Patents

Literature

4565 results about "Sense amplifier" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

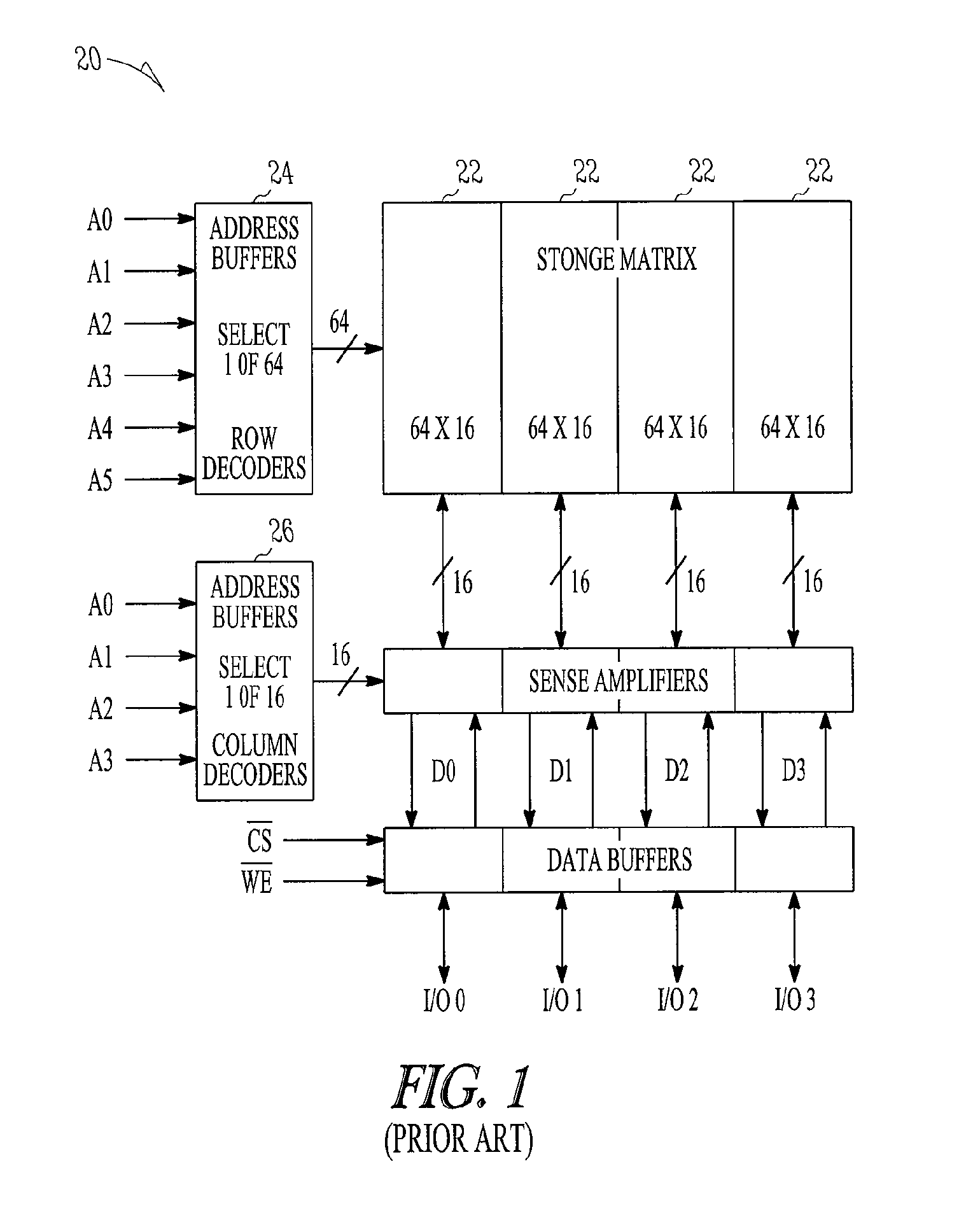

In modern computer memory, a sense amplifier is one of the elements which make up the circuitry on a semiconductor memory chip (integrated circuit); the term itself dates back to the era of magnetic core memory. A sense amplifier is part of the read circuitry that is used when data is read from the memory; its role is to sense the low power signals from a bitline that represents a data bit (1 or 0) stored in a memory cell, and amplify the small voltage swing to recognizable logic levels so the data can be interpreted properly by logic outside the memory.

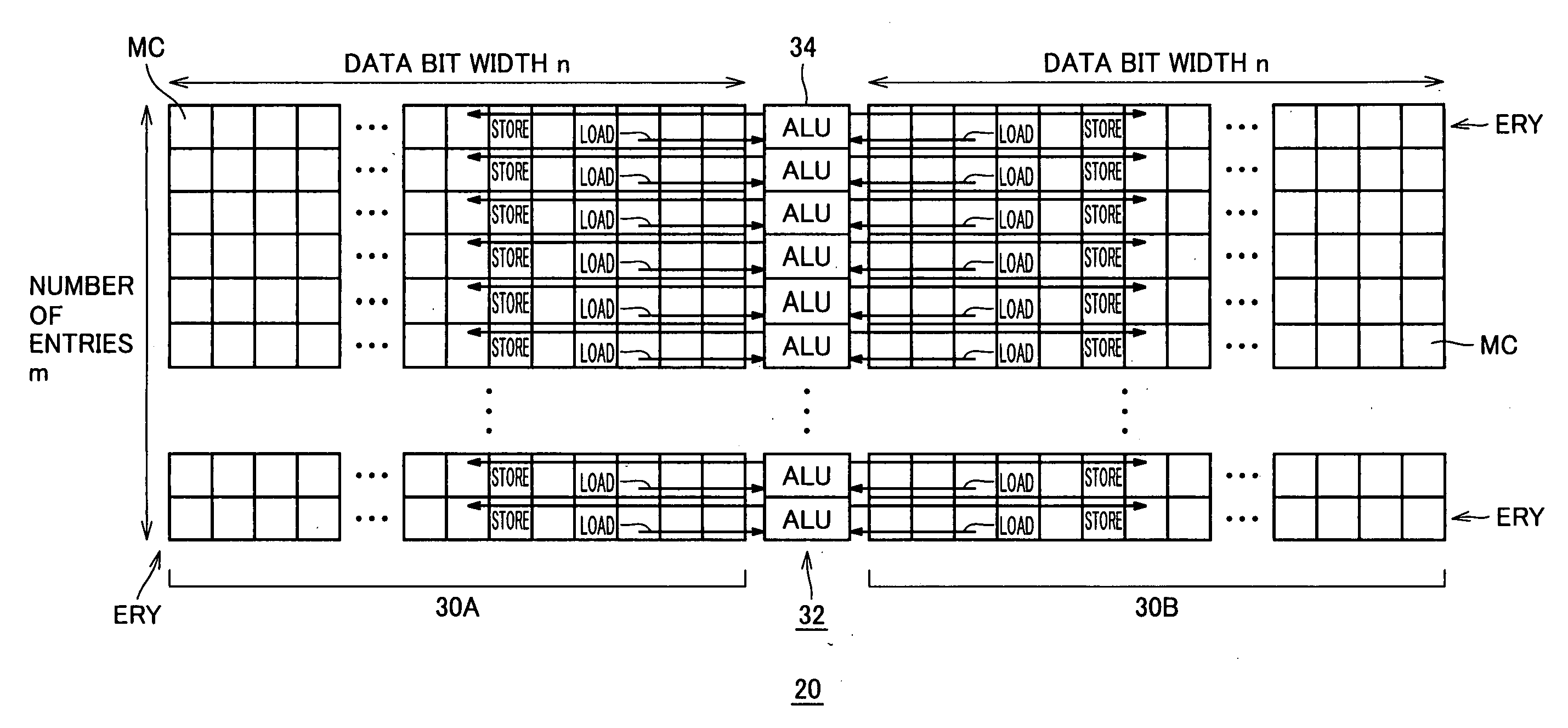

Non-volatile memory and method with shared processing for an aggregate of read/write circuits

InactiveUS20060140007A1Maximum versatilityMinimal componentRead-only memoriesDigital storageAudio power amplifierAssociative processor

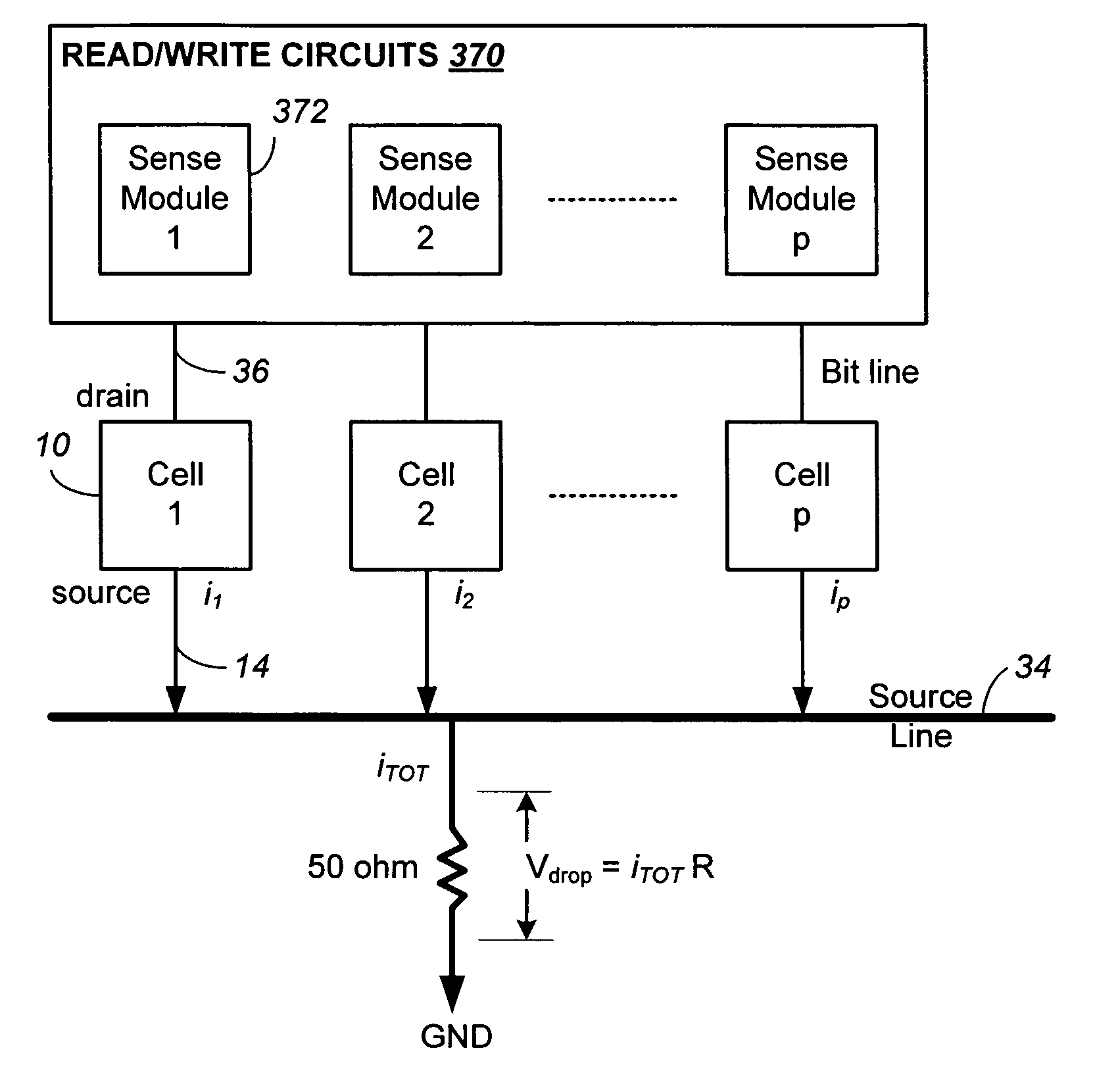

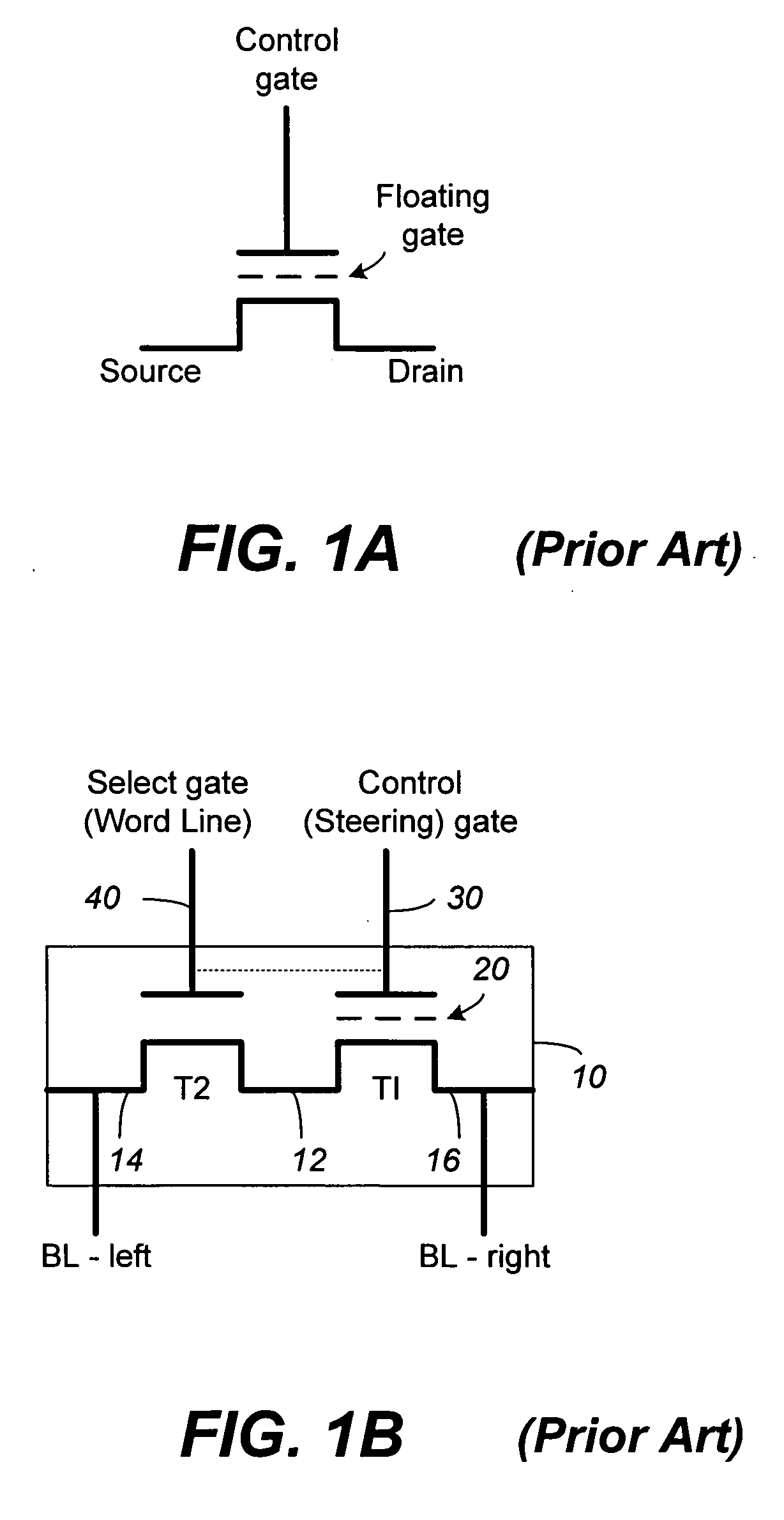

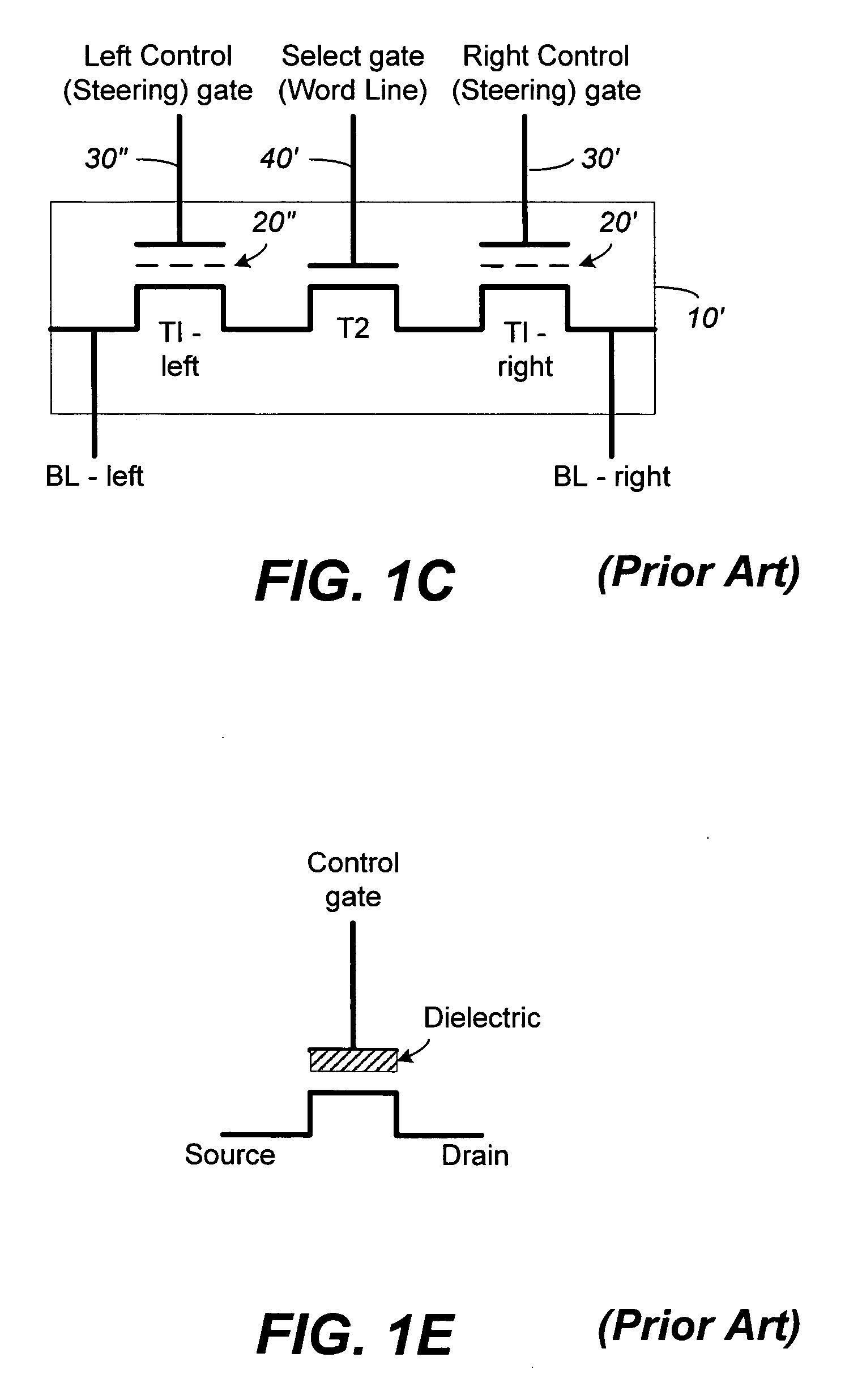

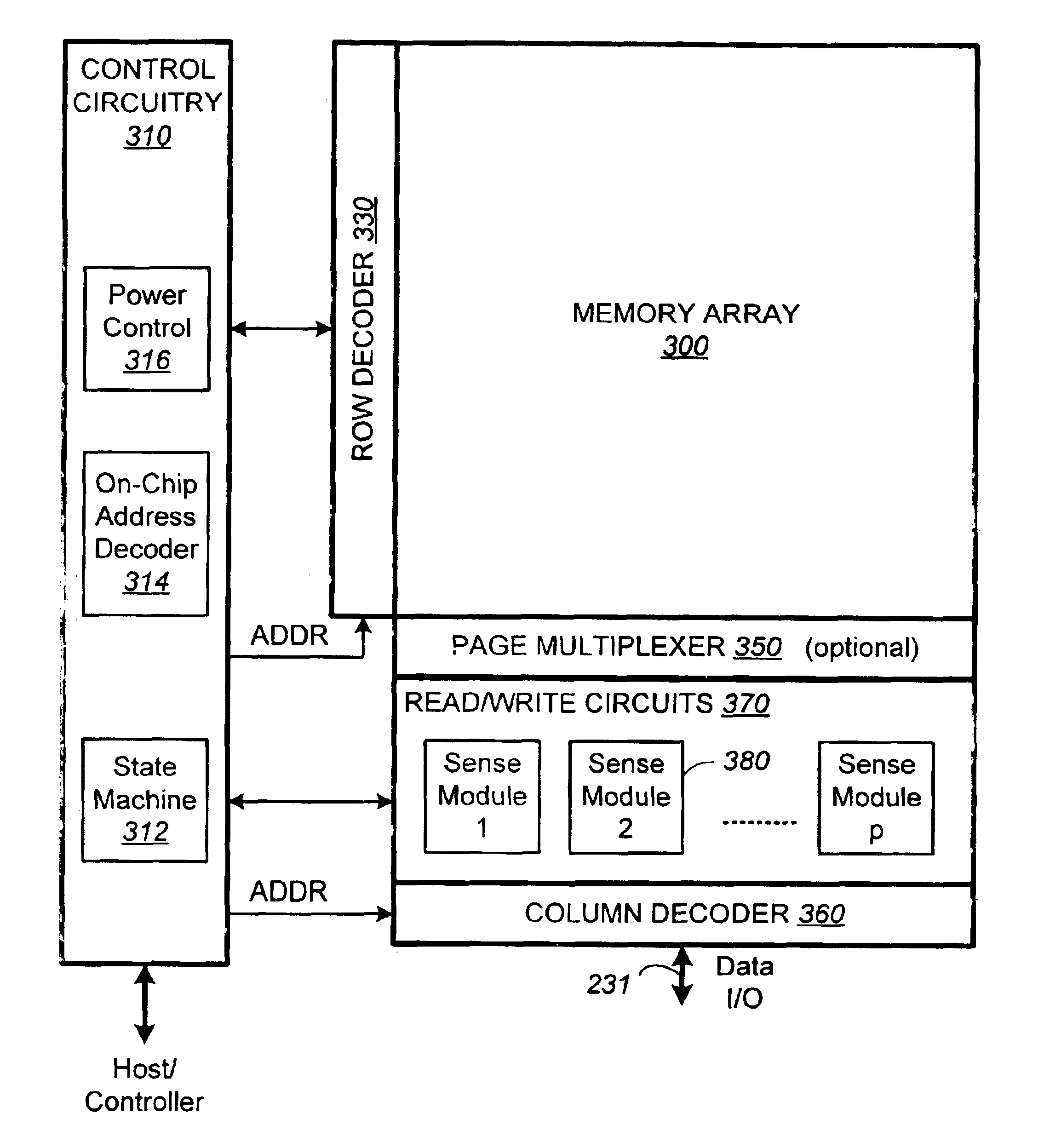

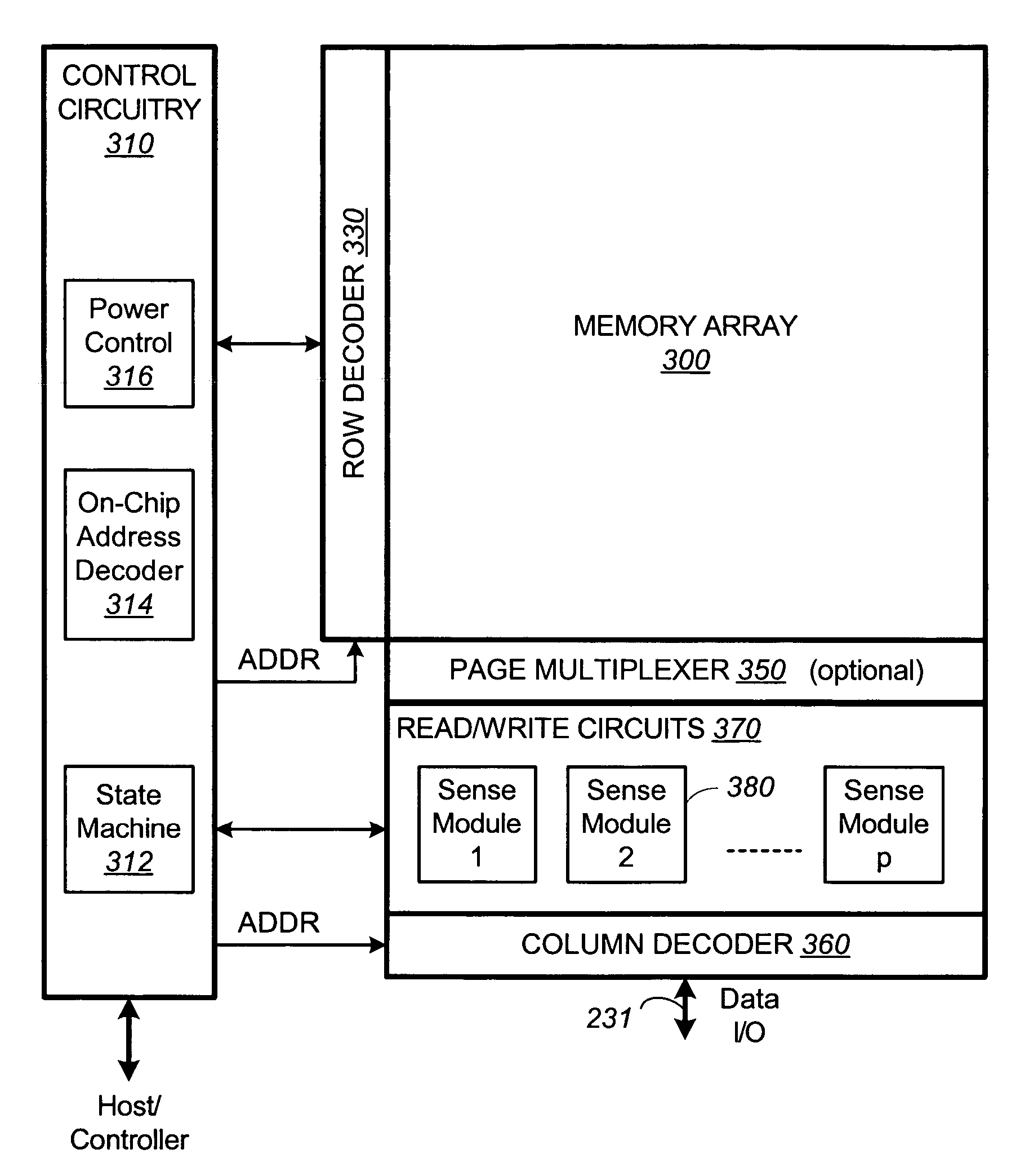

A non-volatile memory device capable of reading and writing a large number of memory cells with multiple read / write circuits in parallel has an architecture that reduces redundancy in the multiple read / write circuits to a minimum. The multiple read / write circuits are organized into a bank of similar stacks of components. Redundant circuits such as a processor for processing data among stacks each associated with multiple memory cells are factored out. The processor is implemented with an input logic, a latch and an output logic. The input logic can transform the data received from either the sense amplifier or the data latches. The output logic further processes the transformed data to send to either the sense amplifier or the data latches or to a controller. This provides an infrastructure with maximum versatility and a minimum of components for sophisticated processing of the data sensed and the data to be input or output.

Owner:SANDISK TECH LLC

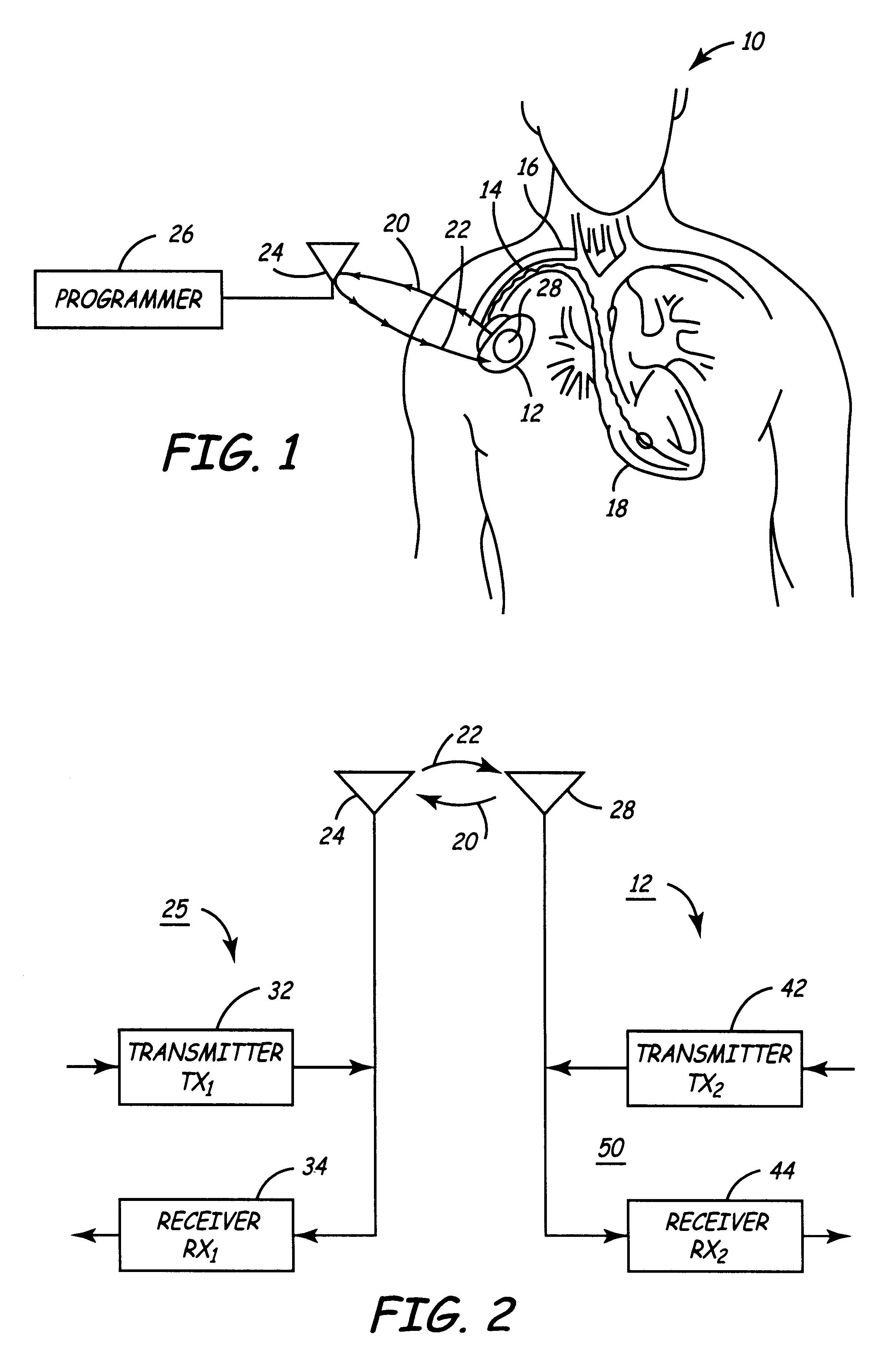

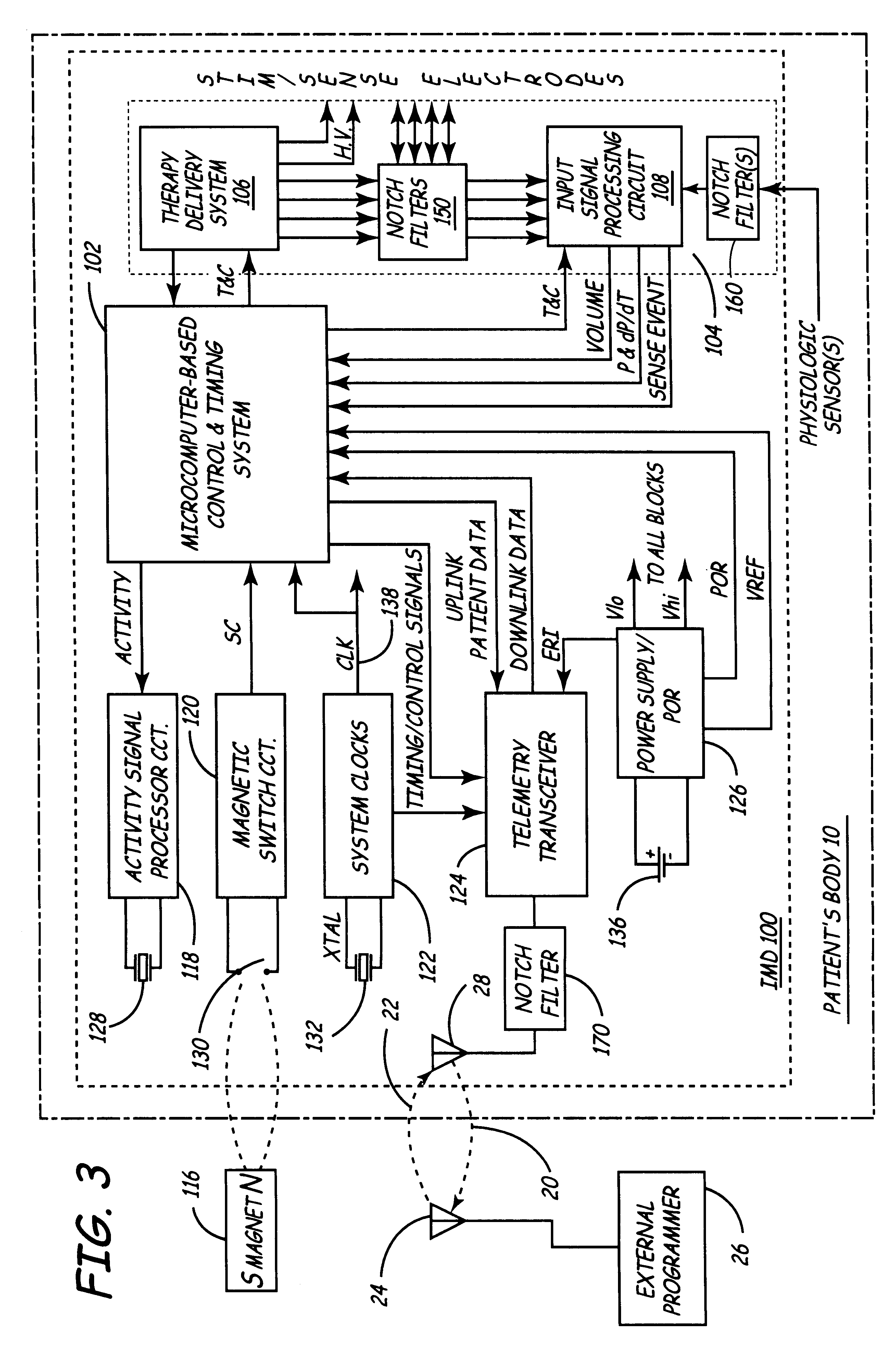

Implantable medical device incorporating integrated circuit notch filters

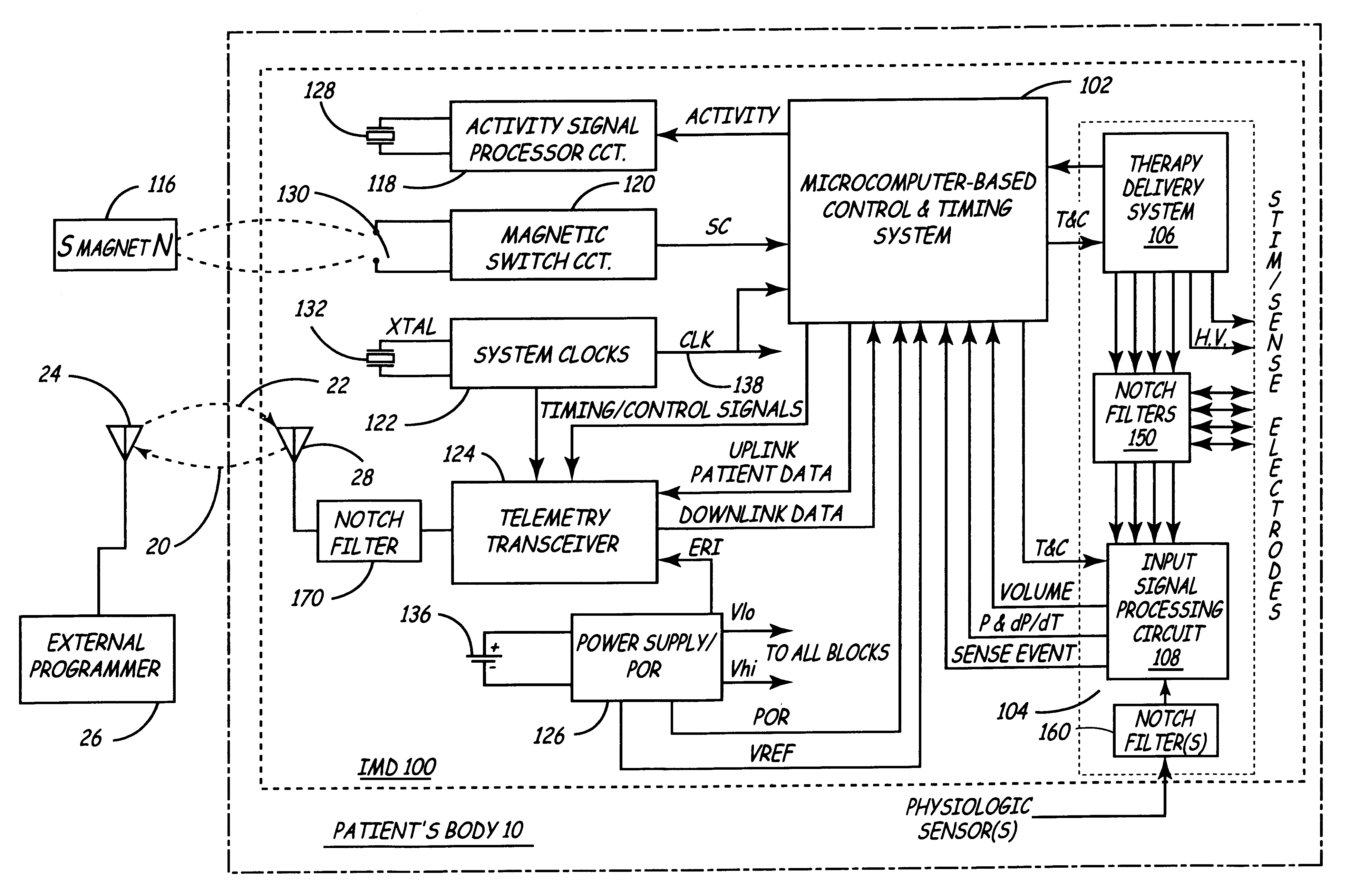

Implantable medical devices (IMDs) having sense amplifiers for sensing physiologic signals and parameters, RF telemetry capabilities for uplink transmitting patient data and downlink receiving programming and interrogation commands to and from an external programmer or other medical device are disclosed. At least one IC chip and discrete components have a volume and dimensions that are optimally minimized to reduce its volumetric form factor. Miniaturization techniques include forming notch filters of MEMS structures or forming discrete circuit notch filters by one or more of: (1) IC fabricating inductors into one or more IC chips mounted to the RF module substrate; (2) mounting each IC chip into a well of the RF module substrate and using short bonding wires to electrically connect bond pads of the RF module substrate and the IC chip; and (3) surface mounting discrete capacitors over IC chips to reduce space taken up on the RF module substrate. The IC fabricated inductors are preferably fabricated as planar spiral wound conductive traces formed of high conductive metals to reduce trace height and width while maintaining low resistance, thereby reducing parasitic capacitances between adjacent trace side walls and with a ground plane of the IC chip. The spiral winding preferably is square or rectangular, but having truncated turns to eliminate 90° angles that cause point-to-point parasitic capacitances. The planar spiral wound conductive traces are further preferably suspended over the ground plane of the IC chip substrate by micromachining underlying substrate material away to thereby reduce parasitic capacitances.

Owner:MEDTRONIC INC

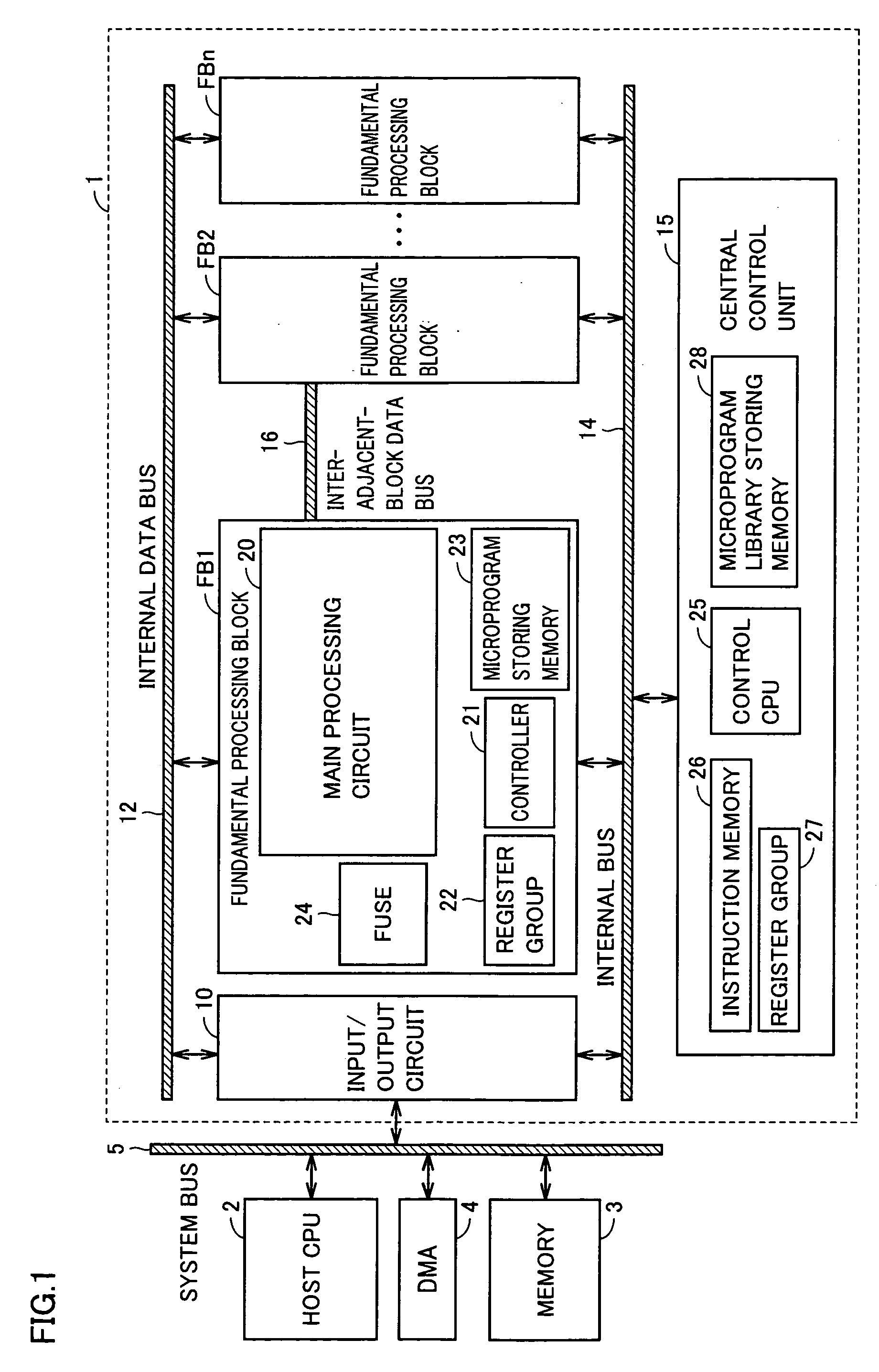

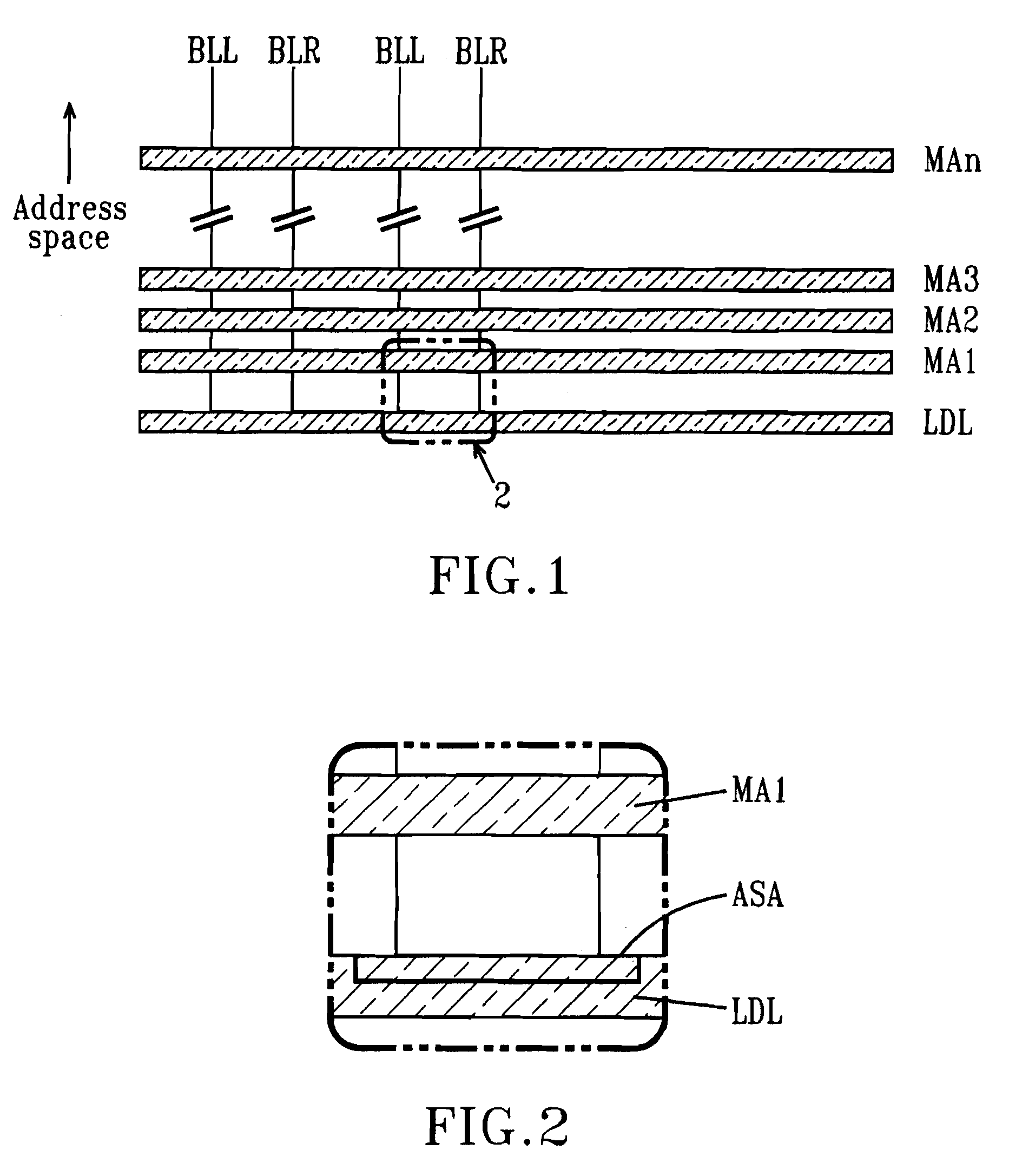

Parallel operational processing device

InactiveUS20070180006A1Easy to operateReduce power consumptionEnergy efficient ICTDigital data processing detailsAudio power amplifierParallel computing

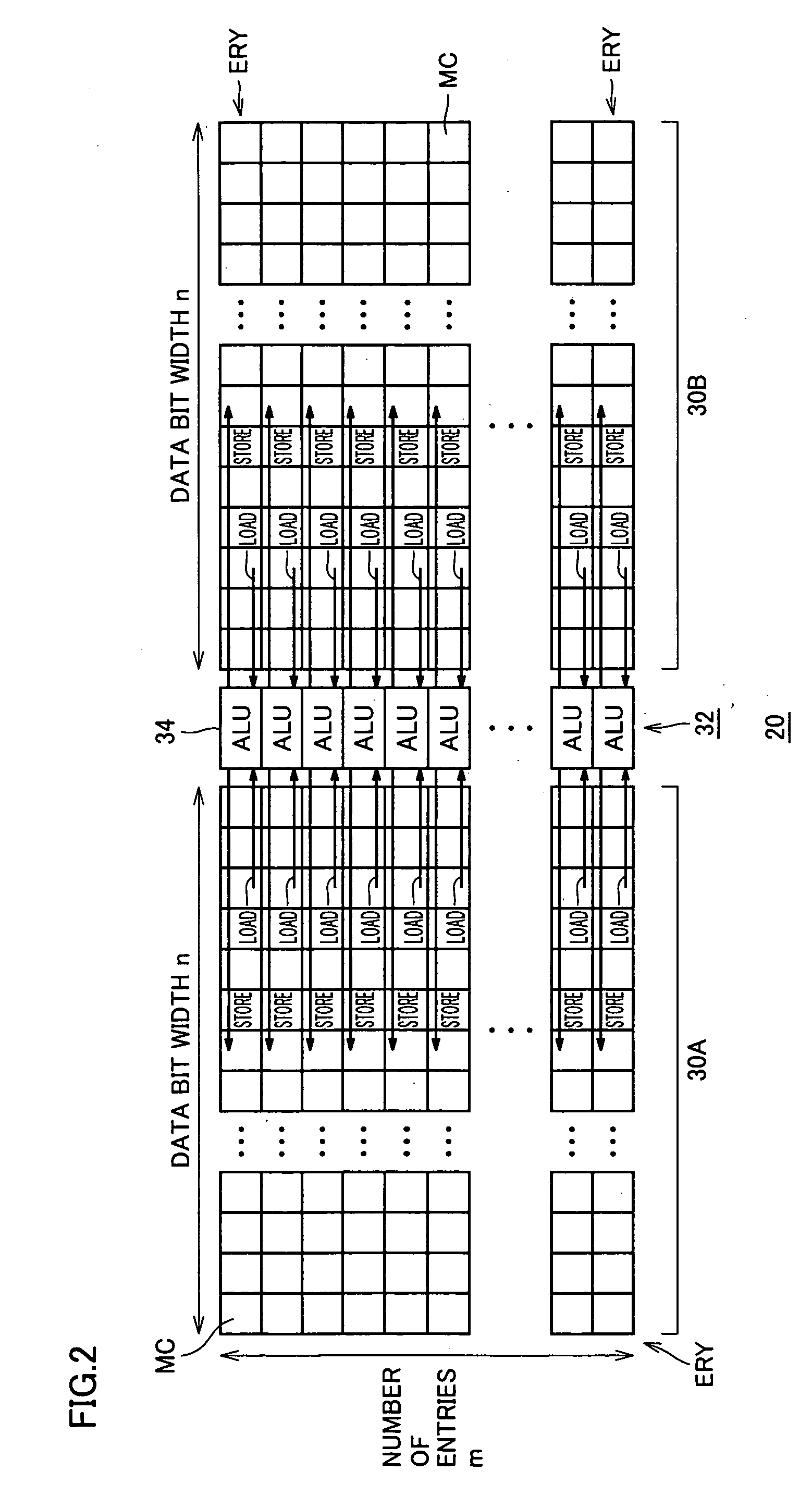

In a parallel operational processing device having an operational processing unit arranged between memory blocks each having a plurality of memory cells arranged in rows and columns, the respective columns of each memory block are alternately connected to the operational processing units on the opposite sides of the memory block. By selecting one word line in one memory block, data can be transferred to two operational processing units. The number of the word lines selected per one operational processing unit is reduced, and power consumption is reduced. The bit operation units and sense amplifiers / write drivers of the operational processing units have arrangement pitch conditions mitigated and are reduced in number, and an isolation region between the memory blocks is not required and the layout area is reduced. Thus, the parallel operational processing device with a layout area and the power consumption reduced, can achieve a fast operation.

Owner:RENESAS ELECTRONICS CORP

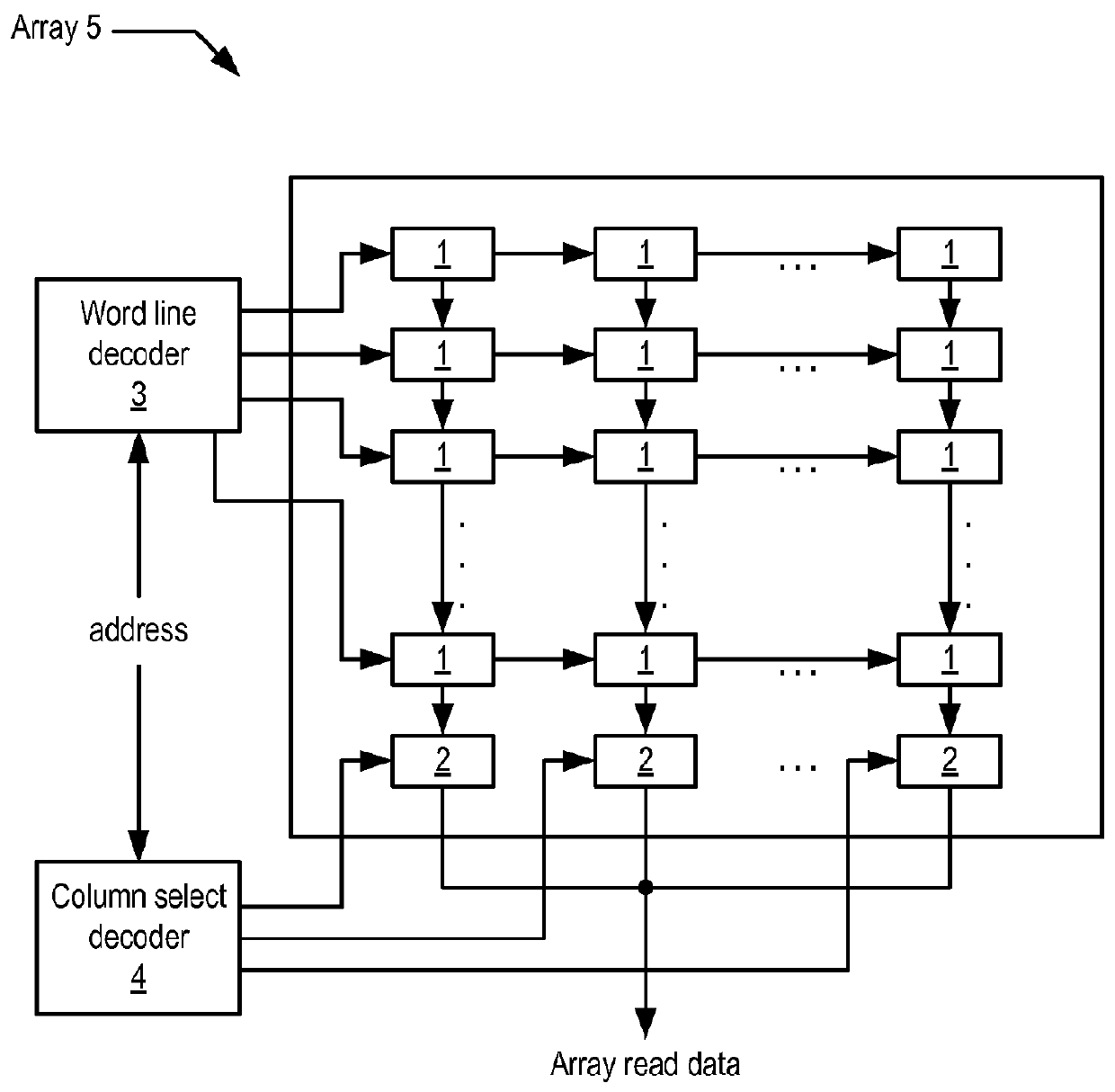

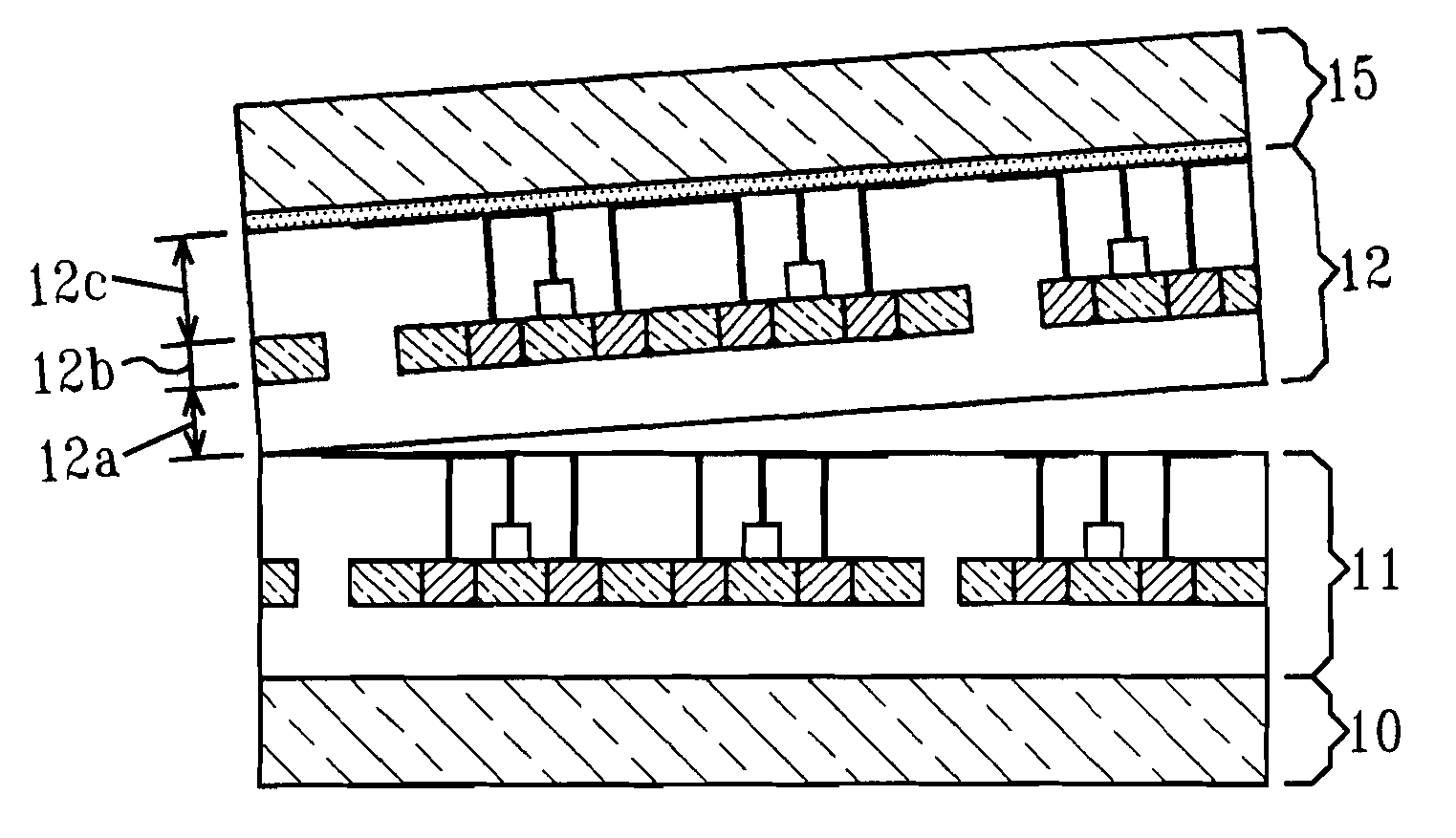

Dram-like nvm memory array and sense amplifier design for high temperature and high endurance operation

InactiveUS20110267883A1Improve threshold voltage sensing marginLarge silicon areaRead-only memoriesDigital storageBit lineAudio power amplifier

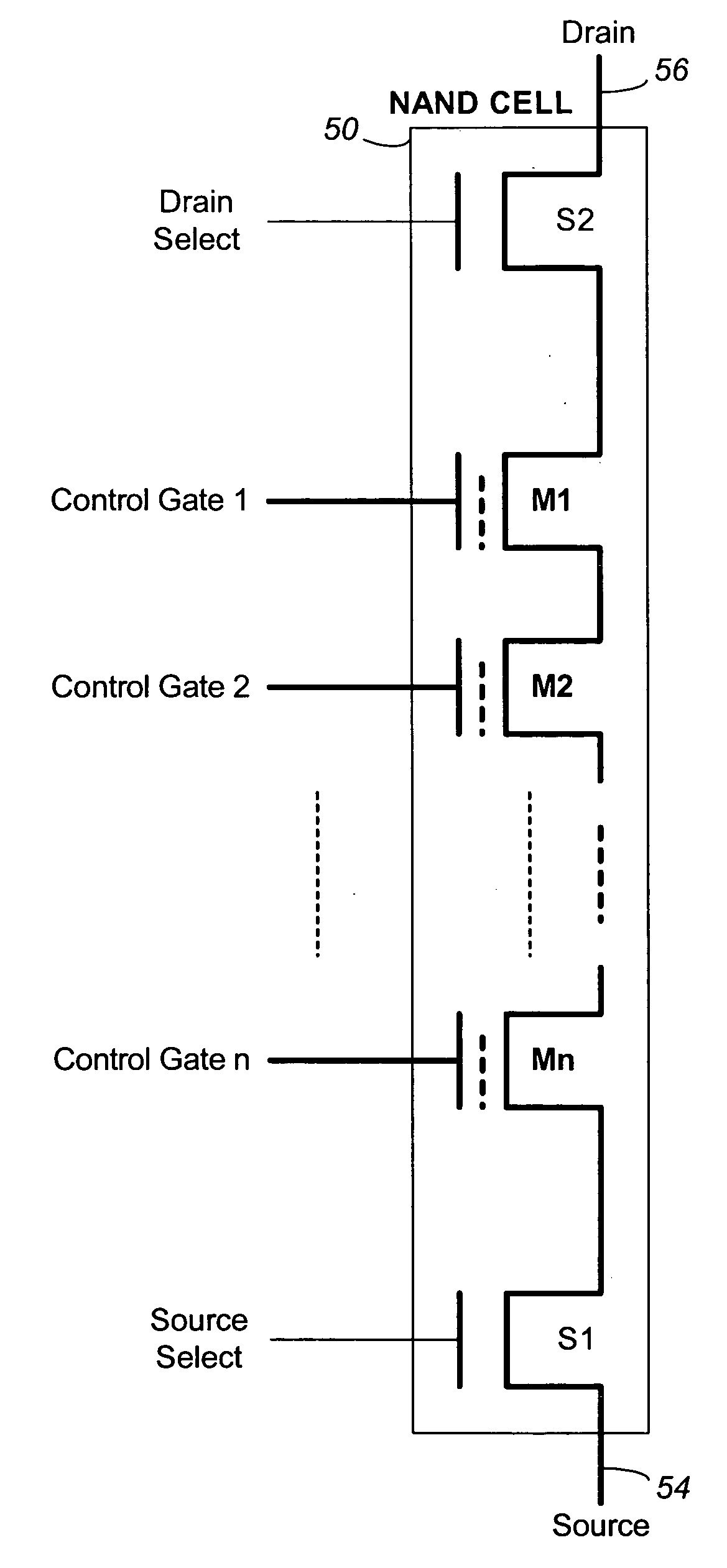

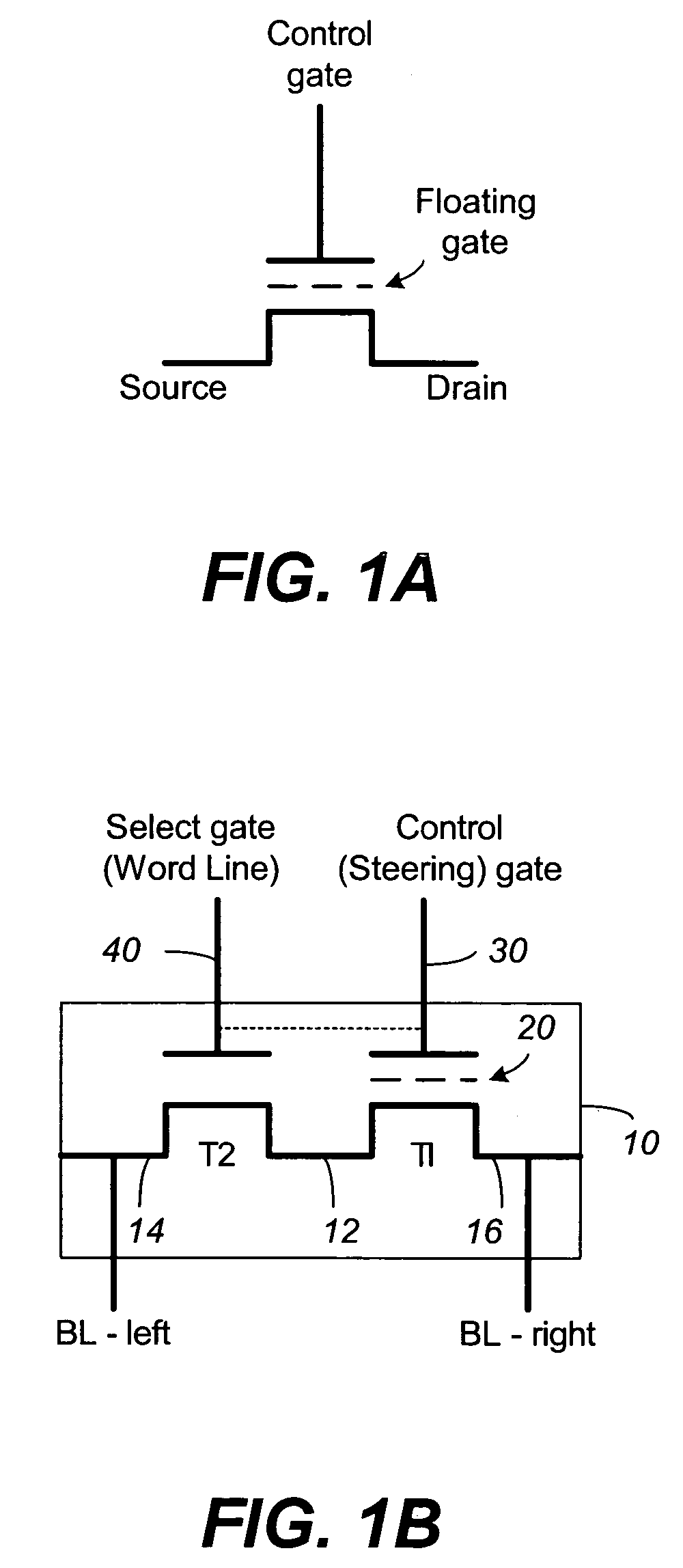

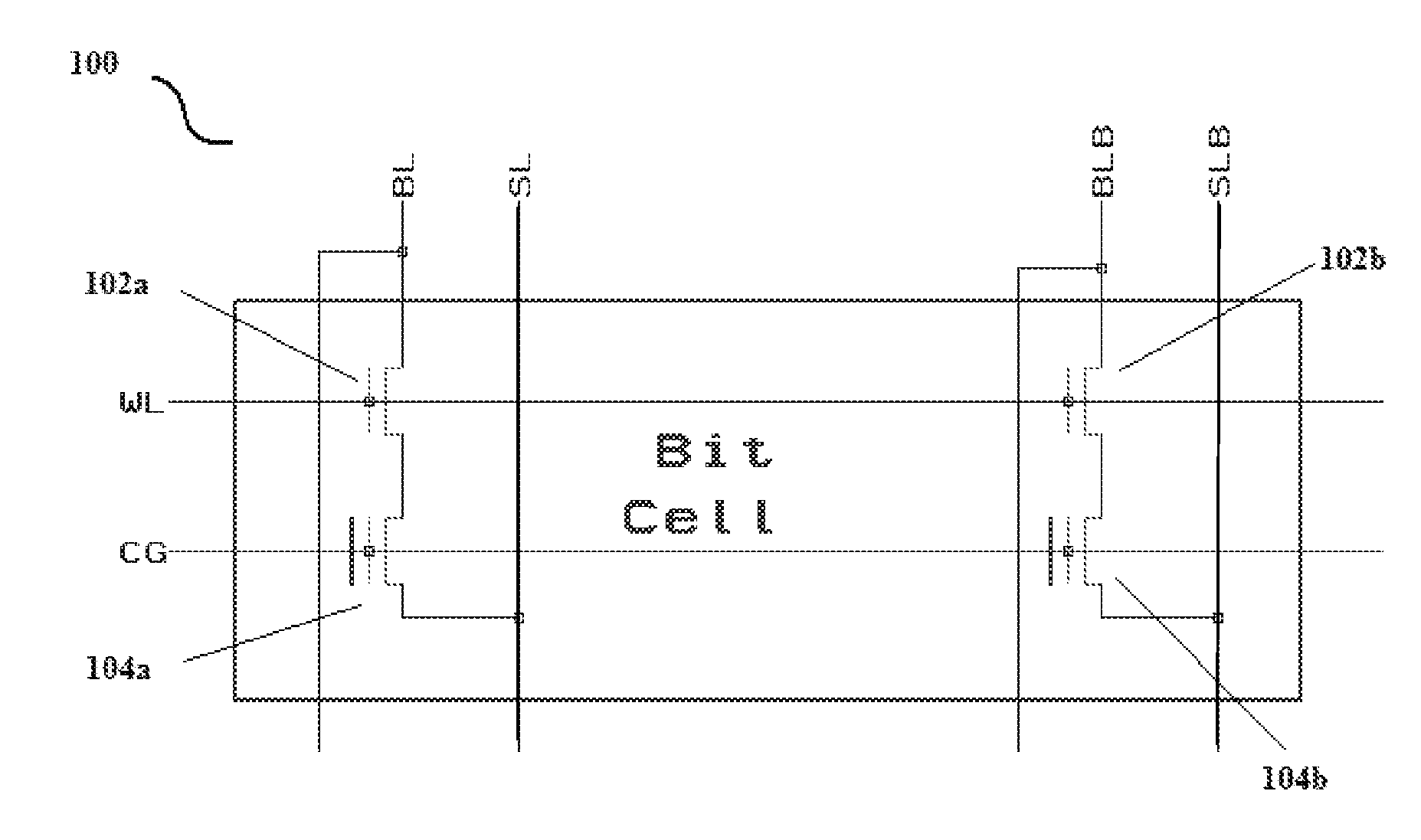

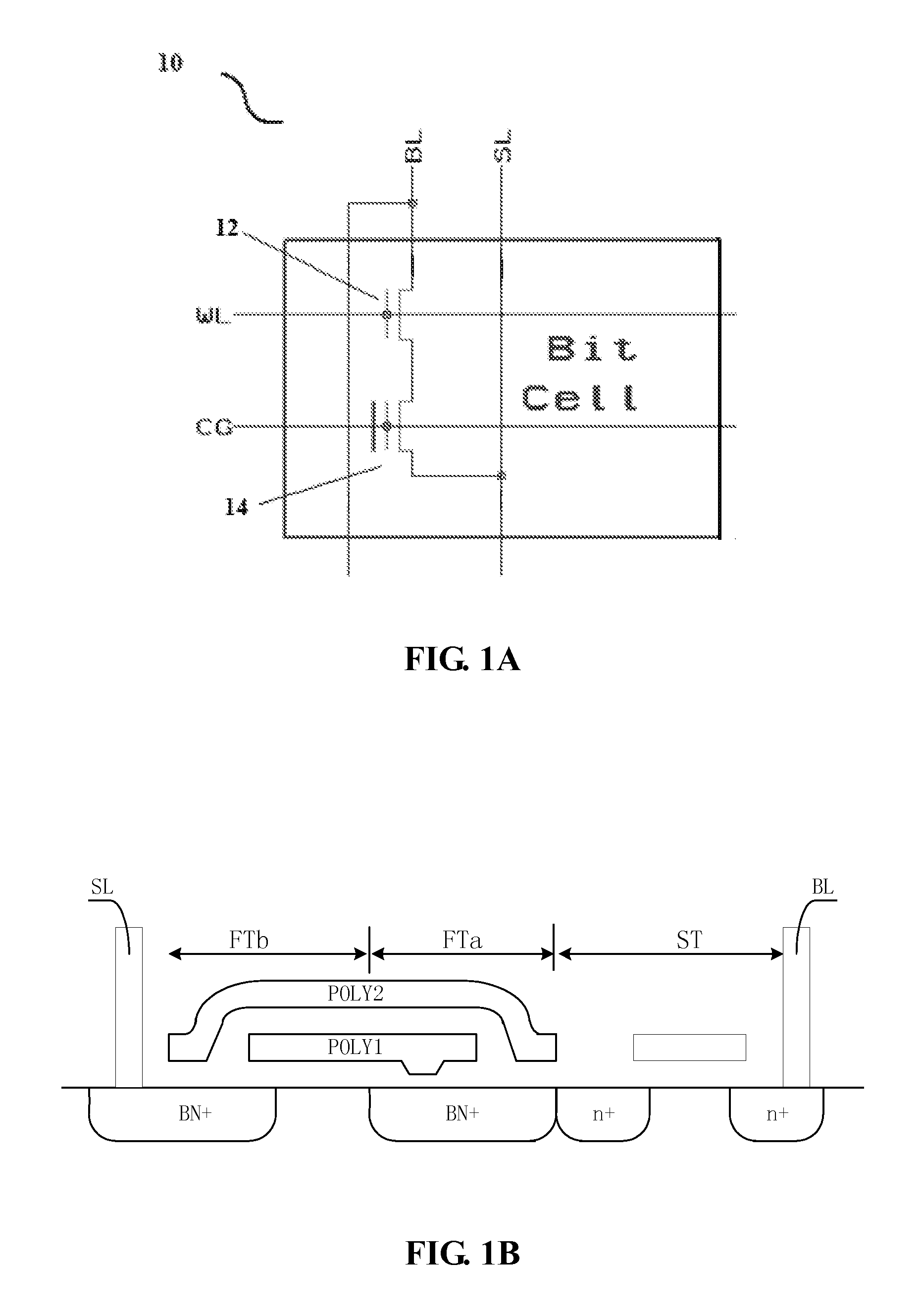

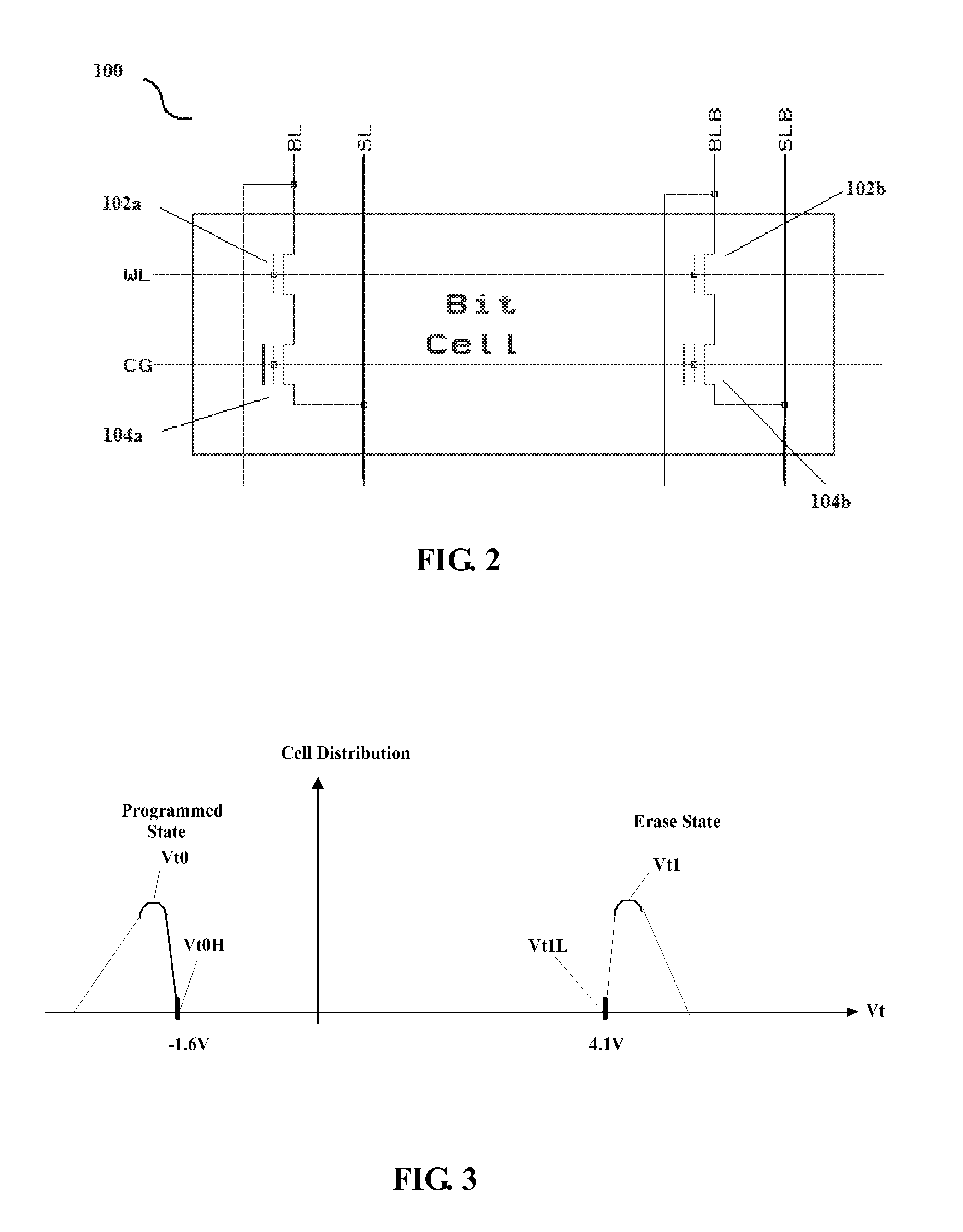

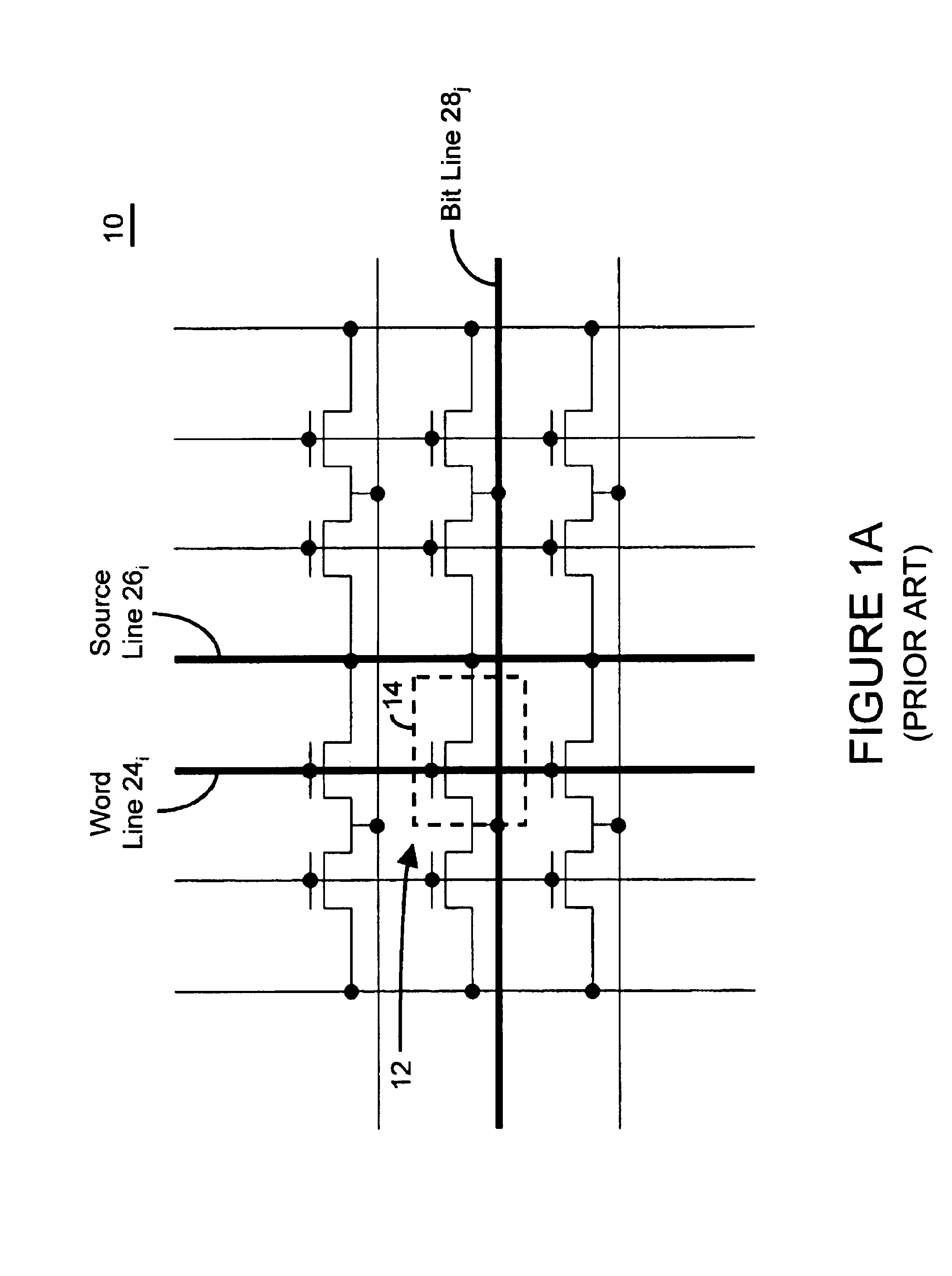

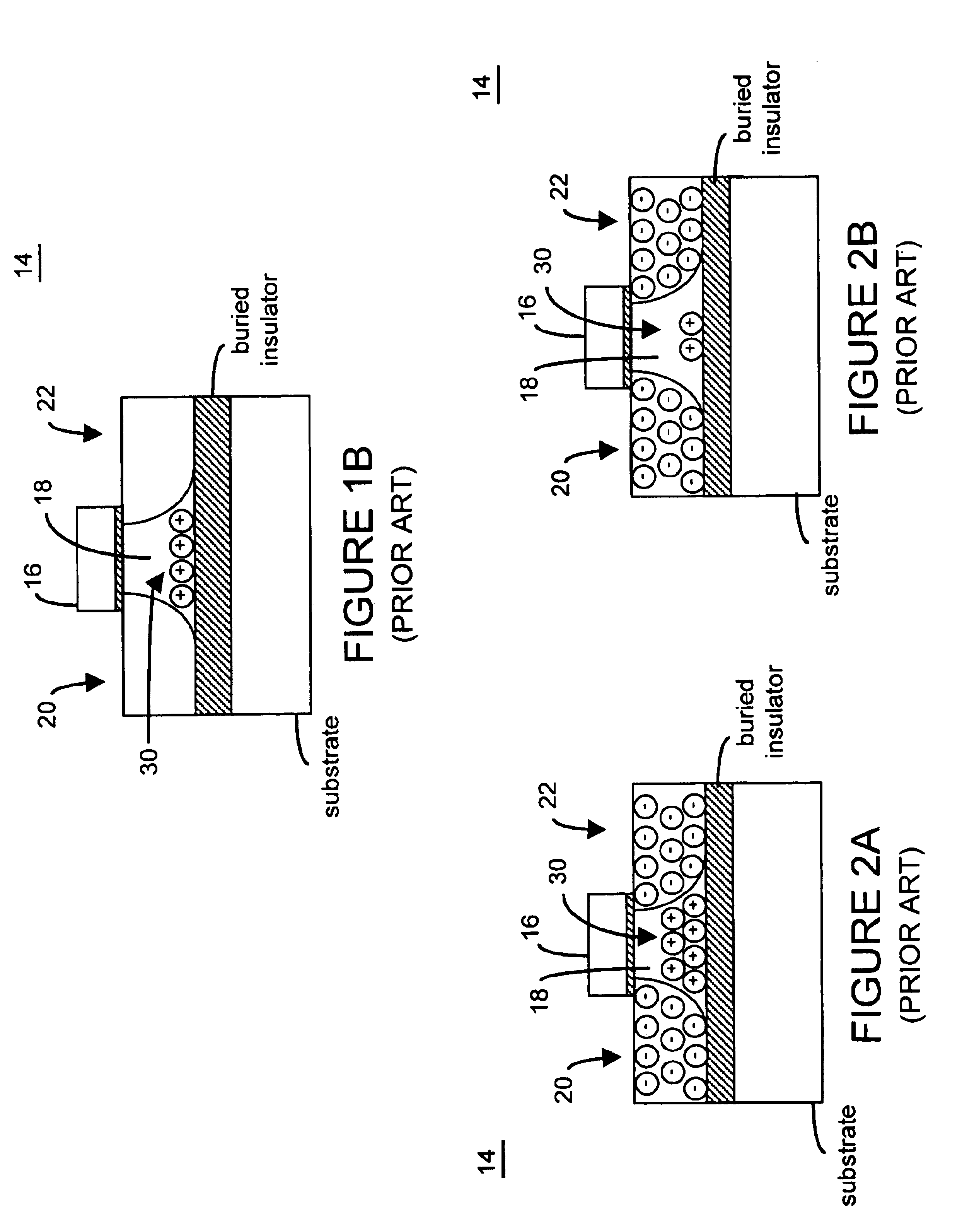

A DRAM-like non-volatile memory array includes a cell array of non-volatile cell units with a DRAM-like cross-coupled latch-type sense amplifier. Each non-volatile cell unit has two non-volatile cell devices with respective bit lines and source lines running in parallel and laid out perpendicular to the word line associated with the non-volatile cell unit. The two non-volatile cell devices are programmed with erased and programmed threshold voltages as a pair for storing a single bit of binary data. The two bit lines of each non-volatile cell unit are coupled through a Y-decoder and a latch device to the two respective inputs of the latch-type sense amplifier which provides a large sensing margin for the cell array to operate properly even with a narrowed threshold voltage gap. Each non-volatile cell device may be a 2 T FLOTOX-based EEPROM cell, a 2 T flash cell, 11 T flash cell or a 1.5 T split-gate flash cell.

Owner:APLUS FLASH TECH

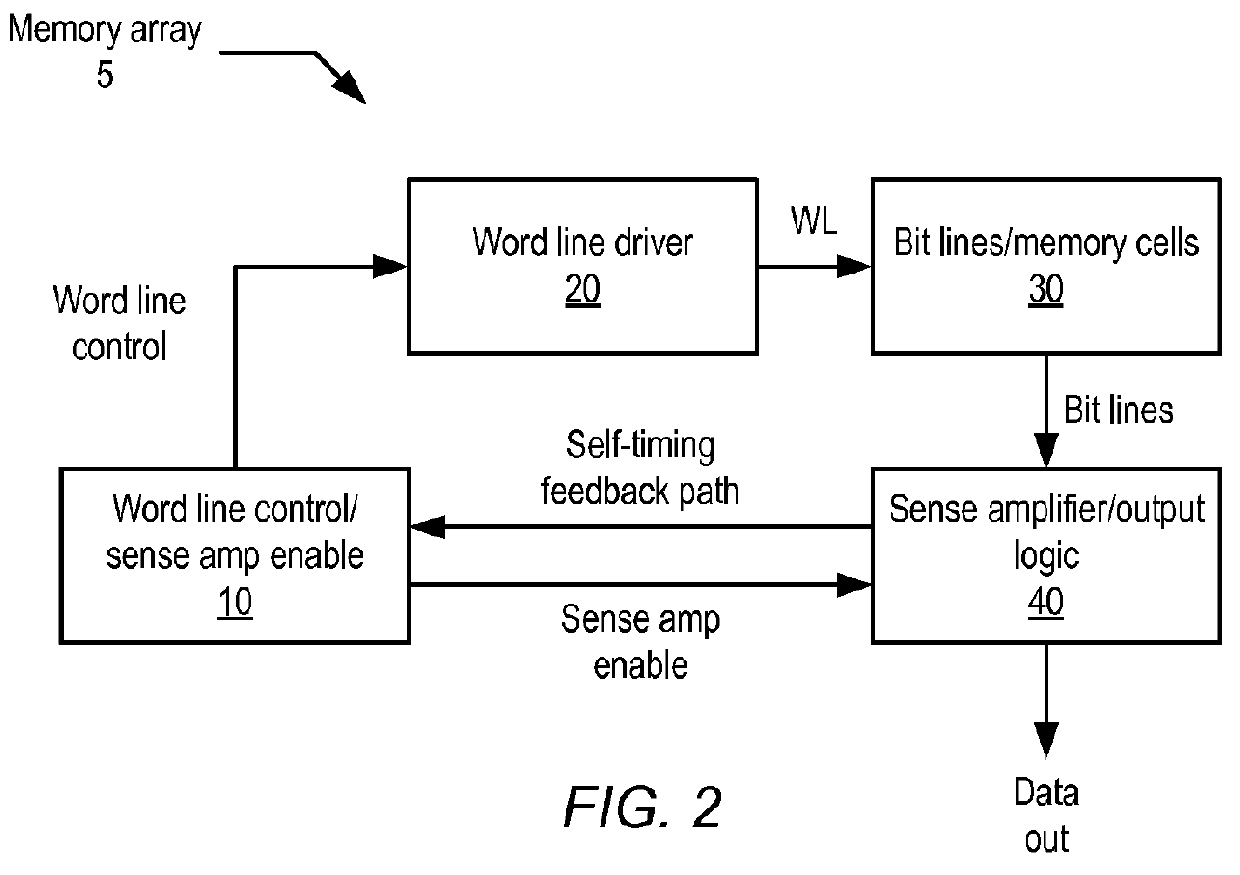

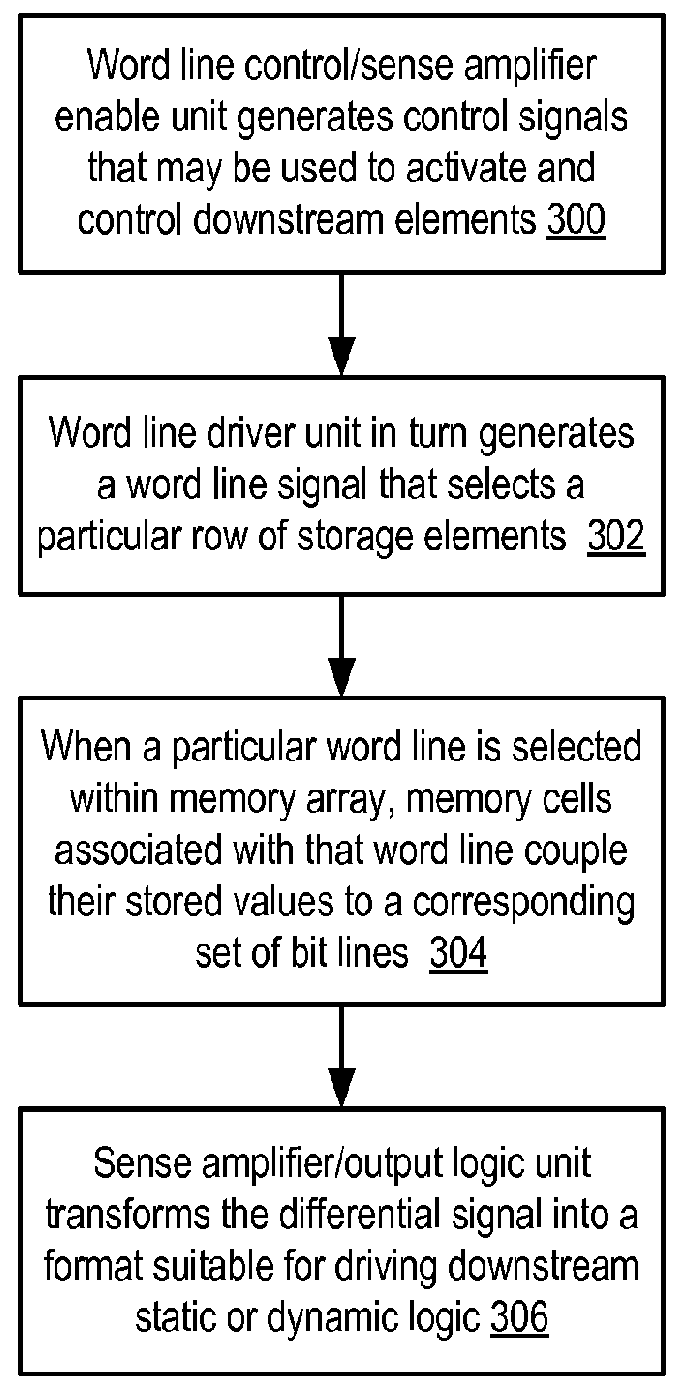

Sense amplifier and sense amplifier latch having common control

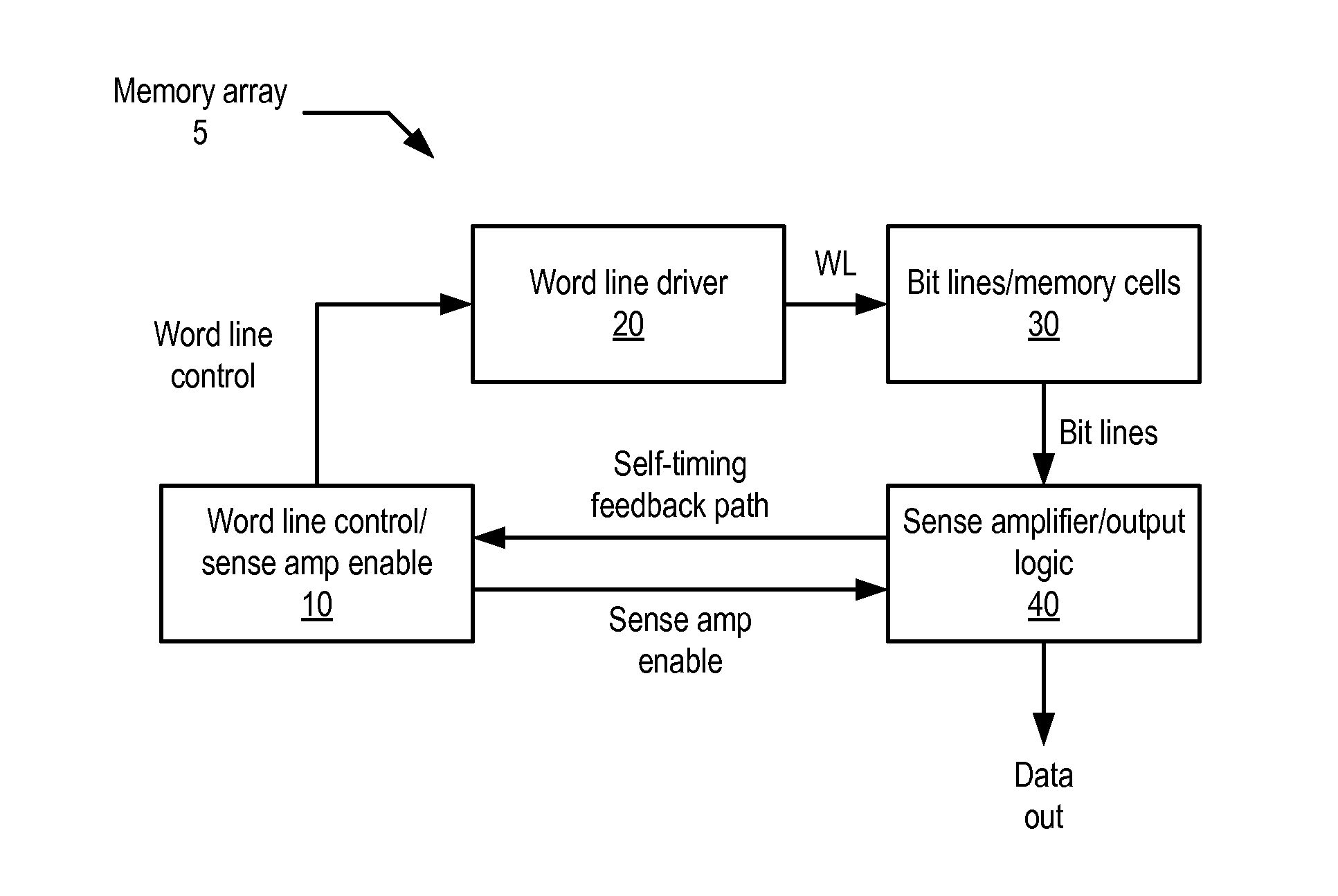

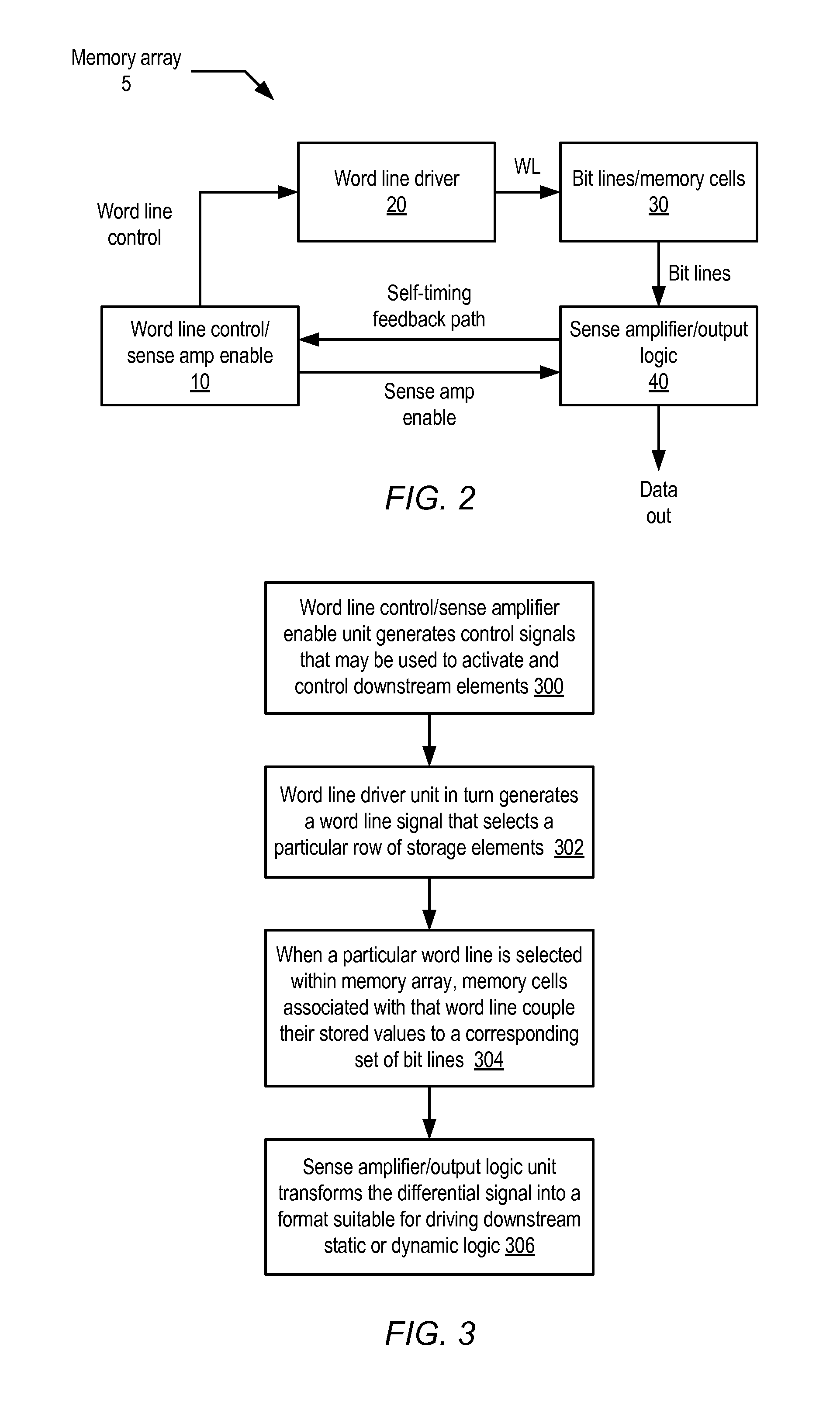

A sense amplifier of a memory array may be provided to amplify data presented from storage cells of the memory array. Additionally, a sense amplifier latch may be provided to store data received from the sense amplifier. The sense amplifier may be enabled for operation by a sense amplifier enable signal that is distinct from a clock signal. Moreover, the latch enable signal of the sense amplifier latch may be controlled by the sense amplifier enable signal, such that the sense amplifier latch opens in response to activation of the sense amplifier and closes in response to deactivation of the sense amplifier.

Owner:APPLE INC

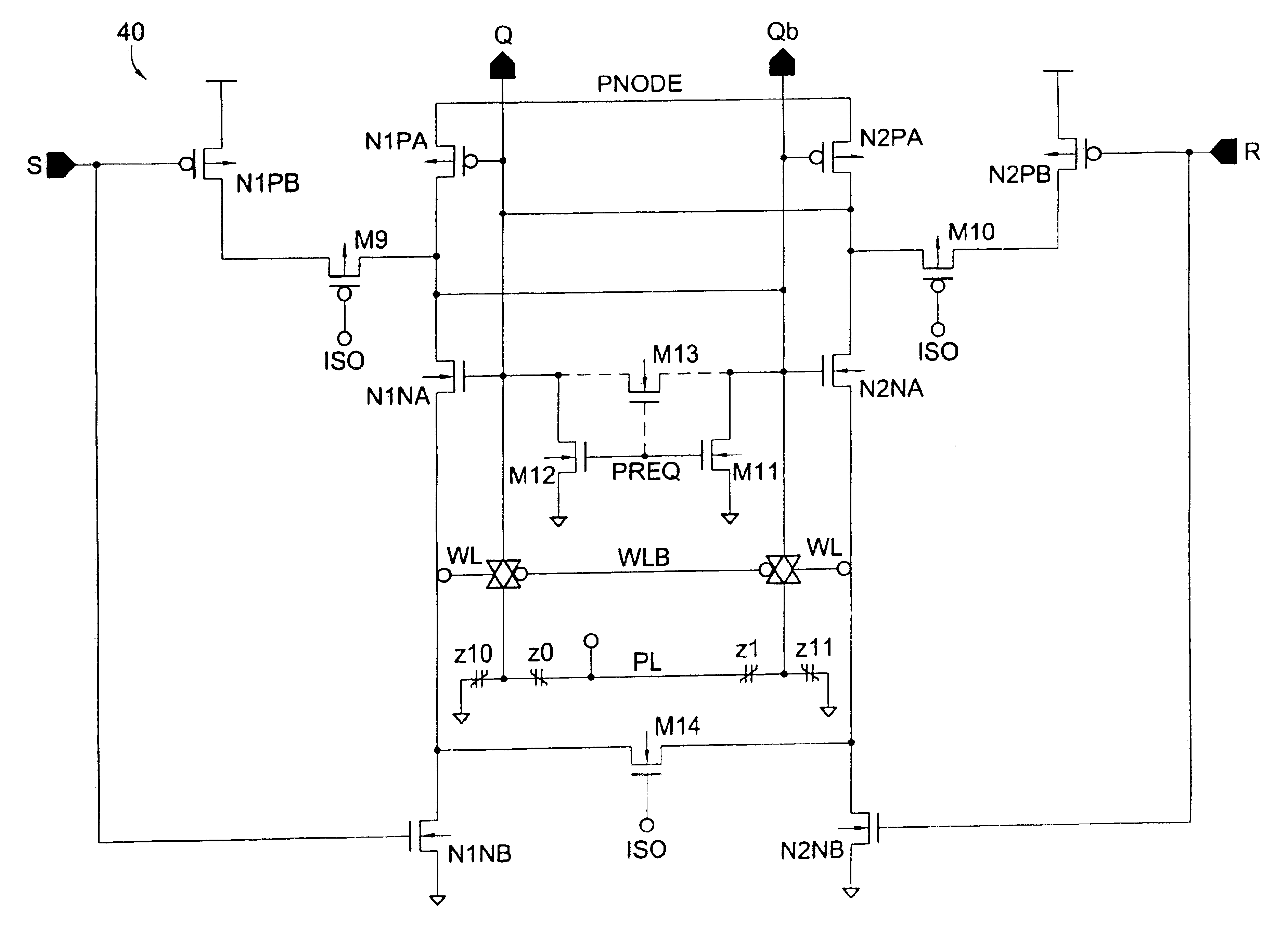

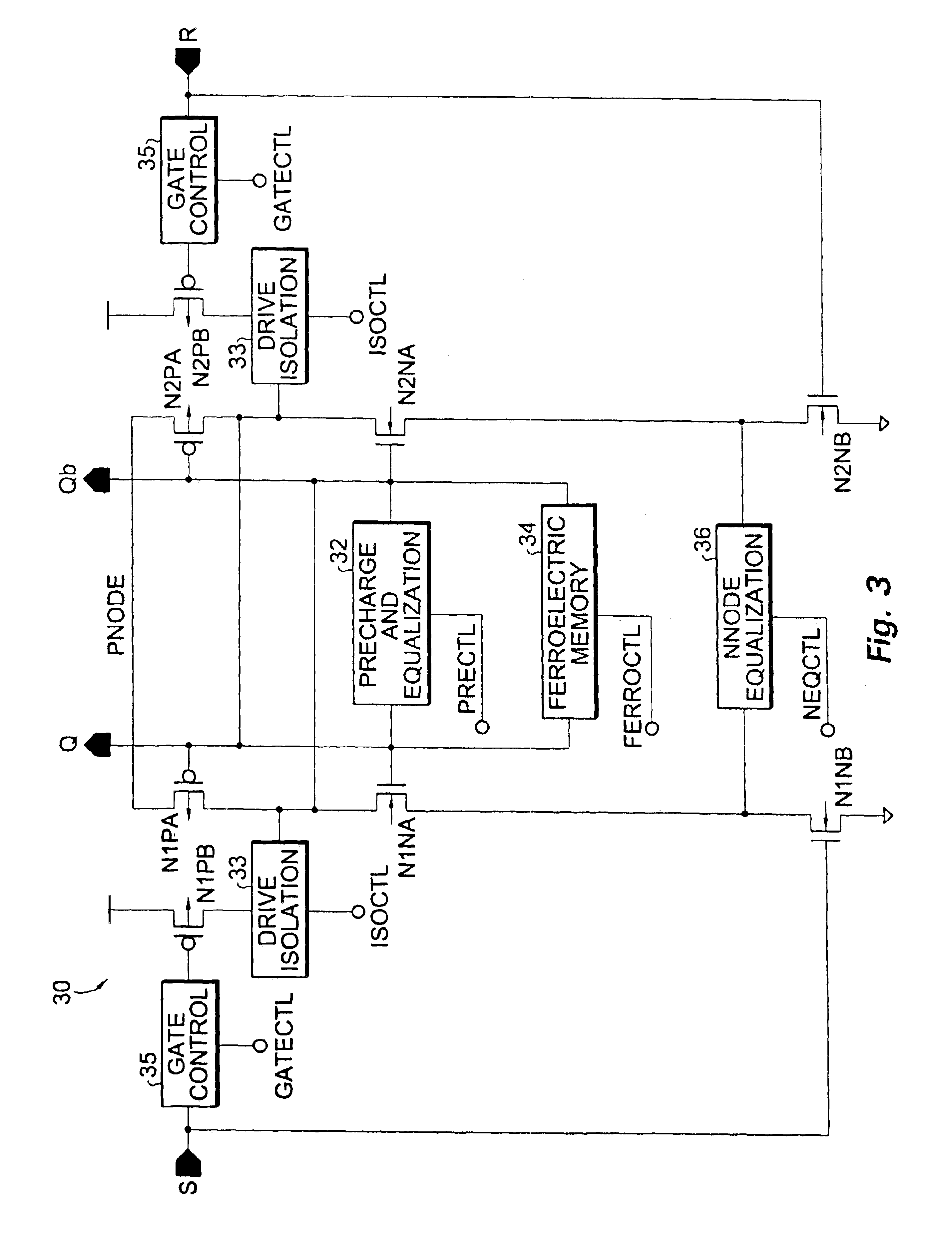

Ferroelectric non-volatile logic elements

InactiveUS6894549B2Easy translationImprove performanceTransistorPulse generation by non-linear magnetic/dielectric devicesShift registerAudio power amplifier

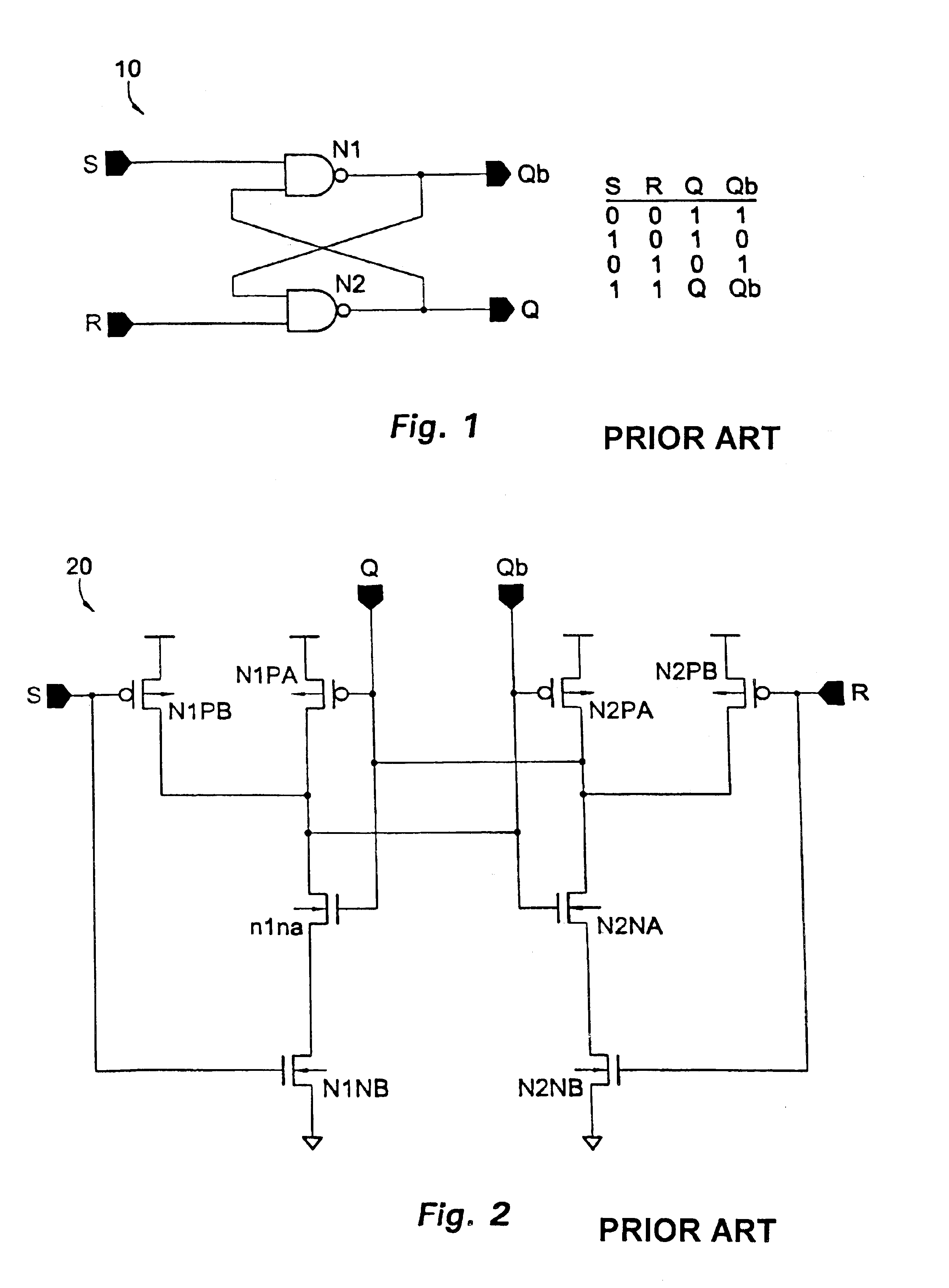

Various logic elements such as SR flip-flops, JK flip-flops, D-type flip-flops, master-slave flip-flops, parallel and serial shift registers, and the like are converted into non-volatile logic elements capable of retaining a current output logic state even though external power is removed or interrupted through the strategic addition of ferroelectric capacitors and supporting circuitry. In each case, the building blocks of a cross-coupled sense amplifier are identified within the logic element and the basic cell is modified and / or optimized for sensing performance.

Owner:MONTEREY RES LLC

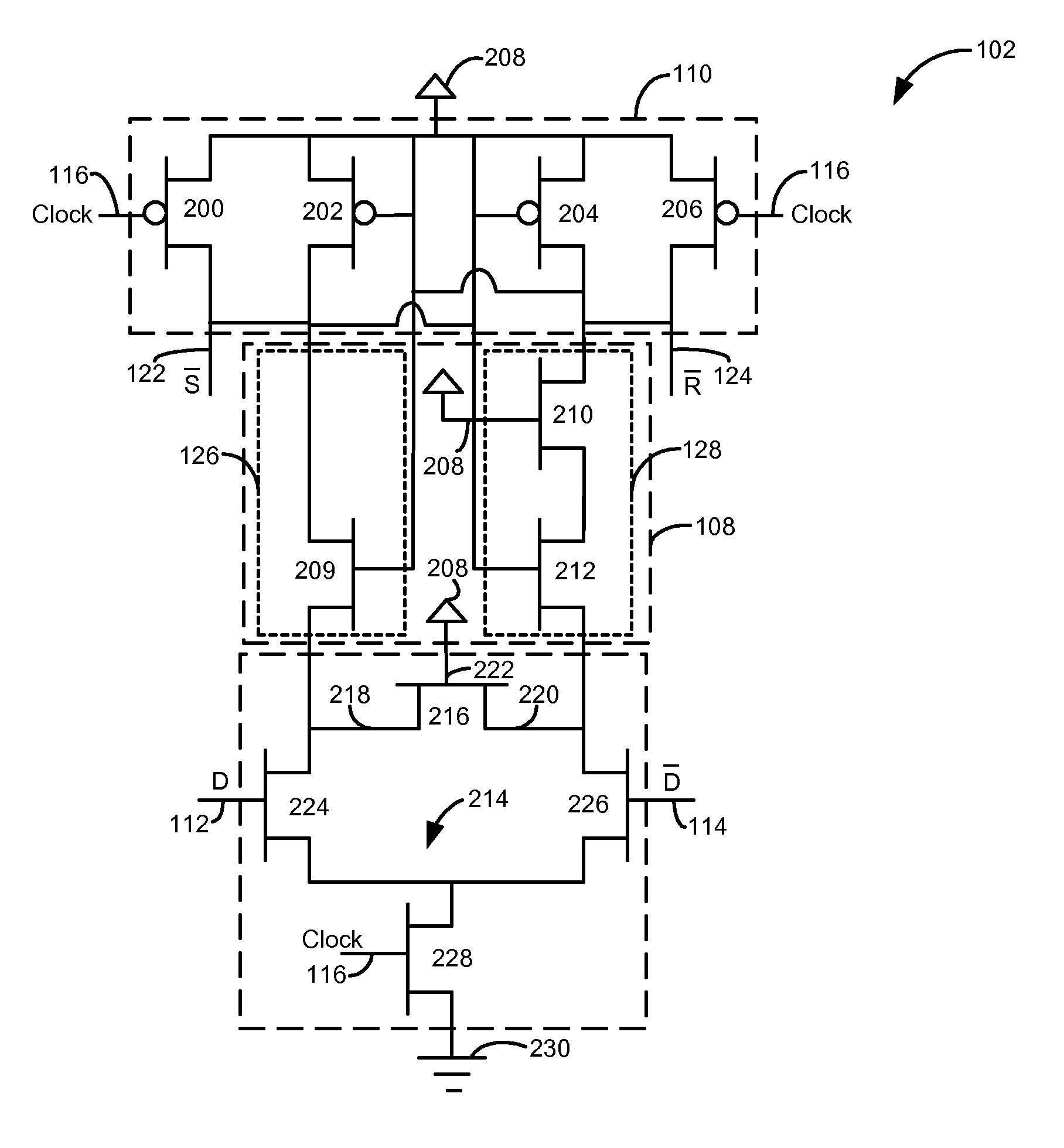

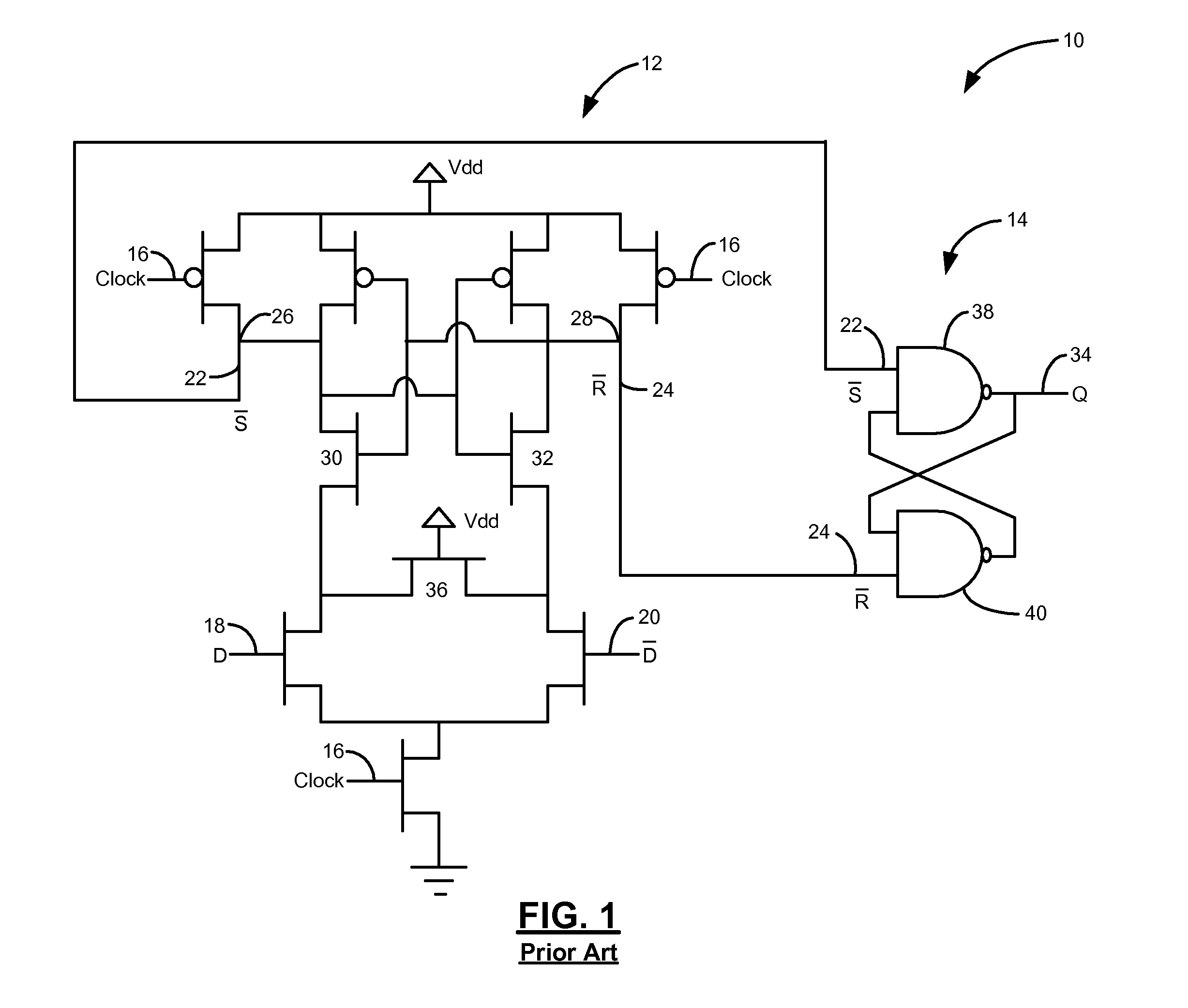

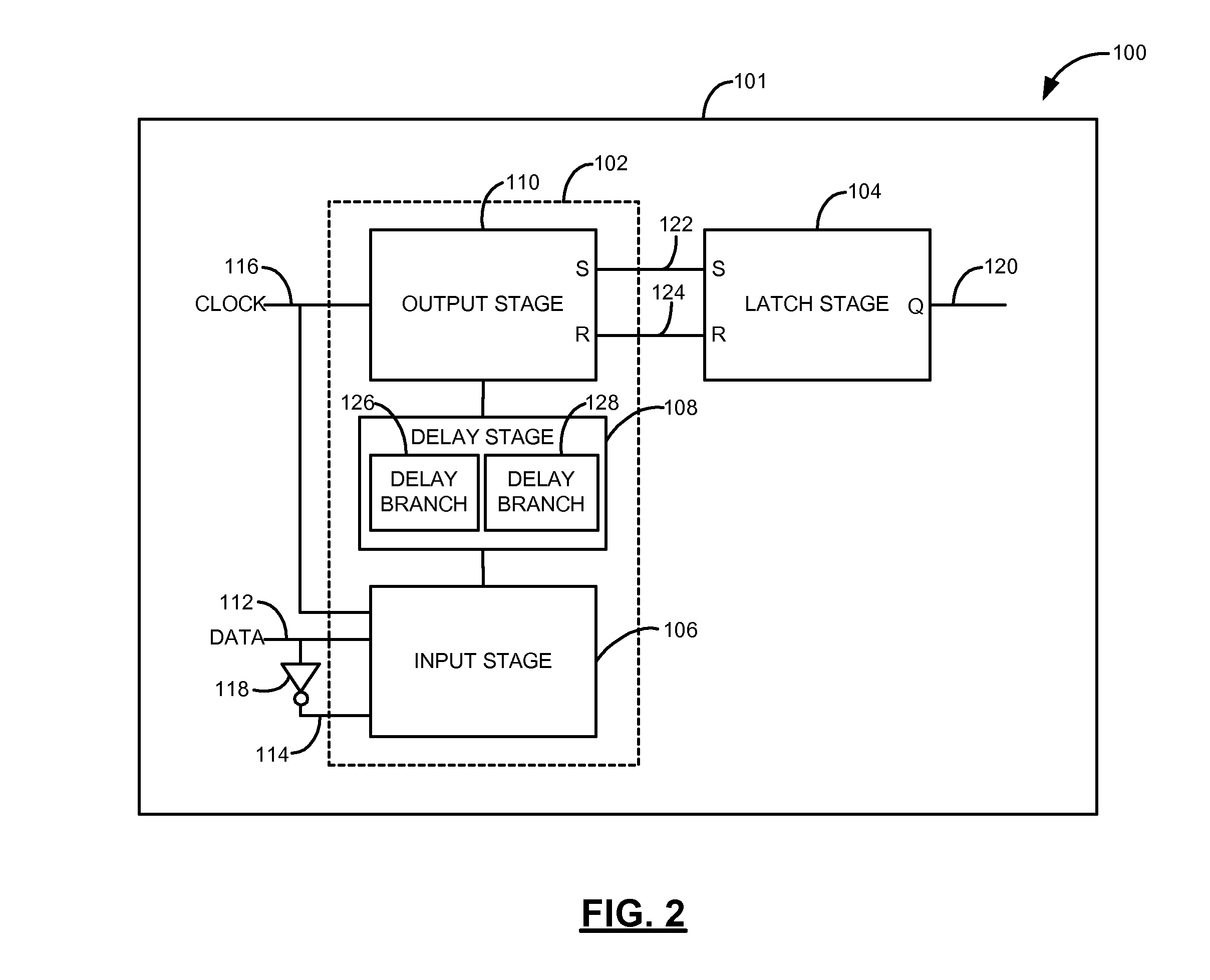

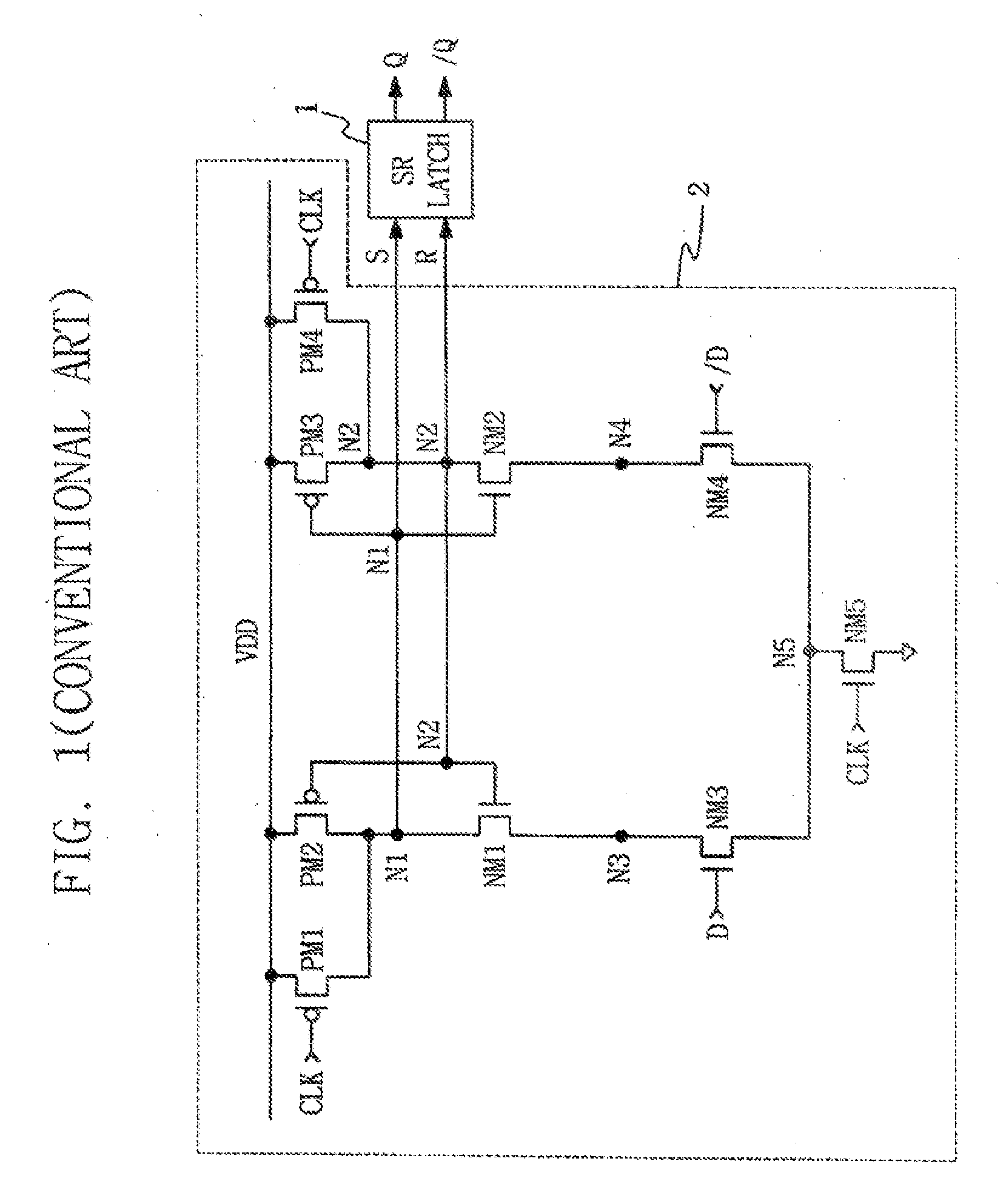

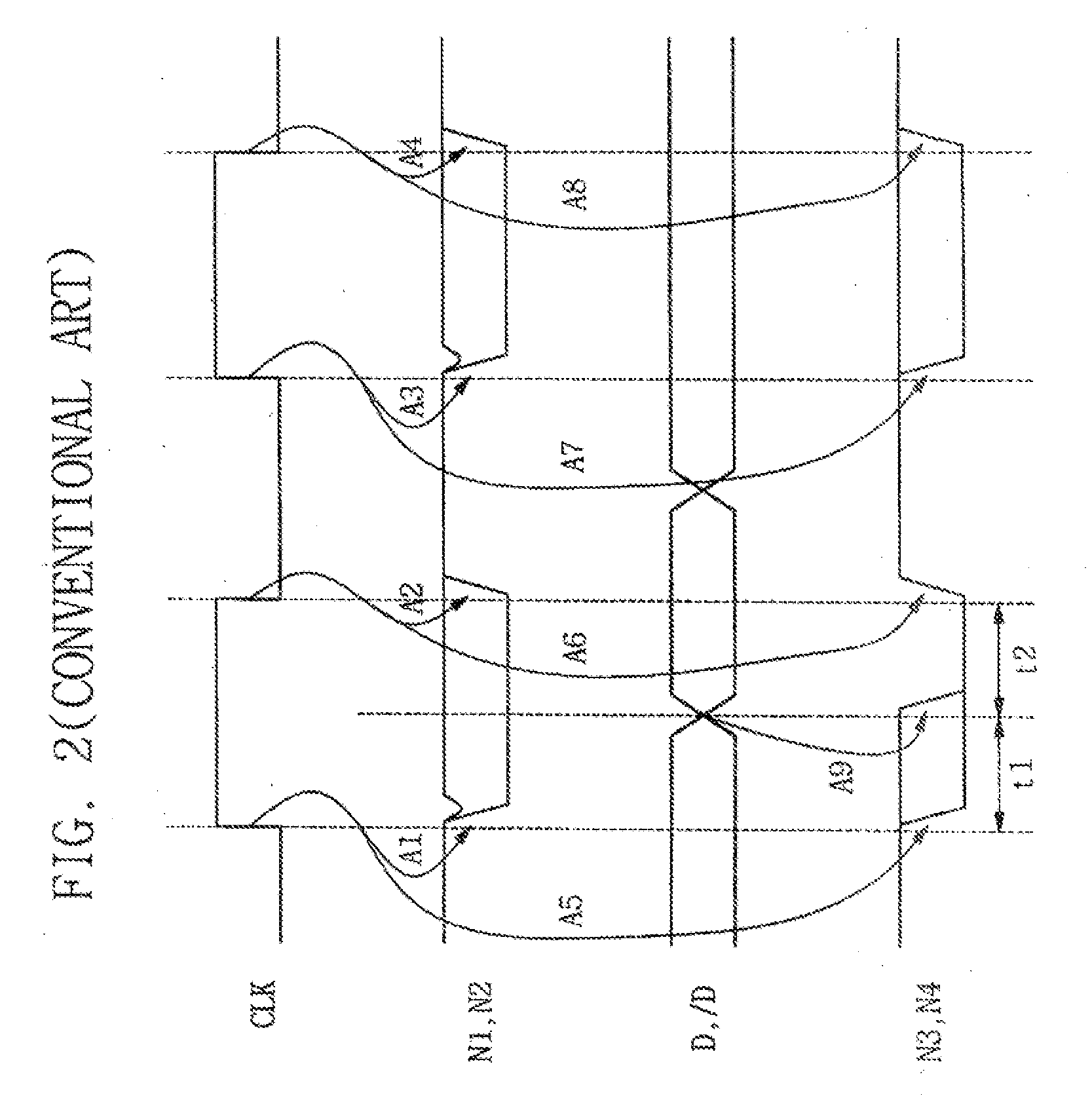

Sense amplifier based flip-flop

A circuit includes an input stage, an output stage, and a delay stage. The input stage is operative to receive a clock signal and a first and second input signal. The output stage is operative to receive the clock signal. The output stage is also operative to generate a first and second output signal based on the clock signal and the first and second input signals. The delay stage is operatively coupled to the input and output stages. The delay stage includes a first and second branch. The second branch includes at least one more delay element than the first branch.

Owner:ATI TECH INC

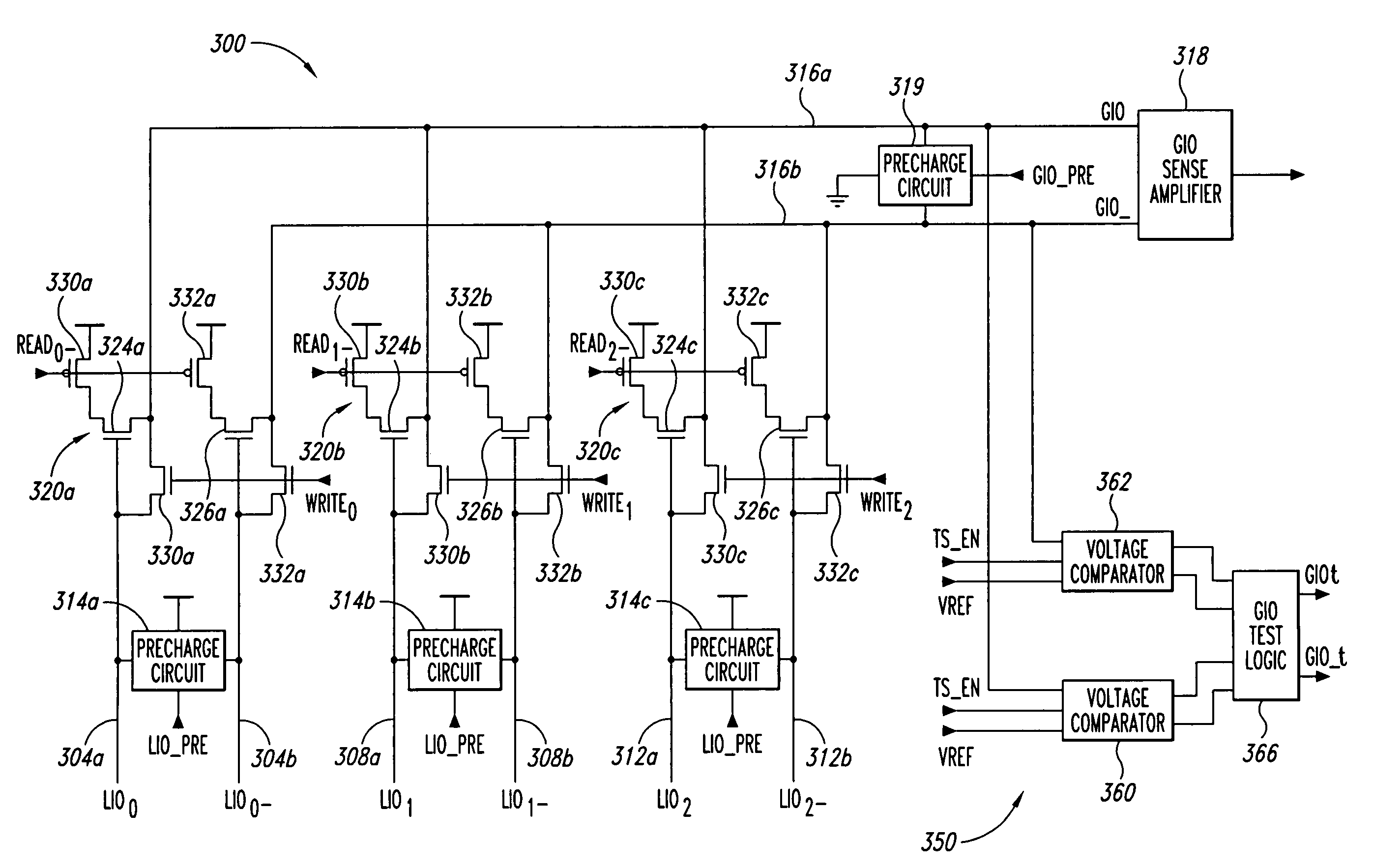

Data path having grounded precharge operation and test compression capability

A data path for coupling data between a memory cell and an input / output (IO) line sense amplifier. An IO line coupling circuit is coupled to a pair of global data lines and a pair of local data lines to couple and decouple each of the global data lines to and from a voltage supply based on the voltage levels of the local data lines for the memory read operation. For the memory write operation, the IO line coupling circuit couples and decouples each of the global data lines to and from a respective one of the local data lines. The data path also includes a first precharge circuit coupled to the global data lines to couple the global data lines to ground to precharge the signal lines prior to a memory read or write operation, and can further include a test compression circuit coupled to the global data lines.

Owner:MOSAID TECH

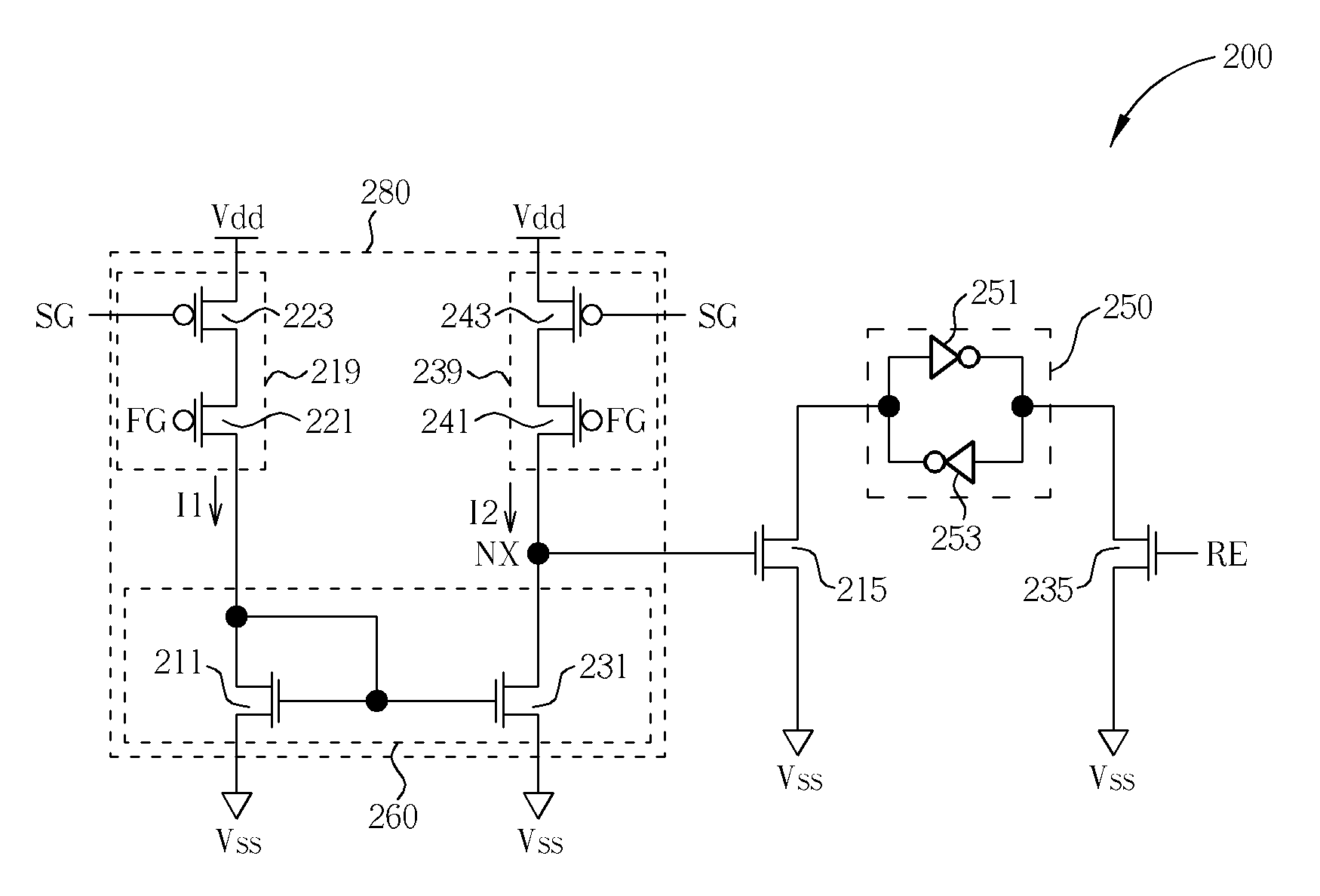

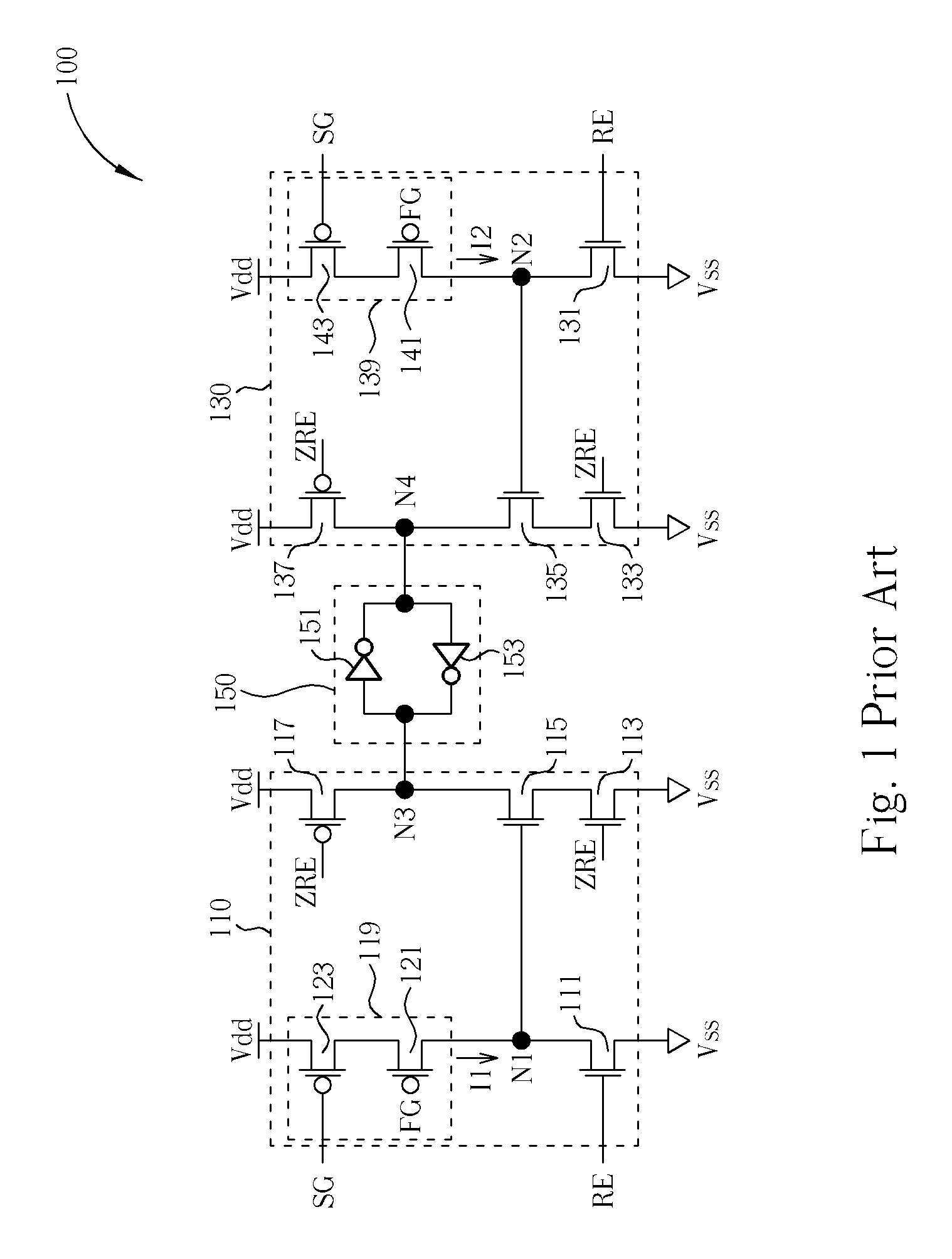

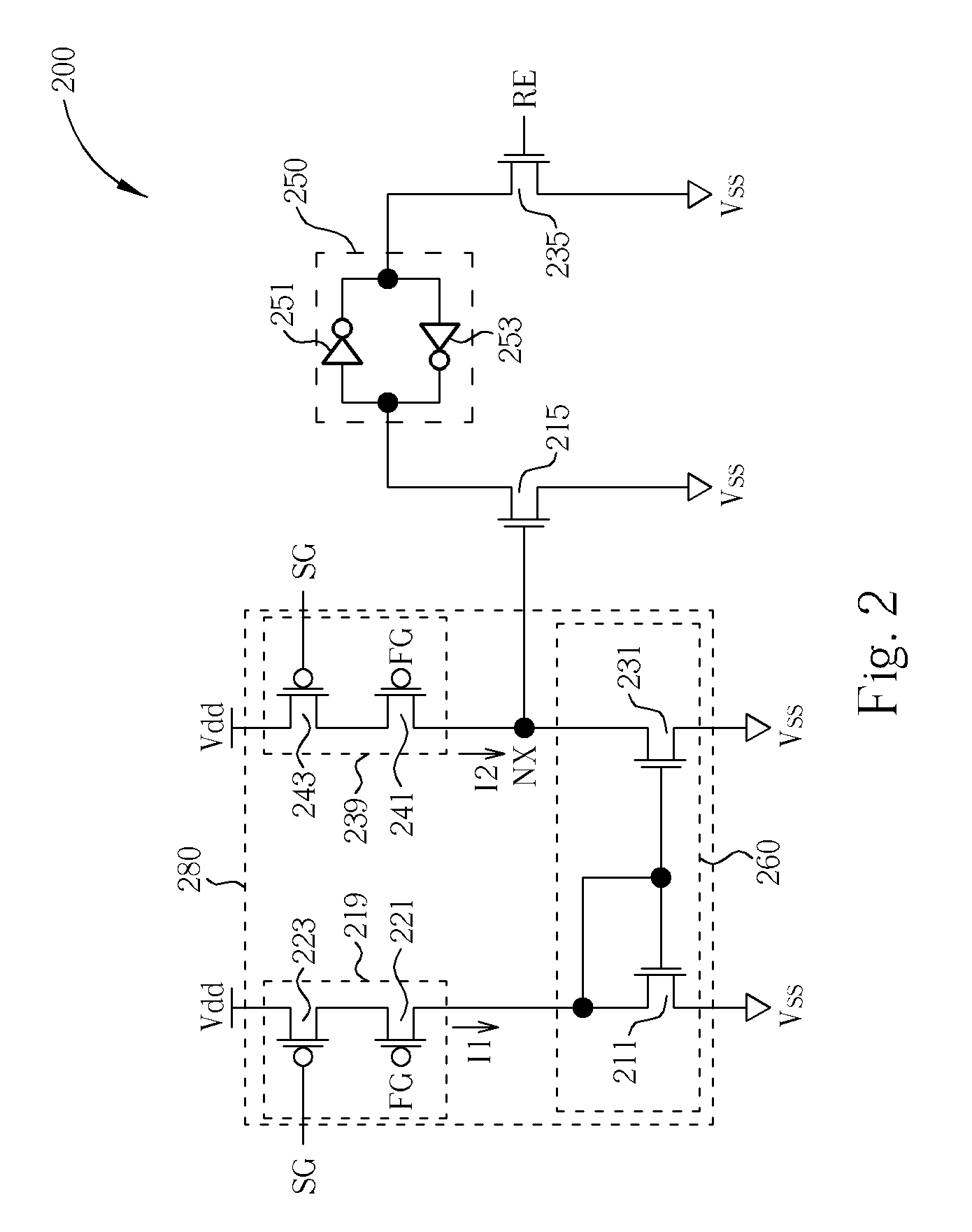

Sense amplifier circuit having current mirror architecture

A sense amplifier circuit for use in a semiconductor memory device has complemented logic states at opposite sides of the latch circuit in the sense amplifier circuit determinate all the time in operation. The sense amplifier circuit takes advantage of a current mirror circuit for ascending or descending a voltage level at the gate of a transistor by charge accumulation or charge dissipation, which turns on or off the transistor so as to control the logic states at opposite sides of the latch circuit in the sense amplifier circuit.

Owner:EMEMORY TECH INC

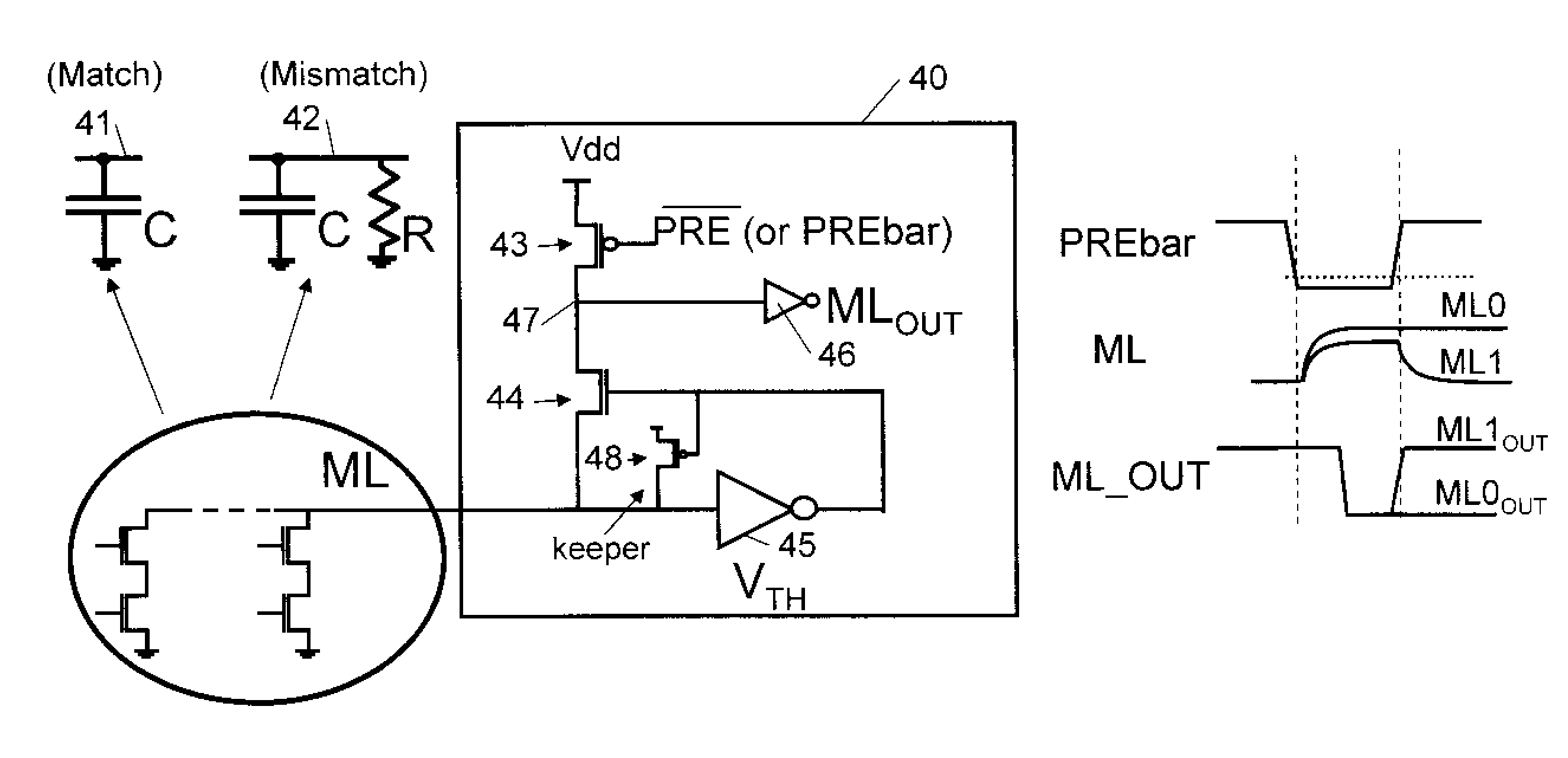

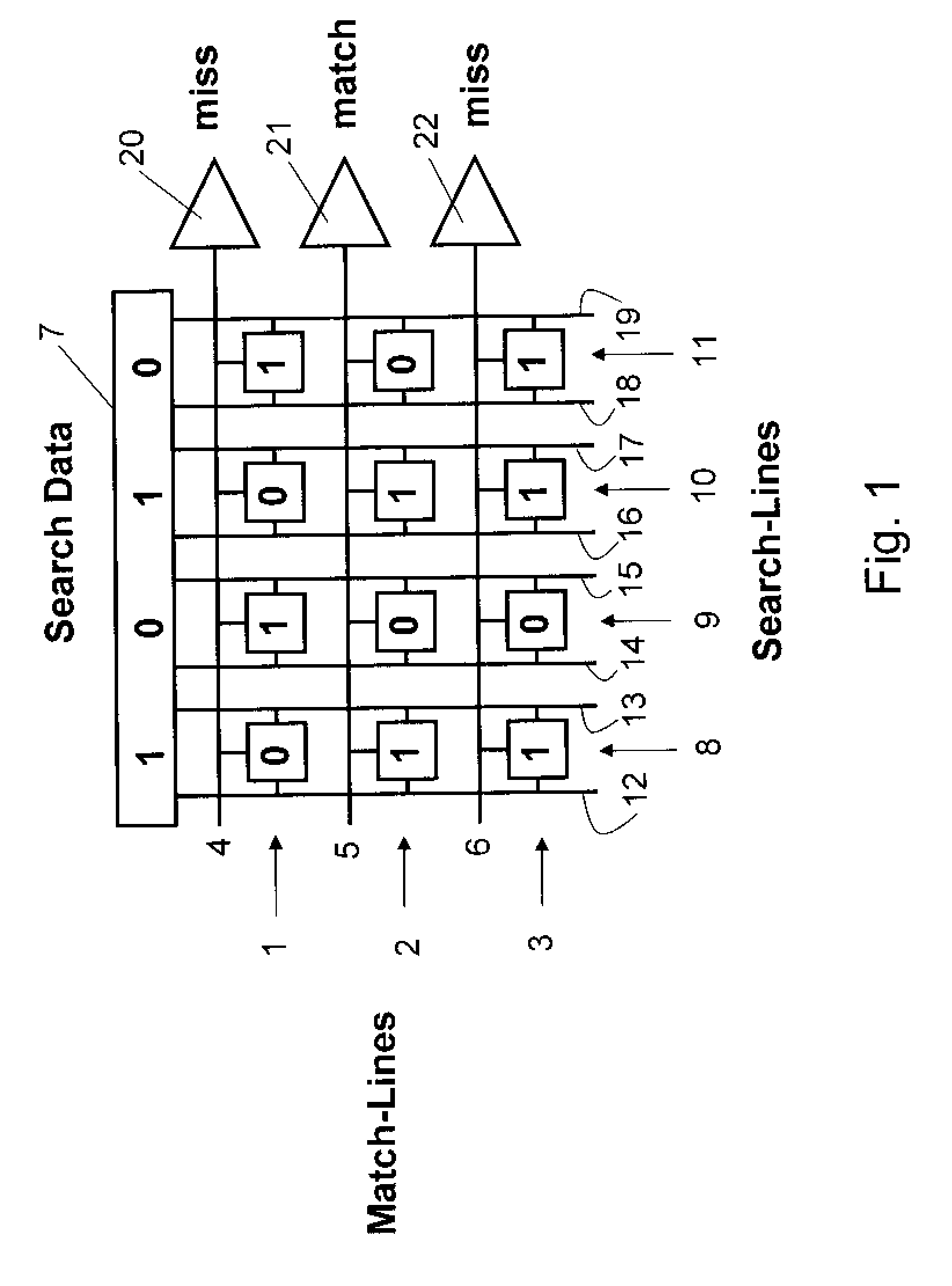

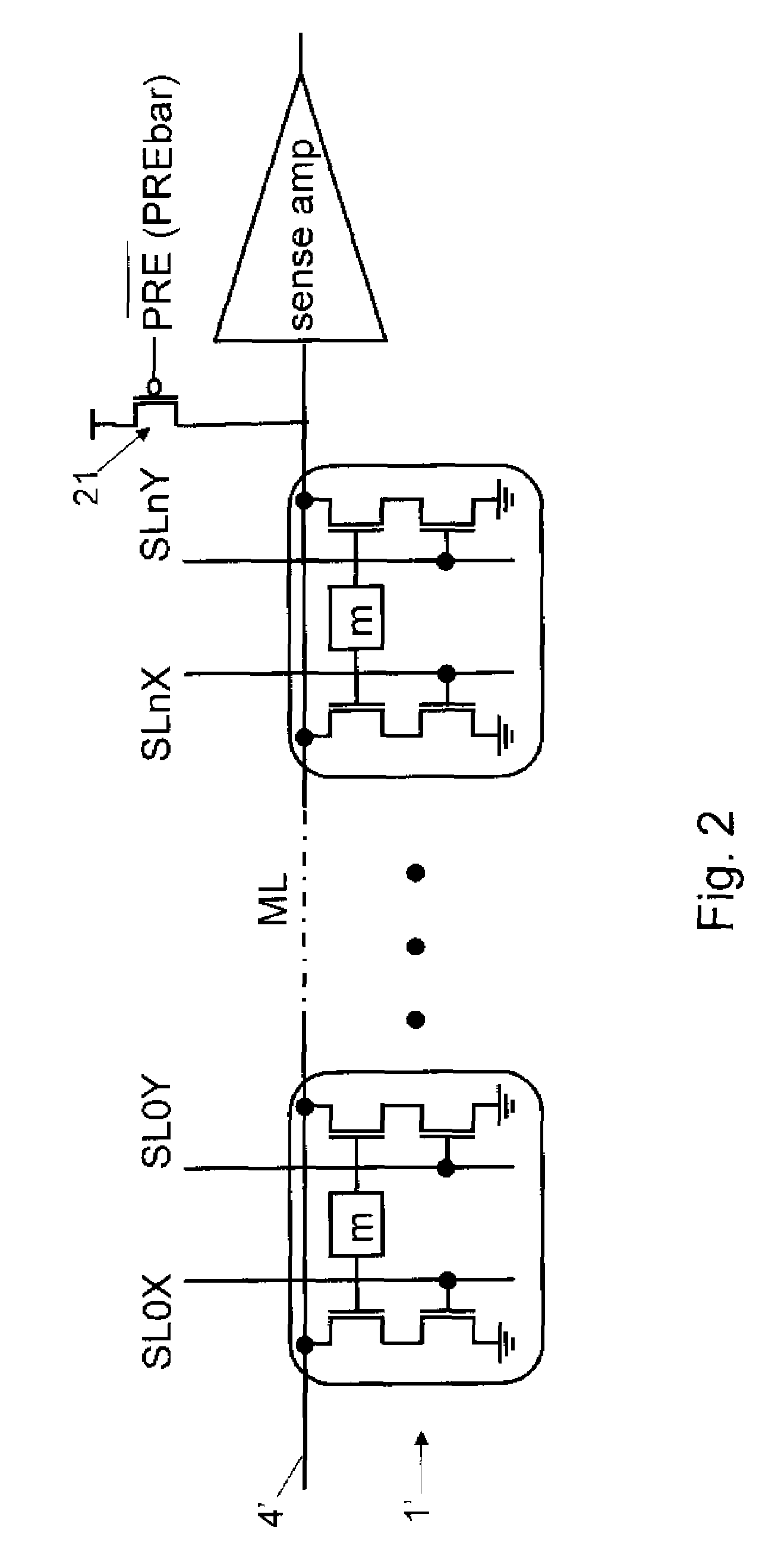

Self-Referenced Match-Line Sense Amplifier For Content Addressable Memories

ActiveUS20080025073A1Reduce the impactReduce impactCurrent/voltage measurementDigital storageAudio power amplifierComputer science

A content addressable memory (CAM) device and process for searching a CAM. The CAM device includes a plurality of CAM cells, match-lines (MLs), search lines, and ML sense amplifiers. The ML sense amplifiers are capable of self-calibration to their respective thresholds to reduce effects of random device variation between adjacent sense amplifiers.

Owner:MARVELL ASIA PTE LTD

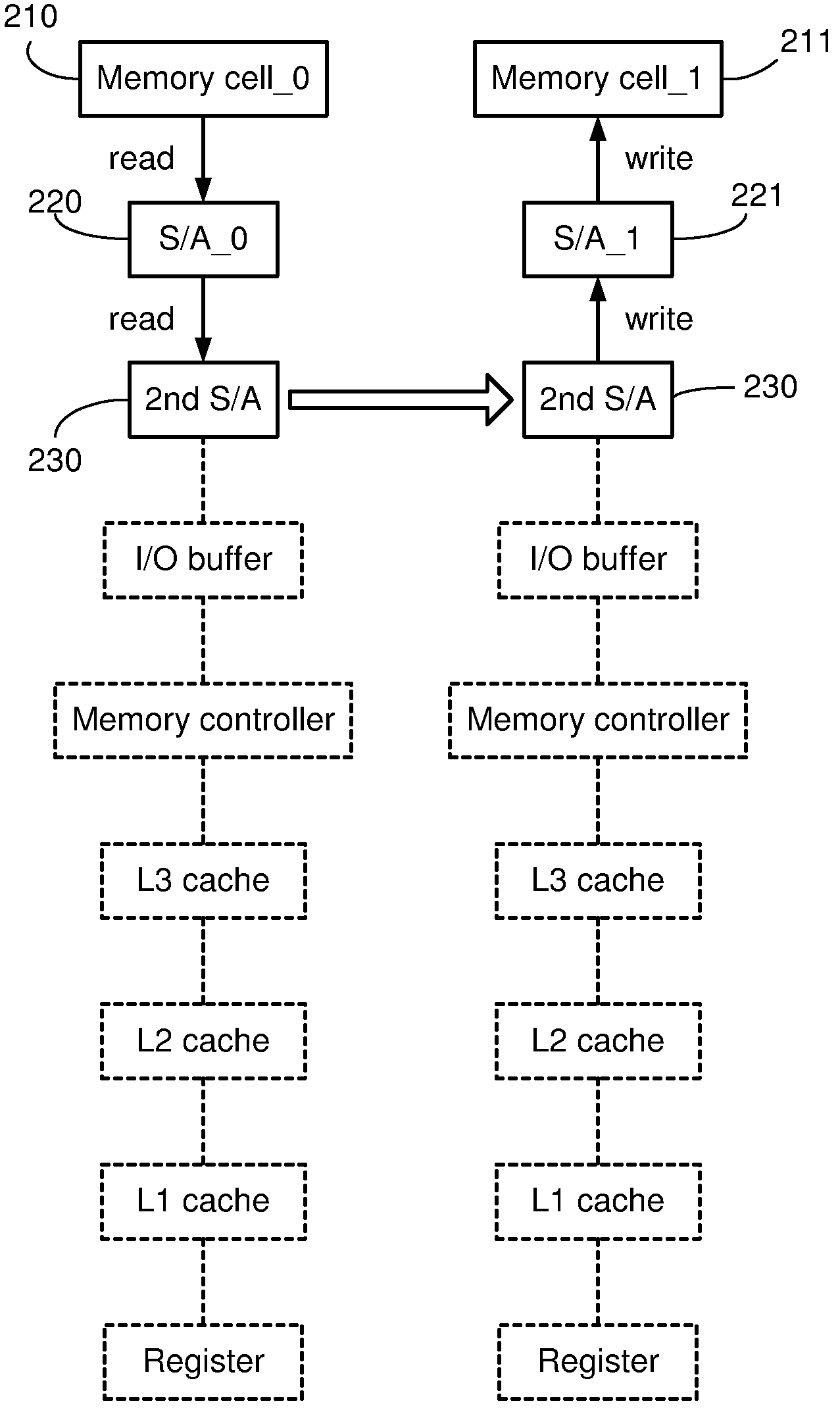

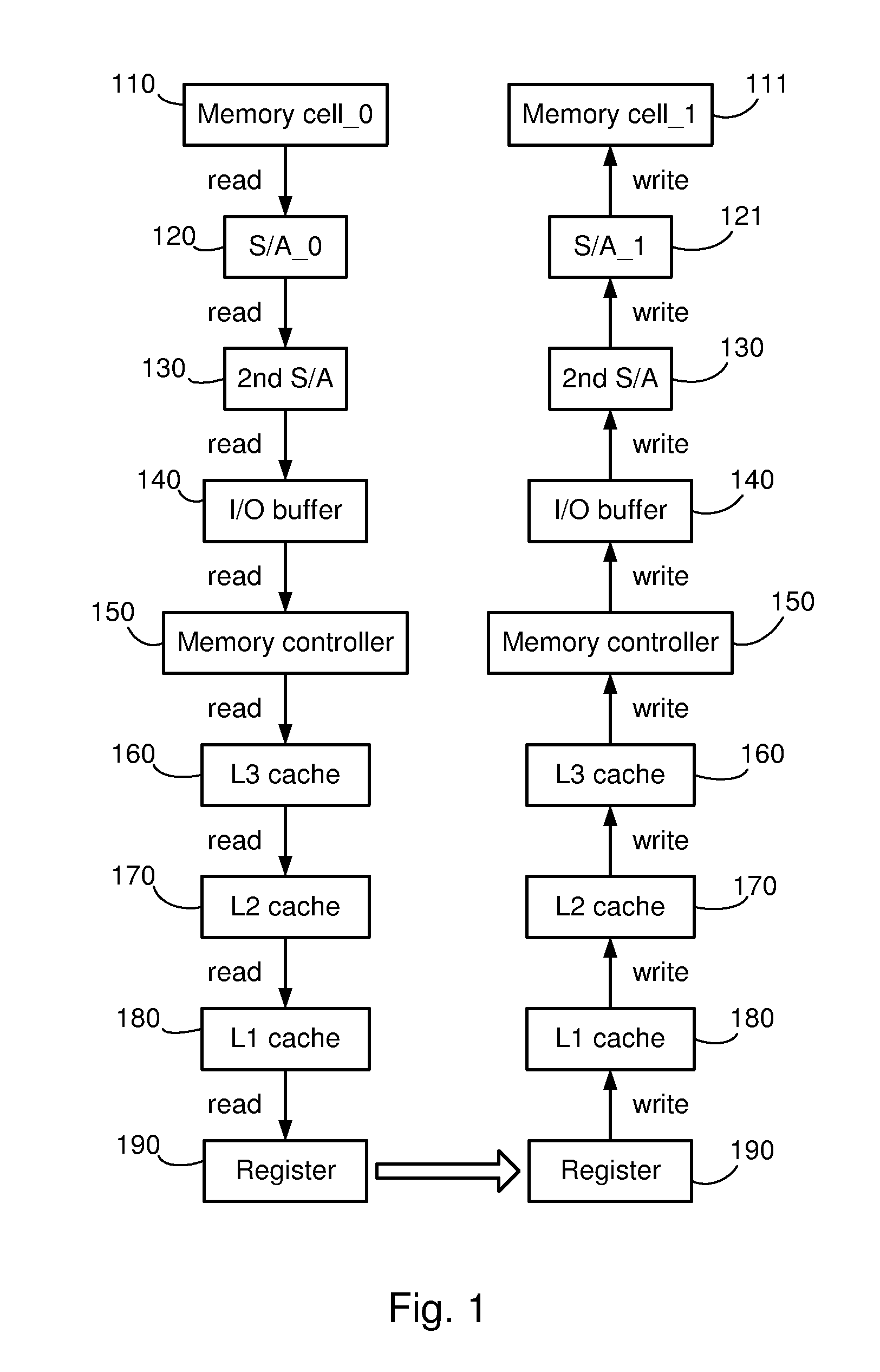

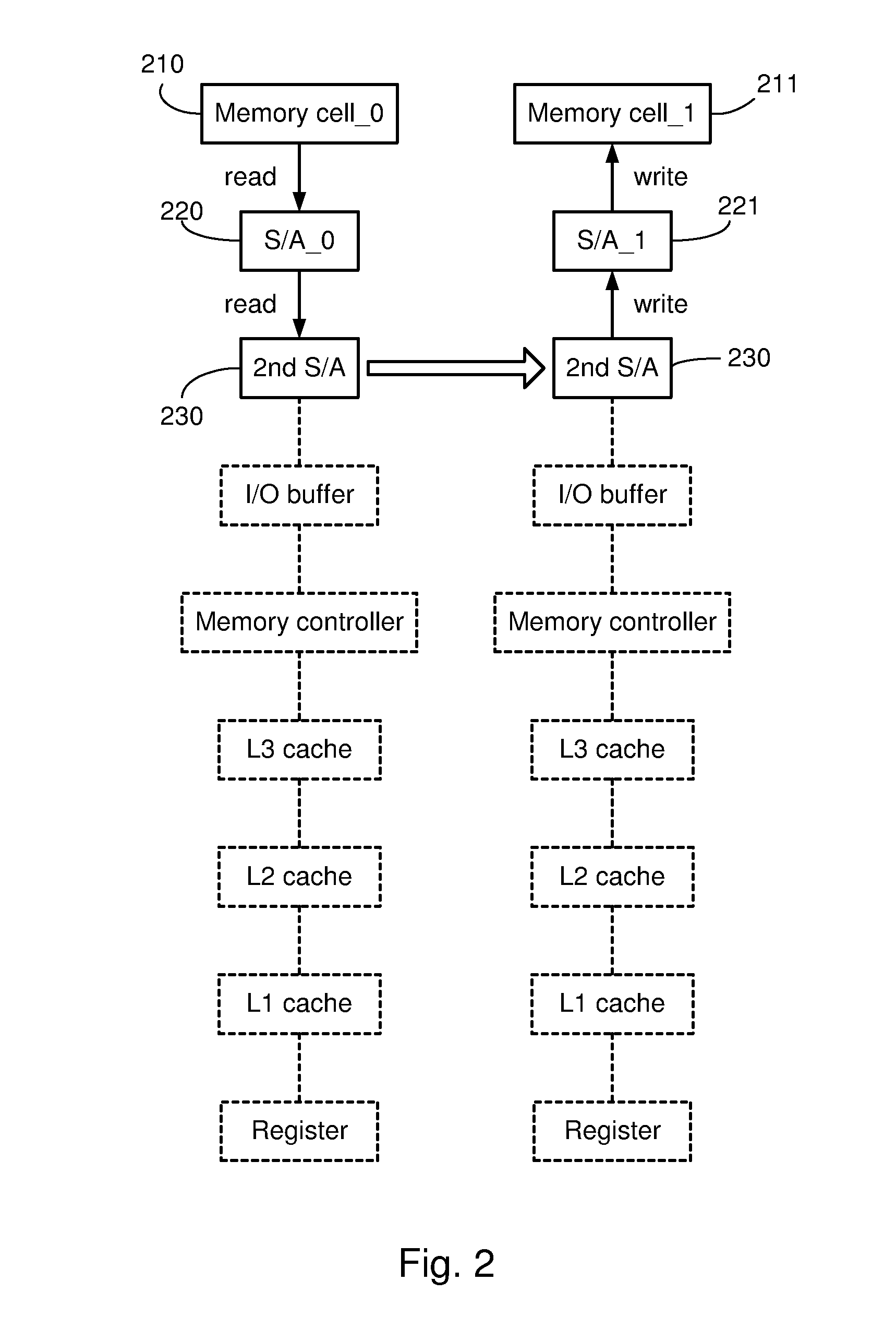

Systems and methods for data transfers between memory cells

Systems and methods for reducing the latency of data transfers between memory cells by enabling data to be transferred directly between sense amplifiers in the memory system. In one embodiment, a memory system uses a conventional DRAM memory structure having a pair of first-level sense amplifiers, a second-level sense amplifier and control logic for the sense amplifiers. Each of the sense amplifiers is configured to be selectively coupled to a data line. In a direct data transfer mode, the control logic generates control signals that cause the sense amplifiers to transfer data from a first one of the first-level sense amplifiers (a source sense amplifier) to the second-level sense amplifier, and from there to a second one of the first-level sense amplifiers (a destination sense amplifier.) The structure of these sense amplifiers is conventional, and the operation of the system is enabled by modified control logic.

Owner:TOSHIBA AMERICA ELECTRONICS COMPONENTS

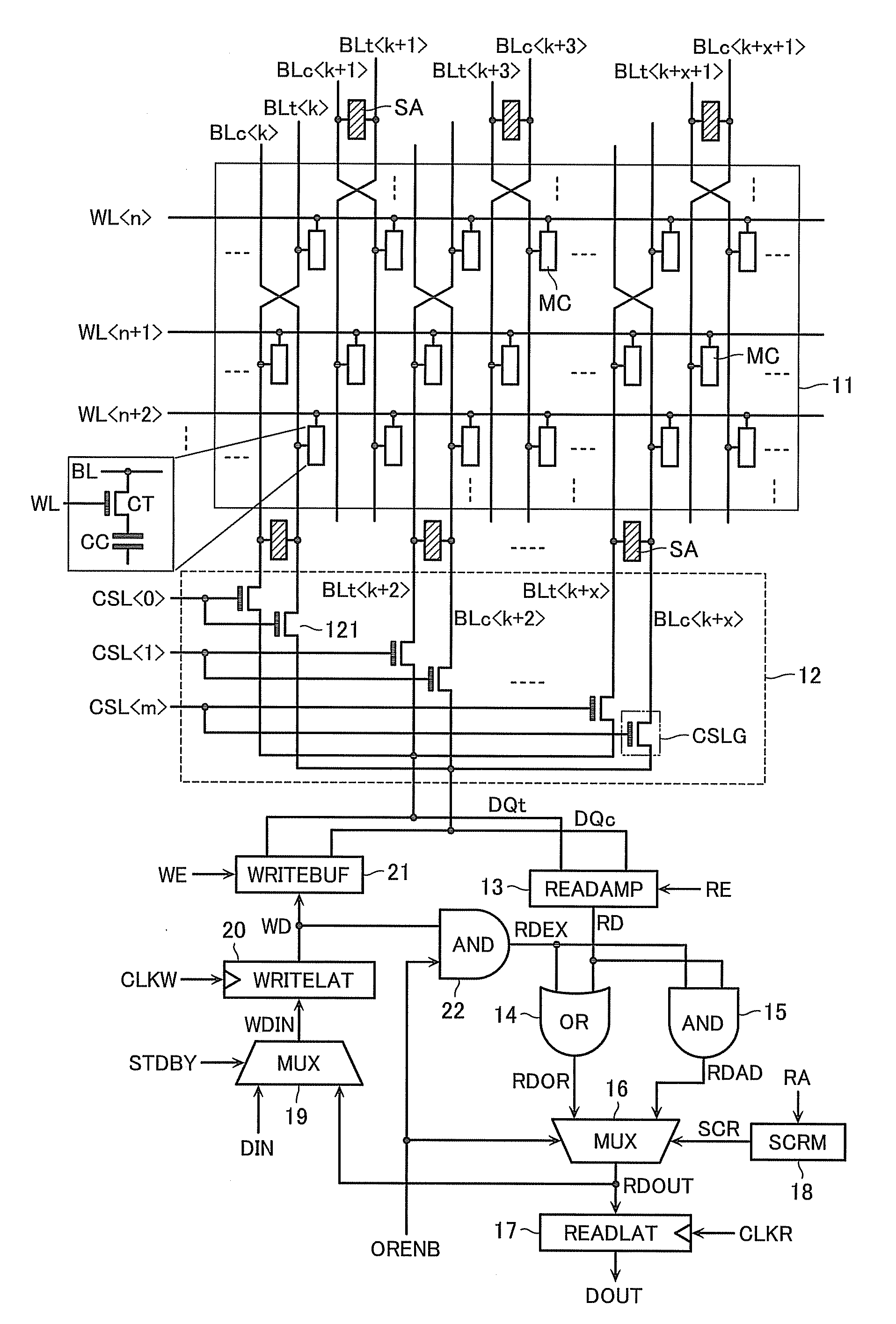

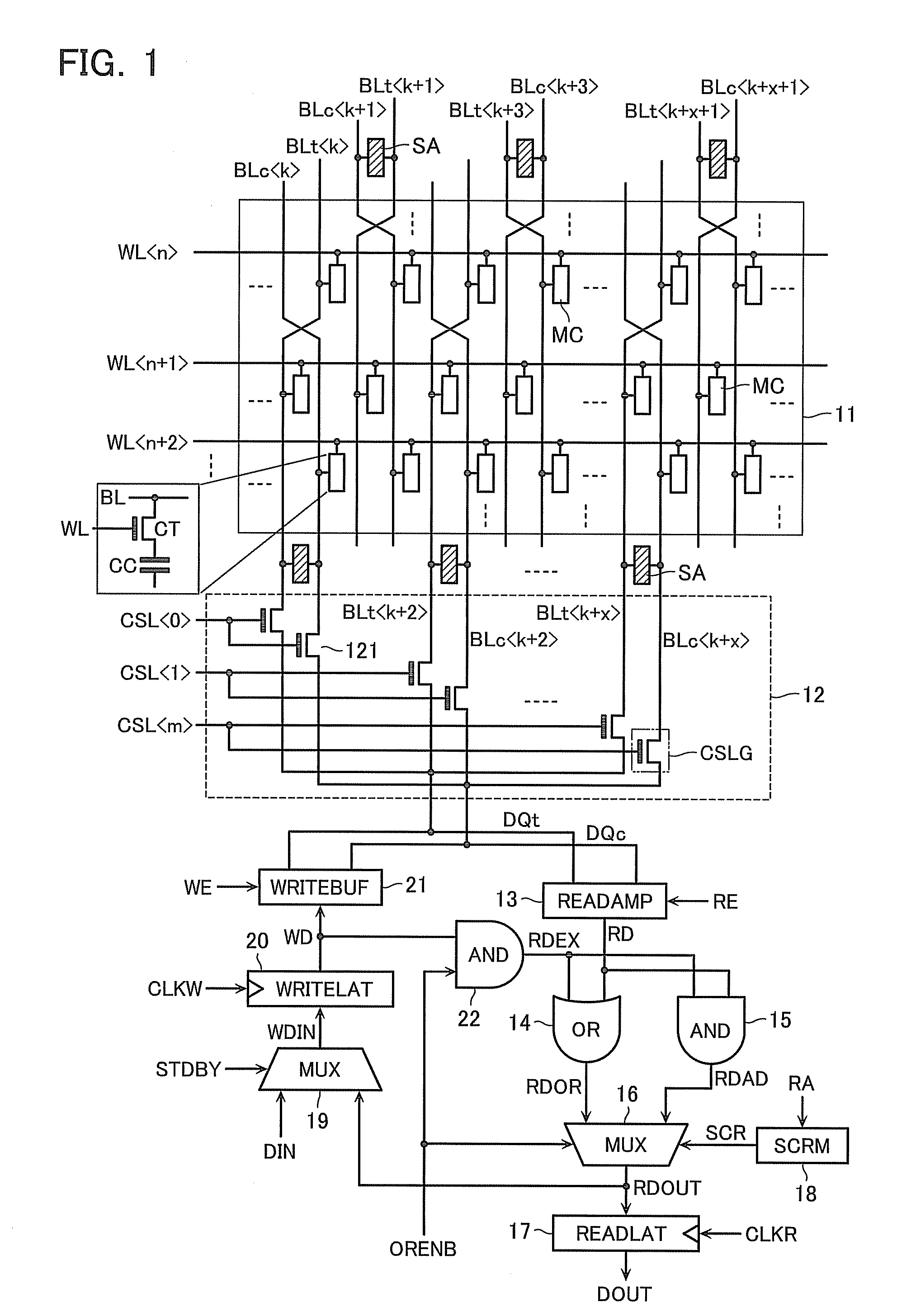

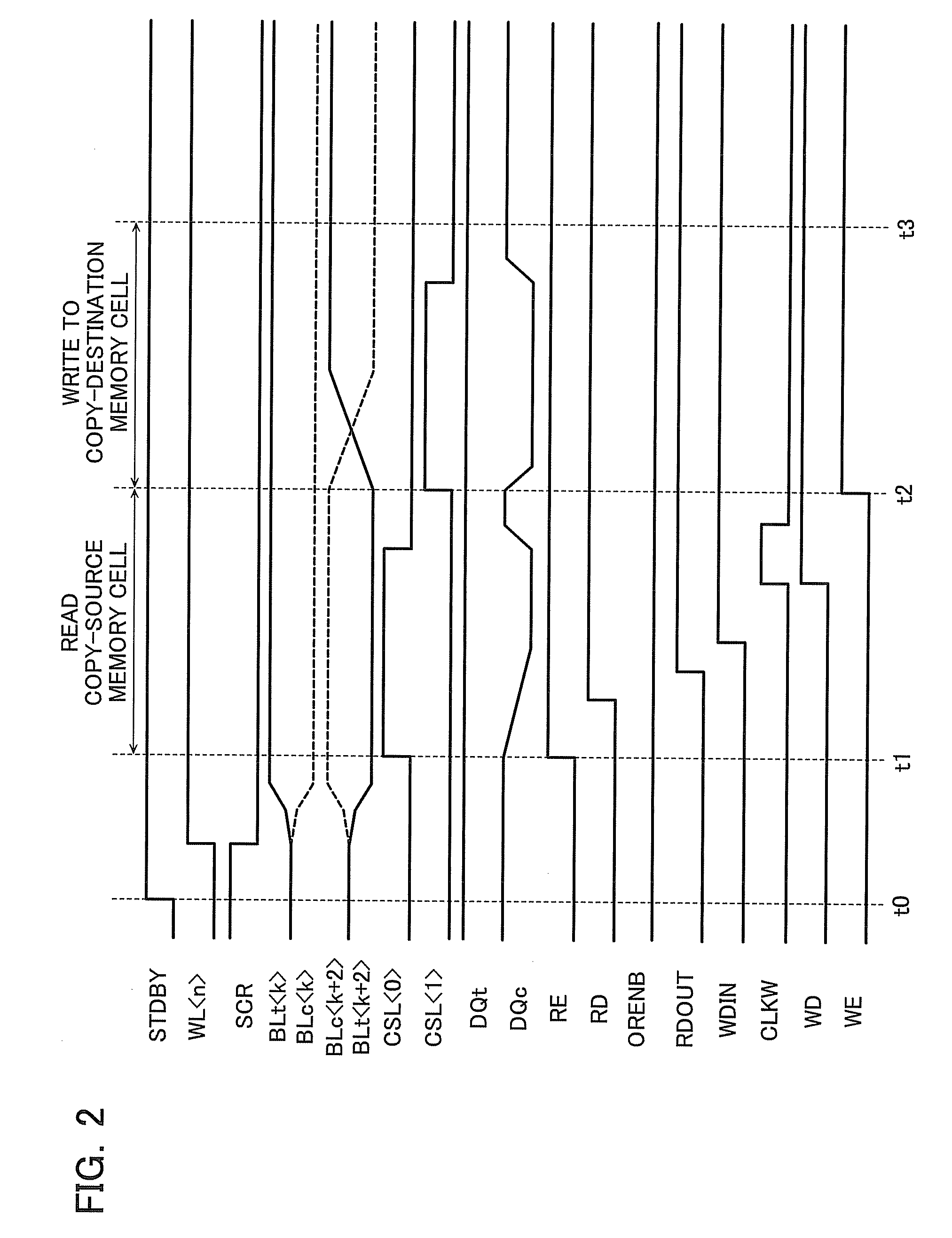

Semiconductor memory device

A sense amplifier circuit senses and amplifies a signal read from memory cells arranged at intersections of word-lines and bit-lines. A write circuit reads first data held in a first memory cell of the memory cells, and writes second data corresponding to the first data in a second memory cell different from the first memory cell. A data latch circuit holds data read from the first memory cell. A logic operation circuit performs a logic operation using data read from the second memory cell and data held in the data latch circuit as input values and outputs third data as an operation value. A write-back circuit writes the third data back to the first memory cell.

Owner:KIOXIA CORP

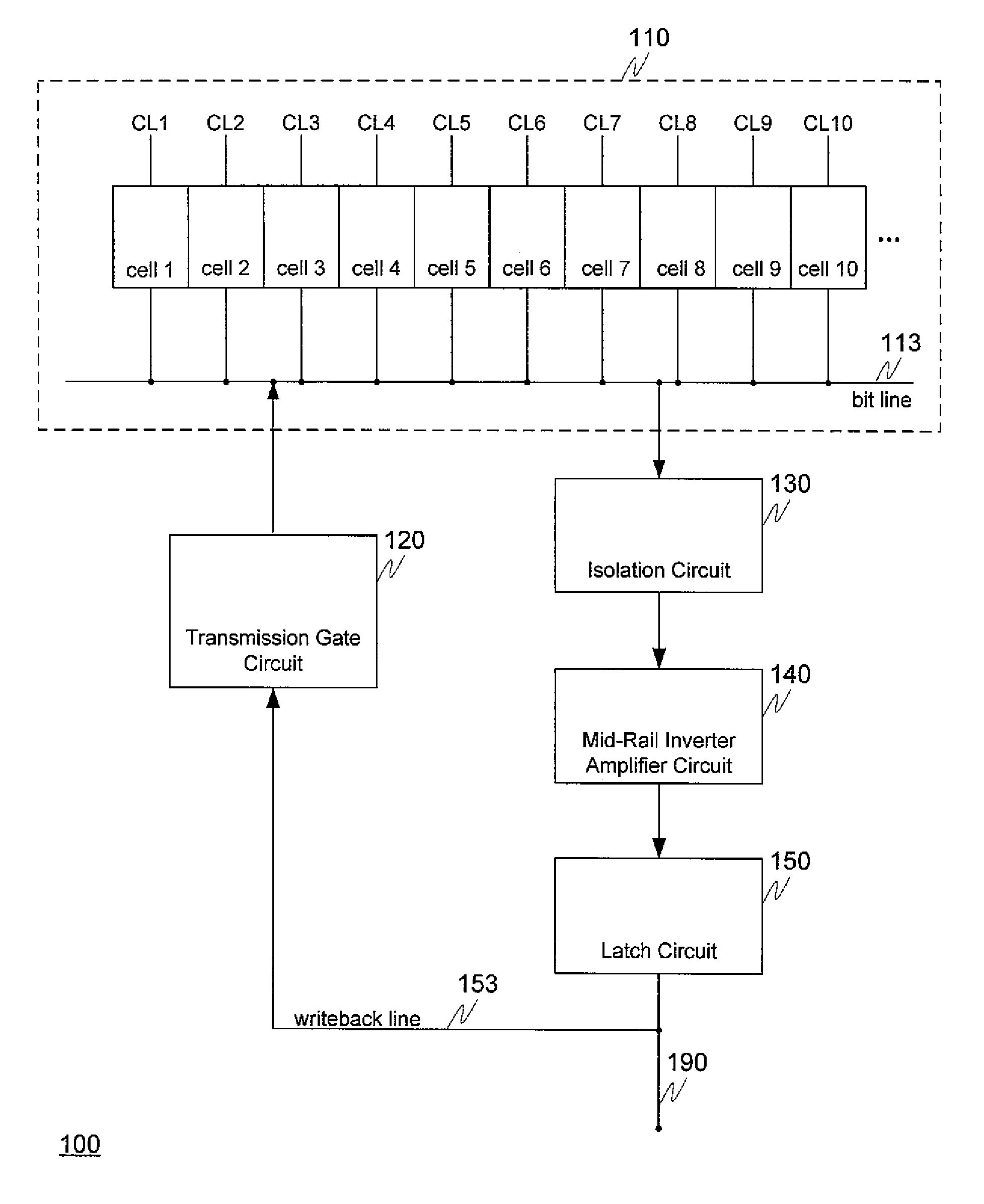

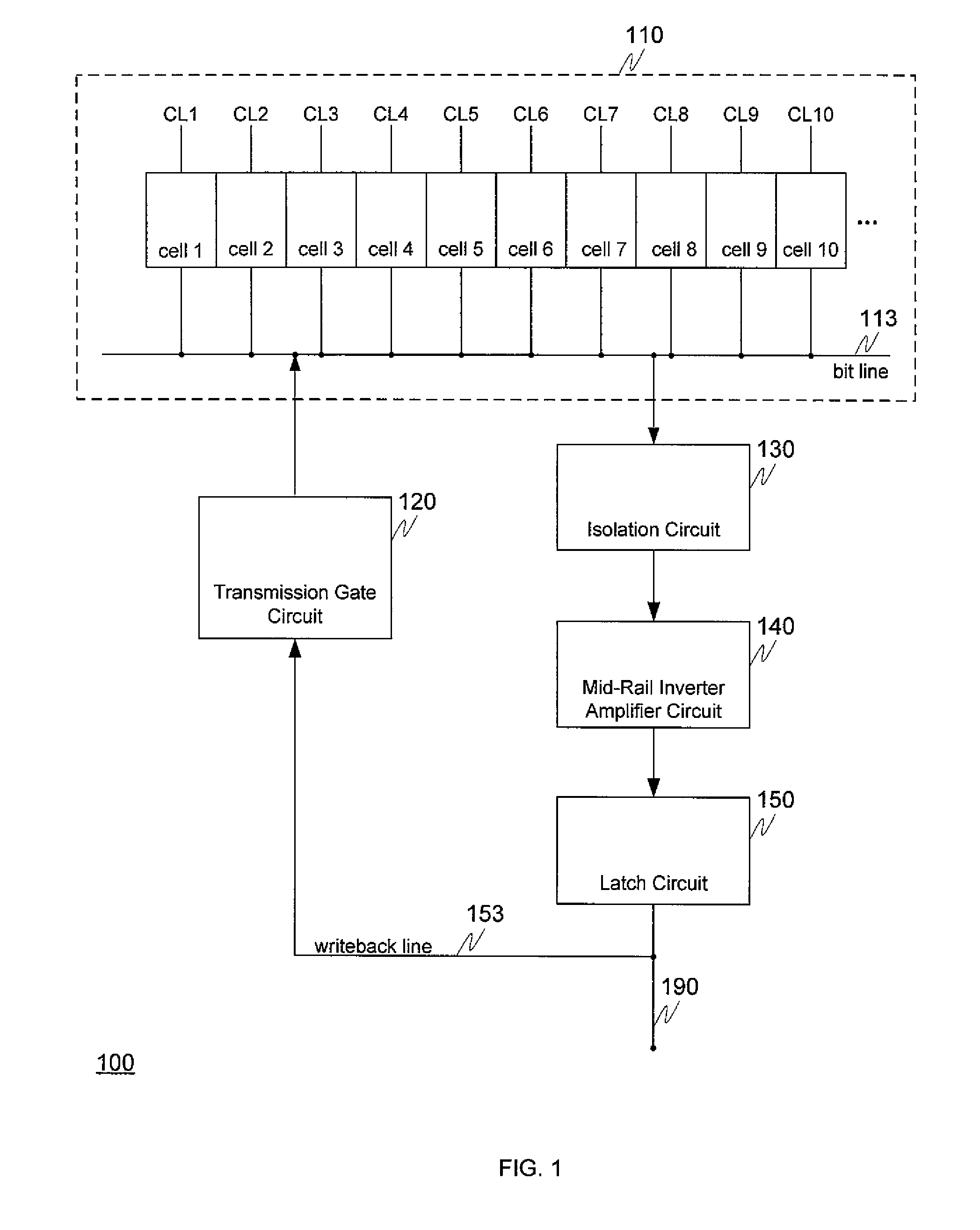

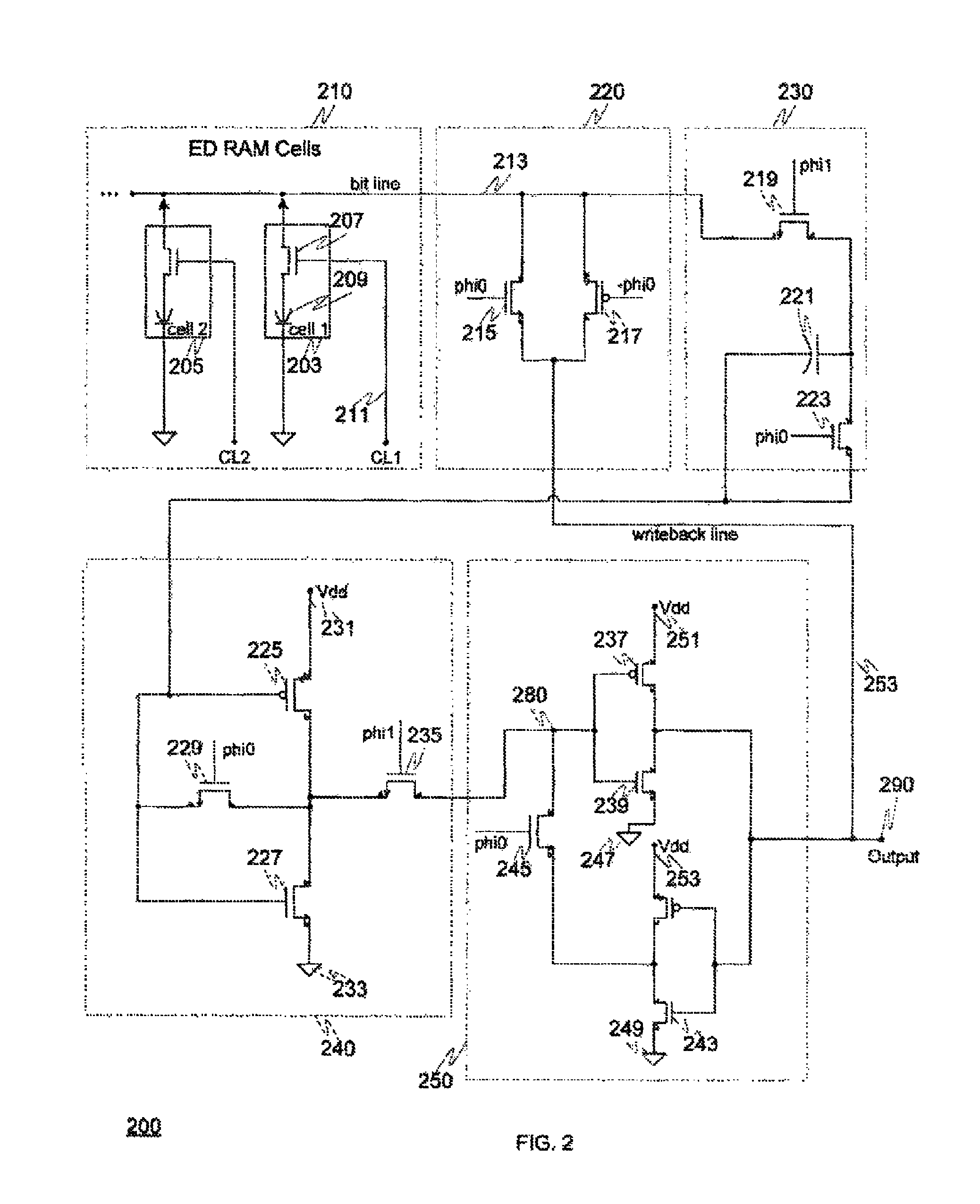

High performance eDRAM sense amplifier

Embedded dynamic random access memory (eDRAM) sense amplifier circuitry in which a bit line connected to each of a first plurality of eDRAM cells is controlled by cell control lines tied to each of the cells. During a READ operation the eDRAM cell releases its charge indicating its digital state. The digital charge propagates through the eDRAM sense amplifier circuitry to a mid-rail amplifier inverter circuit which amplifies the charge and provides it to a latch circuit. The latch circuit, in turn, inverts the charge to correctly represent at its output the logical value stored in the eDRAM cell being read, and returns the charge through the eDRAM sense amplifier circuitry to replenish the eDRAM cell.

Owner:INT BUSINESS MASCH CORP

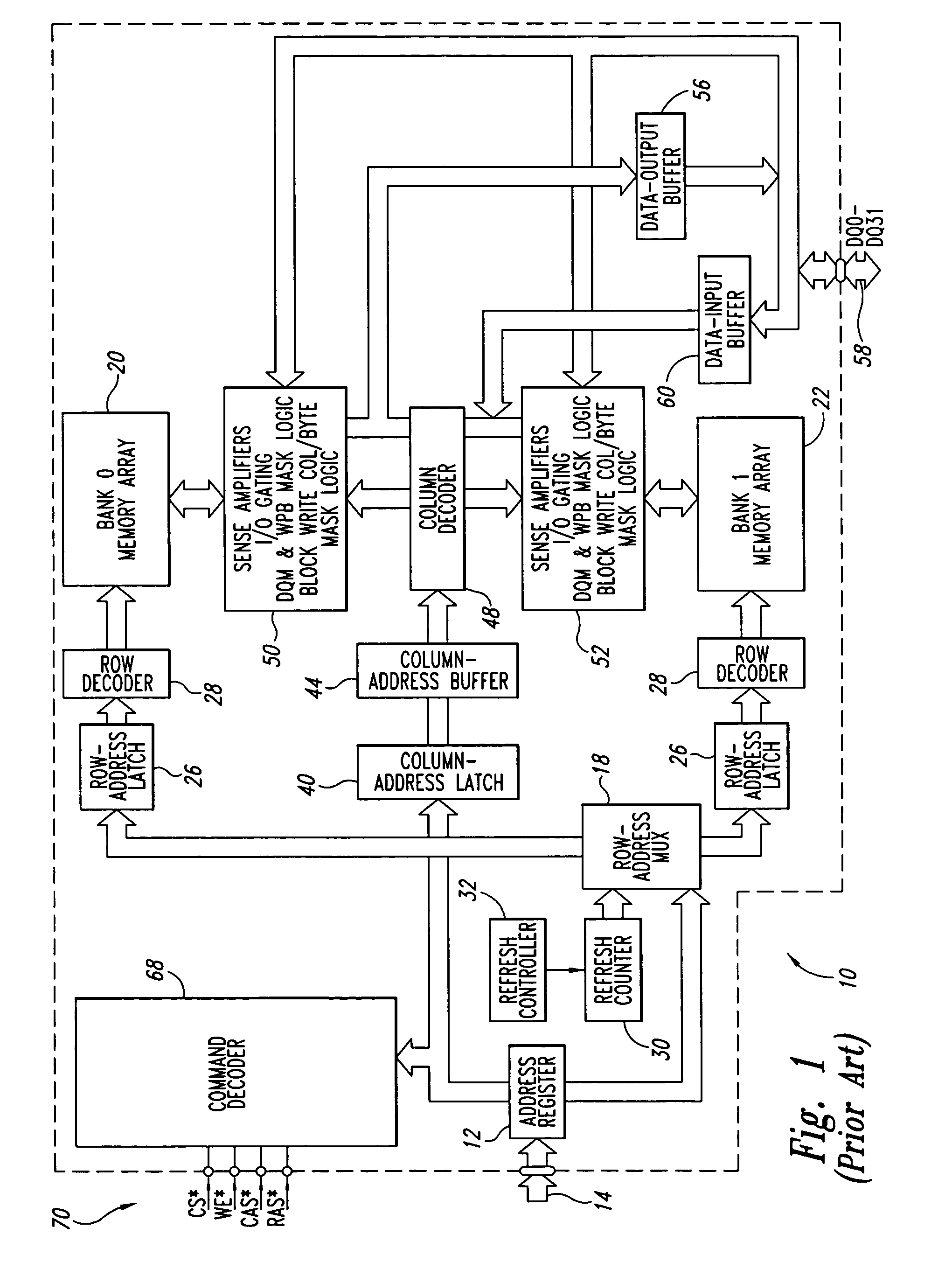

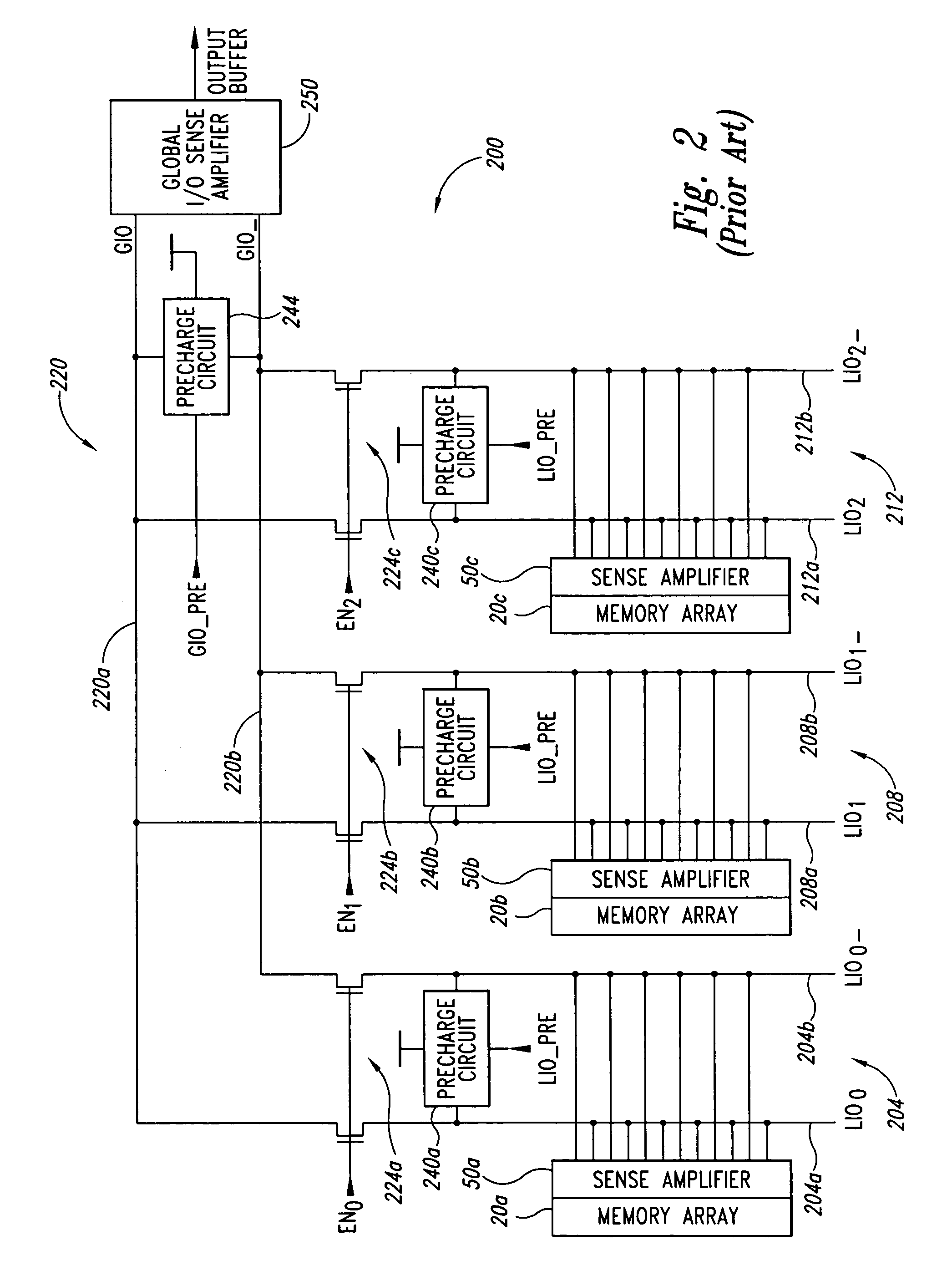

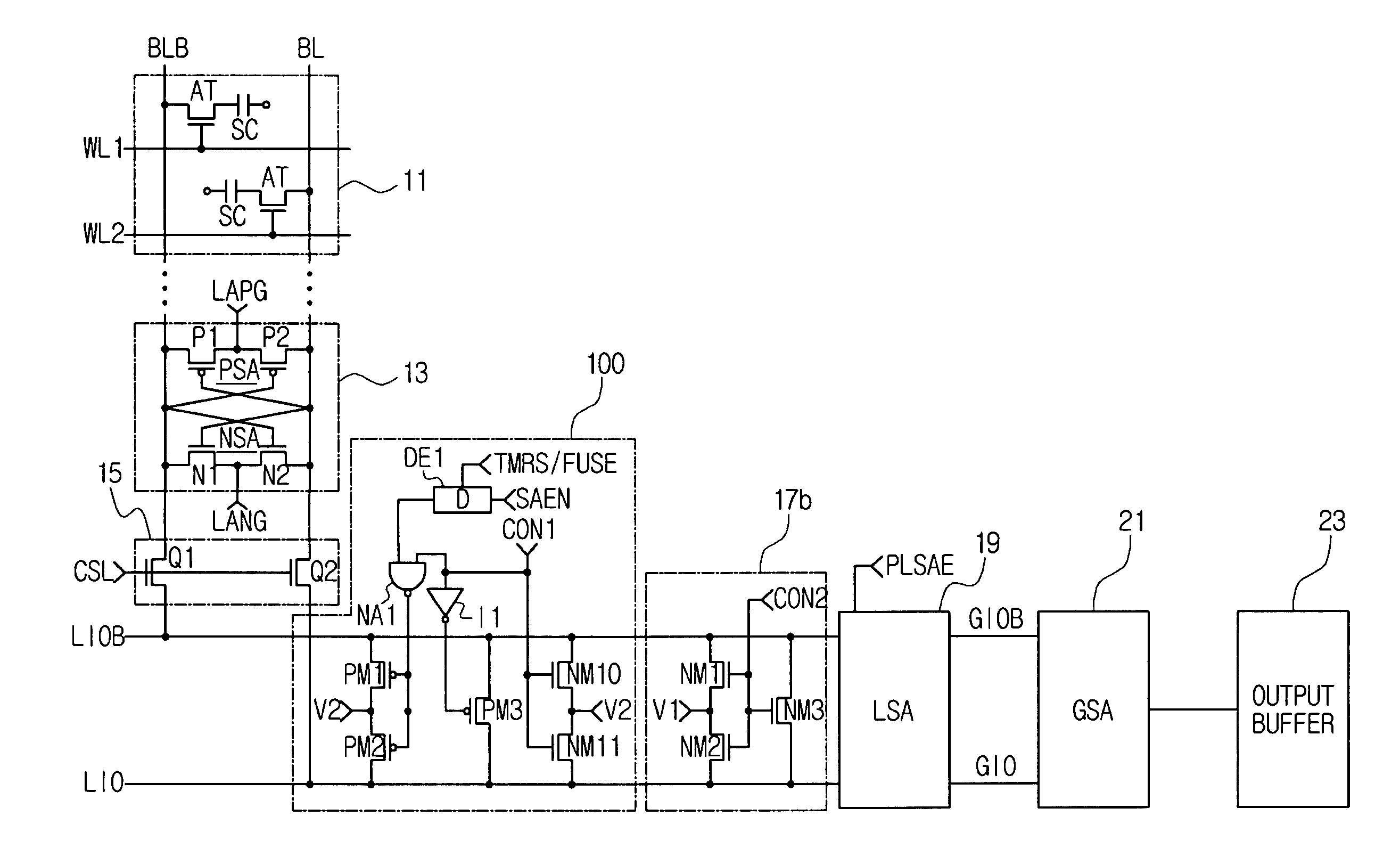

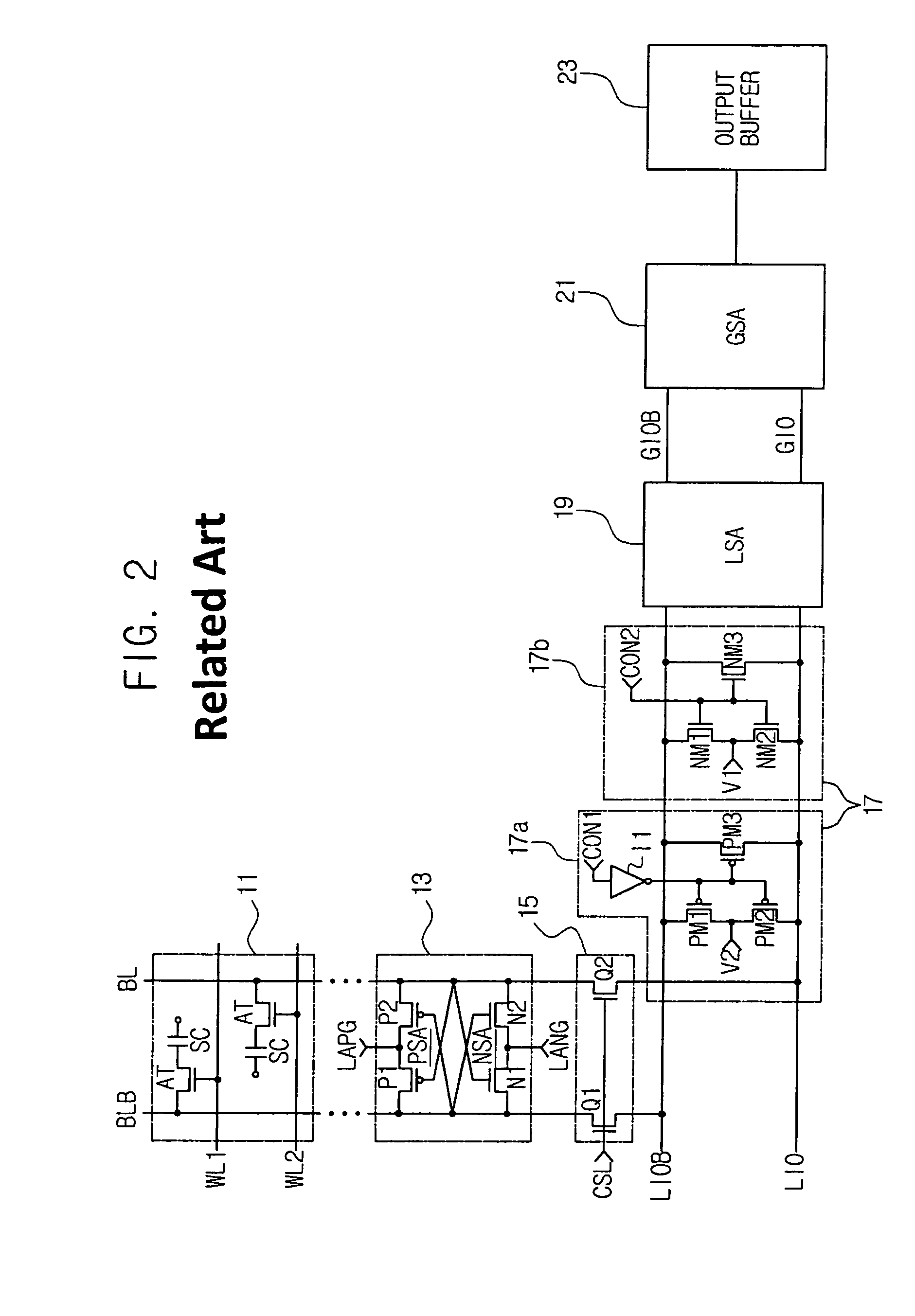

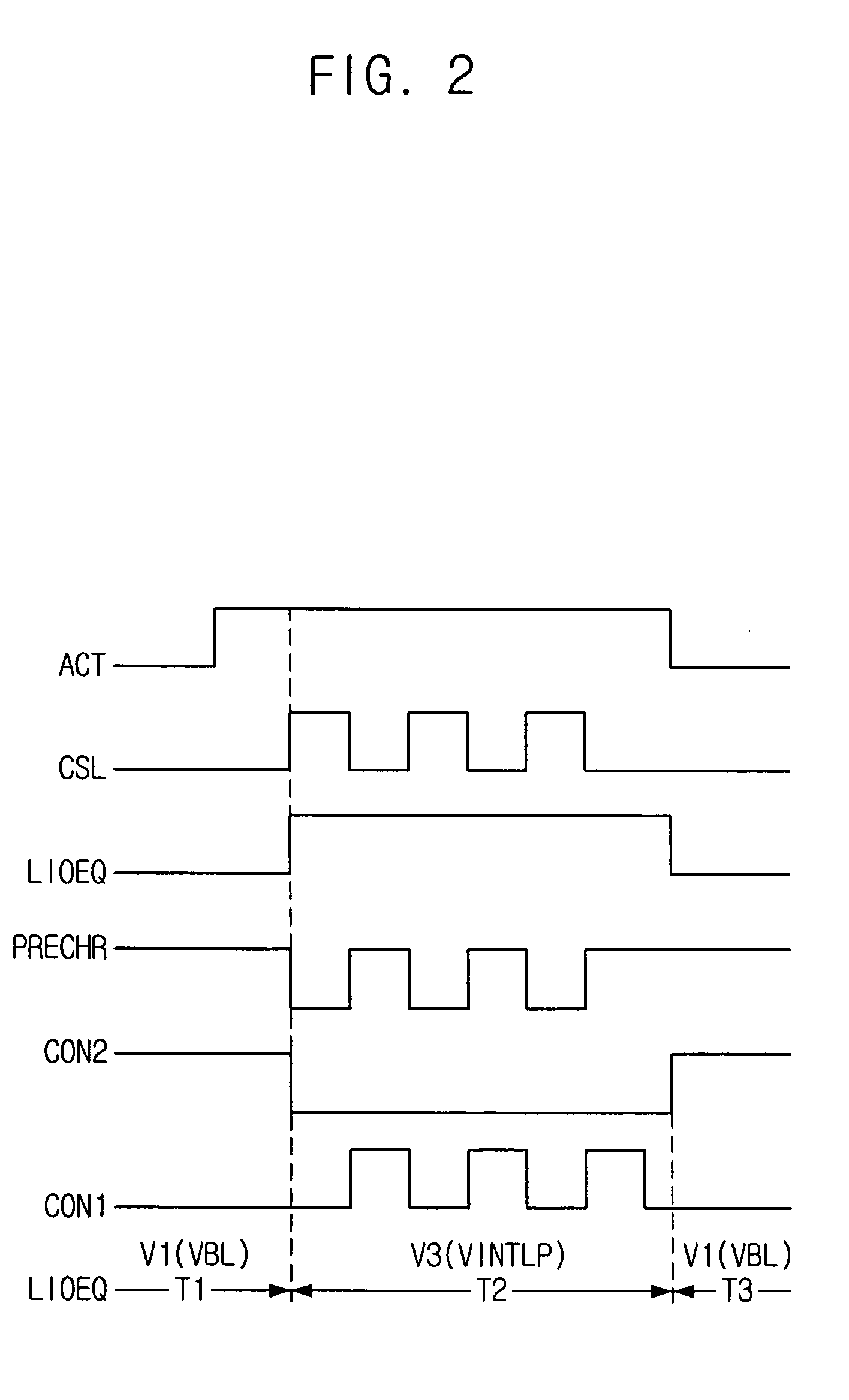

Semiconductor memory device adopting improved local input/output line precharging scheme

A semiconductor memory device capable of preventing or minimizing bit line disturbance and performing a low-voltage high-speed operation includes a read data path circuit including a bit line sense amplifier, a local input / output line sense amplifier, a column selecting unit to operationally connect bit lines connected to the bit line sense amplifier to local input / output lines connected to the local input / output line sense amplifier in response to a column selection signal, and a local input / output line precharging unit to precharge the pair of local input / output lines by a first precharging unit, equalizing the pair of local input / output lines by an equalizing unit, and to precharge the local input / output lines by a second precharging unit following an elapsed time after the bit line sense amplifier is activated, while the column selection is deactivated.

Owner:SAMSUNG ELECTRONICS CO LTD

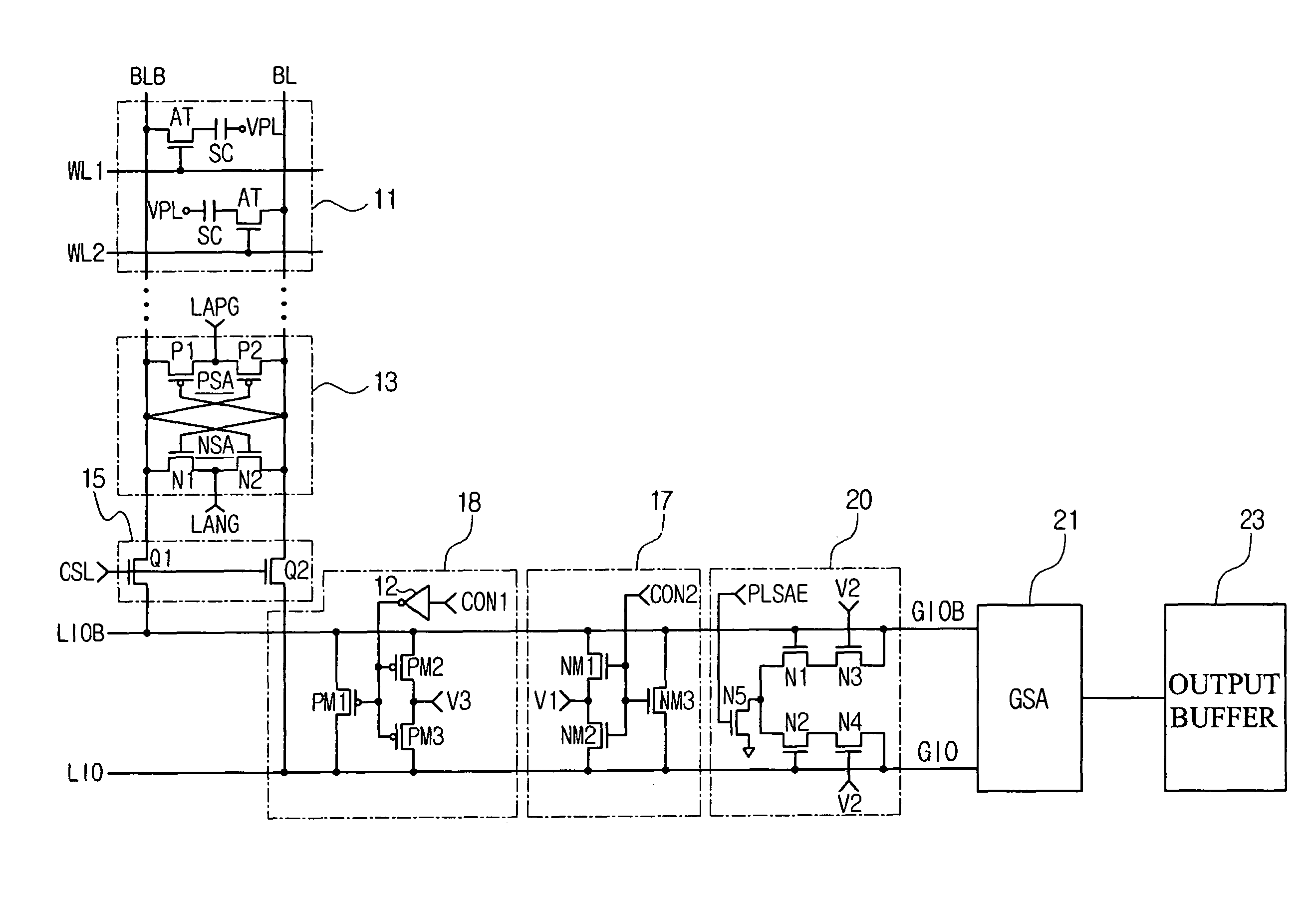

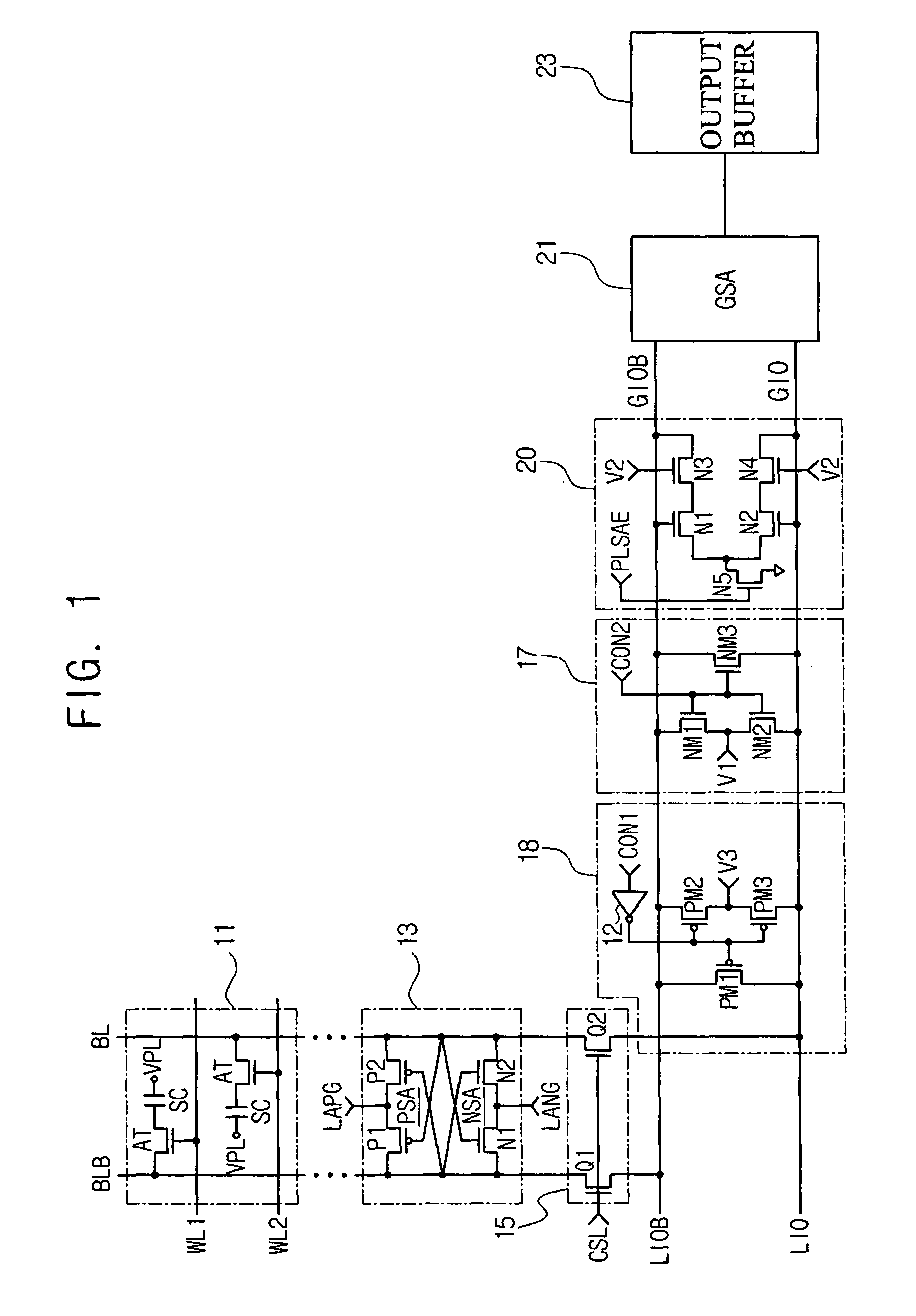

Semiconductor memory device having improved local input/output line precharge scheme

ActiveUS8213248B2Preventing bit line disturbanceRun at high speedDigital storageBit lineDatapath circuits

A data path circuit of a semiconductor memory device includes: a bit line sense amplifier driven by a first power supply voltage; a local input / output line sense amplifier; a column selecting unit operatively connecting a pair of bit lines connected to the bit line sense amplifier and a pair of local input / output lines connected to the local input / output line sense amplifier in response to a column selection signal; and a local input / output line precharge unit precharging the pair of local input / output lines with a second power supply voltage different from the first power supply voltage during a period for which the column selection signal is in an inactive state.

Owner:SAMSUNG ELECTRONICS CO LTD

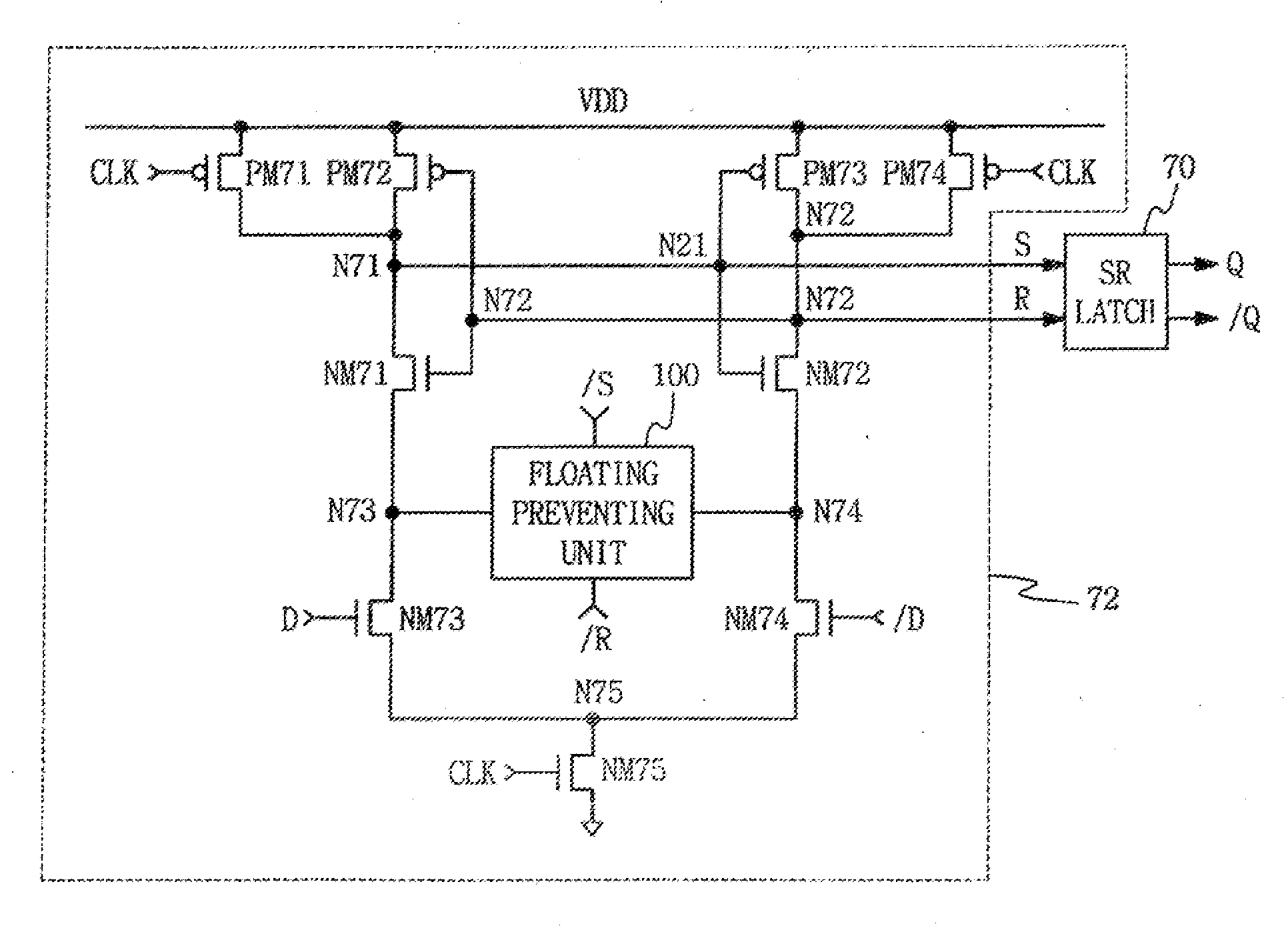

Sense amplifier circuit and sense amplifier-based flip-flop having the same

ActiveUS20070285131A1Reducing signal delay timePrevent degradation of outputCurrent/voltage measurementDigital storageAudio power amplifierControl delay

A sense amplifier-based flip-flop includes a first latch, a second latch, a floating reduction unit, an input signal applying unit, a ground switch and a delay reduction unit. The first latch outputs a signal to a first output terminal pair, and outputs an evaluation signal pair corresponding to an input single pair to the first output terminal pair. The second latch latches the evaluation signal pair and outputs the evaluation signal pair to a second output terminal pair. The floating reduction unit is controlled by signals of the first output terminal pair and is operationally connected between current passing nodes of the first latch to prevent the first output terminal pair from floating. The input signal applying unit is disposed between the current passing nodes and a ground terminal, and receives the input signal pair. The ground switch is disposed between the input signal applying unit and the ground terminal, and is controlled by the clock signal. The delay reduction unit is disposed between the input signal applying unit and the ground switch, and reduces a signal delay from when the clock signal to when the evaluation signal pair is output from the second output terminal pair.

Owner:SAMSUNG ELECTRONICS CO LTD

Reference sense amplifier for non-volatile memory

InactiveUS20060158947A1Large capacityImprove performanceRead-only memoriesDigital storageAudio power amplifierReference current

One or more sense amplifiers for sensing the conduction current of non-volatile memory is controlled by signals that are timed by a reference sense amplifier having similar characteristics and operating conditions. In one aspect, a sensing period is determined by when the reference sense amplifier sensing a reference current detects an expected state. In another aspect, an integration period for an amplified output is determined by when the reference sense amplifier outputs an expected state. When these determined timings are used to control the one or more sense amplifiers, environment and systemic variations are tracked.

Owner:SANDISK TECH LLC

Non-volatile memory and method with improved sensing

InactiveUS7023736B2Large capacityImprove performanceRead-only memoriesDigital storageAudio power amplifierMultiple pass

A method for reducing source line bias is accomplished by read / write circuits with features and techniques for multi-pass sensing. When a page of memory cells are being sensed in parallel, each pass helps to identify and shut down the memory cells with conduction current higher than a given demarcation current value. In particular, the identified memory cells are shut down after all sensing in the current pass have been completed. In this way the shutting down operation does not disturb the sensing operation. Sensing in subsequent passes will be less affected by source line bias since the total amount of current flow is significantly reduced by eliminating contributions from the higher current cells. In another aspect of sensing improvement, a reference sense amplifier is employed to control multiple sense amplifiers to reduce their dependence on power supply and environmental variations.

Owner:SANDISK TECH LLC

Memory sensing circuit and method for low voltage operation

InactiveUS7046568B2Large capacityImprove performanceRead-only memoriesDigital storageBit lineAudio power amplifier

A sensing module operates with a sense amplifier sensing a conduction current of a memory cell via a coupled bit line under constant voltage condition in order to minimize bit-line to bit-line coupling. The rate of discharge of a dedicated capacitor as measured by a change in the voltage drop there across in a predetermined period is used to indicate the magnitude of the conduction current. The voltage cannot drop below a minimum level imposed by a circuit for maintaining the constant voltage condition on the bit line. A voltage shifter is used to boost the voltage during the discharge and to unboost the voltage after the discharge, so that the change in voltage drop properly reflects the rate of discharge without running into the minimum level.

Owner:SANDISK TECH LLC

Sense amplifier latch with integrated test data multiplexer

A sense amplifier latch may be provided to controllably latch the output of a sense amplifier. The latch may open in response to assertion of a latch enable signal to receive data, and close in response to deassertion of the latch enable signal to capture and store the received data. Additionally, a multiplexer may be provided to select from among multiple sources of test data, such as scan data and bypass data. The multiplexer may produce a test data input to the sense amplifier latch that encodes a data value and a control value that causes the data value to be selected. Depending on the state of the test data input, the sense amplifier latch may output either a value received from the sense amplifier or a value encoded in the test data input.

Owner:ALLLE INC

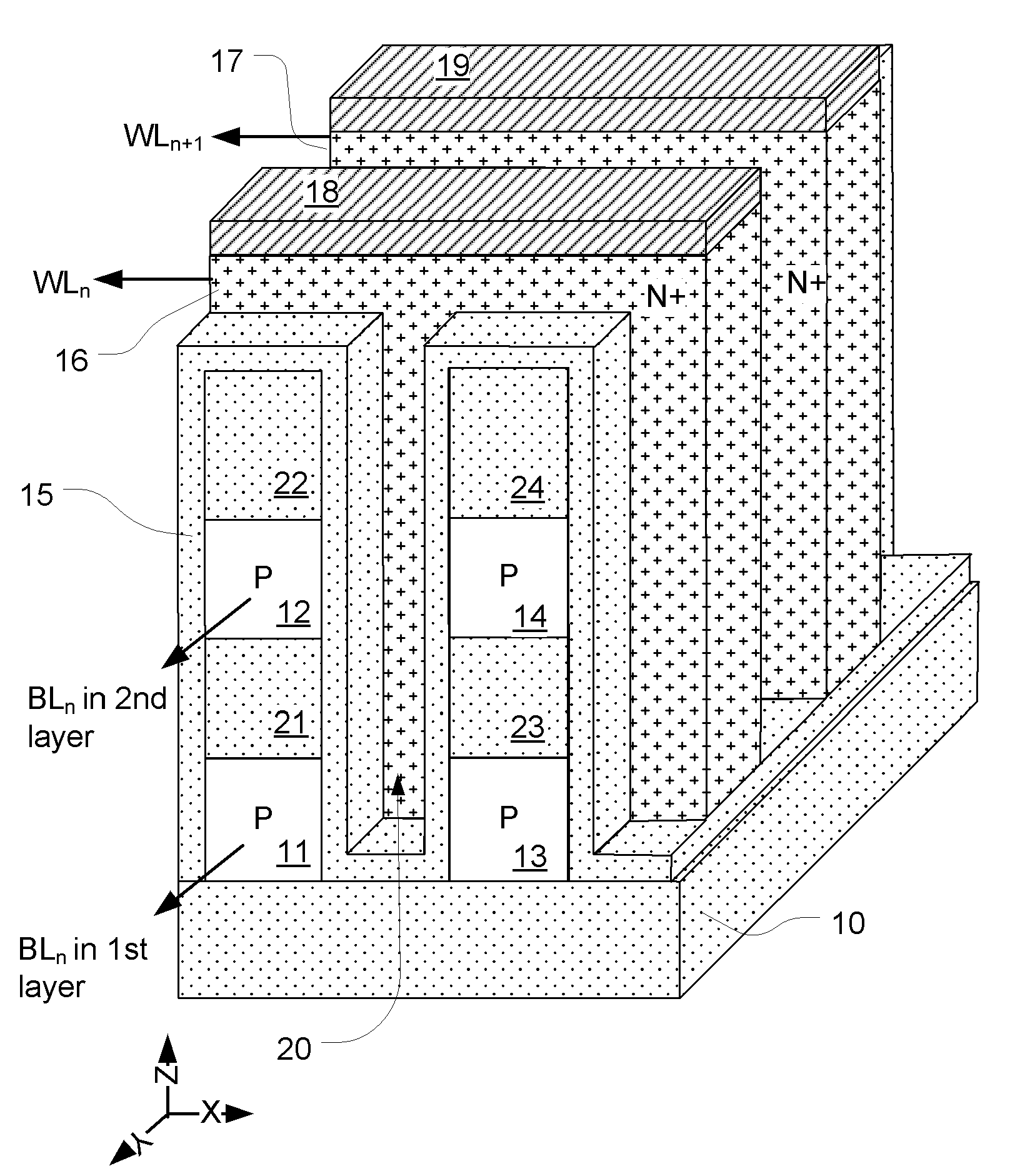

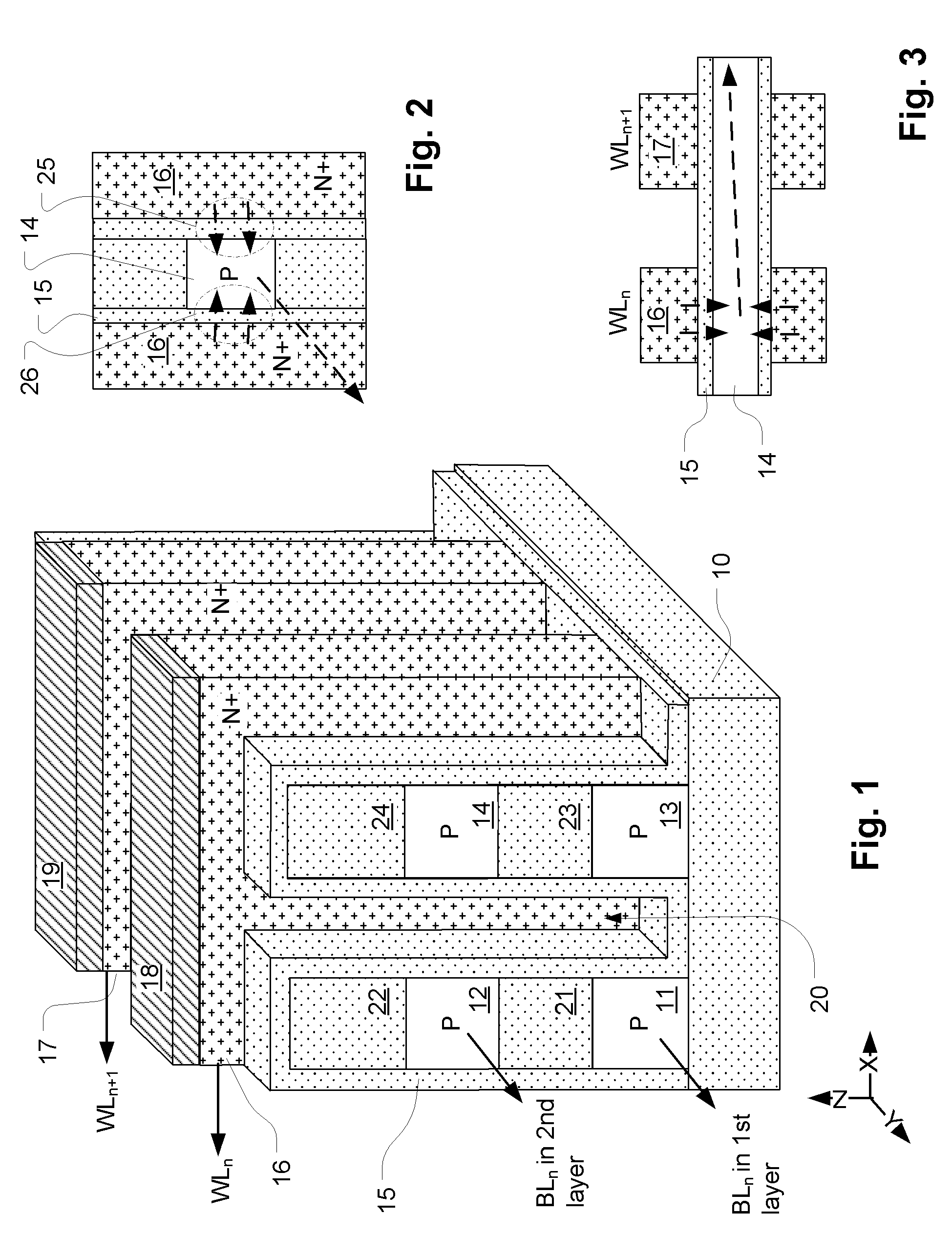

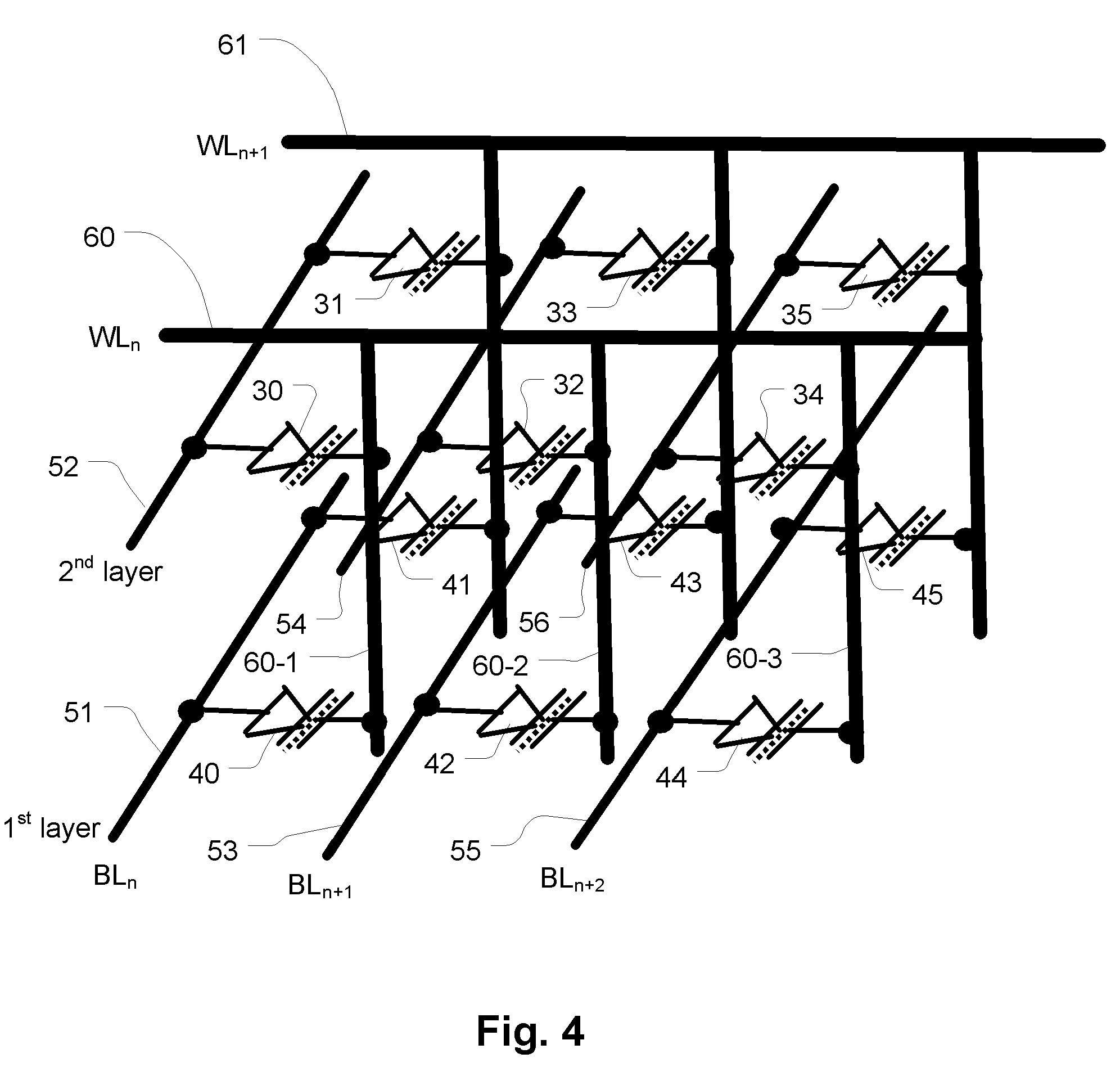

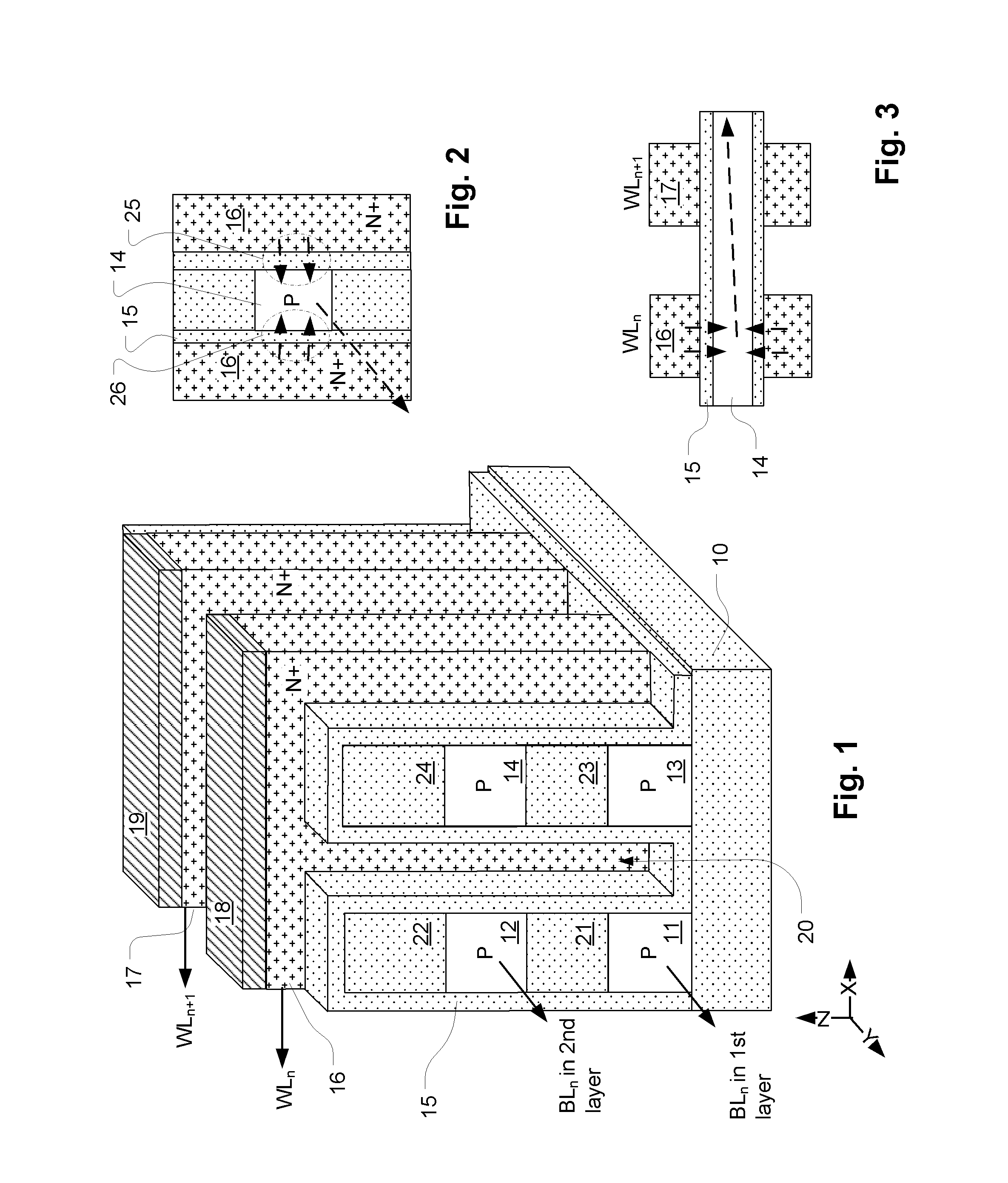

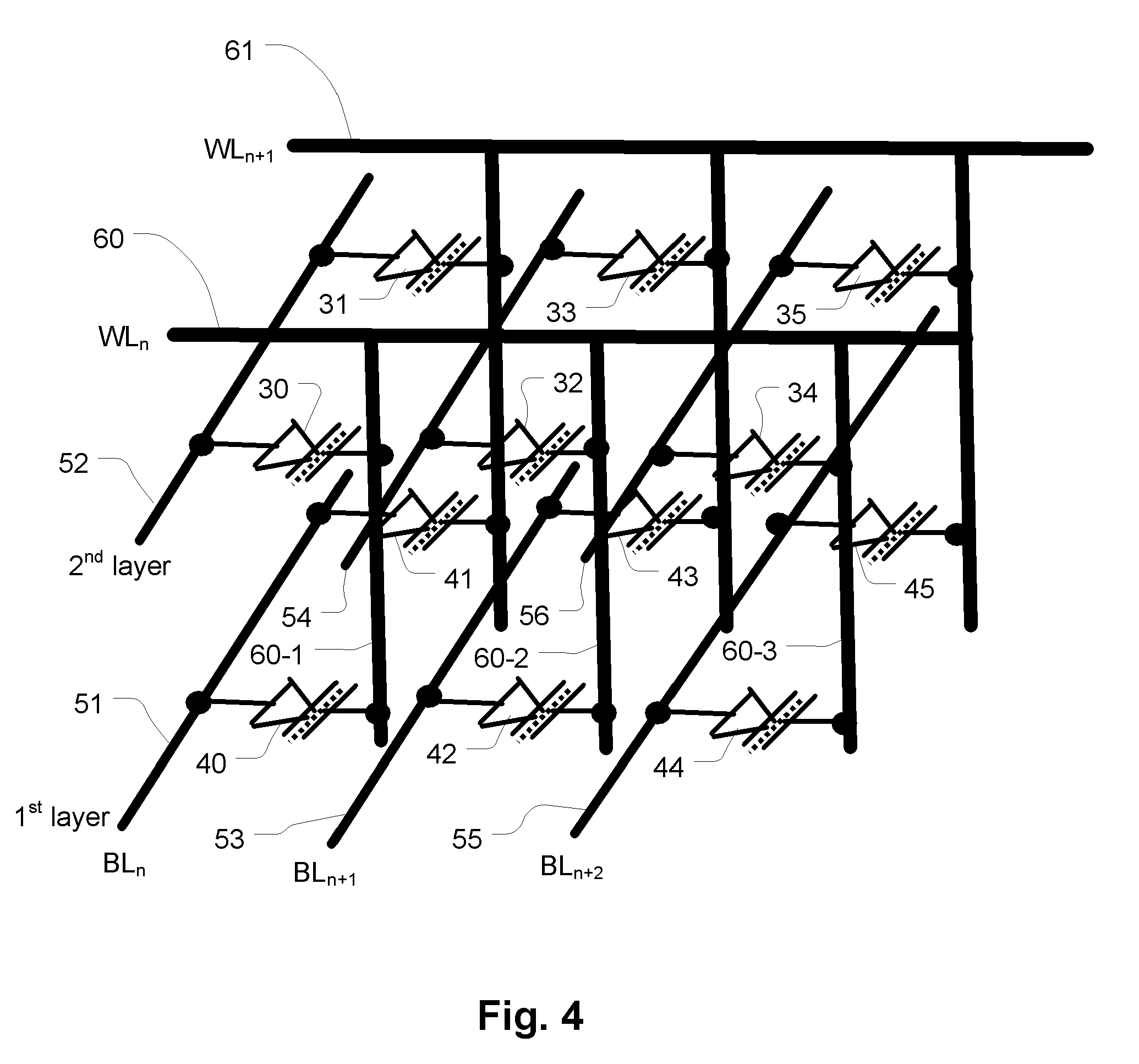

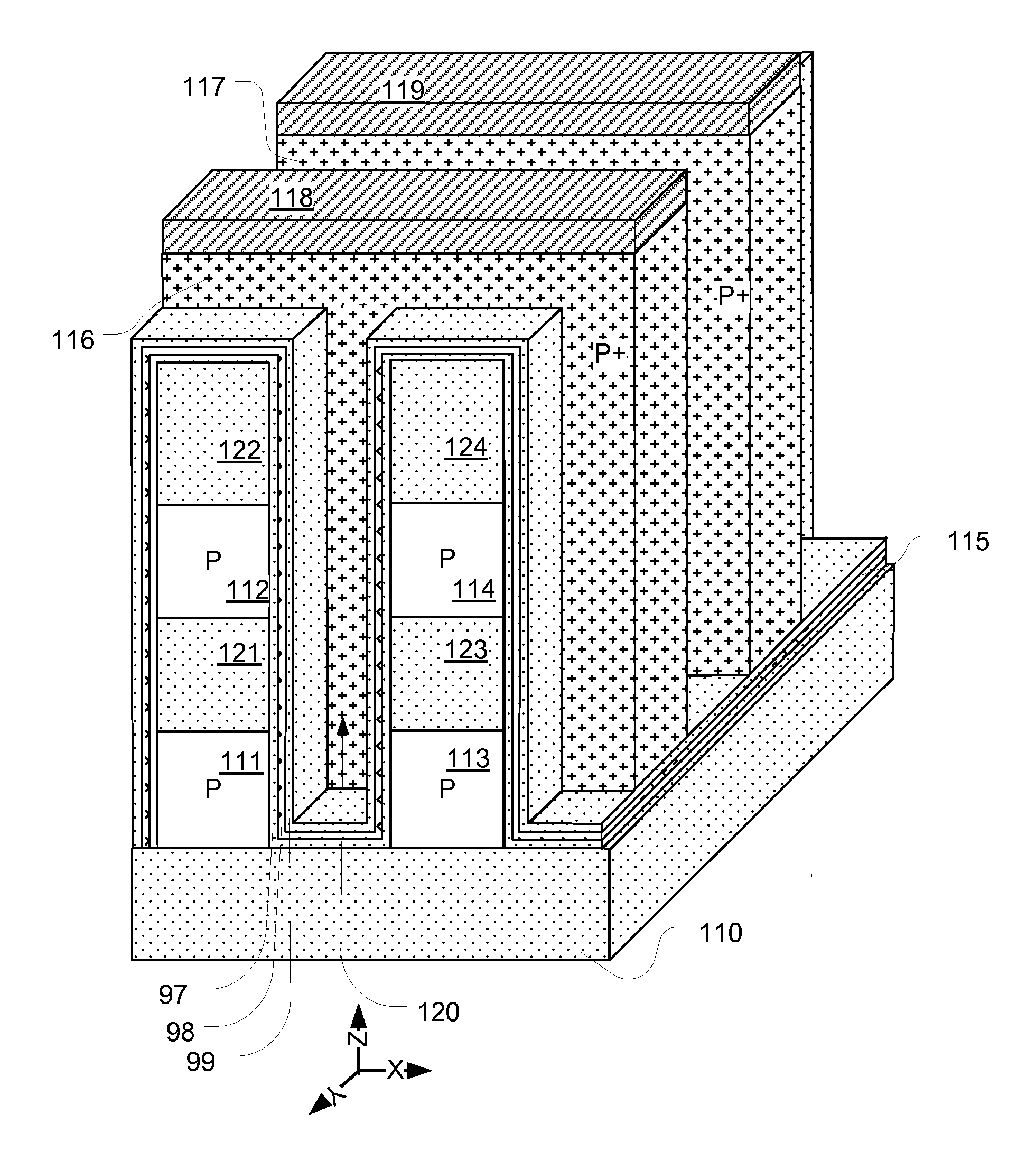

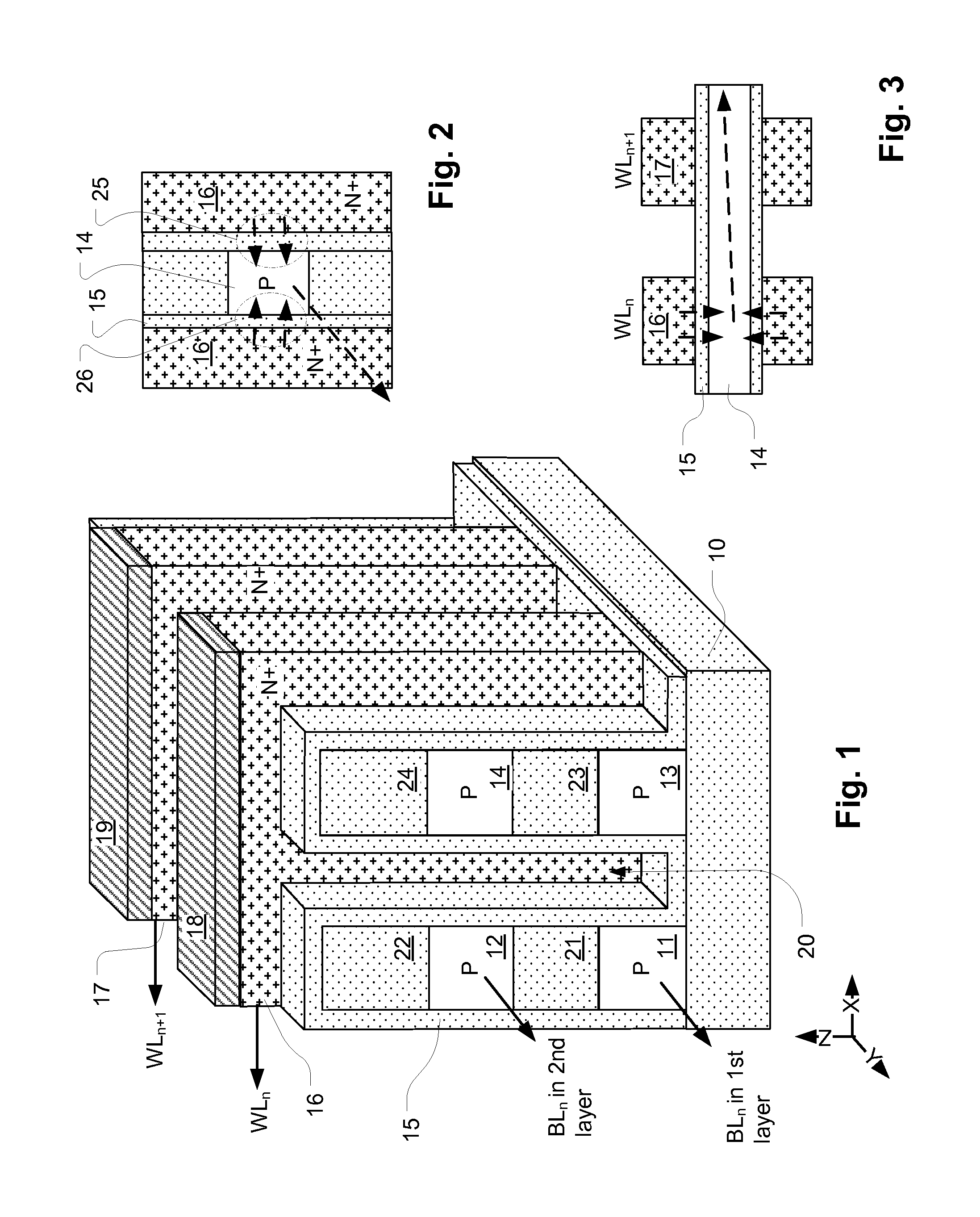

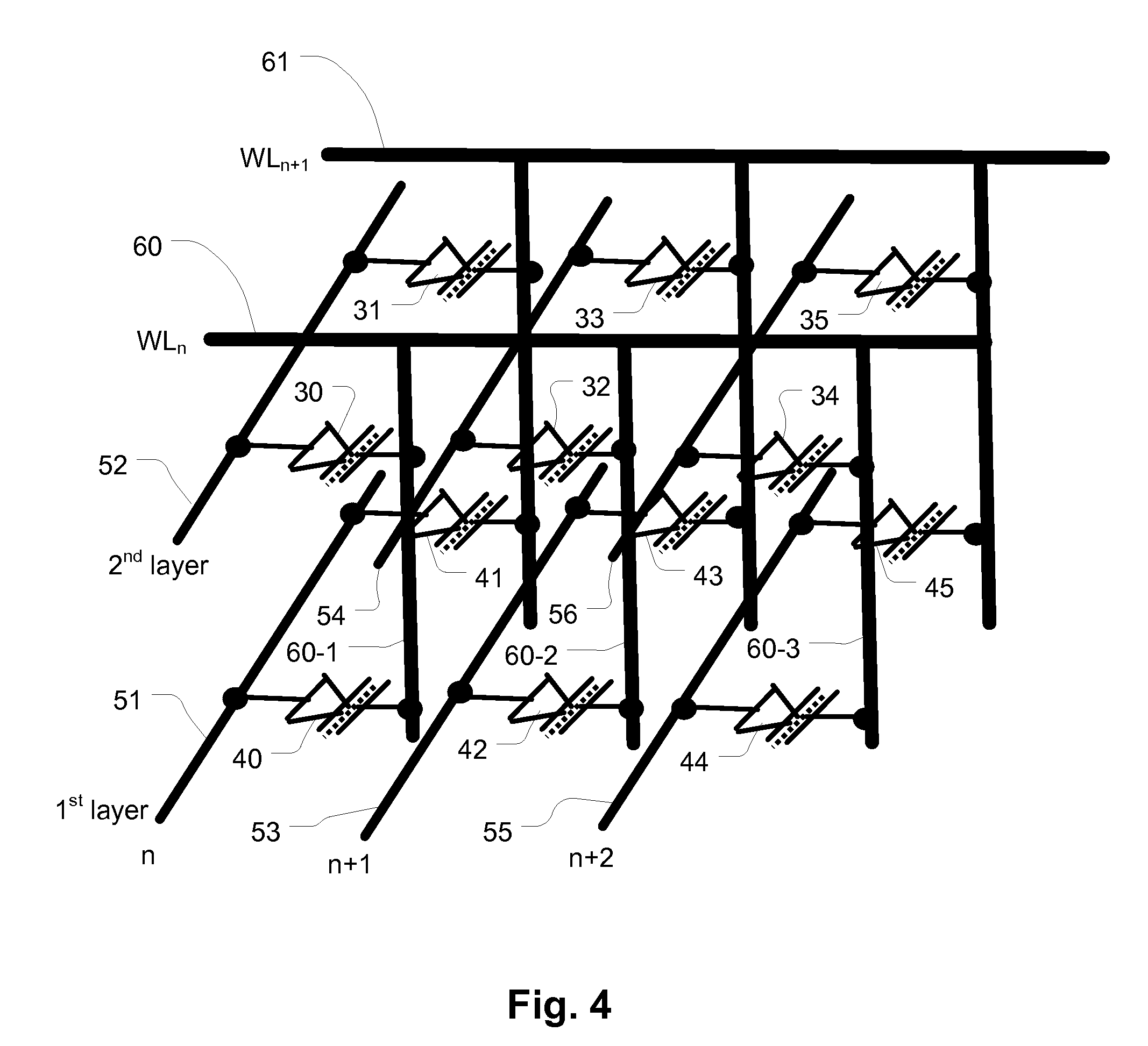

Integrated circuit self aligned 3D memory array and manufacturing method

A 3D memory device includes a plurality of ridge-shaped stacks, in the form of multiple strips of conductive material separated by insulating material, arranged as bit lines which can be coupled through decoding circuits to sense amplifiers. The strips of conductive material have side surfaces on the sides of the ridge-shaped stacks. A plurality of conductive lines arranged as word lines which can be coupled to row decoders, extends orthogonally over the plurality of ridge-shaped stacks. The conductive lines conform to the surface of the stacks. Memory elements lie in a multi-layer array of interface regions at cross-points between side surfaces of the conductive strips on the stacks and the conductive lines. The memory elements are programmable, like the anti-fuses or charge trapping structures. The 3D memory is made using only two critical masks for multiple layers.

Owner:MACRONIX INT CO LTD

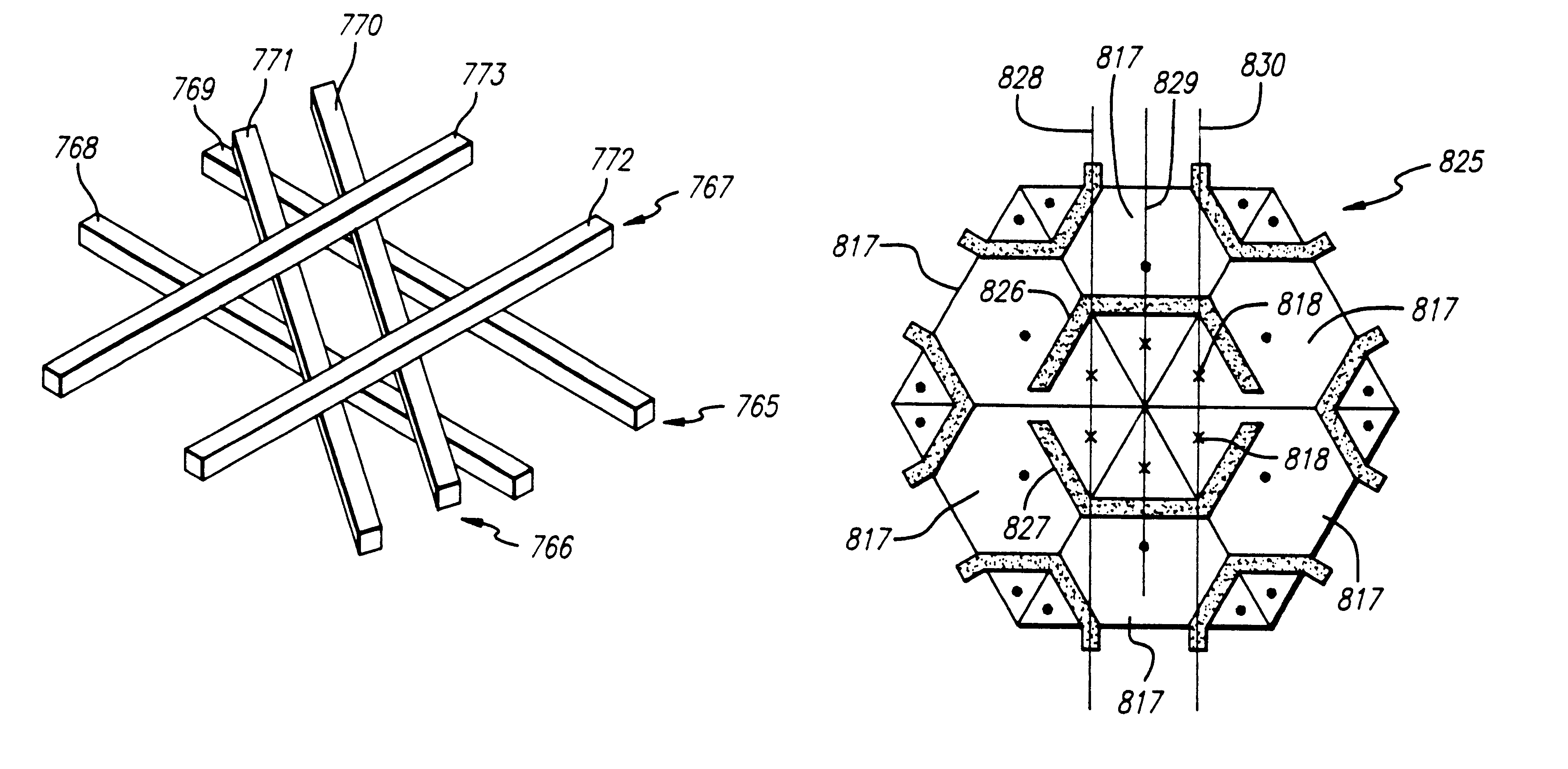

Hexagonal architecture

InactiveUS6407434B1Reduce total wirelength interconnect congestionReduce the numberTransistorSemiconductor/solid-state device detailsCapacitanceElectrical conductor

Several inventions are disclosed. A cell architecture using hexagonal shaped cells is disclosed. The architecture is not limited to hexagonal shaped cells. Cells may be defined by clusters of two or more hexagons, by triangles, by parallelograms, and by other polygons enabling a variety of cell shapes to be accommodated. Polydirectional non-orthogonal three layer metal routing is disclosed. The architecture may be combined with the tri-directional routing for a particularly advantageous design. In the tri-directional routing arraingement, electrical conductors for interconnecting terminals of microelectronic cells of an integrated circuit preferrably extend in three directions that are angularly displaced from each other by 60°. The conductors that extend in the three directions are preferrably formed in three different layers. A method of minimizing wire length in a semiconductor device is disclosed. A method of minimizing intermetal capacitance in a semiconductor device is disclosed. A novel device called a "tri-ister" is disclosed. Triangular devices are disclosed, including triangular NAND gates, triangular AND gates, and triangular OR gates. A triangular op amp and triode are disclosed. A triangular sense amplifier is disclosed. A DRAM memory array and an SRAM memory array, based upon triangular or parallelogram shaped cells, are disclosed, including a method of interconnecting such arrays. A programmable variable drive transistor is disclosed. CAD algorithms and methods are disclosed for designing and making semiconductor devices, which are particularly applicable to the disclosed architecture and tri-directional three metal layer routing.

Owner:BELL SEMICON LLC

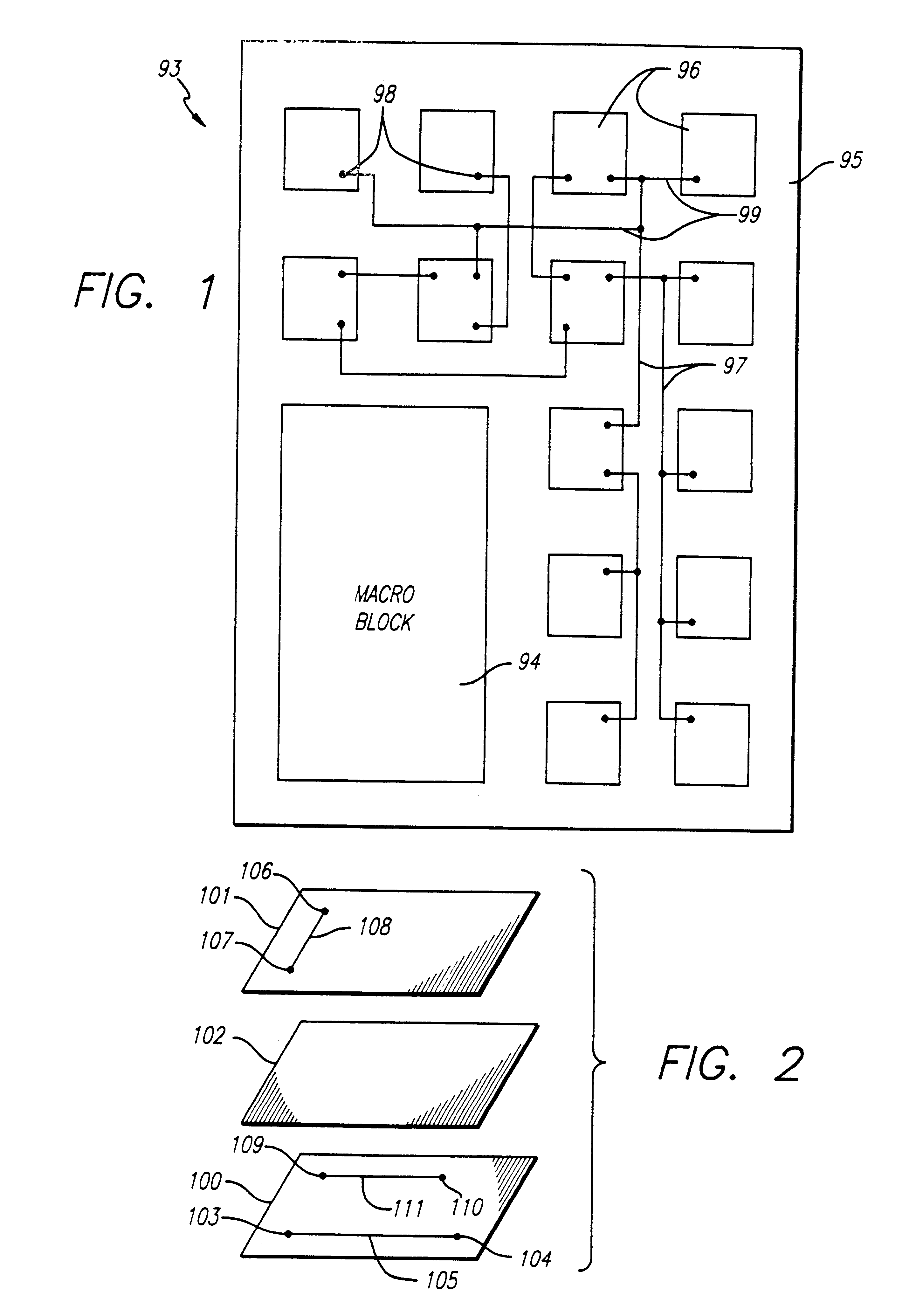

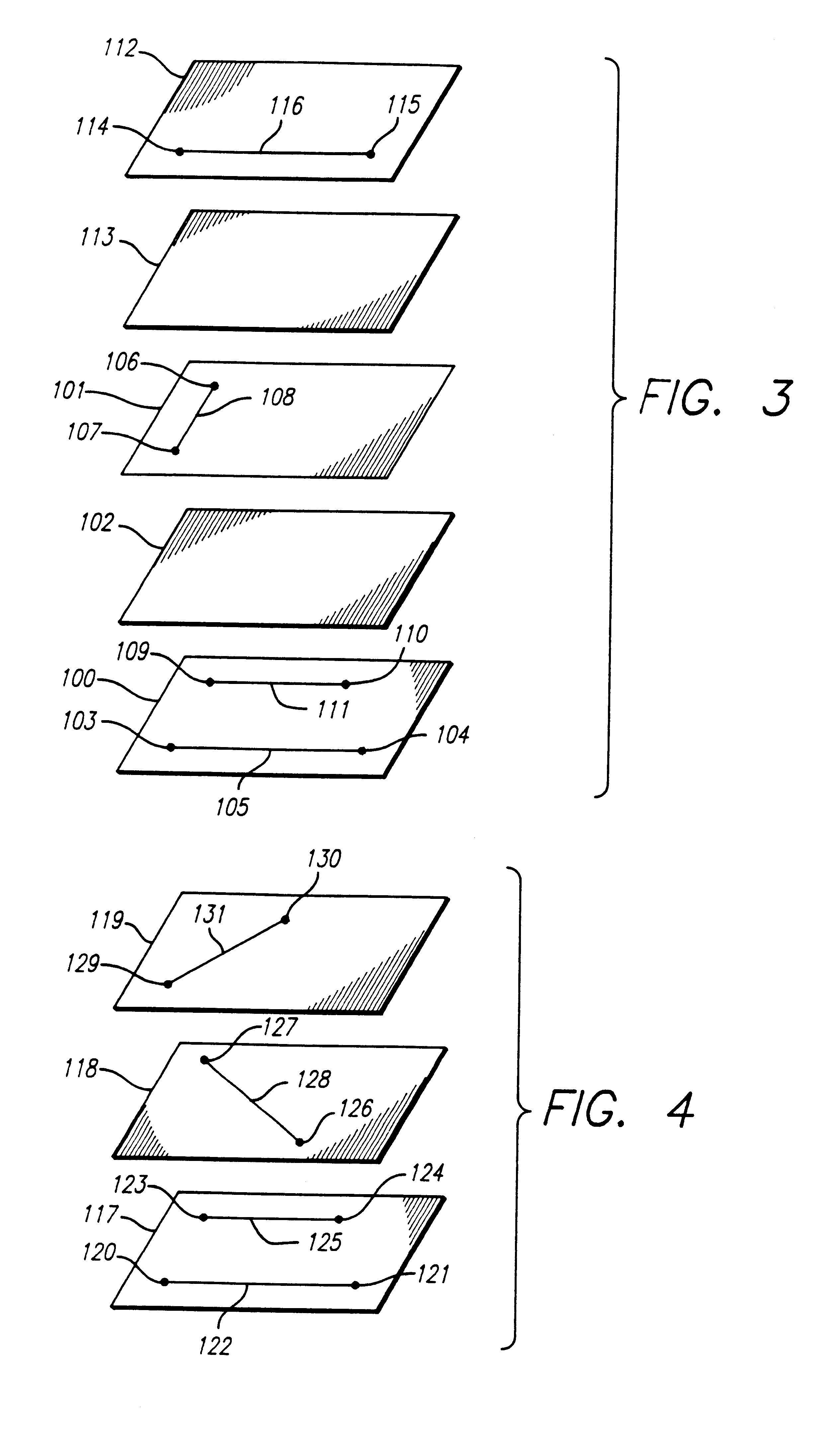

3-dimensional integrated circuit architecture, structure and method for fabrication thereof

ActiveUS20070228383A1Solid-state devicesSemiconductor/solid-state device manufacturingPerformance enhancementAudio power amplifier

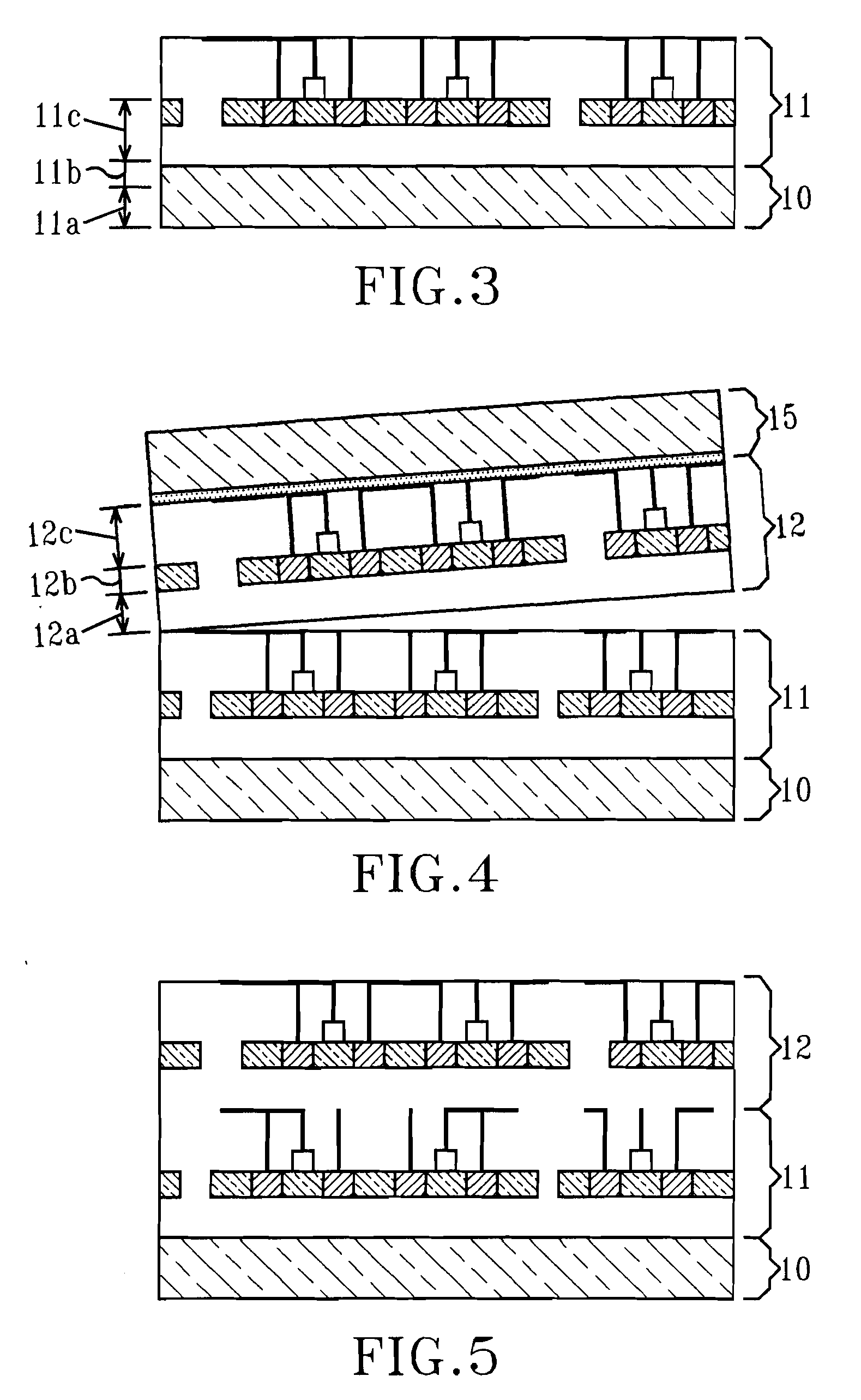

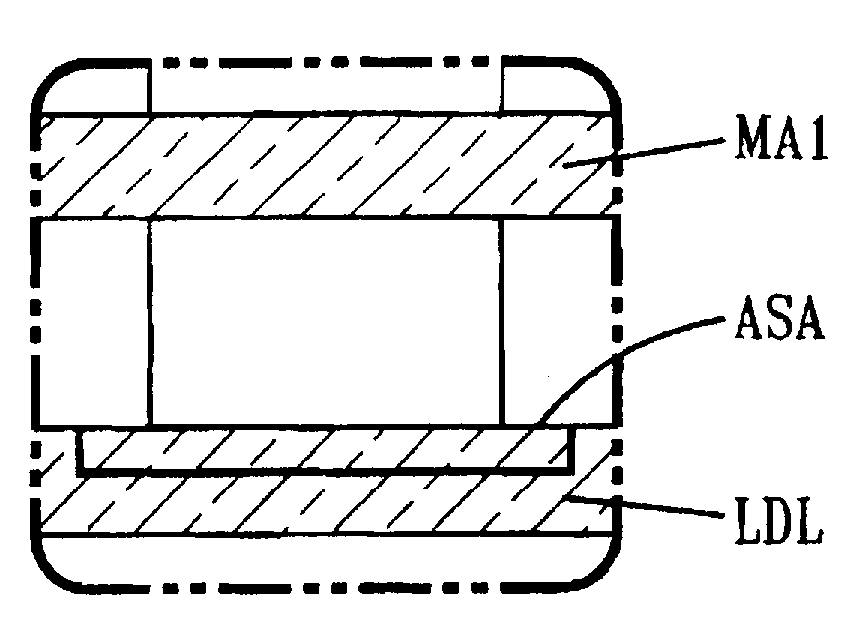

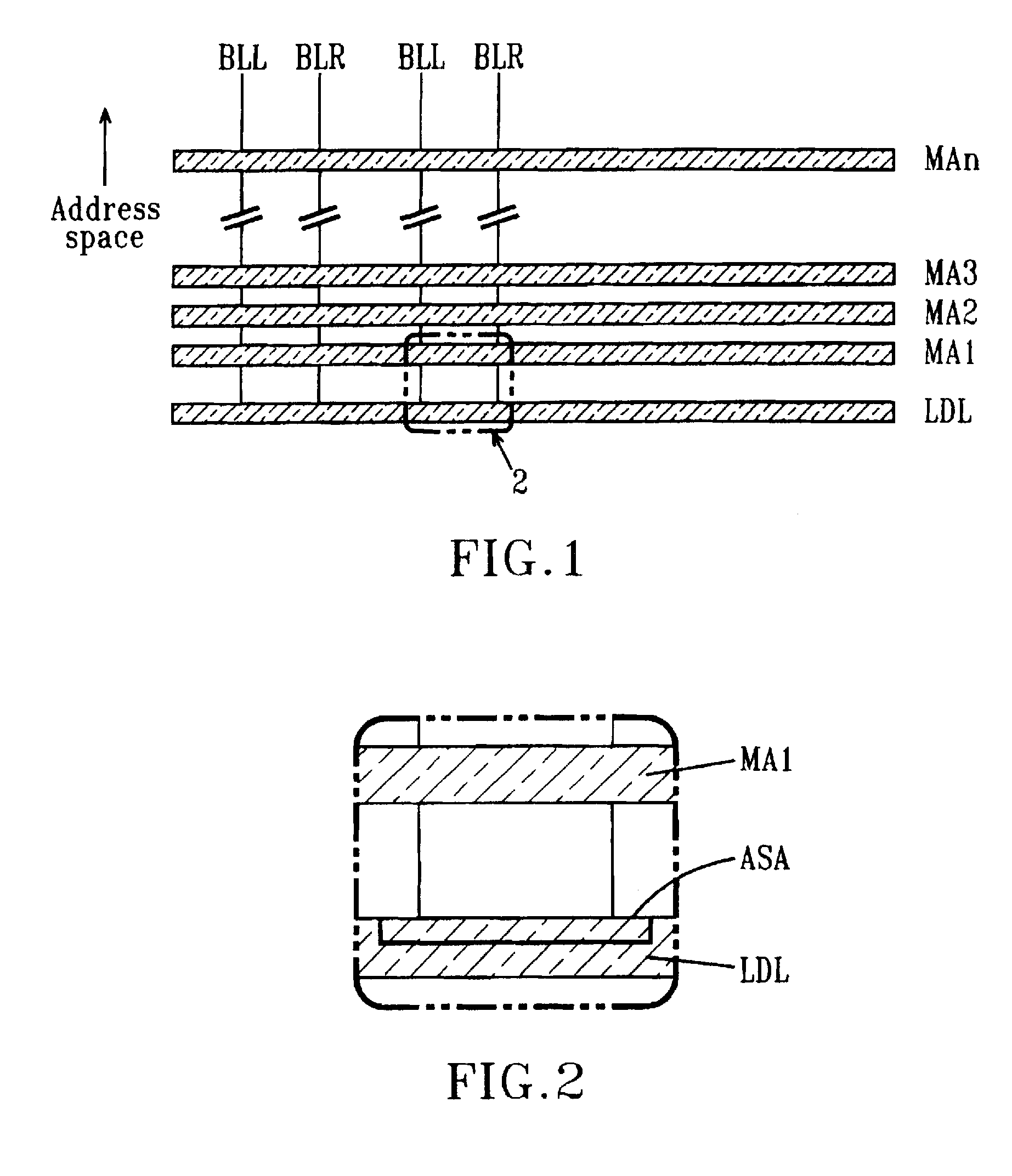

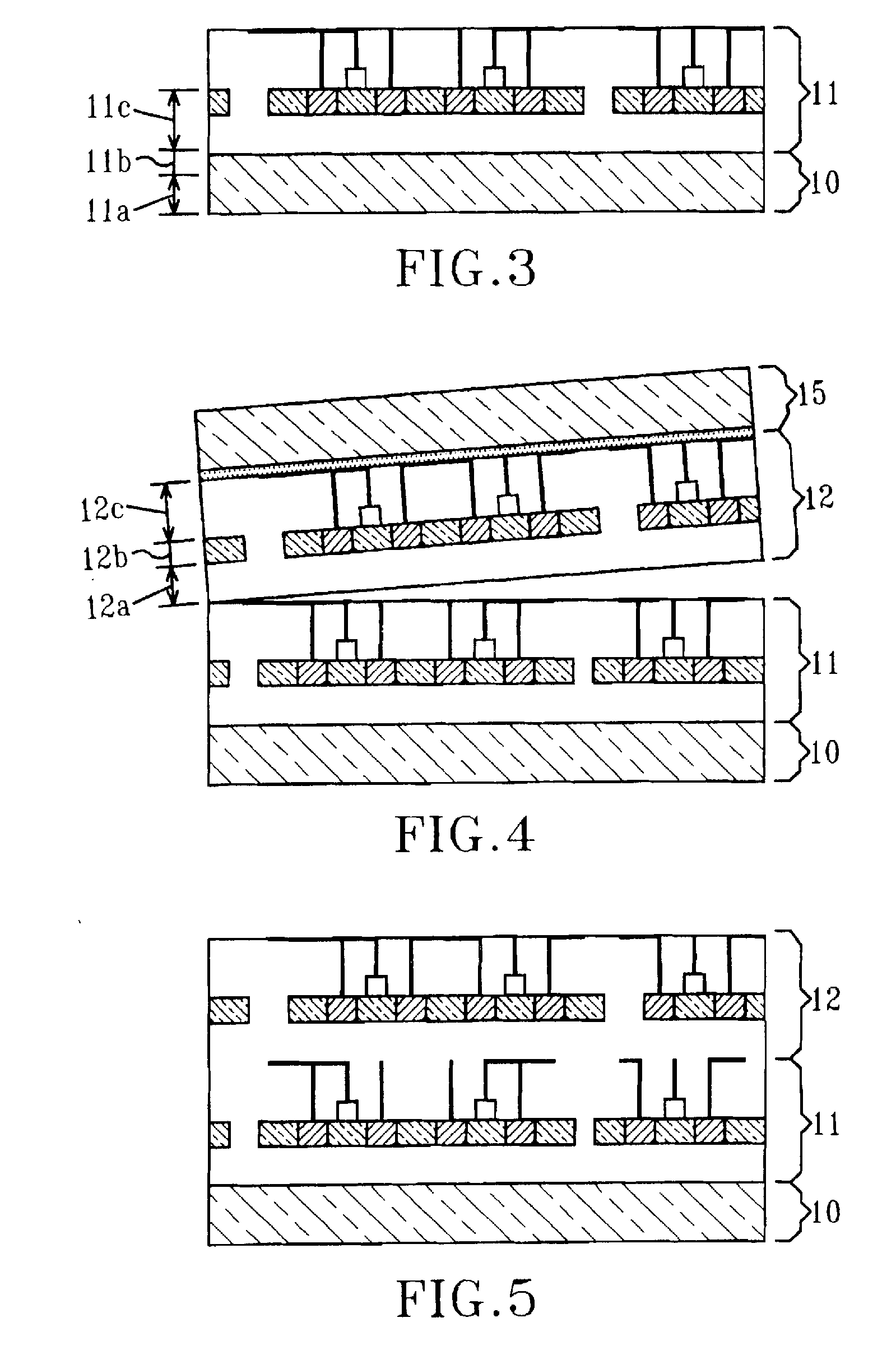

An integrated circuit design, structure and method for fabrication thereof includes at least one logic device layer and at least two additional separate memory array layers. Each of the logic device layer and the at least two memory array layers is independently optimized for a particular type of logic device or memory device disposed therein. Preferably also disposed within the logic device layer are array sense amplifiers, memory array output drivers and like higher performance circuitry otherwise generally disposed within memory array layer substrates. All layers may be independently powered to provide additional performance enhancement.

Owner:IBM CORP

Structure comprising 3-dimensional integrated circuit architecture, circuit structure, and instructions for fabrication thereof

ActiveUS20070283298A1Allow optimizationSolid-state devicesSemiconductor/solid-state device manufacturingAudio power amplifierPerformance enhancement

A design structure comprising an integrated circuit architecture, circuit structure, and / or instructions for fabrication thereof. The circuit structure includes at least one logic device layer and at least two additional separate memory array layers. Each of the logic device layer and the at least two memory array layers is independently optimized for a particular type of logic device or memory device disposed therein. Preferably also disposed within the logic device layer are array sense amplifiers, memory array output drivers and like higher performance circuitry otherwise generally disposed within memory array layer substrates. All layers may be independently powered to provide additional performance enhancement.

Owner:IBM CORP

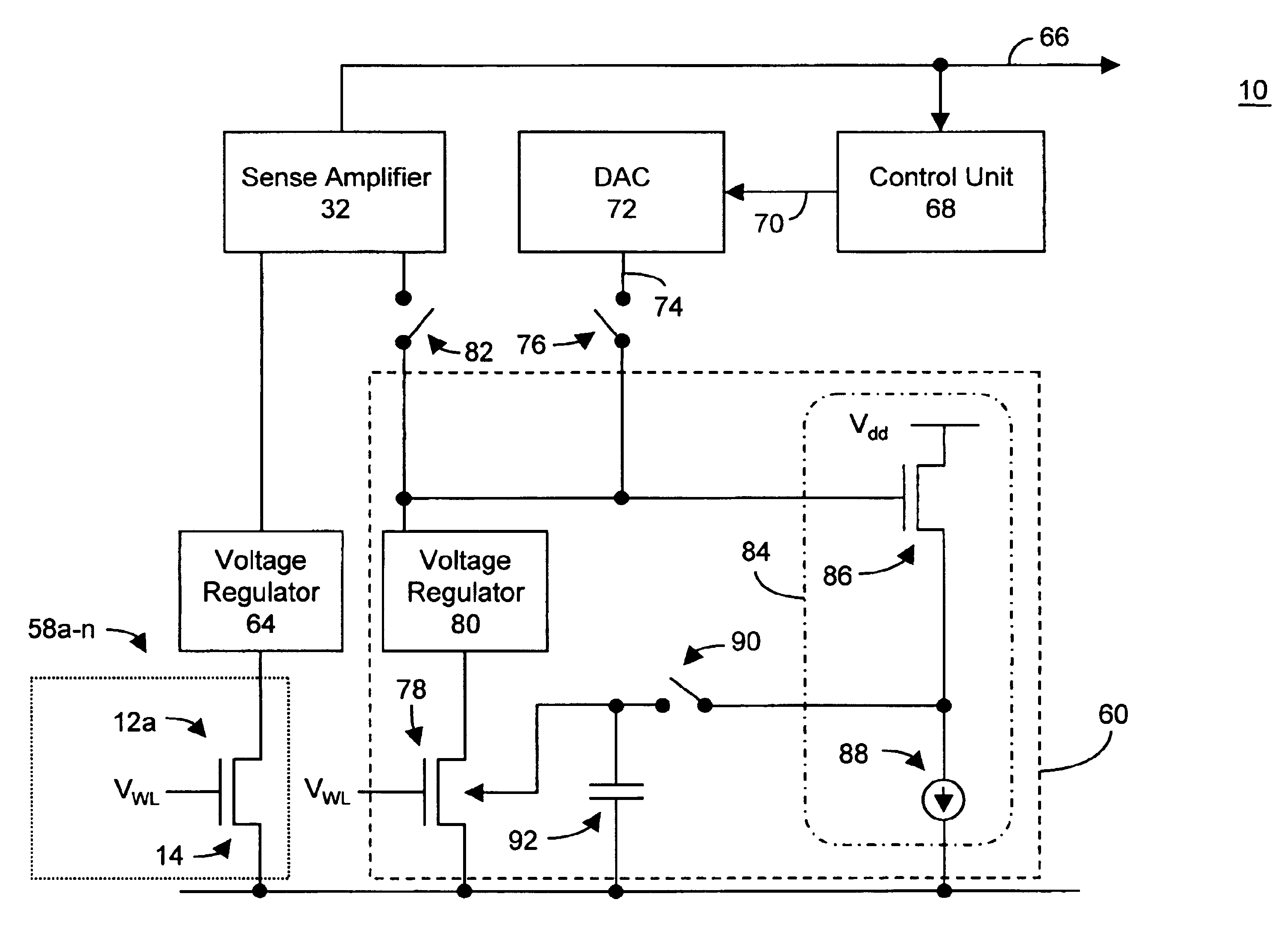

Reference current generator, and method of programming, adjusting and/or operating same

There are many inventions described and illustrated herein. In a first aspect, the present invention is a technique and circuitry for reading data that is stored in memory cells. In one embodiment of this aspect, the present invention is a technique and circuitry for generating a reference current that is used, in conjunction with a sense amplifier, to read data that is stored in memory cells of a DRAM device. The technique and circuitry for generating a reference current may be implemented using an analog configuration, a digital configuration, and / or combinations of analog and digital configurations.

Owner:MICRON TECH INC

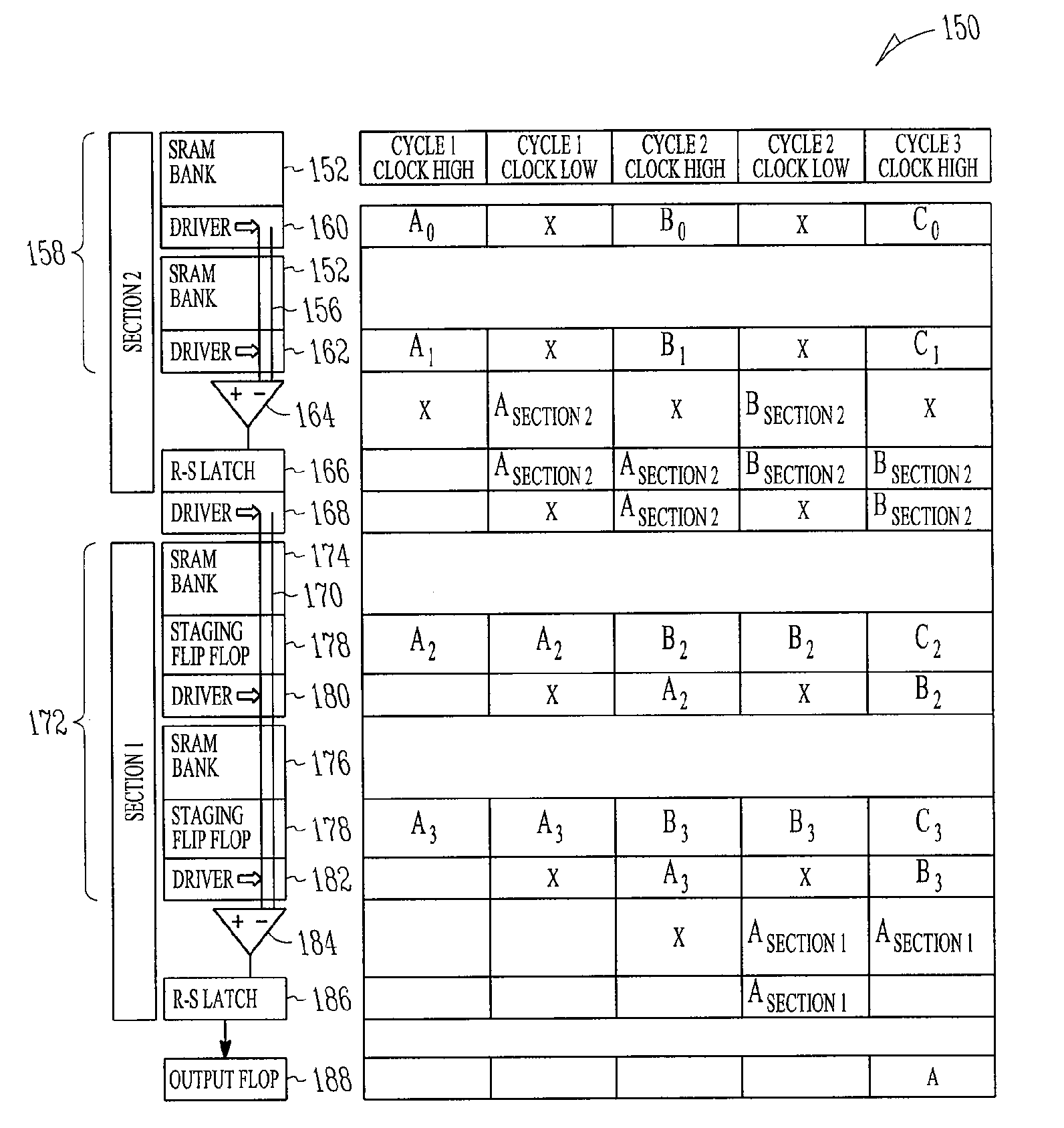

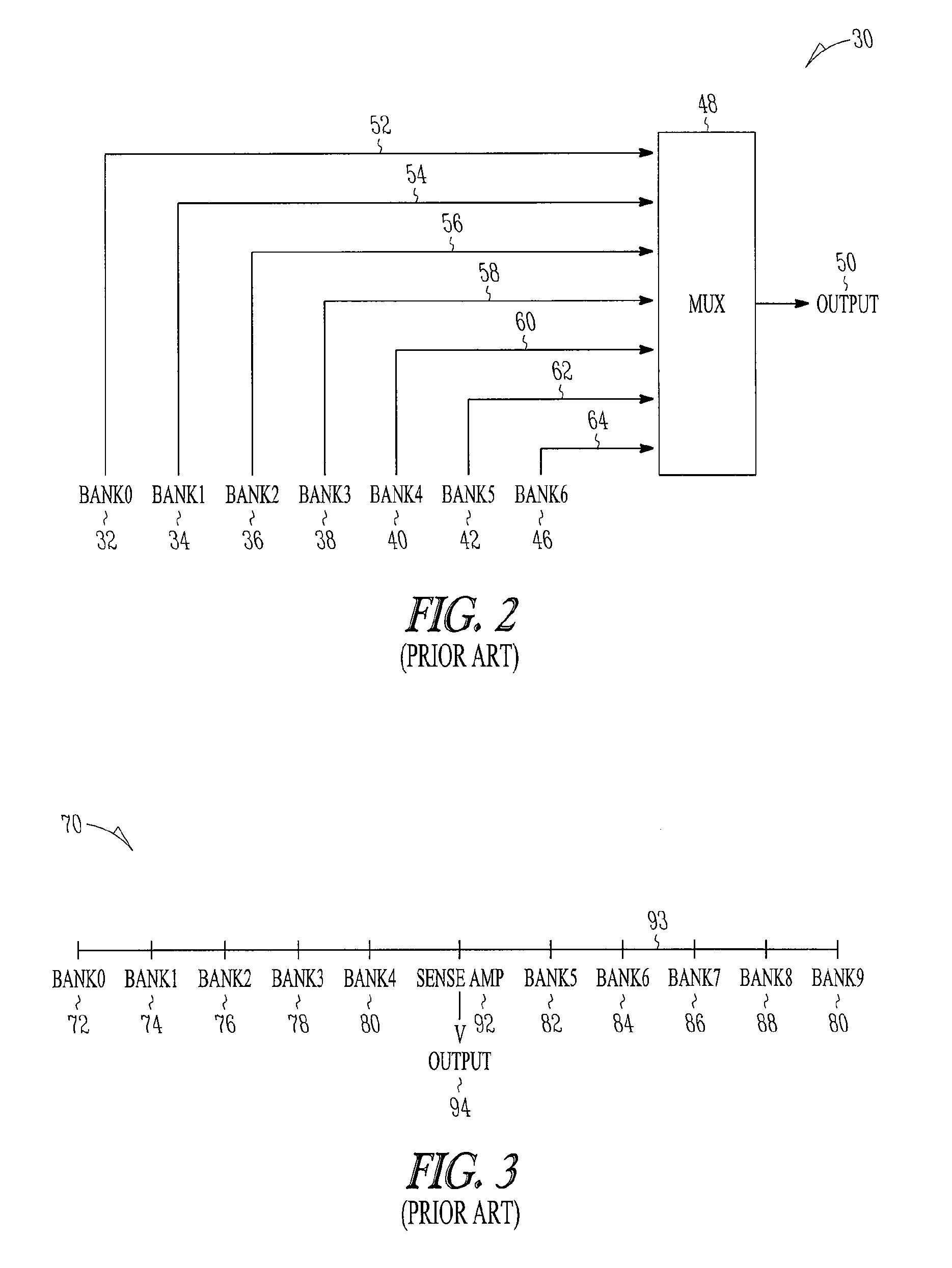

Static random access memory architecture

An architecture for a semiconductor static random access memory (SRAM) is described. In one example, a first set or group or stage of SRAM banks are coupled to a first data bus formed using bit line pairs, and a second set or group or stage of SRAM banks are coupled to a second data bus formed using other bit line pairs. The number of banks coupled to each bit line pair is determined by the SRAM's operating frequency and size. Each data bus is coupled to a sense amplifier. The output from the sense amplifier is then coupled to the bit line pair of a group of SRAM banks. This adjacent group has staging logic coupled to each SRAM bank to store the output of the SRAM bank until the contents from the first group is placed on the bit line of the adjacent stage of SRAM banks. The output from either the first stage or from one of the SRAM banks in the adjacent stage's SRAM banks, which had been stored in the adjacent stage's staging logic, is driven to the sense amplifier coupled to the adjacent stage. Successive stages of SRAM banks can be coupled together until an arbitrary number of stages of SRAM banks have been coupled together.

Owner:CISCO TECH INC

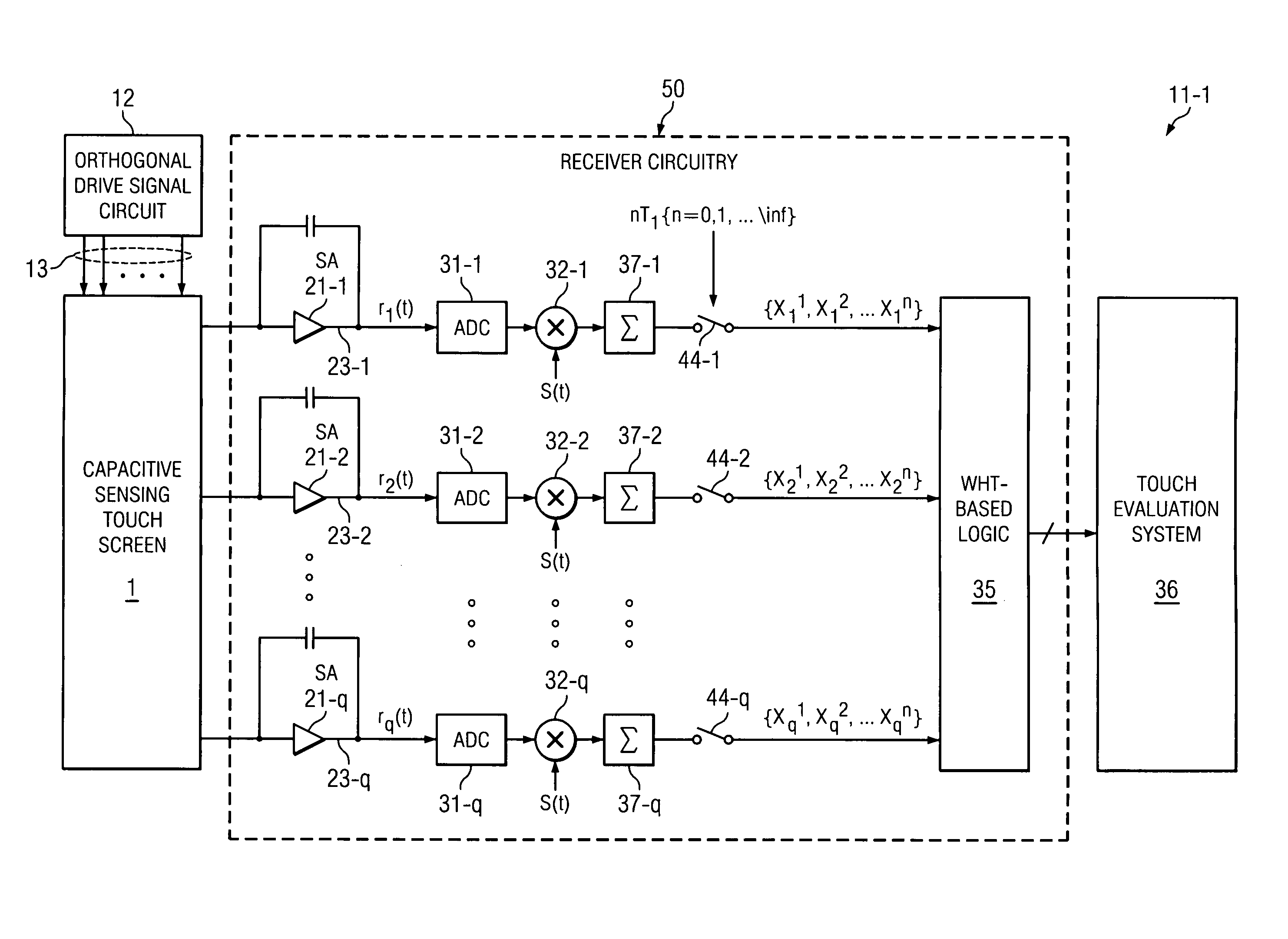

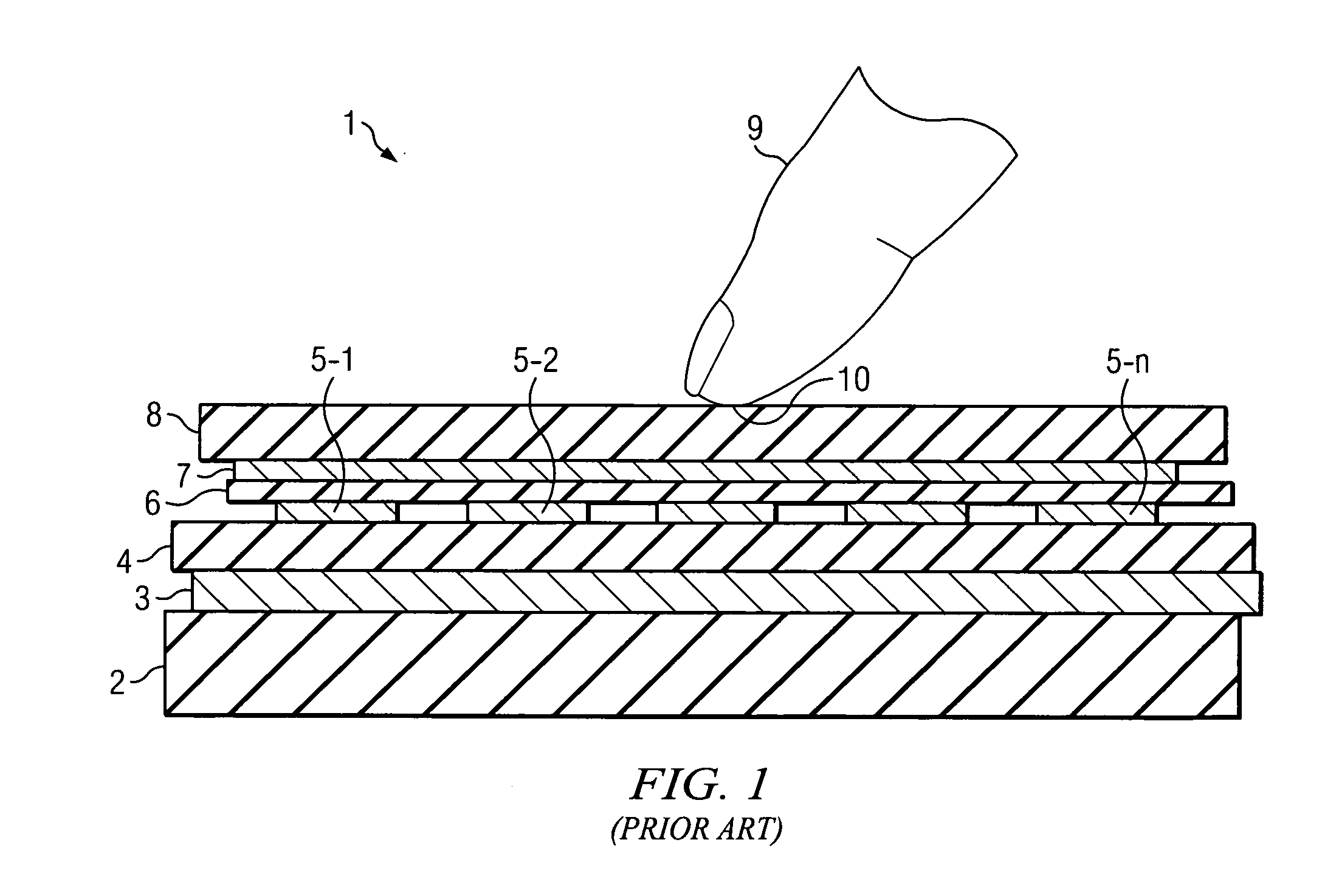

Touch-sensitive interface and method using orthogonal signaling

InactiveUS20120056841A1Improve touch sensitivityScan rate can be decreasedCathode-ray tube indicatorsInput/output processes for data processingCapacitanceAudio power amplifier

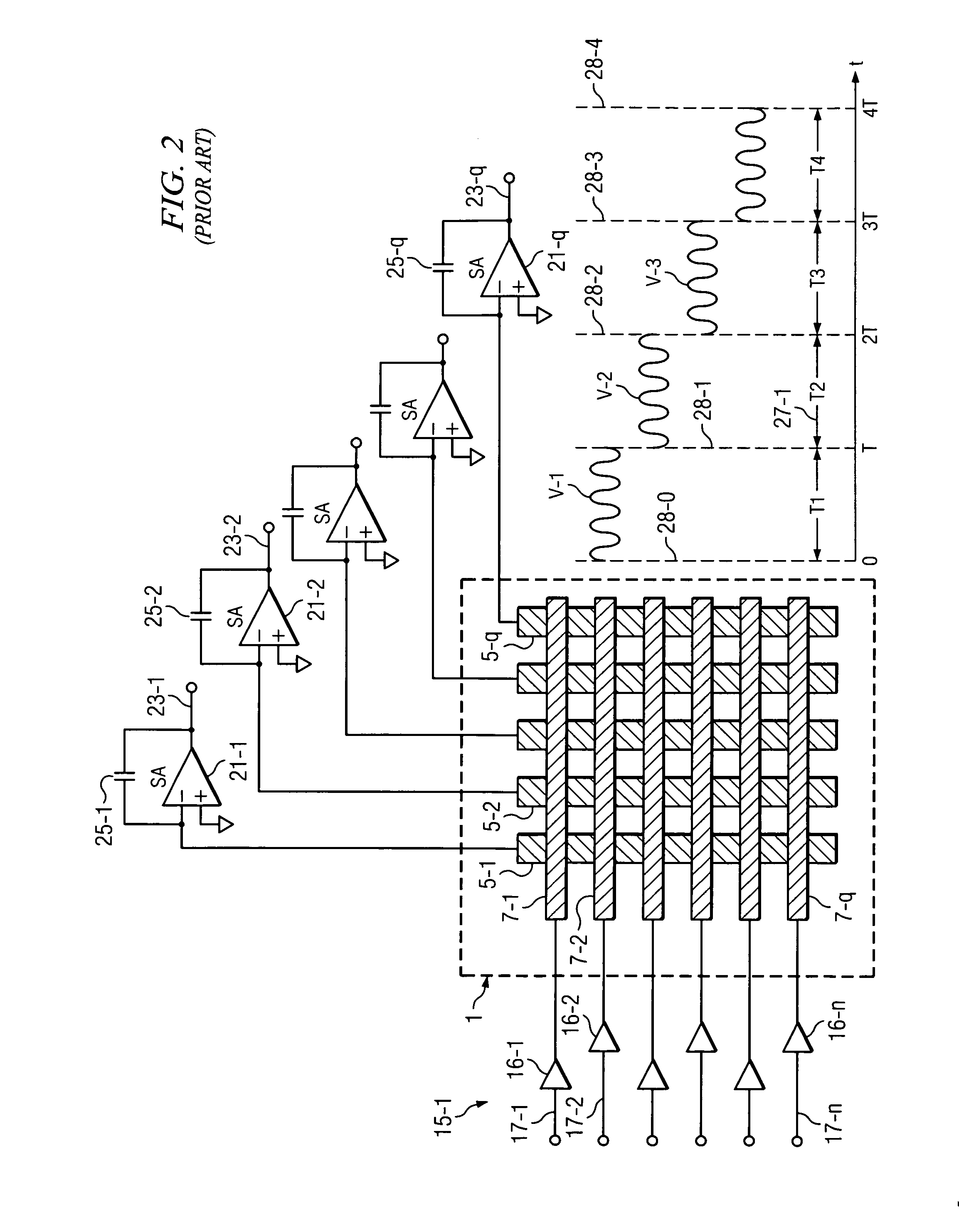

A touch screen system includes a capacitive touch screen (1) including a plurality of row conductors (7-1,2 . . . n) and a column conductor (5-1). A plurality of cotemporaneous orthogonal excitation signals (S1(t), S2(t) . . . Sn(t)) are simultaneously driven onto the row conductors, respectively. The capacitively coupled signals on the column conductor may be influenced by a touch (10) on the capacitive touch screen. Receiver circuitry (50) includes a sense amplifier (21-1) coupled to generate an amplifier output signal (r1(t)) in response to signals capacitively coupled onto the column conductor. WHT-based circuitry (35) determines amounts of signal contribution capacitively coupled by each of the excitation signals, respectively, to the amplifier output signal.

Owner:INTEL CORP

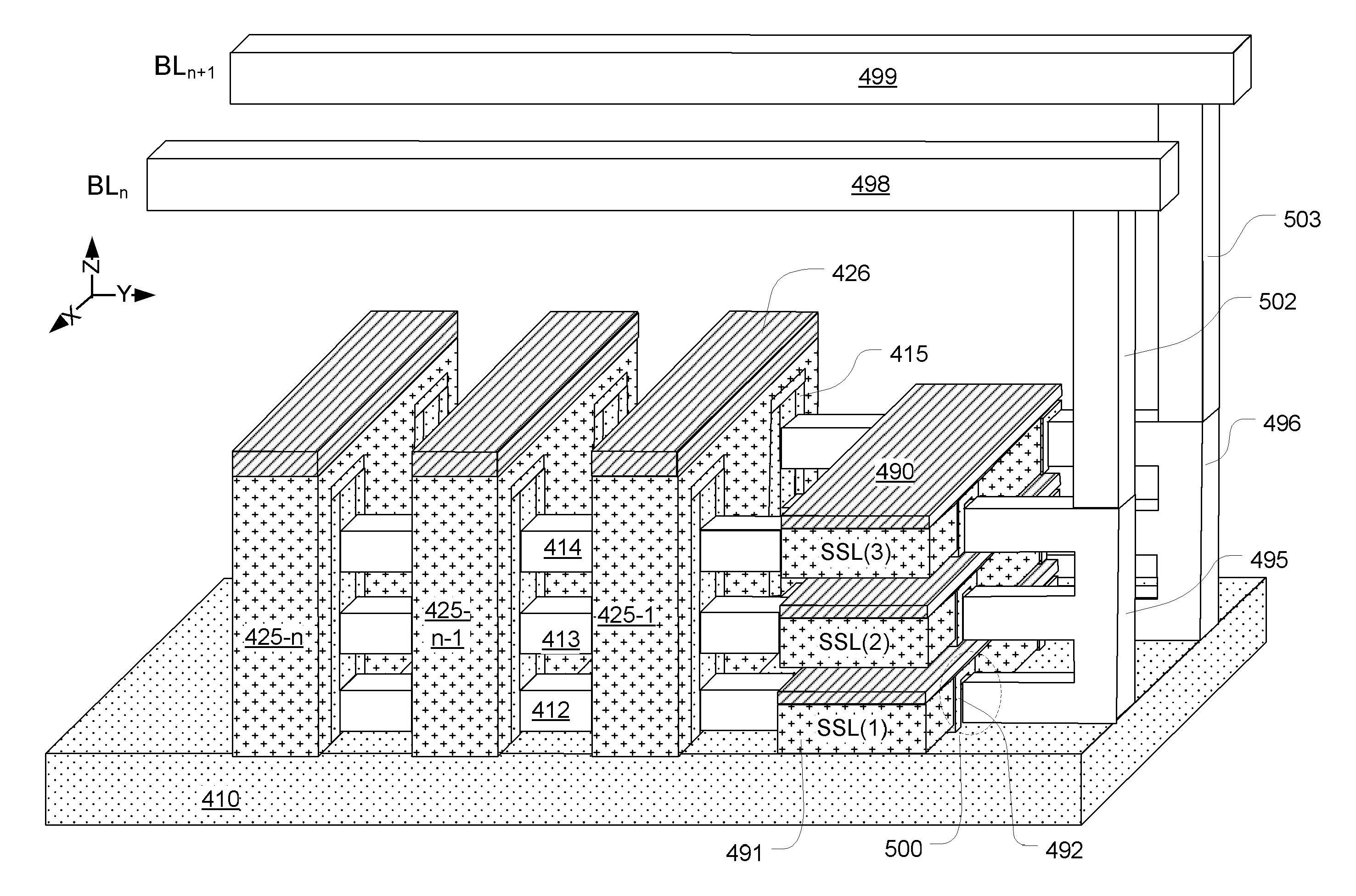

Integrated circuit self aligned 3D memory array and manufacturing method

ActiveUS20100226195A1Semiconductor/solid-state device detailsSolid-state devicesBit lineAudio power amplifier

A 3D memory device includes a plurality of ridge-shaped stacks, in the form of multiple strips of conductive material separated by insulating material, arranged as bit lines which can be coupled through decoding circuits to sense amplifiers. The strips of conductive material have side surfaces on the sides of the ridge-shaped stacks. A plurality of conductive lines arranged as word lines which can be coupled to row decoders, extends orthogonally over the plurality of ridge-shaped stacks. The conductive lines conform to the surface of the stacks. Memory elements lie in a multi-layer array of interface regions at cross-points between side surfaces of the conductive strips on the stacks and the conductive lines. The memory elements are programmable, like the anti-fuses or charge trapping structures. The 3D memory is made using only two critical masks for multiple layers.

Owner:MACRONIX INT CO LTD

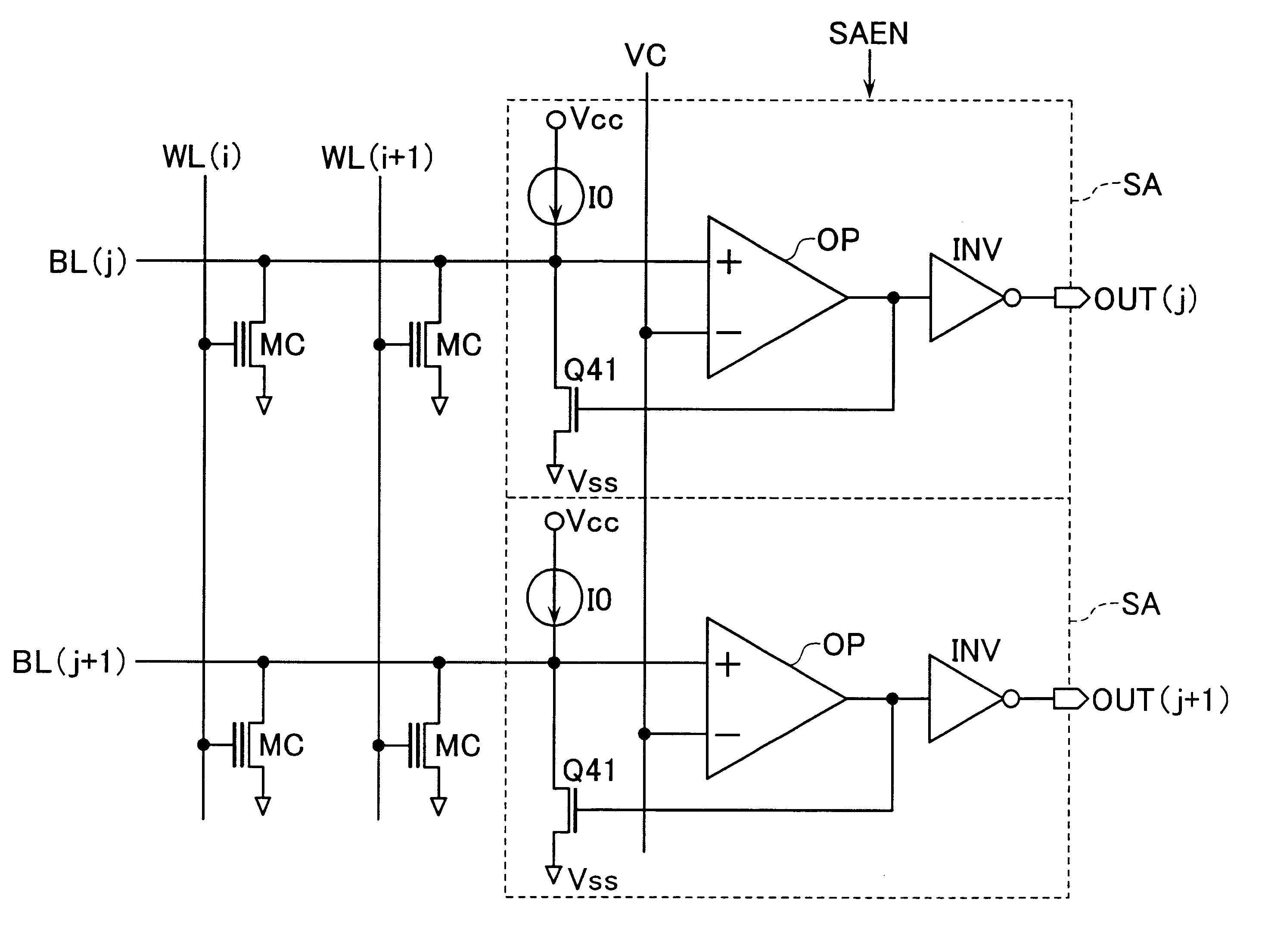

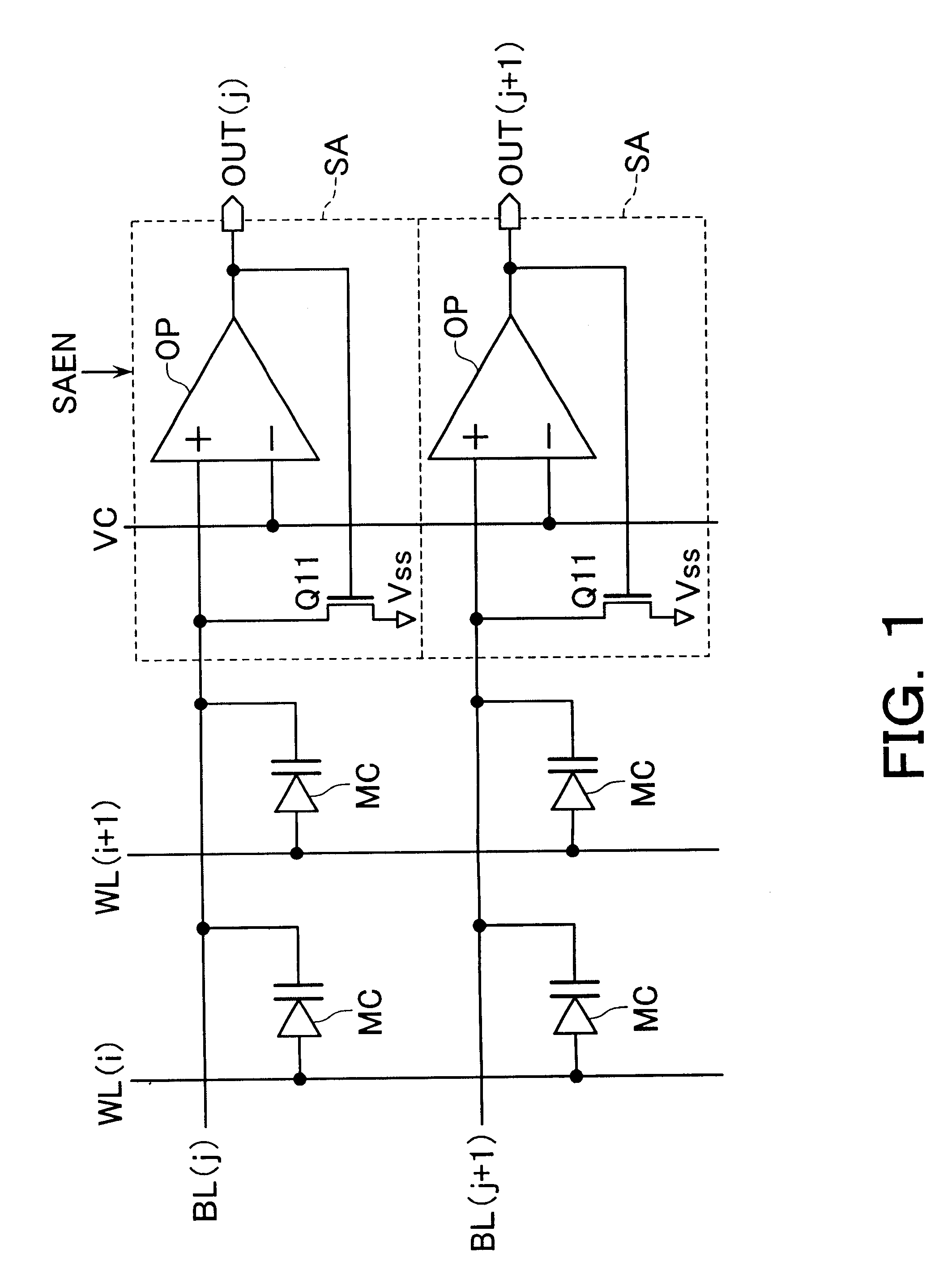

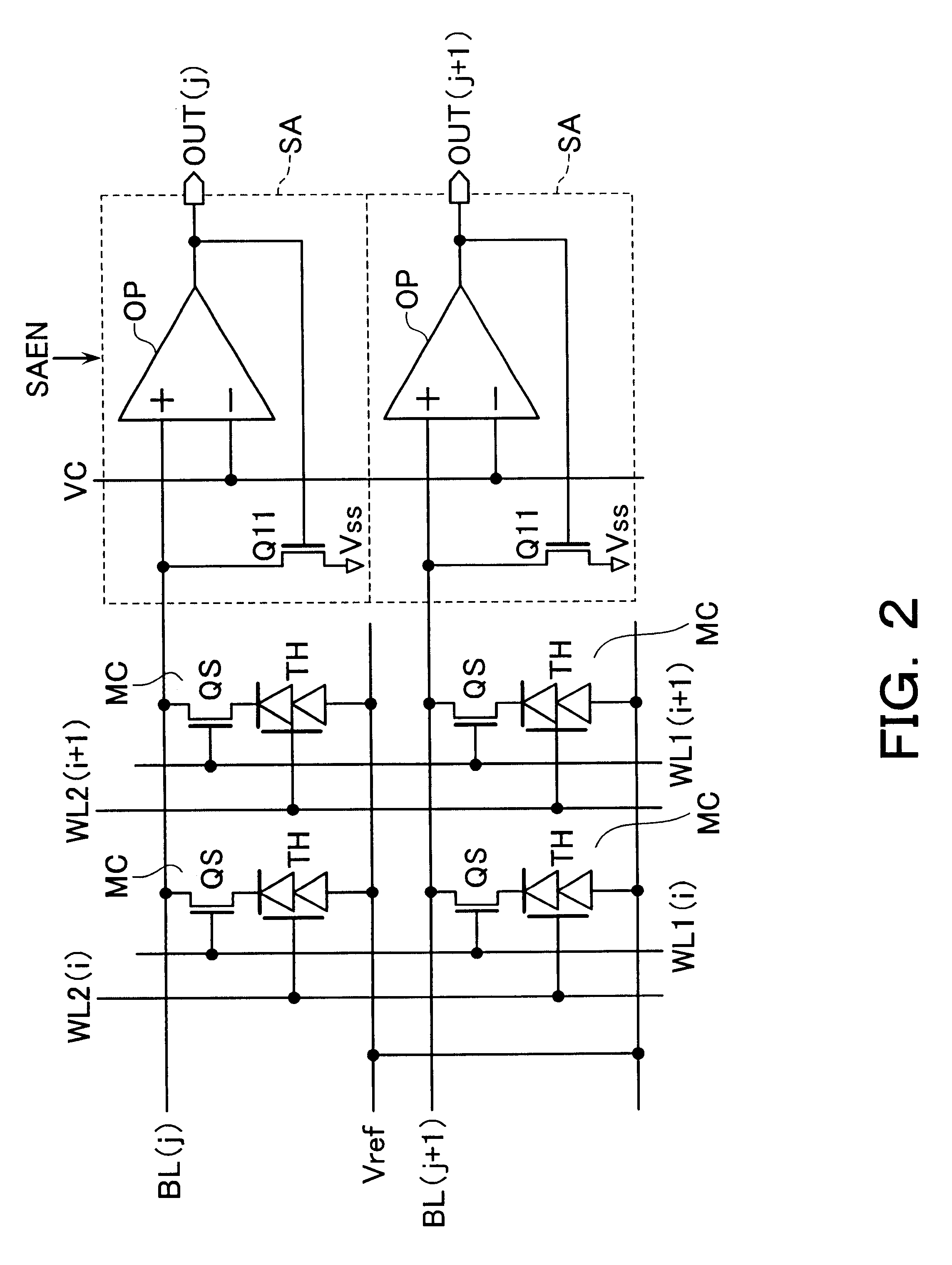

Magnetoresistive memory device

An integrated semiconductor memory device with an array of memory cells MC using magnetic tunnel junction (MTJ) cells is disclosed. A sense amplifier SA that is connected to a bit line BL for data readout of a selected memory cell MC is arranged using an operational amplifier OP. The operational amplifier OP has an inverting input terminal which is connected to the bit line BL and a non-inverting input terminal, to which a potentially fixed constant voltage VC is given. A PMOS transistor Q31 is provided, which can also do double-duty as a current source load. This PMOS transistor has its drain and gate that are connected to the inverting input terminal, and a source as connected to an output terminal of the operational amplifier OP whereby the transistor is under feedback control in response to an output of the operational amplifier OP so that a clamped voltage potential of the bit lime BL is fixed to the voltage VC.

Owner:KK TOSHIBA

Memory Architecture of 3D Array With Alternating Memory String Orientation and String Select Structures

ActiveUS20120182806A1Increase pitchImproved gate structureSolid-state devicesRead-only memoriesArray data structureConductive materials

Owner:MACRONIX INT CO LTD