Patents

Literature

76results about "Pulse generation by non-linear magnetic/dielectric devices" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

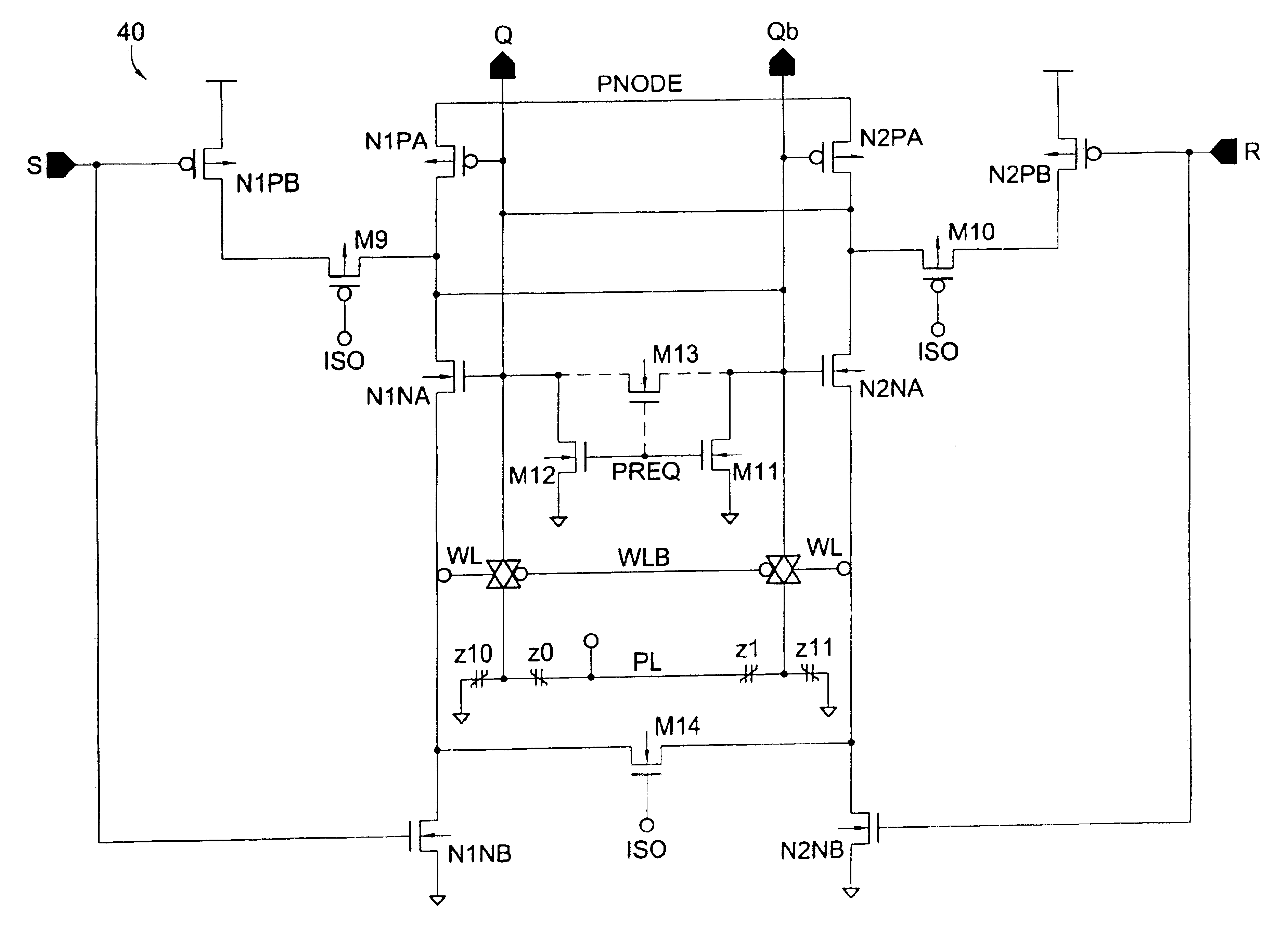

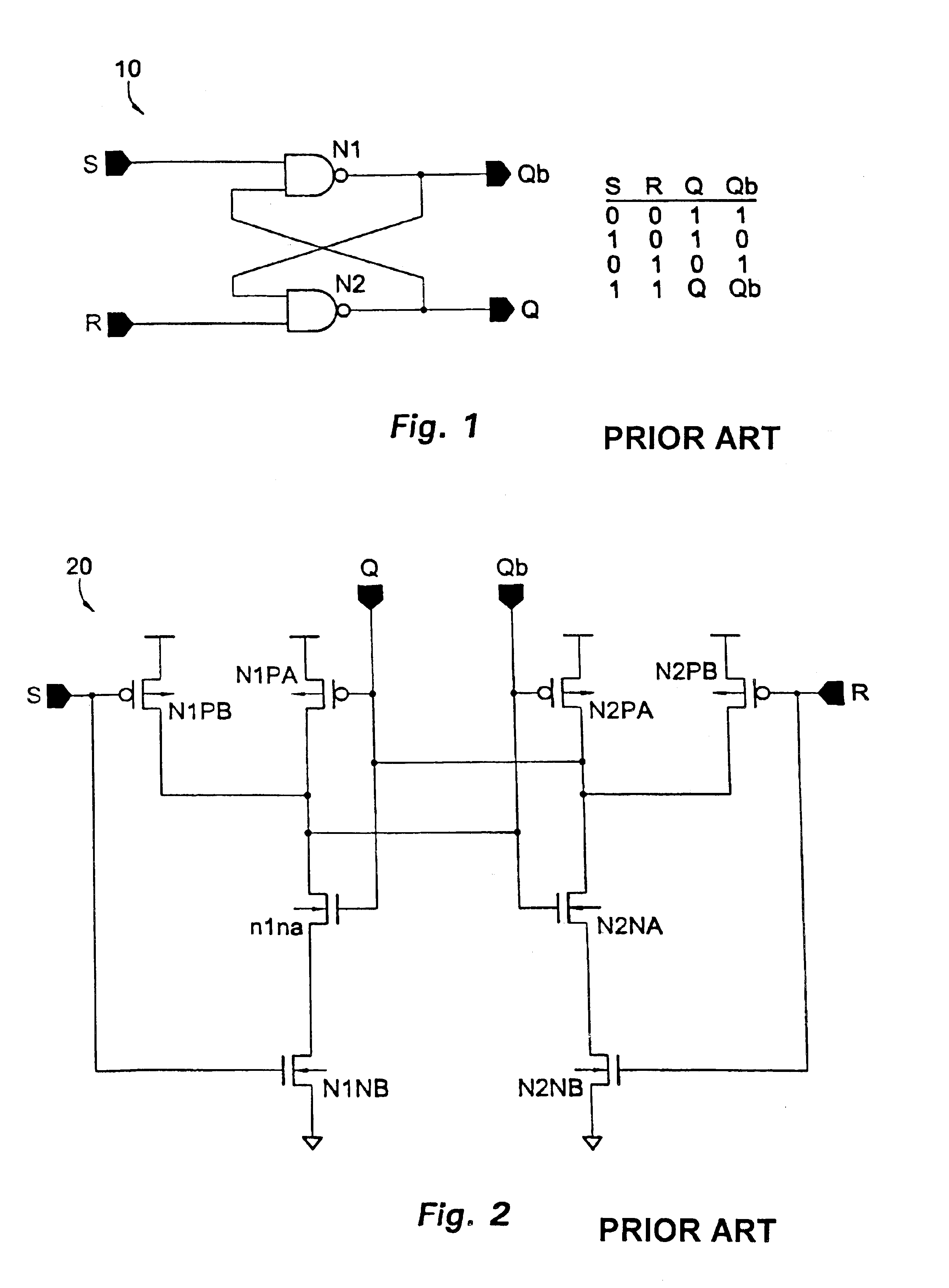

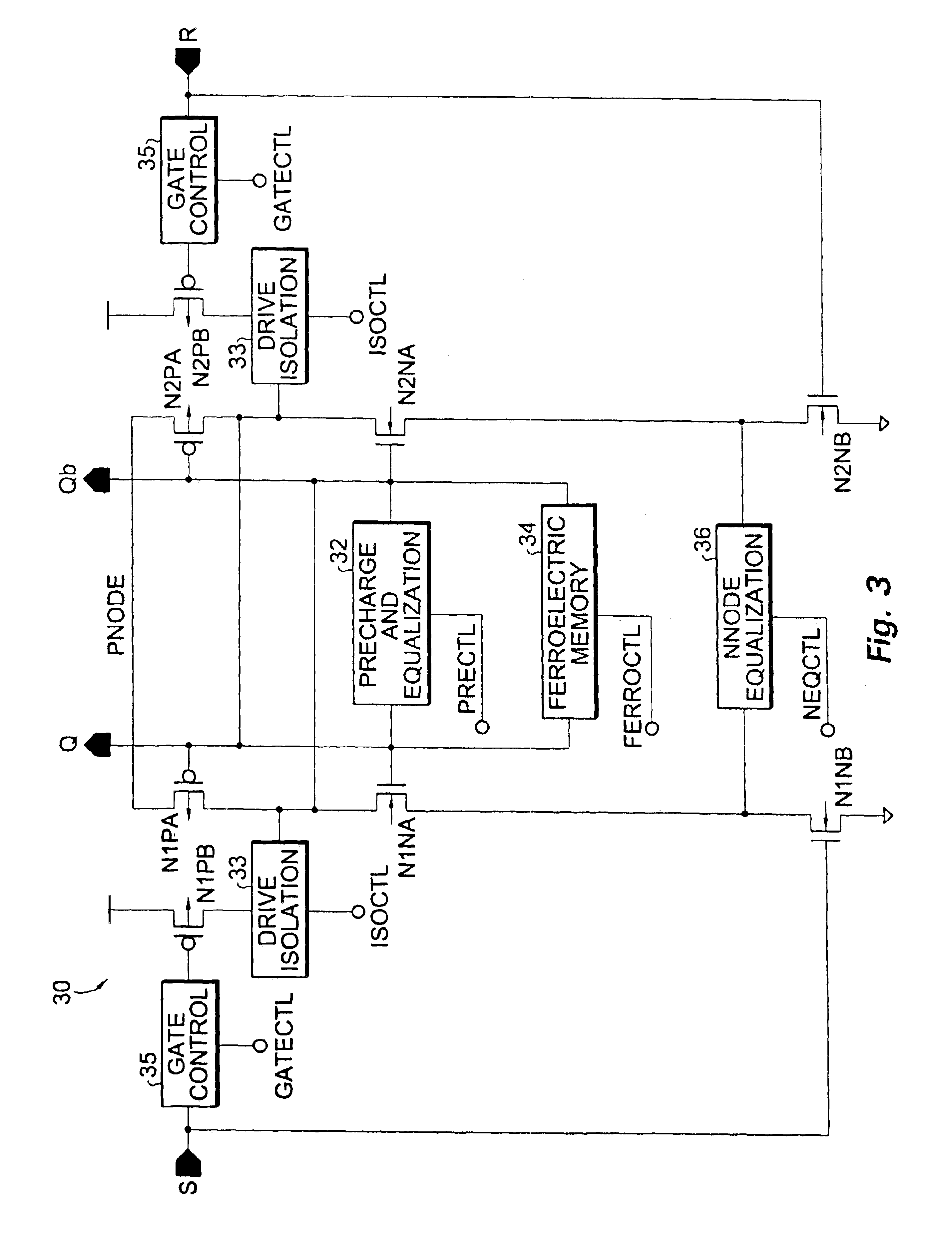

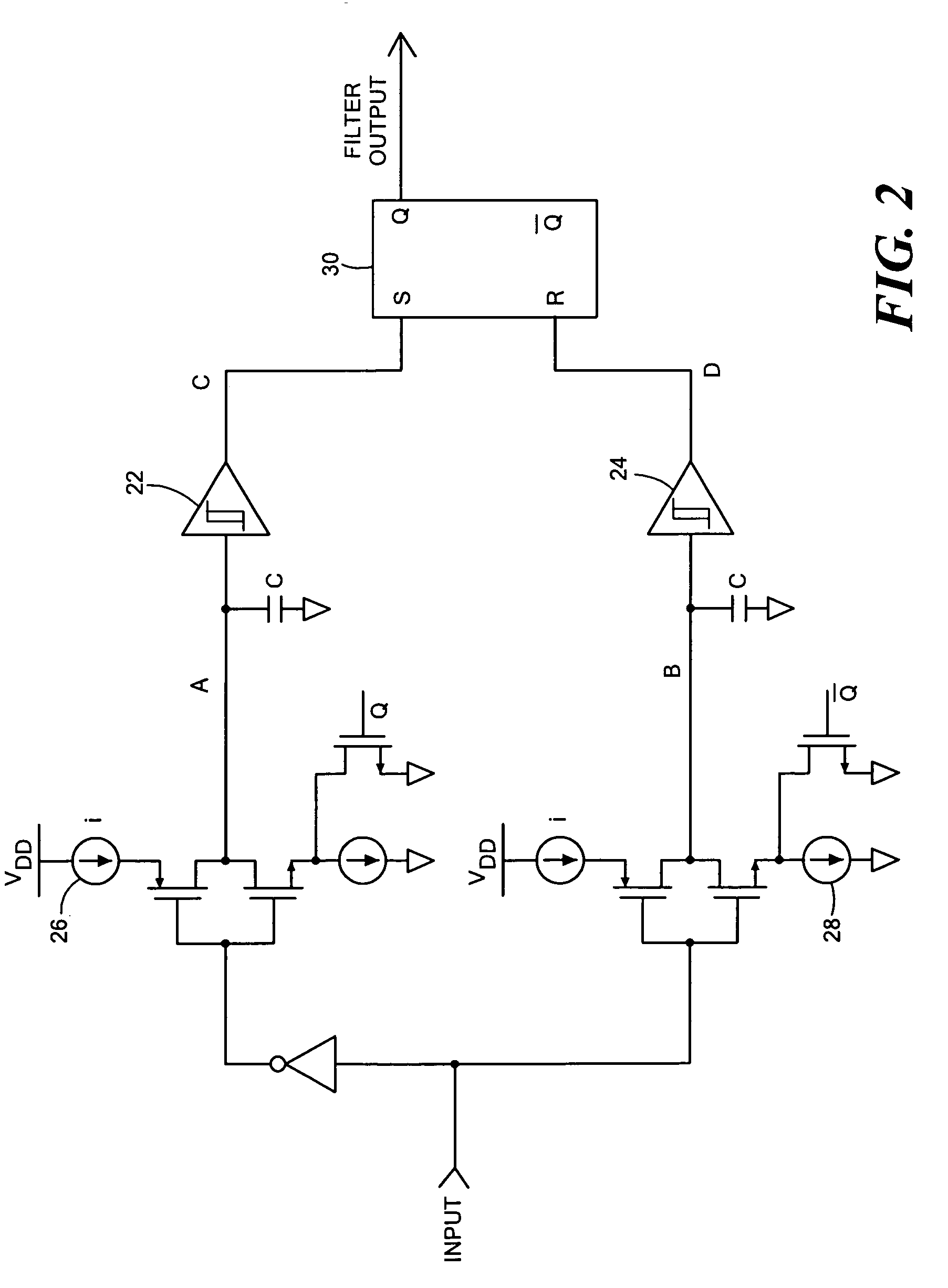

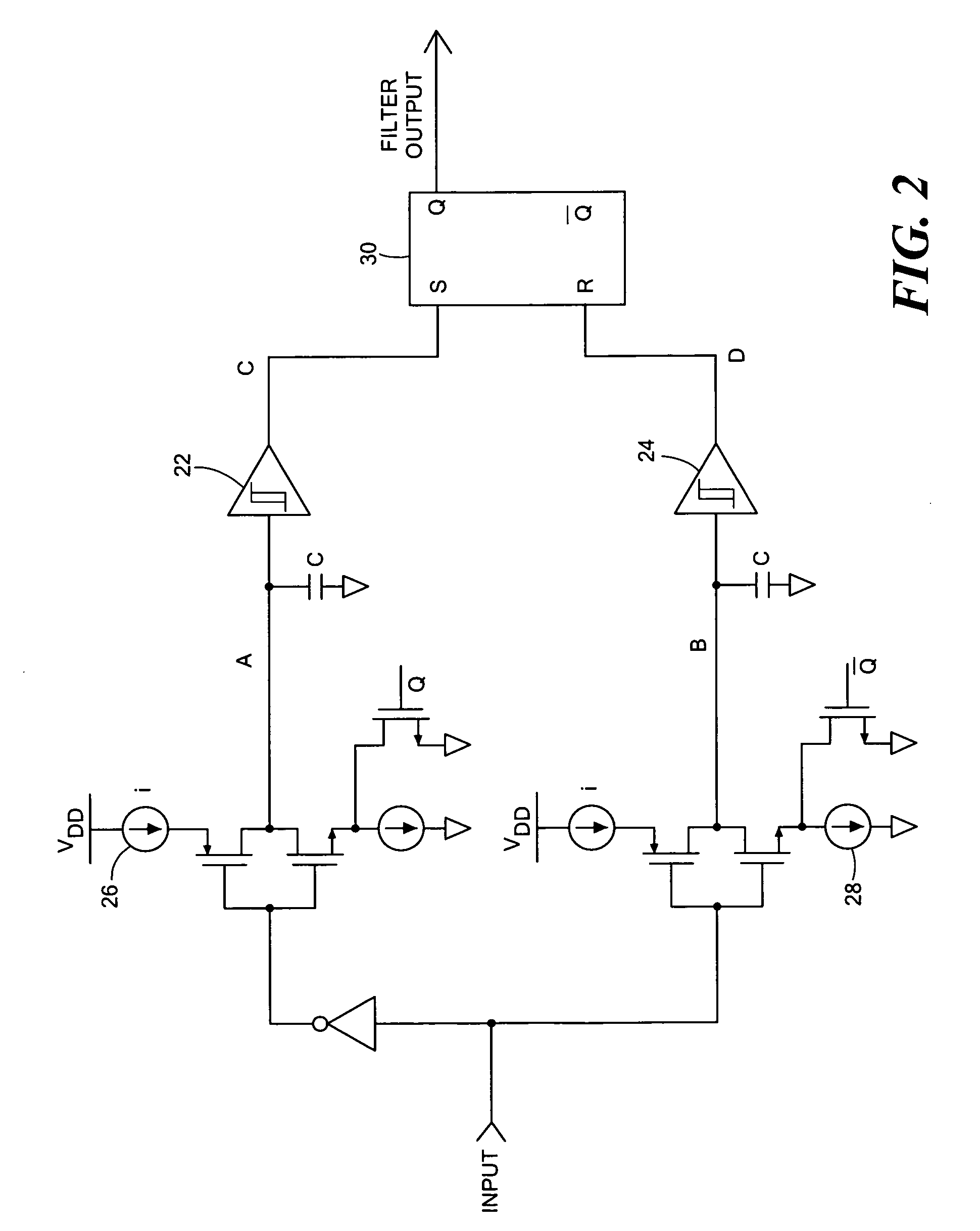

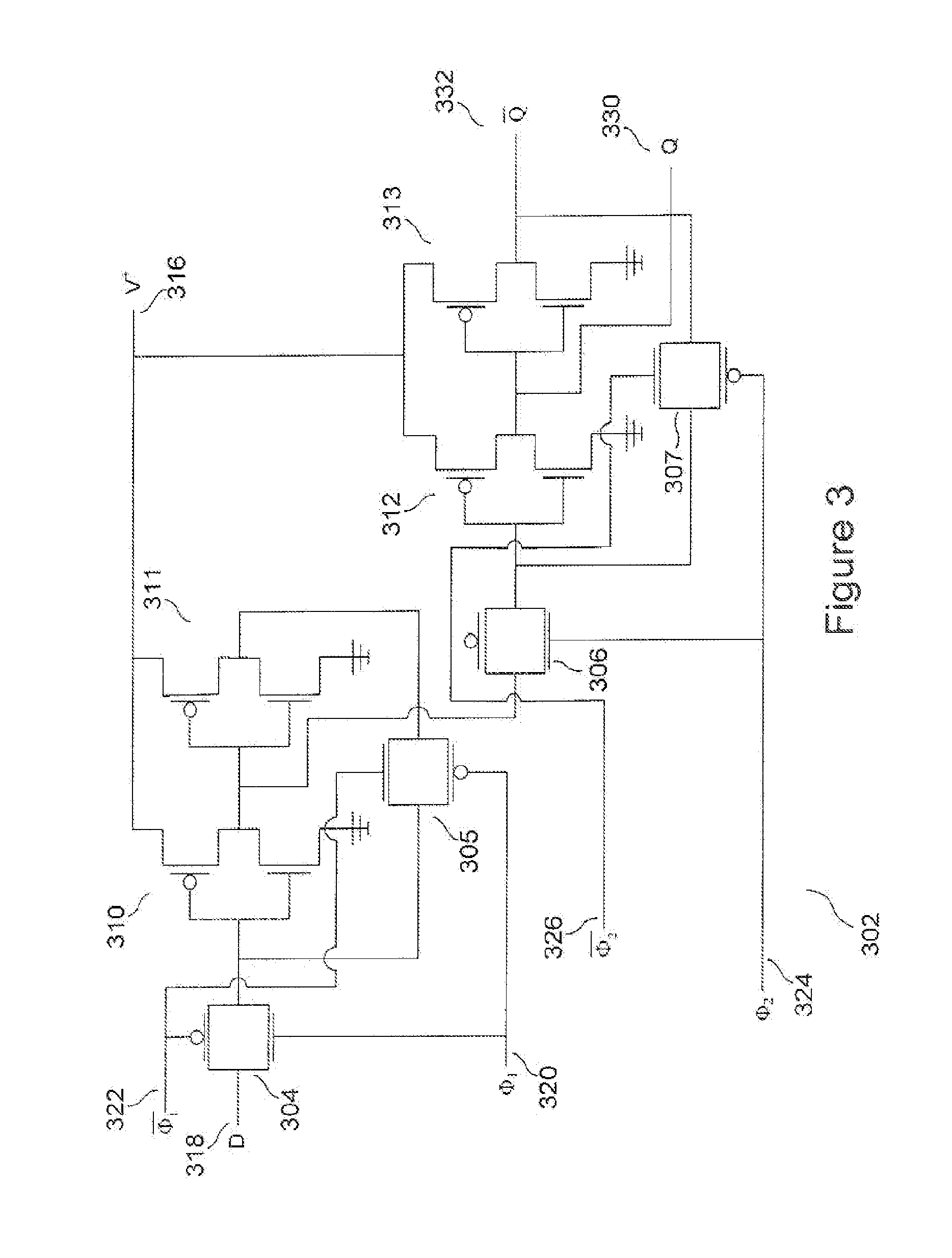

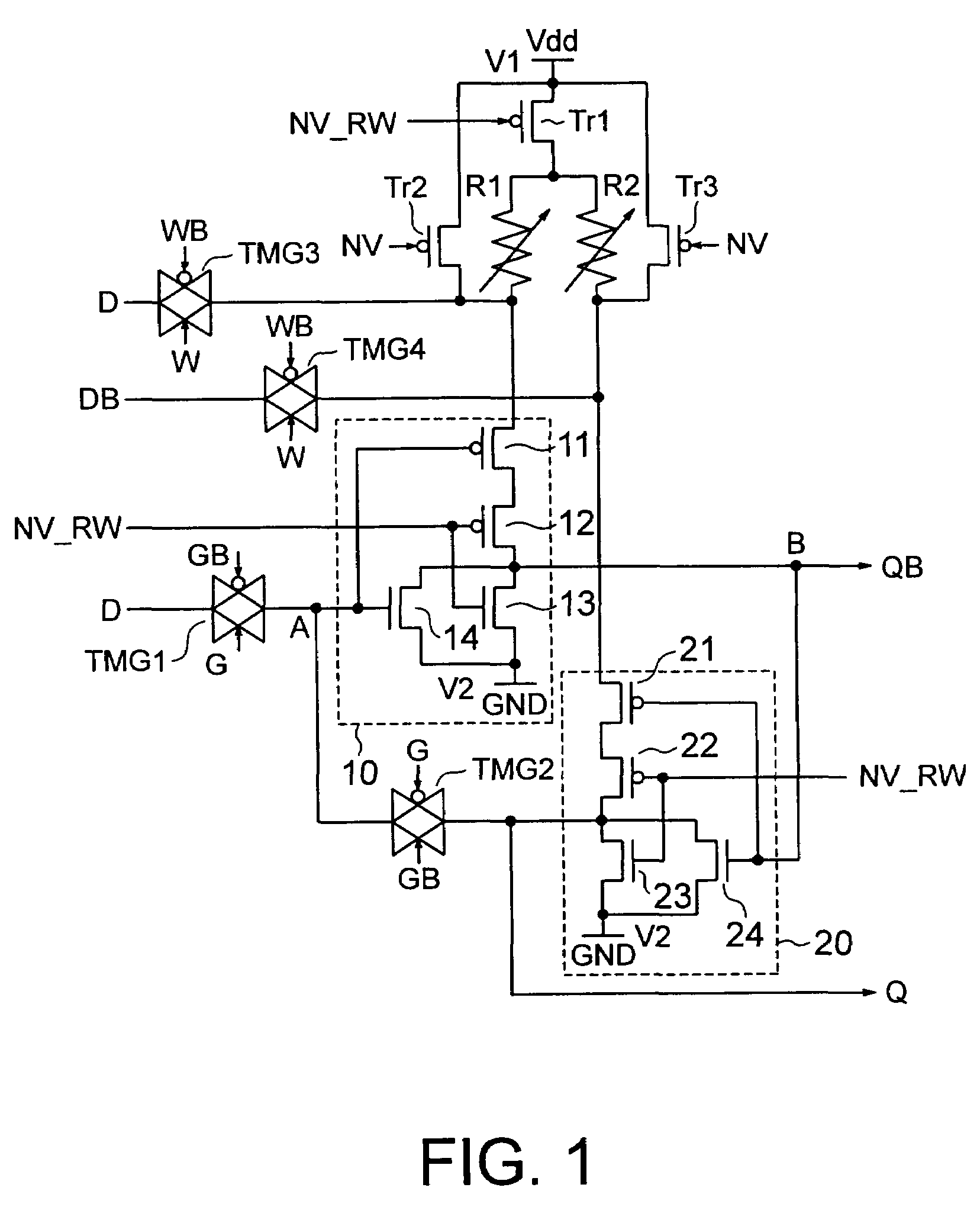

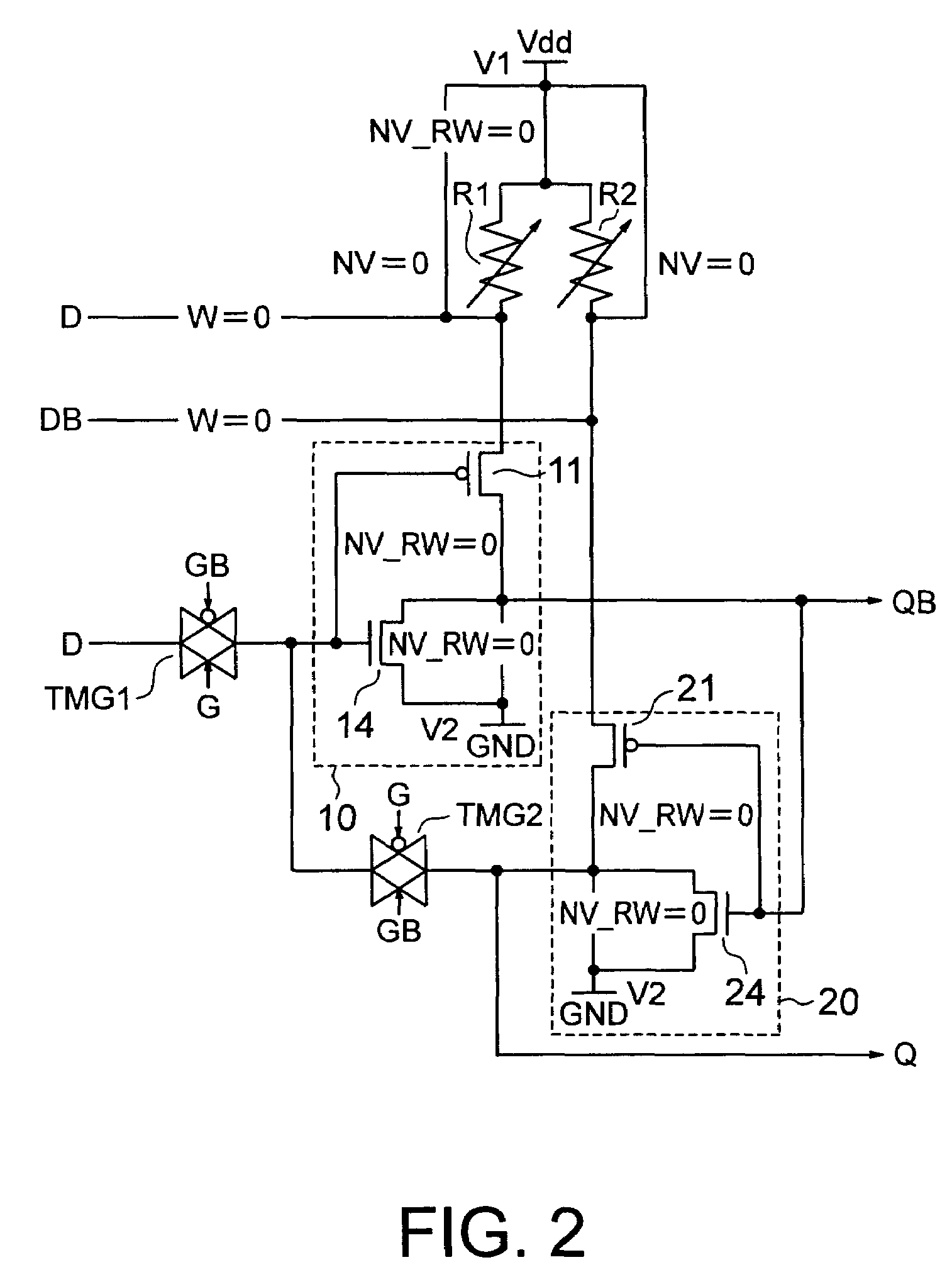

Ferroelectric non-volatile logic elements

InactiveUS6894549B2Easy translationImprove performanceTransistorPulse generation by non-linear magnetic/dielectric devicesShift registerAudio power amplifier

Various logic elements such as SR flip-flops, JK flip-flops, D-type flip-flops, master-slave flip-flops, parallel and serial shift registers, and the like are converted into non-volatile logic elements capable of retaining a current output logic state even though external power is removed or interrupted through the strategic addition of ferroelectric capacitors and supporting circuitry. In each case, the building blocks of a cross-coupled sense amplifier are identified within the logic element and the basic cell is modified and / or optimized for sensing performance.

Owner:MONTEREY RES LLC

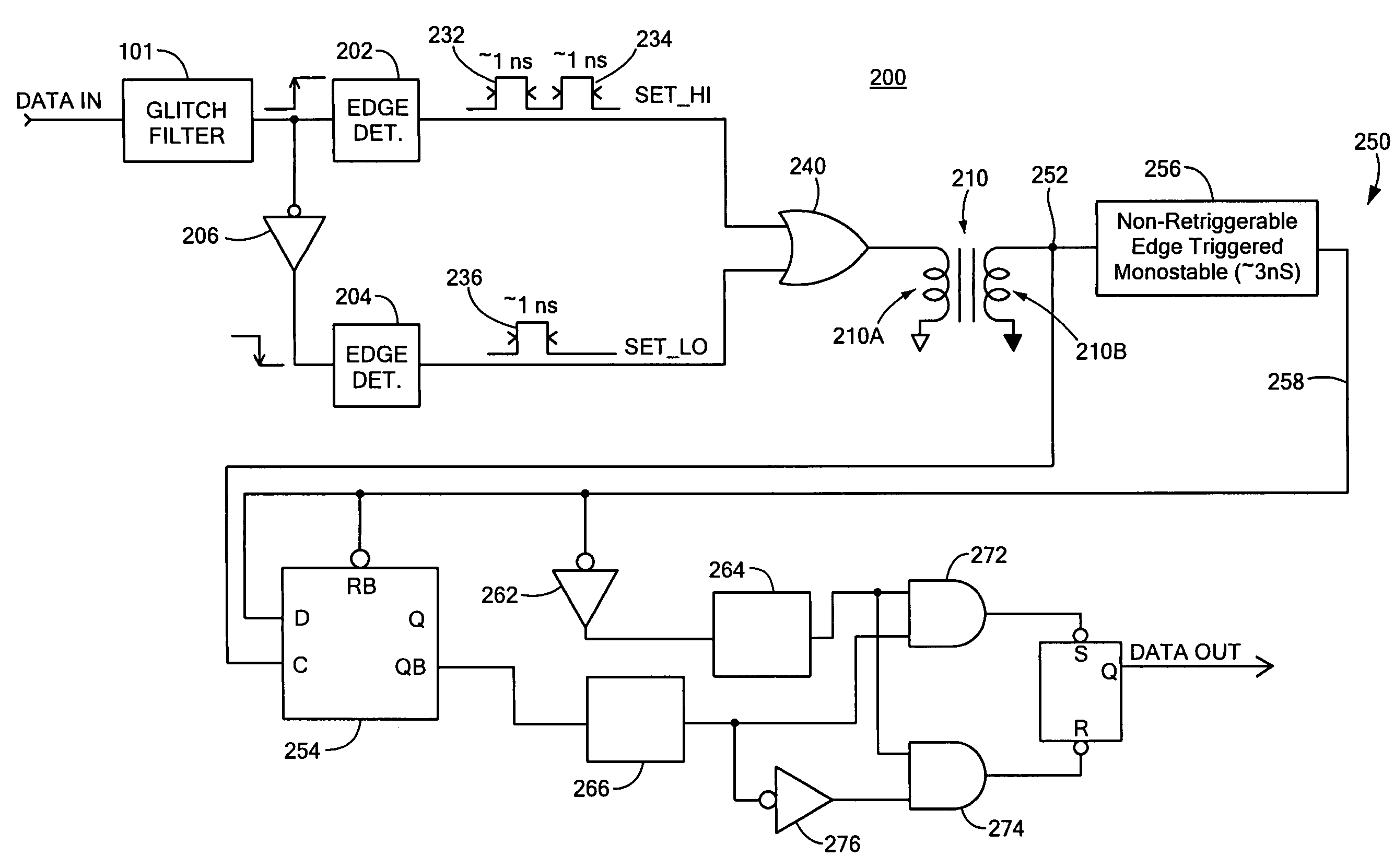

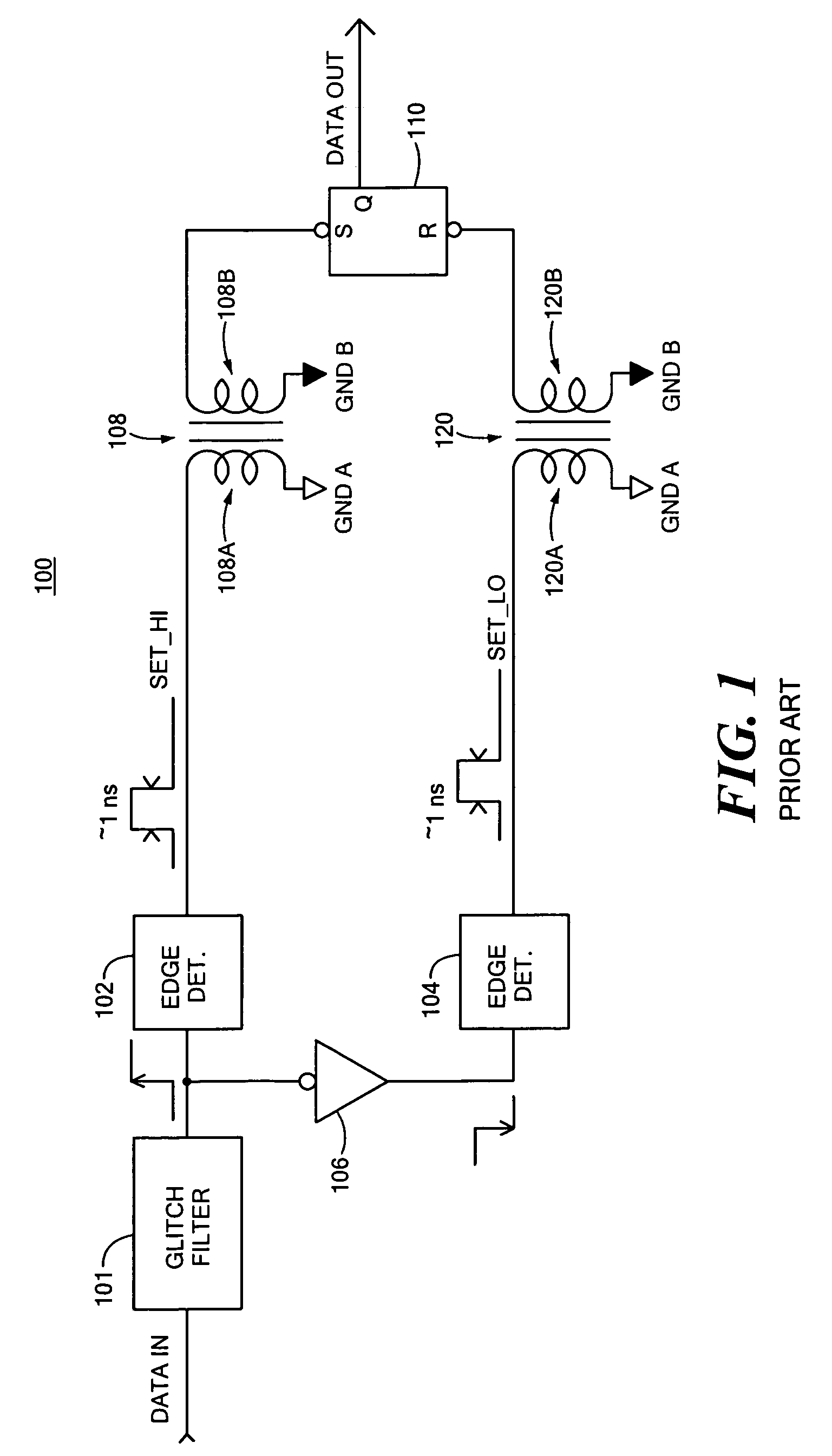

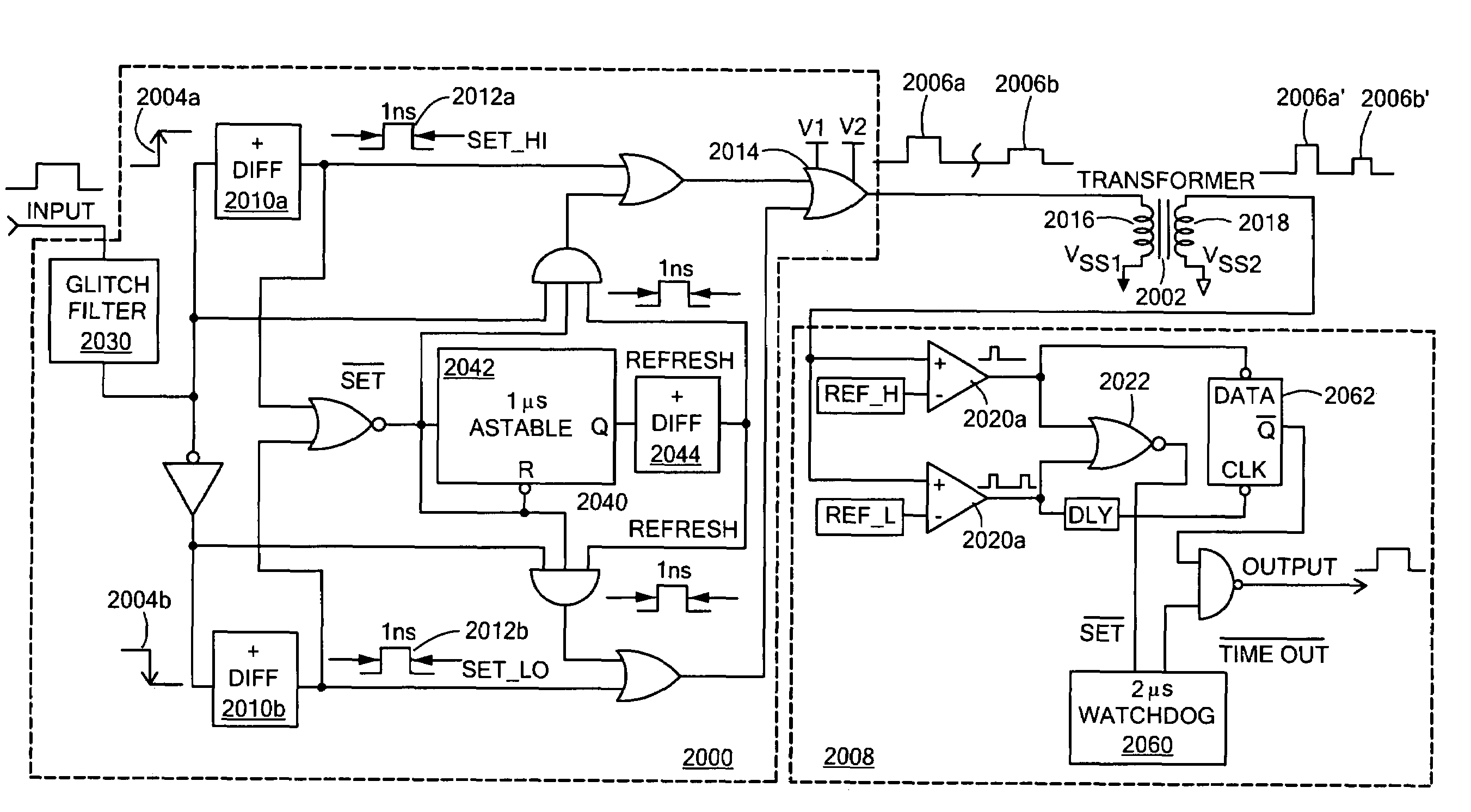

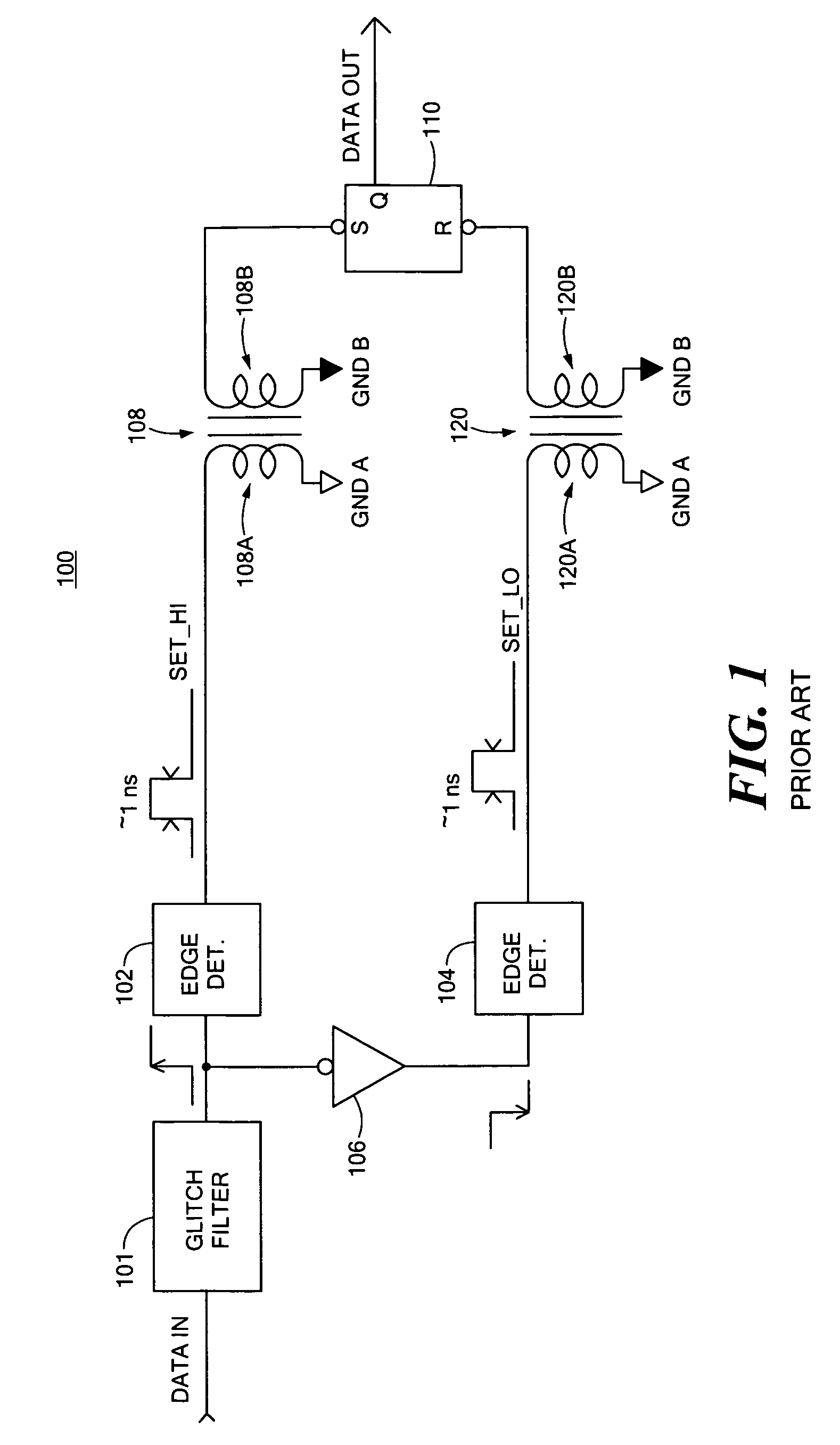

Signal isolators using micro-transformers

ActiveUS7075329B2Reliability increasing modificationsSemiconductor/solid-state device detailsTransformerEngineering

A logic signal isolator comprising a transformer having a primary winding and a secondary winding; a transmitter circuit which drives said primary winding in response to a received logic signal, such that in response to a first type of edge in the logic signal, a signal of a first predetermined type is supplied to the primary winding and in response to a second type of edge in the logic signal, a signal of a second predetermined type is supplied to said primary winding, the primary winding and the transmitter being referenced to a first ground; and the secondary winding being referenced to a second ground which is galvanically isolated from the first ground and said secondary winding supplying to a receiver circuit signals received in correspondence to the signals provided to the primary winding, the receiver reconstructing the received logic signal from the received signals.

Owner:ANALOG DEVICES INC

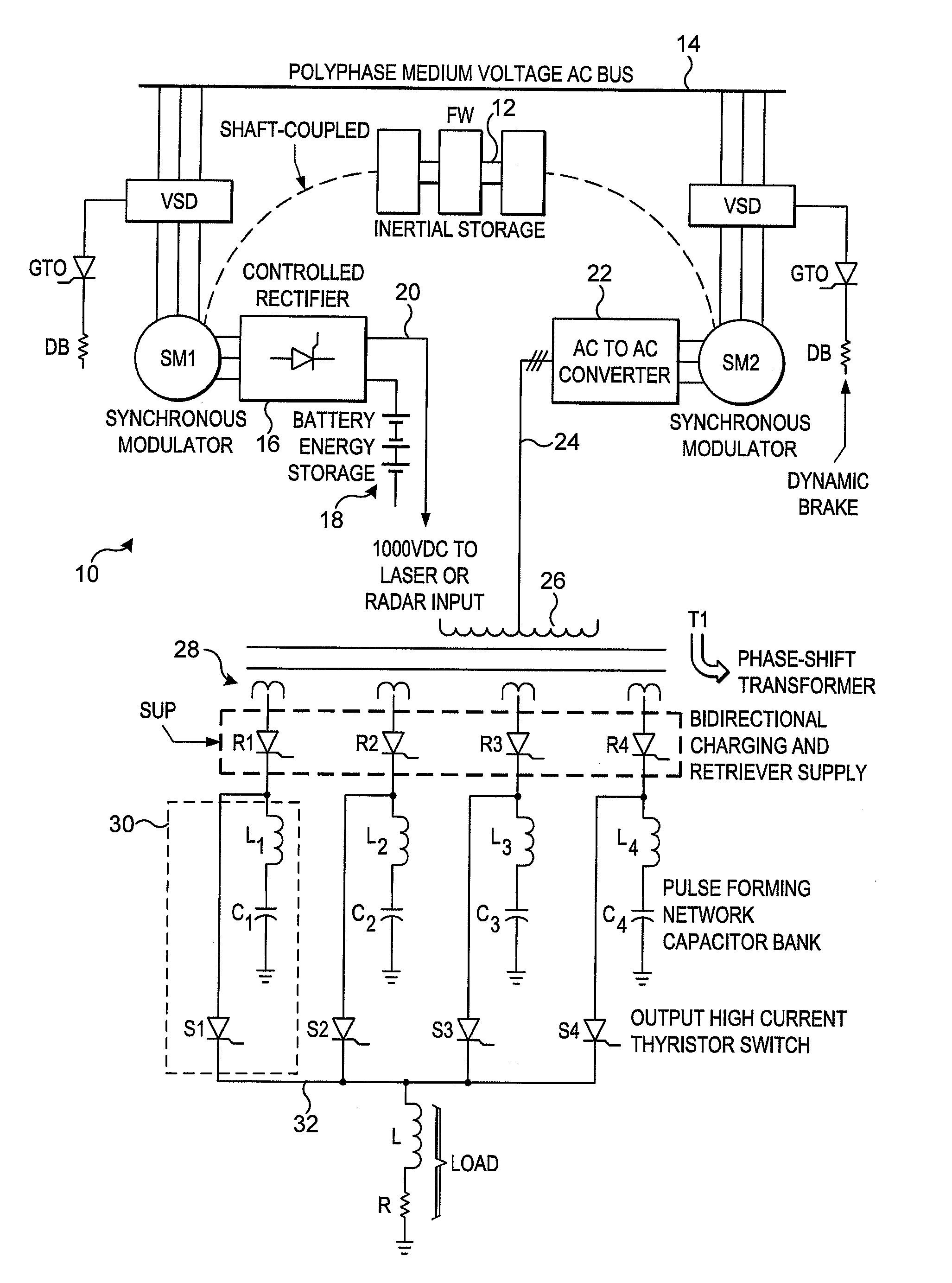

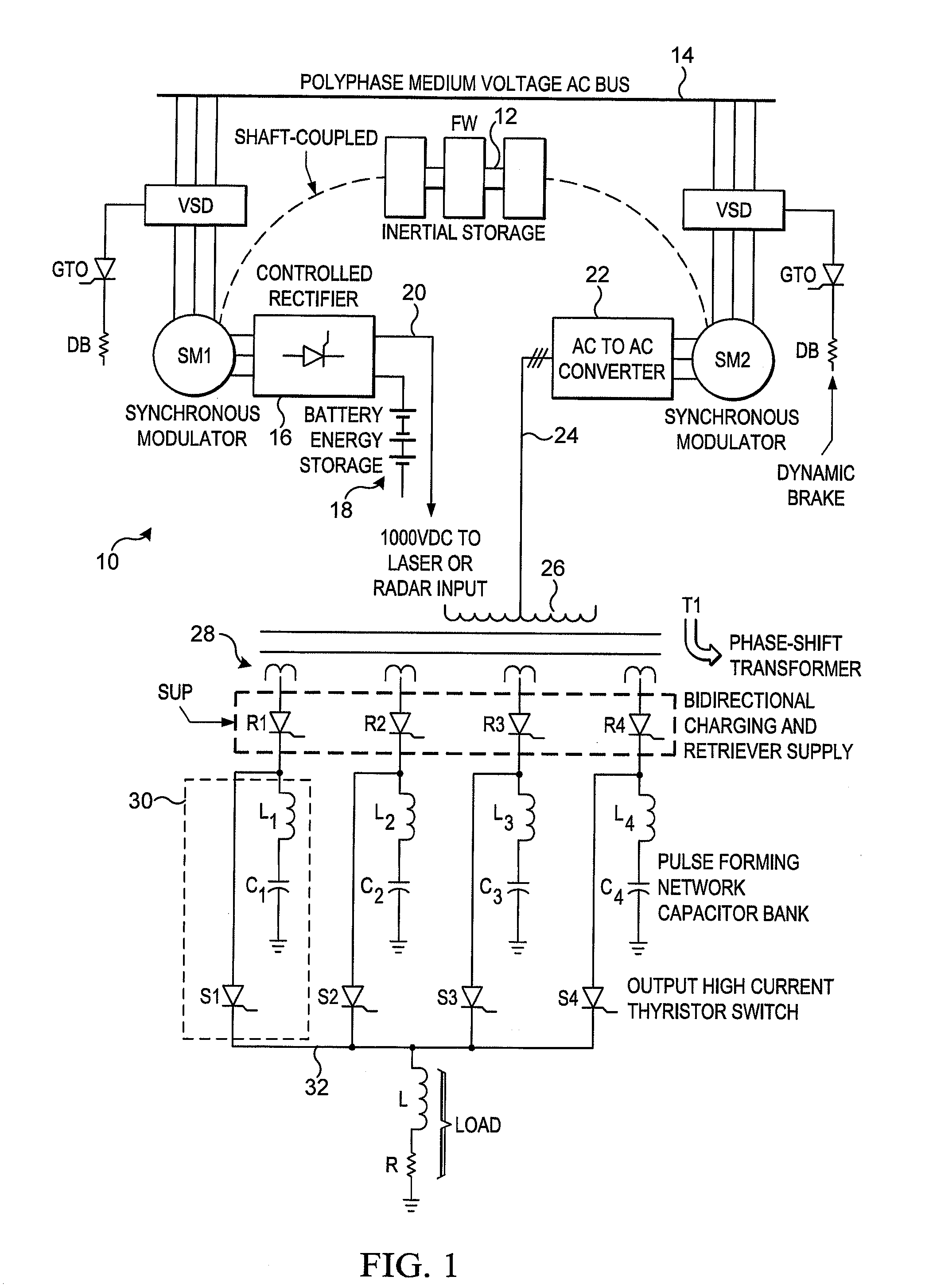

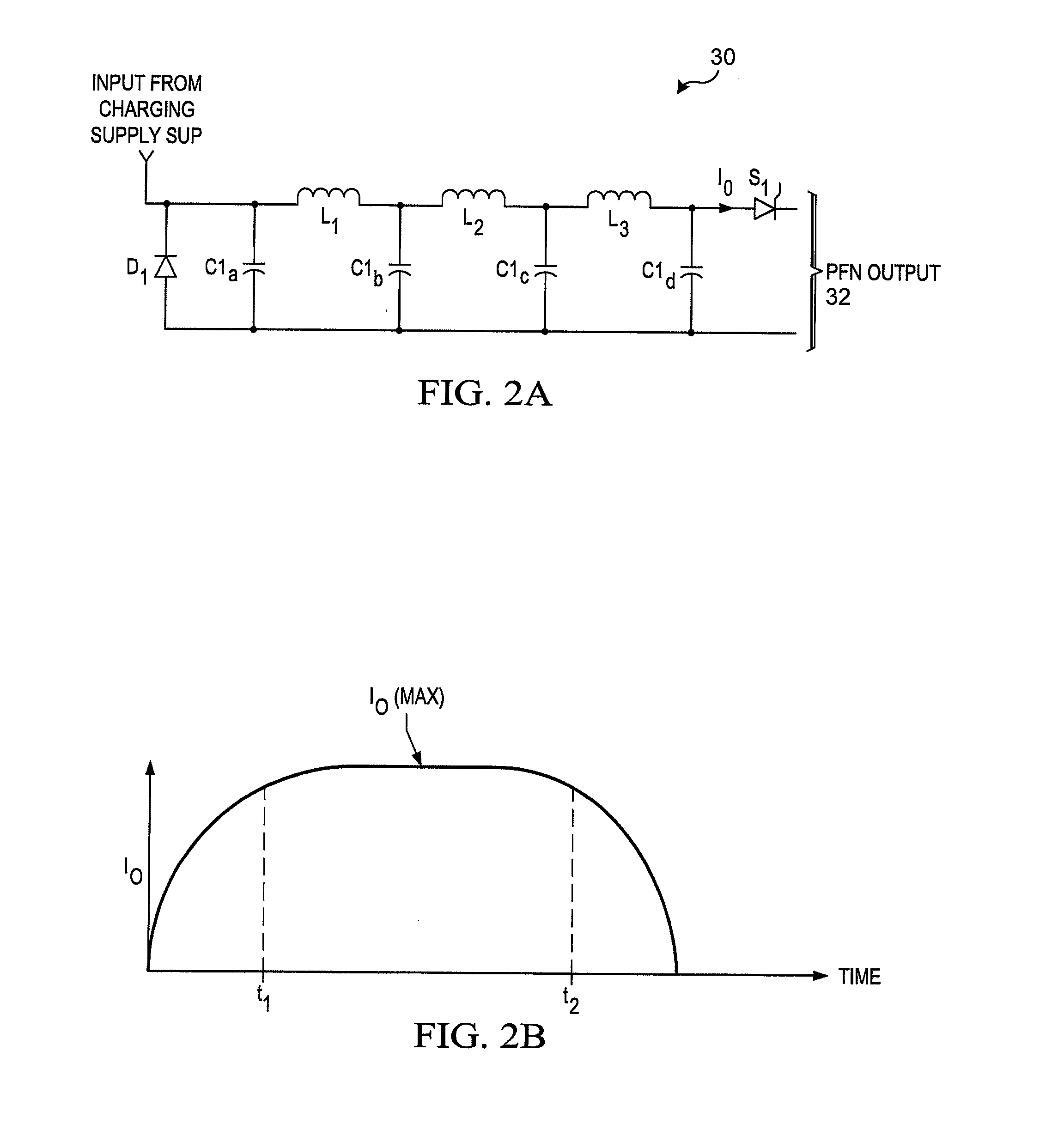

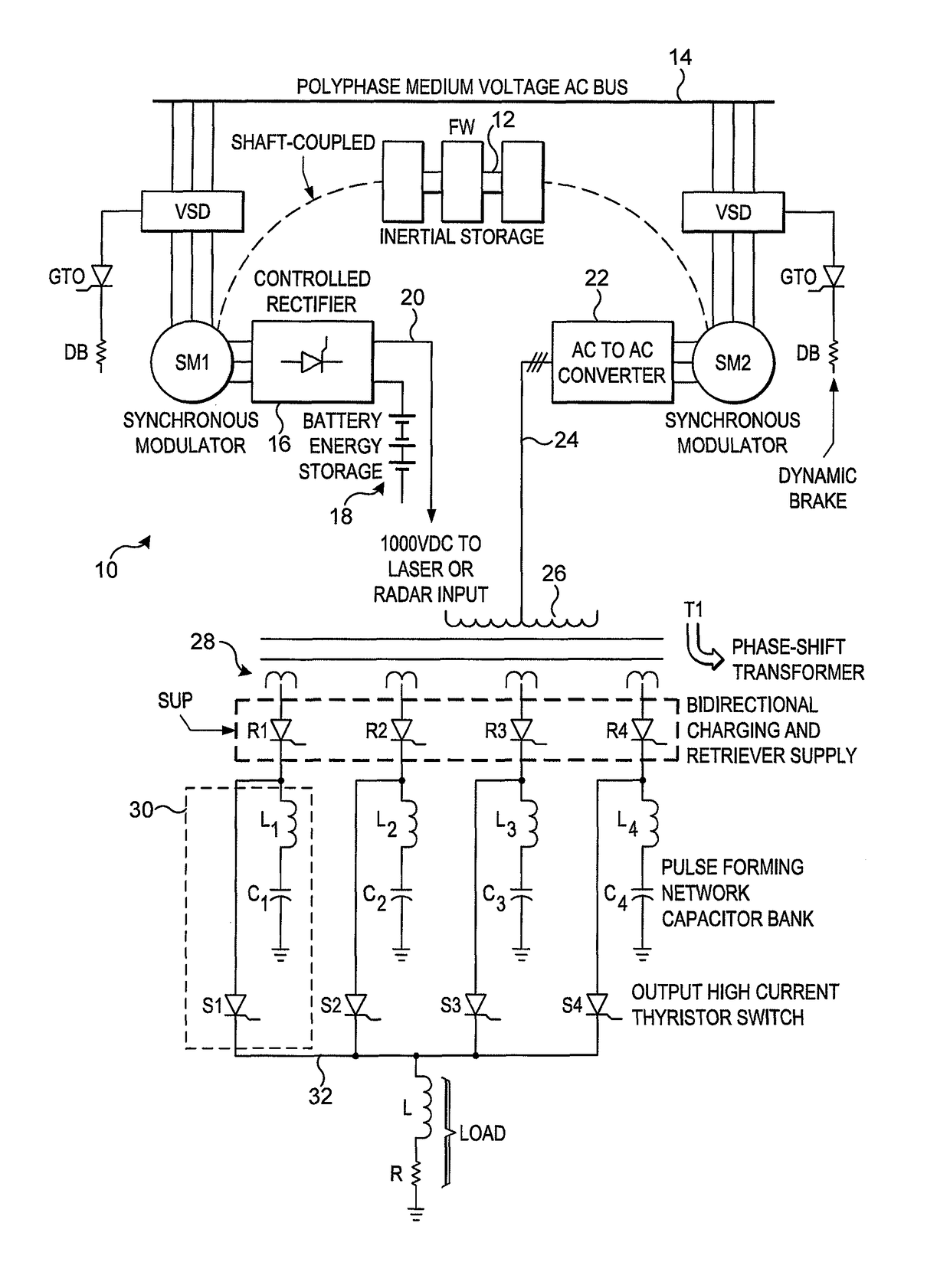

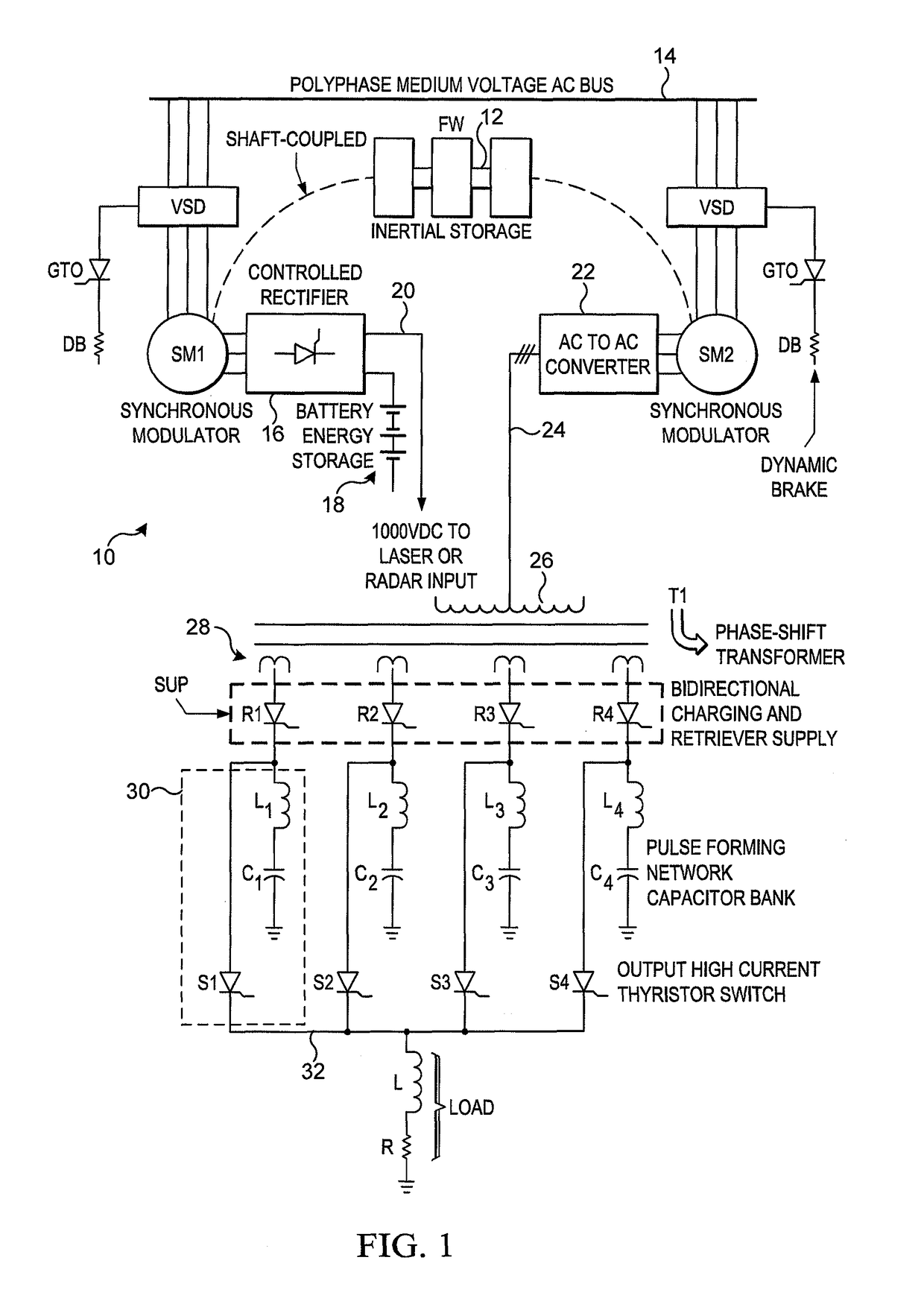

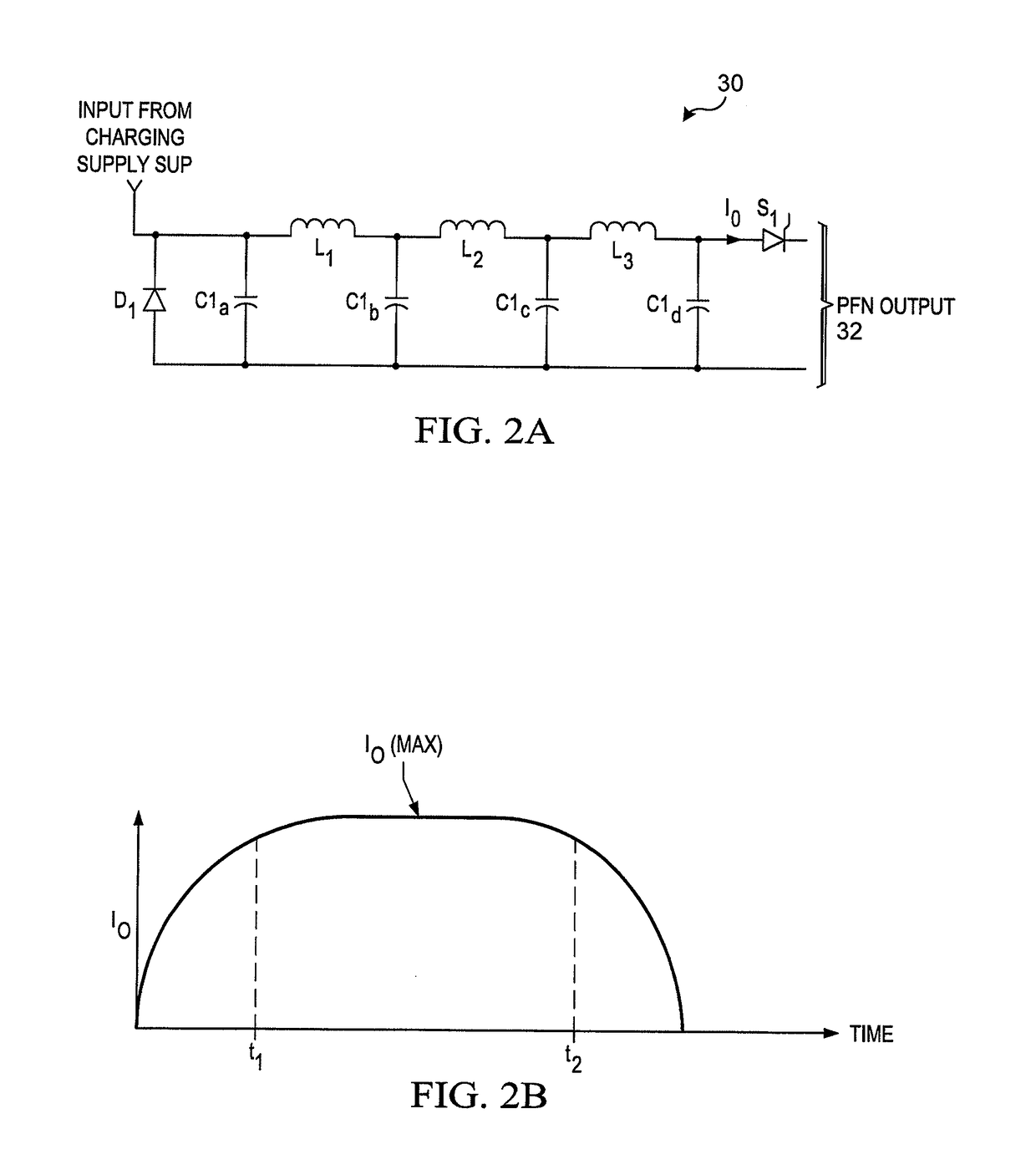

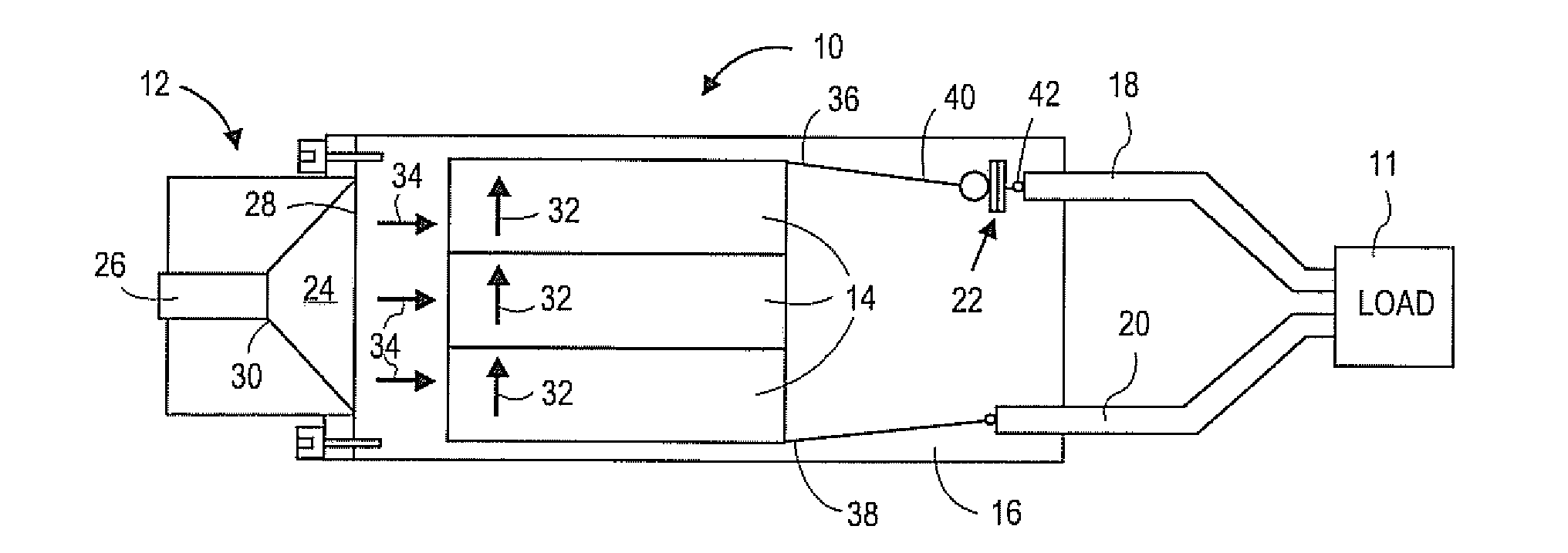

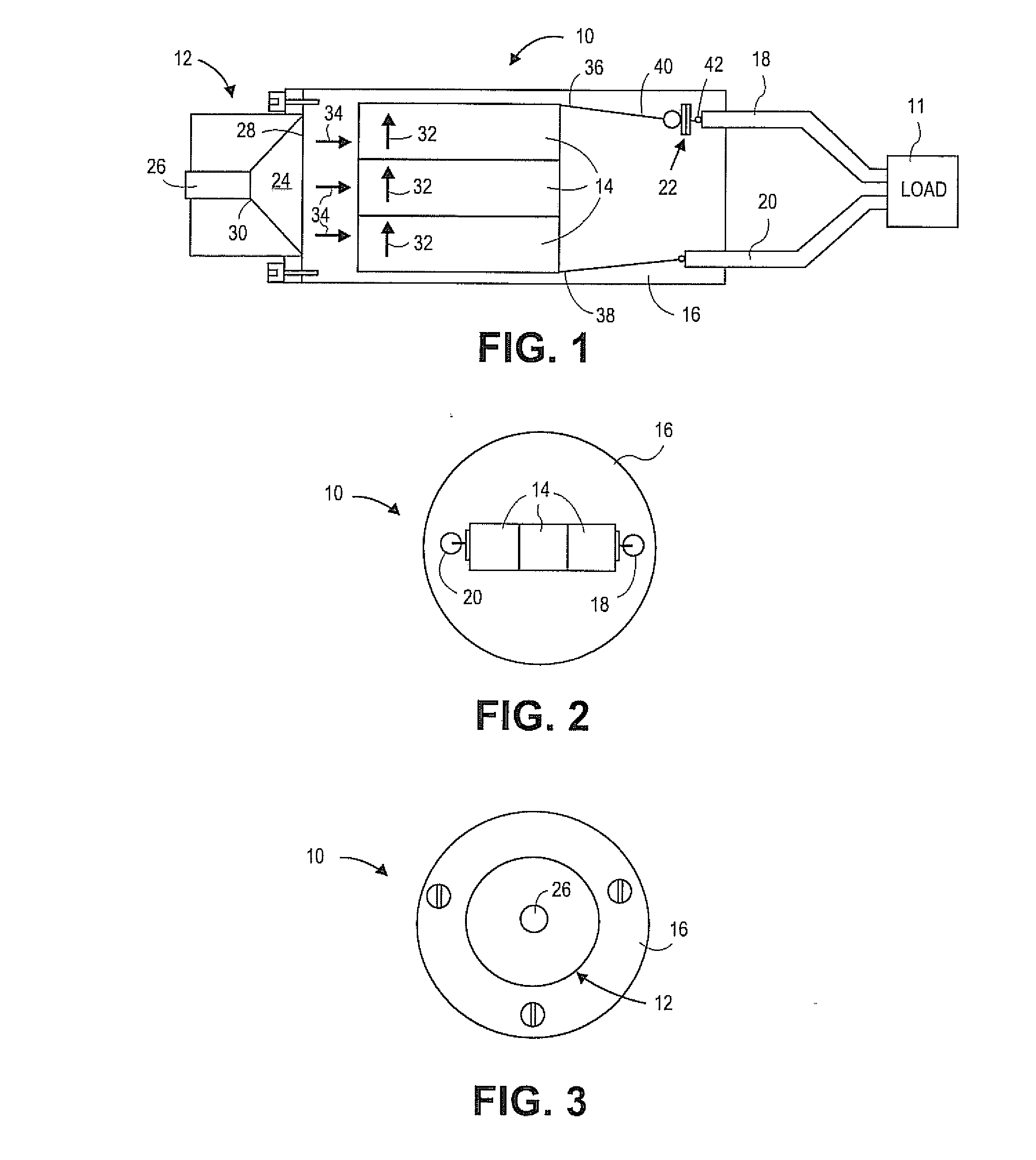

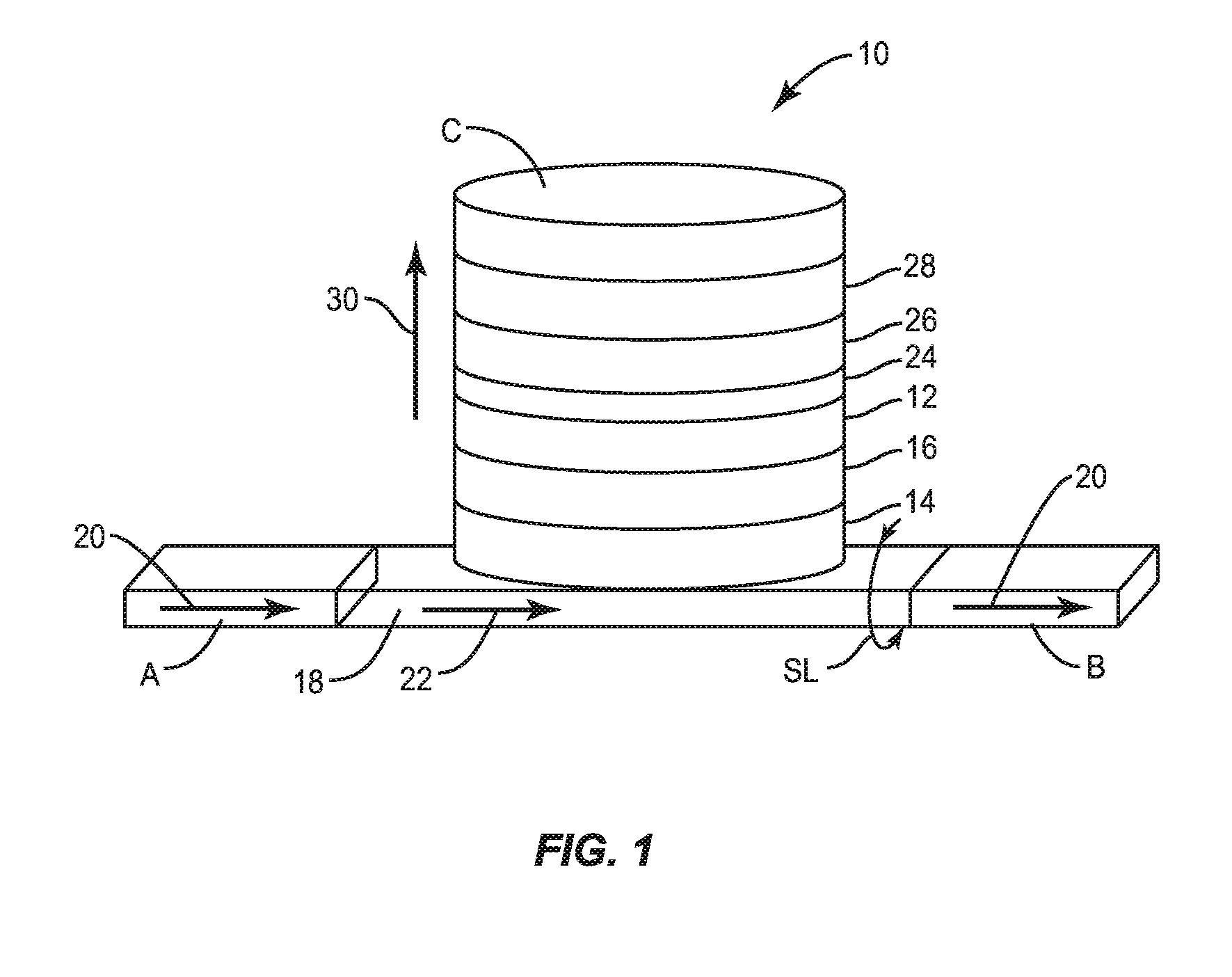

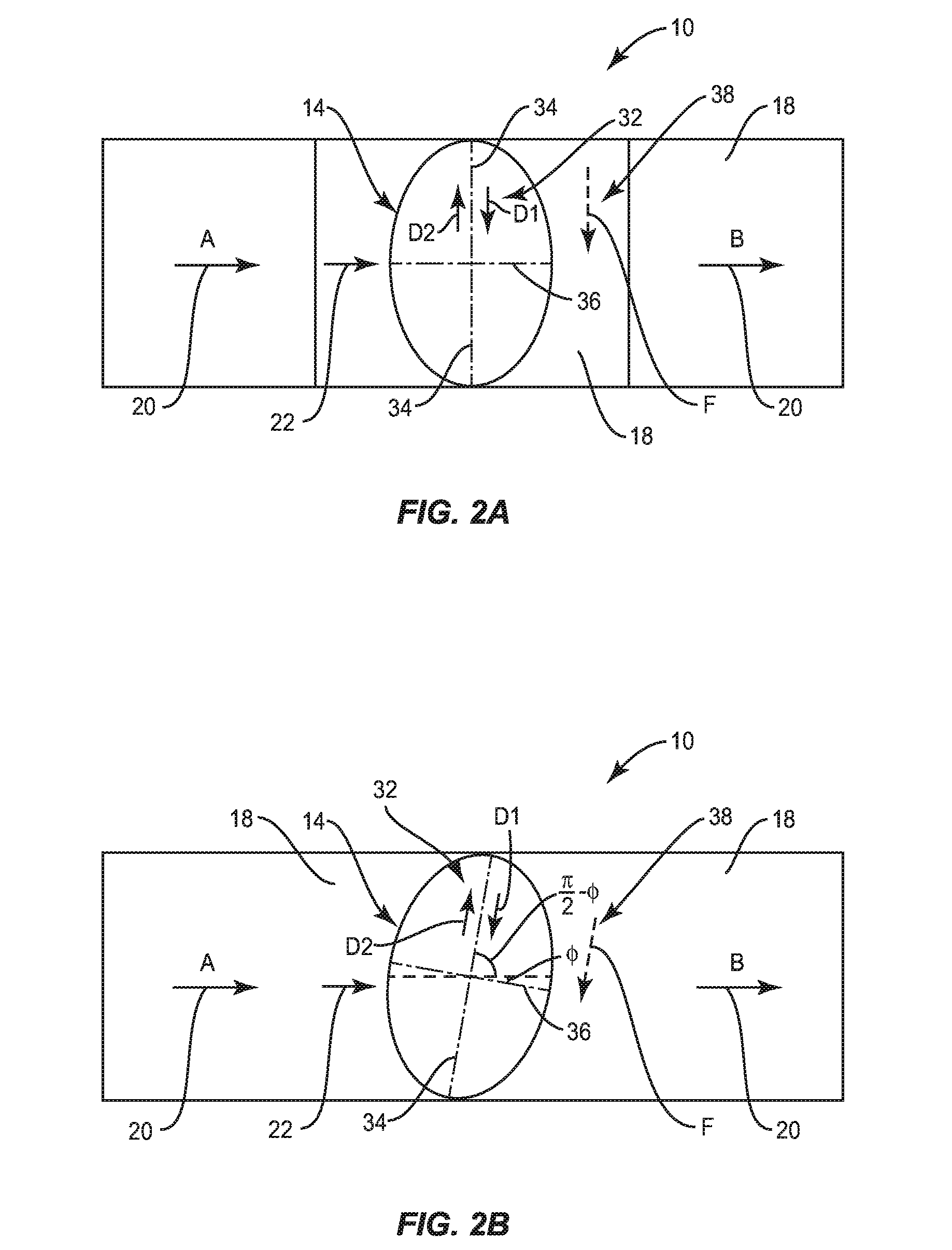

Method and apparatus for control of pulsed power in hybrid energy storage module

ActiveUS20160197600A1Pulse generation by non-linear magnetic/dielectric devicesLoad balancing in dc networkConductor CoilMultiple input

A hybrid energy storage system is configured to control pulsed power. A first dynamo-electric machine is coupled to an inertial energy storage device and has multiple input stator windings configured to accept input power from a source. A polyphase output stator winding is configured to deliver electric power having a first response time to a DC bus. A secondary energy storage system is coupled to the DC bus and is configured to convert its stored energy to electric power in a bidirectional manner. A second dynamo-electric machine has an input stator winding and at least one polyphase output stator winding coupled to a converter, the converter coupled to a DC output. A polyphase boost exciter is configured to derive energy from the DC bus and excite the second machine input stator winding, wherein the second machine is configured to be excited at a faster rate than the first response time of the first machine.

Owner:RAYTHEON CO

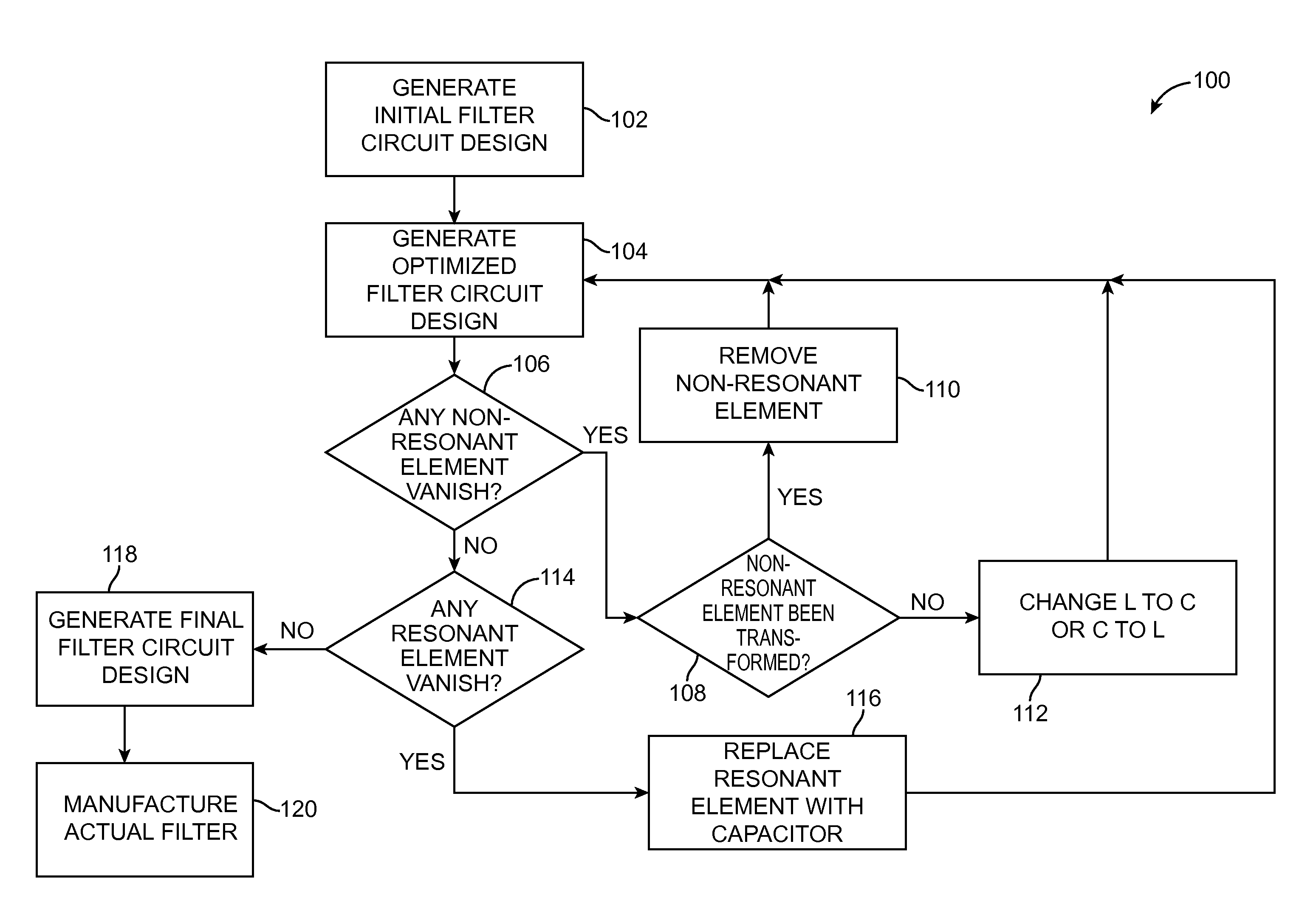

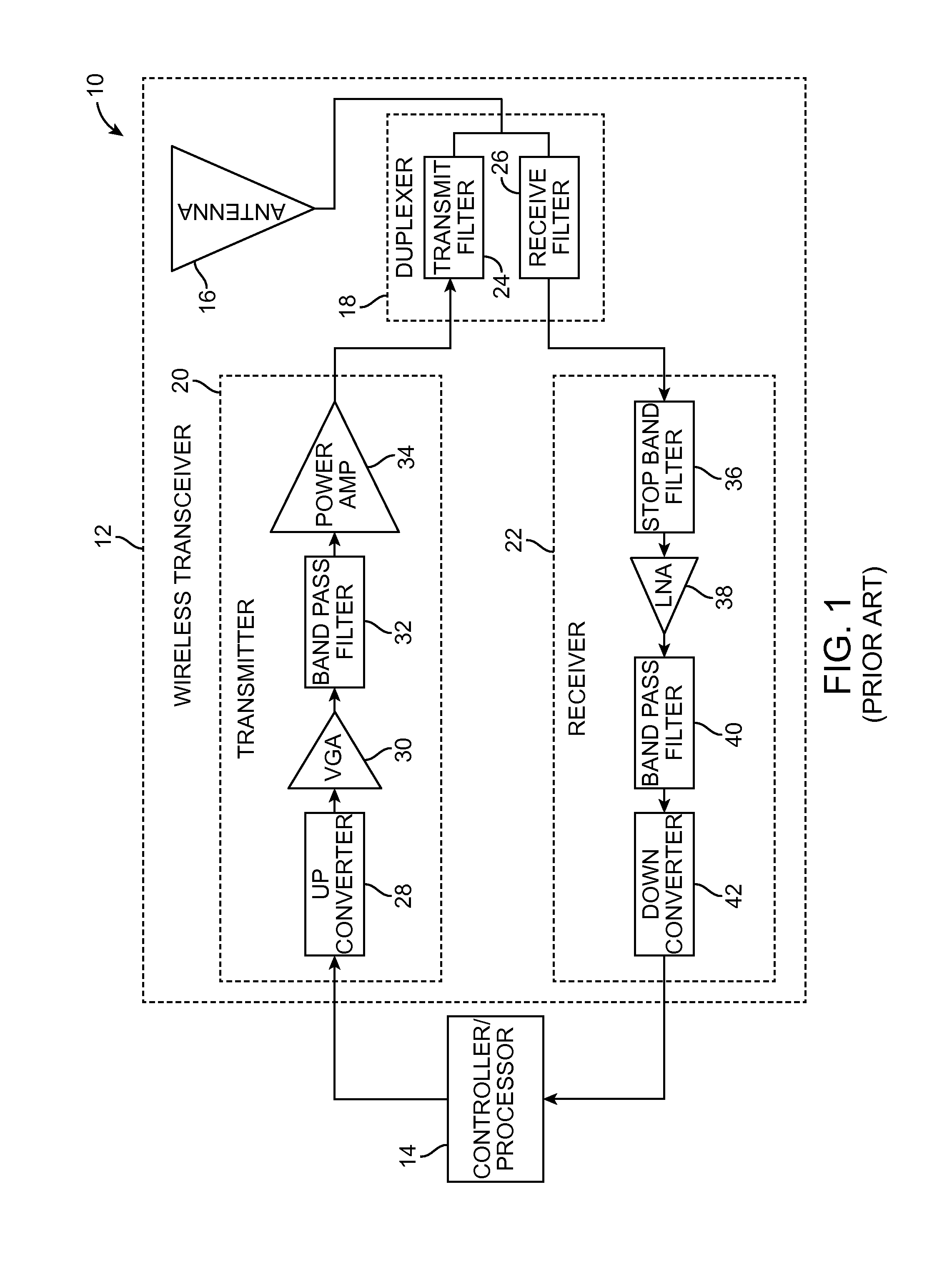

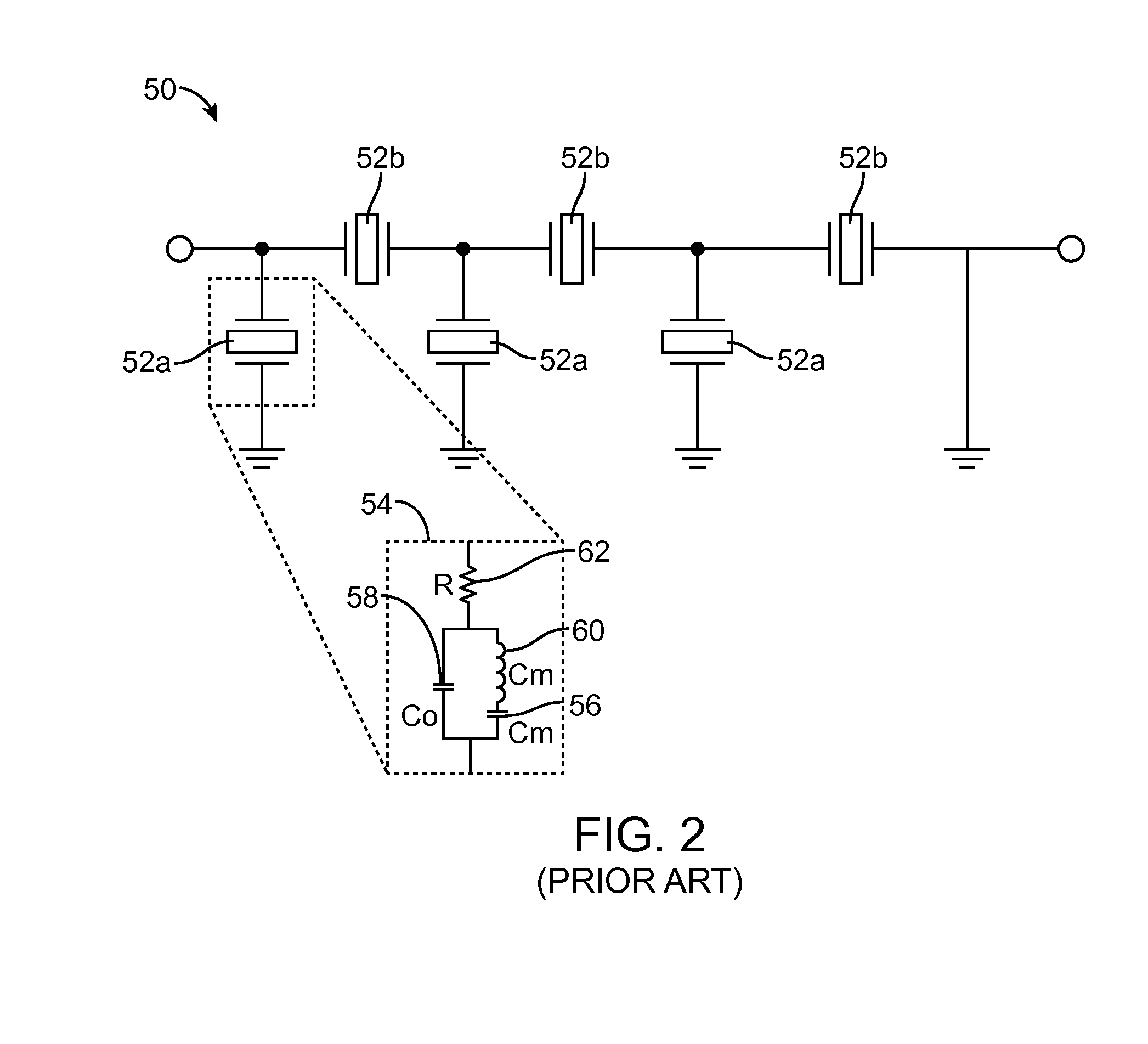

Element removal design in microwave filters

ActiveUS8751993B1Multiple-port networksPulse generation by non-linear magnetic/dielectric devicesGeneration processEngineering

A method of designing a microwave filter using a computerized filter optimizer, comprises generating a filter circuit design in process (DIP) comprising a plurality of circuit elements having a plurality of resonant elements and one or more non-resonant elements, optimizing the DIP by inputting the DIP into the computerized filter optimizer, determining that one of the plurality of circuit elements in the DIP is insignificant, removing the one insignificant circuit element from the DIP, deriving a final filter circuit design from the DIP, and manufacturing the microwave filter based on the final filter circuit design.

Owner:MURATA MFG CO LTD

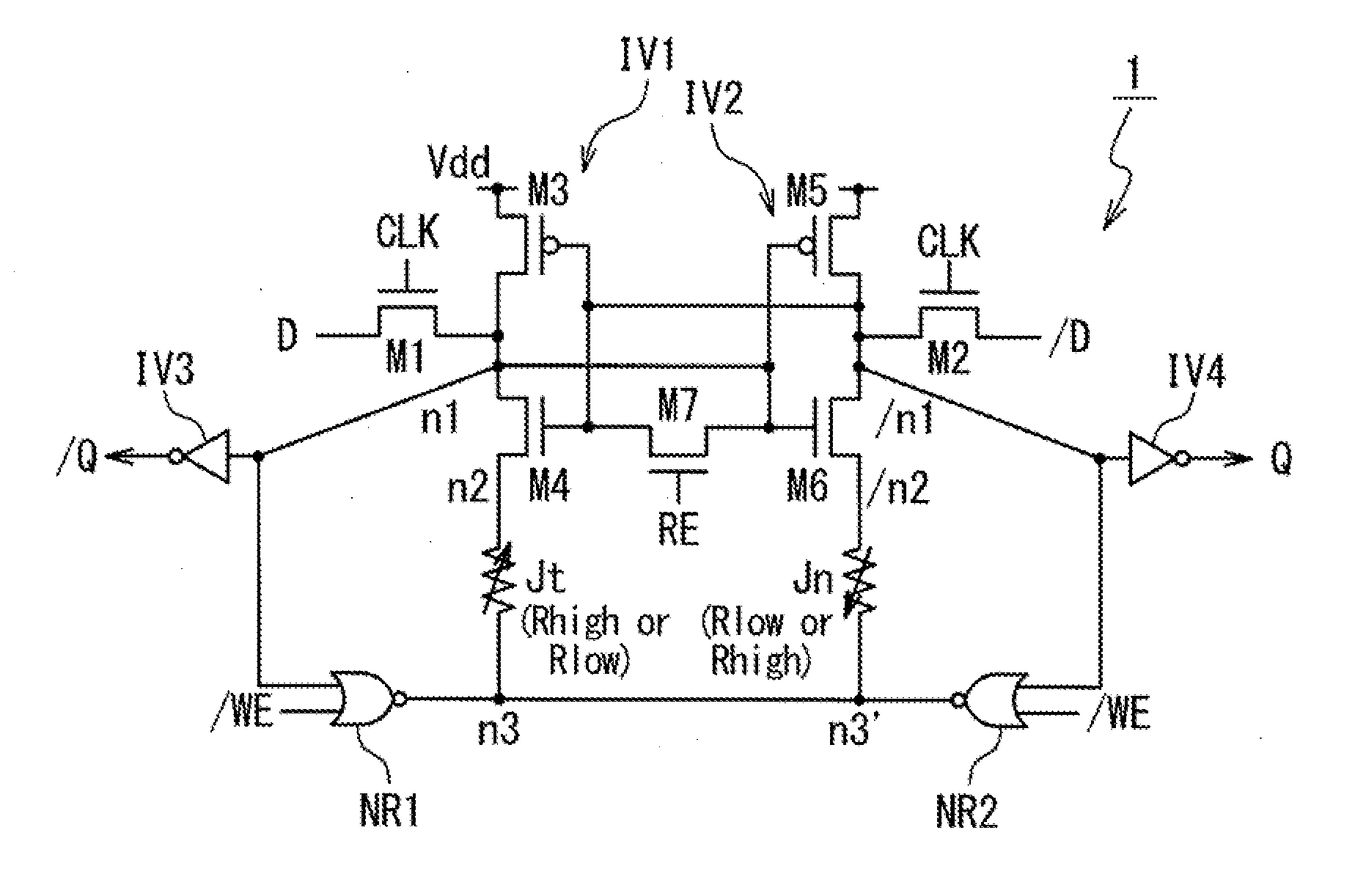

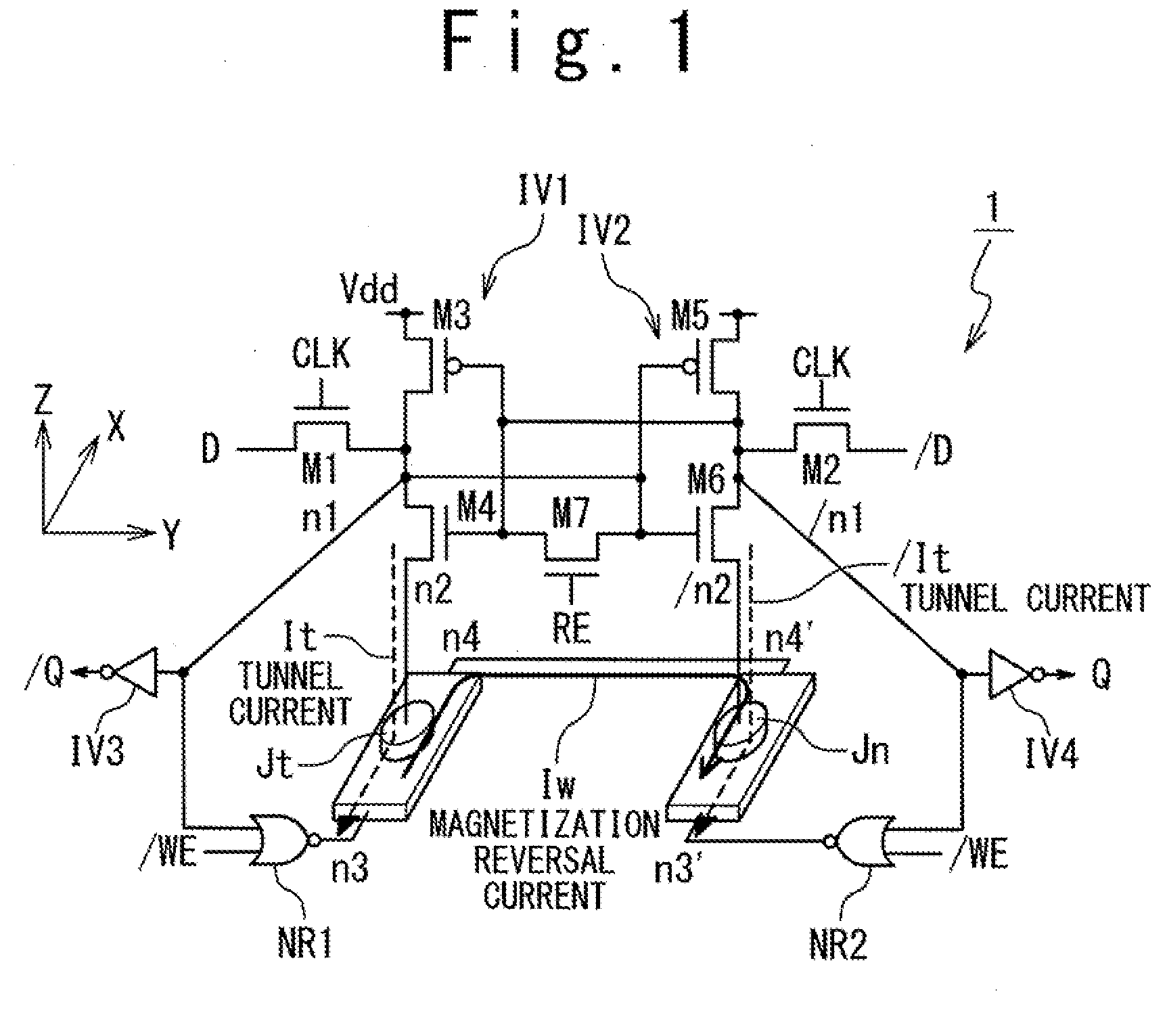

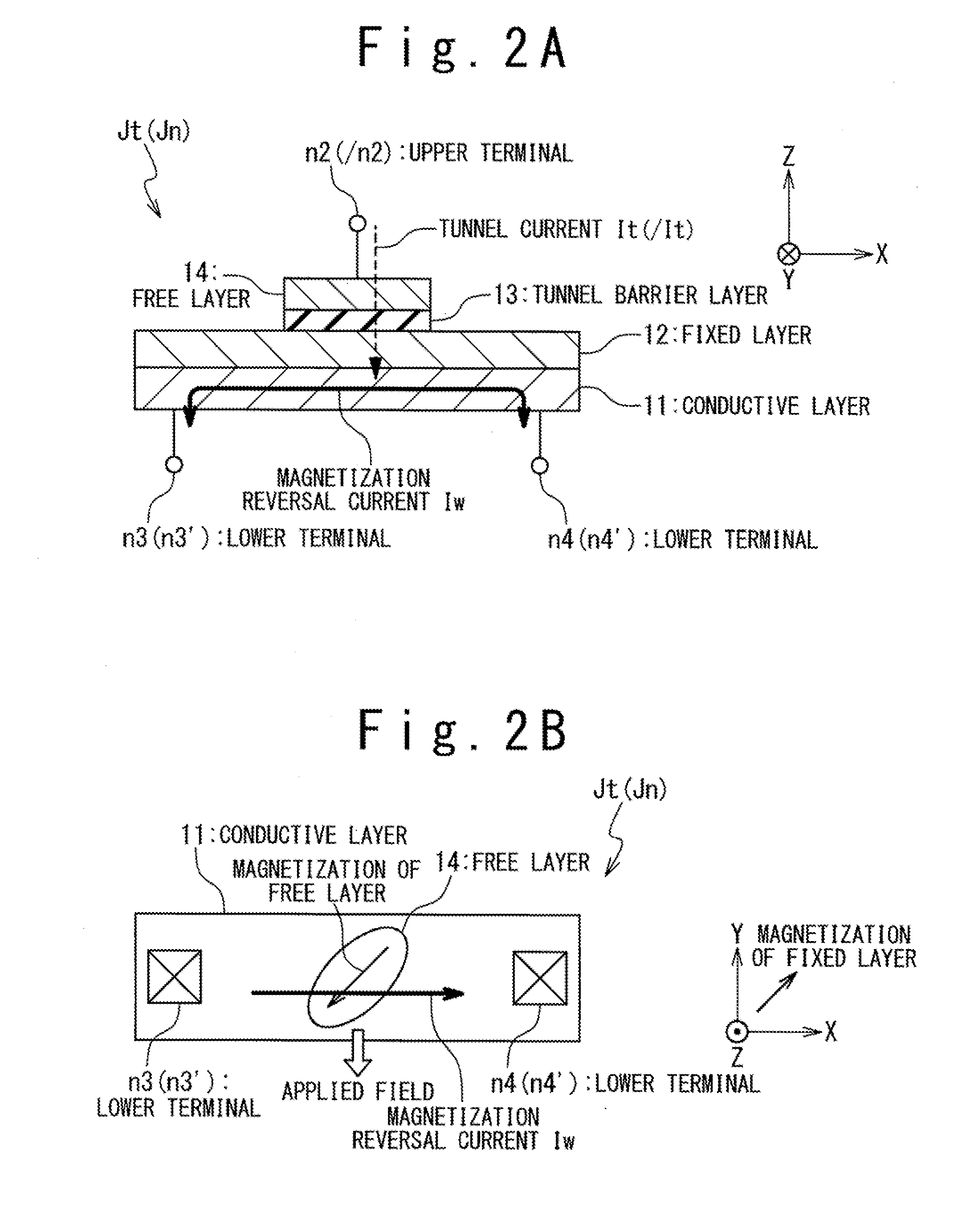

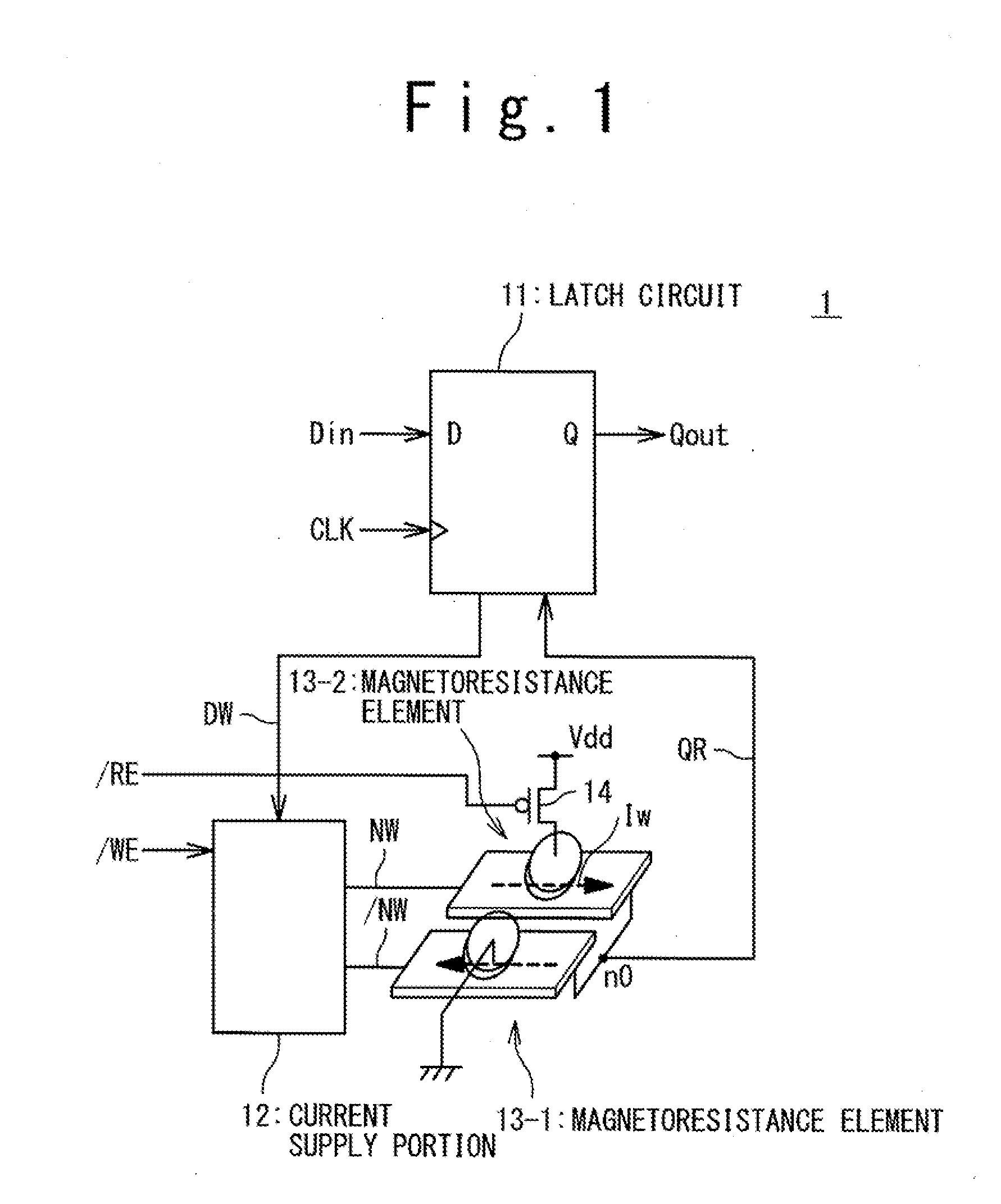

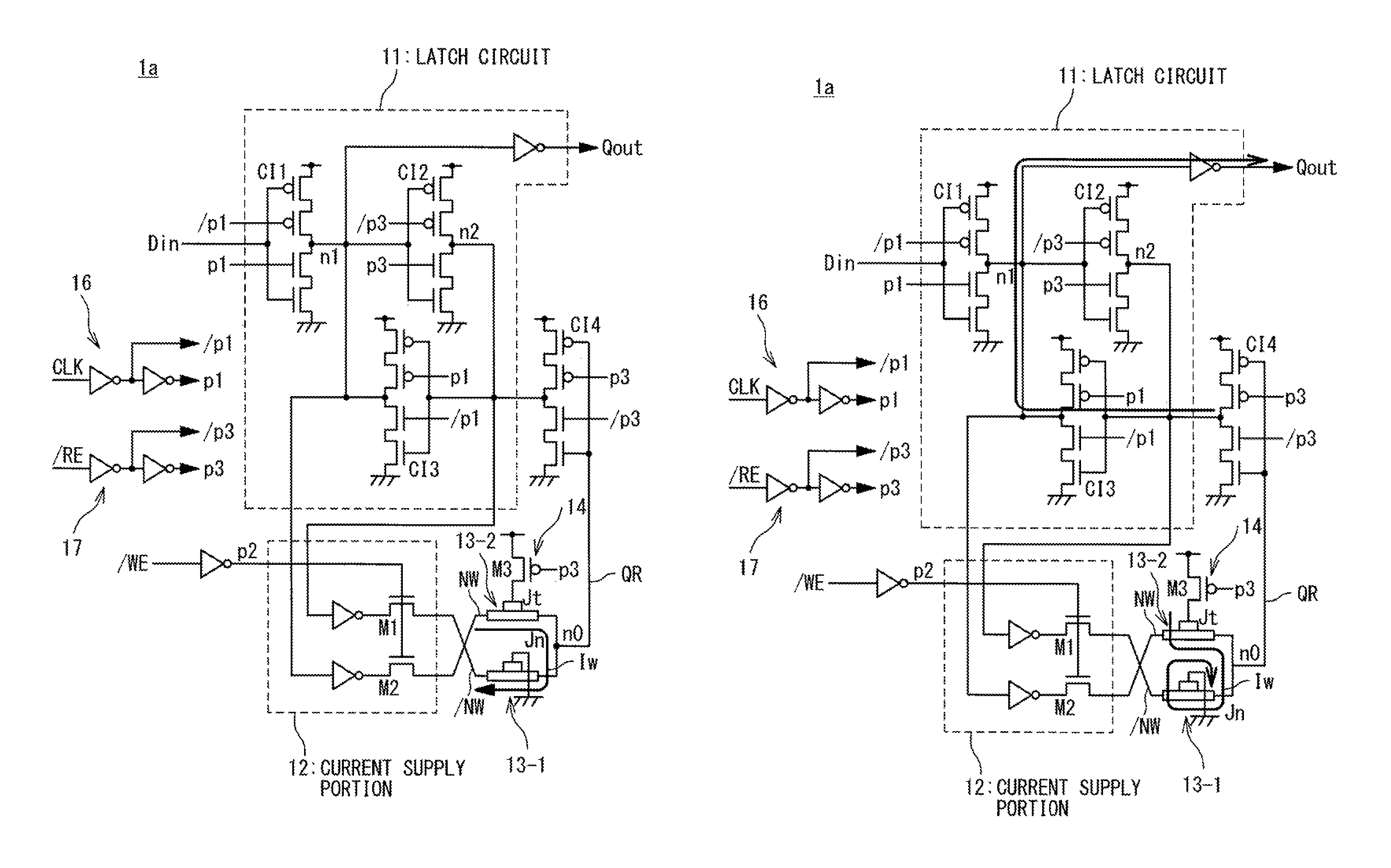

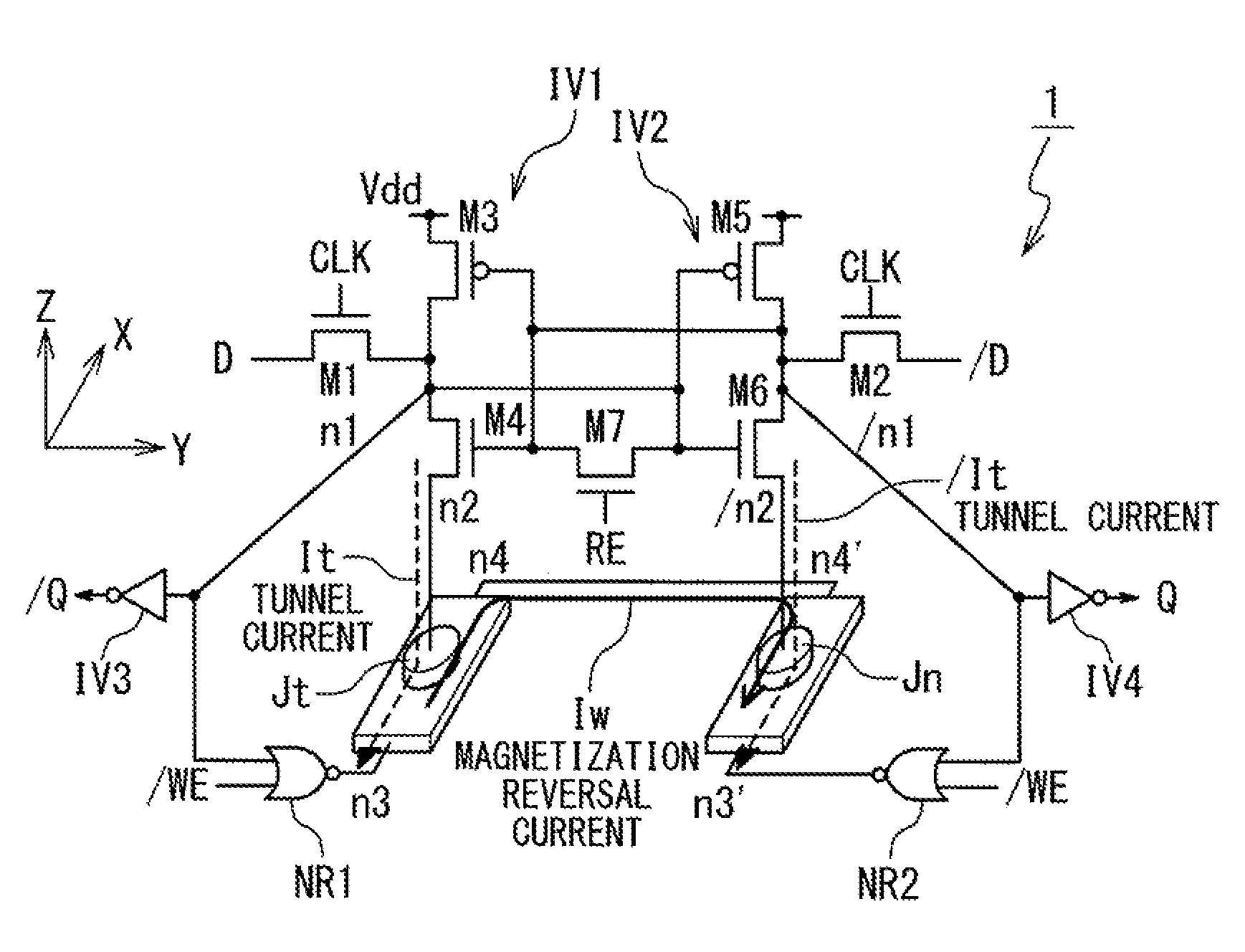

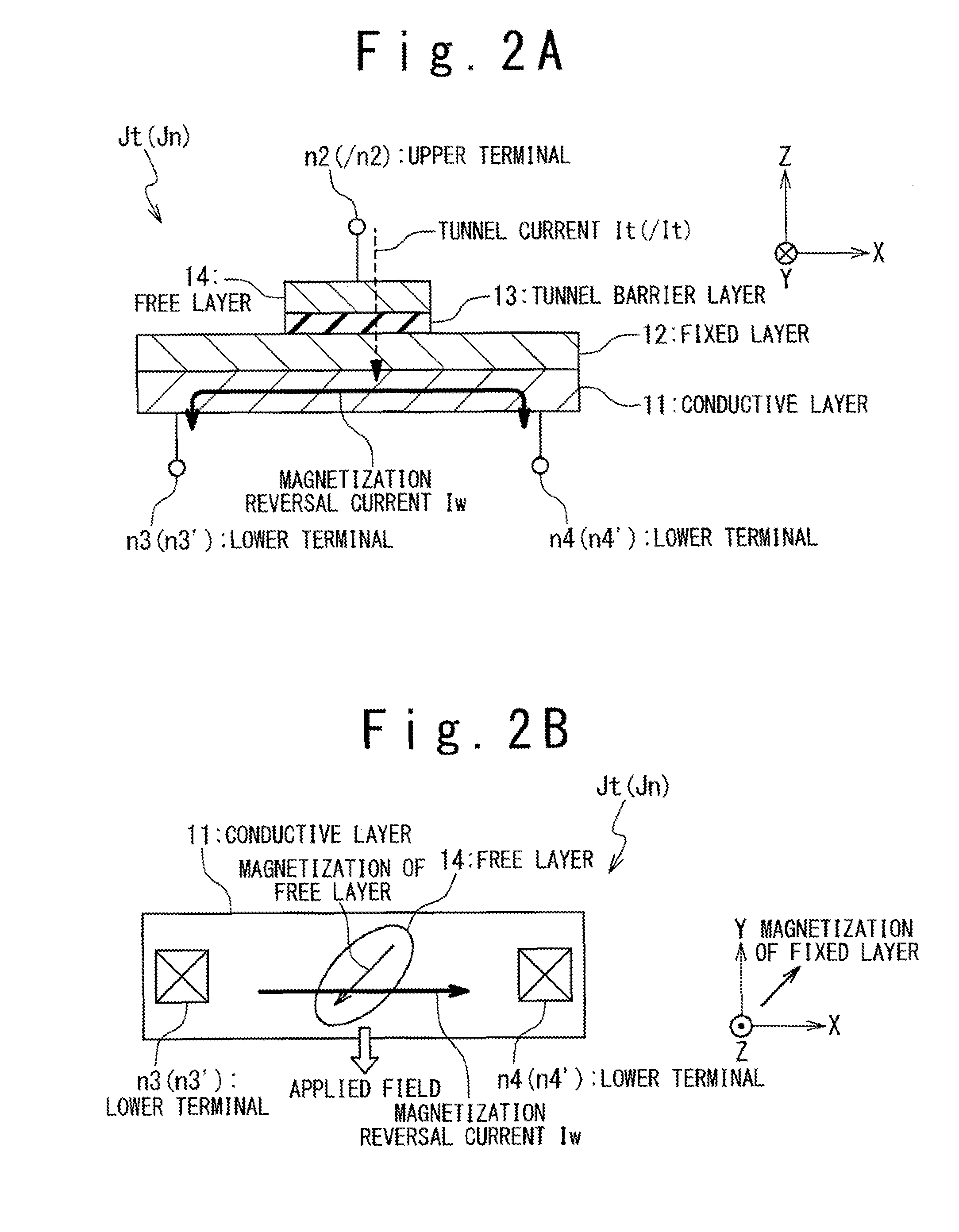

Nonvolatile latch circuit

ActiveUS20100271866A1Total current dropReduces magnetization reversal currentNanotechPulse generation by non-linear magnetic/dielectric devicesReverse currentHemt circuits

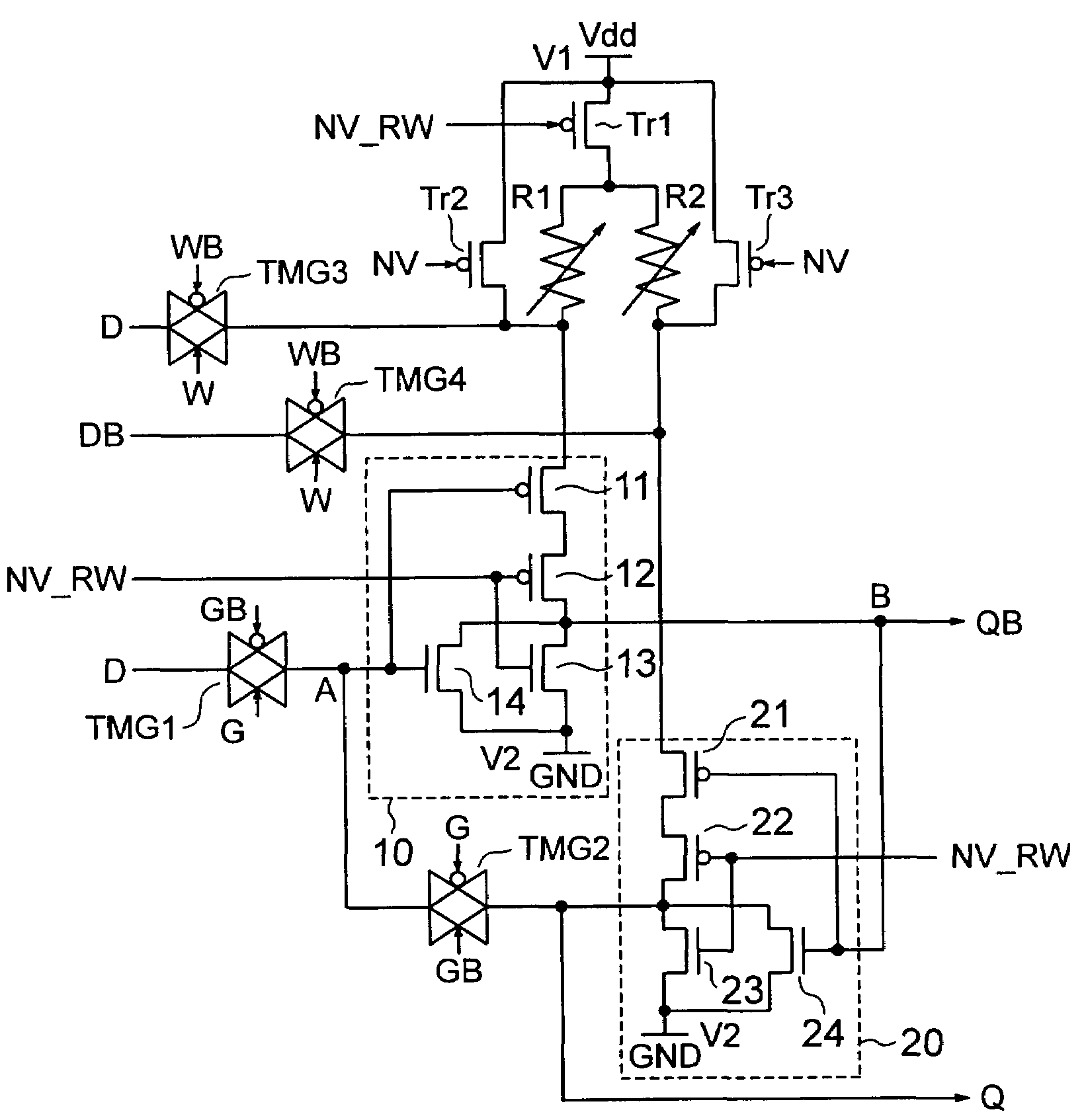

A nonvolatile latch circuit includes: first and second inverters cross-coupled to hold 1-bit data; first and second magnetoresistive elements each having first to third terminals; and a current supply circuitry configured to supply a magnetization reversal current for changing the magnetization states of the first and second maqnetoresistive elements in response to the 1-bit data. The power terminal of the first inverter is connected to the first terminal of the first magnetoresistive element and the power terminal of the second inverter is connected to the first terminal of the second magnetoresistive element. The current supply circuitry is configured to supply the magnetization reversal current to the second terminals of the first and second magnetoresistive elements. The third terminal of the first magnetoresistive element is electrically connected to the third terminal of the second magnetoresistive element.

Owner:NEC CORP

Signal isolator using micro-transformers

ActiveUS7719305B2Reliability increasing modificationsPulse generation by non-linear magnetic/dielectric devicesTransformerEngineering

A logic signal isolator including a micro-transformer with a primary winding and a secondary winding. A transmitter circuit drives the primary winding in response to a received input logic signal such that, in response to a first type of edge in the logic signal, at least a first amplitude signal is supplied to the primary winding and, in response to a second type of edge in the logic signal, a second different amplitude signal is supplied to the primary winding. A receiver circuit receives corresponding first amplitude and second amplitude signals from the secondary winding and reconstructs the received logic input signal from the received signals.

Owner:ANALOG DEVICES INC

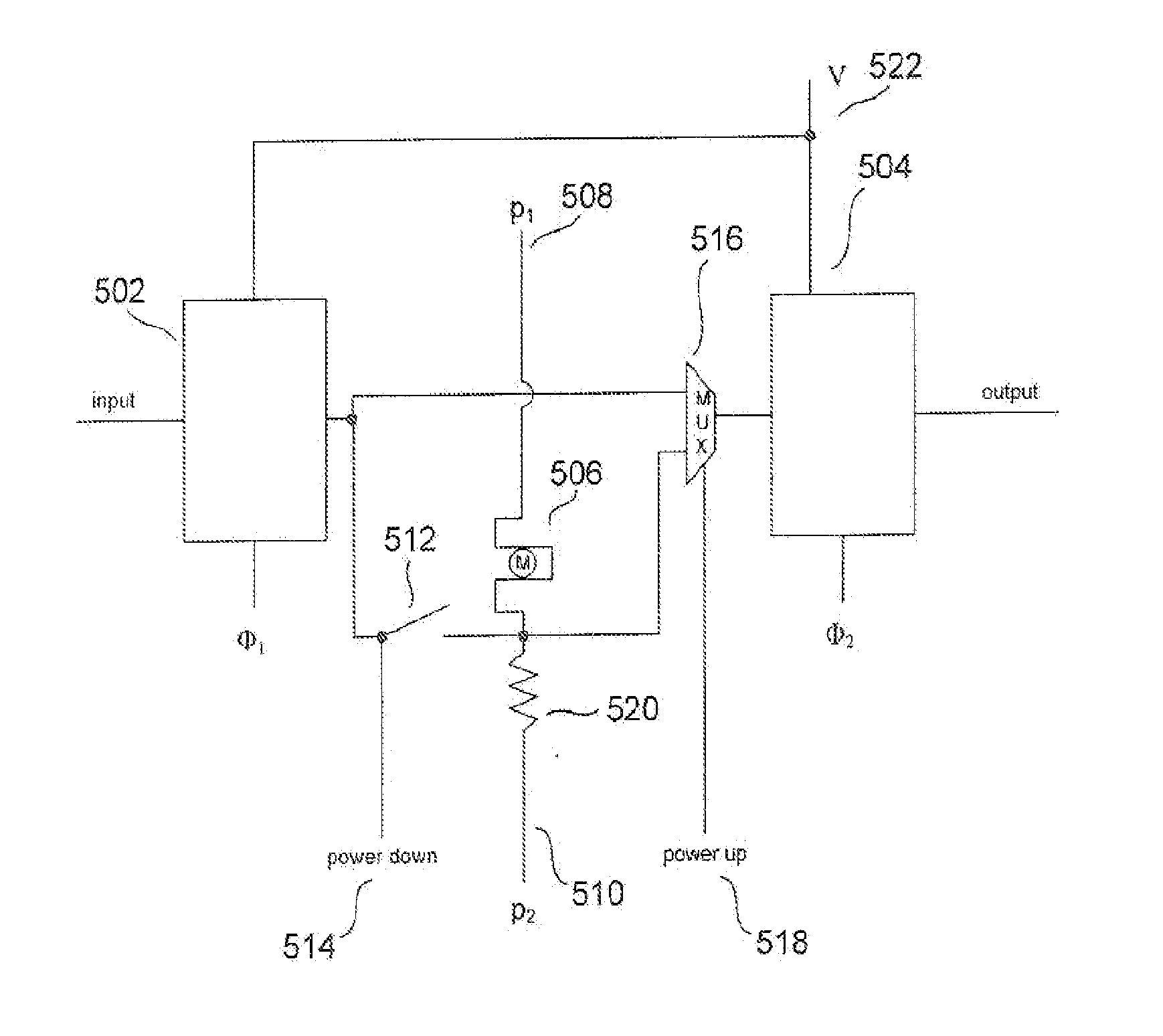

Non-volatile data-storage latch

InactiveUS20120014169A1Pulse generation by non-linear magnetic/dielectric devicesRead-only memoriesComputer scienceTransistor

One embodiments of the present invention is directed to a single-bit memory cell comprising transistor-based bit latch having a data state and a memristor, coupled to the transistor-based bit latch, in which the data state of the transistor-based bit latch is stored by a store operation and from which a previously-stored data state is retrieved and restored into the transistor-based bit latch by a restore operation. Another embodiment of the present invention is directed to a single-bit memory cell comprising a master-slave flip flop and a slave flip flop, and a power input, a memristor, a memory-cell power input, a first memory-cell clock input, a second memory-cell clock input, a memory-cell data input, a memory-cell data output, and two or more memory-cell control inputs.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP

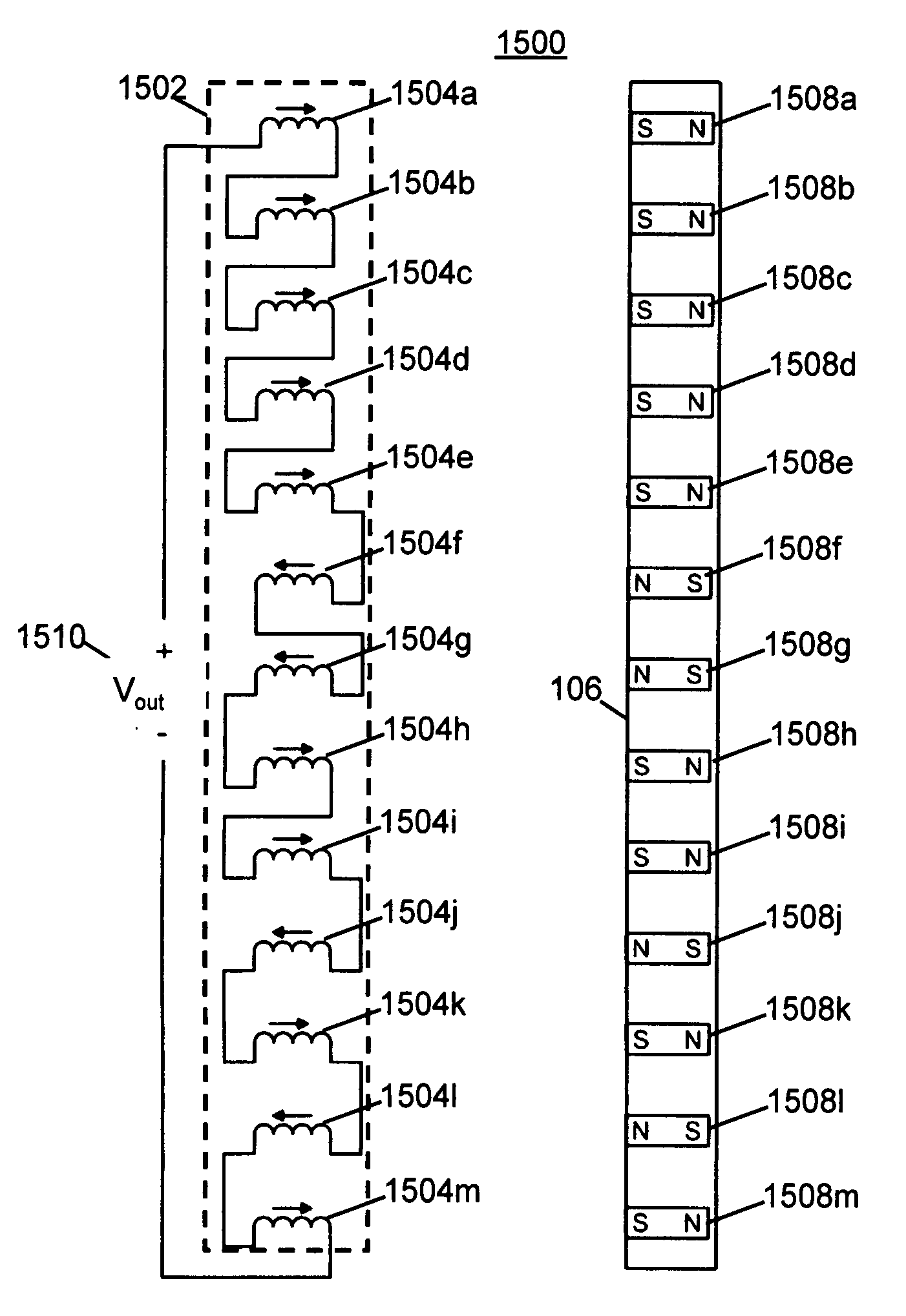

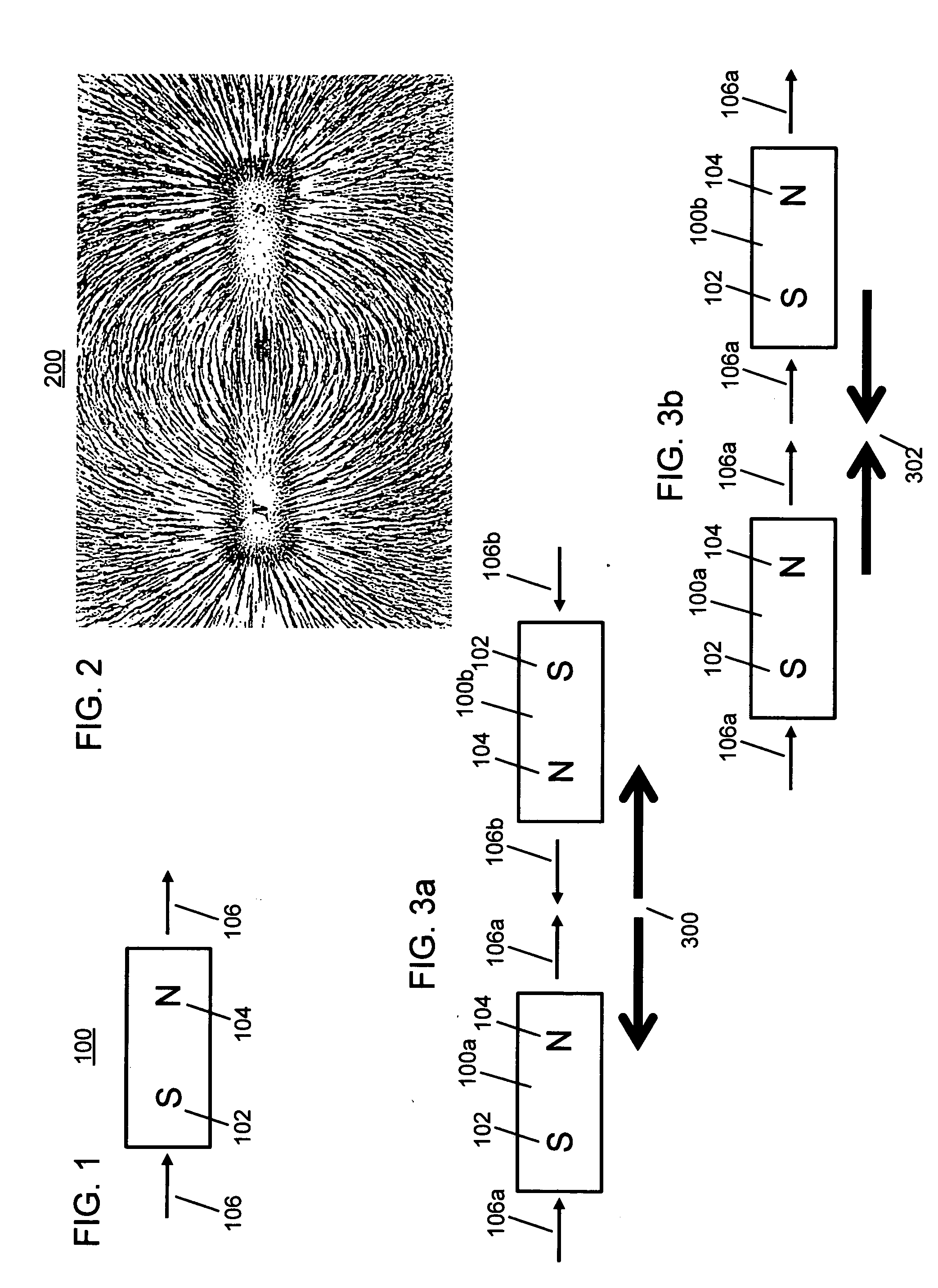

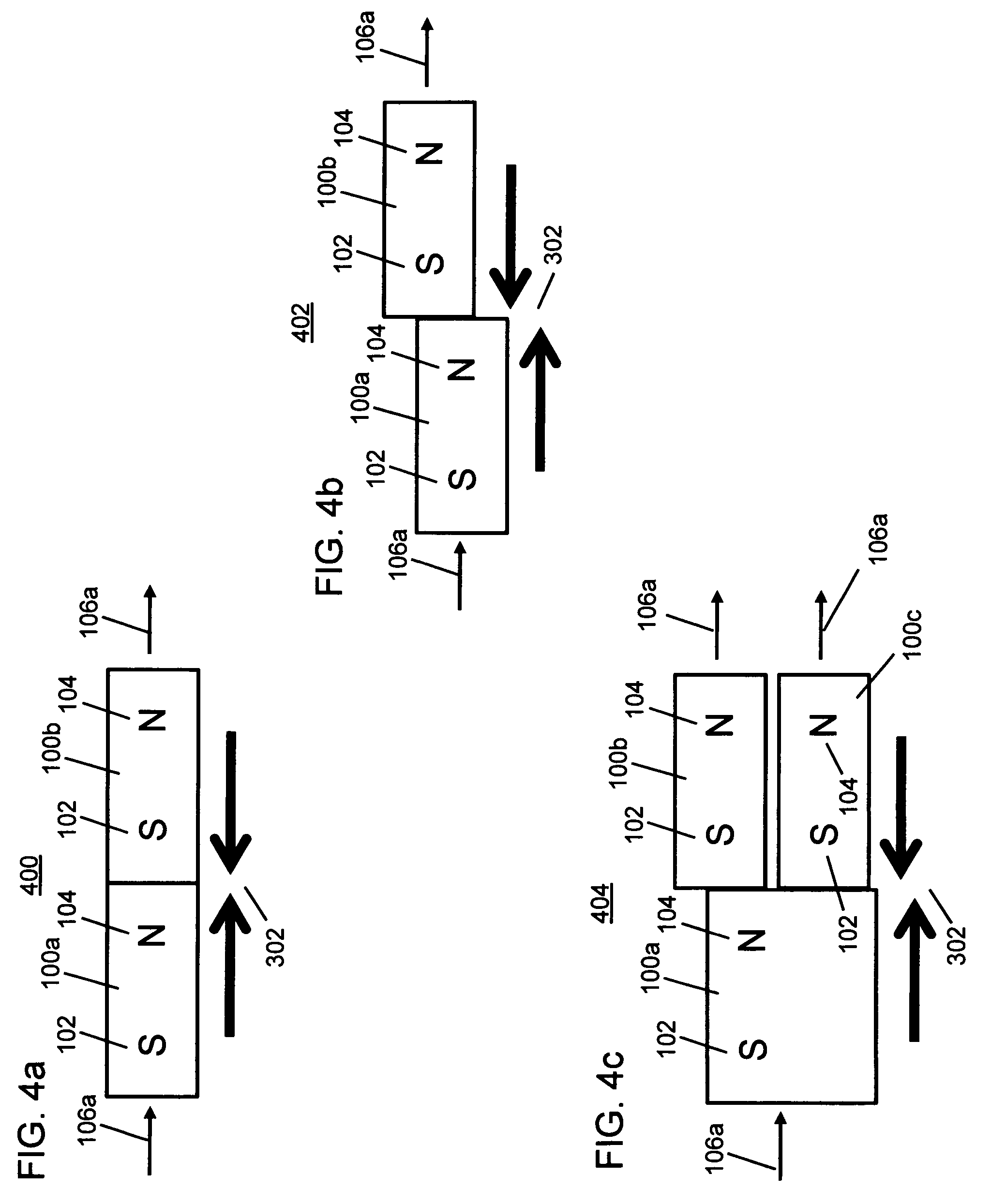

Techniques for producing an electrical pulse

InactiveUS20090250032A1Pulse generation by non-linear magnetic/dielectric devicesCombustion enginesElectrical polarityElectrical impulse

Embodiments of the present invention provide an apparatus, comprising a field emission source having polarities and positions in accordance with a code, a plurality of connected coils adapted to move proximate to said field emission source and having positions in accordance with said code, and wherein an electrical pulse is created when said field emission source is aligned with said plurality of connected coils according to said code.

Owner:CORRELATED MAGNETICS RES LLC

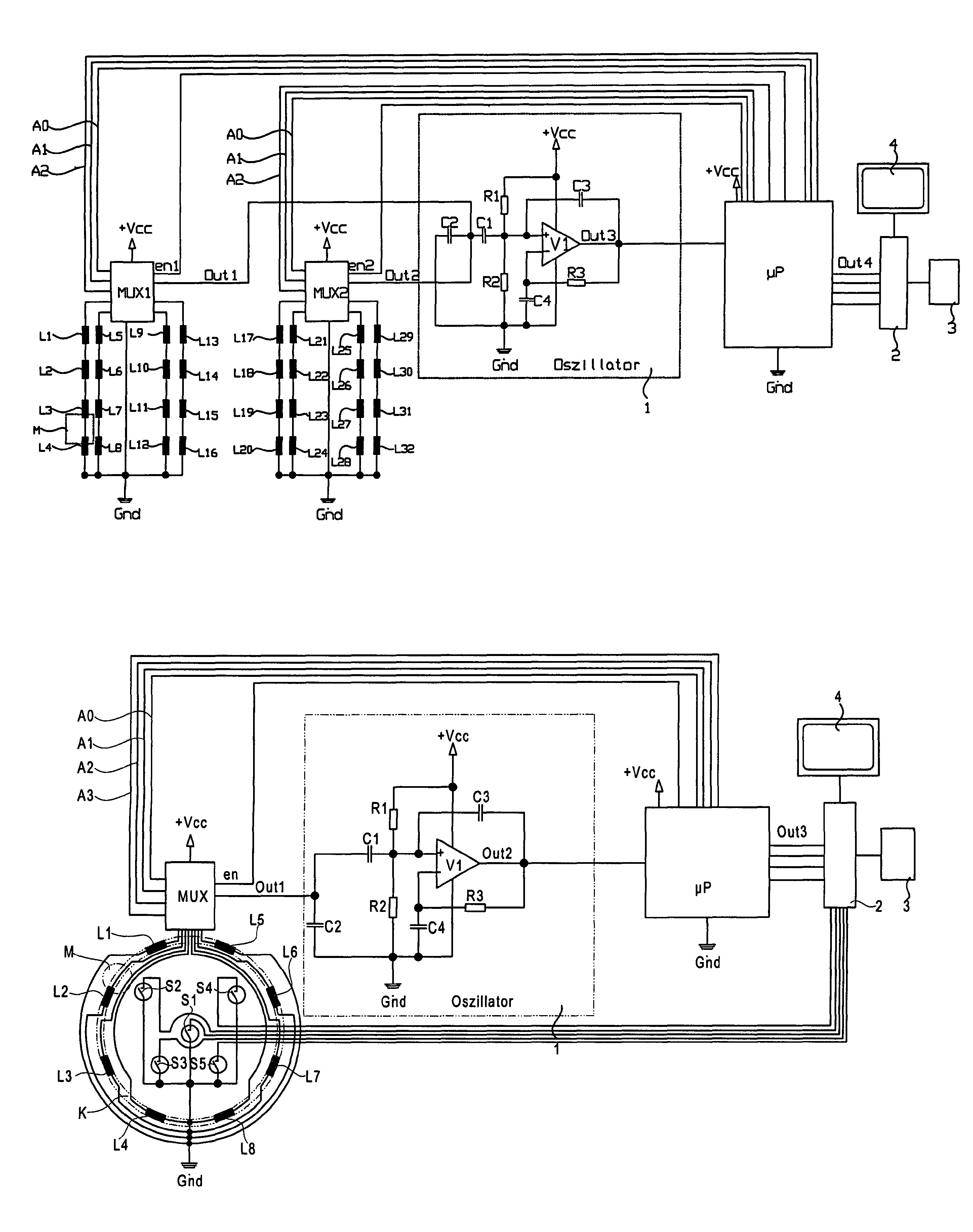

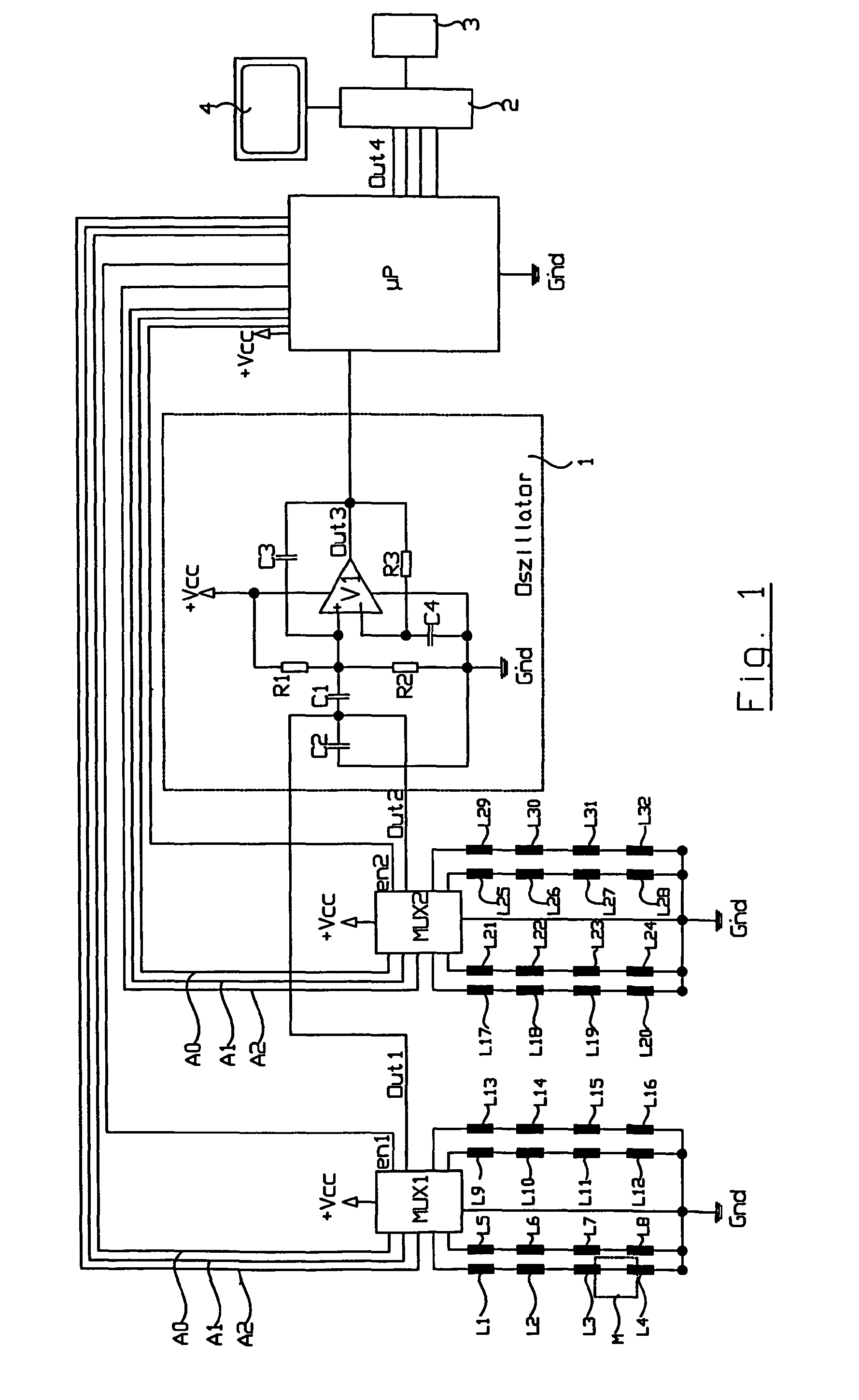

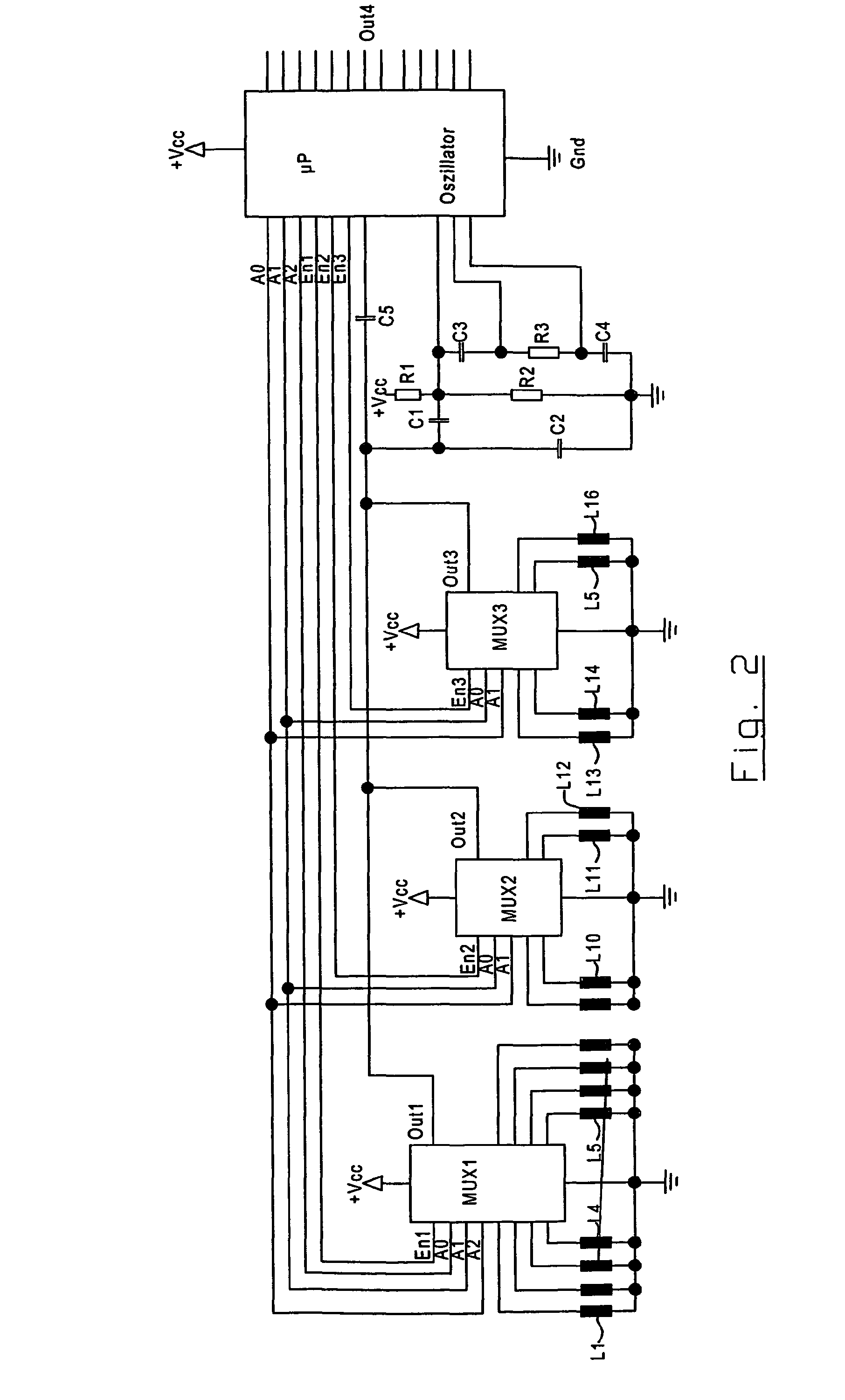

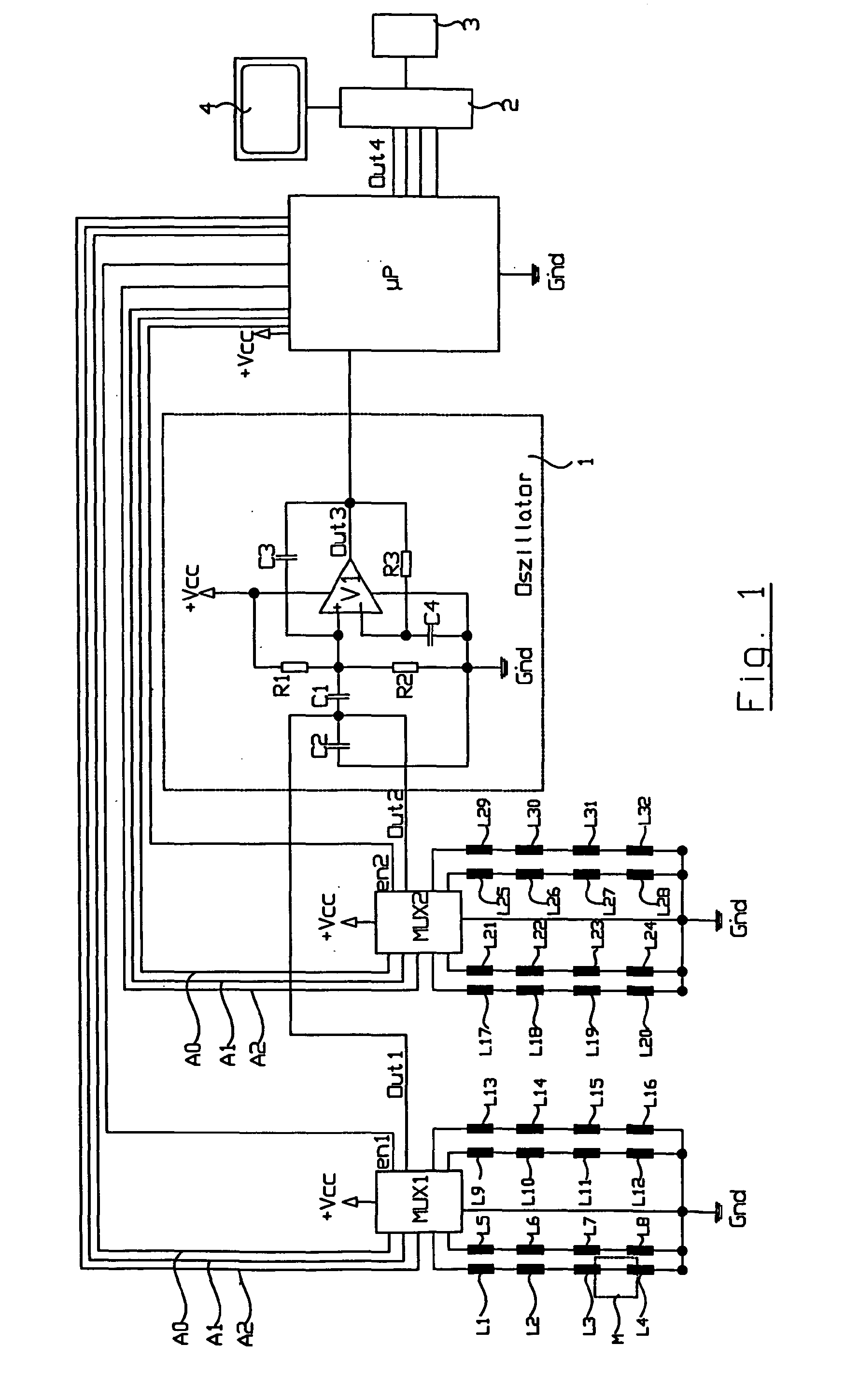

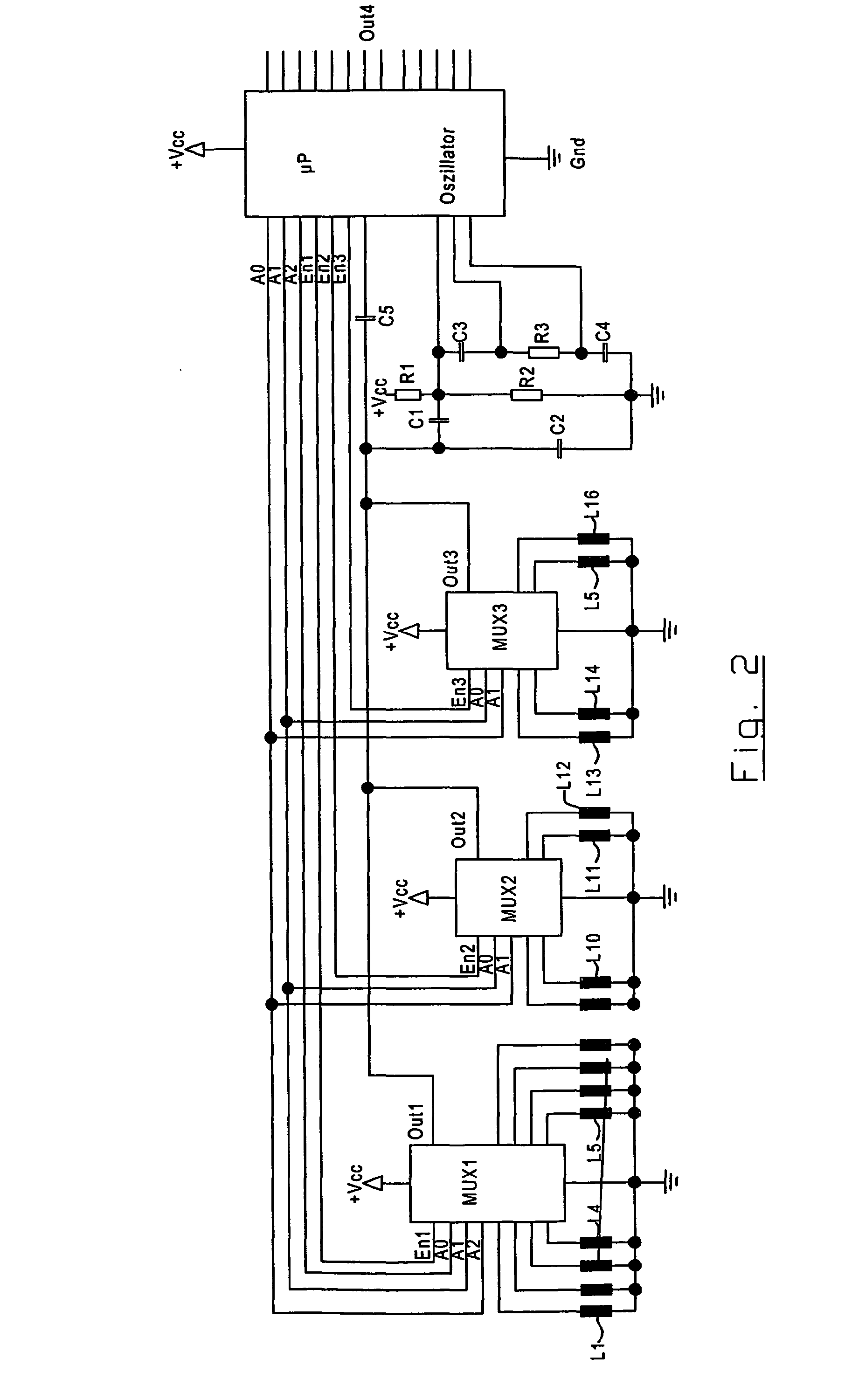

Input apparatus with haptic feedback

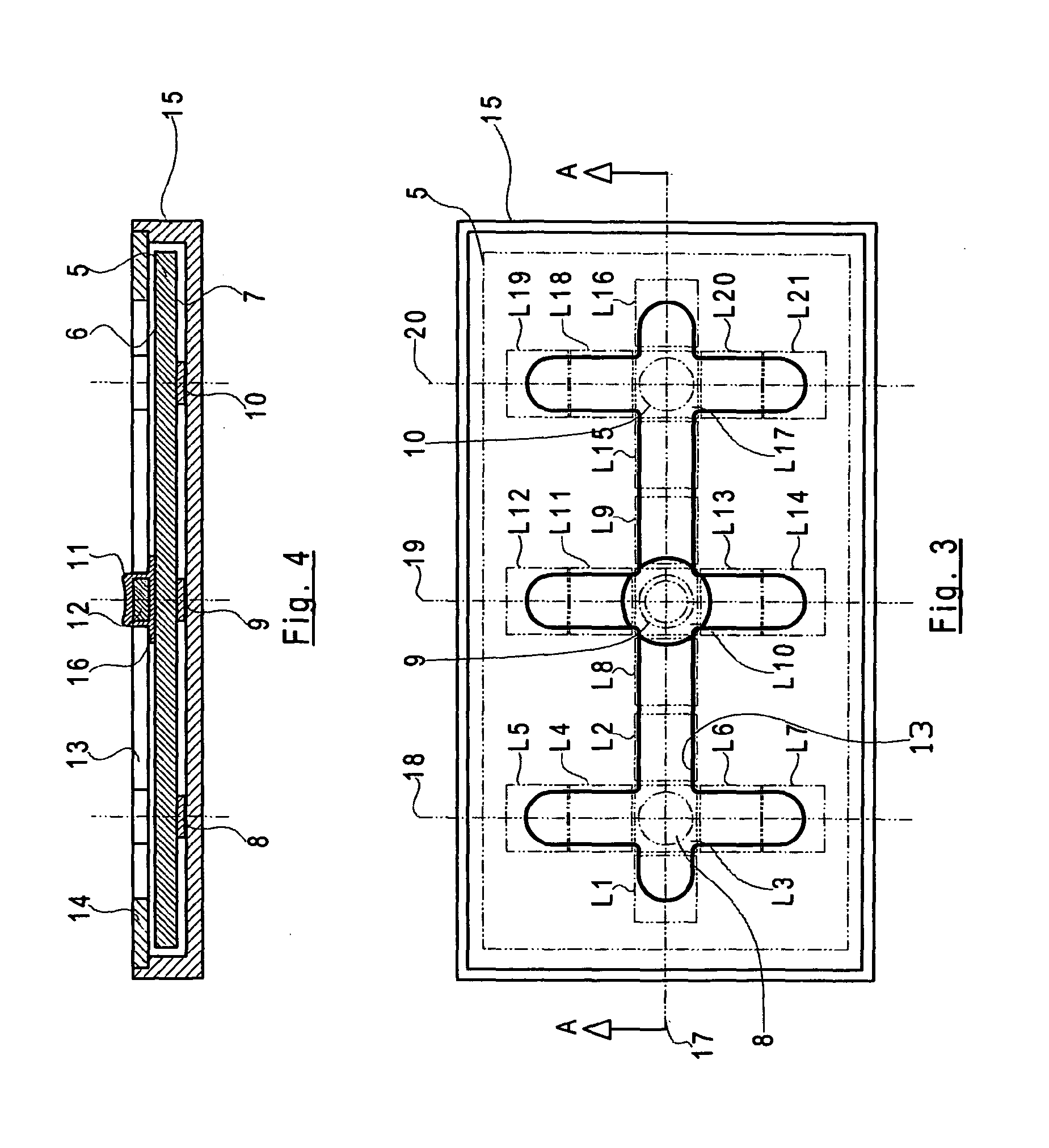

InactiveUS8907661B2Reduce frictionMagnetic measurementsPulse generation by non-linear magnetic/dielectric devicesEngineeringPrinted circuit board

The input device has a printed circuit board (5) to which a plurality of coils (L1-L8) has been fitted which, together with a capacitor (C2), each form a frequency-determining element of an oscillator (1). The coils (L1-L8) are arranged so as to be distributed along a path (K), which may also be a circular path. A movable magnet portion (M) can be displaced relative to the printed circuit board (5). At least one further stationary magnet portion (M1-M8) is mounted on the printed circuit board (5), which is opposite the movable magnet portion (M).

Owner:FM MARKETING

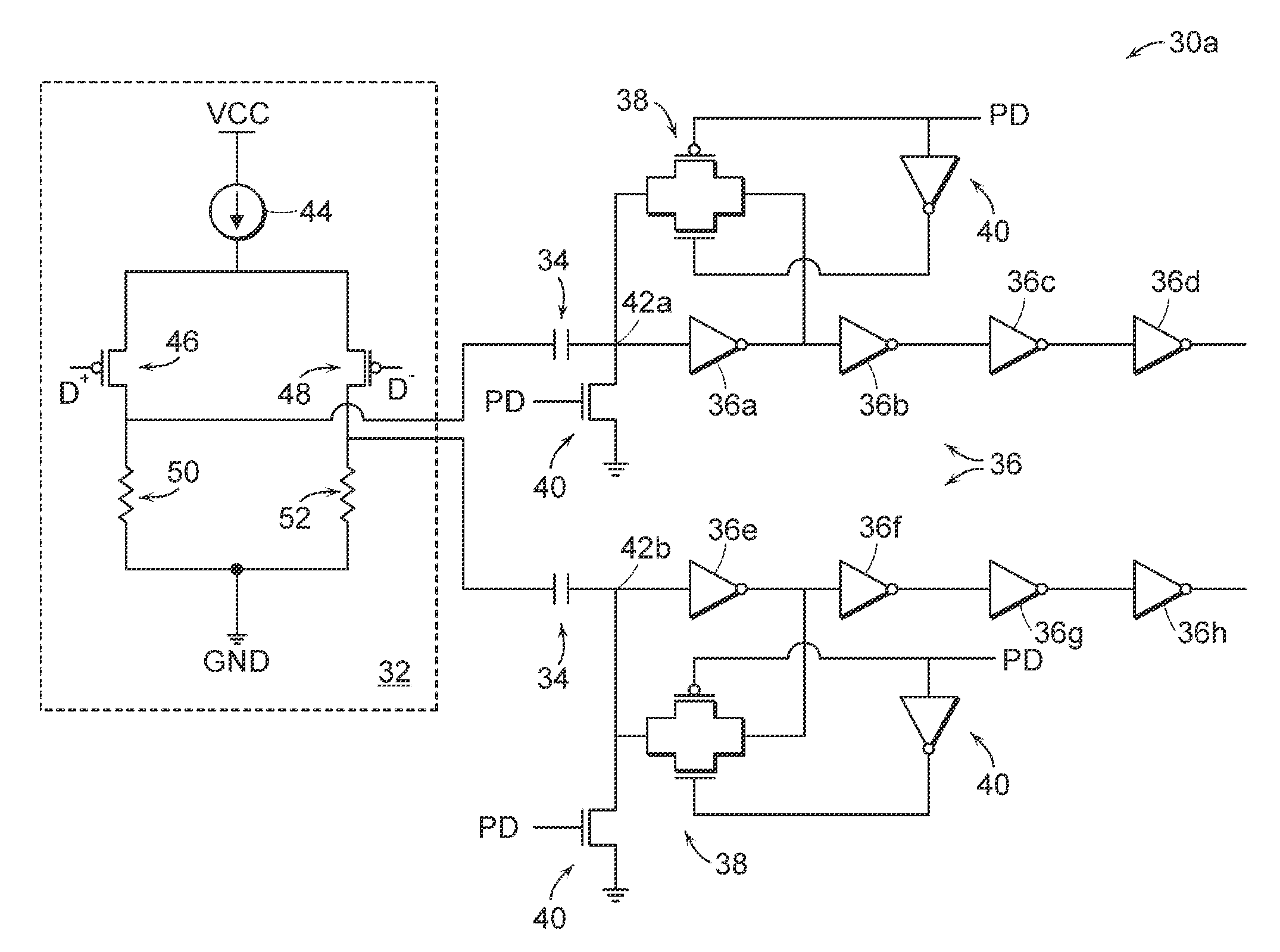

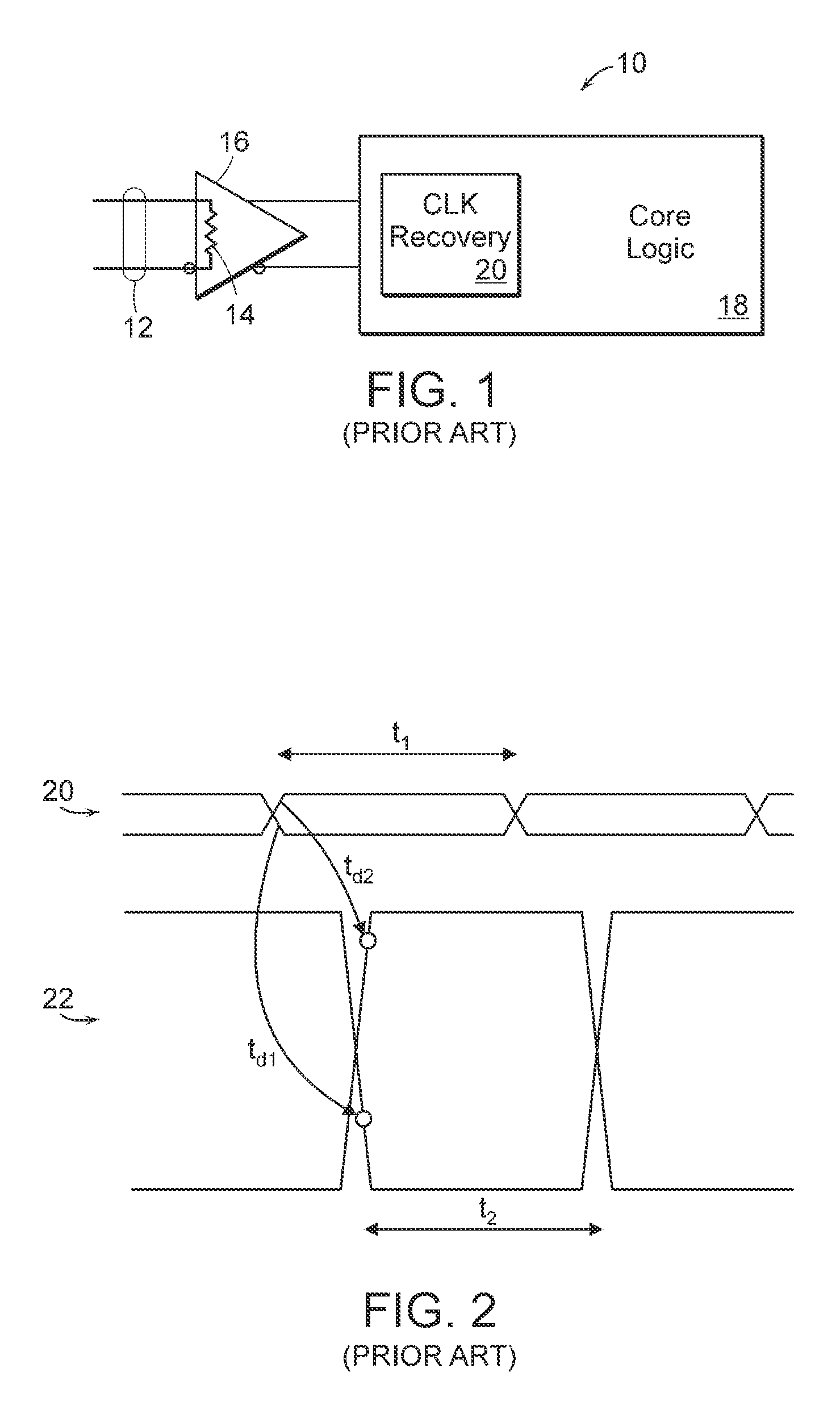

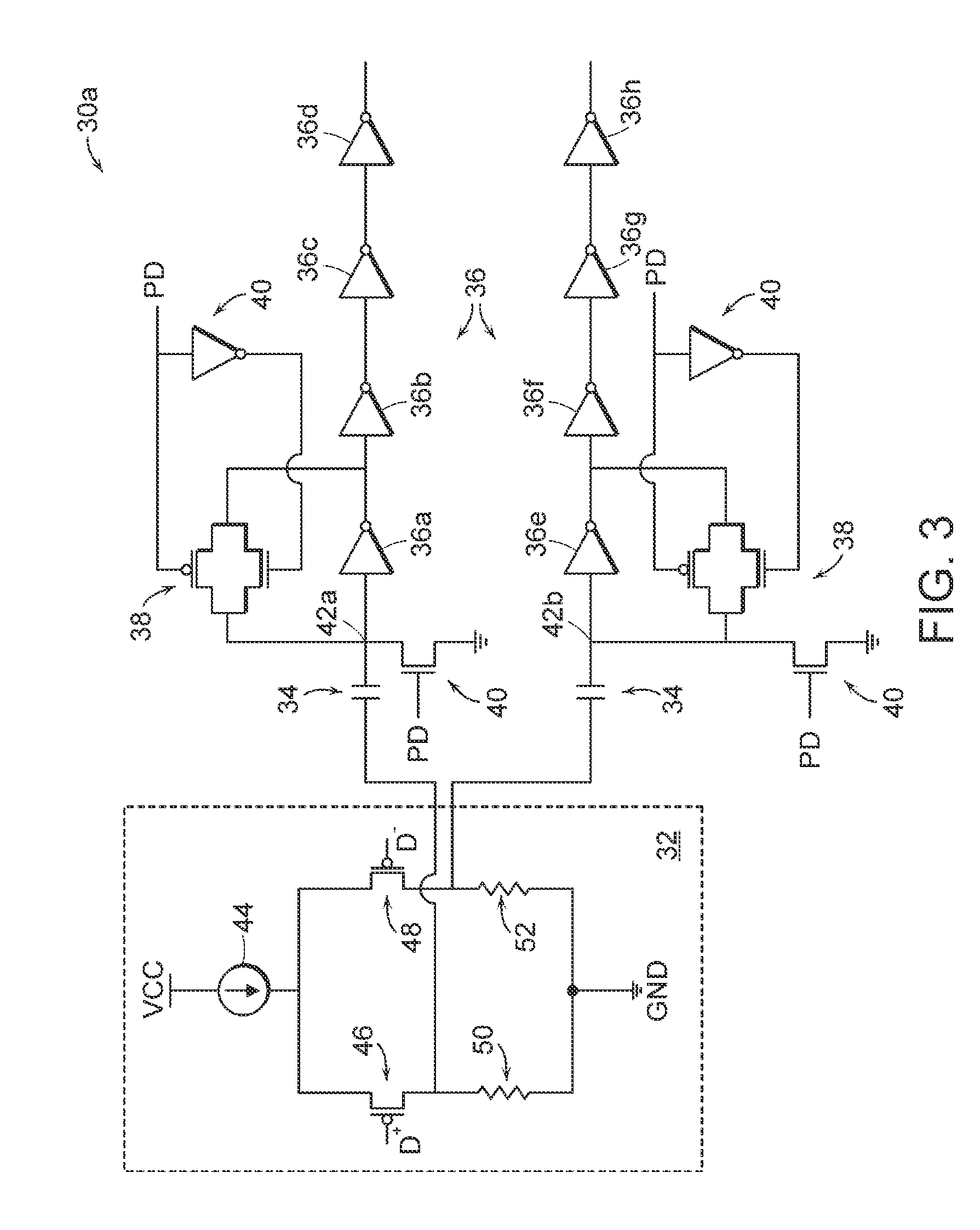

Low duty cycle distortion differential to CMOS translator

ActiveUS7176720B1Easy to implementReduce dependencePulse generation by non-linear magnetic/dielectric devicesDifferential amplifiersCMOSTransmission gate

Disclosed is a circuit comprising a differential input amplifier stage, a capacitor stage, an inverter chain stage, and a biasing circuit. The inverter chain stage may be formed with or without feedback depending on whether a clock signal or data signal is to be translated using the disclosed circuit. The biasing circuit can be formed using either inverters or transmission gates. Moreover, the biasing circuit, the inverter chain stage, and the amplifier stage can be connected to a power down circuit which, when the translator is not being used, will ensure various circuitry of the translator will not consume extensive power. The inverter chain stage, biasing circuit, and capacitor stage are formed on both an upper and lower section to produce true and complementary outputs that have a consistent and equal delay from the transitions of the incoming differential input signal so as to minimize jitter and associated duty cycle of the translated output.

Owner:CYPRESS SEMICON CORP

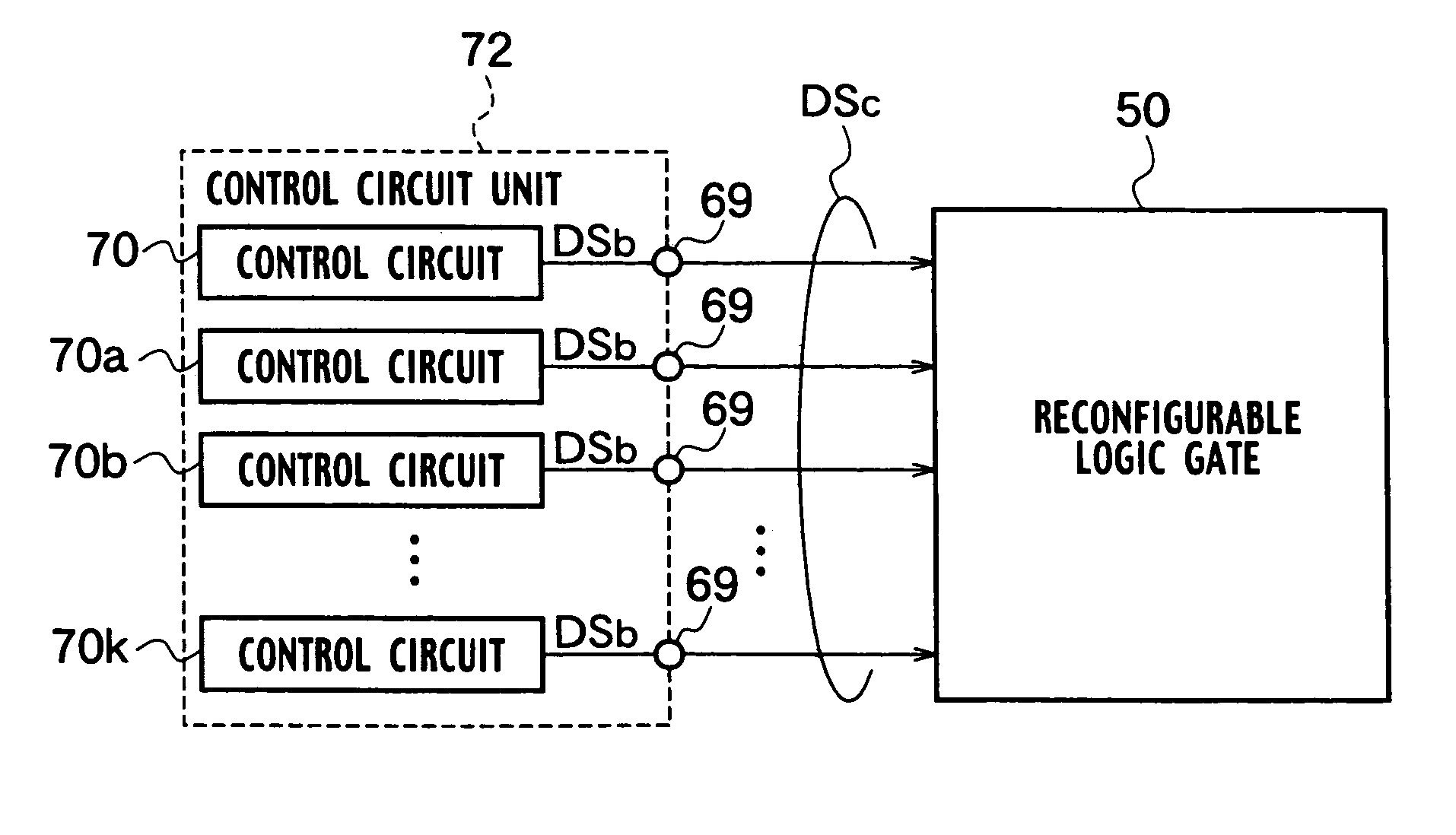

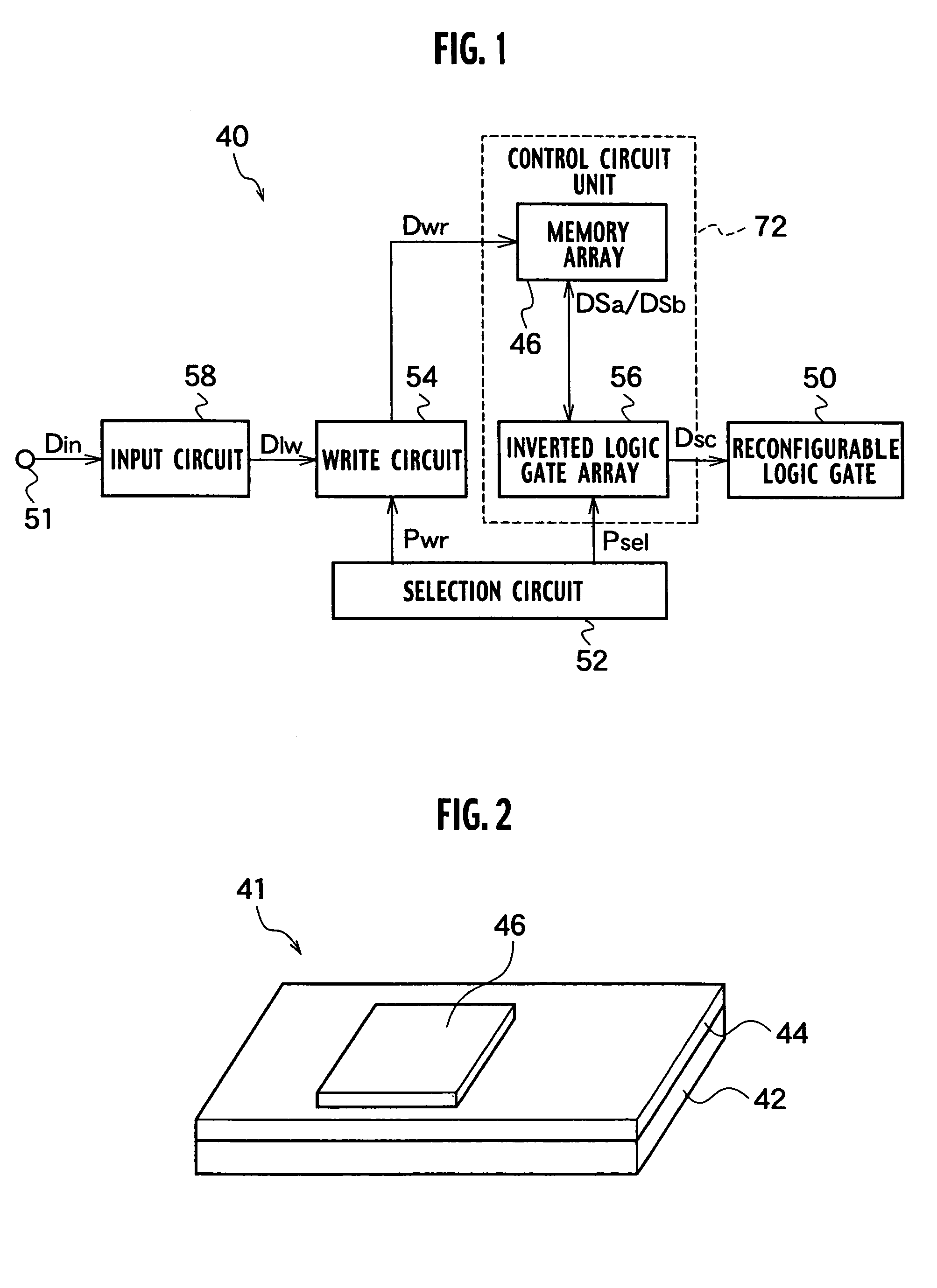

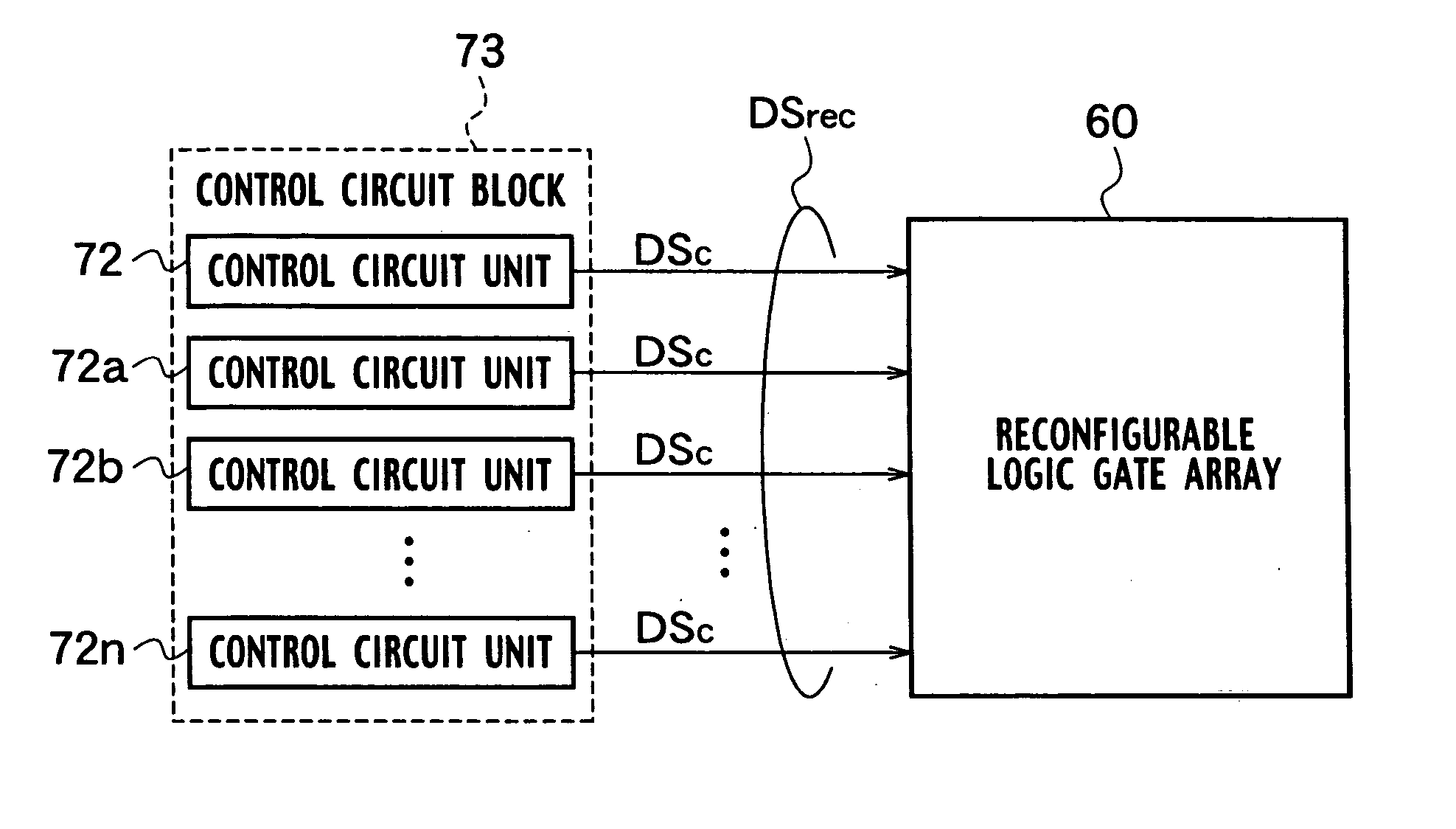

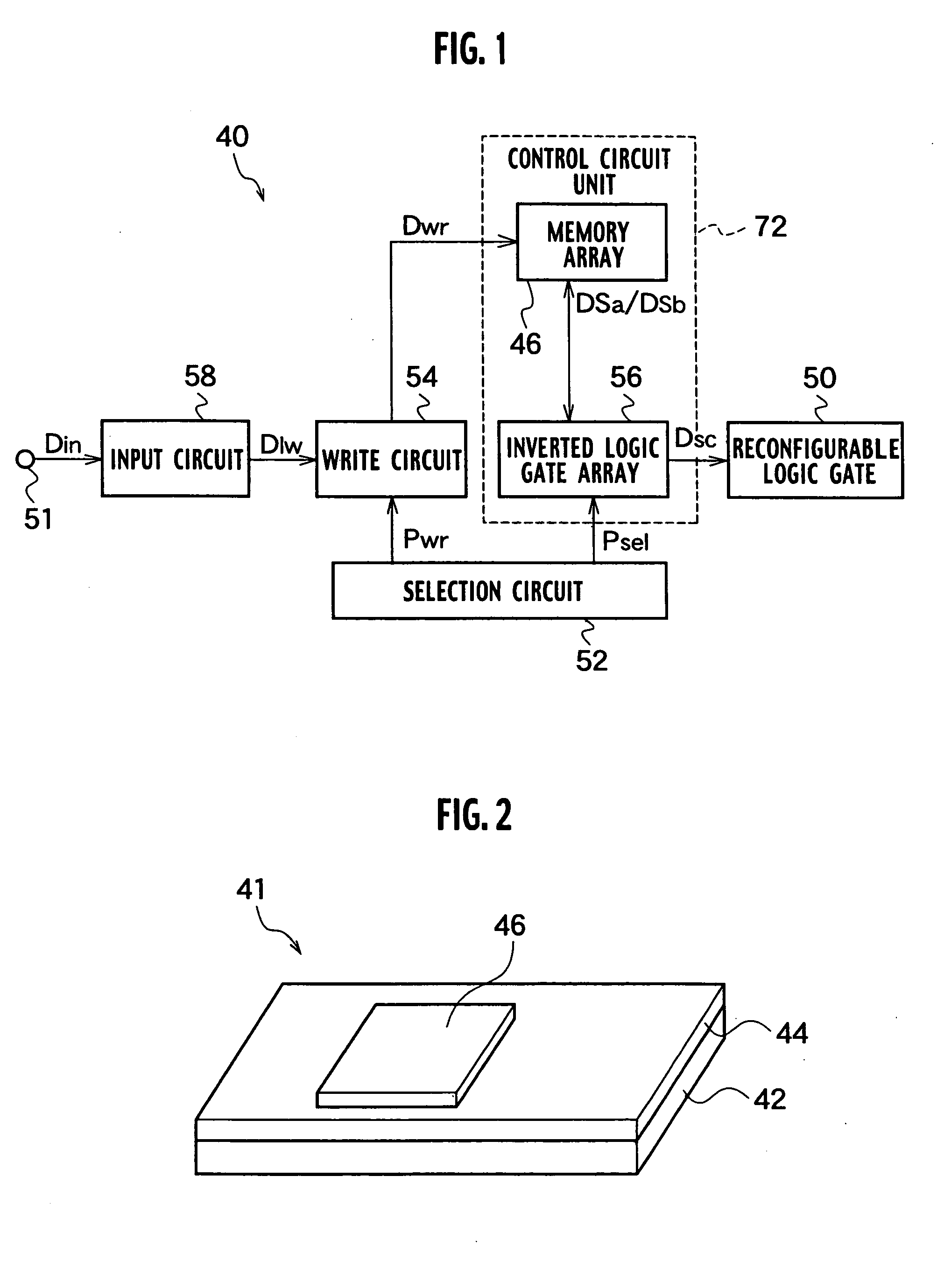

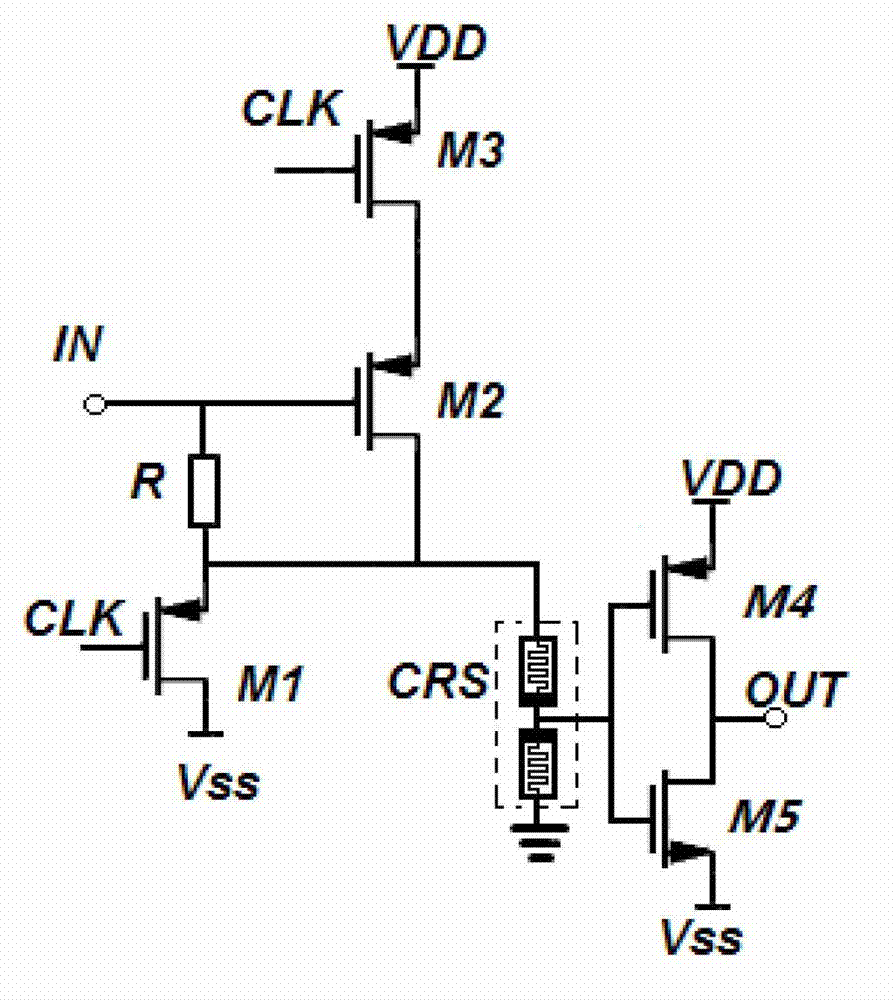

Control circuit and reconfigurable logic block

ActiveUS7068069B2Shorten the timeLogic circuits characterised by logic functionPulse generation by non-linear magnetic/dielectric devicesControl signalInverter

A control circuit for providing a control signal to build a logic circuit includes a latch circuit including first and second inverted logic gates; a first variable resistive memory provided between an output of the first inverted logic gate and an input of the second inverted logic gate, the first variable resistive memory configured to store a resistance value in accordance with a write signal; and a resistive element provided between an input of the first inverted logic gate, wherein the output of the second inverted logic gate serves to transmit the control signal.

Owner:KK TOSHIBA

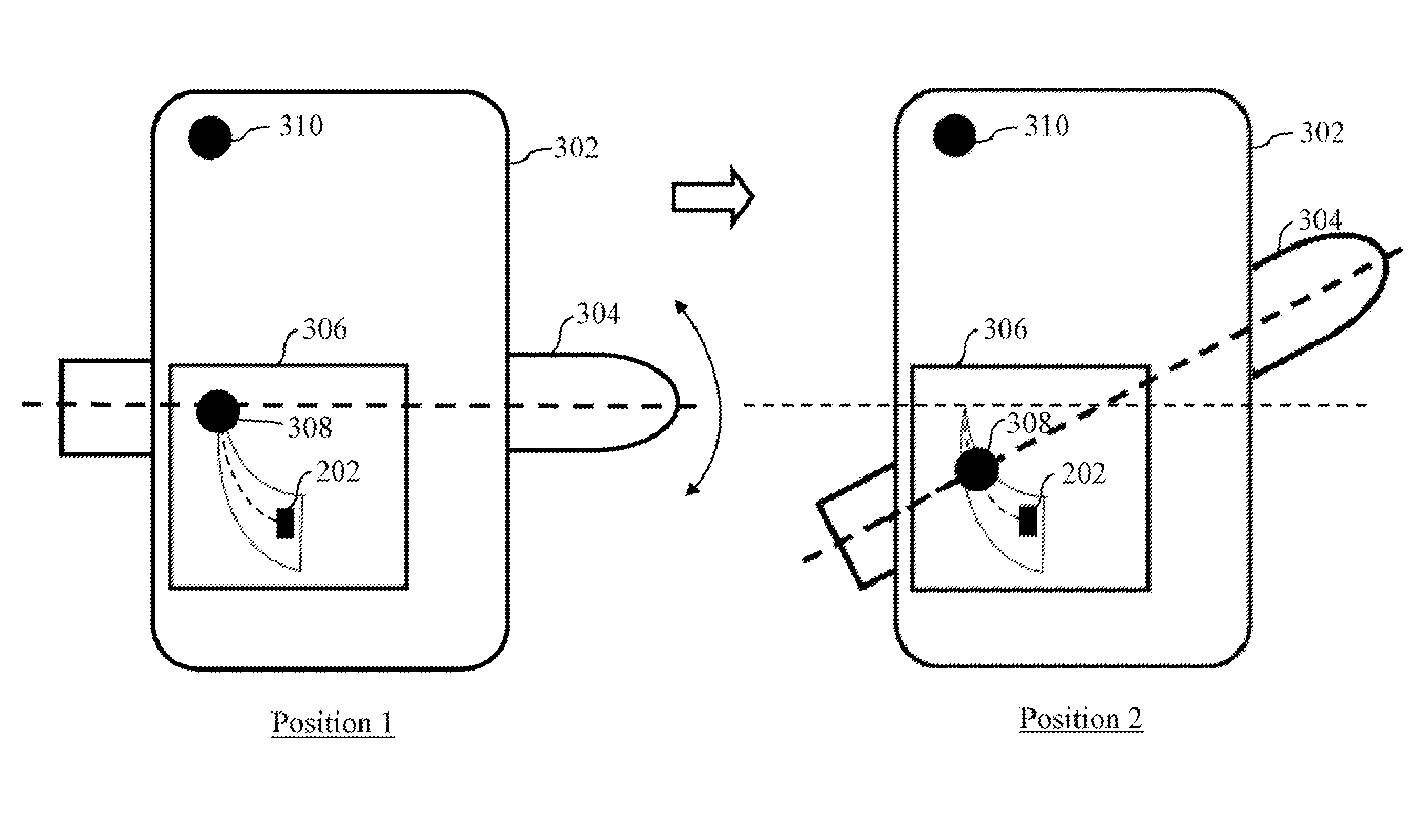

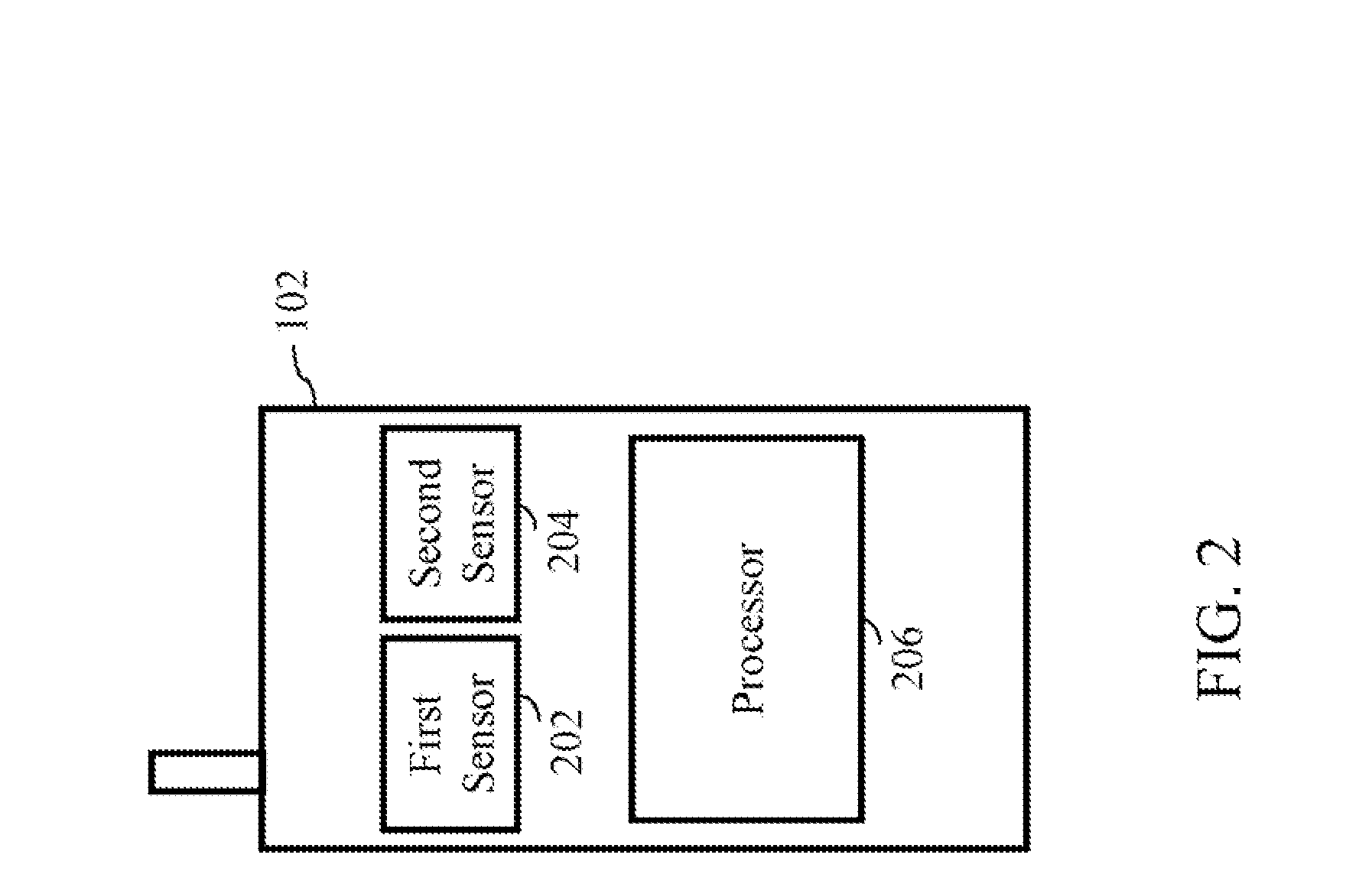

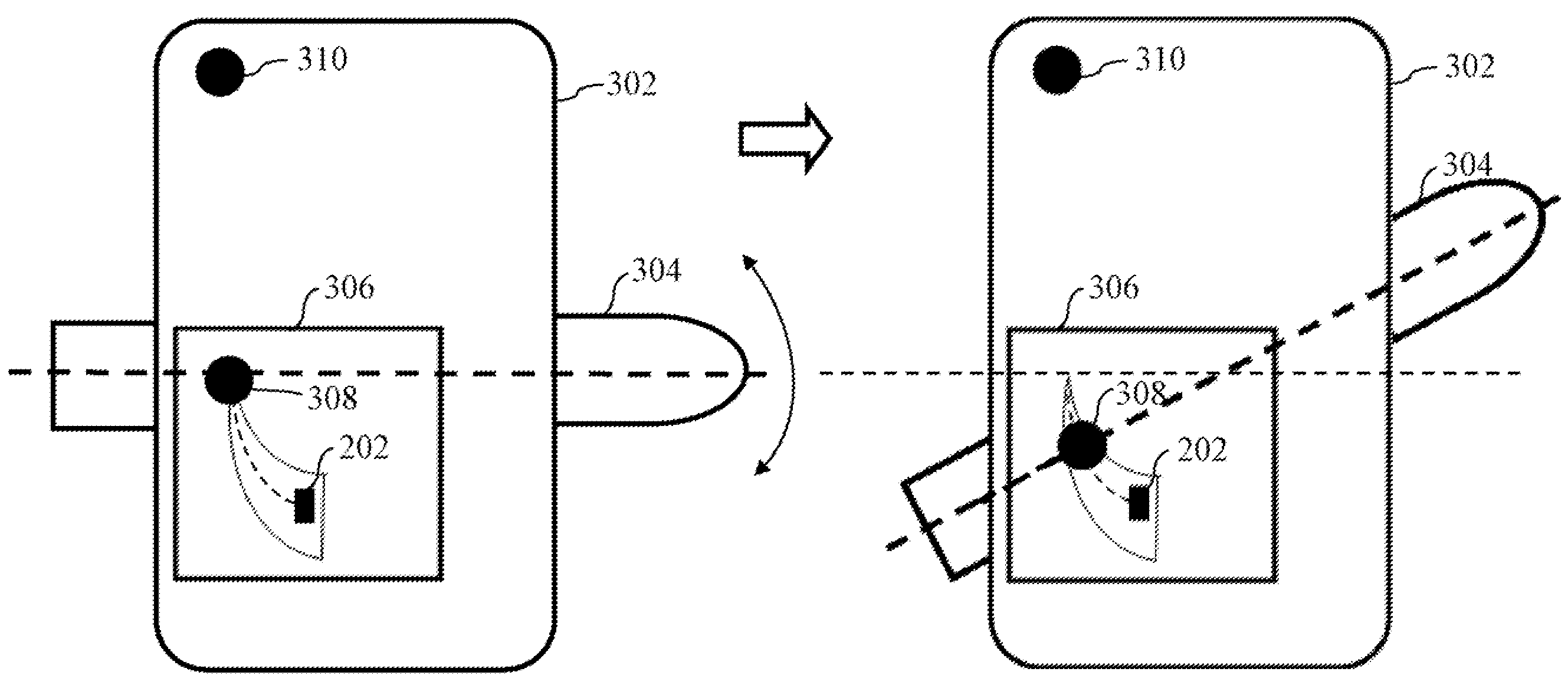

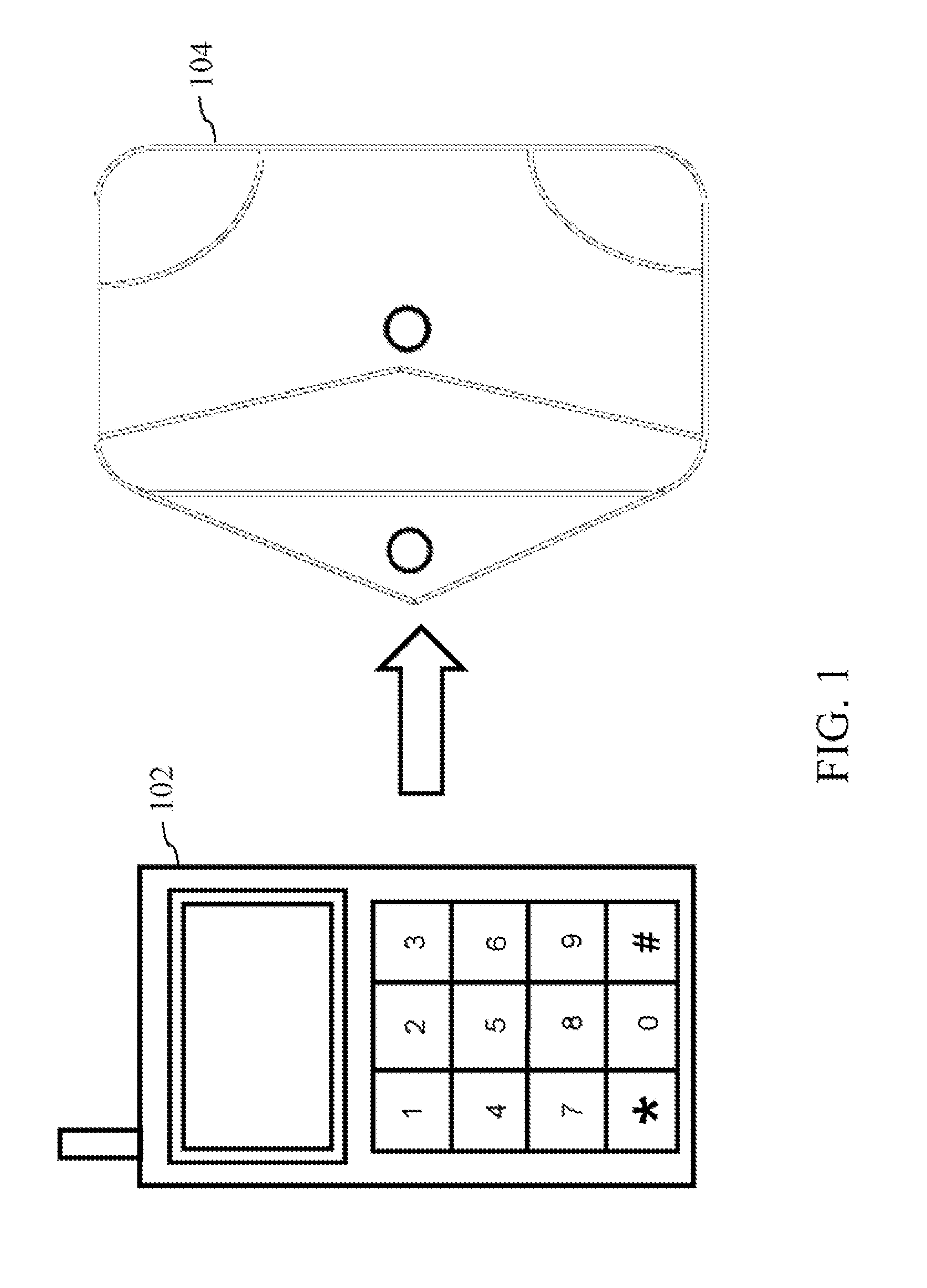

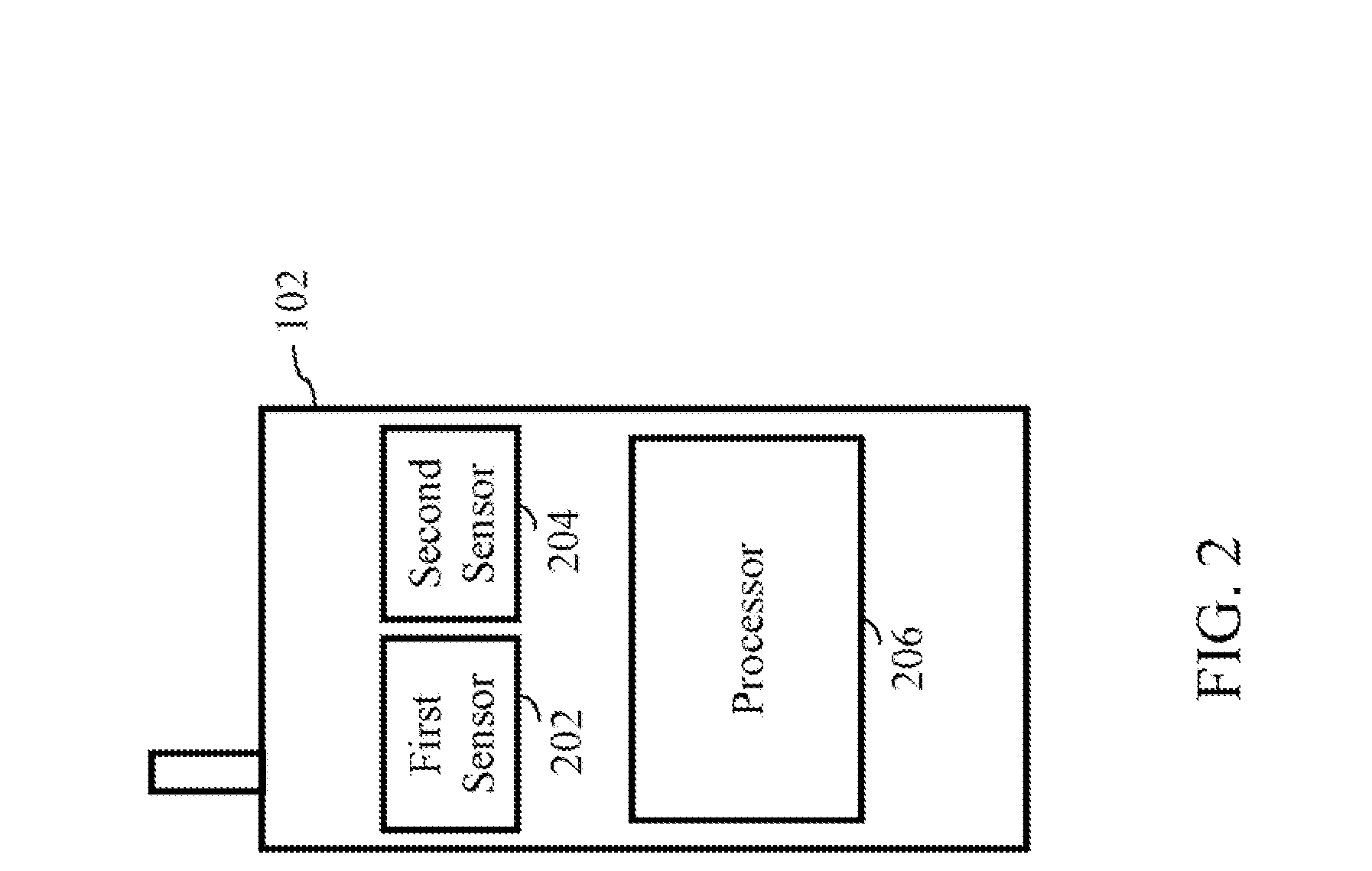

Method and system for controlling a handheld electronic device

ActiveUS7523012B2Travelling carriersPulse generation by non-linear magnetic/dielectric devicesElectricityComputer science

A method (500), a handheld electronic device (102) and an external accessory (402) for controlling at least one function of a plurality of functions of the handheld electronic device is provided. The method includes determining (504) whether the handheld electronic device is docked in an external accessory. Further, the method includes measuring (506) a first magnetic field density when the handheld electronic device is docked in the external accessory. Furthermore, the method includes generating (508) a signal to activate at least one function, based on an electrical parameter.

Owner:MOTOROLA SOLUTIONS INC

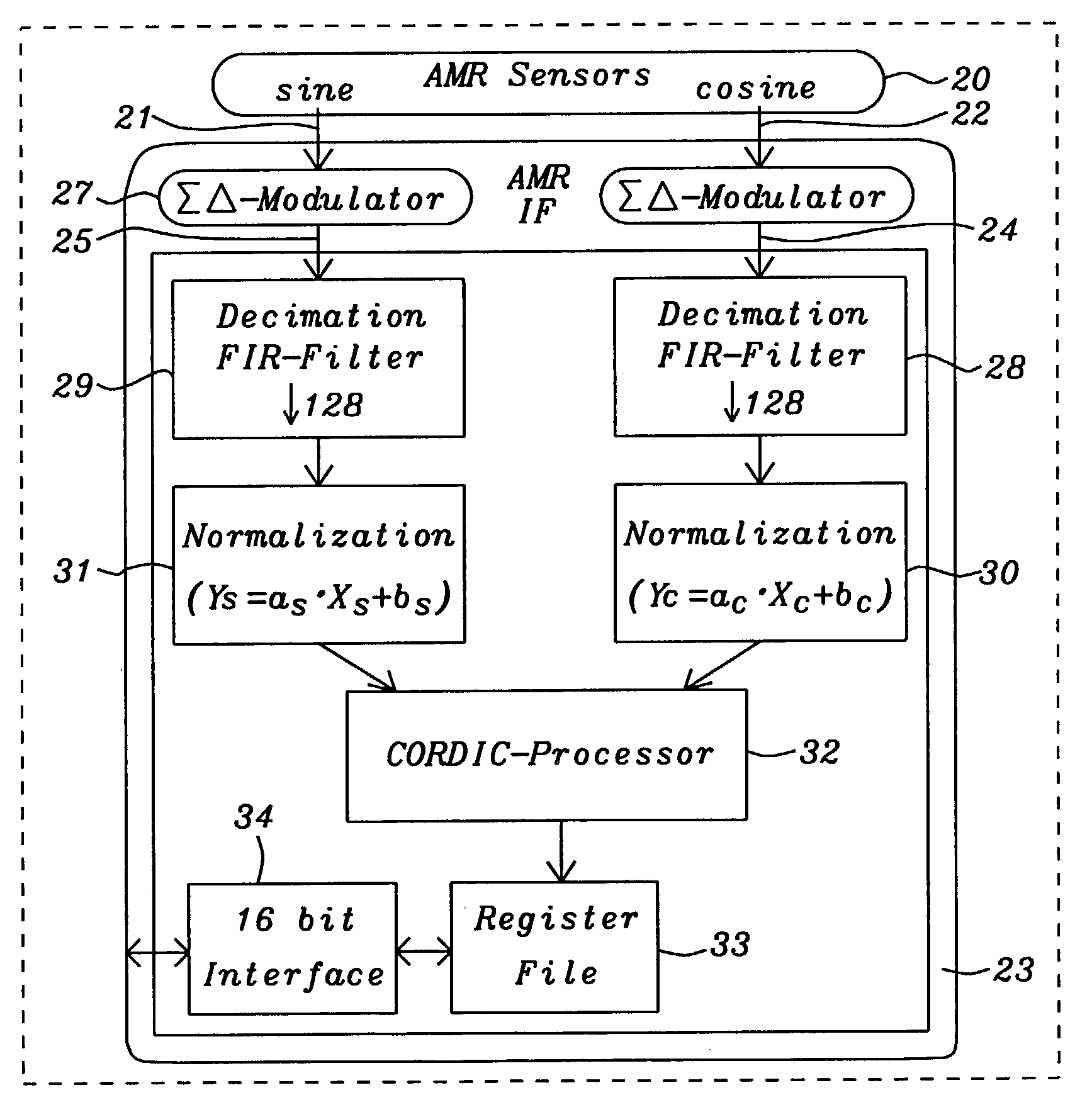

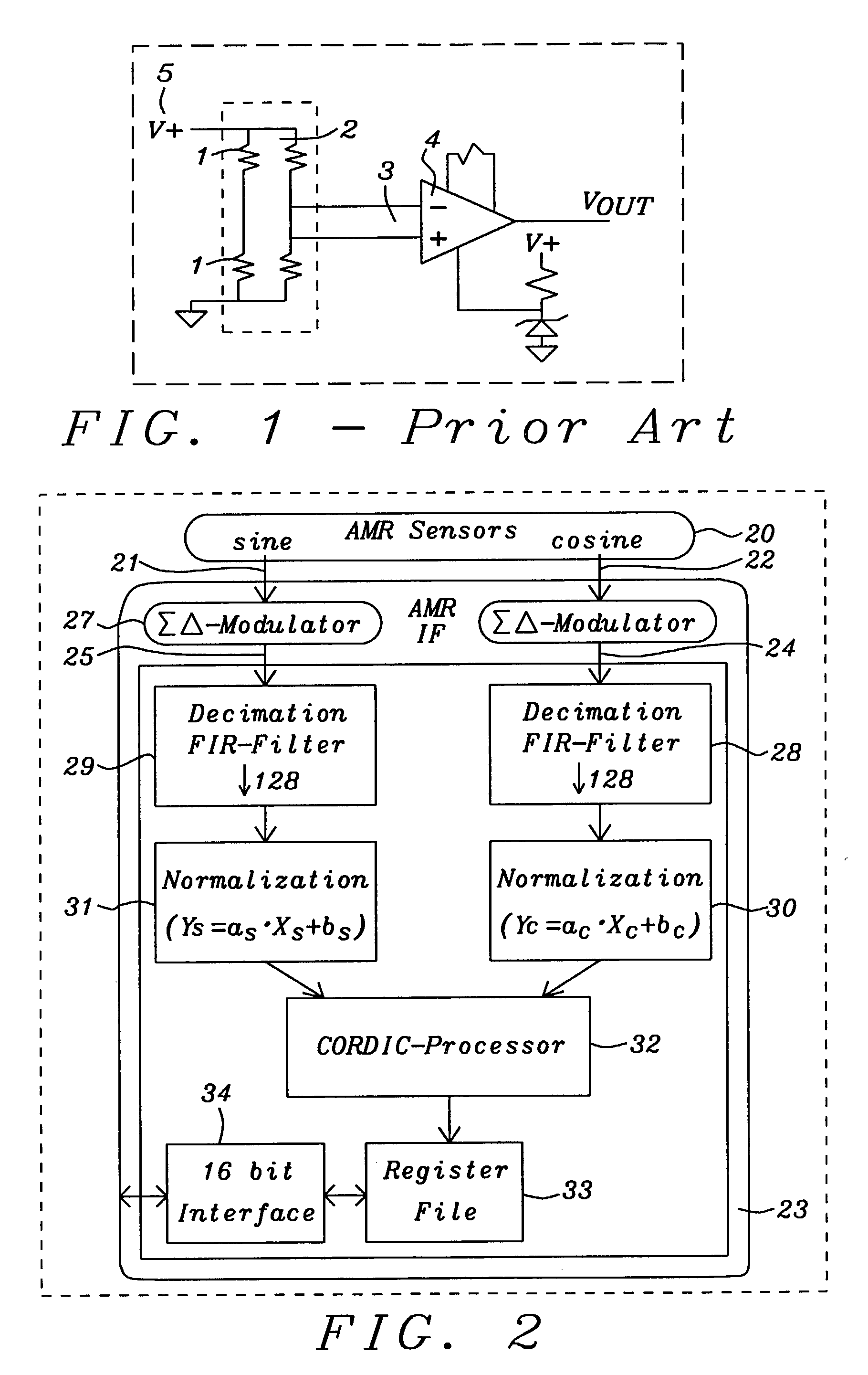

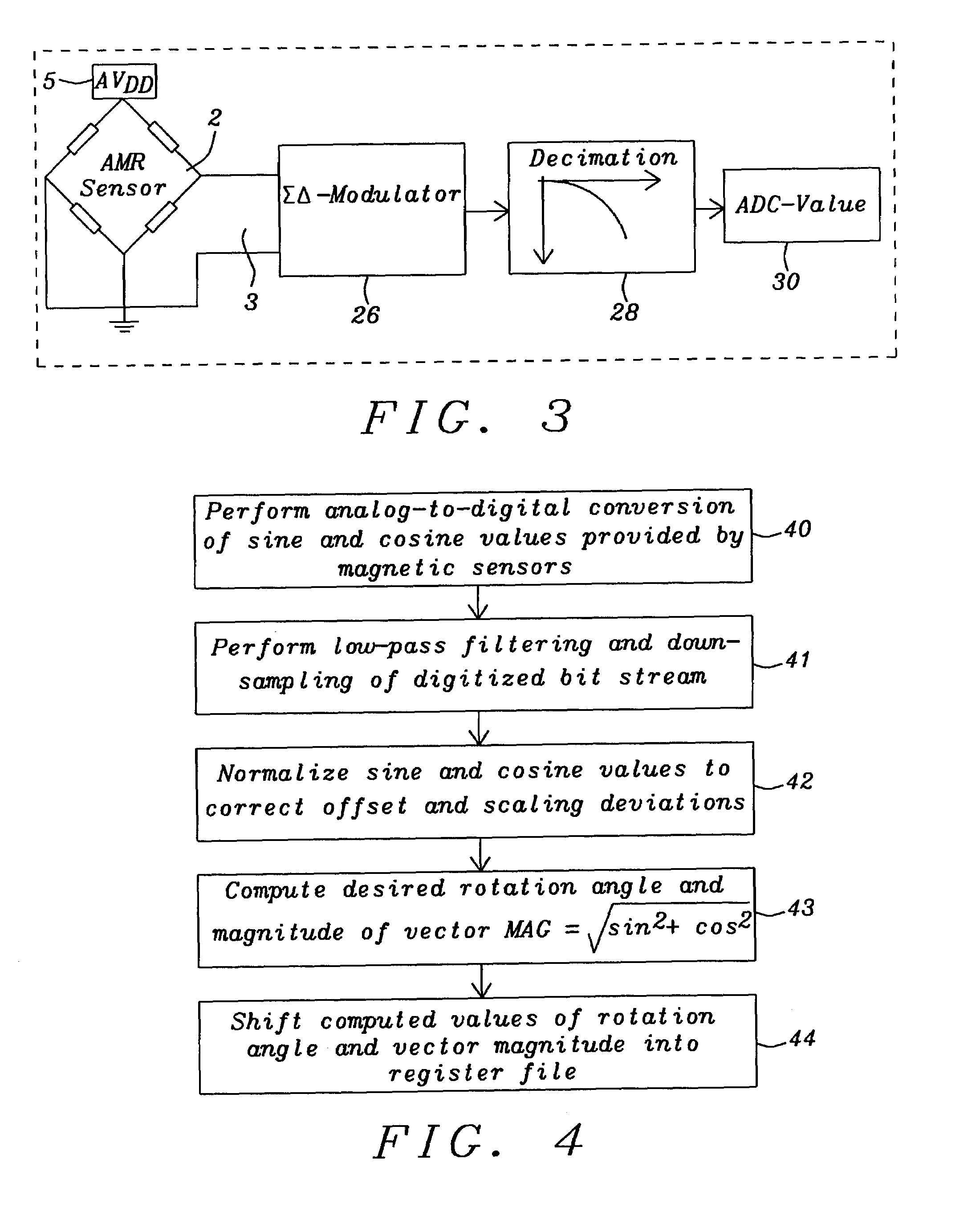

Magnetic sensor digital processing interface for electrical motor application

InactiveUS7064538B2Pulse generation by non-linear magnetic/dielectric devicesSolid-state devicesShift-and-addAnalog signal

A system and methods for an interface for magnetic sensors to determine a rotational angle has been achieved. This interface can be used for magnetic sensors providing analog signals of the sine and cosine values of the angle to be determined. Analog signals are being processed in two measurement paths for the sine and cosine signal each until the desired angle is computed by a CORDIC processor. The first stage of the measurement path is the conversion of the sine and cosine signals from analog to digital by 2nd order delta-sigma modulators with an over-sampling ratio. A low-pass decimation filter with sinc3 characteristic performs the digital value computation. The next stage normalizes the digitized sine and cosine values to correct offset and scaling deviations. The CORDIC processor computes the angle by decomposing the desired rotation angle into iterations of pre-defined elementary rotation angles performing the rotation operation by simple shift-and-add operations and the magnitude of the vector using the output from the normalization stages.

Owner:DIALOG SEMICONDUCTOR GMBH

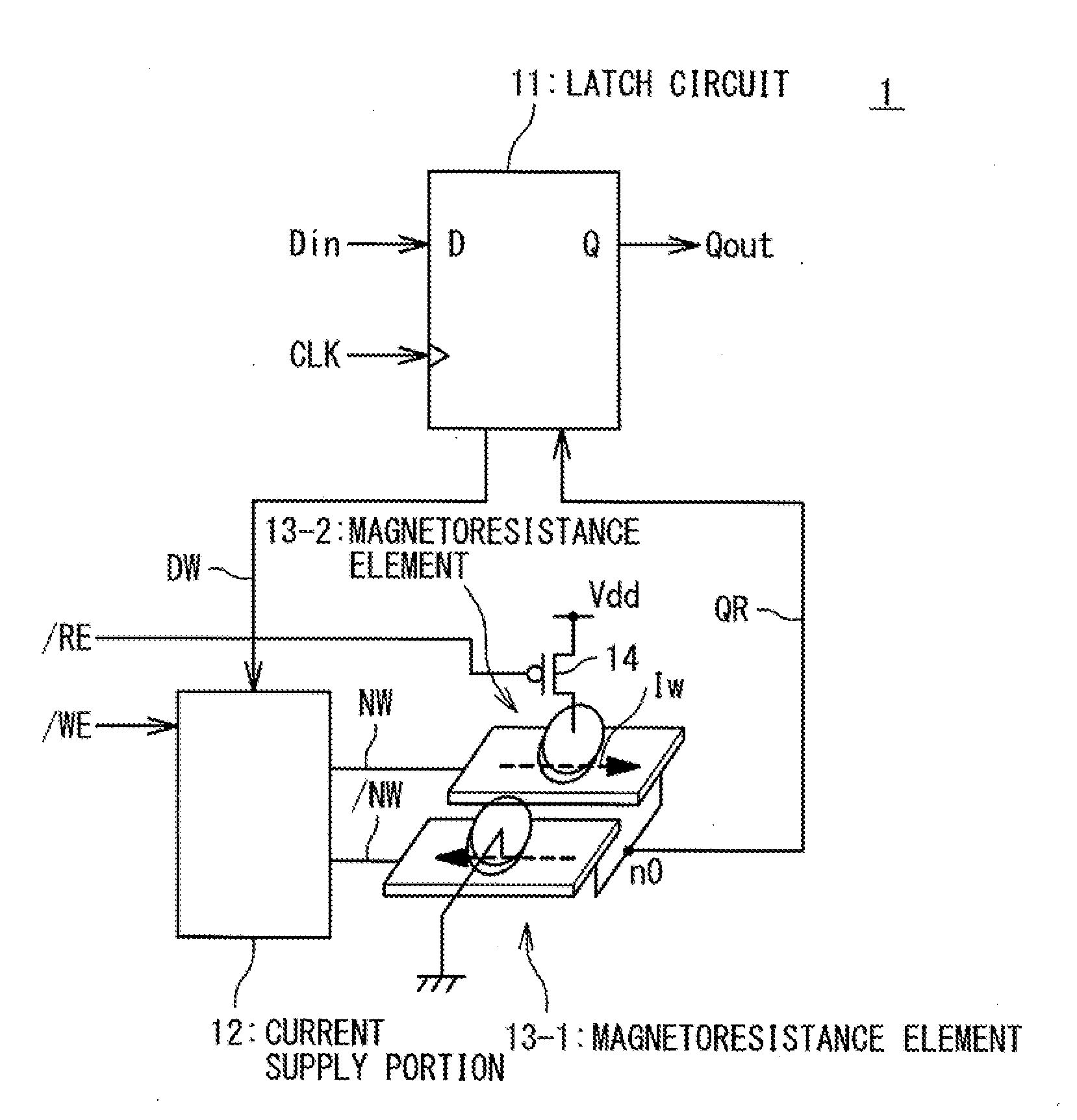

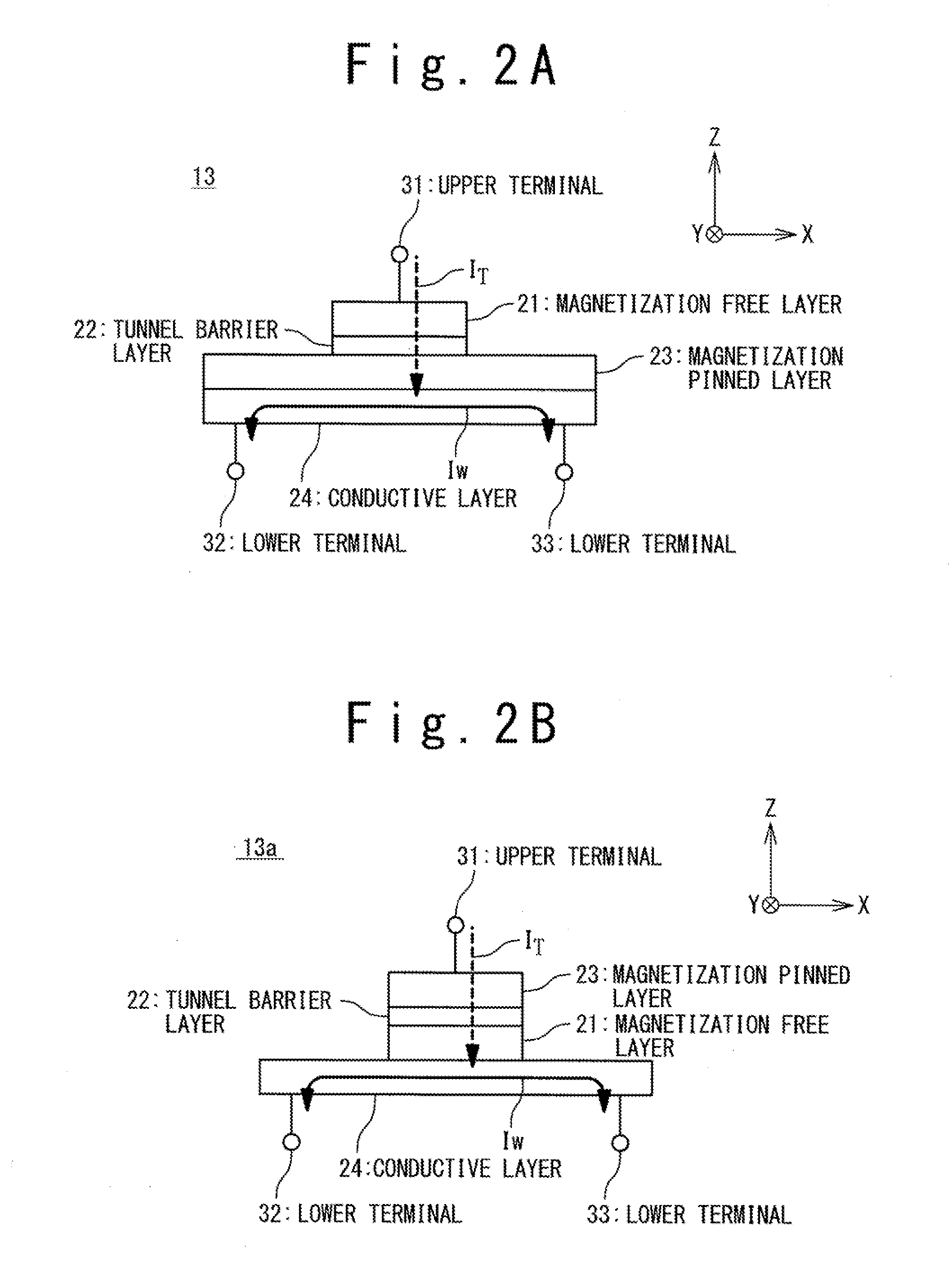

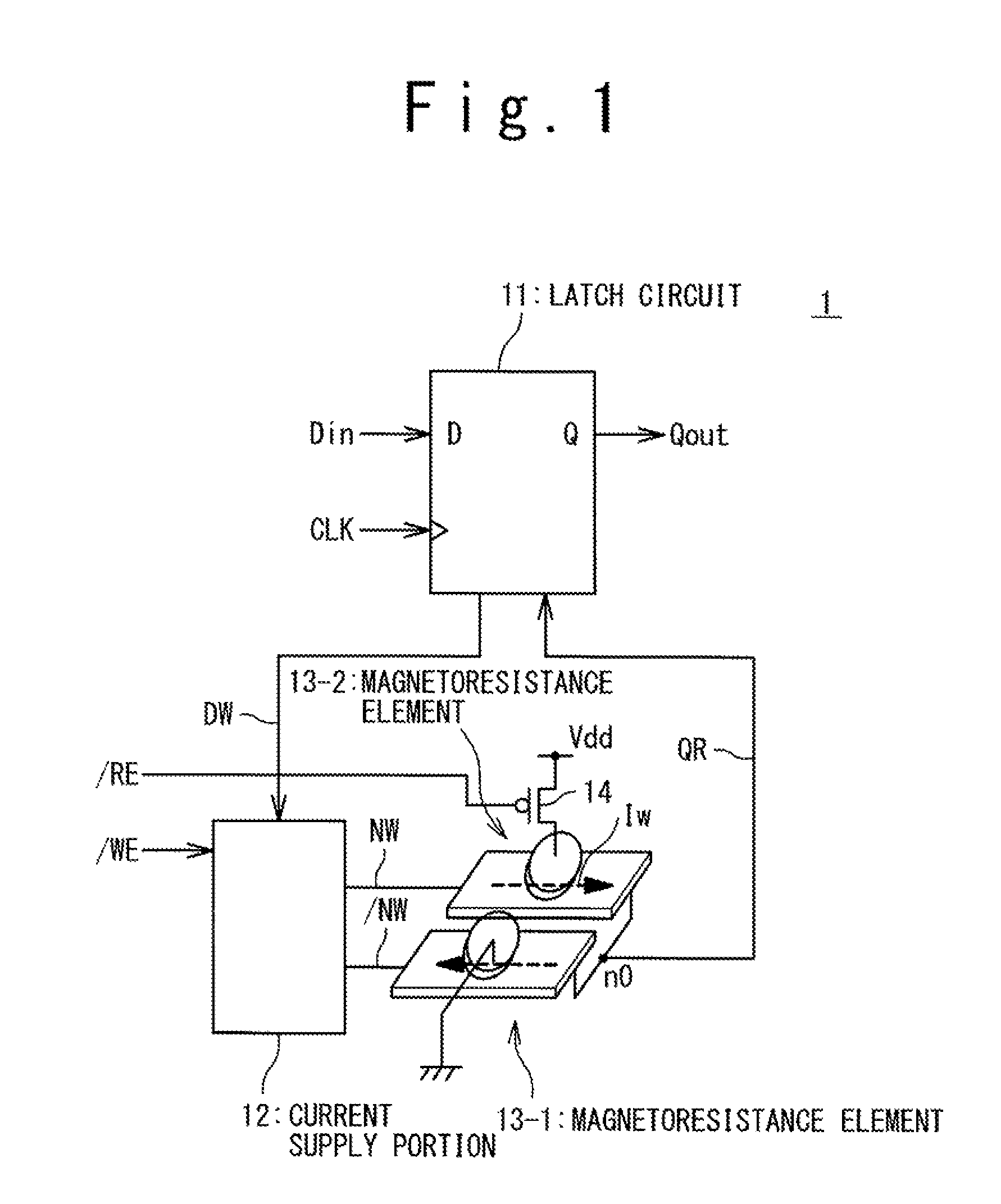

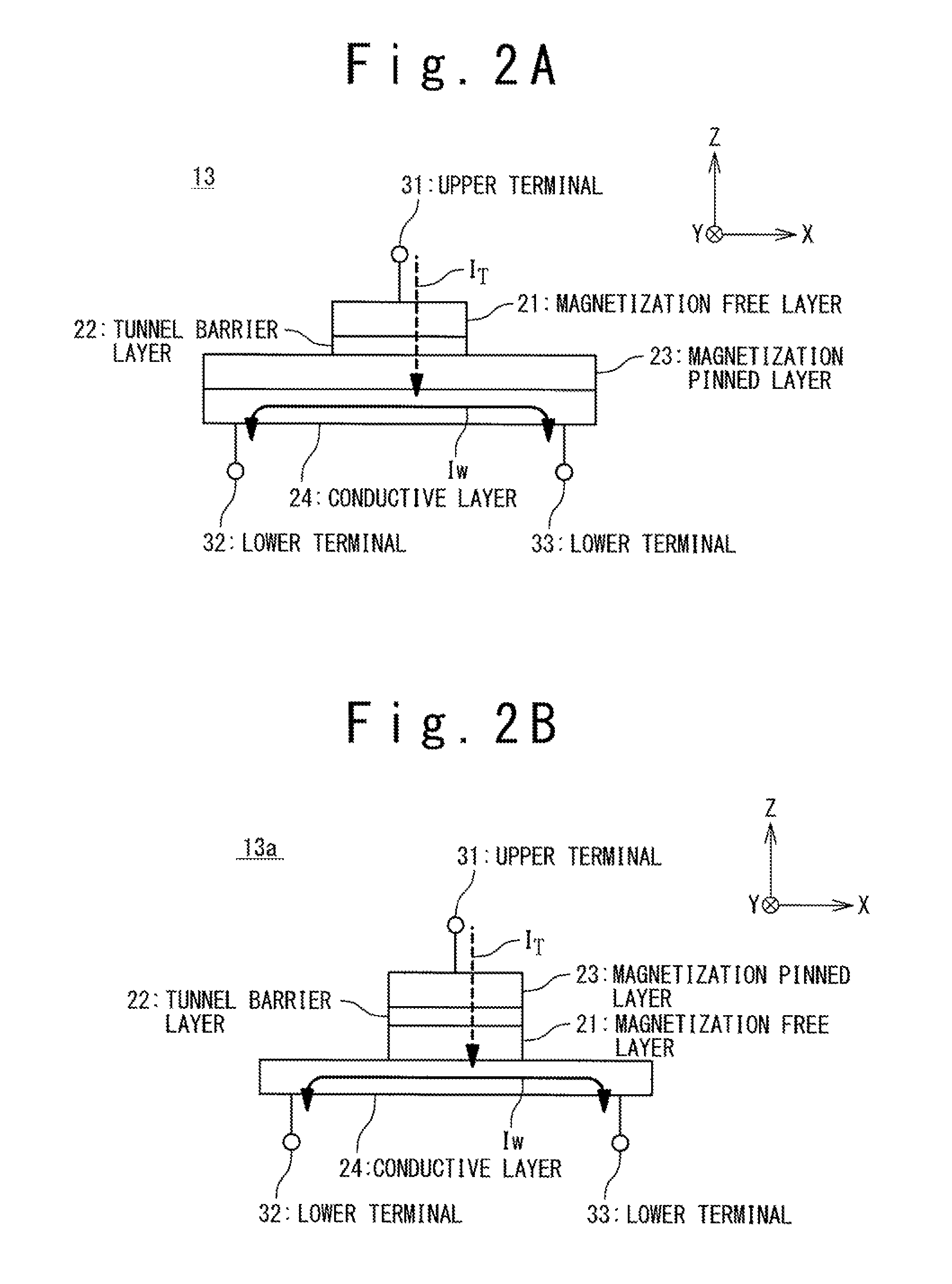

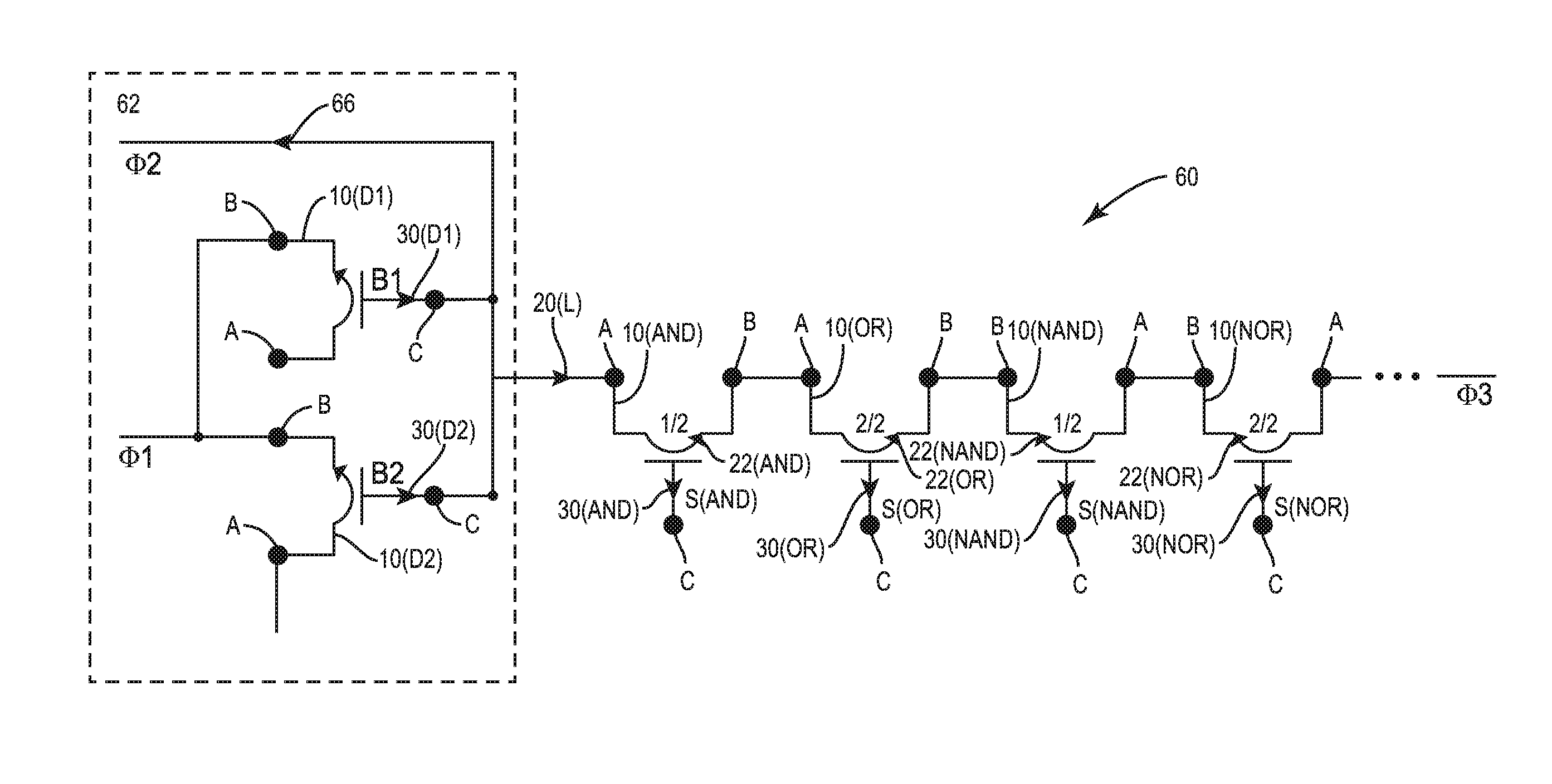

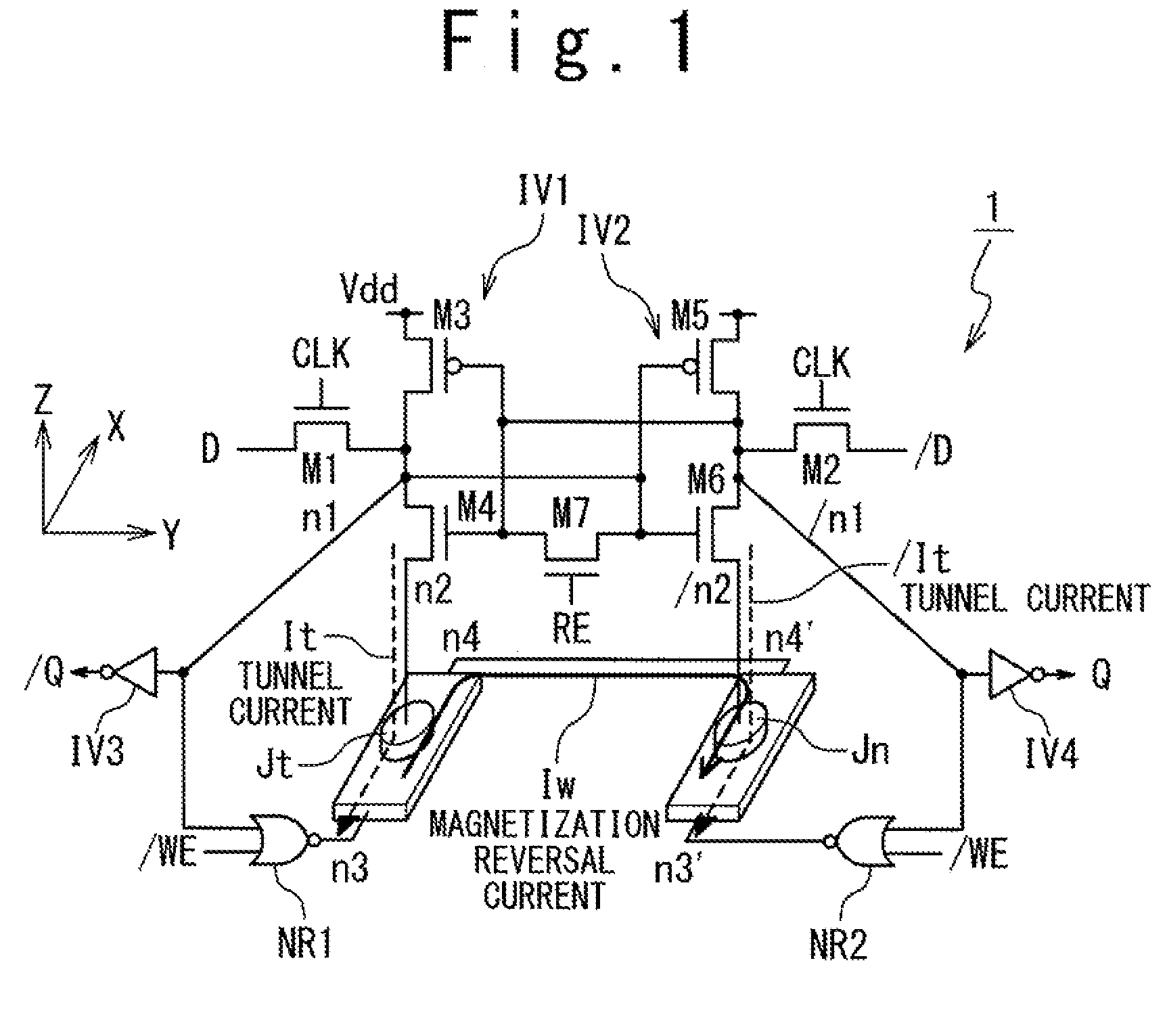

Nonvolatile latch circuit and logic circuit using the same

ActiveUS20100265760A1Effective holdingImprove reliabilityPulse generation by non-linear magnetic/dielectric devicesMagnetic-field-controlled resistorsHemt circuitsMagnetic reluctance

A nonvolatile latch circuit includes: a latch circuit; a first magnetoresistance element and a second magnetoresistance element; and a current supply portion. The latch circuit temporarily holds data. Each of the first magnetoresistance element and the second magnetoresistance element includes a first magnetic layer and a second magnetic layer that are stacked with an insulating film sandwiched therebetween. The current supply portion complementarily changes magnetization states of the first magnetoresistance element and the second magnetoresistance element based on a state of the latch circuit. The first magnetic layer of the first magnetoresistance element and the first magnetic layer of the second magnetoresistance element are series-connected to each other in. The latch circuit has a function that brings data corresponding to the magnetization states to data held by the latch circuit.

Owner:NEC CORP

Input apparatus with haptic feedback

InactiveUS20130002341A1Reduce frictionPulse generation by non-linear magnetic/dielectric devicesElectronic switchingEngineeringPrinted circuit board

The input device has a printed circuit board (5) to which a plurality of coils (L1-L8) has been fitted which, together with a capacitor (C2), each form a frequency-determining element of an oscillator (1). The coils (L1-L8) are arranged so as to be distributed along a path (K), which may also be a circular path. A movable magnet portion (M) can be displaced relative to the printed circuit board (5). At least one further stationary magnet portion (M1-M8) is mounted on the printed circuit board (5), which is opposite the movable magnet portion (M).

Owner:FM MARKETING

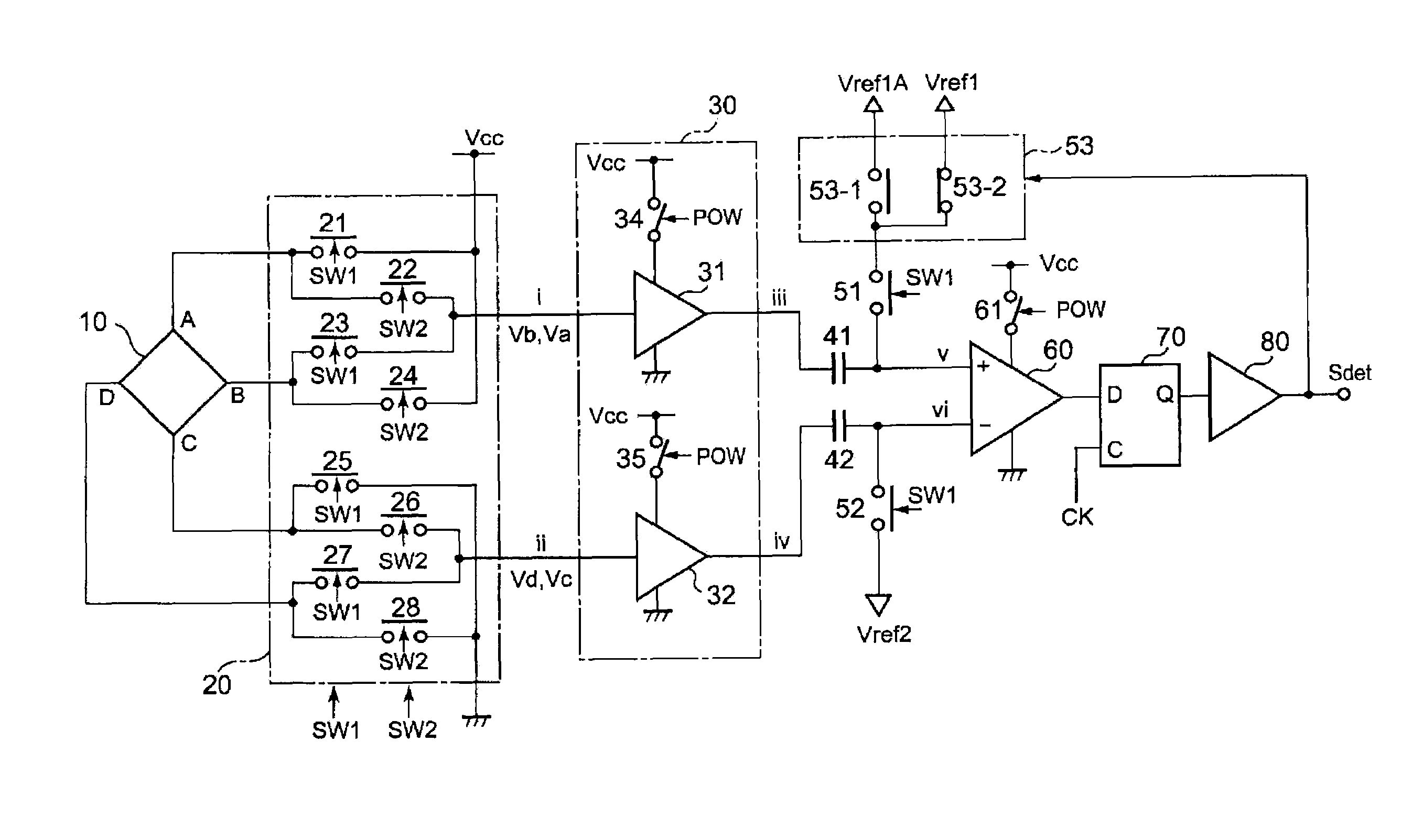

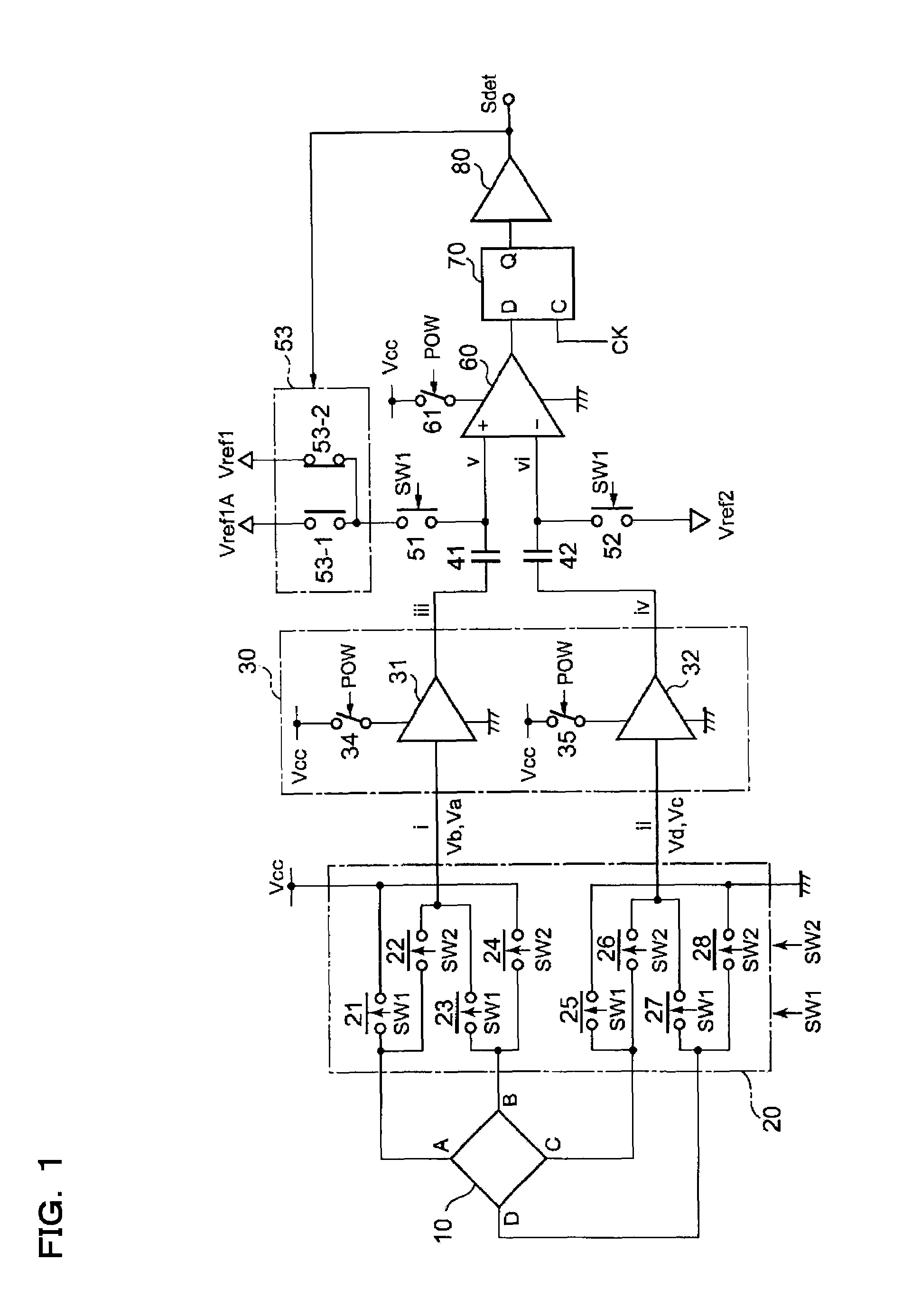

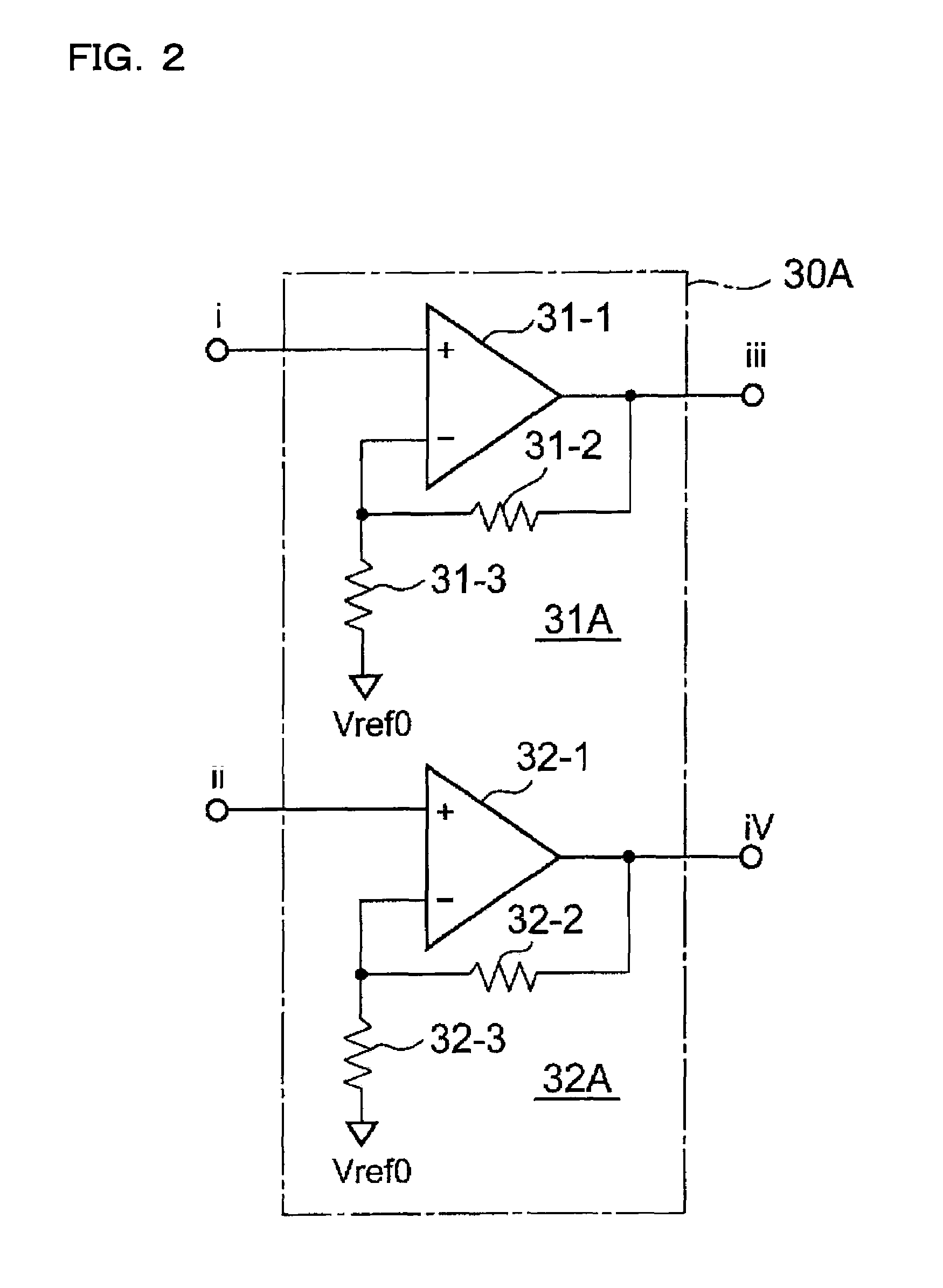

Sensor circuit, semiconductor device, and electronic apparatus

InactiveUS7659716B2Simple structureTotal current dropPulse generation by non-linear magnetic/dielectric devicesMagnetic field measurement using galvano-magnetic devicesCurrent consumptionEngineering

A sensor circuit has: a sensor portion that obtains, as an electrical signal, information on an object to be measured or detected; and a control circuit that controls the operation of the sensor portion. The control circuit receives a start input signal inputted thereto from outside for making the sensor portion operate only for a given duration after the start input signal is inputted thereto. With this configuration, it is possible to reduce the current consumption by arbitrarily controlling a period of an intermittent operation of the sensor circuit.

Owner:ROHM CO LTD

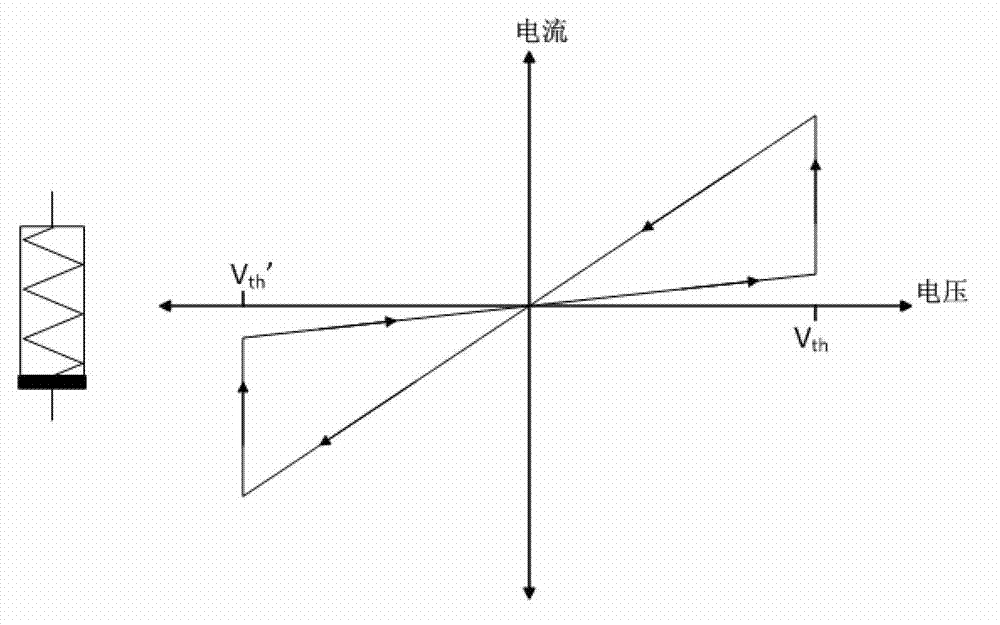

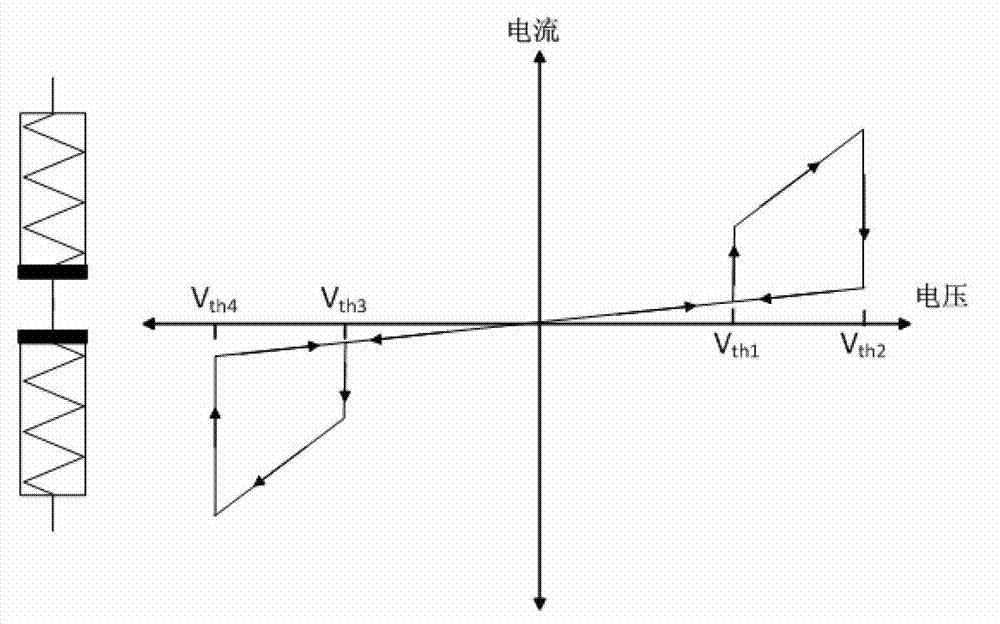

Data holding device

ActiveUS20110128769A1Reduce operating speedIncreased power consumptionPower reduction by control/clock signalPulse generation by non-linear magnetic/dielectric devicesHysteresisEngineering

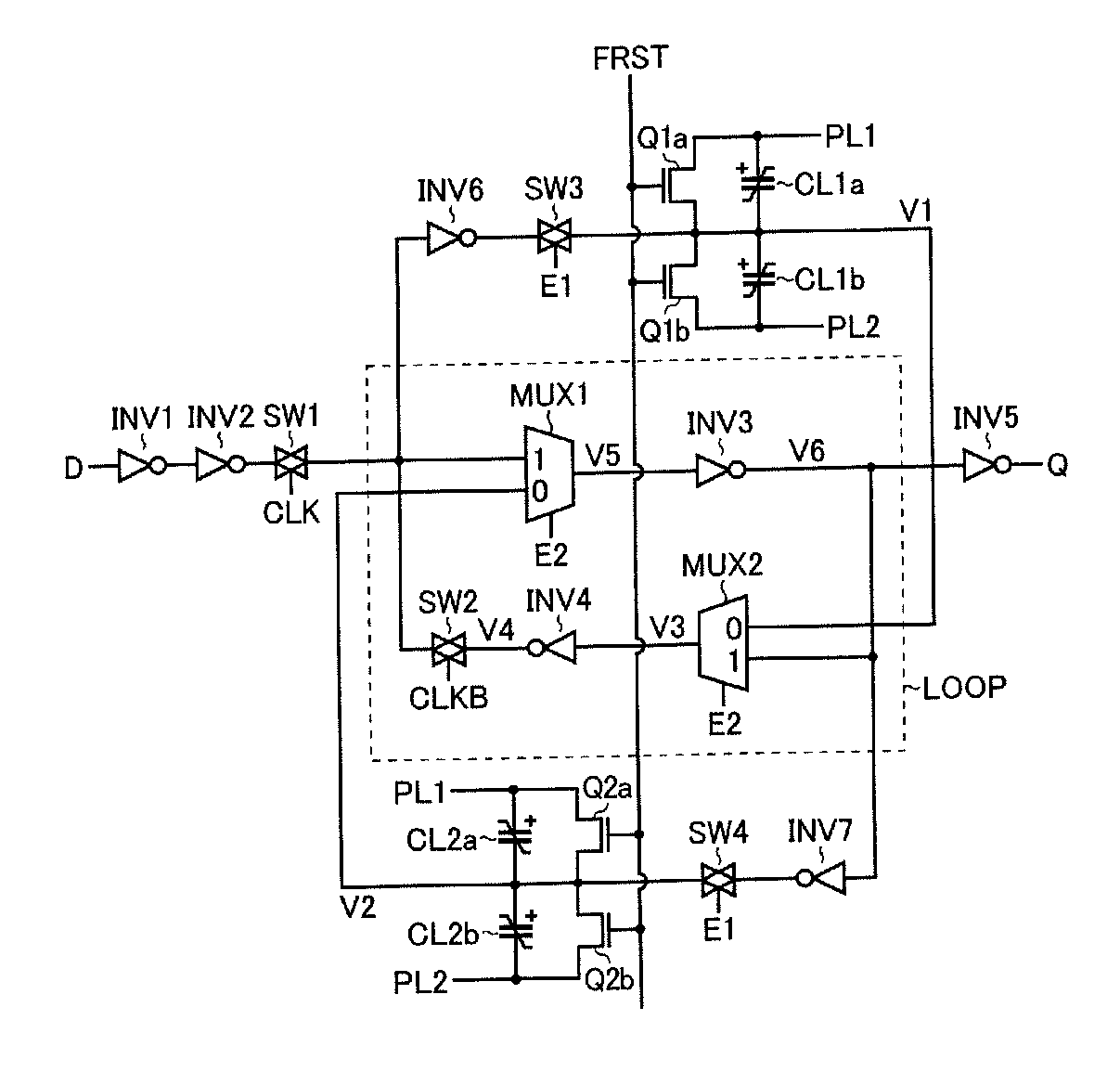

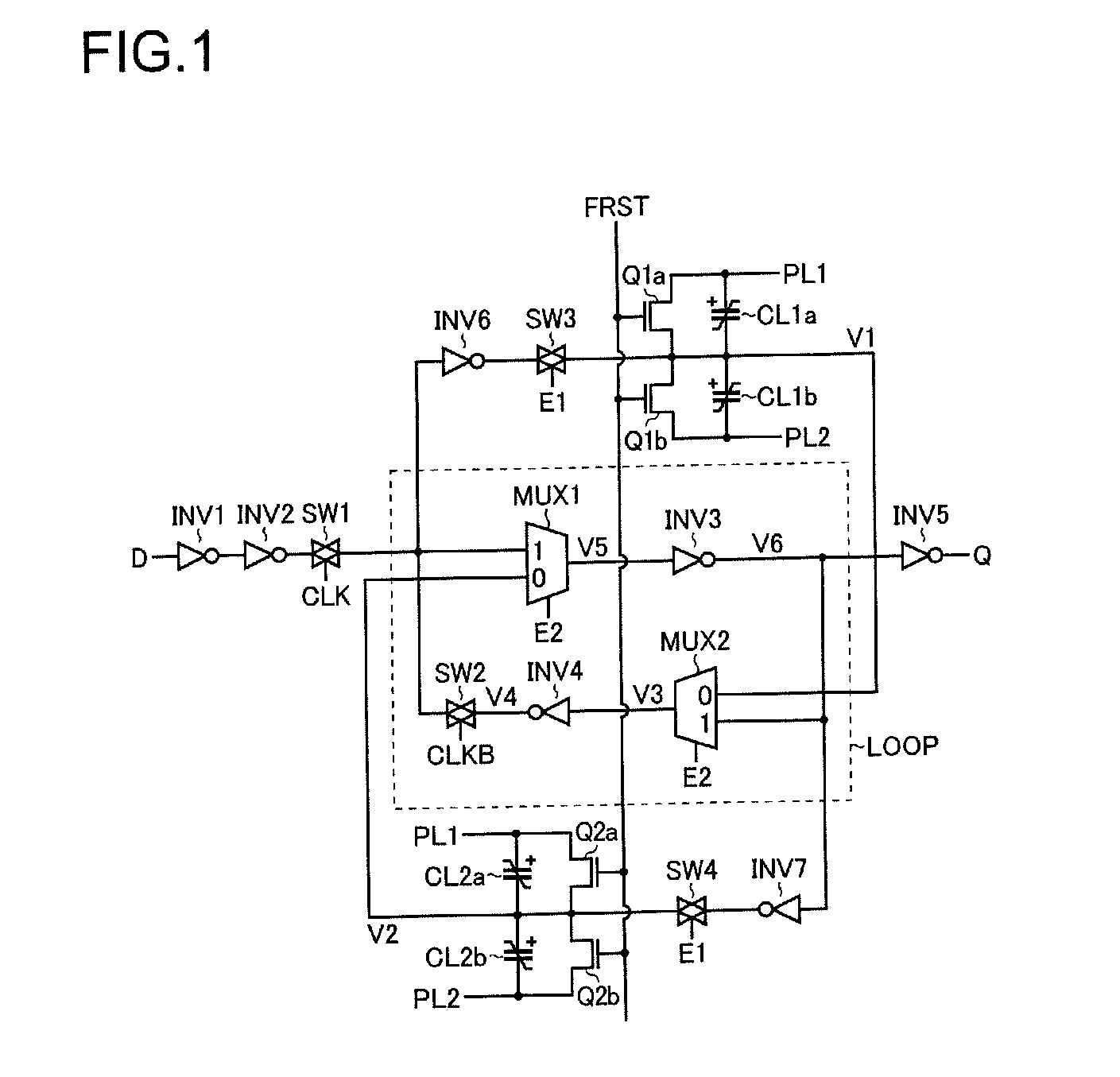

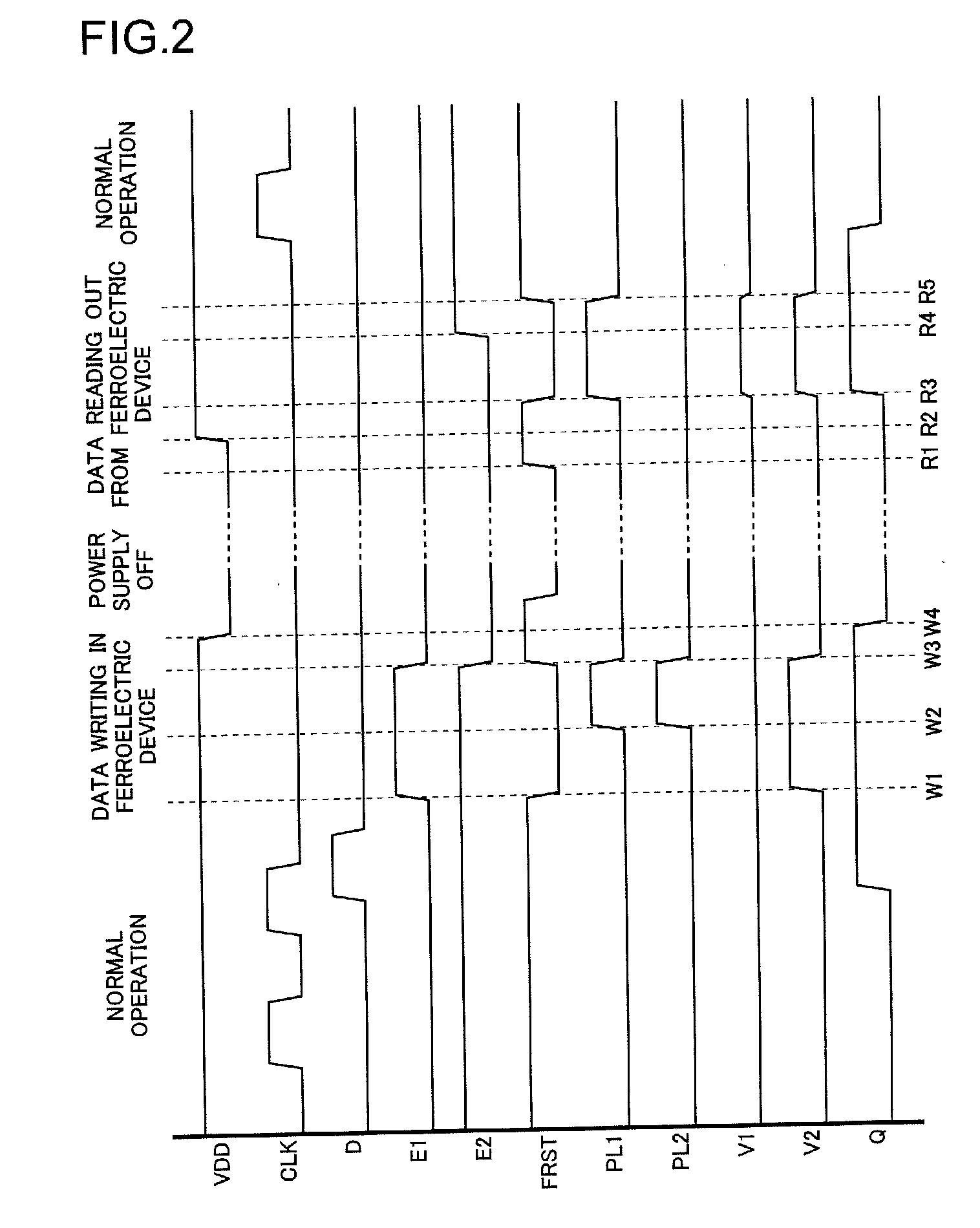

A data holding device comprises a loop structure part (LOOP) that holds data by use of logic gates connected in a loop (e.g., inverters INV3 and INV4 of FIG. 1); a nonvolatile storage part (CL1a, CL1b, CL2a, CL2b, Q1a, Q1b, Q2a and Q2b) that utilizes the hysteresis characteristic of a ferroelectric element to store, in a nonvolatile manner, the data held in the loop structure part (LOOP); and a circuit isolating part (MUX1, MUX2, INV6, INV7, SW3 and SW4) that electrically isolates the loop structure part (LOOP) from the nonvolatile storage part.

Owner:ROHM CO LTD

Nonvolatile latch circuit and nonvolatile flip-flop circuit

ActiveUS7733145B2Improve good performanceImprove staminaPulse generation by non-linear magnetic/dielectric devicesDigital storageControl signalLogic gate

A nonvolatile latch circuit includes: a first gate part controlling to load or intercept an input signal based on a gate signal; a first logic gate functioning as an inverter or a gate outputting a constant voltage in response to the first control signal; a second logic gate functioning as an inverter or a gate outputting the constant voltage in response to the first control signal; a second gate part controlling to load or intercept the output of the second logic gate based on an inverted signal of the gate signal and sends the output of the second logic gate to an first input terminal of the first logic gate; and first and second injection type MTJ elements provided between the driving power supply and the first and second logic gates and changing in resistance depending upon a current flow direction.

Owner:KIOXIA CORP

Method and apparatus for control of pulsed power in hybrid energy storage module

ActiveUS9837996B2Electrical storage systemPulse generation by non-linear magnetic/dielectric devicesConductor CoilMultiple input

A hybrid energy storage system is configured to control pulsed power. A first dynamo-electric machine is coupled to an inertial energy storage device and has multiple input stator windings configured to accept input power from a source. A polyphase output stator winding is configured to deliver electric power having a first response time to a DC bus. A secondary energy storage system is coupled to the DC bus and is configured to convert its stored energy to electric power in a bidirectional manner. A second dynamo-electric machine has an input stator winding and at least one polyphase output stator winding coupled to a converter, the converter coupled to a DC output. A polyphase boost exciter is configured to derive energy from the DC bus and excite the second machine input stator winding, wherein the second machine is configured to be excited at a faster rate than the first response time of the first machine.

Owner:RAYTHEON CO

Nonvolatile latch circuit and logic circuit using the same

ActiveUS8243502B2Effective holdingImprove reliabilityPulse generation by non-linear magnetic/dielectric devicesMagnetic-field-controlled resistorsHemt circuitsMagnetic reluctance

Owner:NEC CORP

Method and system for controlling a handheld electronic device

ActiveUS20090009233A1Travelling carriersPulse generation by non-linear magnetic/dielectric devicesElectricityComputer science

A method (500), a handheld electronic device (102) and an external accessory (402) for controlling at least one function of a plurality of functions of the handheld electronic device is provided. The method includes determining (504) whether the handheld electronic device is docked in an external accessory. Further, the method includes measuring (506) a first magnetic field density when the handheld electronic device is docked in the external accessory. Furthermore, the method includes generating (508) a signal to activate at least one function, based on an electrical parameter.

Owner:MOTOROLA SOLUTIONS INC

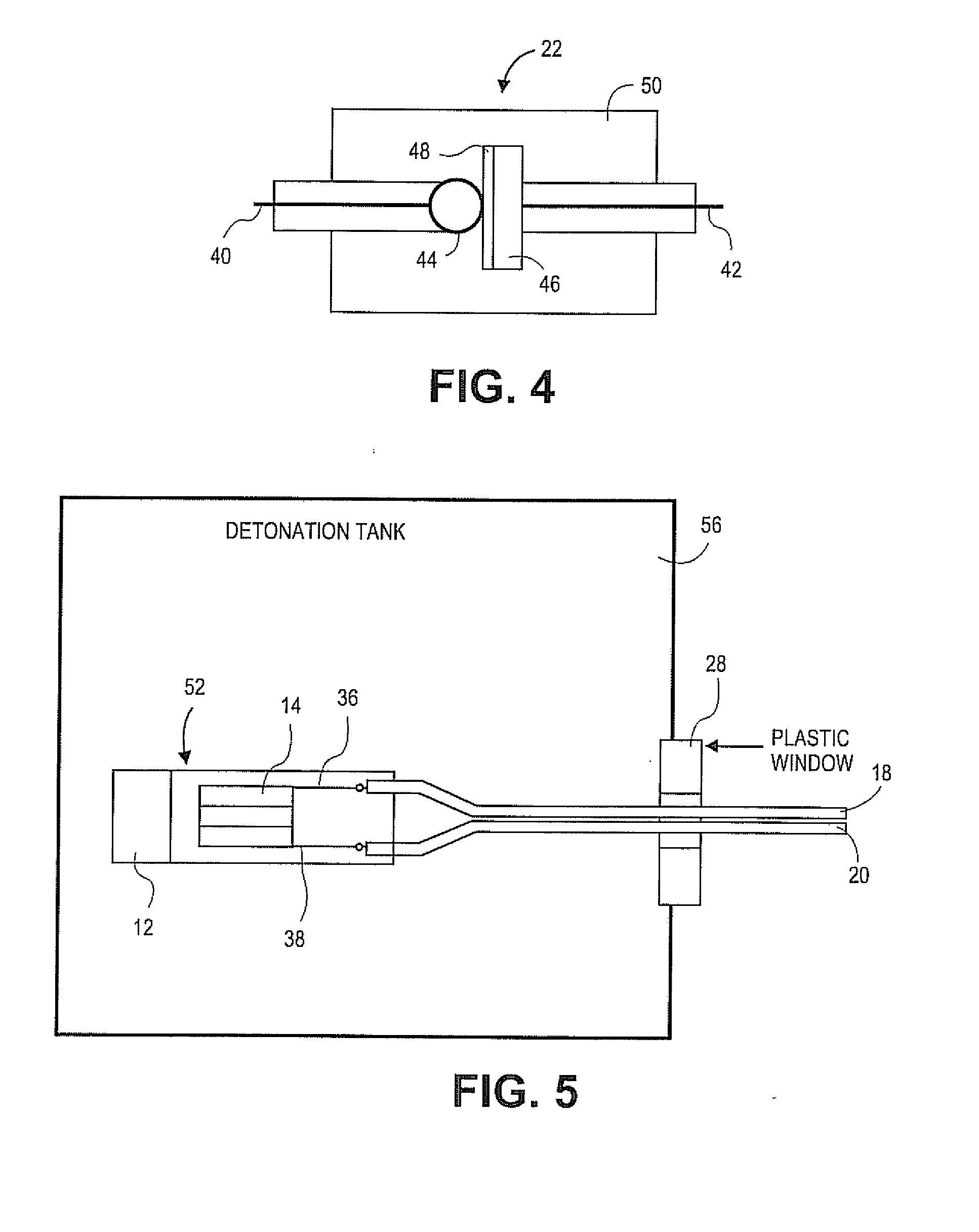

Energy generator systems with a voltage-controlled switch

ActiveUS20110006614A1Well formedPiezoelectric/electrostriction/magnetostriction machinesPulse generation by non-linear magnetic/dielectric devicesElectricityDetonation

A first energy generating system comprises a ferromagnetic generator coupled to a voltage controlled switch. The ferromagnetic generator includes a ferromagnetic element generating a magnetic field and positioned within a pulse generating coil and near an explosive charge. Detonation of the explosive charge decreases the magnetic field and induces a pulse of electric energy in the pulse generating coil. When the magnitude of the electric energy reaches a certain level, the voltage controlled switch closes. A second energy generating system comprises a flux compression generator coupled to a voltage controlled switch. The flux compression generator includes a inductance coil generating a magnetic field within a metallic armature that includes an explosive charge. Detonation of the explosive charge changes the magnetic field and induces a pulse of electric energy in the inductance coil. When the magnitude of the electric energy reaches a certain level, the voltage controlled switch closes.

Owner:LOKI

Control circuit and reconfigurable logic block

ActiveUS20050093574A1Shorten the timeLogic circuits characterised by logic functionPulse generation by non-linear magnetic/dielectric devicesControl signalInverter

A control circuit for providing a control signal to build a logic circuit includes a latch circuit including f0irst and second inverted logic gates; a first variable resistive memory provided between an output of the first inverted logic gate and an input of the second inverted logic gate, the first variable resistive memory configured to store a resistance value in accordance with a write signal; and a resistive element provided between an input of the first inverted logic gate, wherein the output of the second inverted logic gate serves to transmit the control signal.

Owner:KK TOSHIBA

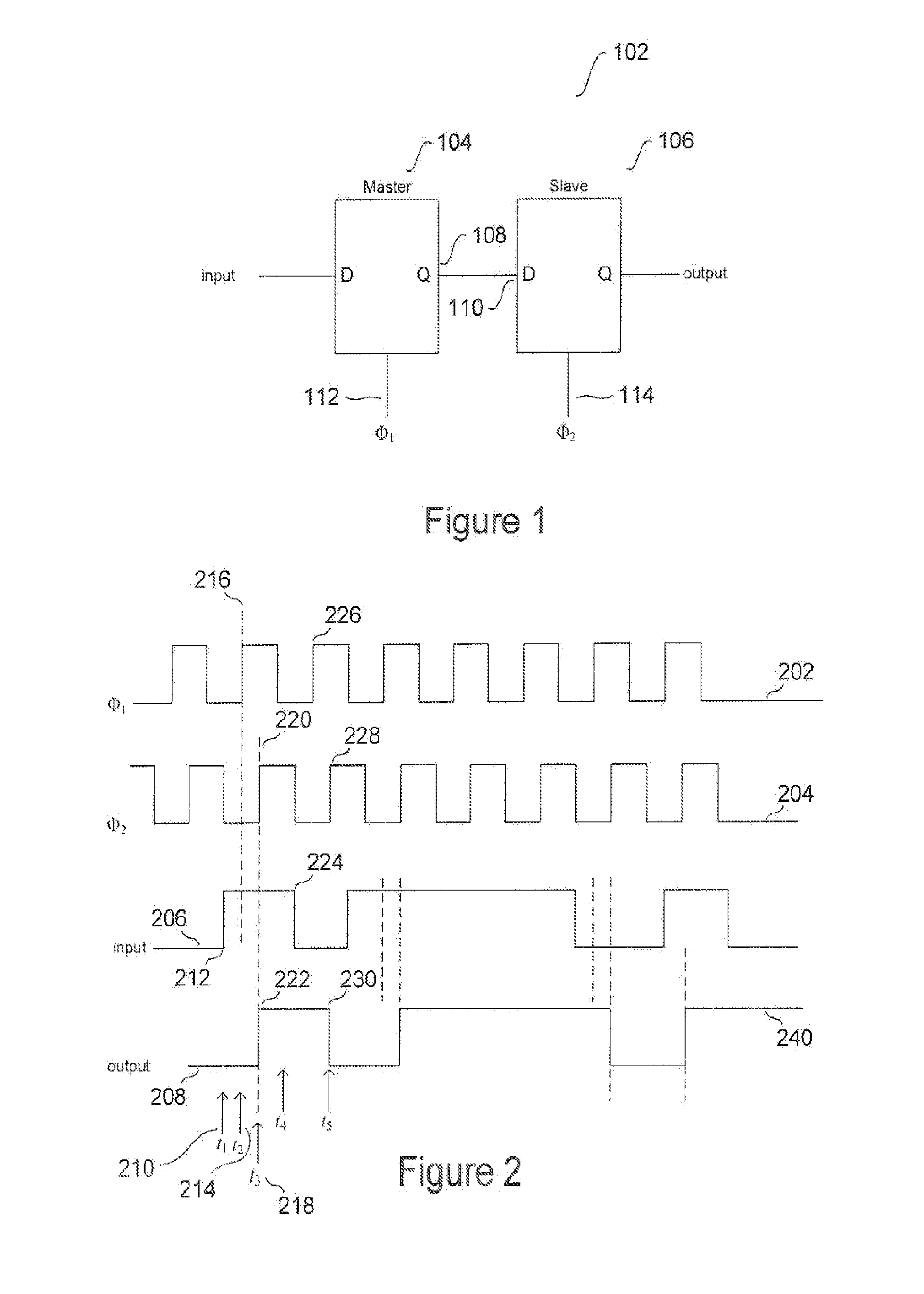

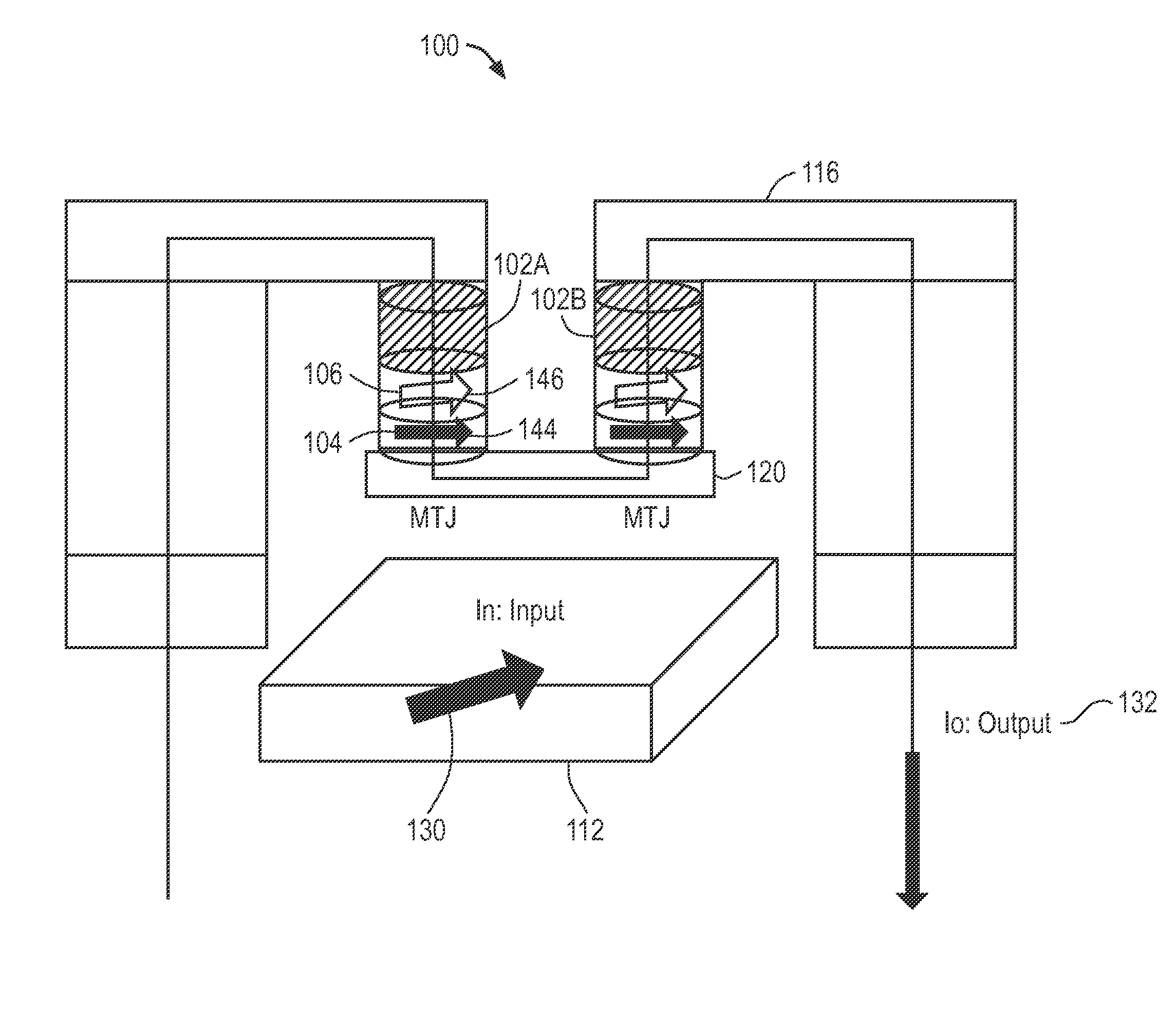

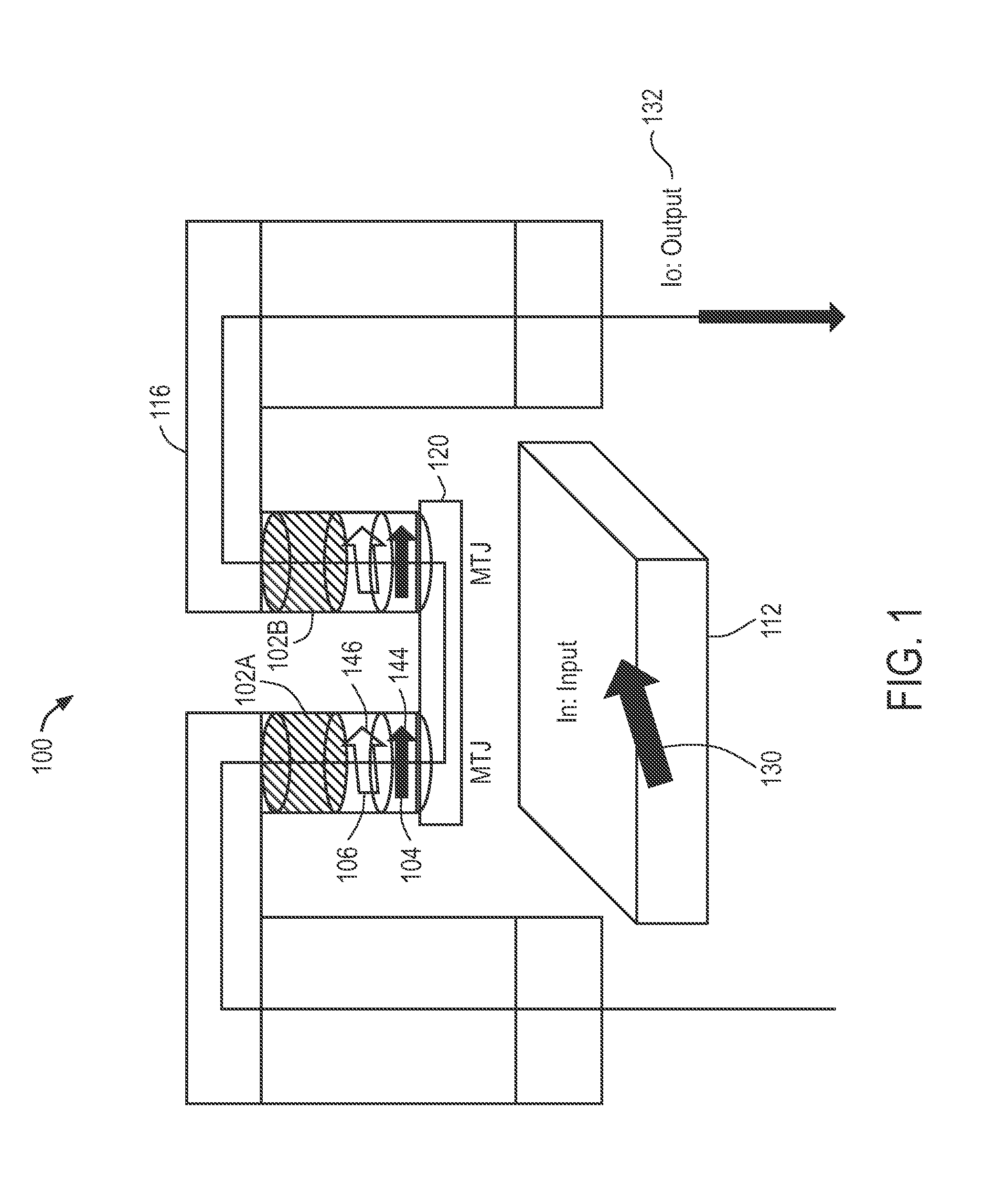

Spintronic logic gates employing a giant spin hall effect (GSHE) magnetic tunnel junction (MTJ) element(s) for performing logic operations, and related systems and methods

InactiveUS20150145576A1Improve power efficiencyImprove processing speedLogic circuits characterised by logic functionPulse generation by non-linear magnetic/dielectric devicesCharge currentSpin Hall effect

Aspects described herein are related to pipeline circuits employing a Giant Spin Hall Effect (GSHE) magnetic tunnel junction (MTJ) element(s) for performing logical operations. In one aspect, a pipeline circuit is disclosed. The pipeline circuit includes a first pipeline stage and a second pipeline stage. The first pipeline stage is configured to store a first bit set and to generate a first charge current representing the first bit set. The second pipeline stage includes a first GSHE MTJ element. The first GSHE MTJ element is configured to set a first bit state for the first logical operation, and has a first threshold current level. The first GSHE MTJ element is configured to generate a first GSHE spin current in response to the first charge current. In this manner, the first GSHE MTJ element is also configured to perform the first logical operation on the first bit set.

Owner:QUALCOMM INC

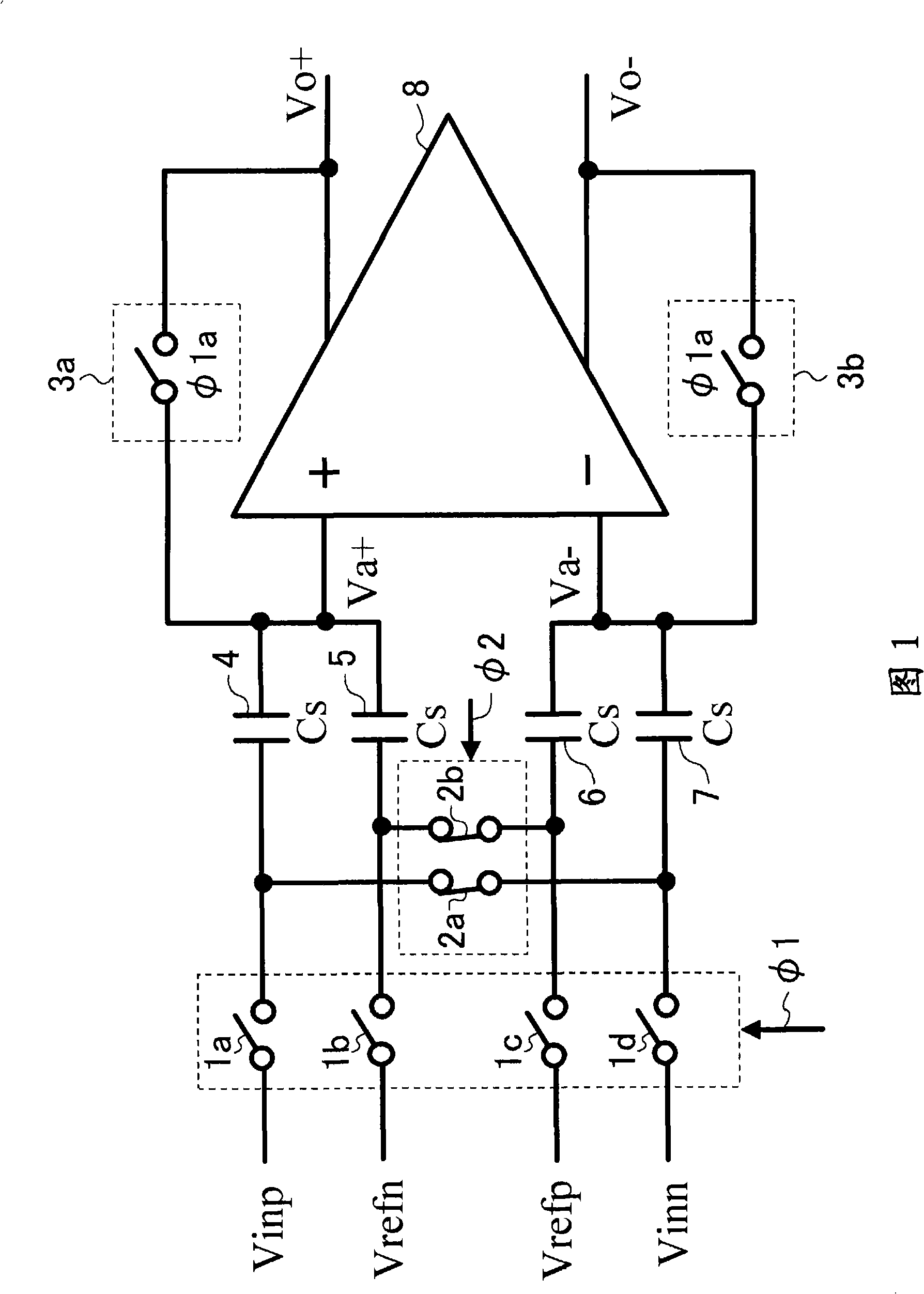

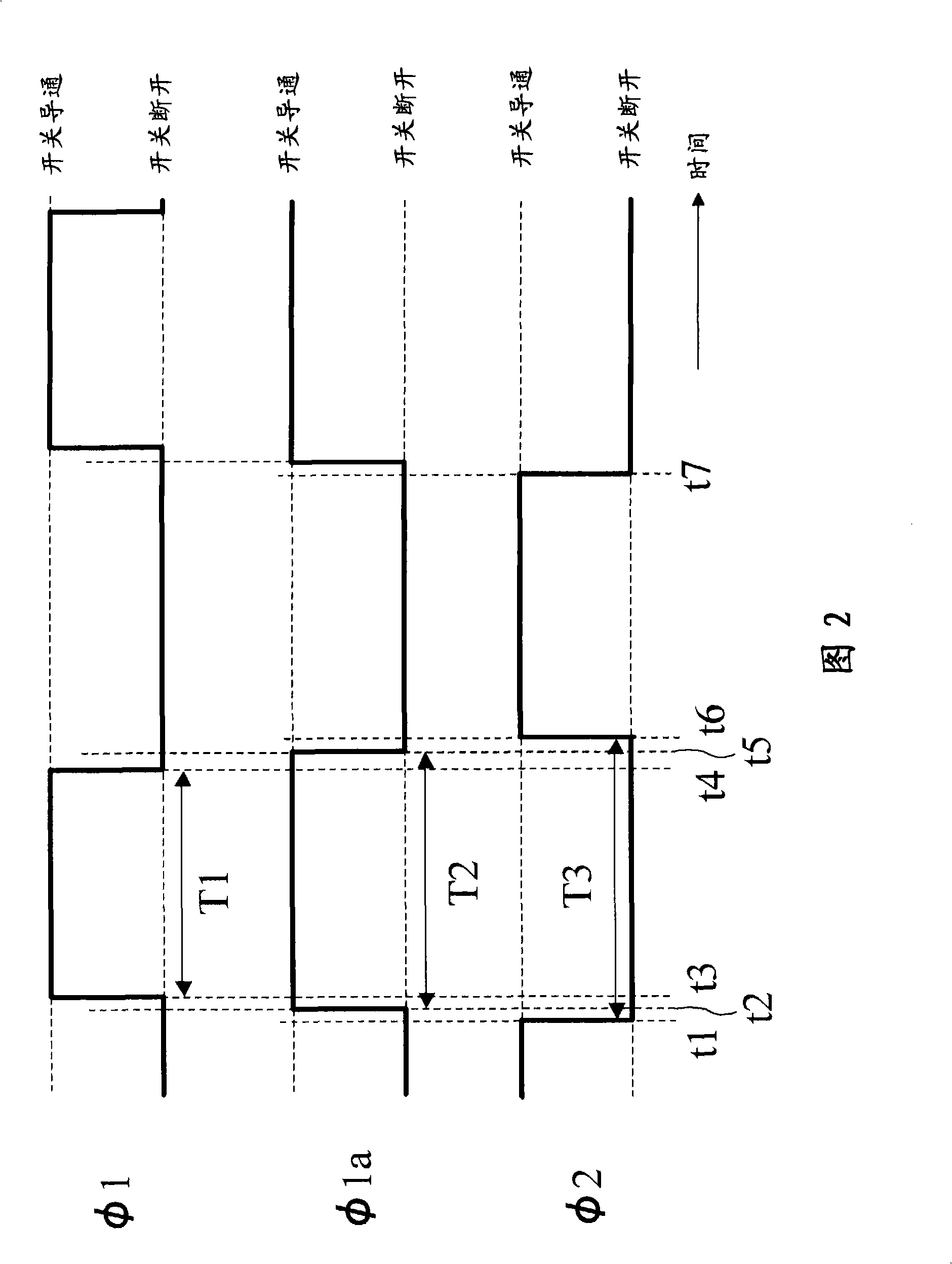

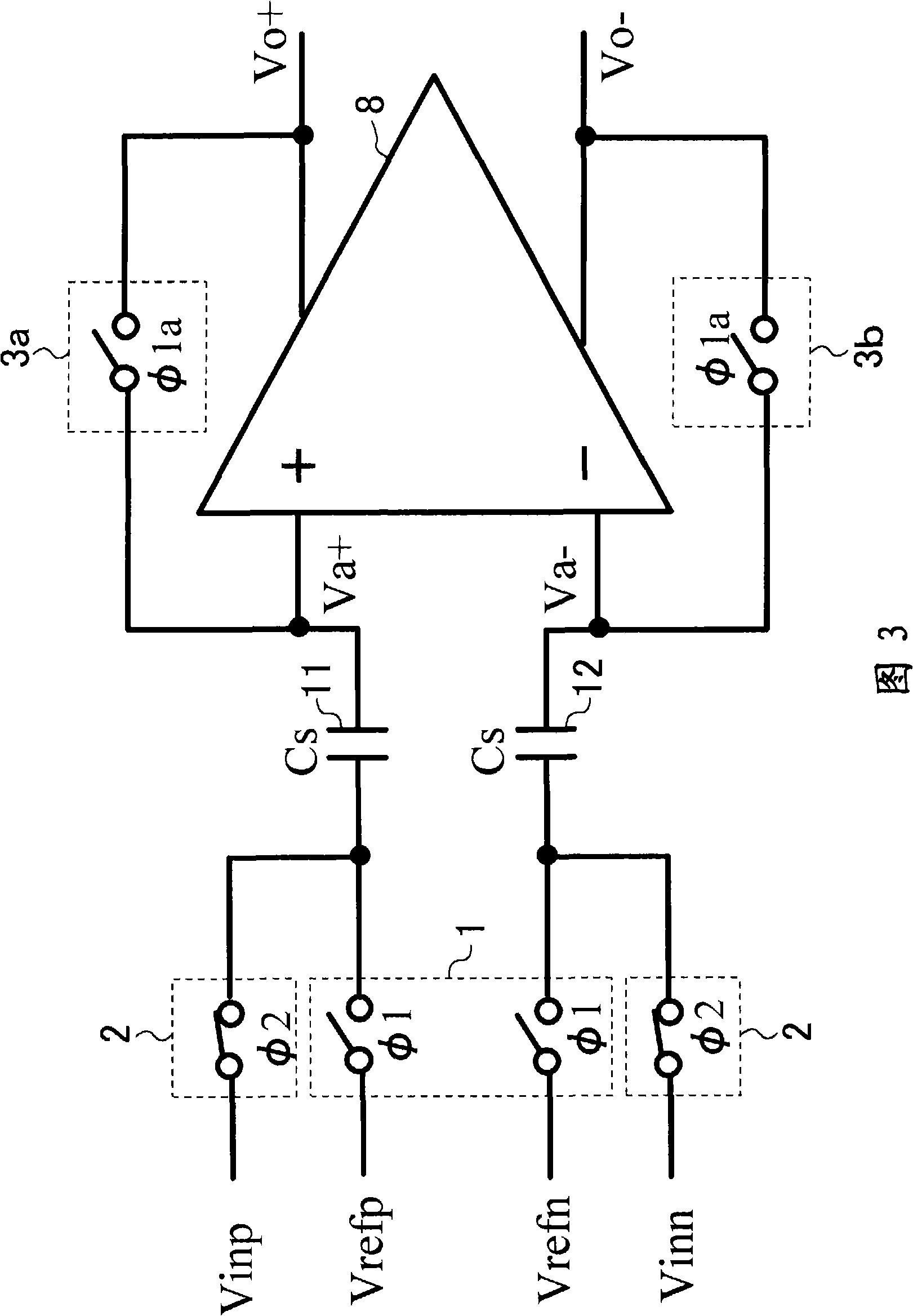

Fully differential comparator and fully differential amplifier

InactiveCN101313468AImprove use valueIncrease power consumptionMultiple input and output pulse circuitsPulse generation by non-linear magnetic/dielectric devicesCapacitanceEngineering

A first to a fourth sampling switch (1a to 1d), a first to a fourth sampling capacitor (4 to 7), and a first and a second charge redistribution switch (2a, 2b) are provided on the input side of a differential amplifier (8). A first and a second reset switch (3a, 3b) are provided between the input and the output of the differential amplifier (8). An input signal voltage (Vinp) having a positive polarity, a comparison reference voltage (Vrefn) having a negative polarity, a comparison reference voltage (Vrefp) having a positive polarity, and an input signal voltage (Vinn) having a negative polarity are respectively applied through a first to a fourth sampling switch (1a to 1d) to one end of each of the first to the fourth sampling capacitor (4 to 7). During a reset period, the reset of the differential amplifier (8) is released after sampling of each voltage is completed, and during a comparison period, the first and the second charge redistribution switch (2a, 2b) are electrically connected.

Owner:PANASONIC CORP

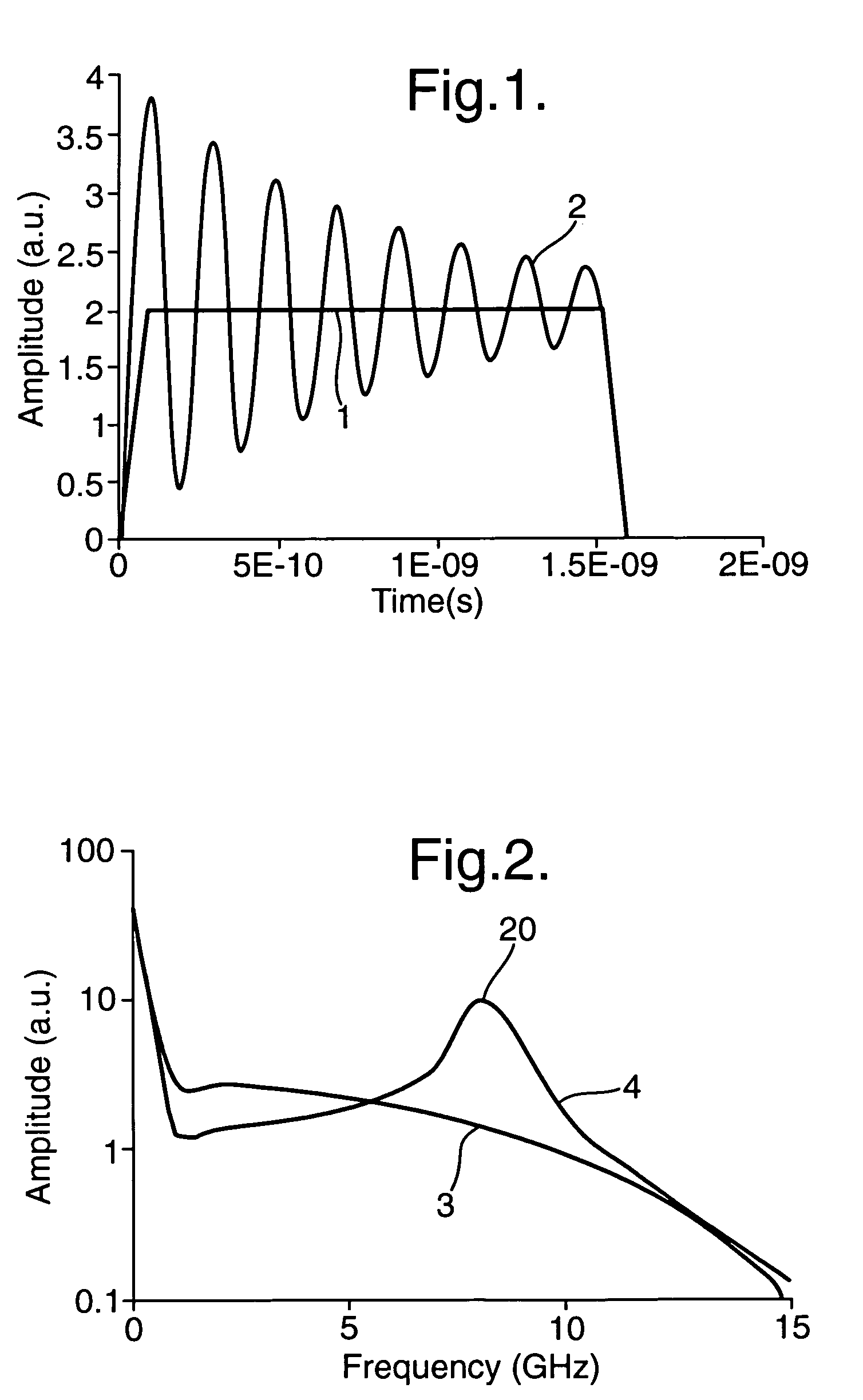

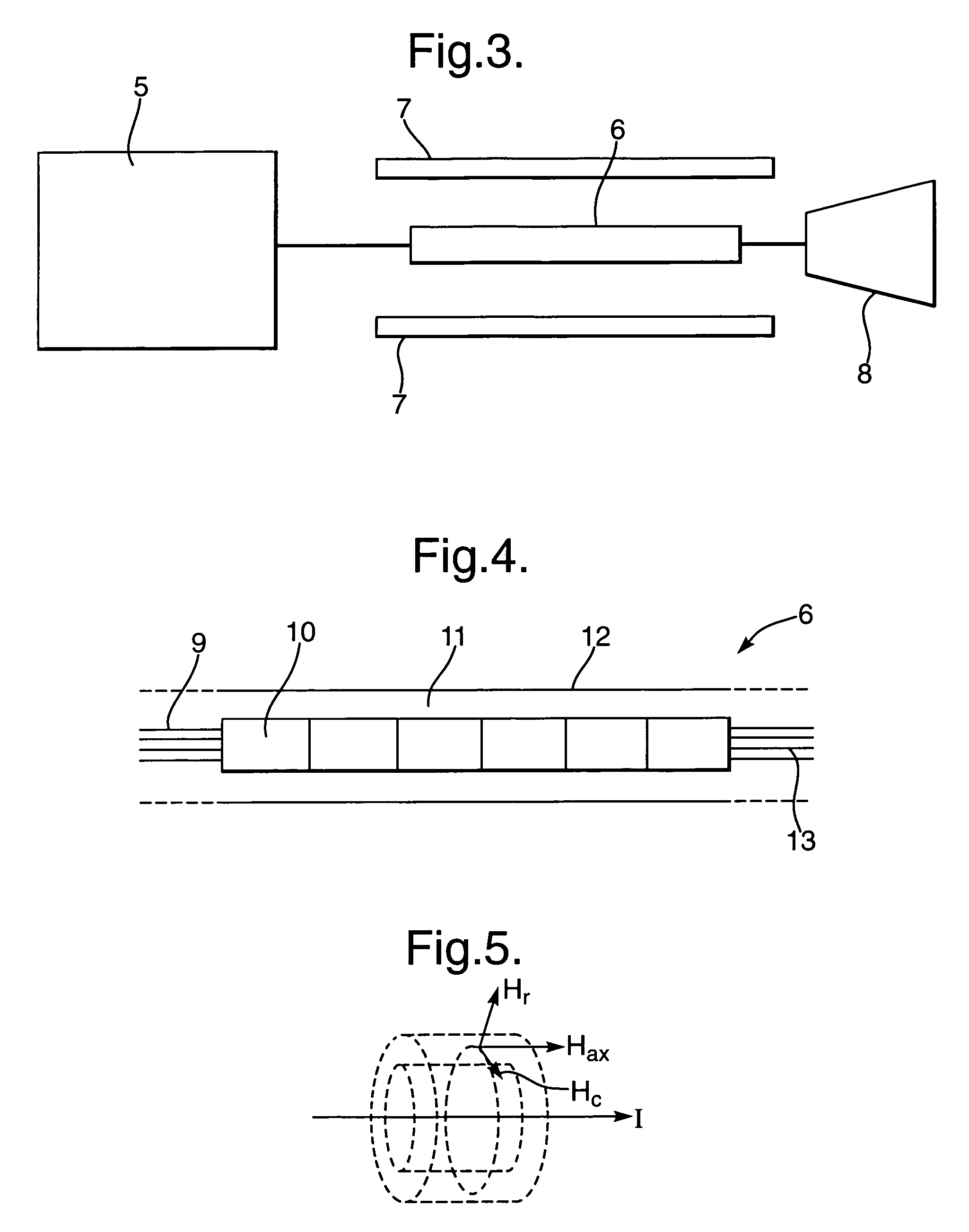

Radio frequency and microwave signals

InactiveUS7498978B2High energyIncreases the radiated fieldPulse modulationOscillations generatorsMicrowave rangePulse energy

A device for generating high powered Radio Frequency (RF) or microwave signals comprising a fast rise-time video pulse generator, a modulator to modify the generated UWB pulses by gyromagnetic action to transfer a portion of the UWB pulse energy from lower frequencies to frequencies in the RF or microwave range thereby producing a resultant RF or microwave waveform that can be radiated.

Owner:BAE SYSTEMS PLC

Nonvolatile latch circuit

ActiveUS8174872B2Total current dropReduces magnetization reversal currentNanotechPulse generation by non-linear magnetic/dielectric devicesReverse currentHemt circuits

A nonvolatile latch circuit includes: first and second inverters cross-coupled to hold 1-bit data; first and second magnetoresistive elements each having first to third terminals; and a current supply circuitry configured to supply a magnetization reversal current for changing the magnetization states of the first and second maqnetoresistive elements in response to the 1-bit data. The power terminal of the first inverter is connected to the first terminal of the first magnetoresistive element and the power terminal of the second inverter is connected to the first terminal of the second magnetoresistive element. The current supply circuitry is configured to supply the magnetization reversal current to the second terminals of the first and second magnetoresistive elements. The third terminal of the first magnetoresistive element is electrically connected to the third terminal of the second magnetoresistive element.

Owner:NEC CORP

Memristor-based non-volatile D trigger

ActiveCN103051307ARealize functionOperation continuedPulse generation by non-linear magnetic/dielectric devicesDigital storageEngineeringApplication areas

Owner:HUAZHONG UNIV OF SCI & TECH

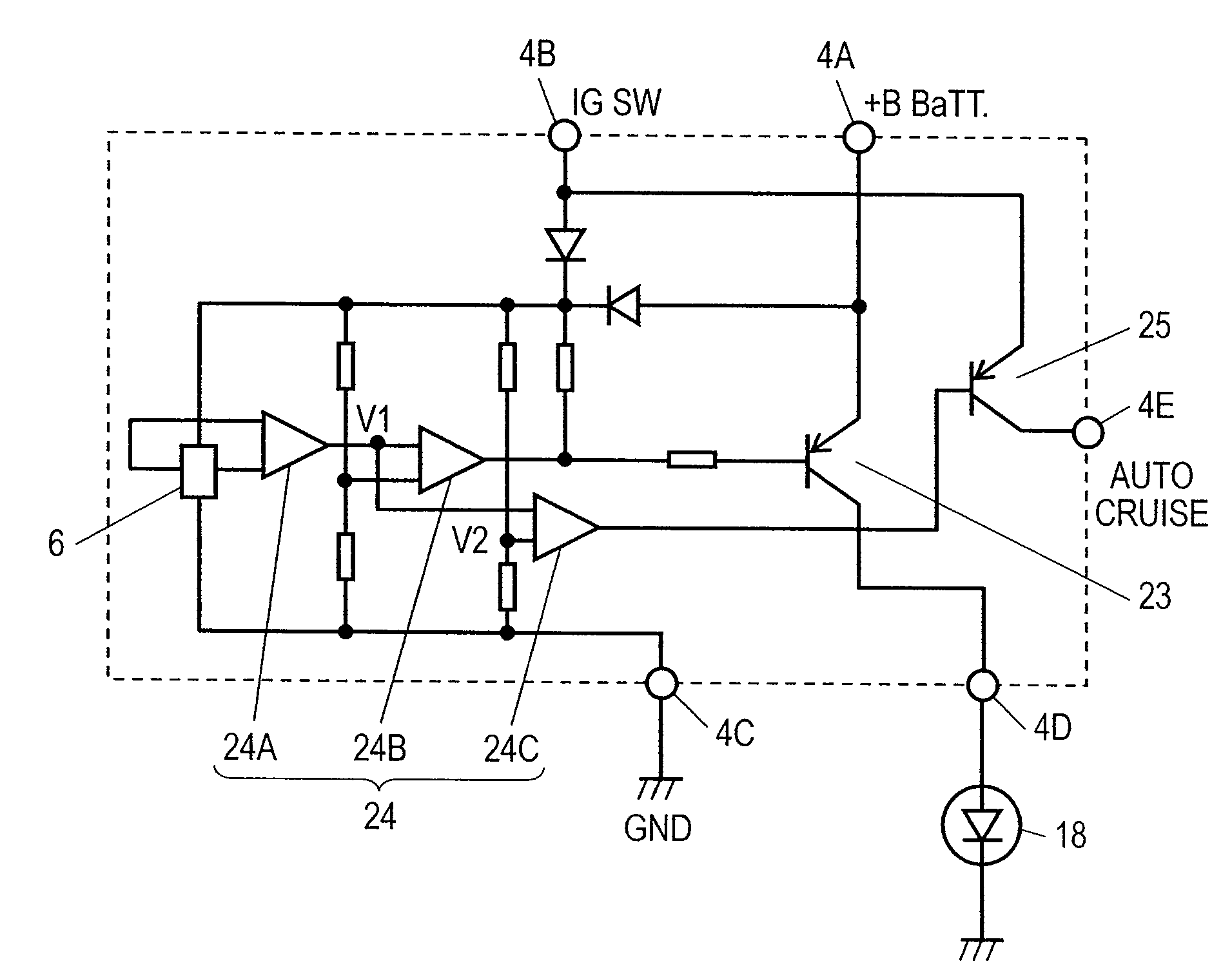

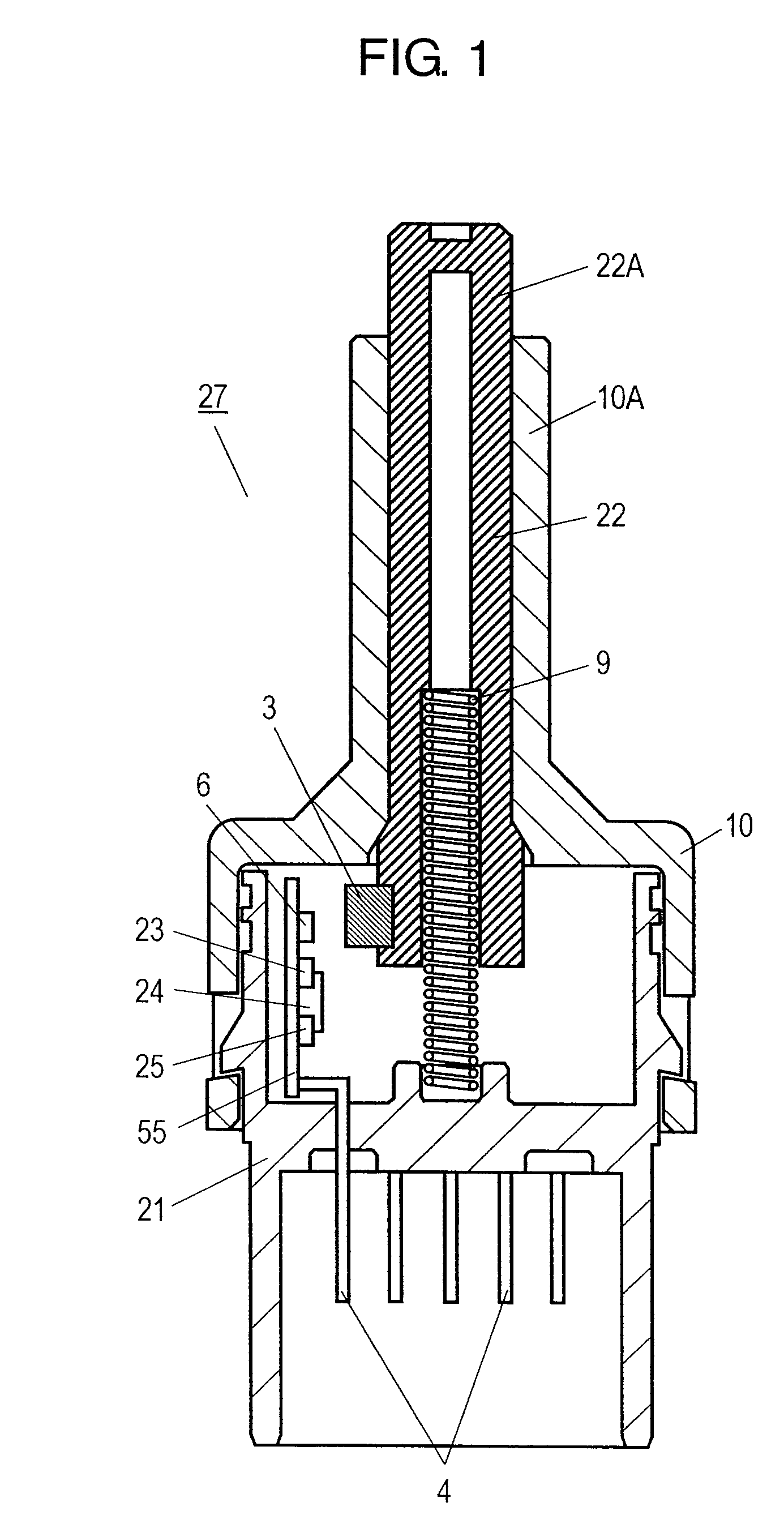

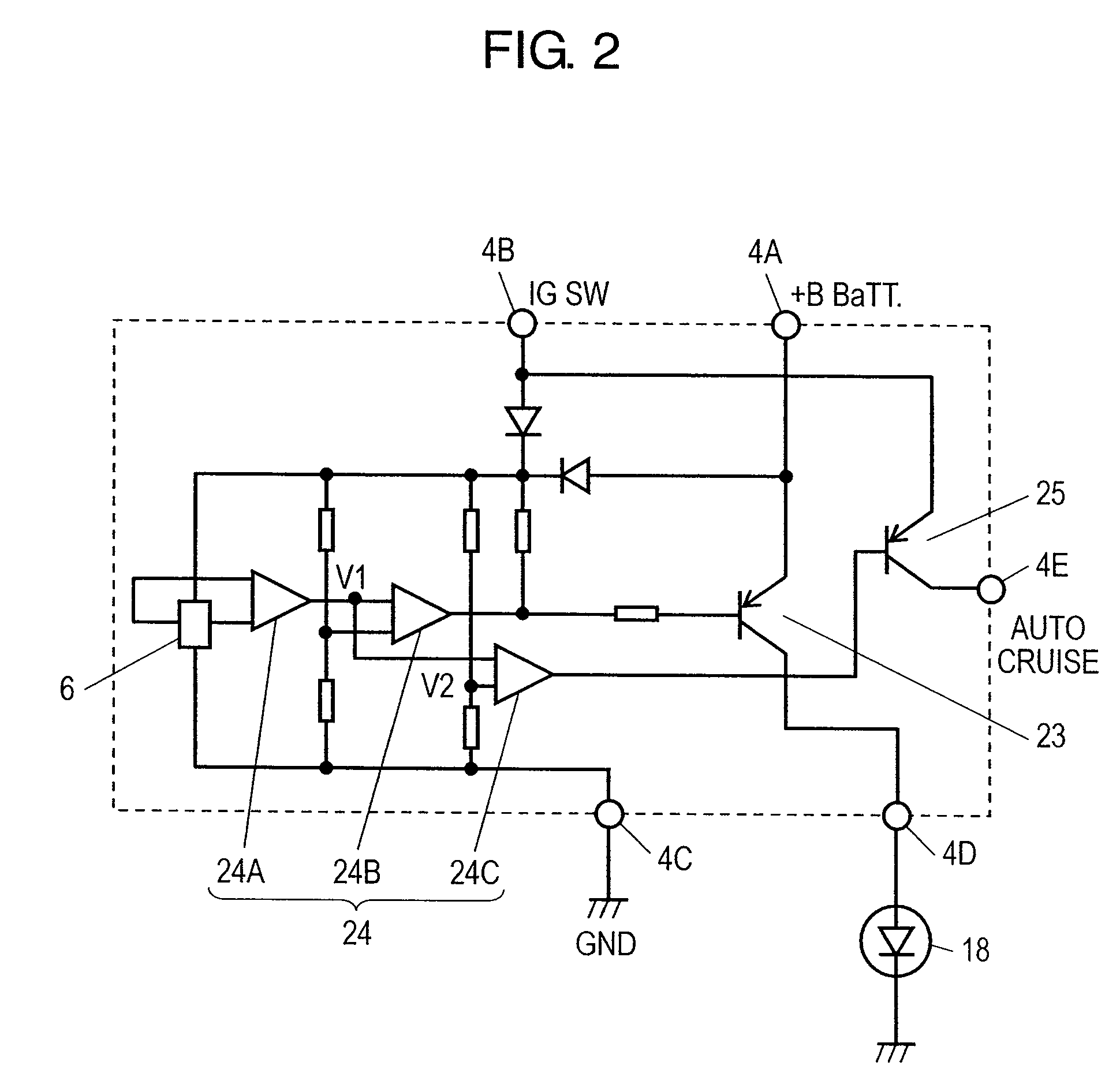

Switch for vehicles

Provided is a switch for vehicles, including a first switching device which performs the electrical connection / disconnection between a battery and a stop lamp and a second switching device connected to a control device which opens and closes the first switching device based on the magnitude of the magnetism of a magnet mounted on an operating body. Various controls such as auto-cruise control and so on as well as the turn on / off of the stop lamp can be simultaneously performed by the one magnet mounted on the operating body of the switch for vehicles.

Owner:PANASONIC CORP

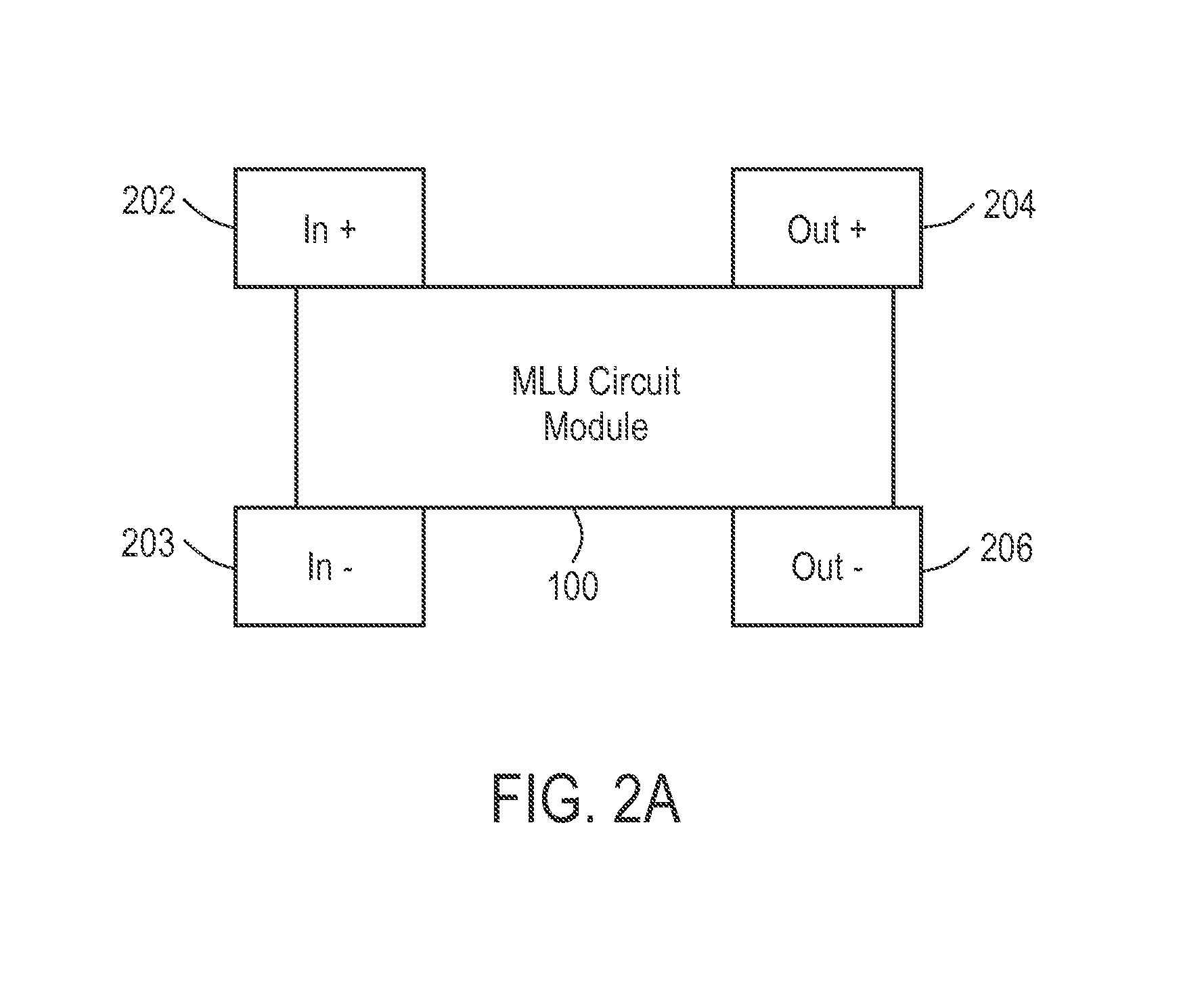

Analog Circuits Incorporating Magnetic Logic Units

ActiveUS20150214953A1Modulation transferencePulse generation by non-linear magnetic/dielectric devicesElectricityLogic cell

Owner:CROCUS TECHNOLOGY

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com