Patents

Literature

1405 results about "Memristor" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

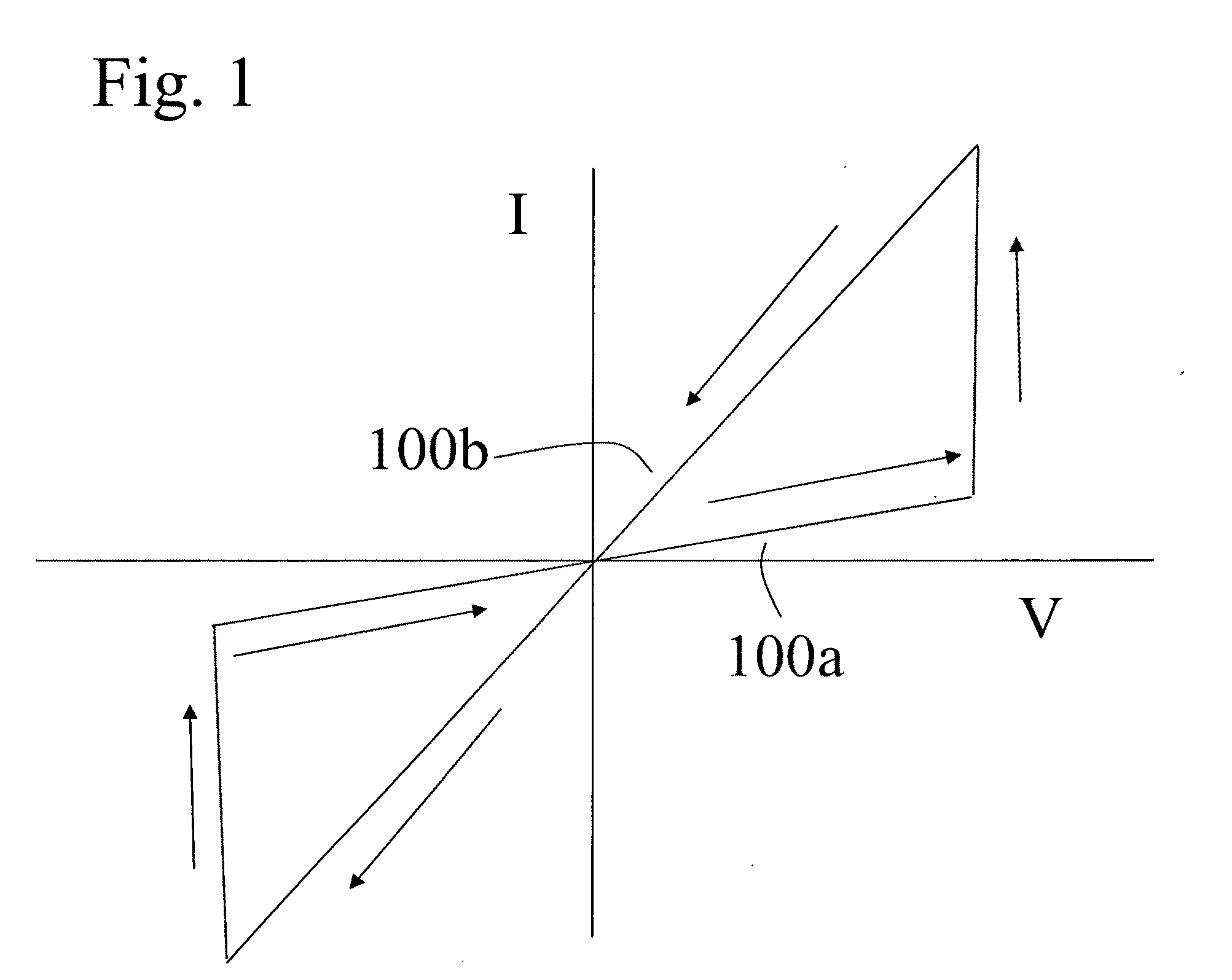

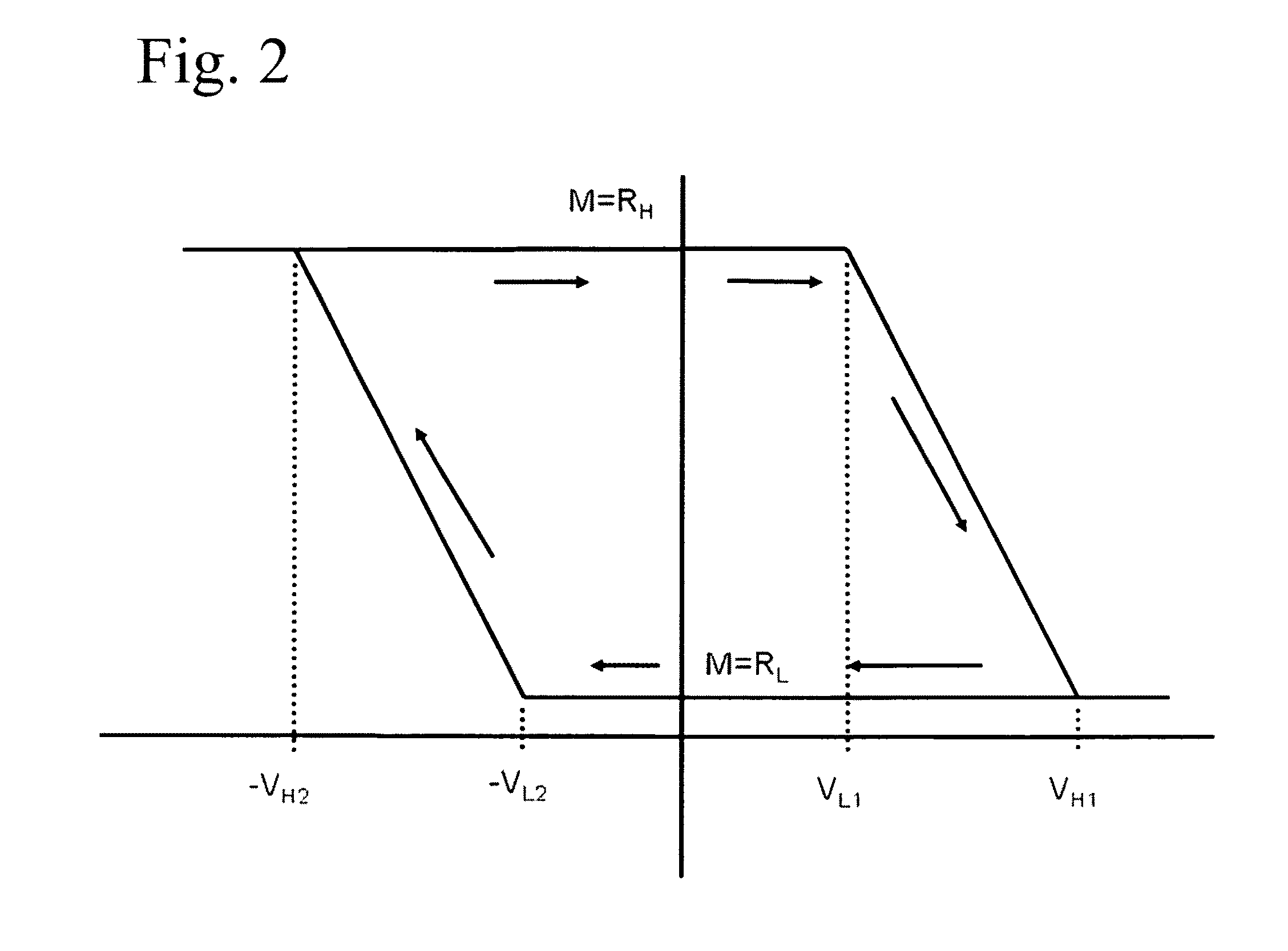

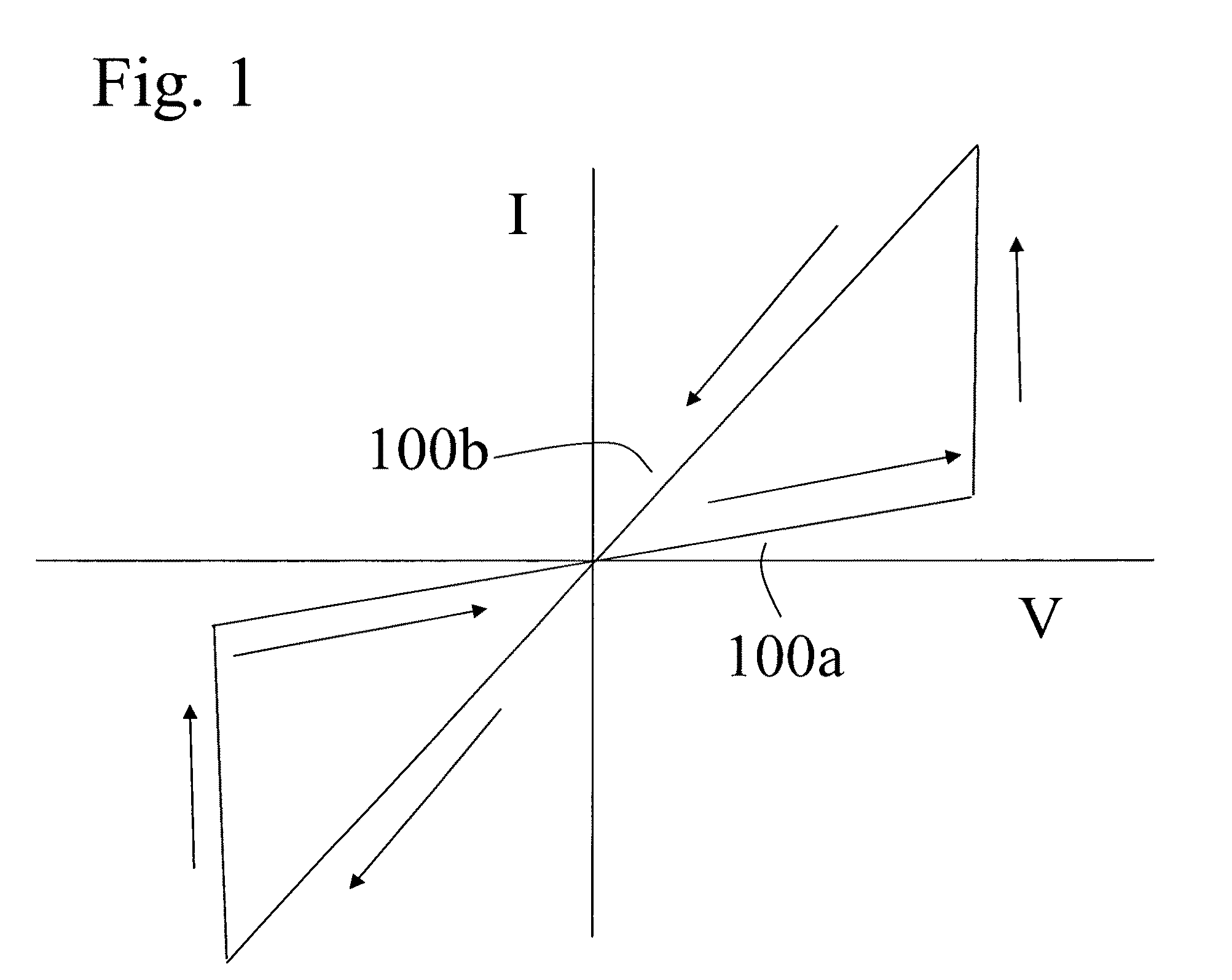

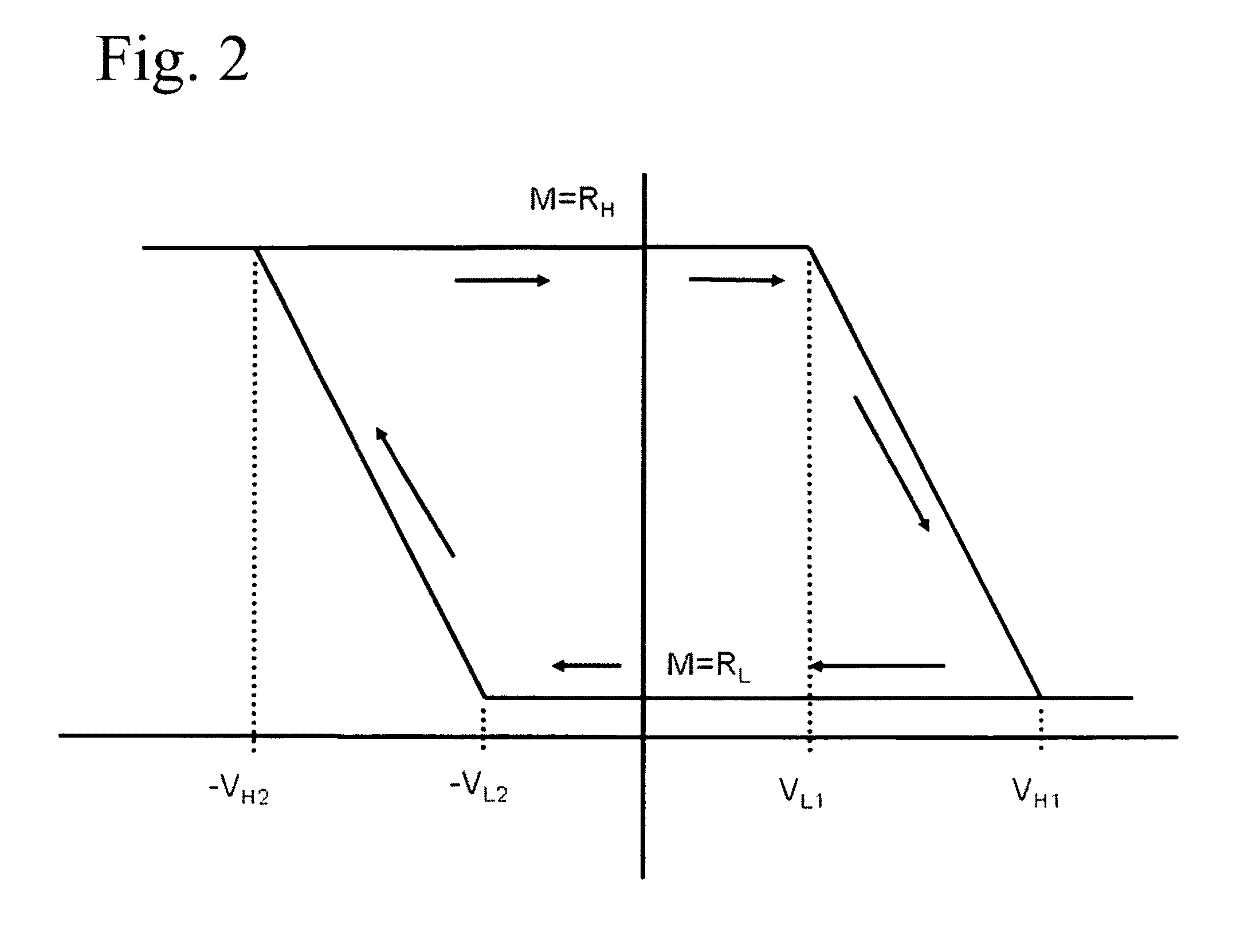

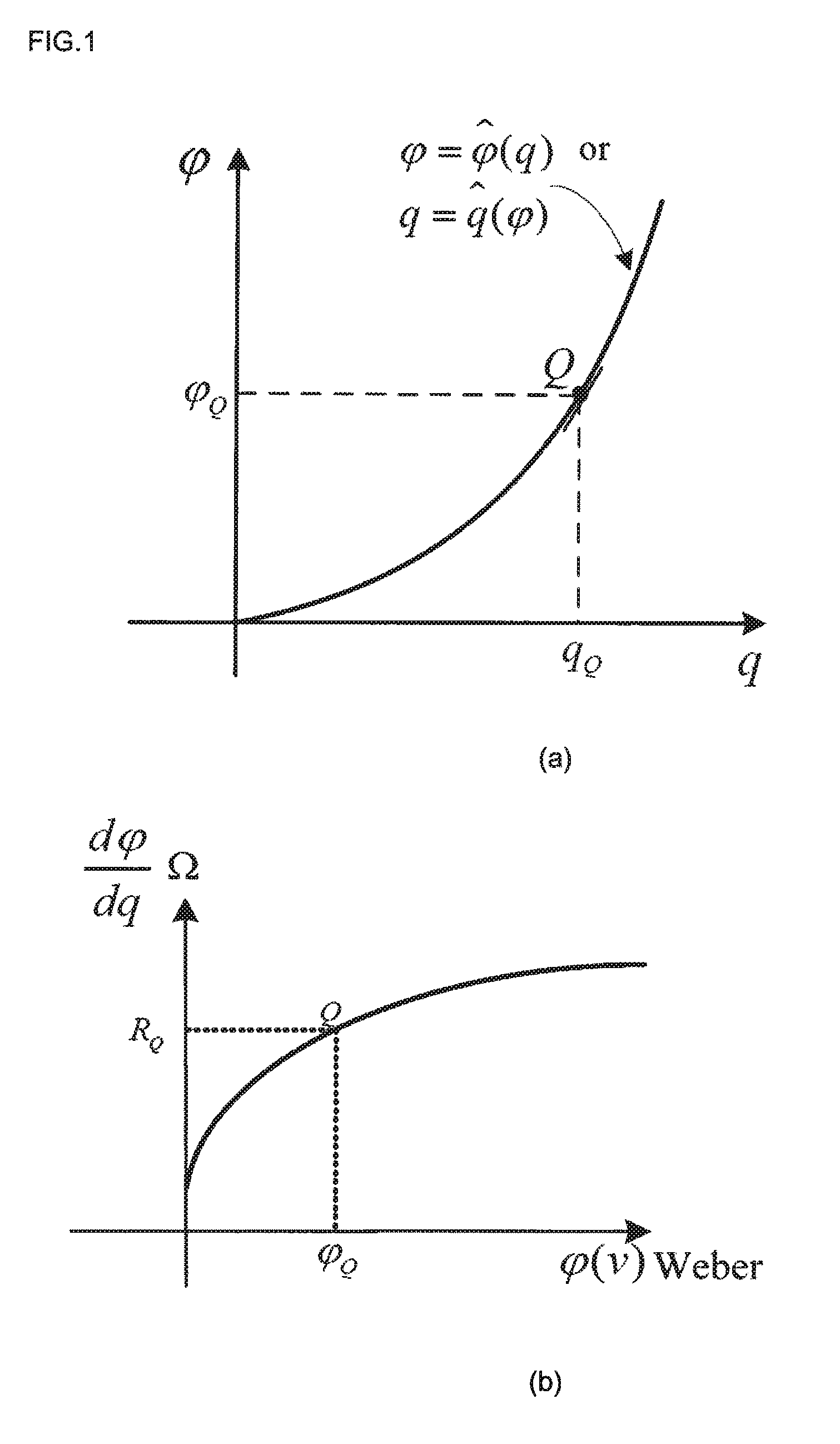

A memristor (/ˈmɛmrɪstər/; a portmanteau of memory resistor) is a hypothetical non-linear passive two-terminal electrical component relating electric charge and magnetic flux linkage. It was envisioned, and its name coined, in 1971 by circuit theorist Leon Chua. According to the characterizing mathematical relations, the memristor would hypothetically operate in the following way: the memristor's electrical resistance is not constant but depends on the history of current that had previously flowed through the device, i.e., its present resistance depends on how much electric charge has flowed in what direction through it in the past; the device remembers its history—the so-called non-volatility property. When the electric power supply is turned off, the memristor remembers its most recent resistance until it is turned on again.

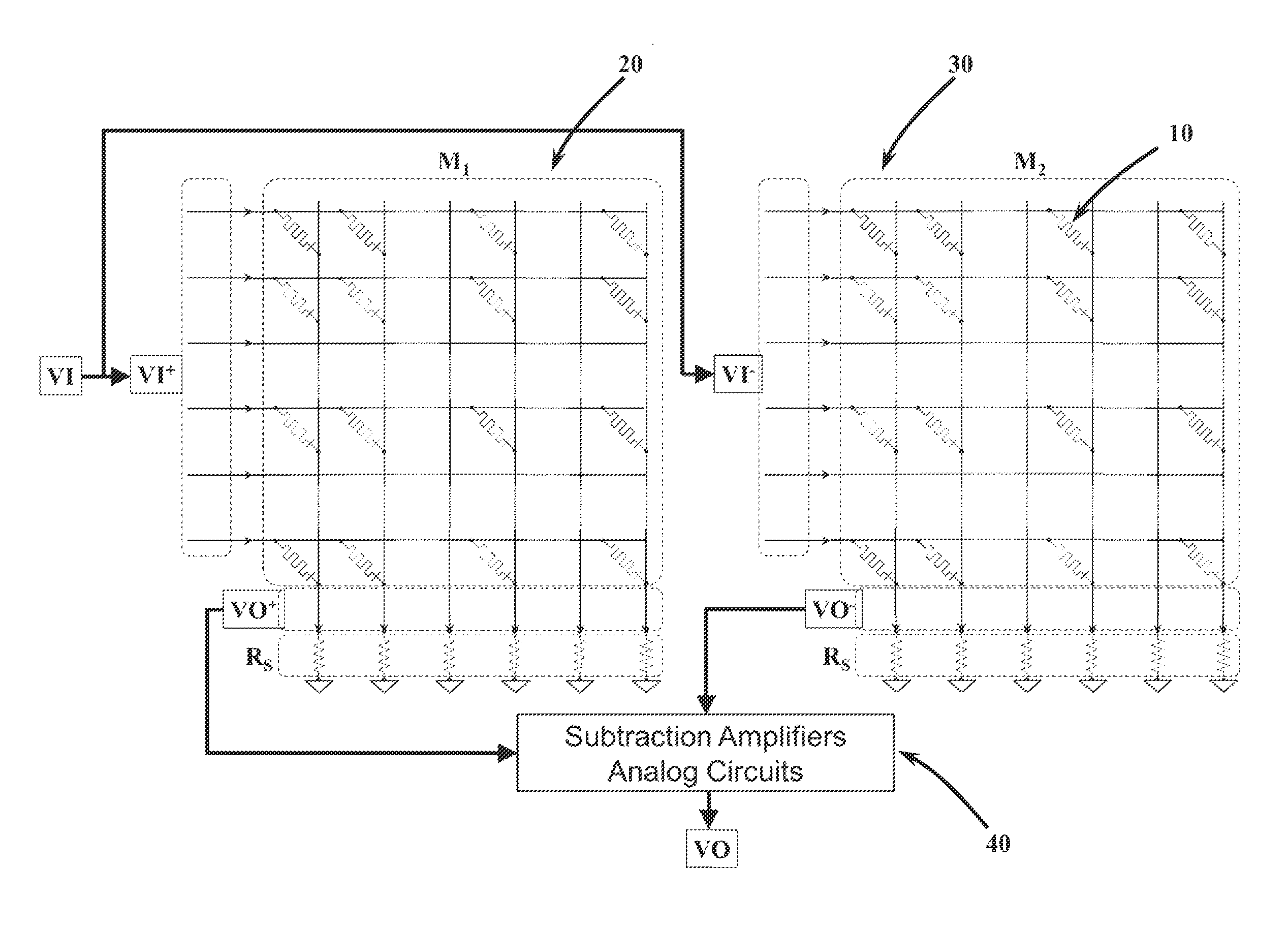

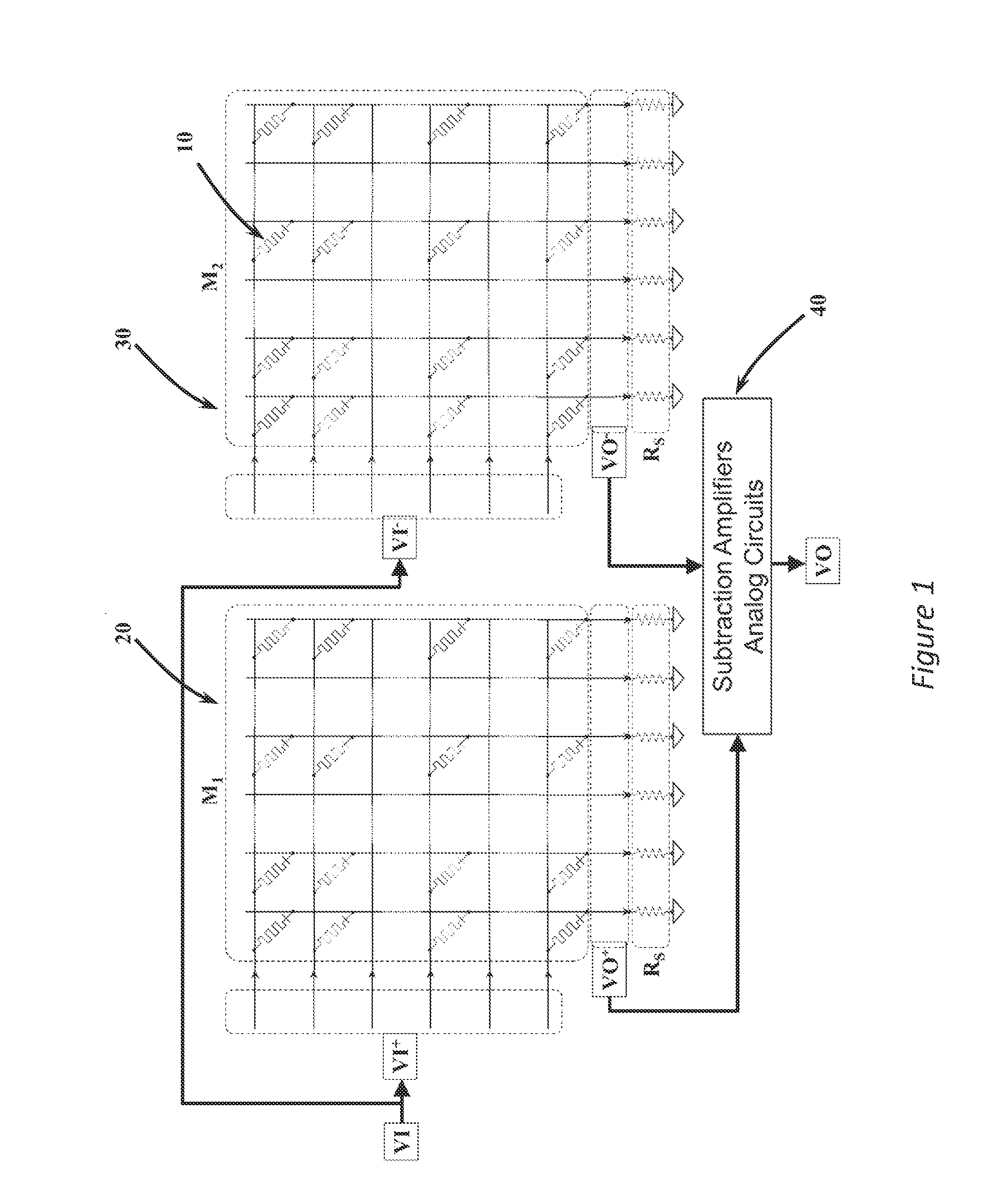

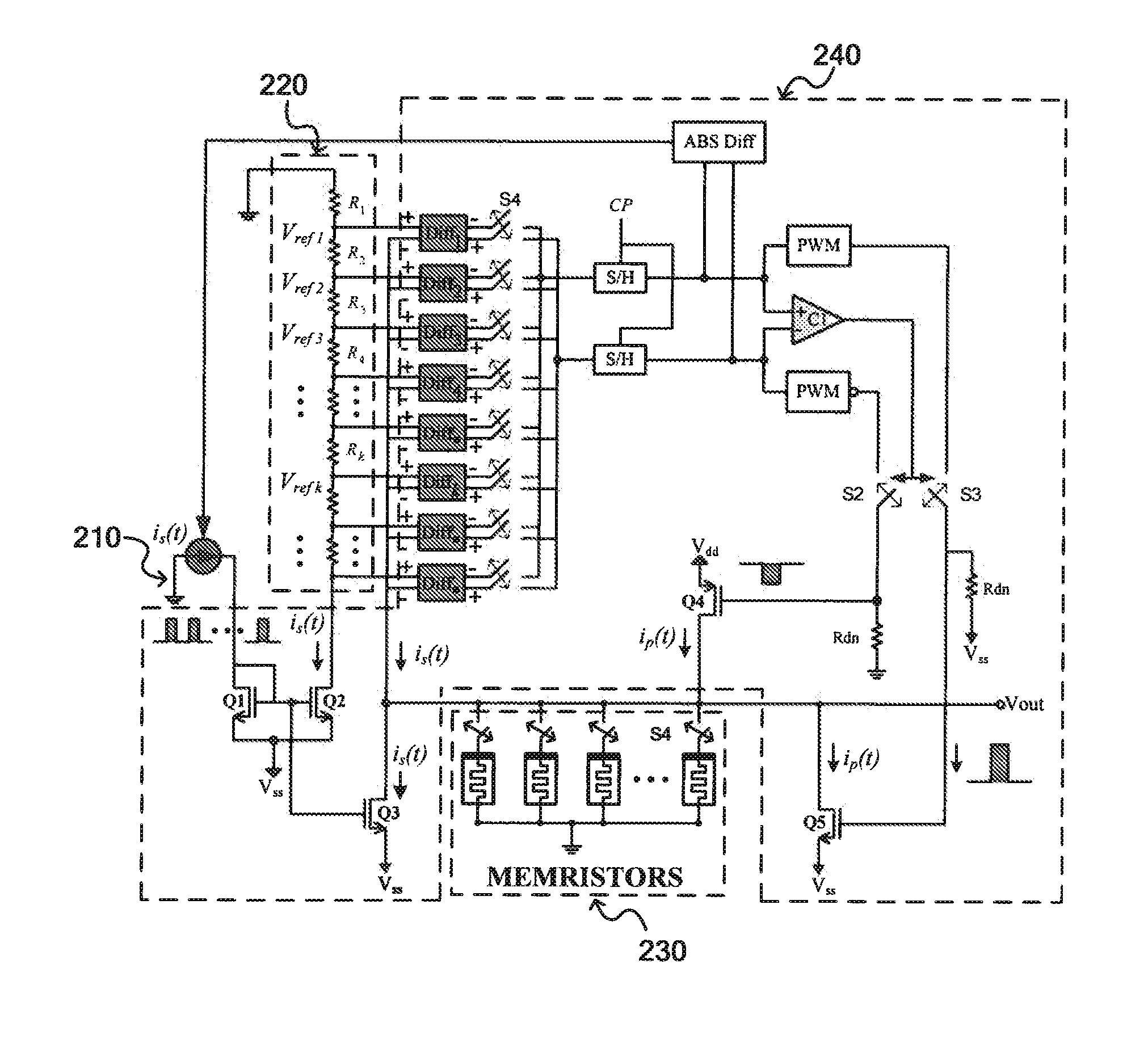

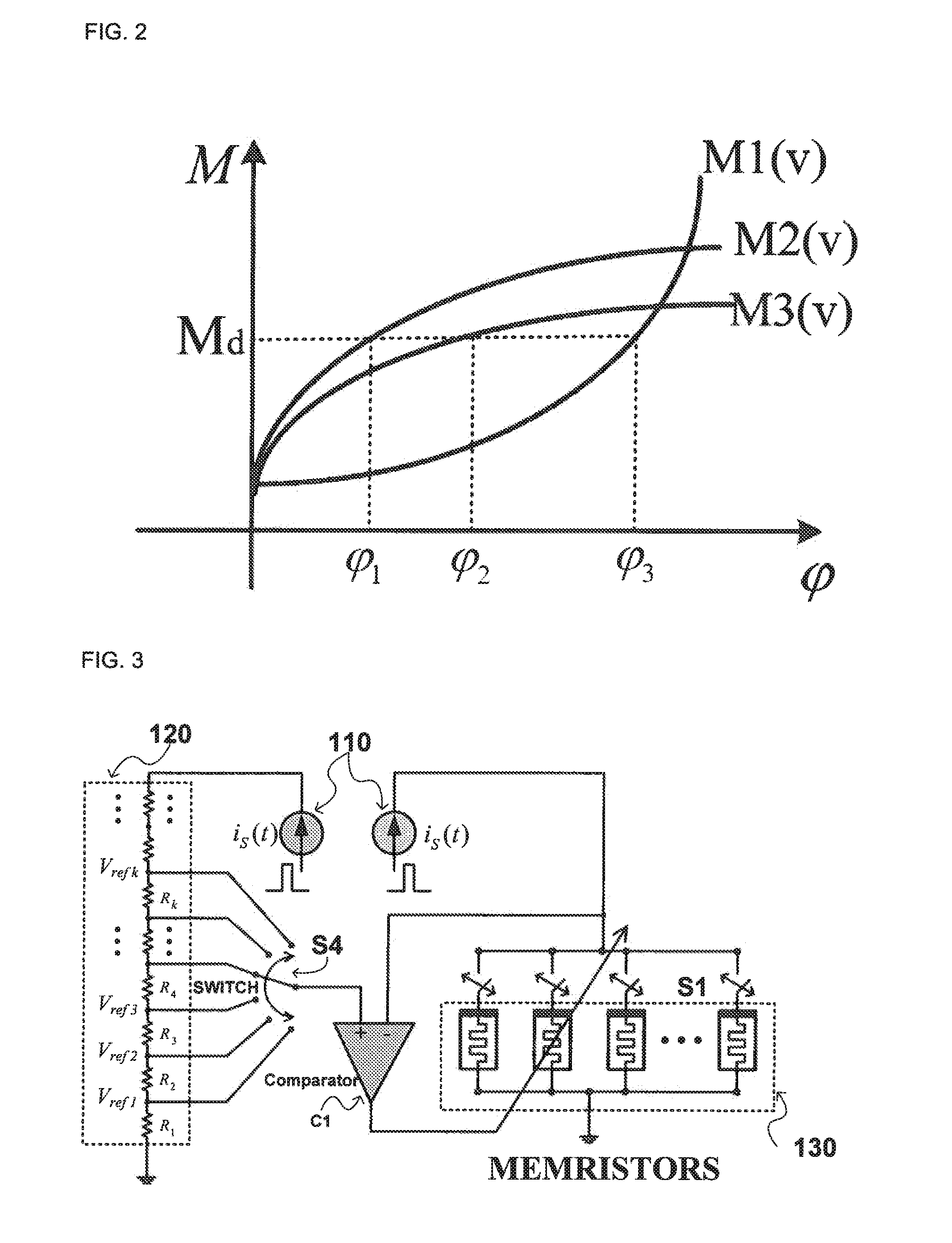

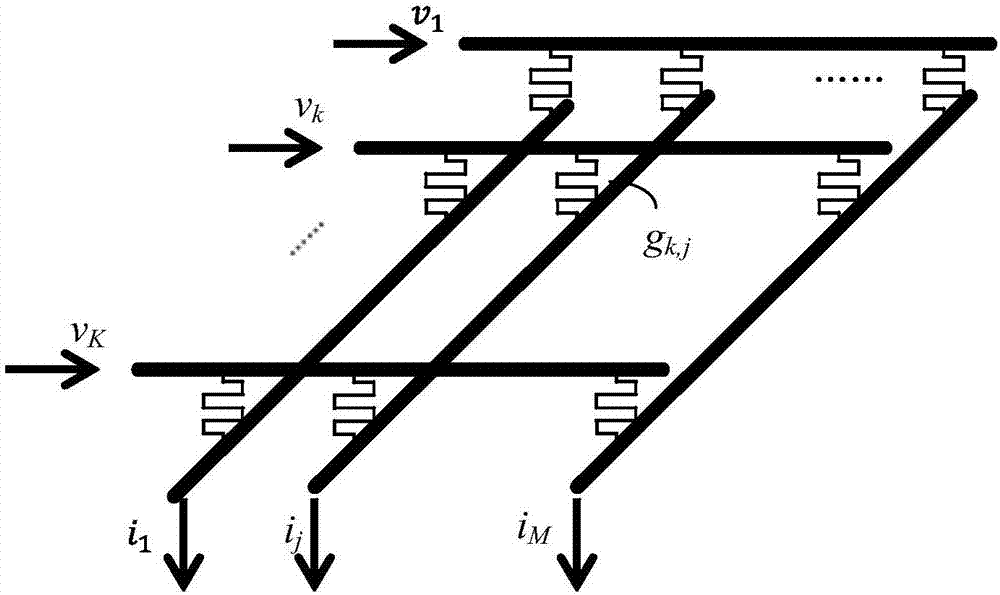

Method and apparatus for performing close-loop programming of resistive memory devices in crossbar array based hardware circuits and systems

ActiveUS20150170025A1Reduce Design ComplexityConvenient and accurateDigital computer detailsDigital storageObservational errorElectrical resistance and conductance

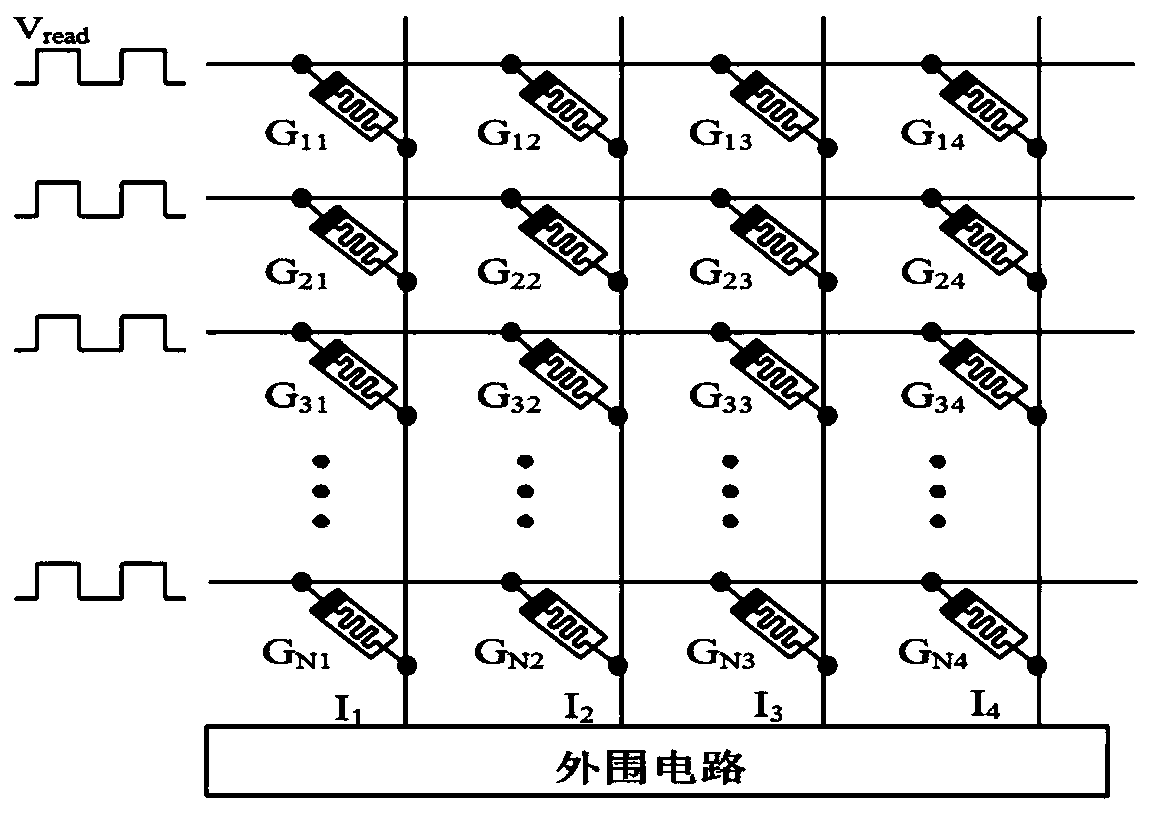

Method and apparatus for performing close-loop programming of resistive memory devices in crossbar array based hardware circuits and systems. Invention provides iterative training of memristor crossbar arrays for neural networks by applying voltages corresponding to selected training patterns. Error is detected and measured as a function of the actual response to the training patterns versus the expected response to the training pattern.

Owner:THE UNITED STATES OF AMERICA AS REPRESETNED BY THE SEC OF THE AIR FORCE

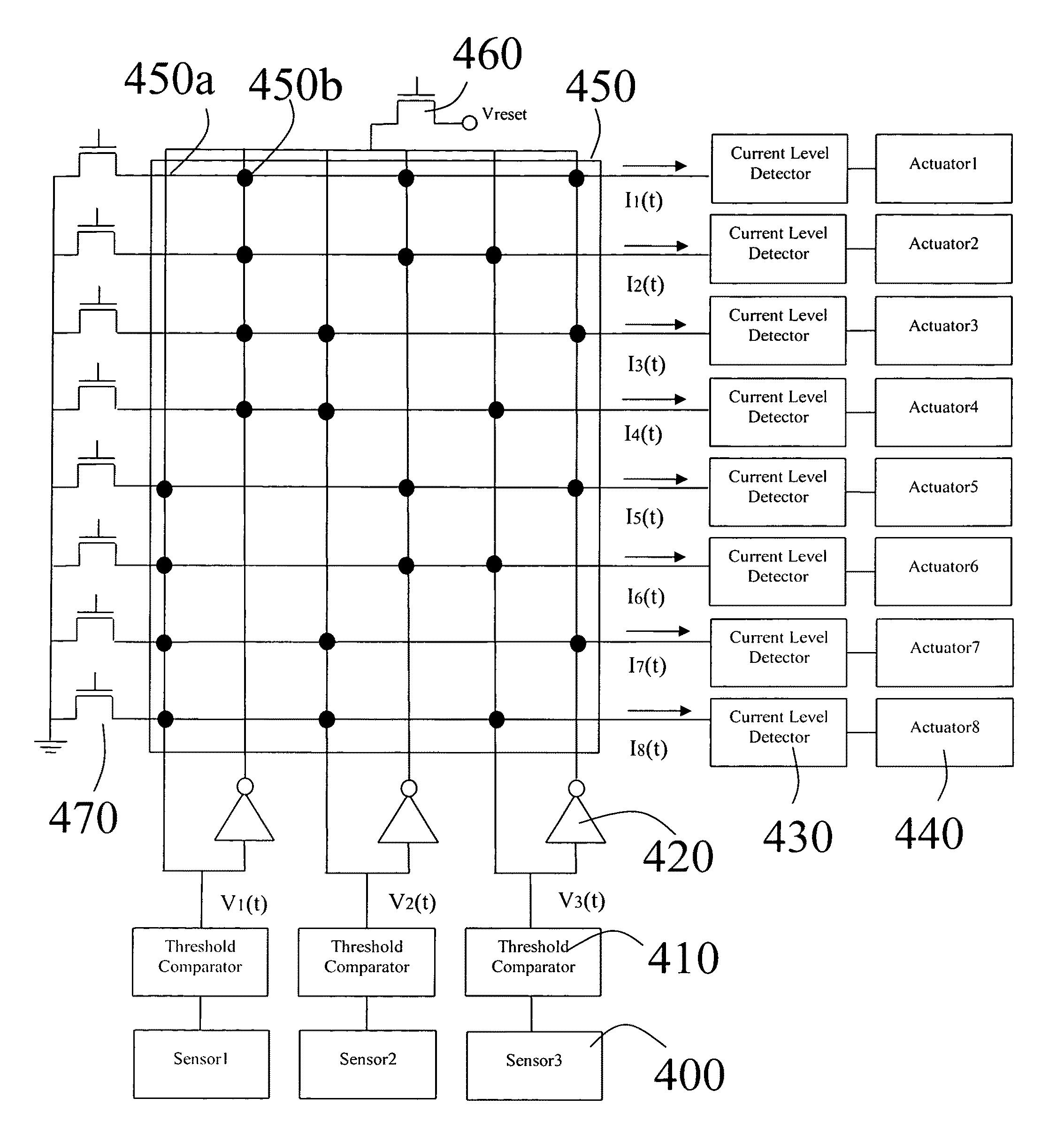

Memristor crossbar neural interface

InactiveUS20090163826A1Improve adaptabilityIncrease speedNanotechSolid-state devicesElectrical resistance and conductanceProsthesis

A device includes an array of electrodes configured for attachment in or on the human head interconnected to control circuitry via a programmable crossbar signal processor having reconfigurable resistance states. In various embodiments the device may be used as a controller for a video game console, a robotic prosthesis, a portable electronic device, or a motor vehicle.

Owner:MOUTTET BLAISE LAURENT

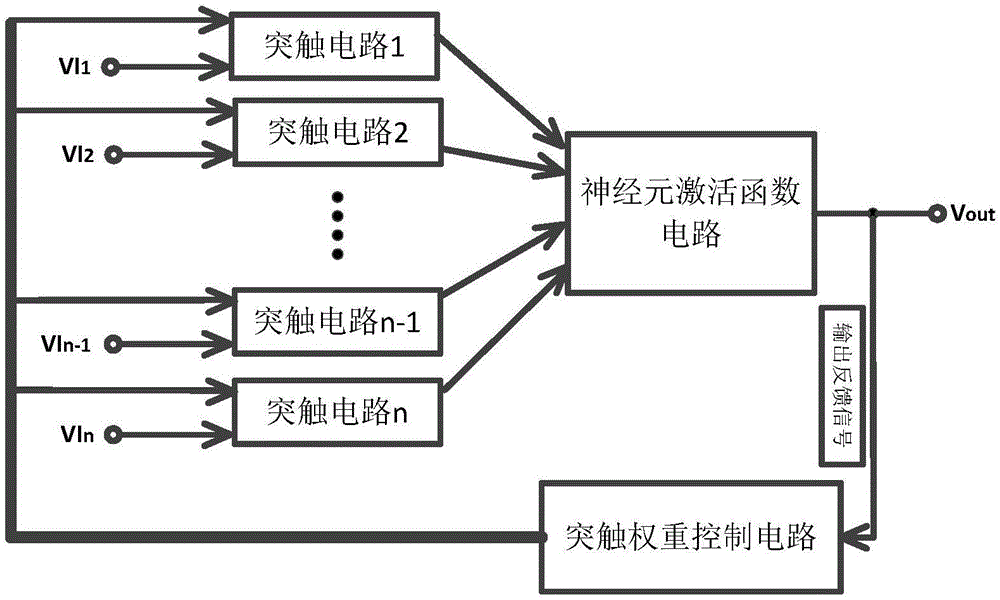

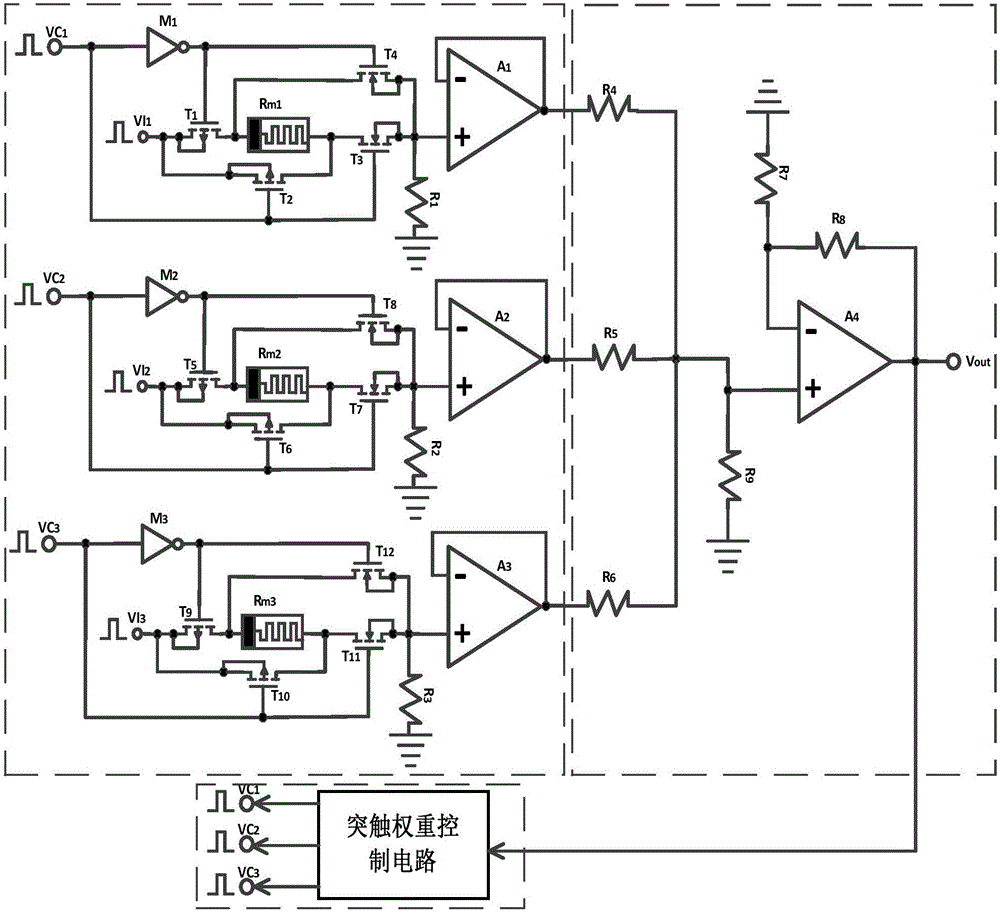

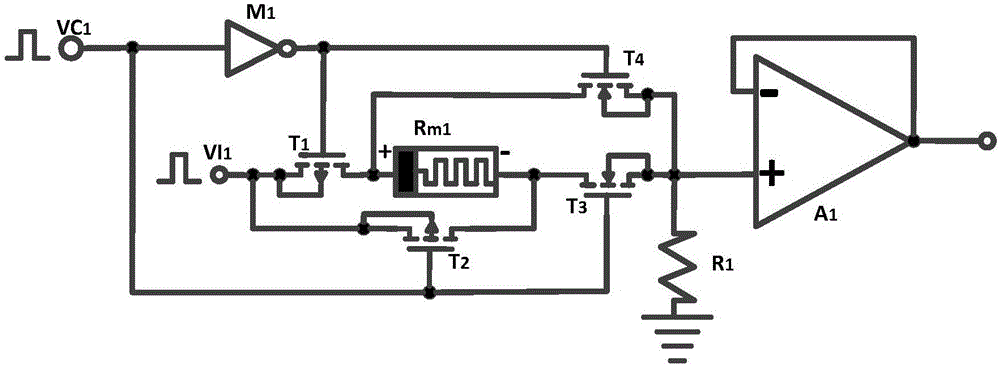

Memristor-based neuron circuit

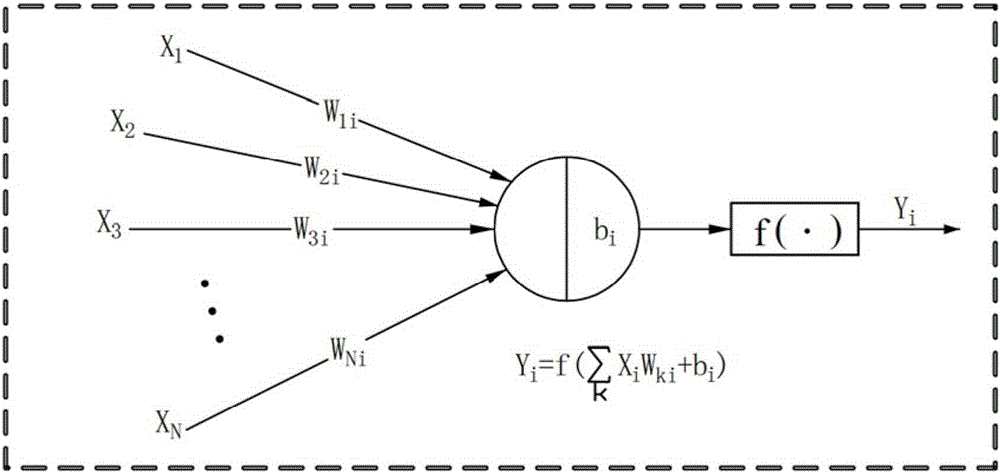

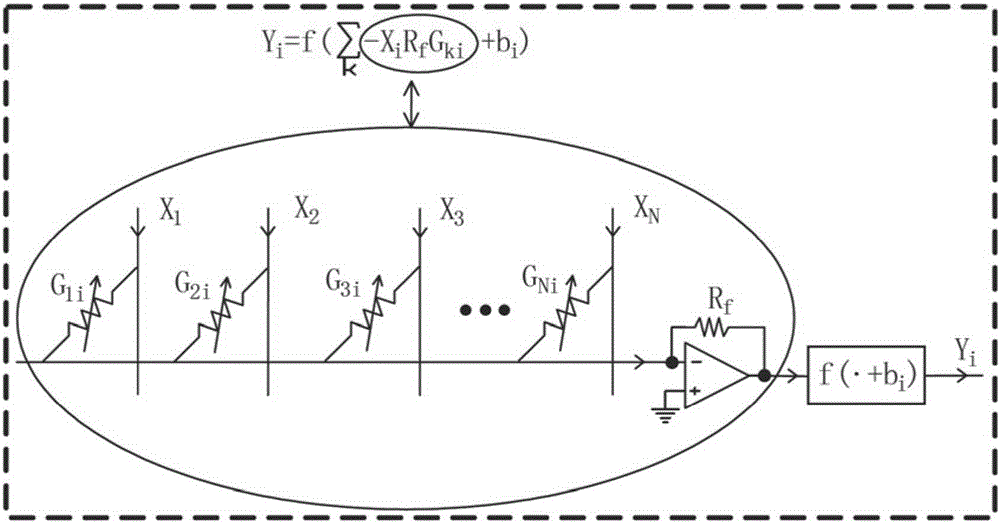

ActiveCN106815636AGood effectEasy compositionNeural architecturesPhysical realisationActivation functionNerve network

The invention discloses a memristor-based neuron circuit, comprising a synaptic circuit, a neuron activation function circuit and a synaptic weight control circuit. In the synaptic circuit, a memristor, under the control of four MOS tubes, changes the memristor value to simulate the change of the synaptic weight in the neuron network. The designed neuron synaptic circuit is capable of being directly connected with a digital logic electrical level so as to achieve convenient and real-time adjustment to the synaptic weight and through the use of the feature that the output voltage of an operational amplifier is restricted by the power supply voltage, the neuron circuit activation function can be realized as a saturated linear function. The neuron synaptic weight change circuit can utilize the existing CMOS micro-controller and at the same time, the micro-controller can be loaded by the neuron network algorithm to change the synaptic weight to realize corresponding functions. According to the invention, a plurality of neuron circuits could be connected into a large-scale neuron network for complicated functions such as mode identification, signal processing, associated memory and non-linear mapping, etc.

Owner:HUAZHONG UNIV OF SCI & TECH

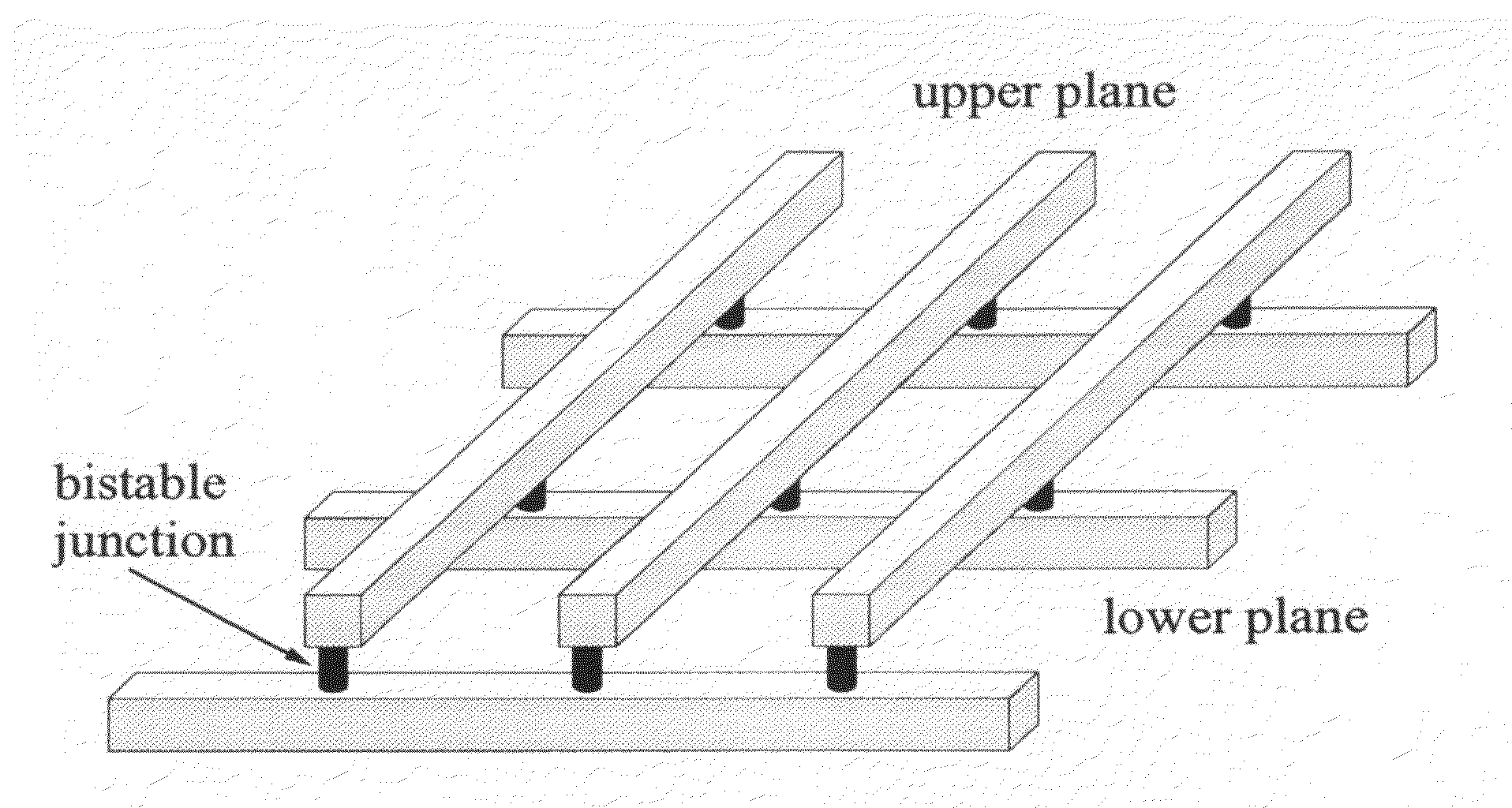

Memristor crossbar neural interface

InactiveUS7902867B2Improve adaptabilityIncrease speedNanotechSolid-state devicesElectrical resistance and conductanceCrossbar switch

A device includes an array of electrodes configured for attachment in or on the human head interconnected to control circuitry via a programmable crossbar signal processor having reconfigurable resistance states. In various embodiments the device may be used as a controller for a video game console, a robotic prosthesis, a portable electronic device, or a motor vehicle.

Owner:MOUTTET BLAISE LAURENT

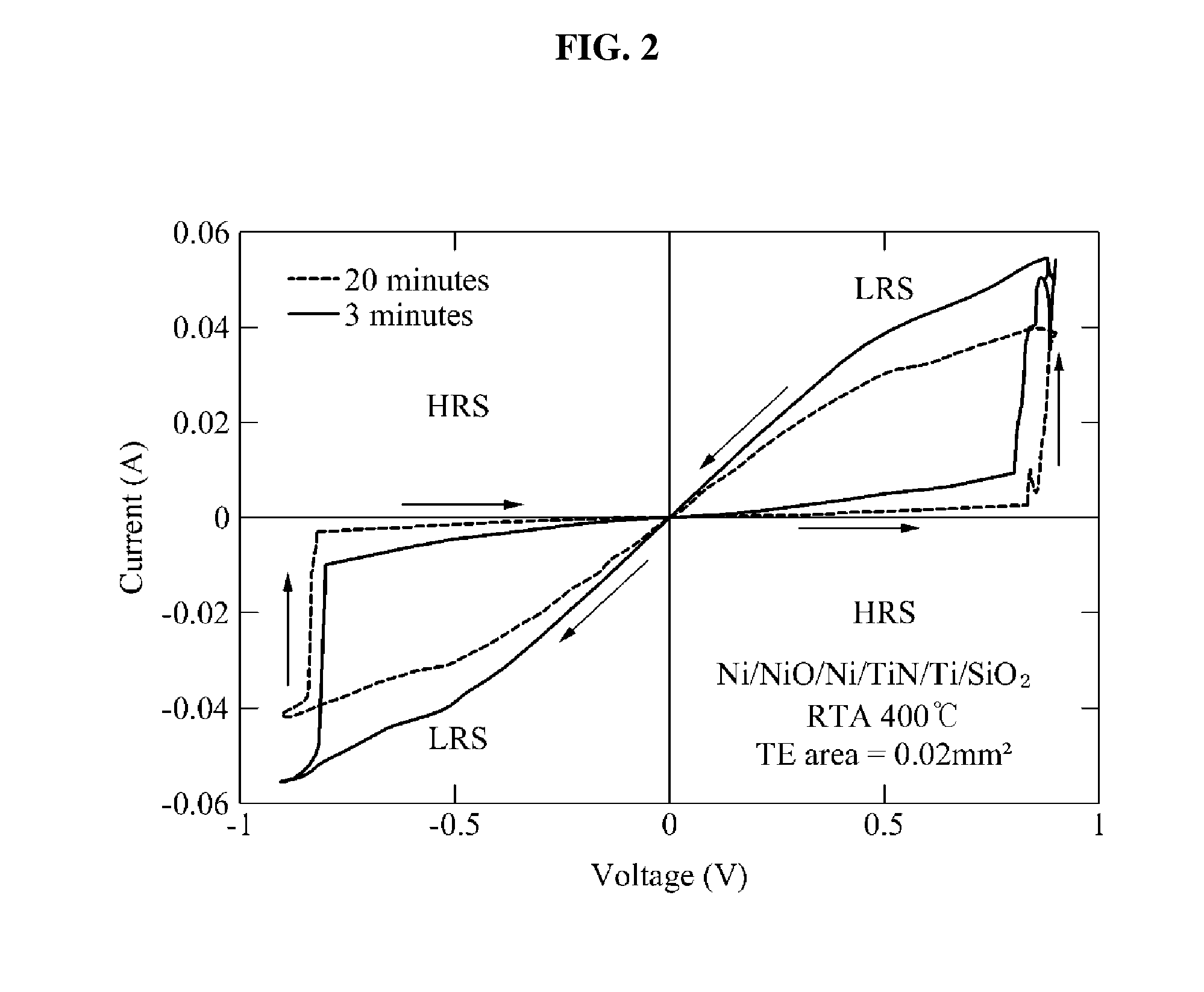

Method of implementing memristor-based multilevel memory using reference resistor array

The present invention relates to a memristor, and more particularly, to a method of implementing a memristor-based multilevel memory using a reference resistor array and a write-in circuit and a read-out / restoration circuit for the memristor-based multilevel memory, in which a memristor can be used as a multilevel memory. In the present invention, a reference resistance value is written in a selected memristor of a memristor array by applying repeatedly the current pulses of which widths are proportional to the difference between the resistances of the selected memristor and the selected node of the reference resistor array.

Owner:IND COOP FOUND CHONBUK NAT UNIV +1

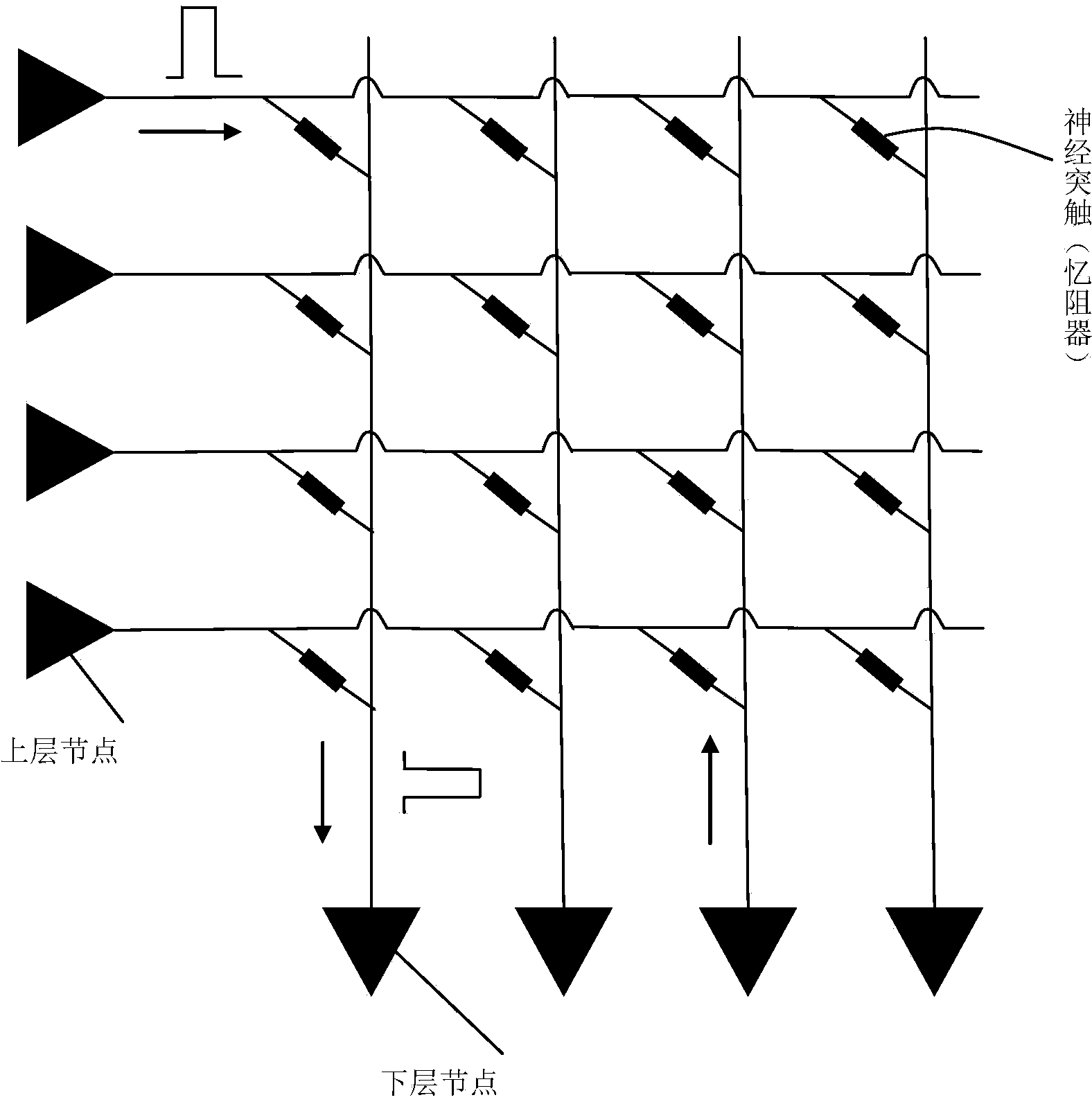

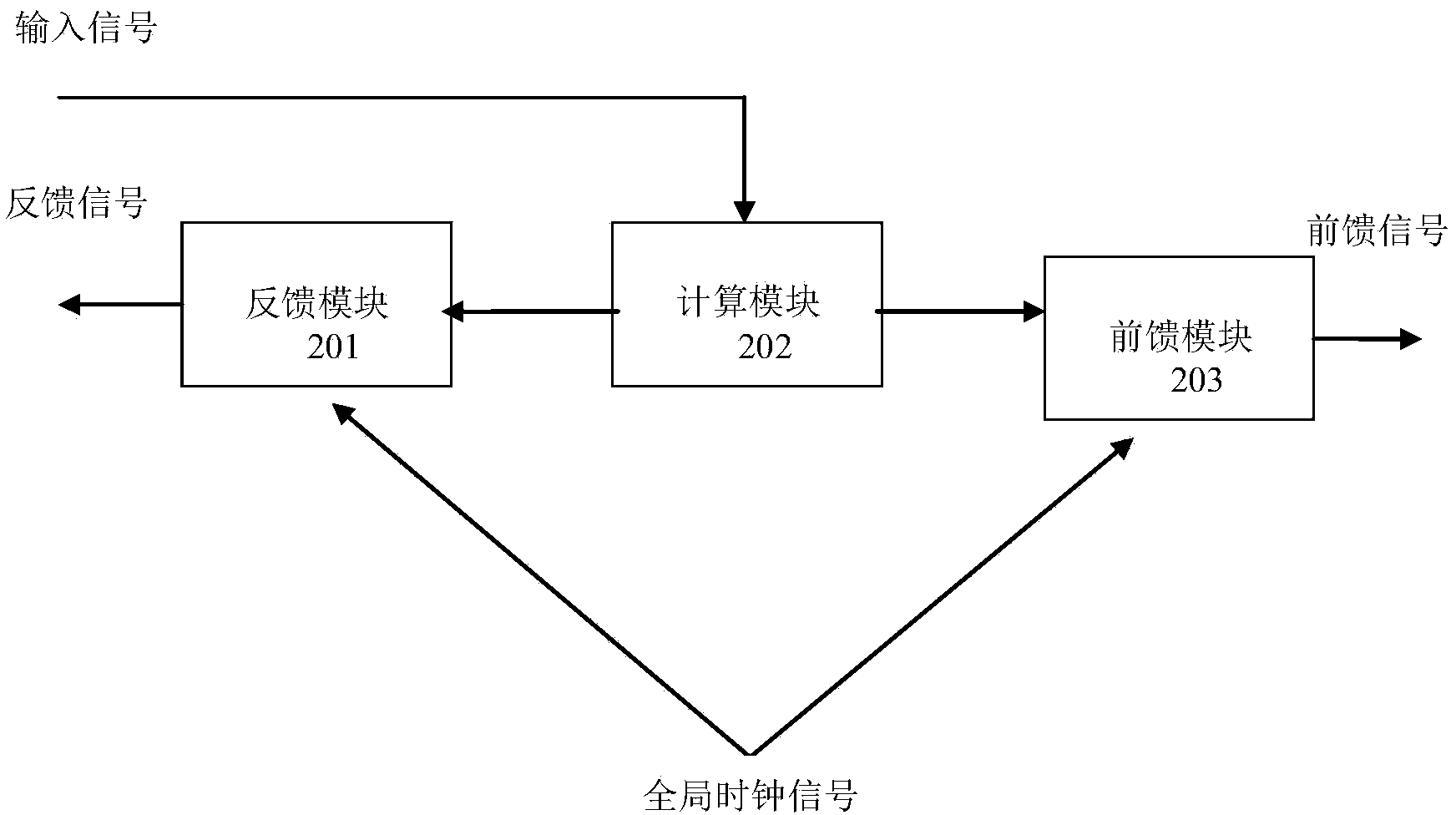

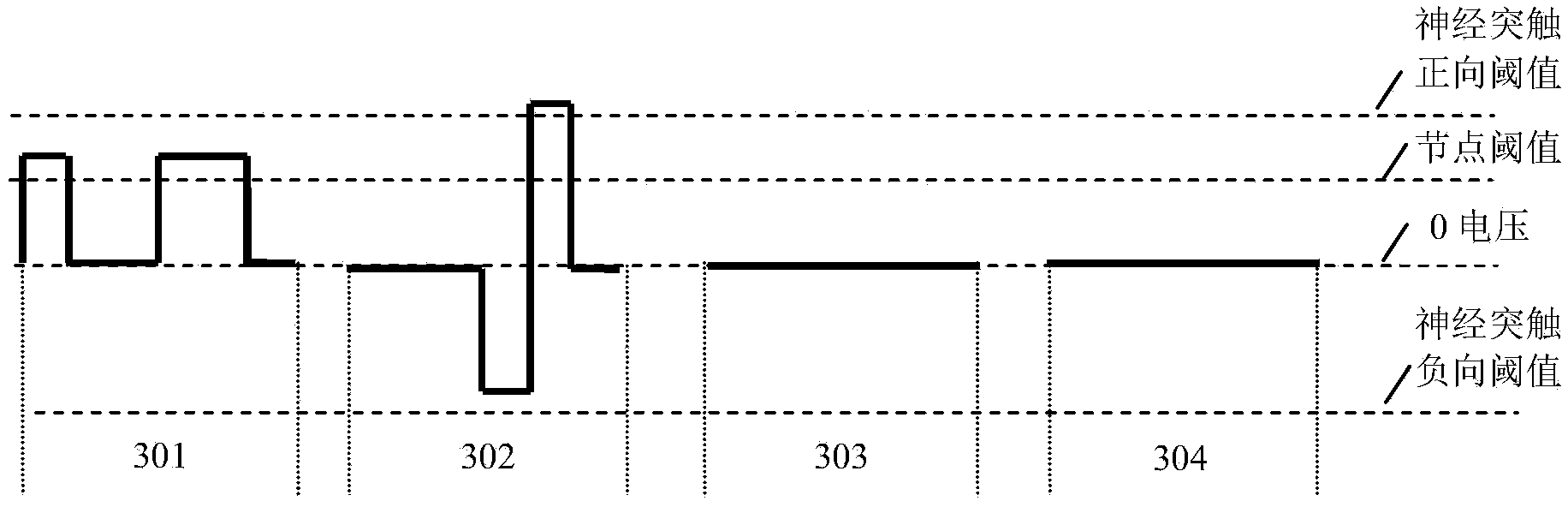

Feedback artificial neural network training method and feedback artificial neural network calculating system

InactiveCN103455843AFast convergenceReduce energy consumptionBiological neural network modelsSynaptic weightNerve network

The invention discloses a feedback artificial neural network training method and a feedback artificial neural network calculating system and belongs to the field of calculation of neural networks. According to the artificial neural network training method, the synapse weight is adjusted according to a feedforward signal and a feedback signal at the two ends of each neural synapse; when the signals at the two ends of each neural synapse are an excitation feedforward signal and an excitation feedback signal respectively, the synapse weight is adjusted to the maximum value; when the signals at the two ends of each neural synapse are a tranquillization feedforward signal and an excitation feedback signal respectively, the synapse weight is adjusted to the minimum value. According to the feedback artificial neural network calculating system, each node circuit comprises a calculating module, a feedforward module and a feedback module and the node circuits are connected through the neural synapses simulated by memristors, and a series of pulse signals are adopted to achieve the feedback artificial neural network training method. An artificial neural network provided by the system and the method is high in rate of convergence, and the artificial neural network calculating system is few in control element, low in energy consumption and capable of being applied to data mining, pattern recognition, image recognition and other respects.

Owner:HUAZHONG UNIV OF SCI & TECH

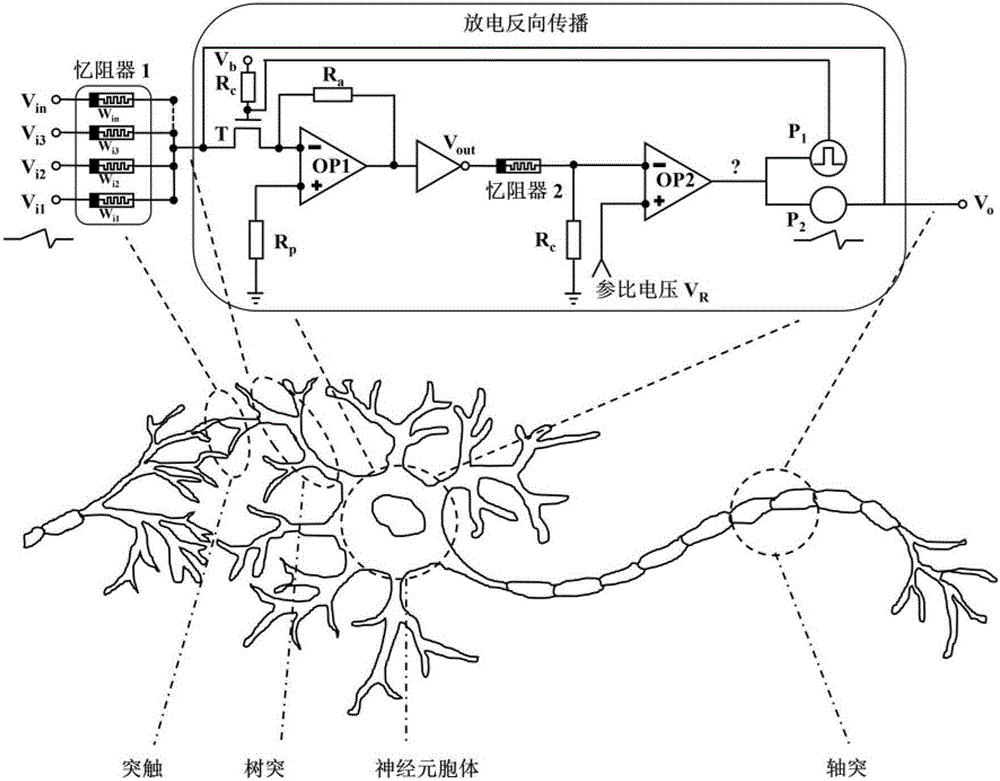

Memristor-based neuron circuit

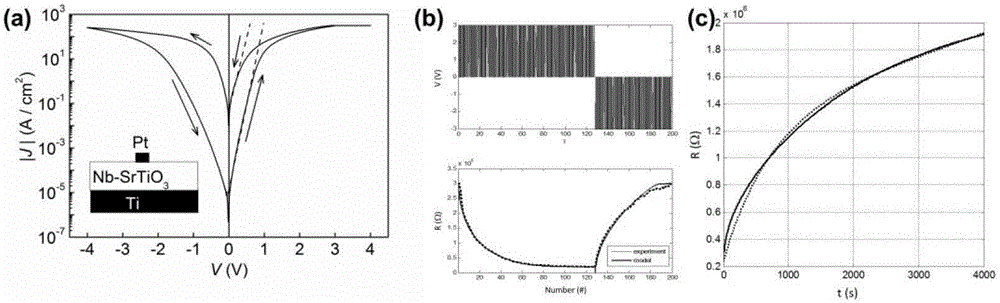

ActiveCN106845634ARealize integrated discharge functionImplement time encodingPhysical realisationInformation processingSynapse

The invention discloses a memristor-based neuron circuit. According to the neuron circuit, partially volatile bipolar resistive transition devices are selected and used as memristors of a synapse array, and a volatile resistive transition device is selected and used as a memristor for expressing membrane potential of neurons, so that the neuron circuit is formed; and synapse basis units are arranged. The neuron circuit can realize an integral discharge function in biological neurons and express local graded potentials; and synapses have partial volatility, can express spike-timing-dependent plasticity, and have great similarity with biological neurons and synapses in the aspects of information storage, transmission and processing. According to the neuron circuit, the basic units can be provided for hardware to simulate a cerebral neural network structure; the technical problems of neuron discharge time delay, difficulty in realizing high-density integration and the like in the prior art are solved; and the neuron circuit can be used for constructing a brain-like information processing system, can quickly process a large amount of information in parallel, and has a greatly high application value in realizing a cerebral neurologic calculation network.

Owner:HUAZHONG UNIV OF SCI & TECH

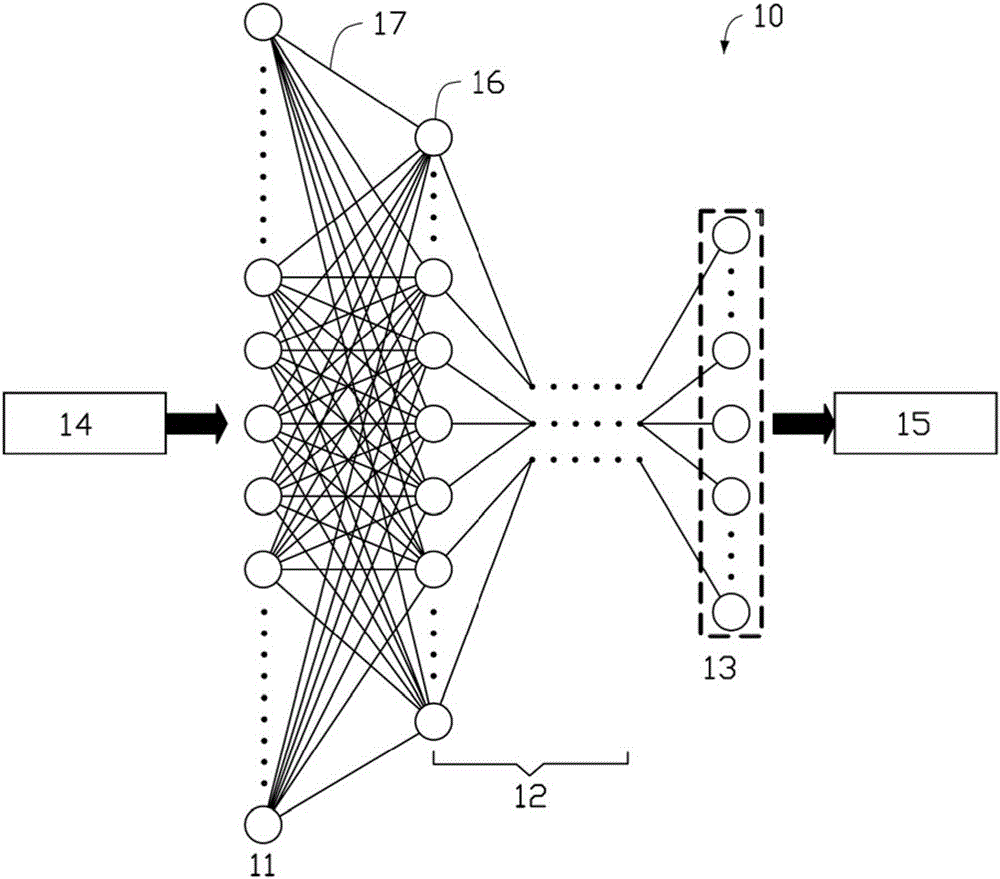

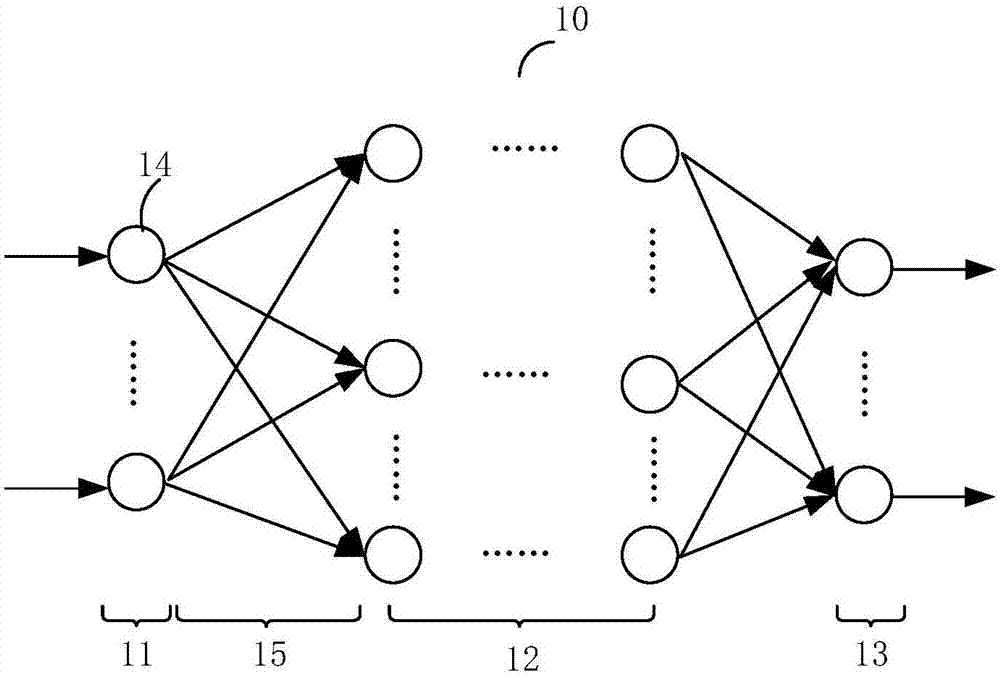

Deep neural network system based on memristor

ActiveCN105224986AIncrease computing speedHigh densityNeural architecturesInformation processingNerve network

The invention provides a deep neural network system based on a memristor, which comprises an input layer, an output layer and multiple hidden layers, wherein the input layer receives an external information input mode, the external information input mode is calculated and converted layer by layer, and an external output result is generated finally by the output layer. A synaptic weight of the deep neural network adopts the memristor for simulation, and the feature that resistance of the memristor changes along with applied electric signals is used to simulate a connection strength behavior of a connection synapse between neural networks. The invention further provides an information processing system for the deep neural network system based on the memristor.

Owner:TSINGHUA UNIV

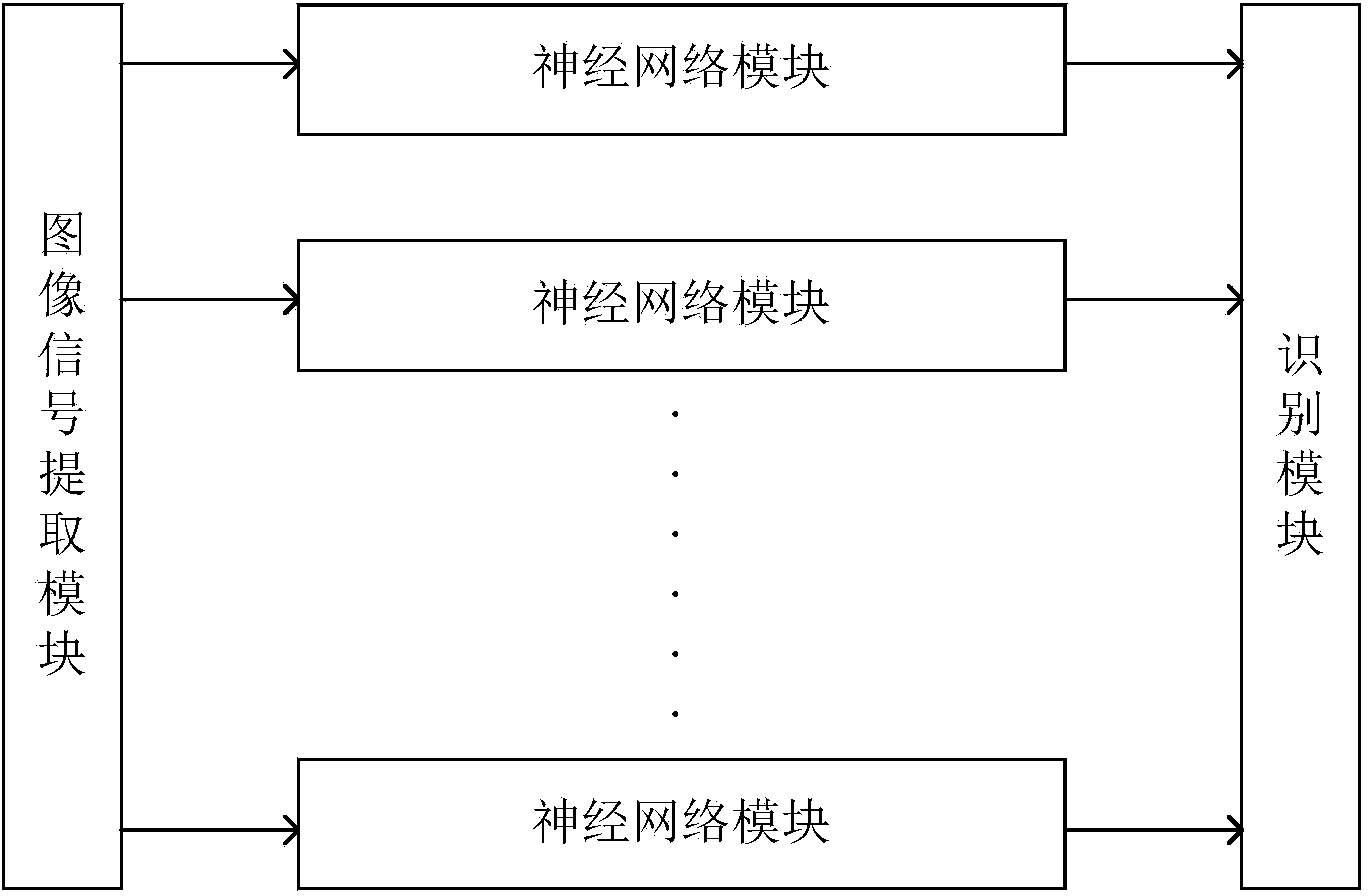

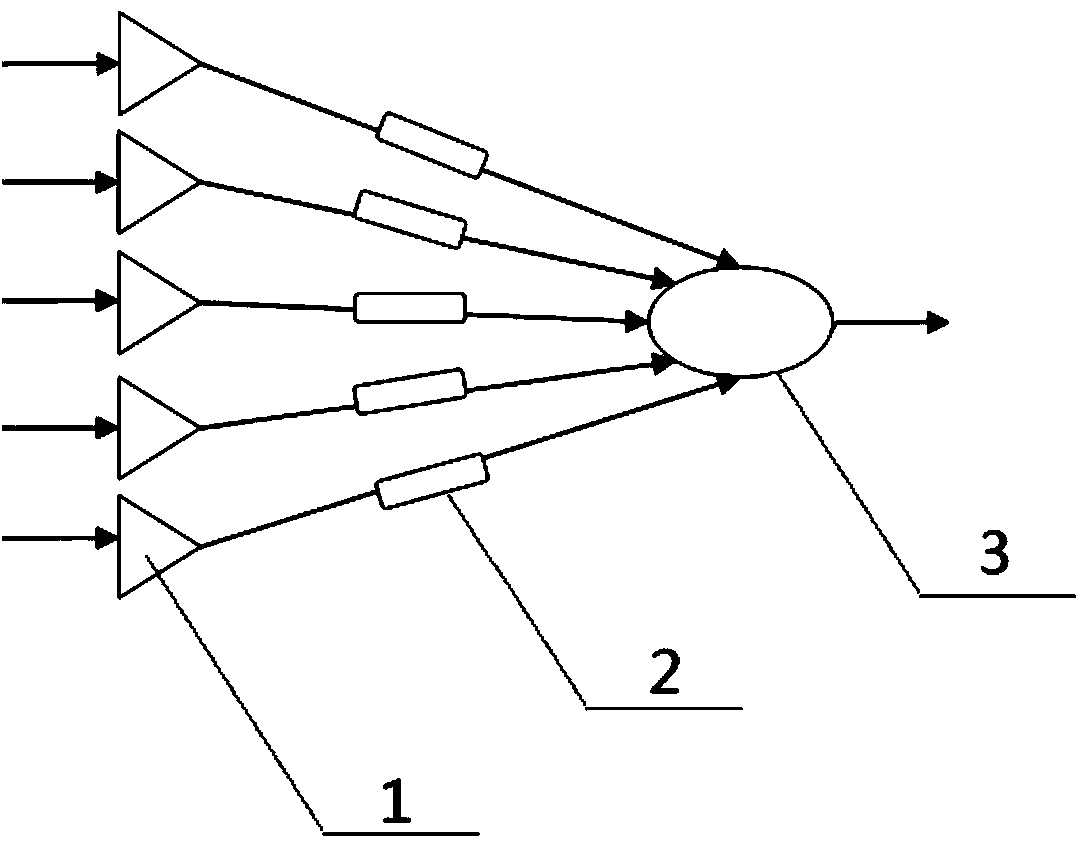

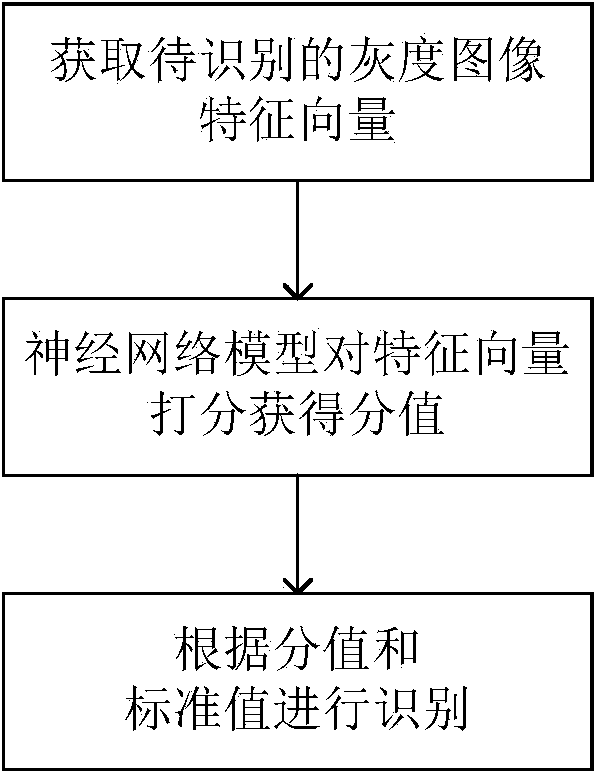

Memristor based image identification system and method

InactiveCN103810497AShorten the timeReduce energy consumptionCharacter and pattern recognitionFeature vectorTime complexity

The invention discloses a memristor based image identification system and method. The system comprises an image signal extracting module, a plurality of memristor based neural network modules, and an identification module, wherein an input end of the identification module is connected with an output end of each neural network module, and an input end of each neural network module is connected with an output end of the signal extracting module. The method includes the following steps that (1) a feature vector of a gray level image to be identified is acquired and input into the neural network modules; (2) each neural network module grades and identifies the feature vector according to an image model of each neural network module; (3) a difference value between a value of each neural network module and obtained standard values during training is calculated, and the classification of an image to be identified is judged according to the difference value. The memristor based image identification system has good expansibility, high integration density, and low power consumption; the method has low time complexity and high identification accuracy.

Owner:HUAZHONG UNIV OF SCI & TECH

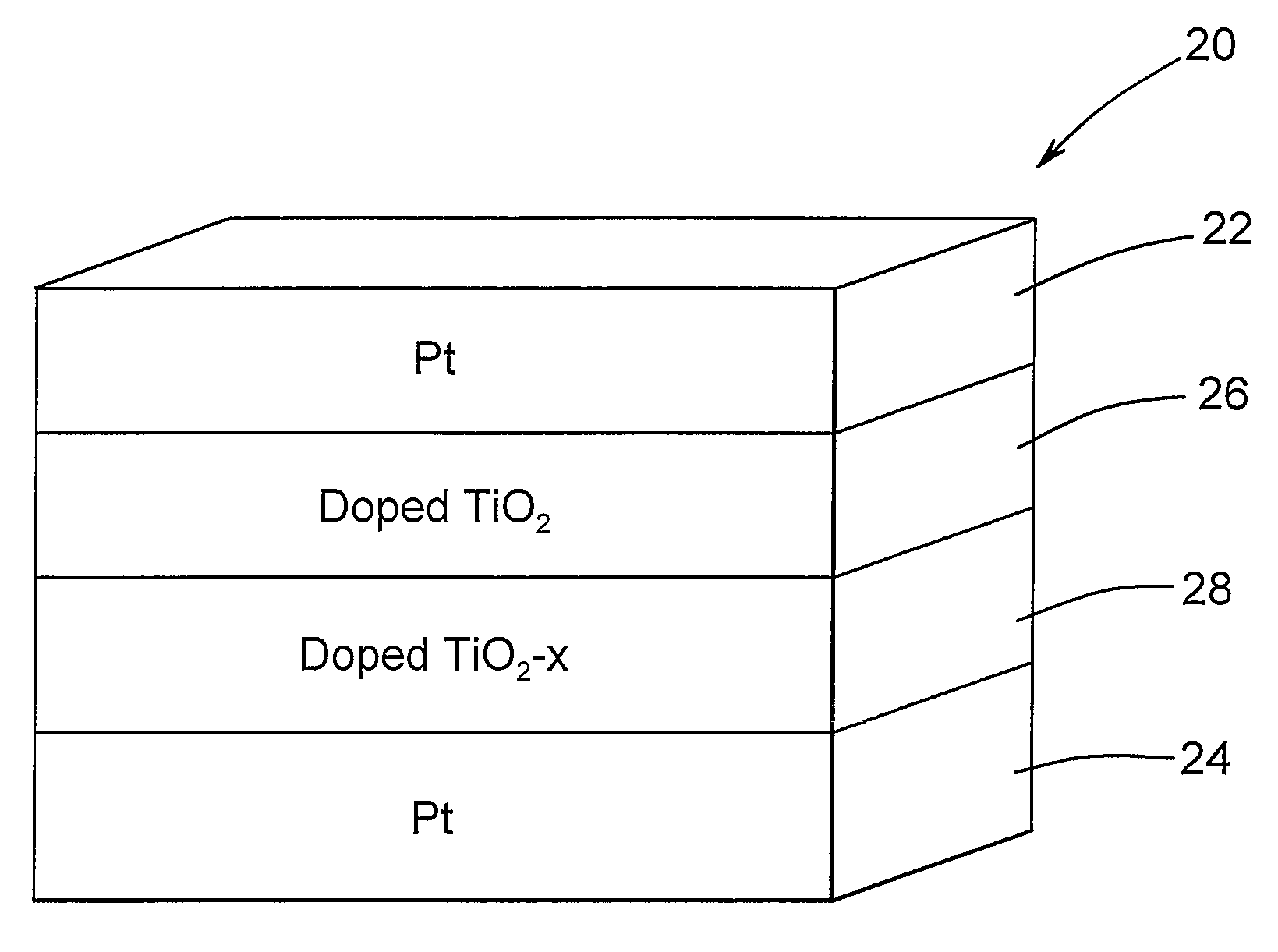

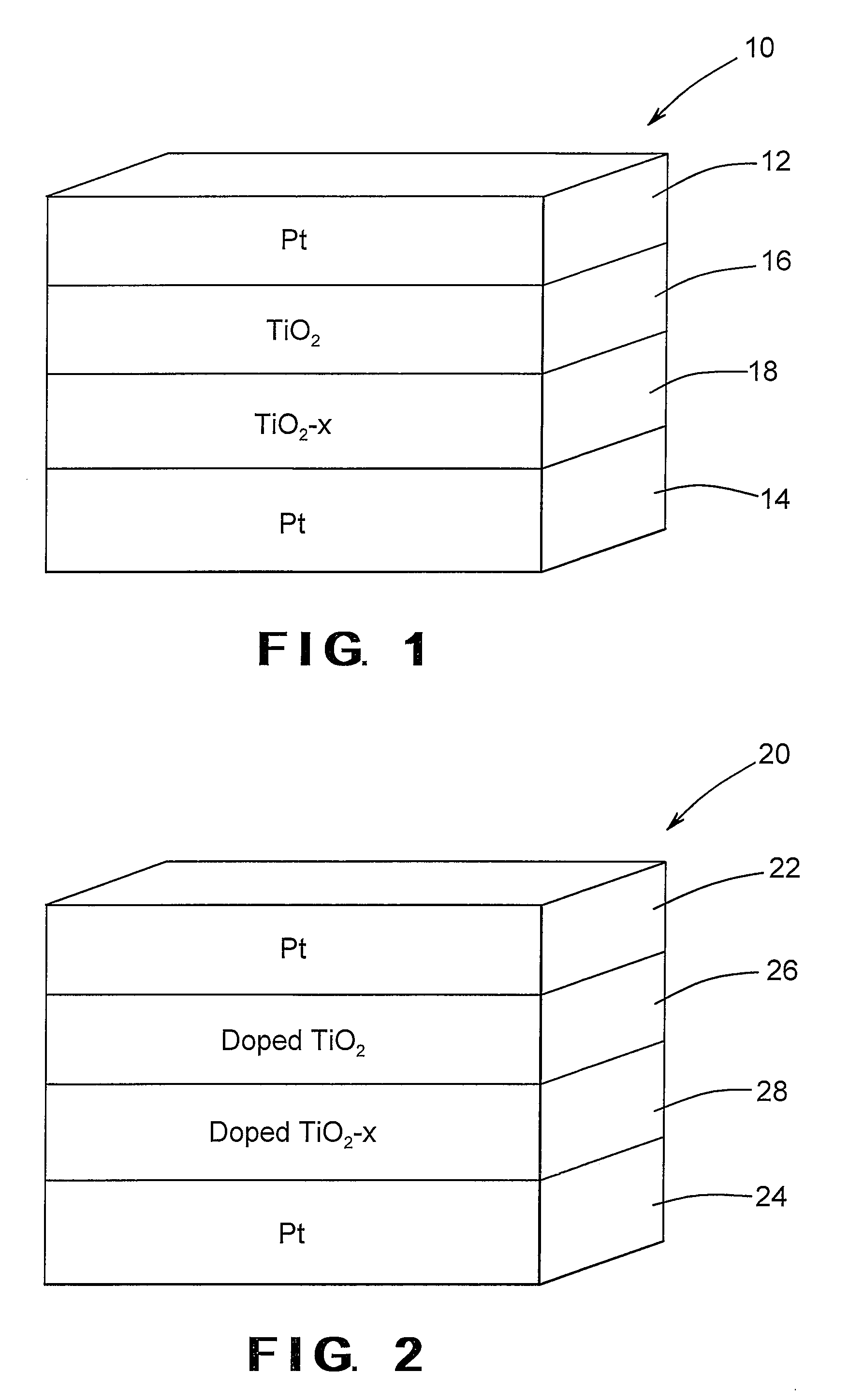

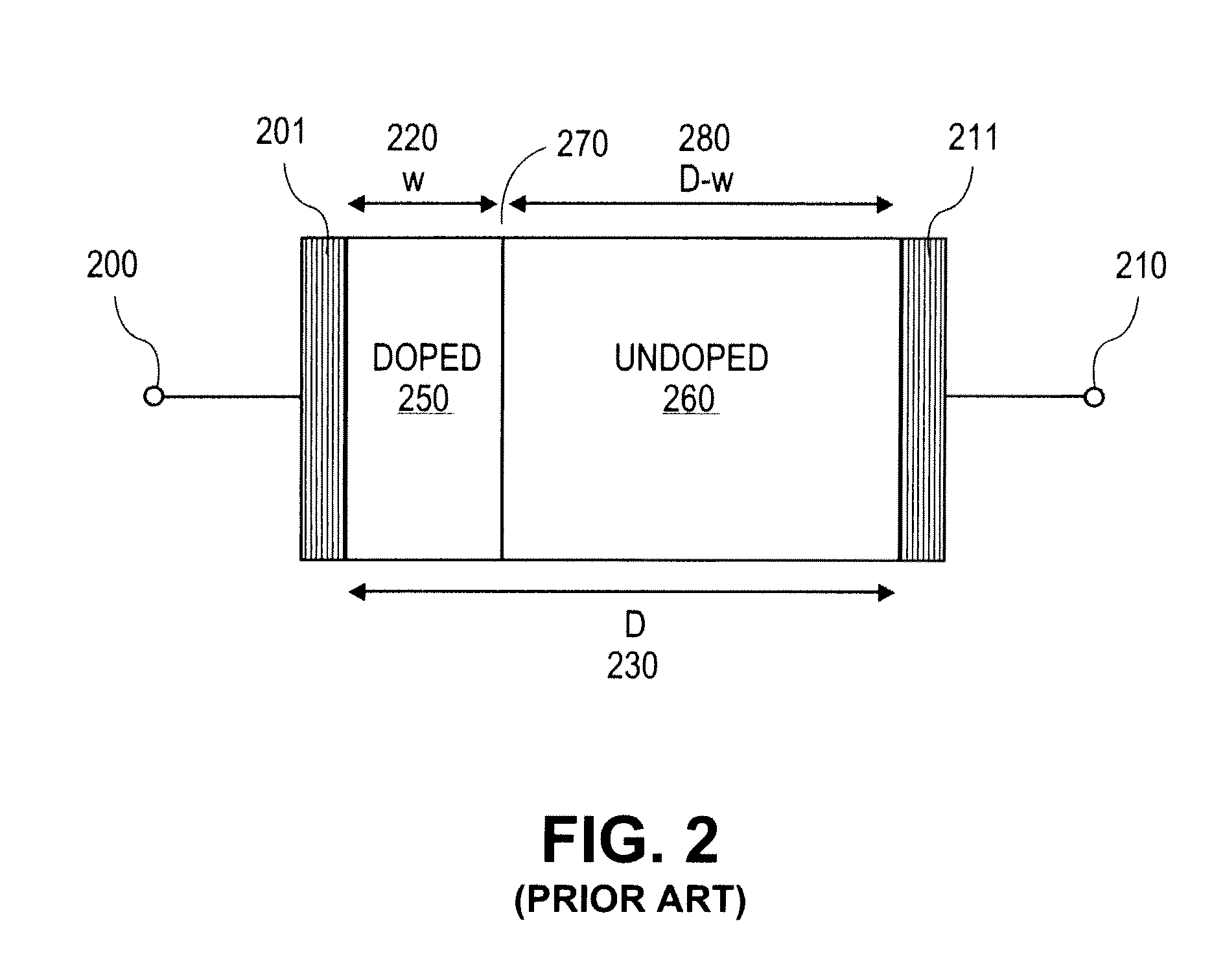

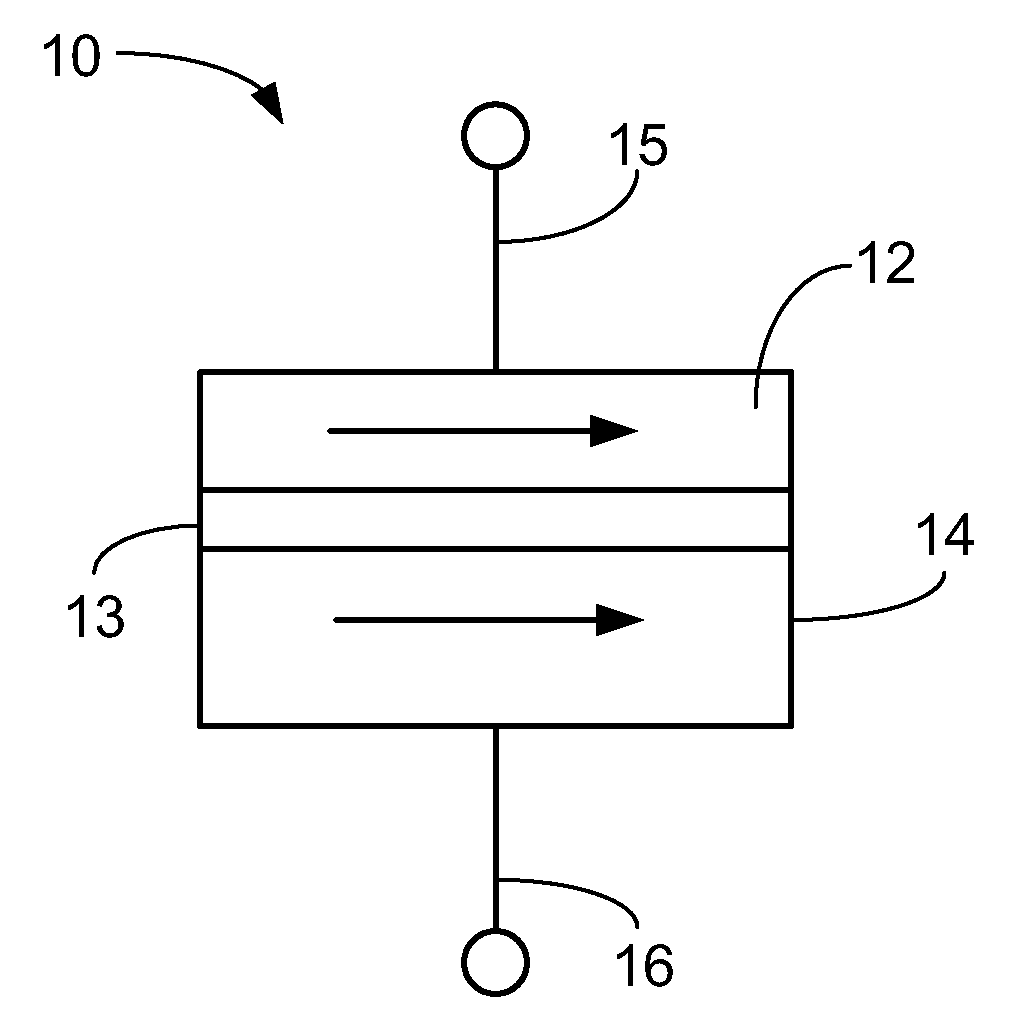

Nanoelectric memristor device with dilute magnetic semiconductors

A nanoelectric memristor device includes a first electrode and a layer of oxygen-vacancy-rich metal oxide deposited upon a surface of the first electrode. A layer of oxygen-rich / stochiometric metal oxide is deposited upon a surface of the oxygen-vacancy-rich metal oxide layer that is opposite from said first electrode. At least one of the oxygen-vacancy-rich metal oxide and oxygen-rich / stochiometric metal oxide layers is doped with one of a magnetic and a paramagnetic material. A second electrode is adjacent to a surface of the oxygen-rich / stochiometric metal oxide layer that is opposite from the oxygen-rich / stochiometric metal oxide layer.

Owner:UNIVERSITY OF TOLEDO

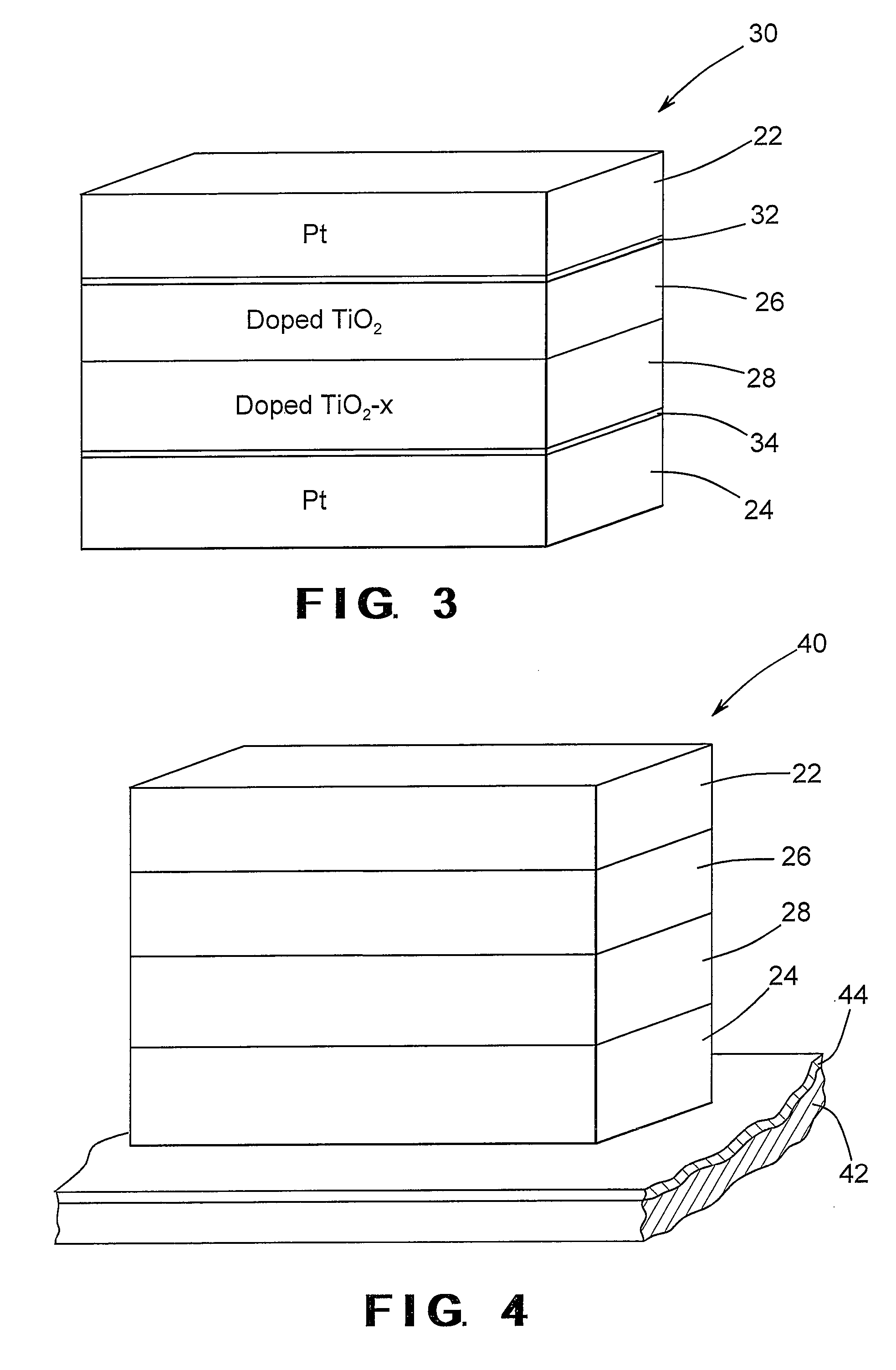

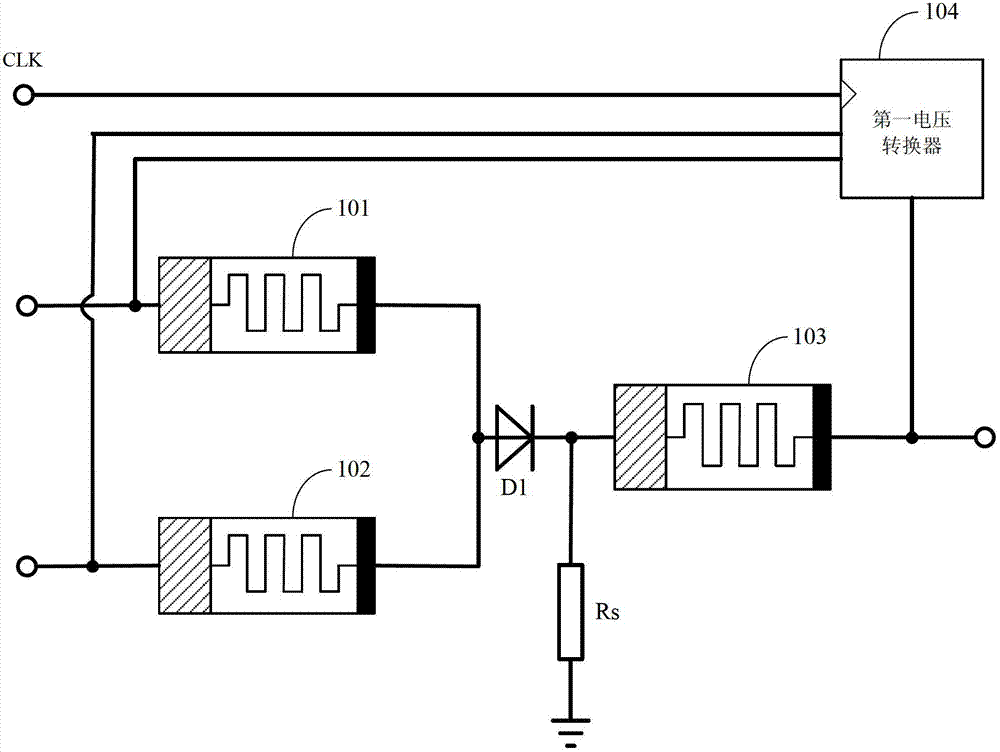

Memristor-based logical gate circuit

InactiveCN102811051ARealize logic processing functionImplement storageDigital storageLogic circuits using elementary logic circuit componentsEngineeringMemristor

The invention discloses a memristor-based logical gate circuit. An and-gate circuit comprises a first memristor, a second memristor, a third memristor, a single-directional conduction element and a first resistor; the input end of the first memristor is used as a first input end of the and-gate circuit, and the input end of the second memristor is used as a second input end of the and-gate circuit; and the output end of the third memristor is used as an output end of the and-gate circuit. An or-gate circuit comprises a fourth memristor, a fifth memristor and a second resistor; the input end of the fourth memristor is used as a first input end of the or-gate circuit, and the input end of the fifth memristor is used as a second input end of the or-gate circuit; and one end of the second resistor is connected with the output end of the fourth memristor and the output end of the fifth memristor, and the other end of the second resistor is used as an output end of the or-gate circuit. A not-gate circuit comprises a sixth memristor, a seventh memristor, a three-state gate and a third resistor; the input end of the sixth memristor is used as an input end of the not-gate circuit; and the output end of the seventh memristor is used as an output end of the not-gate circuit.

Owner:HUAZHONG UNIV OF SCI & TECH

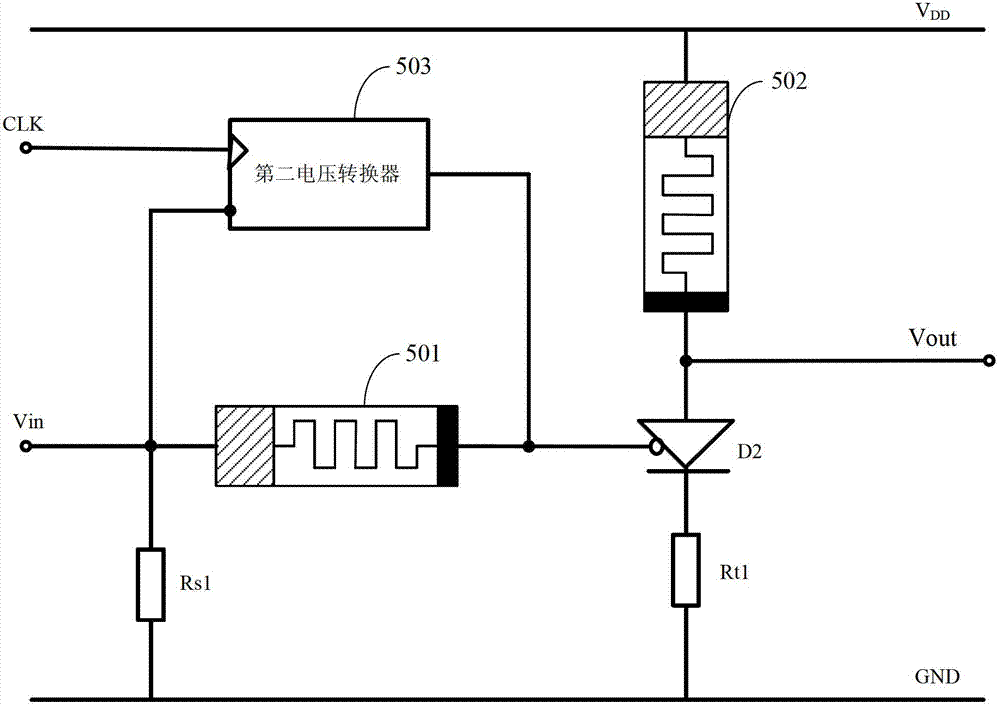

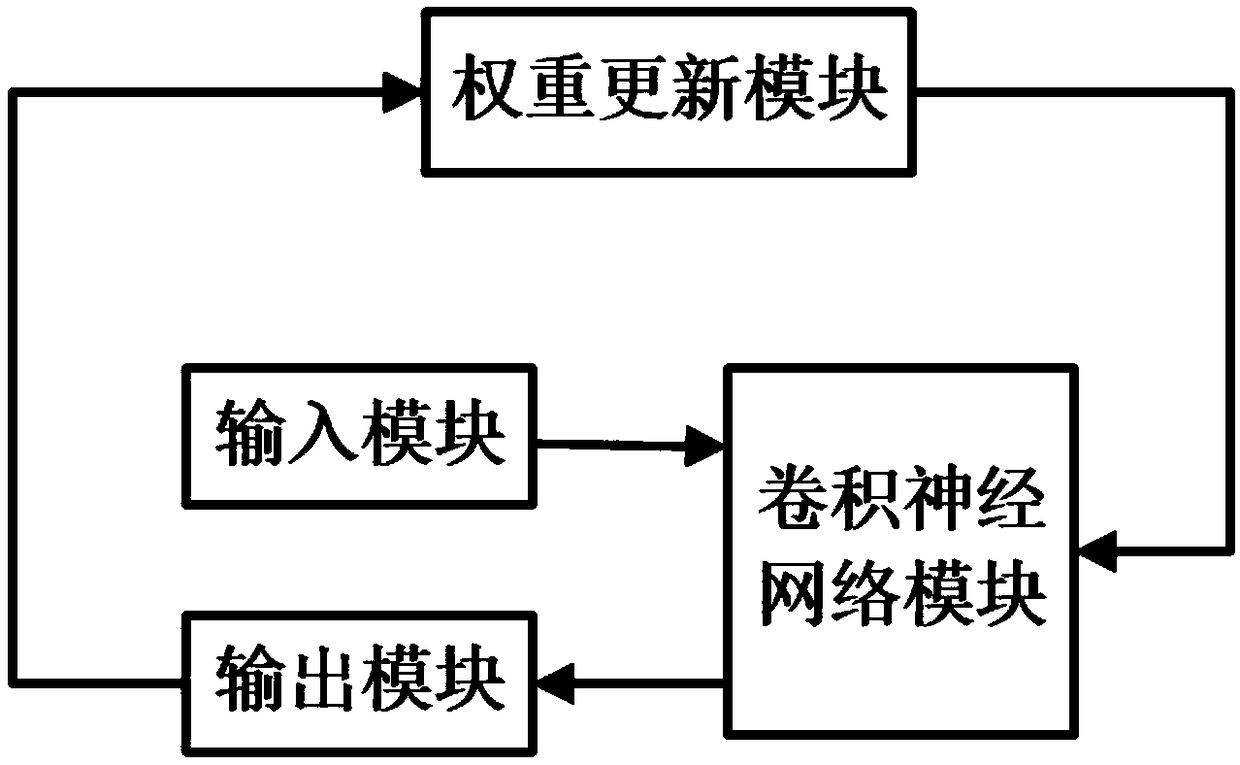

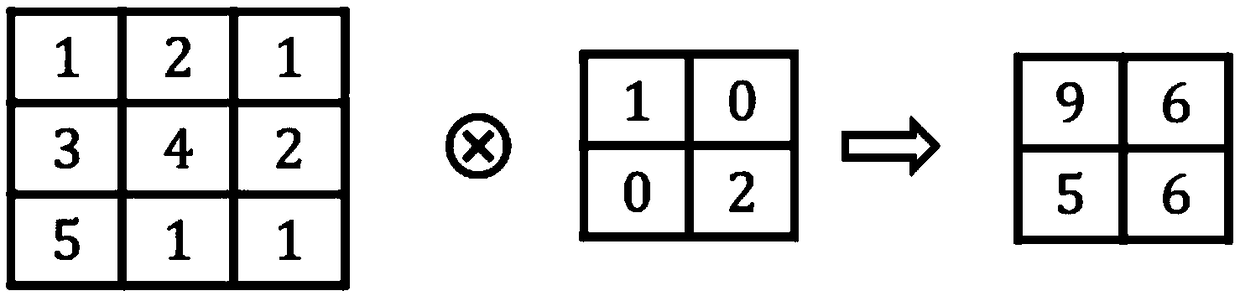

A convolution neural network-on-chip learning system based on nonvolatile memory

ActiveCN109460817AAchieve energy consumptionAvoid disadvantagesNeural architecturesPhysical realisationSynaptic weightSignal transition

The invention discloses a convolution neural network on-chip learning system based on non-volatile memory, comprising an input module, a convolution neural network module, an output module and a weight update module. The on-chip learning of the convolution neural network module utilizes the characteristic that the conductance of the memristor changes with the applied pulse to realize the synapticfunction, and the convolution kernel value or the synaptic weight value is stored in the memristor unit. The input module converts the input signal into the voltage signal required by the convolutional neural network module. The convolutional neural network module transforms the input voltage signal layer by layer and transmits the result to the output module to get the output of the network. Theweight updating module adjusts the conductance value of the memristor in the convolutional neural network module according to the result of the output module, and updates the convolution core value orsynaptic weight value of the network. The invention aims at realizing the on-chip learning of the convolution neural network, realizing the on-line processing of the data, and realizing the requirements of high speed, low power consumption and low hardware cost based on the high parallelism of the network.

Owner:HUAZHONG UNIV OF SCI & TECH

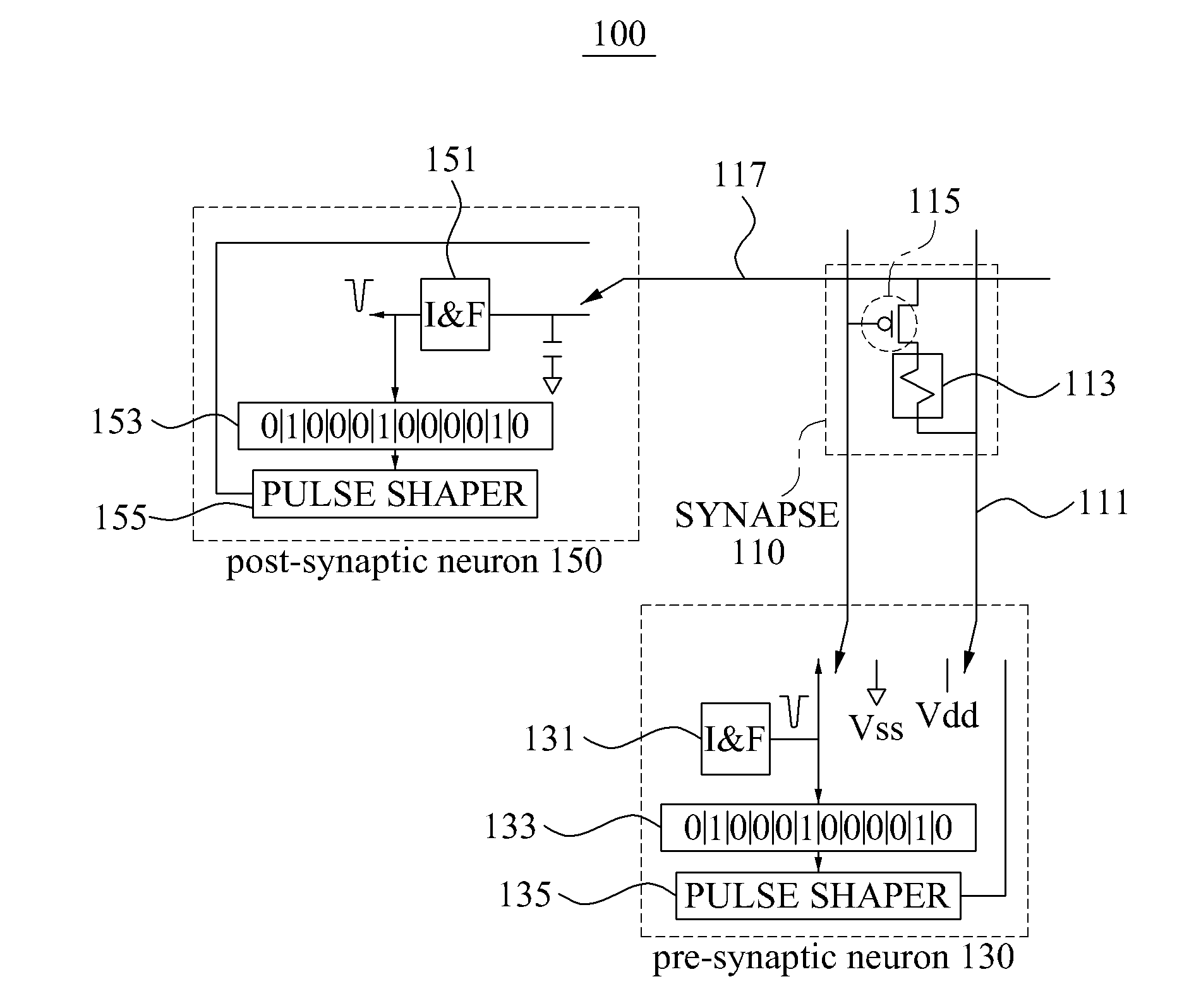

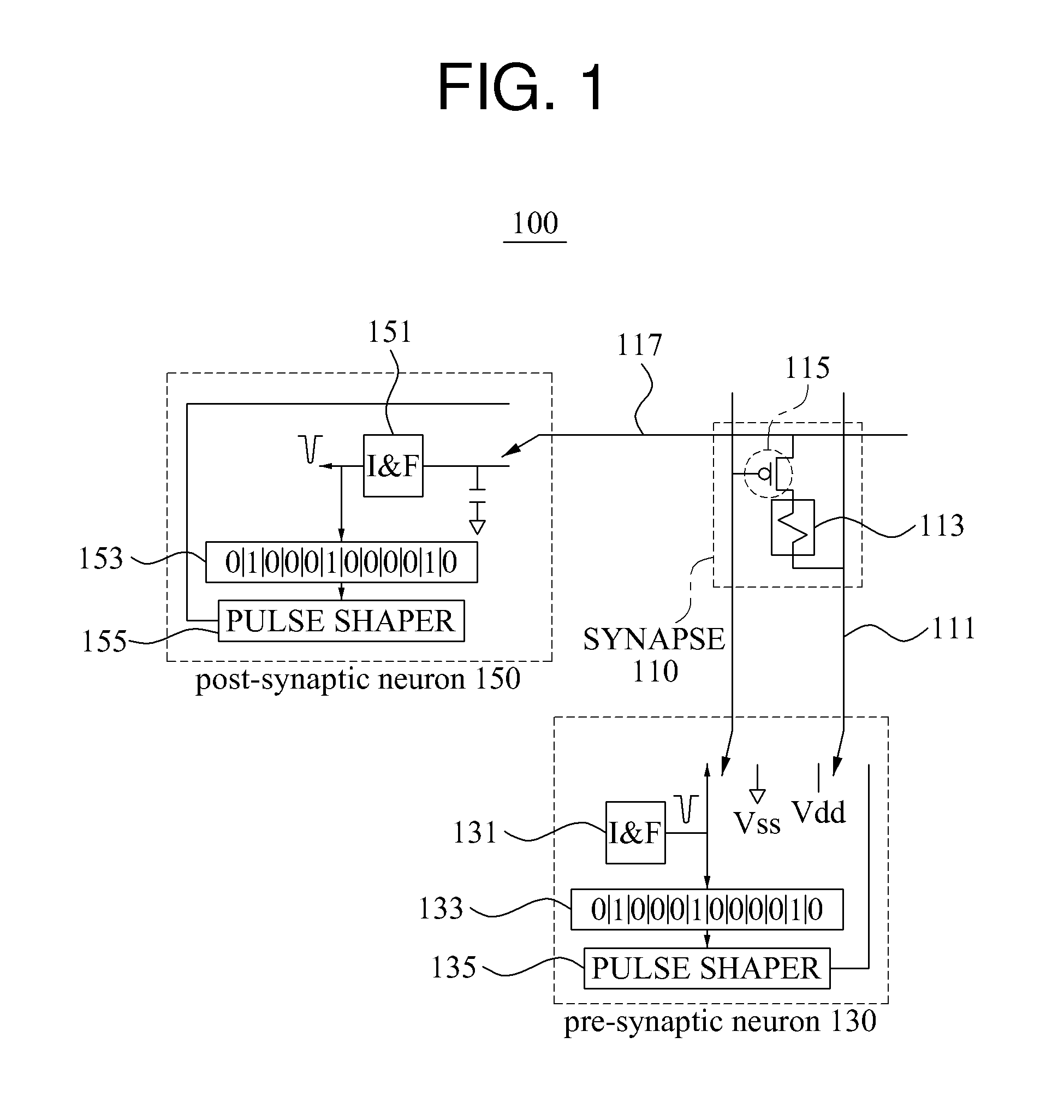

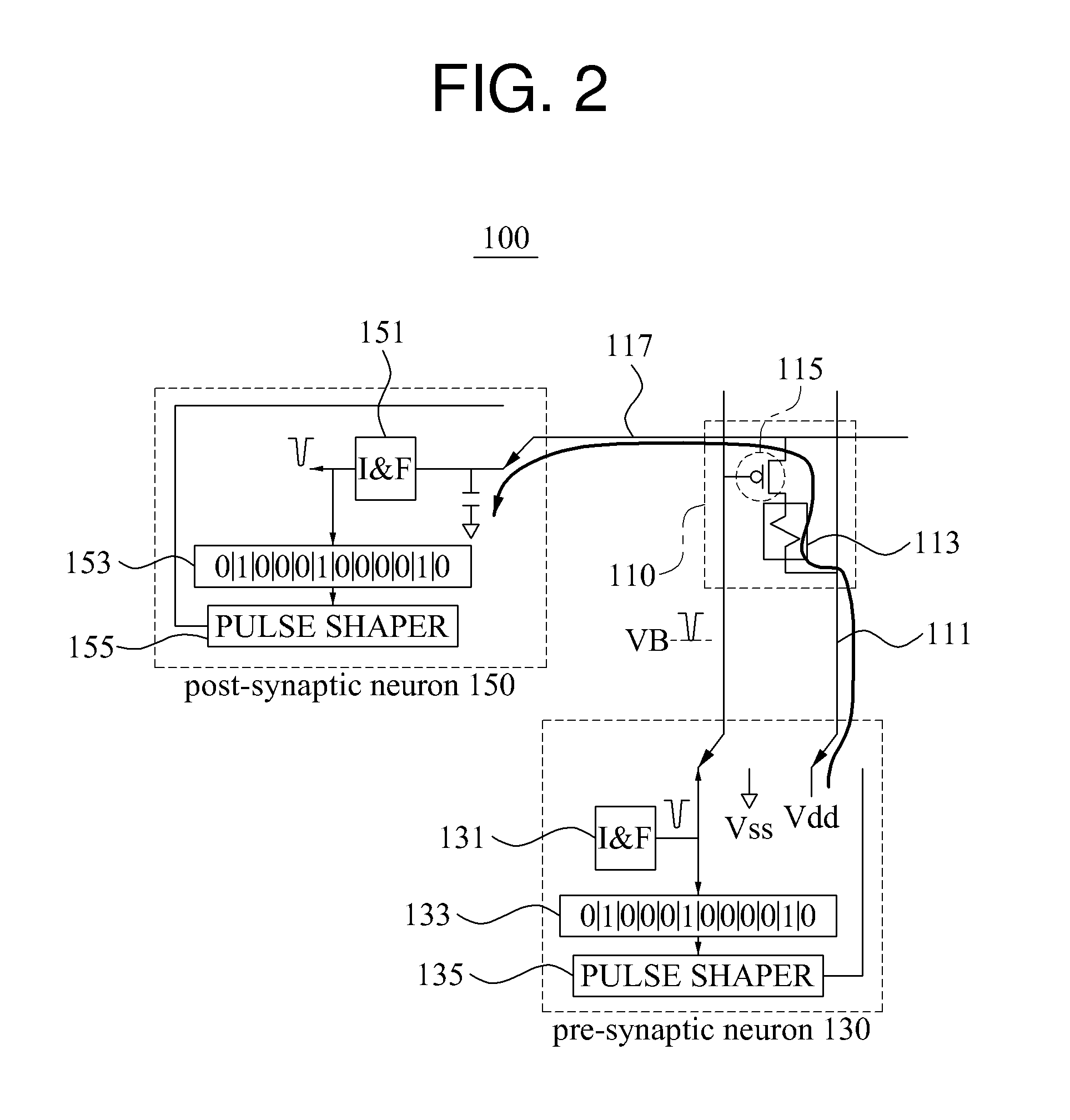

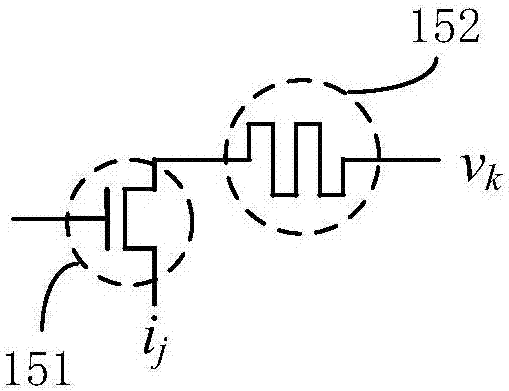

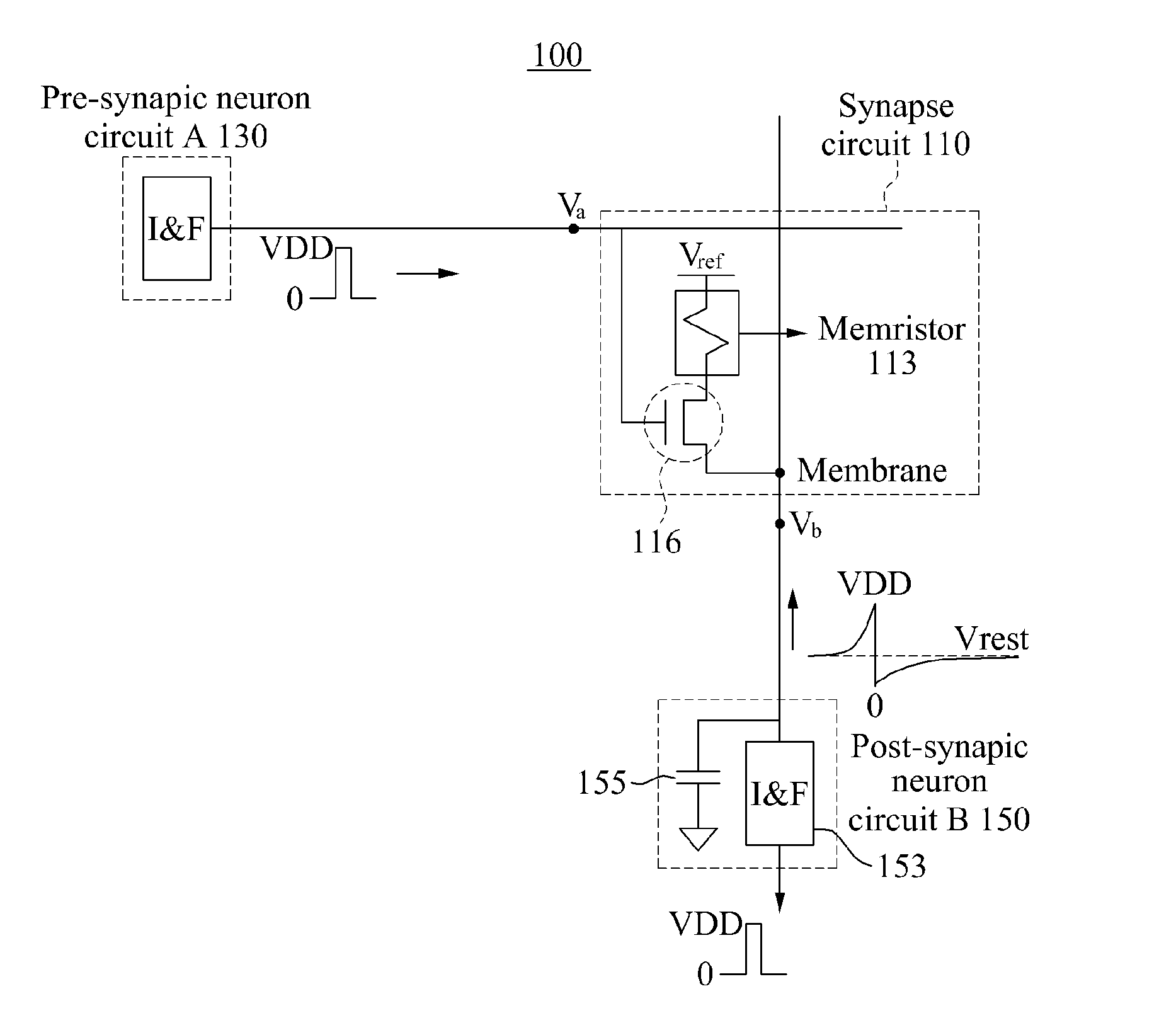

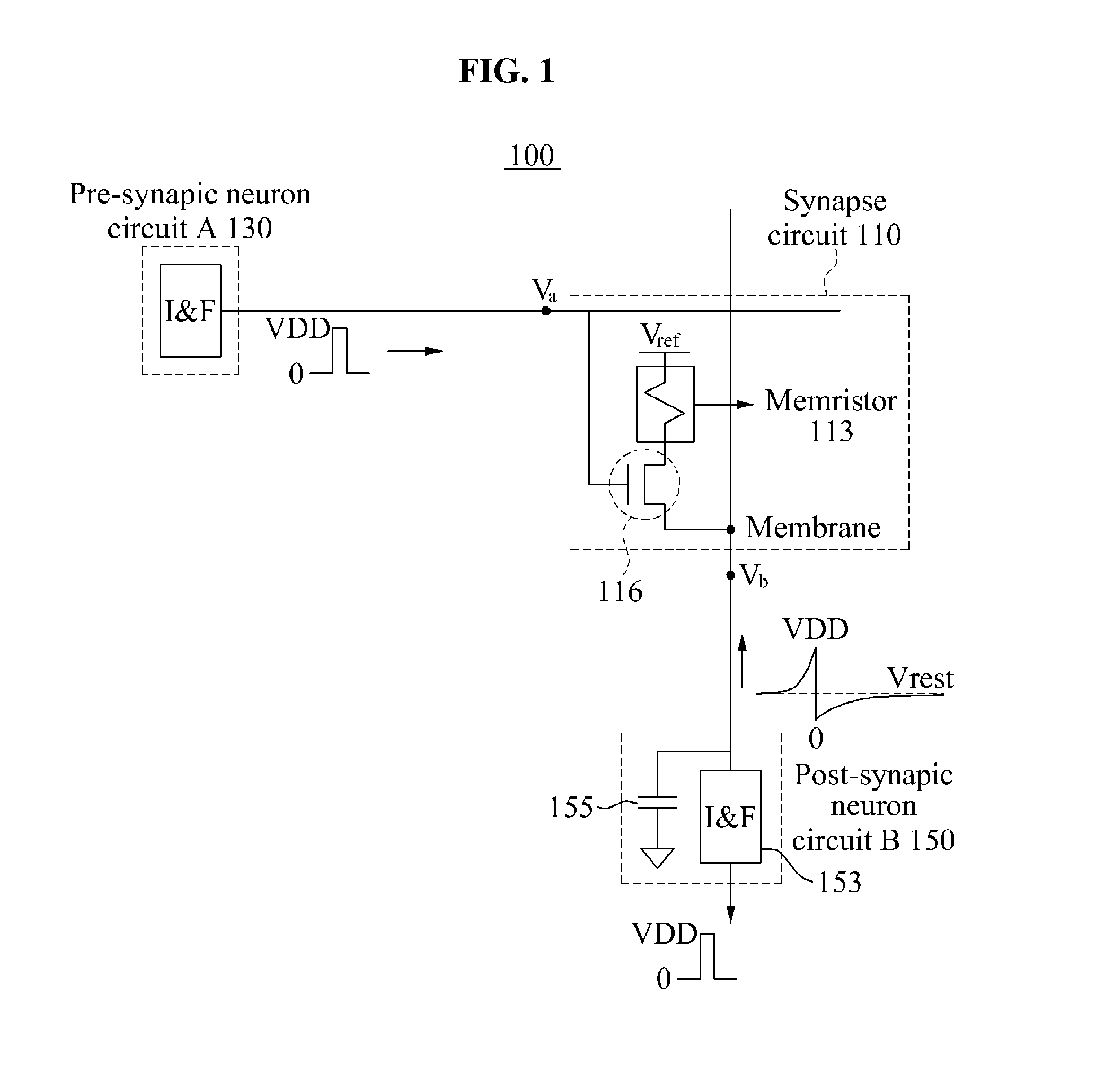

Synapse for function cell of spike timing dependent plasticity (STDP), function cell of stdp, and neuromorphic circuit using function cell of stdp

ActiveUS20120317063A1Synaptic weight can be decreasedReduce resistanceDigital computer detailsDigital storageSpike-timing-dependent plasticityNeuromorphic circuits

A synapse for a spike timing dependent (STDP) function cell includes a memory device having a variable resistance, such as a memristor, and a transistor connected to the memory device. A channel of the memory device is connected in series with a channel of the transistor.

Owner:SAMSUNG ELECTRONICS CO LTD +1

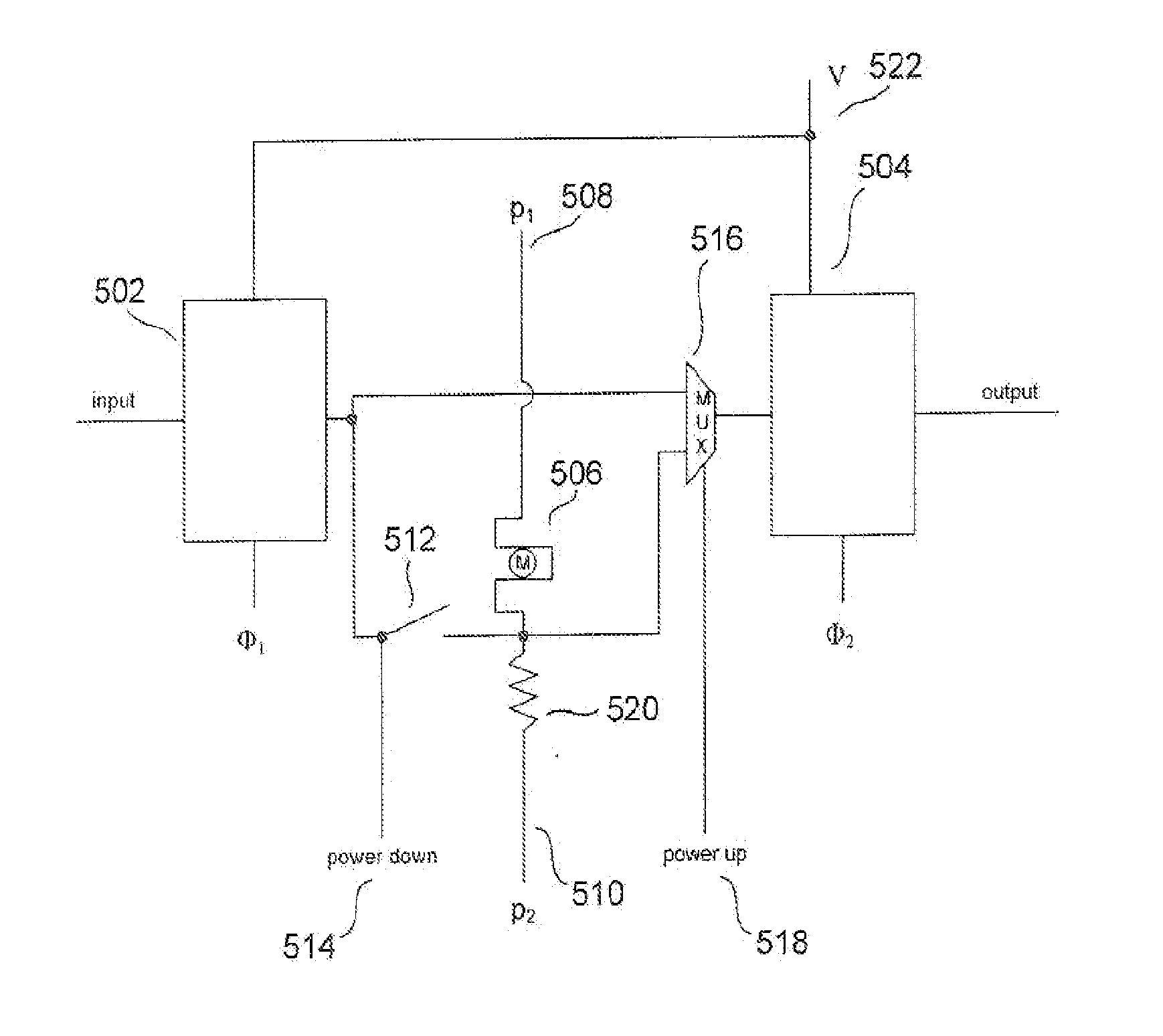

Non-volatile data-storage latch

InactiveUS20120014169A1Pulse generation by non-linear magnetic/dielectric devicesRead-only memoriesComputer scienceTransistor

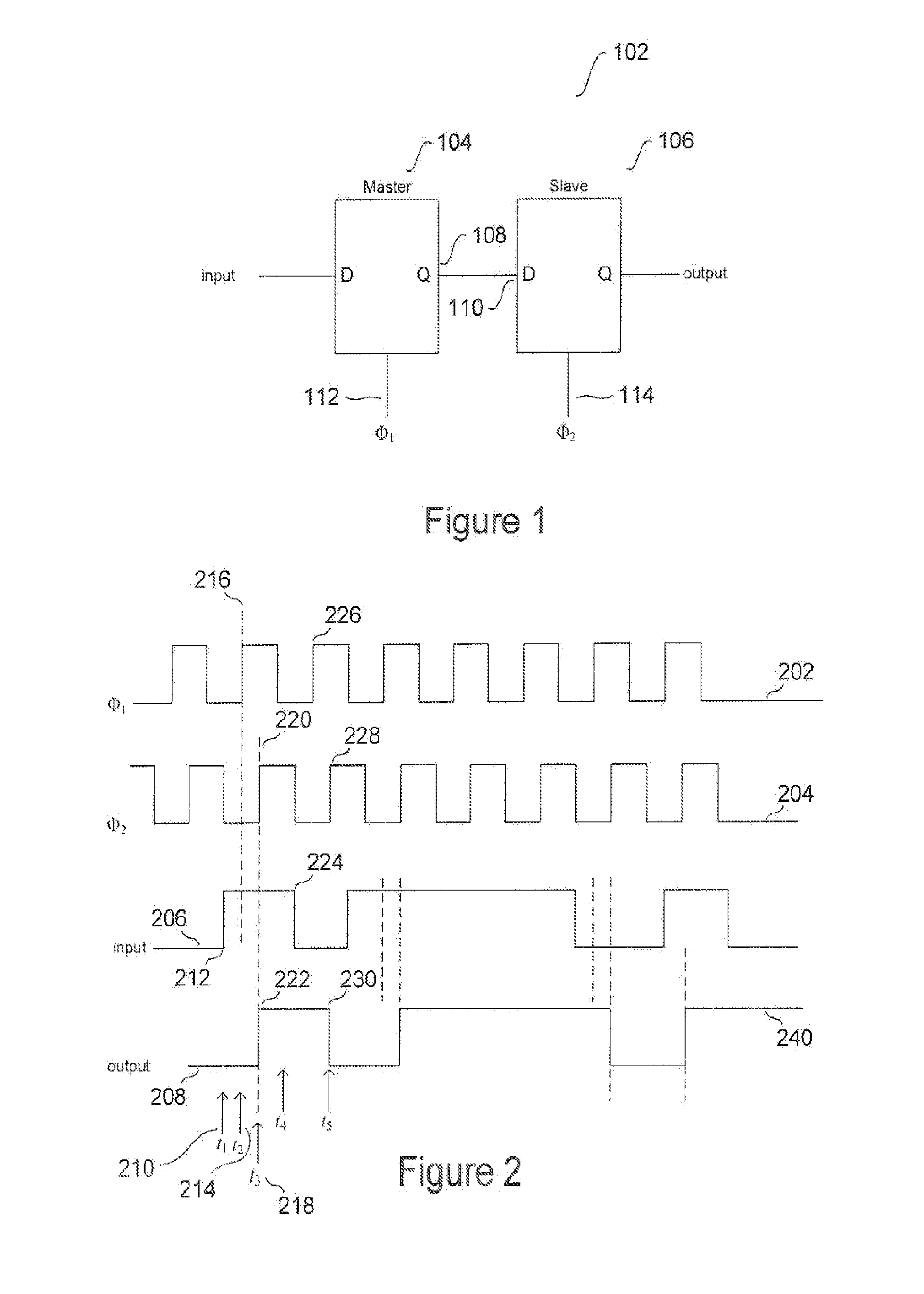

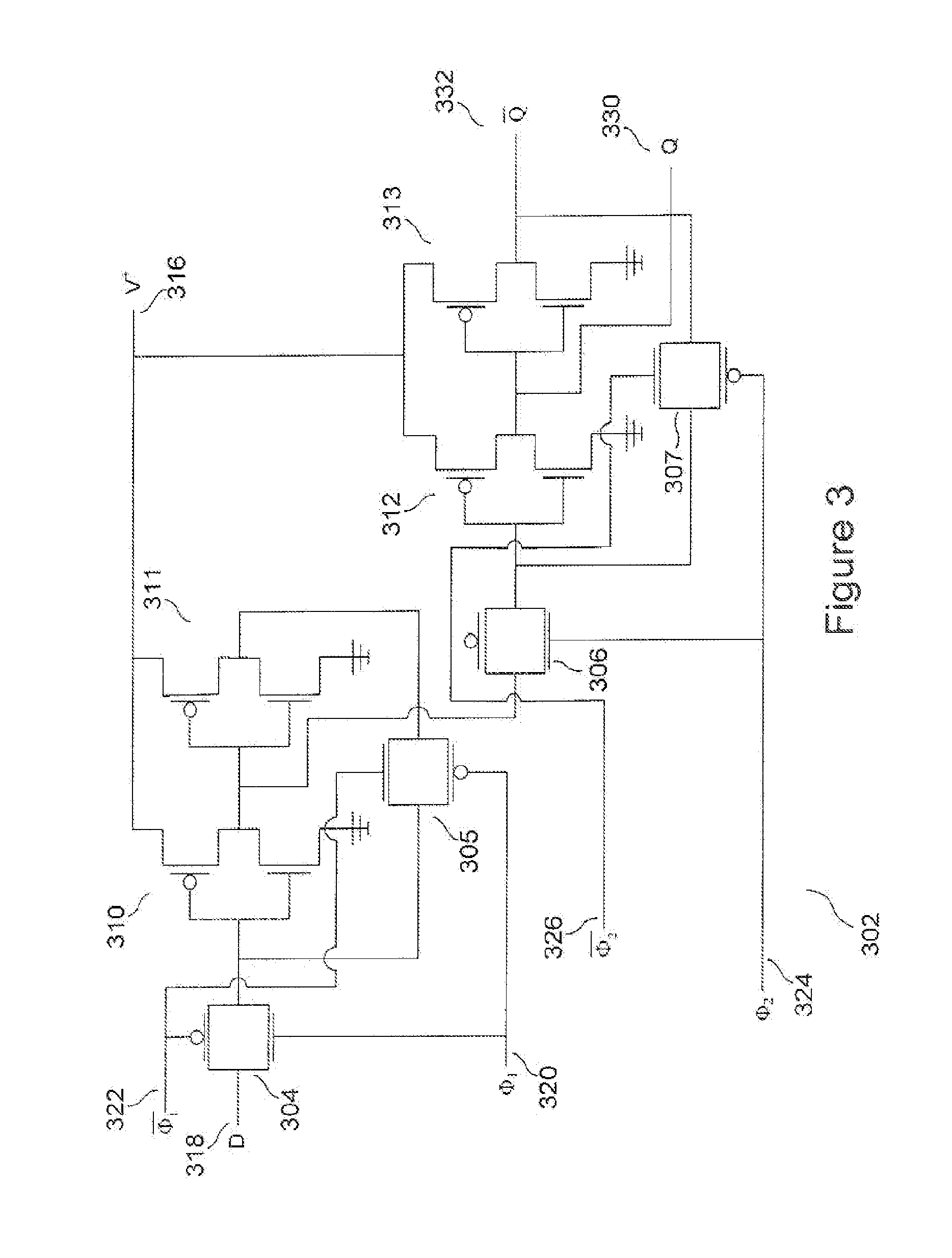

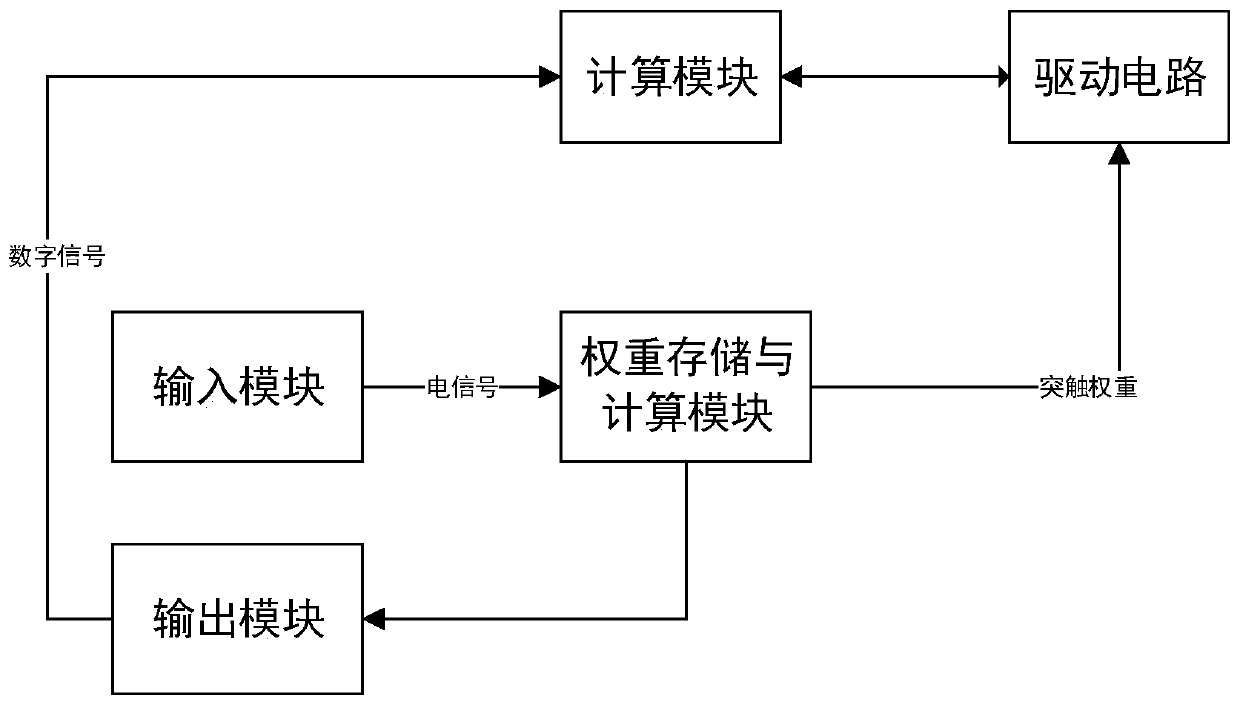

One embodiments of the present invention is directed to a single-bit memory cell comprising transistor-based bit latch having a data state and a memristor, coupled to the transistor-based bit latch, in which the data state of the transistor-based bit latch is stored by a store operation and from which a previously-stored data state is retrieved and restored into the transistor-based bit latch by a restore operation. Another embodiment of the present invention is directed to a single-bit memory cell comprising a master-slave flip flop and a slave flip flop, and a power input, a memristor, a memory-cell power input, a first memory-cell clock input, a second memory-cell clock input, a memory-cell data input, a memory-cell data output, and two or more memory-cell control inputs.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP

Neural network online learning system based on a memristor

ActiveCN109800870AHigh precisionIncrease training speedPhysical realisationOffline learningAlgorithm

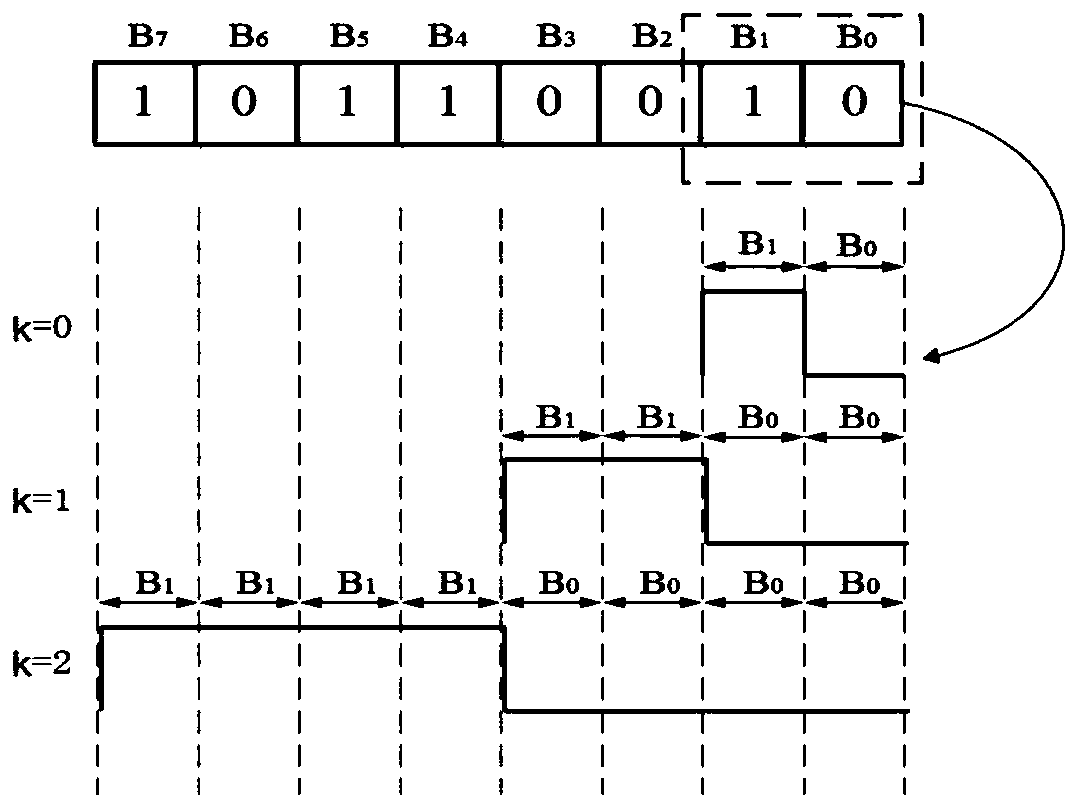

The invention discloses a neural network online learning system based on a memristor. A pulse coding mode of a K-bit input vector is improved; the coding pulse corresponding to each bit is expanded into 2m pulses; In this way, the total number of needed coded pulses is K * 2m, each bit of weighted summation calculation is actually carried out for 2m times, finally, summation averaging operation iscarried out at the output end, the influence of accidental factors and noise on the calculation result in the calculation process is reduced through the mode, and therefore the calculation precisionis improved. The memristor array is simultaneously used for forward weighted summation calculation and weight small storage in the neural network; Different from offline learning, The weight in the memristor array needs to be updated once every time a signal is input through online learning, the variable quantity of the weight is mapped into the number of pulses, then the pulses are applied for one-time weight write-in operation, the neural network training speed can be increased, the hardware cost can be reduced, and the power consumption of neural network training is reduced.

Owner:HUAZHONG UNIV OF SCI & TECH

Semiconductor device and structure

ActiveUS9117749B1Small footprintIncrease speedTransistorSolid-state devicesPower semiconductor deviceSpin-transfer torque

Owner:MONOLITHIC 3D

Training device for memristor-based neural network and training method thereof

The invention discloses a training device for a memristor-based neural network and a training method thereof. The neural network comprises N neuron layers which are connected one by one. The trainingmethod comprises the following steps of: inputting input data into a first neuron layer of the neural network so as to output an output result of the neural network at the Nth neuron layer, and calculating an output error of the Nth neuron layer; and counter-propagating the output error of the Nth neuron layer in a layer-by-layer manner so as to correct weight parameters between the neuron layers;and in the layer-by-layer counter-propagation process, three-valuing an output error of the mth neuron layer, and reversely inputting a voltage signal corresponding to an output result of the three-valuing operation to the mth neuron layer so as to correct a weight parameter of the mth neuron layer, wherein N is an integer greater than or equal to 3, and m is an integer greater than 1 and smallerthan N. According to the training method, the calculation ability of the memristor-based neural network is improved.

Owner:TSINGHUA UNIV

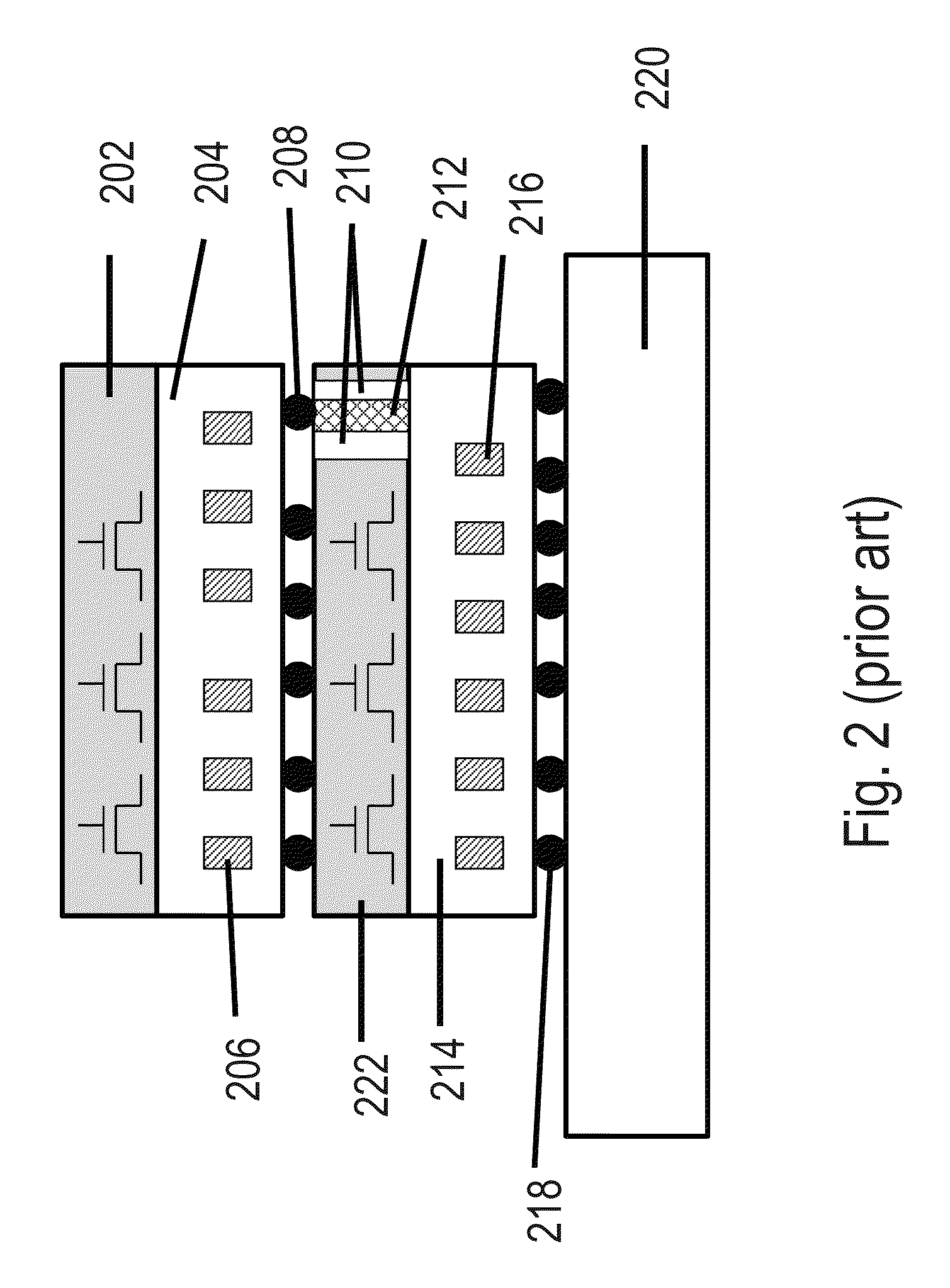

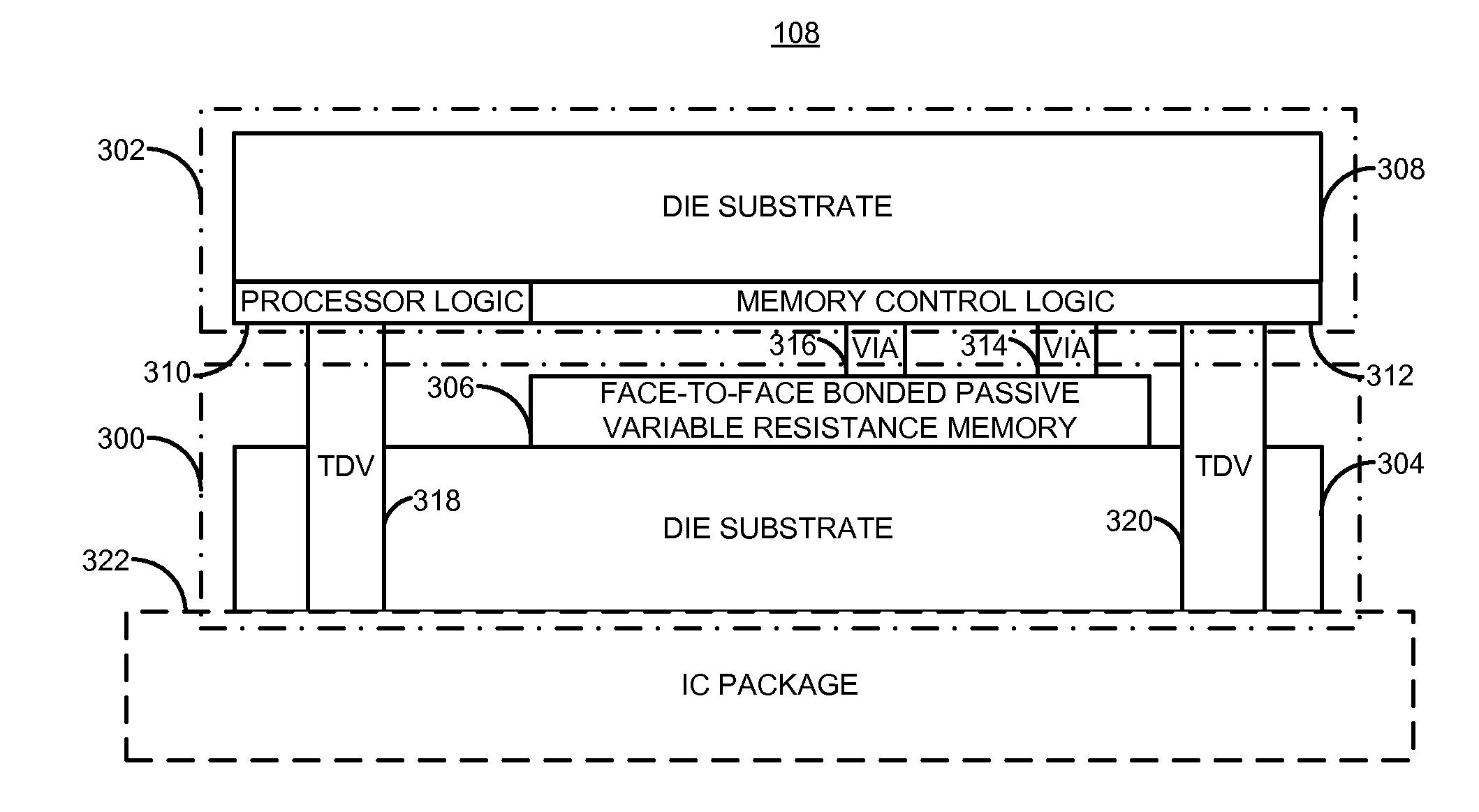

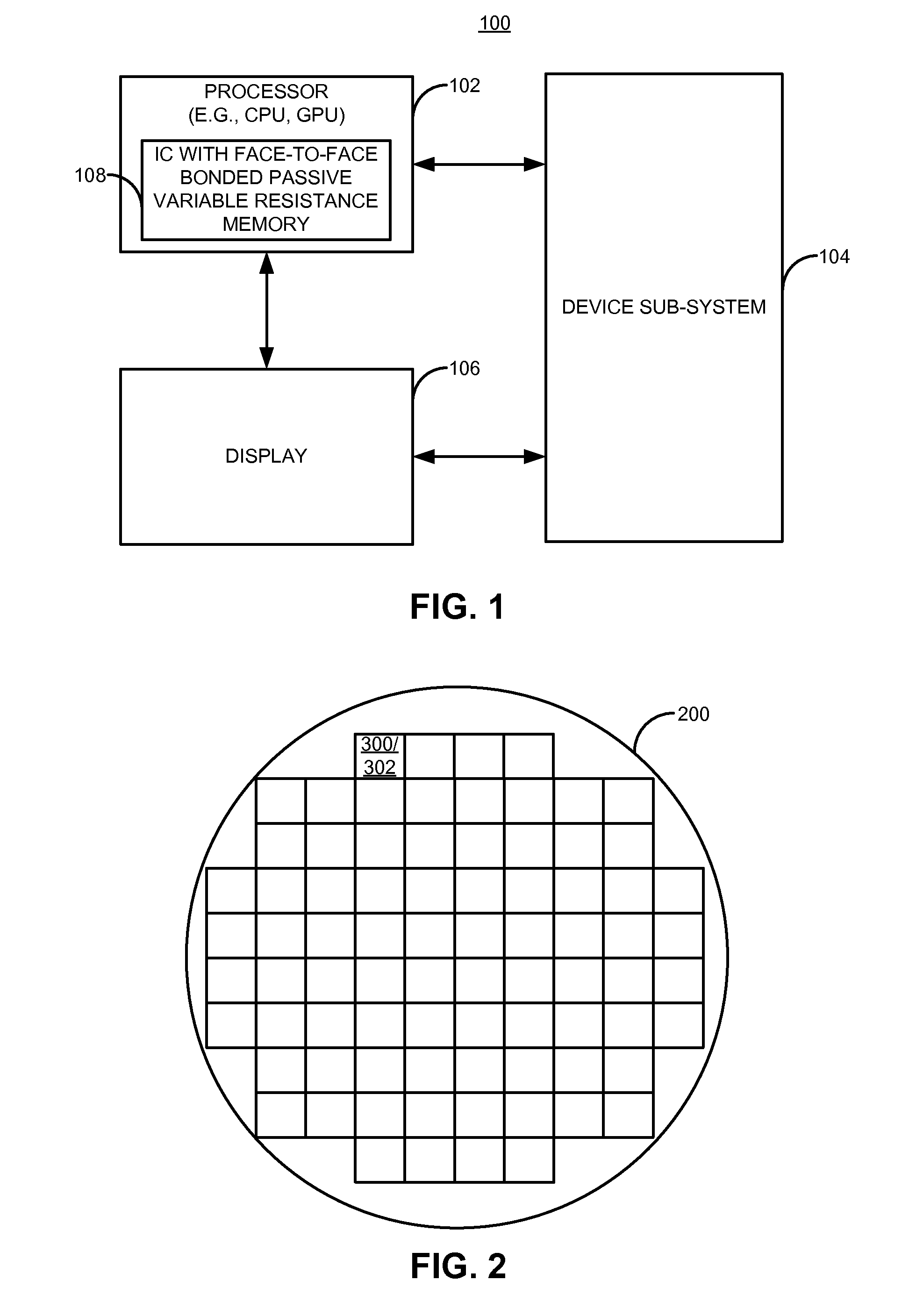

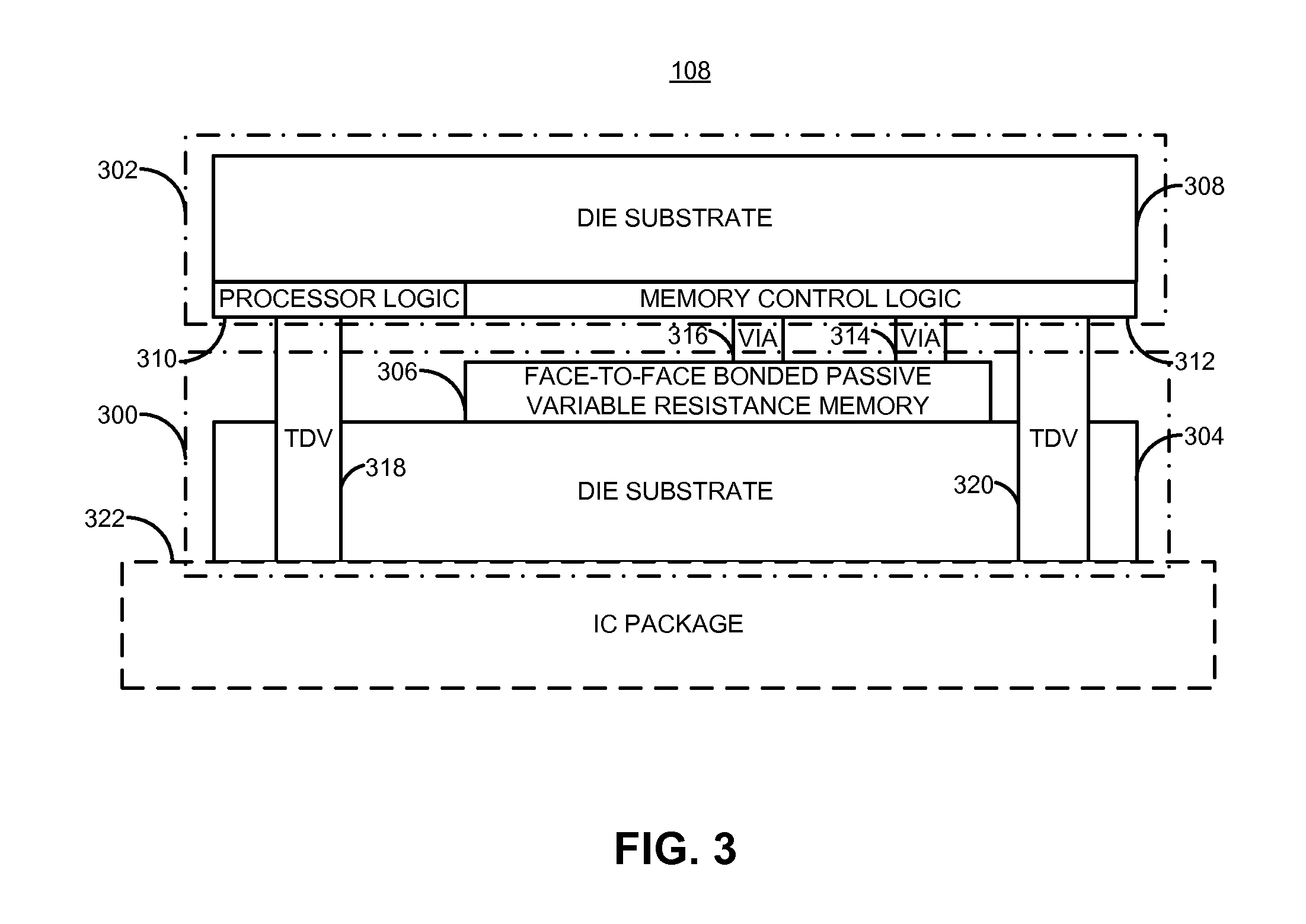

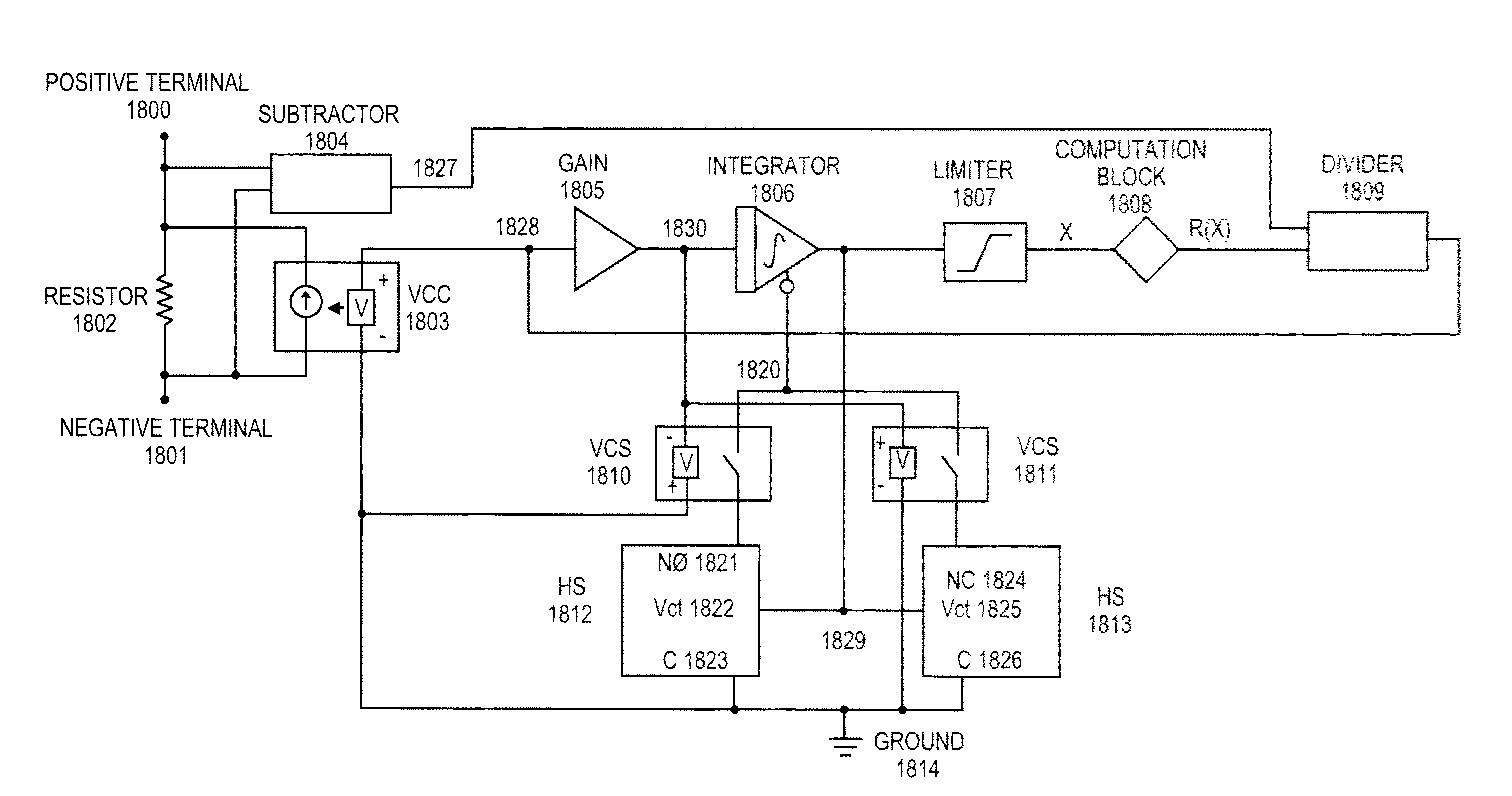

Integrated circuit with face-to-face bonded passive variable resistance memory and method for making the same

In one example, an integrated circuit includes two integrated circuit dies that are face-to-face mounted together. The first integrated circuit die includes passive variable resistance memory and the second integrated circuit die includes memory control logic (e.g., CMOS logic circuit). The passive variable resistance memory, also known as resistive non-volatile memory, may be for example memristors, phase-change memory, or magnetoresistive memory. Each memory cell of the passive variable resistance memory on the first integrated circuit die is electrically connected to the memory control logic on the second integrated circuit die through at least one vertical interconnect accesses (vias). For example, the operation (e.g., write / read) of each passive variable resistance memory cell is controlled by the memory control logic. The integrated circuit may also include processor logic on the second integrated circuit die operatively coupled to the memory control logic.

Owner:ADVANCED MICRO DEVICES INC

Signal-processing devices having one or more memristors

Signal-processing devices having memristors are described for performing frequency-discrimination functions, amplitude-discrimination functions, and time-oriented functions. In each case, the time-domain behavior of the memristors described herein enables these functions to be performed. In one embodiment, memristance of an arrangement of memristors of a device is, after an initial transitional period, predominantly at a first level if frequency of an input signal of the device is less than a first frequency and predominantly at a second level if the frequency of the input signal is greater than a second frequency.

Owner:KOZA JOHN R

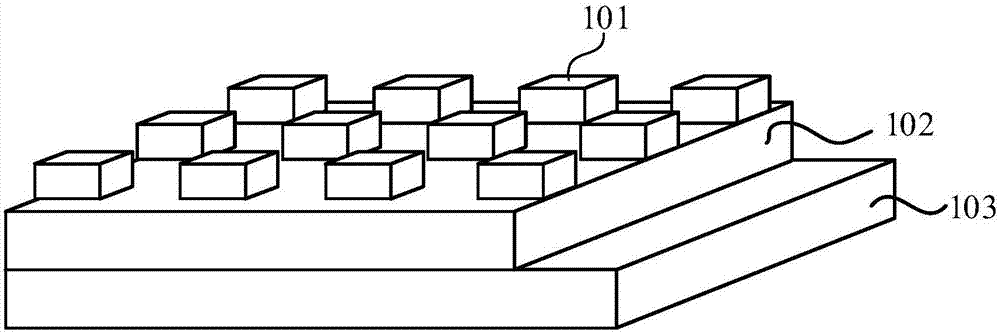

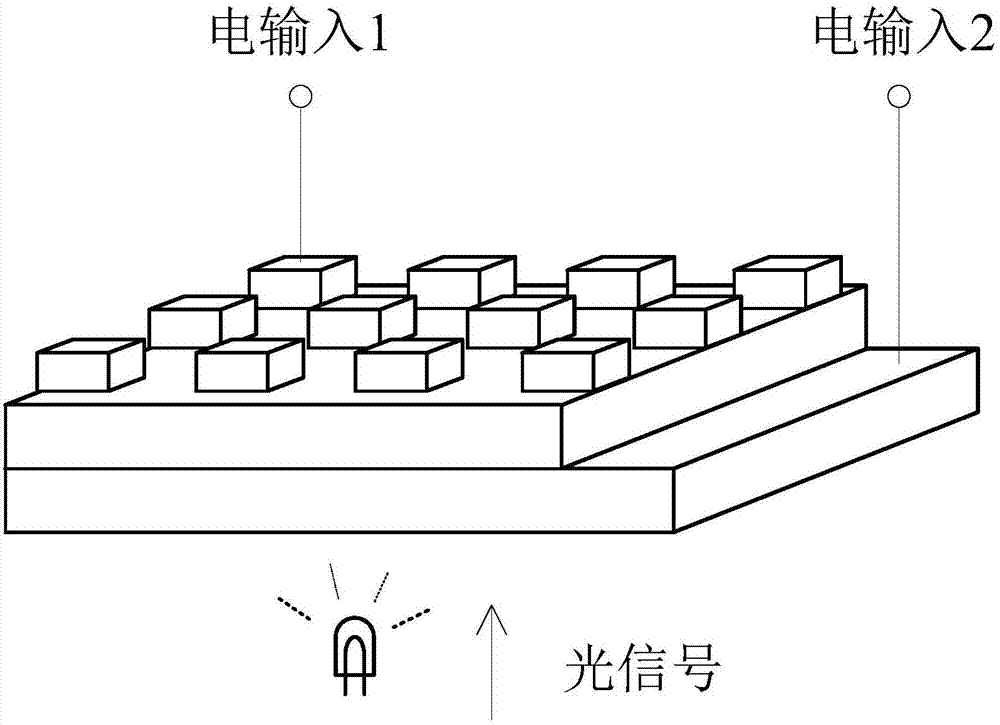

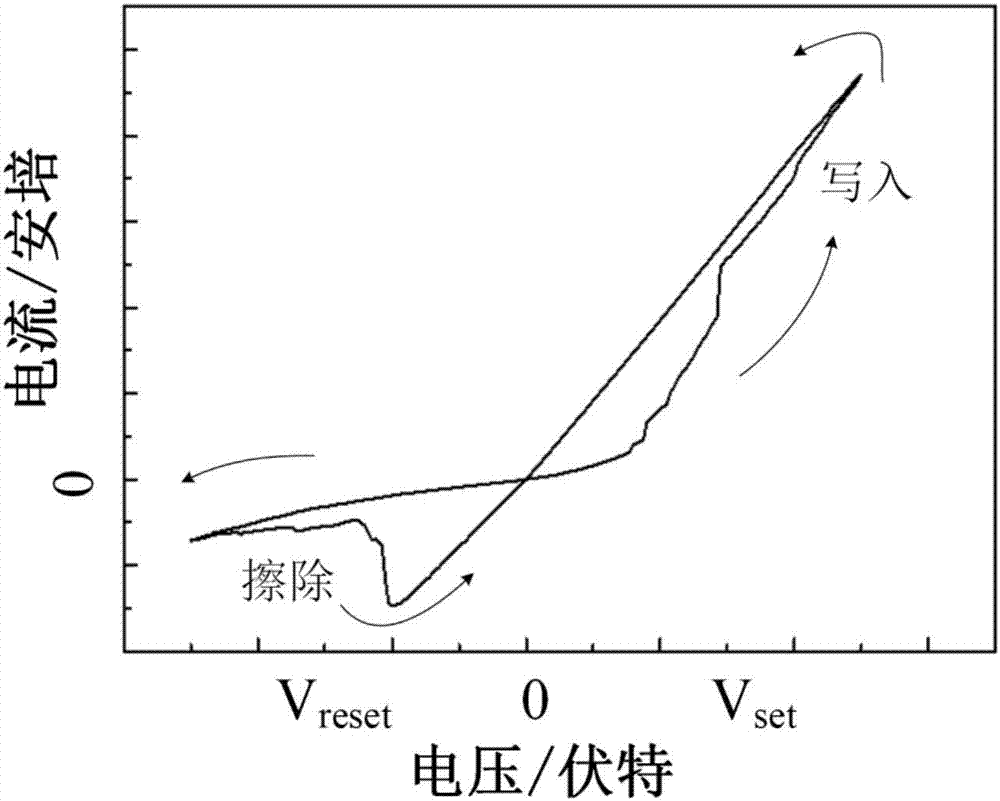

Artificial synaptic device based on photoelectric coupling memristor and modulation method of artificial synapse device

The invention discloses an artificial synaptic device based on a photoelectric coupling memristor and a modulation method of the artificial synaptic device. The artificial synaptic device comprises an upper electrode, a lower electrode and a functional material layer, wherein the functional material layer is arranged between the upper electrode and the lower electrode, the upper electrode, the functional material layer and the lower electrode jointly form a sandwich structure, the functional material layer is made of a material having a photoelectric effect, the lower electrode is a transparent conductive electrode, an electrical signal is input through the upper electrode and the lower electrode, and an optical signal is input through the transparent conductive electrode. In the artificial synaptic device provided by the invention, light is introduced as a control signal of the other end except the electrical signal, two control ends of the artificial synapse device are expanded to three ends, the artificial synaptic device can generate resistance change under an external optical excitation signal by the additionally-arranged end, the artificial synaptic device can be configured to be in a plurality of resistance states correspondingly by selection and control of intensity, frequency and optical pulse time of the optical excitation signal, and various synaptic plasticity functions are correspondingly achieved.

Owner:HUAZHONG UNIV OF SCI & TECH

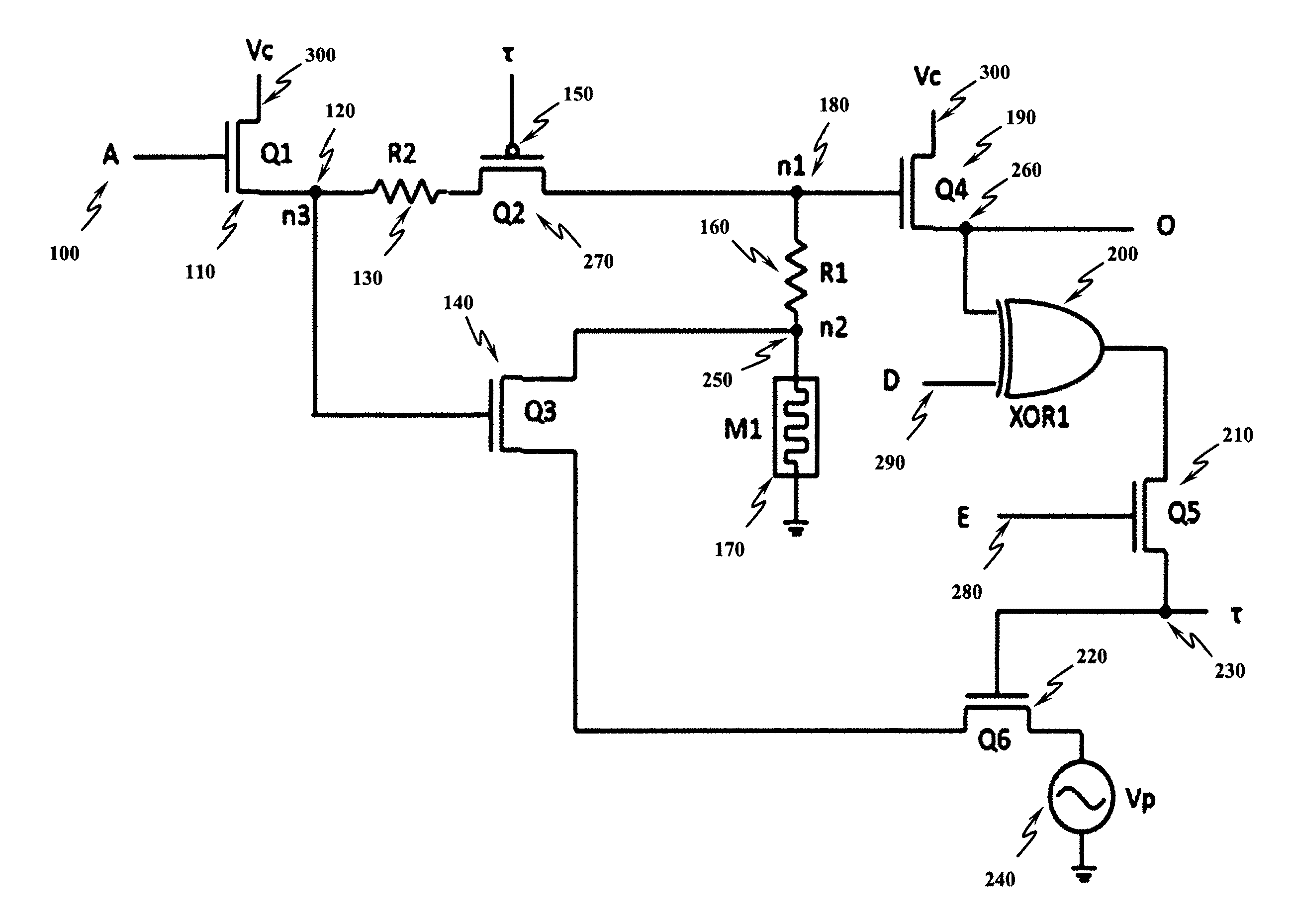

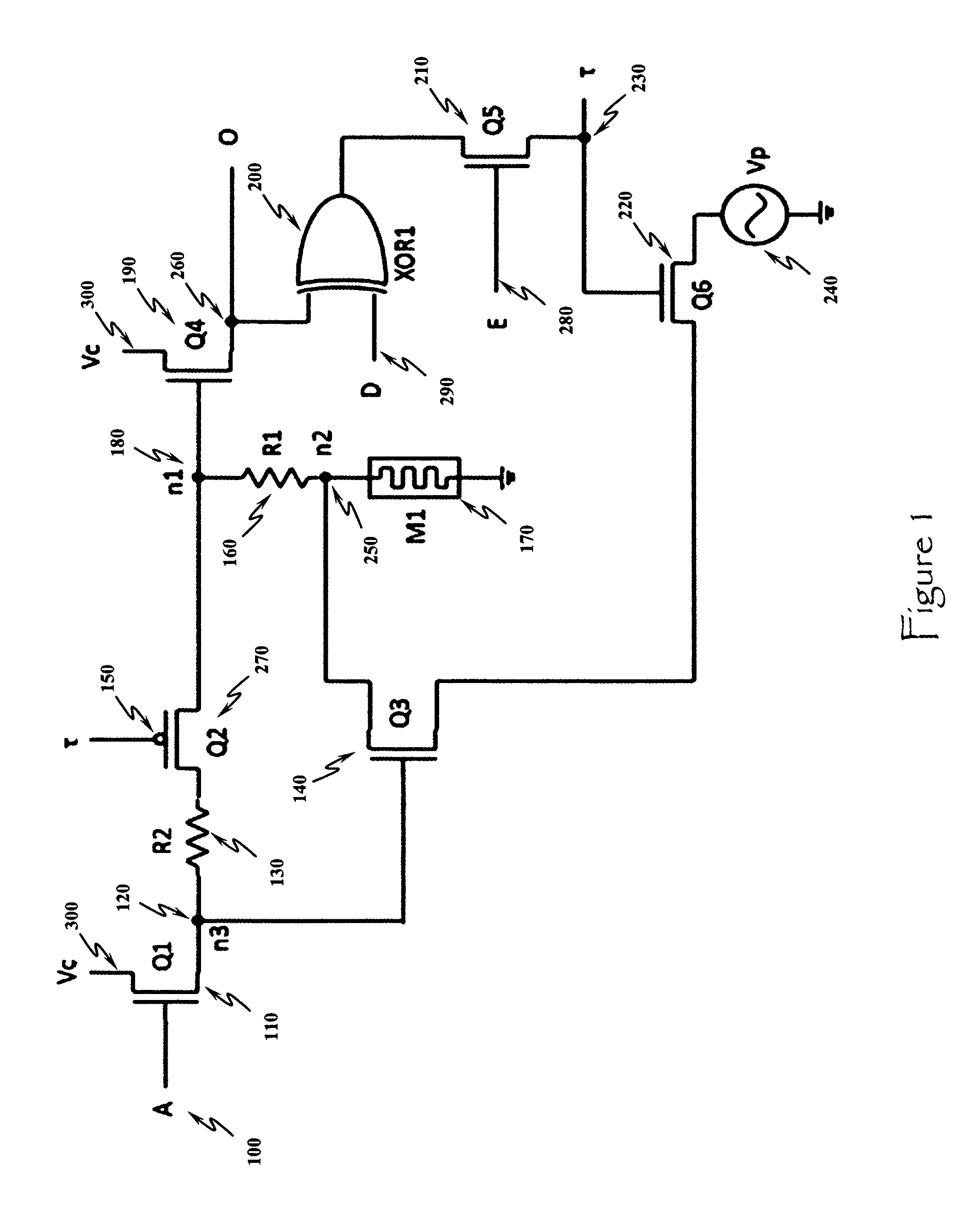

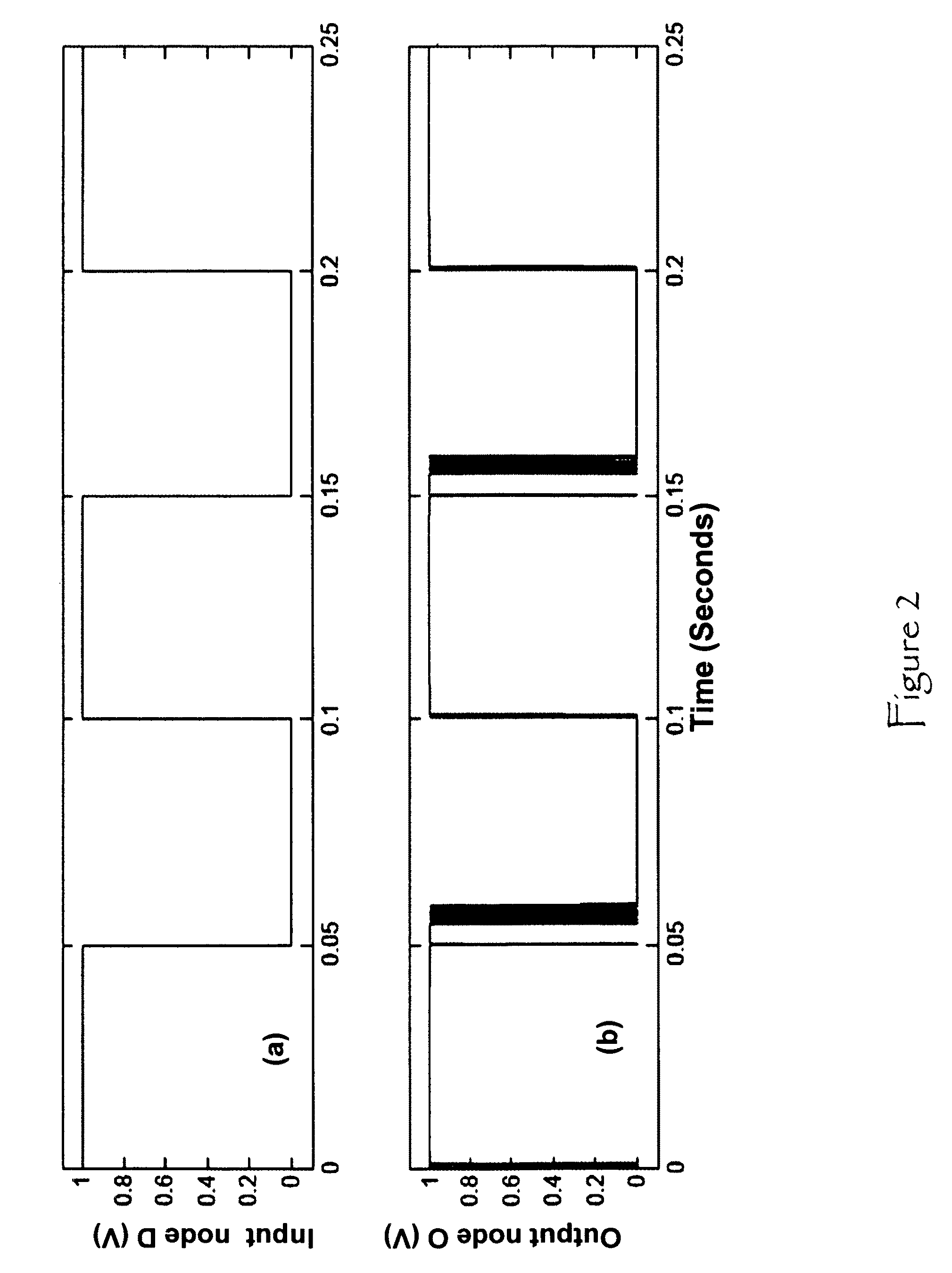

Reconfigurable electronic circuit

InactiveUS7902857B1Reduce power consumptionEliminate needFail-safe circuitsDigital storageElectrical resistance and conductanceEngineering

An apparatus and method provides the foundation for designing reconfigurable electronic computing systems. The invention relies on an ability to change the resistance state of a memristor device to achieve an optimal voltage at specific circuit nodes, whereby this dynamically and autonomously causes the circuit to reconfigure itself and produce a different output for the same input relative to the circuit's initial state. The circuit's state remains constant until the memristor's resistance is changed, at which point the circuit's function is “reprogrammed”.

Owner:THE UNITED STATES OF AMERICA AS REPRESETNED BY THE SEC OF THE AIR FORCE

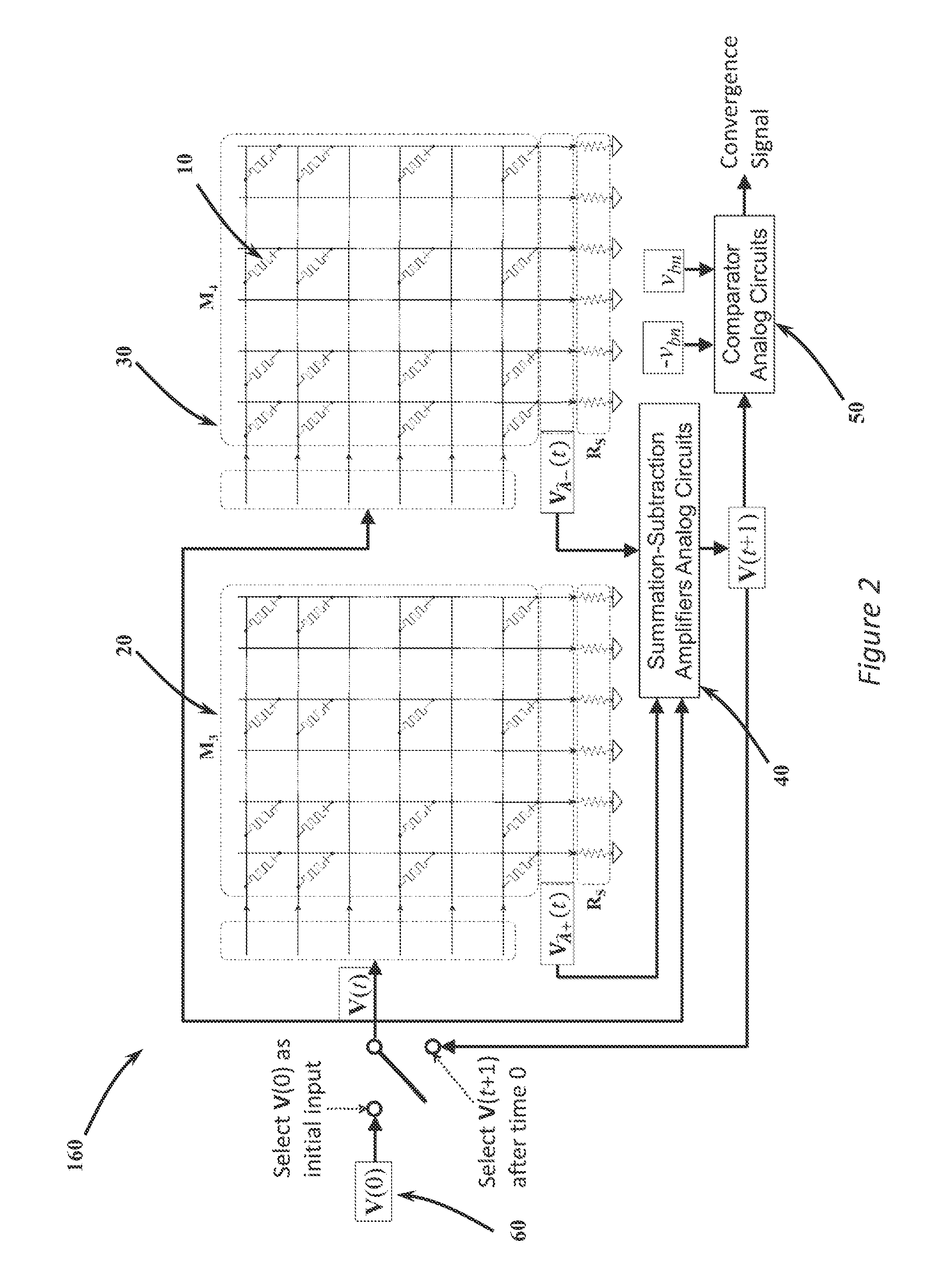

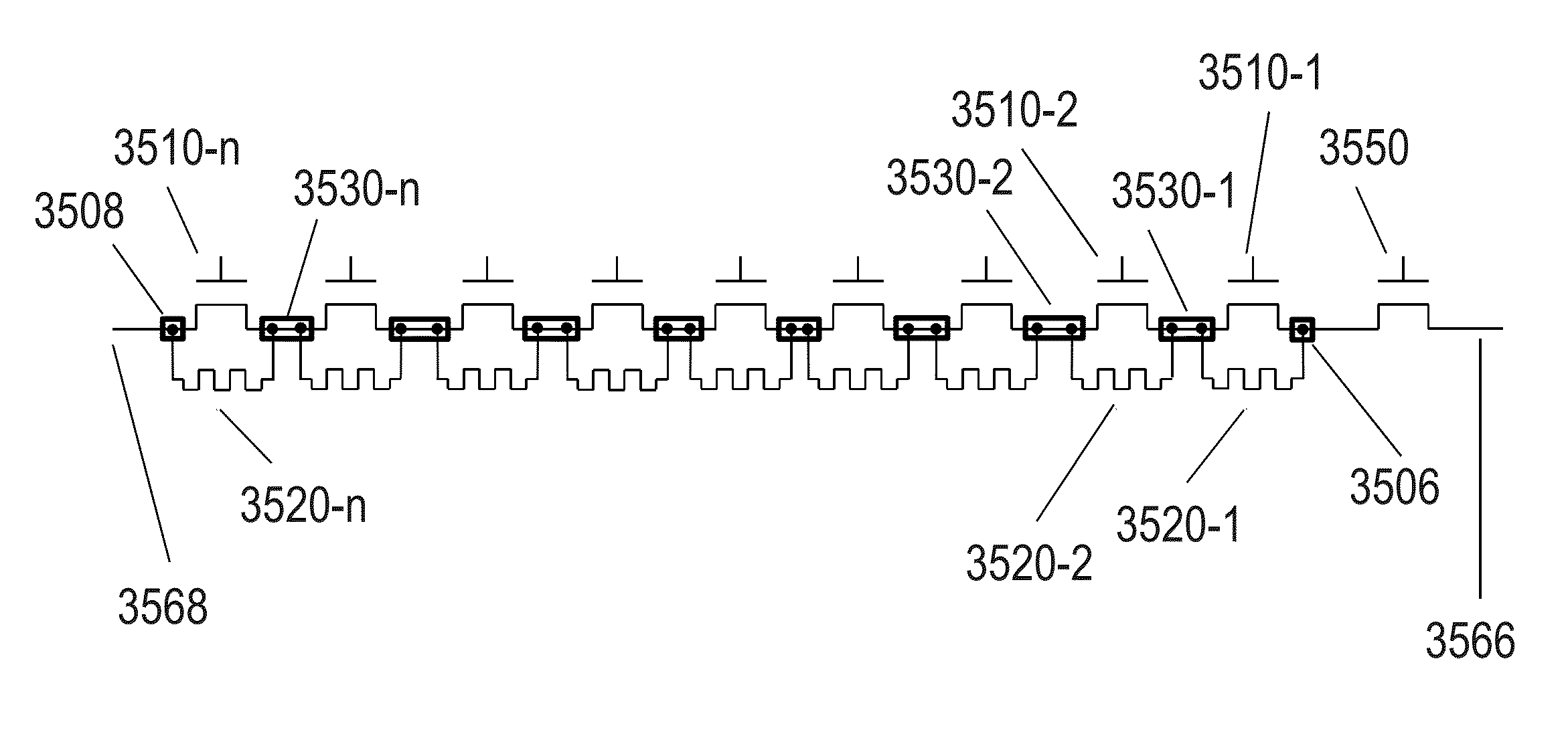

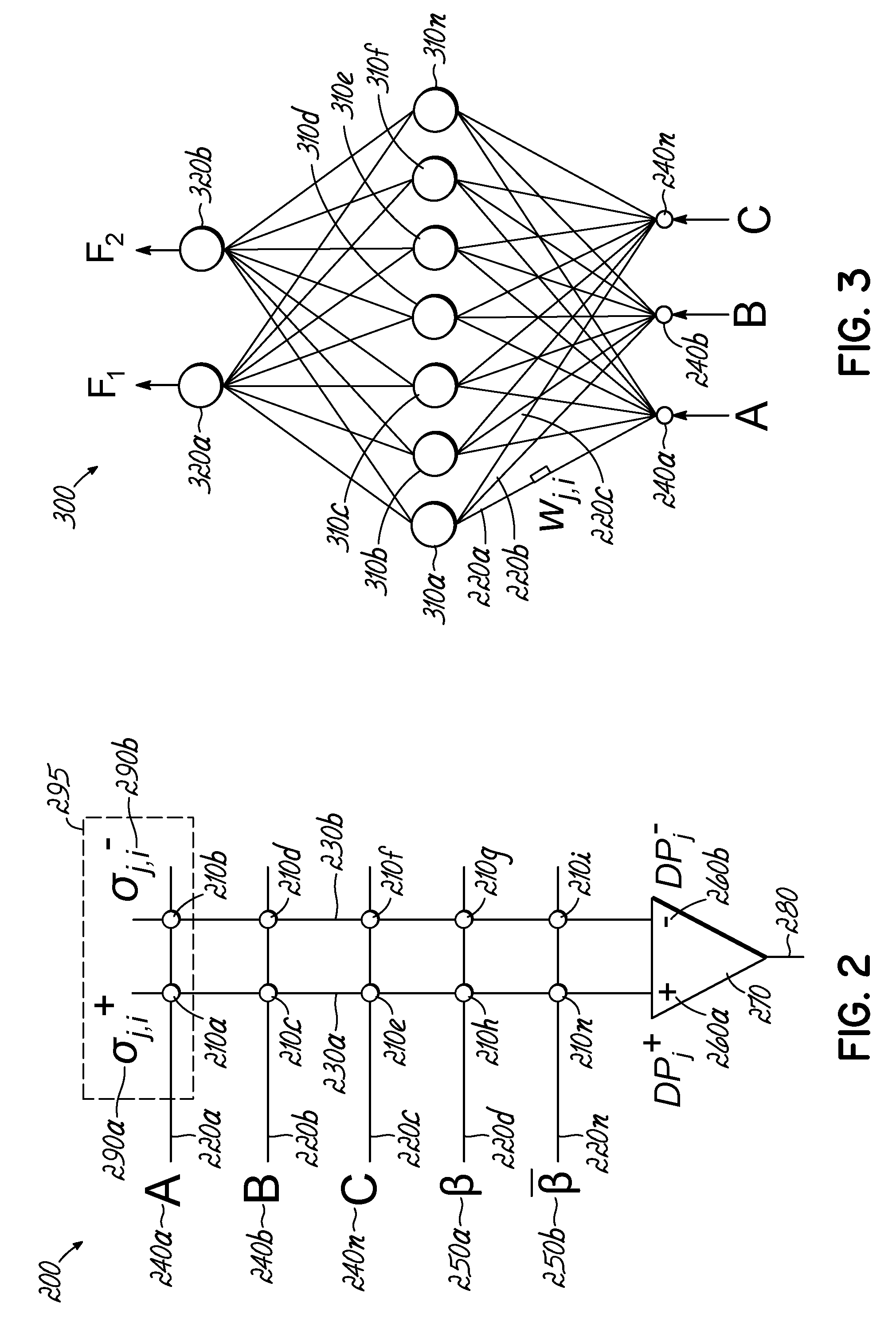

On-chip training of memristor crossbar neuromorphic processing systems

An analog neuromorphic circuit is disclosed having resistive memories that provide a resistance to an input voltage signal as the input voltage signal propagates through the resistive memories generating a first output voltage signal and to provide a resistance to a first error signal that propagates through the resistive memories generating a second output voltage signal. A comparator generates the first error signal that is representative of a difference between the first output voltage signal and the desired output signal and generates the first error signal so that the first error signal propagates back through the plurality of resistive memories. A resistance adjuster adjusts a resistance value associated with each resistive memory based on the first error signal and the second output voltage signal to decrease the difference between the first output voltage signal and the desired output signal.

Owner:UNIV OF DAYTON

Synapse circuit and neuromorphic system including the same

ActiveUS20140358834A1Digital computer detailsDigital storageElectrical resistance and conductanceEngineering

A synapse circuit to perform spike timing dependent plasticity (STDP) operation is provided. The synapse circuit includes a memristor having a resistance value, a transistor connected to the memristor, and the transistor configured to receive at least two input signals. The resistance value of the memristor is changed based on a time difference between the at least two input signals received by the transistor.

Owner:SAMSUNG ELECTRONICS CO LTD +1

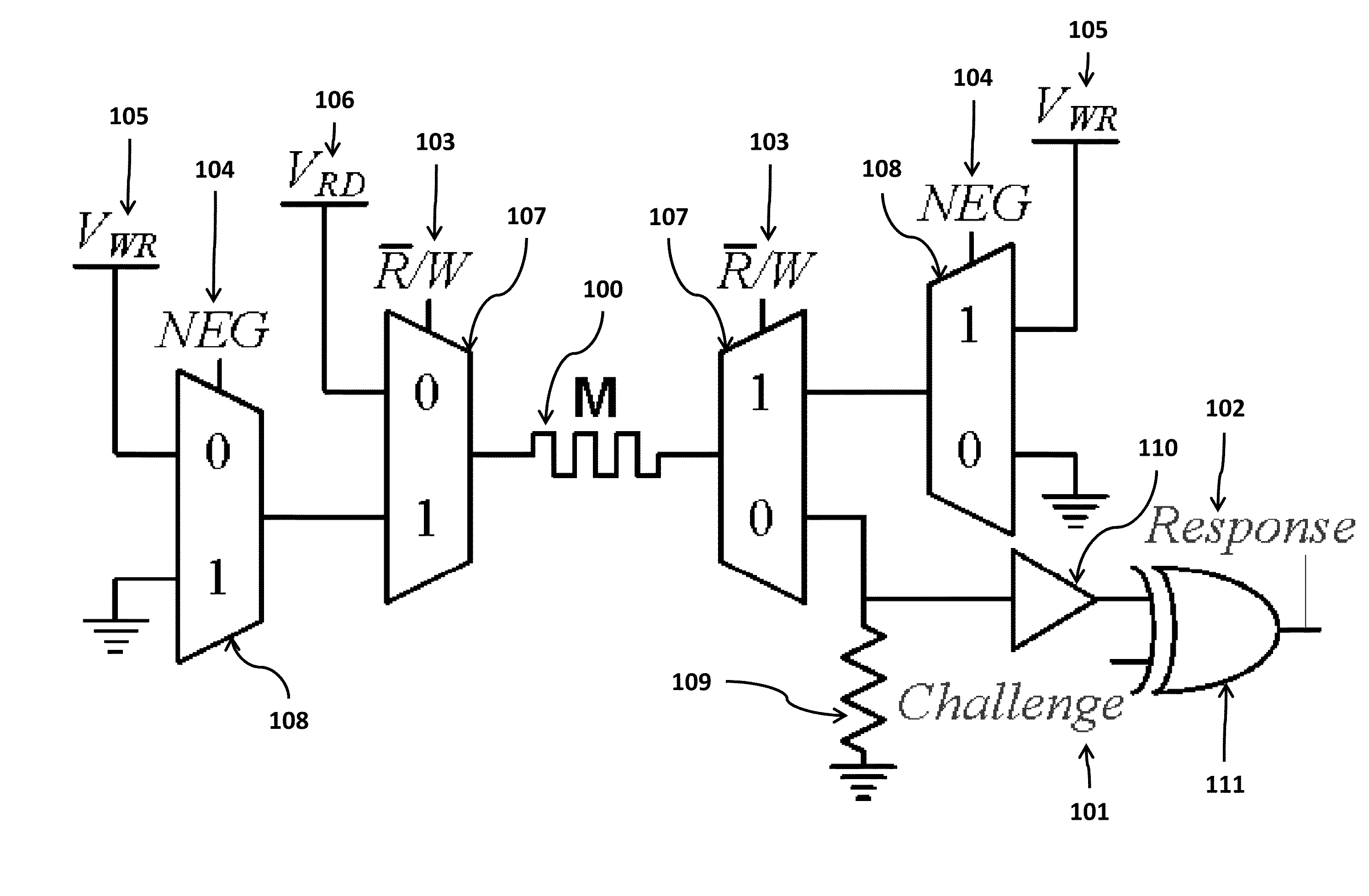

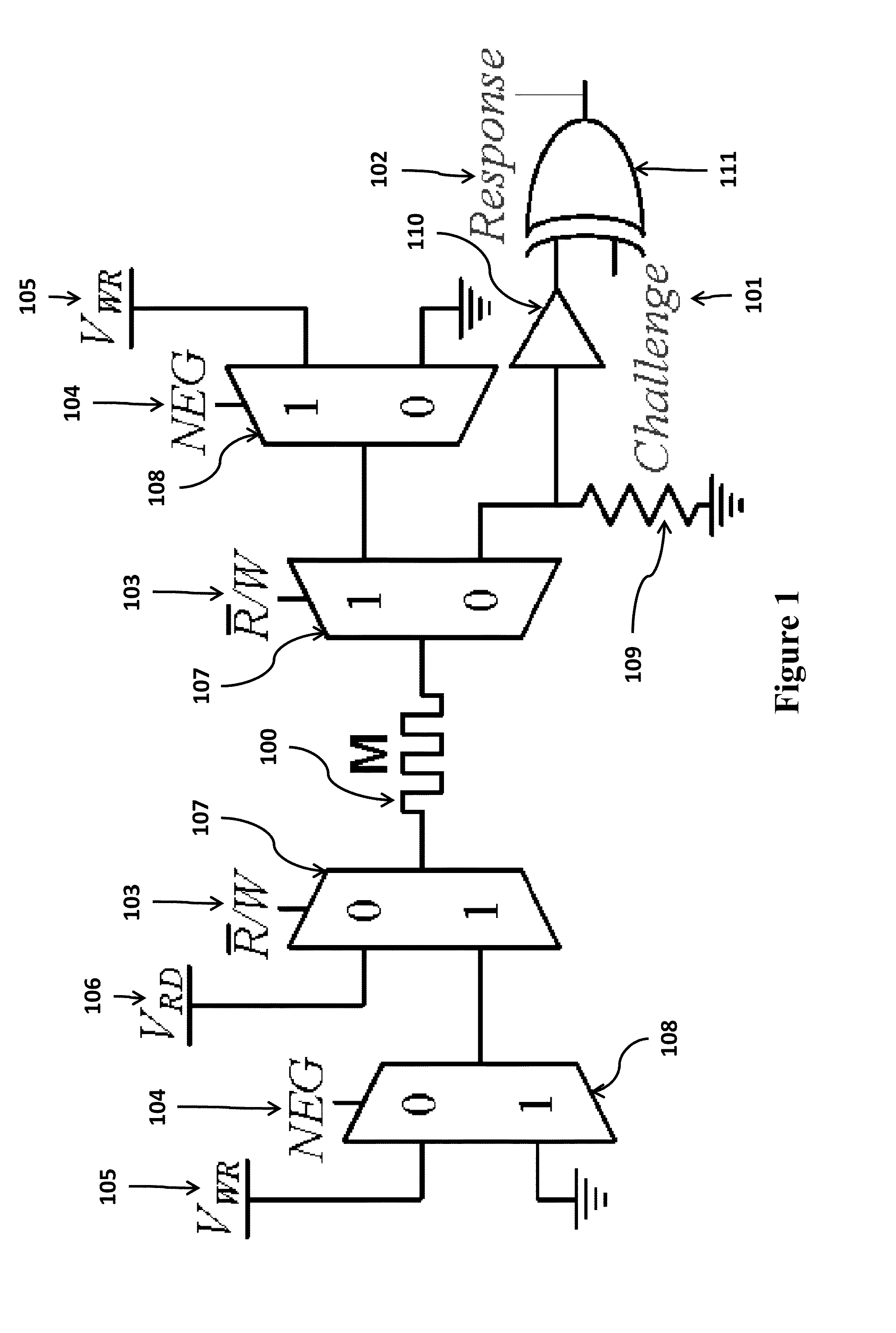

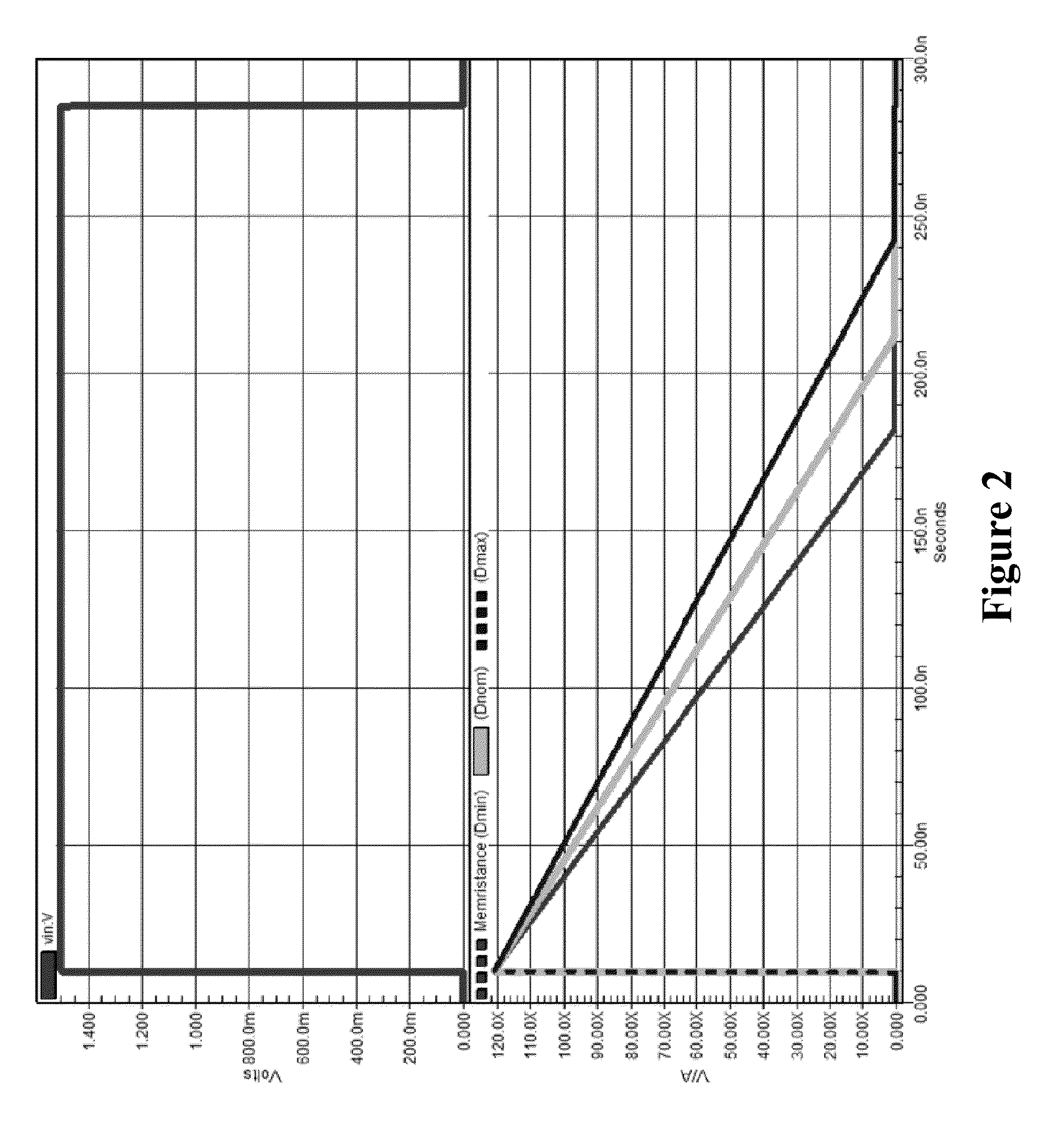

Write-Time Based Memristive Physical Unclonable Function

InactiveUS20140268994A1High resistance stateDigital storageInternal/peripheral component protectionHigh resistancePhysical unclonable function

A physical unclonable function (PUF) device consisting of a hybrid CMOS-memristor circuit that leverages variations in the required write-time of a memristor. Variations in the time required to write, or SET, a memristor from a high to low resistance state arise from variability in physical parameters such as the memristor thickness. When applying a SET voltage across the memristor for the nominal minimum SET time, variability leads to a situation where the memristor will actually SET to the low resistance state only 50% of the time. When the device does not SET it will remain in the high resistance state. Since the to resistance state of the memristor corresponds to reading either a logic 1 or logic 0 on the output of the circuit, the write-time based memristive PUF produces a digital signature directly corresponding to the fabrication process-induced physical variations of an integrated circuit.

Owner:BY THE SEC OF THE AIR FORCE UNITED STATES OF AMERICA AS REPRESENTED

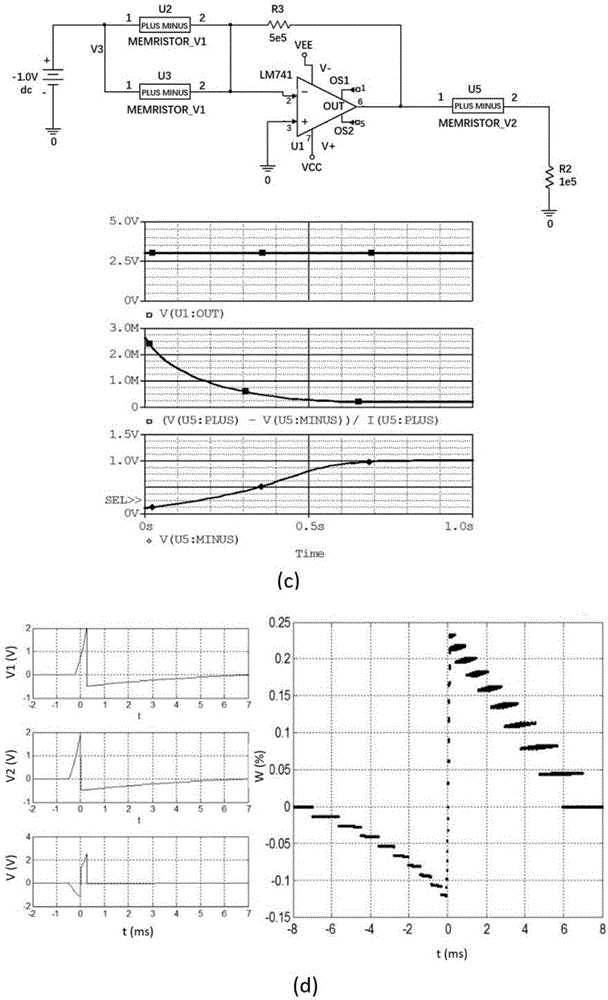

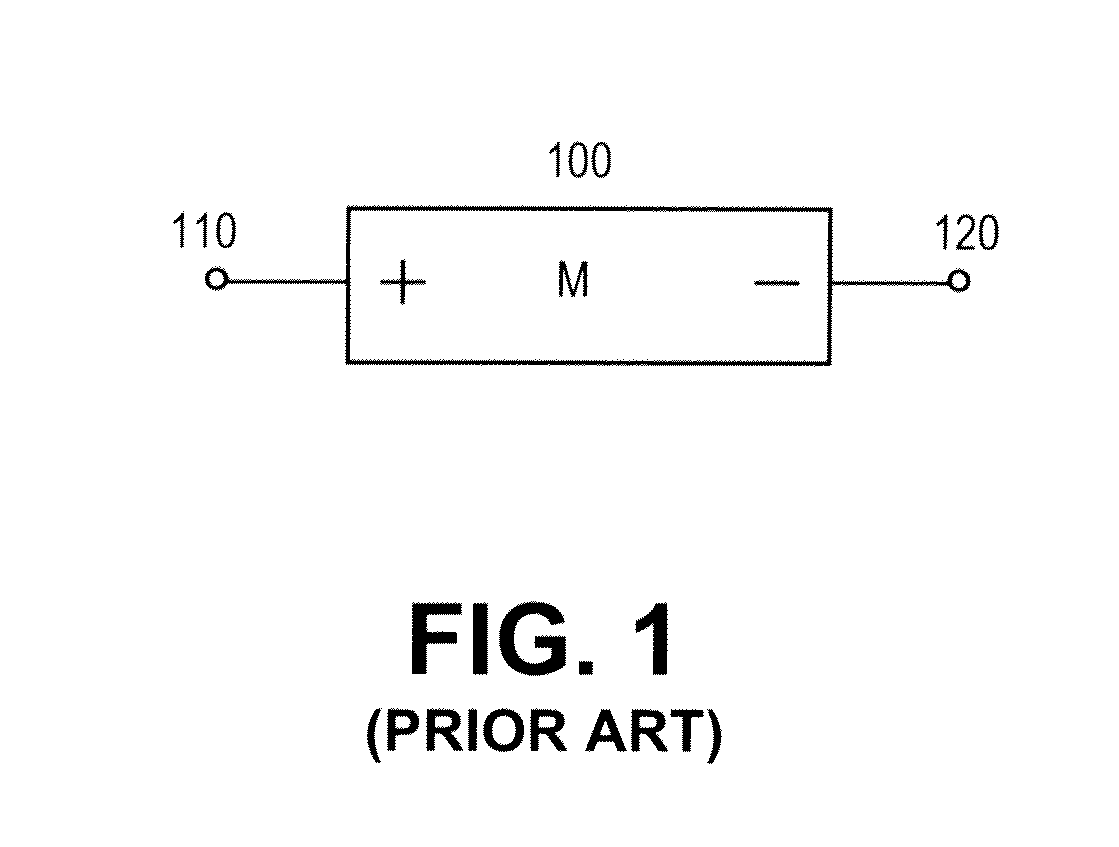

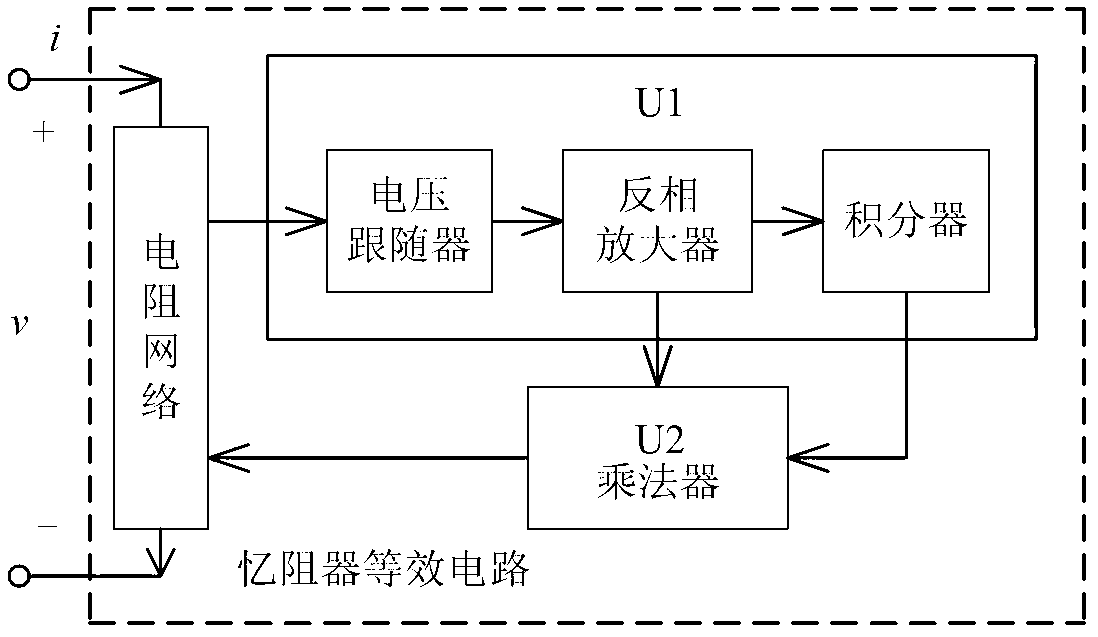

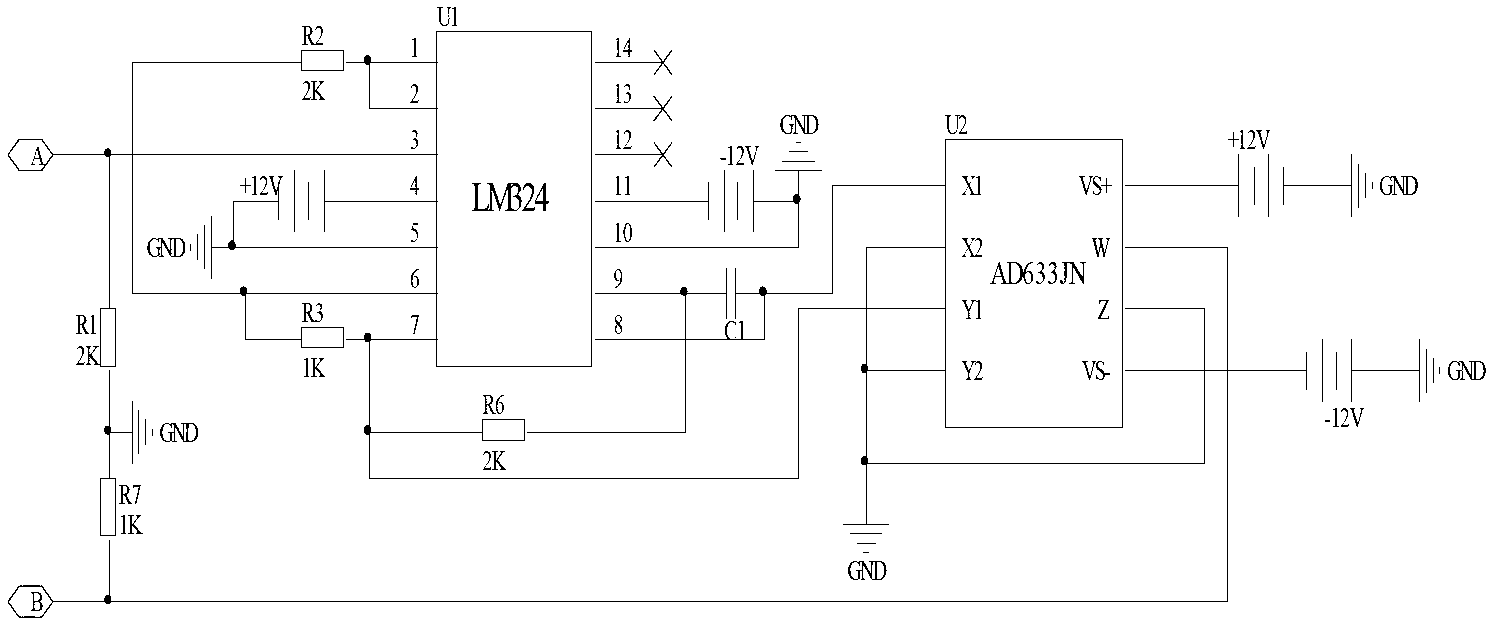

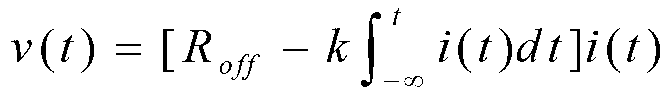

Memristor equivalent simulation circuit

ActiveCN103219983ASimple structureLogic circuitsElectrical resistance and conductanceAudio power amplifier

The invention discloses a memristor equivalent simulation circuit which comprises a resistance network, an integrated operational amplifier U1 and a multiplying unit 2. Two ends of the resistance network are respectively connected input ends (A and B), the resistance network is connected with the integrated operational amplifier U1 which is used for achieving voltage following, reversing amplification and integral operation, the integrated operational amplifier U1 is connected with the multiplying unit 2 connected with the resistance network, and the multiplying unit 2 is used for achieving multiplying of signals. The TiO2 memristor equivalent simulation circuit is used for simulating voltage current characteristics of a memristor and replacing a practical meristor to carry out experiments, application and research.

Owner:ZAOZHUANG SNKSAN INTELLIGENT MACHINERY CO LTD

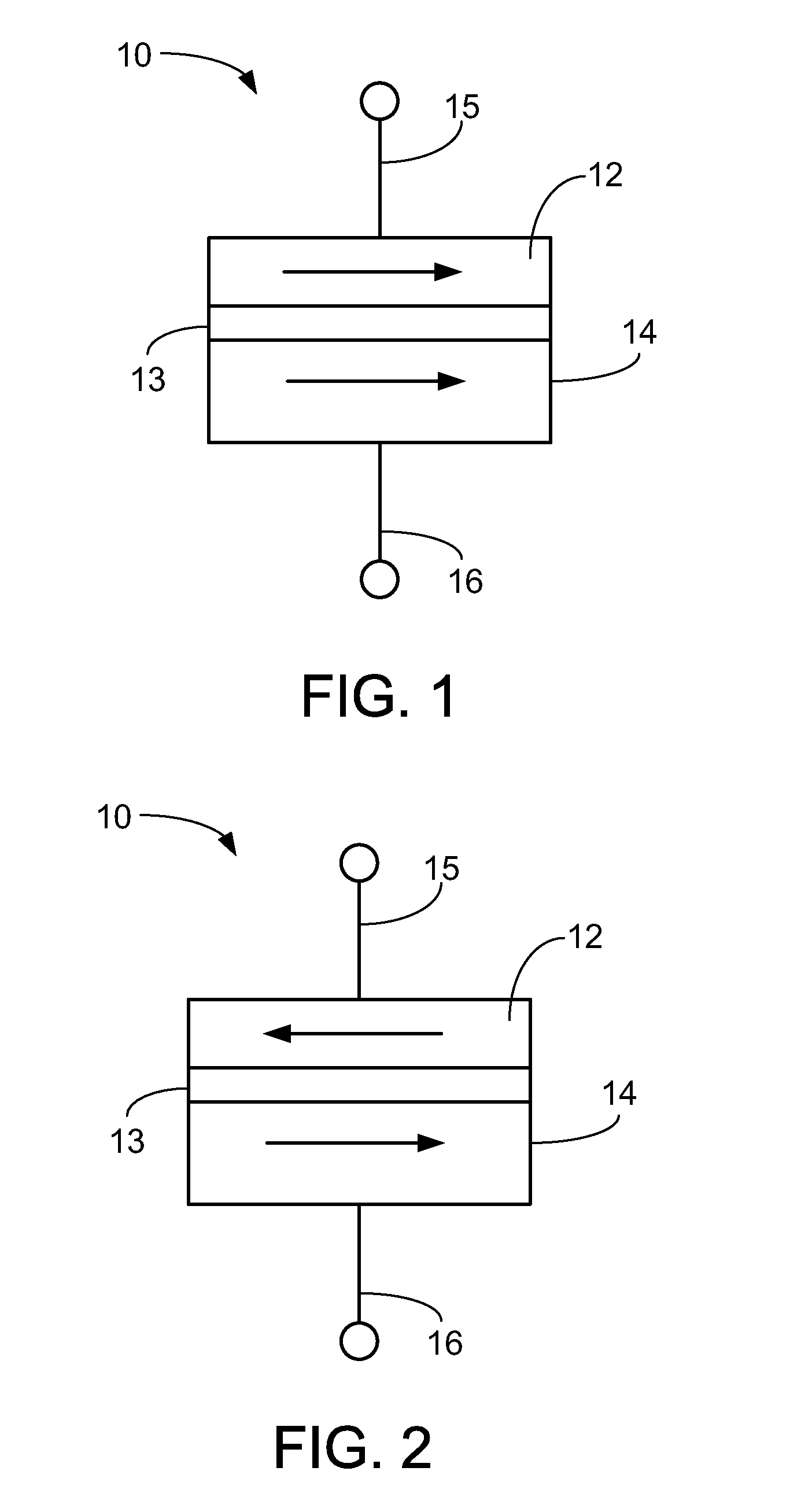

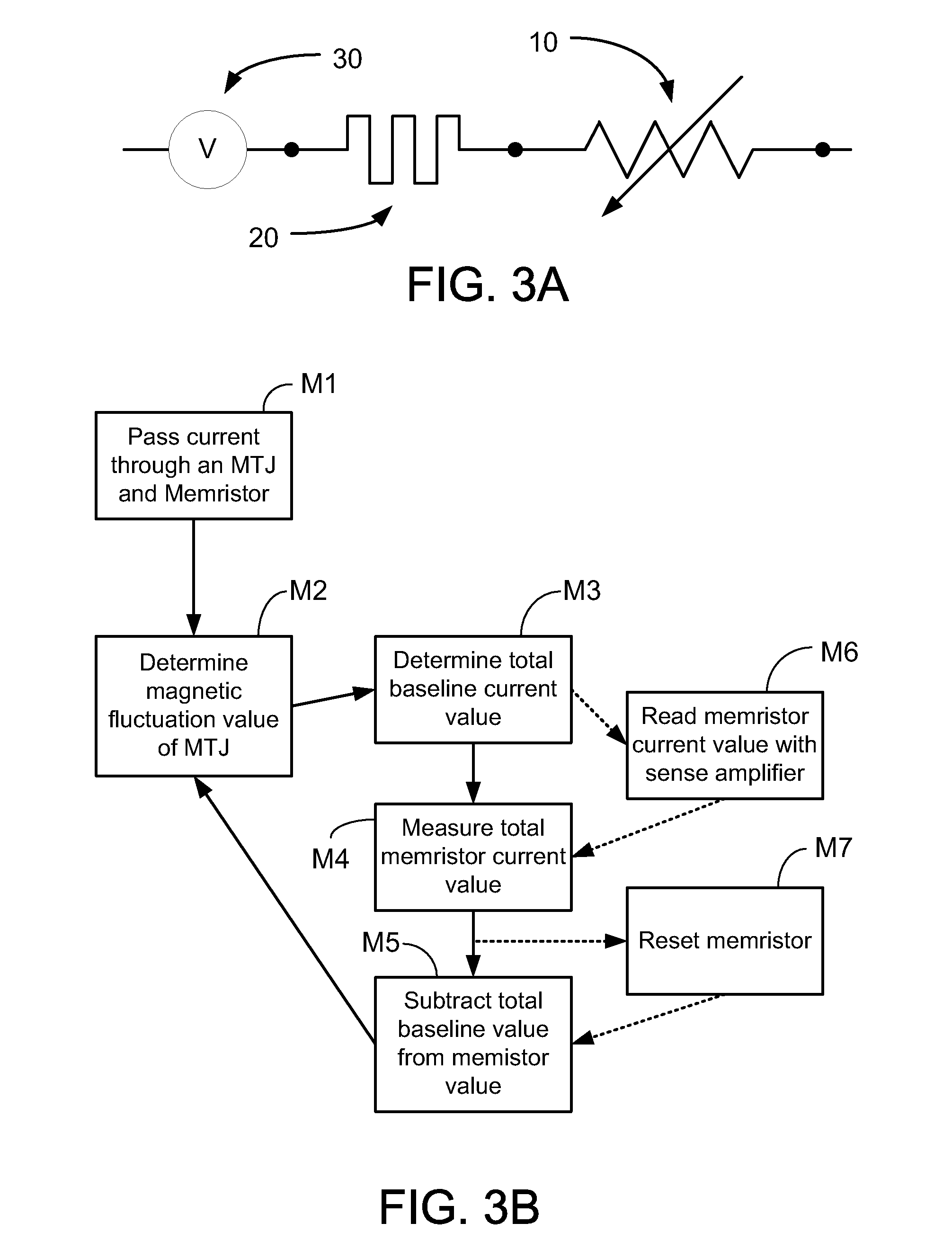

Magnetic Tunnel Junction and Memristor Apparatus

InactiveUS20100109656A1Magnetic-field-controlled resistorsSolid-state devicesHigh resistanceMagnetic memory

A magnetic memory device includes a magnetic tunnel junction having a free magnetic layer having a magnetization orientation that is switchable between a high resistance state magnetization orientation and a low resistance state magnetization orientation and a memristor solid state element electrically coupled to the magnetic tunnel junction. The memristor has a device response that is an integrated voltage versus an integrated current.

Owner:SEAGATE TECH LLC

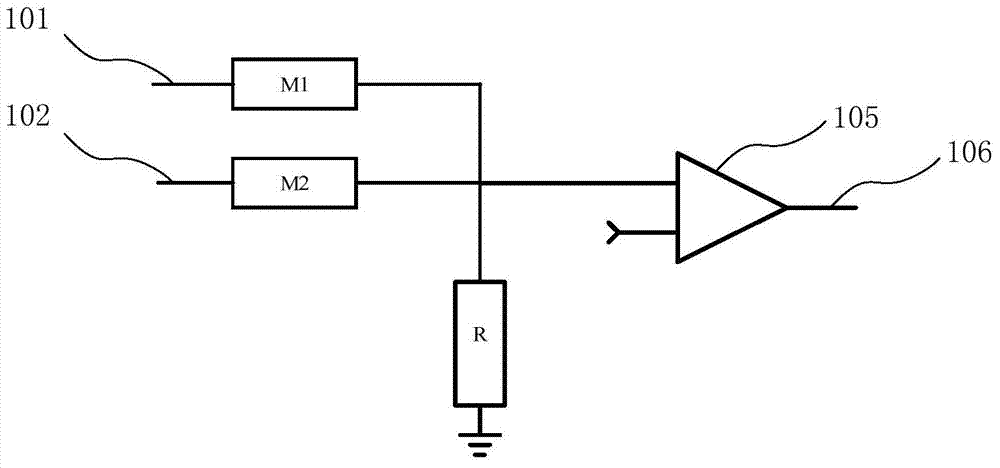

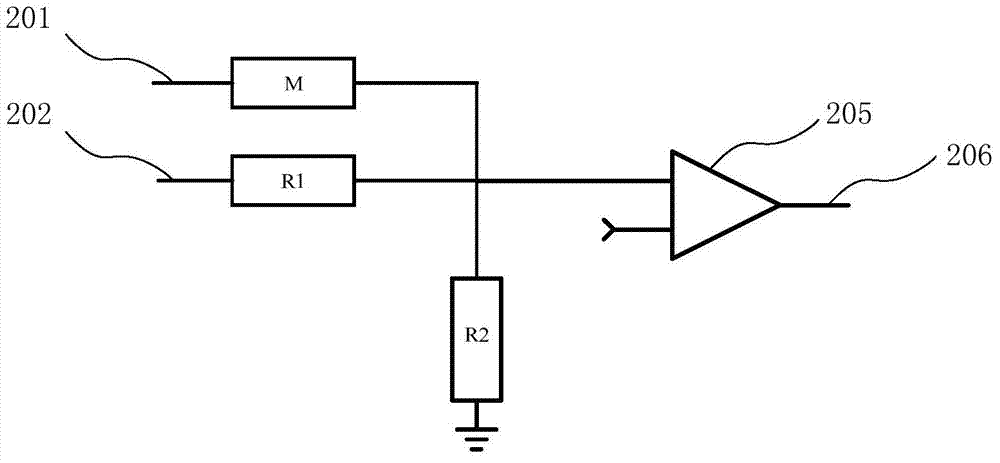

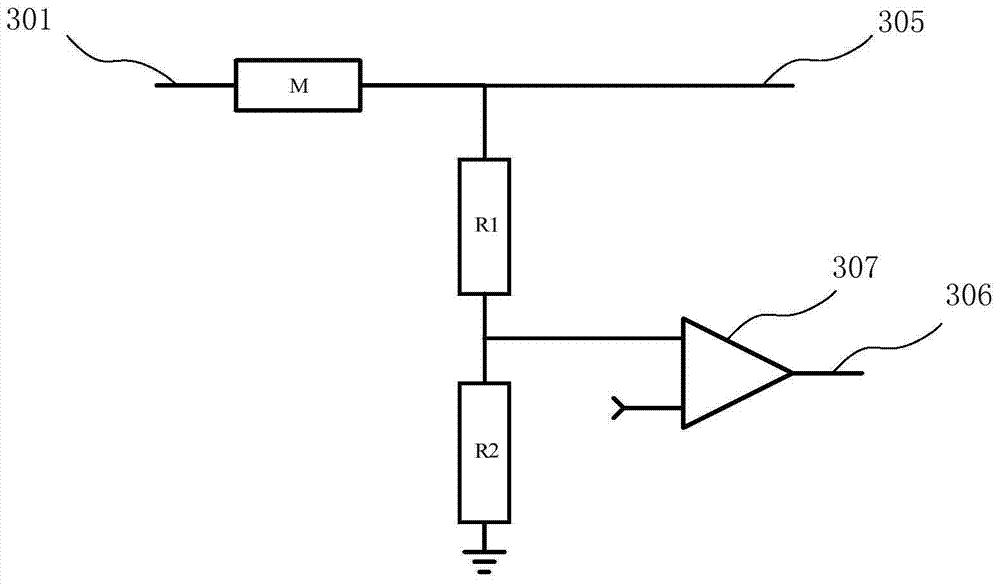

Associative memory circuit based on memory resistor

The invention discloses an associative memory circuit based on a memory resistor. The associative memory circuit based on the memory resistor comprises the memory resistor, a first resistor, a second resistor and a calculation comparator. The first resistor and the memory resistor are connected to a first input end of the calculation comparator in series in sequence. A non-series-connection connecting end of the memory resistor serves as a first input end of the associative memory circuit. A series-connection connecting end of the first resistor and the memory resistor serves as a second input end of the associative memory circuit. One end of the second resistor is connected to the first input end of the calculation comparator and the other end of the second resistor is grounded. A second input end of the calculation comparator is used for being connected with reference voltage. The output end of the calculation comparator is used as the output end of the associative memory circuit. The first input end and the second input end of the associative memory circuit are used for receiving conditioned stimulus signals and receiving unconditioned stimulus signals respectively. The output end of the associative memory circuit is used for outputting response signals. By the adoption of the associative memory circuit based on the memory resistor, the forming process and the forgetting process of biological associative memory can be simulated according to the relation between the application time of the conditioned stimulus signals and the application time of the unconditioned stimulus signals.

Owner:HUAZHONG UNIV OF SCI & TECH

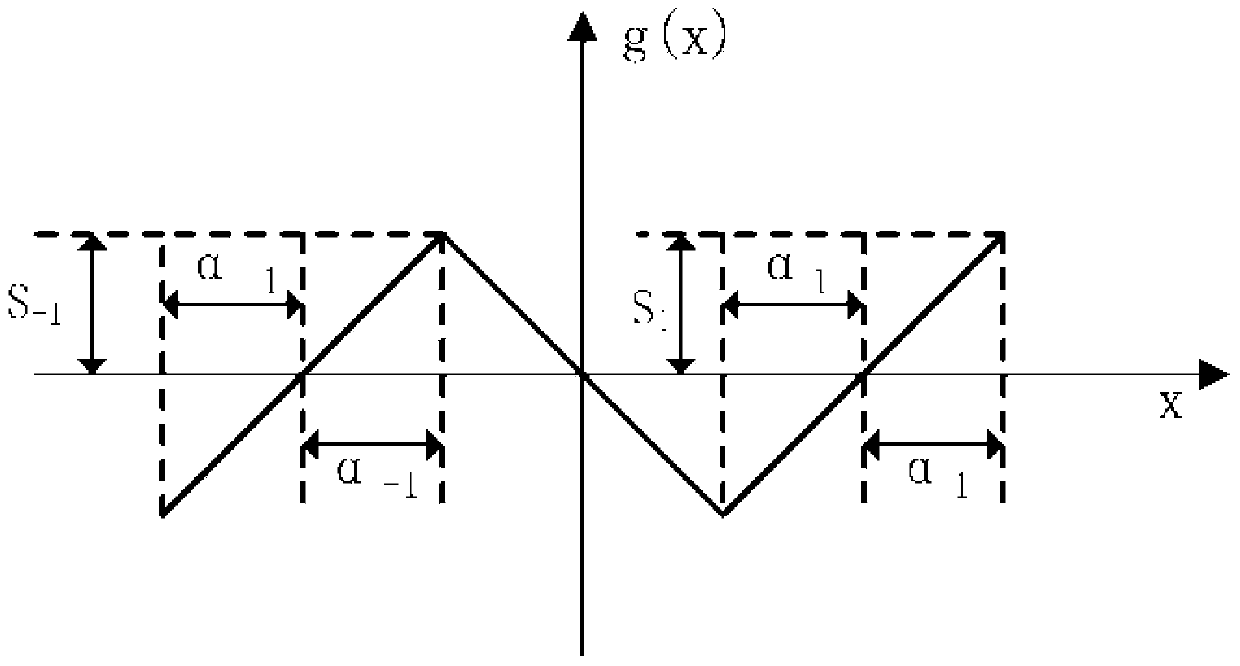

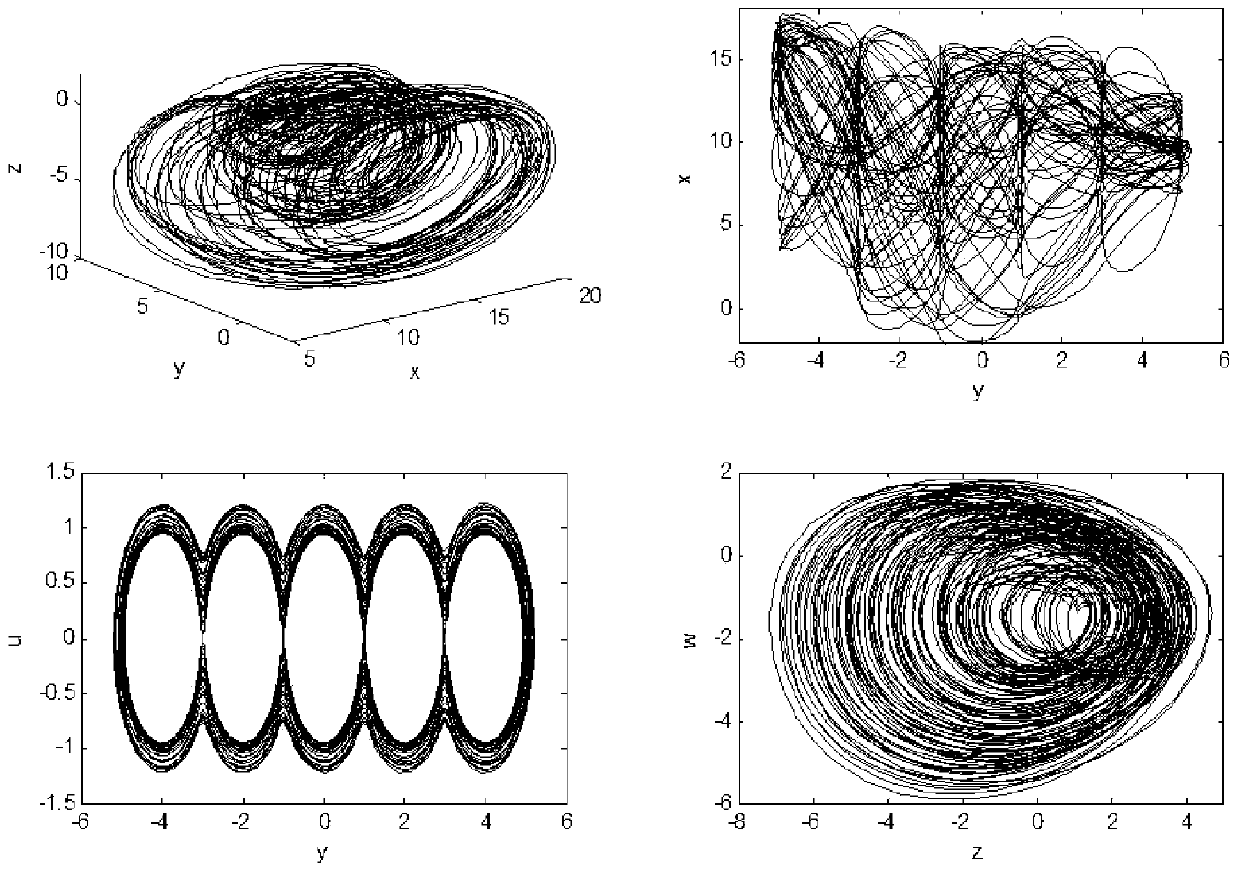

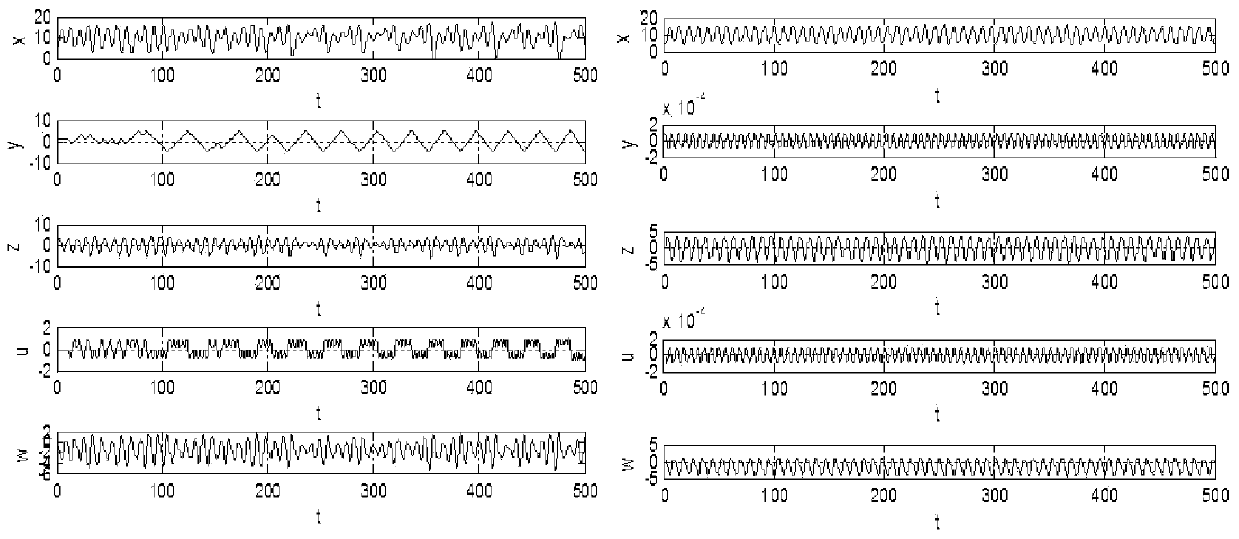

Memristor hyperchaos system and circuit with abundant dynamic behaviors

The invention discloses a memristor hyperchaos system and circuit with abundant dynamic behaviors. The new fifth-order memristor hyperchaos system is provided and has the abundant chaos dynamic behaviors and phase track graphs at different angles, and the different chaos behaviors such as grids and scrolls can be seen. A basic step for generating a complex dynamic chaos system through a memristor in future is made.

Owner:SOUTHWEST UNIVERSITY

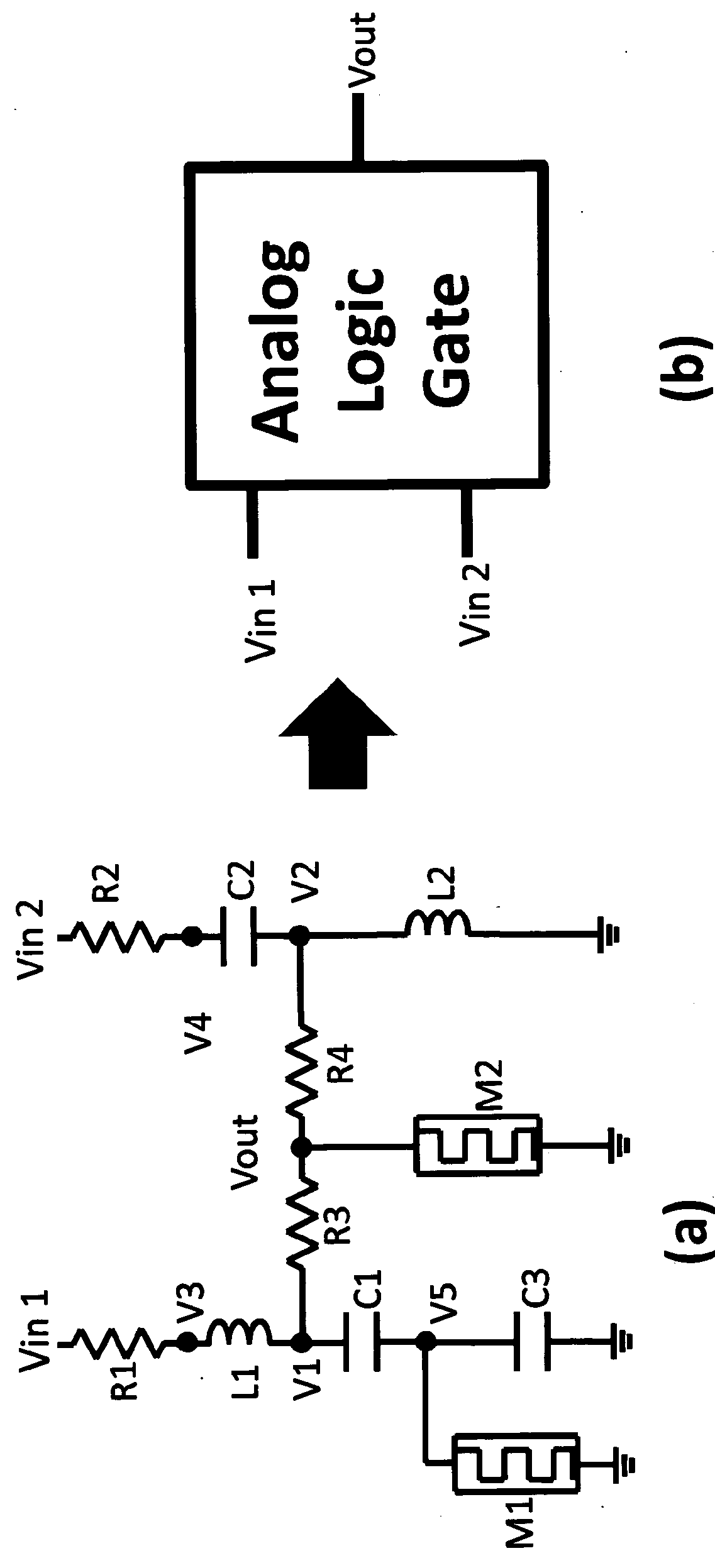

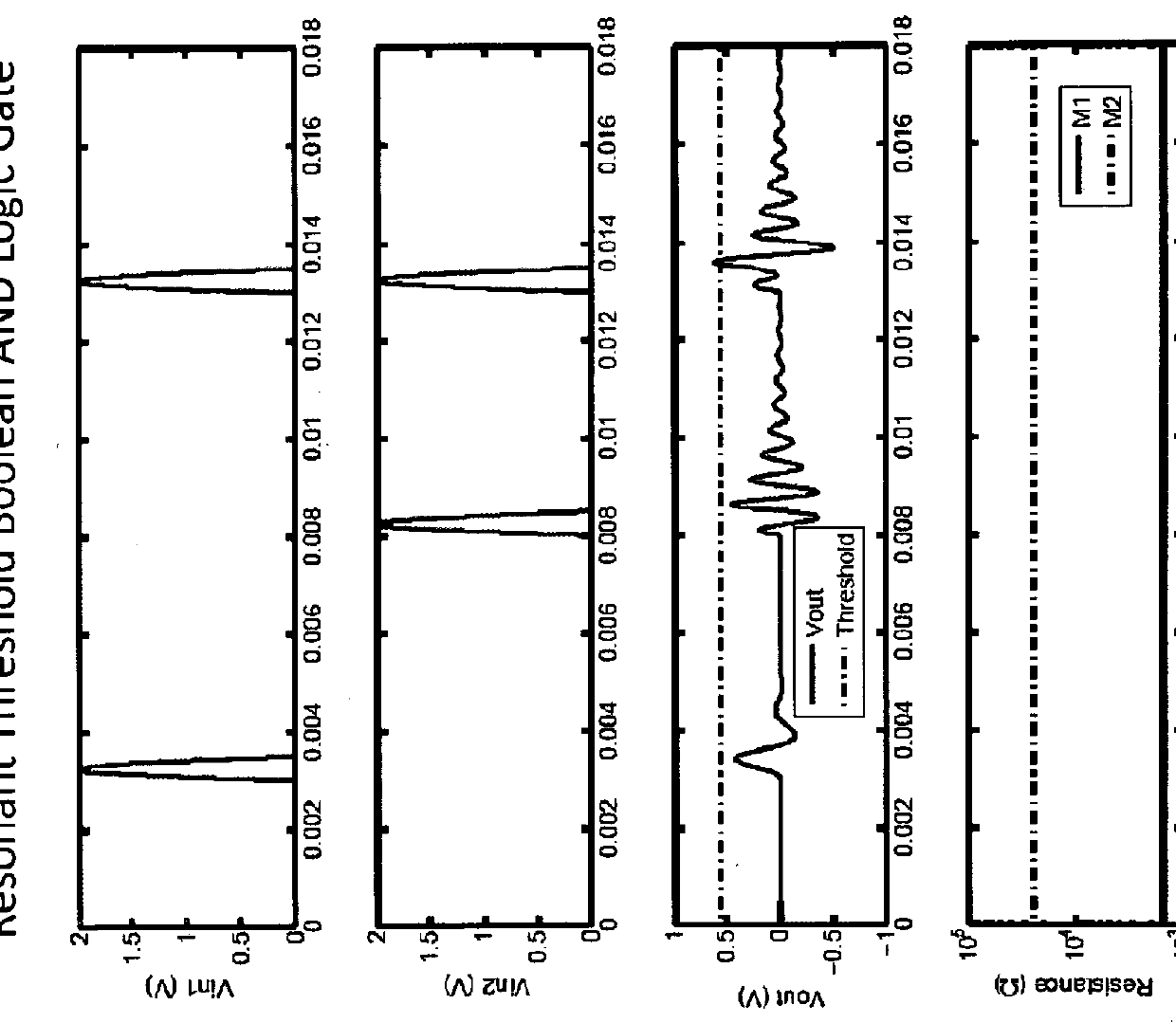

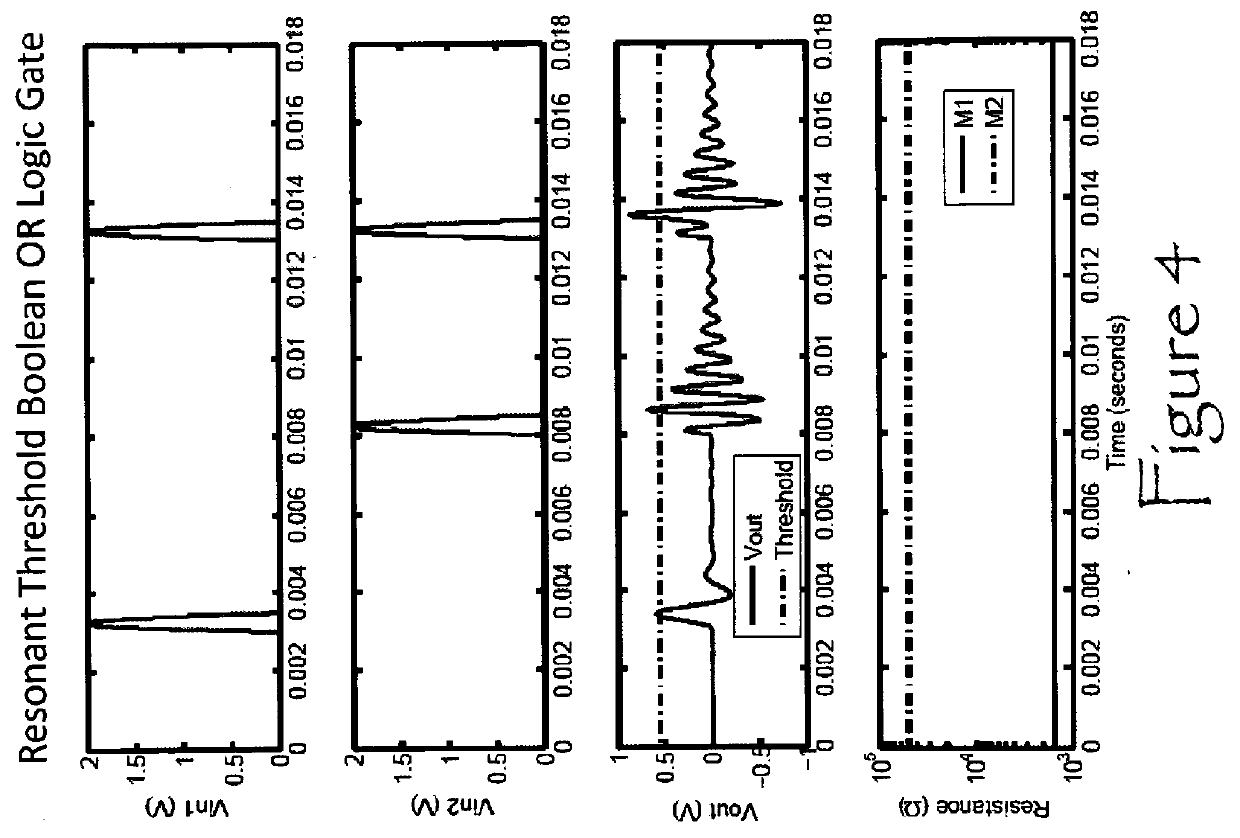

Self-reconfigurable memristor-based analog resonant computer

ActiveUS20120217994A1Logic circuits characterised by logic functionDigital storageComputational logicInductor

An apparatus which provides a self-reconfigurable analog resonant computer employing a fixed electronic circuit schematic which performs computing logic operations (for example OR, AND, NOR, and XOR Boolean logic) without physical re-wiring and whose components only include passive circuit elements such as resistors, capacitors, inductors, and memristor devices. The computational logic self-reconfiguration process in the circuit takes place as training input signals, which are input causing the impedance state of the memristor device to change. Once the training process is completed, the circuit is probed to determine whether the desired logic operation has been programmed.

Owner:THE UNITED STATES OF AMERICA AS REPRESETNED BY THE SEC OF THE AIR FORCE

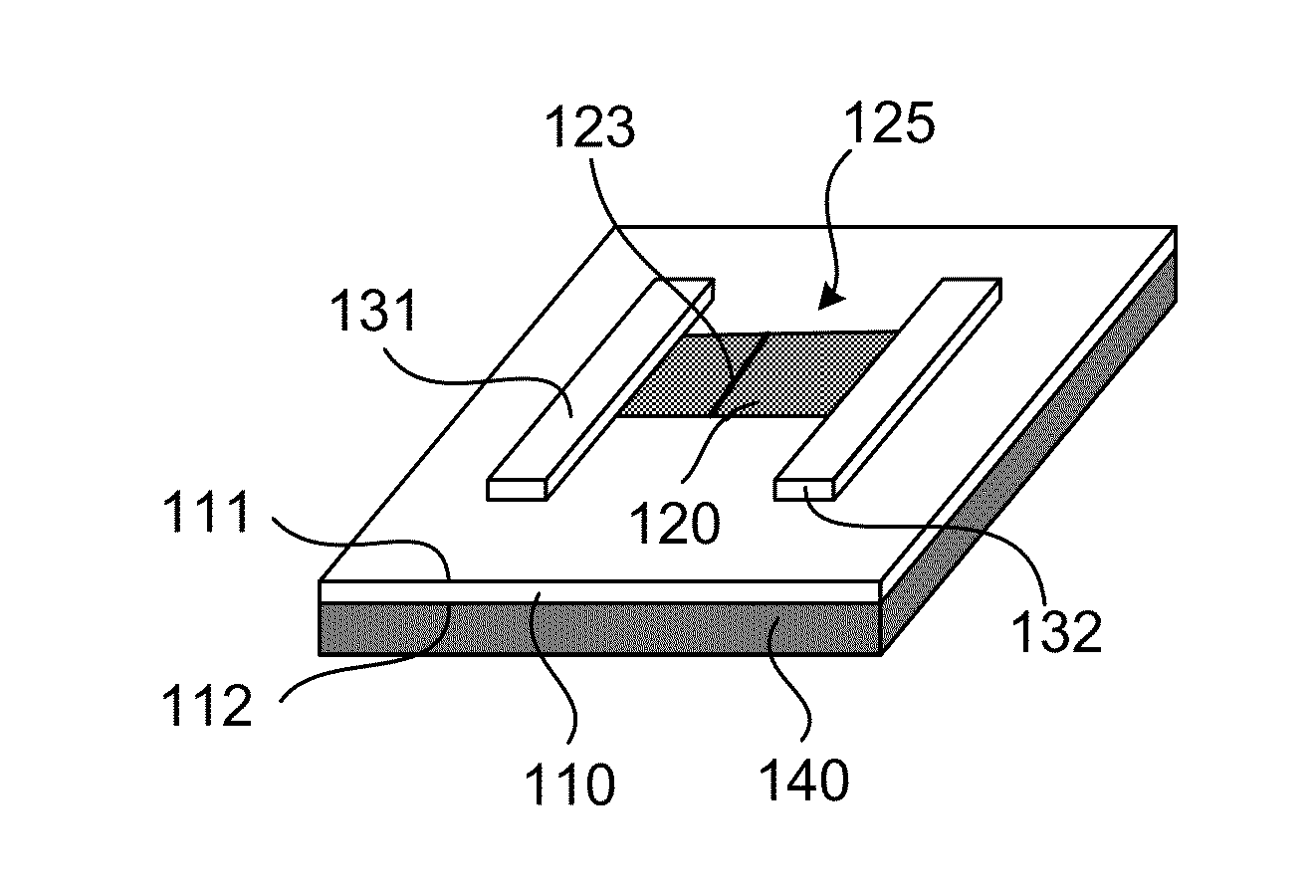

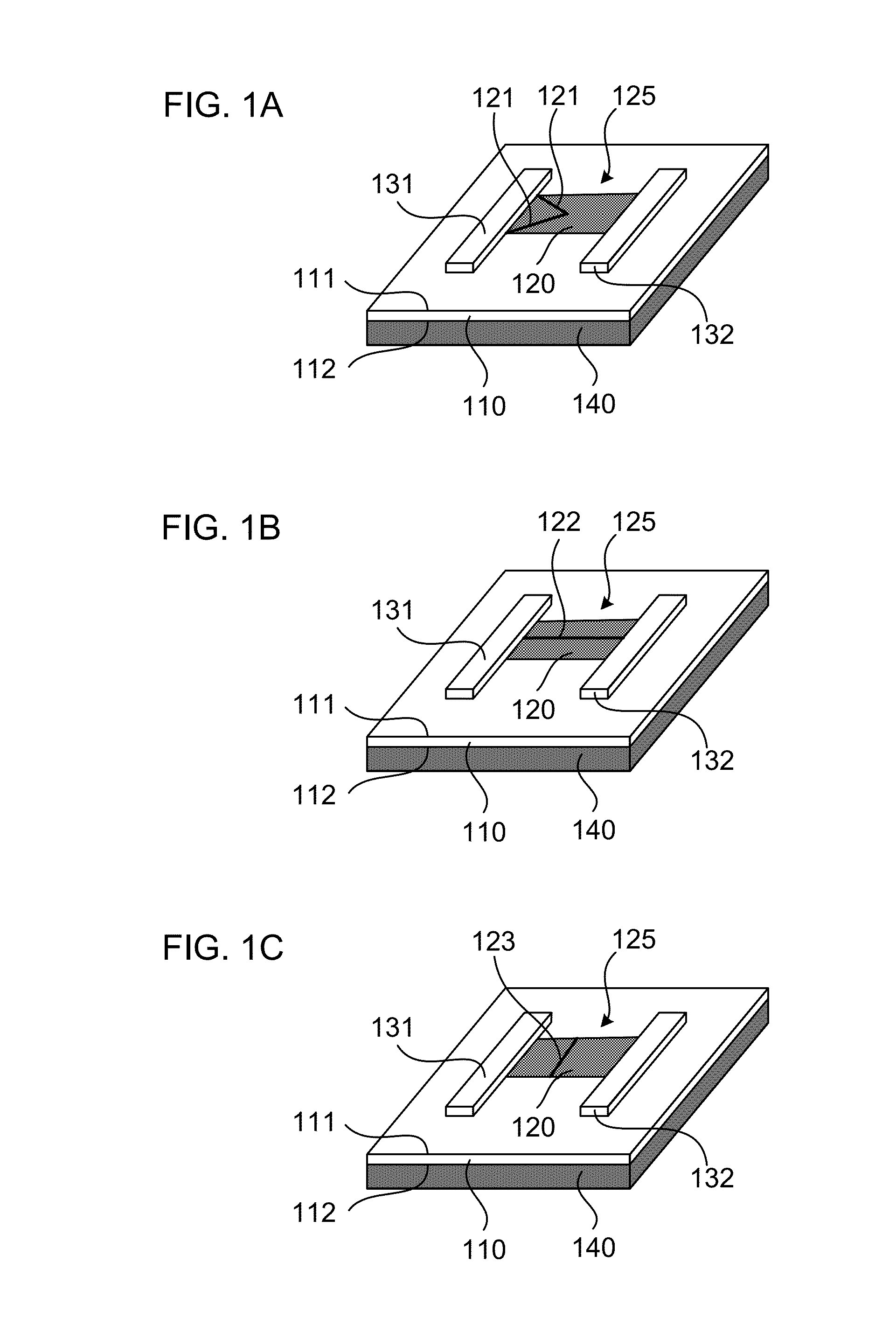

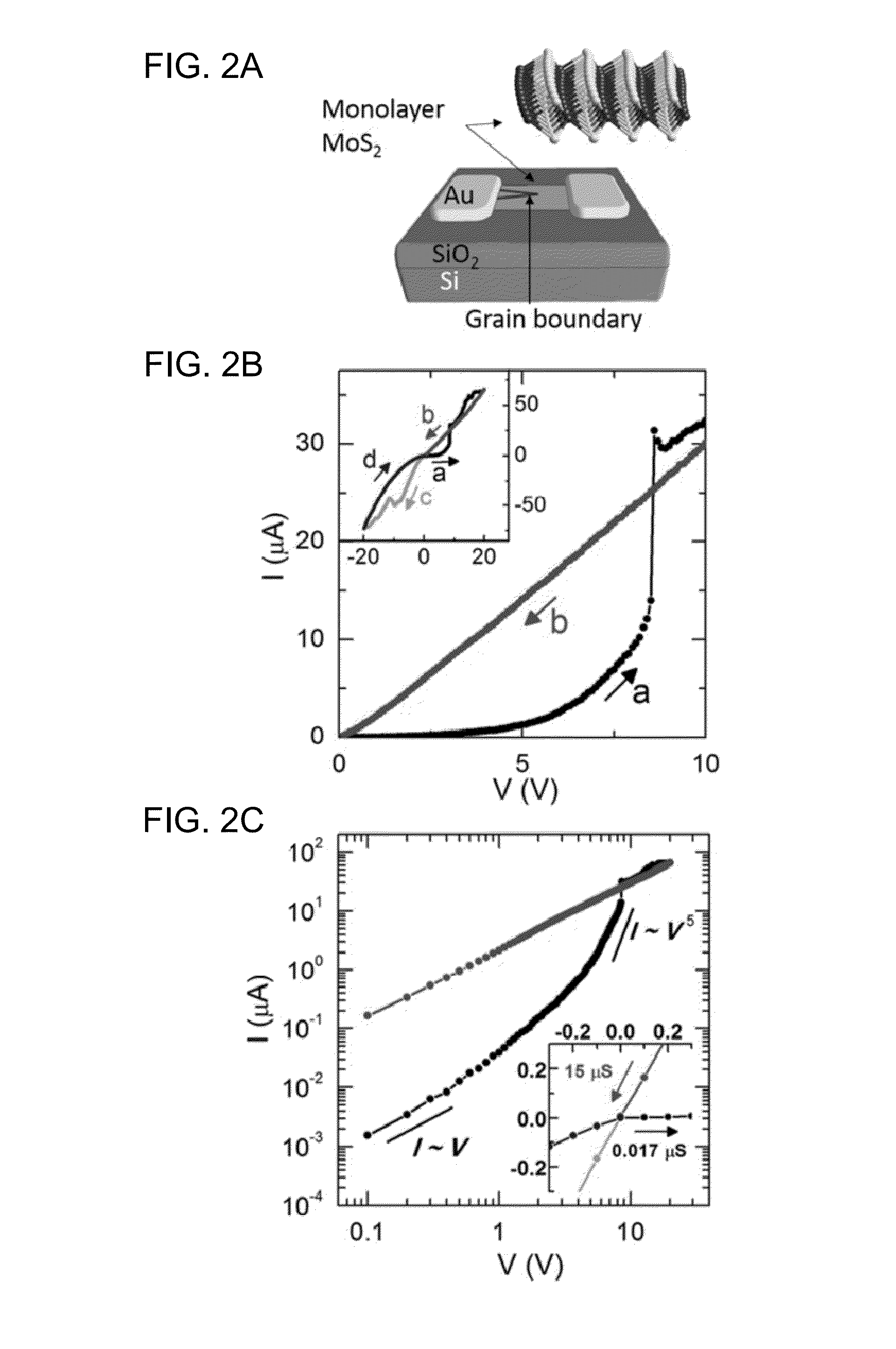

Gate-tunable atomically-thin memristors and methods for preparing same and applications of same

ActiveUS20160248007A1Easy resistanceSolid-state devicesDigital storageCapacitanceCapacitive coupling

In one aspect of the invention, the memristor includes a monolayer film formed of an atomically thin material, where the monolayer film has at least one grain boundary (GB), a first electrode and a second electrode electrically coupled with the monolayer film to define a memristor channel therebetween, such that the at least one GB is located in the memristor channel, and a gate electrode capacitively coupled with the memristor channel.

Owner:NORTHWESTERN UNIV