Patents

Literature

335 results about "Spin-transfer torque" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

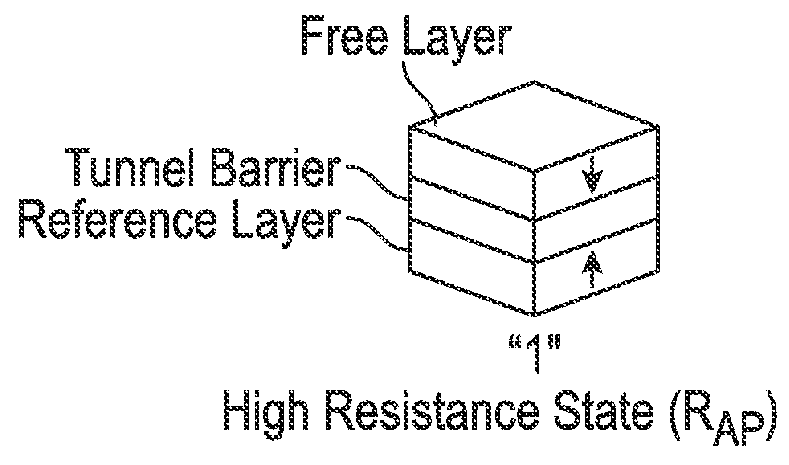

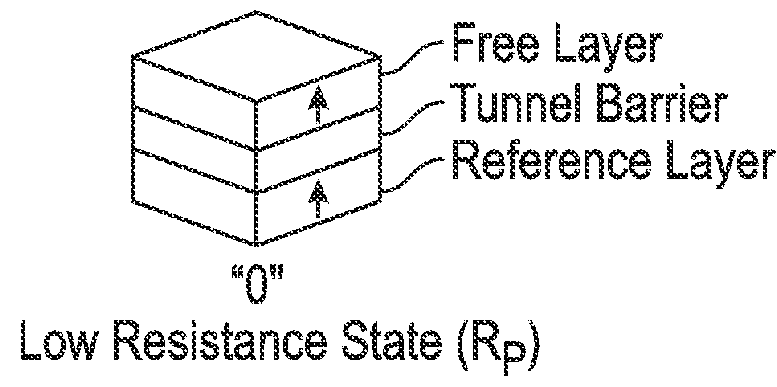

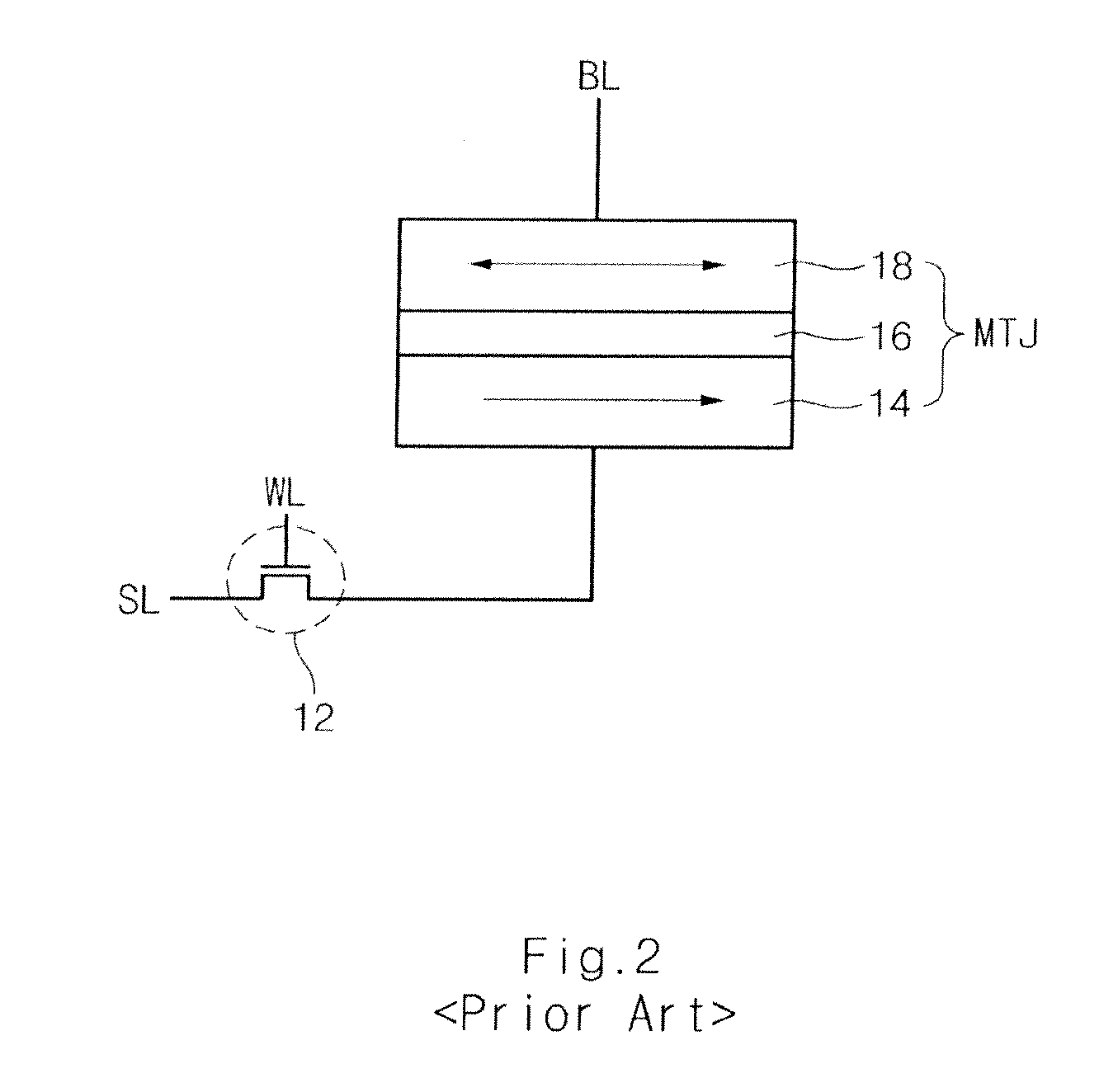

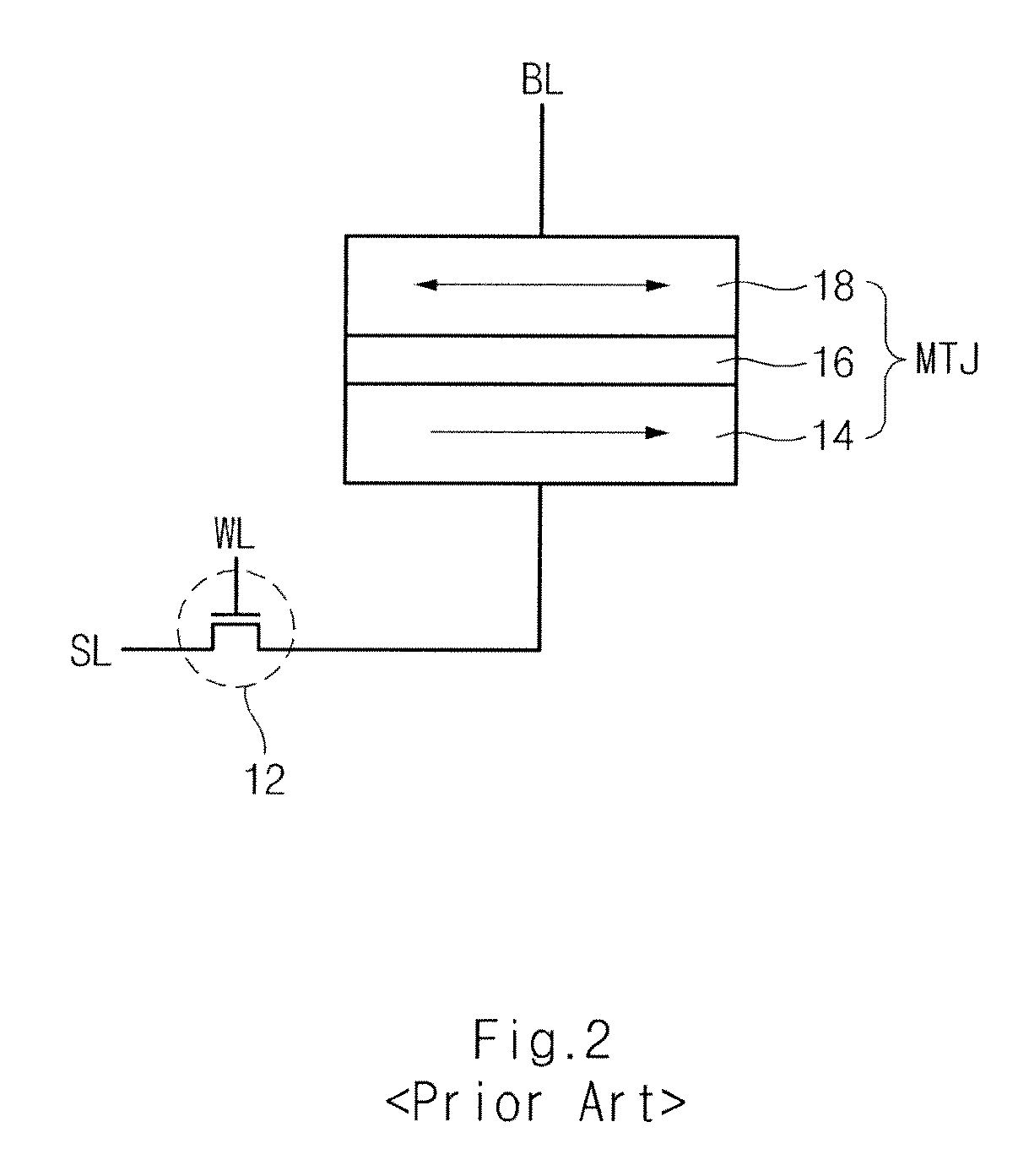

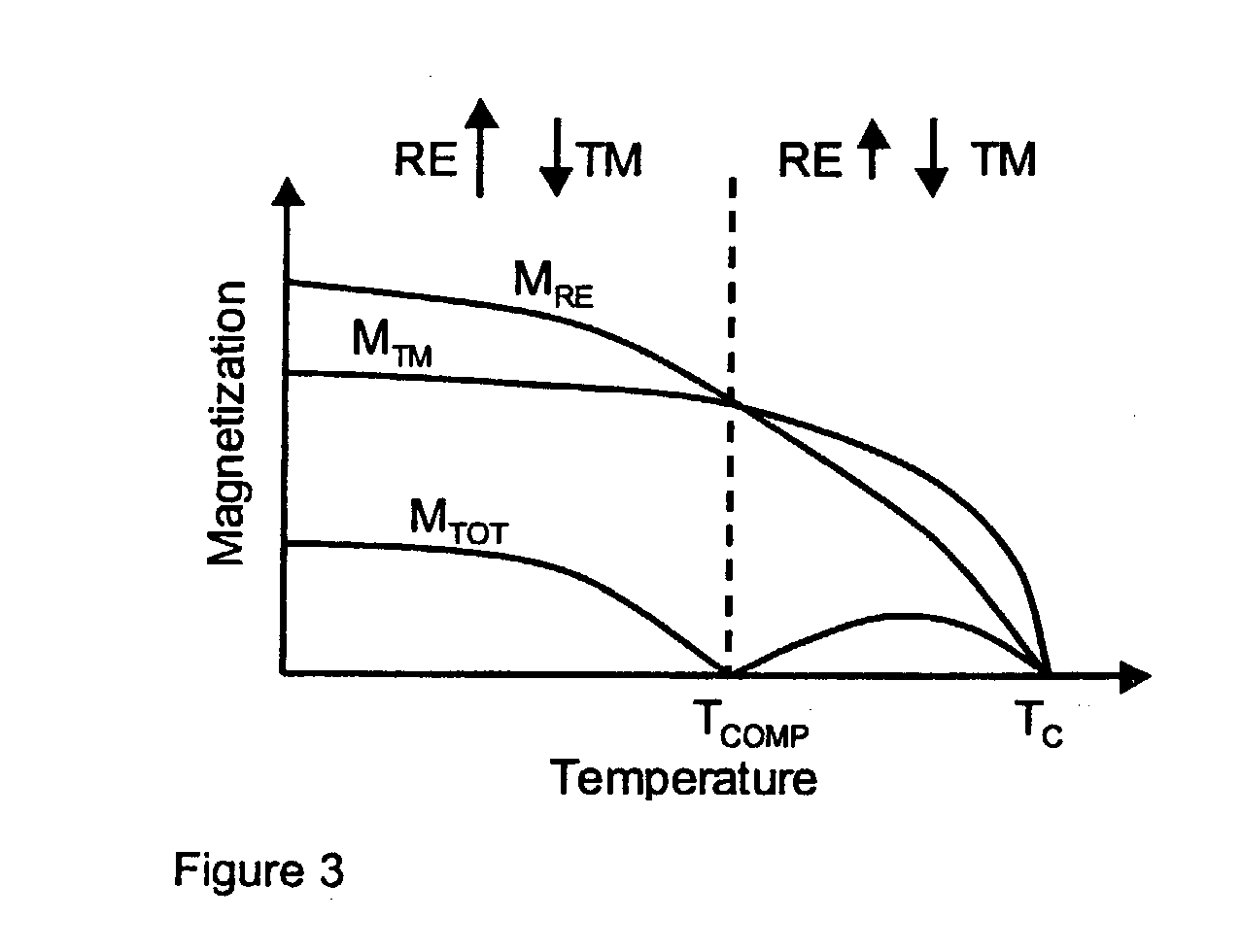

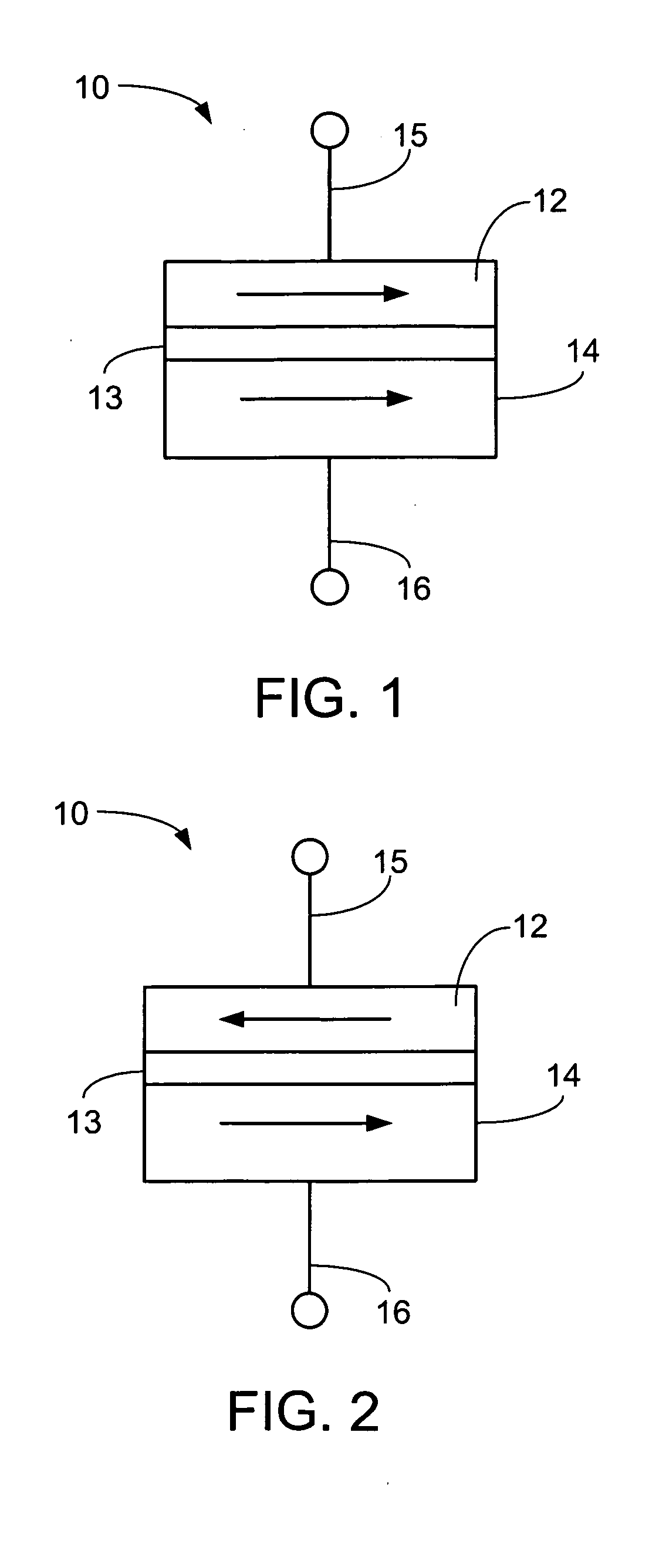

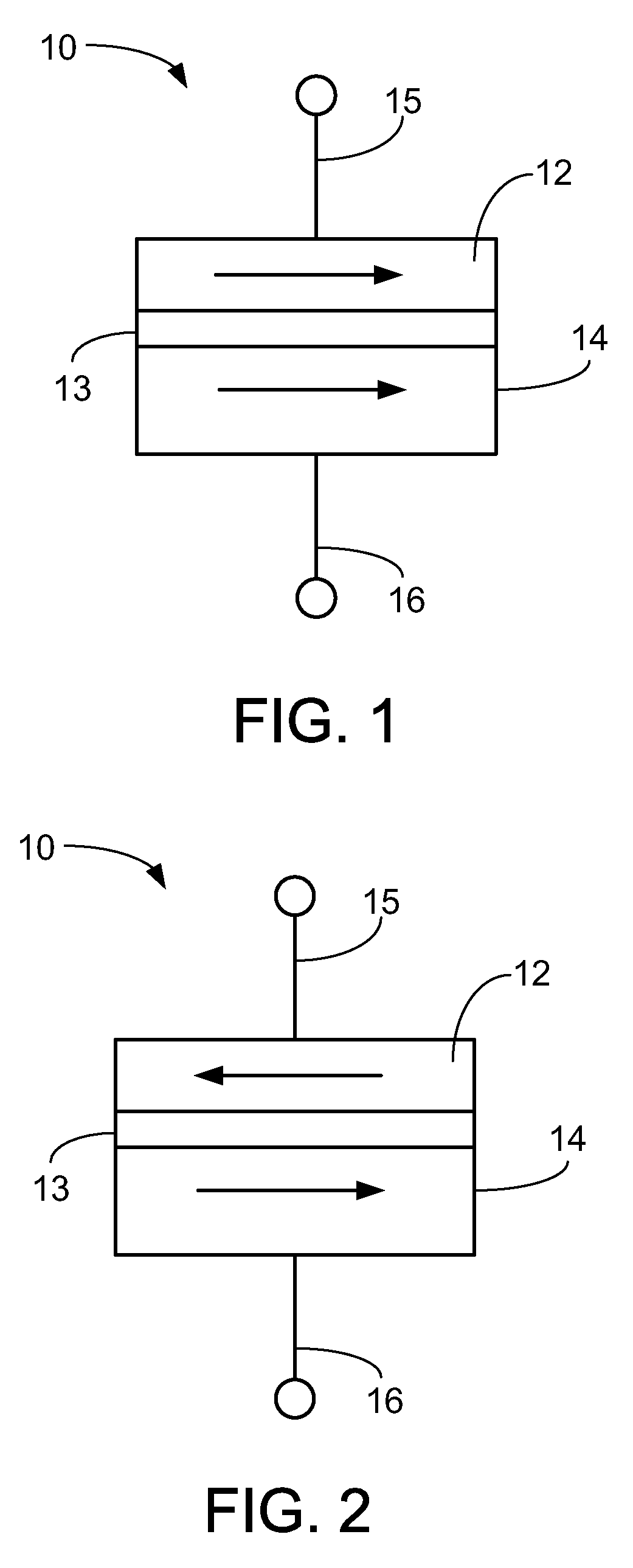

Spin-transfer torque is an effect in which the orientation of a magnetic layer in a magnetic tunnel junction or spin valve can be modified using a spin-polarized current. Charge carriers (such as electrons) have a property known as spin which is a small quantity of angular momentum intrinsic to the carrier. An electric current is generally unpolarized (consisting of 50% spin-up and 50% spin-down electrons); a spin polarized current is one with more electrons of either spin. By passing a current through a thick magnetic layer (usually called the “fixed layer”), one can produce a spin-polarized current. If this spin-polarized current is directed into a second, thinner magnetic layer (the “free layer”), the angular momentum can be transferred to this layer, changing its orientation. This can be used to excite oscillations or even flip the orientation of the magnet. The effects are usually seen only in nanometer scale devices.

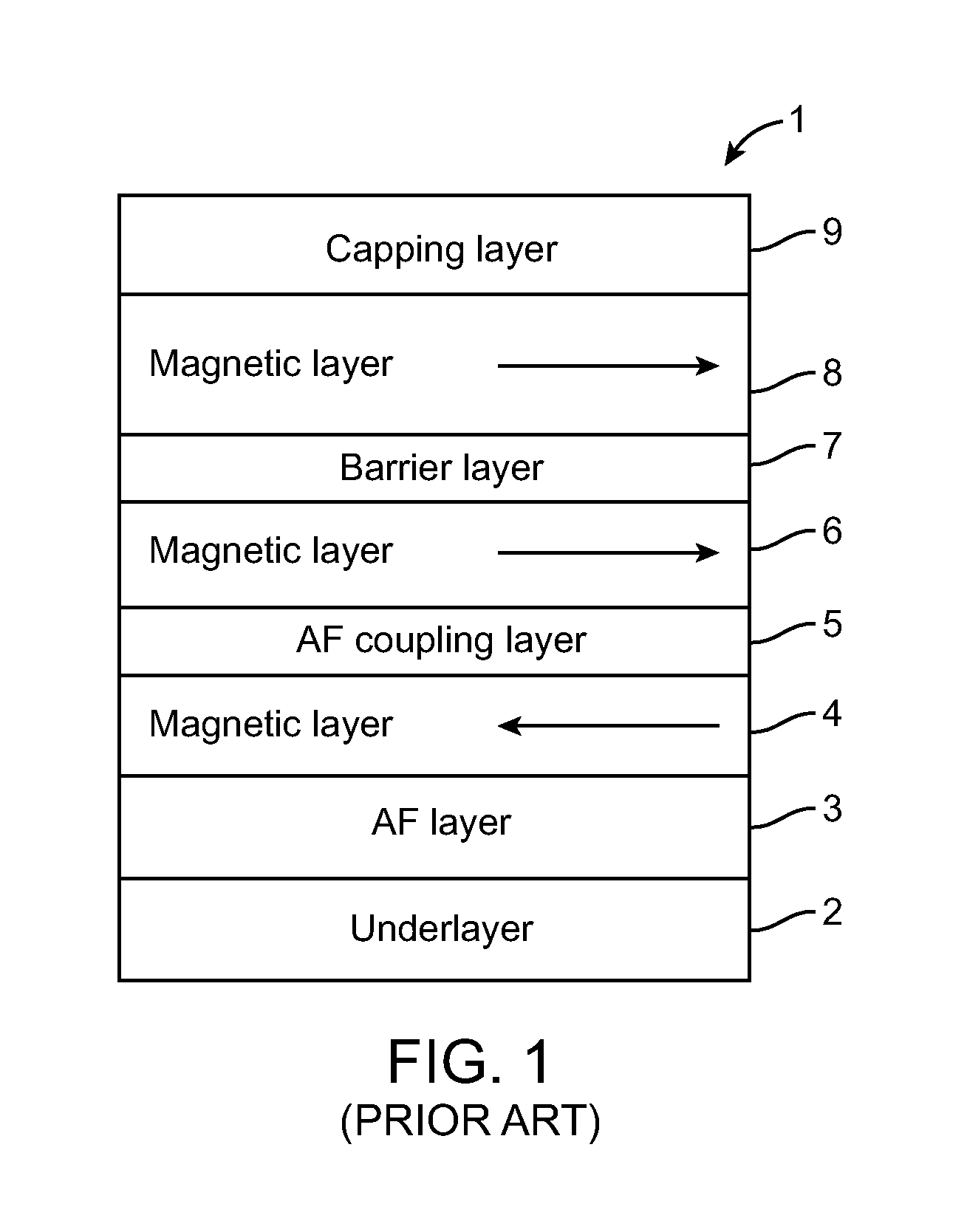

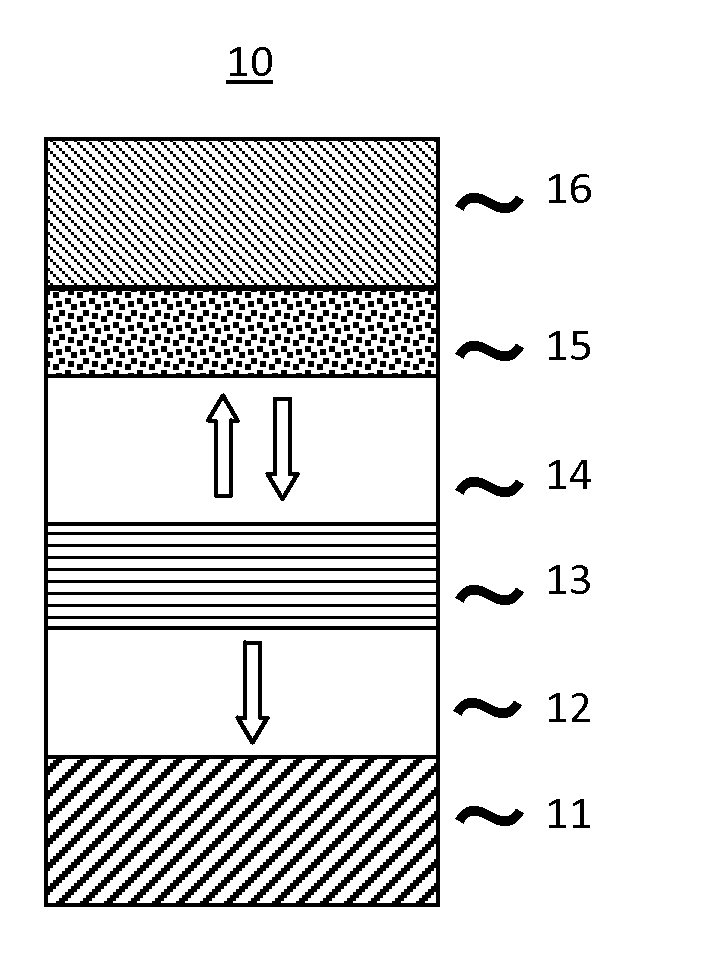

Spin-transfer torque magnetic random access memory having magnetic tunnel junction with perpendicular magnetic anisotropy

A spin-torque transfer memory random access memory (STTMRAM) element includes a fixed layer formed on top of a substrate and a a tunnel layer formed upon the fixed layer and a composite free layer formed upon the tunnel barrier layer and made of an iron platinum alloy with at least one of X or Y material, X being from a group consisting of: boron (B), phosphorous (P), carbon (C), and nitride (N) and Y being from a group consisting of: tantalum (Ta), titanium (Ti), niobium (Nb), zirconium (Zr), tungsten (W), silicon (Si), copper (Cu), silver (Ag), aluminum (Al), chromium (Cr), tin (Sn), lead (Pb), antimony (Sb), hafnium (Hf) and bismuth (Bi), molybdenum (Mo) or rhodium (Ru), the magnetization direction of each of the composite free layer and fixed layer being substantially perpendicular to the plane of the substrate.

Owner:AVALANCHE TECH

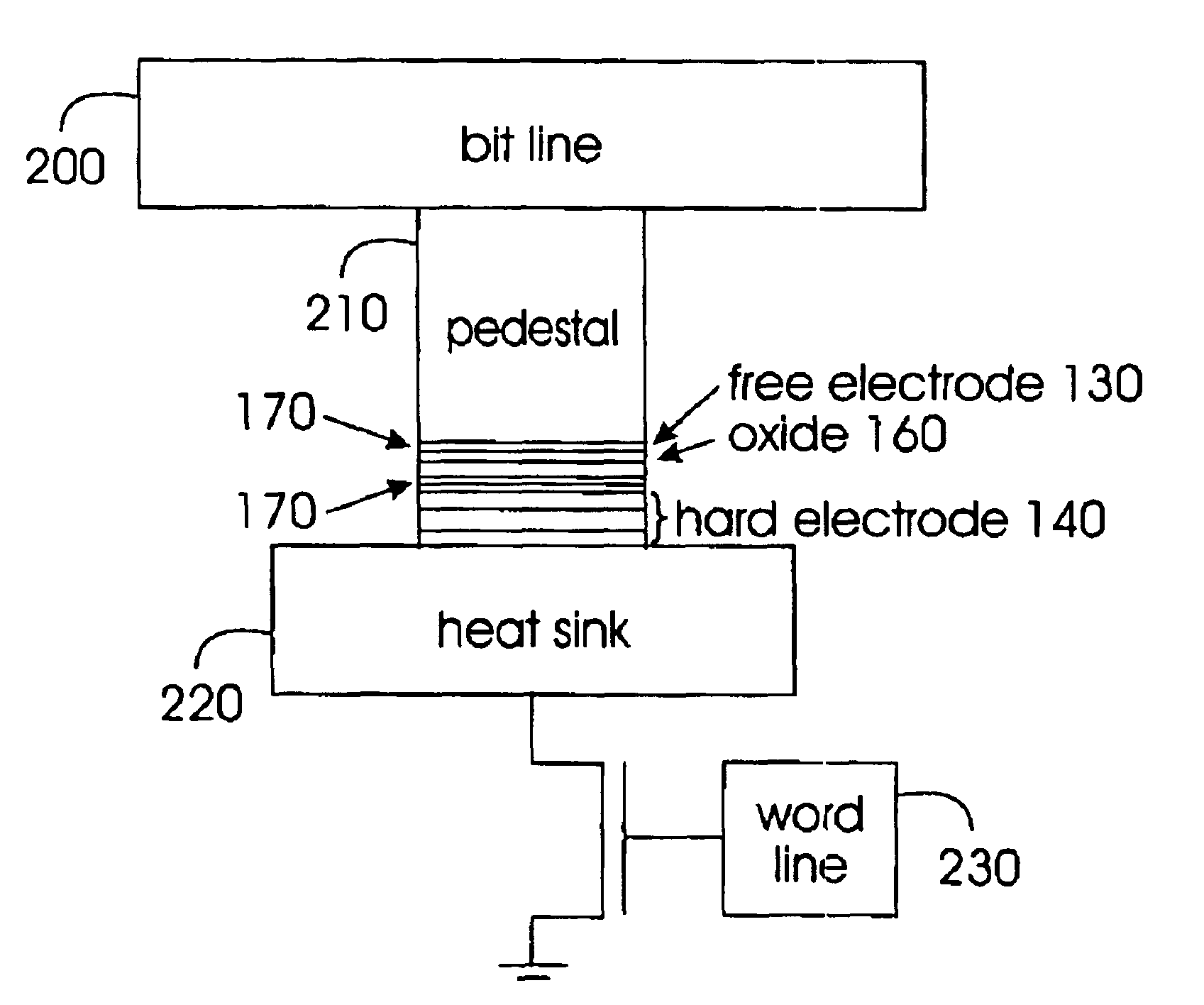

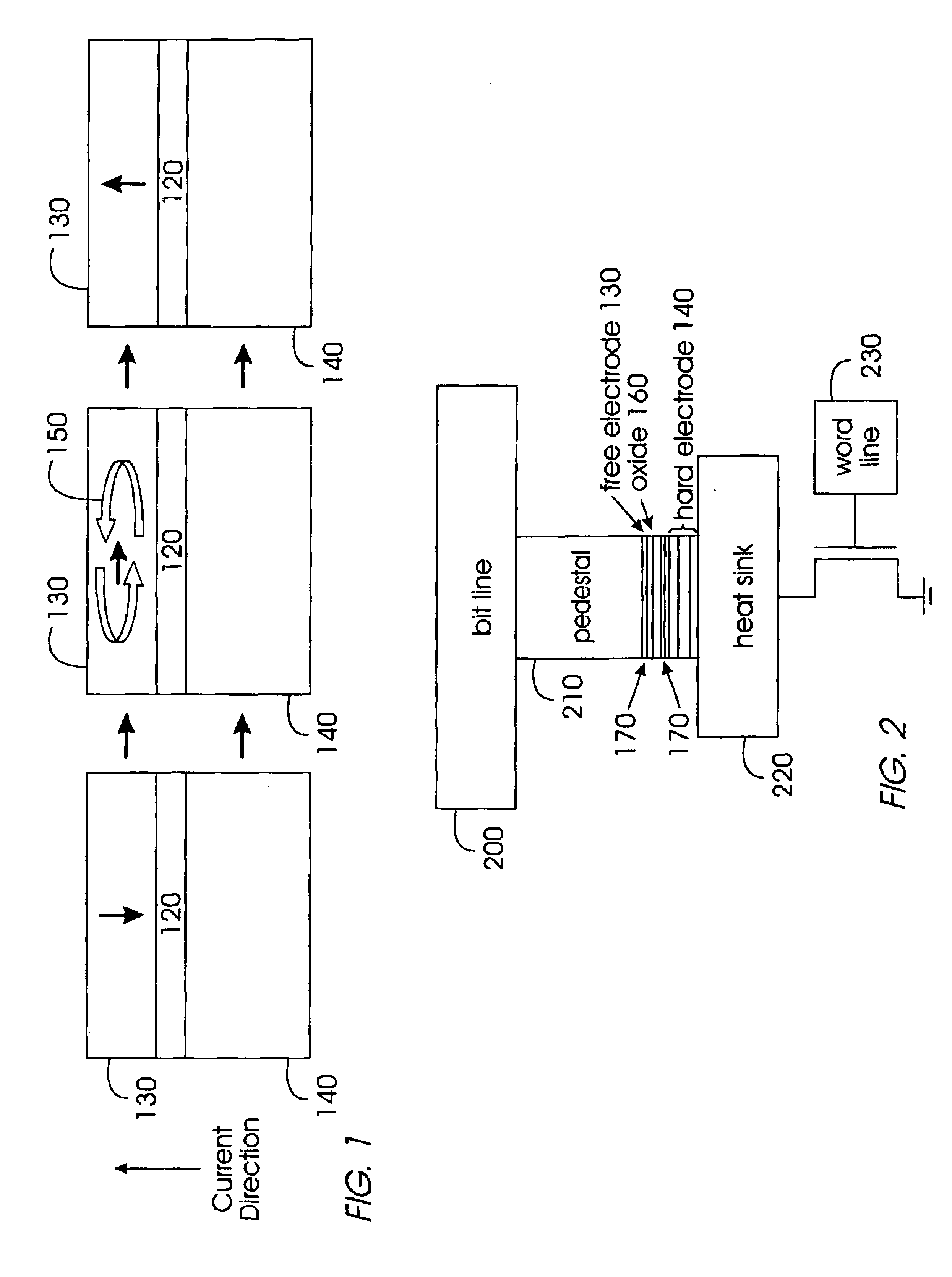

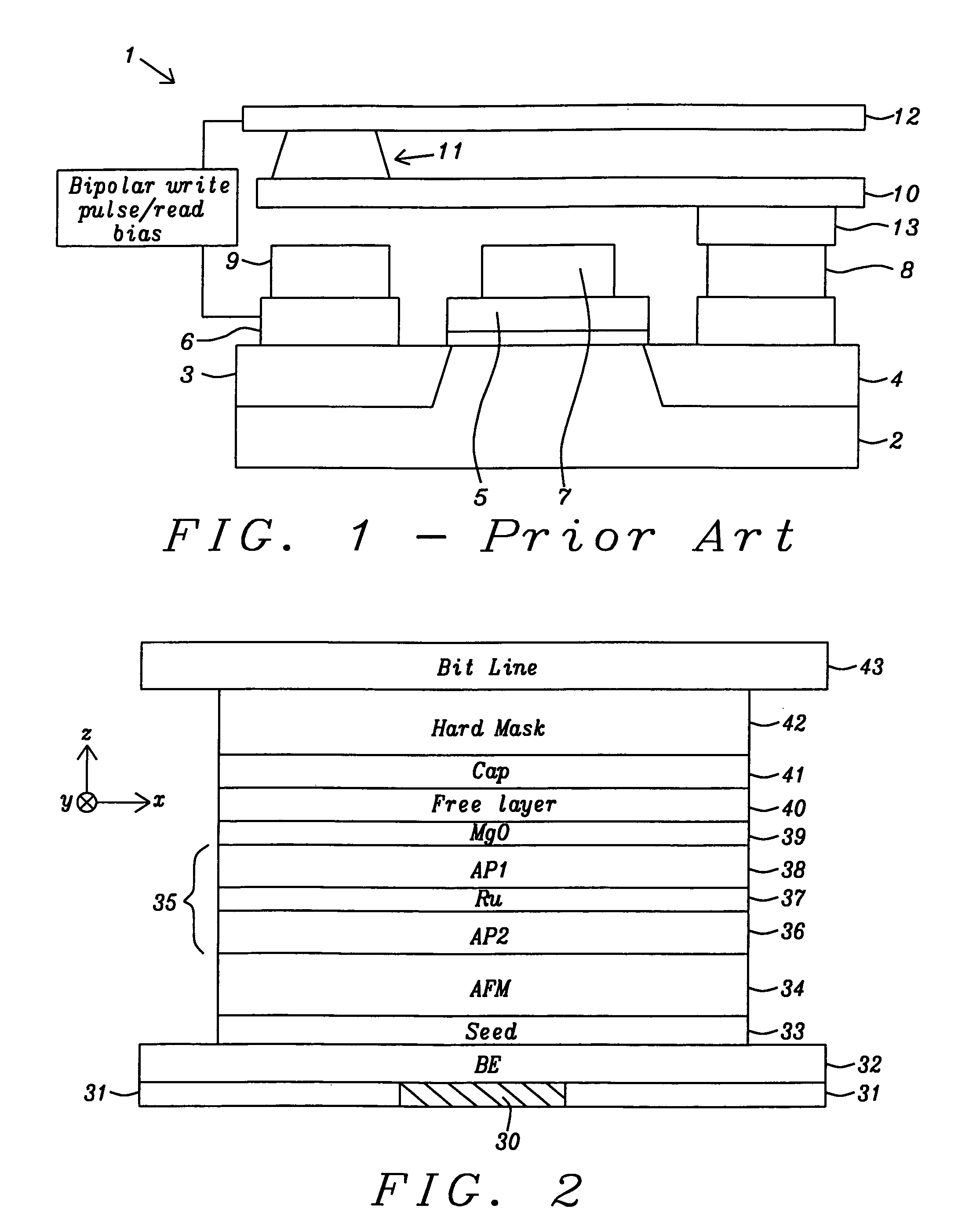

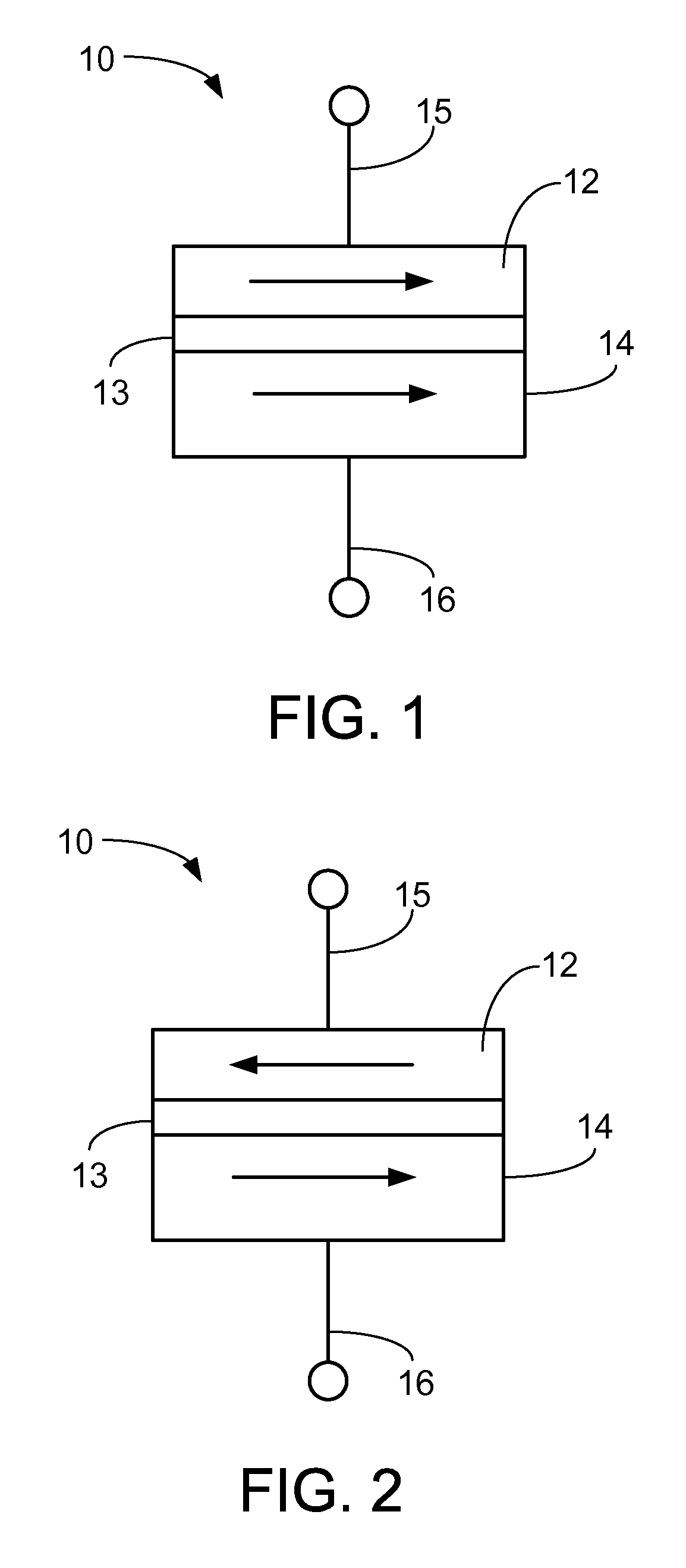

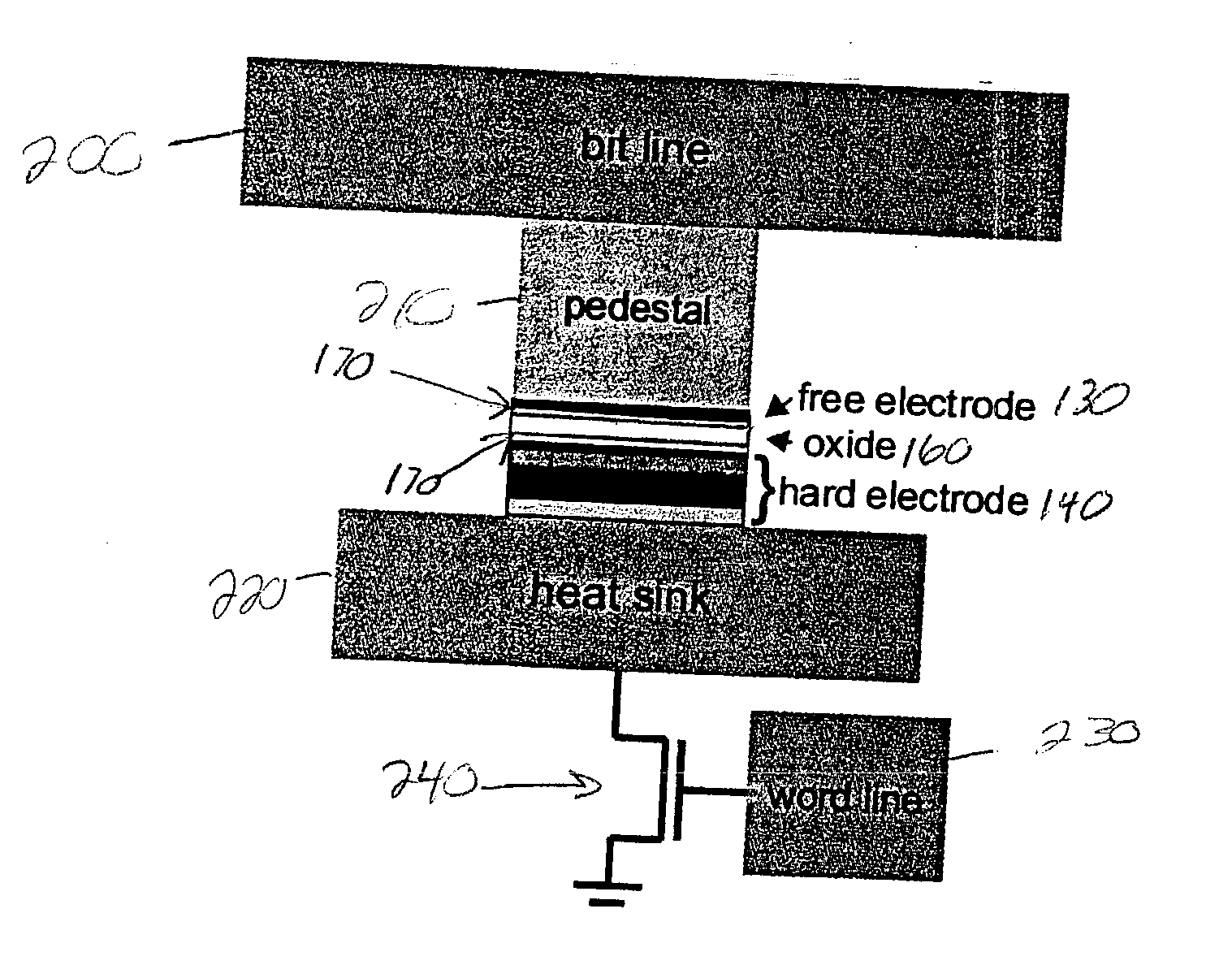

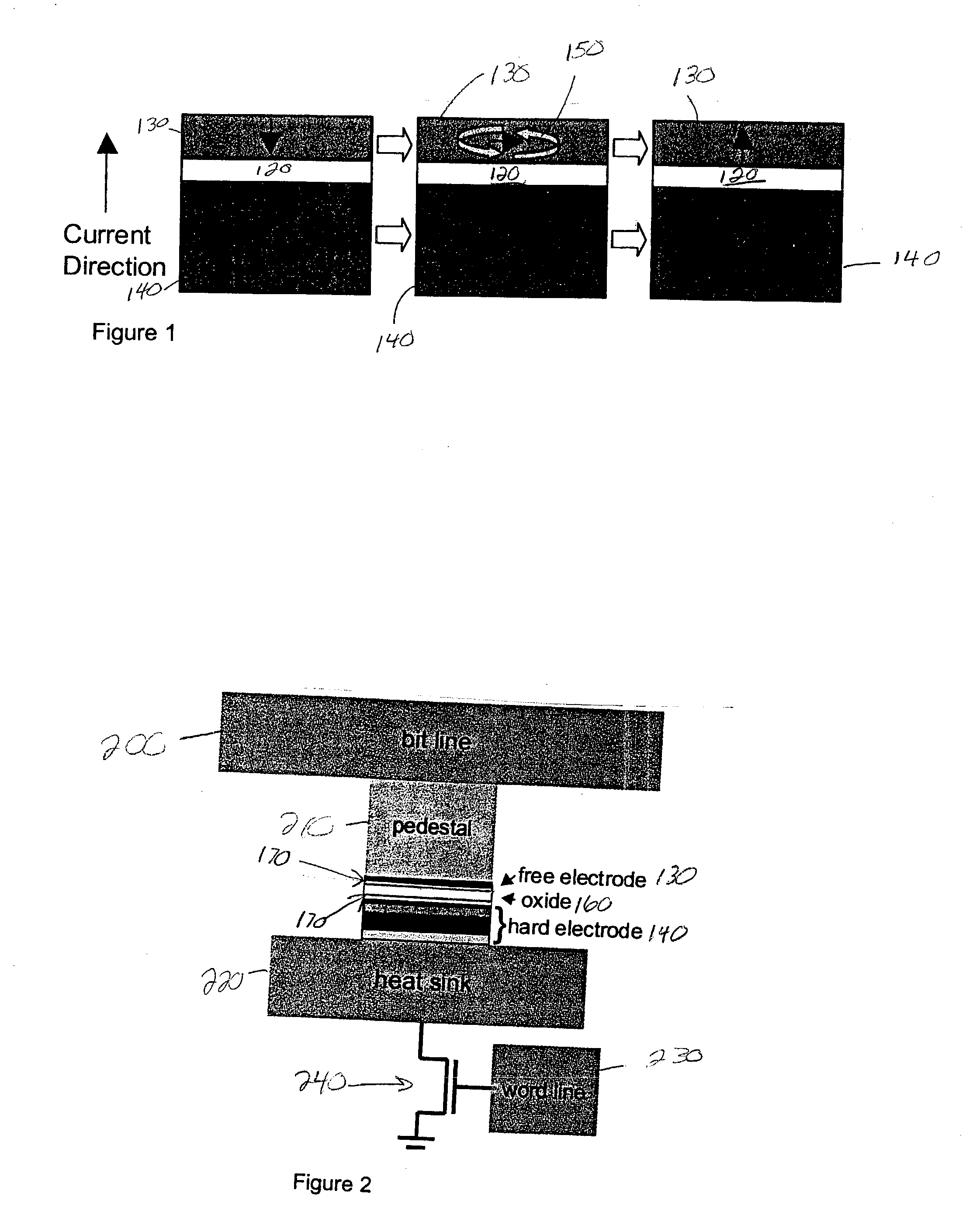

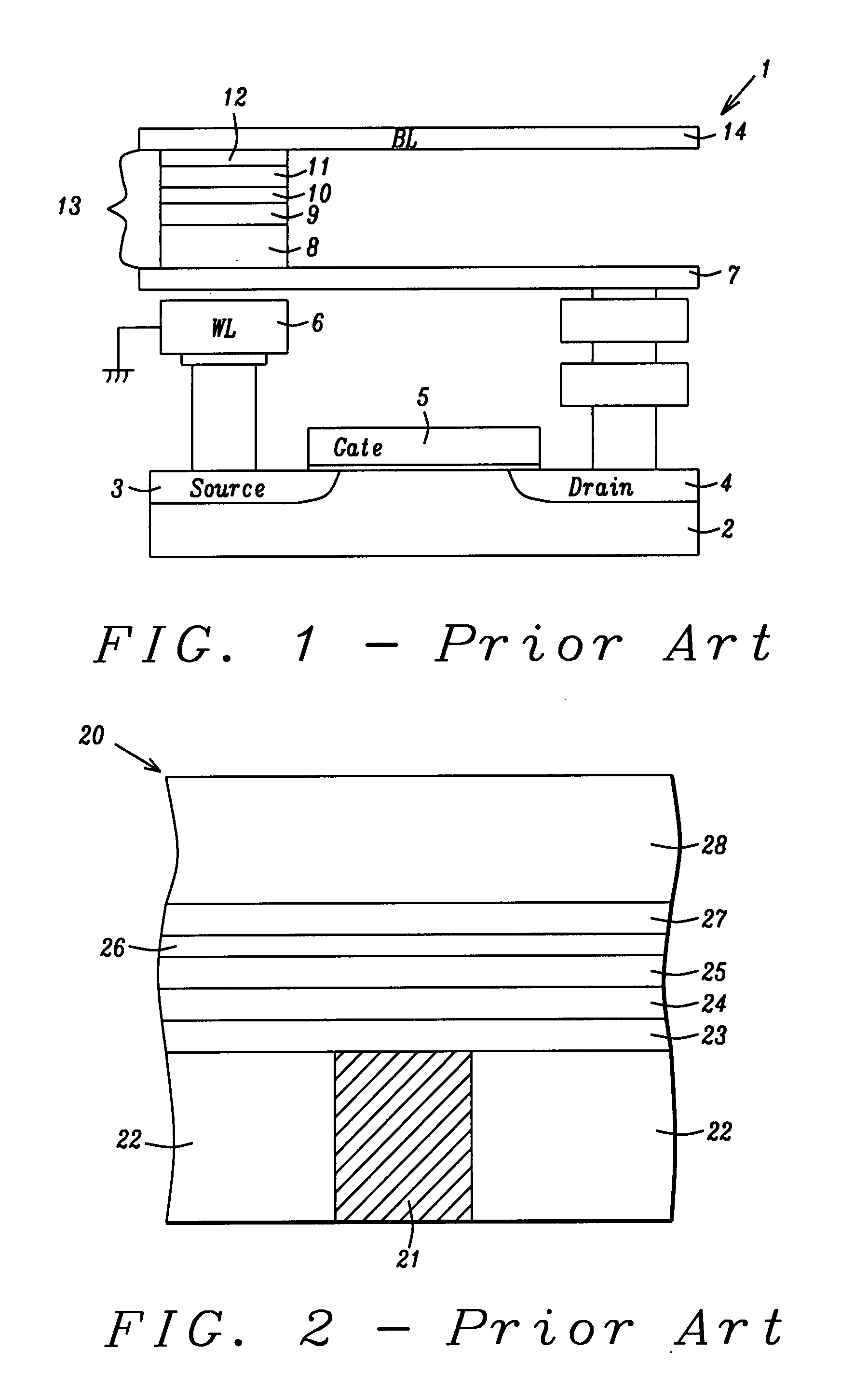

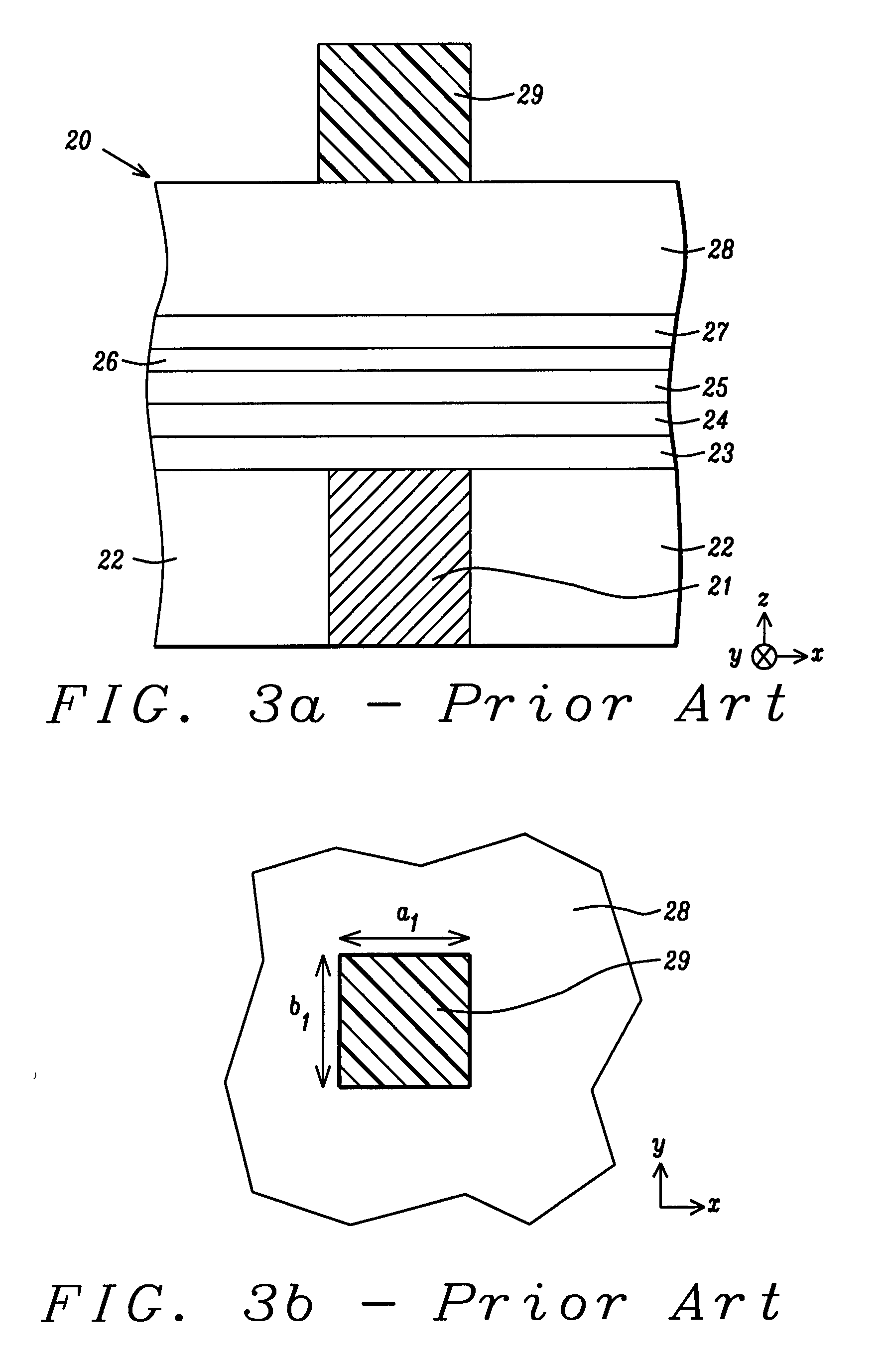

Thermally-assisted magnetic writing using an oxide layer and current-induced heating

InactiveUS6771534B2Increase in sizeIncrease in coercivityNanostructure applicationNanomagnetismElectrical resistance and conductanceElectrical conductor

A method and structure for a non-volatile magnetic random access memory (MRAM) device that has a stable magnetic electrode, an oxide layer adjacent the stable magnetic electrode, and a free magnetic electrode. The oxide layer is between the stable magnetic electrode and the free magnetic electrode. In the invention, a conductor is connected to a stable magnetic electrode. The oxide layer has a resistance at levels to allow sufficient power dissipation to lower the anisotropy of the free magnetic electrode through current induced heating. Current-induced heating is used in combination with spin-transfer torque or a magnetic field to switch the free magnetic electrode.

Owner:GLOBALFOUNDRIES U S INC

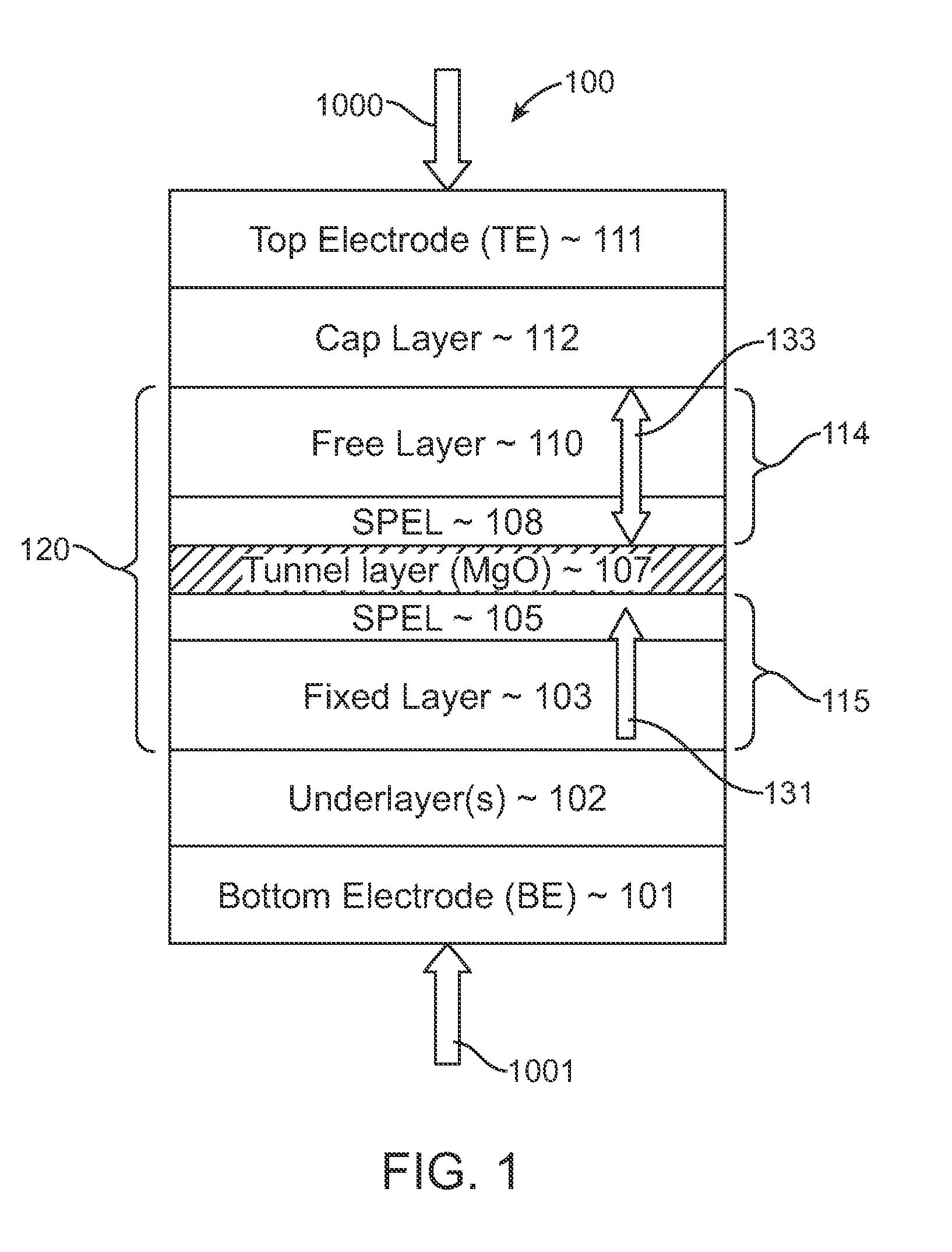

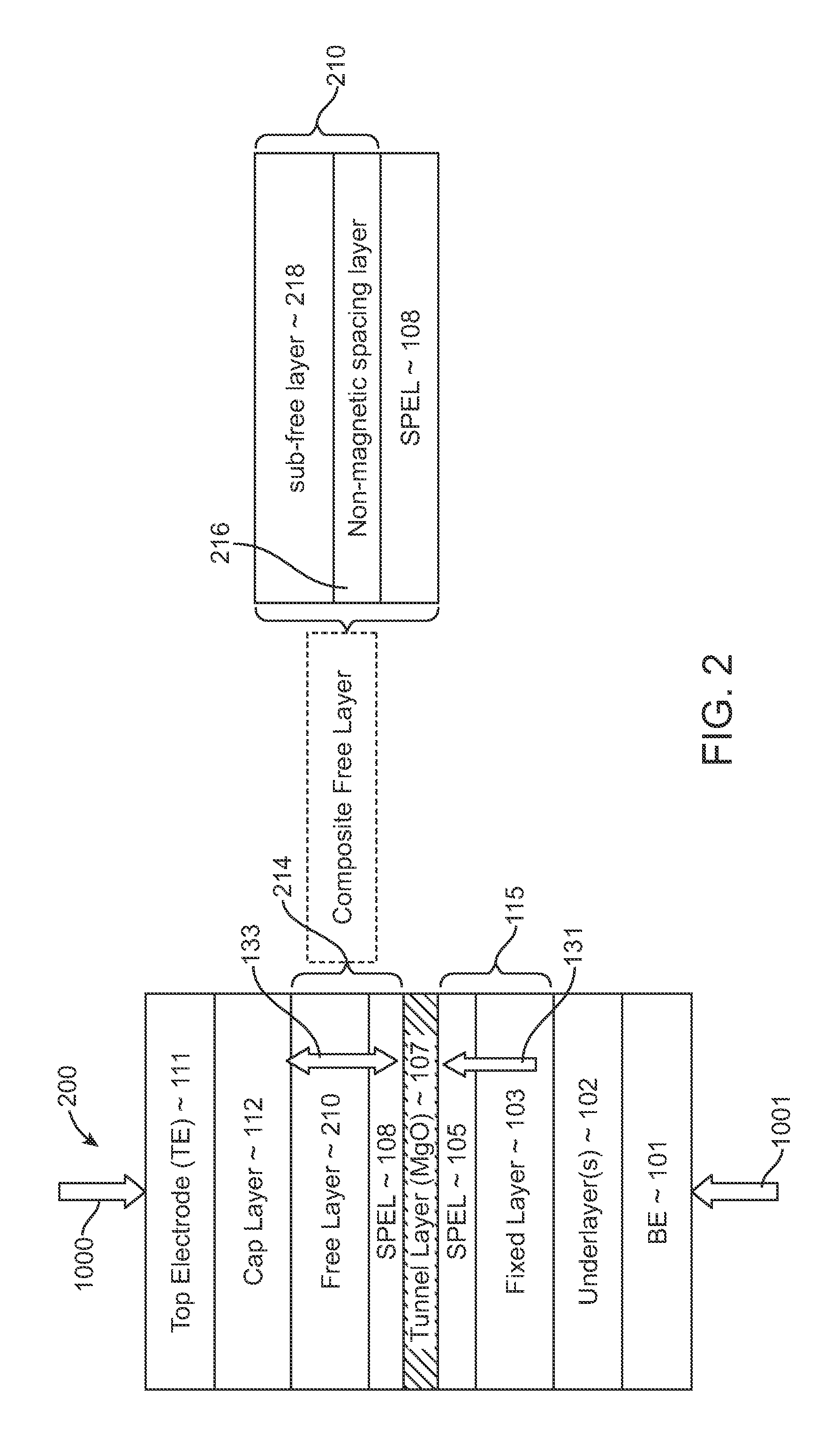

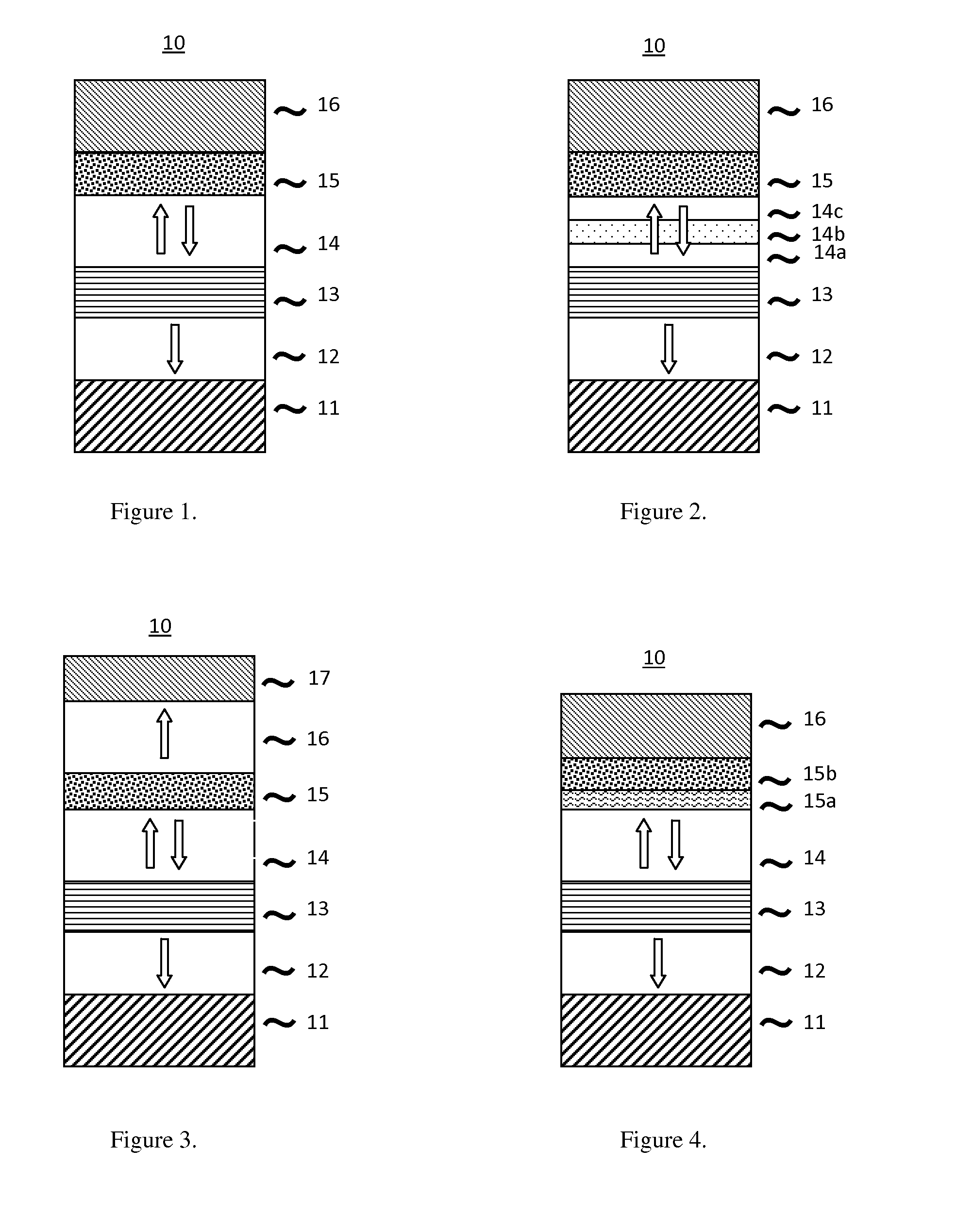

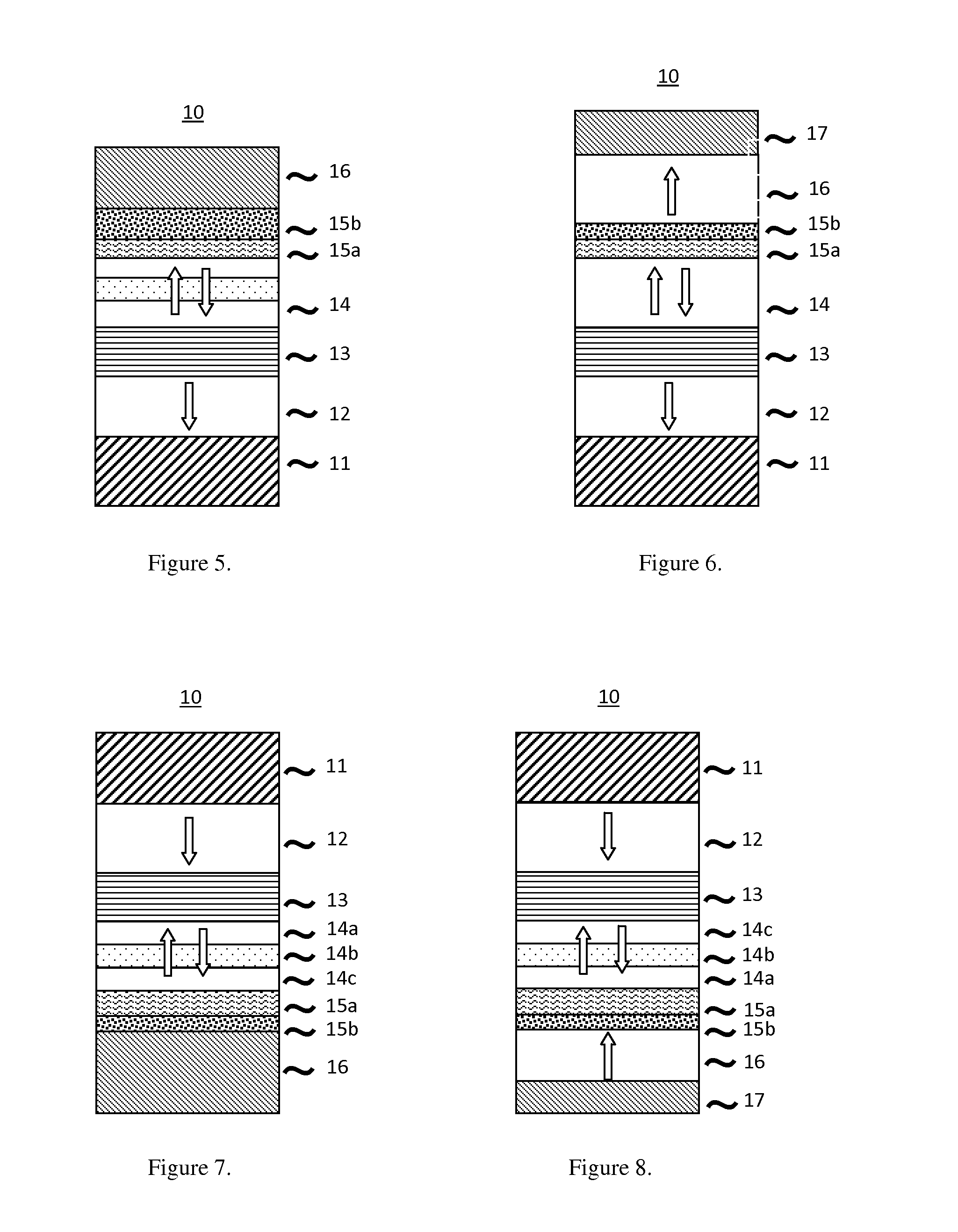

Structure and method to fabricate high performance MTJ devices for spin-transfer torque (STT)-RAM application

ActiveUS20110014500A1High densityIncreased polarizationNanomagnetismMagnetic materials for record carriersPower flowSpin-transfer torque

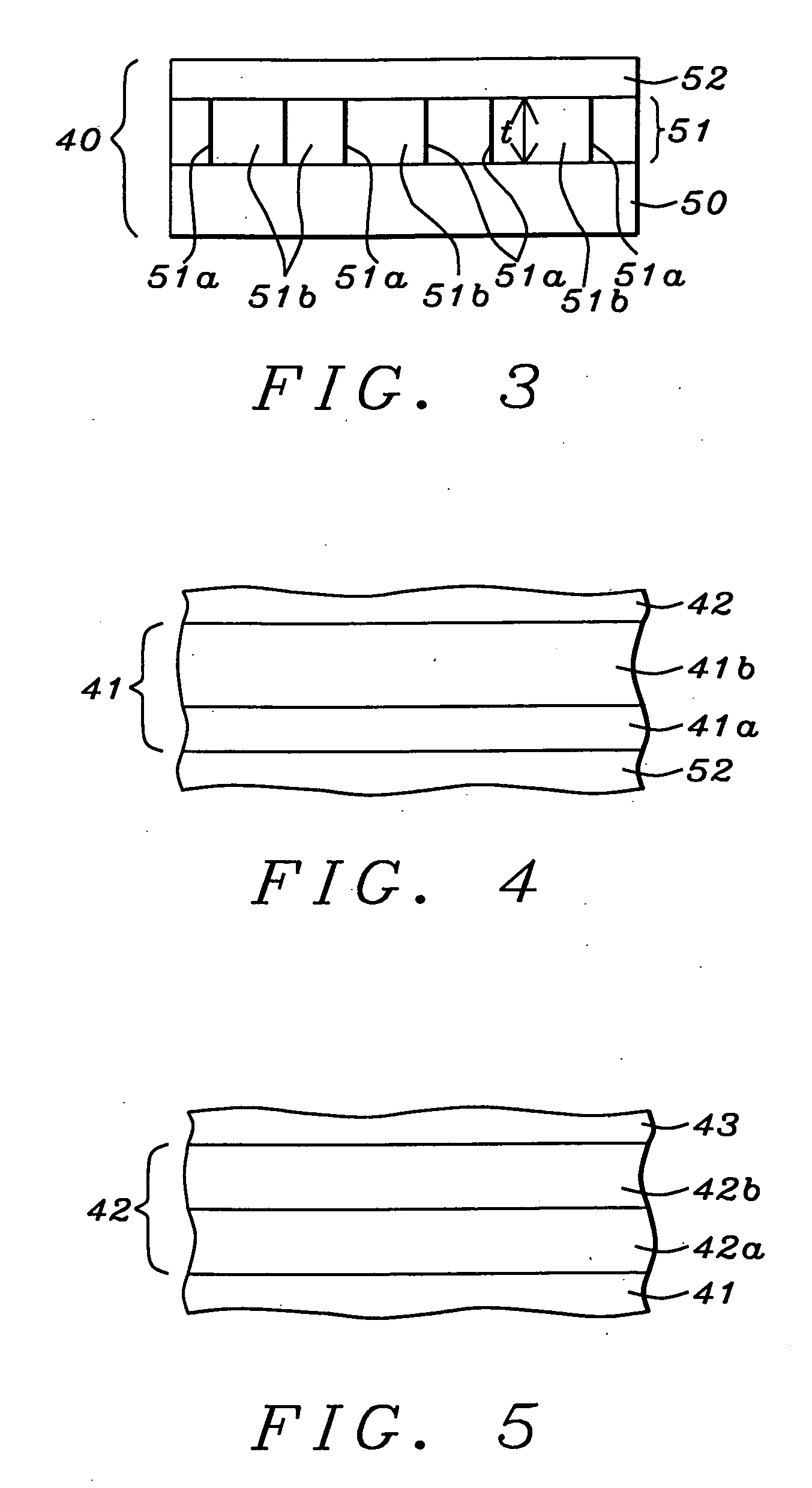

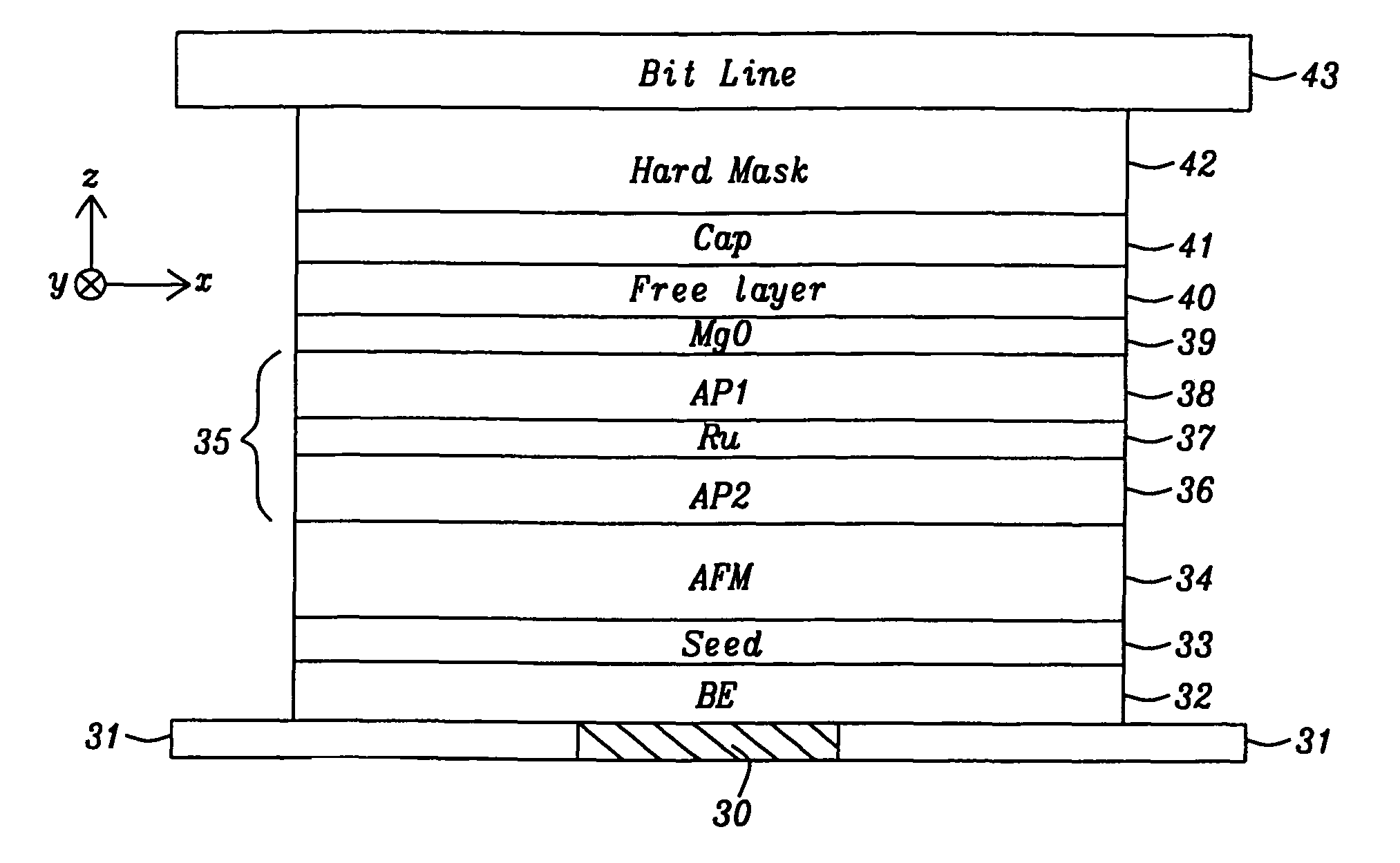

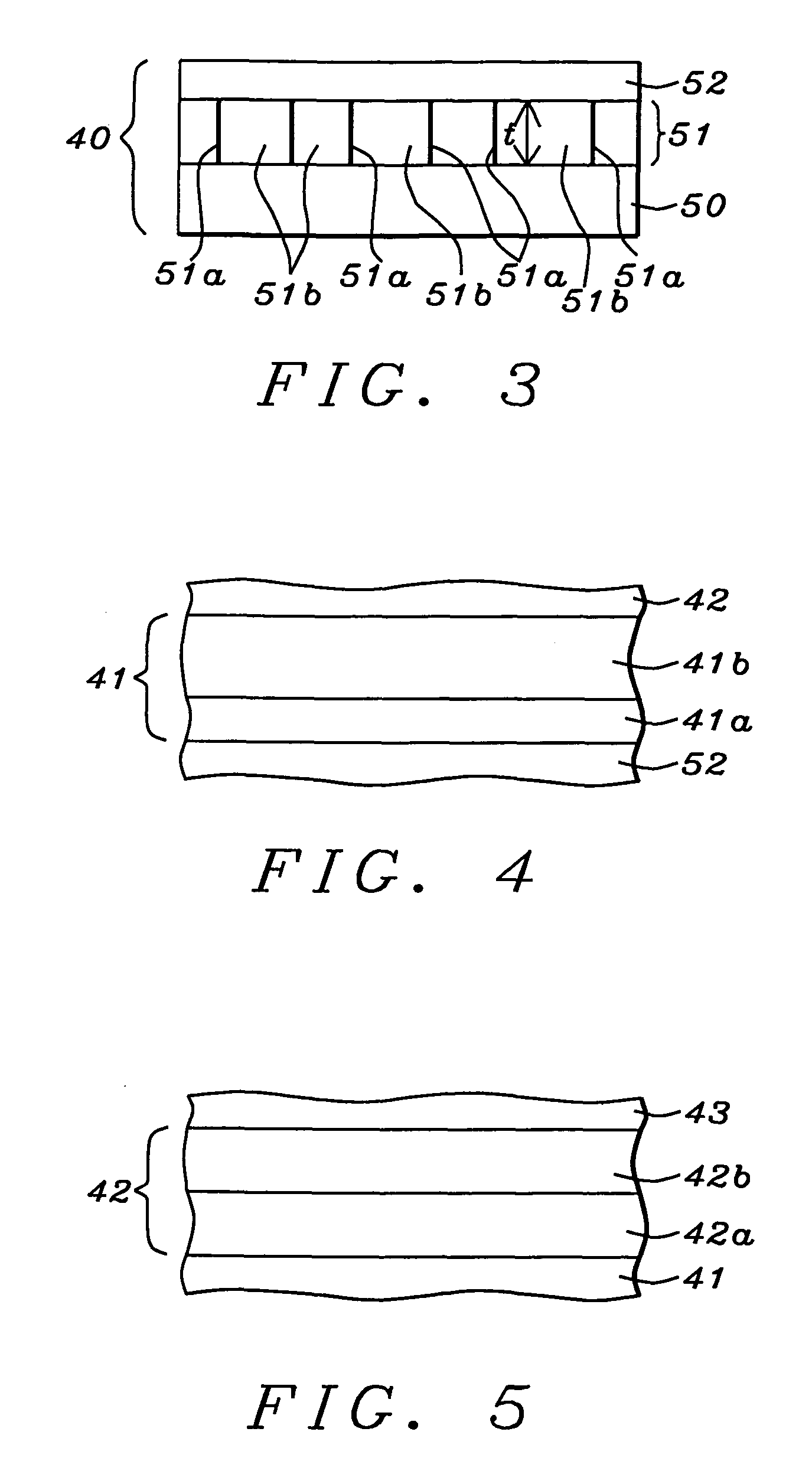

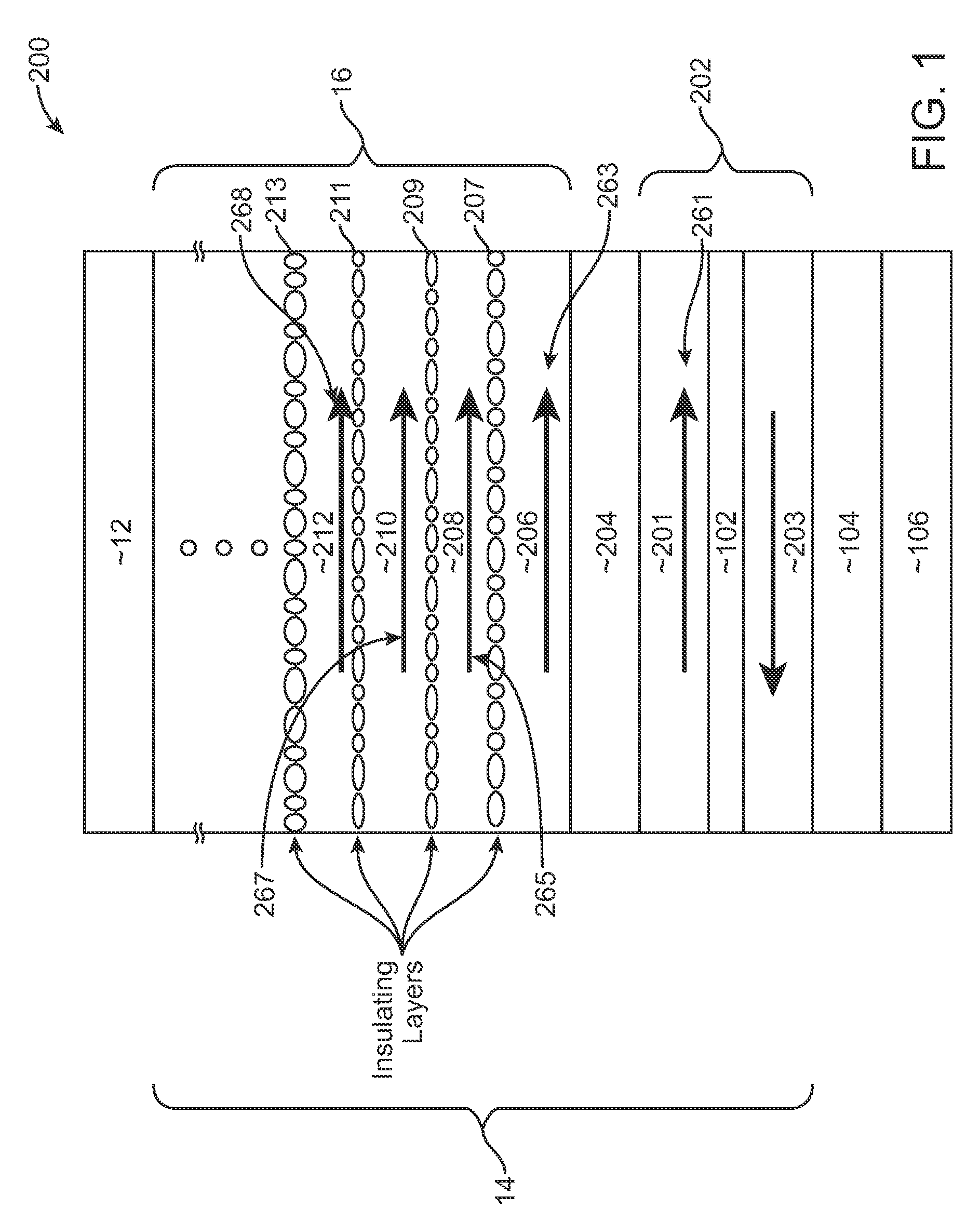

A STT-RAM MTJ is disclosed with a MgO tunnel barrier formed by natural oxidation and containing an oxygen surfactant layer to form a more uniform MgO layer and lower breakdown distribution percent. A CoFeB / NCC / CoFeB composite free layer with a middle nanocurrent channel layer minimizes Jc0 while enabling thermal stability, write voltage, read voltage, and Hc values that satisfy 64 Mb design requirements. The NCC layer has RM grains in an insulator matrix where R is Co, Fe, or Ni, and M is a metal such as Si or Al. NCC thickness is maintained around the minimum RM grain size to avoid RM granules not having sufficient diameter to bridge the distance between upper and lower CoFeB layers. A second NCC layer and third CoFeB layer may be included in the free layer or a second NCC layer may be inserted below the Ru capping layer.

Owner:TAIWAN SEMICON MFG CO LTD

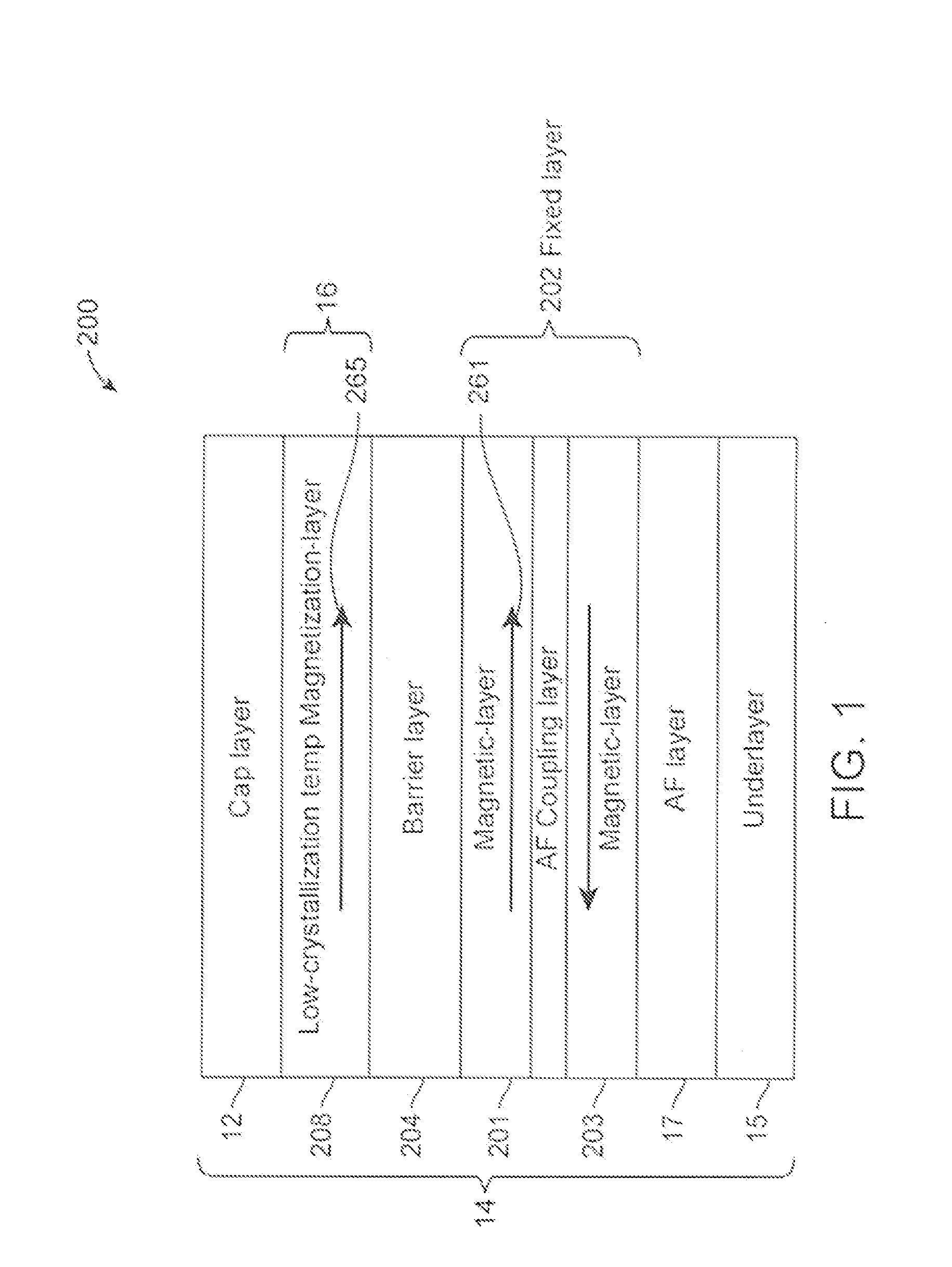

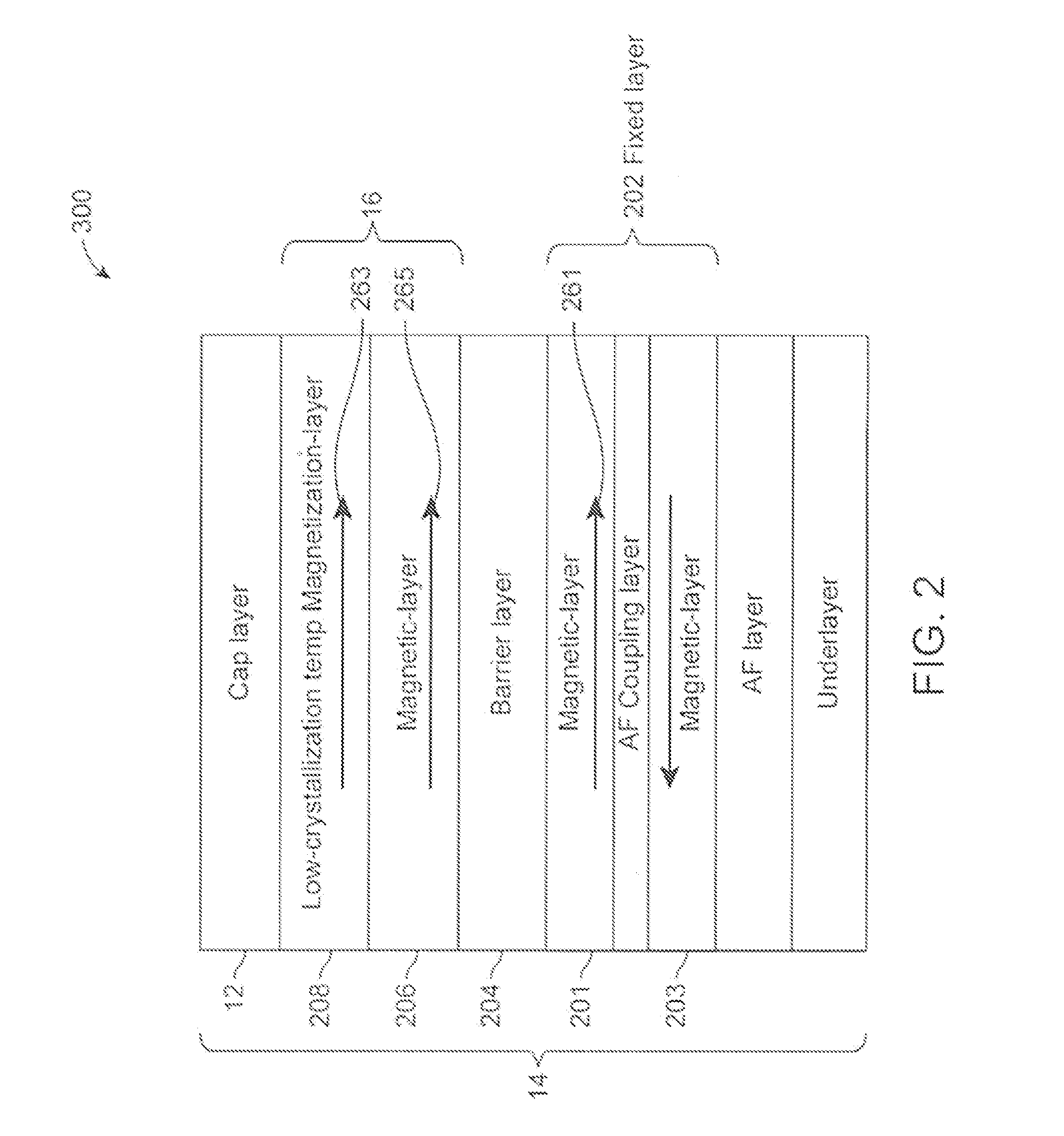

Low-crystallization temperature MTJ for Spin-Transfer Torque Magnetic Random Access Memory (STTMRAM)

A spin-torque transfer memory random access memory (STTMRAM) element is disclosed and has a fixed layer, a barrier layer formed upon the fixed layer, and a free layer comprised of a low-crystallization temperature alloy of CoFeB—Z where Z is below 25 atomic percent of one or more of titanium, (Ti), yittrium (Y), zirconium (Zr), and vanadium (V), wherein during a write operation, a bidirectional electric current is applied across the STTMRAM element to switch the magnetization of the free layer between parallel and anti-parallel states relative to the magnetization of the fixed layer.

Owner:AVALANCHE TECH

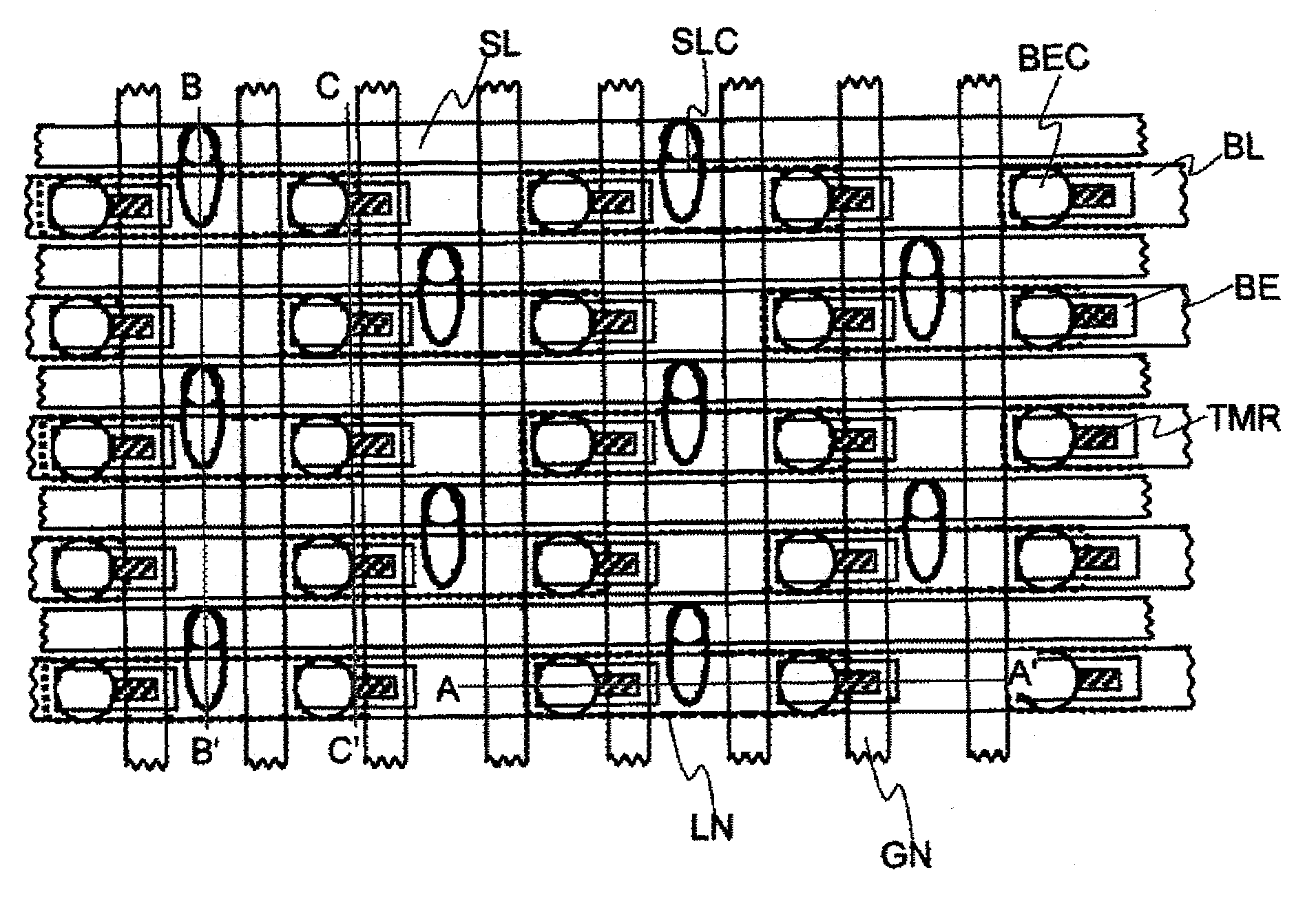

High output nonvolatile magnetic memory

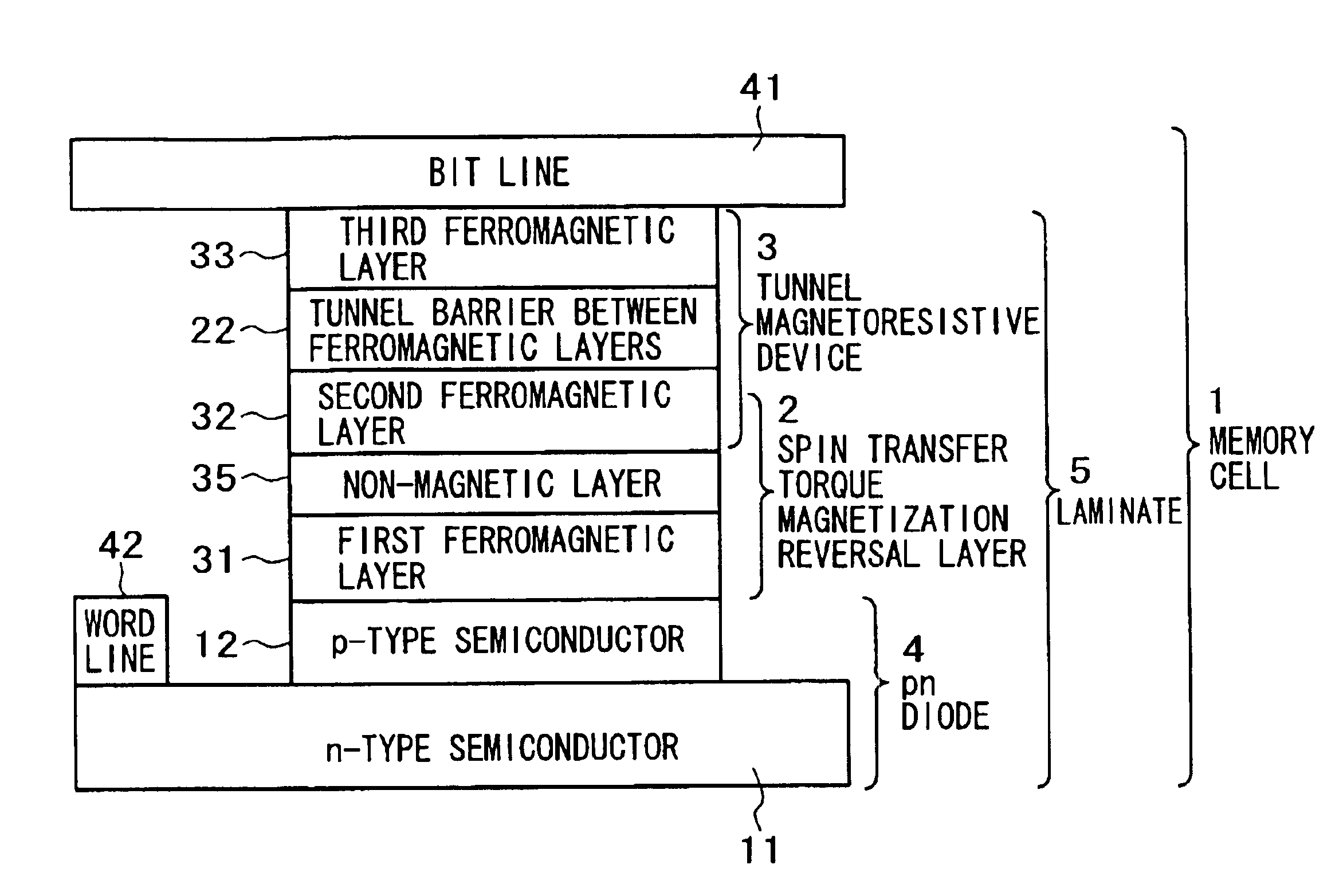

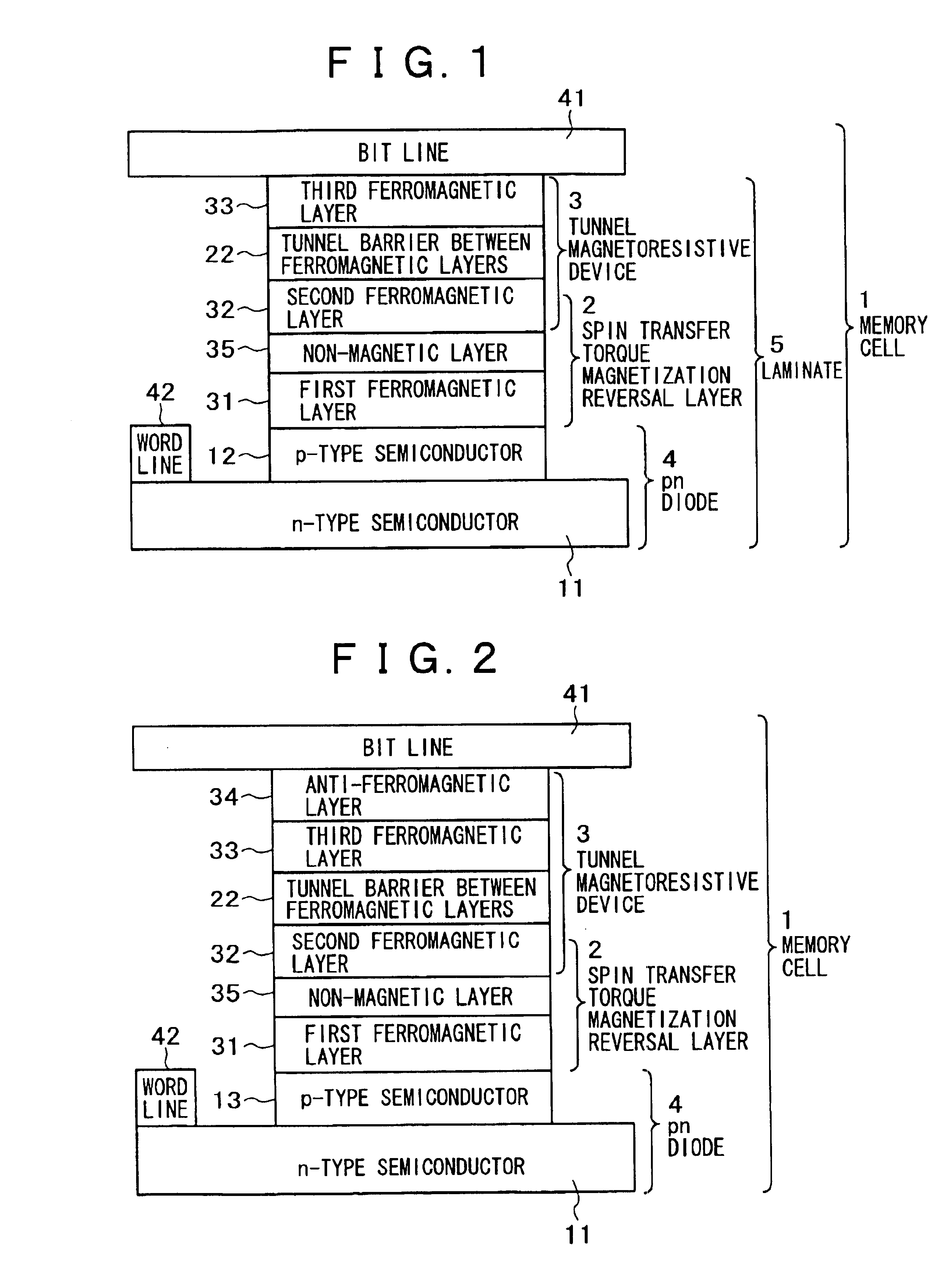

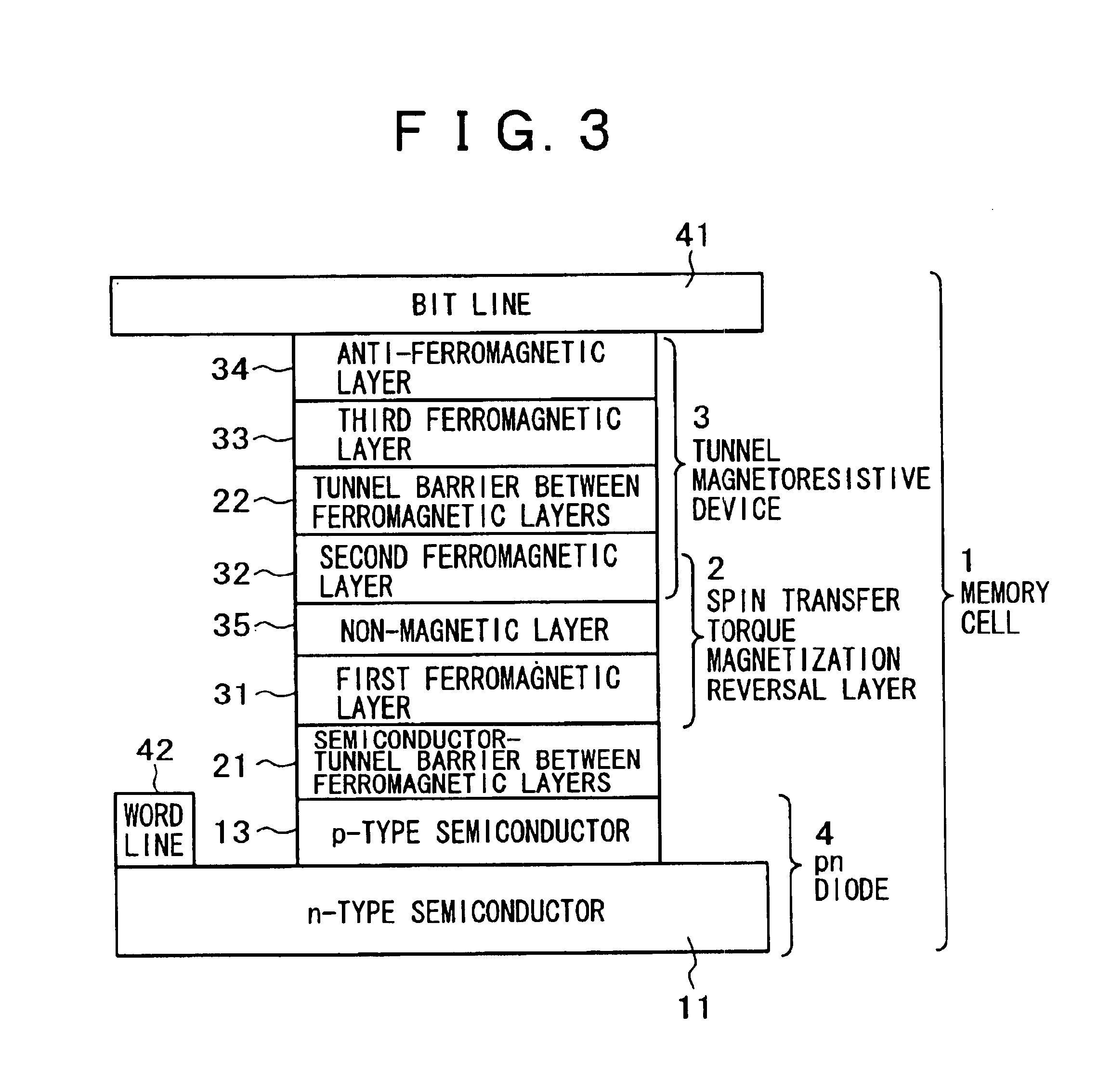

InactiveUS6842368B2Reduce in quantityReduced Power RequirementsNanomagnetismMagnetic-field-controlled resistorsBit lineSpin-transfer torque

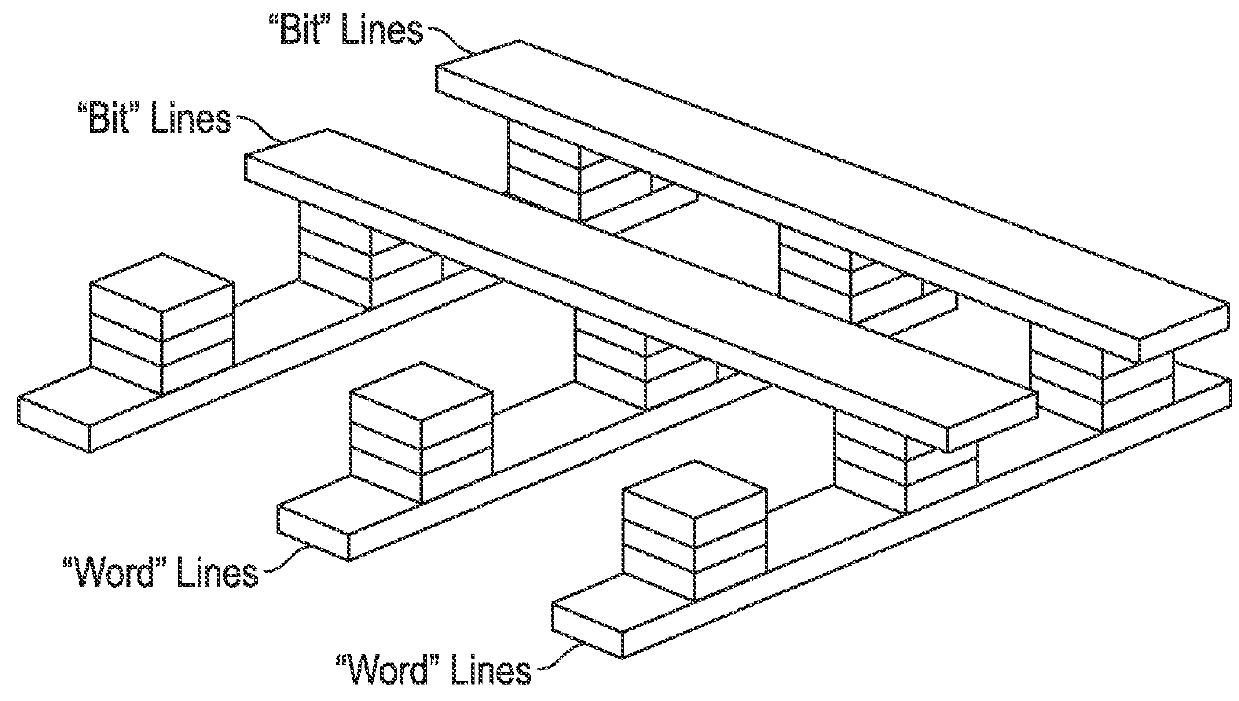

A magnetic memory is provided with a high-output memory cell capable of switching and magnetization reversal operations by means of two terminals. There is formed an MIS junction laminated layer comprising a diode, a spin transfer torque magnetization reversal induction layer, and a tunnel magnetoresistive device. A bit line and a word line are connected to the laminated layer.

Owner:HITACHI LTD

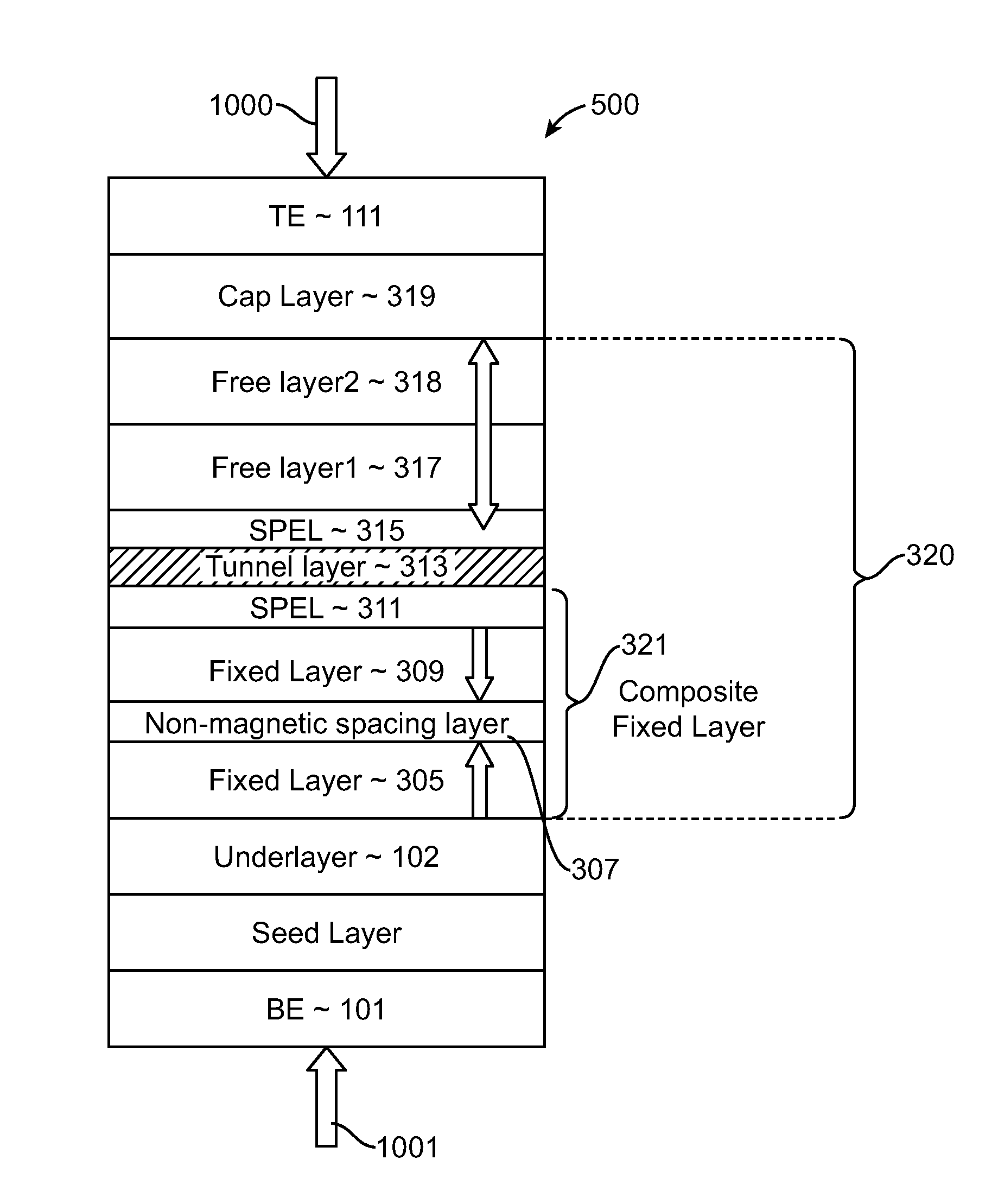

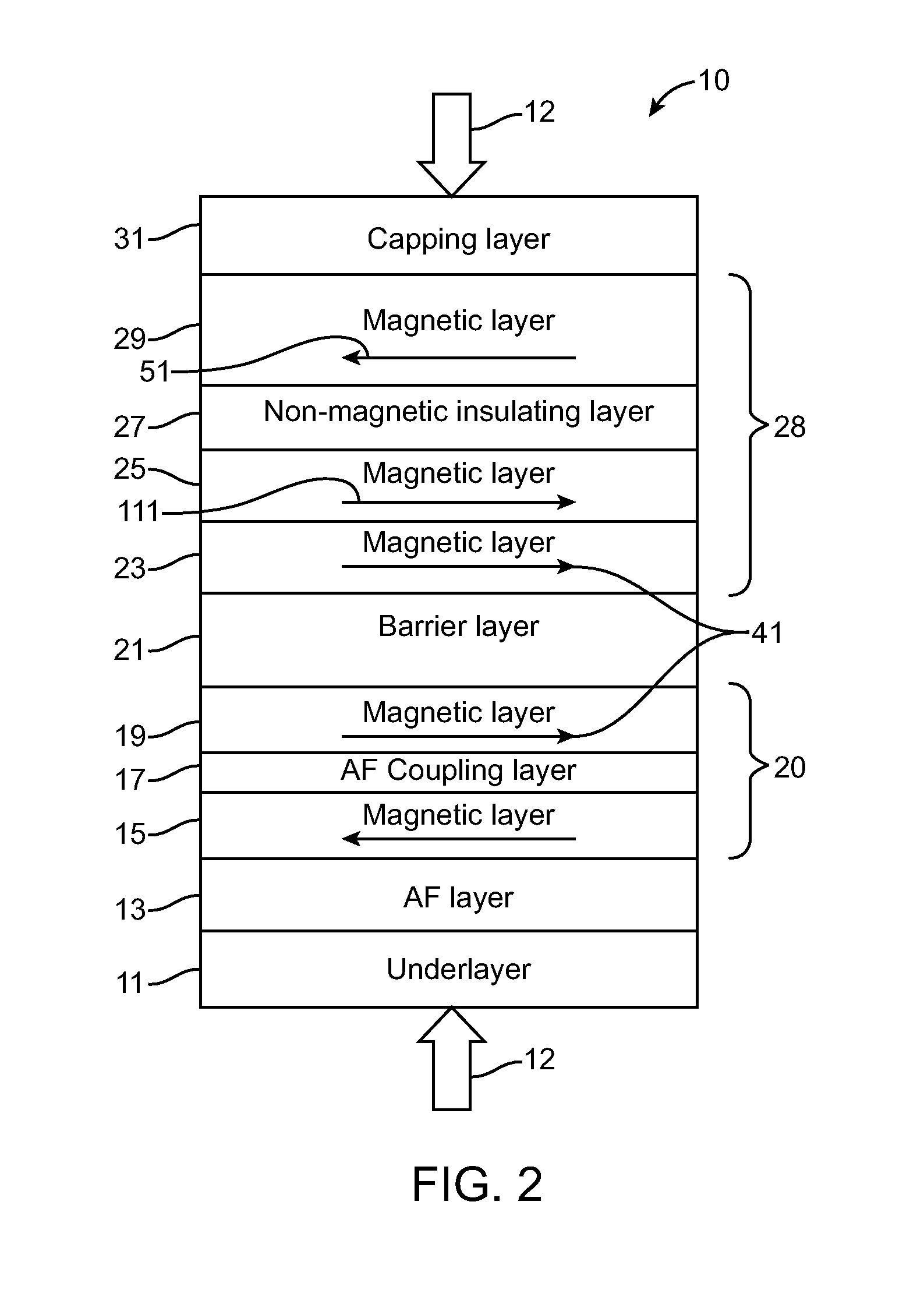

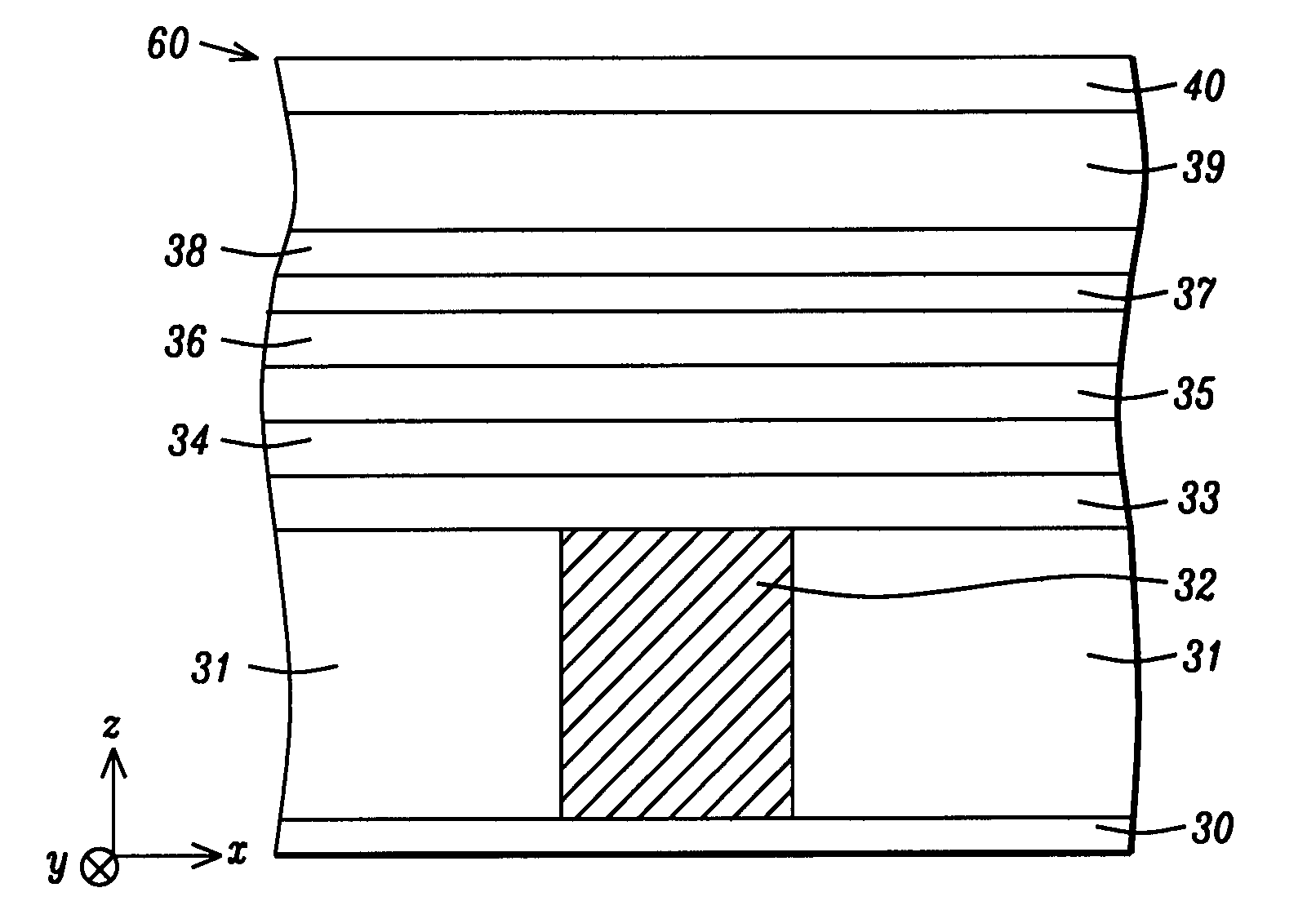

Spin transfer torque magnetic random access memory (sttmram) having graded synthetic free layer

ActiveUS20120018823A1NanomagnetismMagnetic-field-controlled resistorsRandom access memorySpin-transfer torque

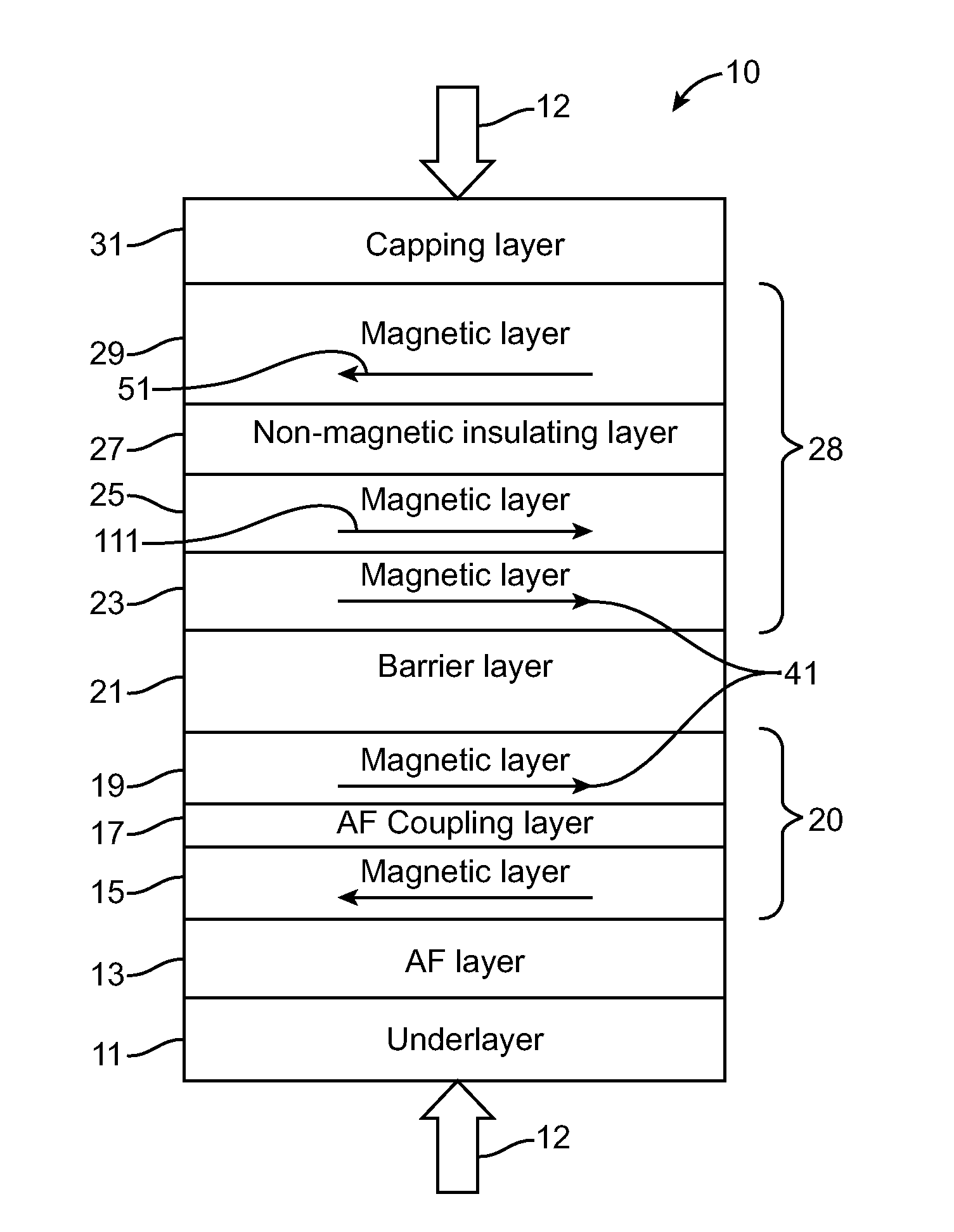

A spin transfer torque memory random access memory (STTMRAM) element is capable of switching states when electrical current is applied thereto for storing data and includes the following layers. An anti-ferromagnetic layer, a fixed layer formed on top of the anti-ferromagnetic layer, a barrier layer formed on top of the second magnetic layer of the fixed layer, and a free layer including a first magnetic layer formed on top of the barrier layer, a second magnetic layer formed on top of the first magnetic layer, a non-magnetic insulating layer formed on top of the second magnetic layer and a third magnetic layer formed on top of the non-magnetic insulating layer. A capping layer is formed on top of the non-magnetic insulating layer.

Owner:AVALANCHE TECH

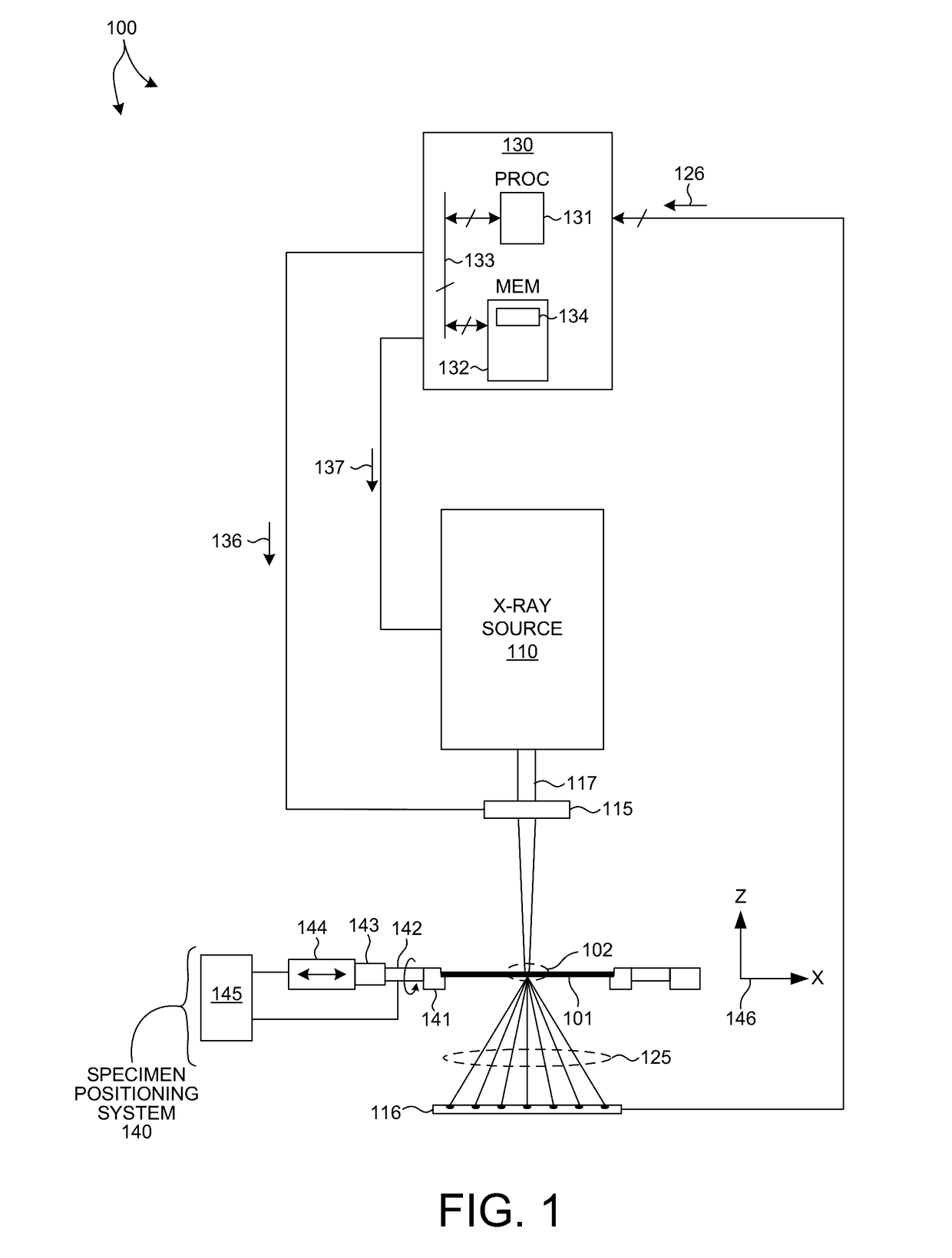

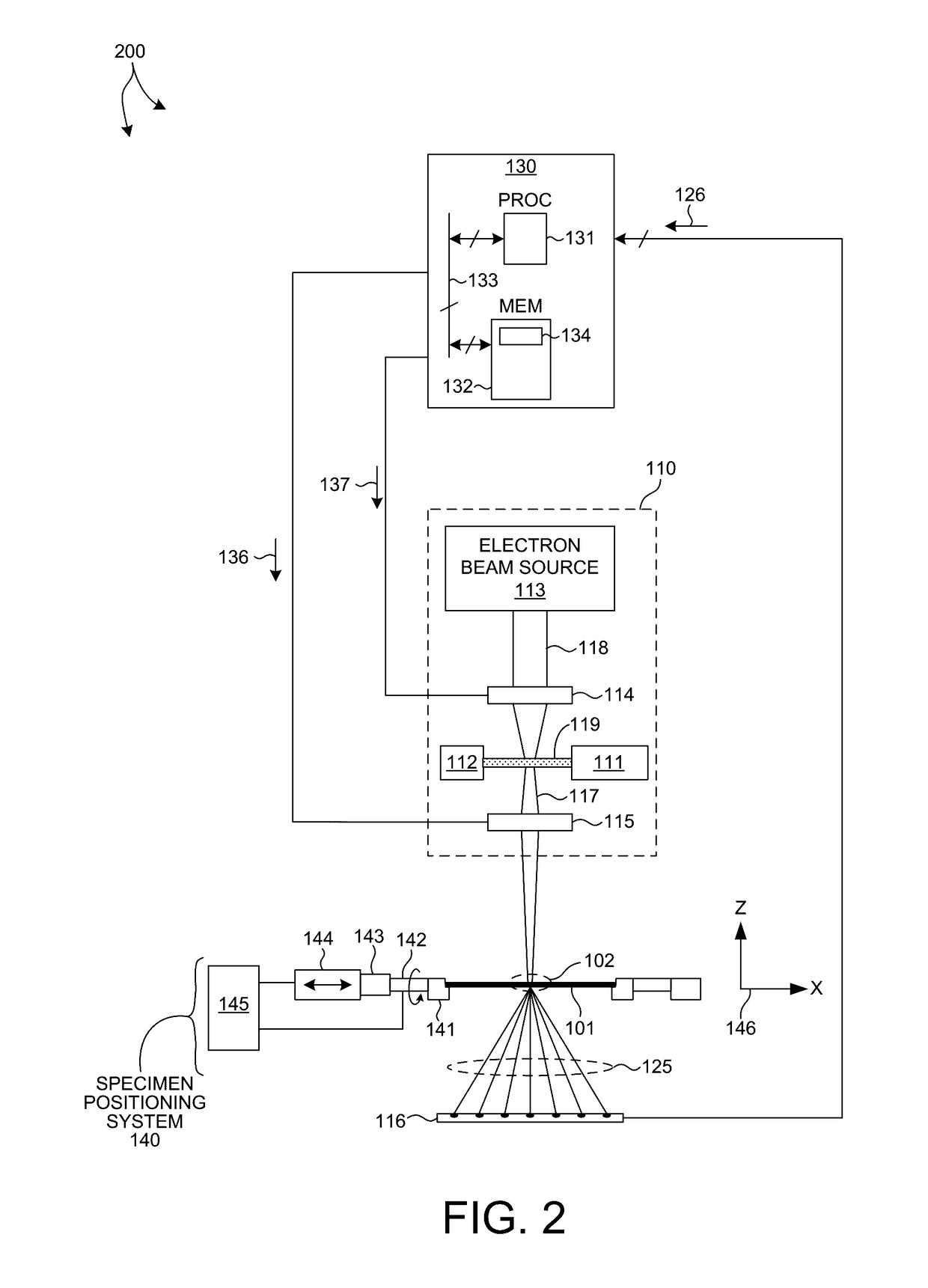

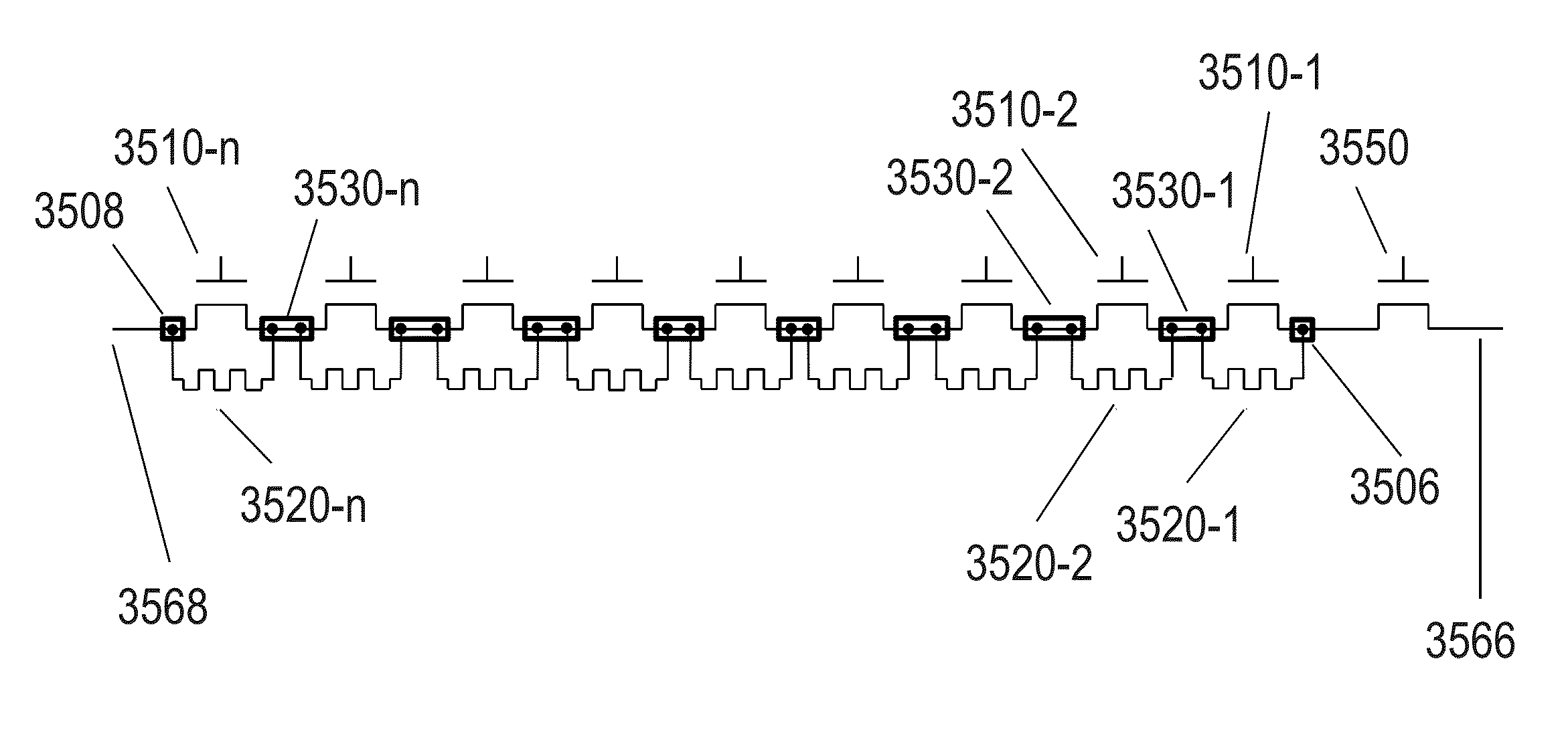

X-Ray Scatterometry Metrology For High Aspect Ratio Structures

ActiveUS20170167862A1Material analysis using wave/particle radiationSemiconductor/solid-state device testing/measurementMetrologyStatic random-access memory

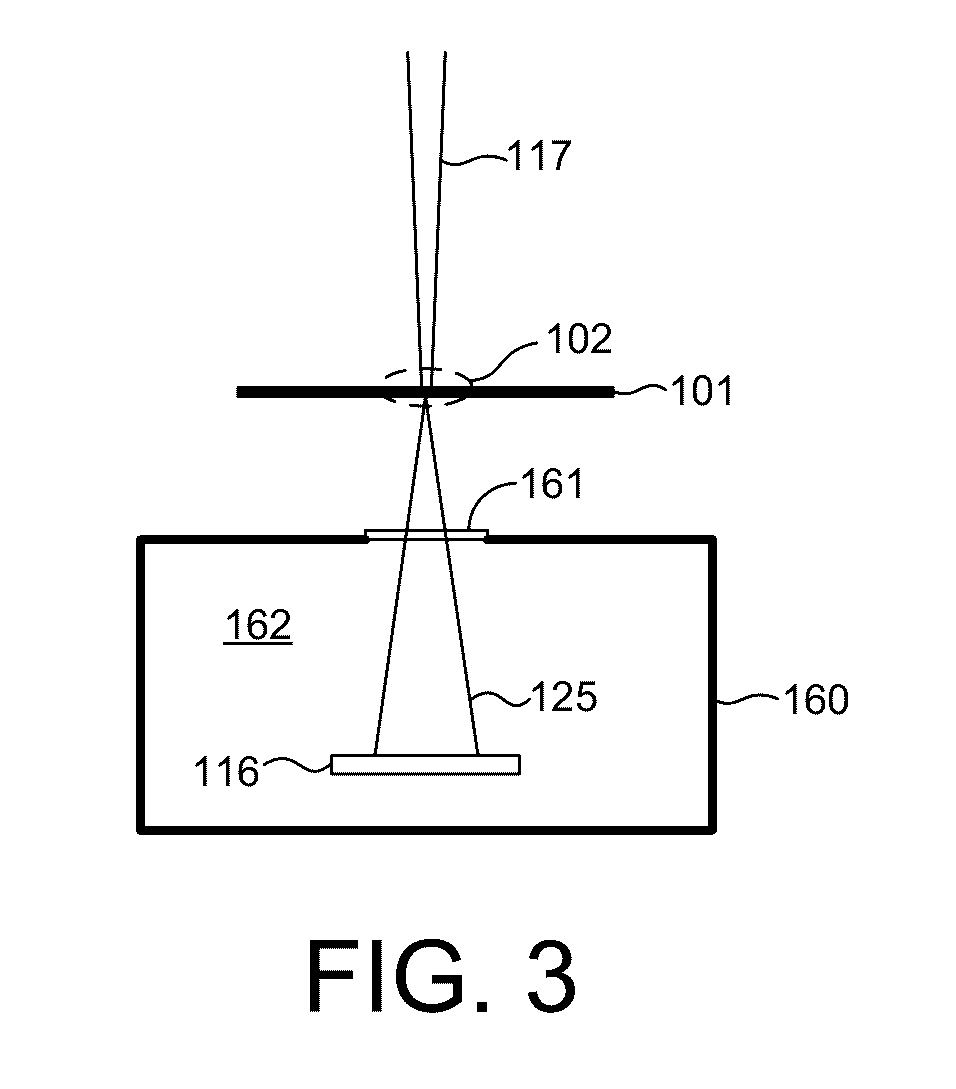

Methods and systems for characterizing dimensions and material properties of high aspect ratio, vertically manufactured devices using transmission, small-angle x-ray scattering (T-SAXS) techniques are described herein. Exemplary structures include spin transfer torque random access memory (STT-RAM), vertical NAND memory (V-NAND), dynamic random access memory (DRAM), three dimensional FLASH memory (3D-FLASH), resistive random access memory (Re-RAM), and PC-RAM. In one aspect, T-SAXS measurements are performed at a number of different orientations that are more densely concentrated near the normal incidence angle and less densely concentrated at orientations that are further from the normal incidence angle. In a further aspect, T-SAXS measurement data is used to generate an image of a measured structure based on the measured intensities of the detected diffraction orders. In another further aspect, a metrology system is configured to generate models for combined x-ray and optical measurement analysis.

Owner:KLA TENCOR TECH CORP

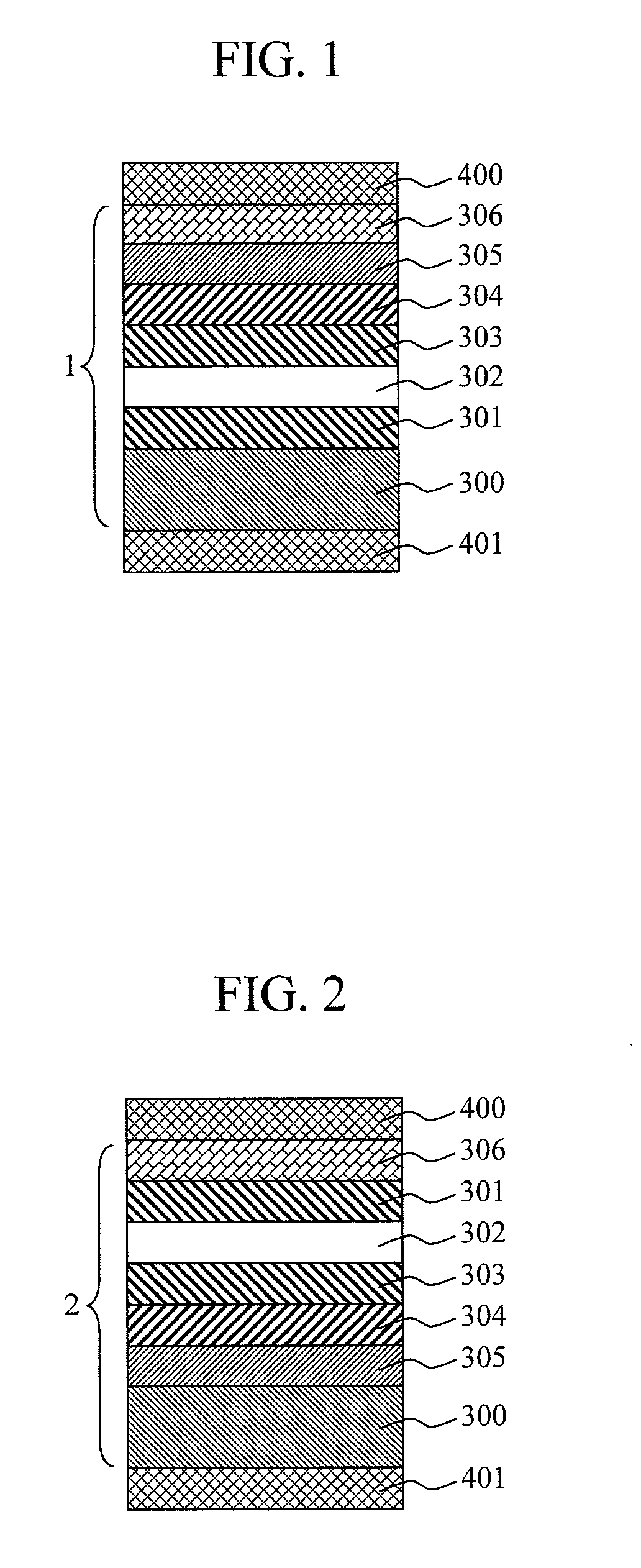

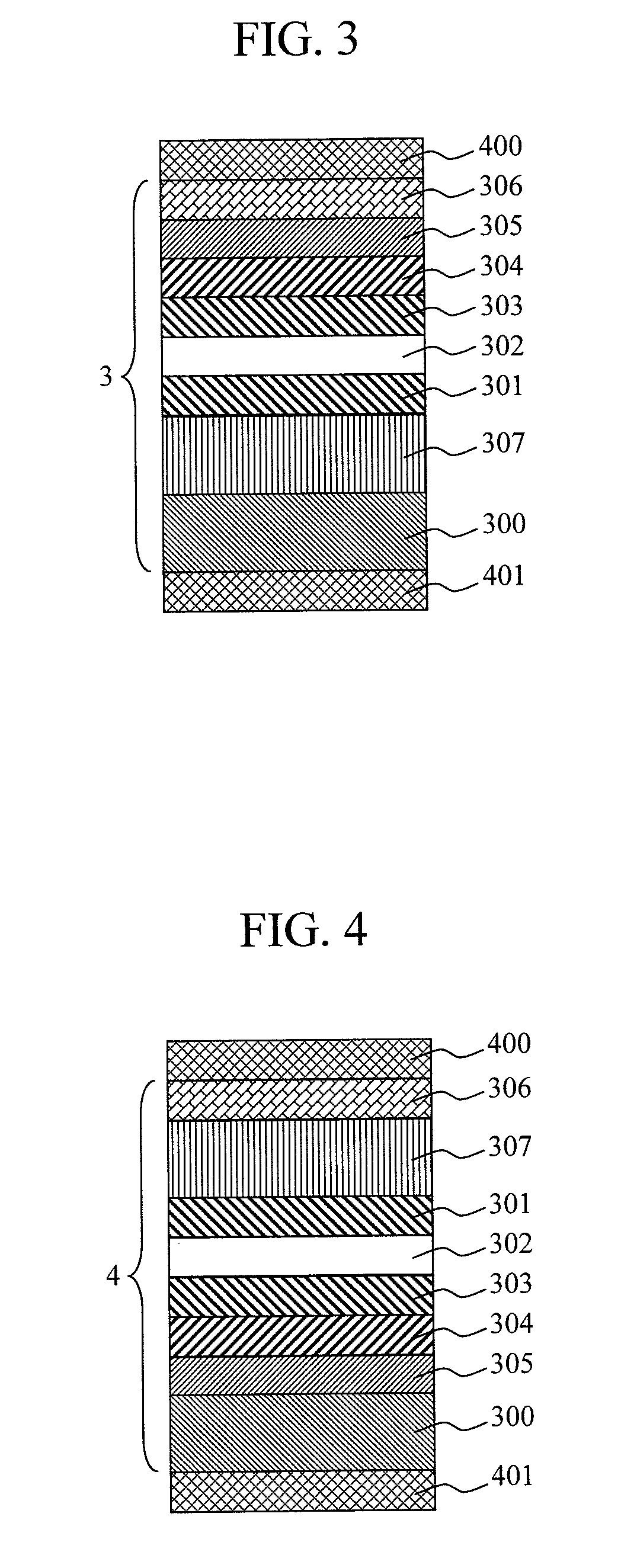

Magnetoresistive Element, Magnetic Memory Cell and Magnetic Random Access Memory Using the Same

ActiveUS20100034014A1Improve thermal stabilityLong retention timeMagnetic-field-controlled resistorsSolid-state devicesSpin-transfer torqueRandom access memory

Provided is a high-speed and ultra-low-power-consumption nonvolatile memory having a high temperature stability at a zero magnetic field. In a tunnel magnetoresistive film constituting a nonvolatile magnetic memory that employs a writing method using a spin-transfer torque, an insulating layer and a nonmagnetic conductive layer are stacked above a ferromagnetic free layer.

Owner:TOHOKU UNIV

Perpendicular spin transfer torque (STT) memory cell with double MgO interface and CoFeB layer for enhancement of perpendicular magnetic anisotropy

ActiveUS9337415B1Increase contentInhibited DiffusionMagnetic-field-controlled resistorsGalvano-magnetic material selectionSpin-transfer torqueMagnetic reluctance

A magnetic tunnel junction (MTJ) for use in a magnetoresistive random access memory (MRAM) has a CoFeB alloy free layer located between the MgO tunnel barrier layer and an upper MgO capping layer, and a CoFeB alloy enhancement layer between the MgO capping layer and a Ta cap. The CoFeB alloy free layer has high Fe content to induce perpendicular magnetic anisotropy (PMA) at the interfaces with the MgO layers. To avoid creating unnecessary PMA in the enhancement layer due to its interface with the MgO capping layer, the enhancement layer has low Fe content. After all of the layers have been deposited on the substrate, the structure is annealed to crystallize the MgO. The CoFeB alloy enhancement layer inhibits diffusion of Ta from the Ta cap layer into the MgO capping layer and creates good crystallinity of the MgO by providing CoFeB at the MgO interface.

Owner:WESTERN DIGITAL TECH INC

High density spin-transfer torque MRAM process

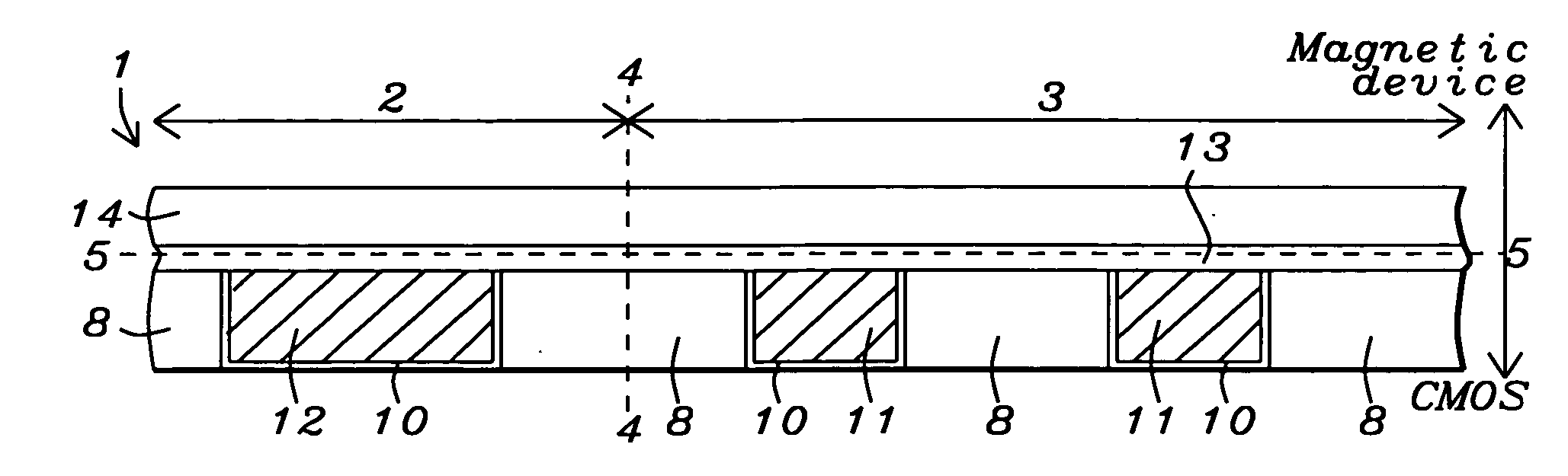

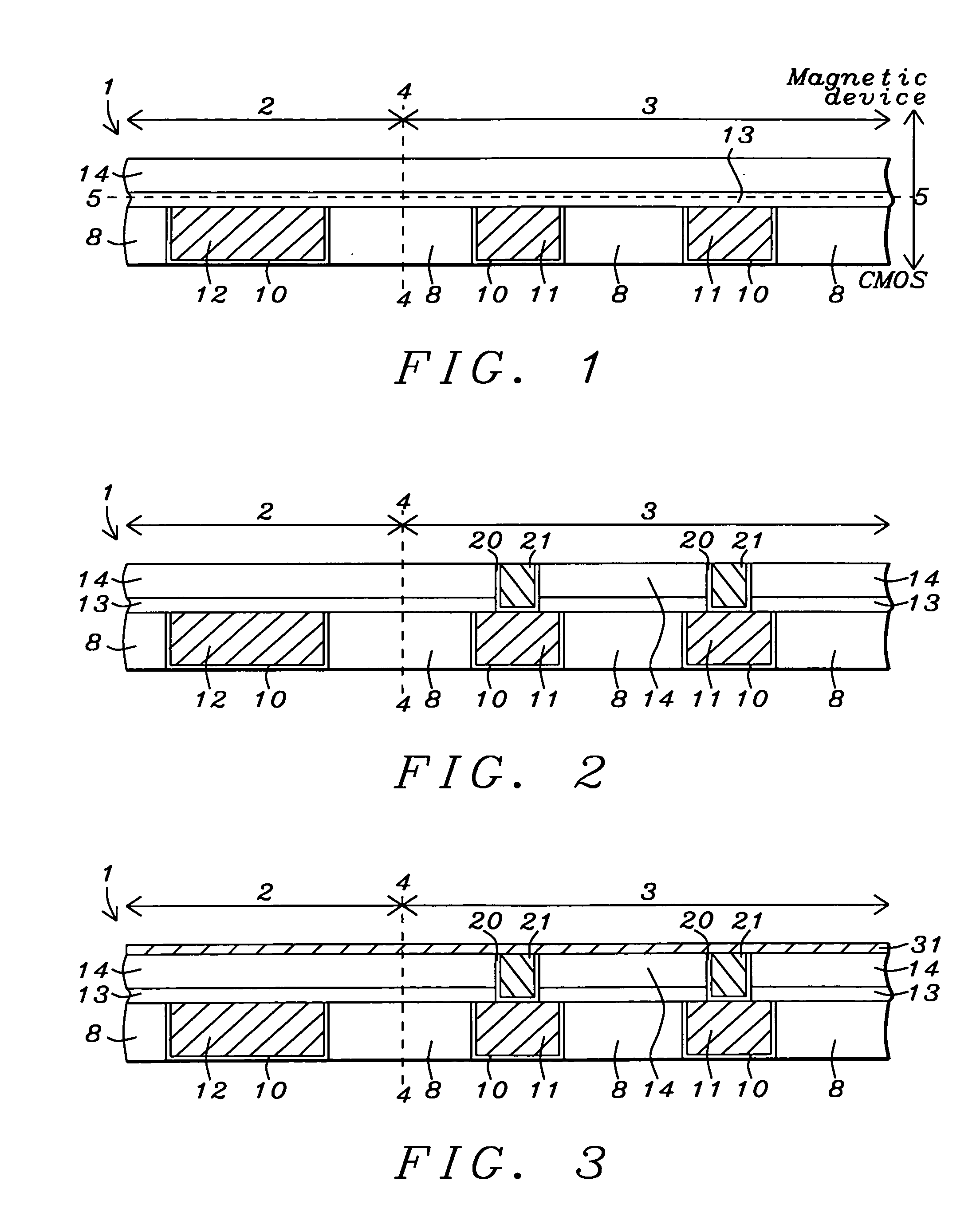

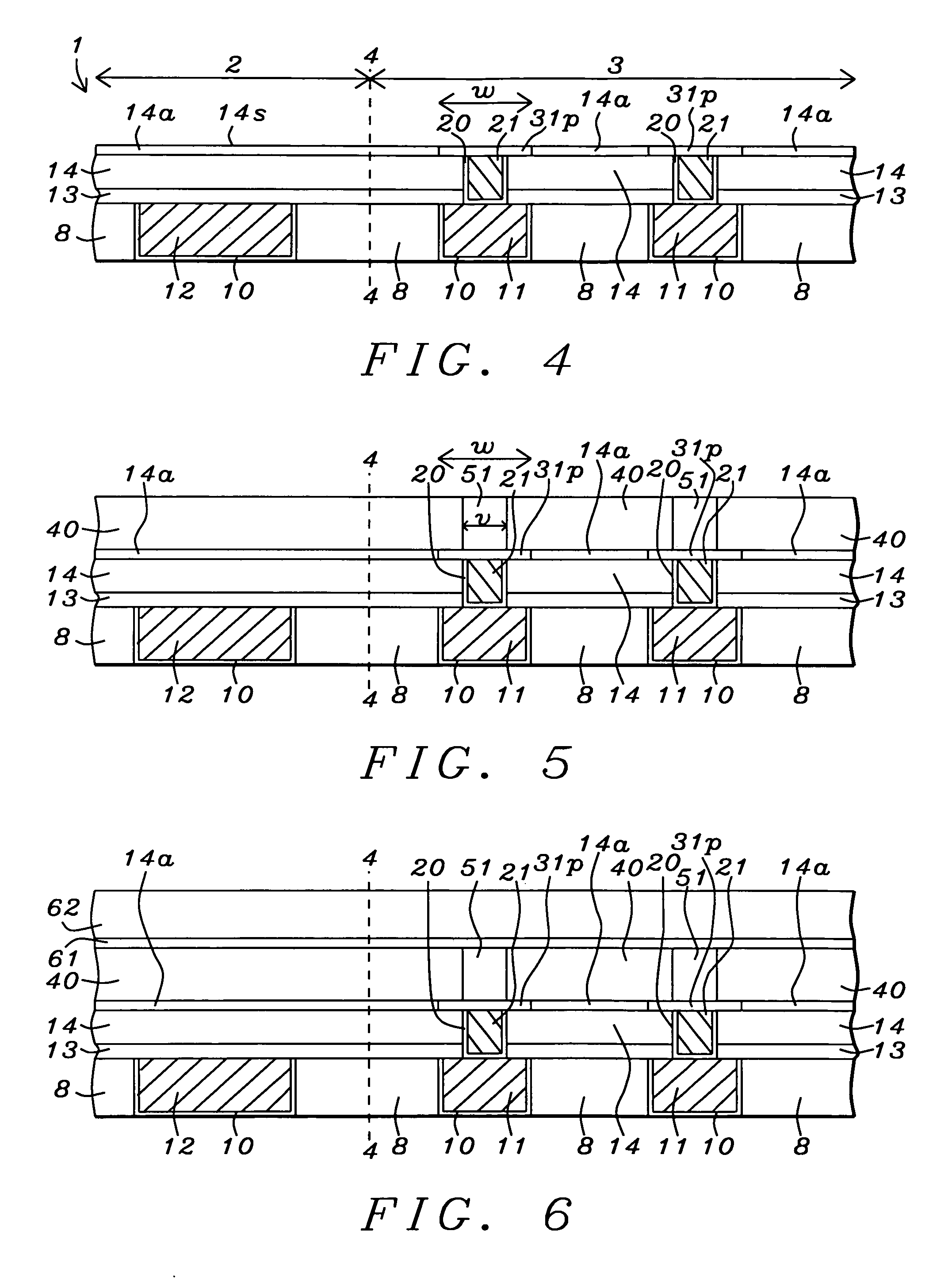

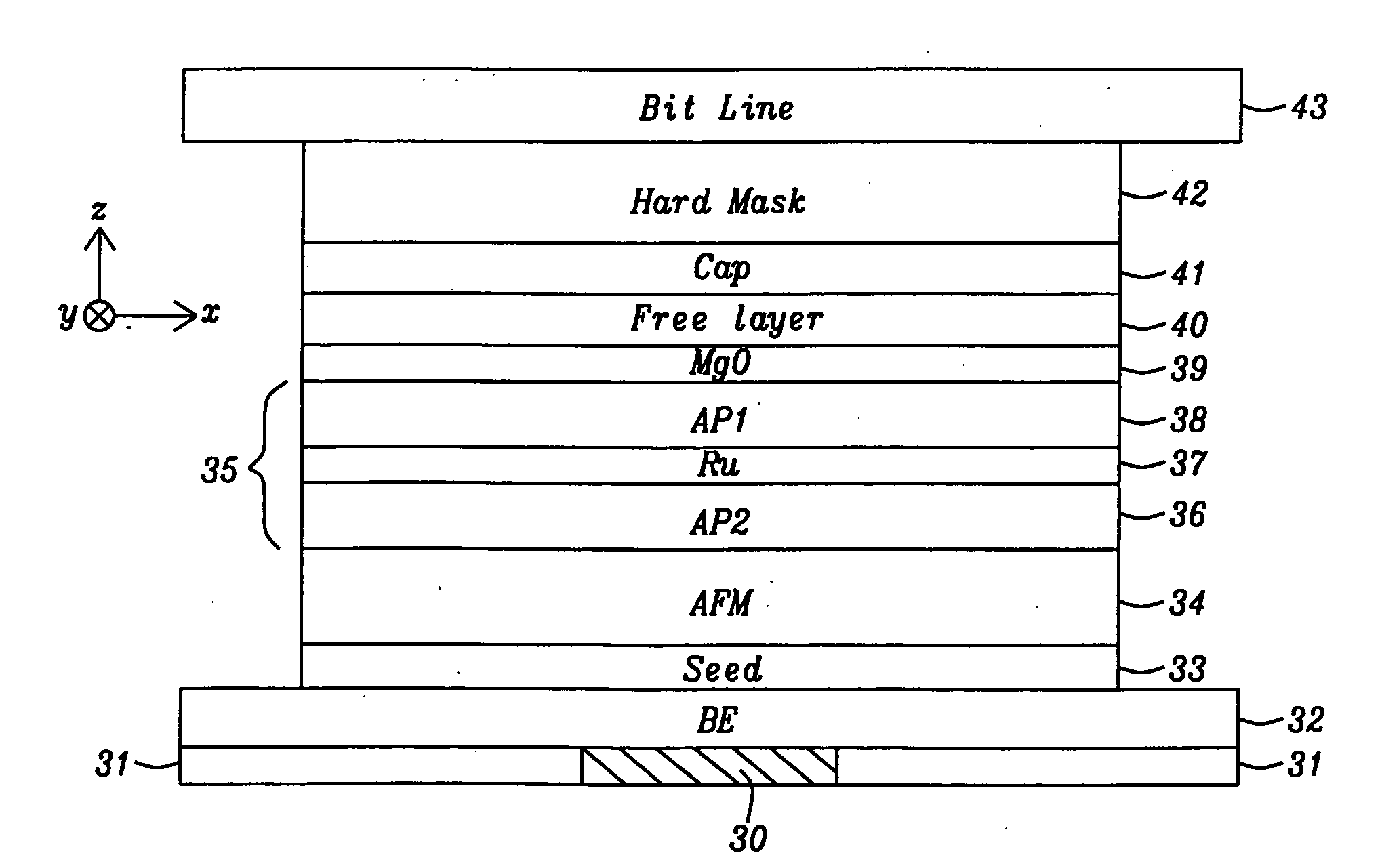

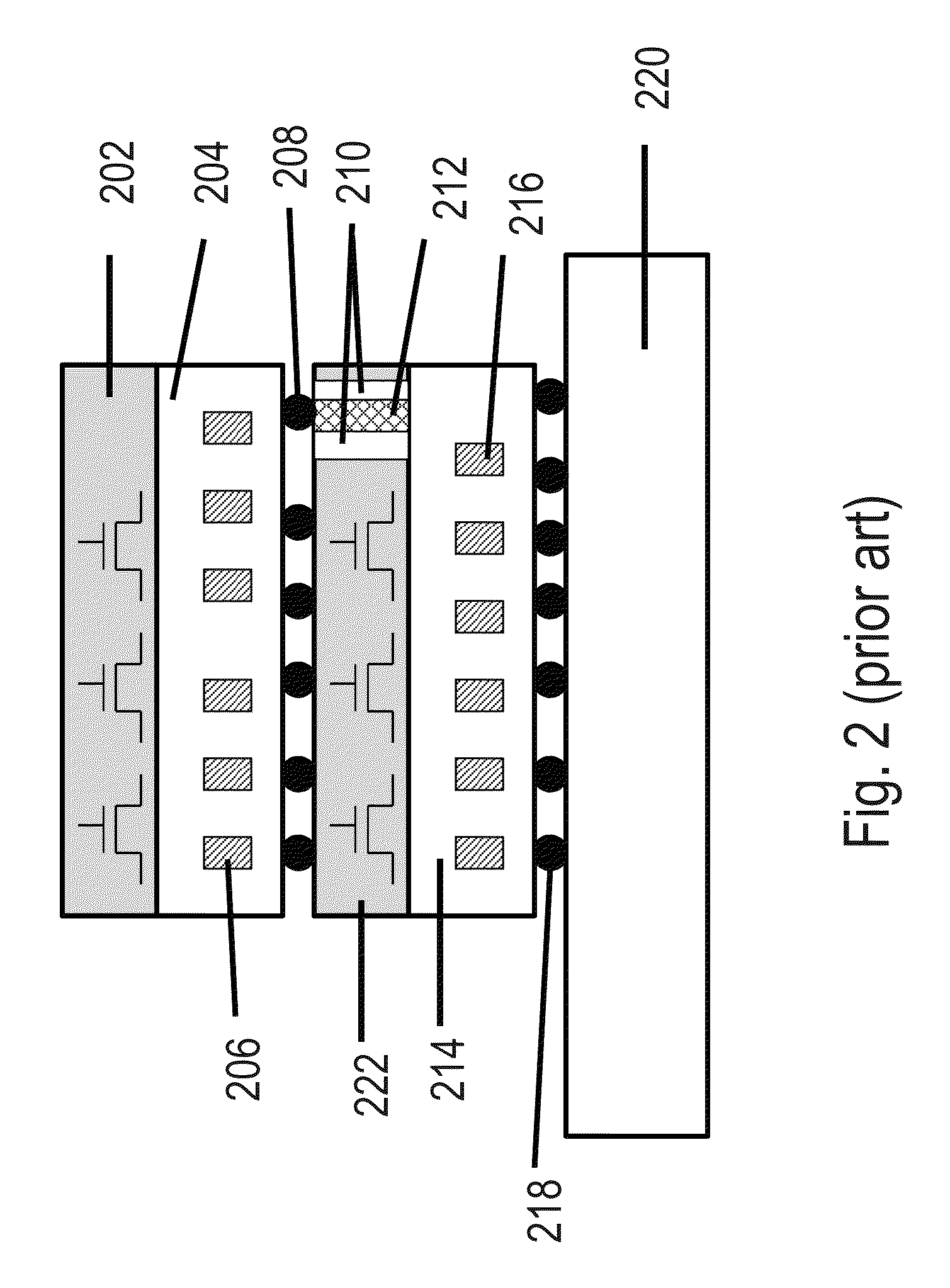

ActiveUS20100109106A1Reduce defectsImprove production yieldSolid-state devicesSemiconductor/solid-state device manufacturingCMOSBit line

A STT-MRAM integration scheme is disclosed wherein the connection between a MTJ and CMOS metal is simplified by forming an intermediate via contact (VAC) on a CMOS landing pad, a metal (VAM) pad that contacts and covers the VAC, and a MTJ on the VAM. A dual damascene process is performed to connect BIT line metal to CMOS landing pads through VAC / VAM / MTJ stacks in a device region, and to connect BIT line connection pads to CMOS connection pads through BIT connection vias outside the device region. The VAM pad is a single layer or composite made of Ta, TaN, or other conductors which serves as a diffusion barrier, has a highly smooth surface for MTJ formation, and provides excellent selectivity with refill dielectric materials during a chemical mechanical polish process. Each VAC is from 500 to 3000 Angstroms thick to minimize additional circuit resistance and minimize etch burden.

Owner:TAIWAN SEMICON MFG CO LTD

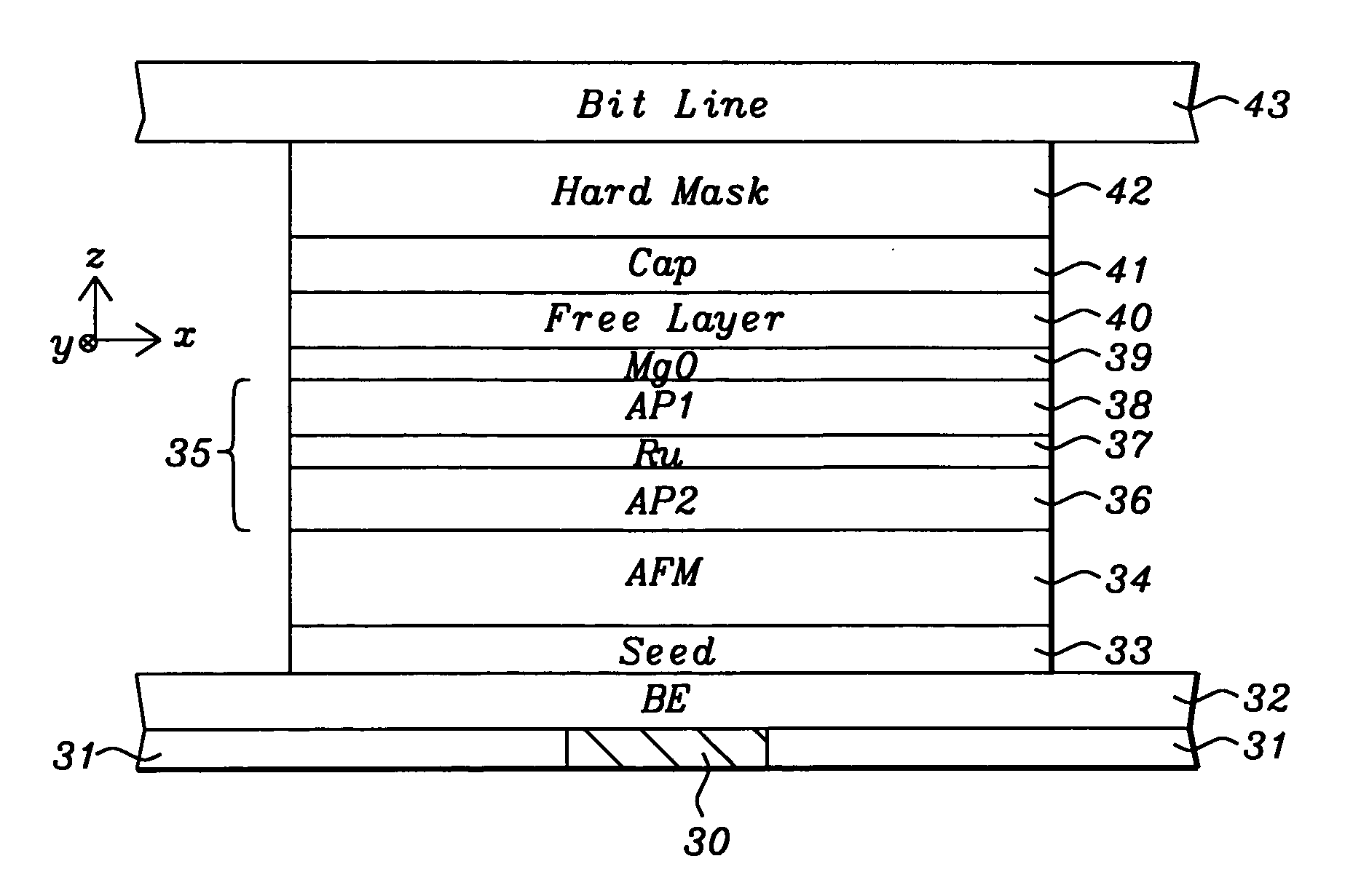

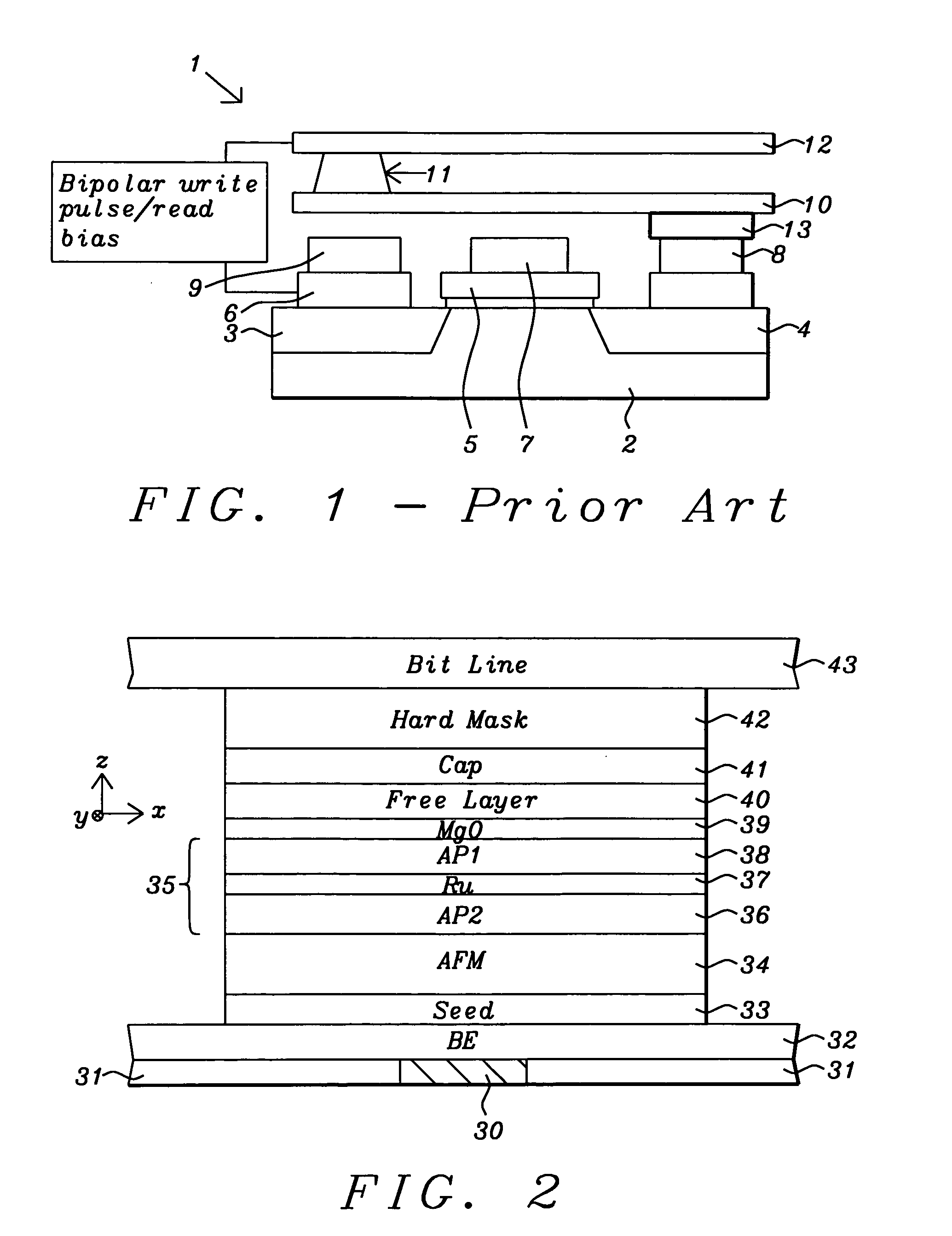

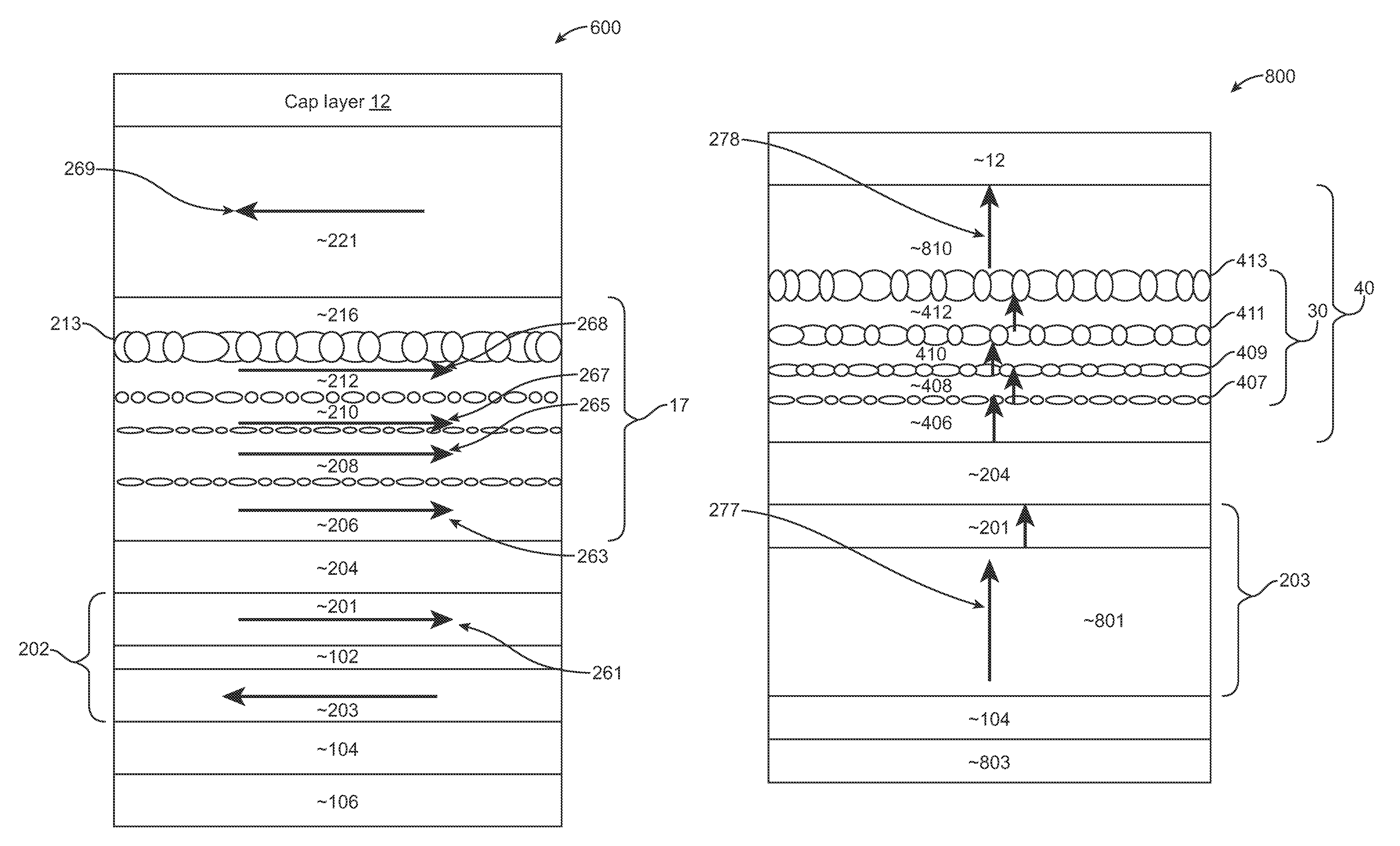

Structure and method to fabricate high performance MTJ devices for spin-transfer torque (STT)-RAM

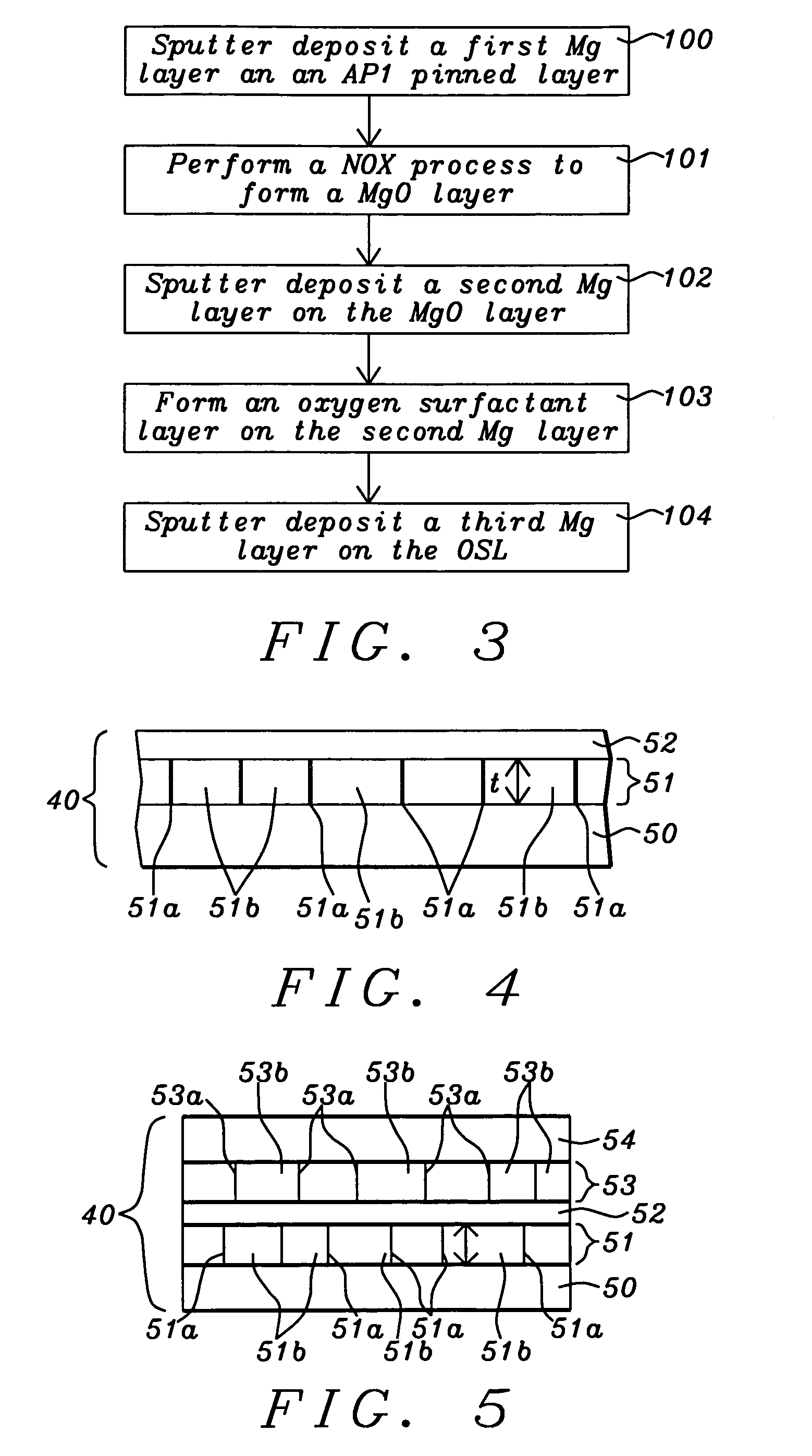

ActiveUS20100065935A1Facilitate magnetization switchingNegatively affectingNanomagnetismSemiconductor/solid-state device manufacturingSpin-transfer torqueEngineering

A STT-RAM MTJ is disclosed with a MgO tunnel barrier formed by a NOX process, a CoFeB / FeSiO / CoFeB composite free layer with a middle nanocurrent channel layer to minimize Jc0, and a Ru capping layer to enhance the spin scattering effect and increase dR / R. Good write margin is achieved by modifying the NOX process to afford a RA less than 10 ohm-μm2 and good read margin is realized with a dR / R of >100% by annealing at 330° C. or higher to form crystalline CoFeB free layers. The NCC thickness is maintained in the 6 to 10 Angstrom range to reduce Rp and avoid Fe(Si) granules from not having sufficient diameter to bridge the distance between upper and lower CoFeB layers. A FeSiO layer may be inserted below the Ru layer in the capping layer to prevent the Ru from causing a high damping constant in the upper CoFeB free layer.

Owner:TAIWAN SEMICON MFG CO LTD

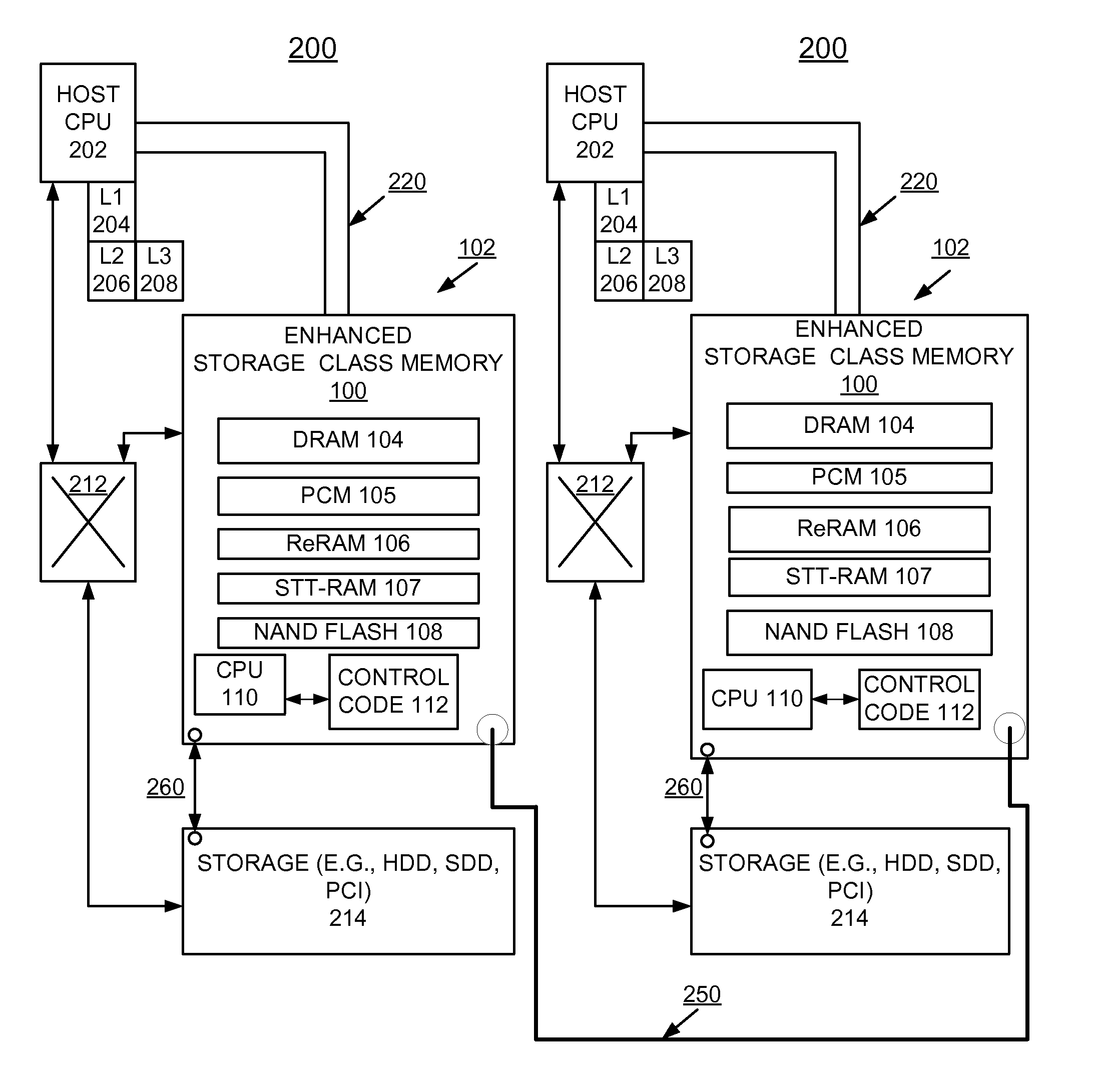

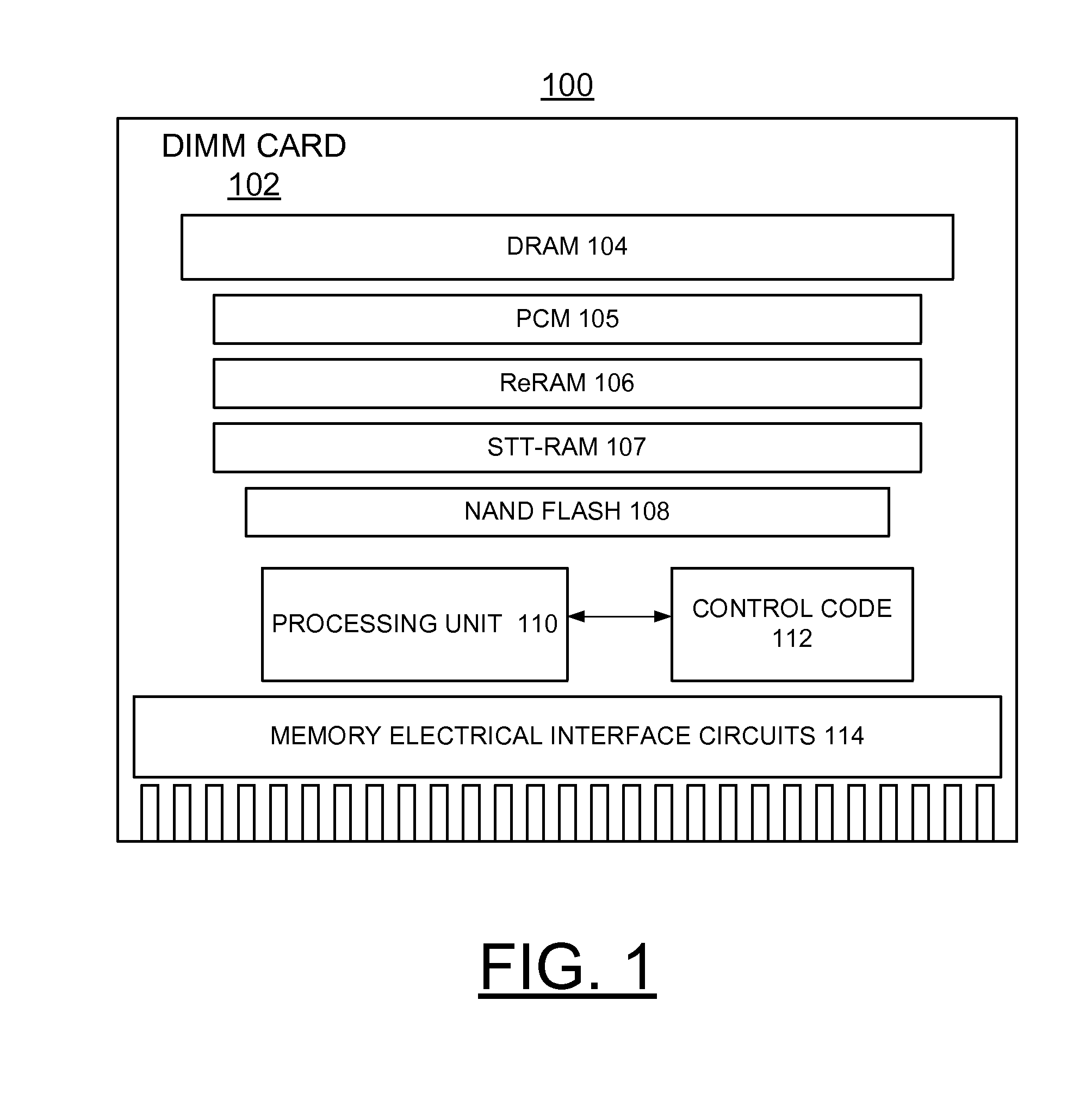

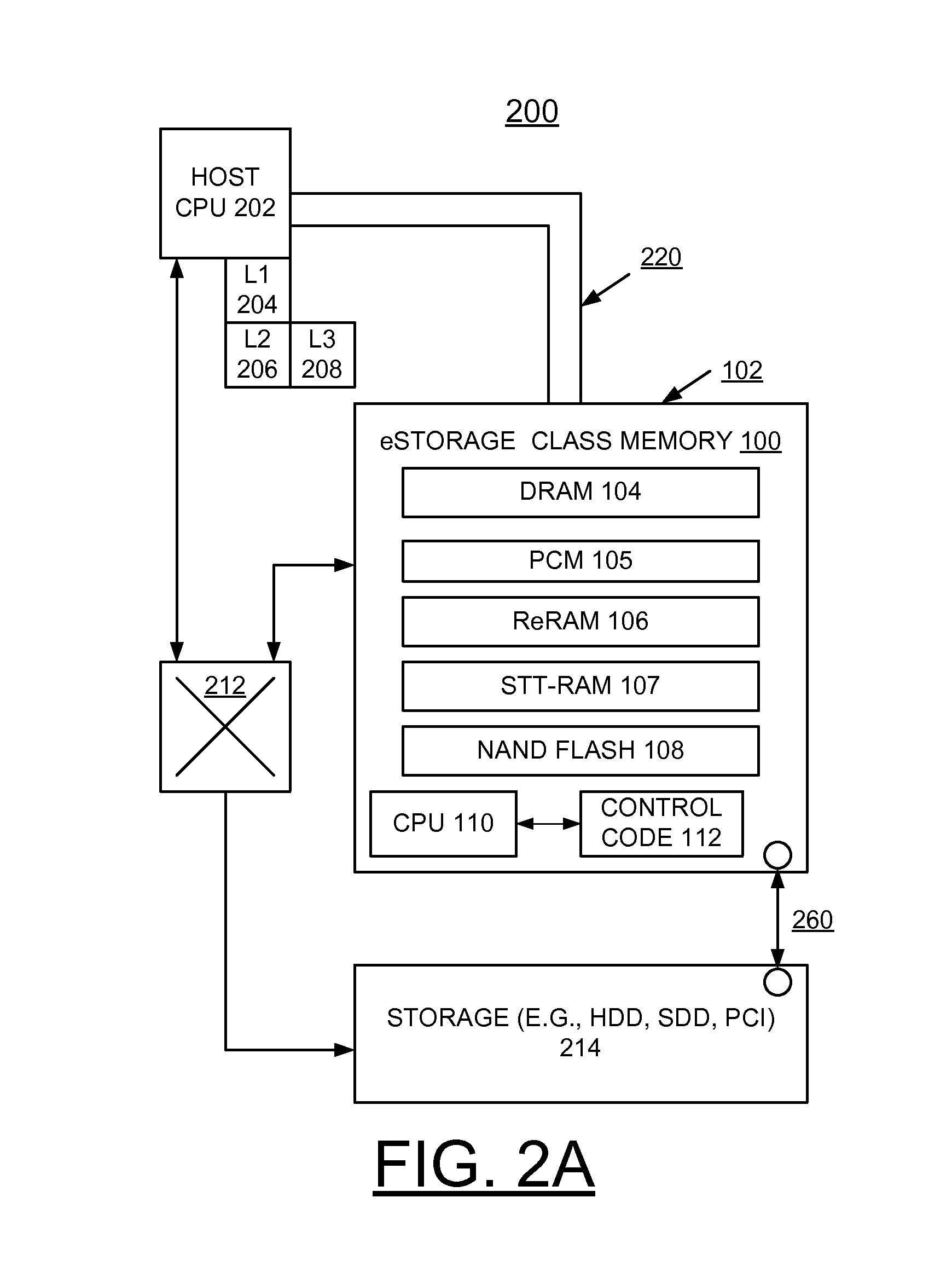

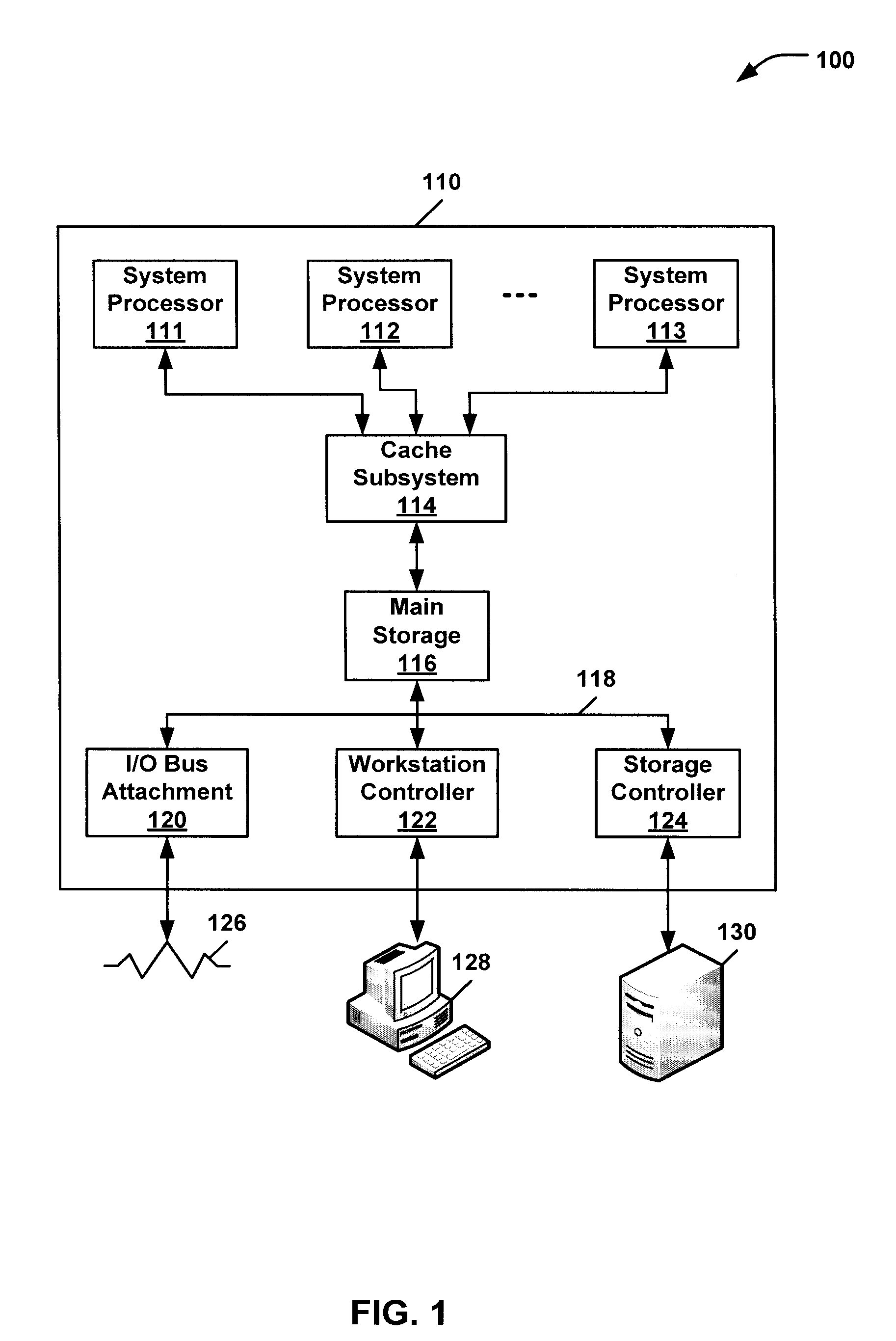

Apparatus and method for low power low latency high capacity storage class memory

InactiveUS20140101370A1Enhanced solid-state storage usageOvercome disadvantagesMemory architecture accessing/allocationMemory adressing/allocation/relocationSolid-state storageDIMM

A method and a storage system are provided for implementing enhanced solid-state storage class memory (eSCM) including a direct attached dual in line memory (DIMM) card containing dynamic random access memory (DRAM), and at least one non-volatile memory, for example, Phase Change memory (PCM), Resistive RAM (ReRAM), Spin-Transfer-Torque RAM (STT-RAM), and NAND flash chips. An eSCM processor controls selectively allocating data among the DRAM, and the at least one non-volatile memory primarily based upon a data set size.

Owner:WESTERN DIGITAL TECH INC

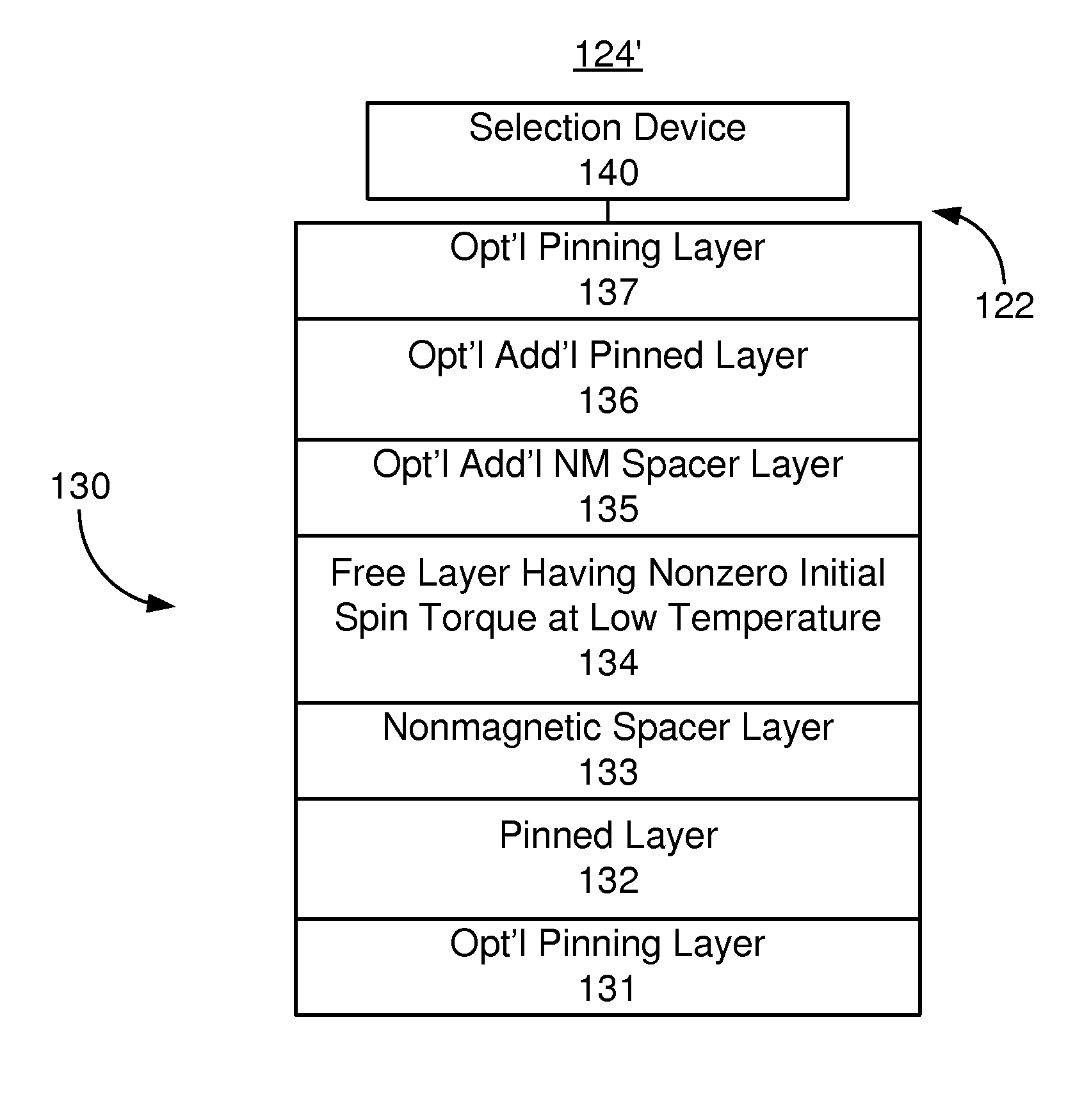

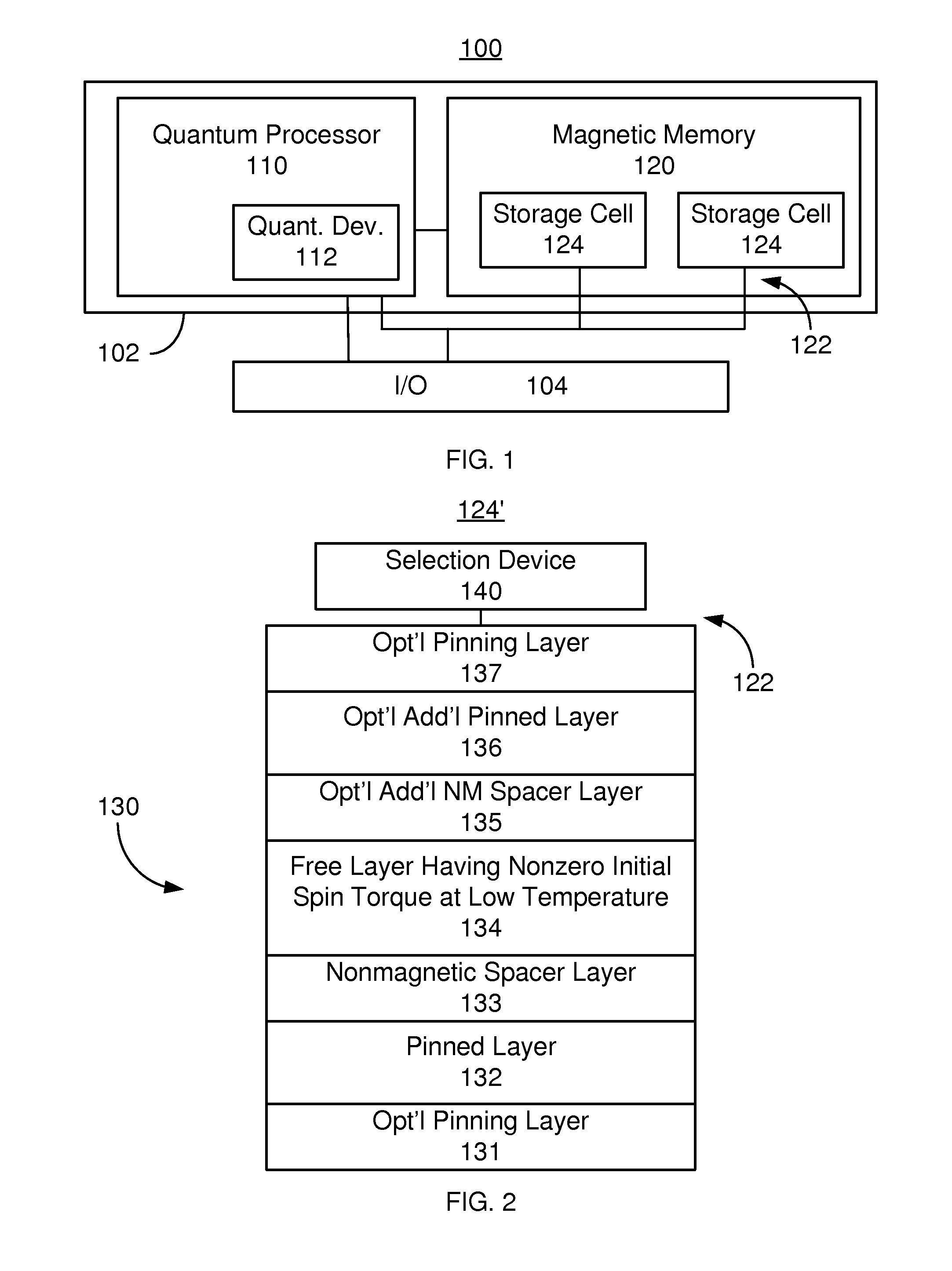

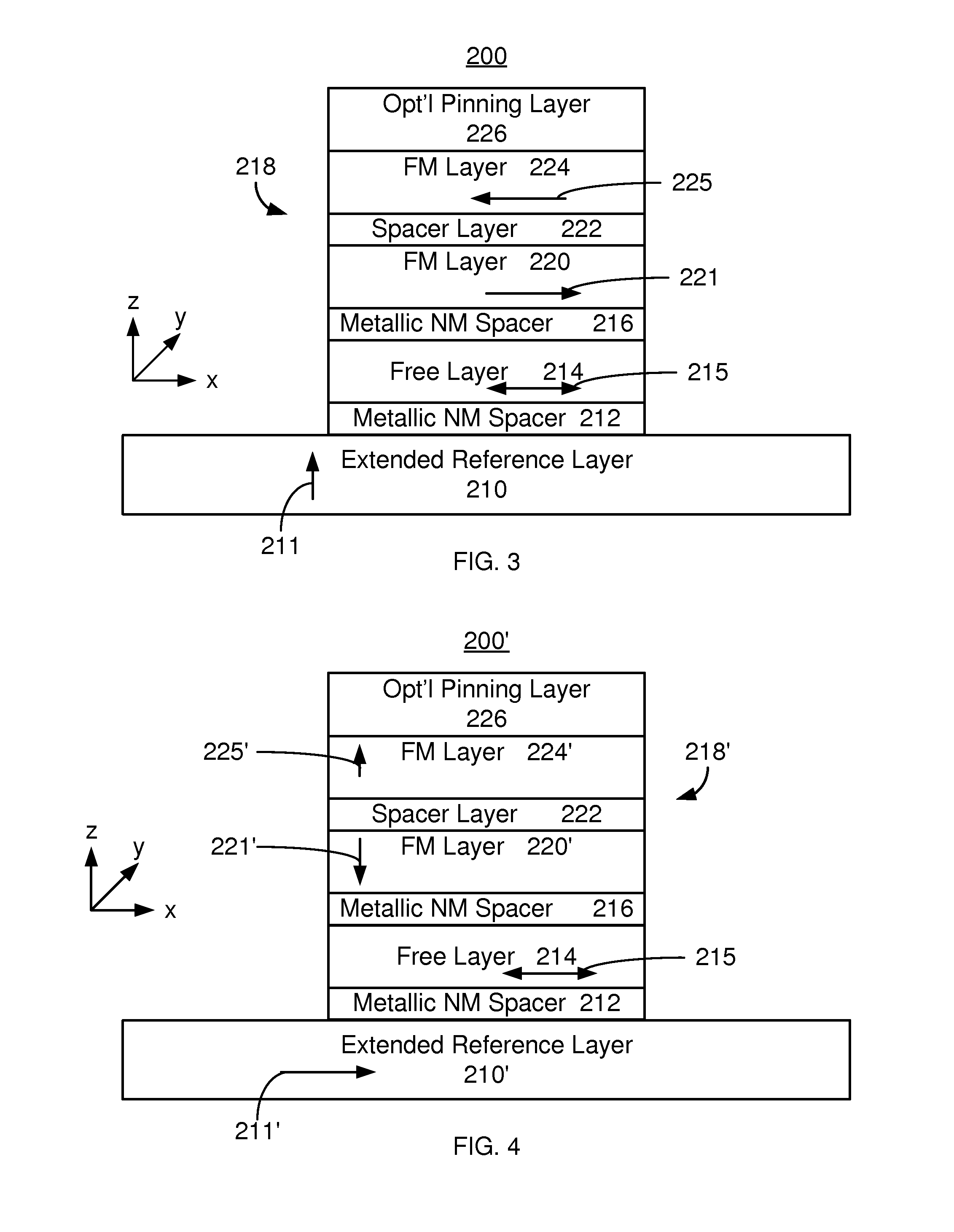

Quantum computing device spin transfer torque magnetic memory

A quantum computing device magnetic memory is described. The quantum computing device magnetic memory is coupled with a quantum processor including at least one quantum device corresponding to at least one qubit. The quantum computing device magnetic memory includes magnetic storage cells coupled with the quantum device(s) and bit lines coupled to the magnetic storage cells. Each of the magnetic storage cells includes at least one magnetic junction. The magnetic junction(s) include a reference layer, a nonmagnetic spacer layer, and a free layer. The nonmagnetic spacer layer is between the reference layer and the free layer. The magnetic junction(s) are configured to allow the free layer to be switched between stable magnetic states. The magnetic junction(s) are configured such that the free layer has a nonzero initial writing spin transfer torque in an absence of thermal fluctuations.

Owner:SAMSUNG ELECTRONICS CO LTD

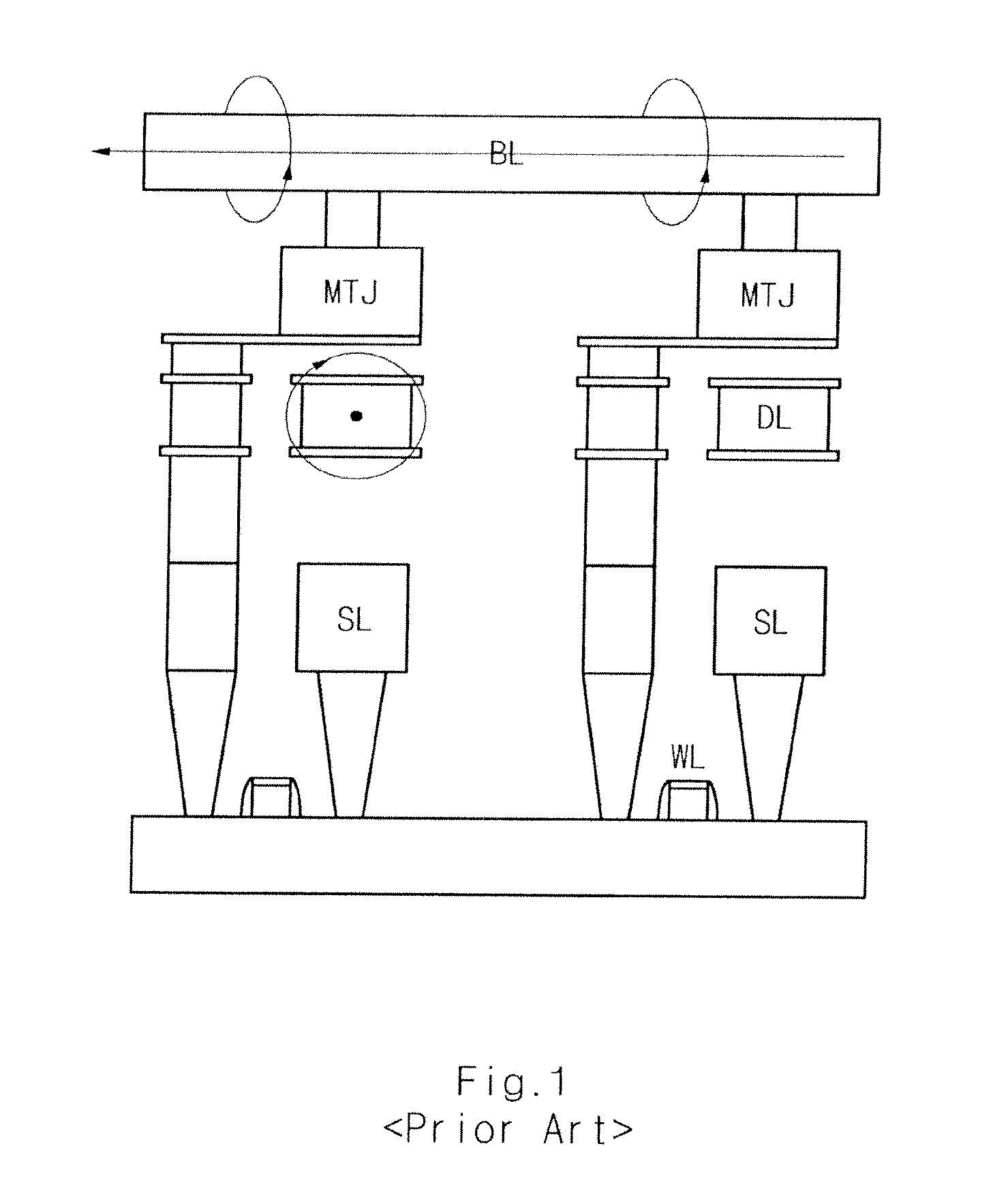

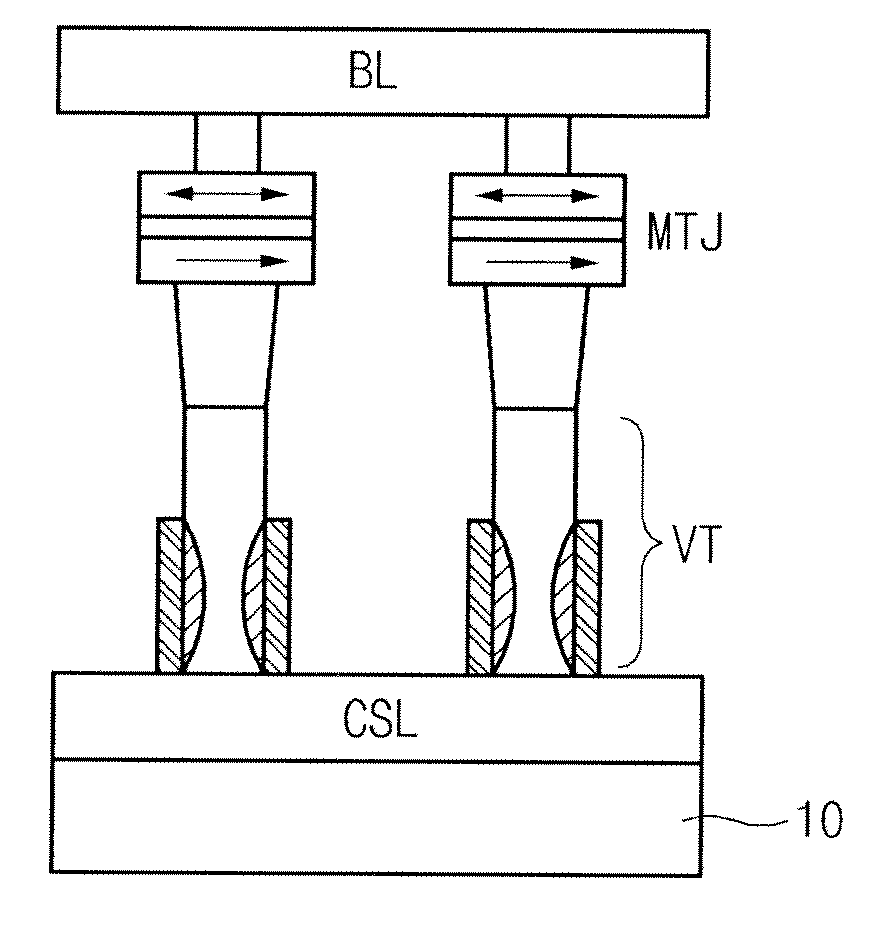

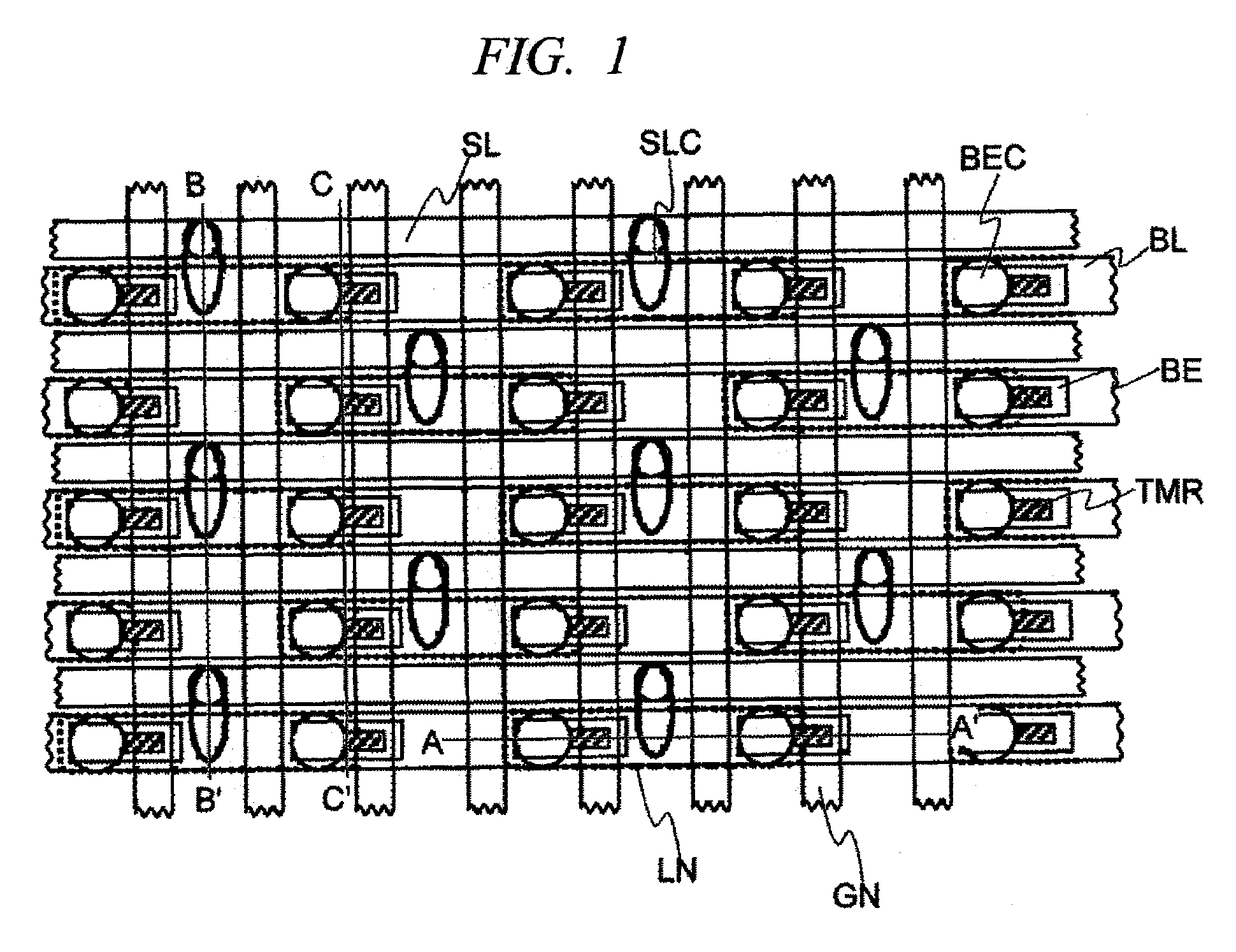

Spin Transfer Torque Memory Device Having Common Source Line and Method for Manufacturing the Same

InactiveUS20110269251A1Reduce resistanceEasy to integrateSolid-state devicesSemiconductor/solid-state device manufacturingSpin-transfer torqueEngineering

Owner:SK HYNIX INC

Structure and method to fabricate high performance MTJ devices for spin-transfer torque (STT)-RAM

A STT-RAM MTJ is disclosed with a MgO tunnel barrier formed by a NOX process, a CoFeB / FeSiO / CoFeB composite free layer with a middle nanocurrent channel layer to minimize Jc0, and a Ru capping layer to enhance the spin scattering effect and increase dR / R. Good write margin is achieved by modifying the NOX process to afford a RA less than 10 ohm-μm2 and good read margin is realized with a dR / R of >100% by annealing at 330° C. or higher to form crystalline CoFeB free layers. The NCC thickness is maintained in the 6 to 10 Angstrom range to reduce Rp and avoid Fe(Si) granules from not having sufficient diameter to bridge the distance between upper and lower CoFeB layers. A FeSiO layer may be inserted below the Ru layer in the capping layer to prevent the Ru from causing a high damping constant in the upper CoFeB free layer.

Owner:TAIWAN SEMICON MFG CO LTD

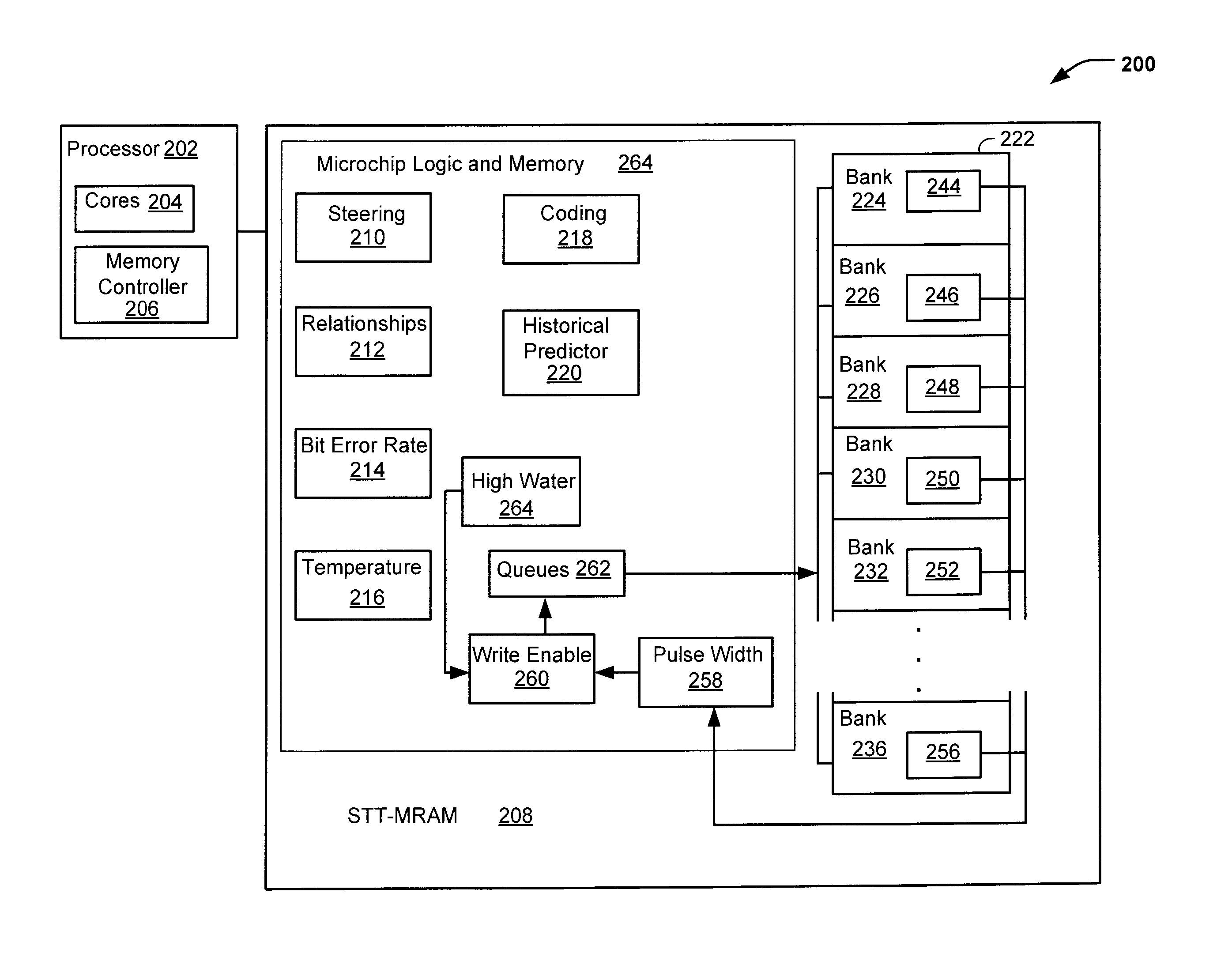

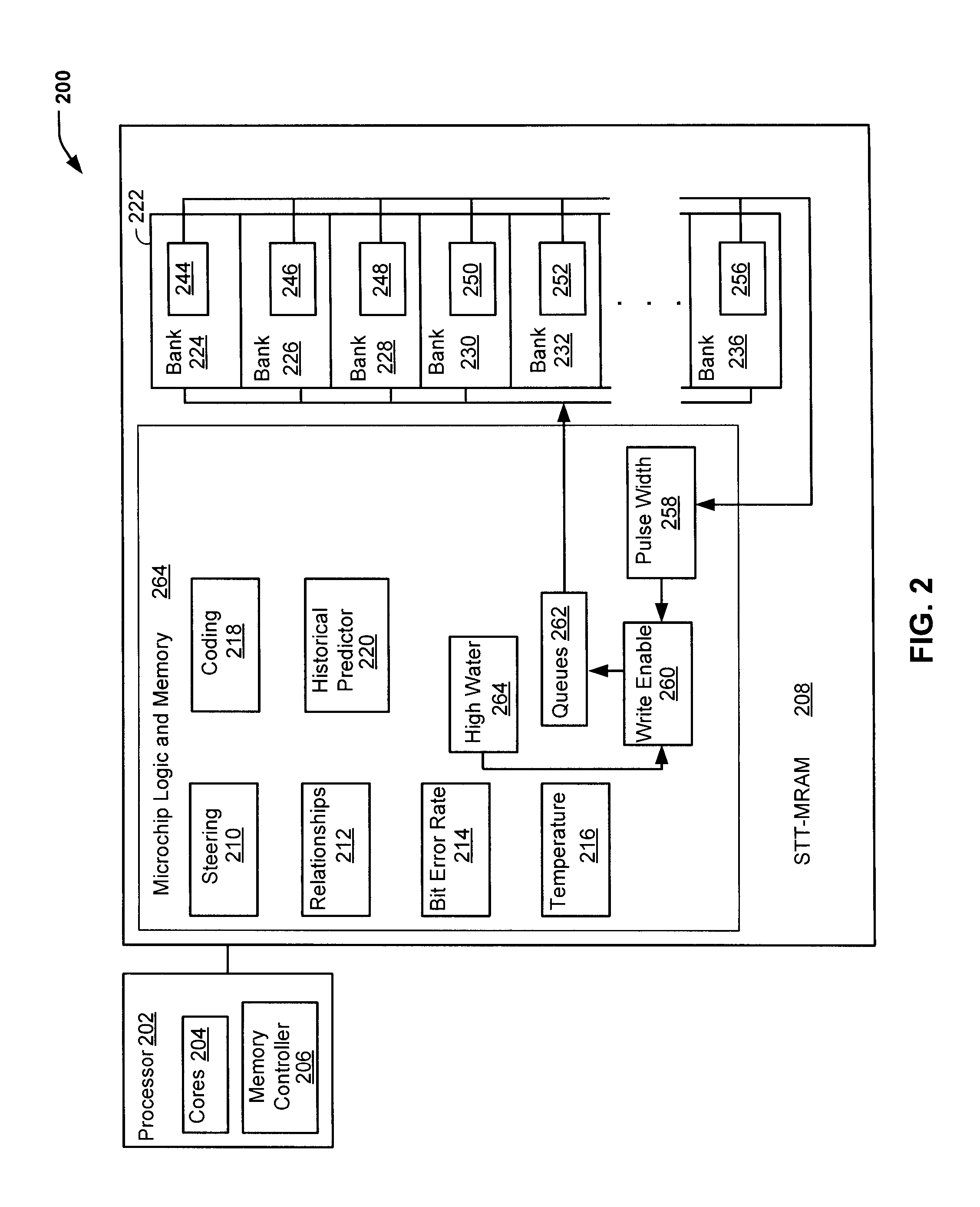

Determining and storing bit error rate relationships in spin transfer torque magnetoresistive random-access memory (STT-MRAM)

ActiveUS9418721B2Reduce consumptionReduce latencyDigital storageSpin-transfer torqueParallel computing

Systems and methods to manage memory on a spin transfer torque magnetoresistive random-access memory (STT-MRAM) are provided. A particular method may include determining a performance characteristic using relationship information that relates a bit error rate to at least one of a programming pulse width, a temperature, a history-based predictive performance parameter, a coding scheme, and a voltage level also associated with a memory. The performance characteristic is stored and used to manage a write operation associated with the memory.

Owner:IBM CORP

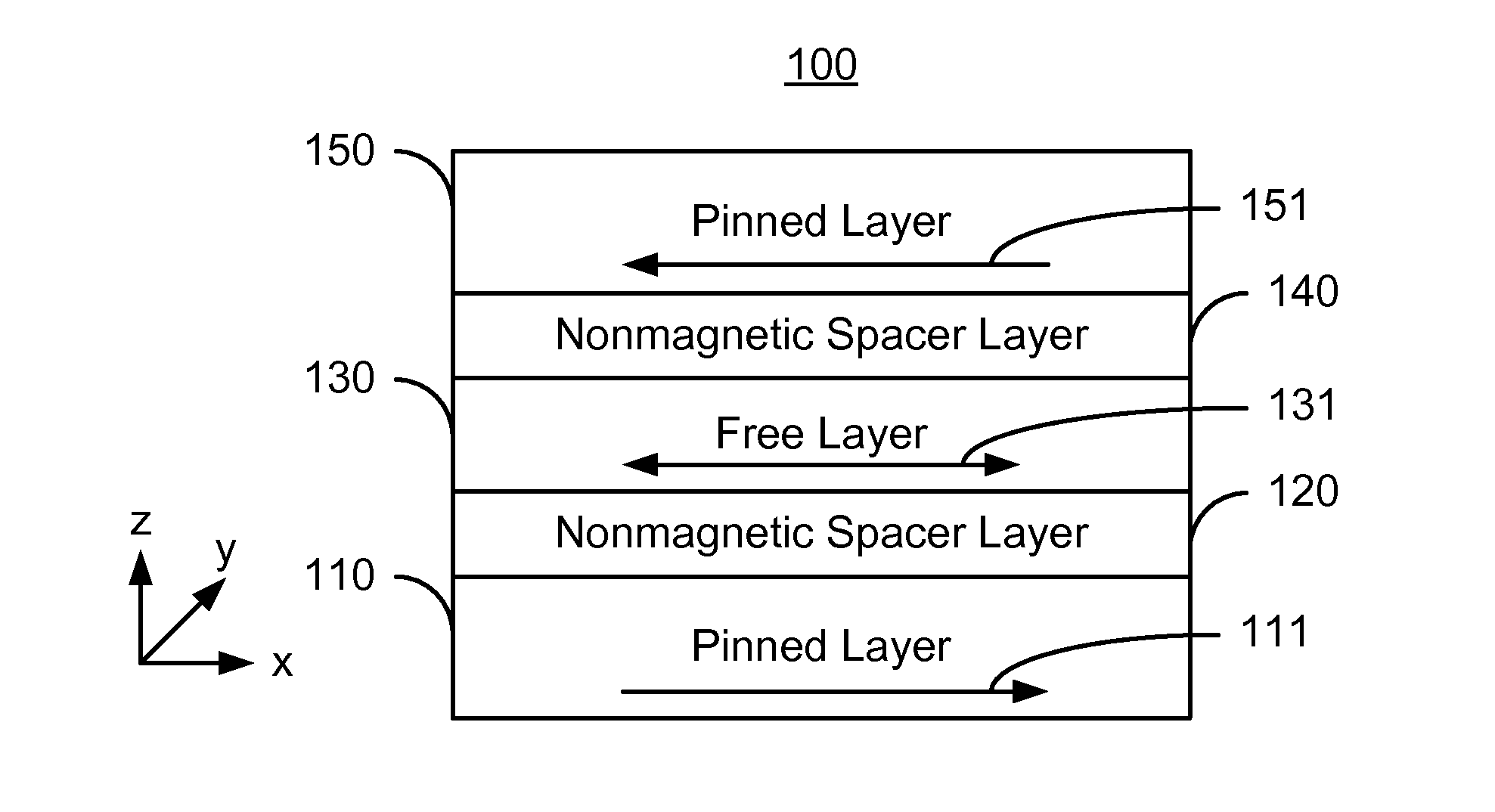

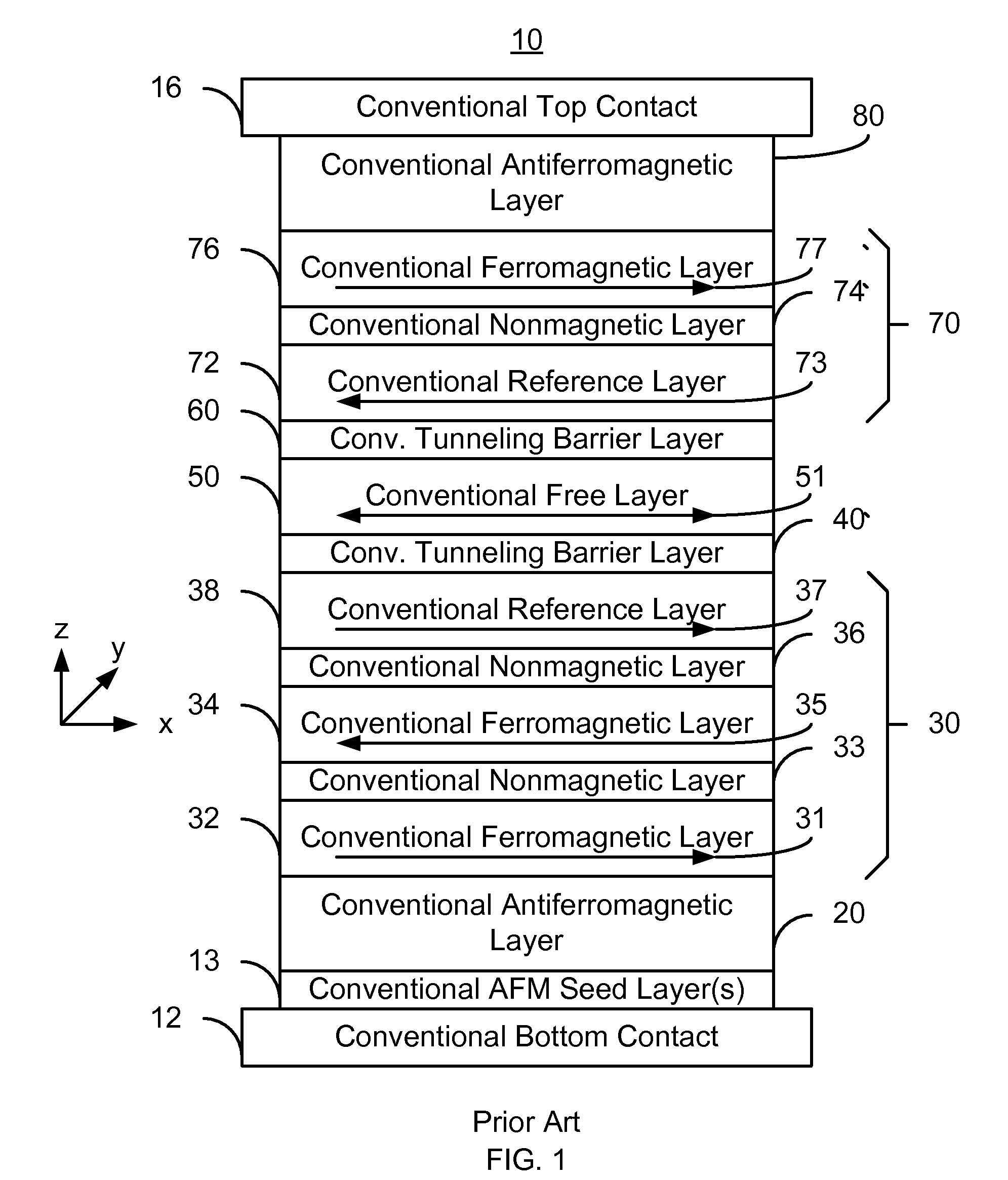

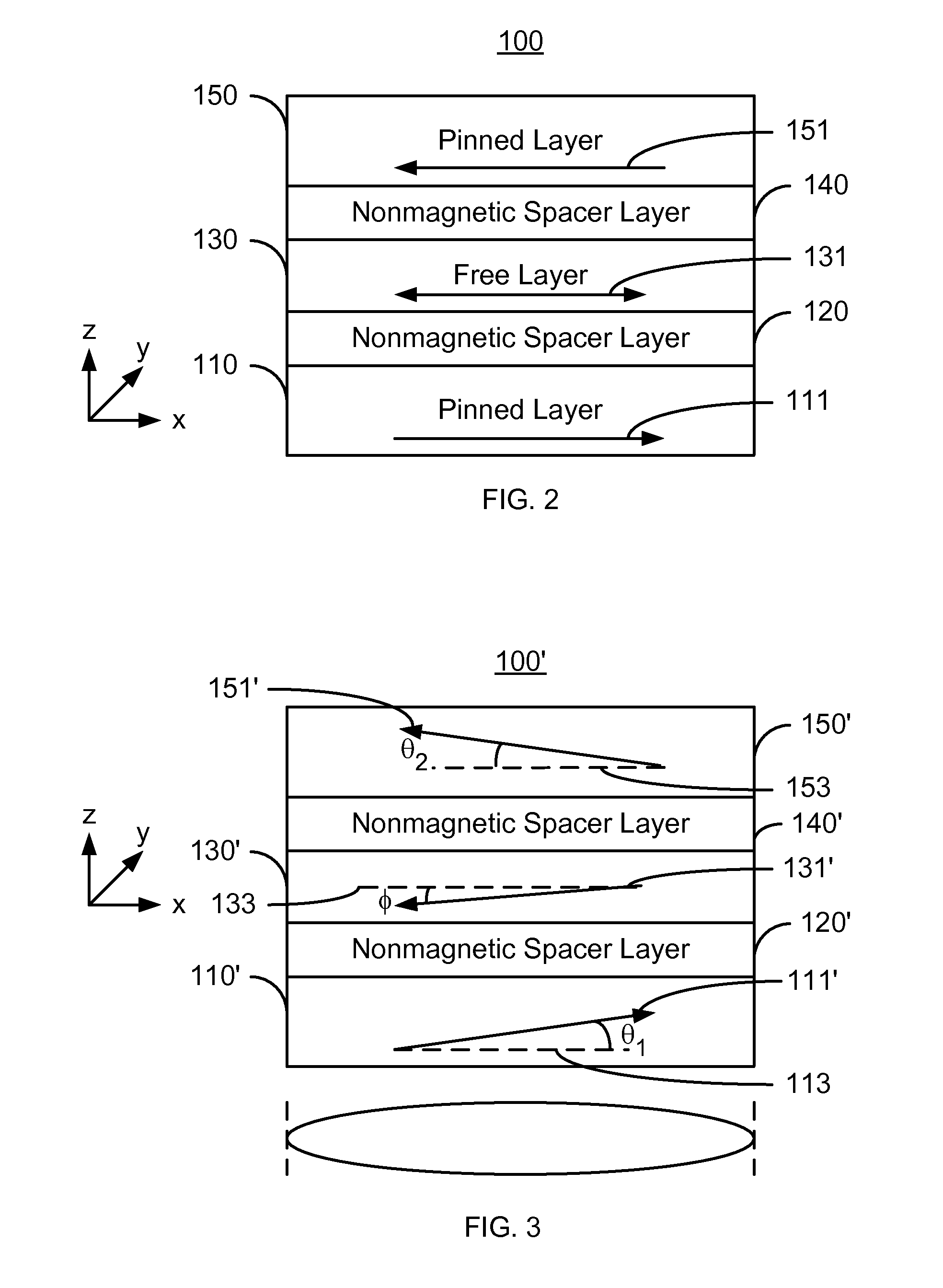

Method and system for providing dual magnetic tunneling junctions usable in spin transfer torque magnetic memories

ActiveUS20110102948A1Magnetic-field-controlled resistorsRecord information storageAntiferromagnetic couplingSpin-transfer torque

A method and system for providing a magnetic junction usable in a magnetic memory are described. The magnetic junction includes first and second pinned layers, first and second nonmagnetic spacer layers, and a free layer. The first pinned layer has a first pinned layer magnetic moment and is nonmagnetic layer-free. The first nonmagnetic spacer layer resides between the first pinned and free layers. The free layer resides between the first and second nonmagnetic spacer layers. The second pinned layer has a second pinned layer magnetic moment and is nonmagnetic layer-free. The second nonmagnetic spacer layer resides between the free and second pinned layers. The first and second pinned layer magnetic moments are antiferromagnetically coupled and self-pinned. The magnetic junction is configured to allow the free layer to be switched between stable magnetic states when a write current is passed through the magnetic junction.

Owner:SAMSUNG SEMICON

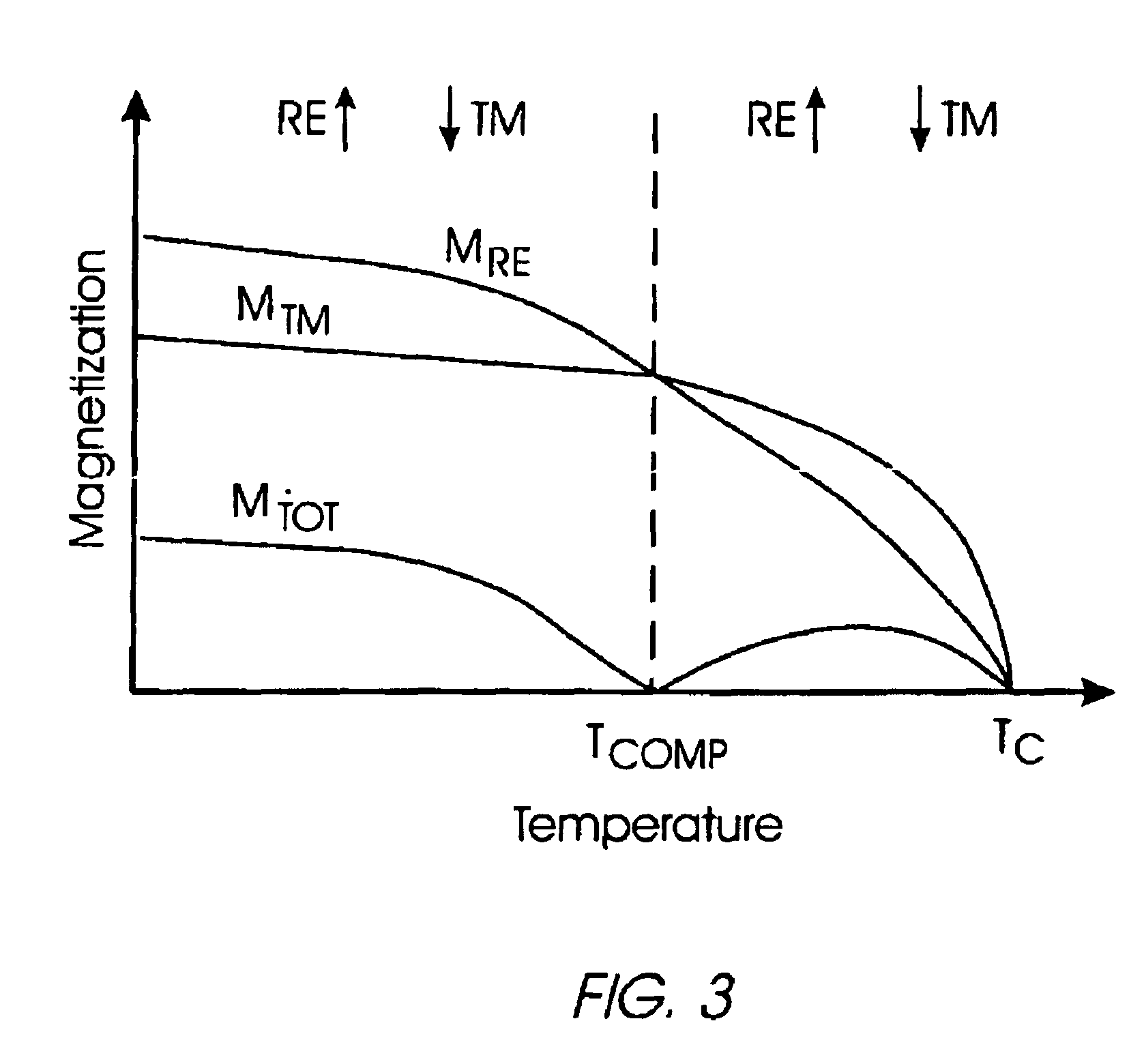

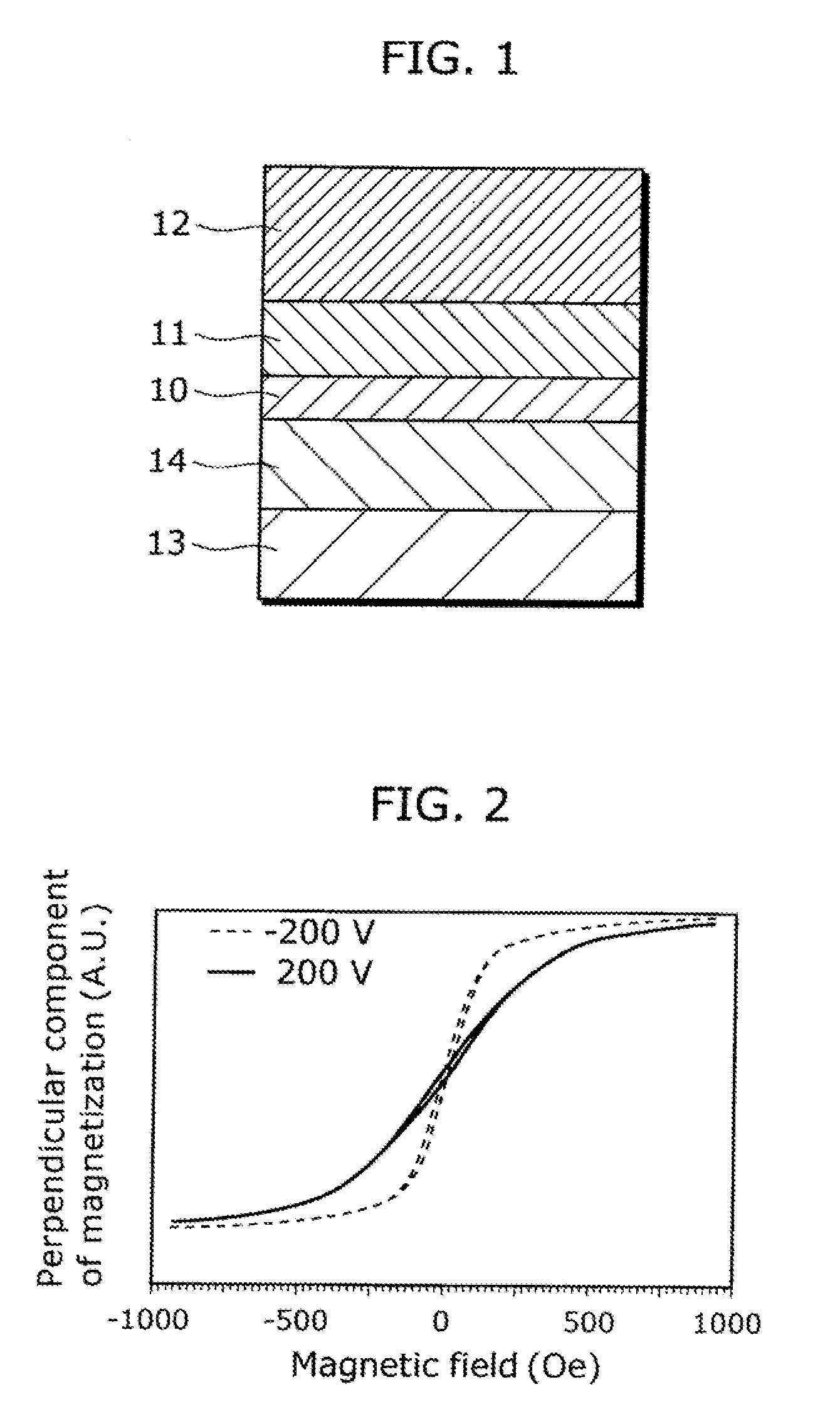

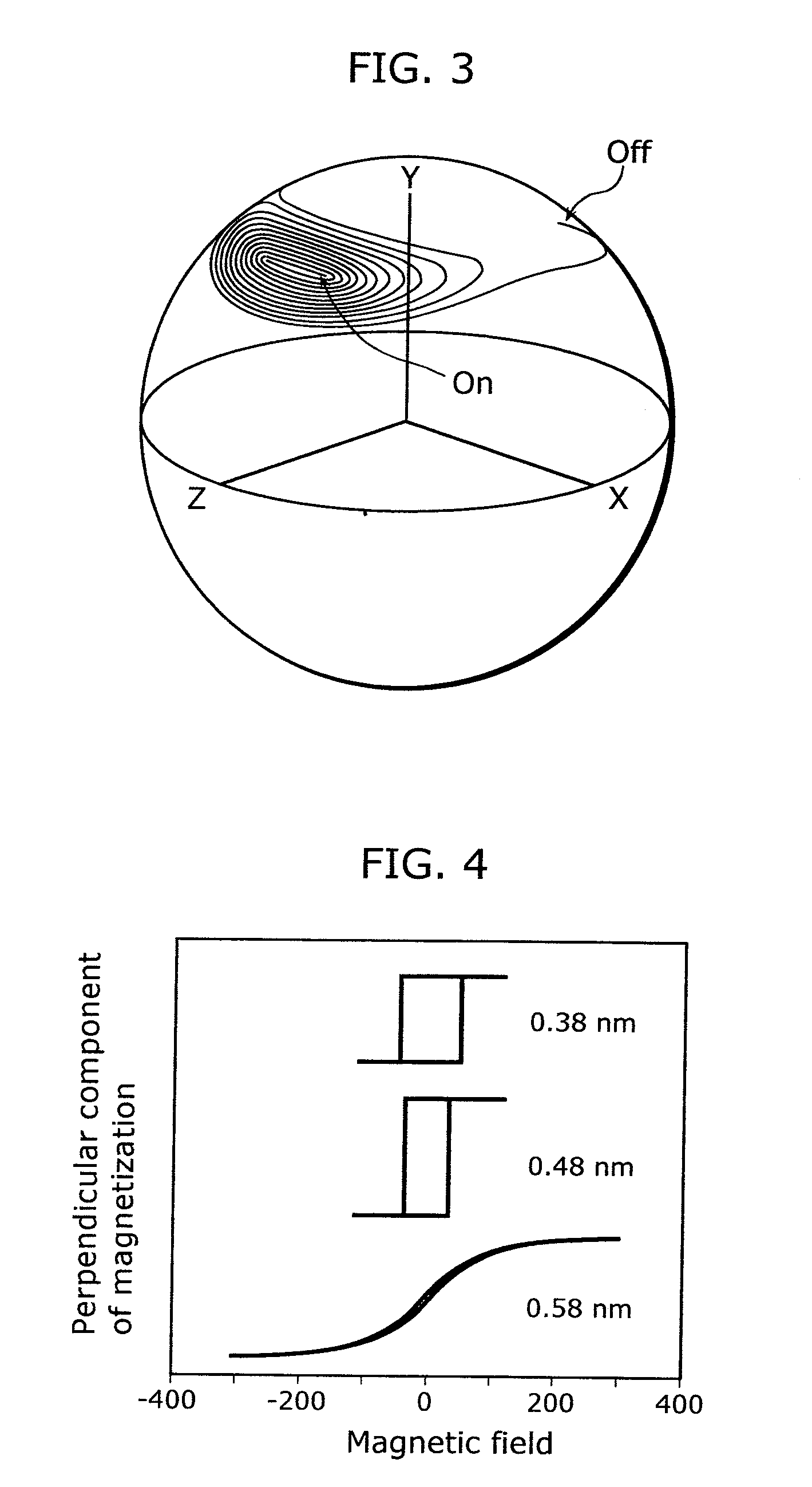

Magnetization control method, information storage method, information storage element, and magnetic function element

InactiveUS20110049659A1Reduce power consumptionIncrease currentElectromagnets without armaturesNanomagnetismMagnetic anisotropySpin-transfer torque

The present invention provides a magnetization control method controlling, utilizing no current-induced magnetic field or spin transfer torque a magnetization direction with low power consumption, an information storage method, an information storage element, and a magnetic function element. The magnetization control method involves controlling a magnetization direction of a magnetic layer, and includes: forming a structure including (i) the magnetic layer which is an ultrathin film ferromagnetic layer having a film thickness of one or more atomic layers and of 2 nm or less, and (ii) an insulating layer provided on the ultrathin film ferromagnetic layer and working as a potential barrier; and controlling a magnetization direction of the ultrathin film ferromagnetic layer by applying either (i) a voltage to opposing electrodes sandwiching the structure and a base layer or (ii) an electric field to the structure to change magnetic anisotropy of the ultrathin film ferromagnetic layer. The magnetization control method further involves controlling a waveform of the applied voltage or the applied electric field to switch the magnetization direction.

Owner:OSAKA UNIV

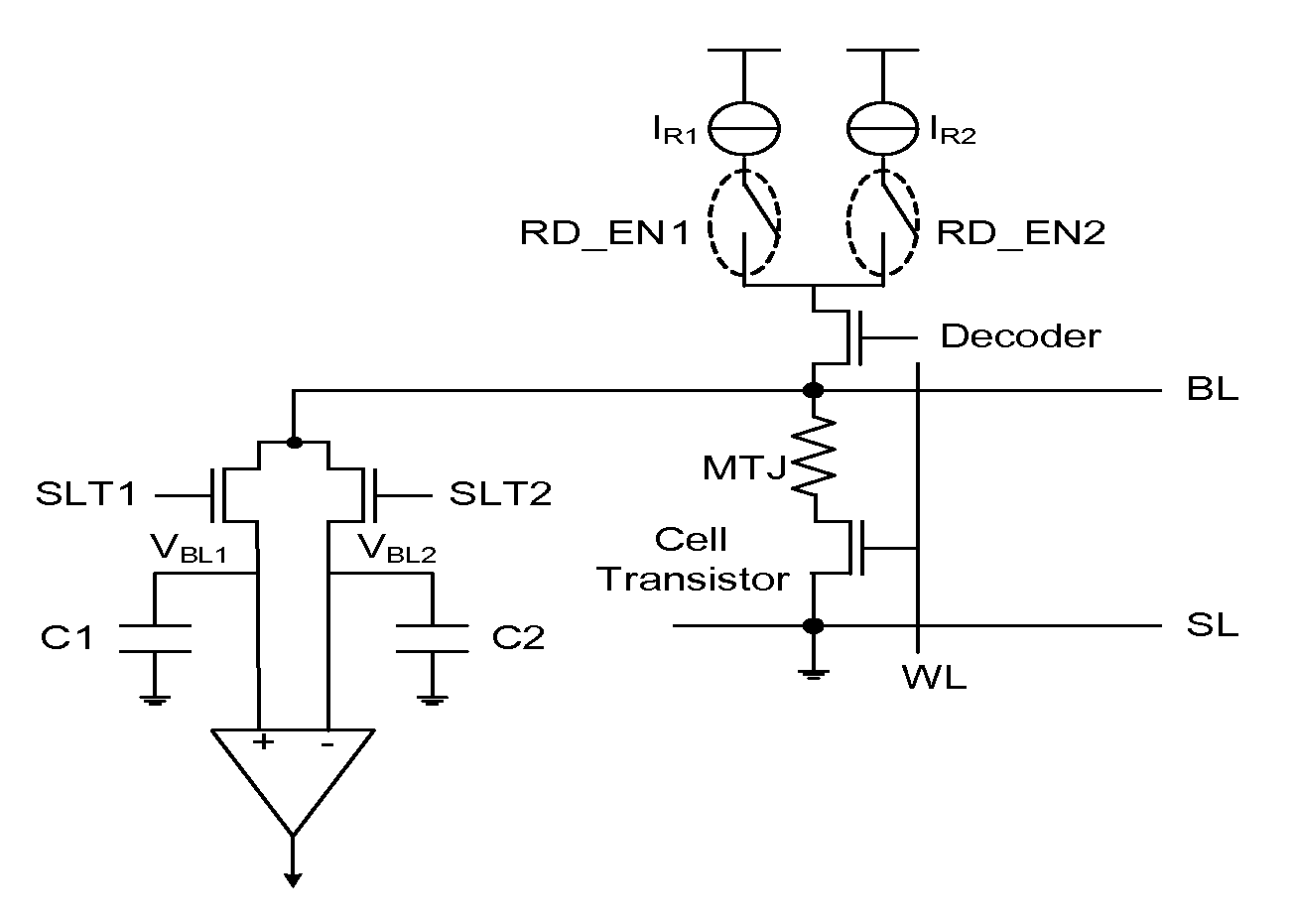

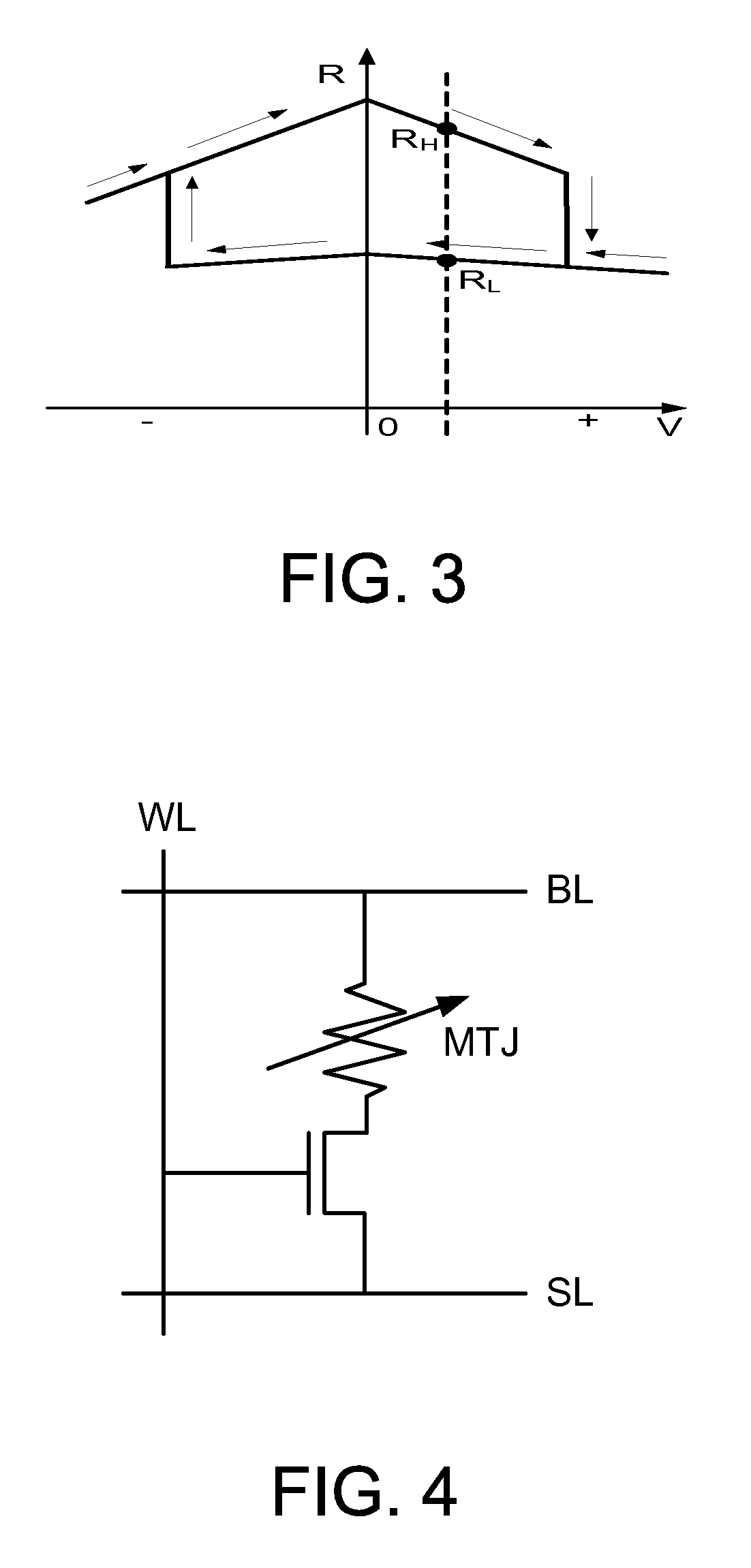

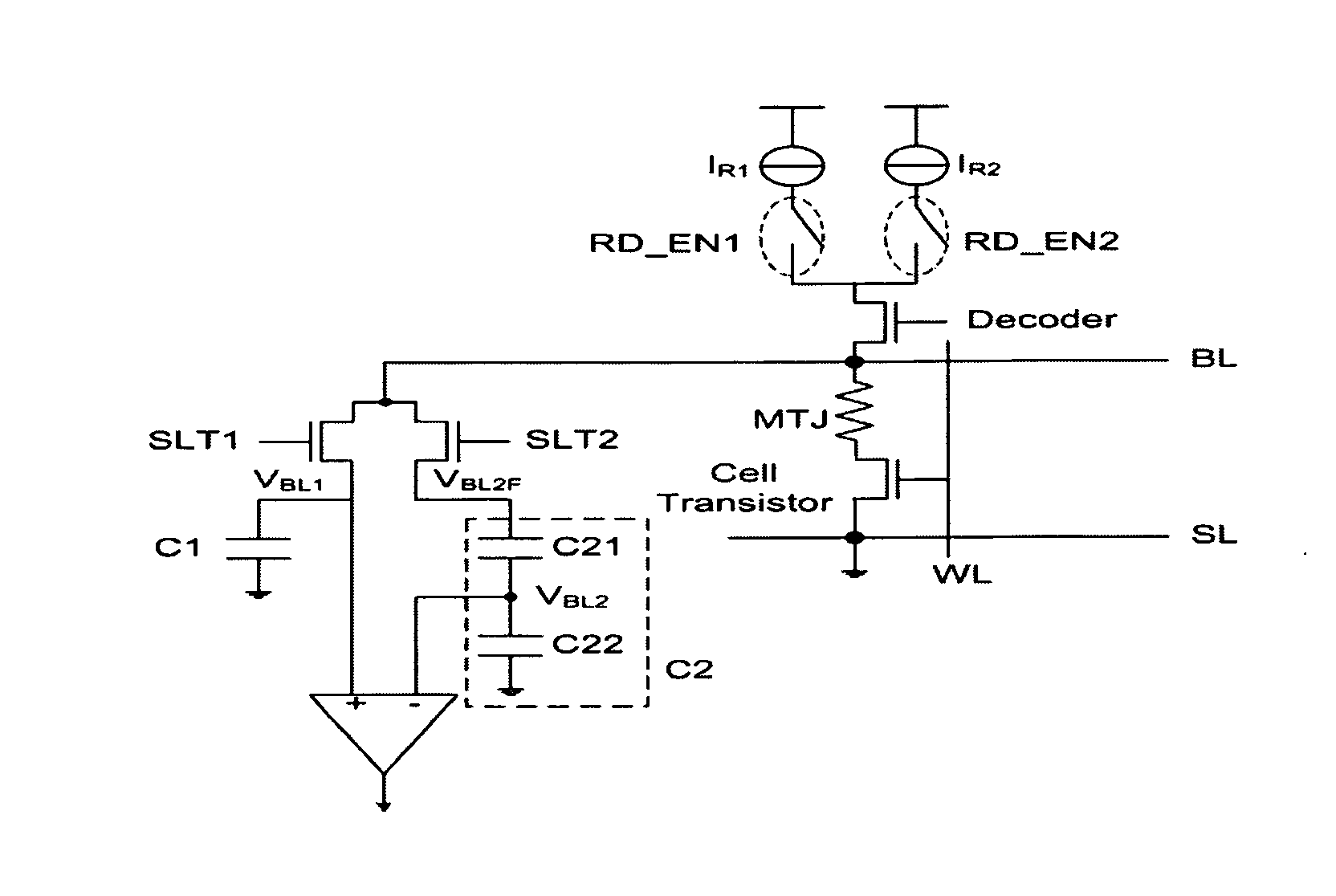

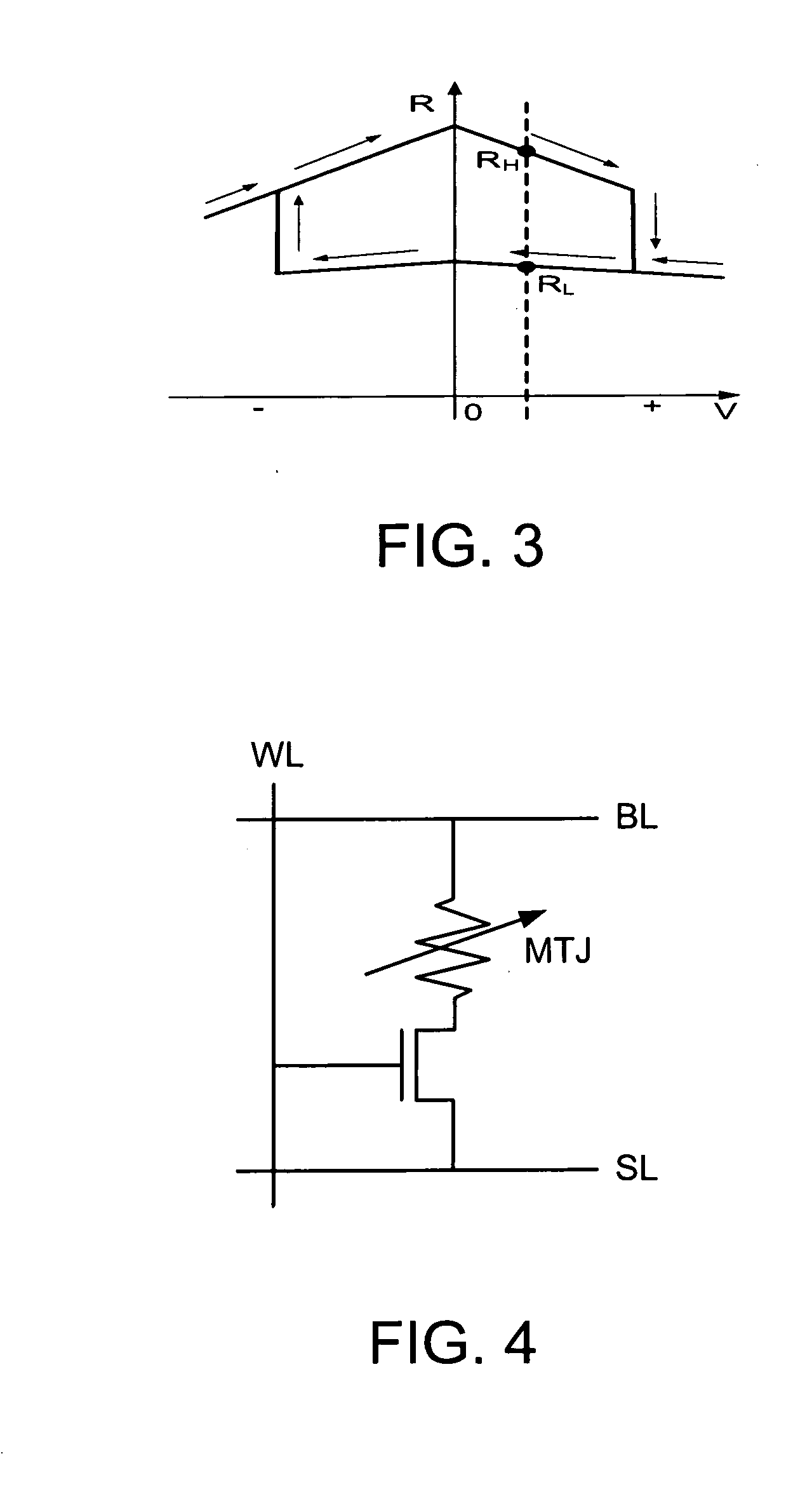

Spin-transfer torque memory self-reference read method

A spin-transfer torque memory apparatus and self-reference read schemes are described. One method of self-reference reading a spin-transfer torque memory unit includes applying a first read current through a magnetic tunnel junction data cell and forming a first bit line read voltage, the magnetic tunnel junction data cell having a first resistance state and storing the first bit line read voltage in a first voltage storage device. Then applying a low resistance state polarized write current through the magnetic tunnel junction data cell, forming a low second resistance state magnetic tunnel junction data cell. A second read current is applied through the low second resistance state magnetic tunnel junction data cell to forming a second bit line read voltage. The second bit line read voltage is stored in a second voltage storage device. The method also includes comparing the first bit line read voltage with the second bit line read voltage to determine whether the first resistance state of the magnetic tunnel junction data cell was a high resistance state or low resistance state.

Owner:SEAGATE TECH LLC

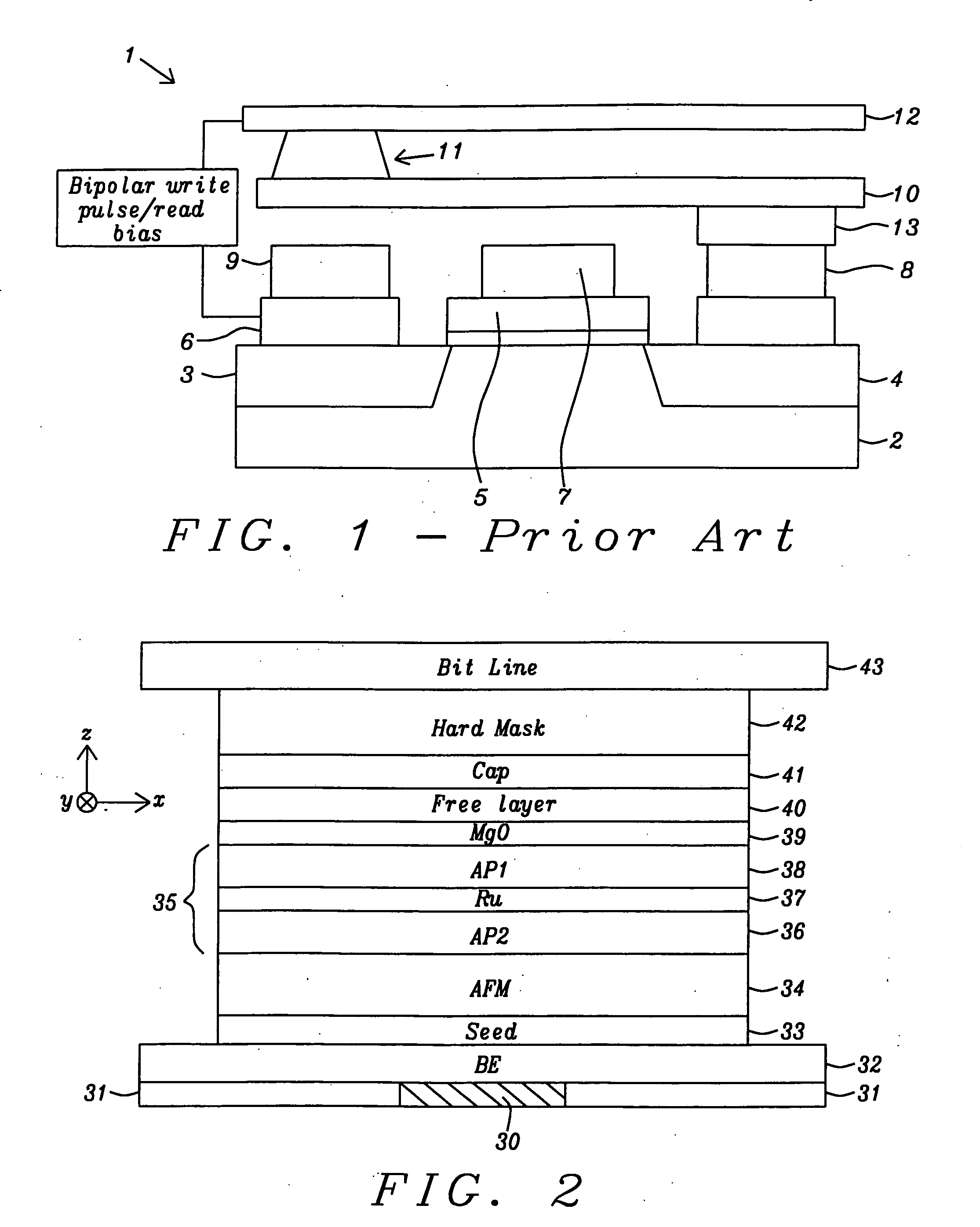

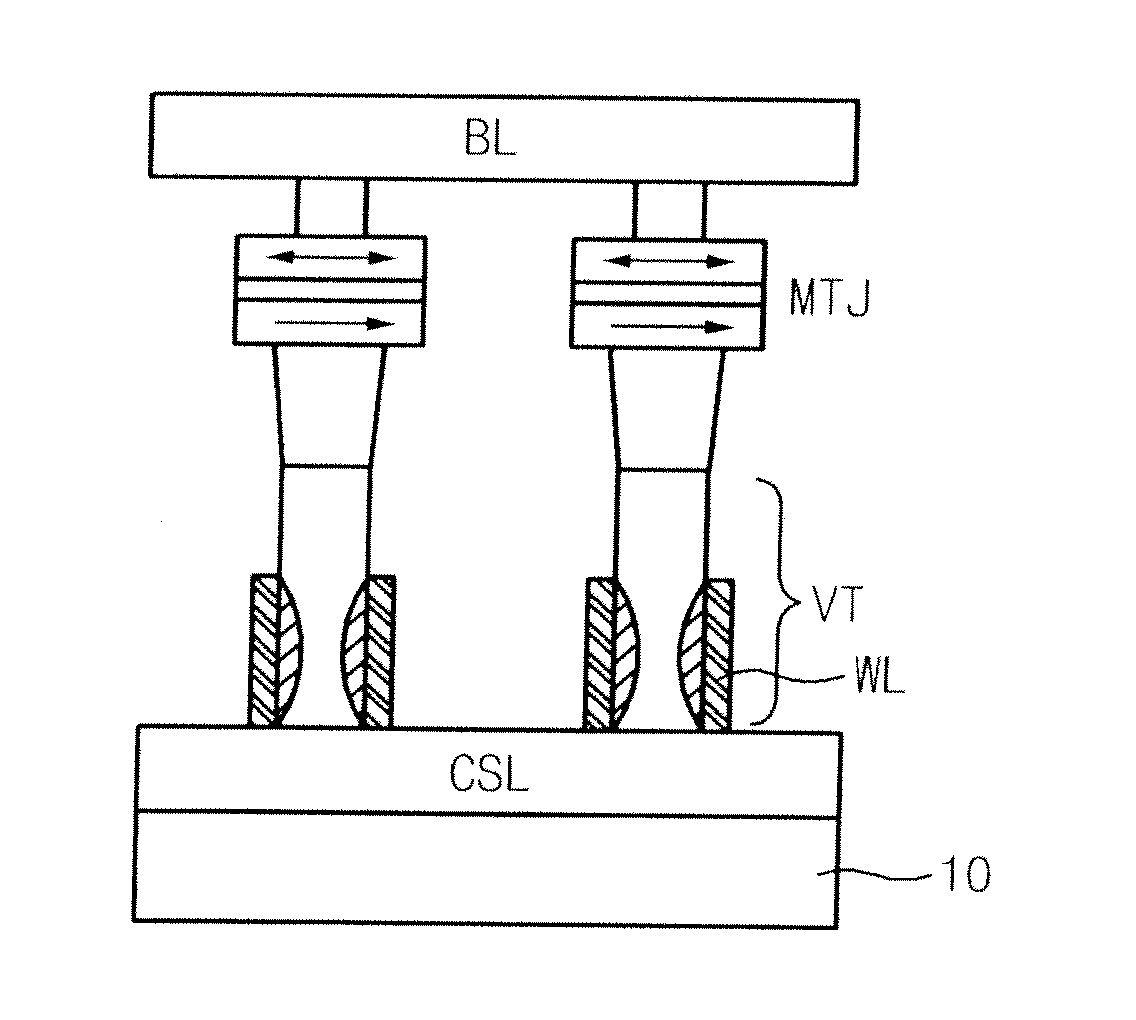

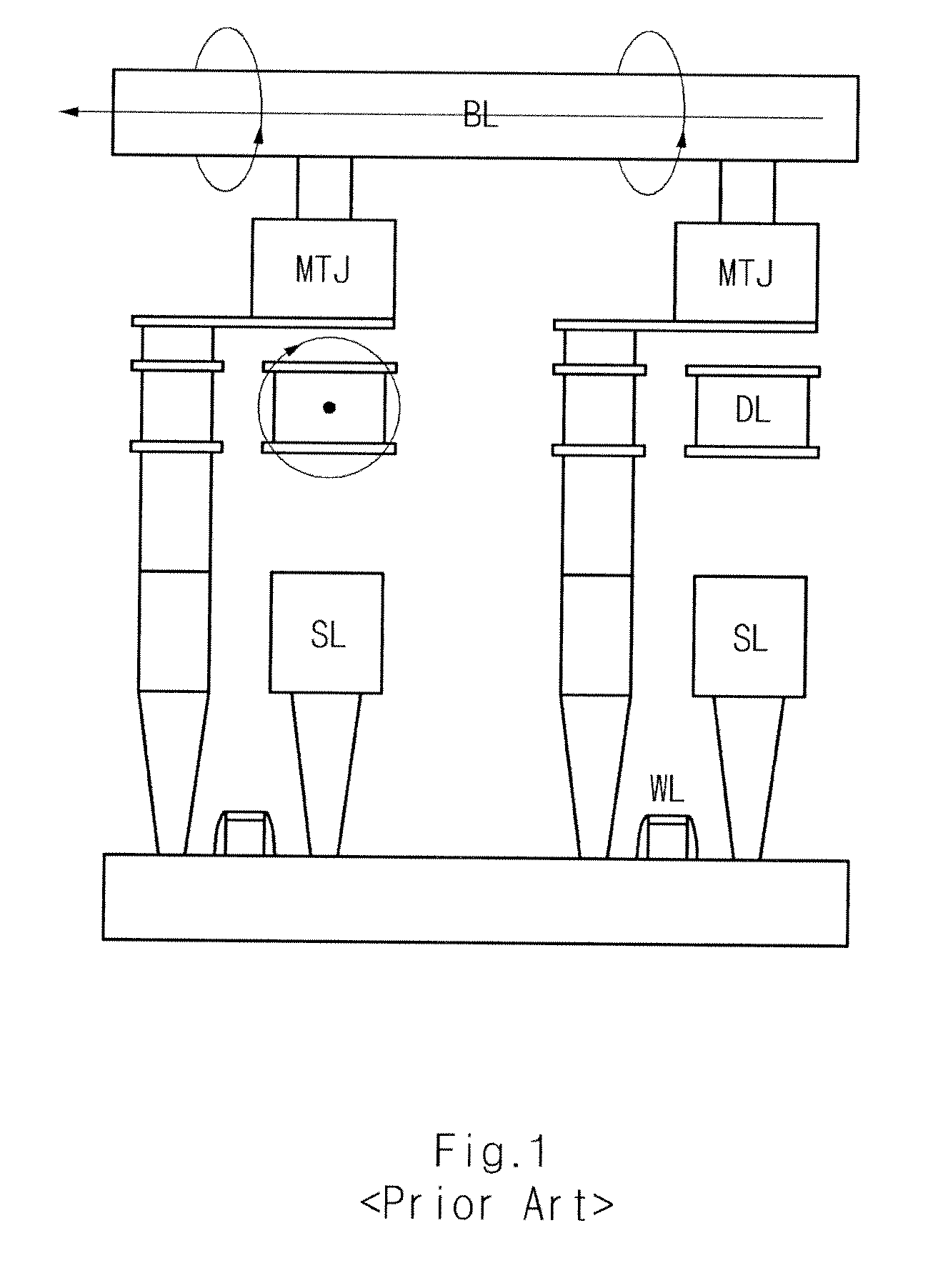

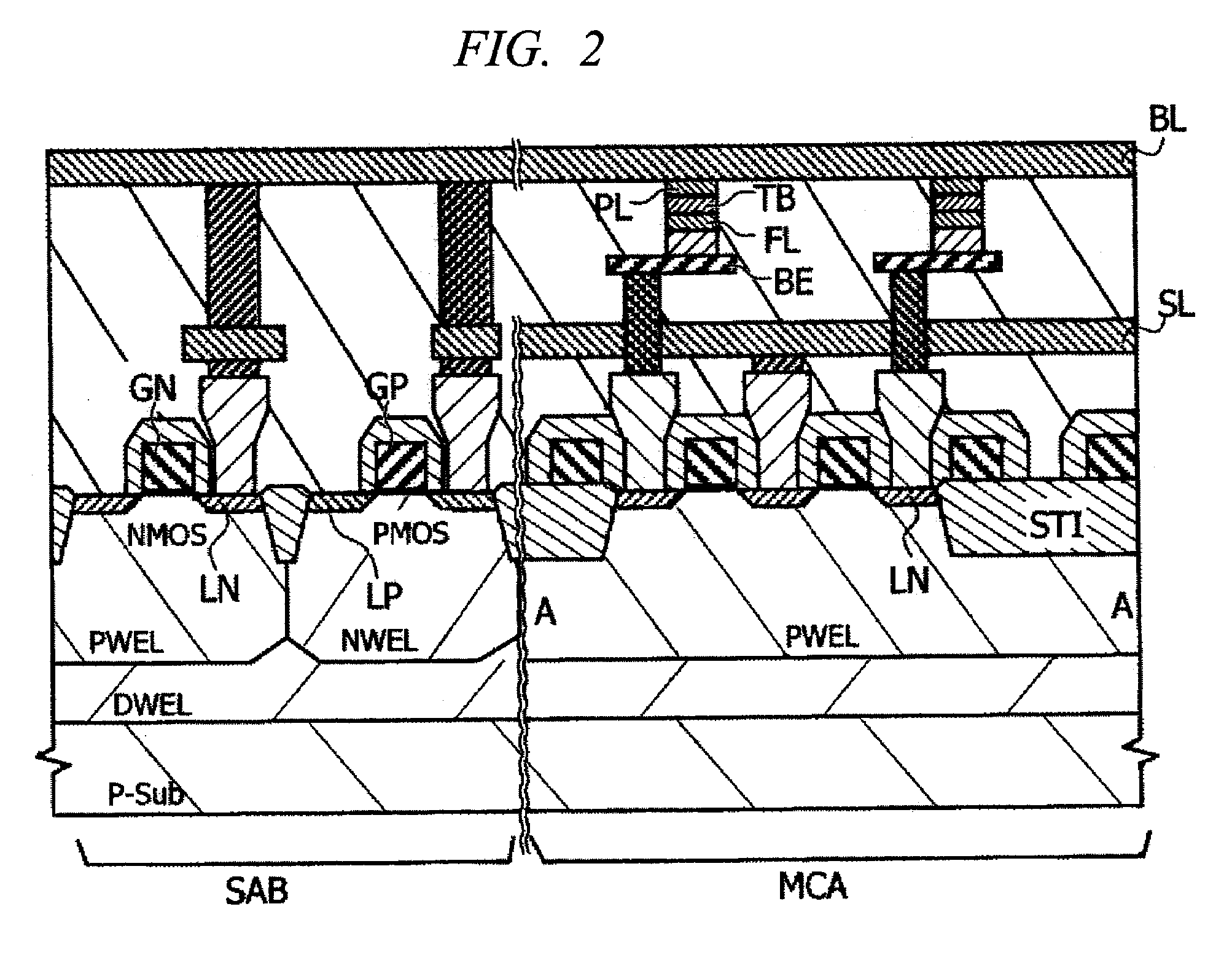

Spin Transfer Torque Memory Device Having Common Source Line and Method for Manufacturing the Same

InactiveUS20100059837A1Easy to optimizeReduce resistance of source lineSolid-state devicesSemiconductor/solid-state device manufacturingSpin-transfer torqueTransistor

A spin transfer torque memory device and a method for manufacturing the same. The spin transfer torque memory device comprises a MRAM cell using a MTJ and a vertical transistor. A common source line is formed in the bottom of the vertical transistor, thereby obtaining the high-integrated and simplified memory device.

Owner:SK HYNIX INC

Thermally-assisted magnetic writing using an oxide layer and current-induced heating

InactiveUS20040095801A1Increase in sizeIncrease in coercivityNanostructure applicationNanomagnetismStatic random-access memoryElectrical conductor

A method and structure for a non-volatile magnetic random access memory (MRAM) device that has a stable magnetic electrode, an oxide layer adjacent the stable magnetic electrode, and a free magnetic electrode. The oxide layer is between the stable magnetic electrode and the free magnetic electrode. In the invention, a conductor is connected to a stable magnetic electrode. The oxide layer has a resistance at levels to allow sufficient power dissipation to lower the anisotropy of the free magnetic electrode through current induced heating. Current-induced heating is used in combination with spin-transfer torque or a magnetic field to switch the free magnetic electrode.

Owner:GLOBALFOUNDRIES US INC

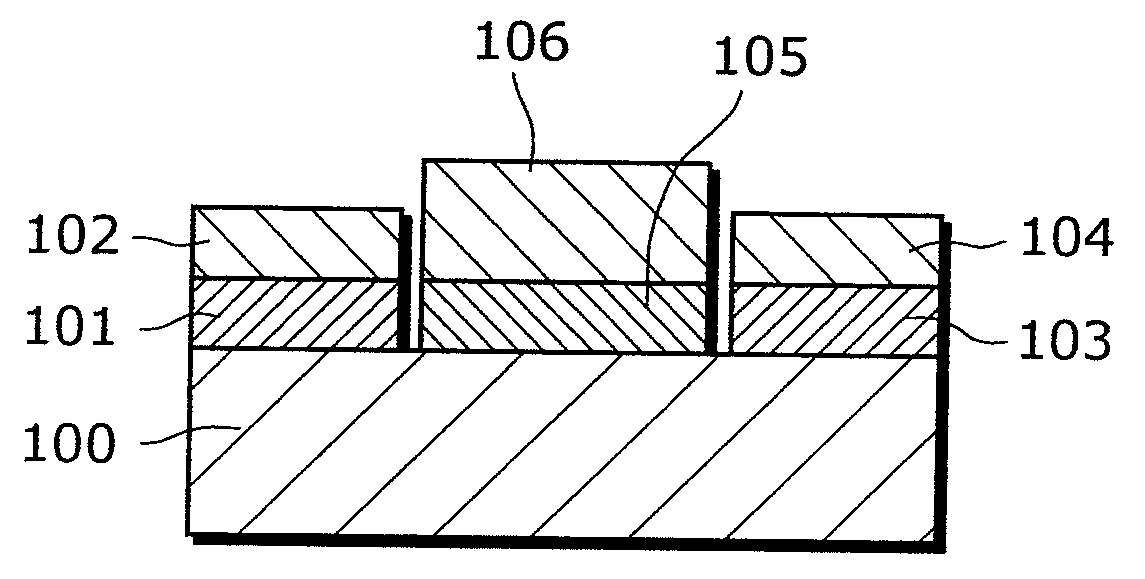

Semiconductor device

InactiveUS20070285974A1Stable reading operationGuaranteed uptimeSolid-state devicesDigital storageBit lineSpin-transfer torque

In MRAM using a spin-transfer torque switching, a sufficient writing operation with a small memory cell is realized, and a reading current is enlarged while a reading disturbance is suppressed. In the case where the free layer of the tunnel magneto-resistance element is located on the side of the bit line, using a PMOS transistor, and in the case where the fixed layer of the tunnel magneto-resistance element is located on the side of the bit line, using an NMOS transistor, an anti-parallel writing in a source grounding operation is performed. The reading and writing operation margin is improved by performing a reading operation in an anti-parallel writing direction.

Owner:HITACHI LTD

Semiconductor device and structure

ActiveUS9117749B1Small footprintIncrease speedTransistorSolid-state devicesPower semiconductor deviceSpin-transfer torque

Owner:MONOLITHIC 3D

Spin-transfer torque memory non-destructive self-reference read method

A spin-transfer torque memory apparatus and non-destructive self-reference read schemes are described. One method of self-reference reading a spin-transfer torque memory unit includes applying a first read current through a magnetic tunnel junction data cell and forming a first bit line read voltage and storing the first bit line read voltage in a first voltage storage device. The magnetic tunnel junction data cell has a first resistance state. Then the method includes applying a second read current thorough the magnetic tunnel junction data cell having the first resistance state and forming a second bit line read voltage and storing the second bit line read voltage in a second voltage storage device. The first read current is less than the second read current. Then the stored first bit line read voltage is compared with the stored second bit line read voltage to determine whether the first resistance state of the magnetic tunnel junction data cell was a high resistance state or low resistance state.

Owner:SEAGATE TECH LLC

Method of magnetic tunneling layer processes for spin-transfer torque MRAM

A method for forming a MTJ in a STT-MRAM is disclosed in which the easy-axis CD is determined independently of the hard-axis CD. One approach involves two photolithography steps and two etch steps to form a post in a hard mask which is transferred through a MTJ stack of layers by a third etch process. Optionally, the third etch may stop on the tunnel barrier or in the free layer. A second embodiment involves forming a first parallel line pattern on a hard mask layer and transferring the line pattern through the MTJ stack with a first etch step. A planar insulation layer is formed adjacent to the sidewalls in the line pattern and then a second parallel line pattern is formed which is transferred by a second etch through the MTJ stack to form a post pattern. Etch end point may be controlled independently for hard-axis and easy-axis dimensions.

Owner:TAIWAN SEMICON MFG CO LTD

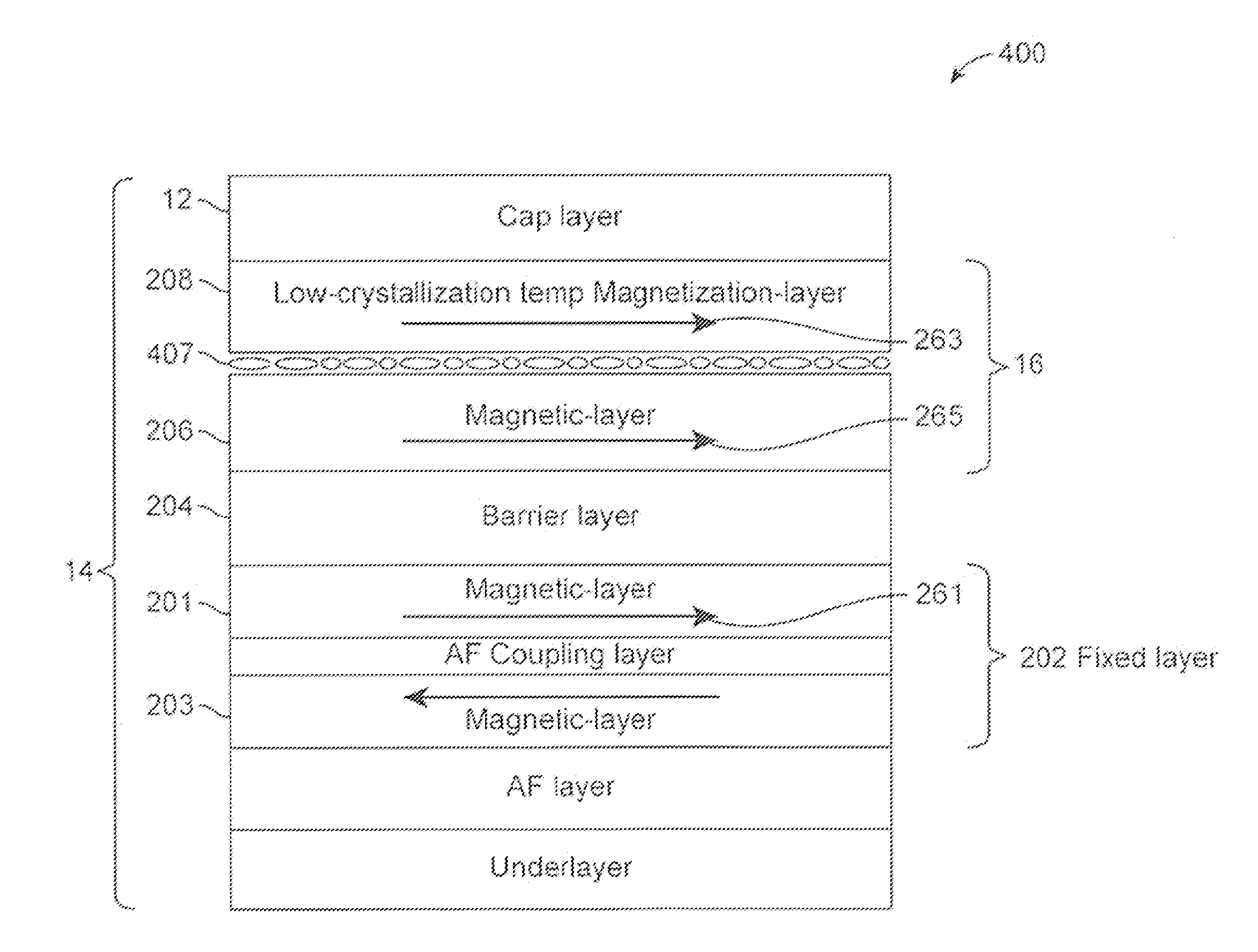

Spin-transfer torque magnetic random access memory (STTMRAM) with laminated free layer

ActiveUS8374025B1NanoinformaticsMagnetic-field-controlled resistorsPower flowPerpendicular anisotropy

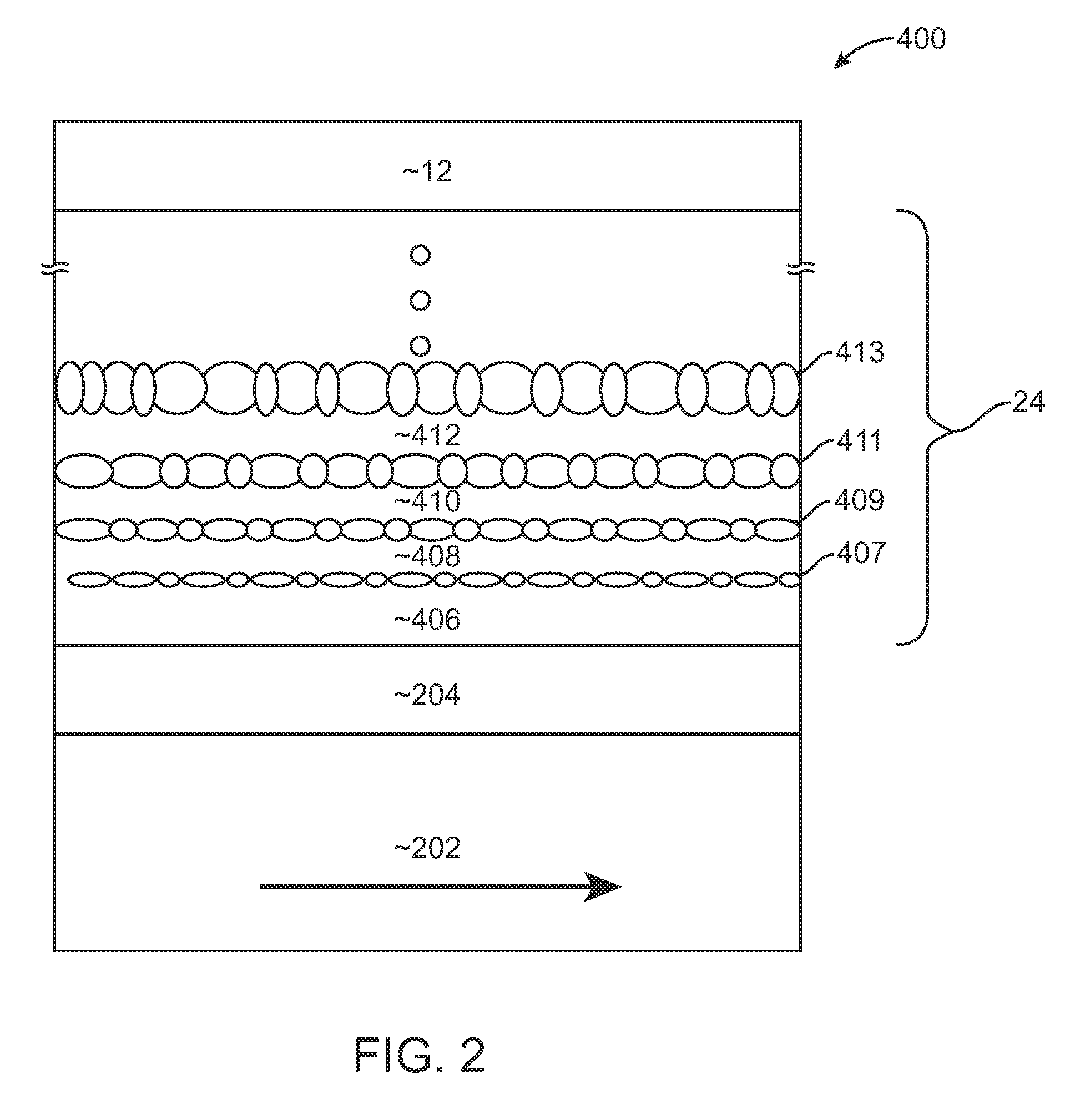

A spin-torque transfer memory random access memory (STTMRAM) element includes a fixed layer having a magnetization that is substantially fixed in one direction and a barrier layer formed on top of the fixed layer and a free layer. The free layer has a number of alternating laminates, each laminate being made of a magnetic layer and an insulating layer. The magnetic layer is switchable and formed on top of the barrier layer. The free layer is capable of switching its magnetization to a parallel or an anti-parallel state relative to the magnetization of the fixed layer during a write operation when bidirectional electric current is applied across the STTMRAM element. Magnetic layers of the laminates are ferromagnetically coupled to switch together as a single domain during the write operation and the magnetization of the fixed and free layers and the magnetic layers of the laminates have either in-plane or perpendicular anisotropy.

Owner:AVALANCHE TECH

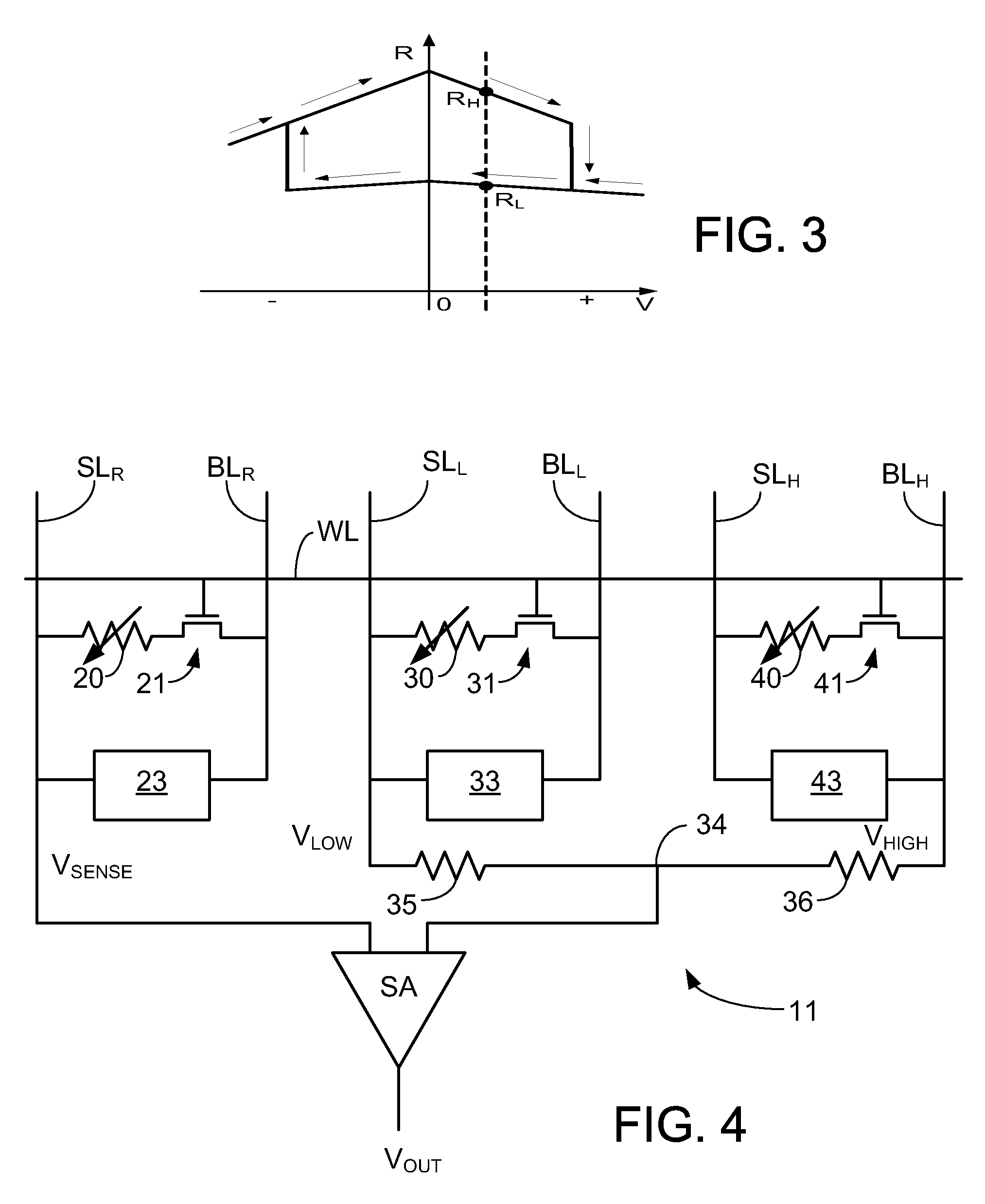

Memory array with read reference voltage cells

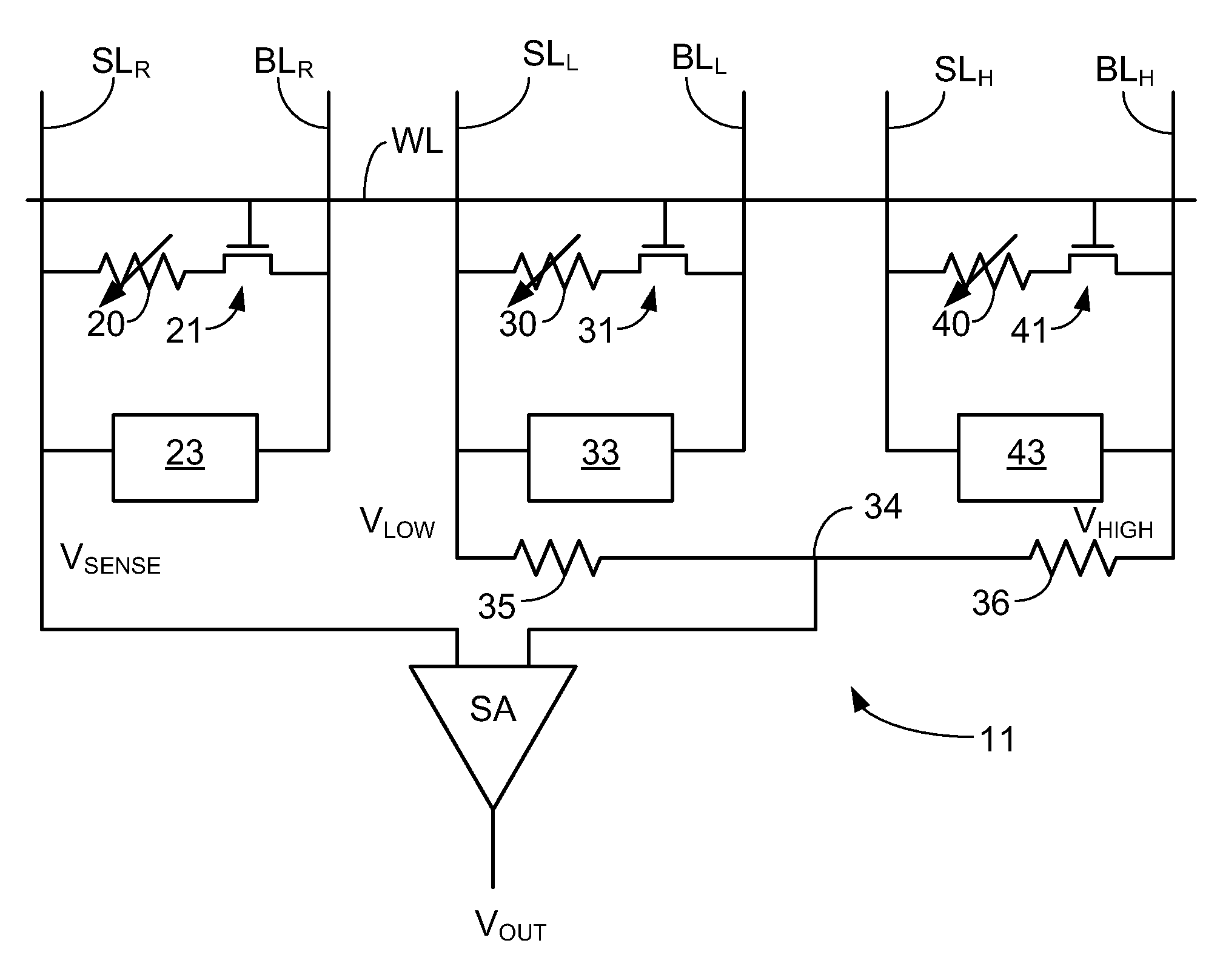

InactiveUS20100067282A1Reliability of reference voltageElectric analogue storesRead-only memoriesHigh resistanceElectrical resistance and conductance

The present disclosure relates to memory arrays with read reference voltage cells. In particular the present disclosure relates to variable resistive memory cell apparatus and arrays that include a high resistance state reference memory cell and a low resistance state reference memory cell that provides a reliable average reference voltage on chip to compare to a read voltage of a selected memory cell and determine if the selected memory cell is in the high resistance state or low resistance state. These memory arrays are particularly suitable for use with spin-transfer torque memory cells and resolves many systematic issues related to generation of a reliable reference voltage.

Owner:SEAGATE TECH LLC

Novel perpendicular magnetoresistive elements

ActiveUS20140217526A1Galvano-magnetic device detailsDigital storageElectrical resistance and conductanceSpin-transfer torque

A perpendicular magnetoresistive element comprises anovel buffer layer provided on a surface of the recording layer, which is opposite to a surface of the recording layer where the tunnel barrier layer is provided, wherein at least the portion of the buffer layer interfacing to the recording layer contains a rocksalt crystal structure having the (100) plane parallel to the substrate plane and at least a portion of the buffer layer comprises a doped element having conductivity enhancement and the perpendicular resistance of the buffer layer is relatively small than that of the tunnel barrier layer. The invention preferably includes materials, configurations and processes of perpendicular magnetoresistive elements suitable for perpendicular spin-transfer torque MRAM applications

Owner:GUO YIMIN

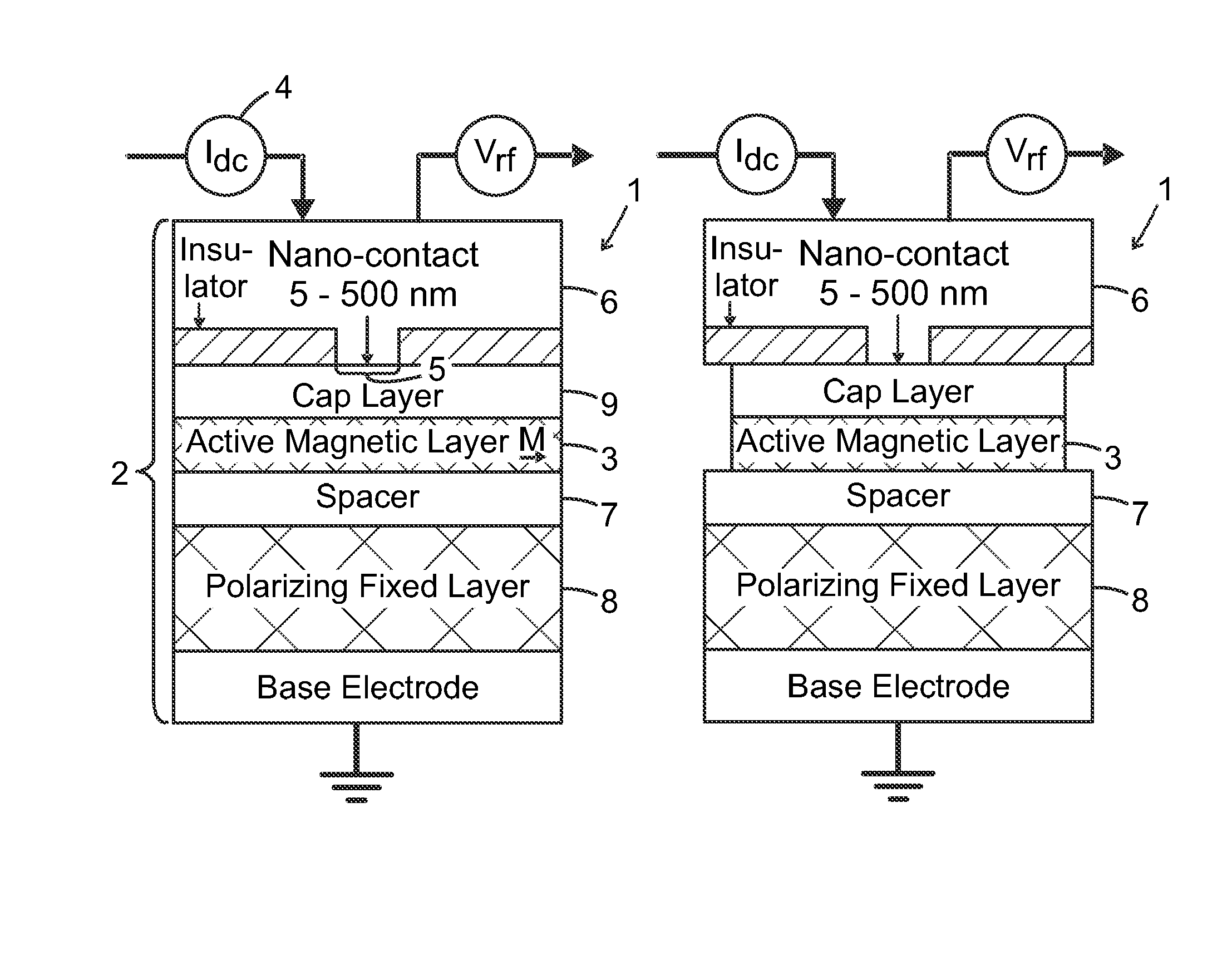

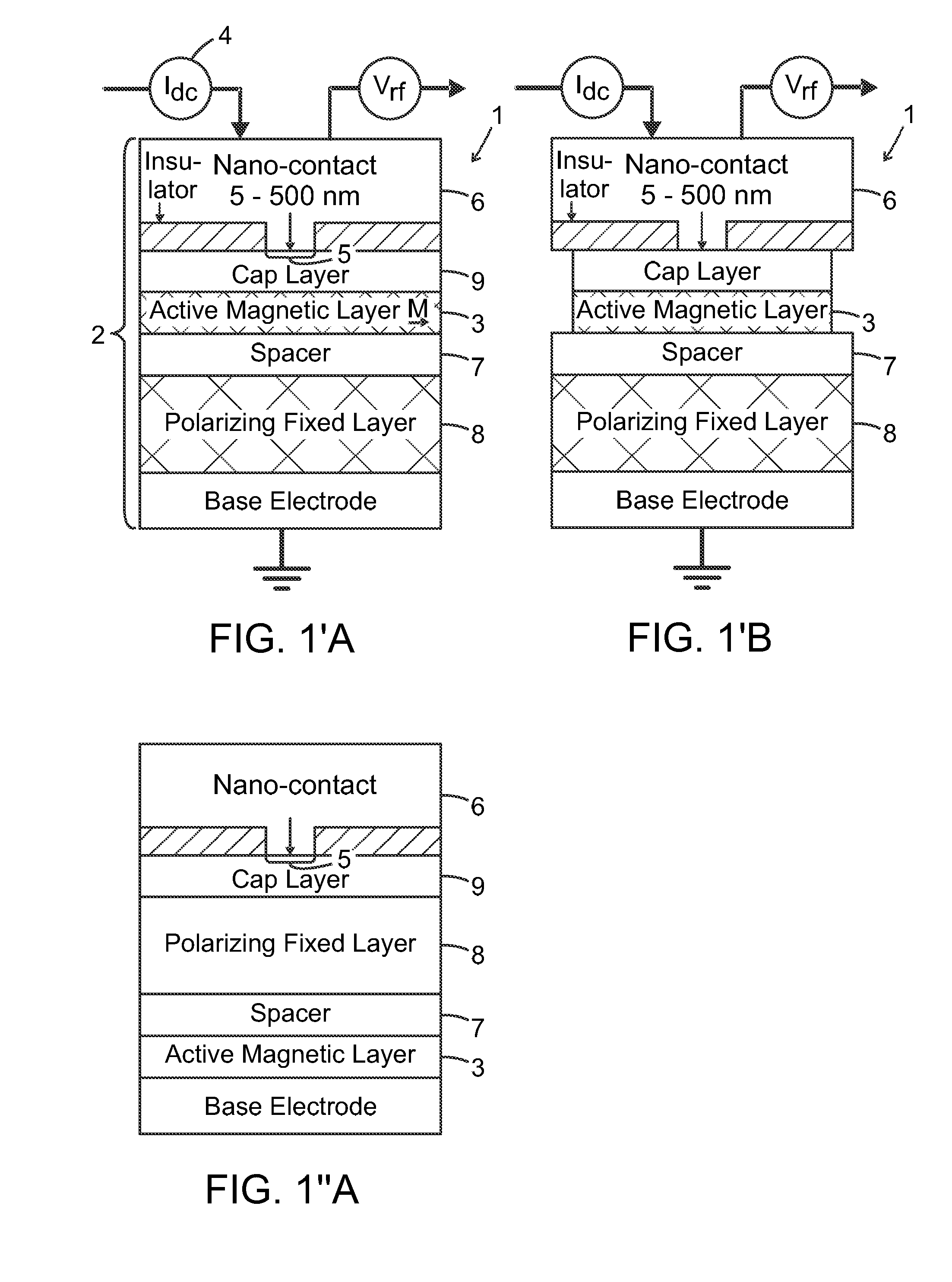

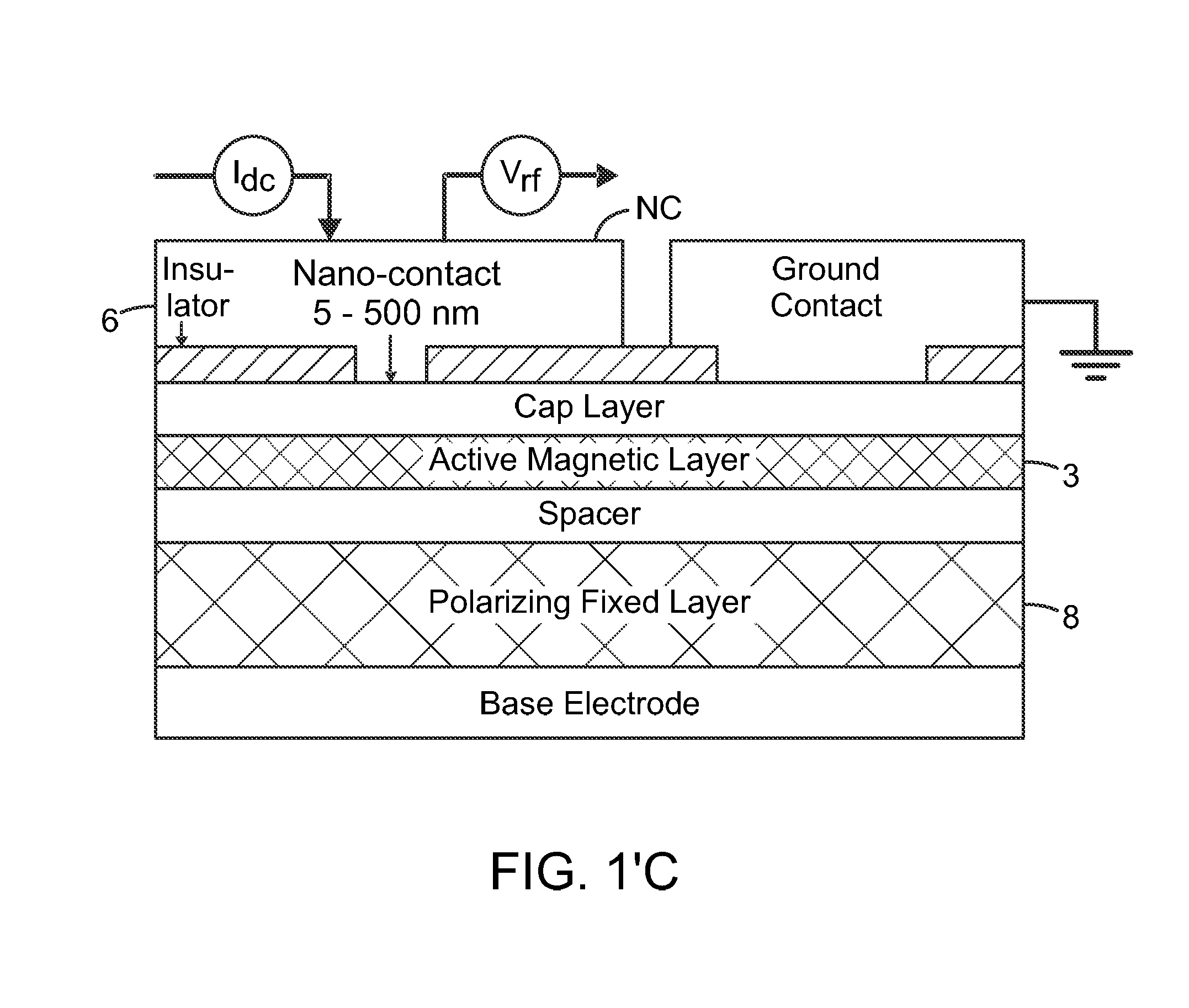

Spin oscillator device

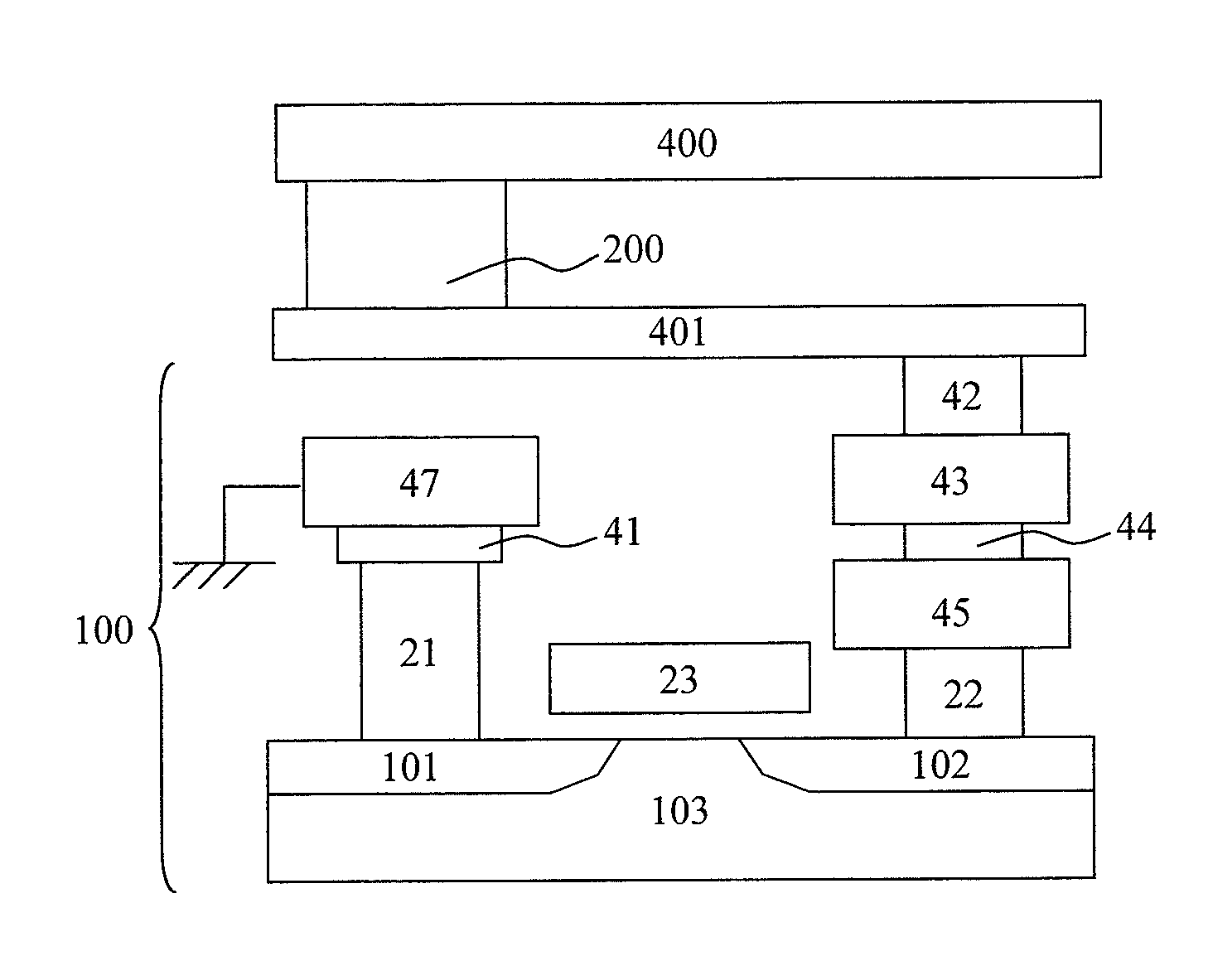

ActiveUS20170033742A1Detection is limitedPulse automatic controlMagnetic-field-controlled resistorsSpin-transfer torqueMagnetic memory

The present invention relates to using spin transfer torque underneath a nanocontact on a magnetic thin film with perpendicular magnetic anisotropy (PMA), provides generation of dissipative magnetic droplet solitons and magnetic droplet-skyrmions and report on their rich dynamical properties. Micromagnetic simulations identify the conditions necessary to nucleate and drive droplet-skyrmions over a wide range of currents and fields. Micromagnetic simulations also demonstrate how droplets and droplet-skyrmions can be used as skyrmion injectors and detectors in skyrmion-based magnetic memories. The droplet-skyrmion can be controlled using both current and magnetic fields, and is expected to have applications in spintronics, magnonics, skyrmionics, and PMA-based domain-wall devices.

Owner:NANOSC AB

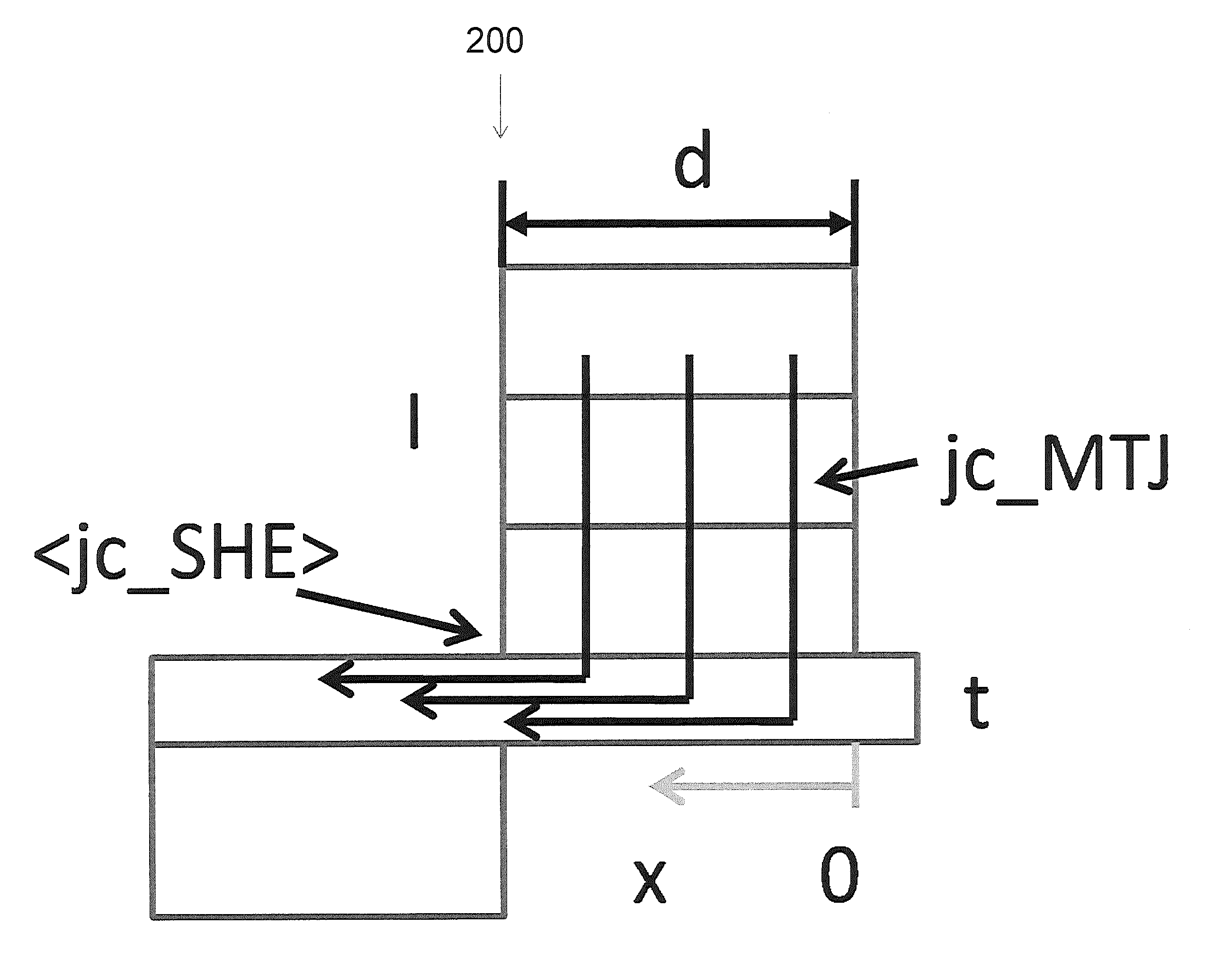

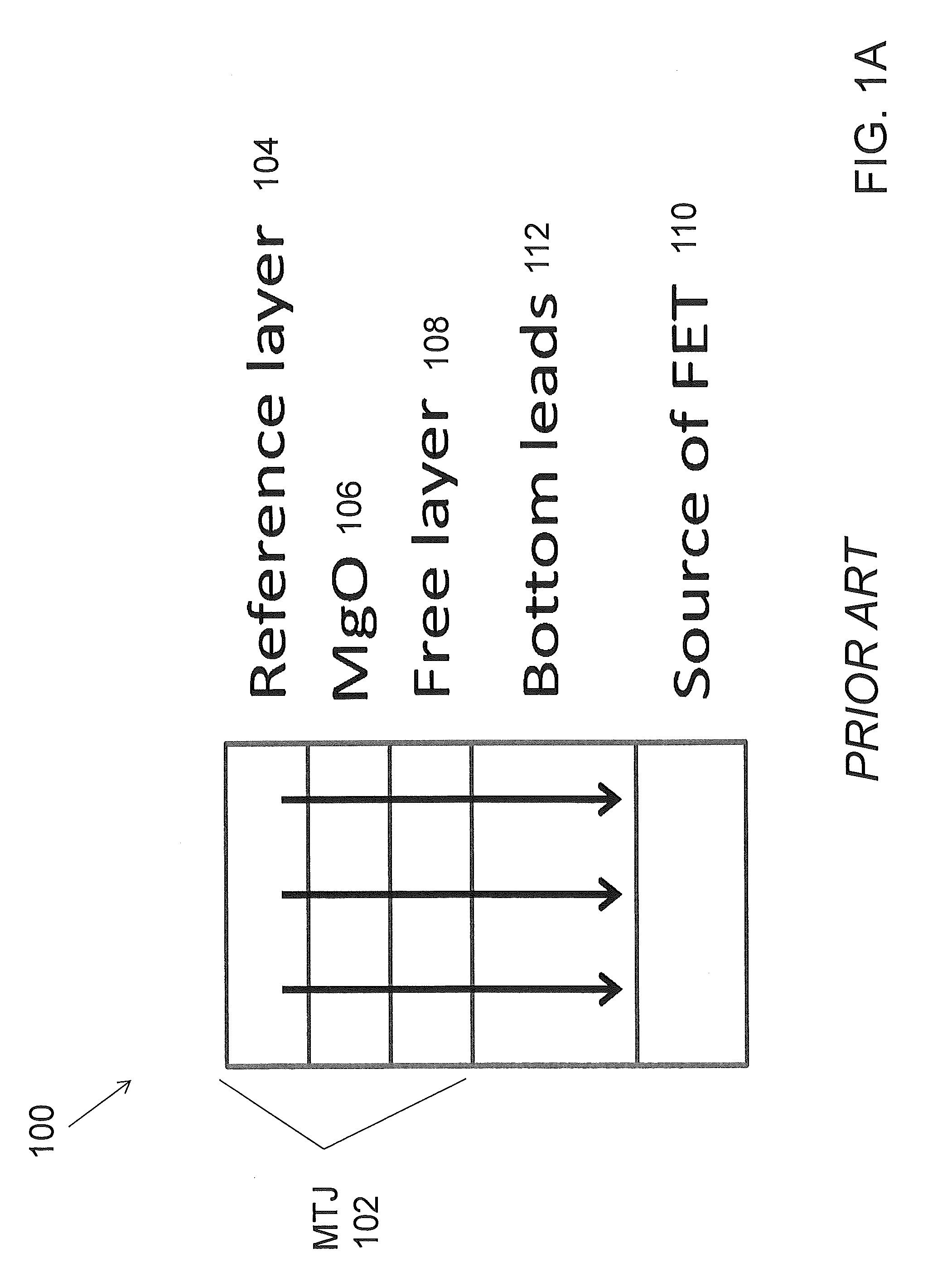

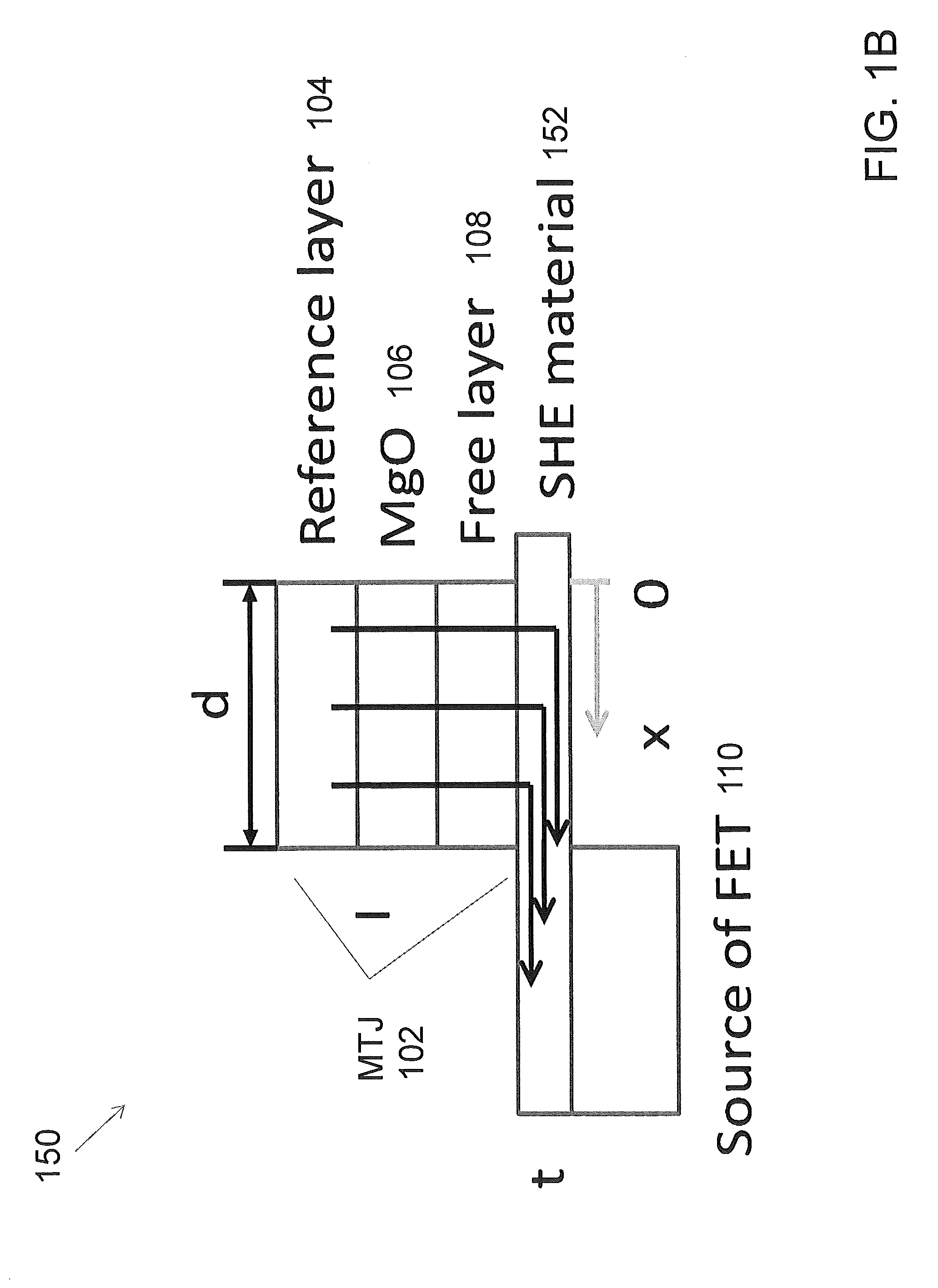

Spin hall effect assisted spin transfer torque magnetic random access memory

ActiveUS20140264513A1Solid-state devicesSemiconductor/solid-state device manufacturingSpin Hall effectSpin-transfer torque

Embodiments are directed to providing a spin hall effect (SHE) assisted spin transfer torque magnetic random access memory (STT-MRAM) device by coupling a magnetic tunnel junction (MTJ) to a SHE material, and coupling the SHE material to a transistor. Embodiments are directed to a spin transfer torque magnetic random access memory (STT-MRAM) device comprising: a magnetic tunnel junction (MTJ) coupled to a spin hall effect (SHE) material, and a transistor coupled to the SHE material.

Owner:IBM CORP