Patents

Literature

6849 results about "Aspect ratio" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

The aspect ratio of a geometric shape is the ratio of its sizes in different dimensions. For example, the aspect ratio of a rectangle is the ratio of its longer side to its shorter side – the ratio of width to height, when the rectangle is oriented as a "landscape".

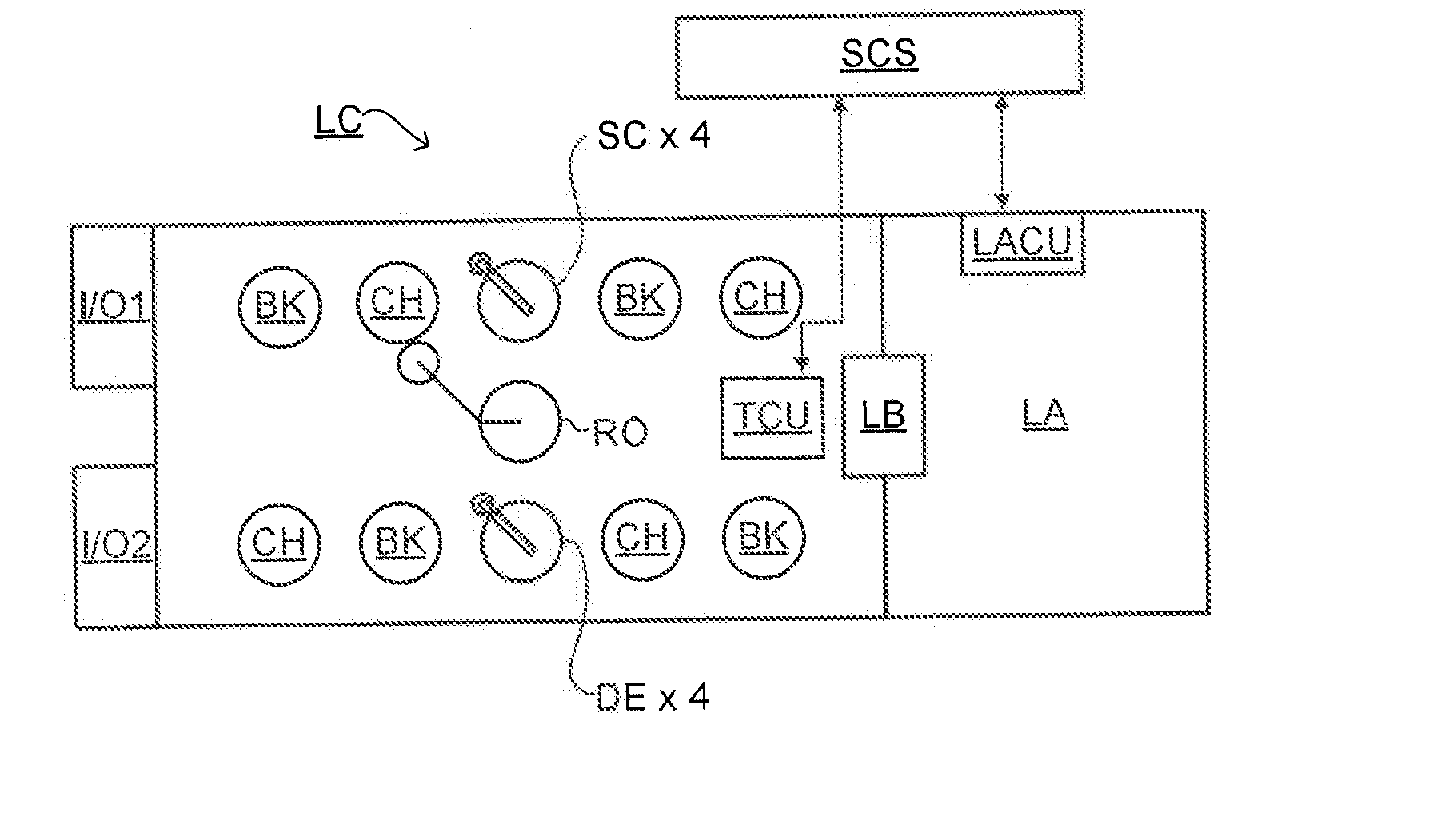

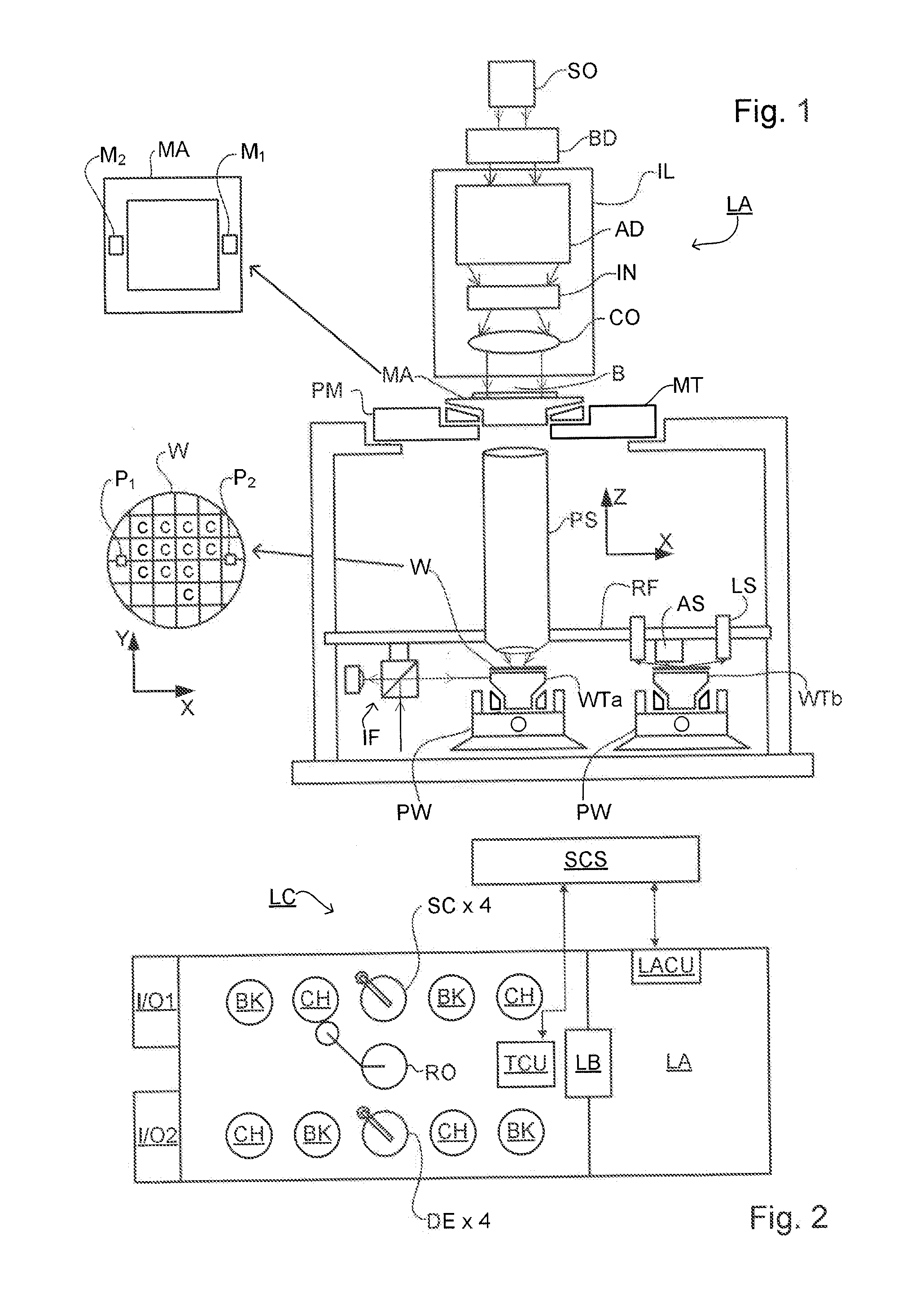

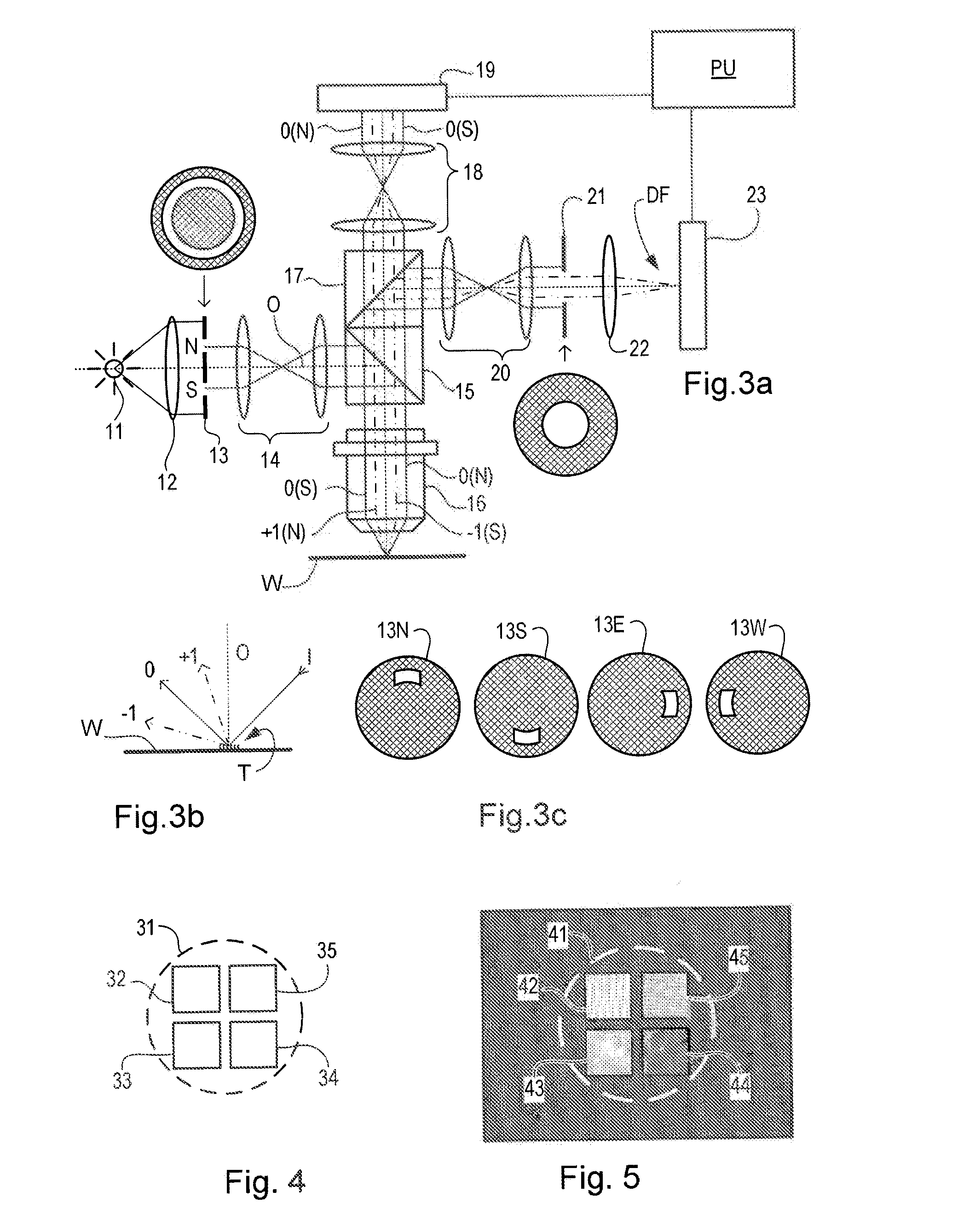

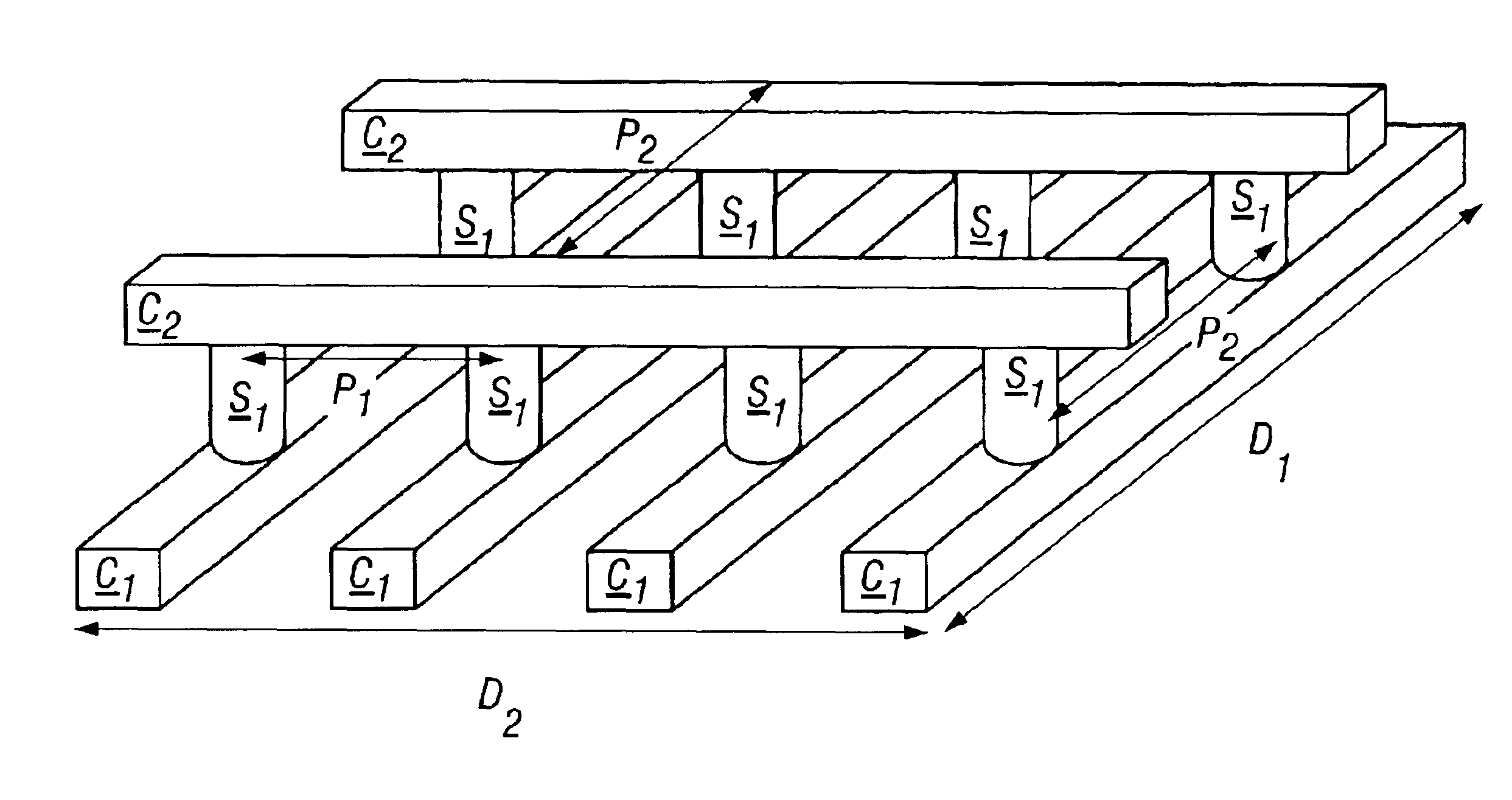

Substrate for Use in Metrology, Metrology Method and Device Manufacturing Method

InactiveUS20120044470A1Efficient packagingPhotomechanical apparatusMaterial analysis by optical meansMetrologyGrating

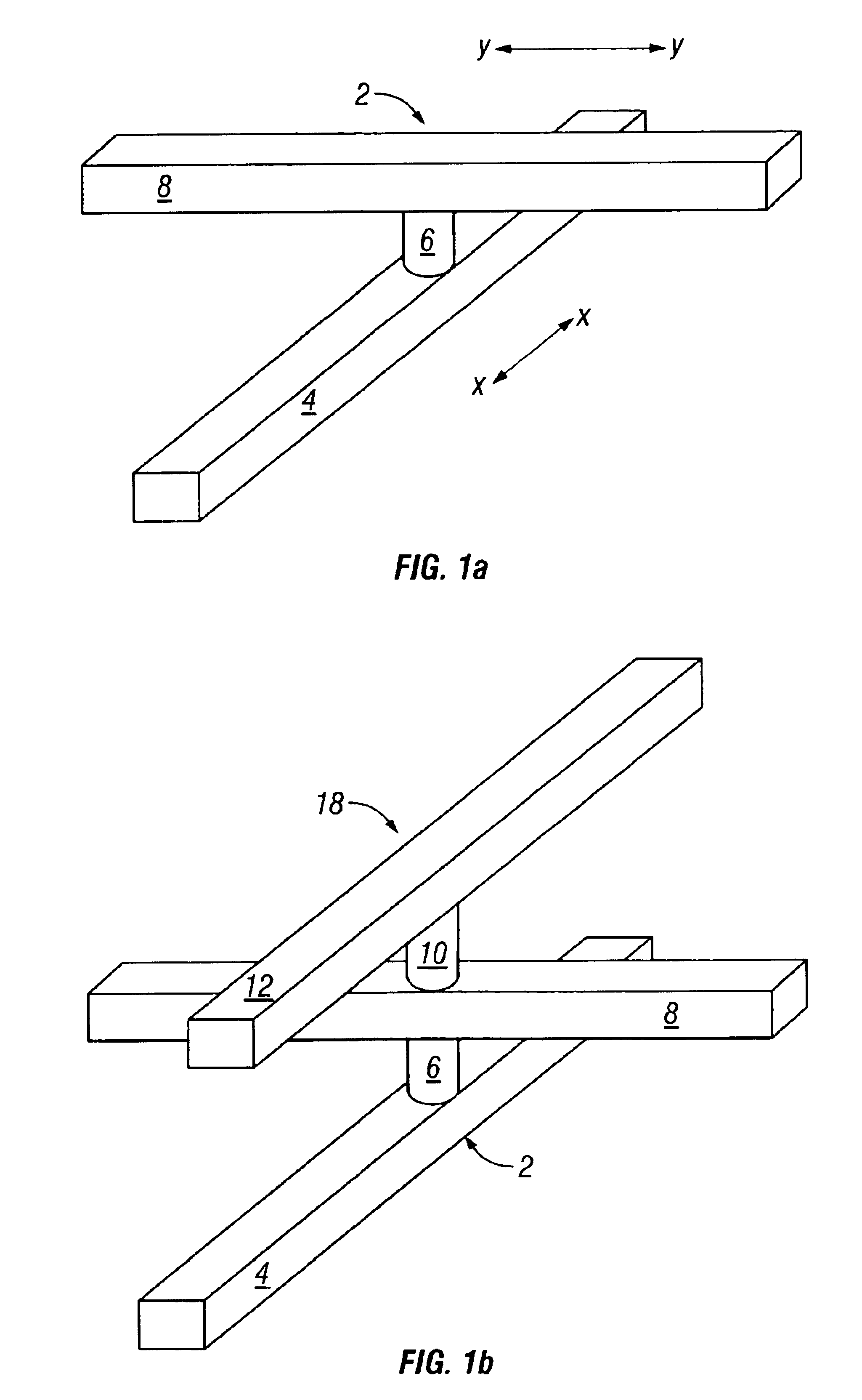

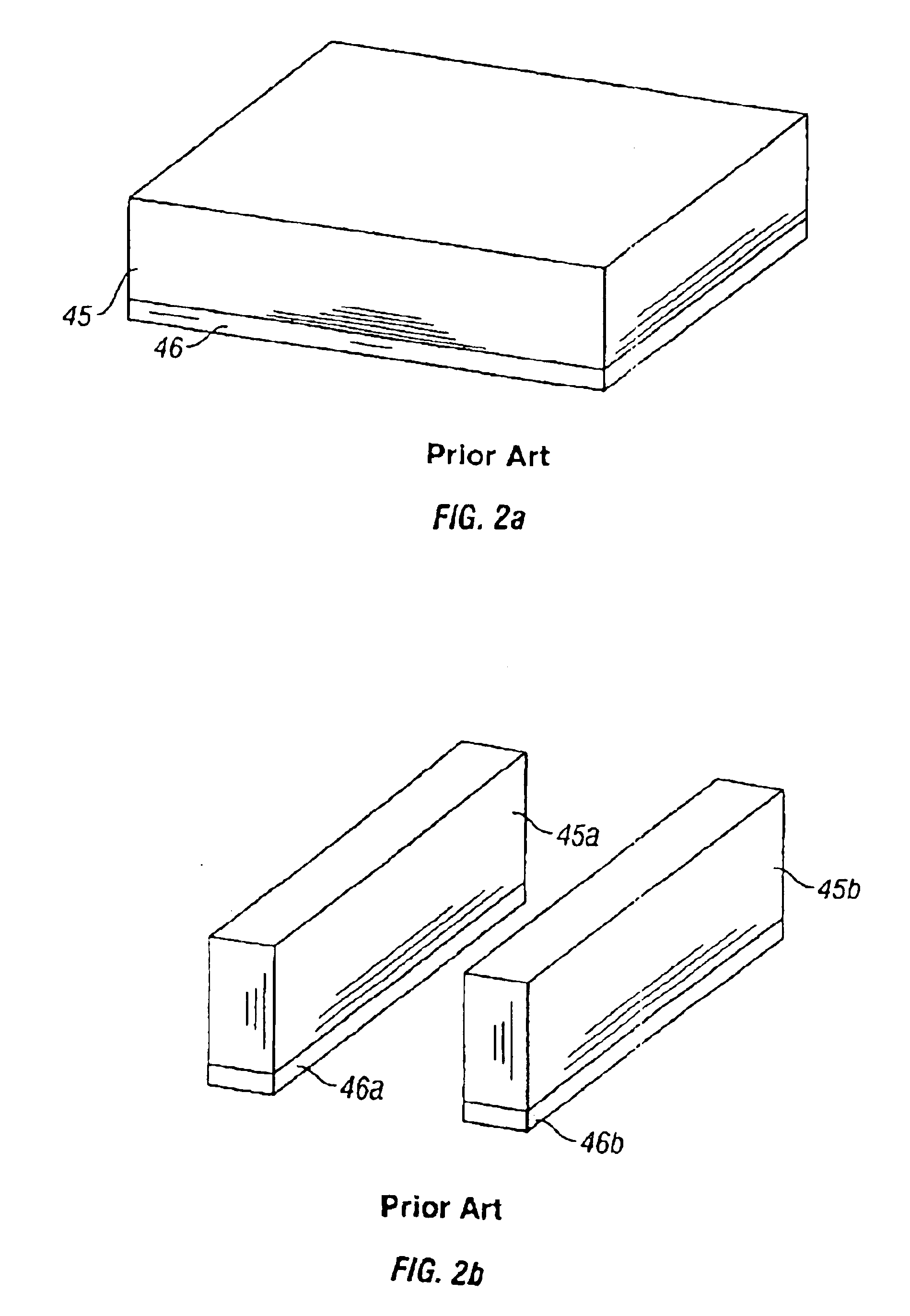

A pattern from a patterning device is applied to a substrate. The applied pattern includes device functional areas and metrology target areas. Each metrology target area comprises a plurality of individual grating portions, which are used for diffraction based overlay measurements or other diffraction based measurements. The gratings are of the small target type, which is small than an illumination spot used in the metrology. Each grating has an aspect ratio substantially greater than 1, meaning that a length in a direction perpendicular to the grating lines which is substantially greater than a width of the grating. Total target area can be reduced without loss of performance in the diffraction based metrology. A composite target can comprise a plurality of individual grating portions of different overlay biases. Using integer aspect ratios such as 2:1 or 4:1, grating portions of different directions can be packed efficiently into rectangular composite target areas.

Owner:ASML NETHERLANDS BV

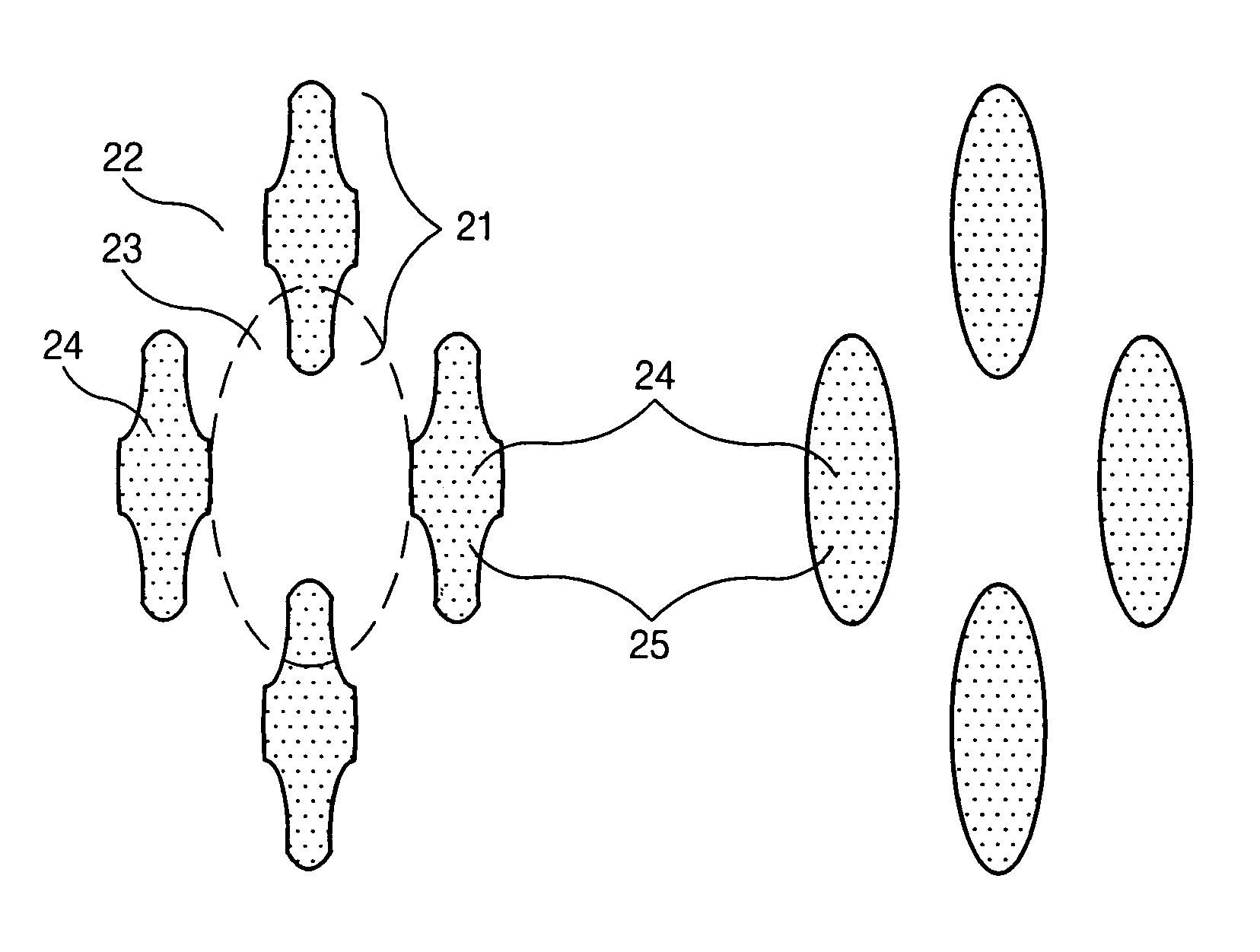

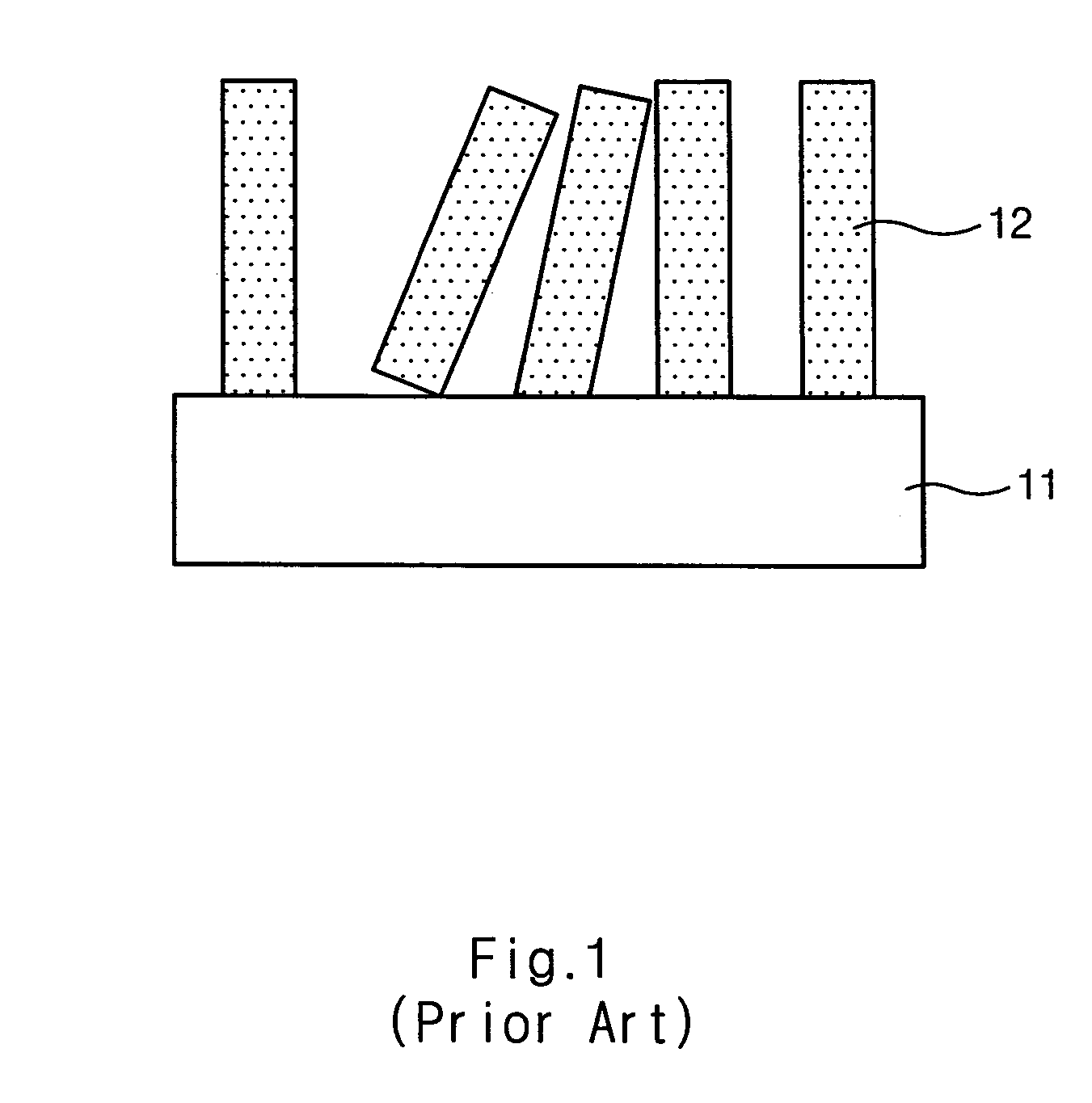

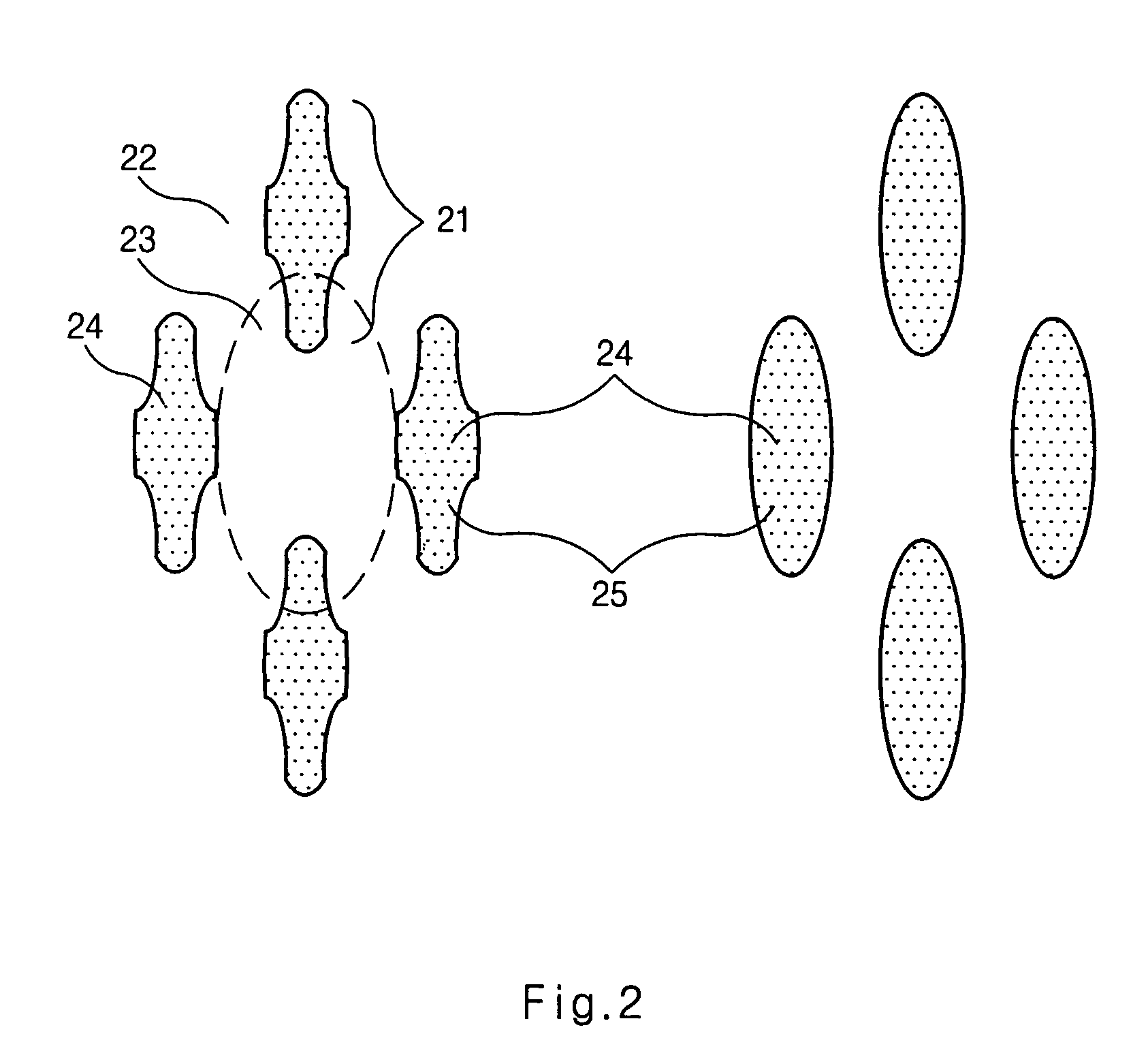

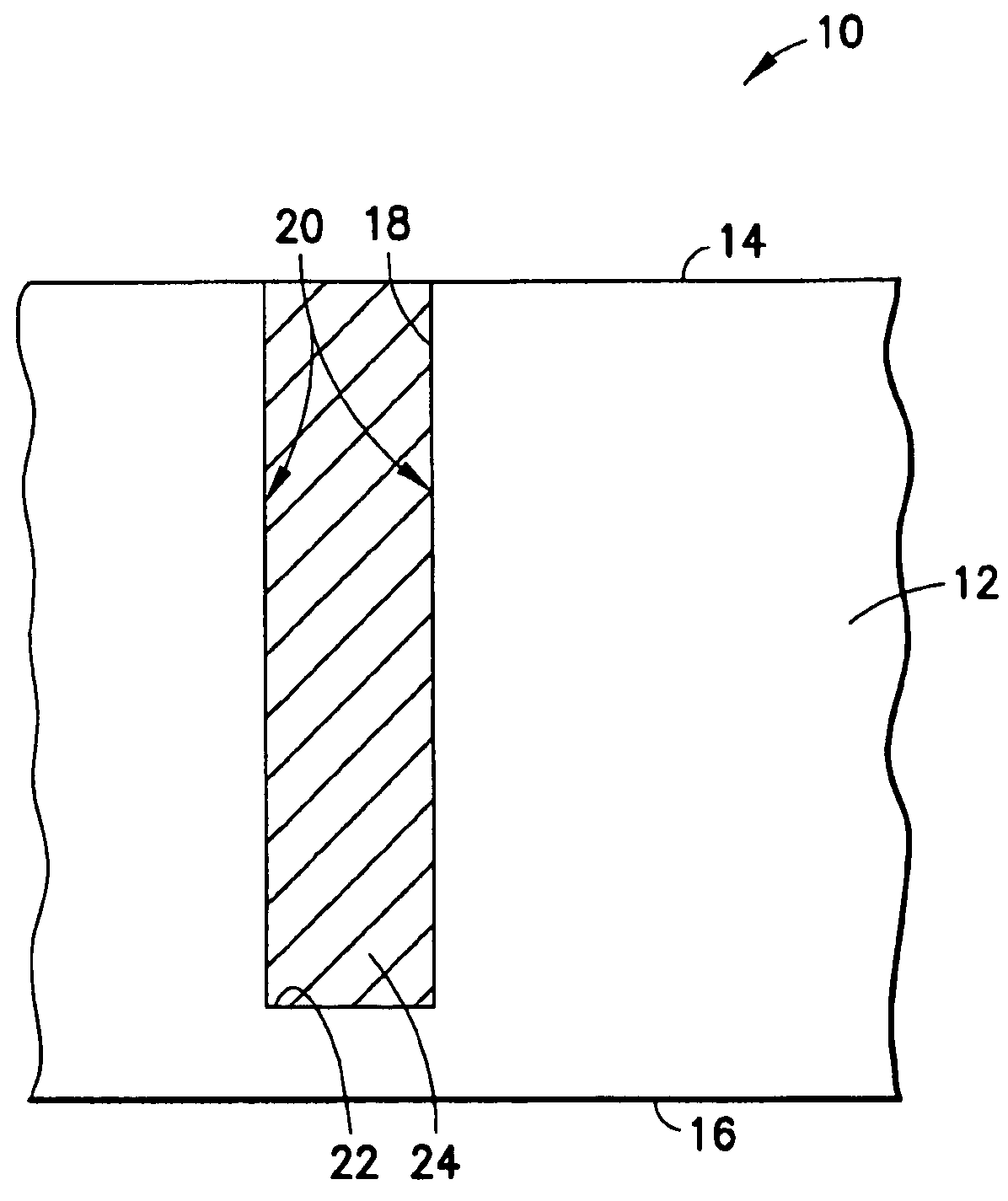

High-density three-dimensional memory cell

InactiveUS6952030B2High densityReduce the overall heightTransistorSemiconductor/solid-state device detailsElectrical conductorHigh density

A three dimensional monolithic memory comprising a memory cell allowing for increased density is disclosed. In the memory cell of the present invention, a bottom conductor preferably comprising tungsten is formed. Above the bottom conductor a semiconductor element preferably comprises two diode portions and an antifuse. Above the semiconductor element are additional conductors and semiconductor elements in multiple stones of memories. The arrangement of processing steps and the choice of materials decreases aspect ratio of each memory cell, improving the reliability of gap fill and preventing etch undercut.

Owner:SANDISK TECH LLC

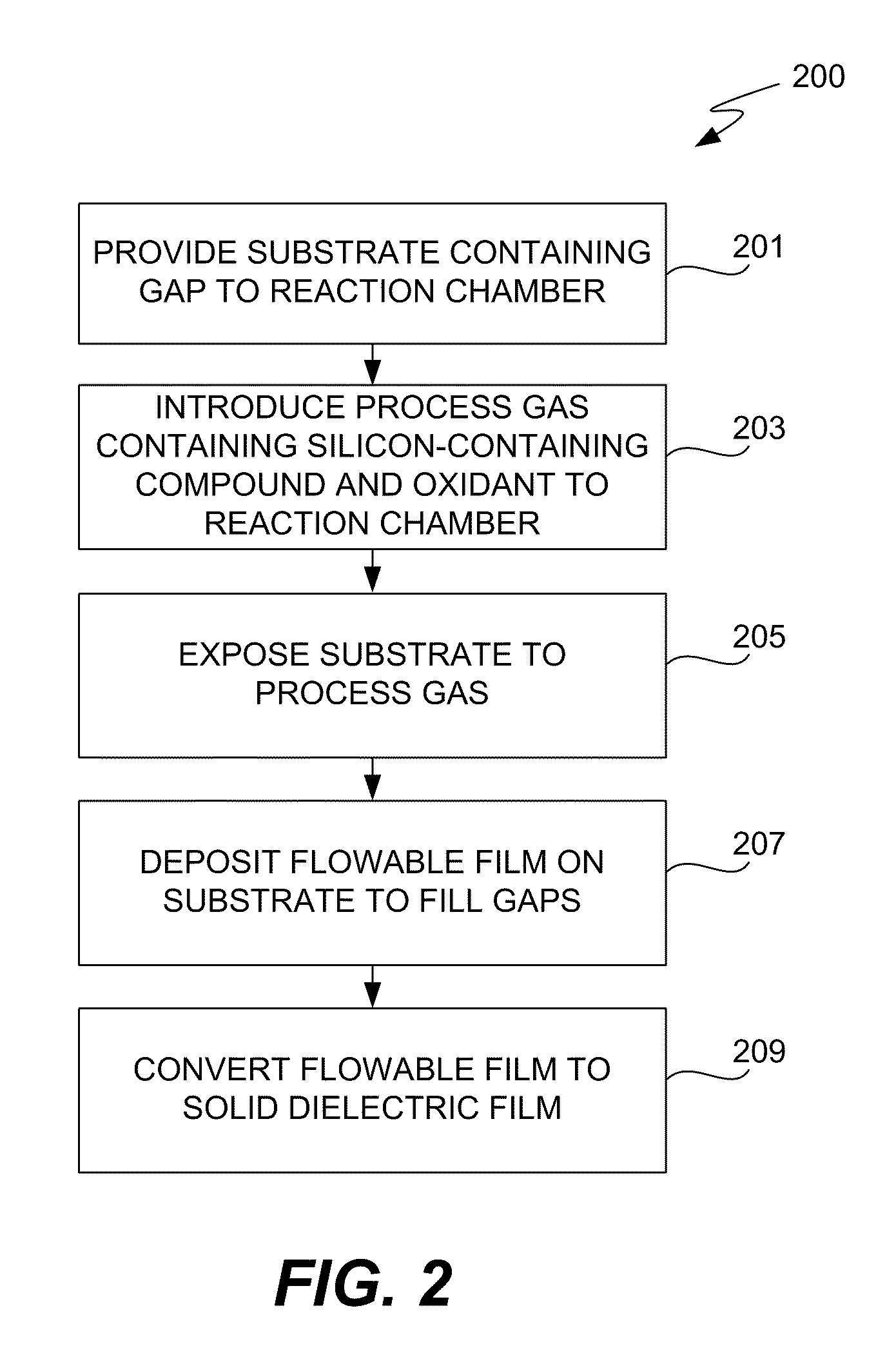

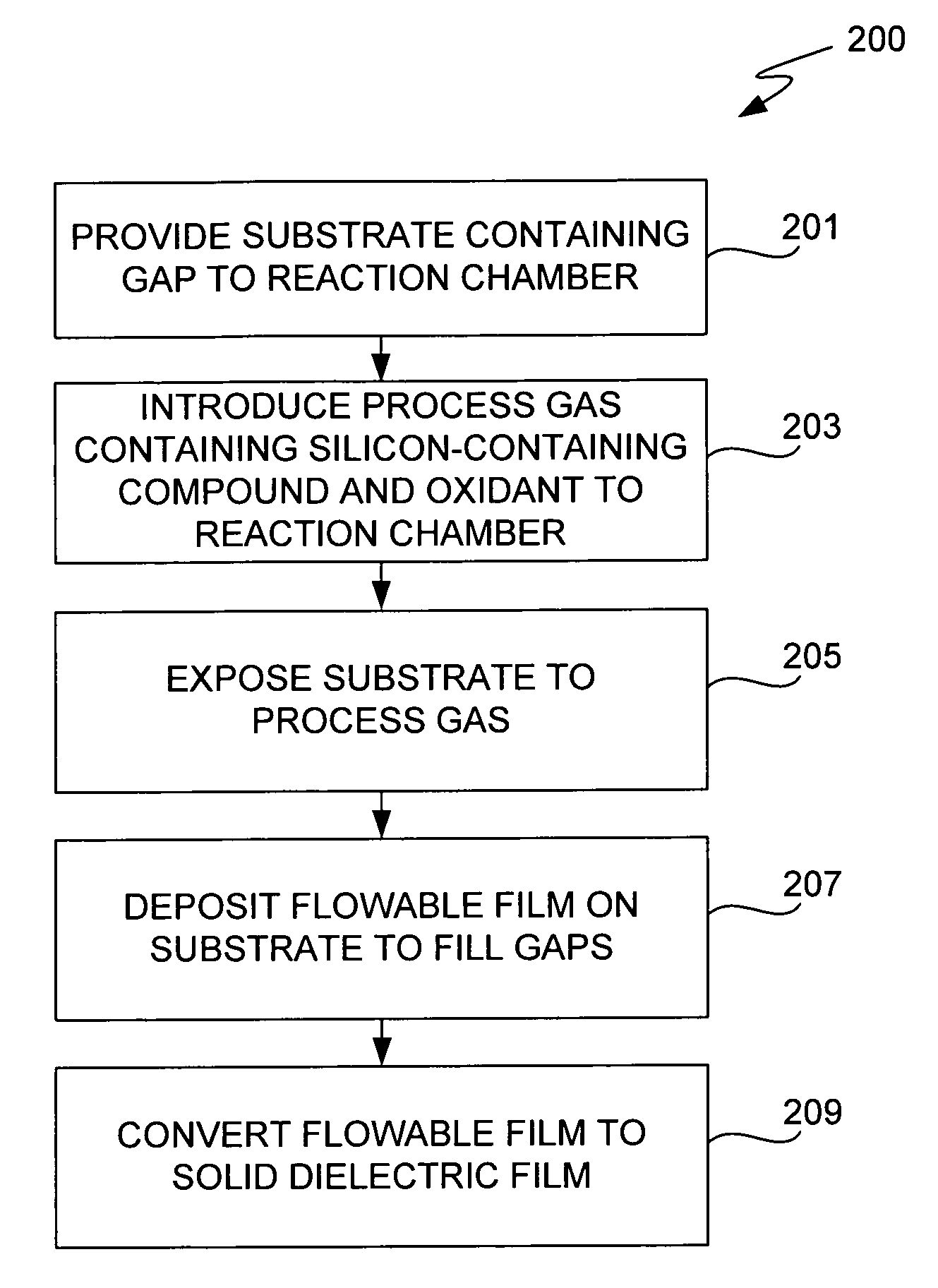

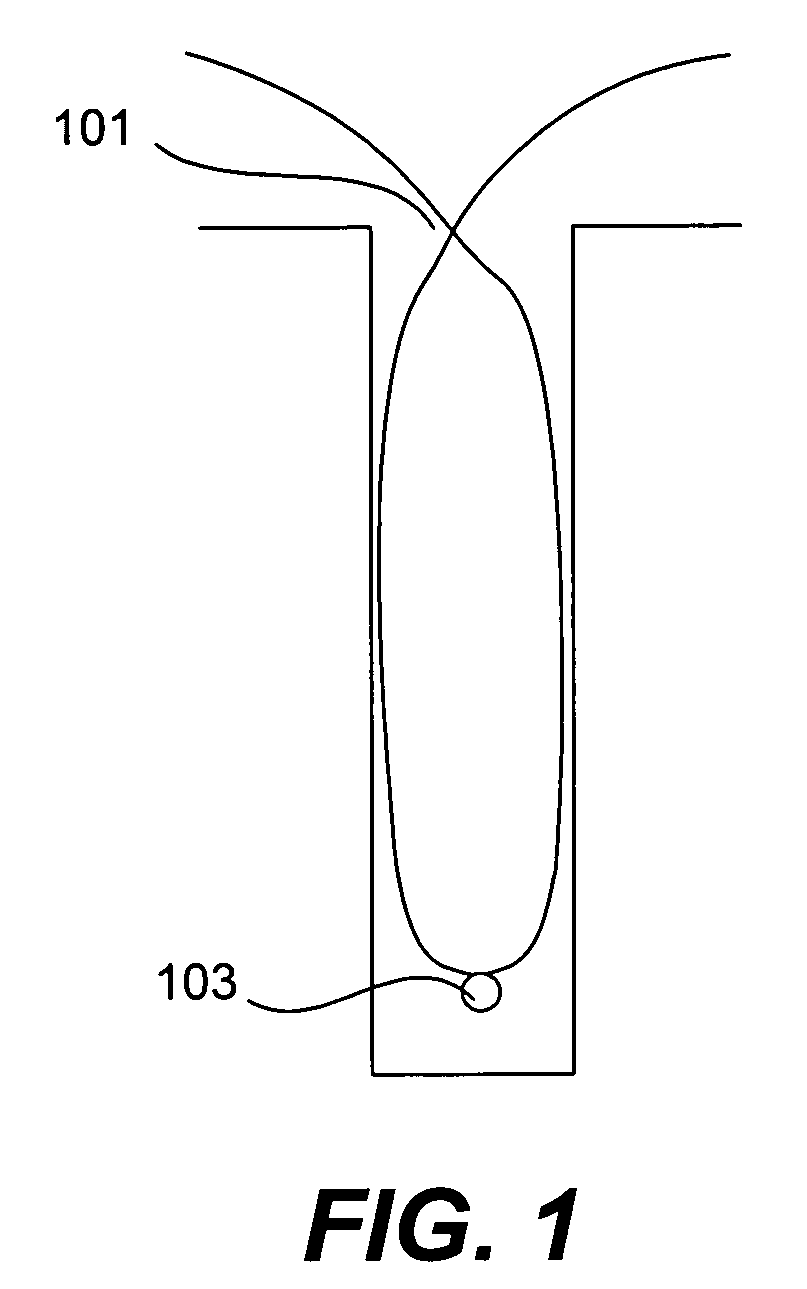

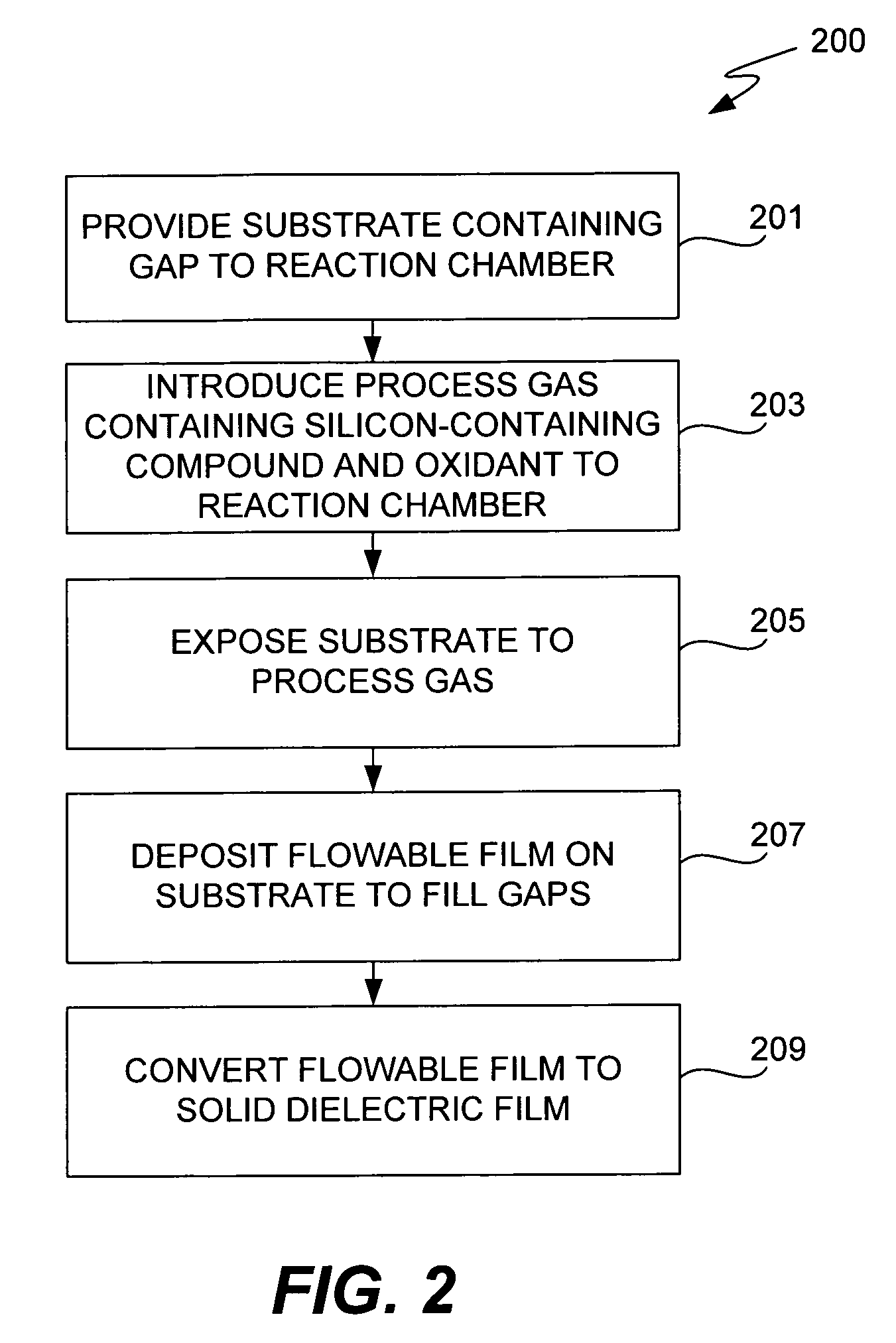

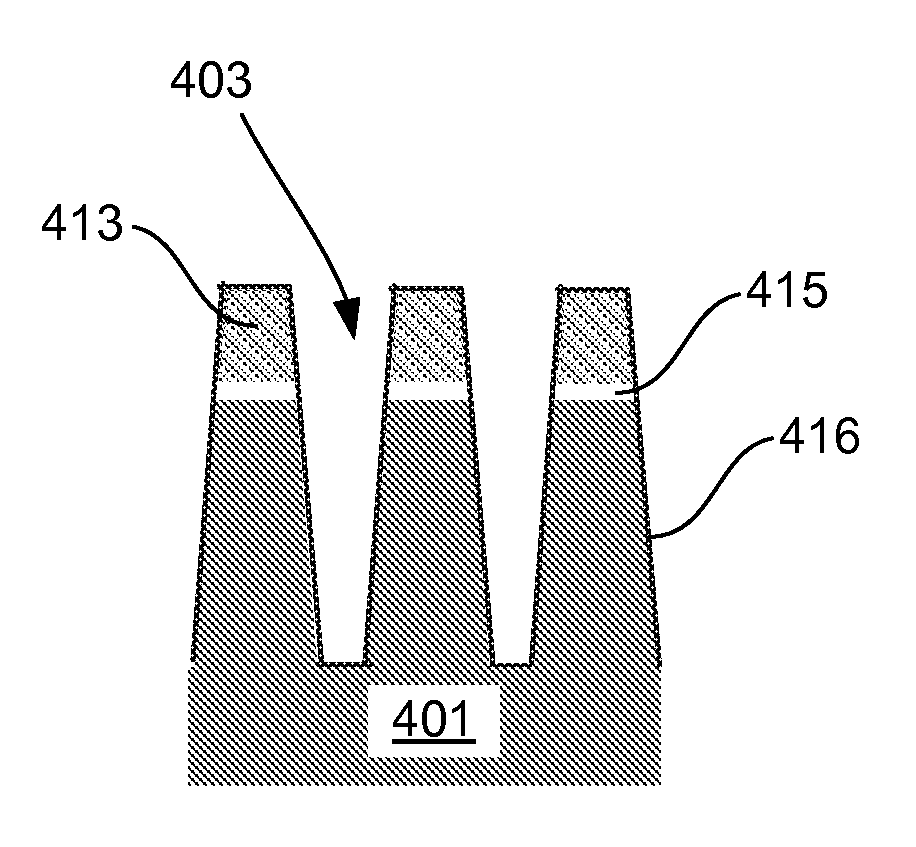

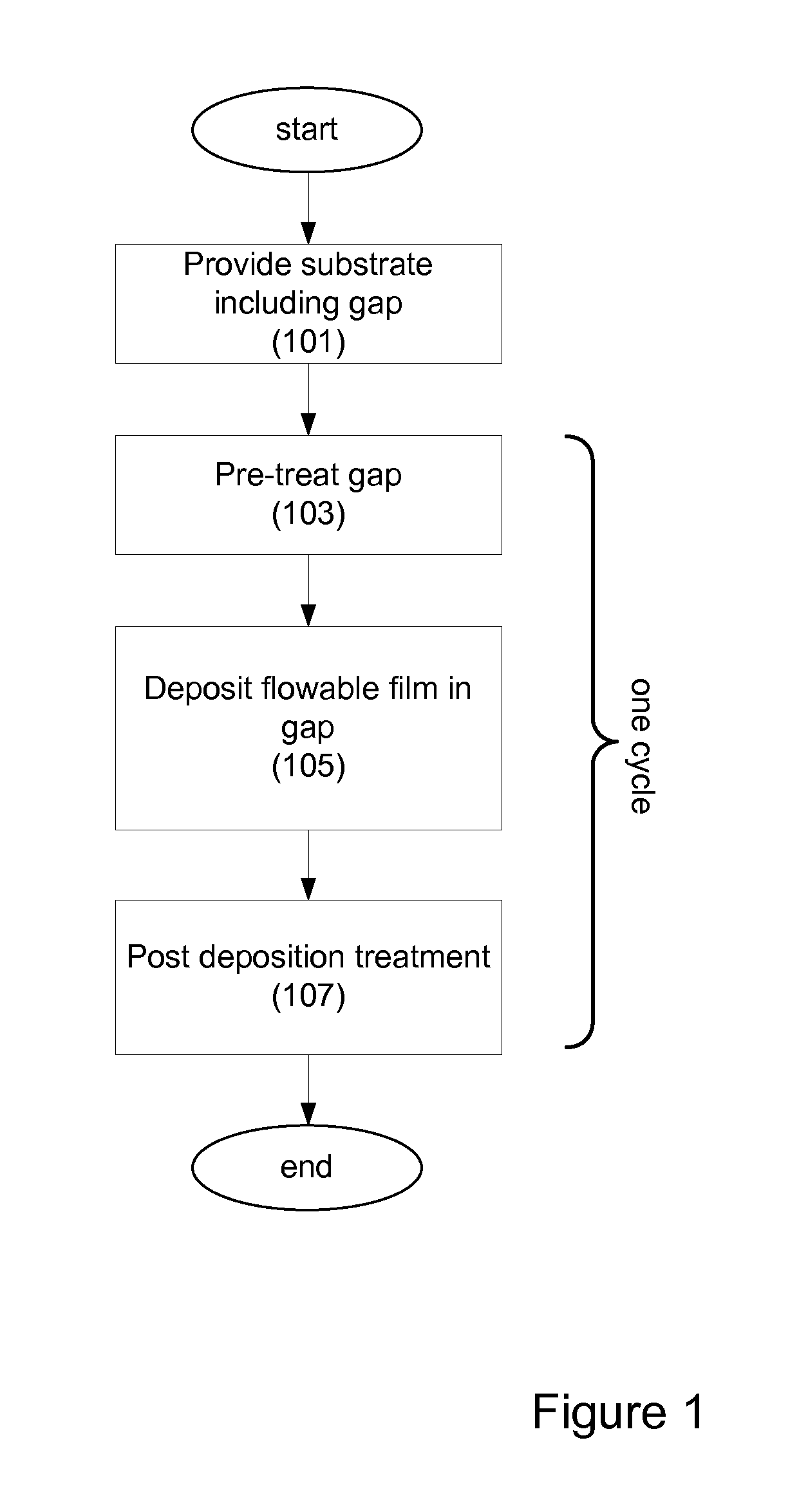

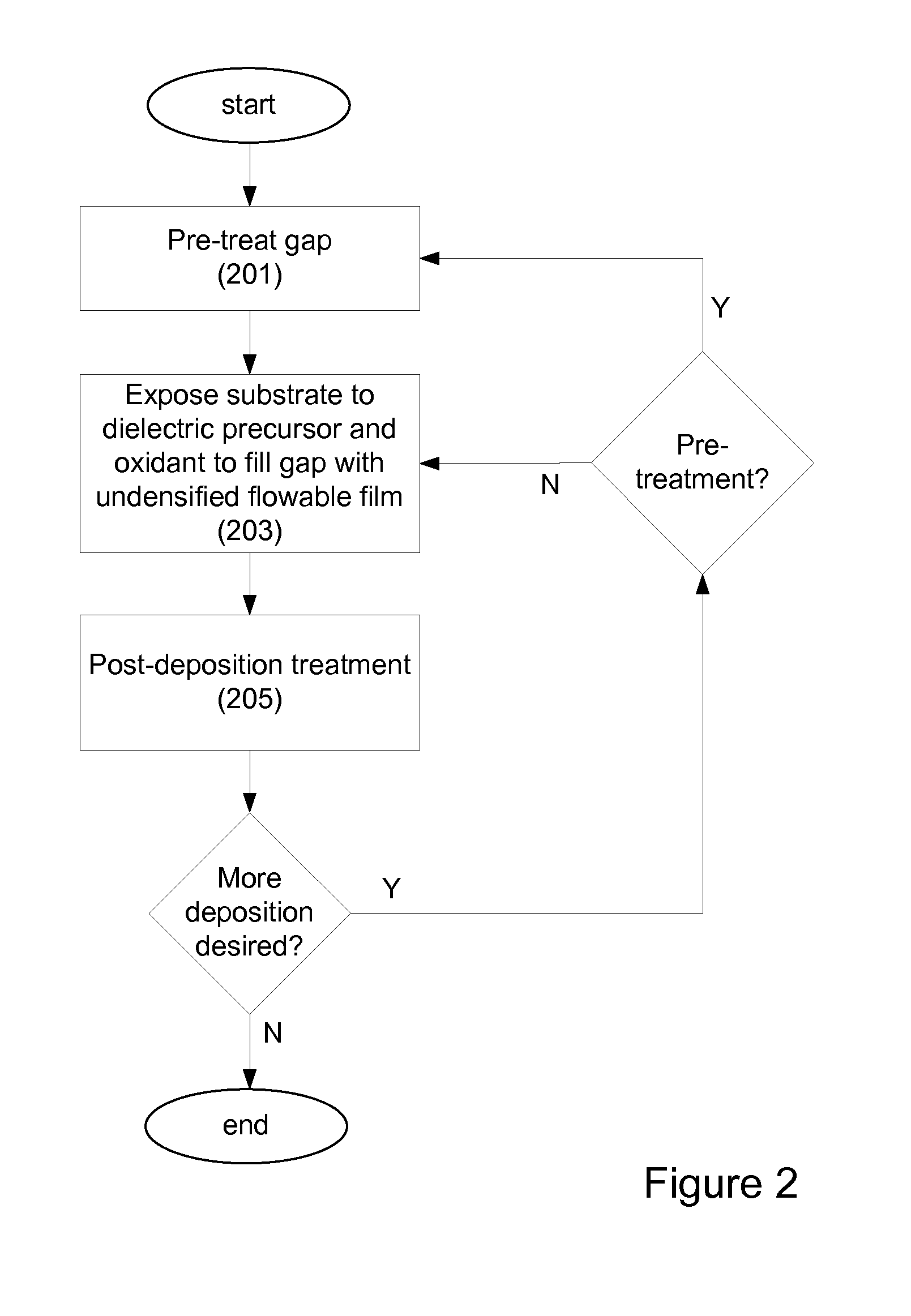

CVD flowable gap fill

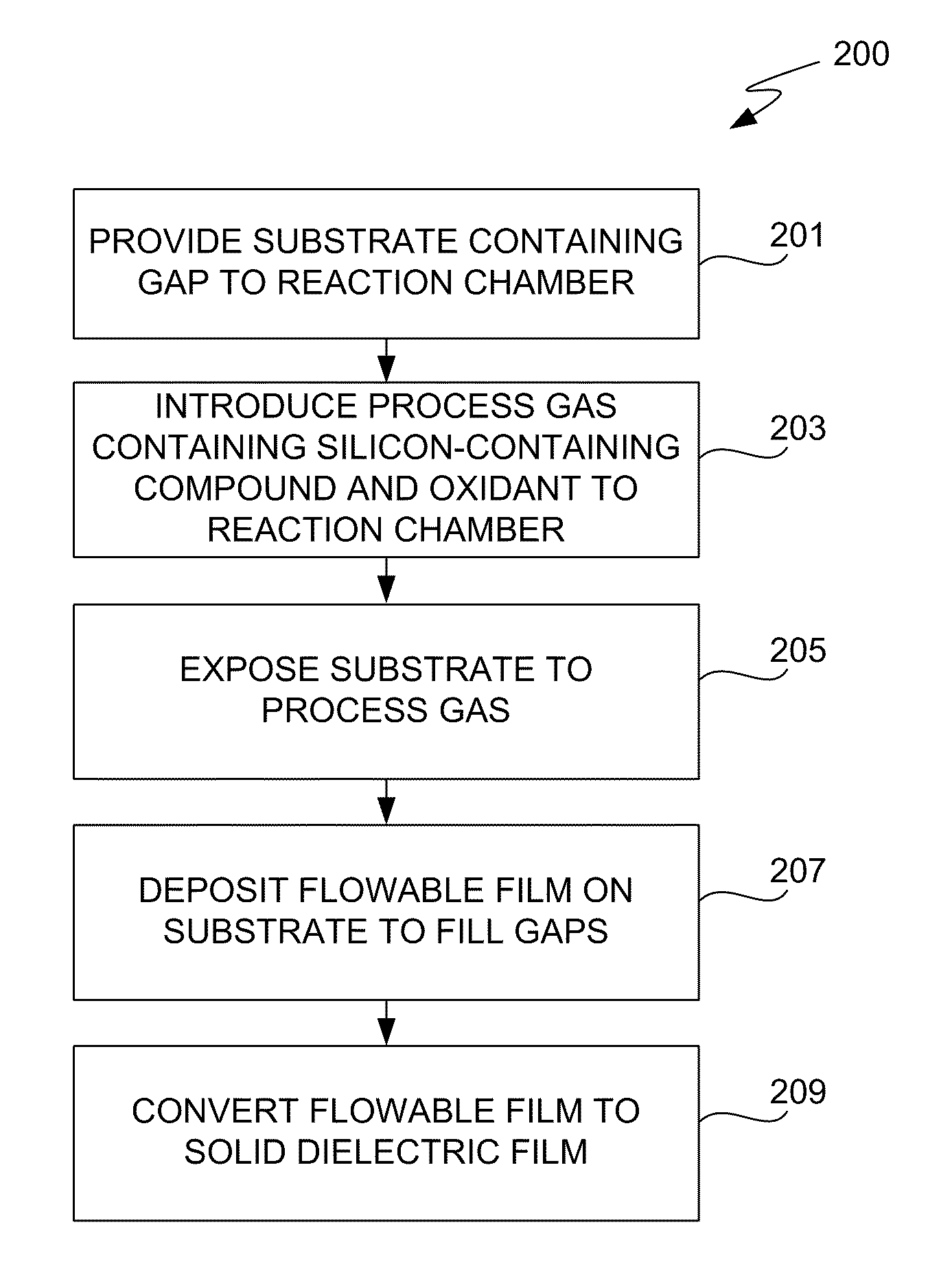

The present invention meets these needs by providing improved methods of filling gaps. In certain embodiments, the methods involve placing a substrate into a reaction chamber and introducing a vapor phase silicon-containing compound and oxidant into the chamber. Reactor conditions are controlled so that the silicon-containing compound and the oxidant are made to react and condense onto the substrate. The chemical reaction causes the formation of a flowable film, in some instances containing Si—OH, Si—H and Si—O bonds. The flowable film fills gaps on the substrates. The flowable film is then converted into a silicon oxide film, for example by plasma or thermal annealing. The methods of this invention may be used to fill high aspect ratio gaps, including gaps having aspect ratios ranging from 3:1 to 10:1.

Owner:NOVELLUS SYSTEMS

CVD flowable gap fill

The present invention meets these needs by providing improved methods of filling gaps. In certain embodiments, the methods involve placing a substrate into a reaction chamber and introducing a vapor phase silicon-containing compound and oxidant into the chamber. Reactor conditions are controlled so that the silicon-containing compound and the oxidant are made to react and condense onto the substrate. The chemical reaction causes the formation of a flowable film, in some instances containing Si—OH, Si—H and Si—O bonds. The flowable film fills gaps on the substrates. The flowable film is then converted into a silicon oxide film, for example by plasma or thermal annealing. The methods of this invention may be used to fill high aspect ratio gaps, including gaps having aspect ratios ranging from 3:1 to 10:1.

Owner:NOVELLUS SYSTEMS

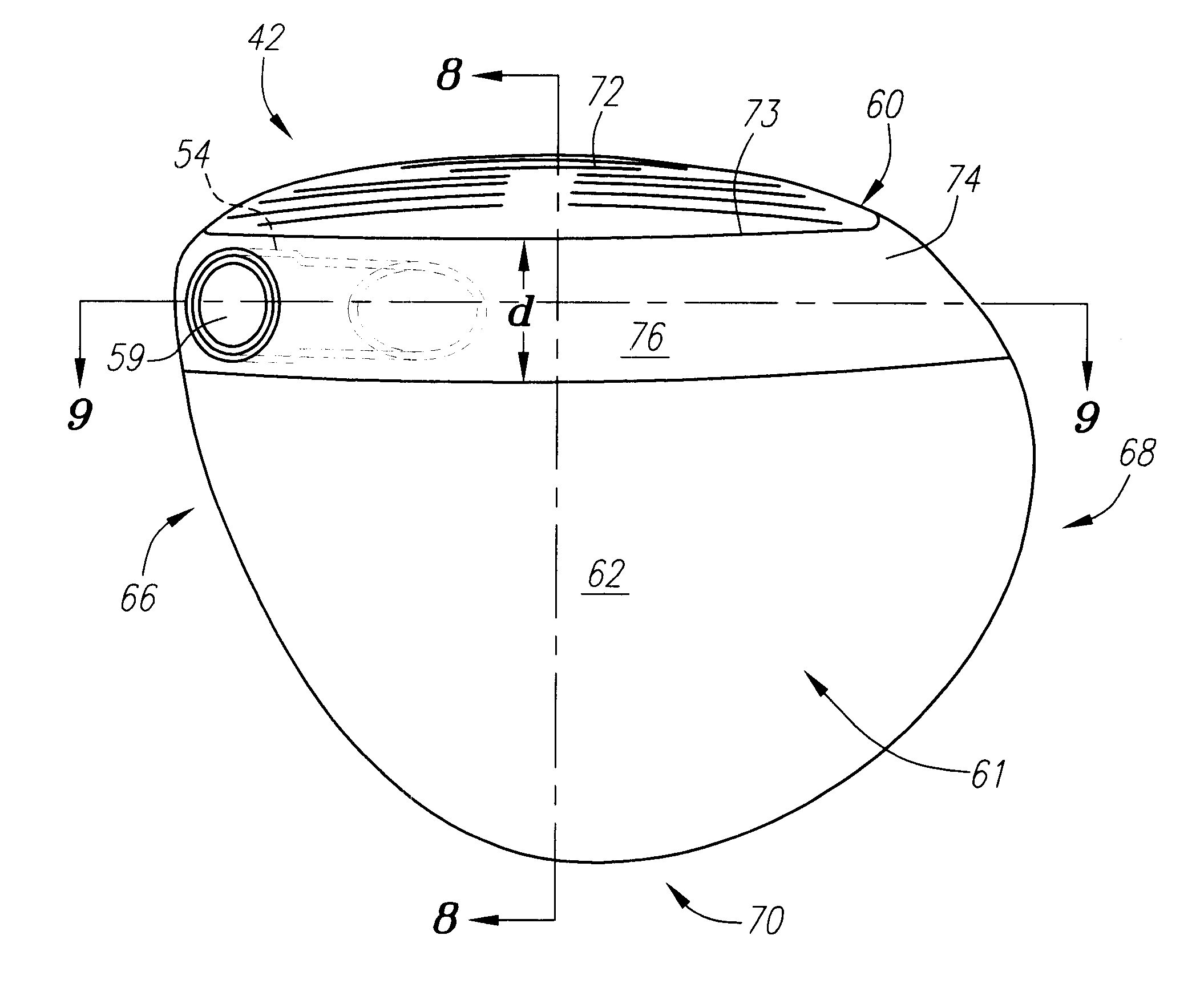

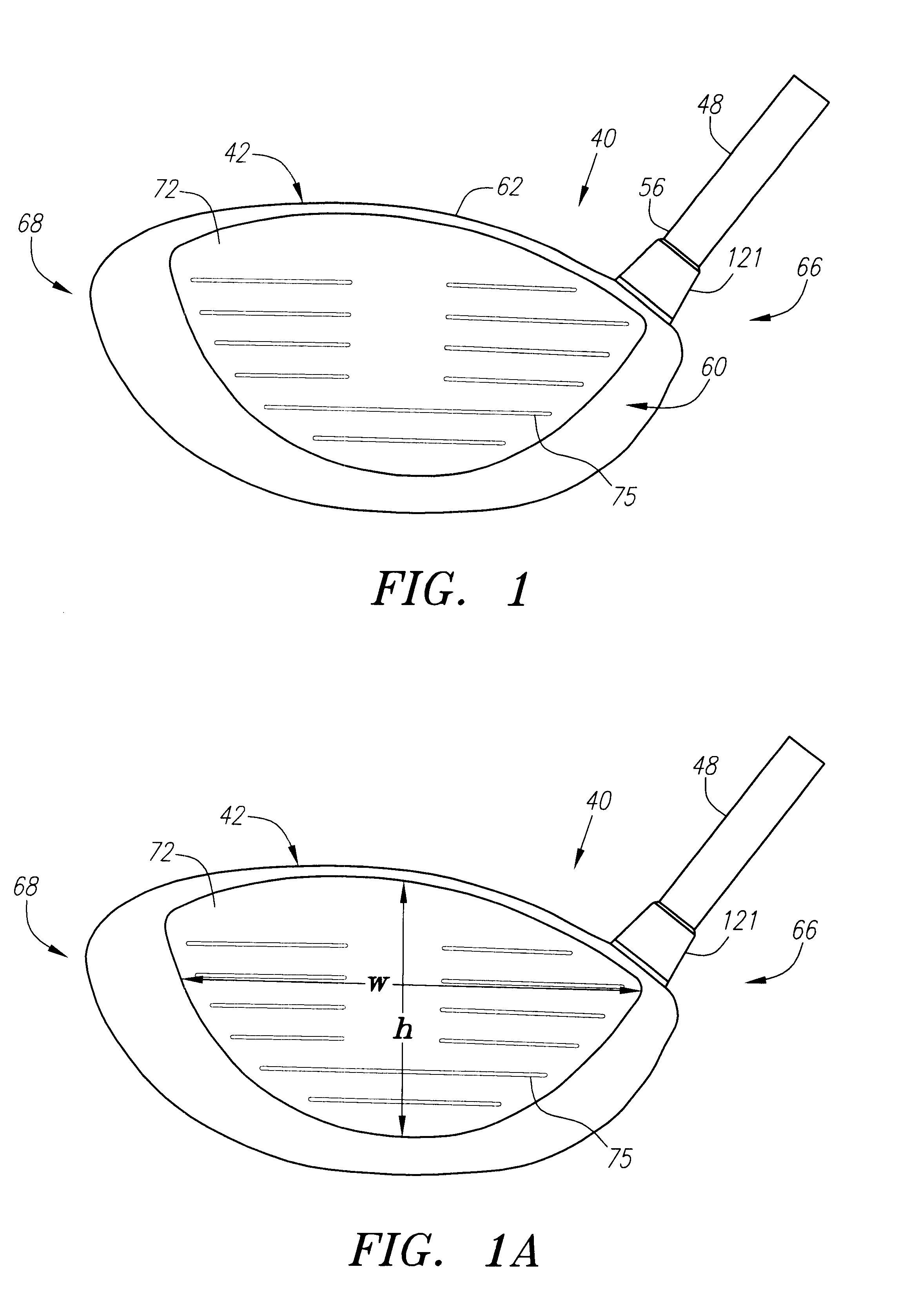

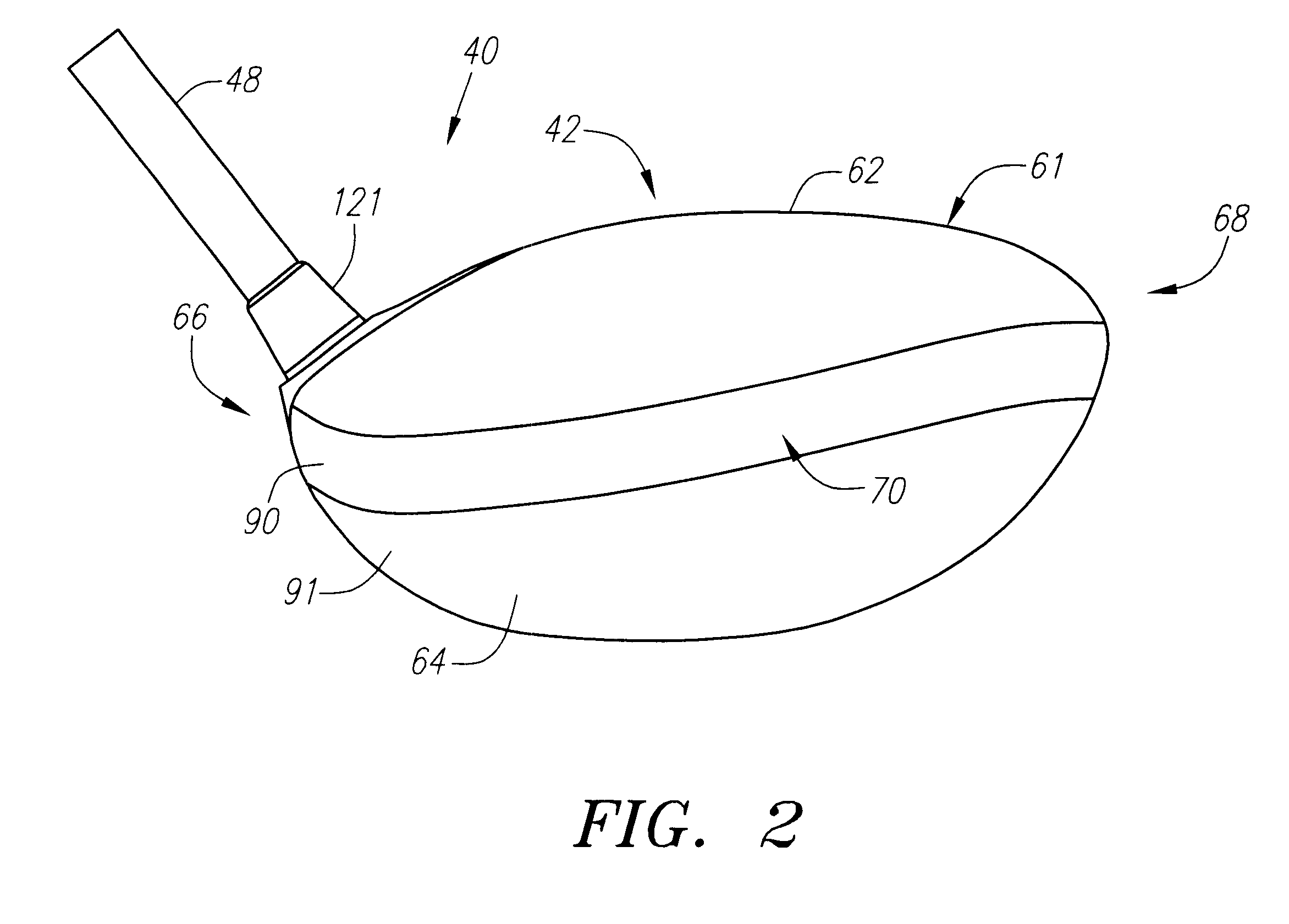

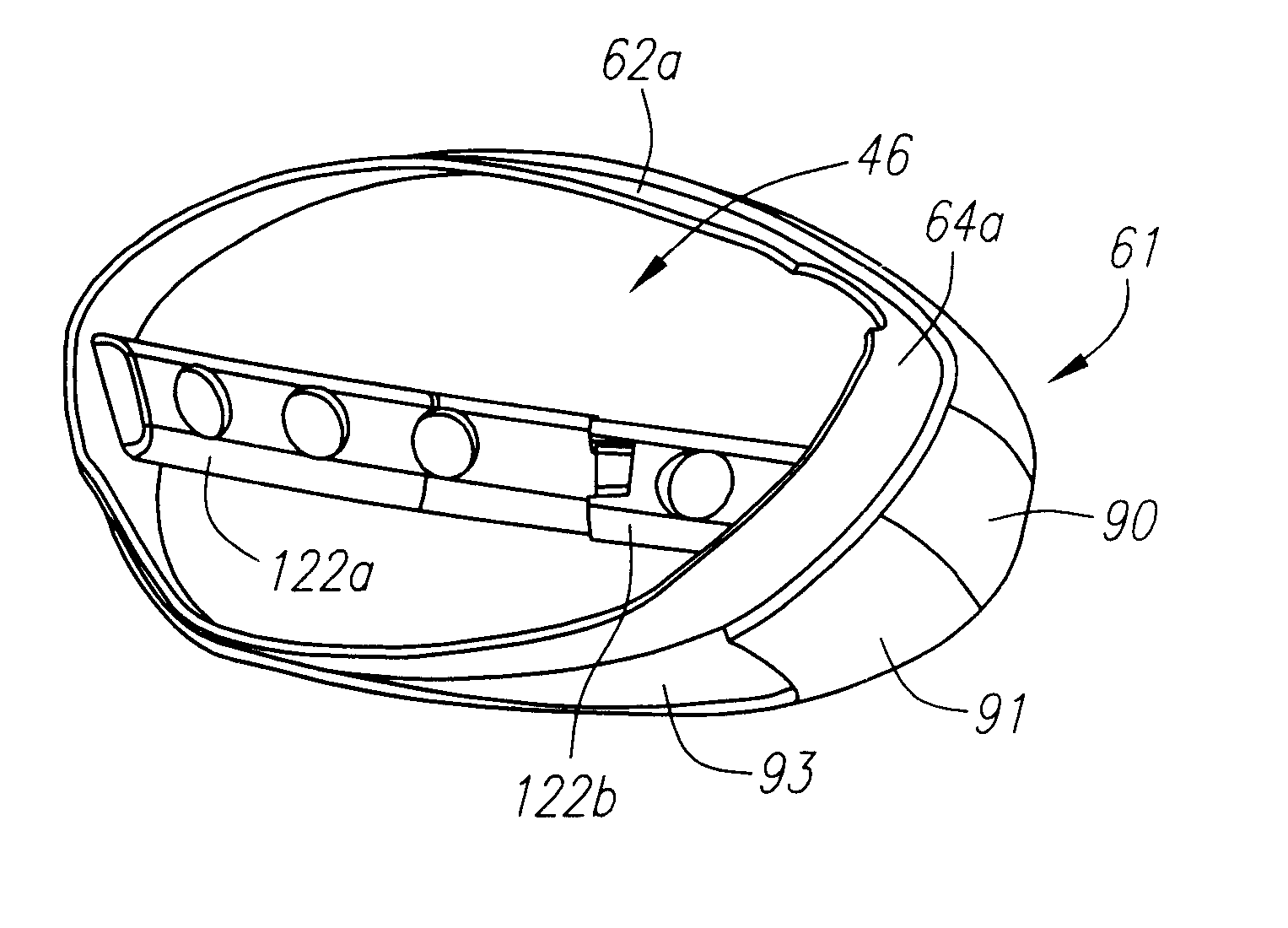

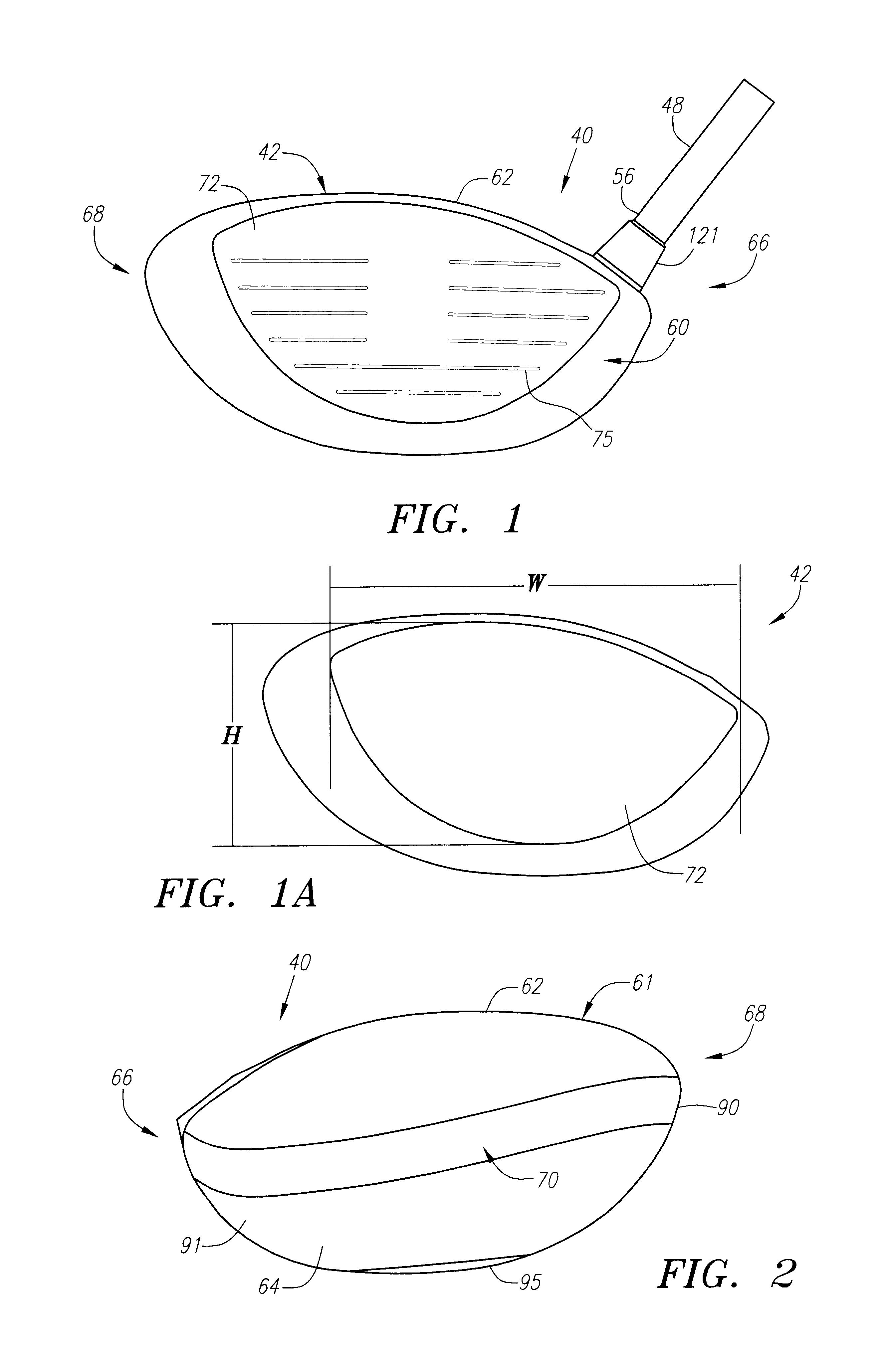

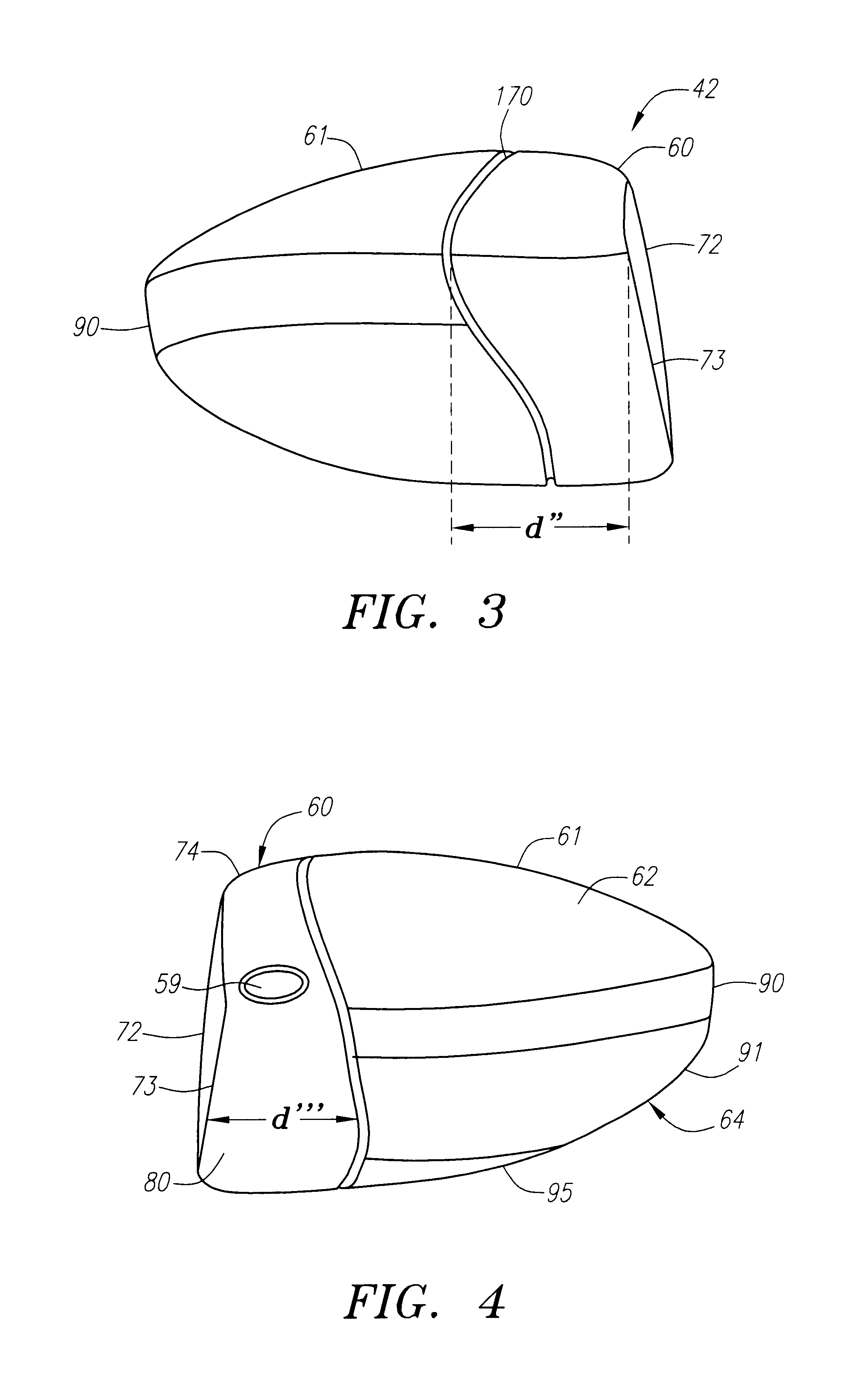

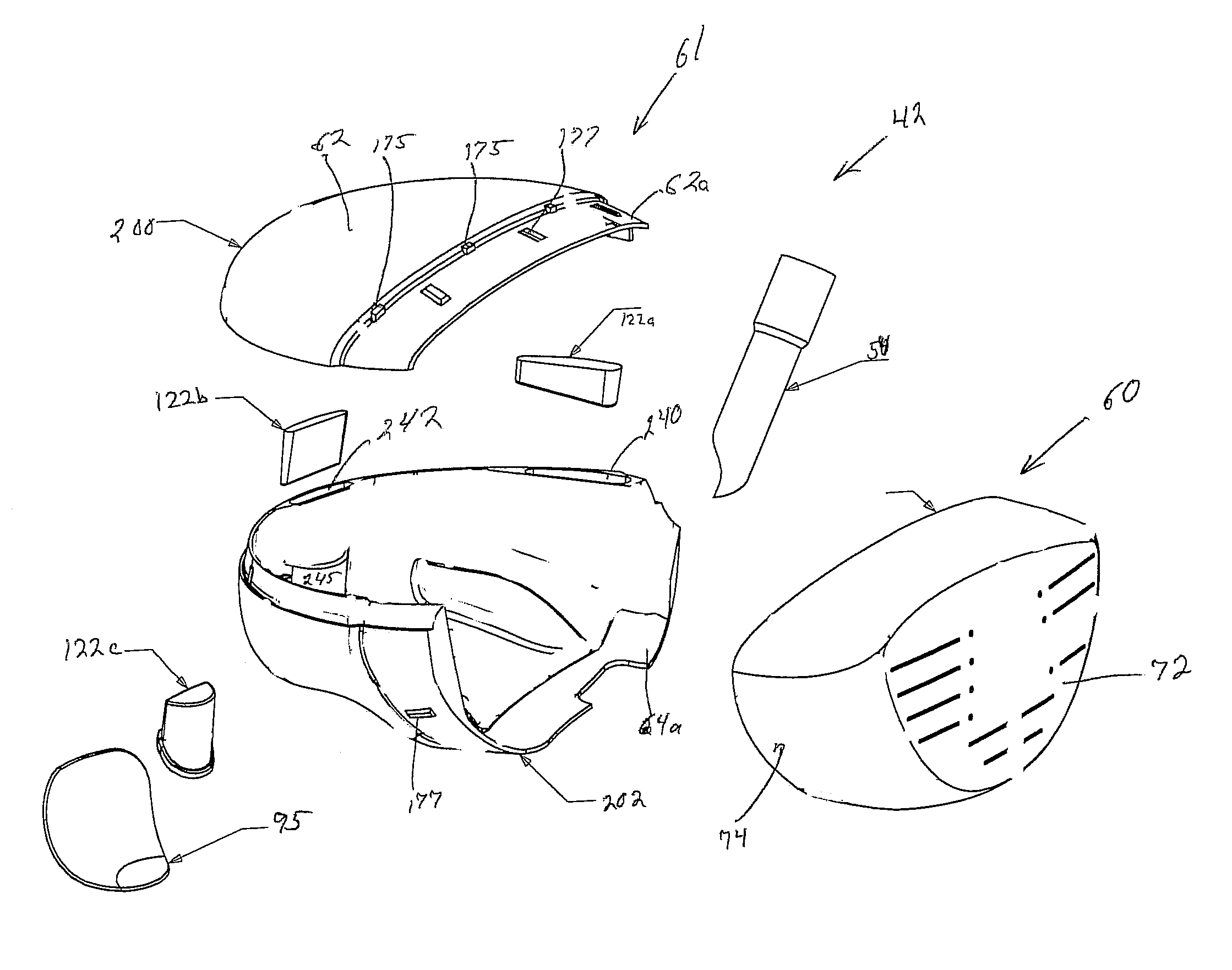

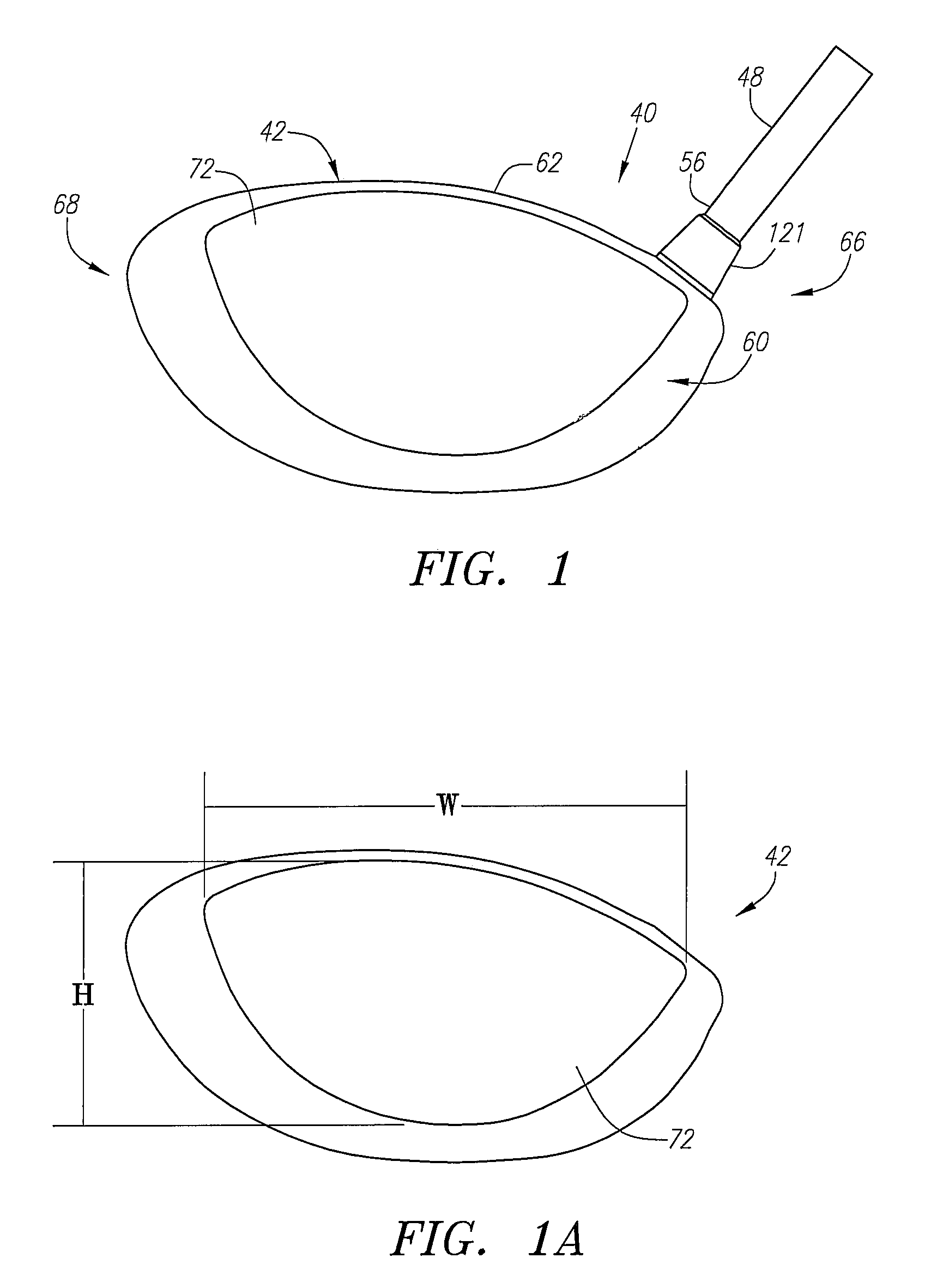

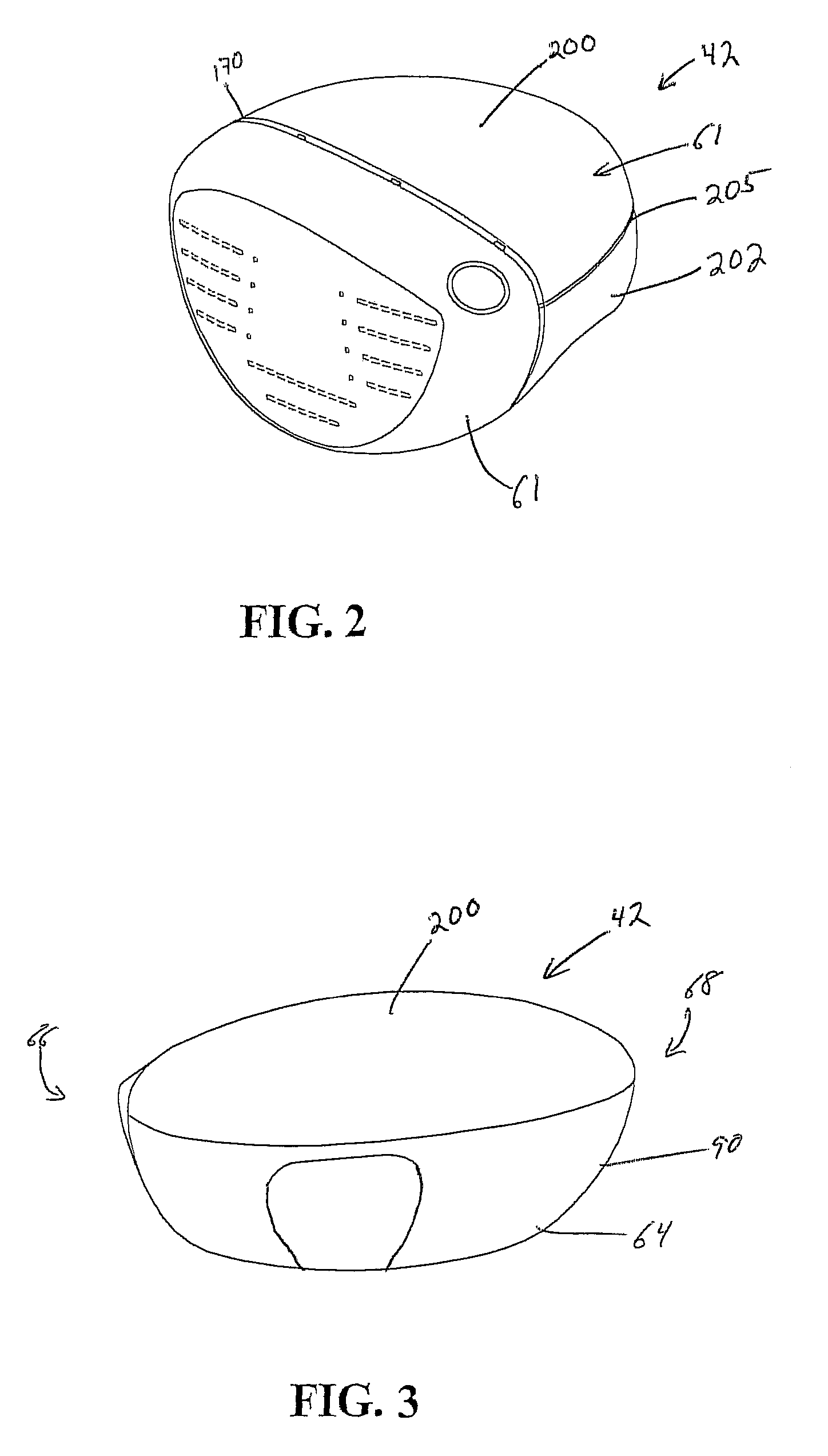

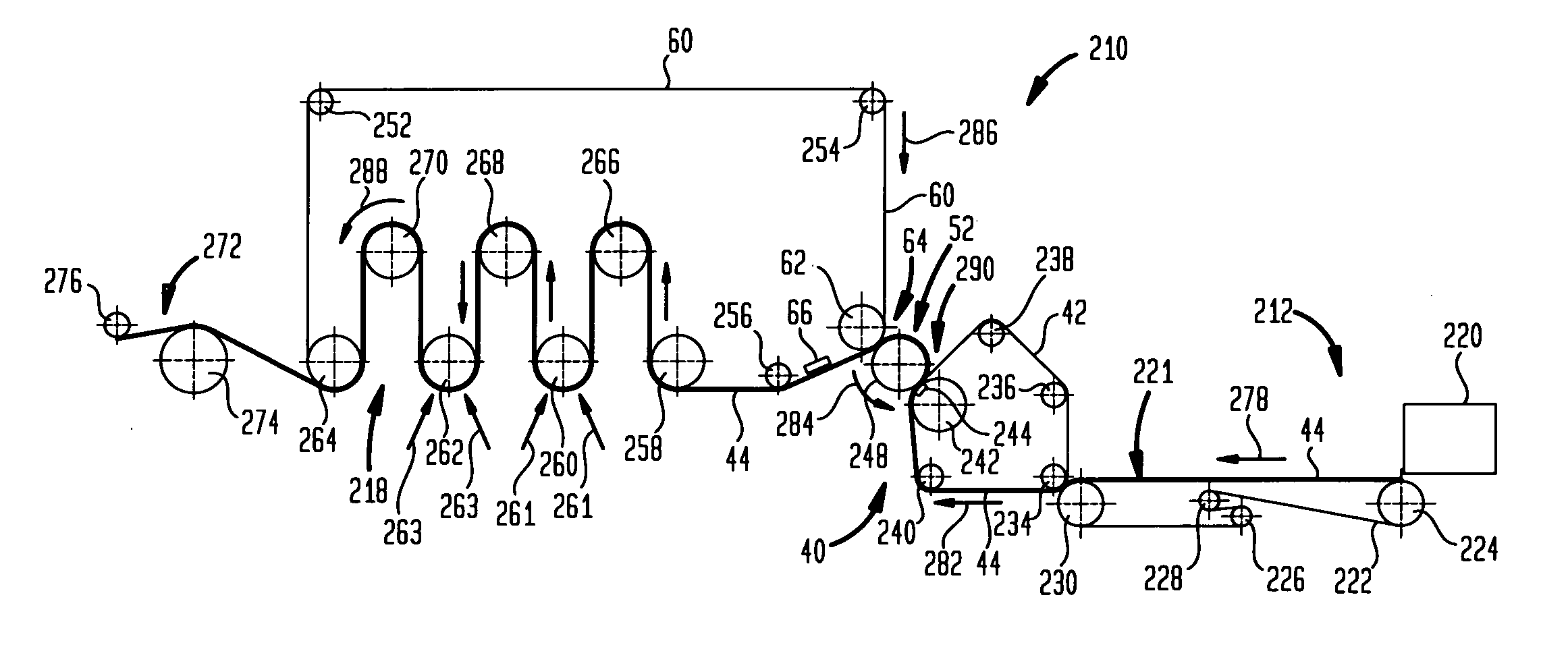

Multiple material golf club head

InactiveUS6491592B2Large coefficientImprove complianceMetal-working apparatusGolf clubsCoefficient of restitutionMetallic materials

A golf club (40) having a club head (42) with a face component (60) and an aft-body (61) is disclosed herein. The face component (60) has a striking plate portion (72) and a return portion (74). The aft-body (61) is composed of a crown portion (62), a sole portion (64) and optionally a ribbon section (90). The face component (60) is composed of a metal material, and the aft-body (61) is composed of a non-metal material such as a composite material or a thermoplastic material. The striking plate portion (72) preferably has an aspect ratio less than 1.7. The striking plate portion (72) preferably has concentric regions of thickness with the thickness portion in the center (102). The club head (42) has a volume in the range of 300 cubic centimeters to 600 cubic centimeters, a weight in the range of 165 grams to 300 grams, and a striking plate portion (72) surface area in the range of 4.00 square inches to 7.50 square inches. The golf club head (42) has a coefficient of restitution greater than 0.81 under test such as the USGA test conditions specified pursuant to Rule 4-1e, Appendix II, of the Rules of Golf for 1998-1999.

Owner:TOPGOLF CALLAWAY BRANDS CORP

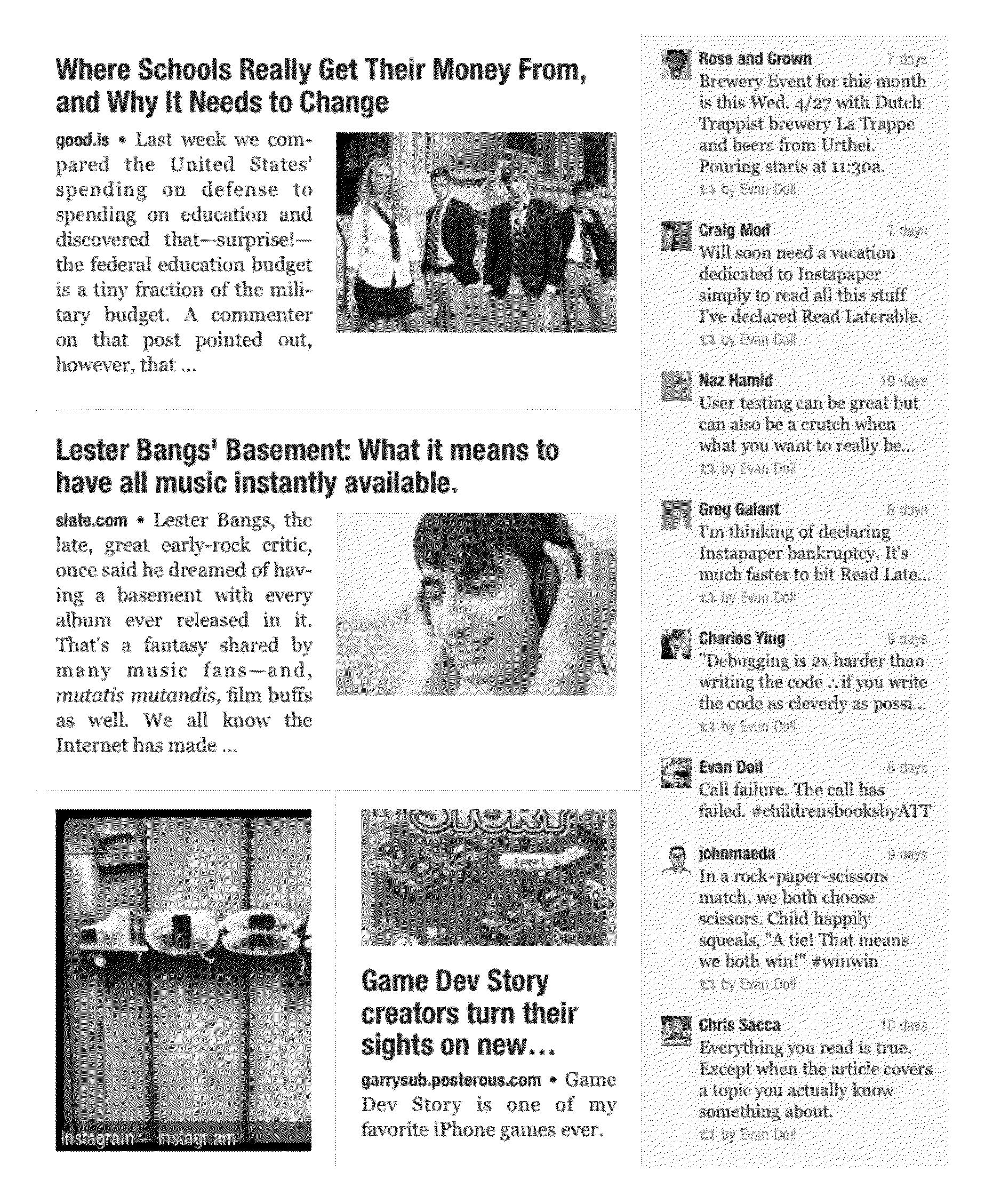

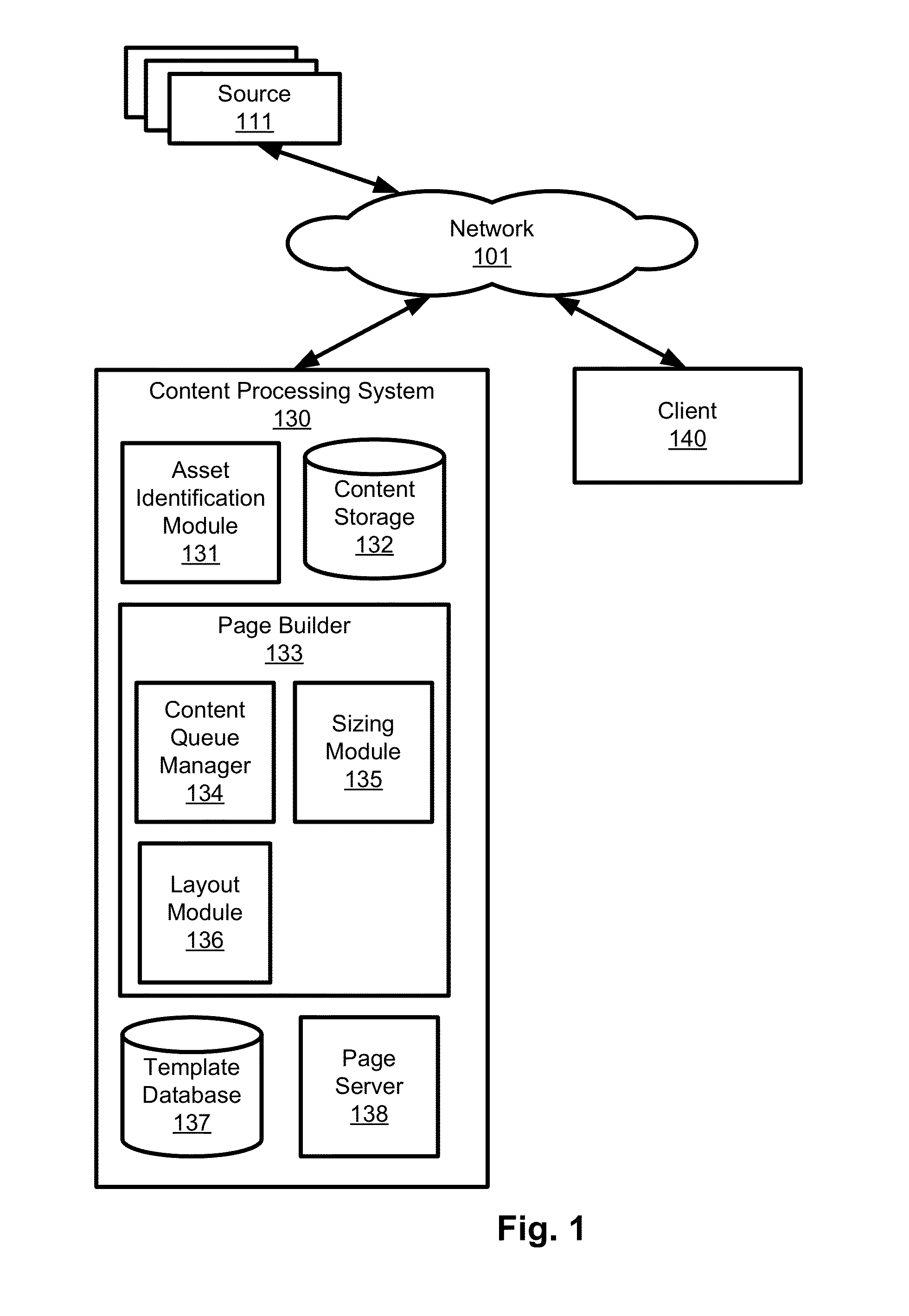

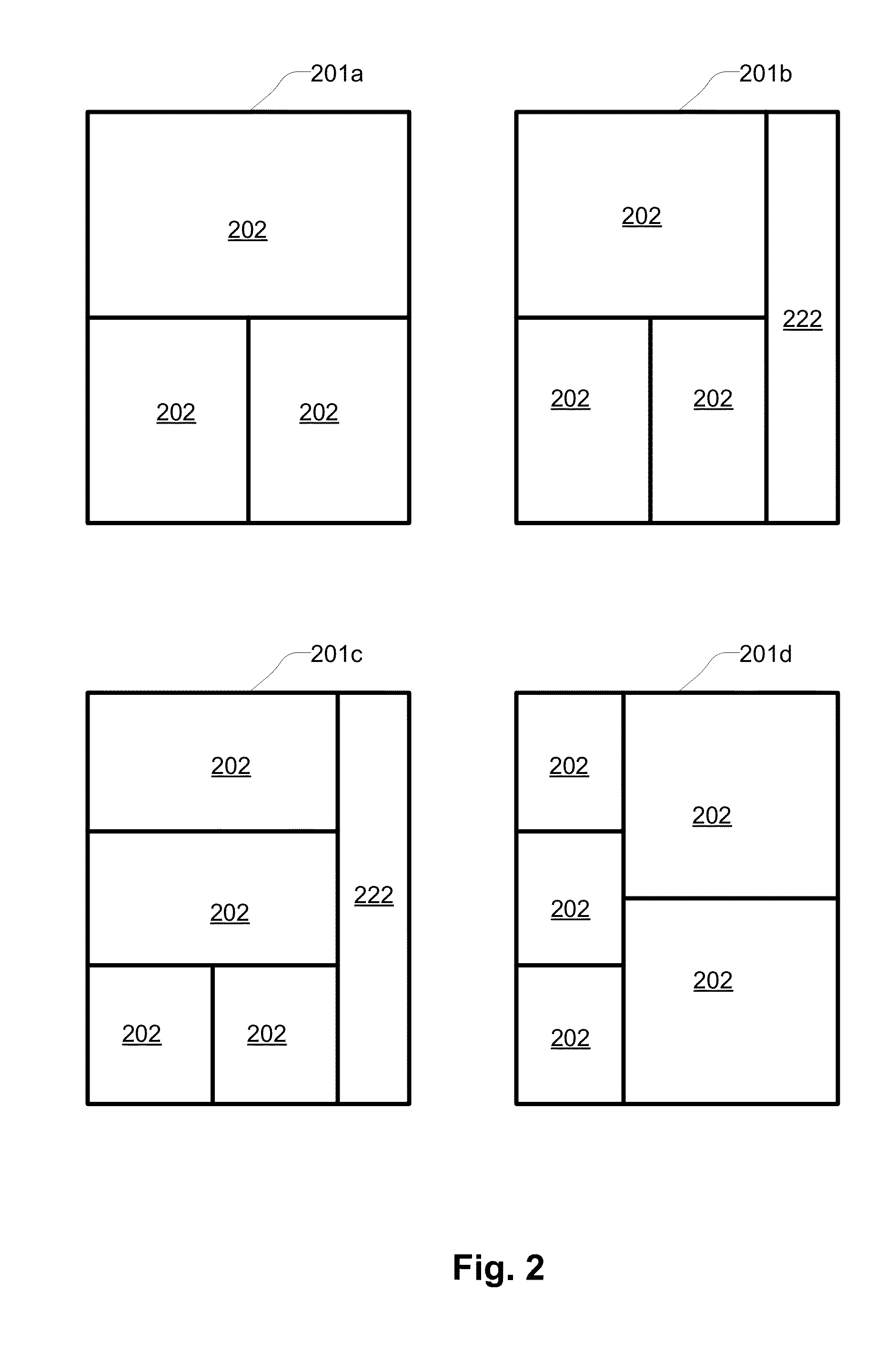

Template-Based Page Layout for Hosted Social Magazines

ActiveUS20130024757A1Data processing applicationsNatural language data processingTemplate basedClient-side

Page layout of content items from a variety of sources is performed. A content processing system queues content items, such as user-generated blogs, tweets, social networking status updates and other postings, received from a variety of sources. Each content item comprises one or more assets from one or more asset types. The asset types include text, images, and video. A page builder retrieves items from the queue and determines the item's size constraints. A template is selected from a template database to use as a layout for the items on a page; each template has a number of slots into which content can be placed. A layout module lays out the items into the slots of the selected template based on the respective size and aspect ratio constraints of the items, in order to build a page to serve a client device.

Owner:FLIPBOARD

Method of forming conformal film having si-N bonds on high-aspect ratio pattern

ActiveUS8394466B2Increasing mobilityIncreasing diffusivitySemiconductor/solid-state device manufacturingChemical vapor deposition coatingSiliconConformal map

Owner:ASM JAPAN

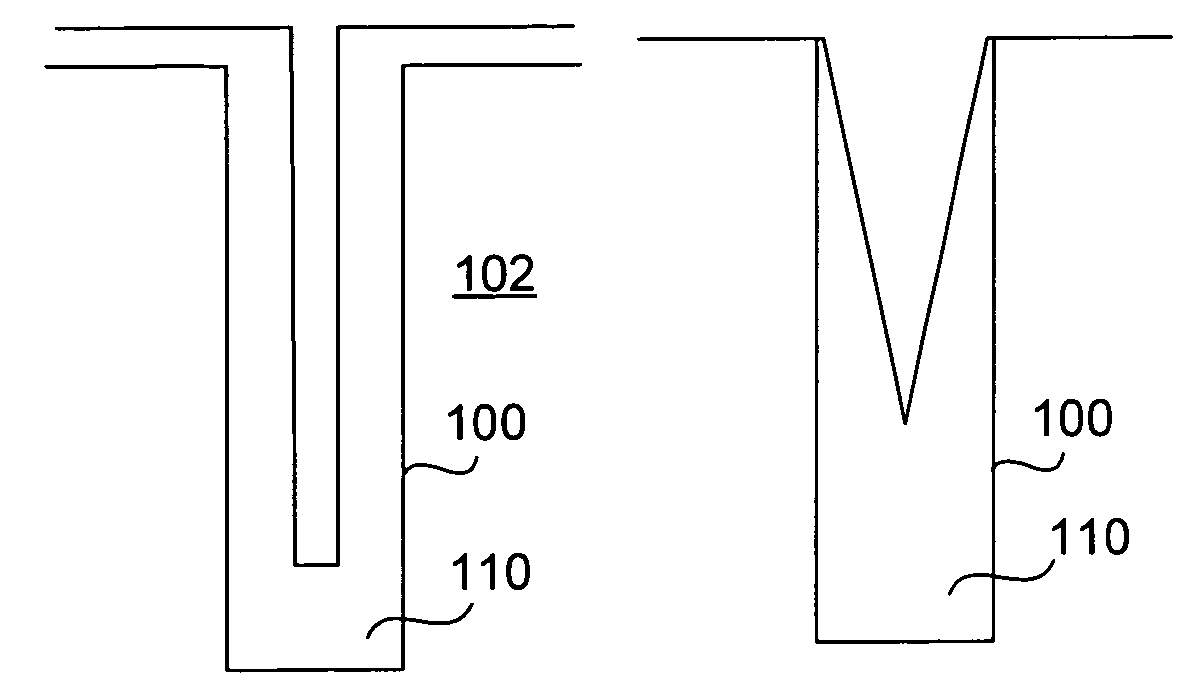

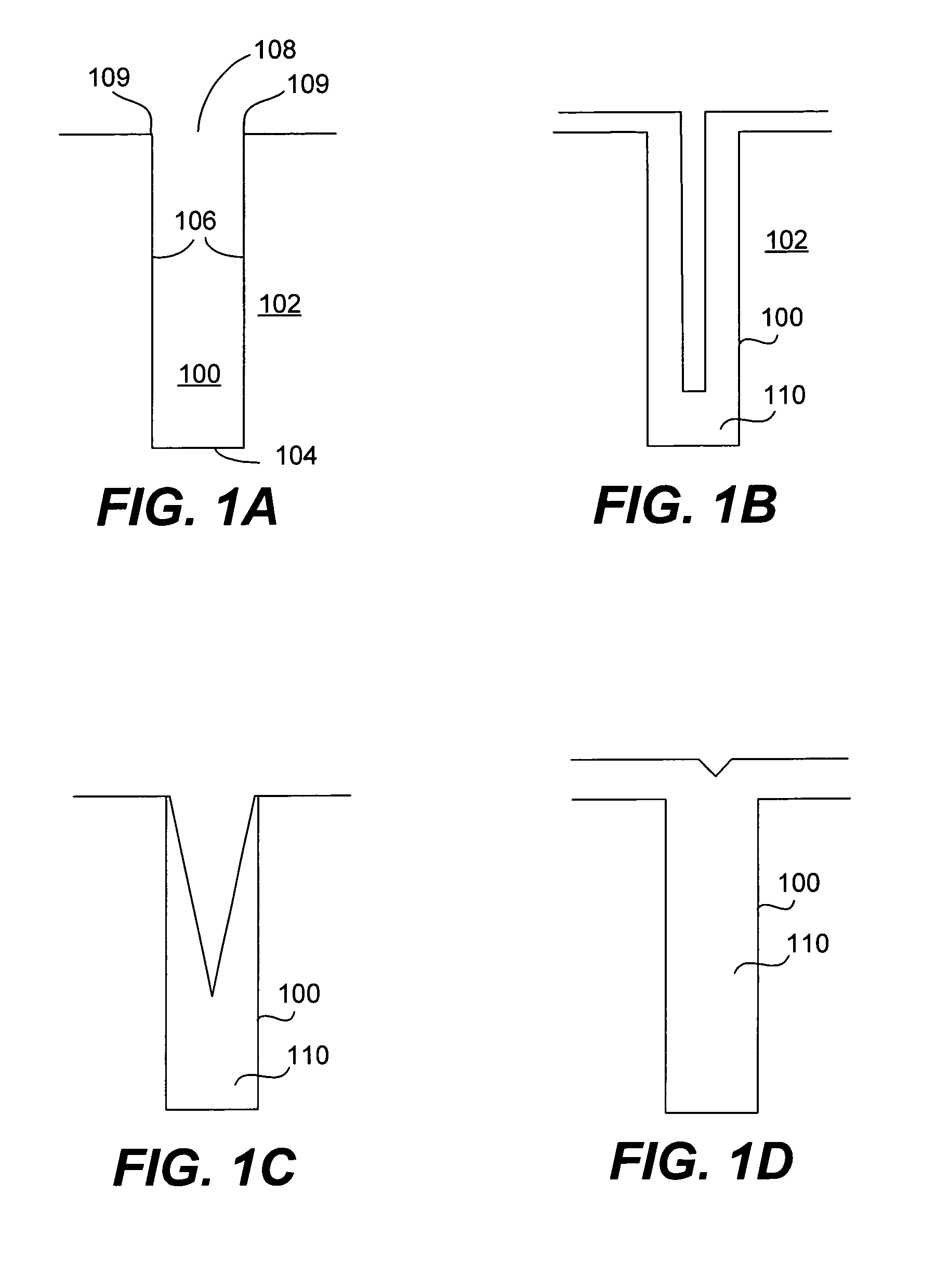

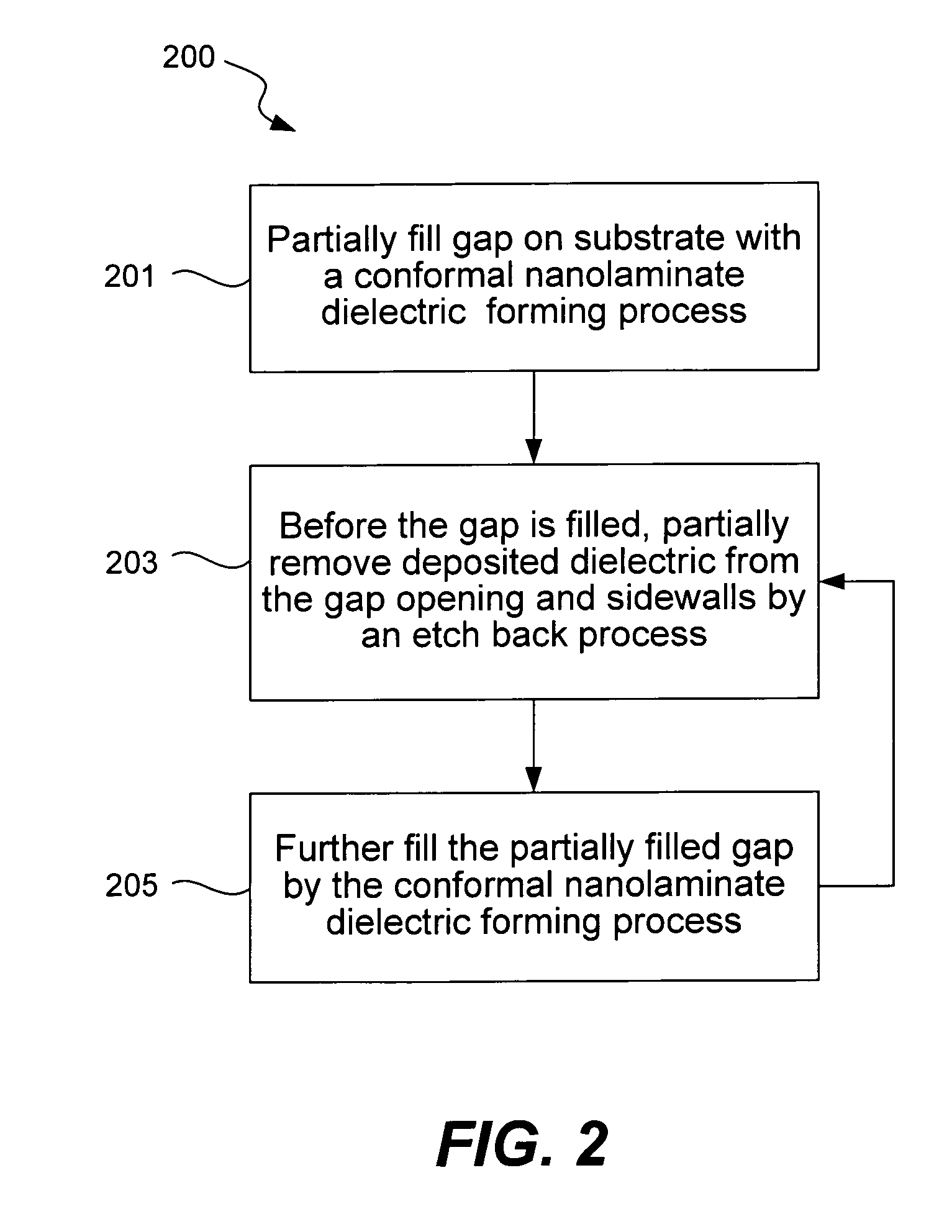

Conformal nanolaminate dielectric deposition and etch back gap fill process

InactiveUS7482247B1Reduce morbidityHigh aspect ratioSemiconductor/solid-state device manufacturingChemical vapor deposition coatingDielectricEngineering

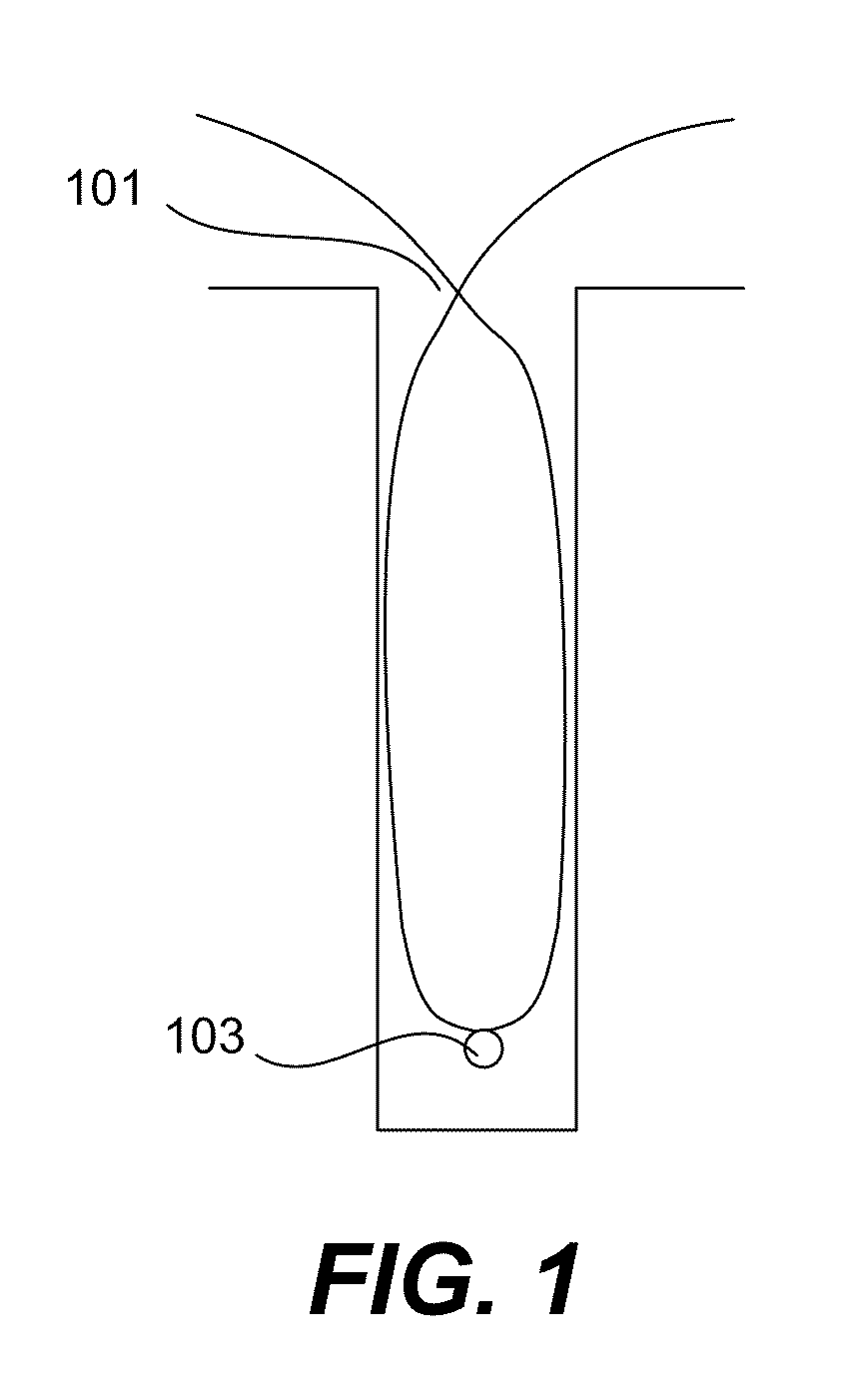

Conformal nanolaminate dielectric deposition and etch back processes that can fill high aspect ratio (typically at least 5:1, for example 6:1), narrow width (typically sub 0.13 micron, for example 0.1 micron or less) gaps with significantly reduced incidence of voids or weak spots involve the use of any suitable confirmal dielectric deposition technique and a dry etch back. The etch back part of the process involves a single step or an integrated multi-step (for example, two-step) procedure including an anisotropic dry etch followed by an isotropic dry etch. The all dry deposition and etch back process in a single tool increases throughput and reduces handling of wafers resulting in more efficient and higher quality nanolaminate dielectric gap fill operations.

Owner:NOVELLUS SYSTEMS

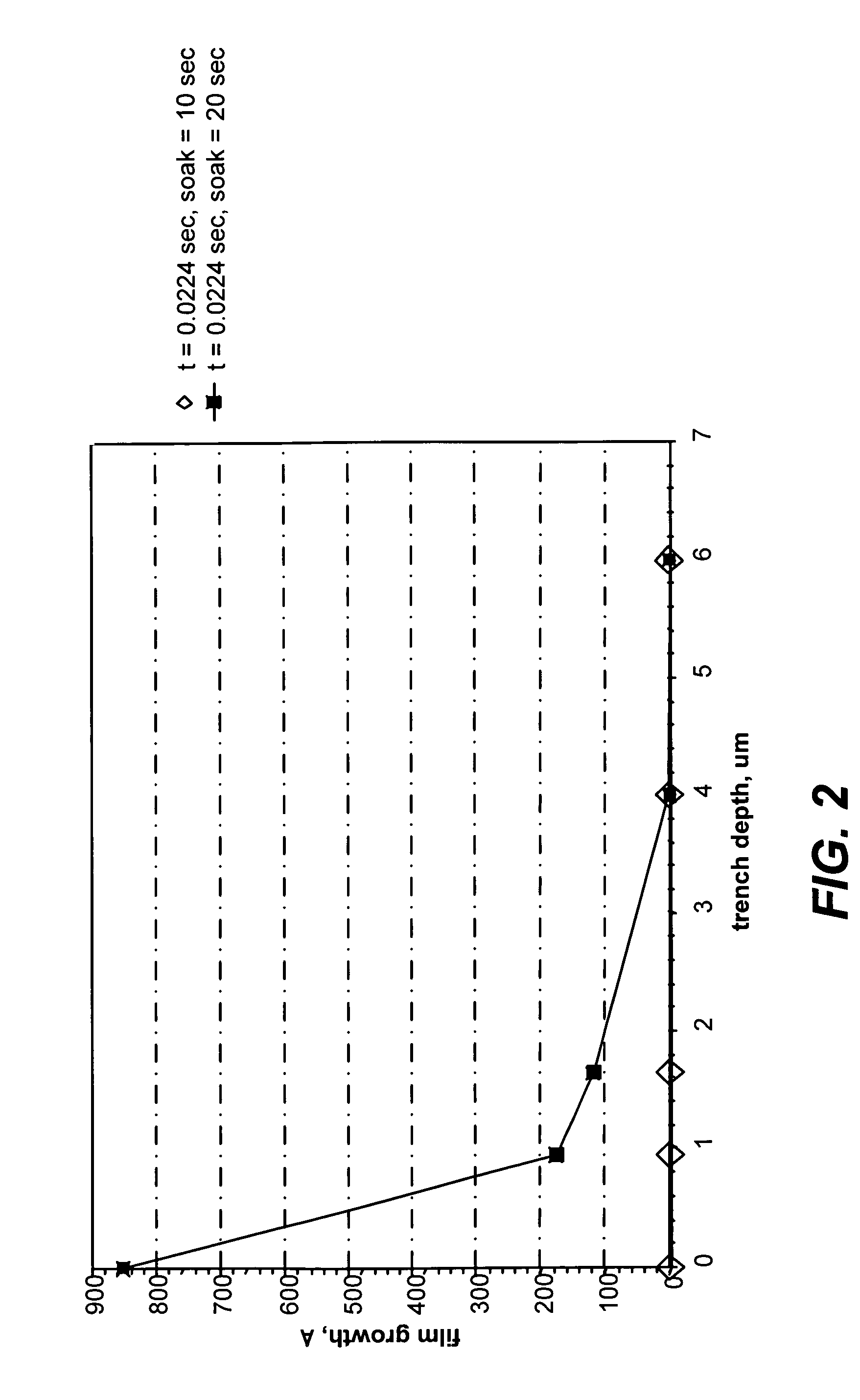

Bottom up fill in high aspect ratio trenches

InactiveUS20120149213A1Improve gap fillingReduce nucleation delayLiquid surface applicatorsSemiconductor/solid-state device manufacturingHydrogenNitrogen

Provided are novel methods of filling gaps with a flowable dielectric material. According to various embodiments, the methods involve performing a surface treatment on the gap to enhance subsequent bottom up fill of the gap. In certain embodiments, the treatment involves exposing the surface to activated species, such as activated species of one or more of nitrogen, oxygen, and hydrogen. In certain embodiments, the treatment involves exposing the surface to a plasma generated from a mixture of nitrogen and oxygen. The treatment may enable uniform nucleation of the flowable dielectric film, reduce nucleation delay, increase deposition rate and enhance feature-to-feature fill height uniformity.

Owner:NOVELLUS SYSTEMS

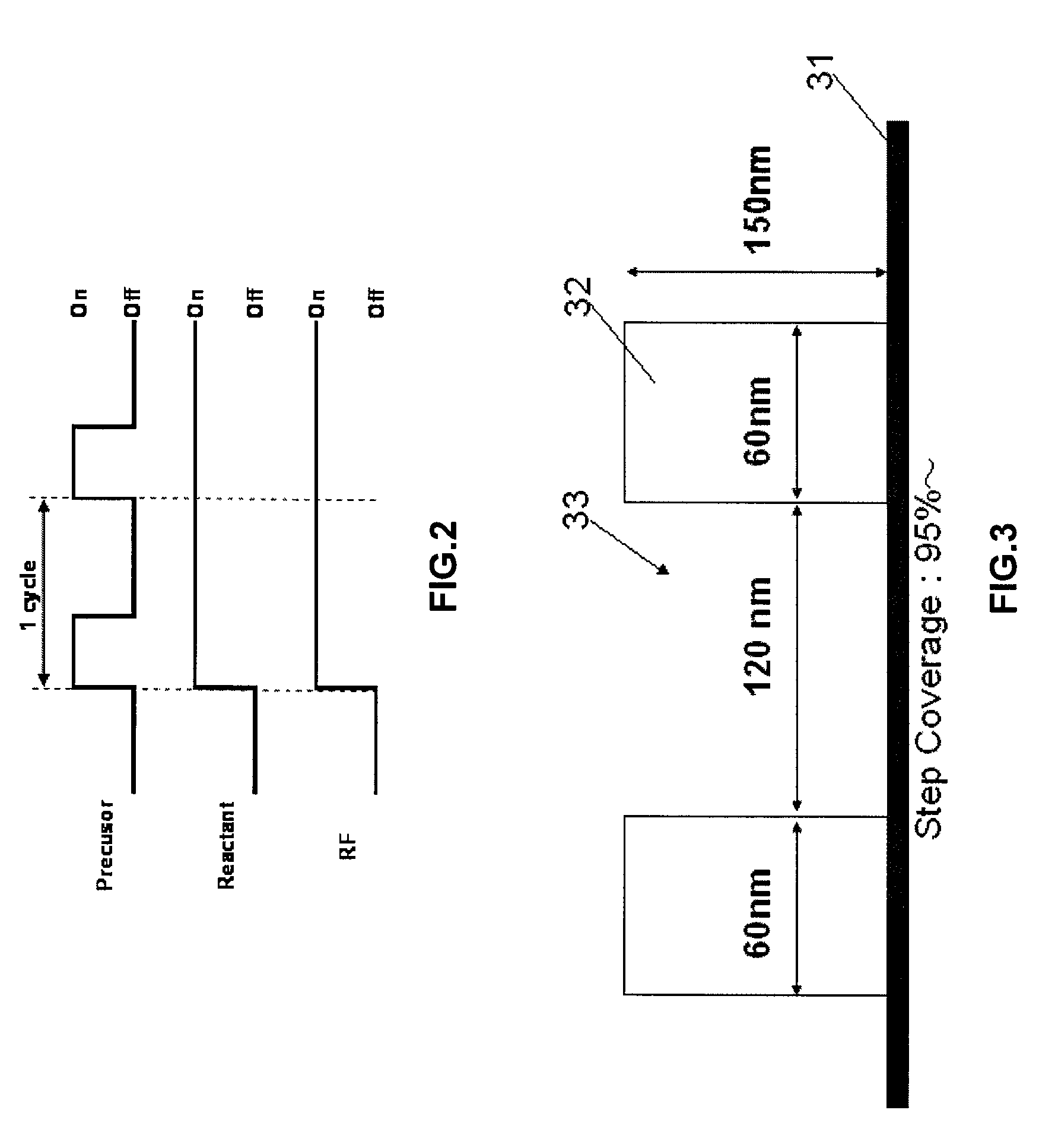

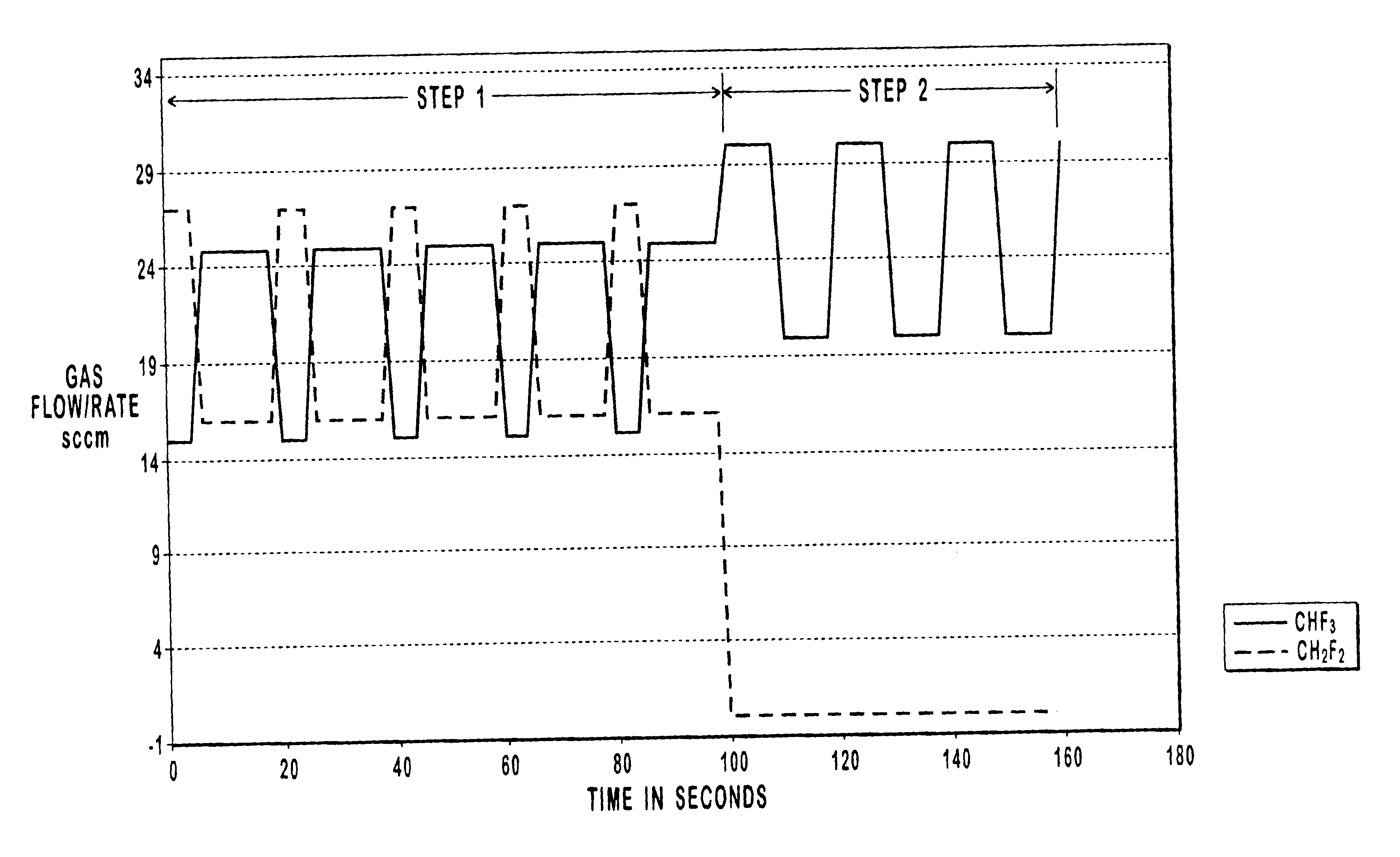

Gas pulsing for etch profile control

InactiveUS6784108B1Increase flow rateReduce flow rateElectric discharge tubesDecorative surface effectsEngineeringAnisotropic etching

Etch profile control with pulsed gas flow and its applications to etching such as anisotropic etching of high aspect ratio features and etching of self-aligned contact structures in various processes. Pulsing can be applied according to this invention to the flow rate of a gas such as an etchant gas, a gas that leads to the deposition of a protective layer, a gas that modifies the deposition of a protective layer, and a gas that modifies etching.

Owner:MICRON TECH INC

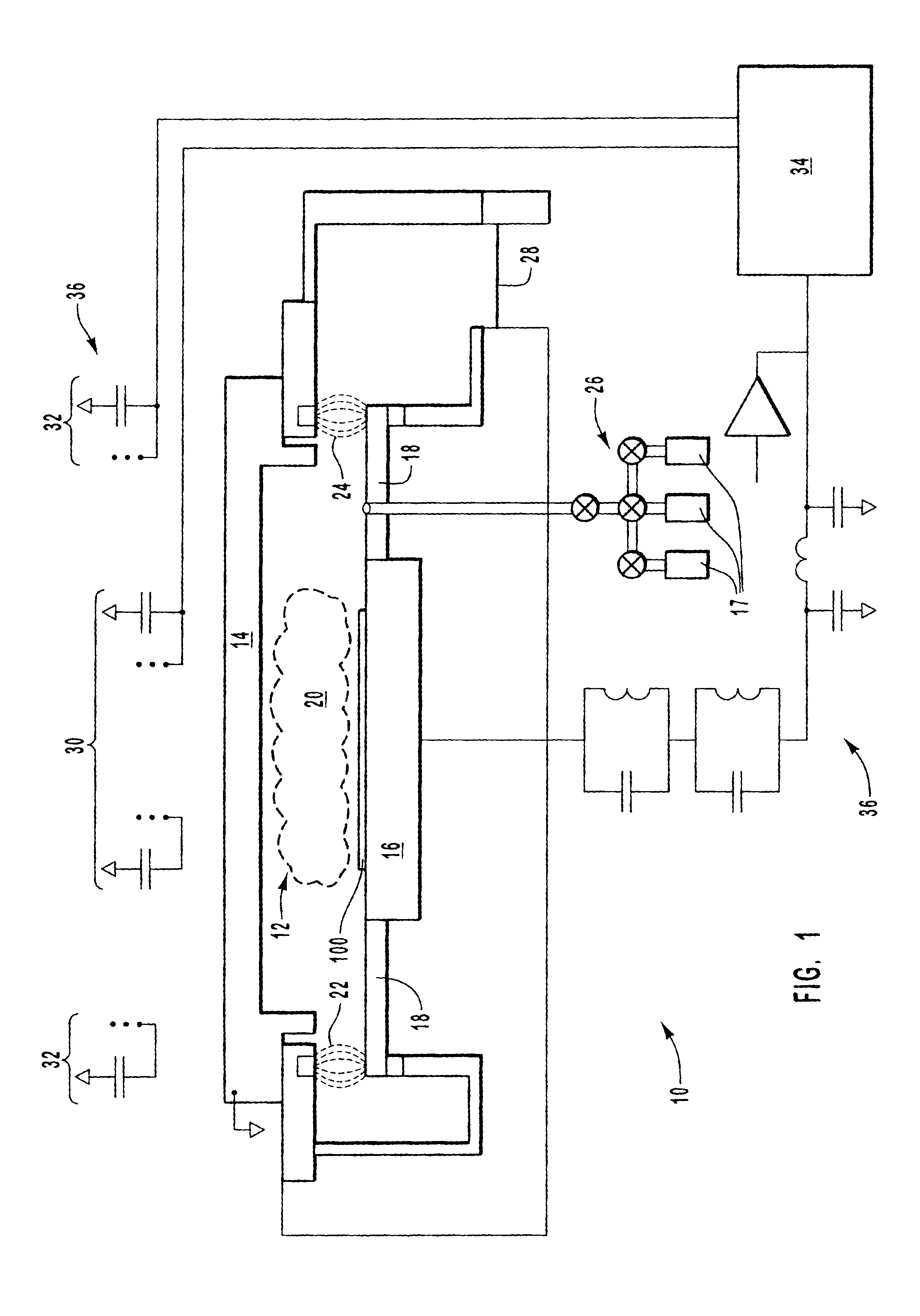

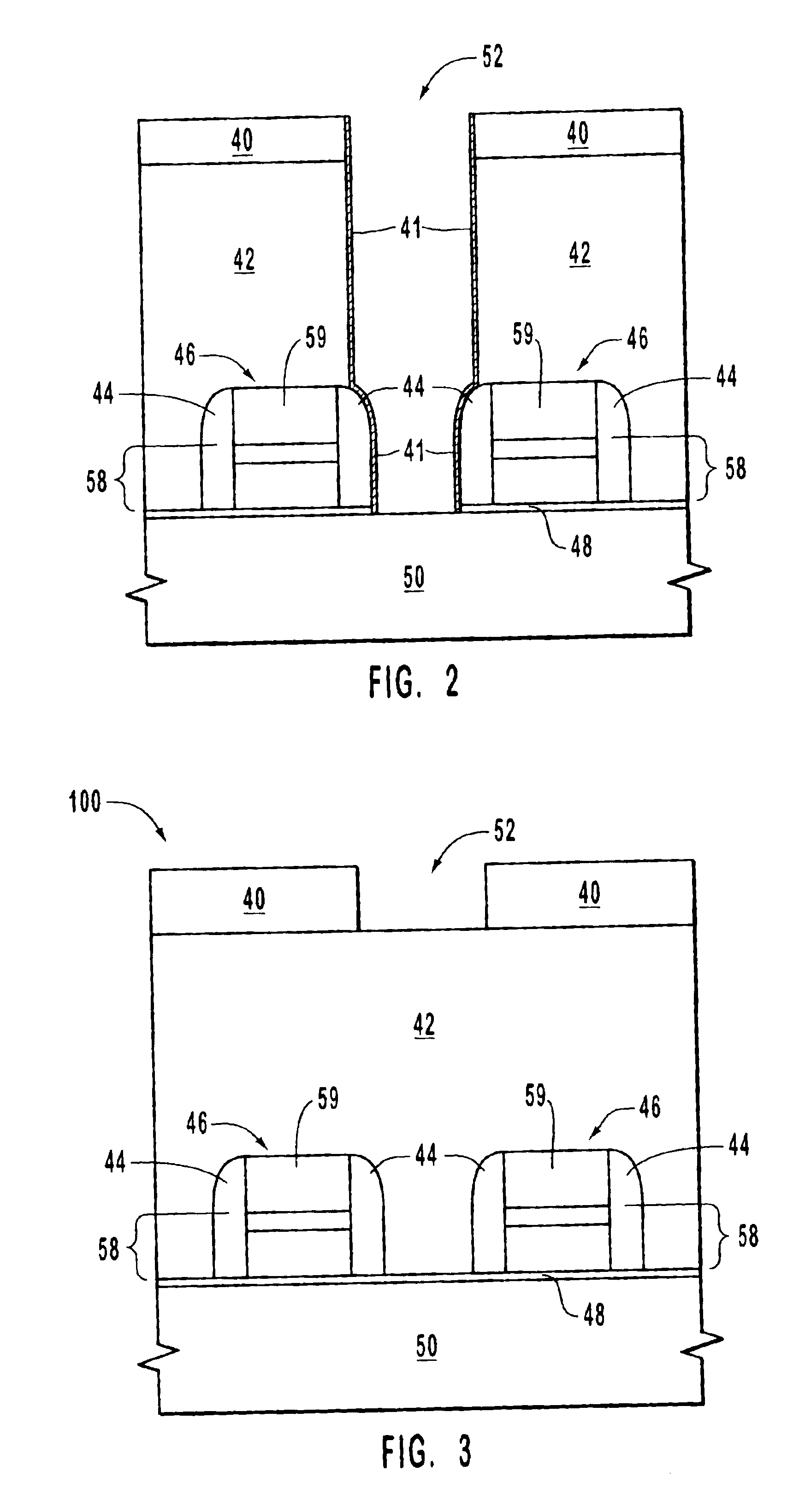

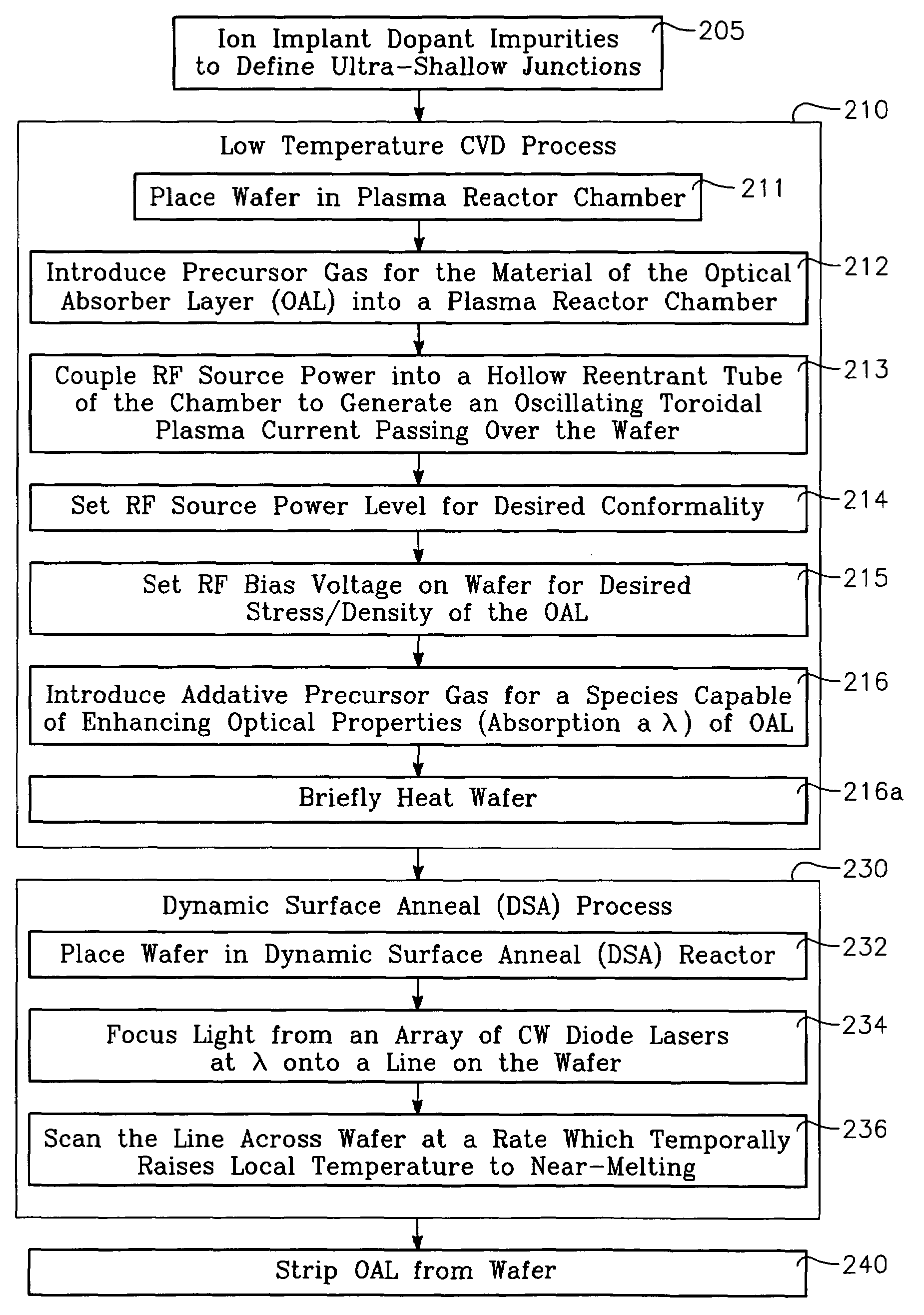

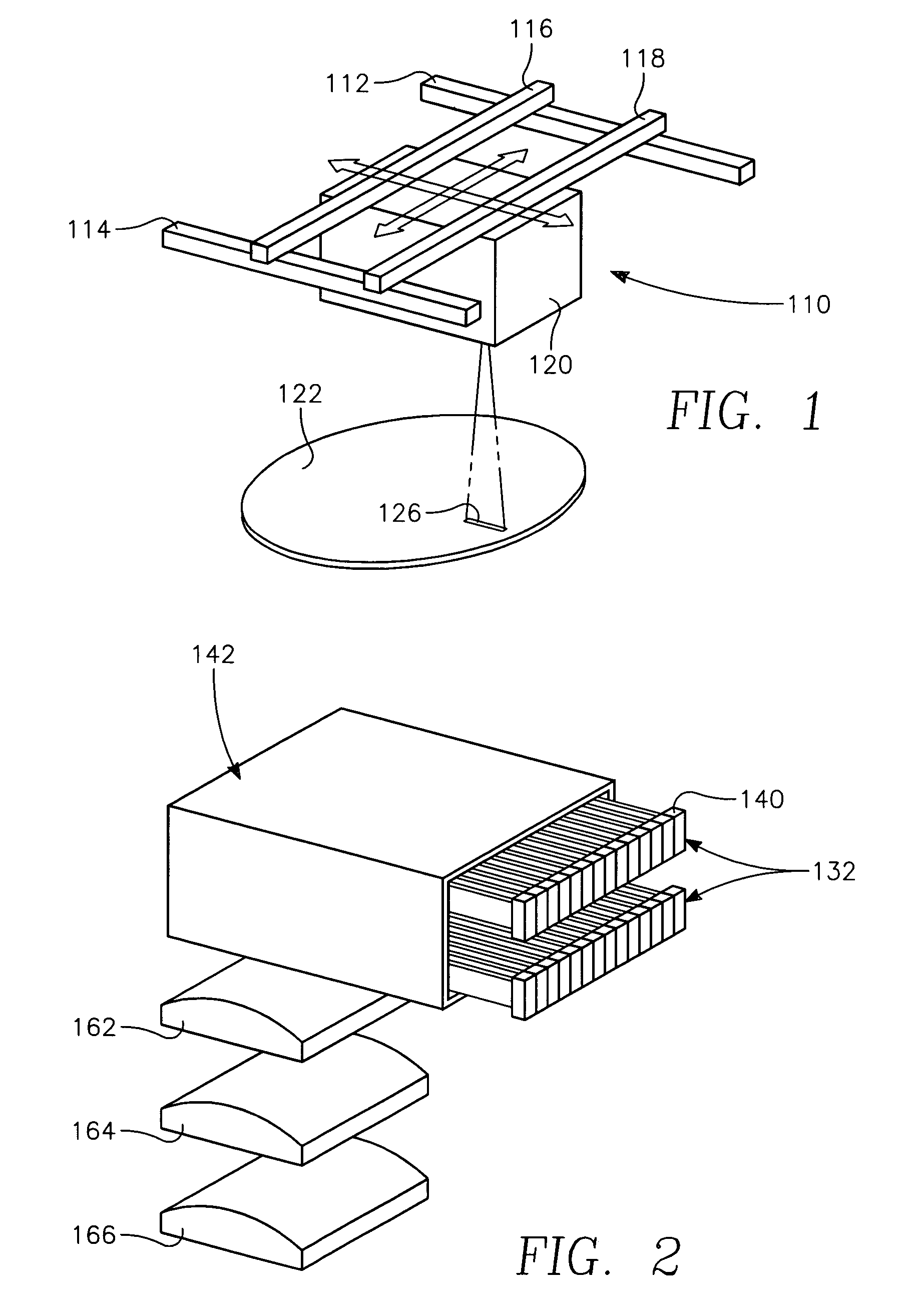

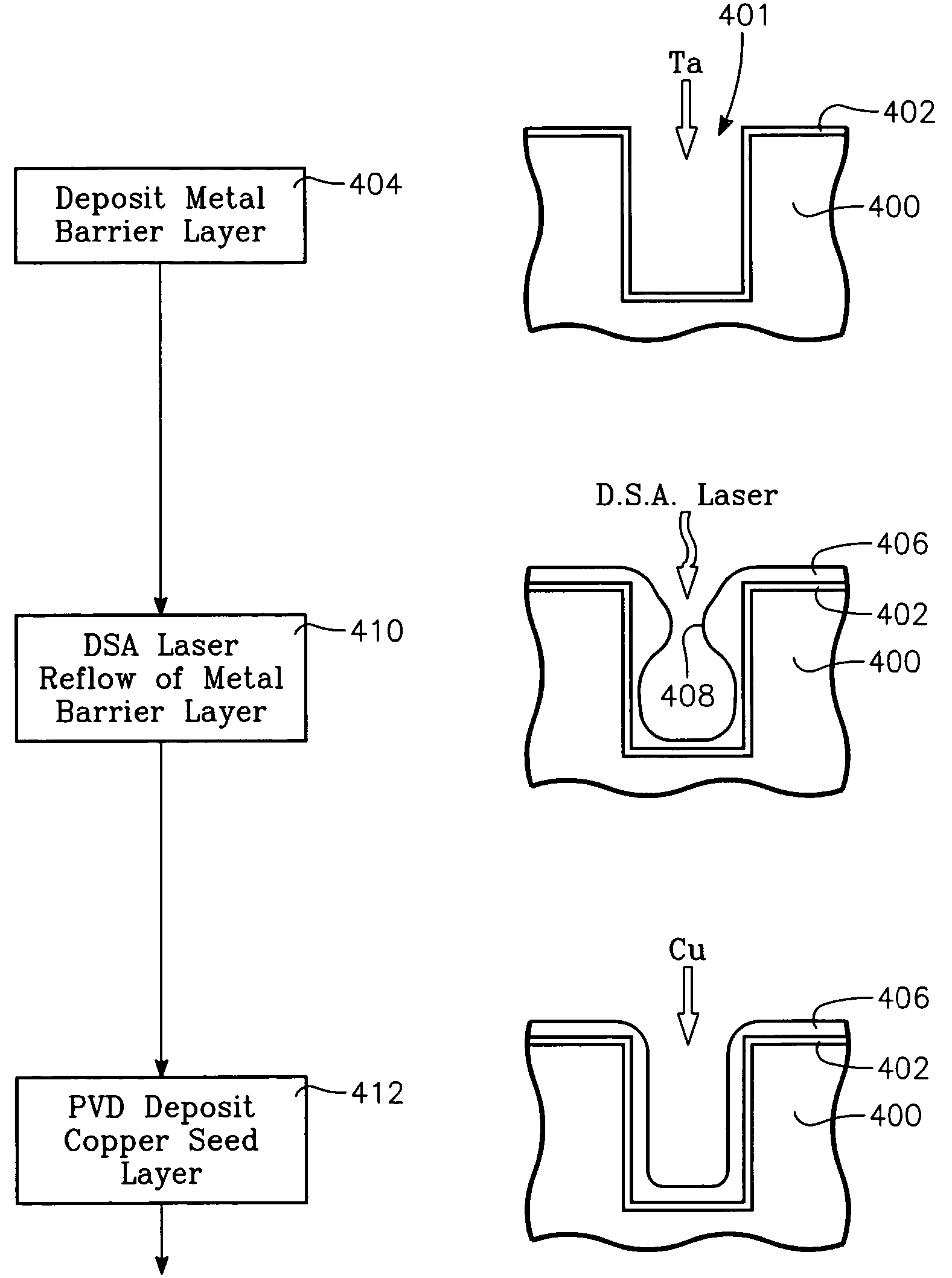

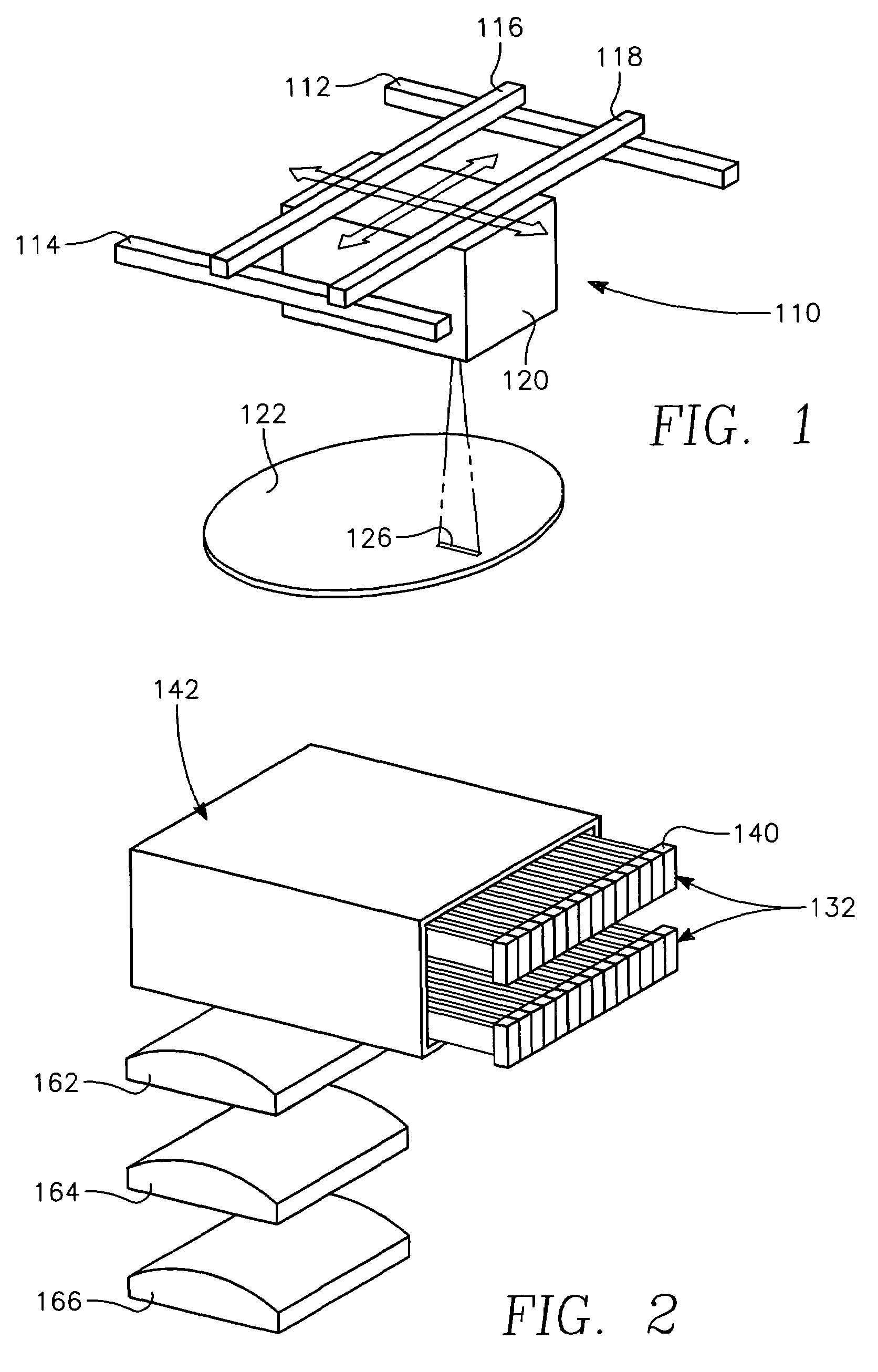

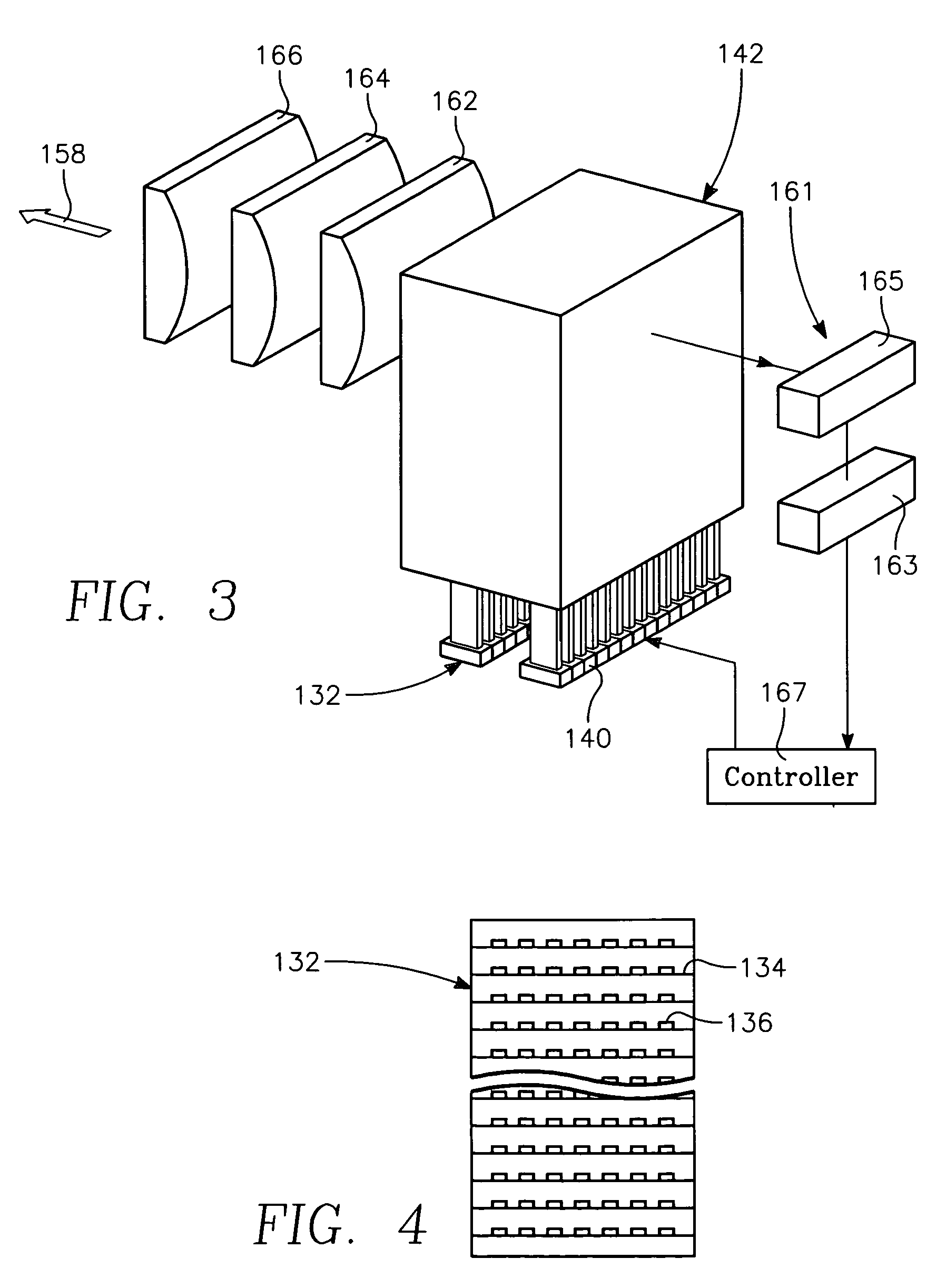

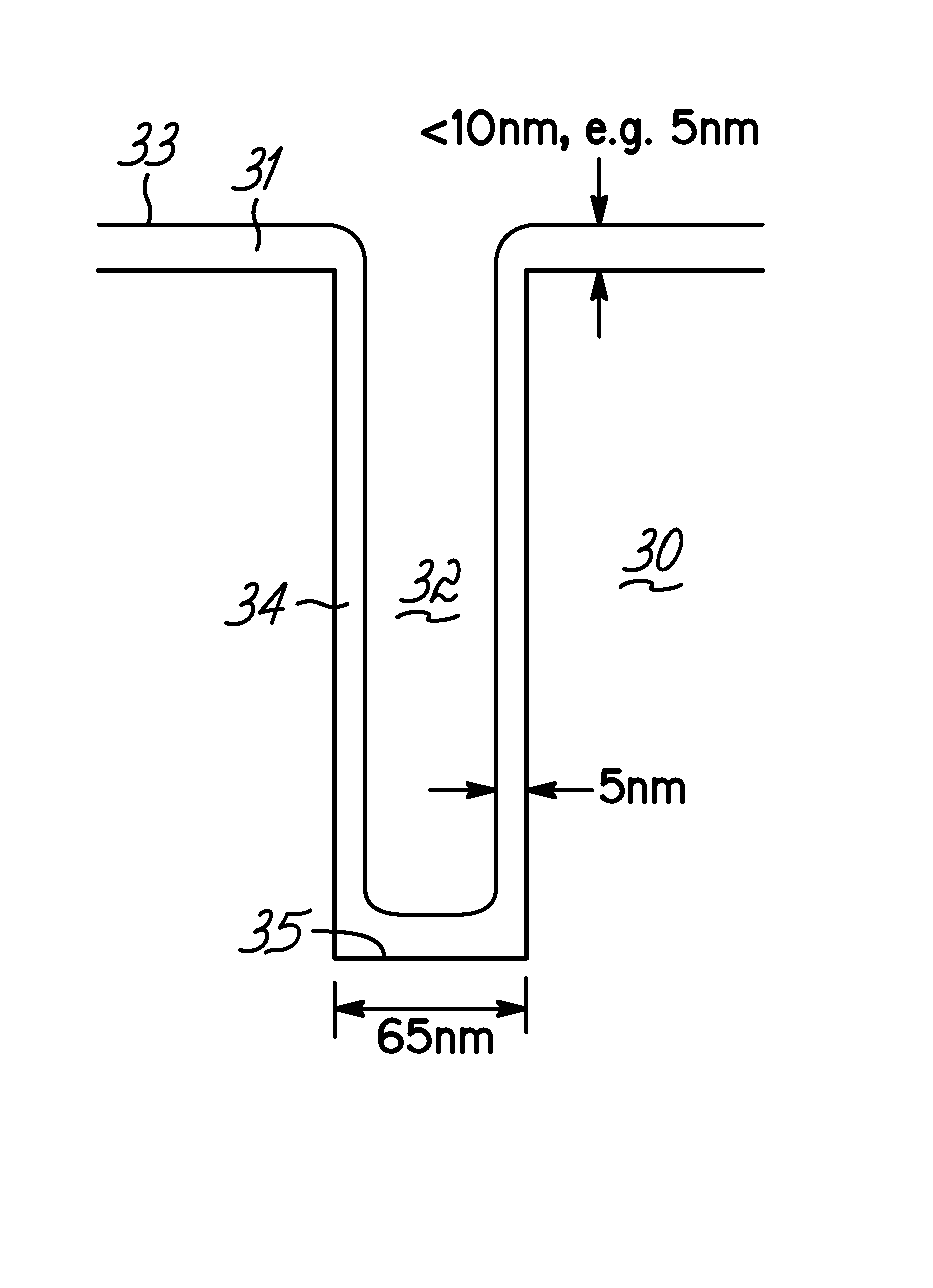

Copper conductor annealing process employing high speed optical annealing with a low temperature-deposited optical absorber layer

InactiveUS7335611B2Semiconductor/solid-state device manufacturingWelding/soldering/cutting articlesCopper conductorLow temperature deposition

A method of forming a conductor in a thin film structure on a semiconductor substrate includes forming high aspect ratio openings in a base layer having vertical side walls, depositing a dielectric barrier layer comprising a dielectric compound of a barrier metal on the surfaces of the high aspect ratio openings including the vertical side walls, depositing a metal barrier layer comprising the barrier metal on the first barrier layer, depositing a main conductor species seed layer on the metal barrier layer and depositing a main conductor layer. The method further includes annealing the main conductor layer by (a) directing light from an array of continuous wave lasers into a line of light extending at least partially across the thin film structure, and (b) translating the line of light relative to the thin film structure in a direction transverse to the line of light. The method of Claim 1 further comprising, prior to the annealing step, depositing an amorphous carbon optical absorber layer on the main conductor layer. The step of depositing an amorphous carbon optical absorber layer includes introducing a carbon-containing process gas into a reactor chamber containing the substrate in a process zone of the reactor, applying RF source power to an external reentrant conduit of the reactor to generate a reentrant toroidal RF plasma current passing through the process zone and applying a bias voltage to the substrate.

Owner:APPLIED MATERIALS INC

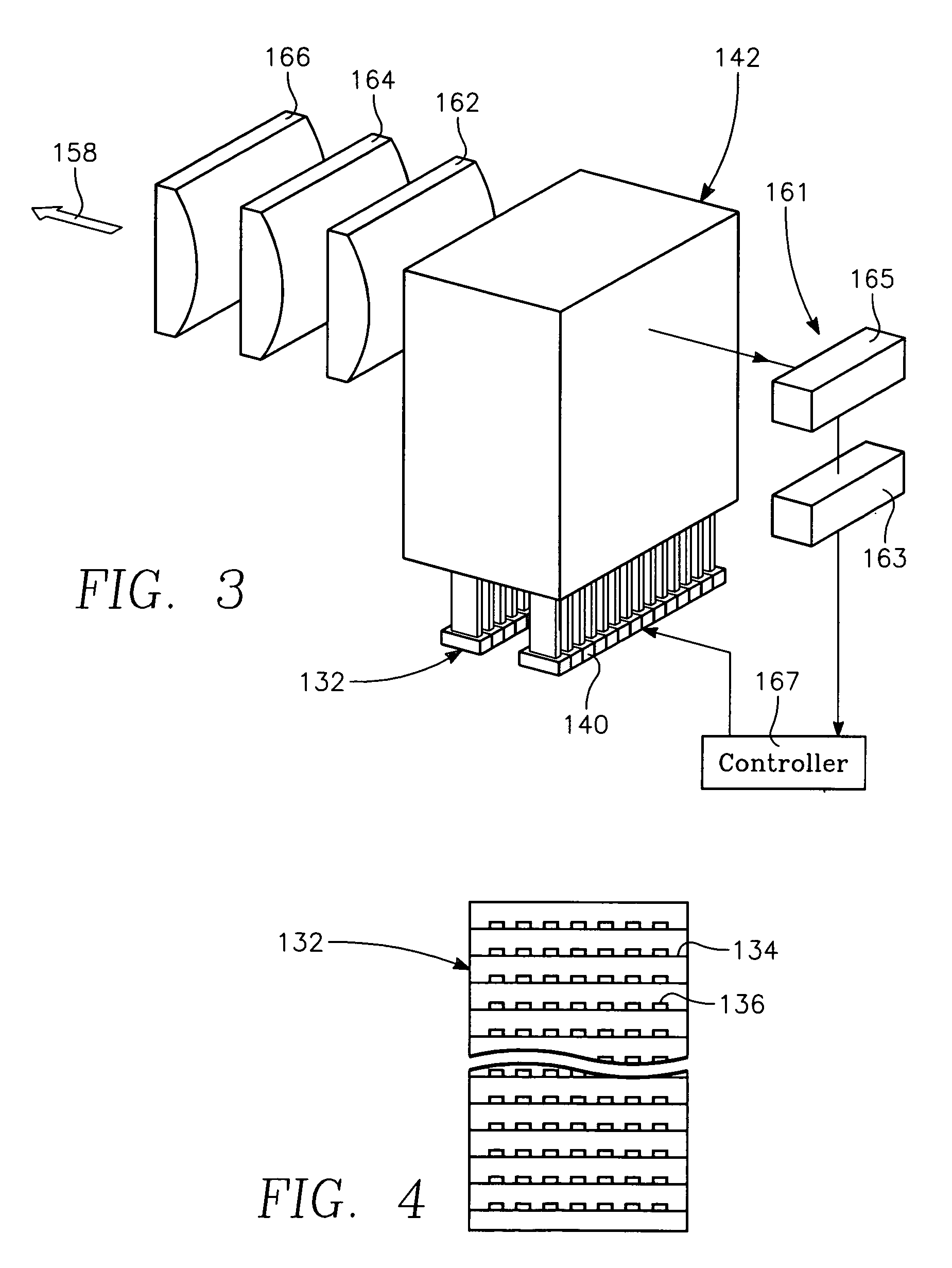

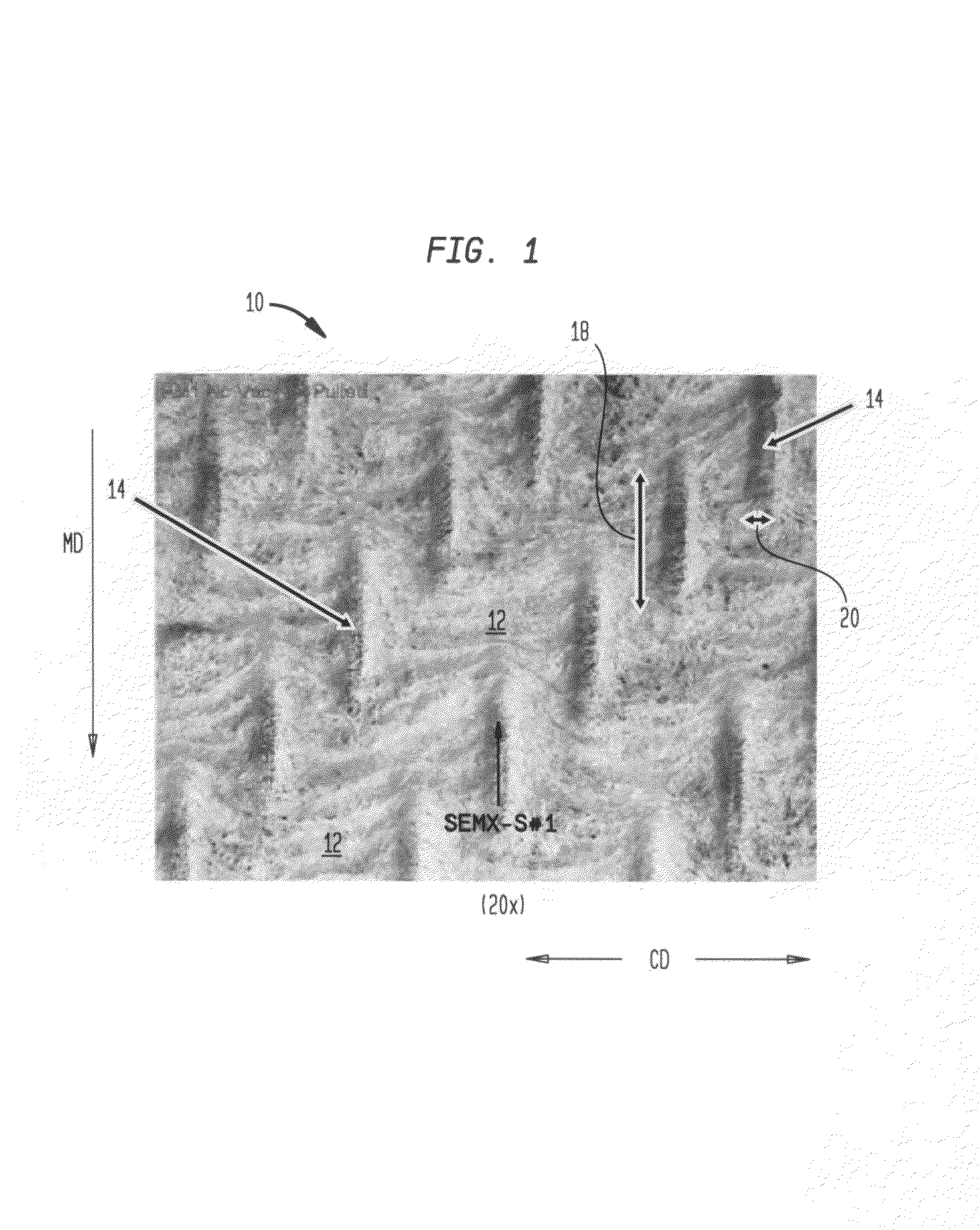

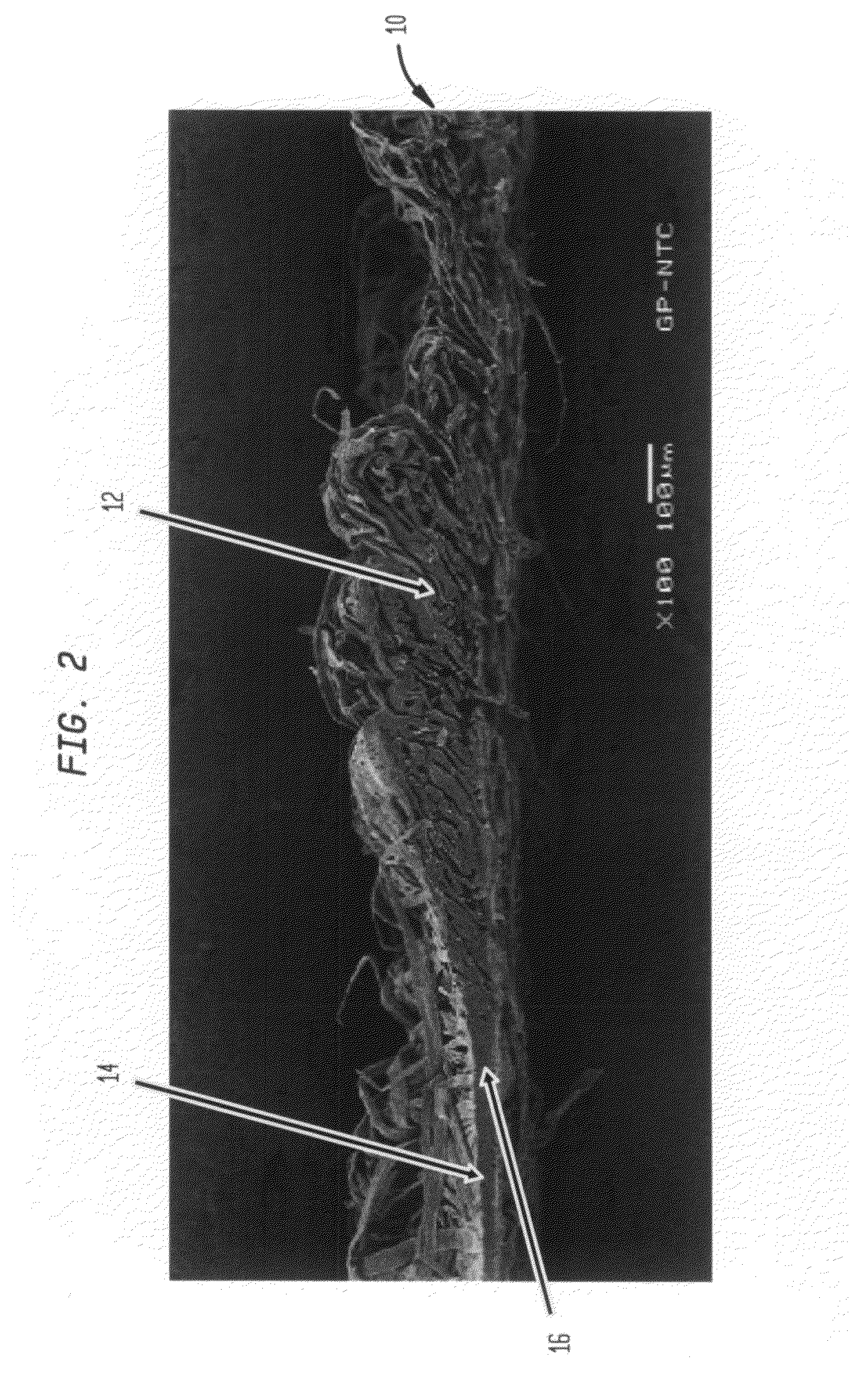

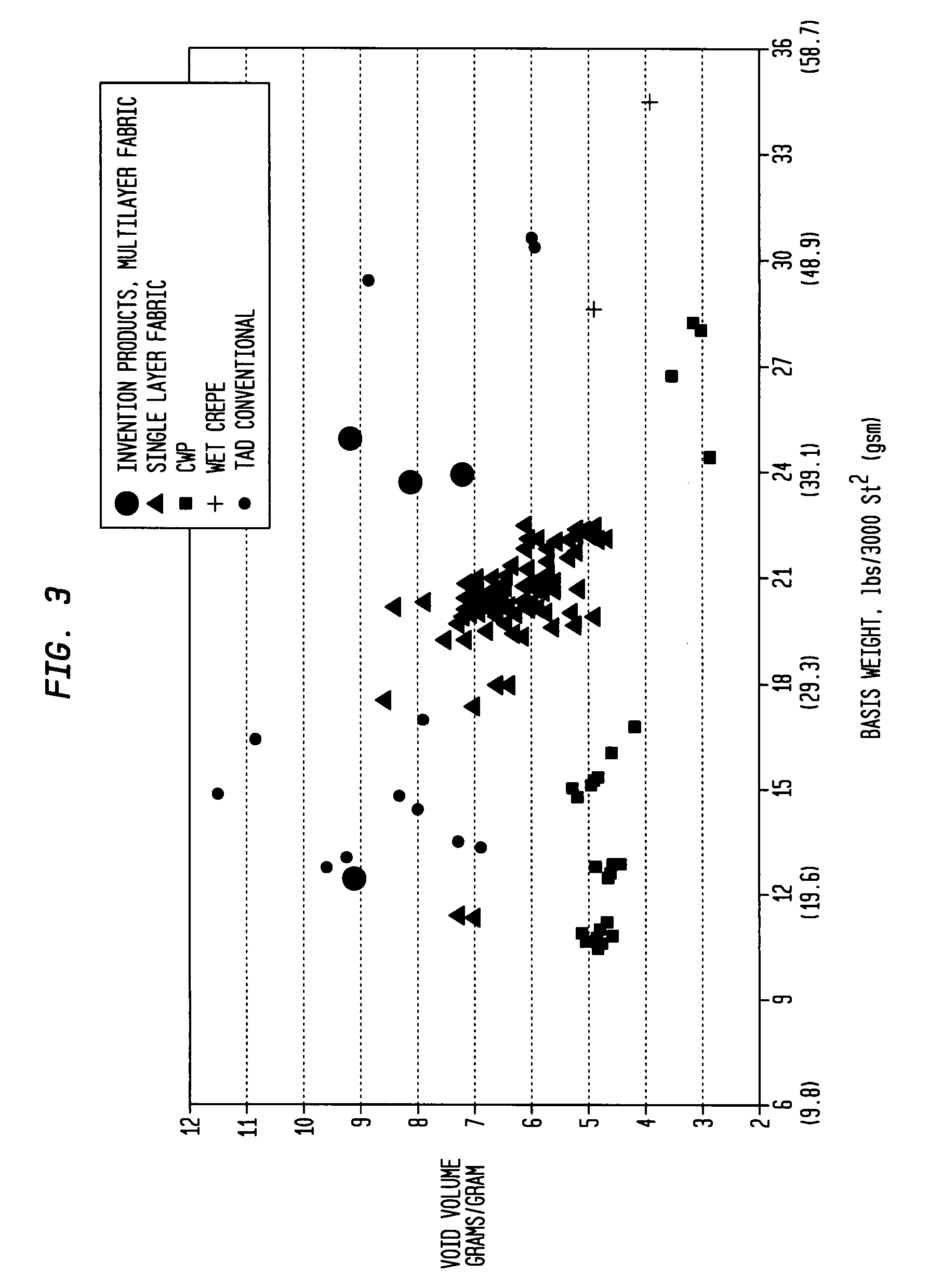

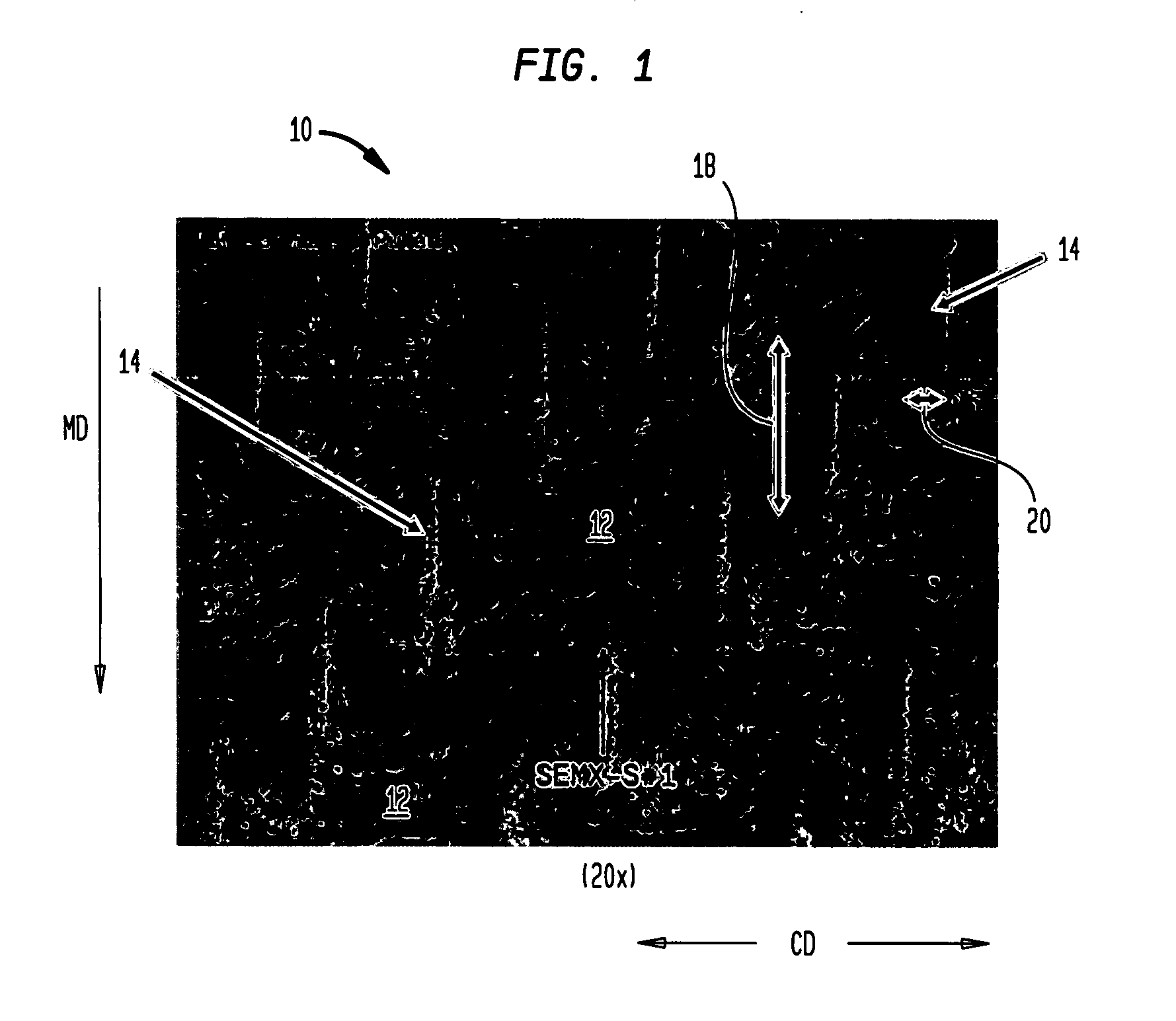

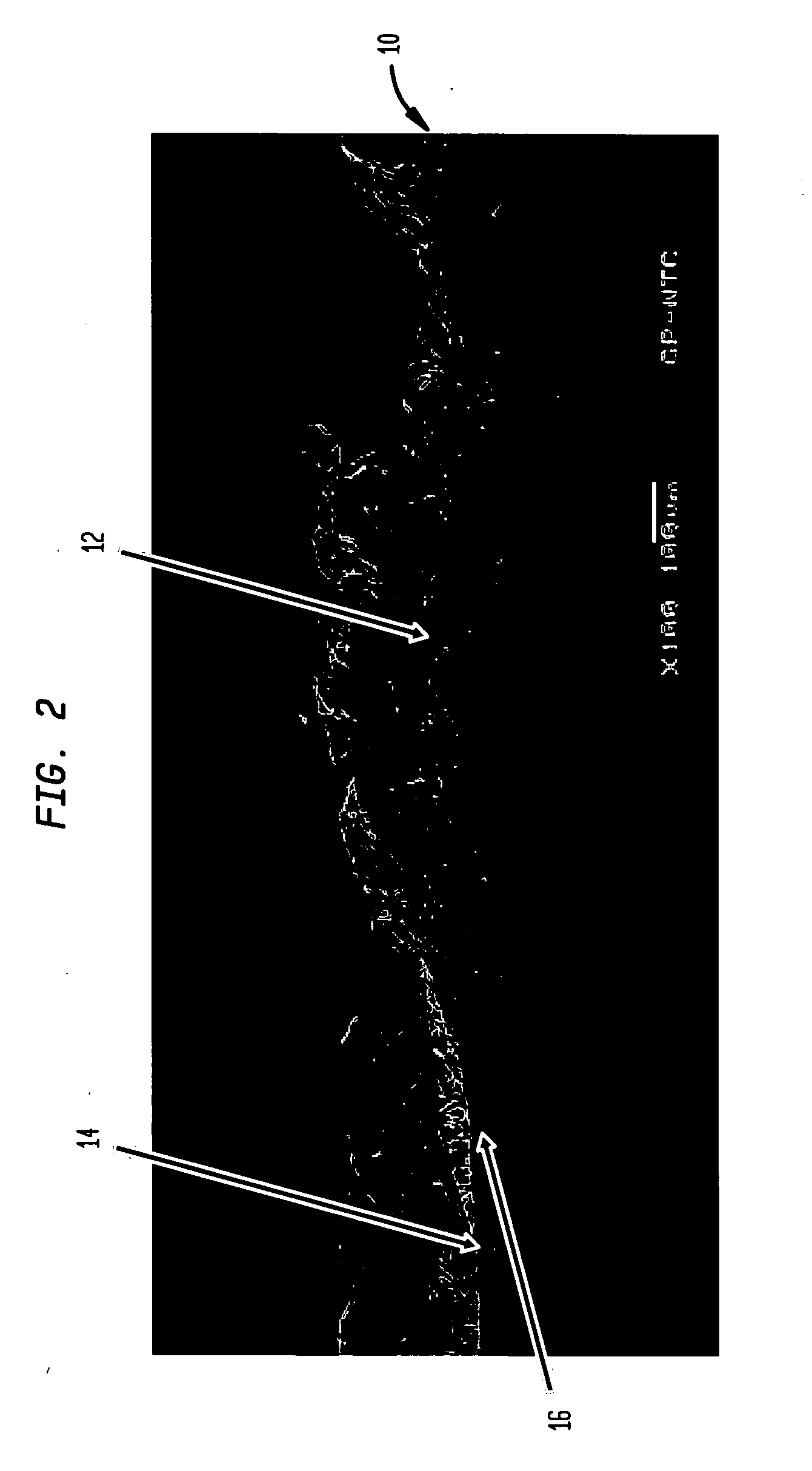

Fabric creped absorbent sheet with variable local basis weight

InactiveUS7494563B2Improve water absorptionSurprising softnessNatural cellulose pulp/paperMechanical working/deformationFiberPapermaking

An absorbent cellulosic sheet having variable local basis weight includes a papermaking-fiber reticulum provided with (i) a plurality of cross-machine direction (CD) extending, fiber-enriched pileated regions of relatively high local basis weight interconnected by (ii) a plurality of elongated densified regions of compressed papermaking fibers. The elongated densified regions have relatively low local basis weight and are generally oriented along the machine direction (MD) of the sheet and have an MD / CD aspect ratio of at least 1.5. The products are most preferably prepared by way of a compactive dewatering / wet crepe process.

Owner:GPCP IP HLDG LLC

Copper barrier reflow process employing high speed optical annealing

A method of forming a barrier layer for a thin film structure on a semiconductor substrate includes forming high aspect ratio openings in a base layer having vertical side walls, depositing a dielectric barrier layer comprising a dielectric compound of a barrier metal on the surfaces of the high aspect ratio openings including the vertical side walls and depositing a metal barrier layer comprising the barrier metal on the first barrier layer. The method further includes reflowing the metal barrier layer by (a) directing light from an array of continuous wave lasers into a line of light extending at least partially across the thin film structure, and (b) translating the line of light relative to the thin film structure in a direction transverse to the line of light.

Owner:APPLIED MATERIALS INC

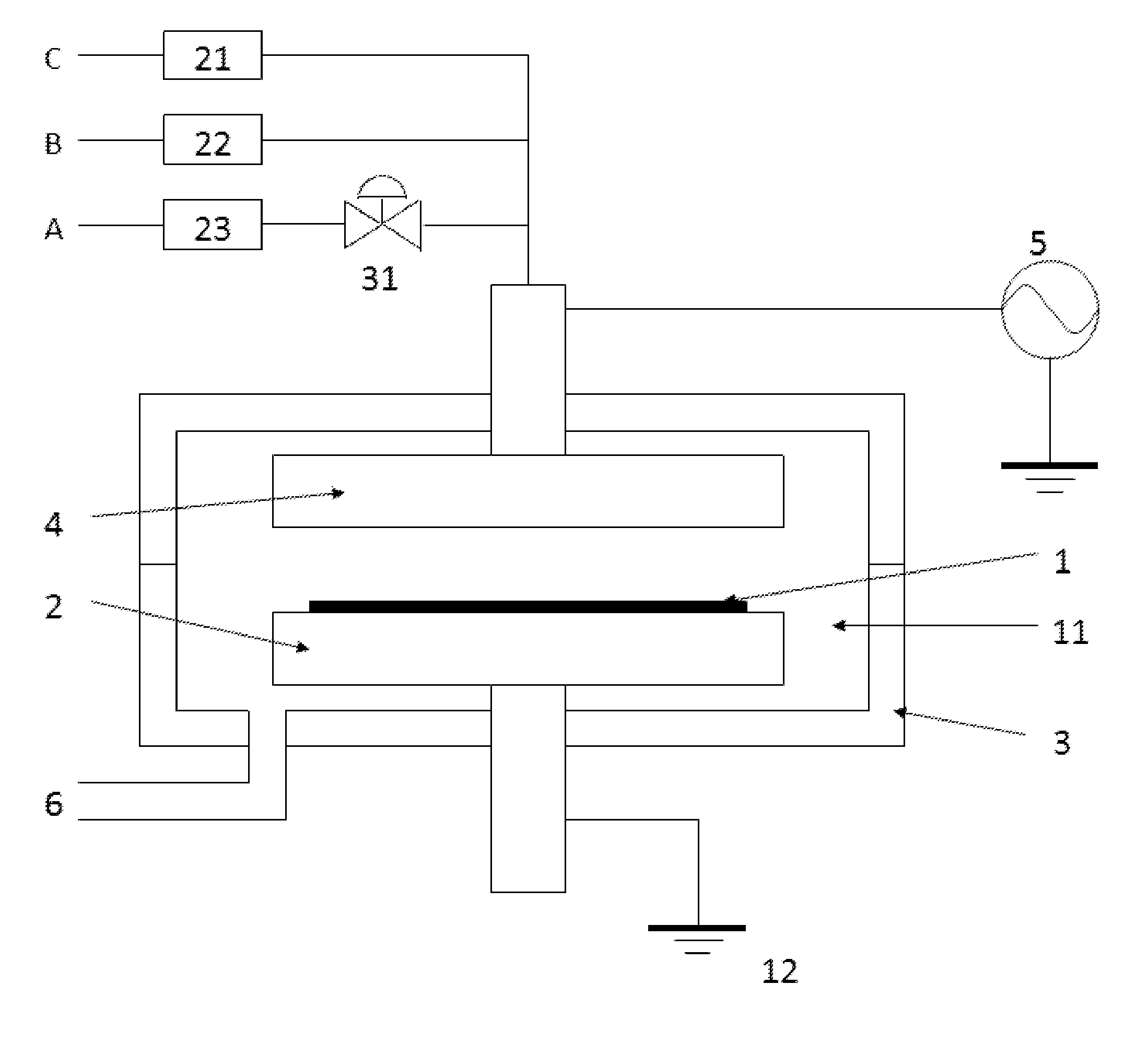

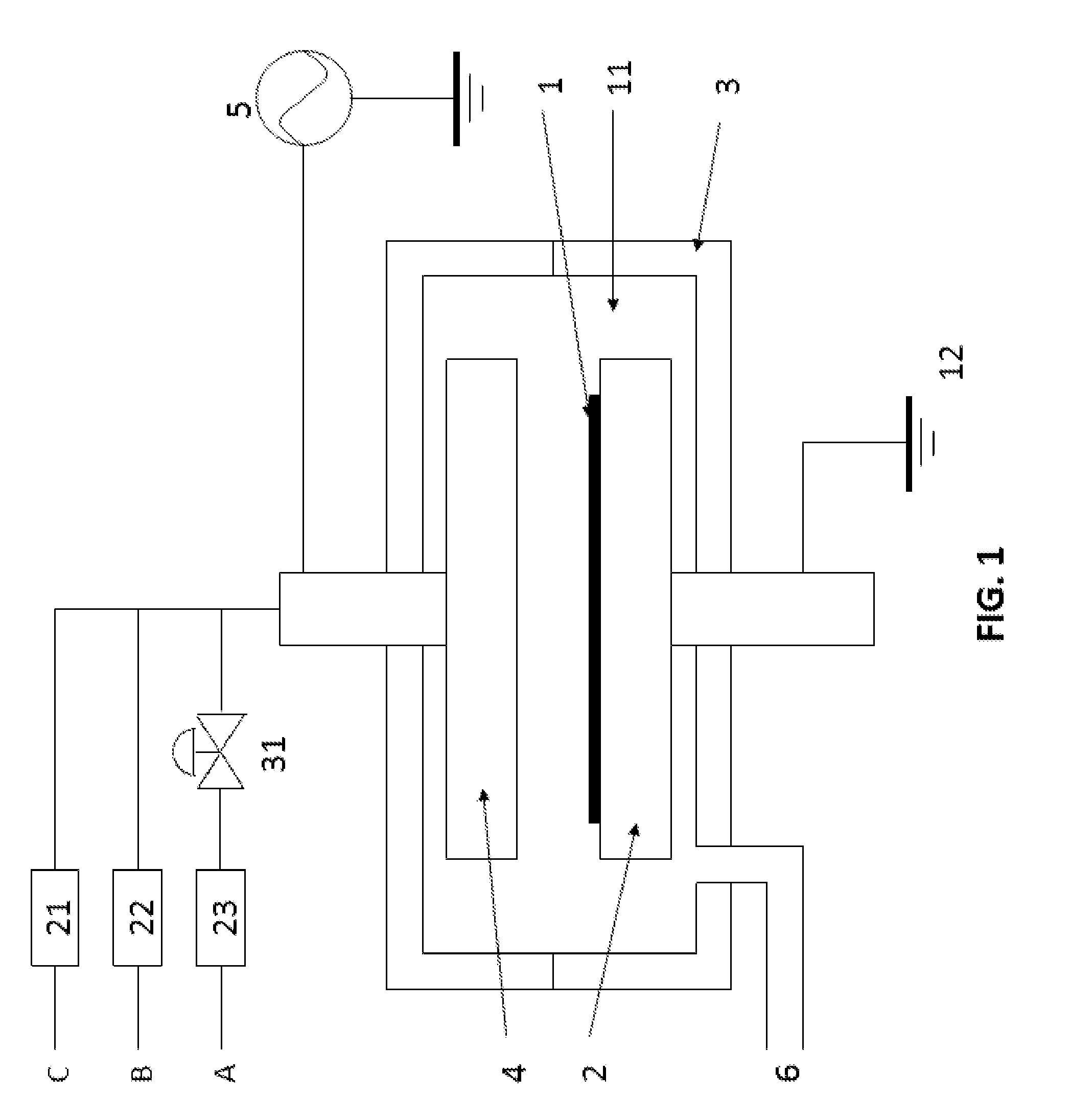

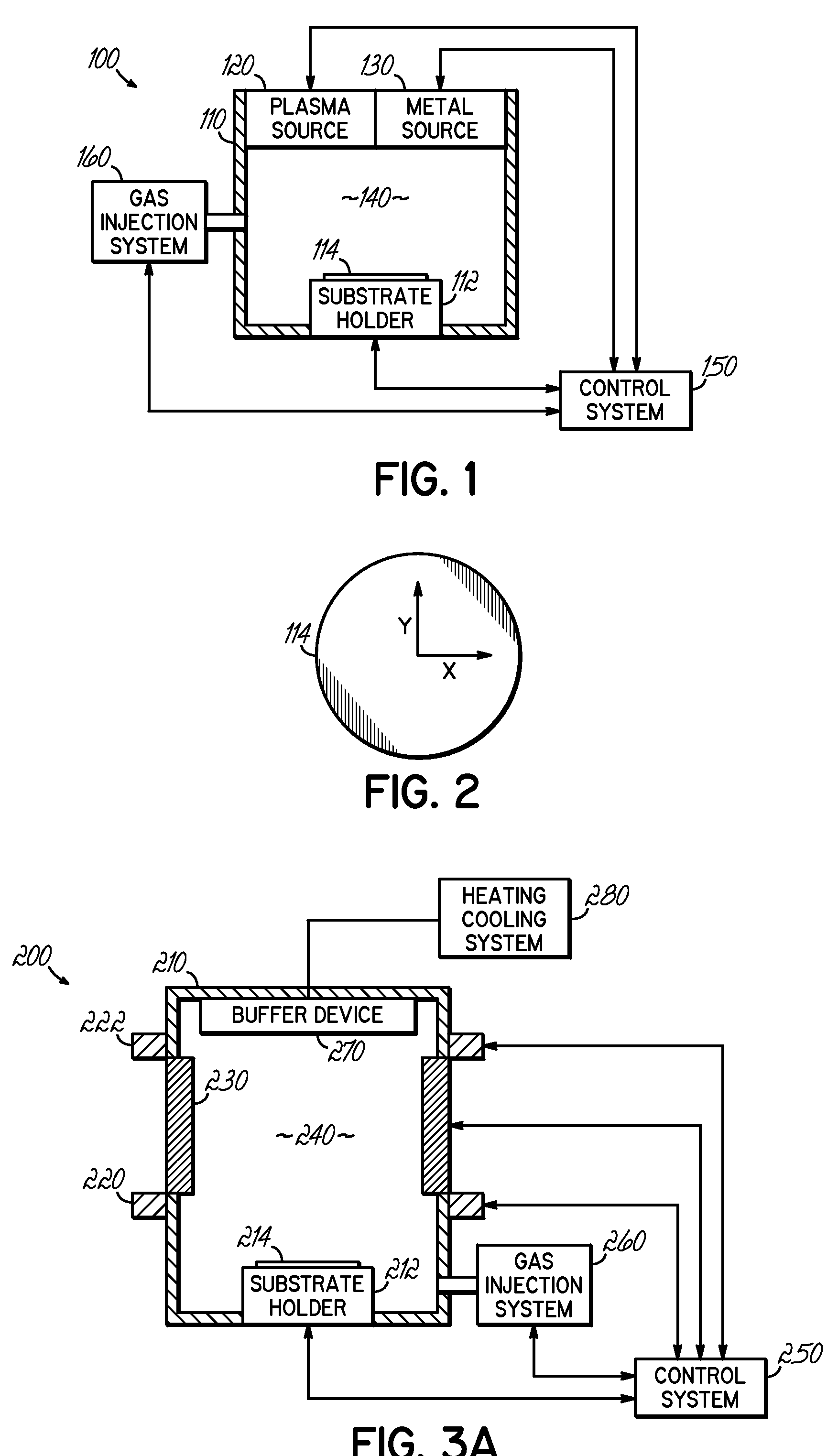

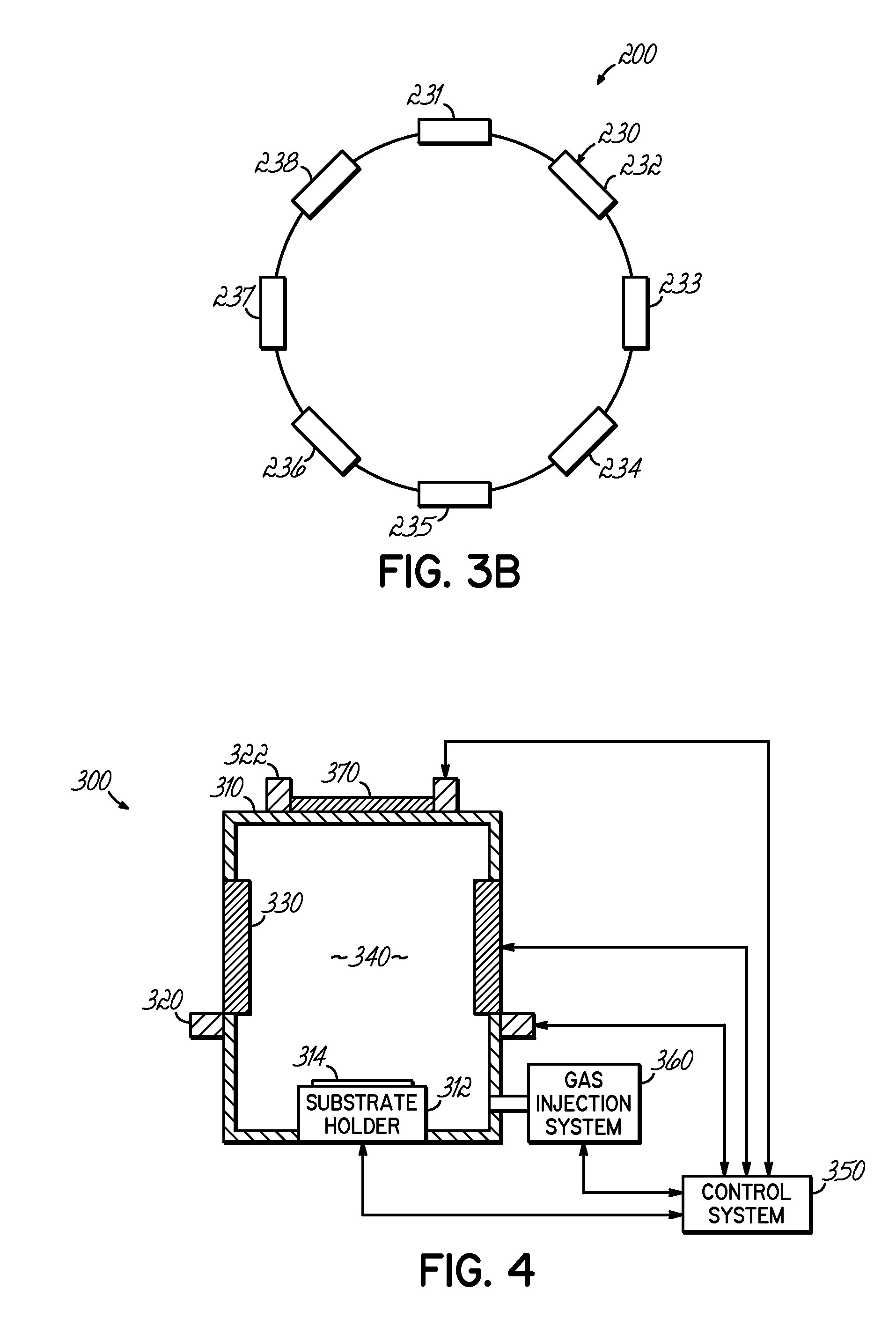

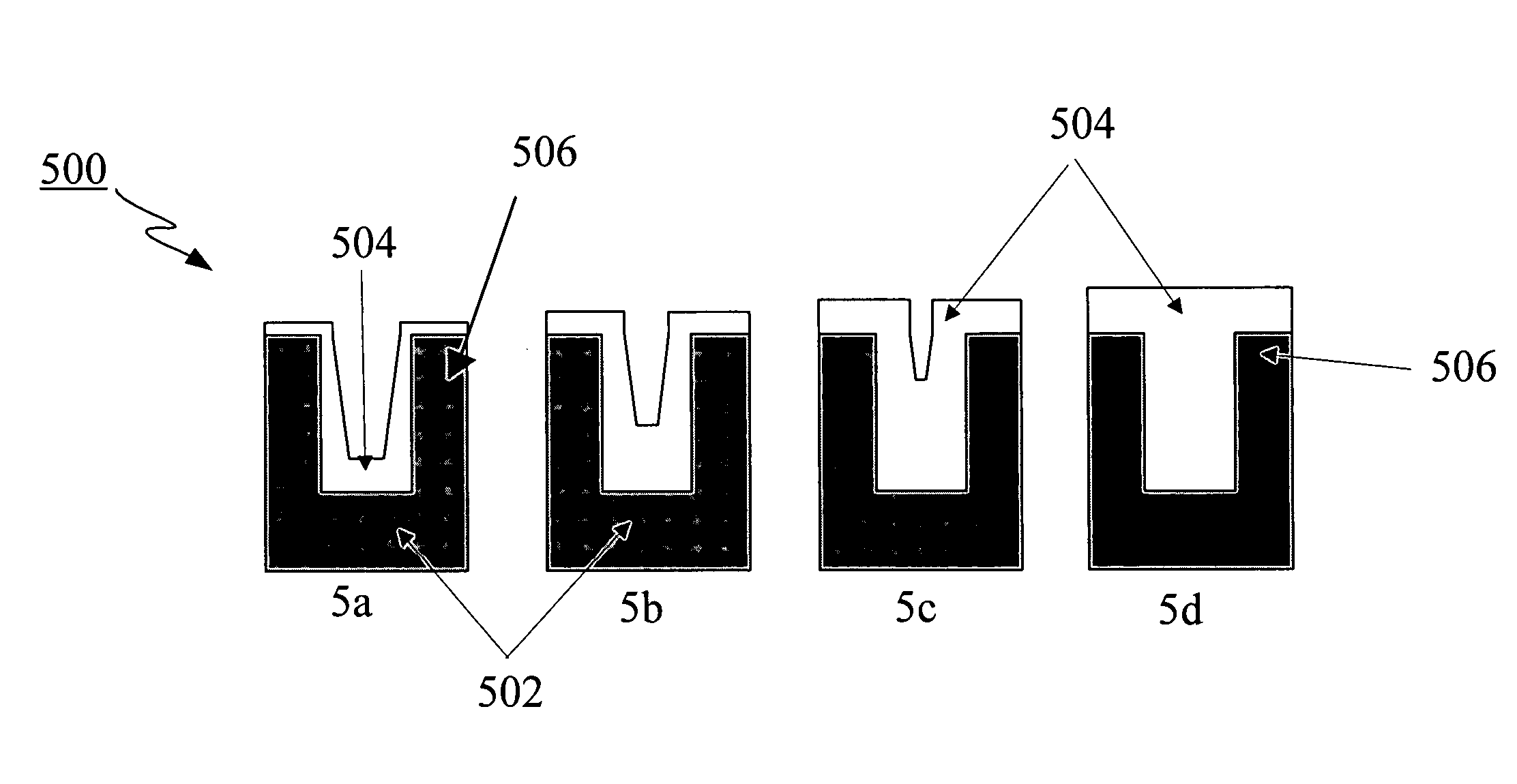

Method and apparatus of distributed plasma processing system for conformal ion stimulated nanoscale deposition process

InactiveUS20080026574A1Good coverageHigh aspect ratio (HAR) featuresVacuum evaporation coatingSputtering coatingPlasma densityHigh density

A deposition system and method of operating thereof is described for depositing a conformal metal or other similarly responsive coating material film in a high aspect ratio feature using a high density plasma is described. The deposition system includes a plasma source, and a distributed metal source for forming plasma and introducing metal vapor to the deposition system, respectively. The deposition system is configured to form a plasma having a plasma density and generate metal vapor having a metal density, wherein the ratio of the metal density to the plasma density proximate the substrate is less than or equal to unity. This ratio should exist at least within a distance from the surface of the substrate that is about twenty percent of the diameter of the substrate. A ratio that is uniform within plus or minus twenty-five percent substantially across the surface of said substrate is desirable. The ratio is particularly effective for plasma density exceeding 1012 cm−3, and for depositing film on substrates having nanoscale features with maximum film thickness less than half of the feature width, for example, at ten percent of the feature width.

Owner:TOKYO ELECTRON LTD

Method of selective coverage of high aspect ratio structures with a conformal film

ActiveUS7625820B1High aspect ratioVacuum evaporation coatingSputtering coatingMetallurgySilicon oxide

Methods for forming thin dielectric films by selectively depositing a conformal film of dielectric material on a high aspect ratio structure have uses in semiconductor processing and other applications. A method for forming a dielectric film involves providing in a deposition reaction chamber a substrate having a gap on the surface. The gap has a top opening and a surface area comprising a bottom and sidewalls running from the top to the bottom. A conformal silicon oxide-based dielectric film is selectively deposited in the gap by first preferentially applying a film formation catalyst or a catalyst precursor on a portion representing less than all of the gap surface area. The substrate surface is then exposed to a silicon-containing precursor gas such that a silicon oxide-based dielectric film layer is preferentially formed on the portion of the gap surface area. The preferential application of the catalyst or catalyst precursor may occur either at the top of the gap, for example to form a sacrificial mask, or at the bottom of the gap to create a seamless and void-free gap fill.

Owner:NOVELLUS SYSTEMS

Multiple material golf club head

InactiveUS6582323B2Increase flexibilityGood coefficientMetal-working apparatusGolf clubsGramMetallic materials

A golf club (40) having a club head (42) with a face component (60) and an aft body (61) is disclosed herein. The face component (60) has a striking plate portion (72) and a return portion (74). The aft-body (61) is composed of a crown portion (62), a sole portion (64) and optionally a ribbon section (90). The face component (60) is composed of a metal material, and the aft-body (61) is composed of a non-metal material such as a composite material or a thermoplastic material. The striking plate portion (72) preferably has an aspect ratio less than 1.7. The striking plate portion (72) preferably has concentric regions of thickness with the thickness portion in the center (102). The club head (42) has a volume in the range of 290 cubic centimeters to 600 cubic centimeters, a weight in the range of 165 grams to 300 grams, and a striking plate portion (72) surface area in the range of 4.00 square inches to 7.50 square inches. The golf club head (42) has a coefficient of restitution greater than 0.81 under test conditions such as the USGA test conditions specified pursuant to Rule 4-1e, Appendix II, of the Rules of Golf for 1998-1999.

Owner:TOPGOLF CALLAWAY BRANDS CORP

Vapor deposition of silicon dioxide nanolaminates

ActiveUS20050112282A1Easy to produceUniform thicknessMaterial nanotechnologySemiconductor/solid-state device manufacturingPorosityElectrical conductor

This invention relates to materials and processes for thin film deposition on solid substrates. Silica / alumina nanolaminates were deposited on heated substrates by the reaction of an aluminum-containing compound with a silanol. The nanolaminates have very uniform thickness and excellent step coverage in holes with aspect ratios over 40:1. The films are transparent and good electrical insulators. This invention also relates to materials and processes for producing improved porous dielectric materials used in the insulation of electrical conductors in microelectronic devices, particularly through materials and processes for producing semi-porous dielectric materials wherein surface porosity is significantly reduced or removed while internal porosity is preserved to maintain a desired low-k value for the overall dielectric material. The invention can also be used to selectively fill narrow trenches with low-k dielectric material while at the same time avoiding deposition of any dielectric on the surface area outside of the trenches.

Owner:PRESIDENT & FELLOWS OF HARVARD COLLEGE

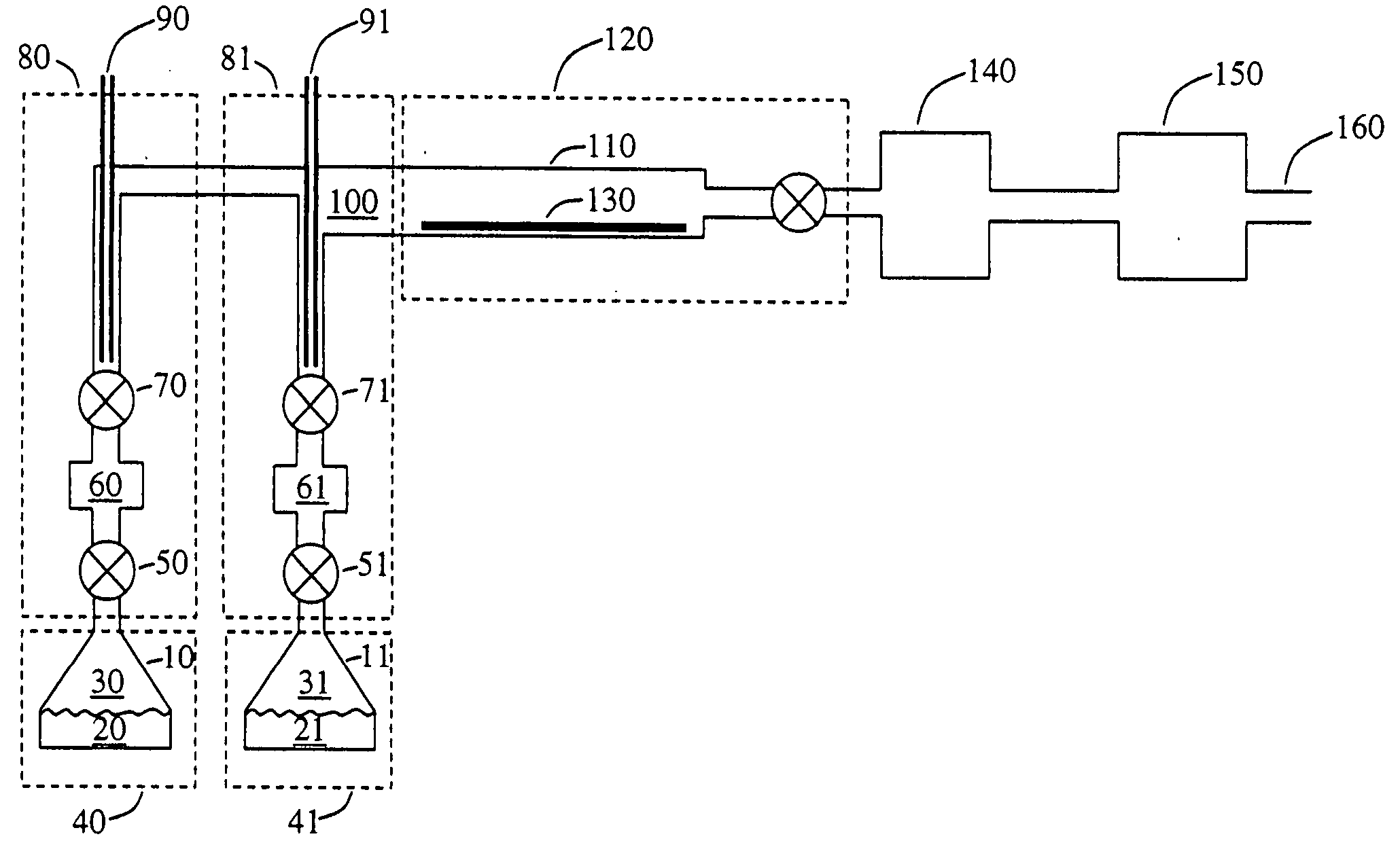

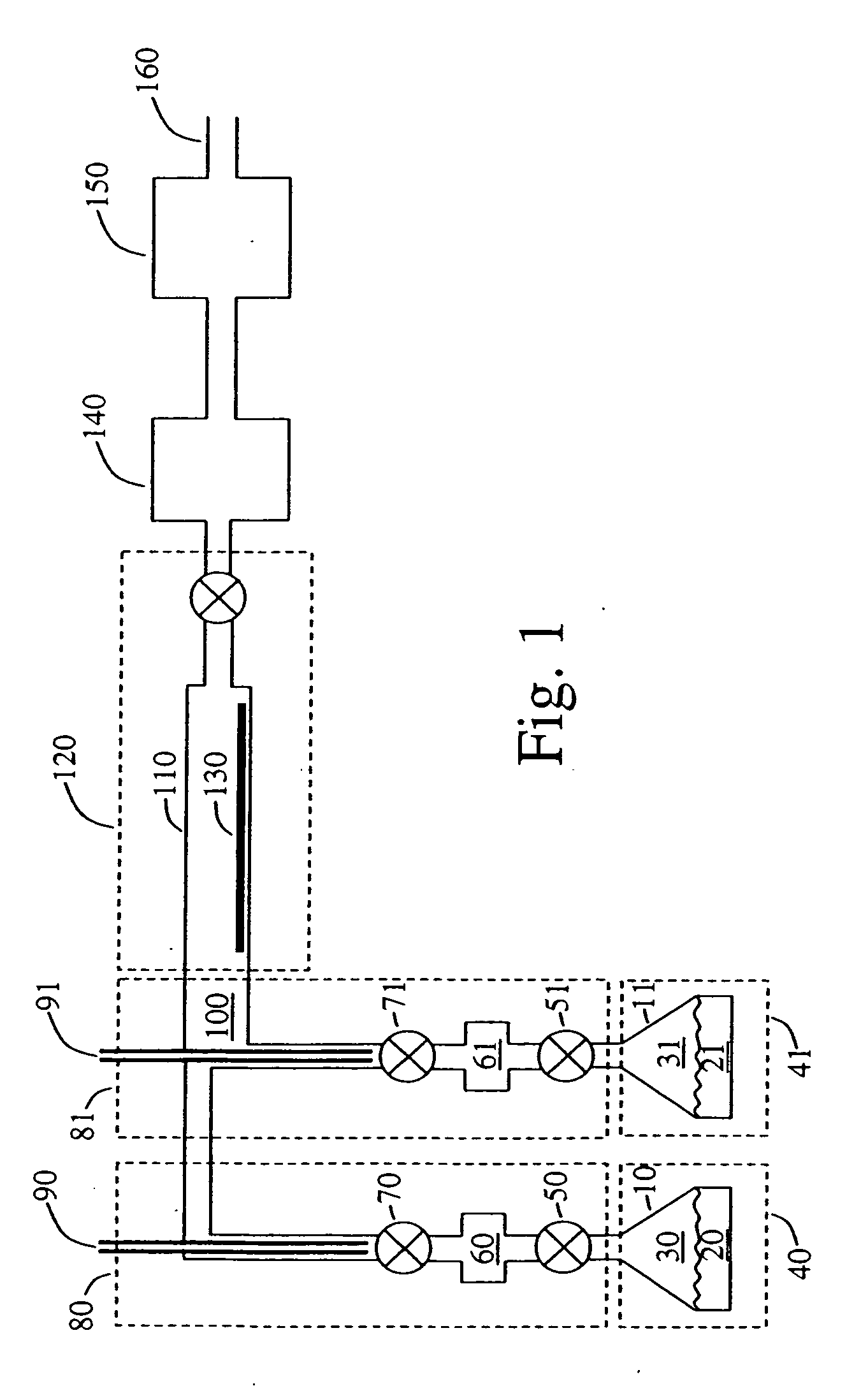

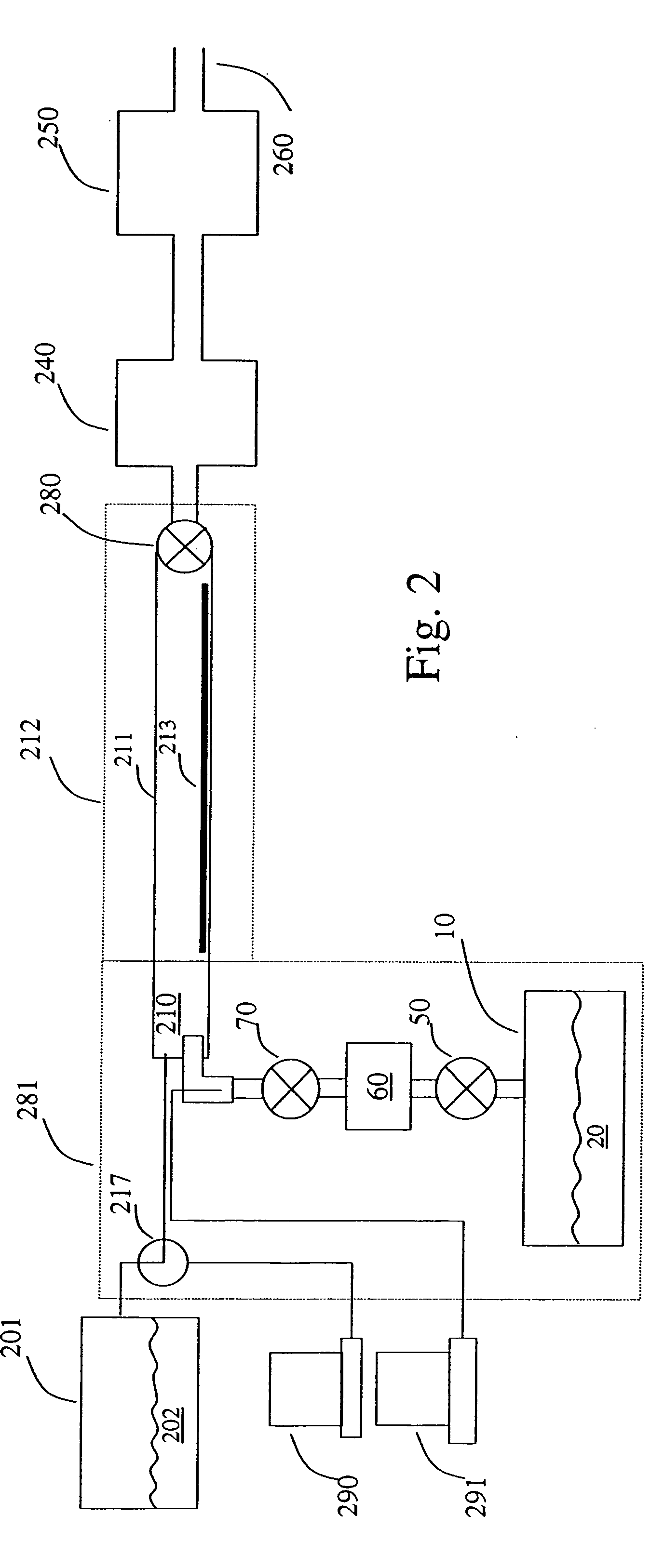

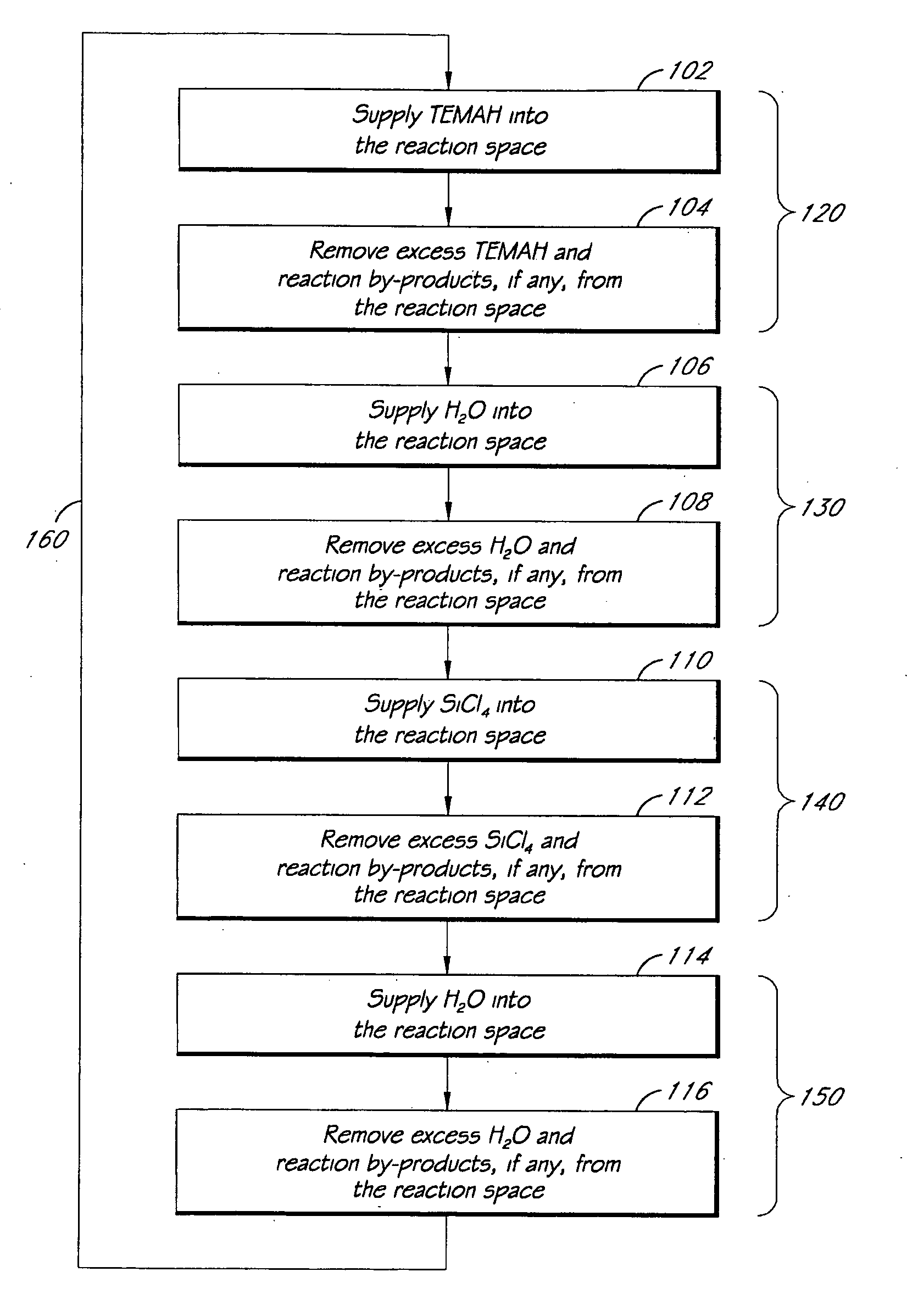

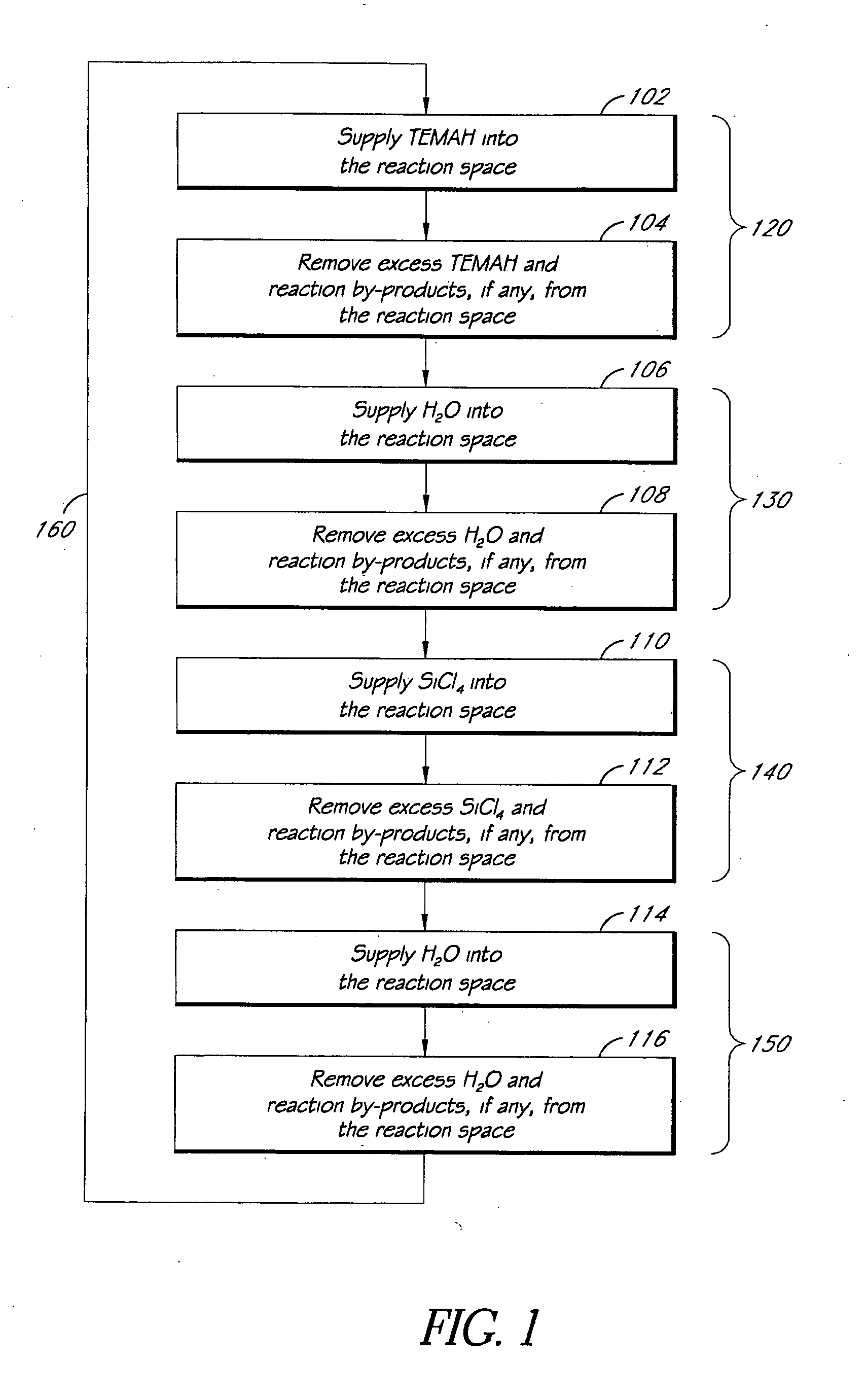

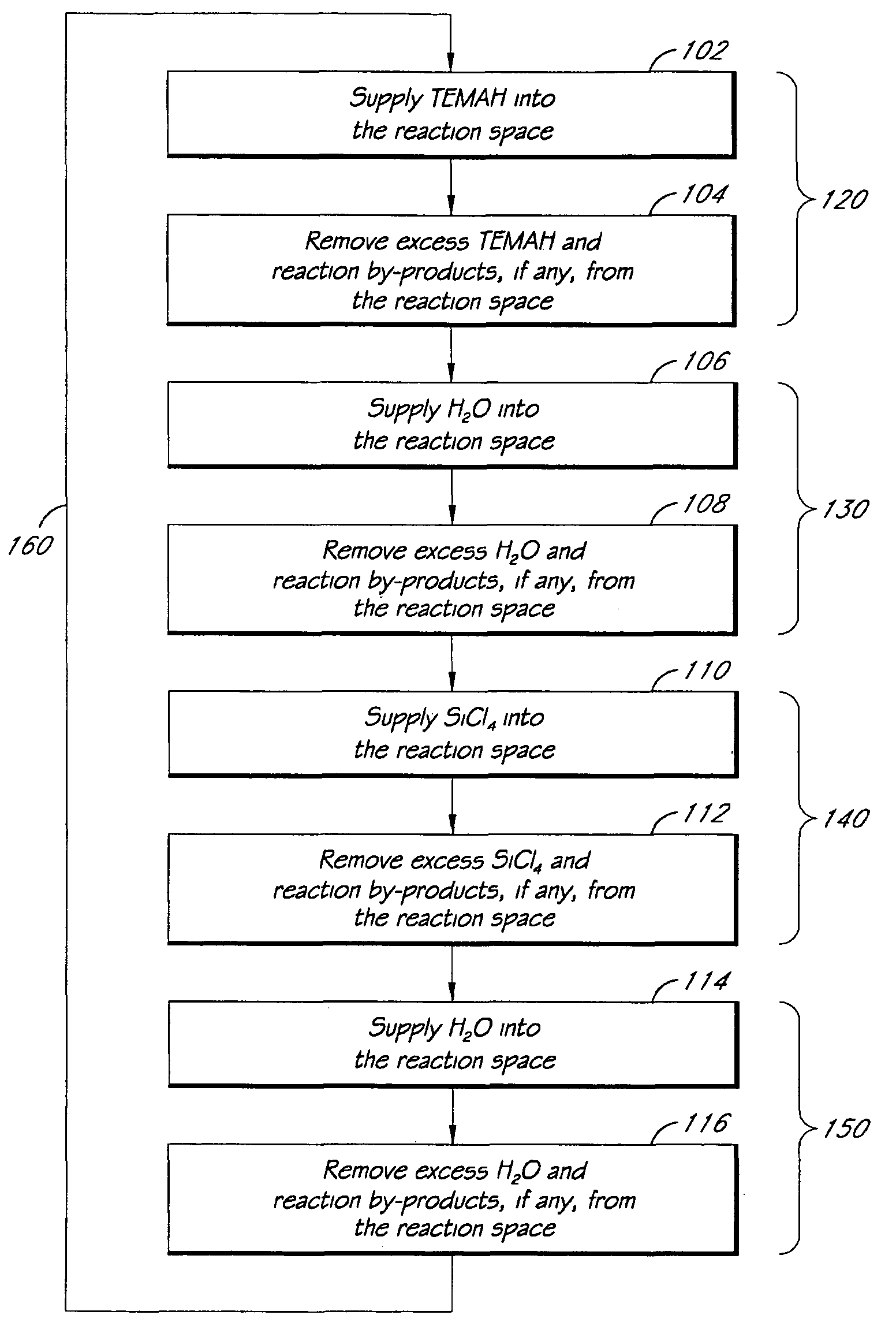

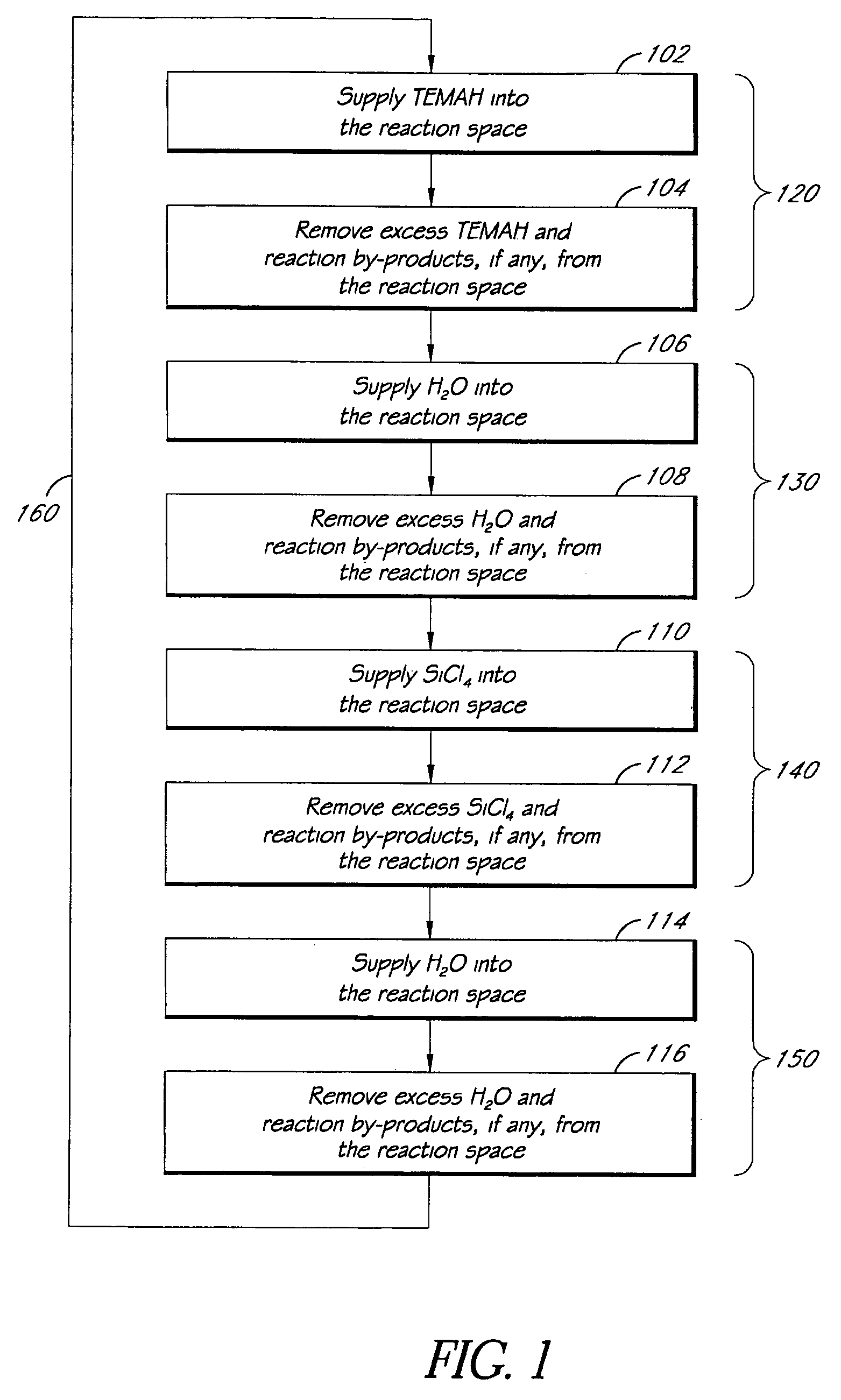

ALD of metal silicate films

ActiveUS20080020593A1Readily apparentSemiconductor/solid-state device manufacturingChemical vapor deposition coatingGas phaseHafnium

Methods for forming metal silicate films are provided. The methods comprise contacting a substrate with alternating and sequential vapor phase pulses of a metal source chemical, a silicon source chemical and an oxidizing agent. In preferred embodiments, an alkyl amide metal compound and a silicon halide compound are used. Methods according to preferred embodiments can be used to form hafnium silicate and zirconium silicate films with substantially uniform film coverages on substrate surfaces comprising high aspect ratio features (e.g., vias and / or trenches).

Owner:ASM IP HLDG BV

Multiple material golf club head

Owner:TOPGOLF CALLAWAY BRANDS CORP

Photoresist polymer and photoresist composition containing the same

InactiveUS7279256B2Enhance the imageImprove the immunityPhotosensitive materialsRadiation applicationsResistEnergy variation

Photoresist polymers and photoresist compositions are disclosed. A photoresist polymer comprising a polymerization repeating unit represented by Formula I is less sensitive to change in the amount of energy due to its higher active energy than that of a conventional photoresist polymer. As a result, a phenomenon where the portion of the pattern for the storage electrode contact region that receives relatively large amount of light becomes too thin is avoided when the device isolation film pattern is formed, and wherein pattern collapse caused by a high aspect ratio due to high etching resistance is prevented or avoided.whereinR1–R10, a, b, c and d are as defined in the description.

Owner:SK HYNIX INC

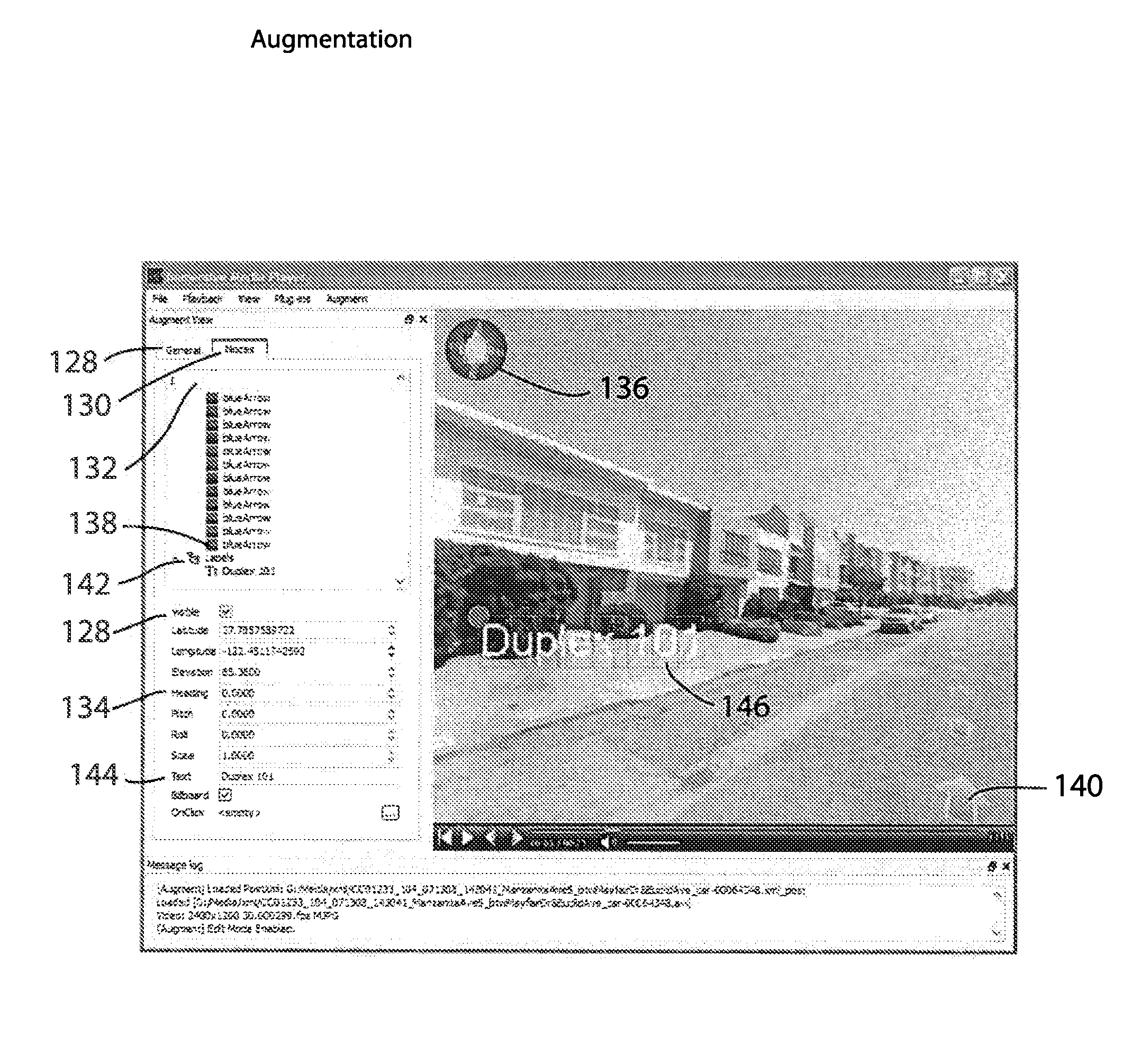

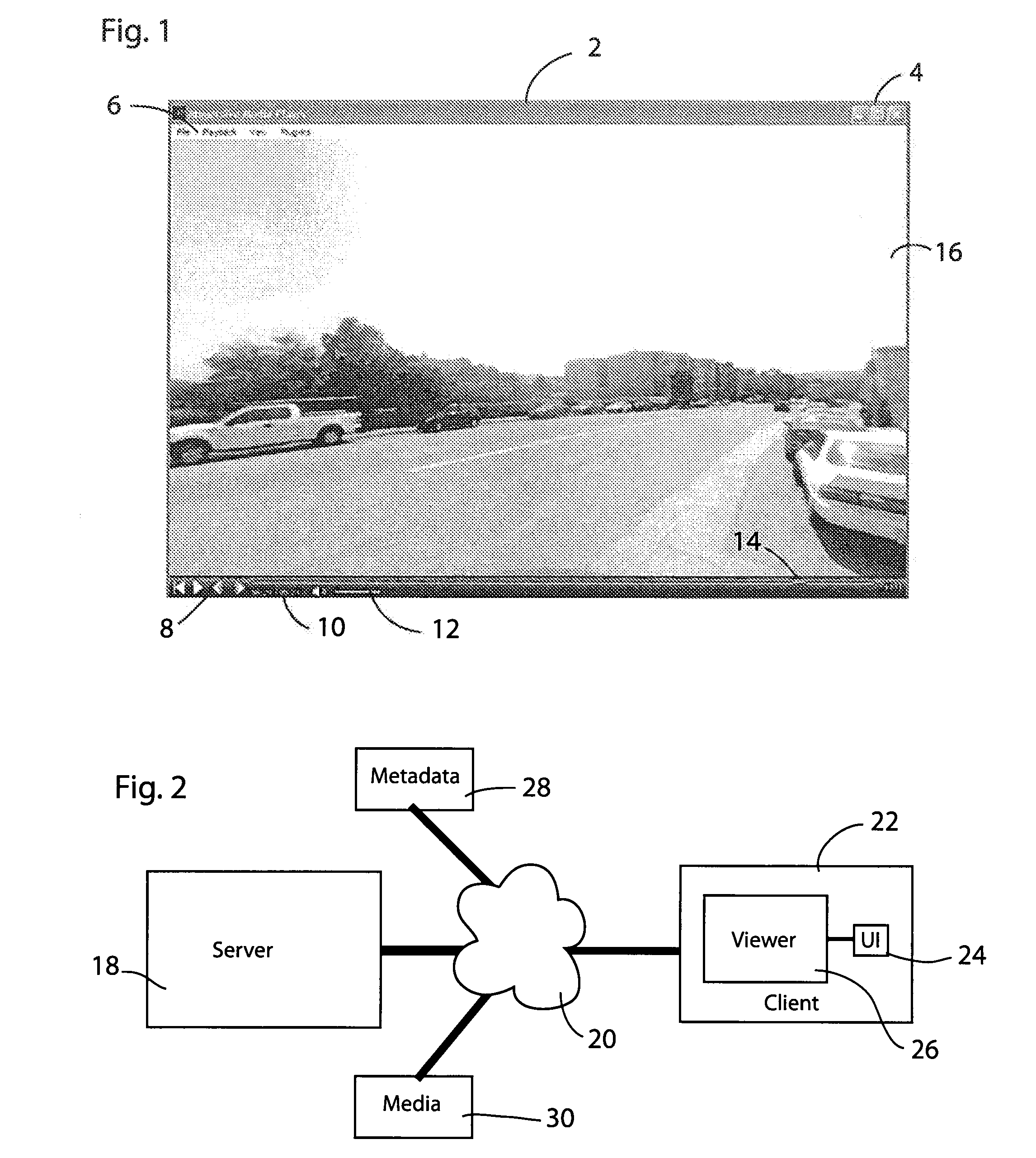

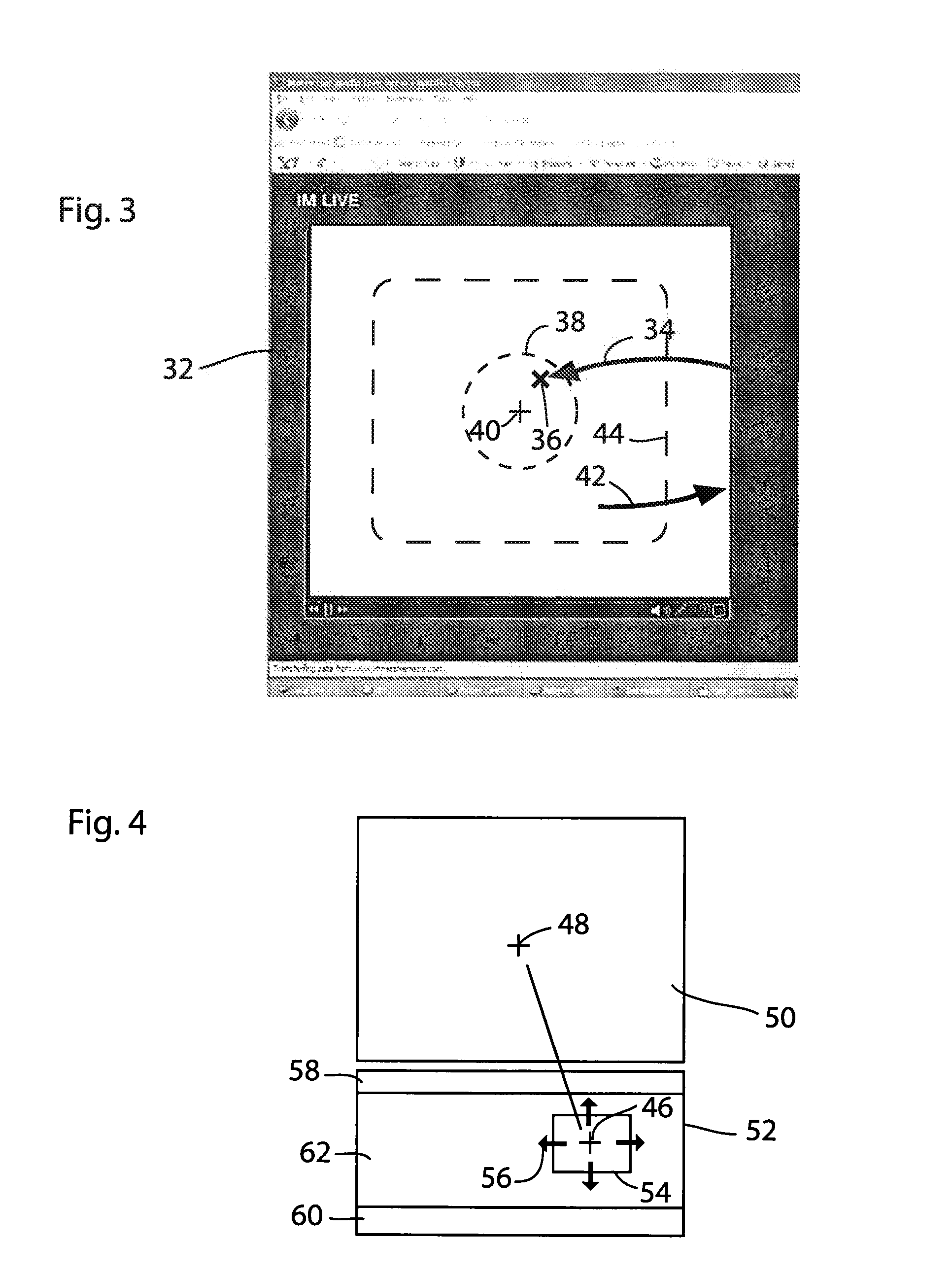

Hybrid media viewing application including a region of interest within a wide field of view

ActiveUS20100299630A1Reduced worldviewTelevision system detailsDigital computer detailsWide fieldDisplay device

A content delivery and display solution includes a viewing application for displaying immersive images with a region of interest, in addition to conventional fixed-aspect-ratio media. The display can include the layered display of metadata, multiple windows, and images or hotspots embedded into the immersive image. The viewing application can be used for the display of either live or prerecorded images, from local or online sources.

Owner:IMMERSIVE MEDIA

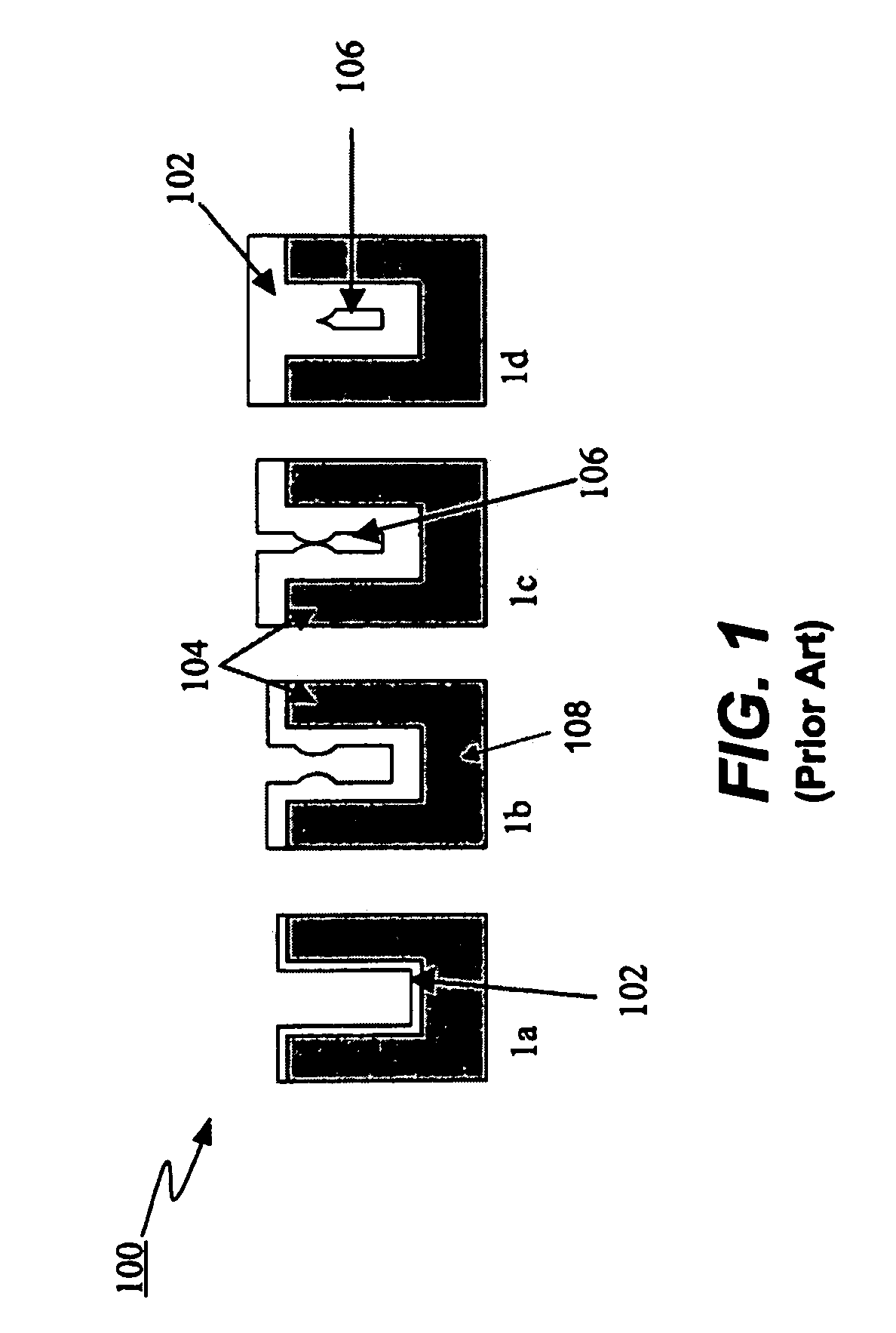

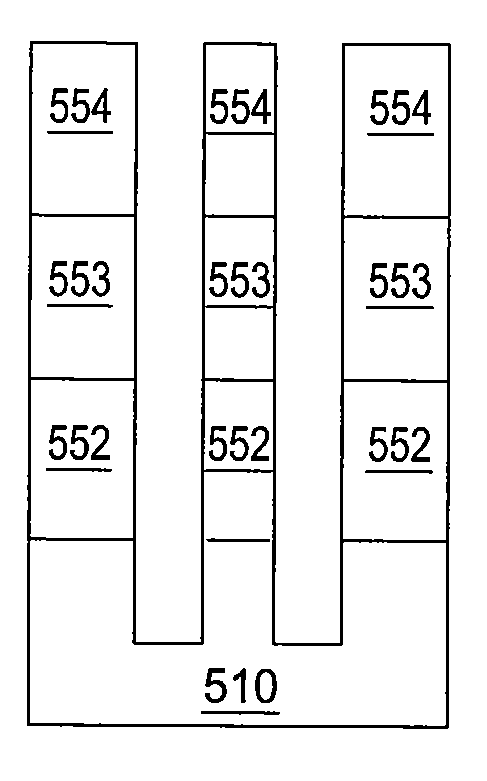

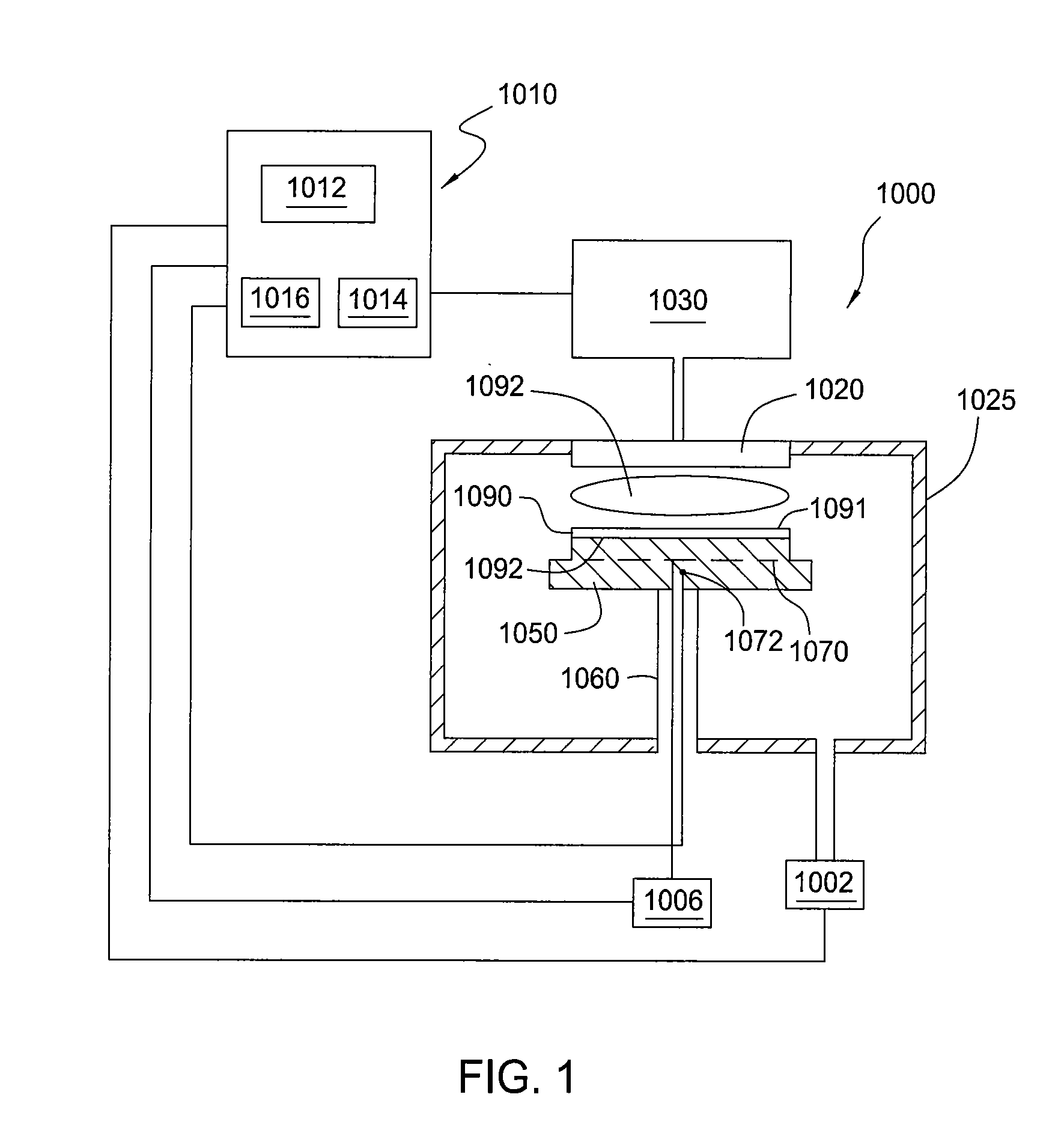

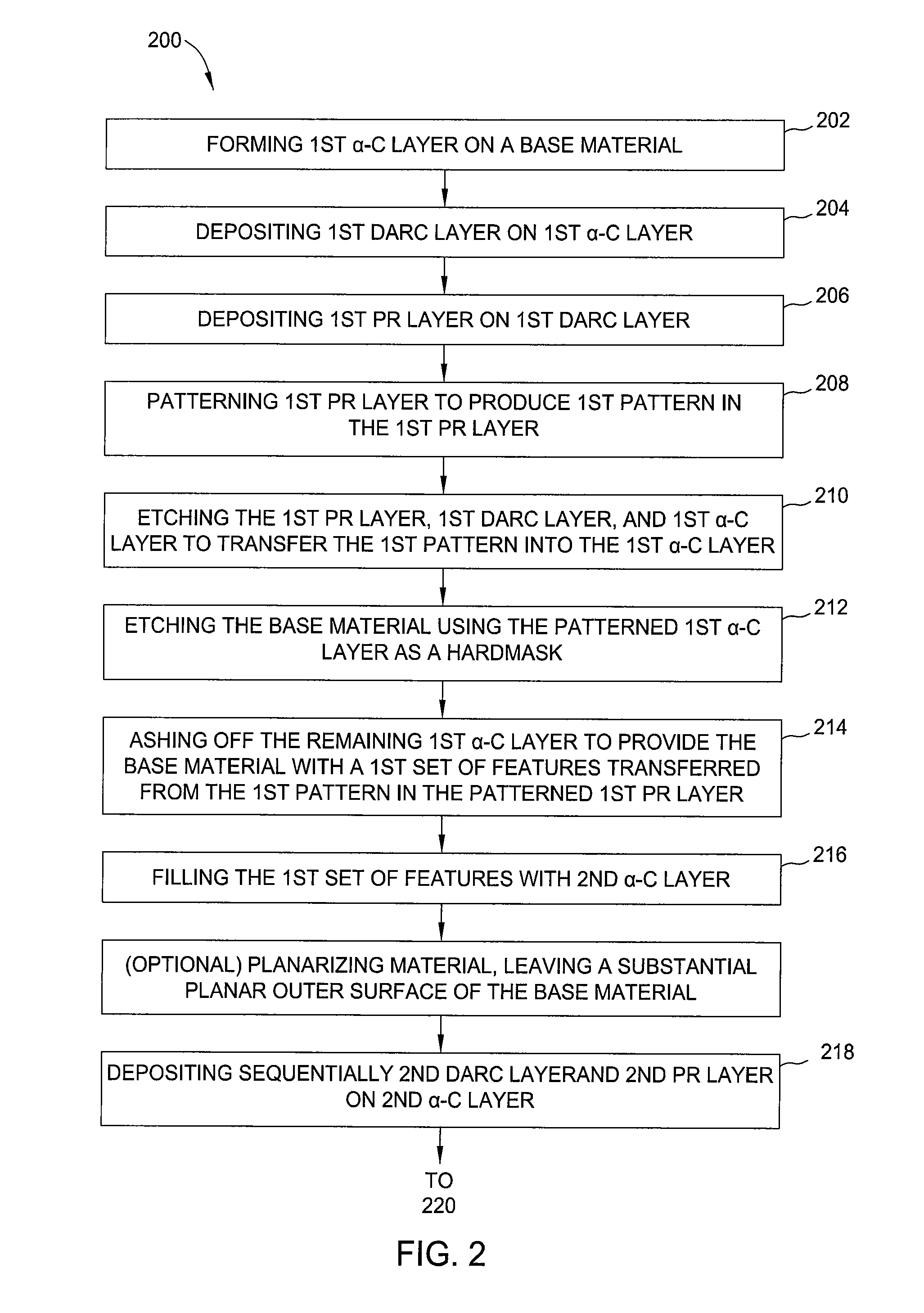

Planarizing etch hardmask to increase pattern density and aspect ratio

InactiveUS20110291243A1Easy to disassembleAdd depthSemiconductor/solid-state device detailsSolid-state devicesAnti-reflective coatingEngineering

Methods for manufacturing a semiconductor device in a processing chamber are provided. In one embodiment, a method includes depositing over a substrate a first base material having a first set of interconnect features, filling an upper portion of the first set of interconnect features with an ashable material to an extent capable of protecting the first set of interconnect features from subsequent processes while being easily removable when desired, planarizing an upper surface of the first base material such that an upper surface of the ashable material filled in the first set of interconnect features is at the same level with the upper surface of the first base material, providing a substantial planar outer surface of the first base material, depositing a first film stack comprising a second base material on the substantial planar outer surface of the first base material, forming a second set of interconnect features in the second base material, wherein the second set of interconnect features are aligned with the first set of interconnect features, and removing the ashable material from the first base material, thereby extending a feature depth of the semiconductor device by connecting the second set of interconnect features to the first set of interconnect features. In another embodiment, a method includes providing a base material having a first film stack deposited thereon, wherein the base material is formed over the substrate and having a first set of interconnect features filled with an amorphous carbon material, the first film stack comprising a first amorphous carbon layer deposited on a surface of the base material, a first anti-reflective coating layer deposited on the first amorphous carbon layer, and a first photoresist layer deposited on the first anti-reflective coating layer, and patterning a portion of the first photoresist layer by shifting laterally a projection of a mask on the first photoresist layer relative to the substrate a desired distance, thereby introducing into the first photoresist layer a first feature pattern to be transferred to the underlying base material, wherein the first feature pattern is not aligned with the first set of interconnect features.

Owner:APPLIED MATERIALS INC

Virtual desktop manager system and method

The present invention comprises a method and computer implemented system for presenting multiple virtual desktops on a display of a computer system. A “pager” window is displayed on a desktop (either real or virtual) which comprises multiple subpanes, each of which contains a scaled virtual desktop having dimensions that are proportional to, but less than the dimensions of a corresponding virtual desktop. Each scaled virtual desktop provides a representation of the corresponding full-size virtual desktop that would display one or more application windows whose content may optionally be replaced by the icon designating the application program or data file displayed therein, for sake of visual clarity. The present invention also provides a mechanism for varying the background image of virtual desktop, and thus, of each scaled virtual desktop pane, in addition to a number of enhancements to the user interface for controlling the virtual desktop environment including transparency hiding of the pager window, constant aspect ratio scaling of the pager window, mouse desktop changing with corner exclusion, display and interaction with window lists, individual pop up menus for windows, starting desktop selection, a method for moving windows between virtual desktops, a method to override virtual desktop behaviors, a method for placing child windows on the same desktop as the parent window, notification of desktop changes, tracking topmost application on other desktops, sticky monitors, and API remote control.

Owner:THOMPSON JEFFREY W +4

Precursors for silicon dioxide gap fill

ActiveUS9337054B2Adverse seam effectSemiconductor/solid-state device manufacturingChemical vapor deposition coatingFilling materialsVolumetric Mass Density

A full fill trench structure is described, including a microelectronic device substrate having a high aspect ratio trench therein and filled with silicon dioxide of a substantially void-free character and substantially uniform density throughout its bulk mass. A method of manufacturing a semiconductor product also is described, involving use of specific silicon precursor compositions for forming substantially void-free and substantially uniform density silicon dioxide material in the trench. The precursor fill composition may include silicon and germanium, to produce a microelectronic device structure including a GeO2 / SiO2 trench fill material. A suppressor component may be employed in the precursor fill composition, to eliminate or minimize seam formation in the cured trench fill material.

Owner:ENTEGRIS INC

High-density plasma process for filling high aspect ratio structures

InactiveUS6846745B1Electric discharge tubesSemiconductor/solid-state device manufacturingHigh densityHydrogen

Chemical vapor deposition processes are employed to fill high aspect ratio (typically at least 3:1), narrow width (typically 1.5 microns or less and even sub 0.15 micron) gaps with significantly reduced incidence of voids or weak spots. This deposition process involves the use of both hydrogen and fluorine as process gases in the reactive mixture of a plasma-containing CVD reactor. The process gas also includes dielectric forming precursors such as silicon and oxygen-containing molecules.

Owner:NOVELLUS SYSTEMS

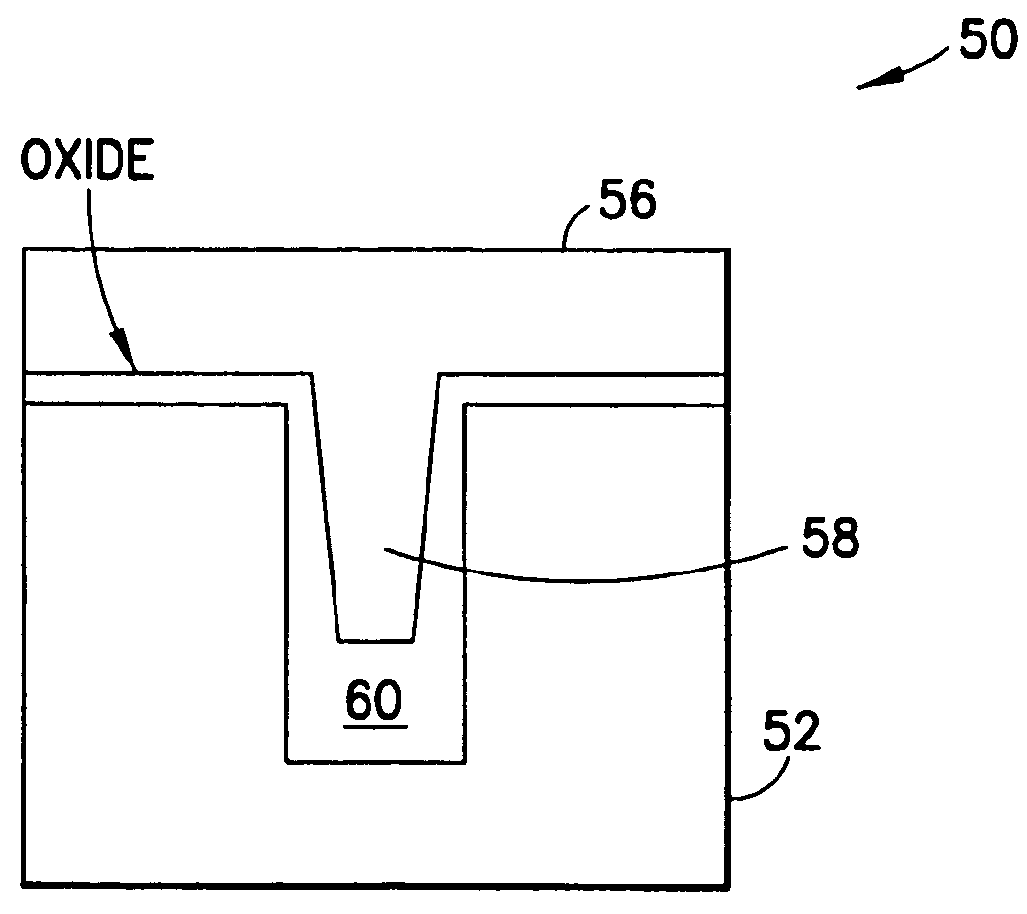

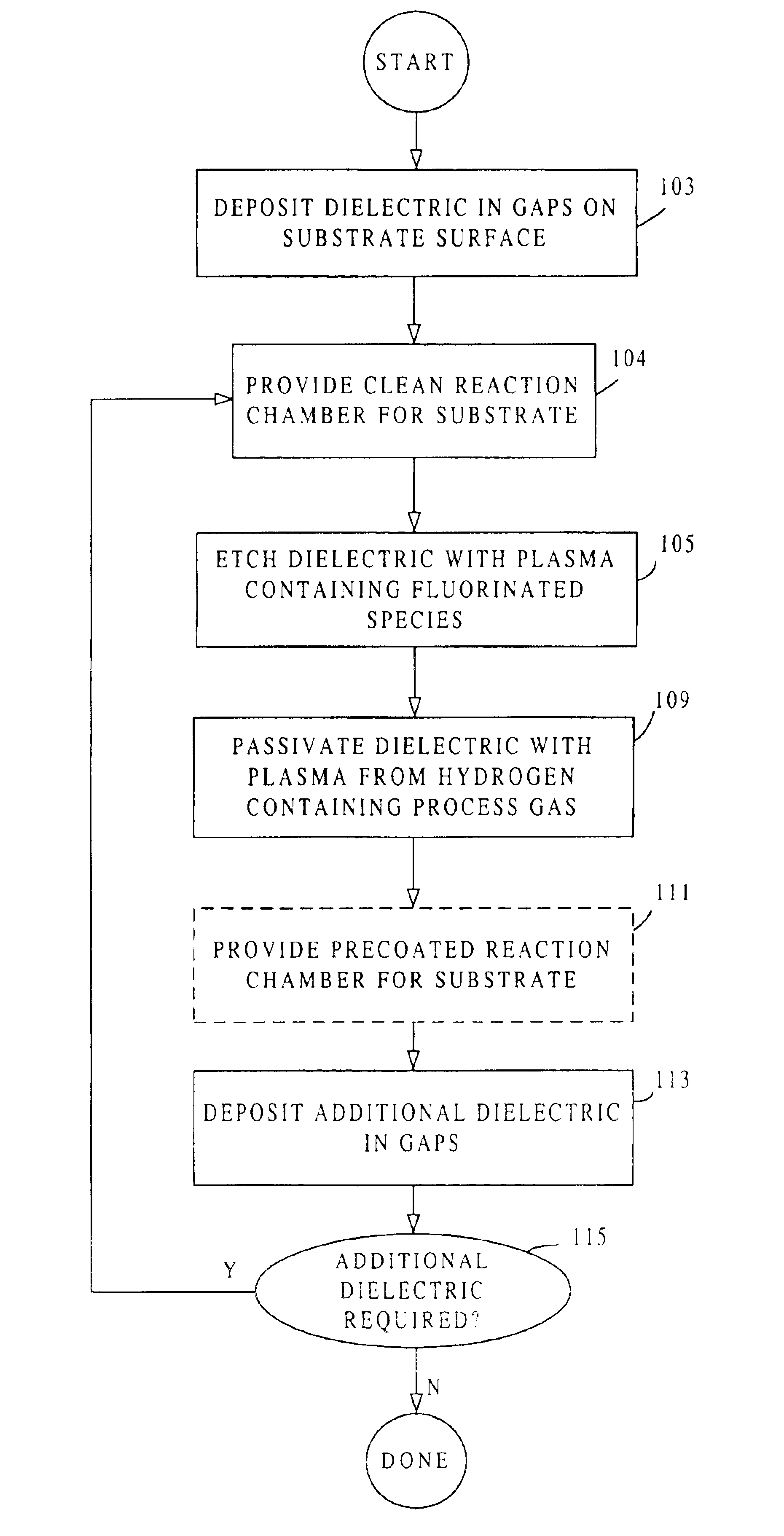

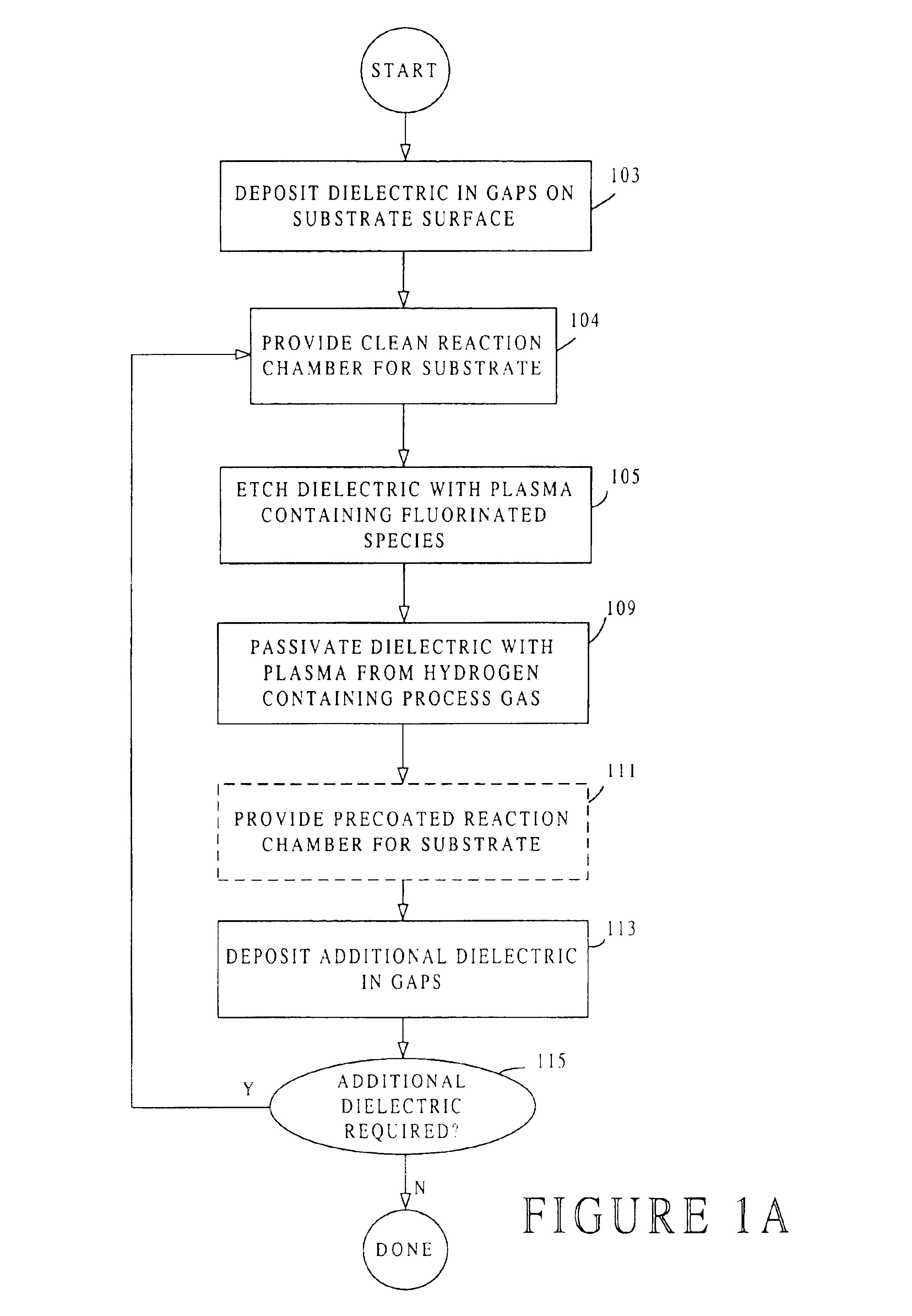

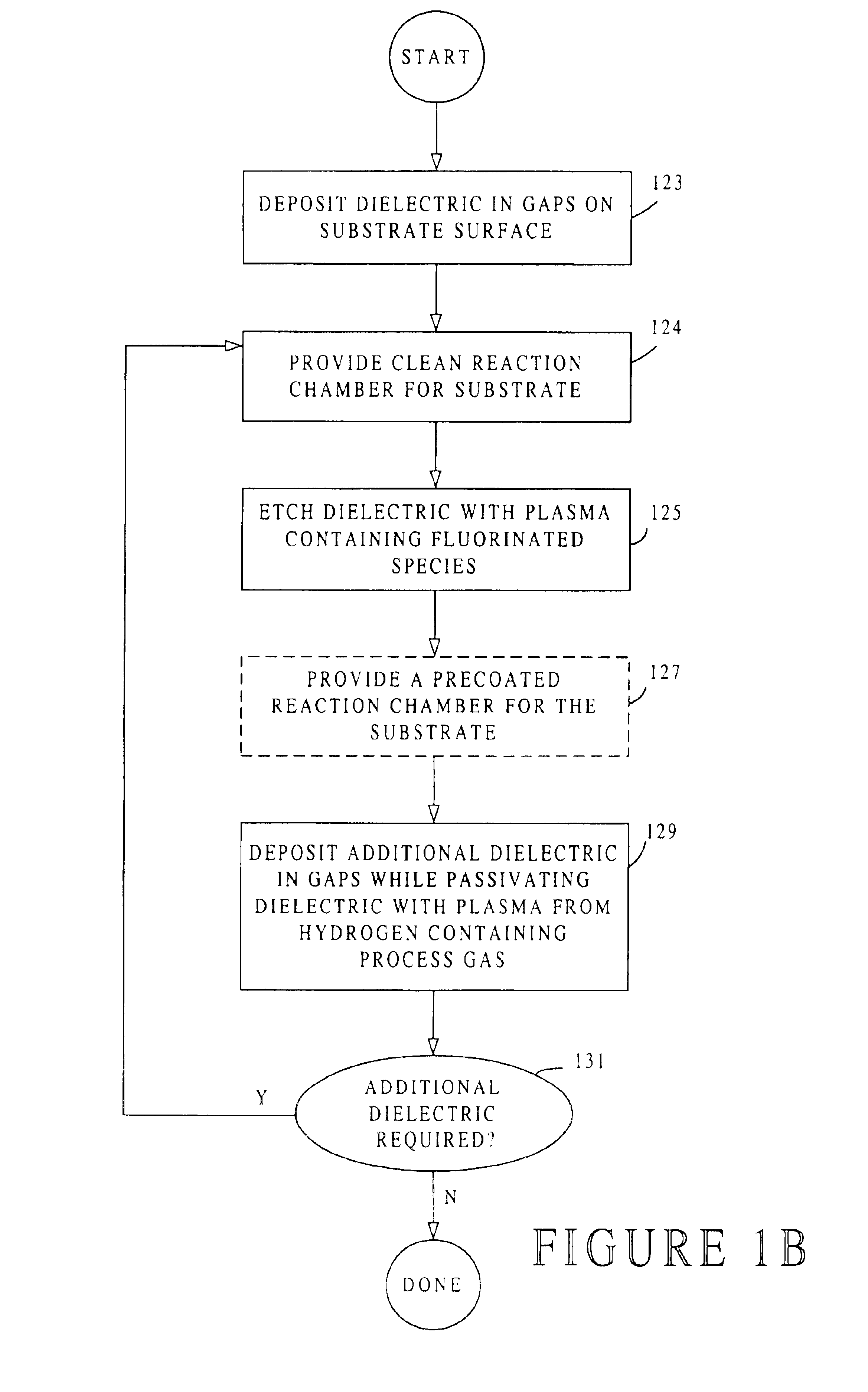

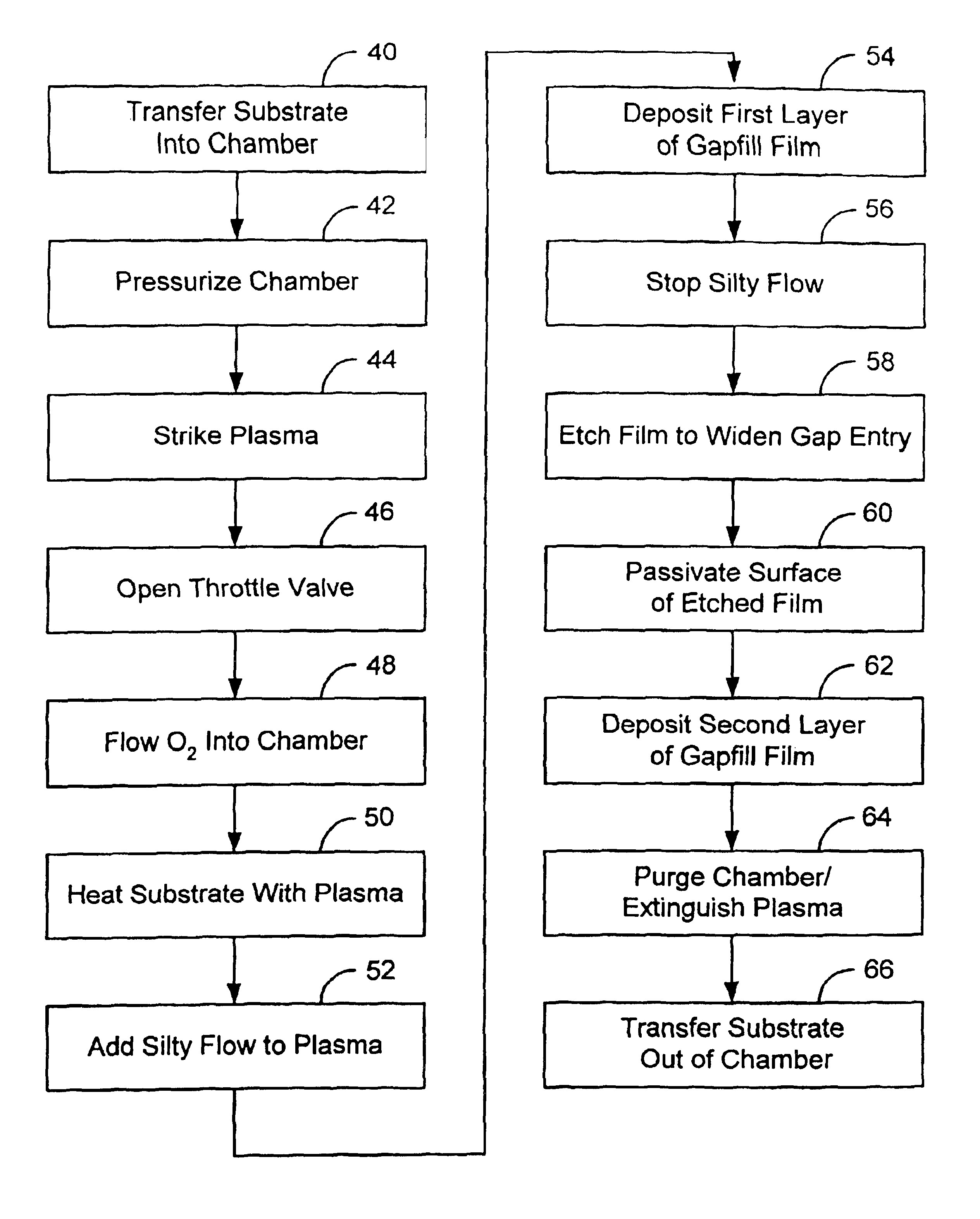

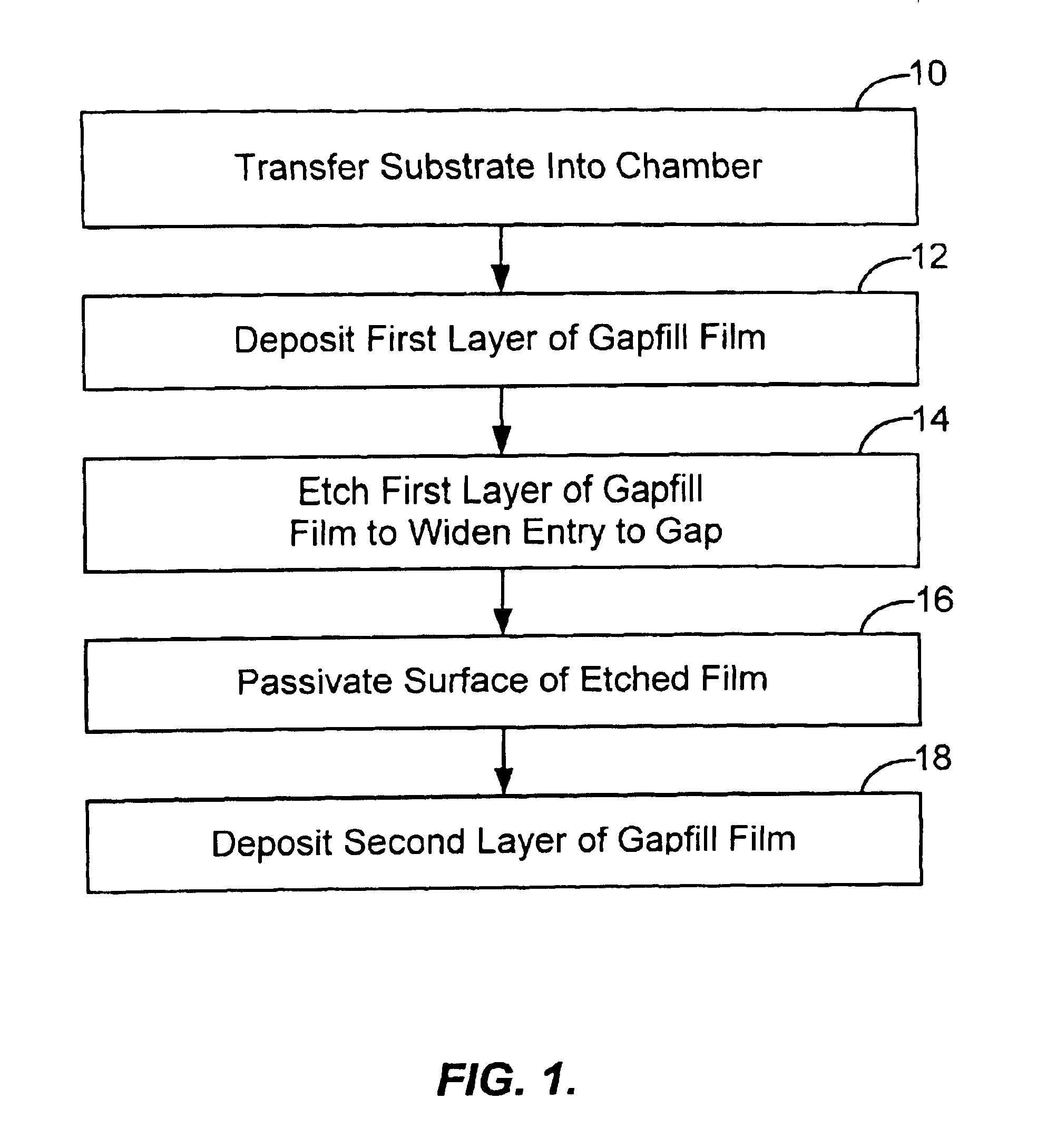

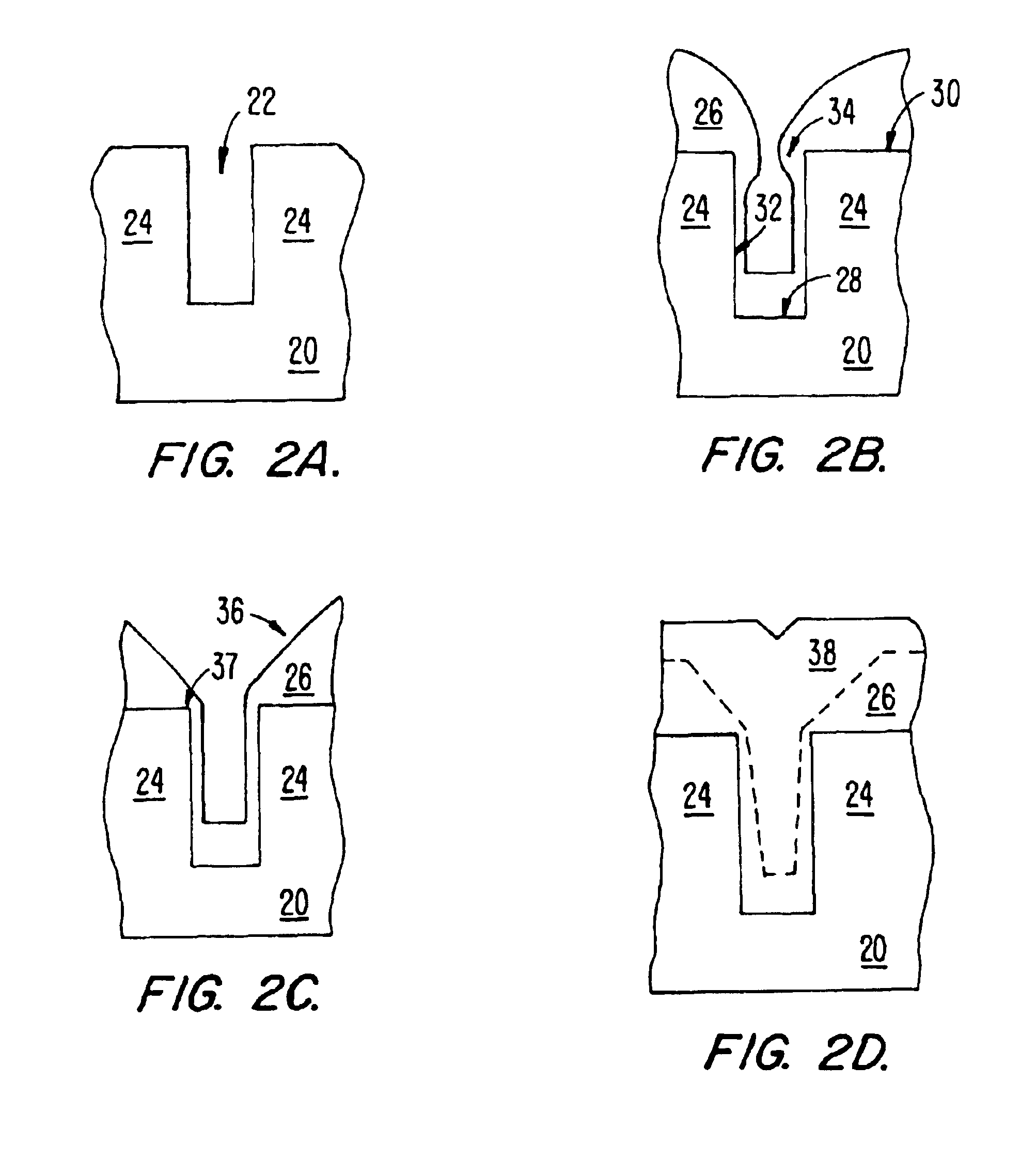

HDP-CVD dep/etch/dep process for improved deposition into high aspect ratio features

InactiveUS6908862B2Improve throughputSuperior gapfillSemiconductor/solid-state device manufacturingChemical vapor deposition coatingHigh densityProduct gas

A method of depositing a film on a substrate disposed in a substrate processing chamber. The method includes depositing a first portion of the film by forming a high density plasma from a first gaseous mixture flown into the process chamber. The deposition processes is then stopped and part of the deposited first portion of the film is etched by flowing a halogen etchant into the processing chamber. Next, the surface of the etched film is passivated by flowing a passivation gas into the processing chamber, and then a second portion of the film is deposited over the first portion by forming a high density plasma from a second gaseous mixture flown into the process chamber. In one embodiment the passivation gas consists of an oxygen source with our without an inert gas.

Owner:APPLIED MATERIALS INC

ALD of metal silicate films

ActiveUS7795160B2Semiconductor/solid-state device manufacturingChemical vapor deposition coatingGas phaseHafnium

Owner:ASM IP HLDG BV

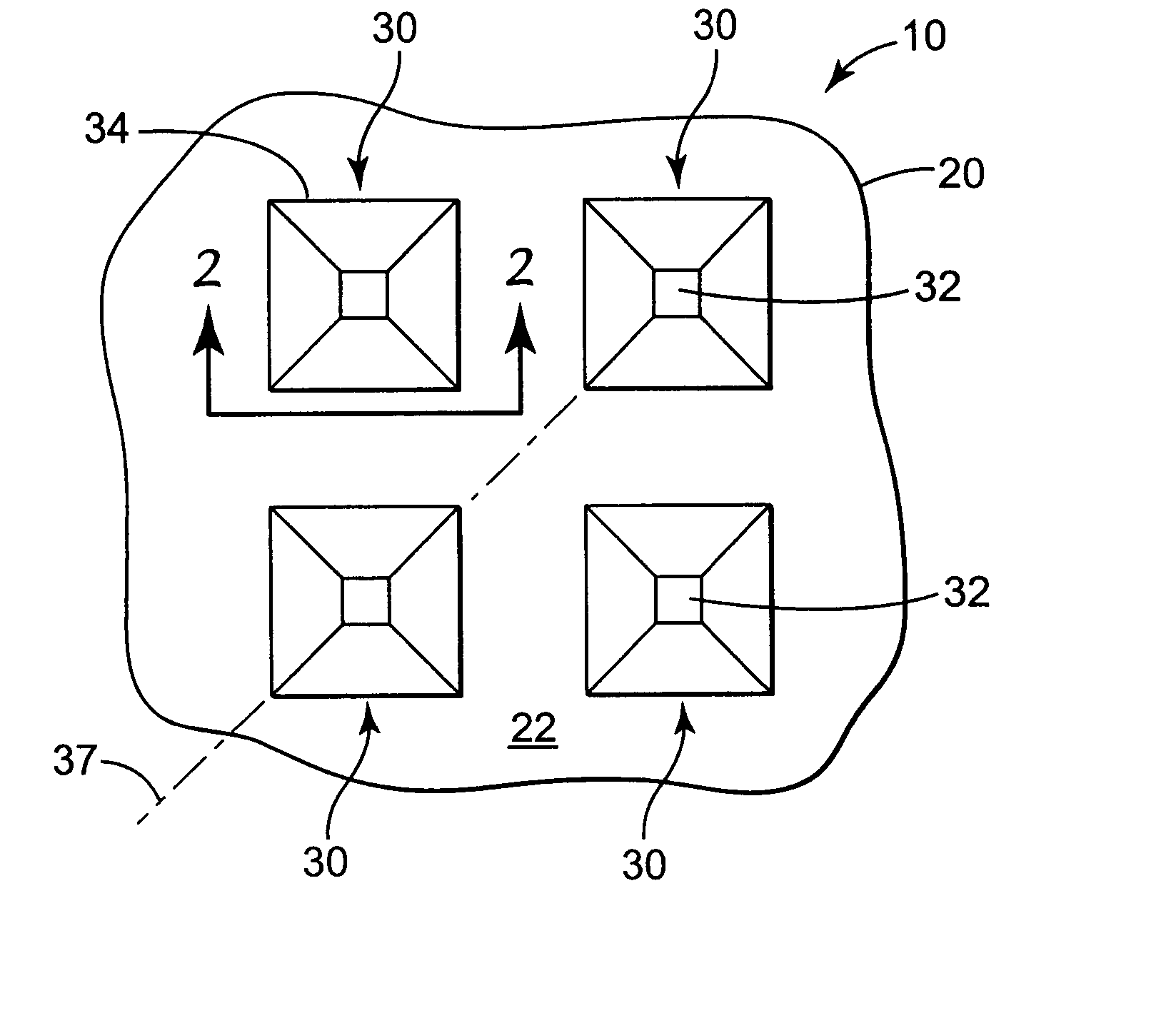

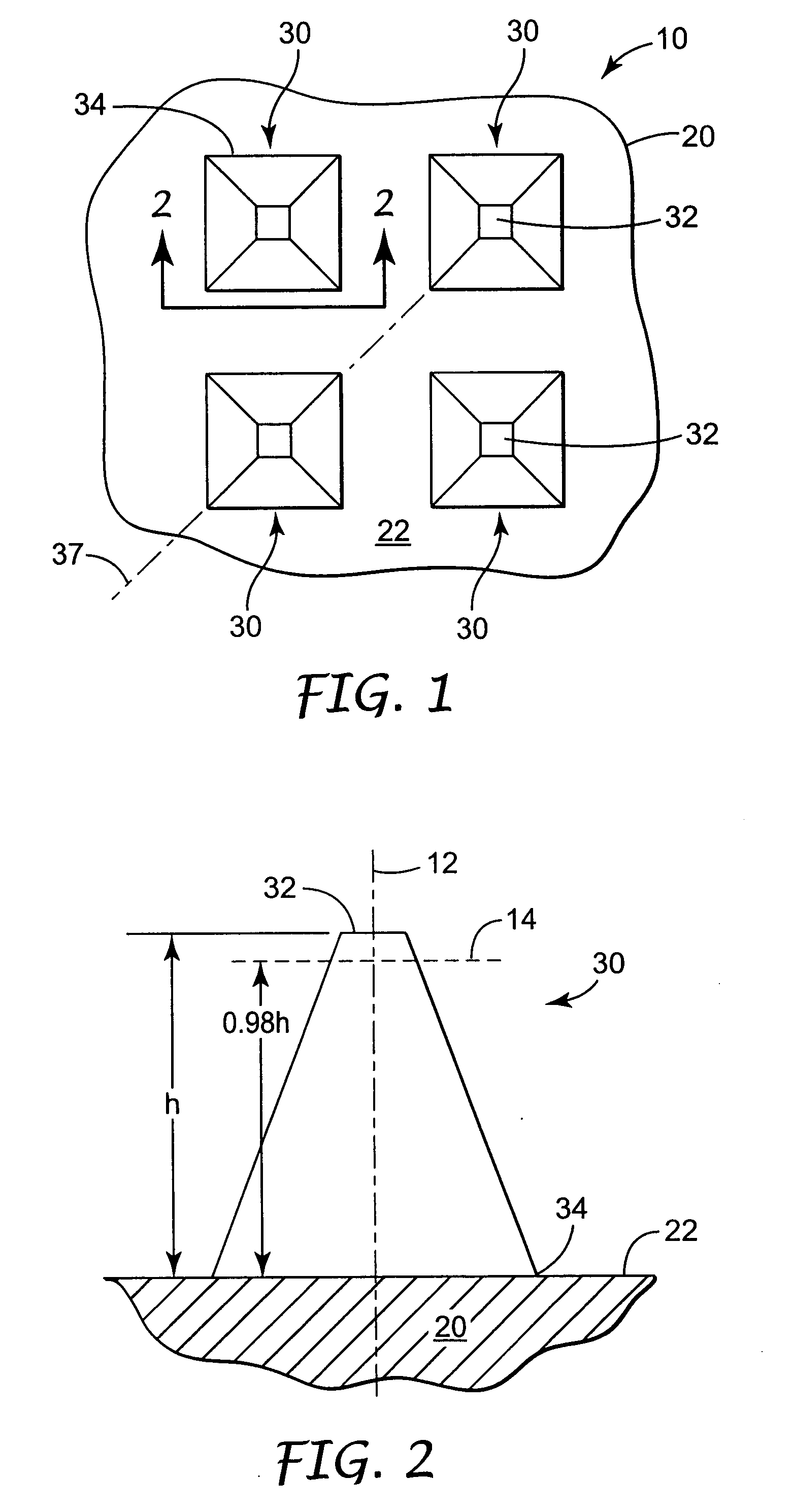

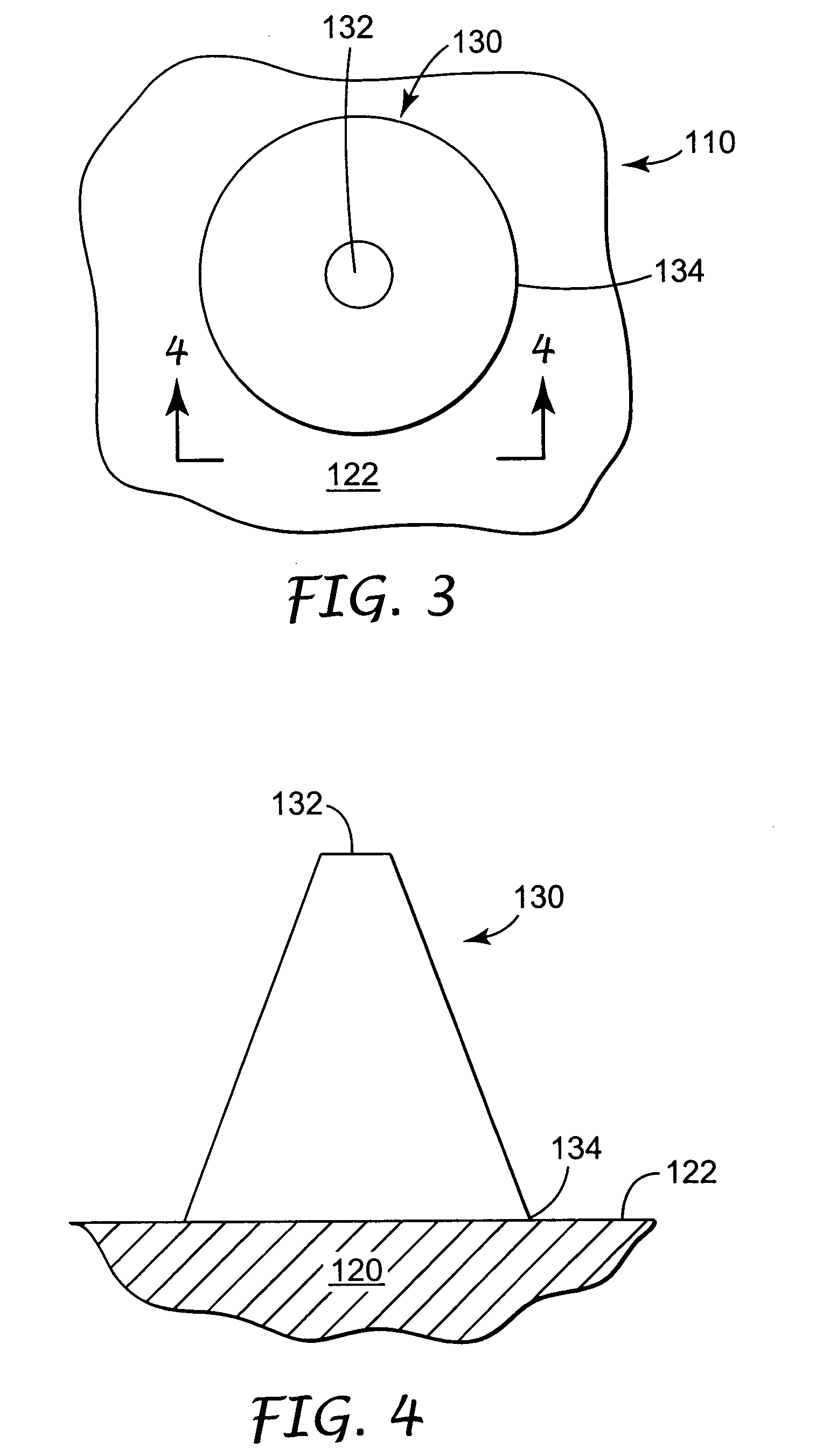

Microneedle devices and microneedle delivery apparatus

InactiveUS20050261631A1Reduces tip fractureEffective perforationSurgical needlesMicroneedlesStratum corneumPain experience

Microneedle devices with microneedles having a truncated tapered shape are disclosed. The microneedles of microneedle devices may also have a controlled aspect ratio. Microneedle delivery apparatus are disclosed that include drivers designed to deliver microneedles at velocities that may enhance perforation of the stratum corneum while limiting the sensation of pain experienced at the delivery site.

Owner:3M INNOVATIVE PROPERTIES CO

Fabric creped absorbent sheet with variable local basis weight

InactiveUS20080029235A1Improve water absorptionSurprising softnessNatural cellulose pulp/paperMechanical working/deformationFiberPapermaking

An absorbent cellulosic sheet having variable local basis weight includes a papermaking-fiber reticulum provided with (i) a plurality of cross-machine direction (CD) extending, fiber-enriched pileated regions of relatively high local basis weight interconnected by (ii) a plurality of elongated densified regions of compressed papermaking fibers. The elongated densified regions have relatively low local basis weight and are generally oriented along the machine direction (MD) of the sheet and have an MD / CD aspect ratio of at least 1.5. The products are most preferably prepared by way of a compactive dewatering / wet crepe process.

Owner:GPCP IP HLDG LLC

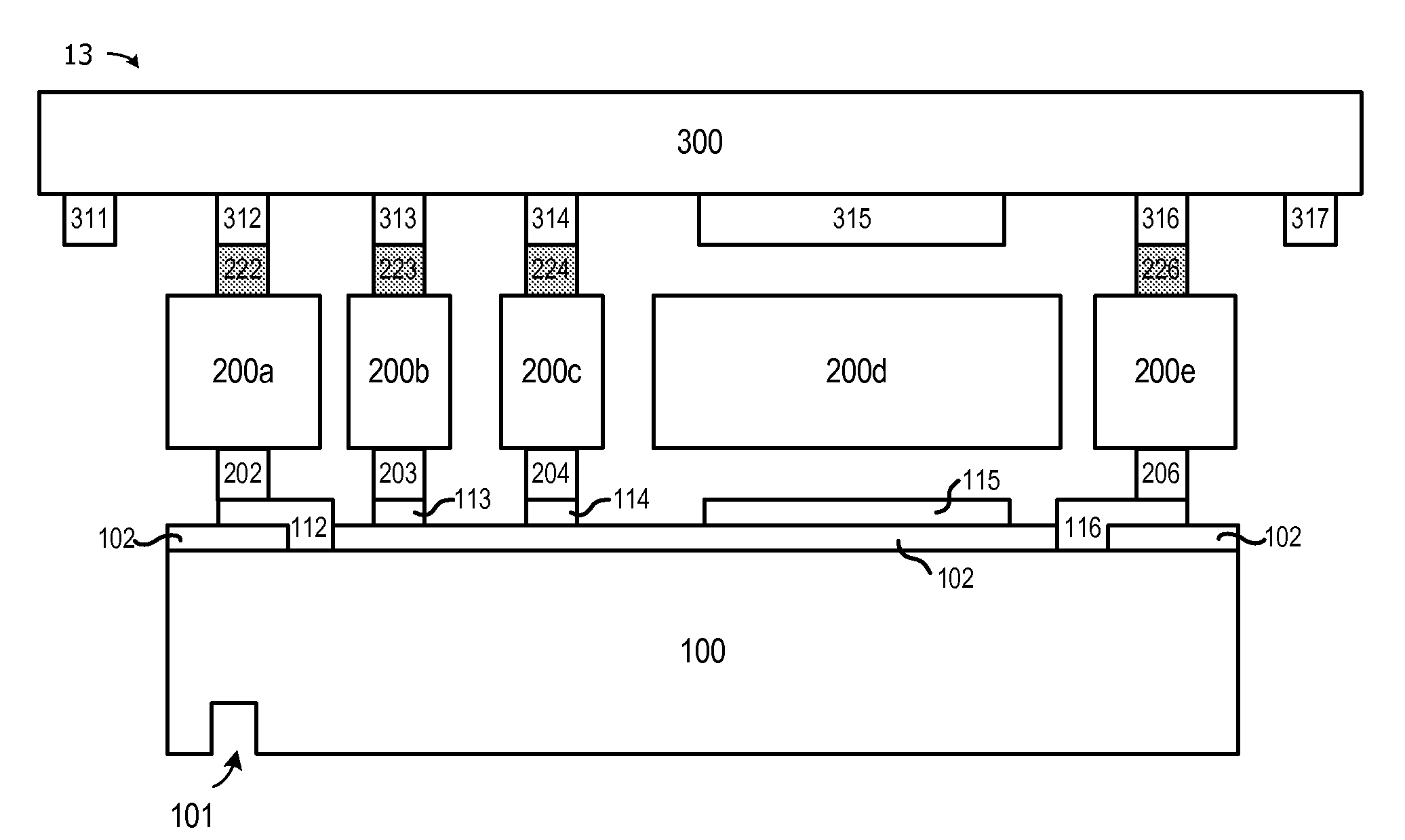

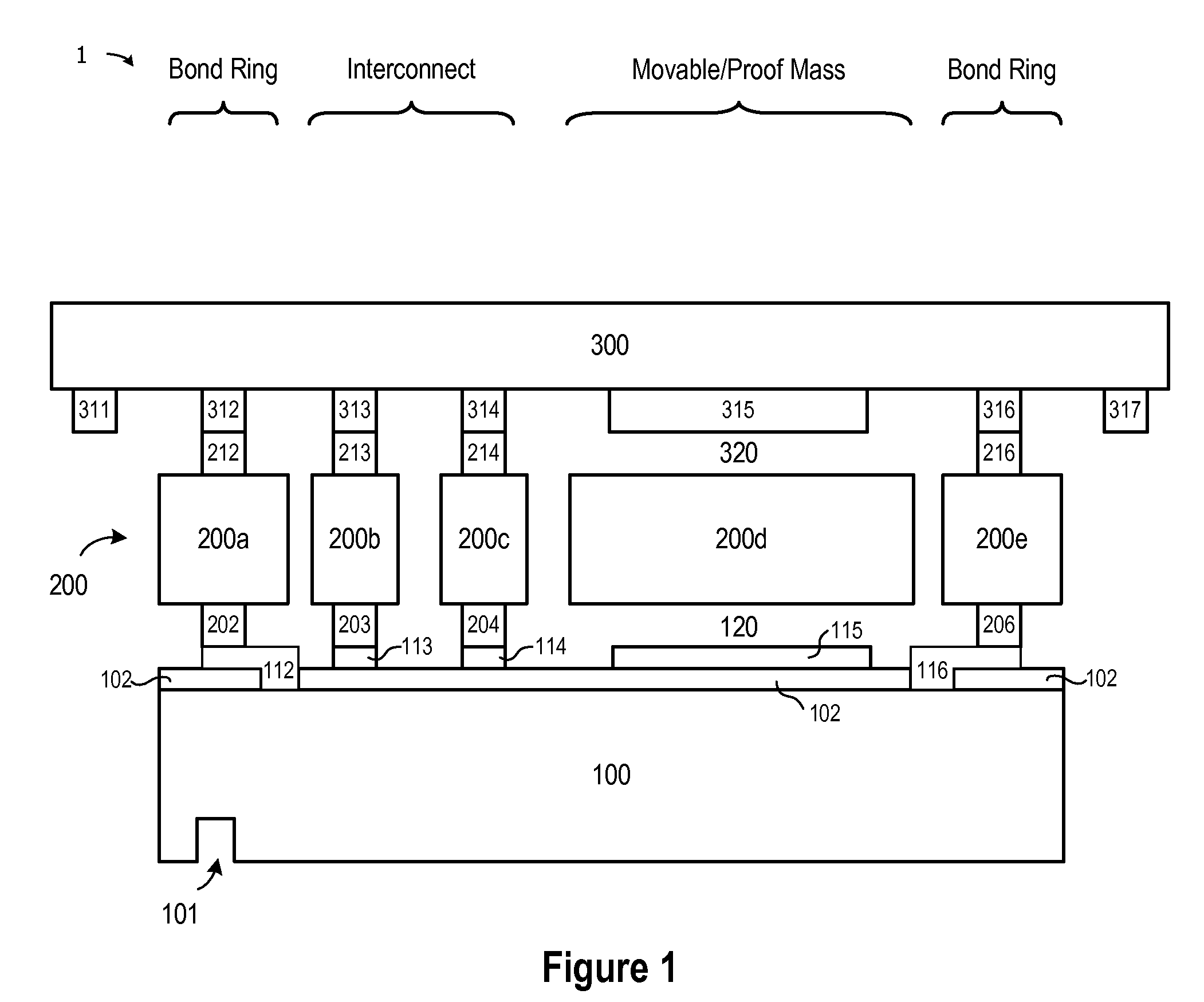

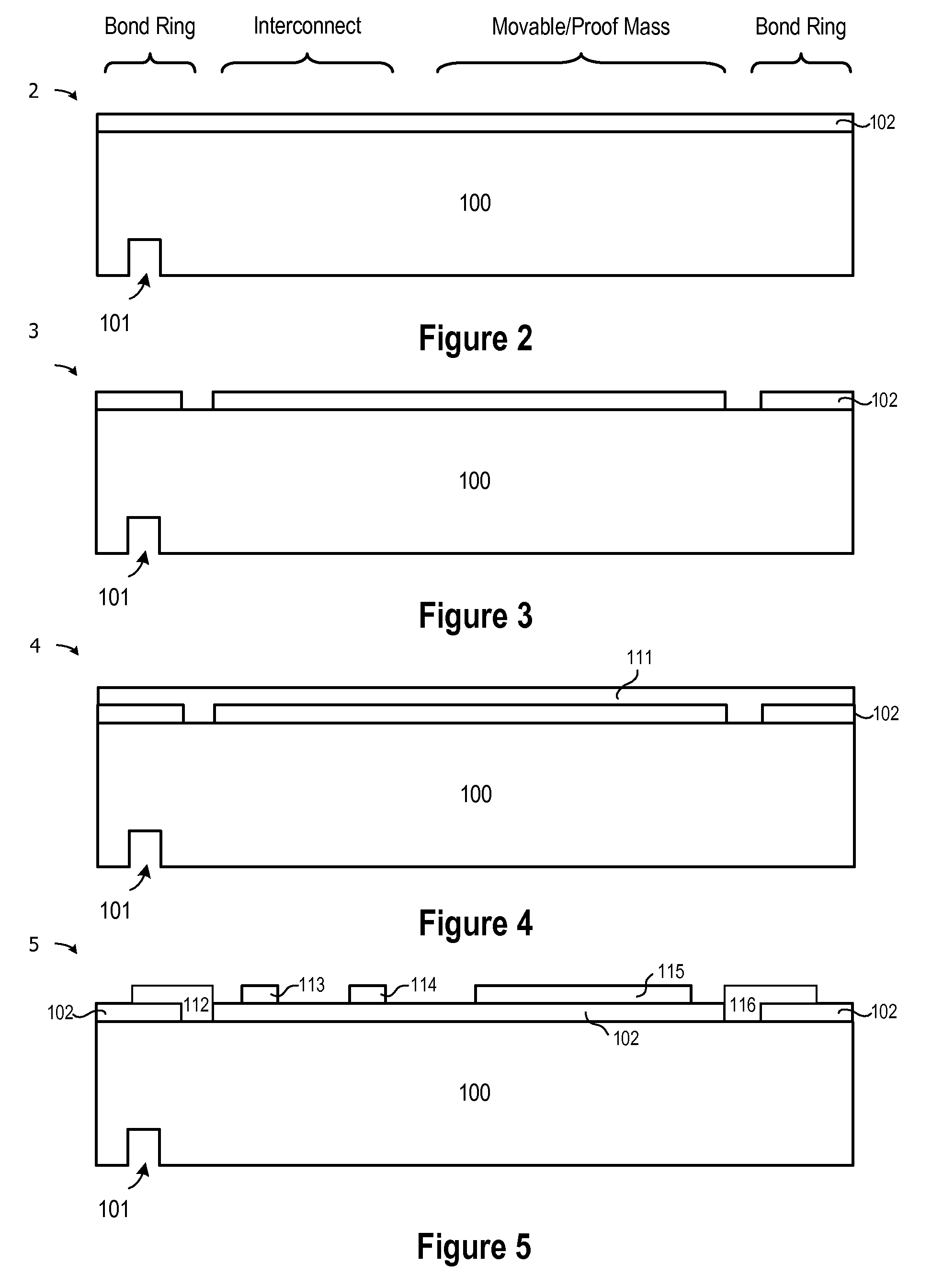

Method of Fabricating High Aspect Ratio Transducer Using Metal Compression Bonding

InactiveUS20100193884A1Television system detailsAcceleration measurement using interia forcesTransducerCapacitive sensing

A method and apparatus are described for fabricating a high aspect ratio MEMS device by using metal thermocompression bonding to assemble a reference wafer (100), a bulk MEMS active wafer (200), and a cap wafer (300) to provide a proof mass (200d) formed from the active wafer with bottom and top capacitive sensing electrodes (115, 315) which are hermetically sealed from the ambient environment by sealing ring structures (112 / 202 / 200a / 212 / 312 and 116 / 206 / 200e / 216 / 316).

Owner:FREESCALE SEMICON INC