Patents

Literature

2134 results about "Resistive random-access memory" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Resistive random-access memory (ReRAM or RRAM) is a type of non-volatile (NV) random-access (RAM) computer memory that works by changing the resistance across a dielectric solid-state material, often referred to as a memristor. This technology bears some similarities to conductive-bridging RAM (CBRAM), and phase-change memory (PCM).

Data boundary management

InactiveUS20050144363A1Reduce the impactReduce impactMemory architecture accessing/allocationMemory adressing/allocation/relocationStatic random-access memoryRandom access memory

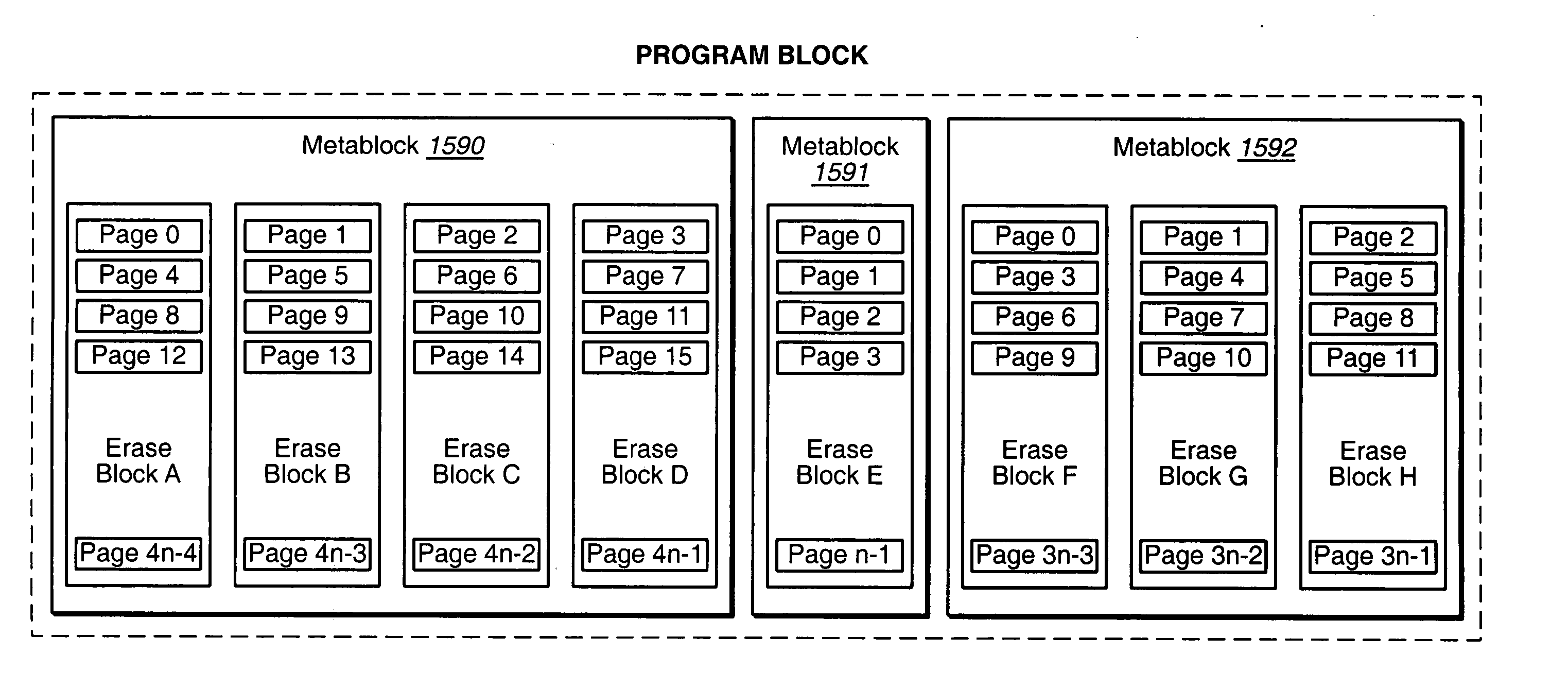

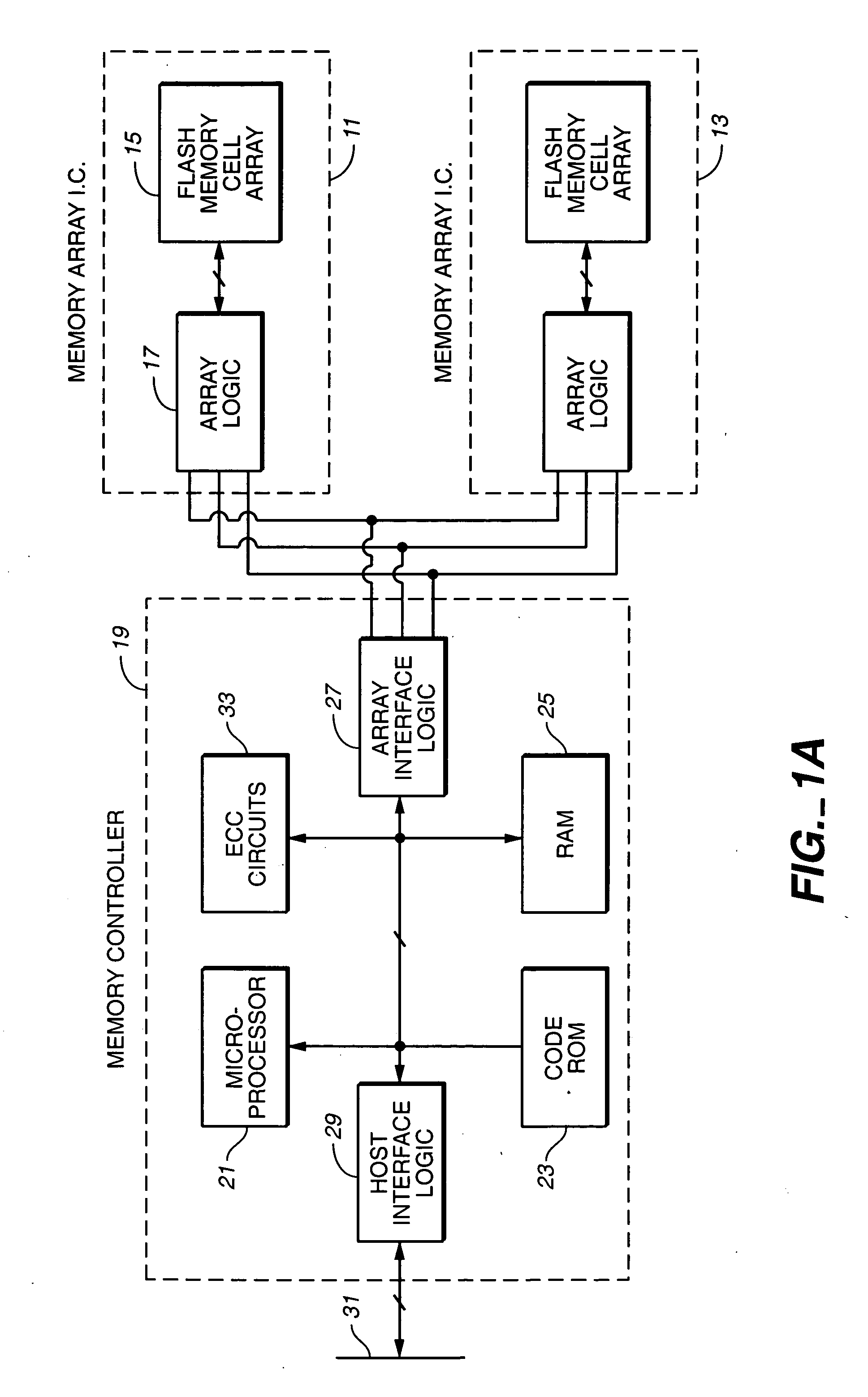

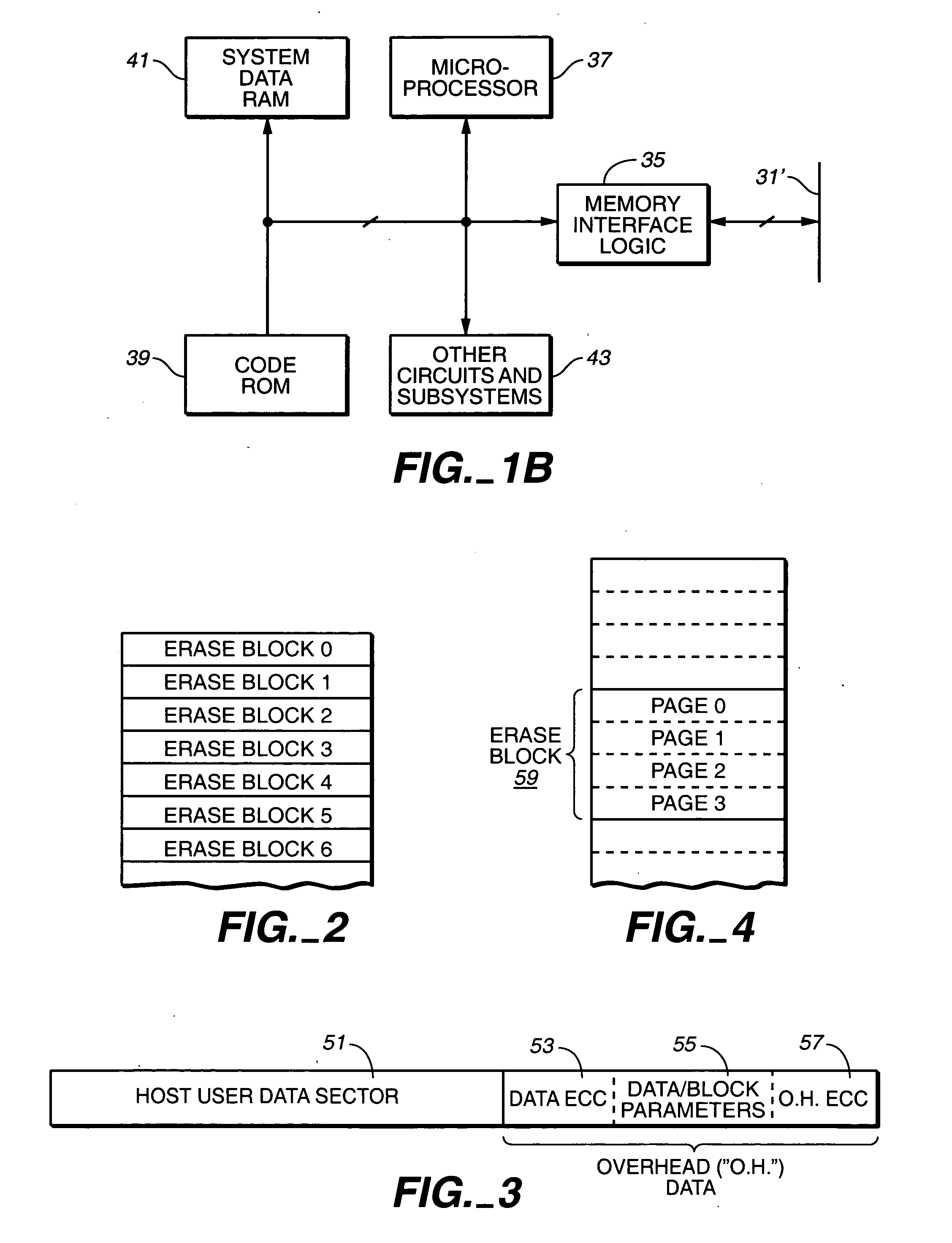

Data may be stored in a non-volatile memory array in adaptive metablocks that are configured according to the locations of data boundaries in the data. Data may be stored in an intermediate format and later copied to adaptive metablocks configured for the data. Data in intermediate format may be stored in non-volatile random access memory or in a portion of the non-volatile memory array.

Owner:SANDISK TECH LLC

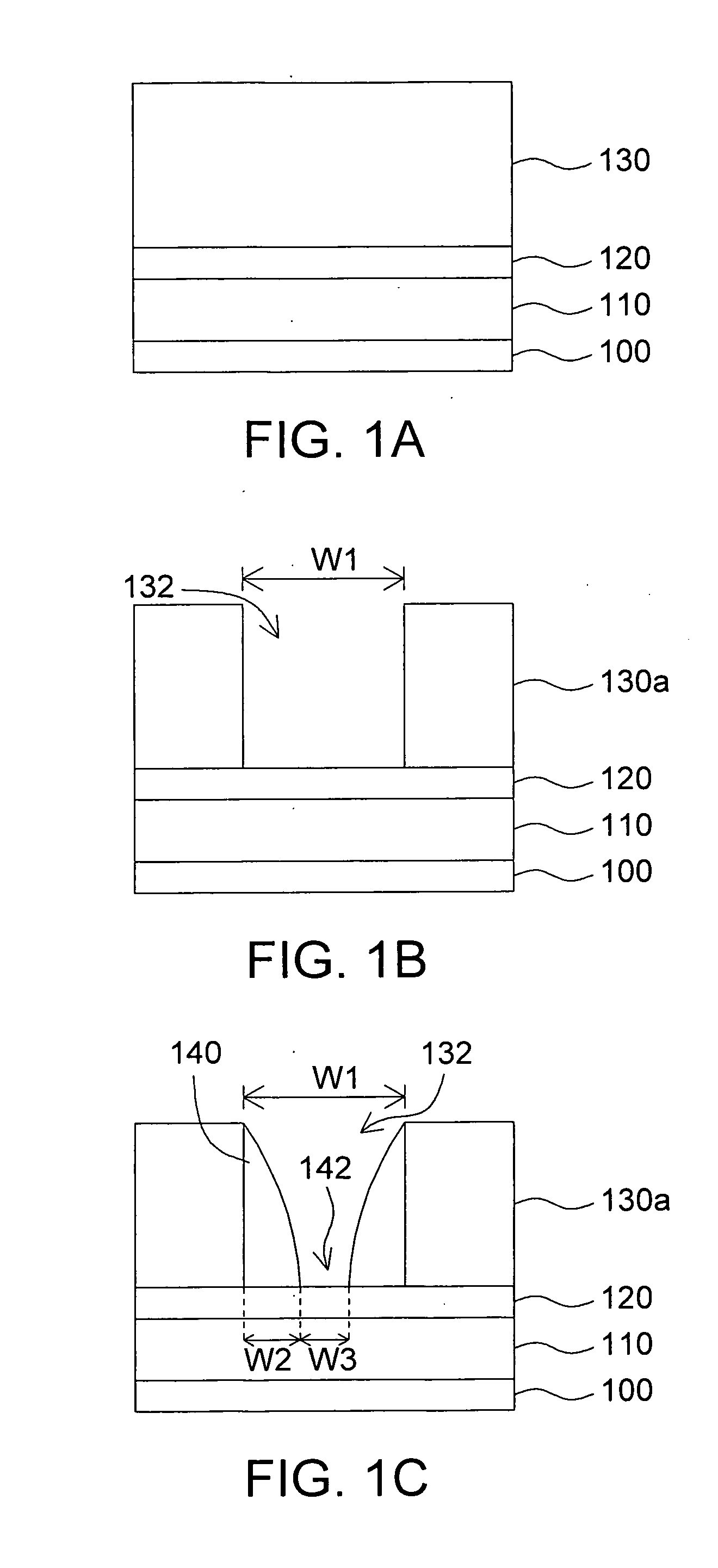

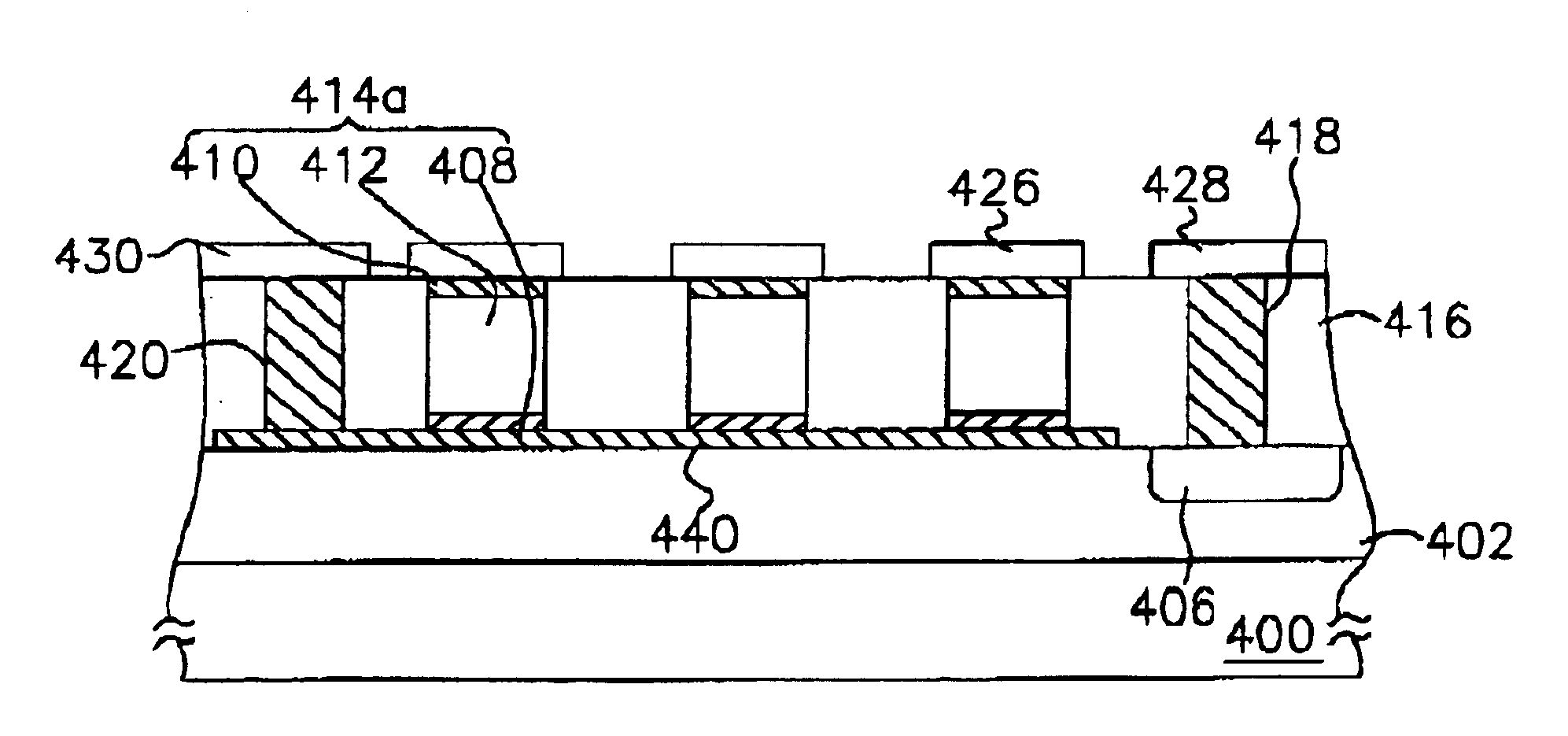

Resistive random access memory and method for manufacturing the same

ActiveUS20100112810A1Improve the immunityReduce power consumptionSemiconductor/solid-state device manufacturingSemiconductor devicesStatic random-access memoryRandom access memory

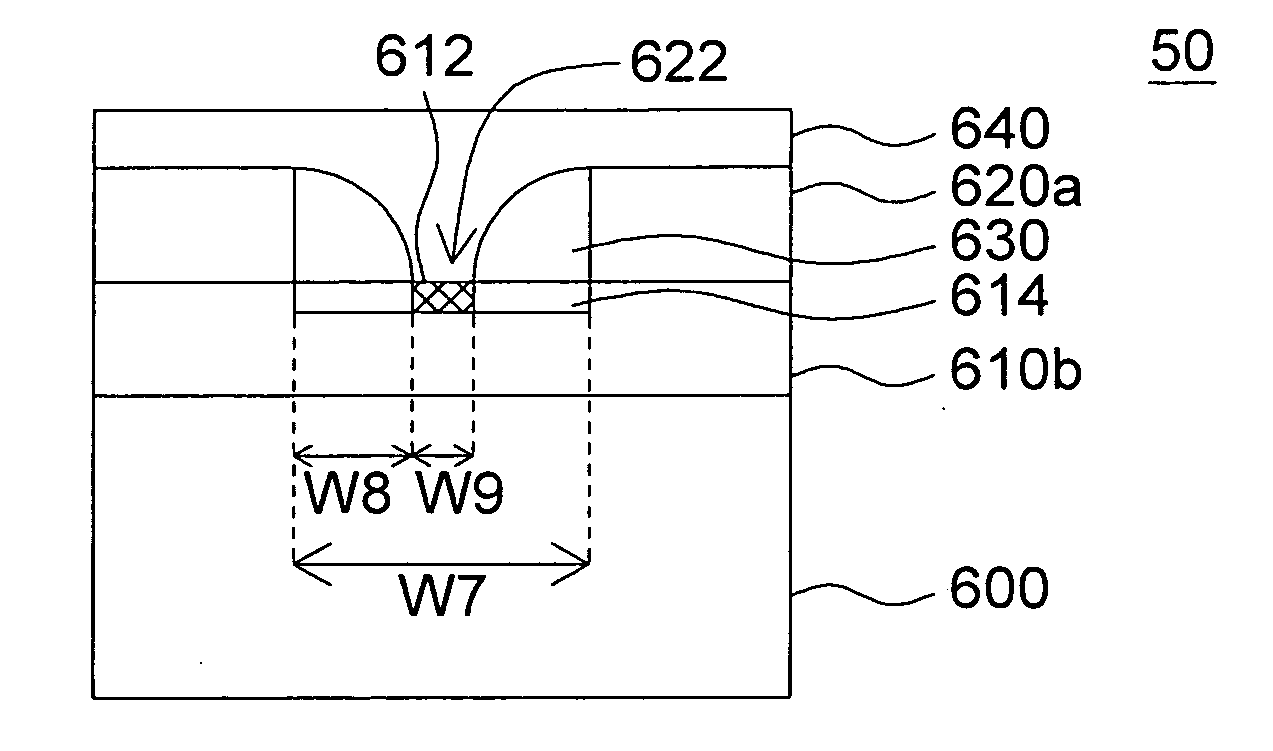

A resistive random access memory including, an insulating layer, a hard mask layer, a bottom electrode, a memory cell and a top electrode is provided. The insulating layer is disposed on the bottom electrode. The insulating layer has a contact hole having a first width. The hard mask layer has an opening. A portion of the memory cell is exposed from the opening and has a second width smaller than the first width. The top electrode is disposed on the insulating layer and is coupled with the memory cell.

Owner:MACRONIX INT CO LTD

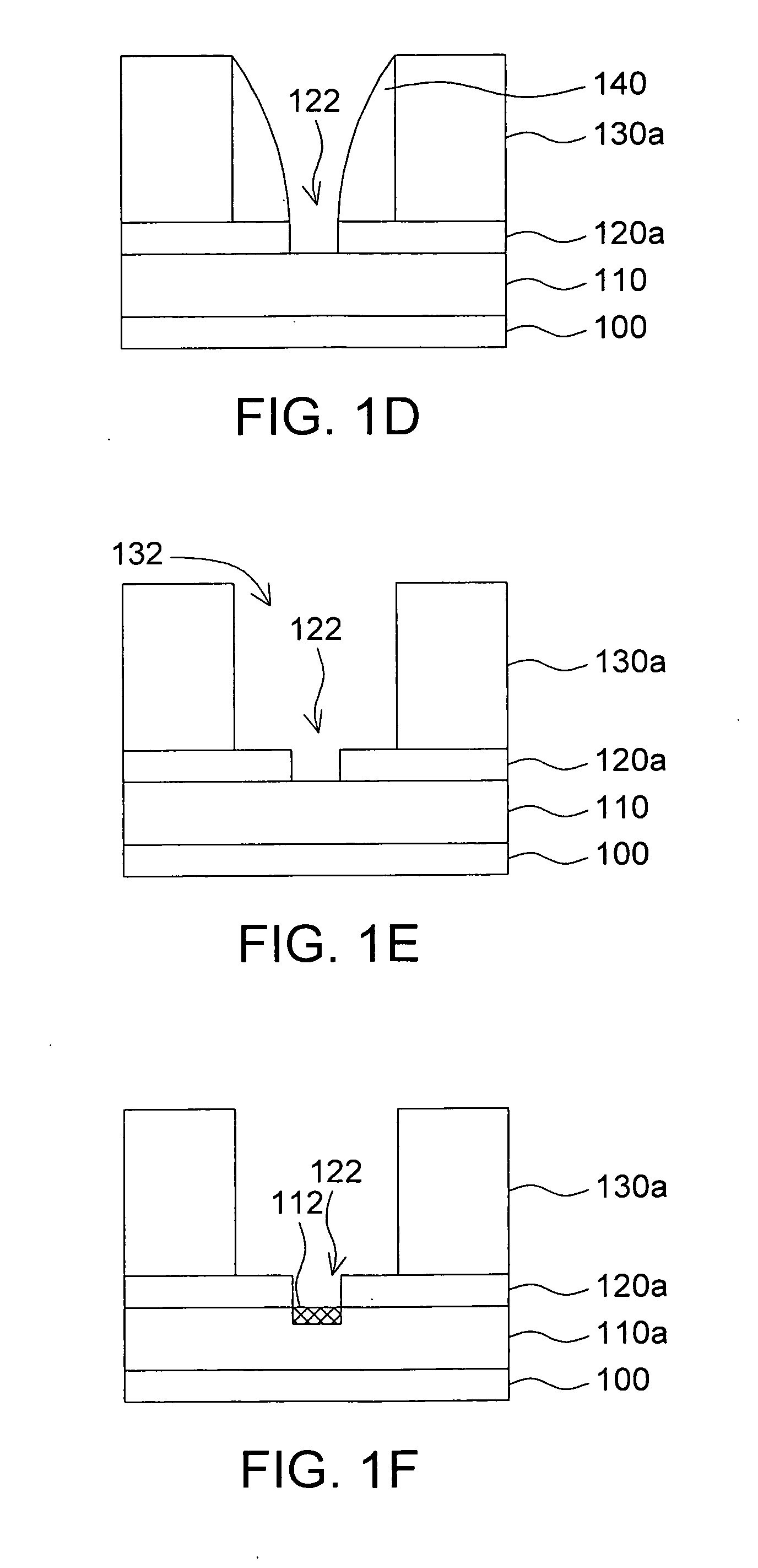

Methods of forming embedded resistors for resistive random access memory cells

Provided are memory cells including resistive switching layers having silicon, oxygen, and nitrogen as well as embedded resistor layers having a metal, silicon, and nitrogen. In some embodiments, silicon may be partially or completely replaced with aluminum. The embedded resistor may also have oxygen. A resistive switching layer directly interfaces an embedded resistor layer of the same cell. A portion of each layer forming this interface may be formed substantially of silicon nitride and may be formed in the same deposition chamber without breaking vacuum. For example, these portions may be formed by sequential atomic layer deposition cycles. However, silicon concentrations in these portions may be different. Specifically, the silicon concentration of the embedded resistor portion may be less than the silicon concentration of the resistive switching layer portion. This variation may be achieved by varying one or more process conditions during fabrication of the memory cell.

Owner:INTERMOLECULAR

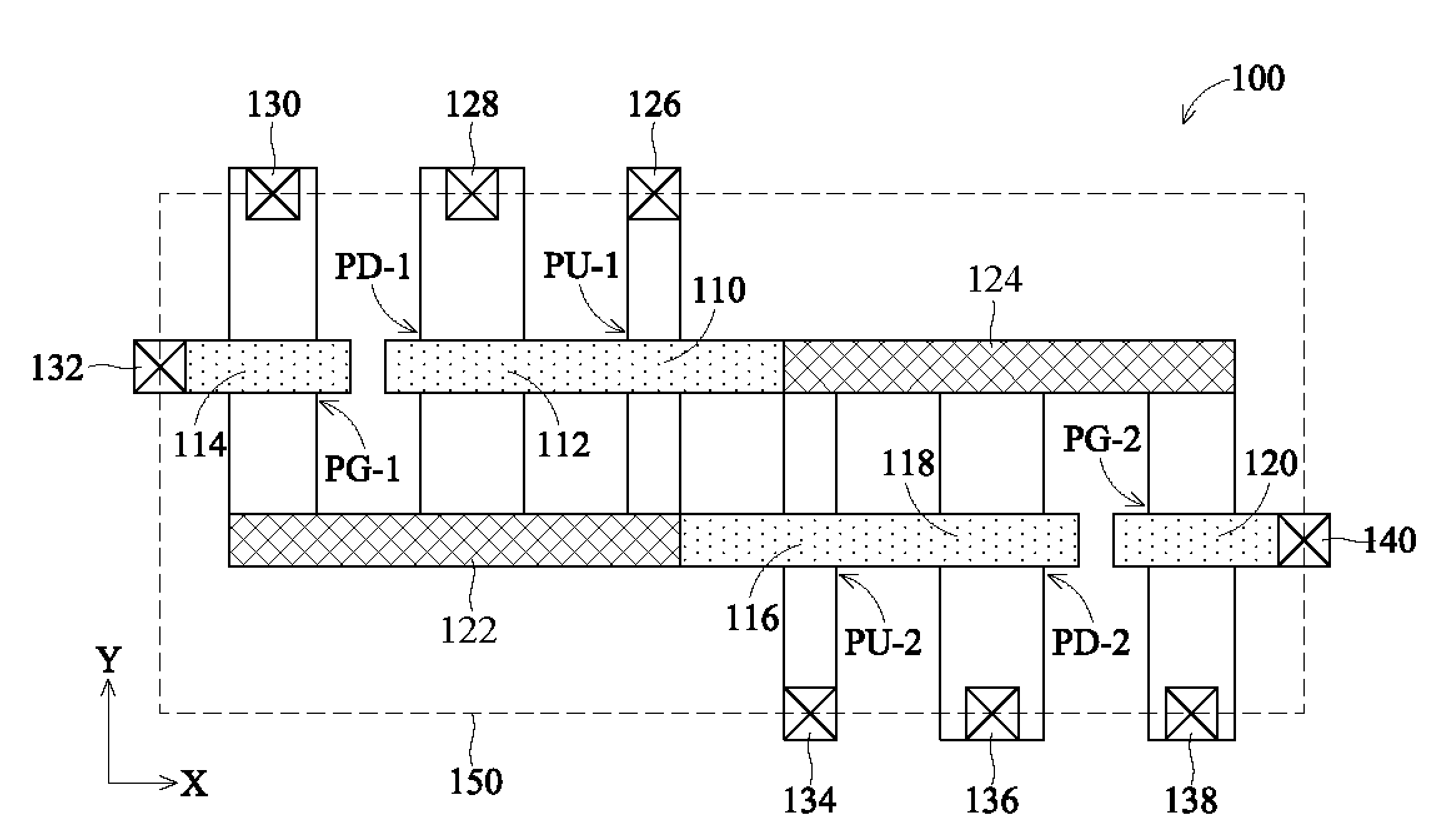

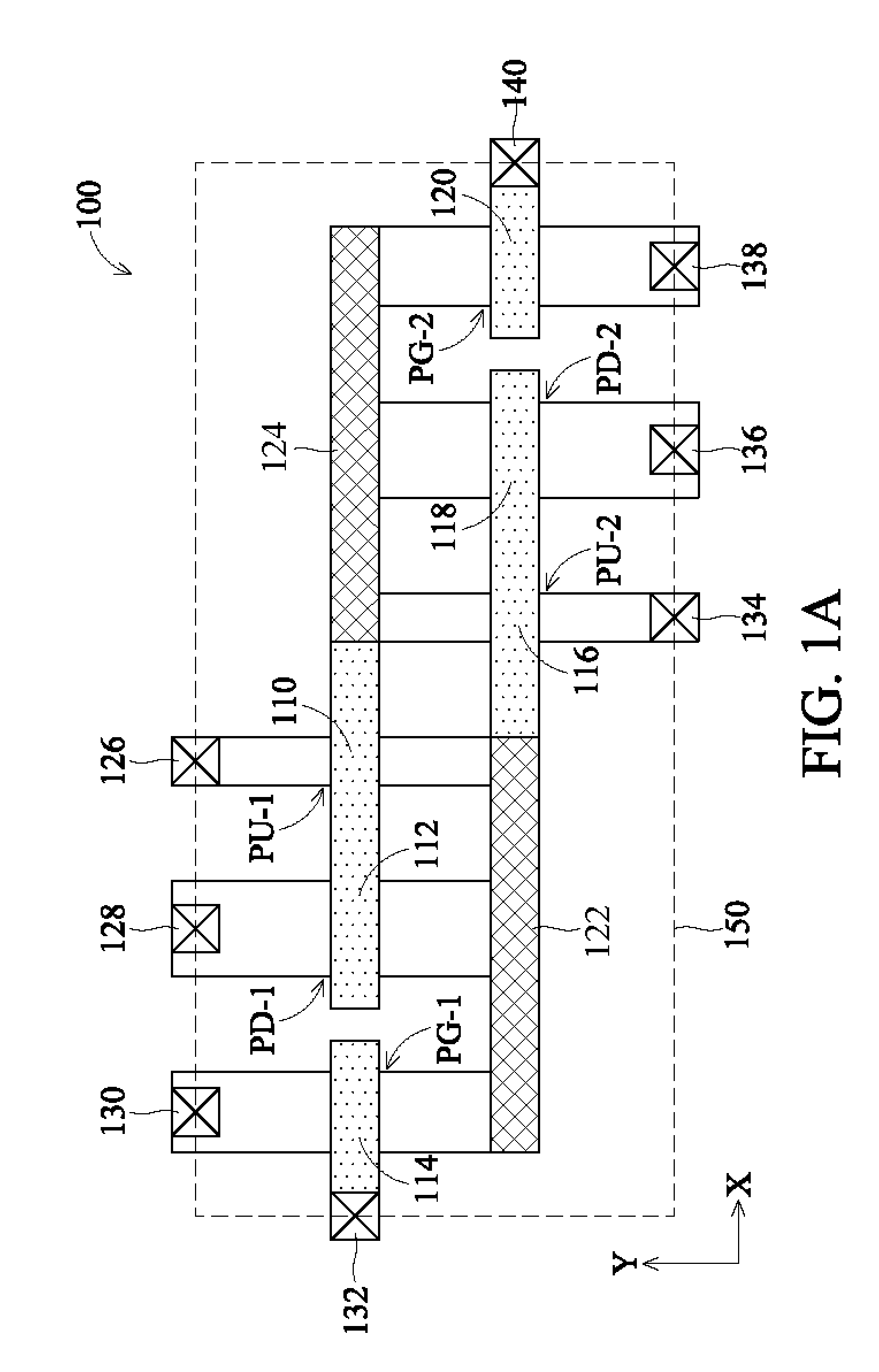

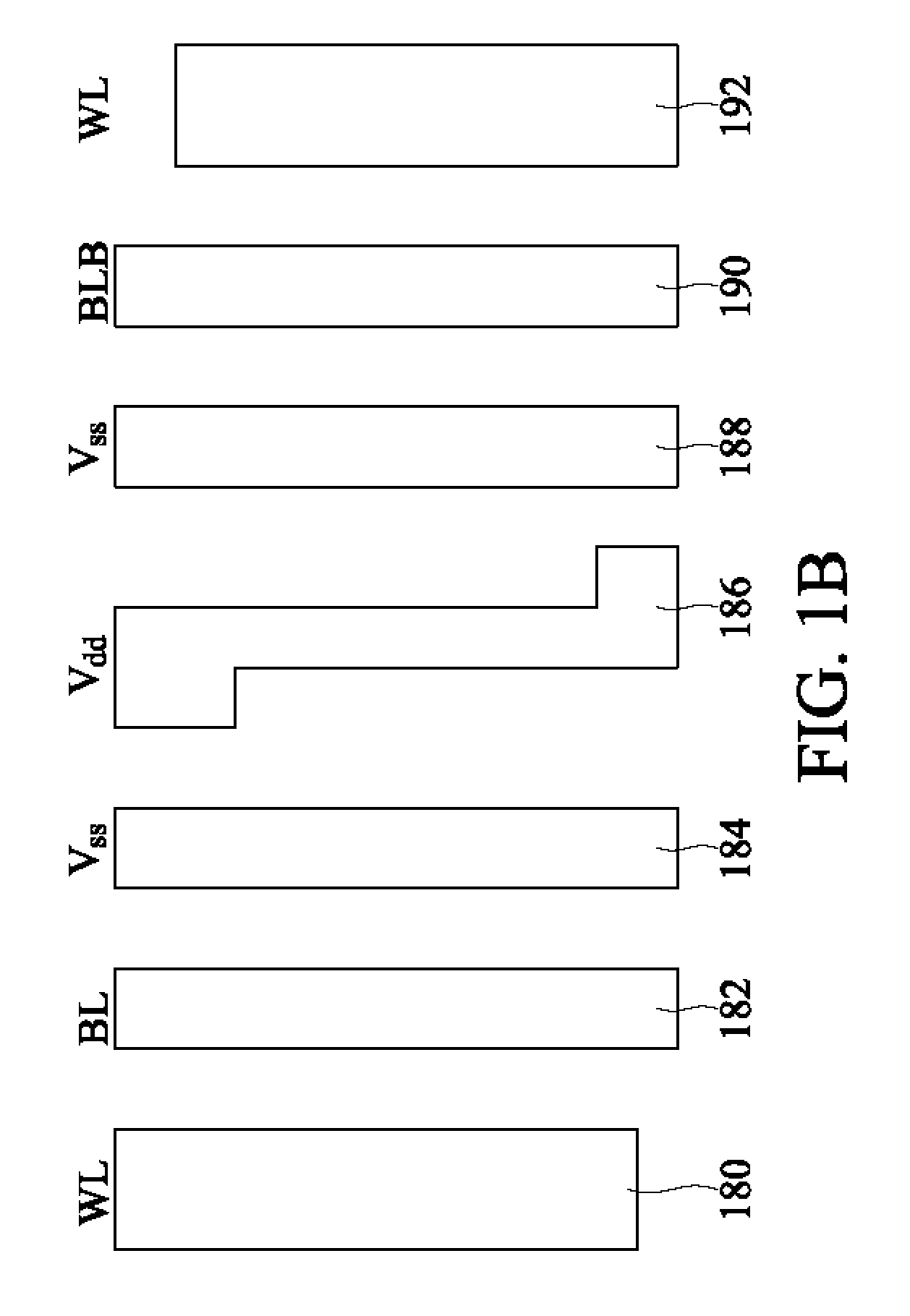

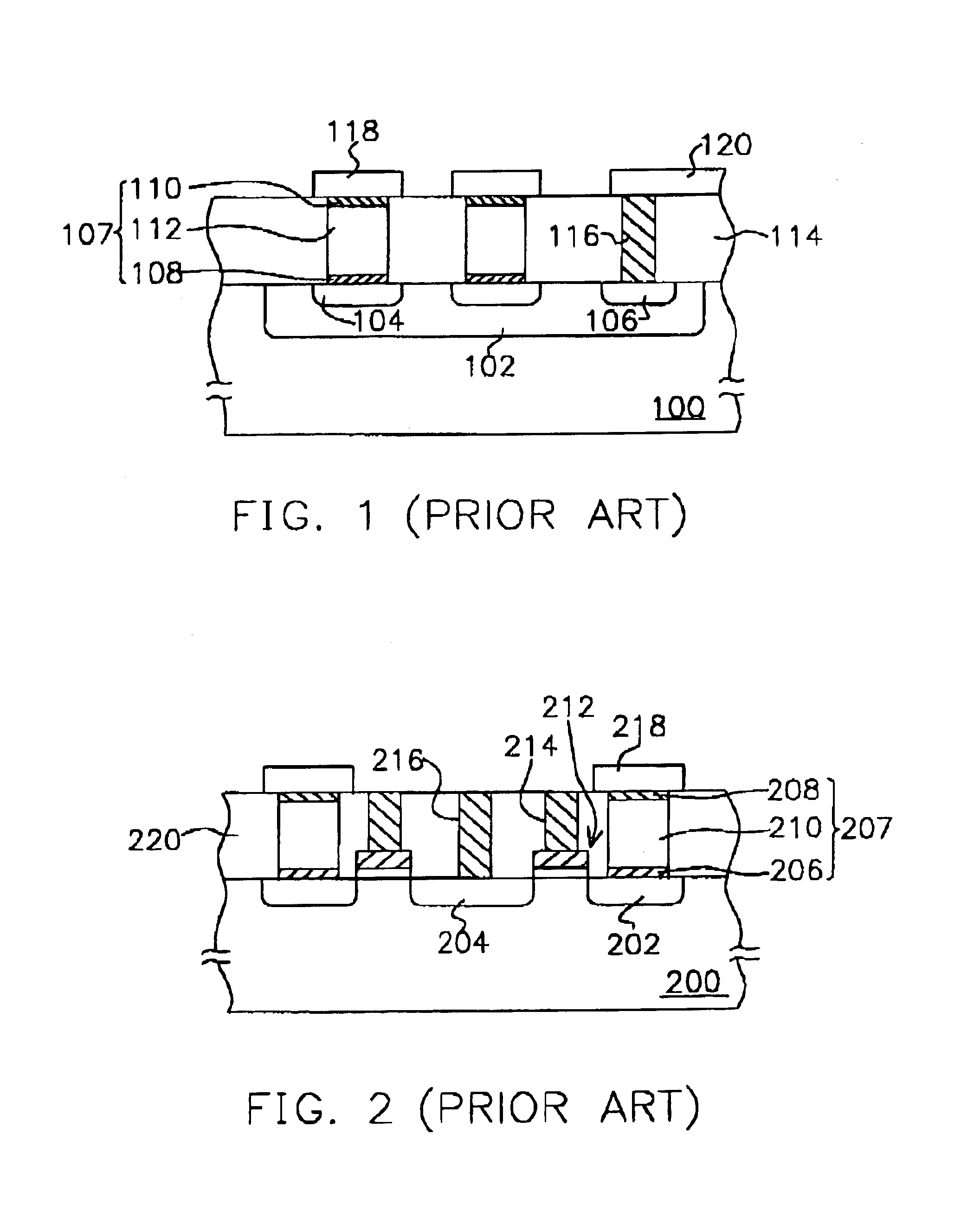

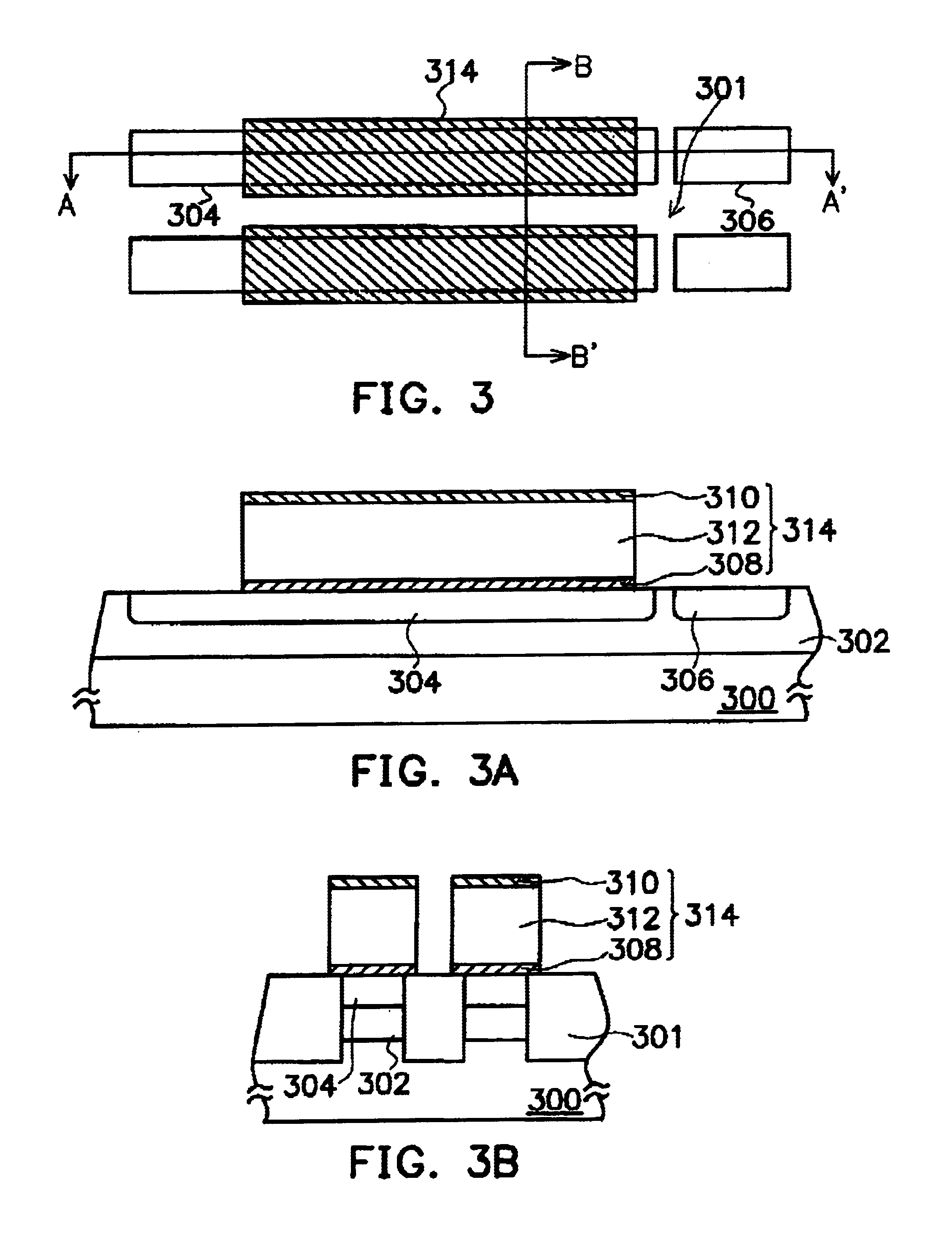

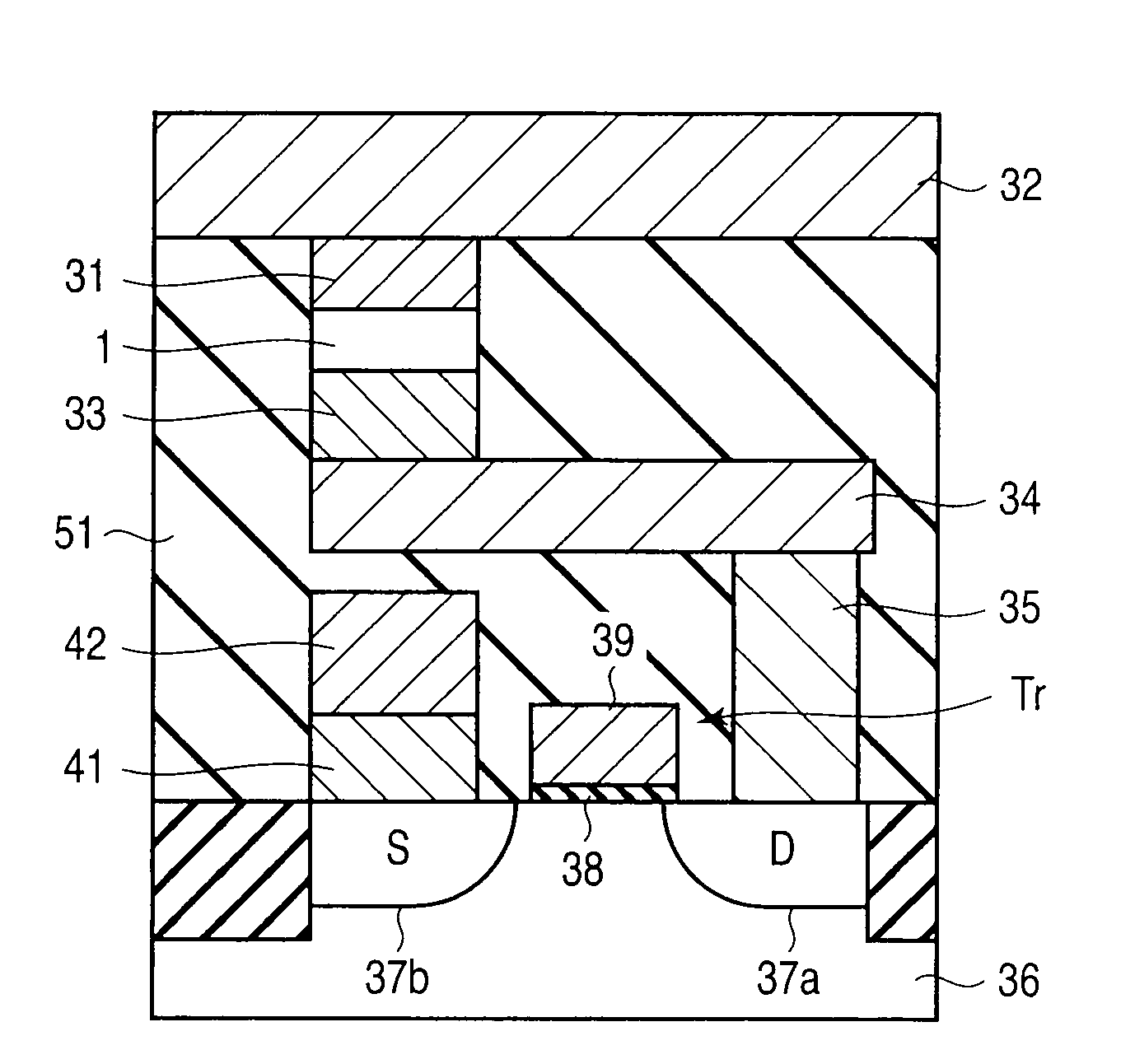

Static random access memory (SRAM) cell and method for forming same

InactiveUS8004042B2High densitySmall sizeTransistorSolid-state devicesStatic random-access memoryRandom access memory

In accordance with an embodiment of the present invention, a static random access memory (SRAM) cell comprises a first pull-down transistor, a first pull-up transistor, a first pass-gate transistor, a second pull-down transistor, a second pull-up transistor, a second pass-gate transistor, a first linear intra-cell connection, and a second linear intra-cell connection. Active areas of the transistors are disposed in a substrate, and longitudinal axes of the active areas of the transistors are all parallel. The first linear intra-cell connection electrically couples the active area of the first pull-down transistor, the active area of the first pull-up transistor, and the active area of the first pass-gate transistor to a gate electrode of the second pull-down transistor and a gate electrode of the second pull-up transistor. The second linear intra-cell connection electrically couples the active area of the second pull-down transistor, the active area of the second pull-up transistor, and the active area of the second pass-gate transistor to a gate electrode of the first pull-down transistor and a gate electrode of the first pull-up transistor.

Owner:TAIWAN SEMICON MFG CO LTD

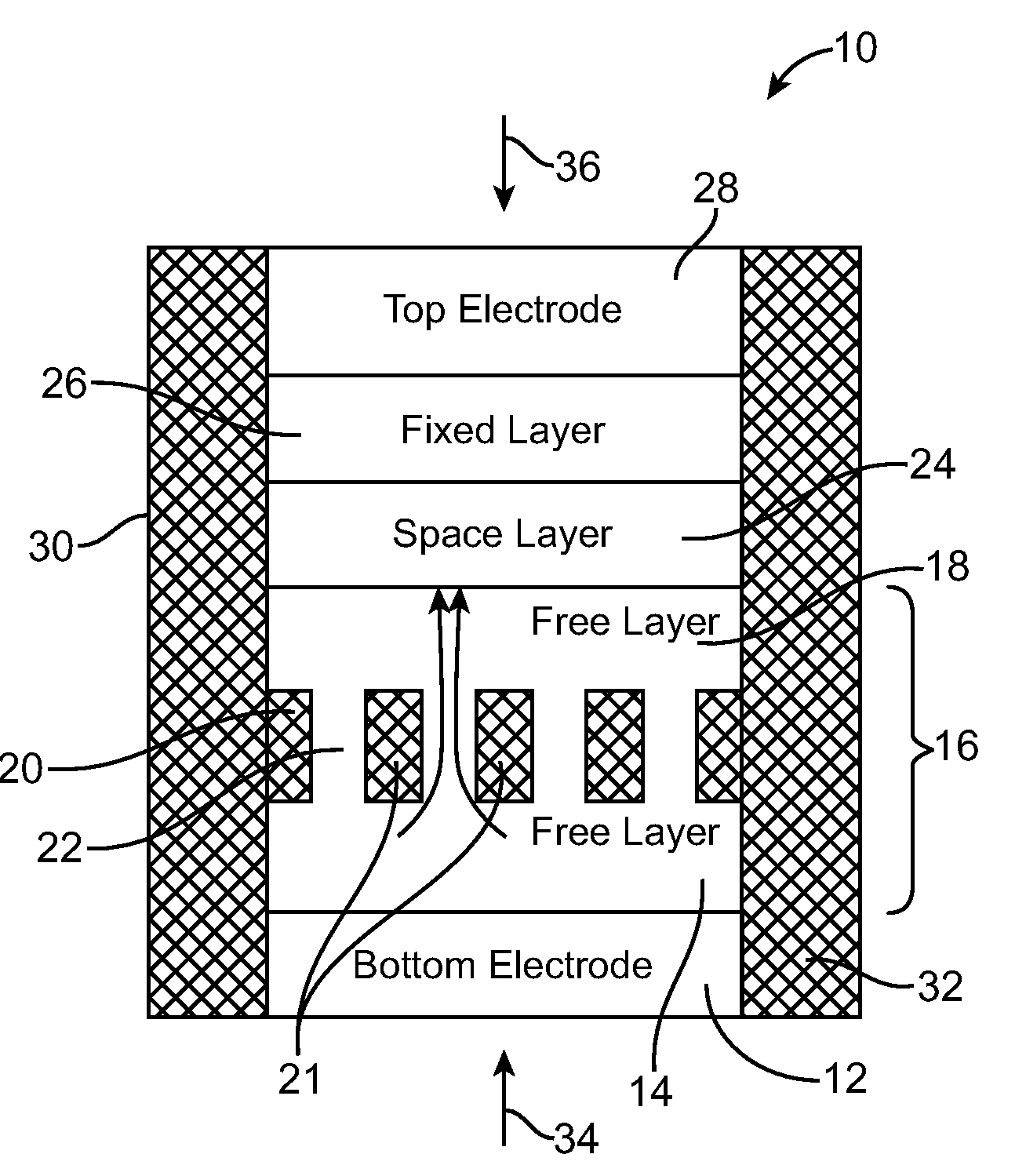

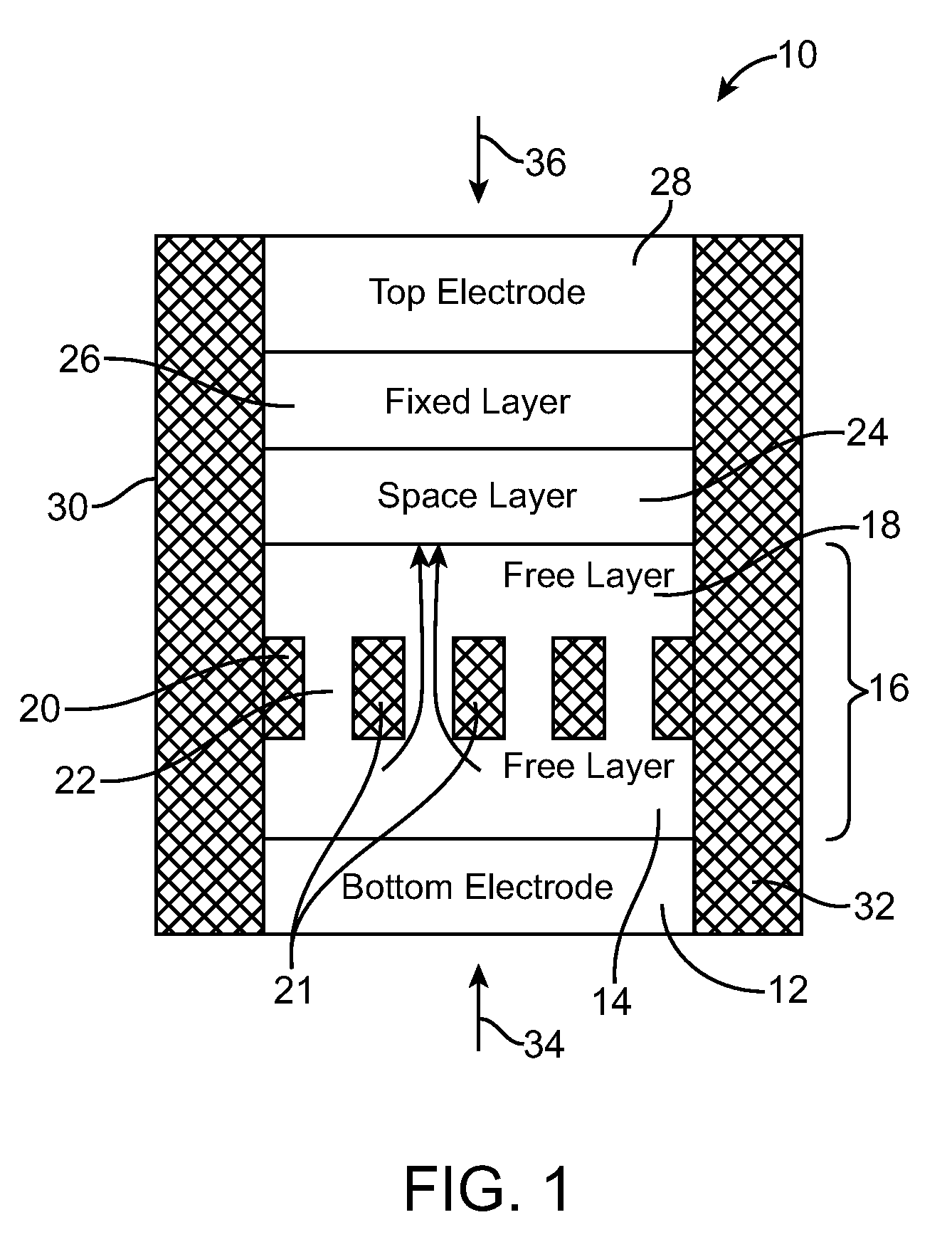

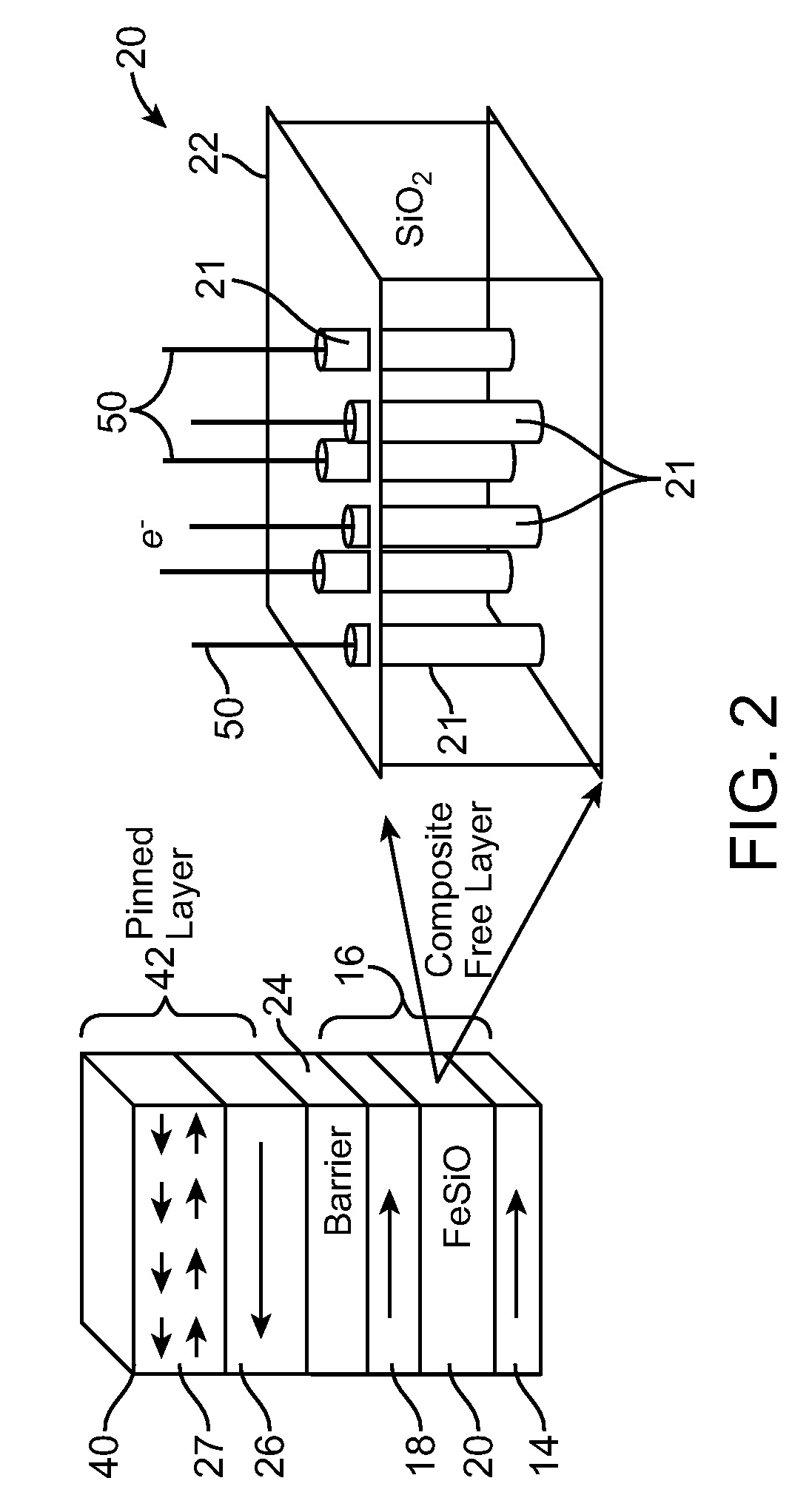

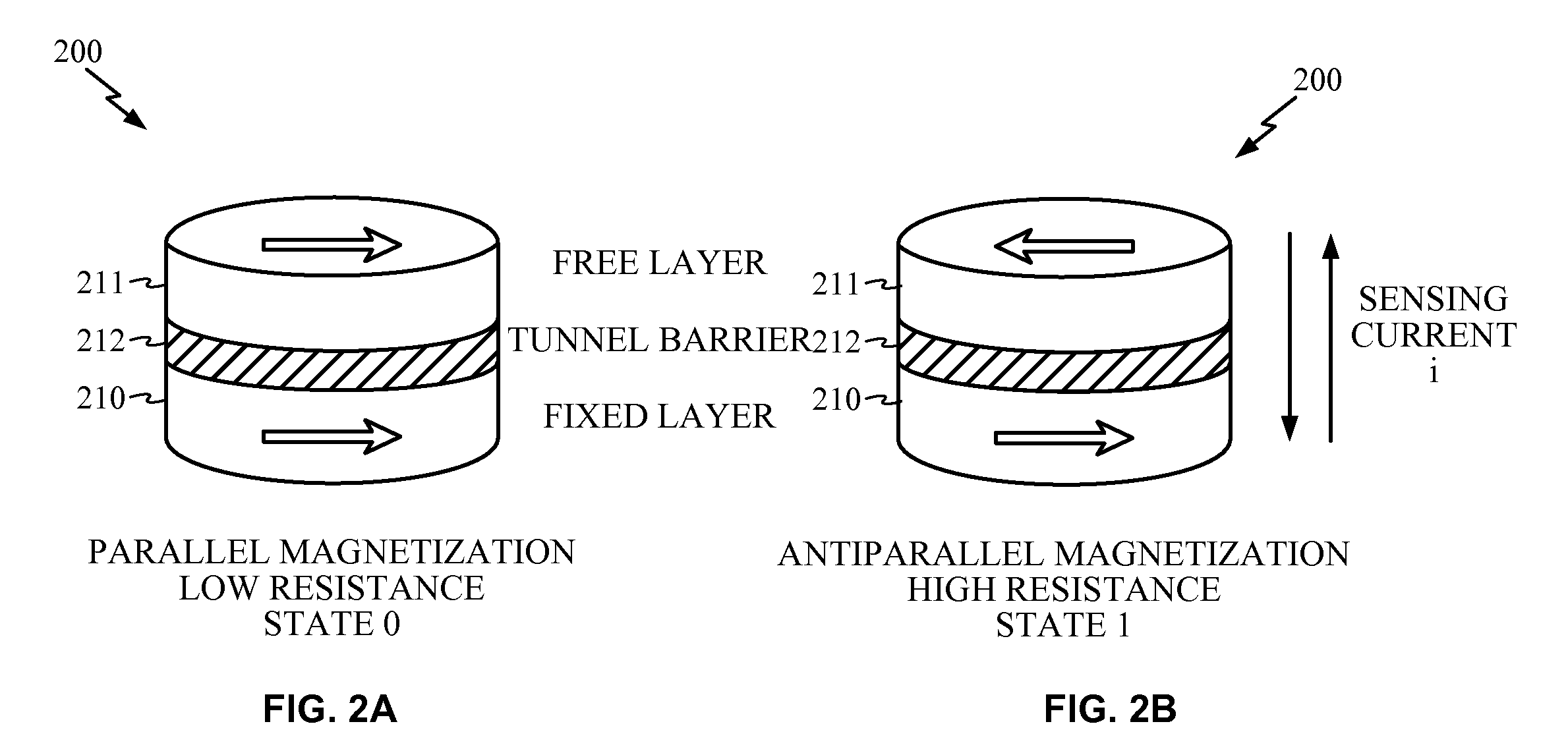

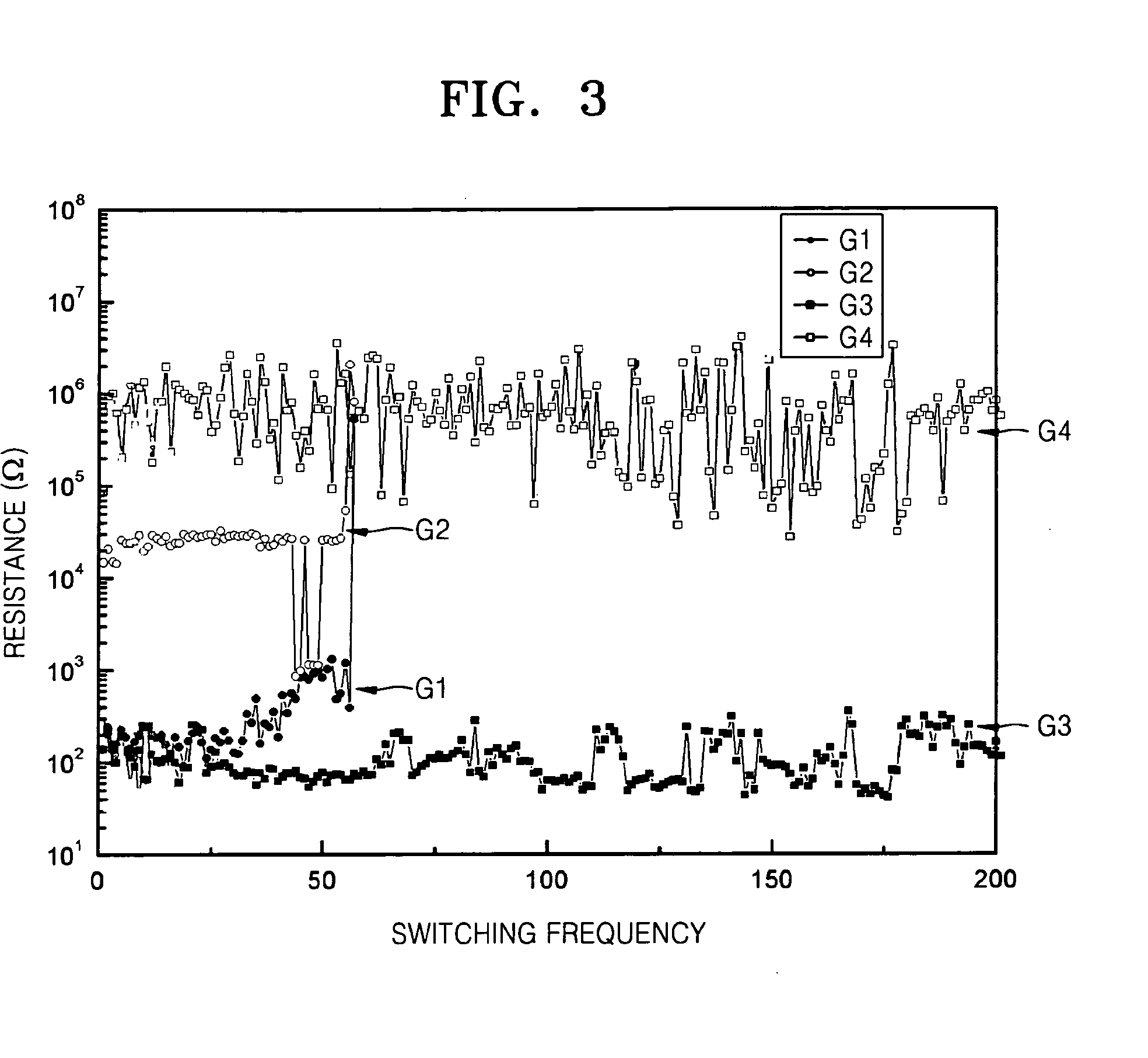

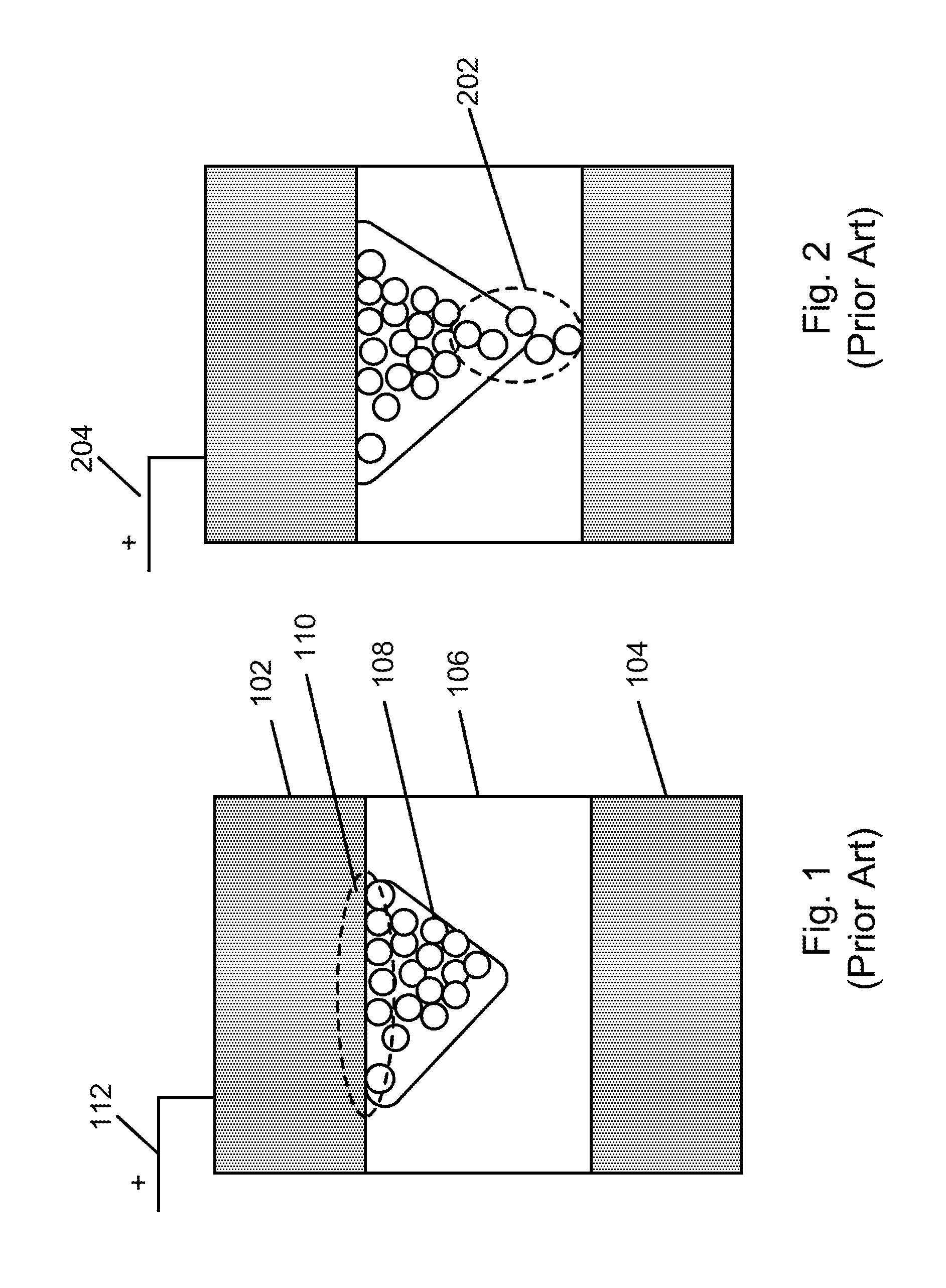

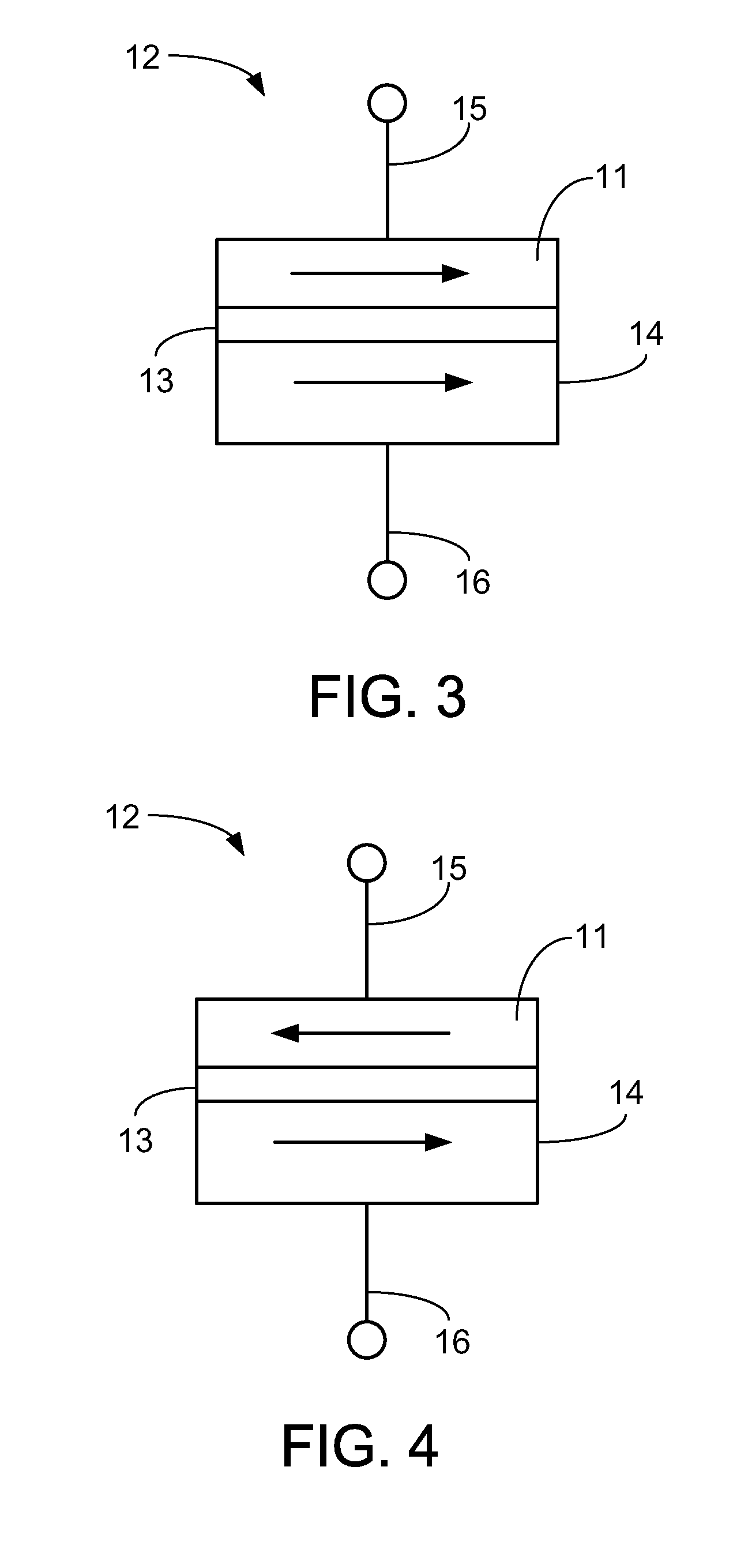

Current-confined effect of magnetic nano-current-channel (NCC) for magnetic random access memory (MRAM)

ActiveUS7732881B2Magnetic-field-controlled resistorsSemiconductor/solid-state device manufacturingCurrent limitingCurrent channel

One embodiment of the present invention includes a memory element having a composite free layer including a first free sub-layer formed on top of the bottom electrode, a nano-current-channel (NCC) layer formed on top of the first free sub-layer, and a second free sub-layer formed on top of the NCC layer, wherein when switching current is applied to the memory element, in a direction that is substantially perpendicular to the layers of the memory element, local magnetic moments of the NCC layer switch the state of the memory element.

Owner:AVALANCHE TECH

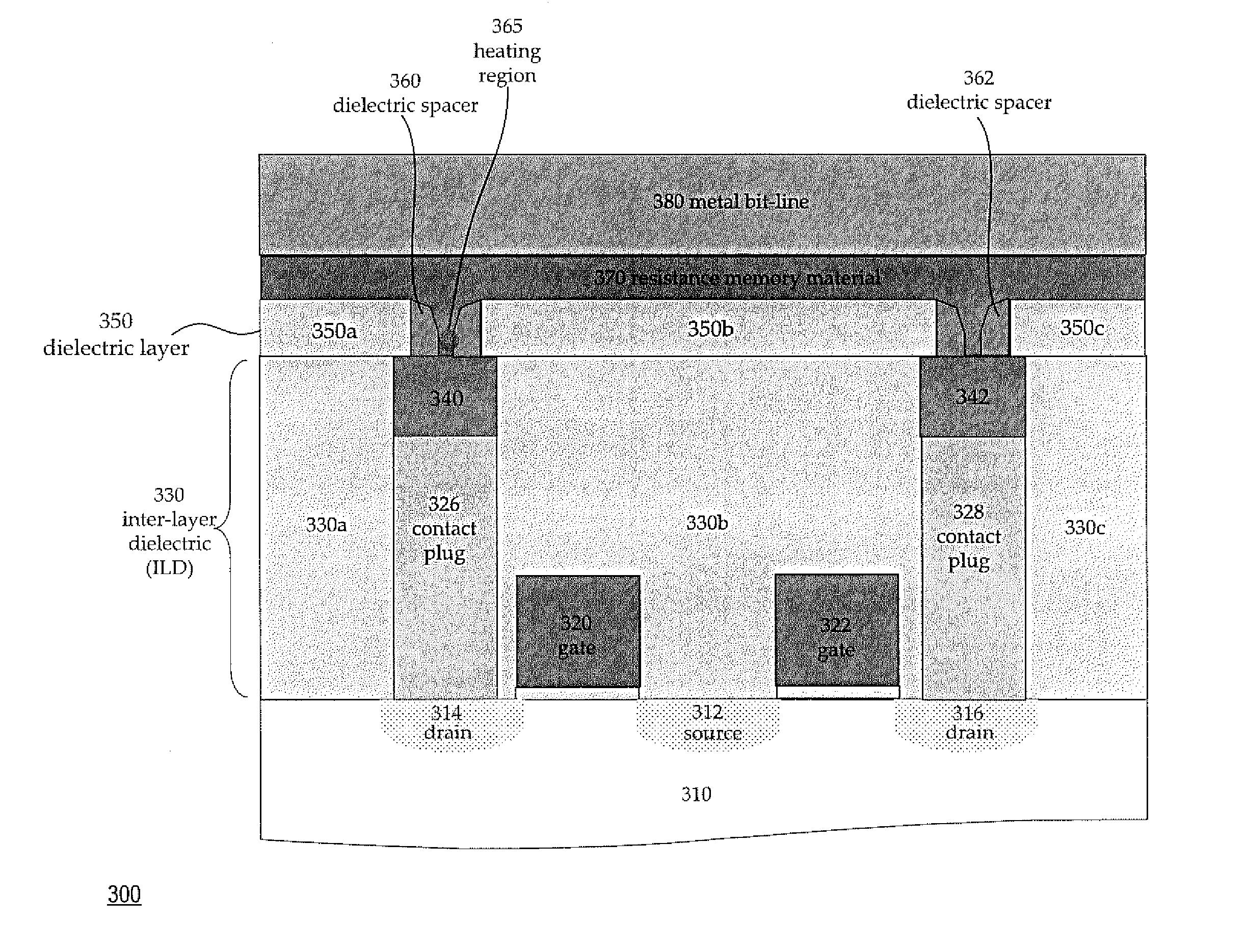

Structures and Methods of a Bistable Resistive Random Access Memory

ActiveUS20070257300A1Reduce heat dissipationReduce heatTransistorSolid-state devicesElectrical resistance and conductanceElectrical conductor

Structures and methods to form a bistable resistive random access memory for reducing the amount of heat dissipation from electrodes by confining a heating region in the memory cell device are described. The heating region is confined in a kernel comprising a programmable resistive memory material that is in contact with an upper programmable resistive memory member and a lower programmable resistive memory member. The lower programmable resistive member has sides that align with sides of a bottom electrode comprising a tungsten plug. The lower programmable resistive member and the bottom electrode function a first conductor so that the amount of heat dissipation from the first conductor is reduced. The upper programmable resistive memory material and a top electrode function as a second conductor so that the amount of heat dissipation from the second conductor is reduced.

Owner:MACRONIX INT CO LTD

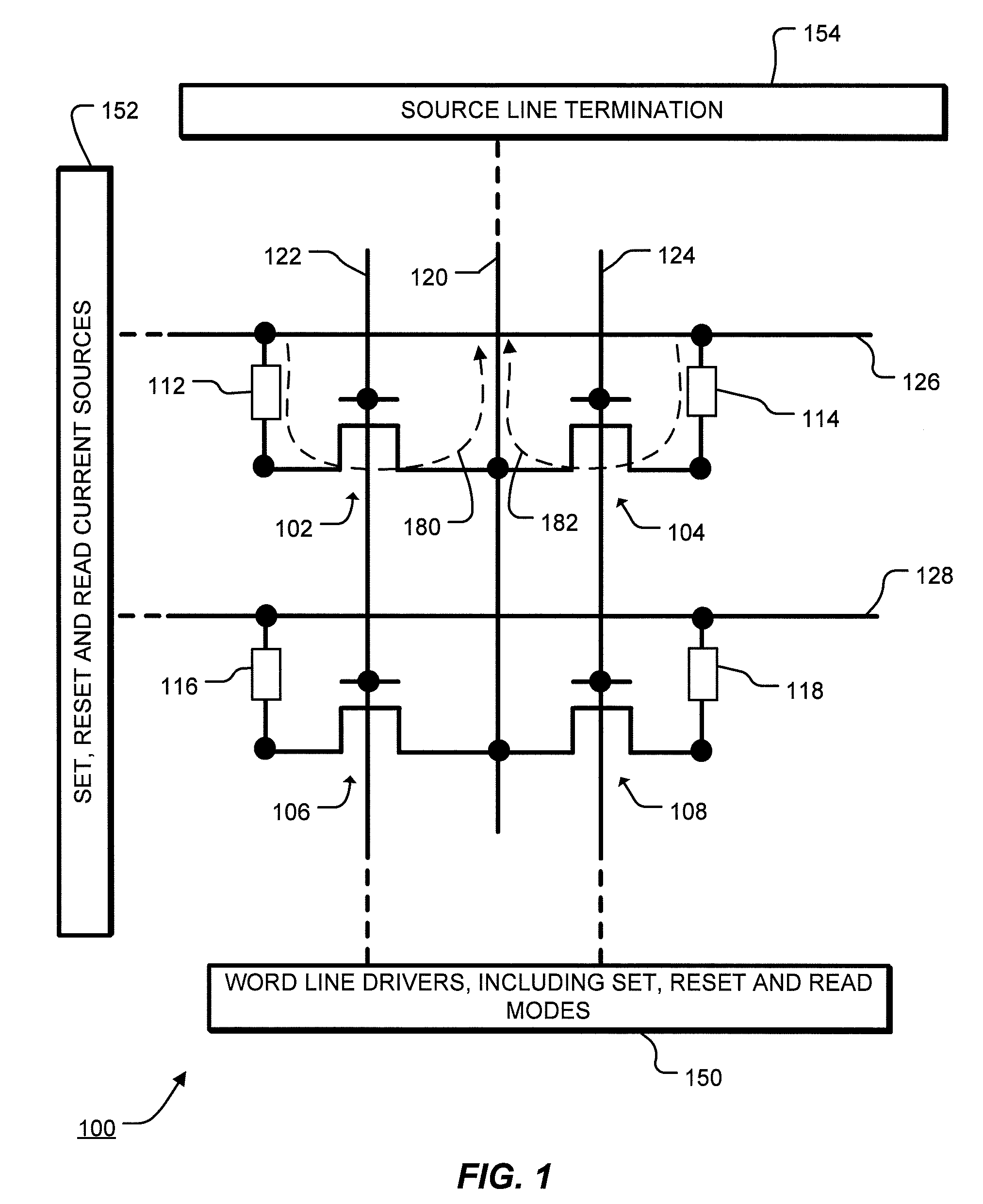

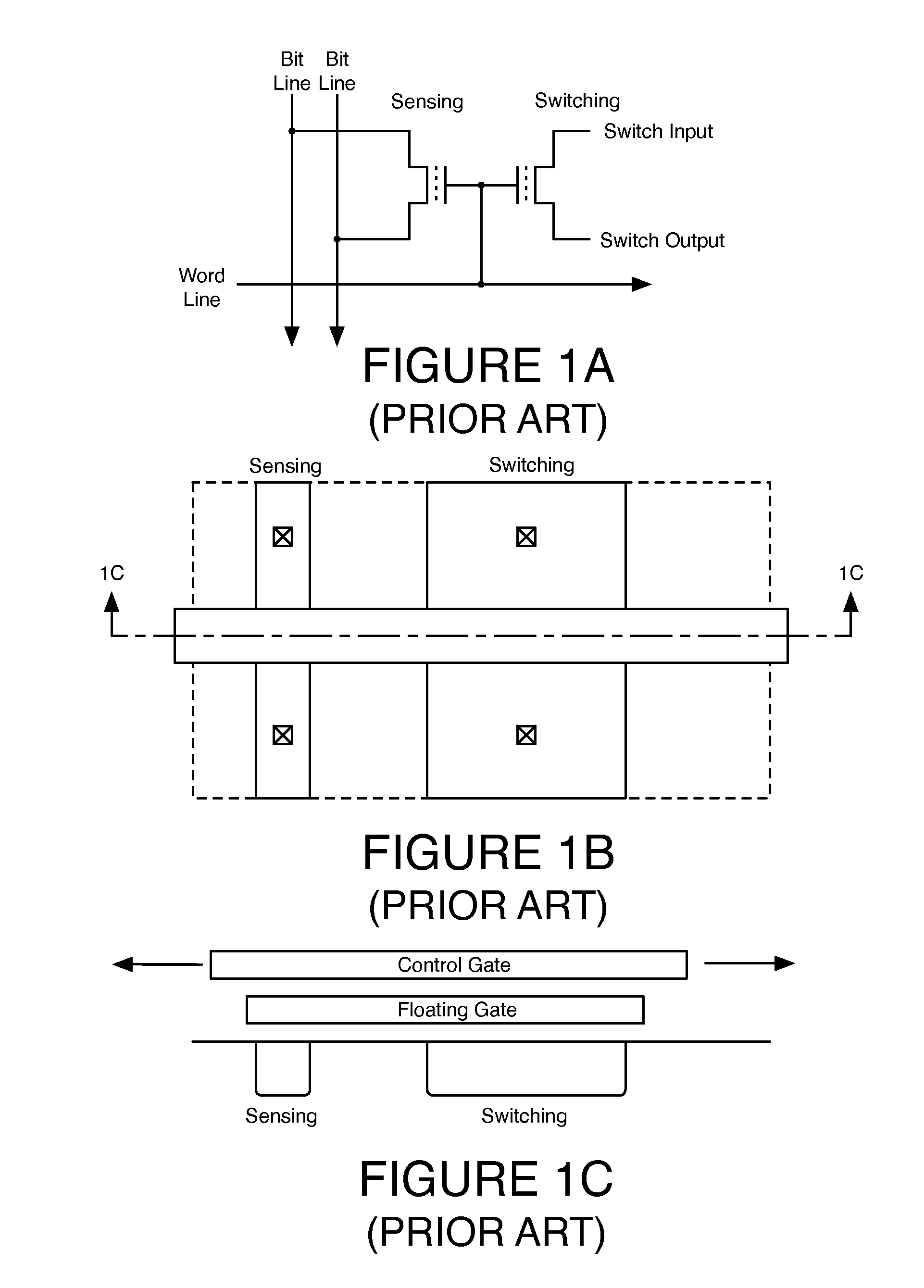

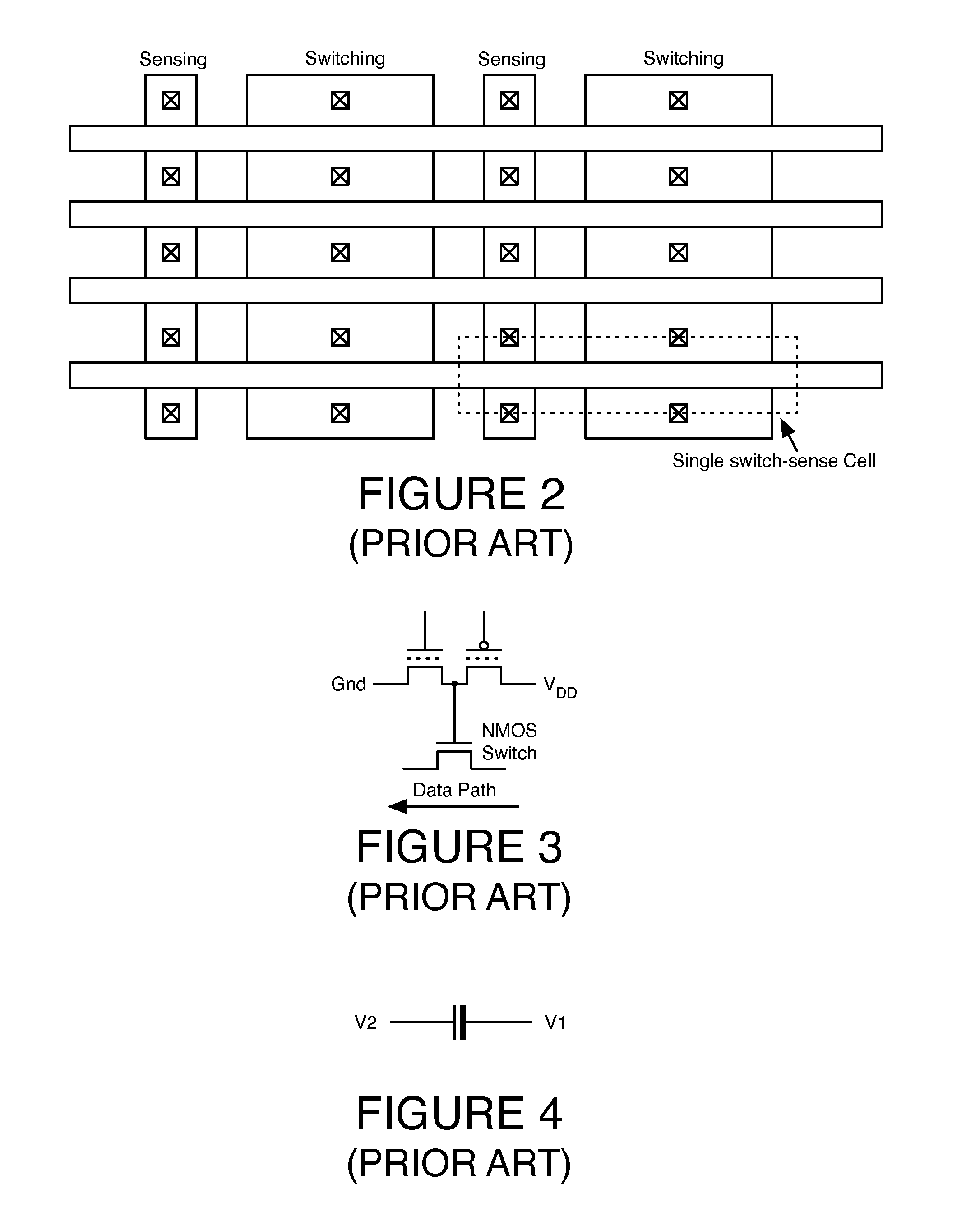

MRAM array having a segmented bit line

InactiveUS6982902B2Reduce leakage currentRaise the ratioDigital storageBit lineStatic random-access memory

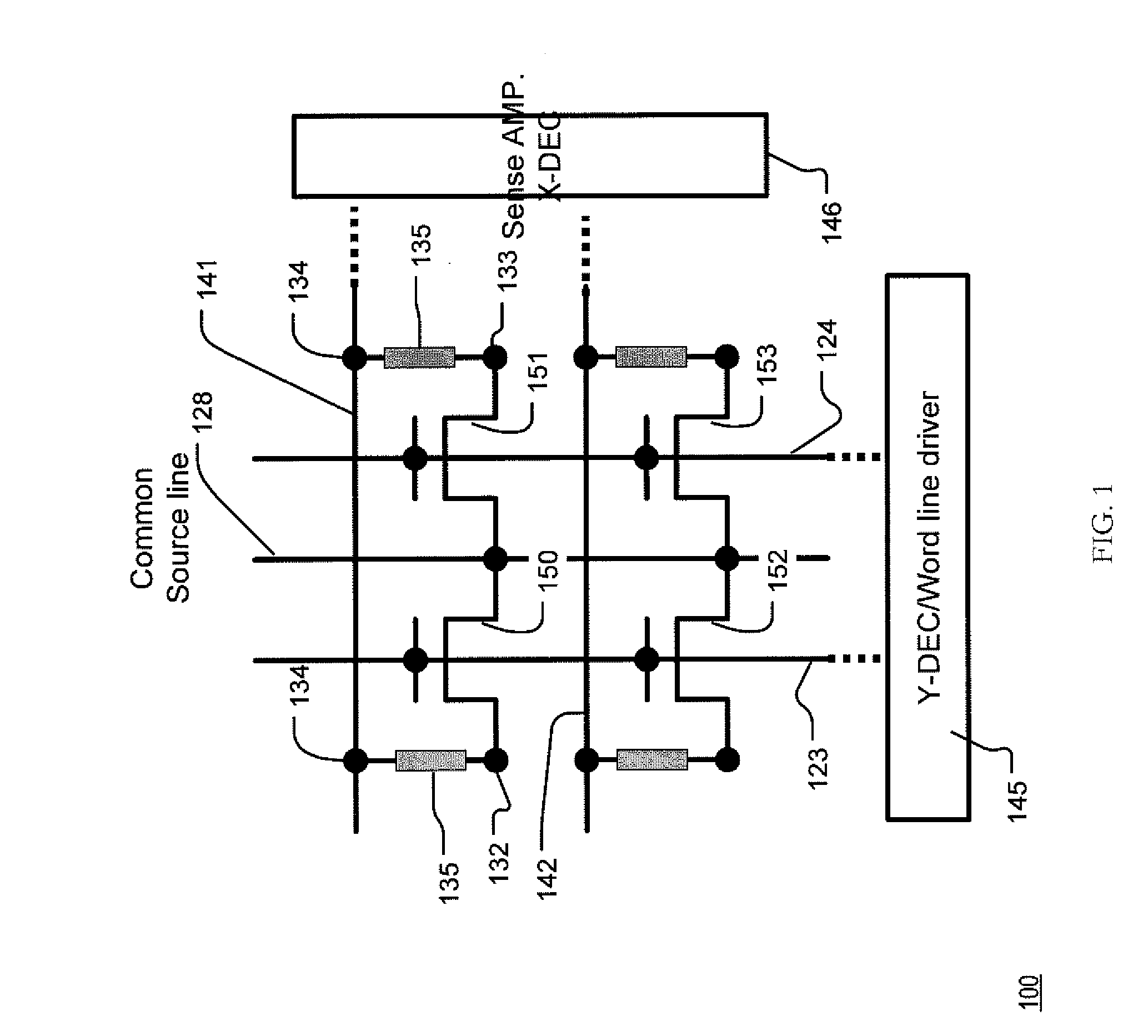

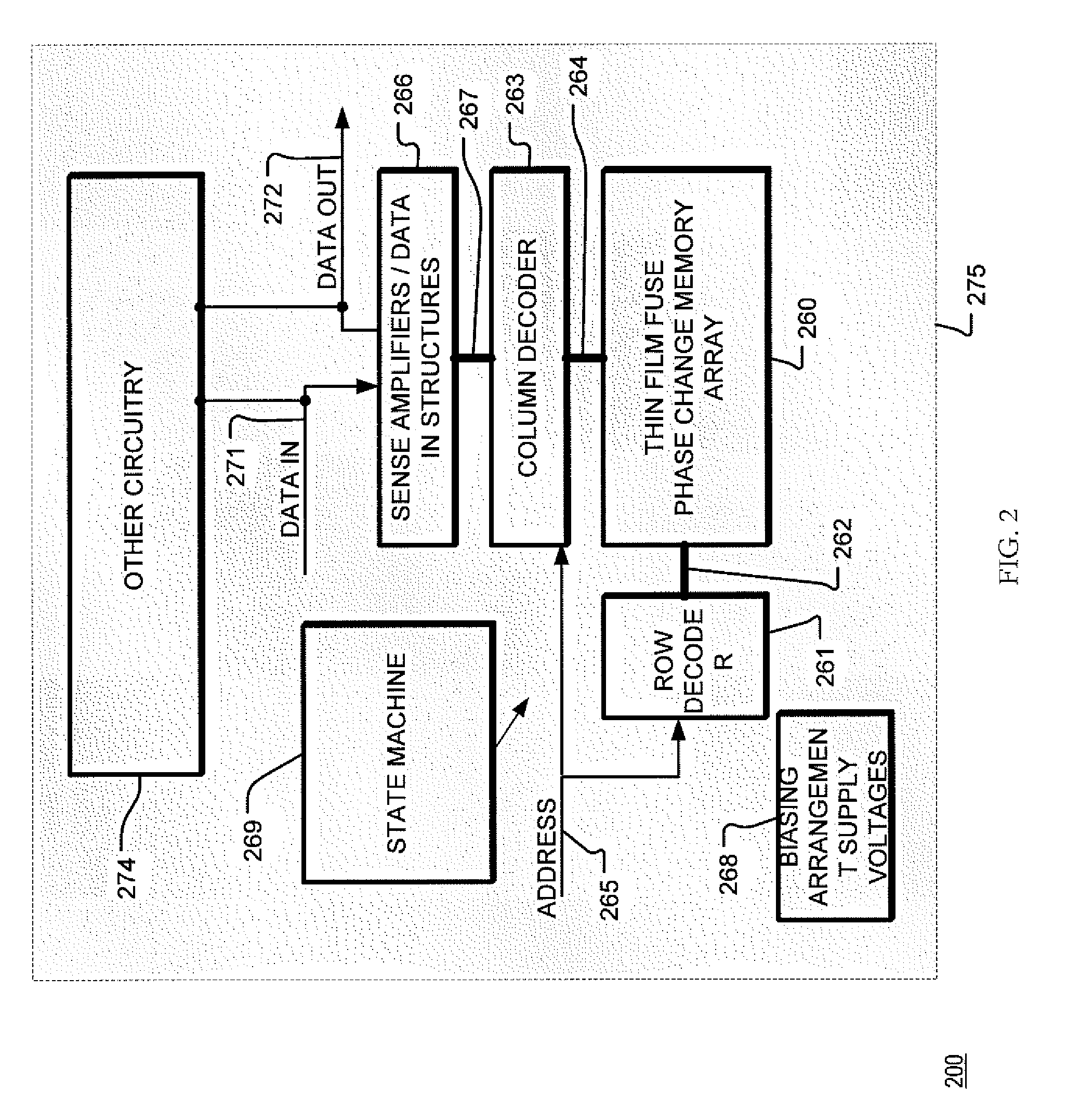

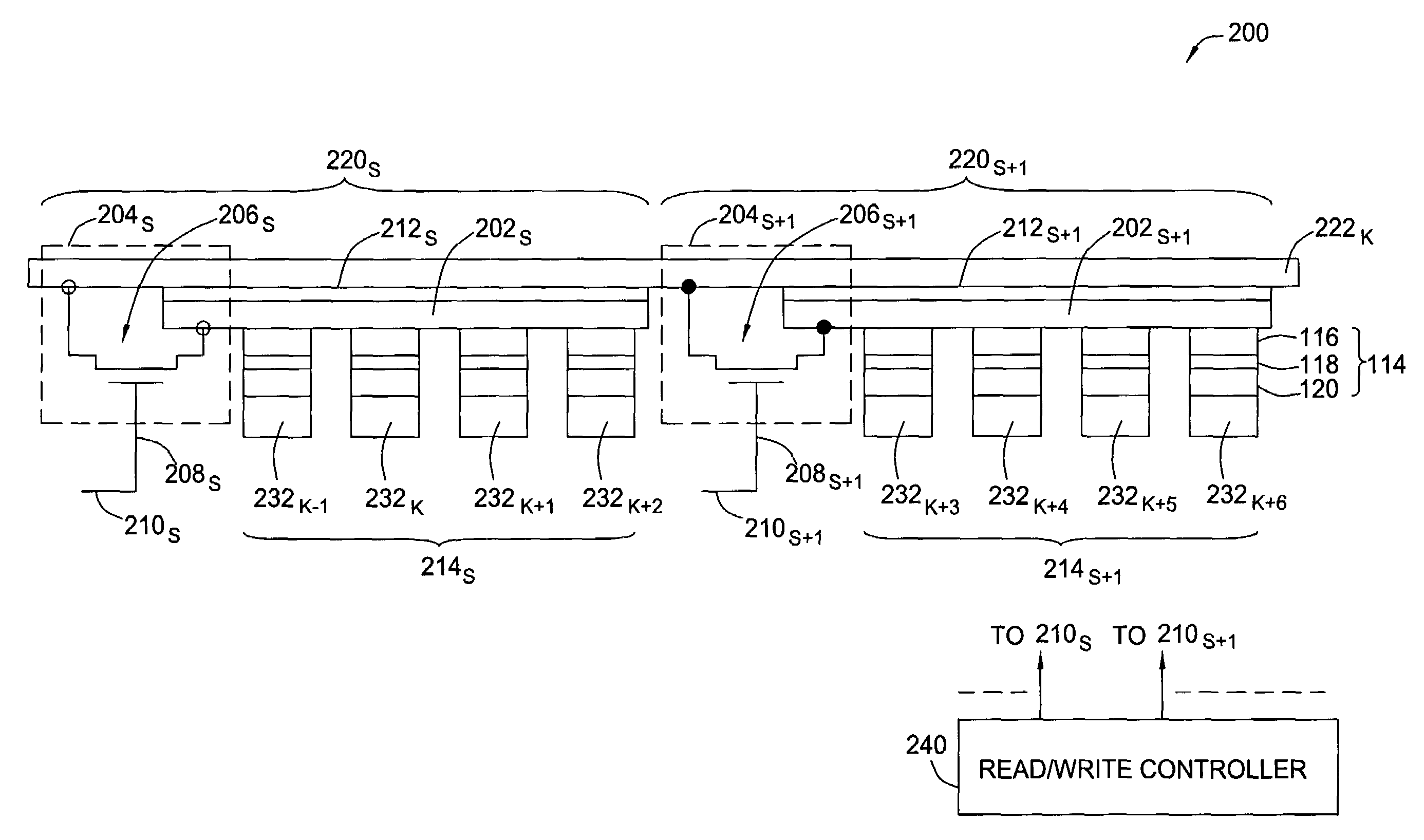

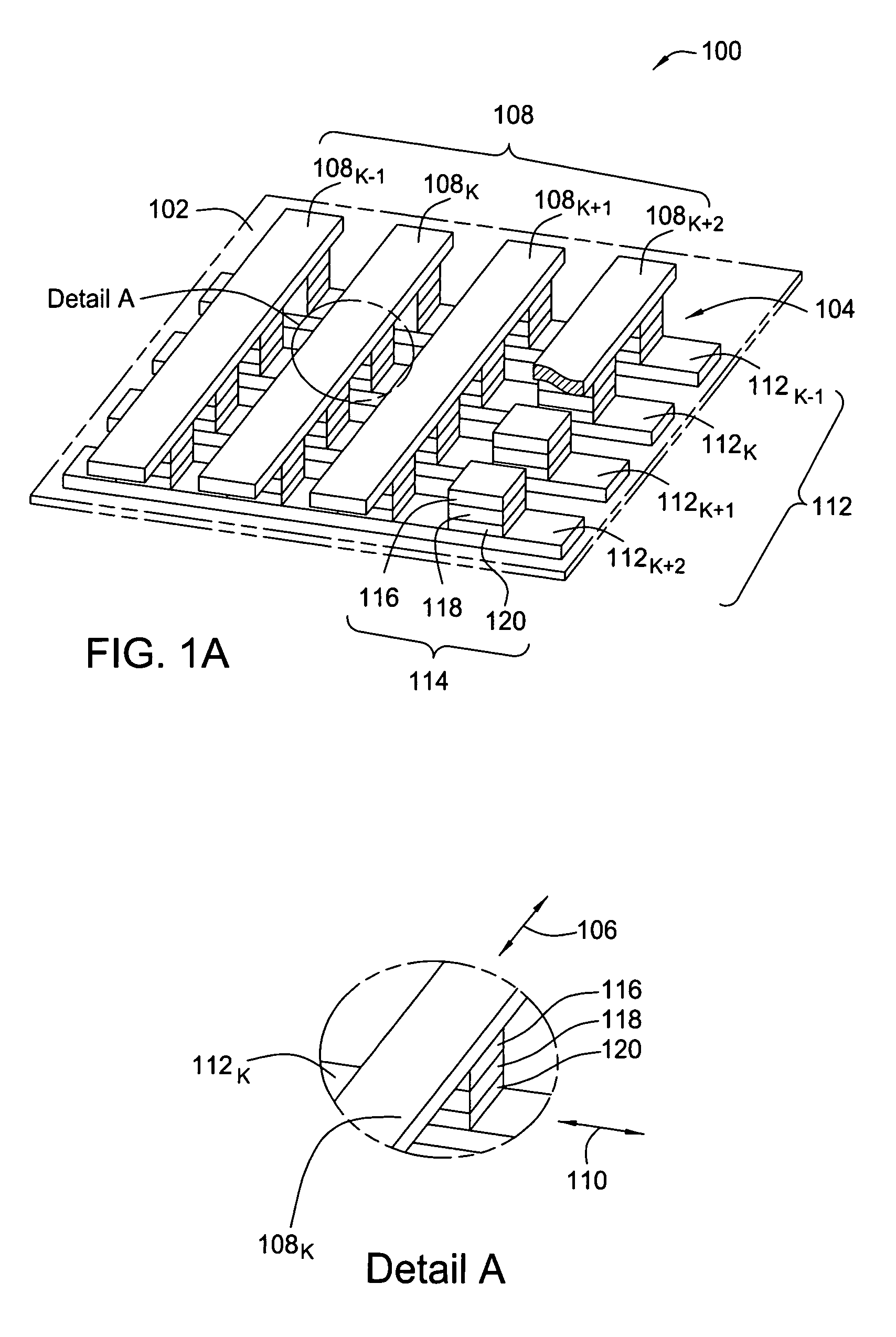

A magneto-resistive random access memory (MRAM) array comprises global bit lines segmented using a plurality of local bit lines. A read / write controller is connected to the switches. Switches couple the global bit line to the local bit lines. The MRAM array has low leakage currents and facilitates a high signal-to-noise (S / N) ratio of read and write operations.

Owner:IBM CORP +1

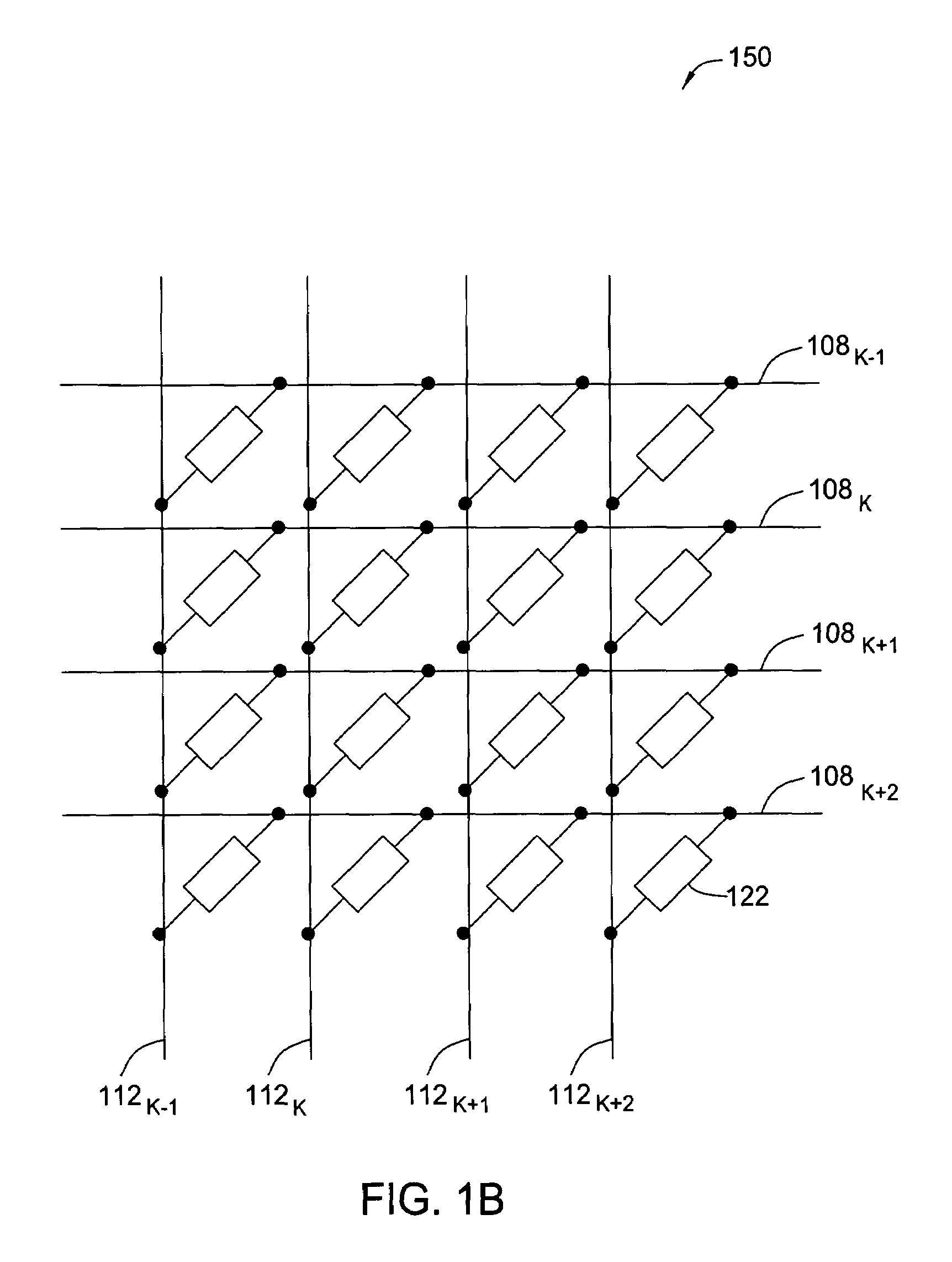

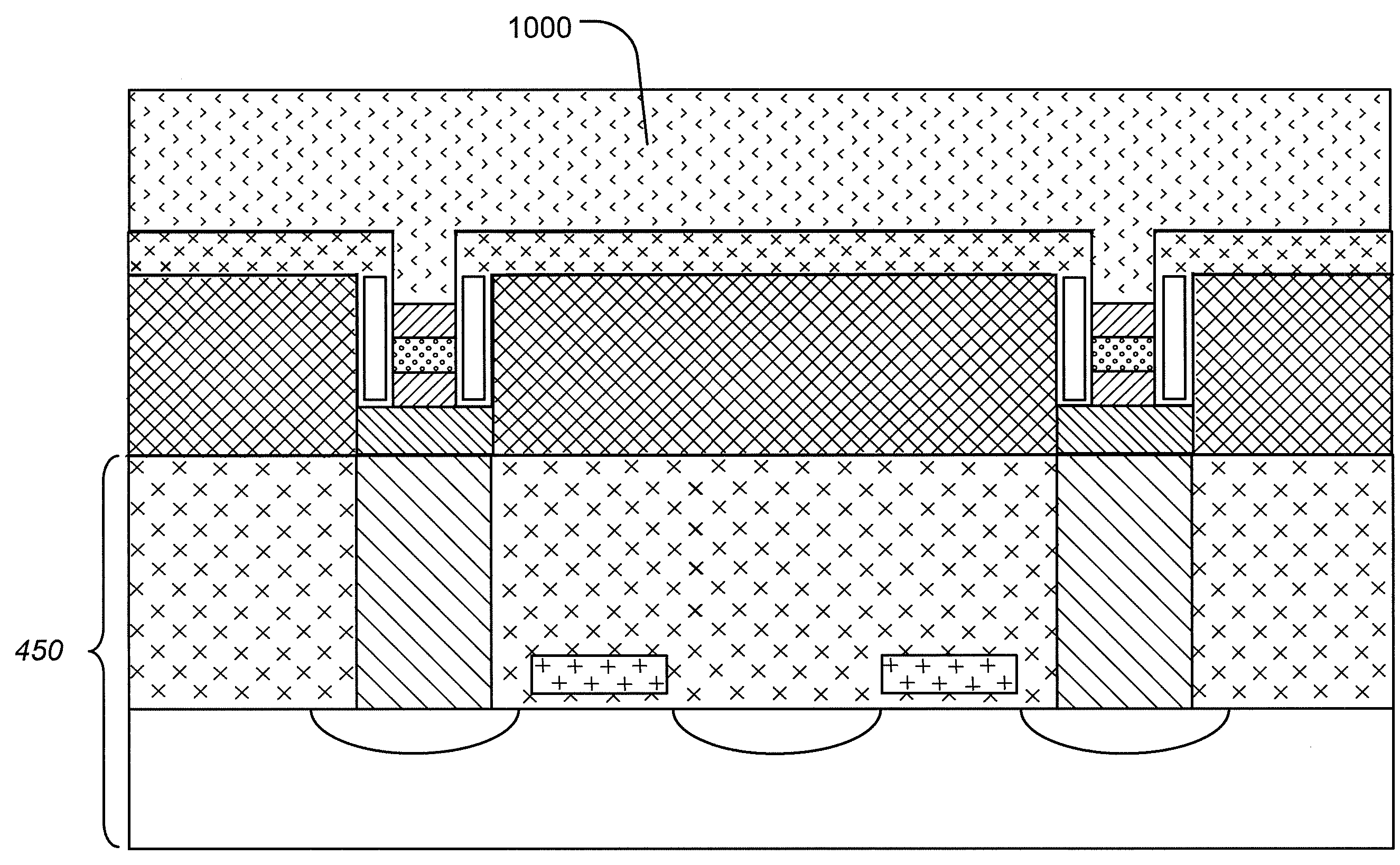

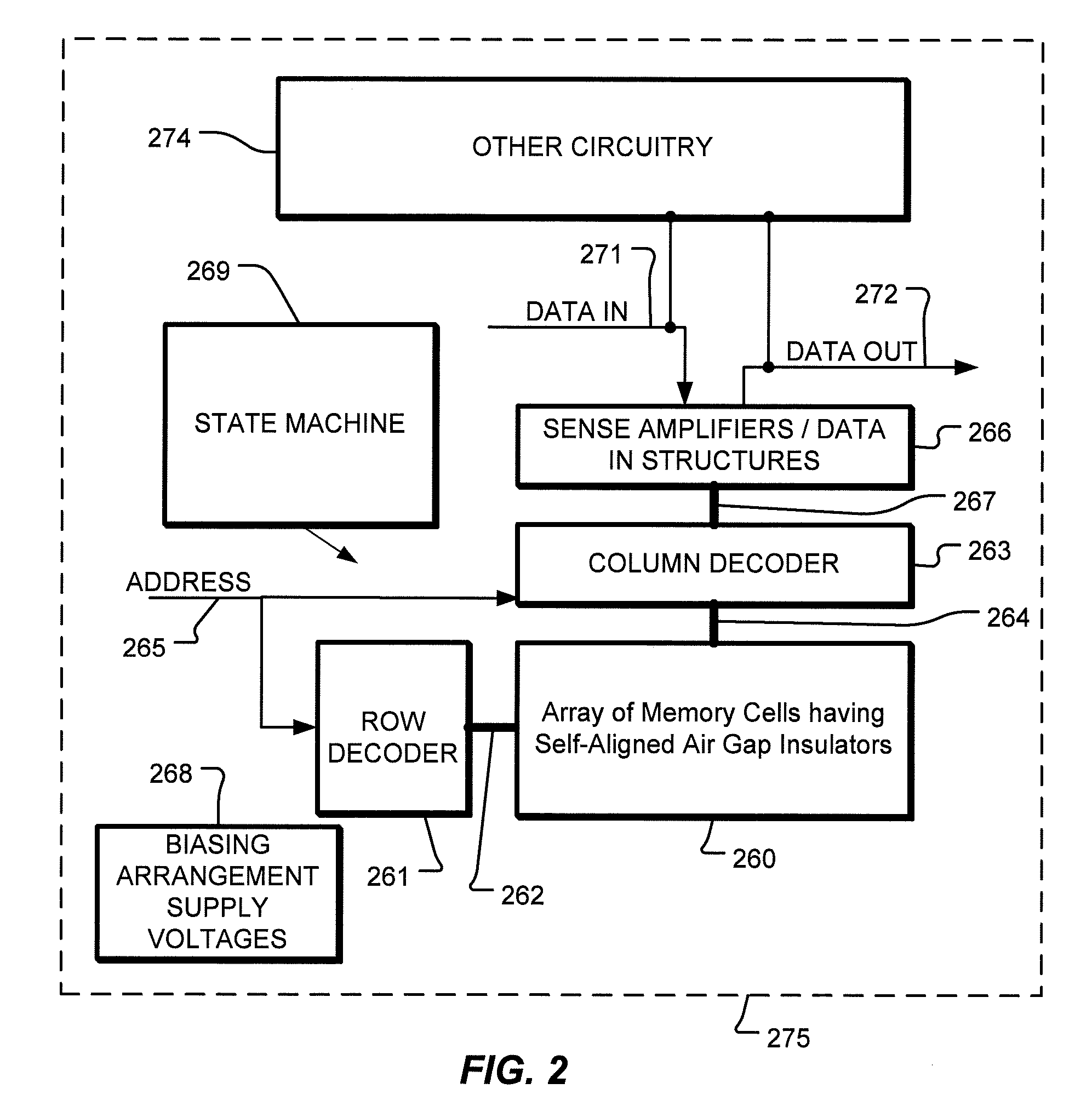

Method for manufacturing a resistor random access memory with a self-aligned air gap insulator

ActiveUS20090101883A1Reduce the amount requiredReduce heat dissipationSemiconductor/solid-state device manufacturingBulk negative resistance effect devicesStatic random-access memoryRandom access memory

Owner:MACRONIX INT CO LTD

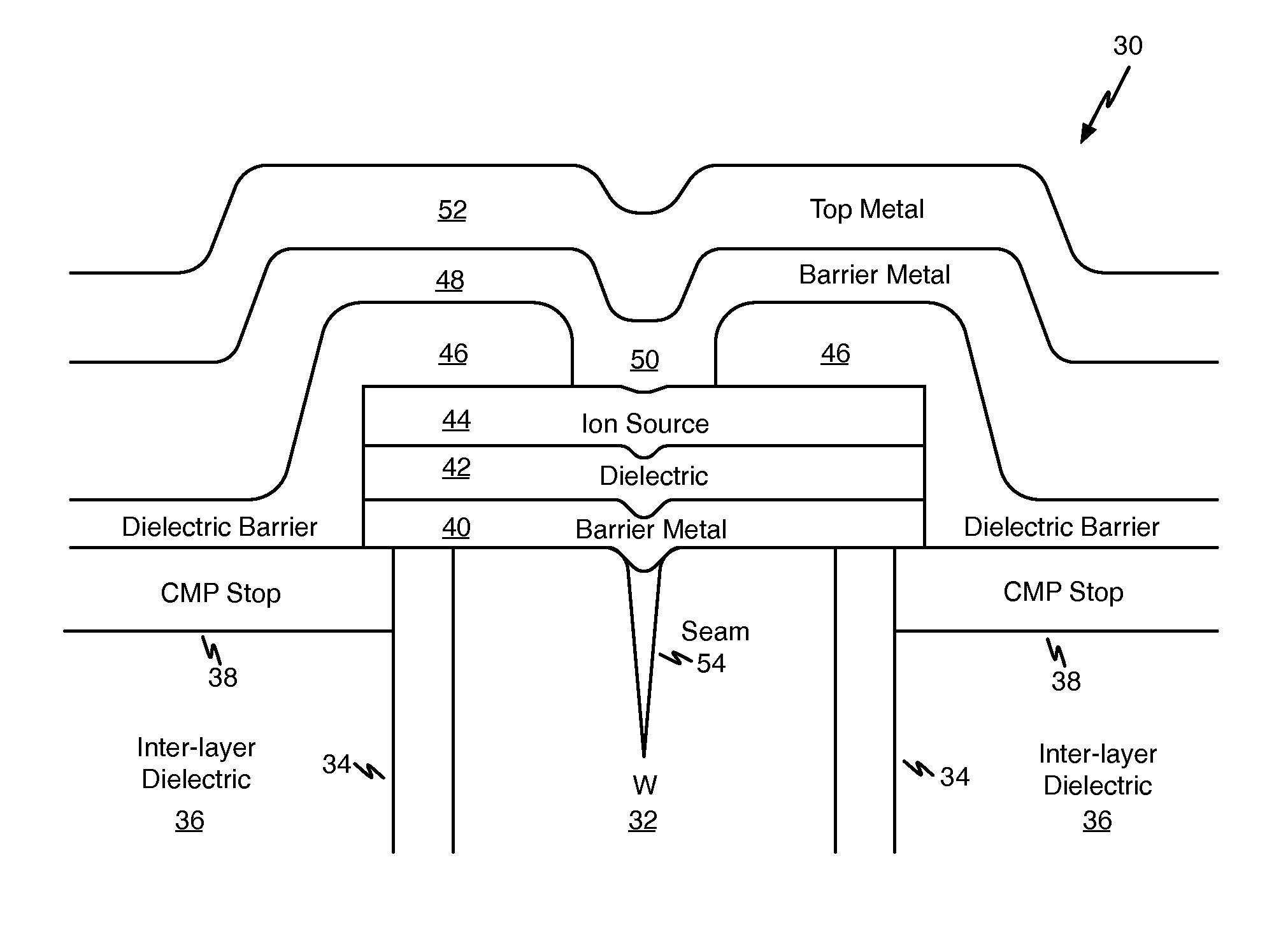

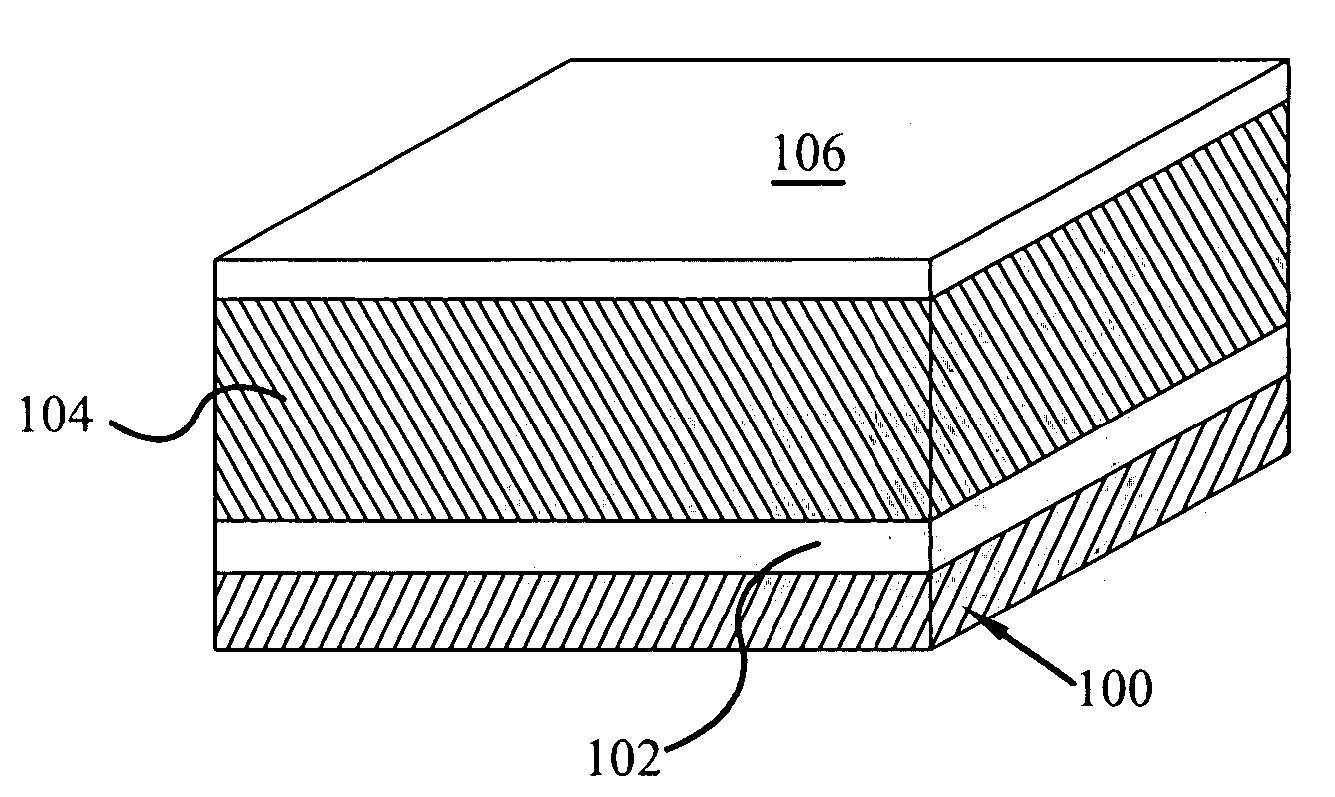

Front to back resistive random access memory cells

A resistive random access memory device formed on a semiconductor substrate comprises an interlayer dielectric having a via formed therethrough. A chemical-mechanical-polishing stop layer is formed over the interlayer dielectric. A barrier metal liner lines walls of the via. A conductive plug is formed in the via. A first barrier metal layer is formed over the chemical-mechanical-polishing stop layer and in electrical contact with the conductive plug. A dielectric layer is formed over the first barrier metal layer. An ion source layer is formed over the dielectric layer. A dielectric barrier layer is formed over the ion source layer, and includes a via formed therethrough communicating with the ion source layer. A second barrier metal layer is formed over the dielectric barrier layer and in electrical contact with the ion source layer. A metal interconnect layer is formed over the barrier metal layer.

Owner:MICROSEMI SOC

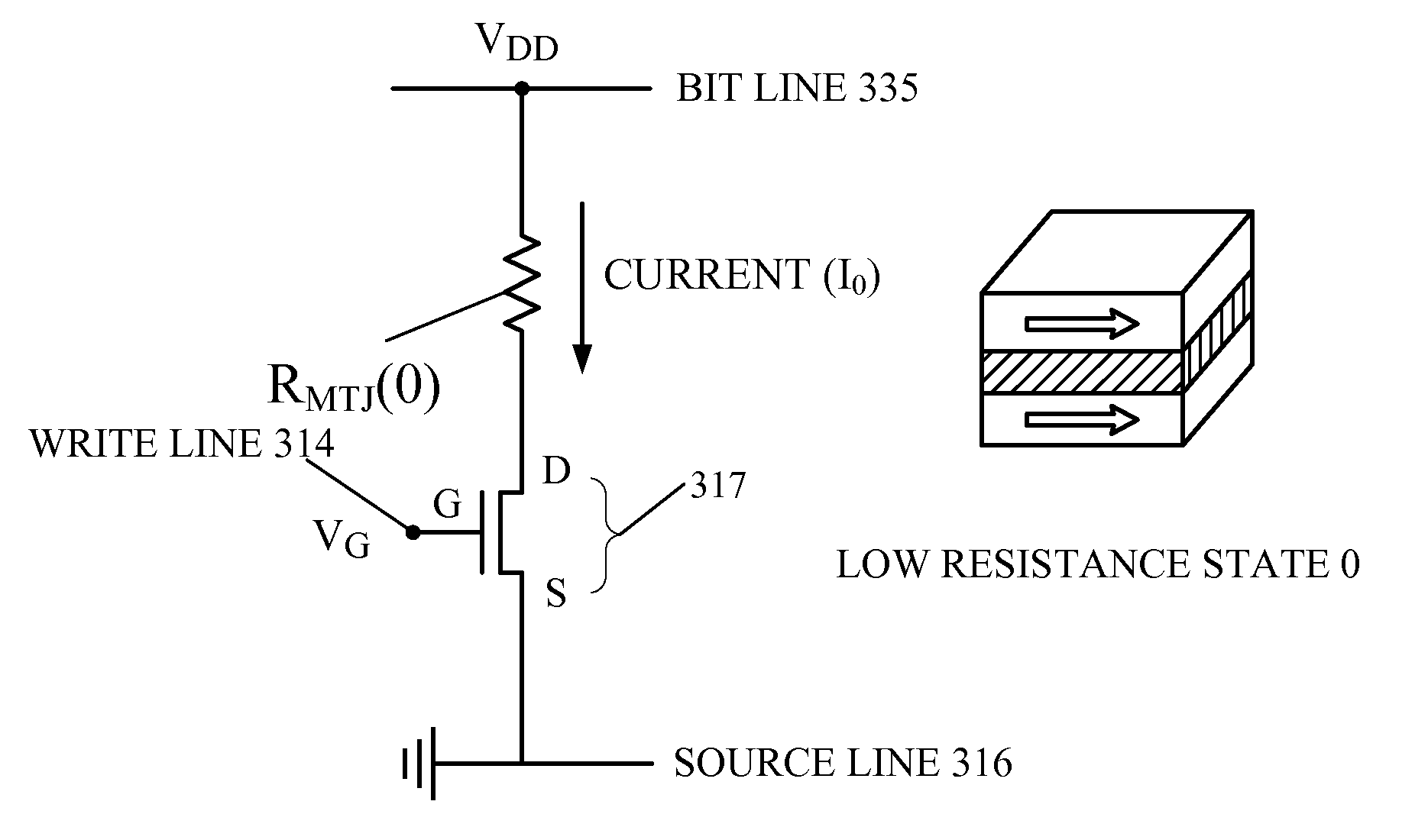

Gate Level Reconfigurable Magnetic Logic

ActiveUS20100039136A1Write currentIncrease current densitySolid-state devicesDigital storageSignal onRandom access memory

A re-programmable gate logic includes a plurality of non-volatile re-configurable resistance state-based memory circuits in parallel, wherein the circuits are re-configurable to implement or change a selected gate logic, and the plurality of non-volatile re-configurable resistance state-based memory circuits are each adapted to receive a logical input signal. An evaluation switch in series with the plurality of parallel non-volatile re-configurable resistance state-based memory circuits is configured to provide an output signal based on the programmed states of the memory circuits. A sensor is configured to receive the output signal and provide a logical output signal on the basis of the output signal and a reference signal provided to the sensor. The reconfigurable logic may be implemented based on using spin torque transfer (STT) magnetic tunnel junction (MTJ) magnetoresistance random access memory (MRAM) as the re-programmable memory elements. The logic configuration is retained without power.

Owner:QUALCOMM INC

Method of making toroidal MRAM cells

InactiveUS20050158881A1Semiconductor/solid-state device manufacturingDigital storageDielectricStatic random-access memory

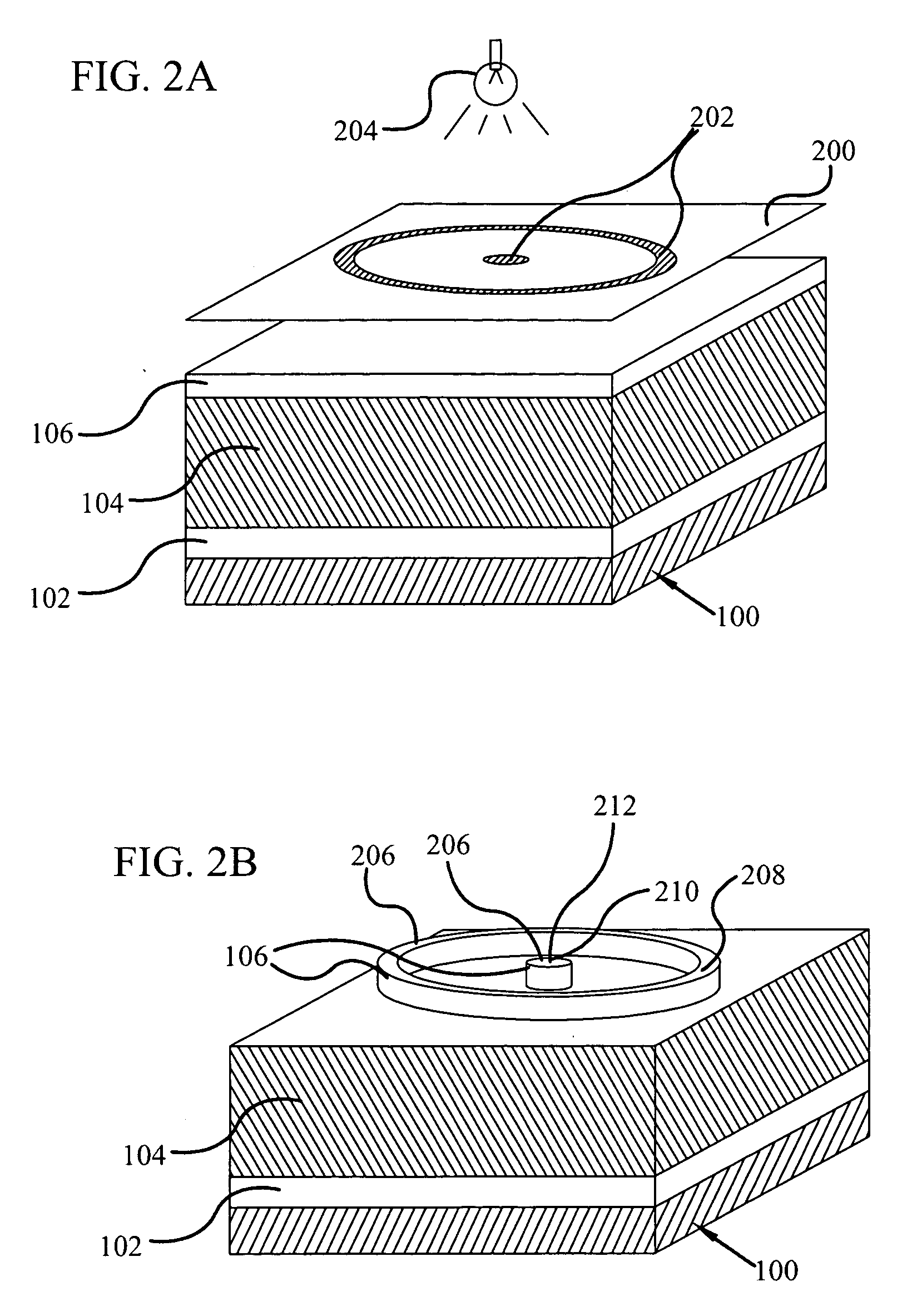

This invention provides a method of making nano-scaled toroidal magnetic memory cells, such as may be used, for example, in magnetic random access memory (MRAM). In a particular embodiment a semiconductor wafer substrate is prepared and a conductor layer is provided upon the wafer. A hard layer is deposited upon the first conductor. From the hard layer, ion etching is employed to form an annular wall about a pillar, the wall and pillar defining an annular slot. A ferromagnetic data layer is deposited within the annular slot and a junction stack is then provided upon at least a portion of the data layer. A dielectric is applied to insulate the structure and then planarized to expose the pillar.

Owner:DATA QUILL

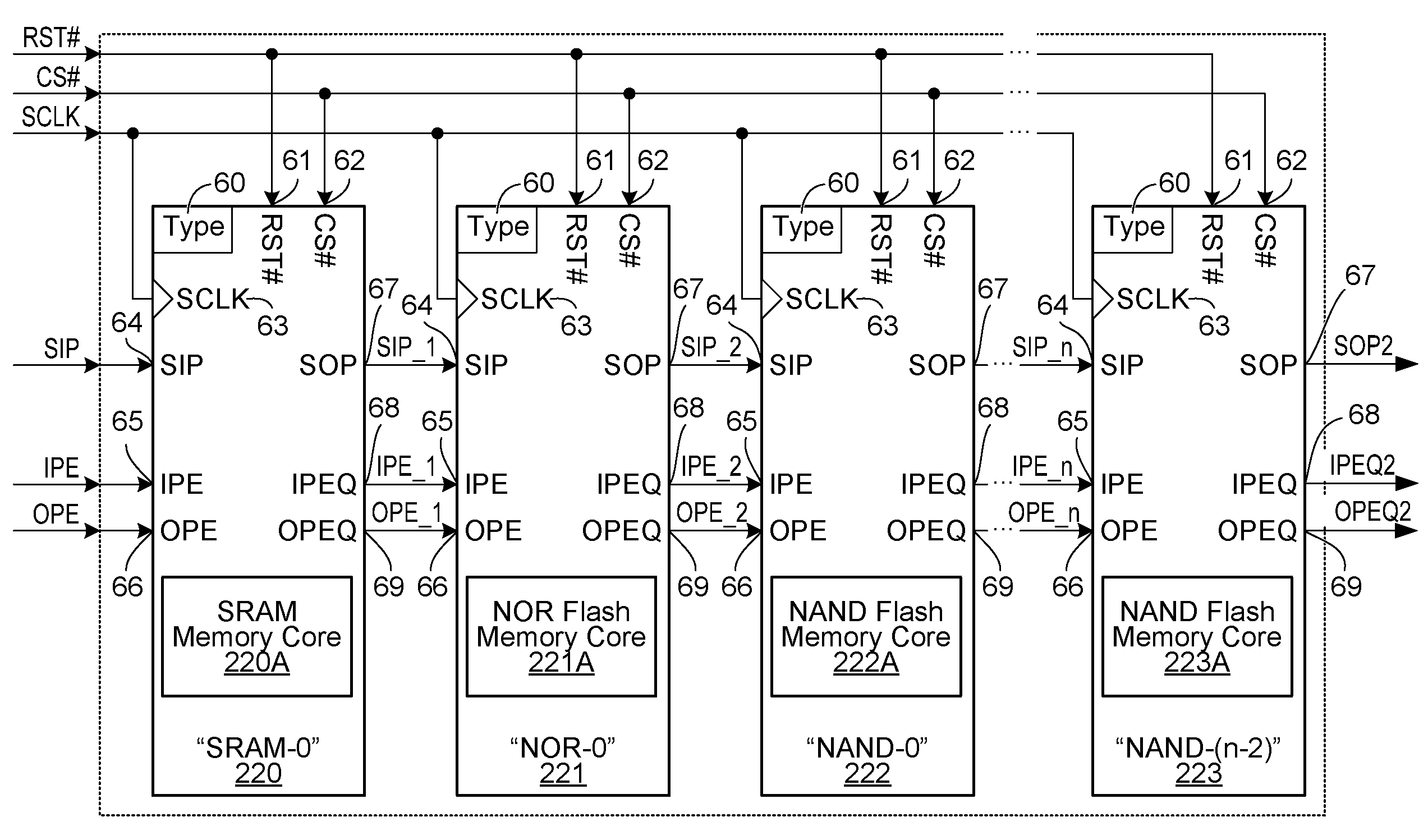

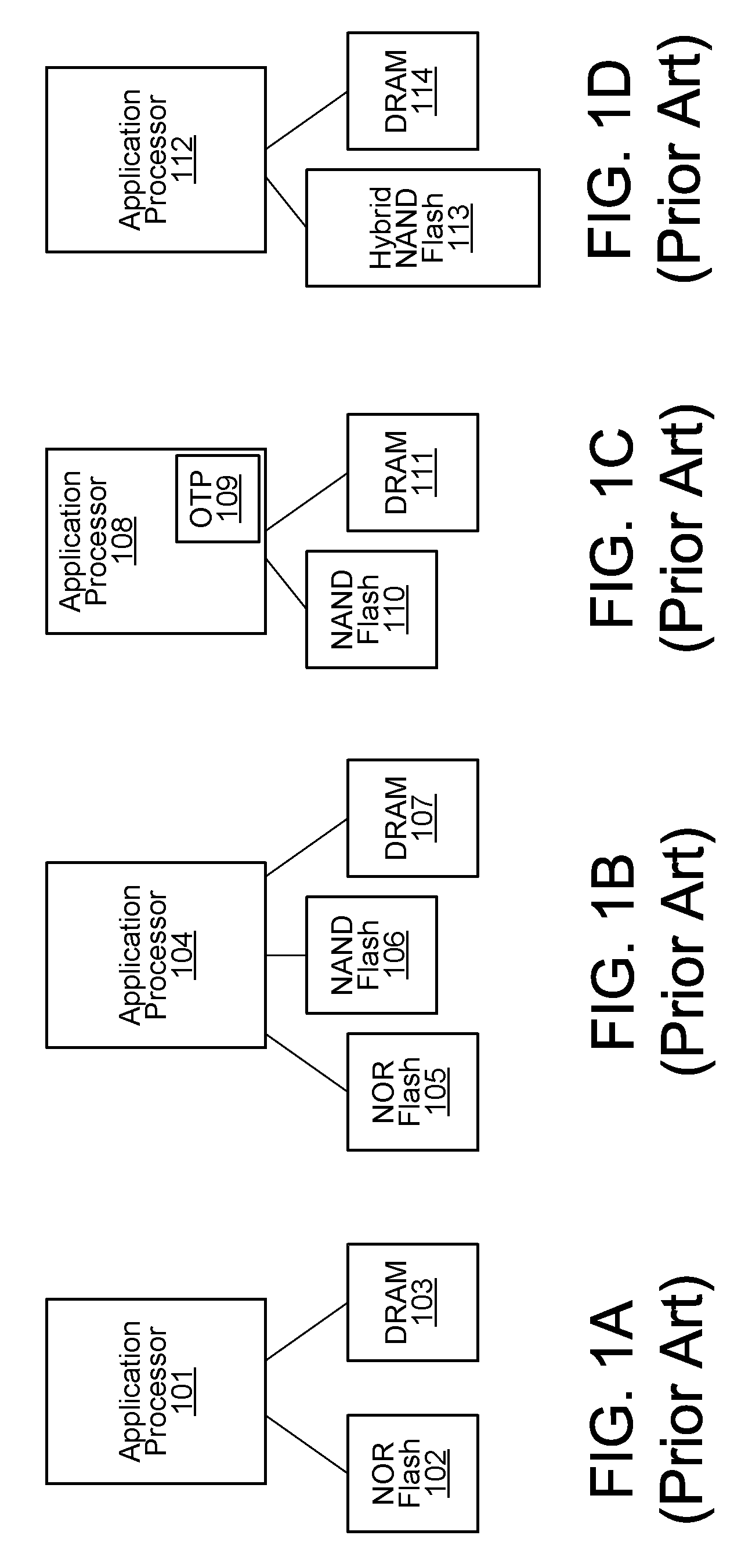

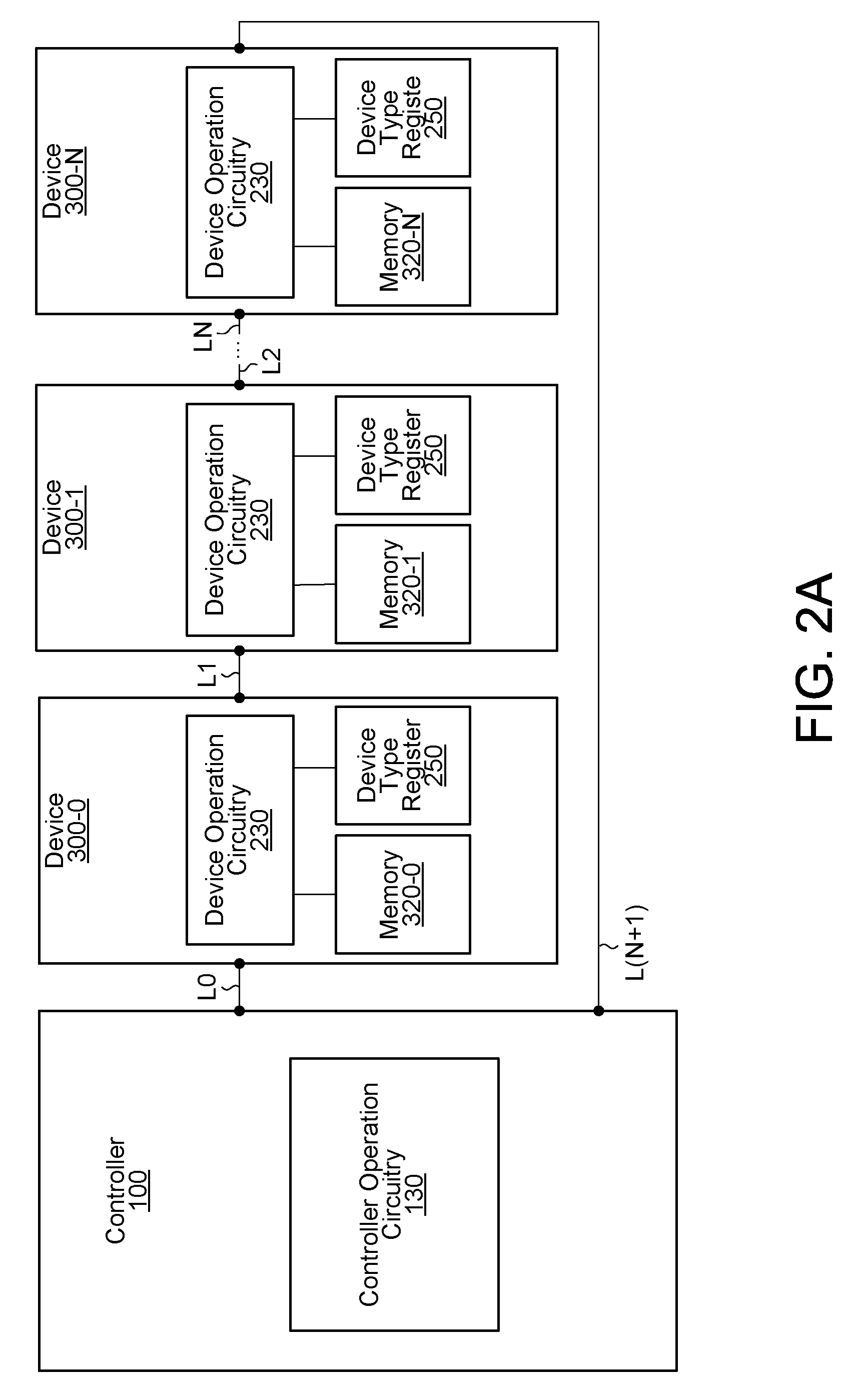

System and method of operating memory devices of mixed type

InactiveUS20080140916A1Memory adressing/allocation/relocationRead-only memoriesHybrid typeStatic random-access memory

A memory system architecture is provided in which a memory controller controls memory devices in a serial interconnection configuration. The memory controller has an output port for sending memory commands and an input port for receiving memory responses for those memory commands requisitioning such responses. Each memory device includes a memory, such as, for example, NAND-type flash memory, NOR-type flash memory, random access memory and static random access memory. Each memory command is specific to the memory type of a target memory device. A data path for the memory commands and the memory responses is provided by the interconnection. A given memory command traverses memory devices in order to reach its intended memory device of the serial interconnection configuration. Upon its receipt, the intended memory device executes the given memory command and, if appropriate, sends a memory response to a next memory device. The memory response is transferred to the memory controller.

Owner:CONVERSANT INTPROP MANAGEMENT INC

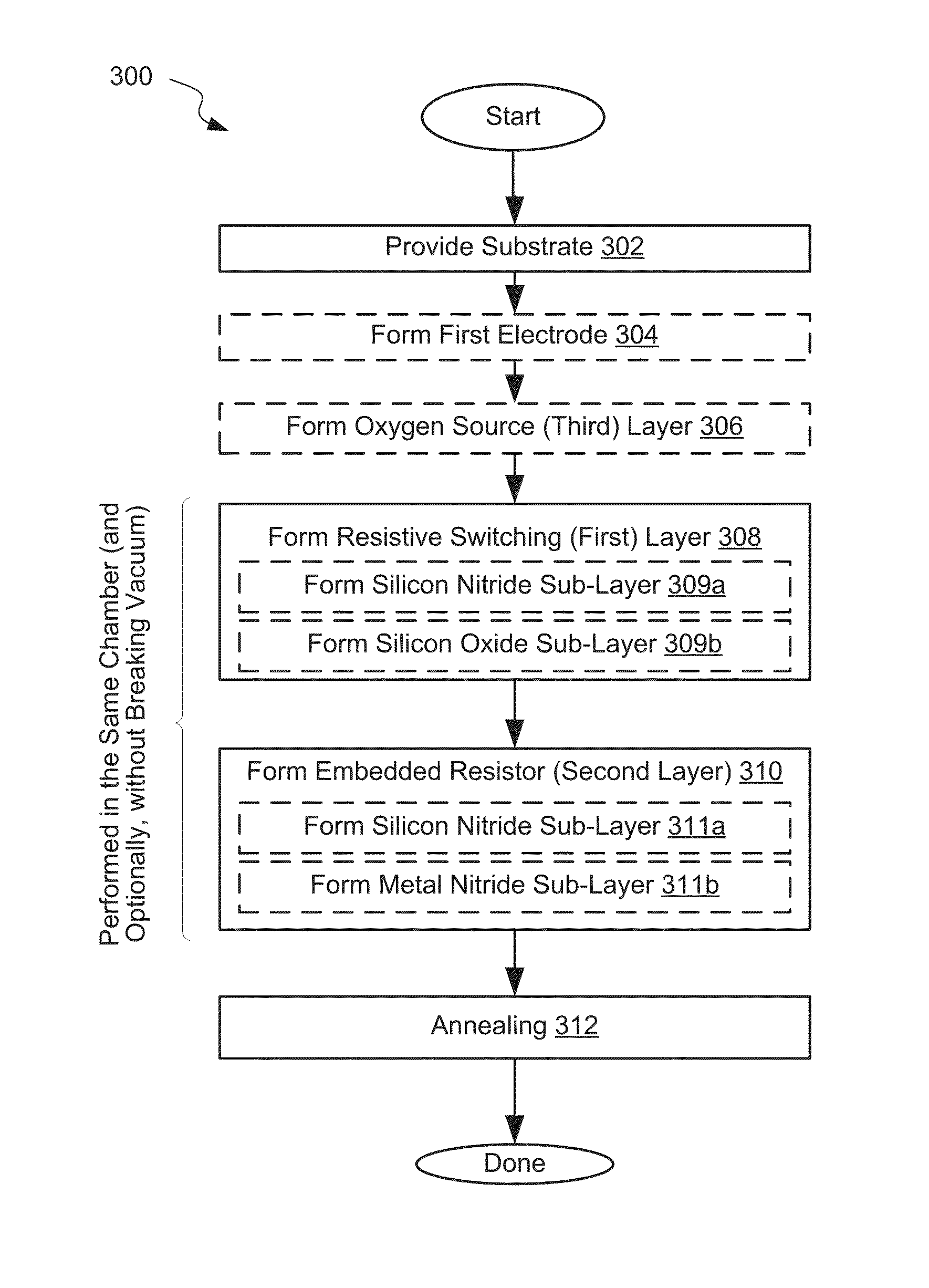

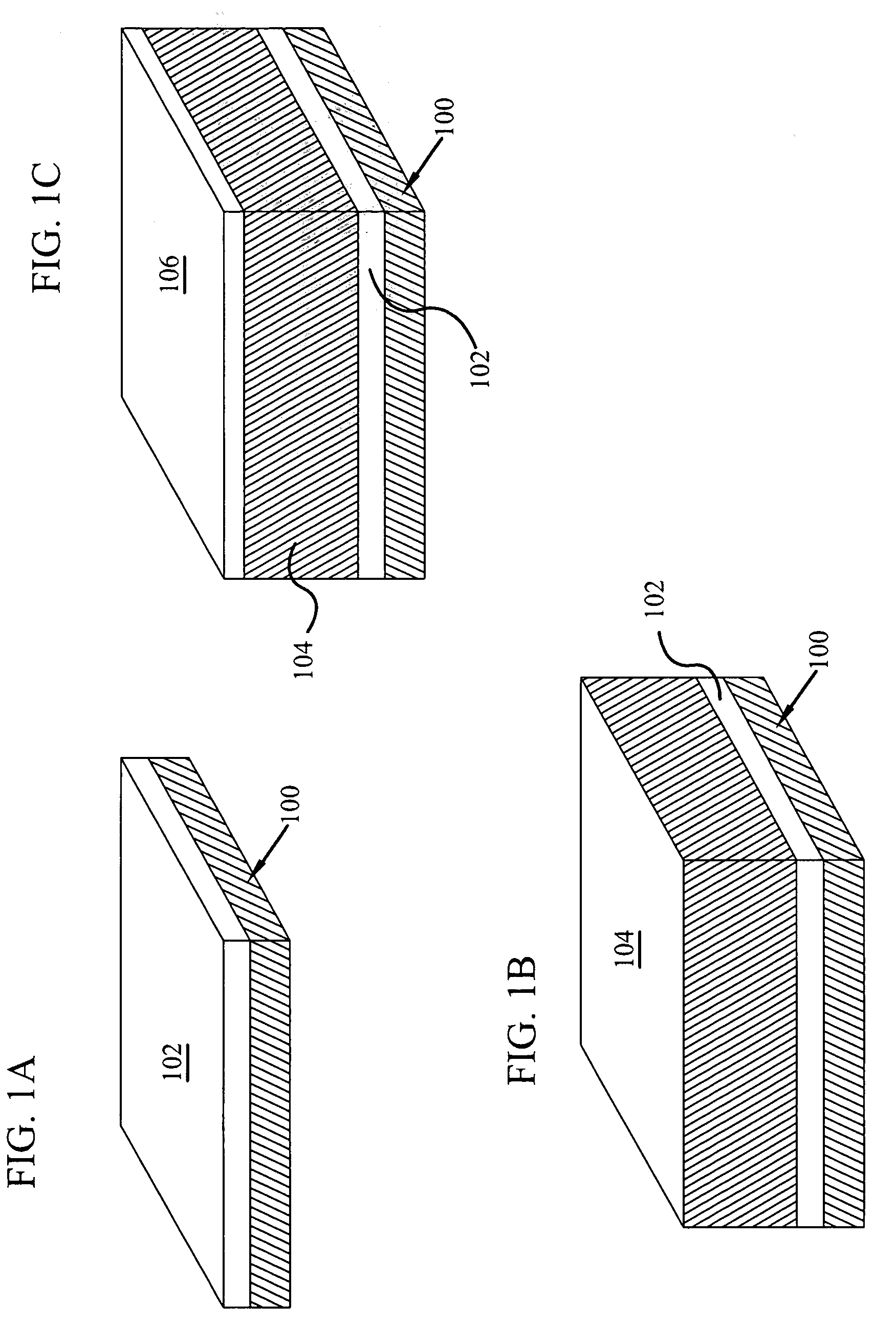

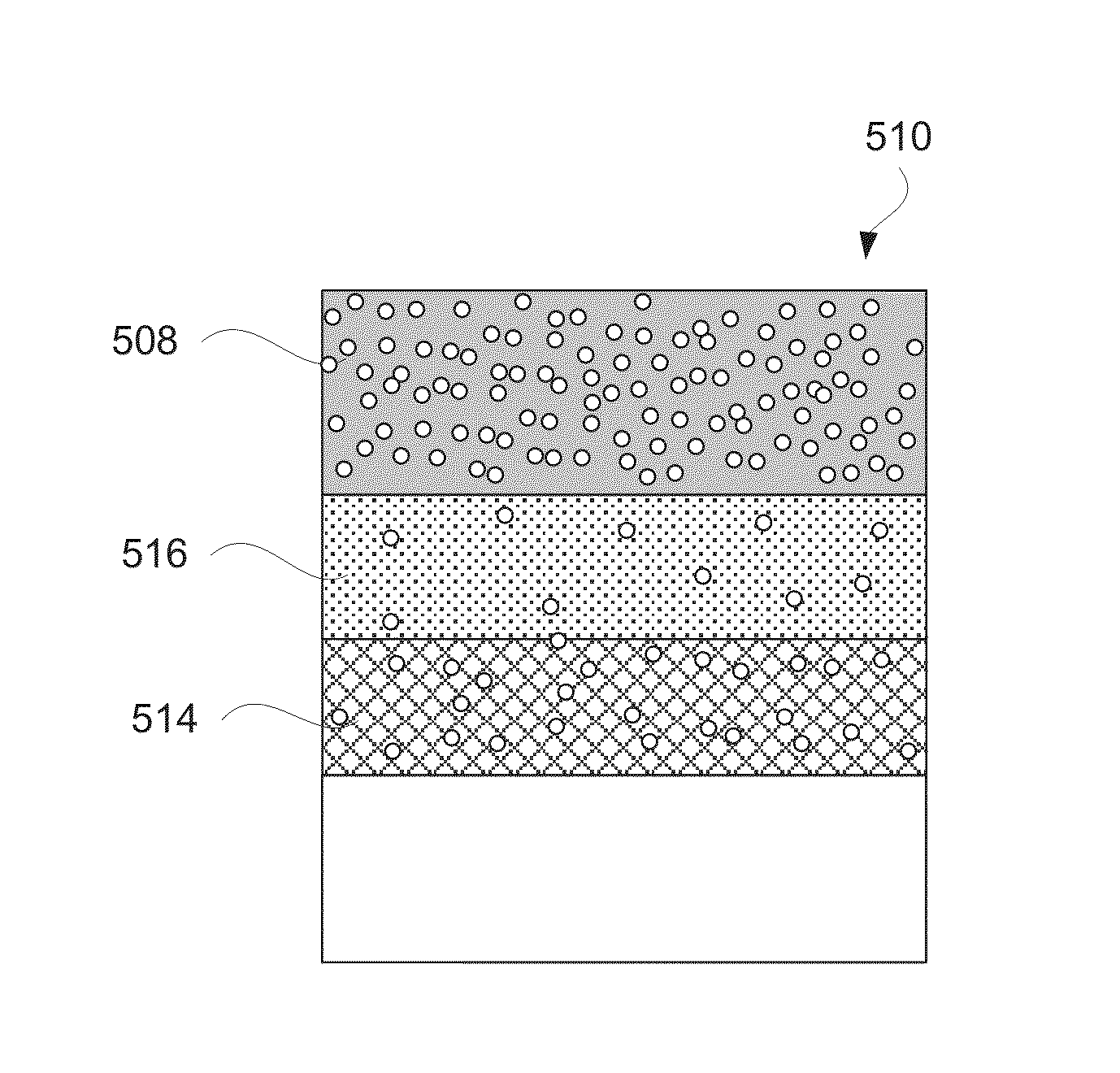

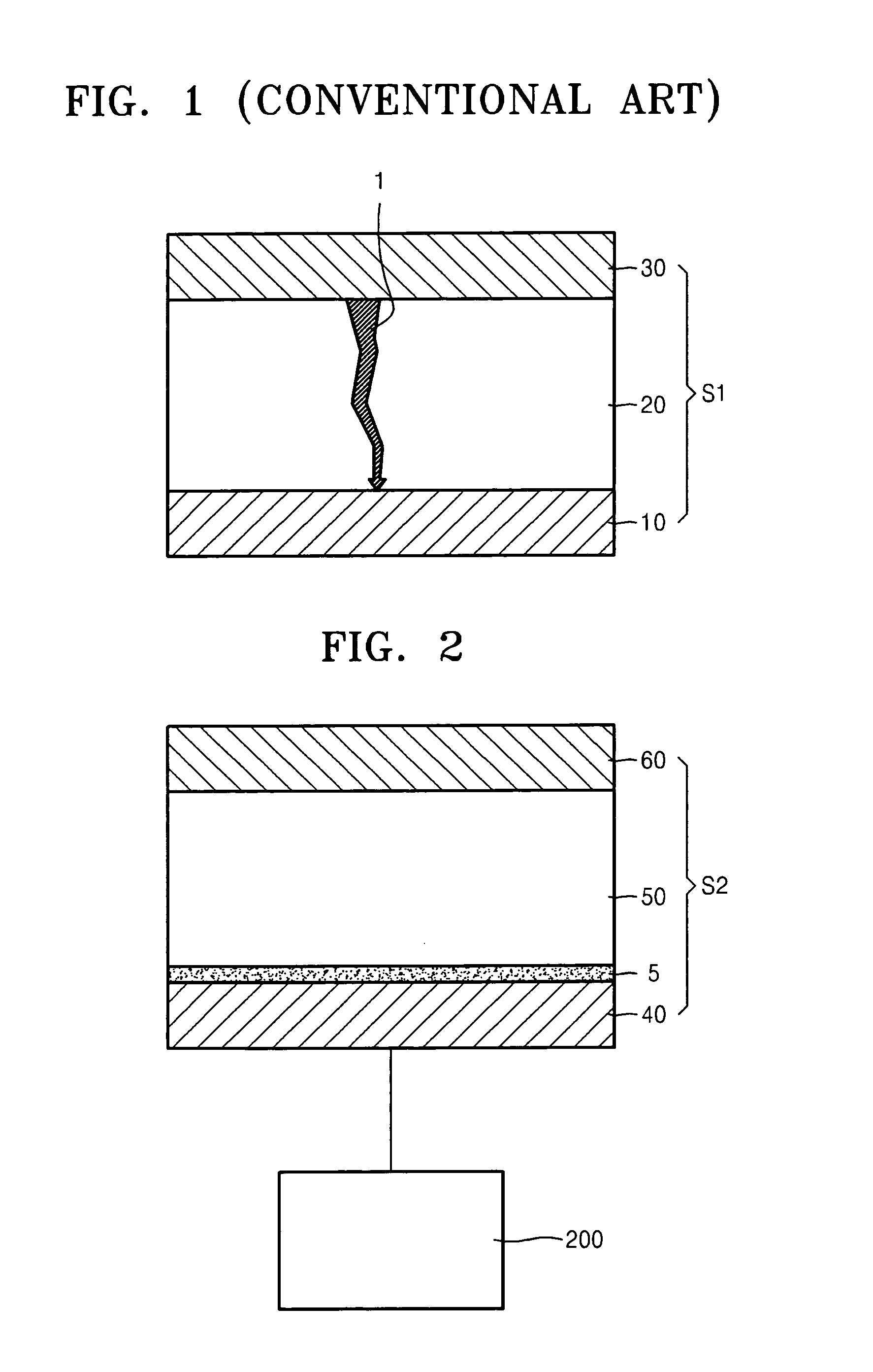

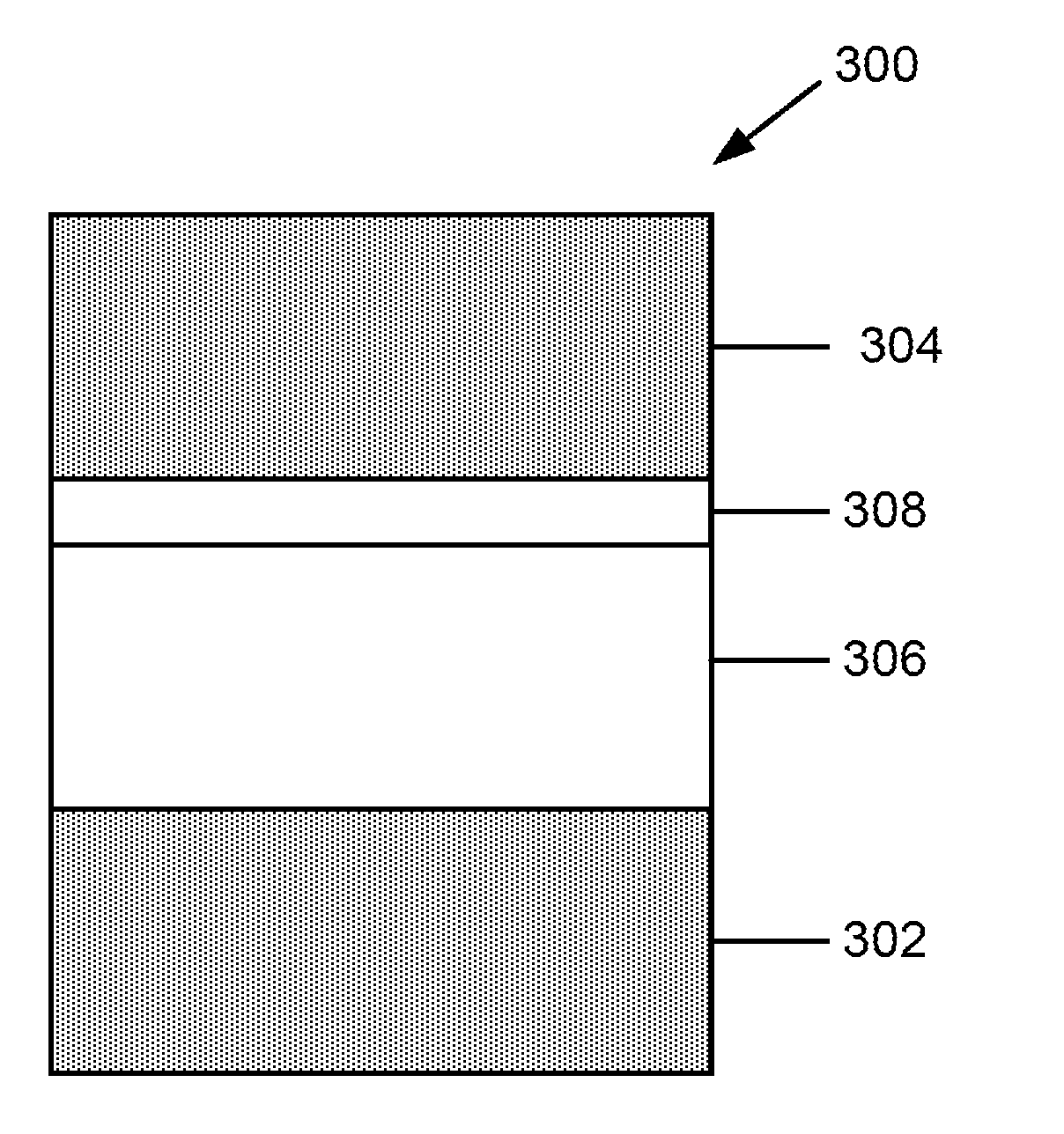

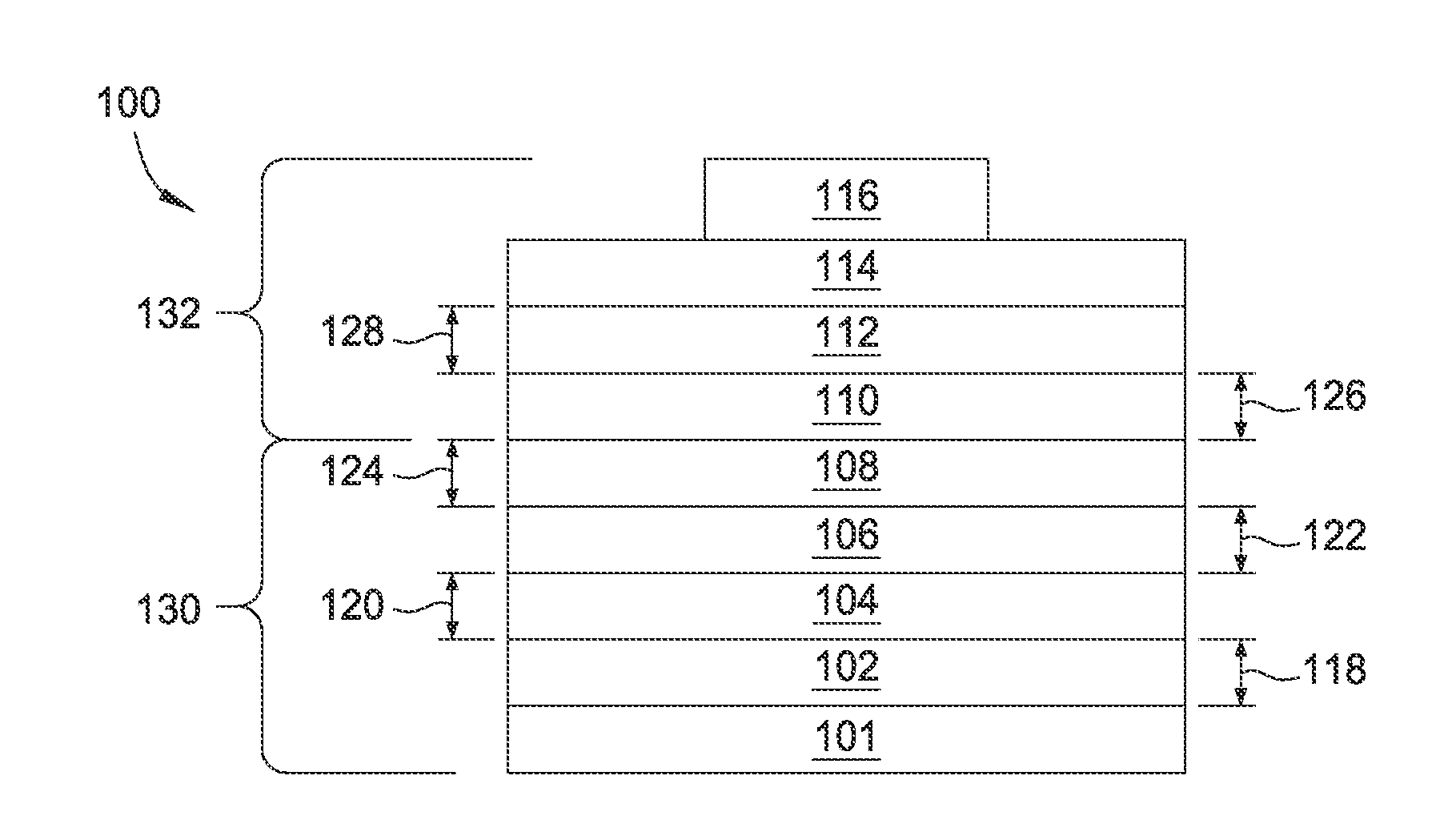

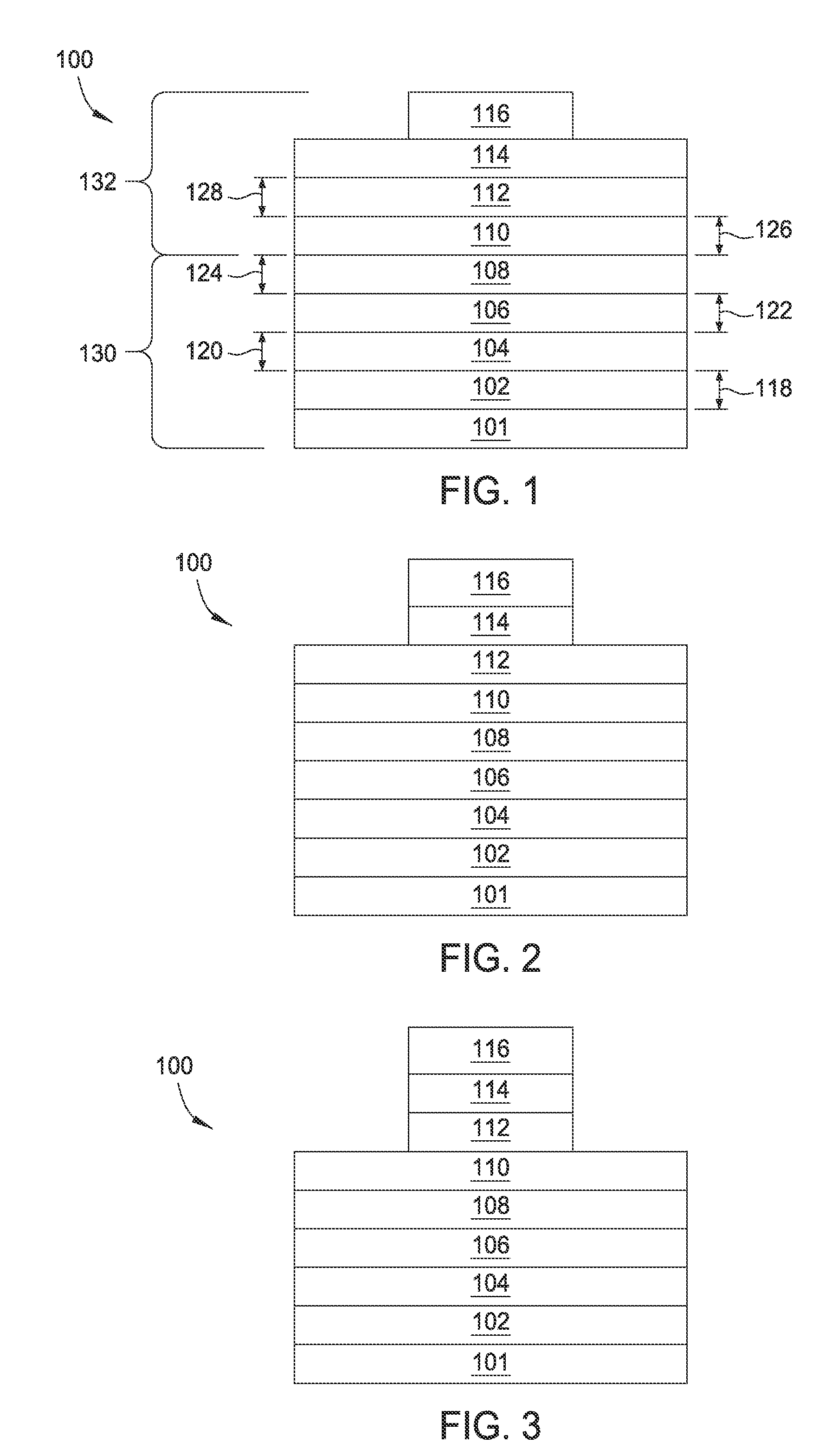

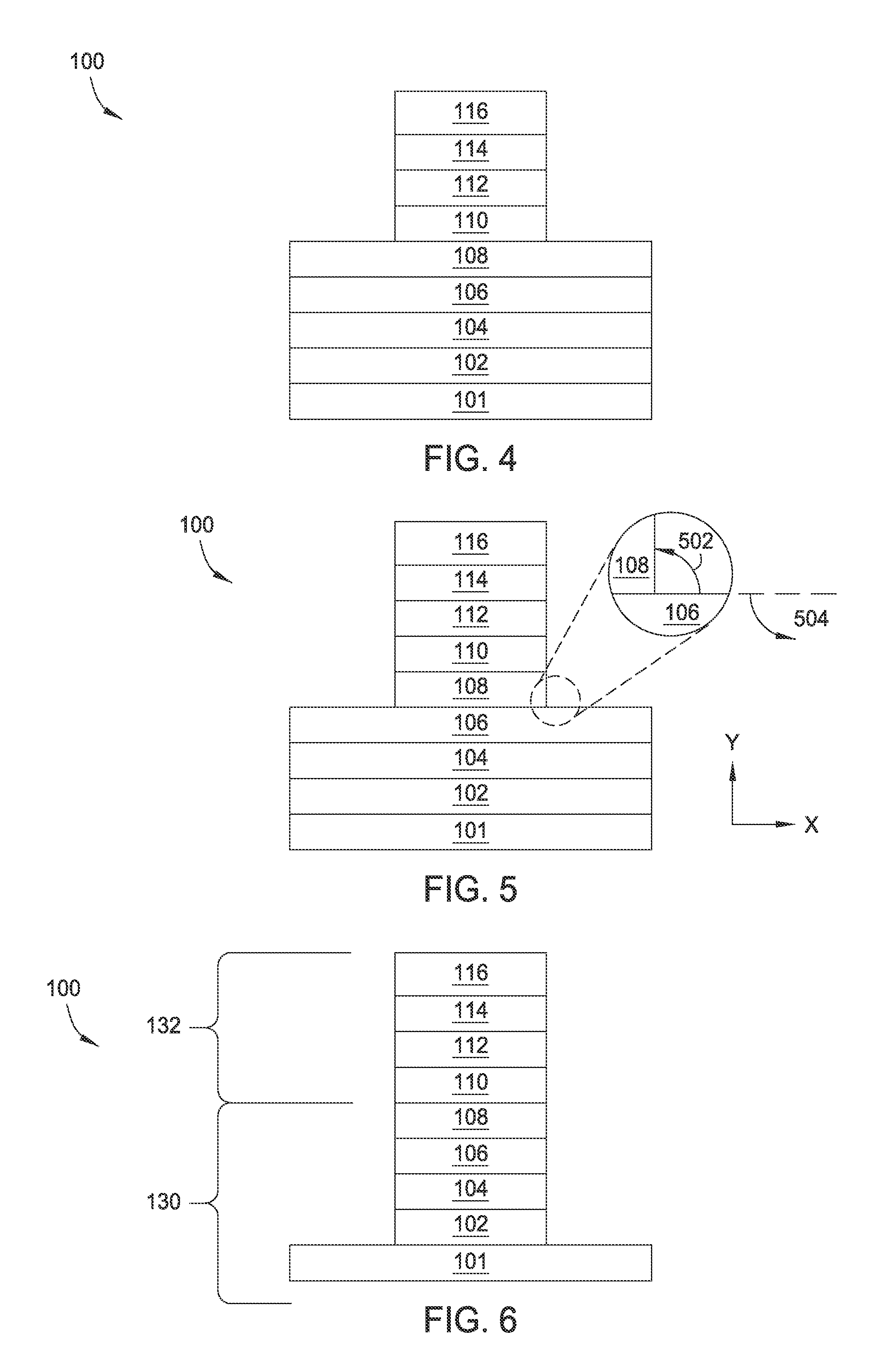

Confined Defect Profiling within Resistive Random Memory Access Cells

ActiveUS20150034898A1Improvement of resistive switching characteristicDigital storageBulk negative resistance effect devicesTitanium nitrideResistive switching

Provided are resistive random access memory (ReRAM) cells and methods of fabricating thereof. A stack including a defect source layer, a defect blocking layer, and a defect acceptor layer disposed between the defect source layer and the defect blocking layer may be subjected to annealing. During the annealing, defects are transferred in a controllable manner from the defect source layer to the defect acceptor layer. At the same time, the defects are not transferred into the defect blocking layer thereby creating a lowest concentration zone within the defect acceptor layer. This zone is responsible for resistive switching. The precise control over the size of the zone and the defect concentration within the zone allows substantially improvement of resistive switching characteristics of the ReRAM cell. In some embodiments, the defect source layer includes aluminum oxynitride, the defect blocking layer includes titanium nitride, and the defect acceptor layer includes aluminum oxide.

Owner:SANDISK TECH LLC

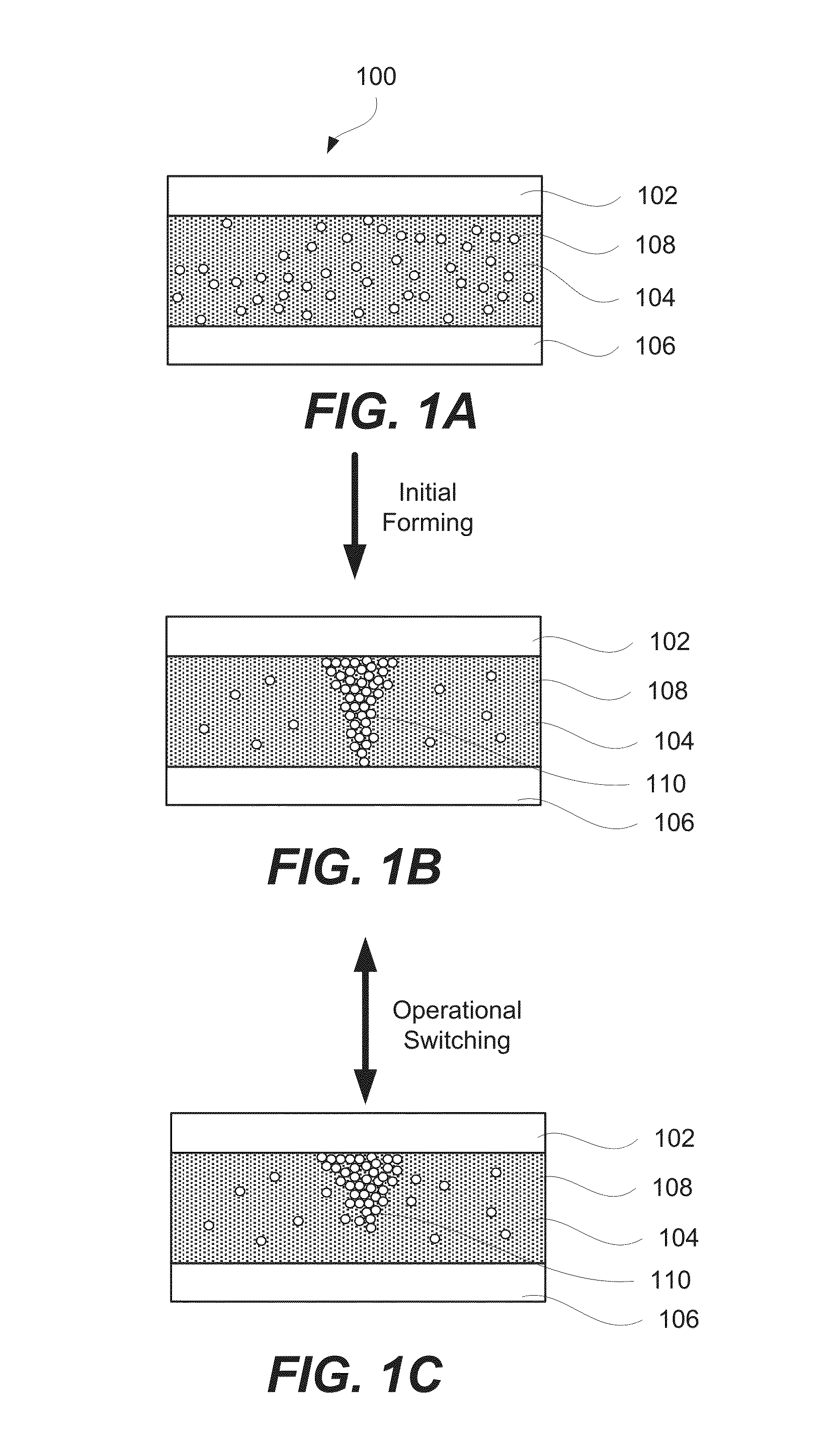

Resistive random access memory and method for fabricating the same

ActiveUS20100038791A1Semiconductor/solid-state device detailsSolid-state devicesOxygen vacancyRandom access memory

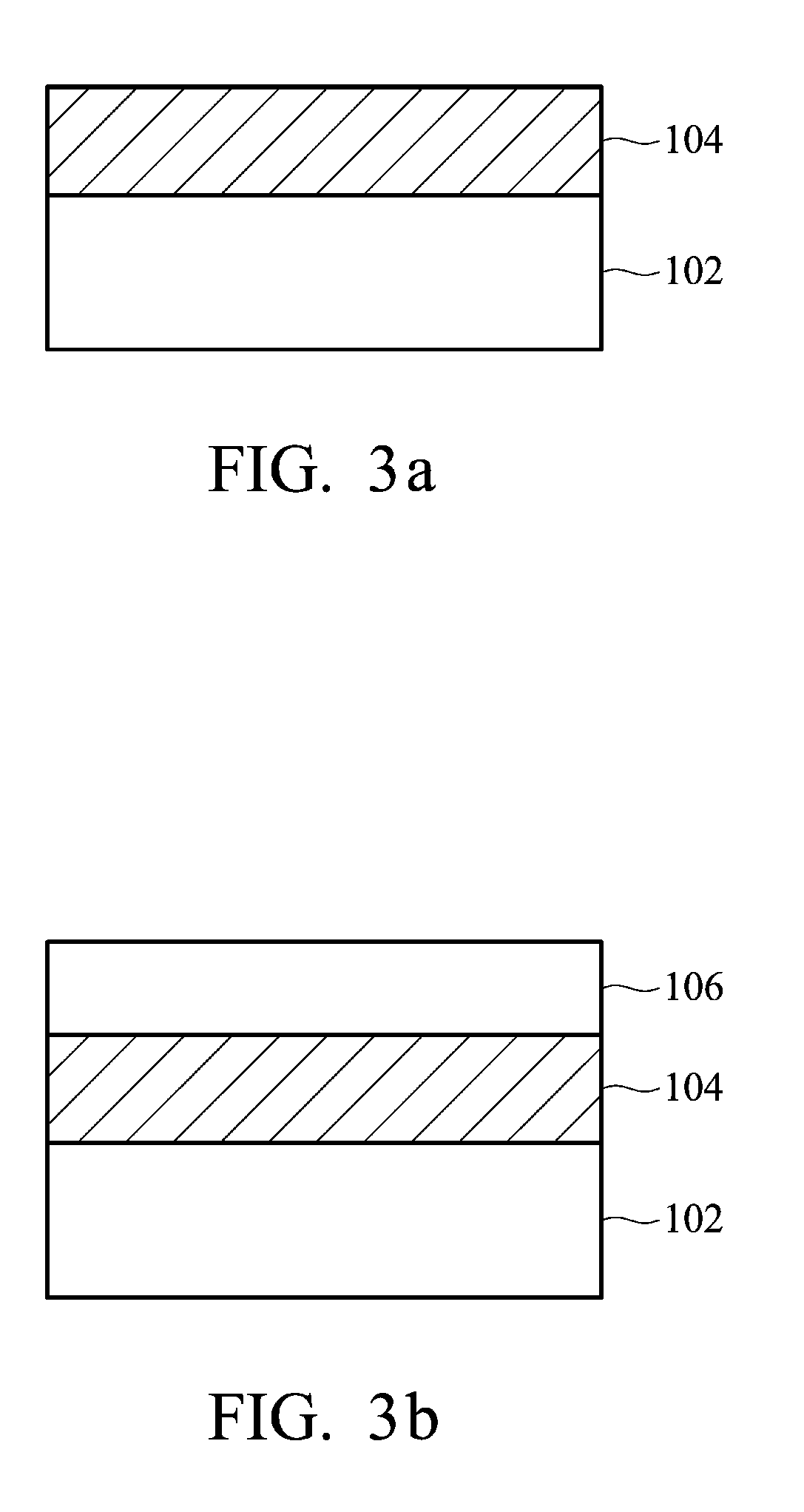

A resistive random access memory and a method for fabricating the same are provided. The method includes providing a bottom electrode formed on a substrate. A metal oxide layer is formed on the bottom electrode. An oxygen atom gettering layer is formed on the metal oxide layer. A top electrode is formed on the oxygen atom gettering layer. The previous mentioned structure is subjected to a thermal treatment, driving the oxygen atoms of the metal oxide layer to migrate into and react with the oxygen atom gettering layer, thus leaving a plurality of oxygen vacancies of the metal oxide layer.

Owner:TAIWAN SEMICON MFG CO LTD

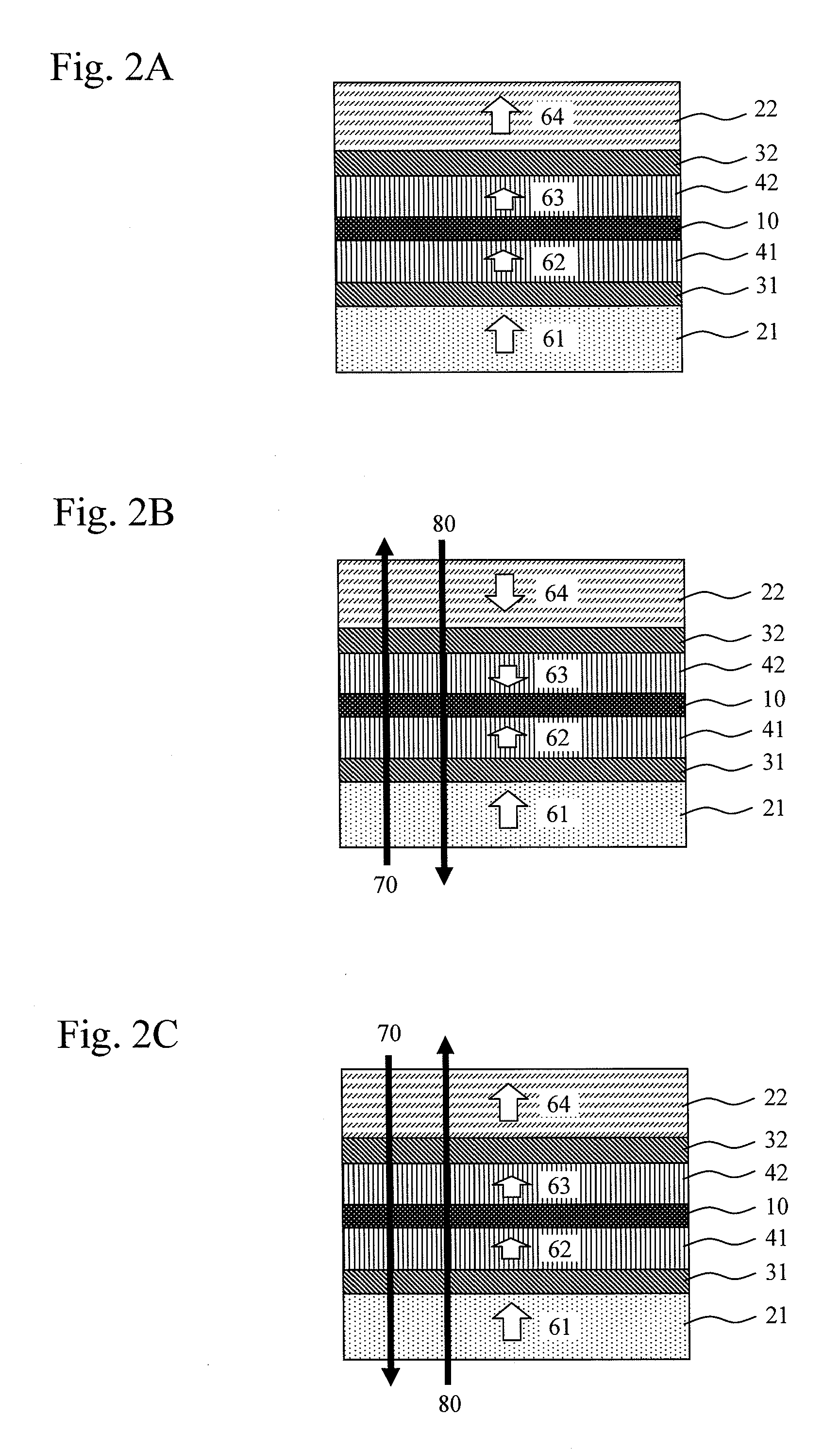

Magnetoresistive effect element, magnetic memory cell using same, and random access memory

ActiveUS20130028013A1Raise the ratioNanomagnetismMagnetic-field-controlled resistorsStatic random-access memoryRandom access memory

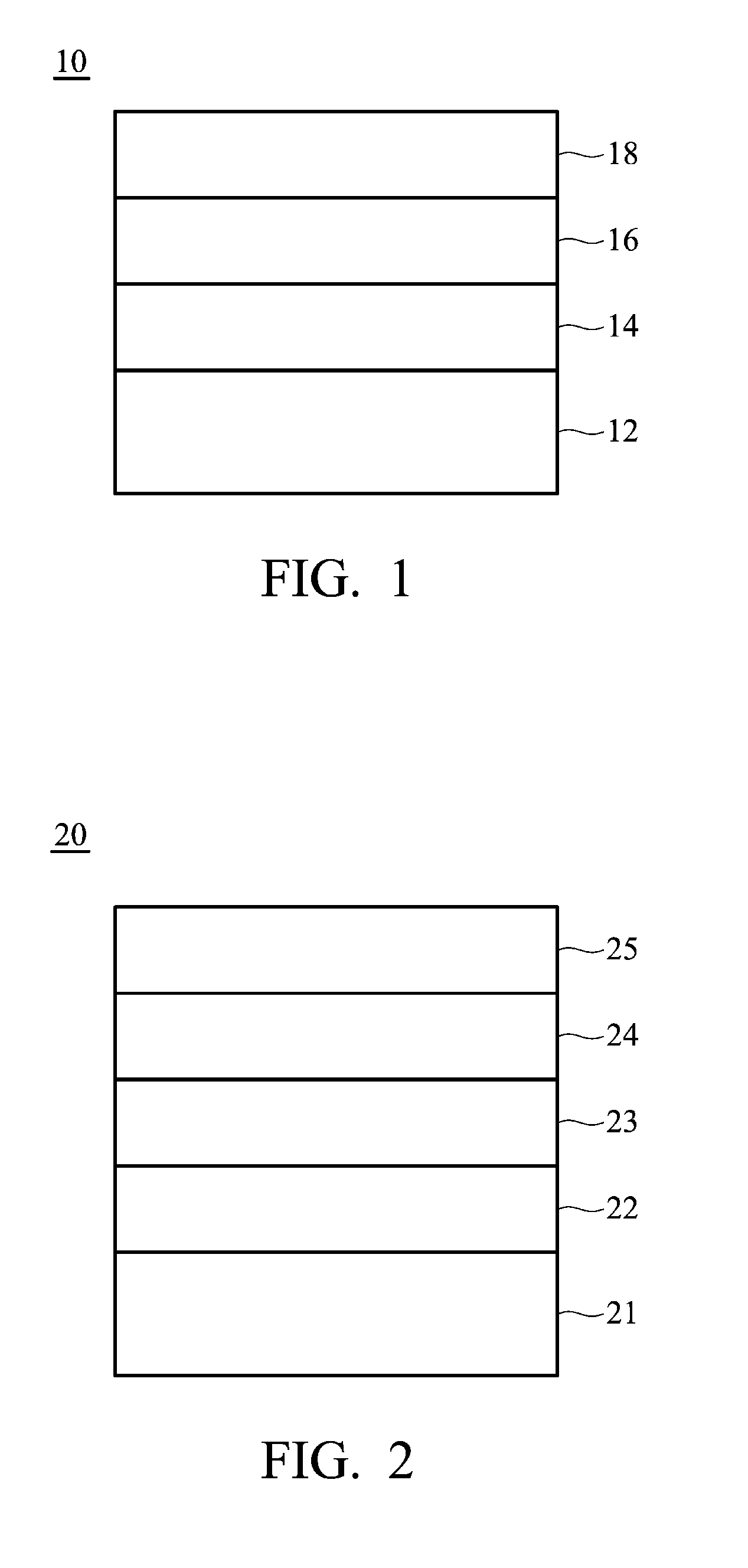

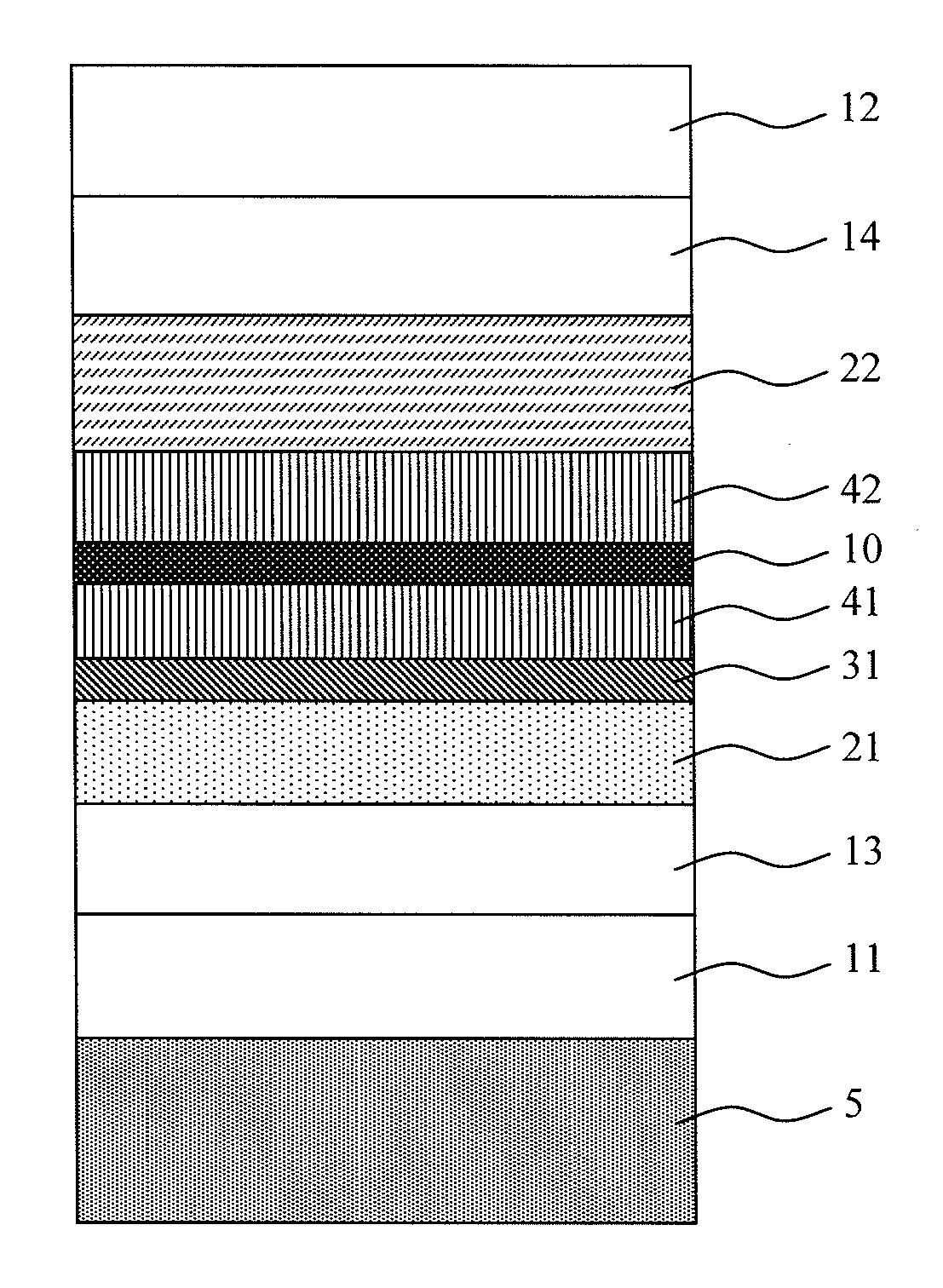

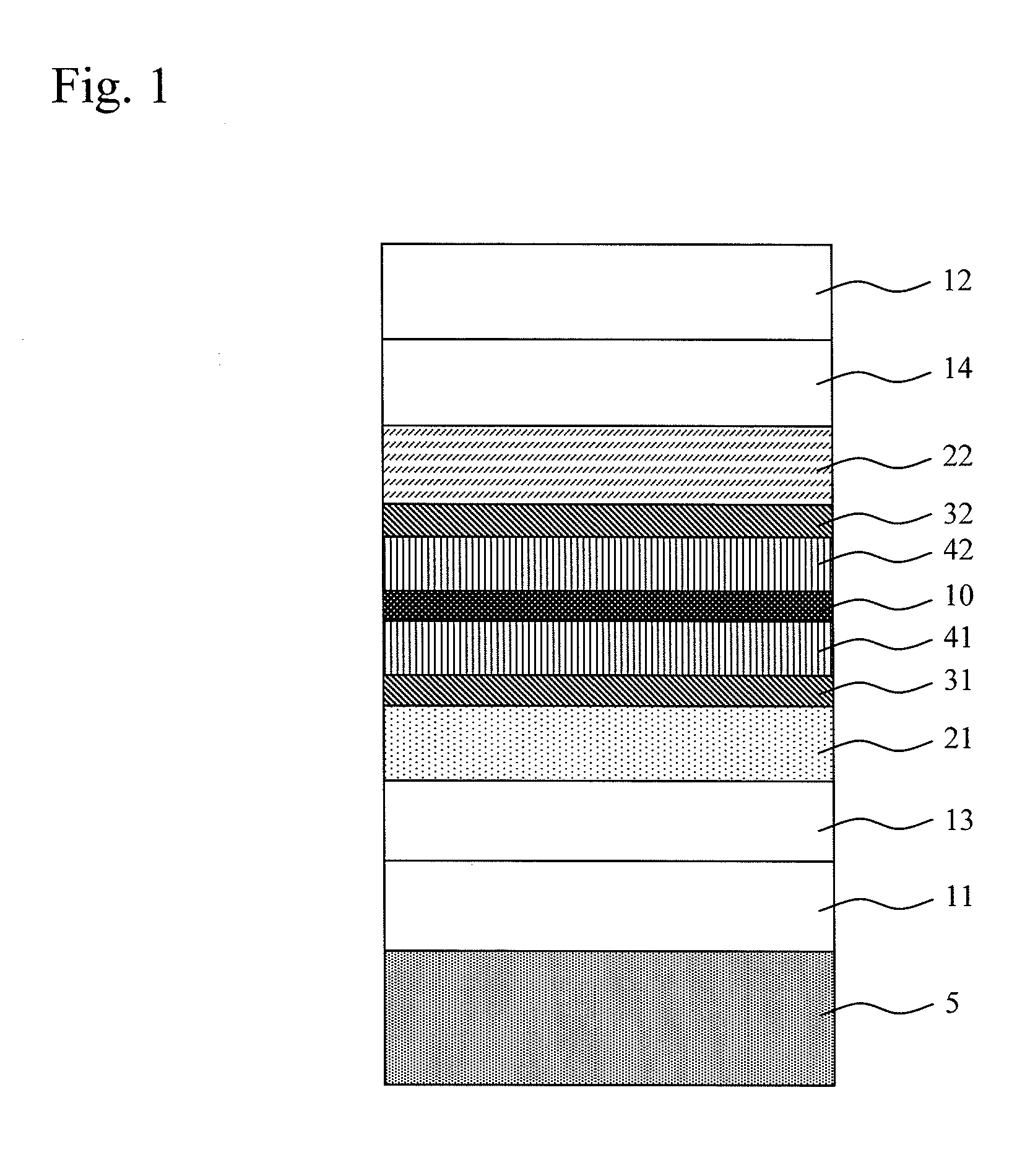

Provided is a magnetoresistive effect element which uses a perpendicularly magnetized material and has a high TMR ratio. Intermediate layers 31, 32 composed of an element metal having a melting point of 1600° C. or an alloy containing the metal on an outside of a structure consisting of a CoFeB layer 41, an MgO barrier layer 10, and a CoFeB layer 42. By inserting the intermediate layers 31, 32, crystallization of the CoFeB layer during annealing is advanced from an MgO (001) crystal side, so that the CoFeB layer has a crystalline orientation in bcc (001).

Owner:TOHOKU UNIV

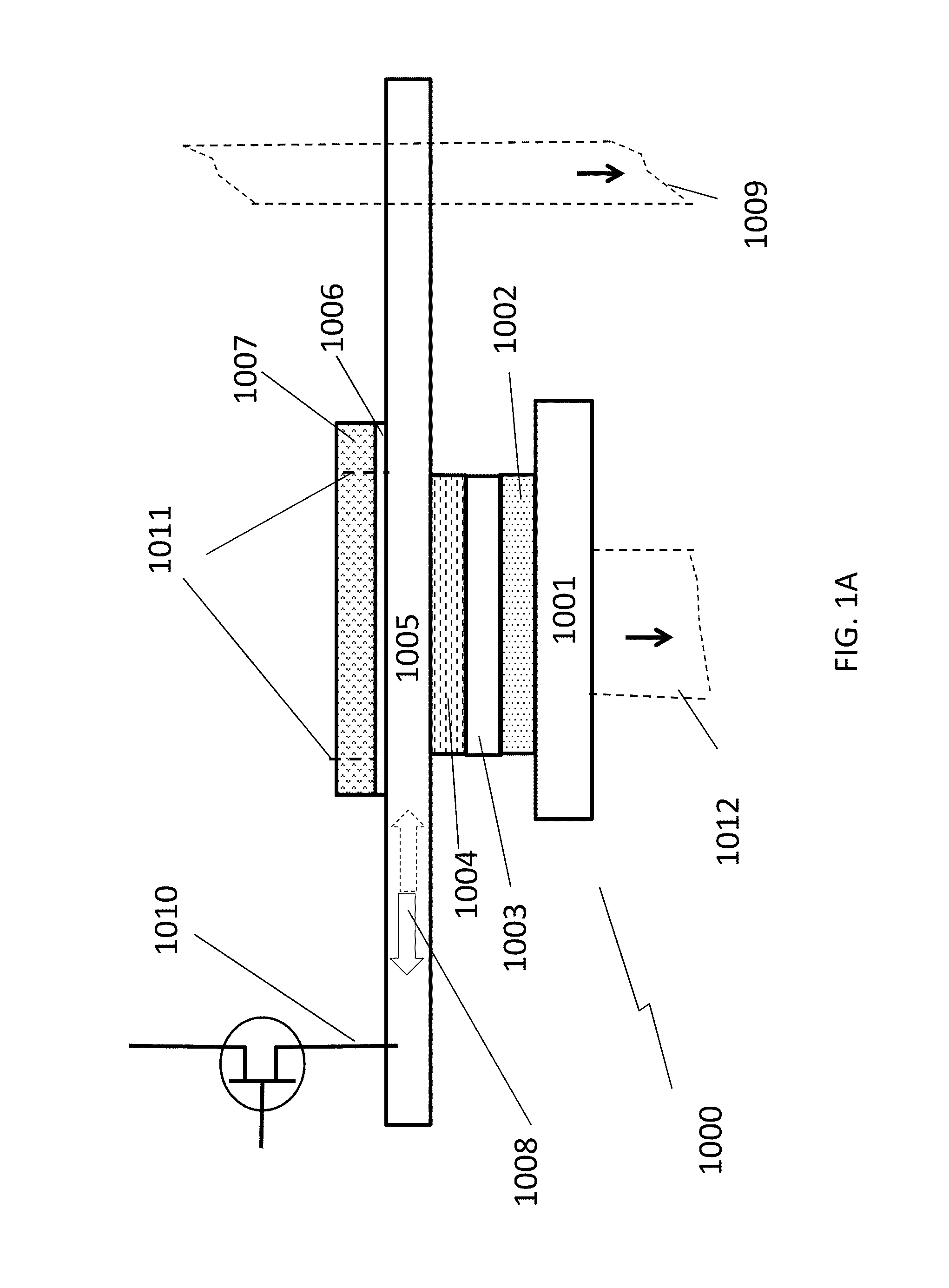

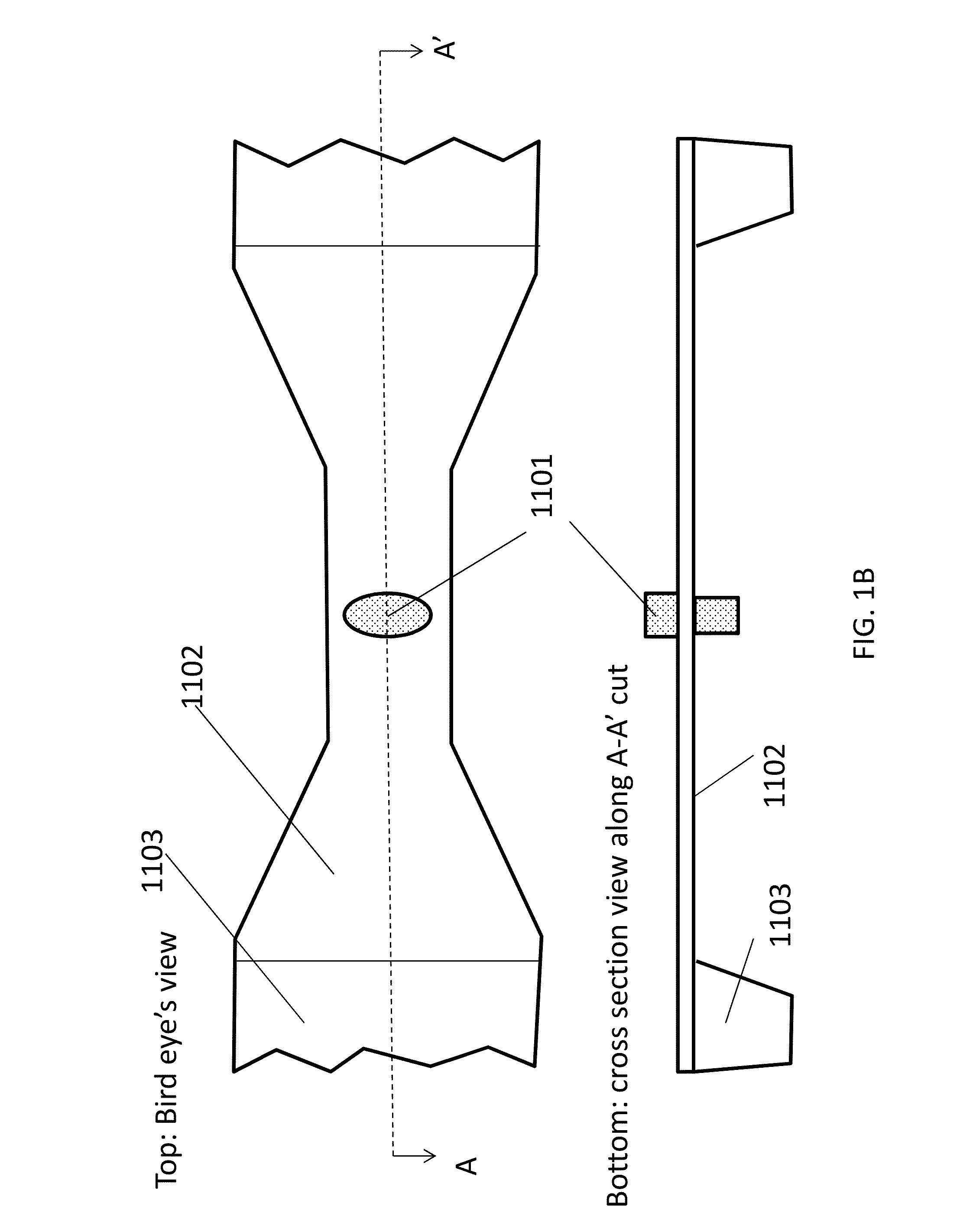

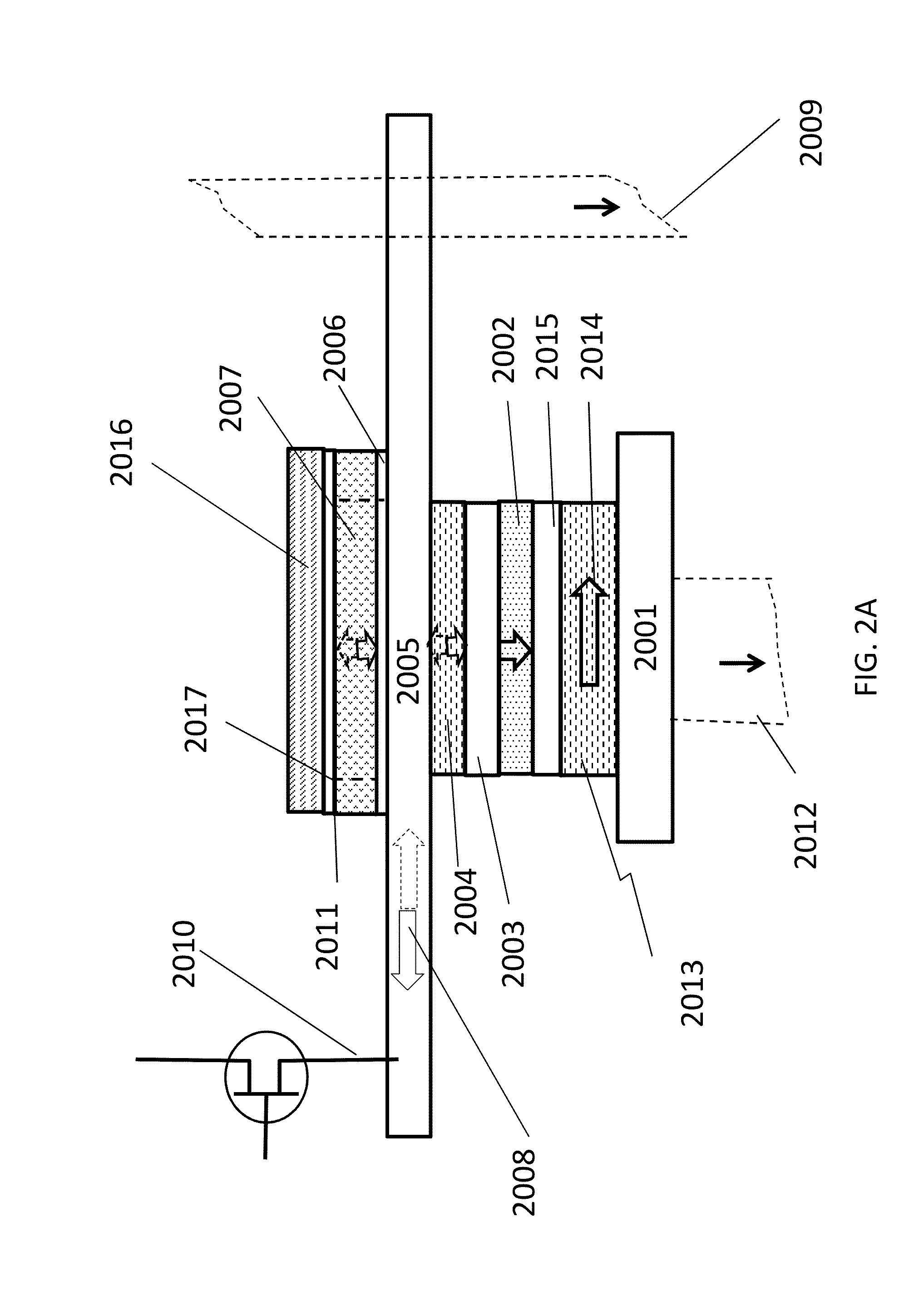

Magnetoresistive random access memory cell and 3D memory cell array

ActiveUS9218864B1Easy to implementImprove thermal stabilityDigital storageMagnetic stabilizationMagnetic reluctance

A novel three-terminal SOT-MRAM memory cell with a unique magnetic stabilization layer or structure is proposed. A complementary magnetic footprint of the data storage layer for the memory cell is able to be created within the magnetic stabilization layer or structure by the magnetic field from the storage layer to enhance the magnetic and thermal stability of the memory cell. Several designs for both perpendicular and in-plane SOT-MRAM memory cell have been invented. With proper wire connection and sensing arrangement, the proposed memory cell is capable of forming not only the 2D array but also 3D array.

Owner:GE YI +1

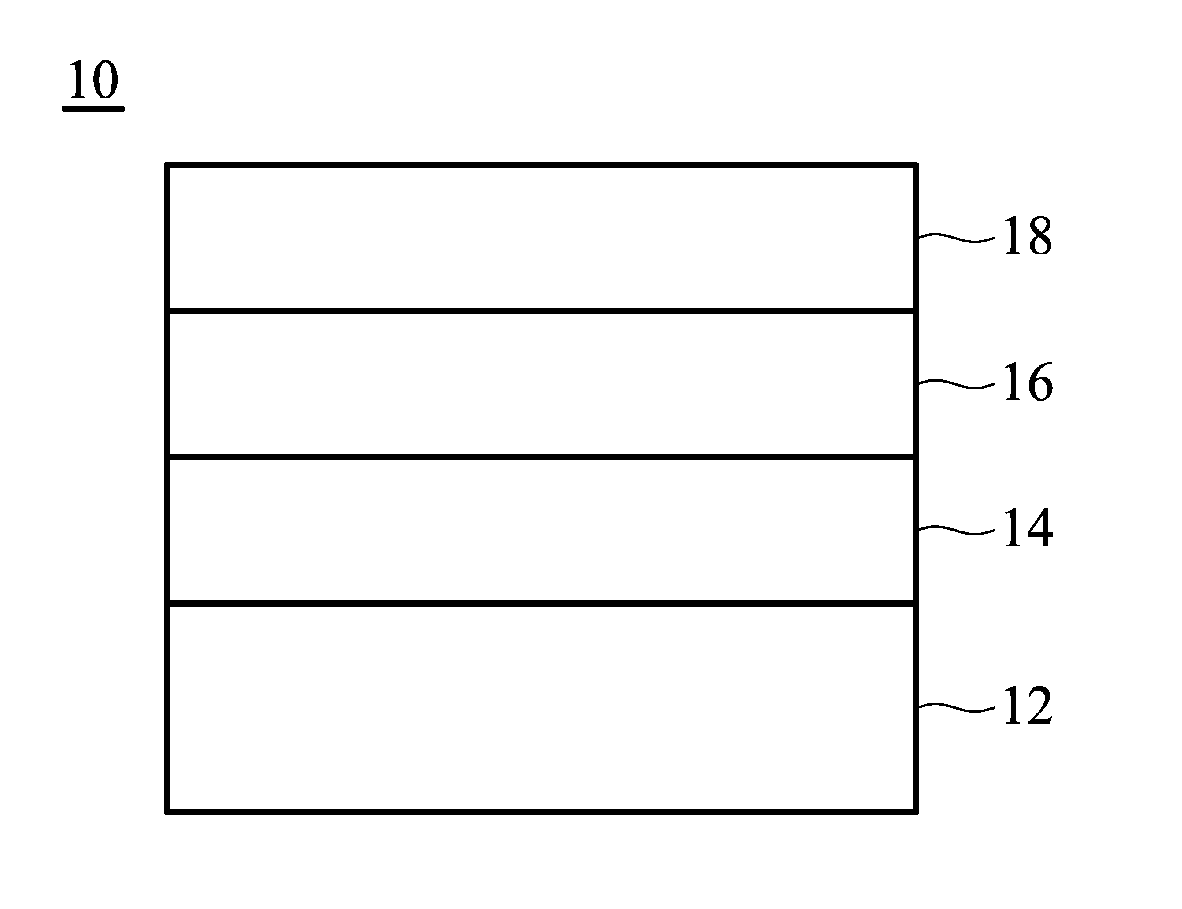

Resistive random access memory device

Provided is a resistive random access memory device that includes a storage node connected to a switching device. The resistive random access memory device includes a first electrode, a resistance variable layer, and a second electrode which are sequentially stacked, wherein a diffusion blocking layer is formed between the first electrode and the resistance variable layer or between the resistance variable layer or / and the second electrode.

Owner:SAMSUNG ELECTRONICS CO LTD

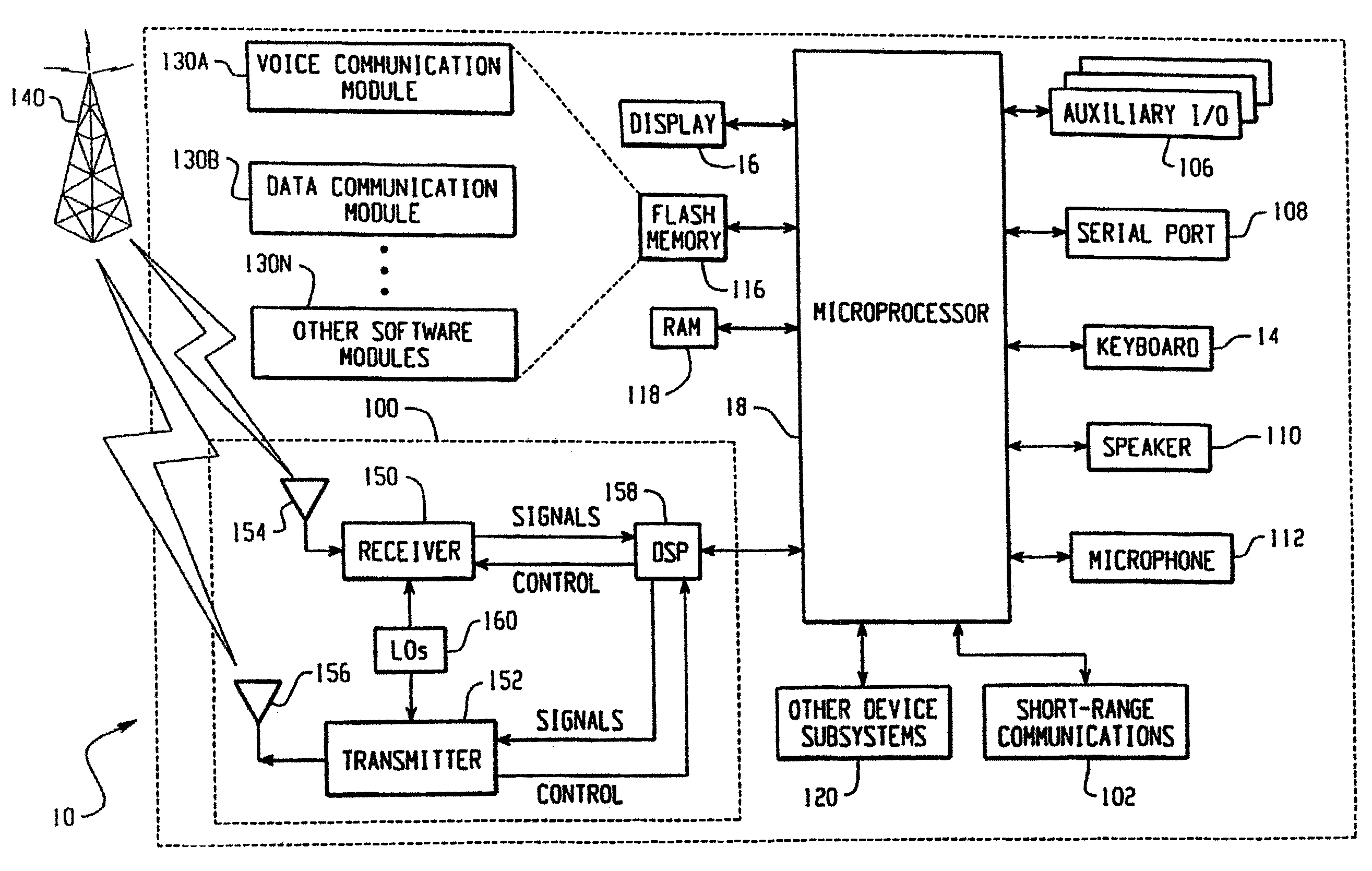

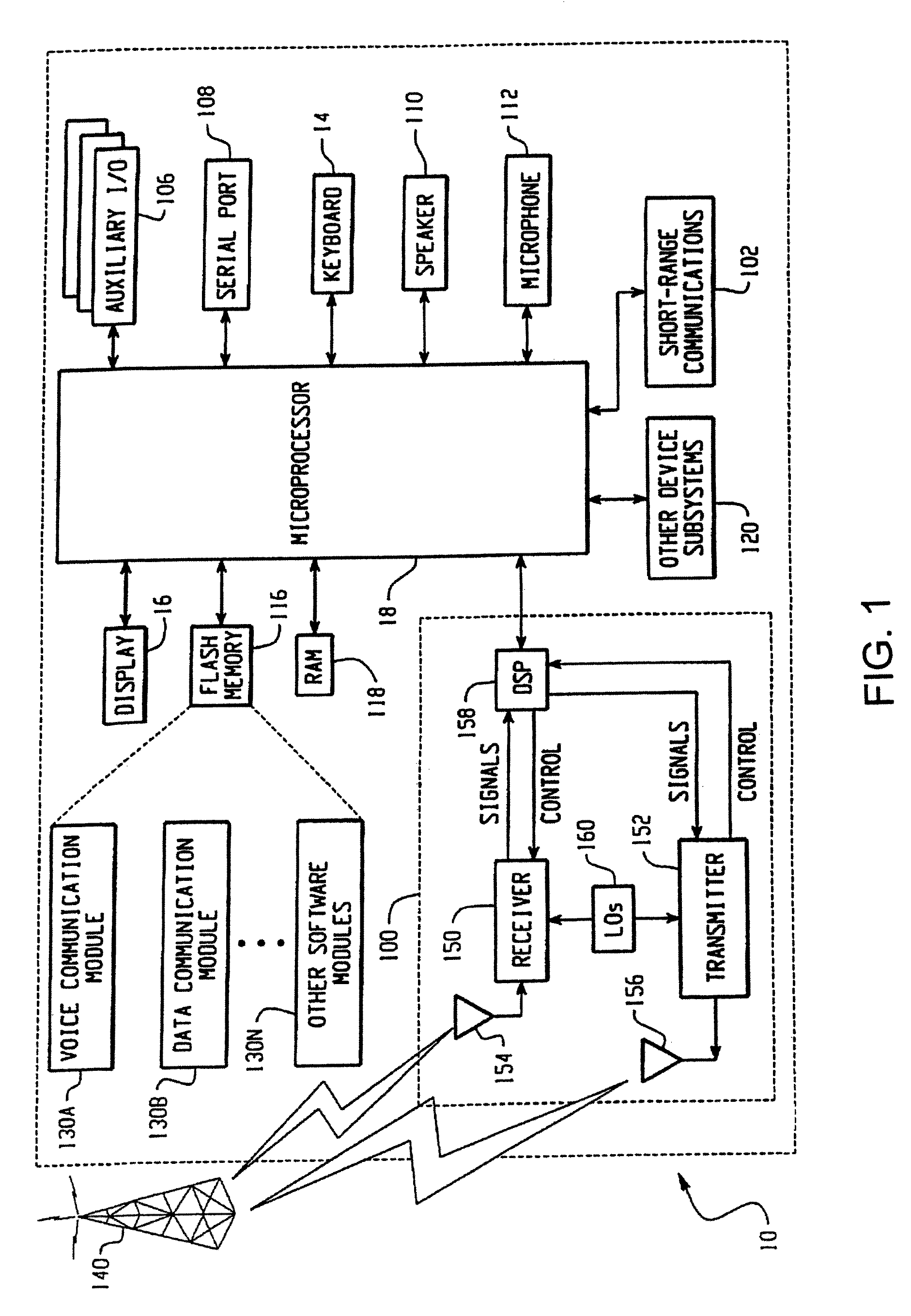

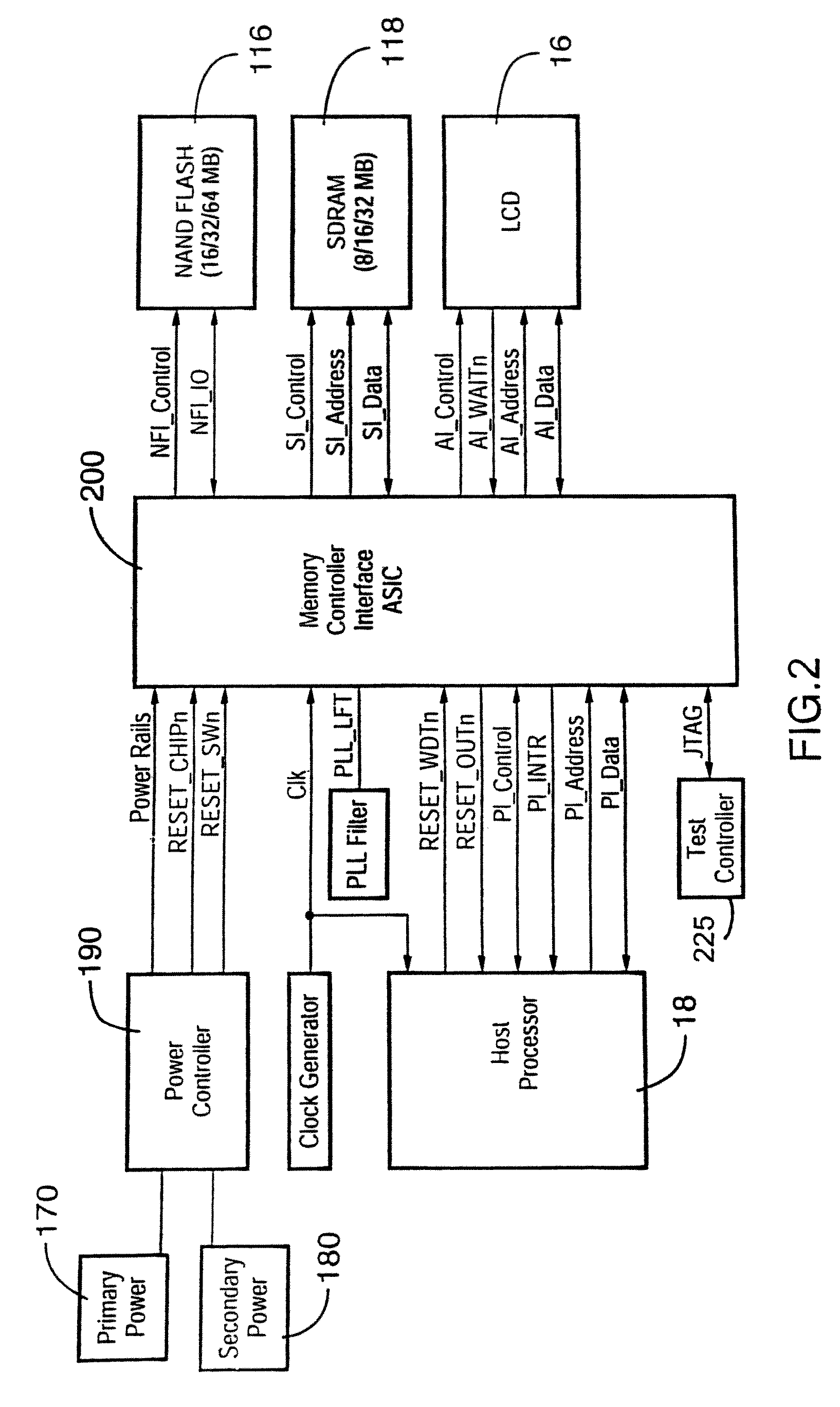

Memory controller interface

ActiveUS7610433B2Memory architecture accessing/allocationMemory loss protectionStatic random-access memoryMemory interface

A memory interface controller and method to allow a processor designed and configured to operate with NOR flash and static random access memory (SRAM) memory devices to instead operate using NAND flash and synchronous dynamic random access memory (SDRAM). The system accomplishes this by caching sectors out of NAND flash into SDRAM, where the data can be randomly accessed by the processor as though it were accessing data from NOR flash / SRAM. Sectors containing data required by the processor are read out of NAND flash and written into SDRAM, where the data can be randomly accessed by the processor.

Owner:MALIKIE INNOVATIONS LTD

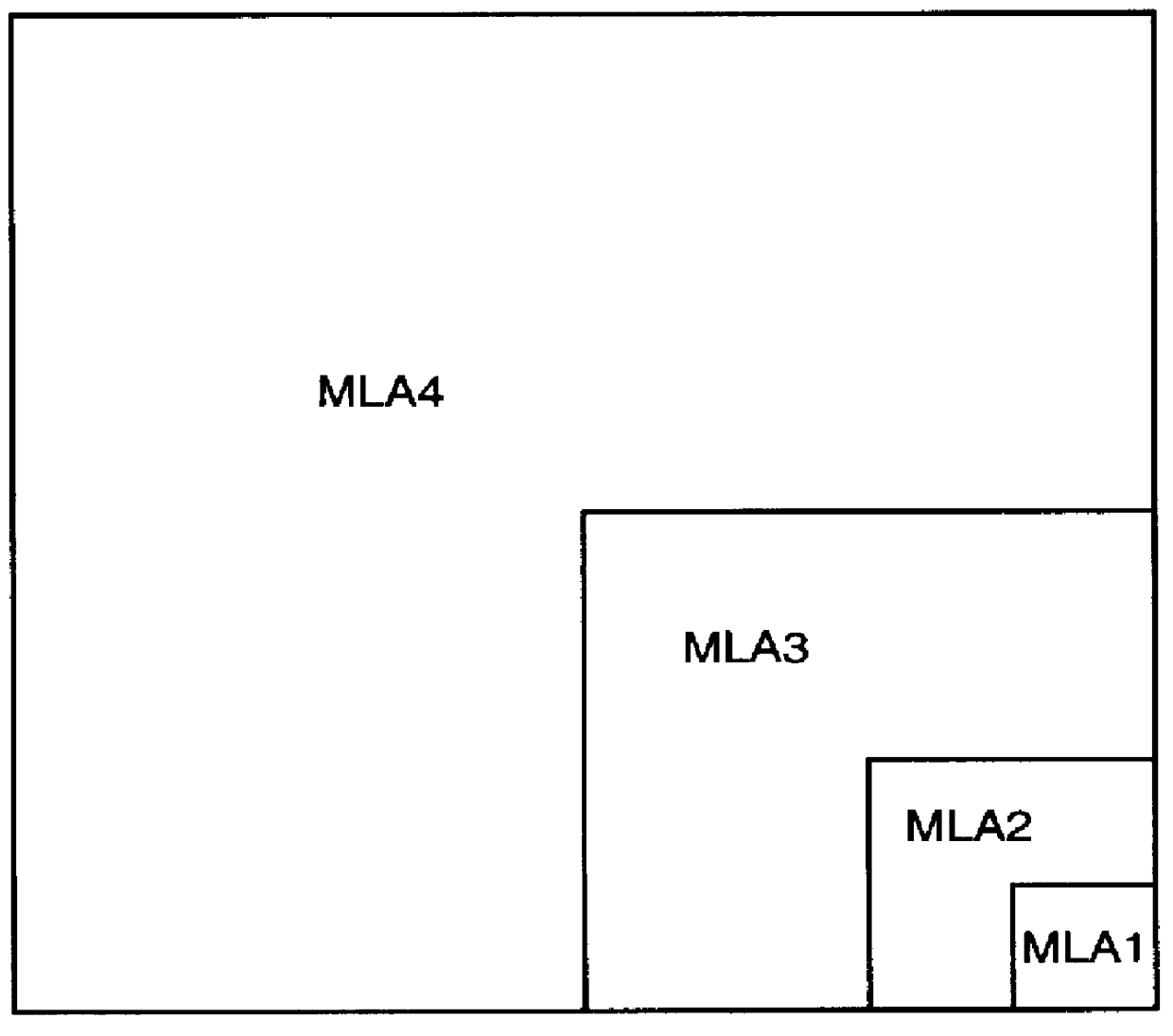

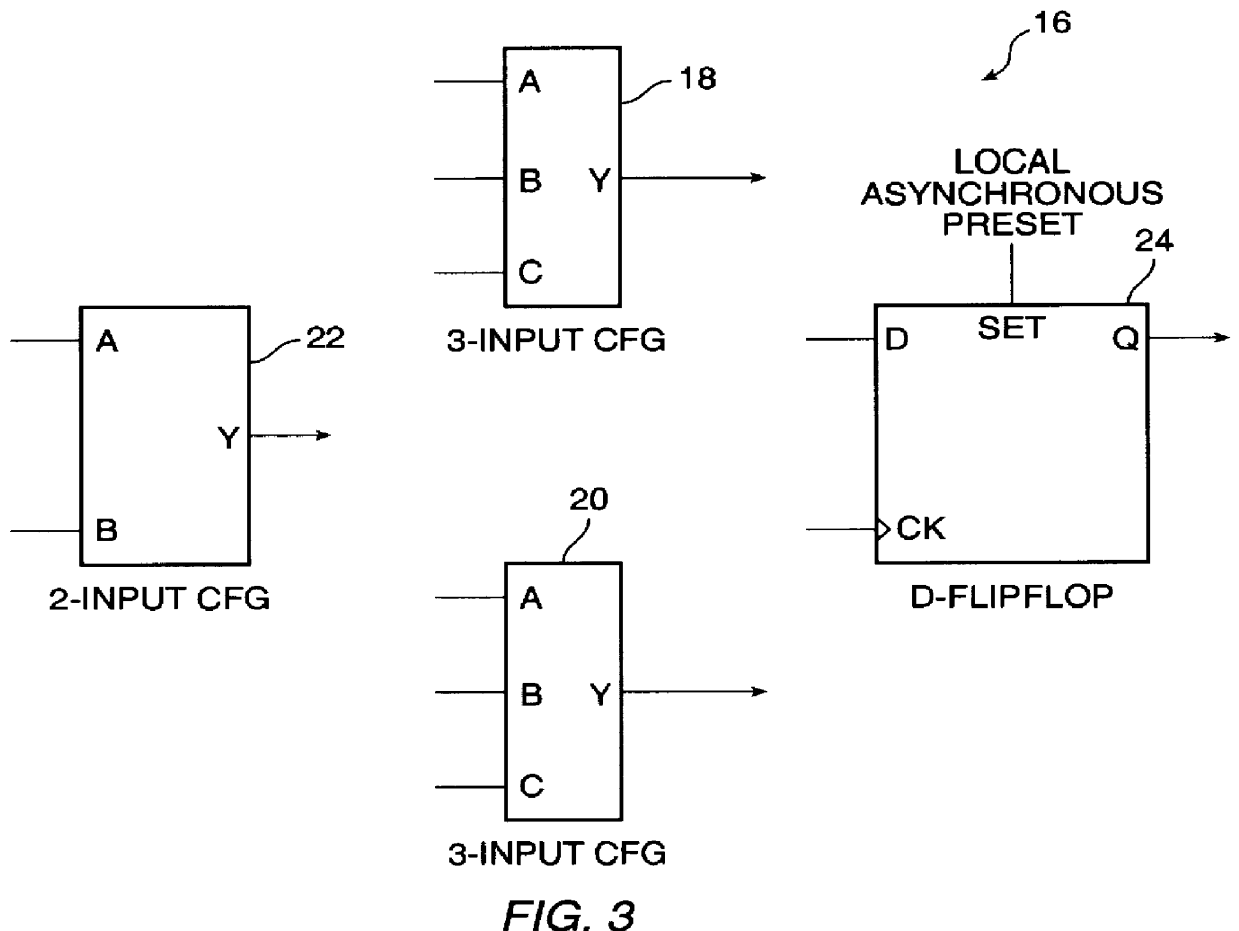

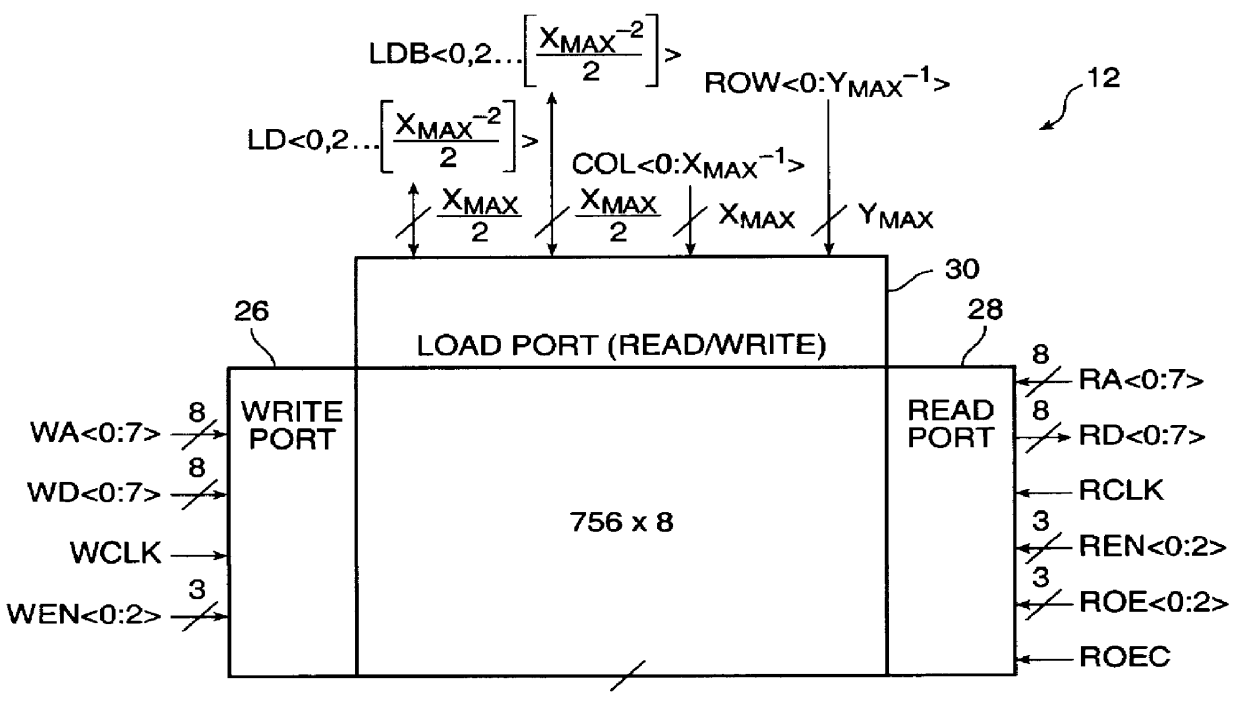

Embedded static random access memory for field programmable gate array

InactiveUS6049487AHigh impedance stateSolve conflictsDetecting faulty hardware by configuration testRead-only memoriesStatic random-access memoryRandom access memory

A dual ported (simultaneous read / write) SRAM block with an additional load port that interacts with the circuitry employed in the loading and testing of the configuration data of the FPGA core is disclosed. Each SRAM block contains circuits in both the read port and the write port that permit the SRAM blocks to be connected into deeper and wider configurations by without any additional logic as required by the prior art. An address collision detector is provided such that when both read and write ports in the SRAM block access the same address simultaneously a choice between the data being read can be made between the data presently in the SRAM block or the new data being written to the SRAM block.

Owner:MICROSEMI SOC

Resistance random access memory

The present invention provides a resistance random access memory structure, including a plurality of word lines in a substrate, a plurality of reset lines coupled to the word lines, a dielectric layer on the substrate, a plurality of memory units in the dielectric layer. Each of the memory units includes a bottom electrode, a top electrode and a resistive thin film between the top electrode and the bottom electrode. The top electrodes of the memory units in a same column e coupled to one of the reset lines and a plurality of the bit lines on the memory units. The bottom electrodes of the memory units in a same row are coupled to one of the bit lines. Because the present invention provides reset lines for Type 1R1D RRAM, it can overcome the non-erasable of the conventional Type 1R1D RRAM.

Owner:WINBOND ELECTRONICS CORP

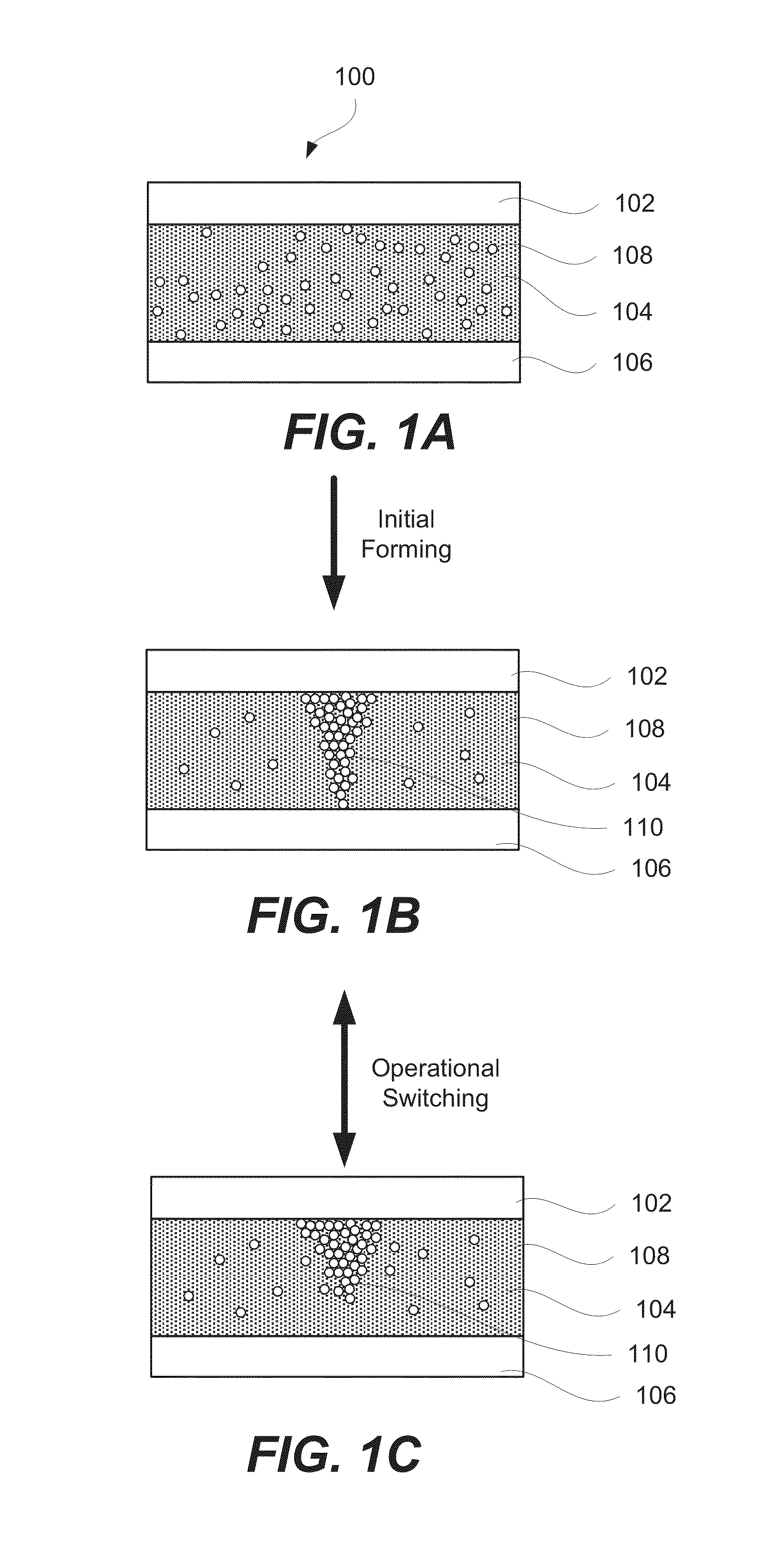

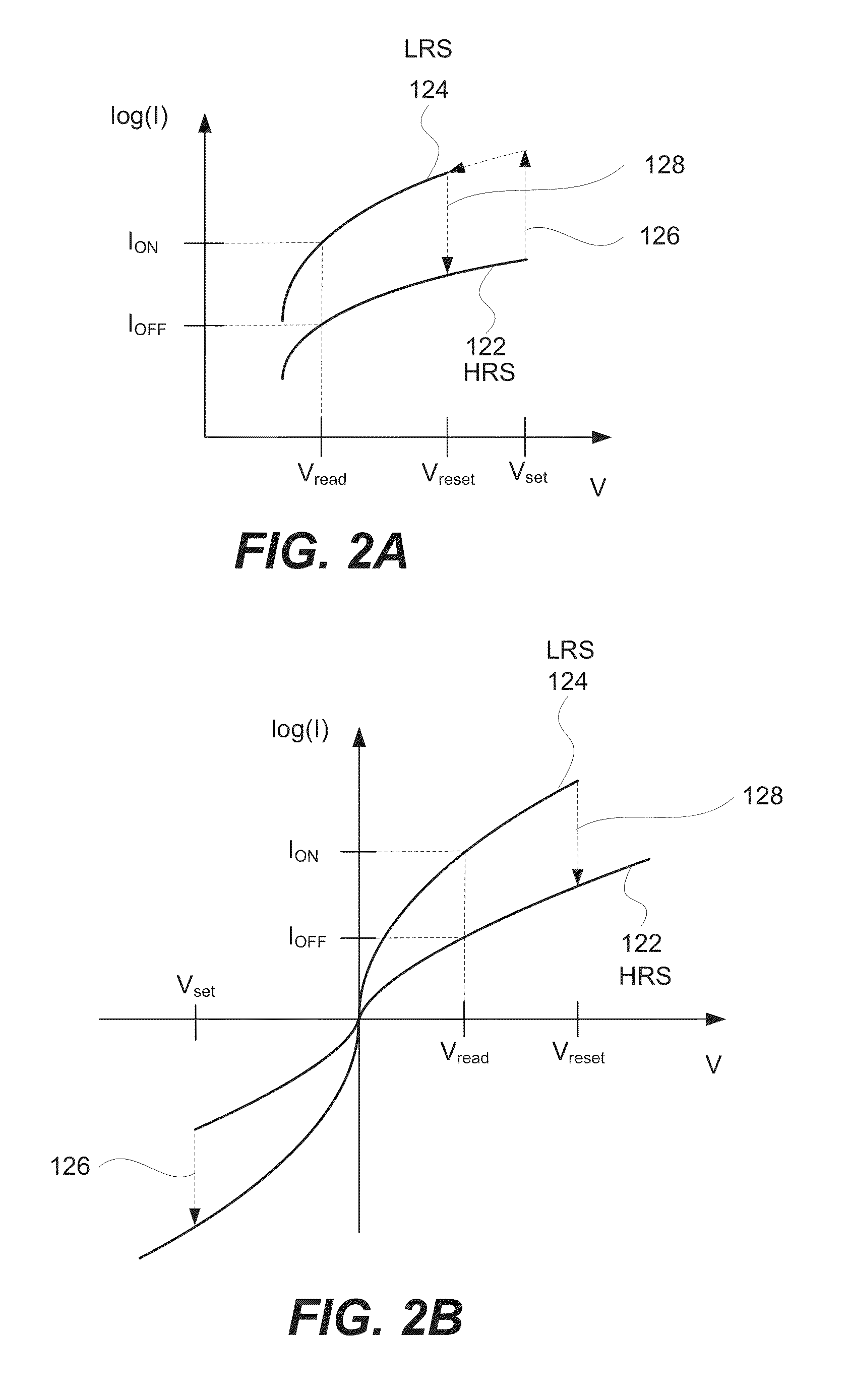

Conductive path in switching material in a resistive random access memory device and control

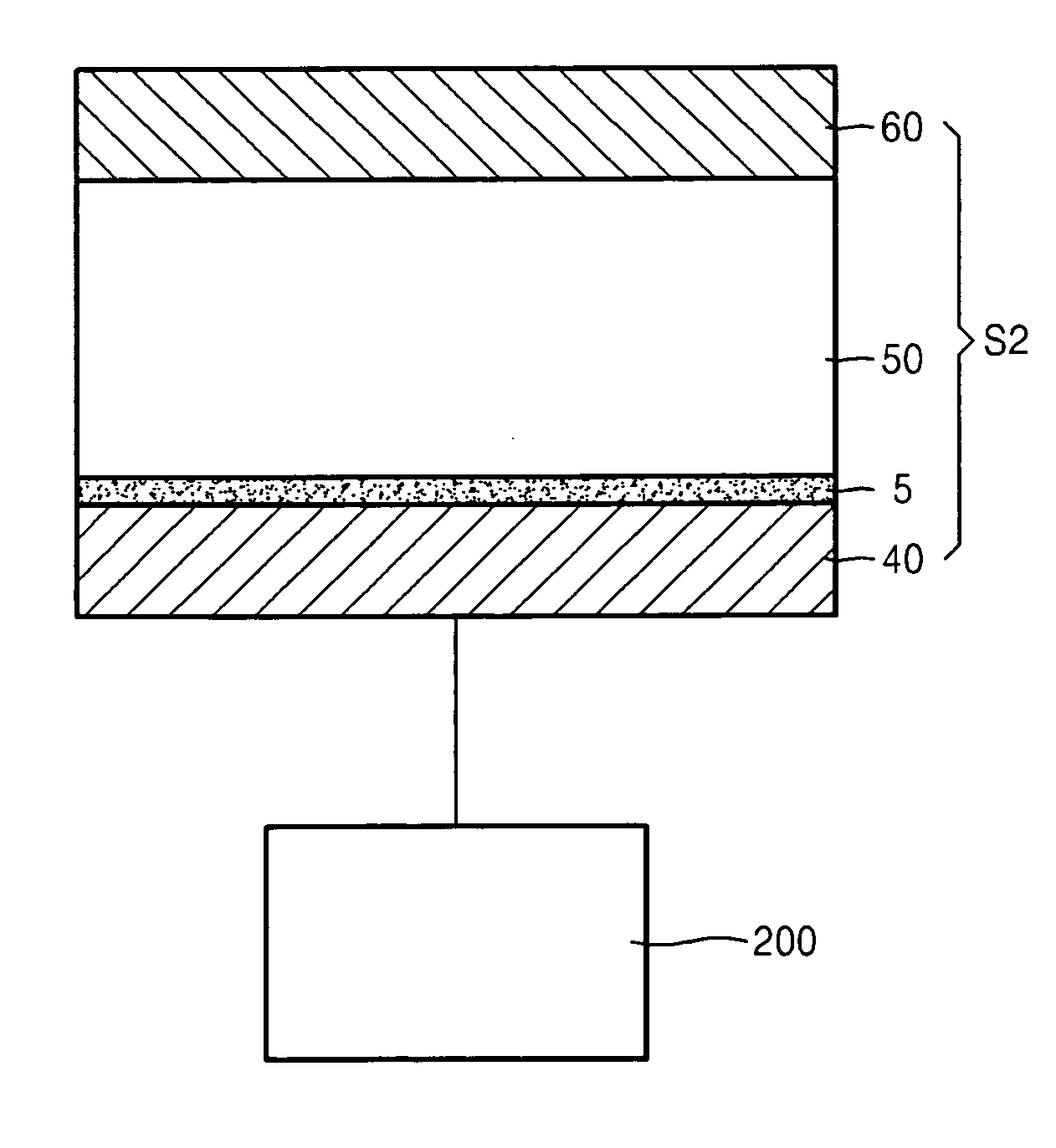

ActiveUS20120074374A1Low forming voltageReduce leakage currentSemiconductor/solid-state device manufacturingBulk negative resistance effect devicesAmorphous siliconResistive switching

A non-volatile memory device structure. The device structure includes a first electrode, a second electrode, a resistive switching material comprising an amorphous silicon material overlying the first electrode, and a thickness of dielectric material having a thickness ranging from 5 nm to 10 nm disposed between the second electrode and the resistive switching layer. The thickness of dielectric material is configured to electrically breakdown in a region upon application of an electroforming voltage to the second electrode. The electrical breakdown allows for a metal region having a dimension of less than about 10 nm by 10 nm to form in a portion of the resistive switching material.

Owner:INNOSTAR SEMICON SHANGHAI CO LTD

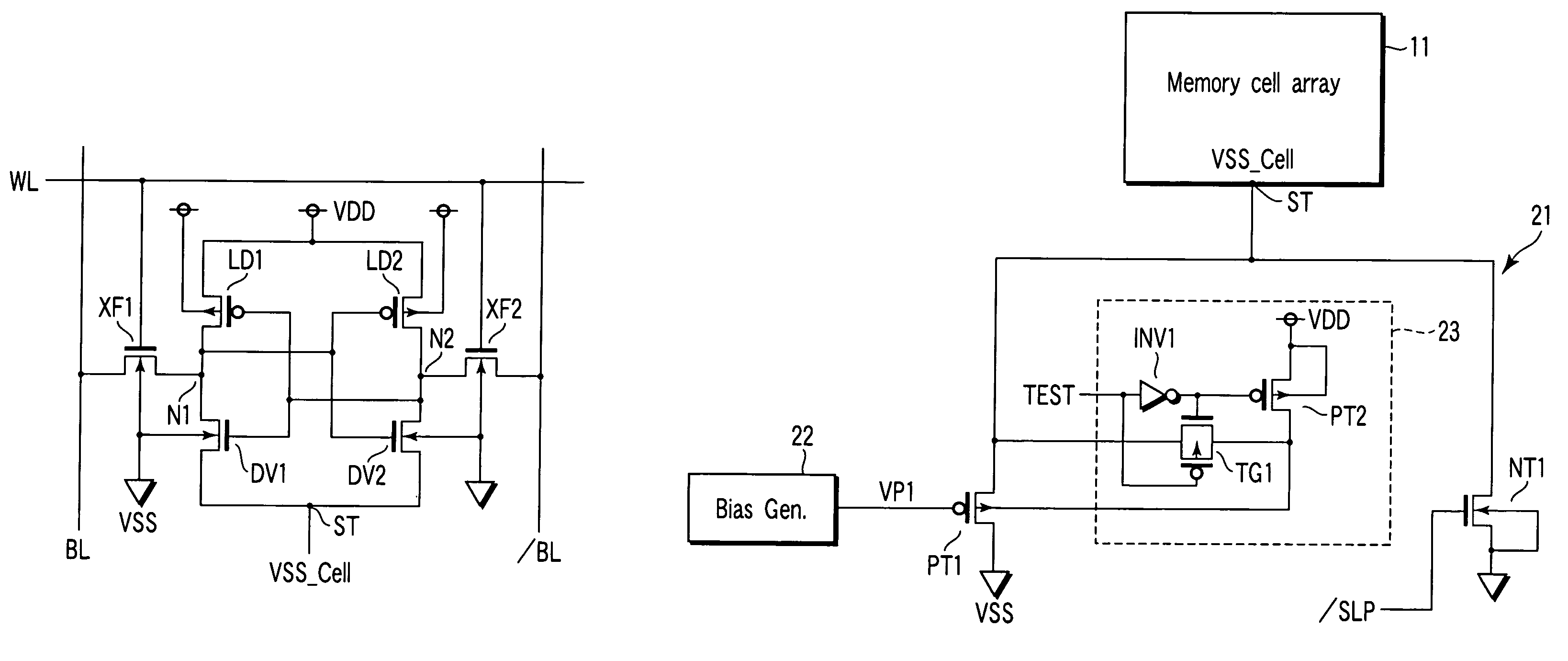

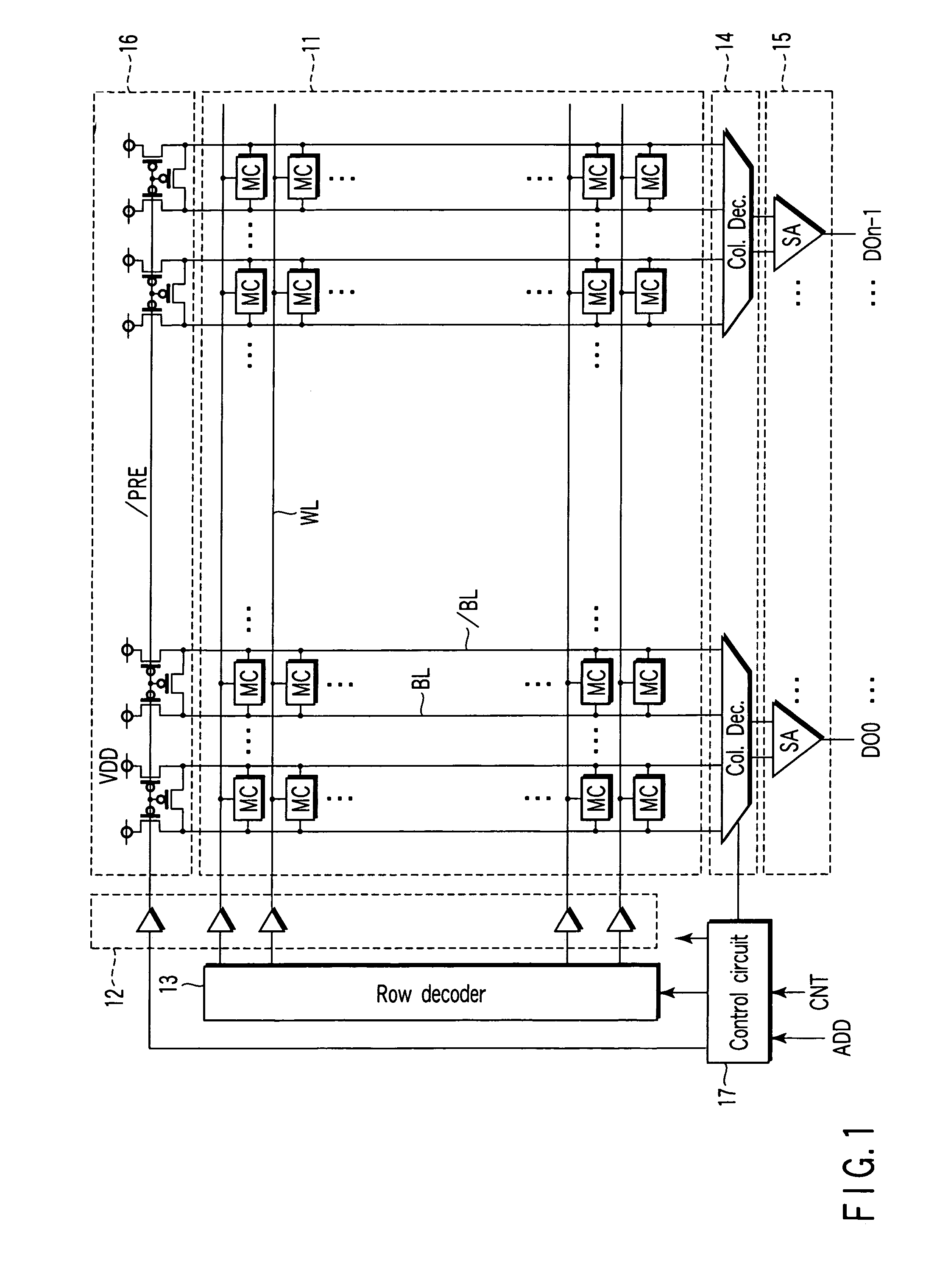

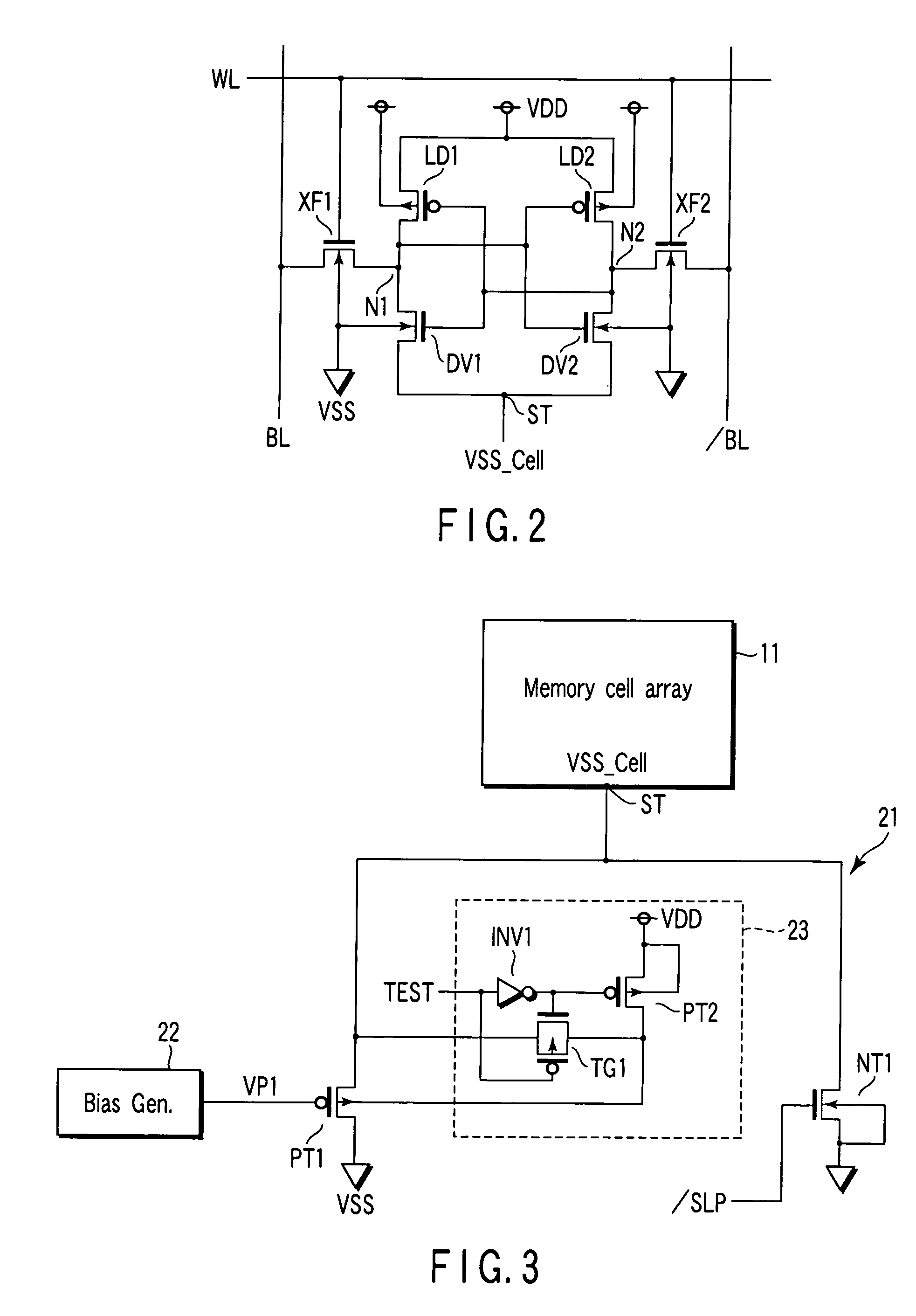

Static random access memory (SRAM) with clamped source potential in standby mode

A semiconductor memory device includes a memory cell array including a plurality of memory cells, a source terminal which supplies a source potential to the memory cells, a first switching element which electrically connects the source terminal and a first power supply potential in an operation mode of the memory cells, and electrically disconnects the source terminal and the first power supply potential in a standby mode of the memory cells, a clamp MIS transistor which is series-connected between the source terminal and the first power supply potential, and clamps the source potential in the standby mode, a bias generation circuit which supplies a first bias potential to a gate terminal of the clamp MIS transistor, and a switching circuit which switches a potential of a back gate terminal of the clamp MIS transistor between a test mode and a non-test mode.

Owner:KK TOSHIBA

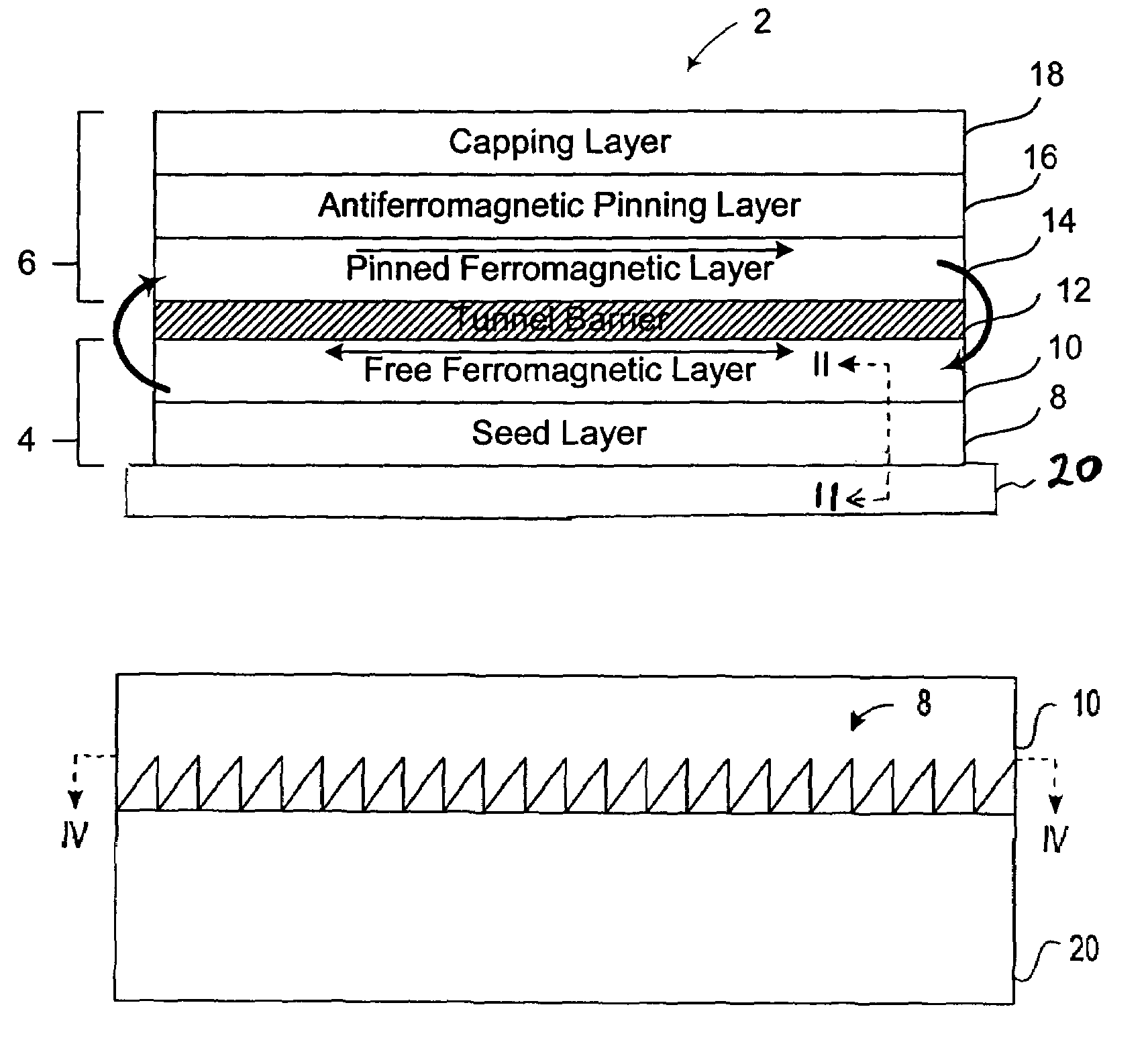

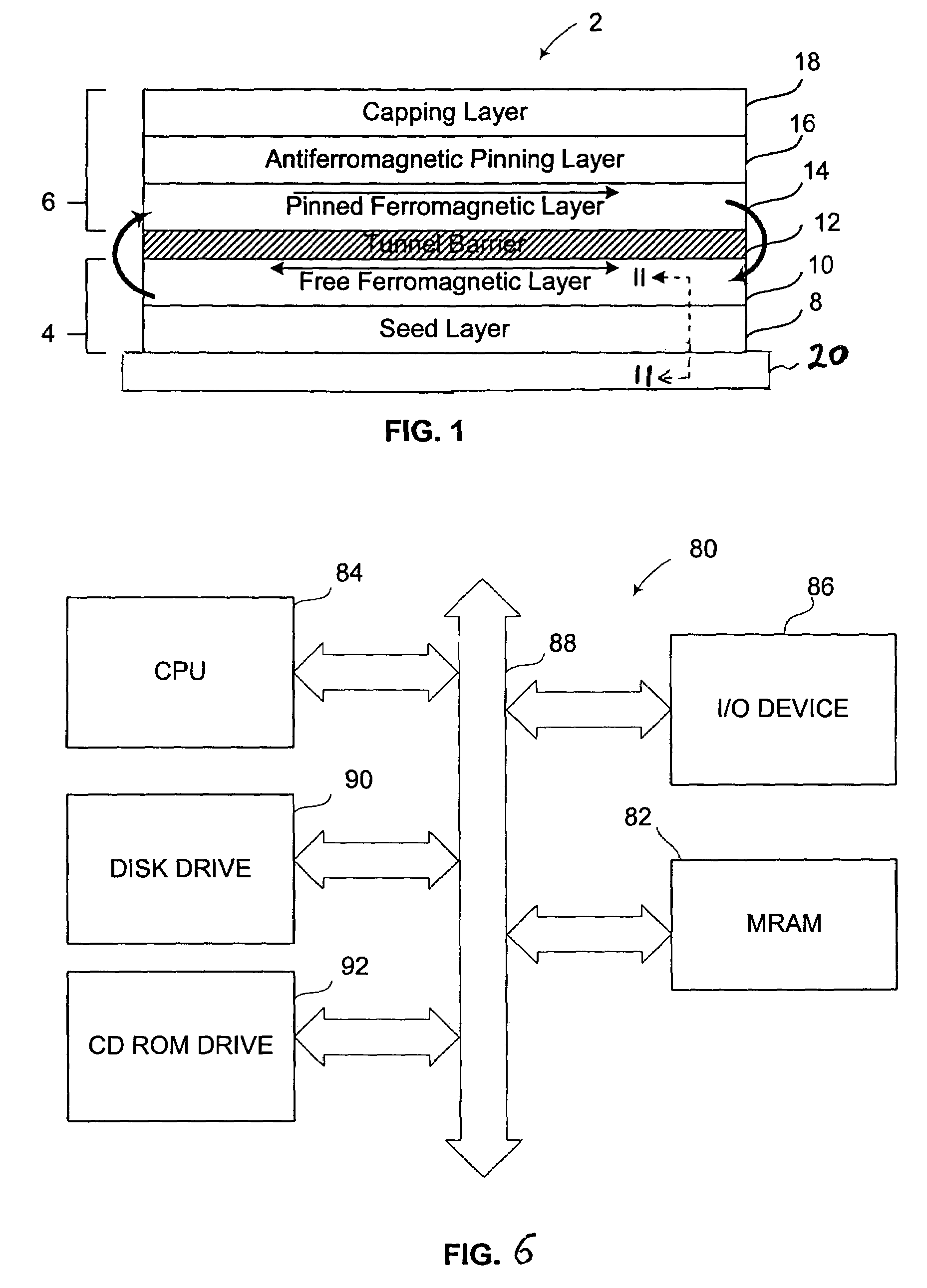

Method for production of MRAM elements

InactiveUS7189583B2Easy to repeatMagnetic-field-controlled resistorsSolid-state devicesLong axisMagnetic reluctance

Magneto-resistive random access memory elements include a ferromagnetic layer having uniaxial anisotropy provided by elongate structures formed in the ferromagnetic film. The magnetic dipole aligns with the long axis of each structure. The structures can be formed in a variety of ways. For example, the ferromagnetic film can be applied to a seed layer having a textured surface. Alternatively, the ferromagnetic film can be stressed to generate the textured structure. Chemical mechanical polishing also can be used to generated the structures.

Owner:MICRON TECH INC

Variable write and read methods for resistive random access memory

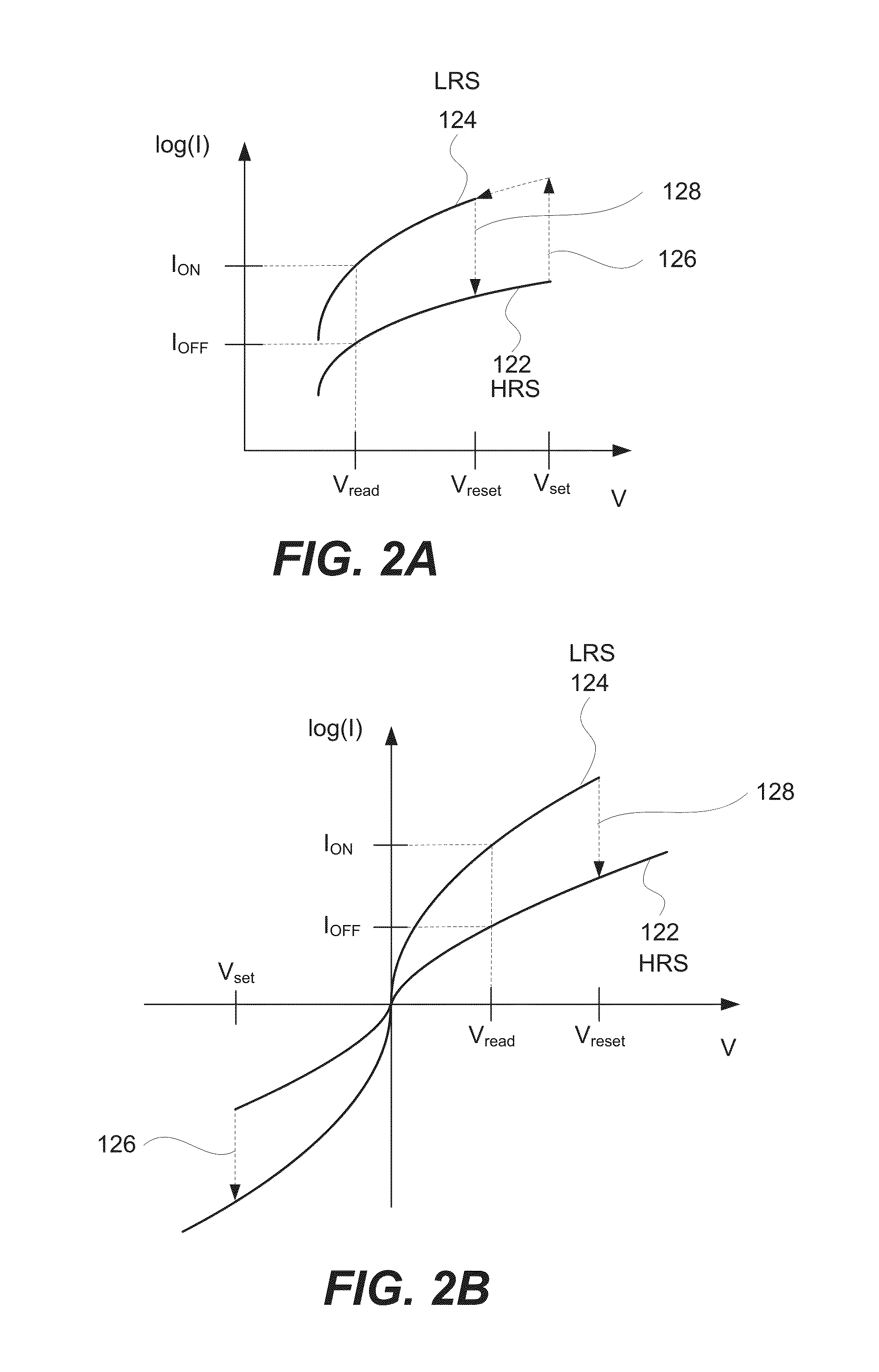

ActiveUS20100067281A1Enhance writabilityImprove readabilityDigital storageStatic random-access memoryRandom access memory

Variable write and read methods for resistance random access memory (RRAM) are disclosed. The methods include initializing a write sequence and verifying the resistance state of the RRAM cell. If a write pulse is needed, then two or more write pulses are applied through the RRAM cell to write the desired data state to the RRAM cell. Each subsequent write pulse has substantially the same or greater write pulse duration. Subsequent write pulses are applied to the RRAM cell until the RRAM cell is in the desired data state or until a predetermined number of write pulses have been applied to the RRAM cell. A read method is also disclosed where subsequent read pulses are applied through the RRAM cell until the read is successful or until a predetermined number of read pulses have been applied to the RRAM cell.

Owner:EVERSPIN TECHNOLOGIES

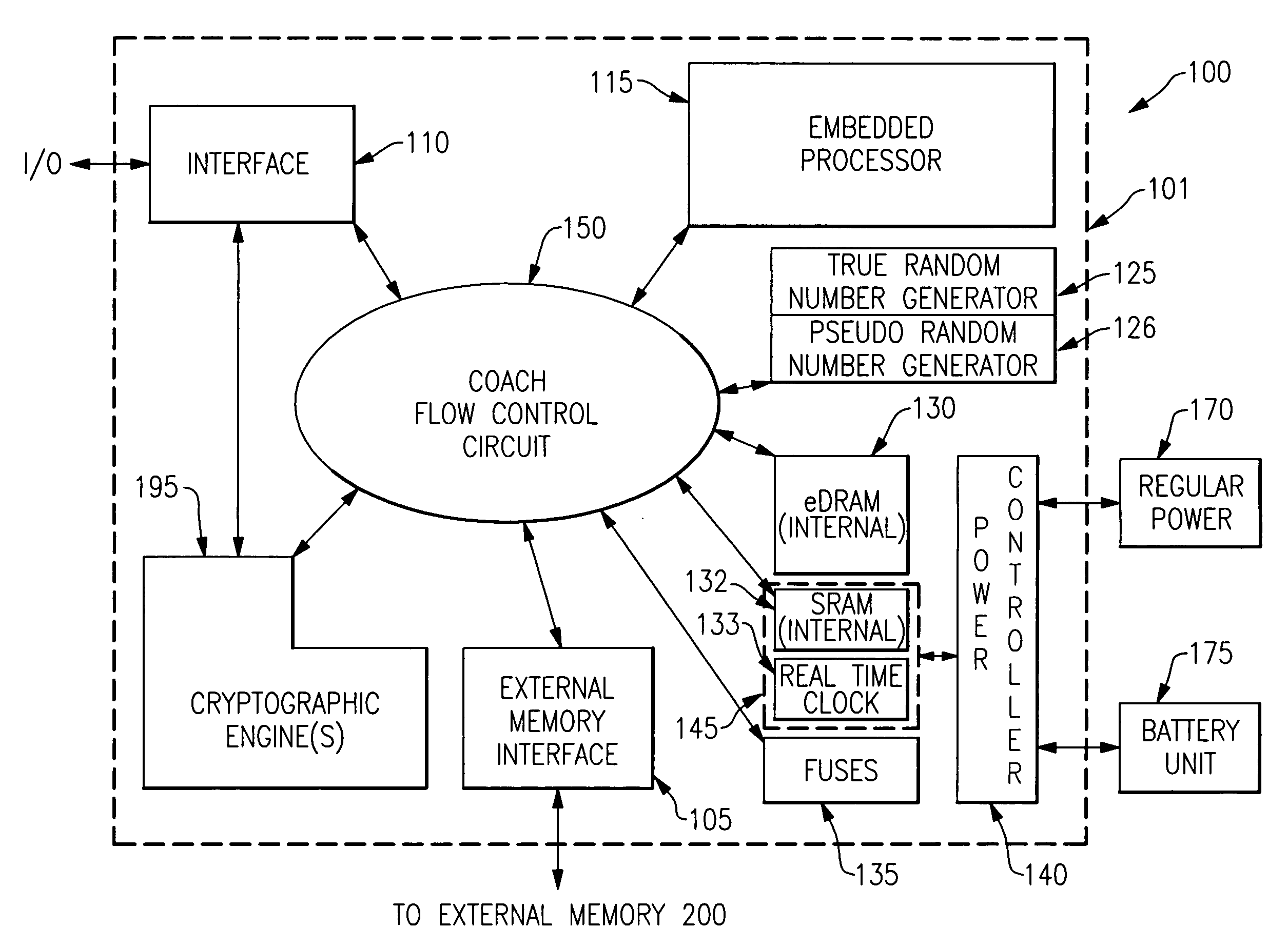

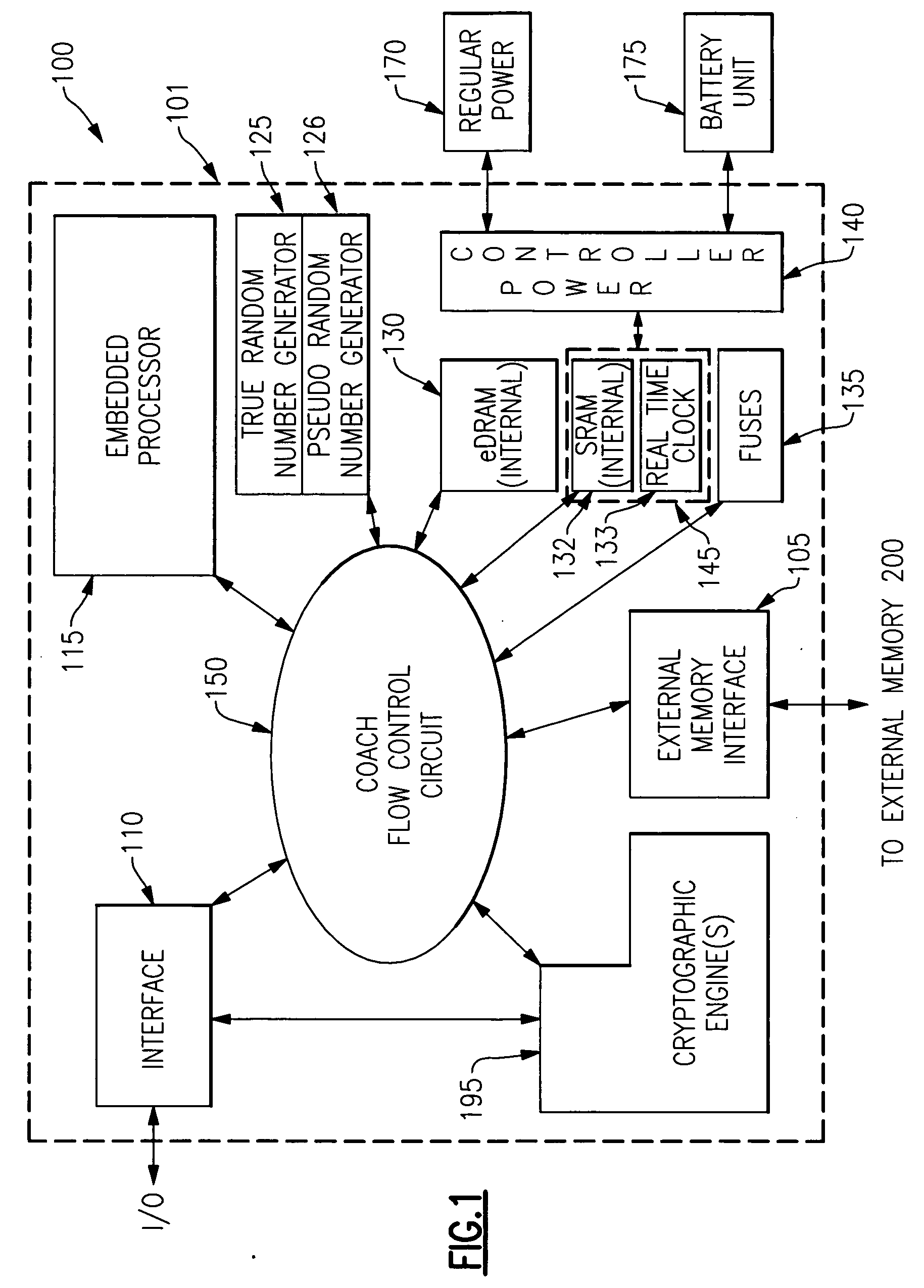

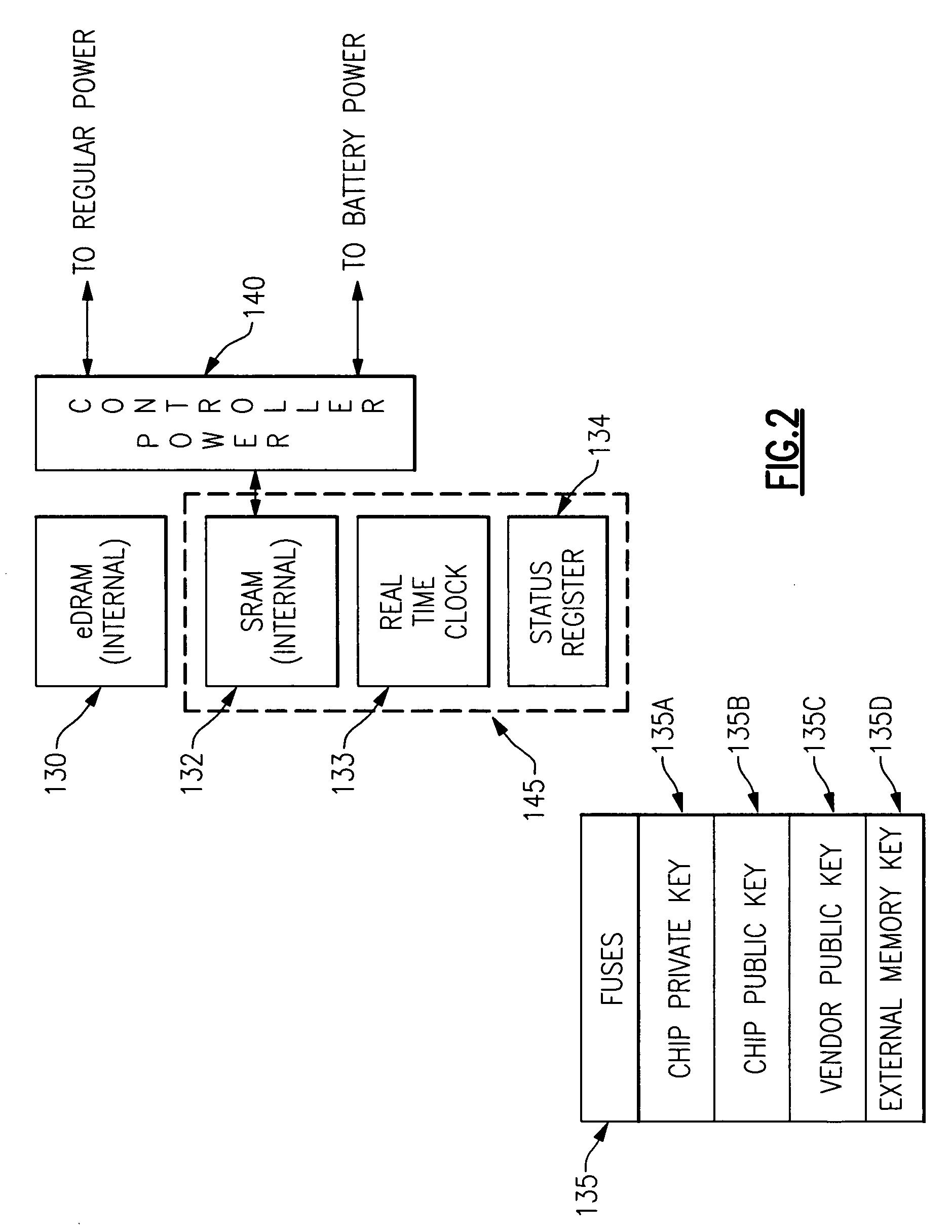

Circuit chip for cryptographic processing having a secure interface to an external memory

InactiveUS20060059369A1Improve process capabilityInhibit involvementUser identity/authority verificationUnauthorized memory use protectionInternal memoryStatic random-access memory

A mechanism is provided in which a secure chip for performing cryptographic and / or other functions is able to securely access a separate random access memory externally disposed with respect to a secure chip boundary. Addressing of the external memory is controlled so as to define certain regions therein which receive and store only encrypted information from the chip. Other regions of the external memory are set aside for the receipt and storage of unencrypted information. Access to the external memory is provided through a controlled interface which communicates with internal chip hardware which operates to control the flow of communication between various internal components such as cryptographic engines, data processors, internal memory of both the volatile and the nonvolatile variety and an external interface which provides the only other access to the chip. The internal chip hardware with which the external memory interface communicates is implemented as a combined ASIC and programmable hardware circuit, wherein the programmable hardware circuit is also securely configurable.

Owner:IBM CORP

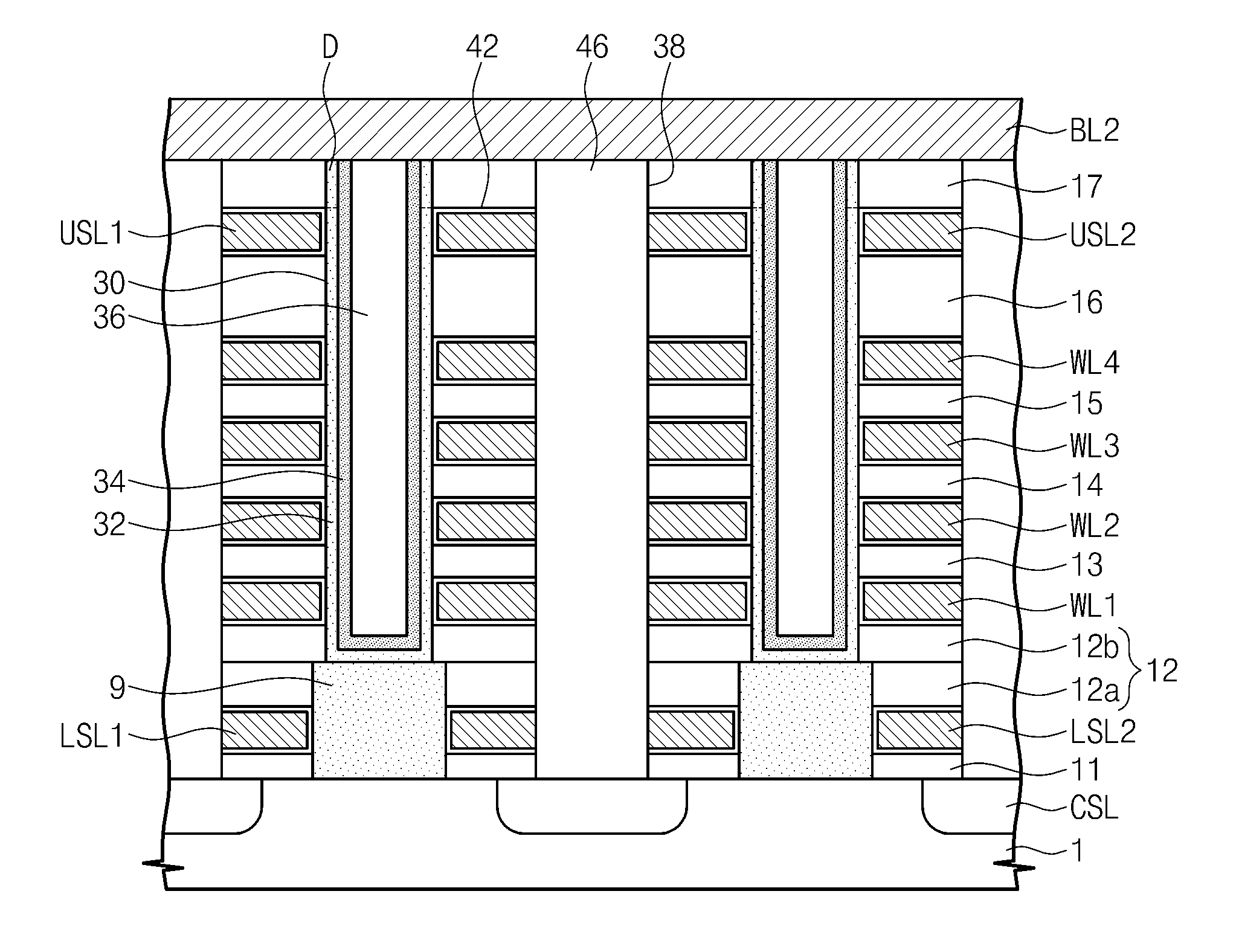

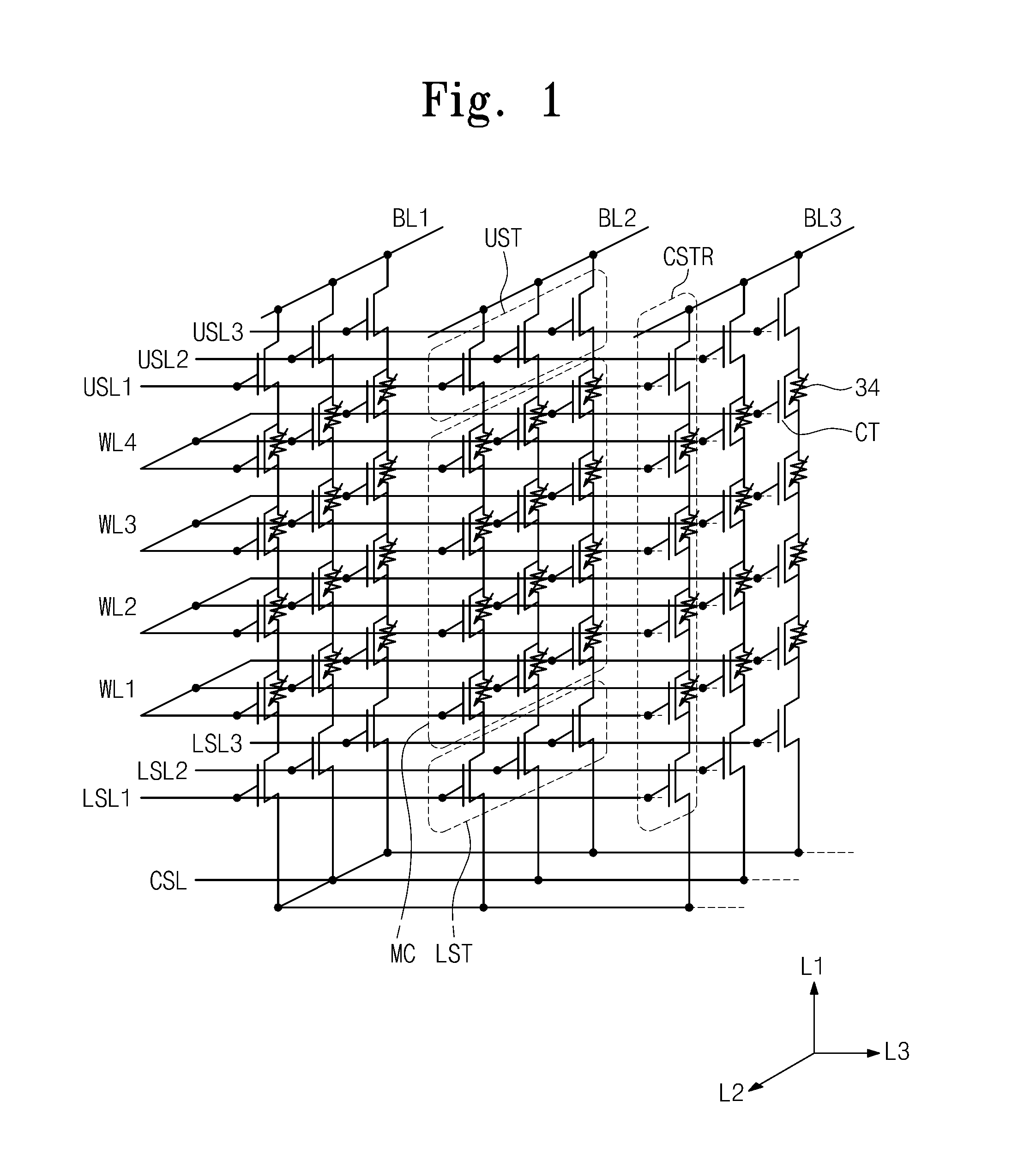

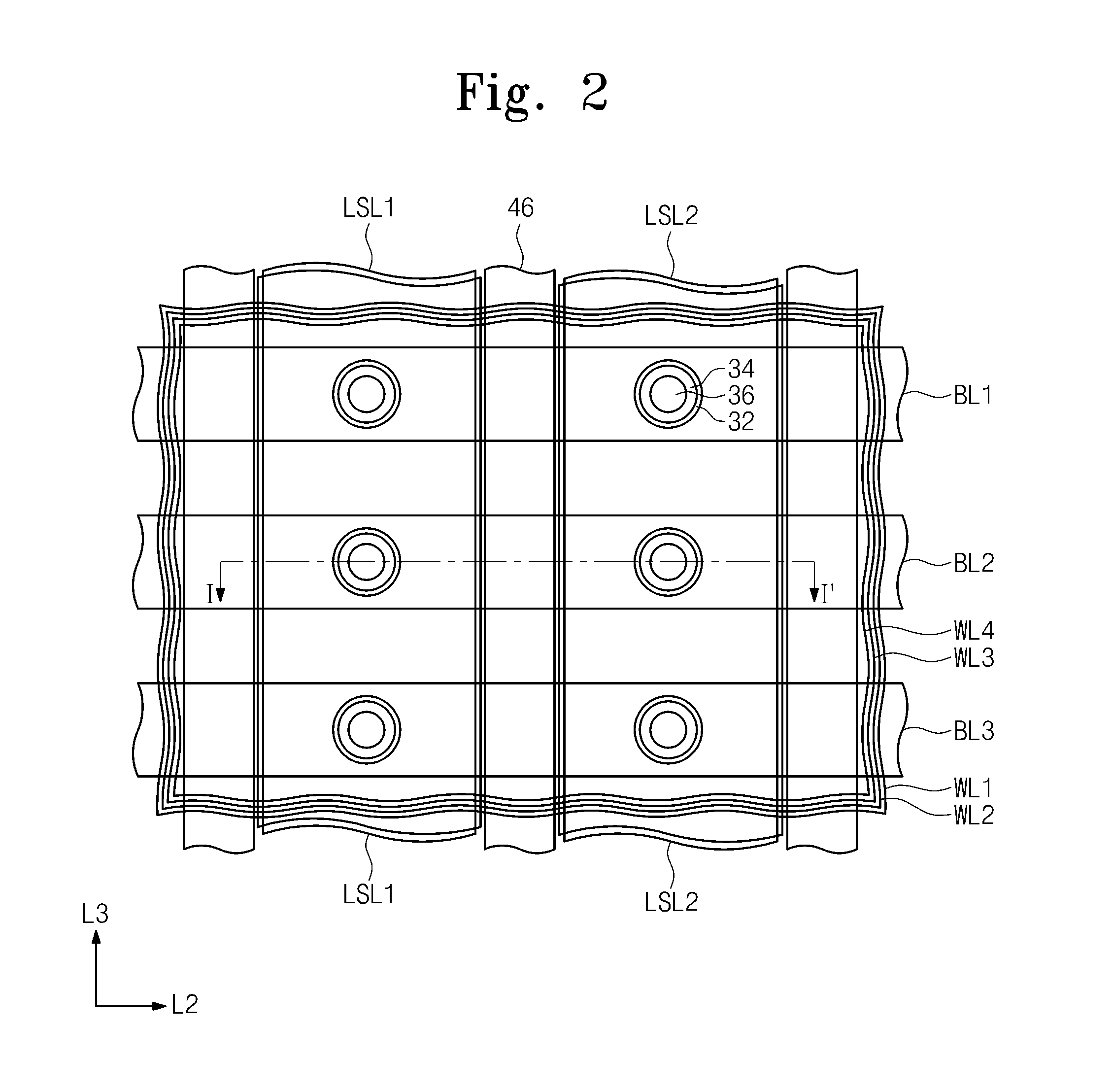

Three-dimensional resistive random access memory devices, methods of operating the same, and methods of fabricating the same

ActiveUS20130328005A1Decrease resistance of variable resistanceIncrease resistance of variable resistiveSolid-state devicesBulk negative resistance effect devicesRandom access memorySemiconductor

A semiconductor device includes a substrate extending in a horizontal direction. An active pillar is present on the substrate extending in a vertical direction relative to the horizontal direction of extension of the substrate. A variable resistive pattern is present on the substrate extending in the vertical direction along the active pillar, an electrical resistance of the variable resistive pattern being variable in response to an oxidation or reduction thereof. A gate is present at a sidewall of the active pillar.

Owner:SAMSUNG ELECTRONICS CO LTD

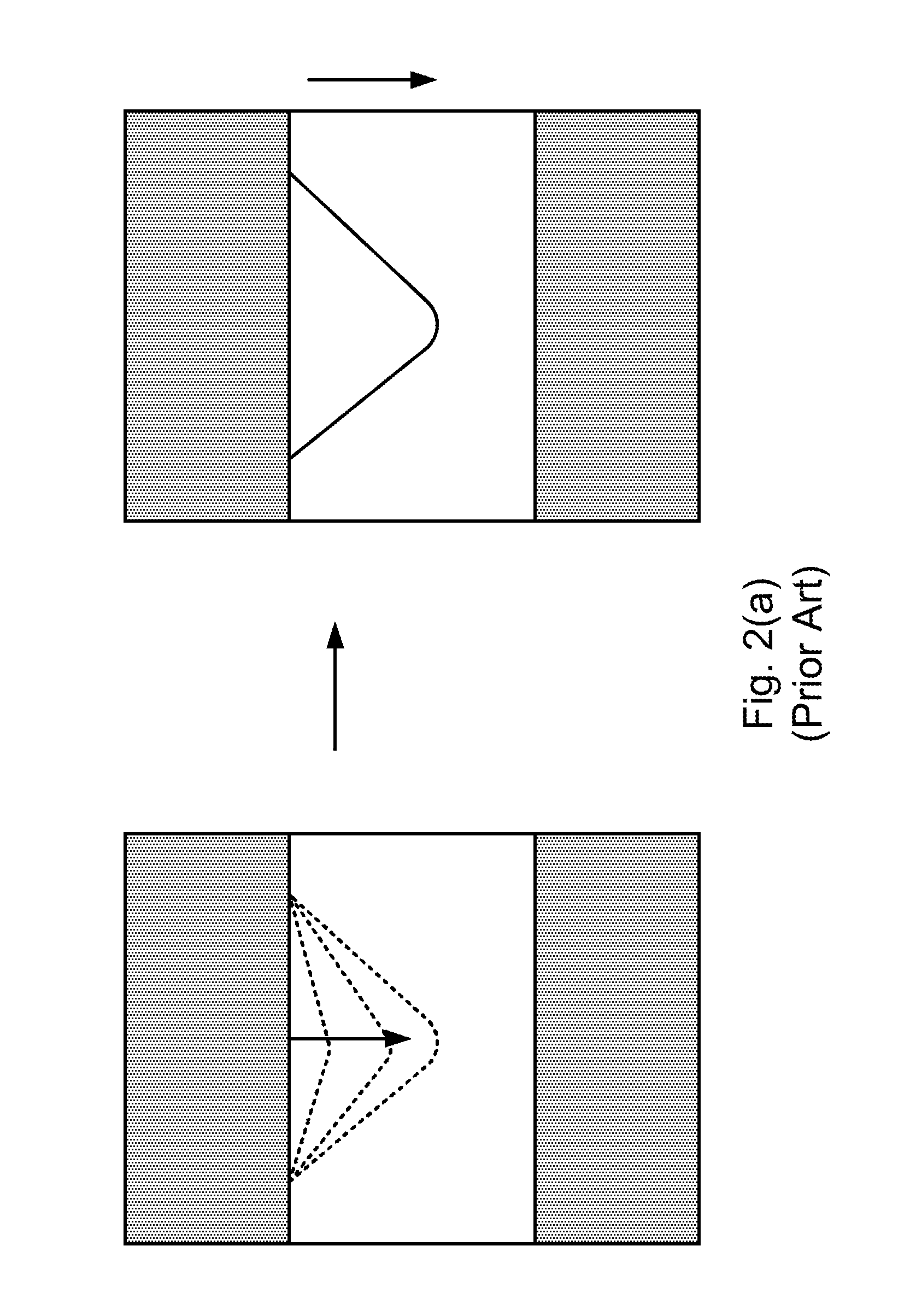

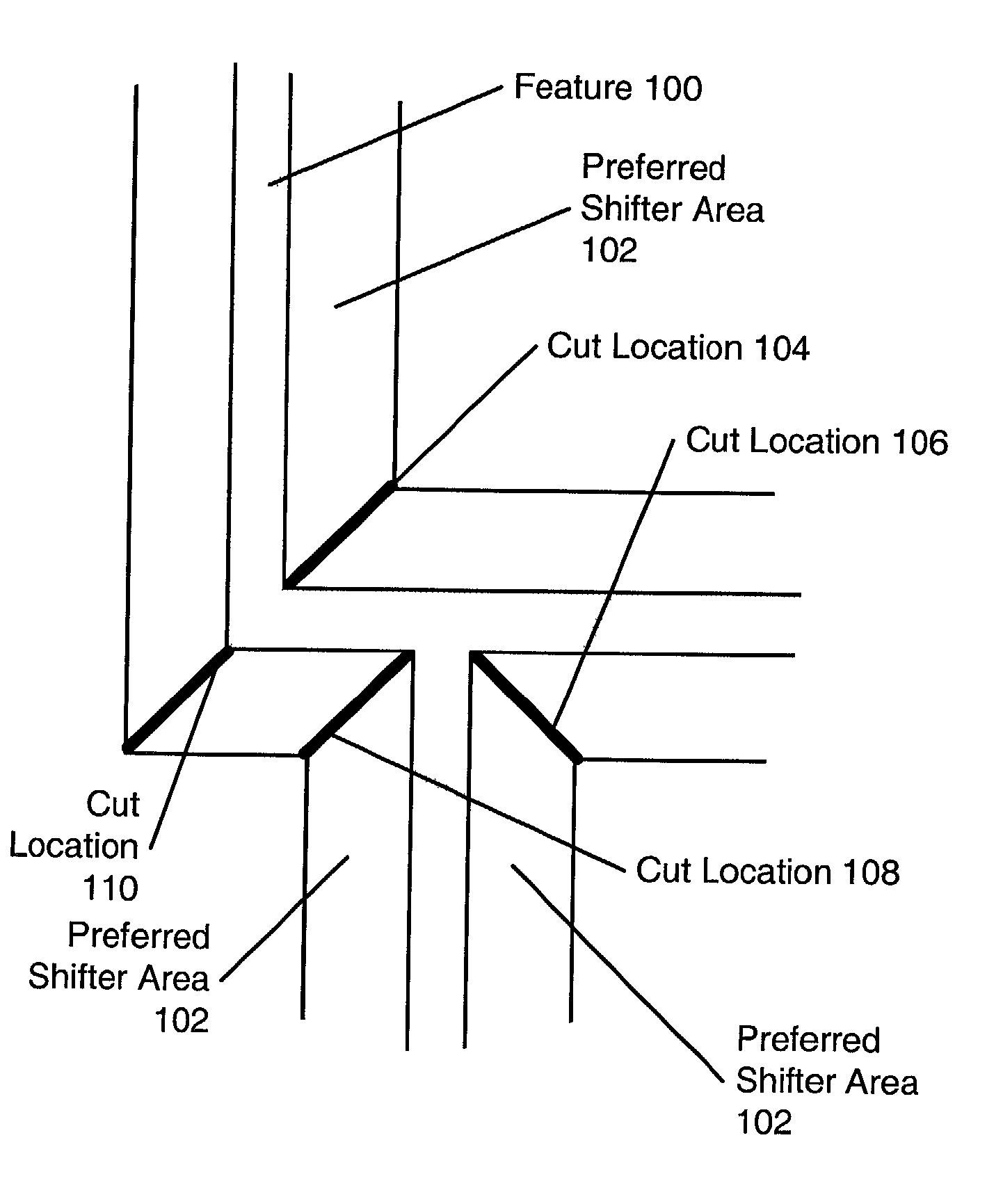

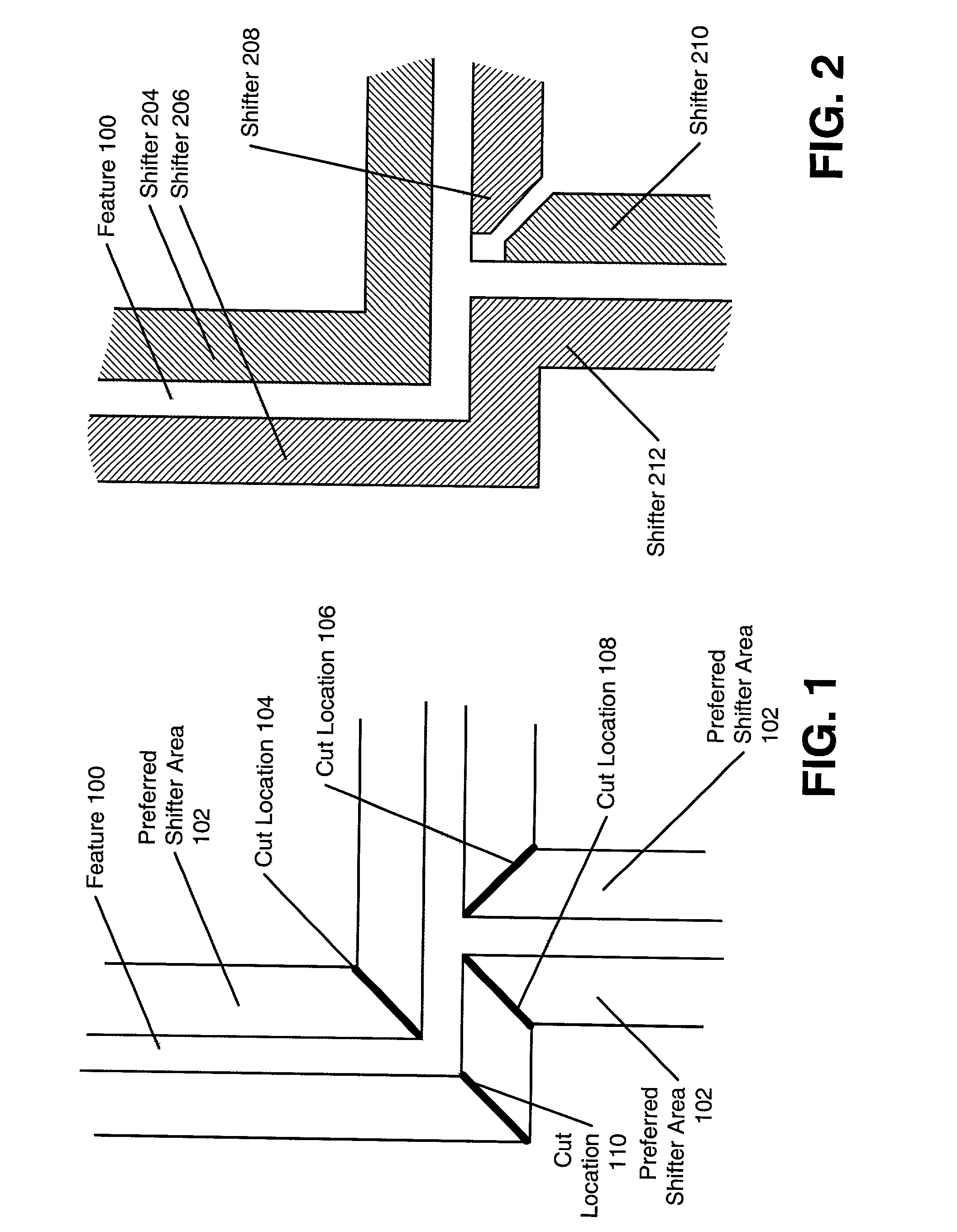

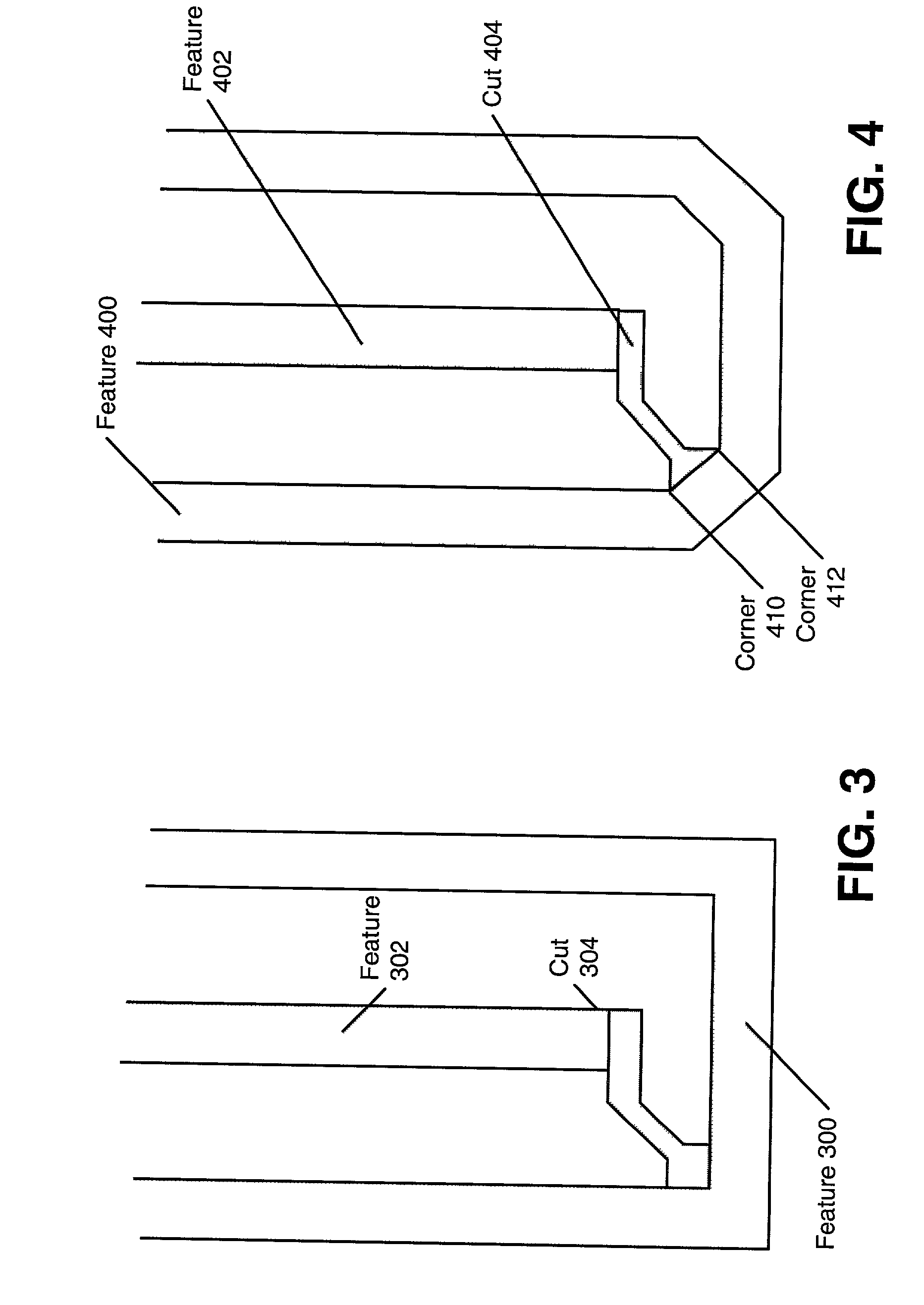

Phase shifting design and layout for static random access memory

InactiveUS20020129327A1Increase productionIncreased circuit densitySemiconductor/solid-state device manufacturingPhotomechanical exposure apparatusStatic random-access memoryRandom access memory

Owner:SYNOPSYS INC

Hard mask for patterning magnetic tunnel junctions

InactiveUS20160351799A1Magnetic-field-controlled resistorsGalvano-magnetic device detailsCarbon layerAnti-reflective coating

Device structures and methods for fabricating device structures are provided herein. Magnetic random access memory (MRAM) devices described herein may include a film stack comprising a magnetic tunneling junction layer, a dielectric capping layer, an etch stop layer, a conductive hard mask layer, a dielectric hard mask layer, a spin on carbon layer, and an anti-reflective coating layer. The film stack may be etched by one or more selected chemistries to achieve improved film stack sidewall verticality. Memory cells having increasingly uniform and reduced critical dimensions may be fabricated utilizing the methods and devices described herein.

Owner:APPLIED MATERIALS INC

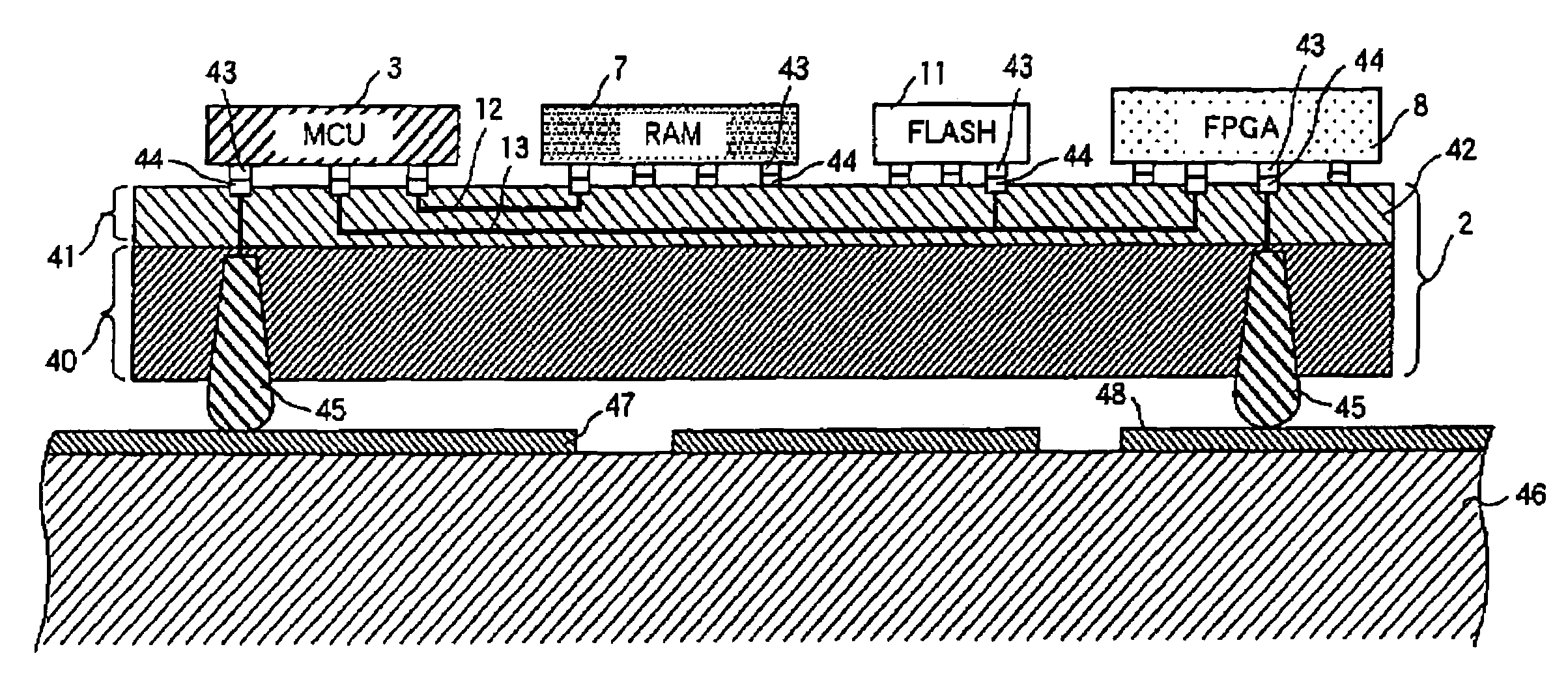

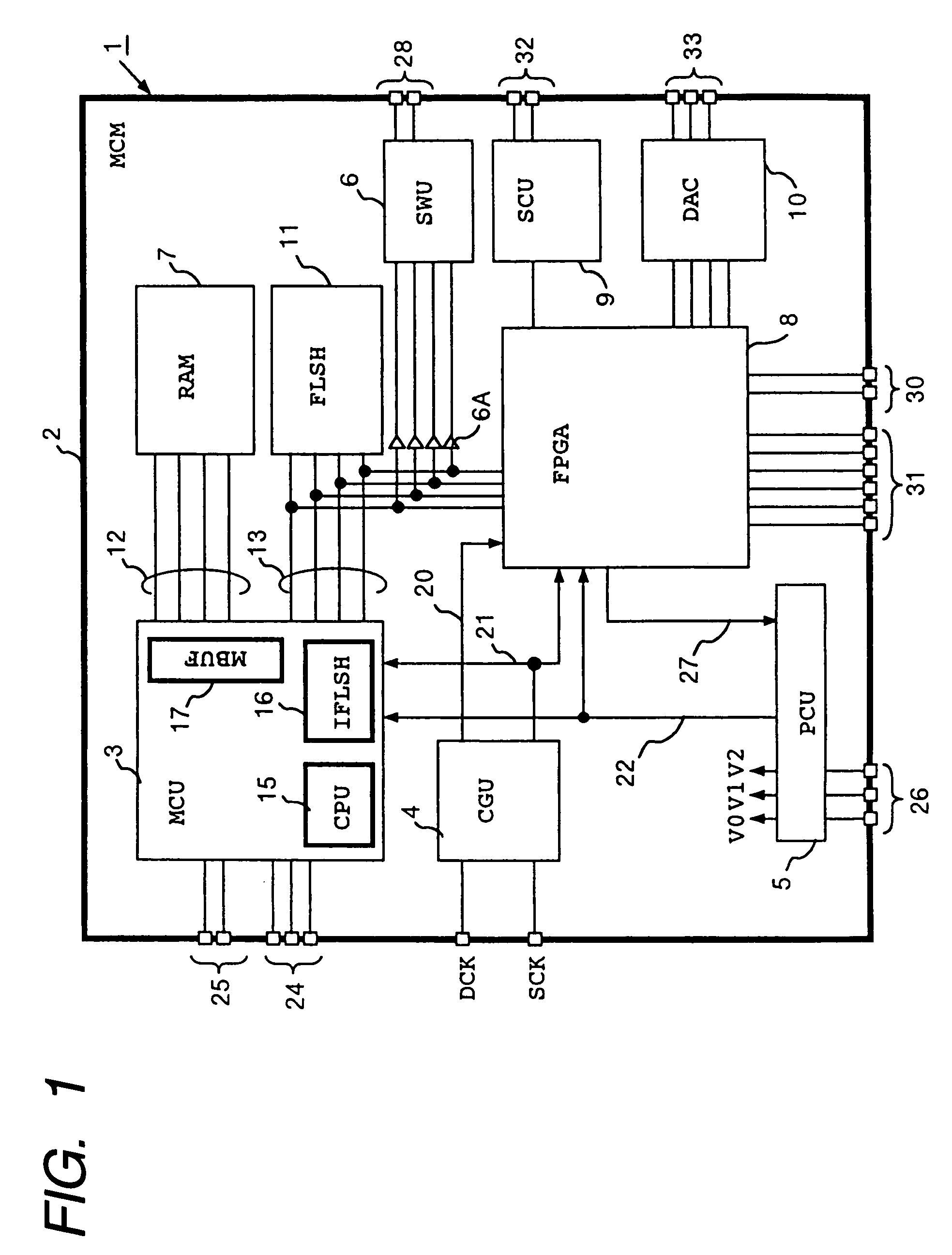

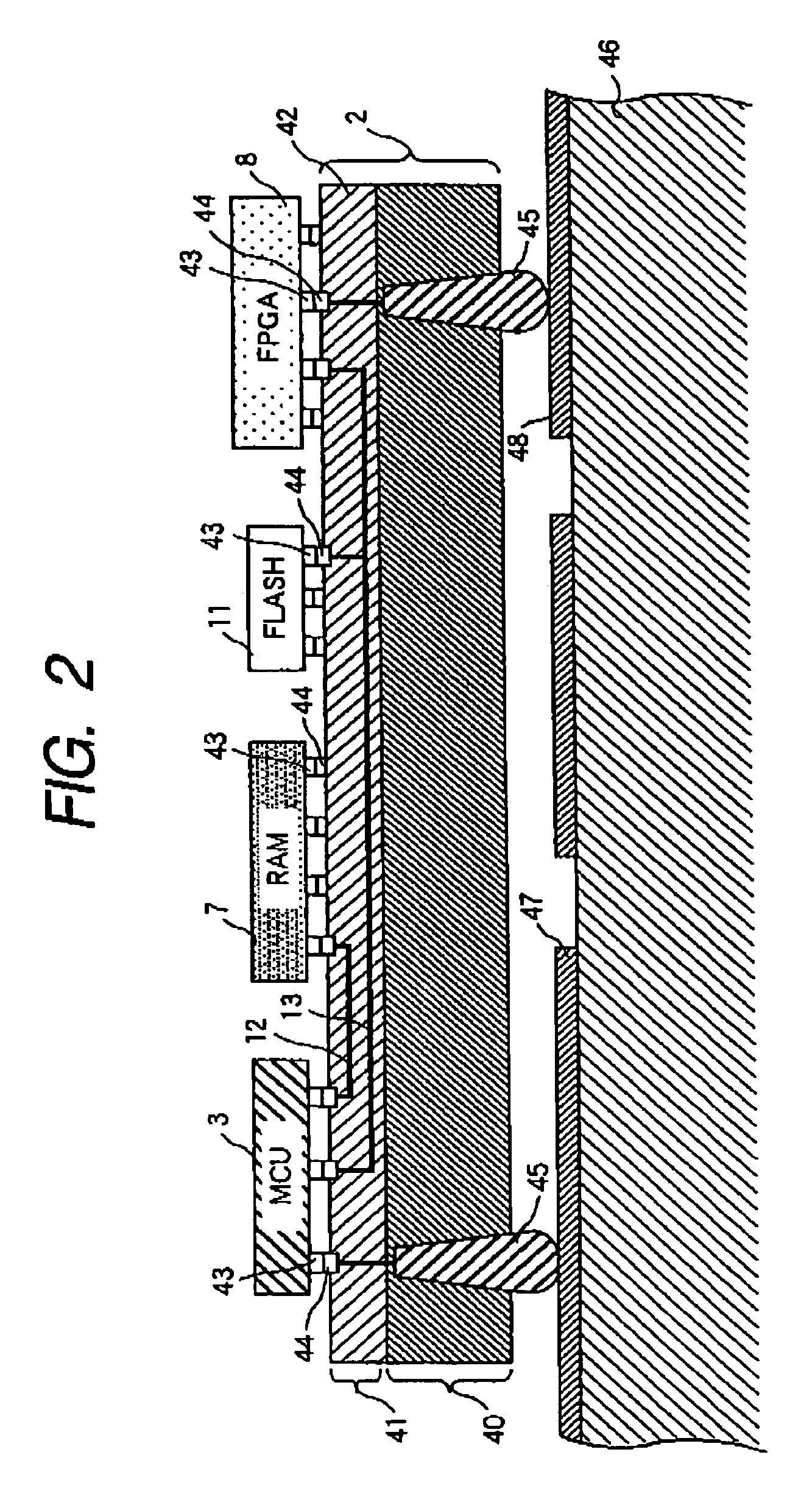

Electronic circuit device

InactiveUS7091598B2Easy to debugLow costError detection/correctionSemiconductor/solid-state device detailsStatic random-access memoryBase function

An electronic circuit device has a high-density mount board, on which are disposed a microcomputer, a random access memory, a programmable device which is a variable logic circuit represented by FPGA, and an electrically-rewritable nonvolatile memory which can store the operation program of the microcomputer. The high-density mount board has external mounting pins on the bottom surface so as to be mounted on a mother board in the same manner as a system on-chip multi-chip module. With an intended logic function being set on the programmable device, a hardware-based function to be realized by the electronic circuit device is simulated. With an operation program being written to the nonvolatile memory, a software-based function to be realized is simulated. Consequently, the device facilitates the debugging at early stages of system development, configures a prototype system, and contributes to the time reduction throughout the system development, prototype fabrication and large-scale production.

Owner:RENESAS TECH CORP

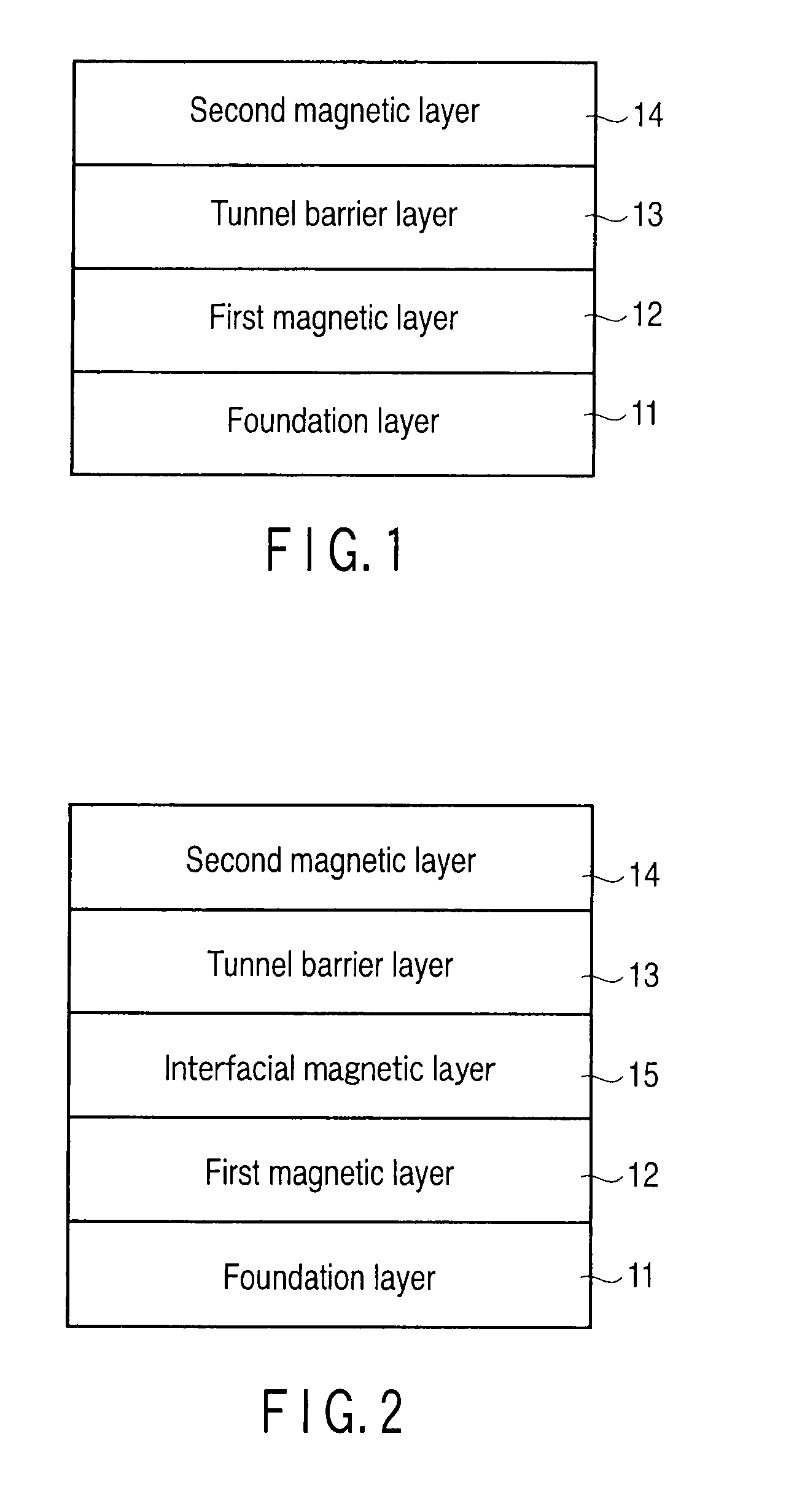

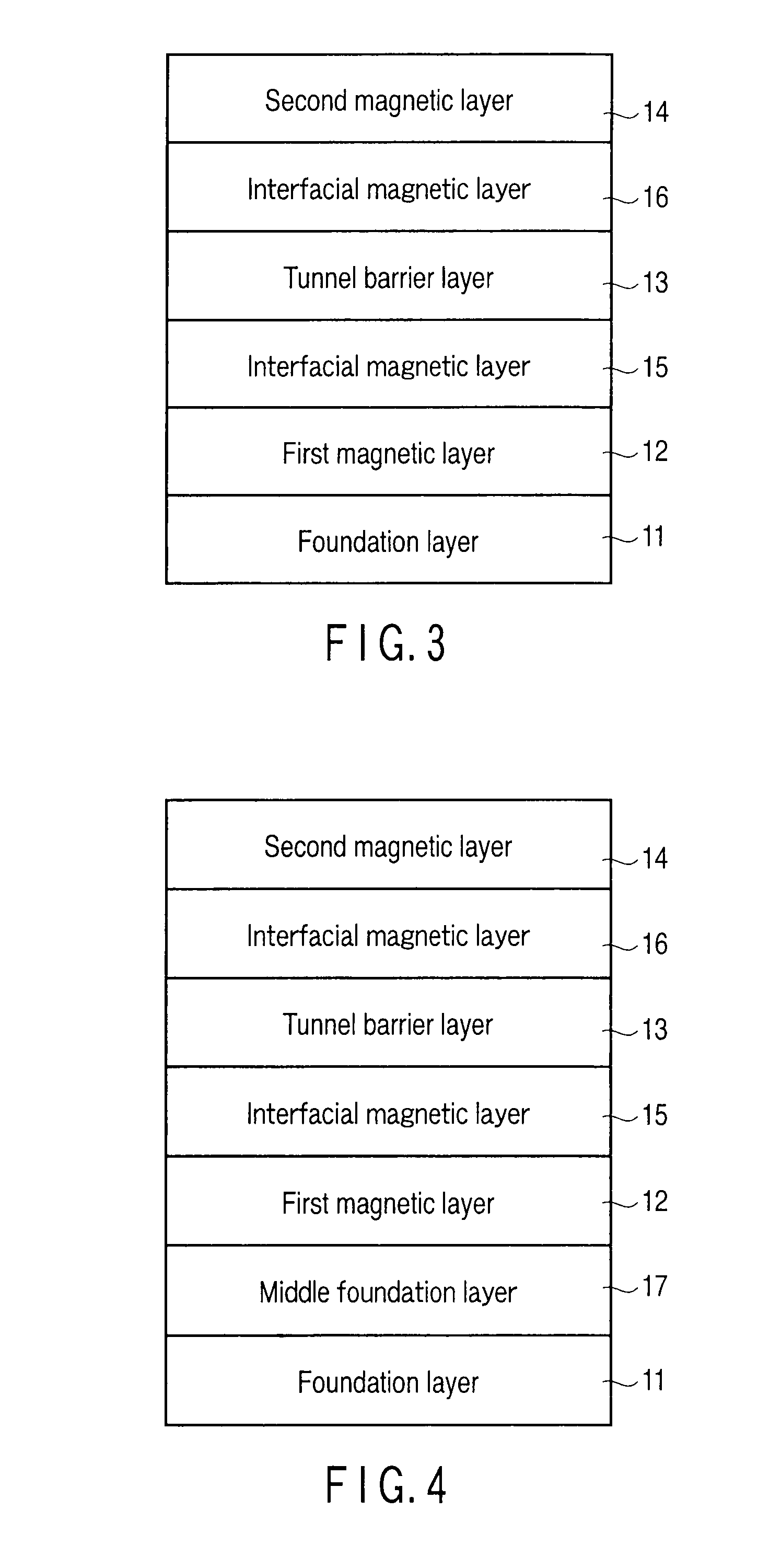

Magnetoresistive element and magnetic random access memory

A magnetoresistive element includes a foundation layer, a first magnetic layer on the foundation layer, a tunnel barrier layer on the first magnetic layer, and a second magnetic layer on the tunnel barrier layer. The first magnetic layer is made of a ferromagnetic metal containing one or more elements selected from a first group consisting of Co, Fe, and Ni, and one or more elements selected from a second group consisting of Cu, Ag, Au, Pd, Pt, Ru, Rh, Ir, and Os. The foundation layer is made of a metal containing one or more elements selected from a third group consisting of Al, Ni, Co, Fe, Mn, Cr, and V.

Owner:KK TOSHIBA