Patents

Literature

8027 results about "Volatile memory" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Volatile memory, in contrast to non-volatile memory, is computer memory that requires power to maintain the stored information; it retains its contents while powered on but when the power is interrupted, the stored data is quickly lost.

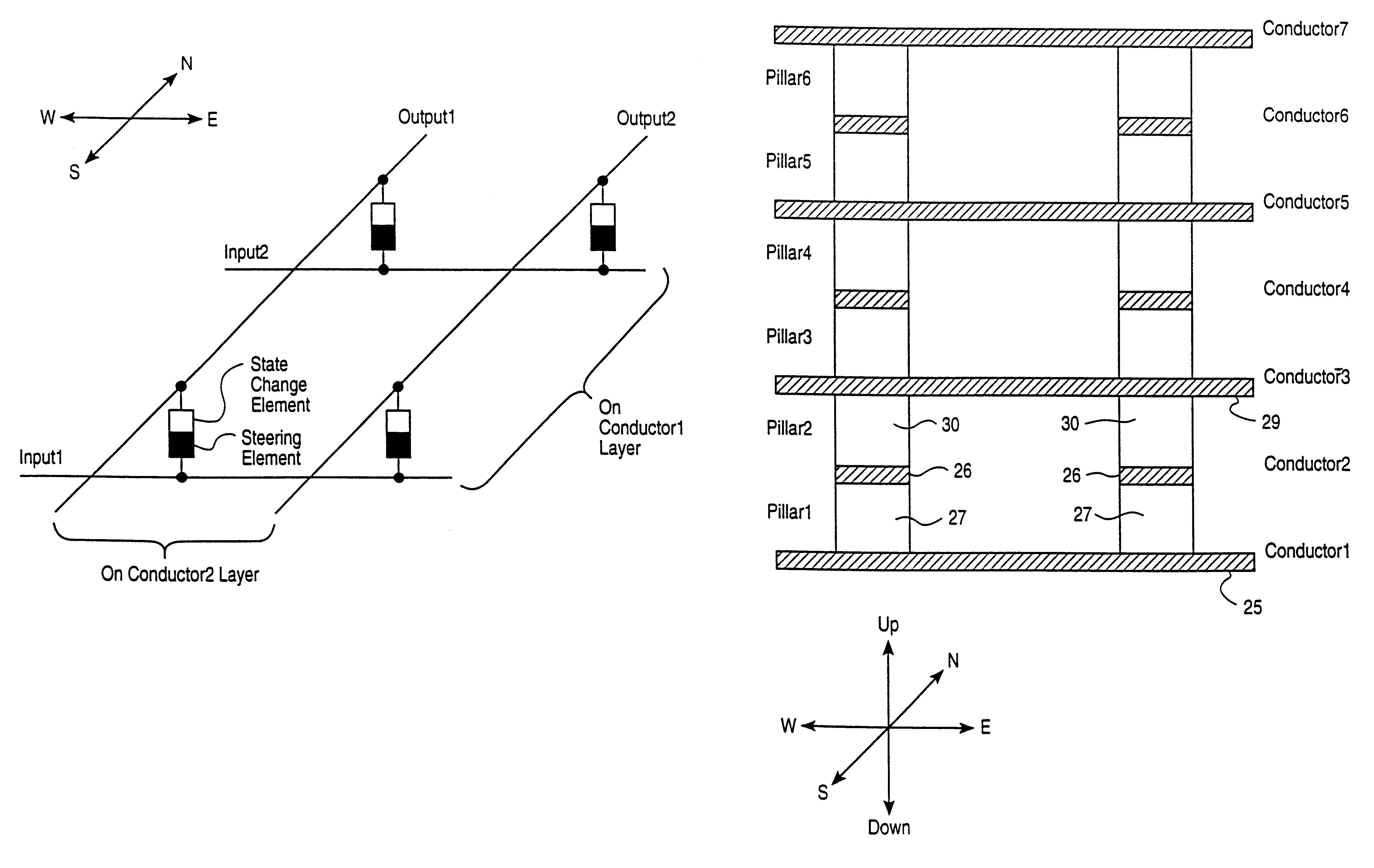

Vertically stacked field programmable nonvolatile memory and method of fabrication

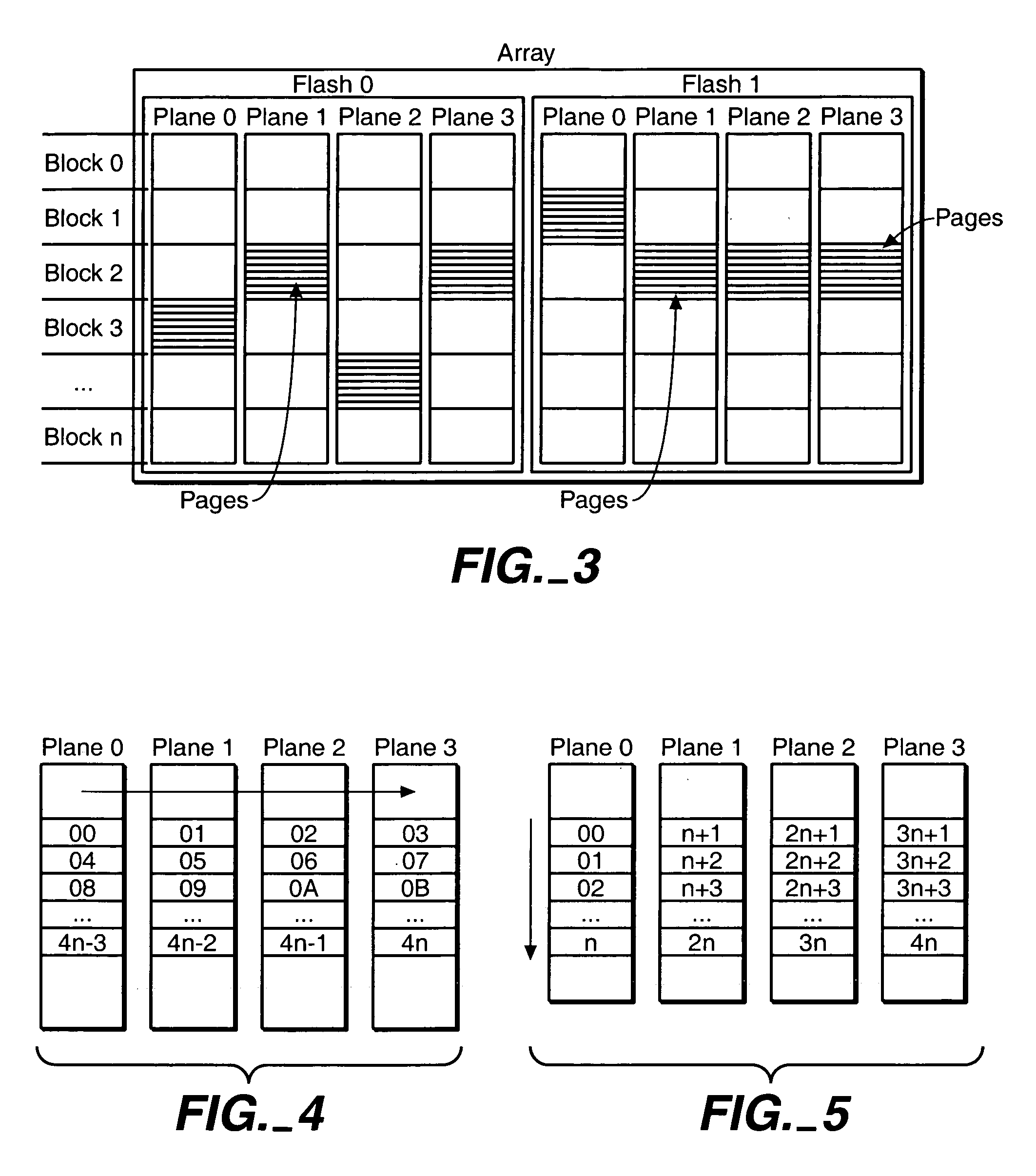

A very high density field programmable memory is disclosed. An array is formed vertically above a substrate using several layers, each layer of which includes vertically fabricated memory cells. The cell in an N level array may be formed with N+1 masking steps plus masking steps needed for contacts. Maximum use of self alignment techniques minimizes photolithographic limitations. In one embodiment the peripheral circuits are formed in a silicon substrate and an N level array is fabricated above the substrate.

Owner:SANDISK TECH LLC

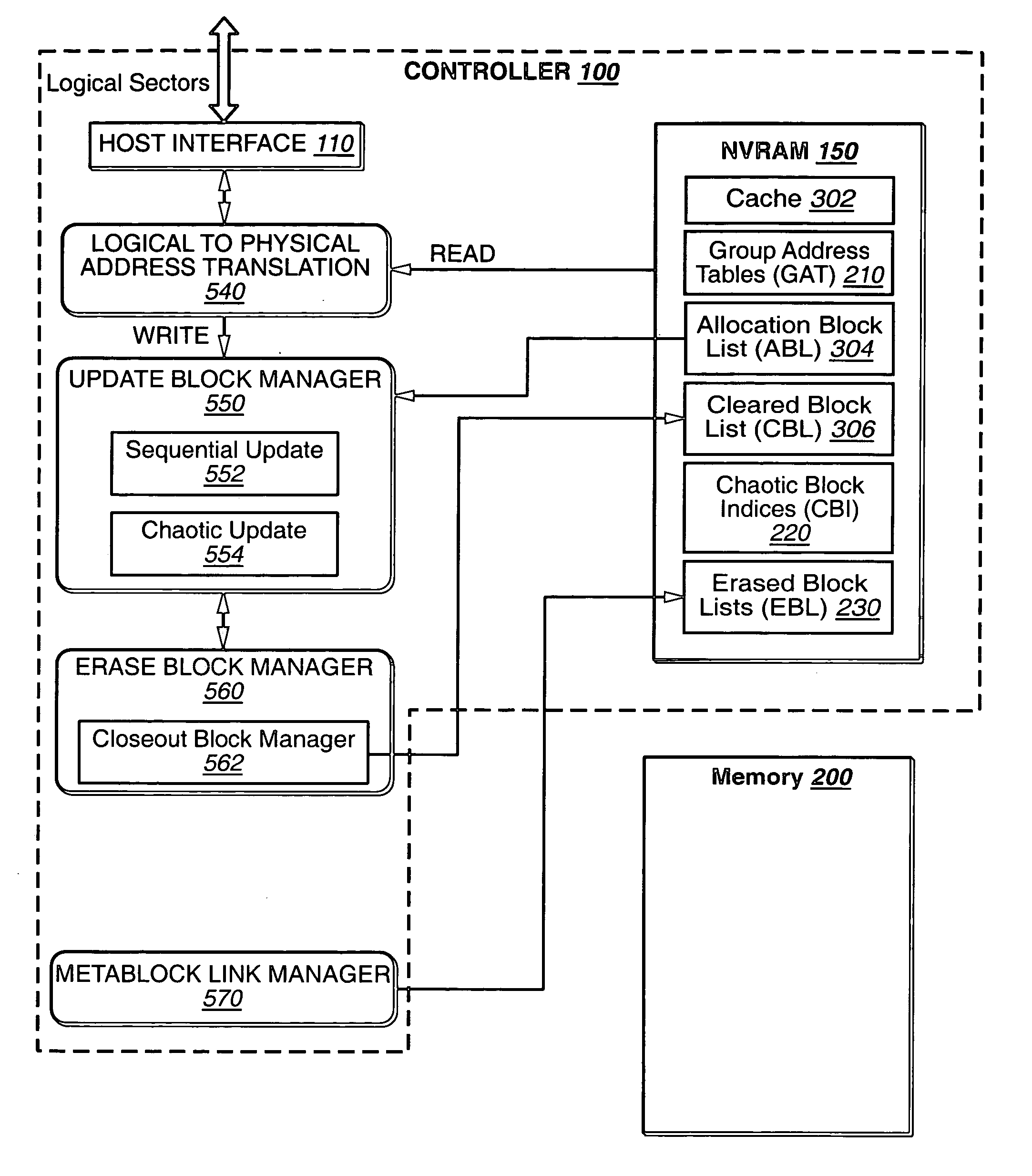

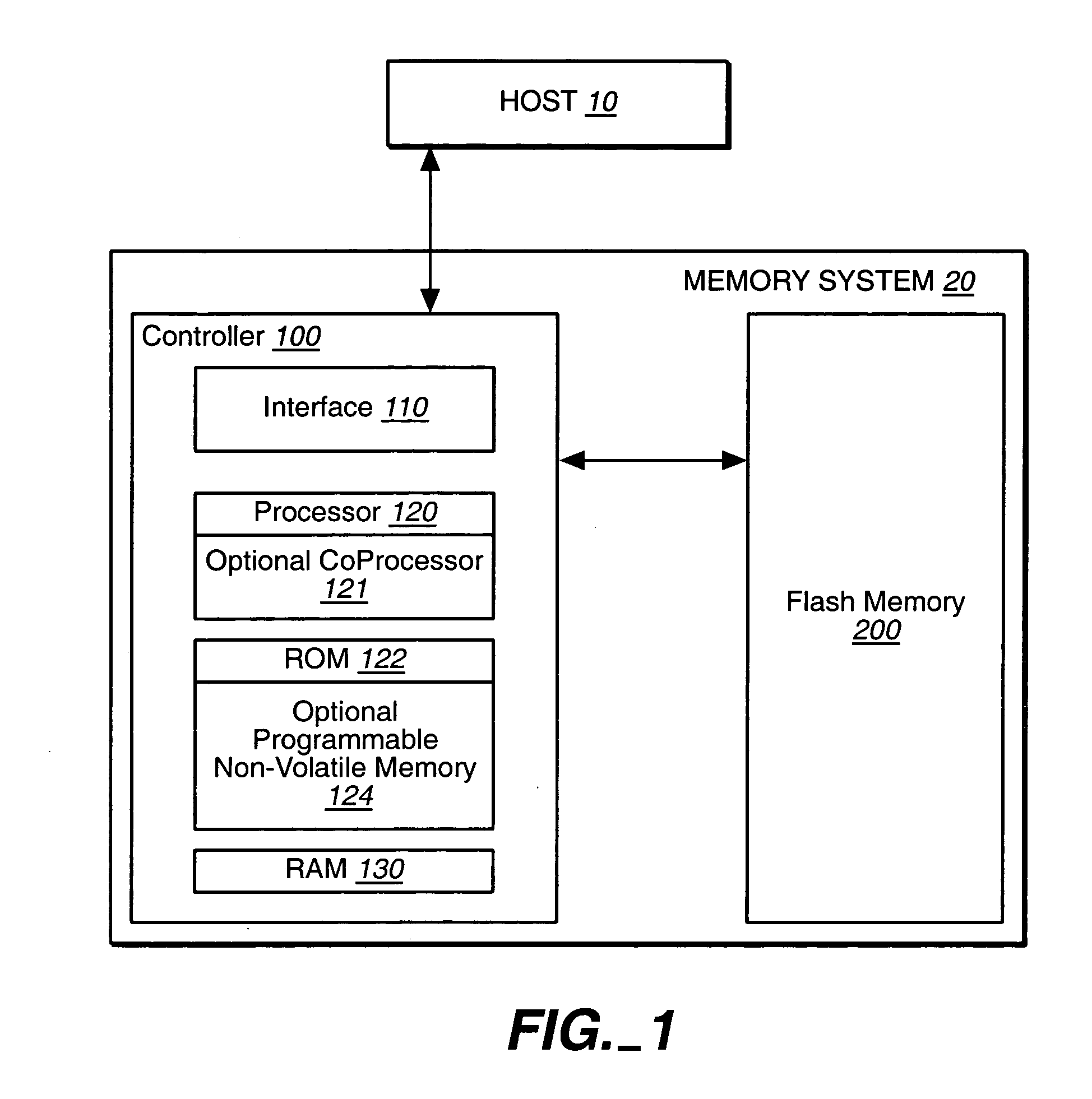

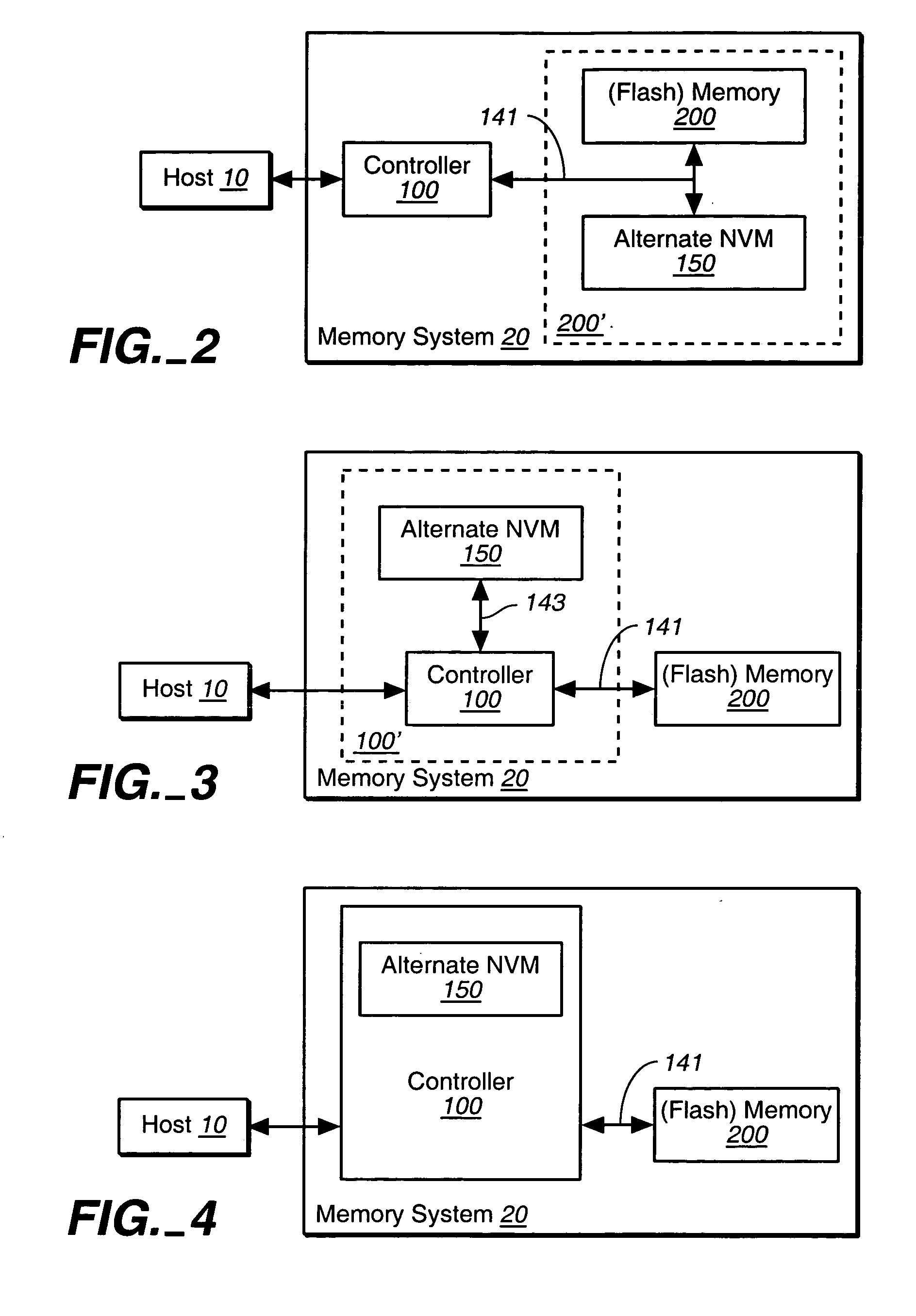

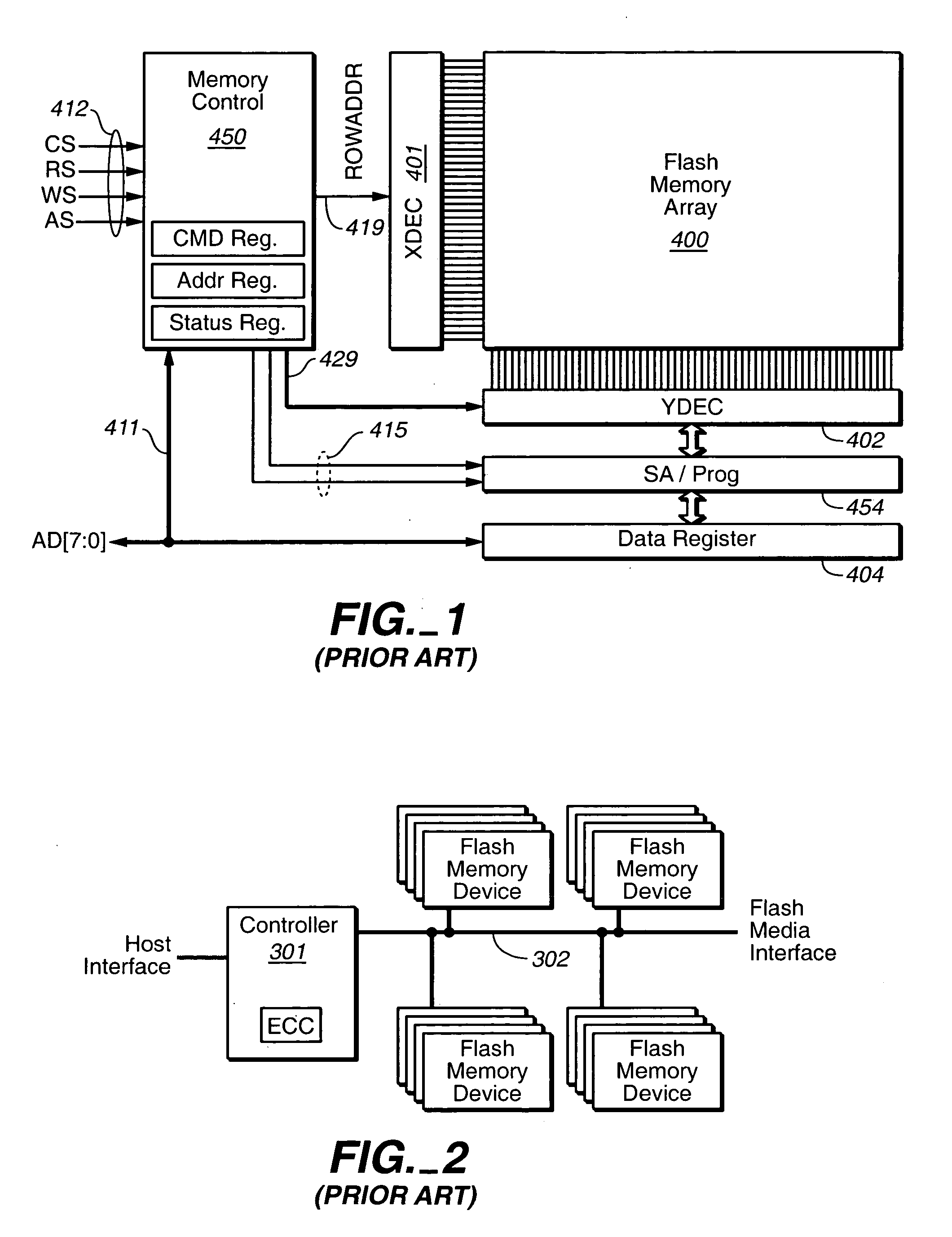

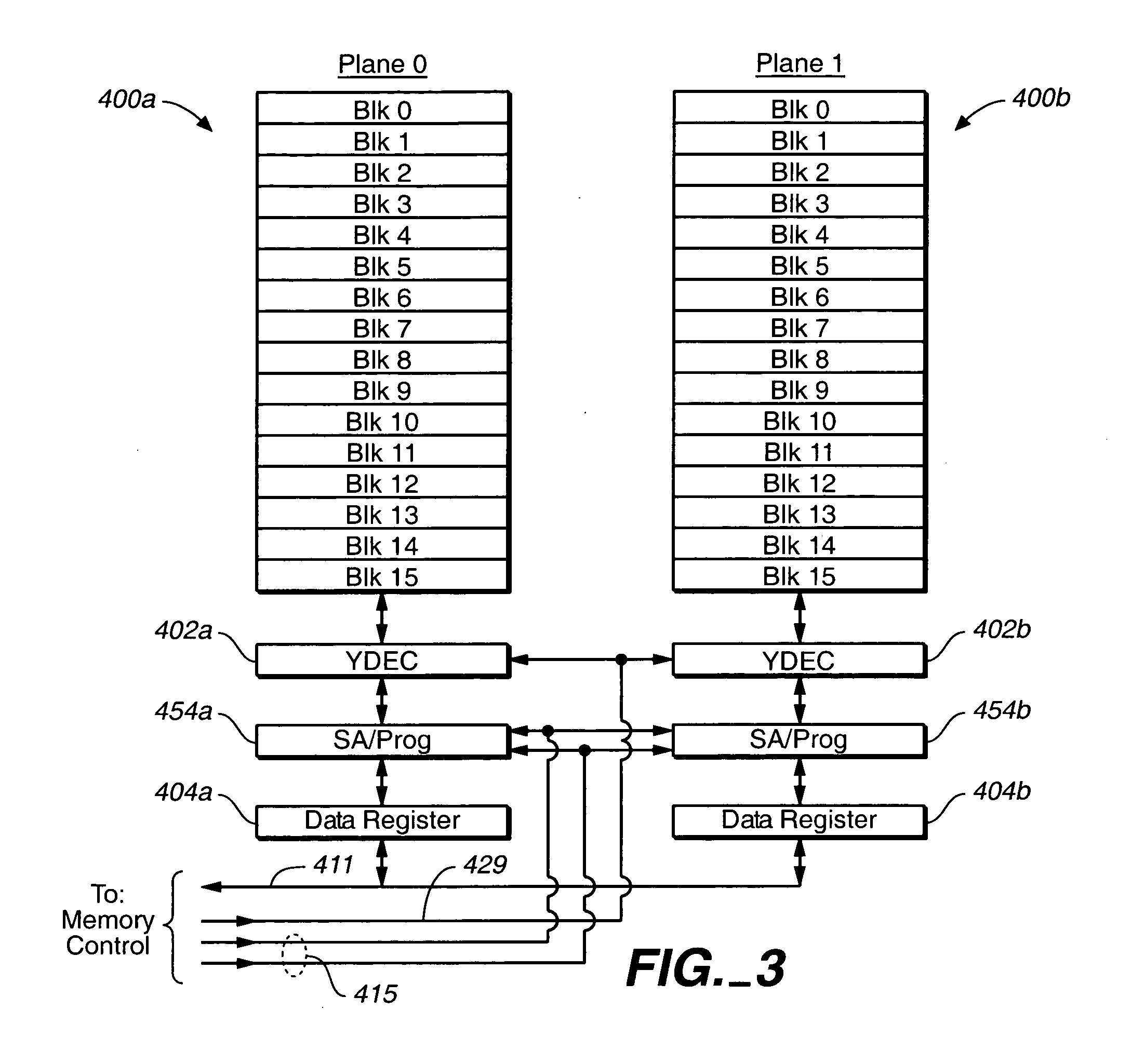

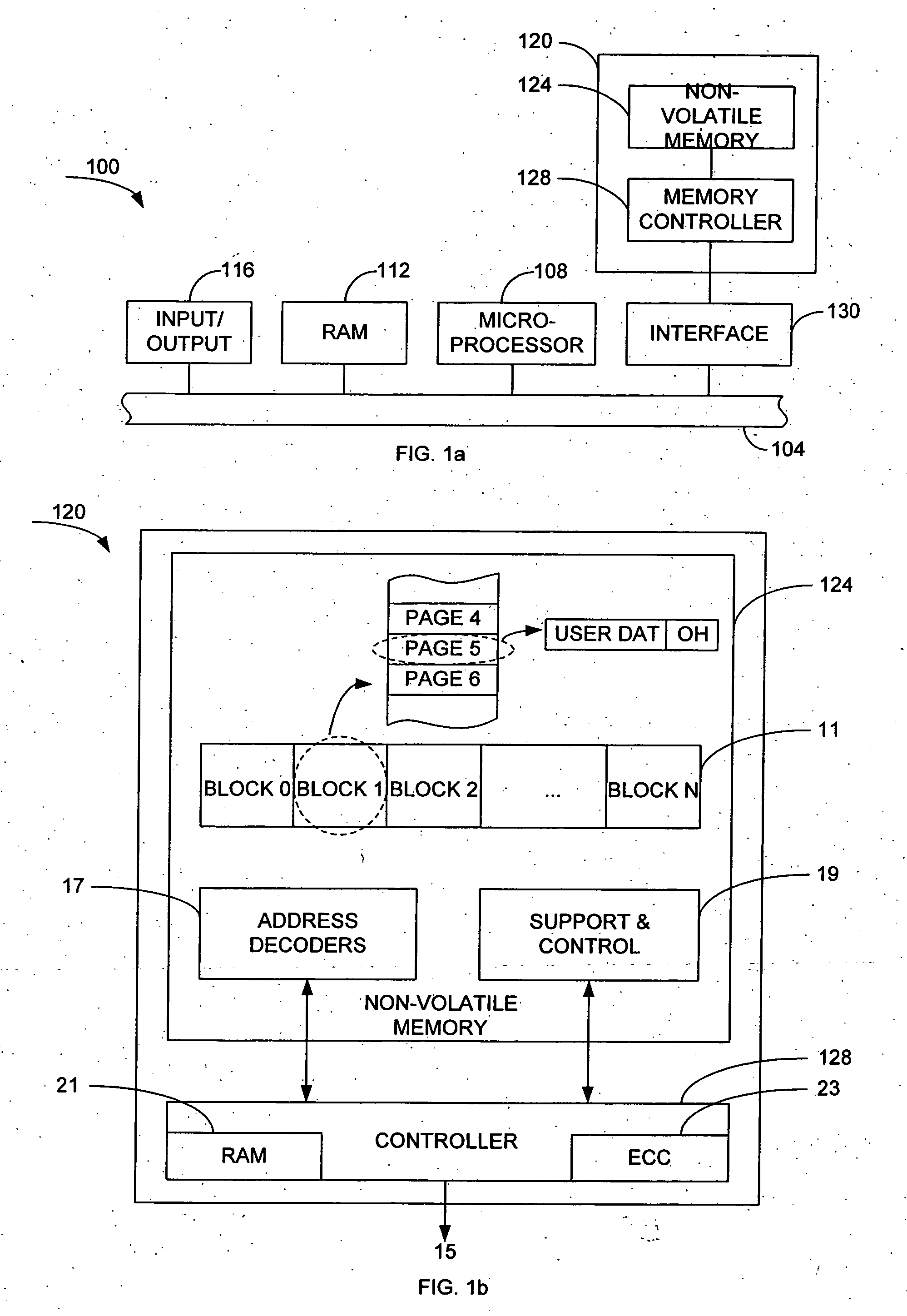

Hybrid non-volatile memory system

InactiveUS20050251617A1Easy accessMemory architecture accessing/allocationInput/output to record carriersData controlControl data

The present invention presents a hybrid non-volatile system that uses non-volatile memories based on two or more different non-volatile memory technologies in order to exploit the relative advantages of each these technology with respect to the others. In an exemplary embodiment, the memory system includes a controller and a flash memory, where the controller has a non-volatile RAM based on an alternate technology such as FeRAM. The flash memory is used for the storage of user data and the non-volatile RAM in the controller is used for system control data used by the control to manage the storage of host data in the flash memory. The use of an alternate non-volatile memory technology in the controller allows for a non-volatile copy of the most recent control data to be accessed more quickly as it can be updated on a bit by bit basis. In another exemplary embodiment, the alternate non-volatile memory is used as a cache where data can safely be staged prior to its being written to the to the memory or read back to the host.

Owner:SANDISK TECH LLC

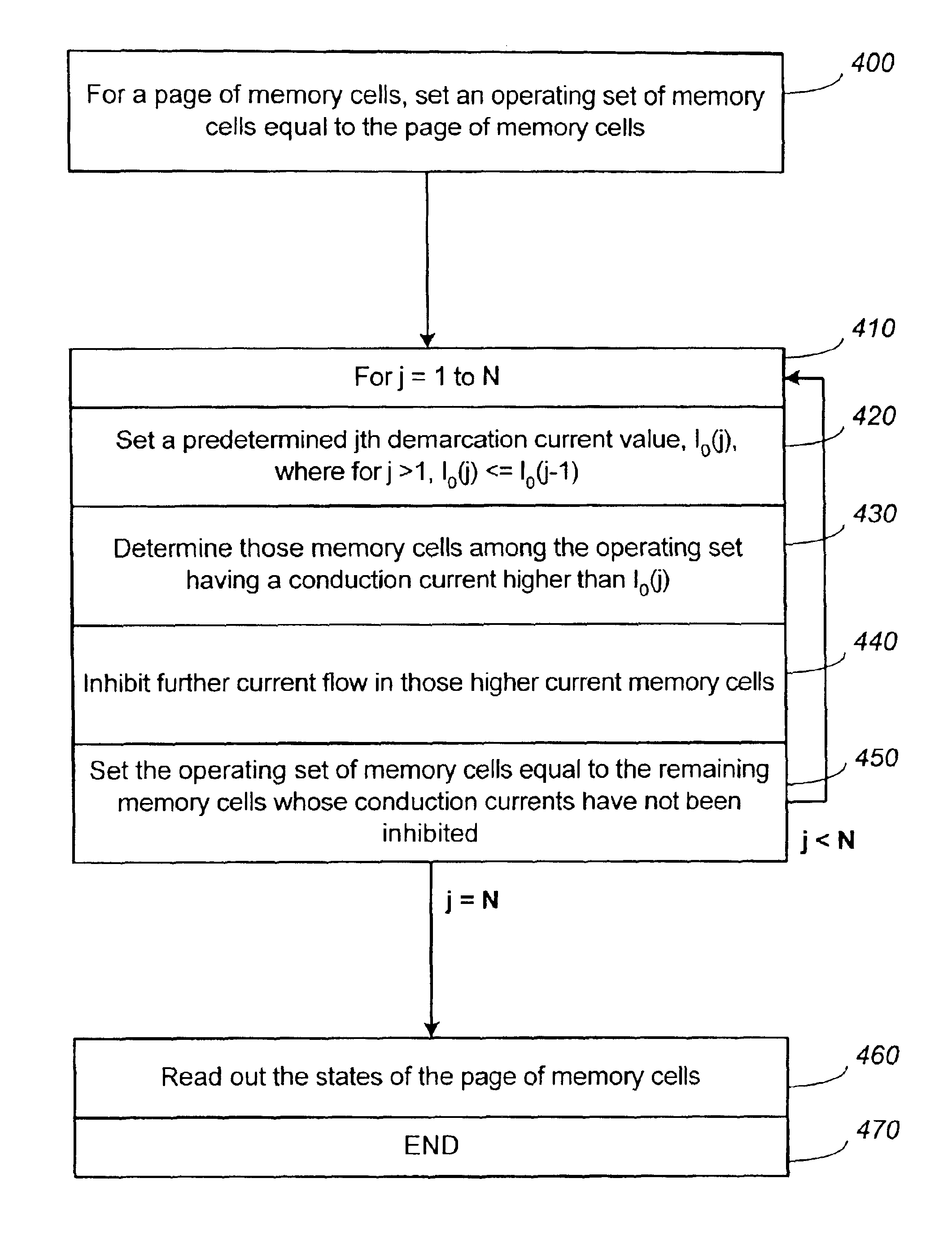

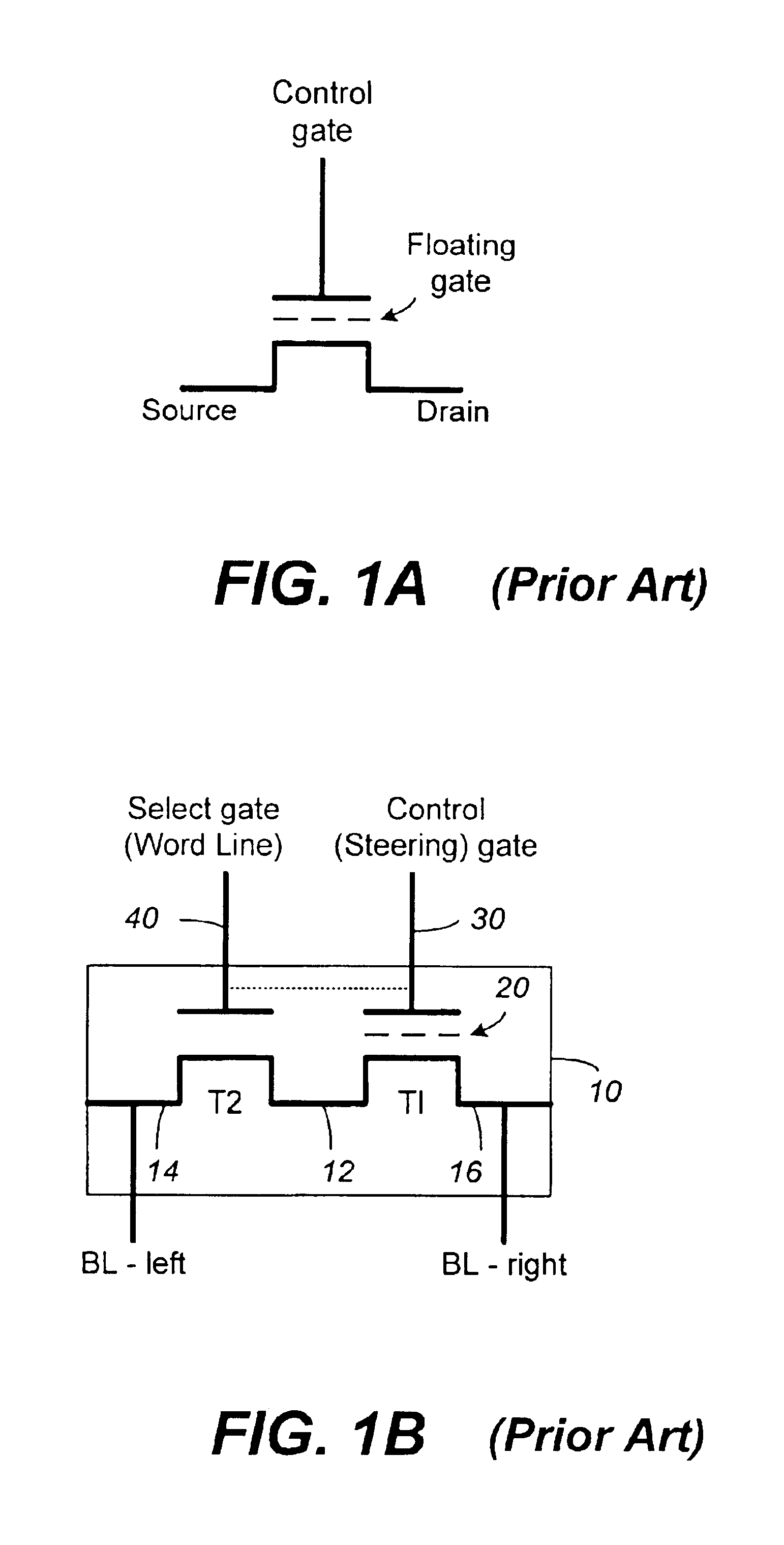

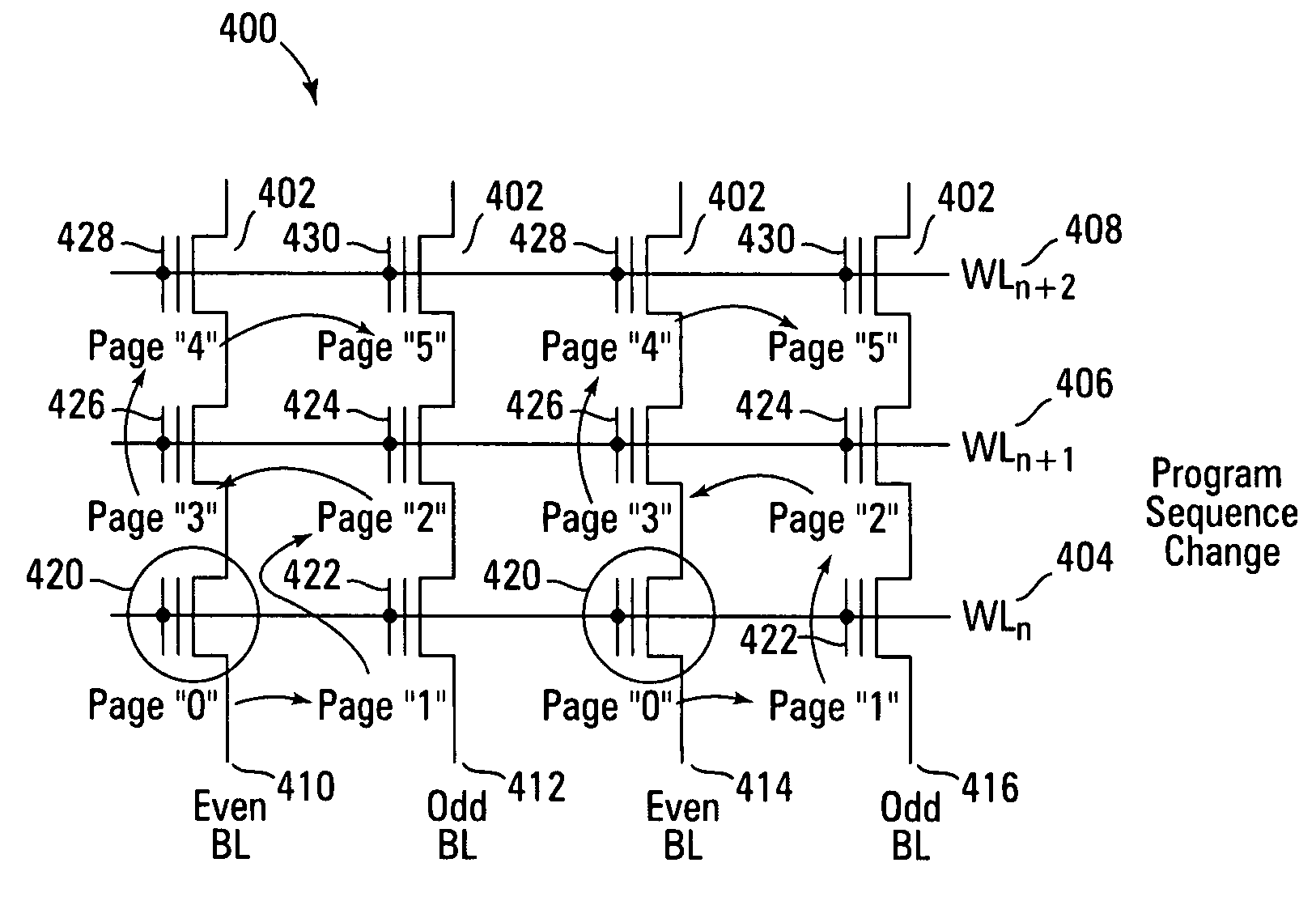

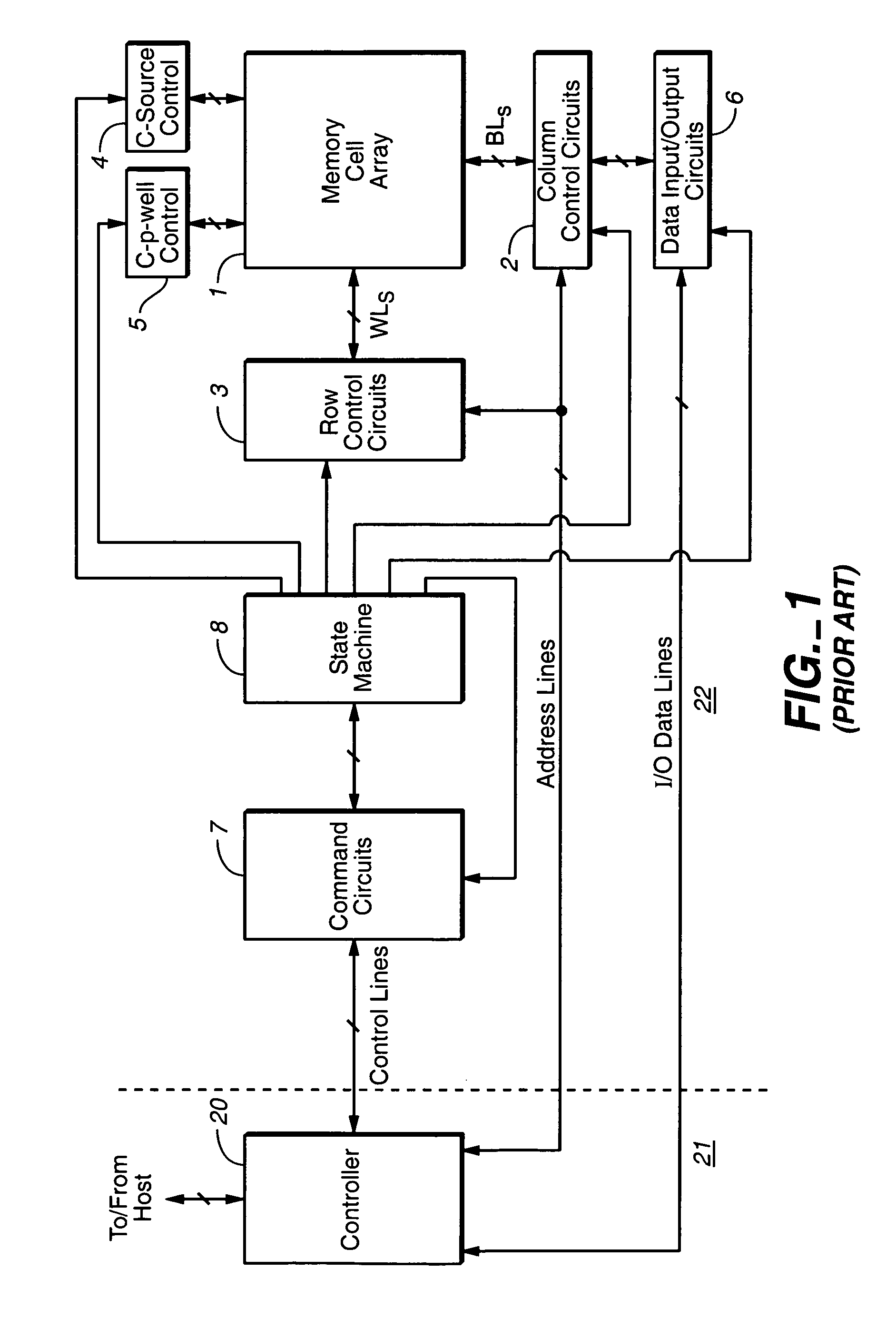

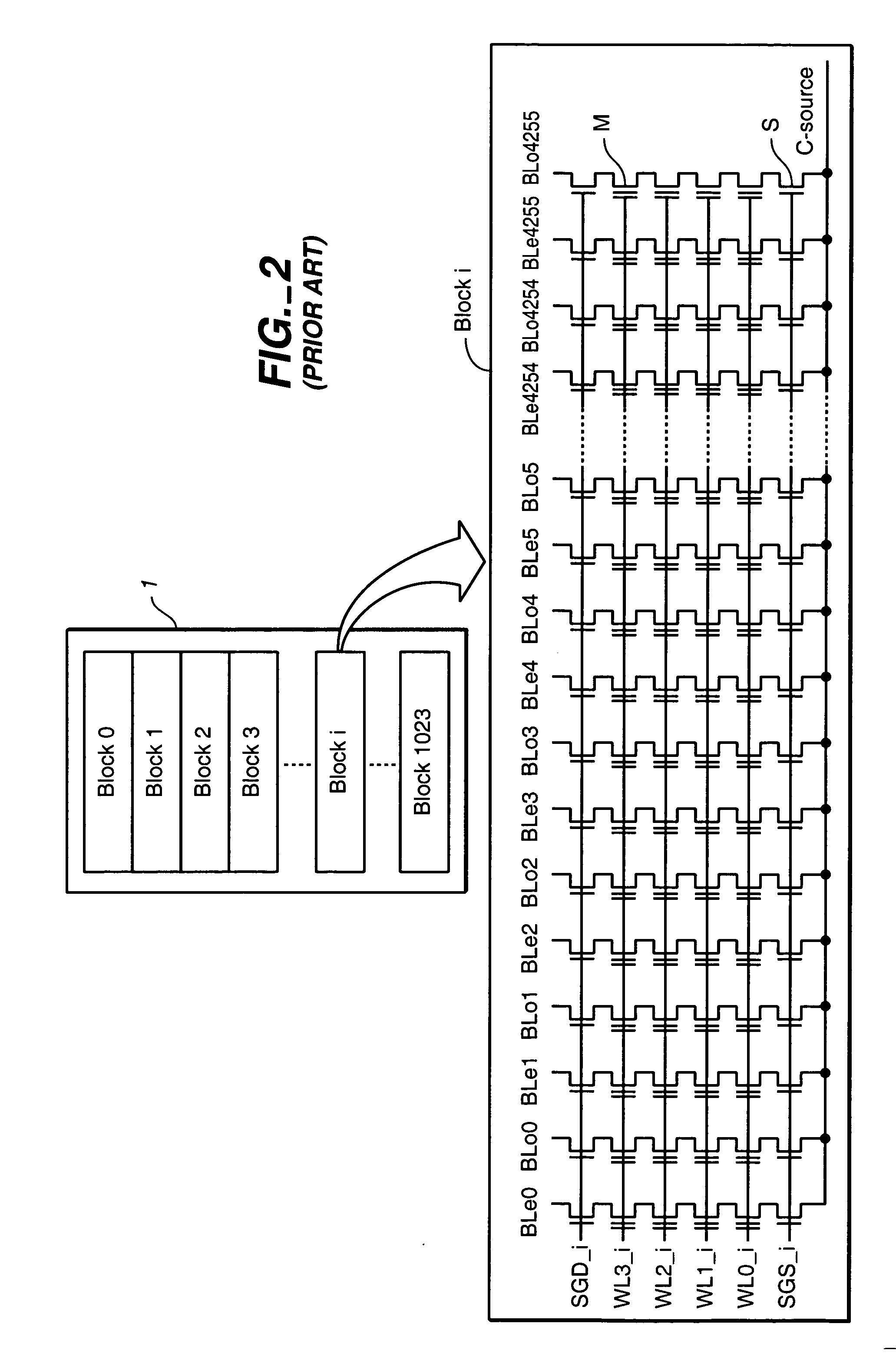

Non-volatile memory and method with reduced neighboring field errors

InactiveUS6987693B2Large capacityImprove performanceRead-only memoriesDigital storageNon-volatile memoryParallel programing

A memory device and a method thereof allow programming and sensing a plurality of memory cells in parallel in order to minimize errors caused by coupling from fields of neighboring cells and to improve performance. The memory device and method have the plurality of memory cells linked by the same word line and a read / write circuit is coupled to each memory cells in a contiguous manner. Thus, a memory cell and its neighbors are programmed together and the field environment for each memory cell relative to its neighbors during programming and subsequent reading is less varying. This improves performance and reduces errors caused by coupling from fields of neighboring cells, as compared to conventional architectures and methods in which cells on even columns are programmed independently of cells in odd columns.

Owner:SANDISK TECH LLC

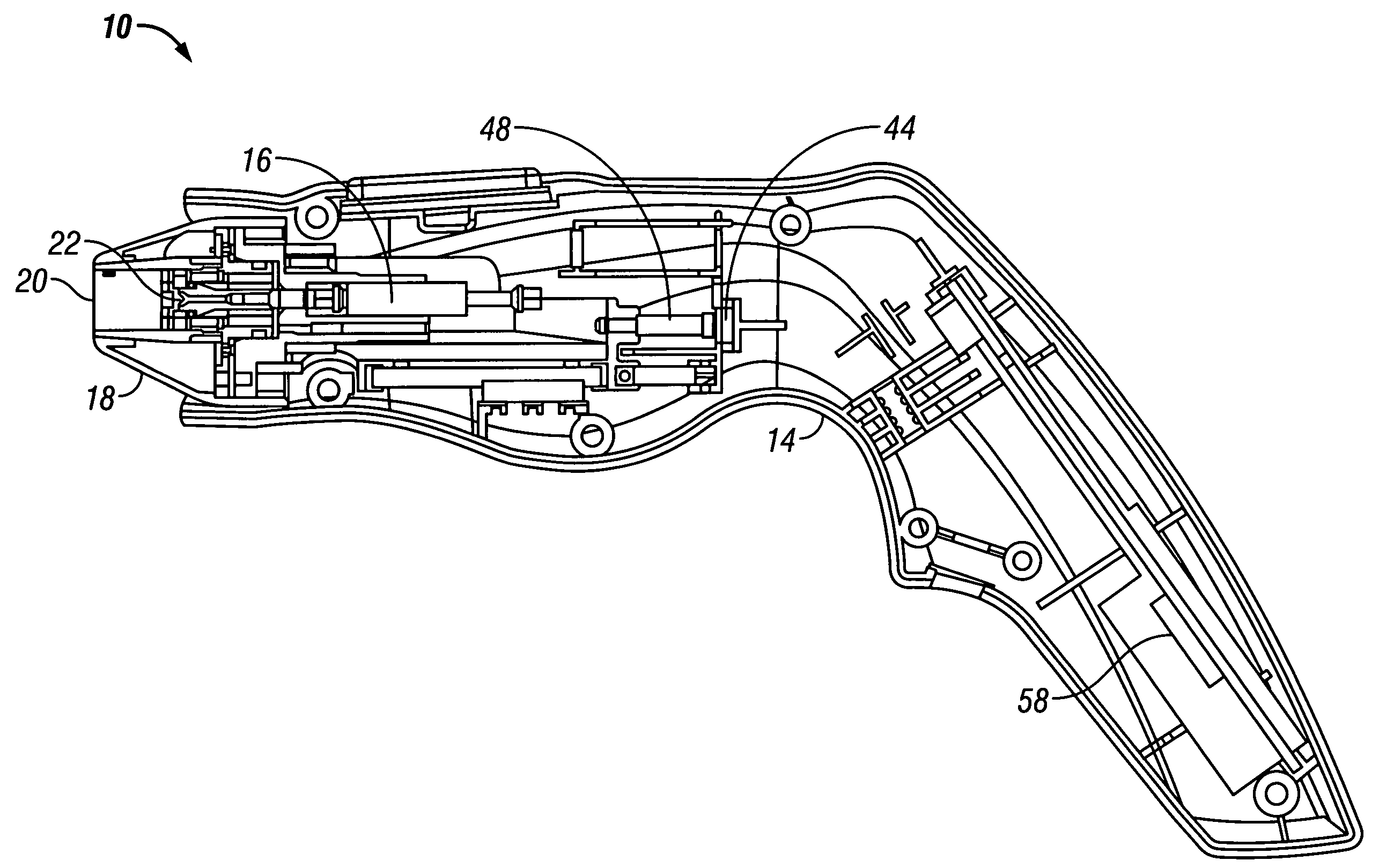

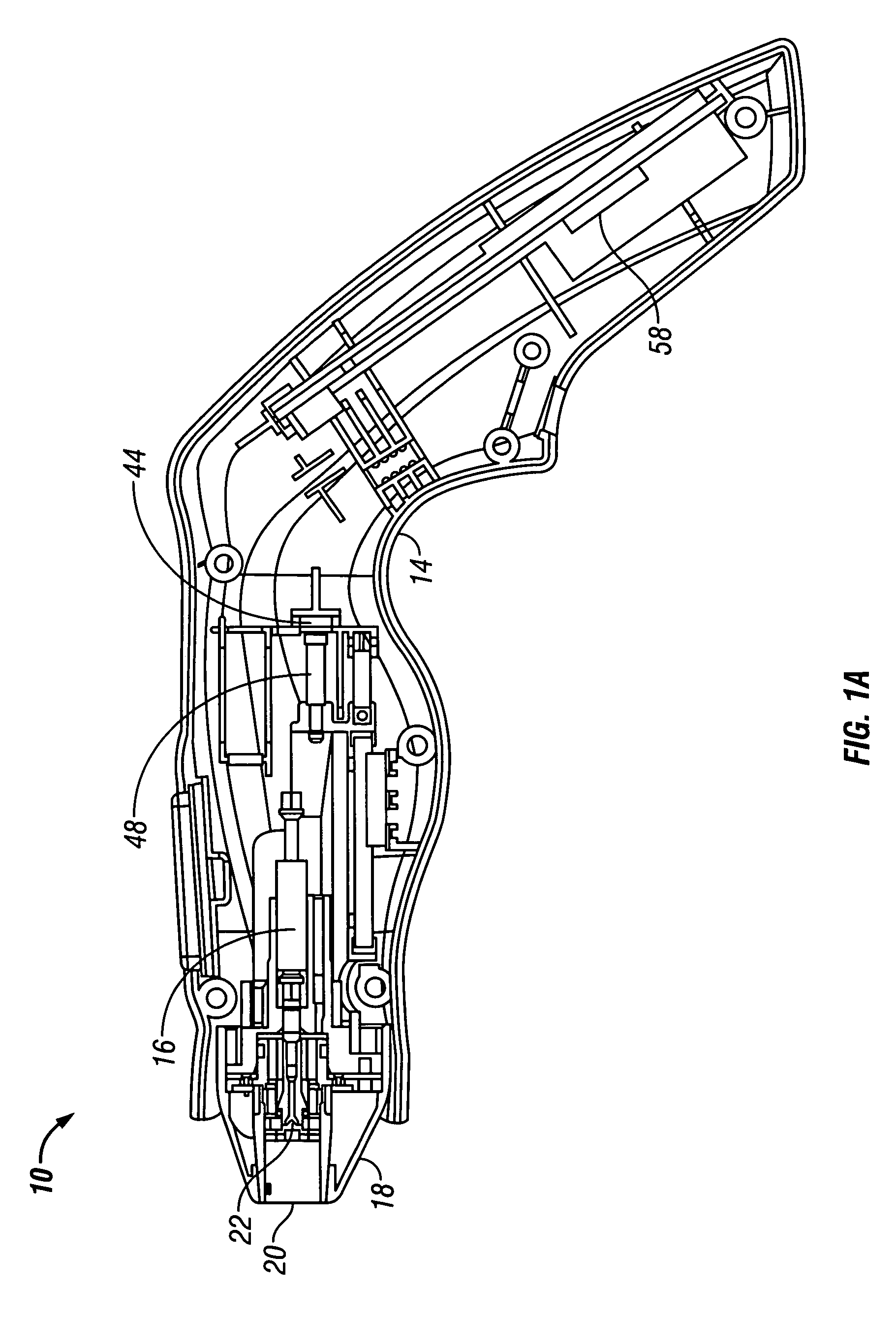

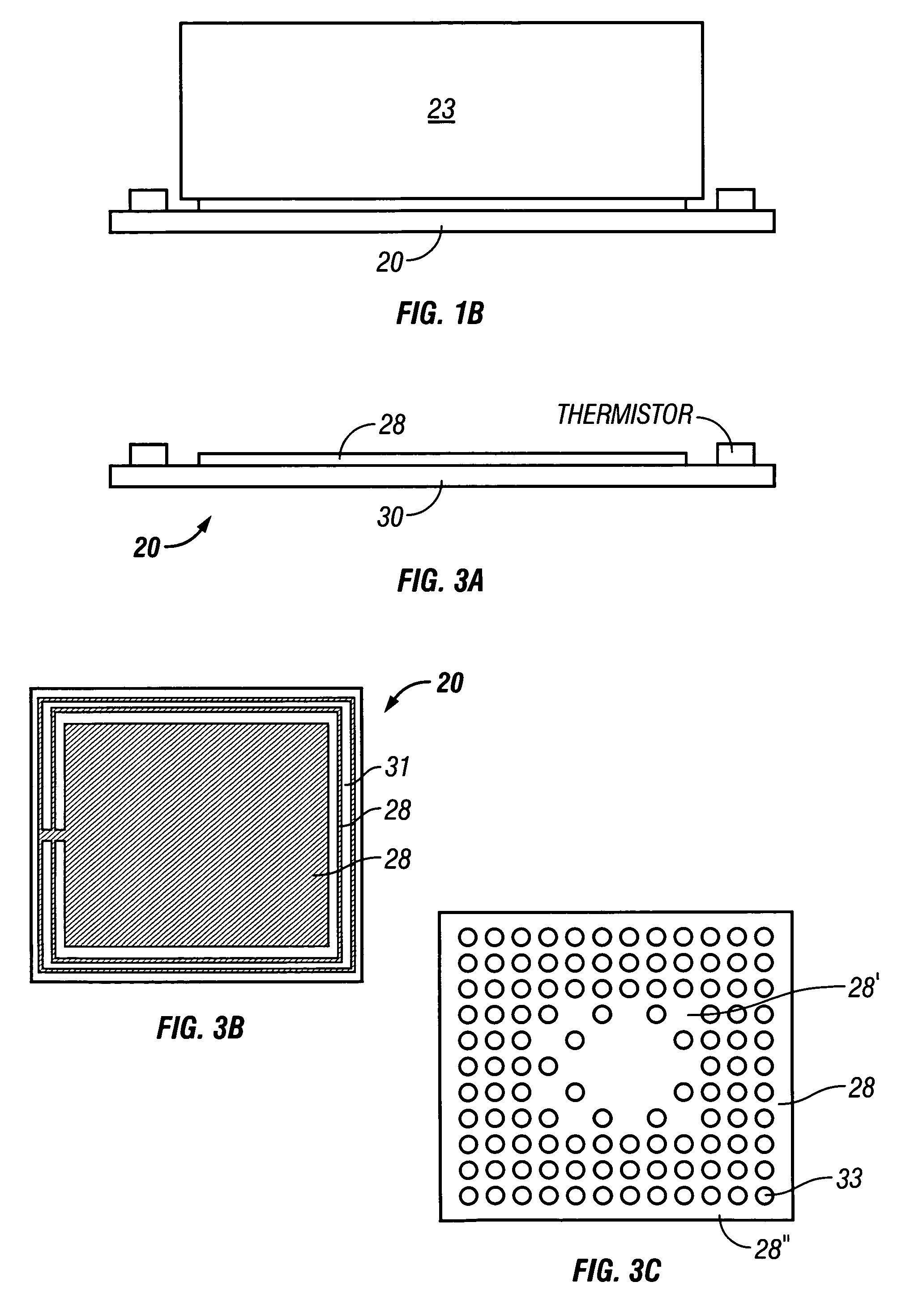

Handpiece with electrode and non-volatile memory

InactiveUS7115123B2Assist in treatmentElectrotherapyPneumatic massageSkin surfaceNon-volatile memory

An apparatus for cooling a skin surface includes an RF device that has an RF electrode with dielectric and conductive portions. The RF device is configured to be coupled to an RF energy source. A cooling member is coupled to the RF device. A memory is coupled to the RF device. The memory is configured to store information to facilitate operation of at least one of the RF electrode, the cooling member, and the RF energy source.

Owner:THERMAGE INC

Maintaining erase counts in non-volatile storage systems

InactiveUS20040080985A1Memory architecture accessing/allocationMemory adressing/allocation/relocationData structureVolatile memory

Methods and apparatus for storing erase counts in a non-volatile memory of a non-volatile memory system are disclosed. According to one aspect of the present invention, a data structure in a non-volatile memory includes a first indicator that provides an indication of a number of times a first block of a plurality of blocks in a non-volatile memory has been erased. The data structure also includes a header that is arranged to contain information relating to the blocks in the non-volatile memory.

Owner:SANDISK TECH LLC

Programming method to reduce gate coupling interference for non-volatile memory

Owner:MICRON TECH INC

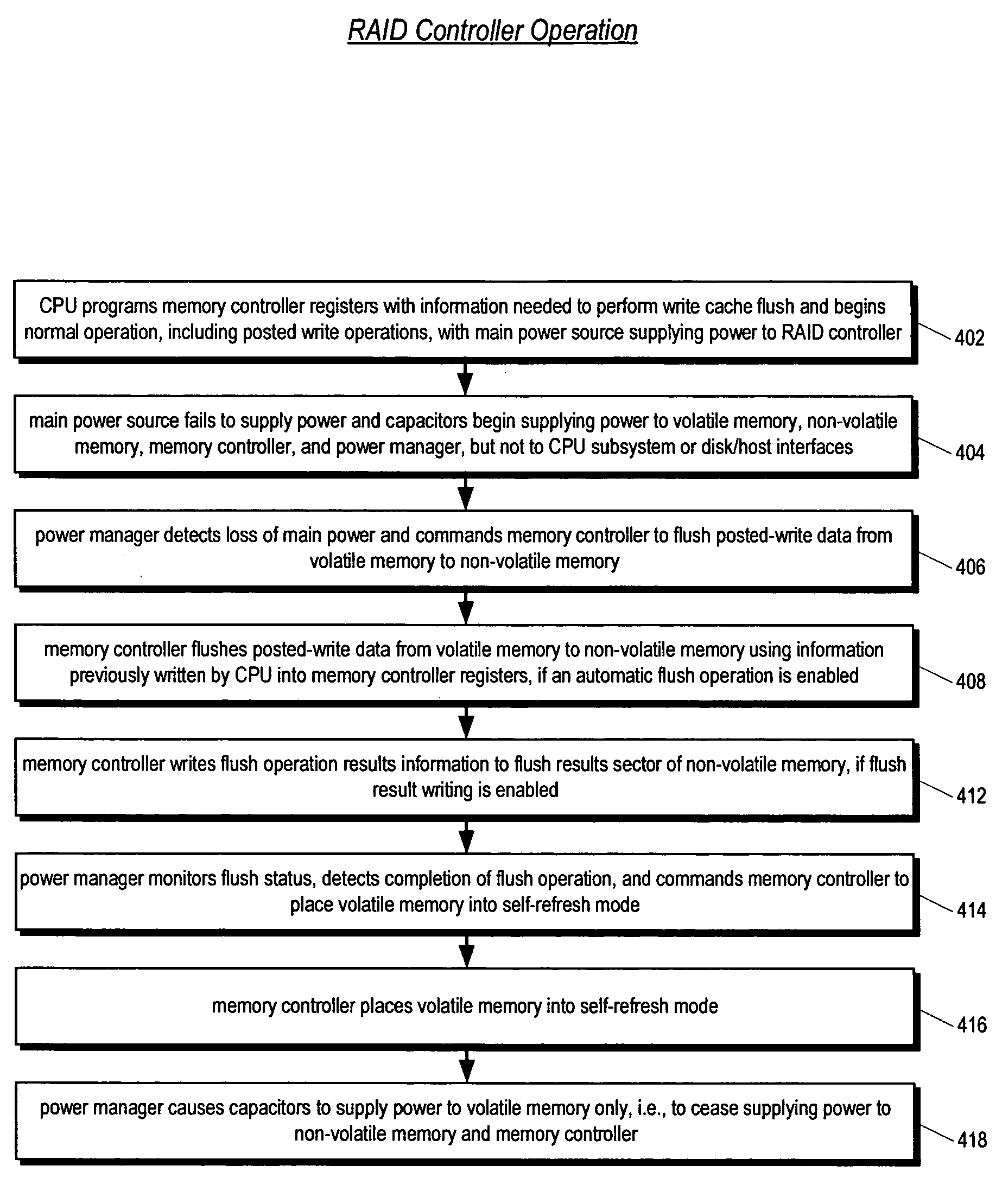

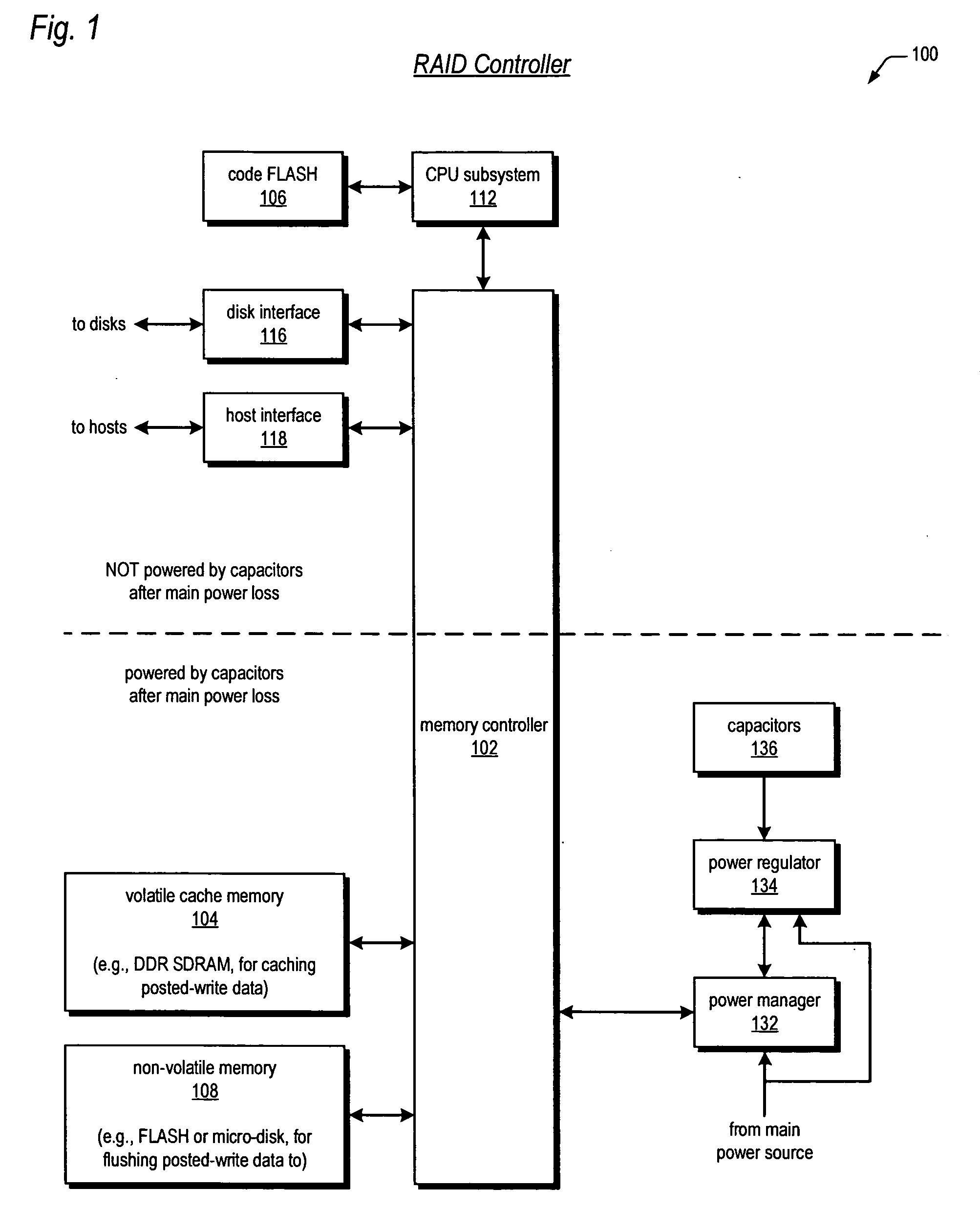

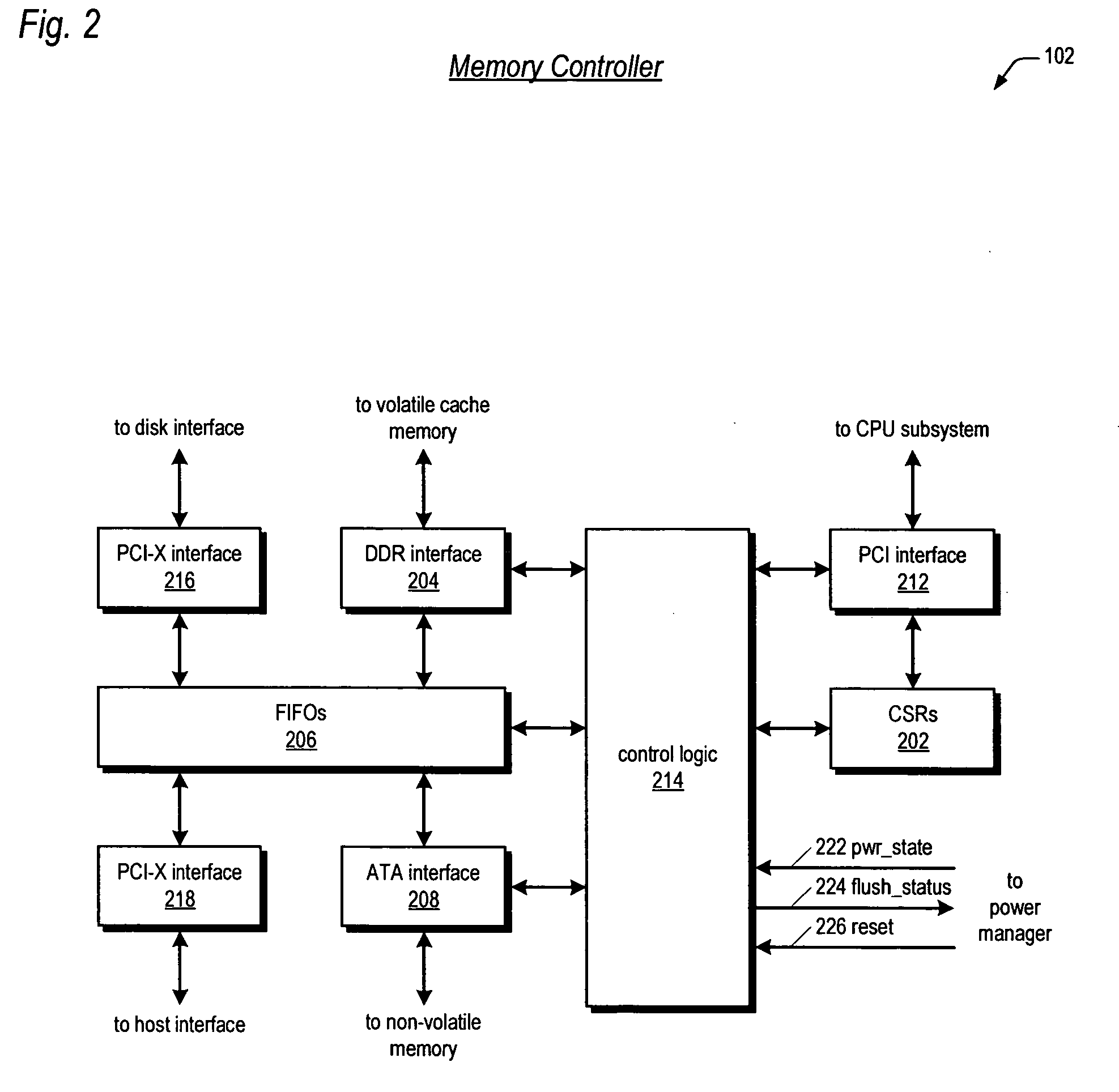

Raid controller using capacitor energy source to flush volatile cache data to non-volatile memory during main power outage

InactiveUS20060015683A1Reduces amount of energy storage capacity requirementLess expensiveEnergy efficient ICTMemory loss protectionRAIDStored energy

A write-caching RAID controller is disclosed. The controller includes a CPU that manages transfers of posted-write data from host computers to a volatile memory and transfers of the posted-write data from the volatile memory to storage devices when a main power source is supplying power to the RAID controller. A memory controller flushes the posted-write data from the volatile memory to the non-volatile memory when main power fails, during which time capacitors provide power to the memory controller, volatile memory, and non-volatile memory, but not to the CPU, in order to reduce the energy storage requirements of the capacitors. During main power provision, the CPU programs the memory controller with information needed to perform the flush operation, such as the location and size of the posted-write data in the volatile memory and various flush operation characteristics.

Owner:DOT HILL SYST

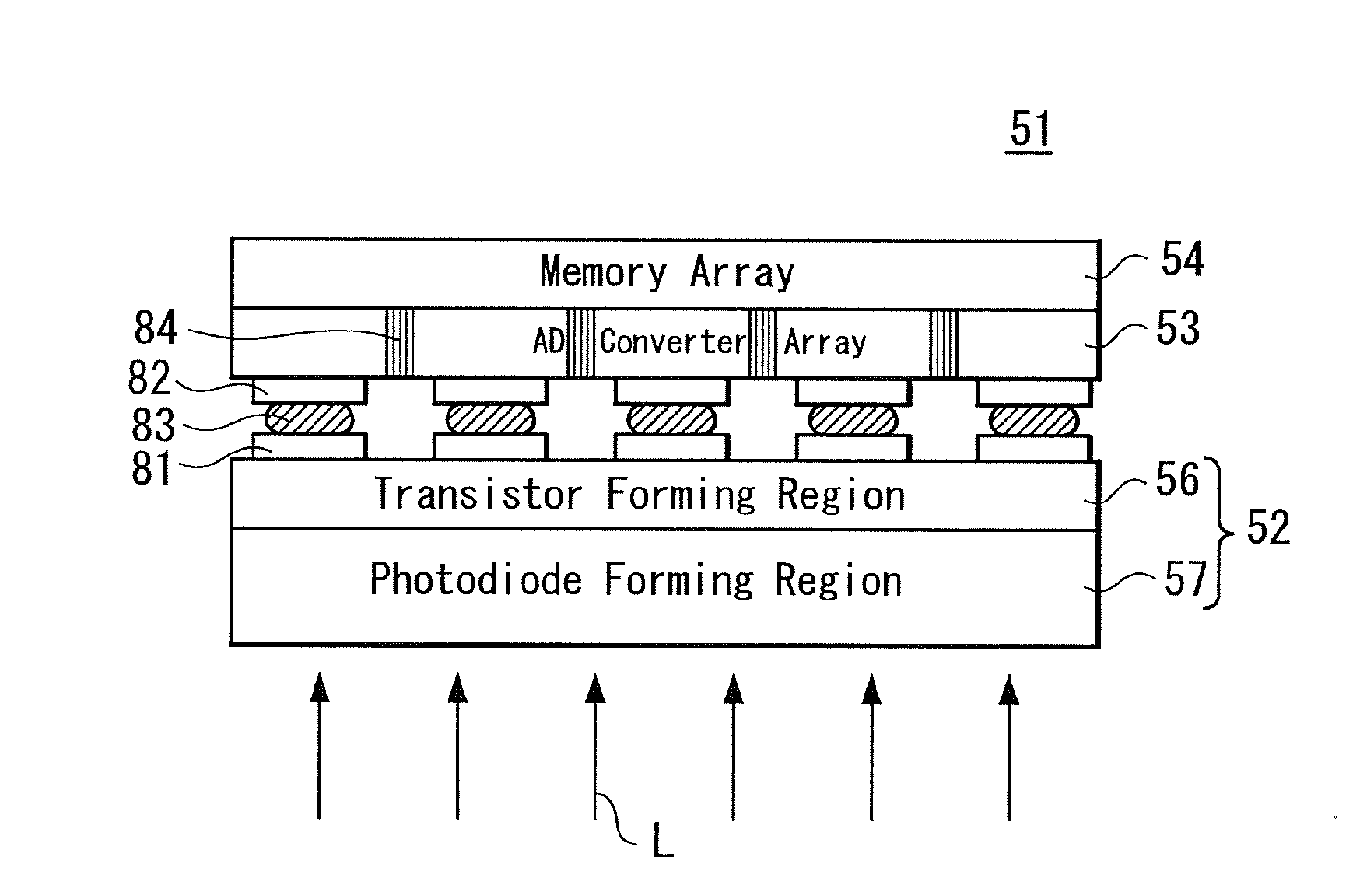

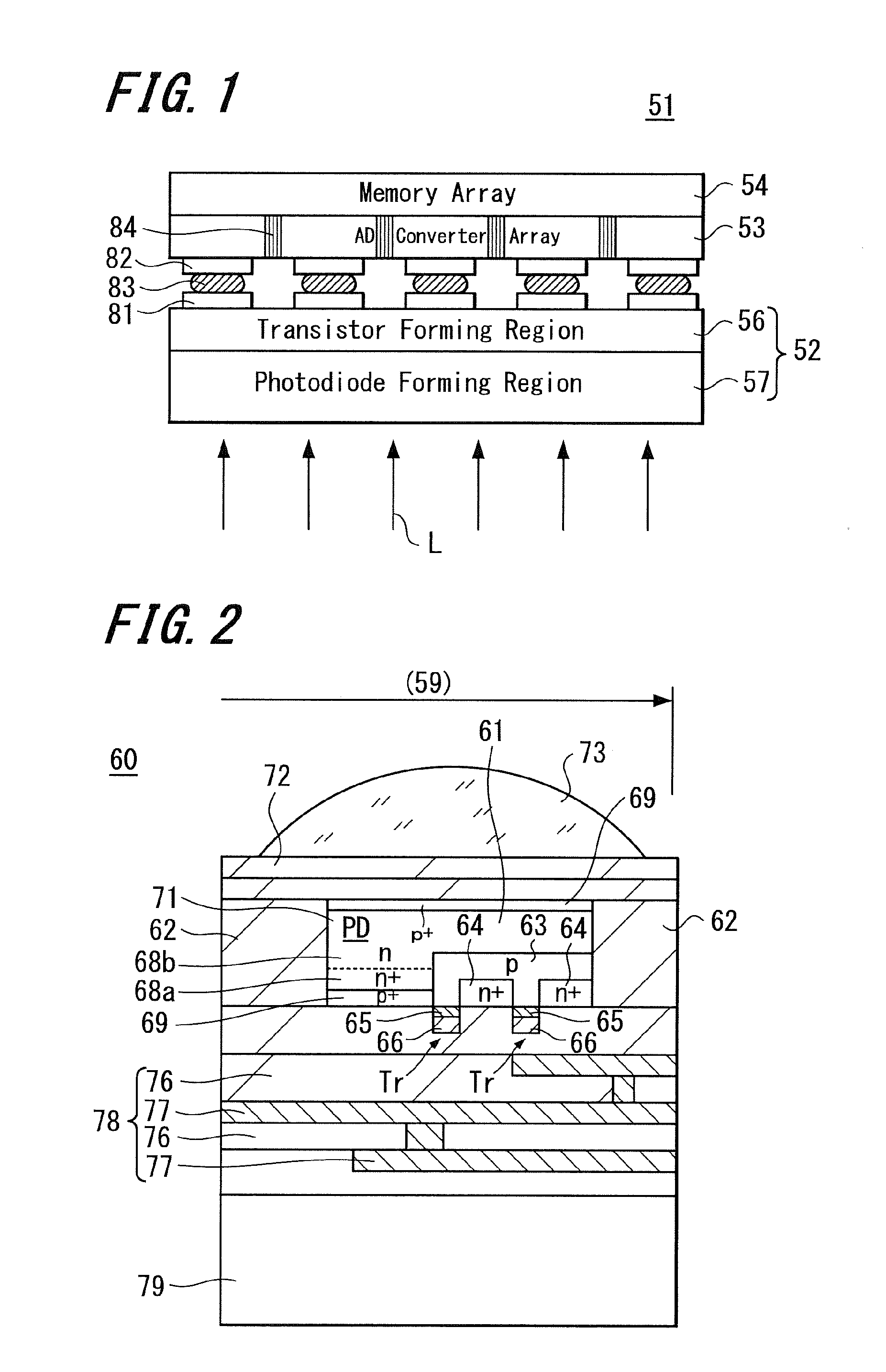

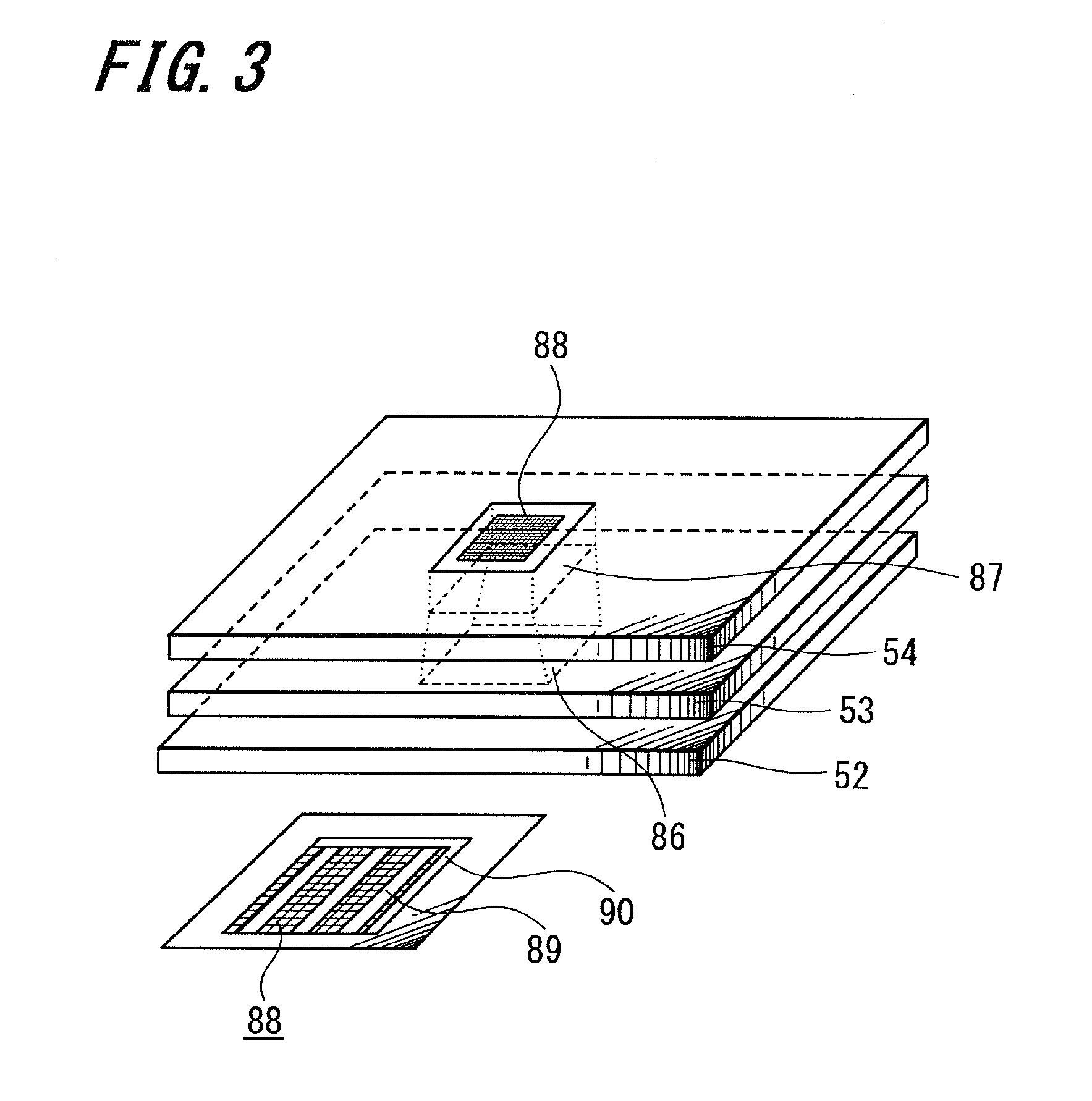

Semiconductor image sensor module and method of manufacturing the same

ActiveUS20100276572A1Increase the aperture ratioIncrease profitTransistorTelevision system detailsCMOSSemiconductor chip

A CMOS type semiconductor image sensor module wherein a pixel aperture ratio is improved, chip use efficiency is improved and furthermore, simultaneous shutter operation by all the pixels is made possible, and a method for manufacturing such semiconductor image sensor module are provided. The semiconductor image sensor module is provided by stacking a first semiconductor chip, which has an image sensor wherein a plurality of pixels composed of a photoelectric conversion element and a transistor are arranged, and a second semiconductor chip, which has an A / D converter array. Preferably, the semiconductor image sensor module is provided by stacking a third semiconductor chip having a memory element array. Furthermore, the semiconductor image sensor module is provided by stacking the first semiconductor chip having the image sensor and a fourth semiconductor chip having an analog nonvolatile memory array.

Owner:SONY CORP

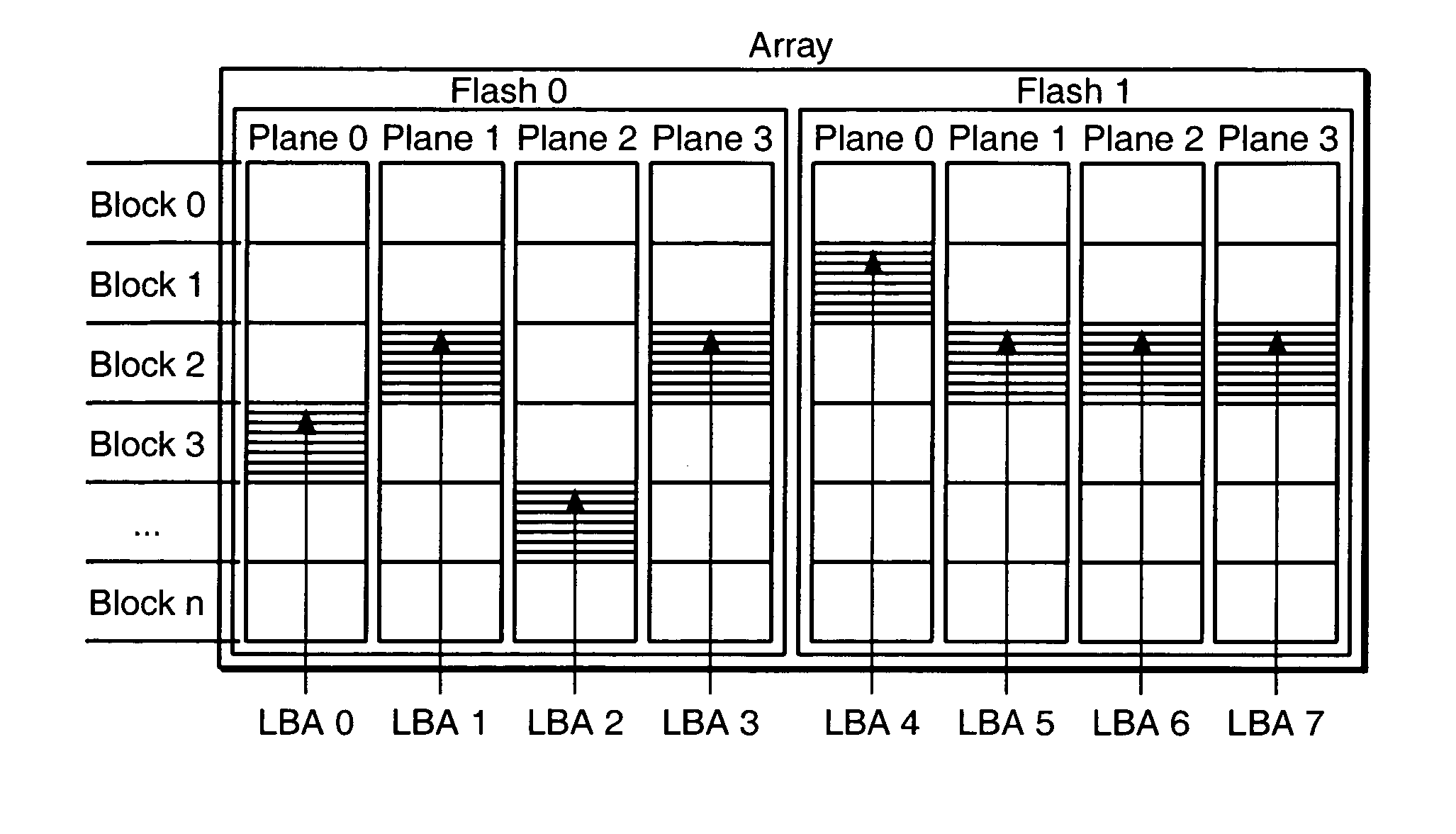

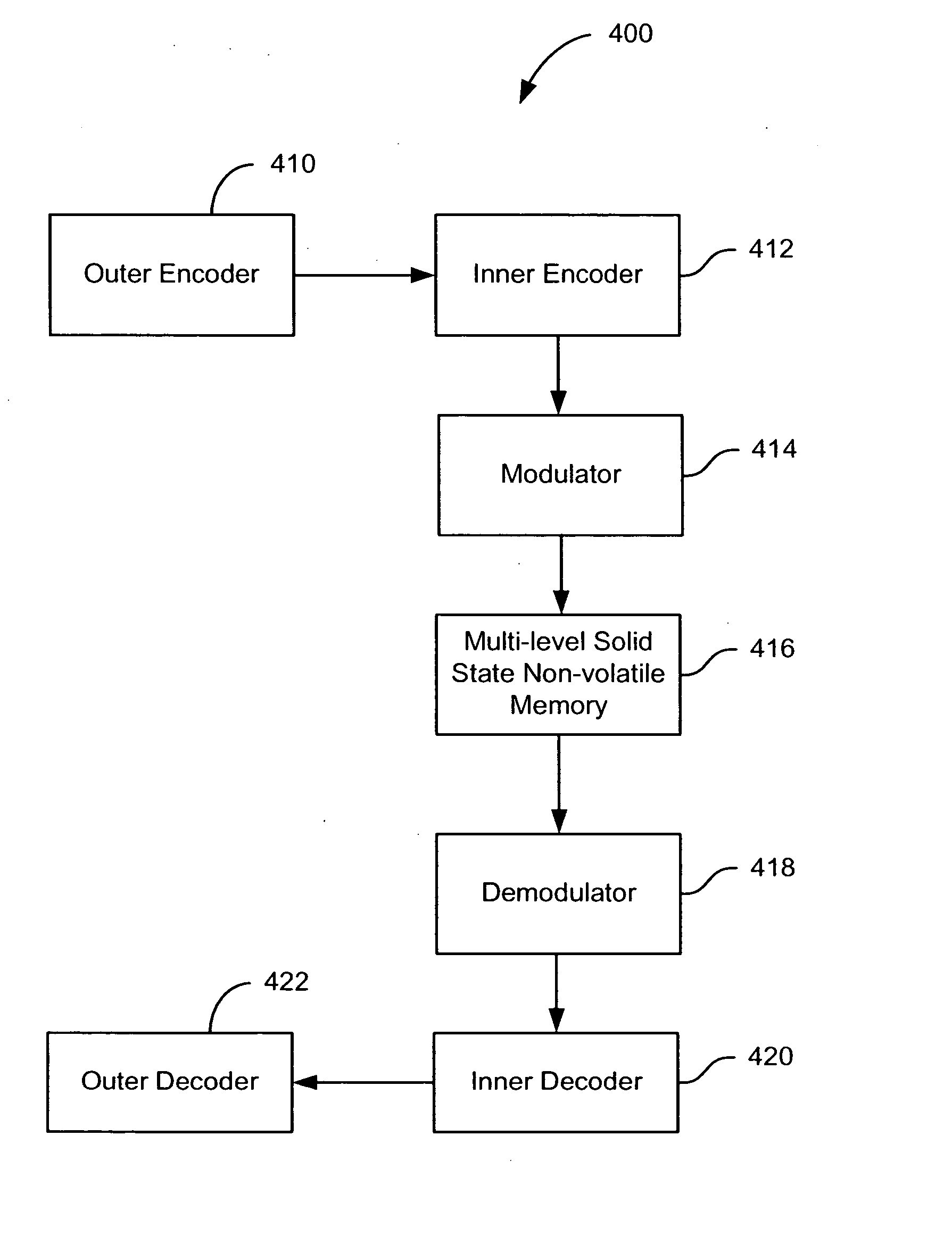

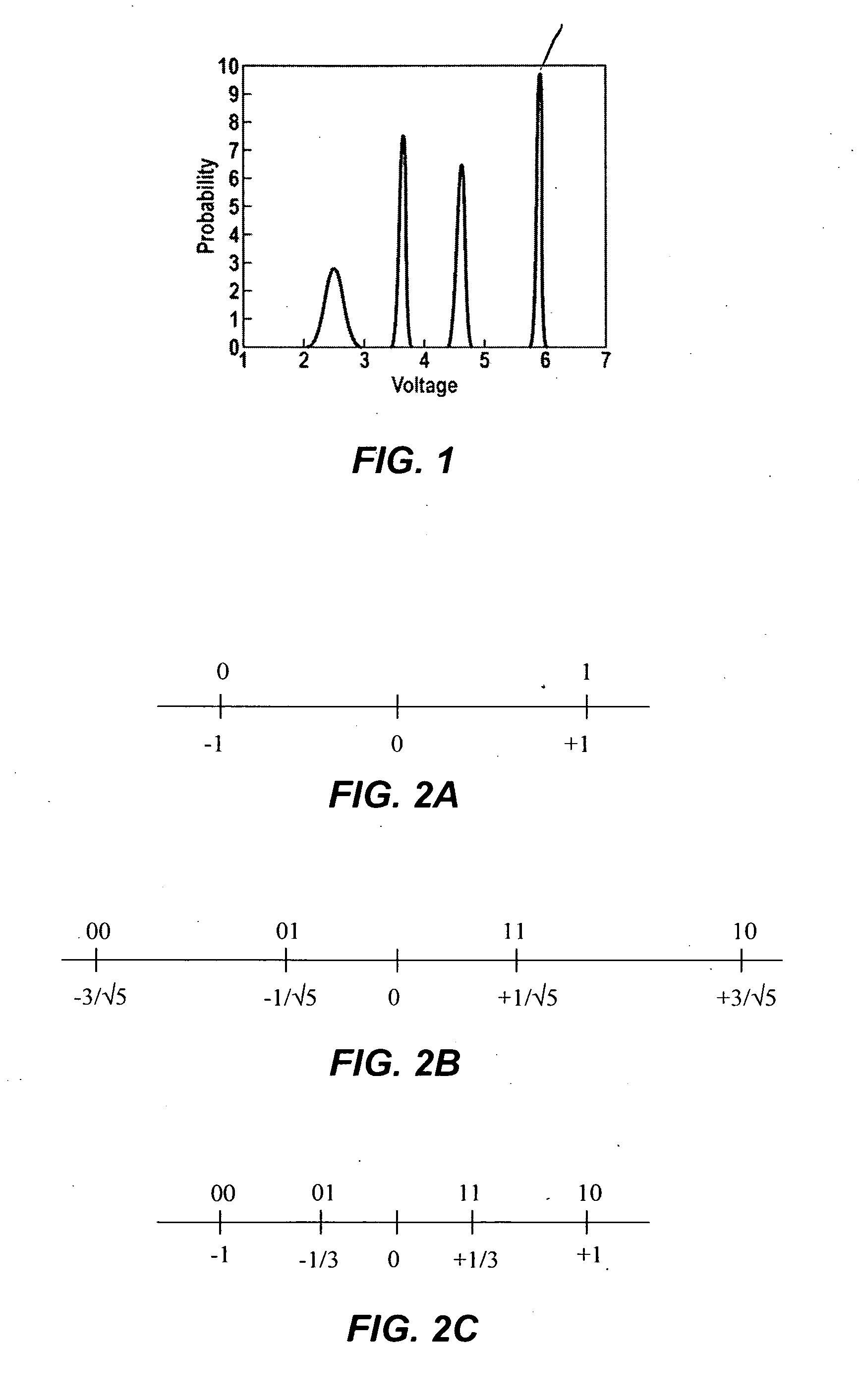

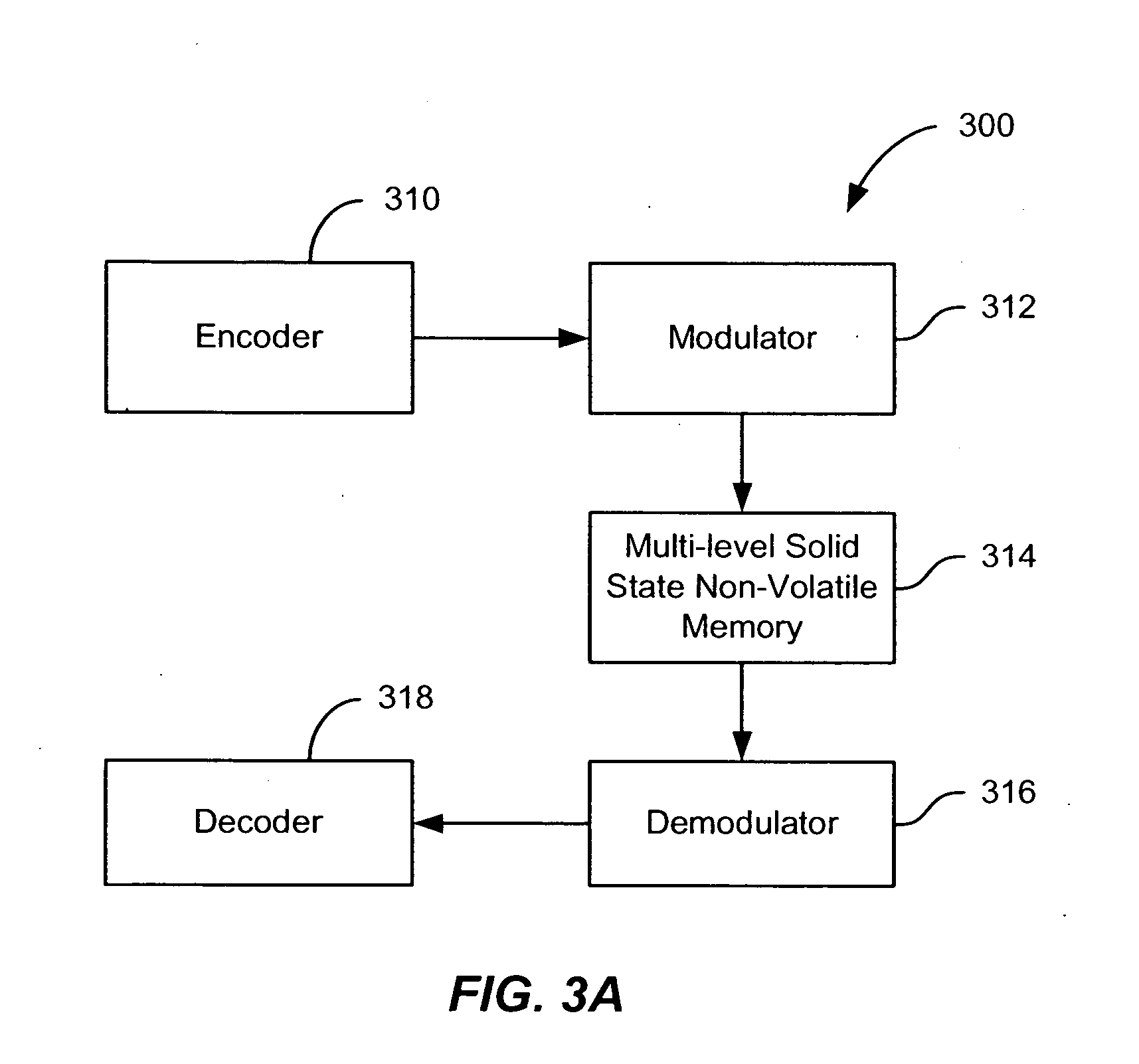

Flash memory with coding and signal processing

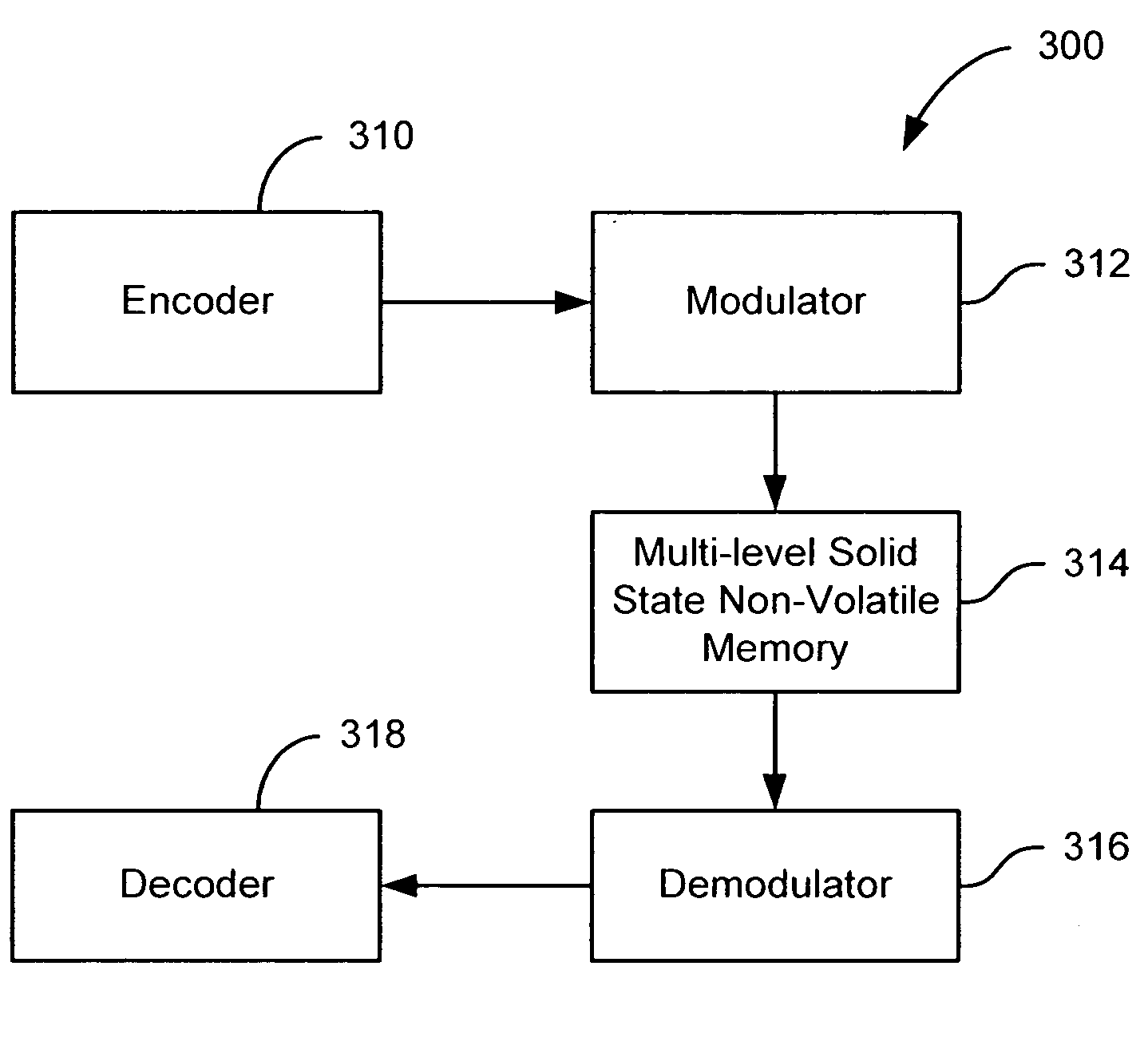

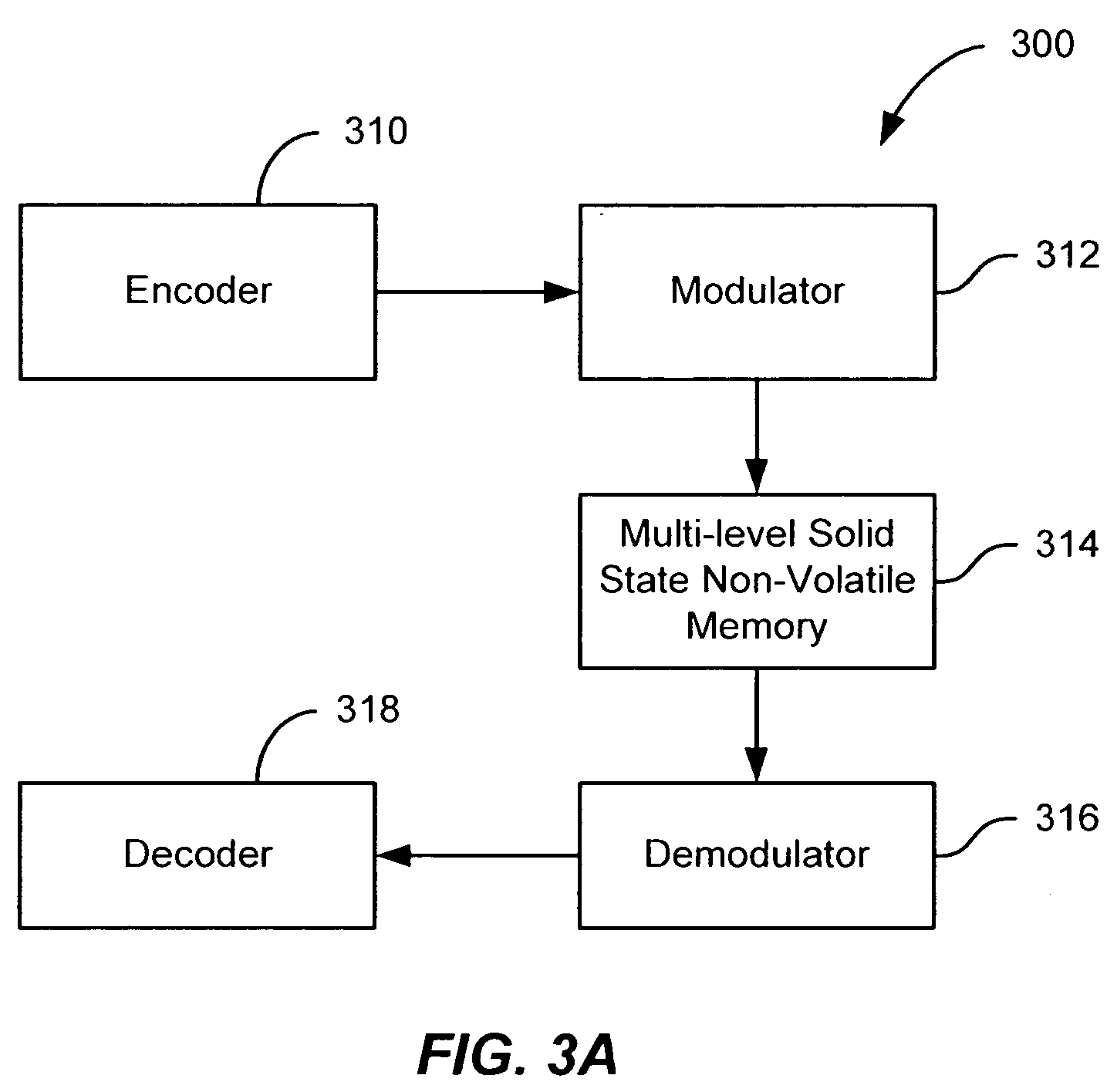

A solid state non-volatile memory unit includes, in part, an encoder, a multi-level solid state non-volatile memory array adapted to store data encoded by the encoder, and a decoder adapted to decode the data retrieved from the memory array. The memory array may be a flash EEPROM array. The memory unit optionally includes a modulator and a demodulator. The data modulated by the modulator is stored in the memory array. The demodulator demodulates the modulated data retrieved from the memory array.

Owner:MARVELL ASIA PTE LTD

Nonvolatile memory unit with specific cache

InactiveUS20050015557A1Reduce frequencyAvoid actionMemory architecture accessing/allocationInput/output to record carriersOperating systemVolatile memory

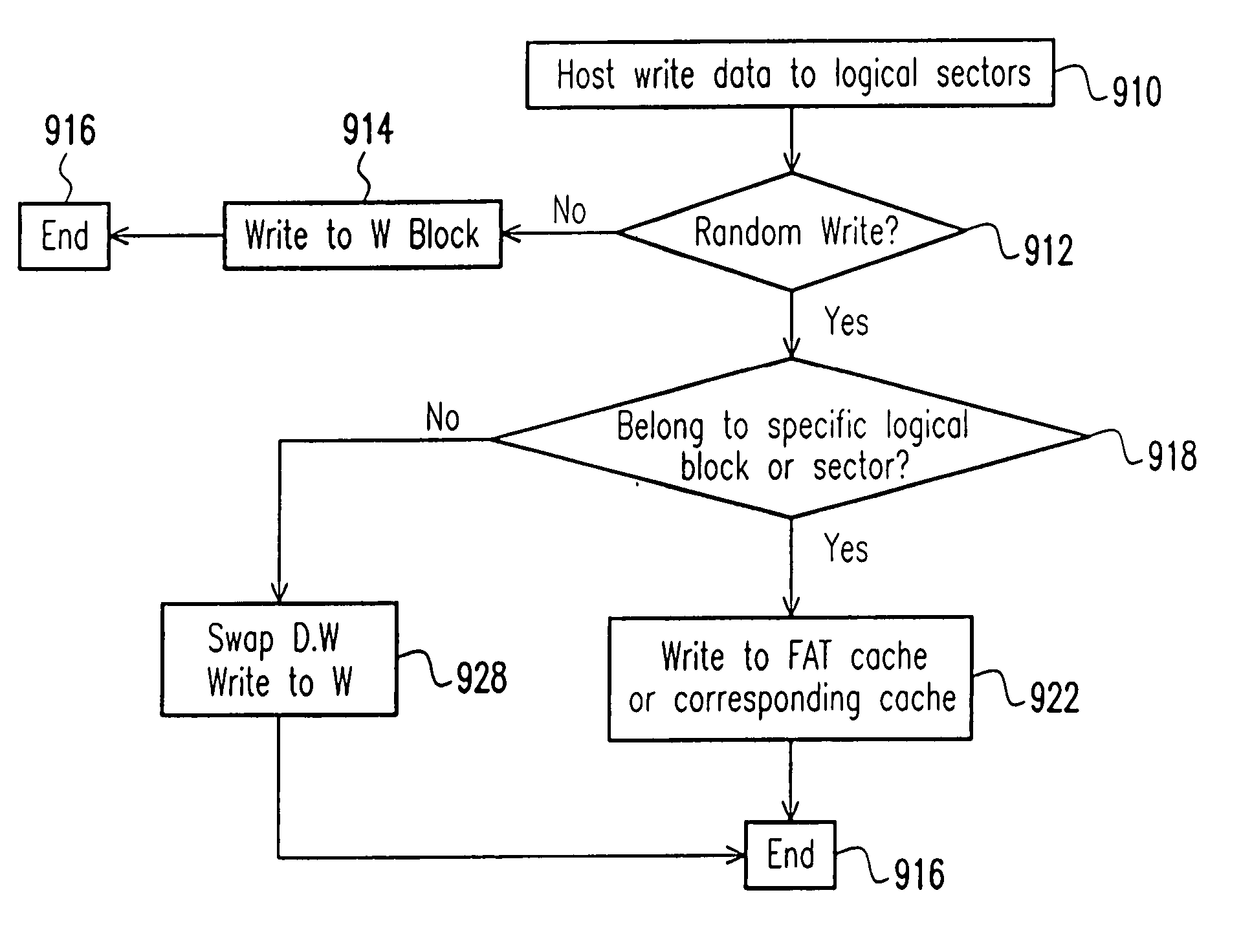

The invention provides a method for organizing a writing operation to a nonvolatile memory. The method comprises setting a specific cache area, into which a specific data belonging to a specific group of logical blocks is to be written. It is determined whether or not the writing operation is a random write. If the writing operation is the random write, then the following steps are performed: determining whether or not the writing operation is to write a data that is belonging to the specific group of logical blocks; and writing the data into the specific cache area if the data is belonging to the specific group of logical blocks. As a result, a swap action between a data block and a writing block can be avoided during a random write operation. A storage structure in a nonvolatile memory device are organized to perform the forgoing writing operation.

Owner:SOLID STATE SYST

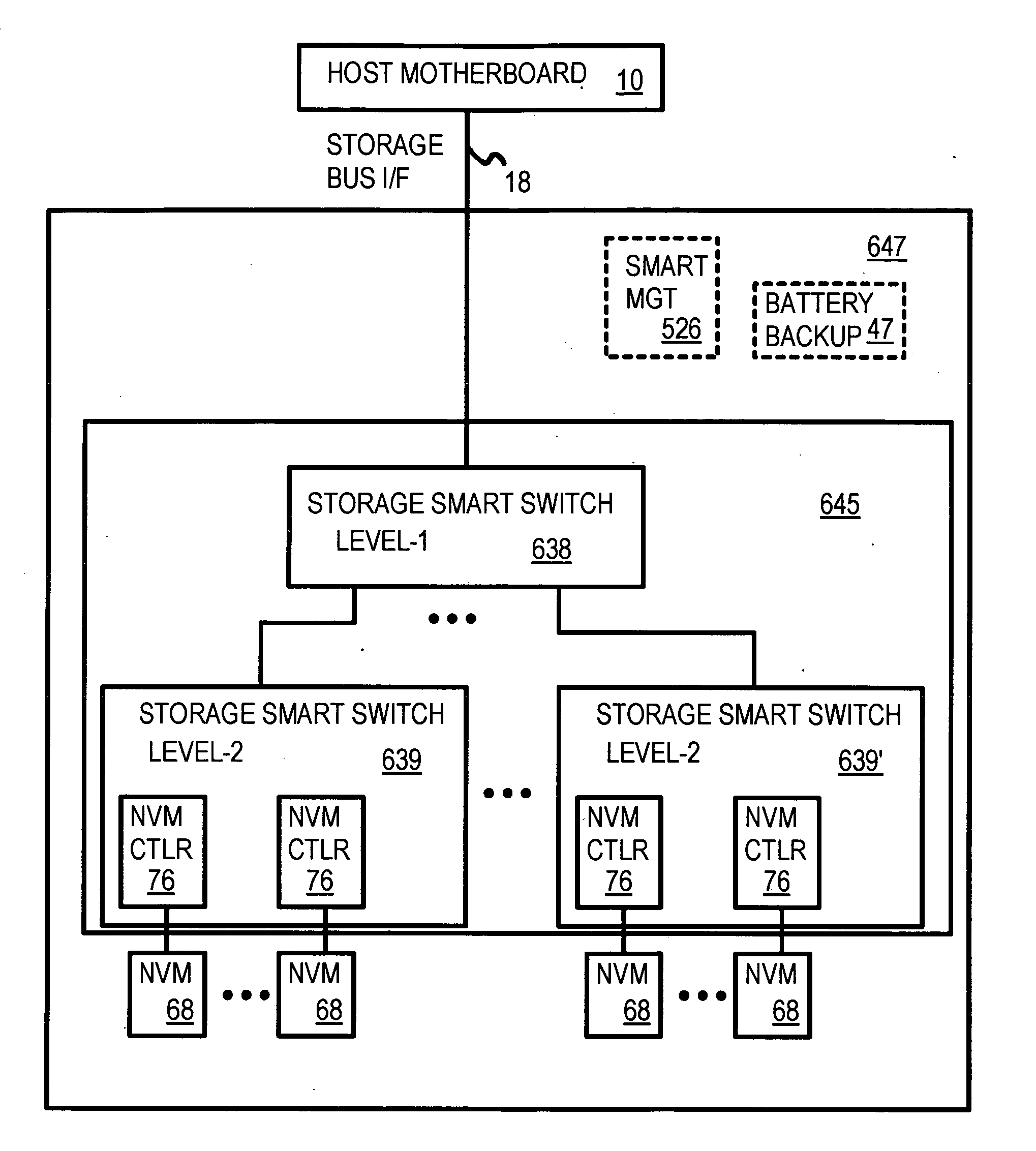

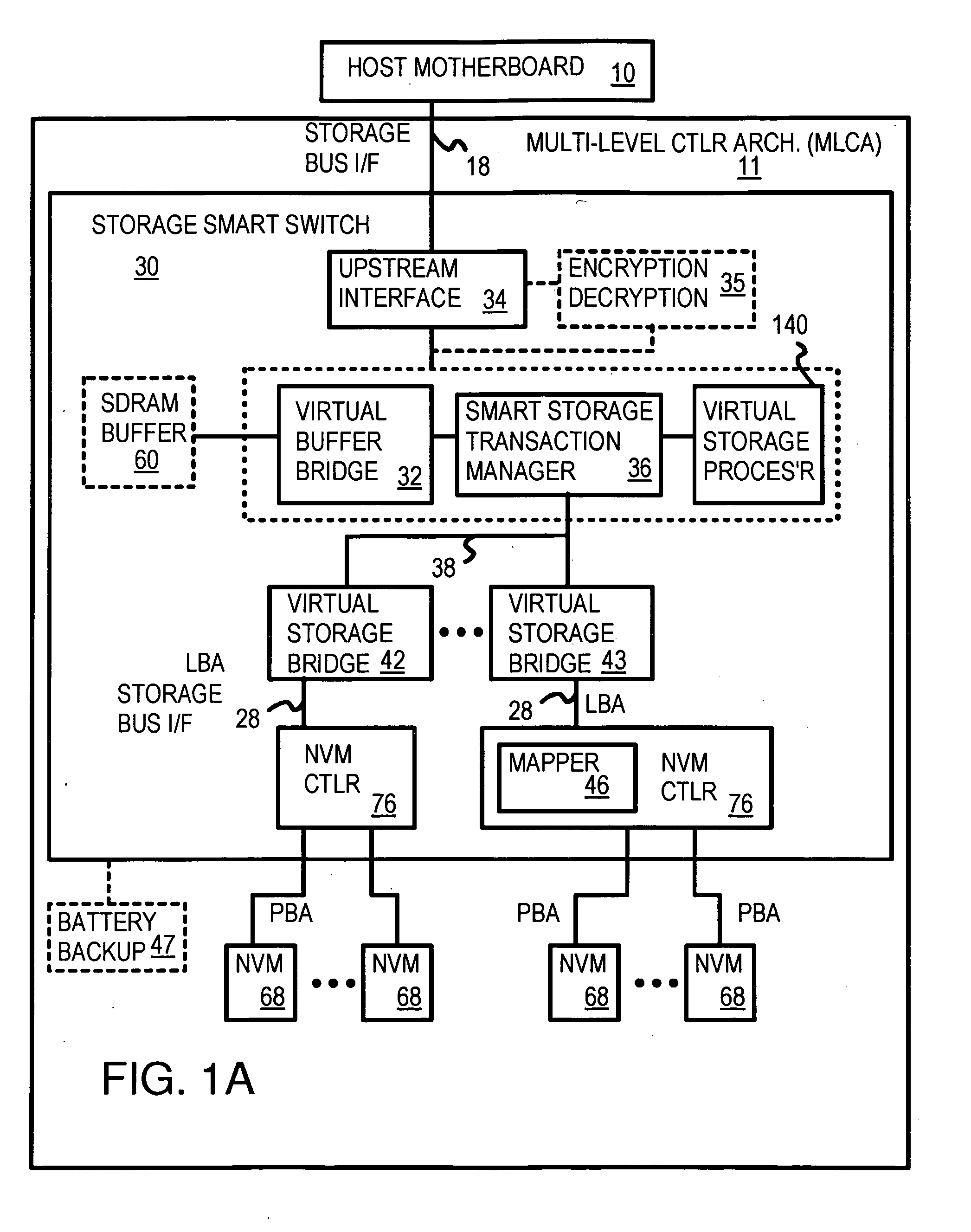

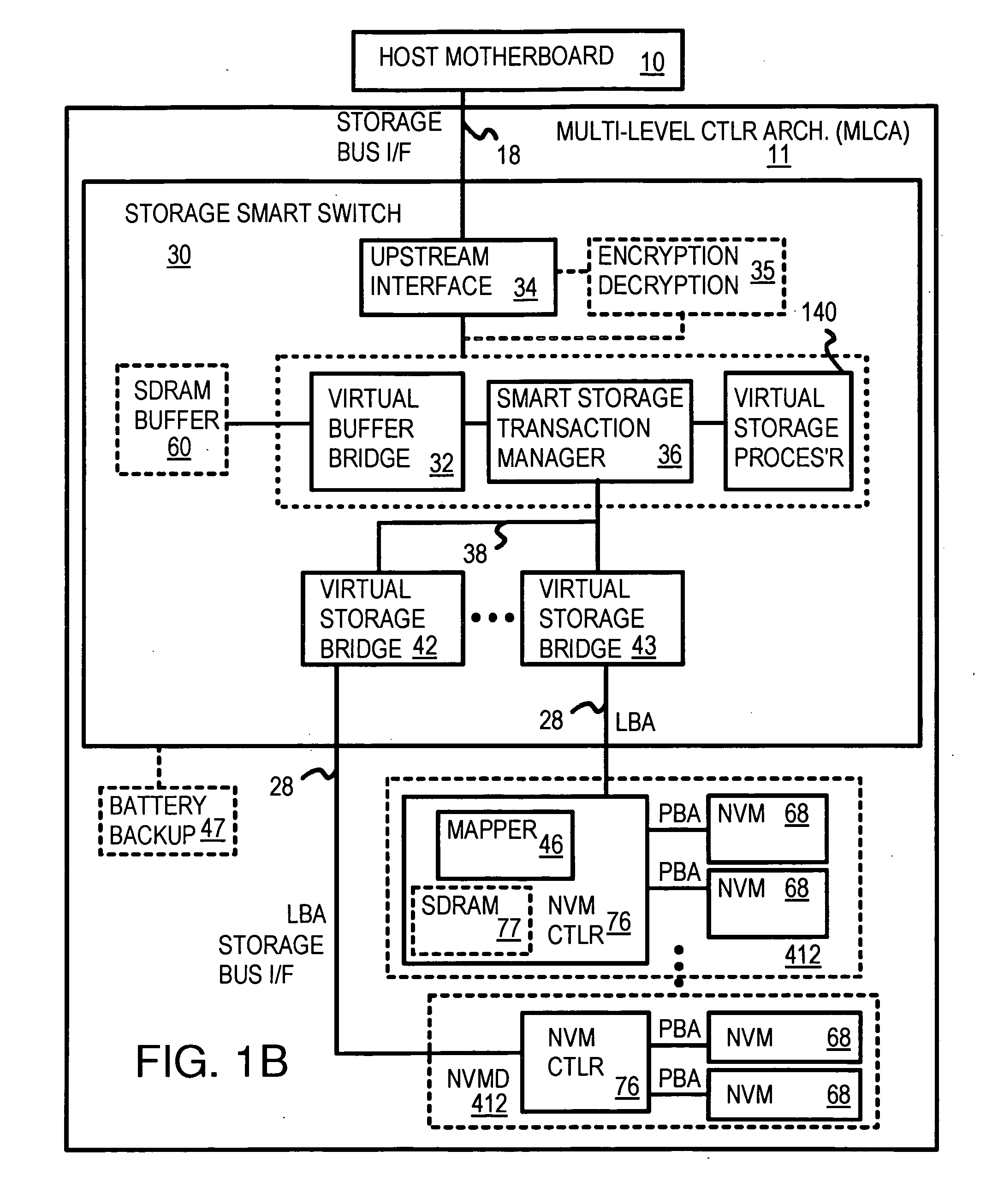

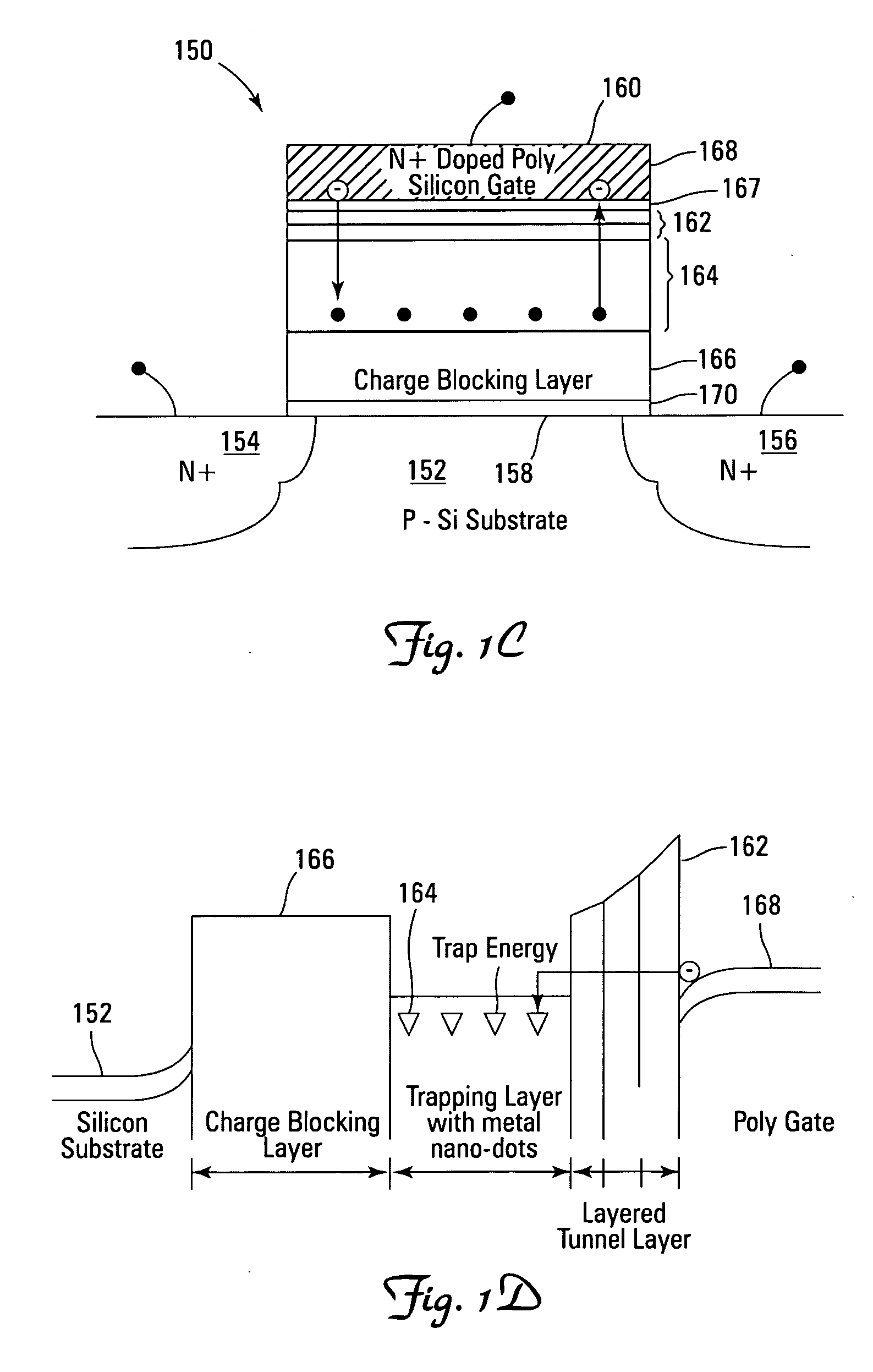

Multi-Level Striping and Truncation Channel-Equalization for Flash-Memory System

InactiveUS20090240873A1Memory architecture accessing/allocationError preventionLogical block addressingData access

Truncation reduces the available striped data capacity of all flash channels to the capacity of the smallest flash channel. A solid-state disk (SSD) has a smart storage switch salvages flash storage removed from the striped data capacity by truncation. Extra storage beyond the striped data capacity is accessed as scattered data that is not striped. The size of the striped data capacity is reduced over time as more bad blocks appear. A first-level striping map stores striped and scattered capacities of all flash channels and maps scattered and striped data. Each flash channel has a Non-Volatile Memory Device (NVMD) with a lower-level controller that converts logical block addresses (LBA) to physical block addresses (PBA) that access flash memory in the NVMD. Wear-leveling and bad block remapping are preformed by each NVMD. Source and shadow flash blocks are recycled by the NVMD. Two levels of smart storage switches enable three-level controllers.

Owner:SUPER TALENT TECH CORP

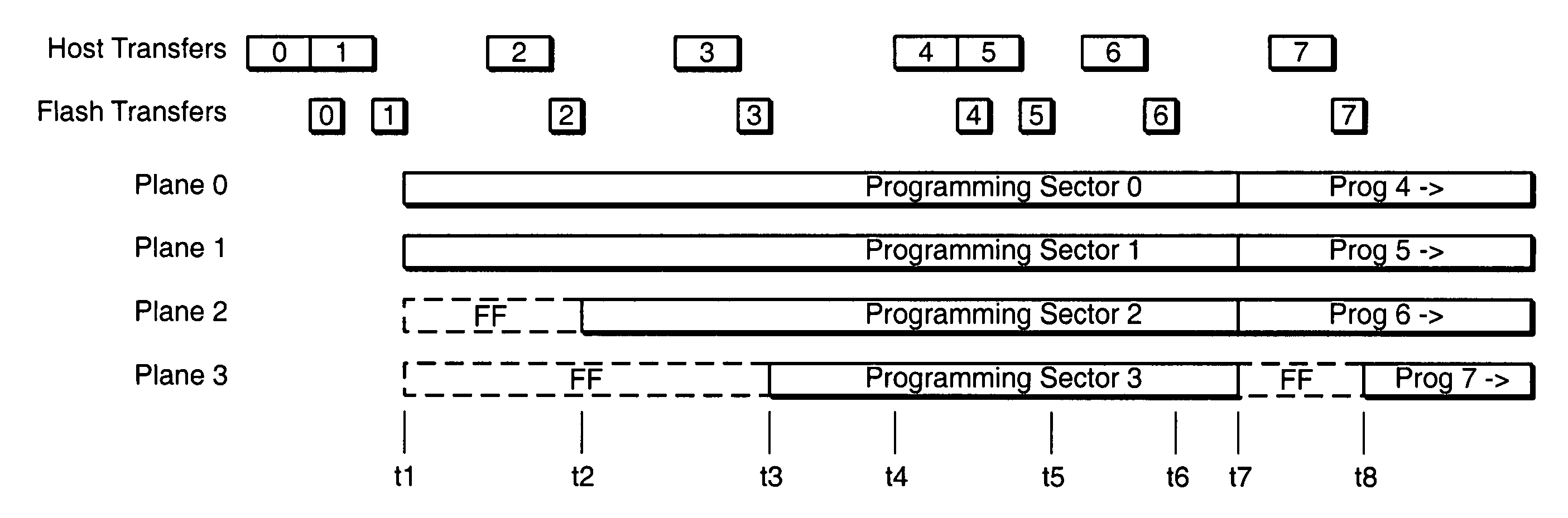

Pipelined programming of non-volatile memories using early data

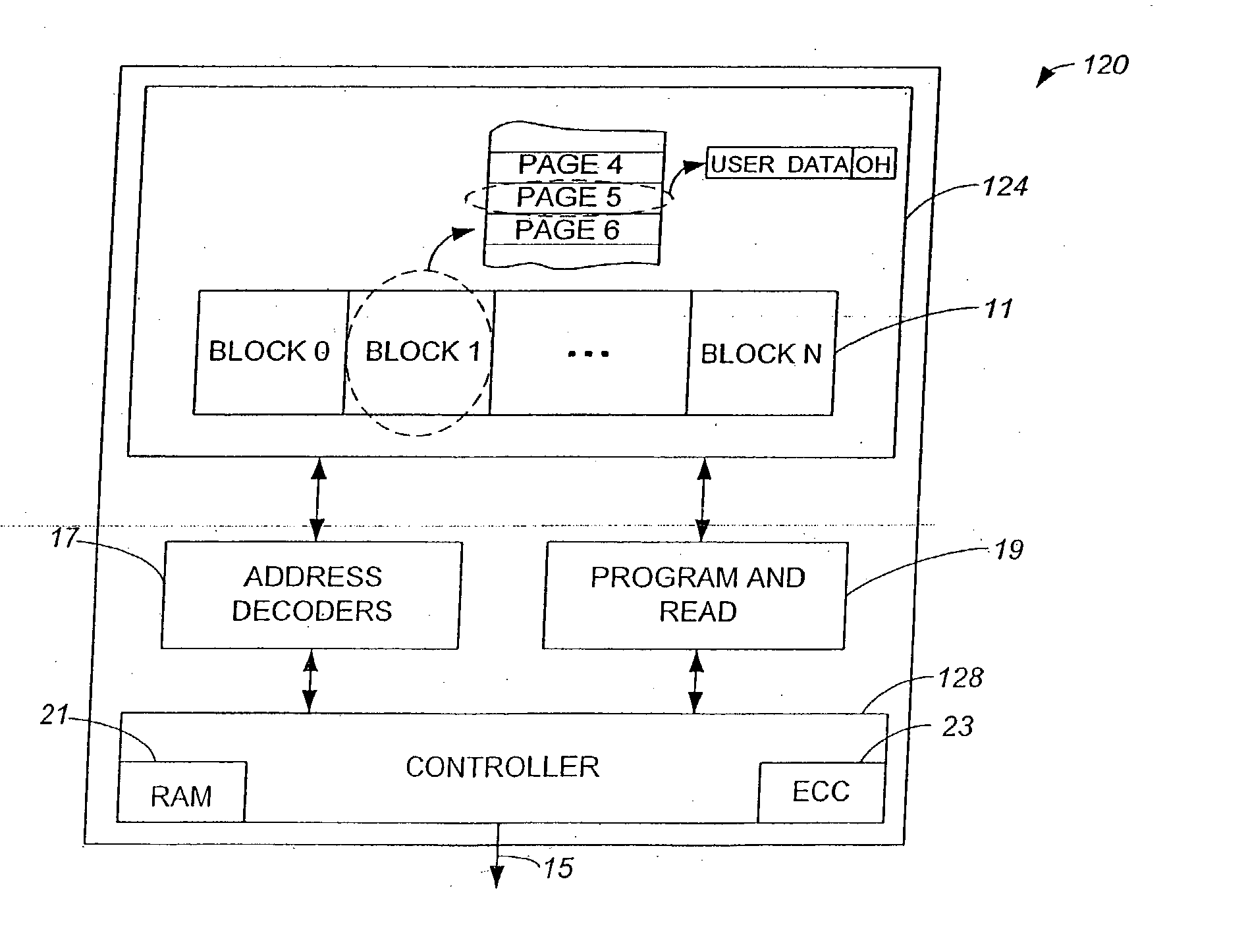

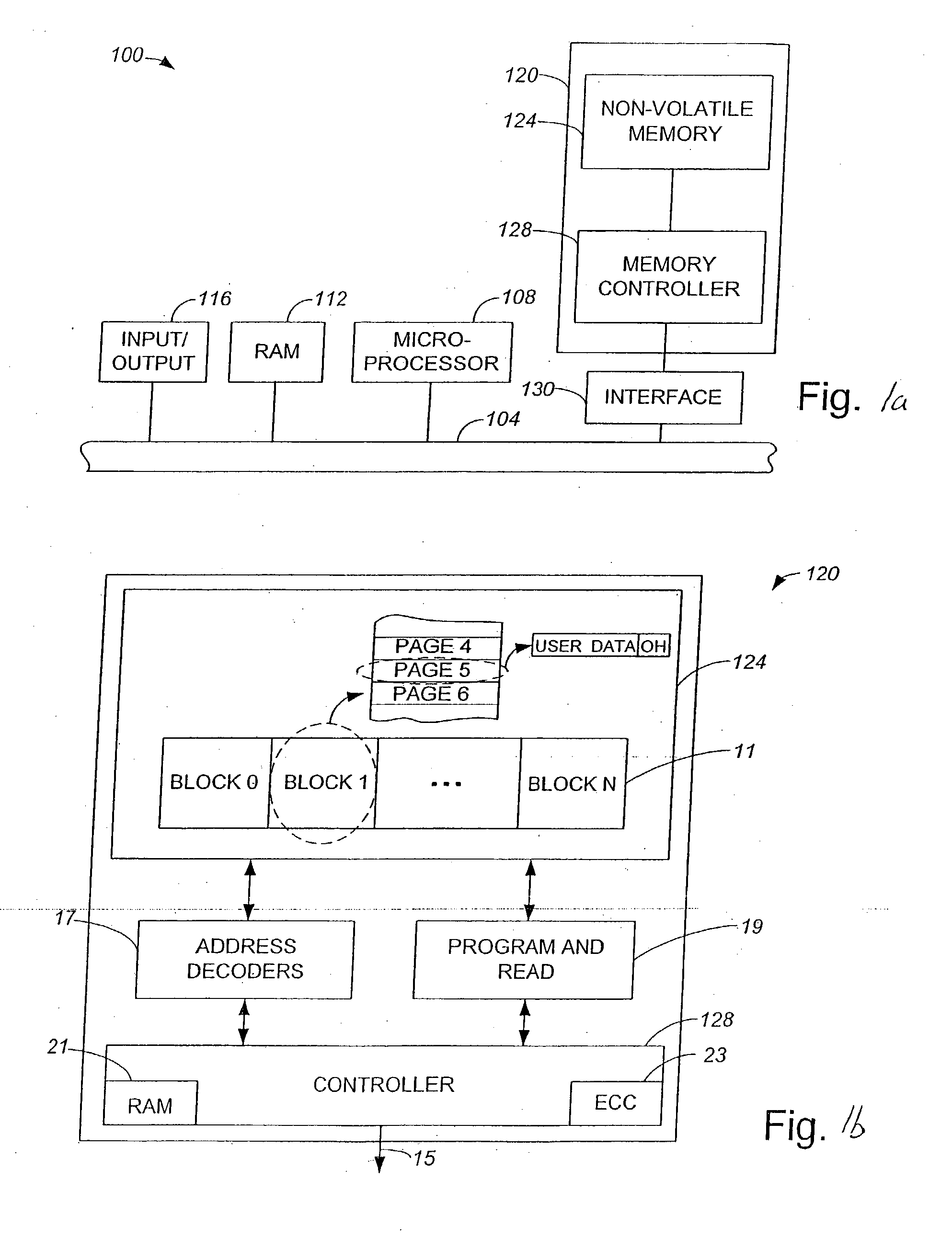

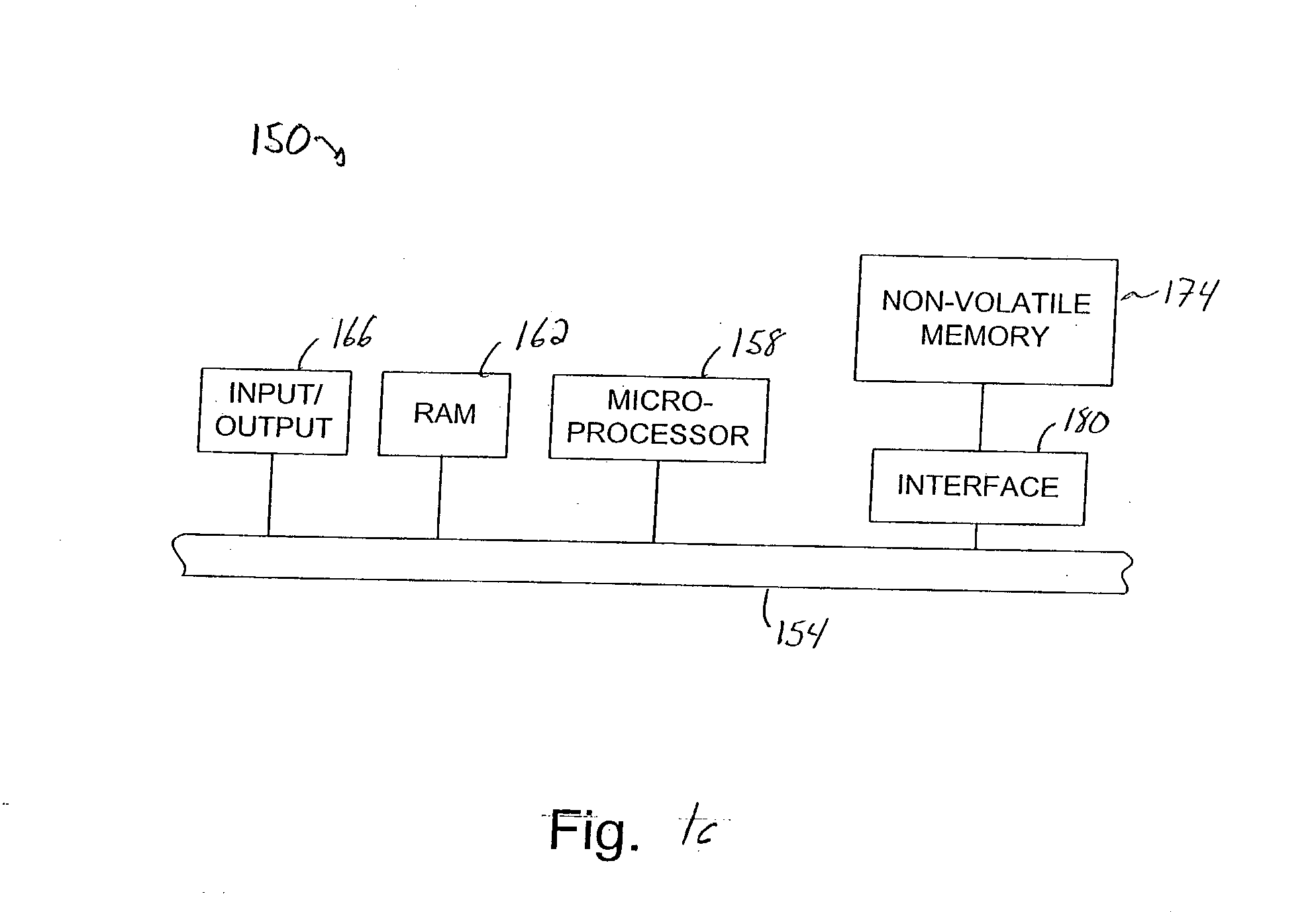

ActiveUS20060126390A1Improve performanceRead-only memoriesDigital storageFull dataProgramming process

The present invention presents techniques whereby a memory system interrupts a programming process and restarts it including additional data. More specifically, when a memory system programs data into a group of cells together as programming unit, programming can begin with less than the full data content which the group can hold. In one embodiment, the present invention allows overlapped programming of upper and lower data pages, where once the memory begins programming the lower logical data page, if data is received for the upper page assigned to the same physical page, programming is interrupted and recommenced with the concurrent programming of both the upper and the loser pages. In a complimentary embodiment, when a page contains multiple sectors of data, programming of the physical page can begin when one or more, but less than all, of the sectors forming the corresponding logical page have been received, stopped and restarted to include additional sectors of the page.

Owner:SANDISK TECH LLC

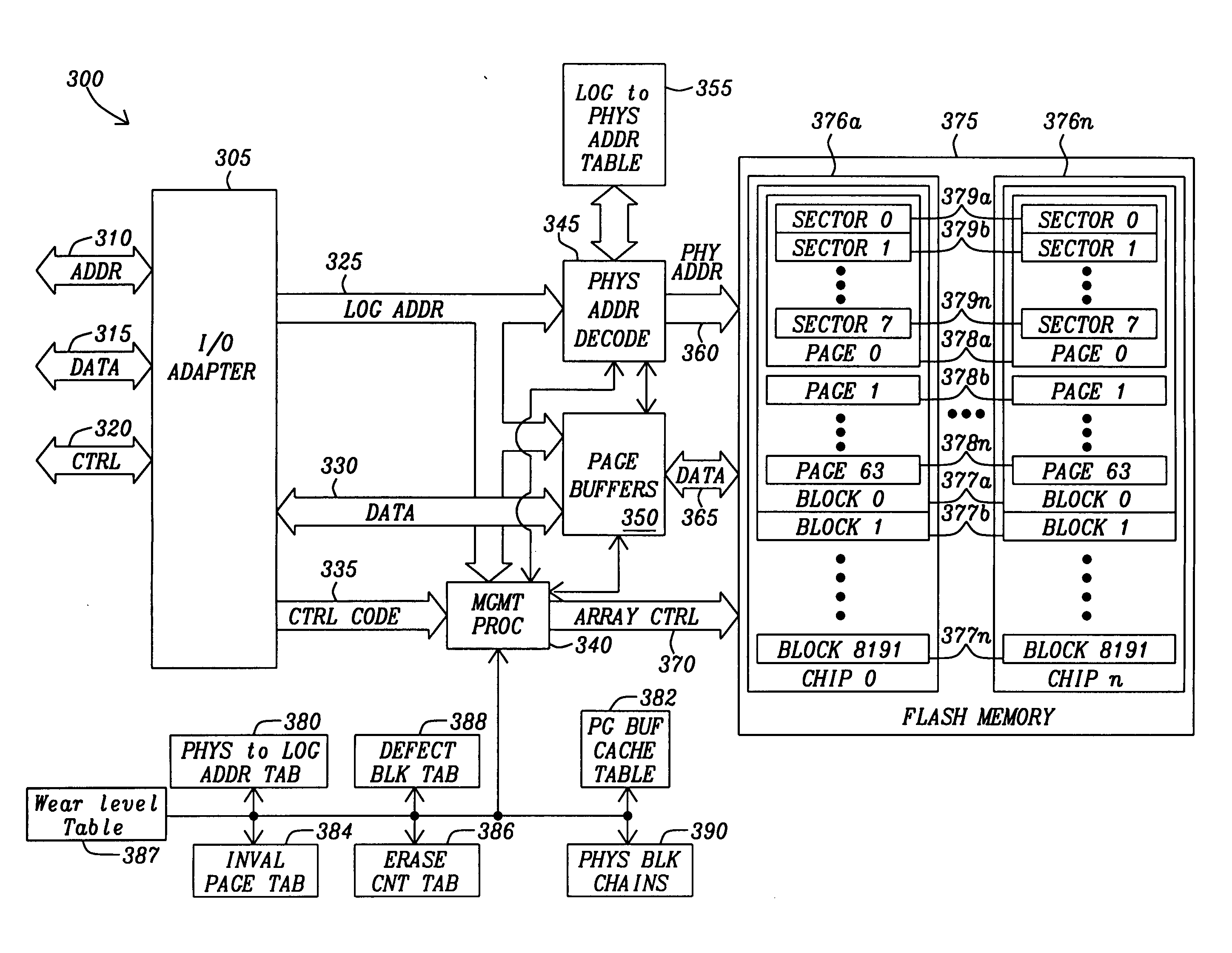

Page based management of flash storage

InactiveUS20110055458A1Memory architecture accessing/allocationMemory adressing/allocation/relocationControl signalPaging

Methods and circuits for page based management of an array of Flash RAM nonvolatile memory devices provide paged base reading and writing and block erasure of a flash storage system. The memory management system includes a management processor, a page buffer, and a logical-to-physical translation table. The management processor is in communication with an array of nonvolatile memory devices within the flash storage system to provide control signals for the programming of selected pages, erasing selected blocks, and reading selected pages of the array of nonvolatile memory devices.

Owner:PIONEER CHIP TECH

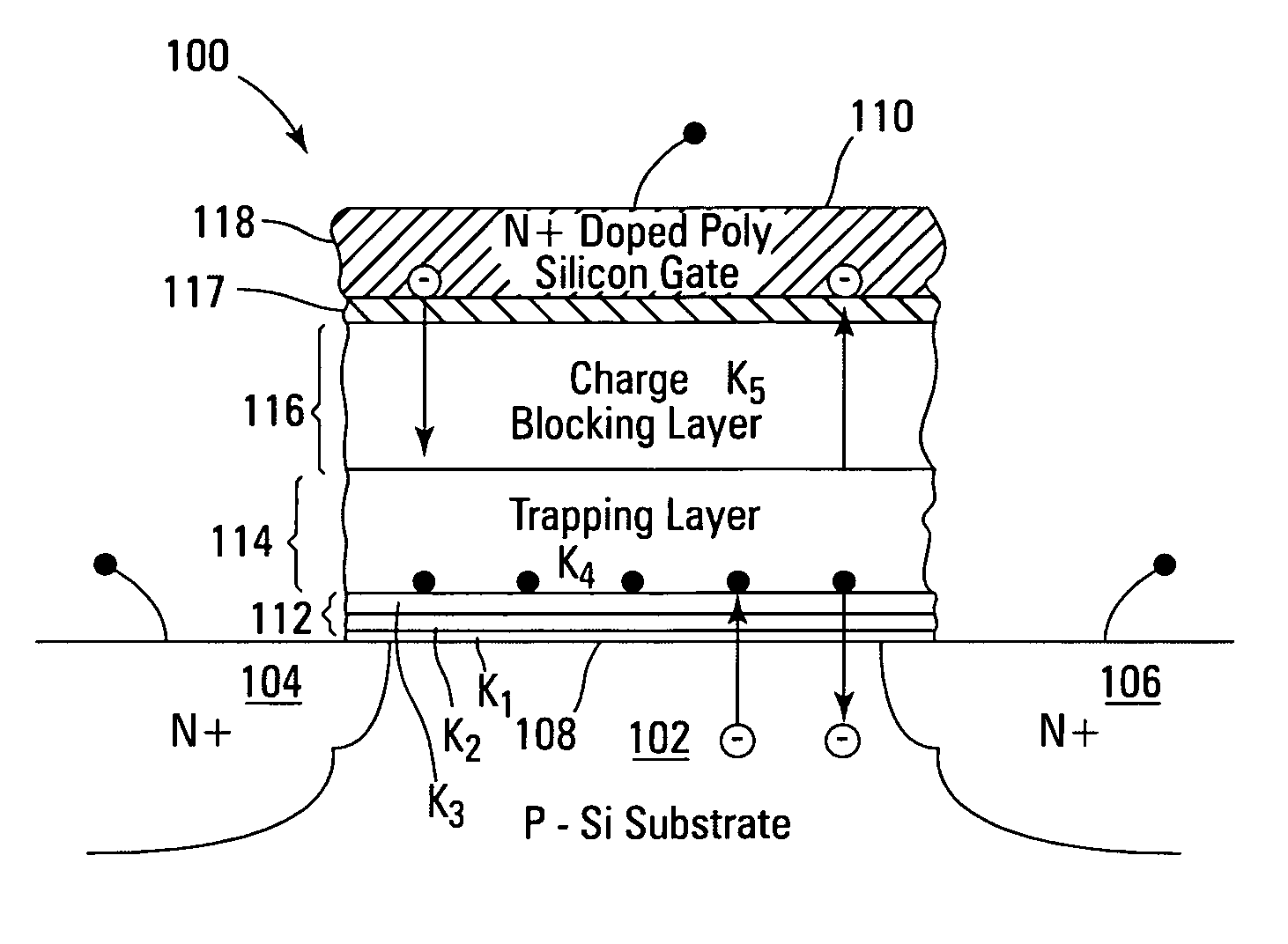

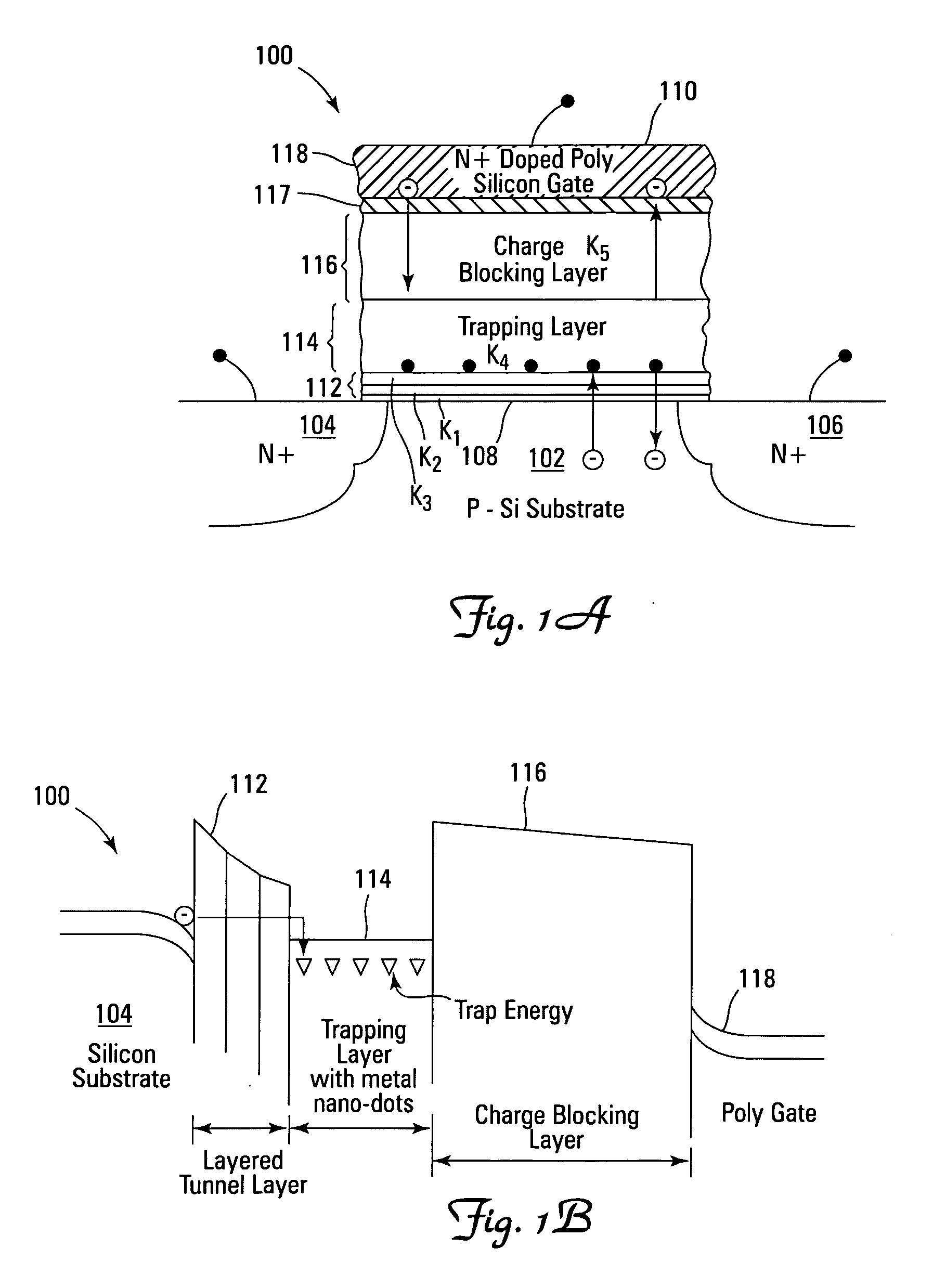

Novel low power non-volatile memory and gate stack

ActiveUS20060261401A1High charge blocking barrierExcellent charge retentionTransistorNanoinformaticsCharge retentionLow voltage

Non-volatile memory devices and arrays are described that facilitate the use of band-gap engineered gate stacks with asymmetric tunnel barriers in reverse and normal mode floating node memory cells in NOR or NAND memory architectures that allow for direct tunnel programming and erase, while maintaining high charge blocking barriers and deep carrier trapping sites for good charge retention. The low voltage direct tunneling program and erase capability reduces damage to the gate stack and the crystal lattice from high energy carriers, reducing write fatigue and enhancing device lifespan. The low voltage direct tunnel program and erase capability also enables size reduction through low voltage design and further device feature scaling. Memory cells of the present invention also allow multiple bit storage. These characteristics allow memory device embodiments of the present invention to operate within the definition of a universal memory, capable of replacing both DRAM and ROM in a system.

Owner:MICRON TECH INC

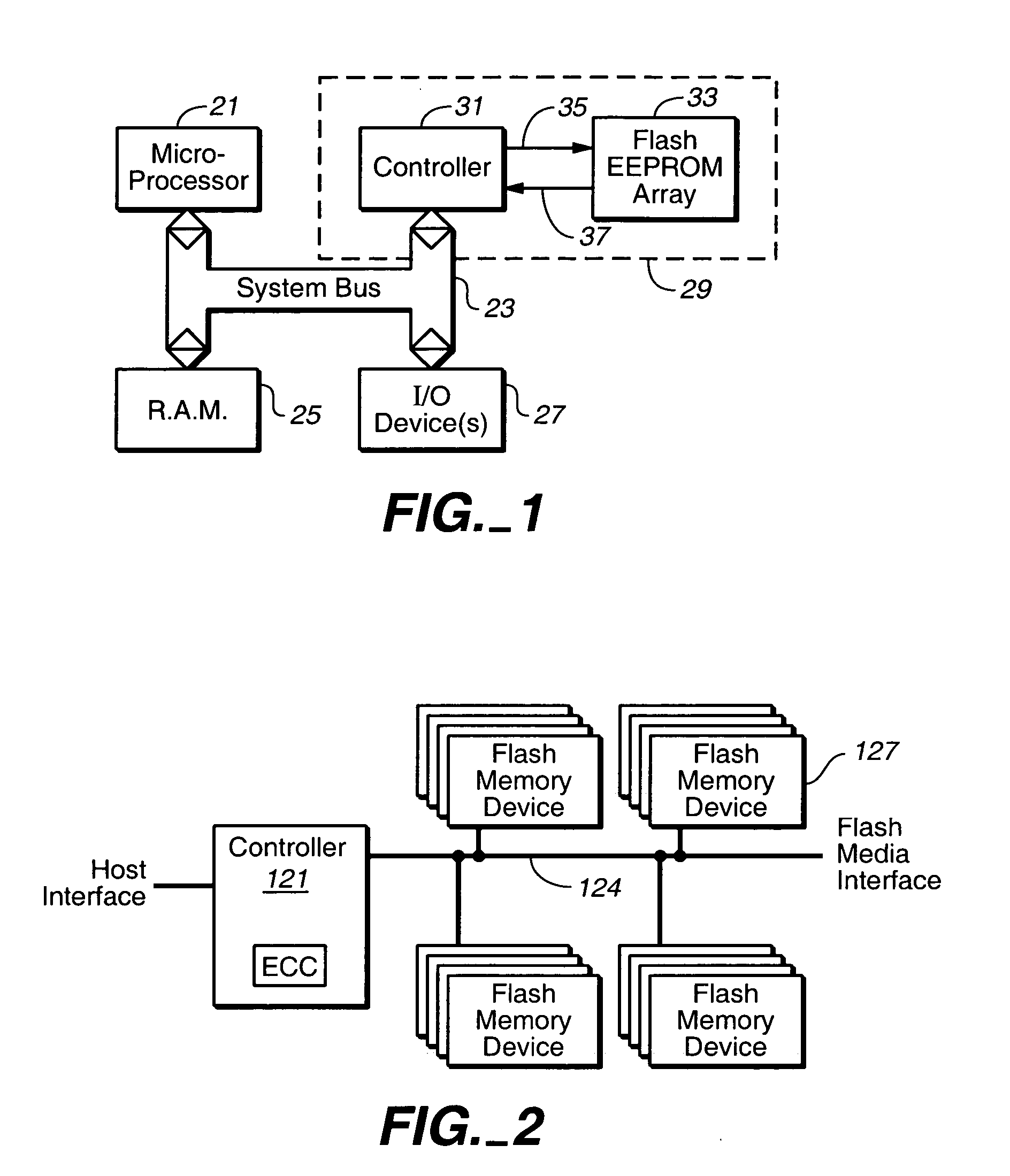

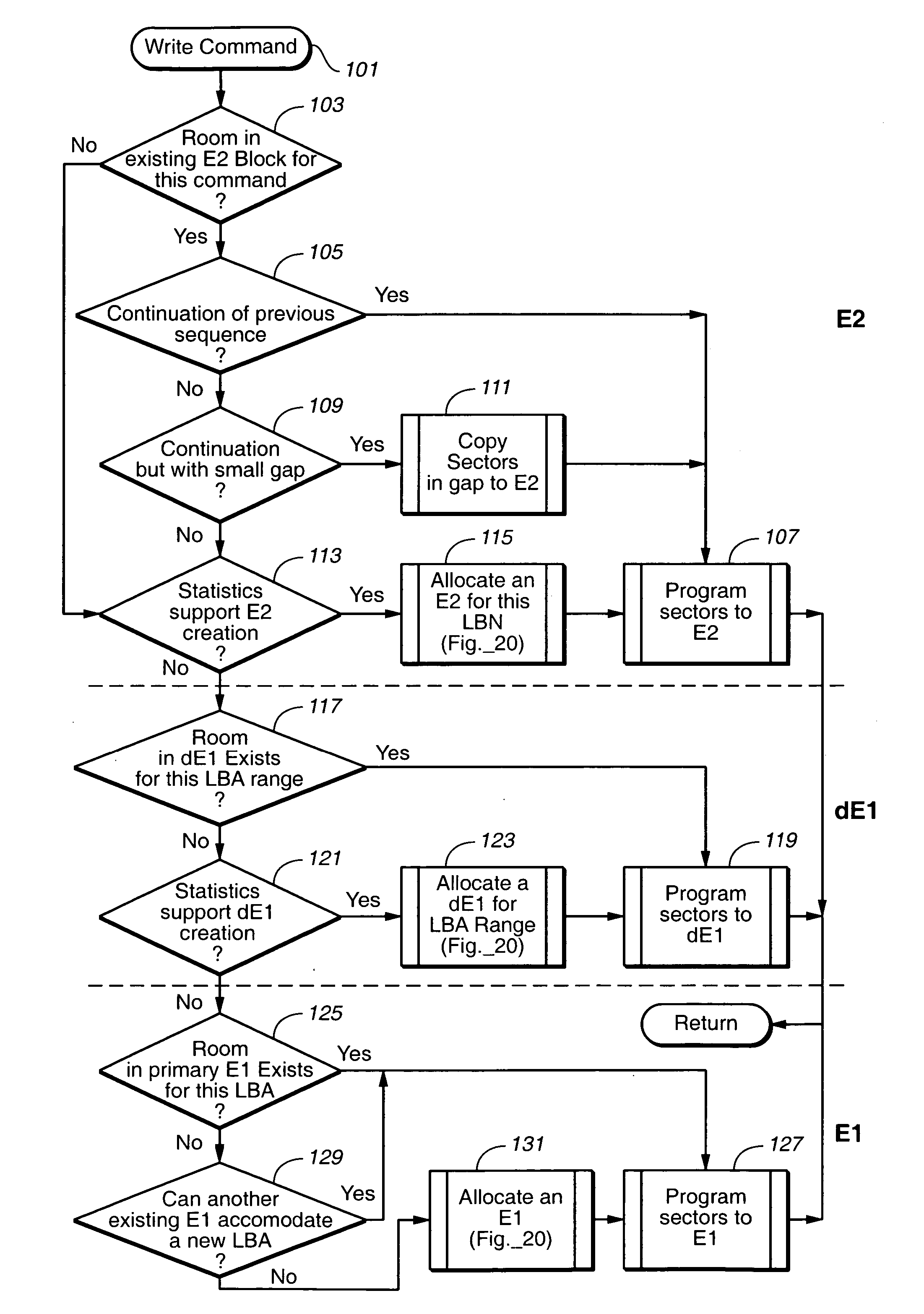

Adaptive mode switching of flash memory address mapping based on host usage characteristics

ActiveUS20050144361A1Reduced useful lifeOptimal performance characteristicMemory architecture accessing/allocationMemory adressing/allocation/relocationDegree of parallelismSelf adaptive

In a non-volatile memory storage system such as a flash EEPROM system, a controller switches the manner in which data sectors are mapped into blocks and metablocks of the memory in response to host programming and controller data consolidation patterns, in order to improve performance and reduce wear. Data are programmed into the memory with different degrees of parallelism.

Owner:SANDISK TECH LLC

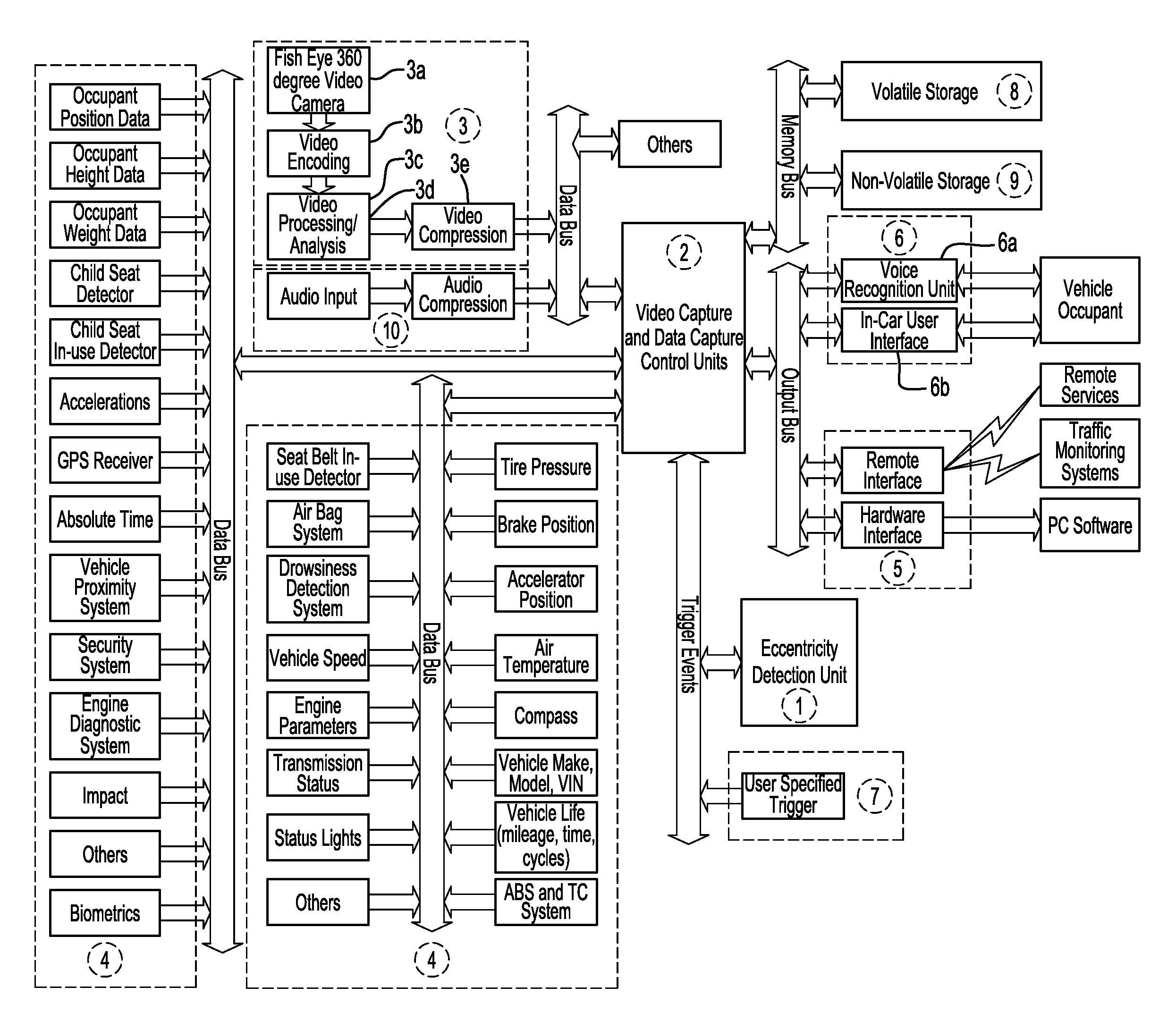

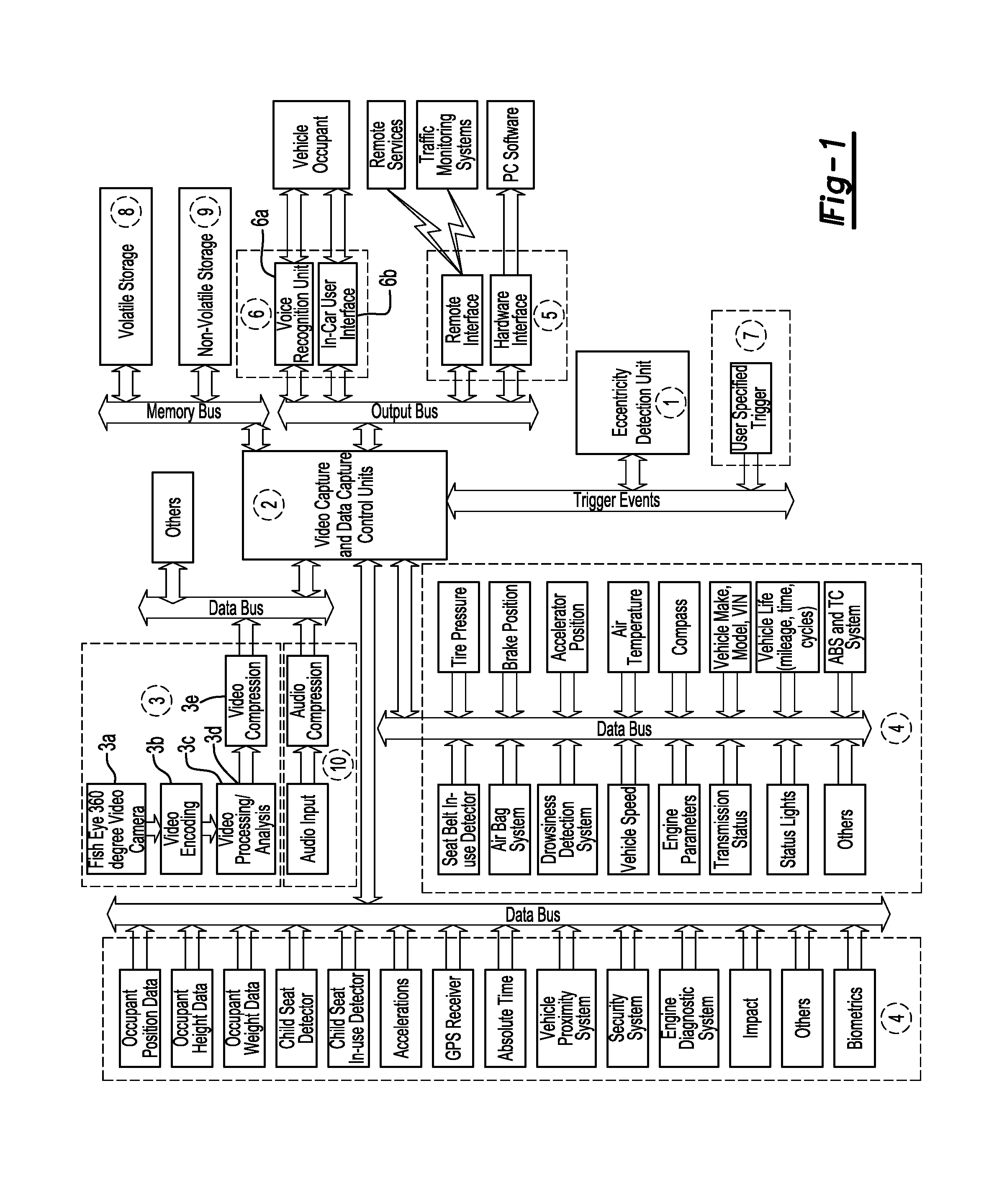

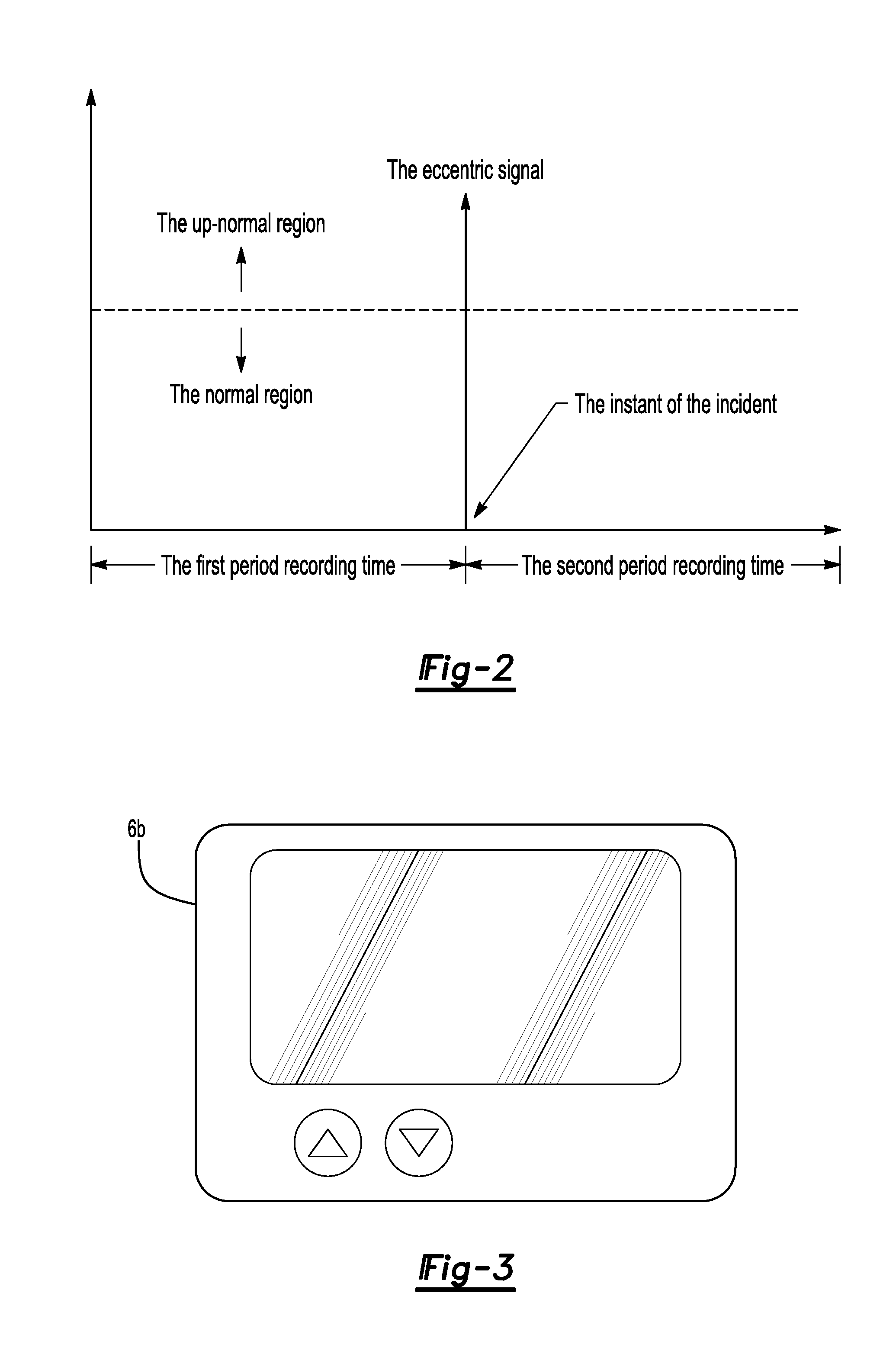

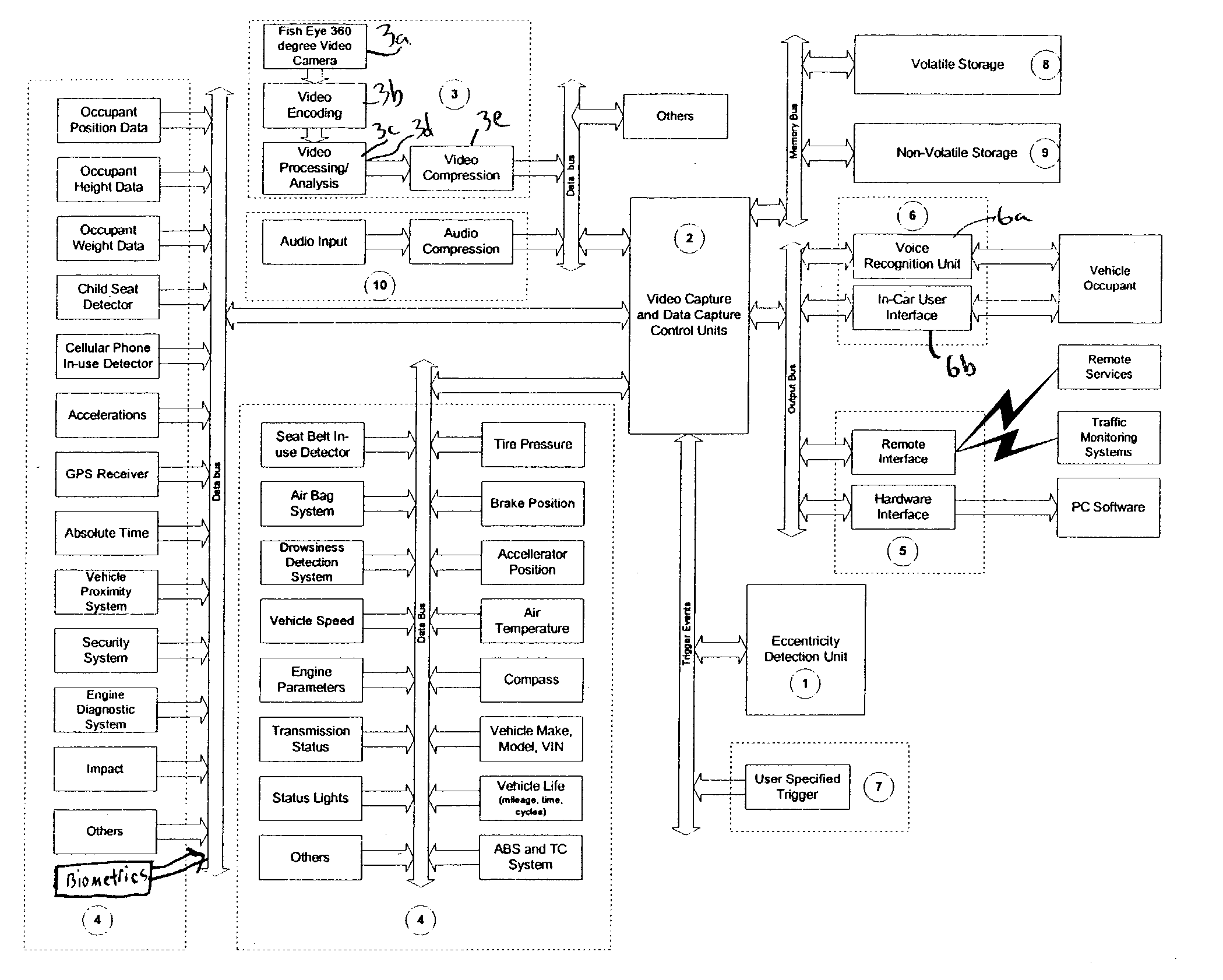

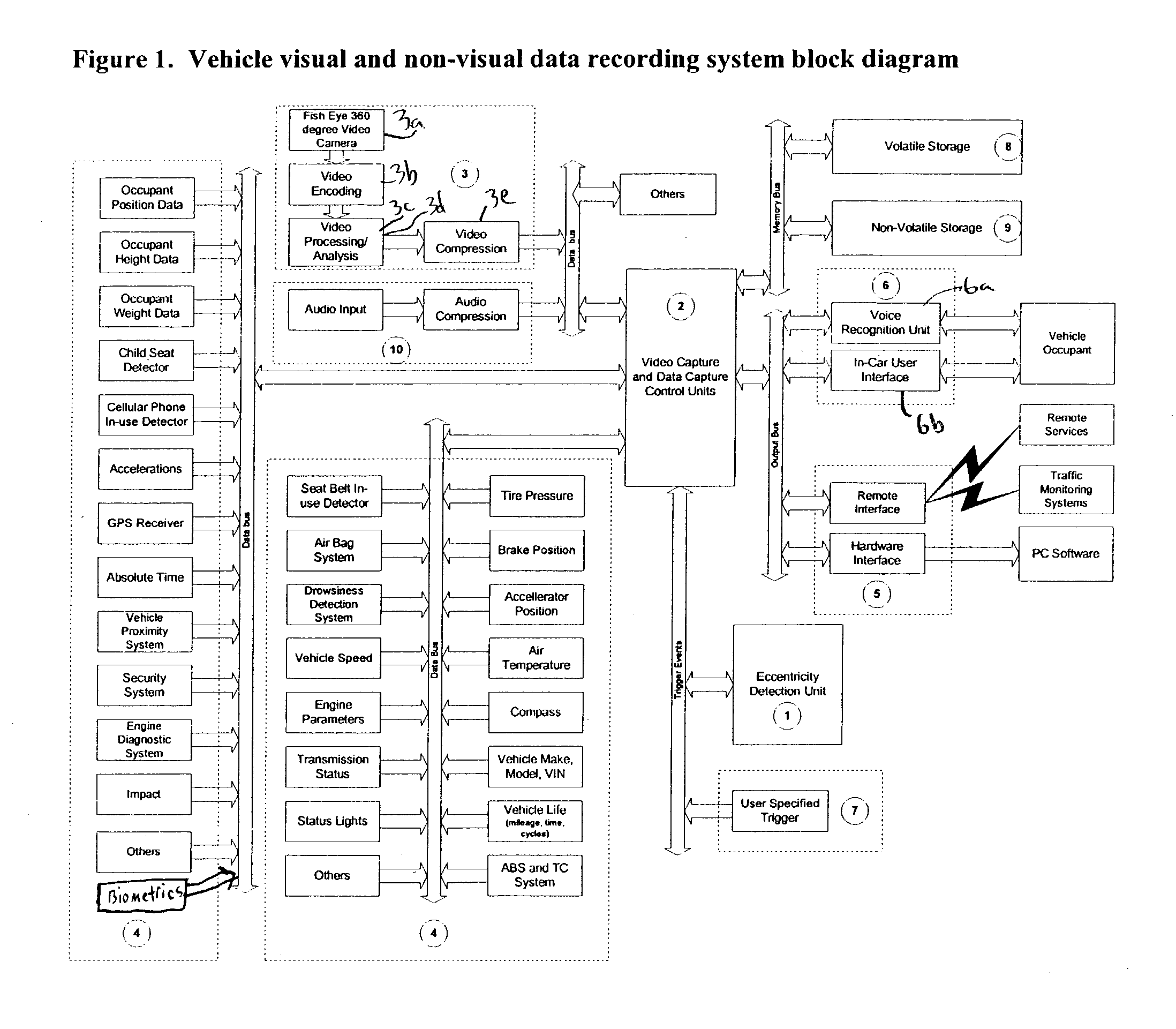

Vehicle visual and non-visual data recording system

ActiveUS7386376B2Vehicle testingRegistering/indicating working of vehiclesData synchronizationDriver/operator

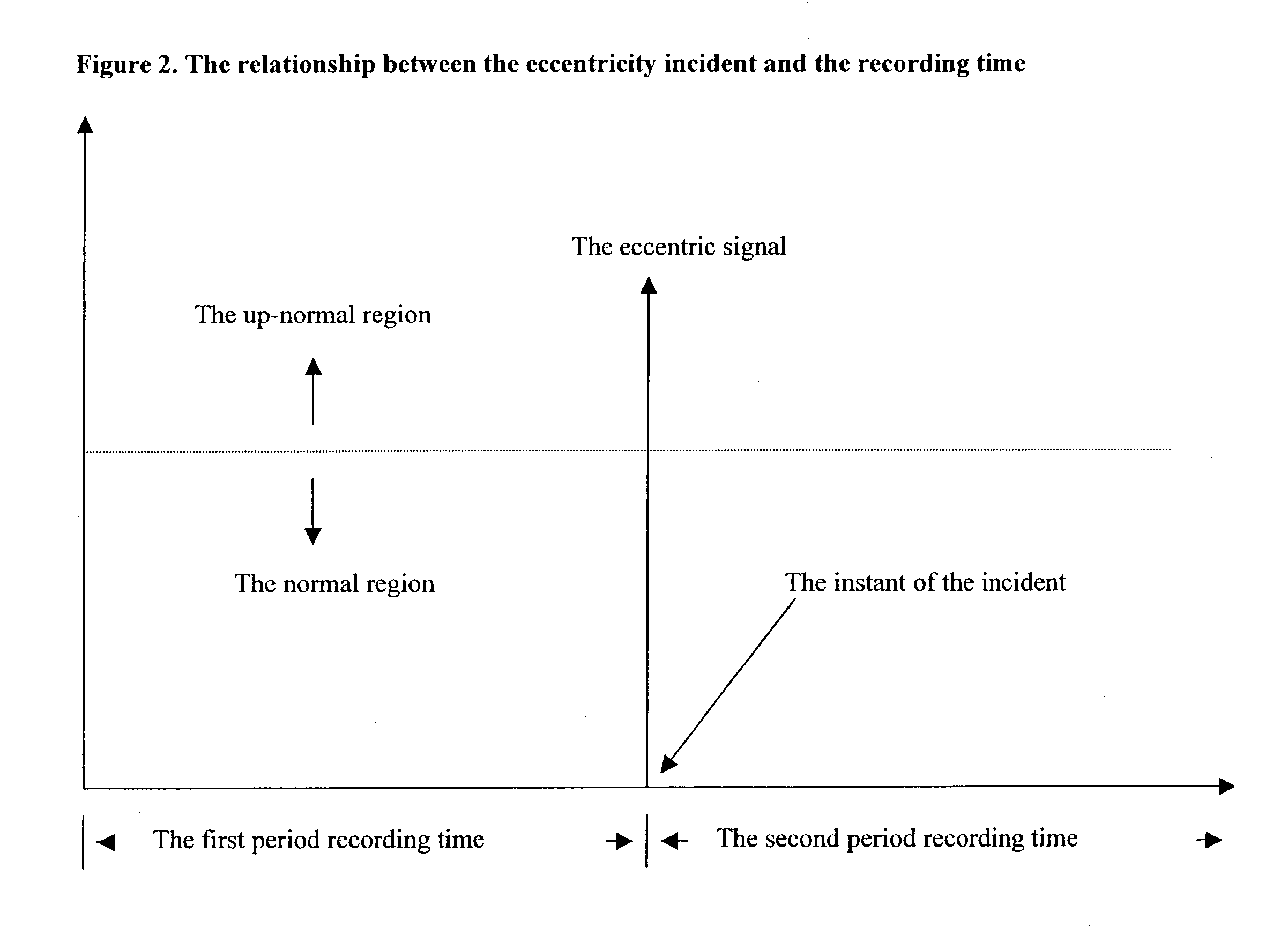

The system described in this invention can be used for monitoring and analyzing real time visual and non-visual information pertaining to the occupant, vehicle, and surroundings prior to, during and post eccentric operating conditions for a given period of time. The system stores vehicle and occupant data from sensors throughout the vehicle and also makes use of existing vehicle sensors that may already be present in the vehicle. The invention also includes a video recording module that makes use of a fish-eye camera to capture video from the inside and the outside of the vehicle. Real-time data analysis is performed to detect and to recognize vehicle occupants, and recognize impending eccentric events. Vehicle, occupant, and video data are stored in circular buffers. When an eccentric event, a collision for example, has been detected, the device continues to record data and video for a fixed period of time. Once this time has elapsed, the data is transferred from volatile to non-volatile memory for later retrieval. A computer may be used to retrieve and display the vehicle and occupant data in a synchronization with the video data for the purposes of accident recreation, driver or vehicle monitoring.

Owner:MINOTAUR SYST LLC

Management of non-volatile memory systems having large erase blocks

ActiveUS20050144358A1Reduce amountImprove system performanceMemory architecture accessing/allocationMemory adressing/allocation/relocationOriginal dataTerm memory

A non-volatile memory system of a type having blocks of memory cells erased together and which are programmable from an erased state in units of a large number of pages per block. If the data of only a few pages of a block are to be updated, the updated pages are written into another block provided for this purpose. Updated pages from multiple blocks are programmed into this other block in an order that does not necessarily correspond with their original address offsets. The valid original and updated data are then combined at a later time, when doing so does not impact on the performance of the memory. If the data of a large number of pages of a block are to be updated, however, the updated pages are written into an unused erased block and the unchanged pages are also written to the same unused block. By handling the updating of a few pages differently, memory performance is improved when small updates are being made. The memory controller can dynamically create and operate these other blocks in response to usage by the host of the memory system.

Owner:SANDISK TECH LLC

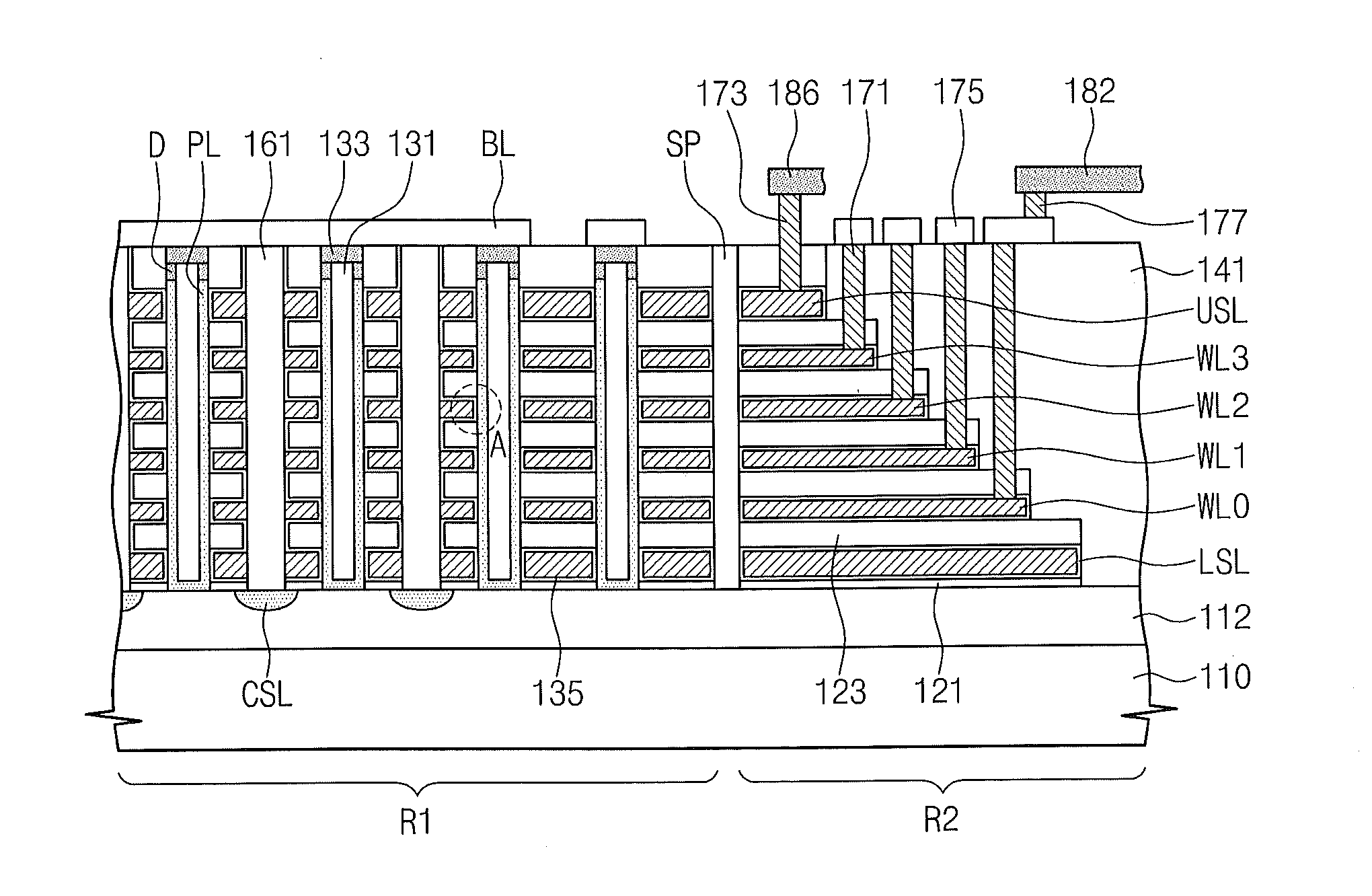

Methods of Forming Nonvolatile Memory Devices Using Nonselective and Selective Etching Techniques to Define Vertically Stacked Word Lines

InactiveUS20120003831A1Solid-state devicesSemiconductor/solid-state device manufacturingEngineeringSecondary layer

Methods of forming nonvolatile memory devices include forming a stack of layers of different materials on a substrate. This stack includes a plurality of first layers of a first material and a plurality of second layers of a second material arranged in an alternating sequence of first and second layers. A selected first portion of the stack of layers is isotropically etched for a sufficient duration to define a first trench therein that exposes sidewalls of the alternating sequence of first and second layers. The sidewalls of each of the plurality of first layers are selectively etched relative to sidewalls of adjacent ones of the plurality of second layers. Another etching step is then performed to recess sidewalls of the plurality of second layers and thereby expose portions of upper surfaces of the plurality of first layers. These exposed portions of the upper surfaces of the plurality of first layers, which may act as word lines of a memory device, are displaced laterally relative to each other.

Owner:SAMSUNG ELECTRONICS CO LTD

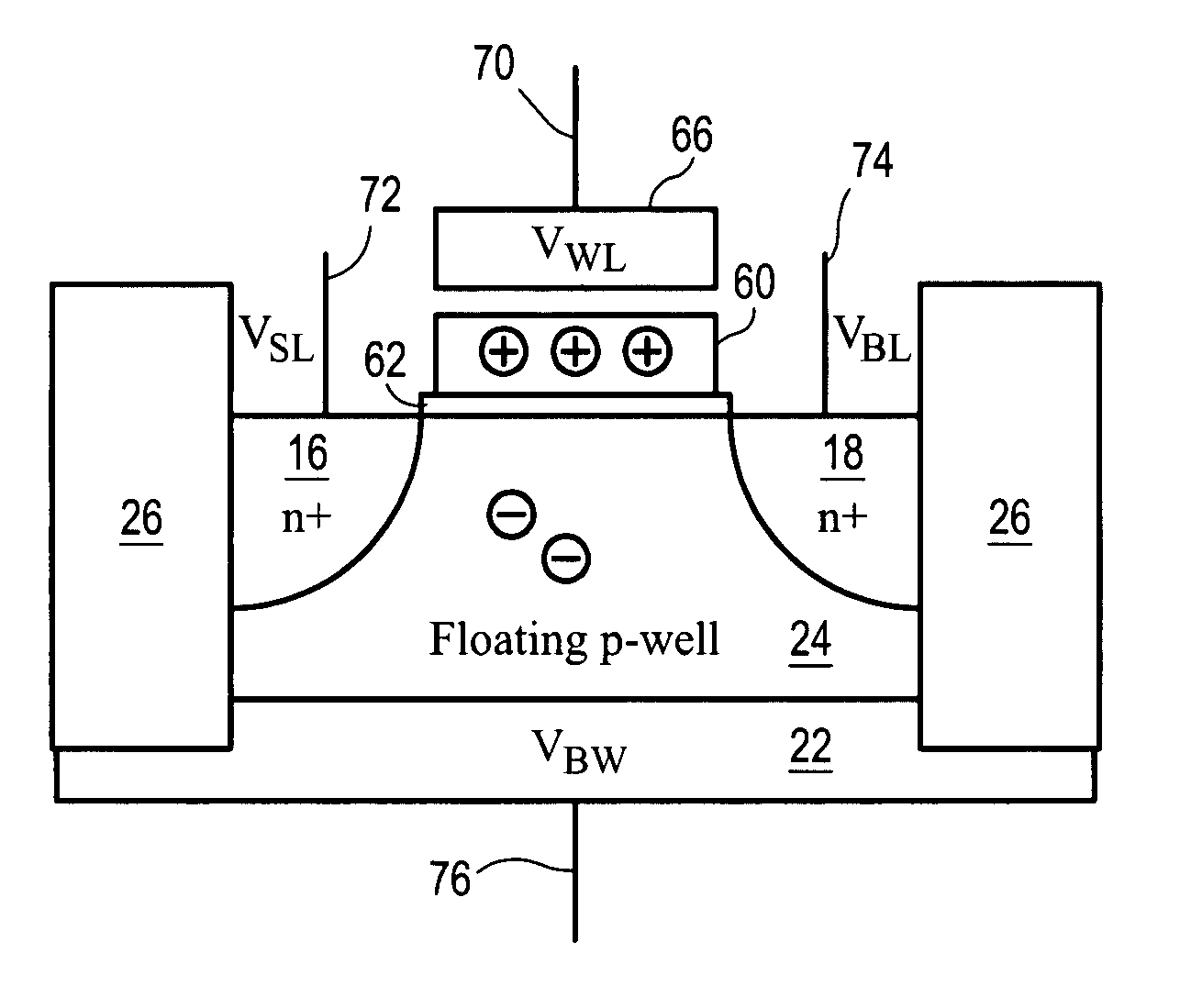

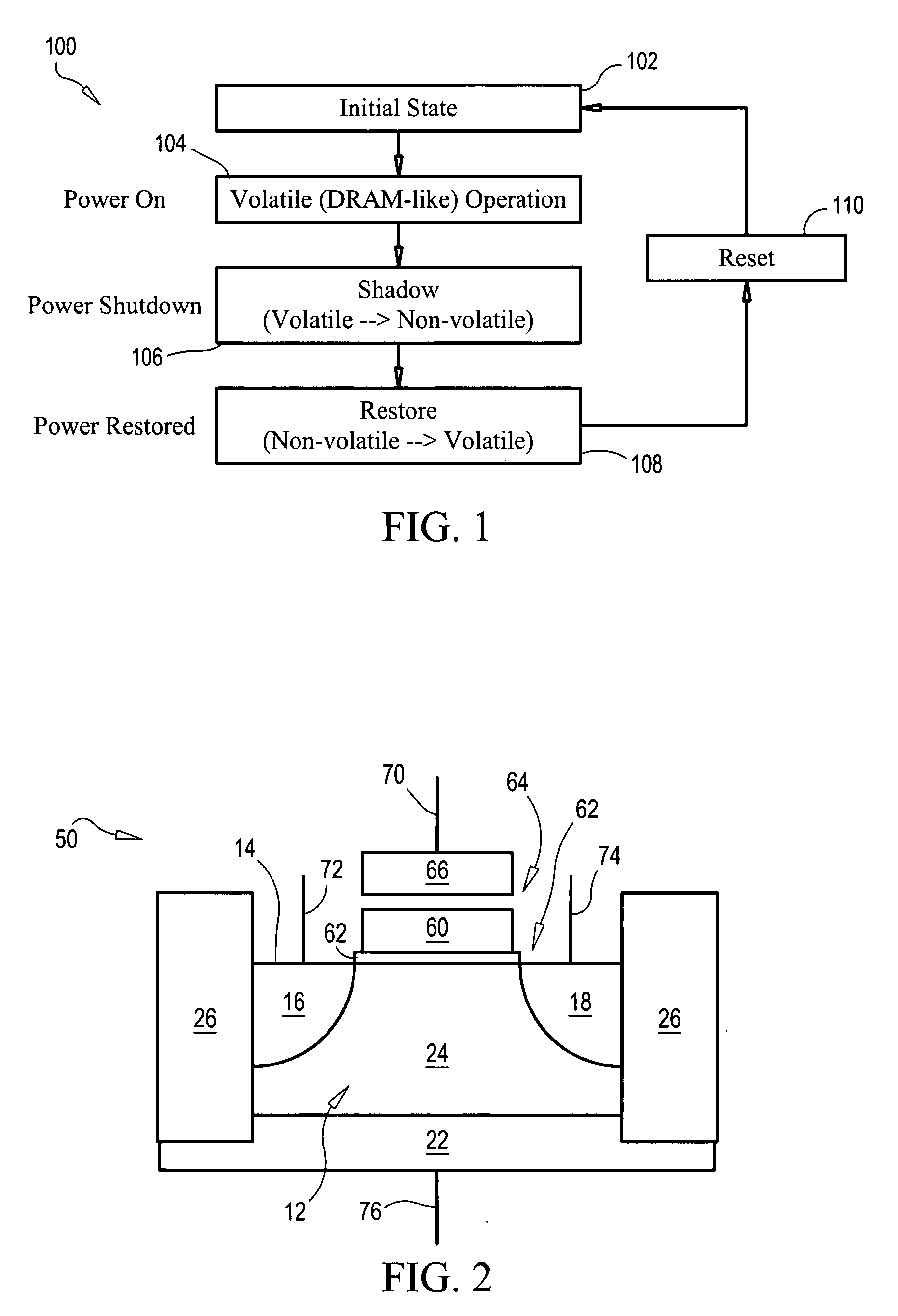

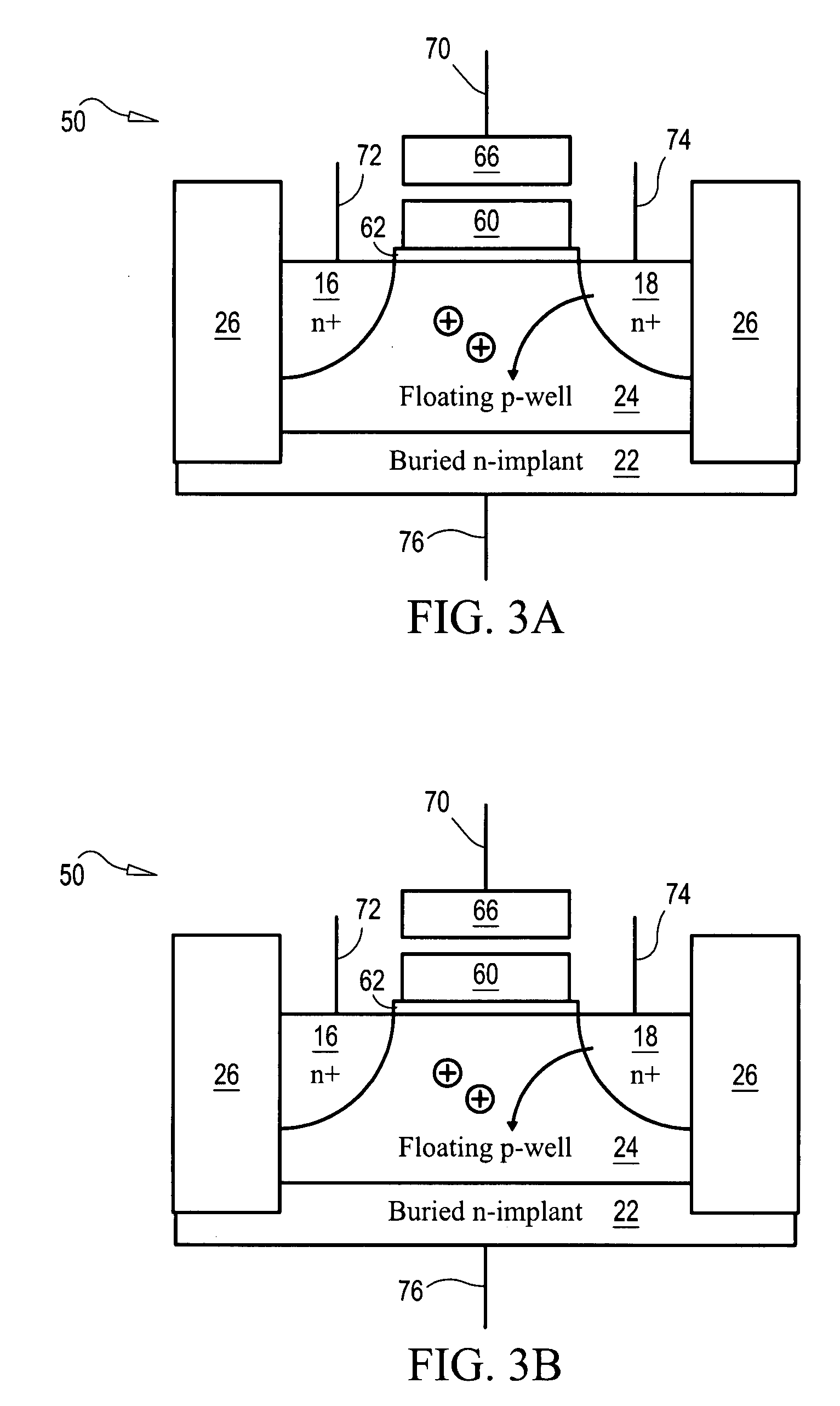

Semiconductor memory having both volatile and non-volatile functionality and method of operating

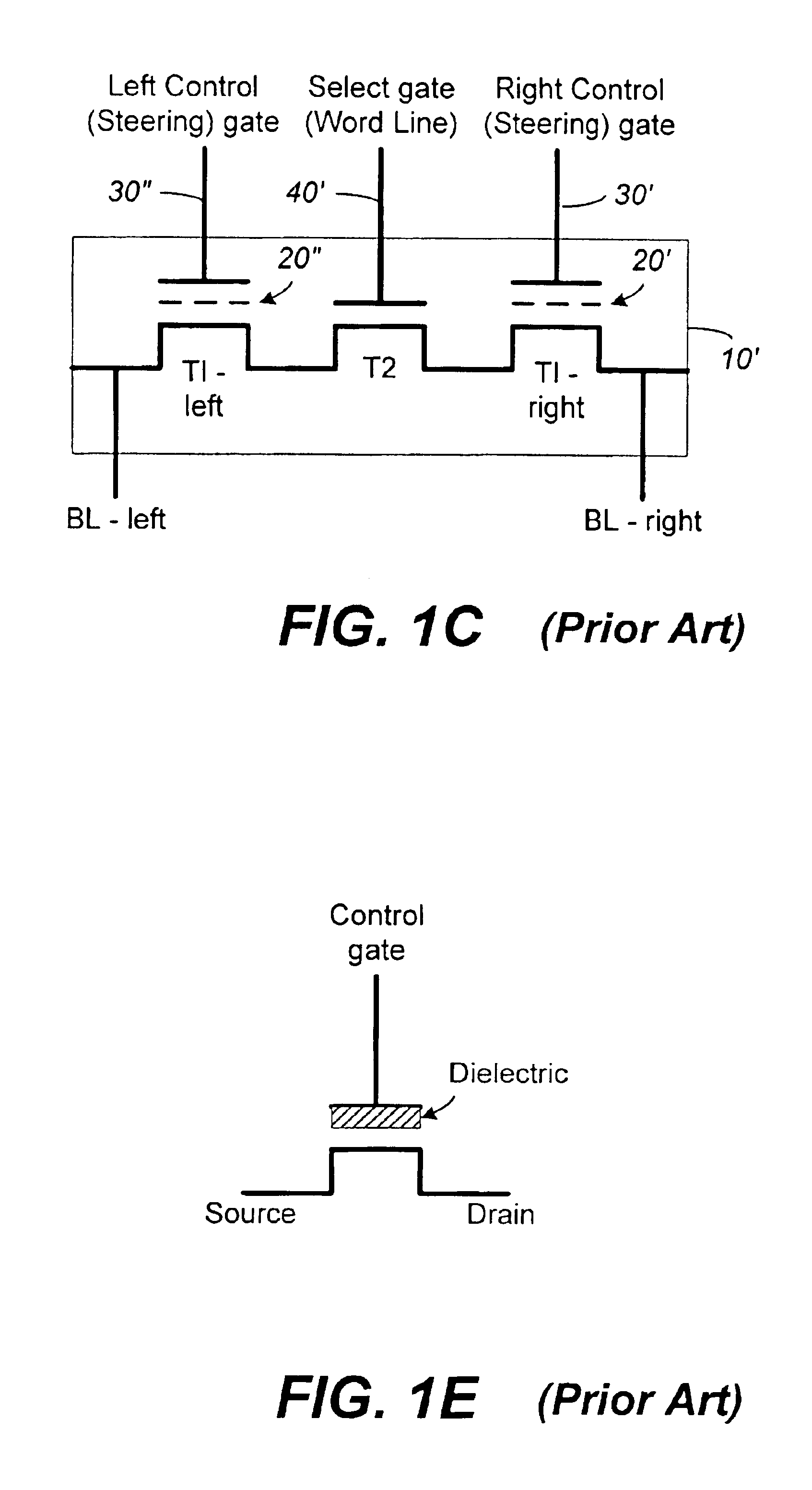

Semiconductor memory having both volatile and non-volatile modes and methods of operation. A semiconductor memory cell includes a substrate having a first conductivity type; a first region embedded in the substrate at a first location of the substrate and having a second conductivity type; a second region embedded in the substrate at a second location the substrate and have the second conductivity type, such that at least a portion of the substrate having the first conductivity type is located between the first and second locations and functions as a floating body to store data in volatile memory; a floating gate or trapping layer positioned in between the first and second locations and above a surface of the substrate and insulated from the surface by an insulating layer; the floating gate or trapping layer being configured to receive transfer of data stored by the volatile memory and store the data as nonvolatile memory in the floating gate or trapping layer upon interruption of power to the memory cell; and a control gate positioned above the floating gate or trapping layer and a second insulating layer between the floating gate or trapping layer and the control gate.

Owner:ZENO SEMICON

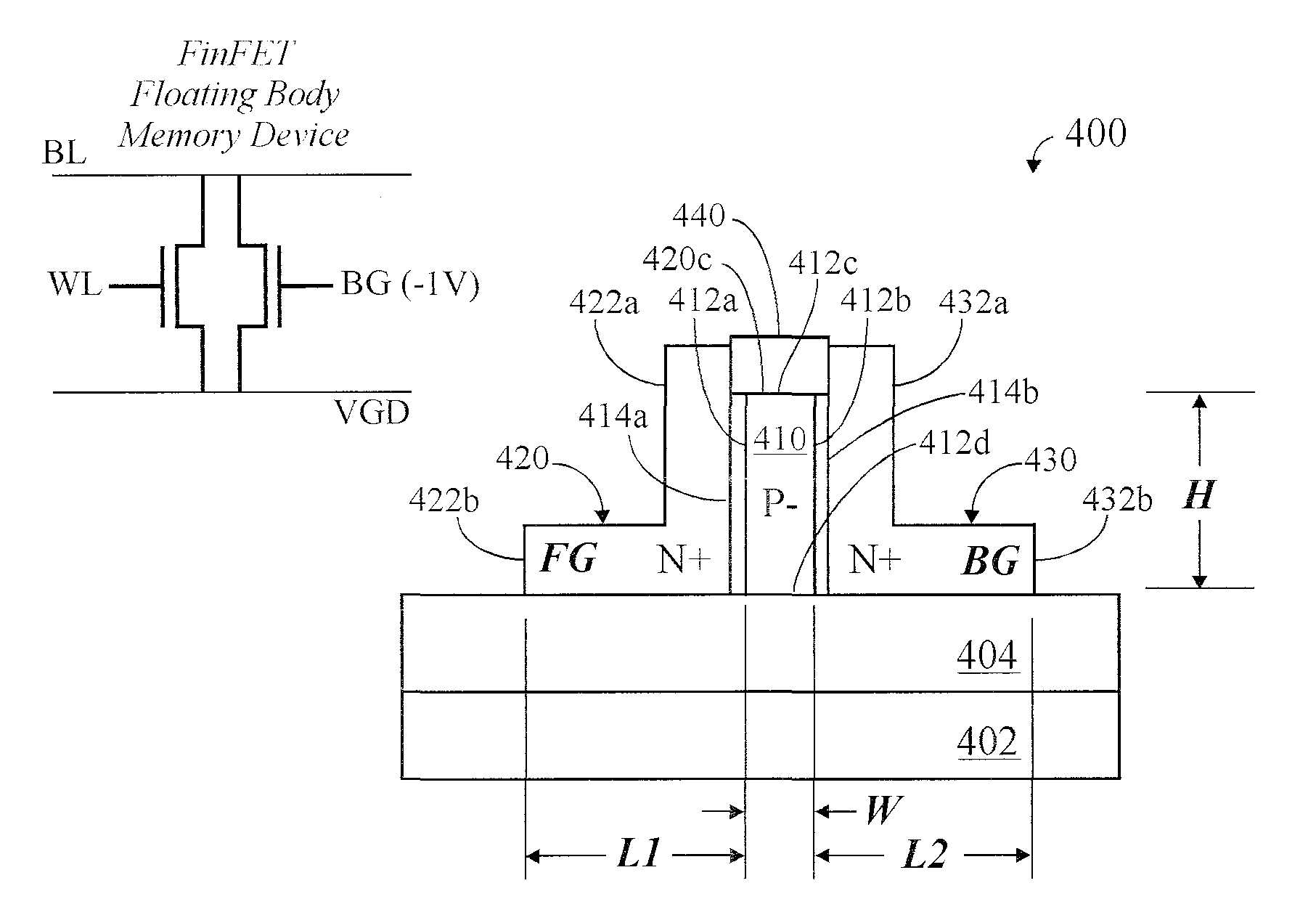

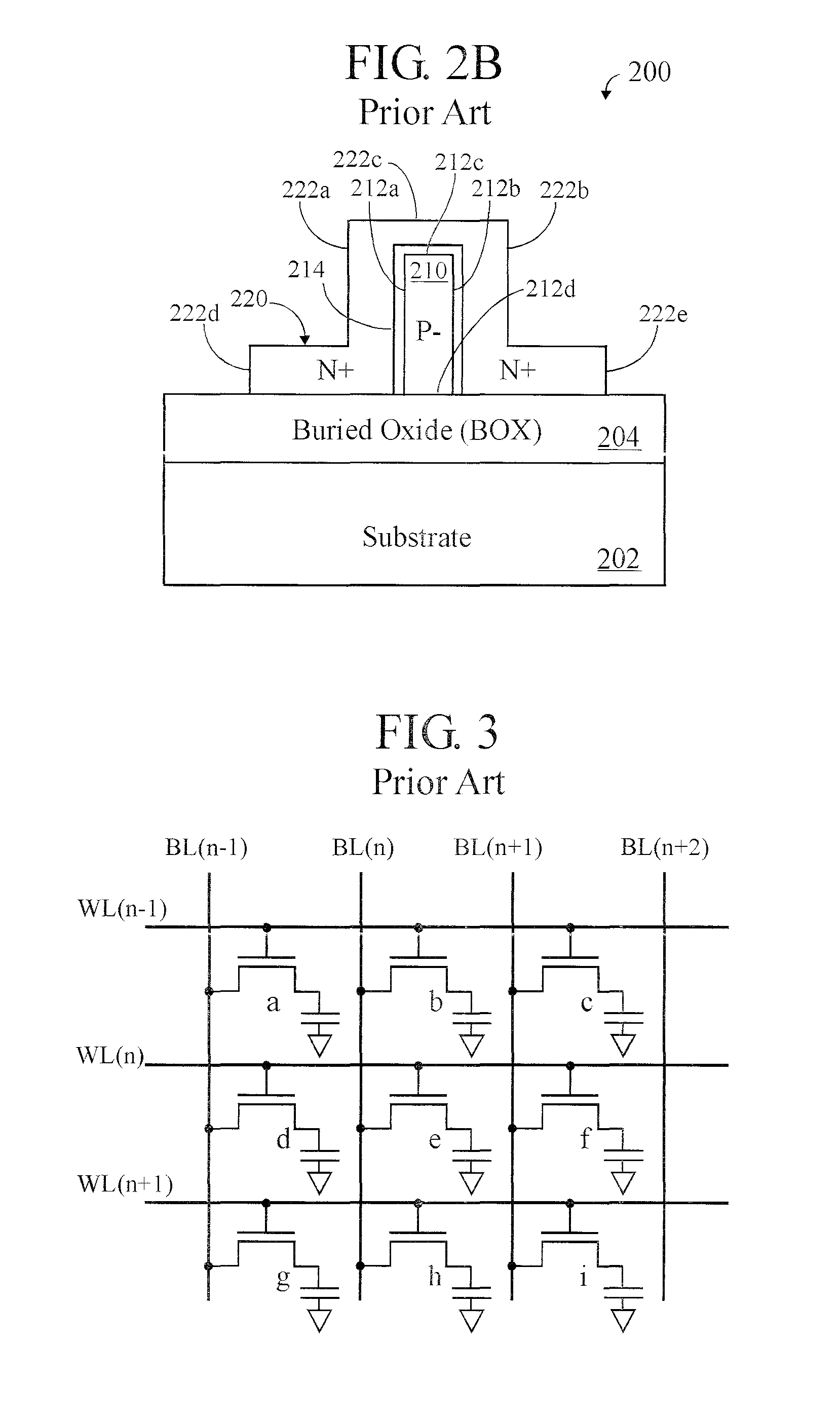

Finfet memory device with dual separate gates and method of operation

InactiveUS20090108351A1Conductivity alteredEnlarging and constricting channelTransistorSolid-state devicesVolatile memoryMemory array

A FinFET device comprises a front gate (FG) and a separate back gate (BG) disposed on opposite sides of the fine. The fin structure may act as a floating body of a volatile memory cell. The front and back gates may be doped with the same or opposite polarity, and may be biased oppositely. A plurality of FinFETs may be connected in a memory array with single column erase, or double column erase capability.

Owner:IBM CORP

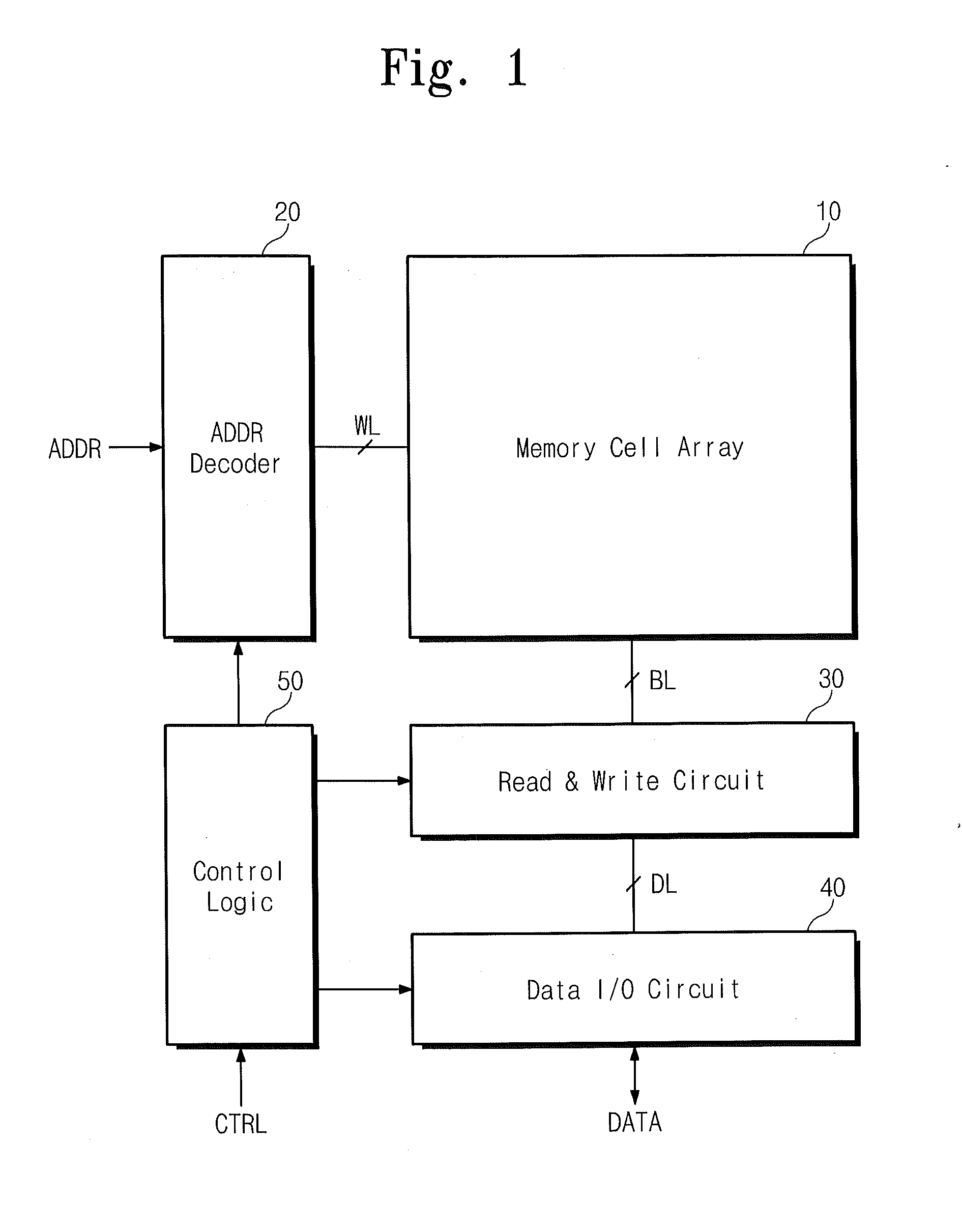

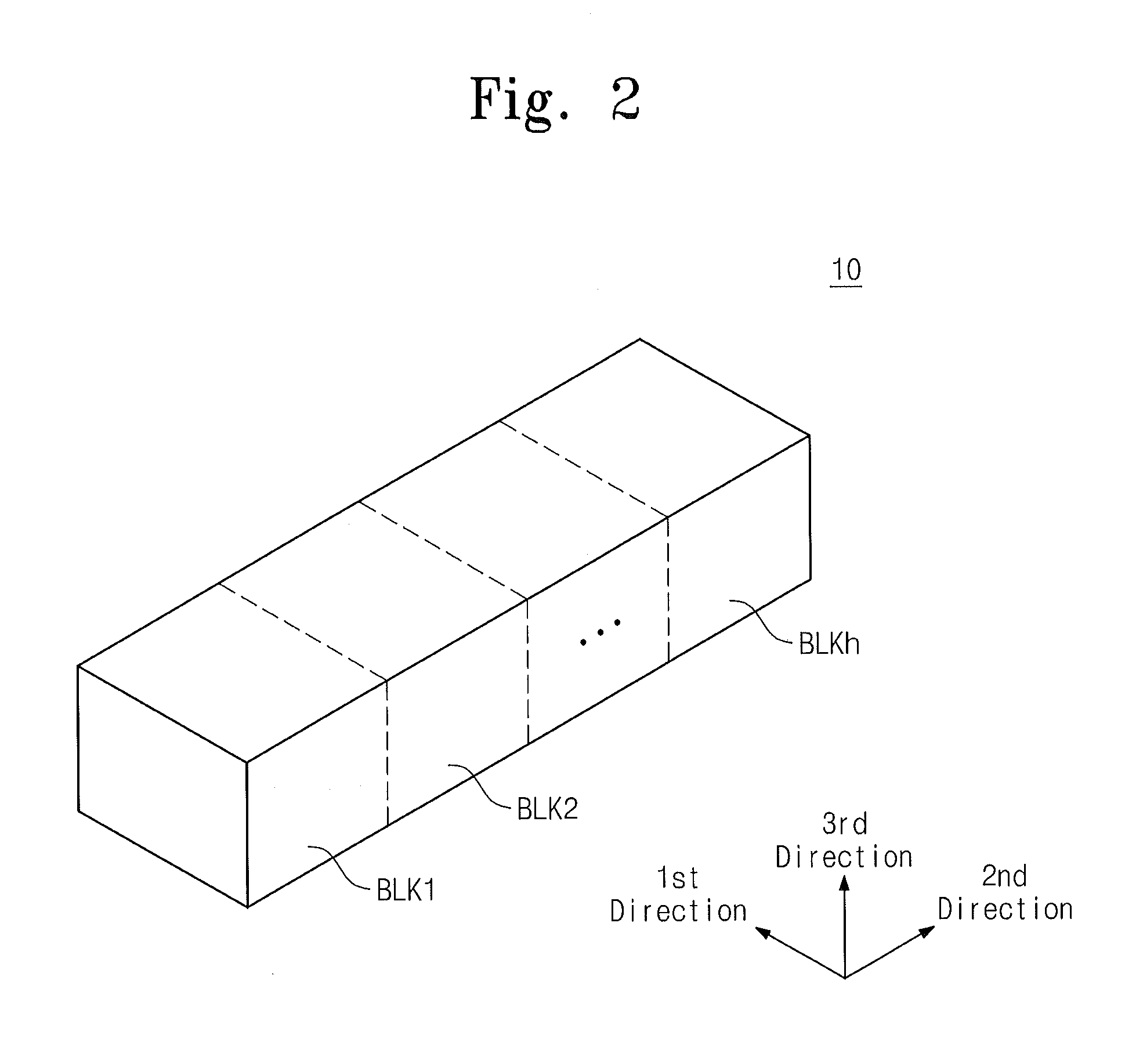

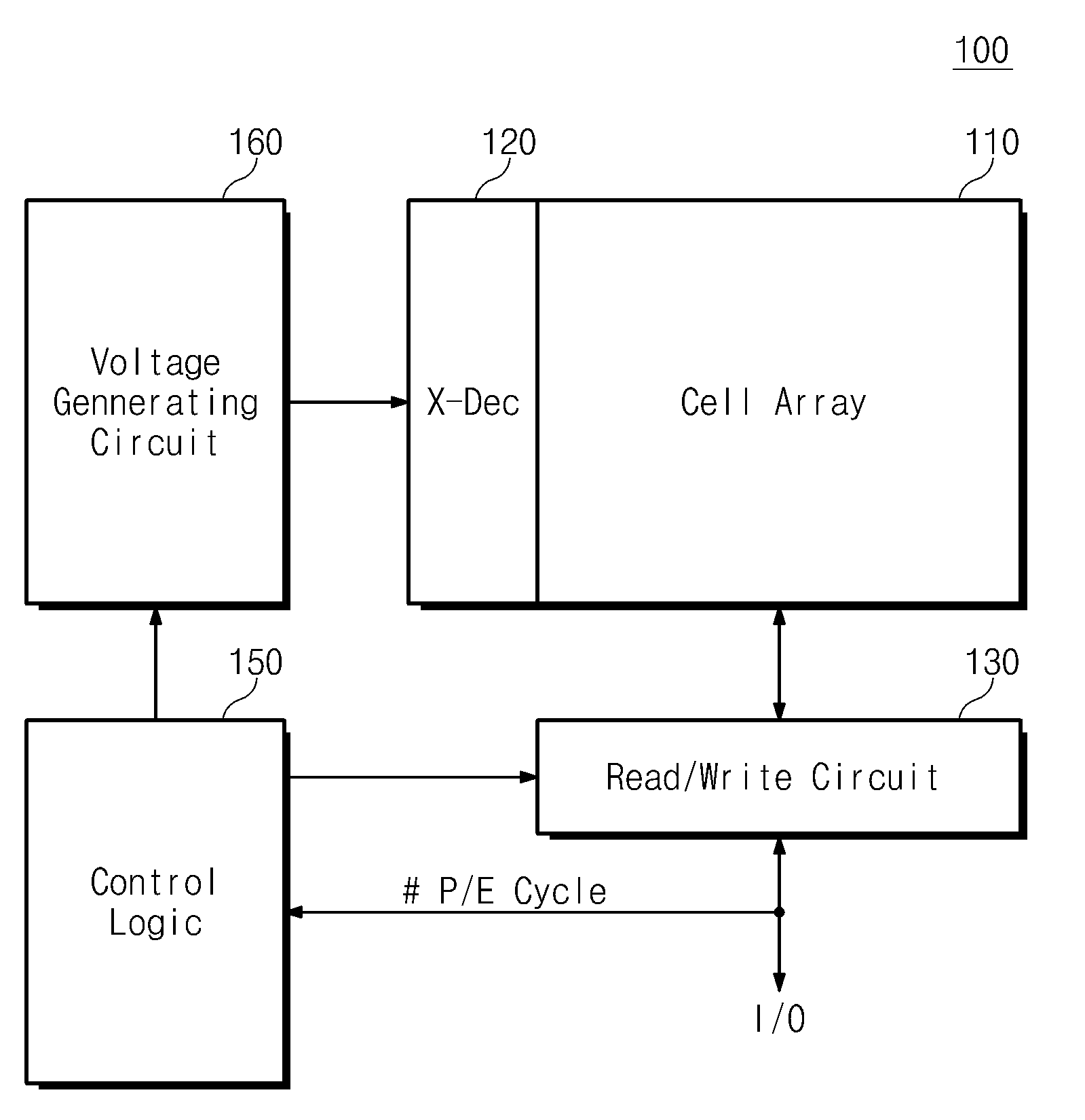

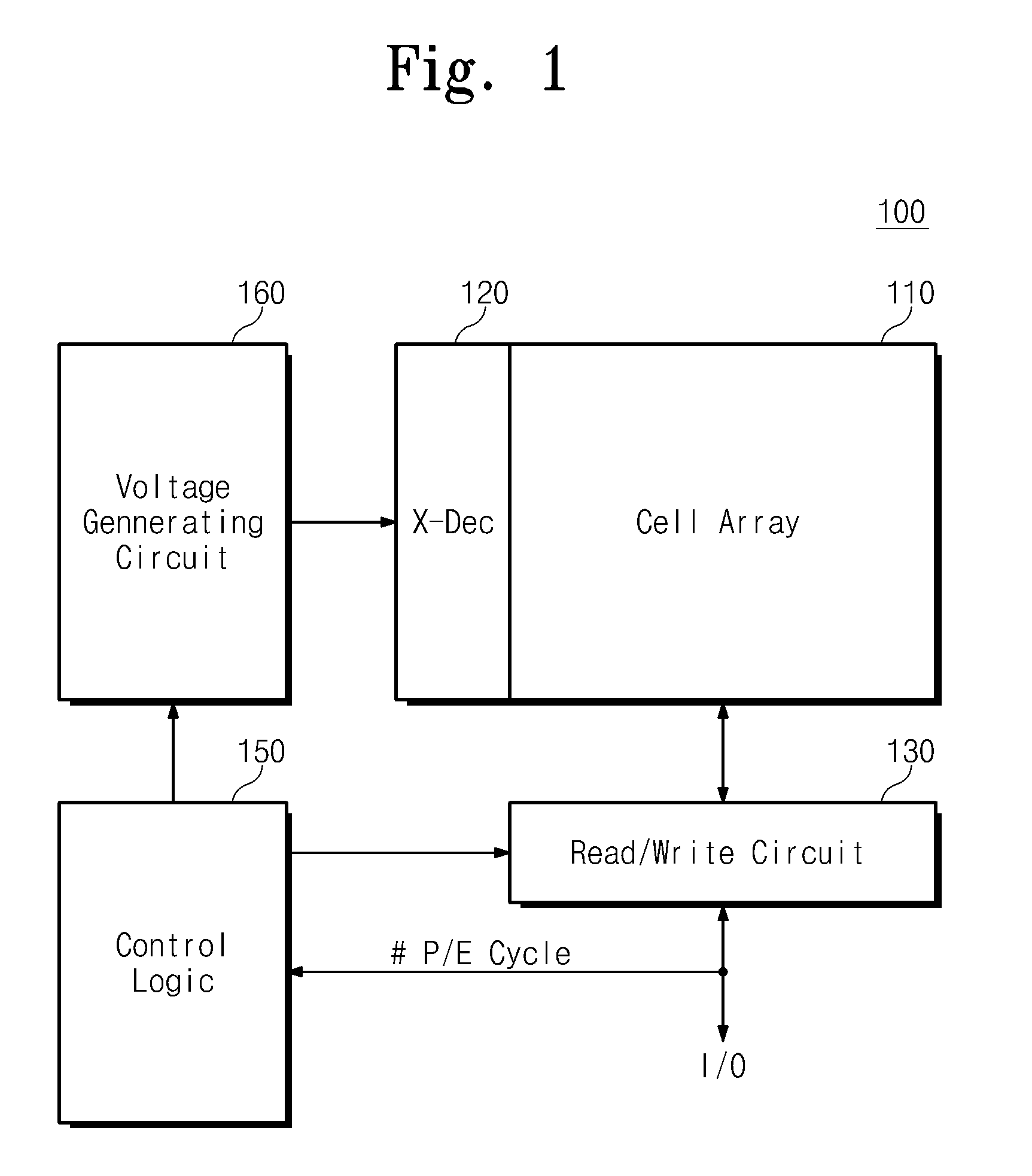

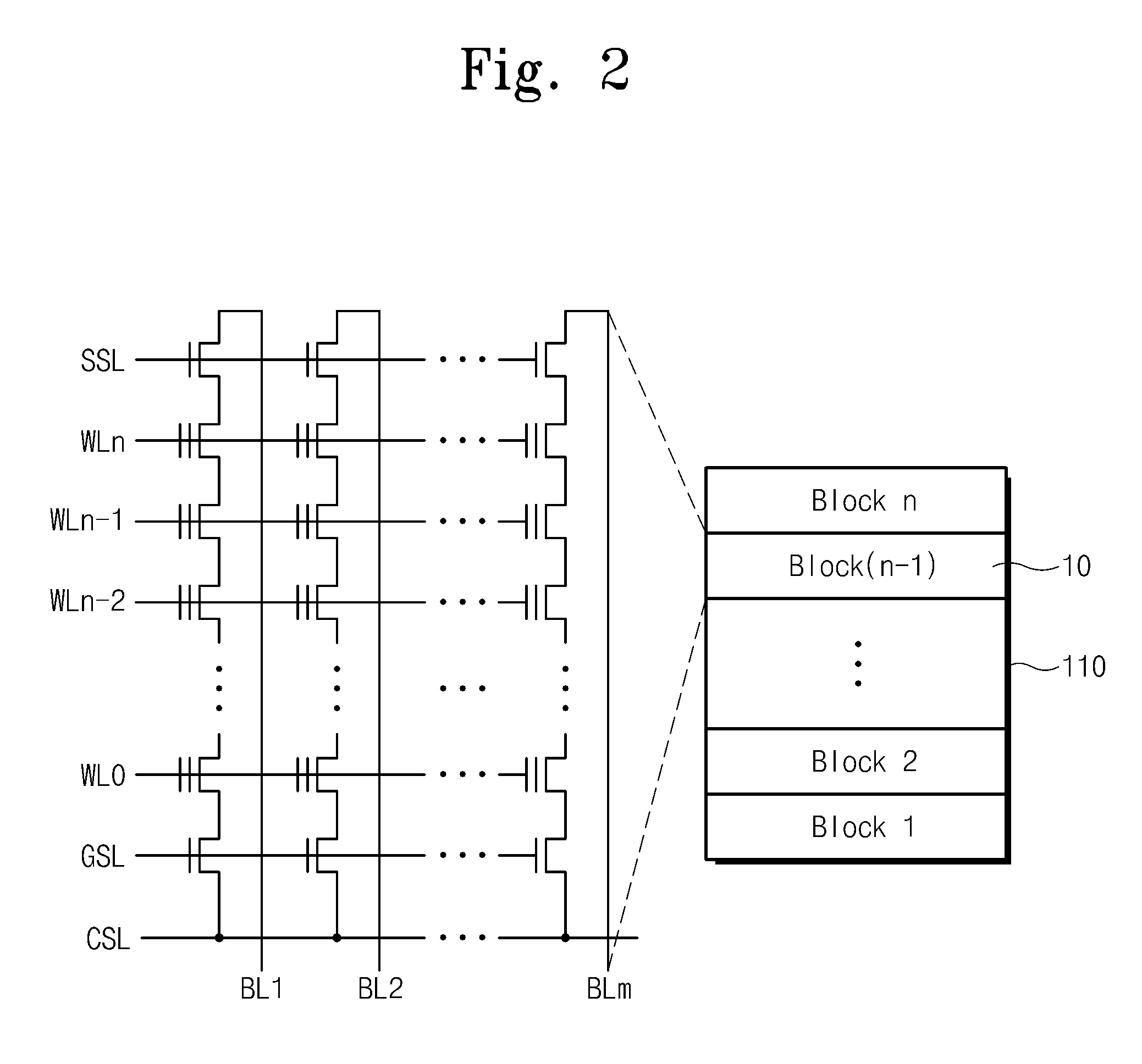

Nonvolatile memory device and related programming method

A nonvolatile memory device comprises a memory cell array comprising a plurality of memory blocks each divided into a plurality of regions, and a control logic component. The control logic component selects a memory block to be programmed based on program / erase cycles of the memory blocks, and selects a program rule used to program the regions of the selected memory block.

Owner:SAMSUNG ELECTRONICS CO LTD

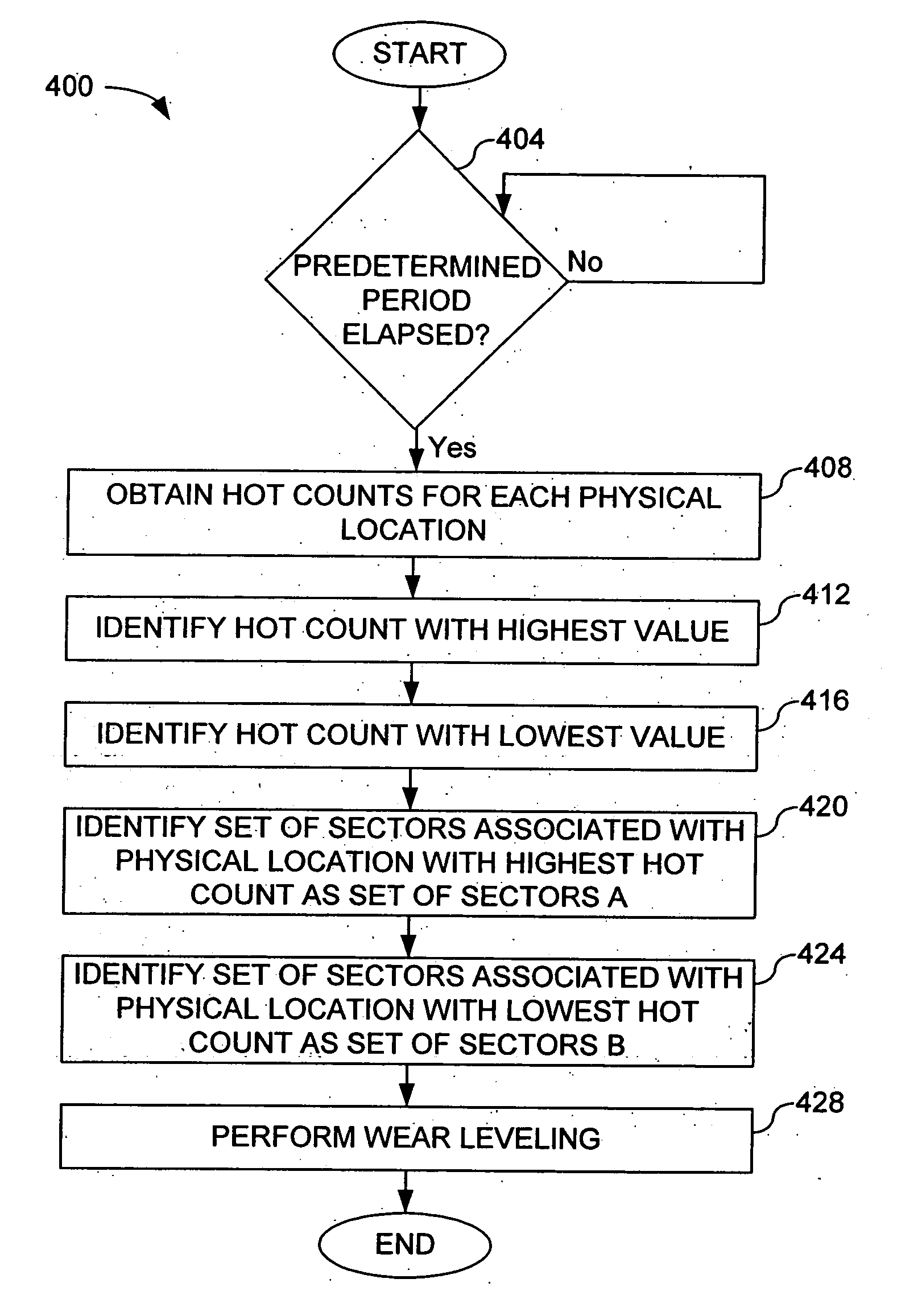

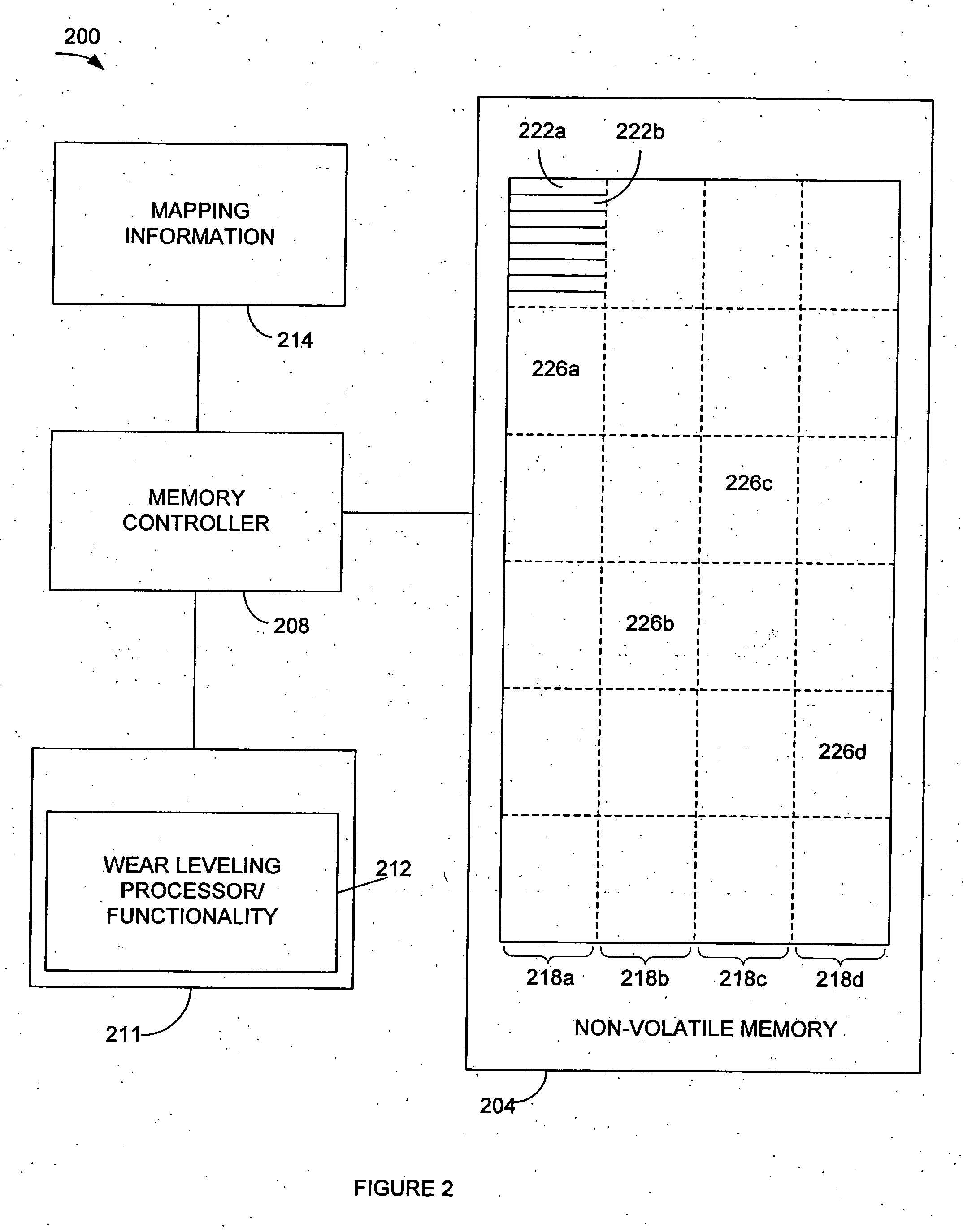

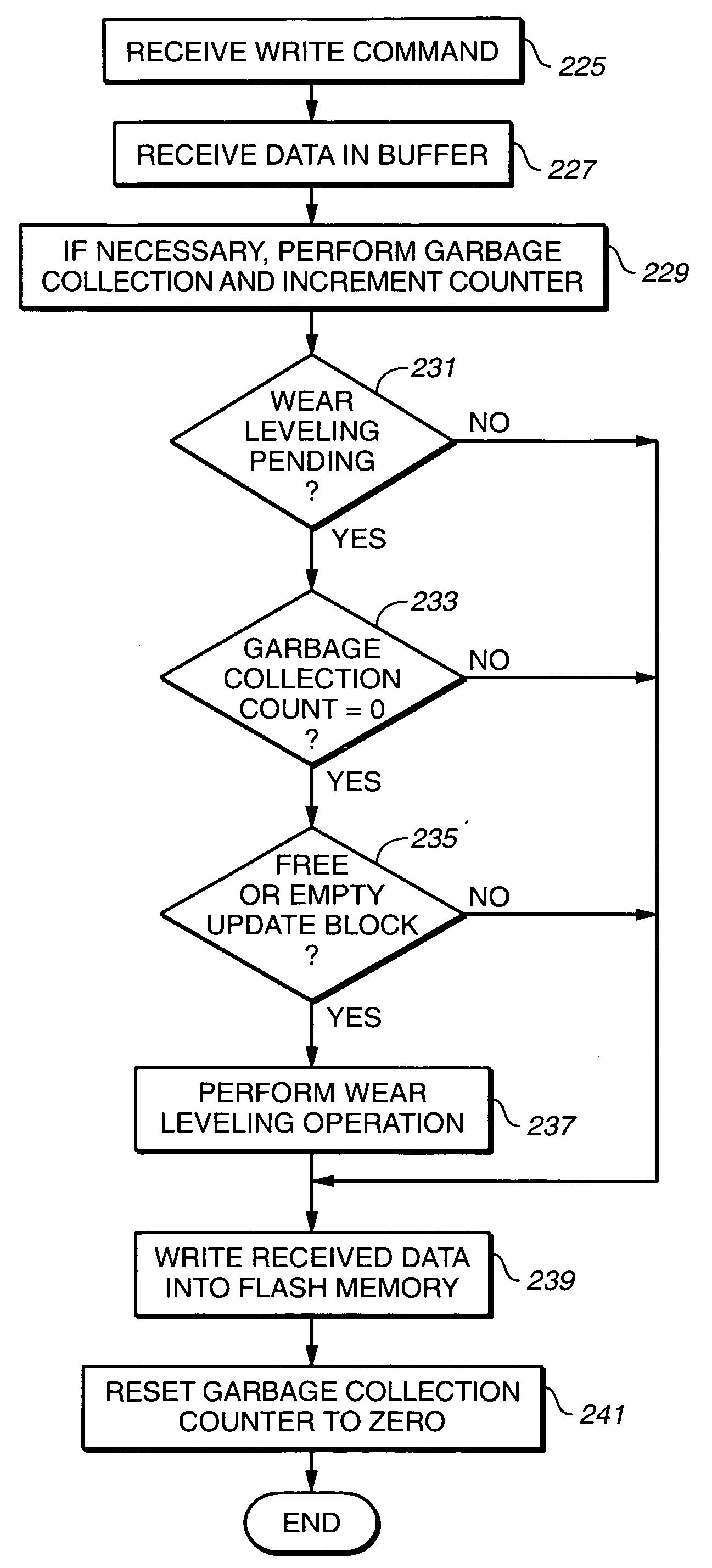

Automated wear leveling in non-volatile storage systems

ActiveUS20040083335A1Precise positioningMemory architecture accessing/allocationMemory adressing/allocation/relocationParallel computingNon-volatile memory

Methods and apparatus for performing wear leveling in a non-volatile memory system are disclosed. Included is a method for performing wear leveling in a memory system that includes a first zone, which has a first memory element that includes contents, and a second zone includes identifying the first memory element and associating the contents of the first memory element with the second zone while disassociating the contents of the first memory element from the first zone. In one embodiment, associating the contents of the first memory element with the second involves moving contents of a second memory element into a third memory element, then copying the contents of the first memory element into the second memory element.

Owner:SANDISK TECH LLC

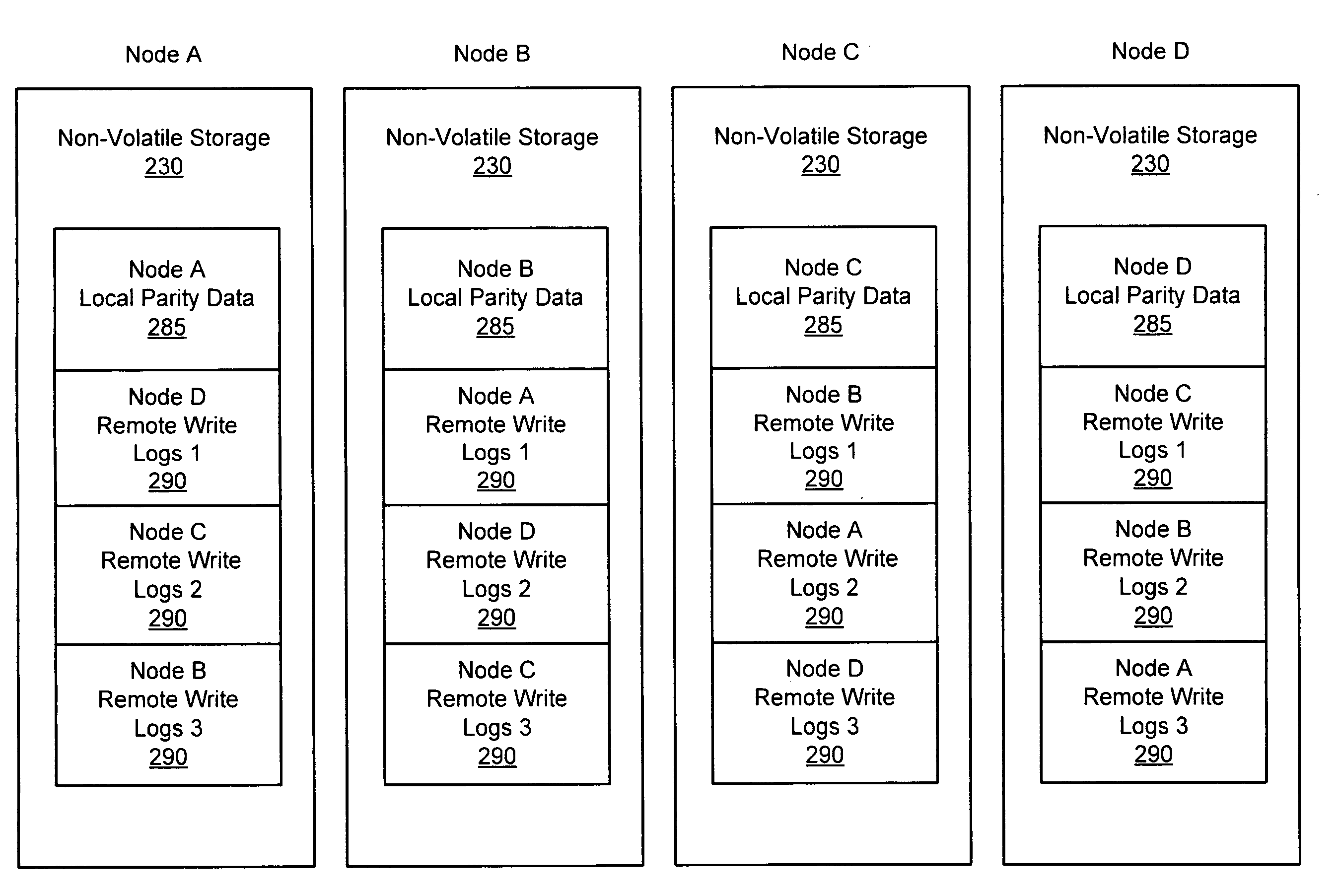

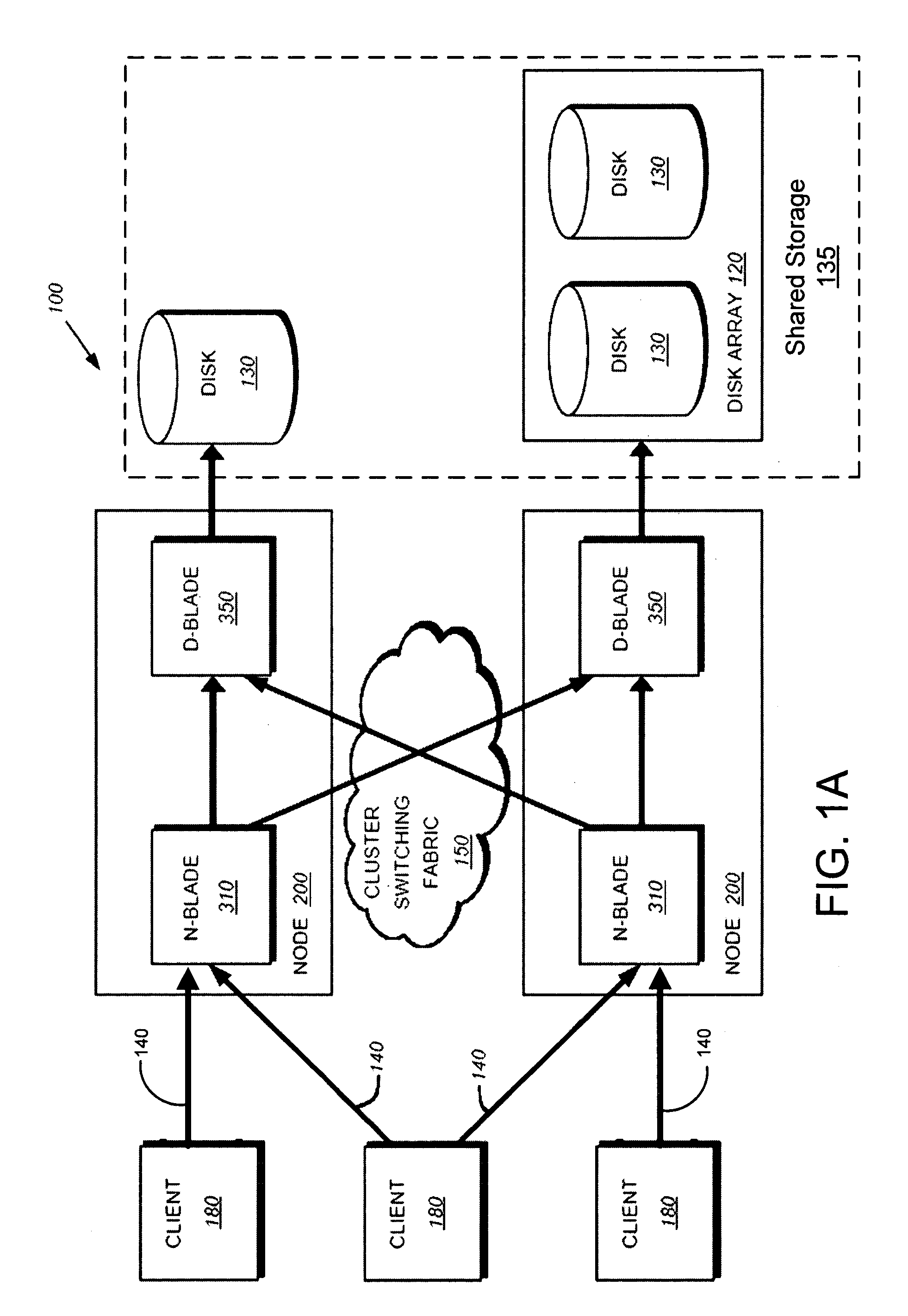

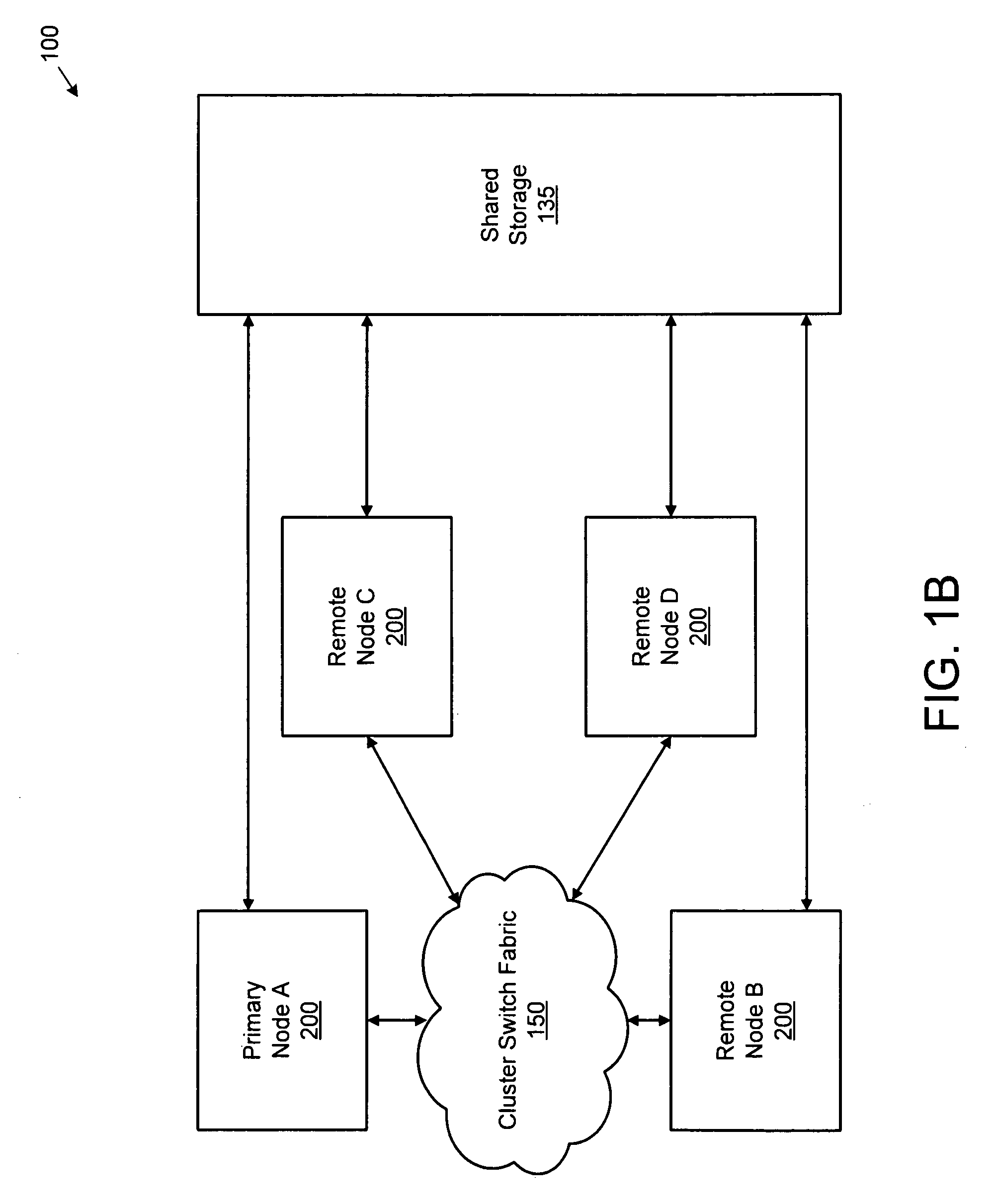

Processing and distributing write logs of nodes of a cluster storage system

ActiveUS8145838B1Short response timeReduce storage spaceError detection/correctionMemory systemsFailoverData store

A cluster storage system comprises a plurality of nodes that access a shared storage, each node having two or more failover partner nodes. A primary node produces write logs for received write requests and produces parity data for the write logs (storing the parity data to local non-volatile storage). By storing parity data rather than actual write logs, the non-volatile storage space within the cluster for storing write logs is reduced. Prior to failure of the primary node, the primary node also sub-divides the write logs into two or more sub-sets and distributes the sub-sets to the two or more partner nodes for storage at non-volatile storage devices. Thus, if the primary node fails, its write logs are already distributed among the partner nodes so each partner node may perform the allotted write logs on the storage, thus improving the response time to the primary node failure.

Owner:NETWORK APPLIANCE INC

Method and system for error correction in flash memory

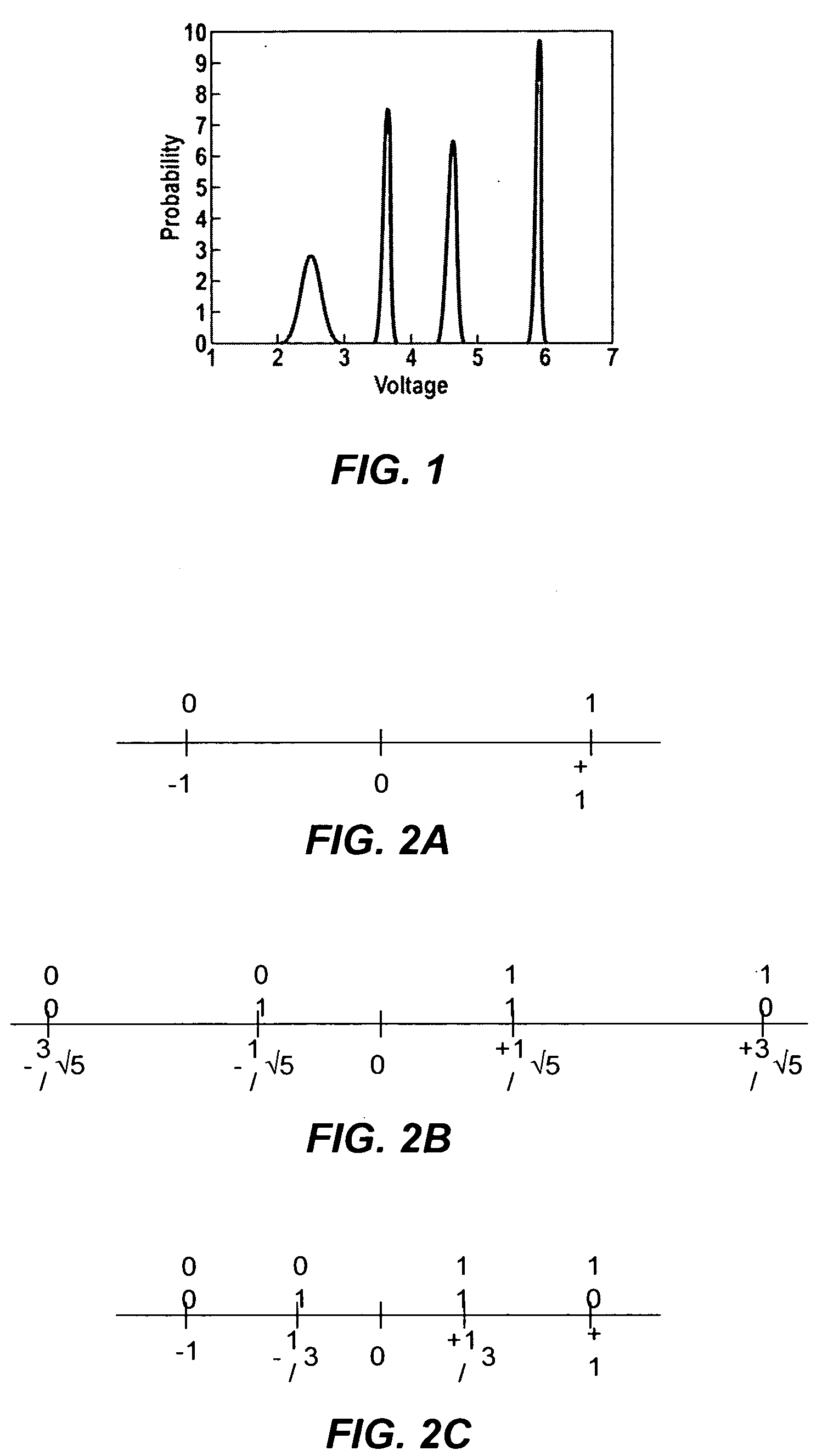

ActiveUS20070171730A1Improve storage densityImprove reliabilityMemory architecture accessing/allocationError detection/correctionA d converterData memory

A solid state non-volatile memory unit. The memory unit includes a multi-level solid state non-volatile memory array adapted to store data characterized by a first number of digital levels. The memory unit also includes an analog-to-digital converter having an input and an output. The input of the analog-to-digital converter is adapted to receive data from the multi-level solid state non-volatile memory array. The output of the analog-to-digital converter is adapted to output a digital signal characterized by a second number of digital levels greater than the first number of digital levels.

Owner:MARVELL ASIA PTE LTD

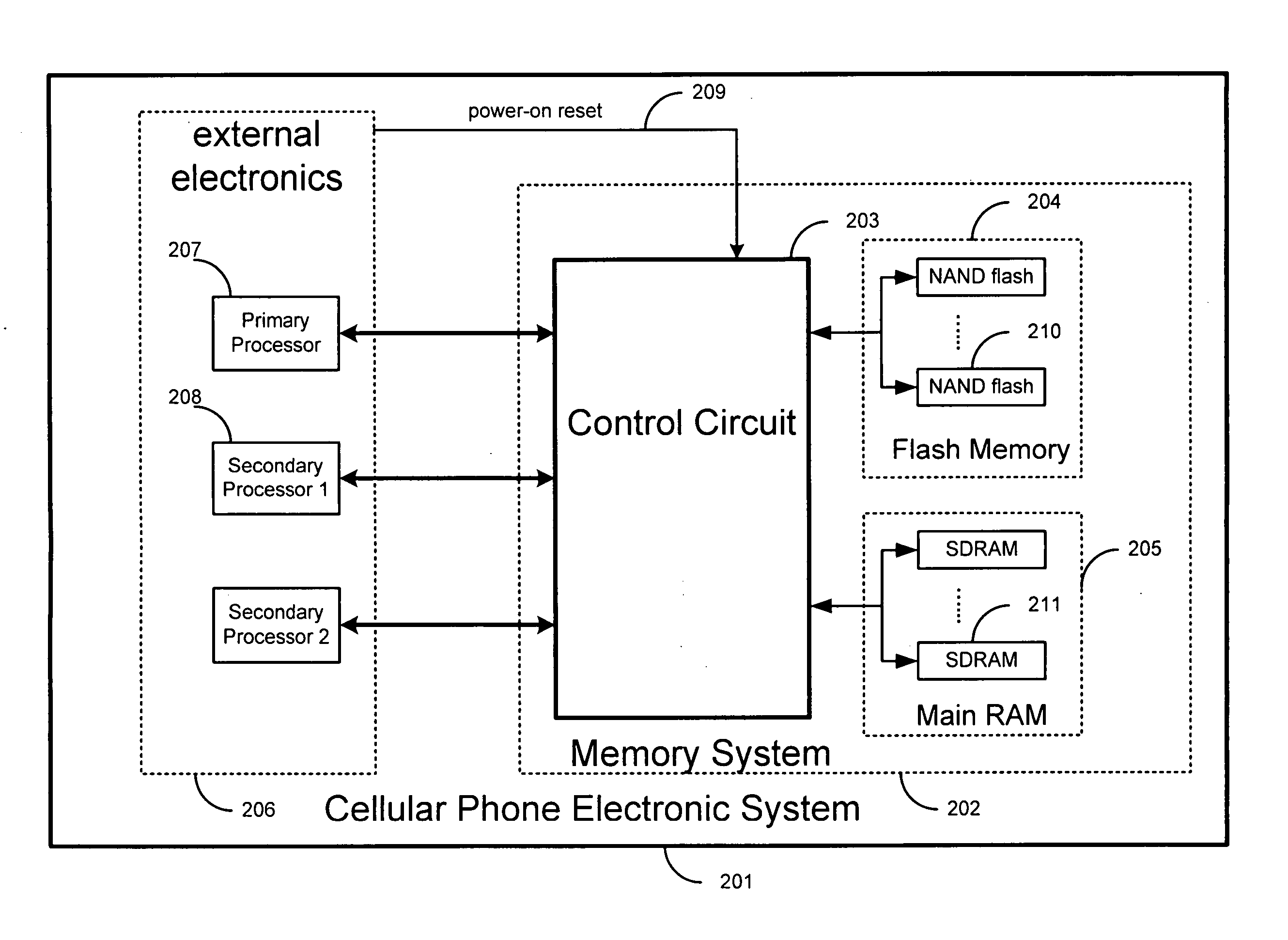

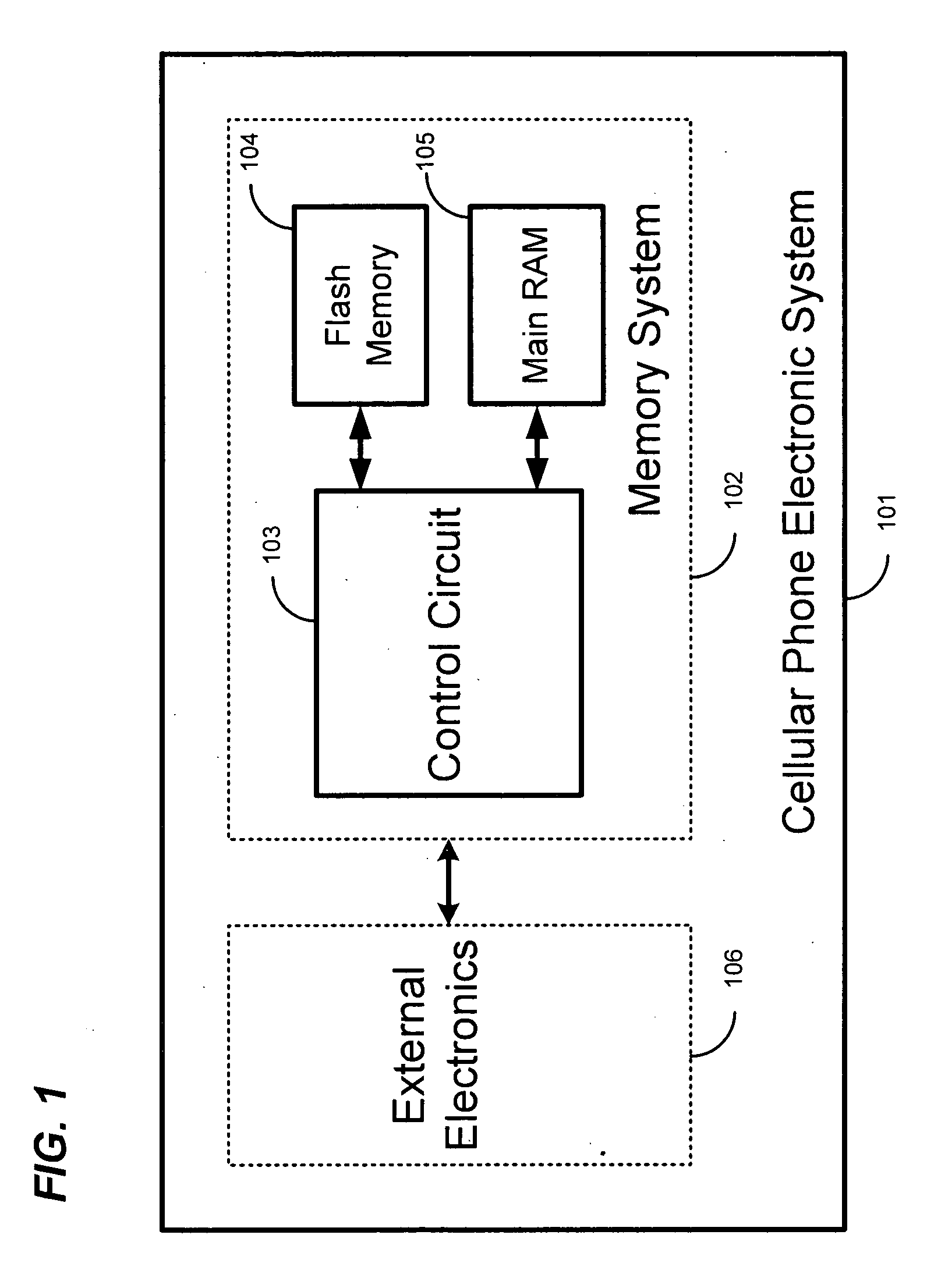

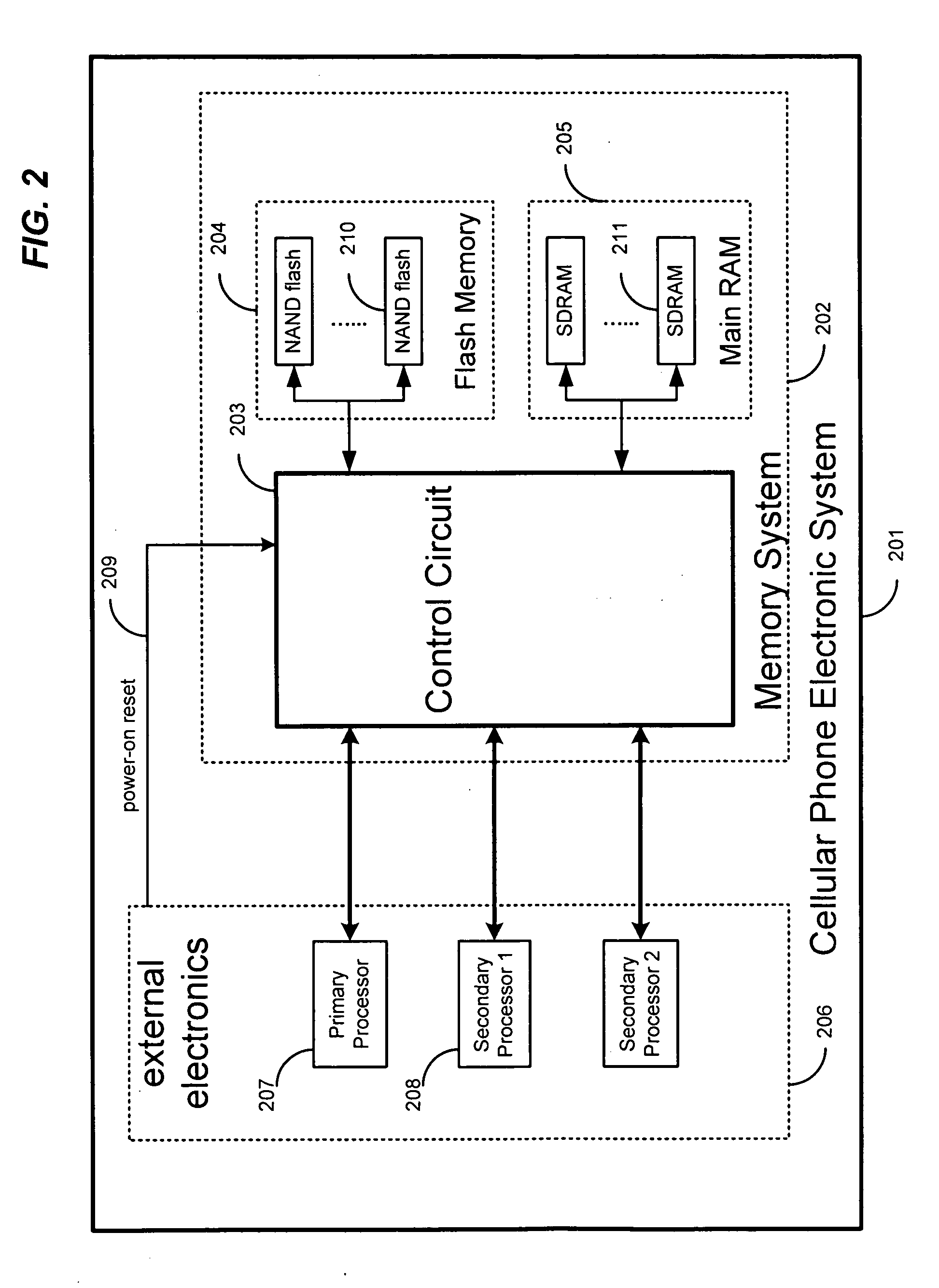

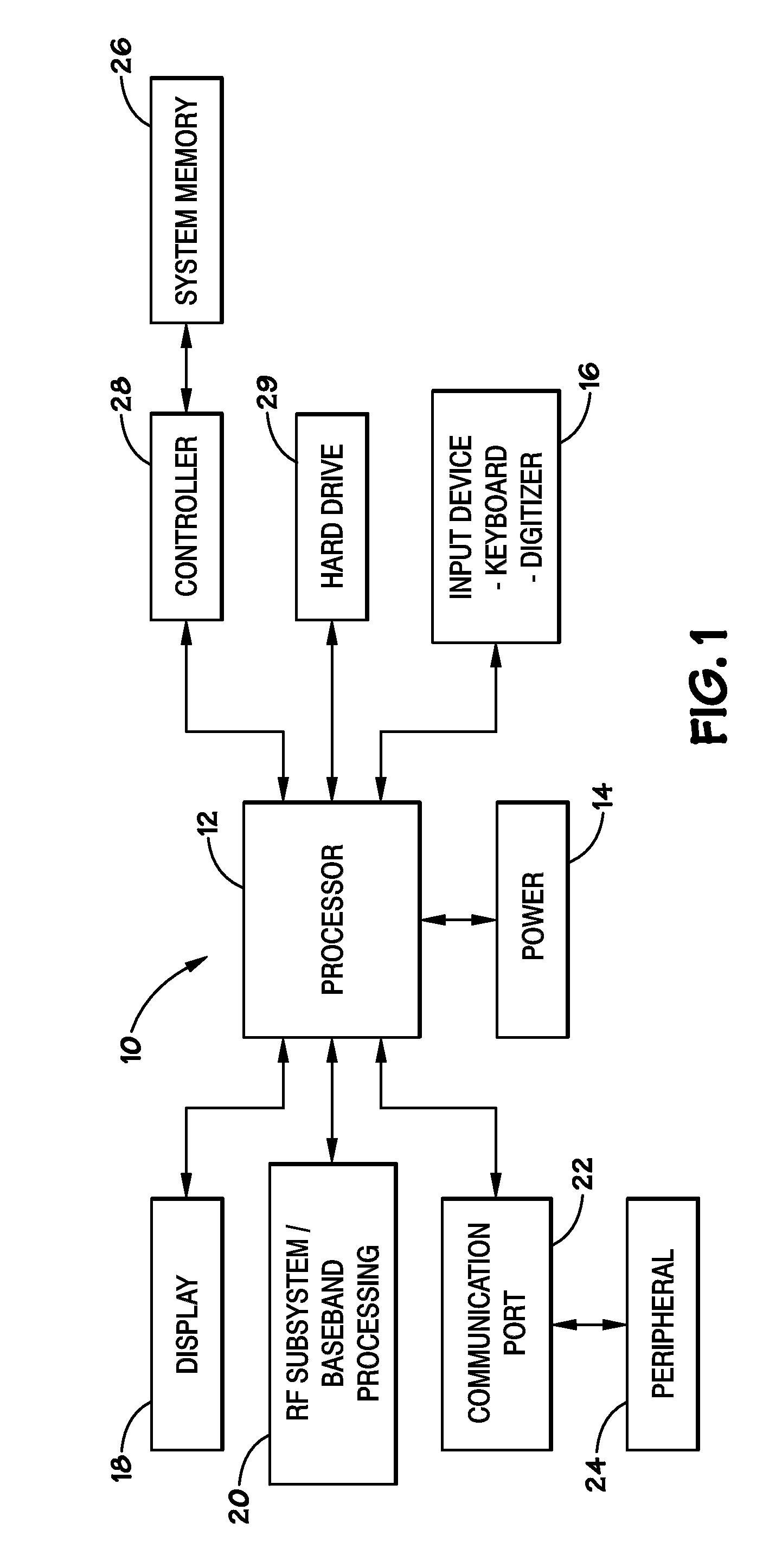

Systems and methods for providing nonvolatile memory management in wireless phones

ActiveUS20060053246A1Low costSmall sizeUnauthorized memory use protectionDigital storageMemory controllerInterface circuits

The present invention is related to memory management, and in particular, to methods and systems for accessing and managing nonvolatile, such as in a wireless phone. A wireless phone memory controller is disclosed that, comprises a first interface circuit configured to be coupled to wireless phone nonvolatile memory, a second interface circuit configured to be coupled to wireless phone volatile memory, a first processor interface configured to be coupled to a first wireless phone processor, wherein the first processor interface is configured to provide the first processor with access to the wireless phone volatile memory, a second processor interface configured to be coupled to a second wireless phone processor, and a controller circuit configured to copy at least a portion of wireless phone nonvolatile memory data to the wireless phone volatile memory.

Owner:GOOGLE LLC

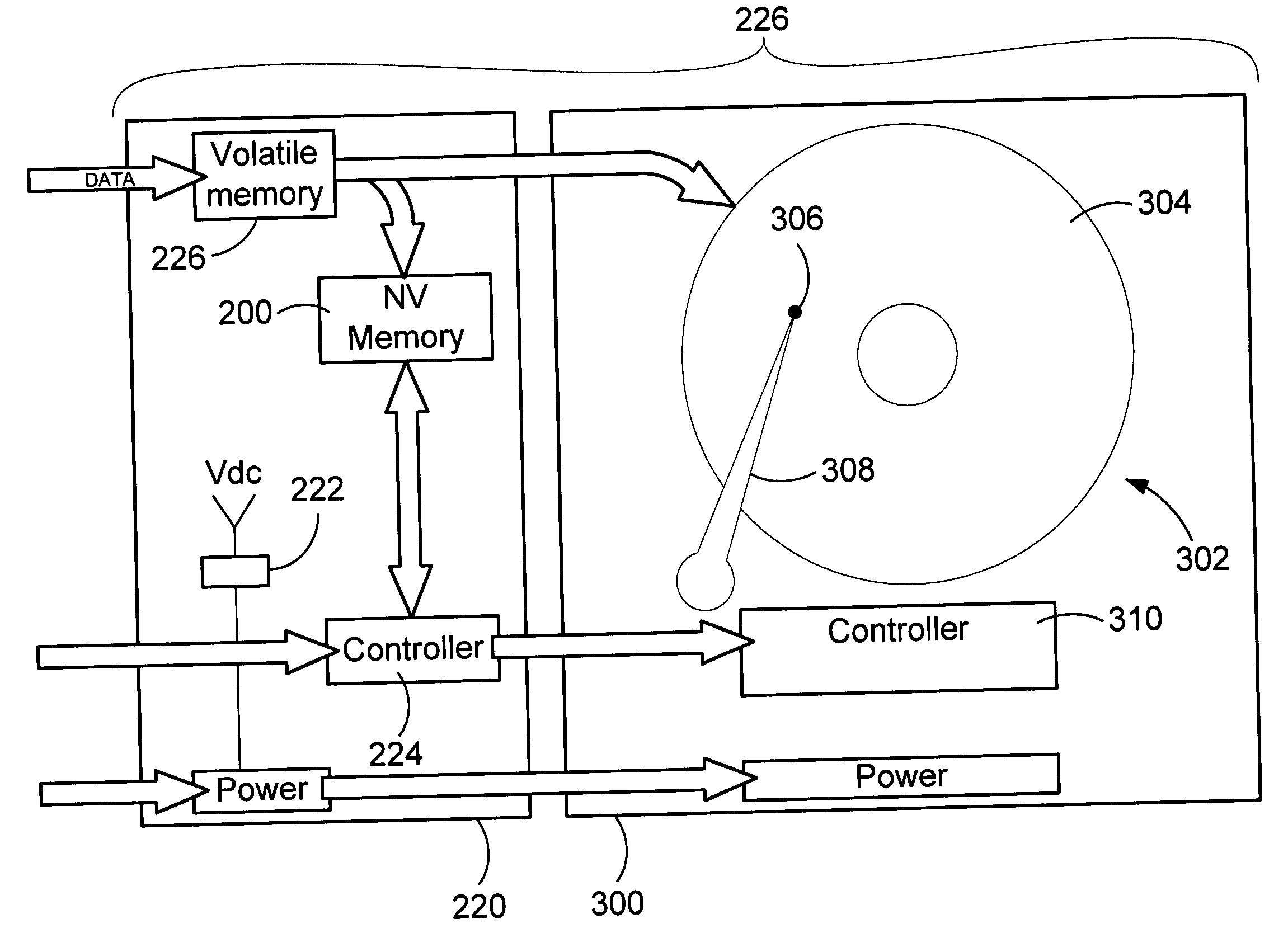

In-line non volatile memory disk read cache and write buffer

ActiveUS20060248387A1Read/write performance of hardReduce the number of timesData buffering arrangementsError detection/correctionHard disc driveWrite buffer

A method and apparatus to improve the read / write performance of a hard drive is presented. A device having solid state, non-volatile (NV) memory is added in-line to the conventional hard drive and acts as a read / write cache. Data specified by the operating system is stored in the NV memory. The operating system provides a list of data to be put in NV memory. The data includes data to be pinned in NV memory and data that is dynamic. Pinned data persists in NV memory until the operating system commands it to be flushed. Dynamic data can be flushed by the hard drive controller. Data sent by an application for storage is temporarily stored in NV memory in data blocks until the operating system commits it to the disk.

Owner:MICROSOFT TECH LICENSING LLC

Vehicle visual and non-visual data recording system

ActiveUS20030154009A1Vehicle testingRegistering/indicating working of vehiclesData synchronizationDriver/operator

The system described in this invention can be used for monitoring and analyzing real time visual and non-visual information pertaining to the occupant, vehicle, and surroundings prior to, during and post eccentric operating conditions for a given period of time. The system stores vehicle and occupant data from sensors throughout the vehicle and also makes use of existing vehicle sensors that may already be present in the vehicle. The invention also includes a video recording module that makes use of a fish-eye camera to capture video from the inside and the outside of the vehicle. Real-time data analysis is performed to detect and to recognize vehicle occupants, and recognize impending eccentric events. Vehicle, occupant, and video data are stored in circular buffers. When an eccentric event, a collision for example, has been detected, the device continues to record data and video for a fixed period of time. Once this time has elapsed, the data is transferred from volatile to non-volatile memory for later retrieval. A computer may be used to retrieve and display the vehicle and occupant data in a synchronization with the video data for the purposes of accident recreation, driver or vehicle monitoring.

Owner:MINOTAUR SYST LLC

Method and apparatus for maintaining data on non-volatile memory systems

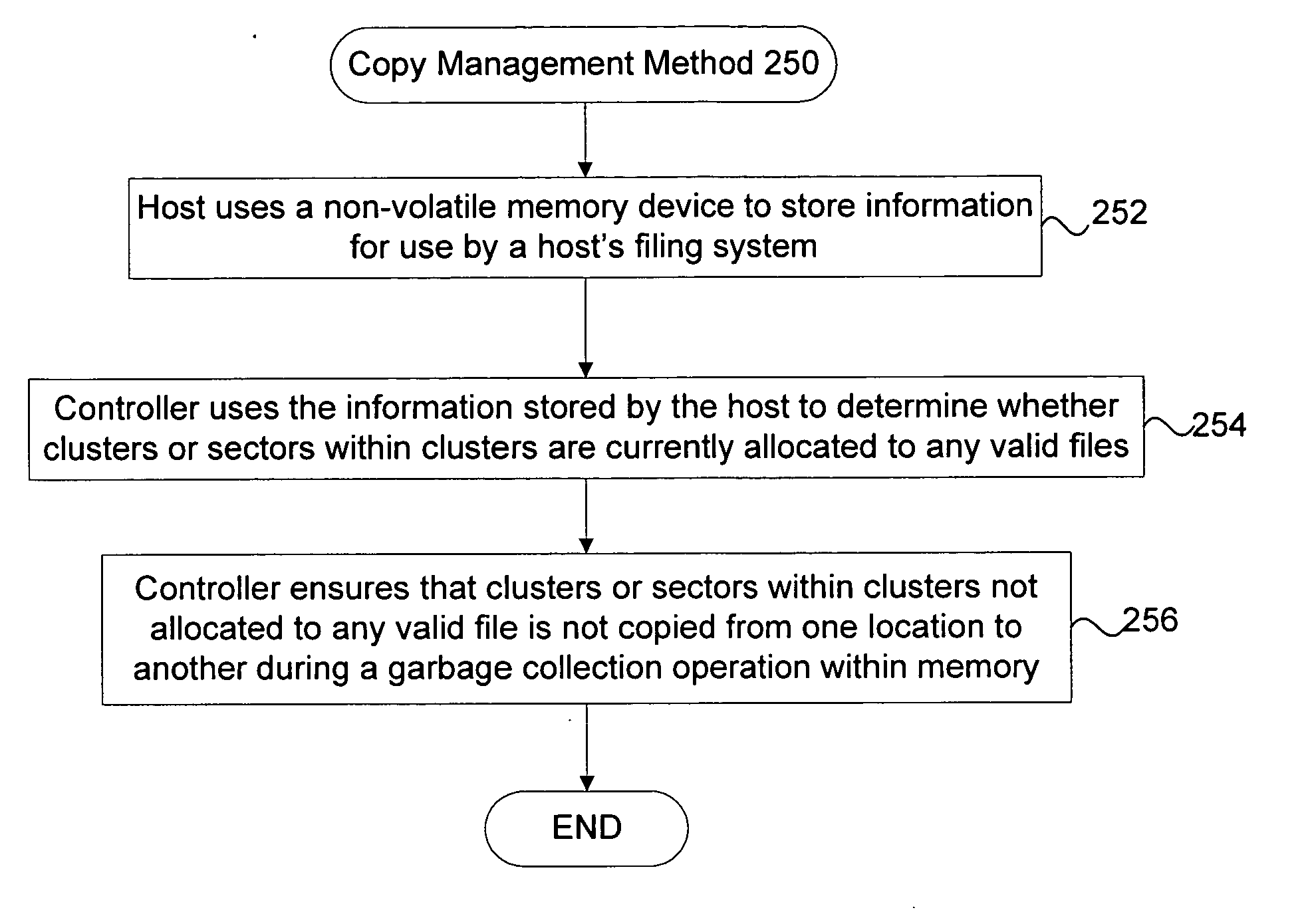

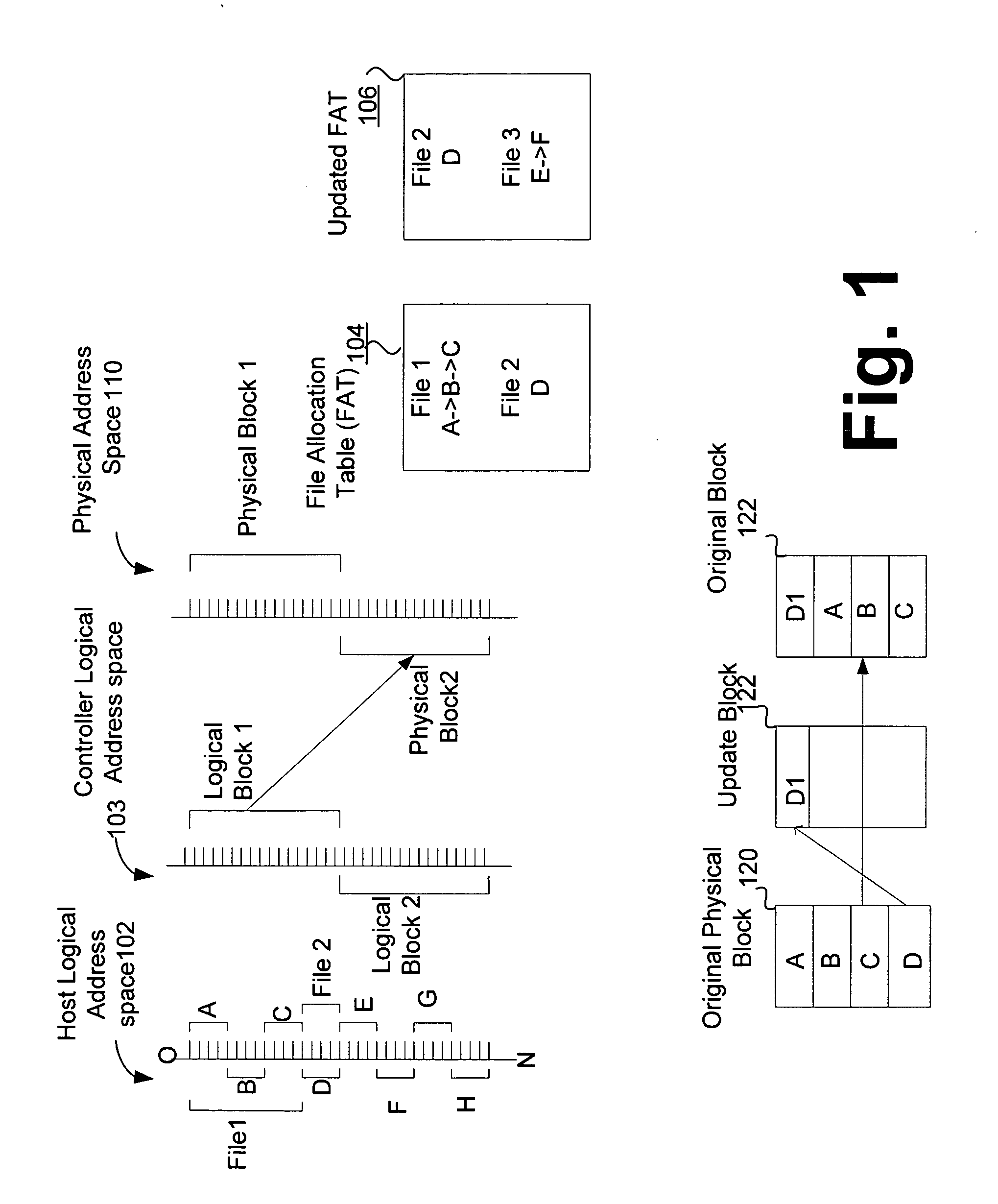

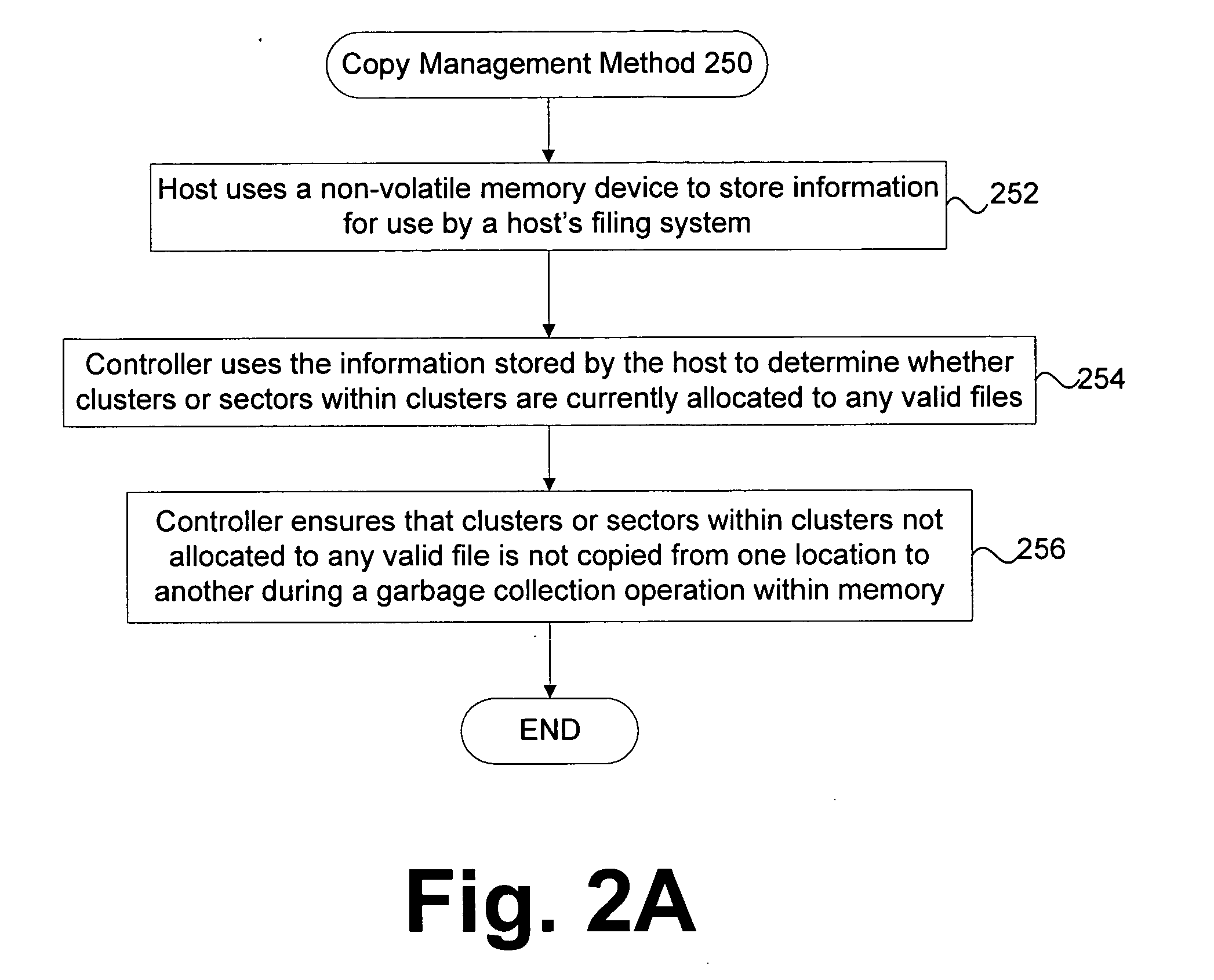

ActiveUS20060020744A1Improve system performanceUnnecessary operationMemory architecture accessing/allocationData processing applicationsCopyingVolatile memory

Techniques for managing data in a non-volatile memory system (e.g., Flash Memory) are disclosed. A controller can use information relating to a host's filing system, which is stored by the host on non-volatile memory, to determine if one or more clusters (or sectors with clusters) are currently allocated. The controller can use the information relating to the host's filing system to ensure that one or more clusters (or one or more sectors within a cluster) are not copied from one location to another location in the memory during a garbage collection cycle. As a result, some unnecessary operations (e.g., copying data) which are conventionally performed can be avoided and system performance can be enhanced.

Owner:SANDISK TECH LLC

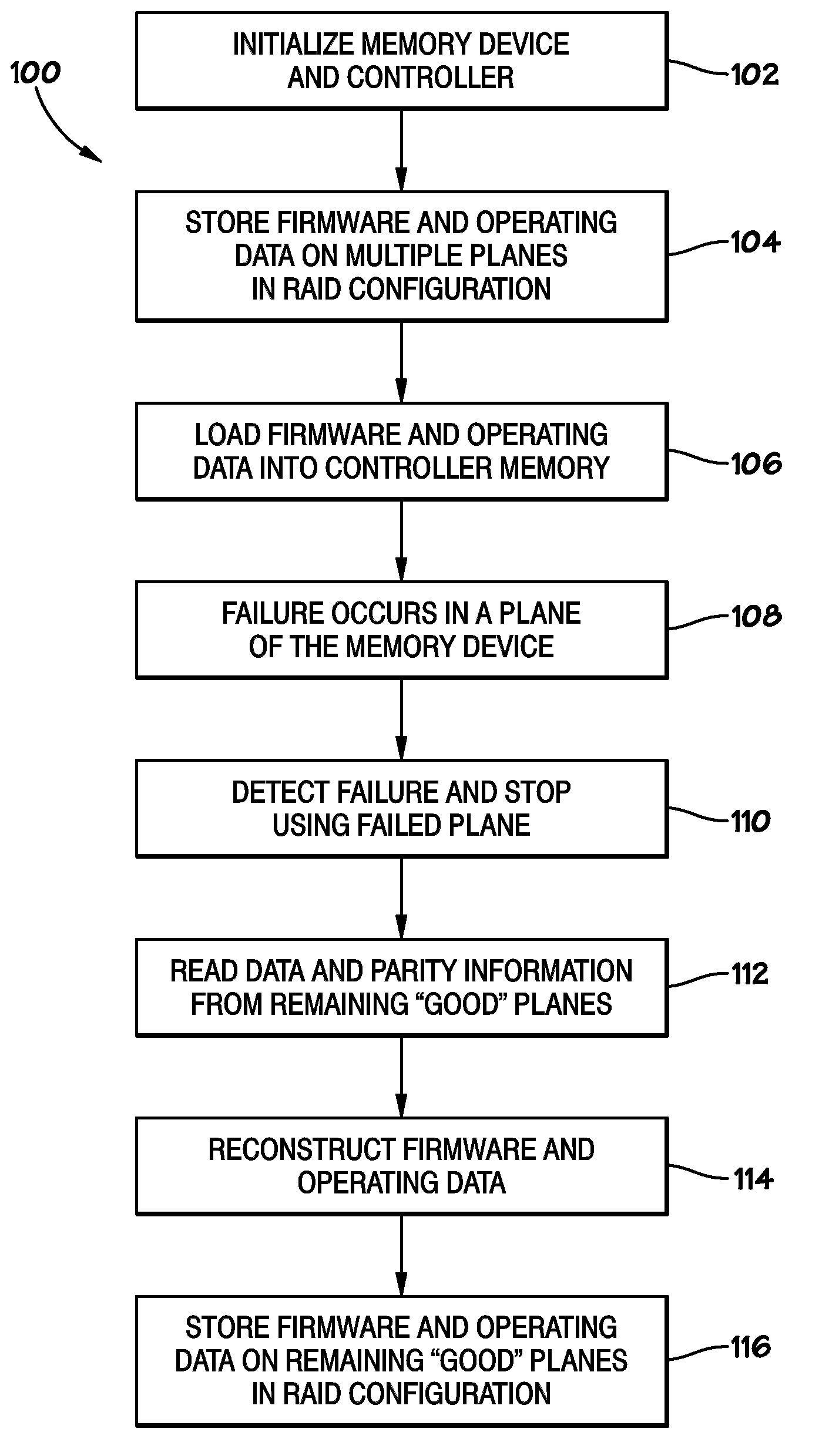

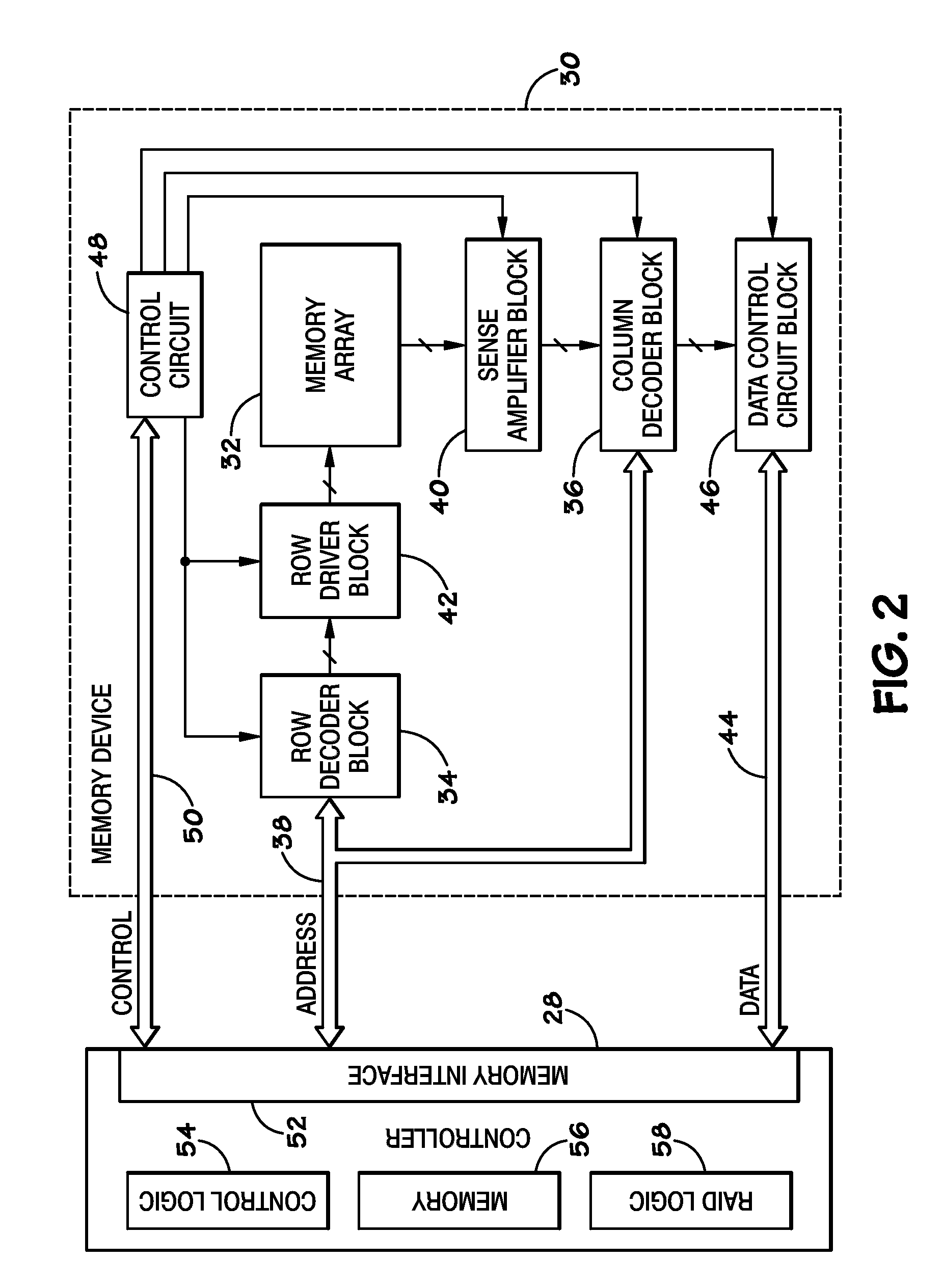

Systems and Methods for Storing and Recovering Controller Data in Non-Volatile Memory Devices

Systems and methods are disclosed for storing the firmware and other data of a flash memory controller, such as using a RAID configuration across multiple flash memory devices or portions of a single memory device. In various embodiments, the firmware and other data used by a controller, and error correction information, such as parity information for RAID configuration, may be stored across multiple flash memory devices, multiple planes of a multi-plane flash memory device, or across multiple blocks or pages of a single flash memory device. The controller may detect the failure of a memory device or a portion thereof, and reconstruct the firmware and / or other data from the other memory devices or portions thereof.

Owner:MICRON TECH INC

Scheduling of housekeeping operations in flash memory systems

ActiveUS20060161728A1Good performanceMemory architecture accessing/allocationRead-only memoriesEEPROMHousekeeping

A re-programmable non-volatile memory system, such as a flash EEPROM system, having its memory cells grouped into blocks of cells that are simultaneously erasable is operated to perform memory system housekeeping operations in the foreground during execution of a host command, wherein the housekeeping operations are unrelated to execution of the host command. Both one or more such housekeeping operations and execution of the host command are performed within a time budget established for executing that particular command. One such command is to write data being received to the memory. One such housekeeping operation is to level out the wear of the individual blocks that accumulates through repetitive erasing and re-programming.

Owner:SANDISK TECH LLC