Patents

Literature

99 results about "Universal memory" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Universal memory refers to a computer data storage device combining the cost benefits of DRAM, the speed of SRAM, the non-volatility of flash memory along with infinite durability. Such a device, if it ever becomes possible to develop, would have a far-reaching impact on the computer market.

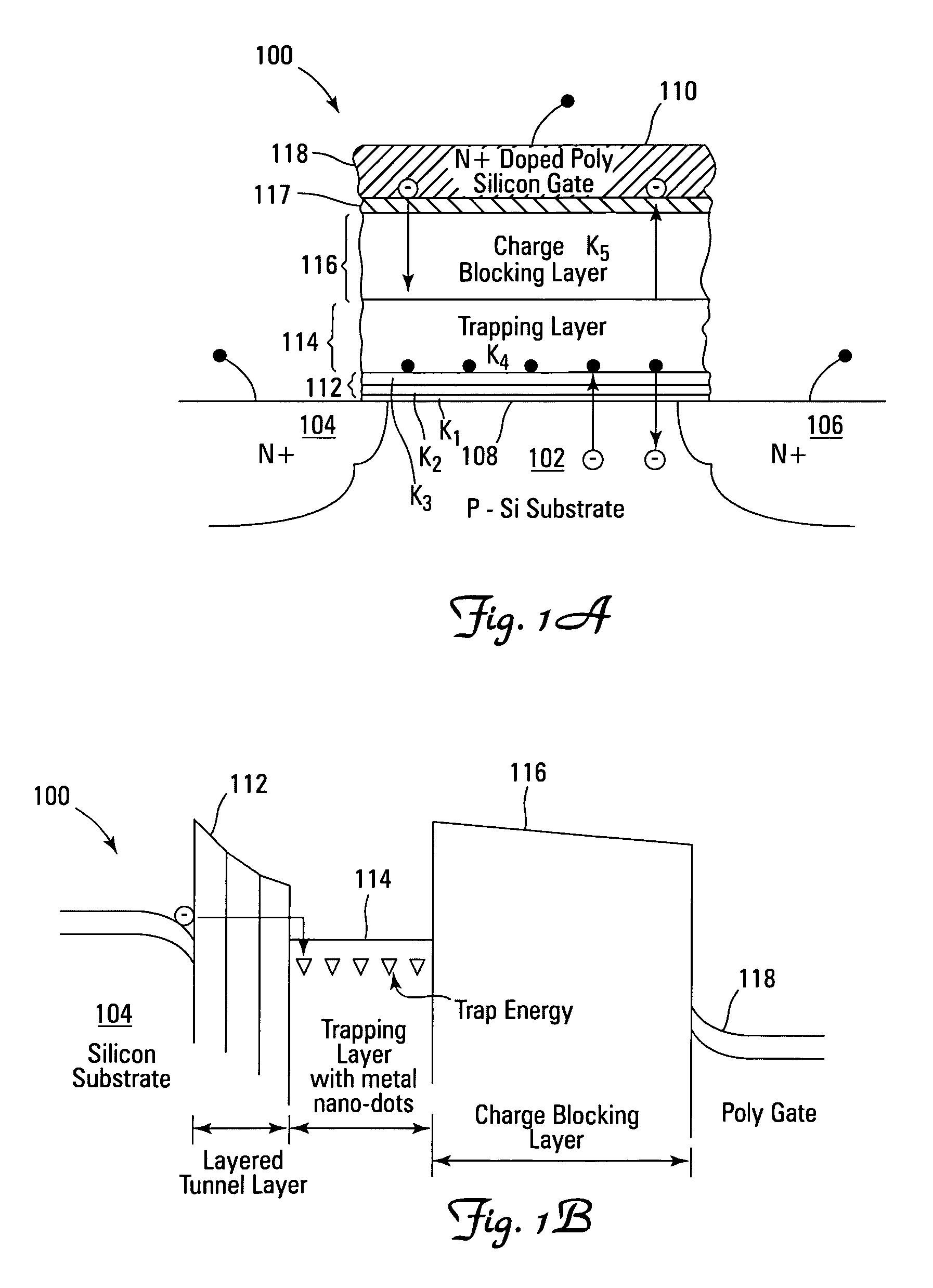

Novel low power non-volatile memory and gate stack

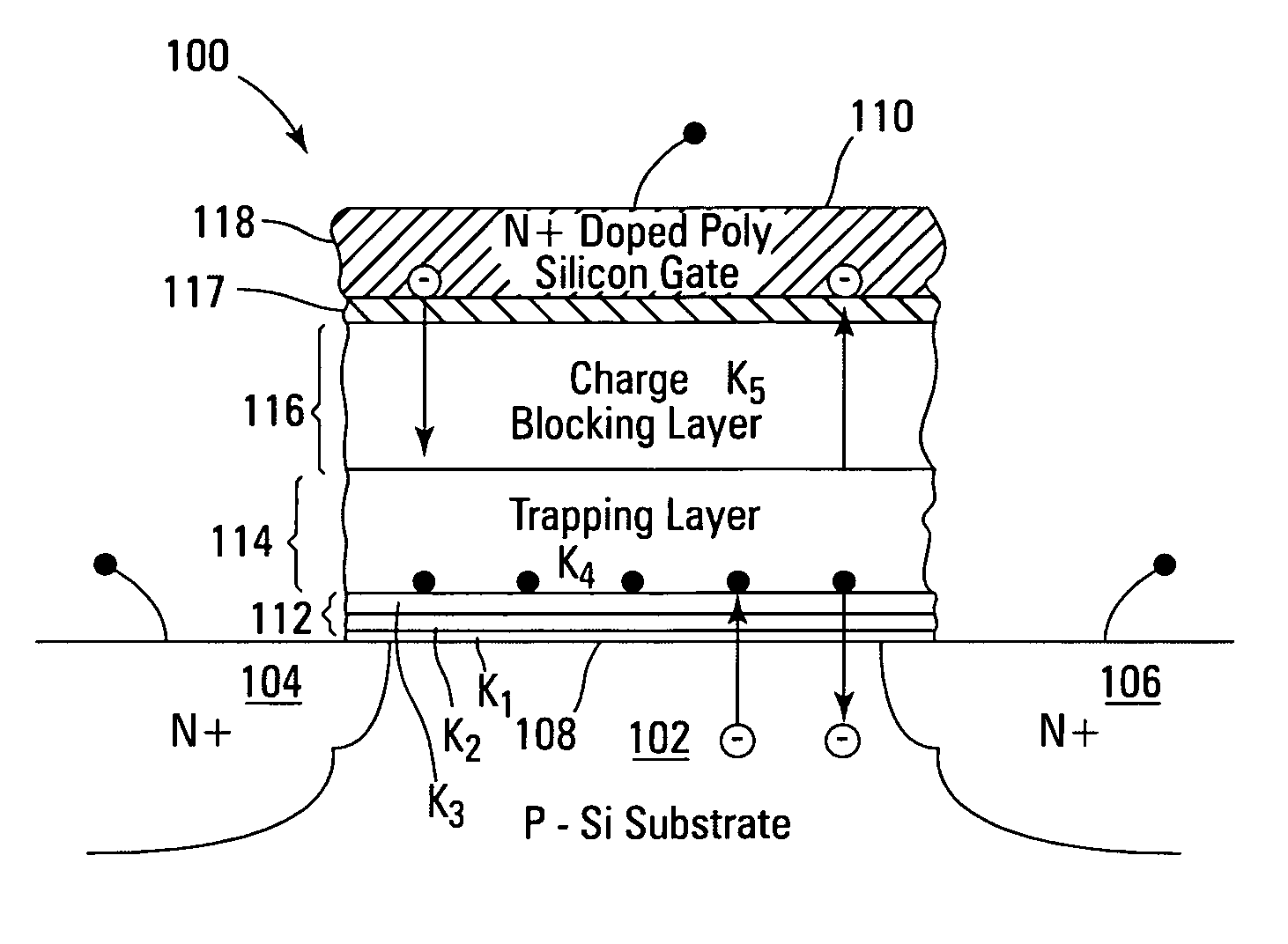

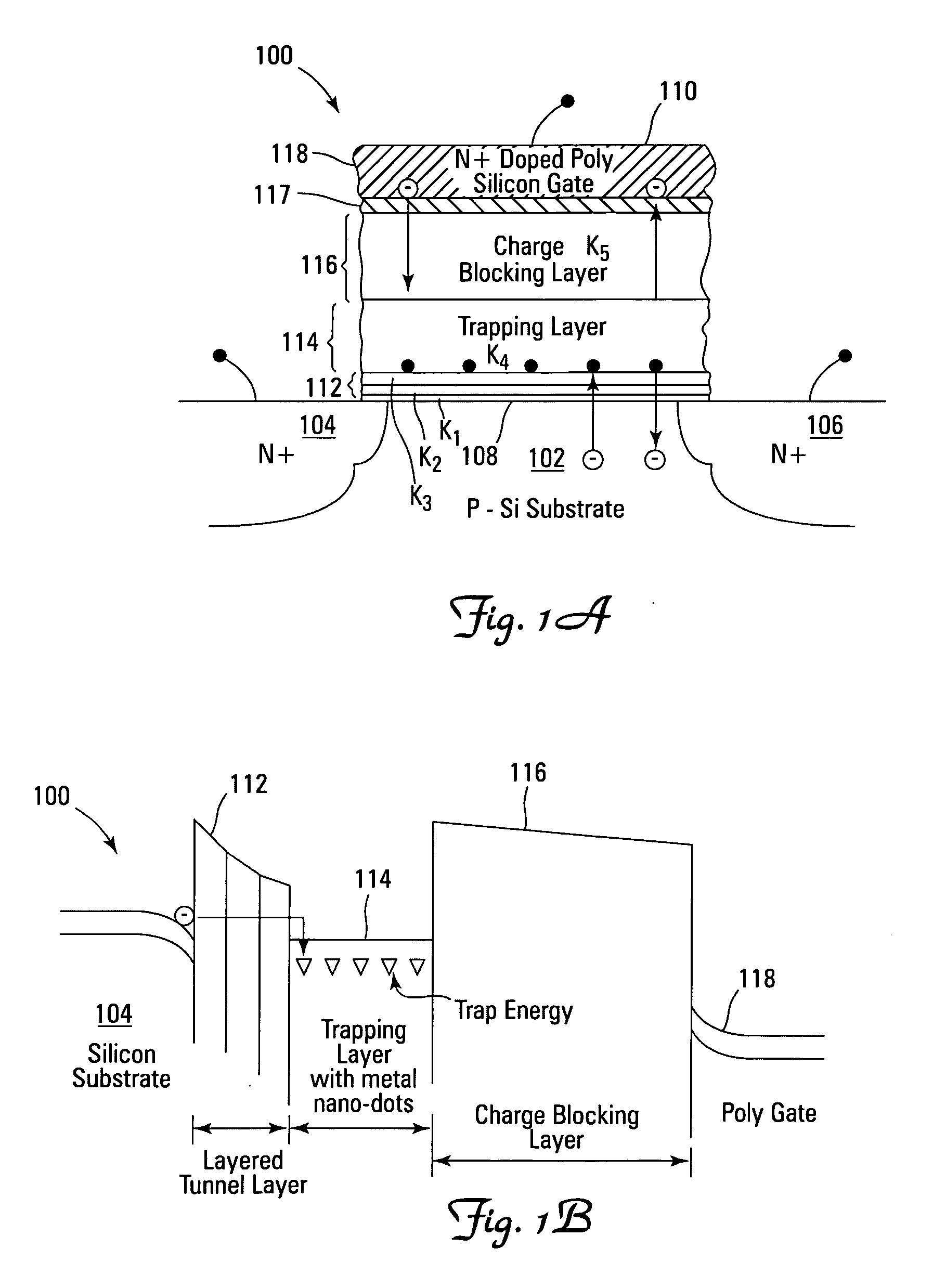

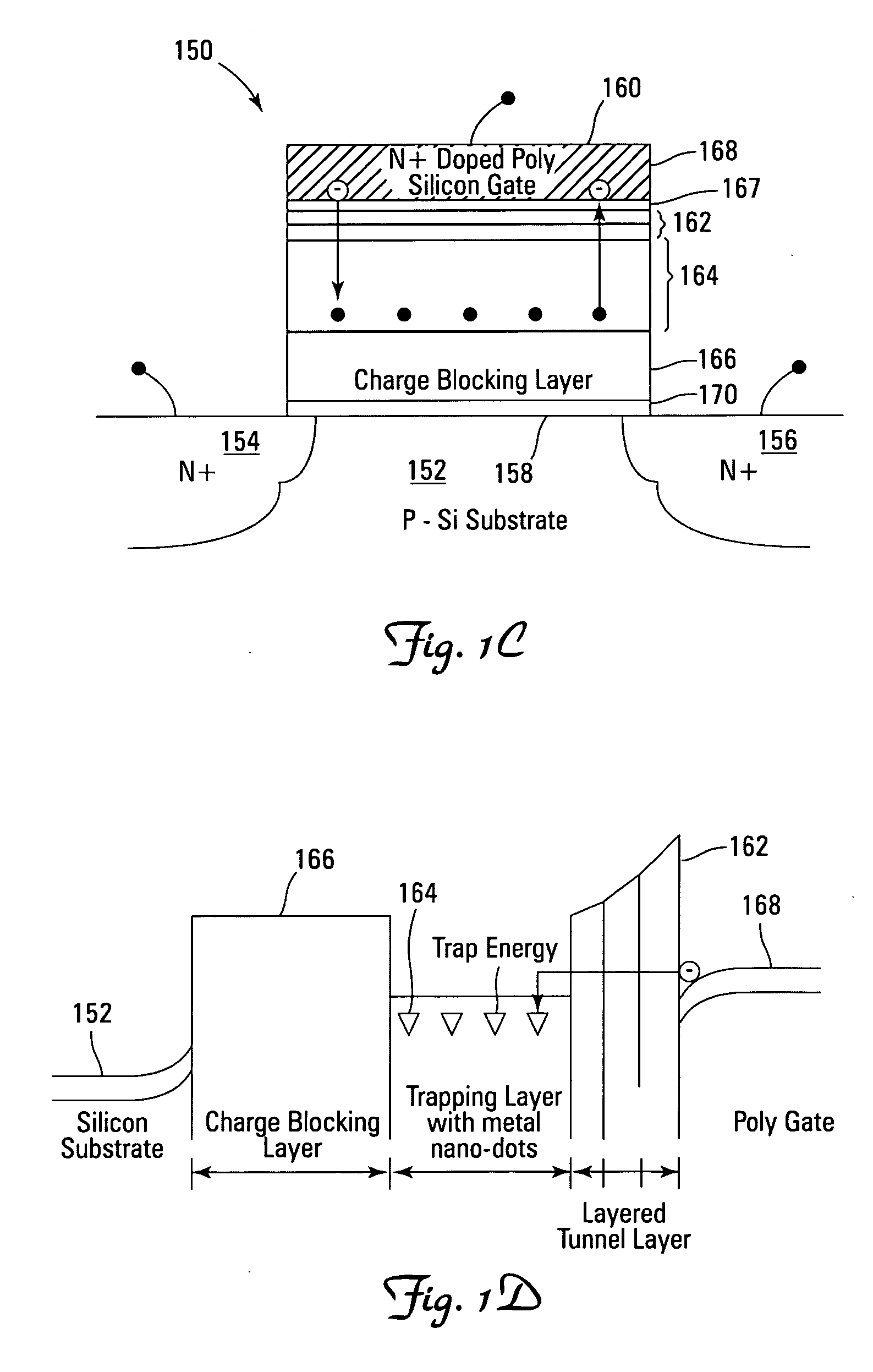

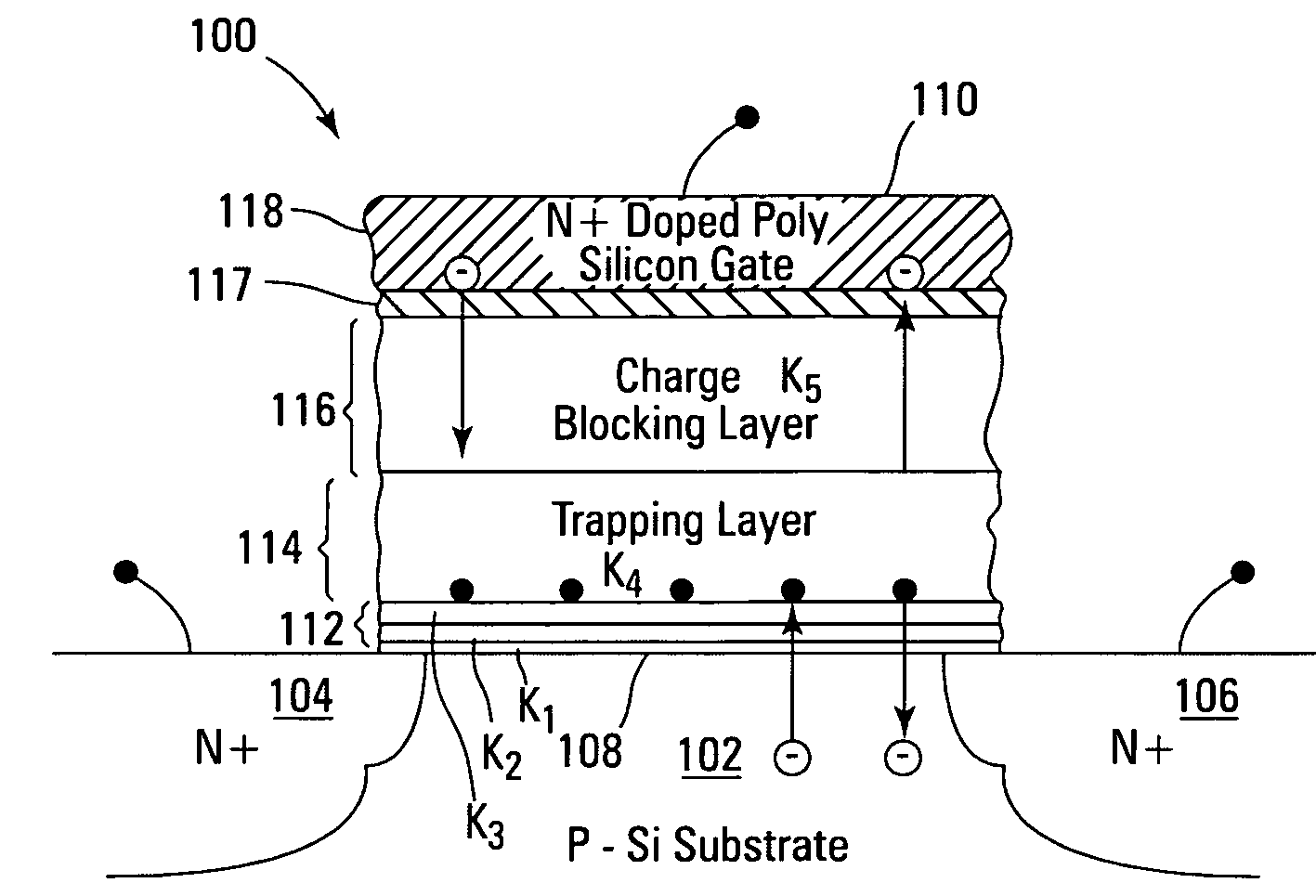

ActiveUS20060261401A1High charge blocking barrierExcellent charge retentionTransistorNanoinformaticsCharge retentionLow voltage

Non-volatile memory devices and arrays are described that facilitate the use of band-gap engineered gate stacks with asymmetric tunnel barriers in reverse and normal mode floating node memory cells in NOR or NAND memory architectures that allow for direct tunnel programming and erase, while maintaining high charge blocking barriers and deep carrier trapping sites for good charge retention. The low voltage direct tunneling program and erase capability reduces damage to the gate stack and the crystal lattice from high energy carriers, reducing write fatigue and enhancing device lifespan. The low voltage direct tunnel program and erase capability also enables size reduction through low voltage design and further device feature scaling. Memory cells of the present invention also allow multiple bit storage. These characteristics allow memory device embodiments of the present invention to operate within the definition of a universal memory, capable of replacing both DRAM and ROM in a system.

Owner:MICRON TECH INC

Low power non-volatile memory and gate stack

Non-volatile memory devices and arrays are described that facilitate the use of band-gap engineered gate stacks with asymmetric tunnel barriers in reverse and normal mode floating node memory cells in NOR or NAND memory architectures that allow for direct tunnel programming and erase, while maintaining high charge blocking barriers and deep carrier trapping sites for good charge retention. The low voltage direct tunneling program and erase capability reduces damage to the gate stack and the crystal lattice from high energy carriers, reducing write fatigue and enhancing device lifespan. The low voltage direct tunnel program and erase capability also enables size reduction through low voltage design and further device feature scaling. Memory cells of the present invention also allow multiple bit storage. These characteristics allow memory device embodiments of the present invention to operate within the definition of a universal memory, capable of replacing both DRAM and ROM in a system.

Owner:MICRON TECH INC

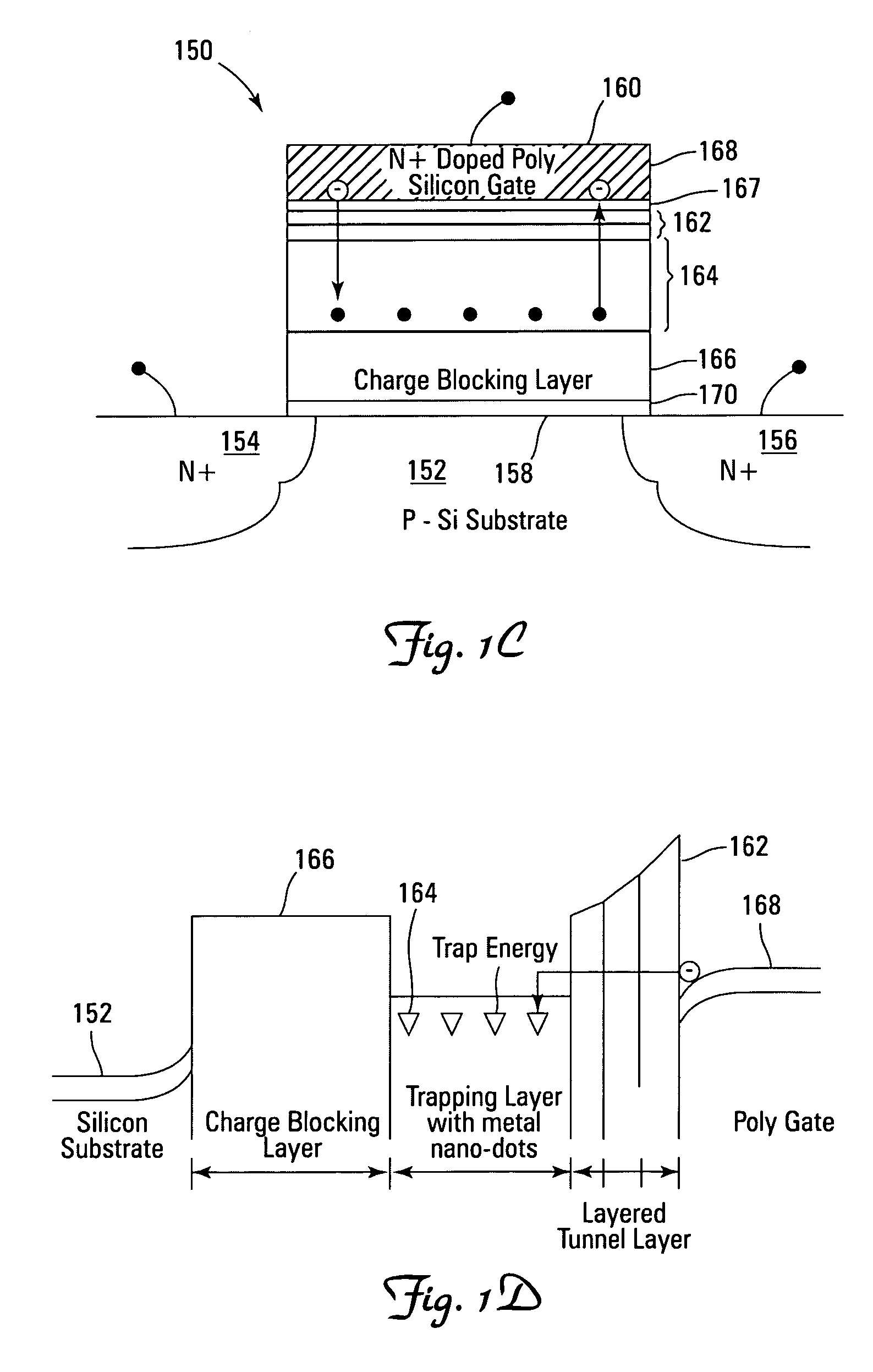

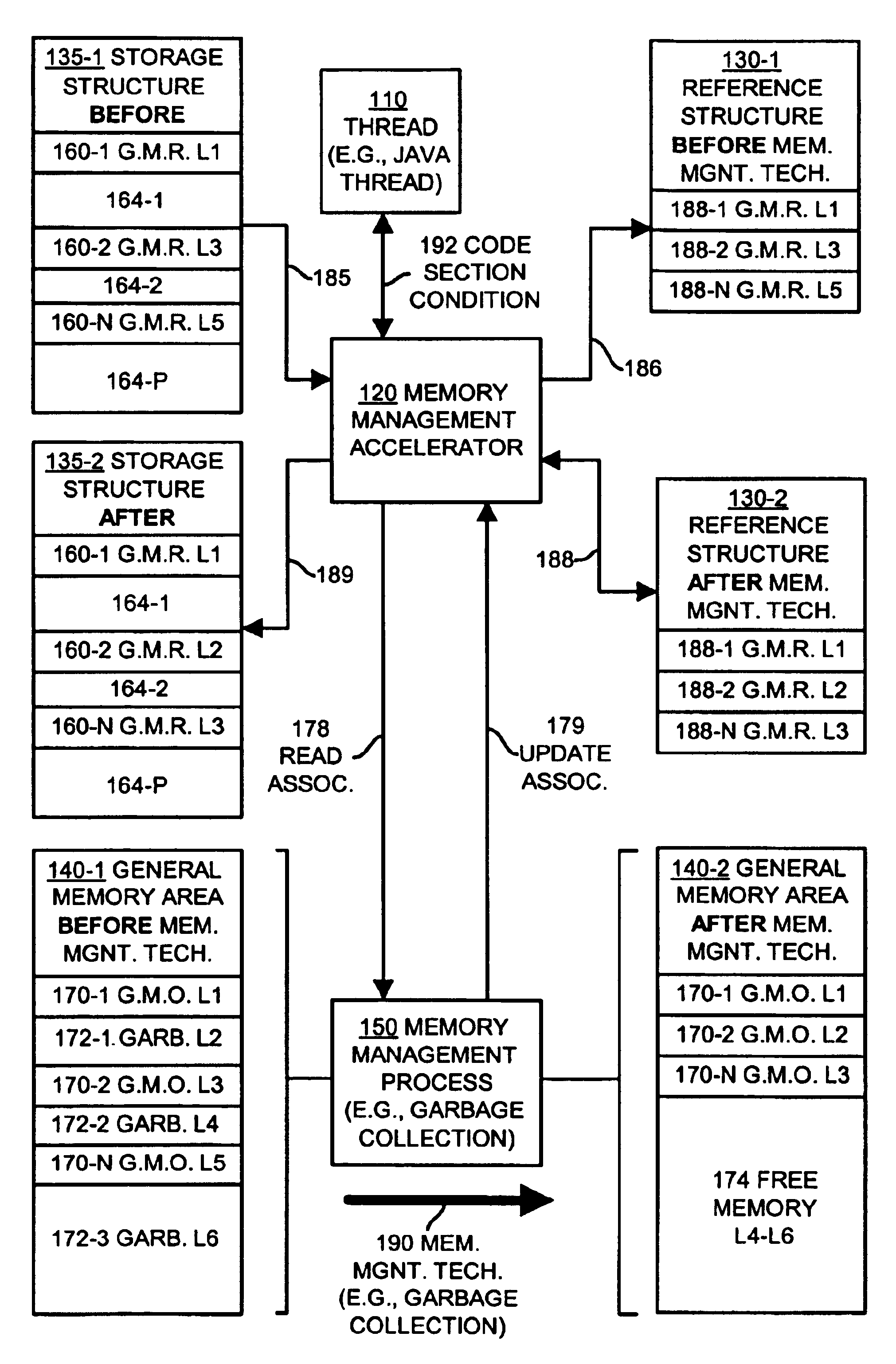

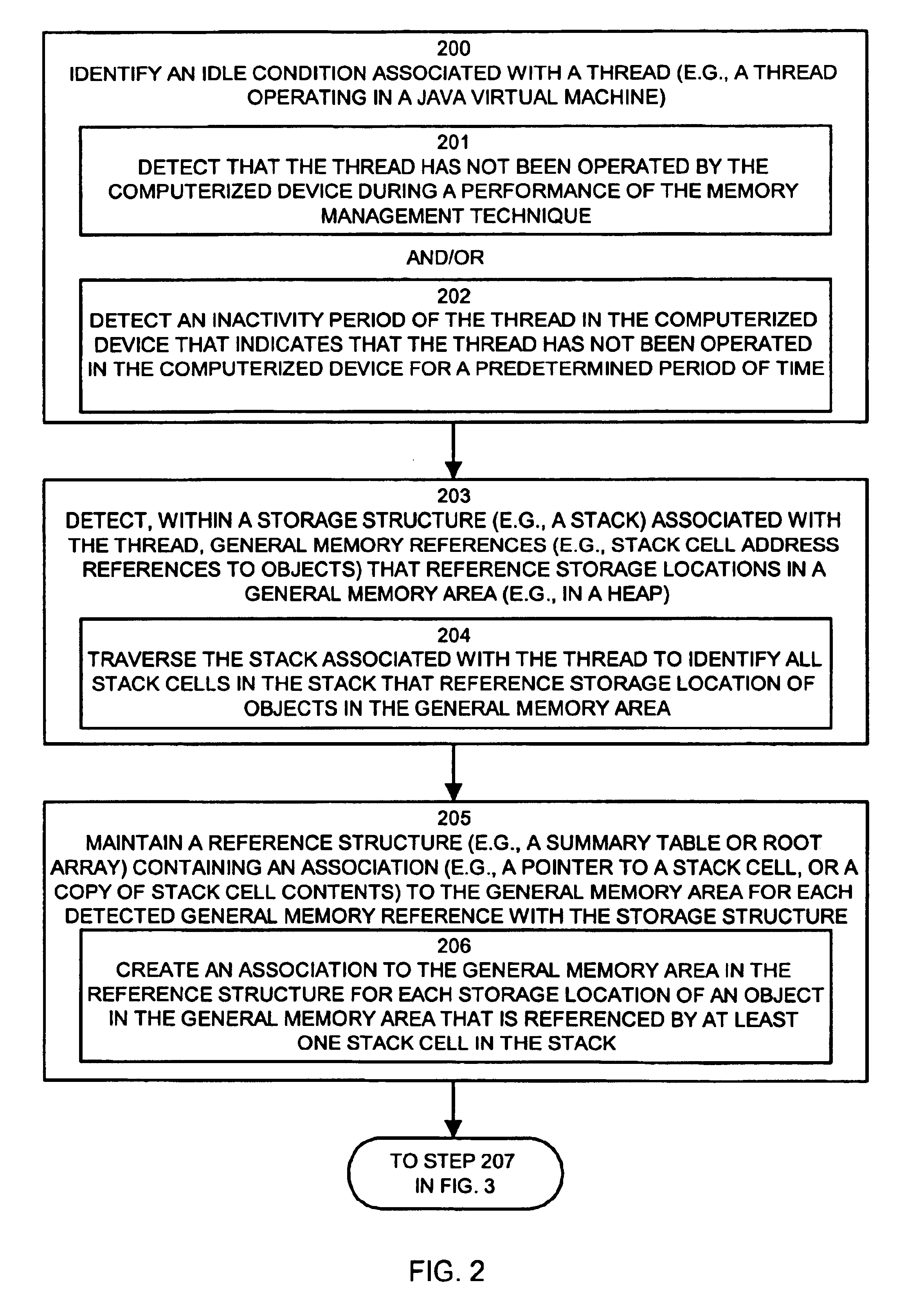

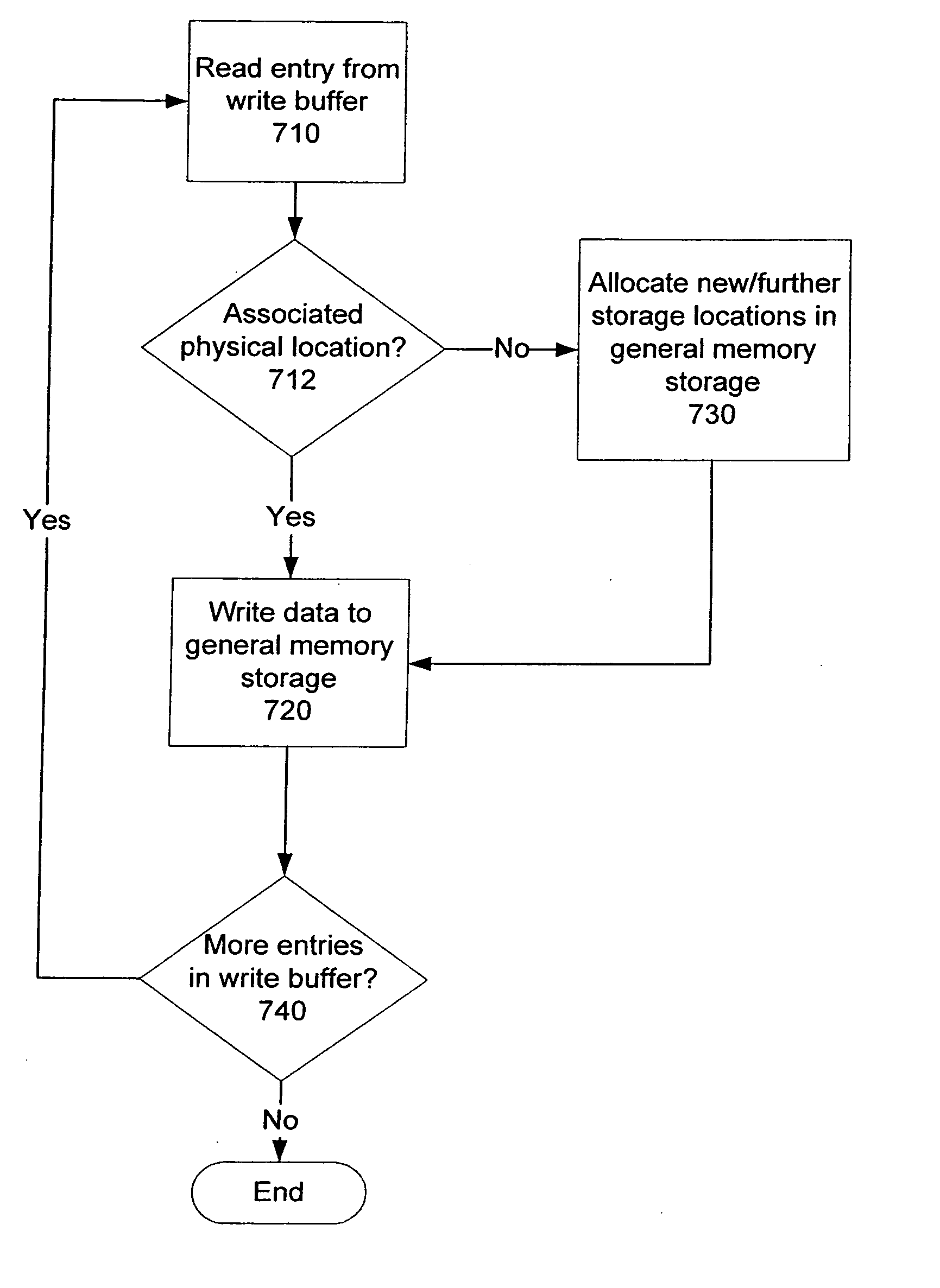

Methods and apparatus for performing a memory management technique

InactiveUS6862674B2Save processing timePrecise maintenanceData processing applicationsMemory adressing/allocation/relocationWaste collectionSystem maintenance

Mechanisms and techniques operate in a computerized device to perform a memory management technique such as garbage collection. The mechanisms and techniques operate to detect, within a storage structure associated with a thread, general memory references that reference storage locations in a general memory area such as a heap. The storage structure may be a stack utilized by the thread, which may be, for example, a Java thread, during operation of the thread in the computerized device. The system maintains a reference structure containing an association to the general memory area for each detected general memory reference within the storage structure. The system then operates a memory management technique on the general memory area for locations in the general memory area other than those for which an association to the general memory area is maintained in the reference structure, thus increasing the performance of the memory management technique.

Owner:ORACLE INT CORP

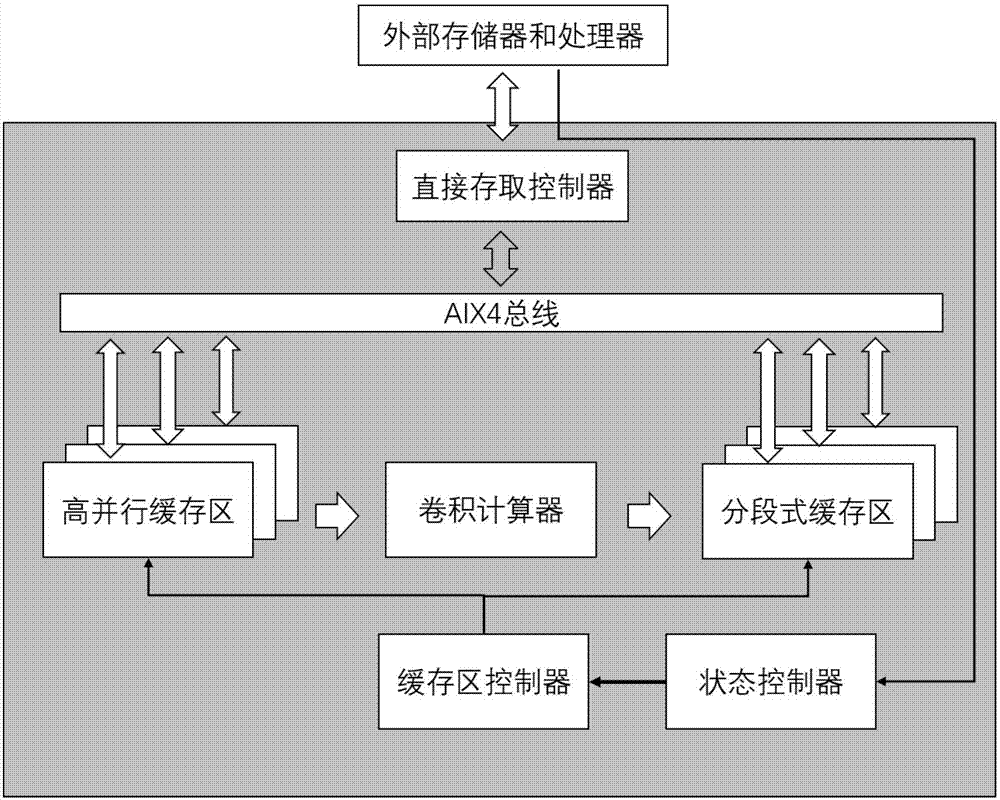

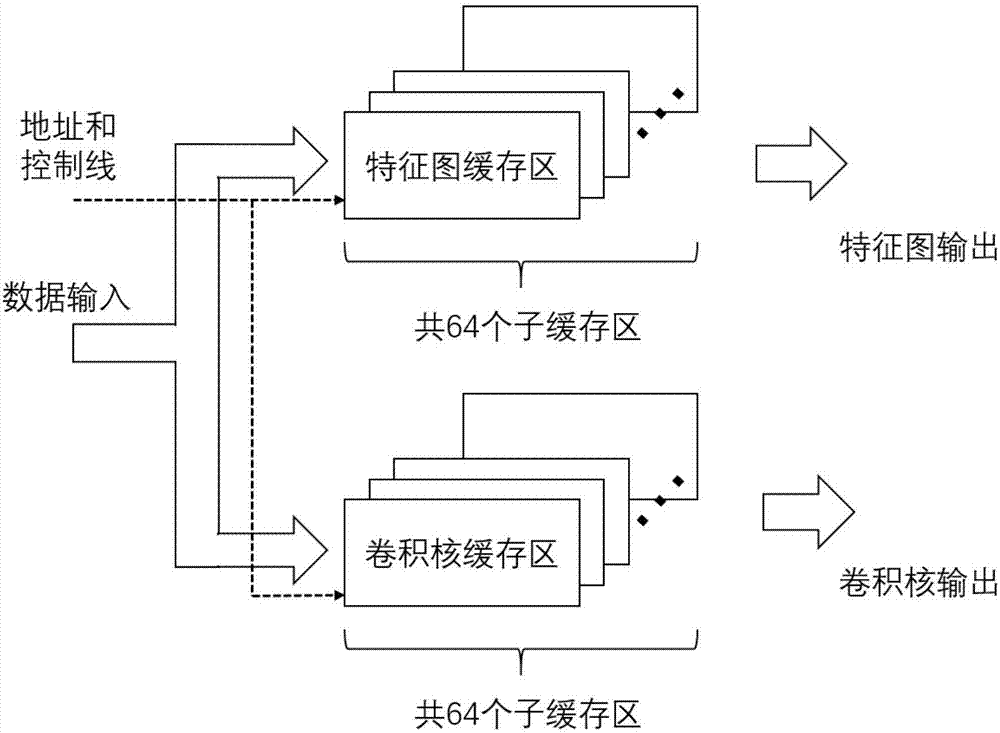

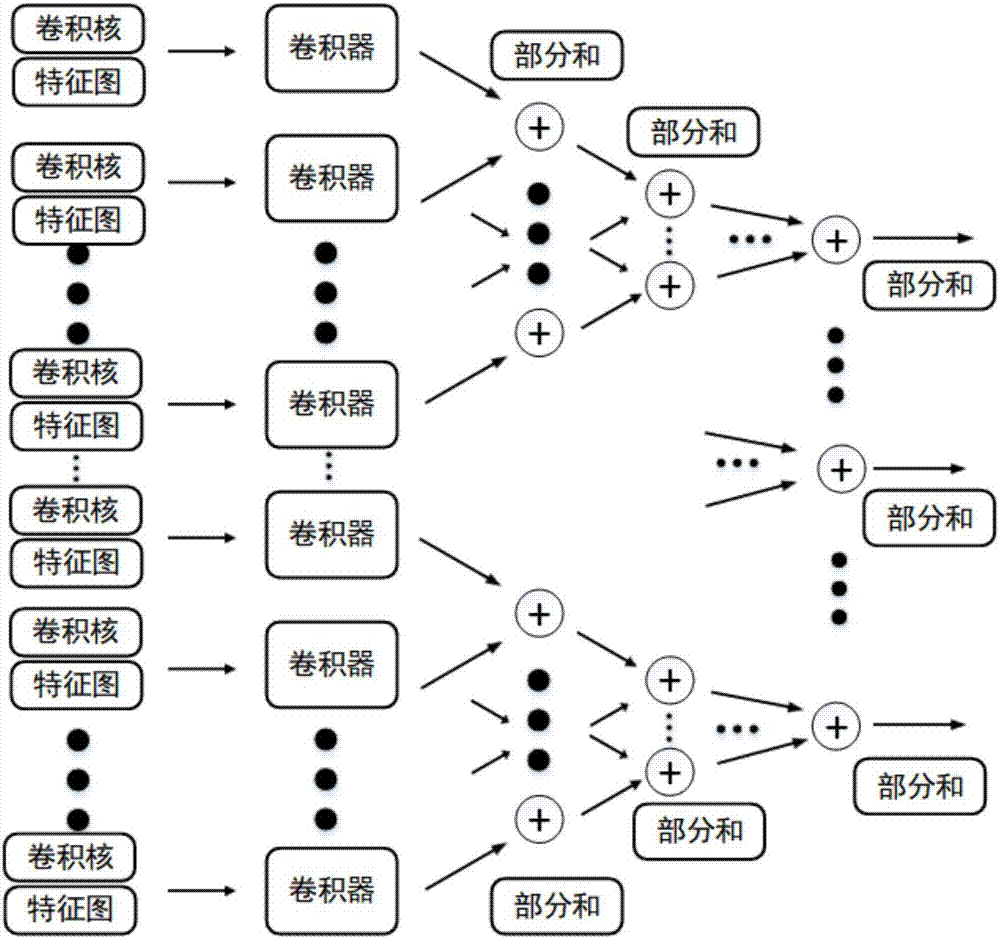

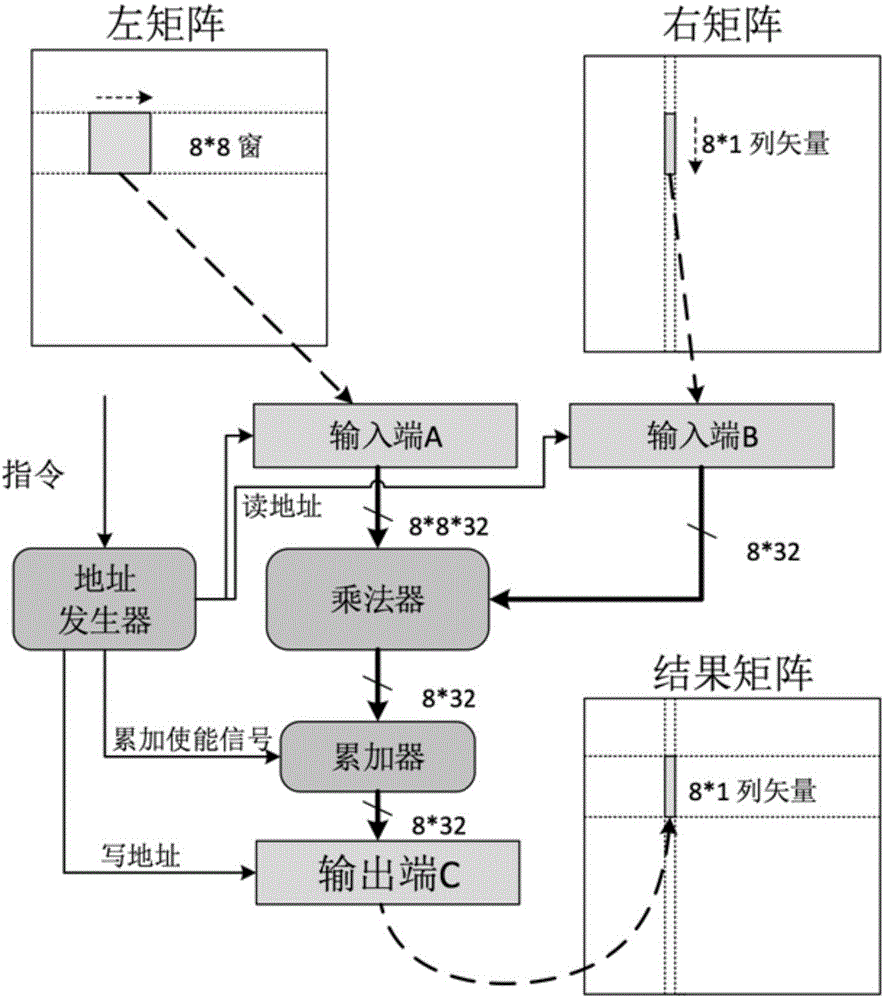

FPGA (field programmable gate array)-based universal fixed-point-number neural network convolution accelerator hardware structure

InactiveCN107392309AImprove versatilityIncrease computing speedPhysical realisationData conversionFace detectionHardware structure

The invention discloses an FPGA (field programmable gate array)-based universal fixed-point-number neural network convolution accelerator hardware structure which comprises a universal AXI4 high-speed bus interface, a universal GPIO (general purpose input / output) interface, a universal convolver, a universal read-write control unit, a universal state controller and a universal convolution result buffer. Universal memory hardware is provided, and high-parallel read-write operations are supported; the universal convolver can be used for accurate configuration of fixed point numbers, configuration of convolution operation levels and high-parallel convolution operation in coordination with high-parallel read-write operations after data storage; the universal read-write control unit includes ram, rom and Fifo read-write control logics and address generating logics; the universal state controller makes corresponding unit operating reactions aiming at a convolution layer and read-write and calculation processes to control an integral calculation process; the universal convolution result buffer is used for high-speed parallel caching and sending of a processing result to a bus according to a convolution result sectional accumulation method. By verification in application to Yolo algorithm based human face detection and CNN (convolutional neural network) based human face recognition, high operating speed and high data precision are embodied.

Owner:SOUTHEAST UNIV WUXI INST OF TECH INTEGRATED CIRCUITS +1

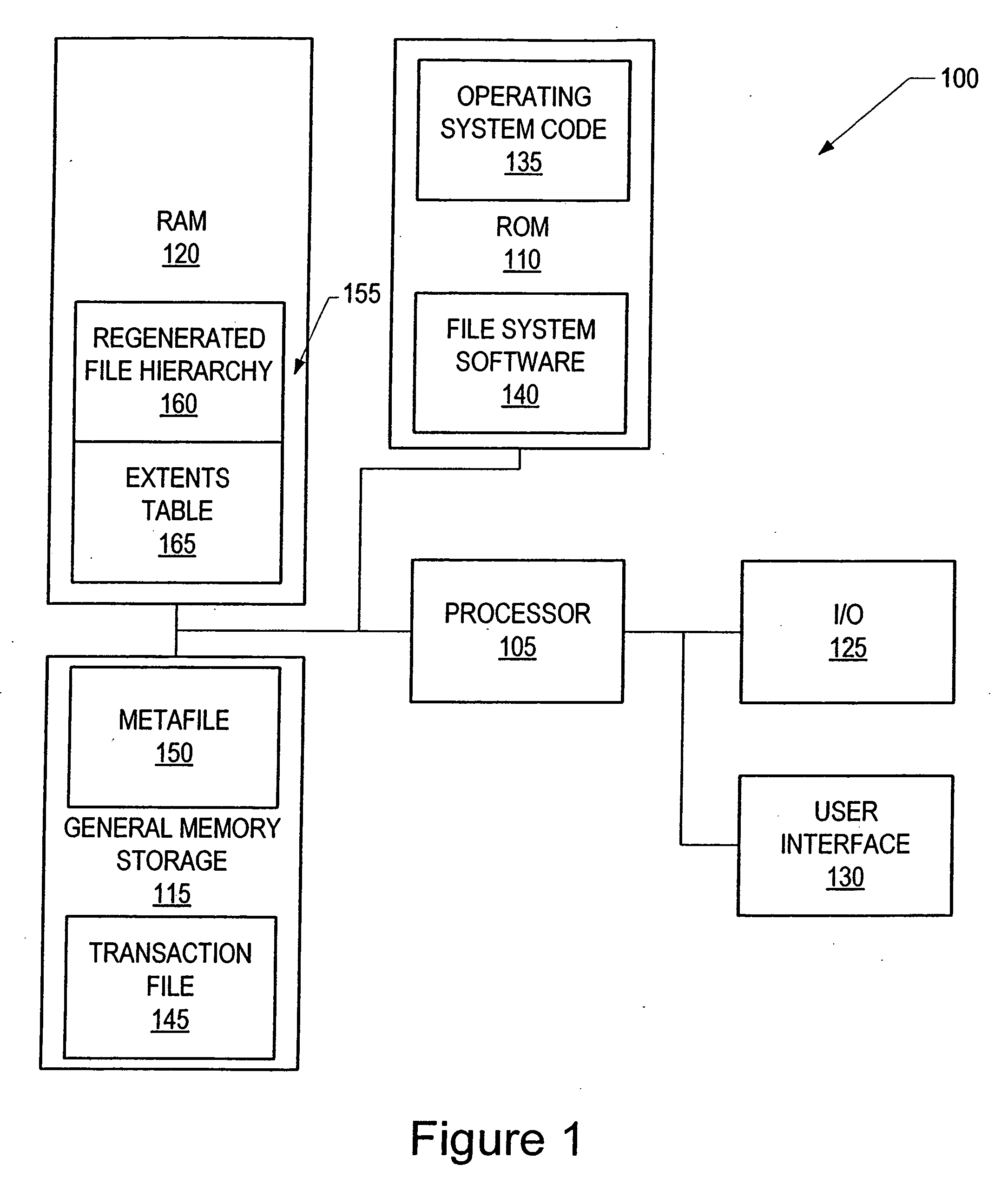

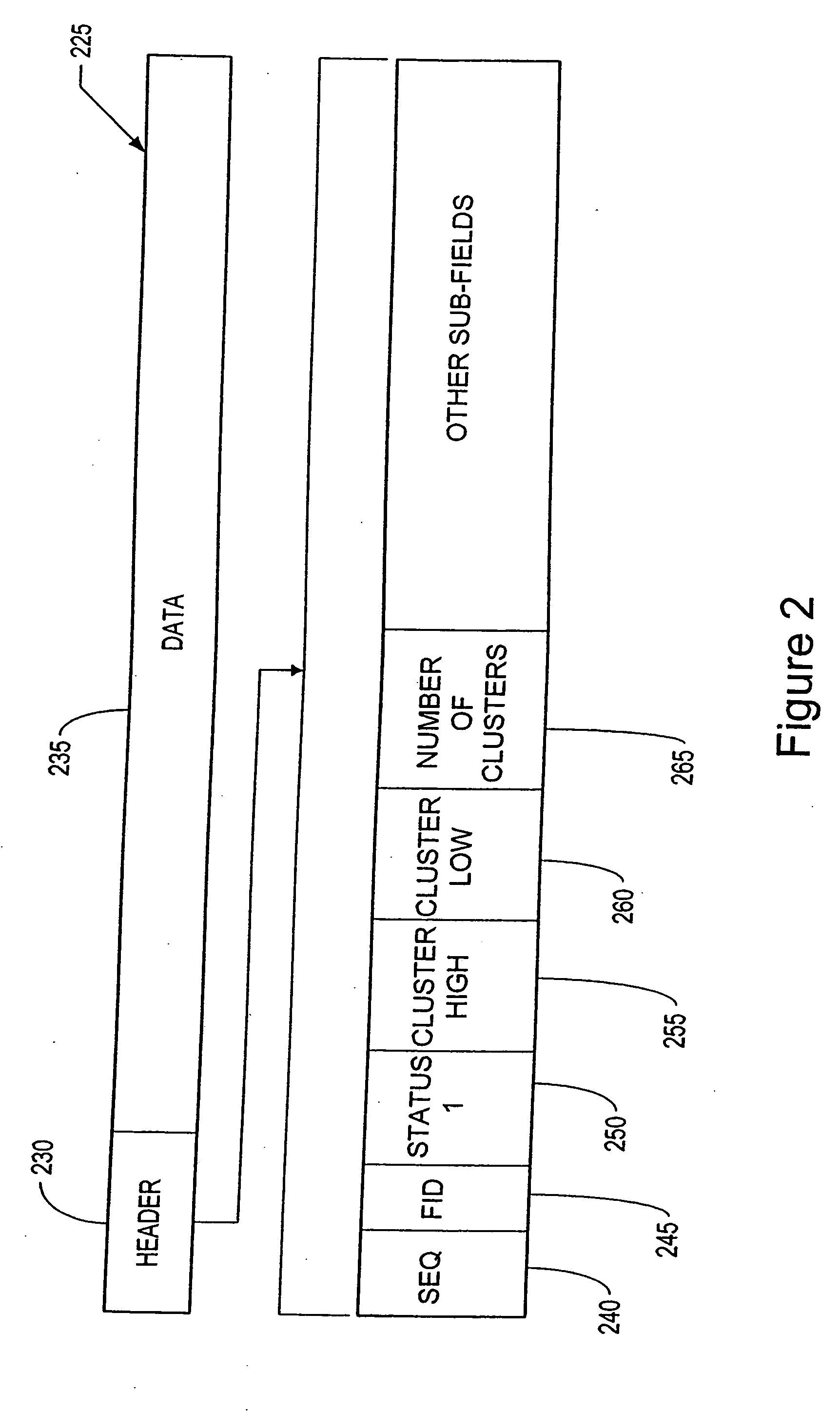

Computer system having logically ordered cache management

ActiveUS20070005894A1Memory architecture accessing/allocationMemory adressing/allocation/relocationConventional memoryFile system

A computer system is set forth that includes a processor, general memory storage, and cache memory for temporarily storing selected data requested from the general memory storage. The computer system also may include file system software that is executed by the processor. The file system software may be used to manage the file data and the structure of the file system for files stored on the general memory storage. Management of the cache memory is placed under the control of cache management software. The cache management software is executed by the processor to manage the contents of the cache memory pursuant to cache hit and cache miss criterion. Sections of the cache memory are organized by the cache management software based on logical addresses of file data requested from the general memory storage.

Owner:MALIKIE INNOVATIONS LTD

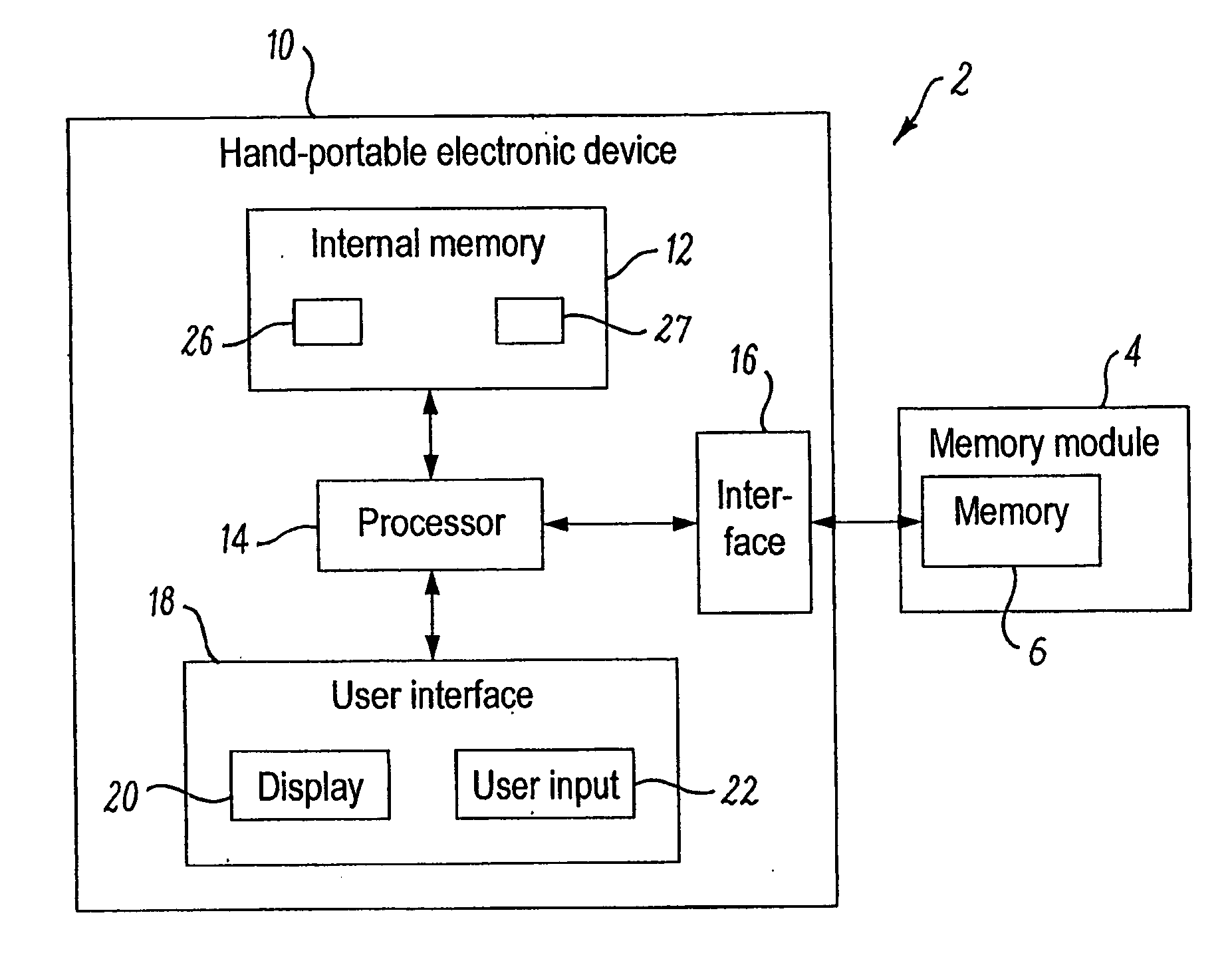

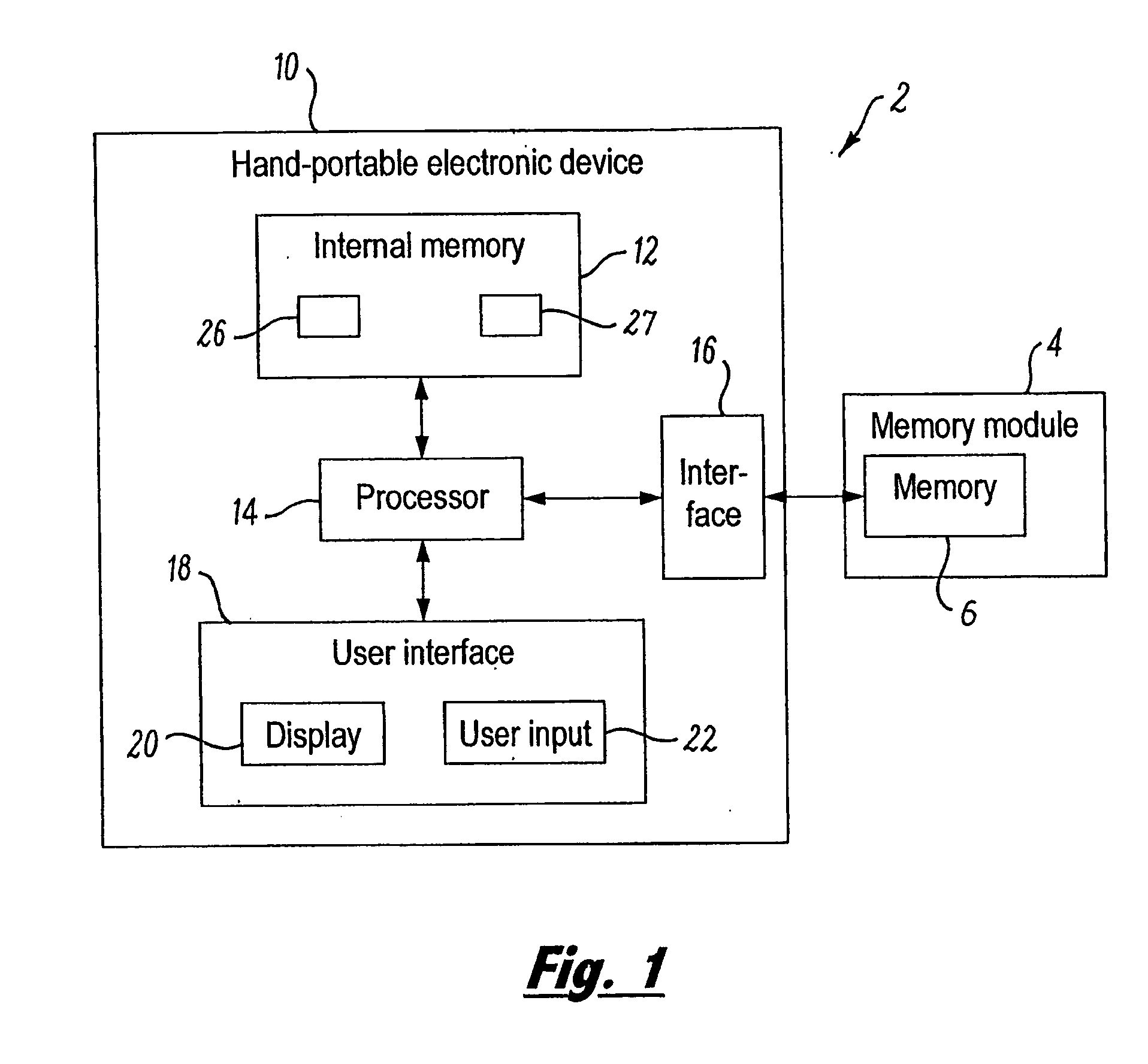

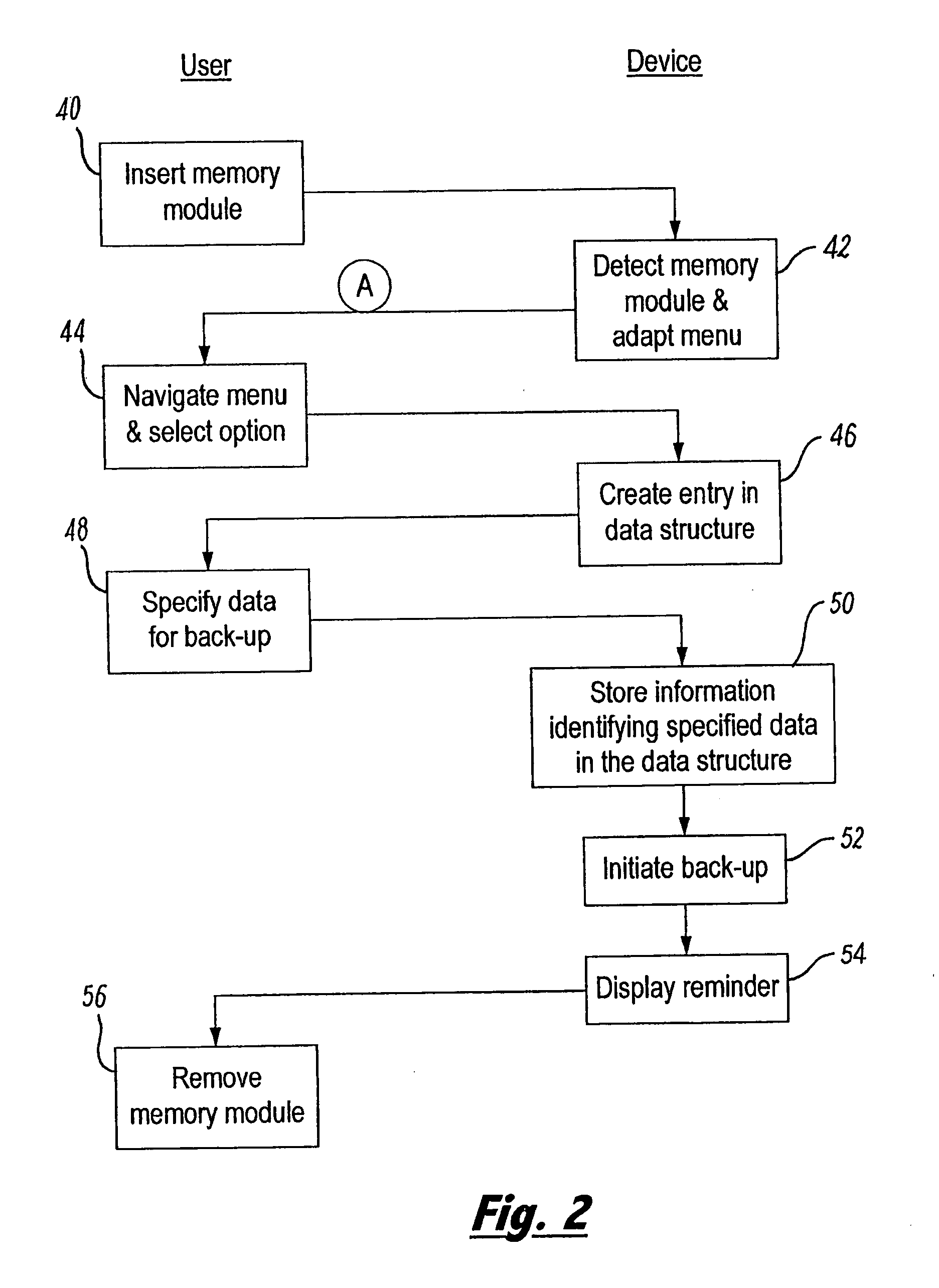

Hardware-Initiated Automated Back-Up of Data from an Internal Memory of a Hand-Portable Electronic Device

InactiveUS20080140736A1Error detection/correctionSpecial data processing applicationsInternal memoryData storing

A hand-portable electronic device configured for hardware-initiated automated back-up, comprising: an internal memory for storing data; an interface for connection and disconnection to any one of a plurality of generic memory modules; a user interface that enables a user of the device to specify the generic memory module connected to the interface for automated back-up of data stored in the internal memory; a controller for automatically backing up data, on connection of a generic memory module to the interface, from the internal memory to the connected generic memory module if the connected generic memory module is identified as a generic memory module that has previously been specified for back-up via the user interface.

Owner:NOKIA CORP

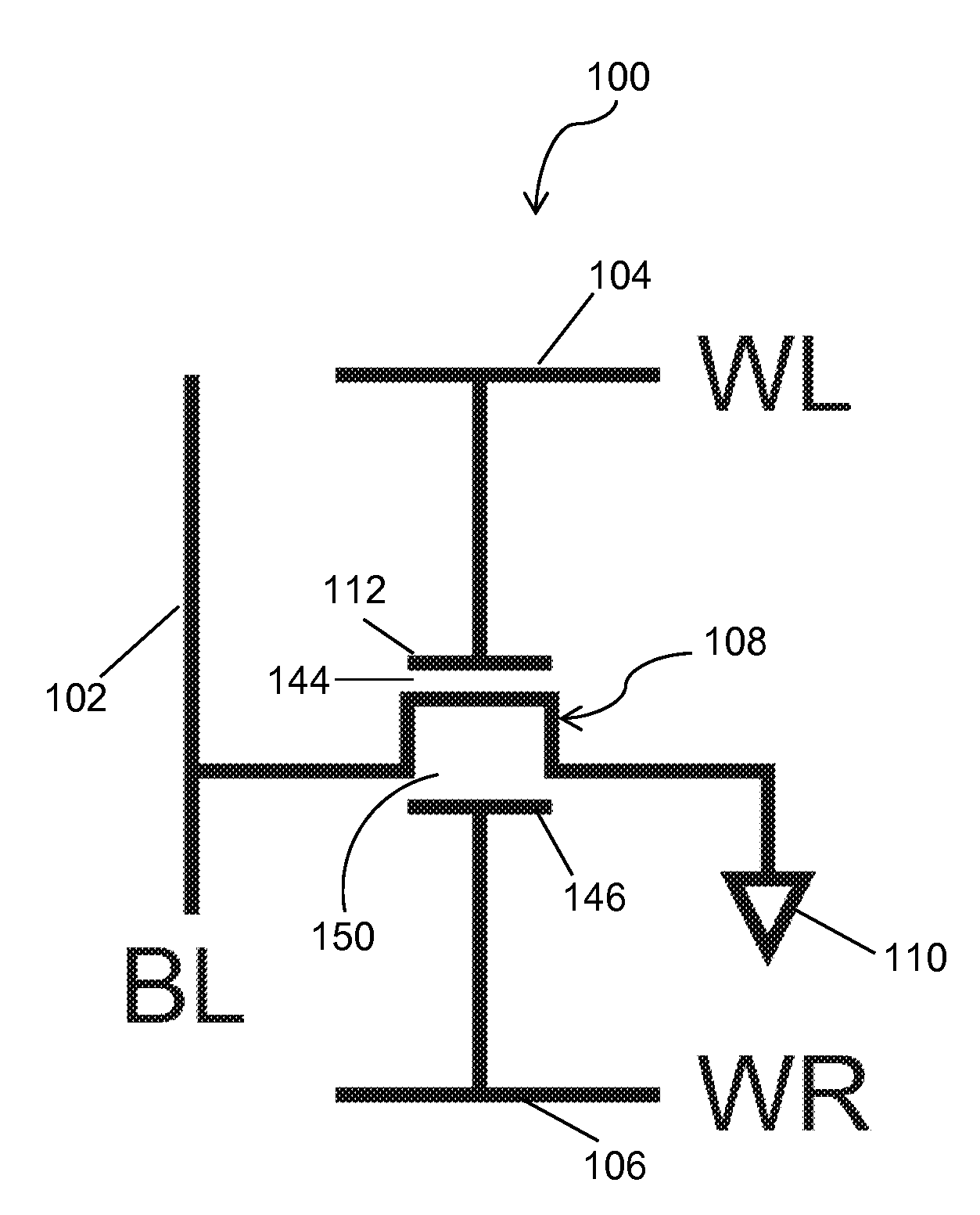

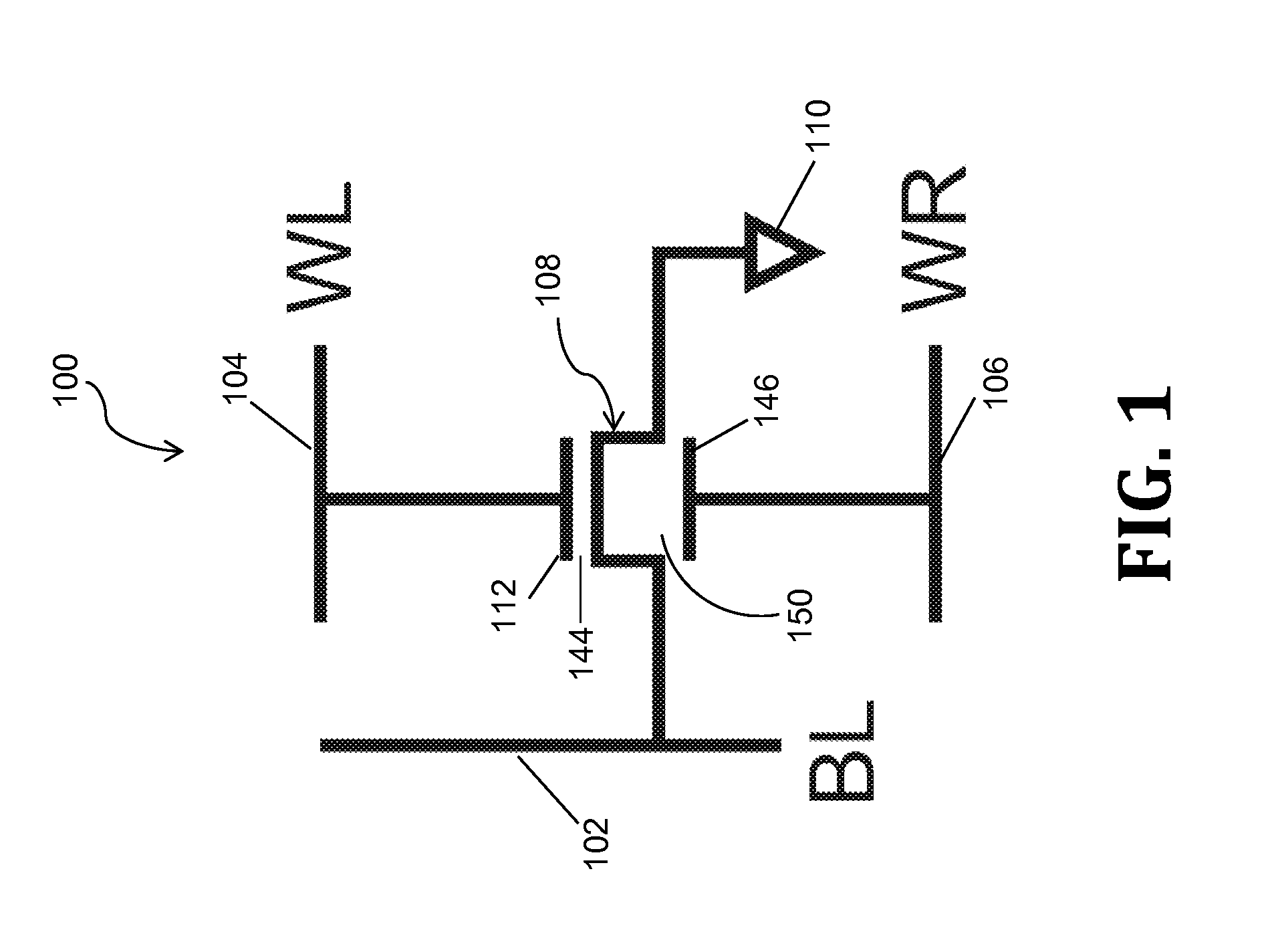

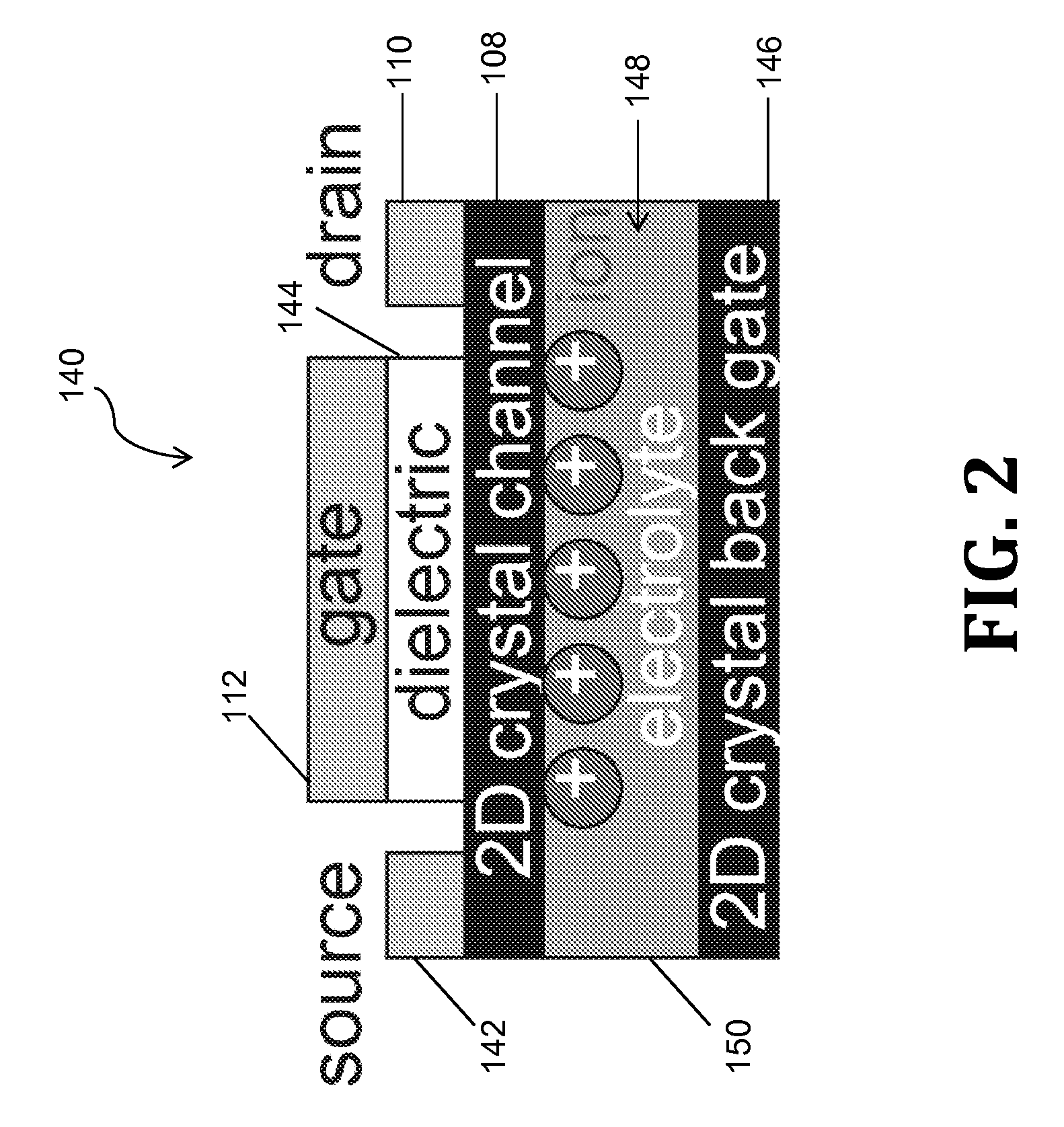

Single transistor random access memory using ion storage in two-dimensional crystals

A single-transistor random access memory (RAM) cell may be used as universal memory. The single-transistor RAM cell generally includes a first gate, a 2D-crystal channel, a source, a drain, an ion conductor, and a second (back) gate. The single-transistor RAM cell is capable of drifting ions towards the graphene channel. The ions in turn induce charge carriers from the source into the graphene channel. The closer the ions are to the graphene channel, the higher the conductivity of the graphene channel. As the ions are spaced from the graphene channel, the conductivity of the graphene channel is reduced. Thus the presence of the charged ions adjacent to the channel is used to modify the channel's conductivity, which is sensed to indicate the state of the memory.

Owner:UNIV OF NOTRE DAME DU LAC

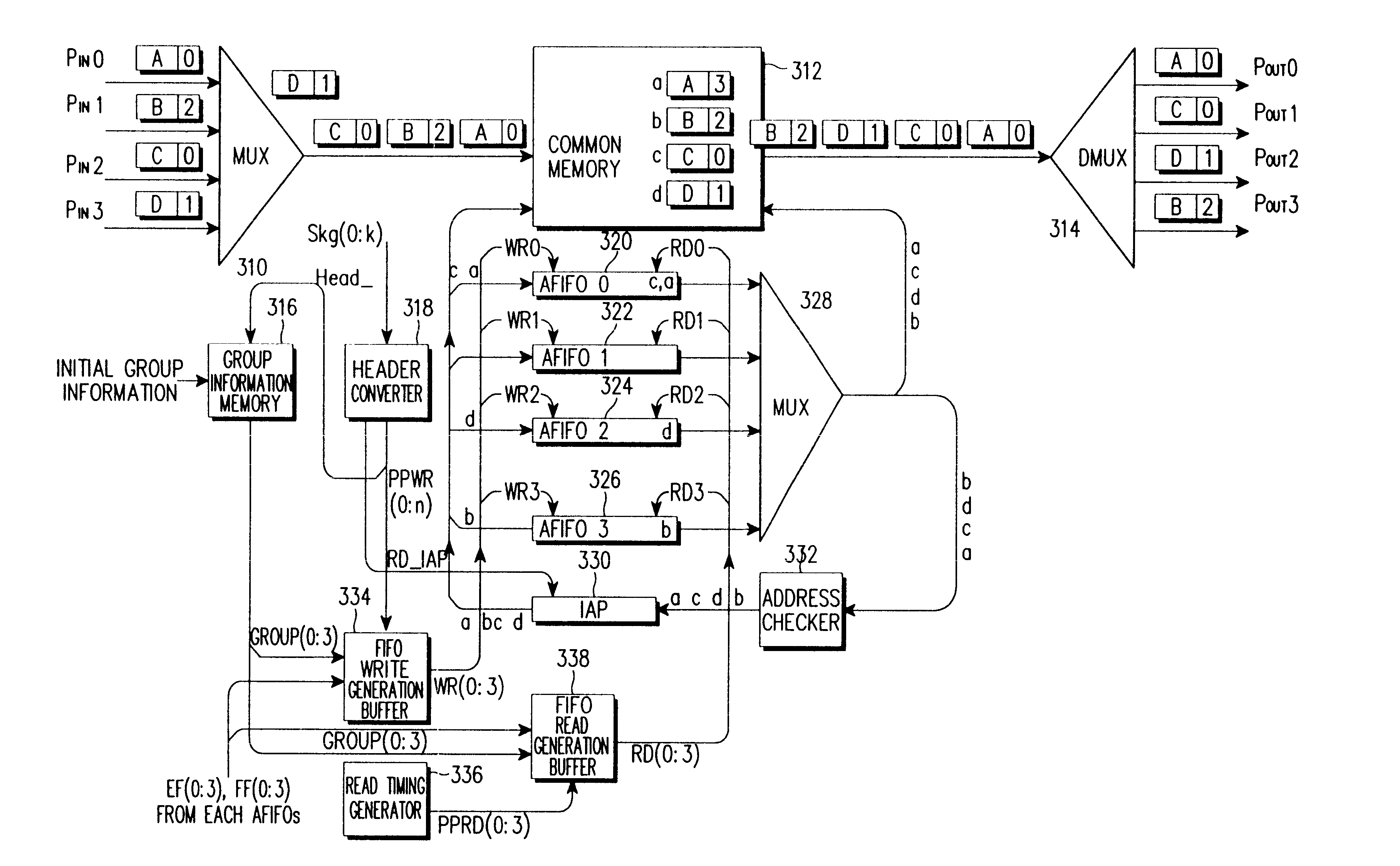

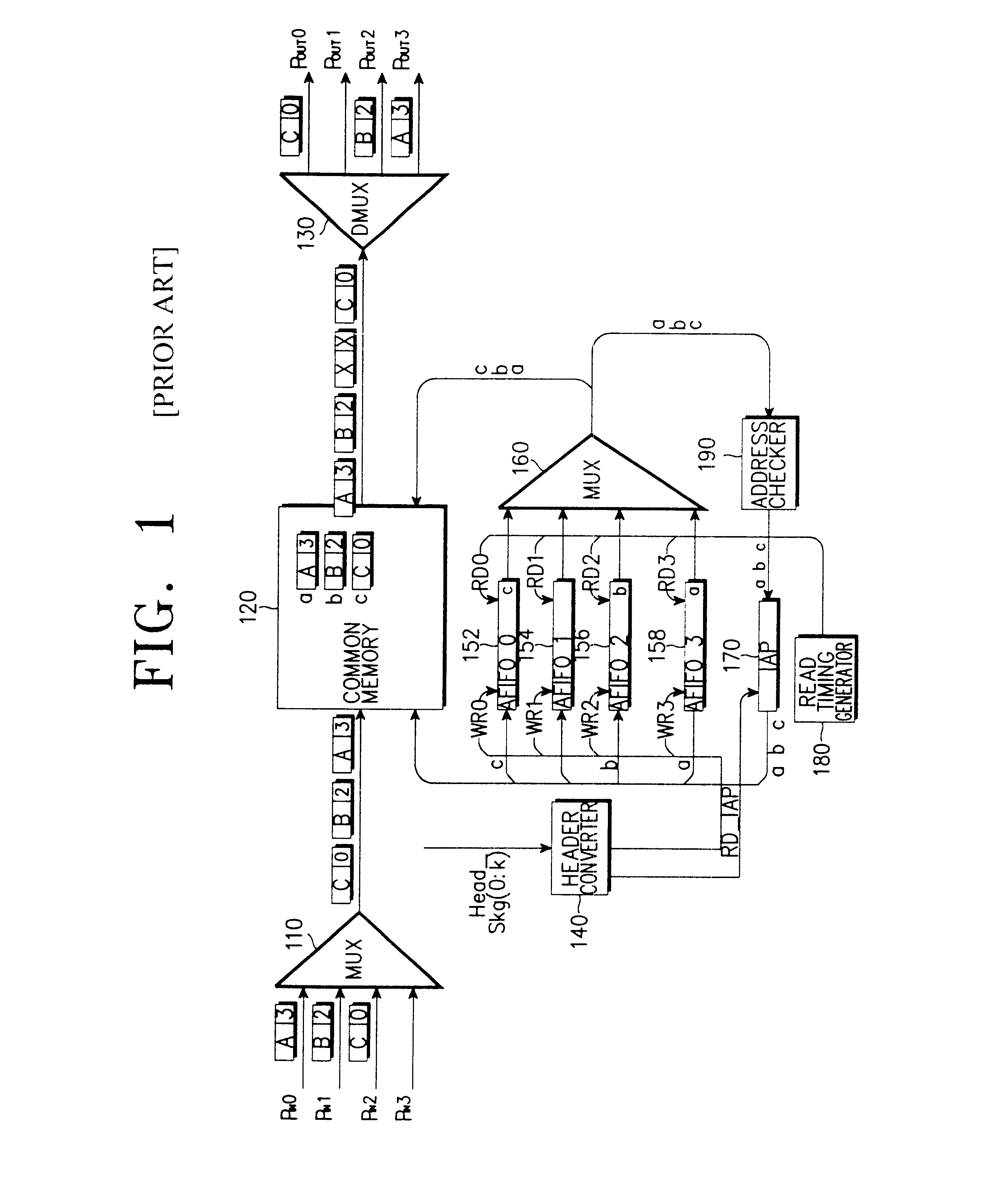

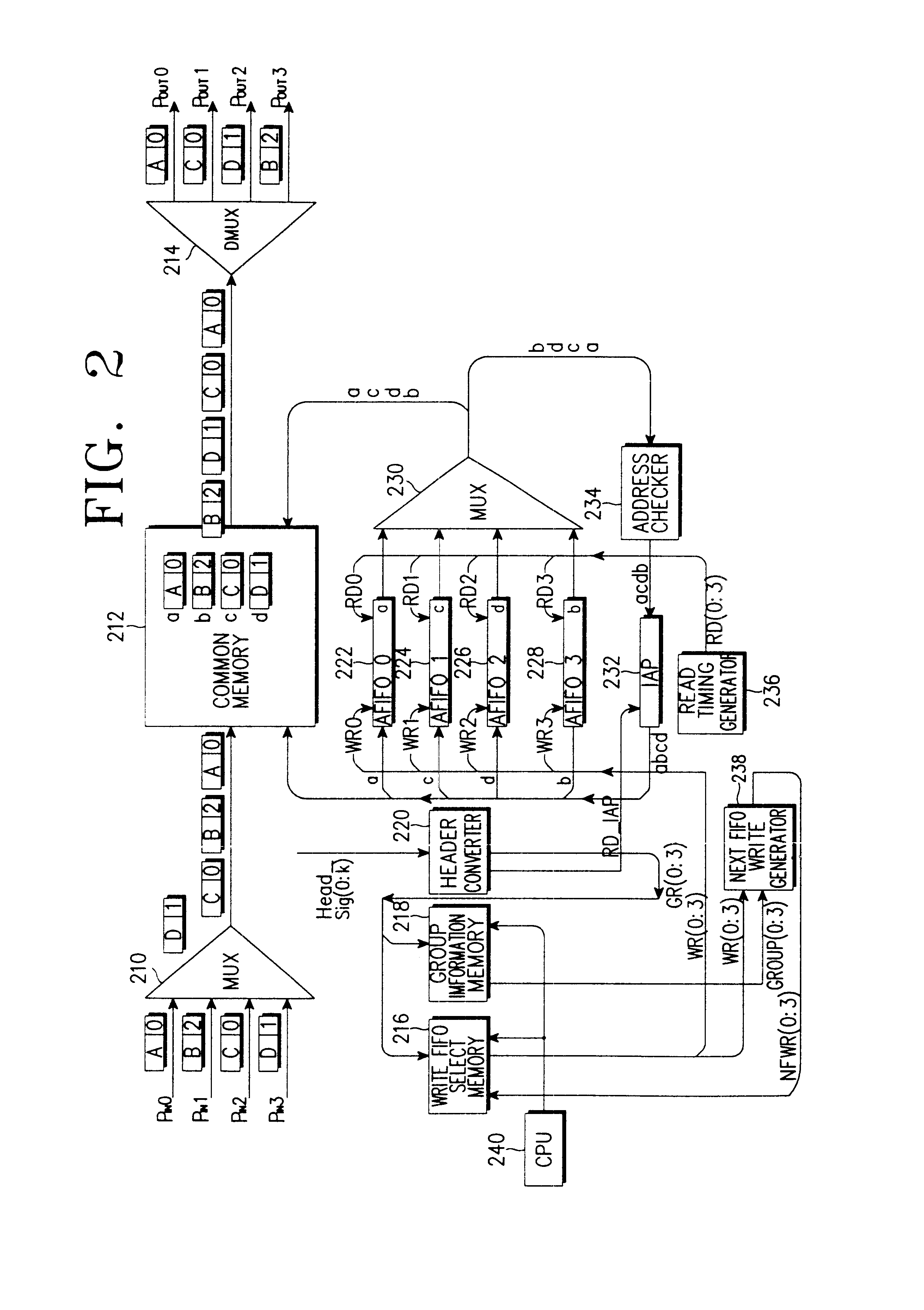

Device and method for processing cell group in a common memory switch

The present invention is related to a device and method for processing a cell group in a common memory switch, in which output ports in the common memory switch are divided into an individualized output port group associated with only one output port and a grouped output port group associated with a plurality of output ports, wherein each output port is assigned to a unique group number.

Owner:SAMSUNG ELECTRONICS CO LTD

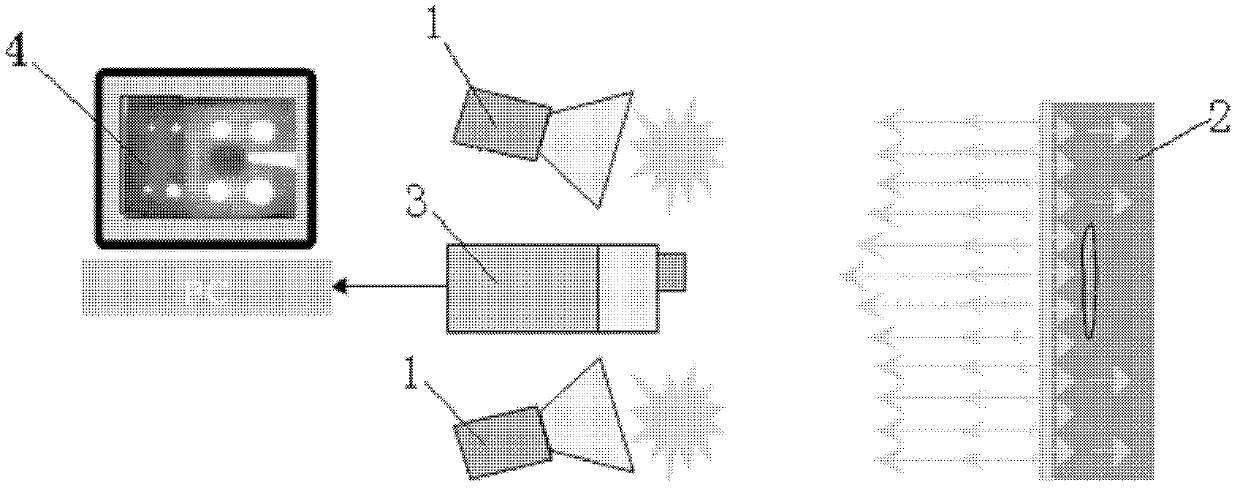

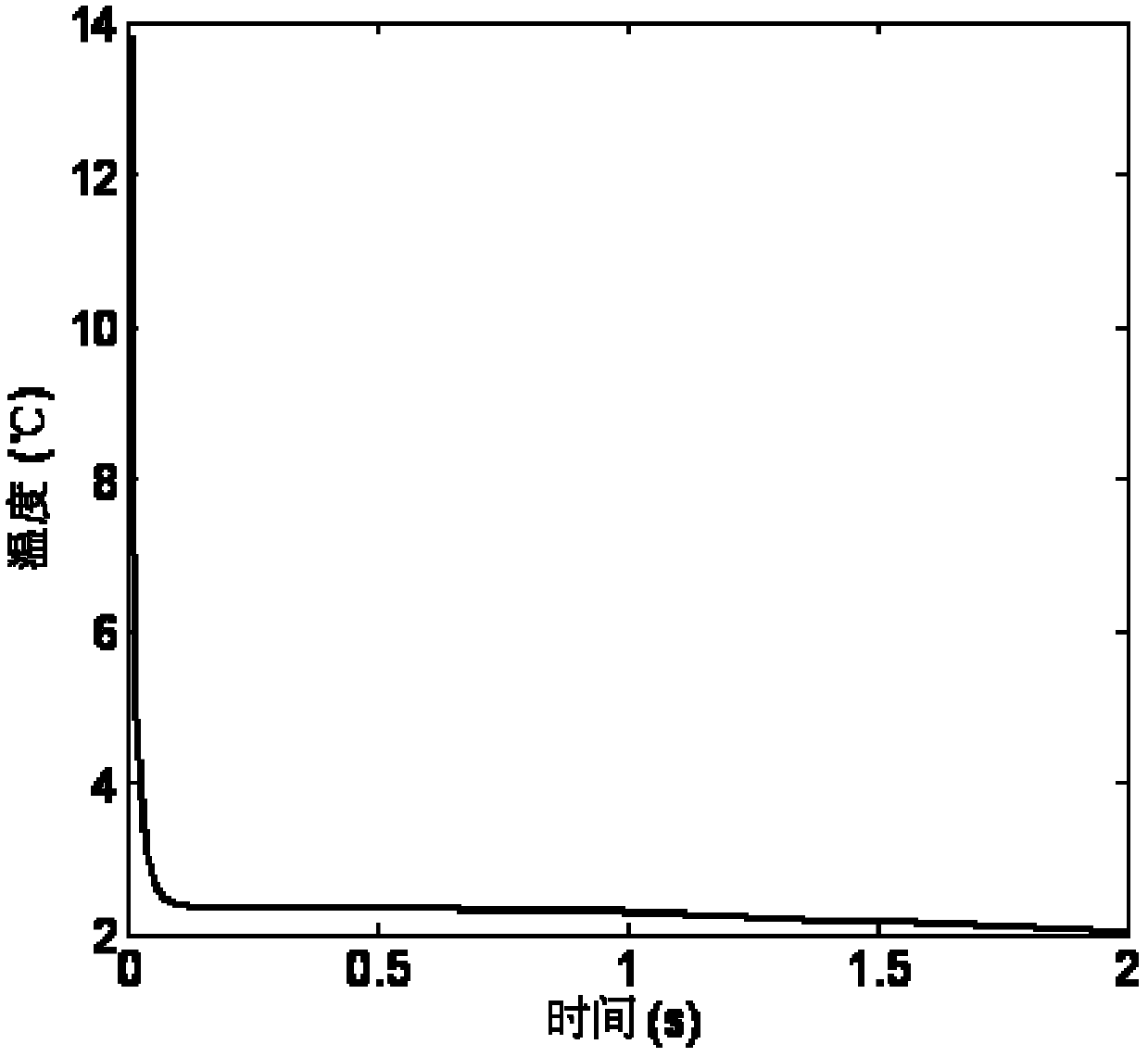

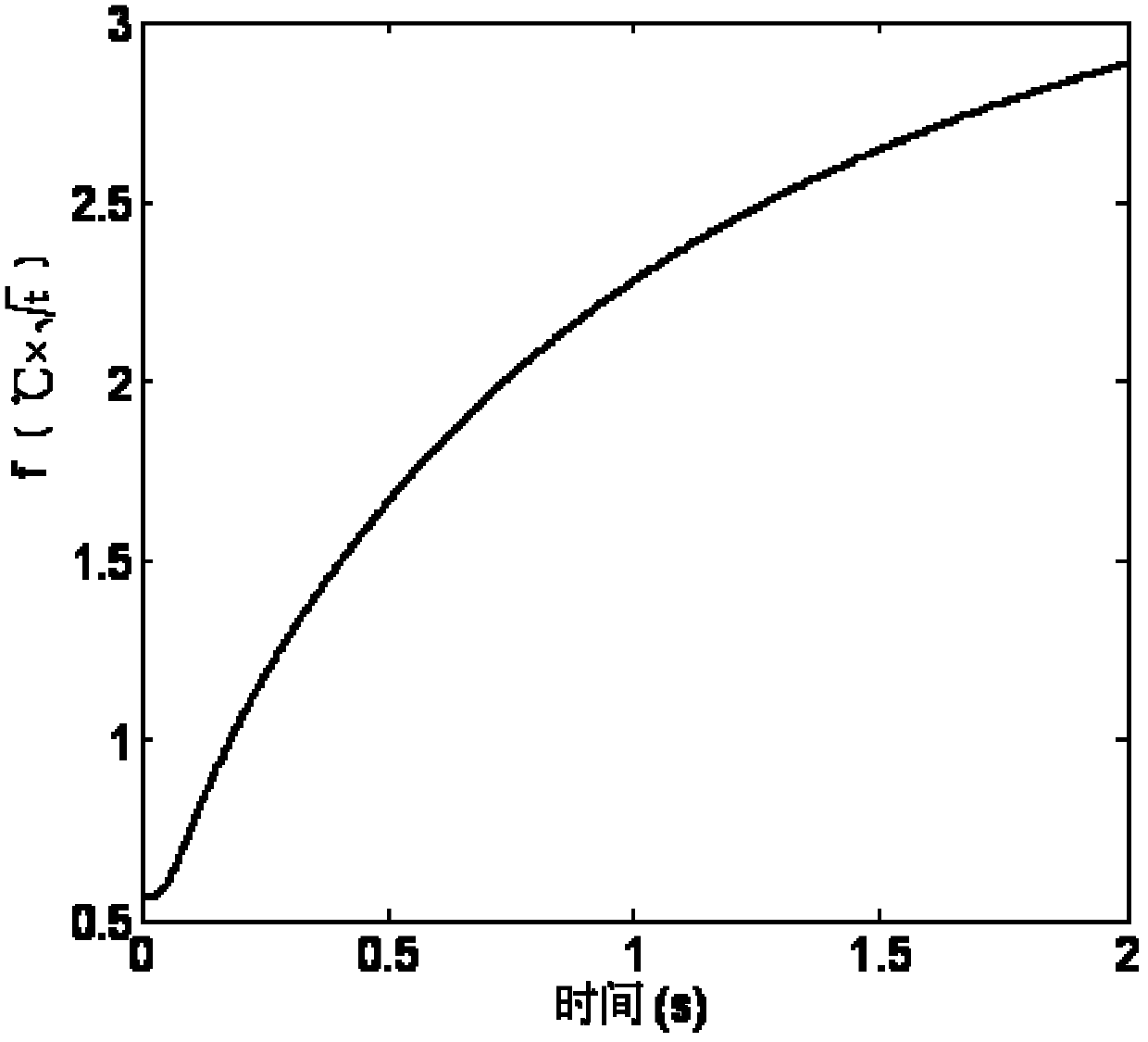

Method for measuring thickness by pulse infrared thermal wave technology

ActiveCN102221339ASimple processing methodMaterial flaws investigationUsing optical meansThermal diffusion coefficientThermodynamics

The invention provides a method for measuring thickness or defect depth by a pulse infrared thermal wave technology, comprising the following steps of (1) heating an object to be measured by pulse heating equipment; obtaining a thermographic sequence on the surface of the object to be measured by an infrared thermal imaging device; memorizing the thermographic sequence in a general memory; (2) multiplying a temperature-time curve of each point in the thermaographic sequence with corresponding time, thus obtaining a new curve f; (3) working out first-order differential on the f; and obtaining a peak time tapst; (4) working out L by a formula, wherein Alpha is thermal diffusion coefficient and L is the thickness or the defect depth of the object to be measured. By adopting the technical scheme, the thickness or detect depth of a part to be measured can be measured, a reference curve is not needed, and only one-order differential treatment is needed for the measurement, so that the processing method is simpler.

Owner:CAPITAL NORMAL UNIVERSITY +1

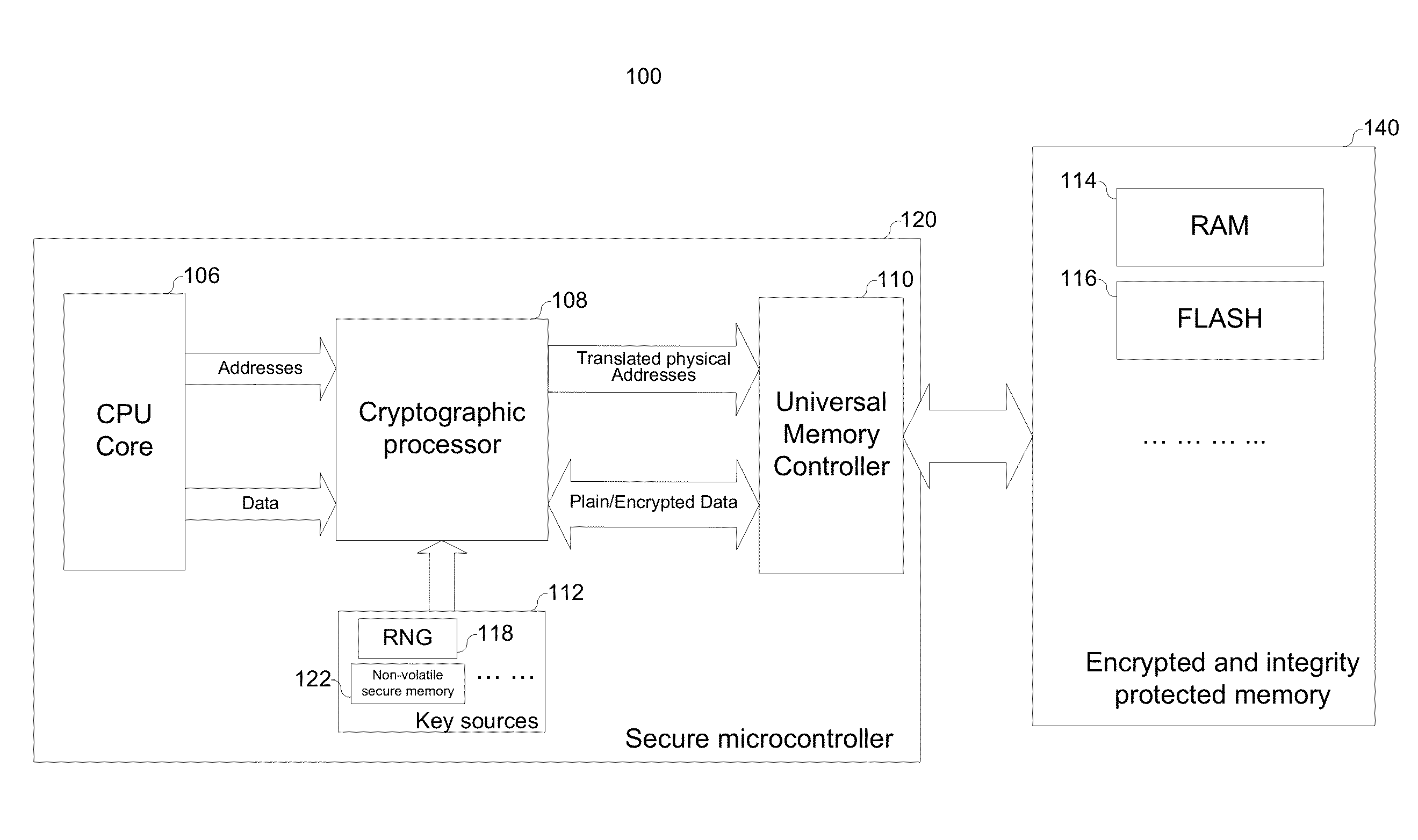

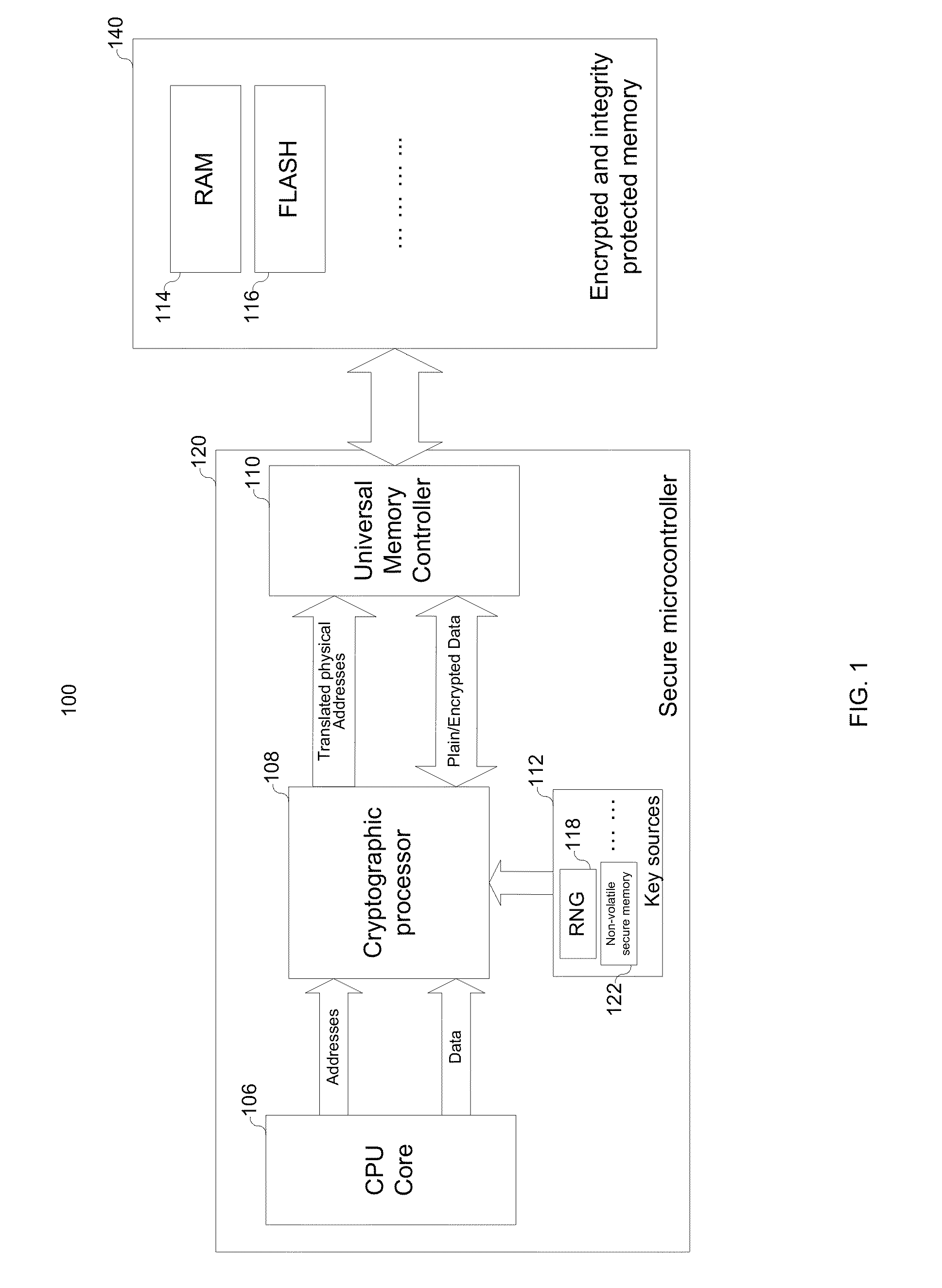

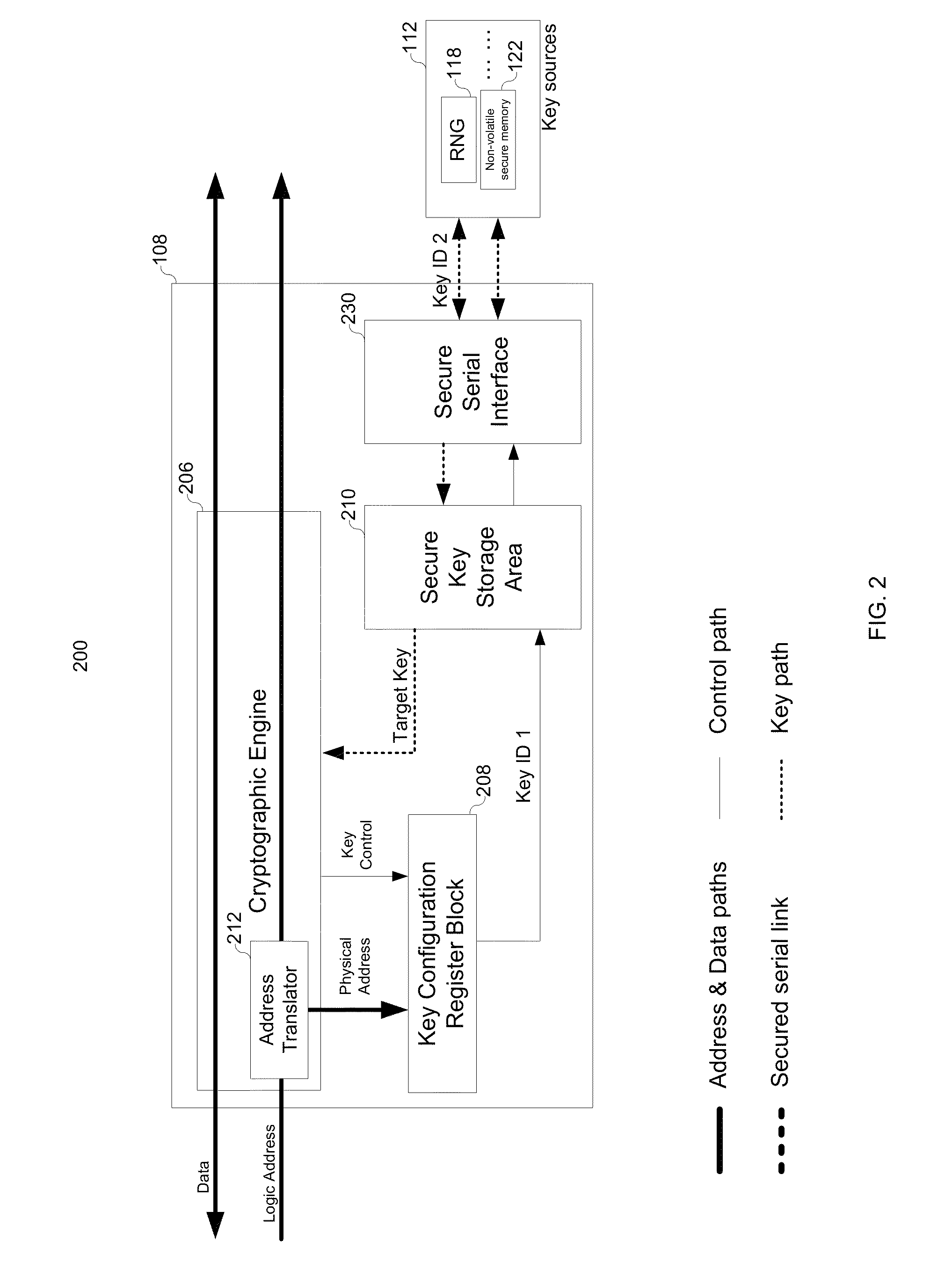

Systems and methods for managing cryptographic keys in a secure microcontroller

ActiveUS20130238907A1Unauthorized memory use protectionHardware monitoringMicrocontrollerOperating system

The present invention relates to key management in a secure microcontroller, and more particularly, to systems, devices and methods of automatically and transparently employing logic or physical address based keys that may also be transferred using dedicated buses. A cryptographic engine translates a logic address to at least one physical address, and processes a corresponding data word based on at least one target key. The target key is selected from a plurality of keys based on the logic or physical address. A universal memory controller stores each processed data word in the corresponding physical address within a memory. Each key is associated with a memory region within the memory, and therefore, the logic or physical address associated with a memory region may be used to automatically identify the corresponding target key. A dedicated secure link may be used to transport key request commands and the plurality of keys.

Owner:MAXIM INTEGRATED PROD INC

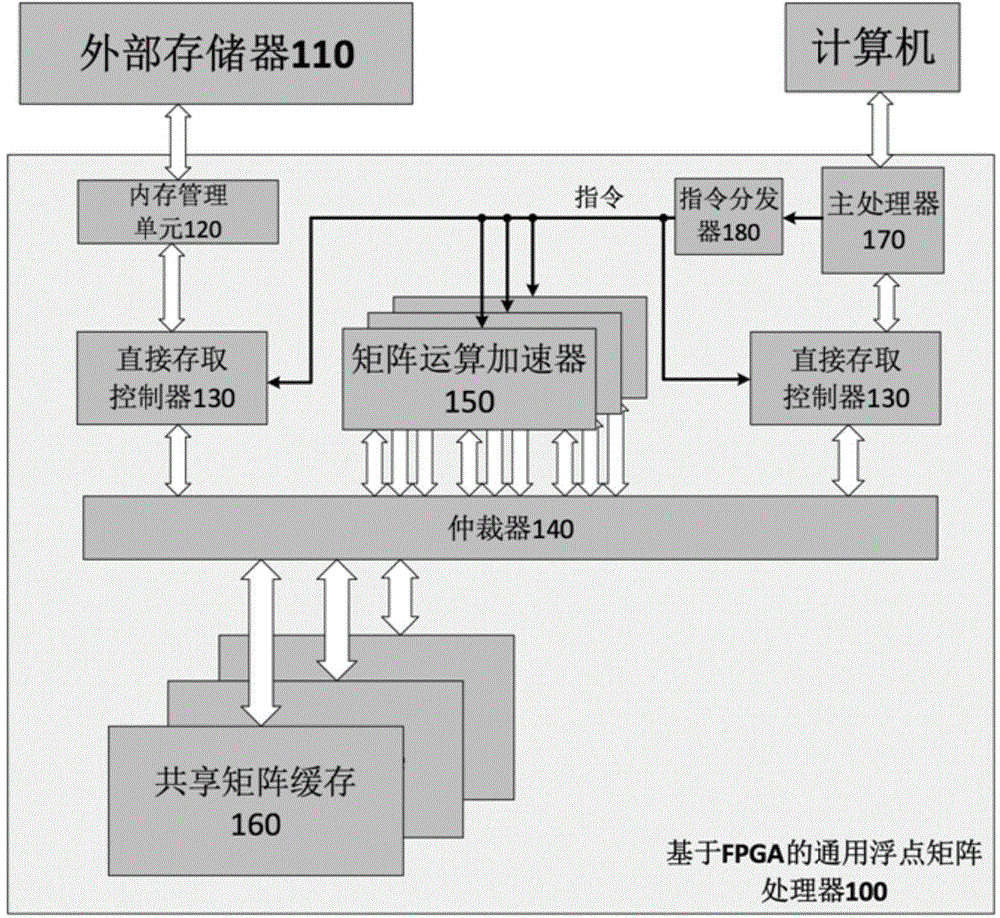

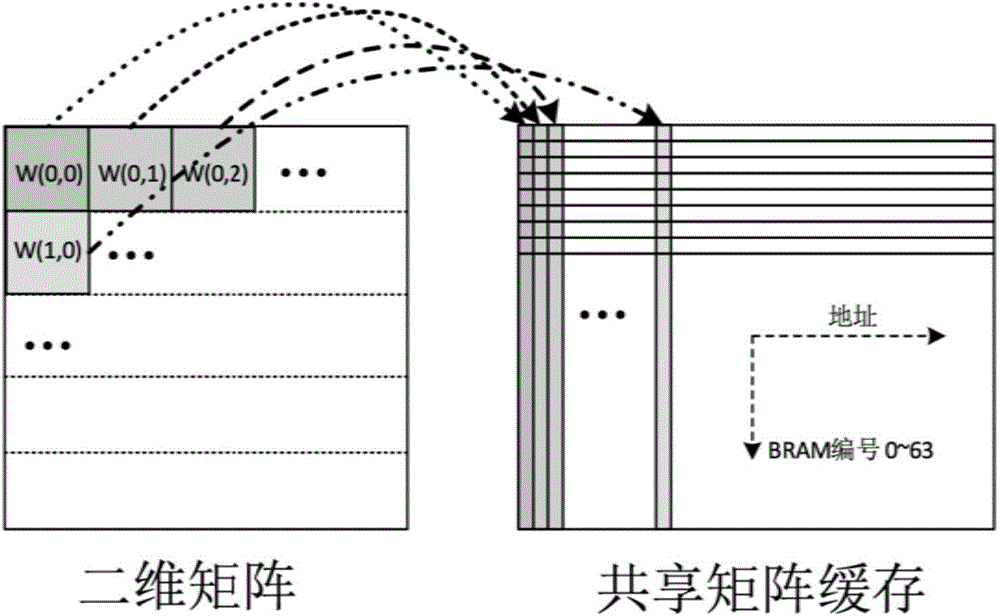

Universal floating point matrix processor hardware structure based on FPGA (field programmable gate array)

ActiveCN104391820AReduce energy consumptionImprove performanceEnergy efficient computingArchitecture with single central processing unitHardware structureExternal storage

The invention discloses a universal floating point matrix processor hardware structure based on an FPGA (field programmable gate array). The universal floating point matrix processor hardware structure comprises a plurality of matrix operation accelerators, a plurality of shared matrix buffer memories, a main processor, an instruction dispatcher, a direct access controller, an arbiter, an external memory and a memory management unit, the shared matrix buffer memories provide universal memory spaces and support high-speed communication on chips between the accelerators, the main processor transmits instructions, dispatches operation and calculates addresses, the instruction dispatcher inspects whether the instructions have occupying conflict or not, the direct access controller finishes data transmission, the arbiter distributes data, the external memory provides buffer, and the memory management unit provides an access interface. The hardware structure can realize 'matrix-matrix' operation on a universal platform, software programs can be modified on the main processor according to different applications, a matrix operation accelerator structure can be conveniently inserted to support various matrix operations, the universal floating point matrix processor hardware structure has high design flexibility and has the advantages of lower energy consumption and higher calculated performance as compared with an embedded processor performing the matrix operations in the past.

Owner:TSINGHUA UNIV

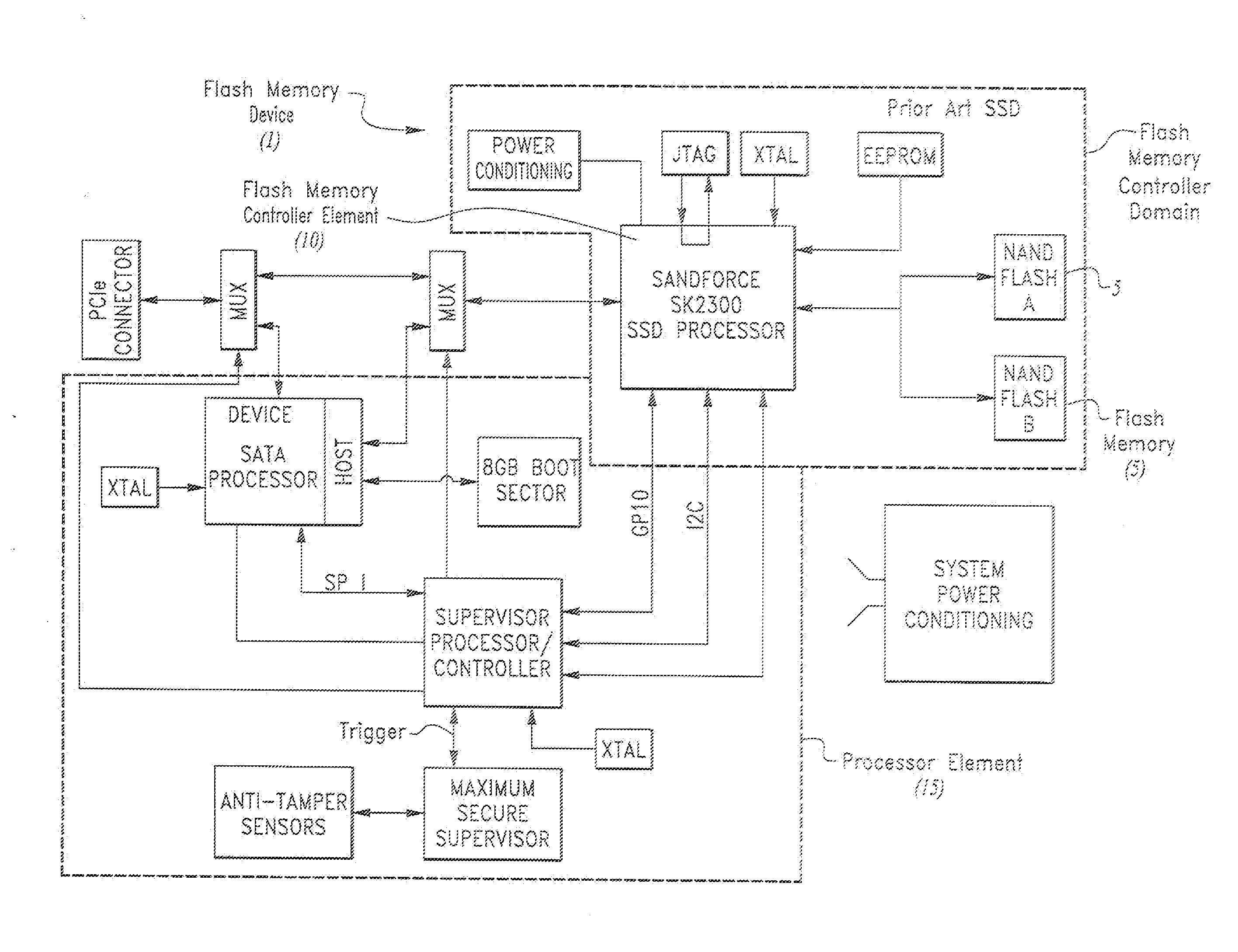

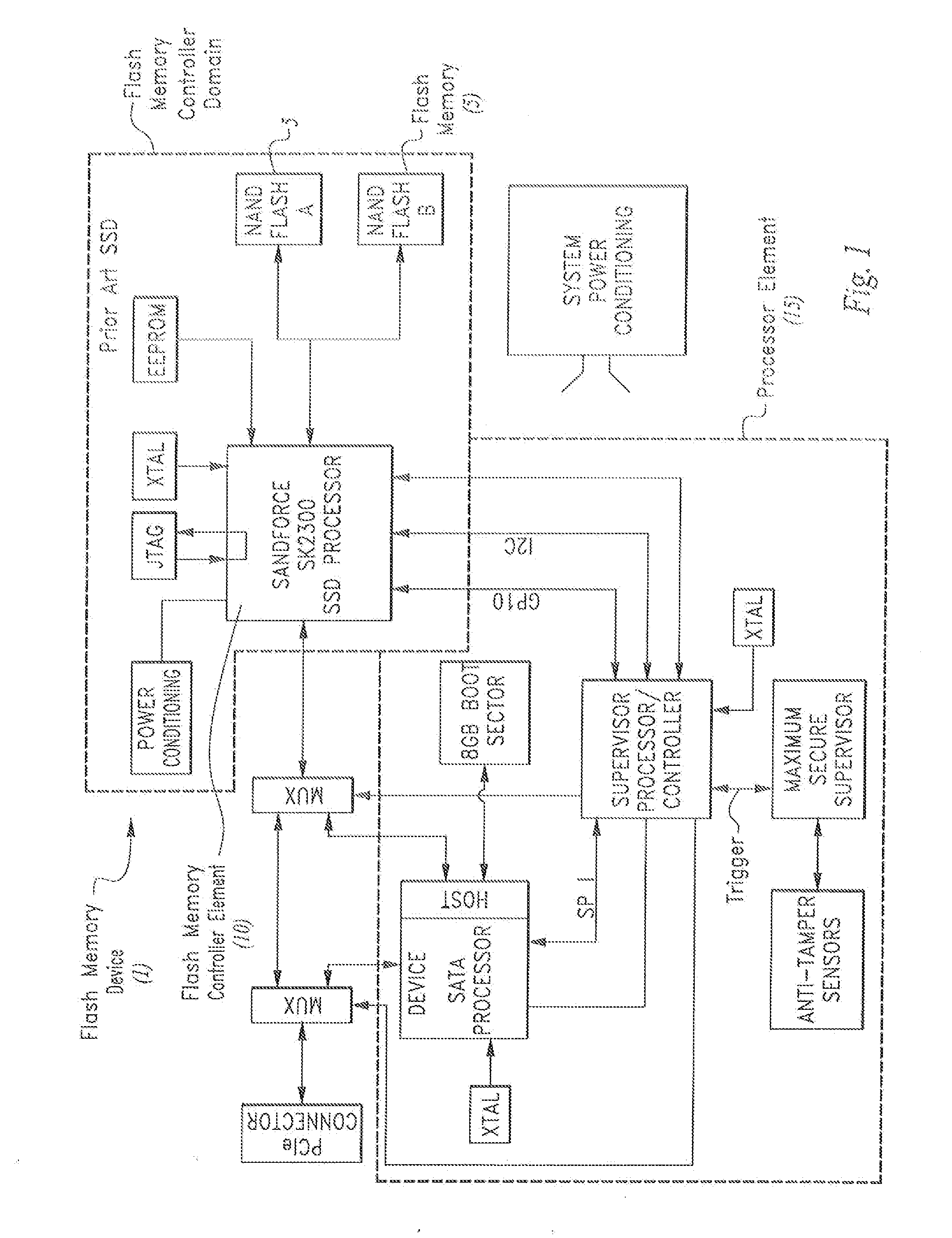

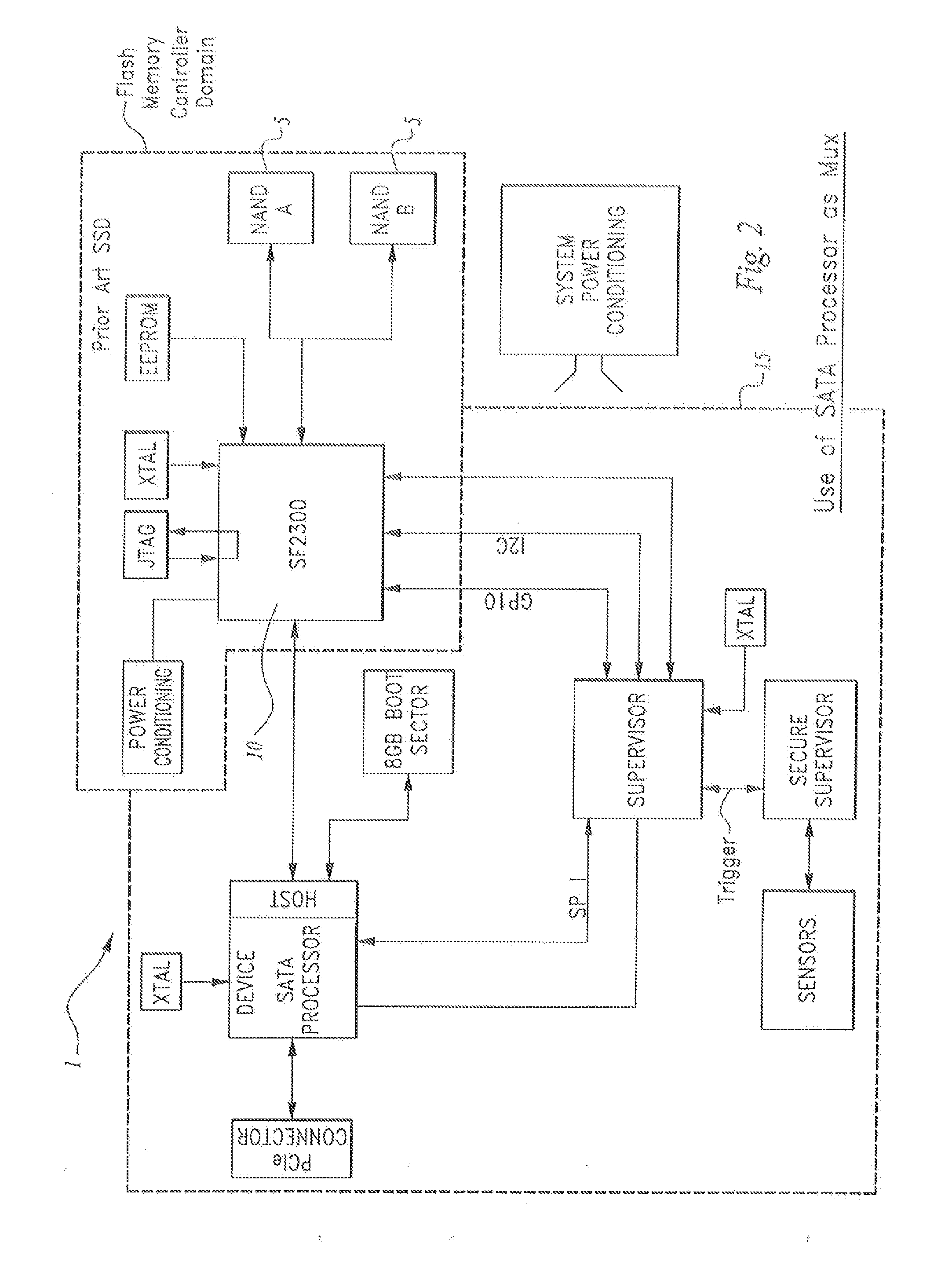

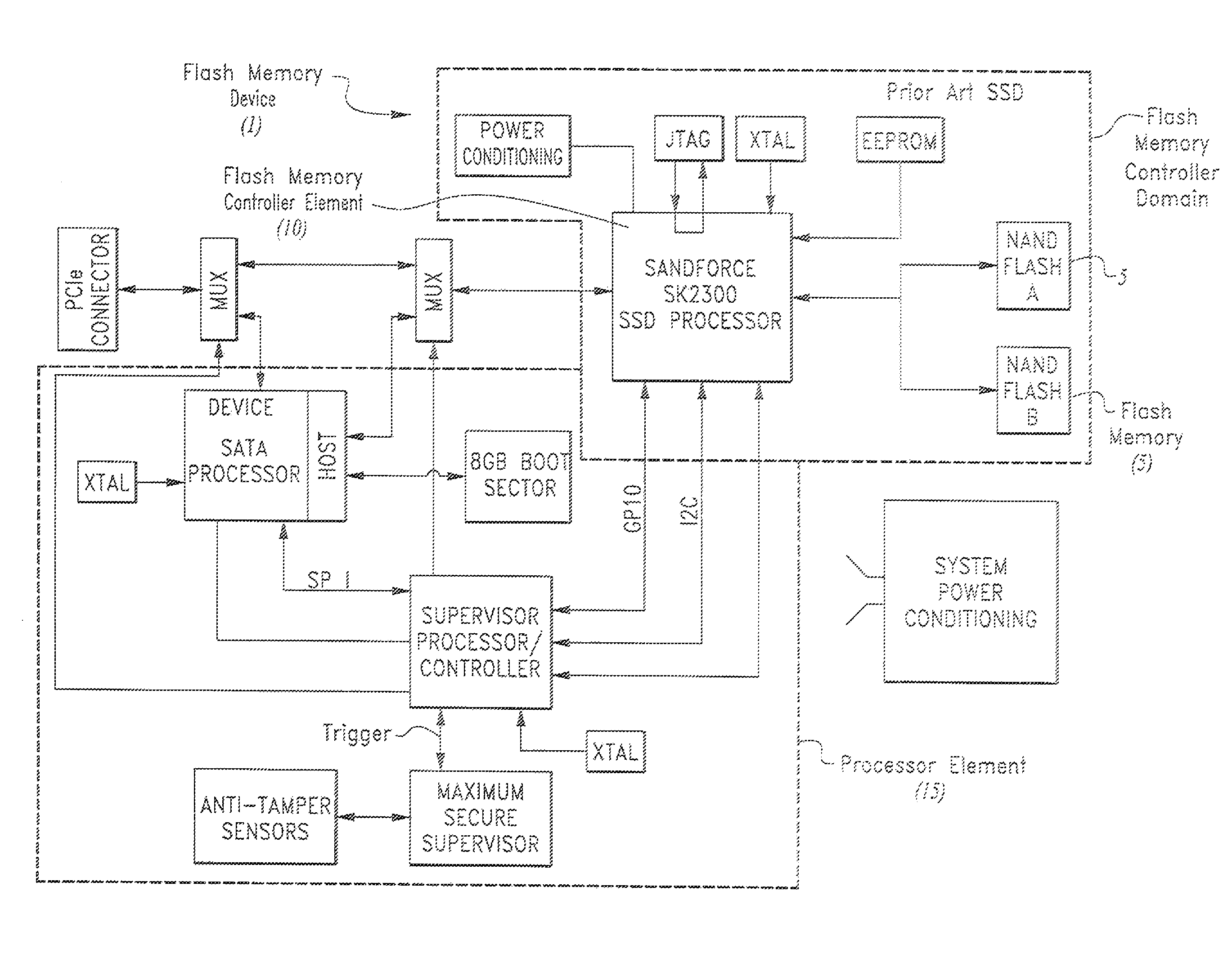

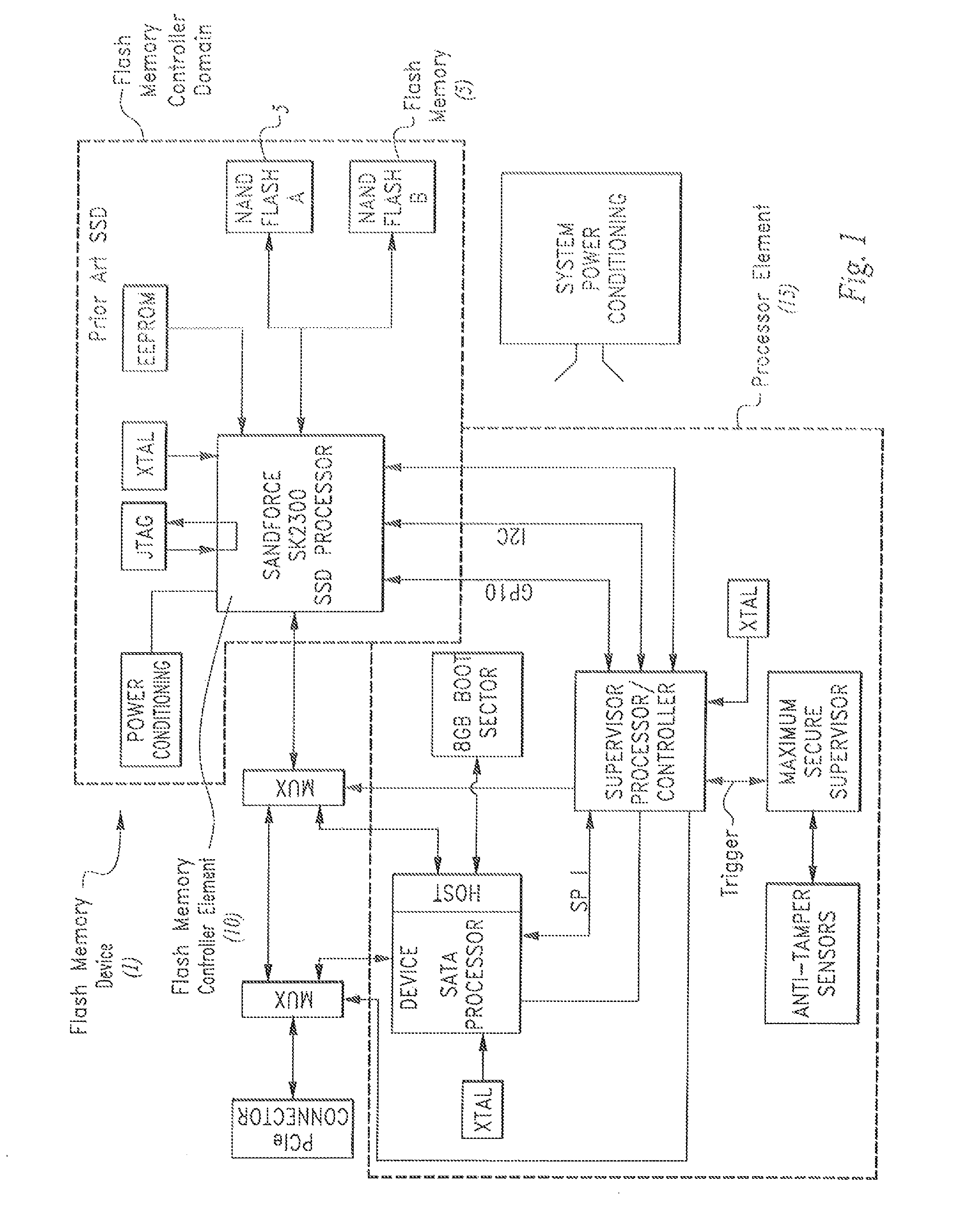

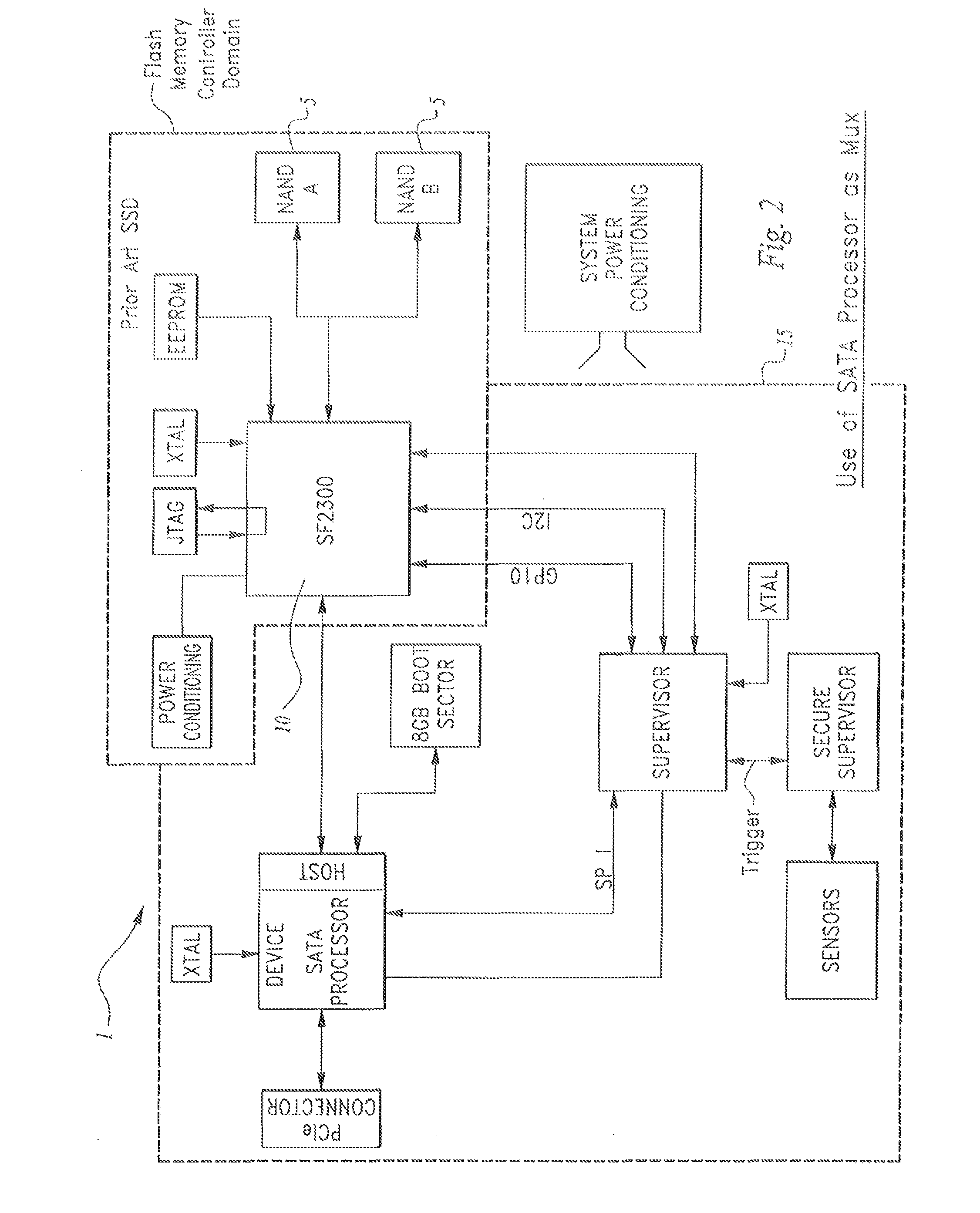

Solid State Drive Memory Device Comprising Secure Erase Function

ActiveUS20140022849A1Quick eraseMemory architecture accessing/allocationRead-only memoriesProcessor elementOperational system

A memory device such as a solid state memory device have a dual-hardware, secure erase feature. A memory controller operating in a memory controller domain provides general memory management and interface operons. Upon receipt of a trigger signal which may be received from a secure supervisor circuit, a separate processor element that is configured to directly access the raw memory cells in the device bypasses the memory controller domain and executes a separately provided secure erase operating system whereby the raw cell data may be erased and rewritten with a predetermined data pattern and whereby the erase operation at the raw cell level may be verified and reported to the user by the processor.

Owner:IRVINE SENSORS

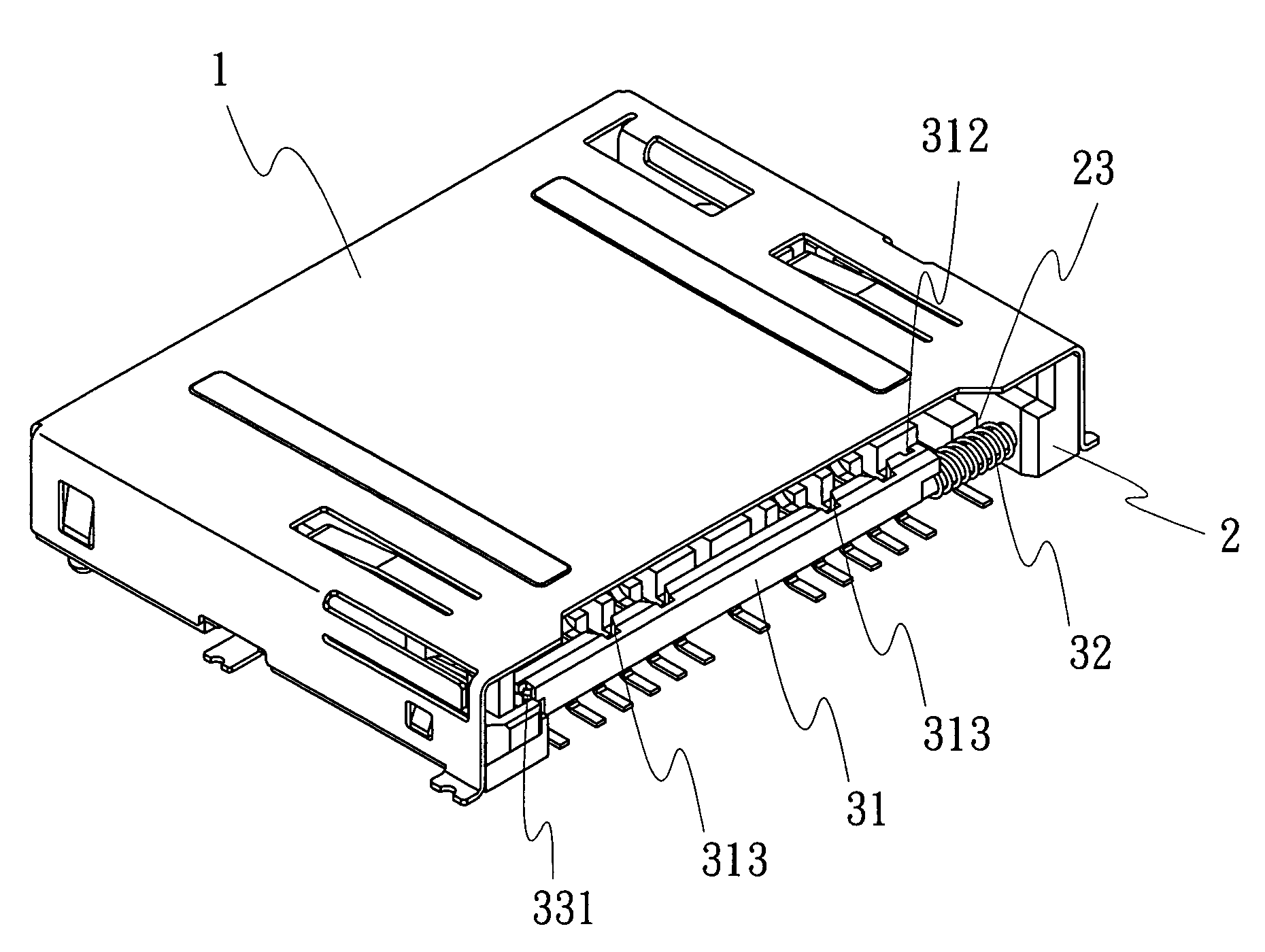

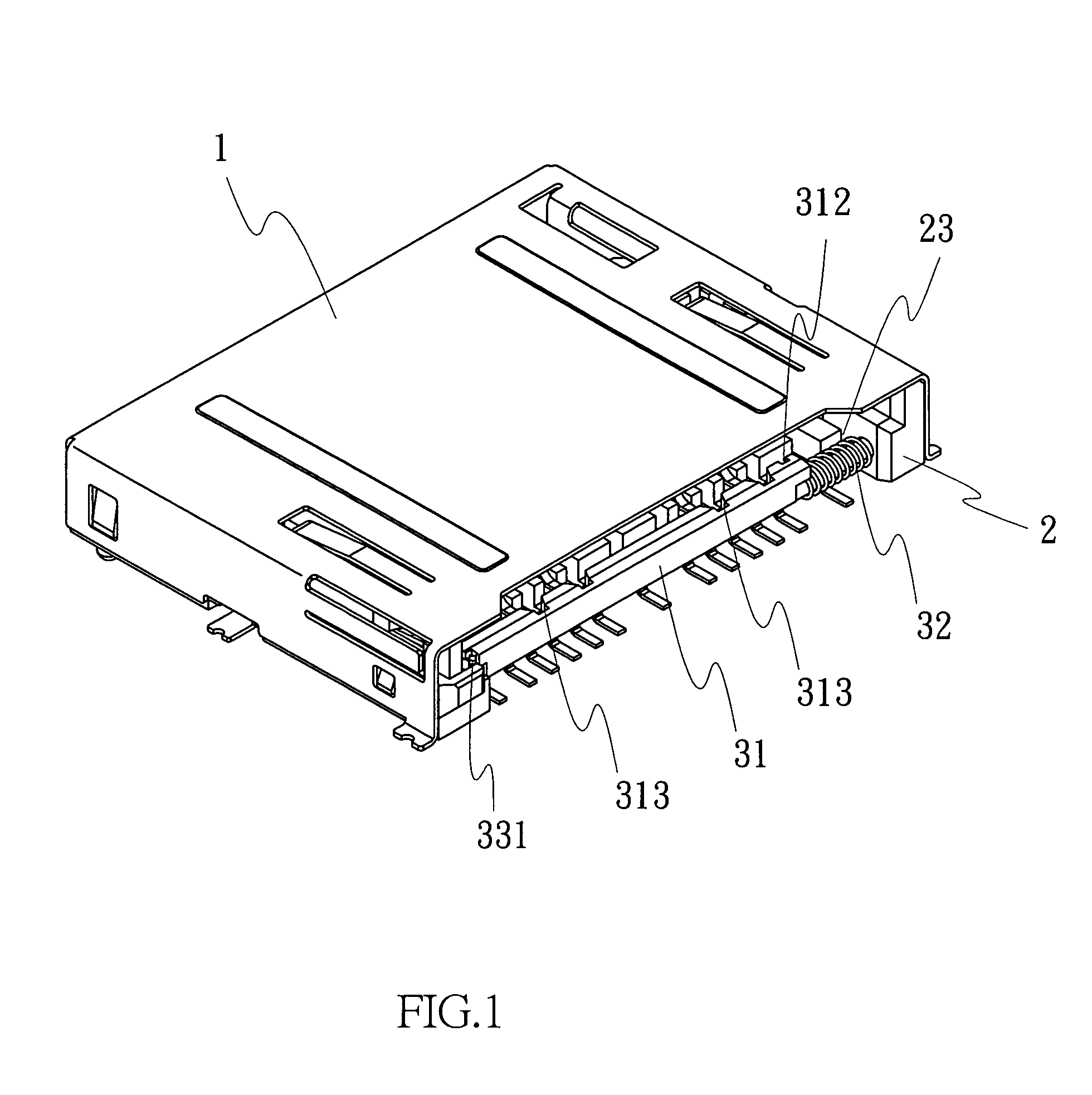

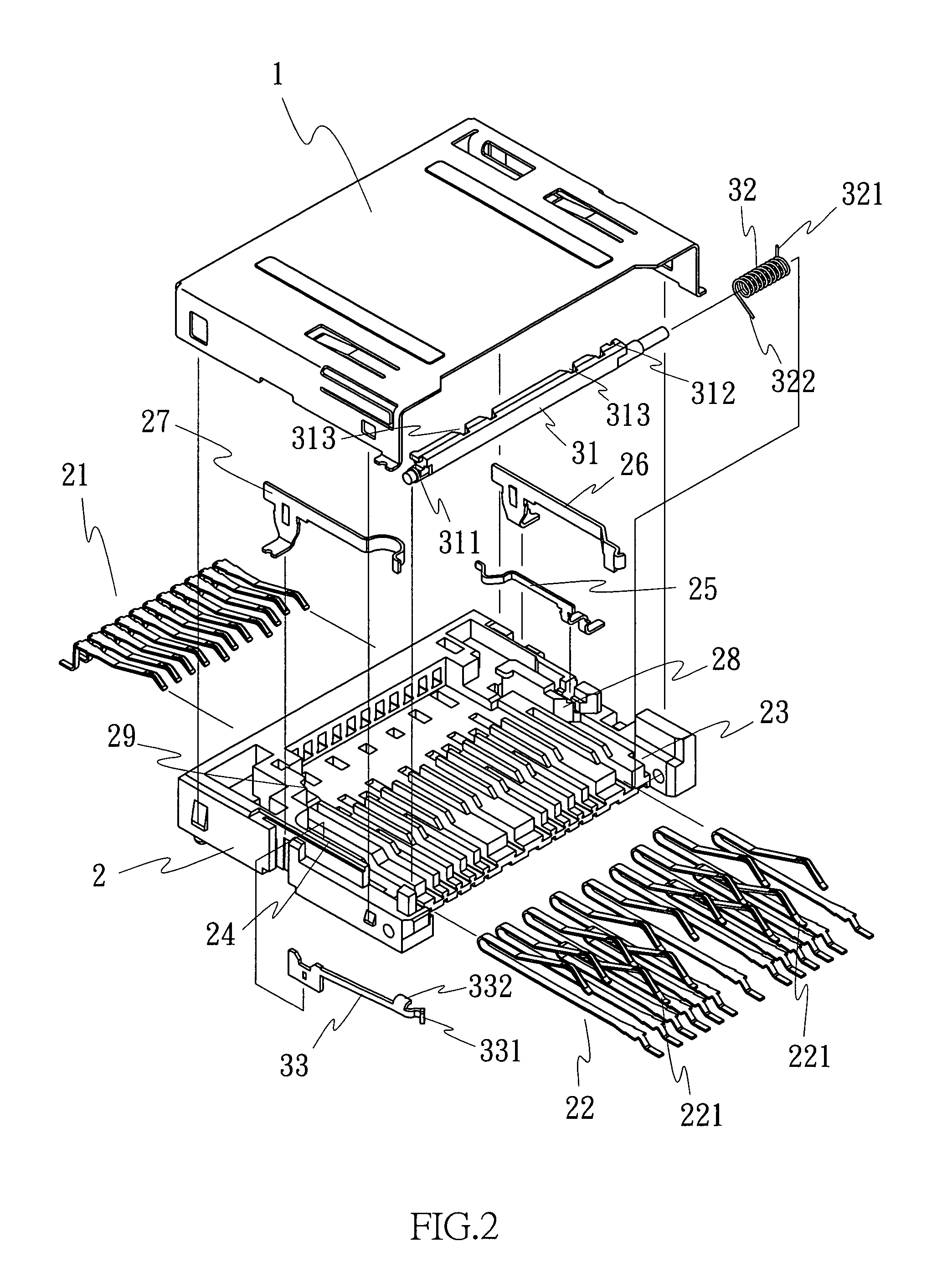

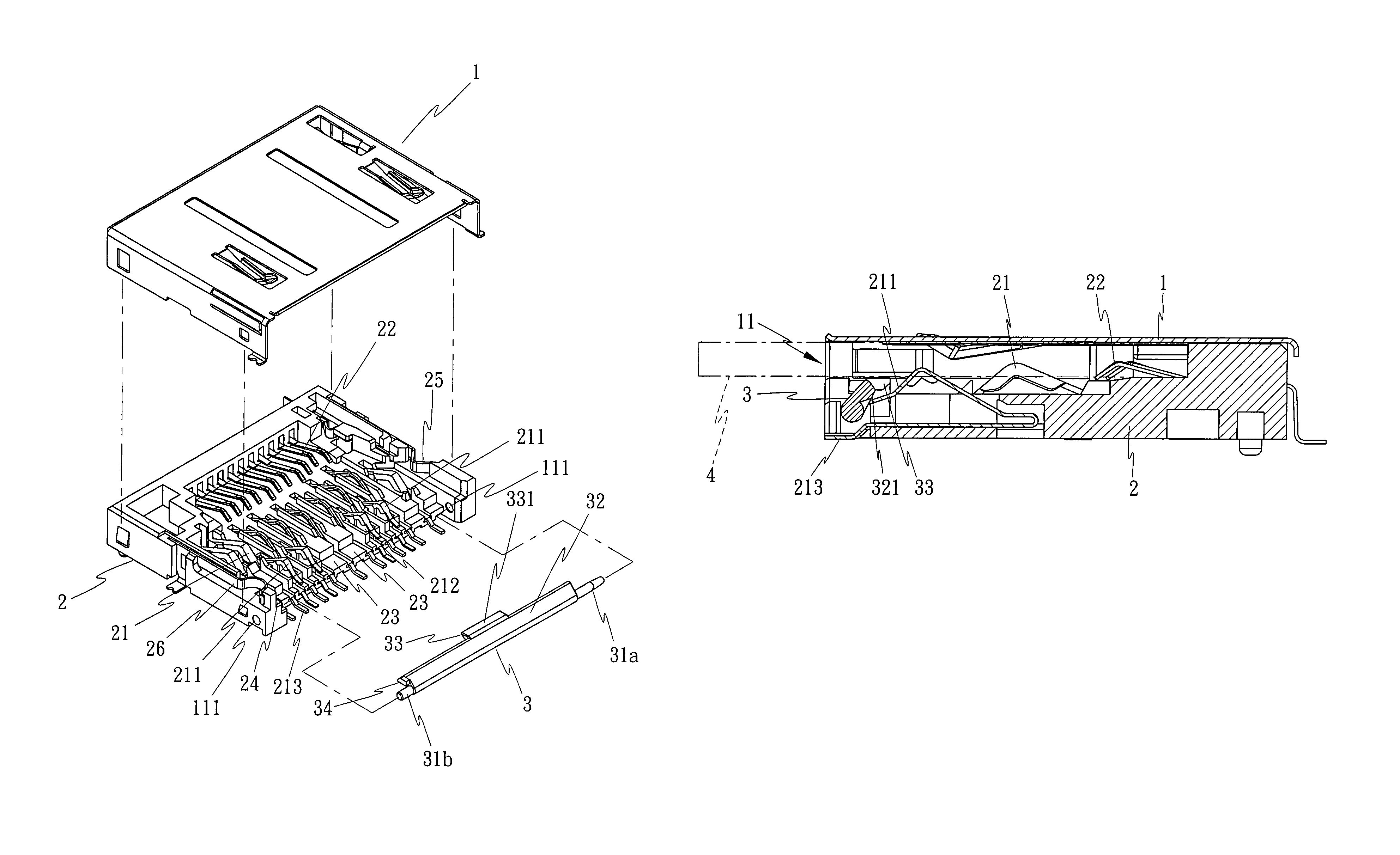

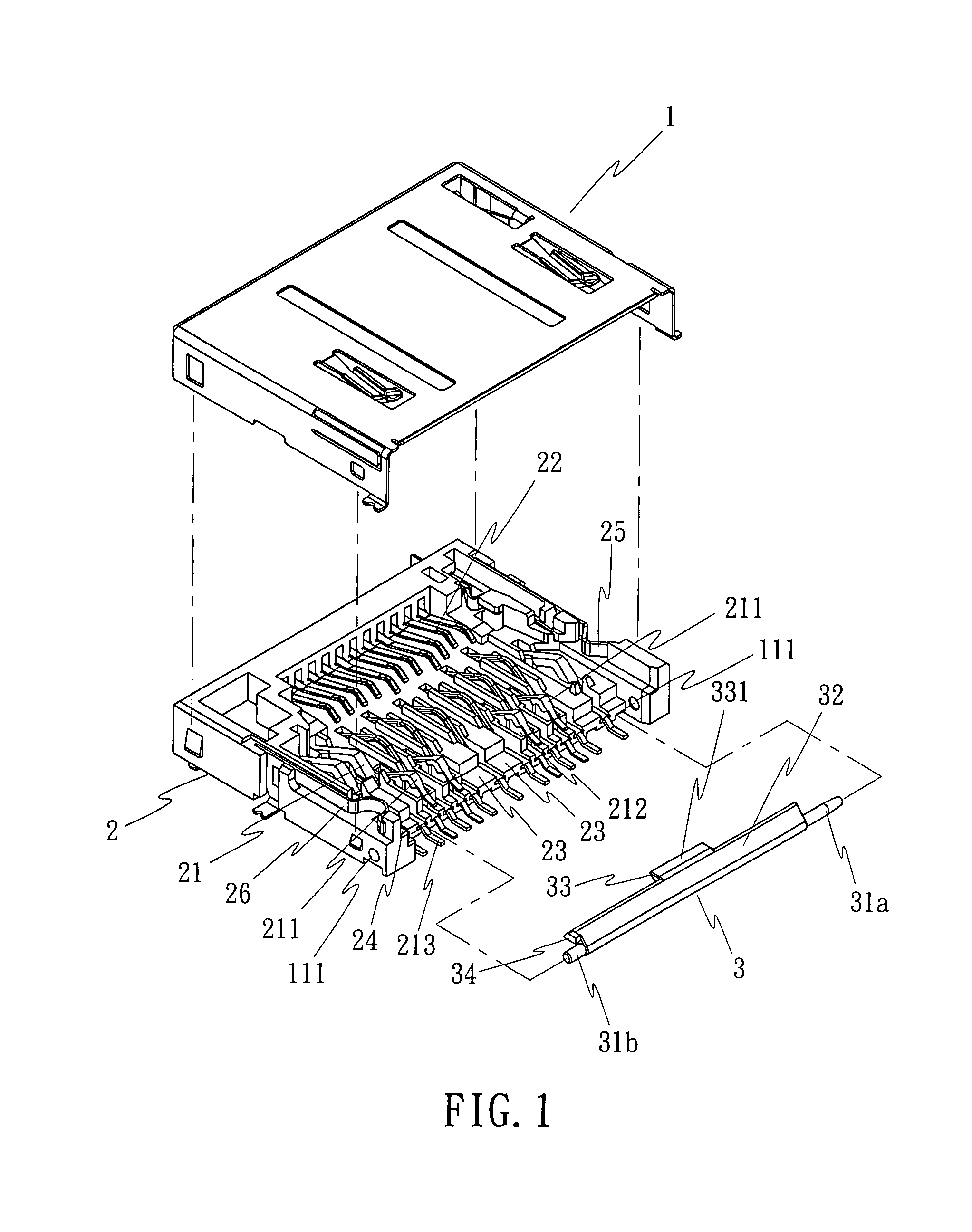

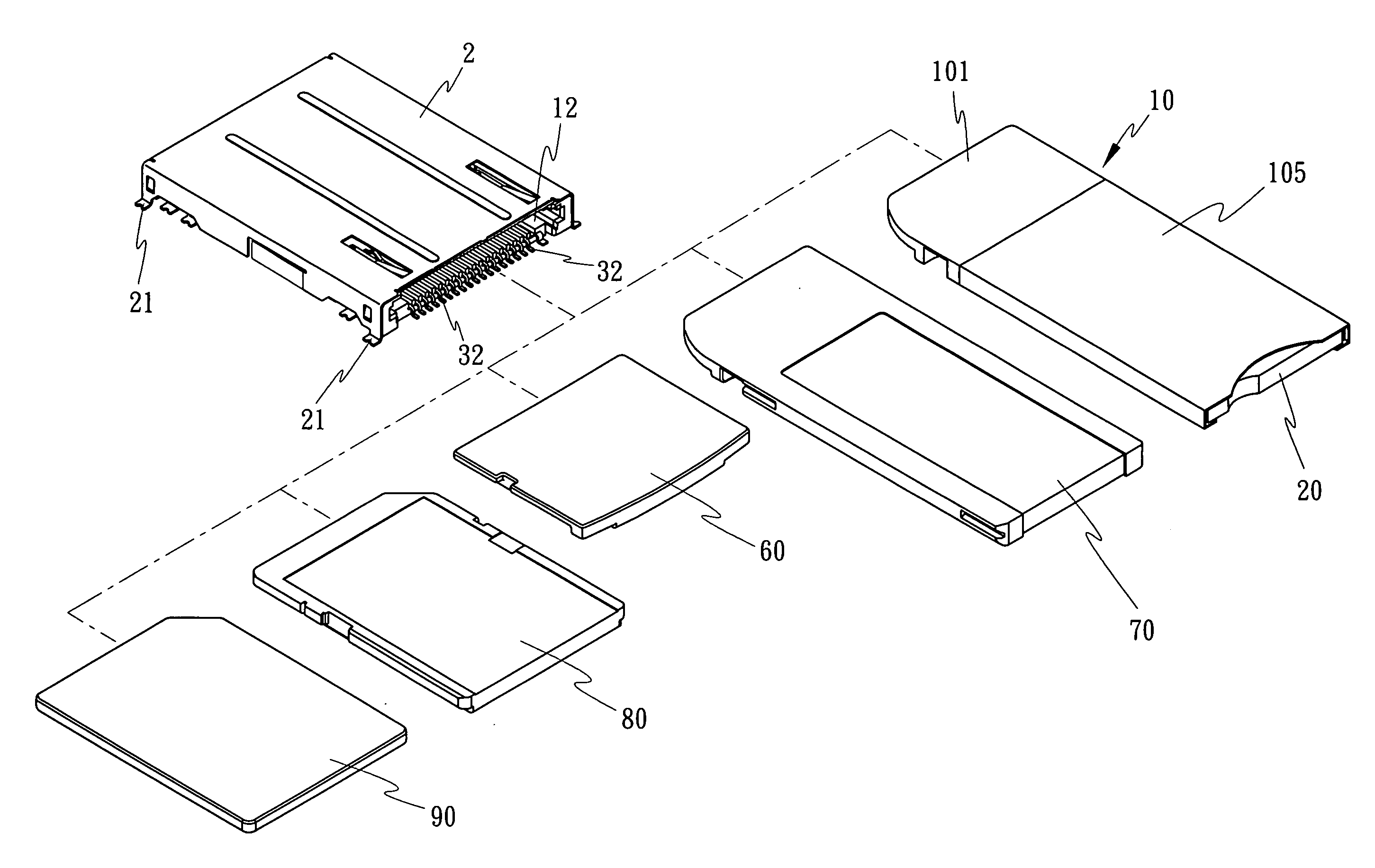

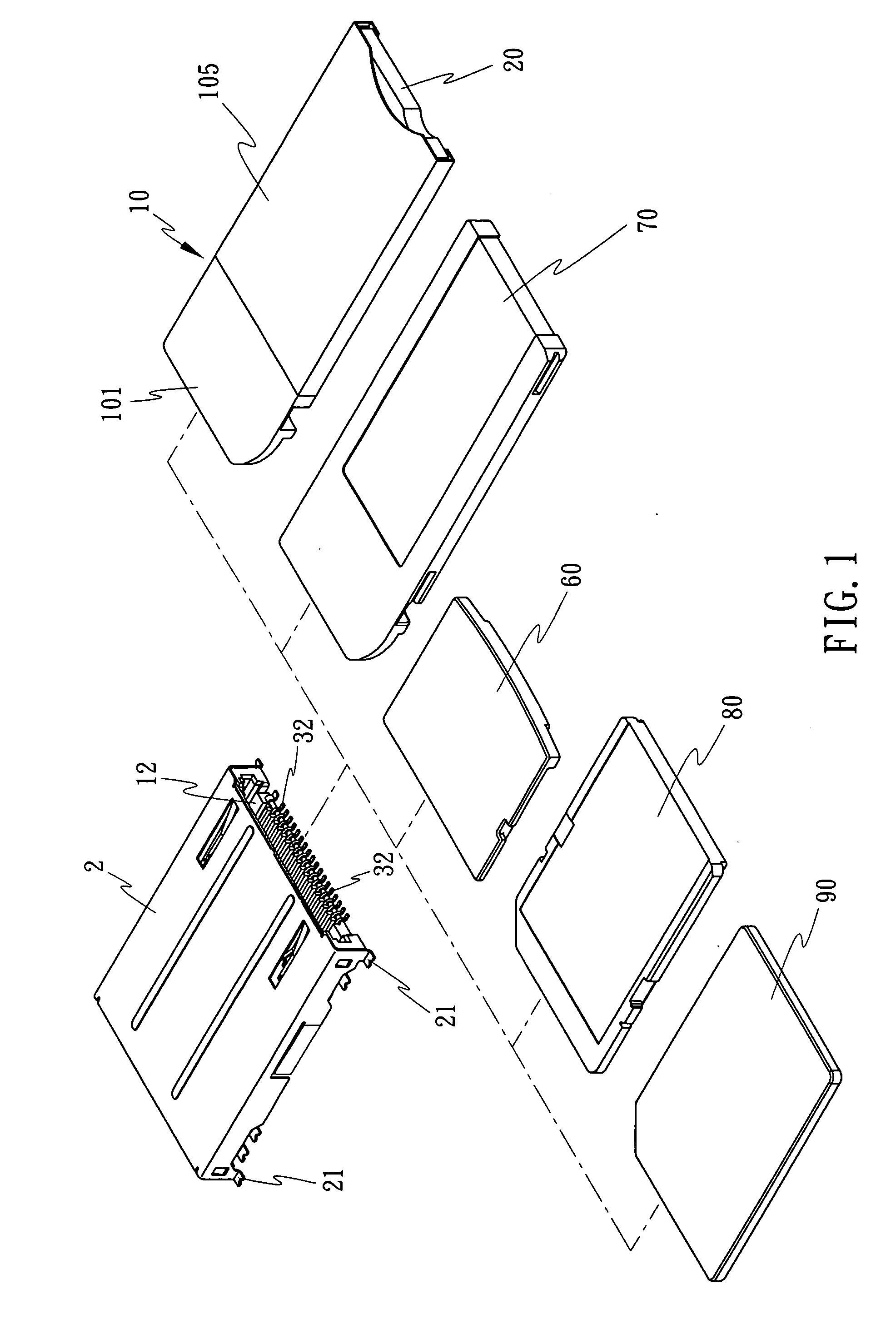

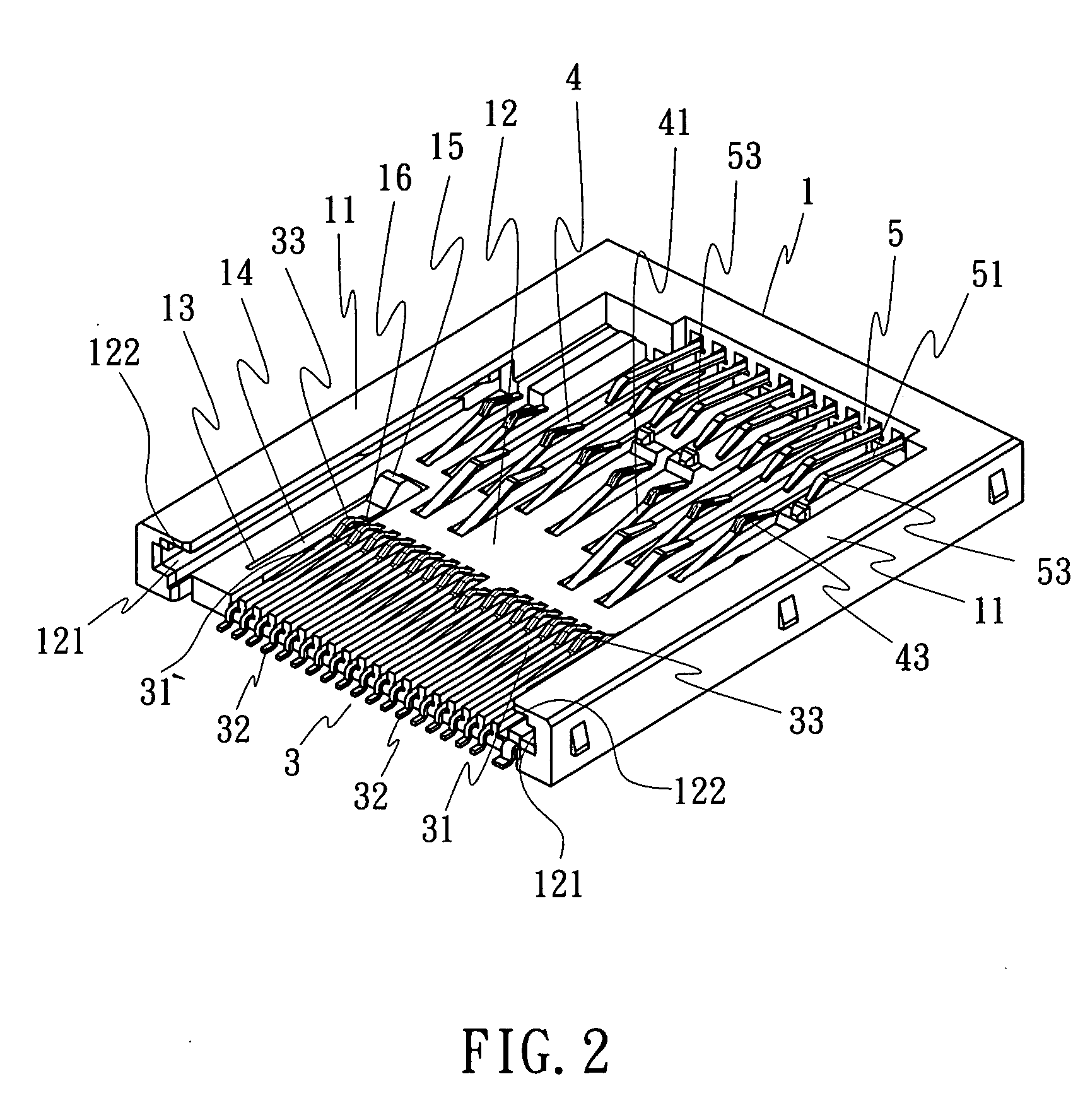

Universal memory card adapter having a movable door

InactiveUS7044757B1Accurate insertionLive contact access preventionRecord carriers used with machinesEngineeringMechanical engineering

A universal memory card adapter is disclosed to have a movable door horizontally pivotally mounted in a stepped receiving open side thereof to control insertion of different memory cards, which movable door has a doorplate pivotally mounted in the stepped receiving open side and dividing the stepped receiving open side into an open type insertion slot and a sheltered insertion slot to match the insertion of different memory cards, a spring member for holding the doorplate in a normal close position, and a control spring strip, which normally stops the doorplate in the normal close position and is disconnected from the doorplate upon insertion of a matching memory card.

Owner:CHANT SINCERE

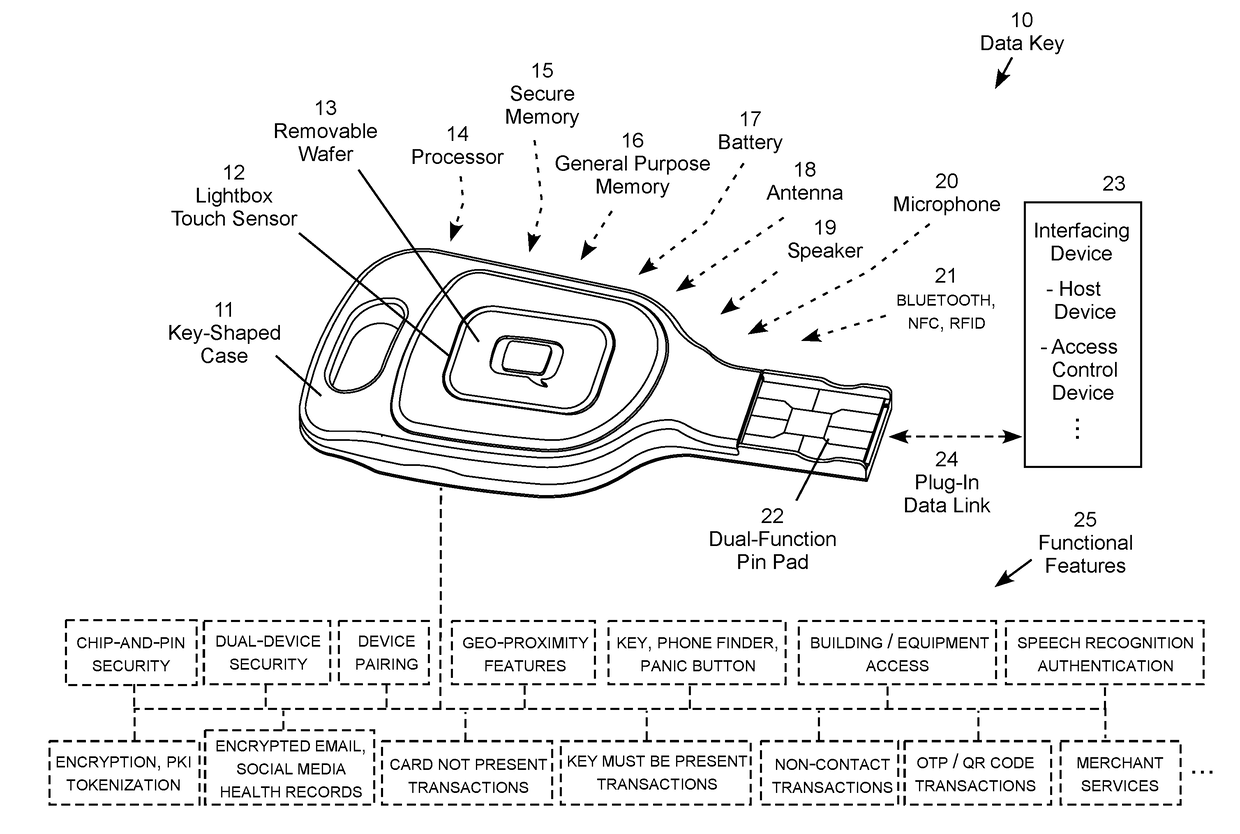

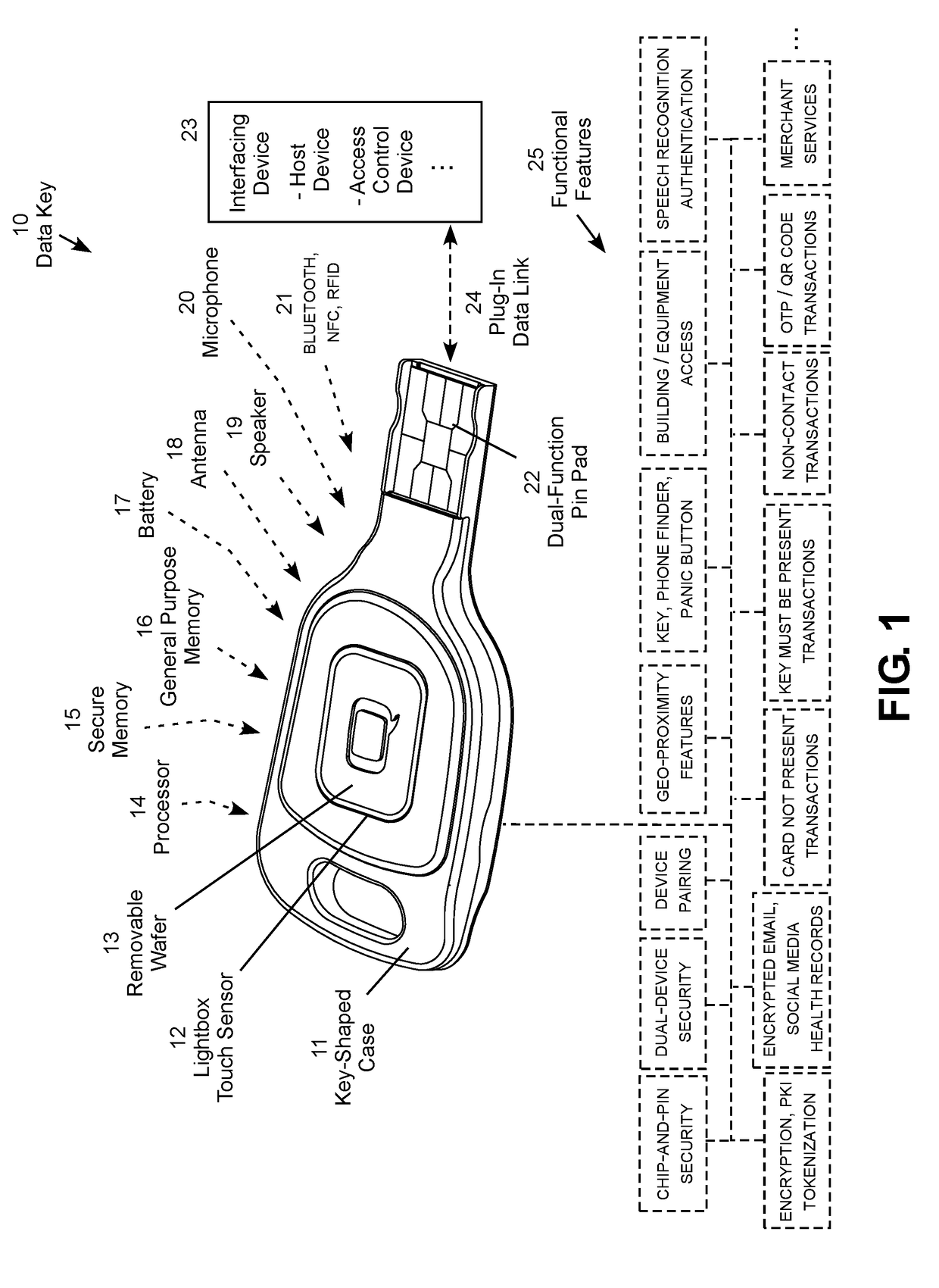

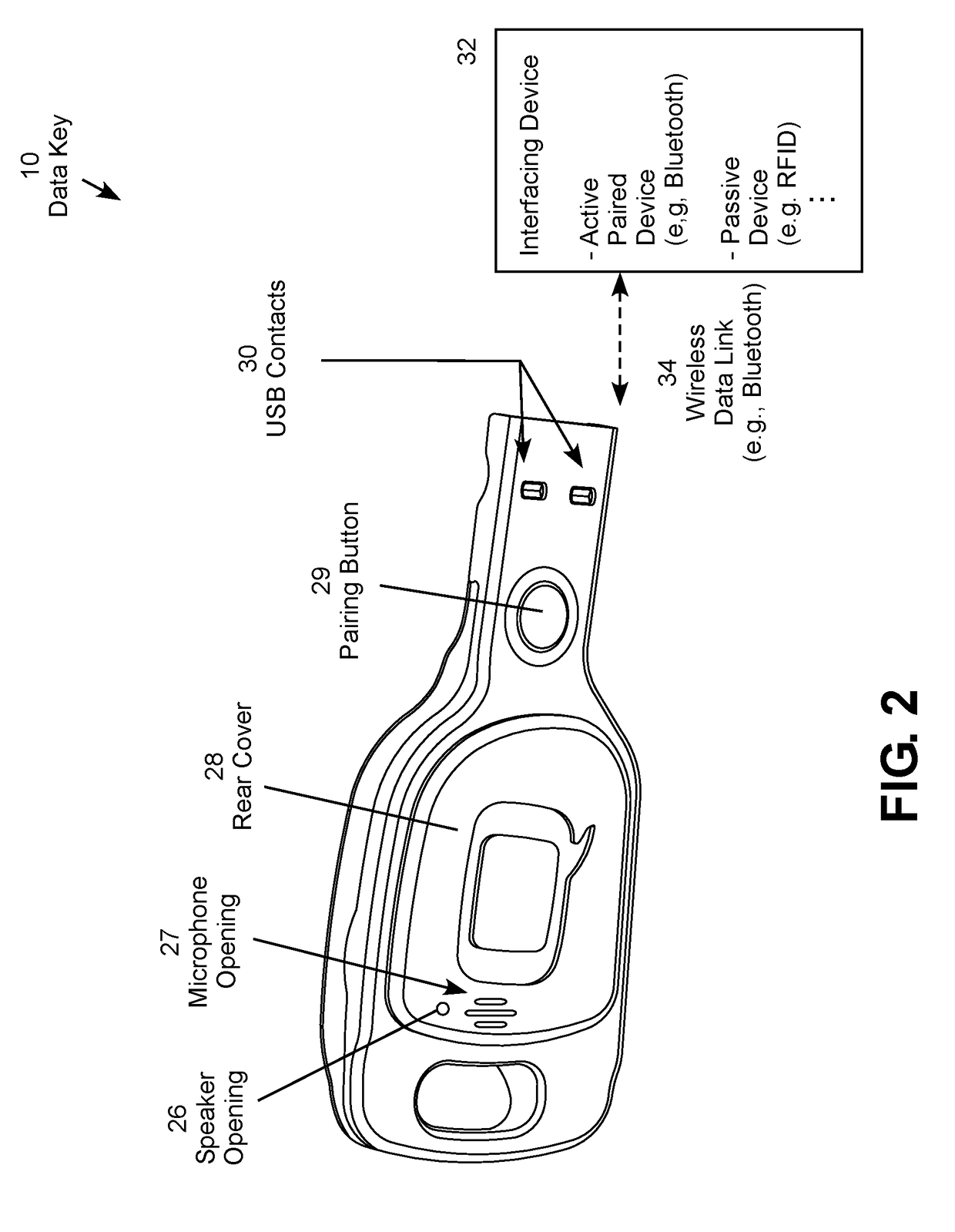

Multi-Function Data Key

A data key for secure financial and other types of data transactions with a key-shaped case, lightbox touch sensor carrying a removable wafer, processor, secure memory, general-purpose memory, battery, antenna, speaker, microphone, and a dual-purpose USB and chip pin pad. Bluetooth, NFC and / or RFID provides the ability to pair the data key through a wireless channel with another device, such as a smartphone, using a pairing button on the back of the data key. The data key provides chip-and-pin type security to online financial transactions. Dual-device security requires both the data key and another communication device registered to an authorized user to be present to activate the data key for secure operations. Device pairing enables geo-proximity features, such as dual-device security with a paired device, key finder, phone finder, and panic button. The data key may provide secure, remotely programmable security for building and equipment access.

Owner:UQONTROL

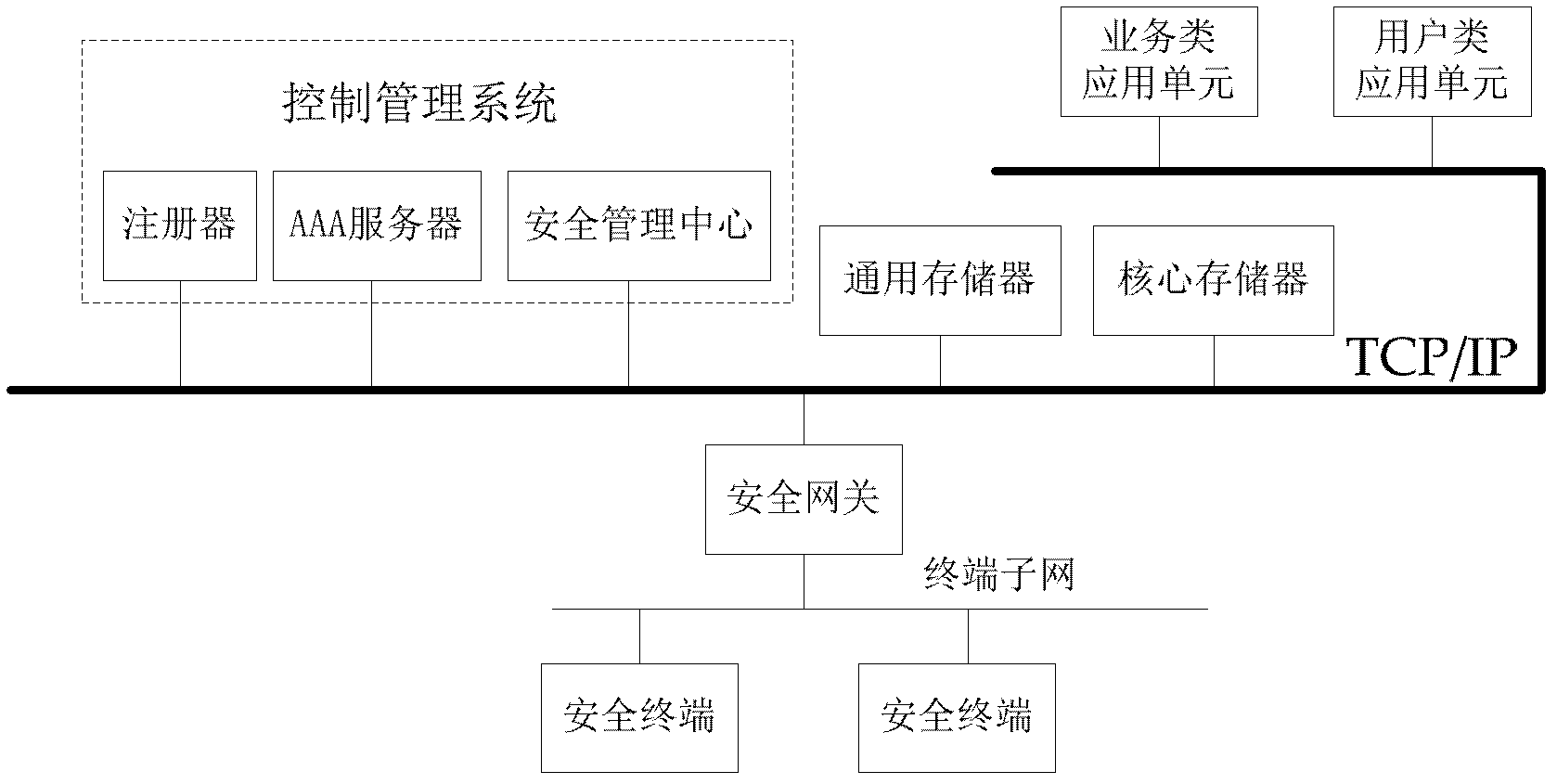

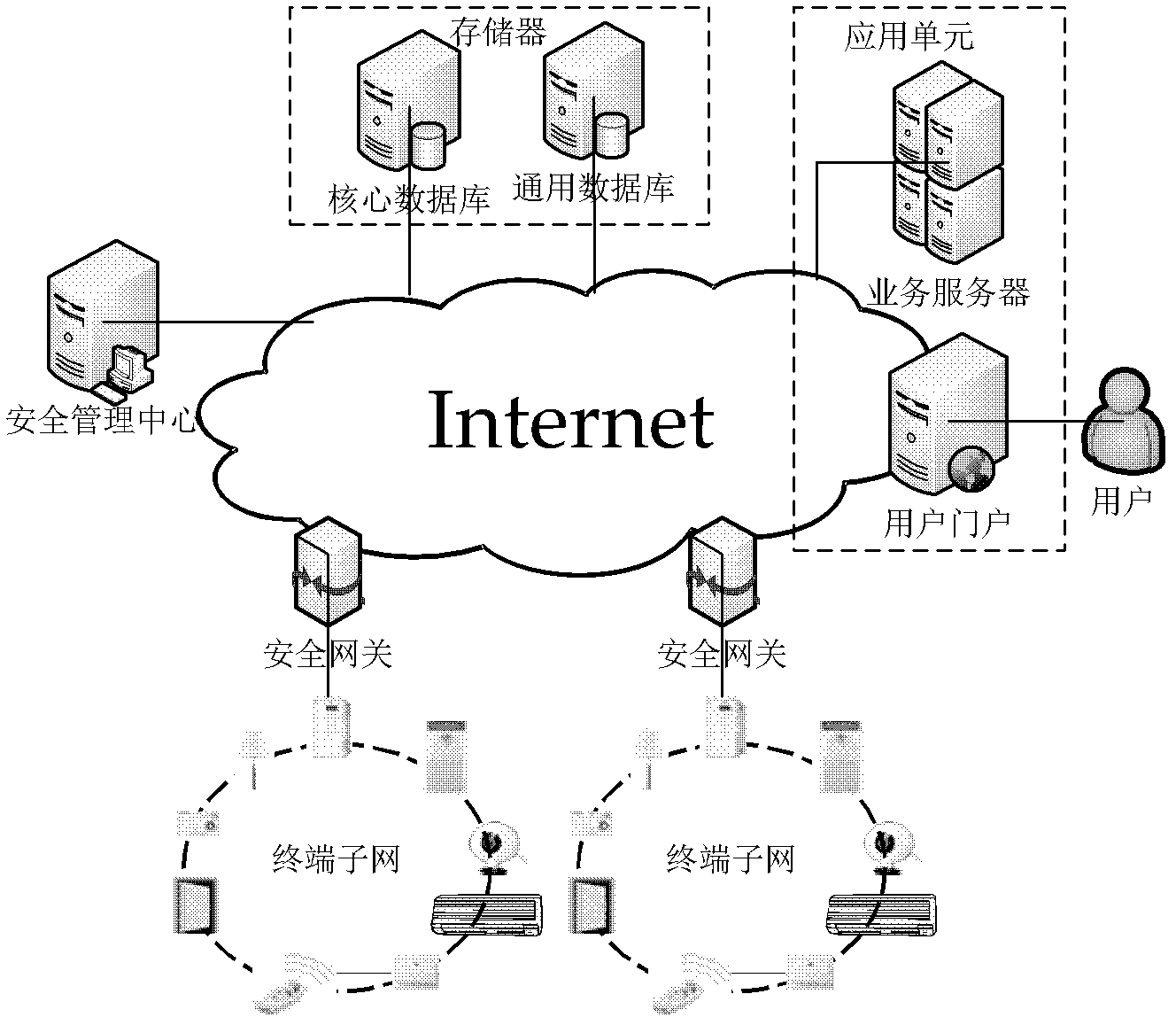

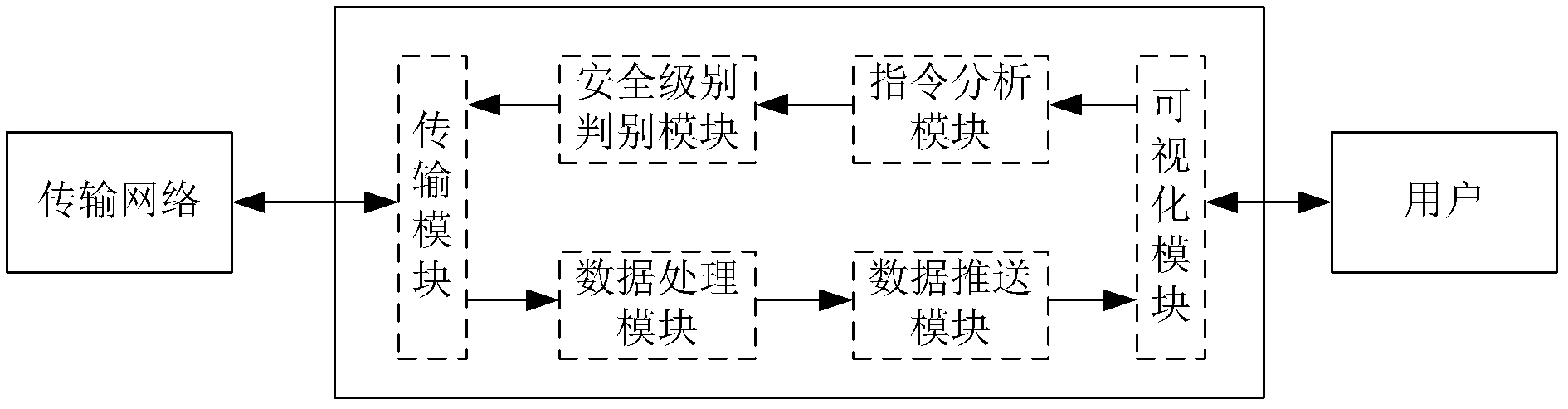

Remote communication security management architecture of ubiquitous green community control network and method for constructing the same

ActiveCN102724175AGuaranteed experienceRealize reasonable schedulingTransmissionNetwork architectureDistributed security

The invention discloses a remote communication security management architecture of a ubiquitous green community control network and a method for constructing the same. For a remote communication process of a ubiquitous green community control network, information transmission and invoking are carried out by a backbone network based on a TCP / IP protocol. According to the security management architecture, on the basis of a ubiquitous green community control network, a new security management center is deployed; security management modules are added to a gateway and terminal equipment, so that the gateway and the terminal equipment are updated as a secure gateway and a secure terminal; and a memory is divided into a general-purpose memory and a core memory and an application unit is further divided into a service type application unit and a user type application unit. According to the disclosed security management method, distributed security management is realized and level-to-level security management with different security levels is supported. And under the precondition that an original network architecture is changed little, effective security guarantees can be realized for the remote communication process of the ubiquitous green community control network by supports for distributed and level-to-level management.

Owner:下一代互联网关键技术和评测北京市工程研究中心有限公司

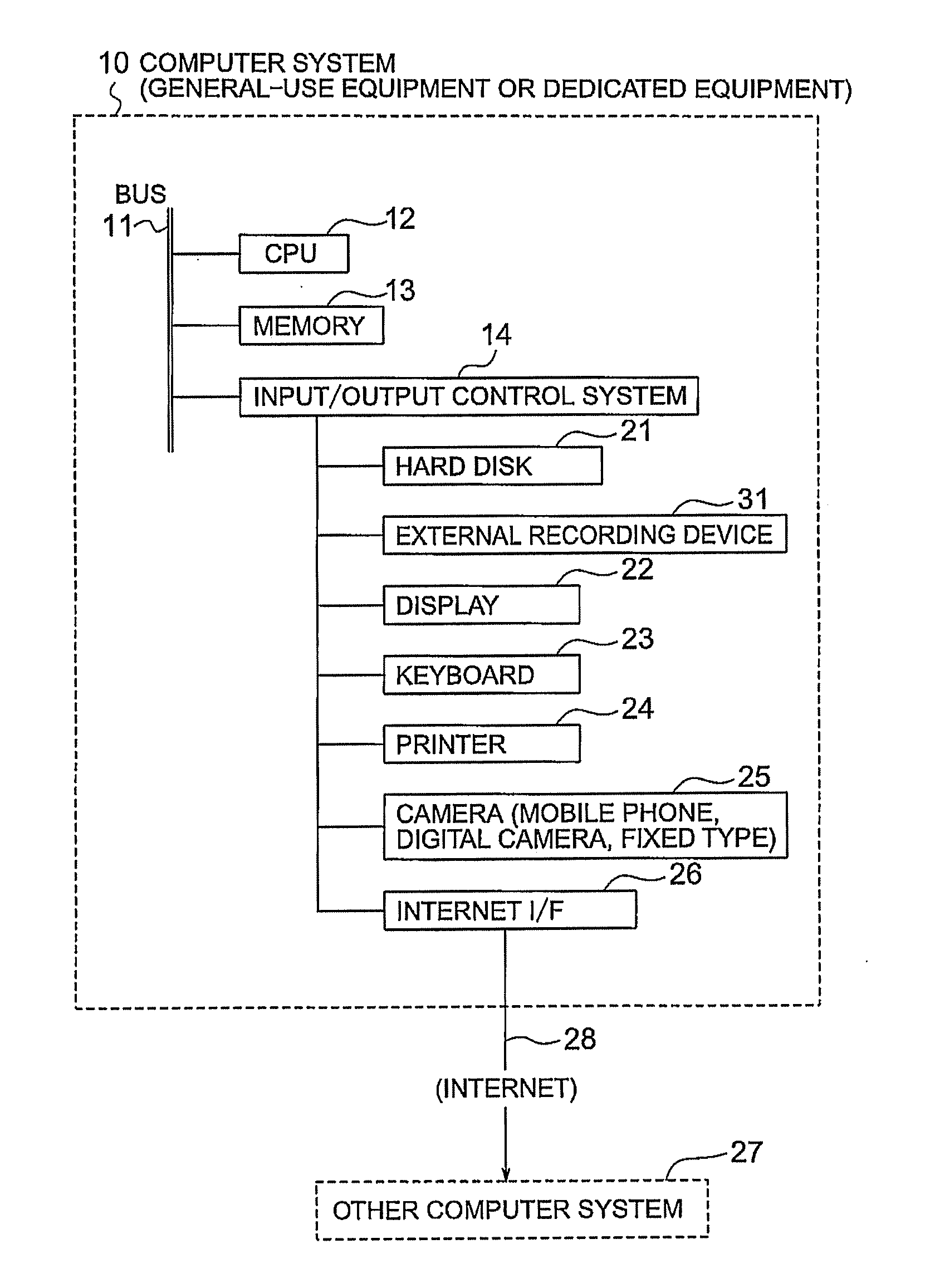

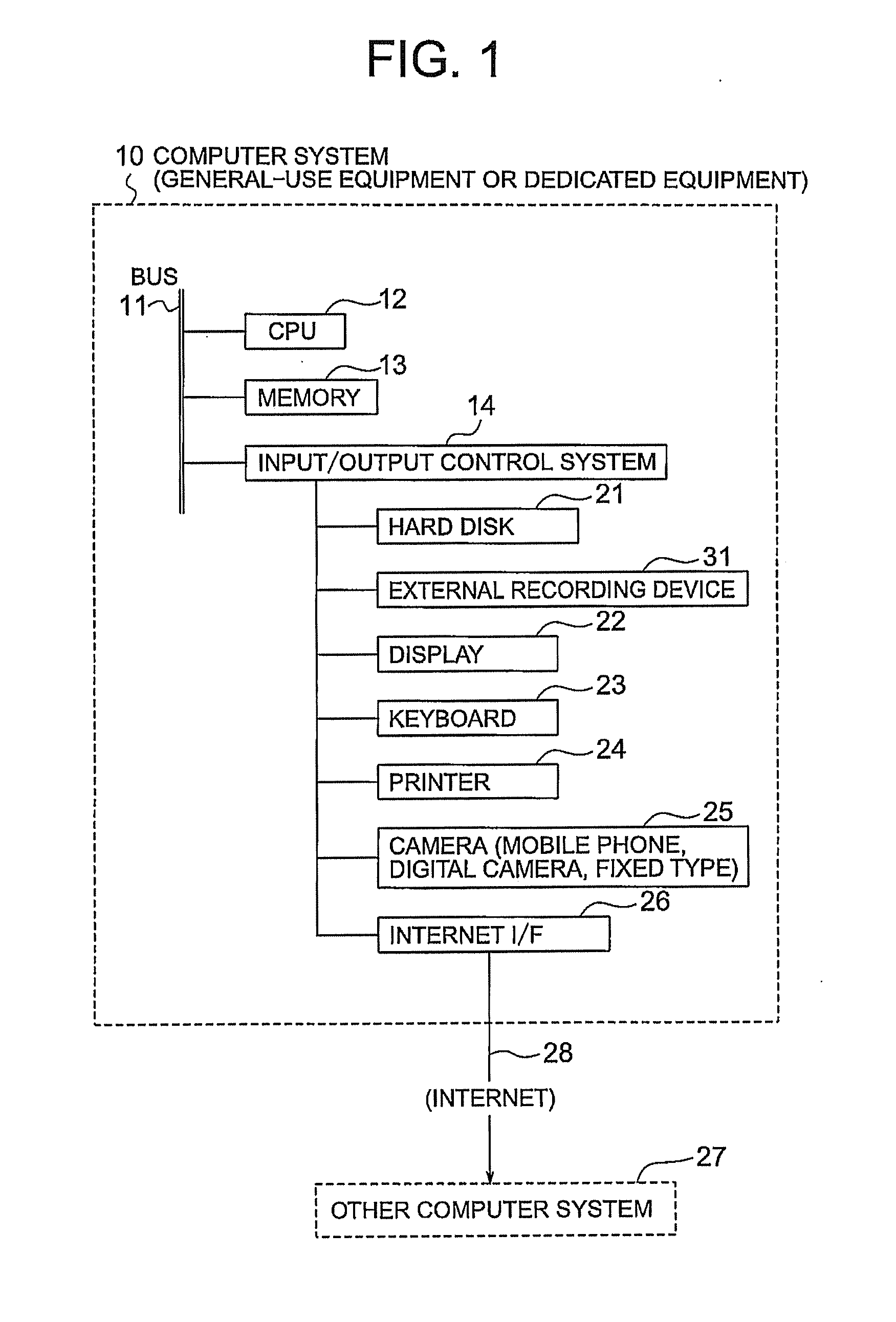

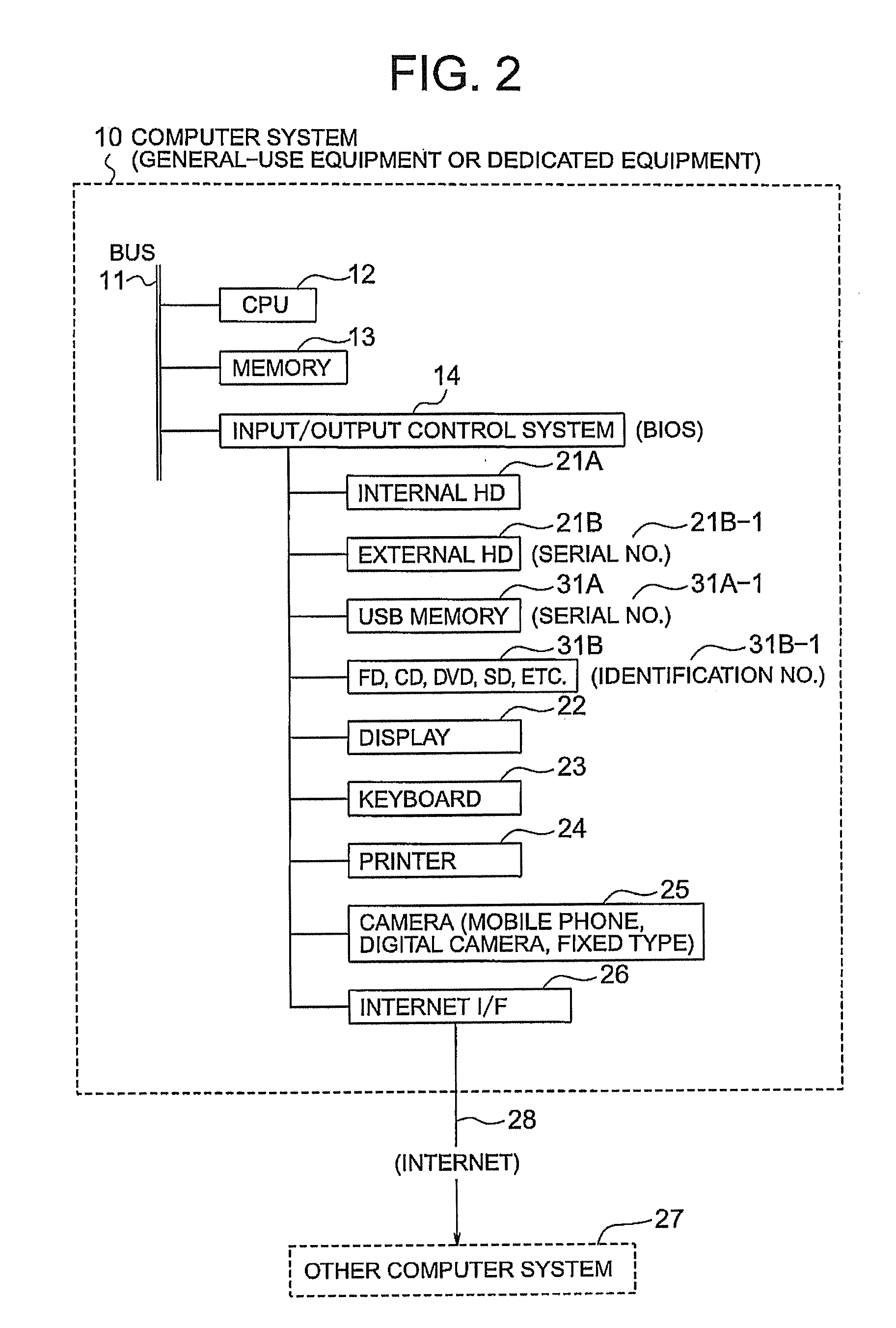

Information management system, information management method and apparatus, and encryption method and program

ActiveUS20110154063A1Reduce loadAvoid Information LeakageUnauthorized memory use protectionHardware monitoringEngineeringData store

An information management system provided with an encrypting means for encrypting an original file to prepare an encrypted file, a data storage memory which stores the encrypted file, a decrypting means, a general memory, an information managing means for decrypting the encrypted file to an editable display file etc. and storing it in the general memory in a regular operational processing cycle, performing the required editing in the form of the display file etc., converting the display file etc. after editing to an encrypted file by the encrypting means, and storing this in the data storage memory, and an information management file which controls processing of or operations on the encrypted file by the information managing means. This standardizes information management at the different levels of an organization, managers, etc., enables secure protection and management of information contained in the different machinery and equipment, lightens the load of information management, prevents leakage of information, and preserves and protects files and prevents their destruction, tampering, and alteration.

Owner:TANI ELECTRONICS IND CO LTD

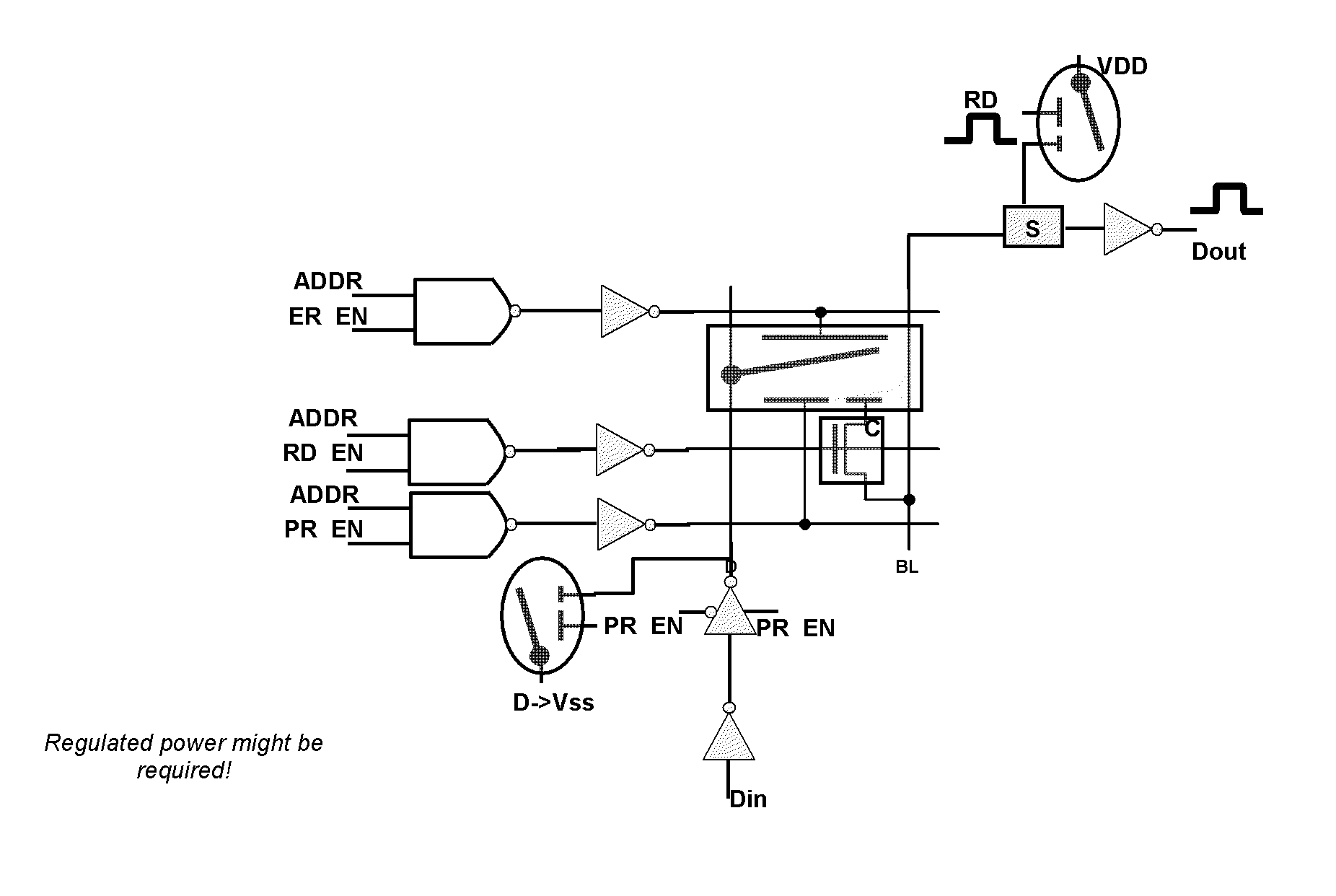

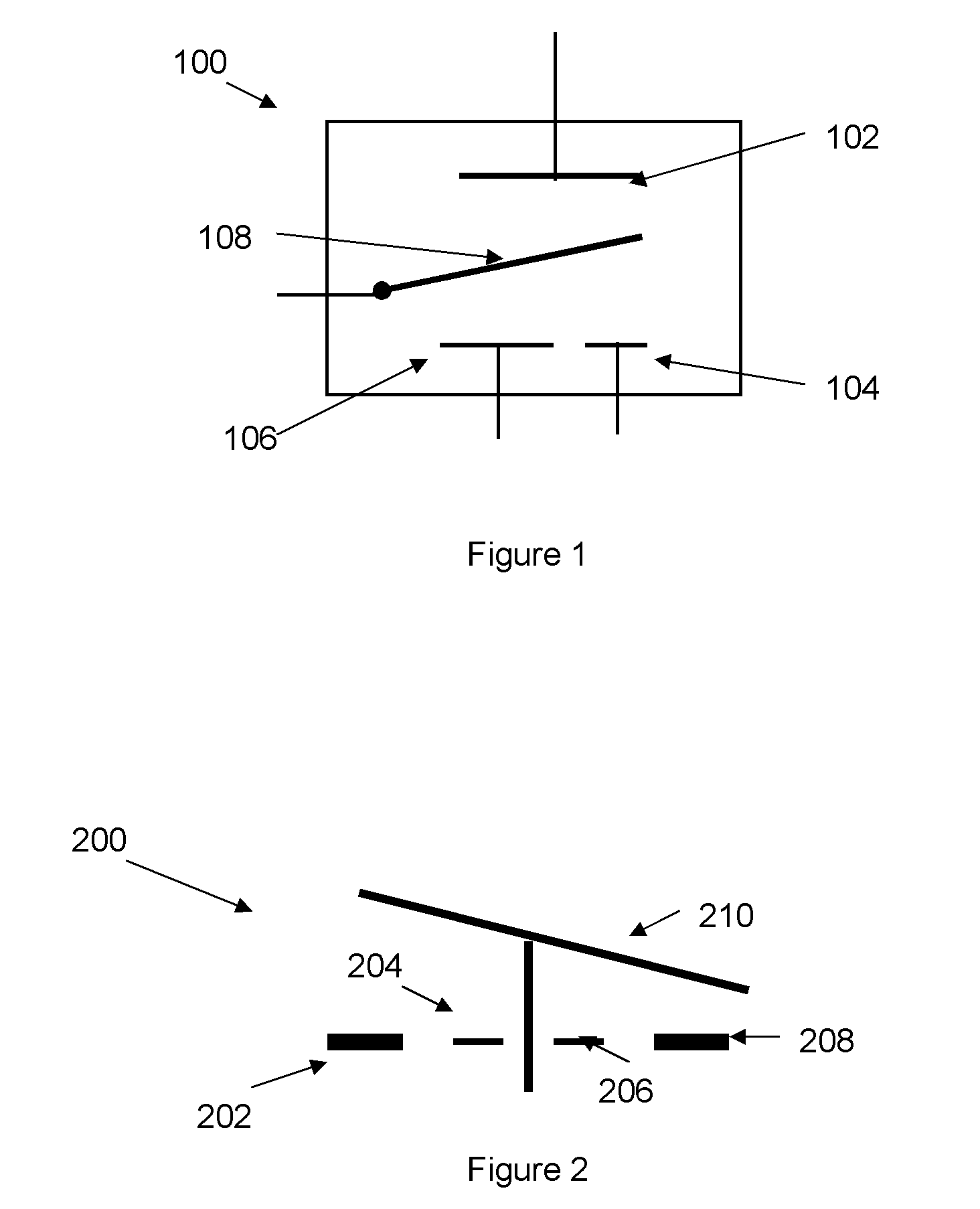

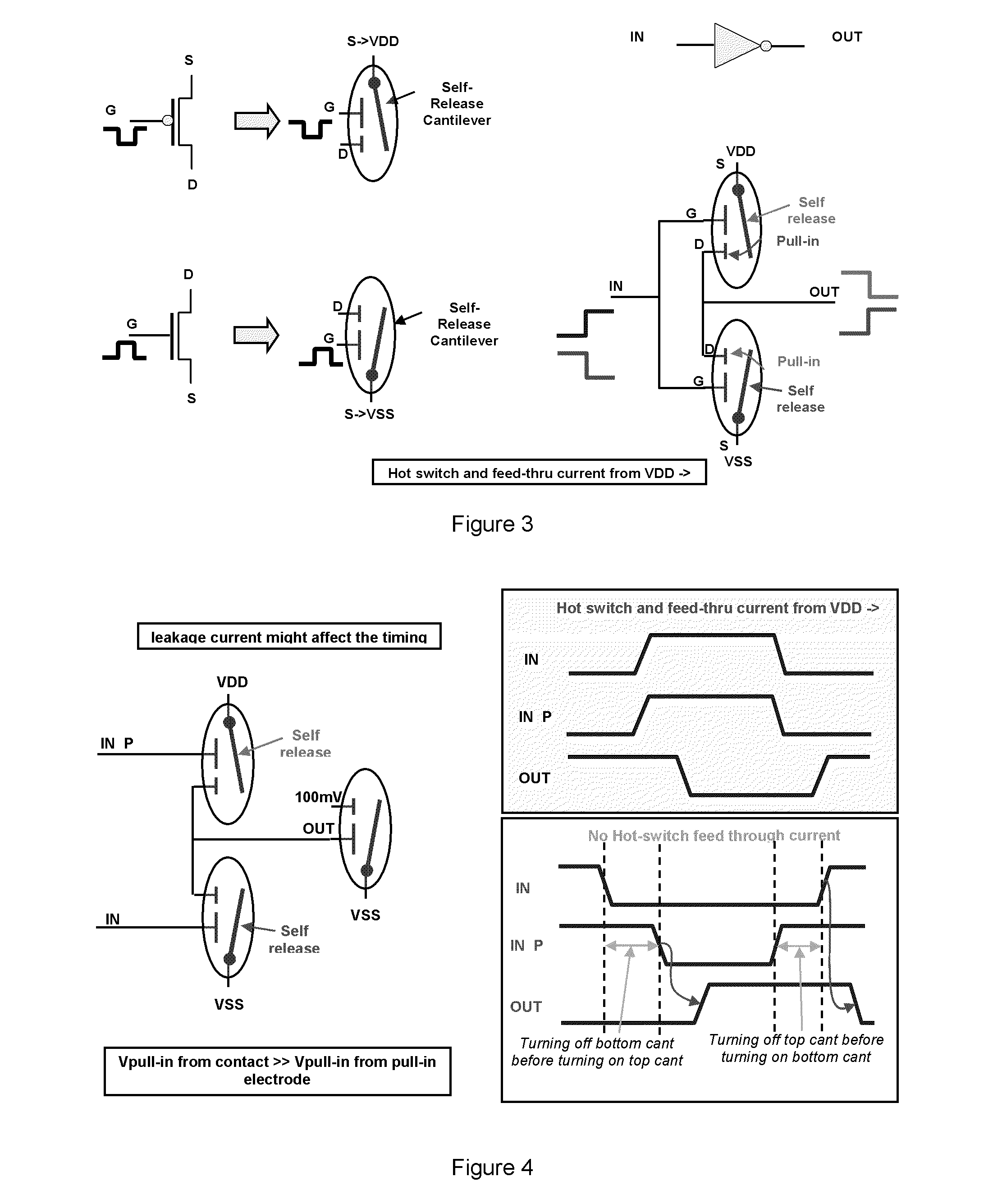

Binary Logic Utilizing MEMS Devices

ActiveUS20110002168A1Space utilizationNecessitating useRead-only memoriesDigital storageNvSRAMTransistor

Embodiments disclosed herein generally relate to switches that utilize micro-electromechanical systems (MEMS). By replacing transistors in many devices with switches such as MEMS switches, the devices may be used for logic applications. MEMS switches may be used in devices such as FPGAs, NAND devices, nvSRAM devices, AMS chips and general memory logic devices. The benefit of utilizing MEMS devices in place of transistors is that the transistors utilize more space on the chip. Additionally, the MEMS devices can be formed in the BEOL without having any negative impacts on the FEOL or necessitating the use of additional layers within the chip.

Owner:QORVO US INC

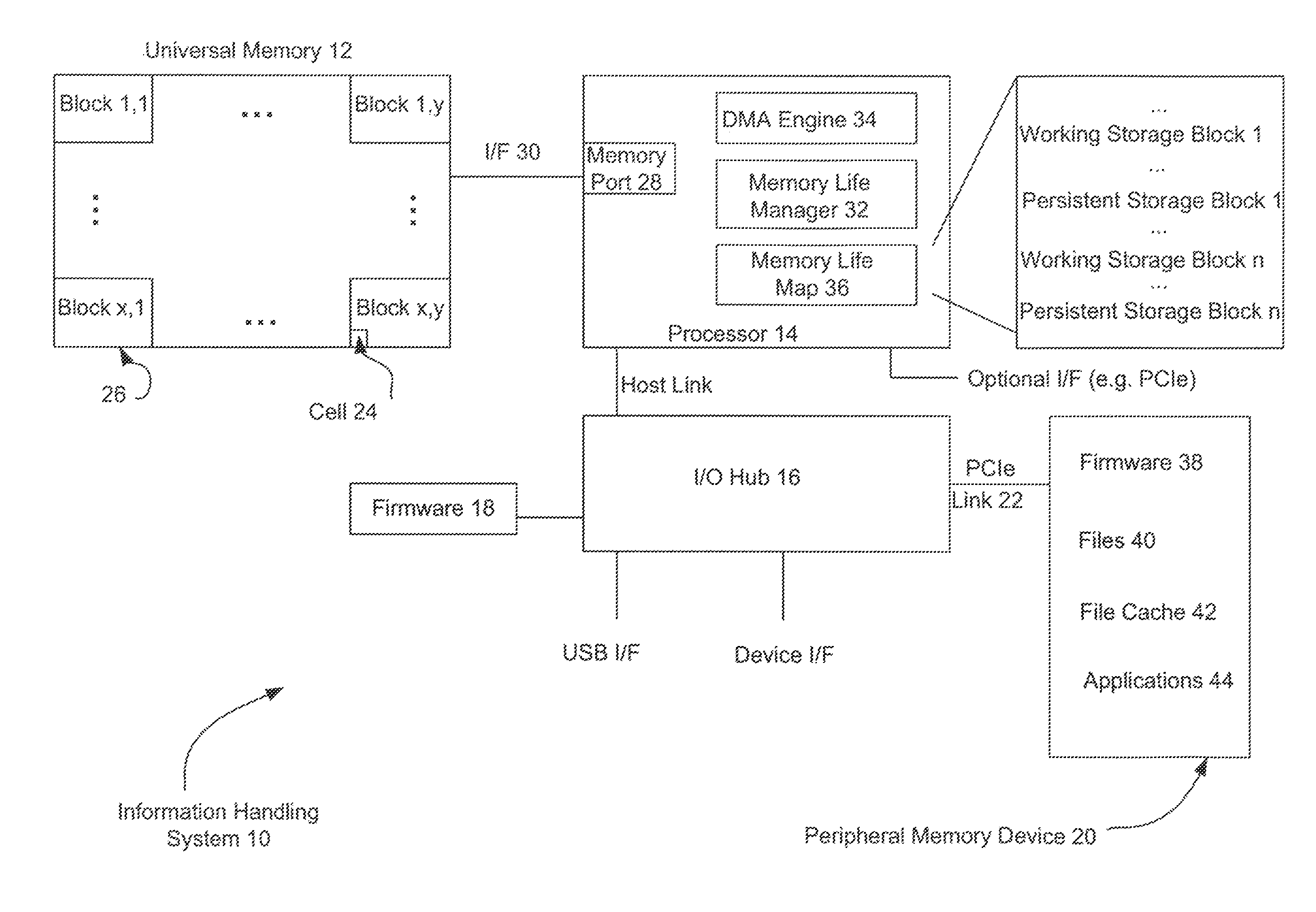

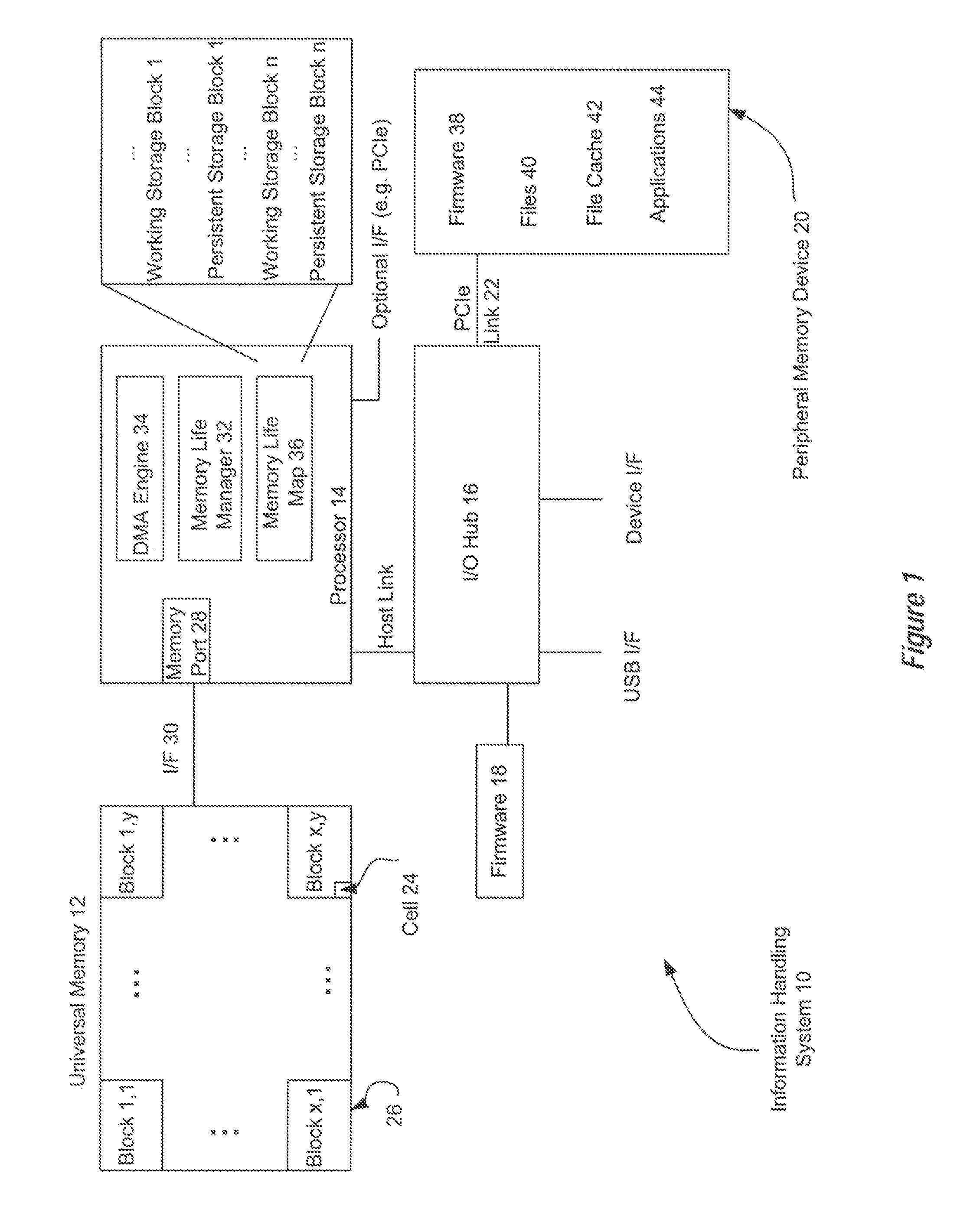

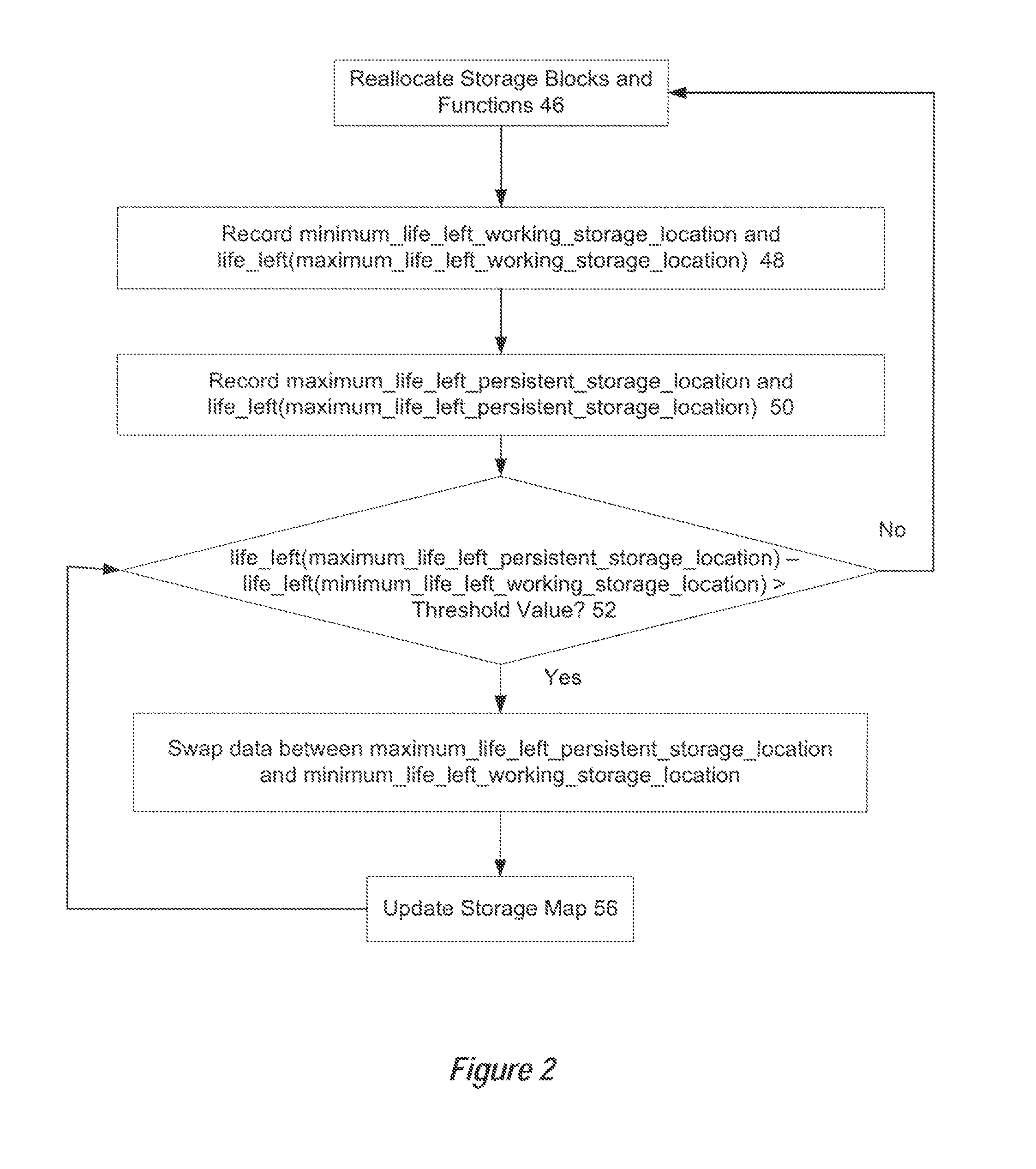

Information Handling System Universal Memory Wear Leveling System and Method

InactiveUS20120017052A1Reduce overheadImproved information handling system operationMemory architecture accessing/allocationMemory systemsParallel computingHandling system

An information handling system universal memory architecture assigns memory blocks to information handling system functions, such as a persistent storage function and a working storage function, that have different relative rates of writes of information. The blocks are periodically analyzed for remaining memory life to reassign blocks to functions that result in wear leveling across the blocks. For example, blocks having relatively low life remaining that are assigned to functions having a relatively high number of writes have their function switched with blocks that have a relatively high life remaining that are assigned to functions having a relatively low number of writes. In addition, wear leveling performed within a block ensures even wear of the memory cells within the block.

Owner:DELL PROD LP

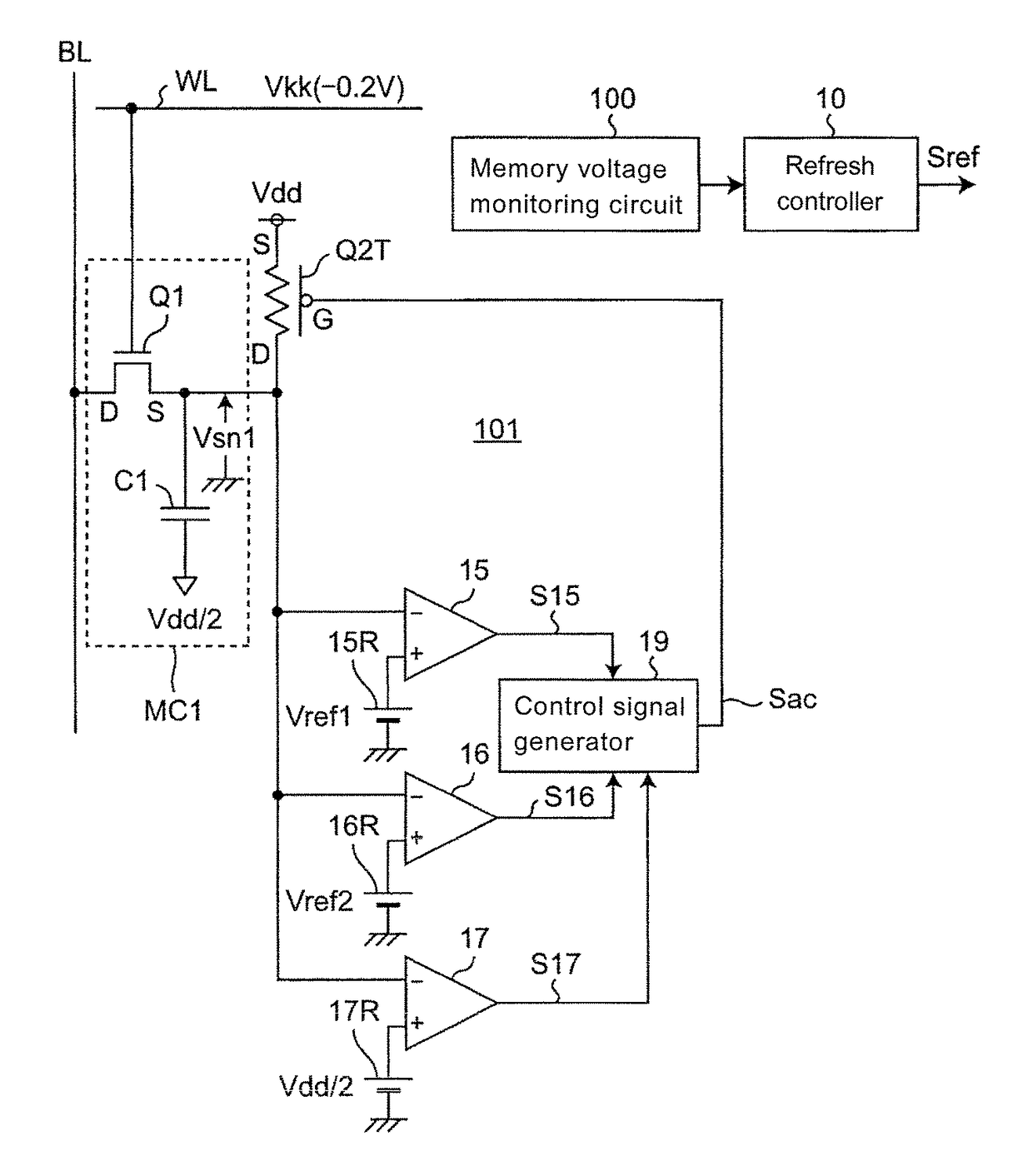

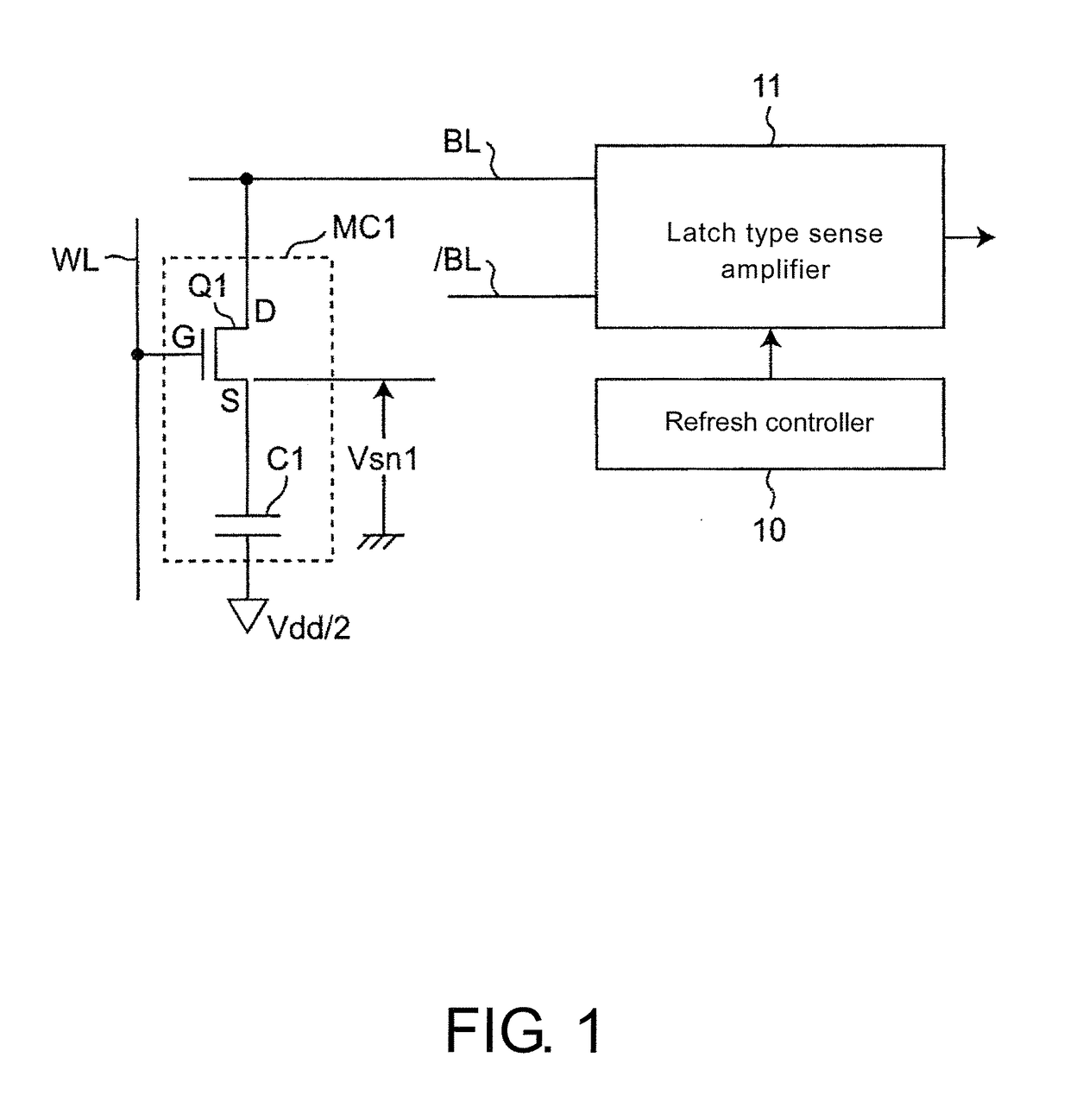

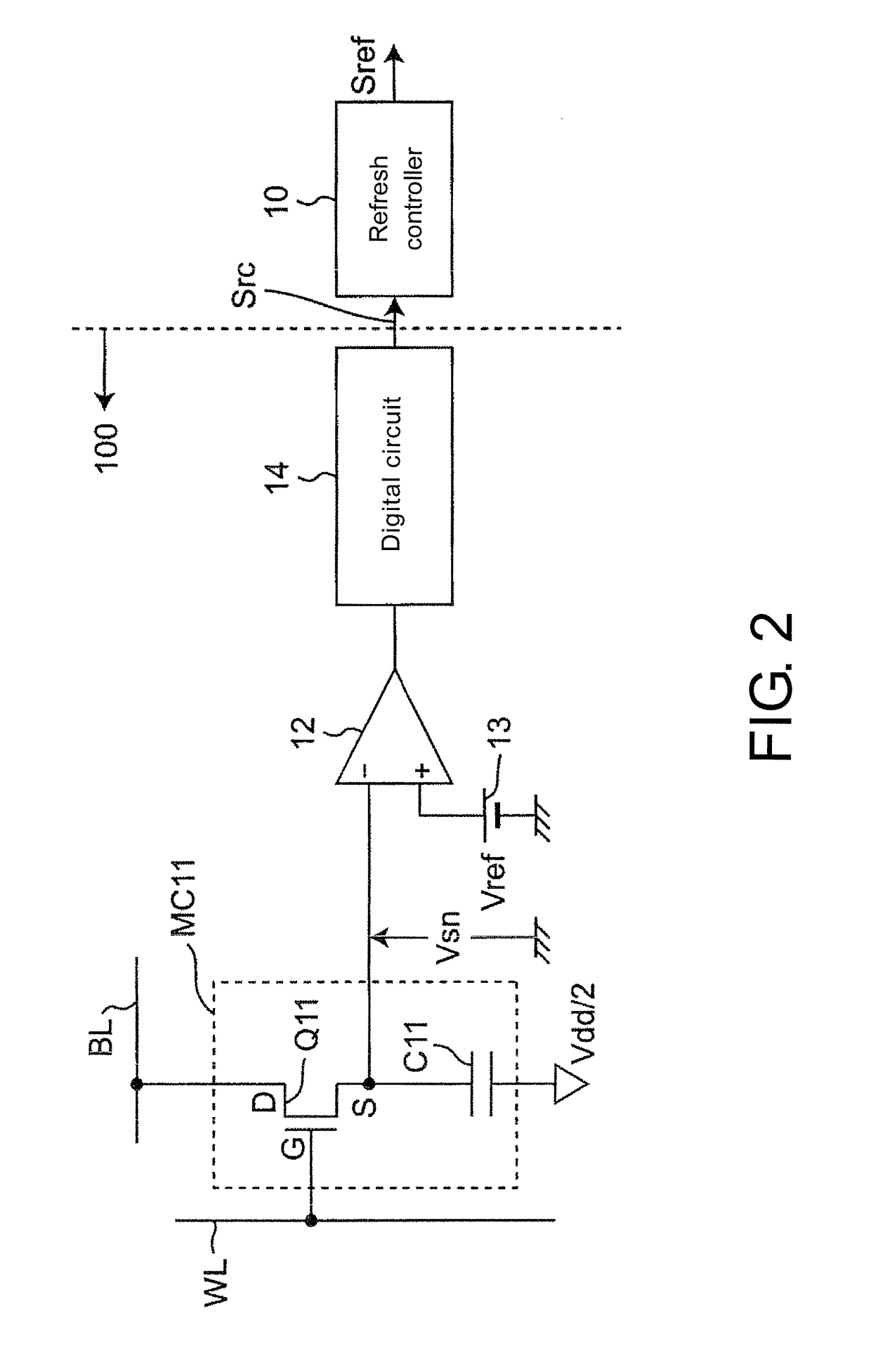

Volatile semicondcutor memory device, refresh control circuit and method thereof

ActiveUS9653142B1Reduce power consumptionSimple circuit structureDigital storageOutput compareControl circuit

A refresh control circuit of a volatile semiconductor memory device is provided, where the volatile semiconductor memory device includes a plurality of memory cells respectively having a select transistor and a memory element, and the refresh control circuit of the volatile semiconductor memory device includes: a first comparison part, which compares a memory voltage of the memory cell of the volatile semiconductor memory device that is different to a general-memorizing memory cell with a specified threshold voltage, and outputs a comparison result signal, and stops self refresh of the memory cell until the memory voltage is decreased to be smaller than the specified threshold voltage. The memory cell is formed in a region adjacent to an array of the general-memorizing memory cell.

Owner:POWERCHIP SEMICON MFG CORP

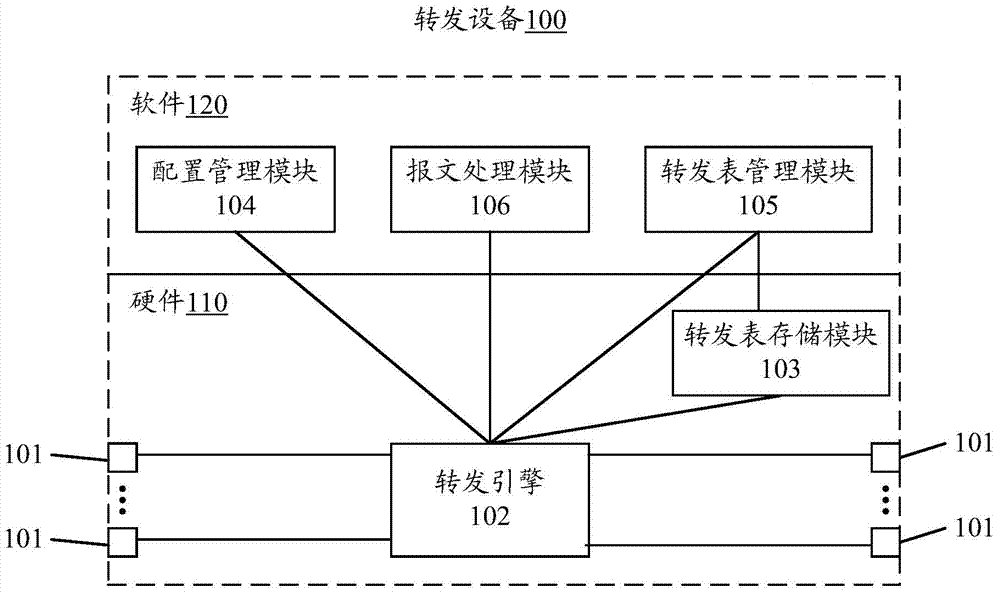

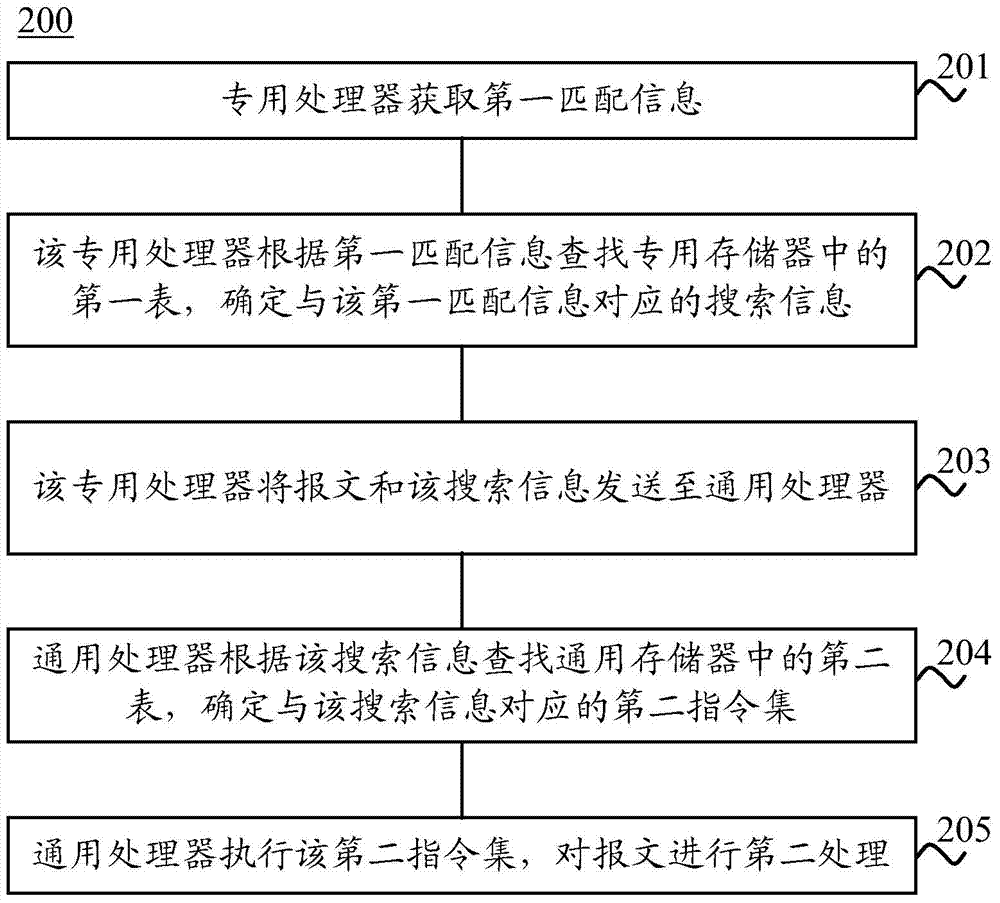

Message processing method and forwarding device

The embodiment of the invention provides a message processing method and a forwarding device. The forwarding device comprises a special processor, a universal processor, a special memorizer and a universal memorizer. When the forwarding device processes a message, the special processor obtains first matching information, looks for a first table in the special memorizer so as to determine search information corresponding to the first matching information, and further sends the message and the search information to the universal processor, and then the universal processor looks for a second table in the universal memorizer with the search information as the index so as to determine a corresponding instruction set and process the message. In this way, when the forwarding device processes the message, the found matching information of the flow tables and the found instruction set are stored in the special memorizer and the universal memorizer respectively, and the flow tables can be stored by reasonably utilizing storage space of the special memorizer of the forwarding device.

Owner:XFUSION DIGITAL TECH CO LTD

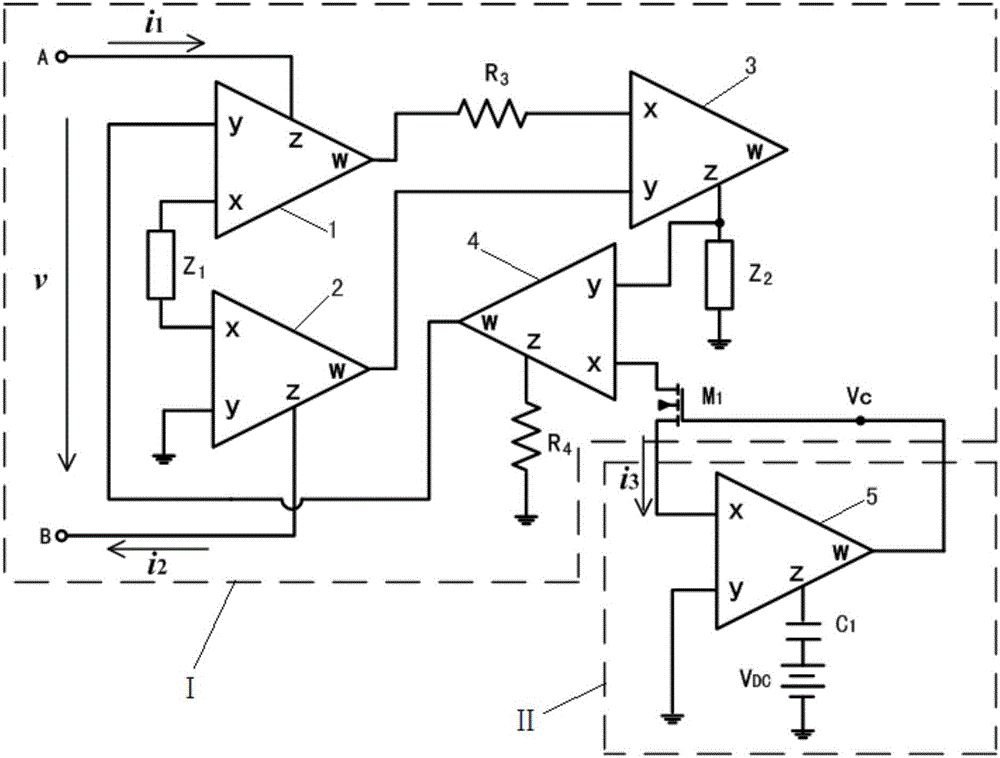

Universal memory device simulator

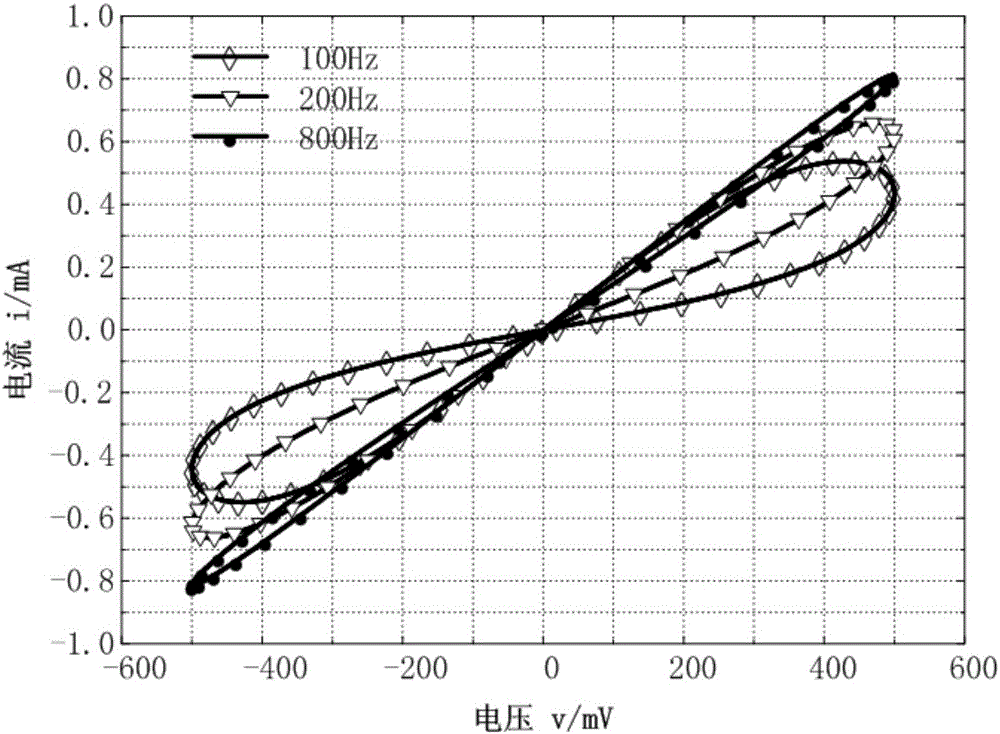

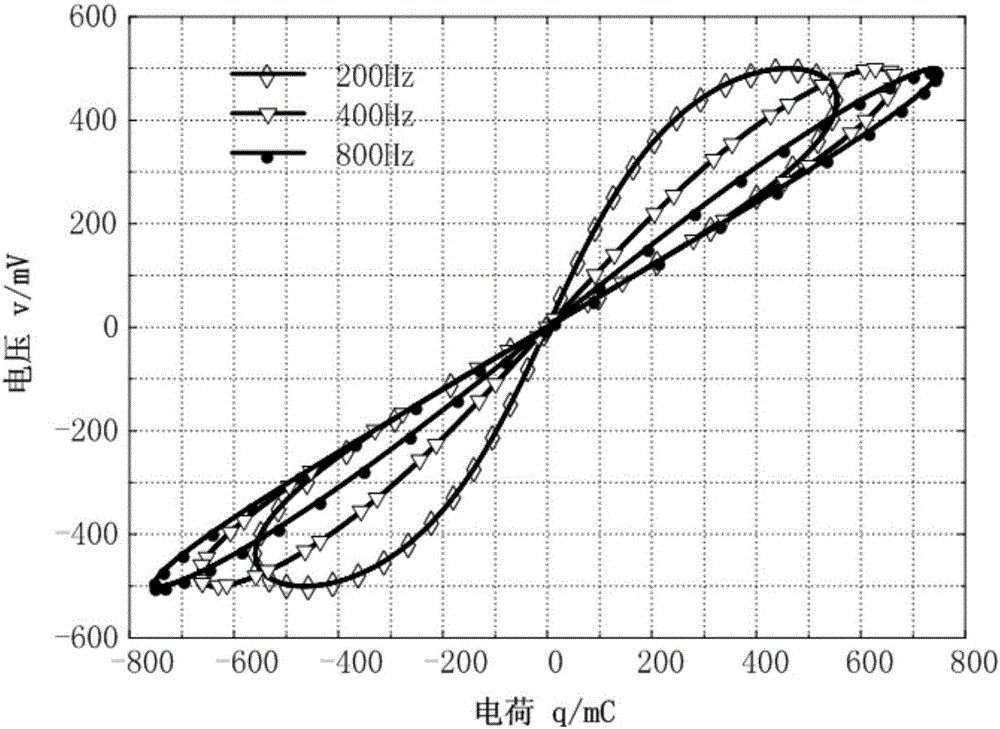

ActiveCN106202796ASimple structureReduce manufacturing costDesign optimisation/simulationCAD circuit designCapacitanceEngineering

The invention discloses a universal memory device simulator. The universal memory device simulator is characterized by comprising a voltage-control floating ground impedance conversion module and a current integration module; the voltage-control floating ground impedance conversion module is used for implementing linear voltage-control resistance, voltage-control capacitance and voltage-control inductance, the current integration module is used for implementing current integration operation, the voltage-control floating ground impedance conversion module comprises a first current feedback operational amplifier, a second current feedback operational amplifier, a third current feedback operational amplifier, a fourth current feedback operational amplifier, a field-effect transistor, a first resistor, a second resistor, a first impedance component and a second impedance component, and the current integration module comprises a fifth current feedback operational amplifier, a capacitor and a direct-current voltage source. The universal memory device simulator has the advantages that the impedance components with different properties can access the universal memory device simulator under the conditions that circuit topological structures are unchanged, accordingly, memristor, memcapacitor and meminductor can be respectively implemented, and the integral universal memory device simulator can be implemented by the aid of only few devices and is simple in structure, low in production cost and wide in application range.

Owner:XIANGTAN UNIV

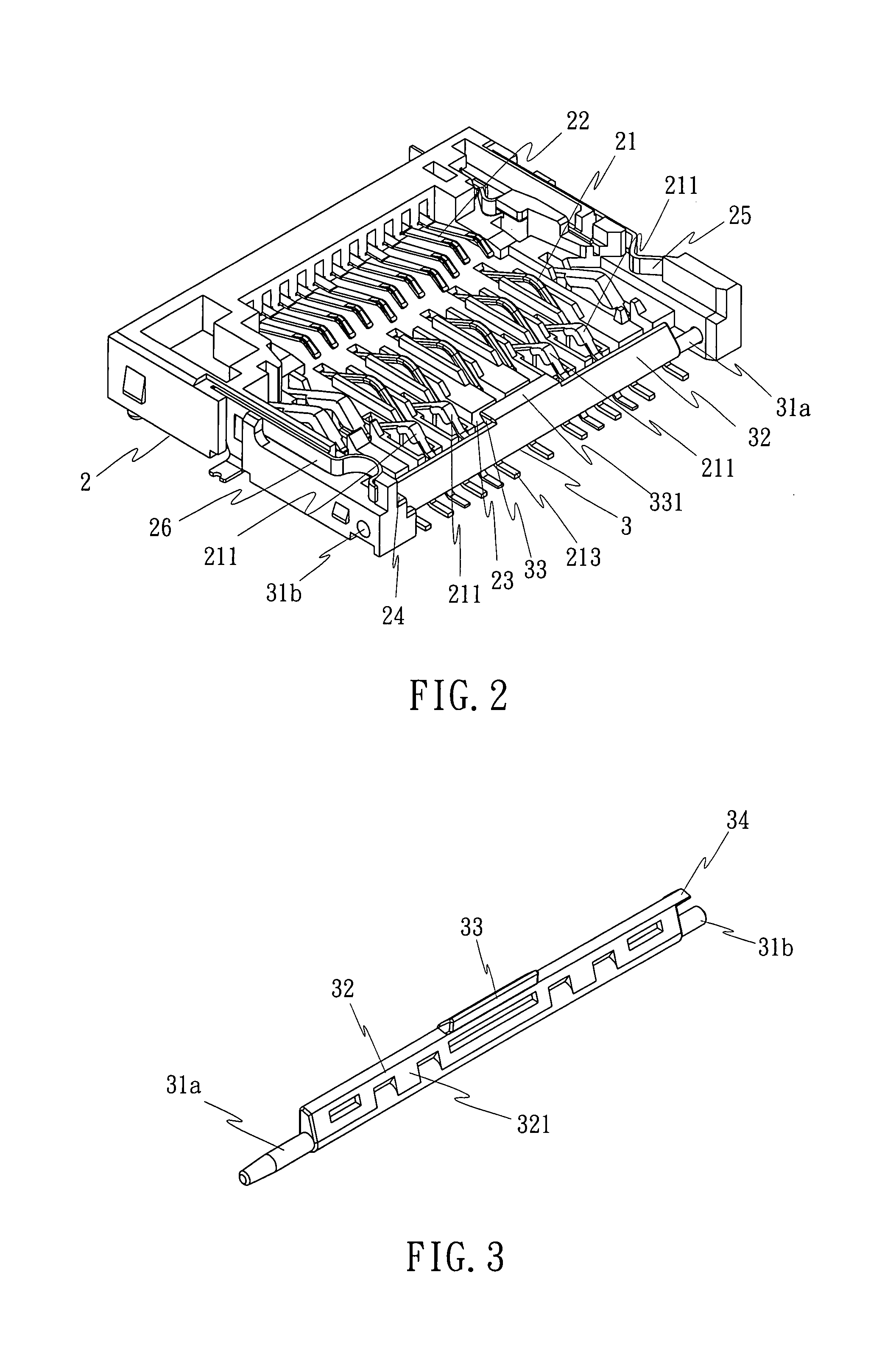

Universal memory card connector

InactiveUS7431595B1Inhibition biasEasy and fast assemblyTwo-part coupling devicesLive contact access preventionEngineeringMemory cards

In a memory card connector, a pivot shaft member is pivotally provided in a front side of the insertion hole for memory card for controlling the gap of the insertion hole for the insertion of a different memory card. The pivot shaft member has a protruding portion protruded from the periphery, and a guide block extending from the protruding portion for guiding the insertion of a thin type memory card into the insertion hole in horizontal. Insertion of a thick memory card into the insertion hole forces the protruding portion to rotate the pivot shaft and to hold down the front row of terminals in the memory card connector, preventing deformation or damage of the terminals due to improper insertion of the memory card into the insertion hole.

Owner:CHANT SINCERE

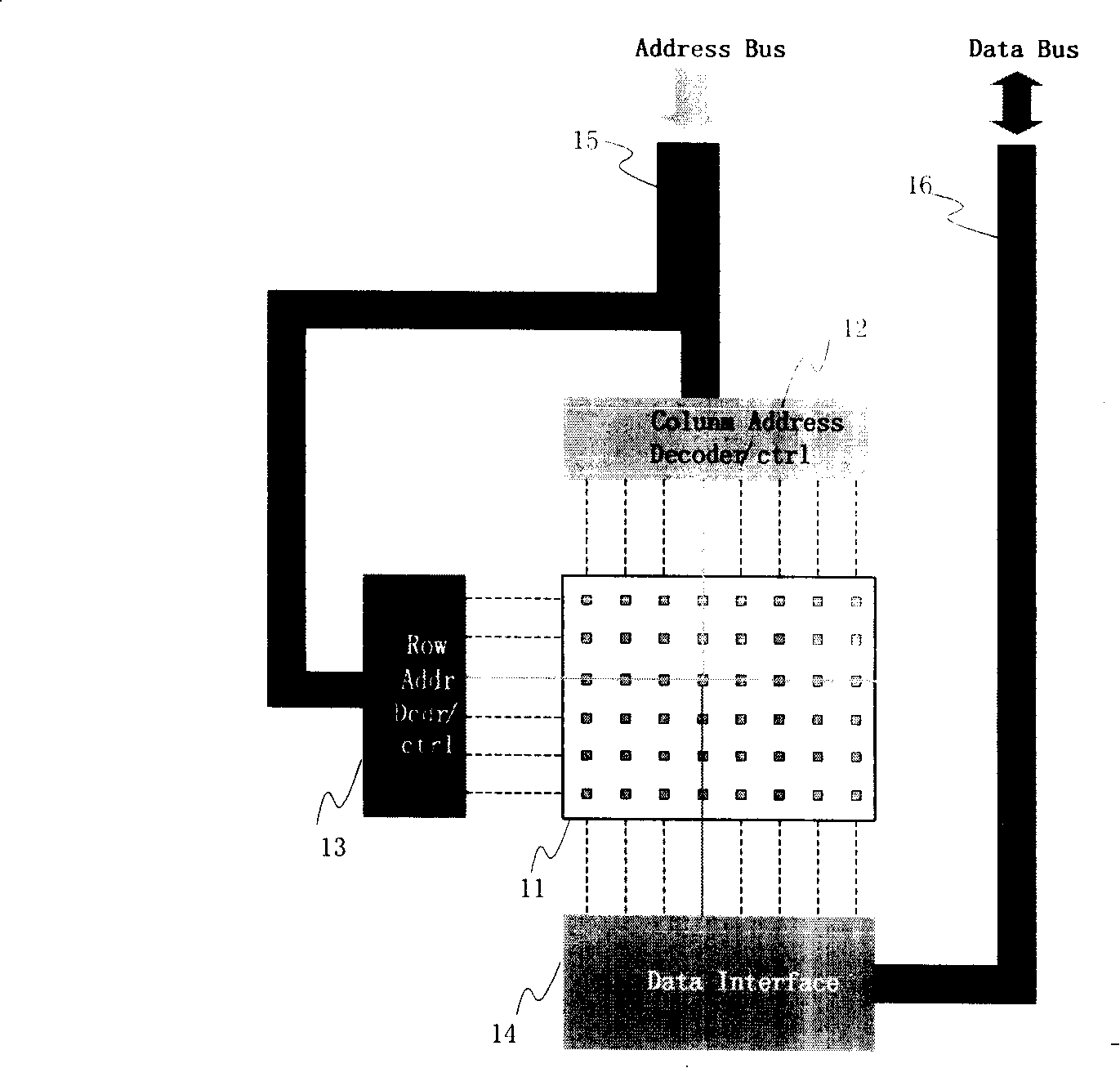

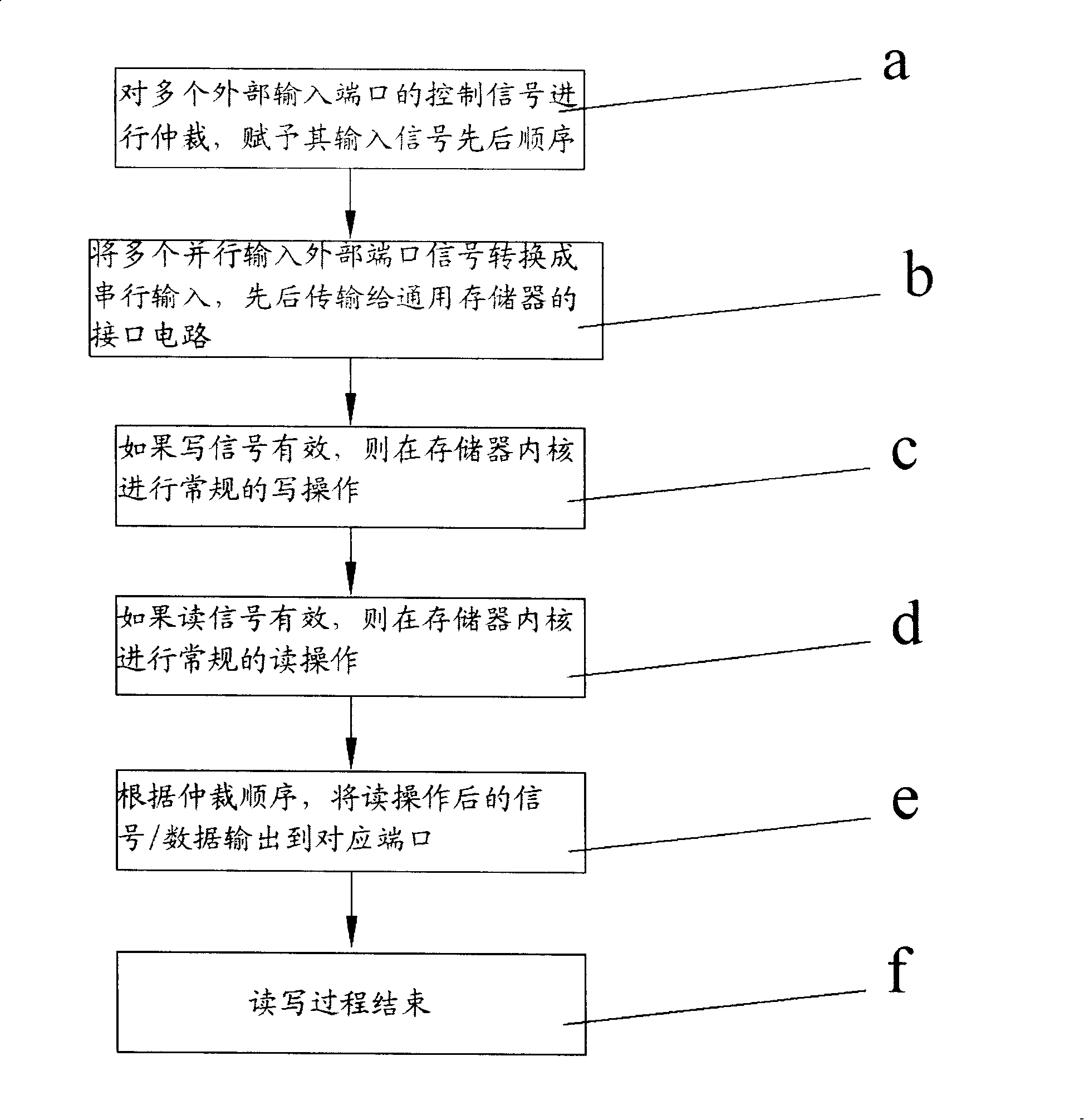

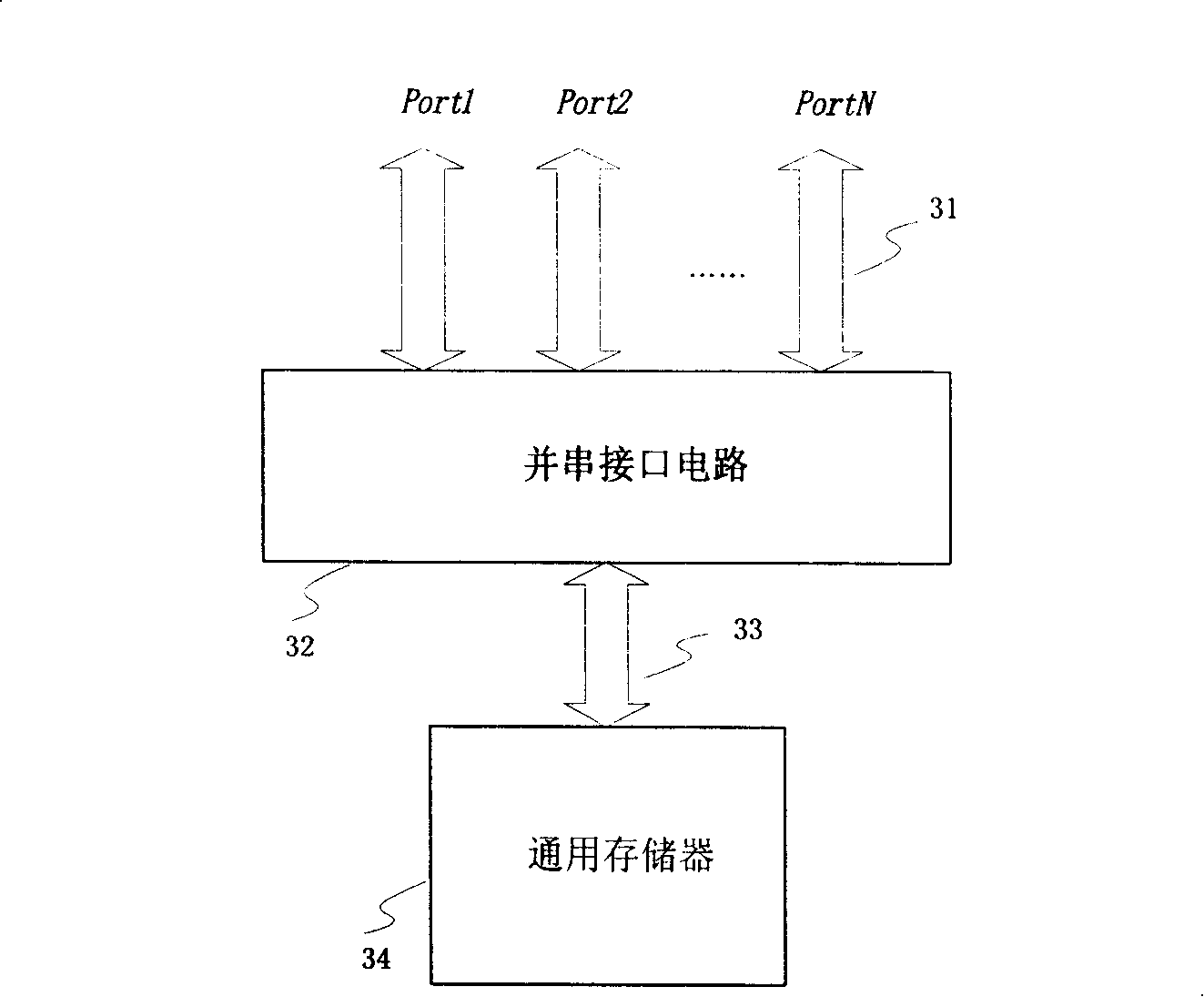

Device and method for single-port memory to realize the multi-port storage function

The invention relates to a device and a method used by a single port storage for realizing a multi-port storage function. The device comprises a general storage and also comprises at least two external access ports, a parallel serial interface circuit and an internal storage unit access port, wherein each port at least comprises a data terminal, an address terminal, a chip selection terminal and a control terminal to realize the input and output of the data; the parallel serial interface circuit is connected with an external access port to complete the parallel serial conversion of the external data and arbitrate the control signals of the external ports; the general storage is connected with the parallel serial interface circuit together by the internal storage unit access port; according to the processing of the parallel serial interface circuit, the data is written into the general storage or the data is read from the general storage, thereby realizing the multiport storage via the single port storage, saving the storage area, improving the storage performance and reducing the cost.

Owner:GIGADEVICE SEMICON (BEIJING) INC

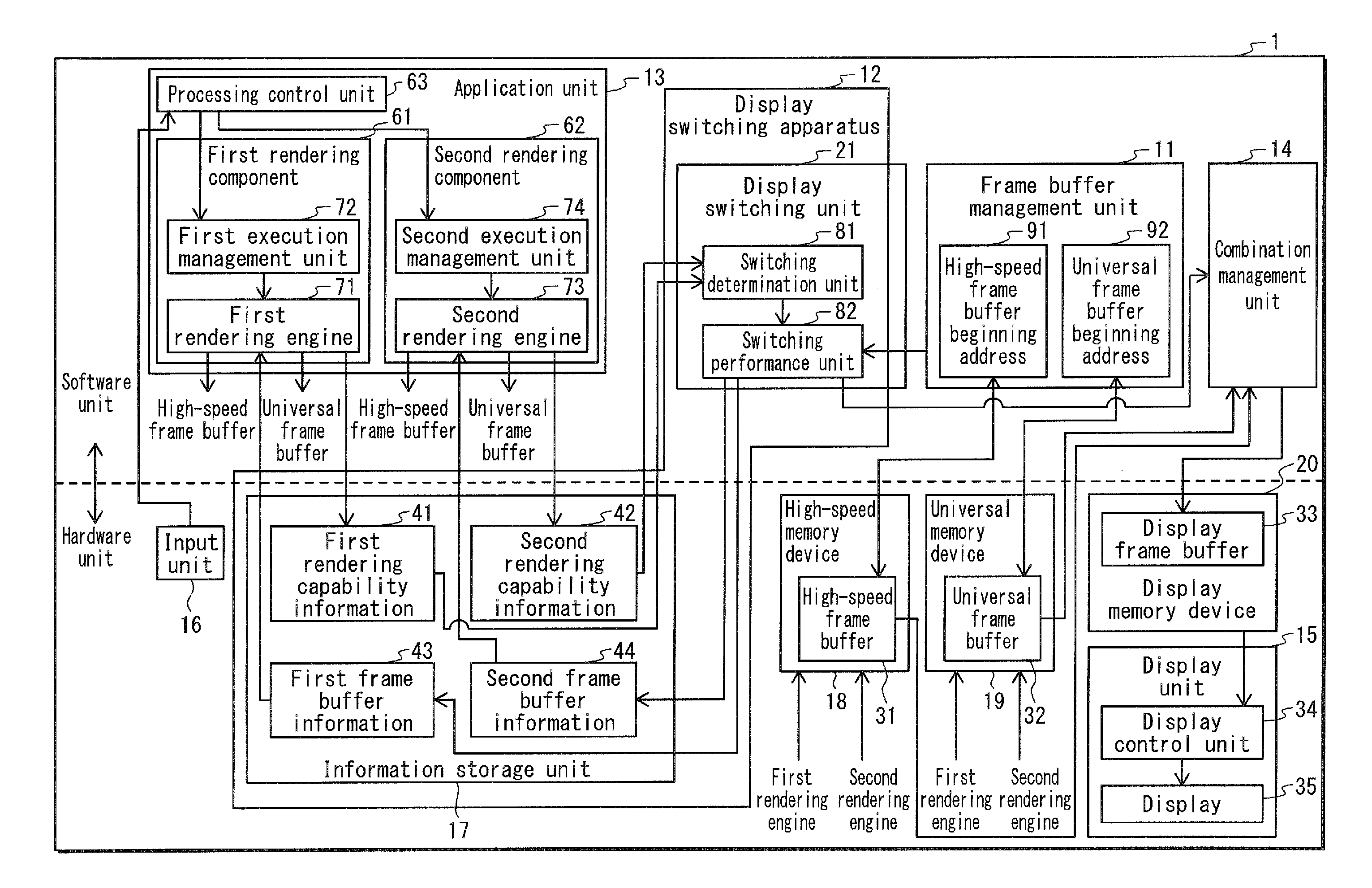

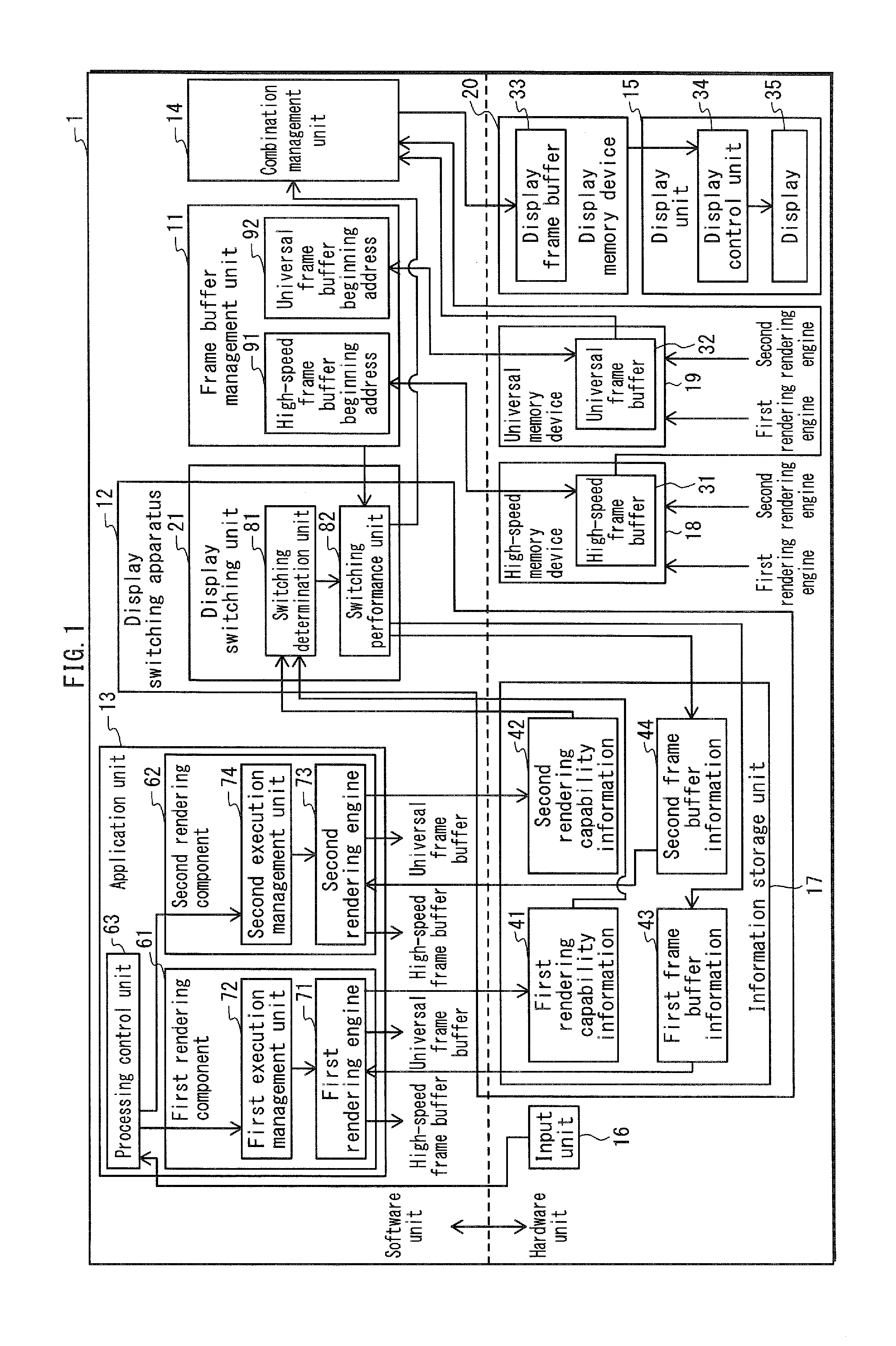

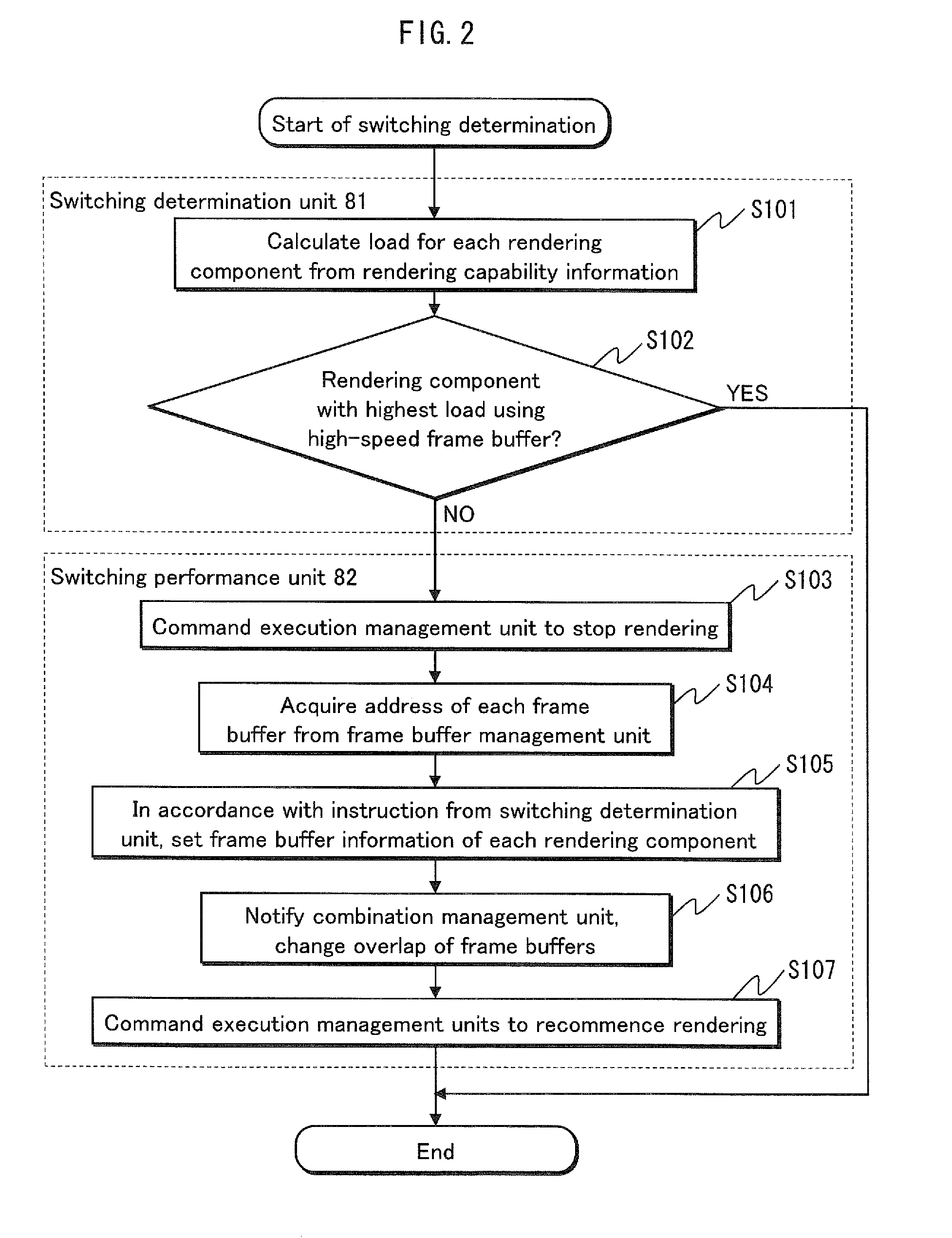

Display switching device

InactiveUS20120062573A1Reduce decreaseProcessing timeDigital computer detailsImage memory managementInformation processingManagement unit

Provided is a display switching apparatus that reduces delayed display, and the like, of frame images. An information processing terminal 1 is provided with a first rendering component 61 that, in each first time interval, generates and writes an image to a buffer, a second rendering component 62 that, in each second time interval, generates and writes an image to a buffer, a frame buffer management unit 11 that allocates a high-speed frame buffer 31 on a high-speed memory device 18 and a universal frame buffer 32 on a universal memory device 19, and a display switching apparatus 12 that includes a switching determination unit 81 that repeatedly calculates a rendering load for each rendering component and a switching performance unit 82 that switches the buffers allocated to the rendering components when the high-speed frame buffer 31 is not allocated to the rendering component with the higher rendering load.

Owner:PANASONIC INTELLECTUAL PROPERTY CORP OF AMERICA

Short-circuit preventive universal memory card connector

A memory card connector having an electrically insulative casing covered with a top cover to house first pins at the front side for the contact of a XD memory card, second pins at the rear side for the contact of a MS memory card, and third pins on the middle for the contact of other memory cards. The casing has an elongated slot in the bottom wall, and a spring arm with a protruding block suspending in the elongated slot to hold the power pin of the first pins, for enabling the power pin to be lowered with the spring arm into the elongated slot to prevent the occurrence of a short circuit accidentally upon insertion of a memory card that is not a XD memory card.

Owner:CHANT SINCERE

Solid state drive memory device comprising secure erase function

InactiveUS9111621B2Memory architecture accessing/allocationRead-only memoriesProcessor elementSolid-state drive

A memory device such as a solid state memory device have a dual-hardware, secure erase feature. A memory controller operating in a memory controller domain provides general memory management and interface operons. Upon receipt of a trigger signal which may be received from a secure supervisor circuit, a separate processor element that is configured to directly access the raw memory cells in the device bypasses the memory controller domain and executes a separately provided secure erase operating system whereby the raw cell data may be erased and rewritten with a predetermined data pattern and whereby the erase operation at the raw cell level may be verified and reported to the user by the processor.

Owner:IRVINE SENSORS

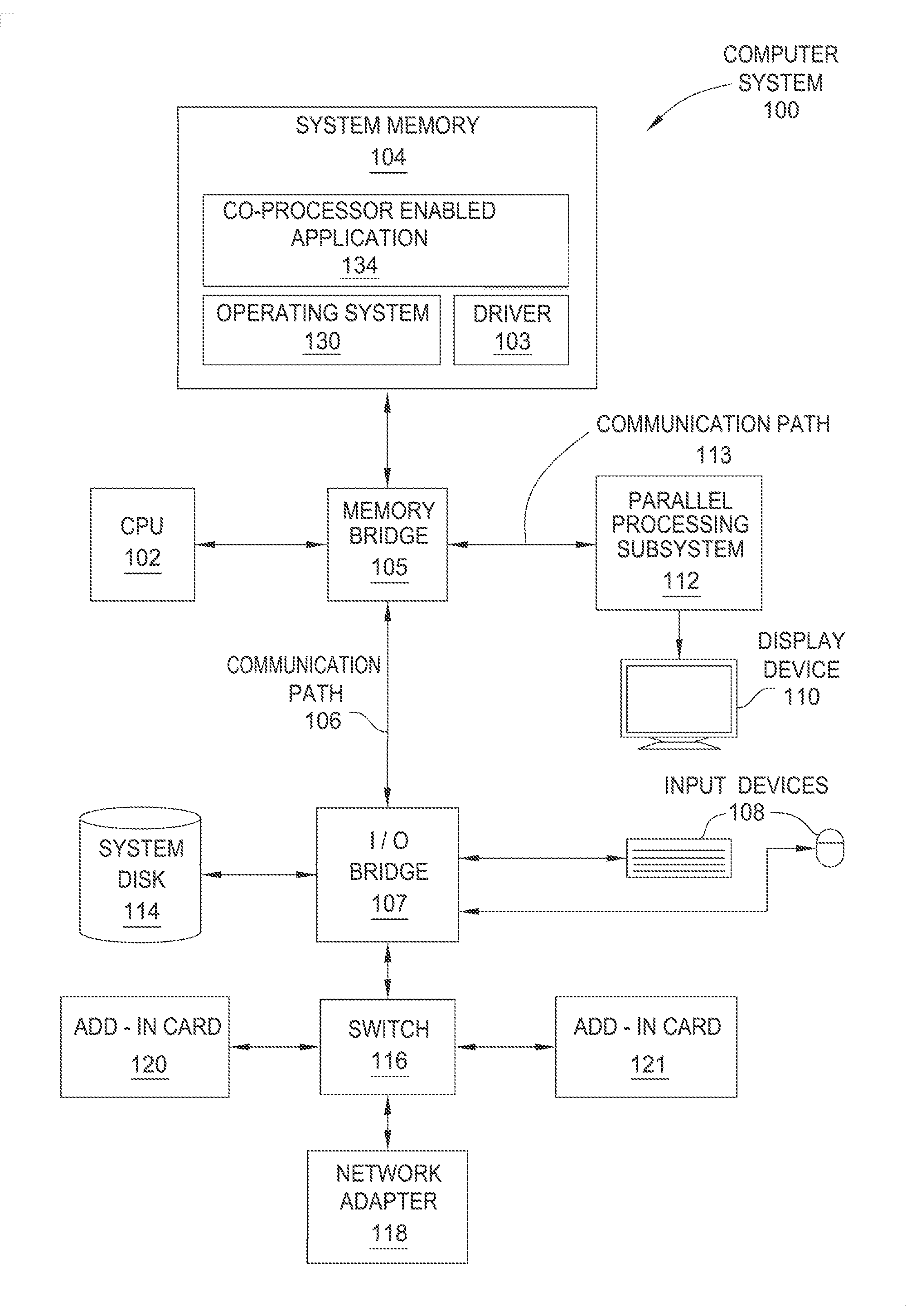

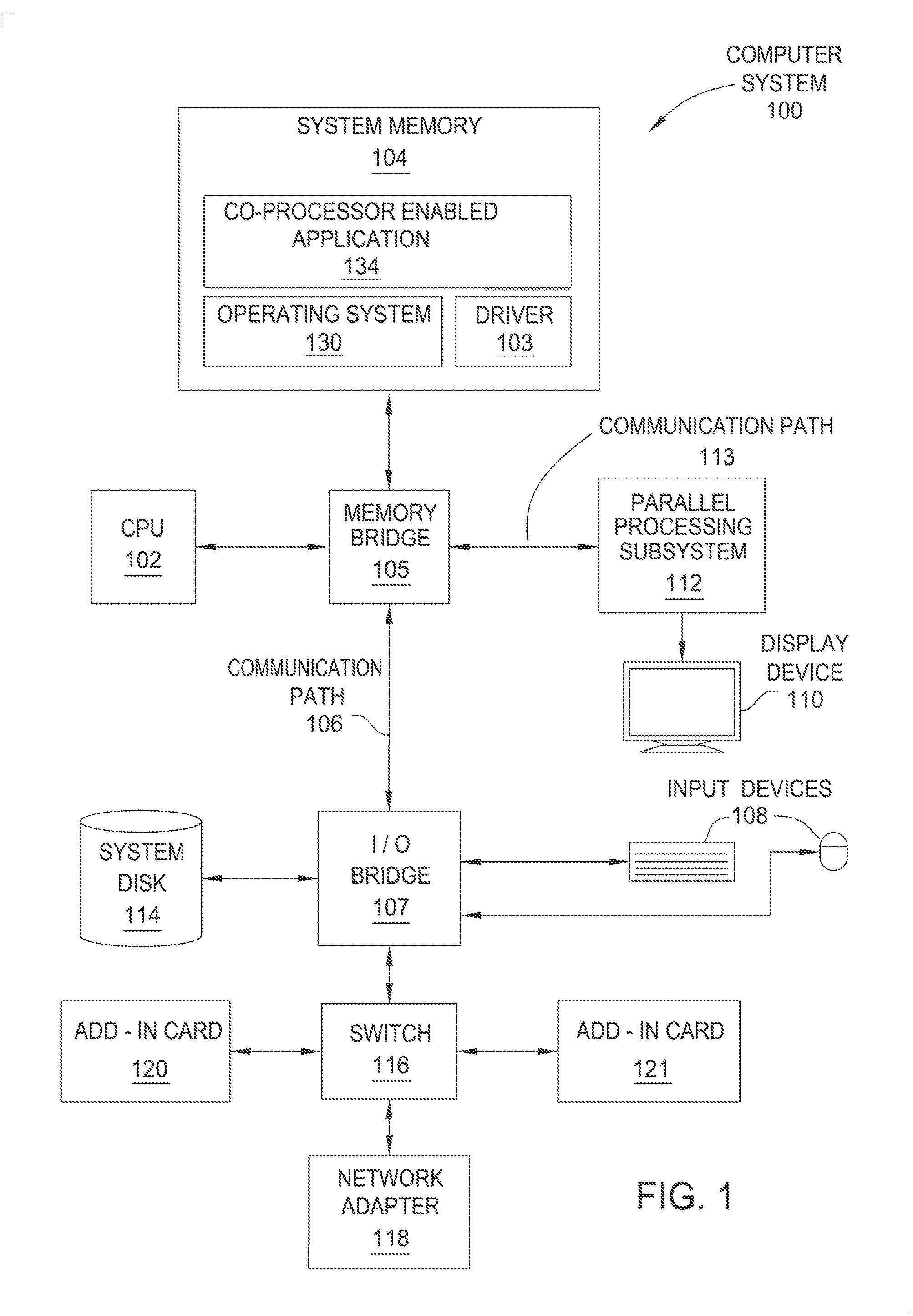

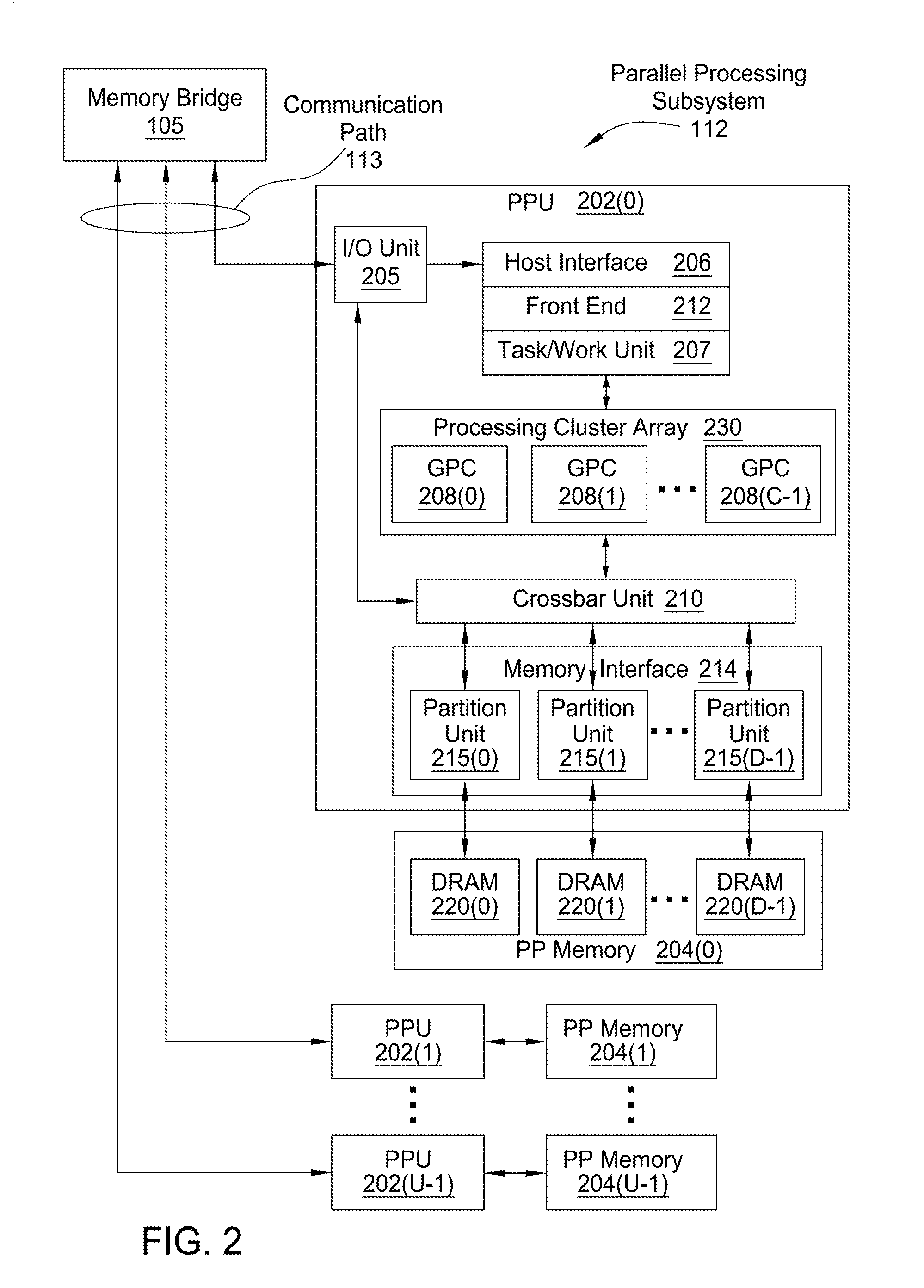

Technique for inter-procedural memory address space optimization in GPU computing compiler

InactiveUS20130113809A1Improve executionSave resourcesProgram controlArchitecture with multiple processing unitsParallel computingProcedural memory

A device compiler and linker is configured to optimize program code of a co-processor enabled application by resolving generic memory access operations within that program code to target specific memory spaces. In situations where a generic memory access operation cannot be resolved and may target constant memory, constant variables associated with those generic memory access operations are transferred to reside in global memory.

Owner:NVIDIA CORP

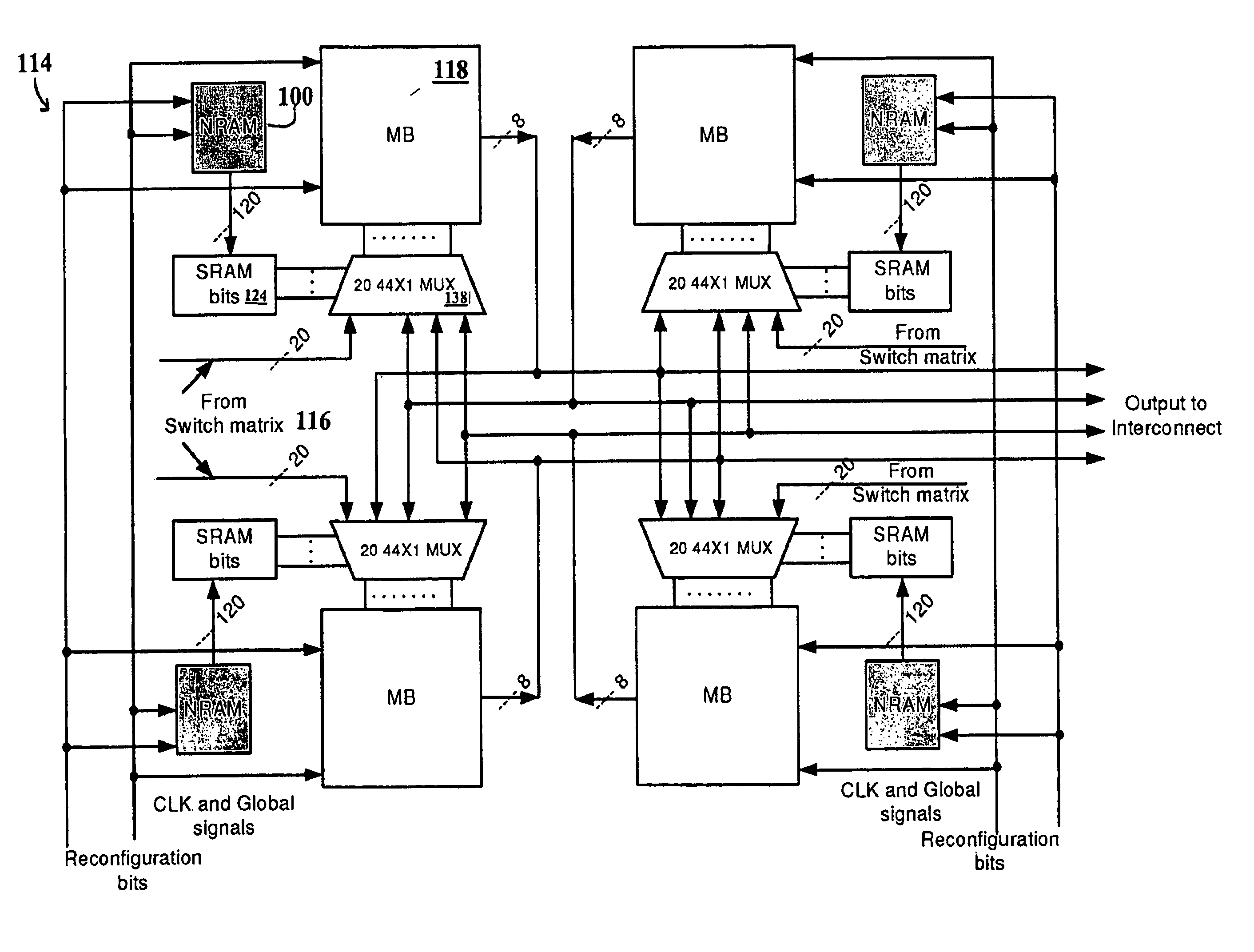

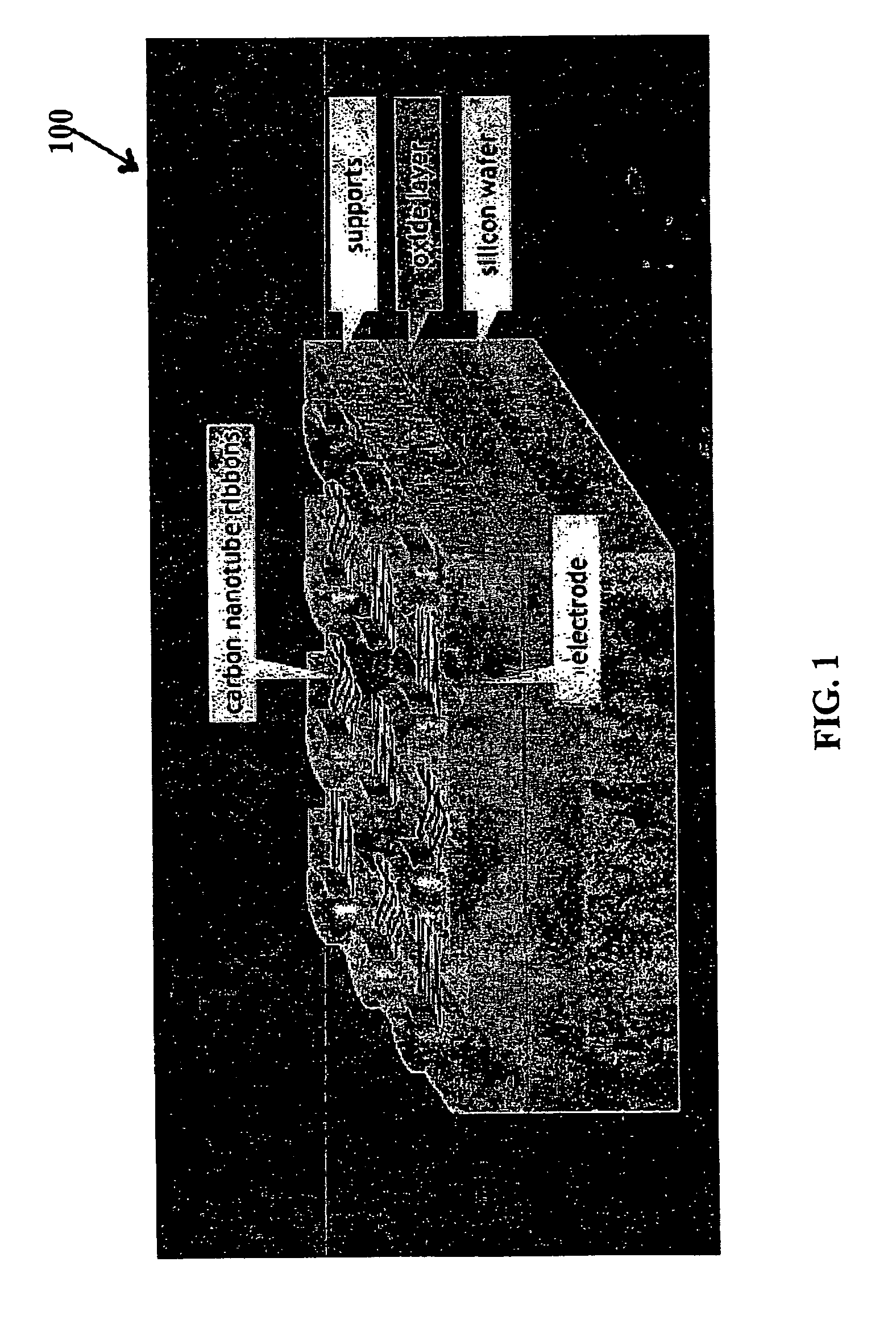

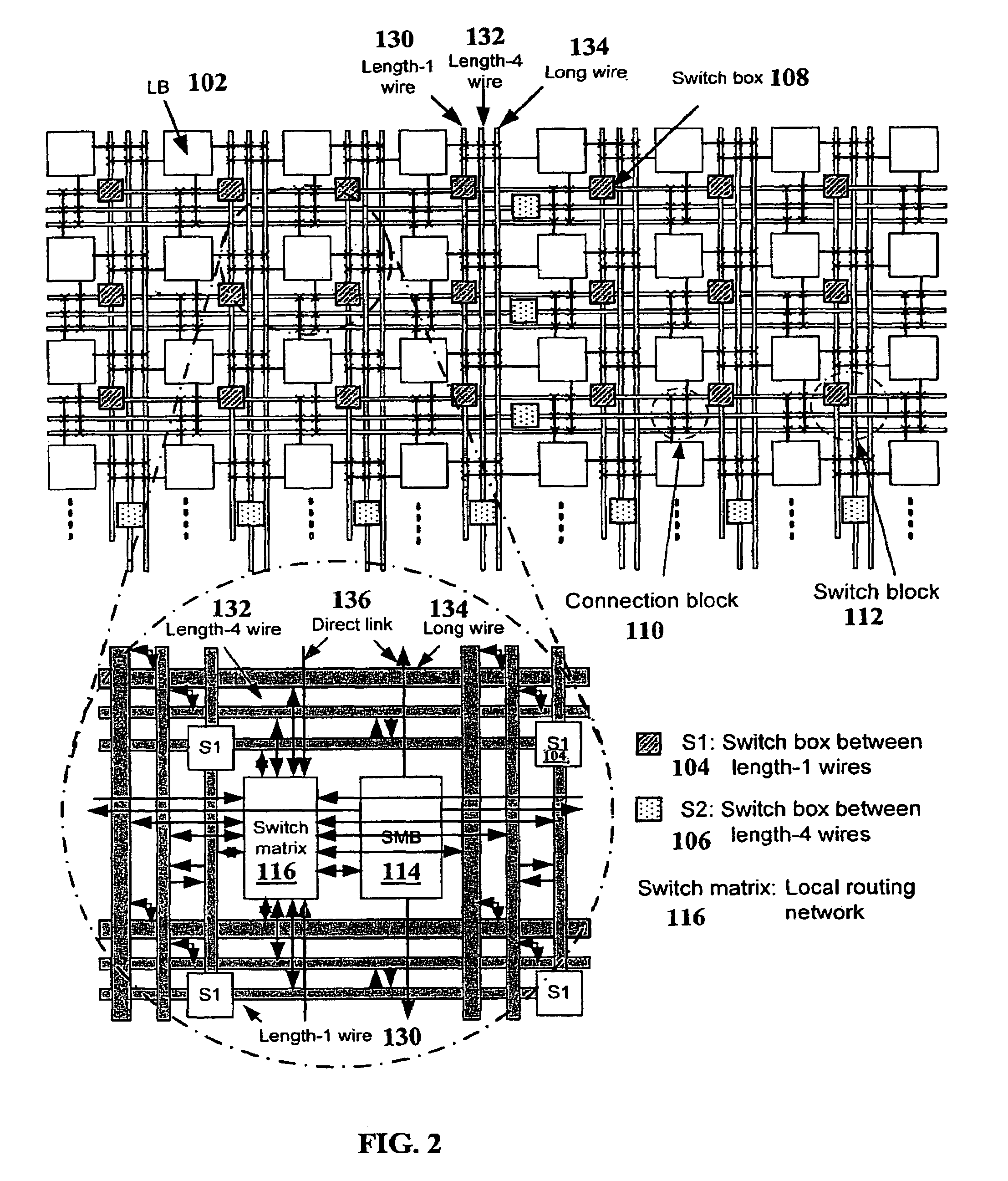

Hybrid nanotube/CMOS dynamically reconfigurable architecture and an integrated design optimization method and system therefor

InactiveUS8117436B2EfficiencyLong latencySolid-state devicesDigital computer detailsLinear temporal logicEngineering

A hybrid nanotube, high-performance, dynamically reconfigurable architecture, NATURE, is provided, and a design optimization flow method and system, NanoMap. A run-time reconfigurable architecture is provided by associating a non-volatile universal memory to each logic element to enable cycle-by-cycle reconfiguration and logic folding, while remaining CMOS compatible. Through logic folding, significant logic density improvement and flexibility in performing area-delay tradeoffs are possible. NanoMap incorporates temporal logic folding during the logic mapping, temporal clustering and placement steps. NanoMap provides for automatic selection of a best folding level, and uses force-direct scheduling to balance resources across folding stages. Mapping can thereby target various optimization objectives and user constraints. A high-density, high-speed carbon nanotube RAM can be implemented as the universal memory, allowing on-chip multi-context configuration storage, enabling fine-grain temporal logic folding, and providing a significant increase in relative logic density.

Owner:QUEENS UNIV OF KINGSTON +1

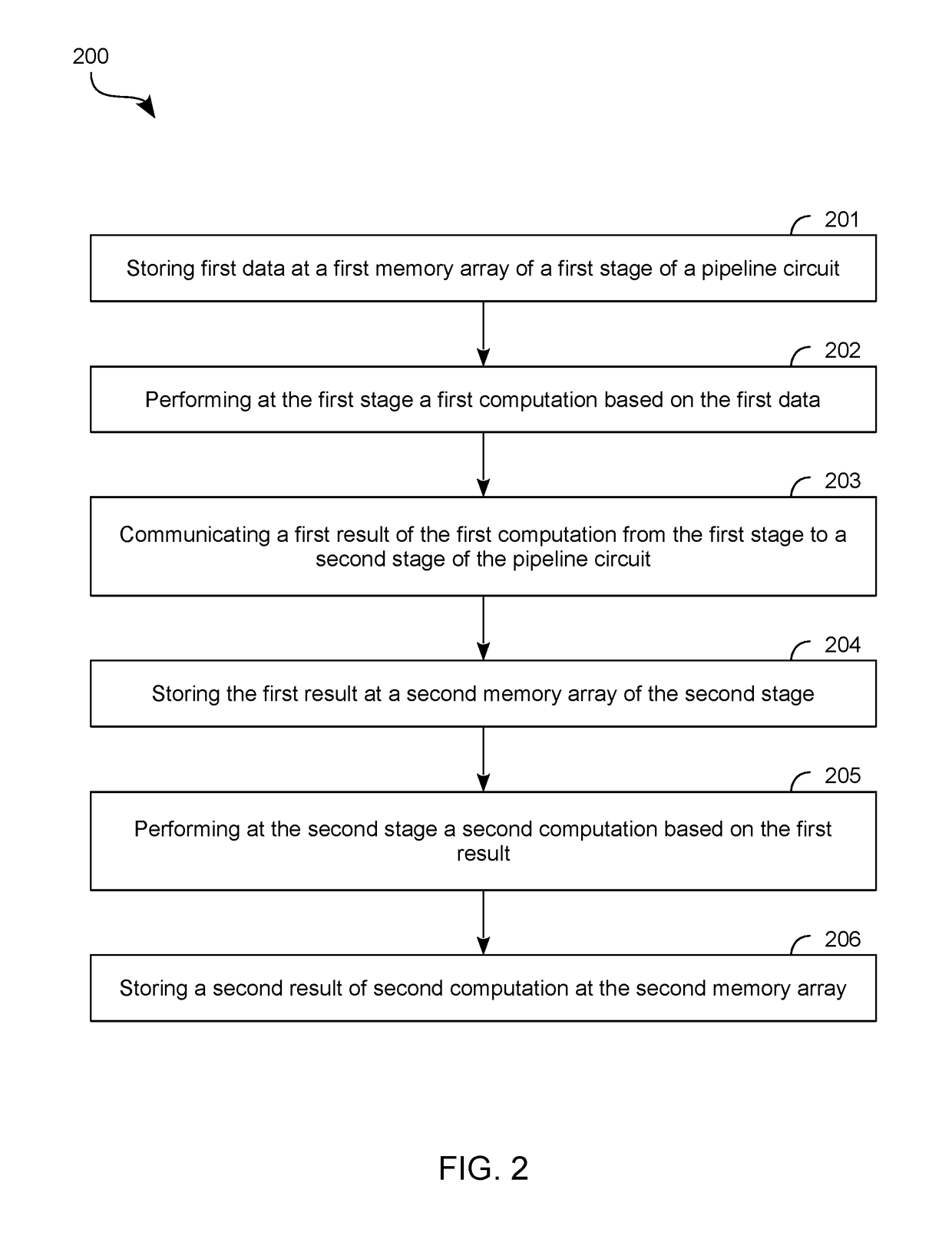

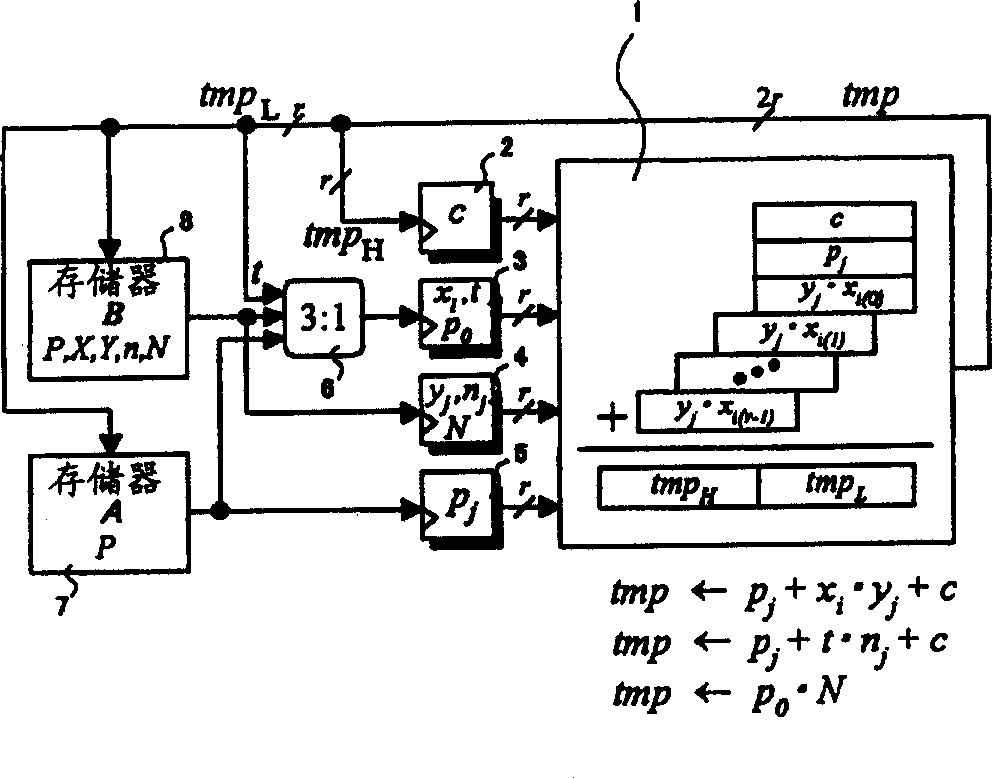

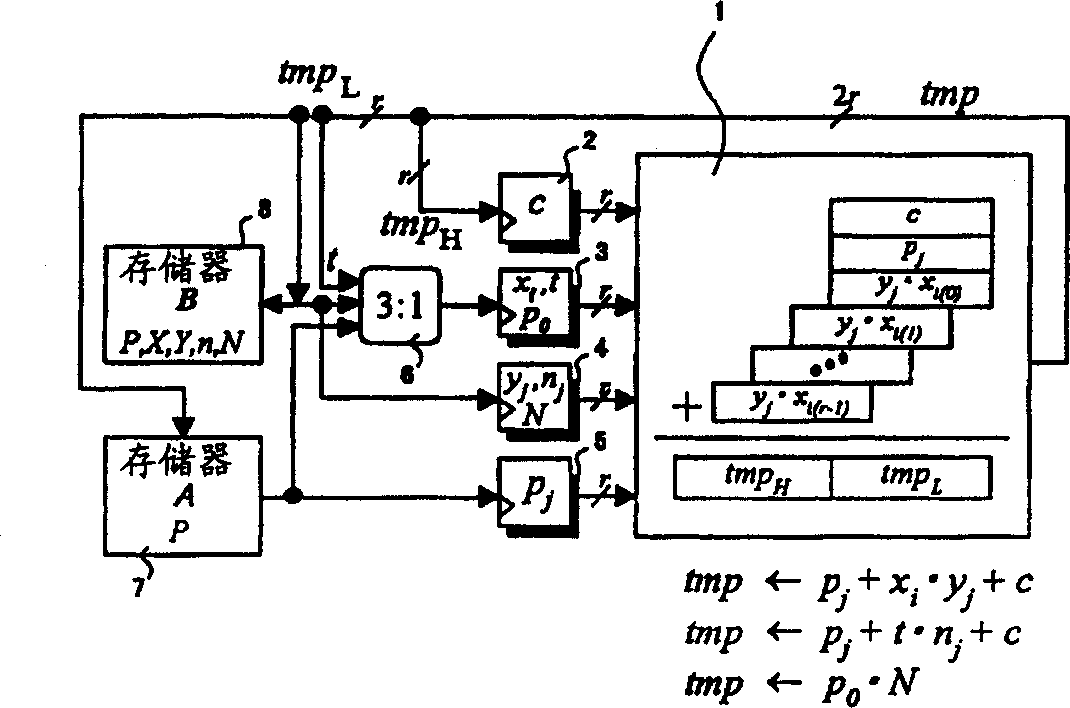

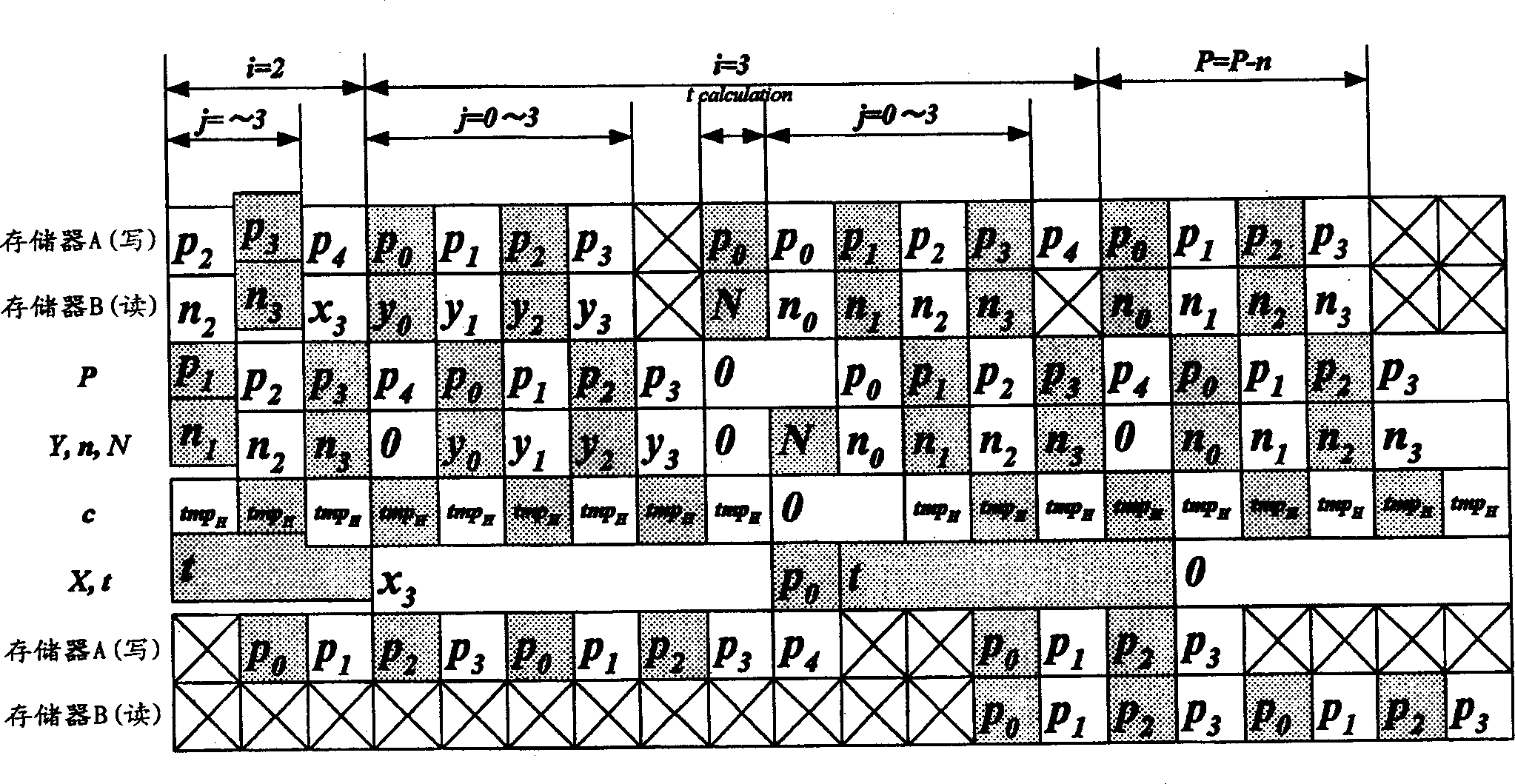

Operation circuit and operation method

InactiveCN1366234ASmall sizeLow costComputations using contact-making devicesMemory adressing/allocation/relocationGeneral purposeProcessor register

The present invention attempts to resolve a Montgomery multiplier bottleneck problem encountered during memory access, by using general-purpose memories having two ports or single port. Two memories 7 and 8 are provided, so that variables that are stored in memory and must be read for an operation can be recorded in different memories. Thereafter, during a reading stage corresponding to a pipeline process, certain of the variables are read from the memory 7 and are loaded in the register 5, while the other variables are read from the memory 8 and are loaded in the other registers.

Owner:IBM CORP