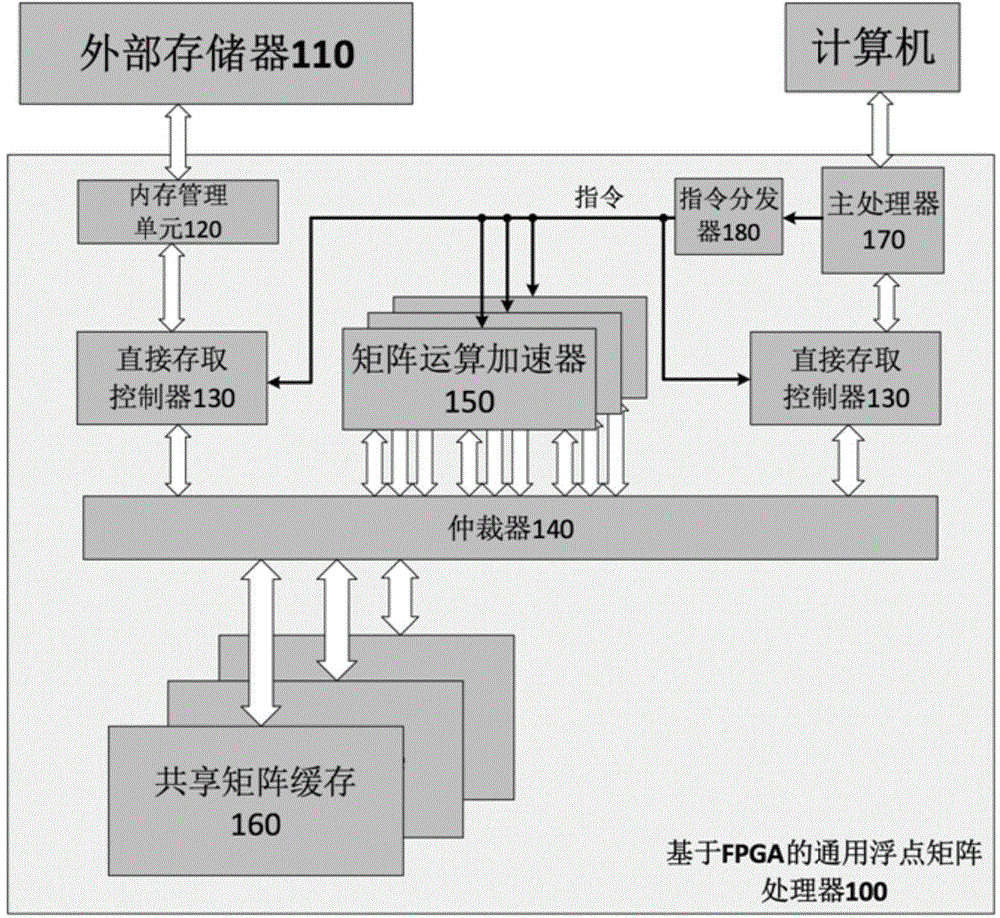

Universal floating point matrix processor hardware structure based on FPGA (field programmable gate array)

A hardware structure and floating-point matrix technology, applied in the architecture with a single central processing unit, general-purpose stored program computer, climate sustainability, etc., can solve the problems of waste of computing resources, increase the workload of the main processor, etc., to achieve The effect of high computing performance, high design flexibility, and low energy consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

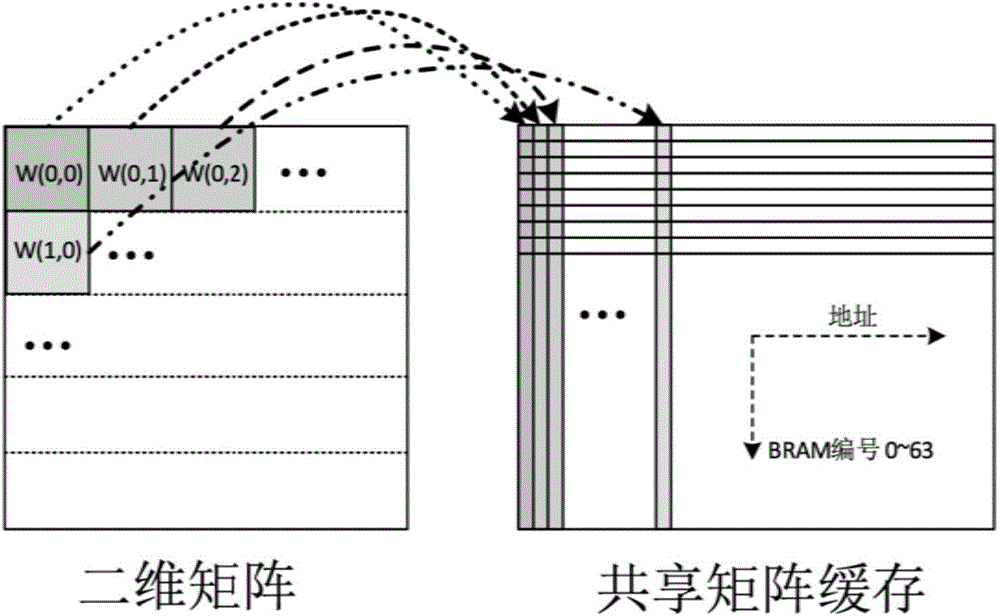

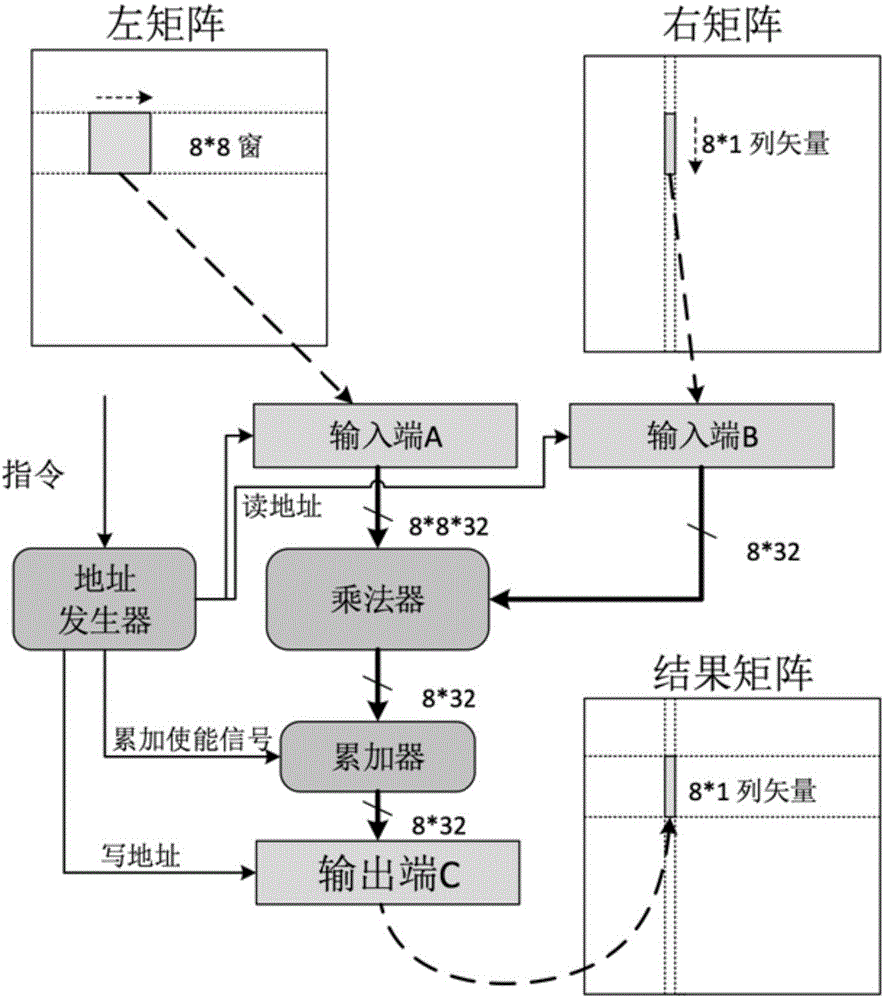

[0032] Embodiments of the present invention are described in detail below, examples of which are shown in the drawings, wherein the same or similar reference numerals designate the same or similar elements or elements having the same or similar functions throughout. The embodiments described below by referring to the figures are exemplary and are intended to explain the present invention and should not be construed as limiting the present invention.

[0033] In addition, the terms "first" and "second" are used for descriptive purposes only, and cannot be interpreted as indicating or implying relative importance or implicitly specifying the quantity of indicated technical features. Thus, a feature defined as "first" and "second" may explicitly or implicitly include one or more of these features. In the description of the present invention, "plurality" means two or more, unless otherwise specifically defined.

[0034] In the present invention, unless otherwise clearly specified...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More