Patents

Literature

1644 results about "Gate array" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A gate array is an approach to the design and manufacture of application-specific integrated circuits (ASICs) using a prefabricated chip with components that are later interconnected into logic devices (e.g. NAND gates, flip-flops,etc.) according to a custom order by adding metal interconnect layers in the factory.

System and method for high speed packet transmission implementing dual transmit and receive pipelines

InactiveUS6901072B1Multiplex system selection arrangementsCircuit switching systemsGigabitStructure of Management Information

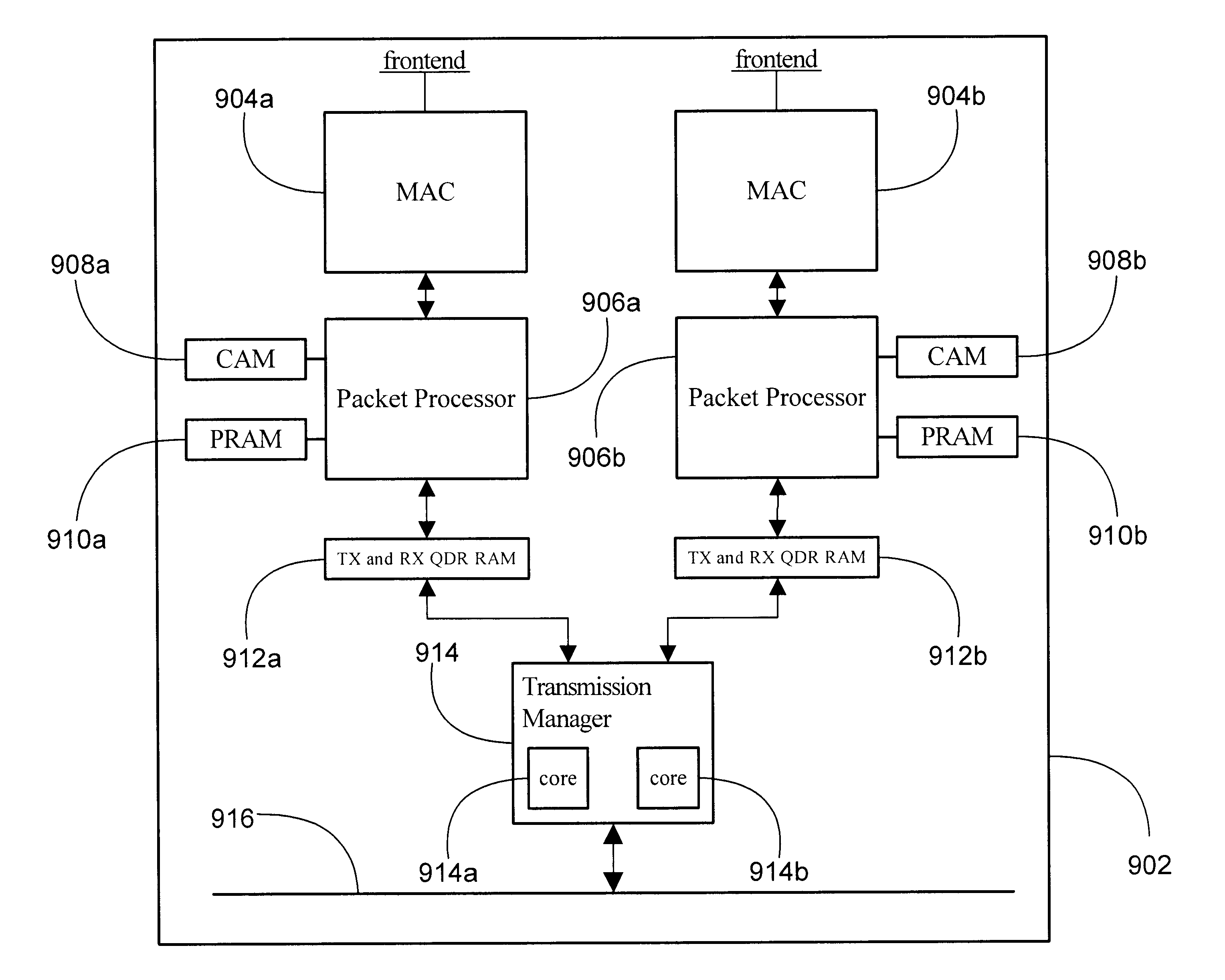

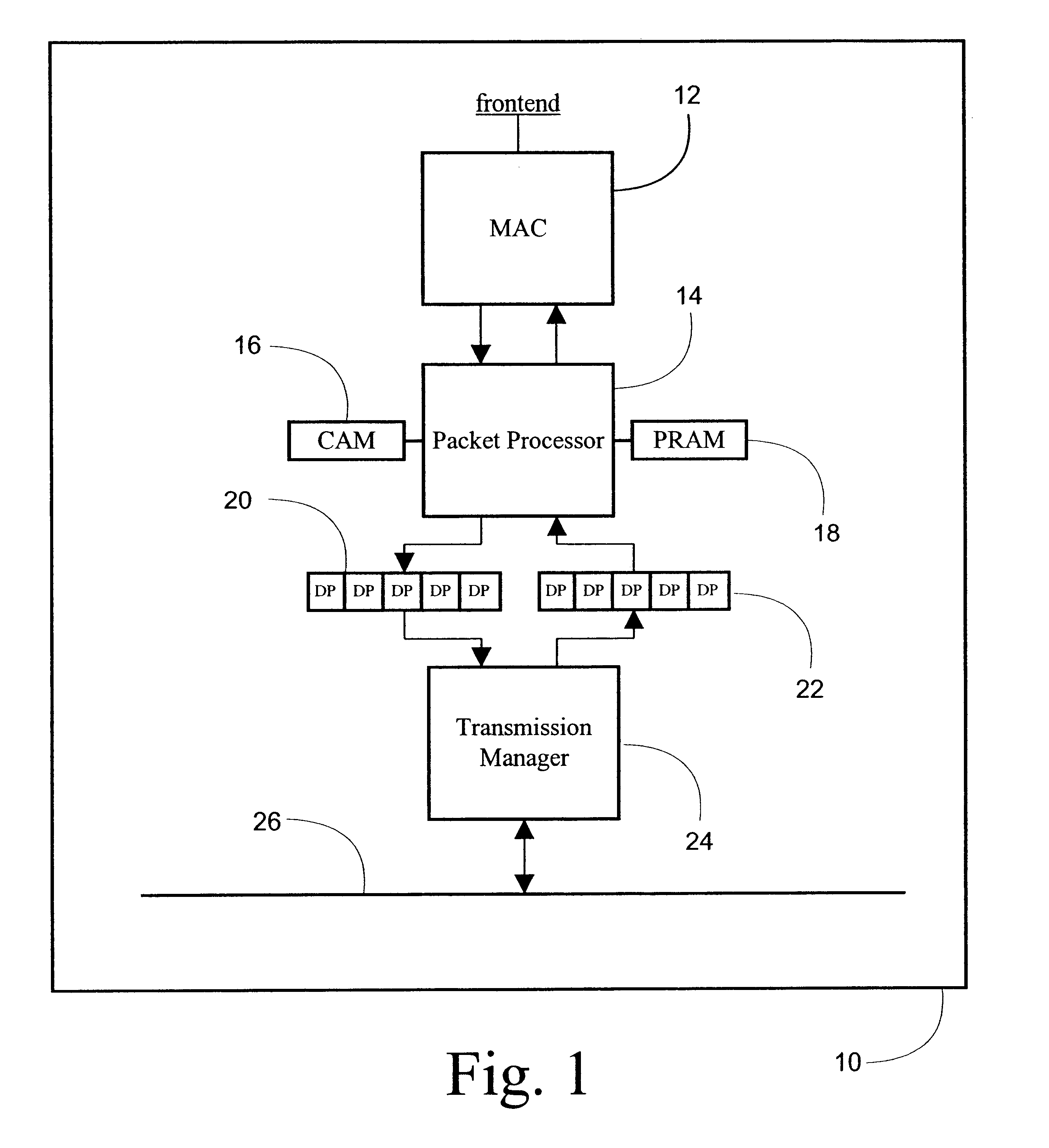

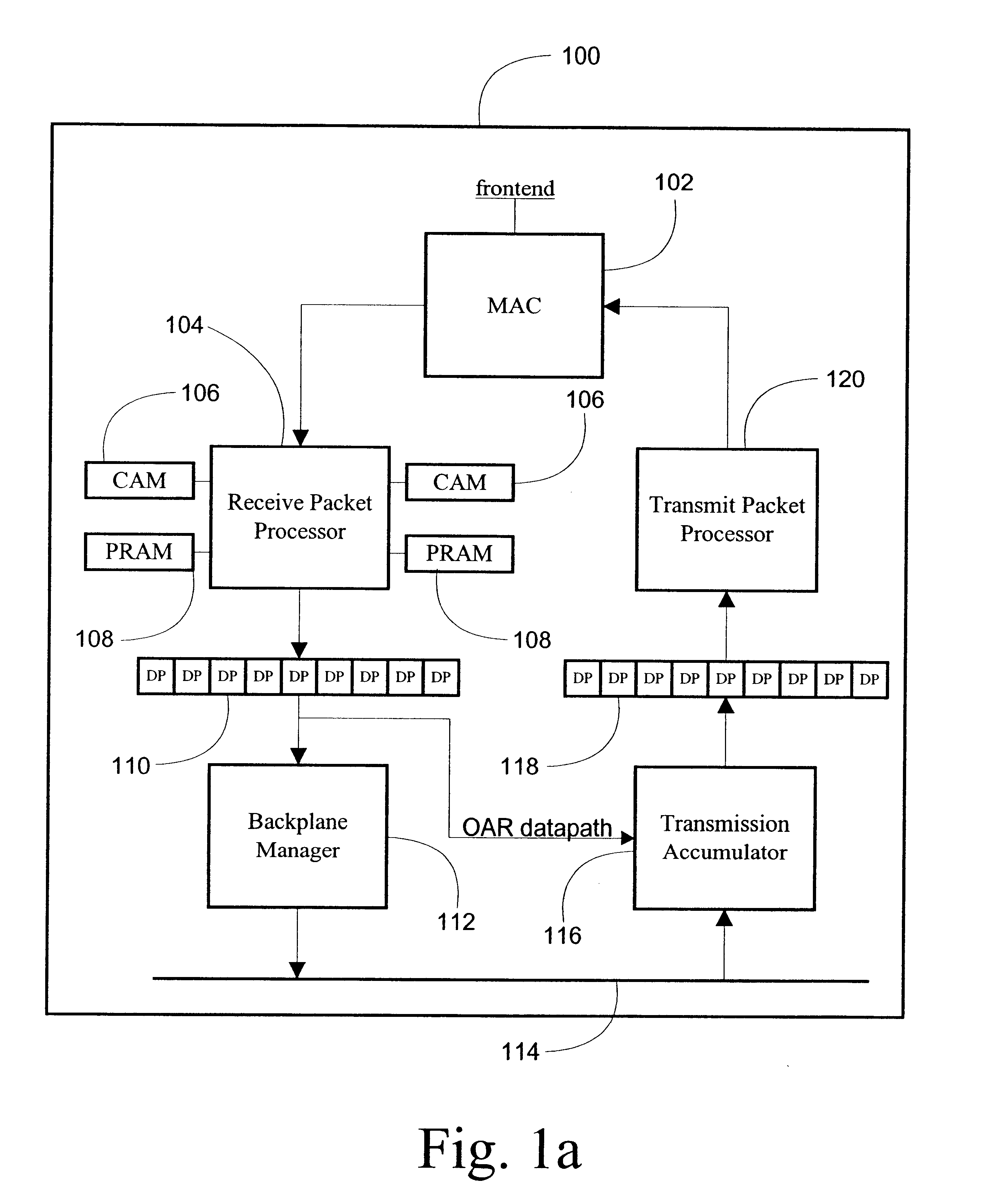

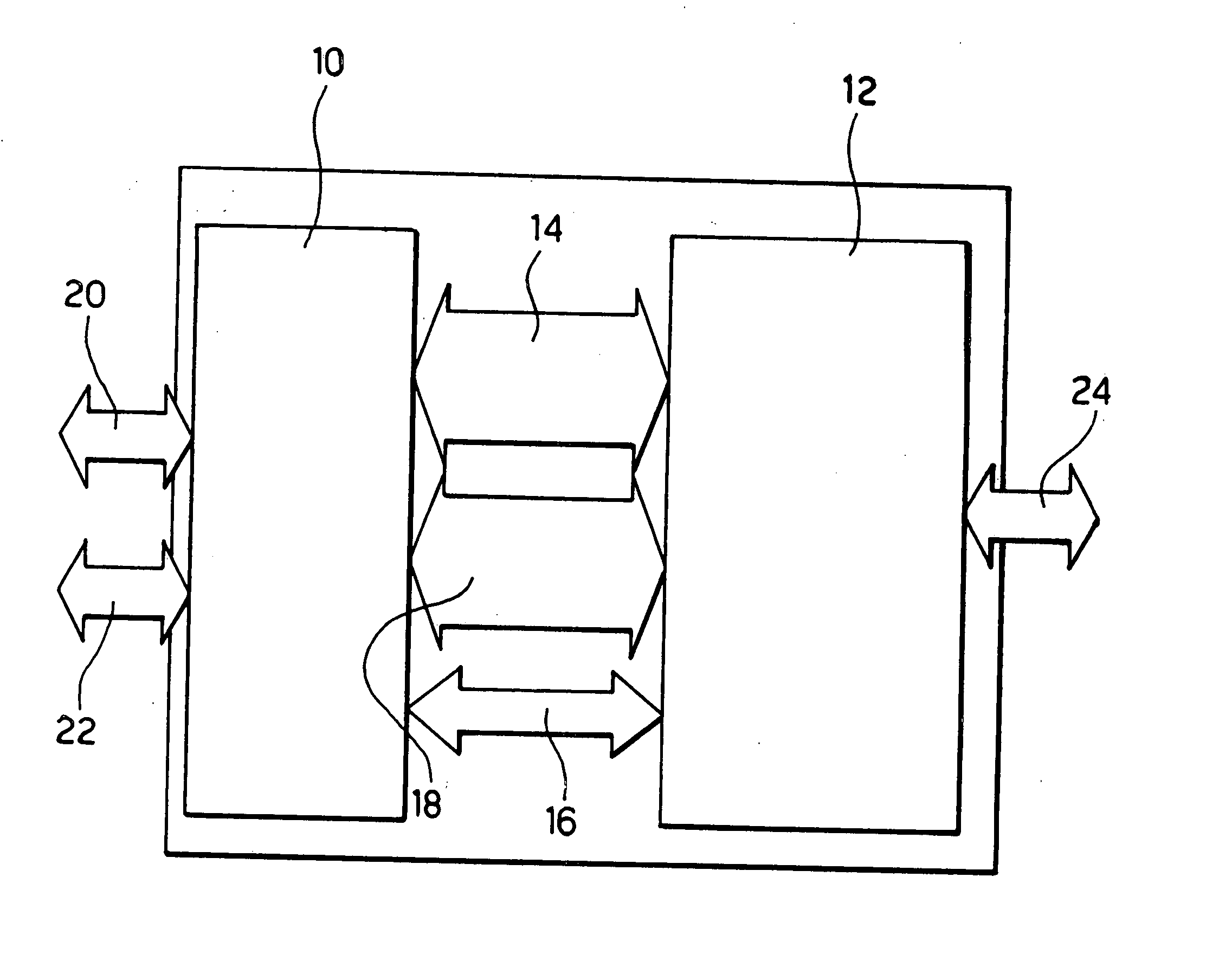

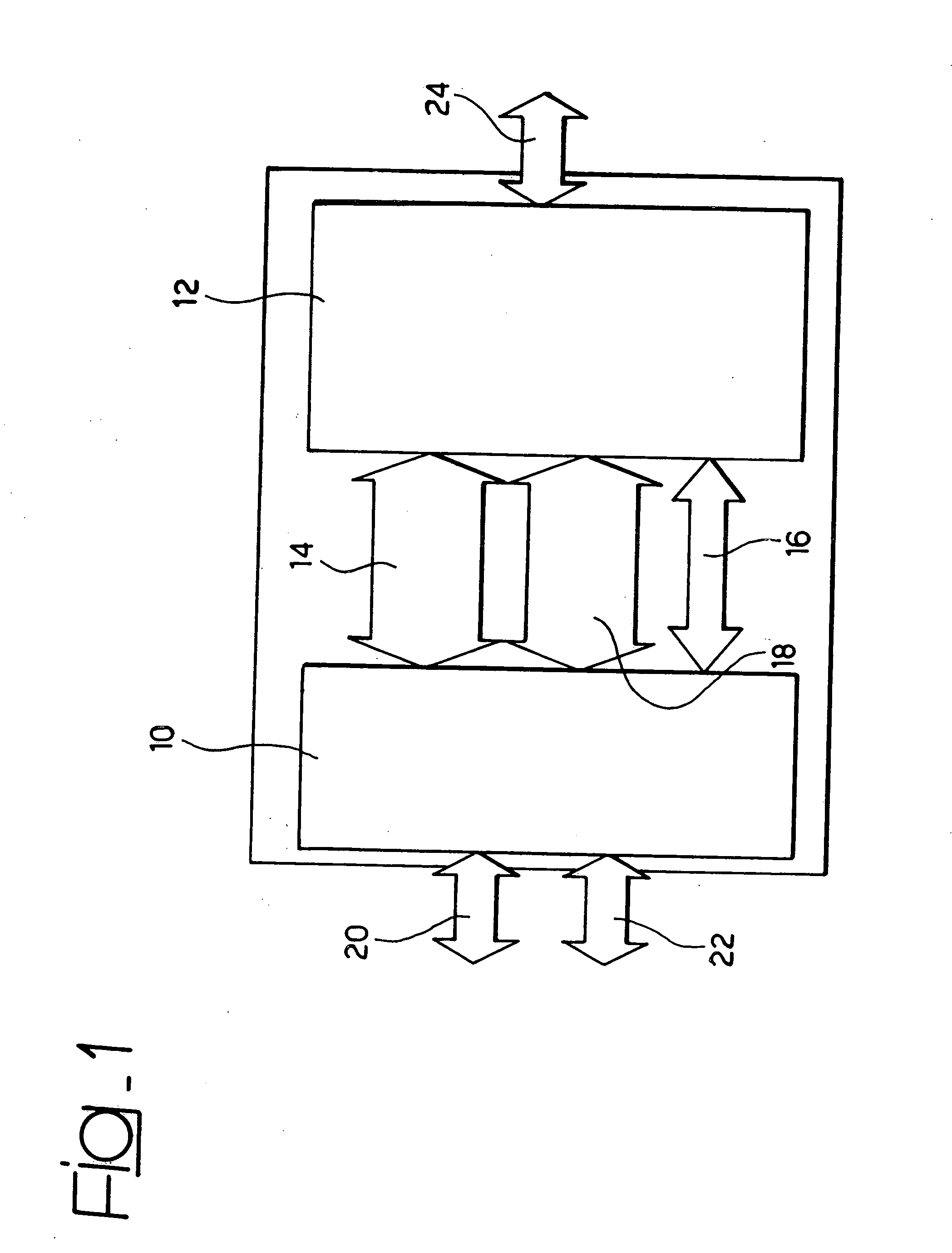

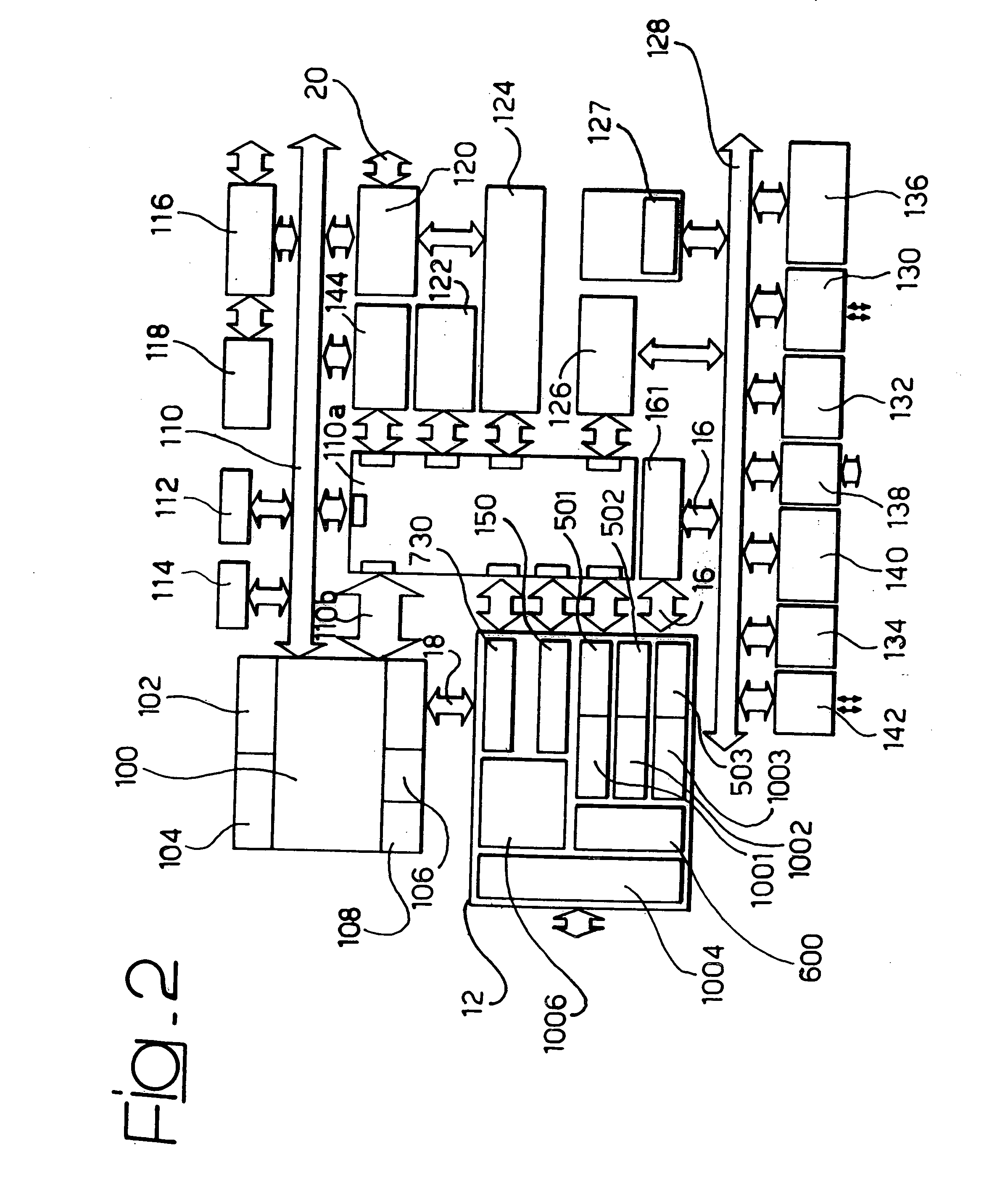

The present invention provides systems and methods for providing data transmission speeds at or in excess of 10 gigabits per second between one or more source devices and one or more destination devices. According to one embodiment, the system of the present invention comprises a first and second media access control (MAC) interfaces to facilitate receipt and transmission of packets over an associated set of physical interfaces. The system also contemplates a first and second field programmable gate arrays (FPGA) coupled to the MAC interfaces and an associated first and second memory structures, the first and second FPGAs are configured to perform initial processing of packets received from the first and second MAC interfaces and to schedule the transmission of packets to the first and second MAC interface for transmission to one or more destination devices. The first and second FPGAs are further operative to dispatch and retrieve packets to and from the first and second memory structures. A third FPGA, coupled to the first and second memory structures and a backplane, is operative to retrieve and dispatch packets to and from the first and second memory structures, compute appropriate destinations for packets and organize packets for transmission. The third FPGA is further operative to receive and dispatch packets to and from the backplane.

Owner:AVAGO TECH INT SALES PTE LTD

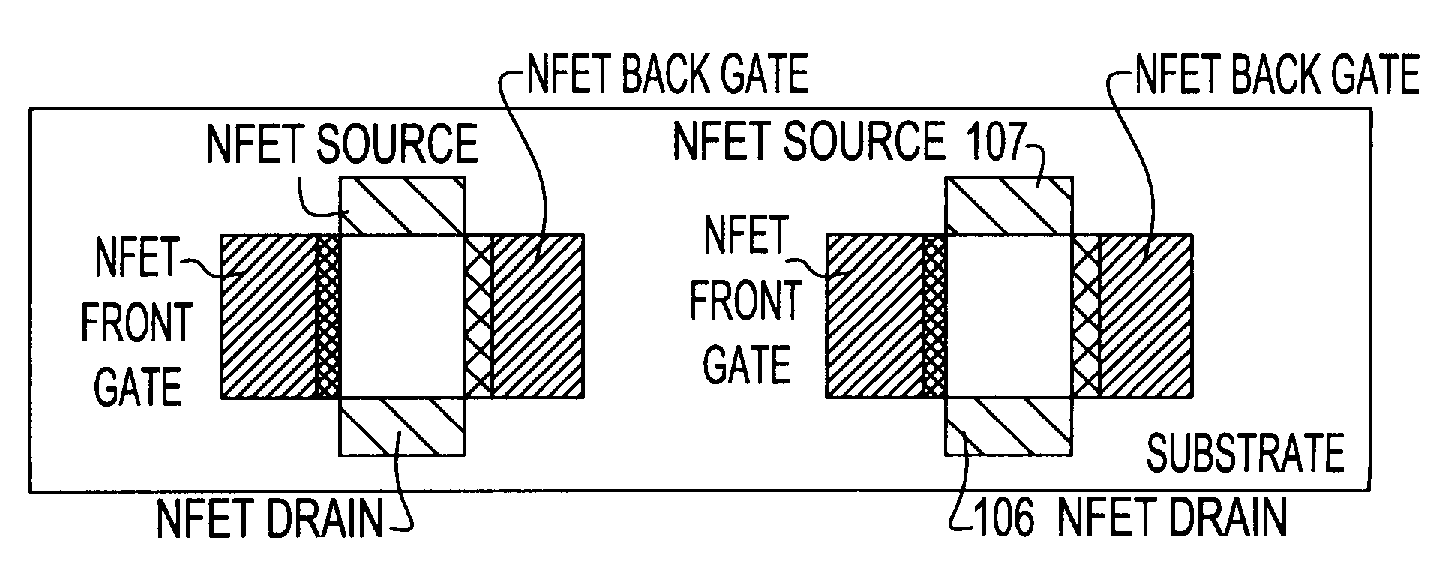

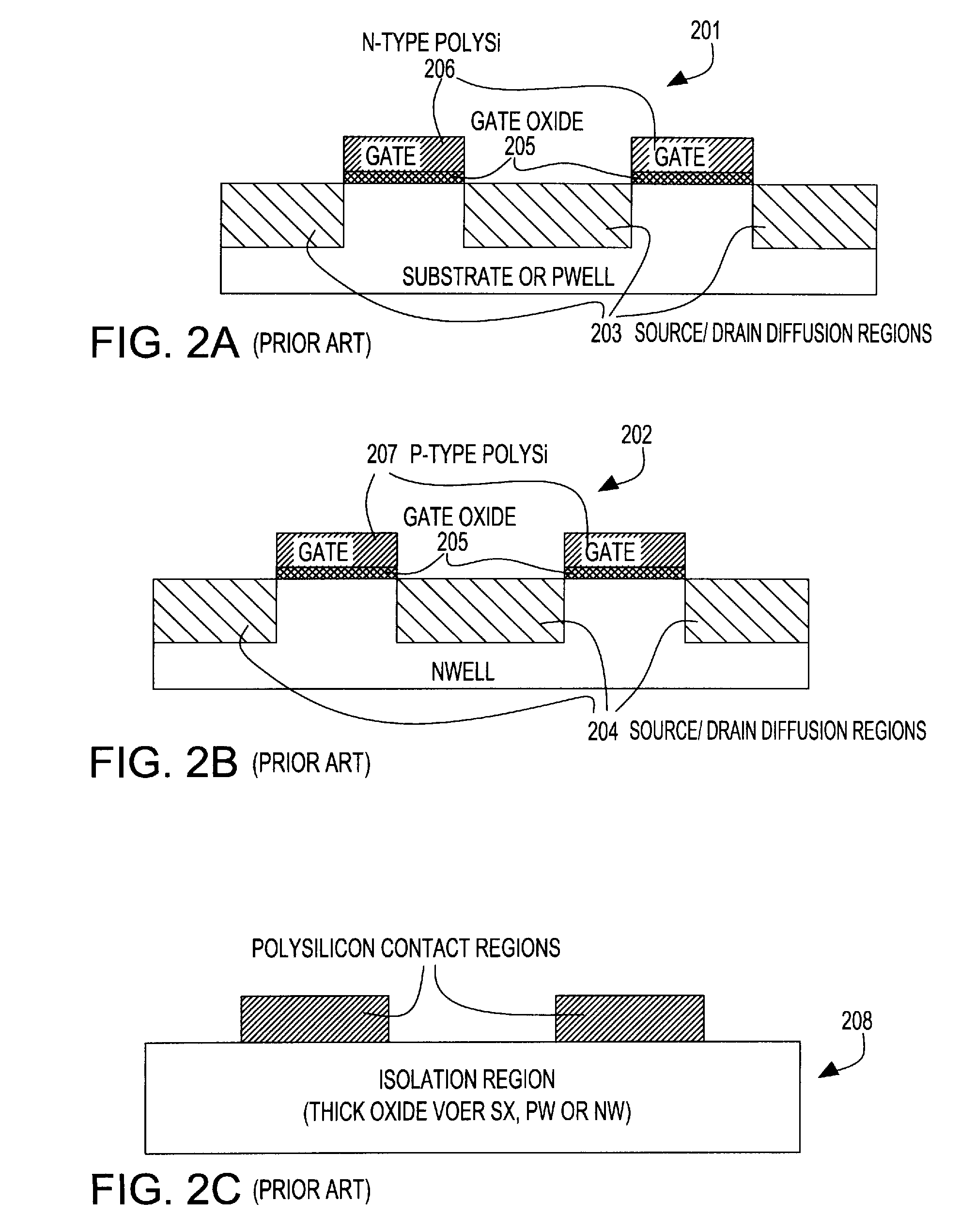

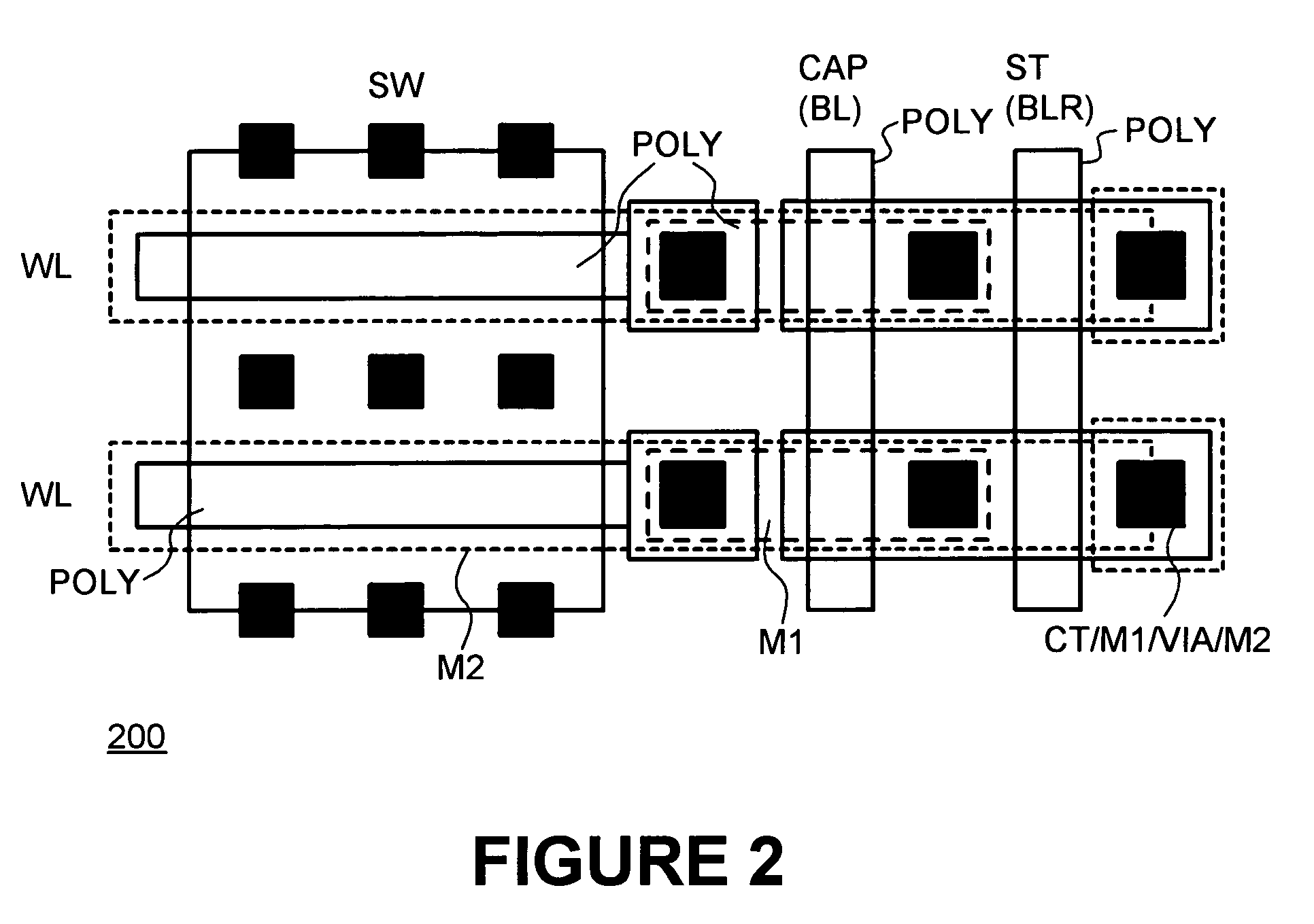

Dual gate fet structures for flexible gate array design methodologies

InactiveUS20090101940A1Easy to operateSolid-state devicesSemiconductor/solid-state device manufacturingGate arrayStandard cell

A gate array cell adapted for standard cell design methodology or programmable gate array that incorporates a dual gate FET device to offer a range of performance options within the same unit cell area. The conductivity and drive strength of the dual gate device may be selectively tuned through independent processing of manufacturing parameters to provide an asymmetric circuit response for the device or a symmetric response as dictated by the circuit application.

Owner:GLOBALFOUNDRIES INC

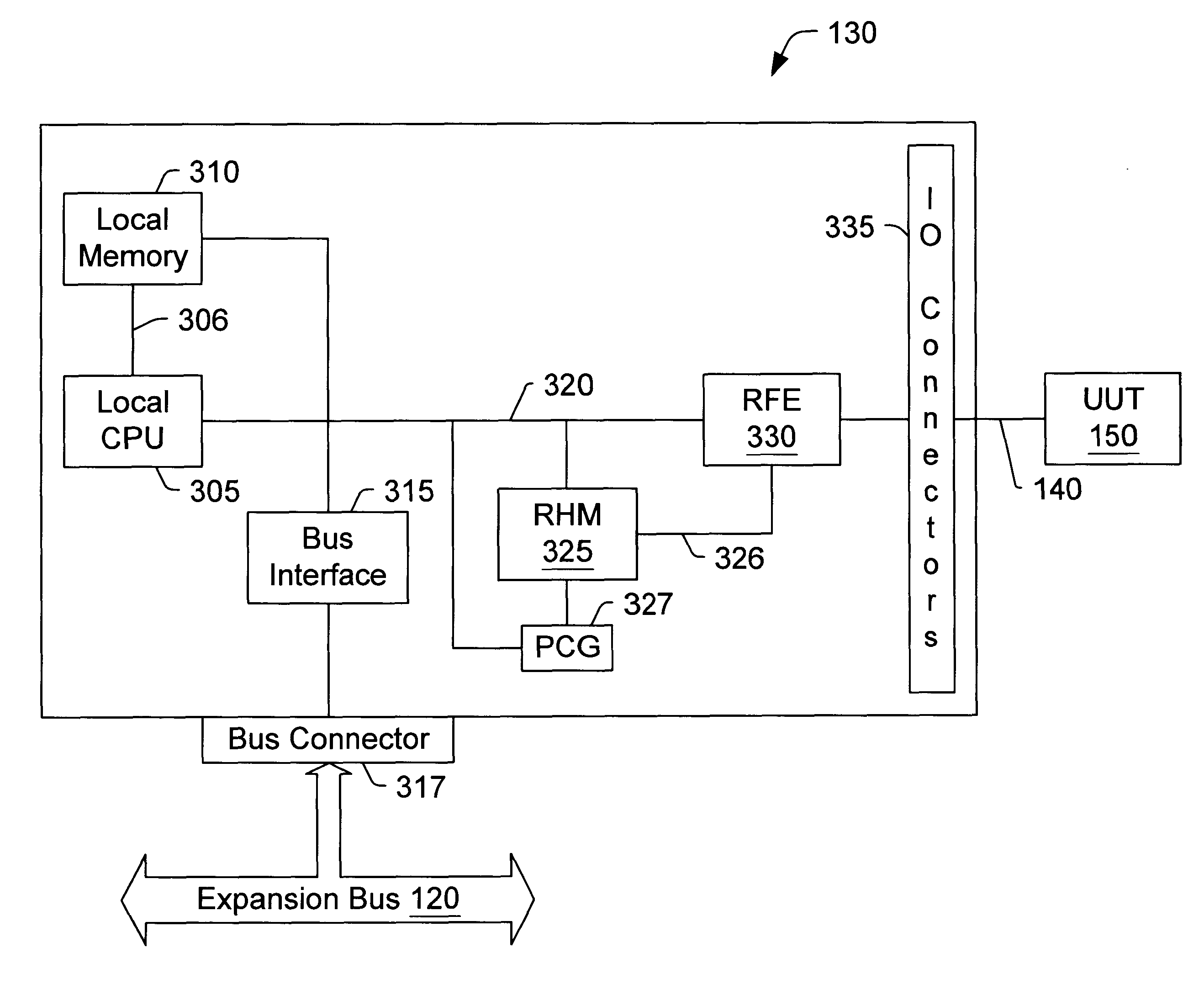

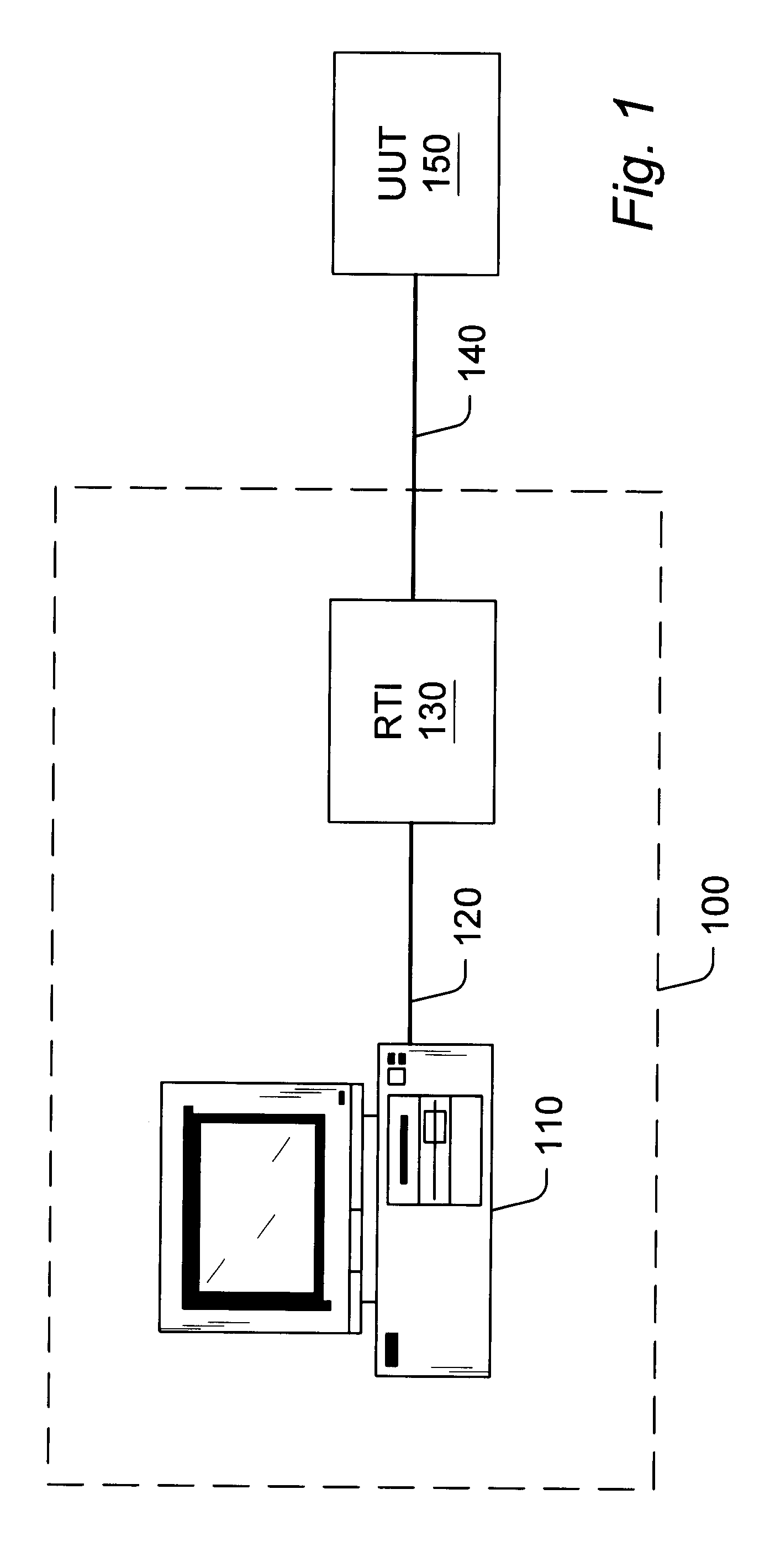

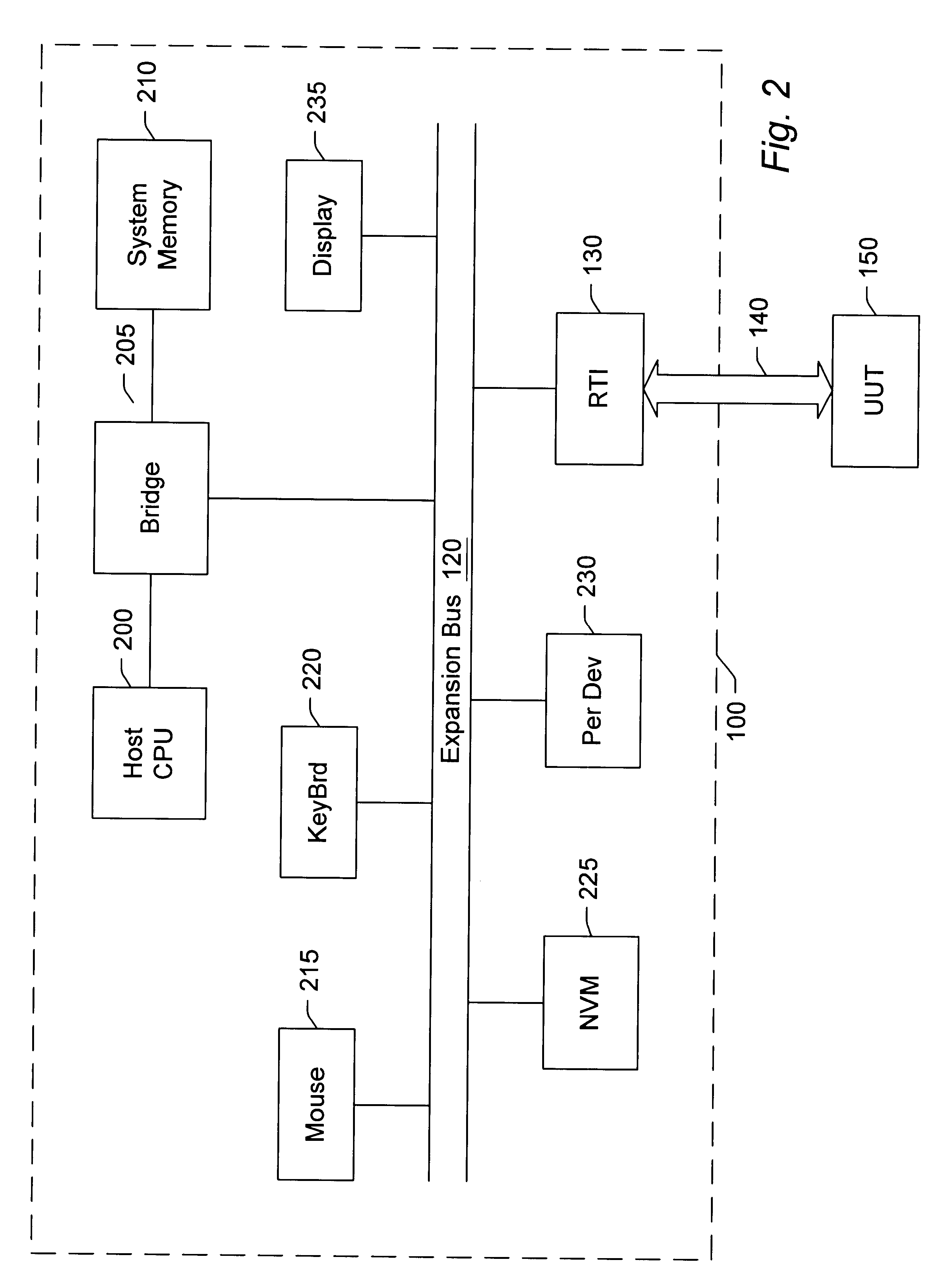

Reconfigurable test system

A reconfigurable test system including a host computer coupled to a reconfigurable test instrument. The reconfigurable test instrument includes reconfigurable hardware-i.e. a reconfigurable hardware module with one or more programmable elements such as Field Programmable Gate Arrays for realizing an arbitrary hardware architecture and a reconfigurable front end with programmable transceivers for interfacing with any desired physical medium-and optionally, an embedded processor. A user specifies system features with a software configuration utility which directs a component selector to select a set of software modules and hardware configuration files from a series of libraries. The modules are embedded in a host software driver or downloaded for execution on the embedded CPU. The configuration files are downloaded to the reconfigurable hardware. The entire selection process is performed in real-time and can be changed whenever the user deems necessary. Alternatively, the user may create a graphical program in a graphical programming environment and compile the program into various software modules and configuration files for host execution, embedded processor execution, or programming the reconfigurable hardware.

Owner:NATIONAL INSTRUMENTS

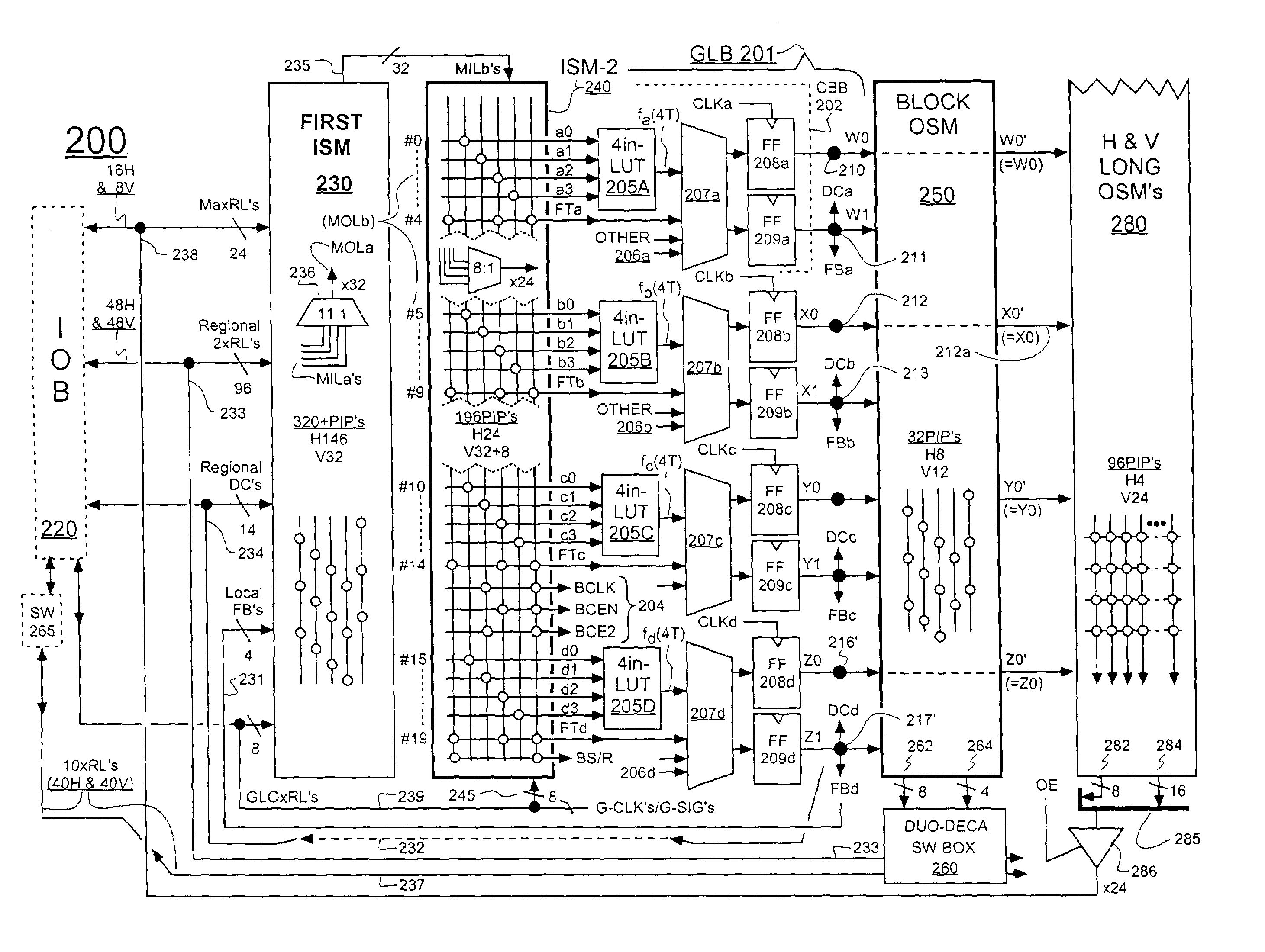

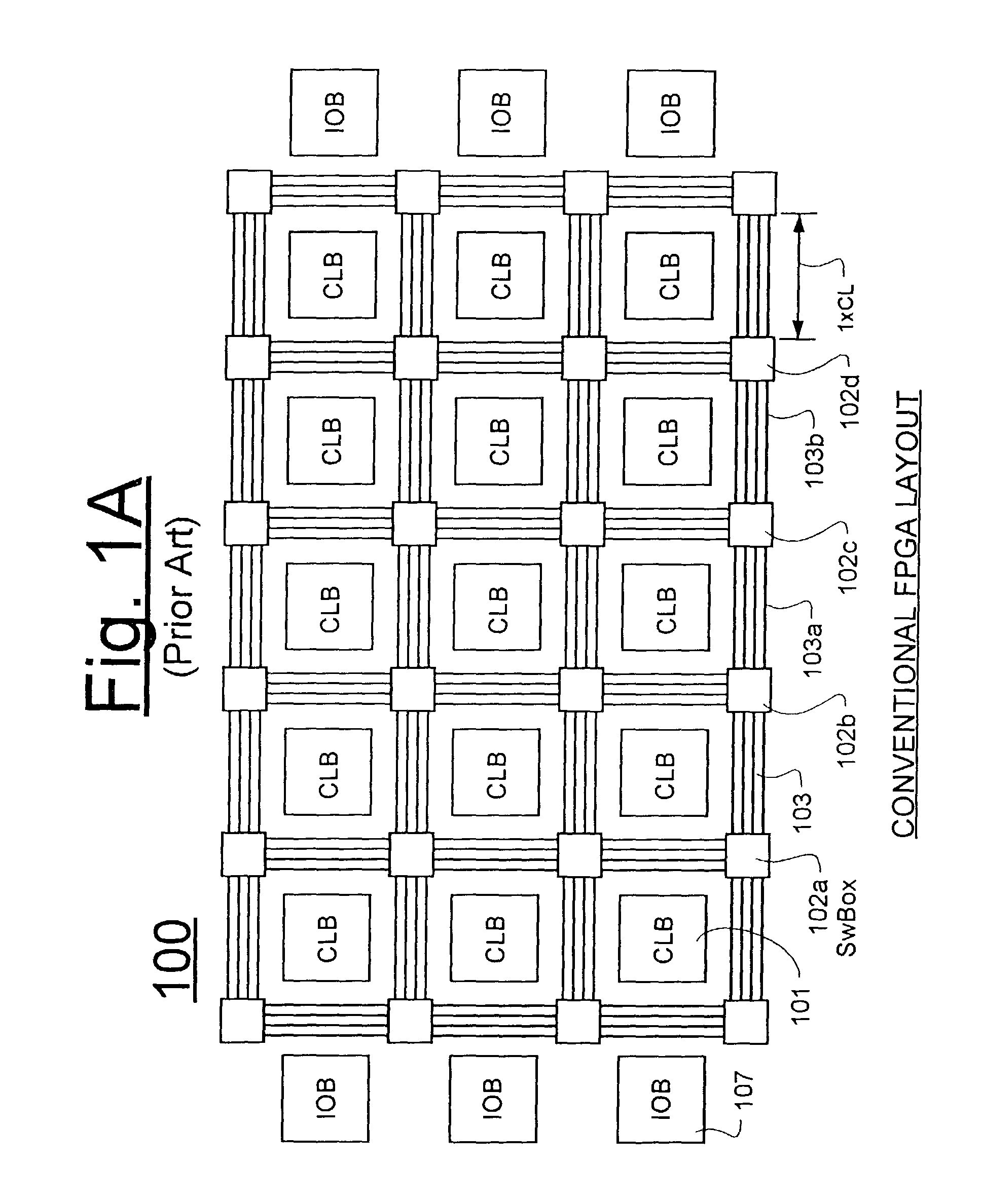

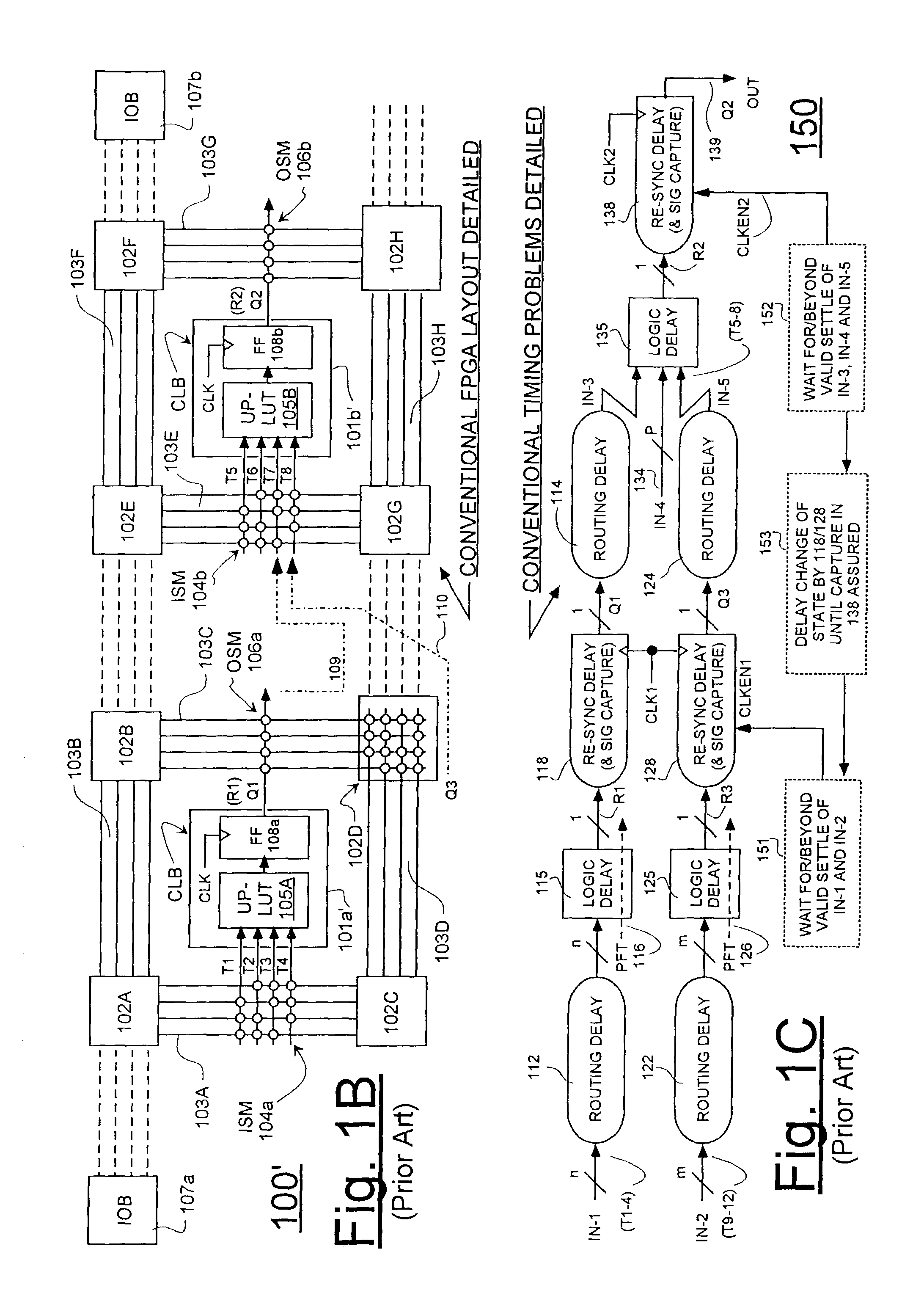

FPGA with register-intensive architecture

ActiveUS7028281B1Minimize resourceReduce consumptionSolid-state devicesCAD circuit designProcessor registerMultiplexer

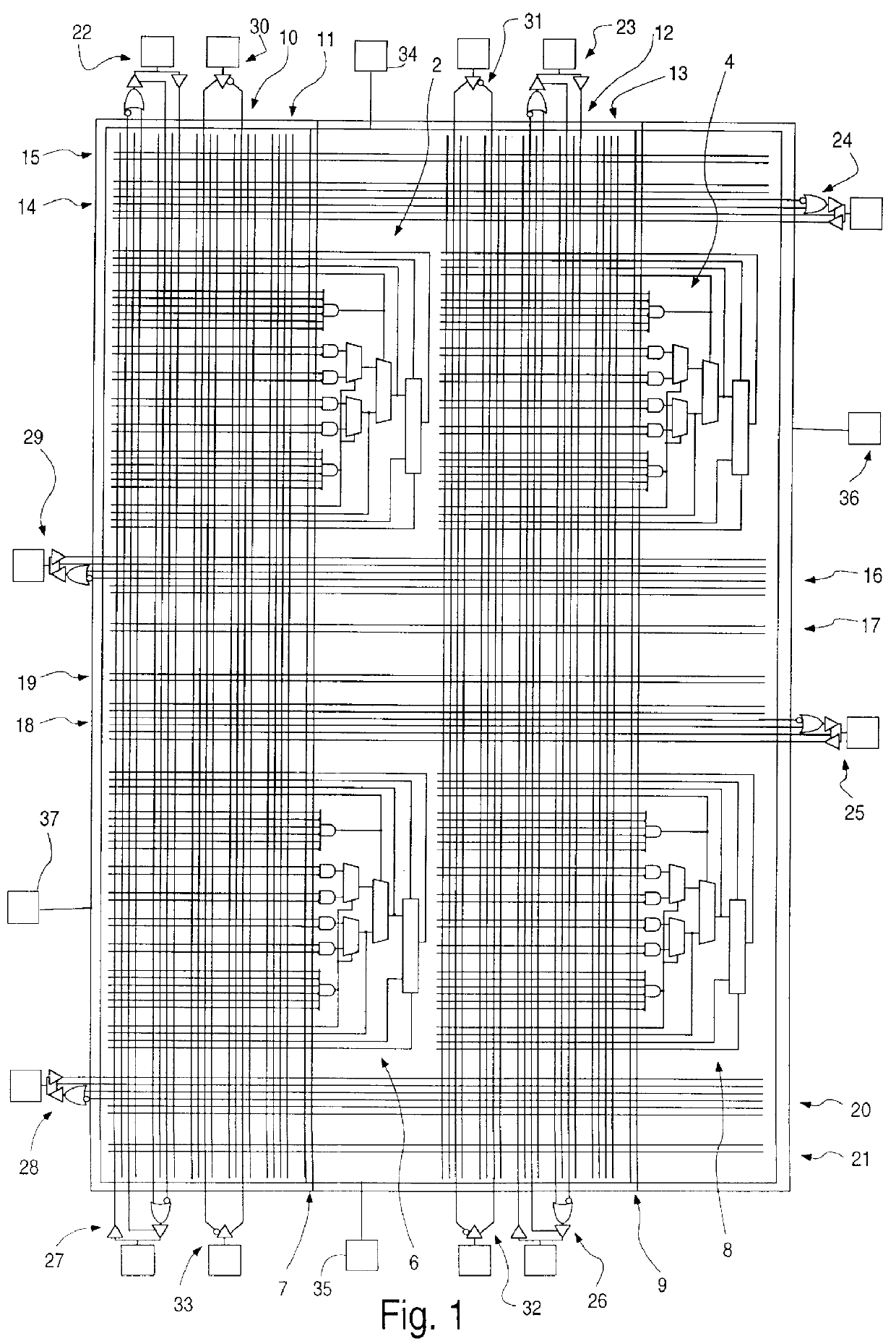

Field programmable gate arrays (FPGA's) may be structured in accordance with the disclosure to have a register-intensive architecture that provides, for each of plural function-spawning LookUp Tables (e.g. a 4-input, base LUT's) within a logic block, a plurality of in-block accessible registers. A register-feeding multiplexer means may be provided for allowing each of the plural registers to equivalently capture and store a result signal output by the corresponding, base LUT of the plural registers. Registerable, primary and secondary feedthroughs may be provided for each base LUT so that locally-acquired input signals of the LUT may be fed-through to the corresponding, in-block registers for register-recovery purposes without fully consuming (wasting) the lookup resources of the associated, base LUT. A multi-stage, input switch matrix (ISM) may be further provided for acquiring and routing input signals from adjacent, block-interconnect lines (AIL's) and / or block-intra-connect lines (e.g., FB's) to the base LUT's and / or their respective, registerable feedthroughs. Techniques are disclosed for utilizing the many in-block registers and / or the registerable feedthroughs and / or the multi-stage ISM's for efficiently implementing various circuit designs by appropriately configuring such register-intensive FPGA's.

Owner:LATTICE SEMICON CORP

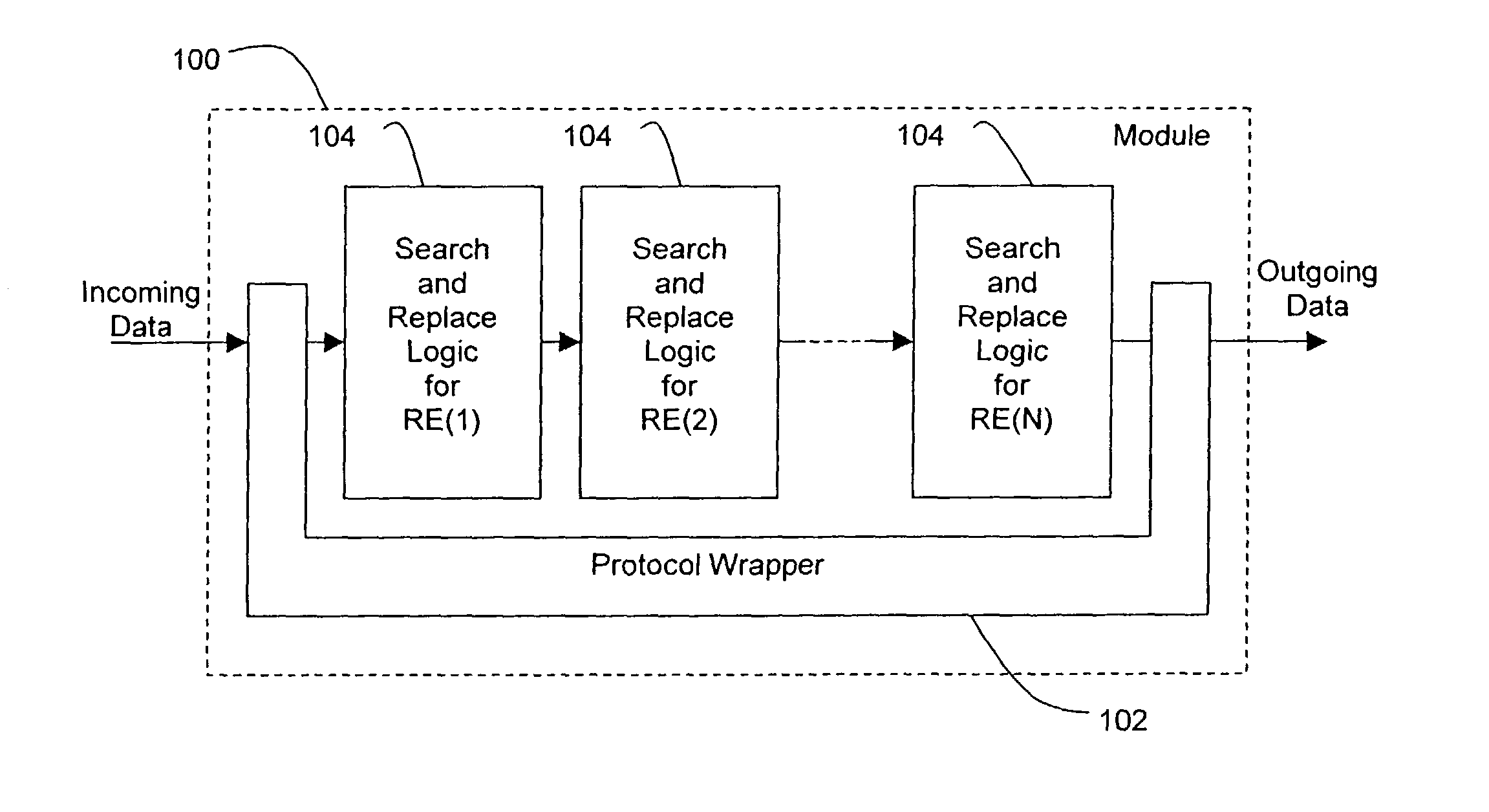

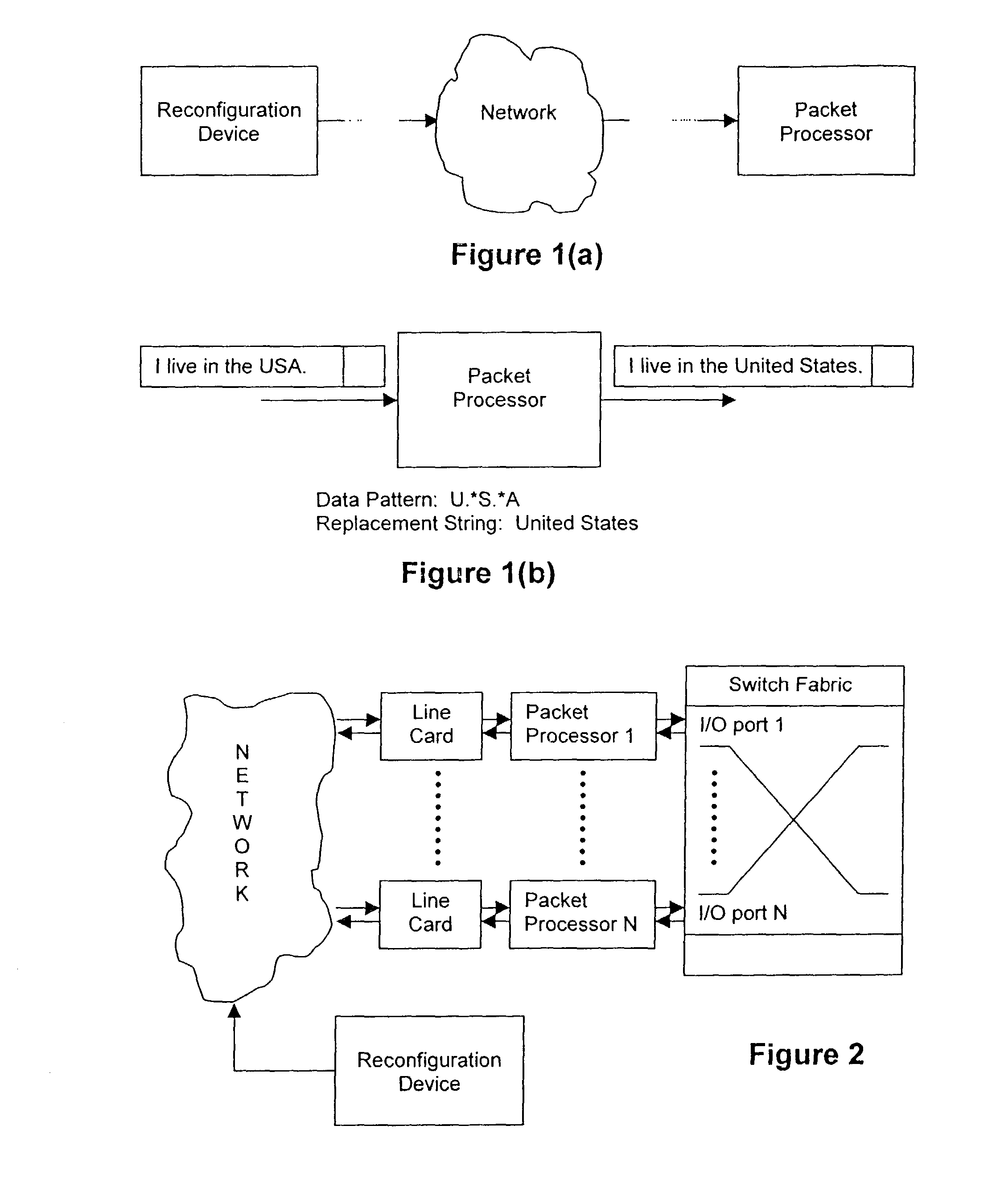

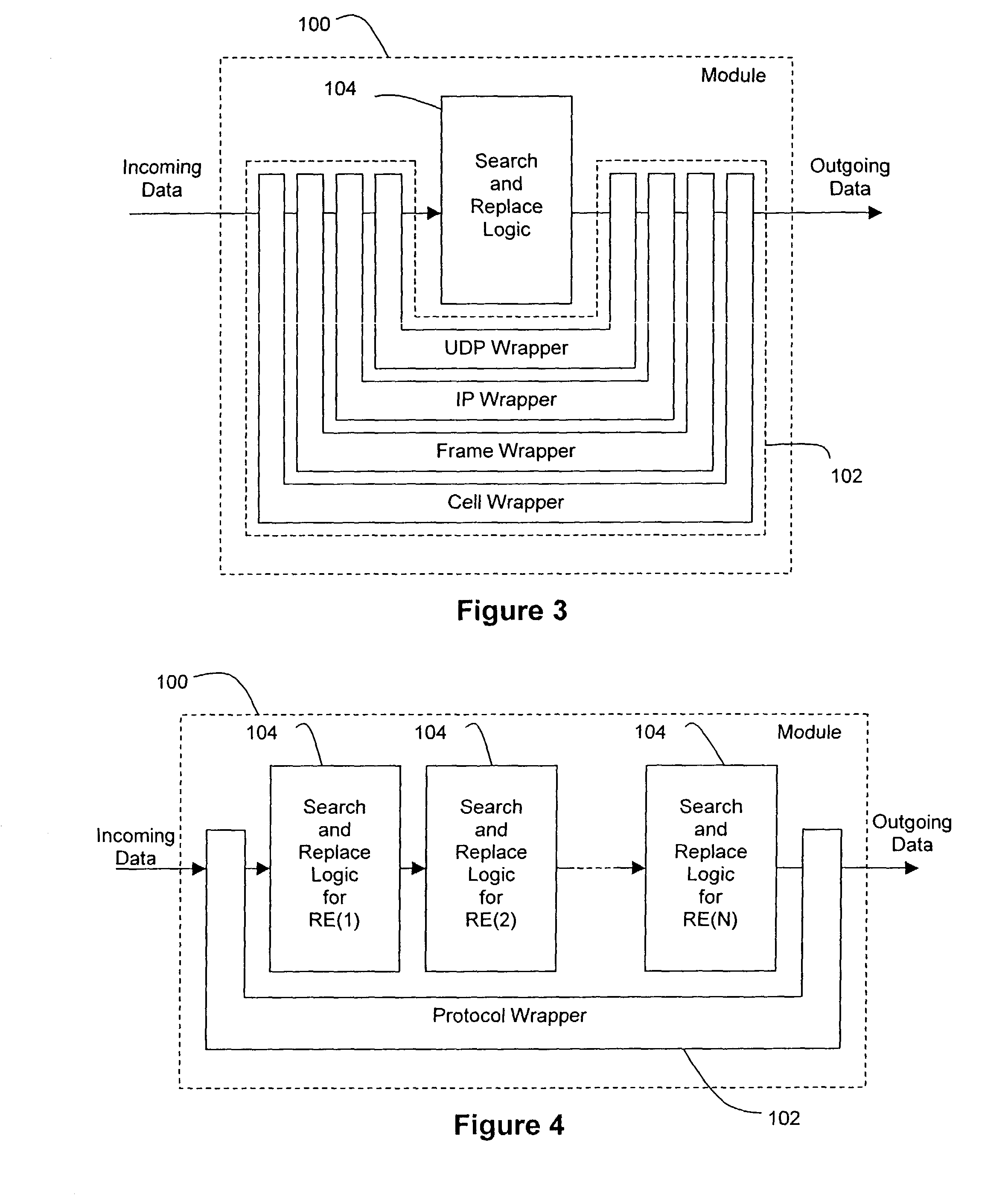

Methods, systems, and devices using reprogrammable hardware for high-speed processing of streaming data to find a redefinable pattern and respond thereto

InactiveUS7093023B2Prevent materialPrevented from reachingError detection/correctionMultiple digital computer combinationsProgrammable logic devicePacket processing

A reprogrammable packet processing system for processing a stream of data is disclosed herein. A reprogrammable data processor is implemented with a programmable logic device (PLD), such as a field programmable gate array (FPGA), that is programmed to determine whether a stream of data applied thereto includes a string that matches a redefinable data pattern. If a matching string is found, the data processor performs a specified action in response thereto. The data processor is reprogrammable to search packets for the presence of different data patterns and / or perform different actions when a matching string is detected. A reconfiguration device receives input from a user specifying the data pattern and action, processes the input to generate the configuration information necessary to reprogram the PLD, and transmits the configuration information to the packet processor for reprogramming thereof.

Owner:WASHINGTON UNIV IN SAINT LOUIS

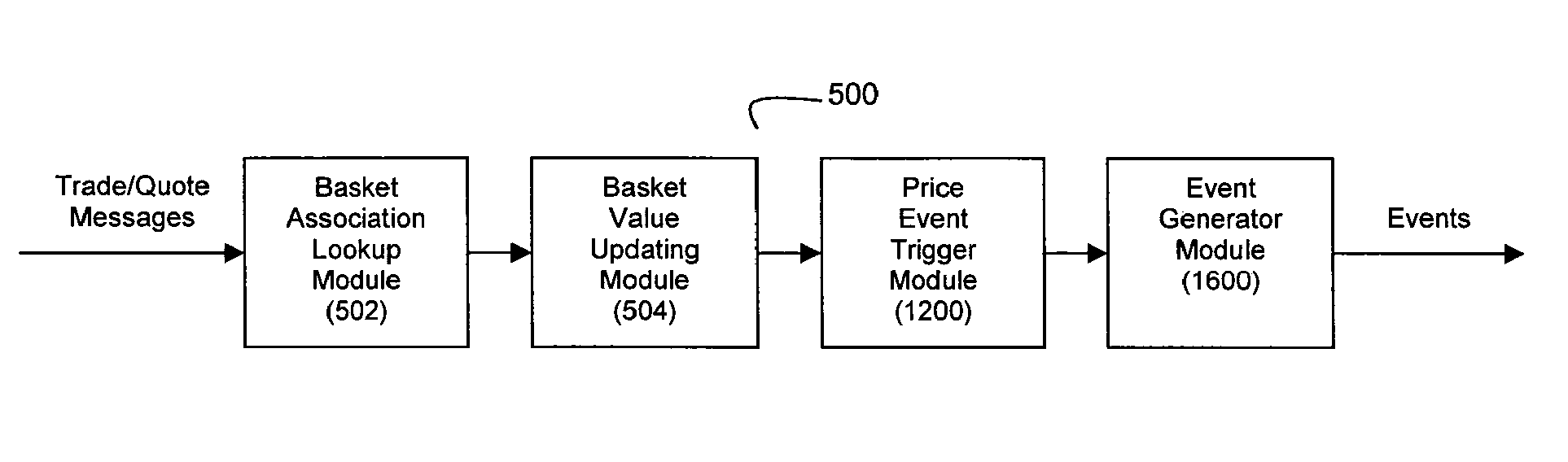

Method and System for Low Latency Basket Calculation

A basket calculation engine is deployed to receive a stream of data and accelerate the computation of basket values based on that data. In a preferred embodiment, the basket calculation engine is used to process financial market data to compute the net asset values (NAVs) of financial instrument baskets. The basket calculation engine can be deployed on a coprocessor and can also be realized via a pipeline, the pipeline preferably comprising a basket association lookup module and a basket value updating module. The coprocessor is preferably a reconfigurable logic device such as a field programmable gate array (FPGA).

Owner:EXEGY INC

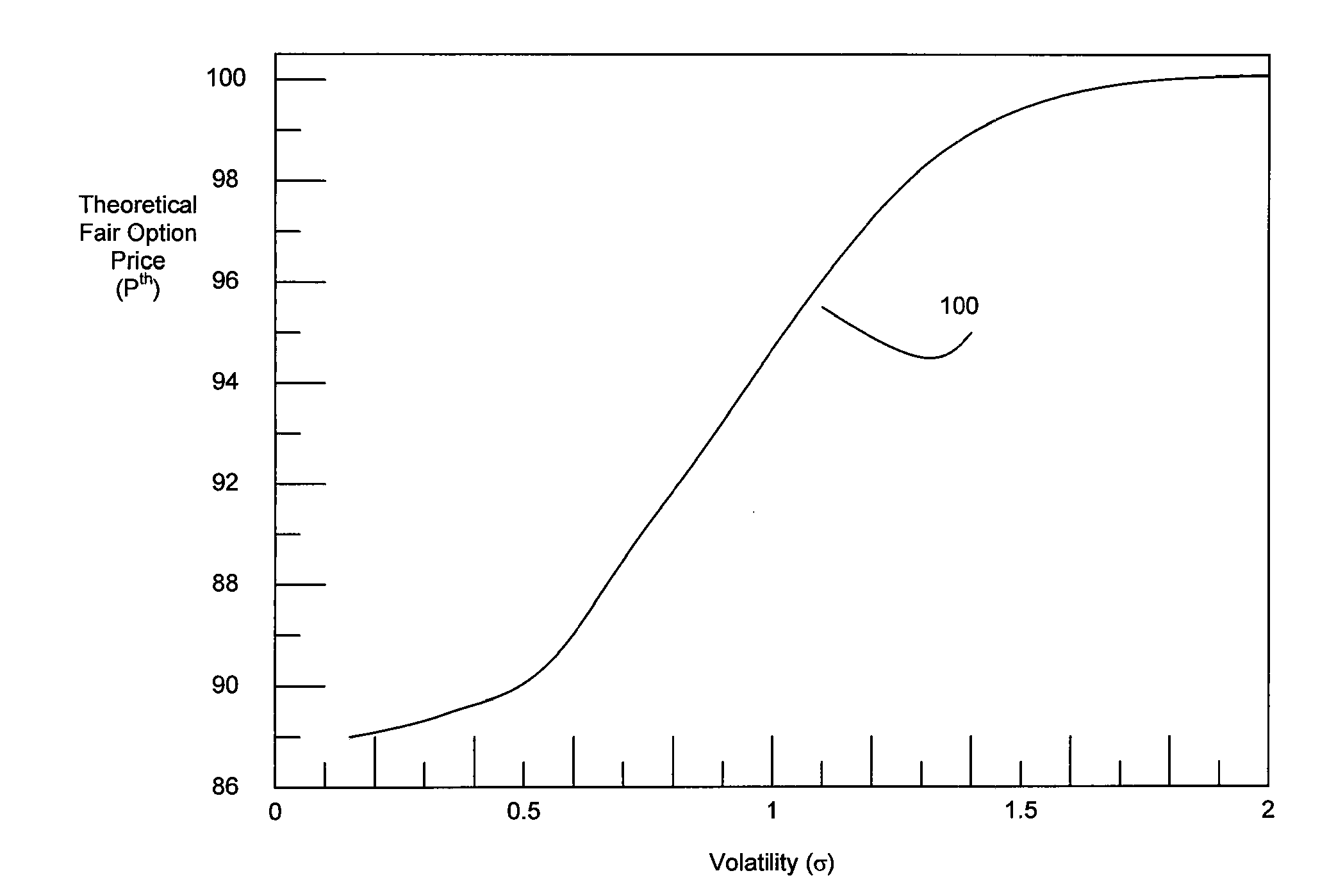

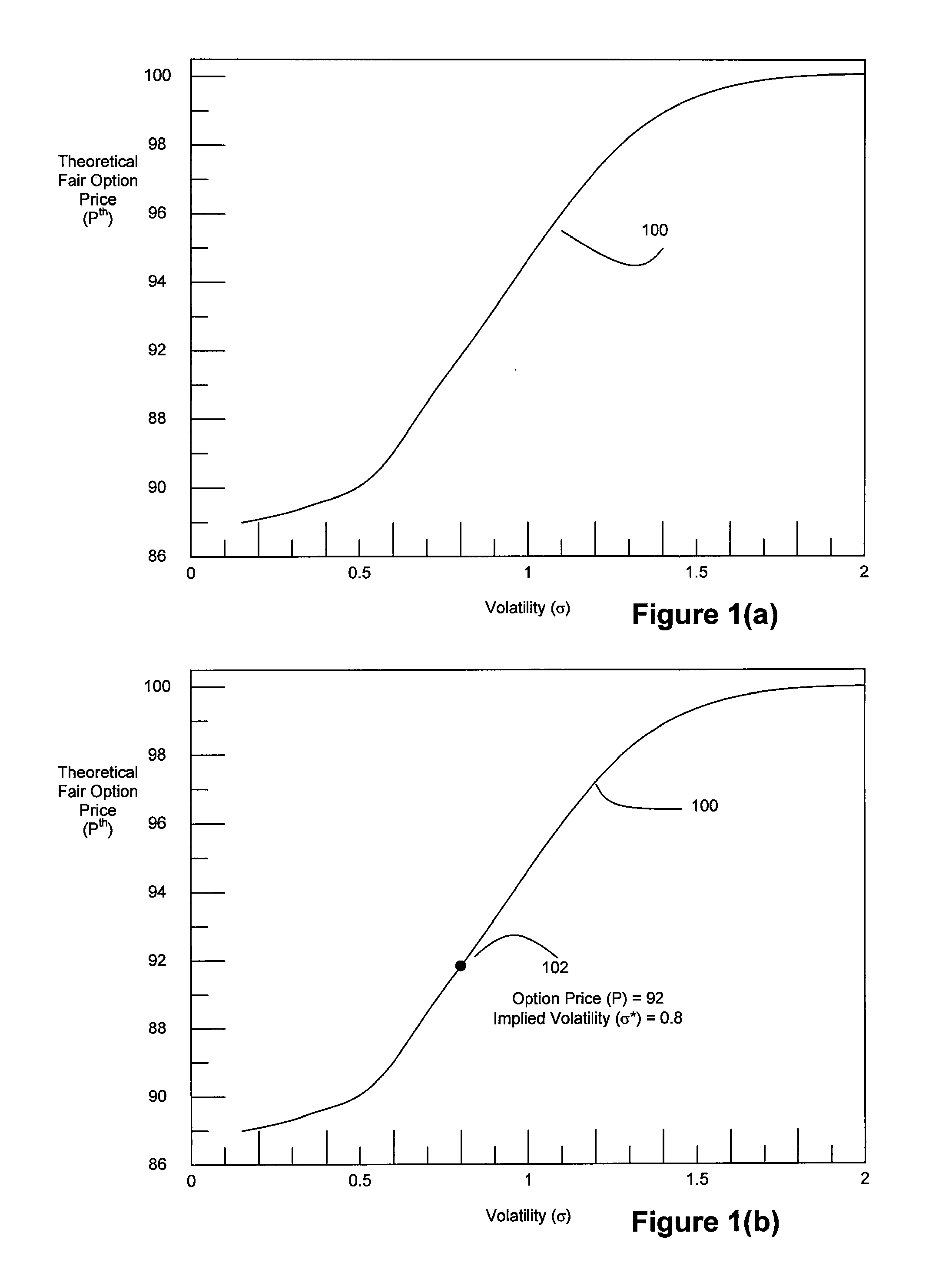

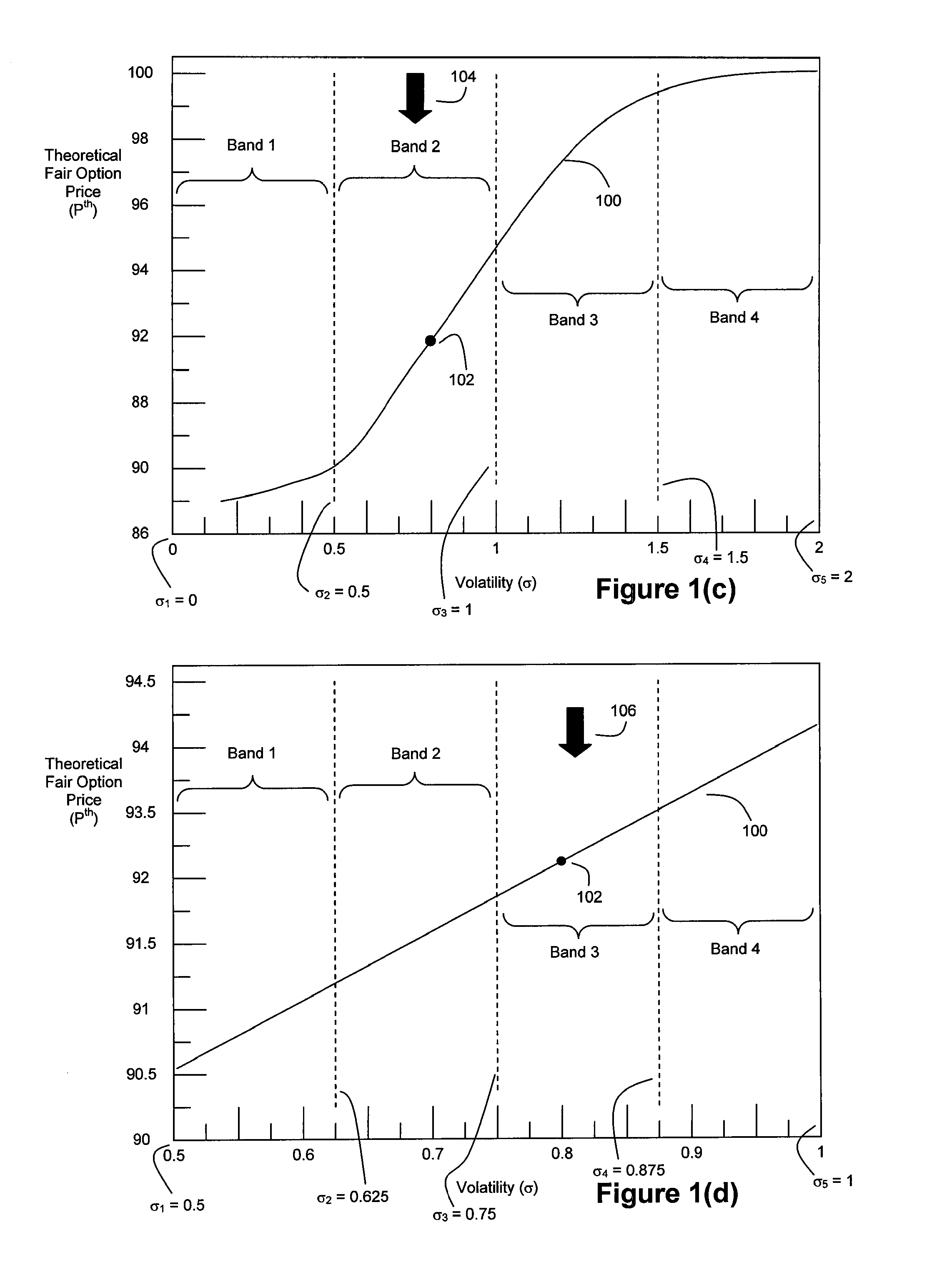

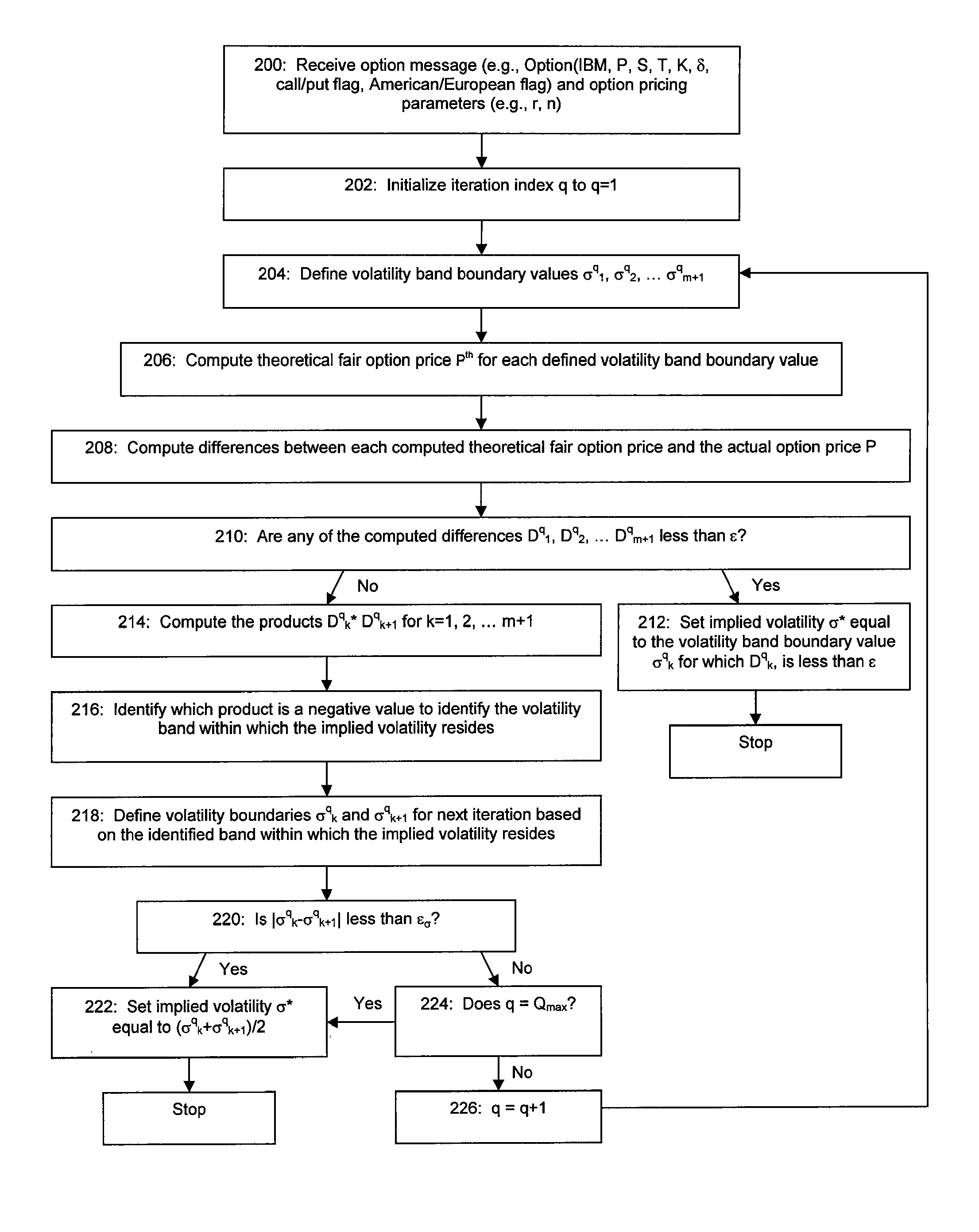

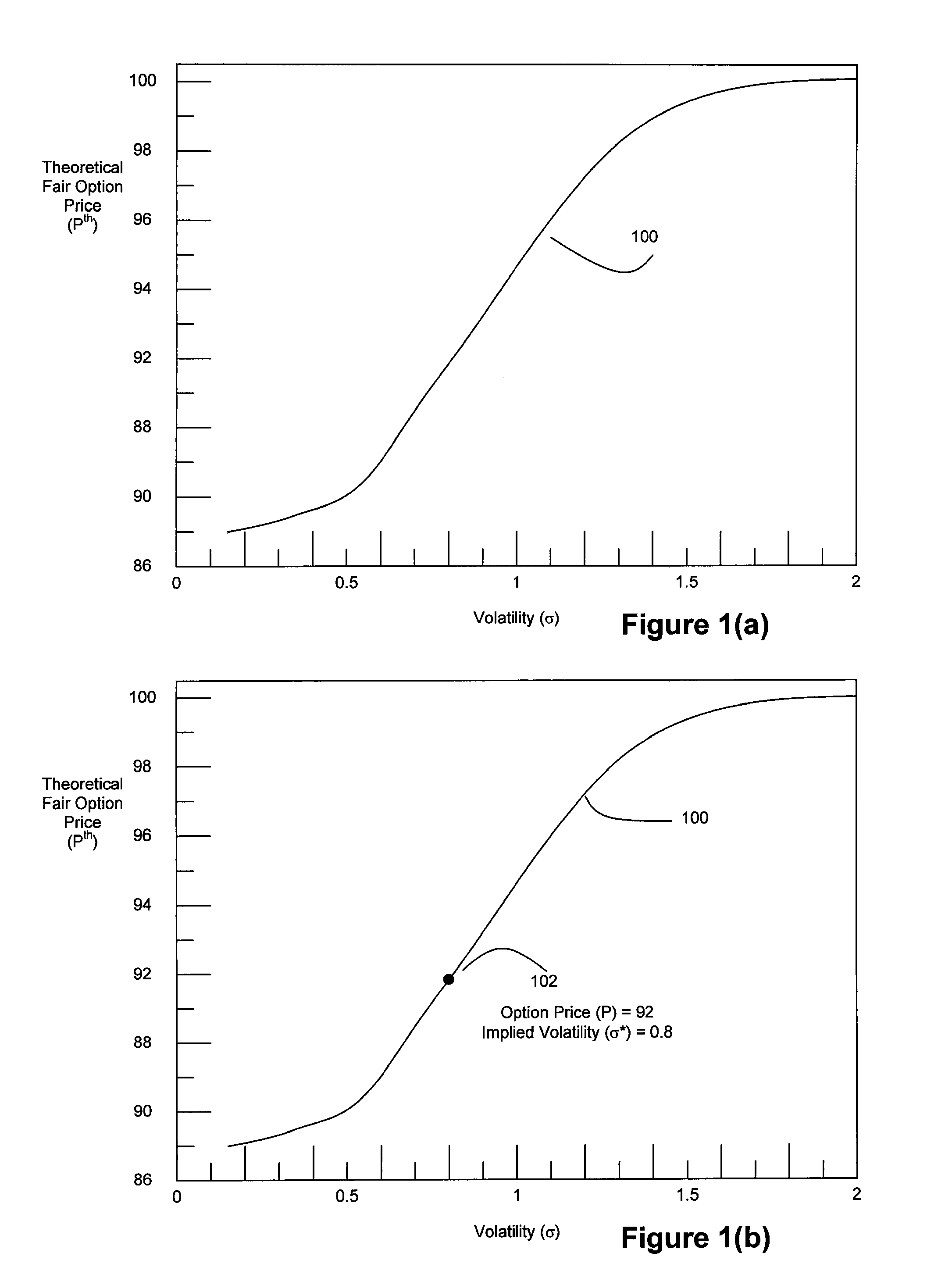

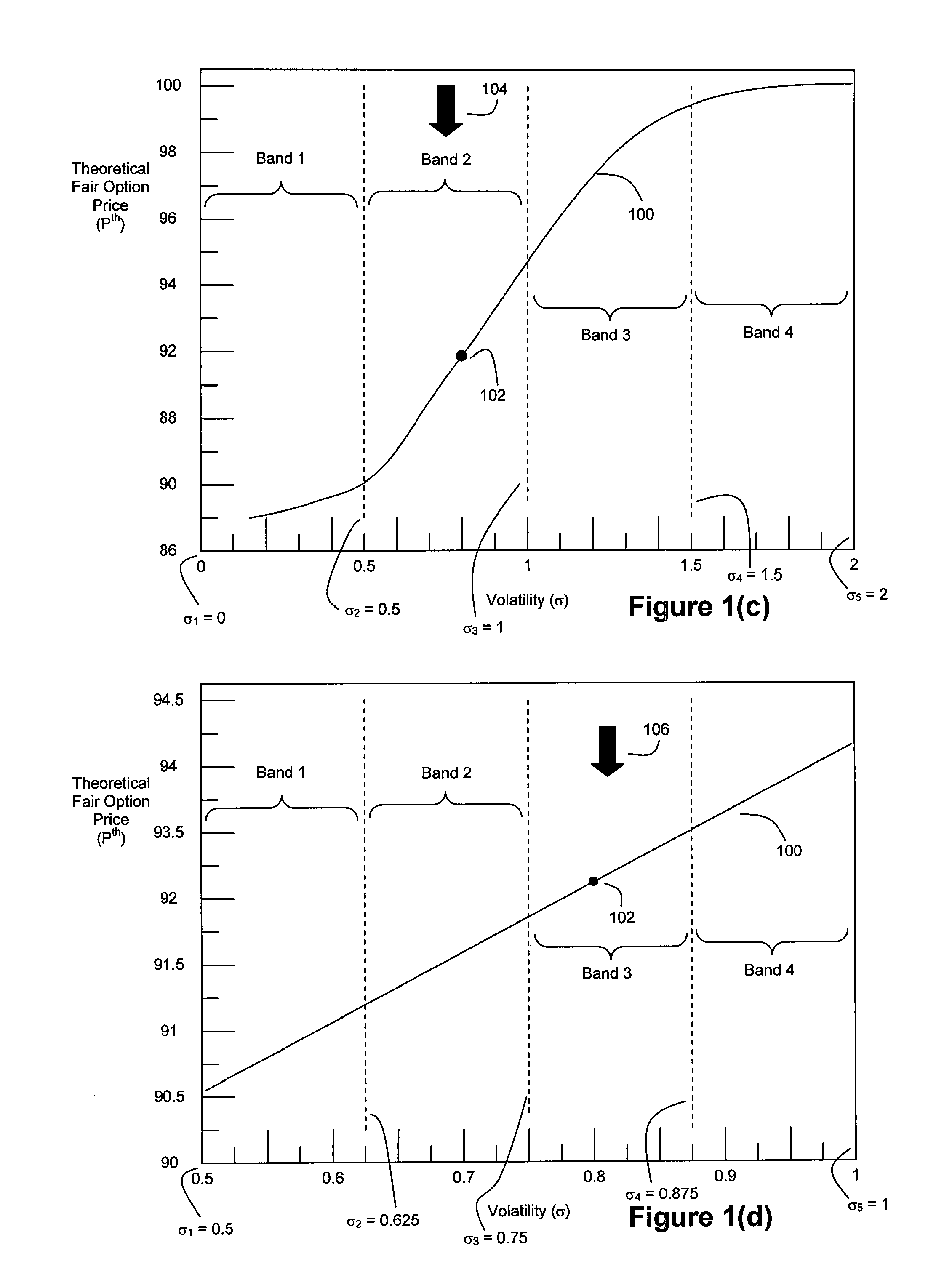

Method and System for High Speed Options Pricing

ActiveUS20070294157A1SpeedReduction of informationFinanceTheoretical computer scienceLatency (engineering)

A high speed technique for options pricing in the financial industry is disclosed that can provide both high throughput and low latency. A parallel / pipelined architecture is disclosed for computing an implied volatility in connection with an option. Parallel / pipelined architectures are also disclosed for computing an option's theoretical fair price. Preferably these parallel / pipelined architectures are deployed in hardware, and more preferably reconfigurable logic such as Field Programmable Gate Arrays (FPGAs) to accelerate the options pricing operations relative to conventional software-based options pricing operations.

Owner:EXEGY INC

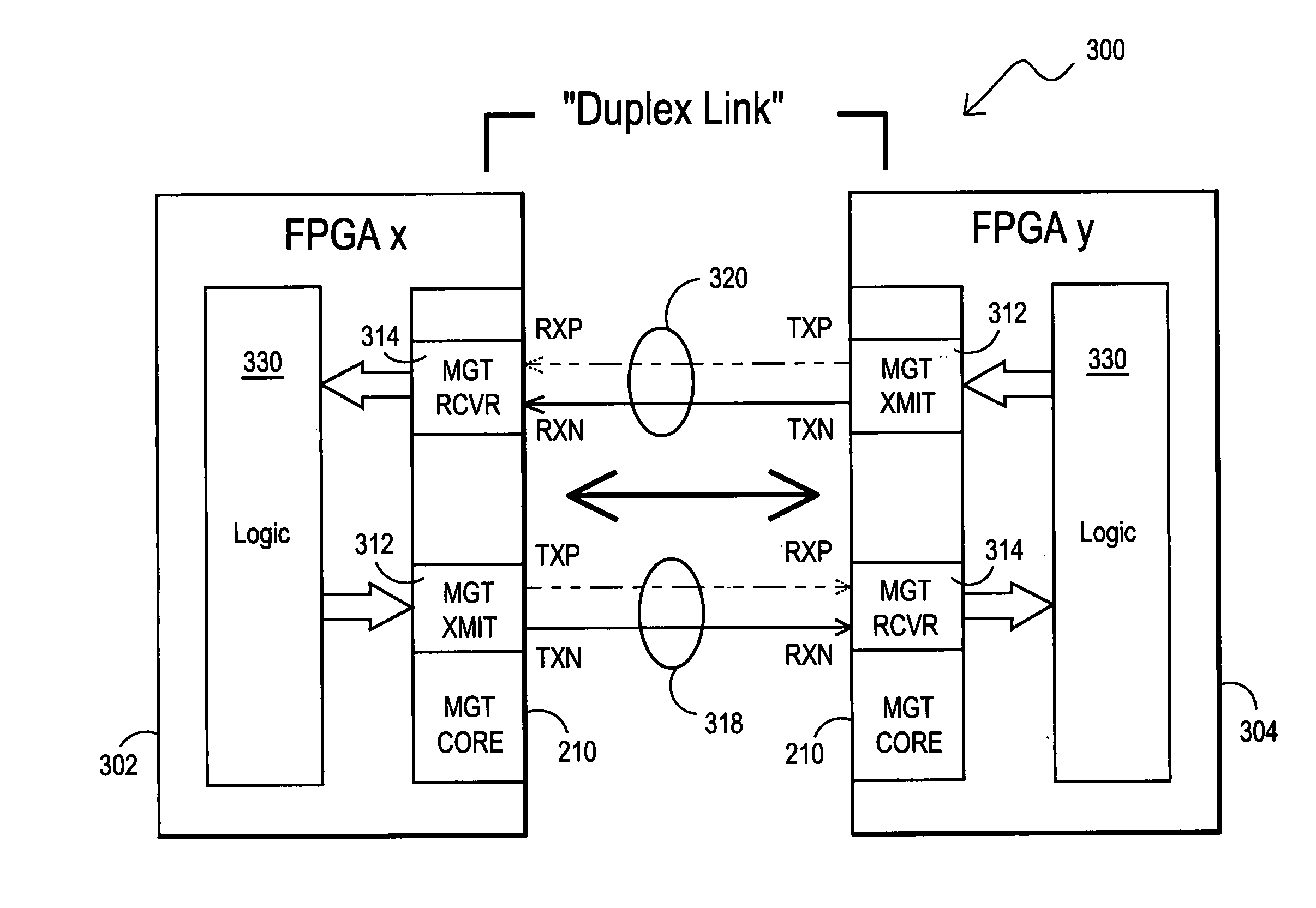

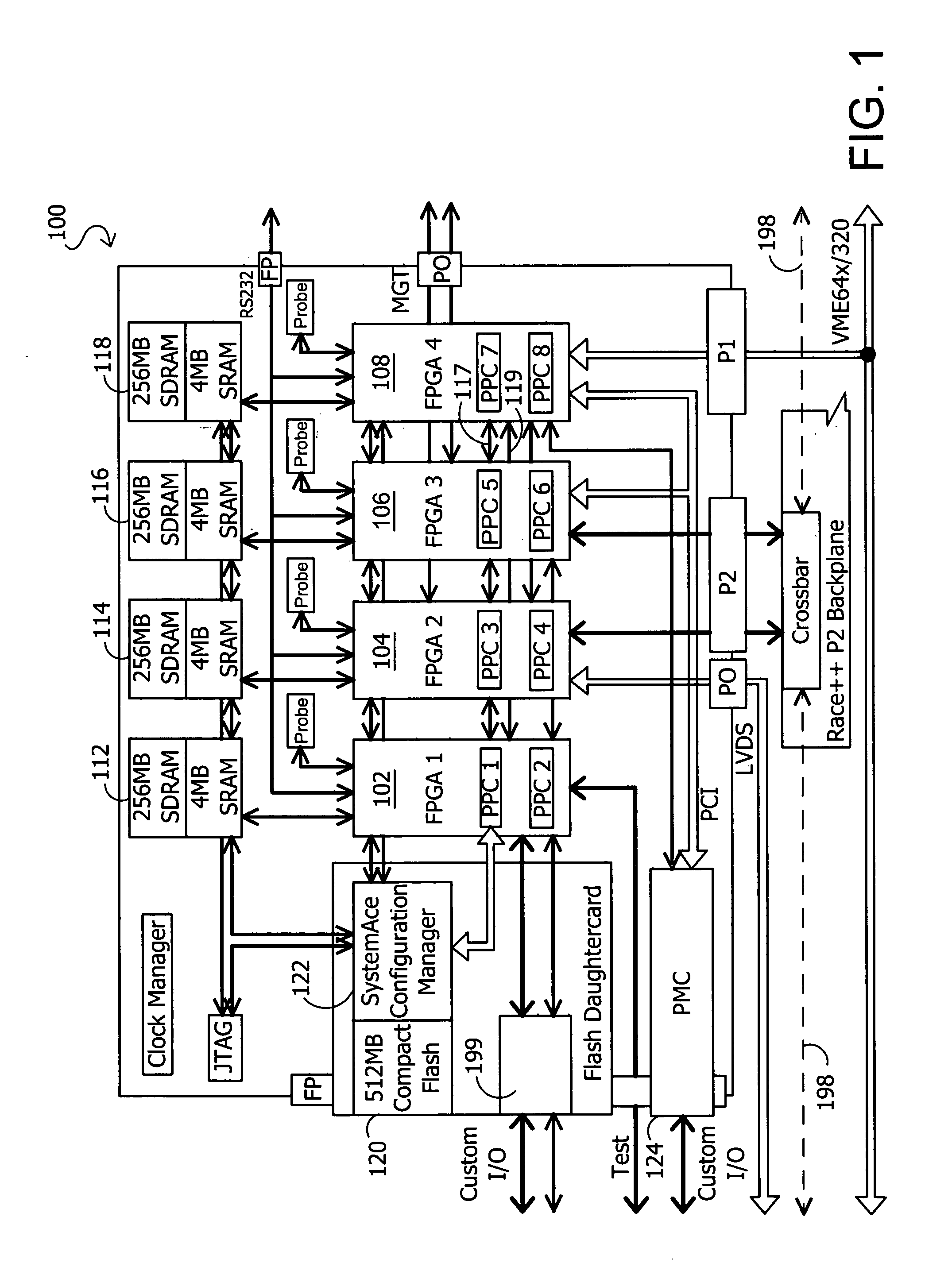

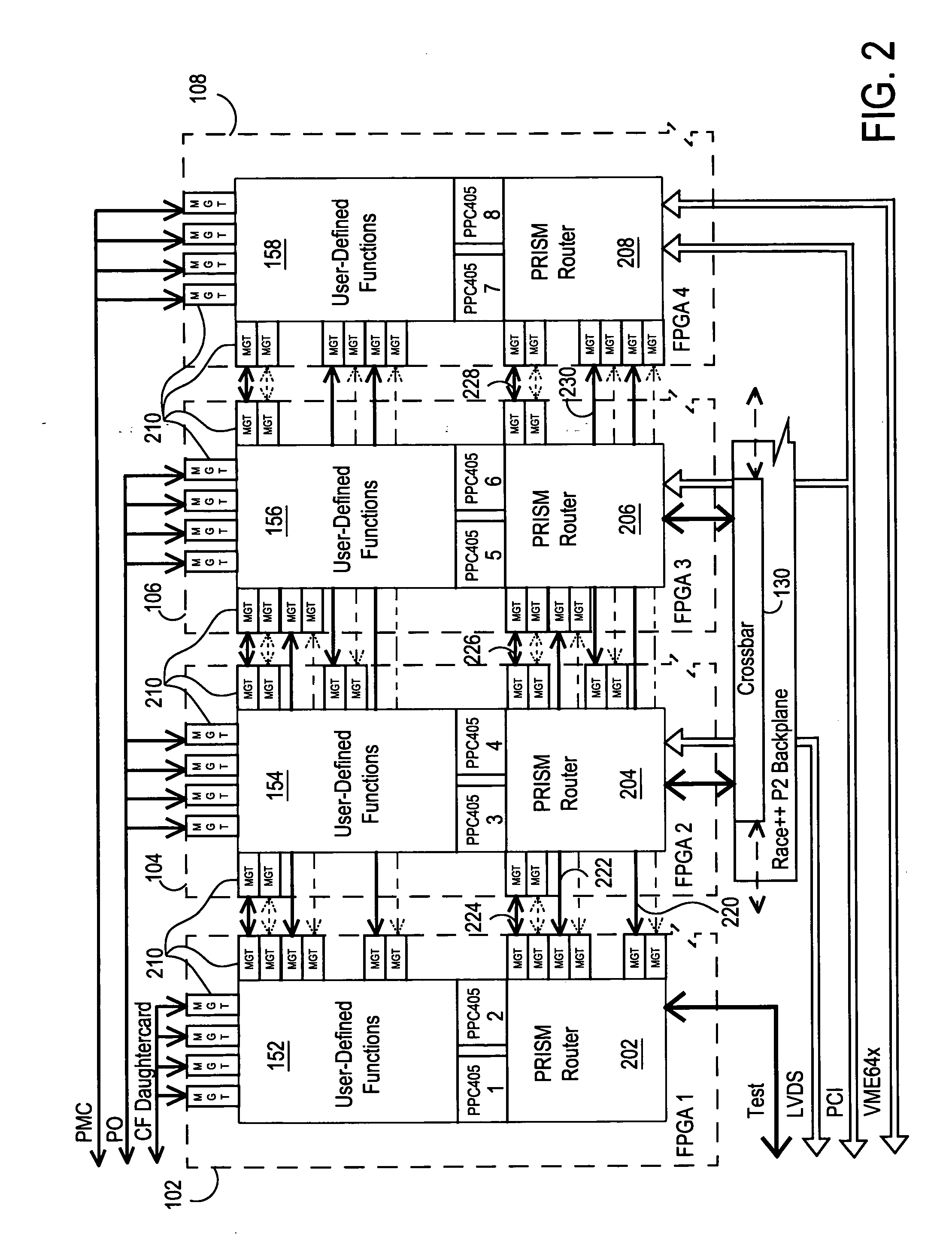

Systems and methods for interconnection of multiple FPGA devices

InactiveUS20050256969A1Promotes commonalityReduce countDigital computer detailsLogic circuits using elementary logic circuit componentsHigh bandwidthIntegrated circuit

Application Specific Integrated Circuit (“ASIC”) devices, such as Field Programmable Gate Arrays (“FPGAs”), may be interconnected using serial I / O connections, such as high speed multi-gigabit serial transceiver (“MGT”) connections. For example, serial I / O connections may be employed to interconnect a pair of ASICs to create a high bandwidth, low signal count connection, and in a manner so that any given pair of multiple ASIC devices on a single circuit card may communicate with each other through no more than one serial data communication link connection step. A reconfigurable hardware architecture (“RHA”) may be configured to include a communications infrastructure that uses a high-bandwidth packet router to establish standard communications protocols between multiple interfaces and / or multiple devices that may be present on a single circuit card. Additionally, a communications infrastructure may be established across multiple circuit cards.

Owner:LIONRA TECH LTD +1

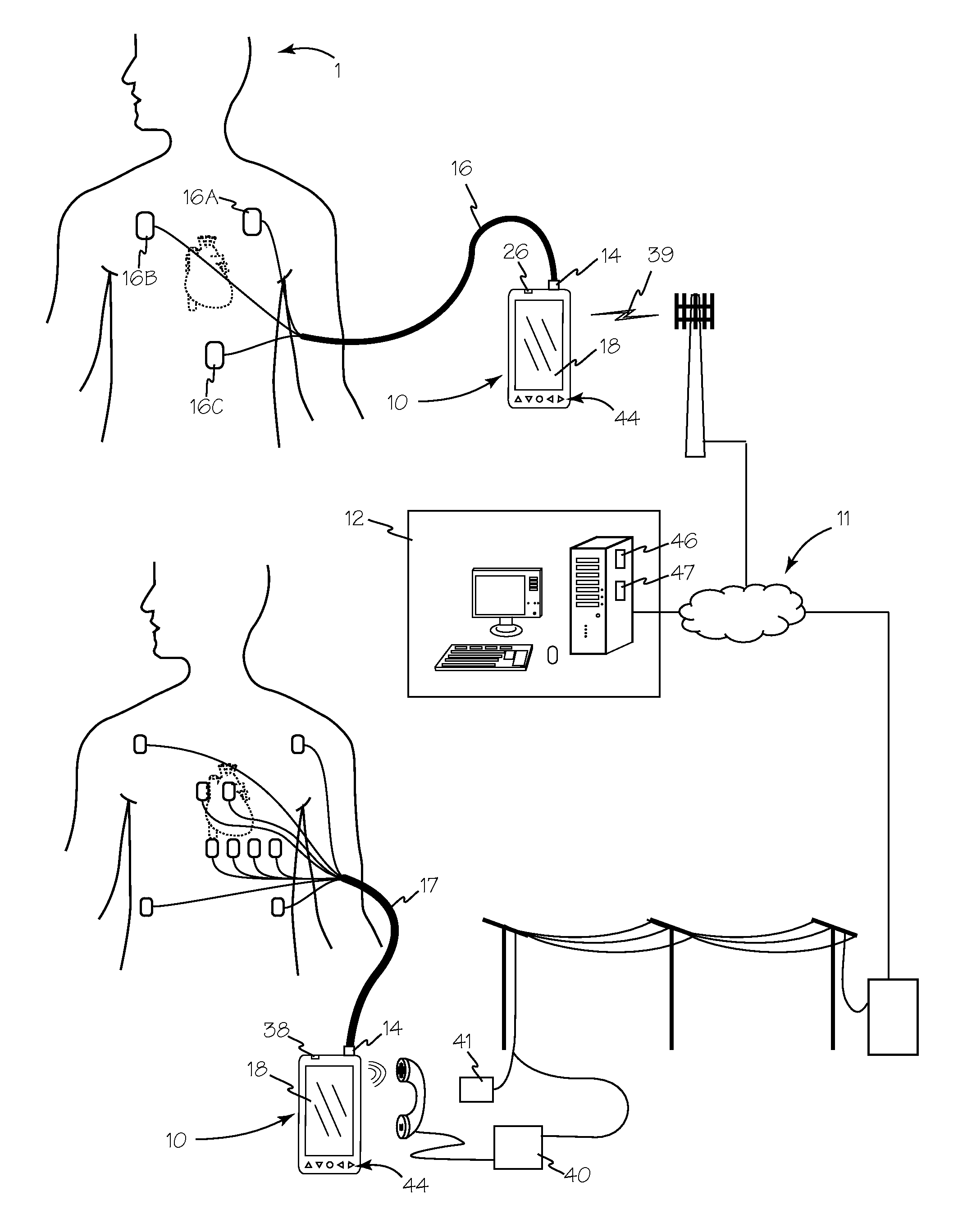

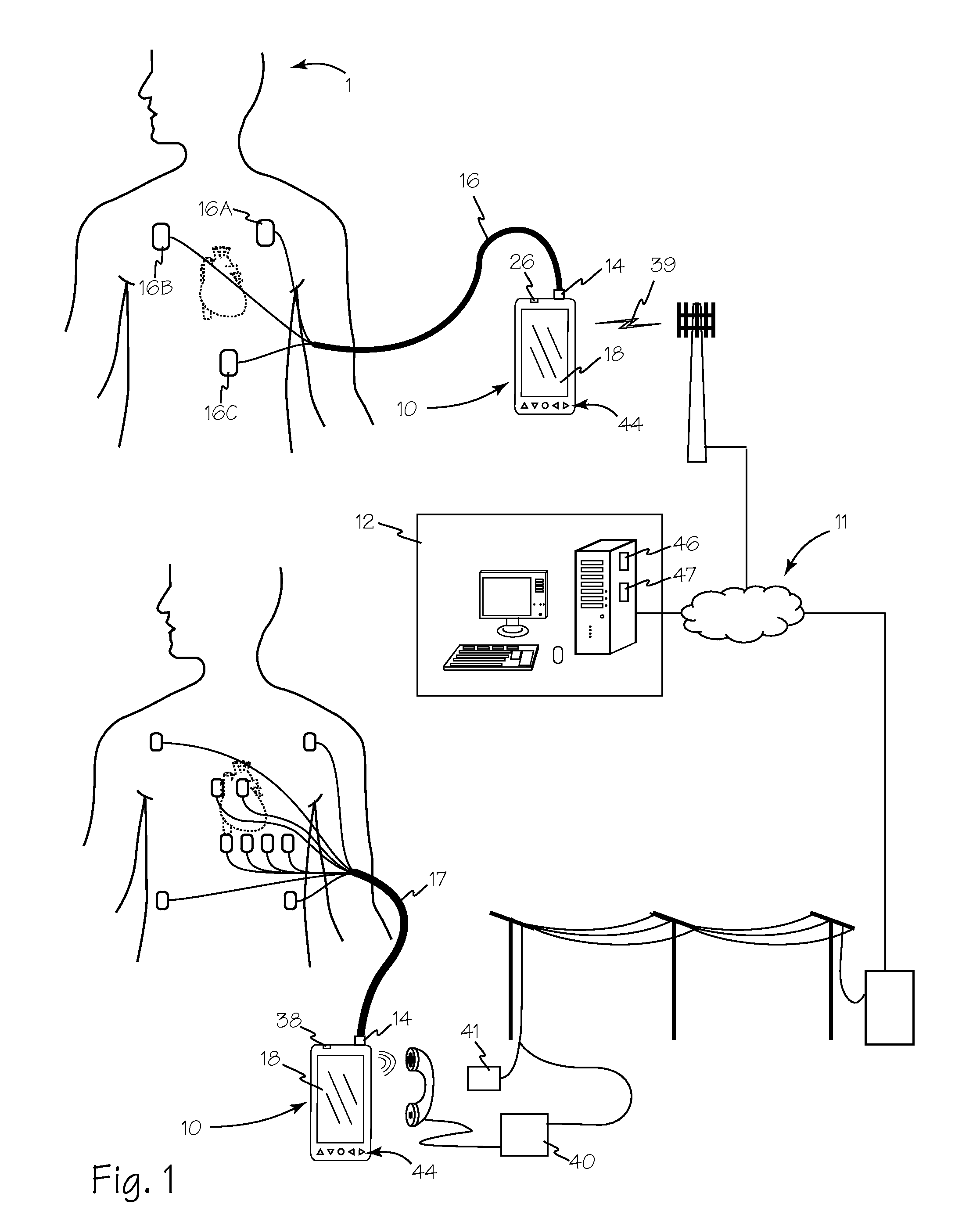

Multi-Function Health Monitor

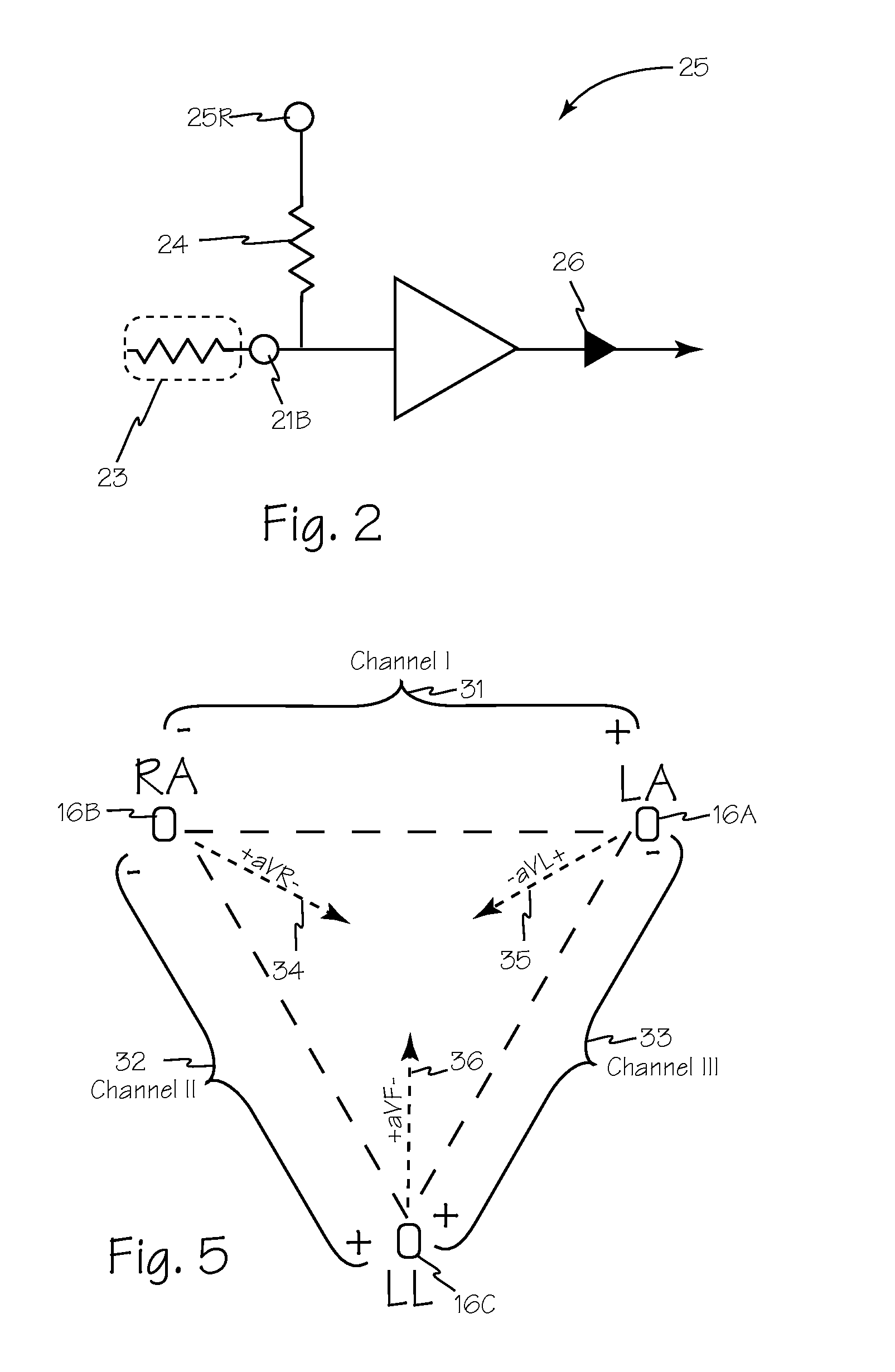

InactiveUS20110270112A1Minimize power consumptionEasy to handleElectrocardiographySensorsHolter monitorHolter Electrocardiography

A multi-function health monitor is capable of performing a resting 12-lead ECG test, an ECG stress test, a 24-hour holter monitor evaluation and or a 30-day MCT monitoring. Using only 3 electrodes, the multifunction health monitor derives 6 channels (Limb leads & Augmented leads) of data with the noise cancellation (ground) effect of a virtual dynamic RL electrode. An electrode resistivity measurement system quantifies and may compensate for increasing resistance the electrodes and the patient that results from the length of time the electrodes are installed on a patient. The multi-function health monitor can provide data analysis through the gate array as the data is acquired. Data may also be stored for remote analysis as well as for transmission to remote stations upon occurrence of one or more threshold events. Parameters for threshold events may be adjusted remotely to obviate the need for a patient to travel for system adjustment.

Owner:ACS DIAGNOSTICS INC

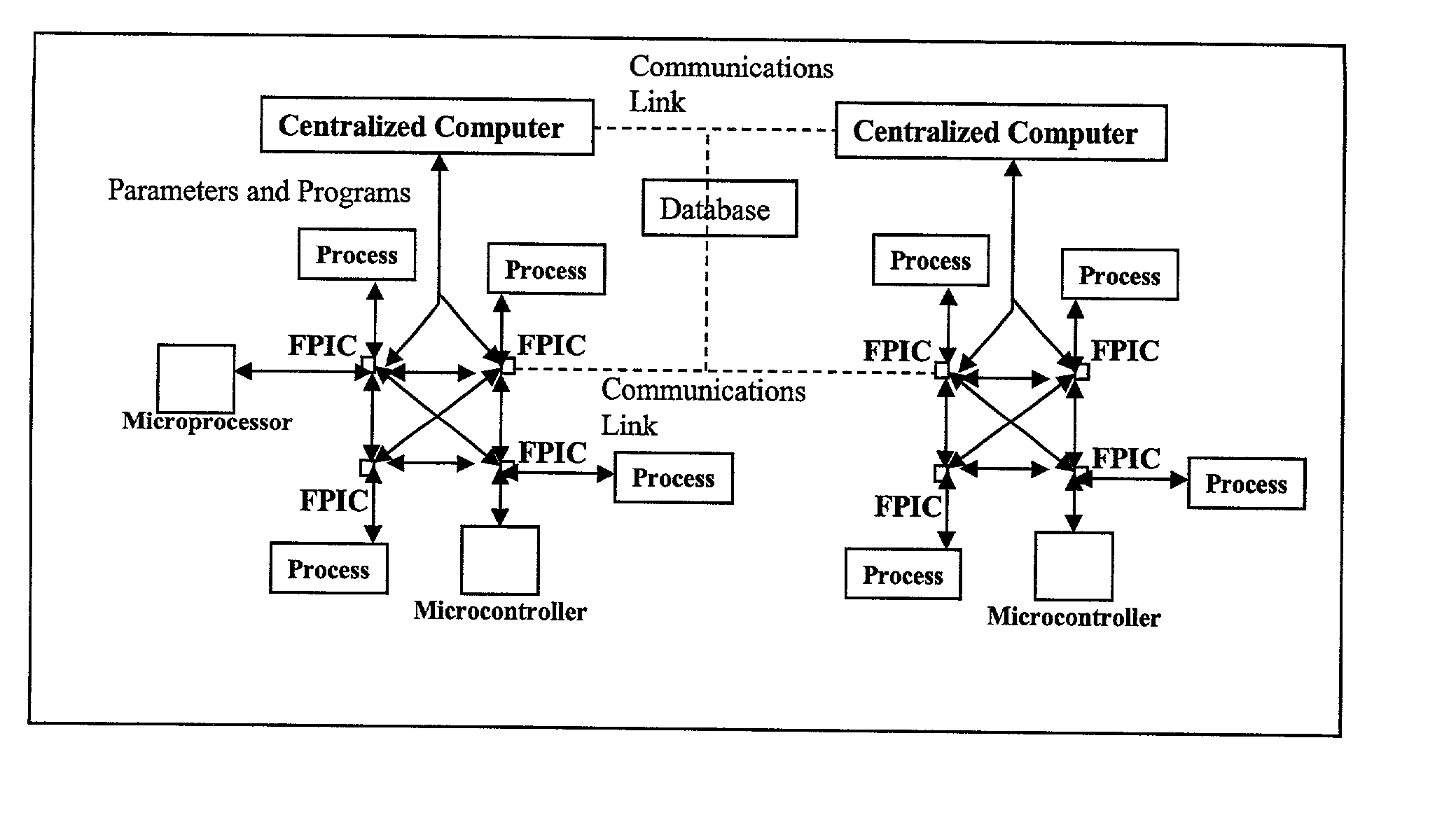

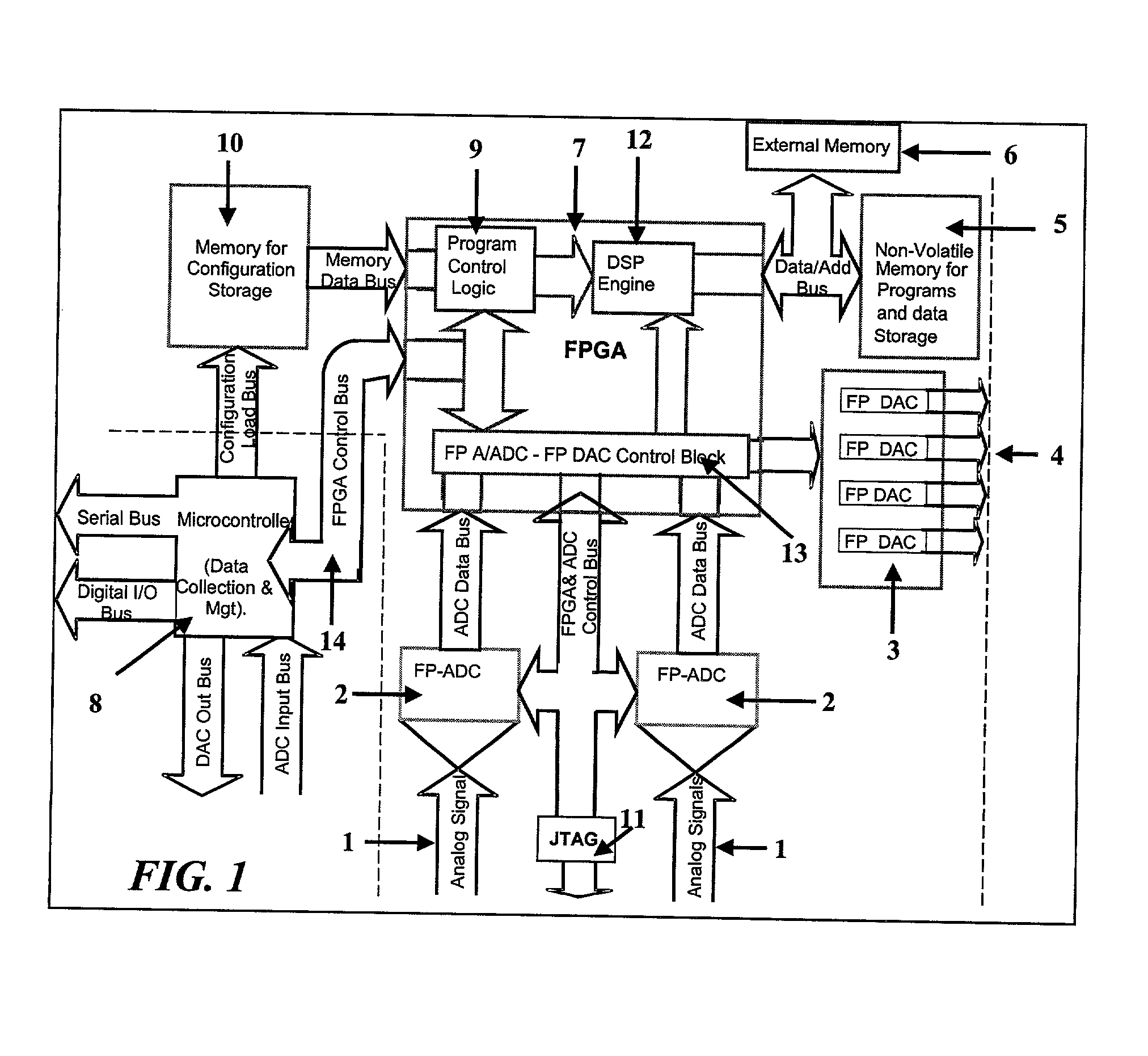

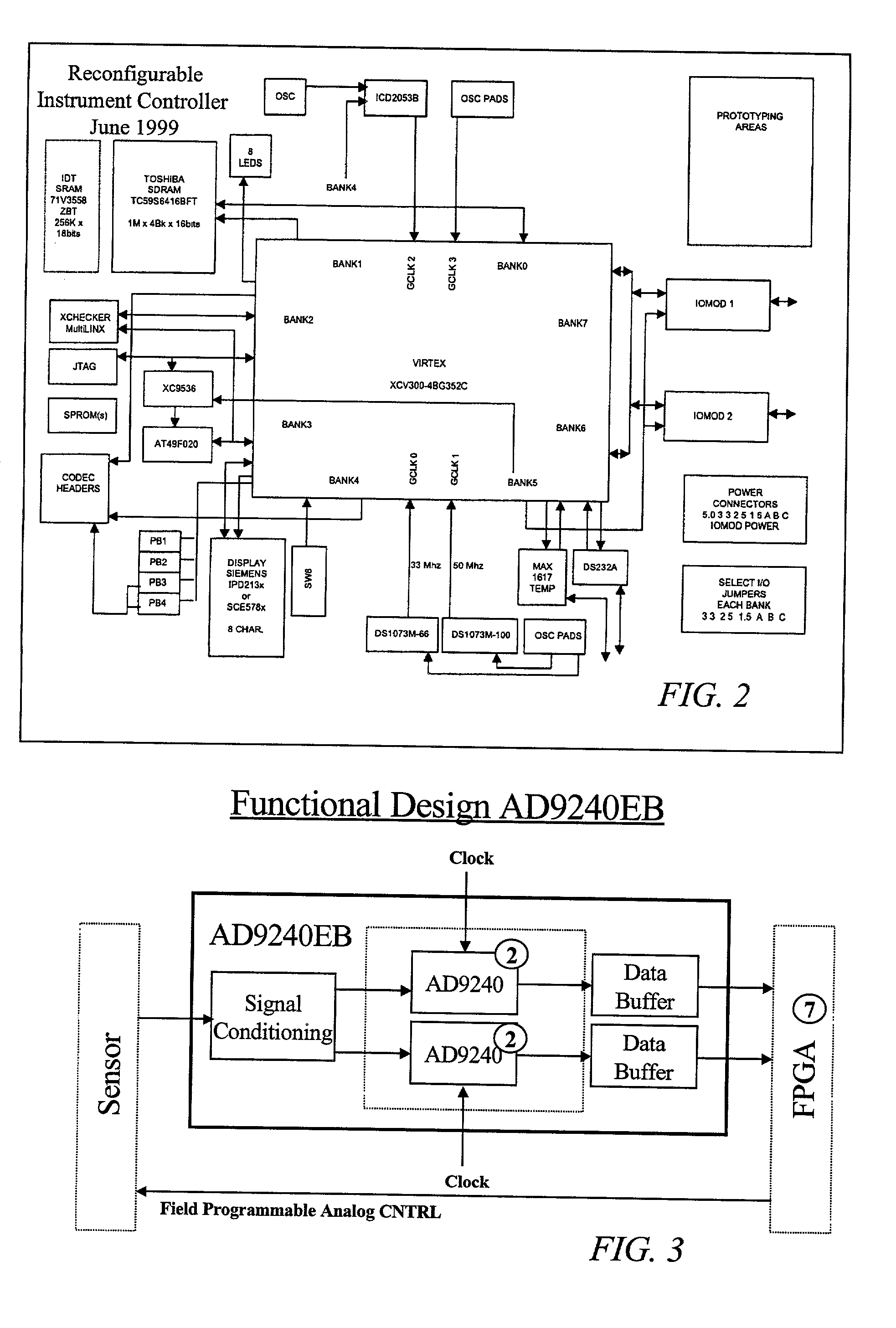

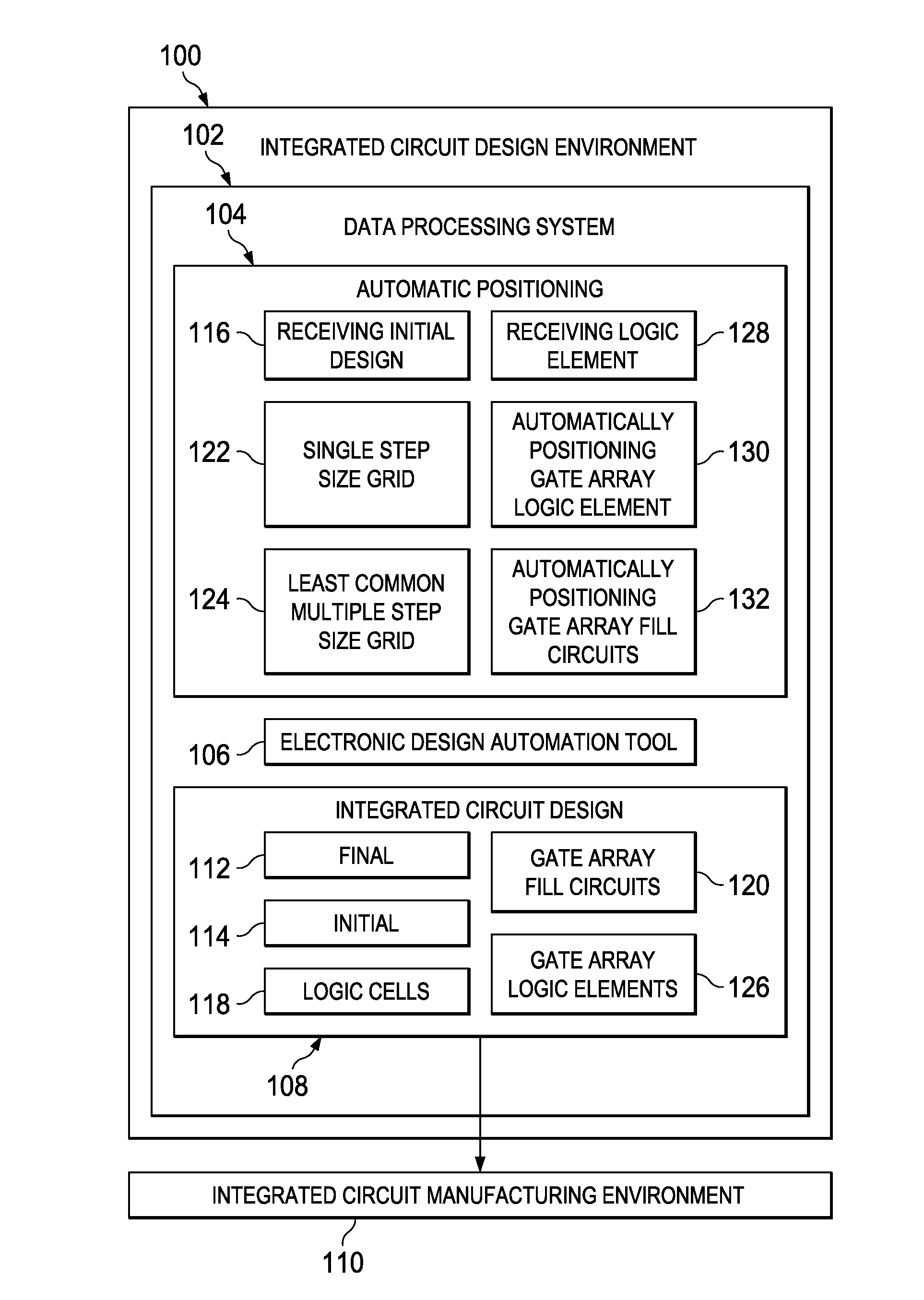

High performance hybrid micro-computer

The Field Programmable Instrument Controller (FPIC) is a stand-alone low to high performance, clocked or unclocked multi-processor that operates as a microcontroller with versatile interface and operating options. The FPIC can also be used as a concurrent processor for a microcontroller or other processor. A tightly coupled Multiple Chip Module design incorporates non-volatile memories, a large field programmable gate array (FPGA), field programmable high precision analog to digital converters, field programmable digital to analog signal generators, and multiple ports of external mass data storage and control processors. The FPIC has an inherently open architecture with in-situ reprogrammability and state preservation capability for discontinuous operations. It is designed to operate in multiple roles, including but not limited to, a high speed parallel digital signal processing; co-processor for precision control feedback during analog or hybrid computing; high speed monitoring for condition based maintenance; and distributed real time process control. The FPIC is characterized by low power with small size and weight.

Owner:BLEMEL KENNETH G

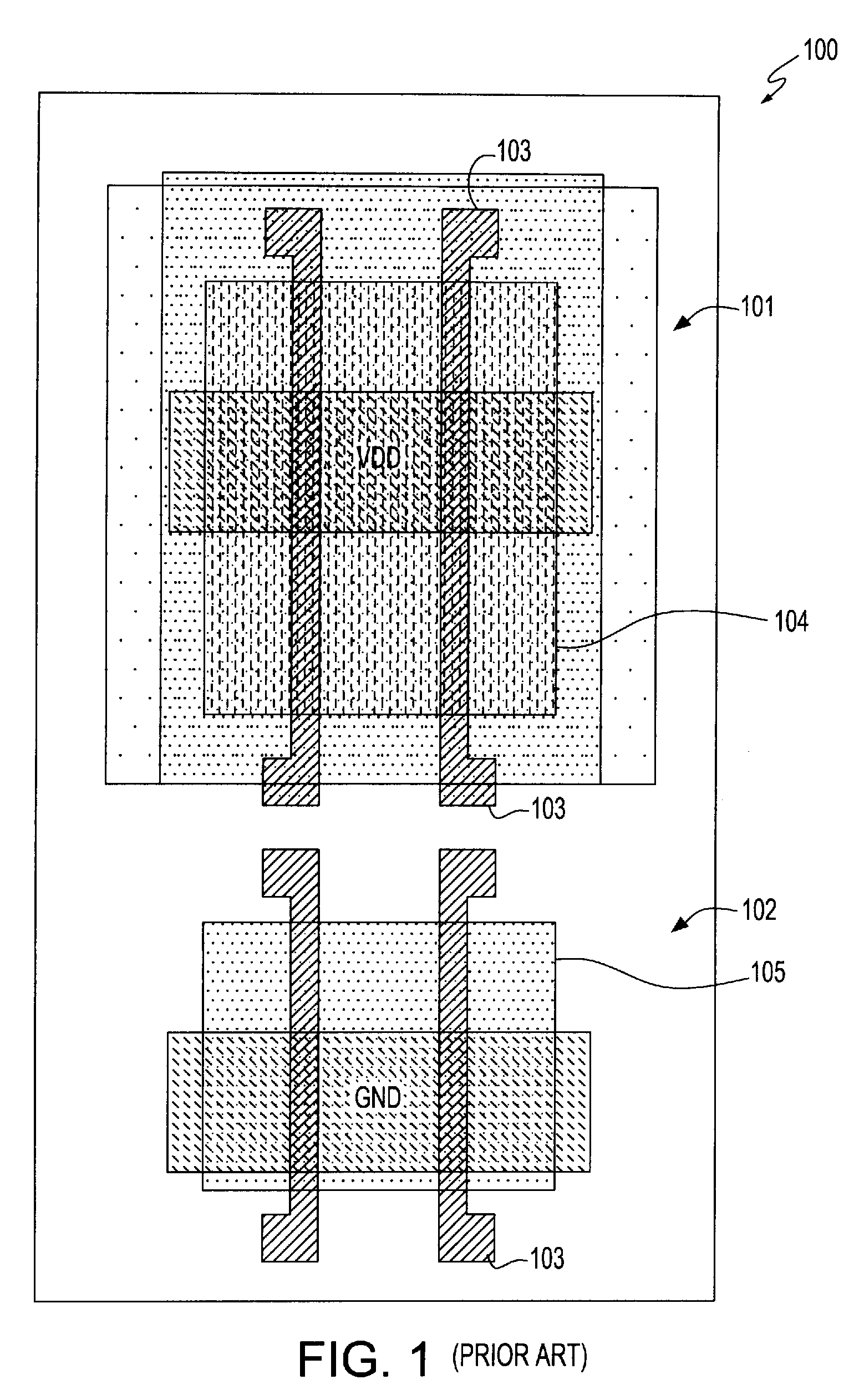

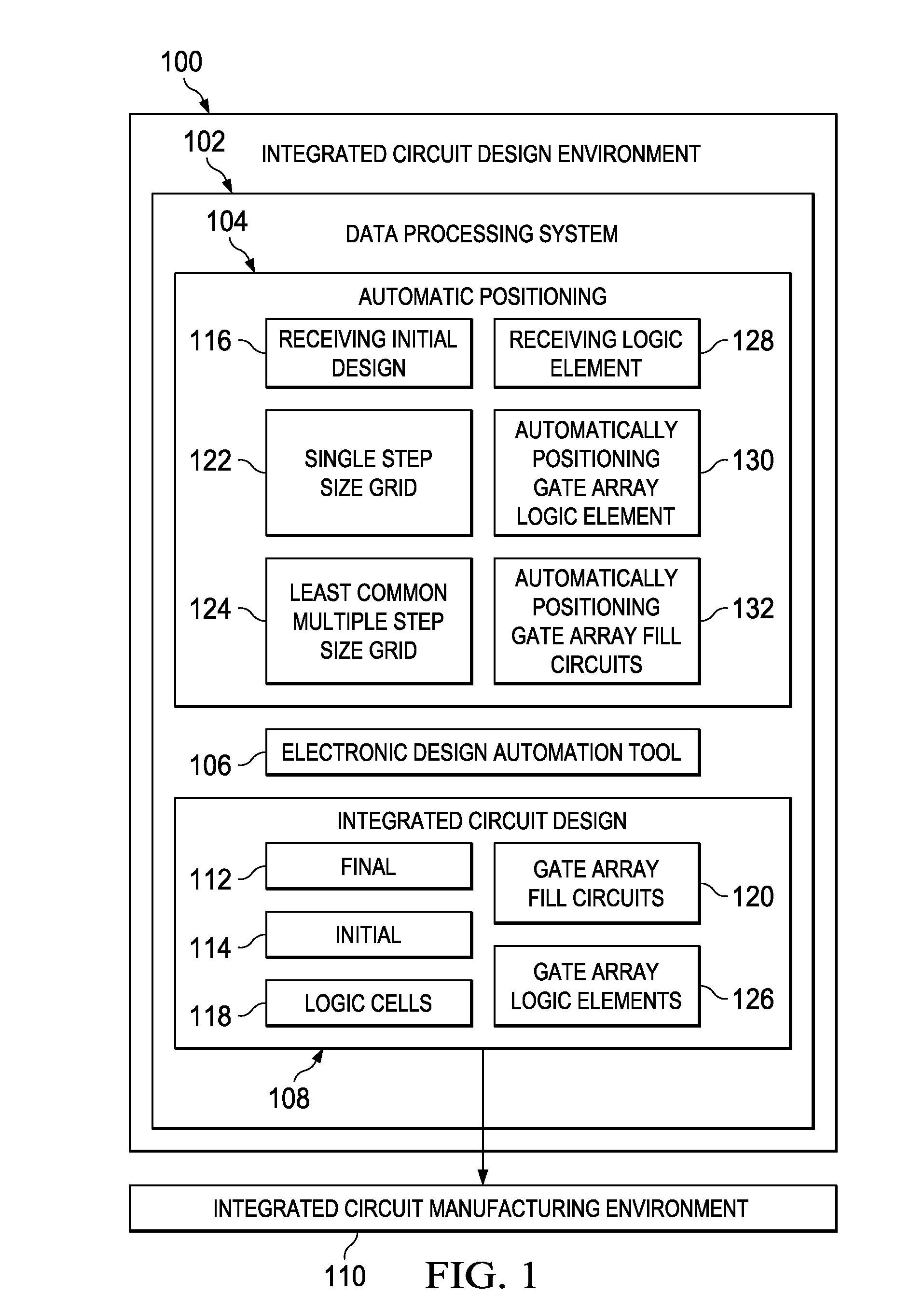

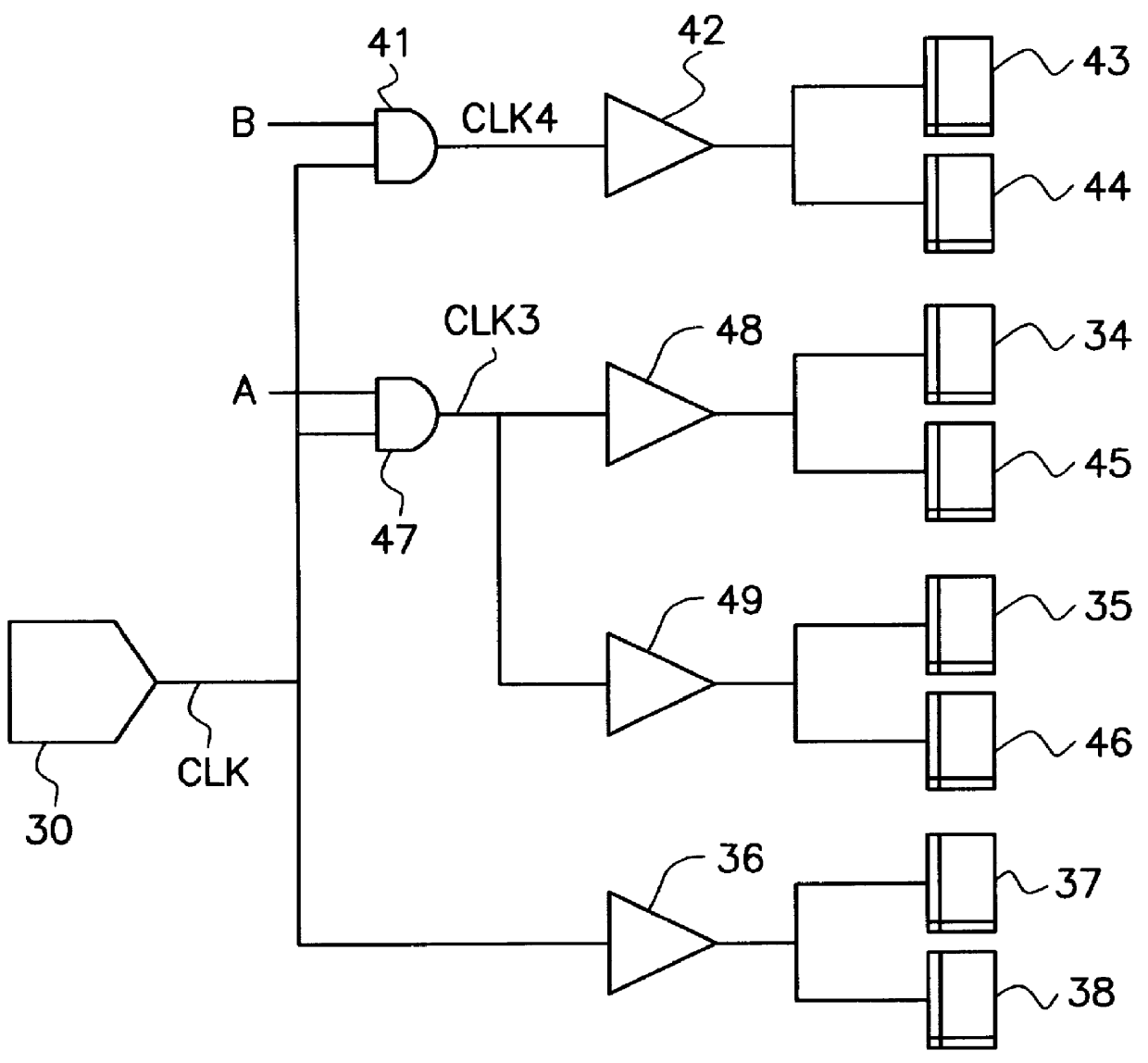

Automatic Positioning of Gate Array Circuits in an Integrated Circuit Design

ActiveUS20110072407A1Computer programmed simultaneously with data introductionComputer aided designLogic cellGate array

An automated method and apparatus for positioning gate array circuits in an integrated circuit design. An initial integrated circuit design includes logic cells and gate array fill circuits positioned thereon. The gate array fill circuits are positioned in available space between the adjacent logic cells so as to fill the available space with the maximum gate array fill circuits. A gate array logic element to be positioned in the integrated circuit design, such as may be required by an engineering change to the circuit design, is automatically positioned between adjacent logic cells so as to allow for full utilization of any space remaining between the adjacent logic cells by gate array fill circuits.

Owner:GLOBALFOUNDRIES US INC

Real-time network monitoring and security

ActiveUS20050108573A1Easy programmingEasy maintenanceWeb data indexingMemory loss protectionHigh bandwidthWire speed

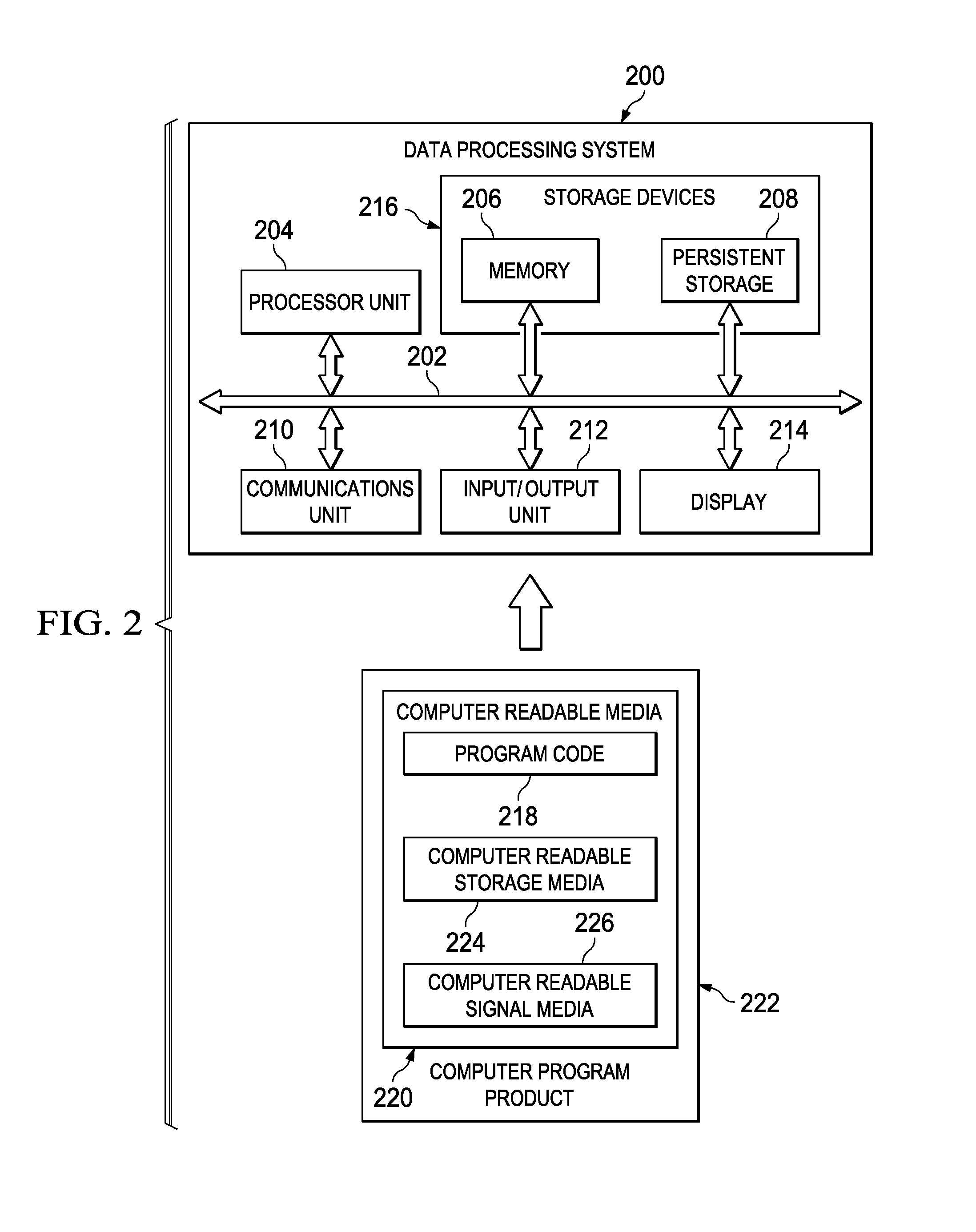

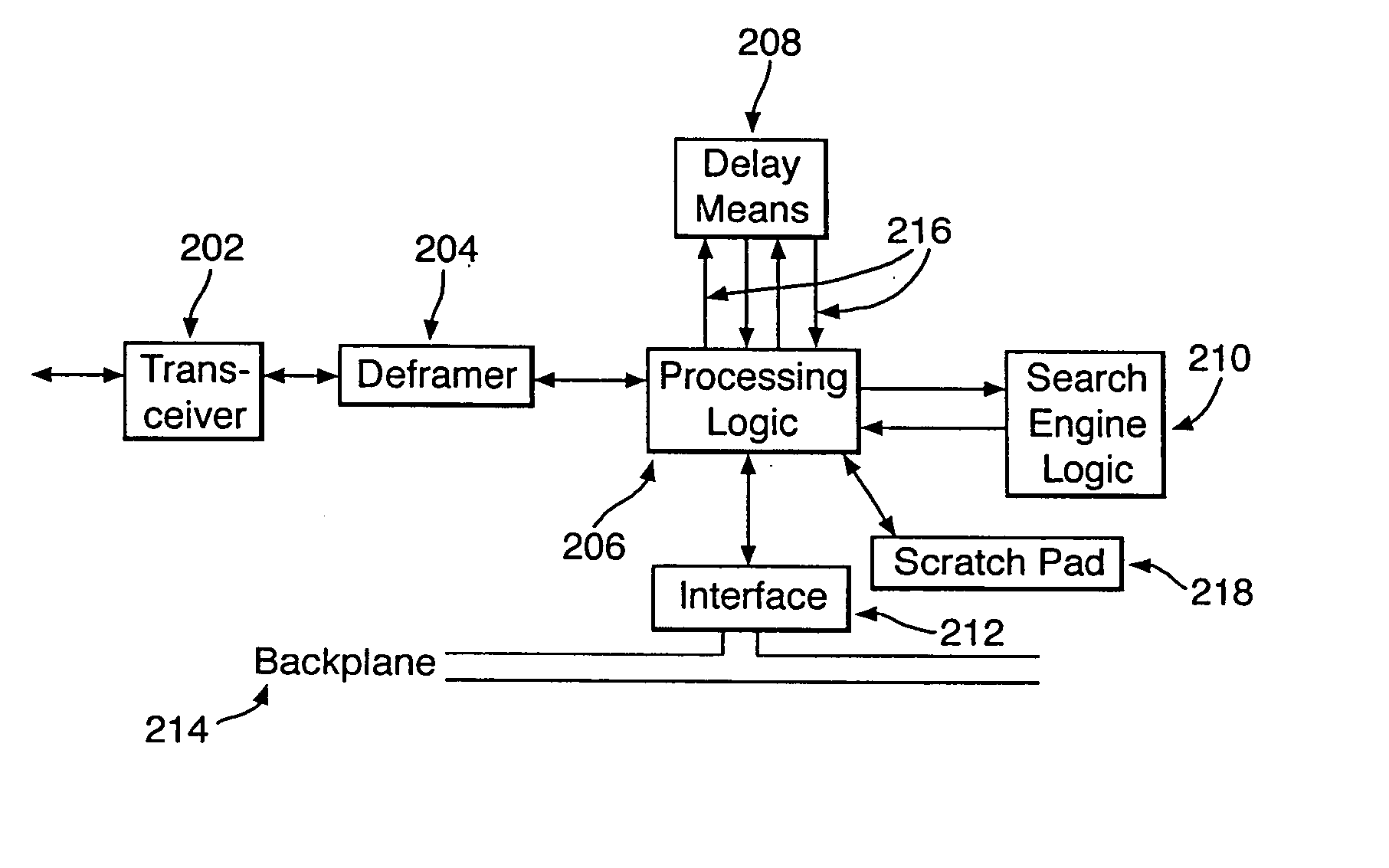

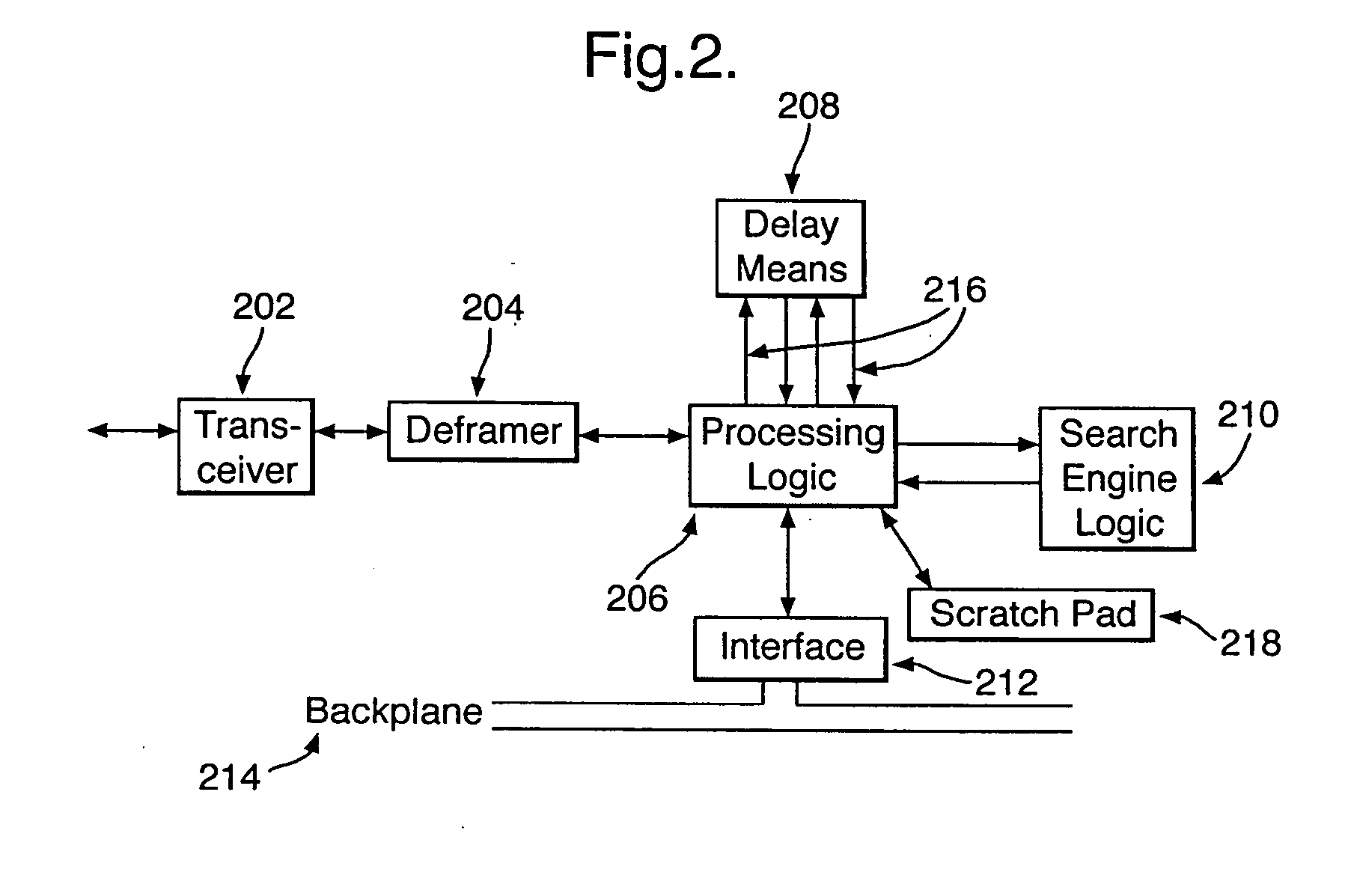

There is provided a hardware device for monitoring and intercepting data packetized data traffic at full line rate. In preferred high bandwidth embodiments, full line rate corresponds to rates that exceed 100 Mbytes / s and in some cases 1000 Mbytes / s. Monitoring and intercepting software, alone, is not able to operate on such volumes of data in real-time. A preferred embodiment comprises: a data delay buffer (208) with multiple delay outputs (216); a search engine logic (210) for implementing a set of basic search tools that operate in real-time on the data traffic; a programmable gate array (206); an interface (212) for passing data quickly to software sub-systems; and control means for implementing software control of the operation of the search tools. The programmable gate array (206) inserts the data packets into the delay buffer (208), extracts them for searching at the delay outputs and formats and schedules the operation of the search engine logic (210). One preferred embodiment uses an IP co-processor as the search engine logic.

Owner:BAE SYSTEMS PLC

Method and System for High Speed Options Pricing

A high speed technique for options pricing in the financial industry is disclosed that can provide both high throughput and low latency. Parallel / pipelined architectures are disclosed for computing an option's theoretical fair price. Preferably these parallel / pipelined architectures are deployed in hardware, and more preferably reconfigurable logic such as Field Programmable Gate Arrays (FPGAs) to accelerate the options pricing operations relative to conventional software-based options pricing operations.

Owner:EXEGY INC

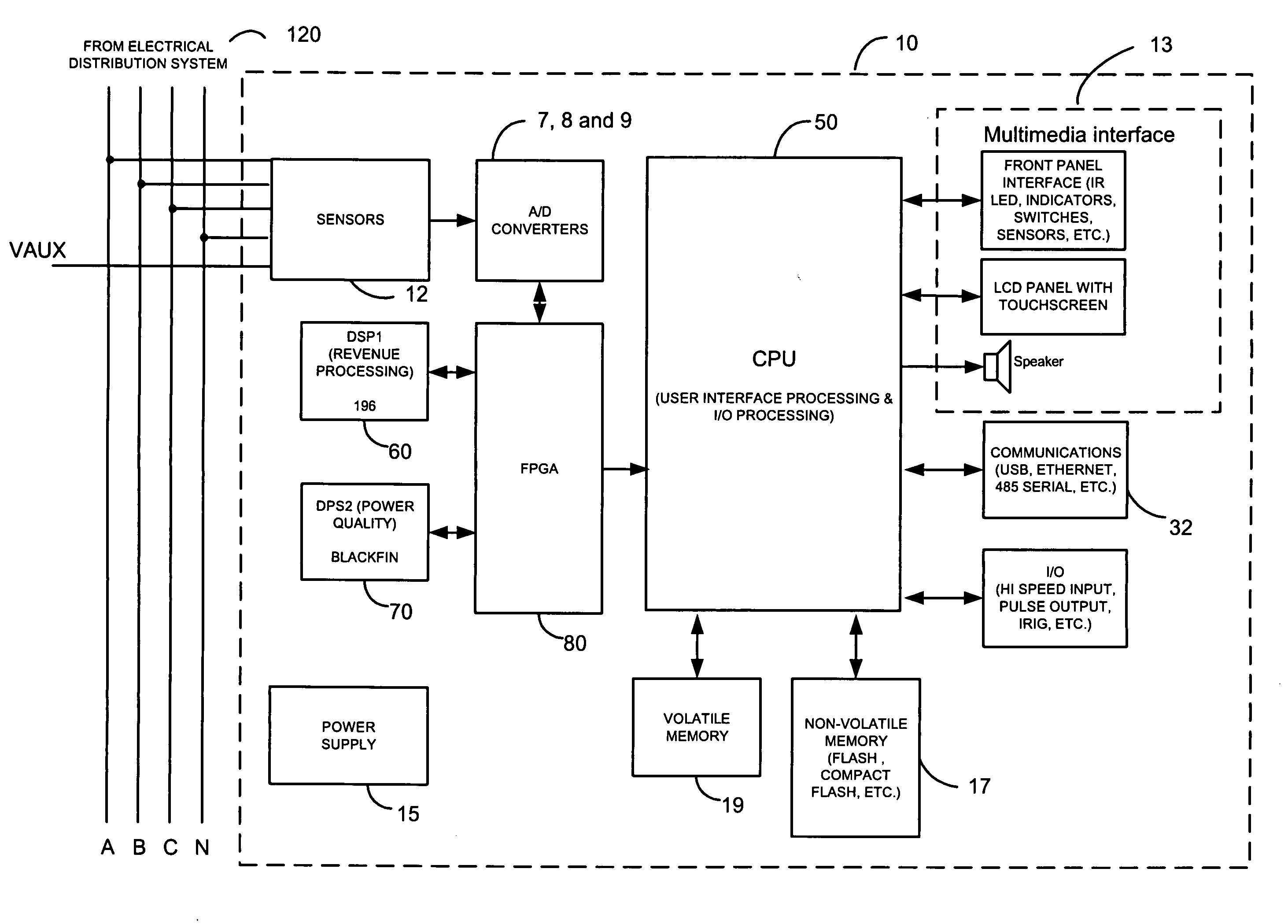

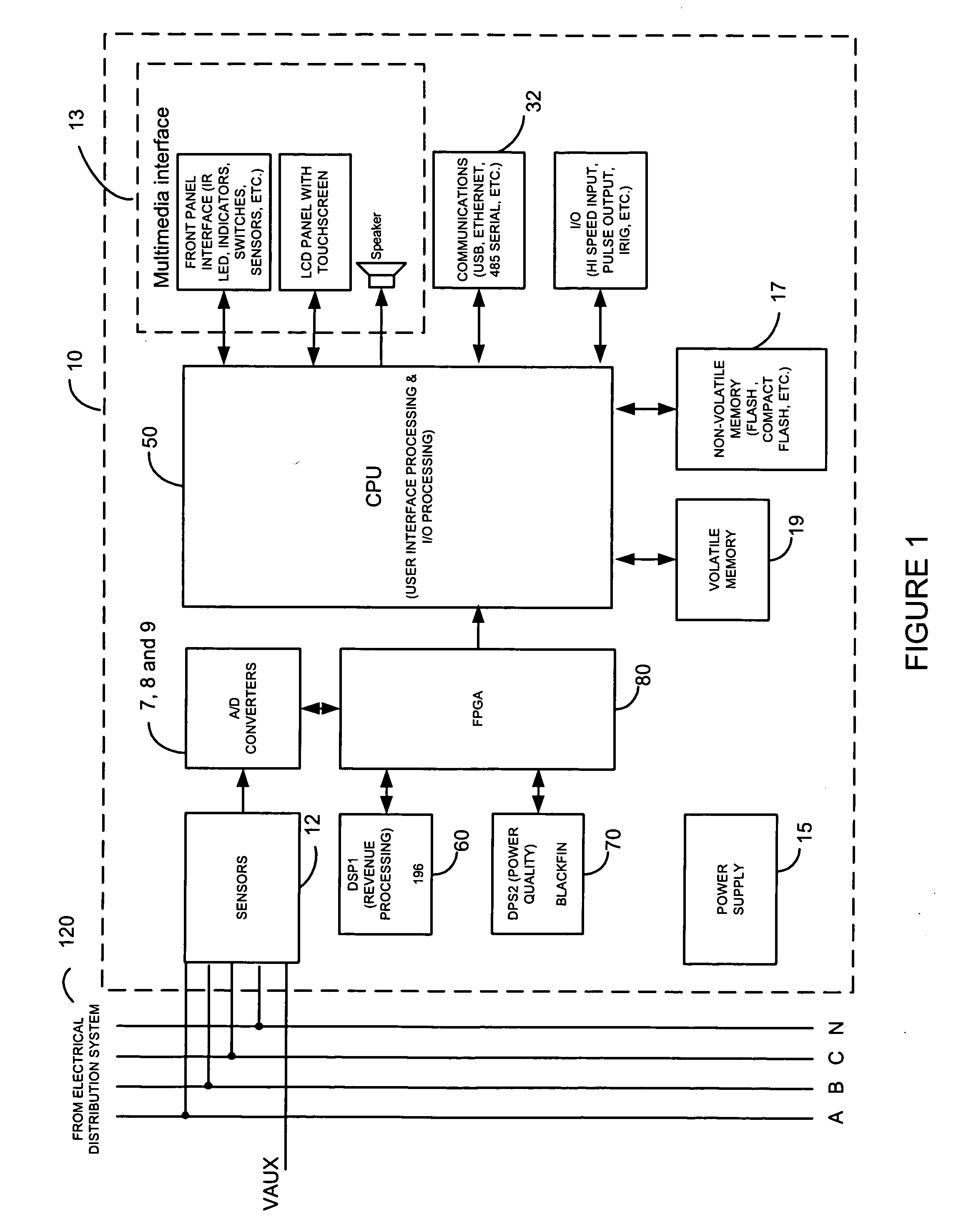

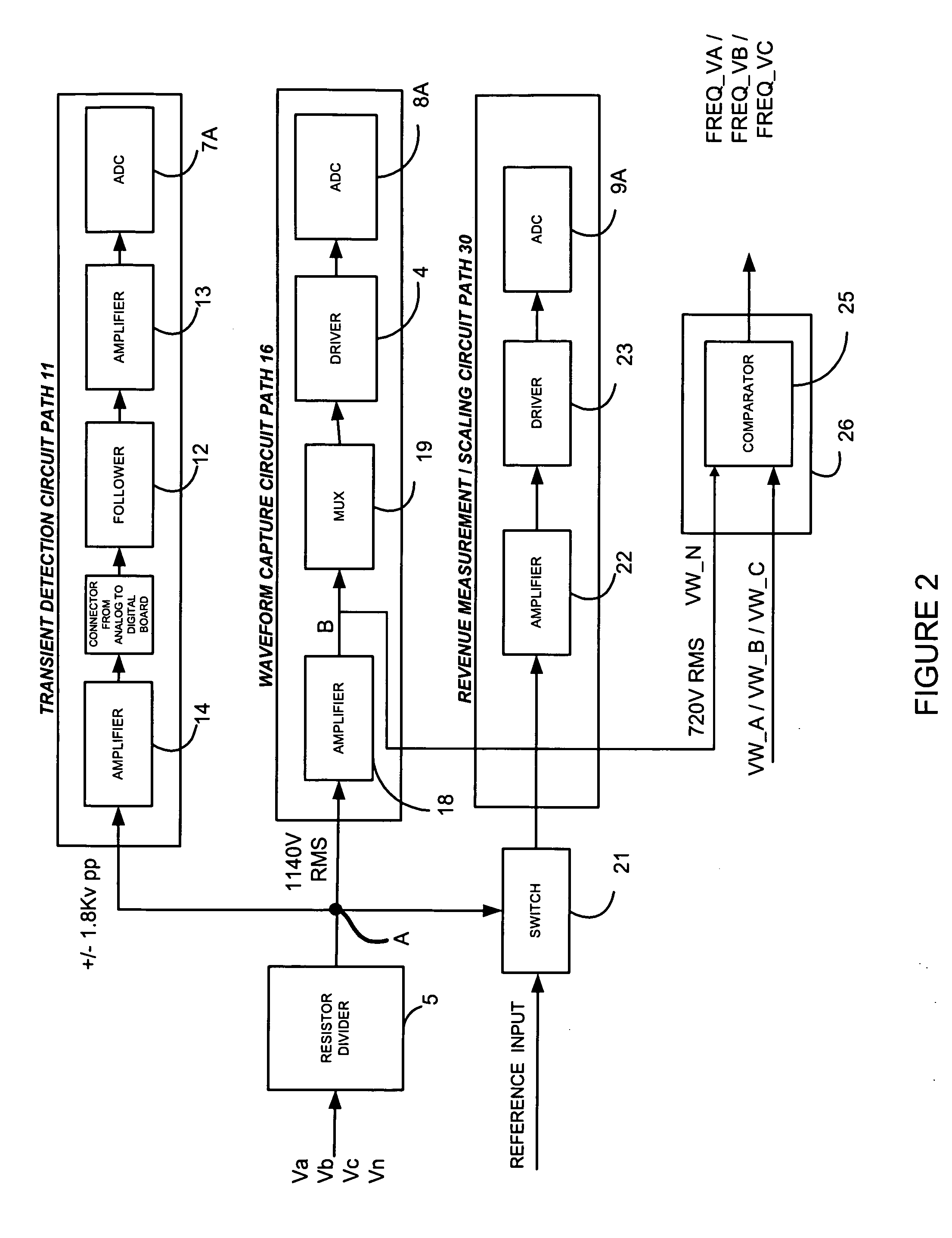

High speed digital transient waveform detection system and method for use in an intelligent device

ActiveUS20080215264A1Avoiding introduction of crosstalkFaster and more sensitive measurementMin-max value modificationElectric devicesVoltageIntelligent electronic device

Owner:ELECTRO INDSGAUGE TECH +1

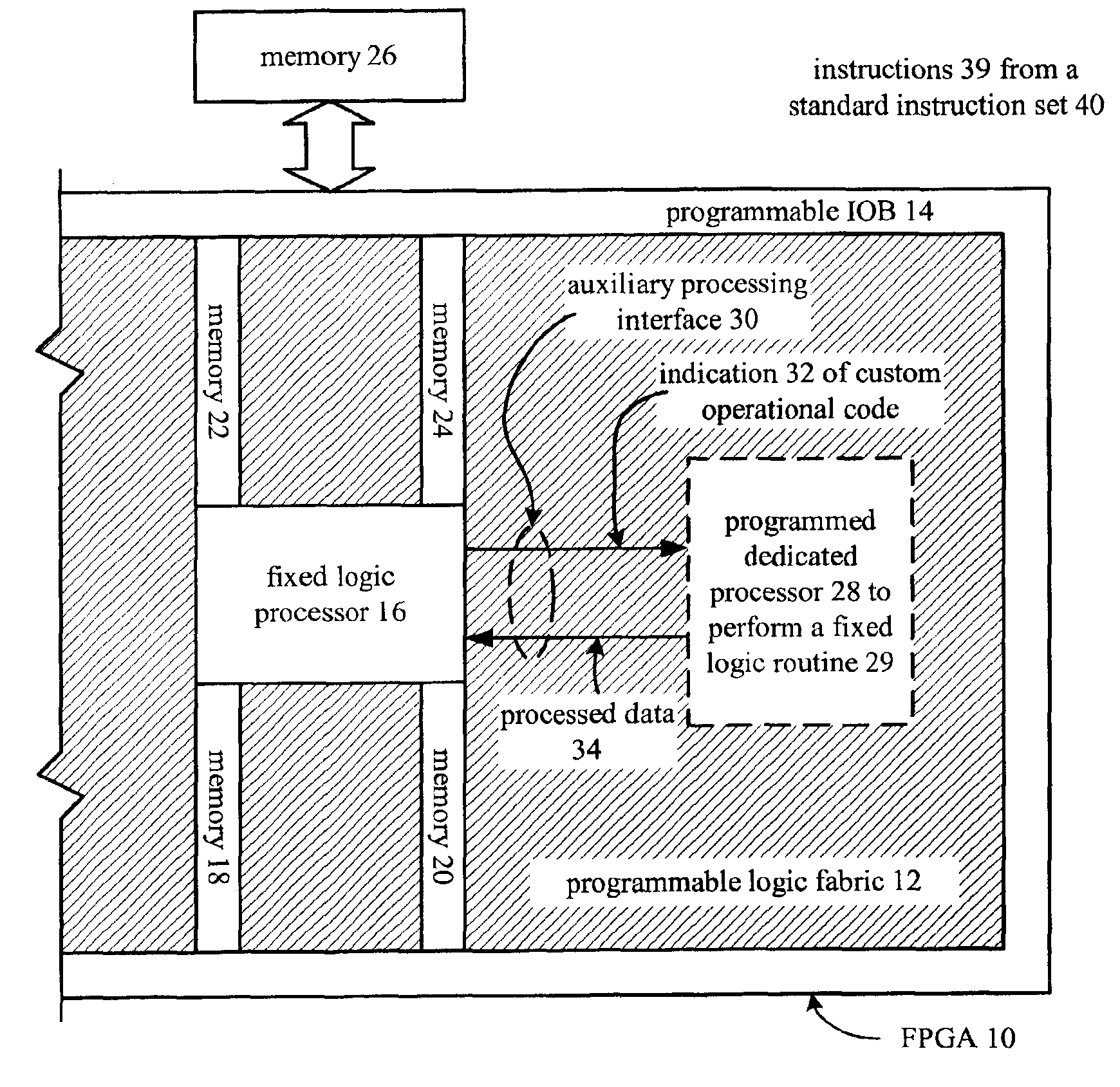

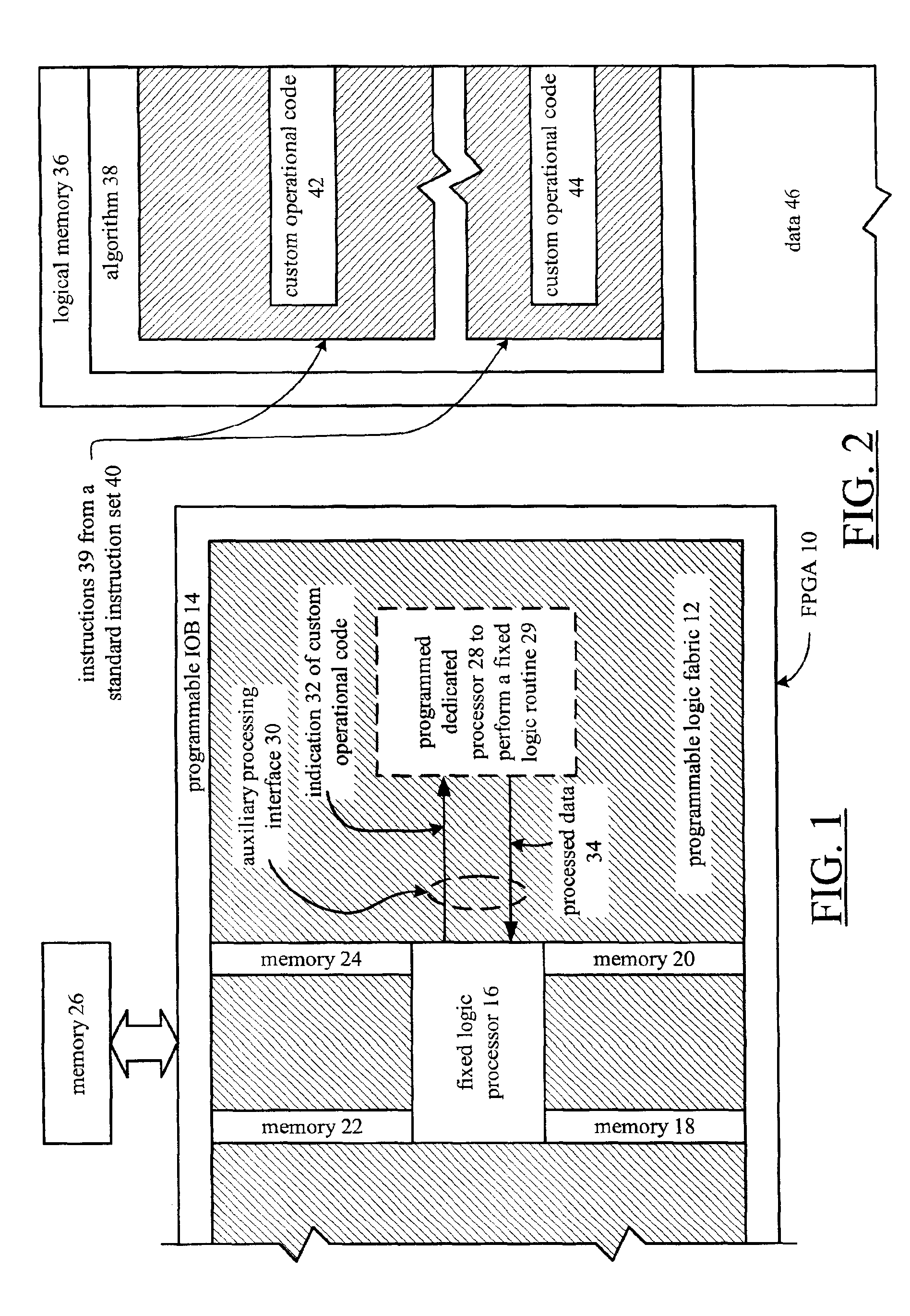

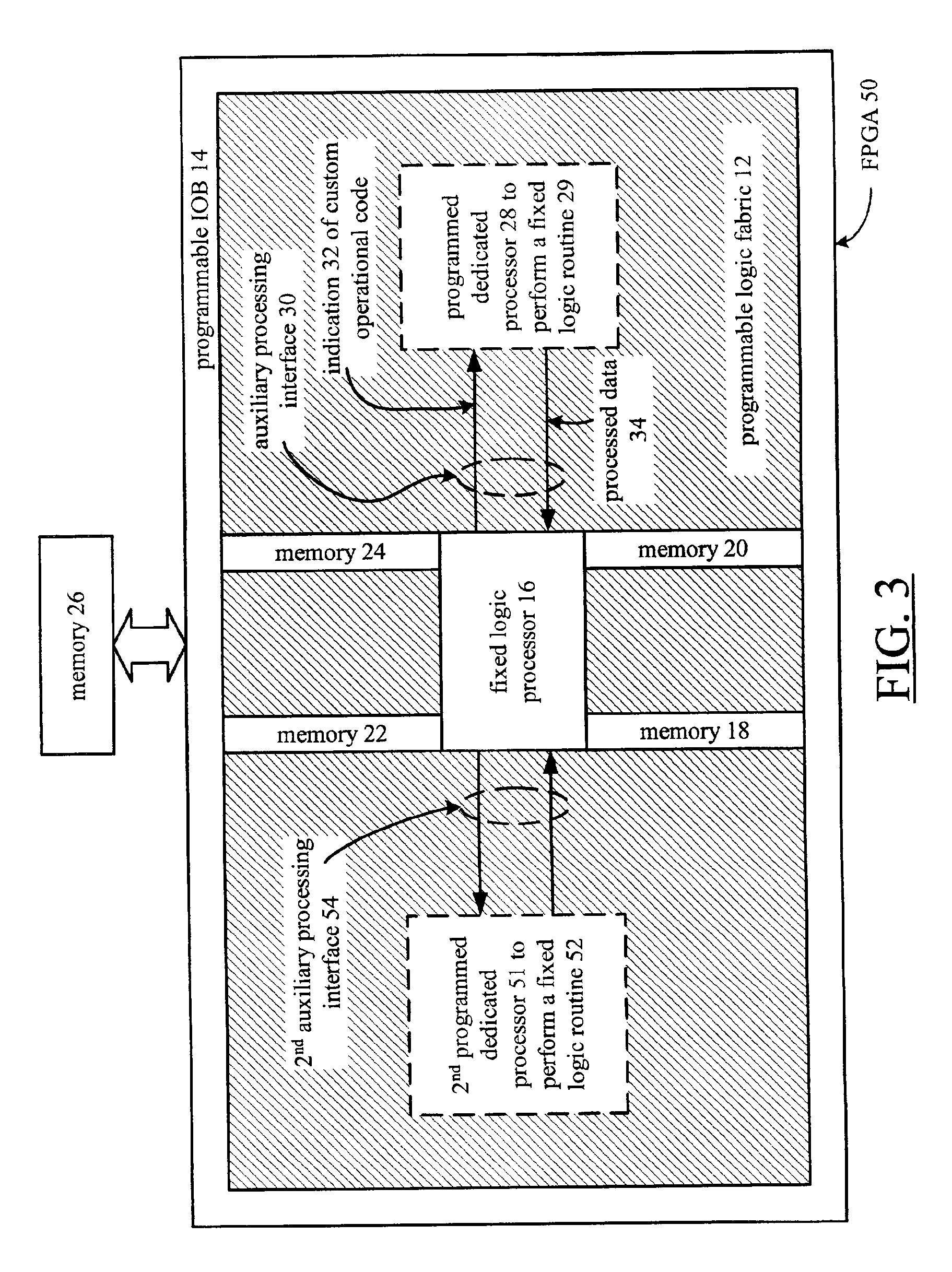

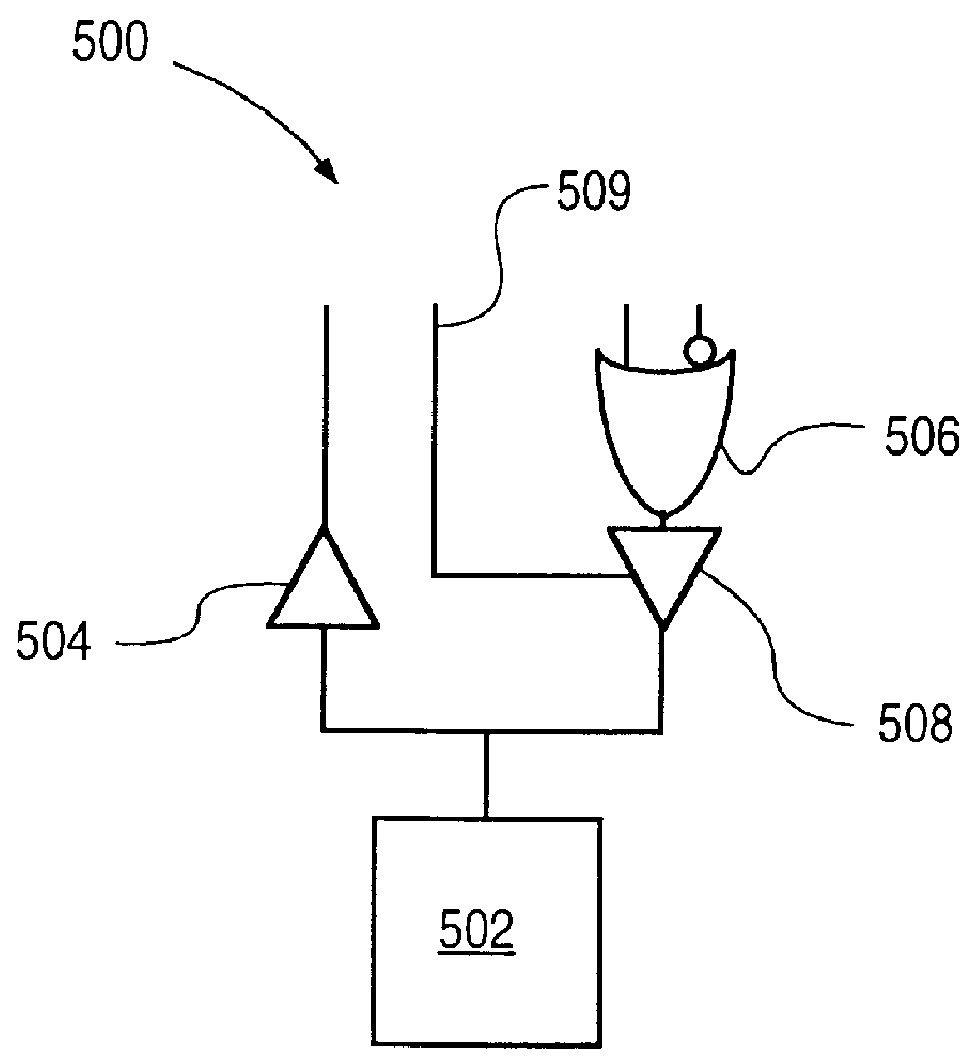

Custom code processing in PGA by providing instructions from fixed logic processor portion to programmable dedicated processor portion

A method and apparatus for processing data within a programmable gate array begins when a fixed logic processor that is embedded within the programmable gate array detects a custom operation code. The processing continues when the fixed logic processor provides an indication of the custom operational code to the programmable gate array. The processing continues by having at least a portion of the programmable gate array, which is configured as a dedicated processor, performing a fixed logic routine upon receiving the indication from the fixed logic processor.

Owner:XILINX INC

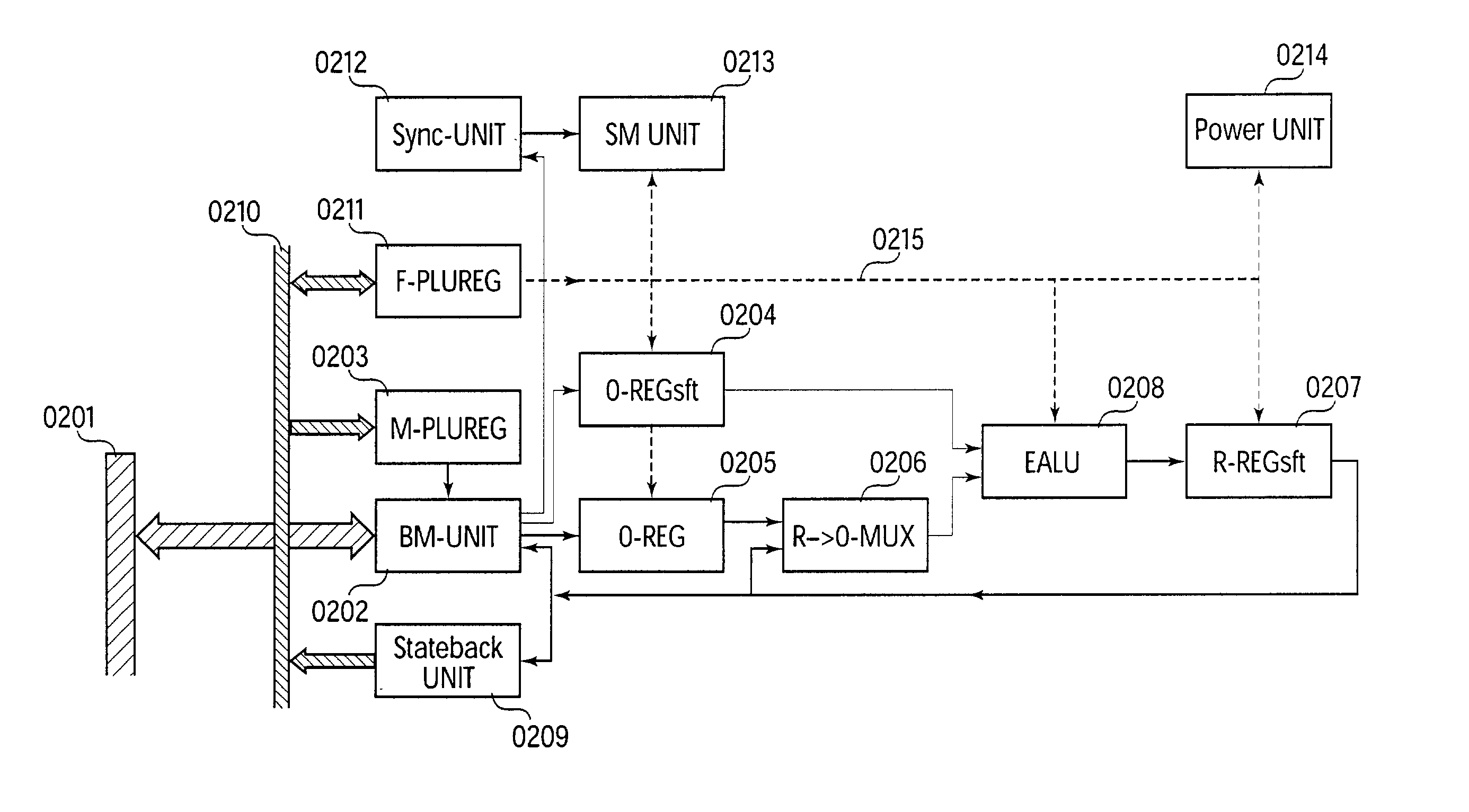

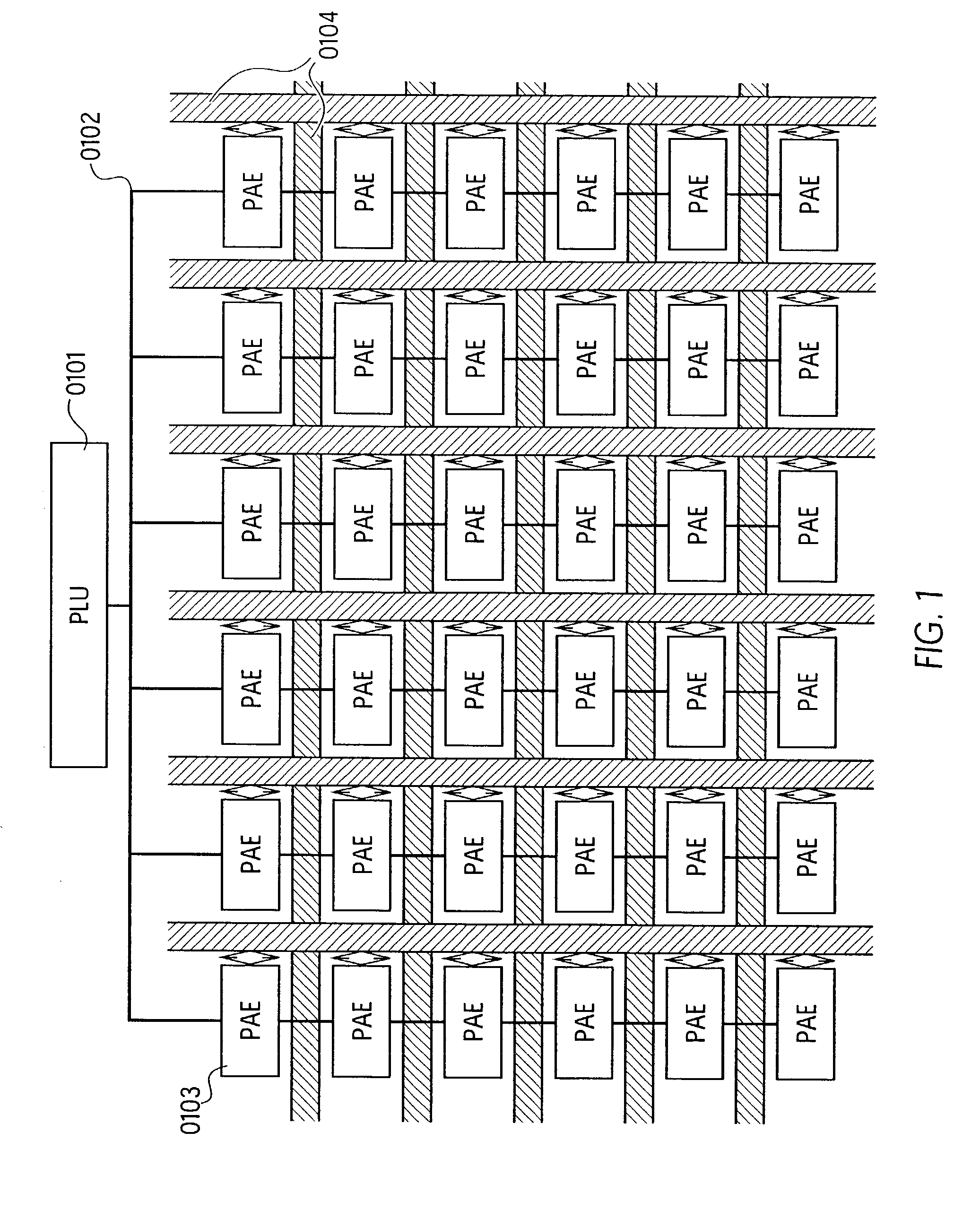

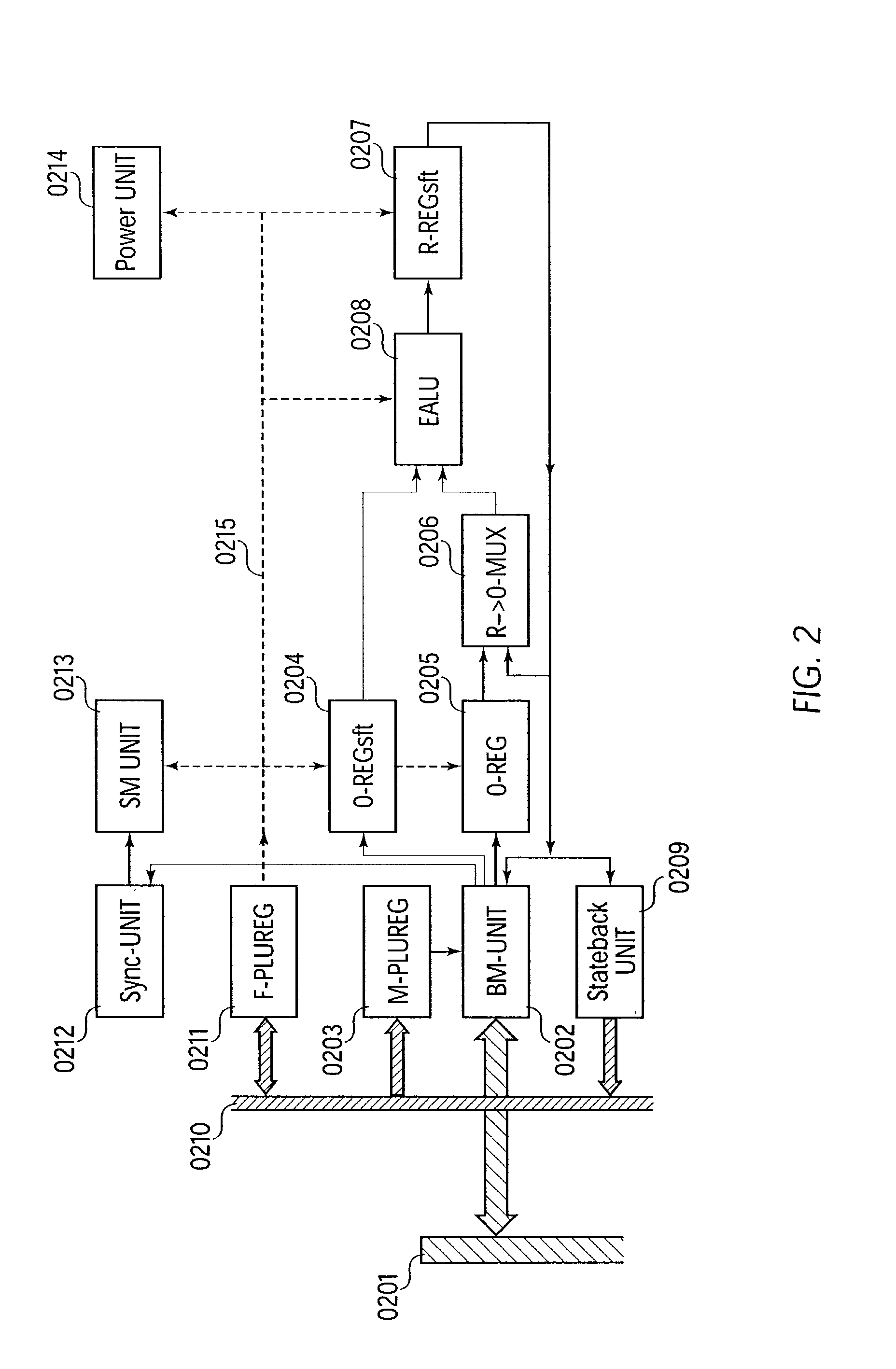

Unit for processing numeric and logic operations for use in central processing units (CPUS), multiprocessor systems, data-flow processors (DSPS), systolic processors and field programmable gate arrays (FPGAS)

InactiveUS20030056085A1The process is convenient and fastSimplifies (re)configurationEnergy efficient ICTMultiple digital computer combinationsBus masteringBroadcasting

An expanded arithmetic and logic unit (EALU) with special extra functions is integrated into a configurable unit for performing data processing operations. The EALU is configured by a function register, which greatly reduces the volume of data required for configuration. The cell can be cascaded freely over a bus system, the EALU being decoupled from the bus system over input and output registers. The output registers are connected to the input of the EALU to permit serial operations. A bus control unit is responsible for the connection to the bus, which it connects according to the bus register. The unit is designed so that distribution of data to multiple receivers (broadcasting) is possible. A synchronization circuit controls the data exchange between multiple cells over the bus system. The EALU, the synchronization circuit, the bus control unit, and registers are designed so that a cell can be reconfigured on site independently of the cells surrounding it. A power-saving mode which shuts down the cell can be configured through the function register; clock rate dividers which reduce the working frequency can also be set.

Owner:PACT +1

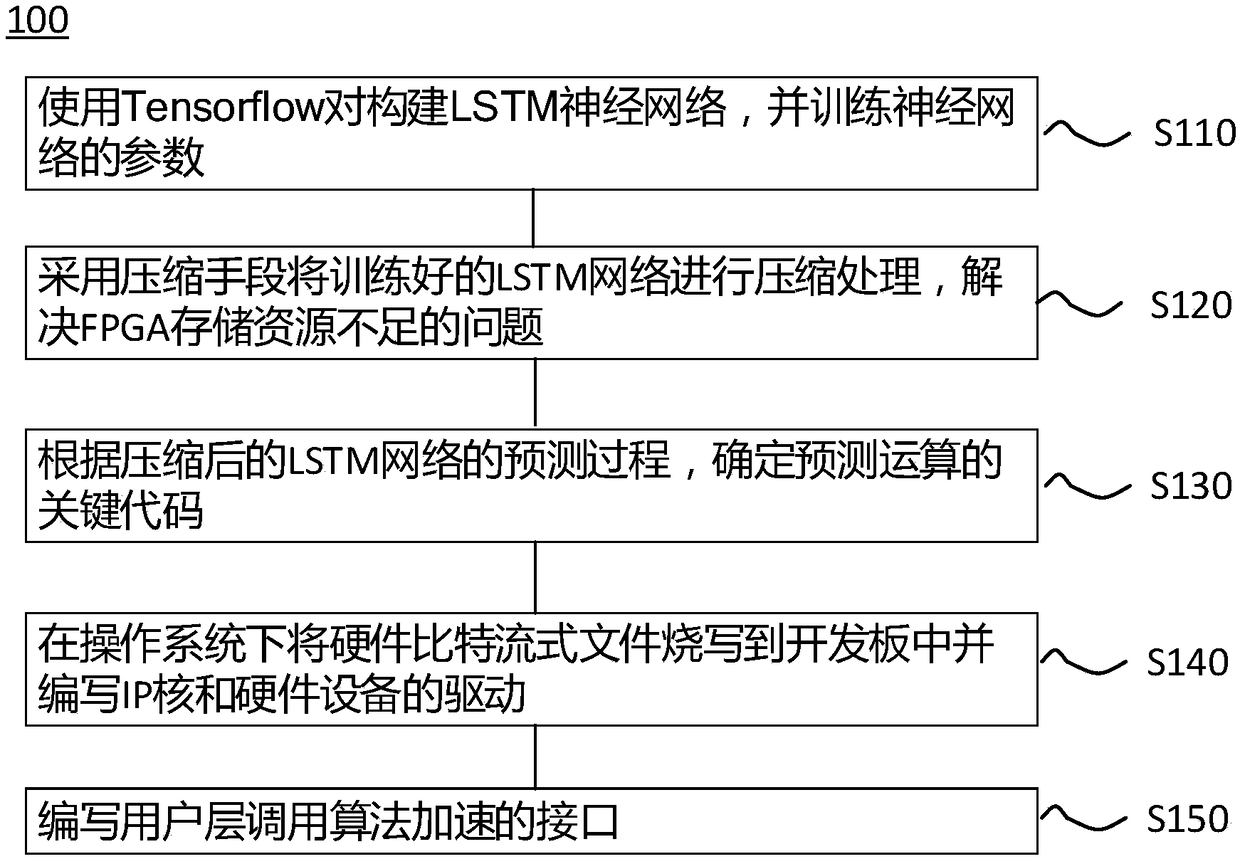

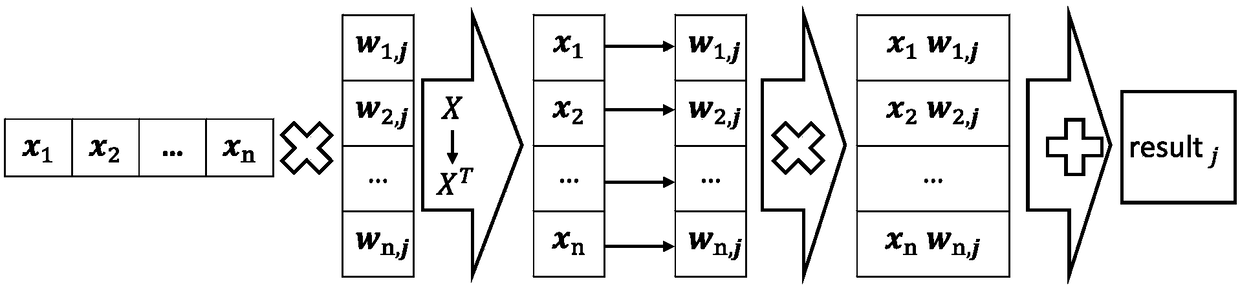

Design method of hardware accelerator based on LSTM recursive neural network algorithm on FPGA platform

InactiveCN108090560AImprove forecastImprove performanceNeural architecturesPhysical realisationNeural network hardwareLow resource

The invention discloses a method for accelerating an LSTM neural network algorithm on an FPGA platform. The FPGA is a field-programmable gate array platform and comprises a general processor, a field-programmable gate array body and a storage module. The method comprises the following steps that an LSTM neural network is constructed by using a Tensorflow pair, and parameters of the neural networkare trained; the parameters of the LSTM network are compressed by adopting a compression means, and the problem that storage resources of the FPGA are insufficient is solved; according to the prediction process of the compressed LSTM network, a calculation part suitable for running on the field-programmable gate array platform is determined; according to the determined calculation part, a softwareand hardware collaborative calculation mode is determined; according to the calculation logic resource and bandwidth condition of the FPGA, the number and type of IP core firmware are determined, andacceleration is carried out on the field-programmable gate array platform by utilizing a hardware operation unit. A hardware processing unit for acceleration of the LSTM neural network can be quicklydesigned according to hardware resources, and the processing unit has the advantages of being high in performance and low in power consumption compared with the general processor.

Owner:SUZHOU INST FOR ADVANCED STUDY USTC

Combination field programmable gate array allowing dynamic reprogrammability and non-votatile programmability based upon transistor gate oxide breakdown

Owner:LATTICE SEMICON CORP +1

Architecture for dynamically reconfigurable system-on-chip arrangements, related methods and computer program product

ActiveUS20070088537A1Increase flexibilitySave energyDigital computer detailsMultiprogramming arrangementsMicrocontrollerExtensibility

A system-on-chip arrangement having, in possible combination with a processor, a plurality of reconfigurable gate array devices, and a configurable Network-on-Chip connecting the gate array devices to render the arrangement scalable. The arrangement lends itself to be operated by mapping in one device of the gate array a set of processing modules, and configuring another device of the plurality of gate array devices as a microcontroller having stored therein software code portions for controlling inter-operation of the processing modules stored in the one device of the plurality. The arrangement is thus adapted, e.g., to handle different computational granularity levels.

Owner:STMICROELECTRONICS SRL

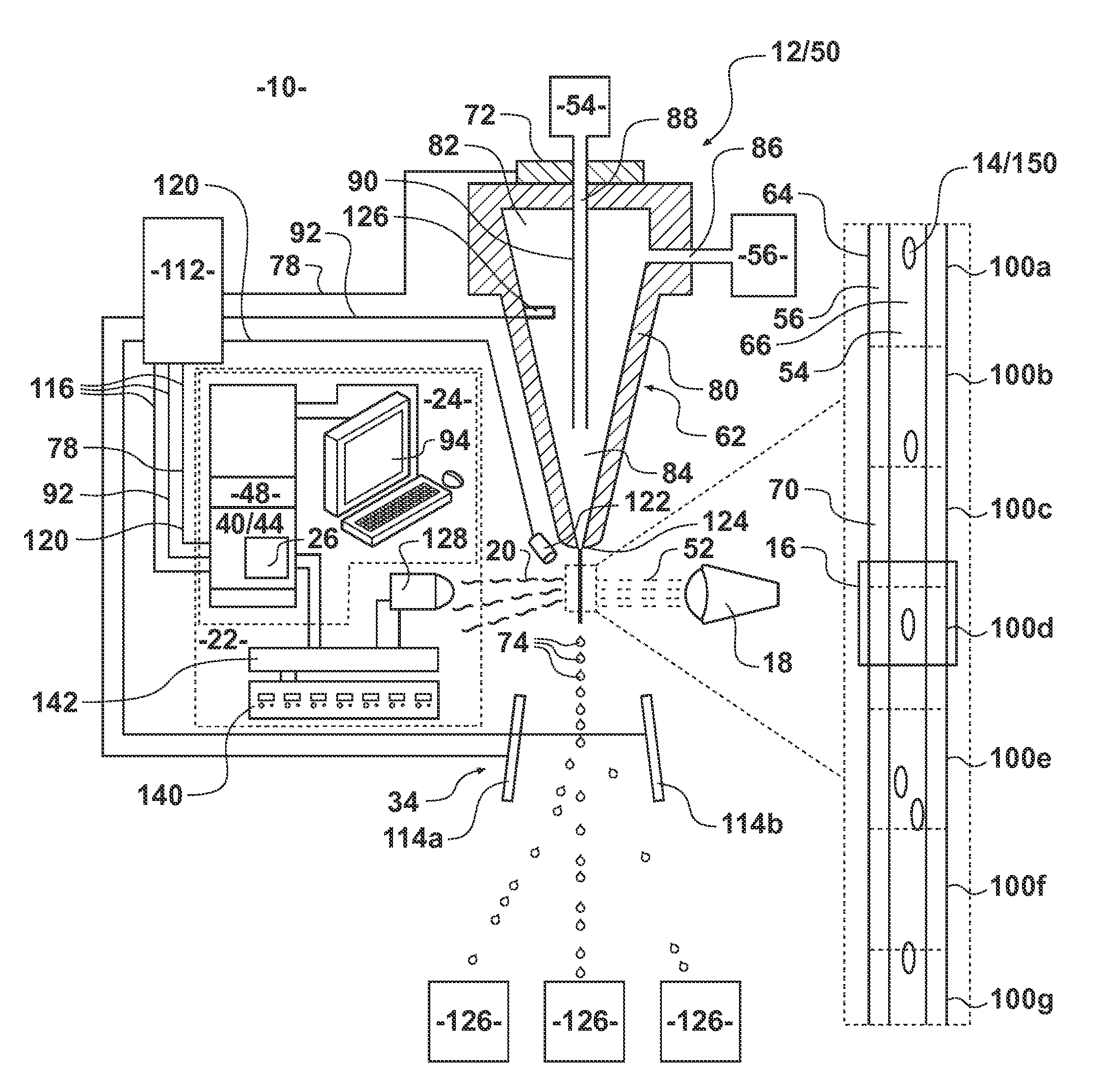

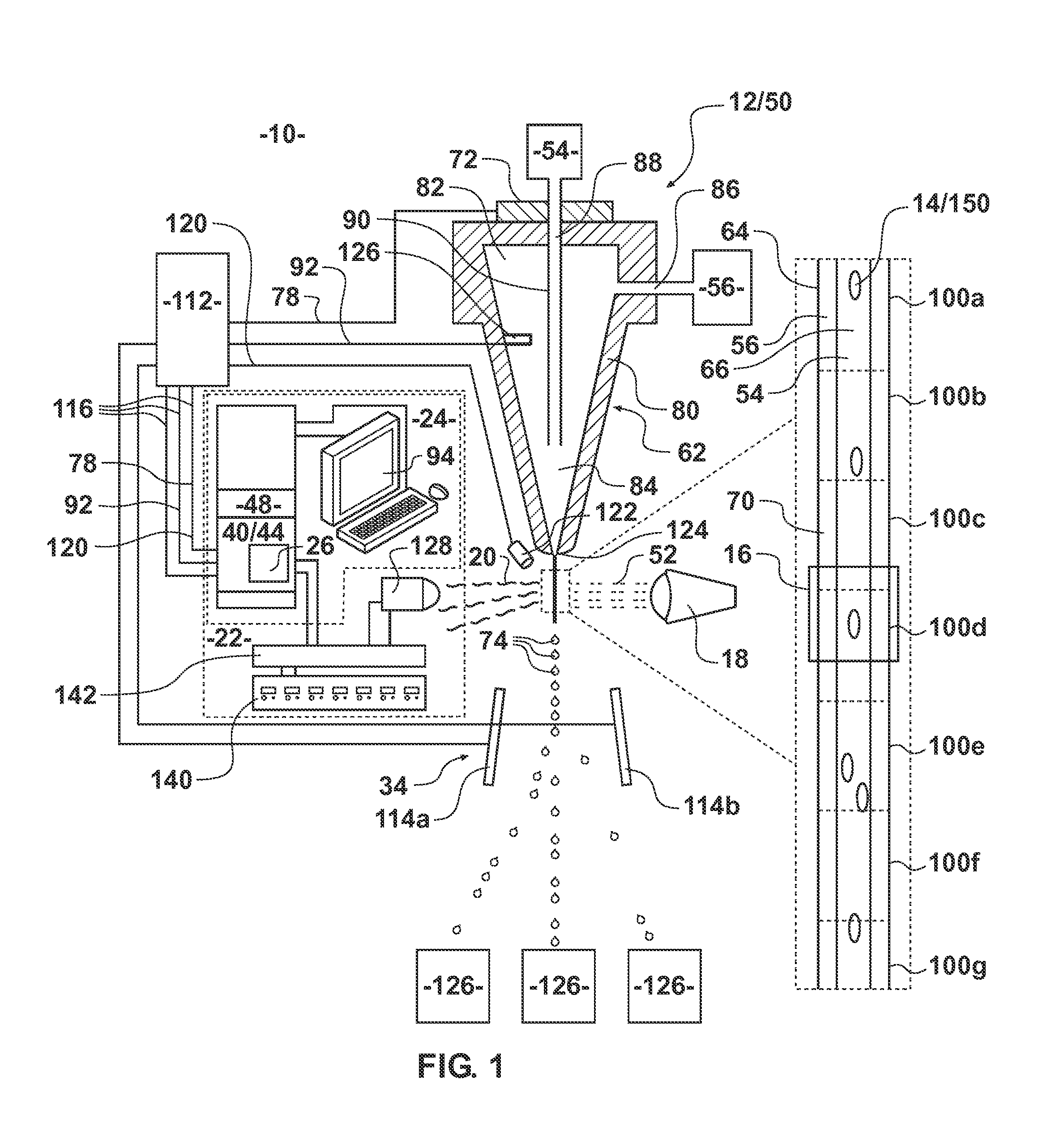

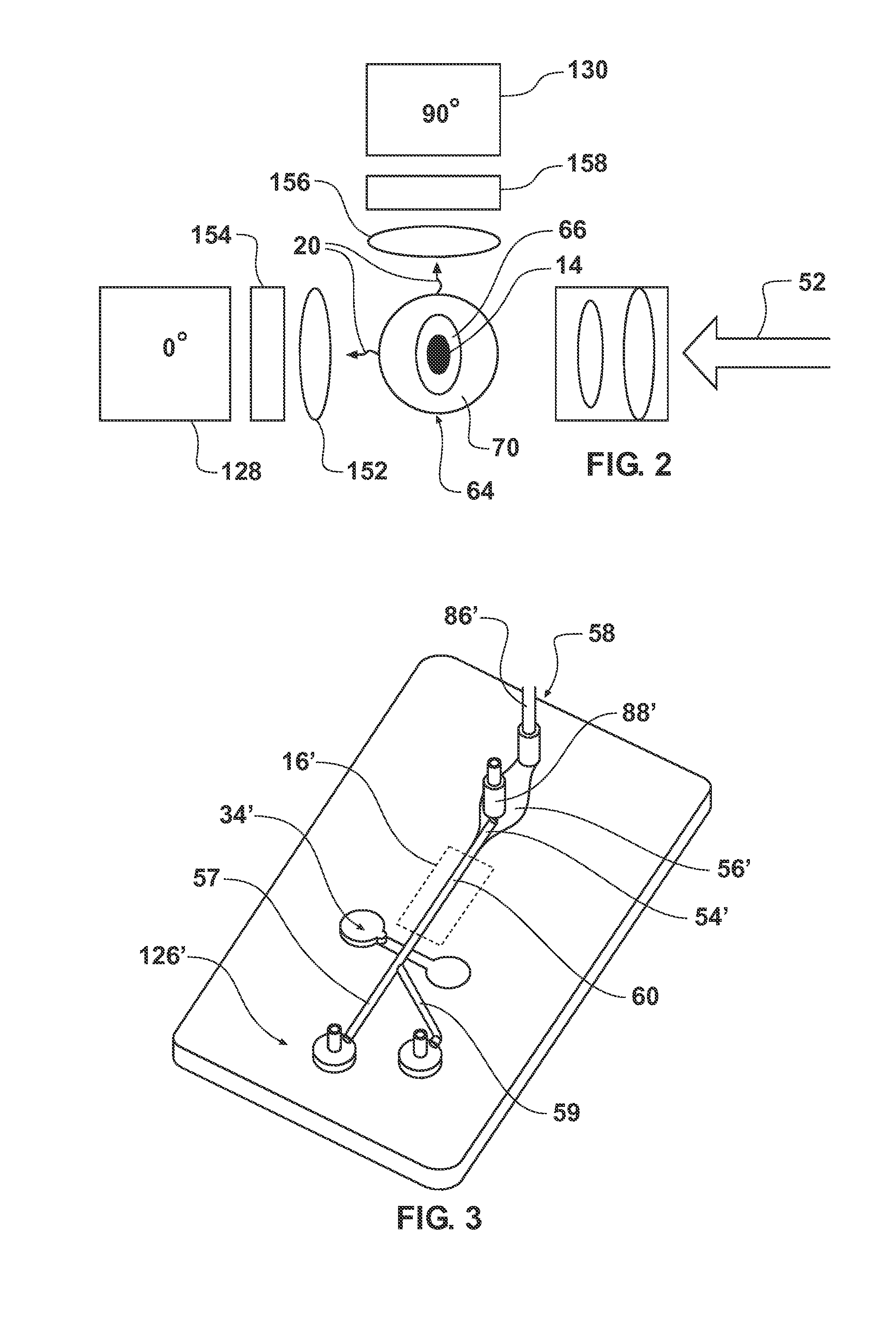

Particle sorting apparatus and method

ActiveUS20120202237A1Accurate trackingEasy to explainMicrobiological testing/measurementWithdrawing sample devicesParticle sortingEngineering

A particle analyzing and / or sorting apparatus and the associated methods. One aspect of the described embodiments relates to an analyzer, or a sorter, having acquisition and sort electronics in the form of a field programmable gate array for processing detected signals. Another aspect relates to a droplet based approach of analyzing and sorting particles and may further include a dynamic element, such a dynamic drop delay. In still another broad aspect, an apparatus and method for dynamically varying other sorting parameters.

Owner:CYTONOMEST

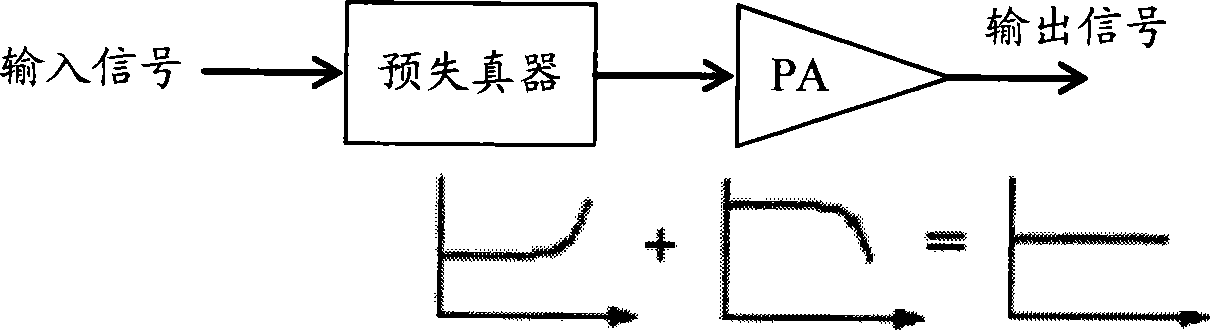

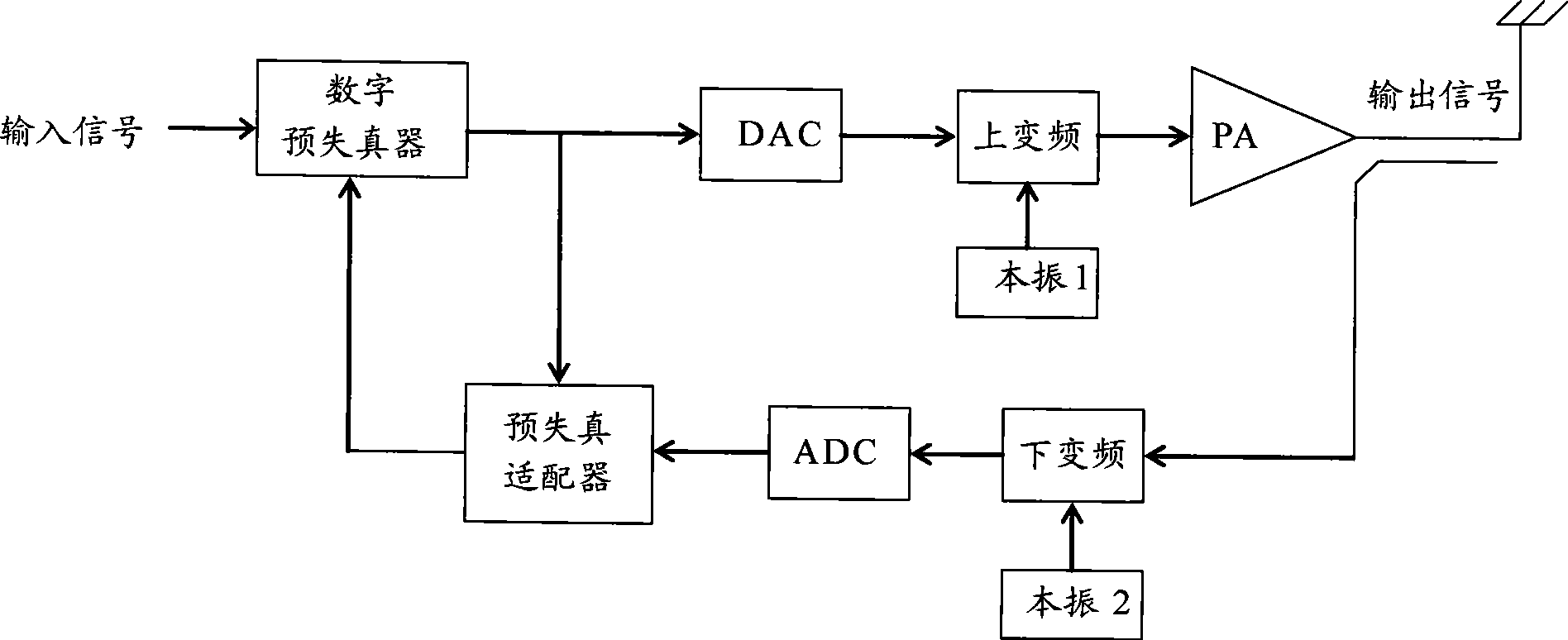

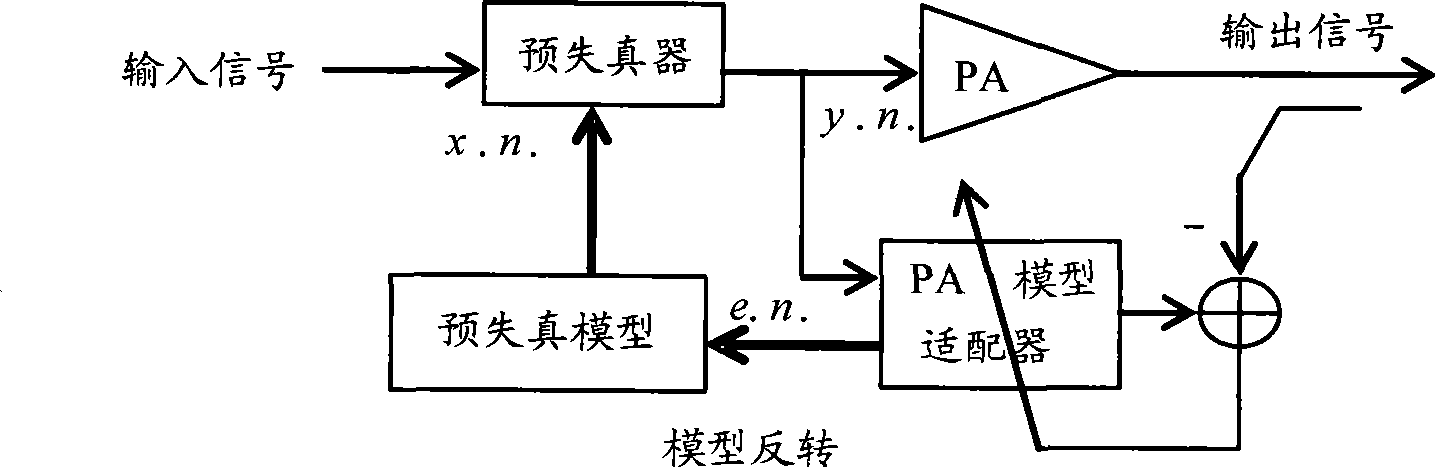

Adaptive pre-distortion method

ActiveCN101459636ANo mistakesNo non-convergence problemAmplifier modifications to reduce non-linear distortionSynchronising arrangementAudio power amplifierGate array

The invention discloses a self-adaptive predistortion method, which comprises the steps: collecting emission data and feedback data, calculating loop delay according to the emission data and the feedback data, carrying out time unifying to input signals according to the loop delay, compensating collected delay of the emission data and the feedback data according to the loop delay, estimating a predistortion model parameter, constructing a matrix according to the set predistortion model parameter, calculating a predistortion parameter corresponding to a power amplifier, adopting a curve fitting method to sample and quantize the predistortion parameter to obtain an LUT table, modifying the predistortion parameter in a digital predistorter according to the LUT table, carrying out digital predistortion to the input signals according to an LUT address and the predistortion parameter which is modified, and generating the LUT address according to the amplitude of the input signals. The technical scheme of the invention saves the hardware implementation cost and can be realized in an FPGA (programmable gate array) easily.

Owner:ZTE CORP

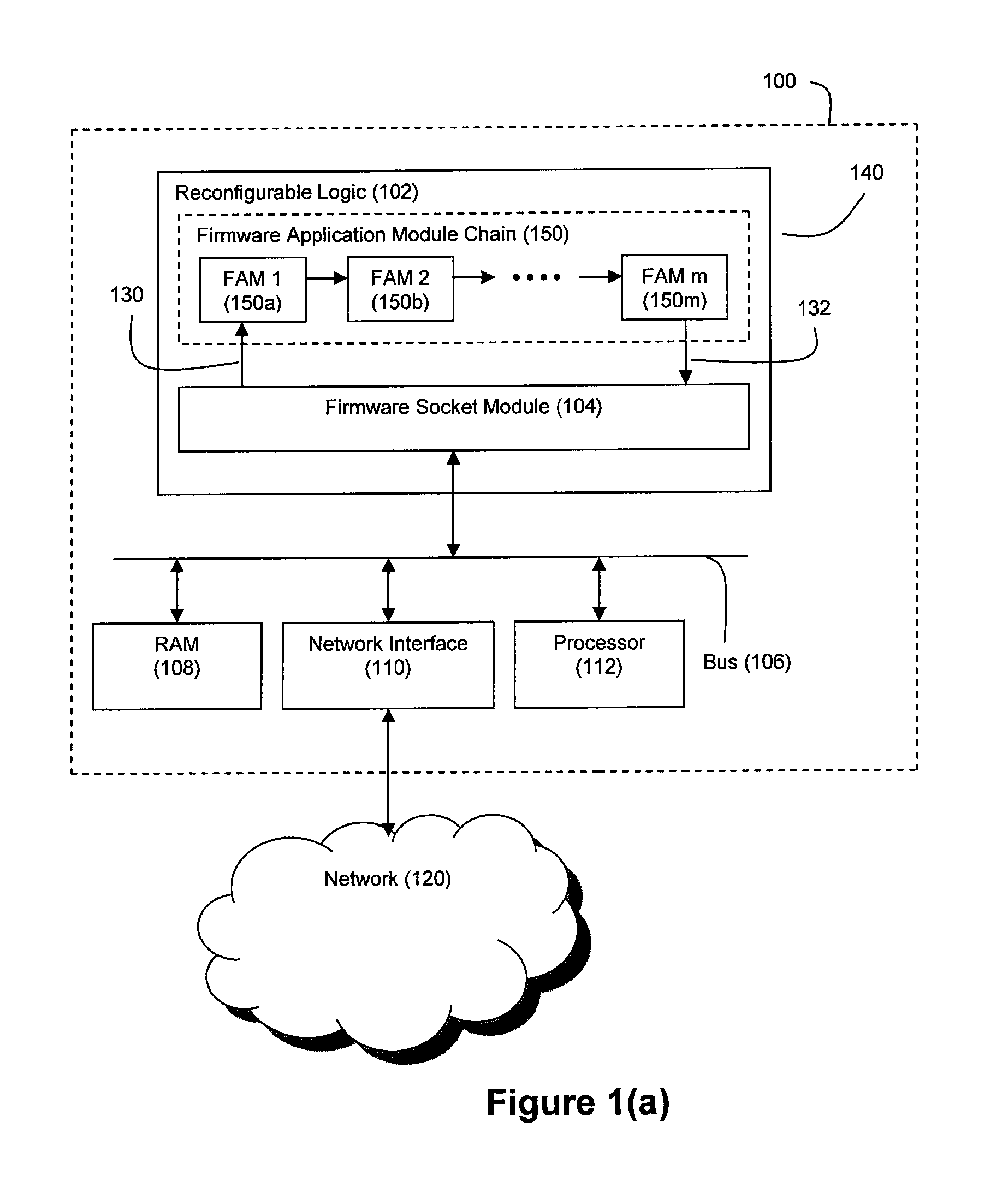

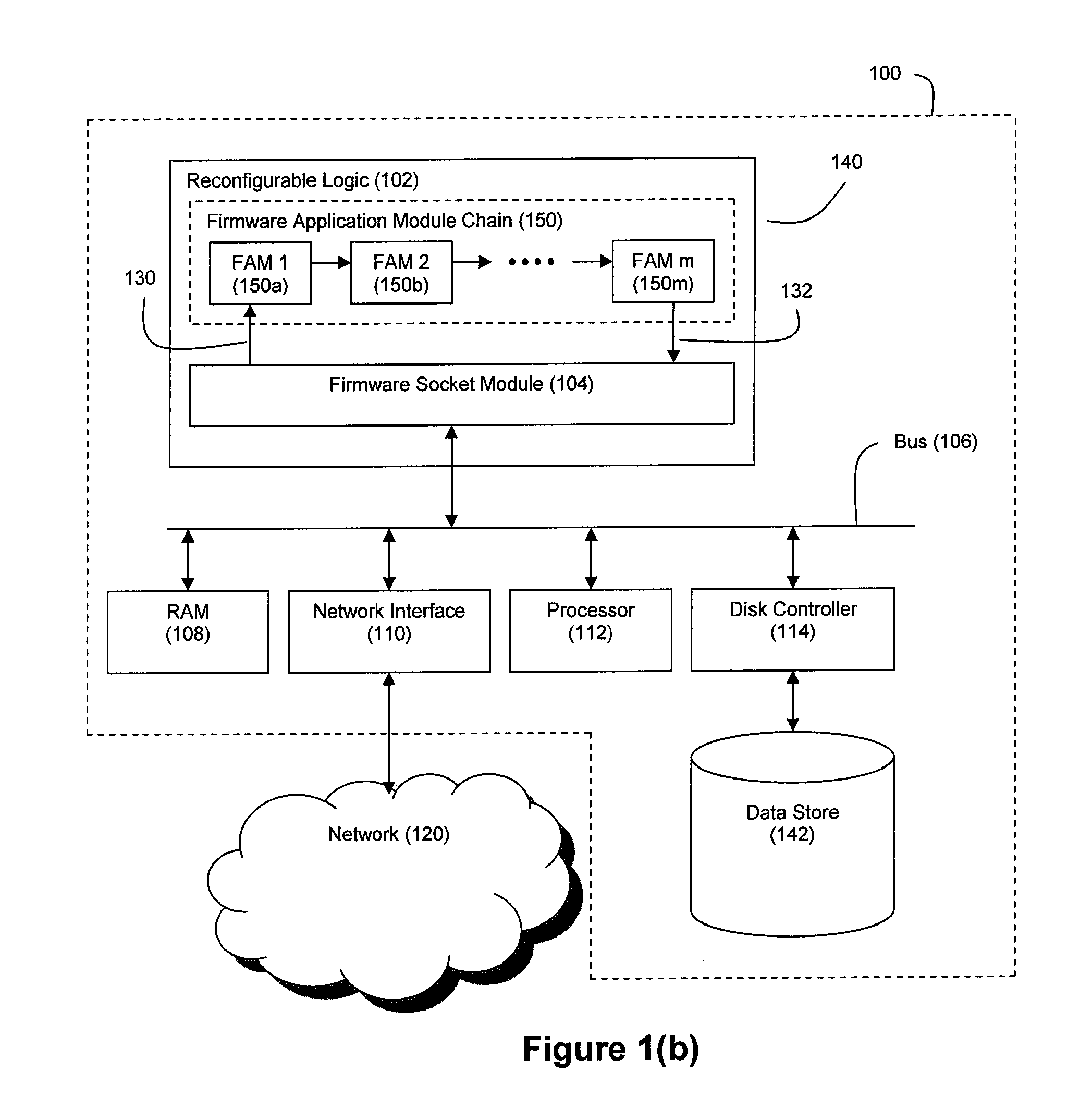

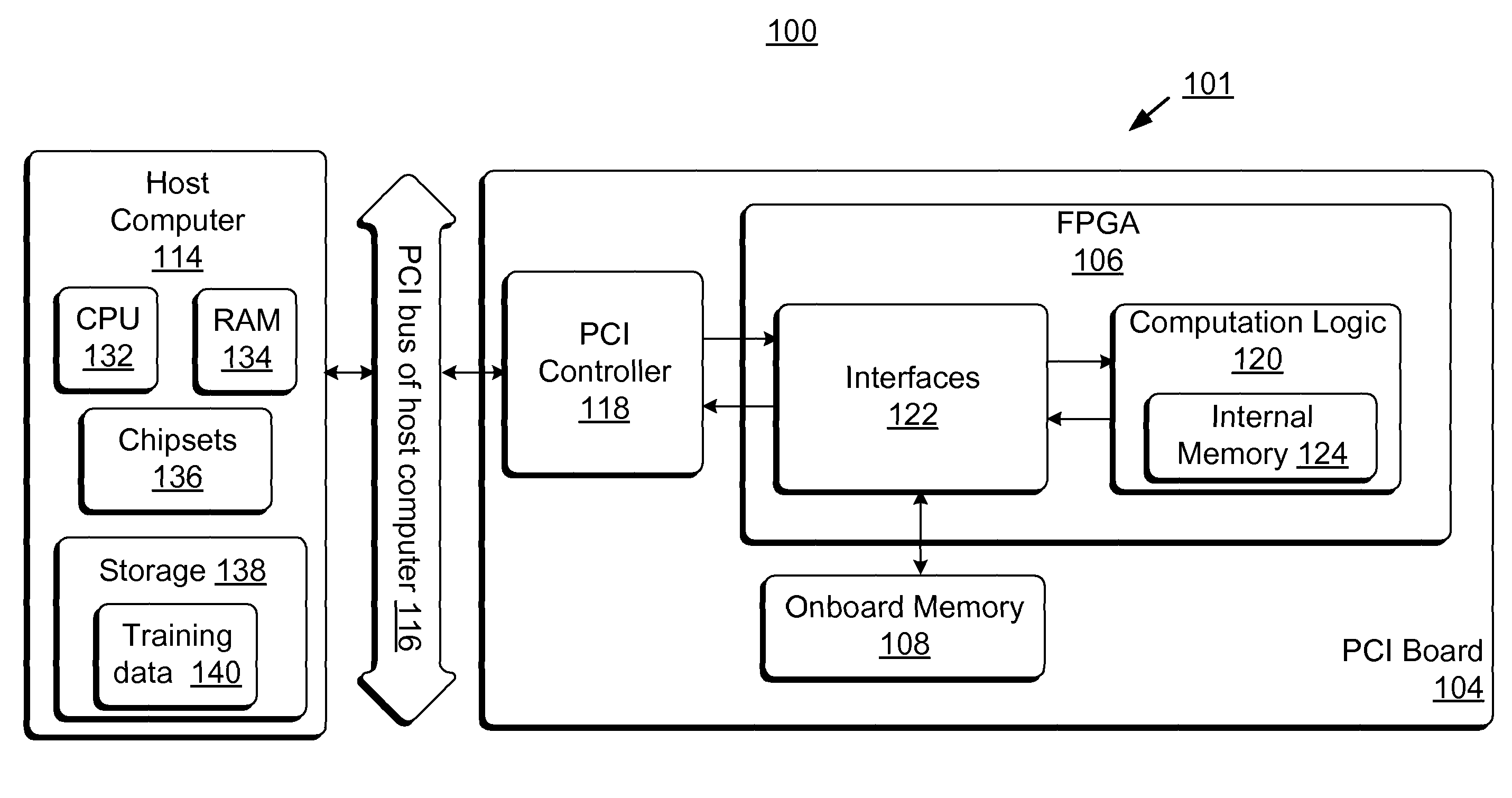

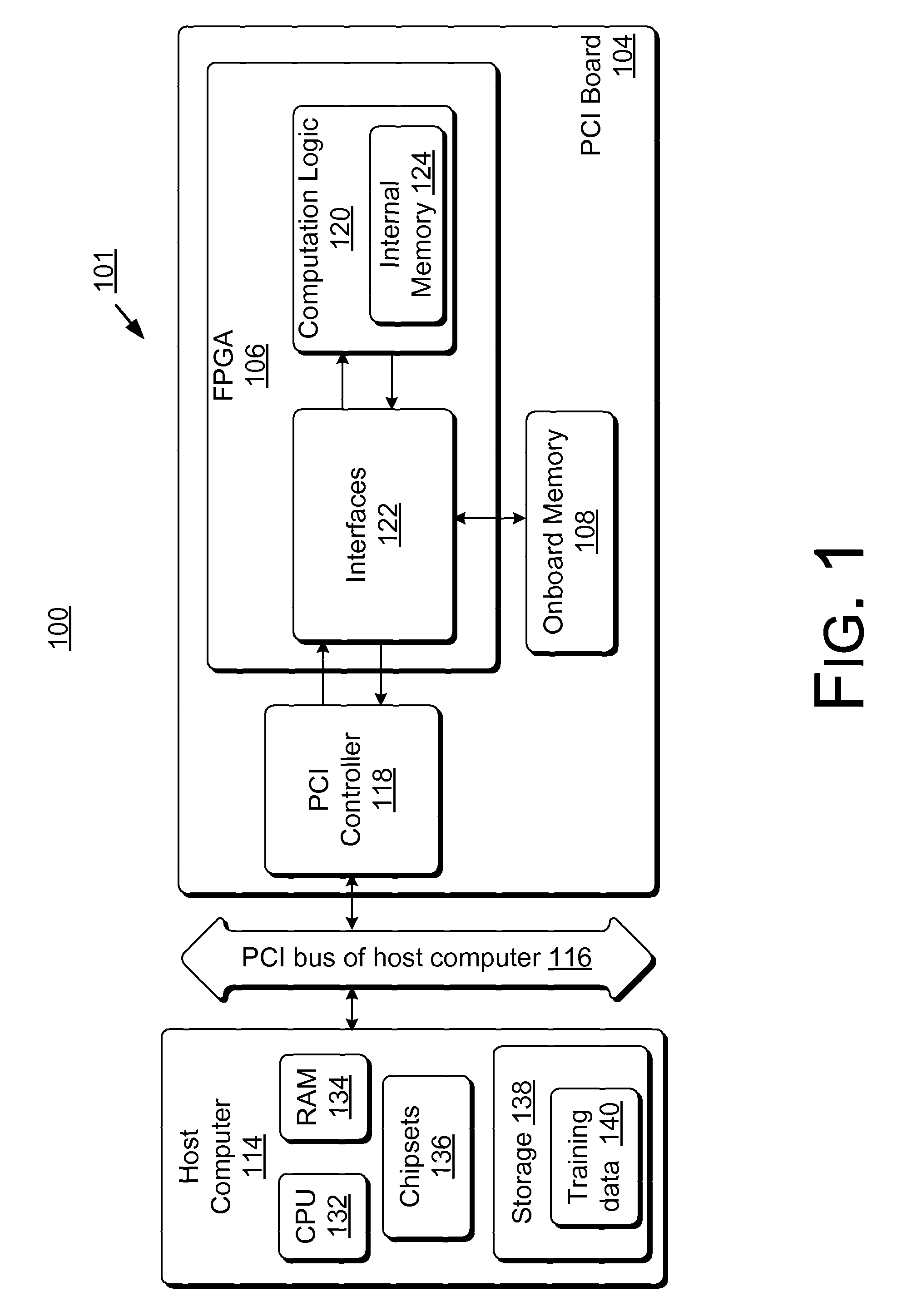

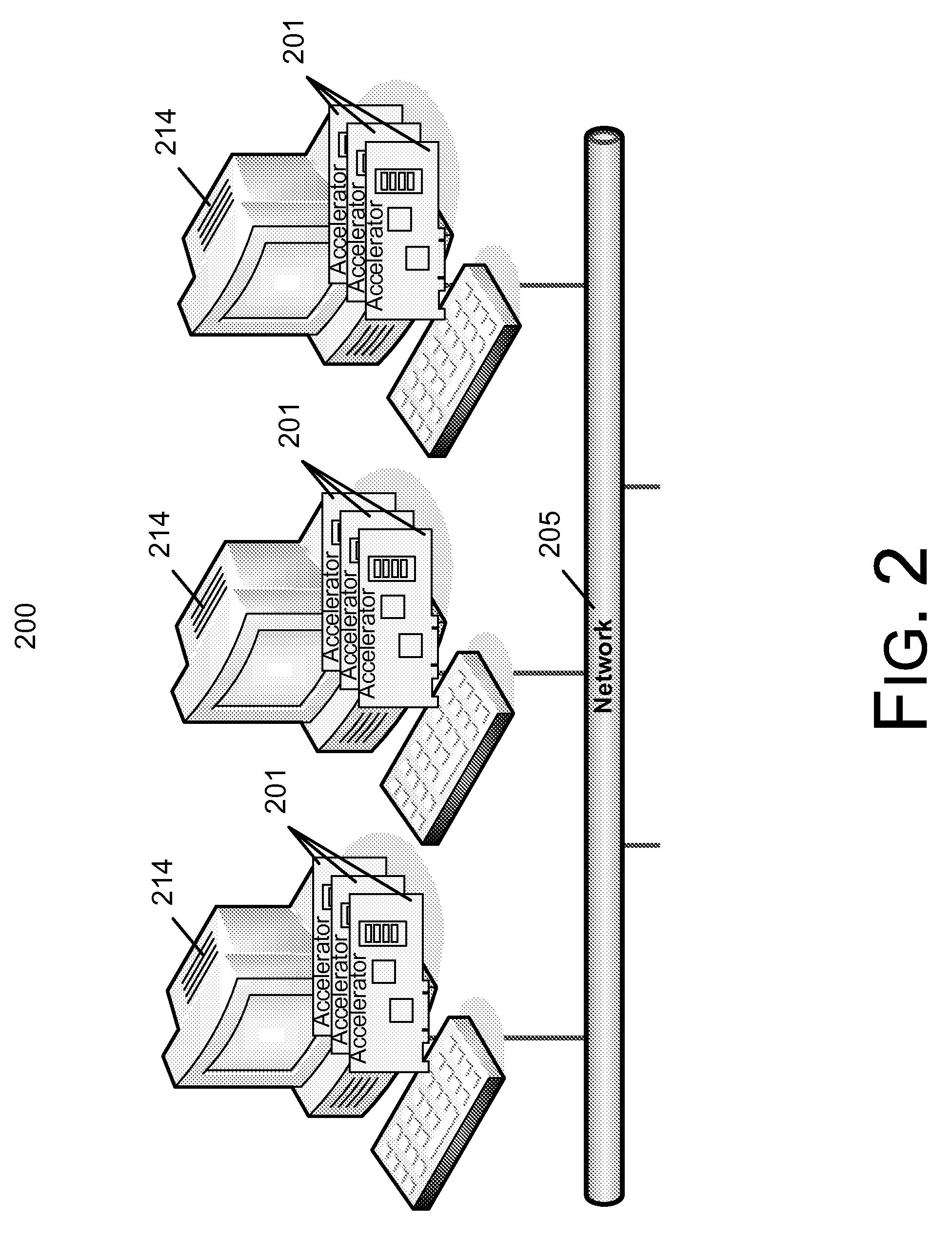

Field-programmable gate array based accelerator system

ActiveUS8131659B2Less timeLess costDigital computer detailsDigital dataHidden layerArithmetic logic unit

Accelerator systems and methods are disclosed that utilize FPGA technology to achieve better parallelism and processing speed. A Field Programmable Gate Array (FPGA) is configured to have a hardware logic performing computations associated with a neural network training algorithm, especially a Web relevance ranking algorithm such as LambaRank. The training data is first processed and organized by a host computing device, and then streamed to the FPGA for direct access by the FPGA to perform high-bandwidth computation with increased training speed. Thus, large data sets such as that related to Web relevance ranking can be processed. The FPGA may include a processing element performing computations of a hidden layer of the neural network training algorithm. Parallel computing may be realized using a single instruction multiple data streams (SIMD) architecture with multiple arithmetic logic units in the FPGA.

Owner:MICROSOFT TECH LICENSING LLC

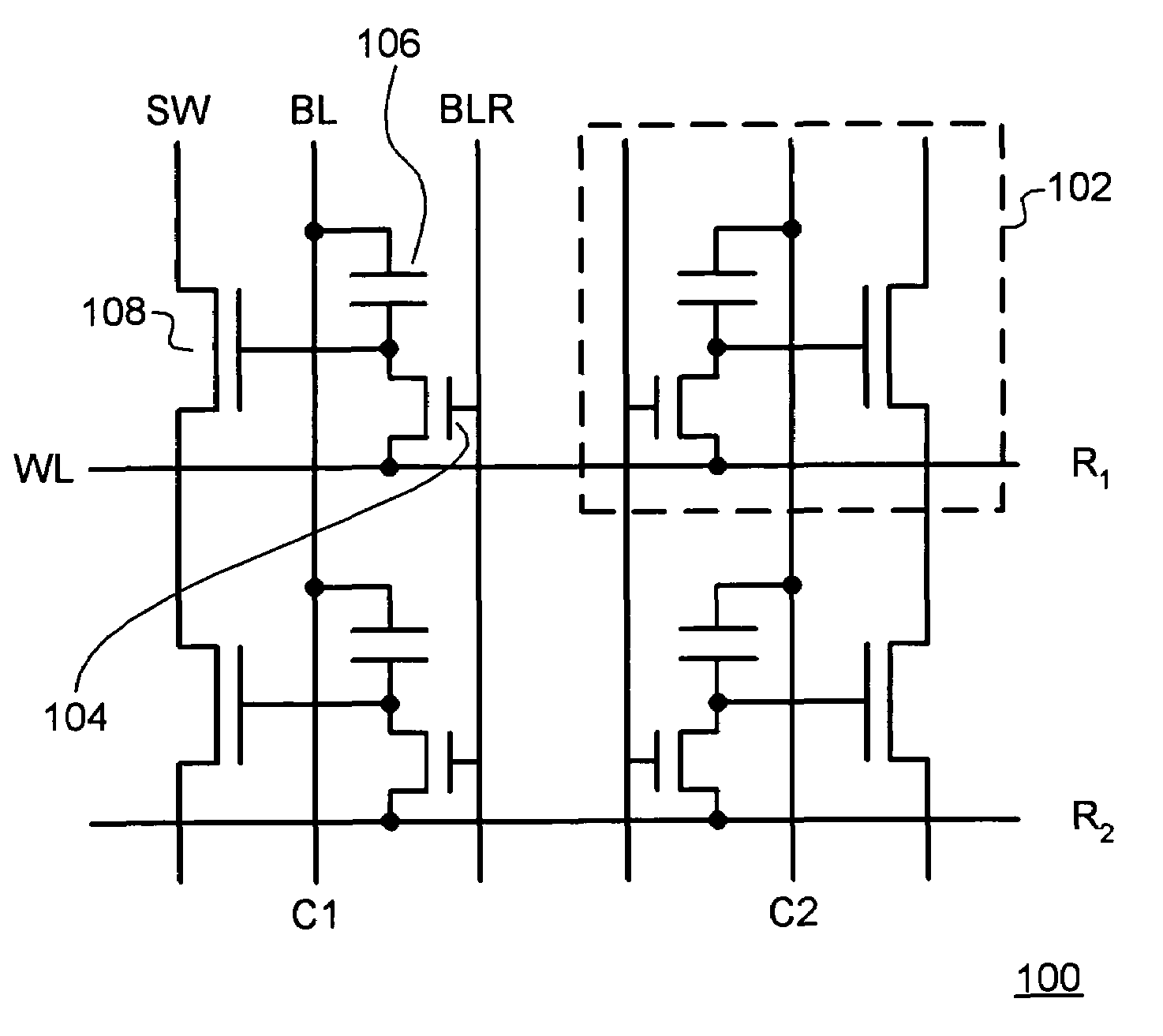

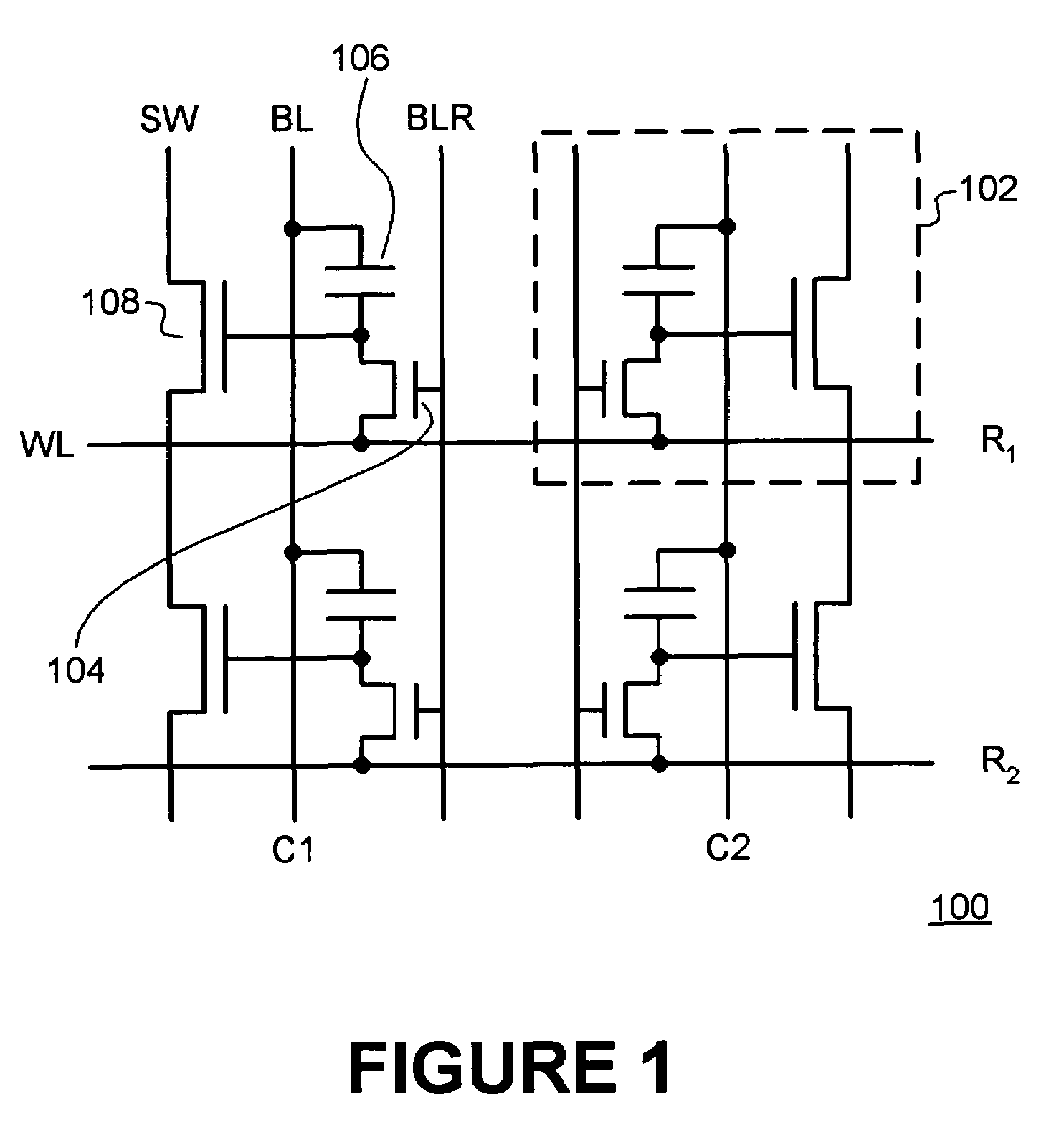

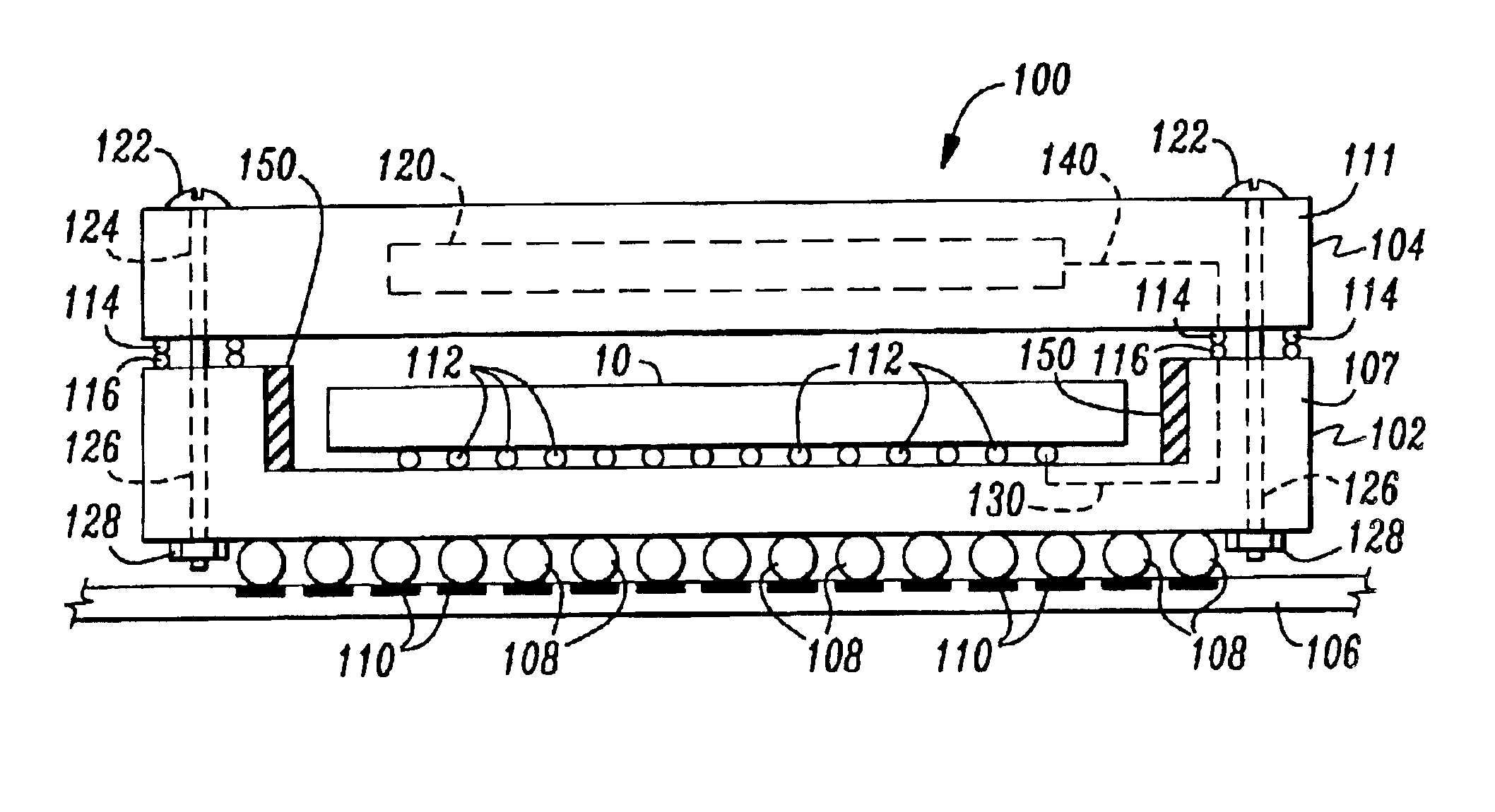

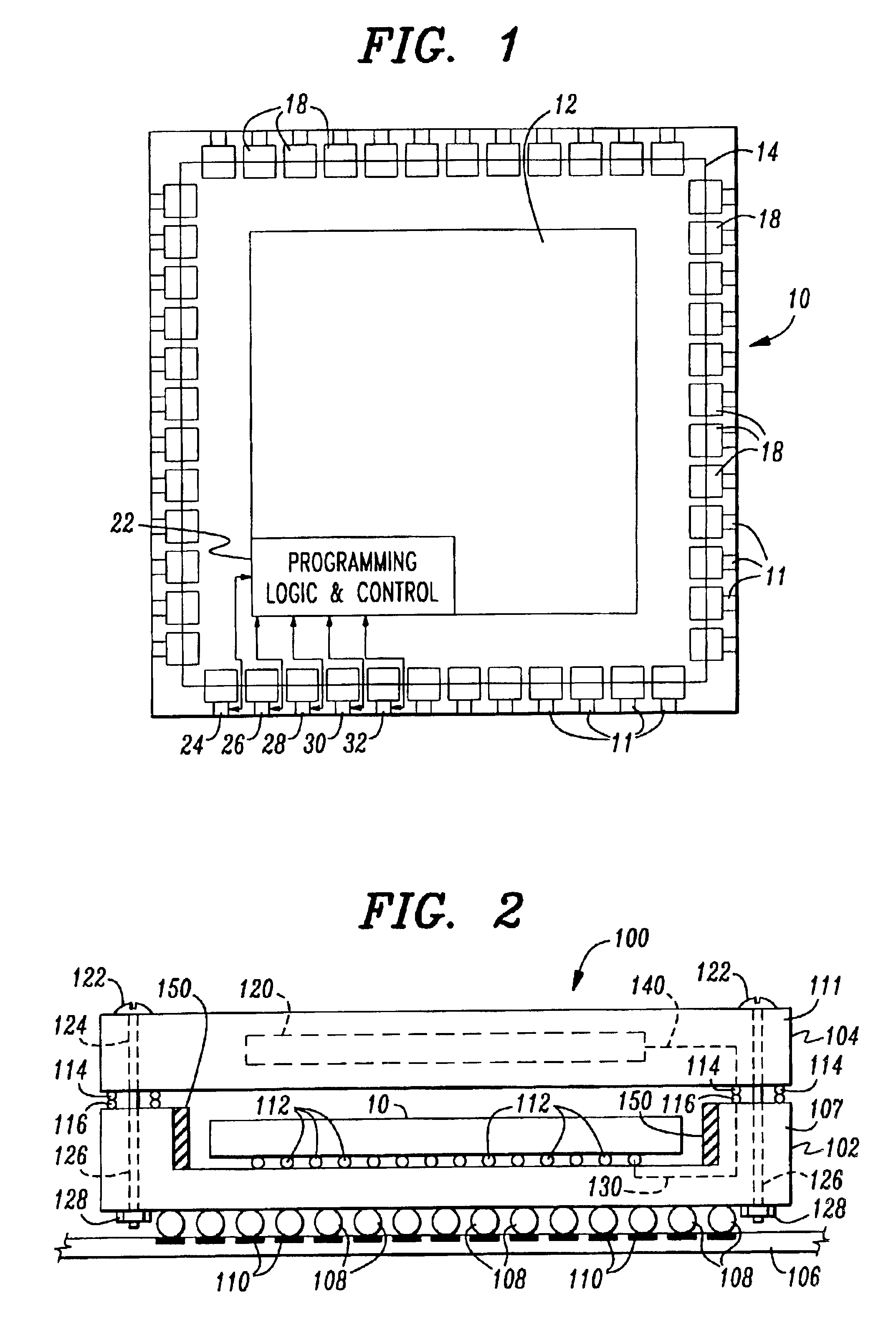

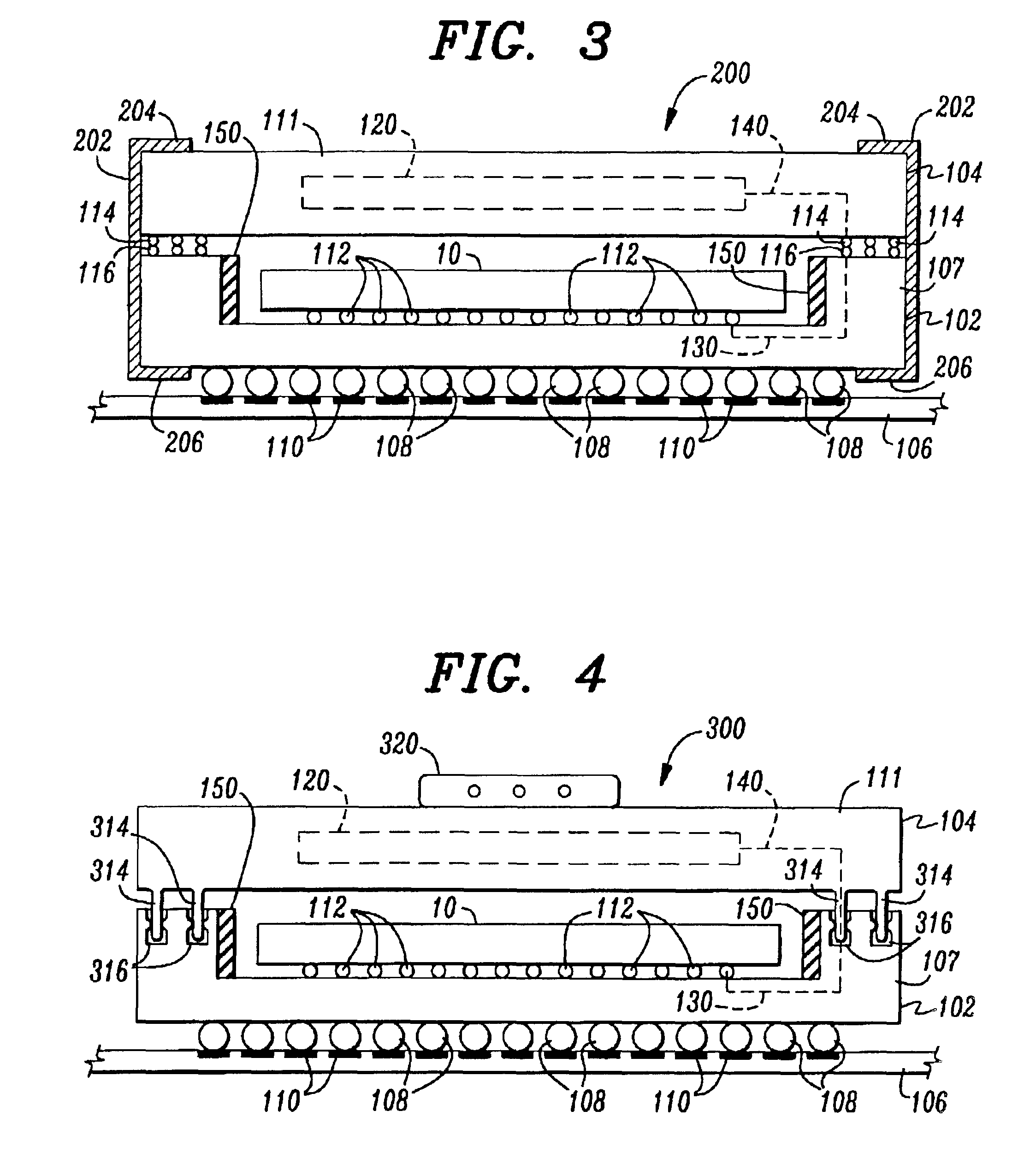

Field programmable gate array assembly

InactiveUS6906407B2FlexibilityPerformanceSemiconductor/solid-state device detailsPrinted circuit aspectsGate arrayCoupling

A field programmable gate array assembly (100, 200, 300) offers the unique functionality typically reserved for custom ICs and application specific integrated circuits (ASICs) with the flexibility of a programmable gate array. This is accomplished by modifying a package for a programmable IC (102), such as a programmable gate array, to electrically and mechanically couple to another IC (104). The preferred electrical and mechanical coupling occurs by stacking the IC on the programmable IC.

Owner:ALCATEL-LUCENT USA INC

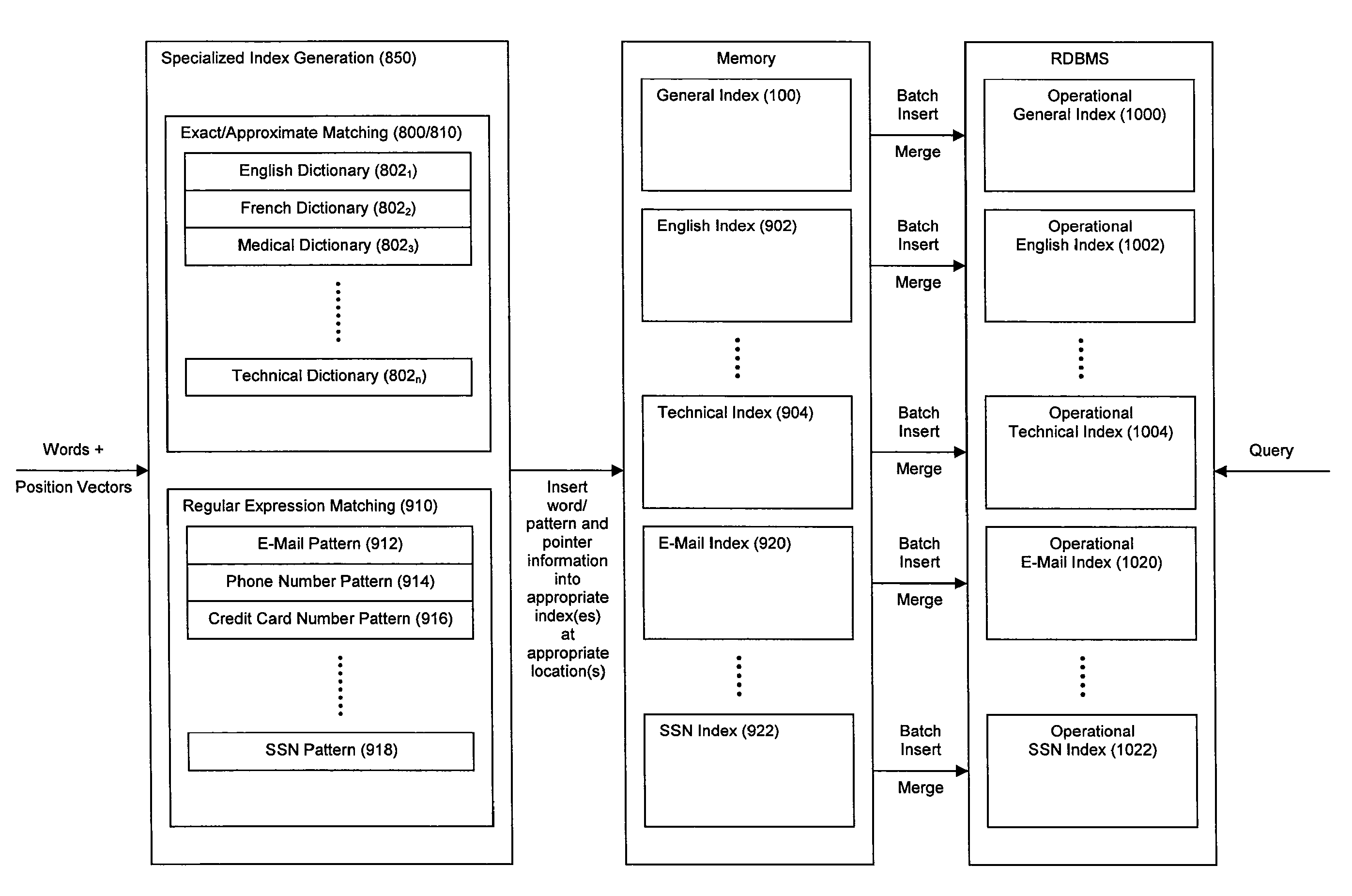

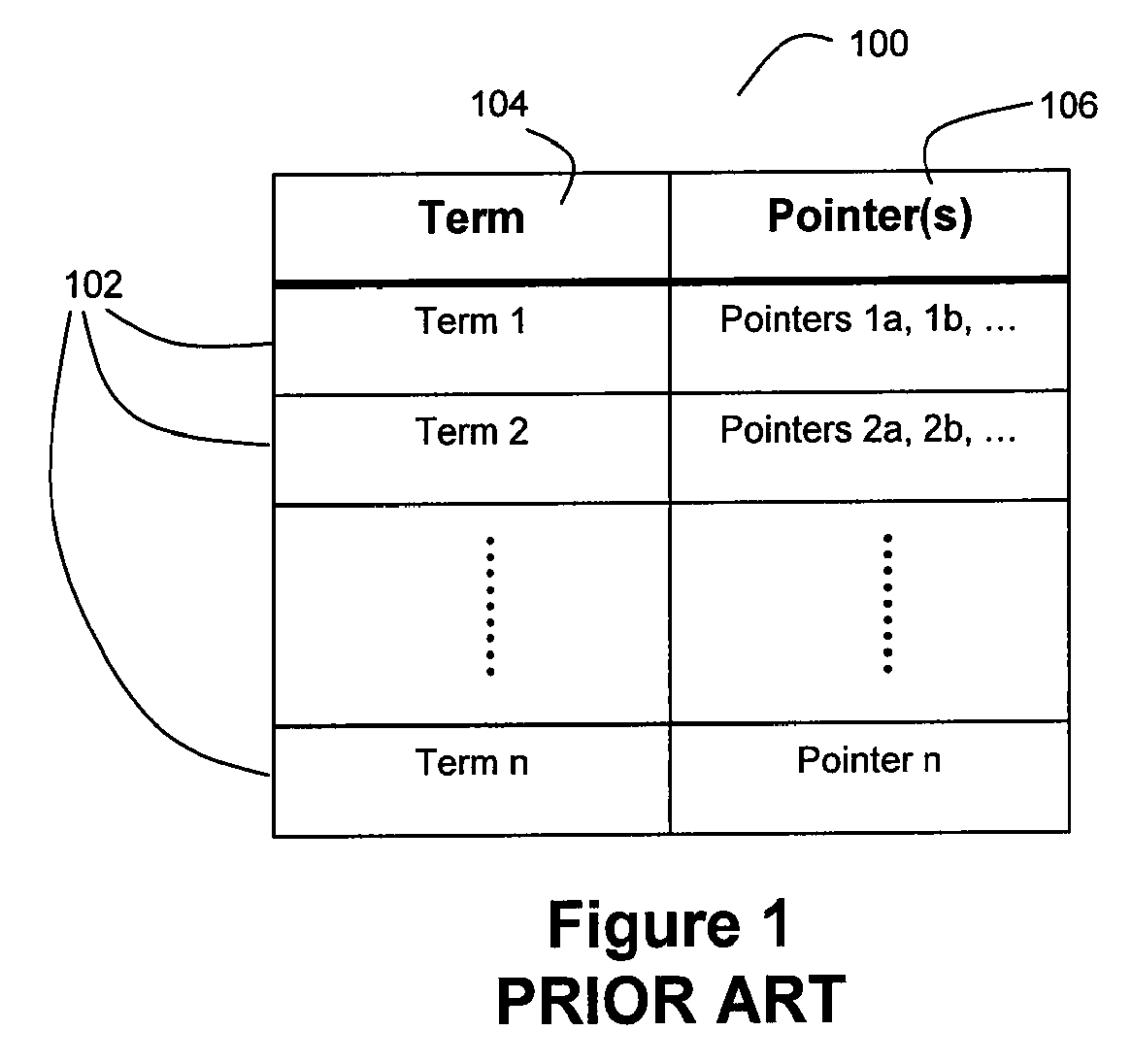

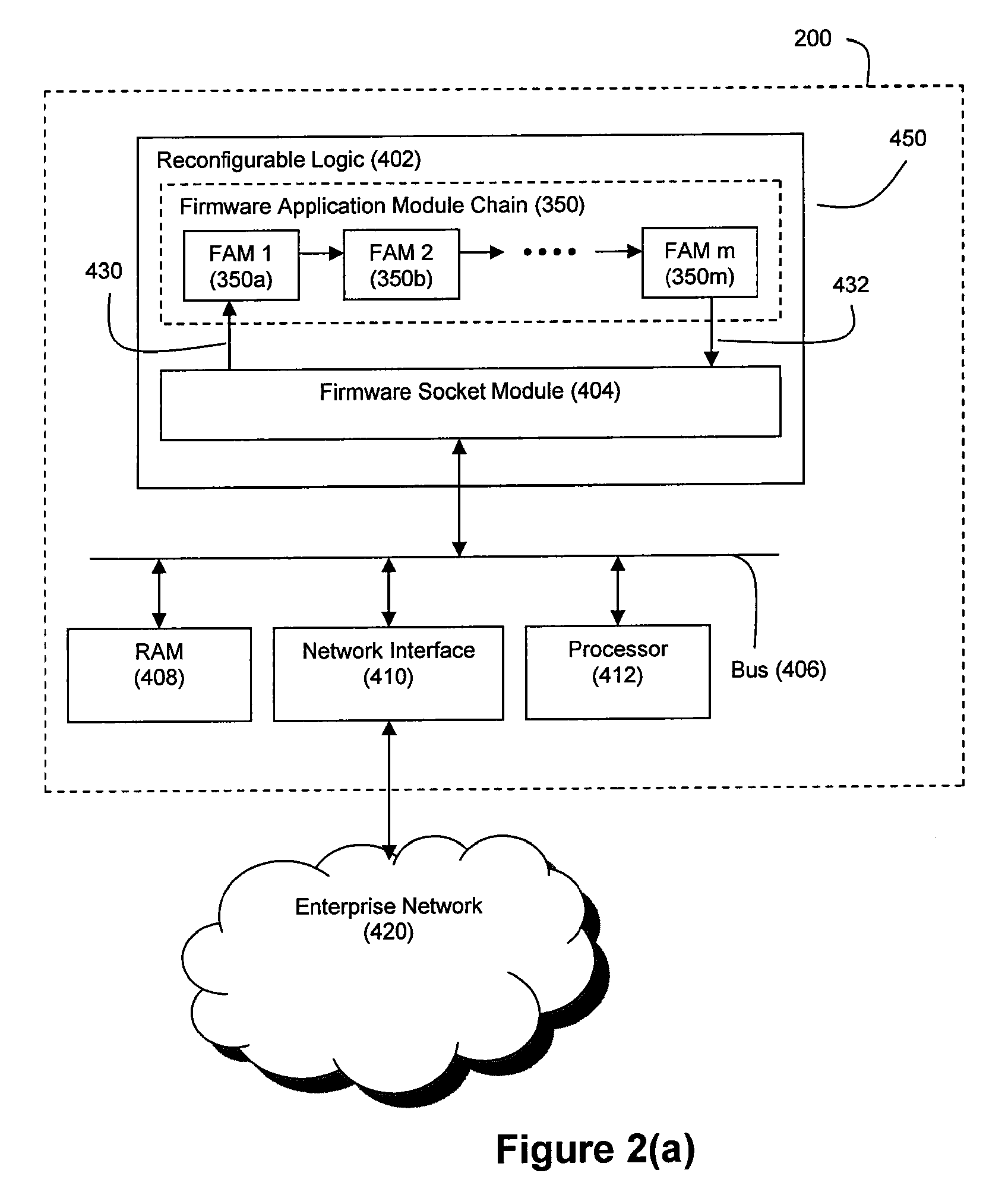

Method and system for high performance data metatagging and data indexing using coprocessors

ActiveUS8326819B2Robust and high performance data searchingHigh indexWeb data indexingDigital data processing detailsData streamCoprocessor

Disclosed herein is a method and system for hardware-accelerating the generation of metadata for a data stream using a coprocessor. Using these techniques, data can be richly indexed, classified, and clustered at high speeds. Reconfigurable logic such a field programmable gate arrays (FPGAs) can be used by the coprocessor for this hardware acceleration. Techniques such as exact matching, approximate matching, and regular expression pattern matching can be employed by the coprocessor to generate desired metadata for the data stream.

Owner:IP RESERVOIR

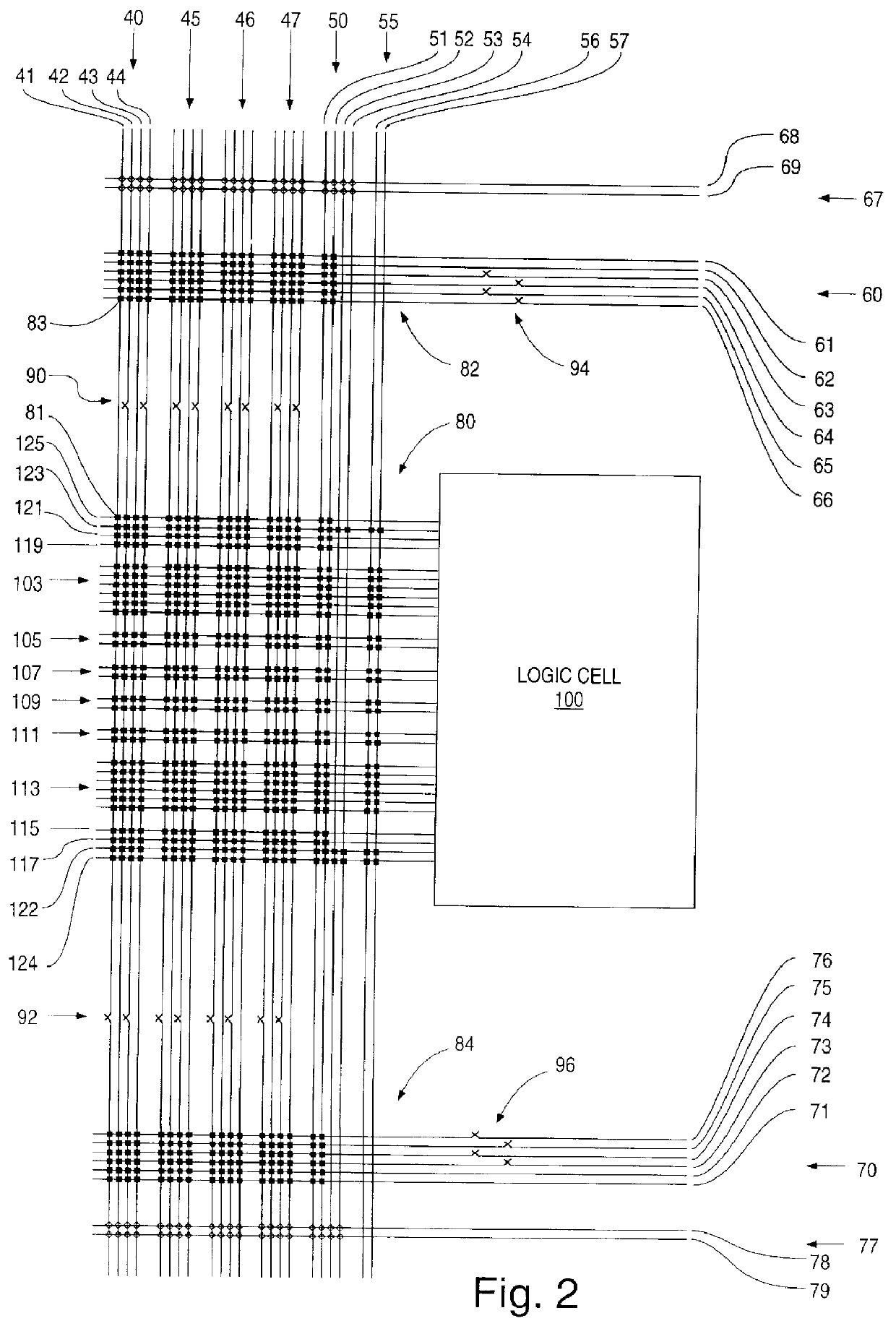

Programmable application specific integrated circuit and logic cell

A field programmable gate array includes a programmable routing network, a programmable configuration network integrated with the programmable routing network; and a logic cell integrated with the programmable configuration network. The logic cell includes four two-input AND gates, two six-input AND gates, three multiplexers, and a delay flipflop. The logic cell is a powerful general purpose universal logic building block suitable for implementing most TTL and gate array macrolibrary functions. A considerable variety of functions are realizable with one cell delay, including combinational logic functions as wide as thirteen inputs, all boolean transfer functions for up to three inputs, and sequential flipflop functions such as T, JK and count with carry-in.

Owner:QUICKLOGIC

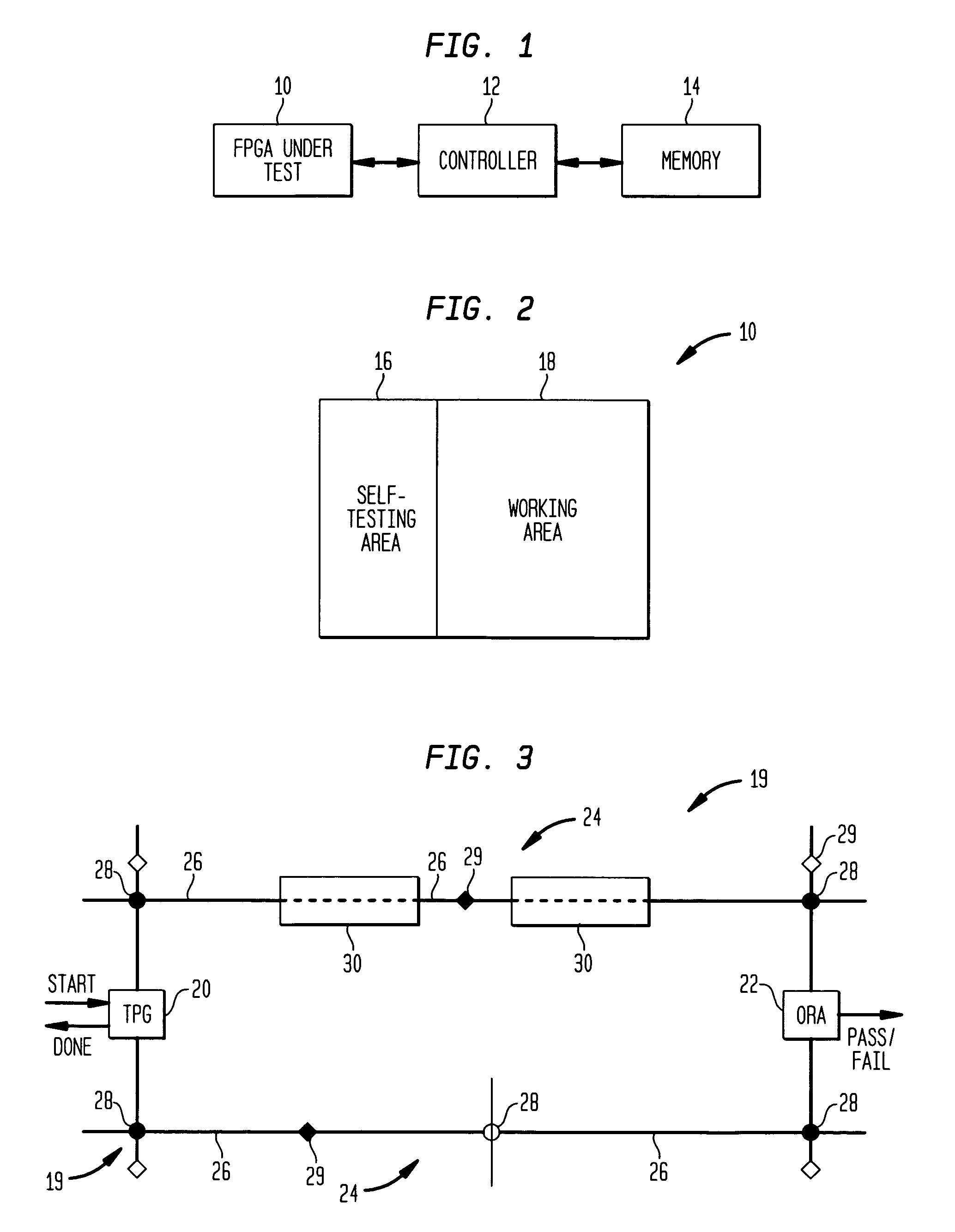

Fault tolerant operation of field programmable gate arrays

ActiveUS6973608B1Extended service lifeMinimize impactElectronic circuit testingRedundant operation error correctionComputer architectureGate array

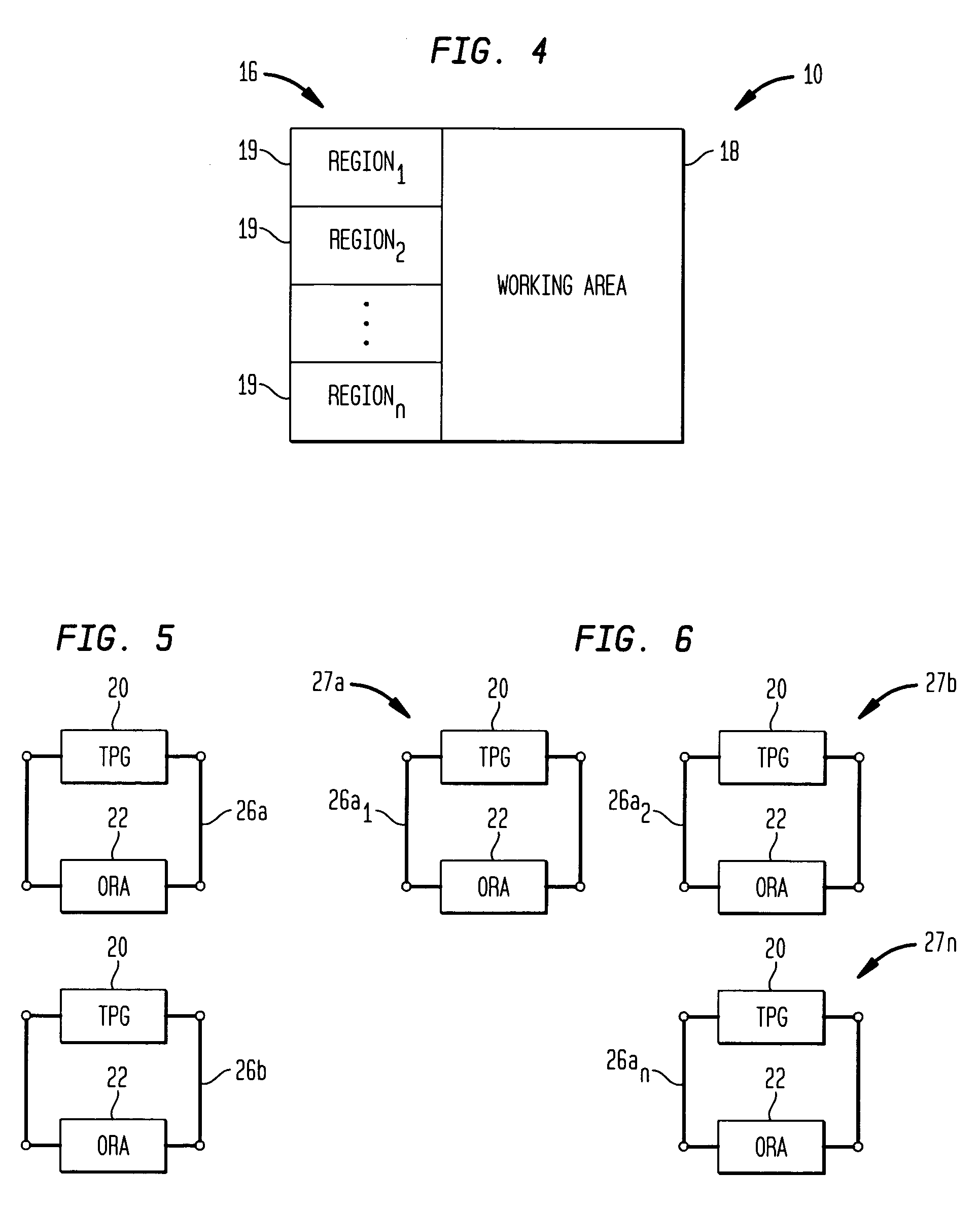

A method of fault tolerant operation of field programmable gate arrays (FPGAs), whether as an embedded portion of a system-on-chip or other application specific integrated circuit, utilizing incremental reconfiguration during normal on-line operation includes configuring an FPGA into a self-testing area and a working area. Within the self-testing area, programmable interconnect resources of the FPGA are tested for faults. Upon the detection of one or more faults within the interconnect resources, the faulty interconnect resources are identified and a determination is made whether utilization of the faulty interconnect resources is compatible with an intended operation of the FPGAs. If the faulty interconnect resources are compatible with the intended operation of the FPGA, utilization of the faulty interconnect resource is allowed to provide fault tolerant operation of the FPGA. If the faulty interconnect resources are not compatible with the intended operation of the FPGA, on the other hand, a multi-step reconfiguration process may be initiated which attempts to minimize the effects of each reconfiguration on the overall performance of the FPGA. In an alternate embodiment, the entire FPGA may be configured as one or more self-testing areas during off-line testing, such as manufacturing testing.

Owner:JUNIVERSITI OF NORT KAROLINA EHT SHARLOTT +1

Gated clock tree synthesis method for the logic design

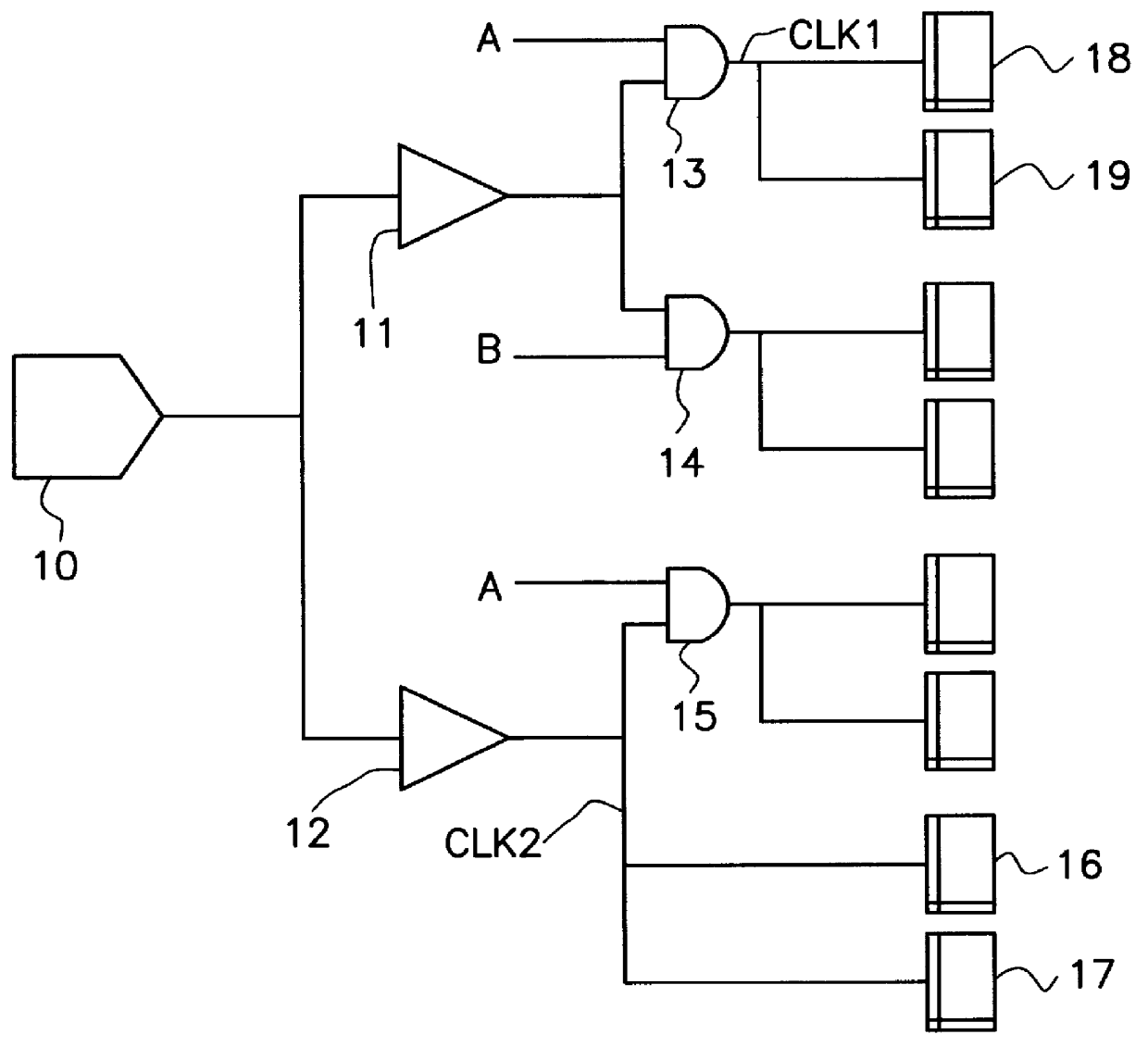

A gated clock tree synthesis (CTS) method is provided for the purpose of synthesizing a gate array logic circuit to allow optimal topological arrangement of the gate array on the logic circuit. This in turn allows the logic circuit to operate more efficiently. The logic circuit includes at least one clock generator, a plurality of control gates each having one input end connected to a control signal and the other input end connected to receive the output clock signal from the clock generator, a plurality of first logic elements that are directly driven by the output clock signal from the clock generator, and a plurality of second logic elements that are driven by the gated clock signal outputted from each of the control gates under control by the control signal. The gated CTS method comprises the steps of grouping the first logic elements into a plurality of groups, connecting each group of the first logic elements via a first buffer to one of the control gates, connecting each of the second logic elements via a second buffer to the clock generator, and connecting one input end of each of the control gates to the clock generator.

Owner:VIA TECH INC

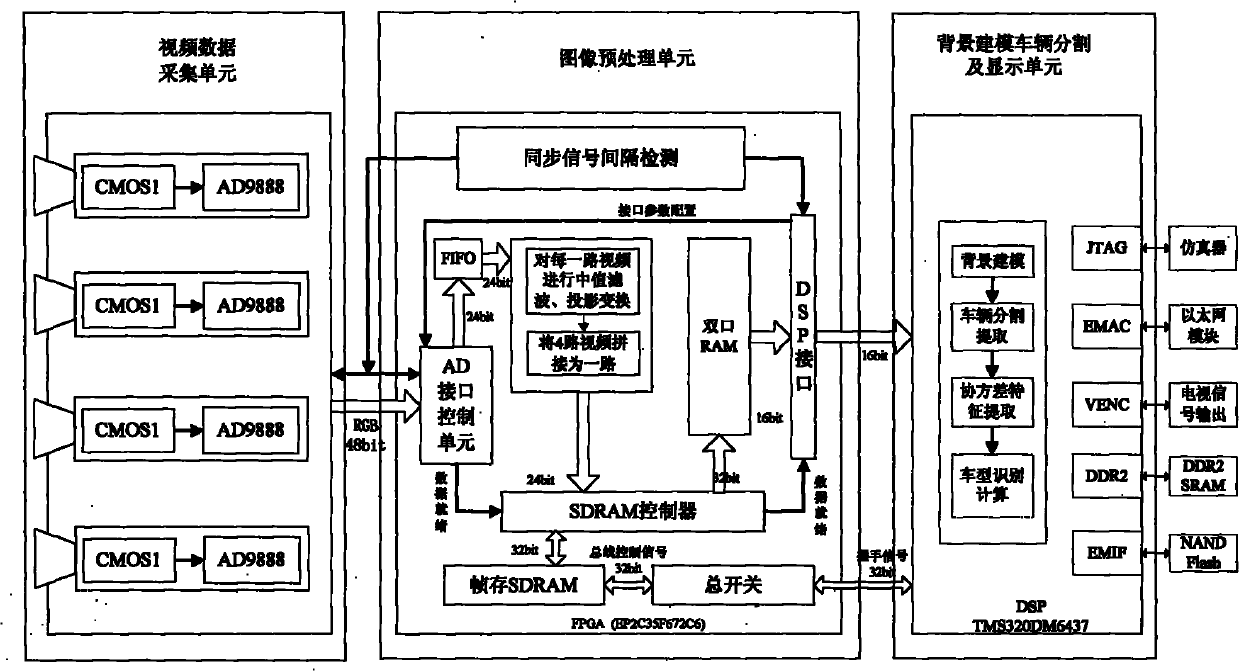

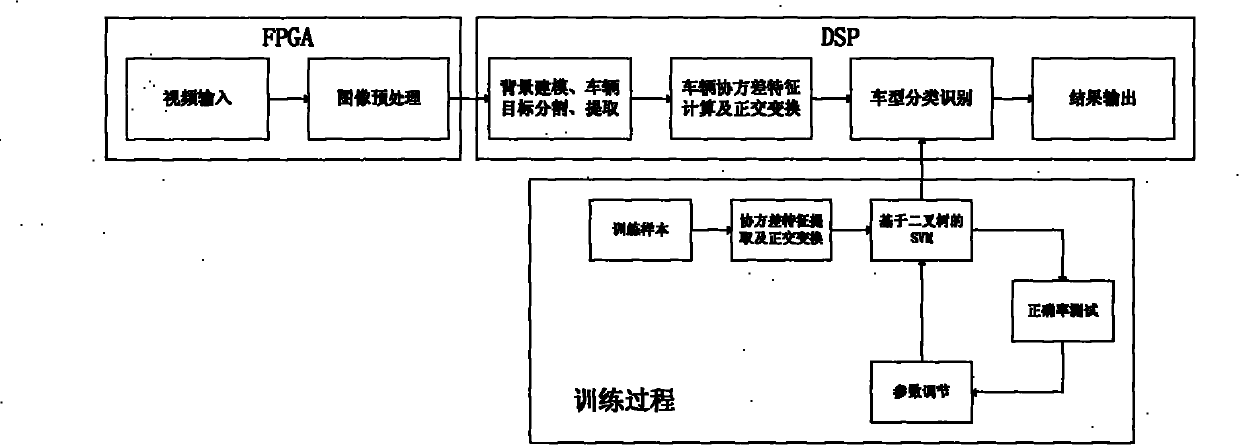

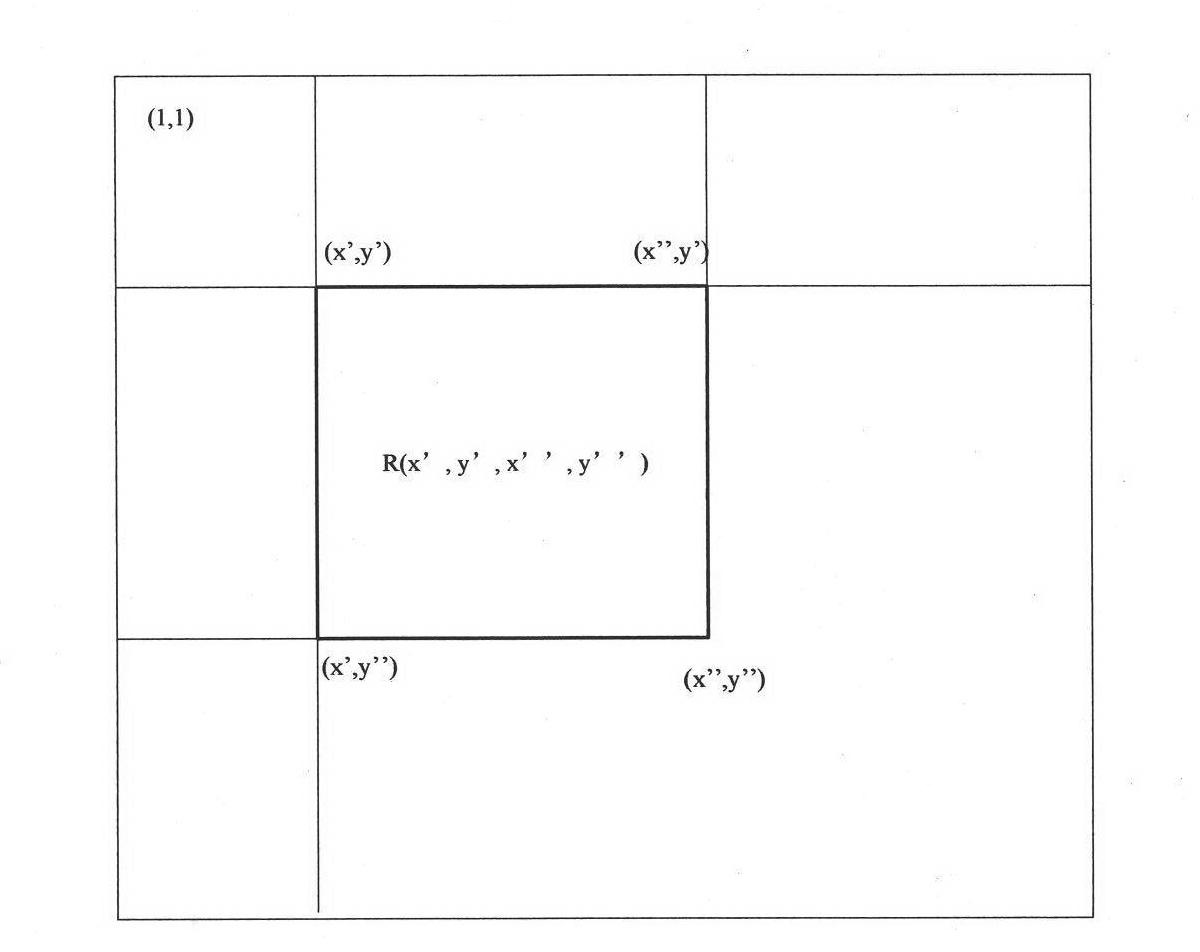

Target detection system and method based on covariance and binary-tree support vector machine

InactiveCN101794515AReduce feature dimensionEasy to handleRoad vehicles traffic controlCharacter and pattern recognitionVideo monitoringCovariance

The invention discloses target detection system and method based on covariance and a binary-tree support vector machine. The system comprises a video data collecting unit, an image preprocessing unit and a background modeling vehicle partitioning and displaying unit. The video data collecting unit is used for acquiring information in real time and carrying out digitization and system conversion on analog videos. The image preprocessing unit comprises an FPGA (Field Programmable Gate Array) and a DSP (Digital Signal Processor), wherein the FPGA is used as a coprocessor; and the DSP is used as a main processor to accomplish the background modeling of video images, the partitioning and the extraction of vehicle targets and the realization of a model identification algorithm. Utilizing the combination of the FPGA and the DSP, the invention can realize multi-video real-time model identification through combining with the model identification algorithm based on the covariance features of the images and the support vector machine. The invention can be widely used for a plurality of fields of intelligent traffic management, intelligent video monitoring and the like.

Owner:HOHAI UNIV

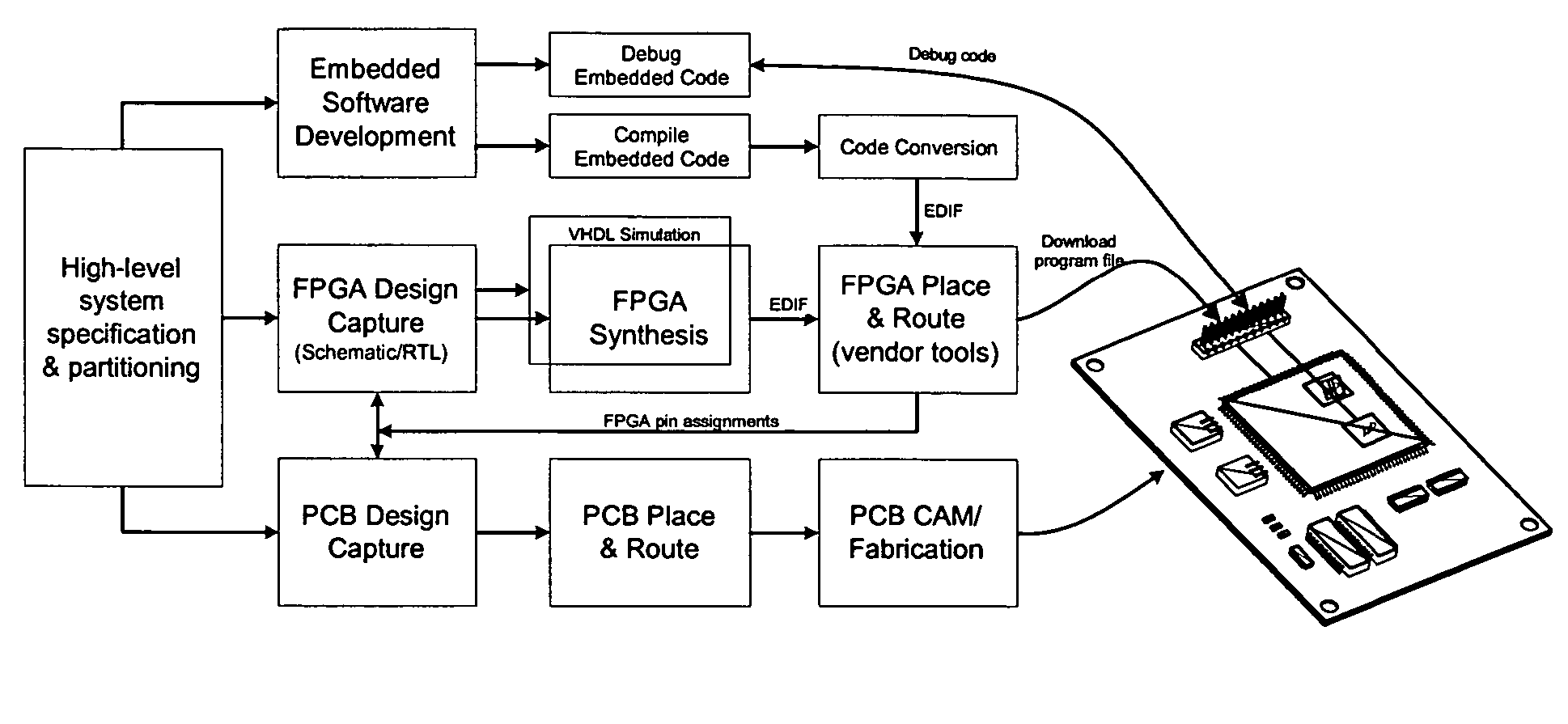

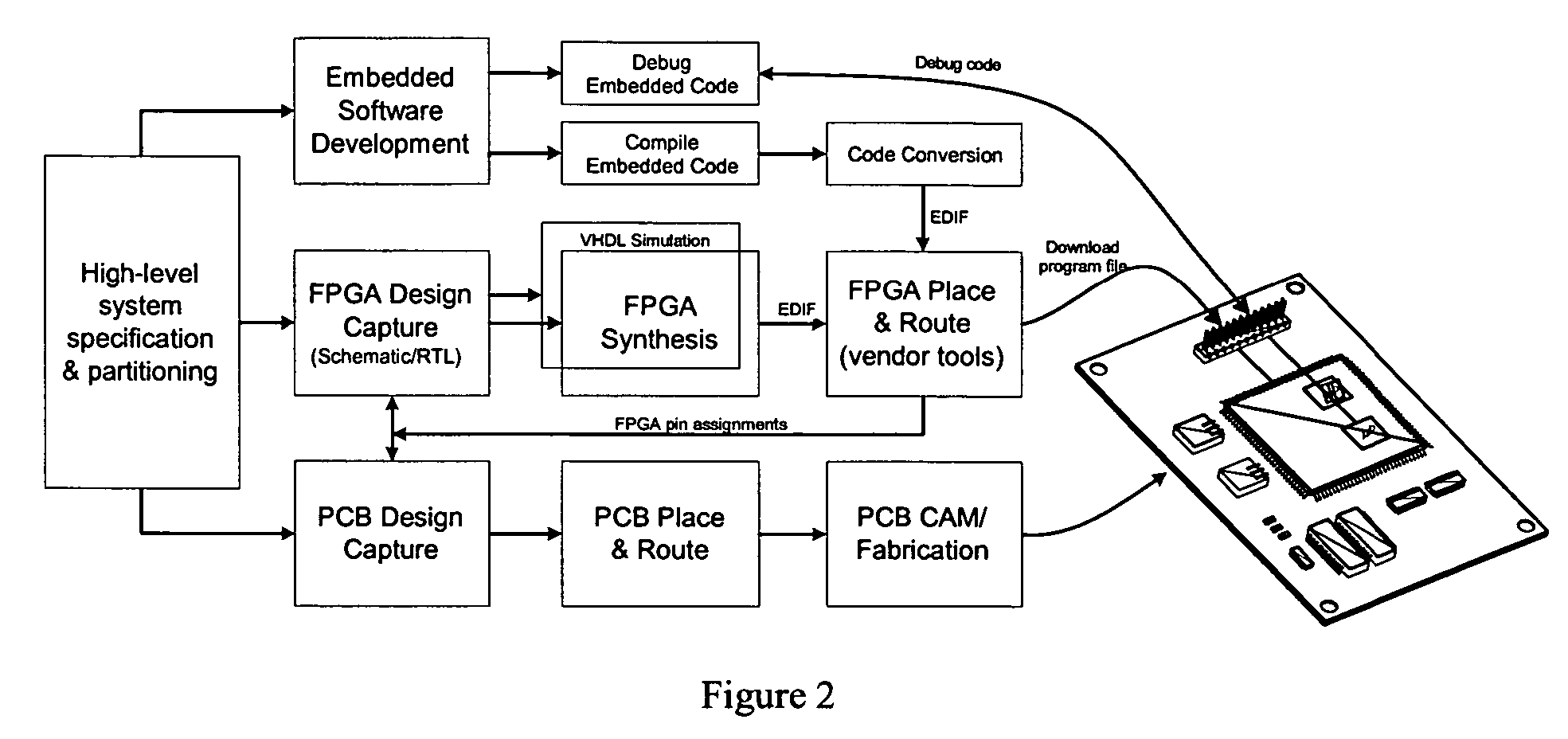

System for designing re-programmable digital hardware platforms

InactiveUS7340693B2Assembly is complexEasy to moveCAD circuit designSpecial data processing applicationsComputer hardwareComputer architecture

A digital design system and method are provided for re-programmable hardware platforms, such as field programmable gate arrays (FPGAs) and other re-programmable system designs. The design system and method bridge the gap between what has previously been a development and prototyping platform used during the design phase of an electronic design system (EDS) project, and commercially viable re-programmable product platforms to replace non-programmable platforms, such as discrete processors and ASICs.

Owner:MITSUBISHI CABLE IND LTD

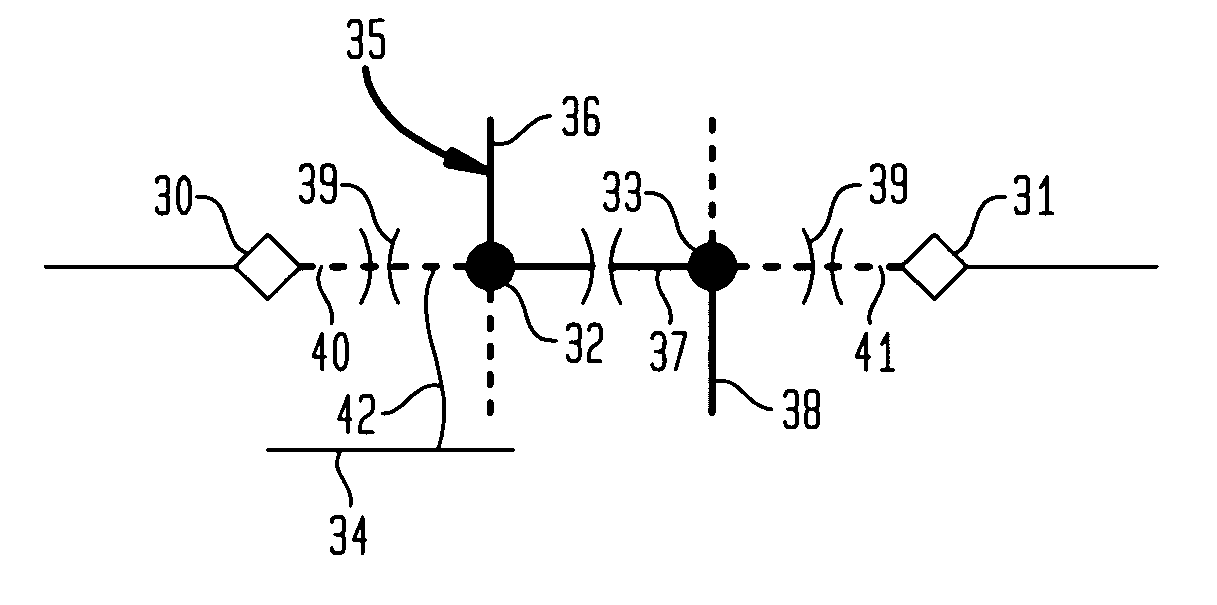

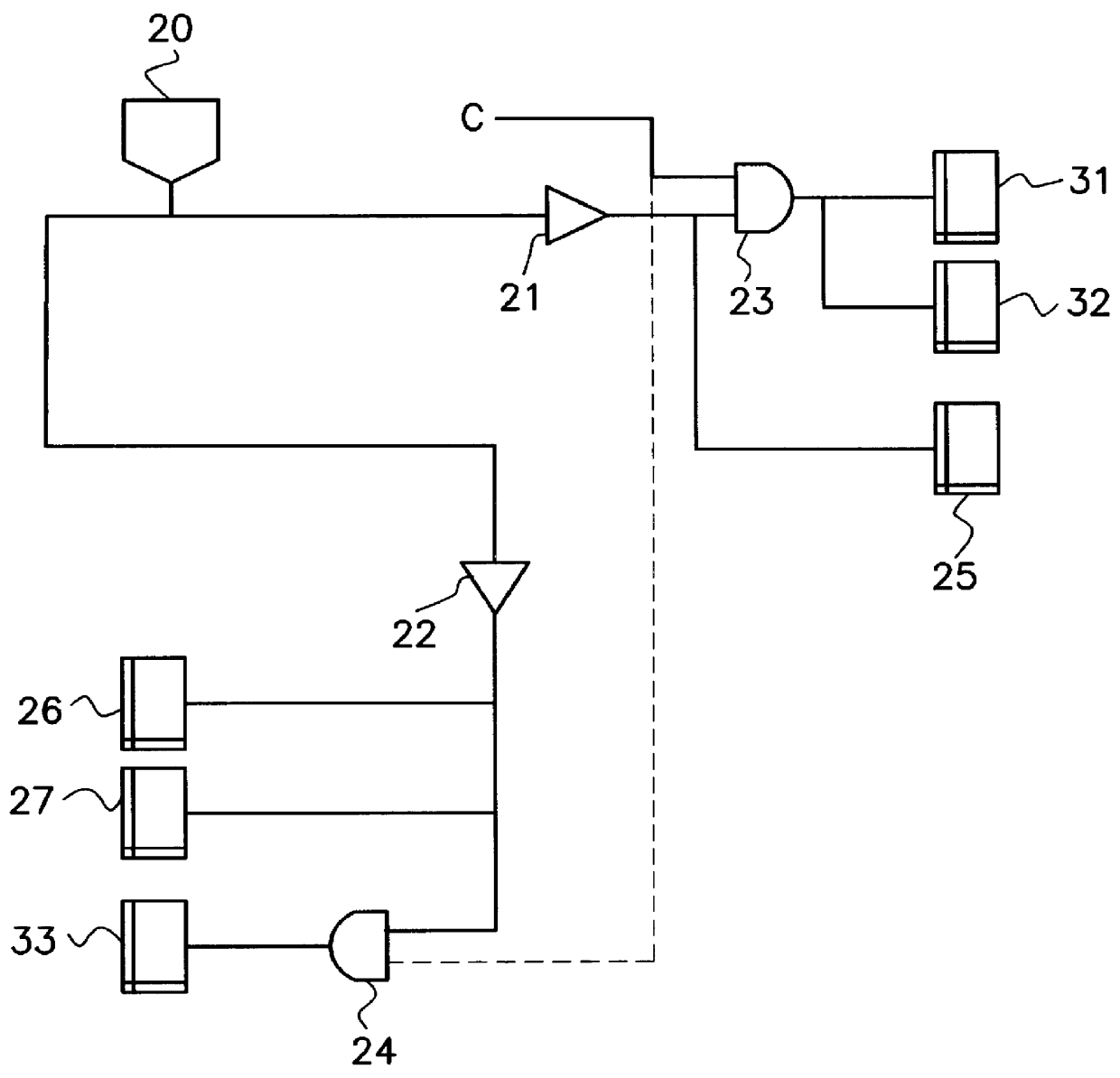

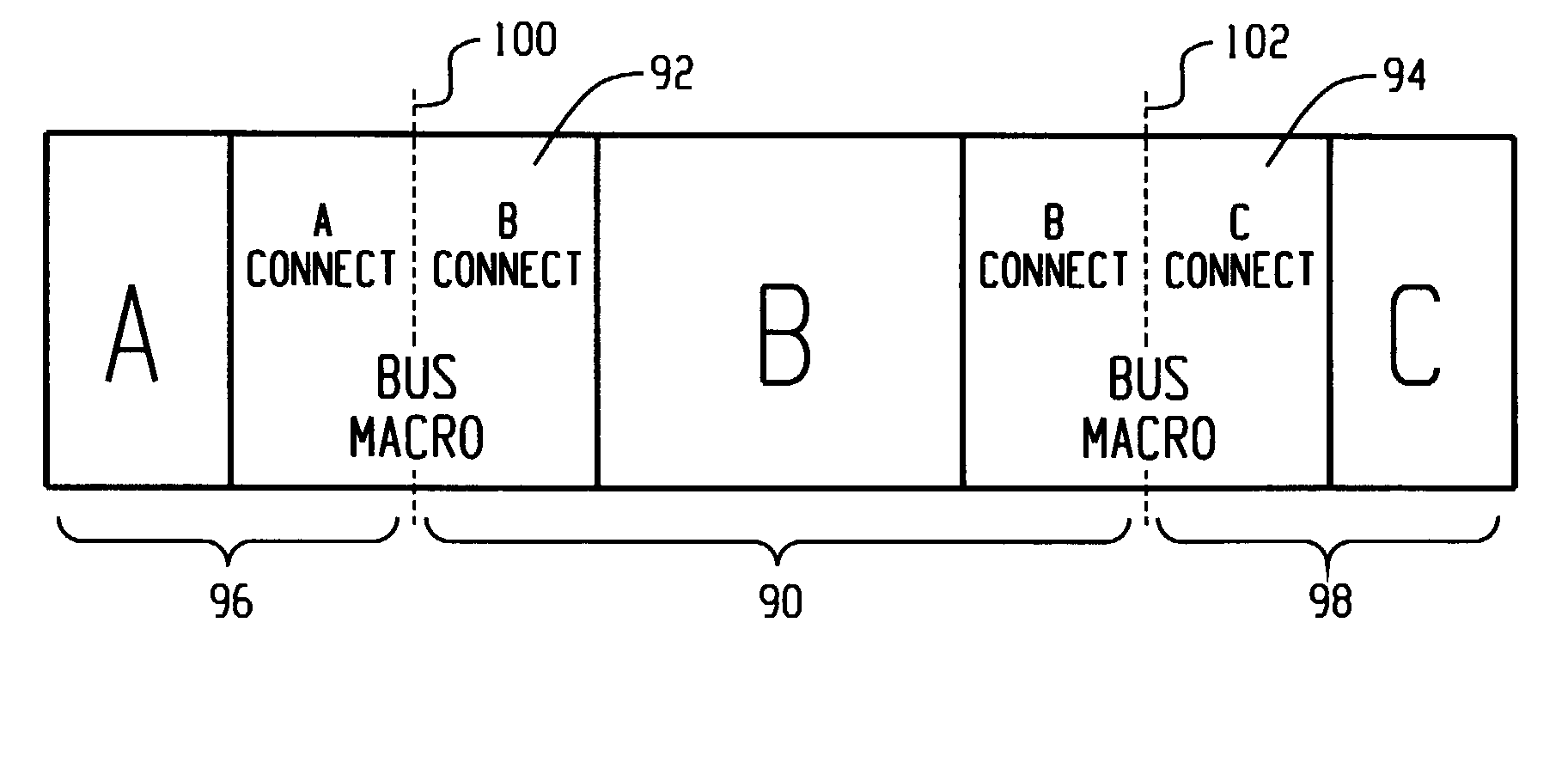

Partial reconfiguration of a programmable gate array using a bus macro

InactiveUS7024651B1Special data processing applicationsLogic circuits using elementary logic circuit componentsSignal routingGate array

A bus macro for use as a routing resource for partial reconfiguration of a field programmable gate array (FPGA) with a design that has interdesign routing with at least one other design programmed into the FPGA comprises: at least one row of bus lines disposed within the FPGA between at least two design areas; a first set of gates disposed within the FPGA for controlling a routing of signals over the at least one row of bus lines from a first design area to a second design area of the FPGA according to a first routing configuration embedded in the first design area; and a second set of gates disposed within the FPGA for controlling a routing of signals over the at least one row of bus lines from the second design area to the first design area of the FPGA according to a second routing configuration embedded in the second design area. A method of partially reconfiguring a field programmable gate array (FPGA) with at least one design that has interdesign routing with at least one other design programmed into the FPGA is also disclosed utilizing at least one bus macro.

Owner:XILINX INC