Patents

Literature

713 results about "Data delay" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Real-time network monitoring and security

ActiveUS20050108573A1Easy programmingEasy maintenanceWeb data indexingMemory loss protectionHigh bandwidthWire speed

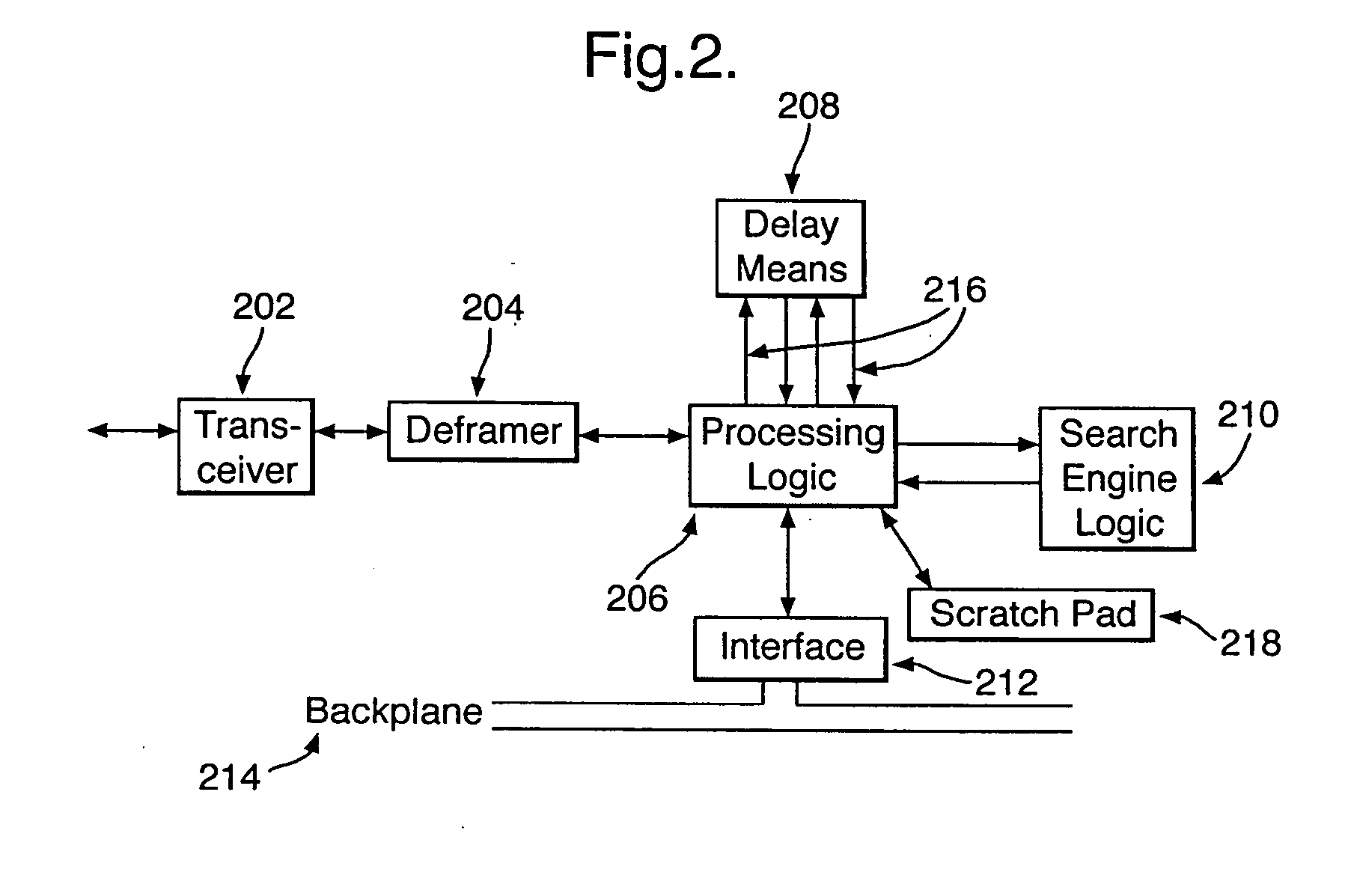

There is provided a hardware device for monitoring and intercepting data packetized data traffic at full line rate. In preferred high bandwidth embodiments, full line rate corresponds to rates that exceed 100 Mbytes / s and in some cases 1000 Mbytes / s. Monitoring and intercepting software, alone, is not able to operate on such volumes of data in real-time. A preferred embodiment comprises: a data delay buffer (208) with multiple delay outputs (216); a search engine logic (210) for implementing a set of basic search tools that operate in real-time on the data traffic; a programmable gate array (206); an interface (212) for passing data quickly to software sub-systems; and control means for implementing software control of the operation of the search tools. The programmable gate array (206) inserts the data packets into the delay buffer (208), extracts them for searching at the delay outputs and formats and schedules the operation of the search engine logic (210). One preferred embodiment uses an IP co-processor as the search engine logic.

Owner:BAE SYSTEMS PLC

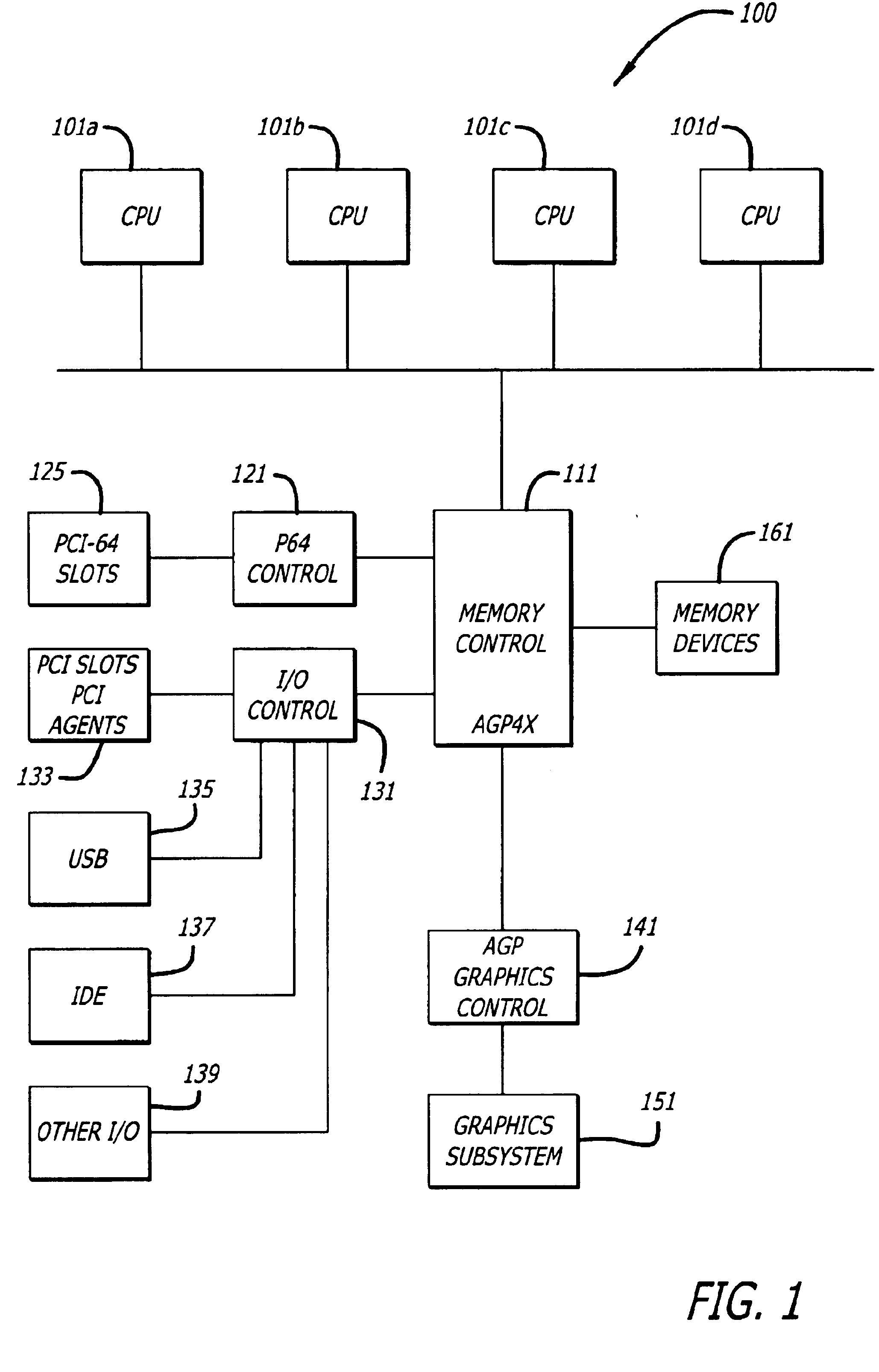

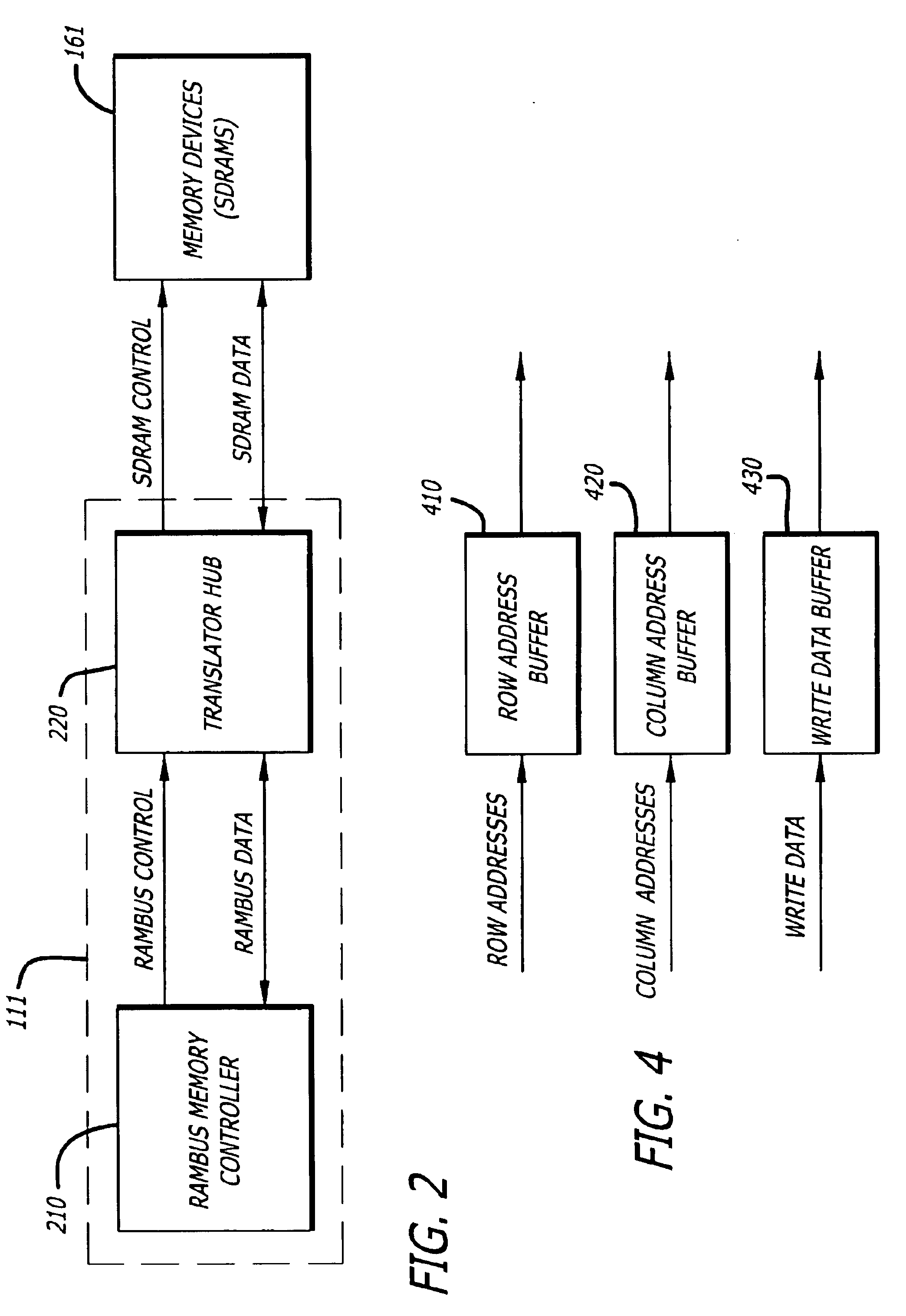

Memory control translators

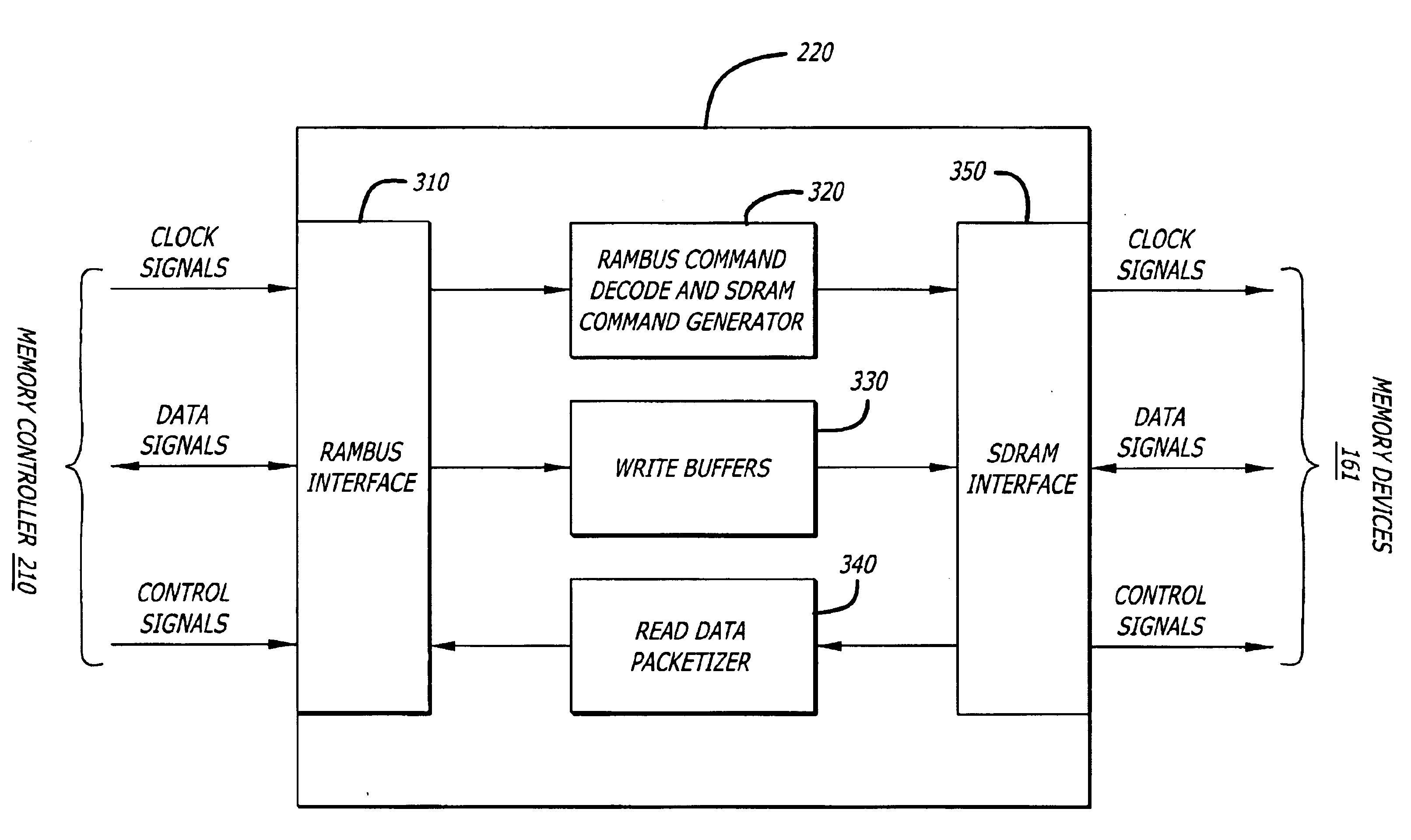

According to one aspect of the invention, a method is provided in which one or more write commands and their corresponding write data are received from a first device. The corresponding write data may be delayed by the first device by a first delay period. The one or more write commands and their corresponding write data are stored in a set of buffers. In response to another write command being received from the first device, a buffered write command and its corresponding write data are sent to a second device for execution, without waiting for the write data corresponding to said another write command to be sent from the first device.

Owner:INTEL CORP

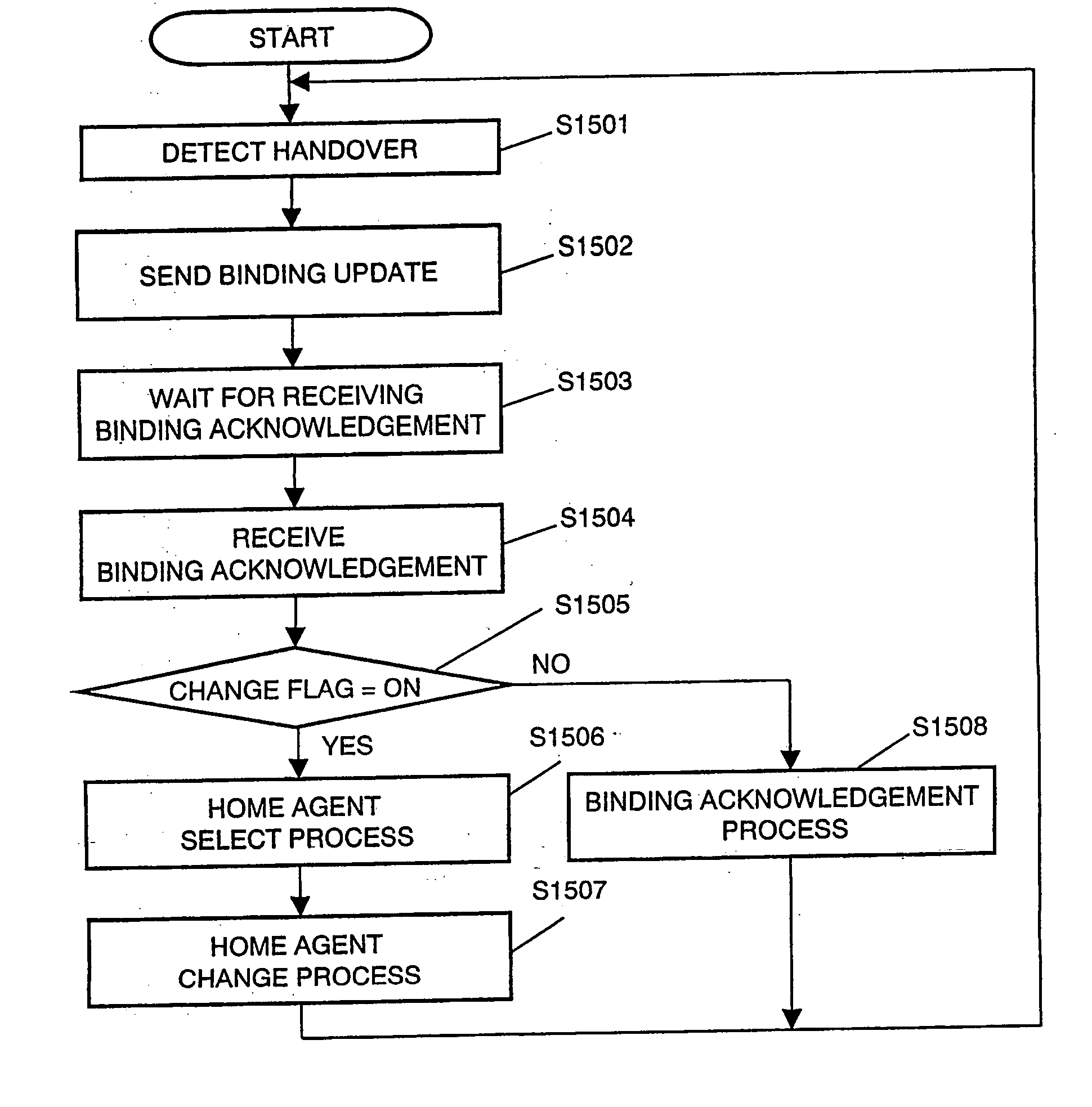

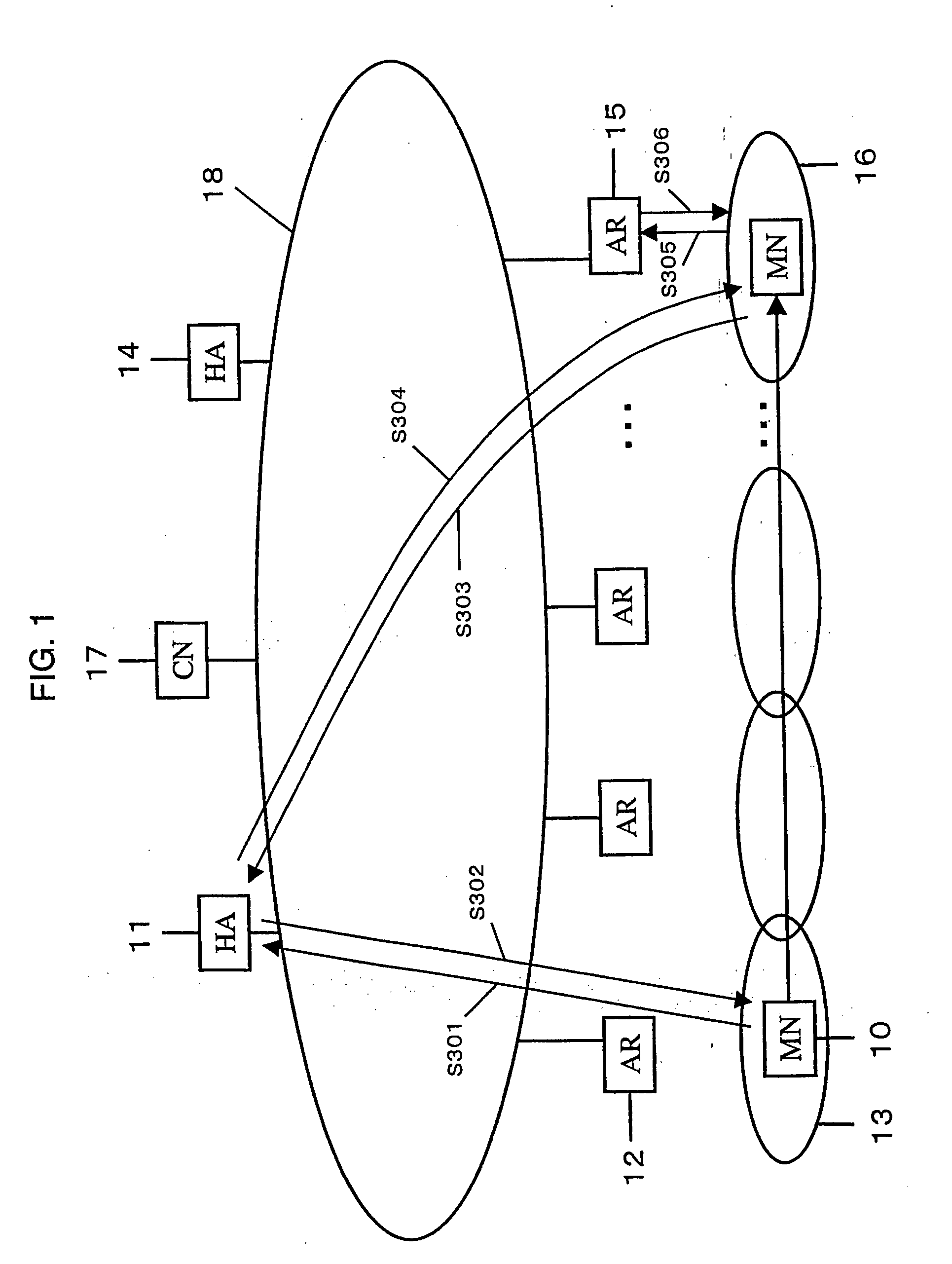

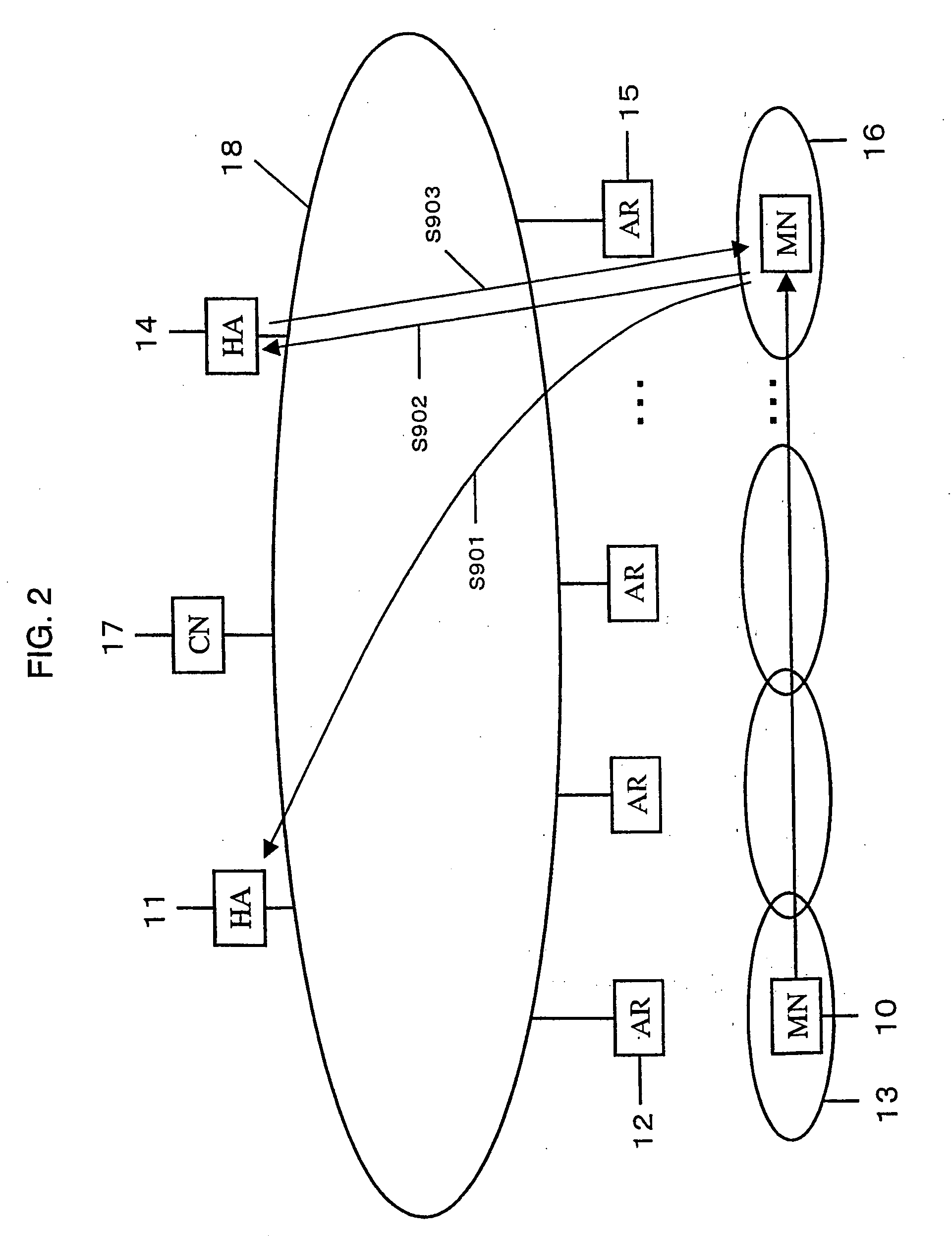

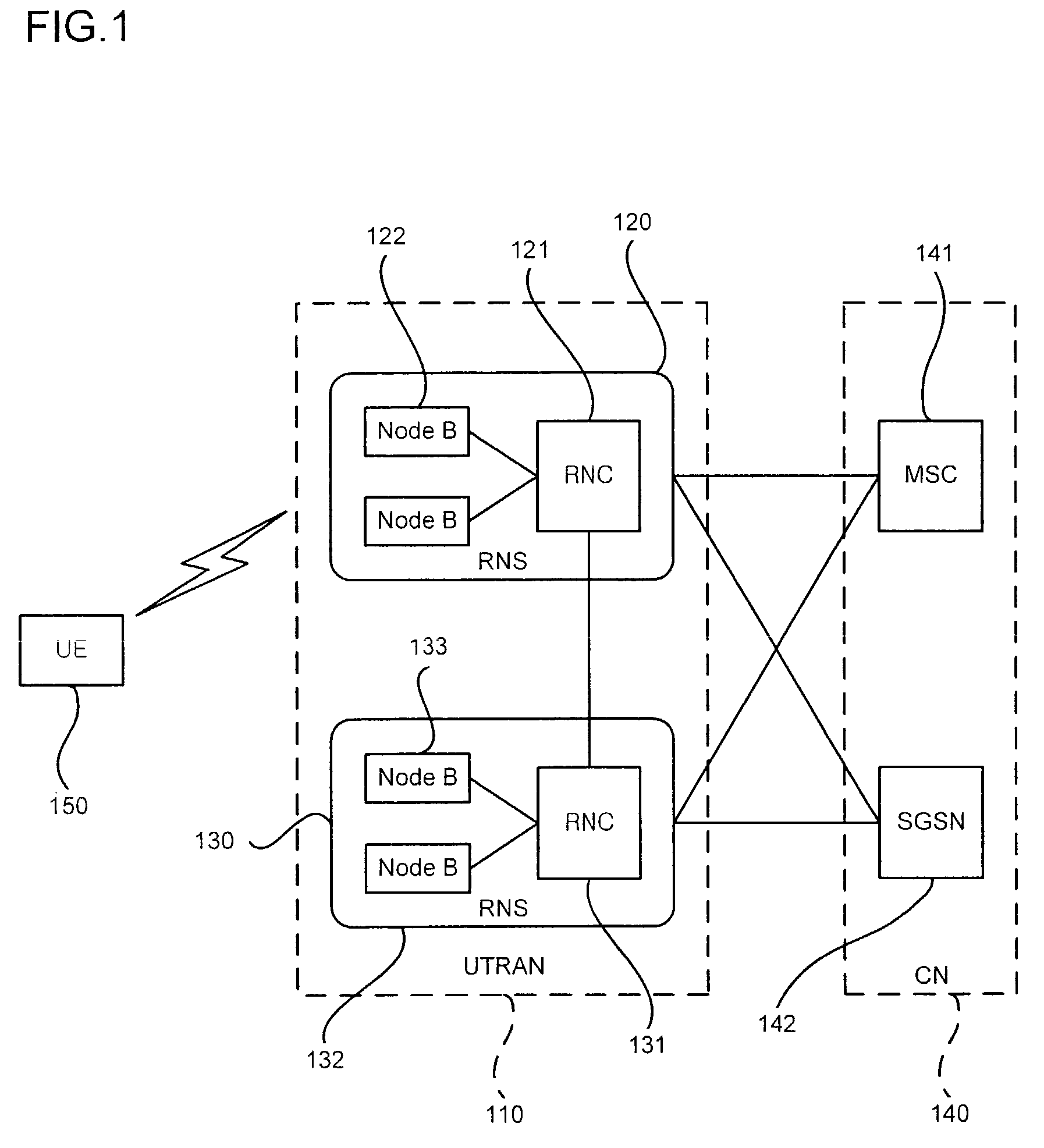

Mobile node, router, server and method for mobile communications under ip version 6 (ipv6) protocol

InactiveUS20050020265A1Smooth handoverQuick eliminationWireless network protocolsRadio/inductive link selection arrangementsDelayed timeMobile communication systems

In a mobile communication system supported with IP version 6, a mobile node measures at least one of a hop number or communication delay time to a belonging home agent. When the result of measurement is equal to or greater than a predetermined value, registration deletion is requested to the belonging home agent while registration is requested to a new home agent. The belonging home agent deletes the registration of mobile node, and the new home agent registers the mobile node. This can reduce the load on an IP network and decrease data delay.

Owner:PANASONIC CORP

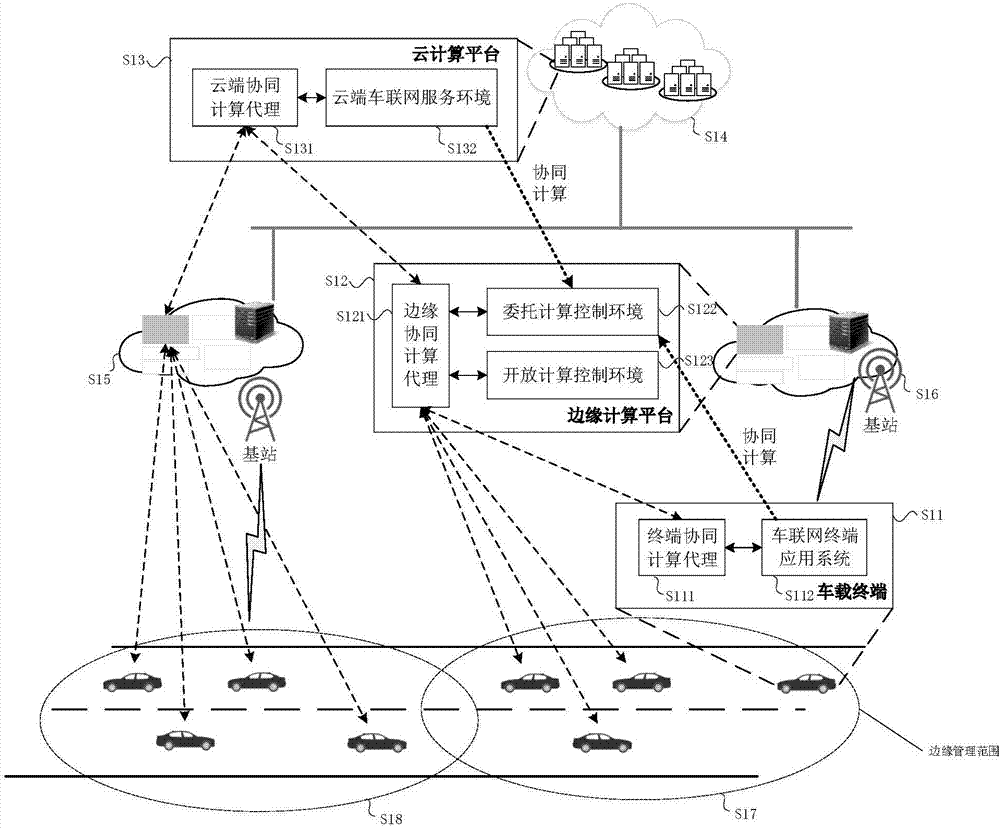

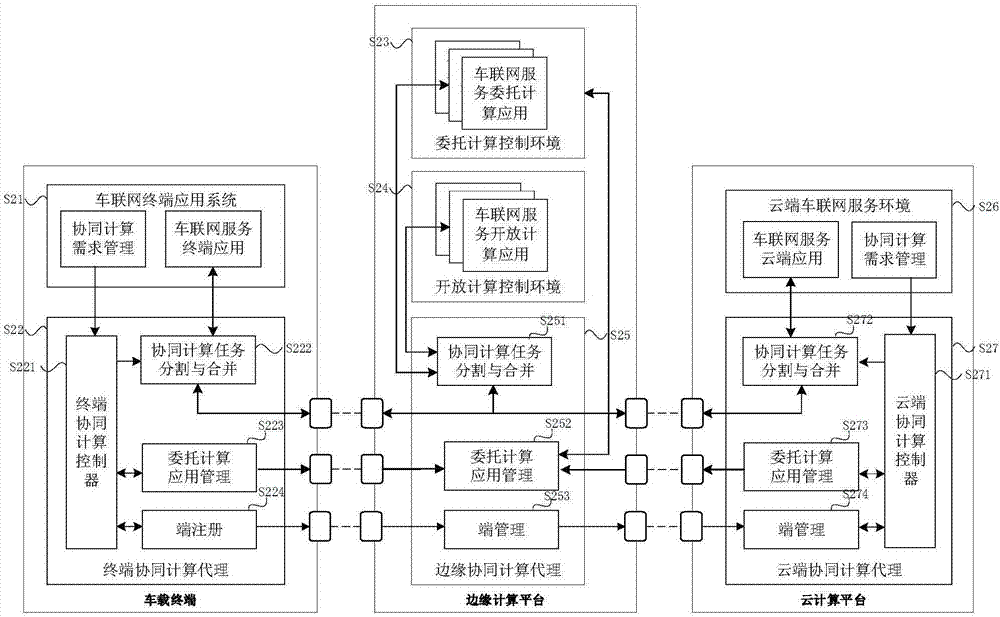

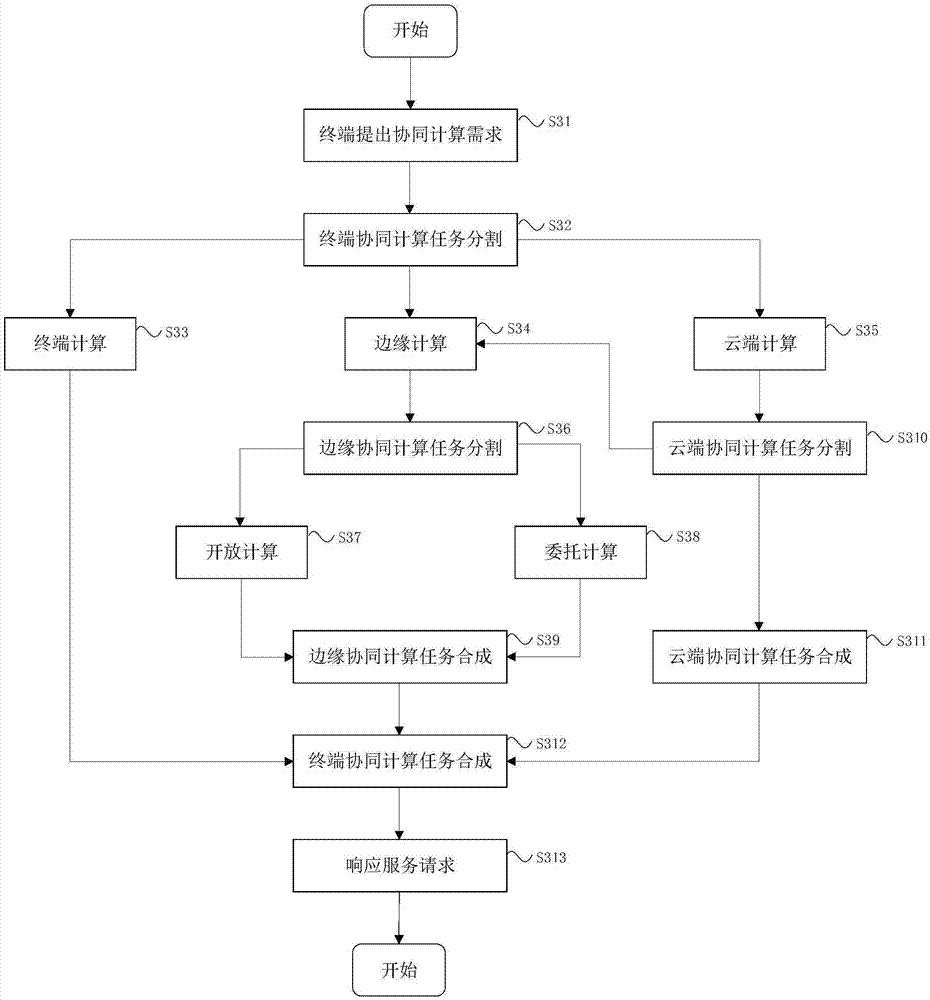

IoV (Internet of Vehicles) service cooperative computation method and system based on cloud end, edge end and vehicle end

ActiveCN107959708AComputing Process SecuritySolve the lack of computing powerTransmissionServices computingThe Internet

The invention discloses an IoV (Internet of Vehicles) service cooperative computation method and system based on a cloud end, an edge end and a vehicle end, and belongs to the field of cloud computation and intelligent driving. According to the computation system and the computation method, firstly, a vehicle-mounted terminal responds to an IoV service request proposed by an IoV terminal application system. A cloud computation platform implements cooperative interactive computation with the vehicle-mounted terminal and an edge computation platform, and provides a service computation resource or a cloud service request by a cloud IoV service environment module. The edge computation platform implements cooperative interactive computation with the vehicle-mounted terminal and the cloud computation platform by an edge cooperative computation agent module, and takes charge of integrating feedback results of a delegation computation control environment module and an open computation controlenvironment module. According to the invention, the unilateral problems of insufficient computation ability of the vehicle end, limited computation resources of the edge end and large data delay of the cloud end are solved, computation efficiency is improved, and user experience is optimized.

Owner:BEIJING UNIV OF POSTS & TELECOMM

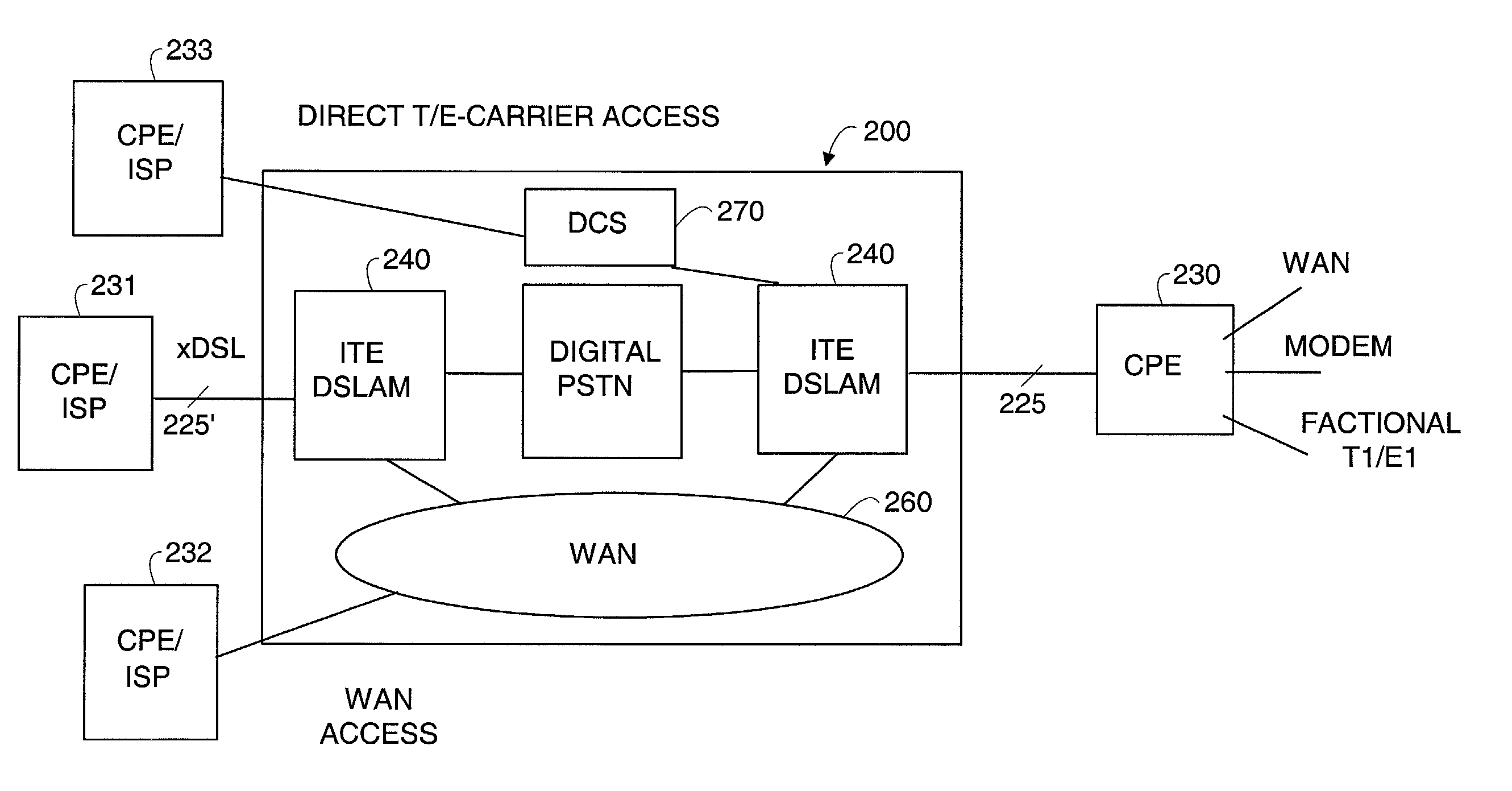

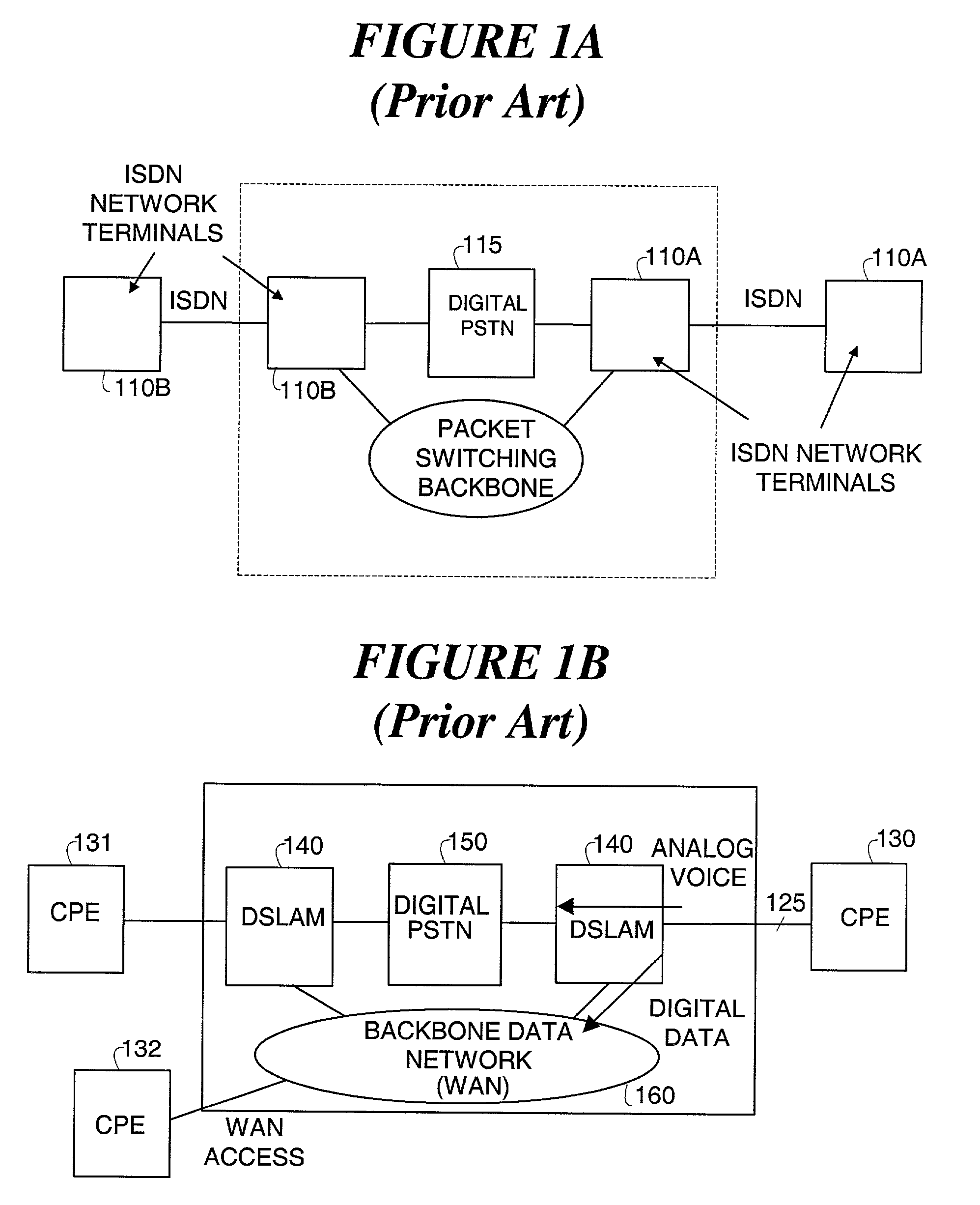

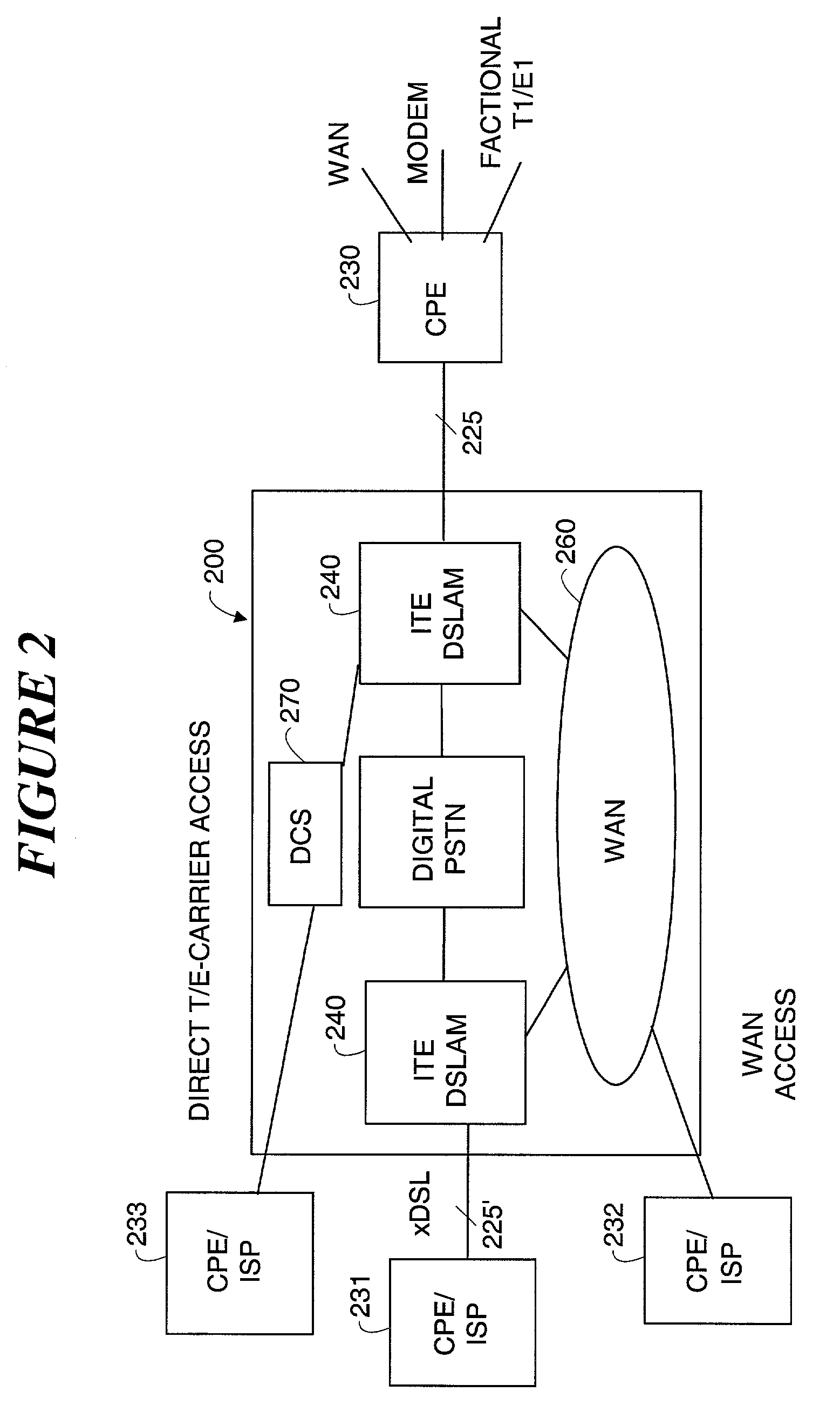

Configurable digital subscriber loop access and end-to-end data and analog voice connection system

InactiveUS7072331B2Improve distributionAppropriate costTime-division multiplexNetworks interconnectionWide areaCross connection

A system that can be dynamically configured to achieve an optimal routing path for an end-to-end data link connection is disclosed. An optimal data path can be determined by a digital subscriber loop (DSL) user based on particular bandwidth requirements, data rate cost constraints, and / or data delay requirements. The data path can be set up to include one or more data routes, including the regular digital public switching telephone network (PSTN), a wide area networks (WAN), or virtual permanent circuit links via digital cross-connects (DCS).

Owner:REALCOMM

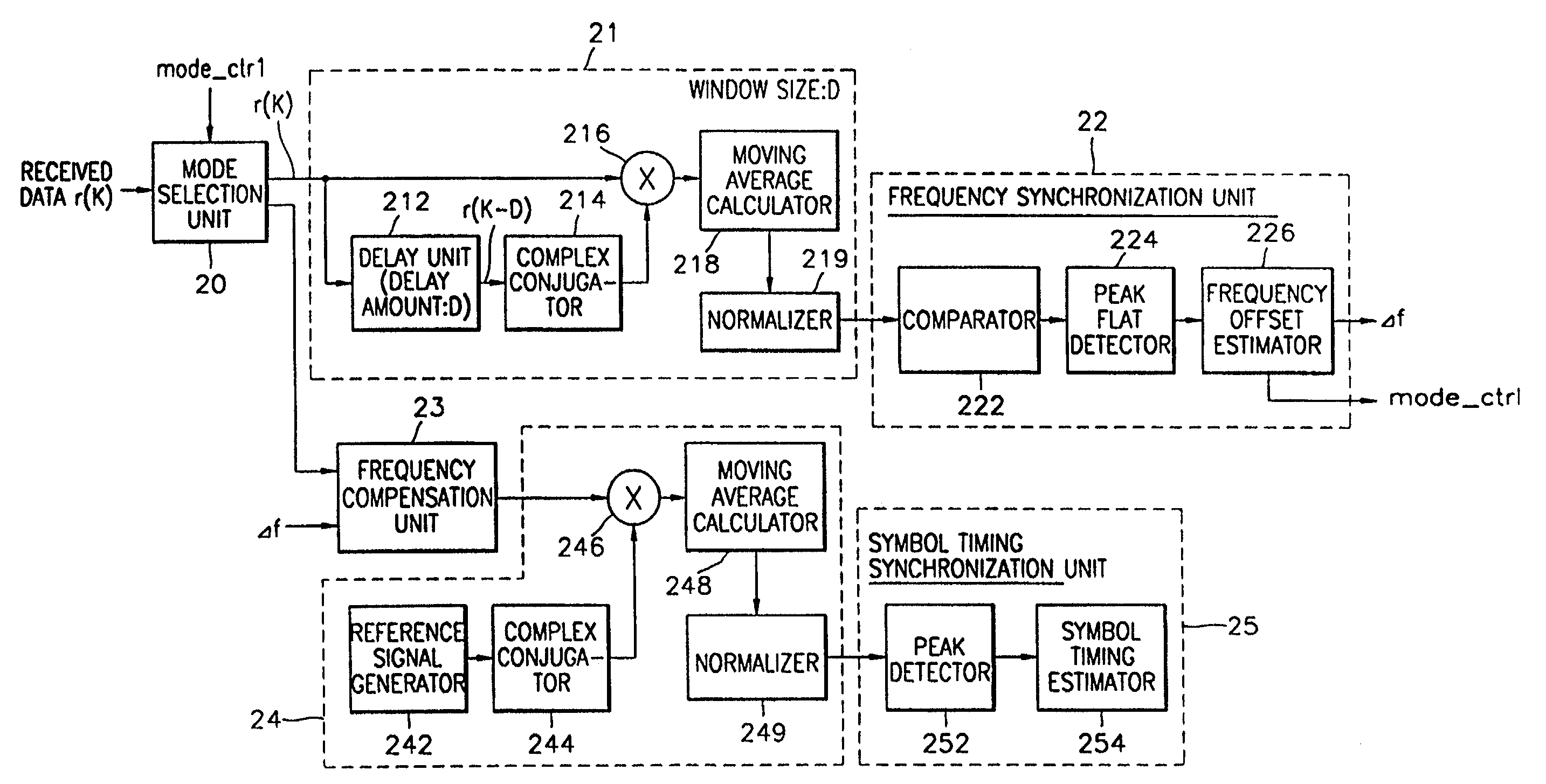

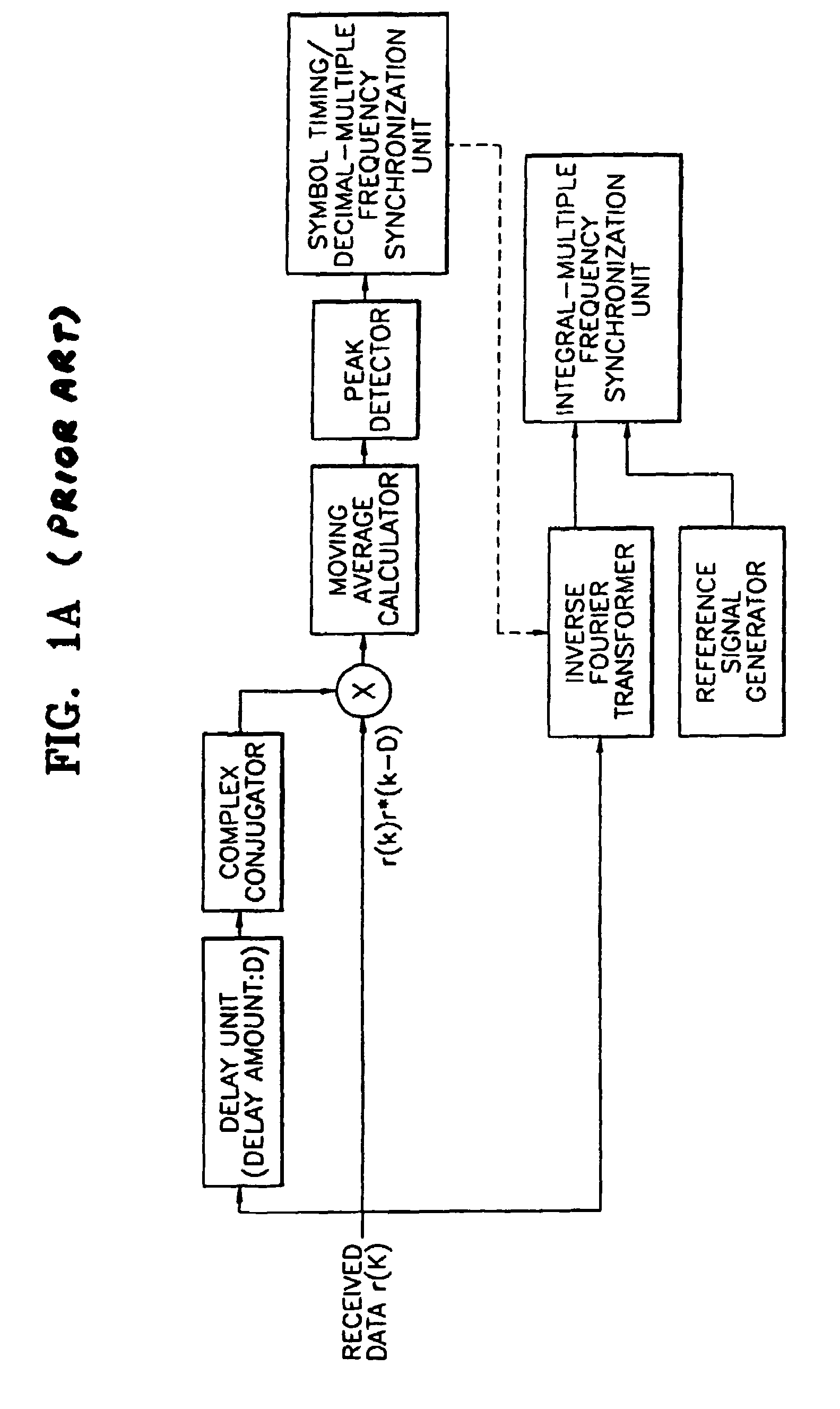

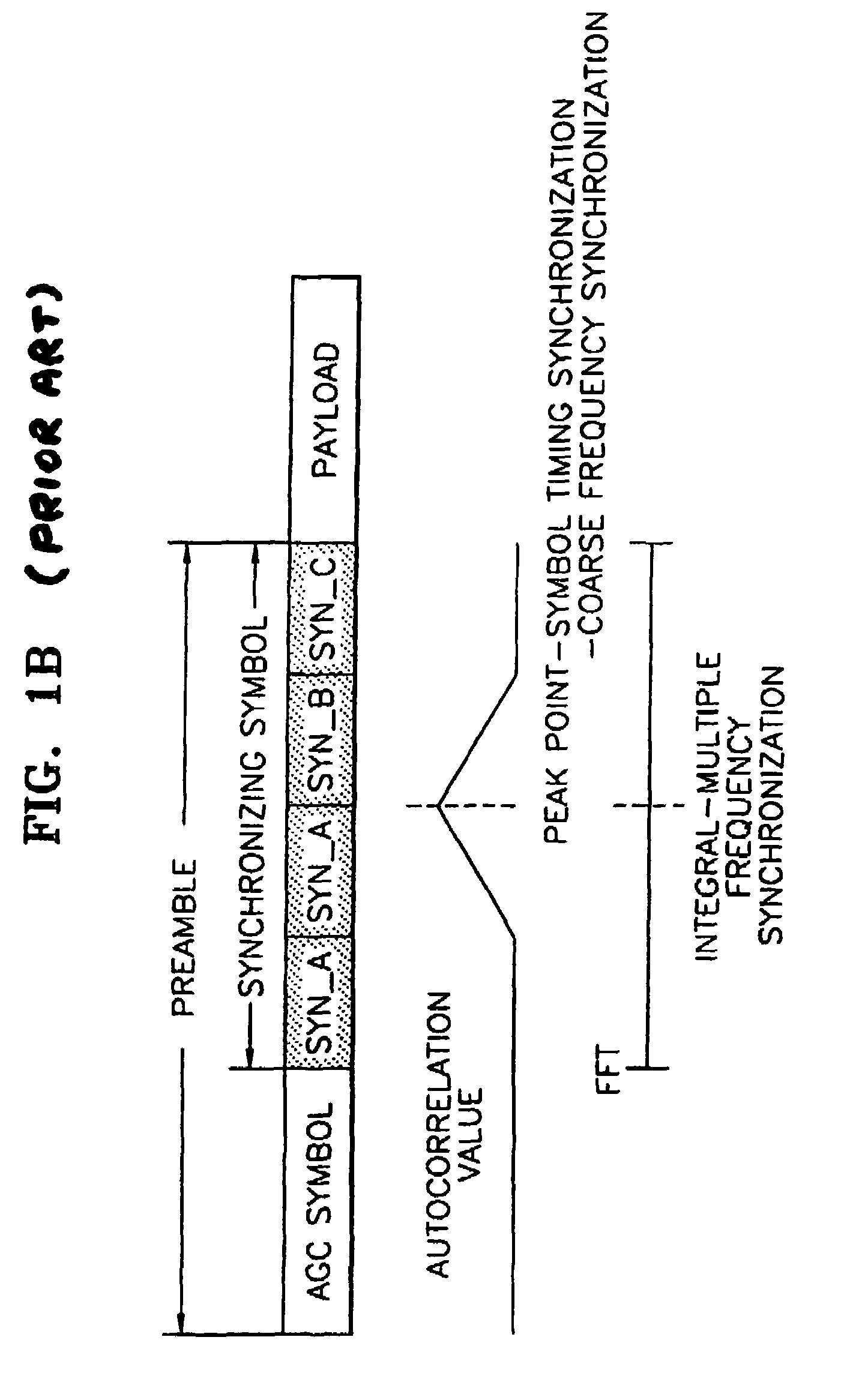

Apparatus and method for achieving symbol timing and frequency synchronization to orthogonal frequency division multiplexing signal

InactiveUS7058151B1Accurate frequency synchronizationAccurate symbol timingCarrier regulationTime-division multiplexFlat detectorPeak value

A frequency and symbol timing synchronization apparatus for orthogonal frequency division multiplexed (OFDM) signals, and a method performed by the apparatus are provided. This apparatus includes an autocorrelation unit, a comparator, a peak flat detector, a frequency offset estimator, a frequency offset compensation unit, a cross correlation unit and a symbol timing synchronization unit. The autocorrelation unit receives data including a synchronizing symbol made up of at least three identical synchronizing signals, delays the received data by a predetermined delay amount, performs autocorrelation between the received data and the delayed data, normalizes an autocorrelated value, and outputs a normalized autocorrelated value. The comparator compares the normalized autocorrelated value with a predetermined threshold value. The peak flat detector detects as a flat section a section where the normalized autocorrelated value is equal to or greater than the threshold value. The frequency offset estimator estimates a frequency offset within the flat section to obtain a frequency offset value. The frequency offset compensation unit compensates for the frequency offset of a received signal using the frequency offset value. The cross correlation unit performs cross correlation using a frequency offset-compensated signal and a reference signal, and normalizes the cross-correlated value to output a normalized cross-correlated value. The symbol timing synchronization unit detects a point where the cross-correlated value is maximum, and performs symbol timing estimation, thereby performing symbol timing synchronization. In the symbol timing and frequency synchronization apparatus and method, accurate frequency synchronization can be achieved because a large sample error can be allowed. Also, a symbol timing error can be reduced since symbol timing synchronization is achieved using a frequency offset-compensated signal.

Owner:SAMSUNG ELECTRONICS CO LTD

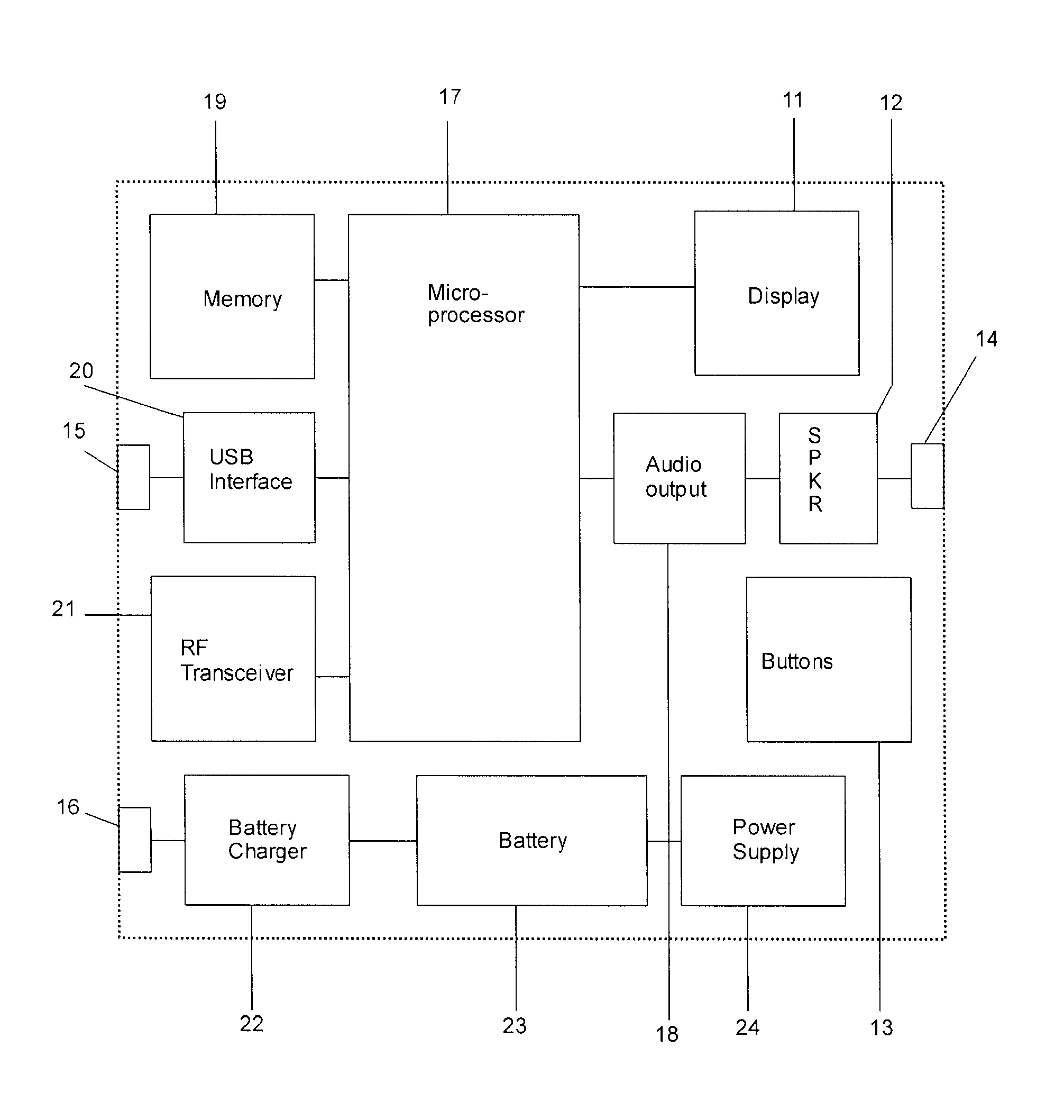

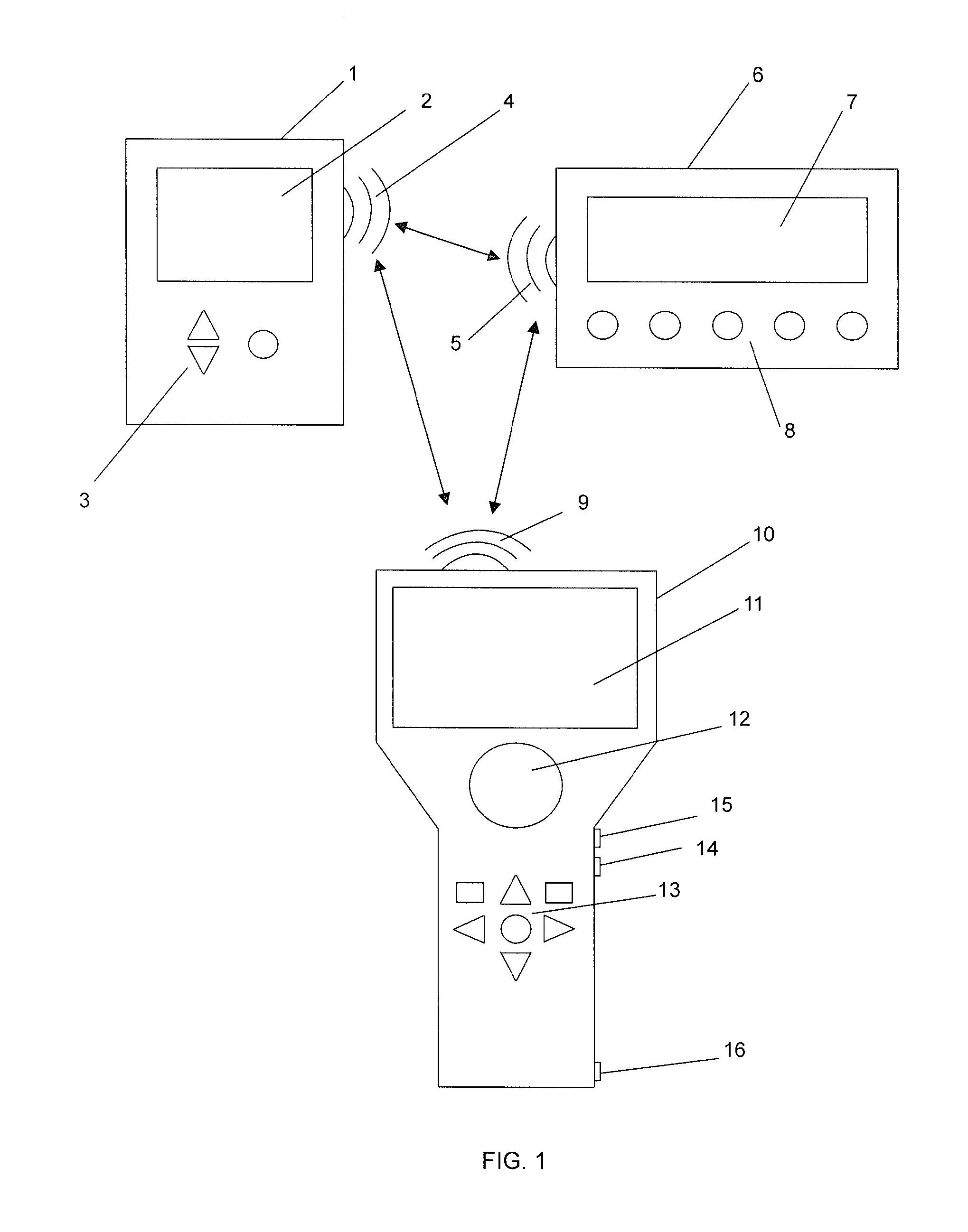

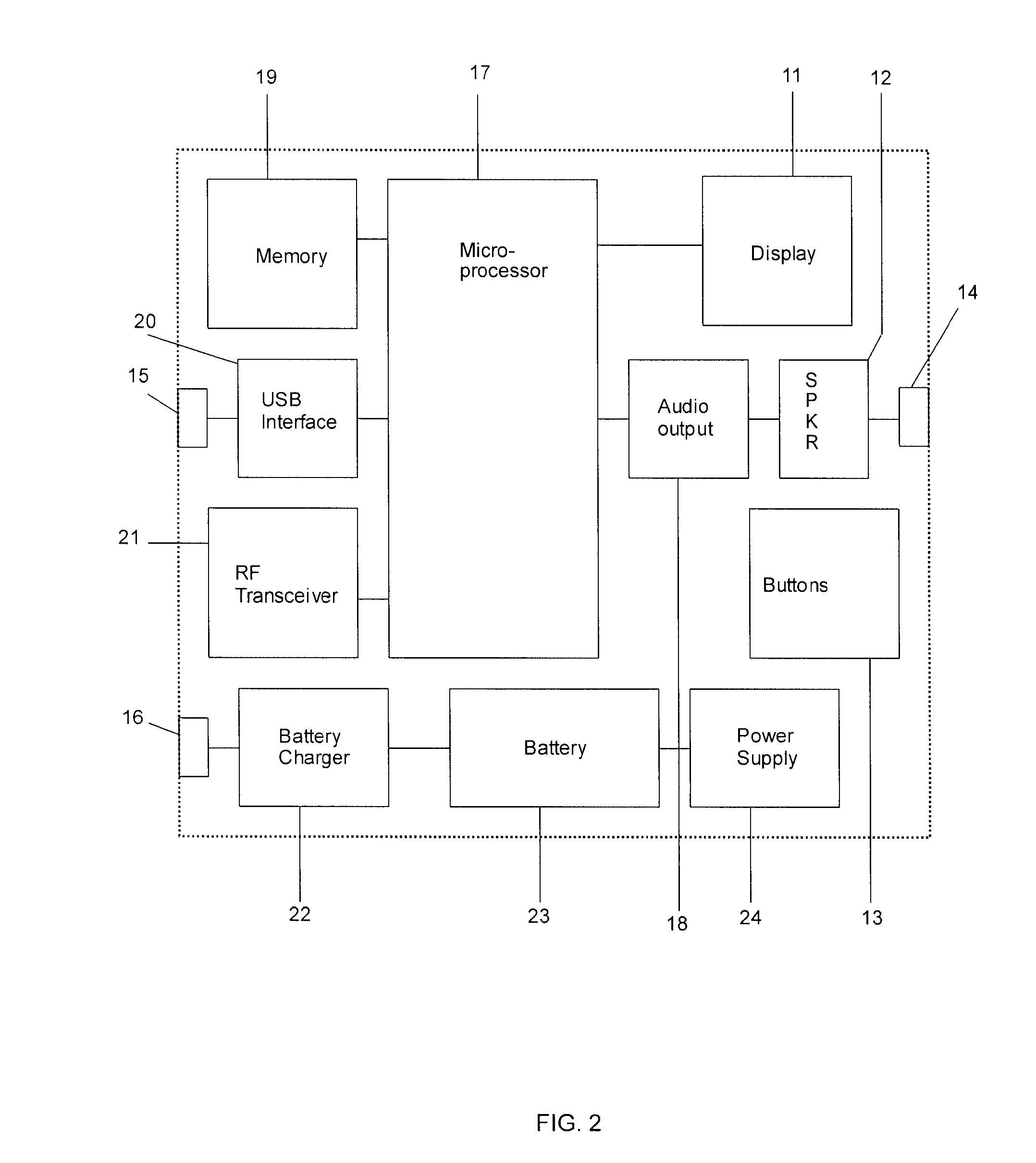

Remote control device for use with insulin infusion systems

InactiveUS20100286653A1Comfortable to holdGuaranteed uptimeMedical devicesPressure infusionInsulin infusionRemote control

Methods and apparatuses providing accessibility options for the blind and poorly sighted for use with insulin therapy systems. A remote control device, with speech output capability and comprehensive speech menu system, may monitor or intercept data generated by a blood glucose meter, and delay, modify and retransmit said data to an insulin pump. The remote control device may also be used to program and set operating parameters of an insulin pump and also record data received from an insulin pump. The remote control device may also be used in conjunction with a personal computing device.

Owner:AXSOL INC

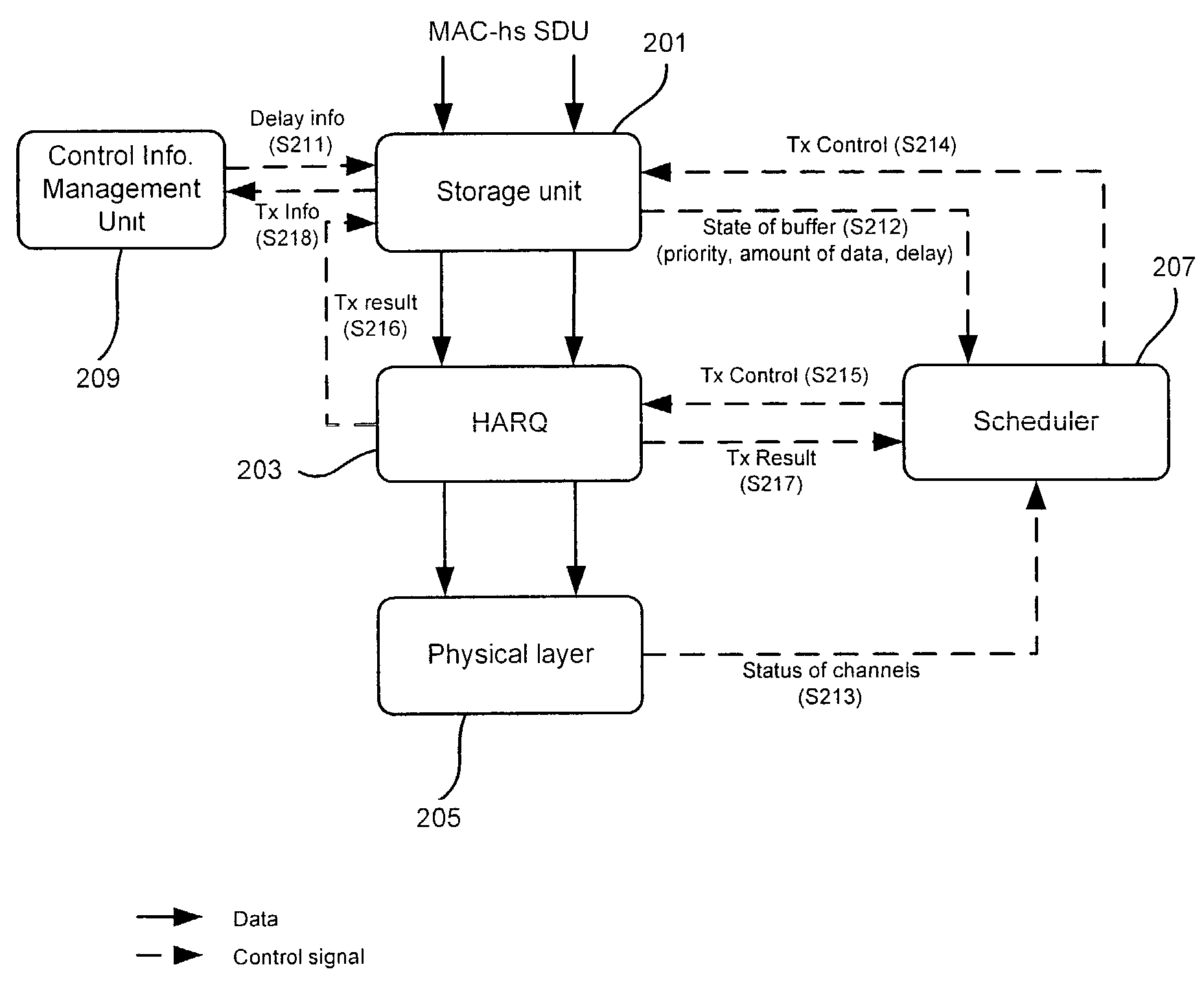

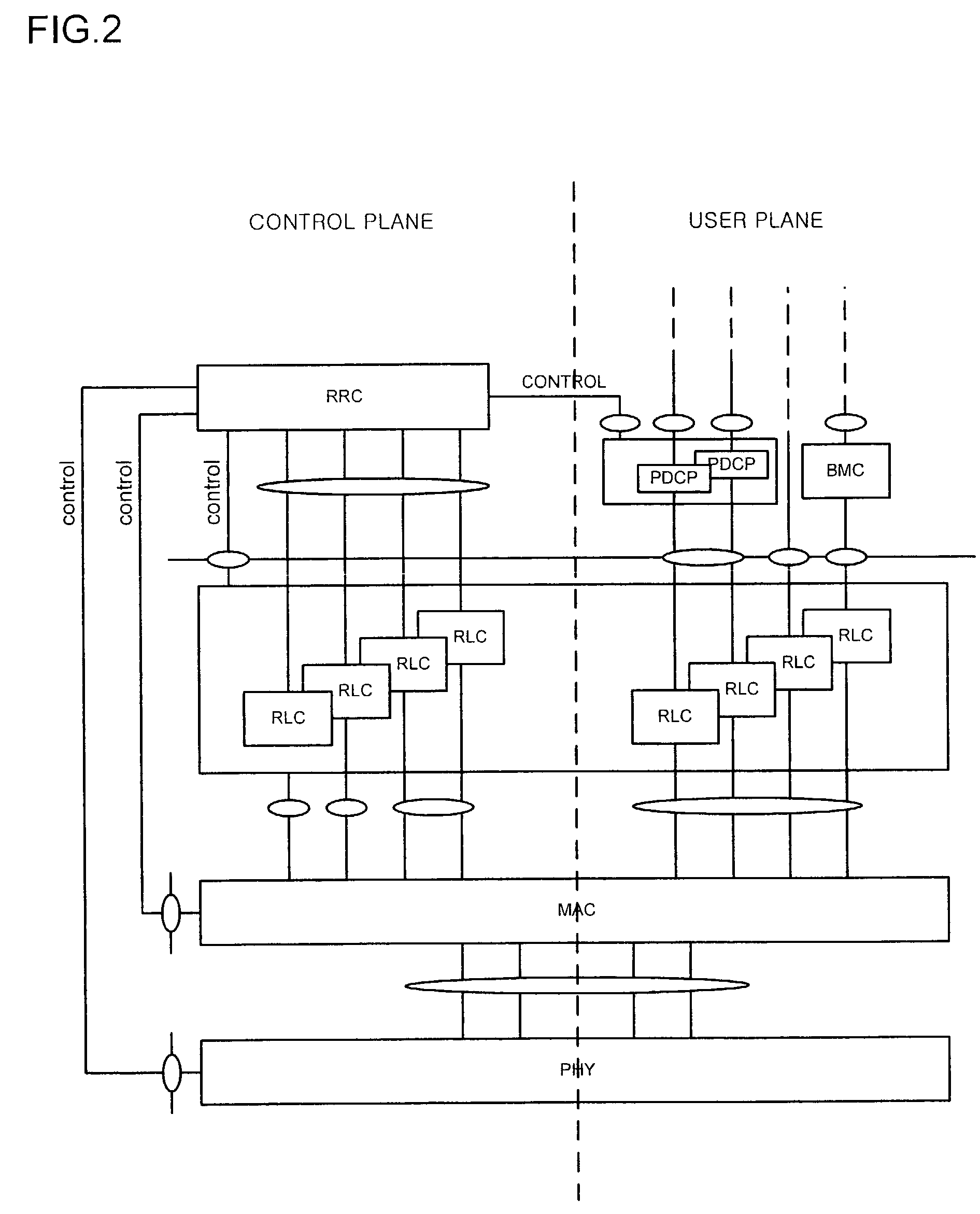

Packet transmission scheduling technique

ActiveUS7515616B2Improve service qualityError preventionTransmission systemsReal time servicesPhysical layer

A packet data transmission method of the HSDPA system includes collecting information on the quality of physical channels, a status of the MAC buffer, the priority level of data, the delay of data, and the like, determining the transmission order of data and the size of a data block to be transmitted based on the collected information, and transmitting the data block through the physical layer according to the order of transmissions. Since the HSDPA scheduler takes into account the delay of data, the quality of real-time services can be improved.

Owner:LG ELECTRONICS INC

Delayed lock-step CPU compare

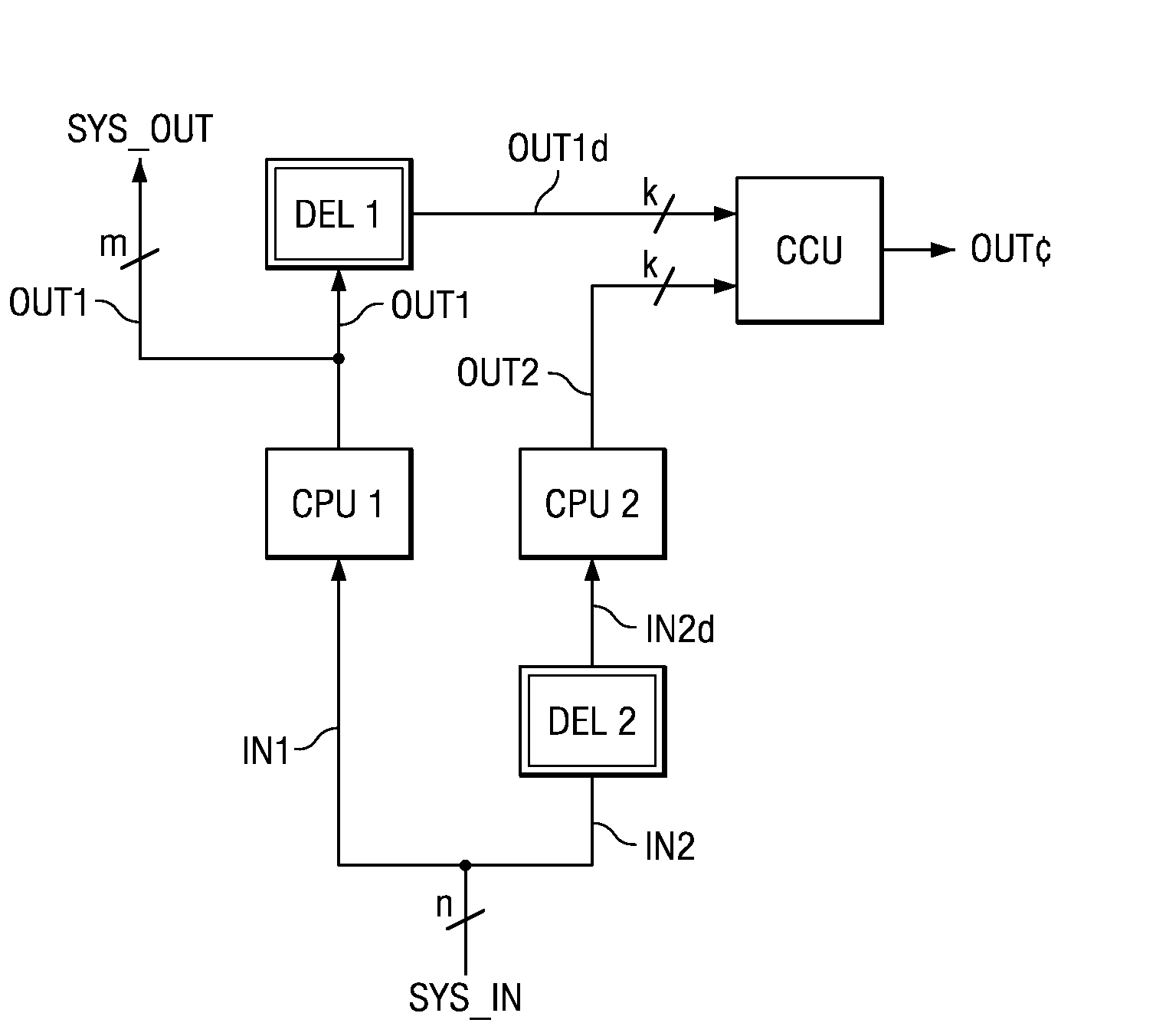

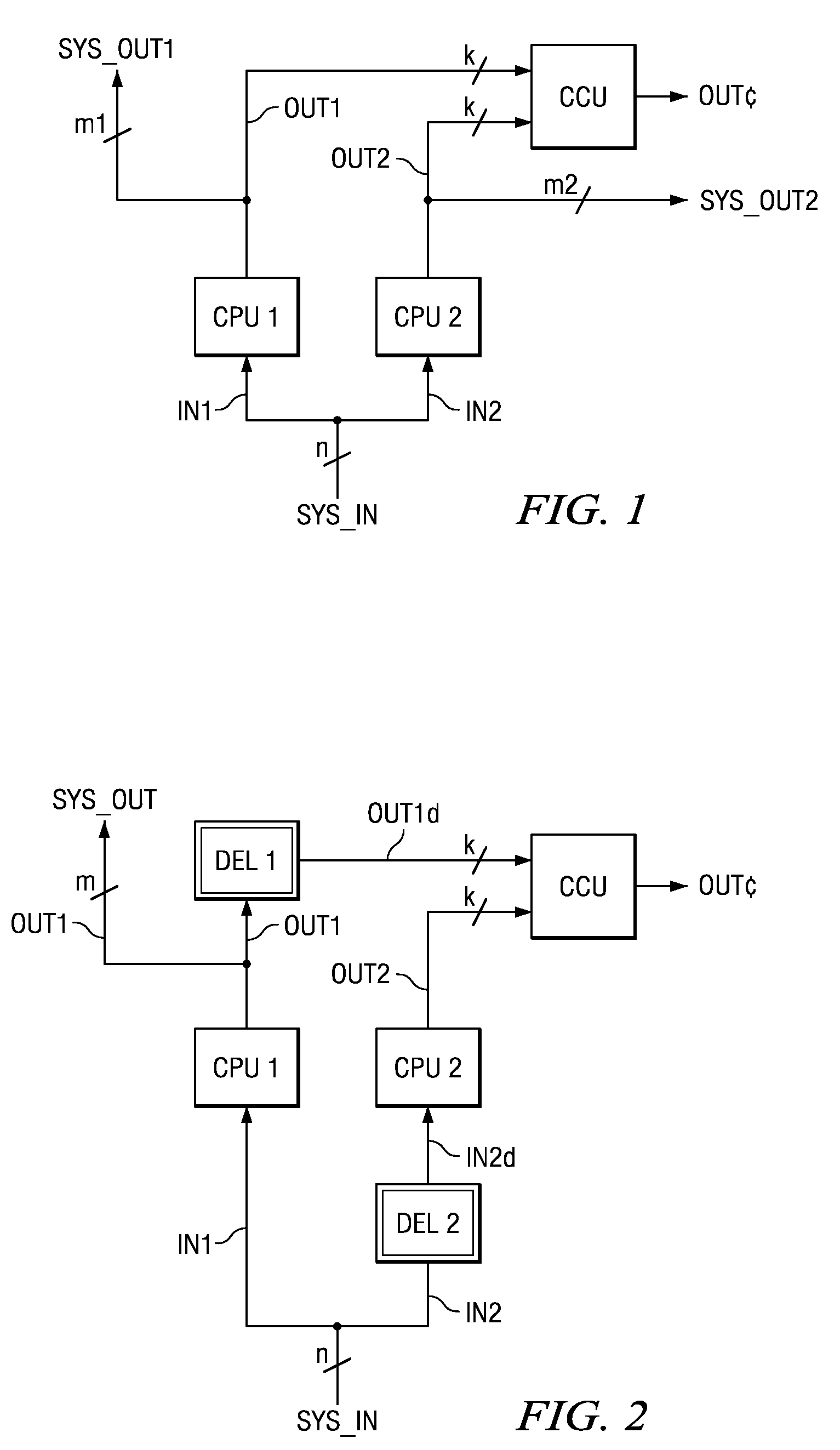

InactiveUS20080244305A1Error detection/correctionGeneral purpose stored program computerMicrocontrollerCpu architecture

The present invention relates to an electronic device comprising a first CPU, a second CPU, a first delay stage and a second delay stage for delaying data propagating on a bus, a CPU compare unit, and wherein the first delay stage is coupled to an output of the first CPU and a first input of the CPU compare unit, an input of the first CPU is coupled to a system input bus, the second delay stage is coupled to the system input bus and to an input of the second CPU, an output of the second CPU (CPU2) is coupled to the CPU compare unit, and wherein the first CPU and the second CPU are adapted to execute the same program code and the CPU compare unit is adapted to compare an output signal of the first delay stage, which is a delayed output signal of the first CPU, with an output signal of the second CPU. In one embodiment, the present invention relates to a method for lock-step comparison of CPU outputs of an electronic device, in particular a microcontroller, having a dual CPU architecture, the method comprising executing the same program code on a first CPU and a second CPU in response to data provided via a system input bus, delaying an output data of the first CPU by a predetermined first delay to receive a delayed output data, delaying the data to be input to the second CPU by a predetermined second delay, and comparing the output data of the second CPU with the delayed output data of the first CPU.

Owner:TEXAS INSTR INC

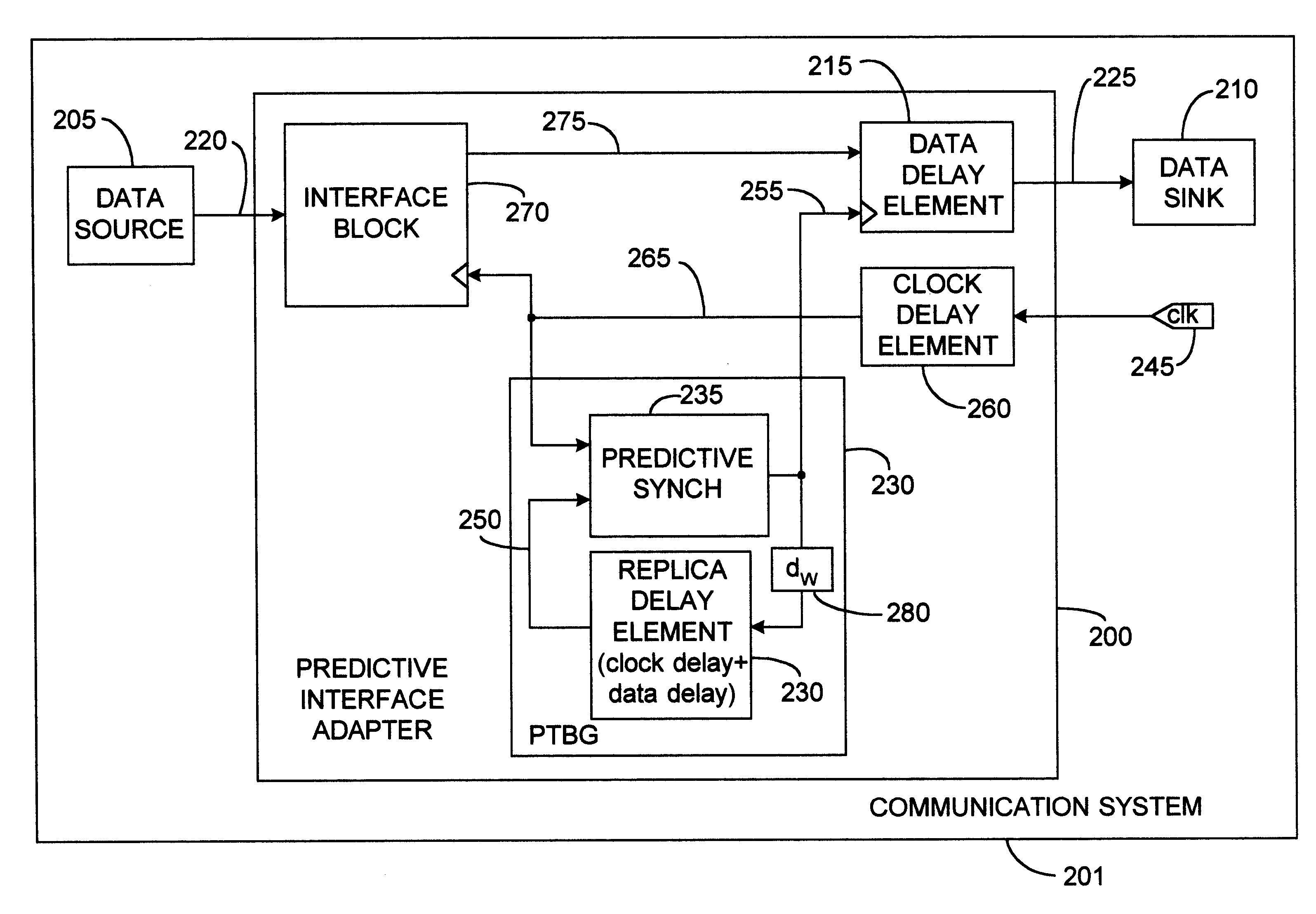

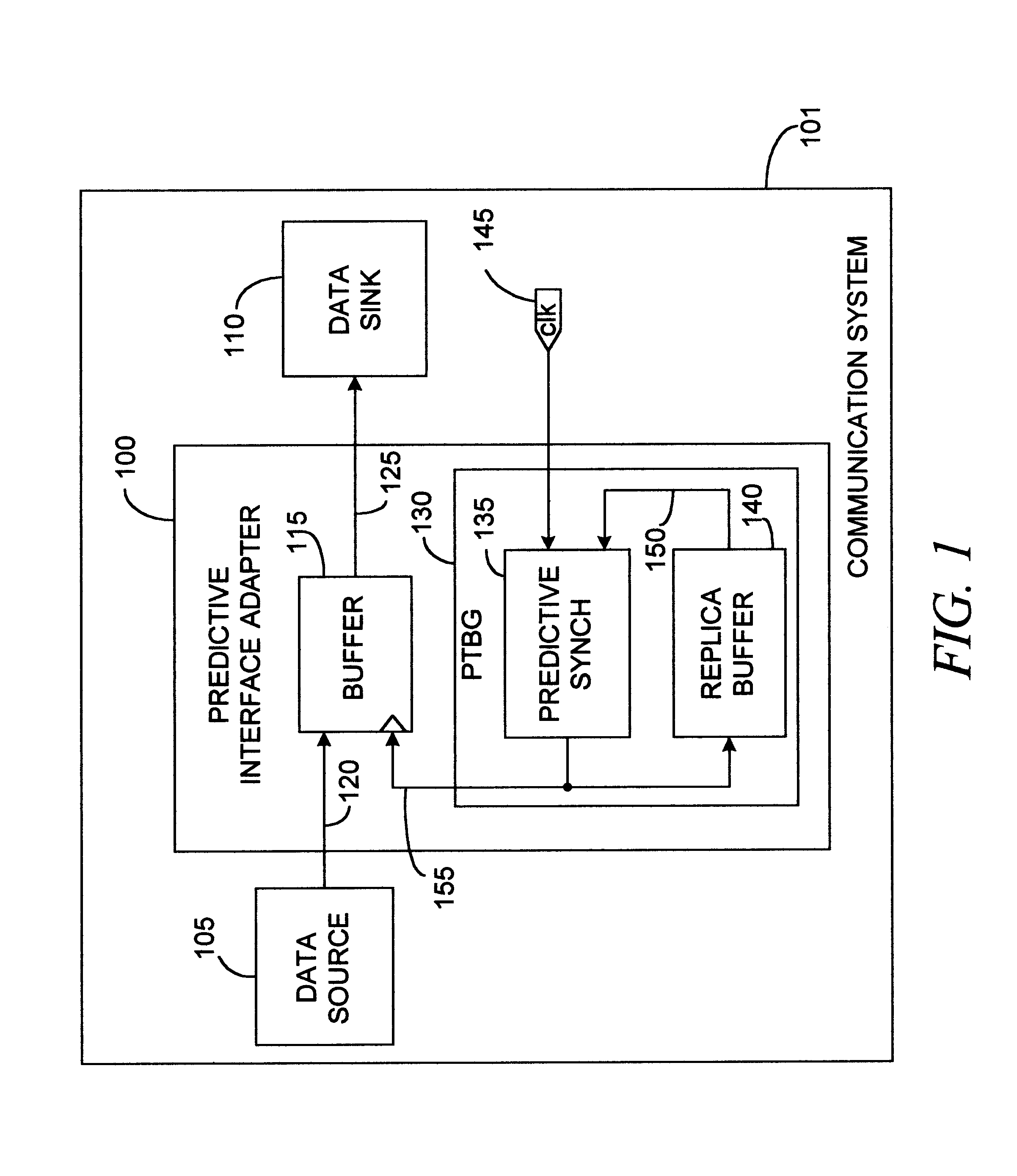

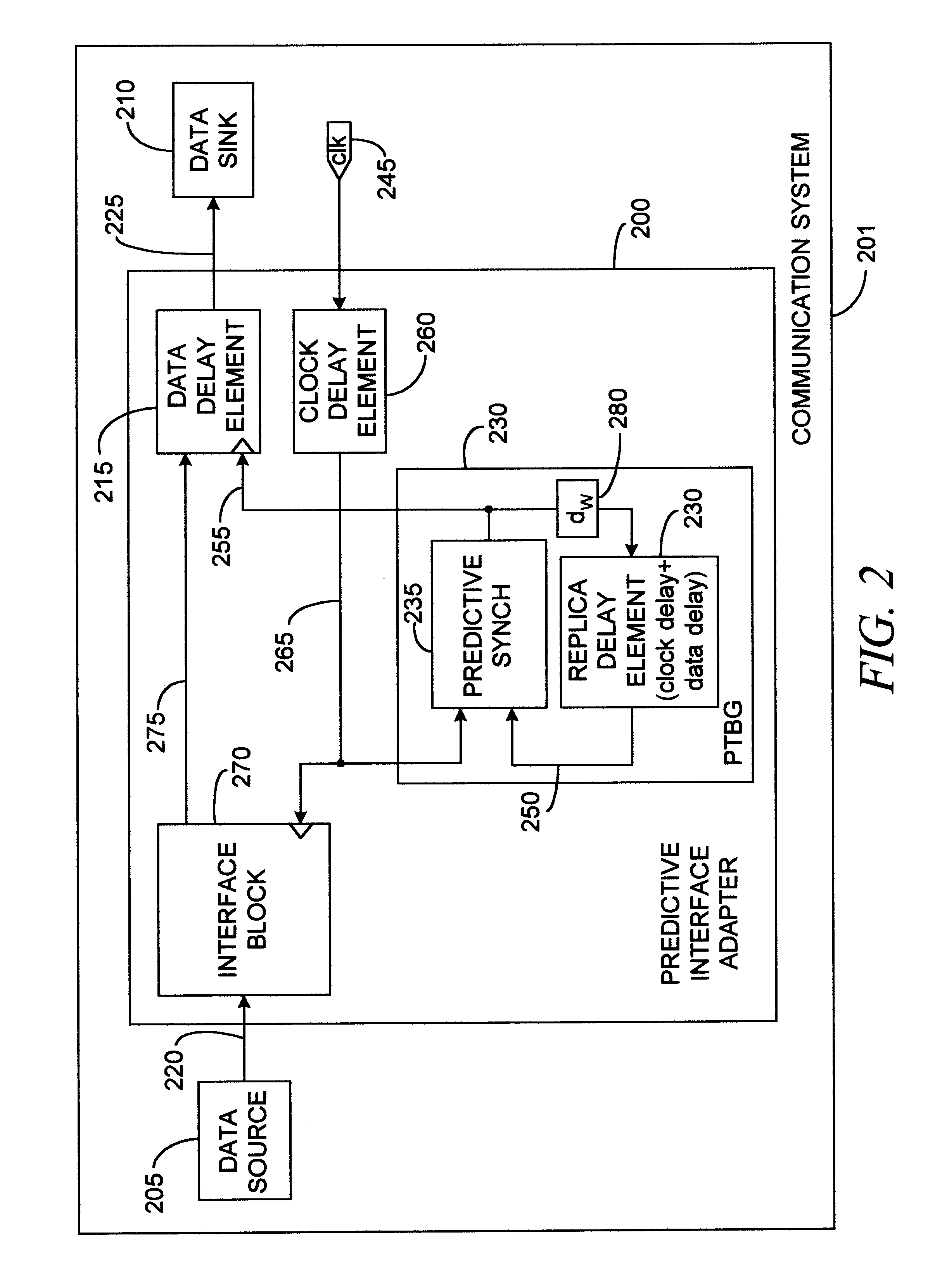

Circuit for optimizing a delay line used to de-skew received data signals relative to a received clock signal

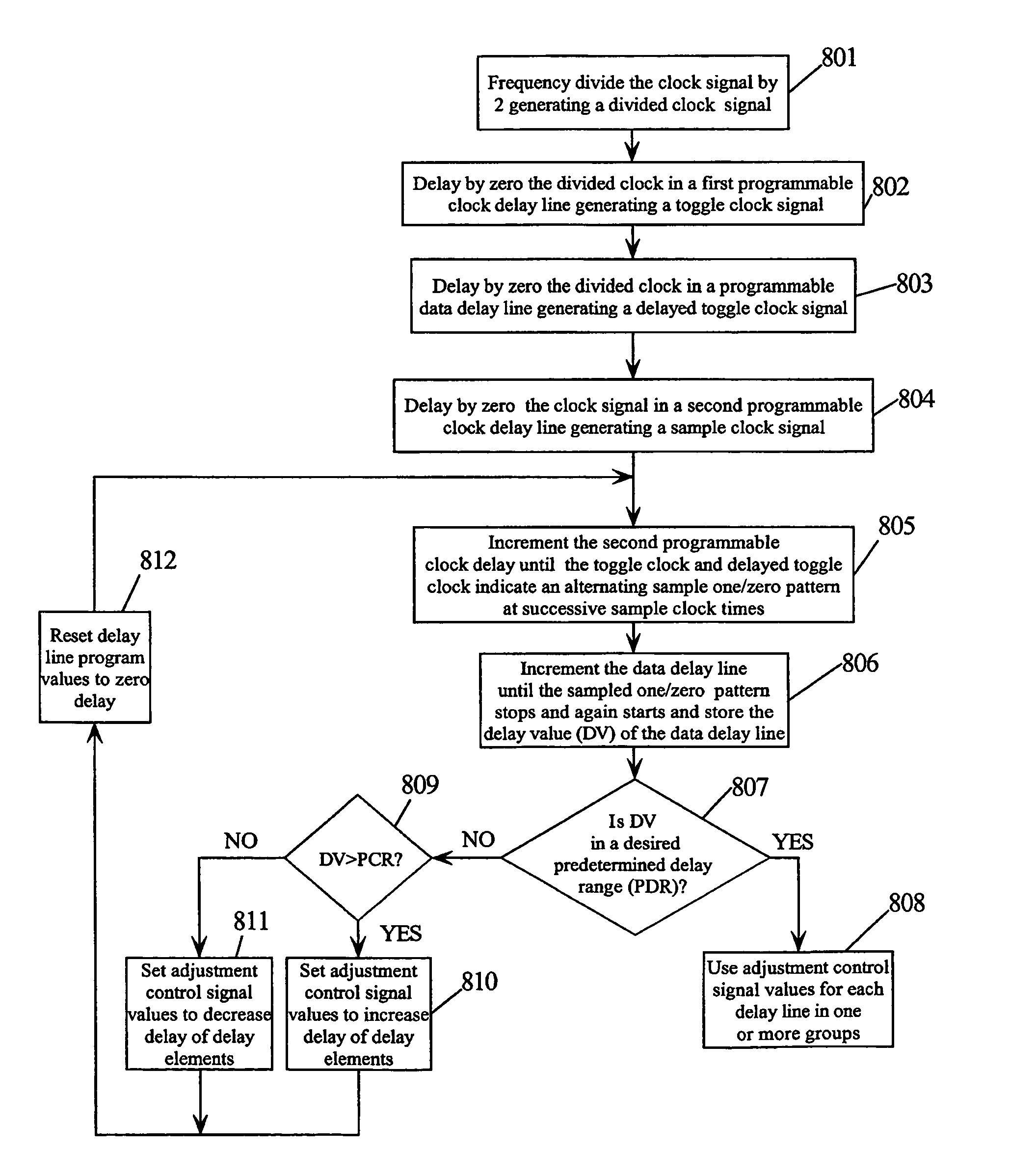

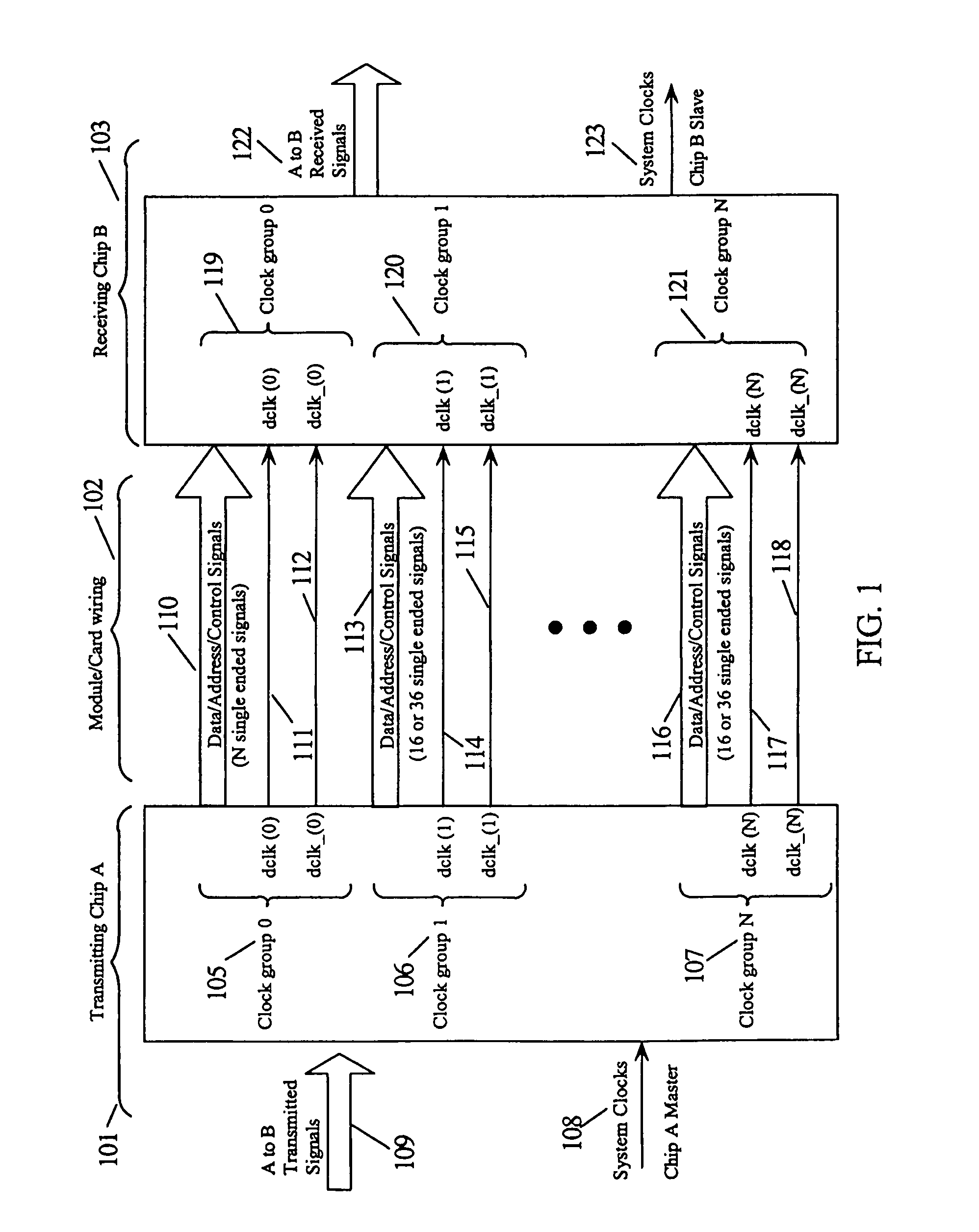

InactiveUS7012956B1Extra delayPrecise alignmentSynchronisation information channelsSynchronisation signal speed/phase controlControl signalData signal

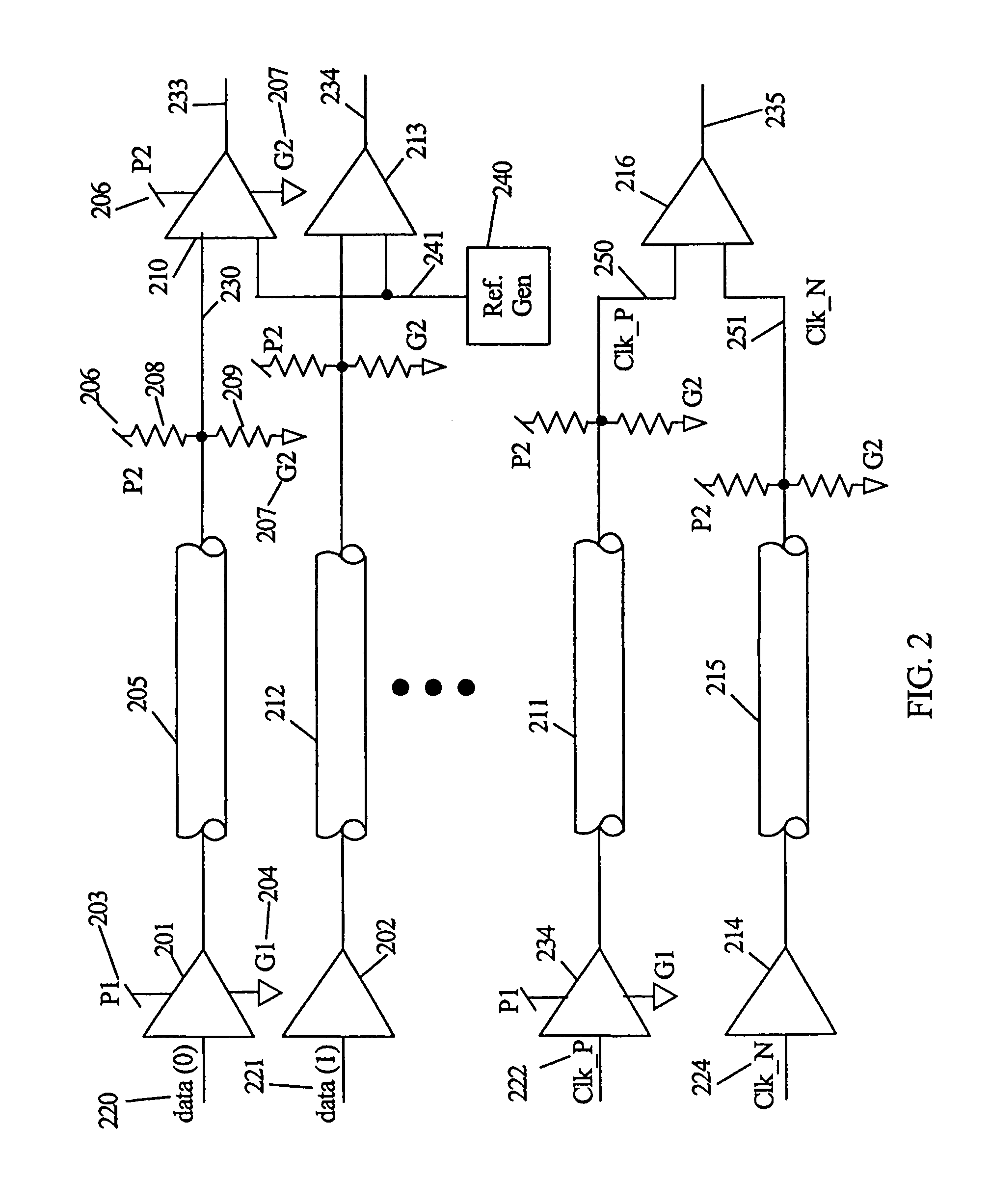

Delay circuits have programmable delay elements to delay data signals so a clock samples the data signals in the middle of the eye window pattern. The clock is frequency divided by two, generating a divided clock coupled to a clock delay circuit and a data delay circuit generating a toggle clock and a delayed toggle clock that are sampled with the clock signal. A state machine varies the number N of delay elements selected in the data delay circuit until successive samples of the toggle clock and the delay toggle clock have opposite logic stages. The resulting number N is the number of delay elements required to generate a delay equal to one period of the clock. The delay of each delay element is adjusted using adjustment control signals until an N is generated that is within a predetermined range. The adjustment control signals are distributed to the data delay circuits.

Owner:IBM CORP

Method and apparatus for improving radio spectrum usage and decreasing user data delay when providing packet PSI status

ActiveUS20060280144A1Improve data throughputAllocated more efficientlyAssess restrictionTime-division multiplexCommunications systemFrequency spectrum

Owner:QUALCOMM INC

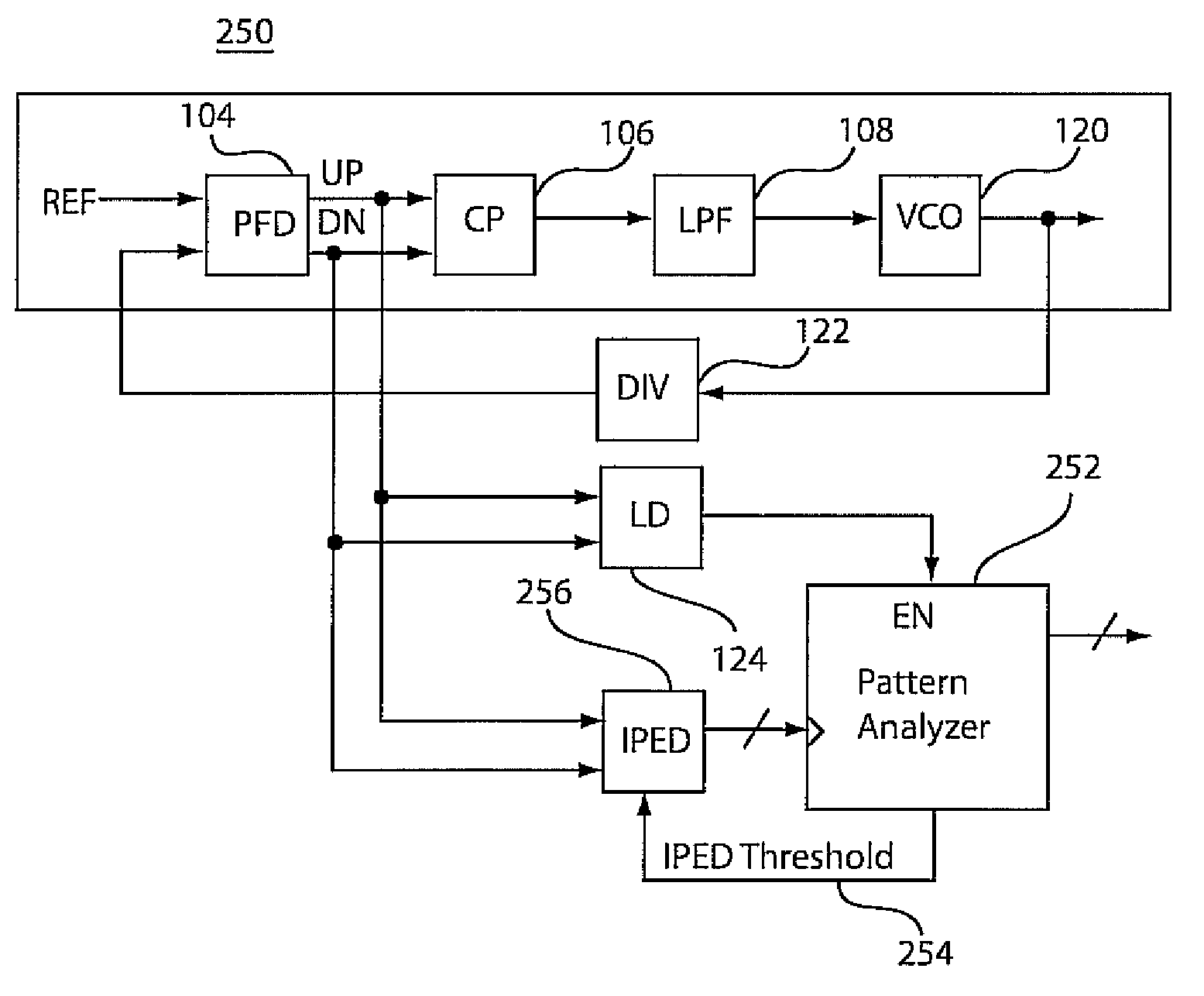

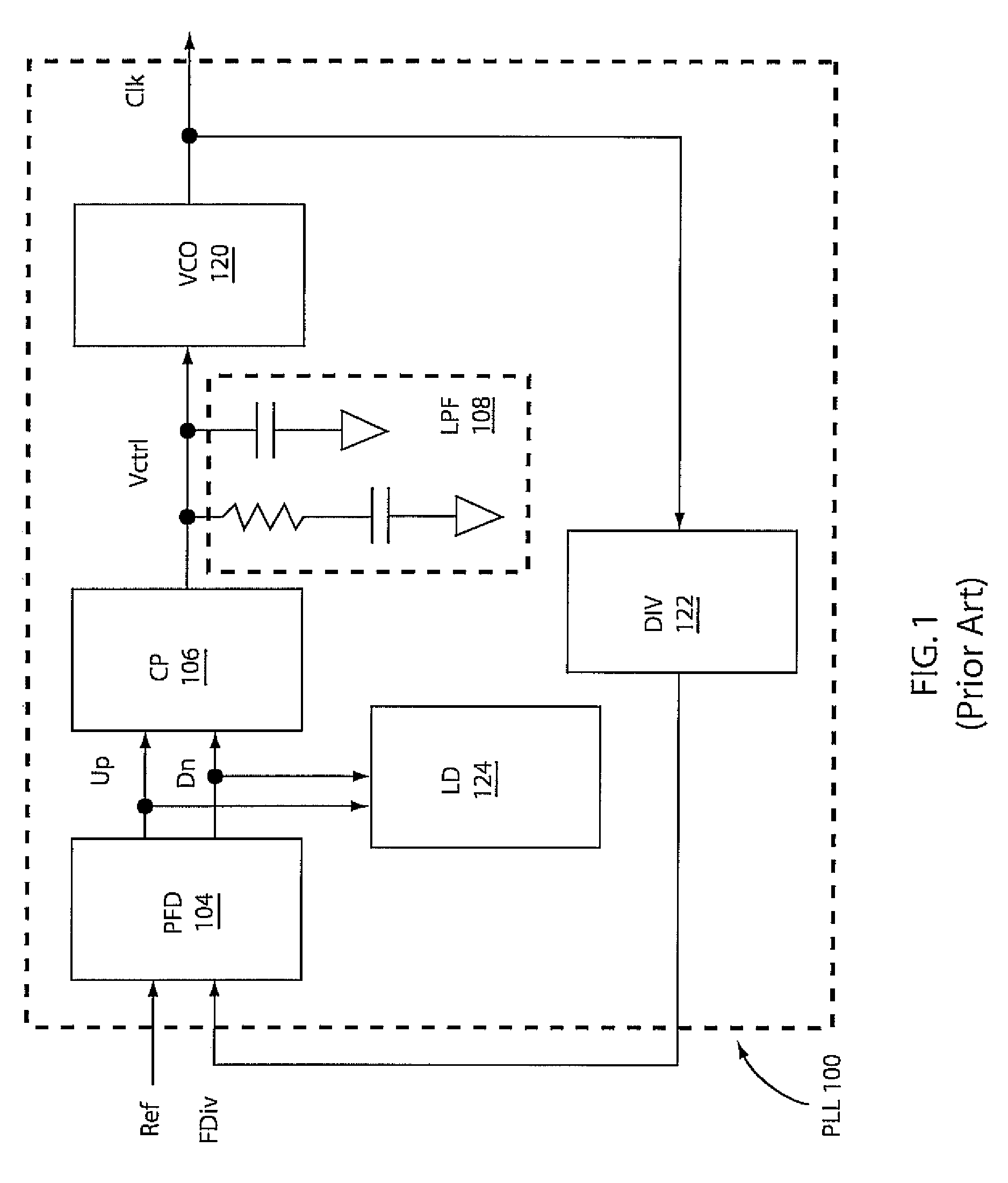

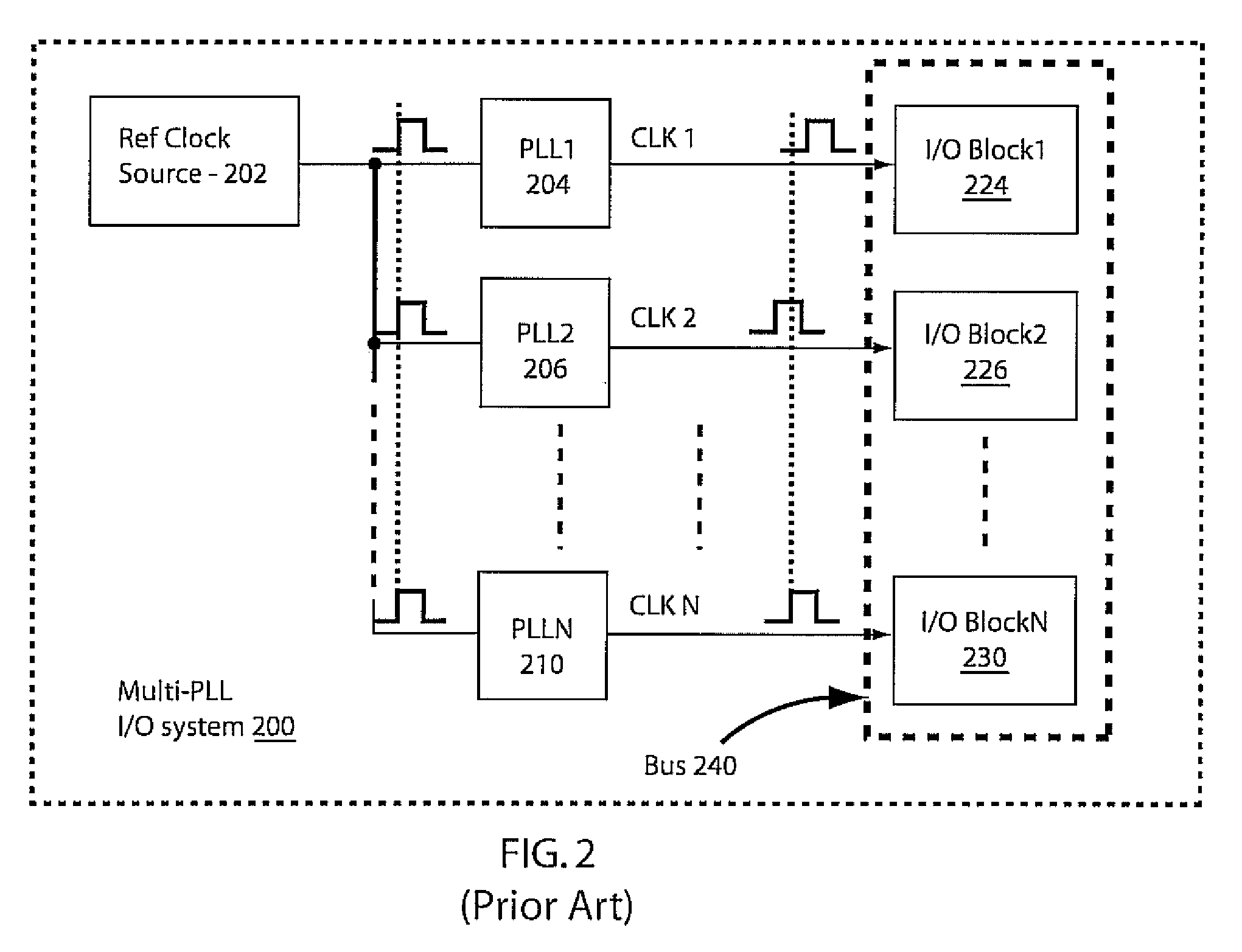

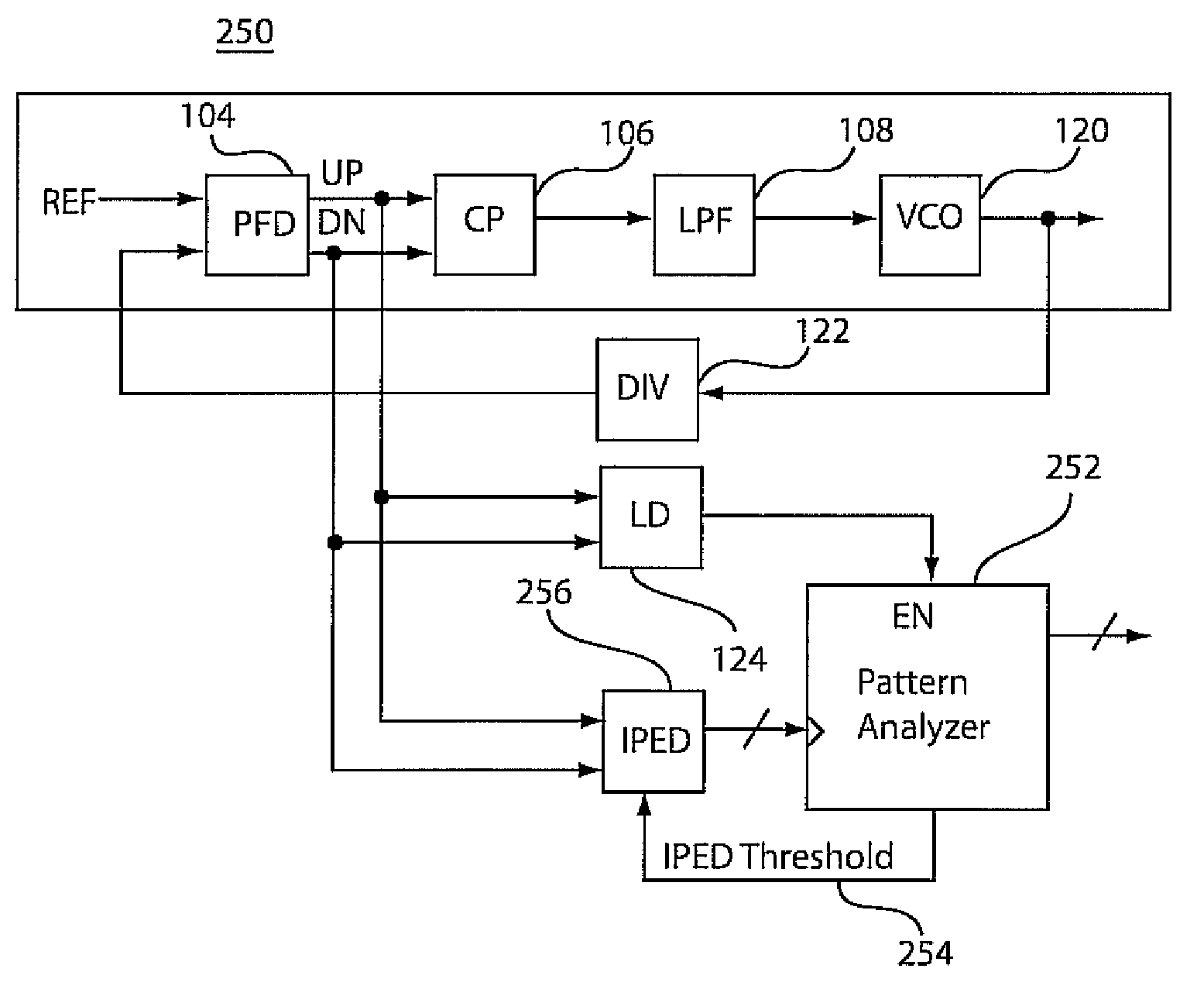

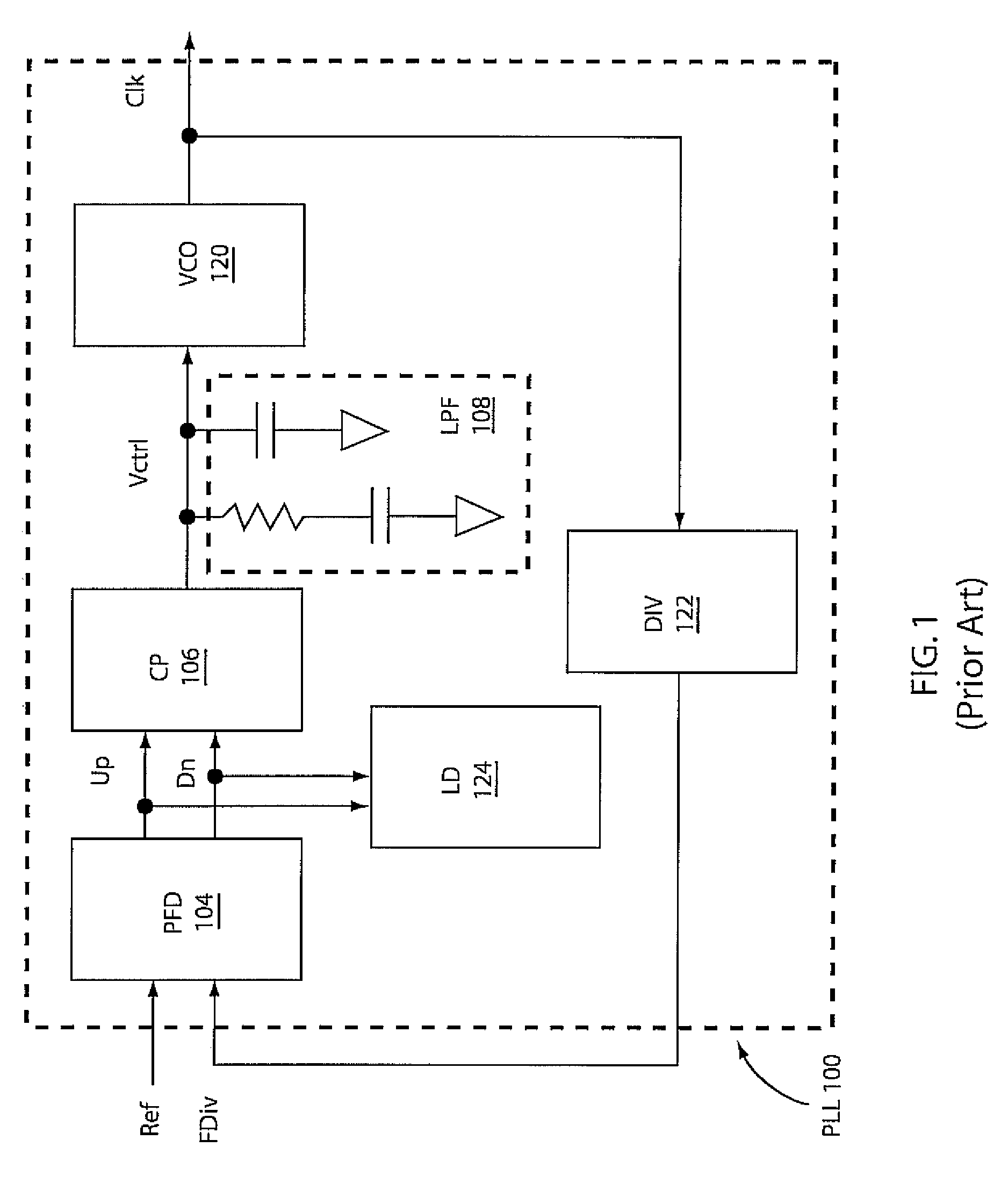

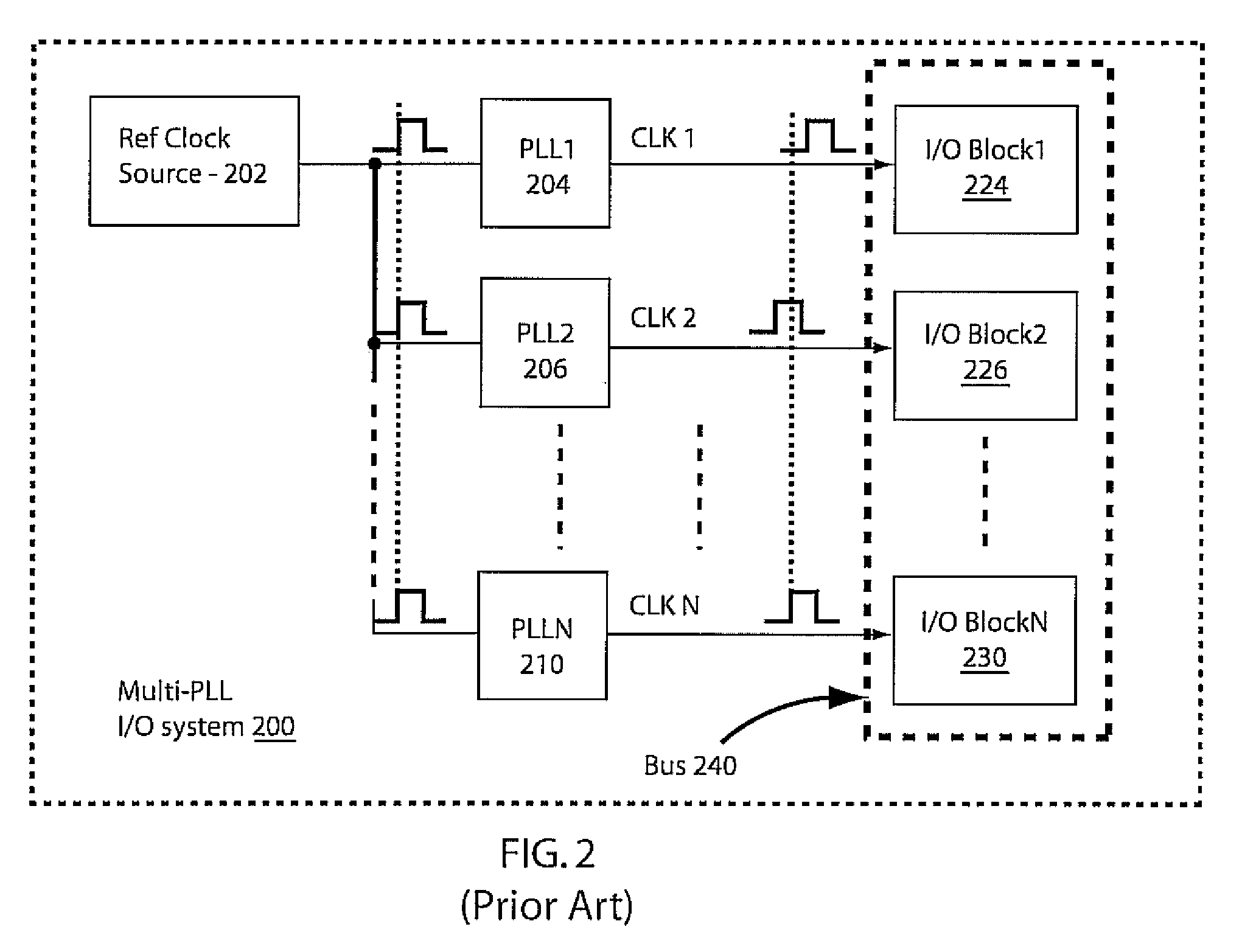

Automatic static phase error and jitter compensation in PLL circuits

InactiveUS7511543B2Enhance the shake effectEffective wayPulse automatic controlVoltage-current phase angleEngineeringLag

An instantaneous phase error detector (IPED) and method includes a first gate configured to logically OR output phase error signals as data to a first latch, and a second gate configured to logically combine the output phase error signals to clock the first latch. A delay element delays to the data to the first latch where the output of the first latch provides instantaneous phase error change information. A second latch is coupled to the output phase error signals to output a lead / lag signal to indicate which of the output phase error signals is leading. A phase-locked loop employing the output of the IPED is also disclosed along with static phase measurement and jitter optimization features.

Owner:GLOBALFOUNDRIES INC

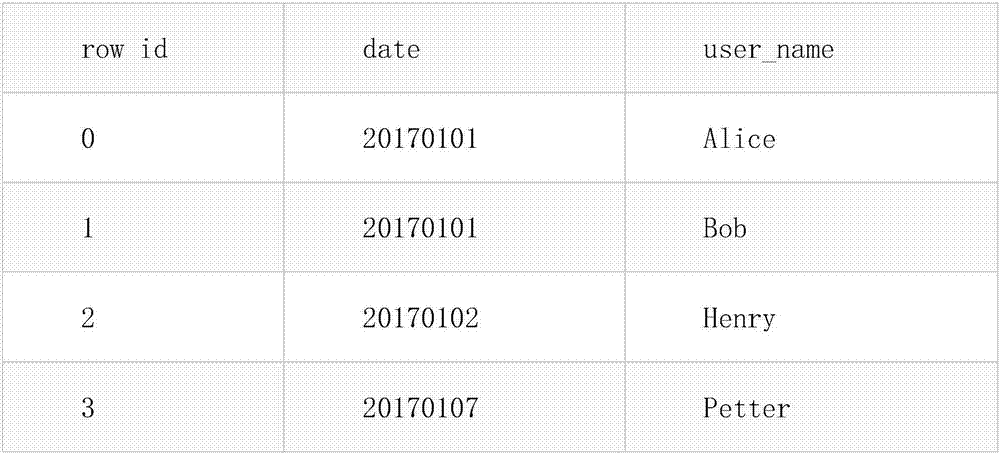

IndexR real-time data analyzing library

InactiveCN107133342ARapid positioningEfficient indexingDatabase distribution/replicationData miningData warehouseData set

The invention discloses an IndexR real-time data analyzing library. The IndexR real-time data analyzing library realizes a structure data format which can be arranged in a distribution environment, can be subjected to parallel processing, is provided with an index and is of a rank type. On the basis of the data format, a data warehouse system is built through the IndexR; mass data sets can be subjected to rapid statistical analysis (OLAP) on the basis of Hadoop ecology; the data can be imported in real time, moreover, the zero delay of querying is realized. The IndexR is deigned to solve the problems such as slow analyzing under a big data scene, data delay, and complex system. According to the IndexR real-time data analyzing library, the data is stored in HDFS; the Zookeeper is used for communicating and negotiating in the cluster; the Hive is used for conveniently managing partitioned data; the data can be rapidly imported in real time through Kafka; an outstanding distributive querying engine Apache Drill is used in a querying layer.

Owner:广州舜飞信息科技有限公司

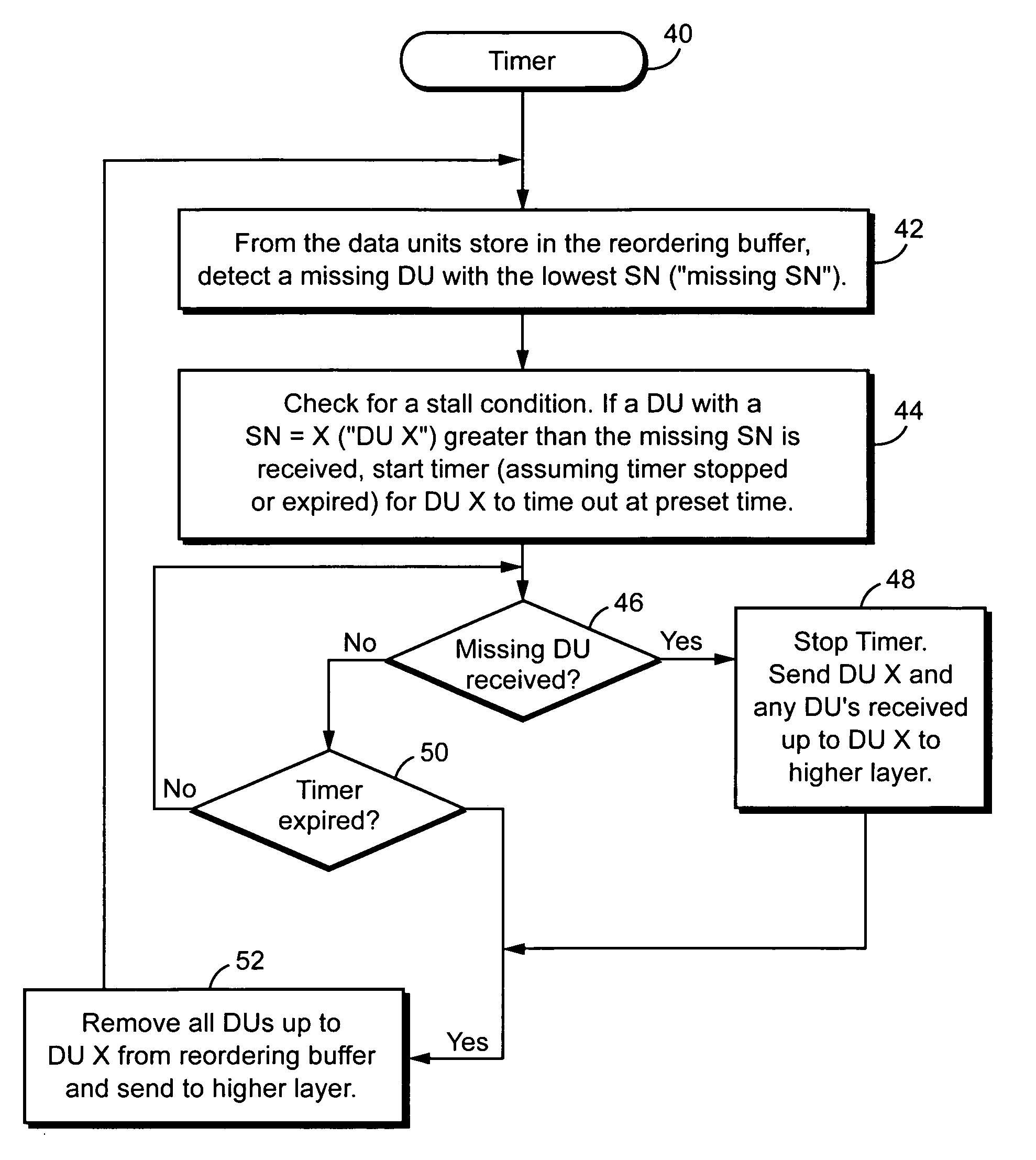

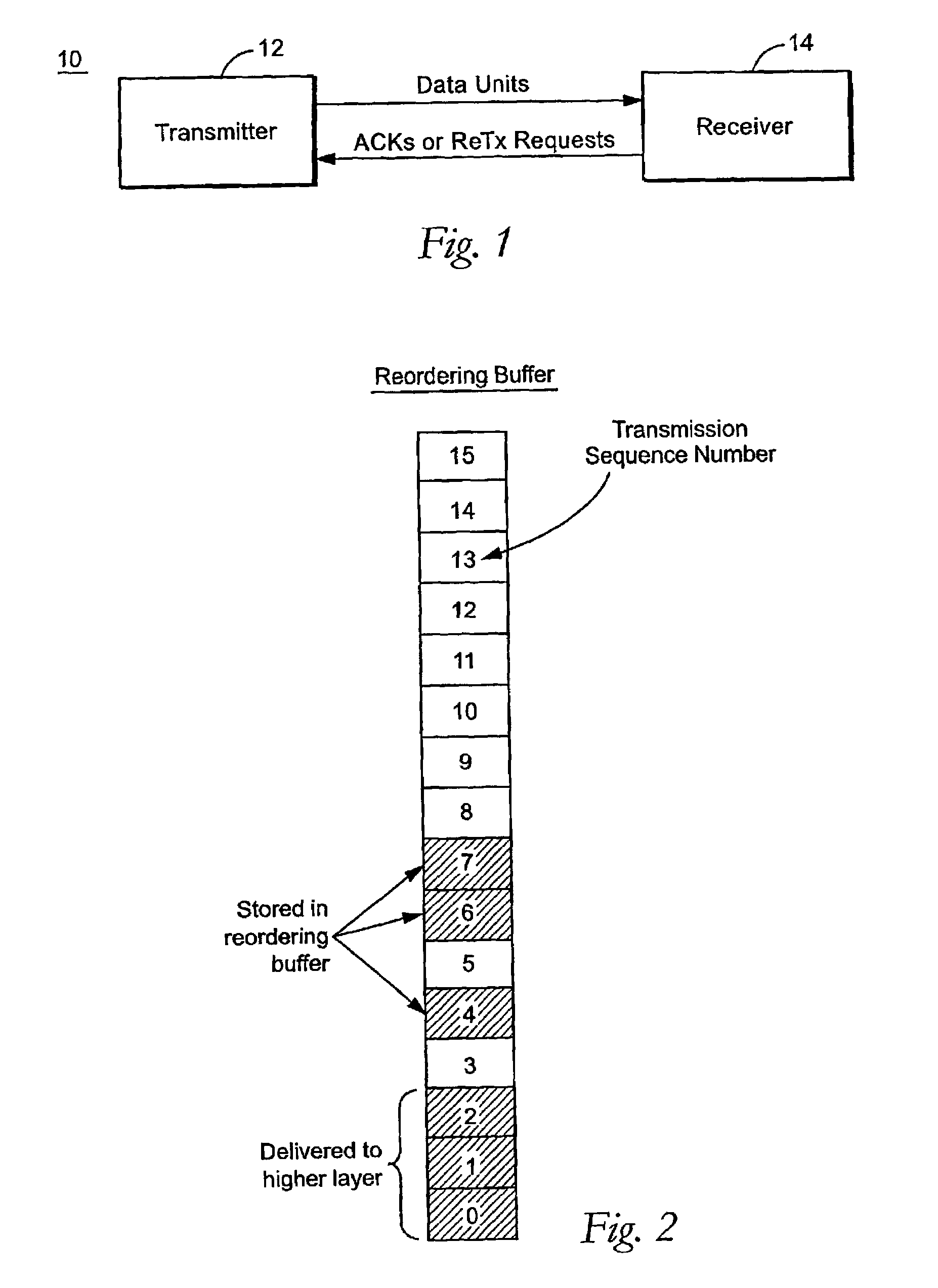

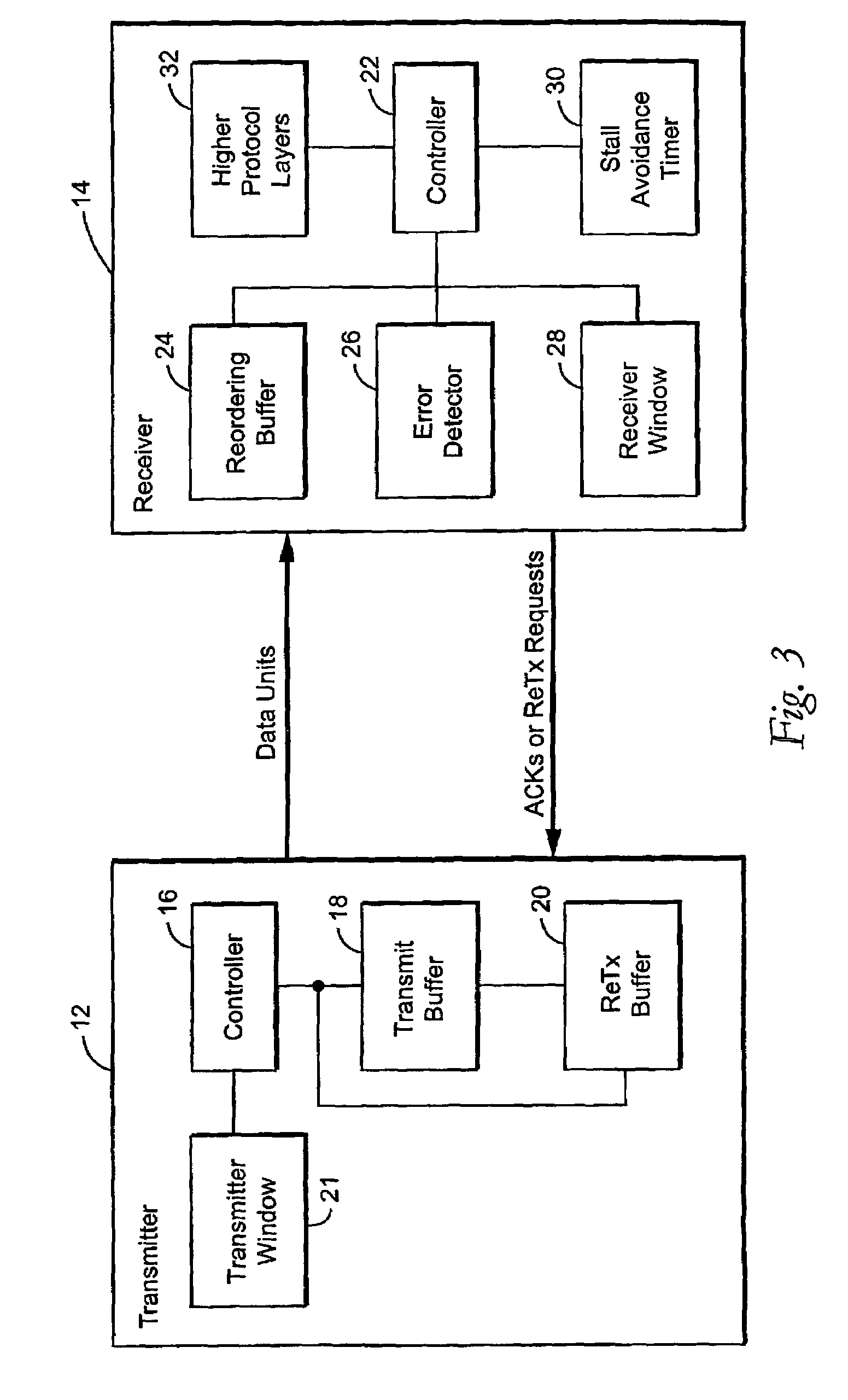

Avoiding stall conditions and sequence number ambiguity in an automatic repeat request protocol

ActiveUS7187677B2Avoid ambiguityReduce data latencyError prevention/detection by using return channelTime-division multiplexMissing dataAutomatic repeat request

The present invention provides a stall avoidance mechanism that may be used alone or in conjunction with an ambiguity avoidance mechanism in an ARQ protocol. Both mechanisms decrease data delays and increase data throughput rates. Stall avoidance is accomplished by determining whether a stall condition exists with respect to receiving a missing data unit. In one example, only a single timer is needed to avoid stalls. Retransmission ambiguities may be avoided using a retransmission window in the transmitter and / or a receive window in the receiver. Although each mechanism may be used independently of the other, a preferred example embodiment uses a stall avoidance timer, a retransmission window in the transmitter, and a receive window in the receiver.

Owner:TELEFON AB LM ERICSSON (PUBL)

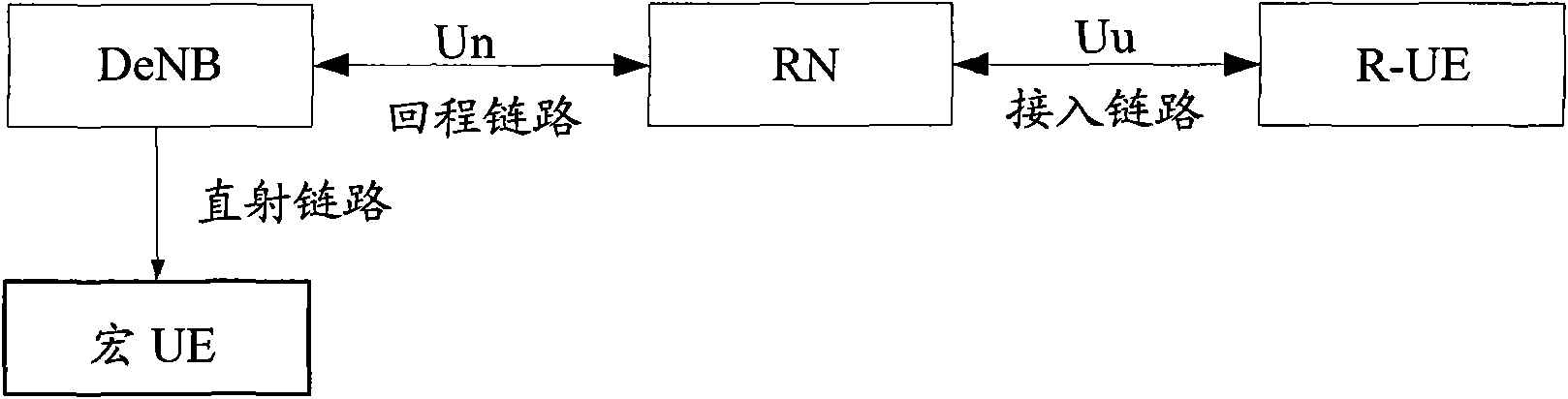

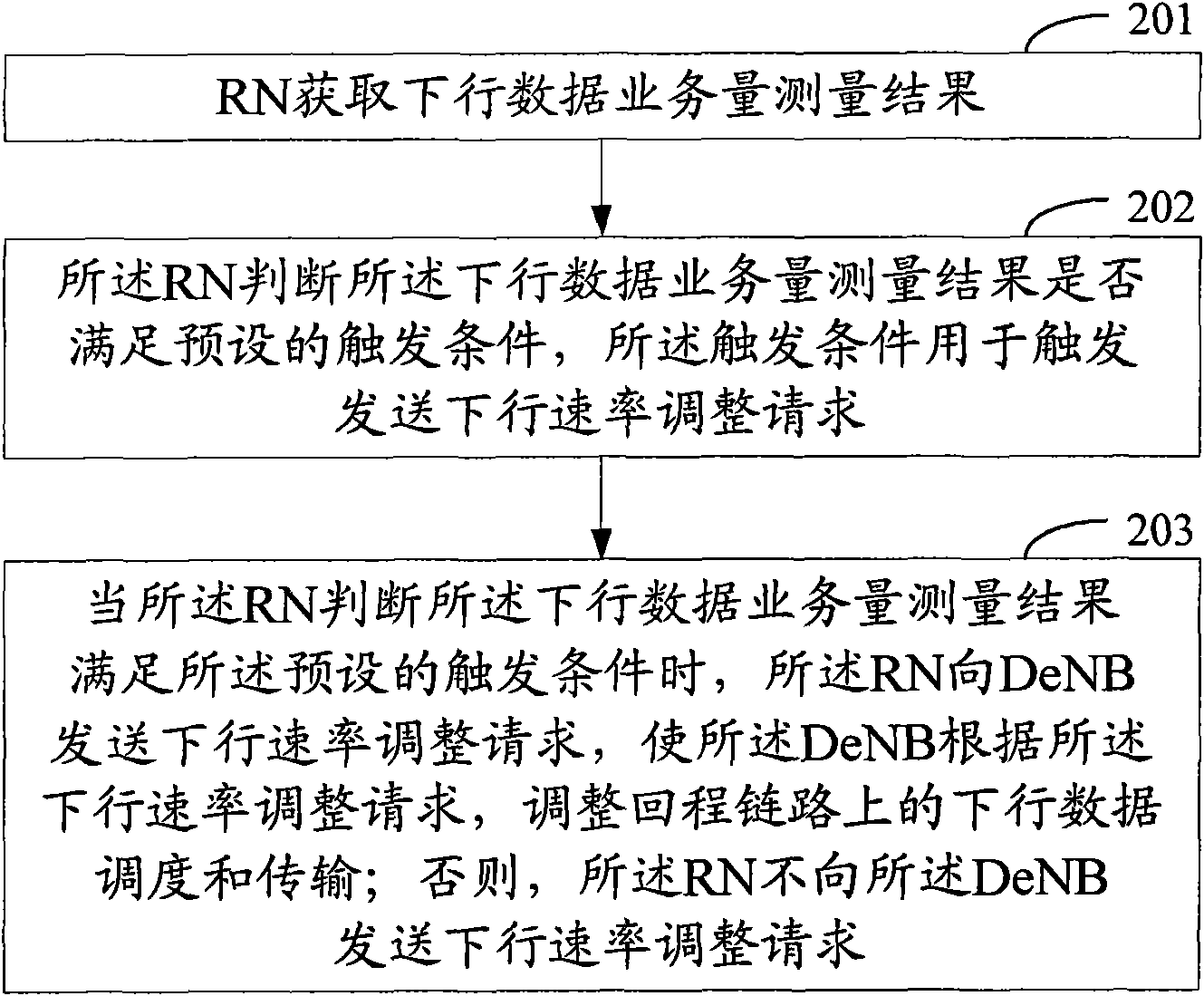

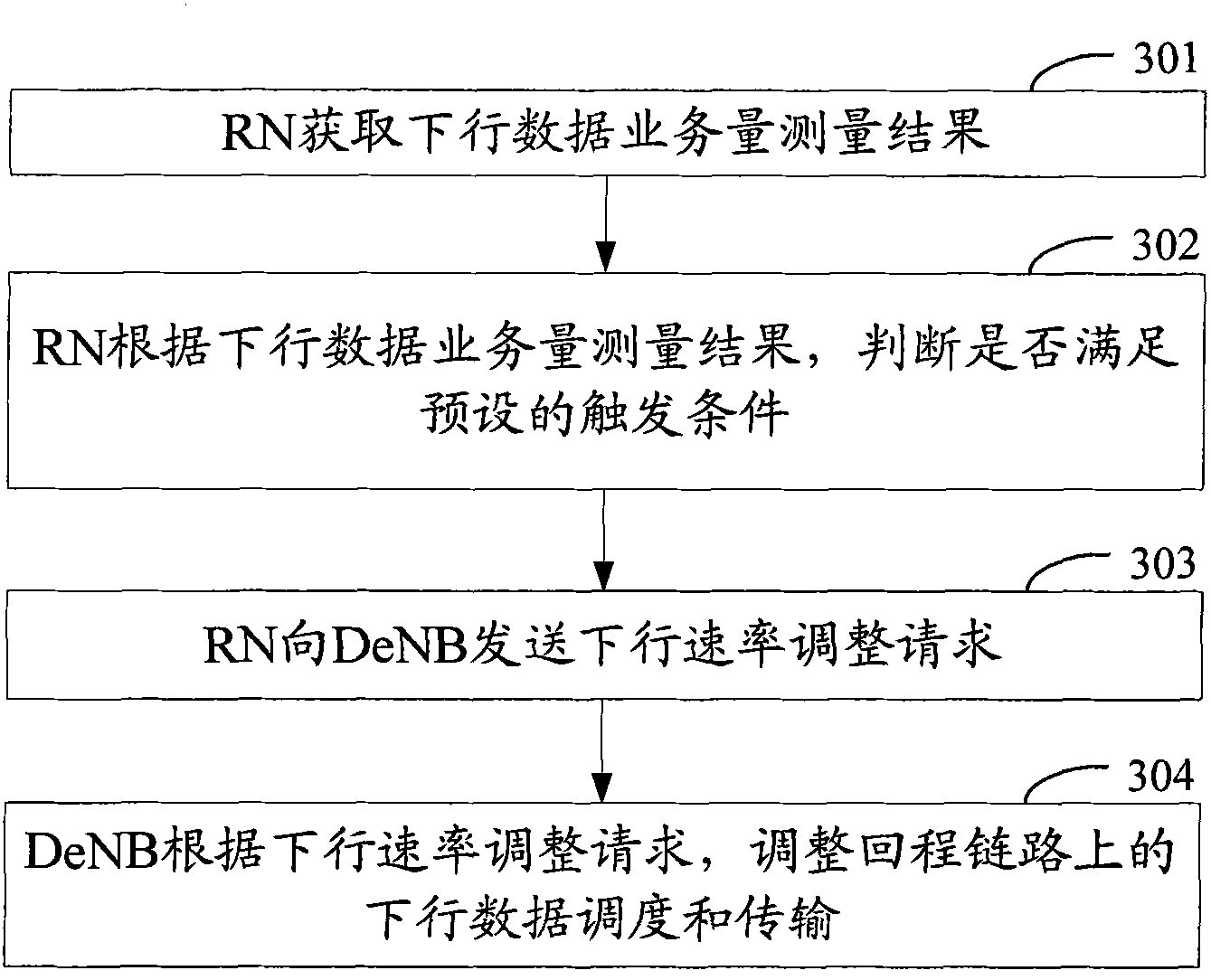

Method, system and equipment for controlling flow of backhaul link

ActiveCN102056242AAvoid mismatchSolve the waste of resourcesError preventionNetwork traffic/resource managementTraffic capacityControl flow

The embodiment of the invention discloses method, system and equipment for controlling the flow of a backhaul link. The method comprises the following steps: a relay node (RN) acquires a downlink data traffic measurement result; the RN judges whether the downlink data traffic measurement result meets a preset trigger condition, wherein the trigger condition is used for triggering to send a downlink speed adjustment request; when the RN judges that the downlink data traffic measurement result meets the preset trigger condition, the RN sends the downlink speed adjustment request to a donor evolved node B (DeNB), so that the DeNB adjusts the downlink data scheduling and transmission on the backhaul link according to the downlink speed adjustment request; and otherwise, the RN doesn't send the downlink speed adjustment request to the DeNB. The invention avoids the mismatch of data stream between the backhaul link and the access link, so as to solve the problem of downlink data congestion of the RN or downlink data delay of the relay user equipment (R-UE), as well as the problem of waste of the resources on the backhaul link.

Owner:DATANG MOBILE COMM EQUIP CO LTD

Automatic static phase error and jitter compensation in pll circuits

InactiveUS20080191746A1Enhance the shake effectEffective wayPulse automatic controlVoltage-current phase angleLagData delay

An instantaneous phase error detector (IPED) and method includes a first gate configured to logically OR output phase error signals as data to a first latch, and a second gate configured to logically combine the output phase error signals to clock the first latch. A delay element delays to the data to the first latch where the output of the first latch provides instantaneous phase error change information. A second latch is coupled to the output phase error signals to output a lead / lag signal to indicate which of the output phase error signals is leading. A phase-locked loop employing the output of the IPED is also disclosed along with static phase measurement and jitter optimization features.

Owner:GLOBALFOUNDRIES INC

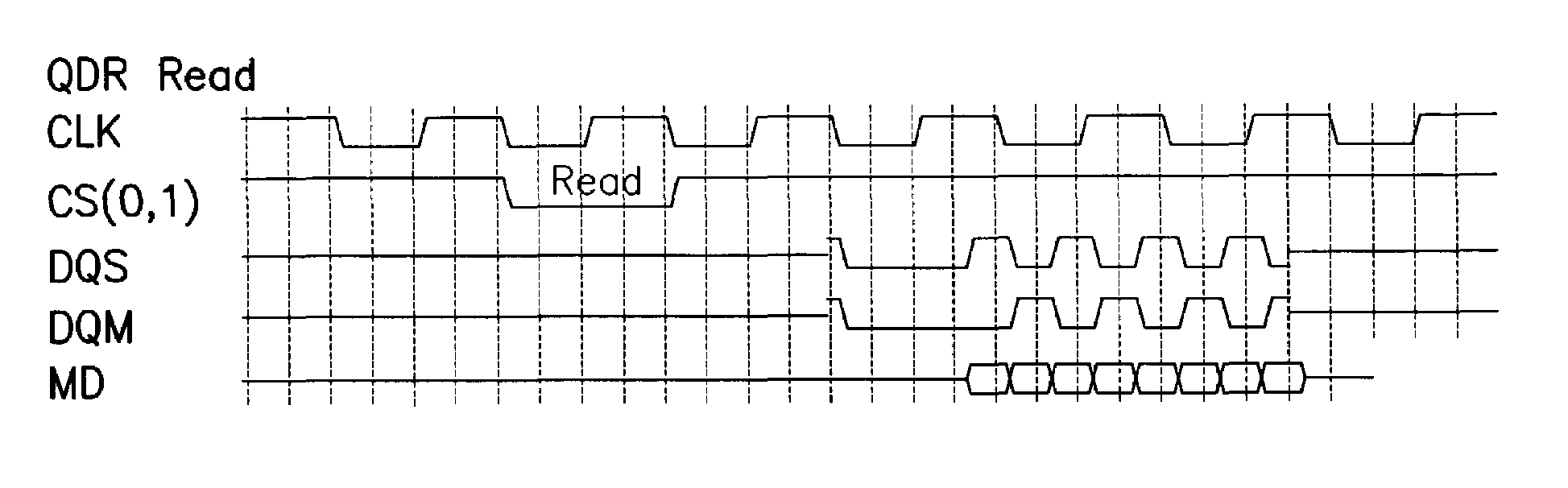

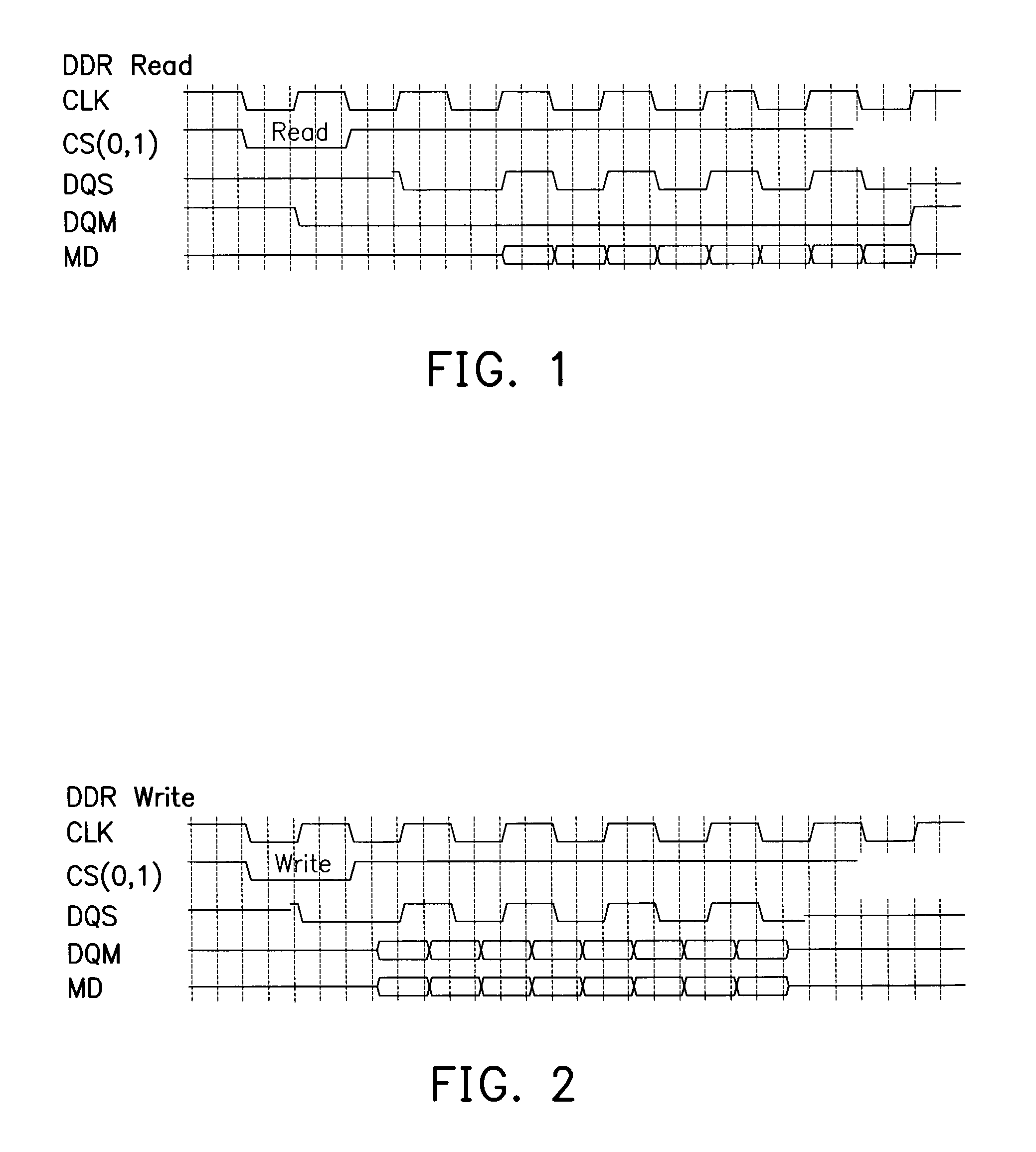

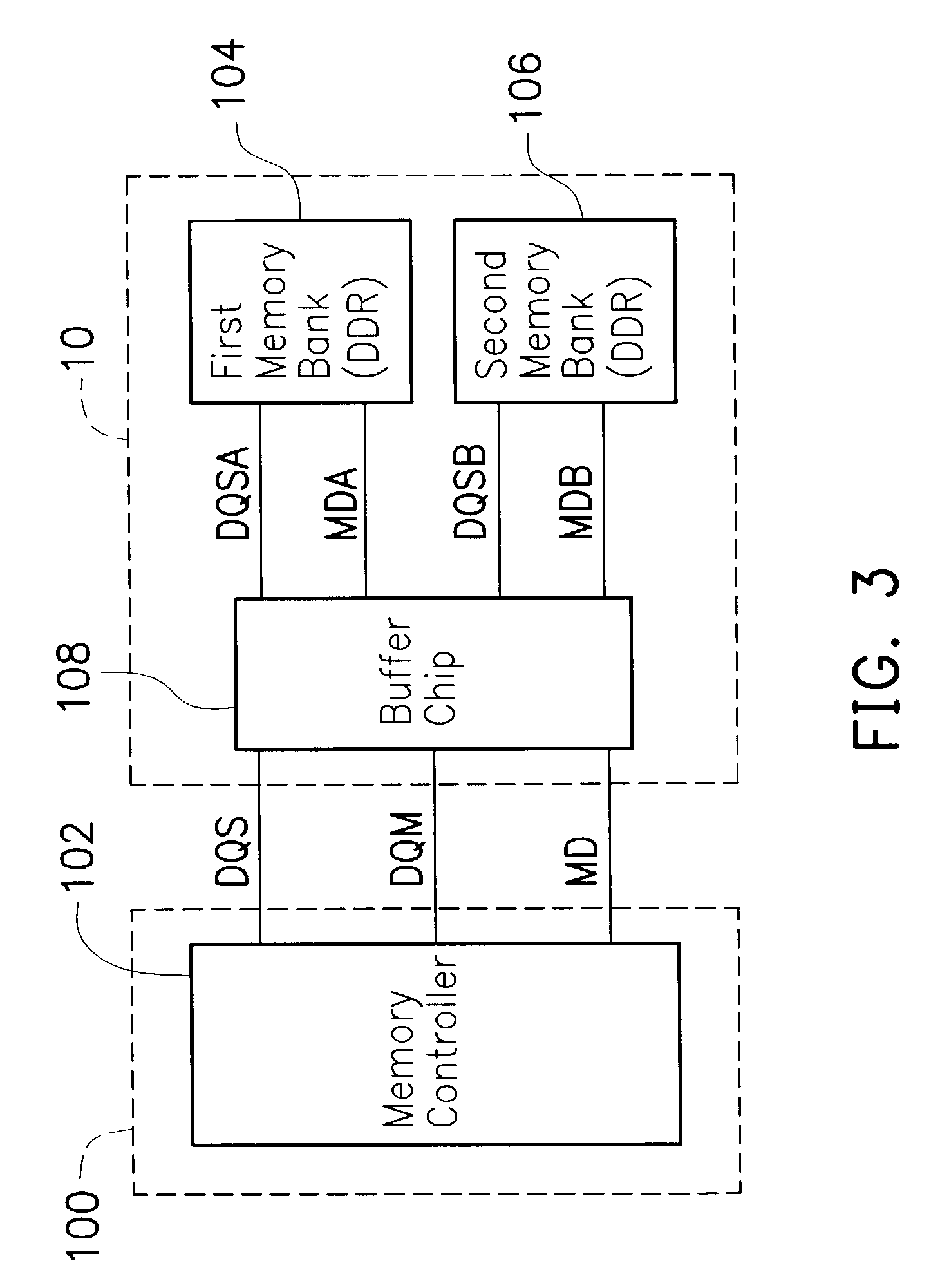

Memory controller for supporting a plurality of different memory accesse modes

A common DRAM controller is provided for supporting a plurality of memory types such as double data rate or quad data rate mode or types. The controller is adapted to use a number of clock signals to process data. The controller can further delay the data for a predetermined time period and capture the same.

Owner:VIA TECH INC

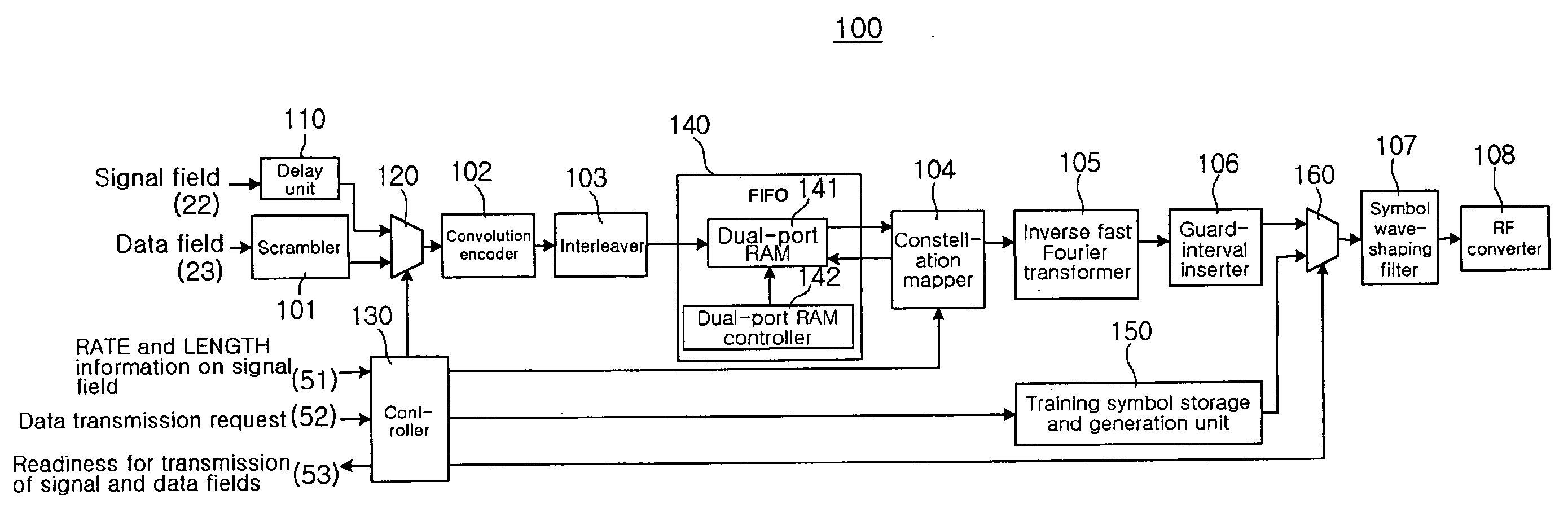

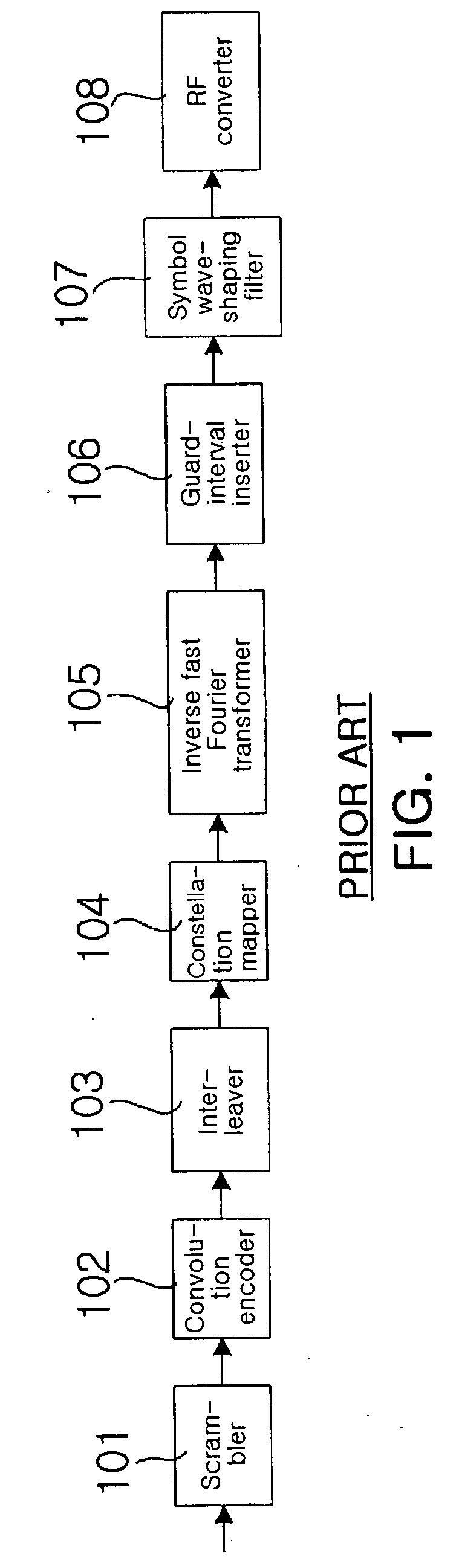

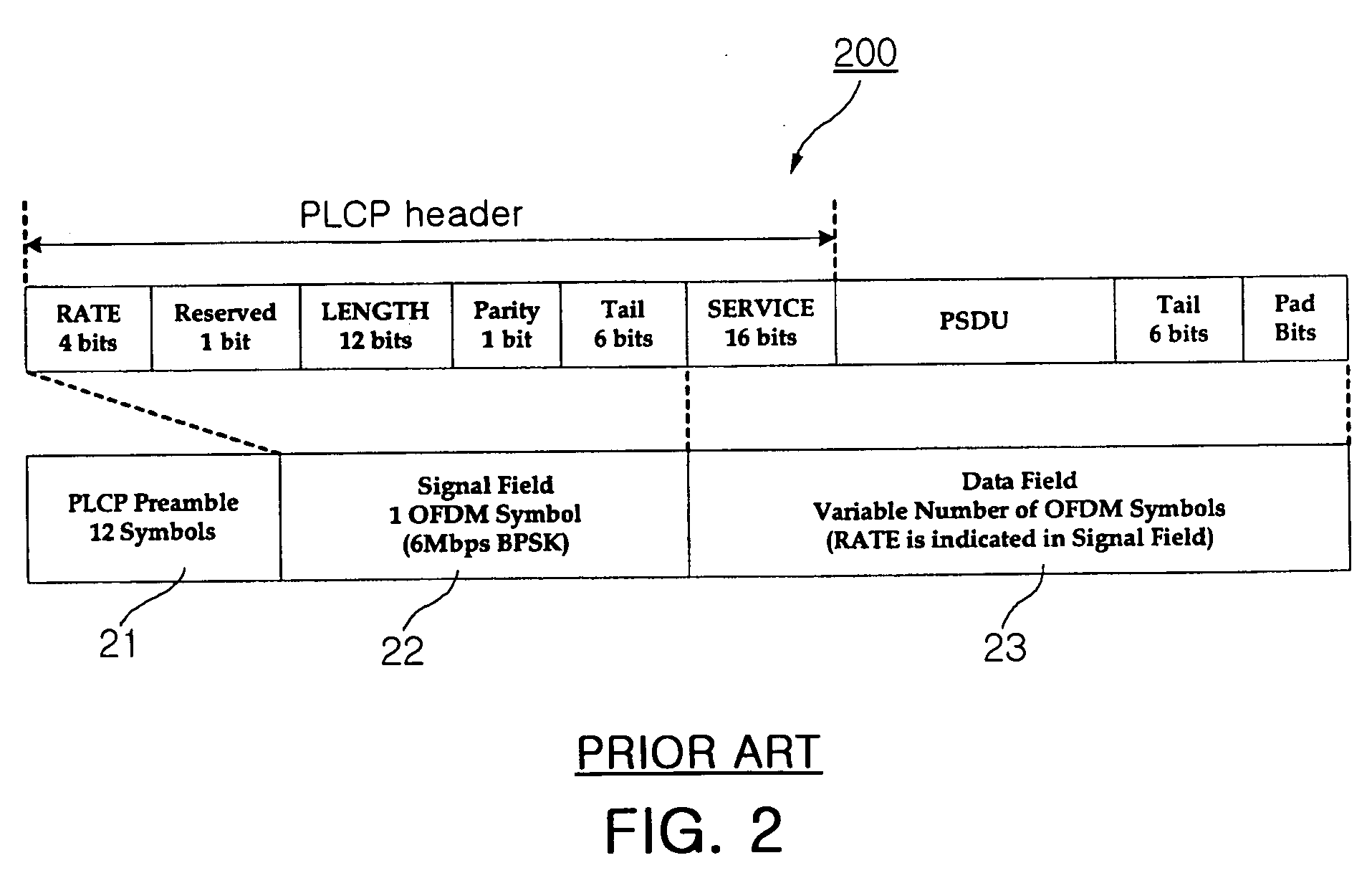

OFDM transmission apparatus and method having minimal transmission delay

ActiveUS20060092825A1Minimized transmission delayMinimal transmission delayFrequency-division multiplex detailsModulated-carrier systemsData fieldTransmission latency

An OFDM transmission apparatus having minimal transmission delay comprises a training symbol storage and generation unit, a delay unit and a controller. The training symbol storage and generation unit stores training symbols for the preamble, and outputs the stored training symbols when a training symbol output request signal is received. The delay unit receives data for the signal field from the MAC layer, delays the received data by the data processing time of the scrambler, and outputs the delayed data to the convolution encoder. The controller outputs the training symbol output request signal, requesting the preamble of the frame, to the training symbol storage and generation unit when a frame transmission request is received from the MAC layer, and outputs a data request signal, requesting the signal field and the data field, to the MAC layer in consideration of total data processing time (TPROCESS).

Owner:ELECTRONICS & TELECOMM RES INST

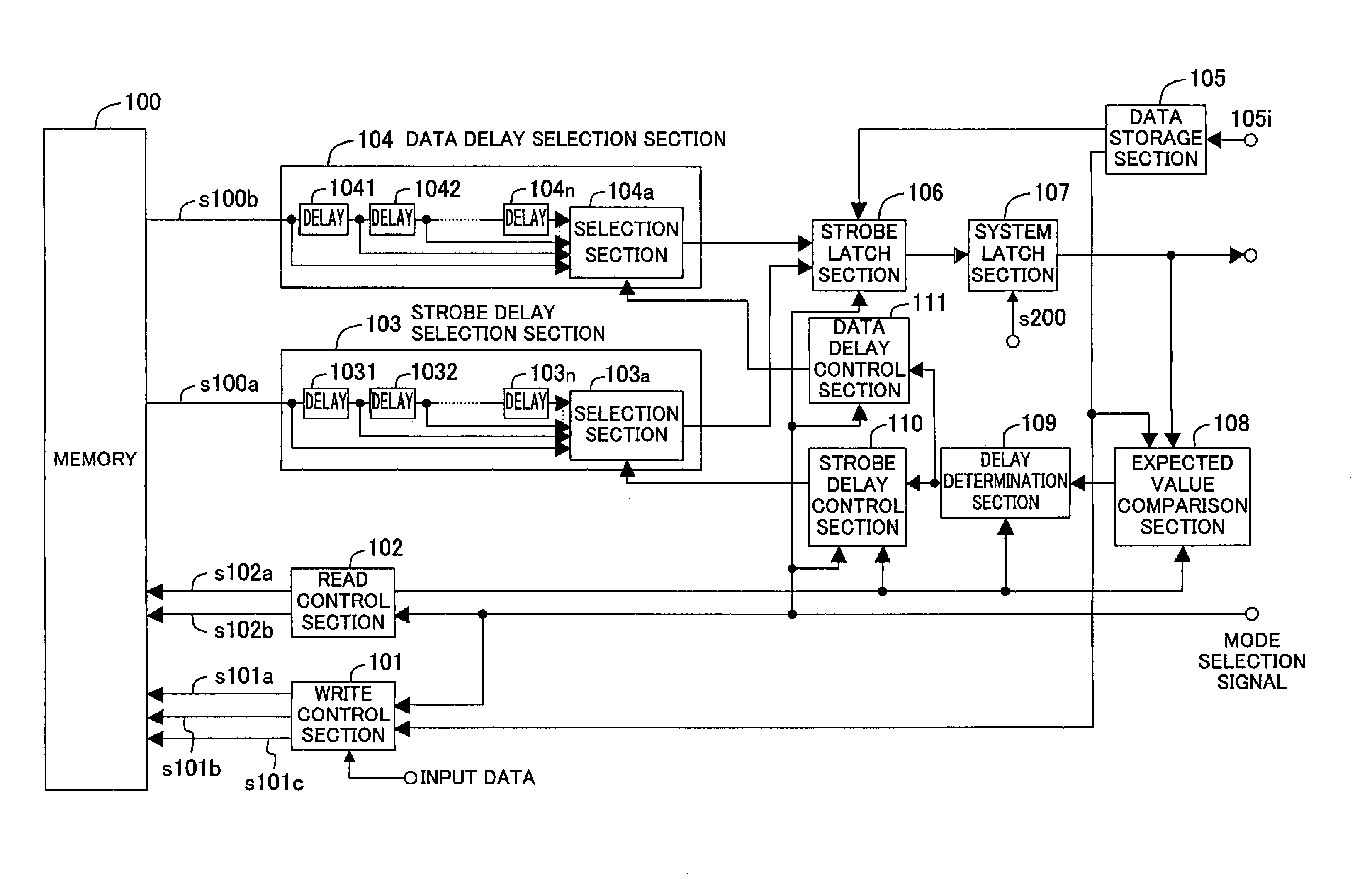

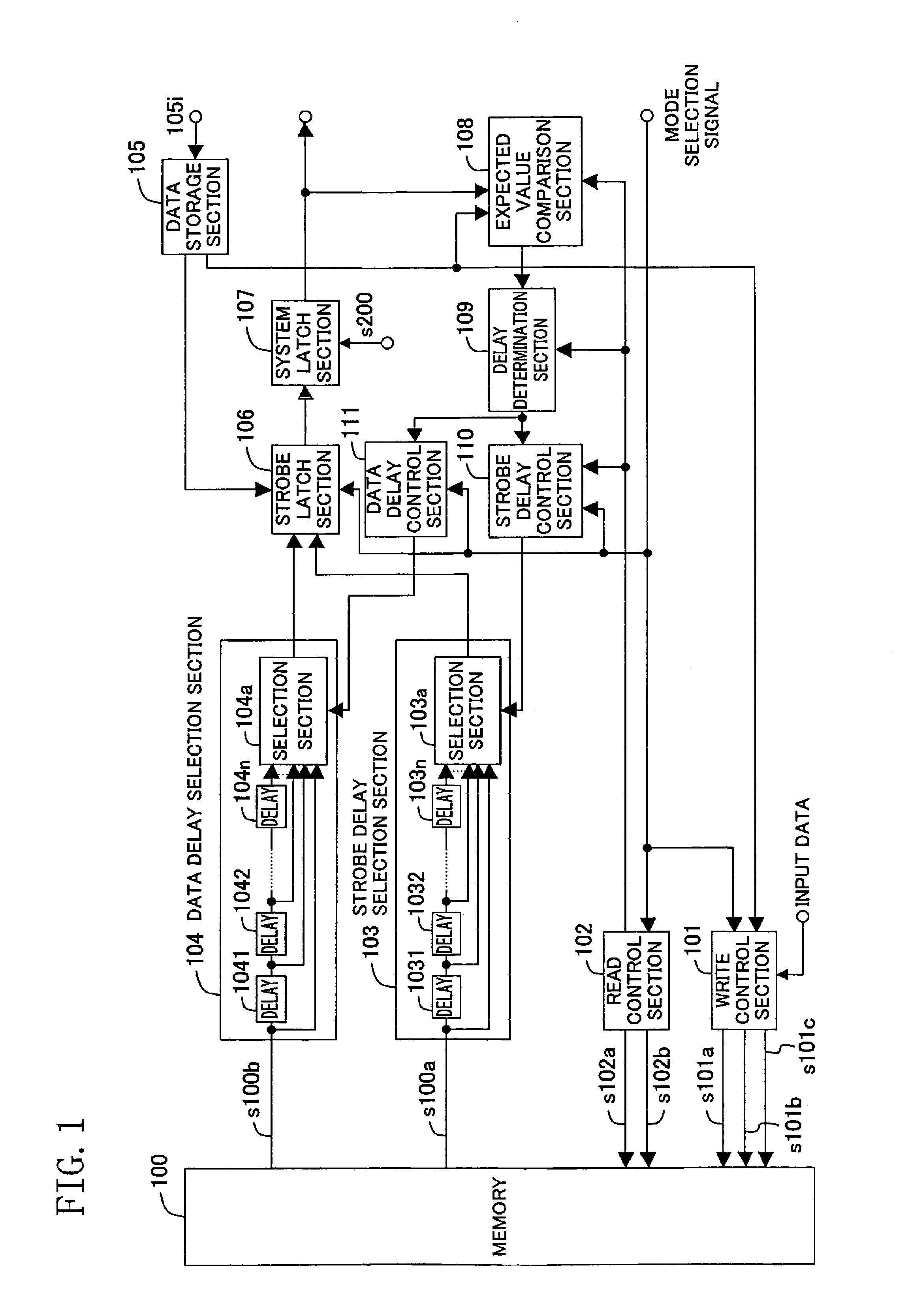

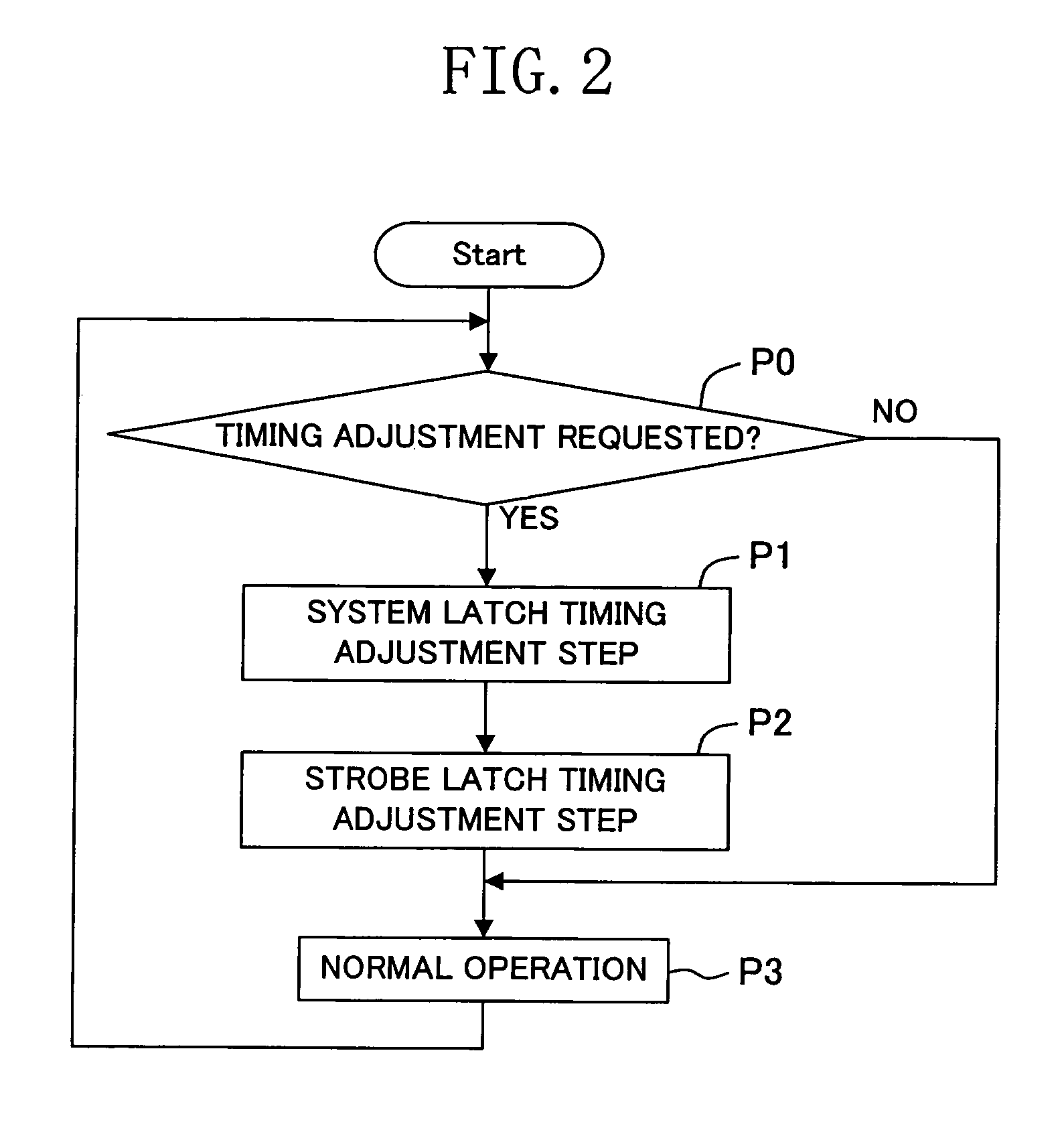

Method and apparatus for timing adjustment

A strobe signal from a memory is delayed through delay circuits of a strobe delay selection section, thus obtaining a plurality of delayed strobe signals. A strobe latch section produces check data in synchronism with each of the delayed strobe signals, and a system latch section latches, with a system clock, check data latched by the strobe latch section. Based on a comparison by an expected value comparison section and a determination by a delay determination section, the optimal strobe signal with the optimal delay is selected from among the delayed strobe signals produced in the strobe delay selection section. Then, data from the memory is delayed through delay circuits in a data delay selection section, thus obtaining a plurality of delayed data, and the optimal data with the optimal delay is selected from among the plurality of delayed data based on the comparison by the expected value comparison section and the determination by the delay determination section.

Owner:SOCIONEXT INC

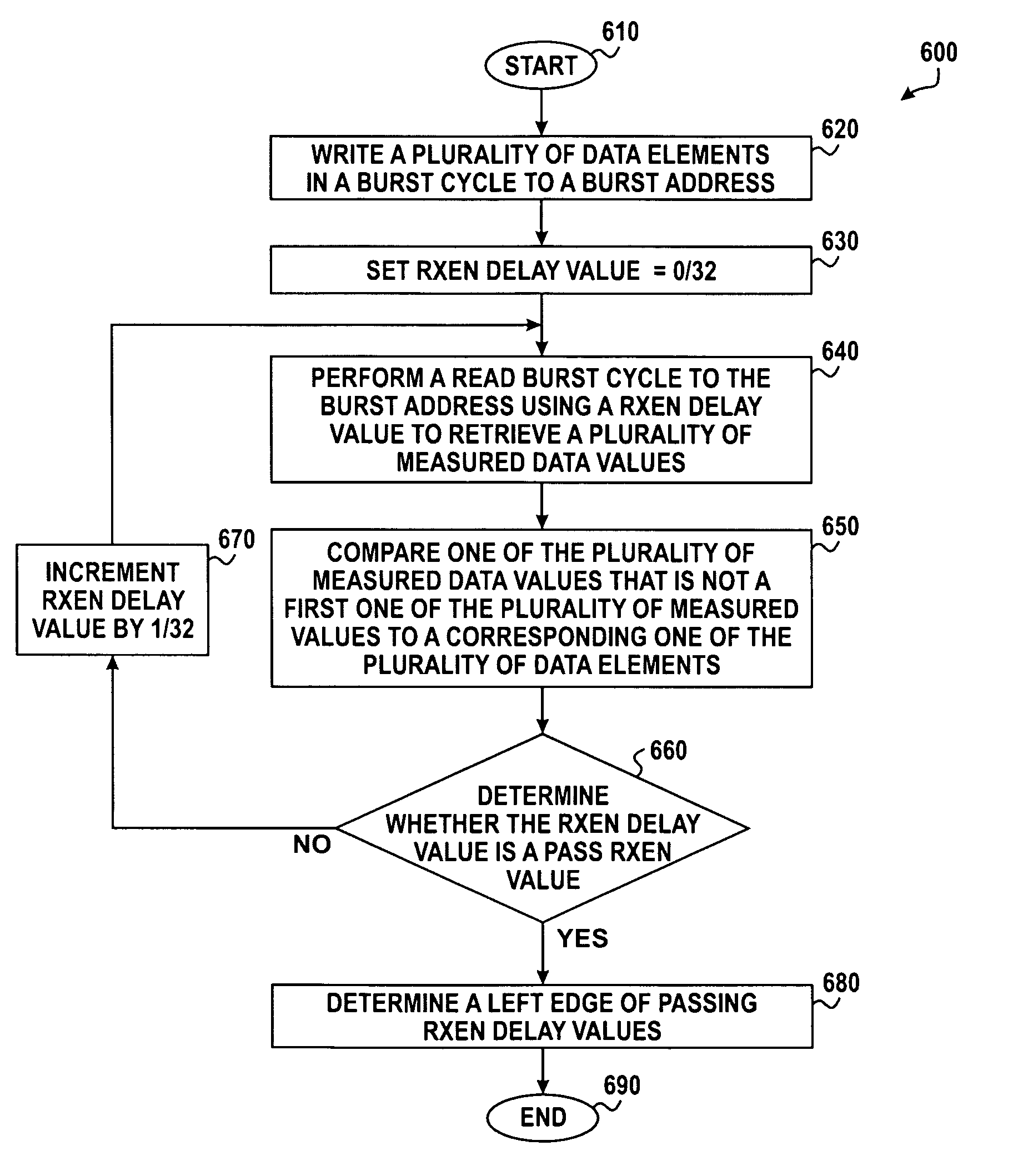

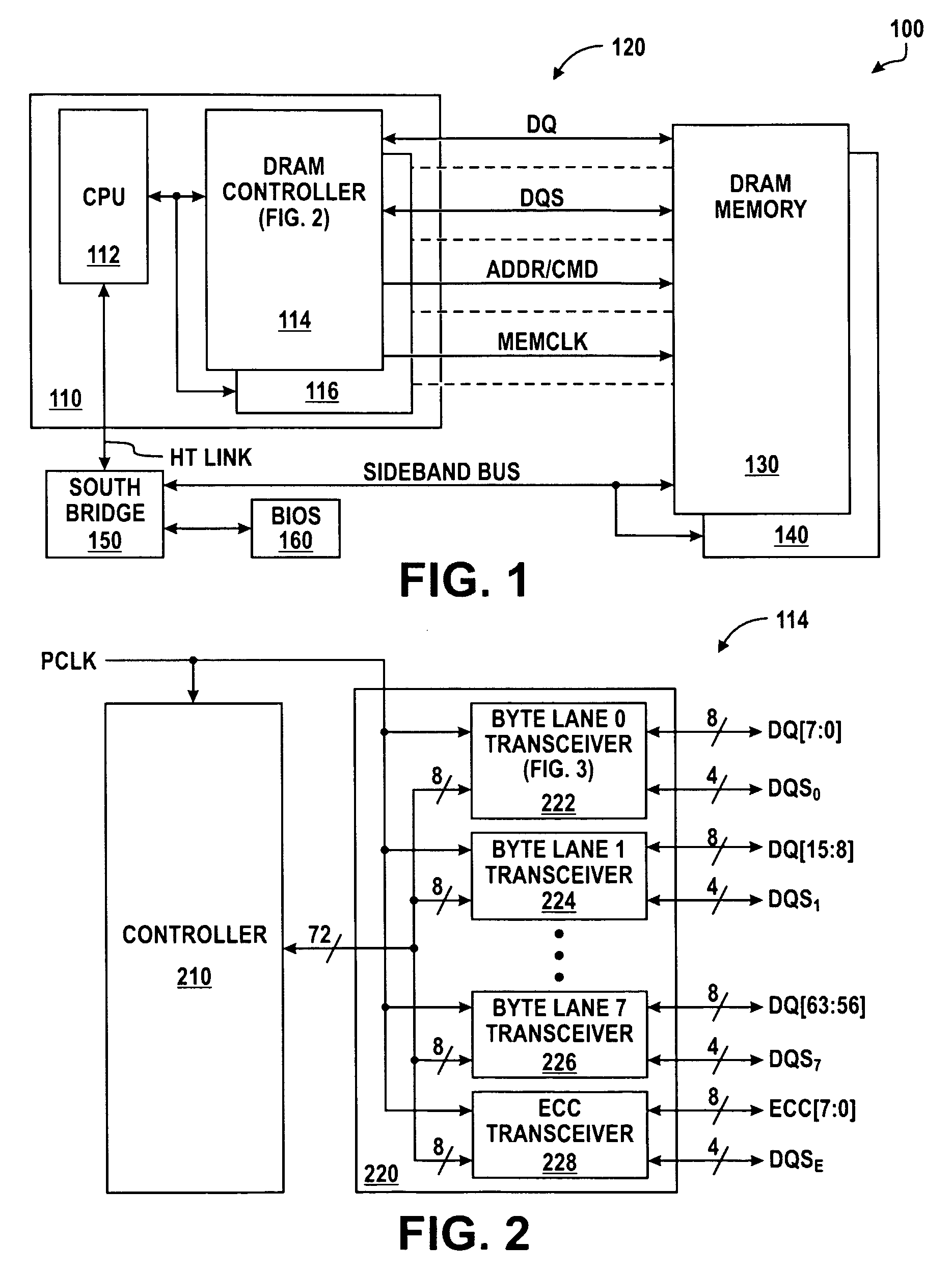

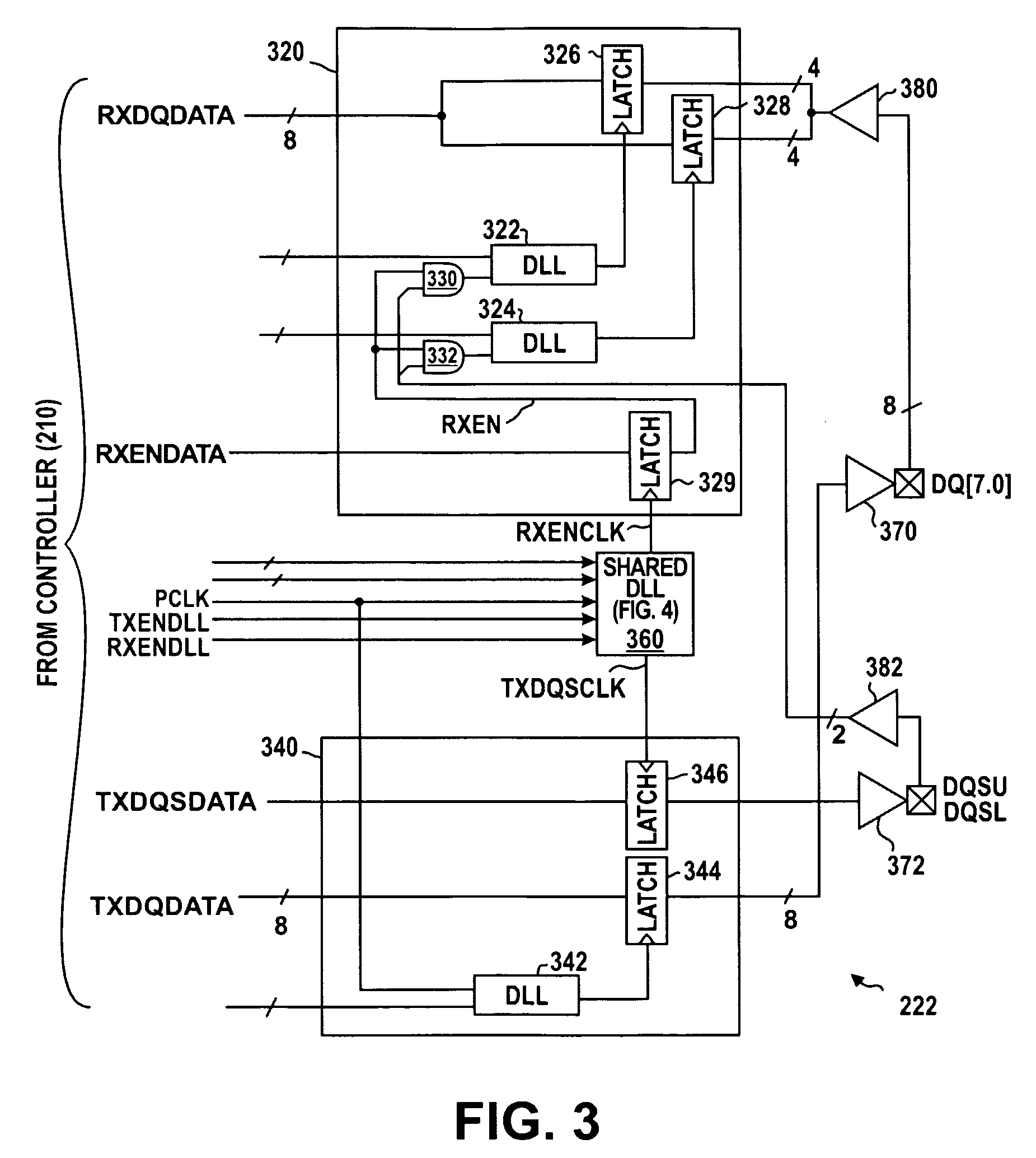

Method for training dynamic random access memory (DRAM) controller timing delays

Timing delays in a double data rate (DDR) dynamic random access memory (DRAM) controller (114, 116) are trained. A left edge of passing receive enable delay values is determined (530). A final value of a receive data strobe delay value and a final value of a transmit data delay value are trained (540). A right edge of passing receive enable delay values is determined using a working value of the receive data strobe delay (550); and a final receive enable delay value intermediate between the left edge of passing receive enable delay values and the right edge of passing receive enable delay values is set (560).

Owner:ADVANCED MICRO DEVICES INC

Multiprotocol computer bus interface adapter and method

Owner:AVAGO TECH INT SALES PTE LTD

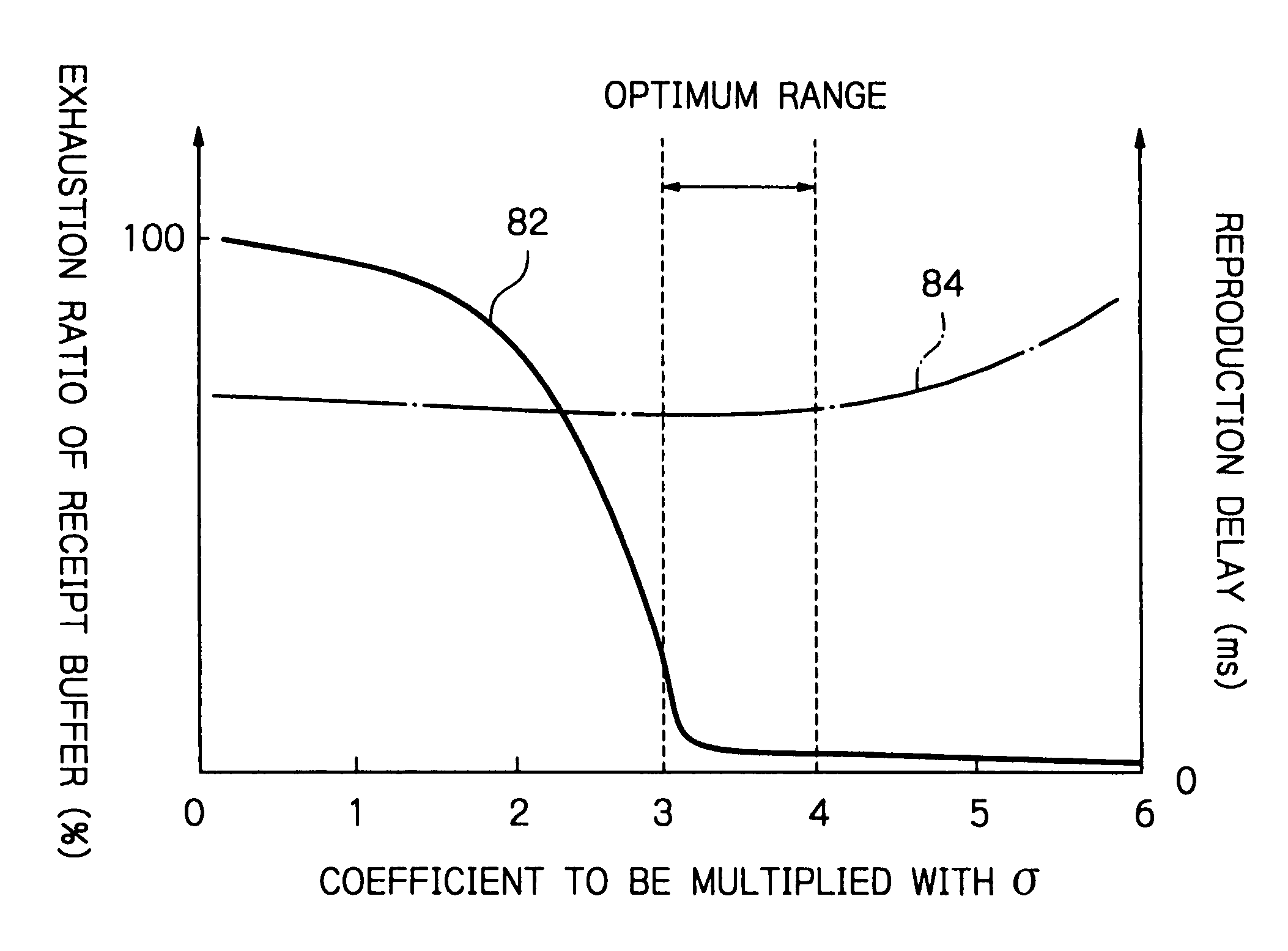

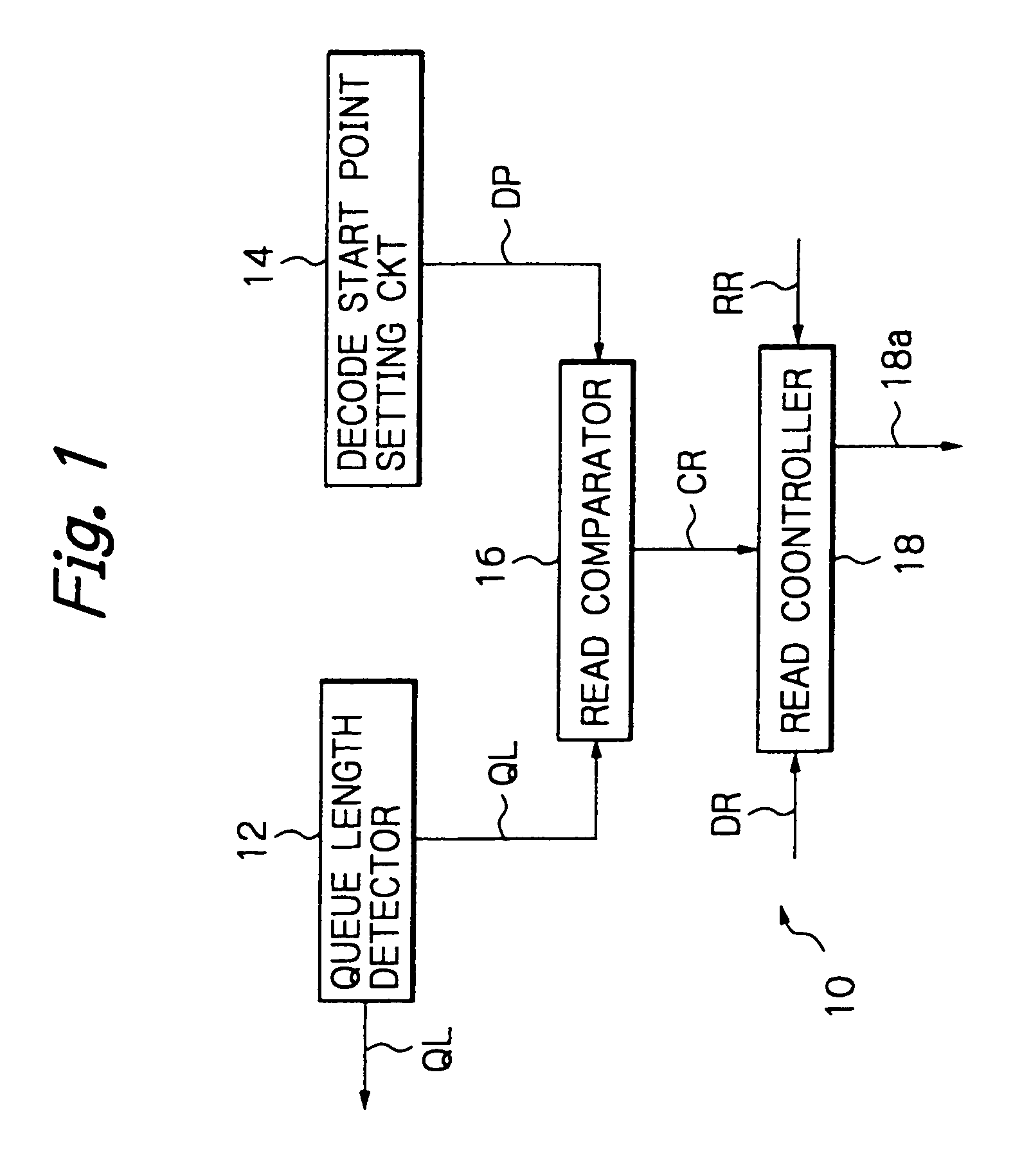

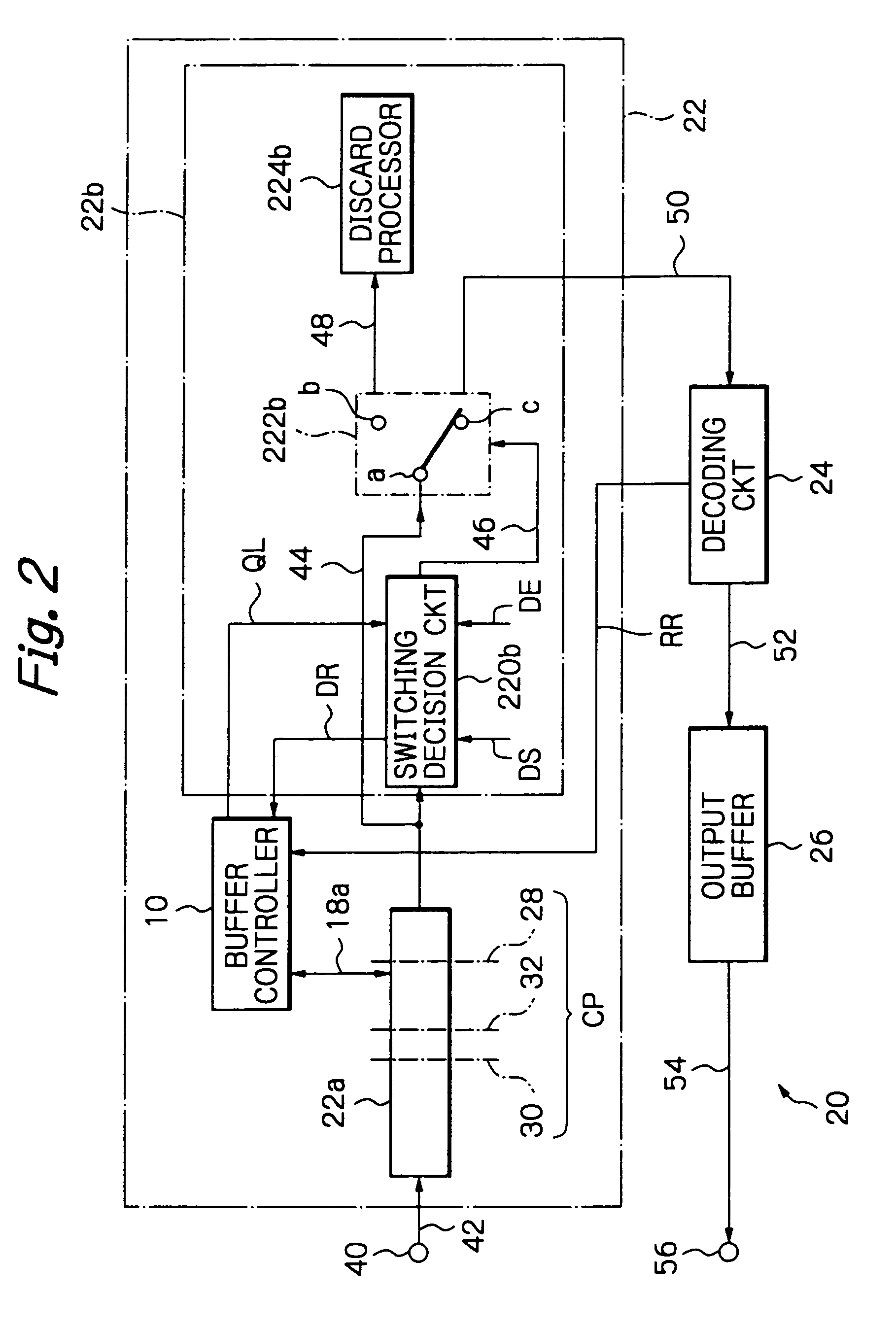

Packet receiver with the influence of jitter and packet losses reduced before a buffer becomes idle due to data delays and packet receiving method using the same

InactiveUS7349330B1Quality improvementError preventionFrequency-division multiplex detailsPacket lossNetwork on

A packet receiver includes a packet memory circuit for temporarily storing received packets in a FIFO (First-In First-Out) fashion in the form of a queue. A read start threshold setting circuit sets, with respect to the length of the queue, a read start threshold at which the received packets should begin to be read out. A read comparing circuit determines whether or not the length of the queue has reached the read start threshold, and outputs a read command signal in accordance with the result of decision. In response to the read command signal, a read control circuit causes the received packets to be read out of the packet memory circuit. The packet receiver reduces the influence of the jitter of a communication network on speech quality. Also, the packet receiver reduces the influence of delays of packets by executing discard processing with the queue.

Owner:OKI ELECTRIC IND CO LTD

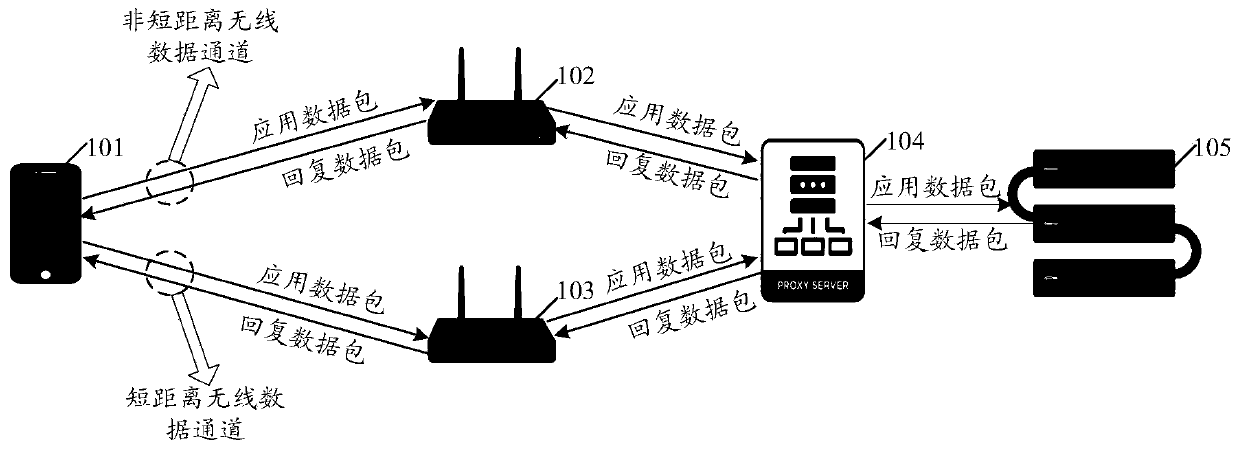

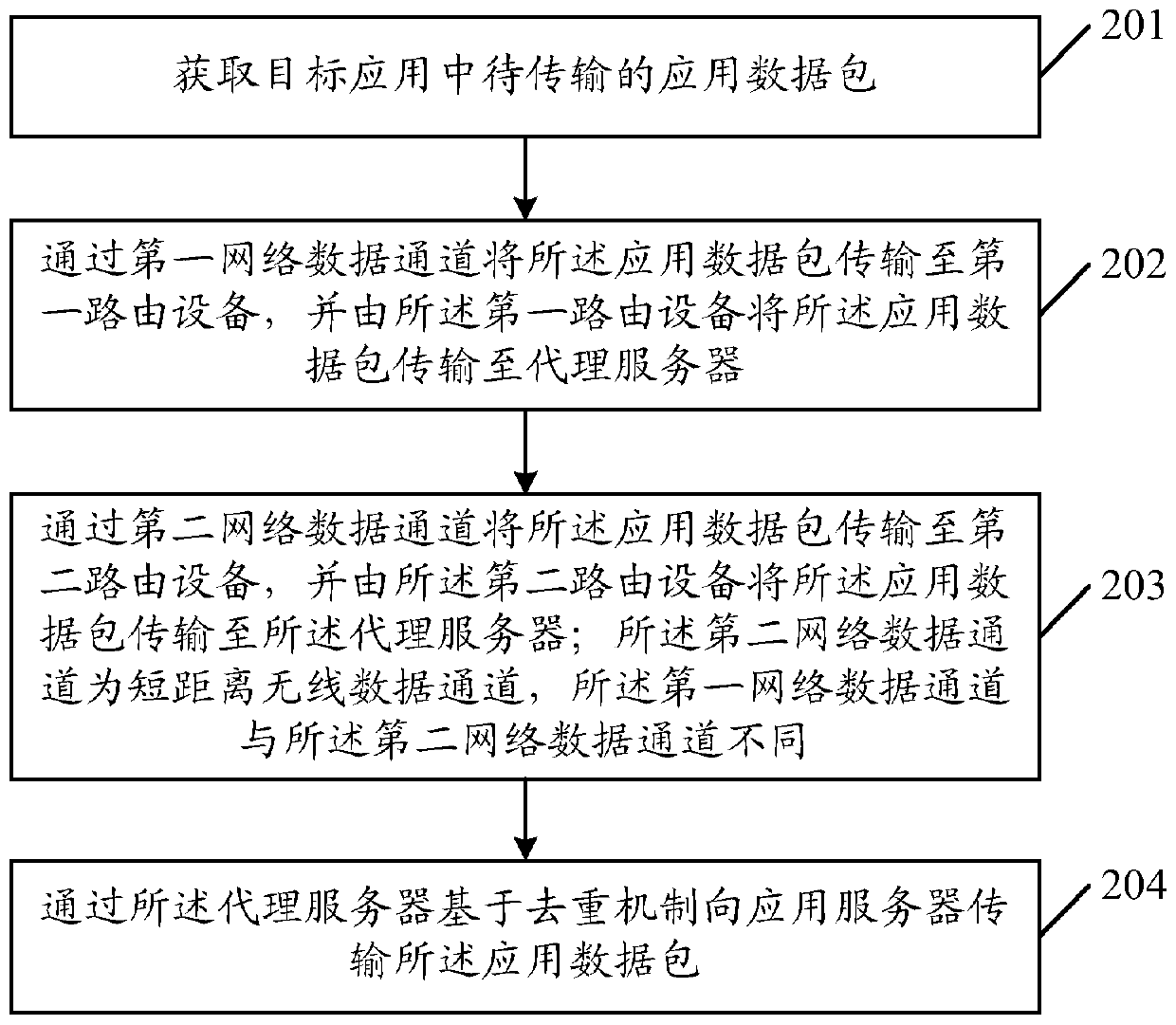

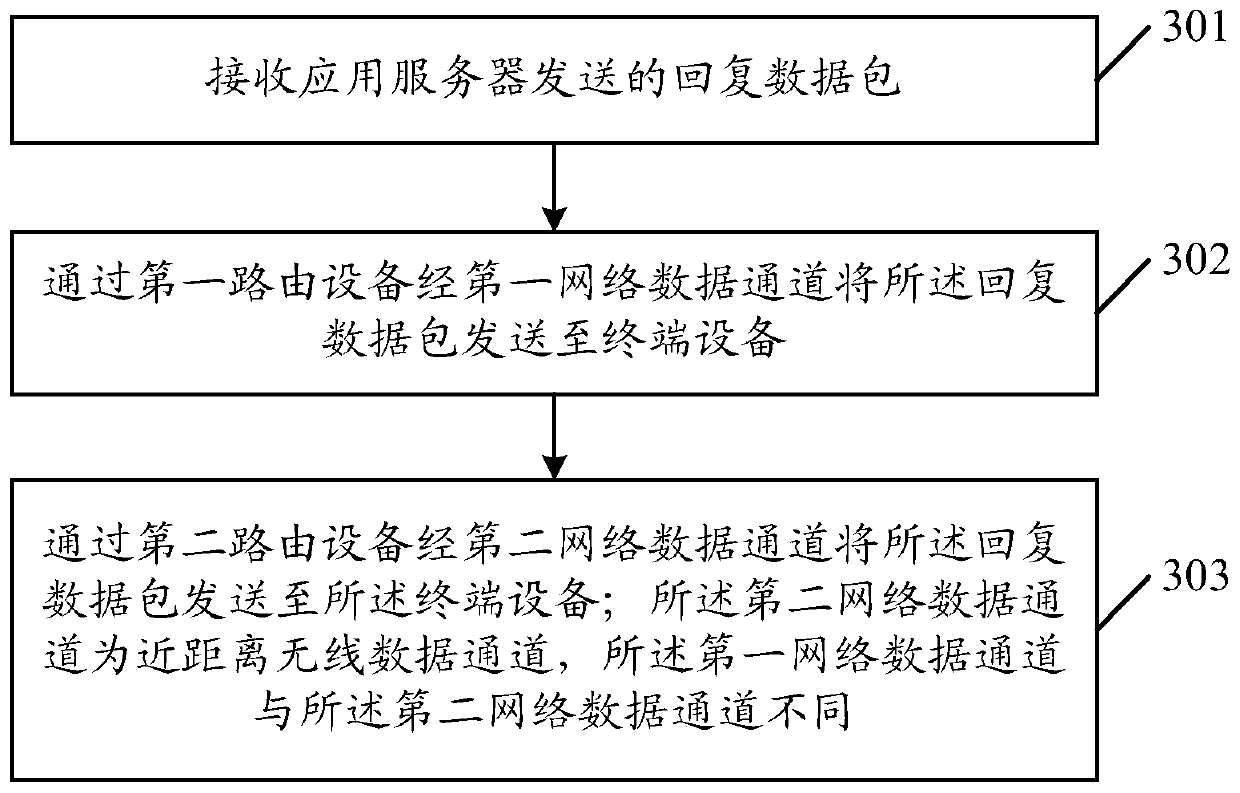

Data transmission method and device, equipment and storage medium

ActiveCN110099403AImprove stabilityConsumes less powerConnection managementTransmissionApplication serverAir interface

The embodiment of the invention discloses a data transmission method and device, equipment and a storage medium. The method comprises: acquring an application data packet to be transmitted in a targetapplication; transmitting the application data packet to first routing equipment through a first network data channel, and transmitting the application data packet to a proxy server by the first routing equipment; meanwhile, transmitting the application data packet to second routing equipment through a second network data channel, and transmitting the application data packet to a proxy server through the second routing equipment, wherein the second network data channel is a short-distance wireless data channel, and the first network data channel is different from the second network data channel; finally, transmitting the application data packet to the application server based on the deduplication mechanism through the proxy server. According to the method, short-distance wireless data isused as an auxiliary channel for data transmission, so that the stability of data transmission between the terminal equipment and the application server is improved, and the air interface packet lossrate and the data delay are effectively reduced.

Owner:TENCENT TECH (SHENZHEN) CO LTD

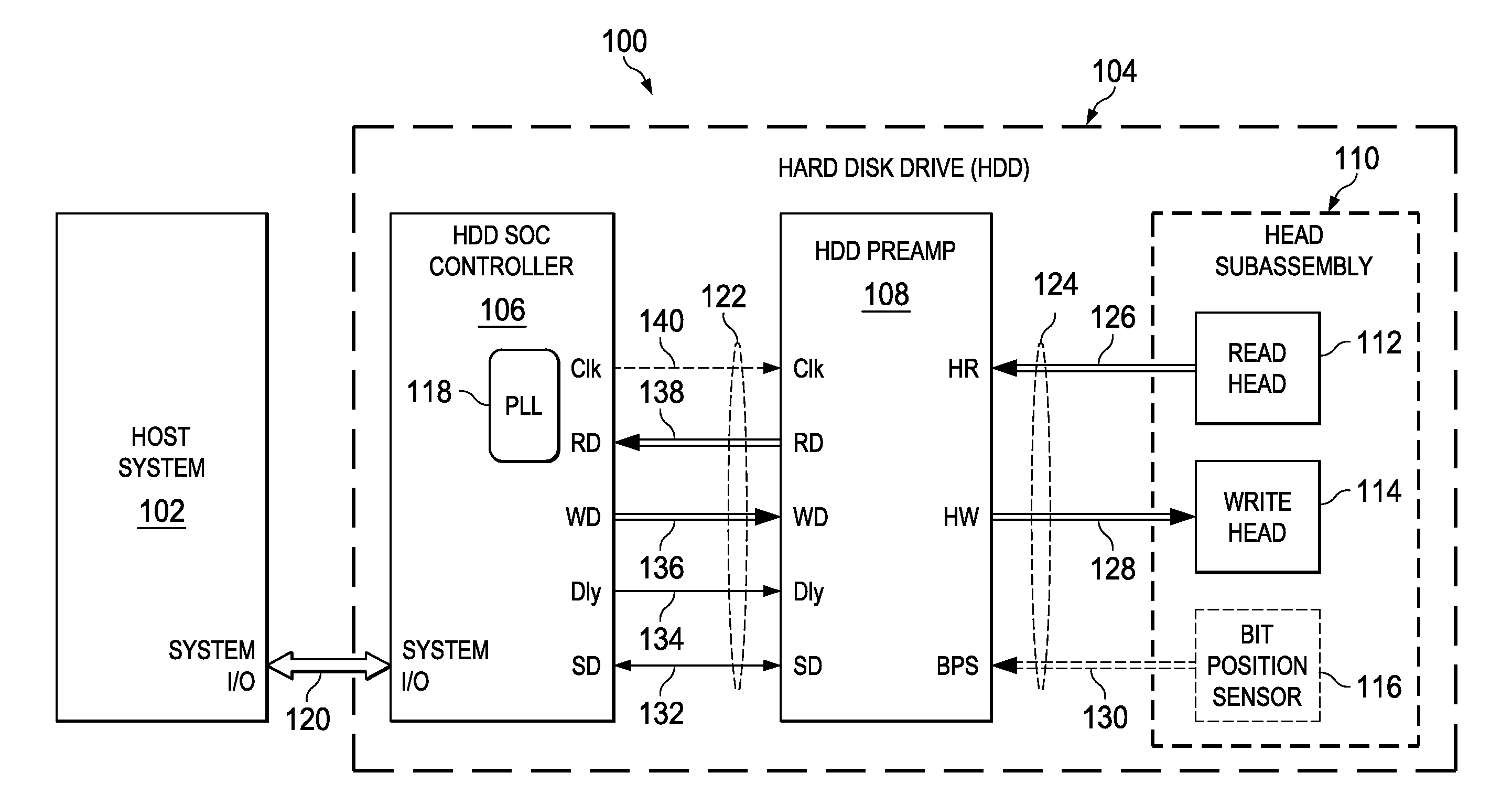

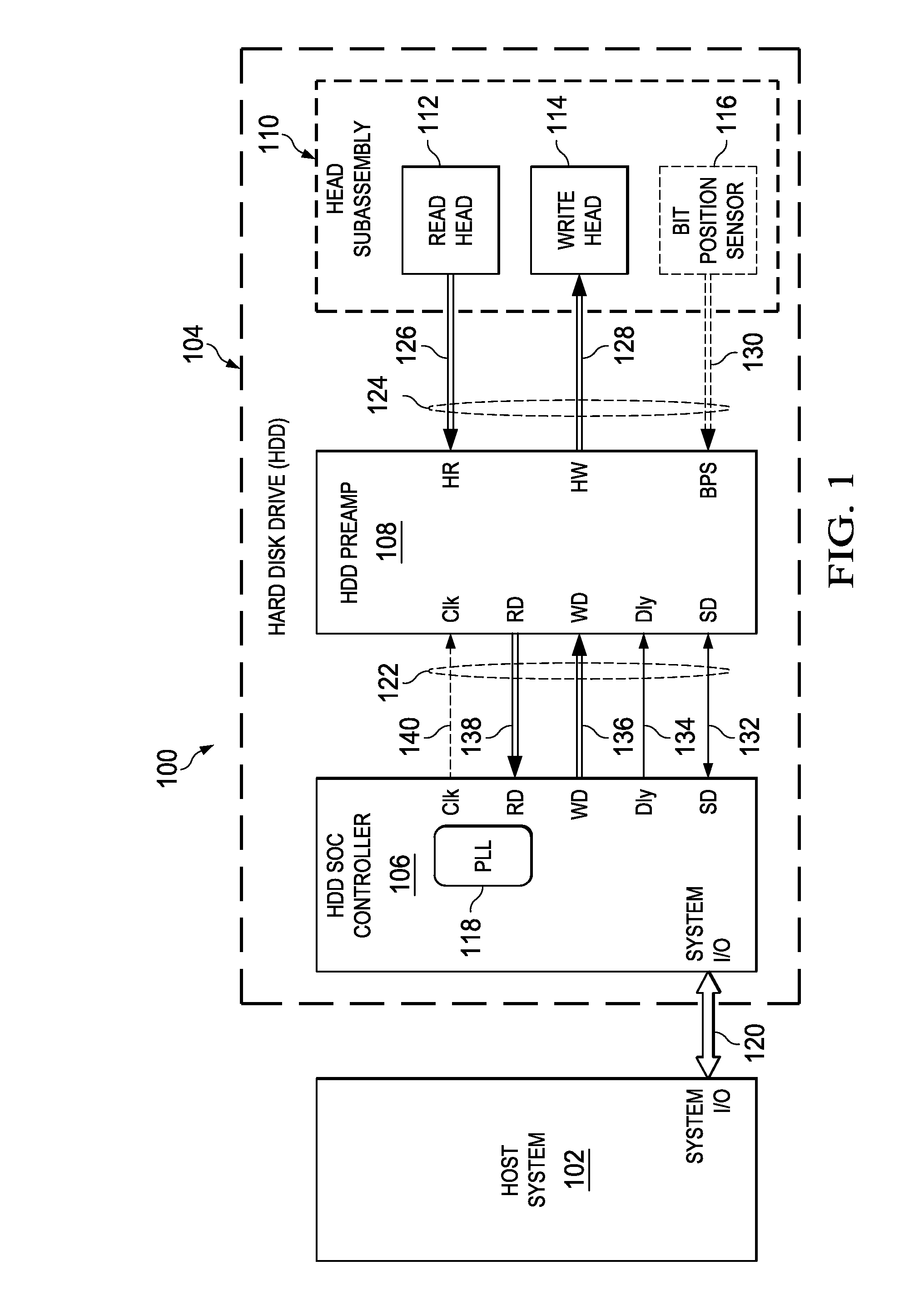

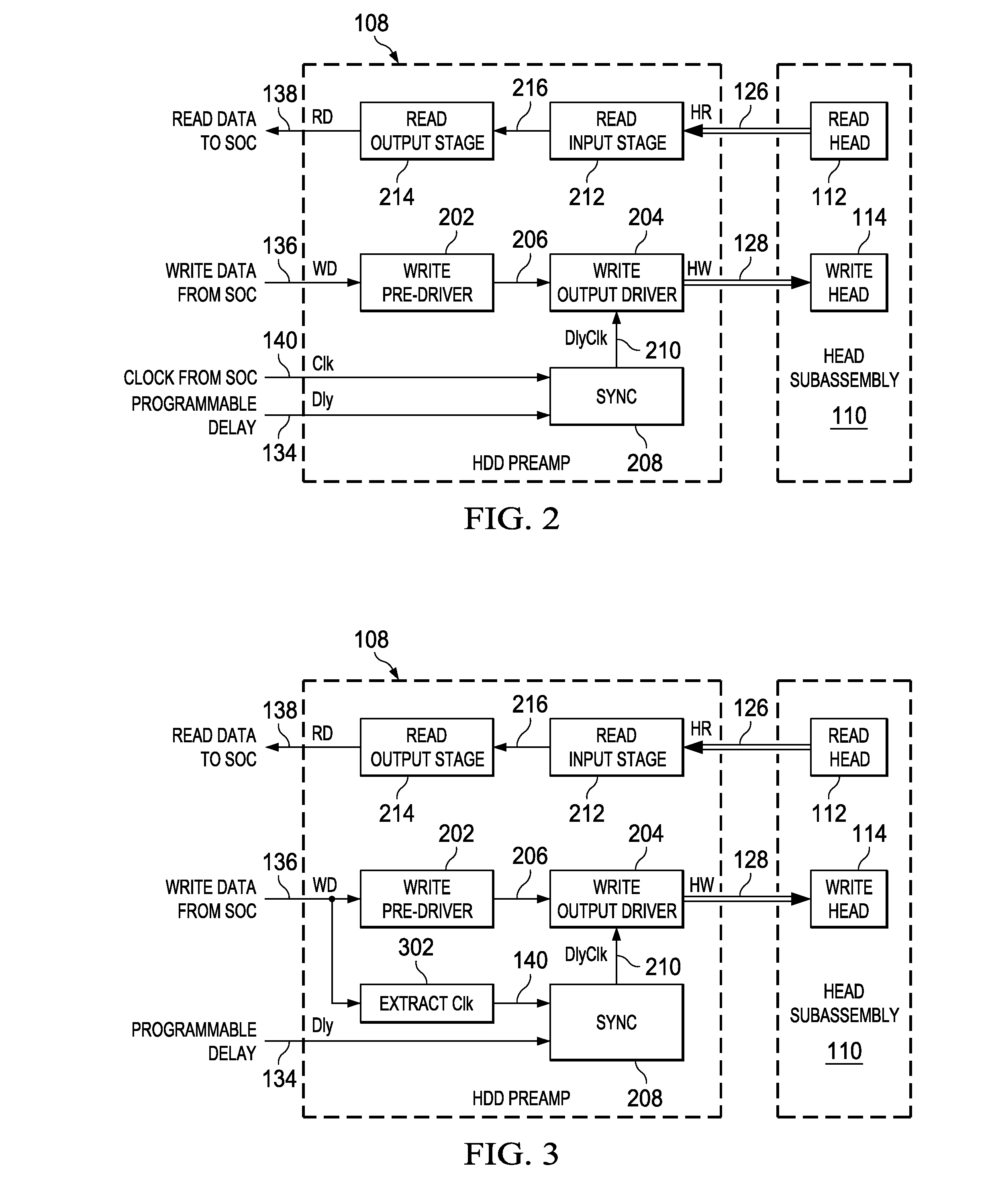

Preamplifier and method for synchronization with bit patterned media

ActiveUS20100246048A1Accurate timingReduce time uncertaintyPatterned record carriersNanoinformaticsAudio power amplifierMagnetic storage

A preamplifier and method writes data synchronized with the passing of a write head in a magnetic storage device over bit islands in discrete patterned recording media. The preamplifier contains a write pre-driver that conditions write data, a synchronization circuit that accepts a delay offset value and a write clock and produces a delayed clock, and a write output driver that is gated by the delayed clock to produce write pulses for magnetizing the bit islands. Gating the write output driver using the delayed clock results in more accurate synchronization than delaying the write data into the preamplifier due to the reduction of the overall length and variability of interconnects and transistors in the intervening circuitry. Write clock generation circuitry, as well as bit position sensor circuitry for use with bit position signals produced by a read head or by a separate bit position sensor, are optionally integrated into the preamplifier, close to the write output driver and write head, for further improvements in delay accuracy and stability. Write pulses produced by the preamplifier are thus well aligned with the bit islands, resulting in higher magnetization and an improved bit error rate.

Owner:TEXAS INSTR INC

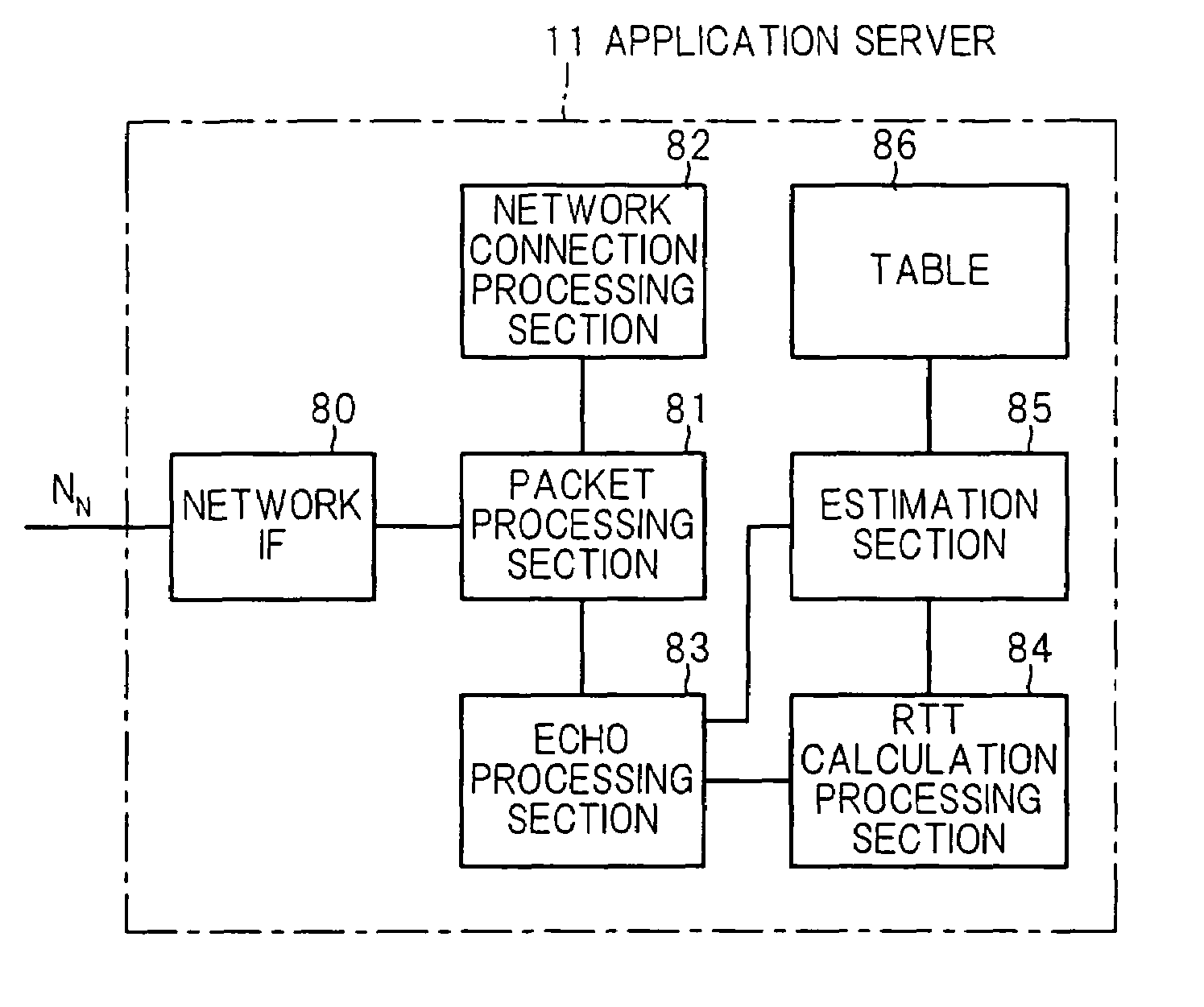

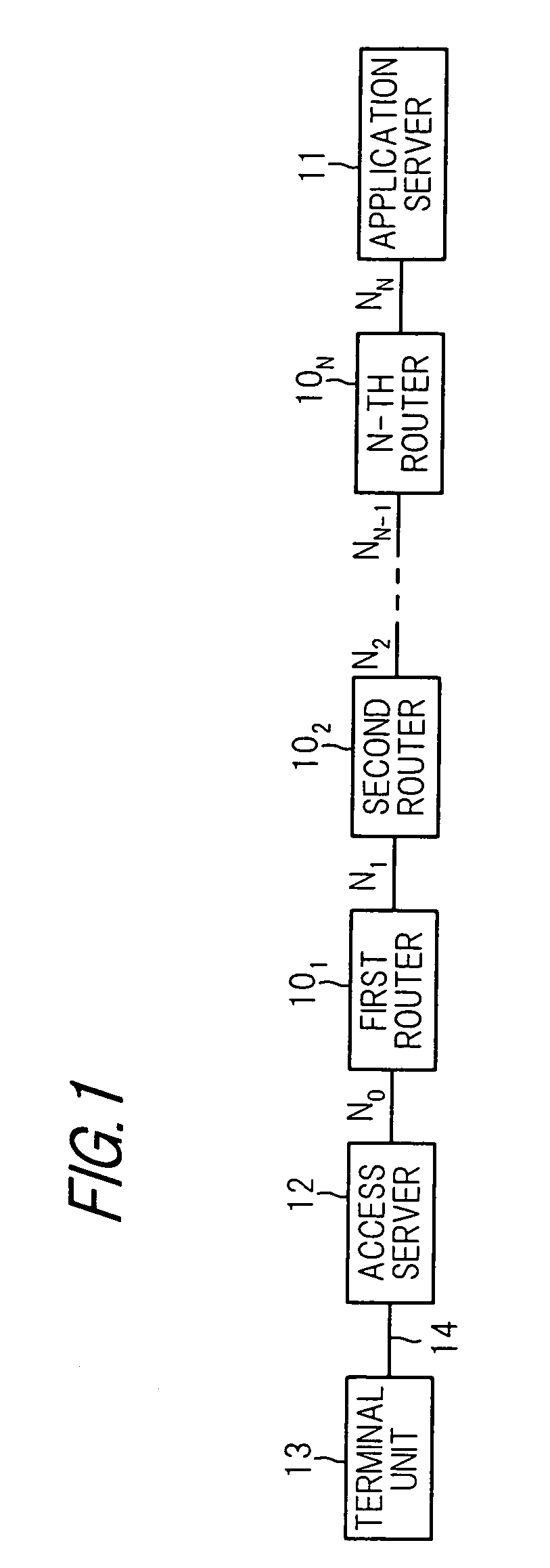

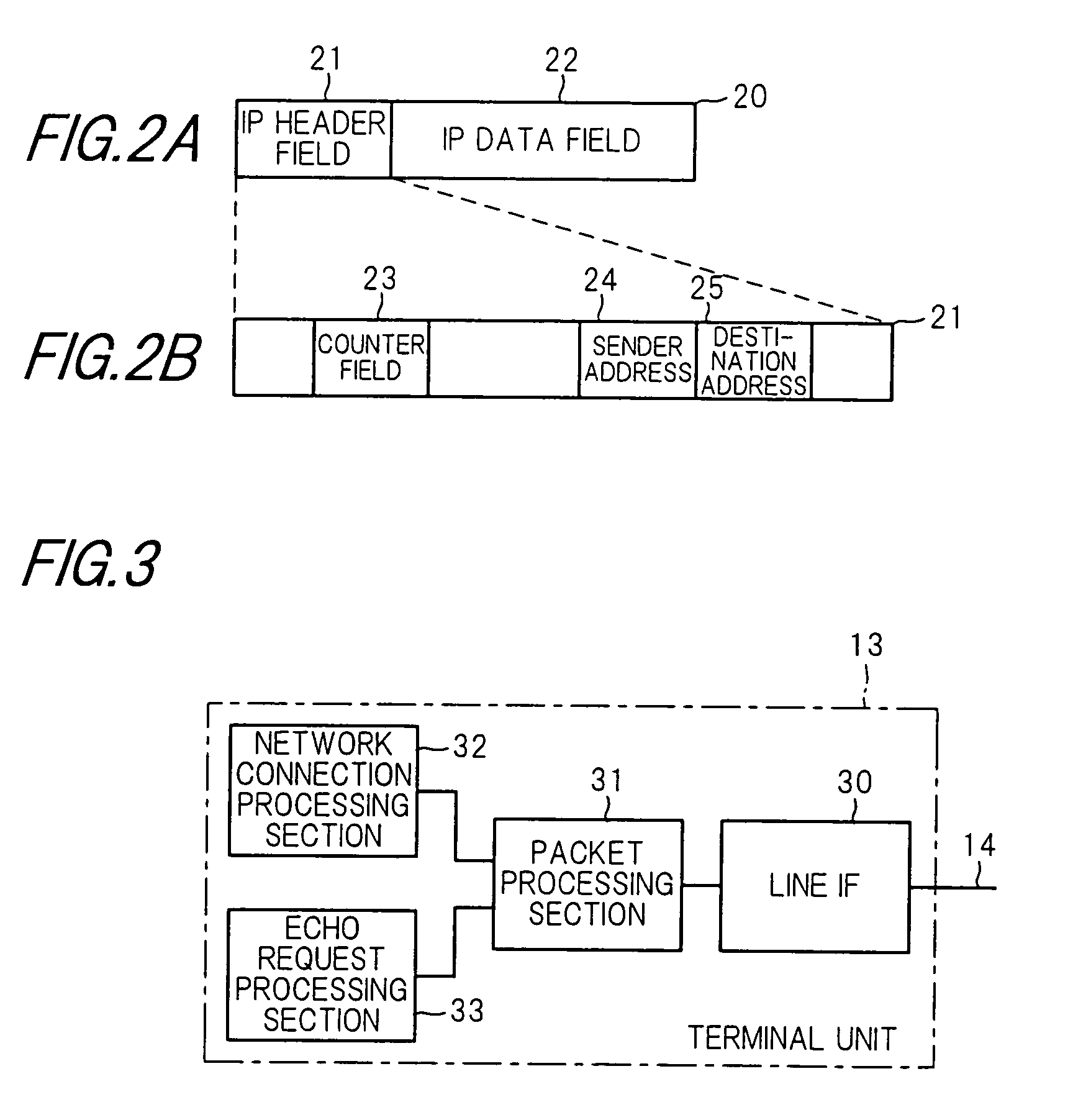

Network system

InactiveUS6965573B1Easily applied to existing Internet systemError preventionTransmission systemsNetworked systemComputer terminal

Disclosed is a network system that has: a communication line having a predetermined bandwidth; a terminal unit that is connected to the communication line and receives data through the communication line; a first unit that includes the terminal unit through the communication line and repeats data to be communicated between the terminal unit and the first unit; and a second unit that sends data to the terminal unit through the first unit according to a bandwidth of the terminal unit that is estimated based on a data delay time of the communication line.

Owner:RAKUTEN GRP INC

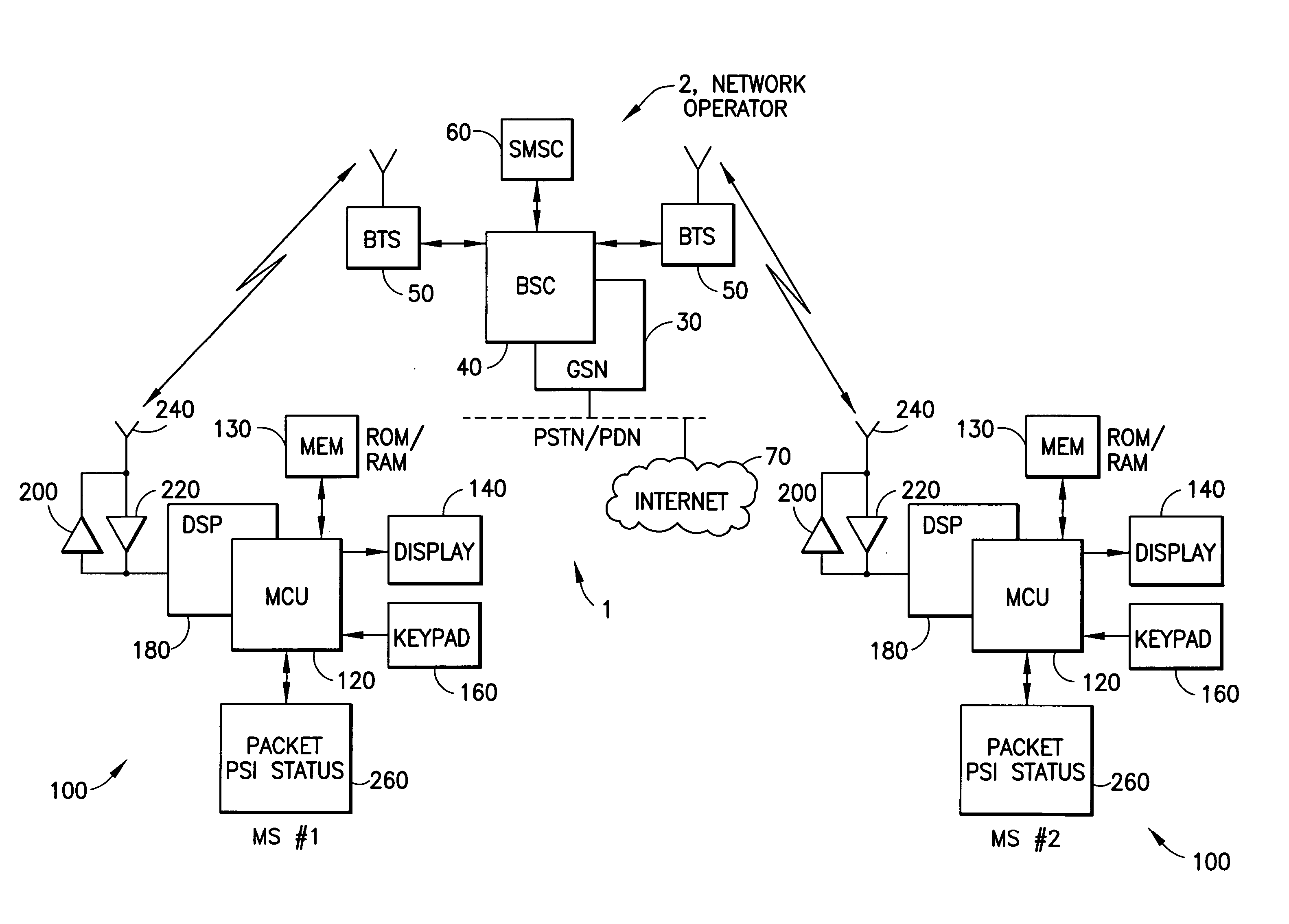

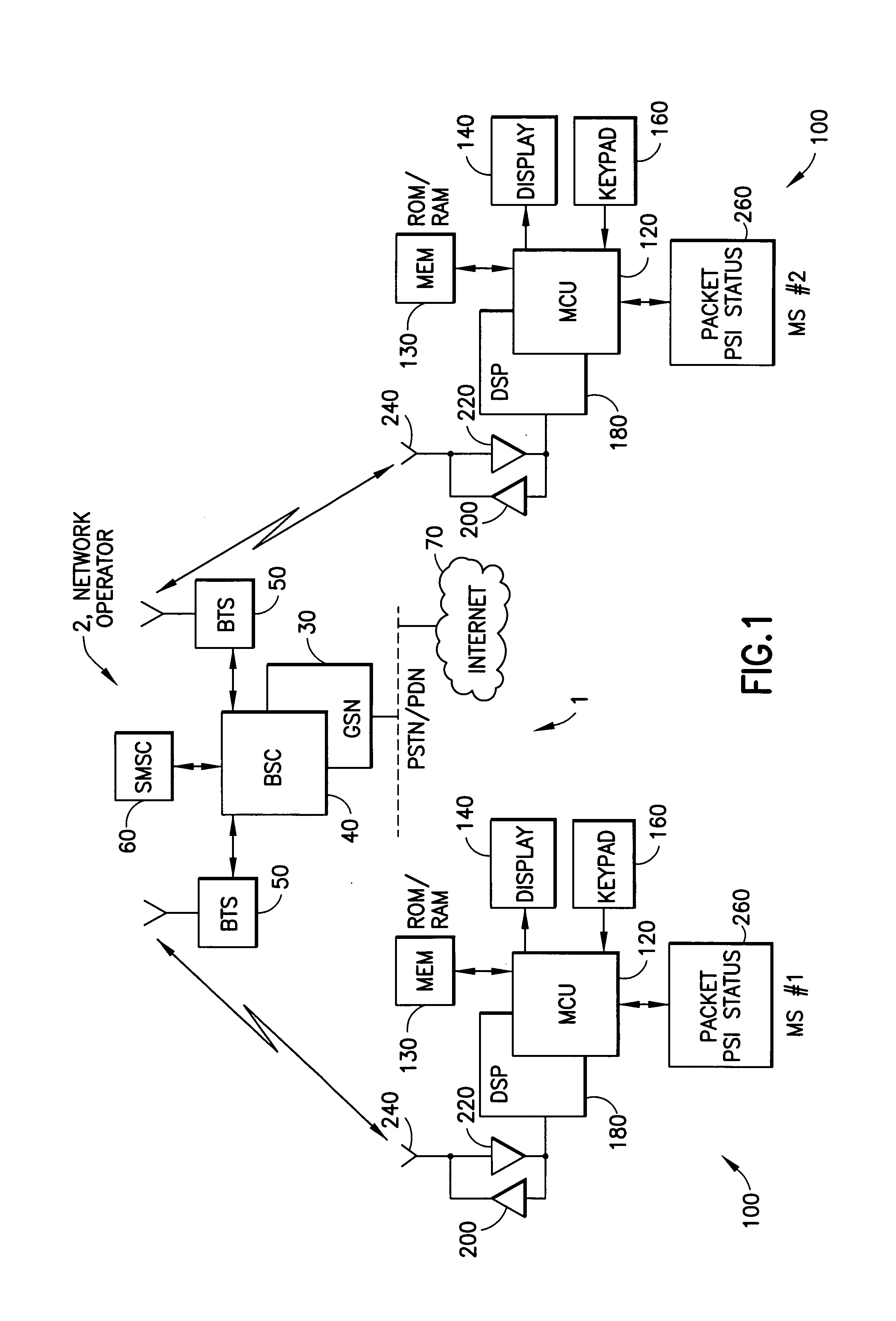

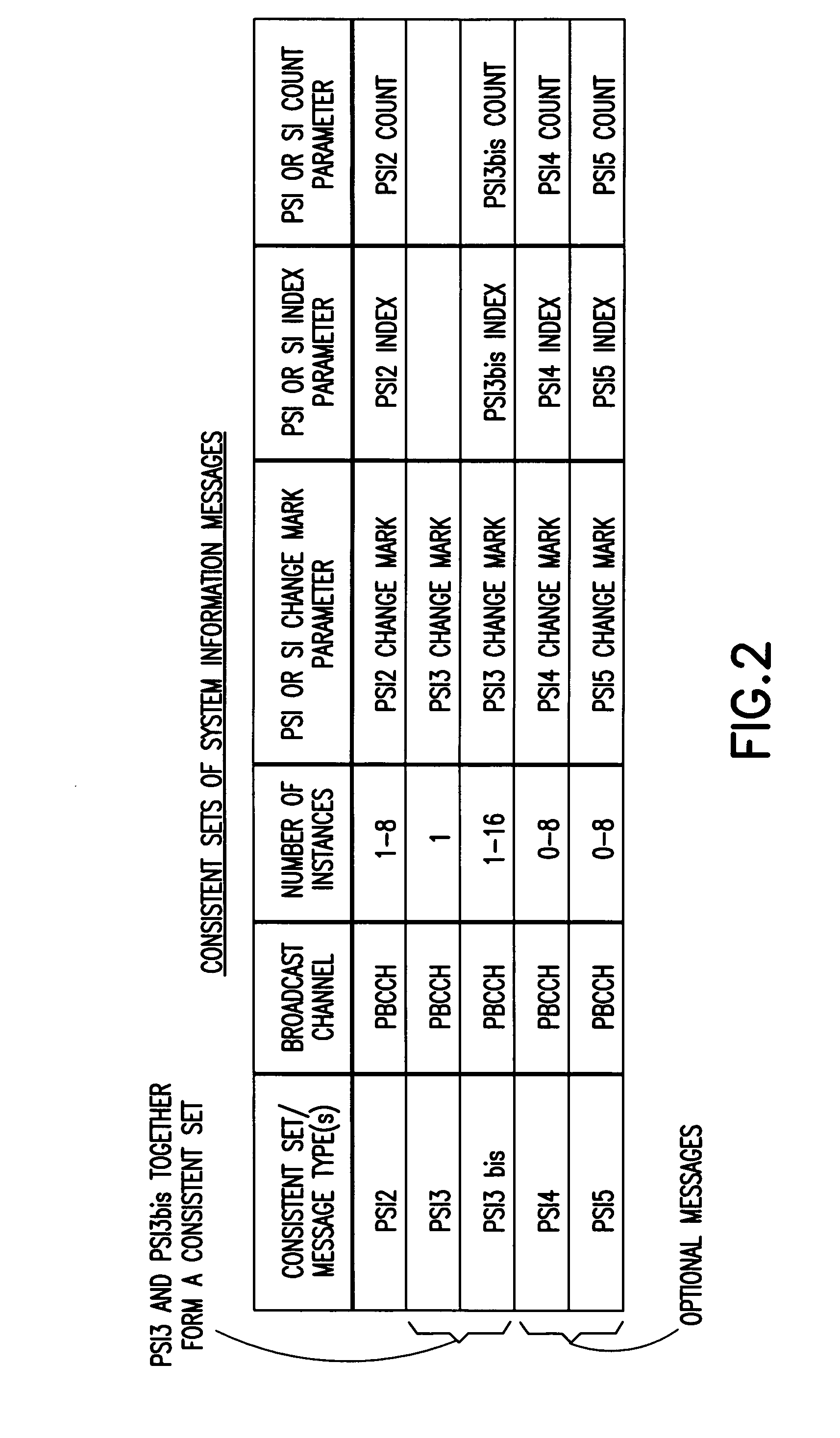

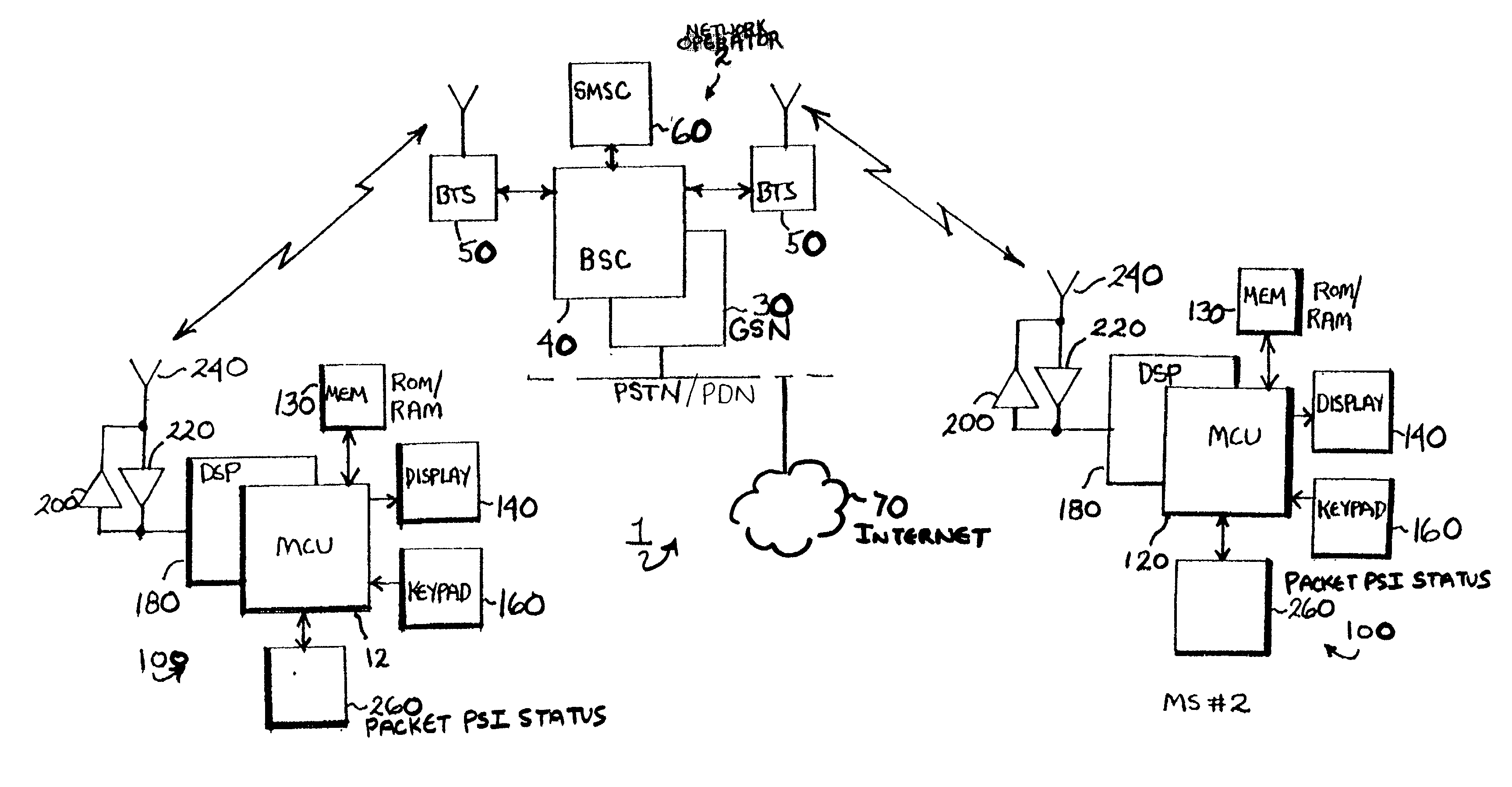

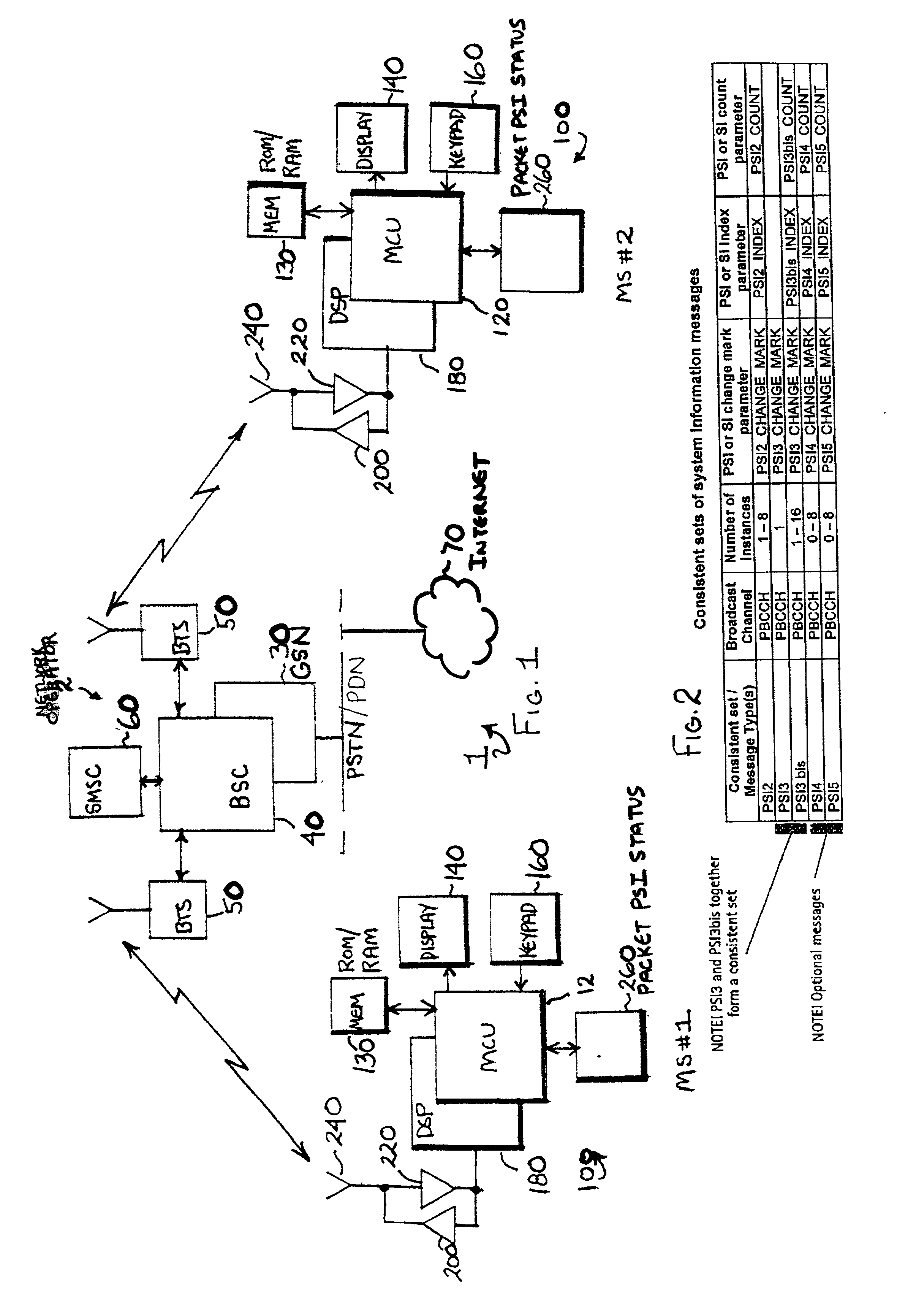

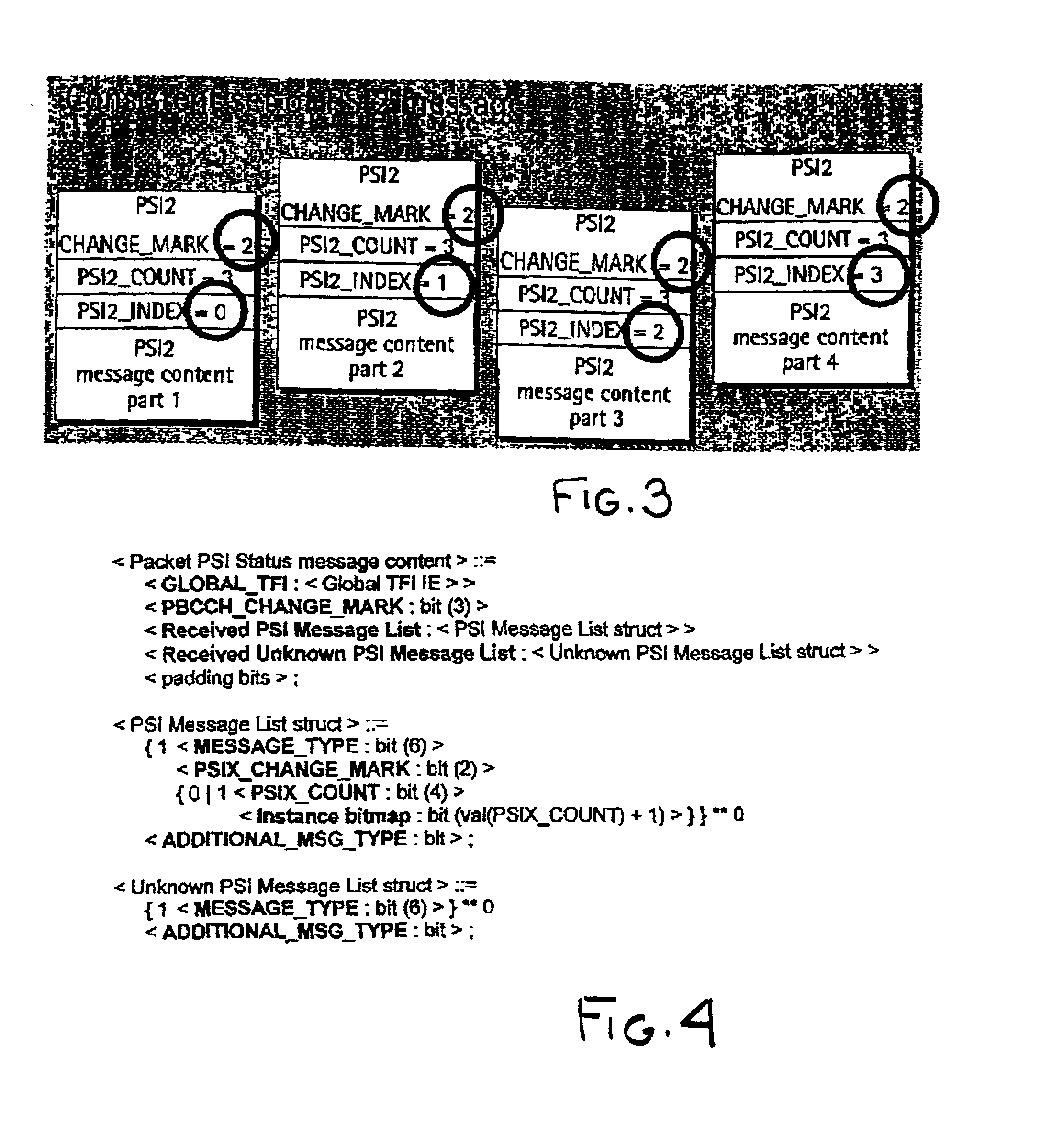

Method and apparatus for improving radio spectrum usage and decreasing user data delay when providing packet PSI status

ActiveUS7136363B2Accelerated programOvercome problemsAssess restrictionTime-division multiplexFrequency spectrumCommunications system

A method provides for operating a wireless communication system having packet data capabilities, and includes steps of: (a) sending a message from a mobile station to a network on a same physical channel that is used to transmit packet data, the message specifying individual ones of packet system information (PSI) messages that are required for reception by the mobile station; and (b) in response to receiving the message, transmitting only the specified individual ones of the PSI messages from the network to the mobile station over the same physical channel used to transmit the packet data.

Owner:QUALCOMM INC

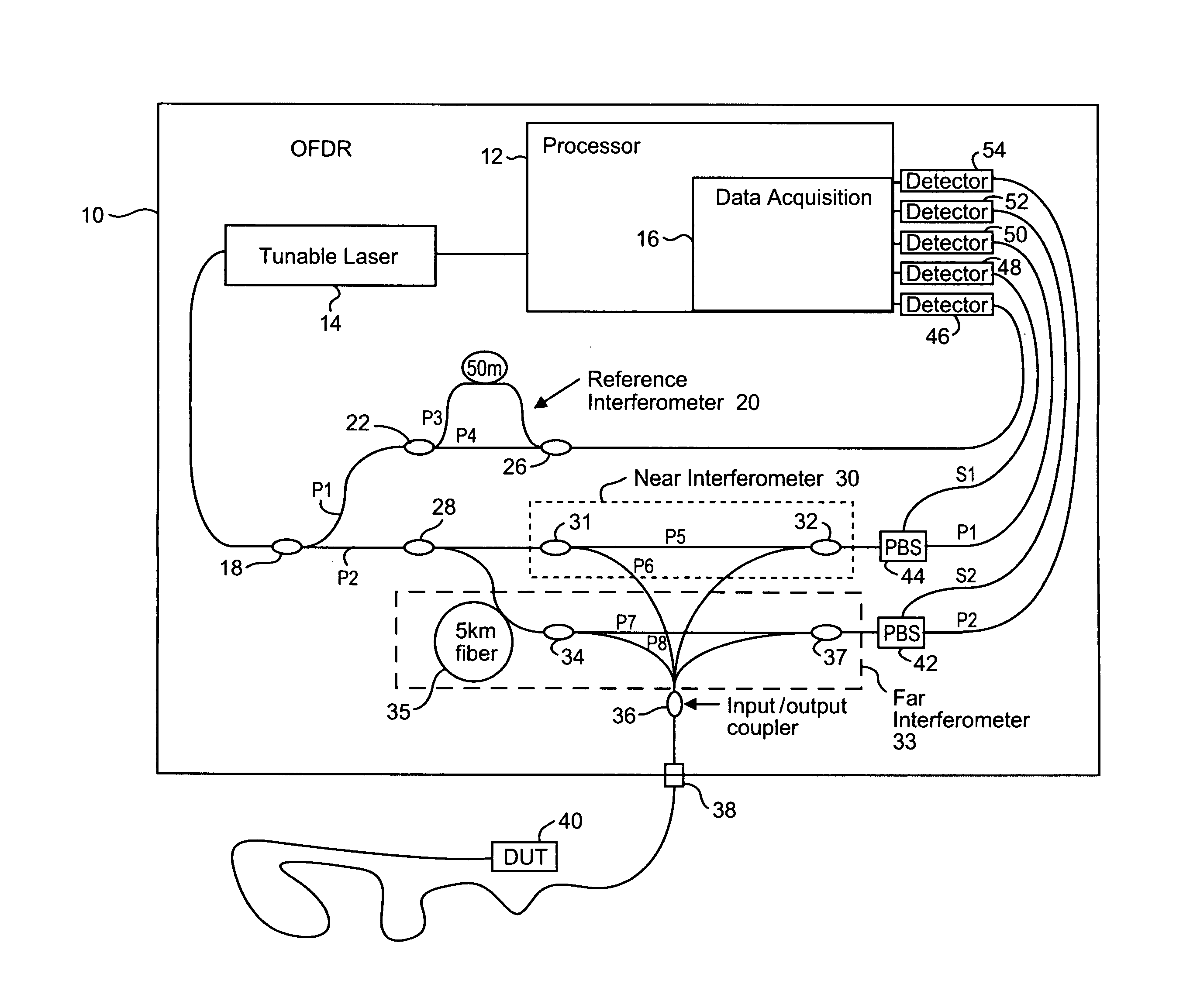

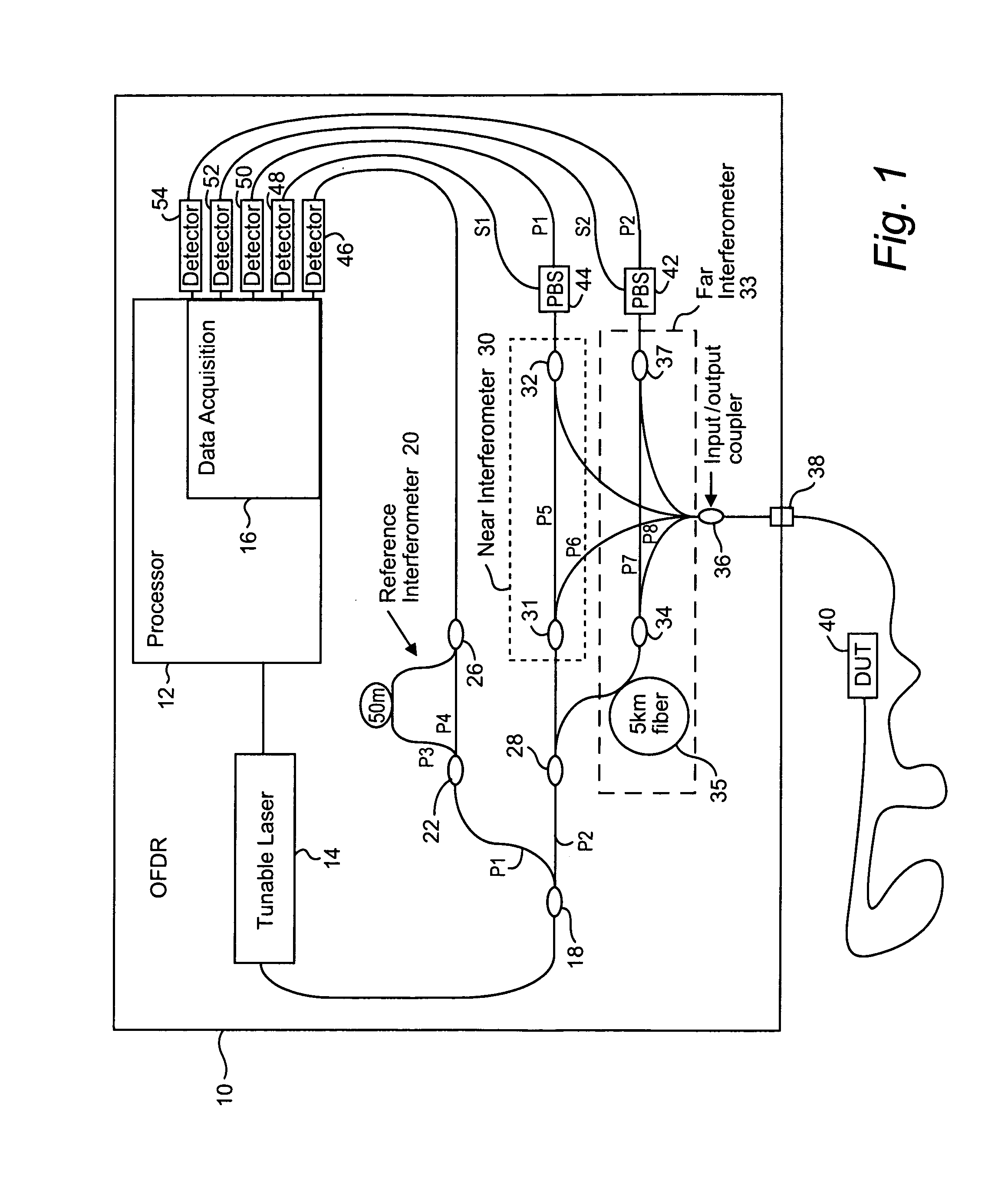

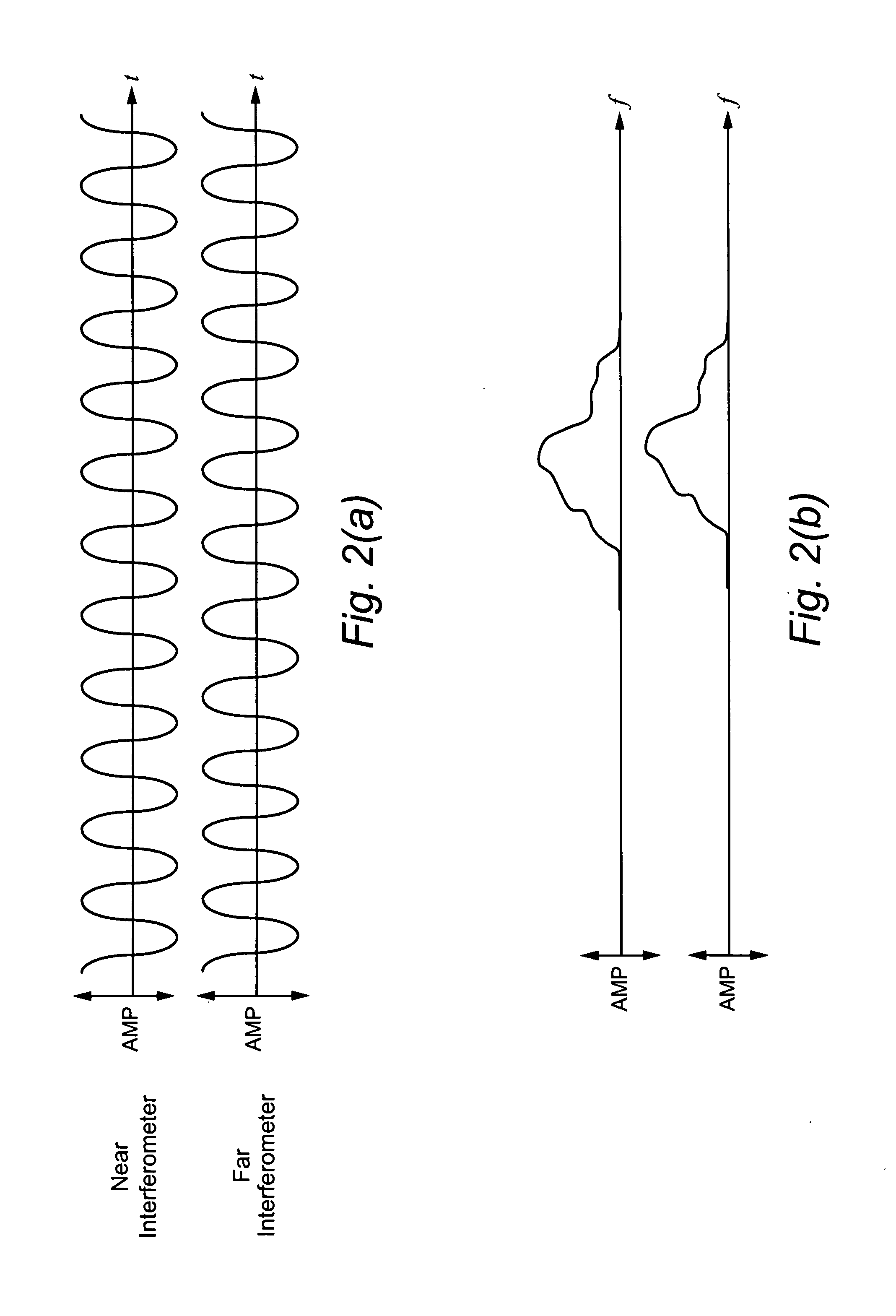

Compensating for time varying phase changes in interferometric measurements

ActiveUS20100321702A1Precise location and determinationIncrease spaceUsing optical meansReflectometers detecting back-scattered light in frequency-domainOptical propertyPhase change

An optical device under test (DUT) is interferometrically measured. The DUT can include one or more of an optical fiber, an optical component, or an optical system. First interference pattern data for the DUT is obtained for a first path to the DUT, and second interference pattern data for the DUT is obtained for a second somewhat longer path to the DUT. Because of that longer length, the second interference pattern data is delayed in time from the first interference pattern data. A time varying component of the DUT interference pattern data is then identified from the first and second interference pattern data. The identified time varying component is used to modify the first or the second interference pattern data to compensate for the time-varying phase caused by vibrations, etc. One or more optical characteristics of the DUT may then be determined based on the modified interference pattern data.

Owner:INTUITIVE SURGICAL OPERATIONS INC

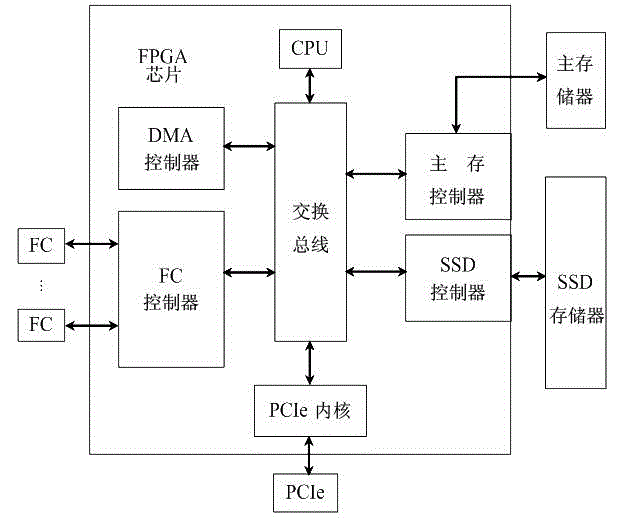

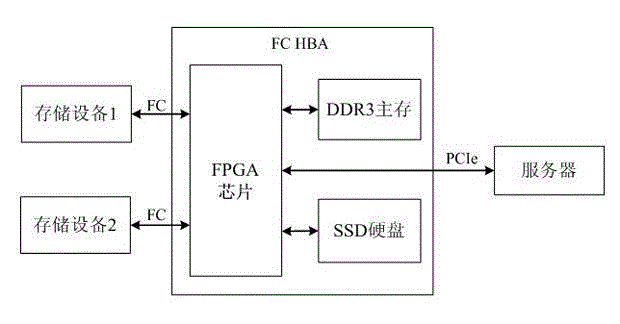

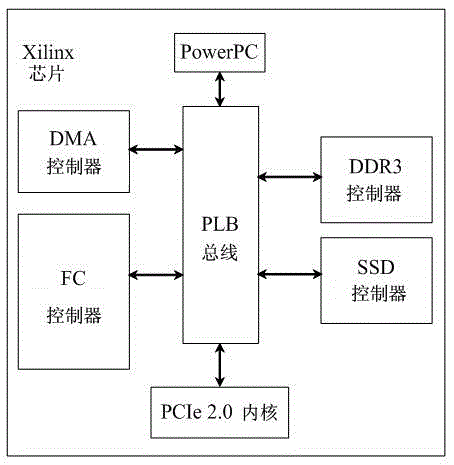

FC HBA (fiber channel host bus adapter) based on SSD (solid state disk) cache and design method thereof

ActiveCN103336745AReduce data latencySSD improvedMemory adressing/allocation/relocationGigabyteEngineering

The invention discloses an FC HBA (fiber channel host bus adapter) based on an SSD (solid state disk) cache and a design method thereof. An SSD memory is used as the buffer memory of the FC HBA, a server is communicated with the FC HBA through a PCIe (peripheral component interface express) interface, a memory device is communicated with the FC HBA through an FC interface; and the SSD buffer memory stores the transmitted data in a buffer manner, and the transmitted data includes the data transmitted between the server and the memory device, and the data transmitted between the memory device and another memory device. The SSD memory is used as the data cache of the FC HBA, namely a large-capacity high-speed buffer memory is provided for the FC HBA, the capacity of the buffer memory can reach 100 GB (gigabyte)-2TB(trillionbyte), or even a larger range. The server only needs to access to the SSD buffer memory in the FC HBA to obtain required data without accessing to the memory device, so that the data delay between the server and the memory device is reduced, and the IOPS (input / output operations per second) of the system is effectively improved. Besides, the SSD memory is used as the cache of the FC HBA, so that the transfer rate of stored network data is effectively improved.

Owner:无锡北方数据计算股份有限公司

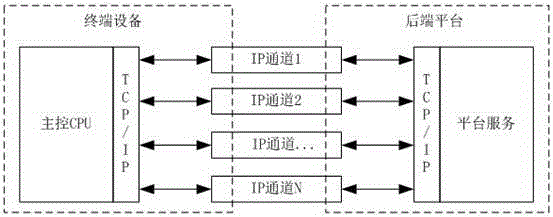

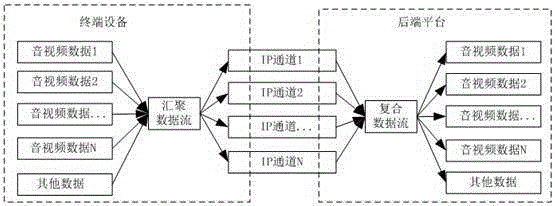

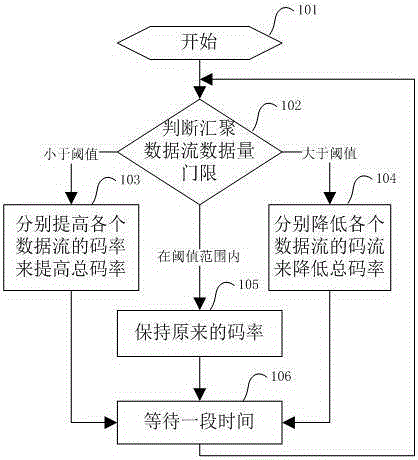

Multichannel real-time data transmission method of self-adaptive bandwidth

InactiveCN105245321AHigh bandwidthMeet transfer requirementsNetwork traffic/resource managementTransmission path multiple useData streamCode rate

The invention provides a multichannel real-time data transmission method of a self-adaptive bandwidth. The method comprises the following steps: compounding a plurality of data streams existent on a terminal device into a converged data stream; self-adaptively adjusting code rate of each data stream according to the total data volume of the converged data stream; dividing the converged data stream into a plurality of data packets suitable for transmission volume of an IP network, and selecting an IP channel for each data packet; transmitting each data packet to a back-end platform through the IP channel selected for the data packet. Through the adoption of the method provided by the invention, a plurality of mobile channels are compounded into a communication channel, the total bandwidth of the mobile communication channel is increased, and a transmission requirement of a higher data bandwidth is satisfied; the sending rate can be self-adaptively adjusted, so that the channel bandwidth can be utilized in maximum efficiency, and the data delay can be controlled in a reasonable range, the demand of real-time video transmission is satisfied.

Owner:ANHUI TSINGLINK INFORMATION TECH

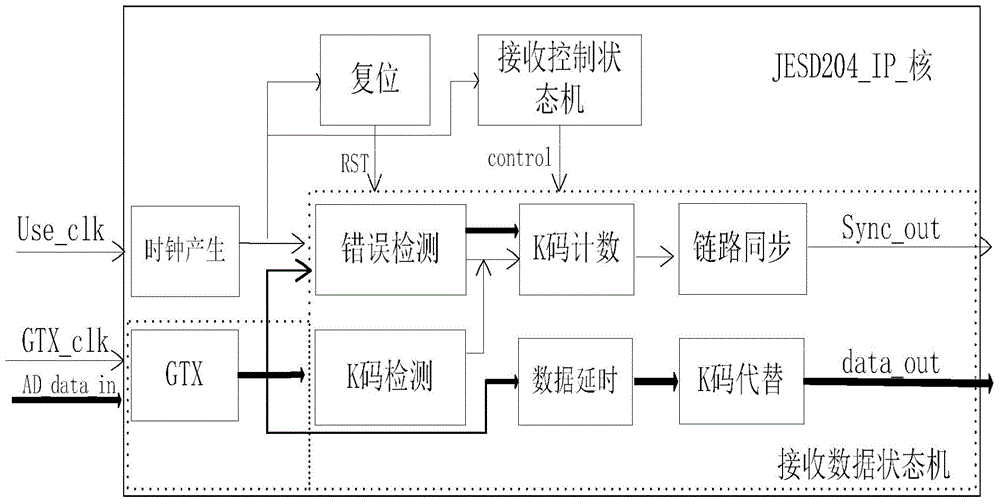

IP core based on JESD 204 protocol

ActiveCN104063342AReduce bit error rateAvoid crosstalkElectric digital data processingTransceiverDifferential signaling

The invention provides an IP core based on the JESD204 protocol and aims to provide an IP core which is strong in anti-interference capability high in transmission rate and unaffected by inter symbol interference and synchronous influence. The IP core based on JESD204 protocol is realized by adopting the following technical proposal; FPGA ( Field Programmable Gate Array) contains multiple GTX interfaces; each GTX interface receives data conforming to the JESD 204 protocol through a pair of differential signaling wires between an analog-digital converter ADC chip and each GTX interface in a serial manner; the IP core based on the JESD 204 protocol is characterized in that a clock generation unit generates all the input clocks required by all the other functional units; a reset function unit logically controls and generates reset signals, so as to receive control signals generated by a control state machine; a physical layer calls a high-speed serial transceiver inside the FPGA, so as to send converted parallel data to a data error detection function unit; the parallel data is further sent to a K code detection function unit for K code detection; the detected k code is sent to a K code count function unit for counting; a link synchronization function unit judges the synchronous state of a high-speed serial transmission link according to the detection results of the K code detection function unit; a data delay function unit conducts a delay treatment on the data from the GTX and provides the delay processed data for a K code substitution function unit.

Owner:10TH RES INST OF CETC