Patents

Literature

18016results about "Networks interconnection" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Reference time distribution over a network

InactiveUS8014423B2Time-division multiplexGenerating/distributing signalsTime informationData stream

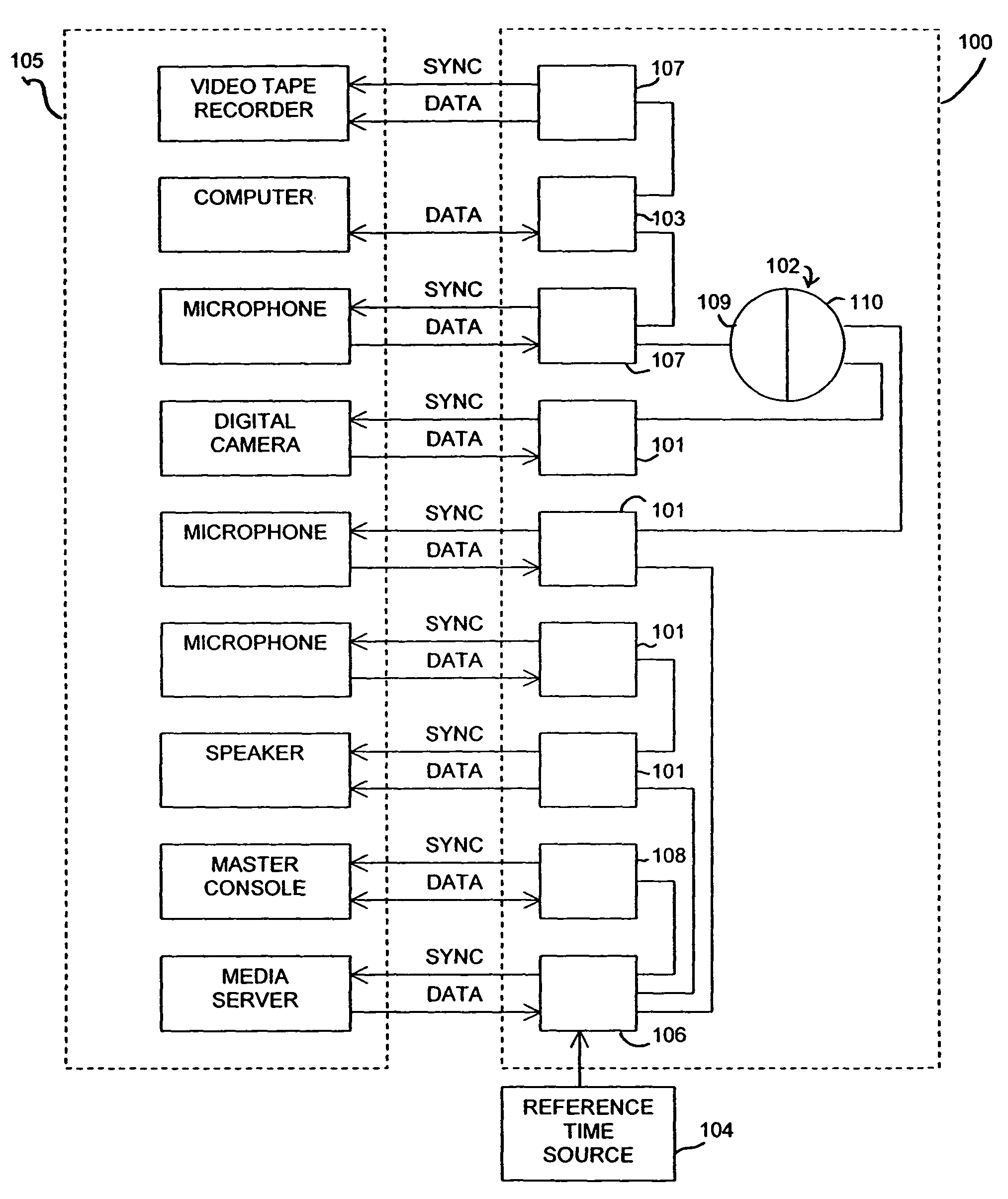

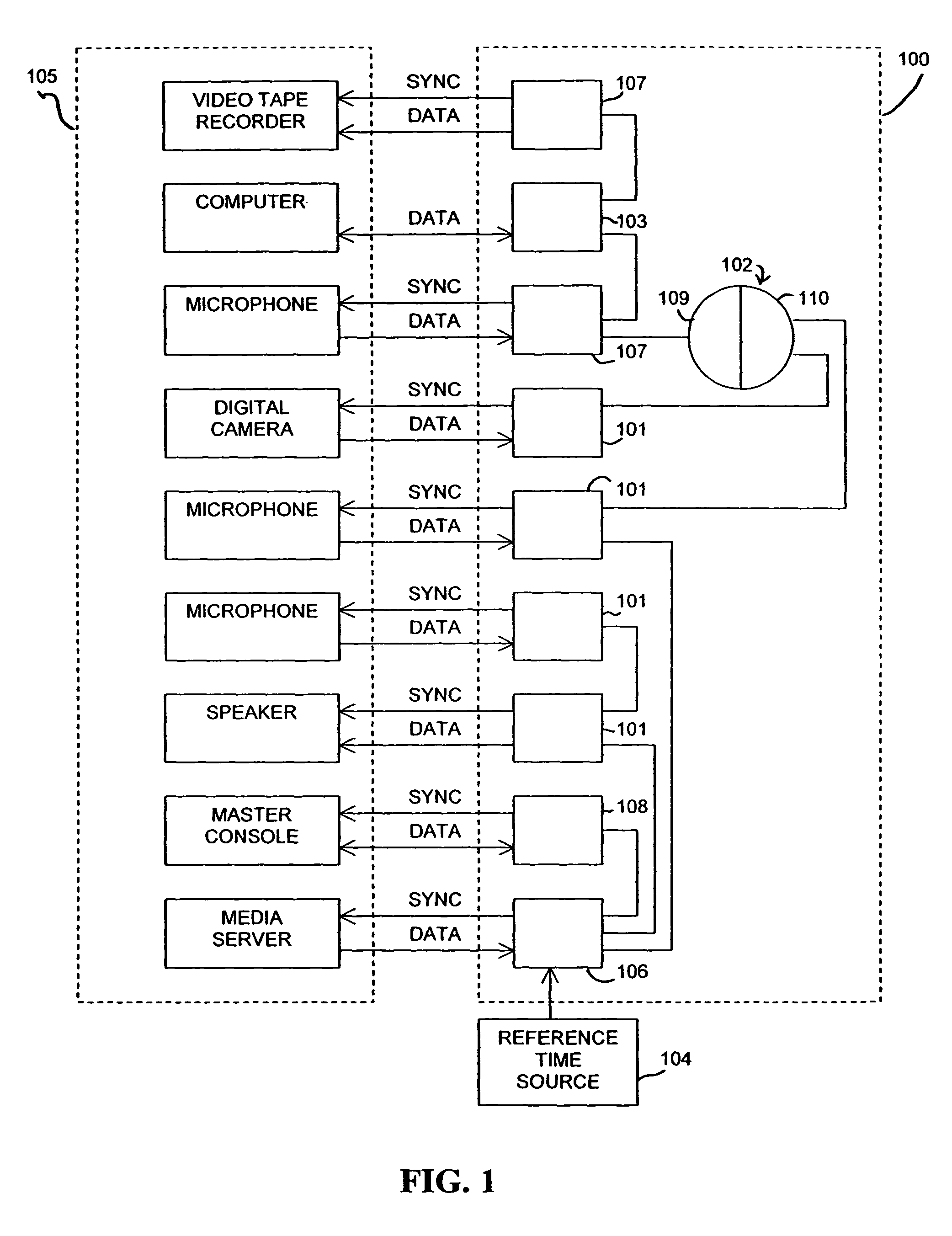

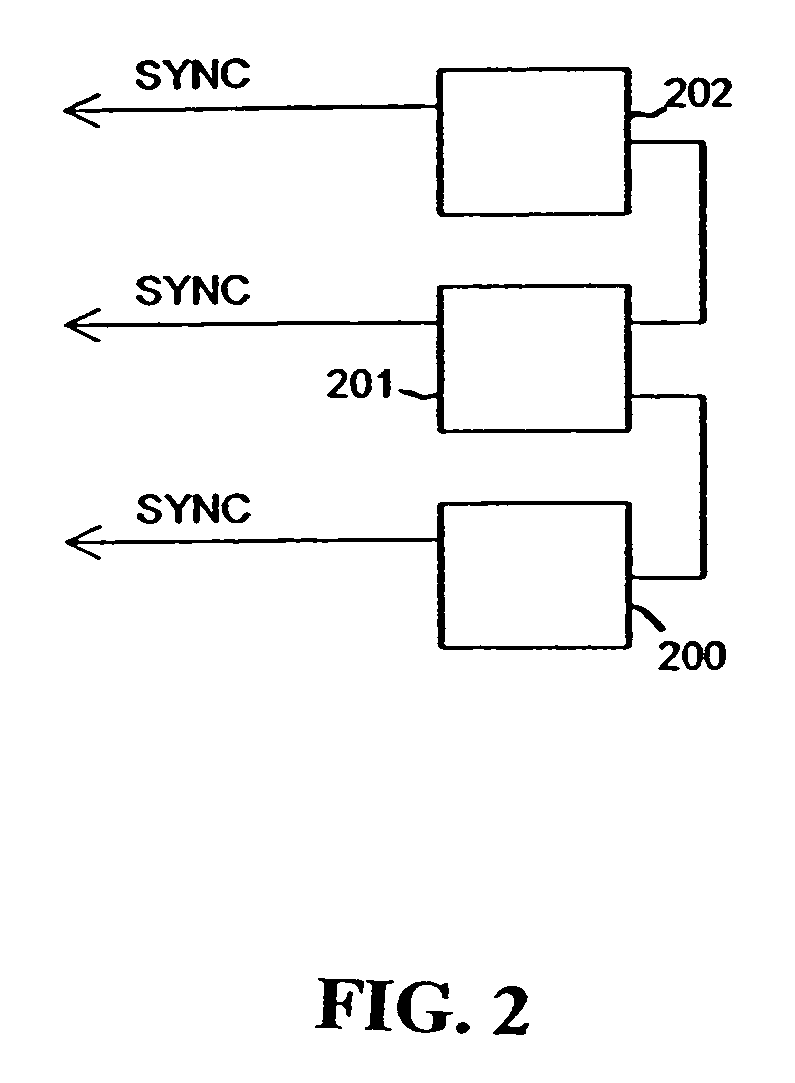

A reference time distribution system and method use a data transmission network having a plurality of nodes to distribute the House Sync signal. A network-wide time signal is generated using a reference time generator, and the network-wide time signal is then distributed over the network to the plurality of nodes. At each node, the network-wide time signal is converted to a local synchronization signal for use in performing synchronization of the timing of each node. Either network-inherent timing and / or additional time signaling is used to provide the nodes attached to this network with a network-wide notion of time. The time information is converted locally into synchronization signals or time information as required by a respective application. When data is transported over the network, delay compensation is performed to simultaneously output different data streams that have been synchronously input into the network, regardless of the data path.

Owner:POLARIS POWERLED TECH LLC

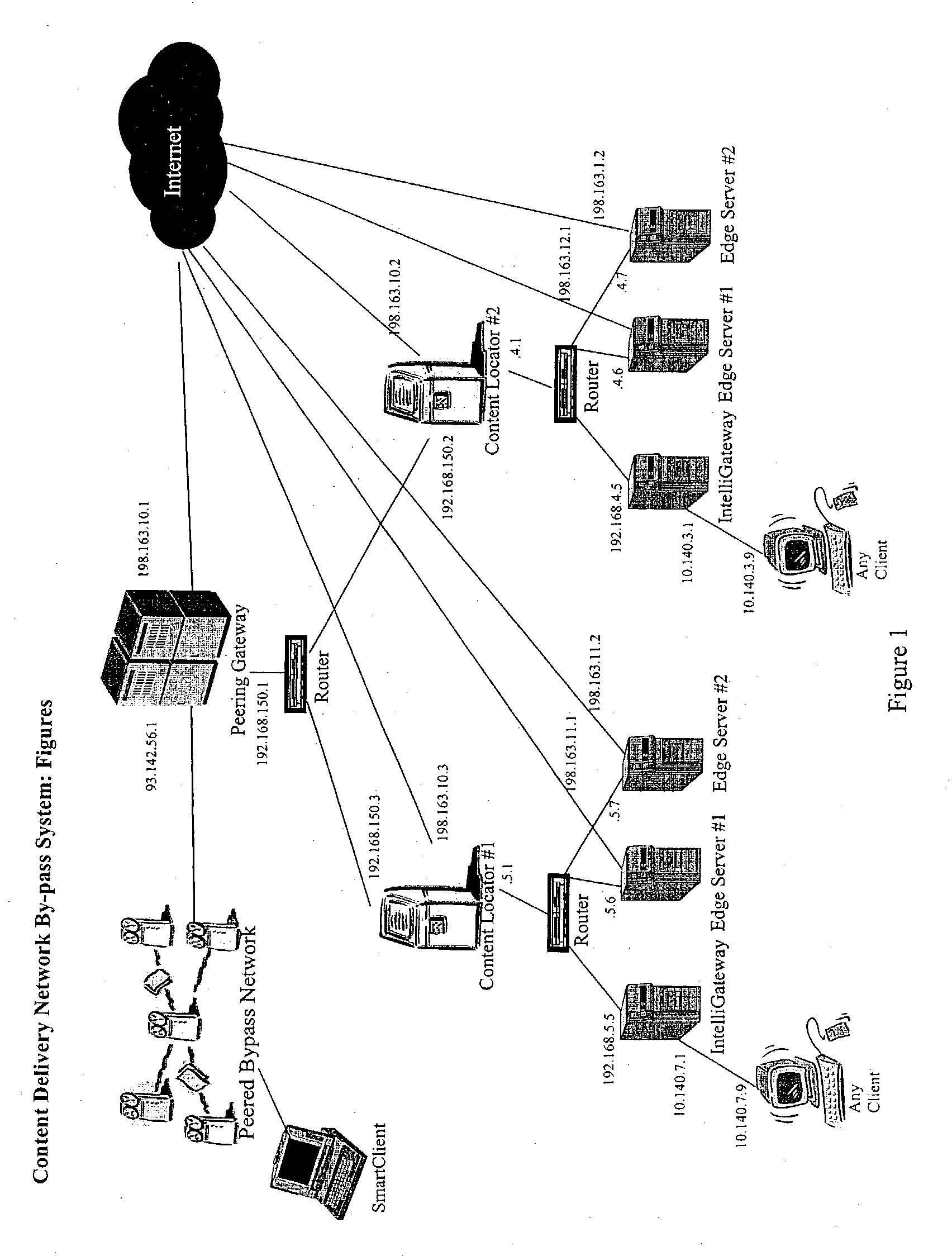

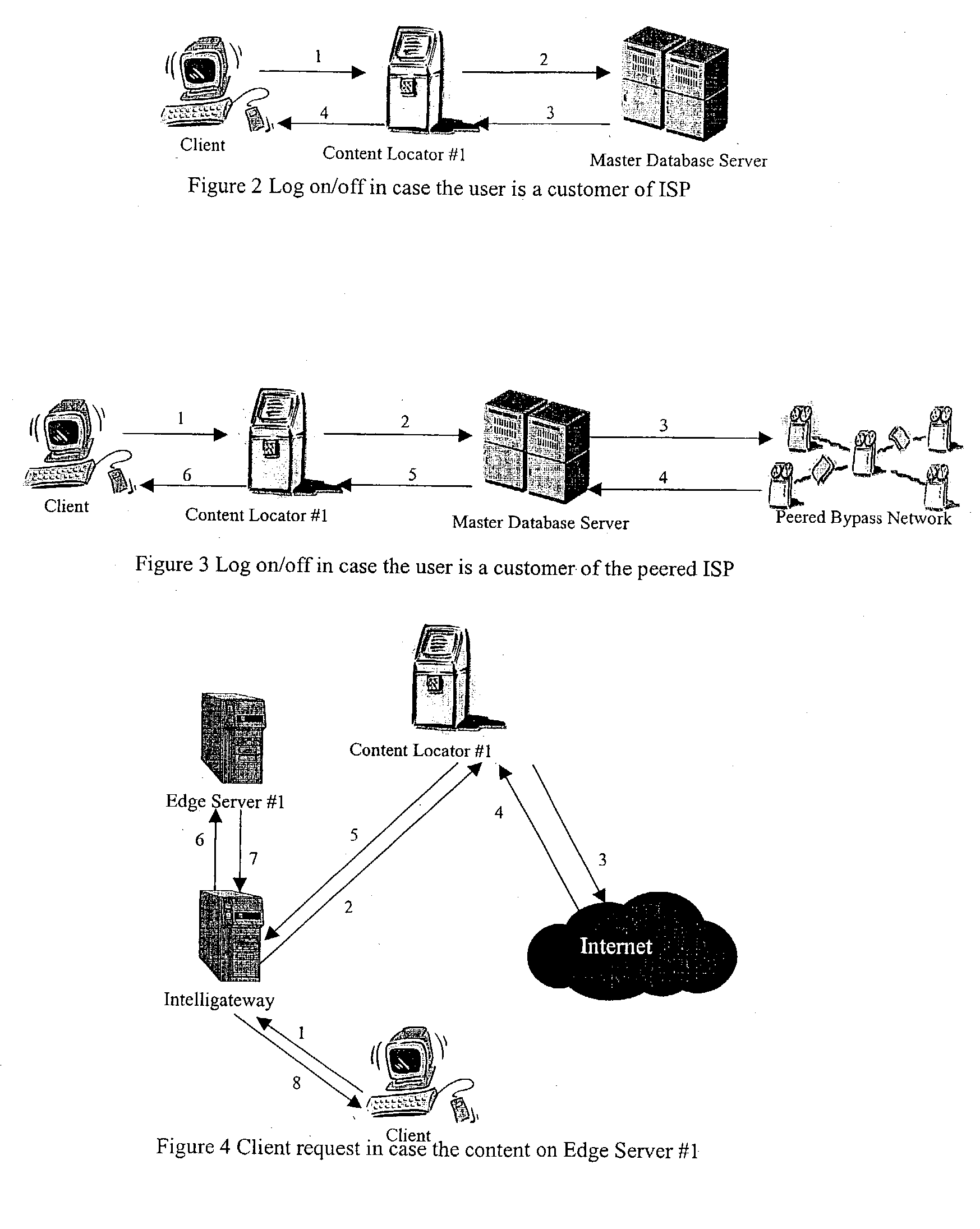

Content delivery network by-pass system

InactiveUS20030174648A1Increase capacityIncrease in sizeError preventionTransmission systemsWeb sitePeering

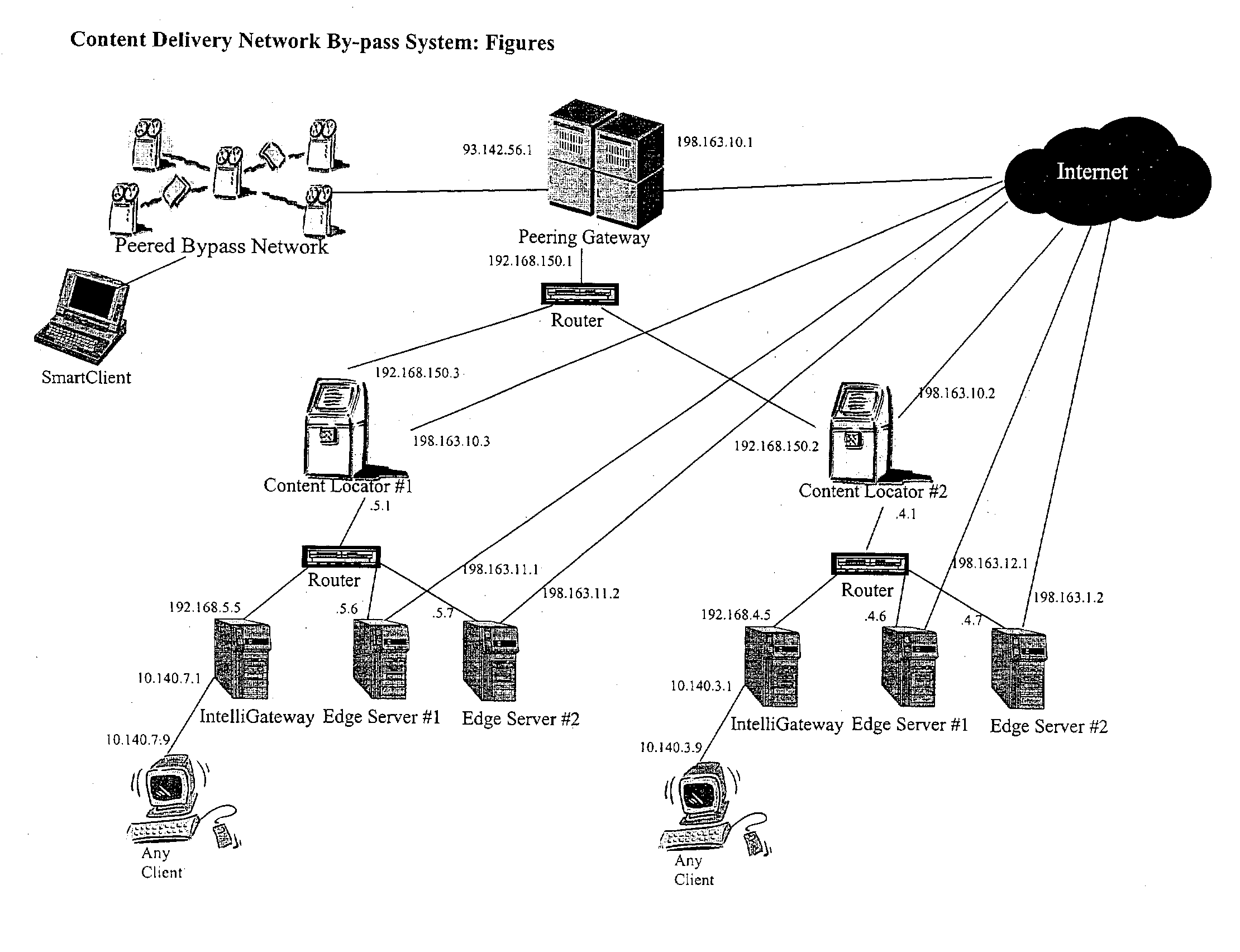

The bypass network is designed to provide fast access and high quality streaming media services anywhere anytime. There are five major components including Peering Gateway, Content Locator, Edge Server, Gateway and Client. The whole bypass network is divided into number of self-managed sub-networks, which are referred as local networks in this document. Each local network contains Edge Servers, gateways, and a Content Locator. The Edge Servers serve as cache storage and streaming servers for the local network. The gateways provide a connection point for the client computers. Each local network is managed by a Content Locator. The Content Locator handles all client requests by communicating with the Peering Gateway and actual web sites, and makes the content available on local Edge Servers. The Content Locator also balances the load on each Edge Server by monitoring the workload on them. One embodiment is designed for home users whose home machine does not move around frequently. A second embodiment is designed for business users who travel around very often where the laptops would self-configure as a client of the network.

Owner:TELECOMM RES LAB

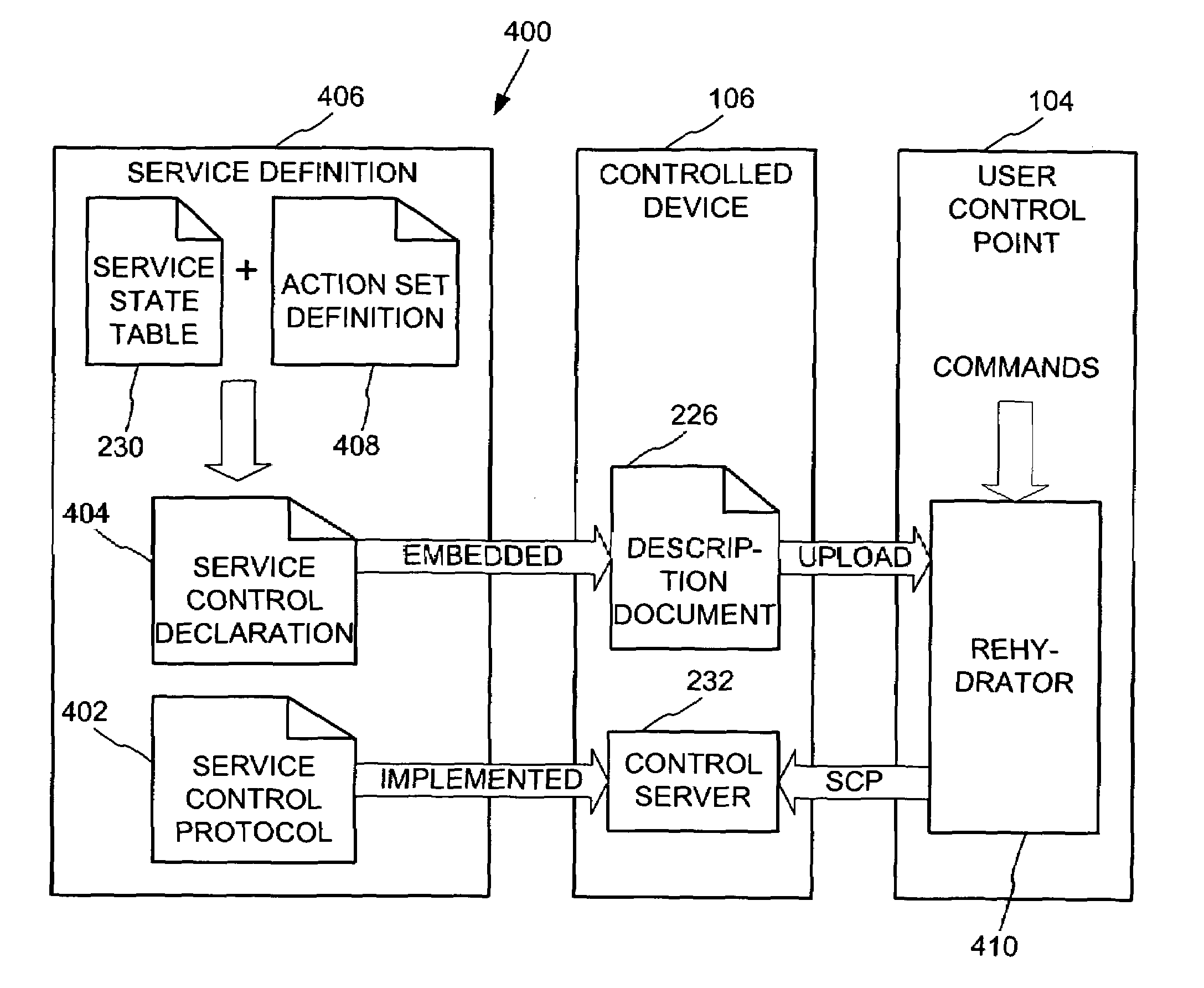

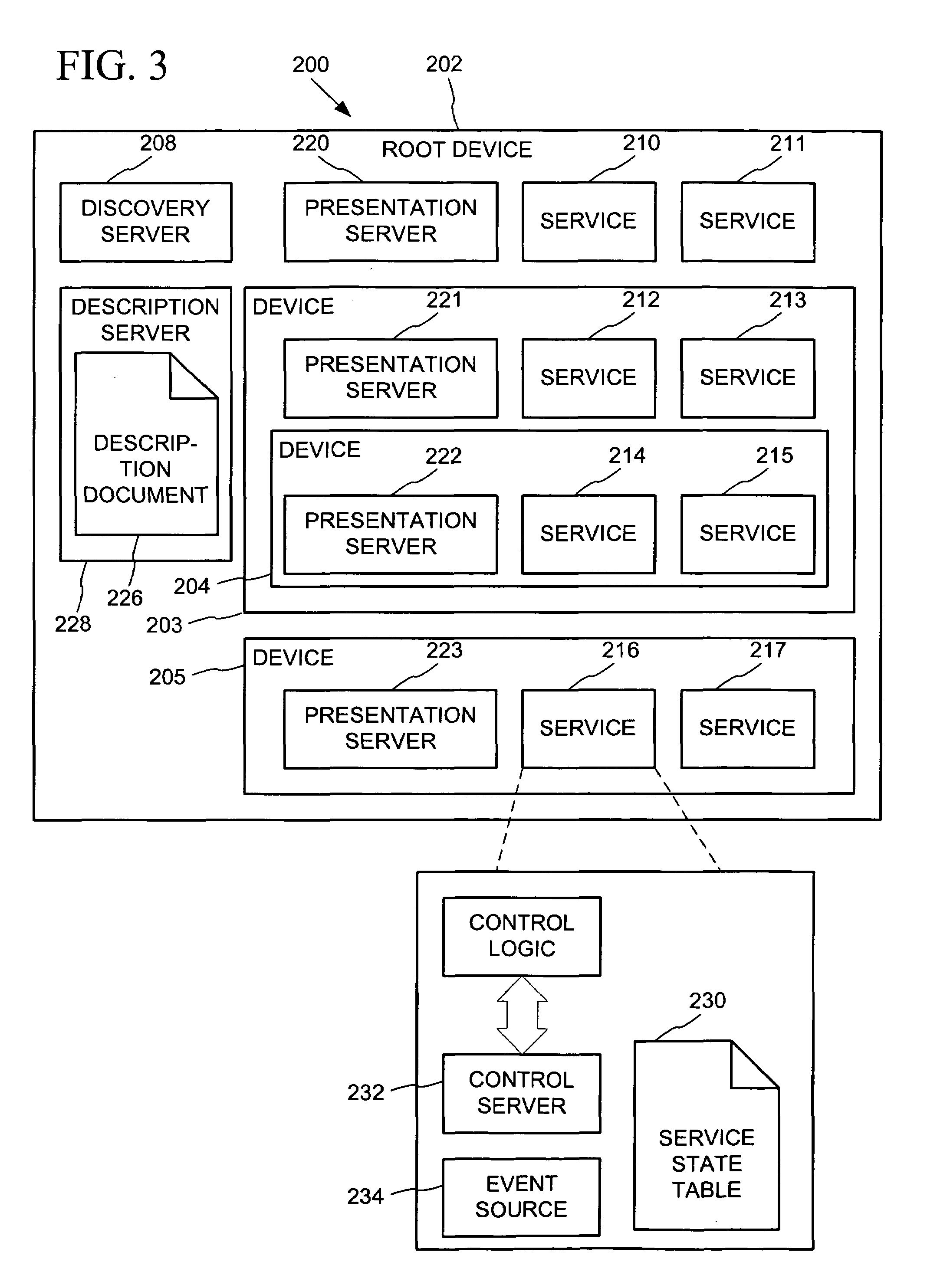

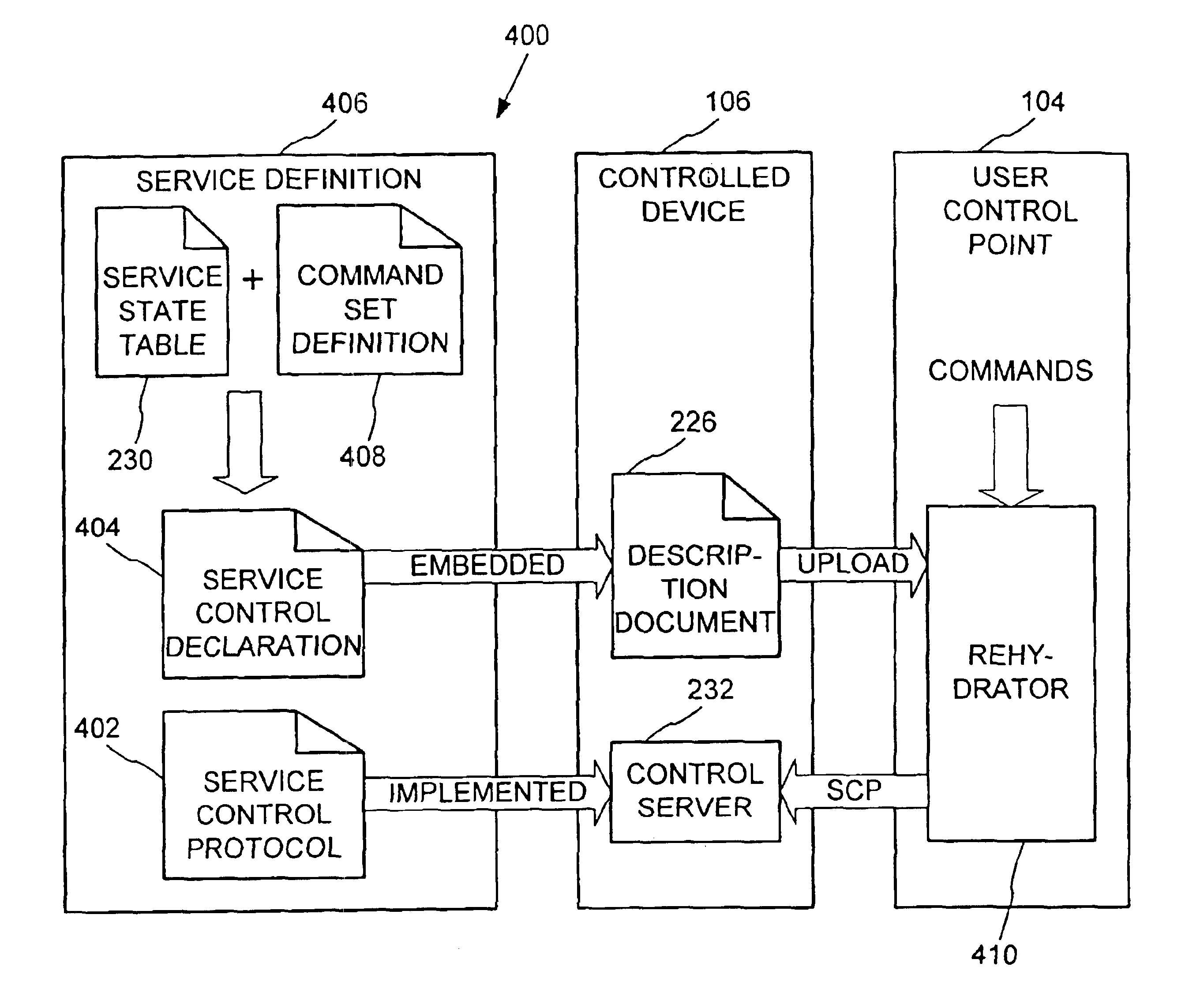

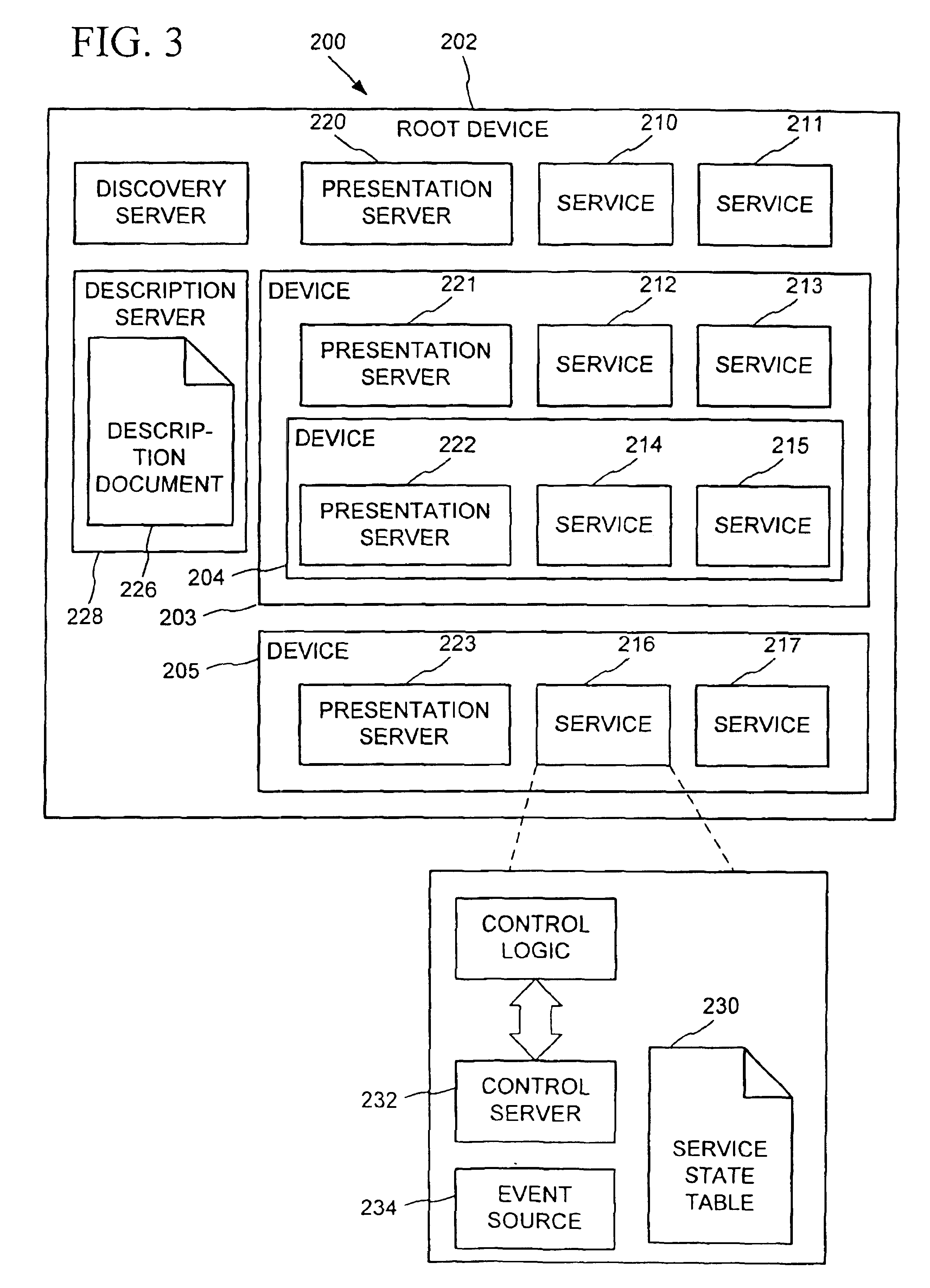

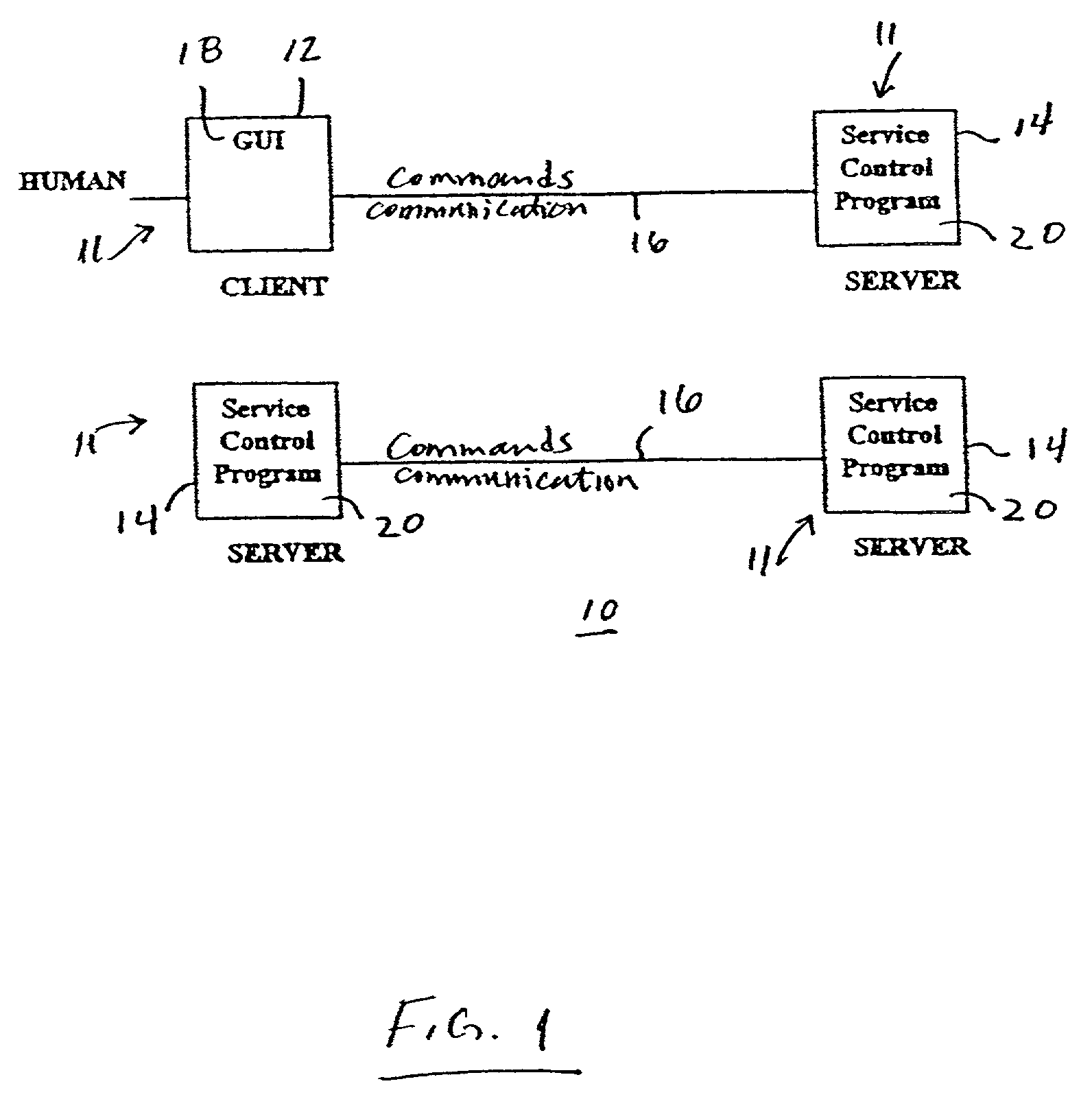

Data driven remote device control model with general programming interface-to-network messaging adapter

InactiveUS7085814B1CostConnectivity solutionMultiple digital computer combinationsNetworks interconnectionService protocolData description

A general programmatic interface-to-network messaging adapter exposes a suitable object integration interface or application programming interface to applications on a controller device and sends network data messages to invoke services or query status of a controlled device. The adapter maps application calls to the interface into network data messages according to service protocols of the controlled device. The general adapter provides the interface suitable to any specific service of a controlled device based on a data description of the interface, and converts the application calls to network data messages based on a data description of a protocol and format for network data messages to interact with the specific service. Once the interface / messaging description is obtained, applications on the controller device can programmatically interact with the adapter, and the adapter then handles appropriate message exchanges with the service of the controlled device. The general adapter allows controller device applications to be written using object-oriented programming, while avoiding code download.

Owner:ROVI TECH CORP

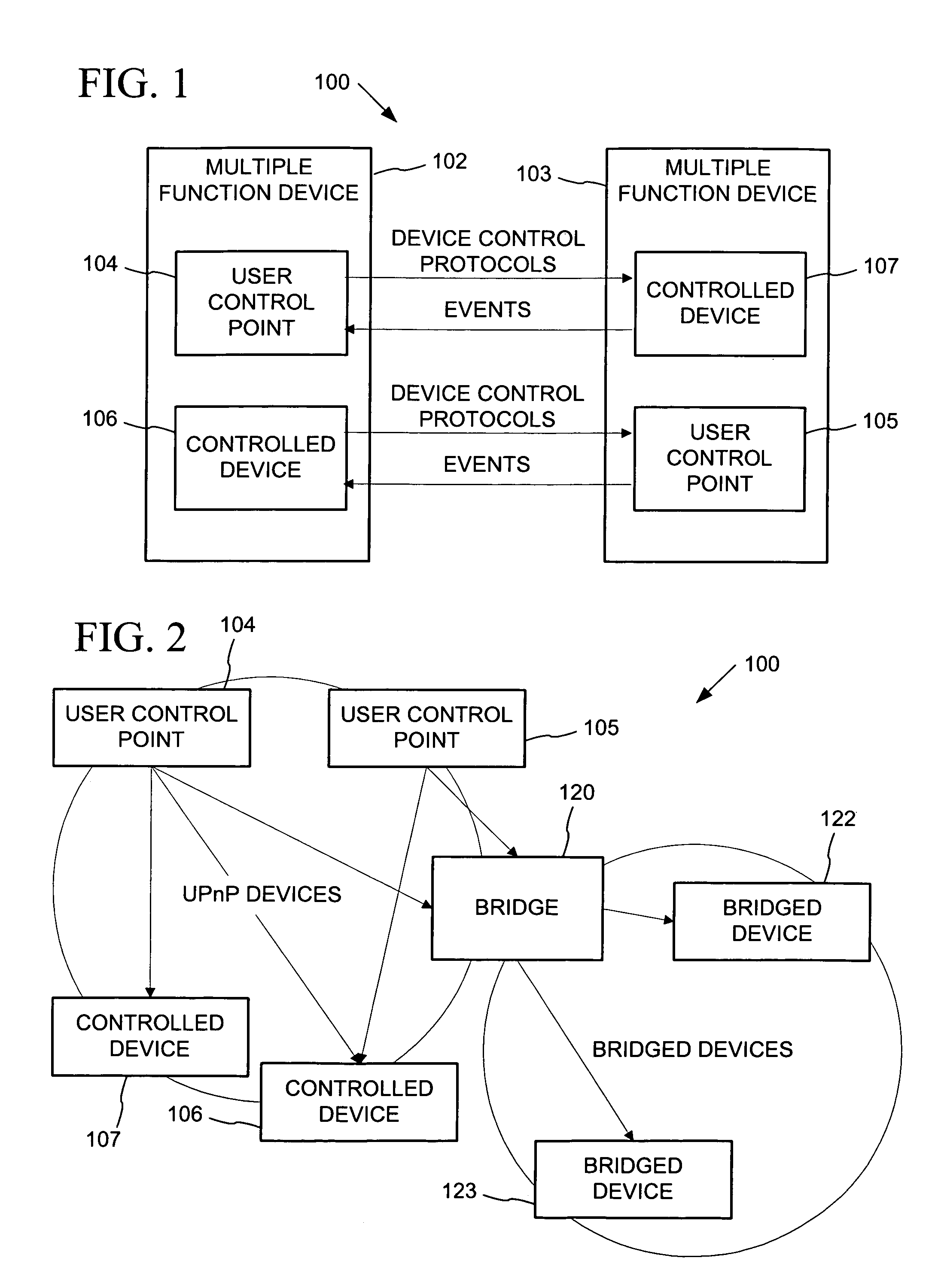

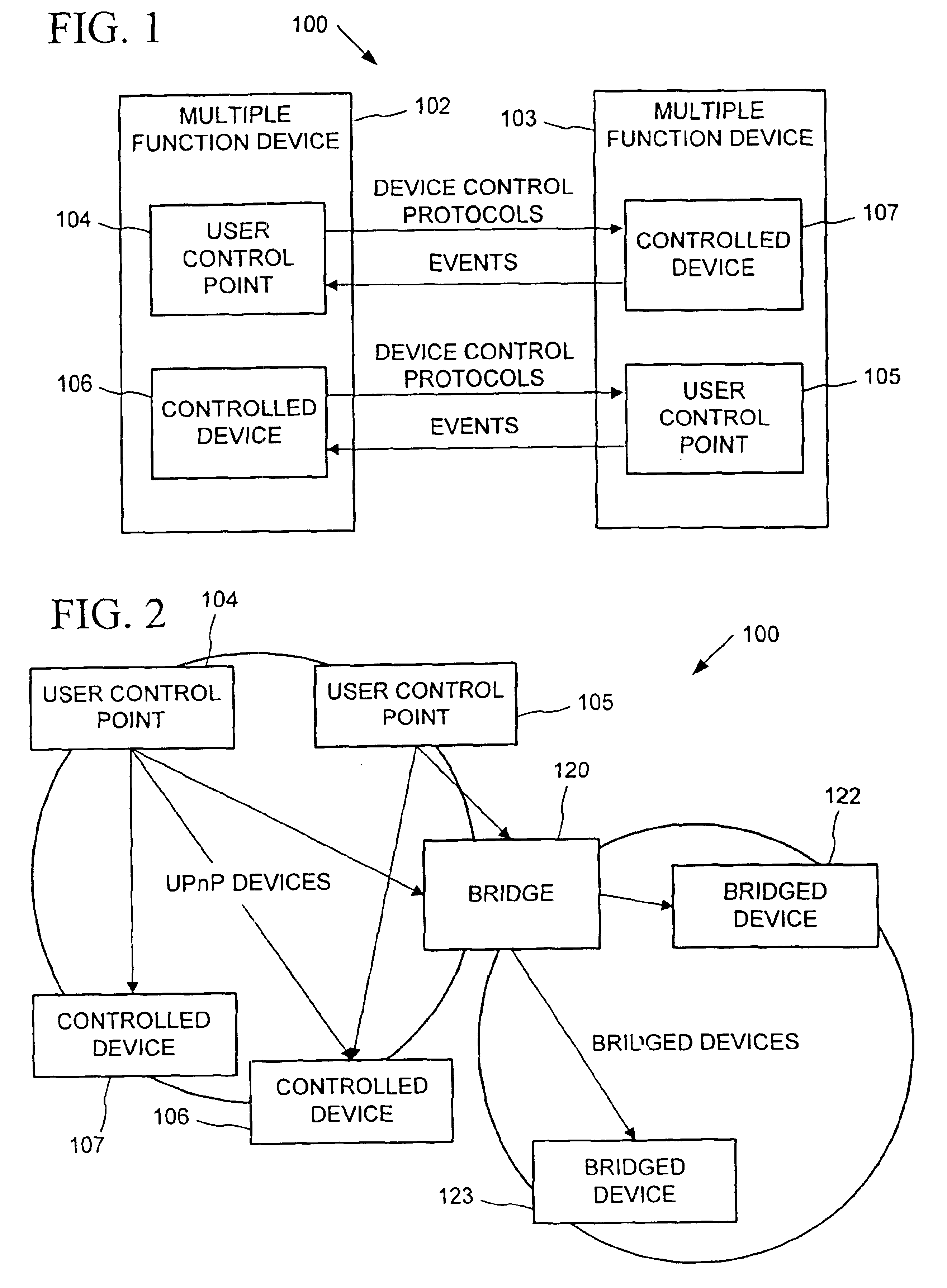

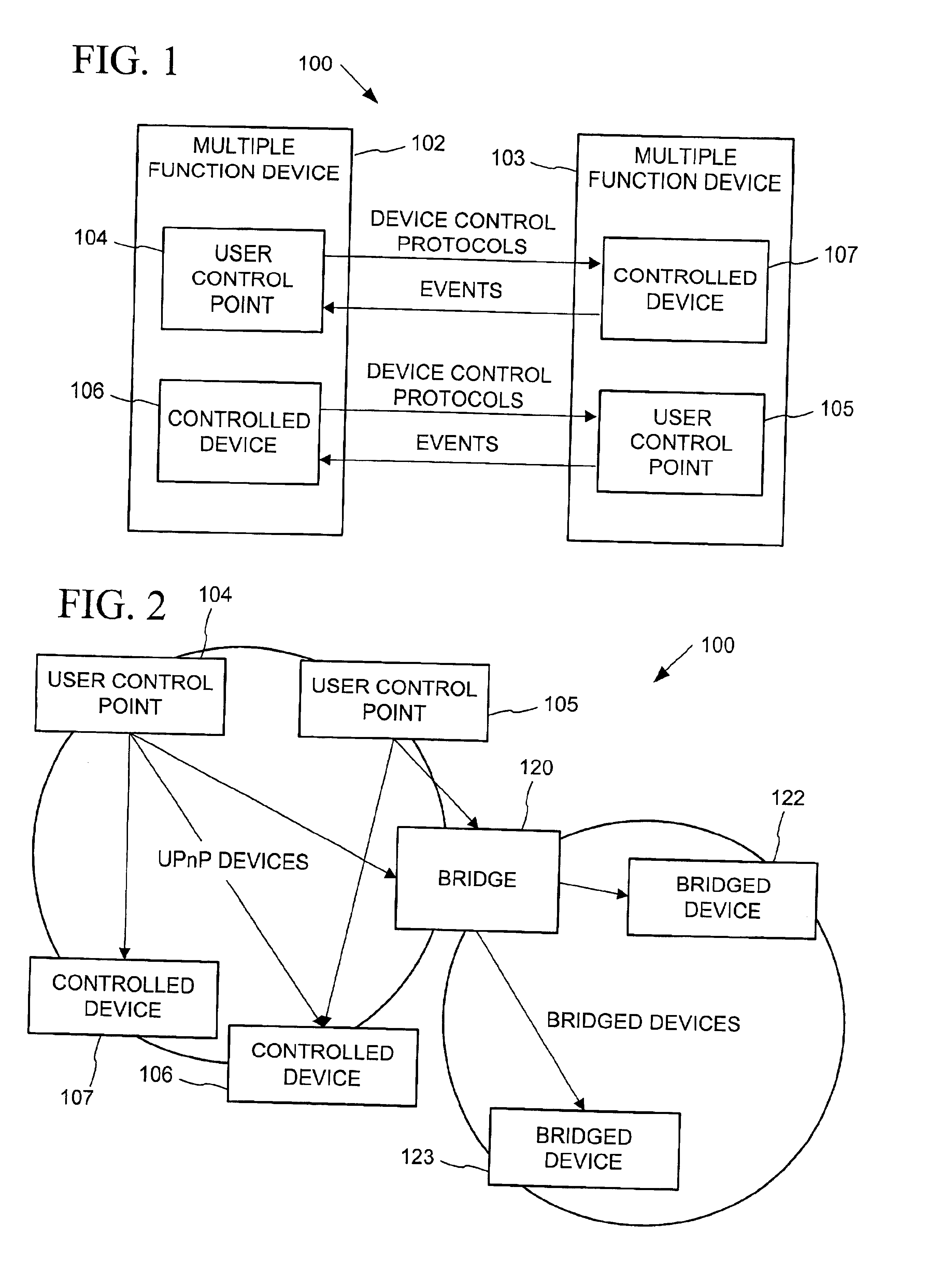

Dynamic self-configuration for ad hoc peer networking using mark-up language formated description messages

InactiveUS6892230B1CostConnectivity solutionDigital computer detailsNetworks interconnectionAuto-configurationHuman language

A device control model provides an integrated set of addressing, naming, discovery and description processes that enables automatic, dynamic and ad-hoc self-setup by devices to interoperate with other devices on a network. This permits a computing device when introduced into a network to automatically configure so as to connect and interact with other computing devices available on the network, without a user installation experience and without downloading driver software or persisting a configuration setup for connecting and interacting with such other computing devices. Upon completing interaction with such other devices, the computing device automatically releases the setup for such other devices so as to avoid persistent device configurations that might create a configuration maintenance and management burden.

Owner:ROVI TECH CORP

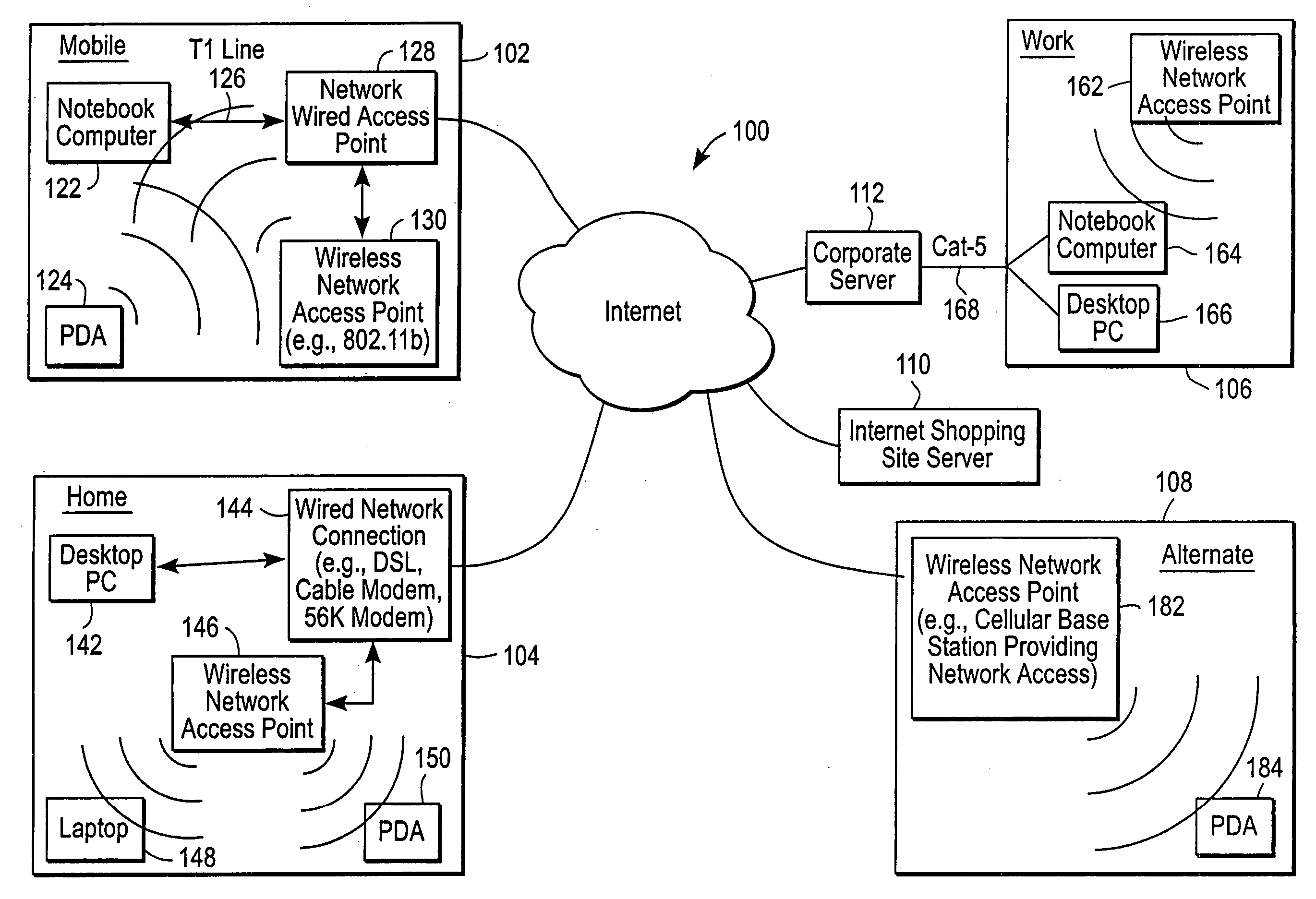

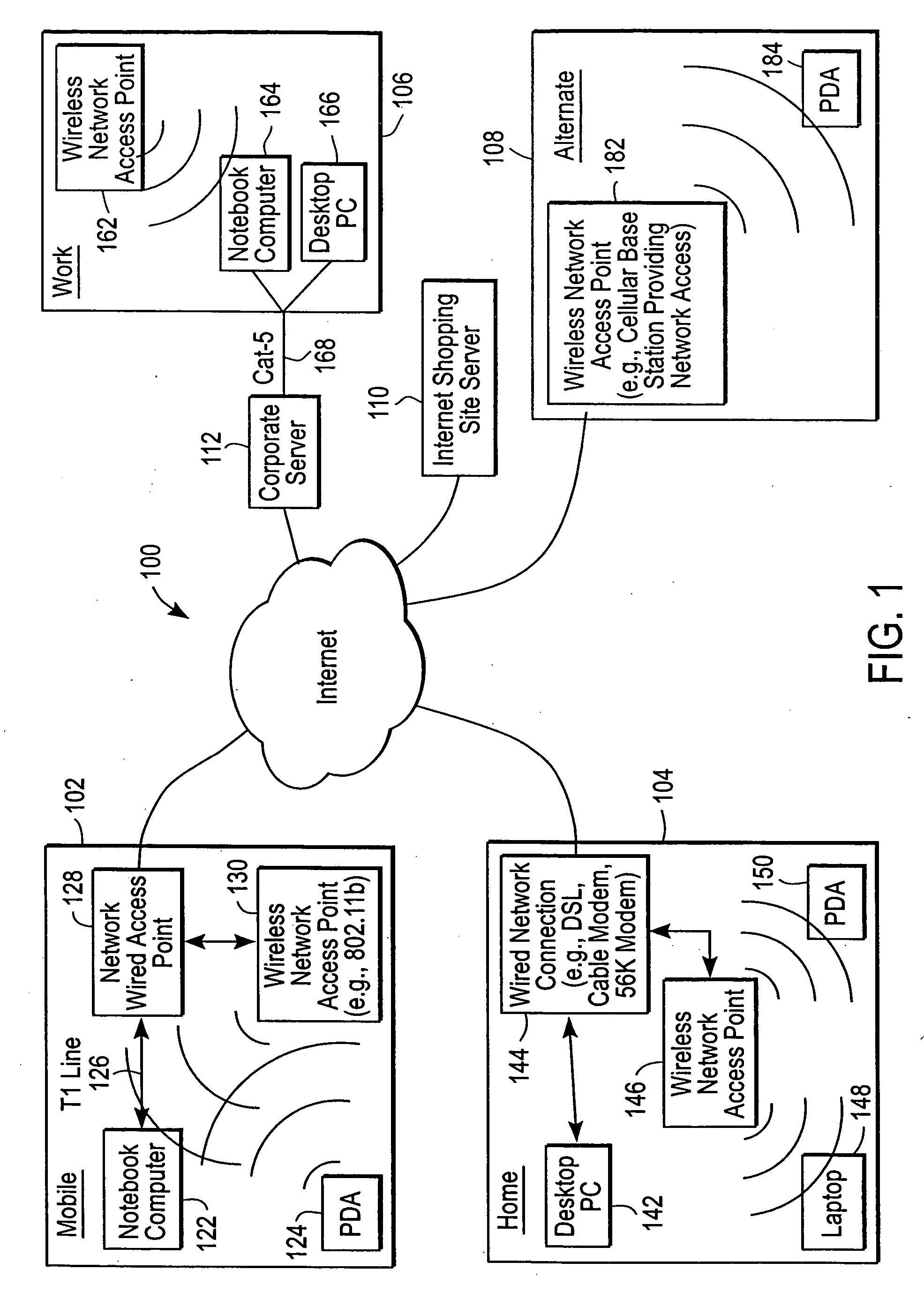

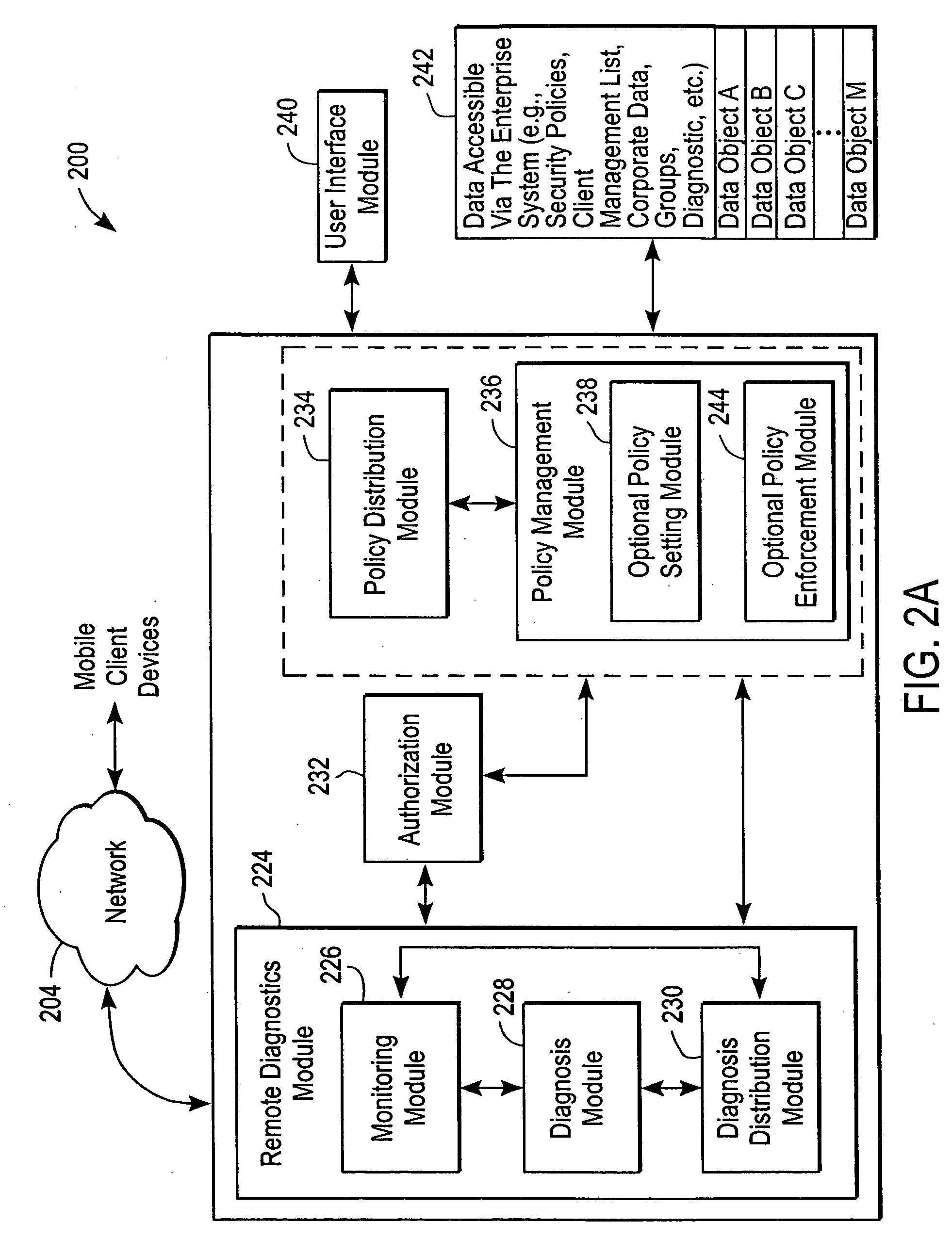

Administration of protection of data accessible by a mobile device

ActiveUS20050055578A1Digital data processing detailsMultiple digital computer combinationsAnti virusEnterprise networking

The protection of data on a client mobile computing device by a server computer system such as within an enterprise network or on a separate mobile computing device is described. Security tools are described that provide different security policies to be enforced based on a location associated with a network environment in which a mobile device is operating. Methods for detecting the location of the mobile device are described. Additionally, the security tools may also provide for enforcing different policies based on security features. Examples of security features include the type of connection, wired or wireless, over which data is being transferred, the operation of anti-virus software, or the type of network adapter card. The different security policies provide enforcement mechanisms that may be tailored based upon the detected location and / or active security features associated with the mobile device. Examples of enforcement mechanisms are adaptive port blocking, file hiding and file encryption.

Owner:APPLE INC

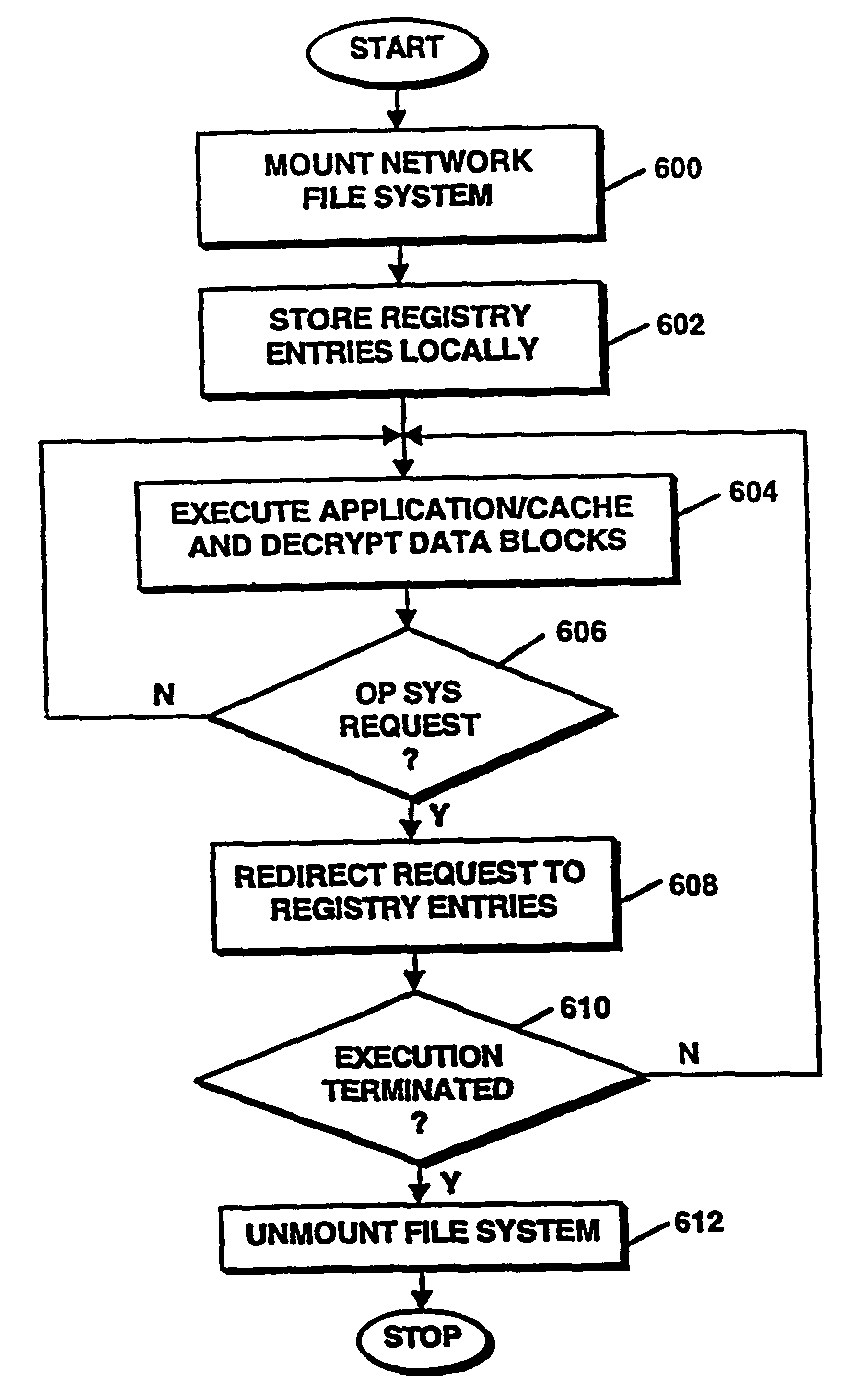

Method and apparatus for installation abstraction in a secure content delivery system

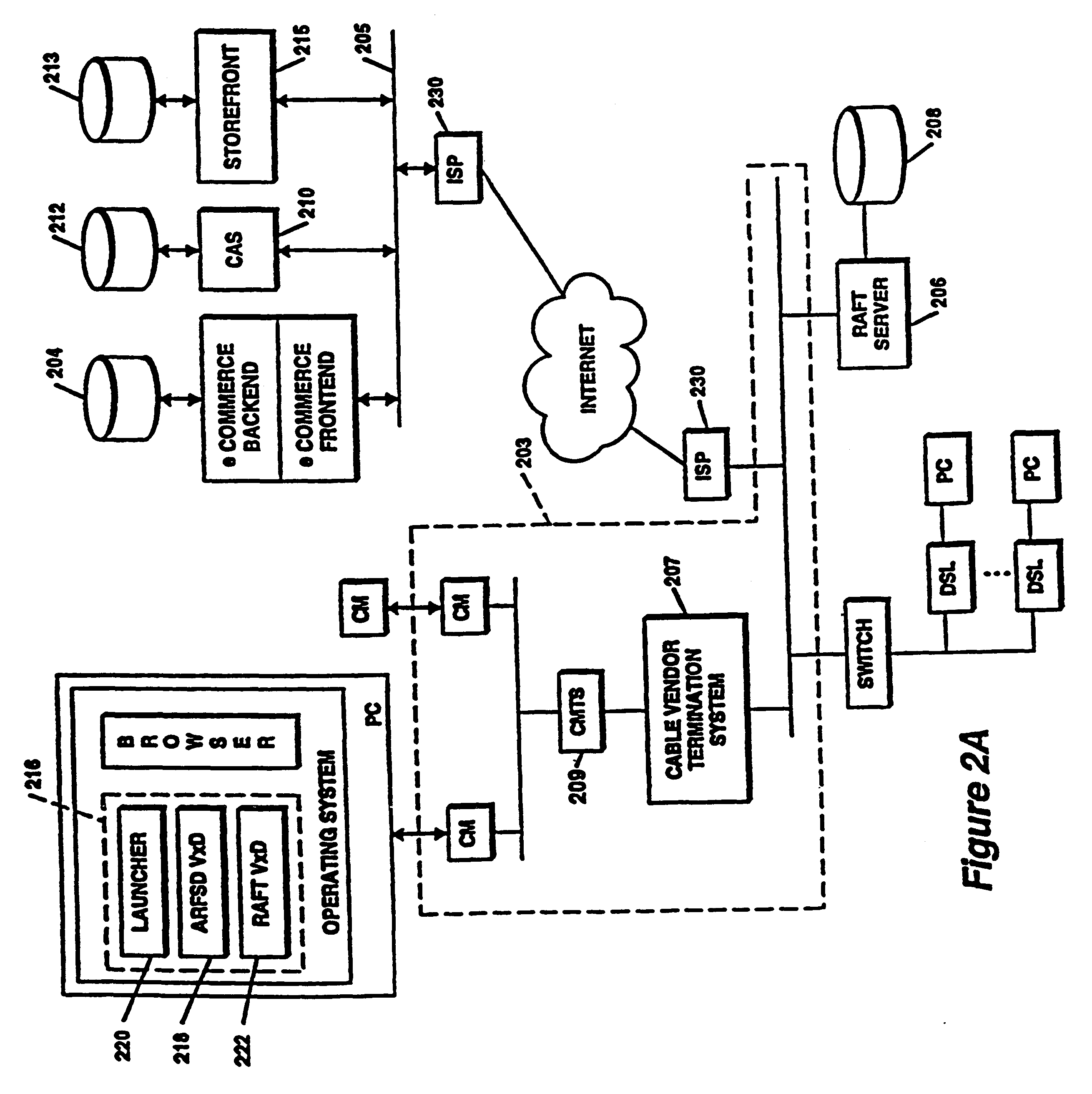

InactiveUS6374402B1Expand accessAvoid leverageTelevision system detailsBroadband local area networksOperational systemNetwork addressing

A system for secure delivery of on-demand content over broadband access networks includes a client application executing on a user's local computer system. The client application interacts with a content server on which a plurality of selectable titles are stored and further interacts with an access server which provides the network address of a title and keying data necessary for to the client process access and execute the title. The client process utilizes an installation abstraction which enables a title to be executed on the local computer system without ever being installed. The abstraction is achieved by mounting a network file system and storing a set of registry entries related to the title on the local computer system. Portions of the title are retrieved from the content server and executed by the local operating system. During title execution, requests from the local operating system are intercepted and redirected to the set of registry entries, as applicable. The times at which the client process may retrieve the title data from the content server are defined by the access server through use of an activator and token.

Owner:MICROSOFT TECH LICENSING LLC

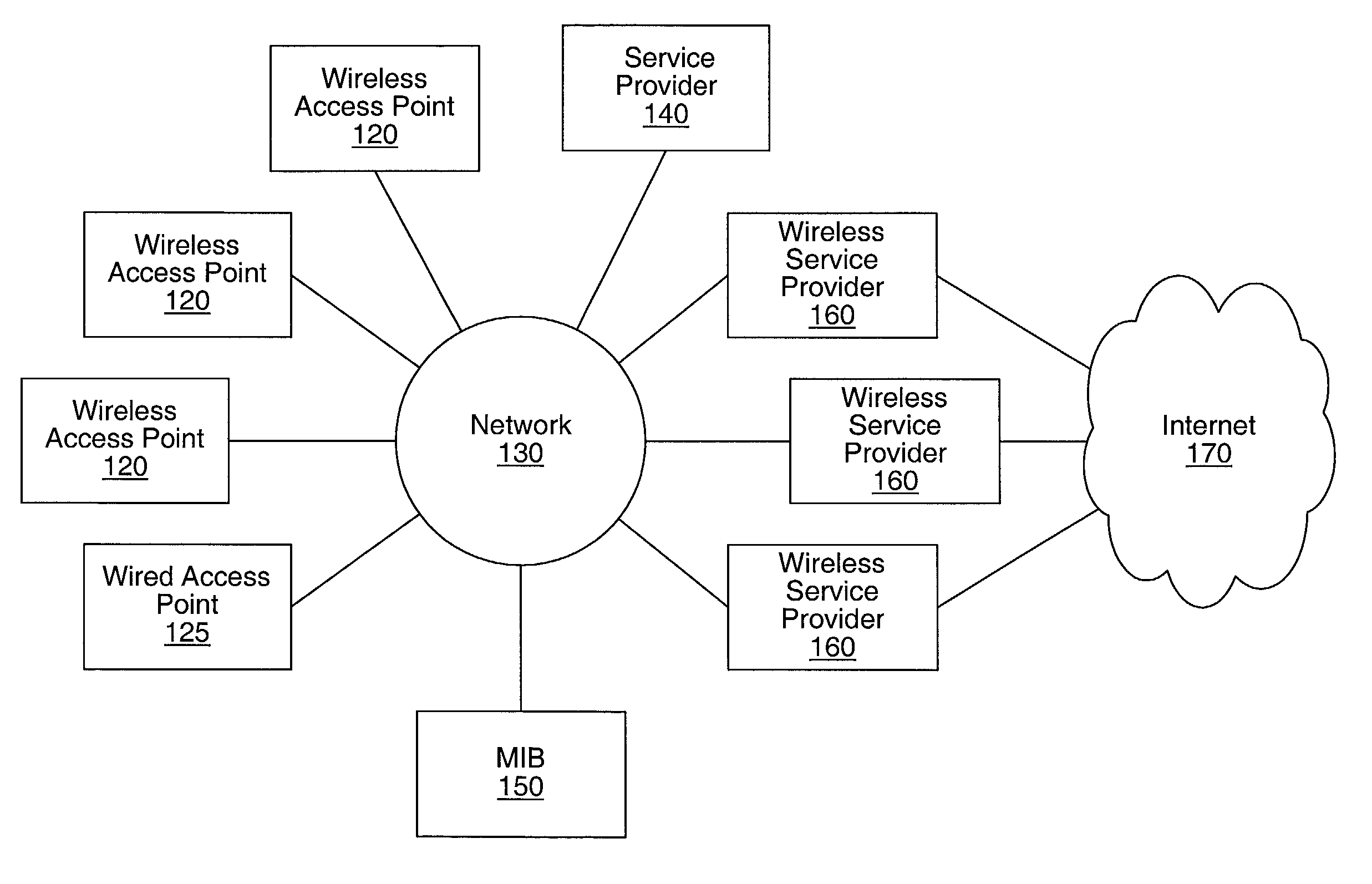

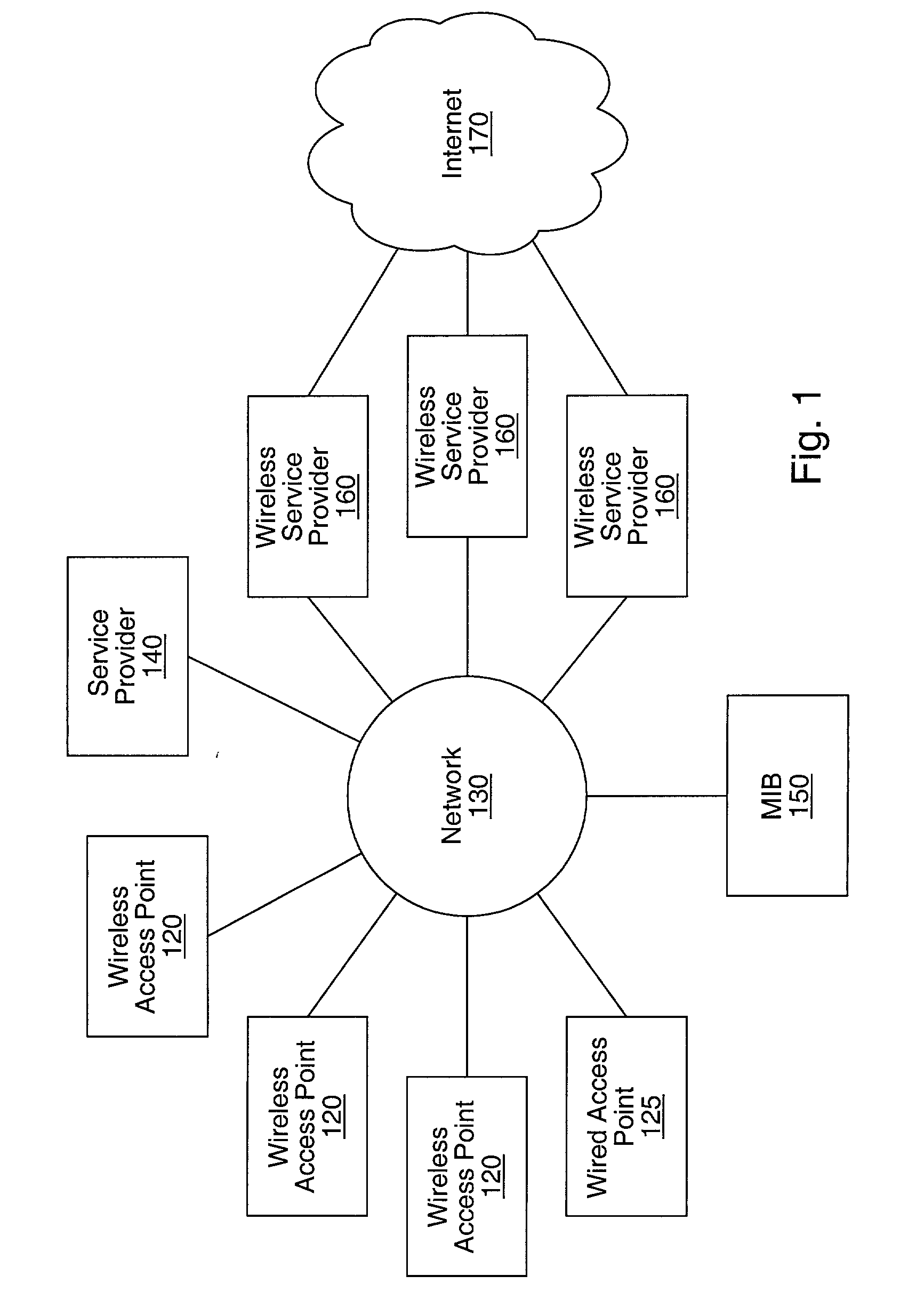

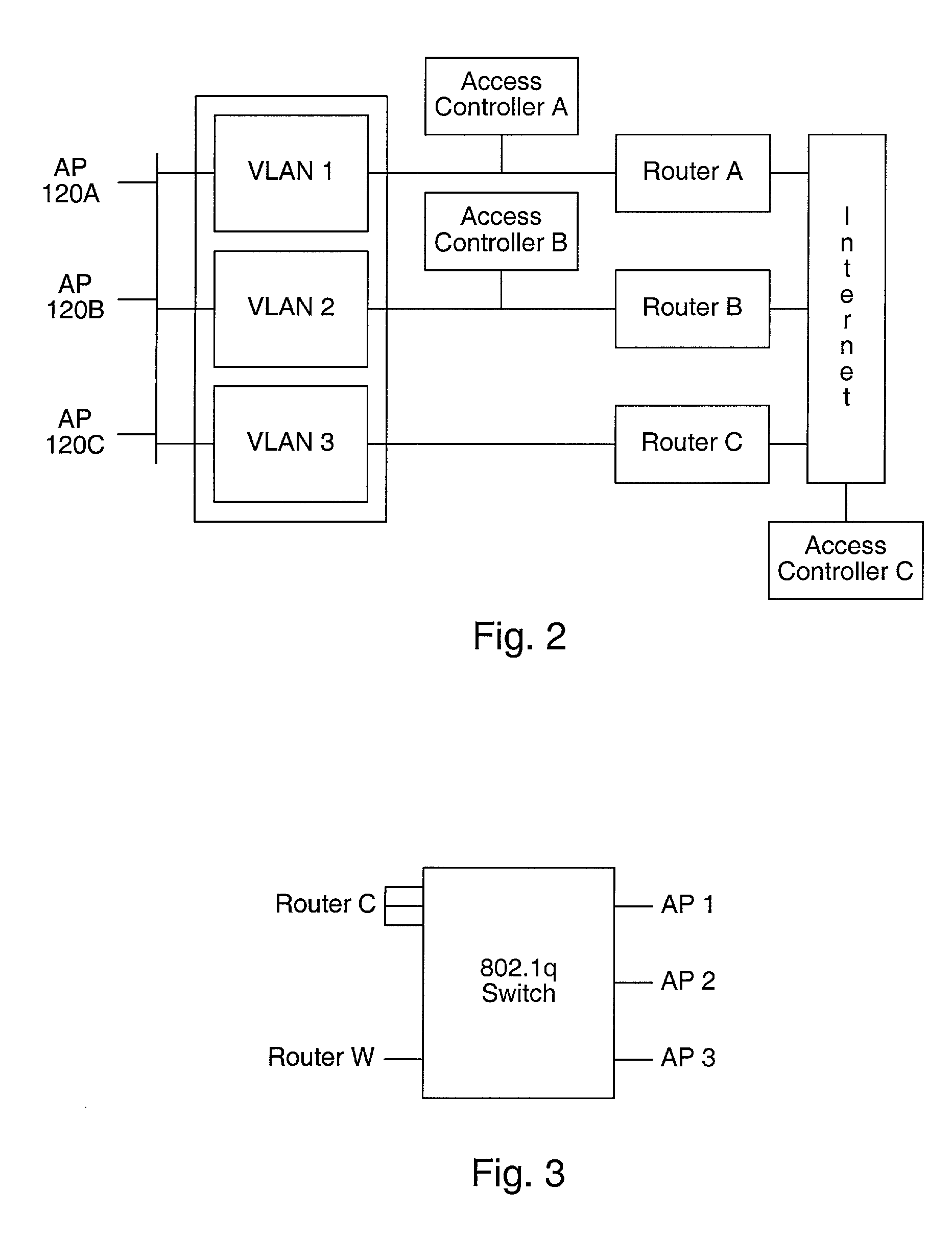

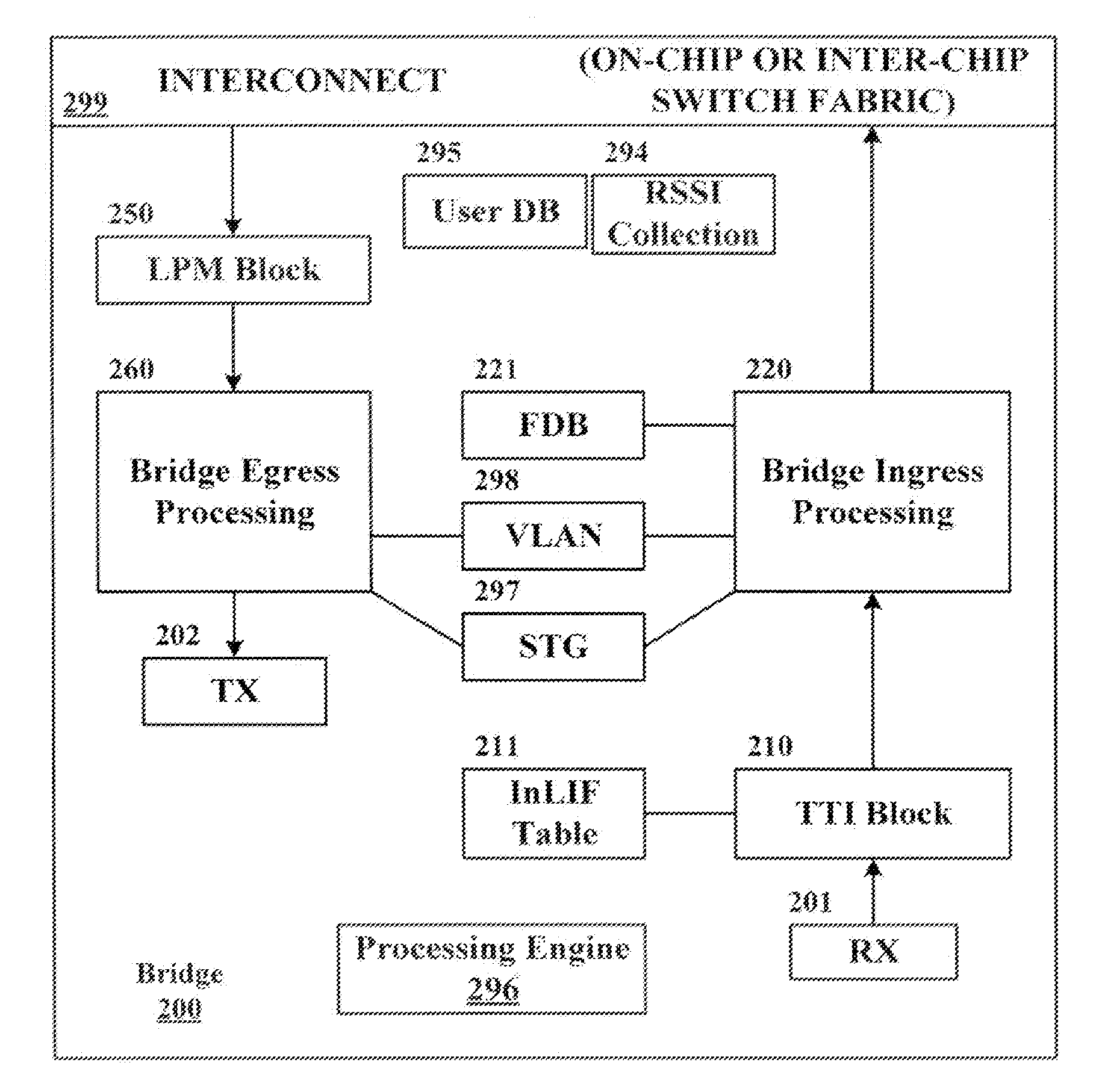

Distributed network communication system which allows multiple wireless service providers to share a common network infrastructure

System and method for providing access to multiple wireless service providers (WSPs) on a shared network infrastructure. The system includes a plurality of access points (APs) coupled to a network which may be distributed in airports, mass-transit stations, businesses, etc. The network may couple to a wide area network, such as the Internet. Each AP may include a plurality of virtual APs (VAPs), each corresponding to a WSP. A portable computing device (PCD) of a user stores identification information indicating a WSP of a plurality of possible WSPs, and which may include an access level of the user. Each AP "listens for" or detects identification information associated with numerous WSPs. When the AP receives the identification information from the PCD, it determines the VAP / WSP for the PCD using the identification information. Network access is then provided to the PCD through the determined WSP at the determined access level.

Owner:CISCO TECH INC

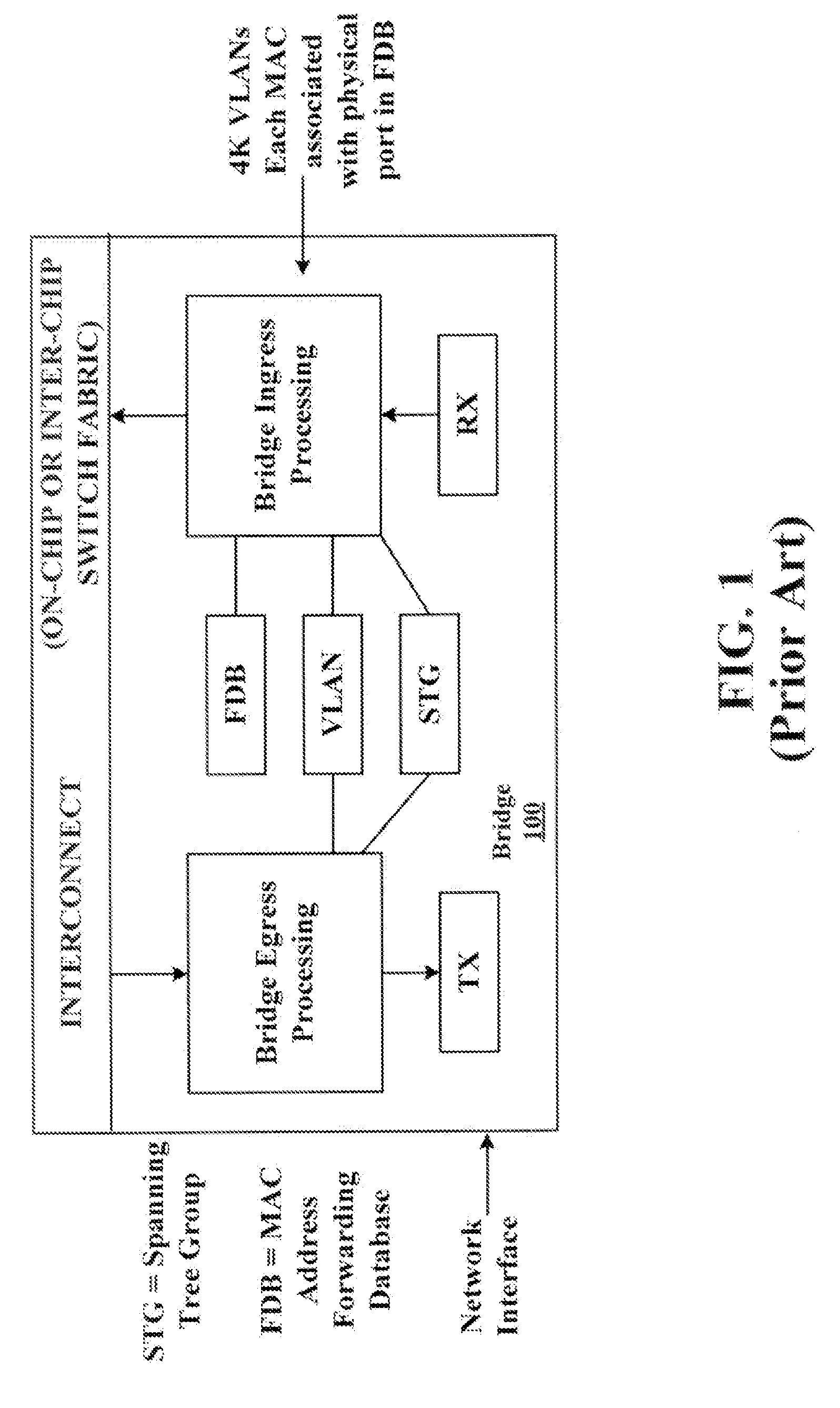

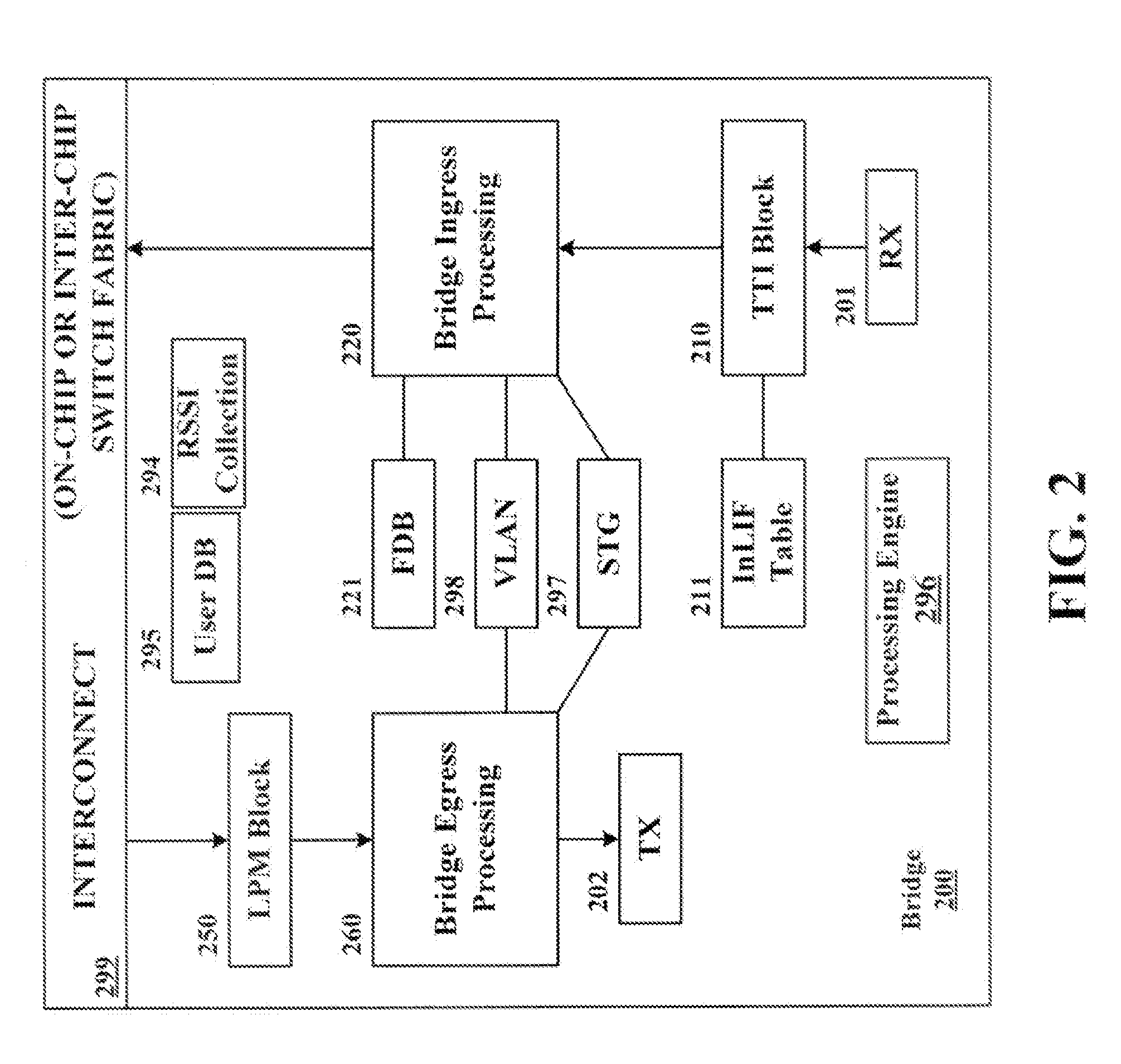

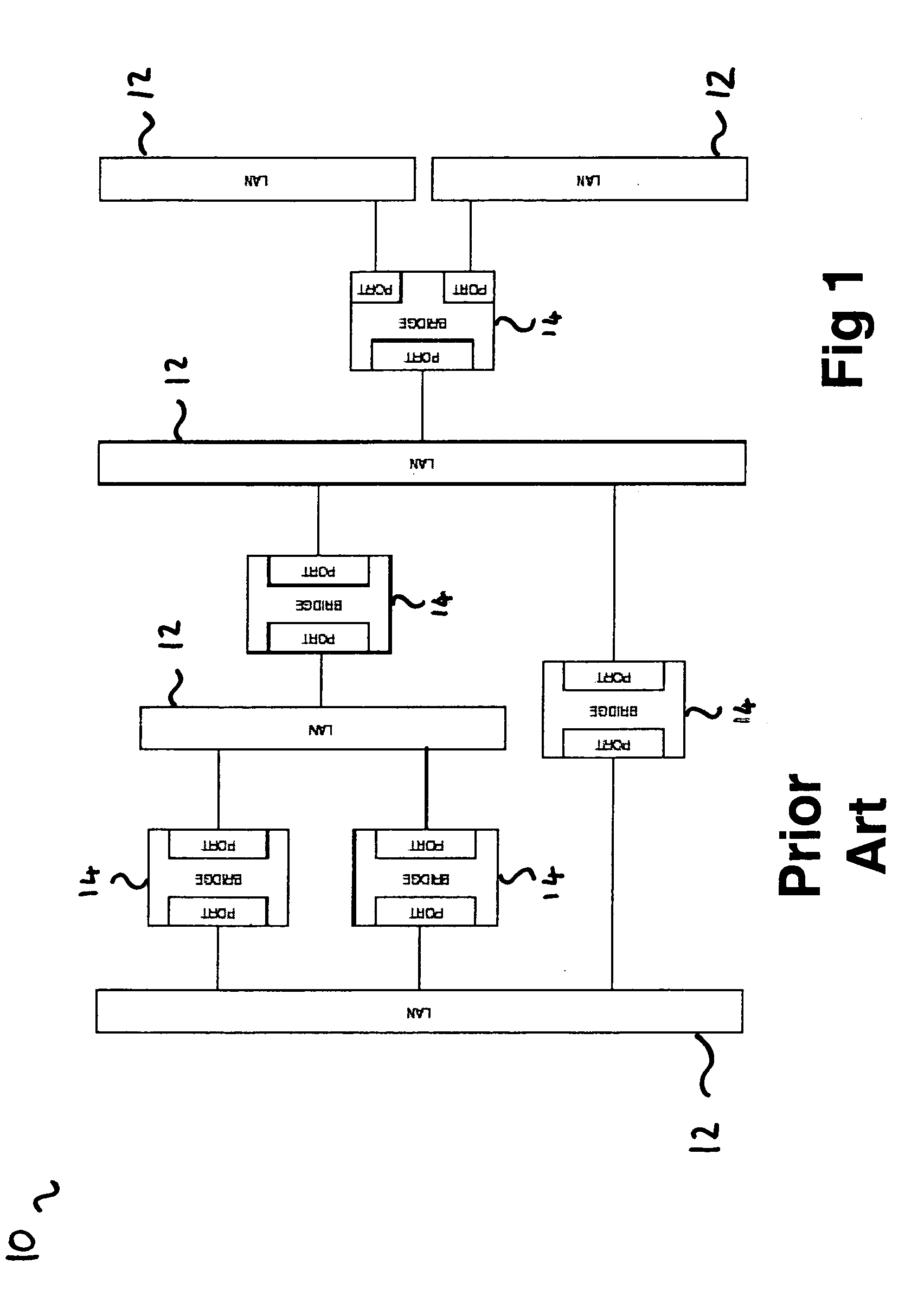

Logical bridging system and method

A system and method of extending a standard bridge to enable execution of logical bridging functionality are disclosed. In some implementations, a logical bridge may assign source logical port information to a data packet based on characteristics of the data packet, employ the source logical port information to learn the source address and to forward the data packet to a logical egress port, and map the logical egress port to a physical egress port at which the data packet is to be egressed. A tunnel interface may optionally be applied to a data packet upon egress.

Owner:MARVELL ISRAEL MISL

Switching system method for discovering and accessing SCSI devices in response to query

InactiveUS7089293B2Simple processRobust systemSpecial service provision for substationMultiplex system selection arrangementsStorage managementComputer engineering

Owner:ORACLE INT CORP

Method and apparatus for performing data flow ingress/egress admission control in a provider network

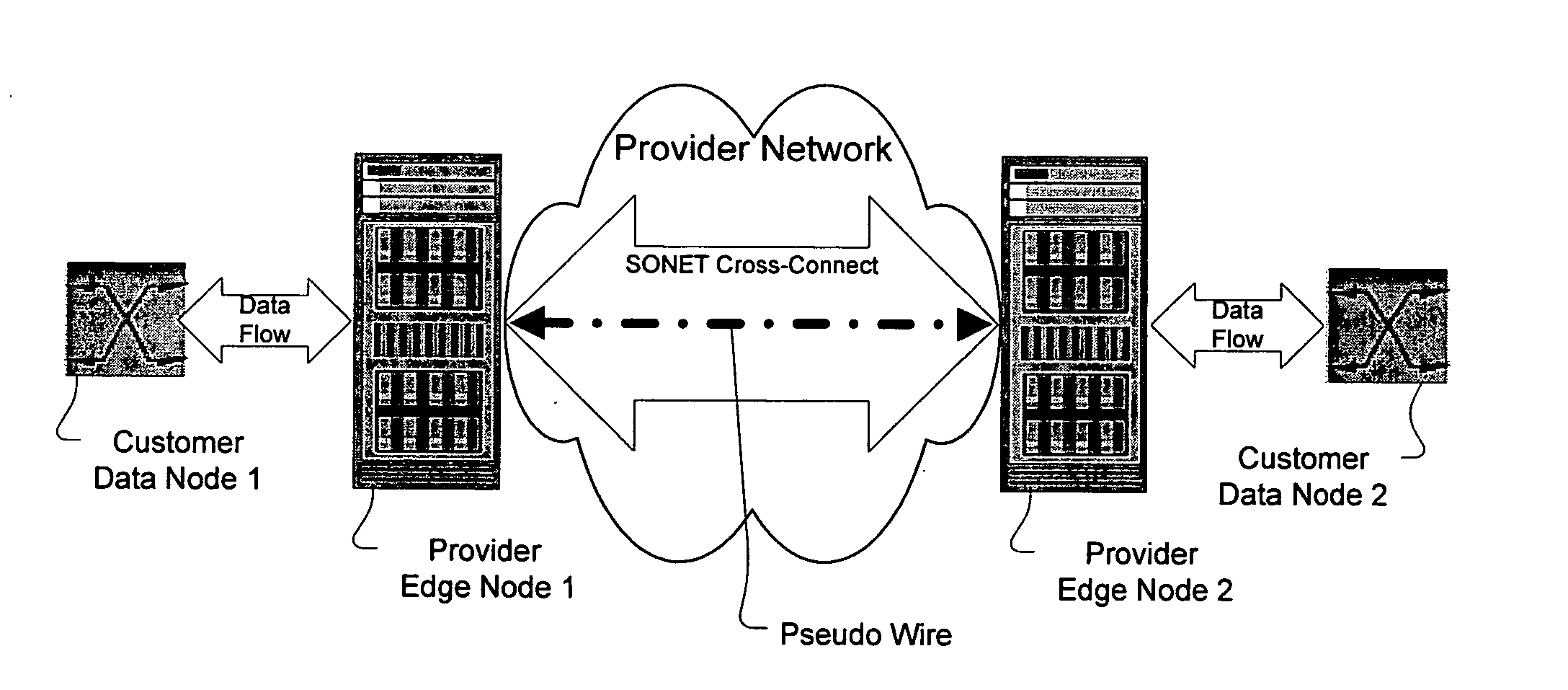

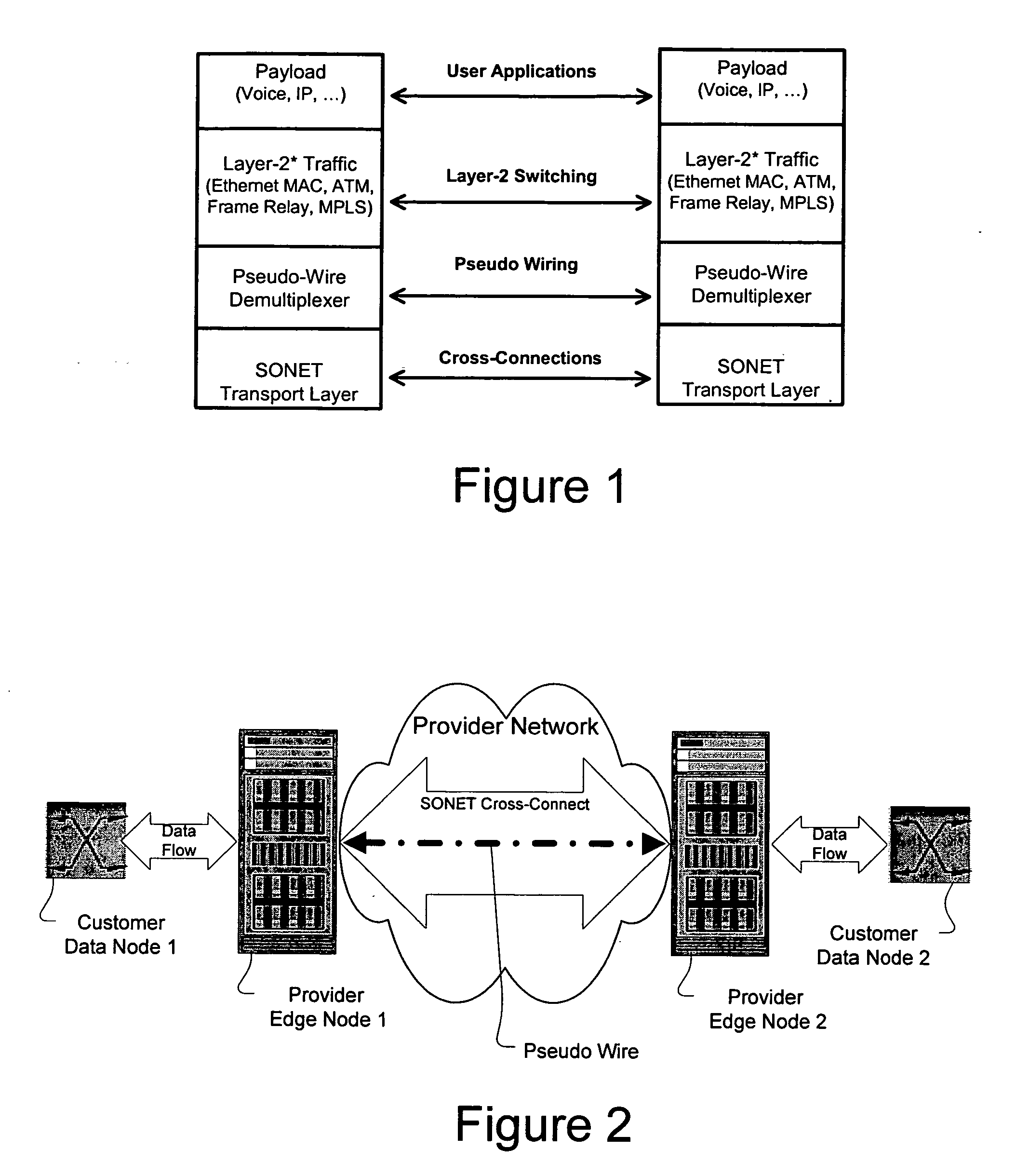

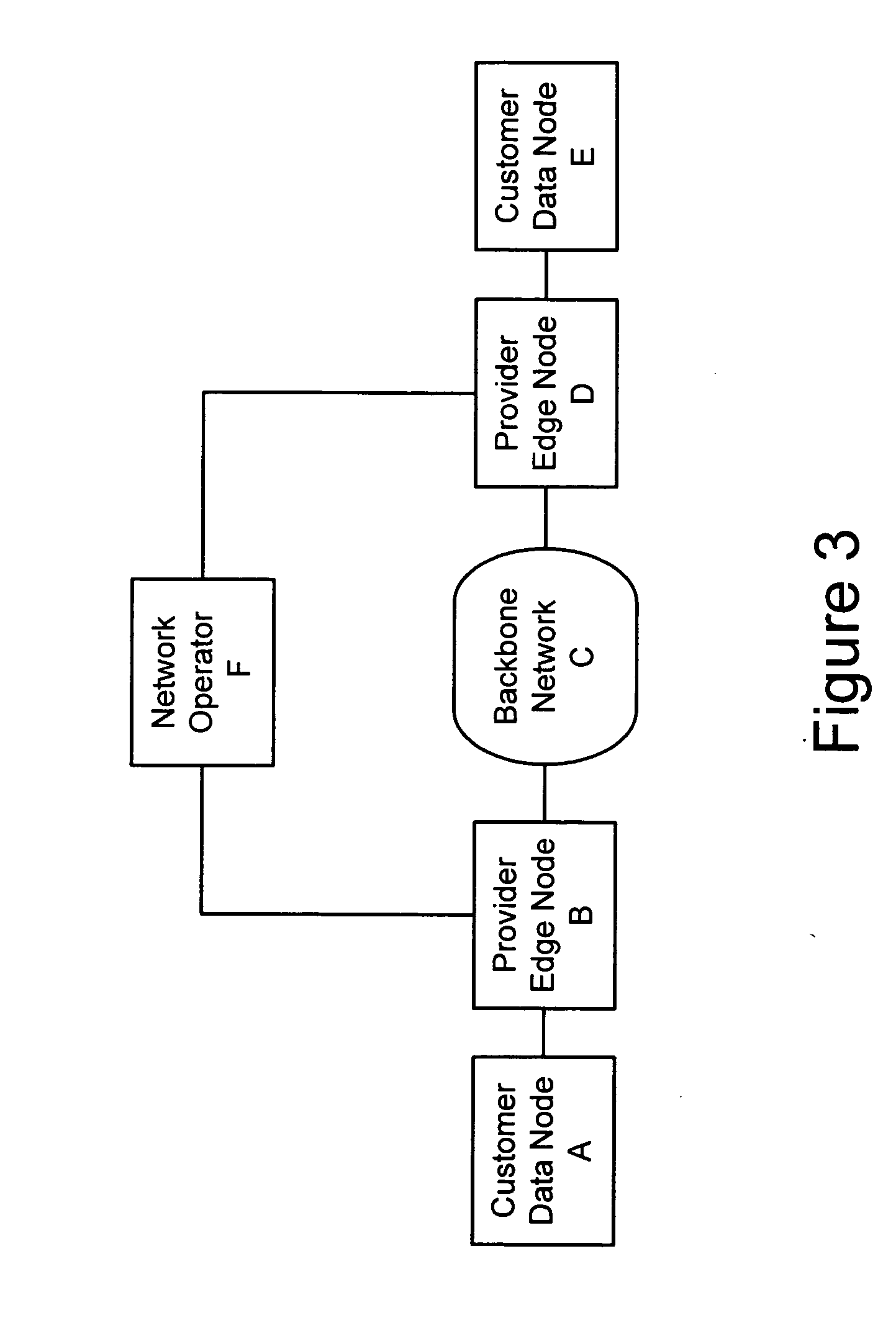

A method, apparatus and network for transporting layer-2 frames, such as Ethernet MAC, ATM AAL5, and Frame Relay, over MPLS, SONET / SDH, or OTN optical transport networks as well as electrical transport networks is disclosed. The method establishes "pseudo-wires" between, for example, routers, Layer-2 packet switches, or SONET / SDH switches. Inter-related ingress and egress resource tables may be used by provider edge nodes to negotiate consistently managed data tunnels across a provider network on behalf of data flowing from / to a diverse base of customer edge nodes. Detailed network resource information particular to each of the data flows is exchanged between provider edge nodes during the creation of pseudo-wires. Admission control algorithms are applied at the ingress and egress points in order to manage the data flows into a provider network and exiting from a provider network to customer equipment. By applying pseudo-wire shuffling and preemption techniques, the providers can make better use of their network resources by admitting more pseudo-wires.

Owner:CIENA

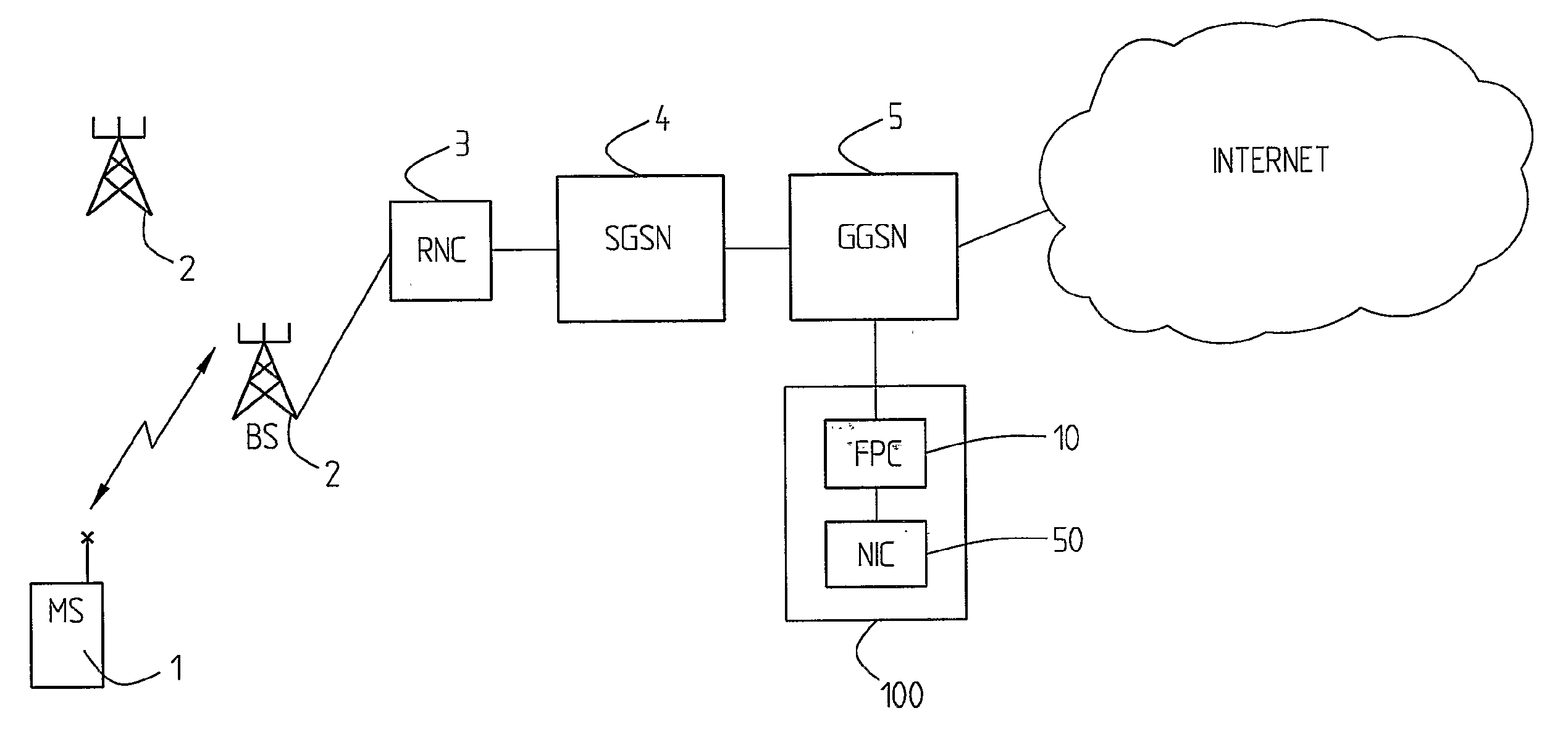

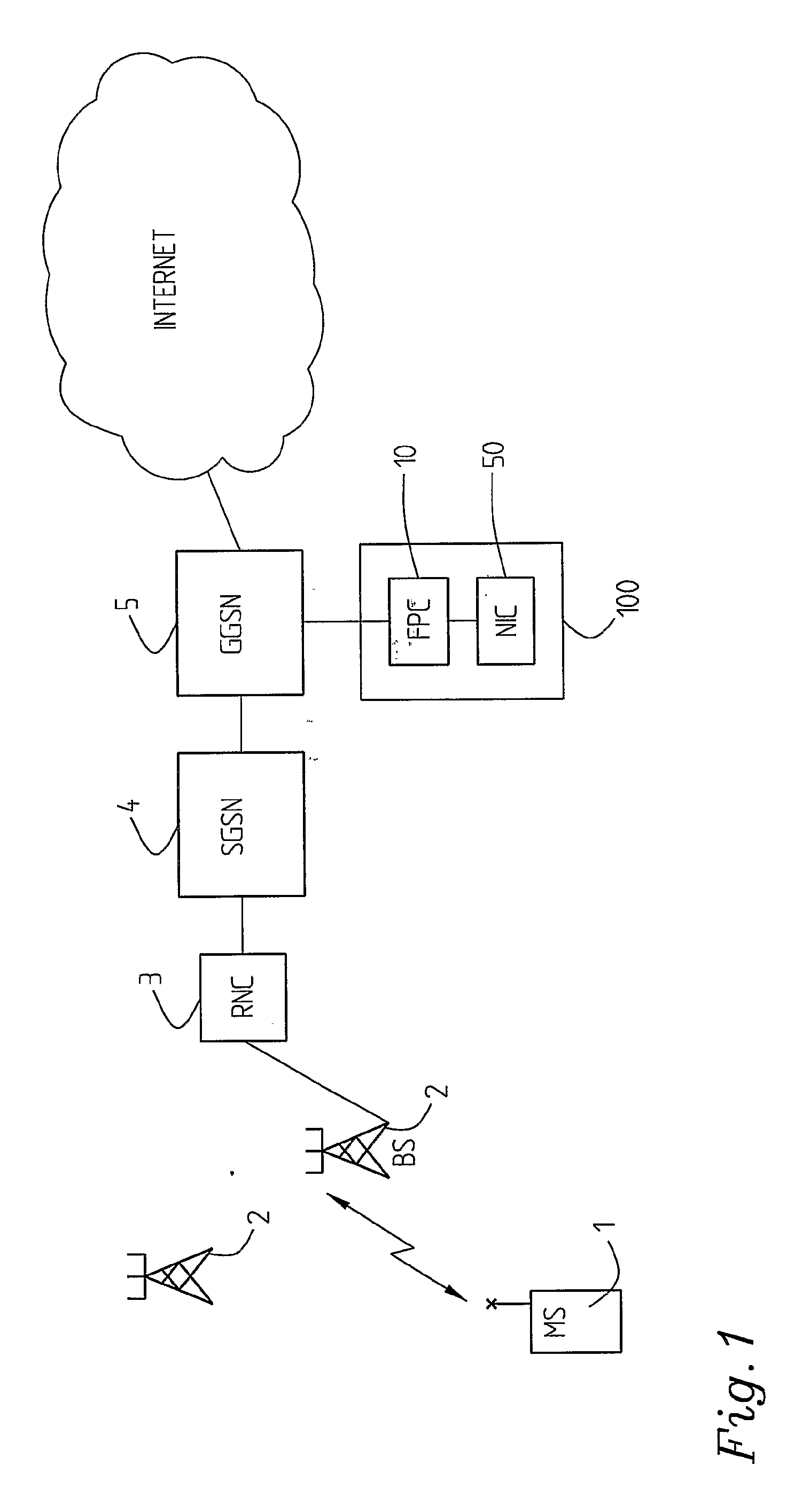

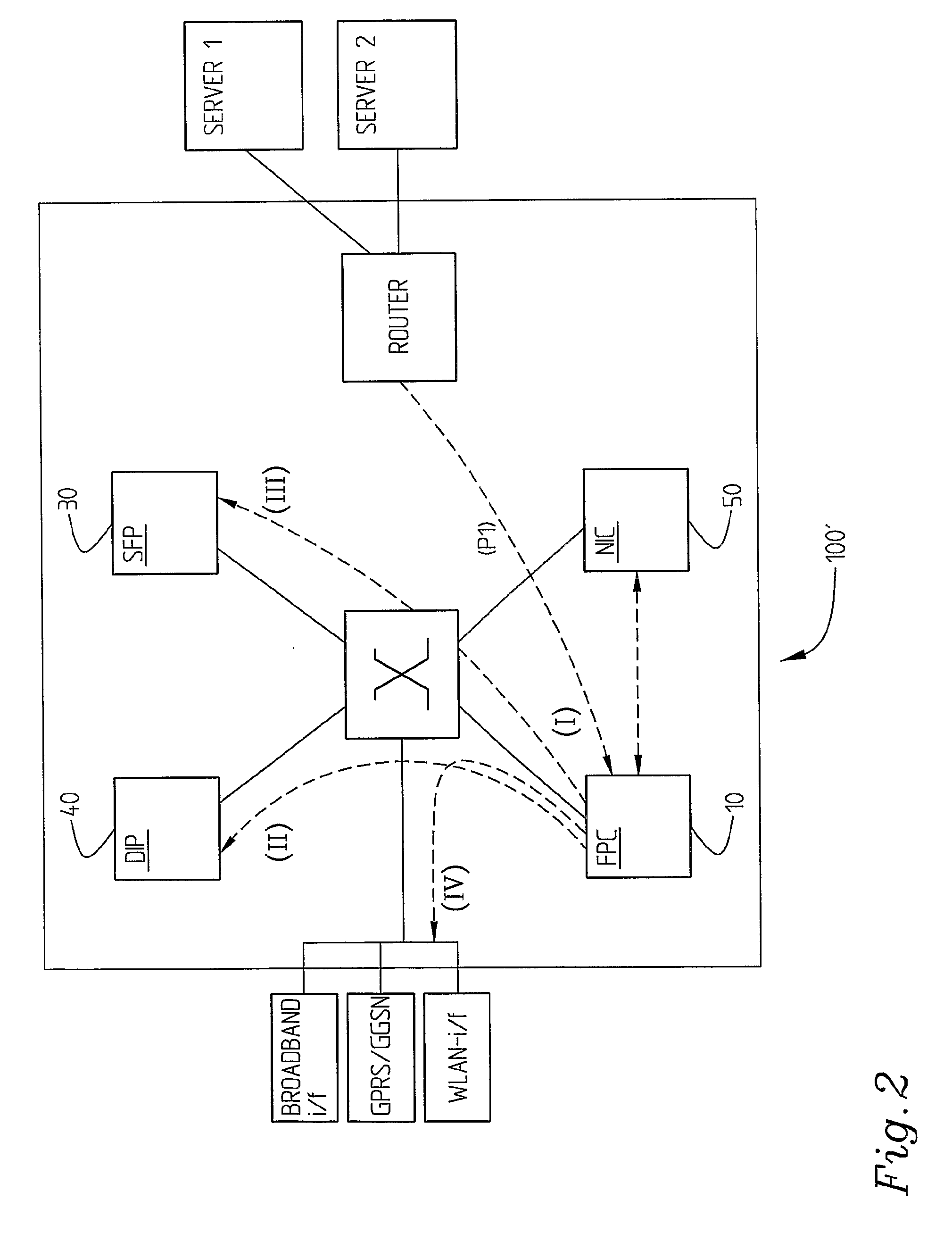

Arrangement and a Method Relating to Flow of Packets in Communication Systems

ActiveUS20080002579A1Precise maintenanceError preventionTransmission systemsProper functionProcessing core

An arrangement, system, and method for switching data packet flows in a communication system. A flow processing core classifies packet flows and defines processing flow sequences applicable to the packet flows. A distributing arrangement directs the packet flows to appropriate functional units or processors according to each packet flow's applicable processing flow sequence. The current position of each packet flow in its respective processing flow sequence is indicated. Packet flow sequence information may be determined so that reclassification of already classified packets is avoided.

Owner:TELEFON AB LM ERICSSON (PUBL)

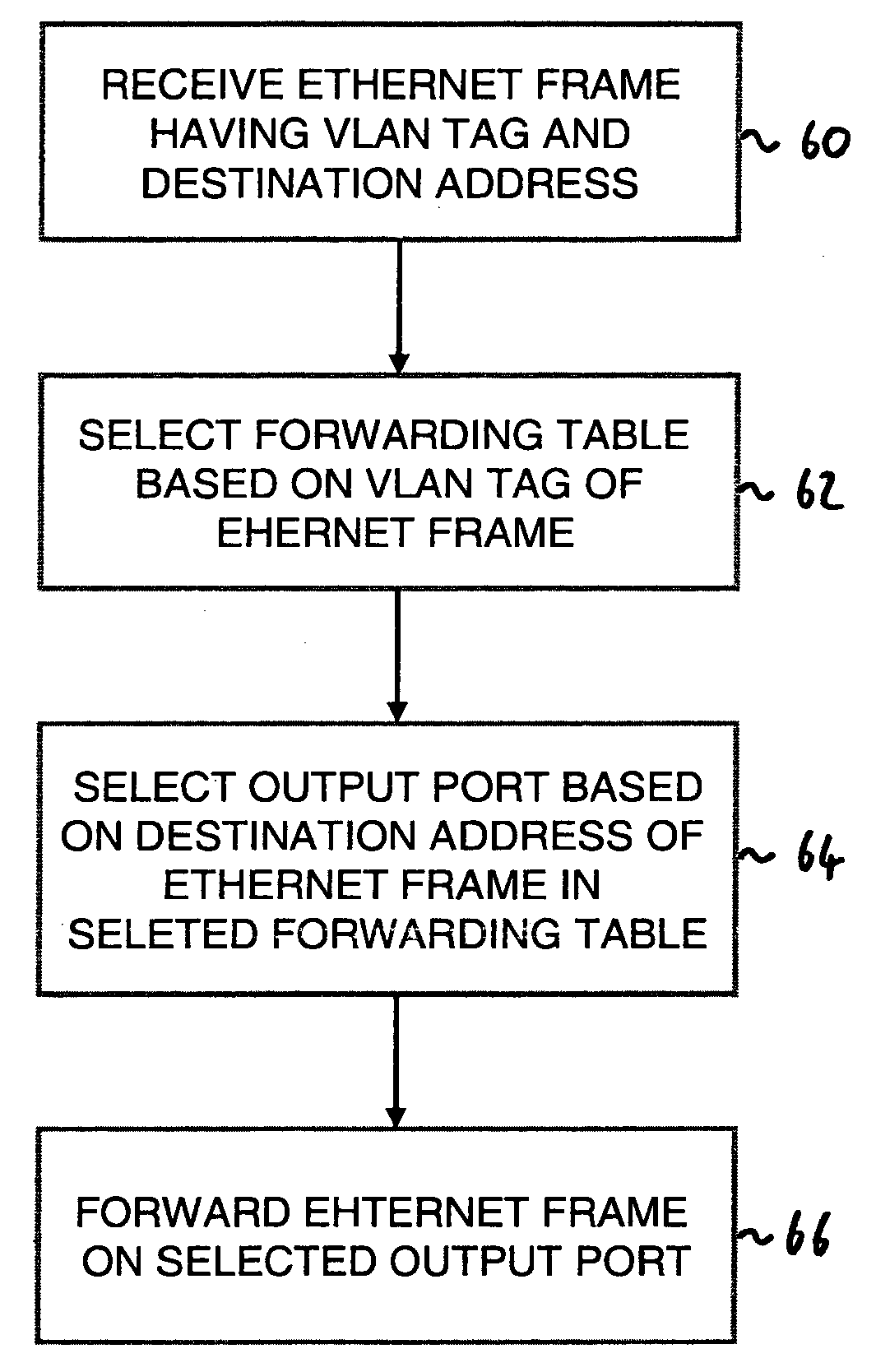

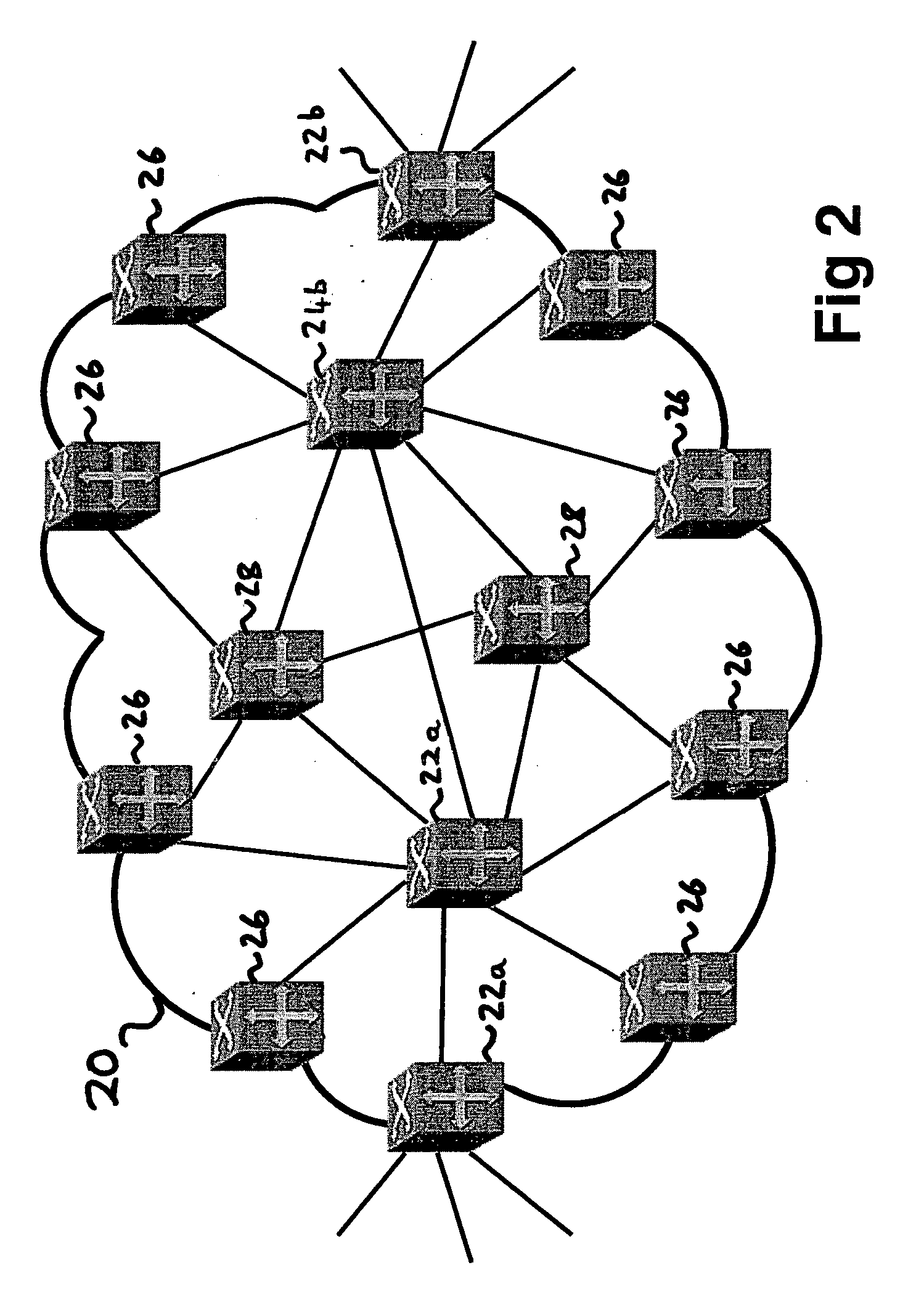

Traffic engineering in frame-based carrier networks

InactiveUS20050220096A1Flexibility connections-egStore-and-forward switching systemsNetworks interconnectionFrame basedEthernet frame

The invention relates to enabling traffic engineering in frame-based networks such as Ethernet networks. There is described a method of and connection controller for establishing connections (76, 77) in a frame-based communications network comprising nodes (71-75 and 78) such as Ethernet switches. The connections are established by configuring, in various of the nodes, mappings for forwarding data frames, such as Ethernet frames. The mappings are from a combination of a) a destination address corresponding to a destination node (73) of the connection and b) an identifier, such as a VLAN tag. The mappings are to selected output ports of the various nodes. By using the combination of destination address AND identifier, the mappings enable data frames belonging to different connections (76, 77) to be forwarded differentially (ie forwarded on different output ports) at a node (75) despite the different connections having the same destination node. This enables flexibility in routing connections—ie the ability to perform traffic engineering.

Owner:RPX CLEARINGHOUSE

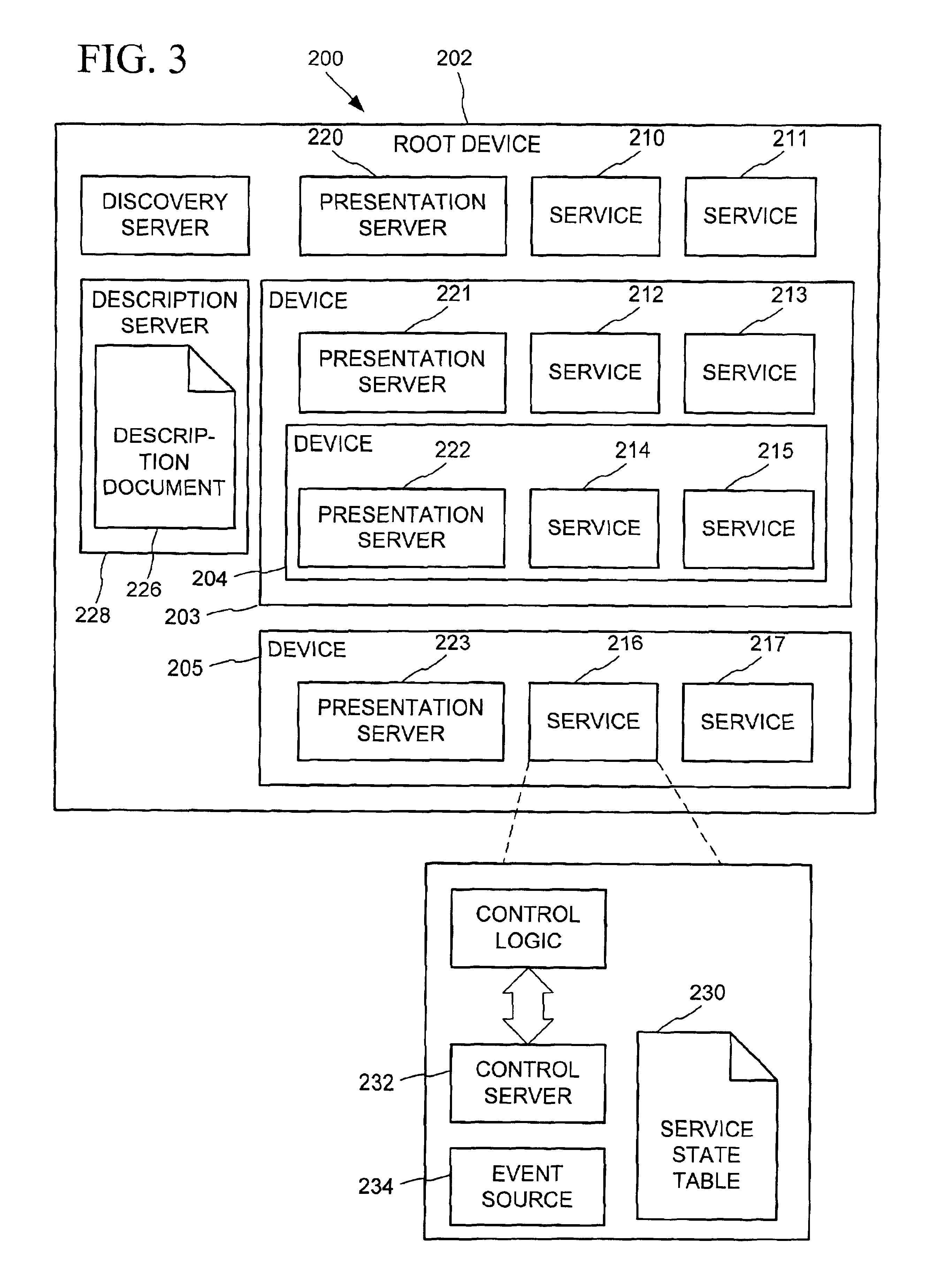

XML-based template language for devices and services

InactiveUS6910068B2CostConnectivity solutionMultiple digital computer combinationsNetworks interconnectionWeb siteProgramming language

A universal plug and play (UPnP) device makes itself known through a set of processes-discovery, description, control, eventing, and presentation. Following discovery of a UPnP device, an entity can learn more about the device and its capabilities by retrieving the device's description. The description includes vendor-specific manufacturer information like the model name and number, serial number, manufacturer name, URLs to vendor-specific Web sites, etc. The description also includes a list of any embedded devices or services, as well as URLs for control, eventing, and presentation. The description is written by a vendor, and is usually based on a device template produced by a UPnP forum working committee. The template is derived from a template language that is used to define elements to describe the device and any services supported by the device. The template language is written using an XML-based syntax that organizes and structures the elements.

Owner:ROVI TECH CORP

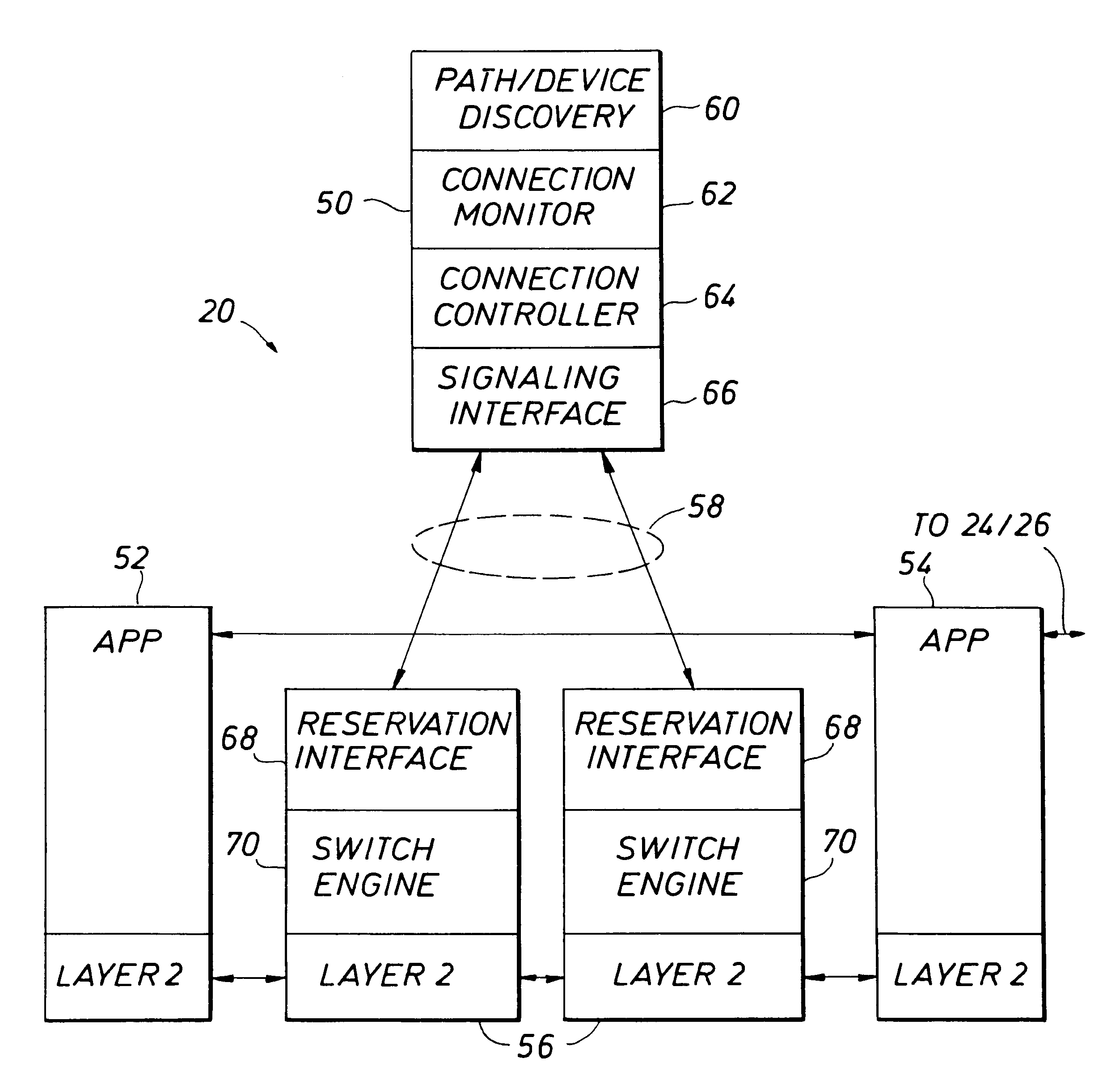

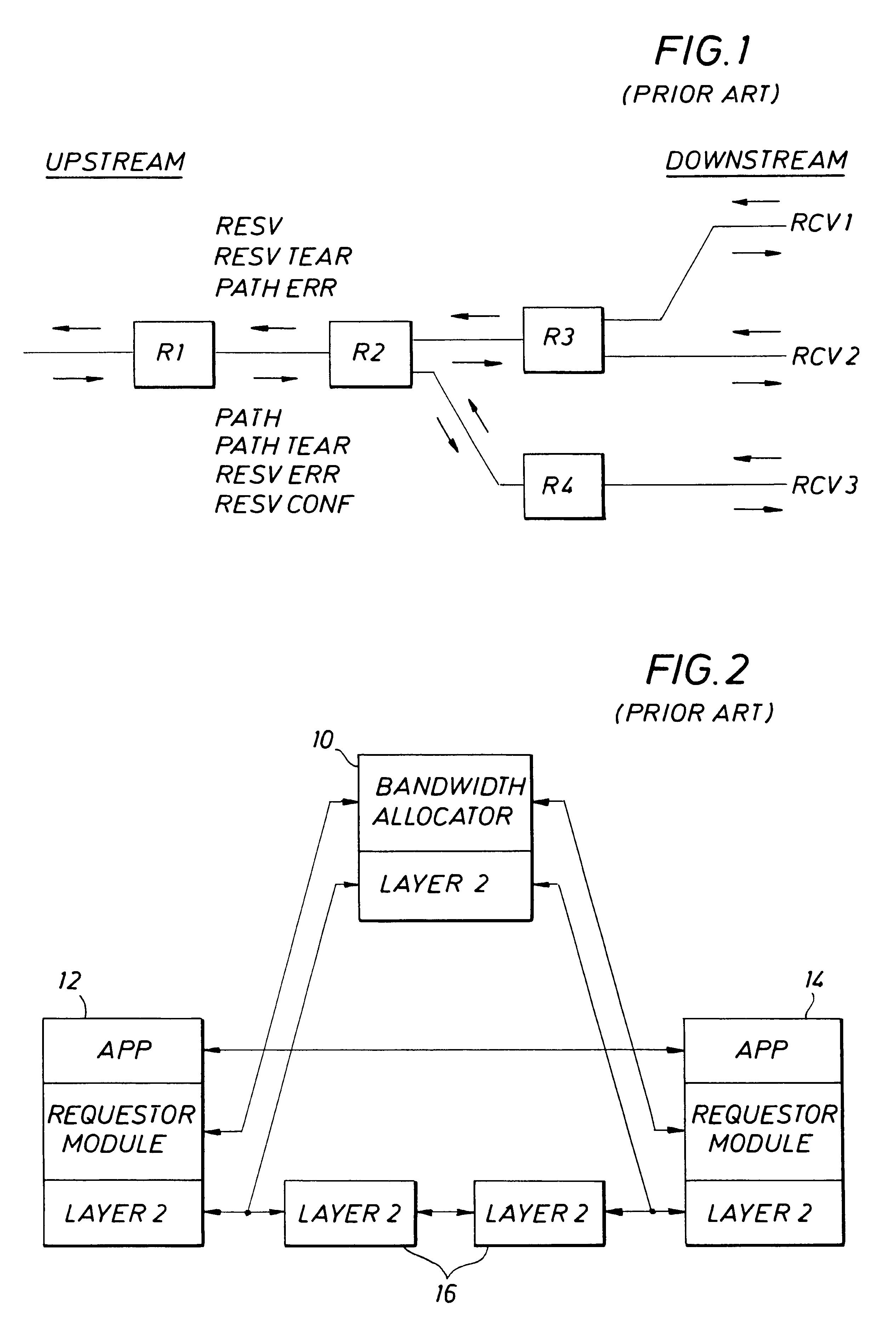

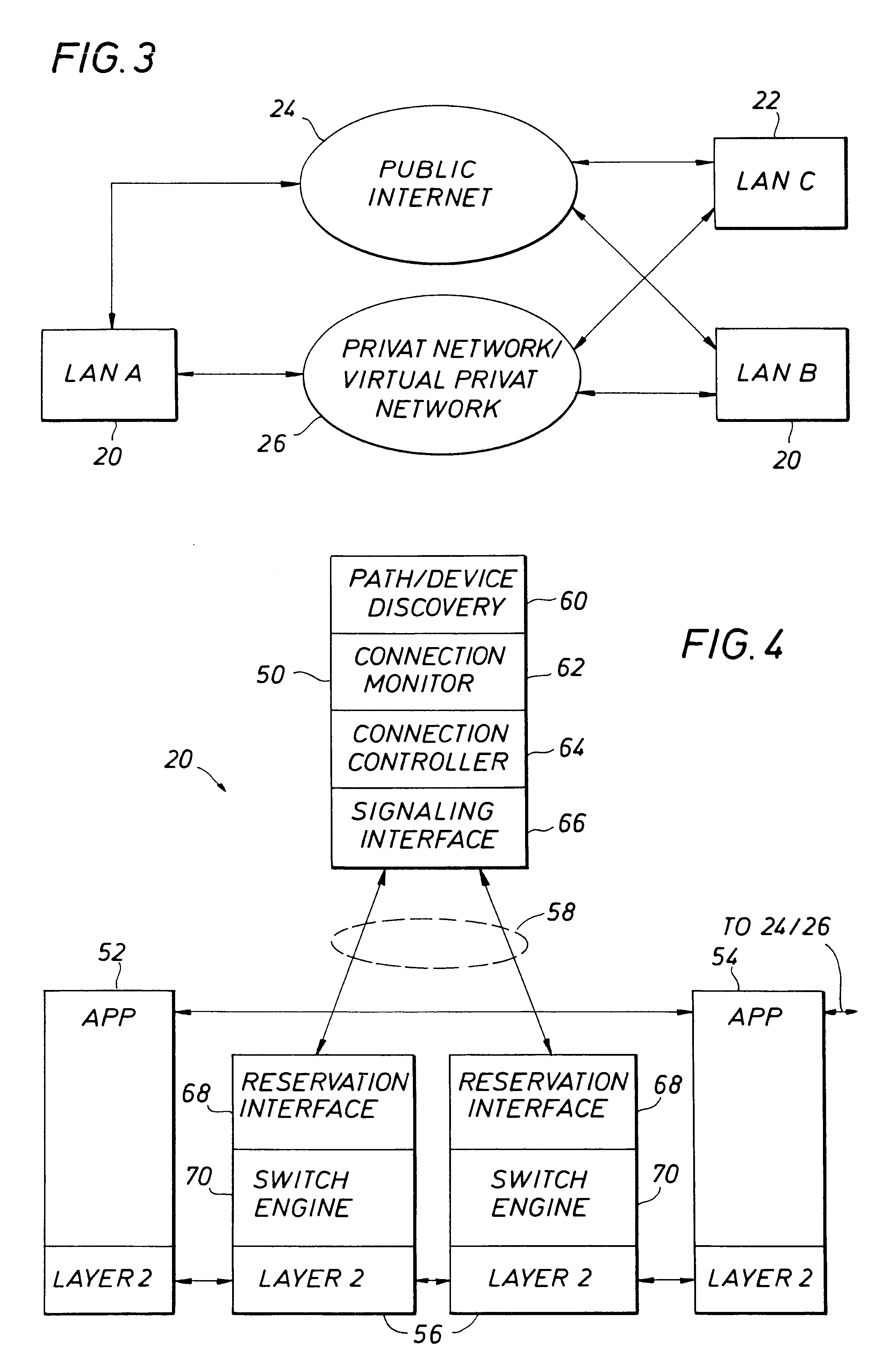

Method and apparatus for providing guaranteed quality/class of service within and across networks using existing reservation protocols and frame formats

InactiveUS6563793B1Error preventionFrequency-division multiplex detailsAssurance qualityClass of service

A method and apparatus provide reserved bandwidth and QOS / COS virtual circuit connections in a network using both conventional and novel reservation protocols and frame formats. An apparatus according to the invention includes an enterprise control point that communicates with switches via a reserved signaling channel. The switches have been upgraded or replaced to include enhanced functionality. The enhanced switches detect packets that include requests for reserved connections according to existing reservation protocols such as RSVP and IEEE 802.1P / Q. Such detected packets are forwarded to the enterprise control point for processing via a reserved signaling channel. The enterprise control point identifies a path within the network that can satisfy the requested QOS / COS and reserves the requested resources all along the path from beginning to end. A method according to the invention includes detecting packets that include requests for reserved connections according to existing reservation protocols such as RSVP and IEEE 802.1P / Q, forwarding detected packets to an enterprise control point for processing via a reserved signaling channel, identifying a path within the network that can satisfy the requested QOS / COS and reserving the requested resources all along the path from beginning to end.

Owner:WARPSPEED COMM

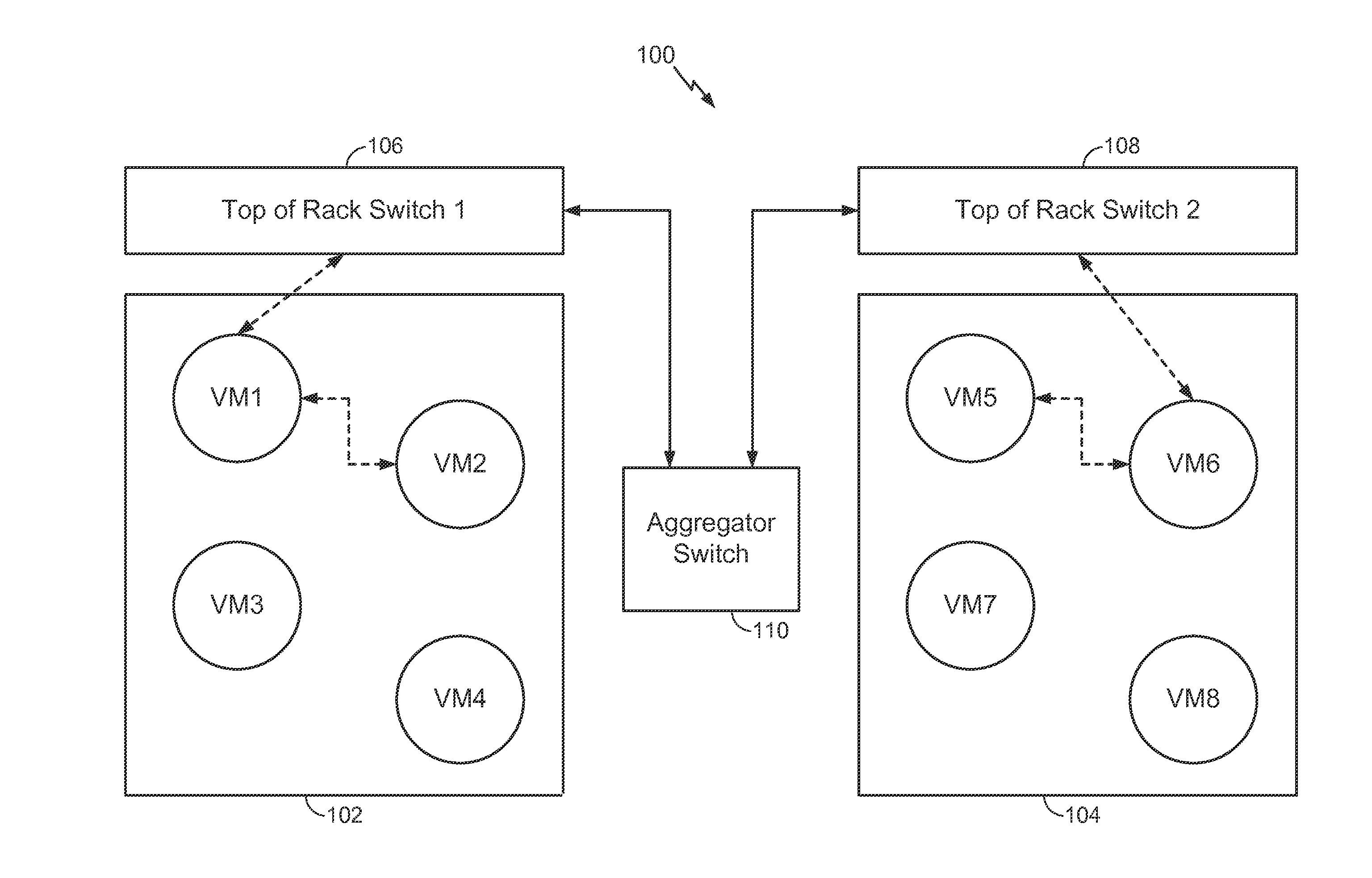

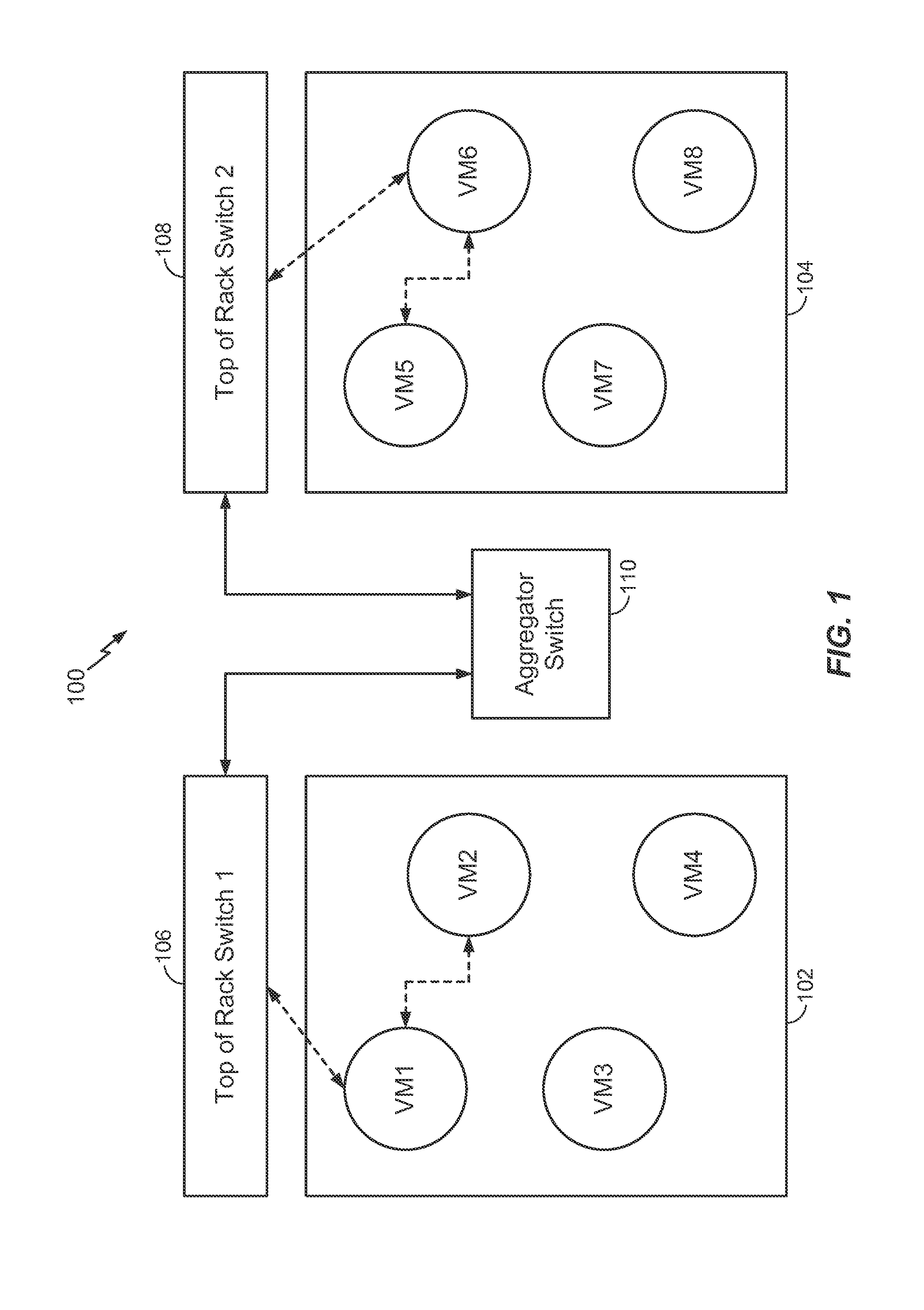

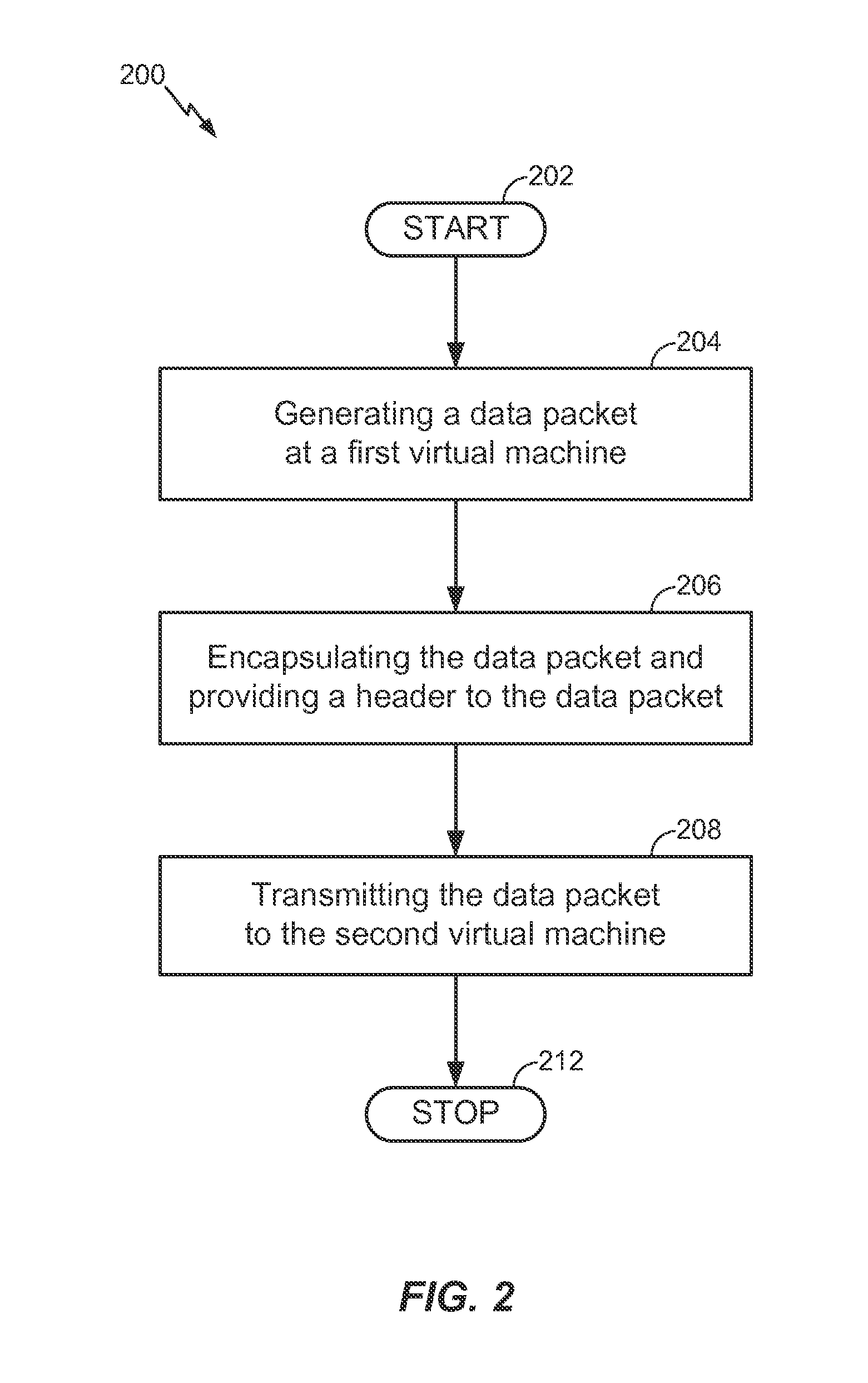

Method for resource optimized network virtualization overlay transport in virtualized data center environments

ActiveUS20150195178A1Error preventionFrequency-division multiplex detailsTransport systemData center

A method for resource optimized network virtualization overlay transport in a virtualized data center environment includes an optimized virtualized transport mechanism based on MPLS-TP tunneling technology. The transport mechanism may include a usage monitoring and resource usage advertisement mechanism based on IGP-TE protocol extension. Also, the transport mechanism may include a path computation engine (PCE) based optimal path computation for a virtualized transport tunnel used to carry VM-to-VM traffic across the virtualized data center. Additionally, the transport mechanism may include a SDN controller for provisioning and control of virtualized machines and a virtualized transport system.

Owner:CIENA

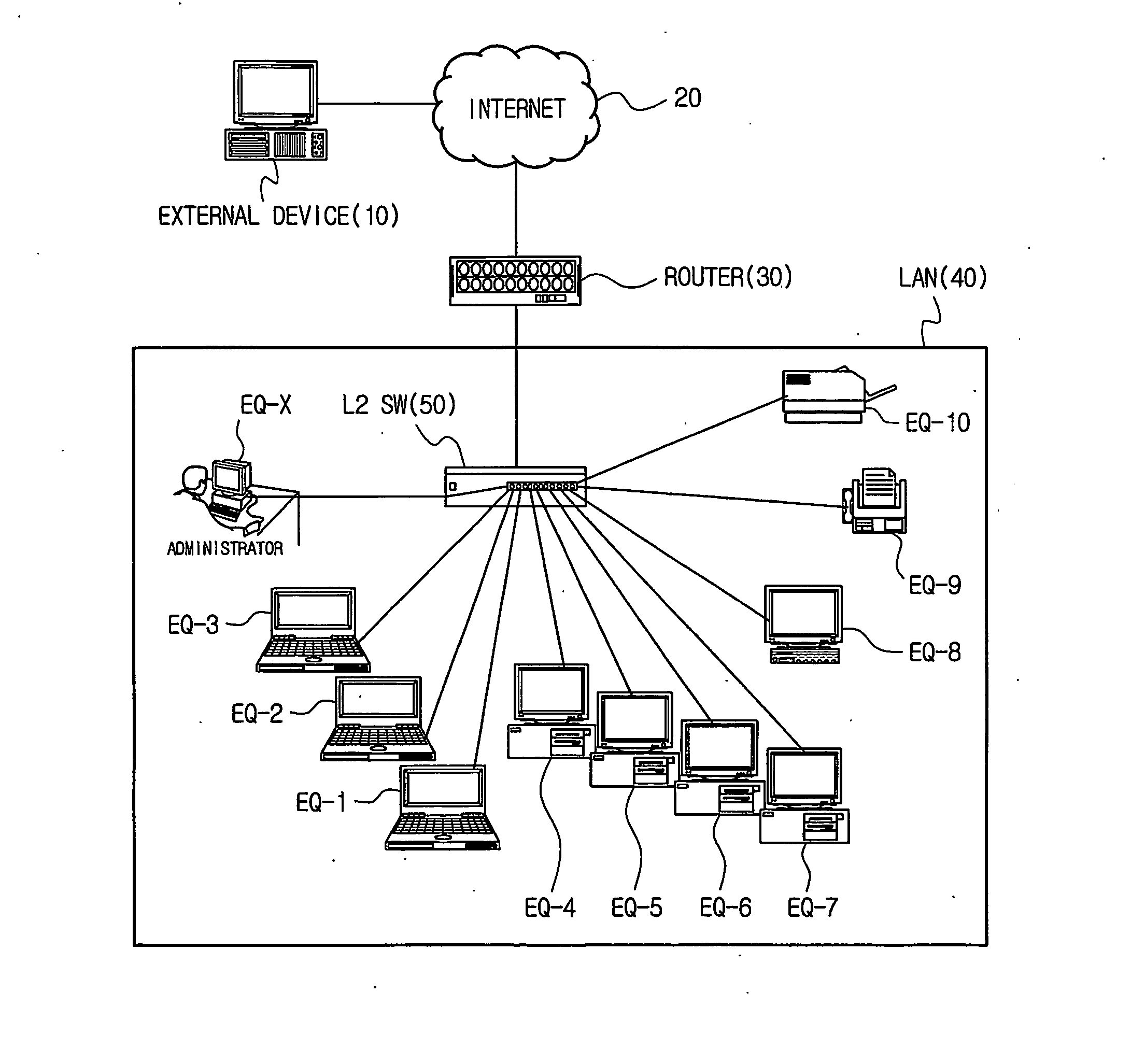

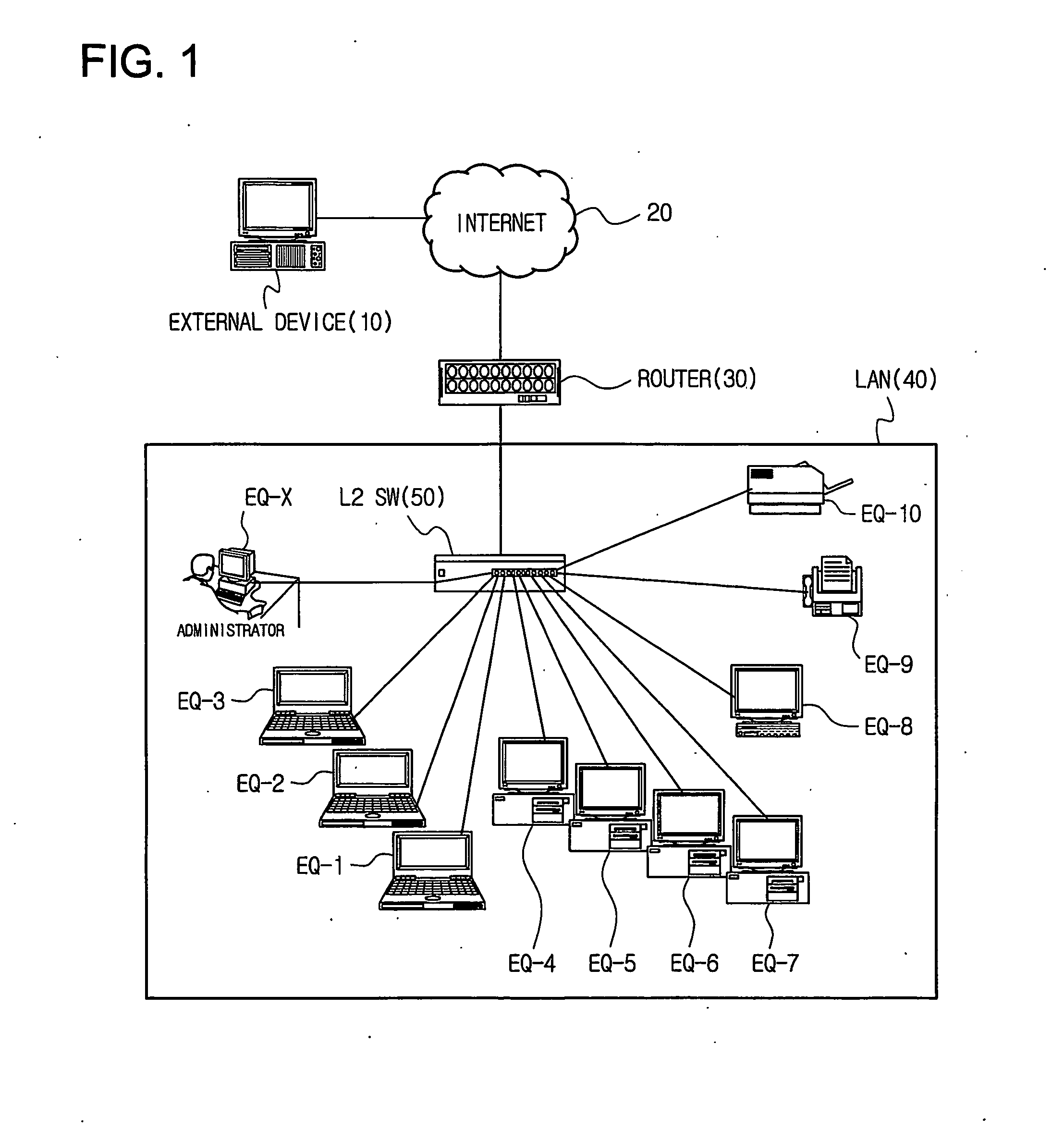

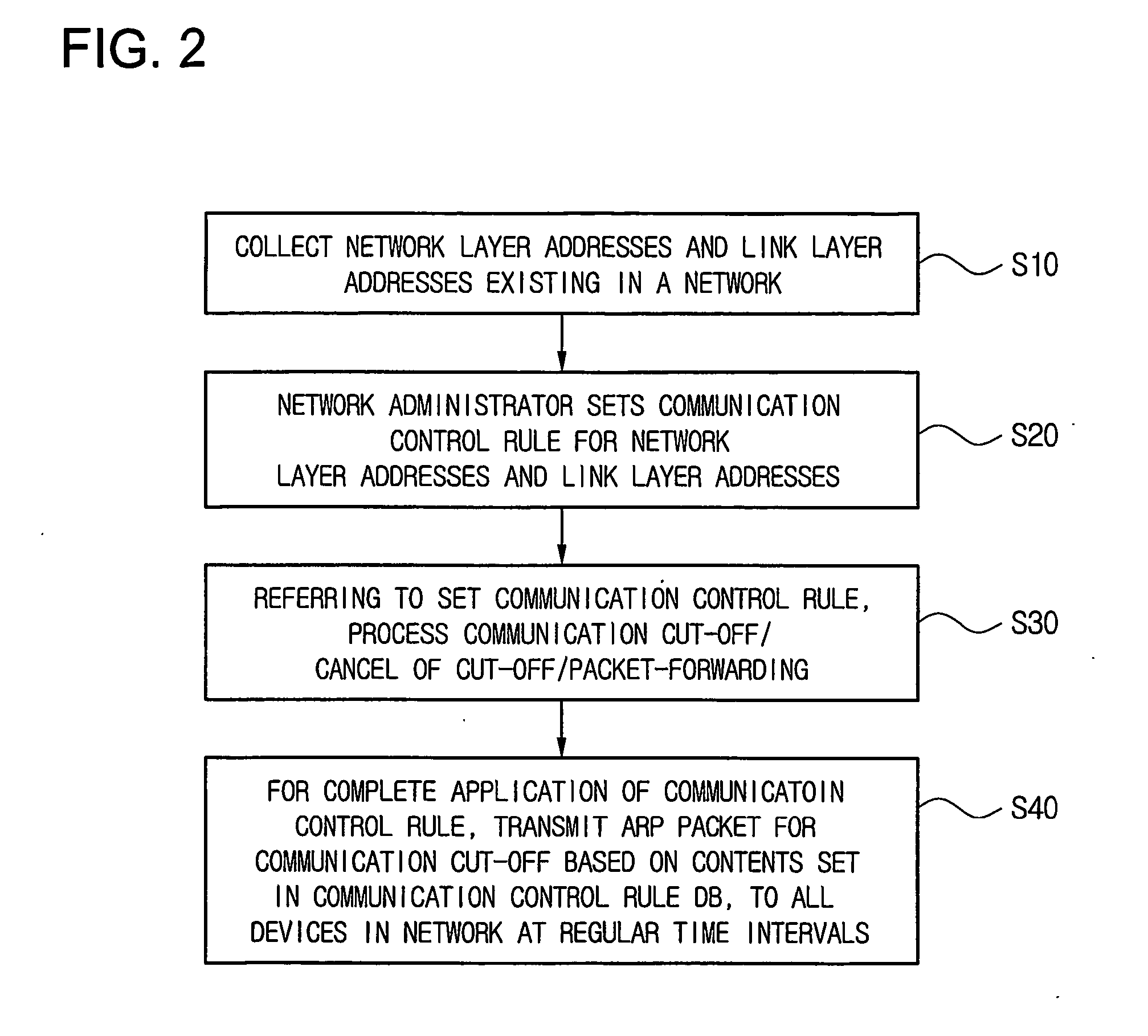

Method of controlling communication between devices in a network and apparatus for the same

InactiveUS20070064689A1Avoid collisionReduce communicationSpecial service provision for substationNetworks interconnectionAddress Resolution ProtocolVirtual firewall

Disclosed is a technology by which rules on communication permission or control are enforced to network internal devices such that an environment which looks as if to have a virtual firewall existing between network internal devices can be established. A communication control apparatus for this is located on the same level in the network as other devices are located. By using this communication control apparatus, an address resolution protocol (ARP) packet in which a data link layer address is manipulated is provided to devices that are the objects of communication cut-off, such that data packets transmitted by the communication cut-off object devices are transmitted to manipulated abnormal addresses. By doing so, communication with the communication cut-off object devices is cut off. For a device which is in a communication cut-off state although the device is not an object of communication cut-off any more, the communication control apparatus transmits an ARP packet including normal address information to the device such that the communication cut-off state is canceled.

Owner:INIMAX

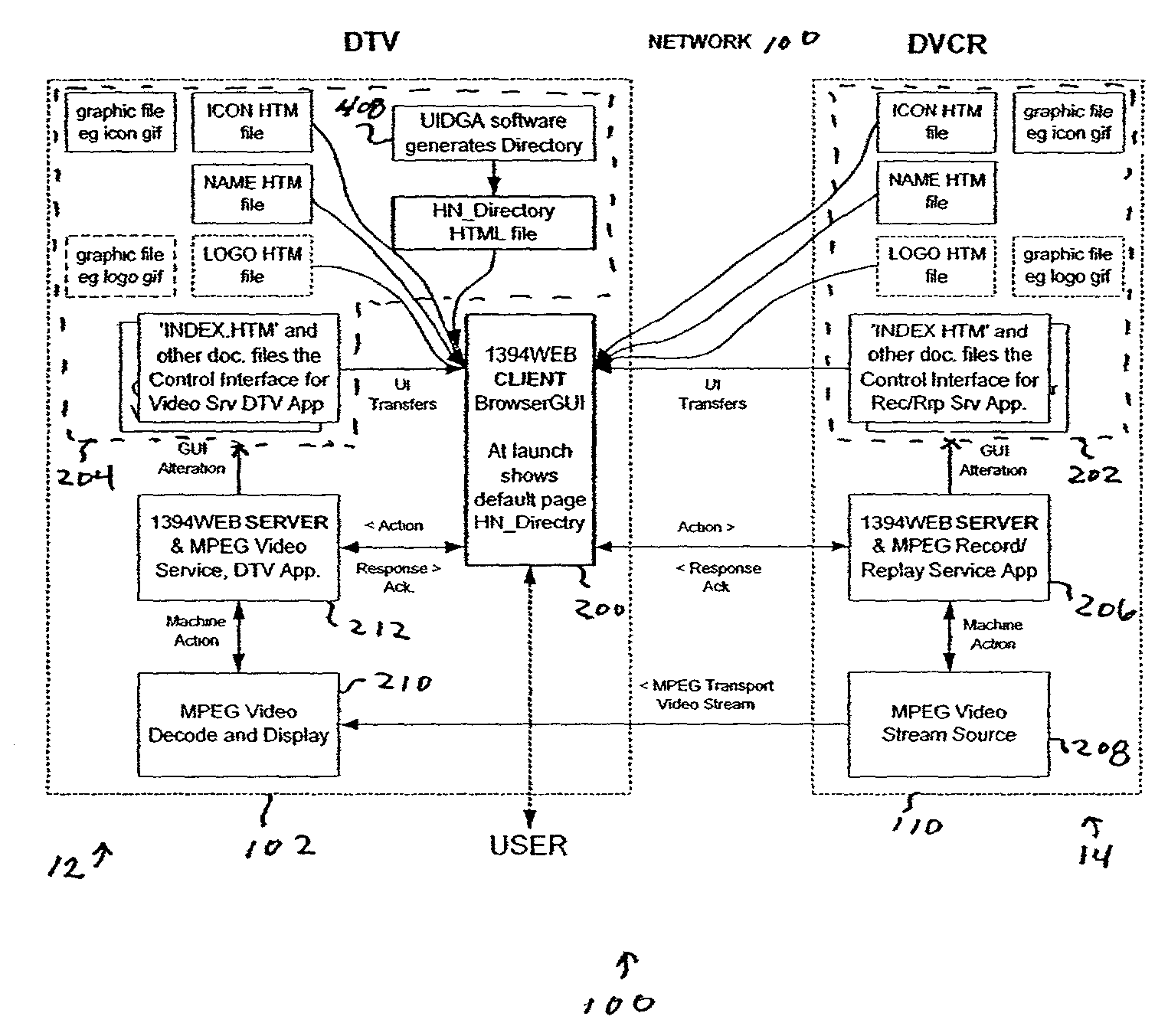

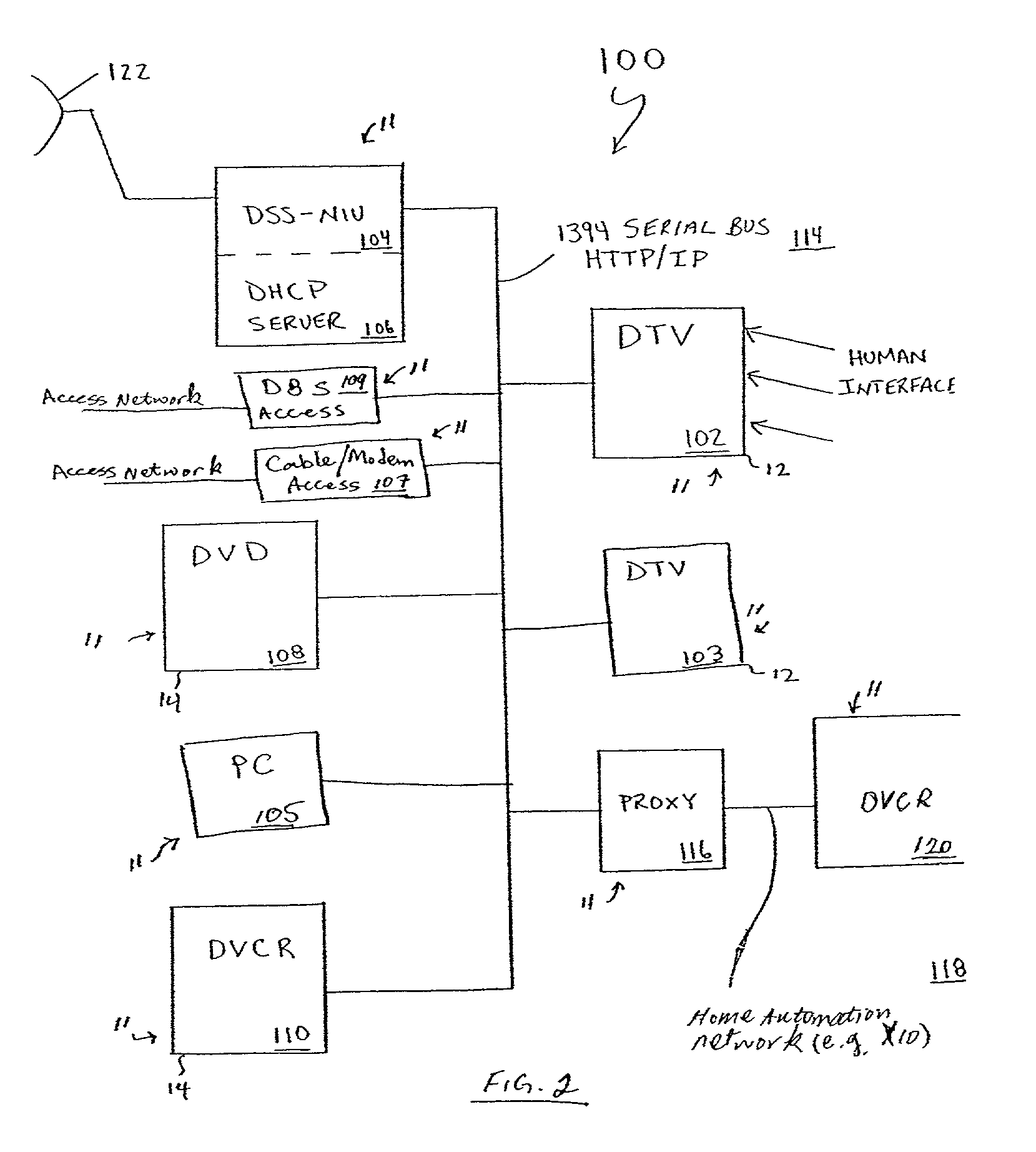

Architecture for home network on world wide web with private-public IP address/URL mapping

InactiveUS7349967B2Special service provision for substationTelevision system detailsIp addressNetwork on

A method for providing user interfaces in a first network to a remote access device, the first network including interconnected first devices and at least one interface device for connecting the first network to a second network. The remote access device establishes communication with the second network and sends a request to the interface device for accessing the first network; at least one of the first devices obtains information from one or more of the first devices, and generates a user interface description including at least one reference associated with the device information, the reference including an external address such that the device is accessible from the remote access device; the interface device sends the user interface description to the remote access device; and the remote access device displays a user interface based on the user interface description.

Owner:SAMSUNG ELECTRONICS CO LTD

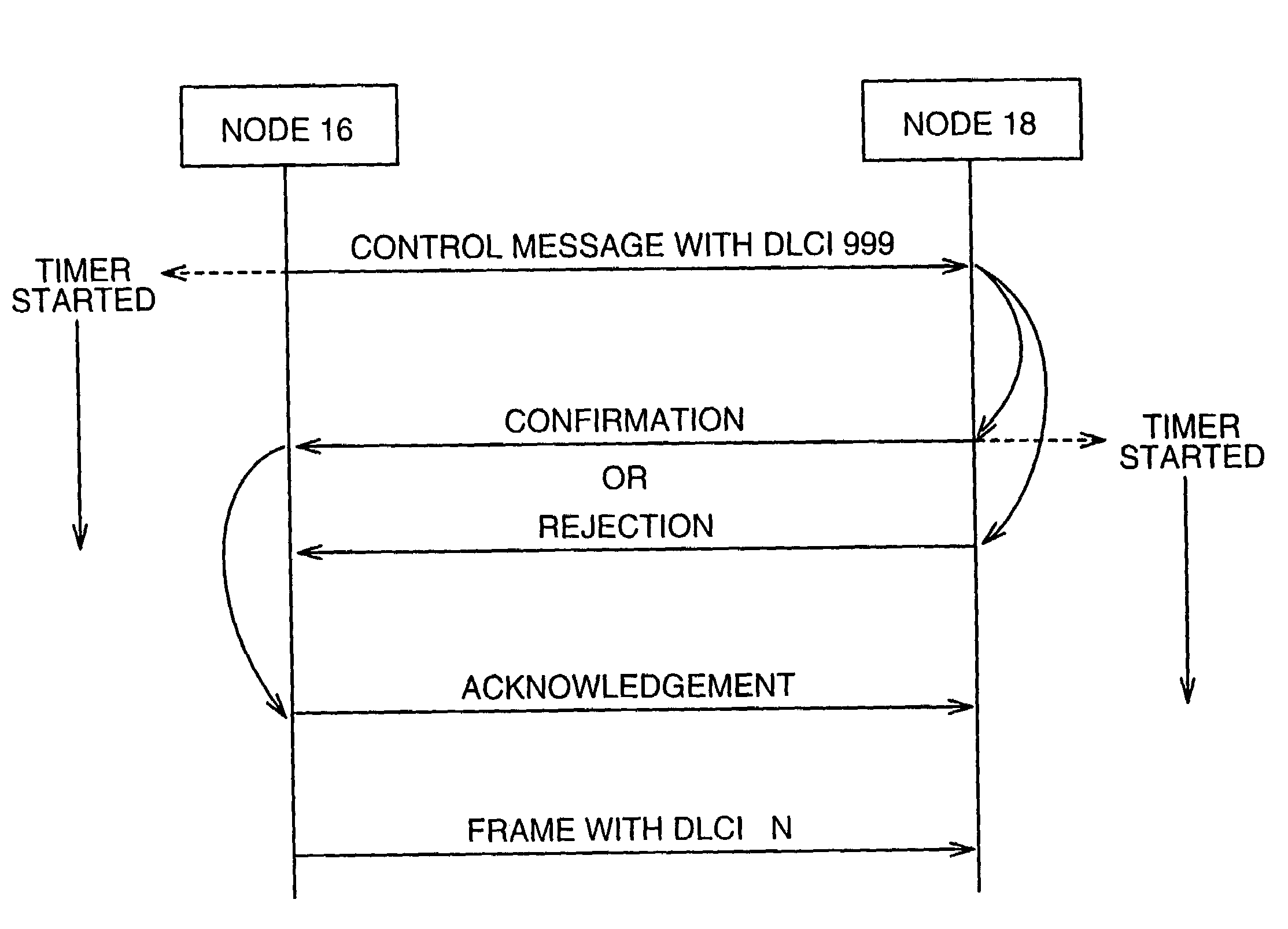

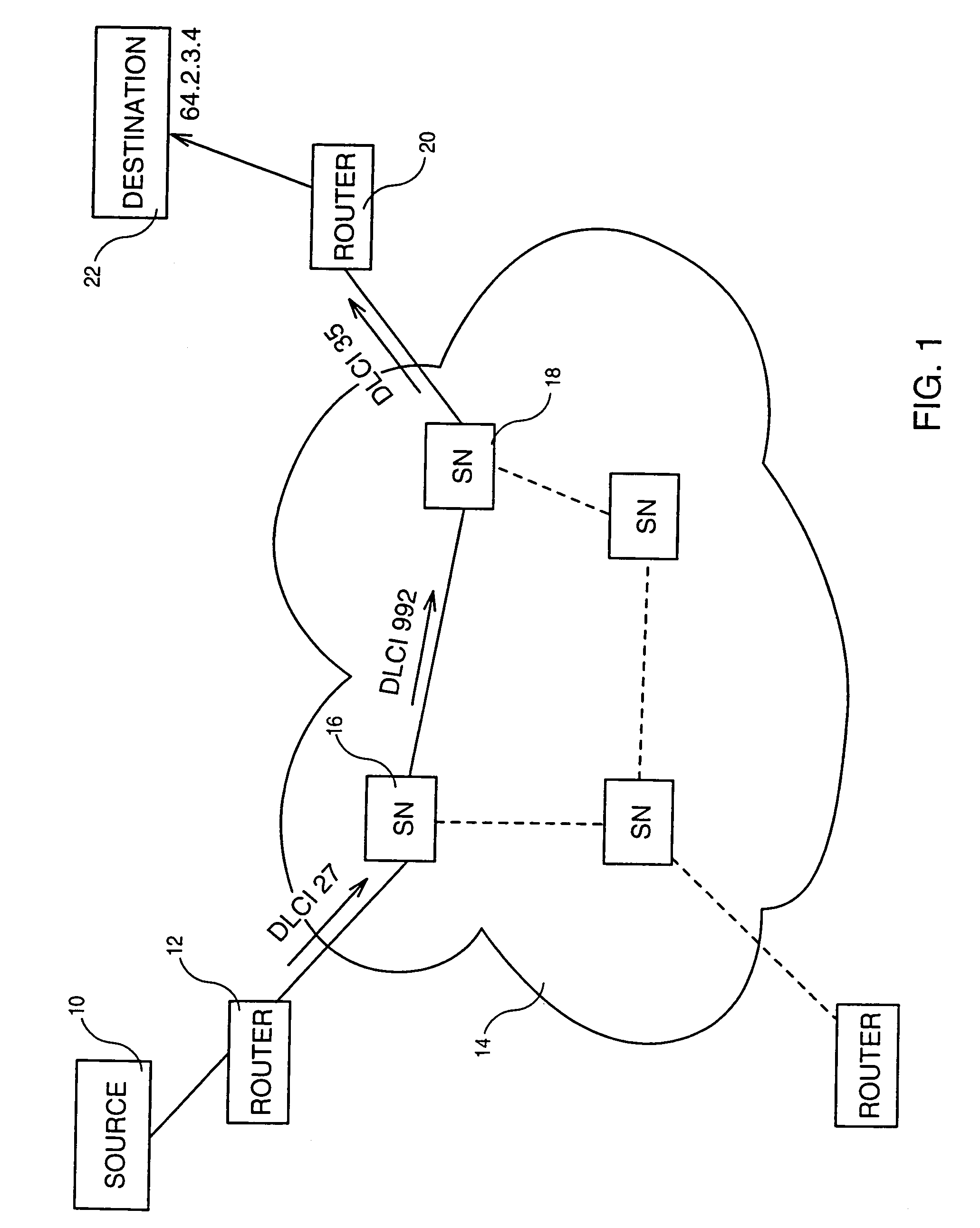

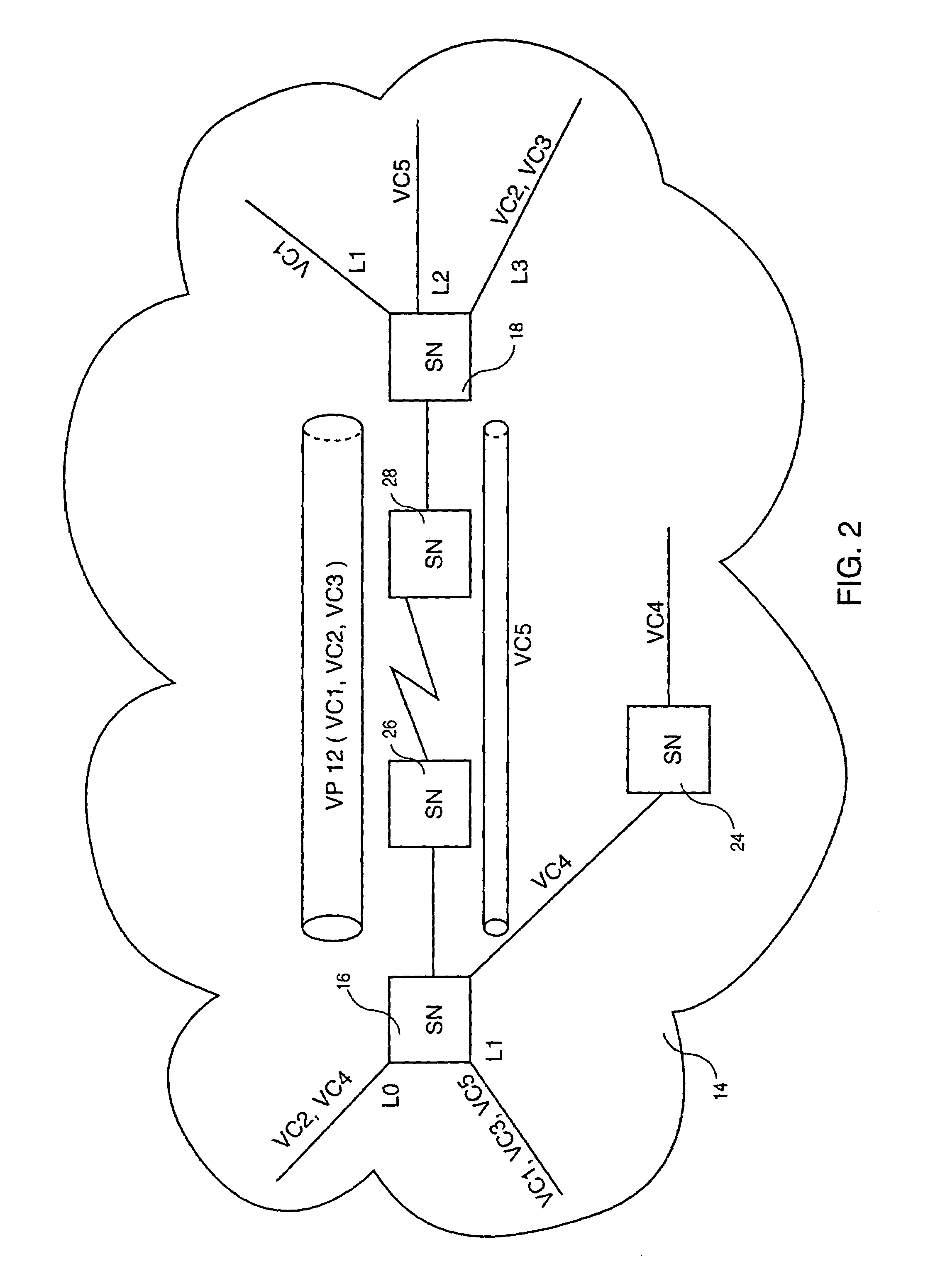

Method and system for establishing a virtual path capability in a frame relay network

A method and system for establishing a Virtual Path (VP12) capability in a Frame Relay network wherein frames are transmitted over a plurality of virtual circuits from a first switching node to a second switching node. A control message is transmitter from the first switching node to the second switching node with a Data Link Connection Identifier (DLCI) having a predetermined value indicating the purpose of the control message which is to define a virtual path aggregating at least two virtual circuits selected from multiple virtual circuits. The control message contains the identification of the virtual circuits aggregated in the defined virtual path.

Owner:IBM CORP

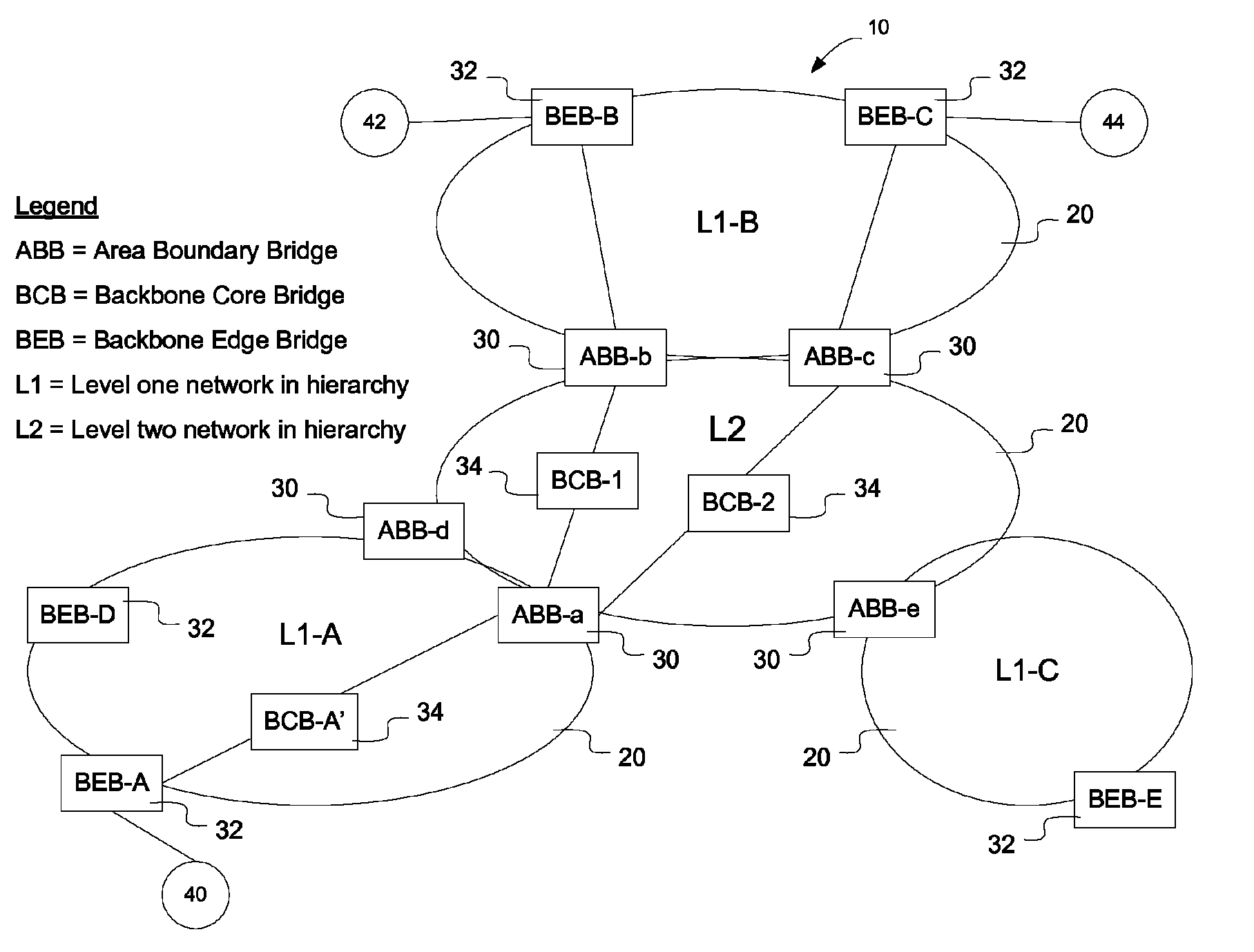

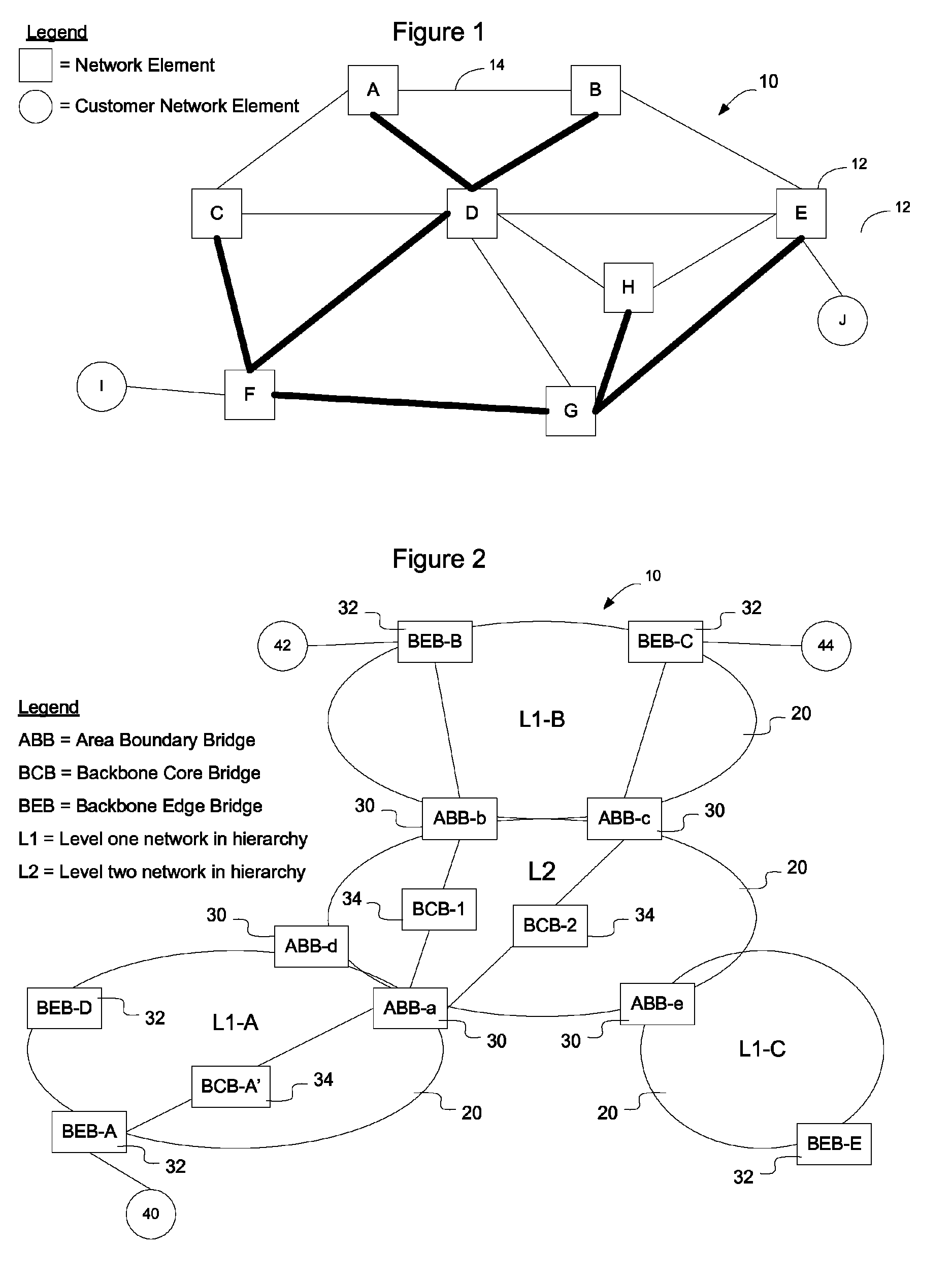

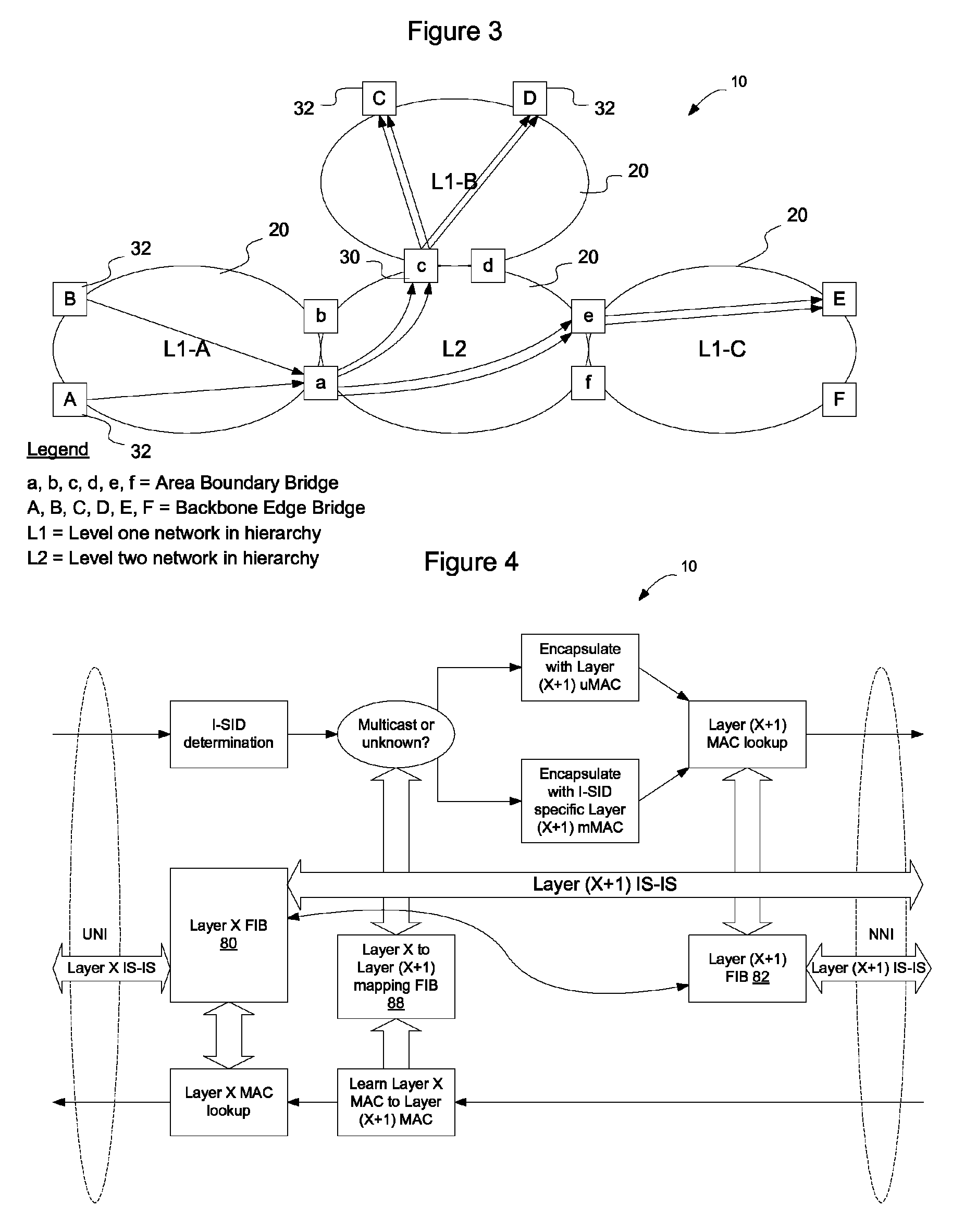

Method and apparatus for exchanging routing information and the establishment of connectivity across multiple network areas

InactiveUS8223668B2Easy to operateMultiple digital computer combinationsNetworks interconnectionStructure of Management InformationNetwork structure

Owner:RPX CLEARINGHOUSE

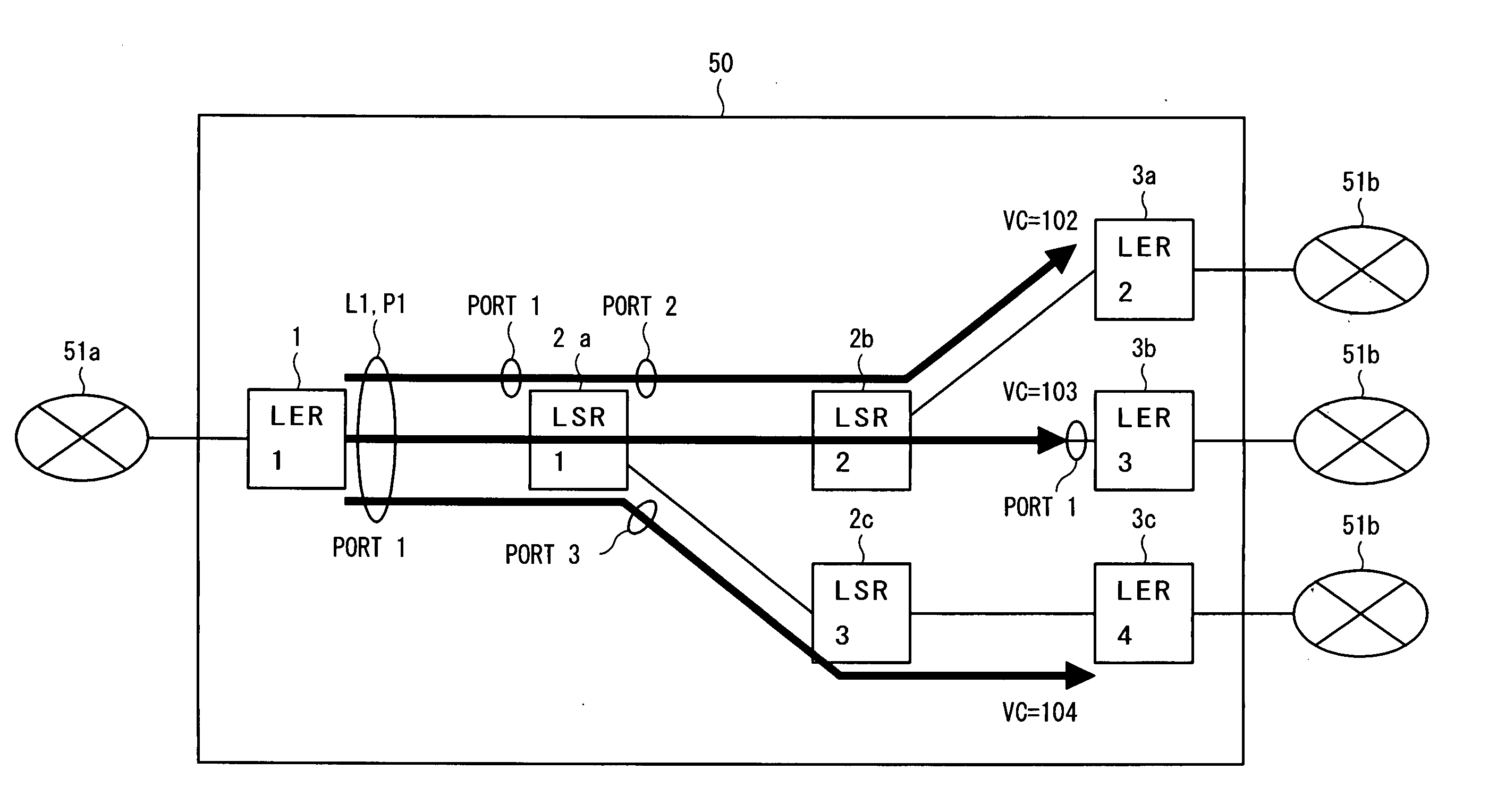

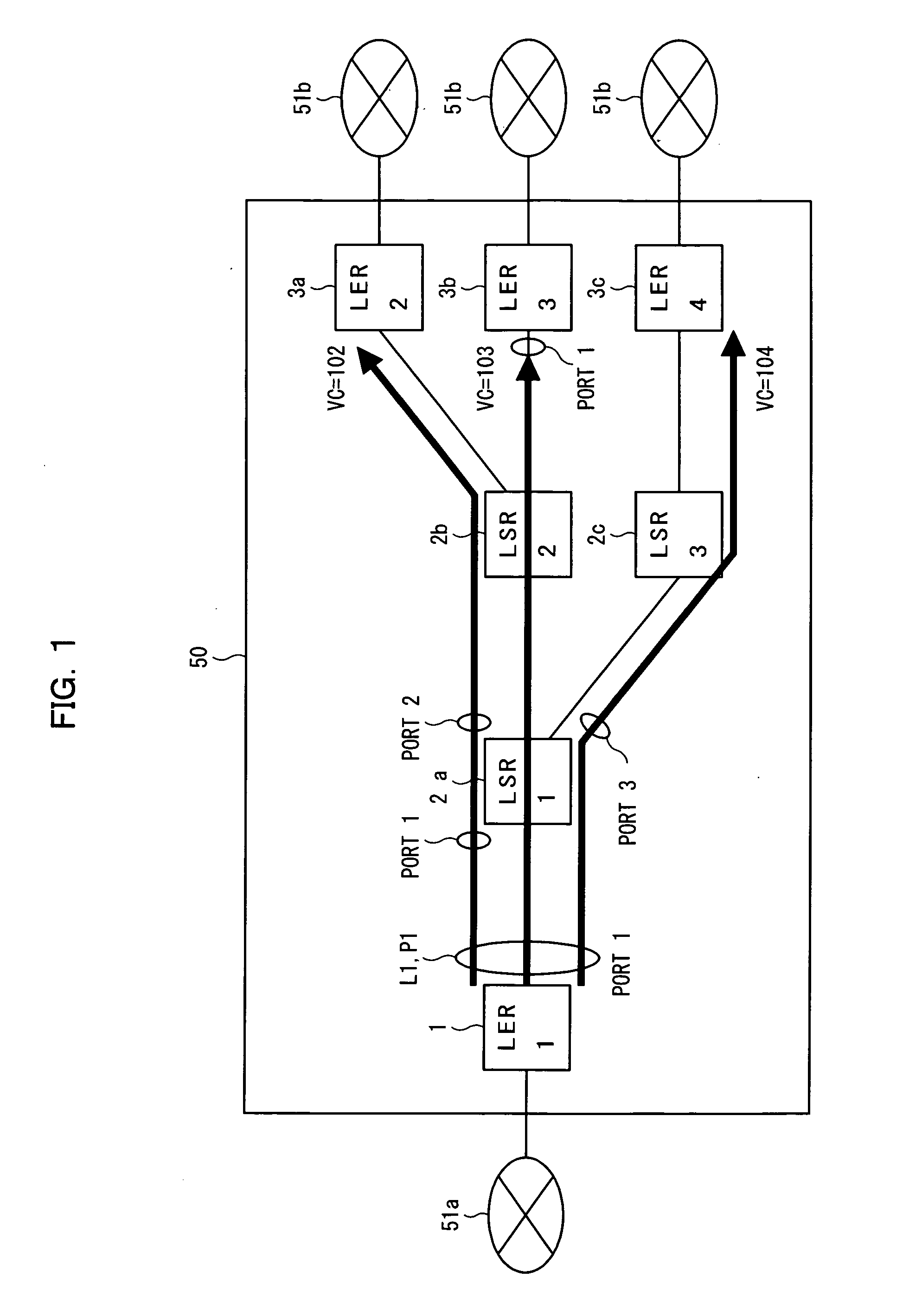

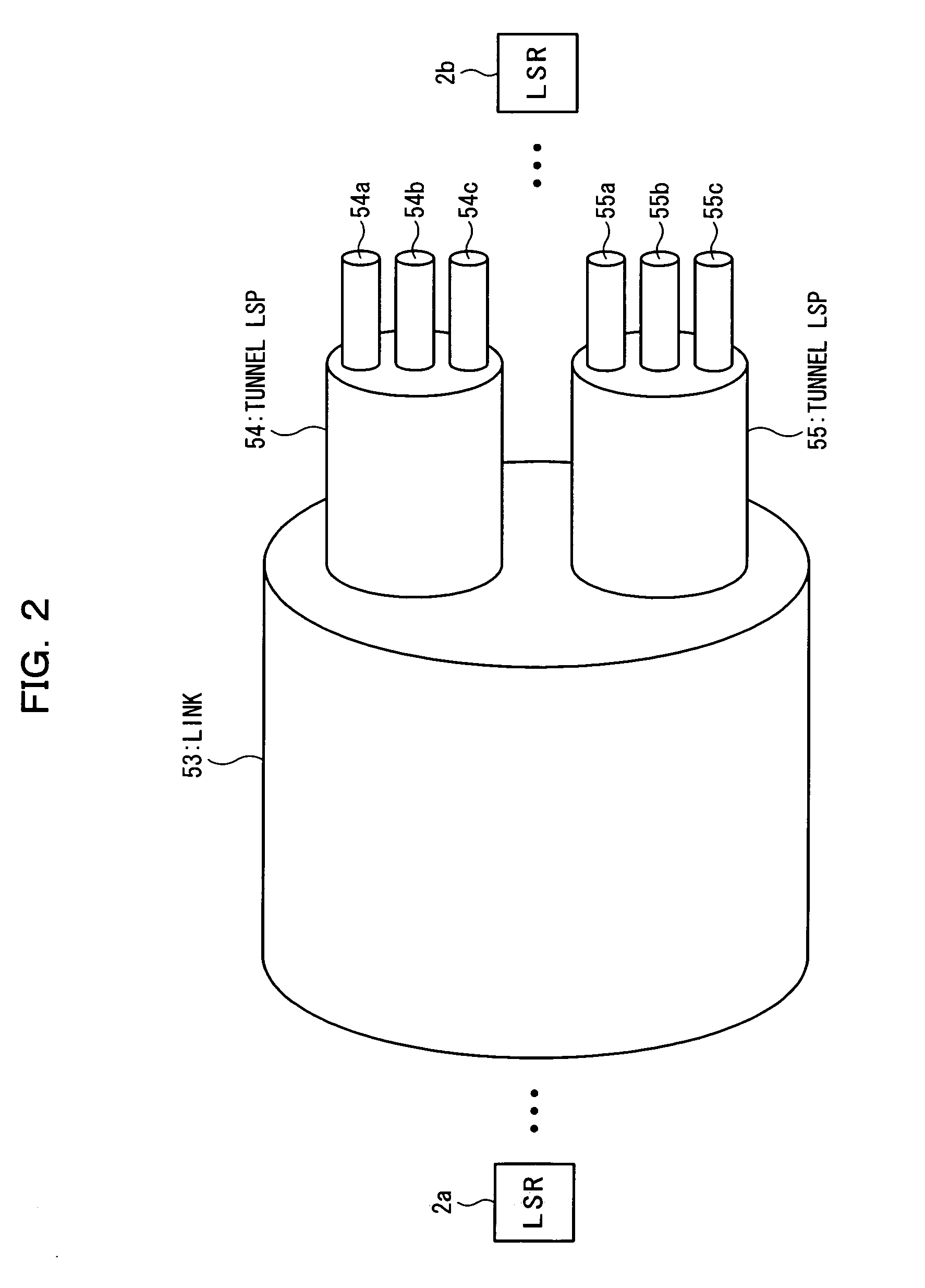

Router, frame forwarding method, and lower layer frame virtual forwarding system

InactiveUS20050169270A1Avoid loadEasy to useTime-division multiplexNetworks interconnectionPhysical addressLabel switching

In an MPLS network, multicast, broadcast and address learning belonging to the layer 2 functions are realized. An ingress router comprises a frame receiving unit, a determining unit, a first frame transmitting unit, a physical address table for multicast, a label switching unit, a tunnel label table, a VCID giving unit, a L2 header creating unit and a second frame transmitting unit. The load on the network is suppressed, the band is efficiently used, and wasteful frame duplication and frame forwarding between edge routers are avoided.

Owner:FUJITSU LTD

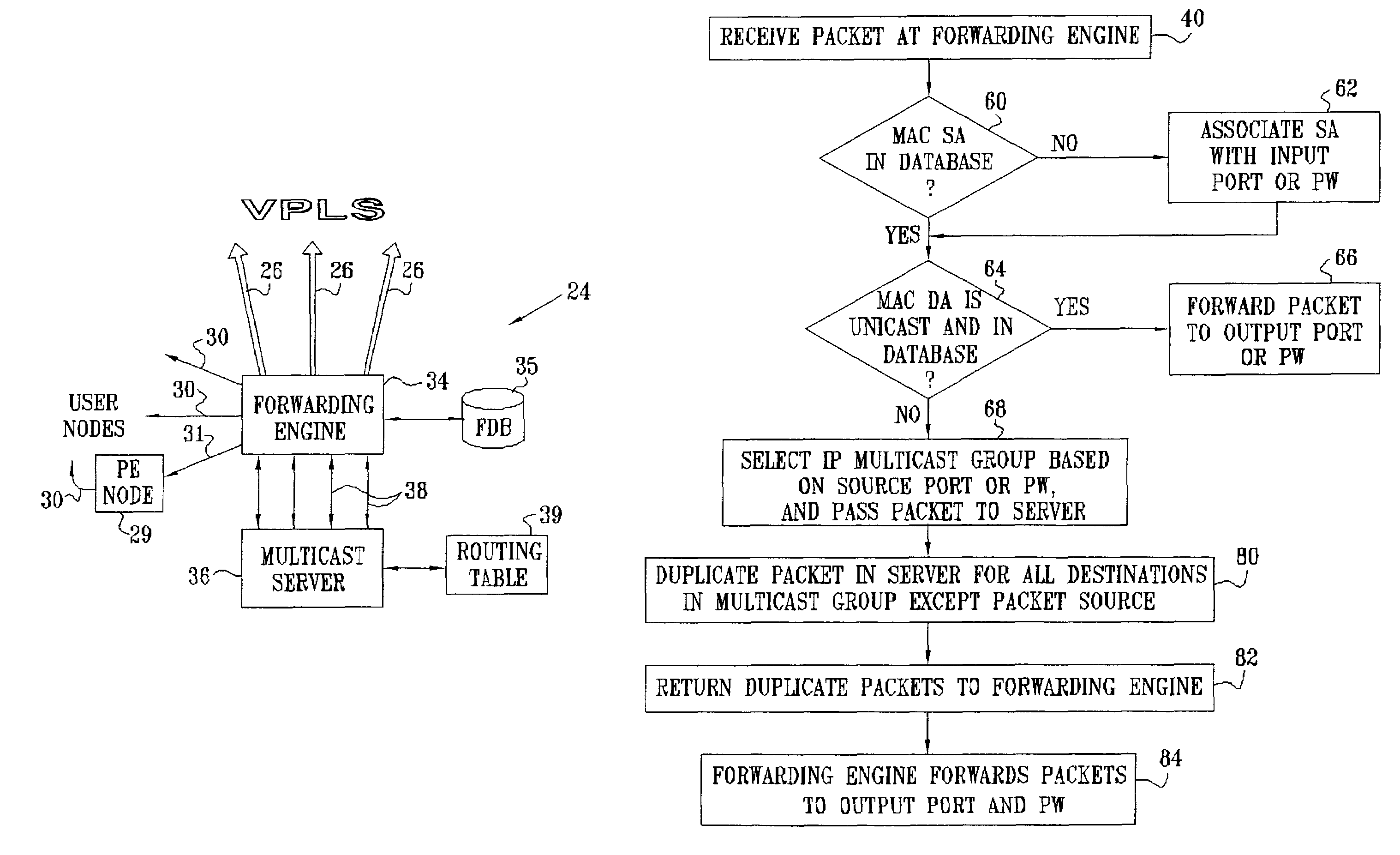

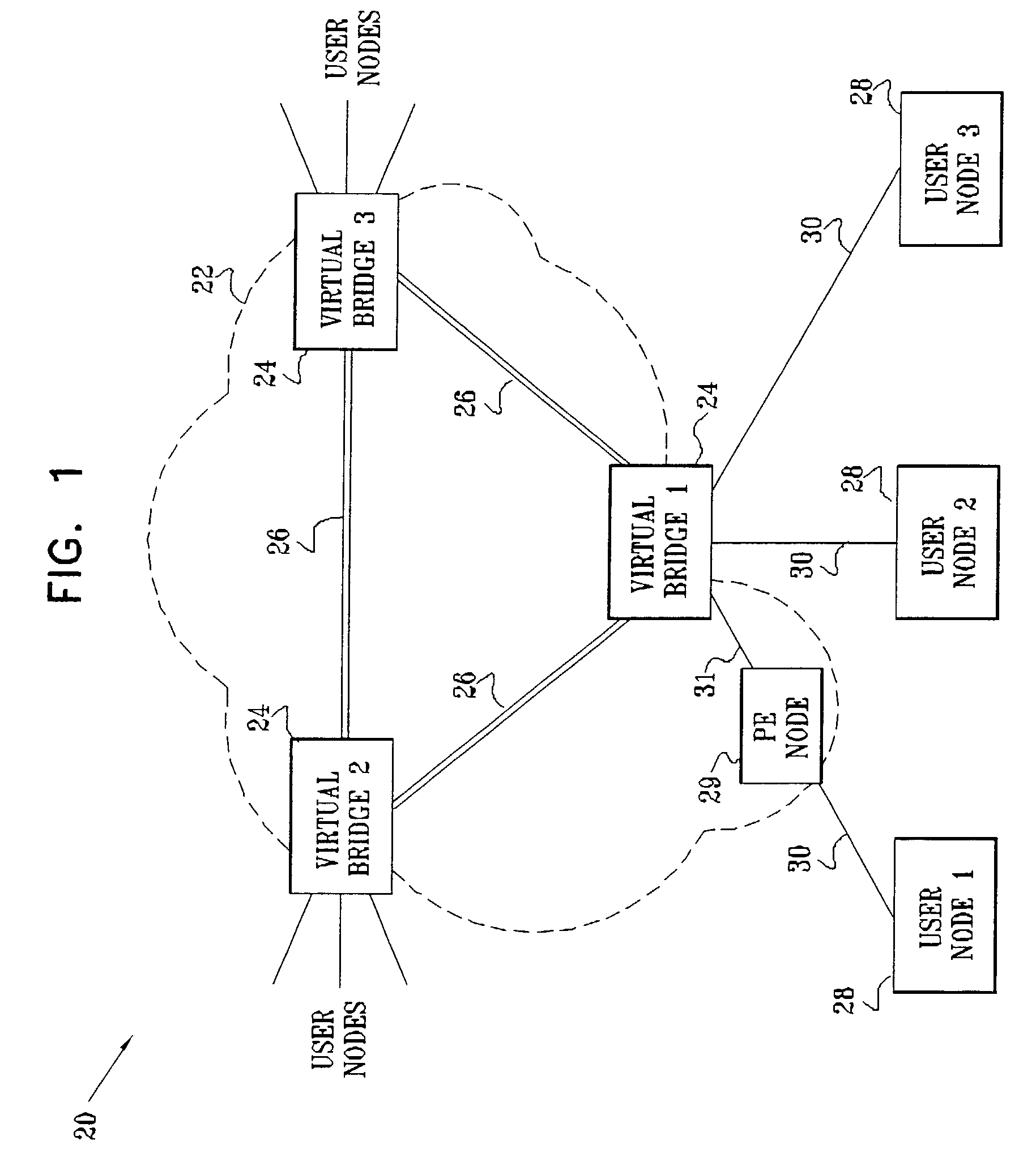

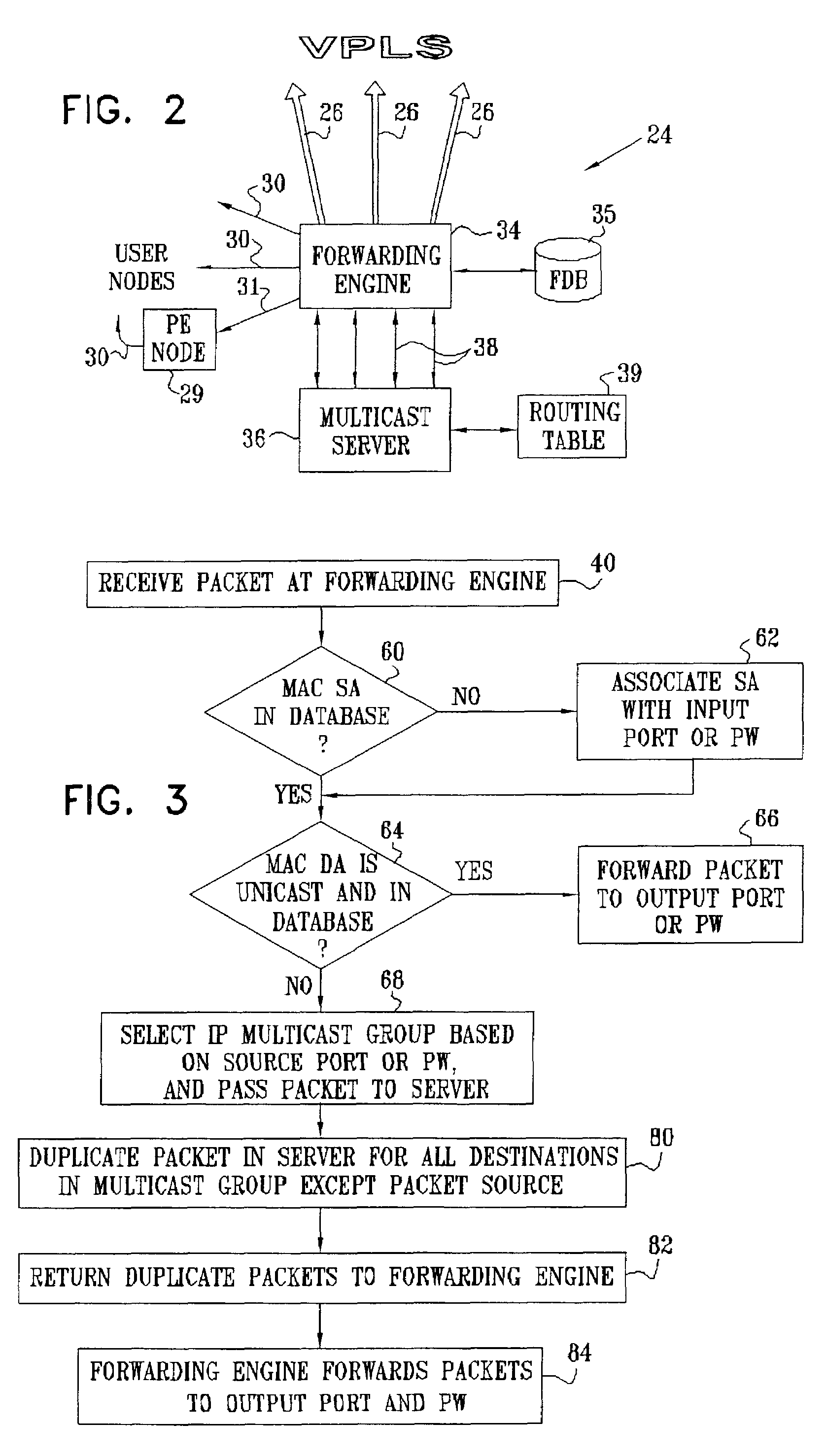

Virtual private LAN service using a multicast protocol

ActiveUS7339929B2Optimization mechanismRemove the burdenSpecial service provision for substationNetworks interconnectionNetworked Transport of RTCM via Internet ProtocolComputer network

A method for data broadcast over a network includes receiving at a virtual bridge a data packet to be flooded over the network, and passing the data packet from the virtual bridge to a multicast-capable router, along with a broadcast indication. Responsive to the broadcast indication, the router determines a group of destination addresses to which the packet should be multicast, and creates copies of the packet for transmission over the network to the destination addresses in the group.

Owner:CORRIGENT CORP

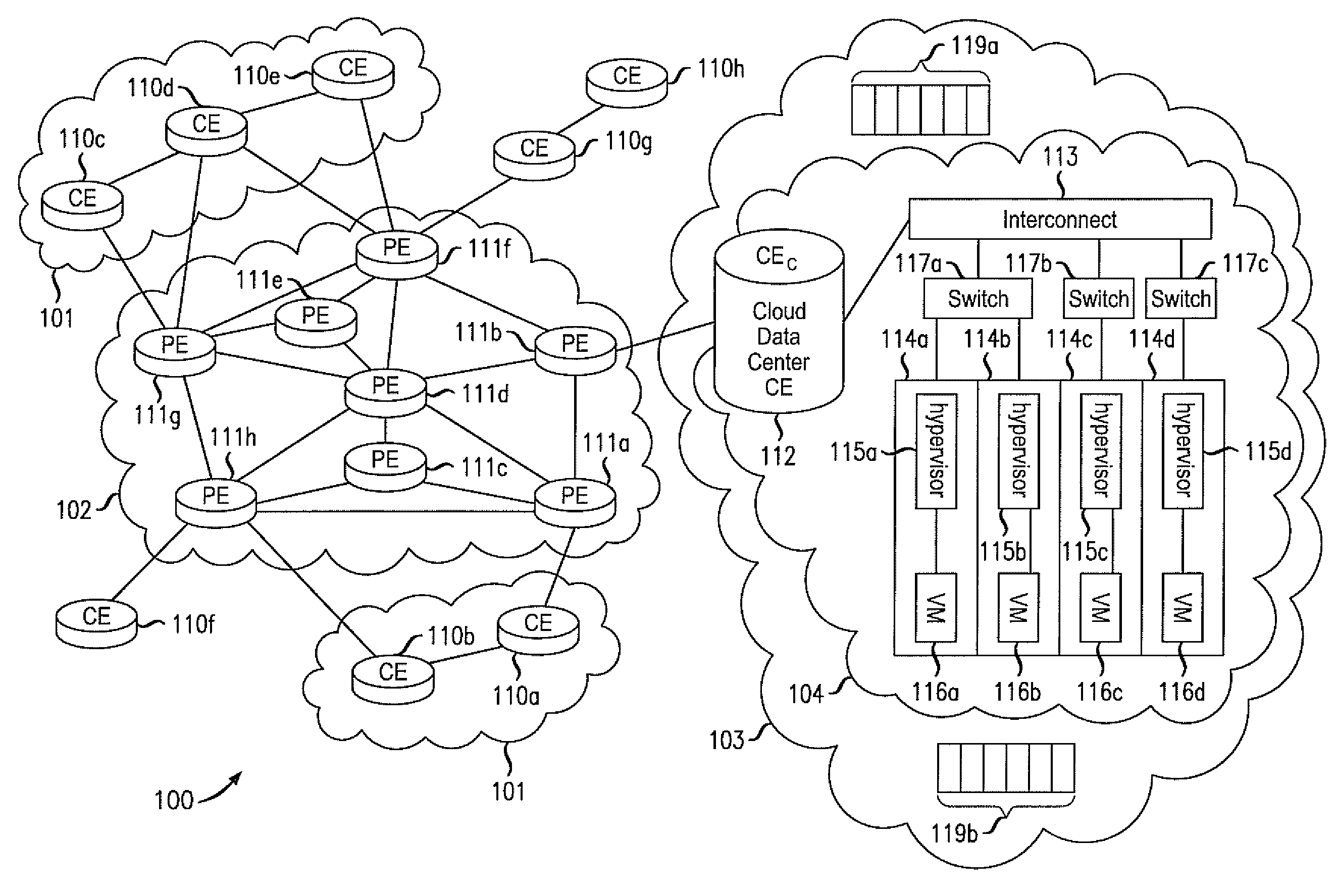

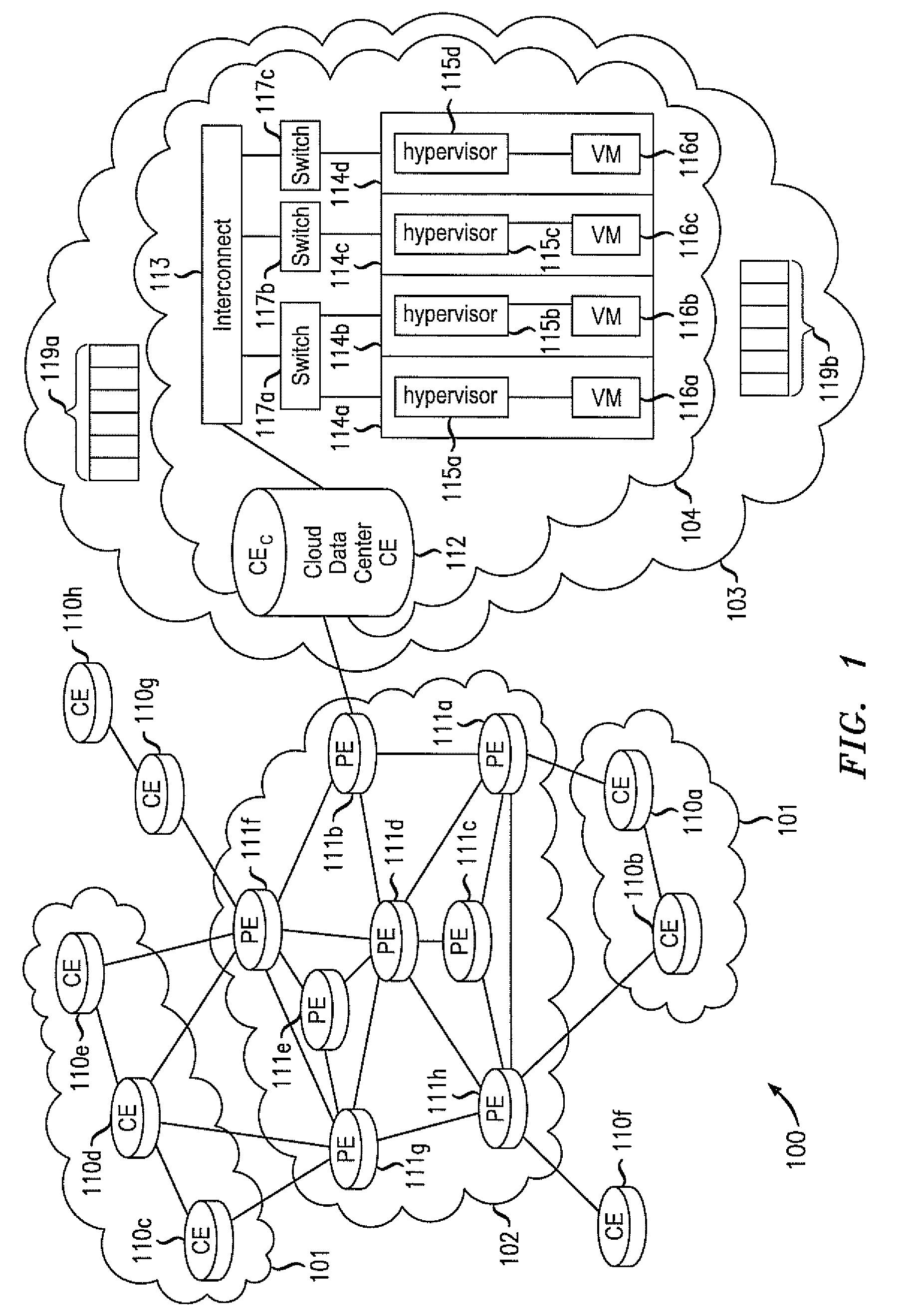

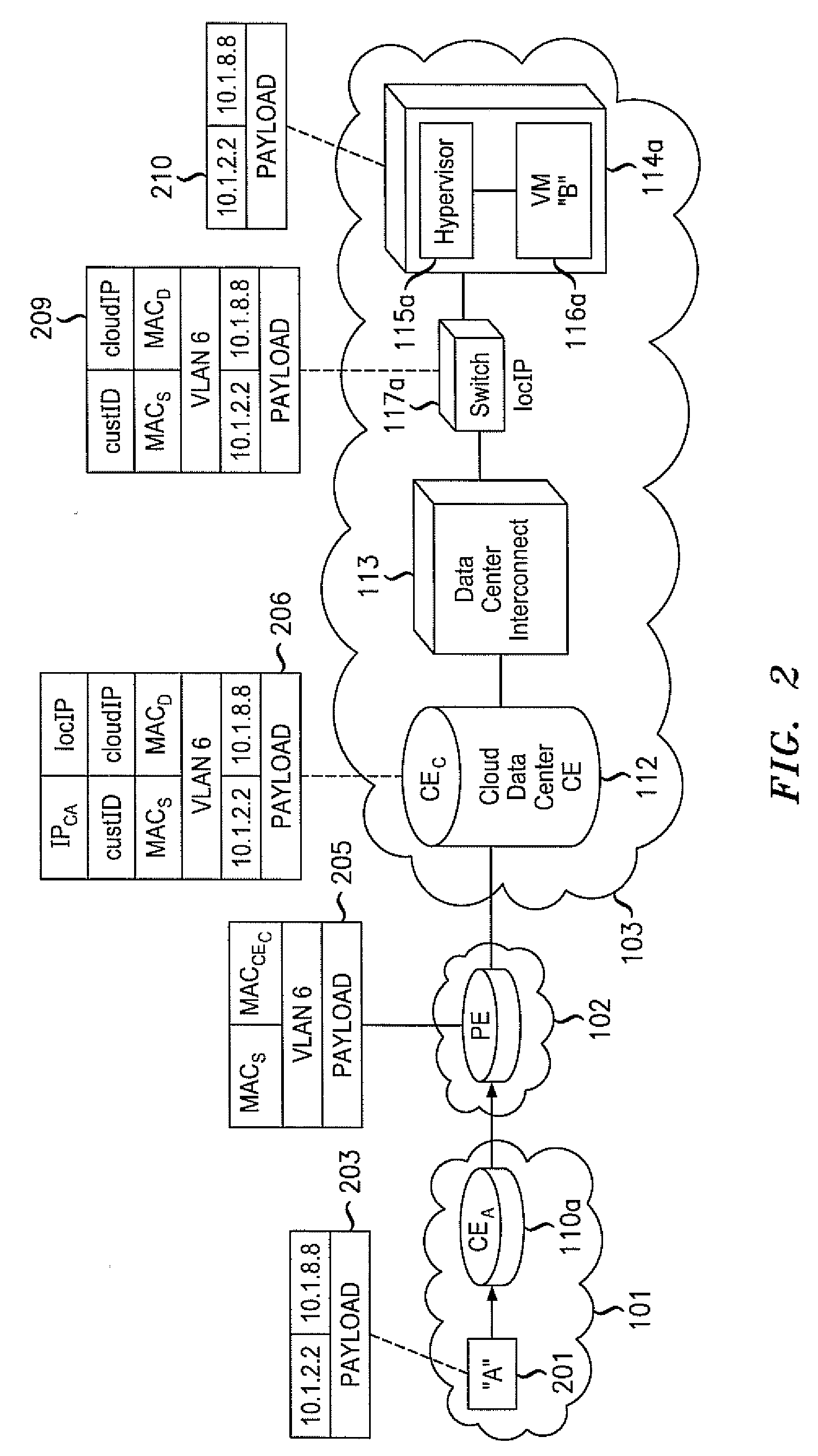

Layer 2 seamless site extension of enterprises in cloud computing

ActiveUS20110075667A1Ensure safetyHighly-dynamic scalability of cloud resourcesMultiple digital computer combinationsNetworks interconnectionNetwork packetIp address

Various embodiments relate to a Cloud Data Center, a system comprising the Cloud Data Center, and a related method. The Cloud Data Center may include a logical customer edge router to send packets between addresses in a private enterprise network and addresses in a logical network within a cloud network using Layer 2 protocol and MAC addressing. The logical network may have resources, known as virtual machines, allocated to the private enterprise network and may share a common IP address space with the private enterprise network. A directory at the Cloud Data Center may correlate the enterprise IP addresses of virtual machines with a MAC address, cloud IP address, and a location IP address within the logical network. The Cloud Data Center may double encapsulate packets with MAC, cloudIP, and locIP headers, when sending a packet to a destination in the logical network.

Owner:ALCATEL LUCENT SAS

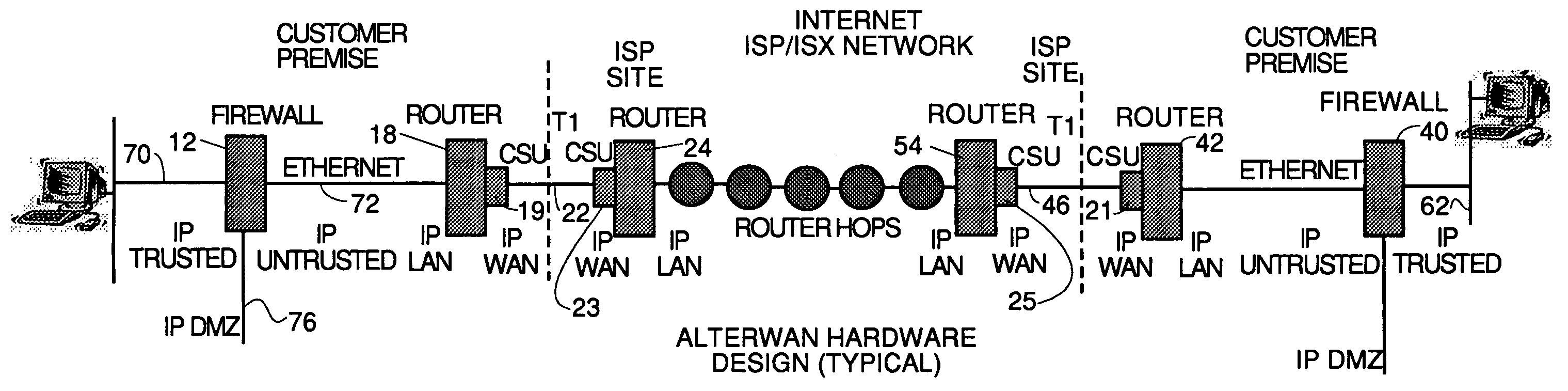

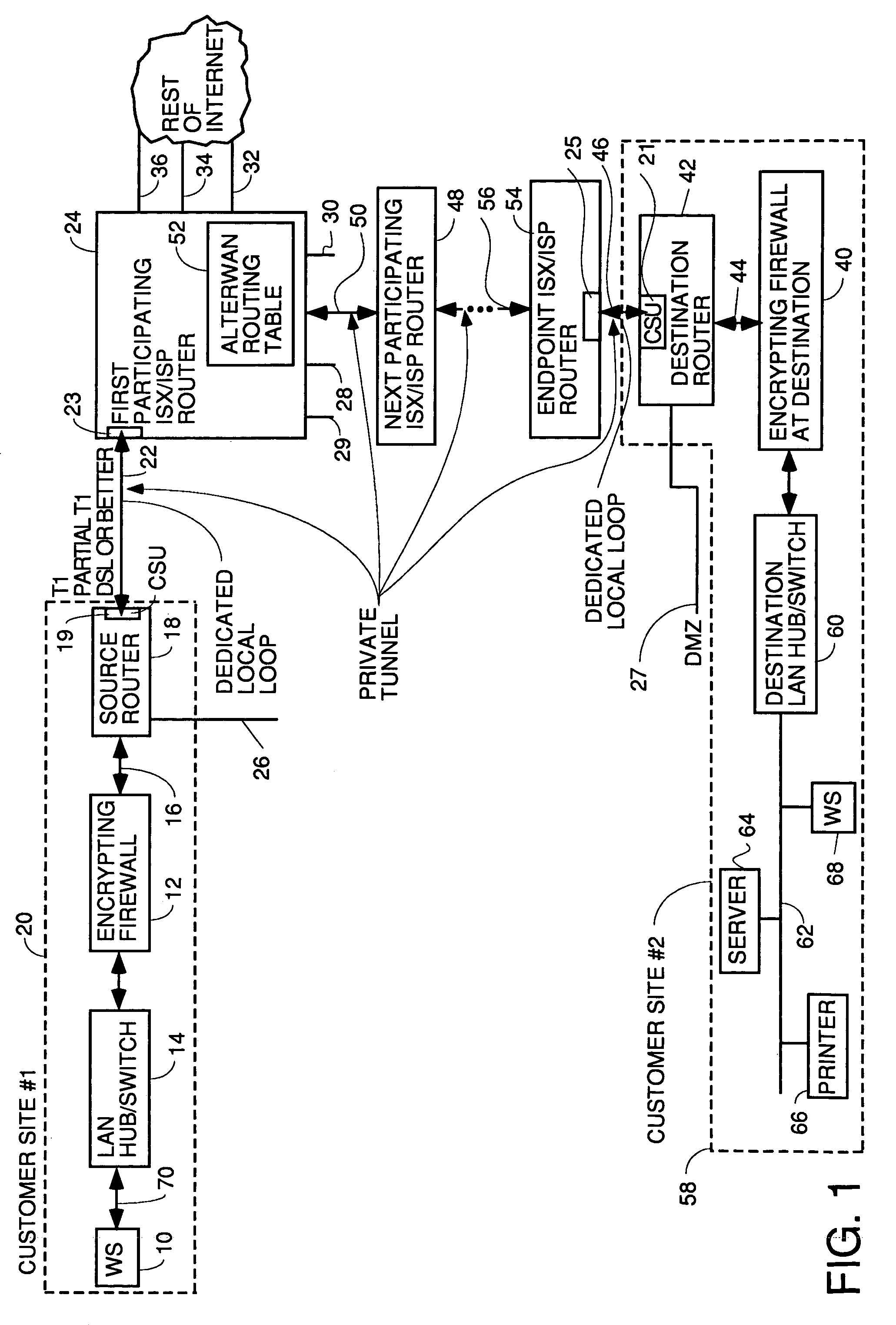

Wide area network using internet with quality of service

InactiveUS7111163B1Reduces monthly costQuality improvementDigital data processing detailsMultiple digital computer combinationsQuality of serviceTTEthernet

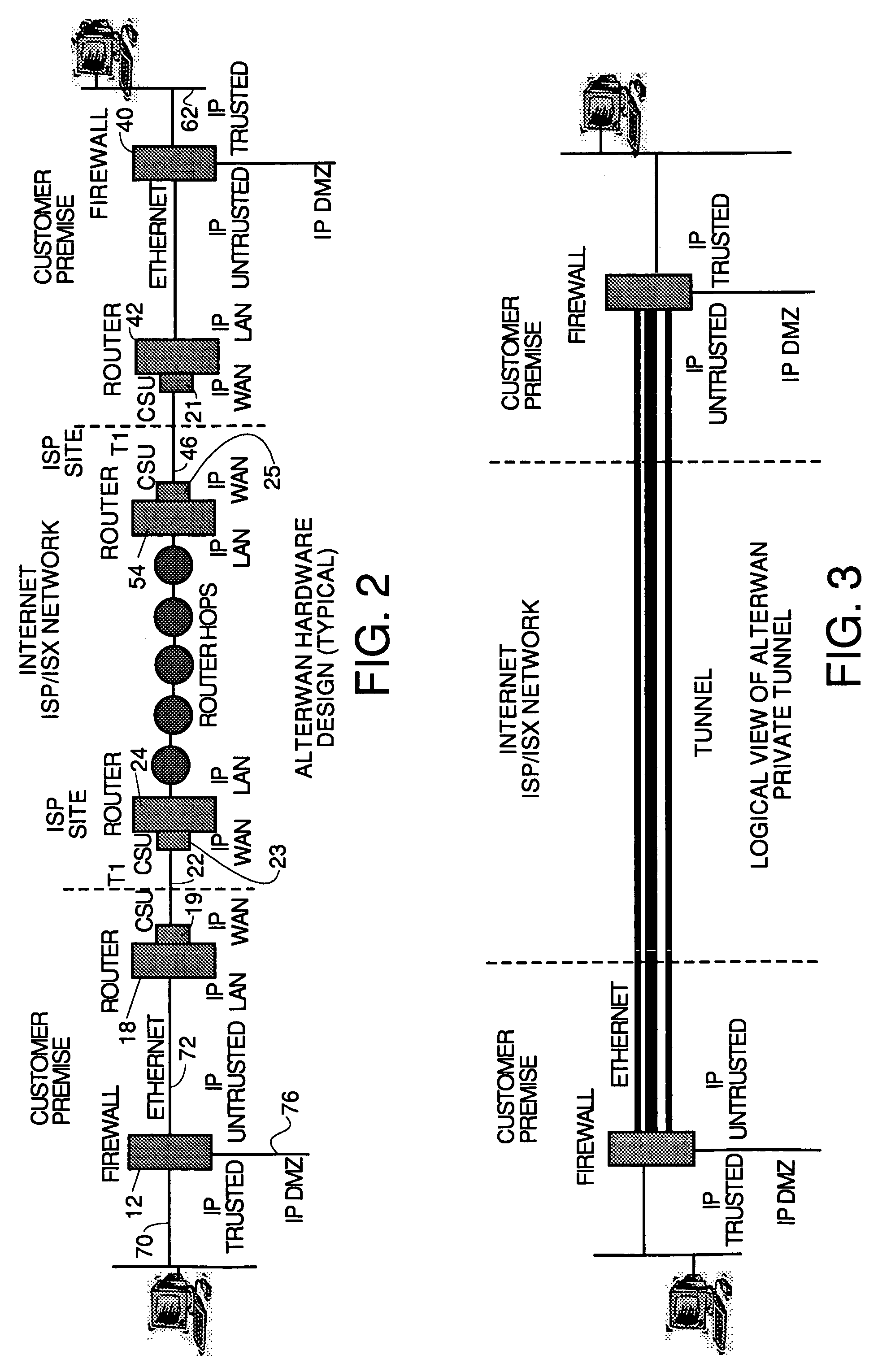

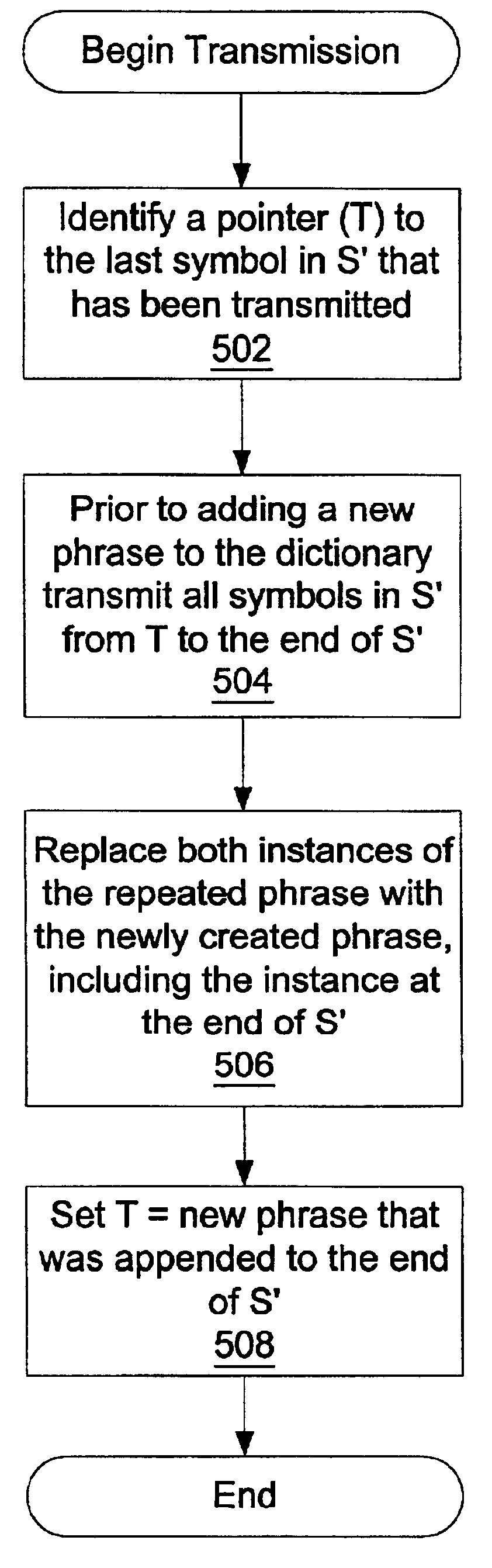

A wide area network using the internet as a backbone utilizing specially selected ISX / ISP providers whose routers route AlterWAN packets of said wide area network along private tunnels through the internet comprised of high bandwidth, low hop-count data paths. Firewalls are provided at each end of each private tunnel which recognize IP packets addressed to devices at the other end of the tunnel and encapsulate these packets in other IP packets which have a header which includes as the destination address, the IP address of the untrusted side of the firewall at the other end of the tunnel. The payload sections of these packets are the original IP packets and are encrypted and decrypted at both ends of the private tunnel using the same encryption algorithm using the same key or keys.

Owner:ALTERWAN

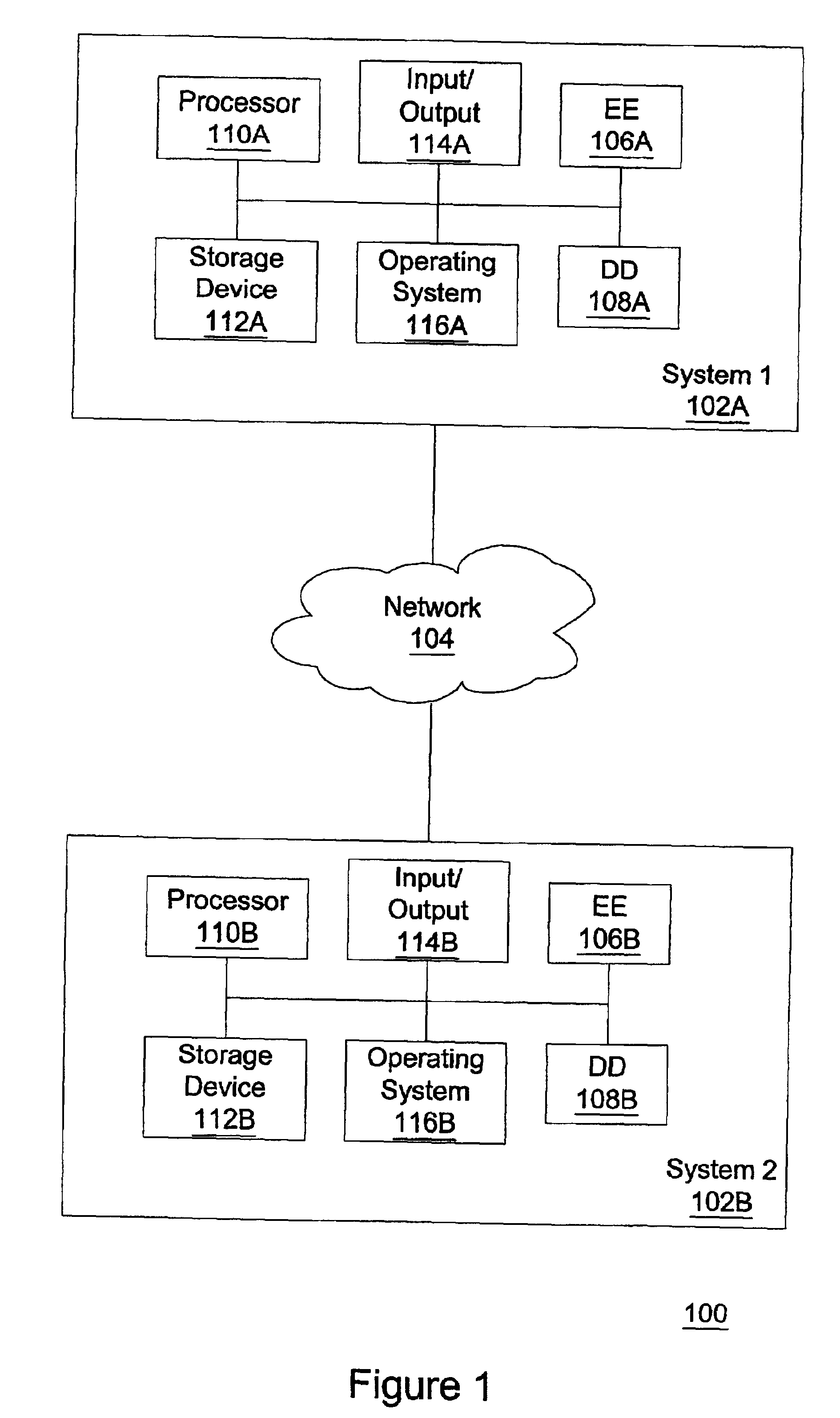

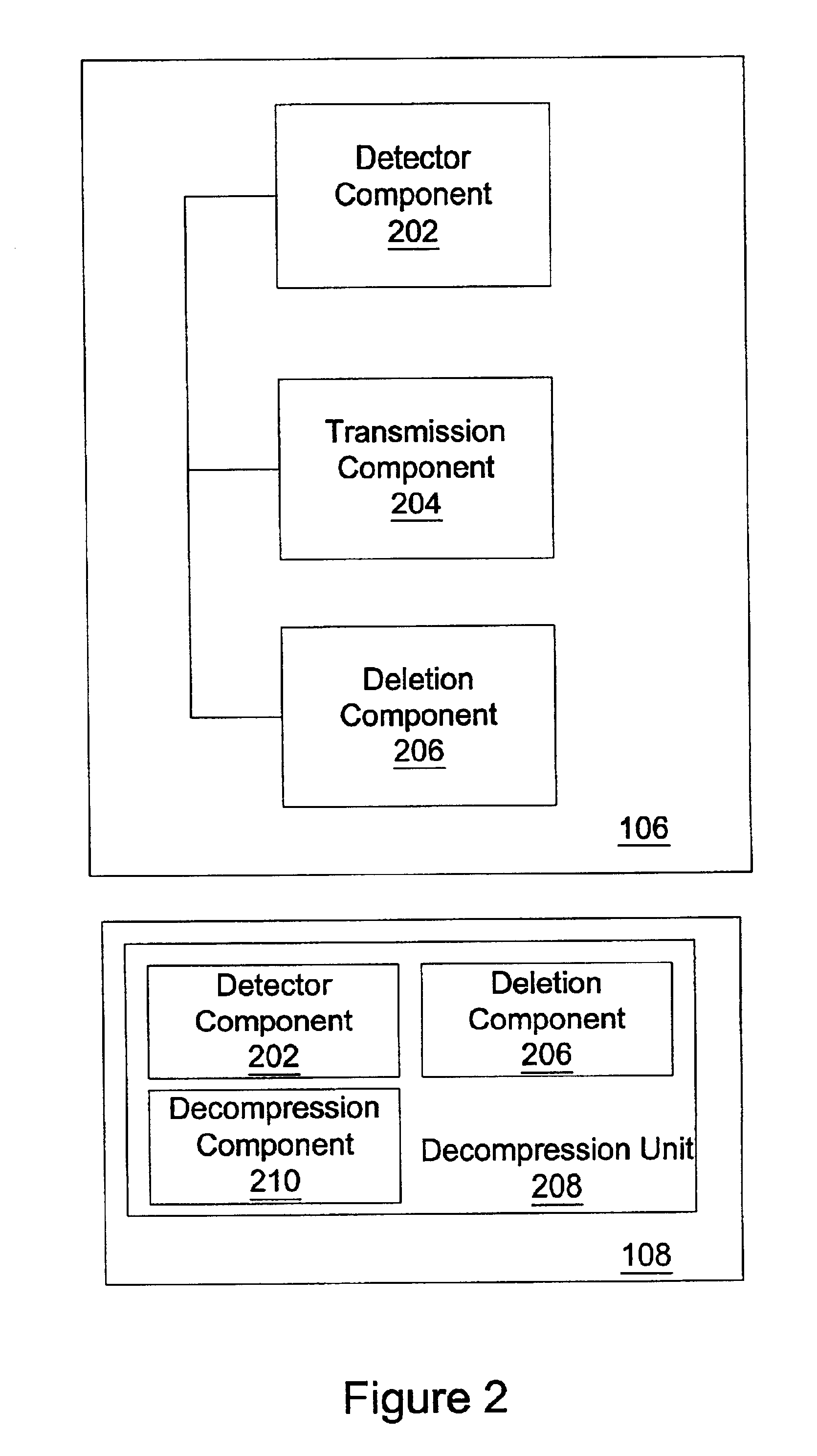

System and method for incremental and continuous data compression

ActiveUS6856651B2Not affect speedEfficient compressionColor television with pulse code modulationColor television with bandwidth reductionData compressionVariable length

A data compression system and method for that is capable of detecting and eliminating repeated phrases of variable length within a window of virtually unlimited size.

Owner:RIVERBED TECH LLC

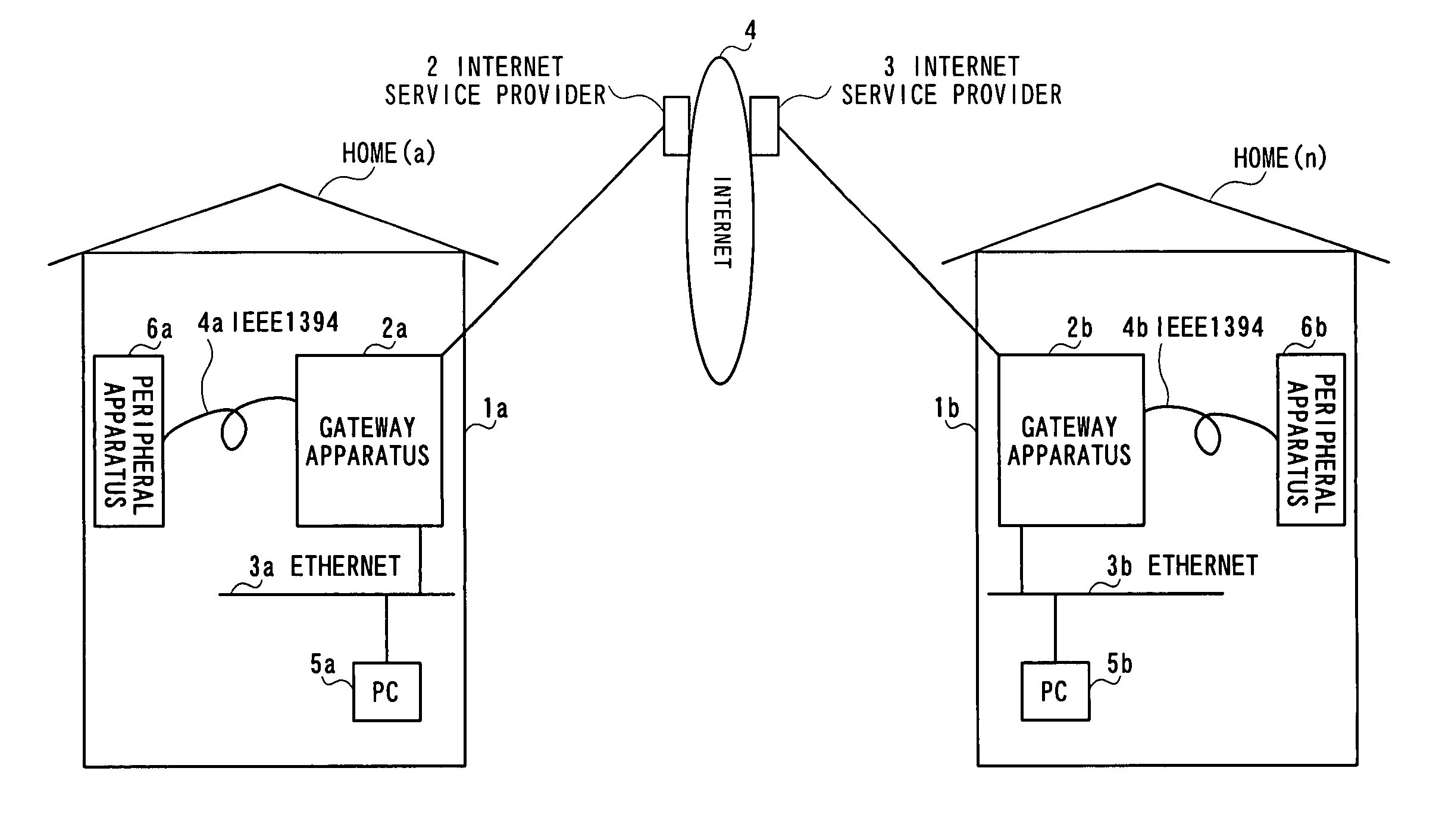

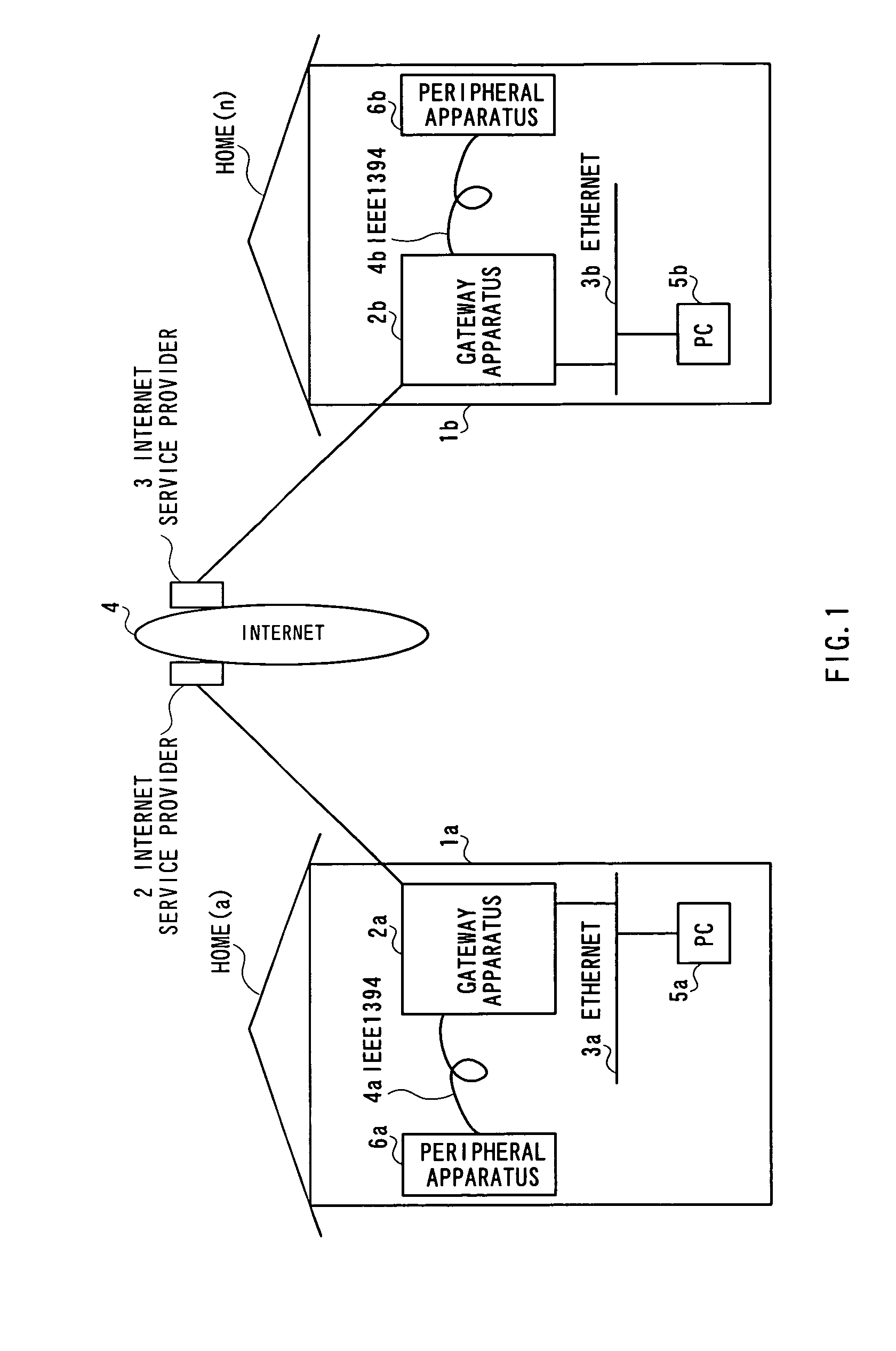

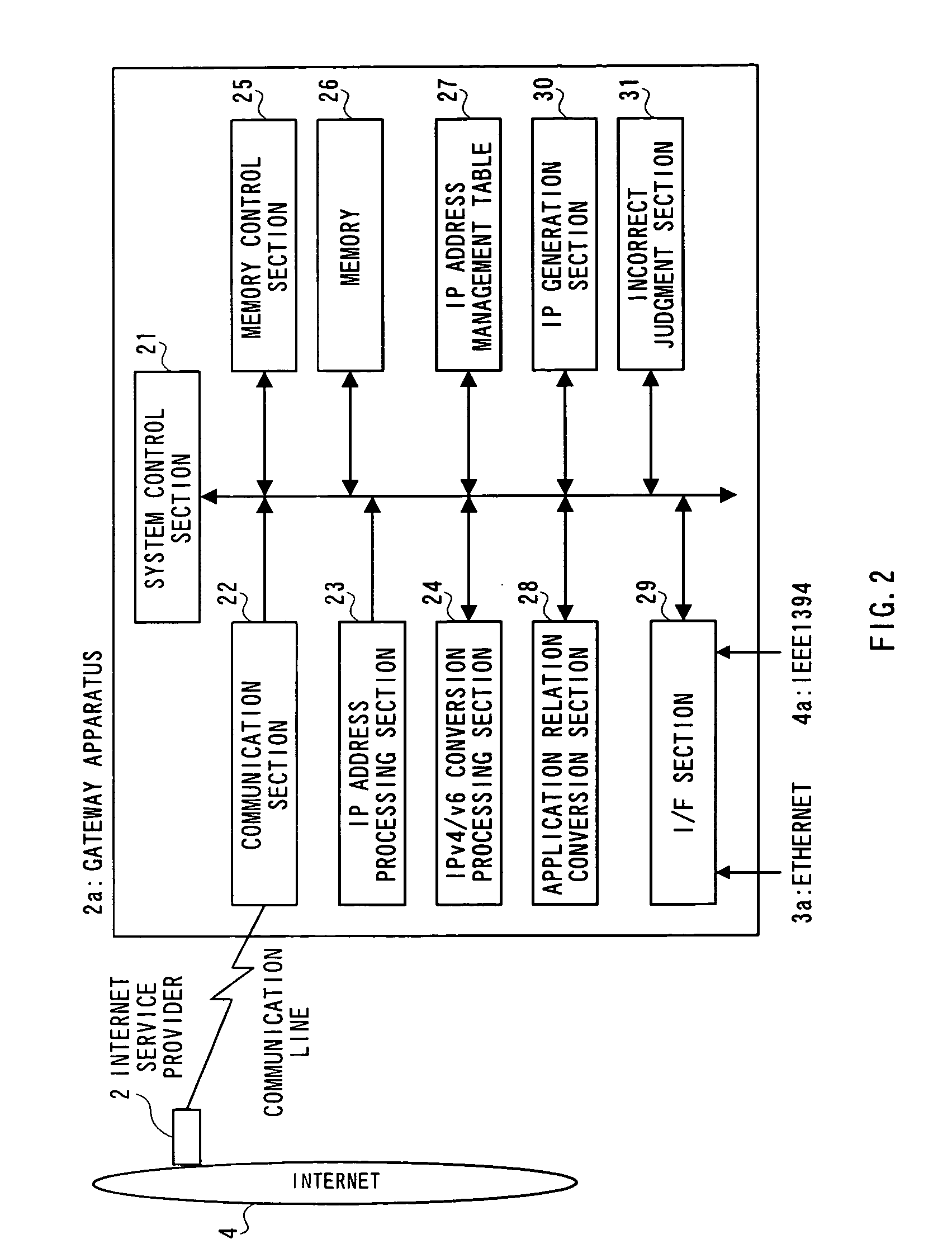

Gateway apparatus for controlling apparatuses on home network

InactiveUS6957275B1Easy to controlAvoid accessMultiple digital computer combinationsNetworks interconnectionIp addressIdentification device

The gateway apparatus has an IP address table that relates a plurality of apparatuses, each of which is one of components constructing a home network, to IP addresses respectively assigned to the apparatuses to store, a reception section that receives data with a destination indicative of one of the apparatuses constructing the home network, a recognition section that recognizes the apparatus with an IP address matching the IP address indicative of the destination contained in received data using the IP address table, and a distribution section that transmits the received data to the recognized apparatus.

Owner:MATSUSHITA GRAPHIC COMM SYST INC

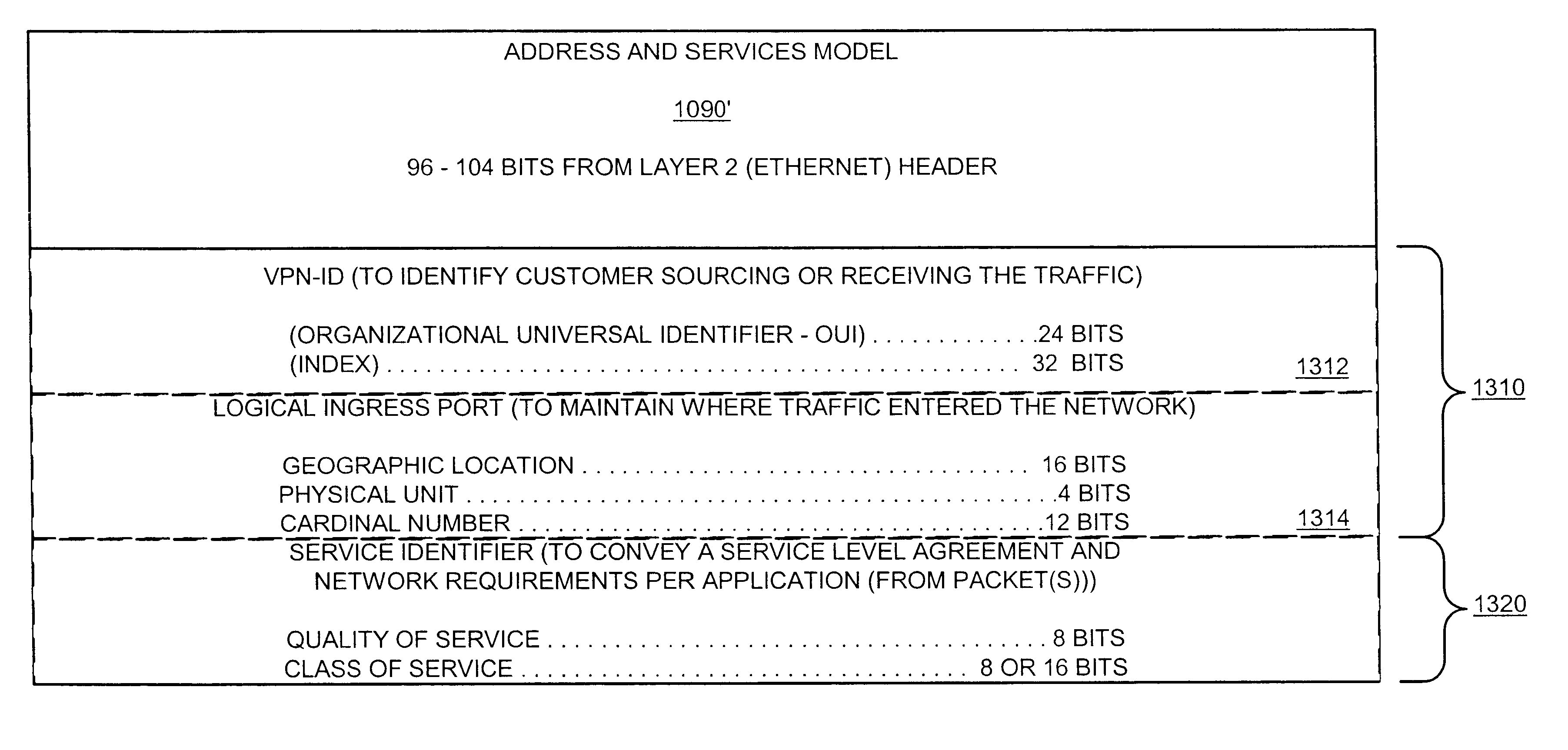

Methods and apparatus and data structures for providing access to an edge router of a network

Aggregating physical connections from customers for presentation to an access router and de-aggregating traffic from a shared link(s) from the access router. Ports of an aggregation unit may be configured such that each has a unique identifier in the place of information (e.g., the layer 2 address) originally in the layer 2 header. The layer 2 (e.g., MAC) address of the customer device connected with the port can be associated with, and therefore determined from, the IP address of the attached device. When a packet is received from a customer, information in the layer 2 header is changed to a unique identifier assigned to a logical port or interface associated with the physical port. When a packet is received from the access router, it is placed on the port assigned to the logical port associated with the destination layer 2 address (or associated with other bits of the unique bit string and at least some of those bits are replaced with the destination layer 2 address of the device associated with the port.

Owner:VERIZON PATENT & LICENSING INC

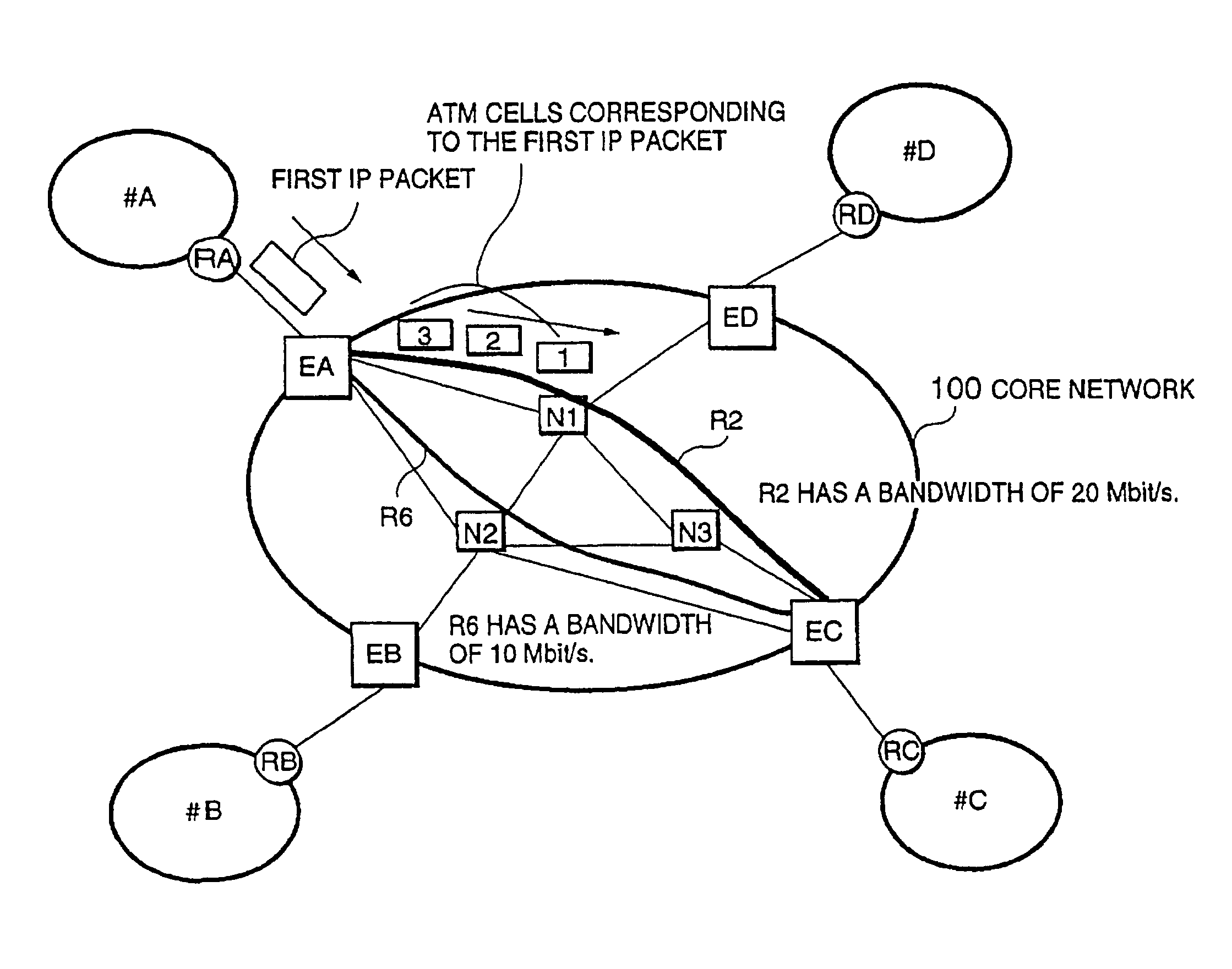

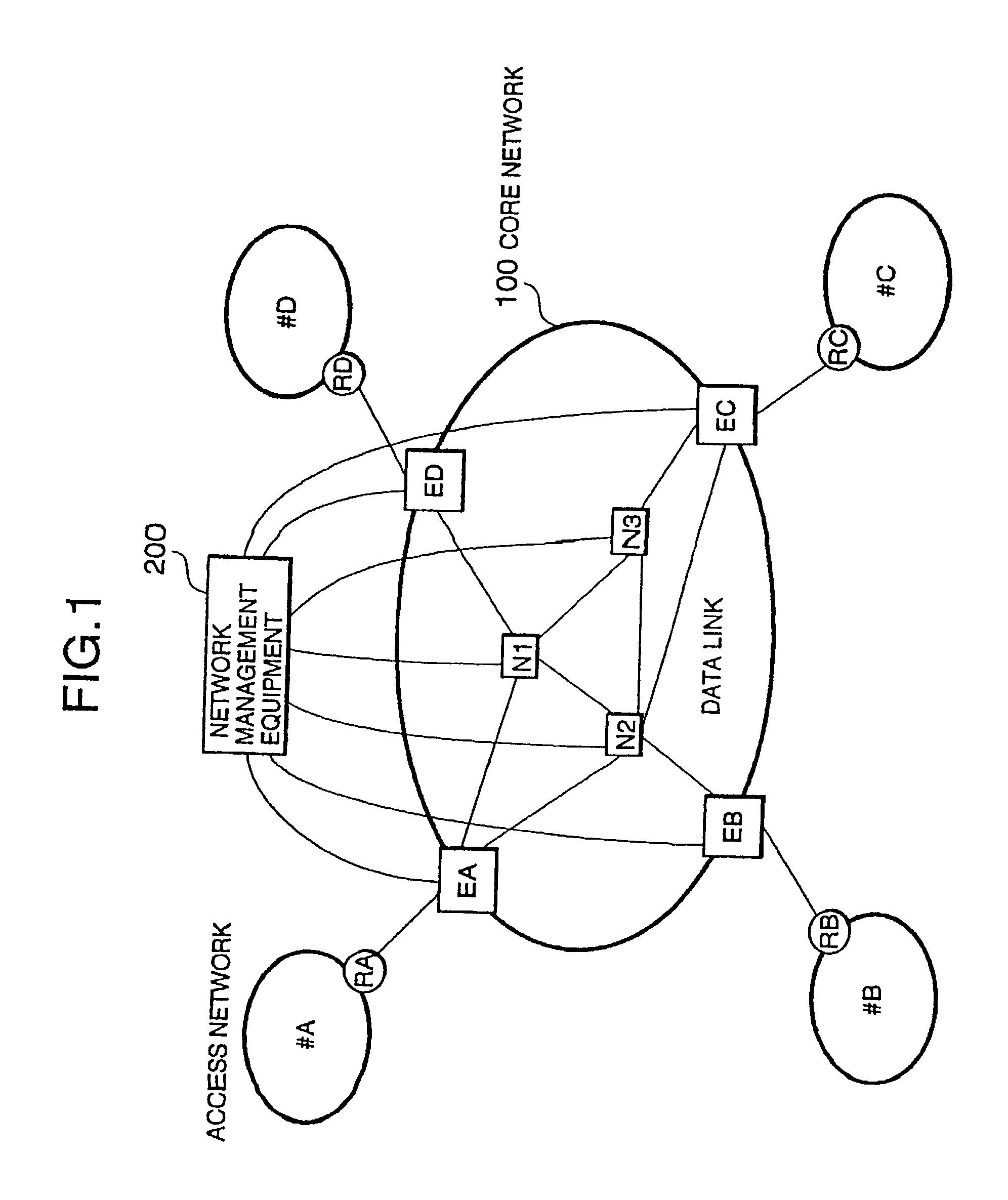

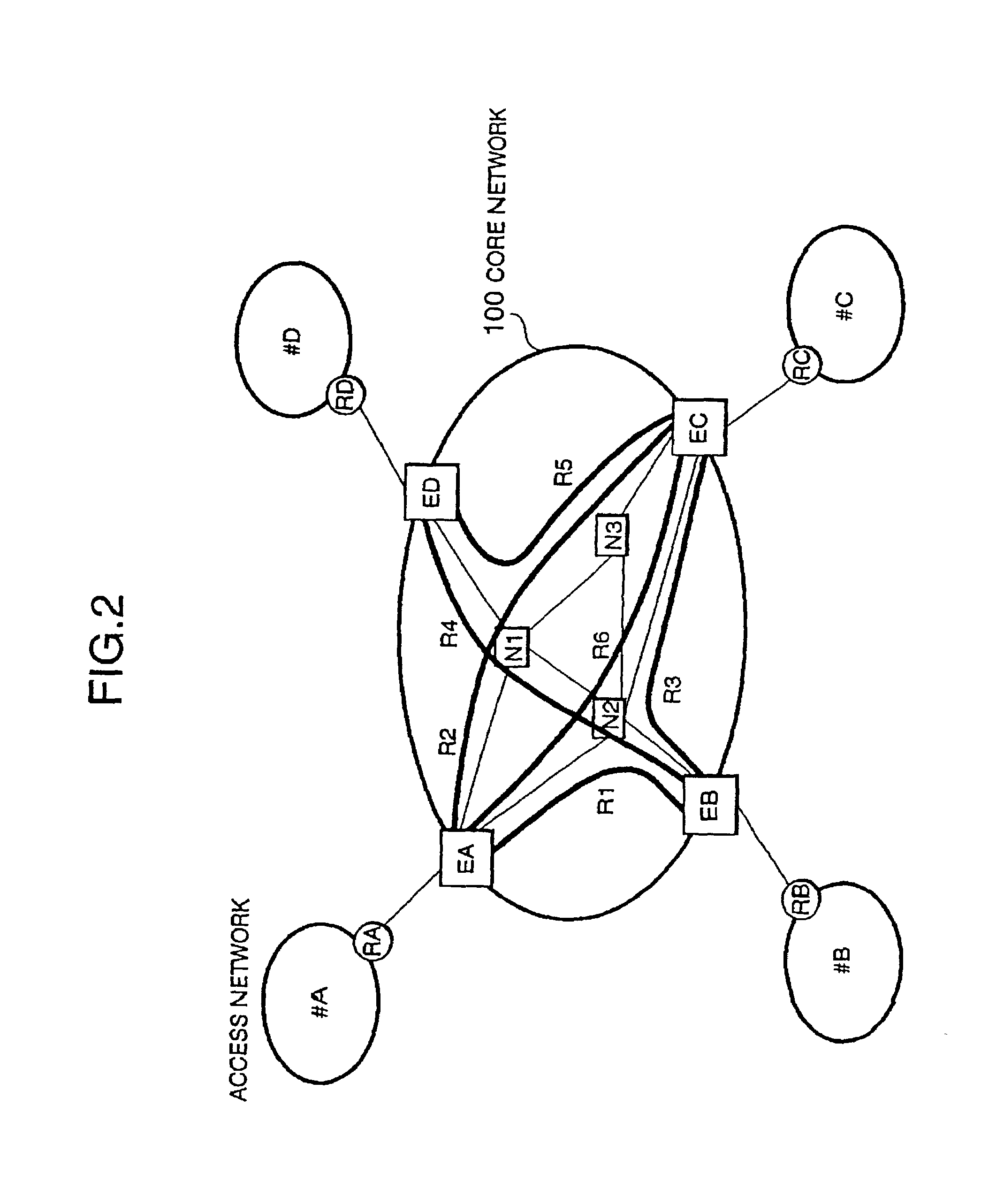

Packet switching network, packet switching equipment and network management equipment

InactiveUS7046630B2Reduces delay variationReduce in quantityError preventionTransmission systemsAccess networkDelayed time

This invention provides a network management equipment and a packet switching equipment which eliminate a connection setup delay time, reduce a delay and a delay variation involved in data transfer, and effectively perform connectionless data flow processing in a large data network. The network is divided into a connection-oriented core network and a plurality of connectionless access networks connected to the core network where a plurality of connections (called permanent virtual route (PVR)) are set up among a plurality of edge nodes. The network management equipment selects one route from a plurality of PVRs for connectionless data flow received from one of the access networks and transfers data along the PVR.

Owner:HITACHI LTD

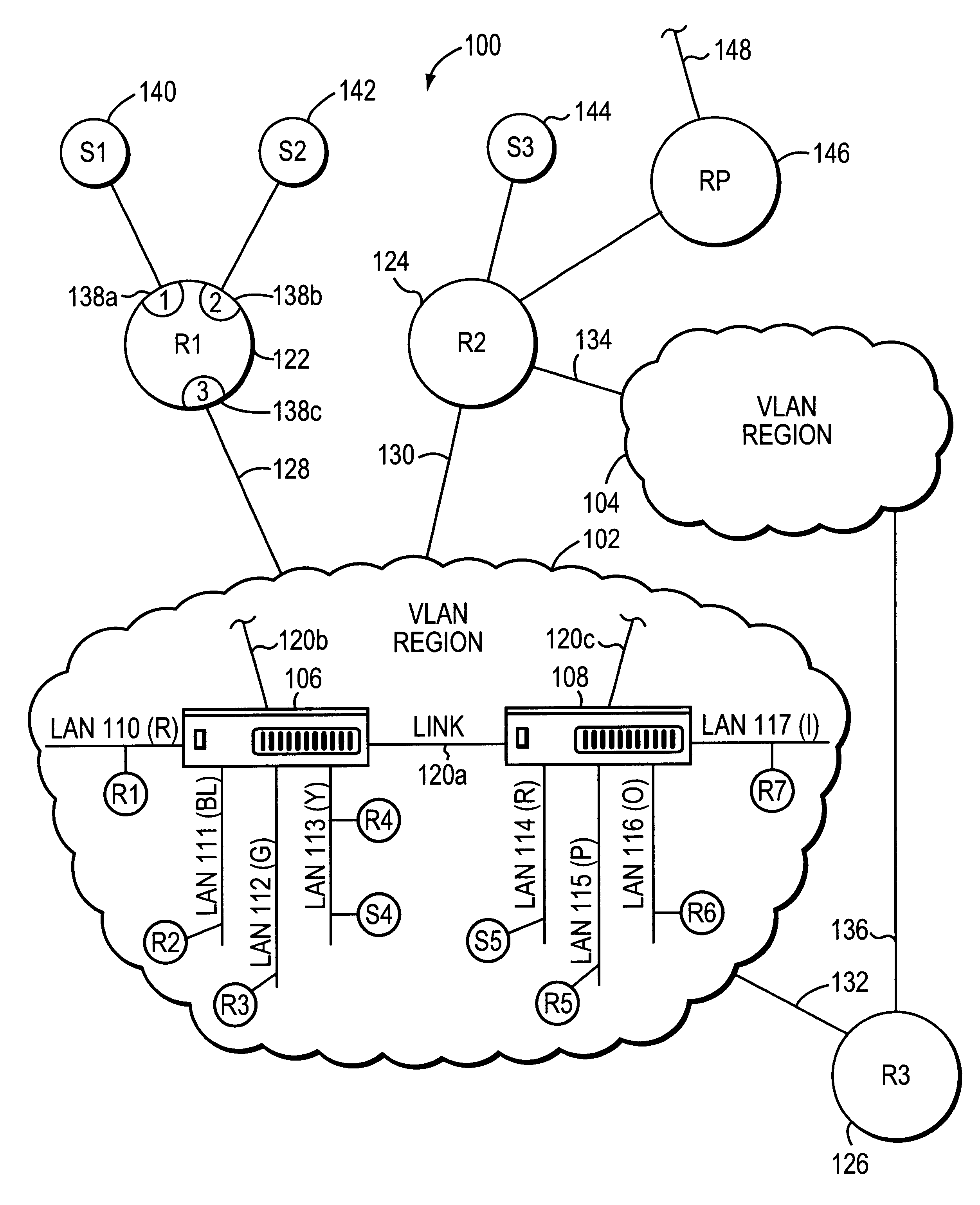

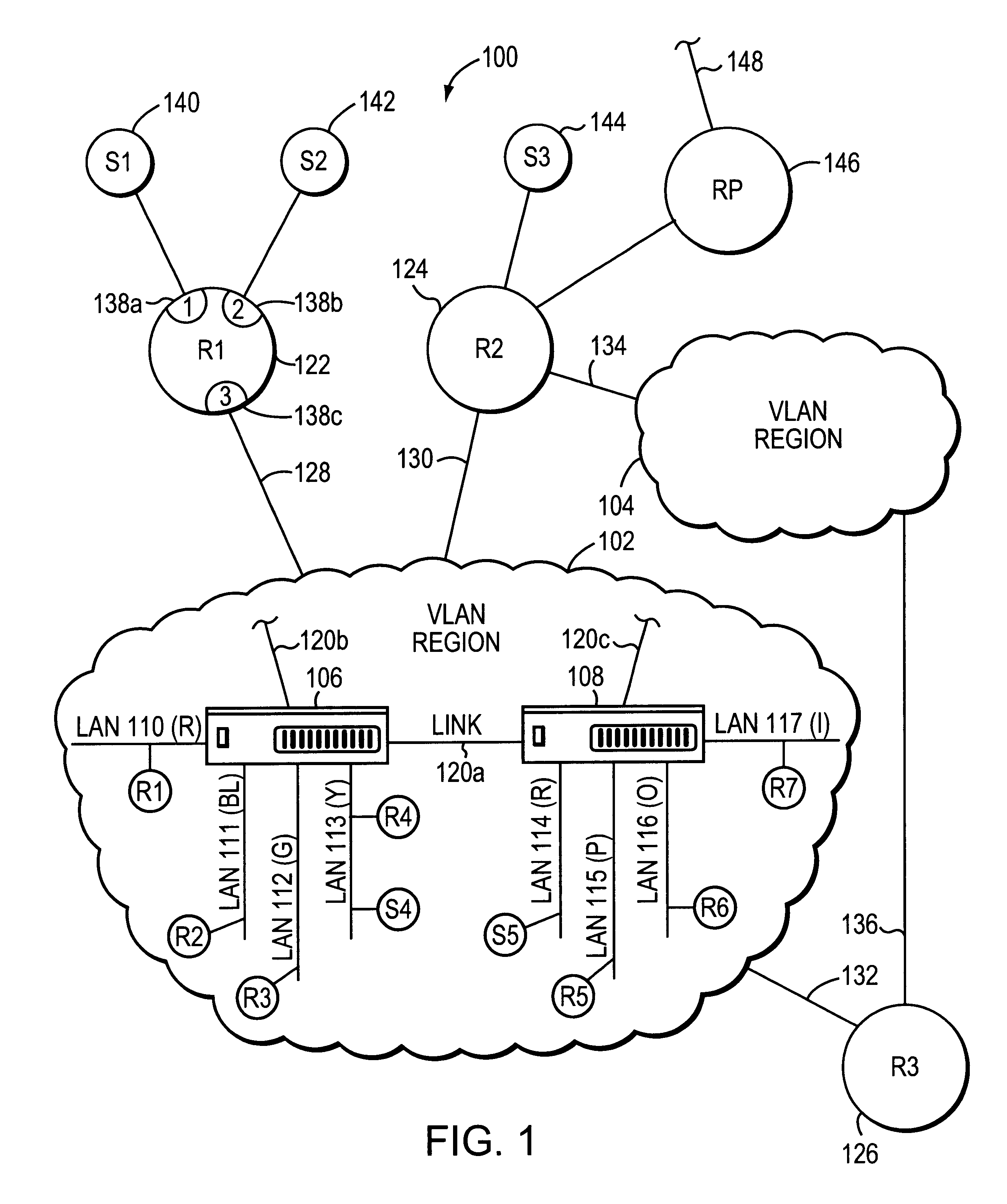

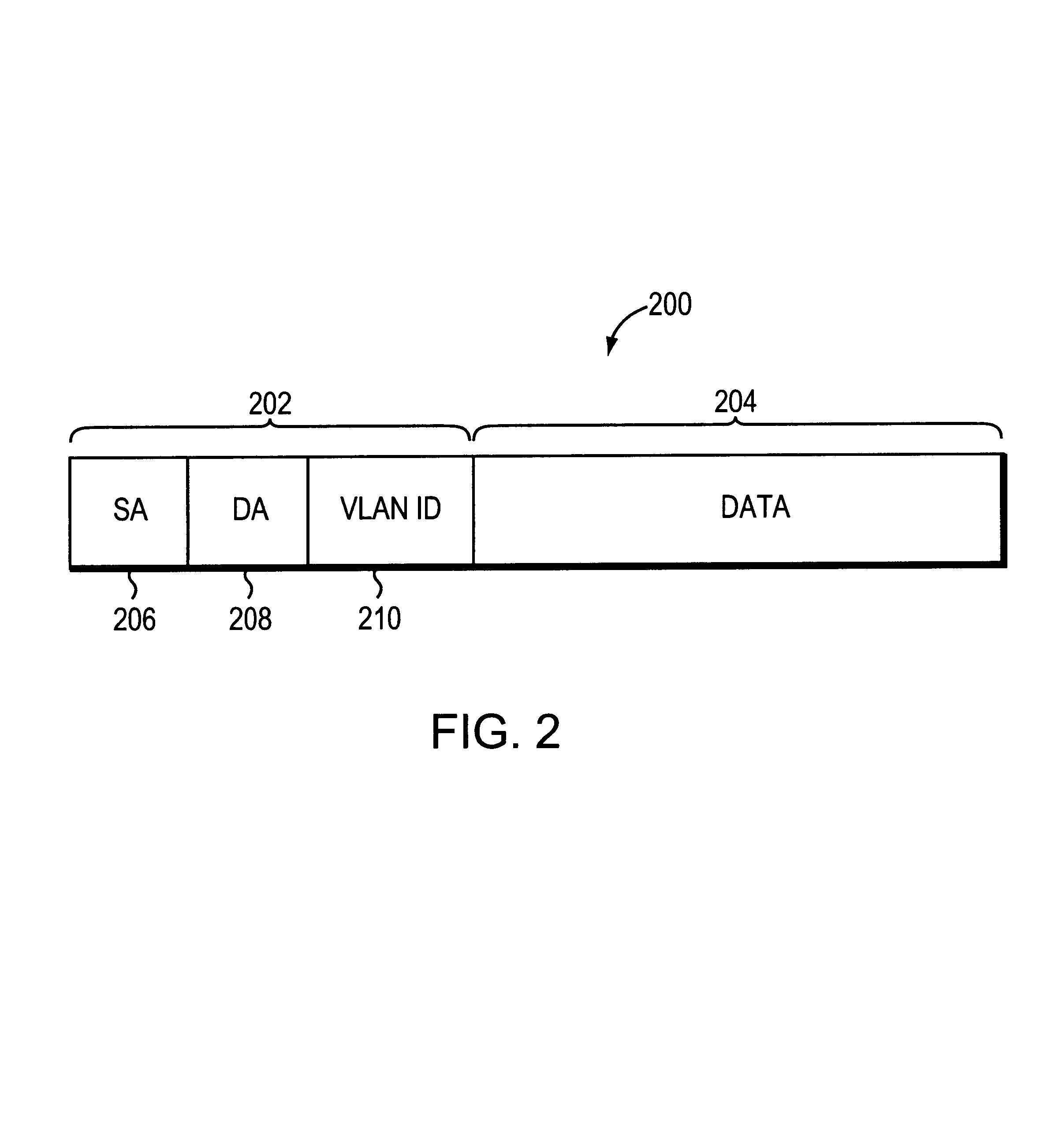

System and method for distributing multicasts in virtual local area networks

InactiveUS6839348B2Effective distributionEfficiently distributedSpecial service provision for substationTime-division multiplexVirtual LANIP multicast

The invention relates to a system and method for efficiently distributing multicast messages within computer networks configured to have one or more virtual local area network (VLAN) domains. A multicast network device (MND), having a plurality of interfaces, includes a multicast controller for efficiently distributing multicast messages among subscribing entities associated with various VLAN domains. The multicast controller, which is in communicating relationship with the interfaces, includes a VLAN assignment engine for assigning responsibility for the VLAN domains to the extent there are multiple MNDs. The multicast controller also accesses a multicast tag source to establish a plurality of novel VLAN tags for efficiently distributing multicast messages, including a sub-regional Multicast VLAN Identifier (MVLAN-ID) that encompasses all of the VLAN domains for which the respective MND is responsible, and one or more color-limited MVLAN-IDs that encompass all of the VLAN domains for which the MND is responsible except for one. The multicast controller then tags multicast messages with its sub-regional or a color-limited MVLAN-ID depending on whether the message is considered internal or external by the respective MND. The tagged messages are then forwarded for distribution to the subscribers associated with the various VLAN domains.

Owner:CISCO TECH INC

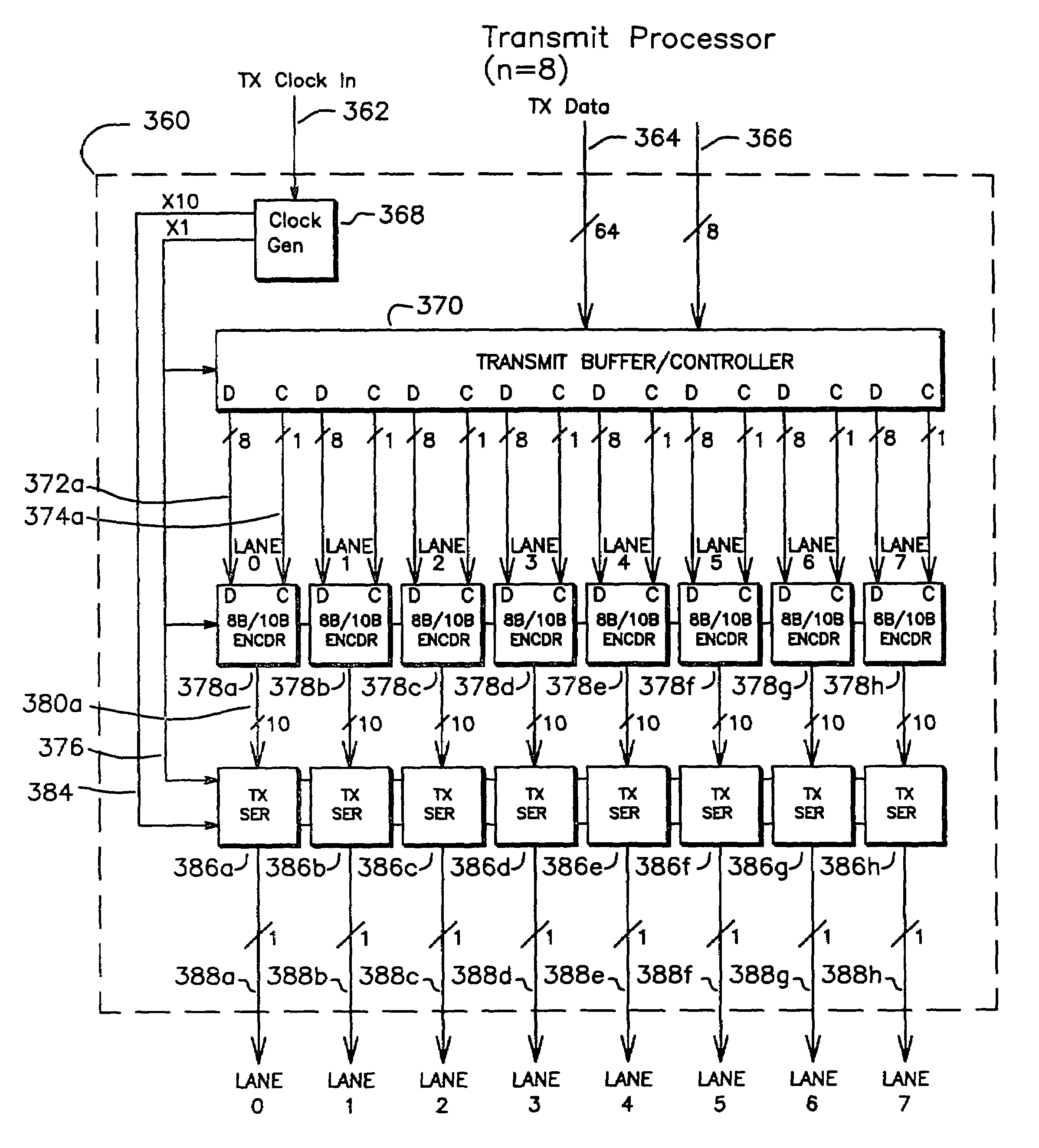

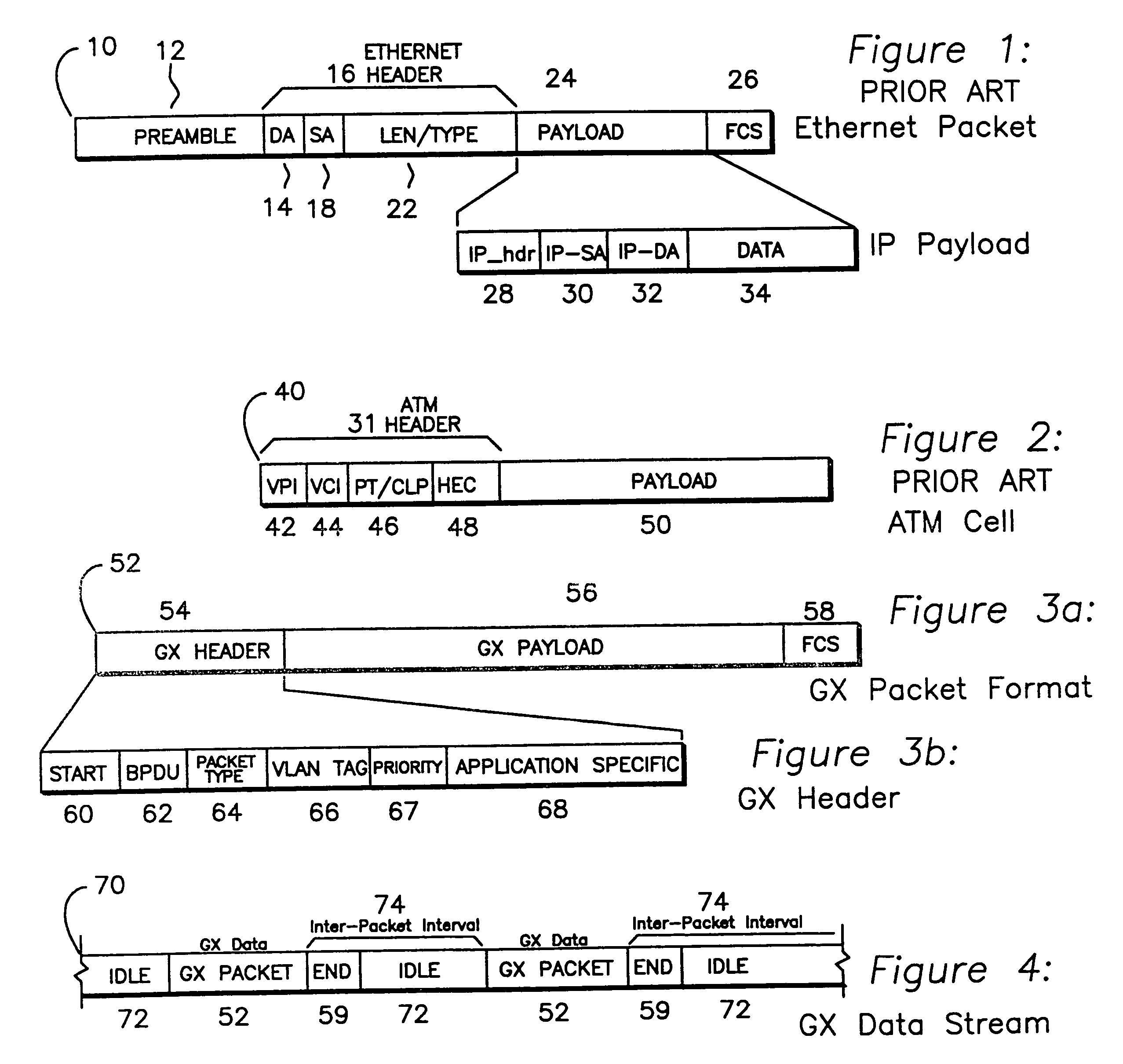

Multi-function high-speed network interface

InactiveUS7573916B1Multiplex system selection arrangementsTime-division multiplexCommunication interfaceClock rate

A high speed communications interface divides data into a plurality of lanes, each lane encoded with clocking information, serialized, and sent to an interface. During cycles when there is no available data to send, IDLE_EVEN and IDLE_ODD cells are sent on alternating cycles. Data is transmitted by sending a header which spans all lanes and includes a START symbol. The final data transaction includes a Frame Check Sequence (FCS) which operates over the entire header and data. The packet is terminated by an END symbol, which is sent after the final data, and the remainder of the lanes are padded with IDLE_EVEN, IDLE_ODD, IDLE_EVEN_BUSY, or IDLE_ODD_BUSY cycles. The interface has a variable clock rate.

Owner:CISCO TECH INC

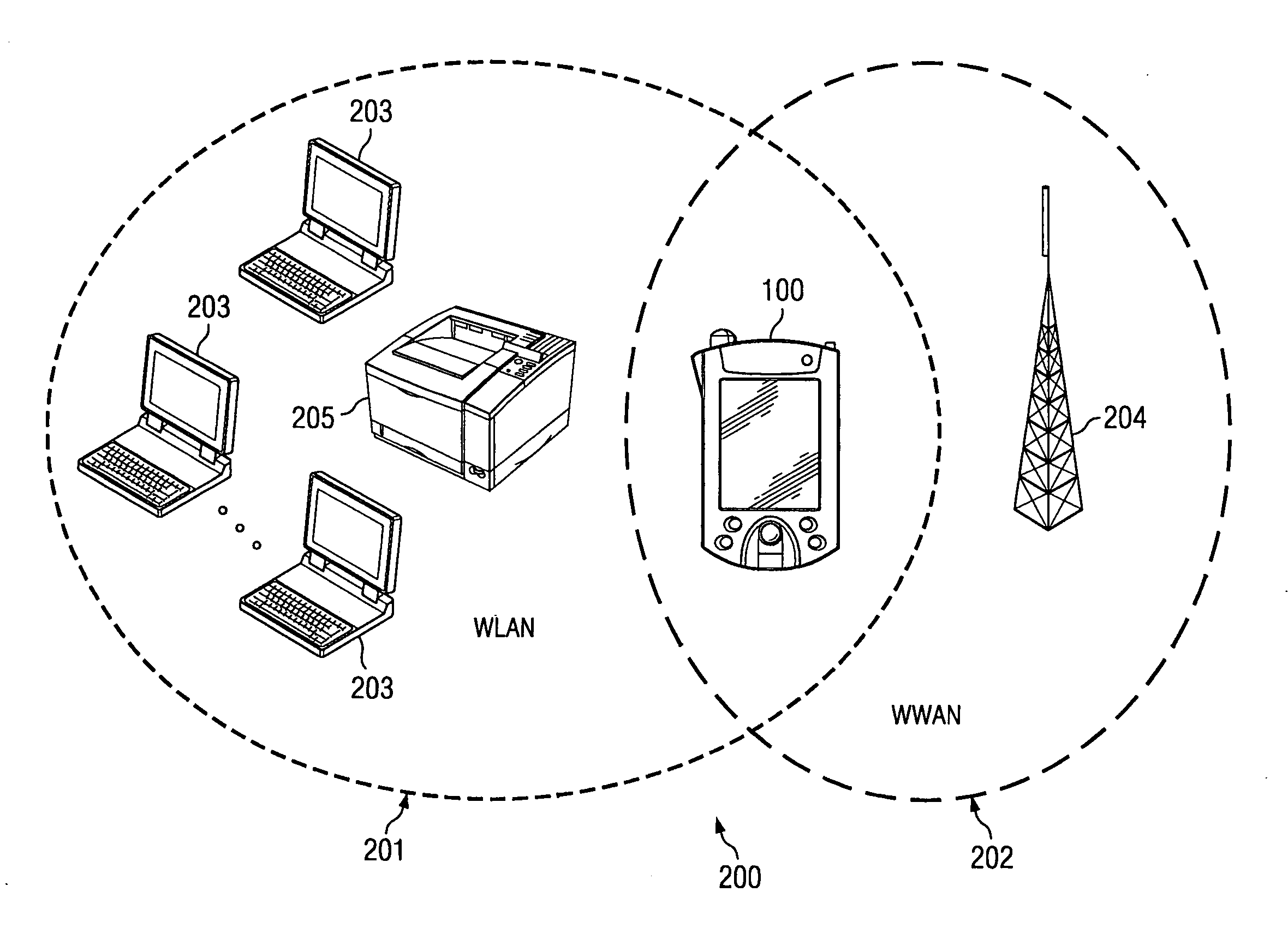

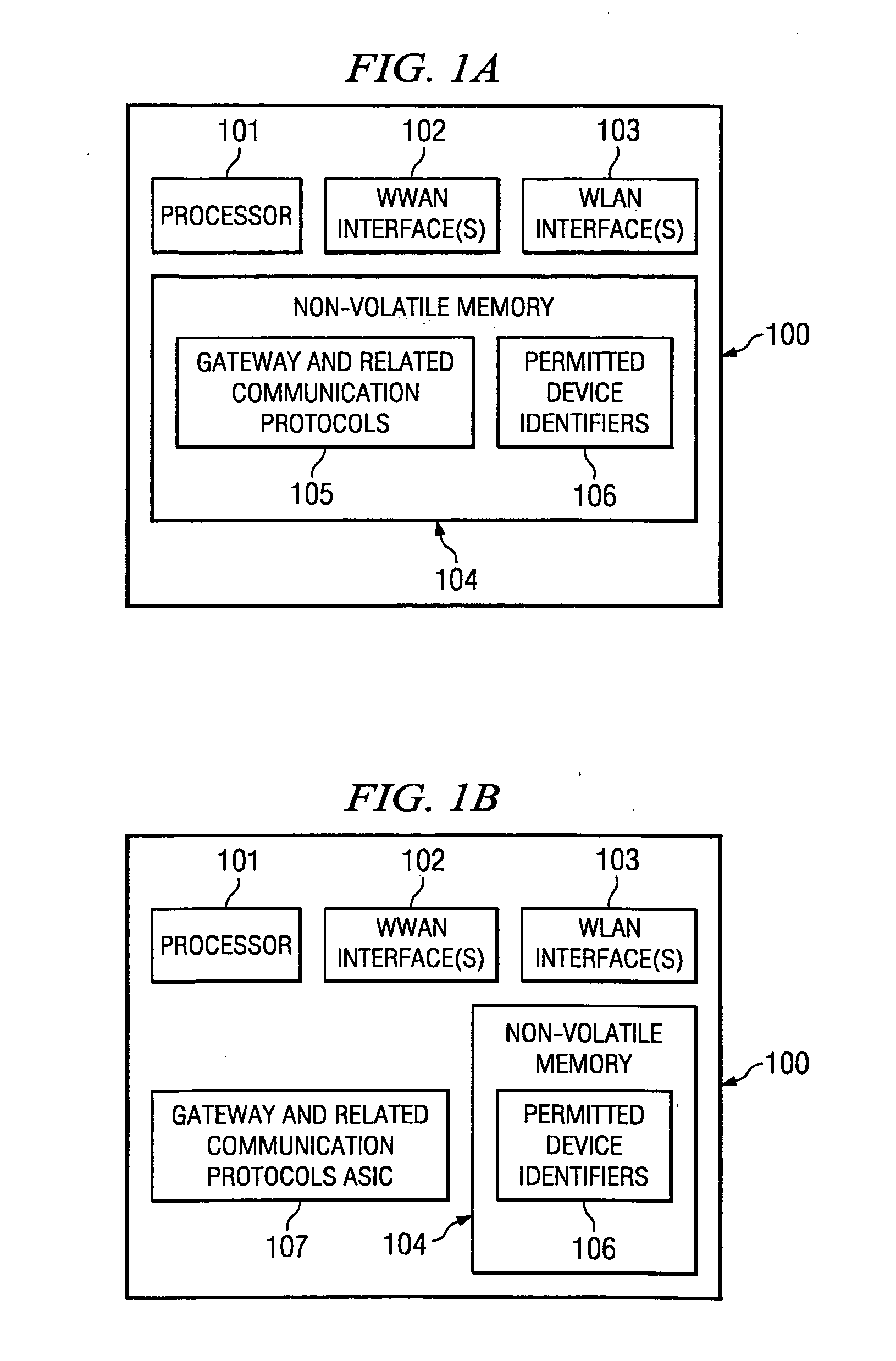

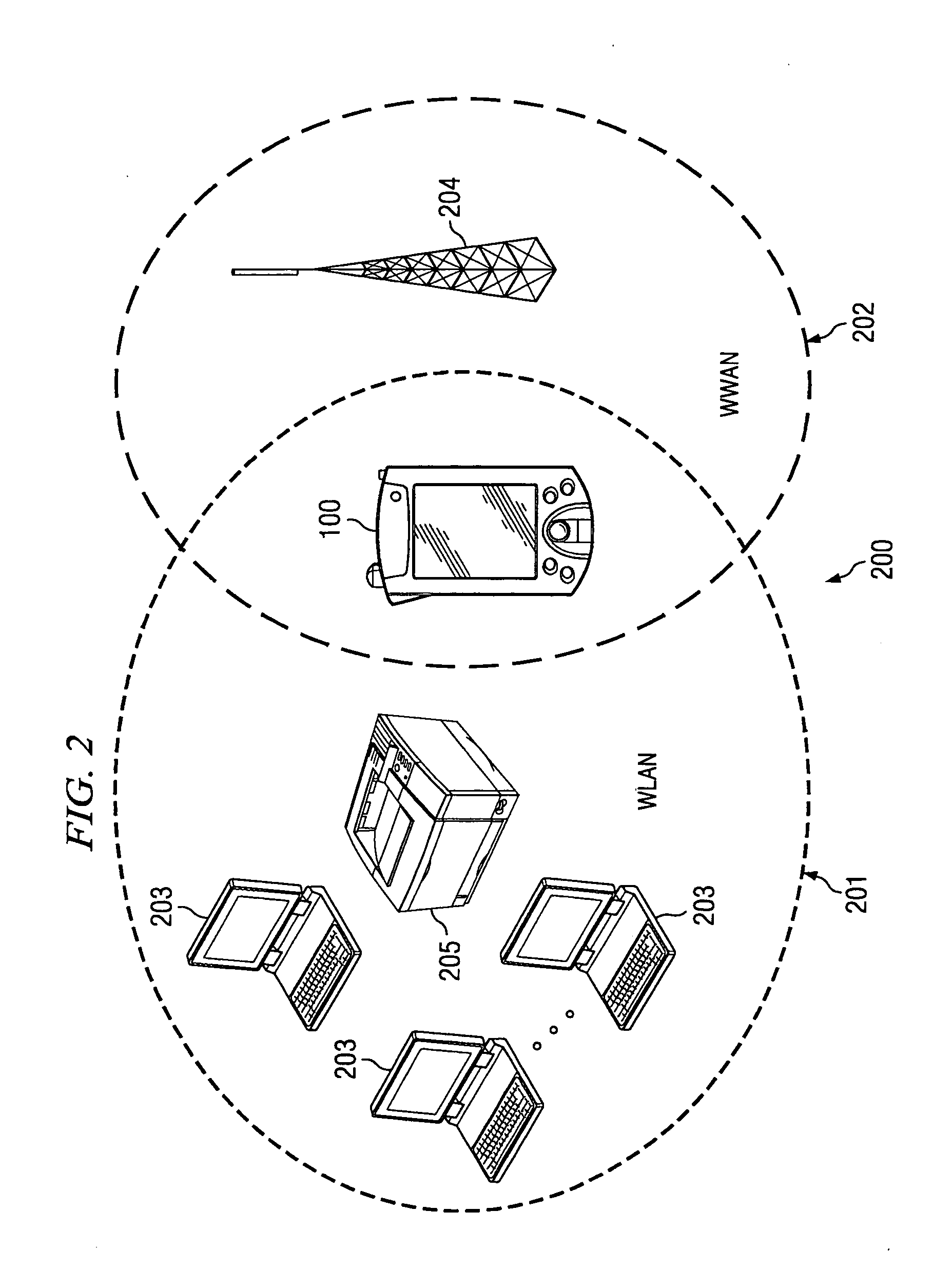

Portable computing device for wireless communications and method of operation

In one embodiment of the present invention, a portable computing device for wireless communications comprises a first network interface for communicating with a public wireless wide area network (WWAN), a second network interface for communicating with a private wireless local area network (WLAN), and a processor executing under control of software instructions, the software instructions defining a gateway protocol, the gateway protocol establishing the portable computing device as an access point within the private WLAN after the wireless presence on the public WWAN is established.

Owner:HEWLETT PACKARD DEV CO LP