IP core based on JESD 204 protocol

A protocol and protocol layer technology, applied in the IP core field, can solve problems such as large area and volume, crosstalk and synchronization, unfavorable technology upgrades, etc., to achieve the effects of avoiding crosstalk problems, improving receiving speed, and high transmission speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

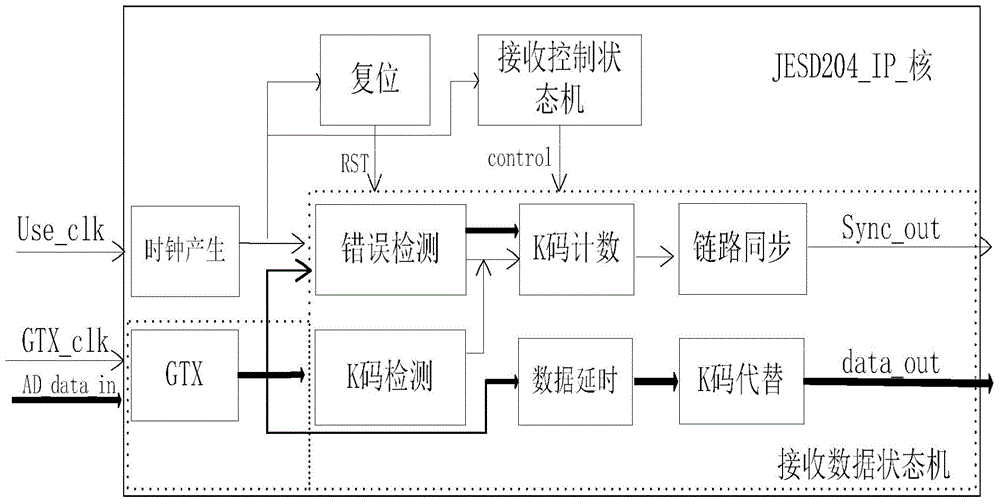

[0017] refer to figure 1 . In the programmable logic gate array FPGA, the physical layer of JESD204IP is realized based on the FPGA on-chip high-speed serial transceiver GTX, and the core protocol layer of JESD204IP is realized by using VHDL language. The FPGA contains multiple GTX interfaces, and each GTX interface receives data in a serial manner through a pair of differential signal lines between the ADC chip and the analog-to-digital converter. FPGA is based on the high-speed serial transceiver GTX, uses VHDL language, and implements the IP core of the JESD204 protocol according to the JESD204 protocol standard provided by the JEDEC international organization. The protocol layer is based on the user input clock User_clk, uses the clock generation unit clk_gen to generate the input clock required by all other functional units, generates the reset signal RST through the reset function unit RESET logic control, and generates the control signal control through the receiving c...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More