Patents

Literature

1703 results about "Netlist" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

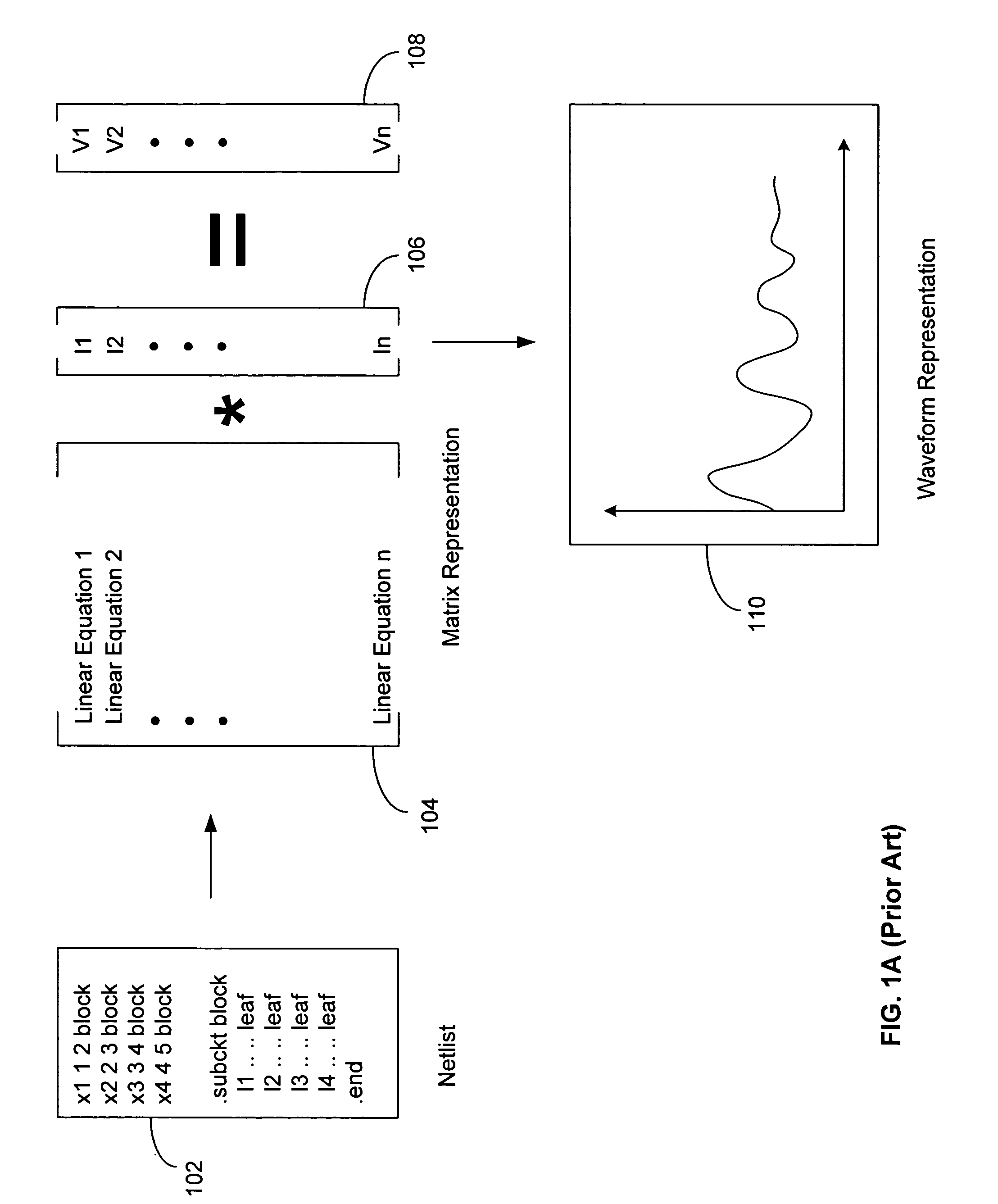

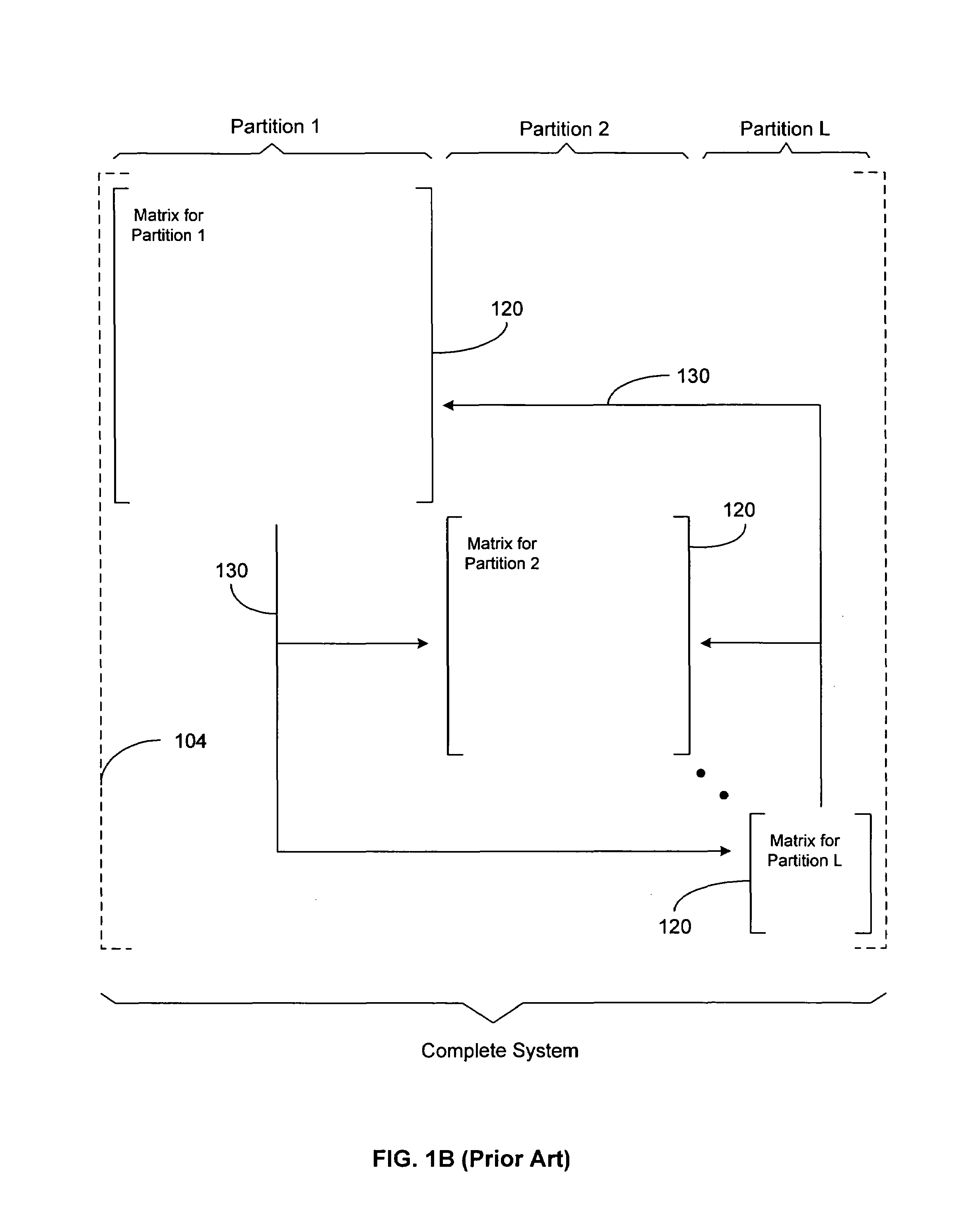

In electronic design, a netlist is a description of the connectivity of an electronic circuit. In its simplest form, a netlist consists of a list of the electronic components in a circuit and a list of the nodes they are connected to. A network (net) is a collection of two or more interconnected components.

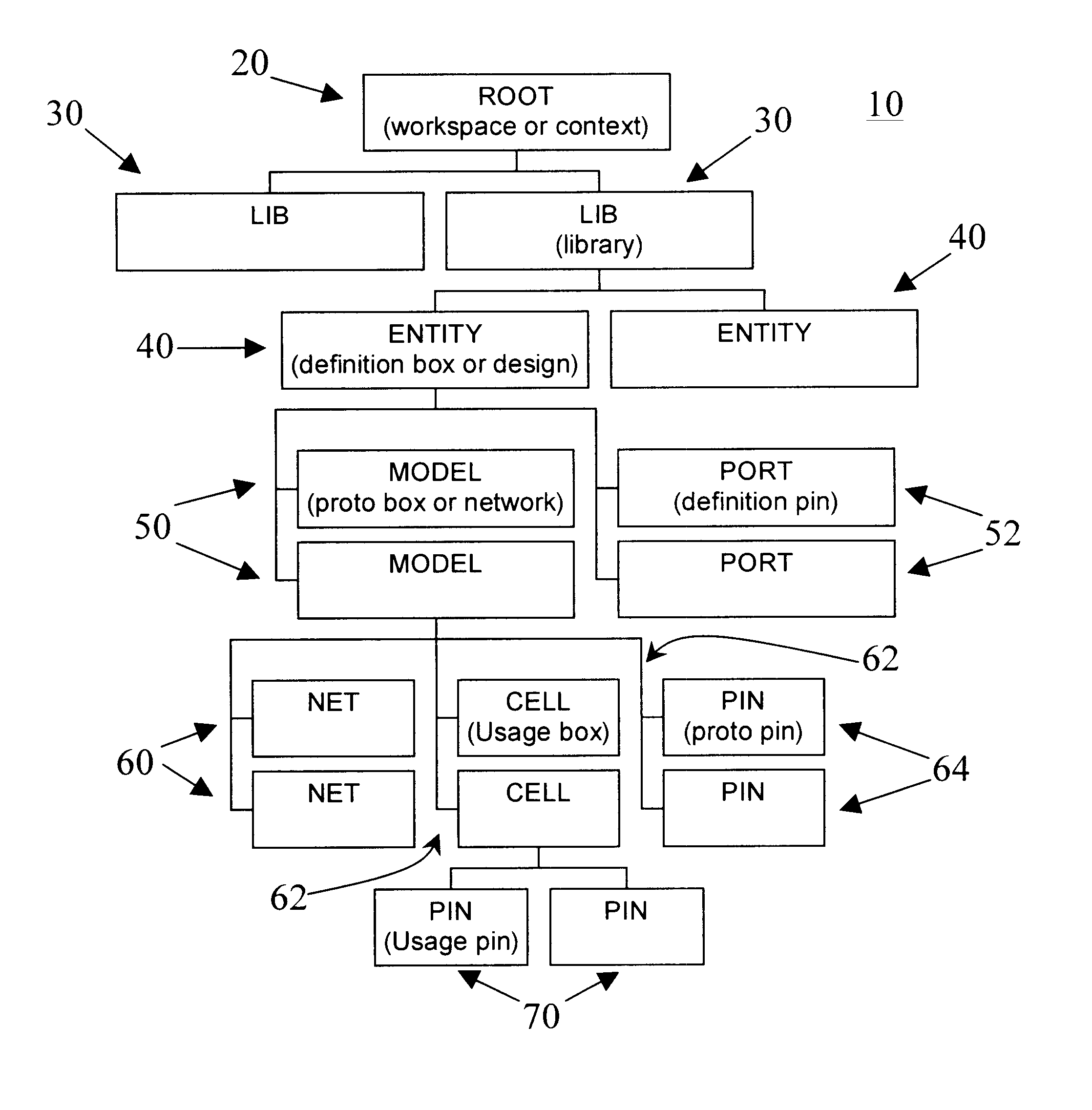

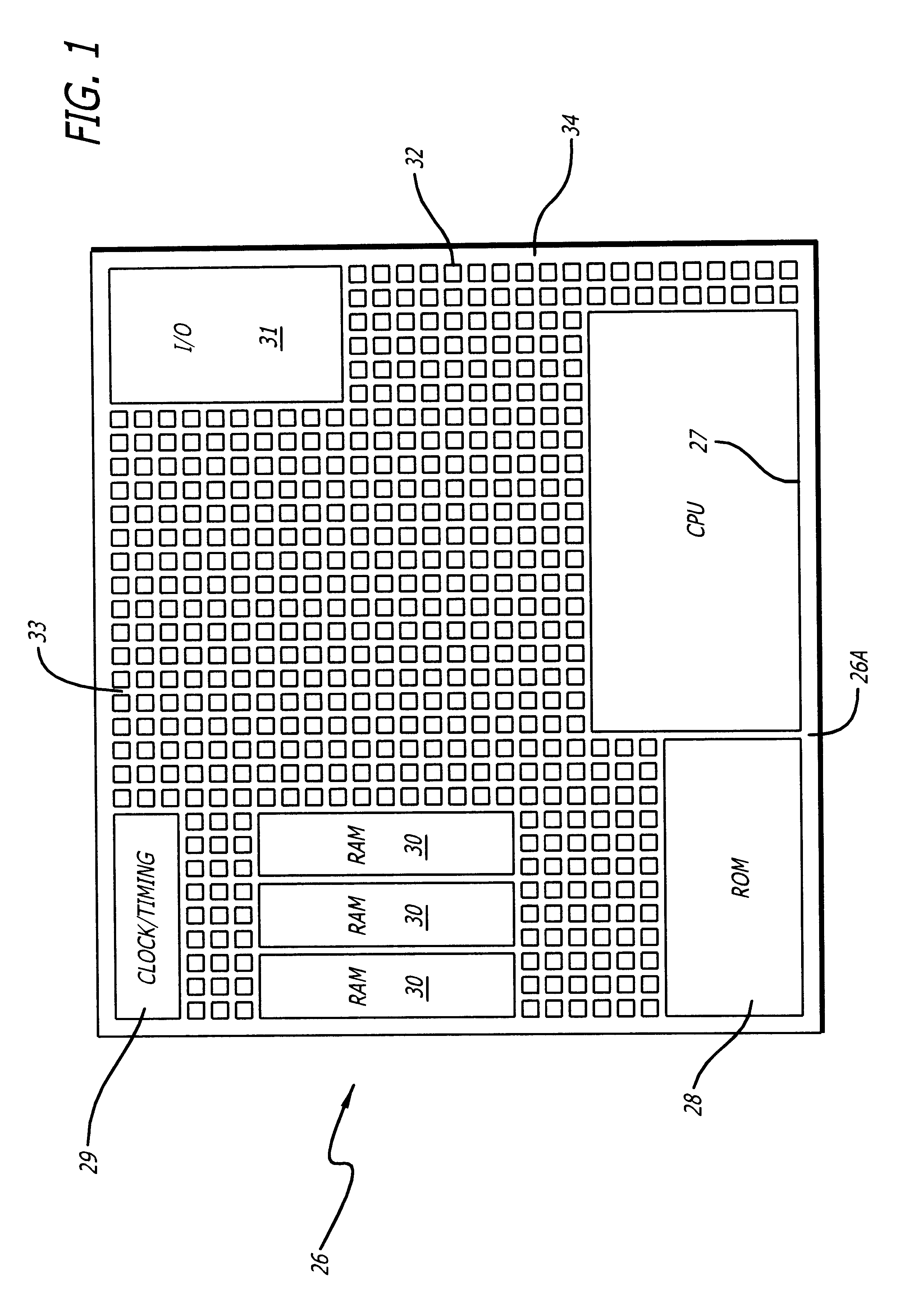

Method for storing multiple levels of design data in a common database

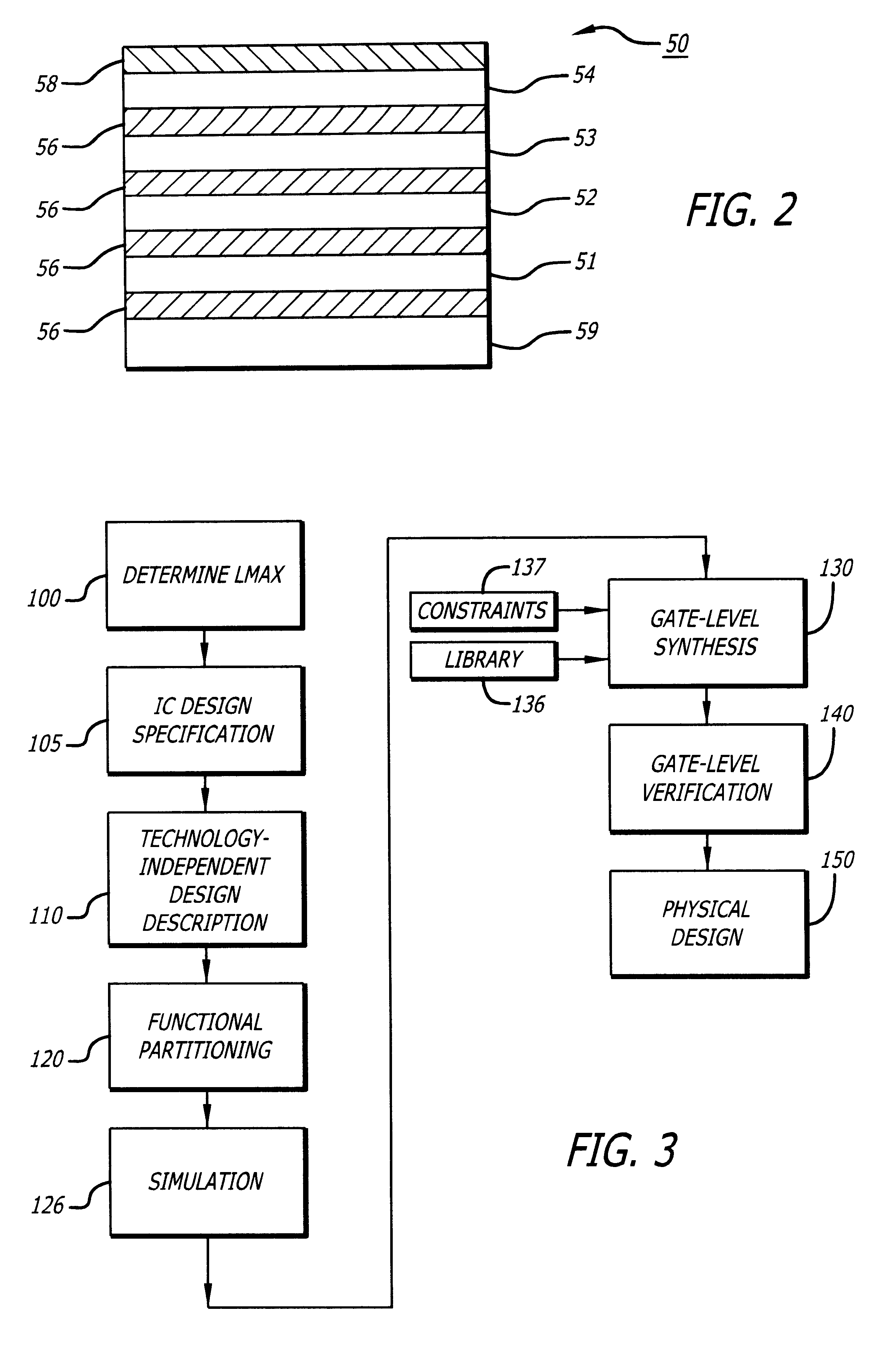

InactiveUS6505328B1Increase flexibilityEasy to integrateSemiconductor/solid-state device manufacturingCAD circuit designGraphicsLogic circuit design

Owner:MAGMA DESIGN AUTOMATION

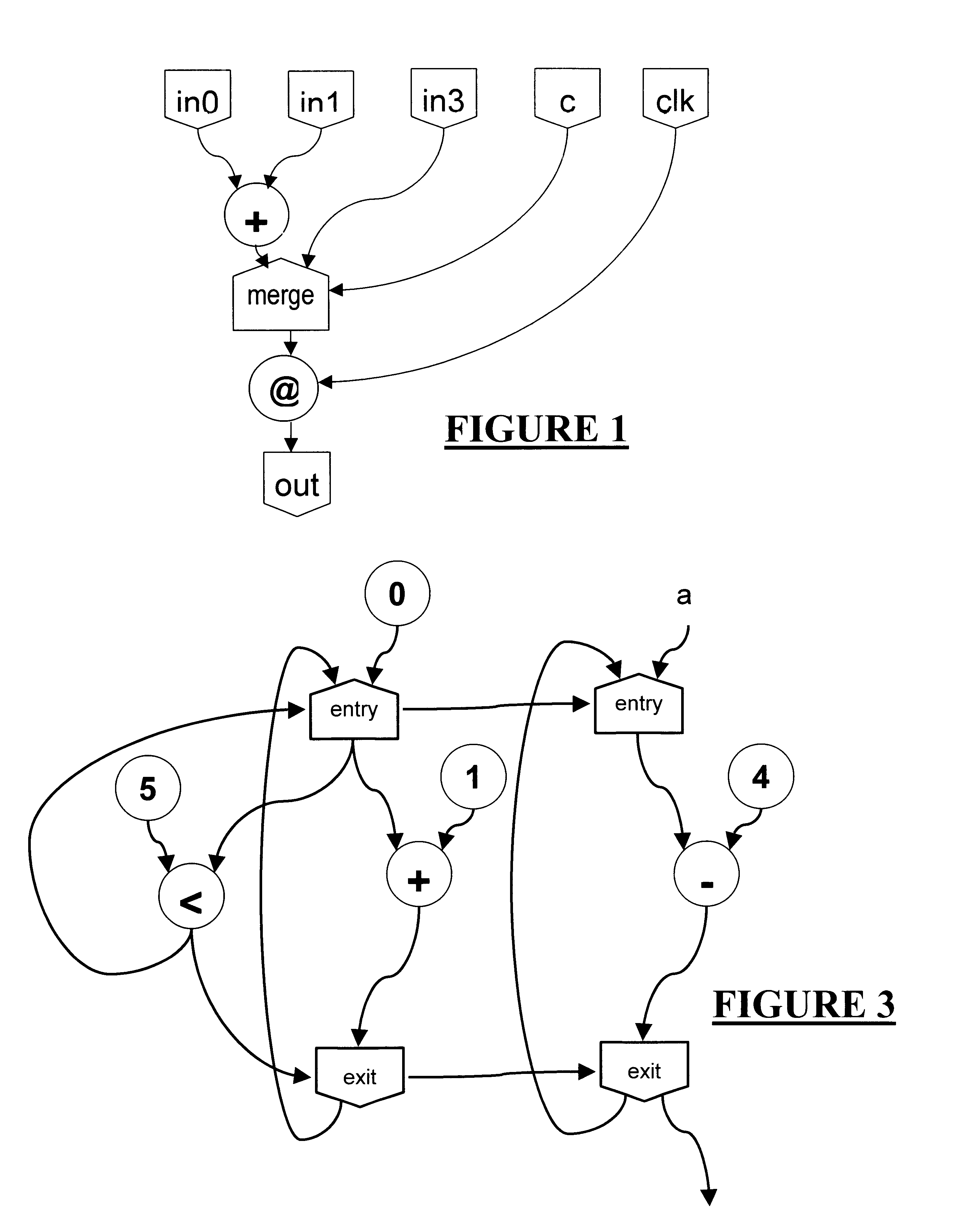

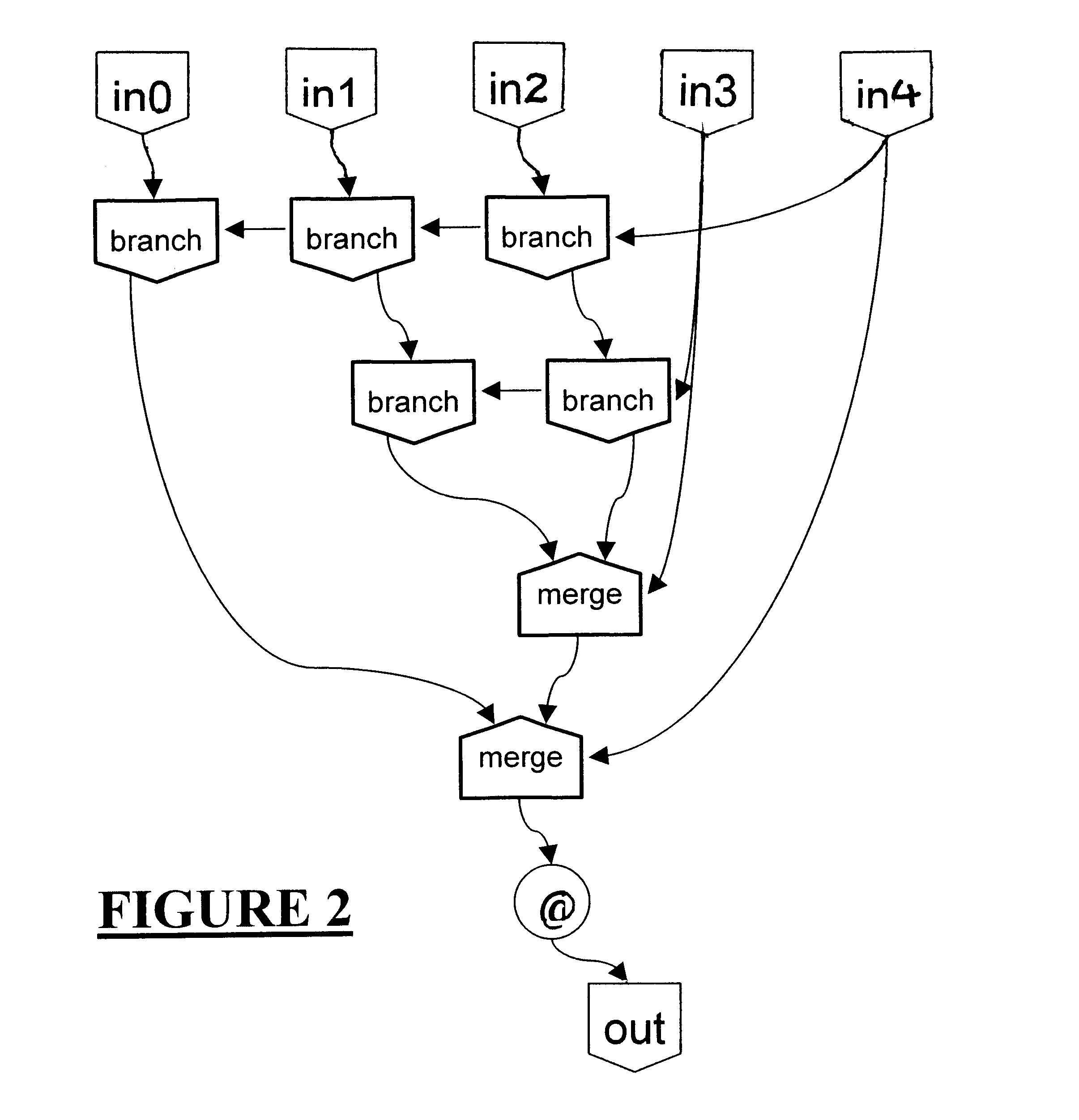

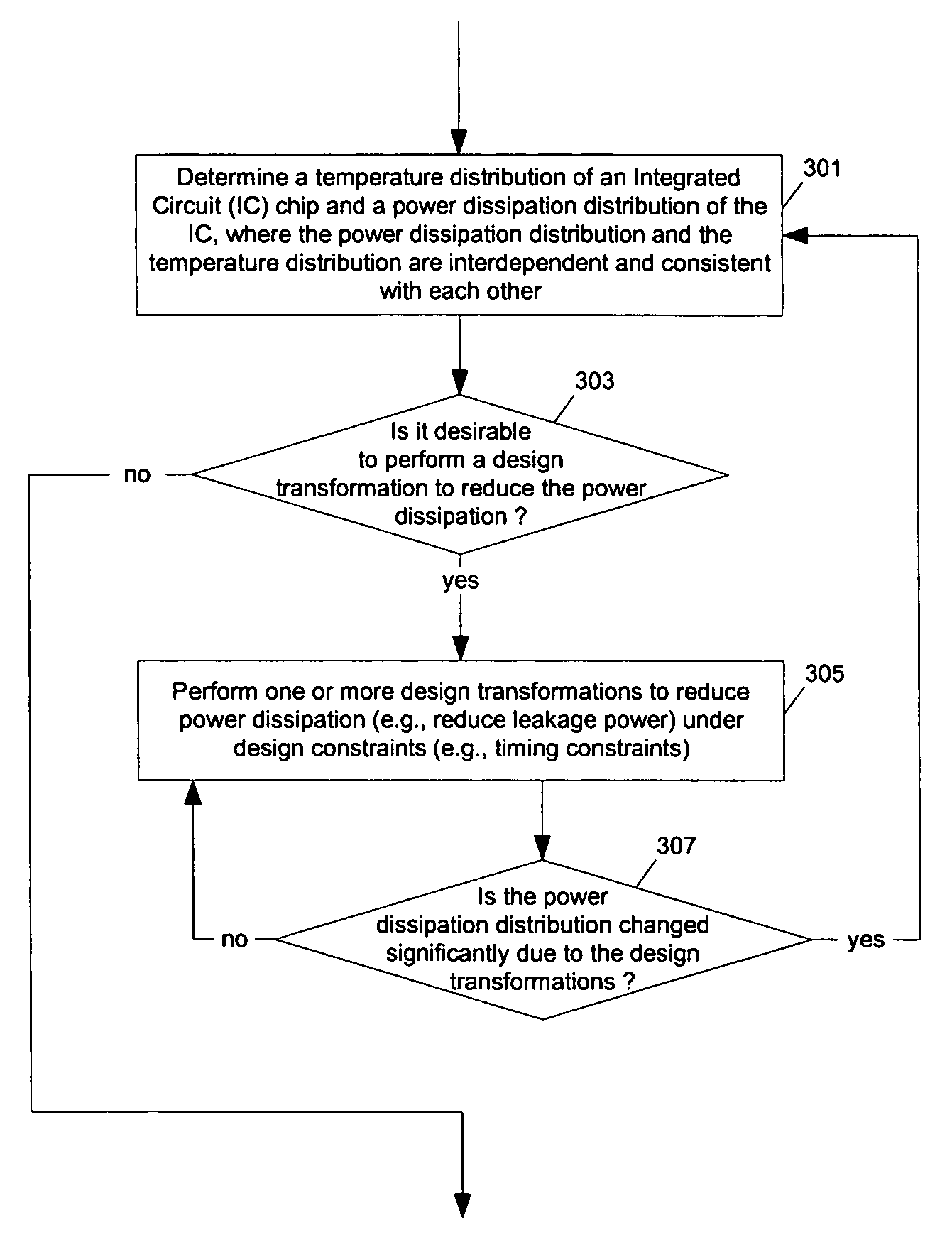

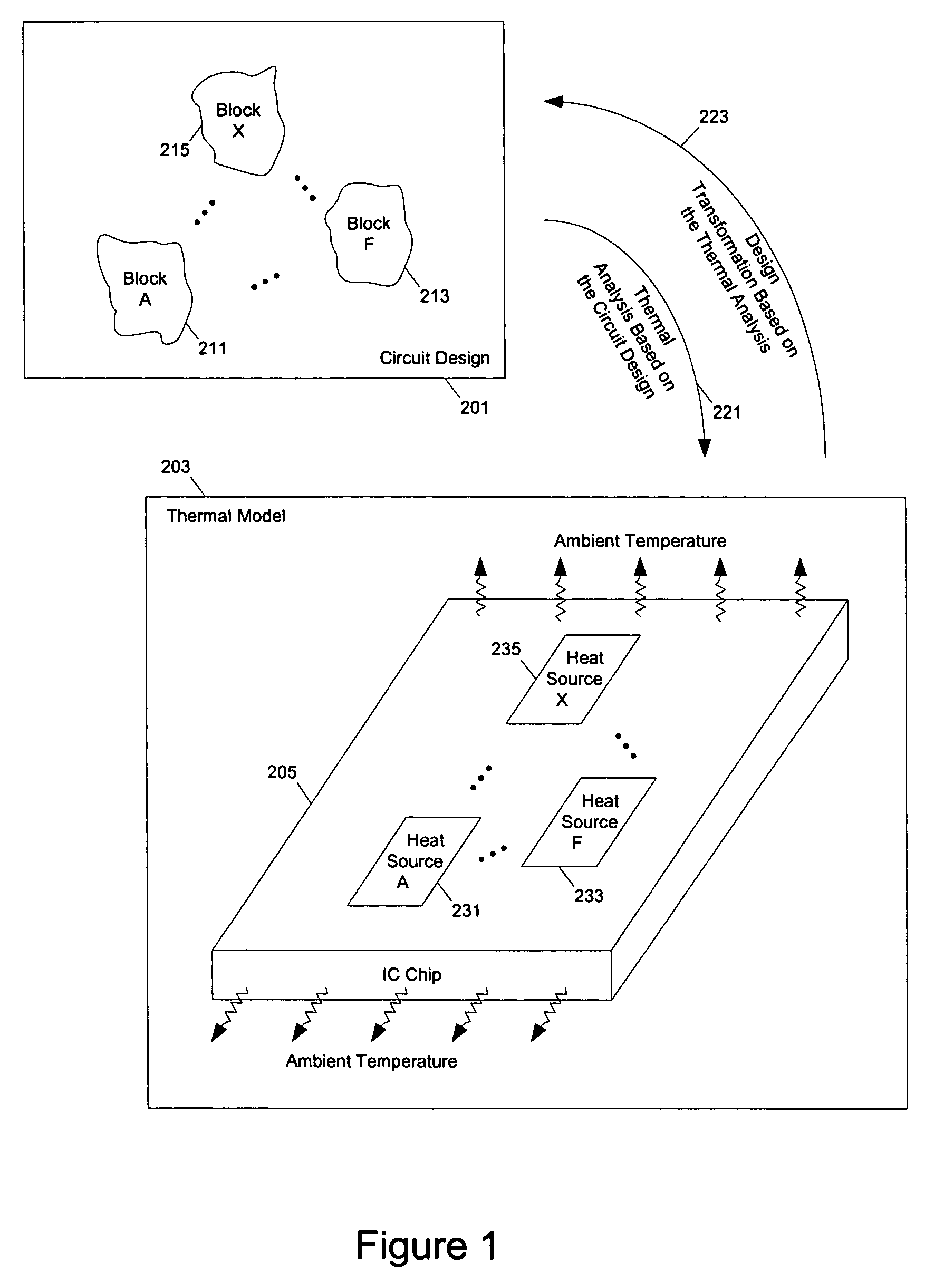

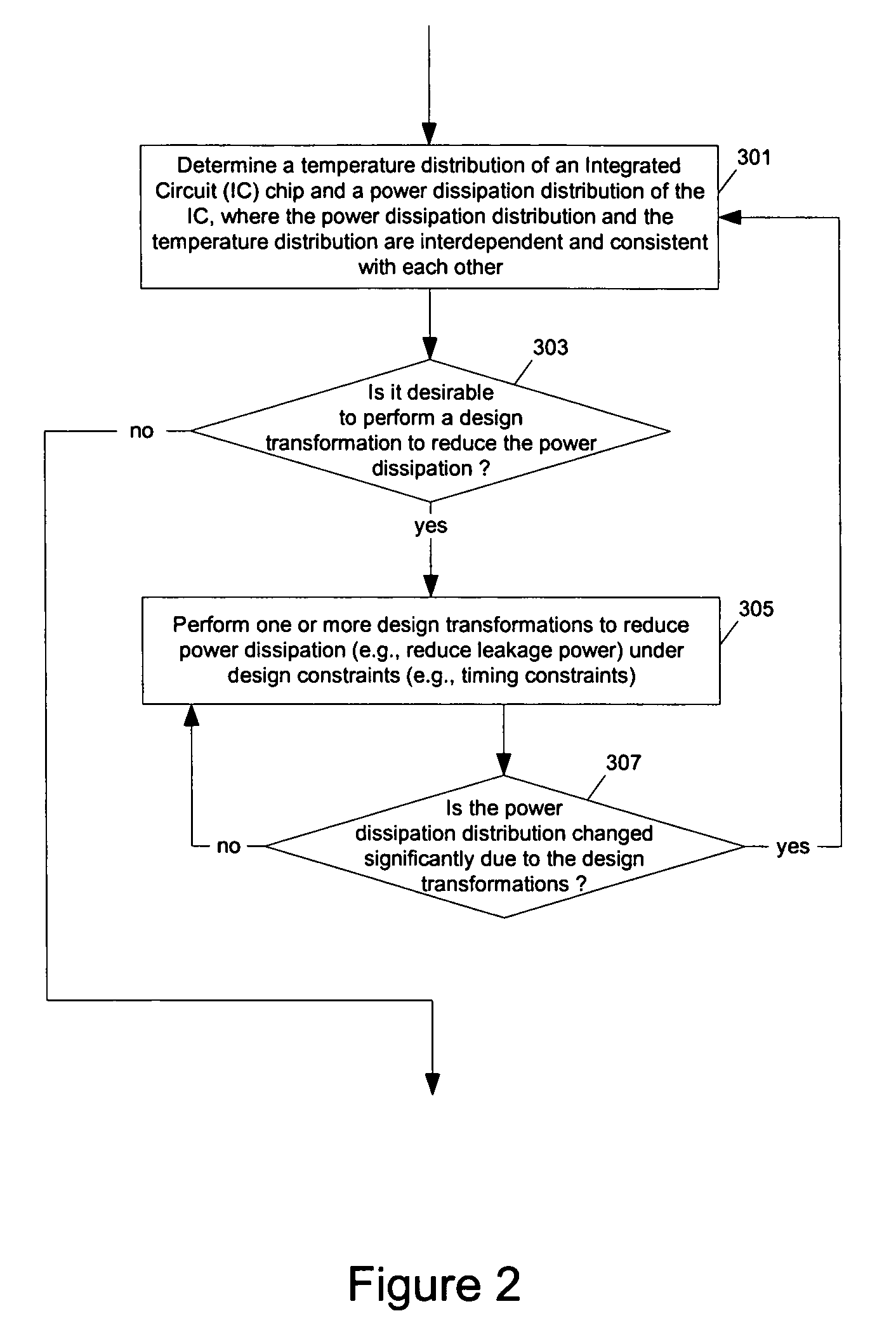

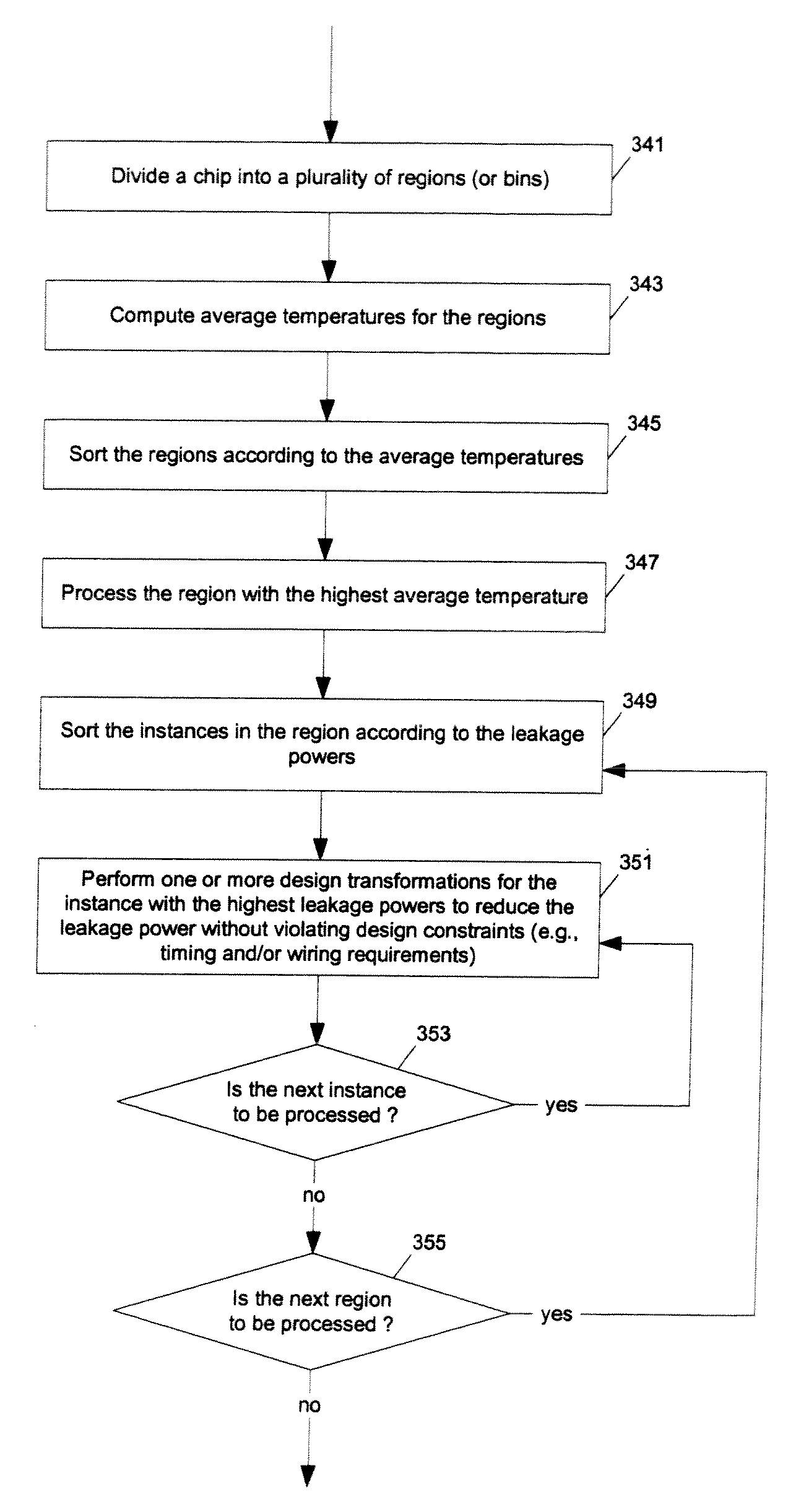

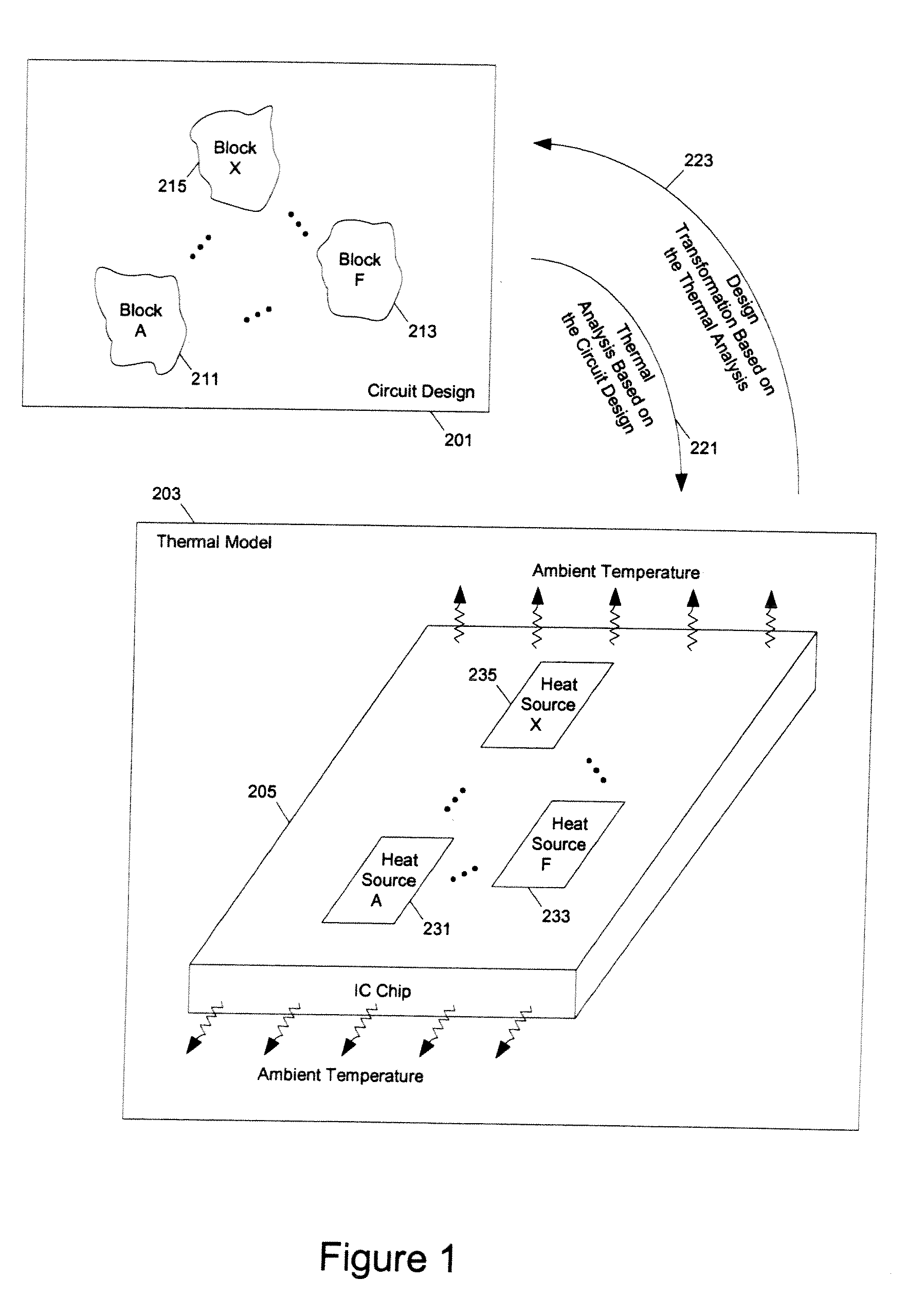

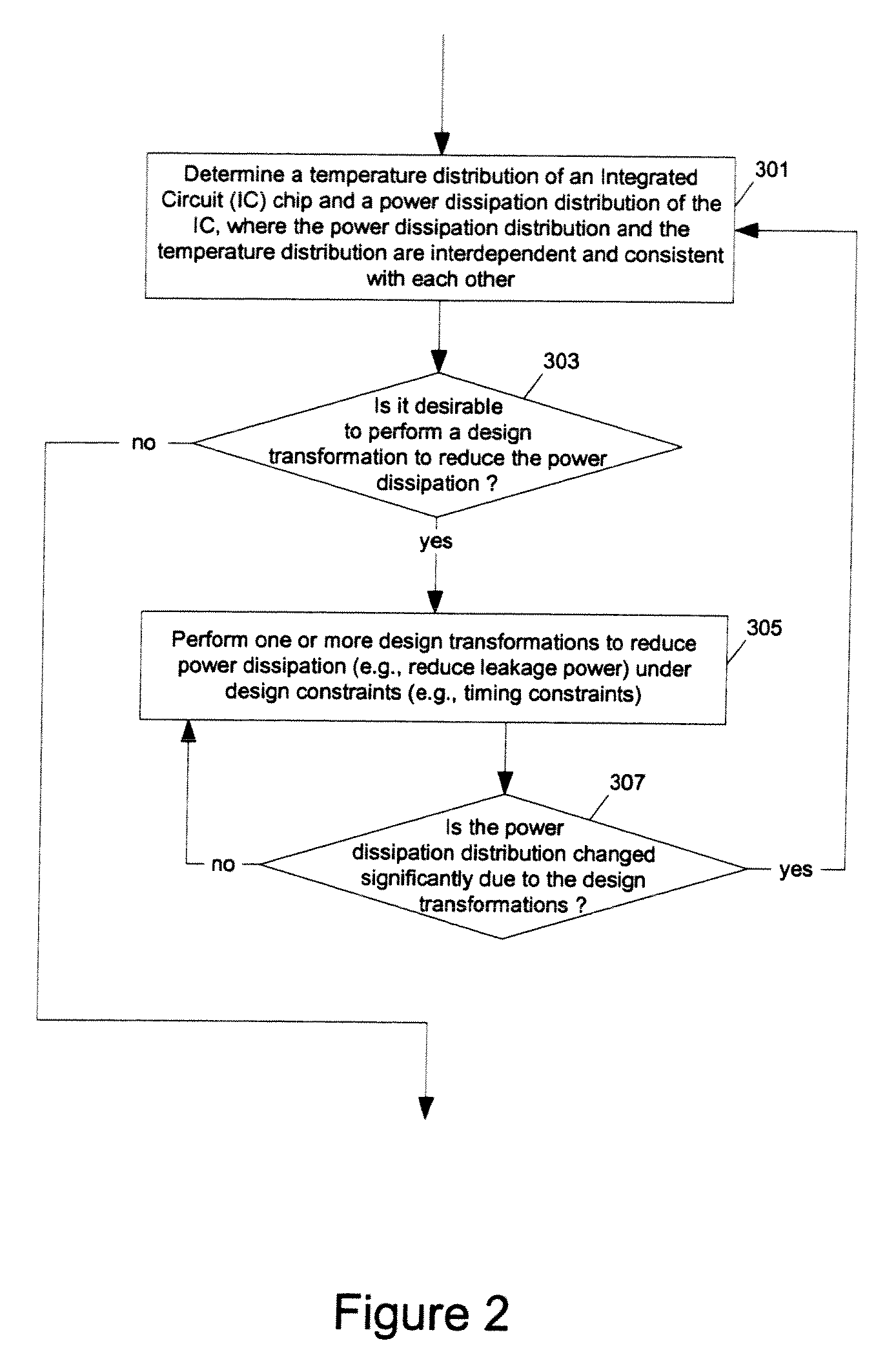

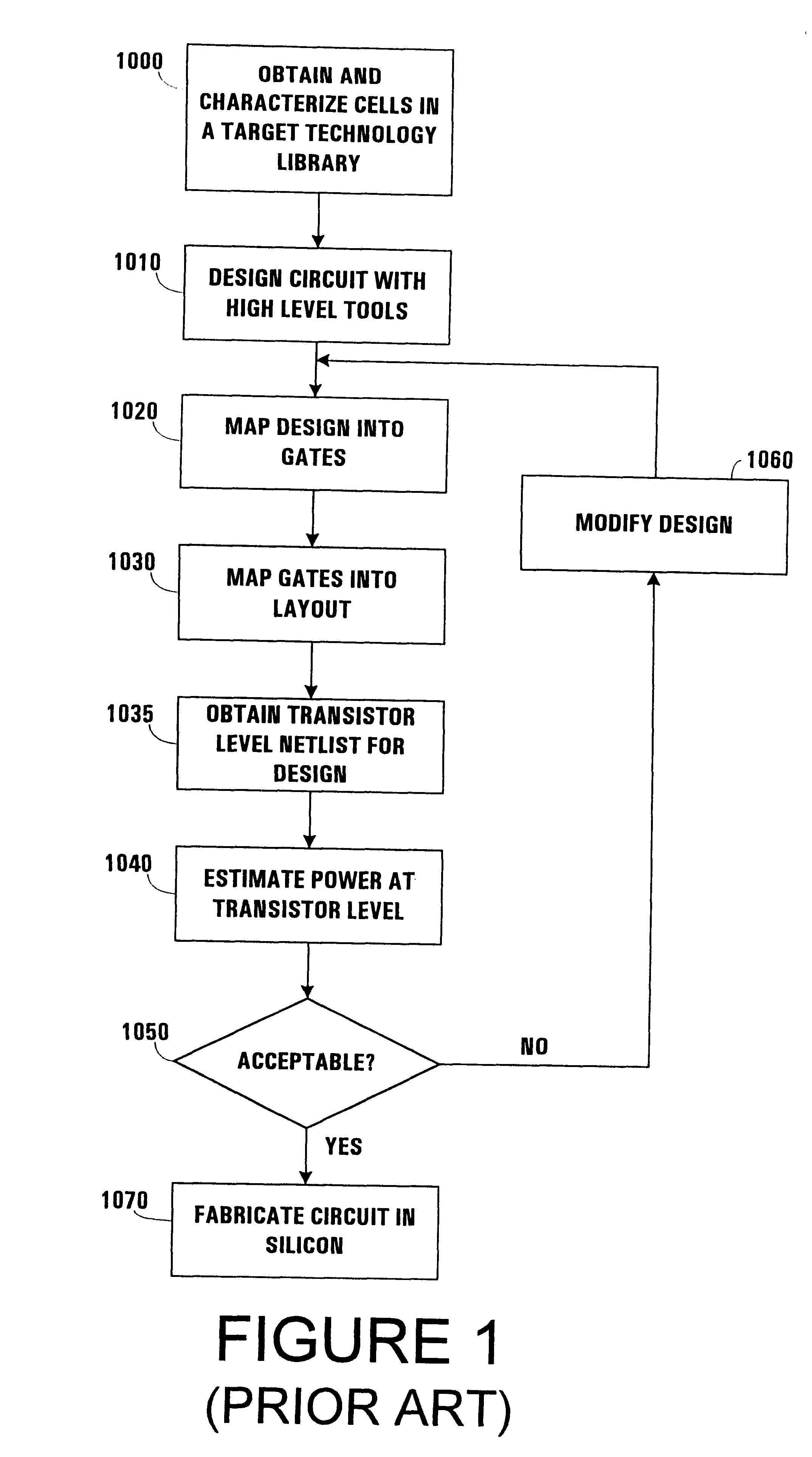

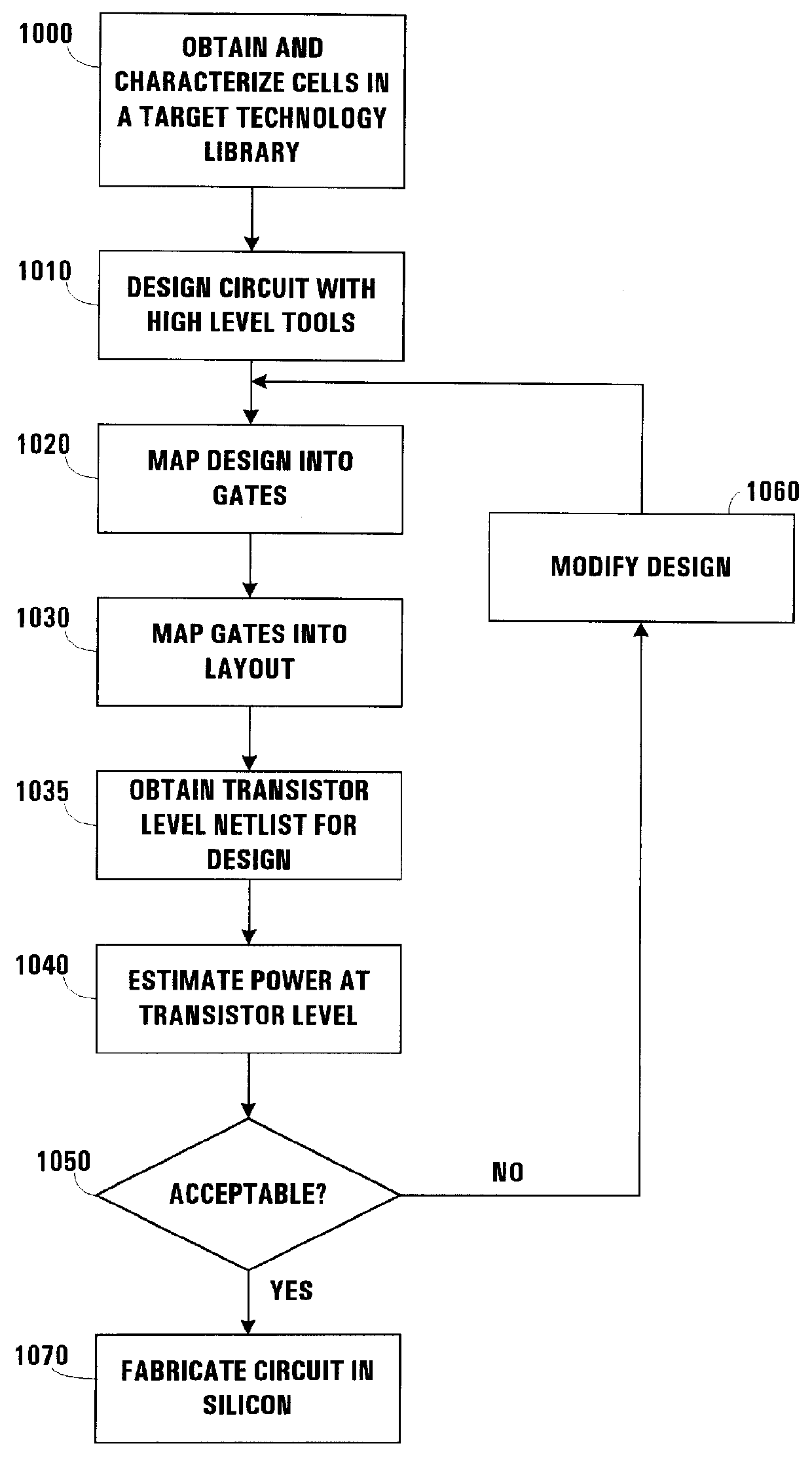

Methods and apparatuses for thermal analysis based circuit design

ActiveUS7366997B1Reduce power consumptionExtension of timeSoftware simulation/interpretation/emulationSpecial data processing applicationsPower usageTransition time

Methods and apparatuses for circuit design to reduce power usage, such as reducing temperature dependent power usage, and / or to improve timing, such as reducing temperature dependent delay or transition time. At least one embodiment of the present invention reduces the power dissipation and improves the timing of an integrated circuit to optimize the design. A thermal analysis is used to determine the temperature dependent power dissipation of a circuit and the temperature distribution of the circuit resulting from dissipating the heat created by the temperature dependent power dissipation. Then, the components of the design are selectively transformed to reduce the power dissipation and to improve timing based on the temperature solution. The transformation may include placement changes and netlist changes, such as the change of transistor threshold voltages for cells or for blocks of the circuit chip.

Owner:SYNOPSYS INC

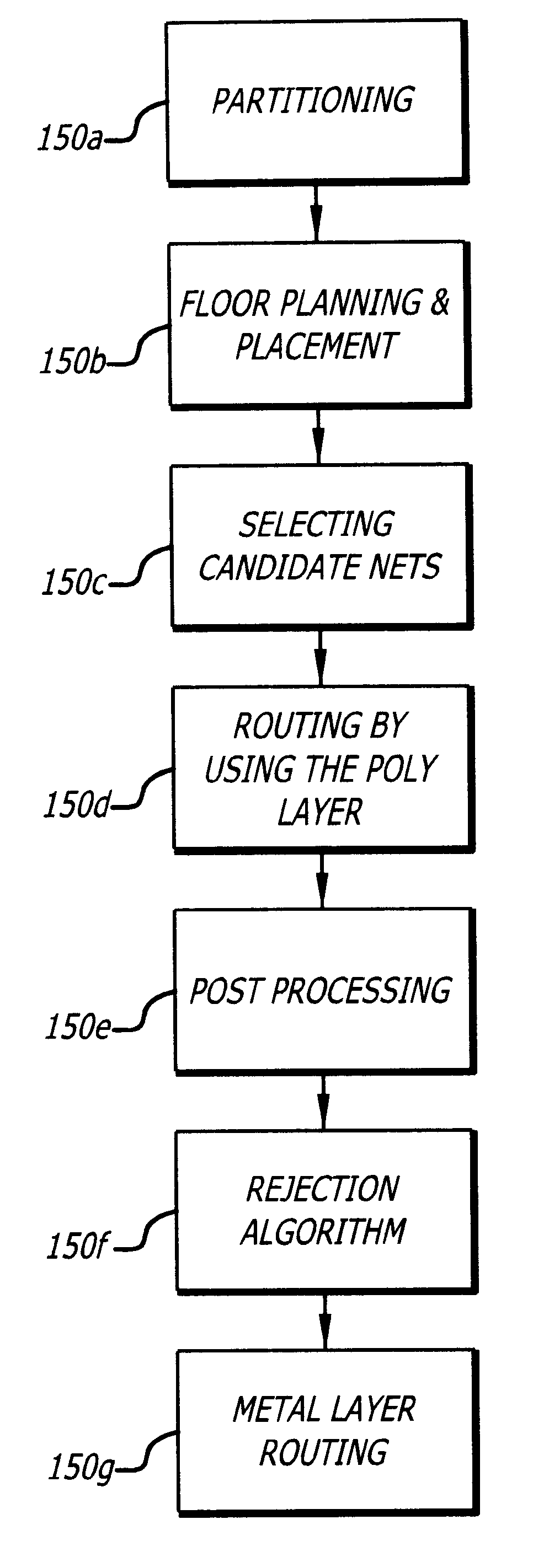

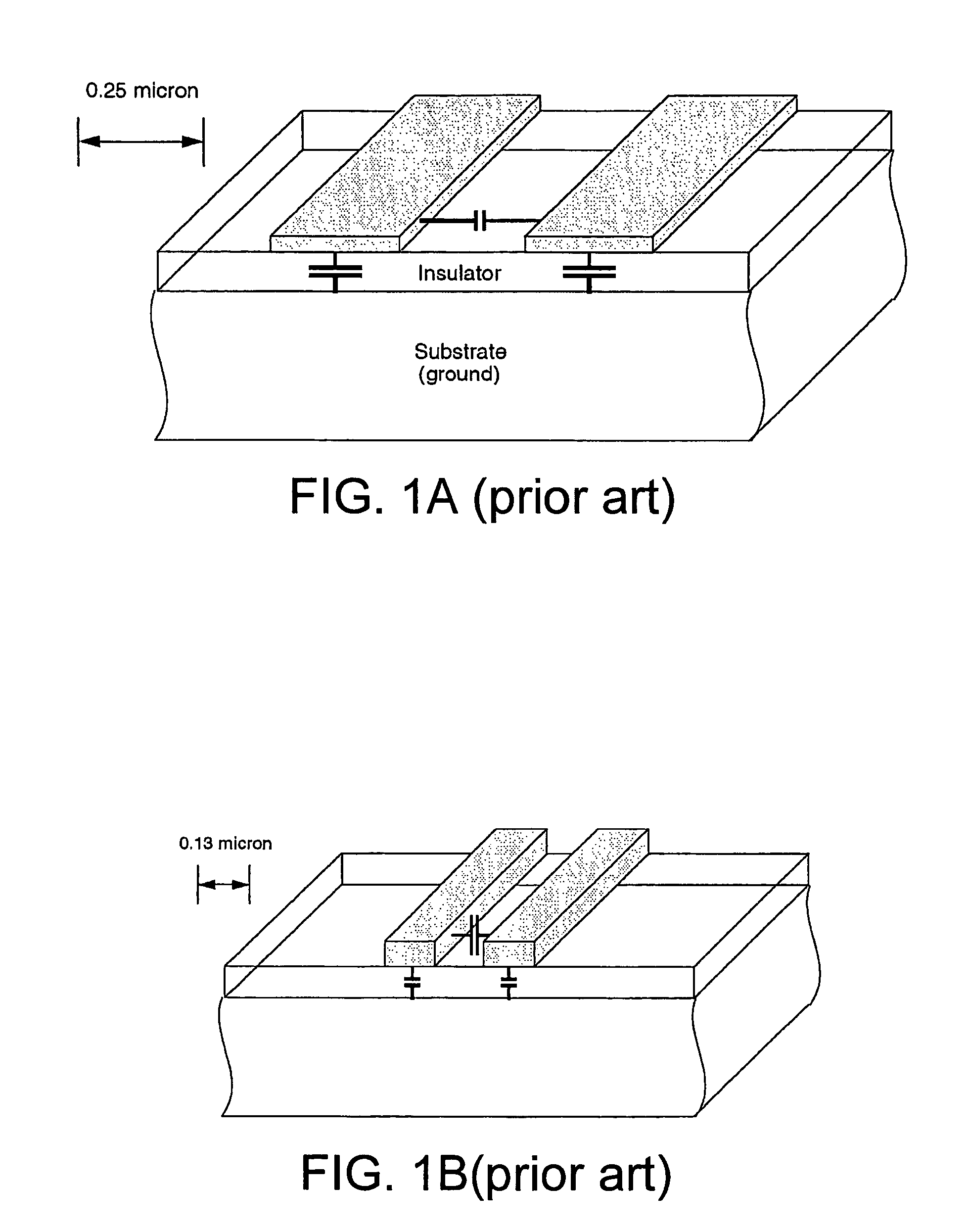

Poly routing for chip interconnects with minimal impact on chip performance

InactiveUS6240542B1Computer aided designSoftware simulation/interpretation/emulationFilter algorithmNetlist

Methods for using the polysilicon layer to route the cells in the ASIC are disclosed. The poly layer of an IC chip is used for routing chip interconnects with minimal impact on the chip performance by selecting nets in the IC chip based on a predetermined or a desired qualification. A maximum allowable length of the poly layer to be used for chip interconnects is determined based on the intended technology of the chip. A filtering algorithm filters the netlist to provide a set of candidate nets that are suitable for poly layer routing based on the predetermined or desired qualification. A routing tool routes the selected nets that have been selected by the filtering algorithm by using the poly layer. Some of the poly layer routings are further rejected by a post processing step.

Owner:BELL SEMICON LLC

Methods and apparatuses for thermal analysis based circuit design

ActiveUS20080168406A1Reduce power consumptionExtension of timeSoftware simulation/interpretation/emulationSpecial data processing applicationsEngineeringPower usage

Methods and apparatuses for circuit design to reduce power usage, such as reducing temperature dependent power usage, and / or to improve timing, such as reducing temperature dependent delay or transition time. At least one embodiment of the present invention reduces the power dissipation and improves the timing of an integrated circuit to optimize the design. A thermal analysis is used to determine the temperature dependent power dissipation of a circuit and the temperature distribution of the circuit resulting from dissipating the heat created by the temperature dependent power dissipation. Then, the components of the design are selectively transformed to reduce the power dissipation and to improve timing based on the temperature solution. The transformation may include placement changes and netlist changes, such as the change of transistor threshold voltages for cells or for blocks of the circuit chip.

Owner:SYNOPSYS INC

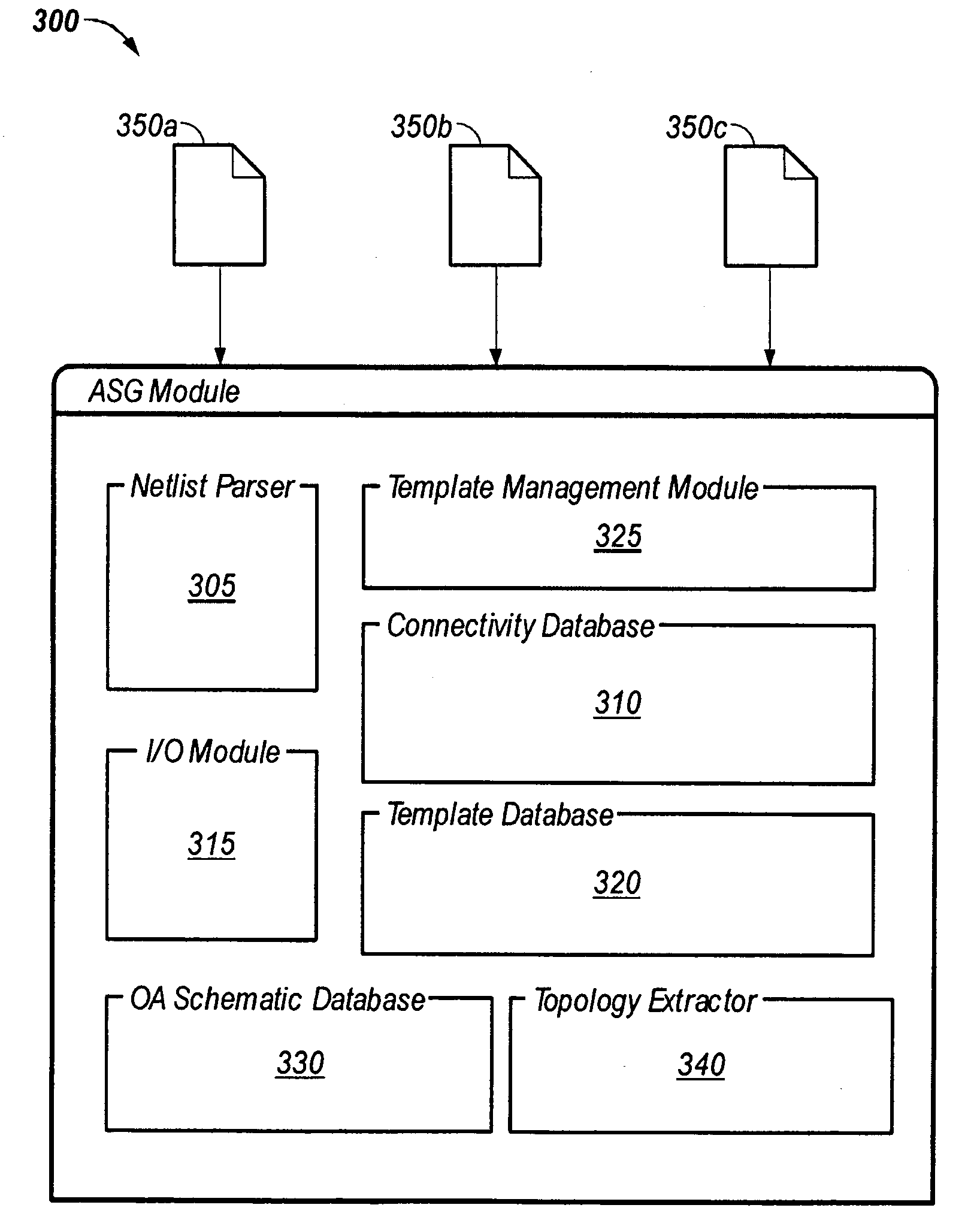

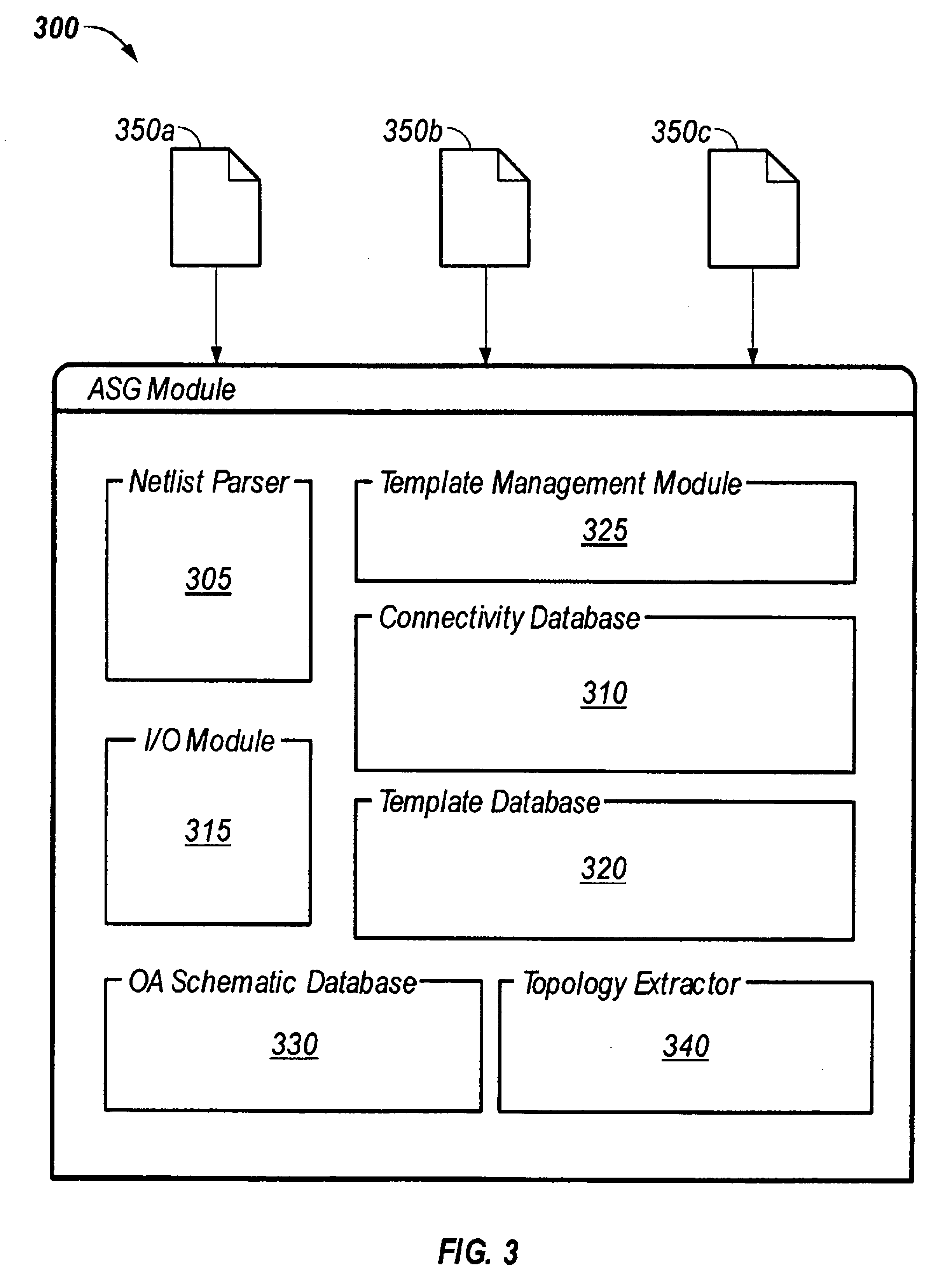

System and method for circuit schematic generation

The present invention provides a system and method for generating circuit schematic that includes extracting connectivity data of a plurality of devices from a netlist, categorizing the plurality of devices into groups, placing Schematic Analog Placement Constraints on all the instances by identifying instances among the groups that match with a circuit template (in-built as well as user-specified), creating a BFS instance tree of tree instances, creating a two terminal device clusters and creating instance attachments. Using the constraints during grid based placement and eventually generated schematic which look like analog schematic.

Owner:CADENCE DESIGN SYST INC

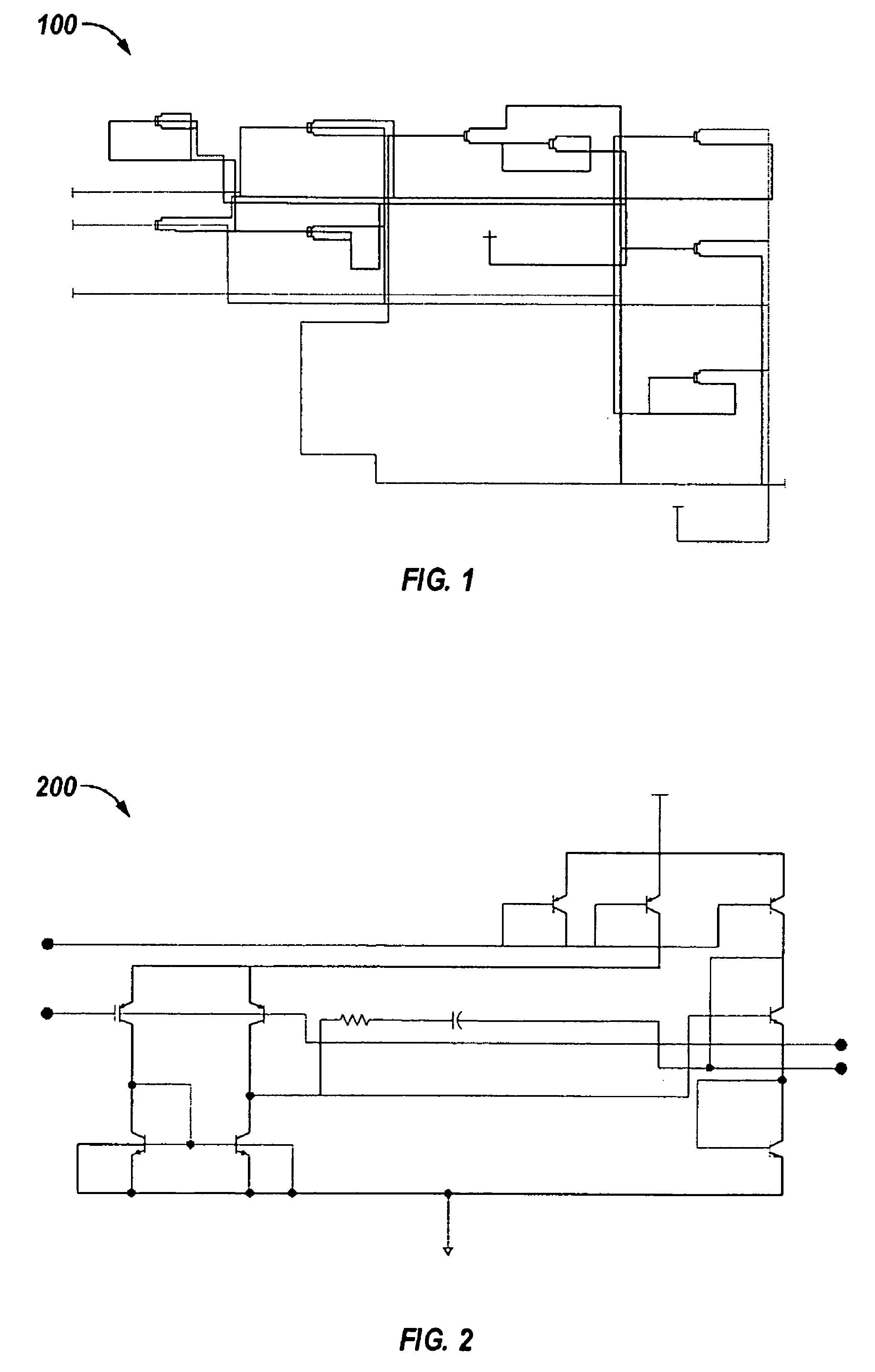

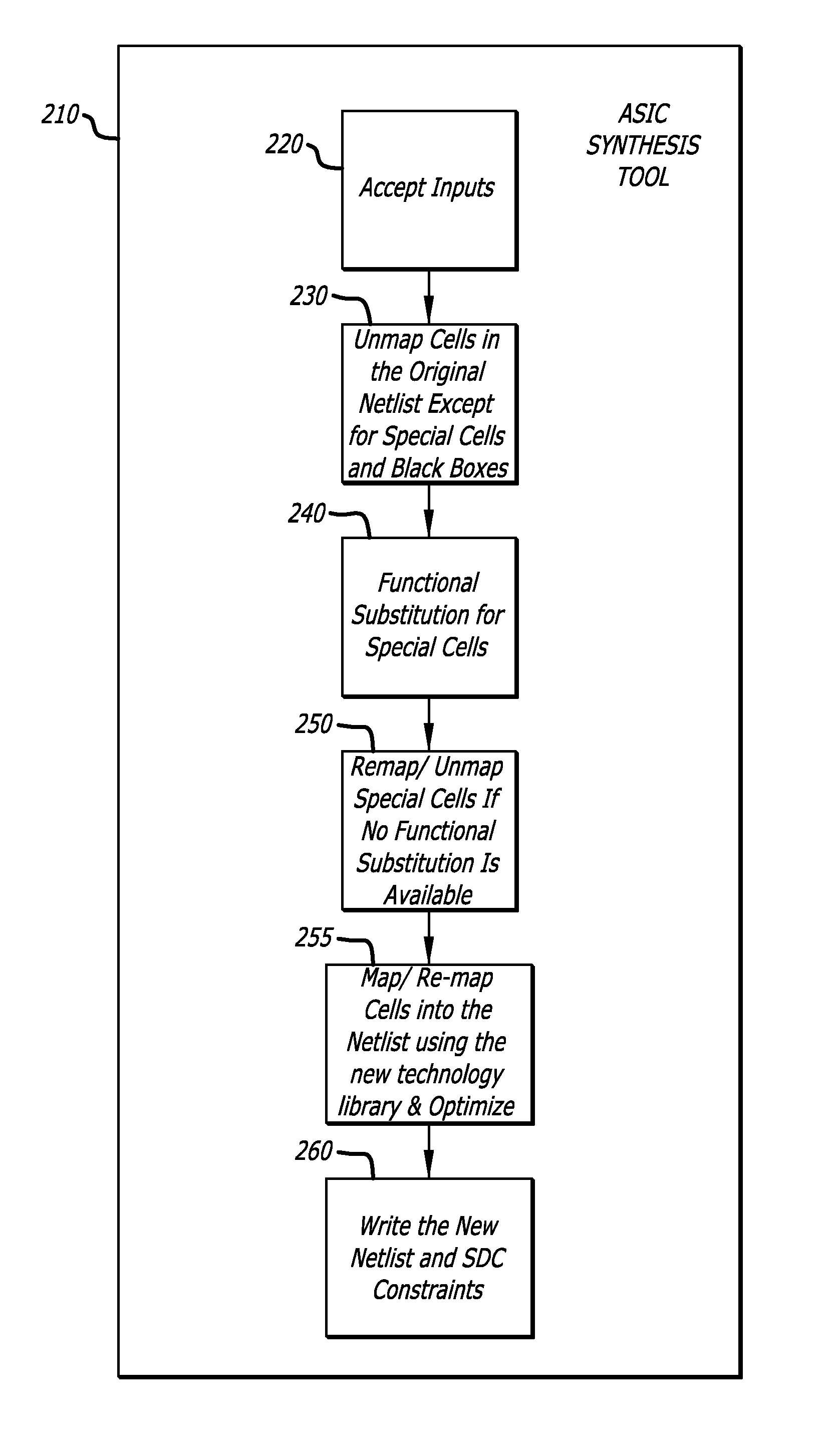

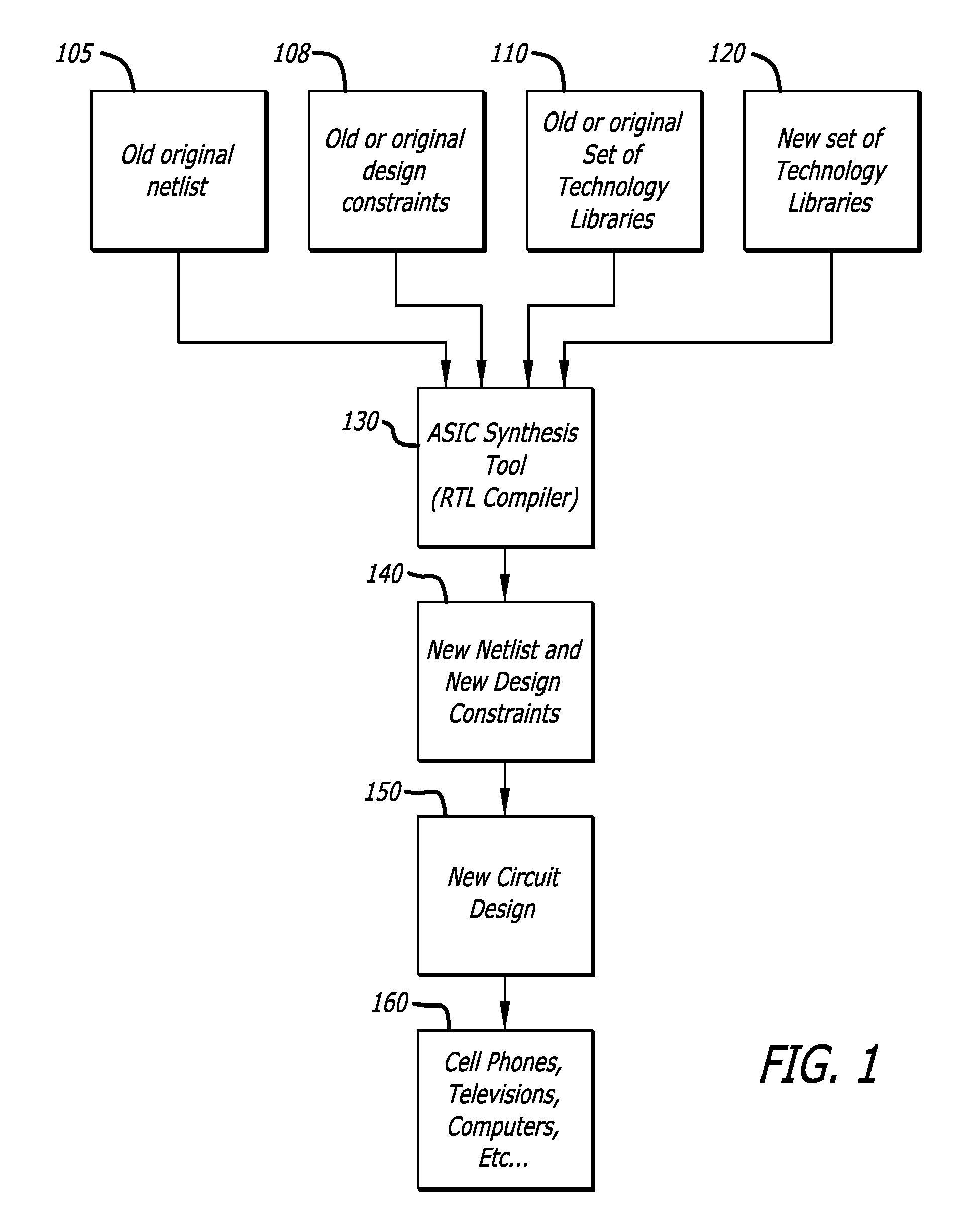

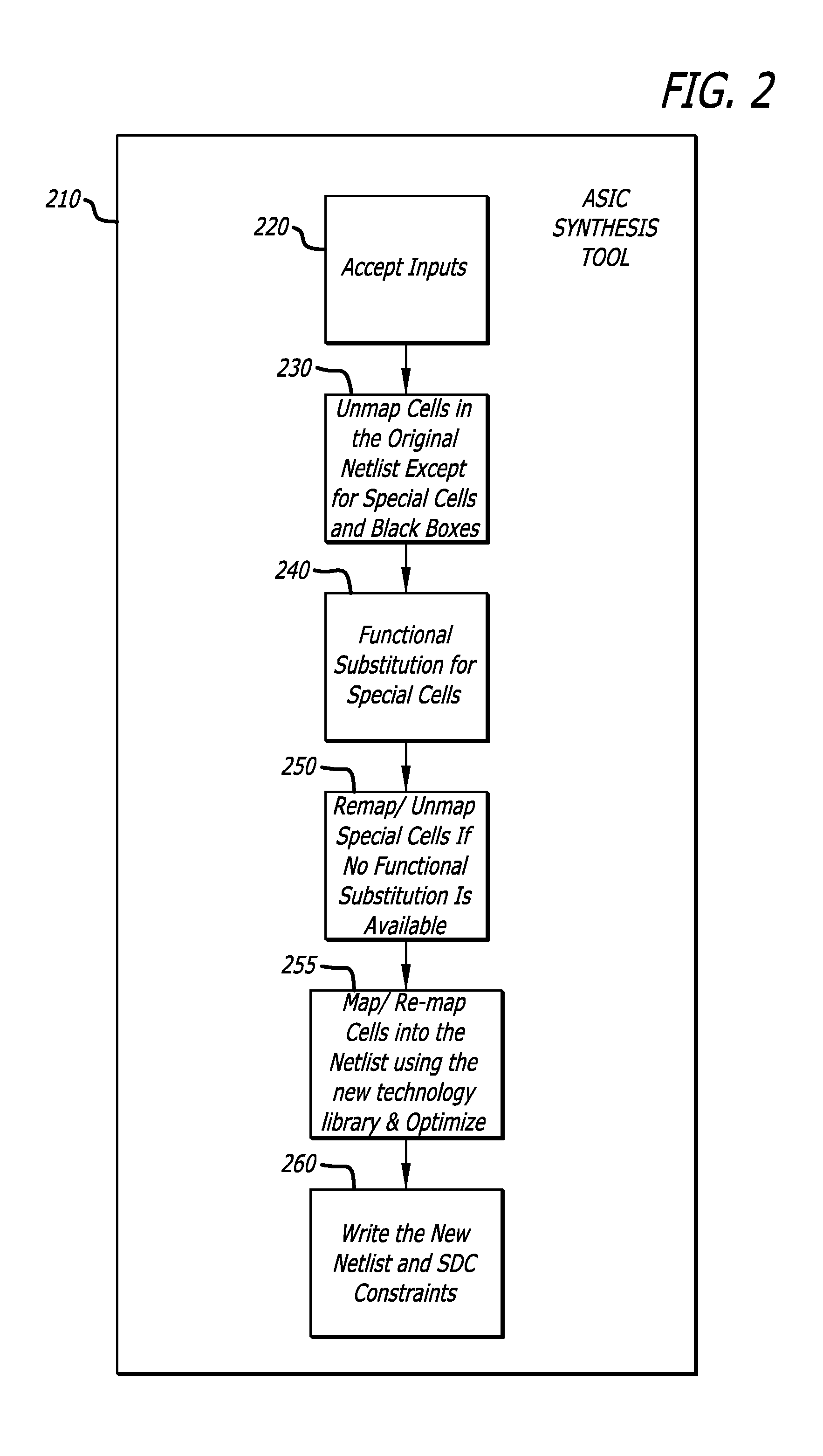

Integrated circuit netlist migration

A method for migrating a netlist from one set of library cells to a new set of library cells with minimal time and effort and without loss of information within an ASCI environment. This methodology ensures that during translation logic equivalence and scan configurations are maintained in the new technology libraries. Additionally, a complete migration of the constraints from the original netlist to the new netlist is also performed. Designer engineers no longer have to start from RTL and execute a complete resynthesis to translate an original design from one technology library to a new technology library.

Owner:CADENCE DESIGN SYST INC

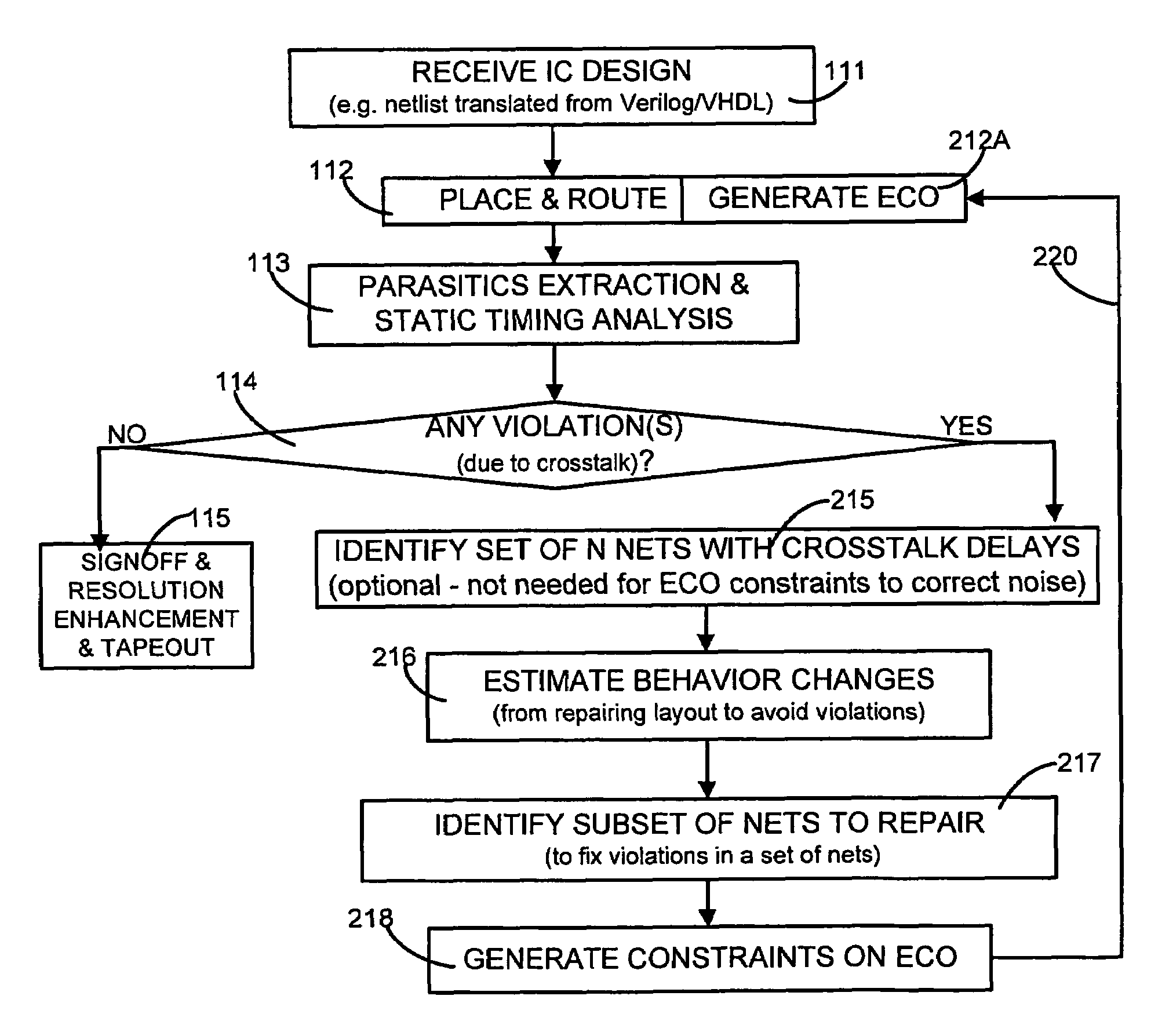

Generation of engineering change order (ECO) constraints for use in selecting ECO repair techniques

ActiveUS7454731B2CAD circuit designSoftware simulation/interpretation/emulationLayoutEngineering change order

Static timing and / or noise analysis are performed on a netlist of an integrated circuit, to estimate behavior of the netlist and to identify at least one violation by said behavior of a corresponding requirement thereon, such as setup time, hold time or bump height in a quiescent net. Thereafter, effect of engineering change order (ECO) to correct the violation are automatically analyzed, based on the layout, the parasitics, the timing and / or noise behavior, and the violation, followed by generation of a constraint on the behavior (called “ECO” constraint), such as a timing constraint and / or a noise constraint. Next, the ECO constraint is automatically used, e.g. in a place and route tool, to select an ECO repair technique, from several ECO repair techniques that can overcome the violation. The selected ECO repair technique is automatically applied to the layout, to generate a modified layout which does not have the violation.

Owner:SYNOPSYS INC

Synthesizing current source driver model for analysis of cell characteristics

InactiveUS7761275B2Analogue computers for electric apparatusCAD circuit designParasitic capacitanceEngineering

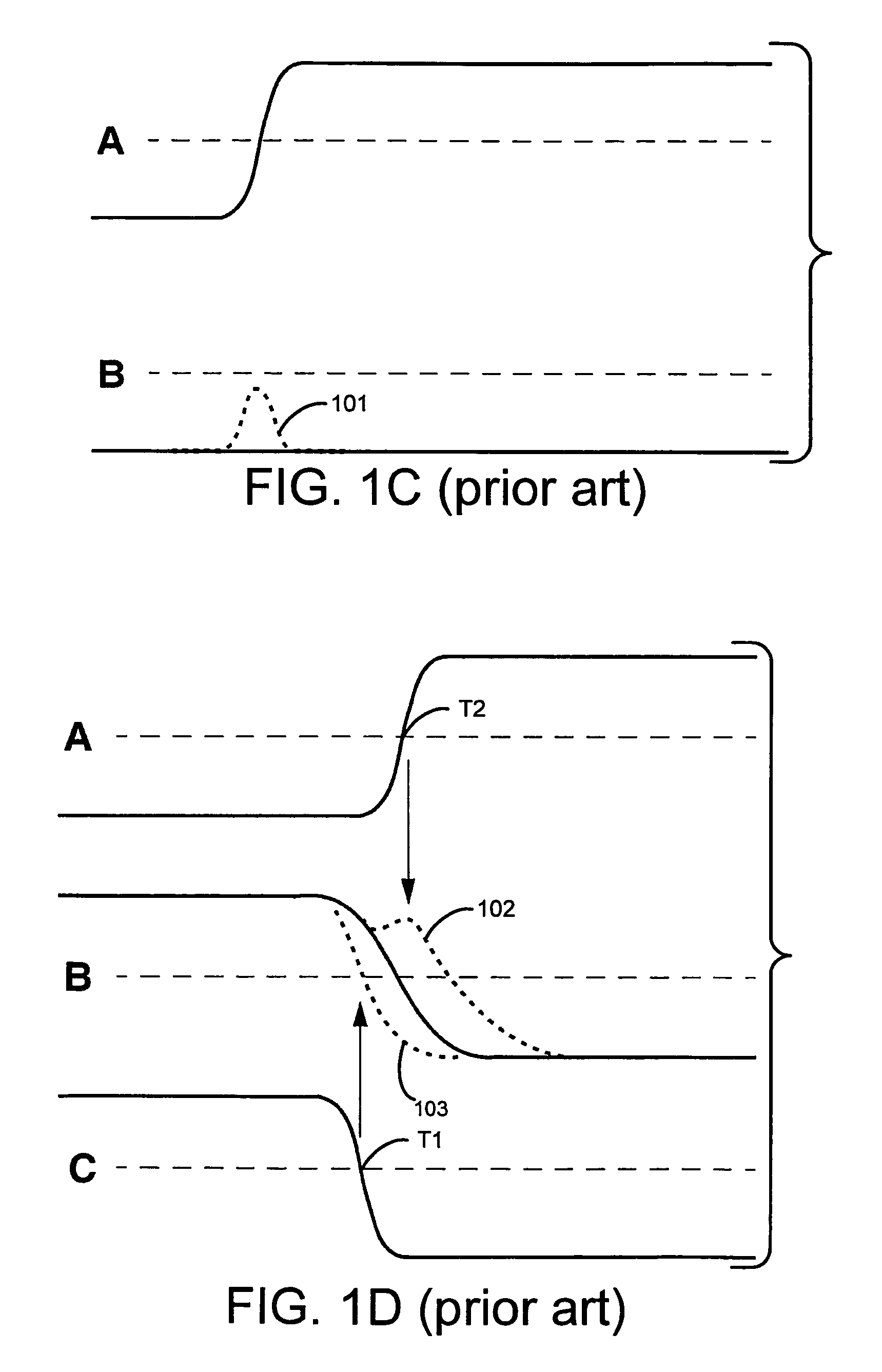

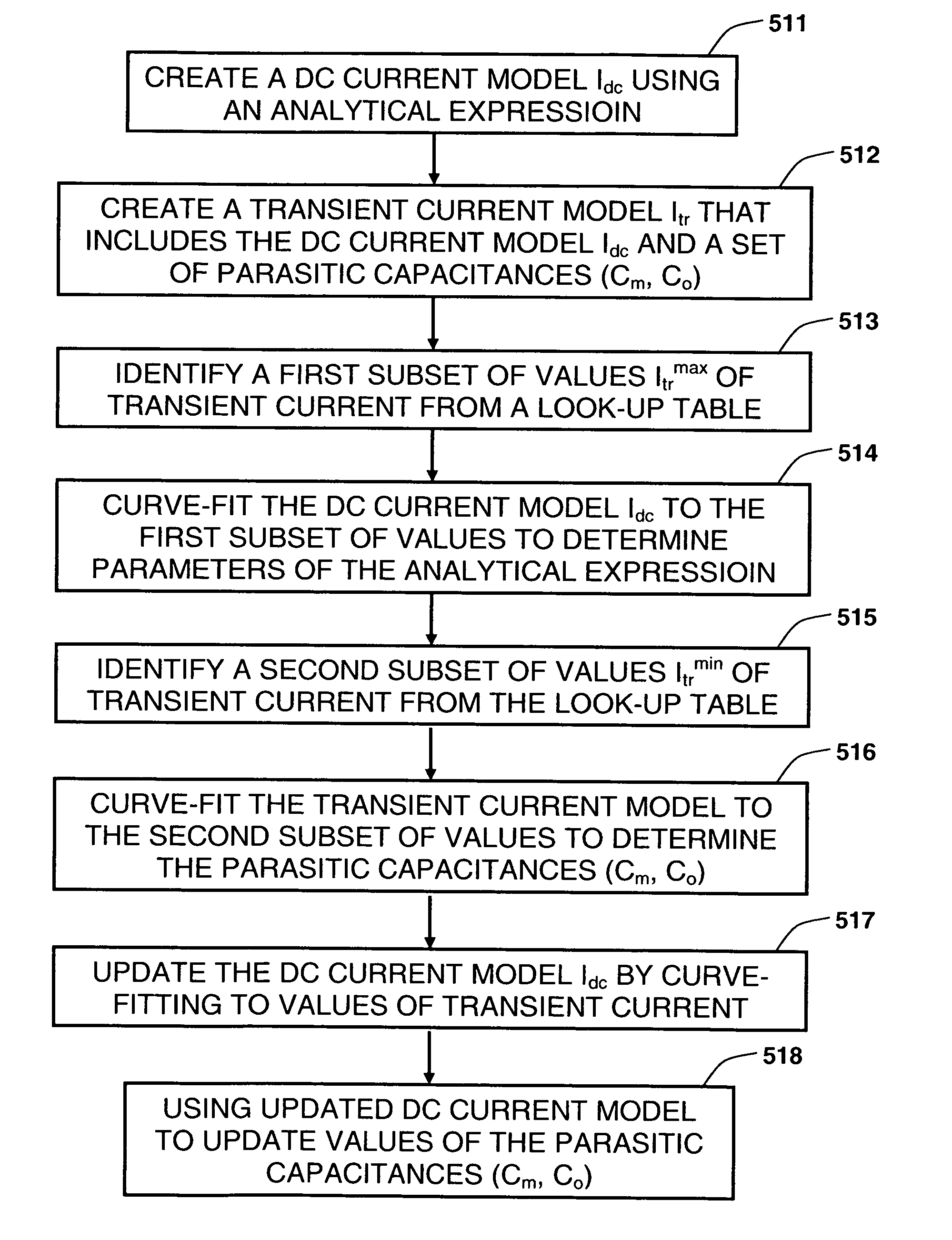

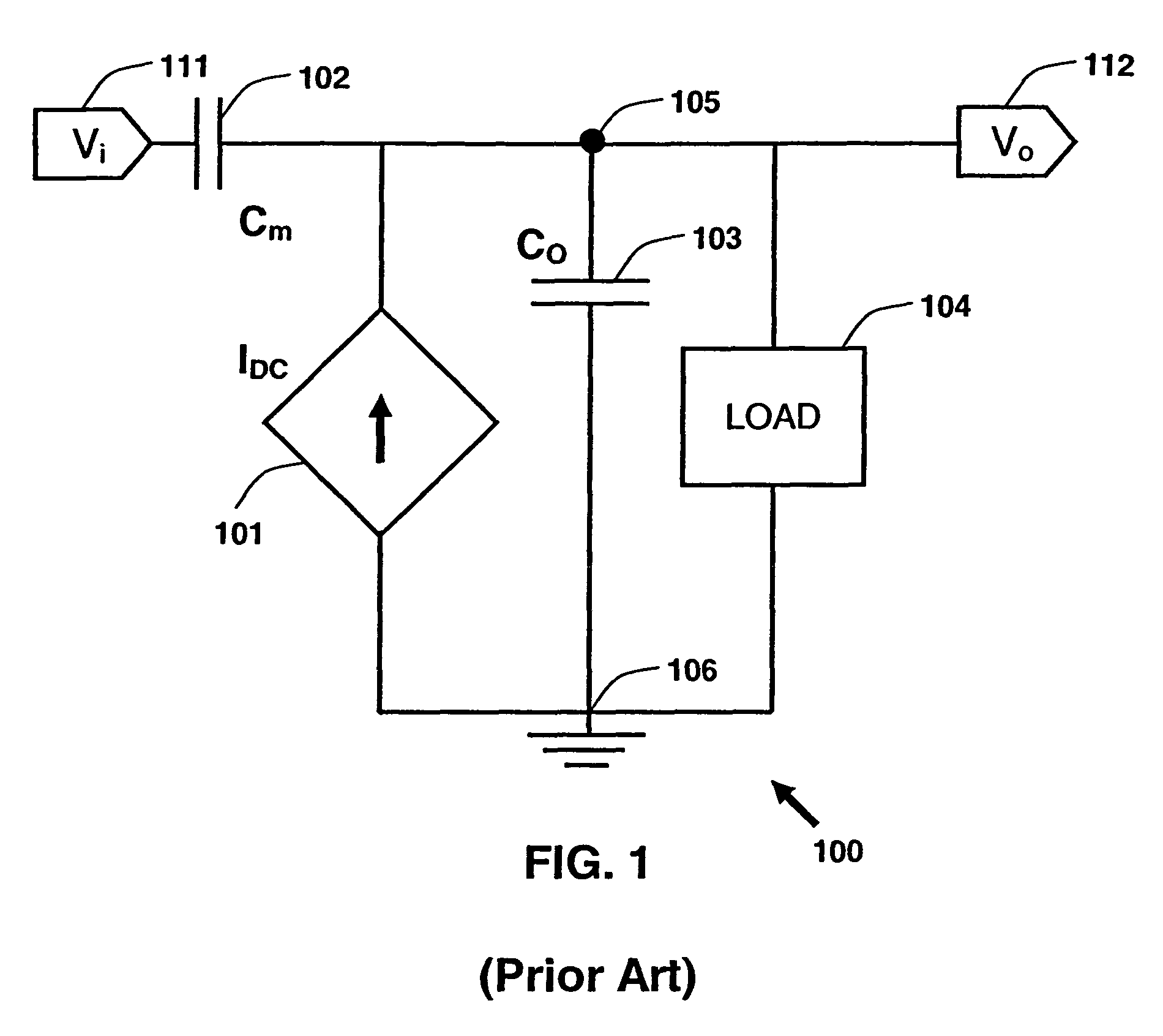

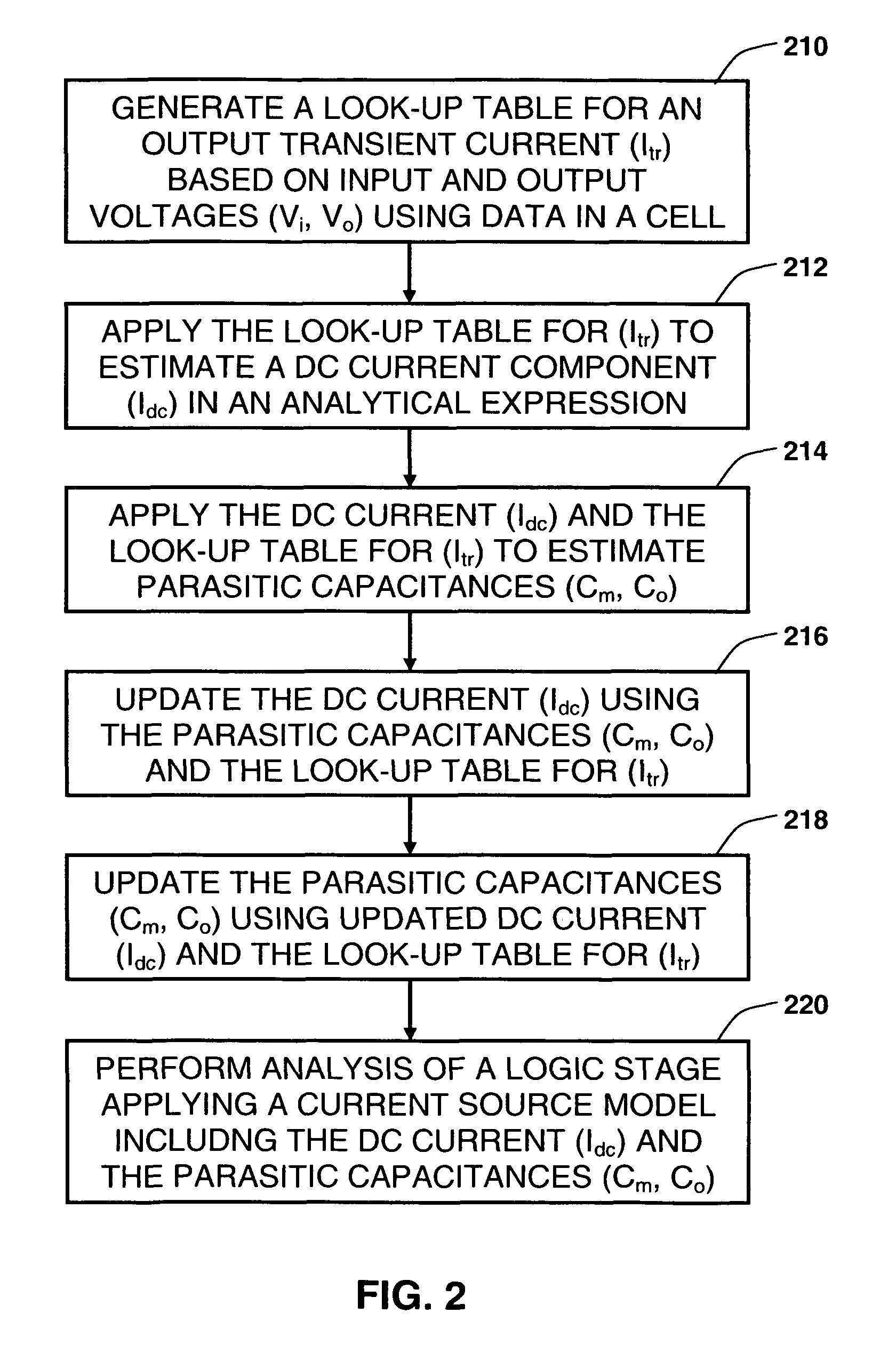

A method for performing an analysis of at least one logic stage in a netlist, which include one or more drivers, is provided. The method includes operations of generating at least one look-up table for an output transient current to be based on values of input and output voltages using data available from a cell library; synthesizing analytically at least one current source model, which includes a DC component and a plurality of parasitic capacitances, using the look-up table; simulating the logic stage using the current source model to model the drivers; and obtaining characteristics of the simulated logic stage. A system and a machine-readable medium for performing the method are also provided.

Owner:INT BUSINESS MASCH CORP

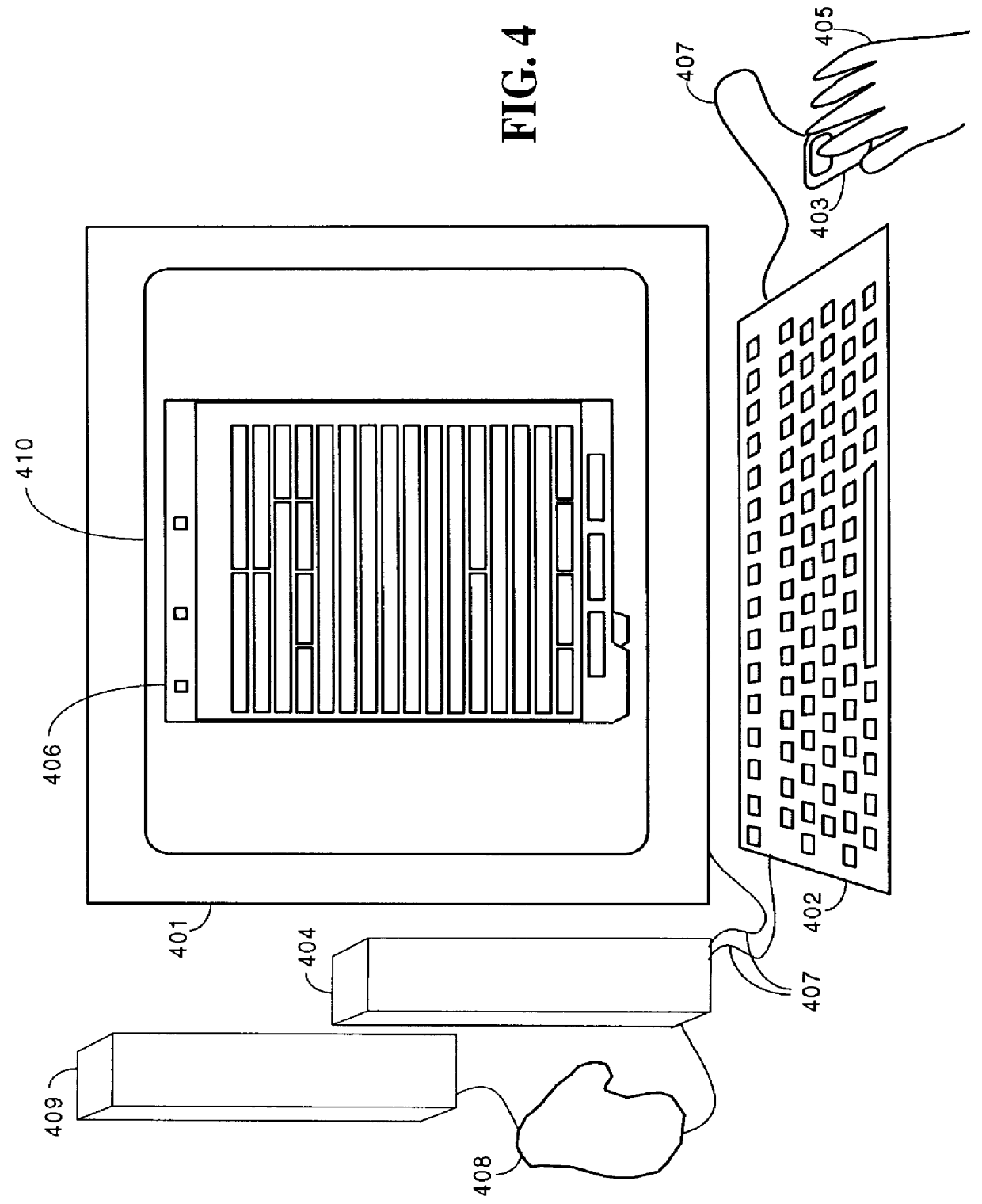

Method for configuring circuits over a data communications link

InactiveUS6023565ACAD circuit designSpecial data processing applicationsTelecommunications linkComputer architecture

A method of specifying design parameters is provided for configuring circuits for programmable ICs. A design database describing a circuit is displayed in table-based format on a computer screen display. The design database may include a memory map including data to be placed in bit-storage space in the target programmable IC. This design database requires no schematics or HDL description of the circuit, even for complicated application-specific circuits. The desired parameters are entered by the user, typically using toggle buttons, pull-down menus, or keyboard entry. The selected parameters are then entered into the design database, thereby configuring the design database in accordance with the selected parameters. Next, the design database is transmitted over a data communications link such as the internet to a second computer, on which the compilation software resides. The design is then compiled and the resulting netlist is transmitted back to the originating computer. In one embodiment, a schematic symbol or HDL instantiation is also generated by the second computer, and transmitted back to the originating computer.

Owner:XILINX INC

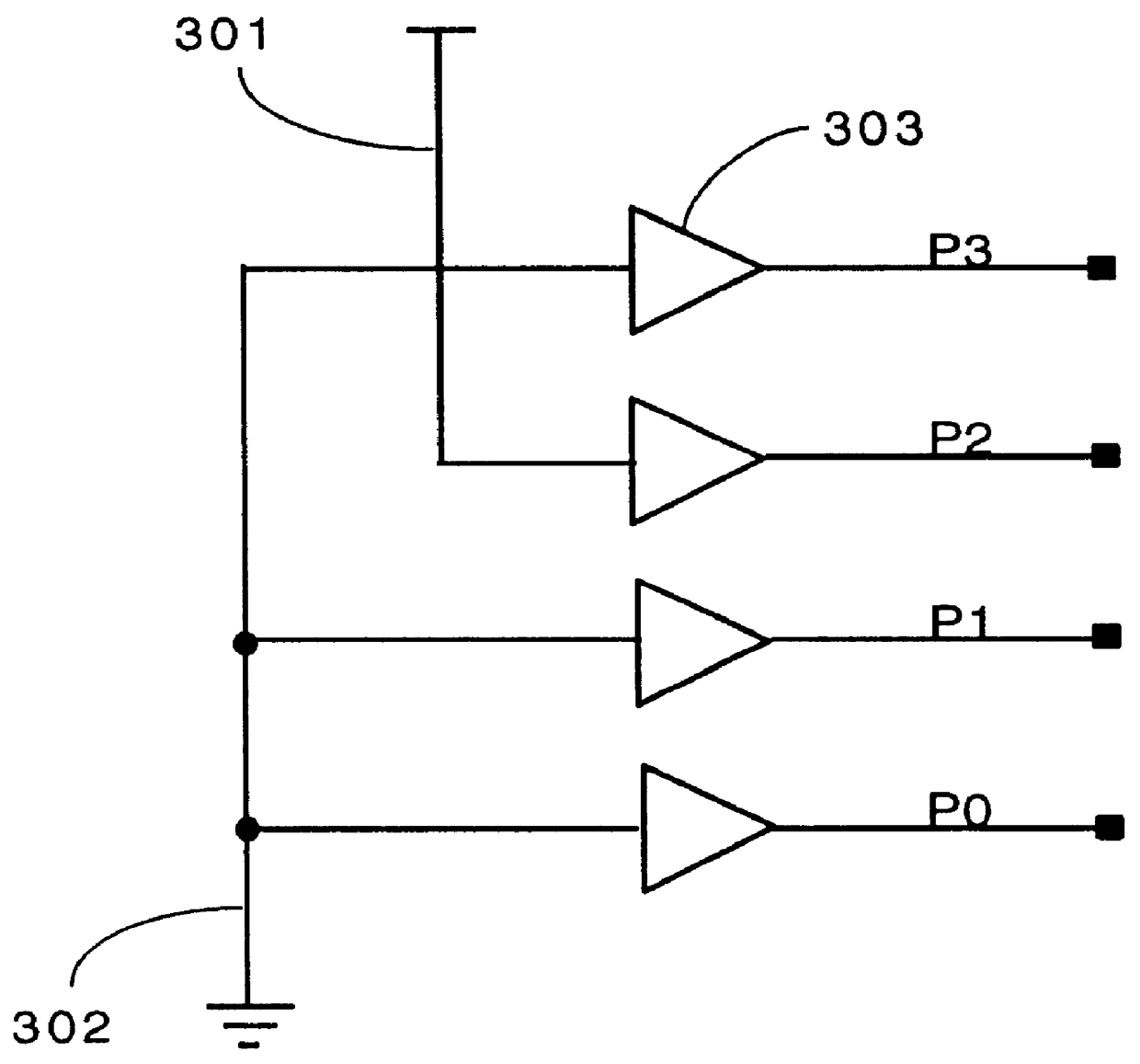

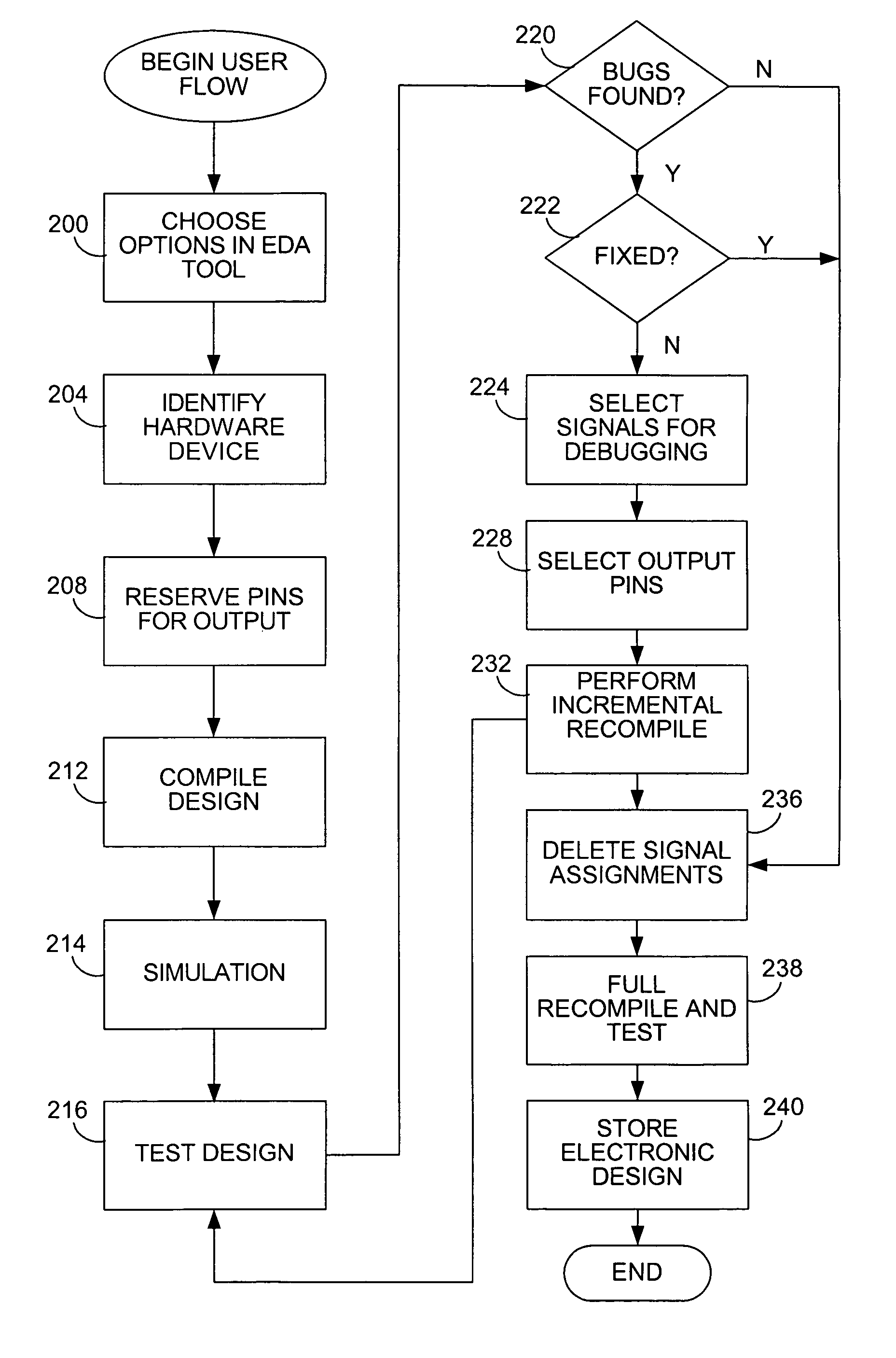

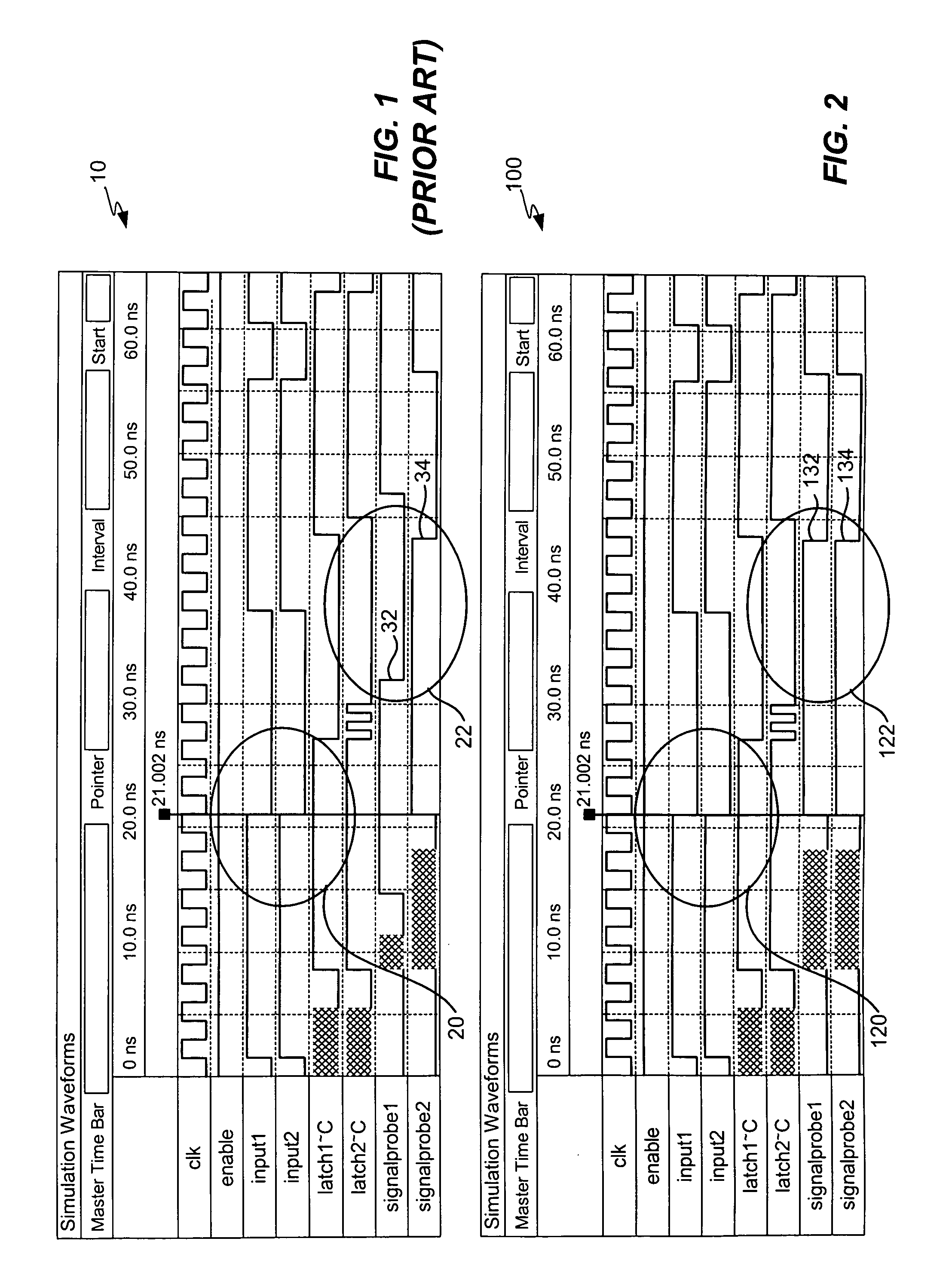

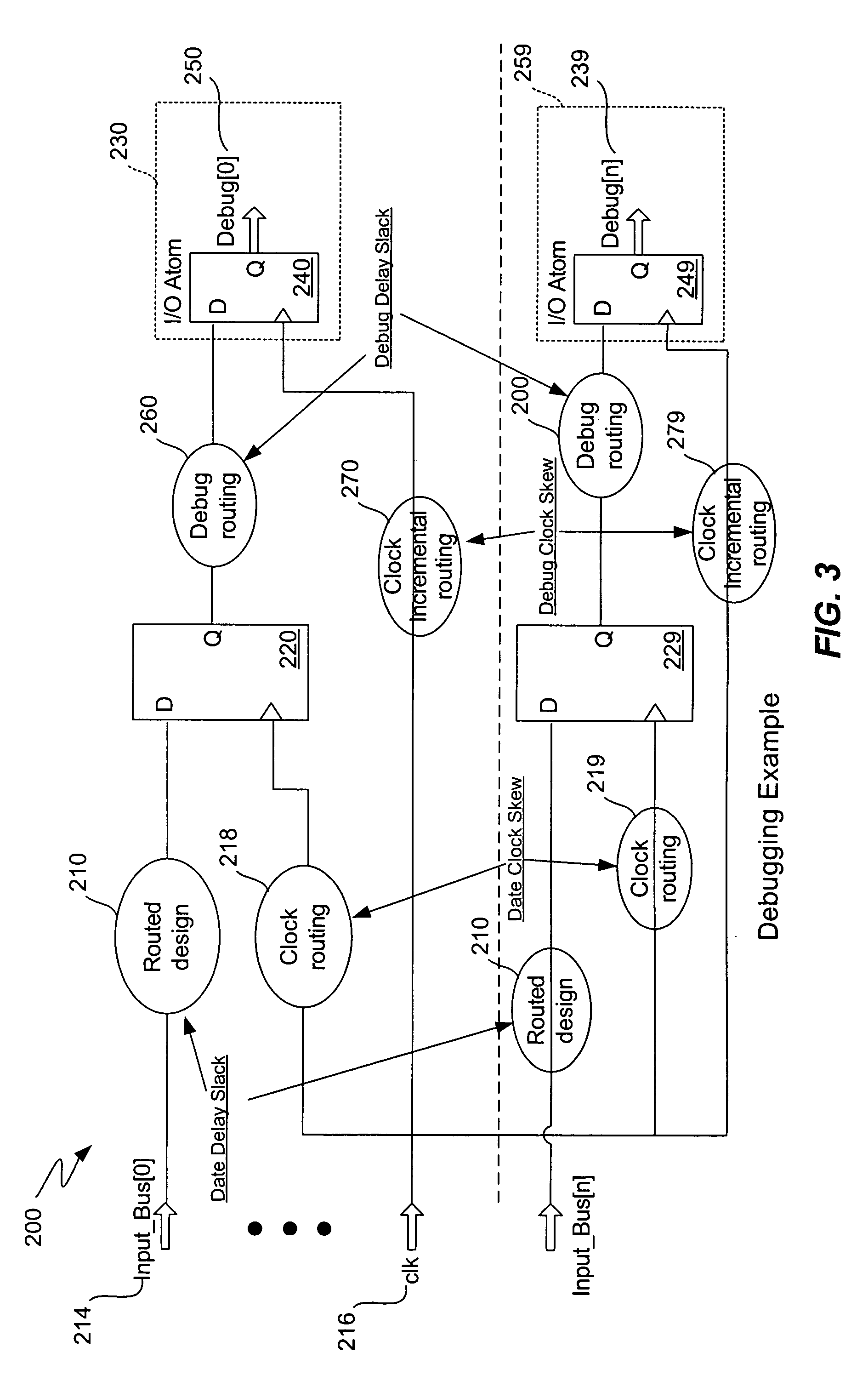

Chip debugging using incremental recompilation and register insertion

InactiveUS7206967B1Efficient solutionError detection/correctionElectrical testingComputer architectureProcessor register

While debugging, a user chooses an incremental recompile. Internal signals of interest and output pins are selected, and a number of additional registers are chosen to insert in the path of each internal signal. A clock is selected for the registers. An incremental recompile of the compiled design compiles a routing from each internal signal to an output pin via the added registers. The database building and logic synthesis stages are skipped. The post-fitting logical netlist and routing netlist are retrieved. The new registers are created and the internal signal is connected to the output pin atom in the logical netlist. The fitter places and routes the connections to create a new routing netlist and then the new routing netlist is output into a programming output file (POF) in a form suitable for programming the PLD. The original routing netlist is undisturbed. The user views the internal signals at the output pins chosen. The user may iterate through this process many times in order to debug the PLD. The debugging assignments may be deleted.

Owner:ALTERA CORP

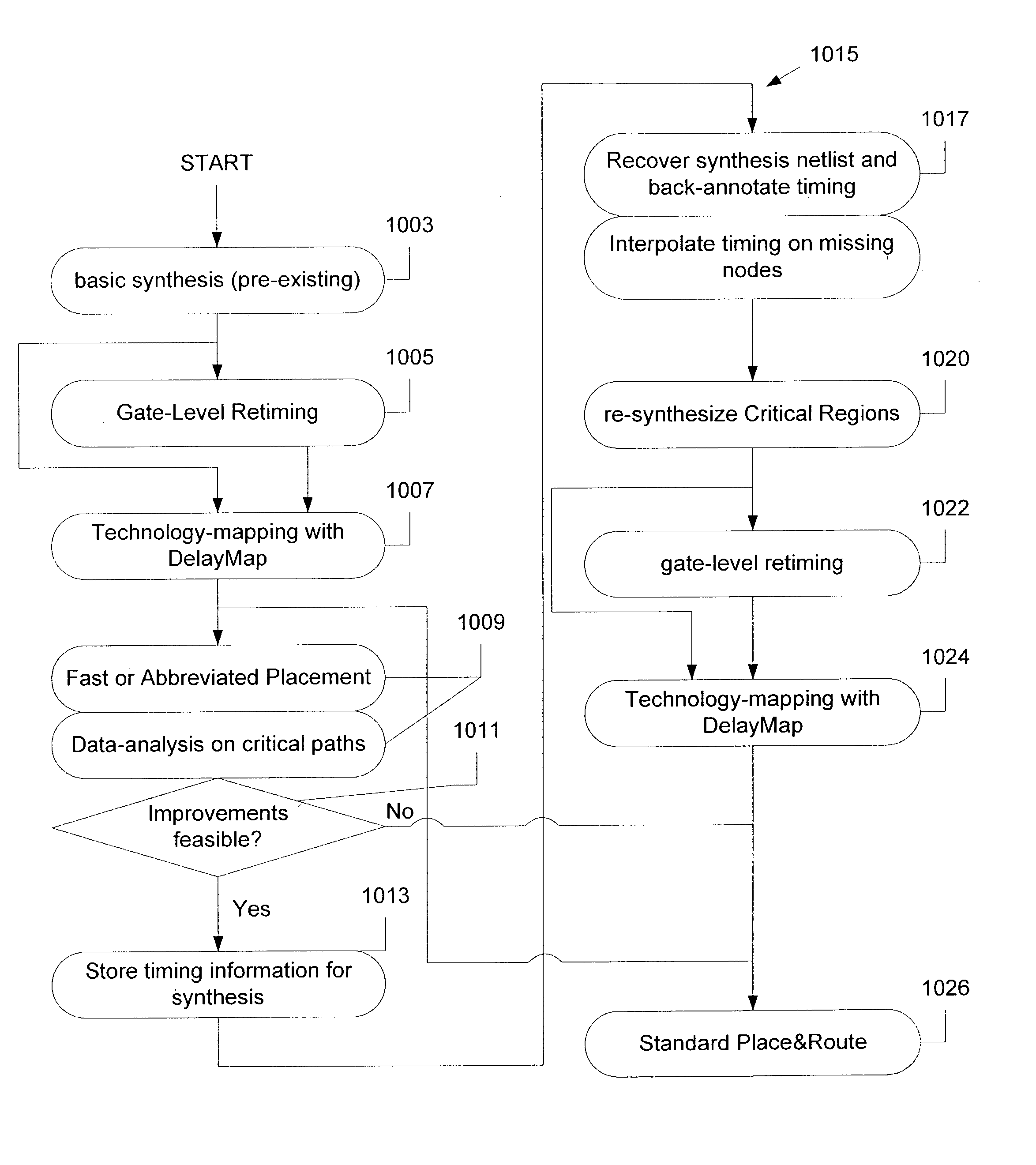

Physical resynthesis of a logic design

InactiveUS7337100B1Simple designMinimize time delayElectronic circuit testingAnalogue computers for electric apparatusThird partyVisibility

A multiple-pass synthesis technique improves the performance of a design. In a specific embodiment, synthesis is performed in two or more passes. In a first pass, a first synthesis is performed, and in a second or subsequent pass, a second synthesis or resynthesis is performed. During the first synthesis, the logic will be mapped to for example, the logic structures (e.g., logic elements, LUTs, synthesis gates) of the target technology such as a programmable logic device. Alternatively a netlist may be provided from a third party. Before the second synthesis, a fast or abbreviated fit may be performed of the netlist to a specific device (e.g., specific programmable logic device product). Before the second synthesis, the netlist obtained from the first synthesis (or provided by a third party) is unmapped and then the second synthesis is performed. Since a partial fit is performed, the second synthesis has more visibility and optimize the logic better than by using a single synthesis pass. After the second synthesis pass, a more detailed fit is performed.

Owner:ALTERA CORP

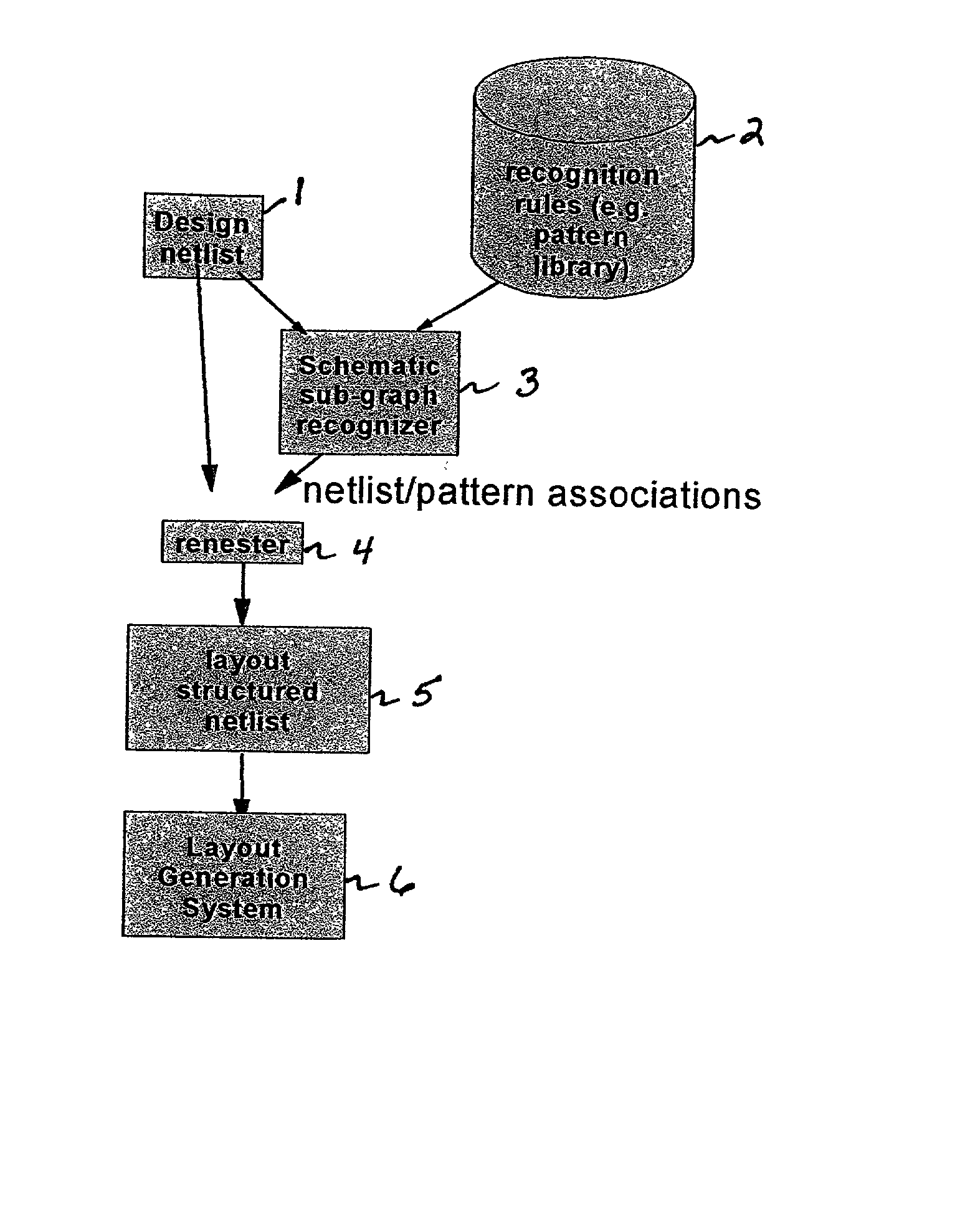

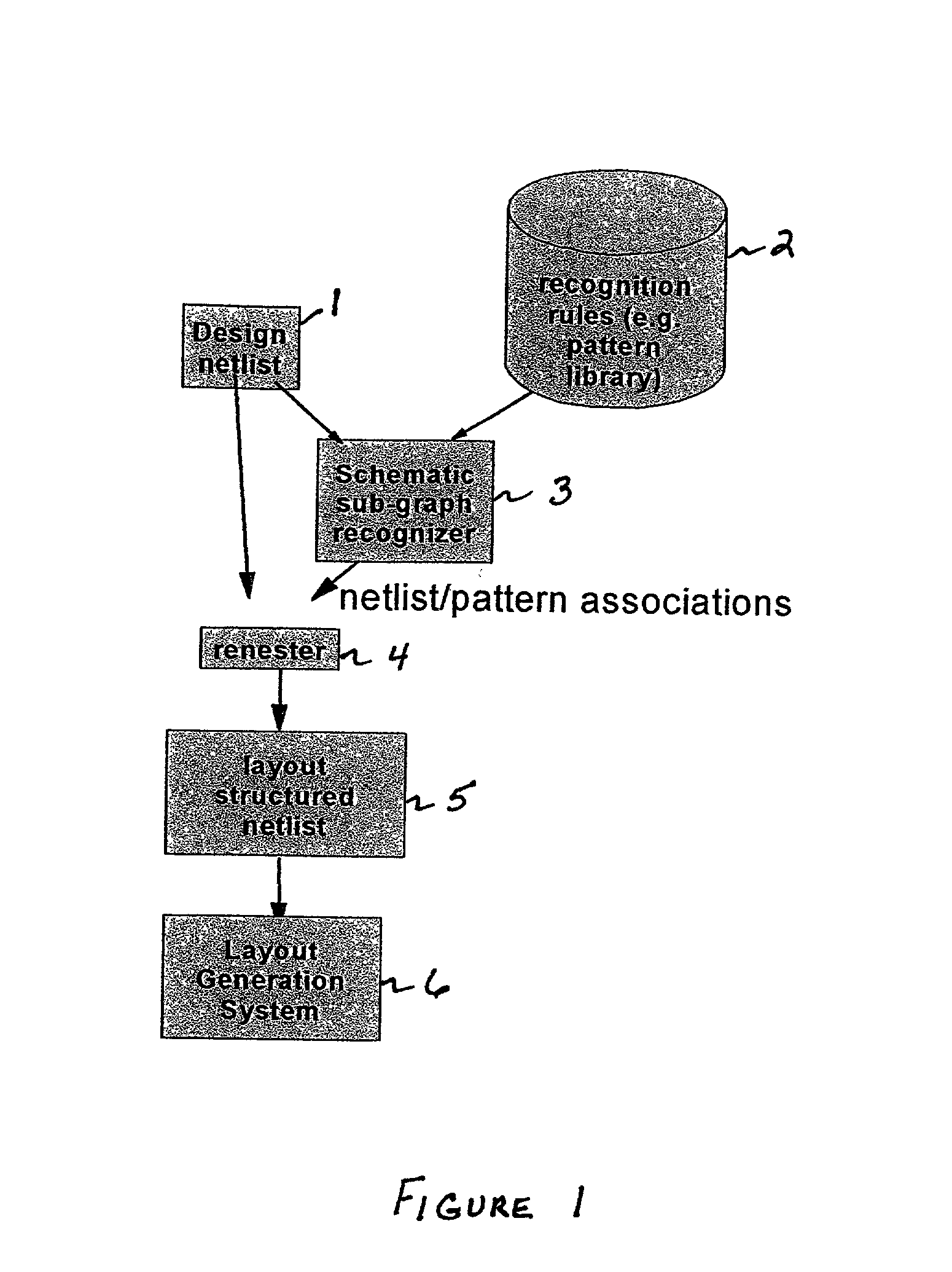

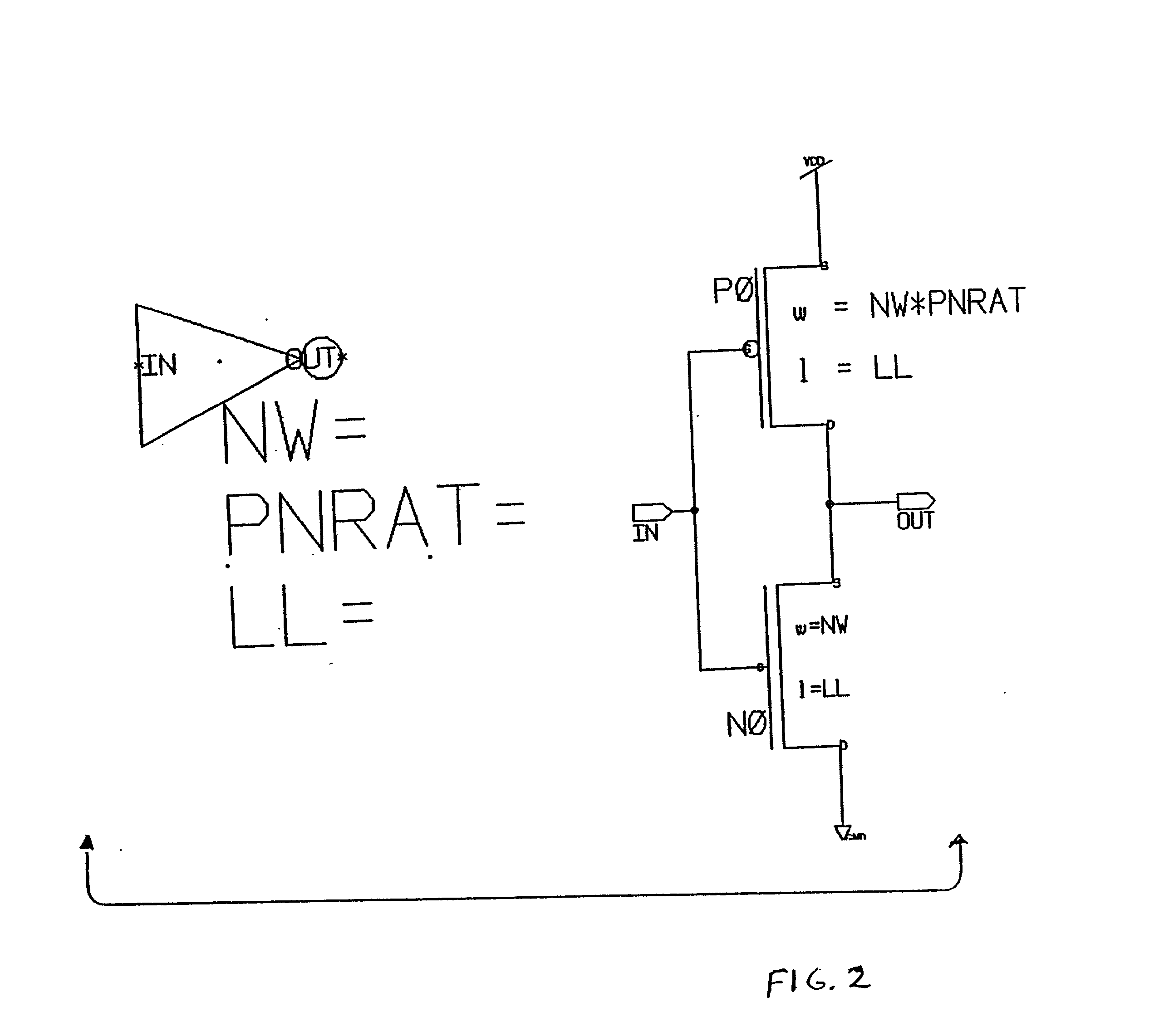

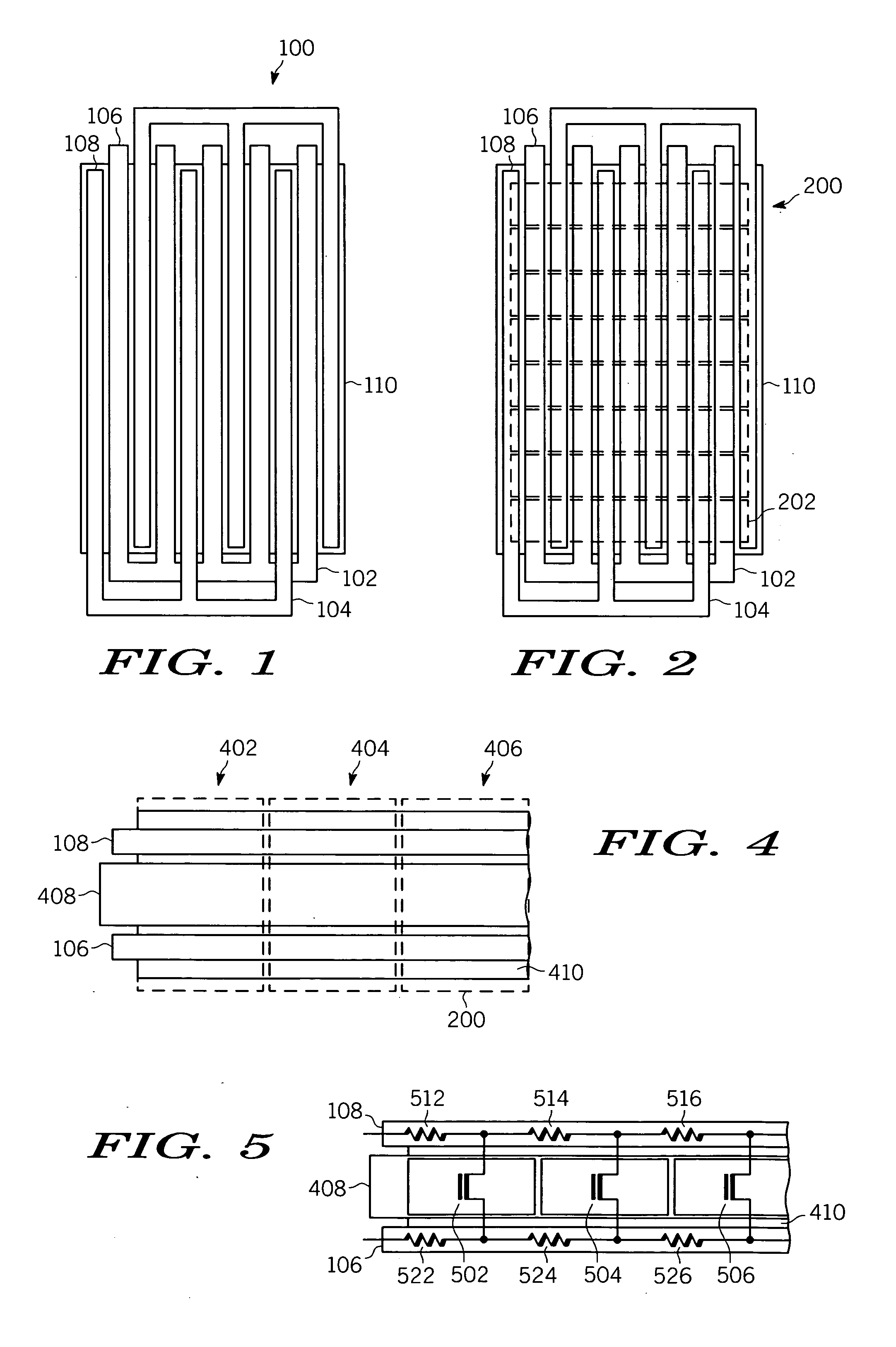

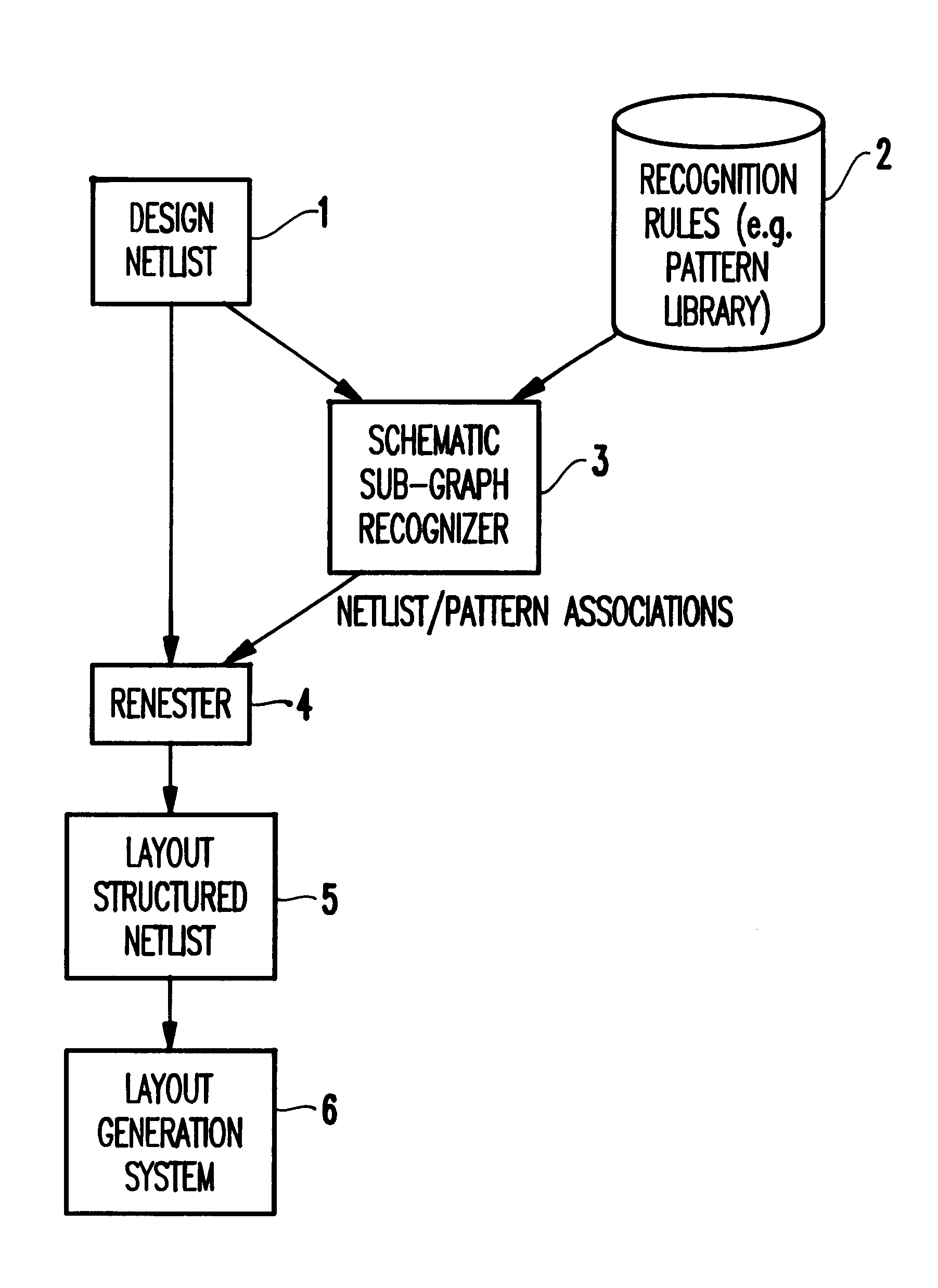

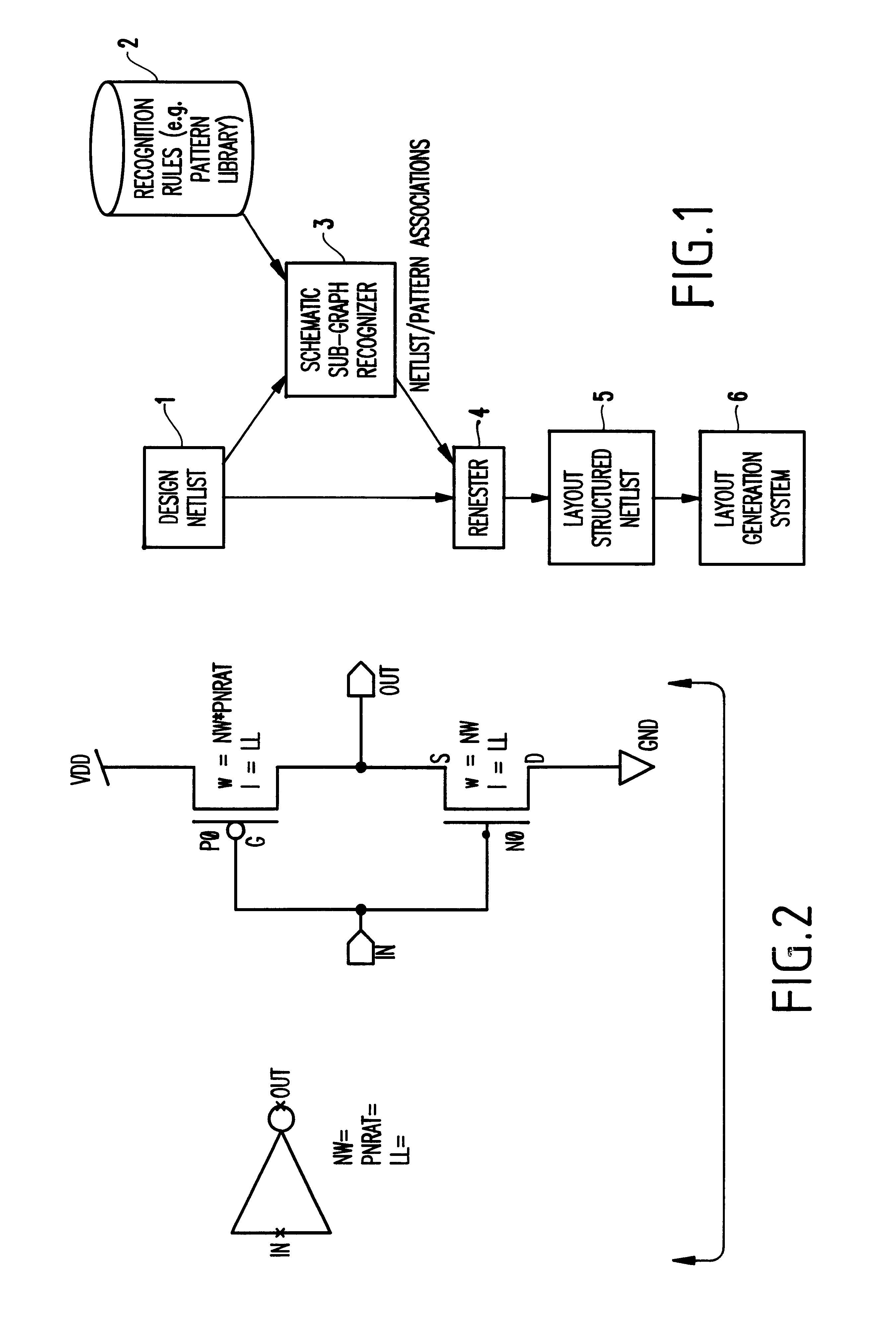

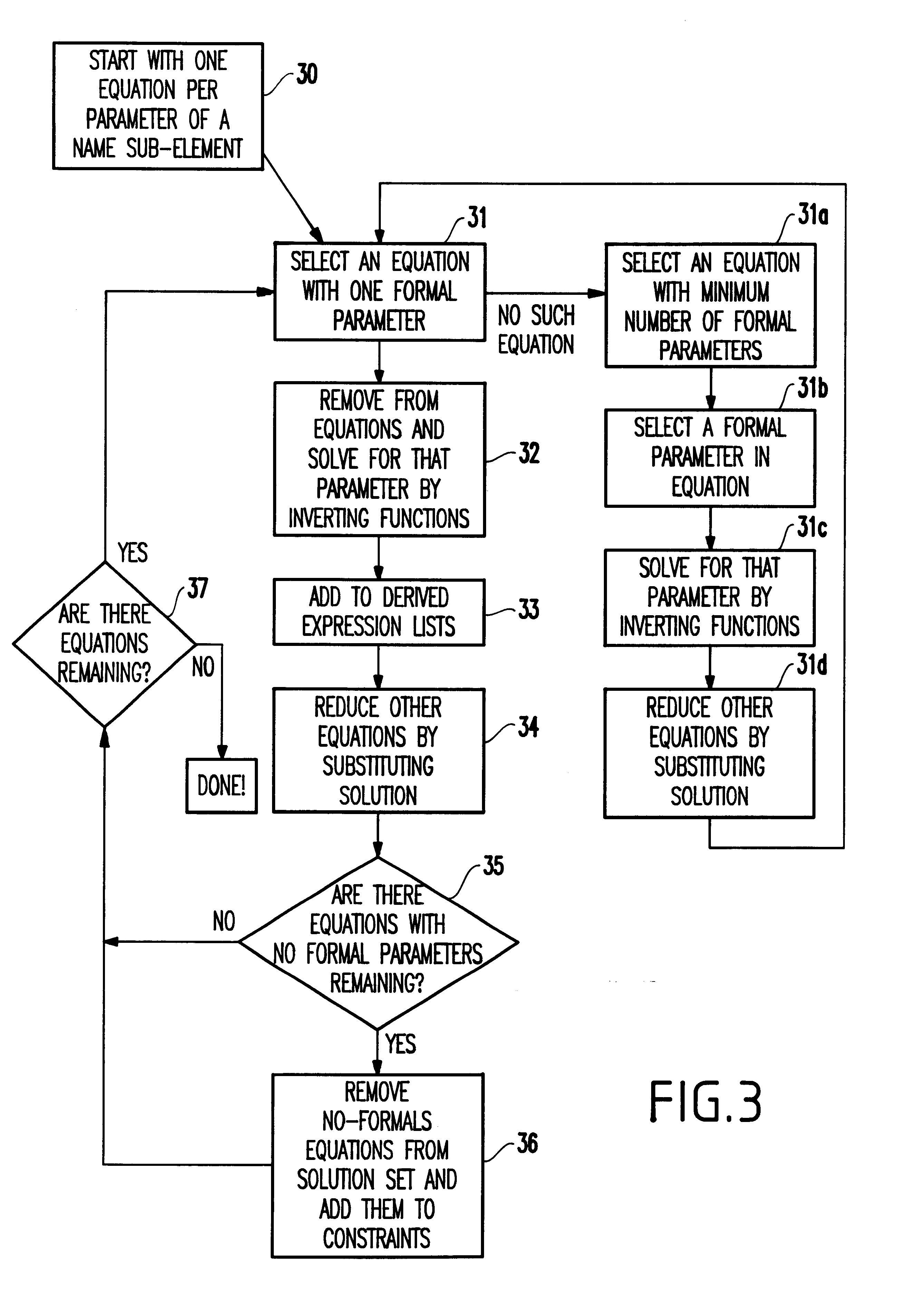

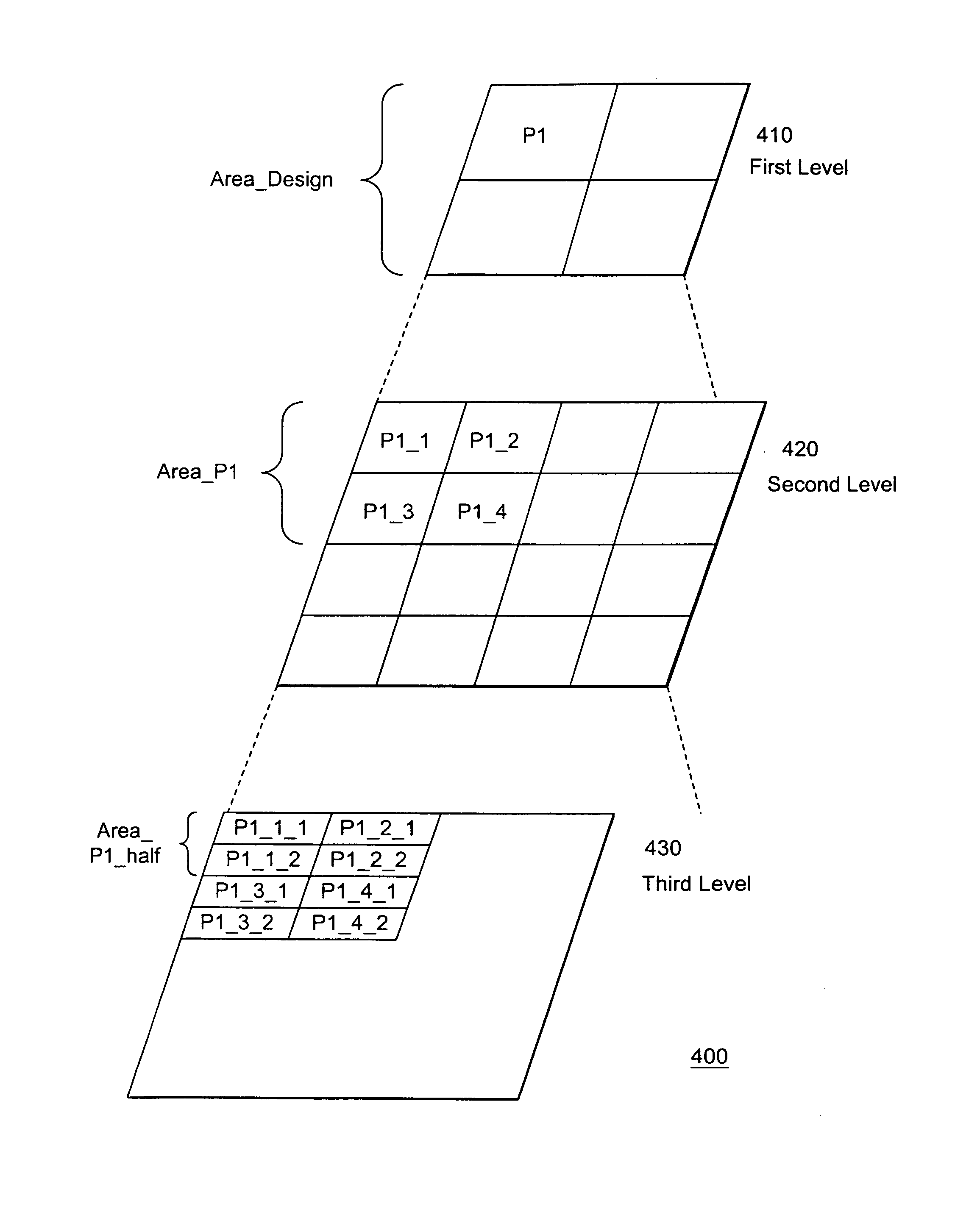

Hierarchical layout method for integrated circuits

InactiveUS20020194575A1Easy to modifyIncrease production capacityCAD circuit designProgram controlComputer architectureGenerative Design

A method for hierarchical layout of an electronic design using an electronic computer aided design system, wherein the method includes generating a parameterized pattern library and using an existing netlist and analyze in a pattern recognizer, from which a list of associations between the pattern library and the netlist is created. Renesting then occurs wherein the netlist using the list of associations is used for generating a hierarchical layout of the electronic components in the design.

Owner:IBM CORP

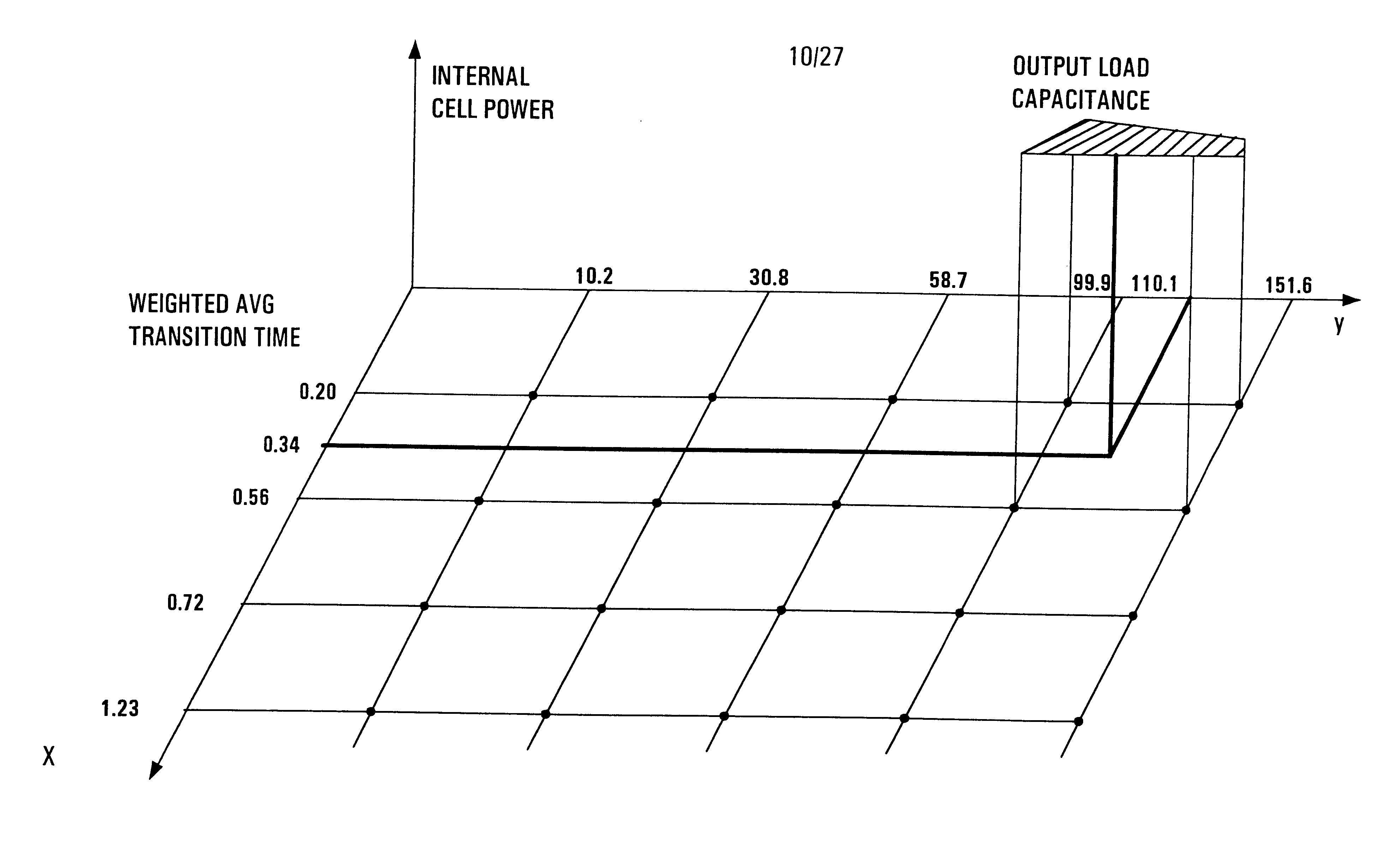

Method and apparatus for estimating internal power consumption of an electronic circuit represented as netlist

InactiveUS6345379B1Improve accuracyEasy to writeCAD circuit designSpecial data processing applicationsTransition timeNetlist

This is a method of quickly computing the power dissipated by a digital circuit using information available at the gate library level. It estimates the short-circuit power by modeling the energy dissipated by the cell per input transition as a function of the transition time or edge rate, and multiplying that value by the number of transitions per second for that input.

Owner:SYNOPSYS INC

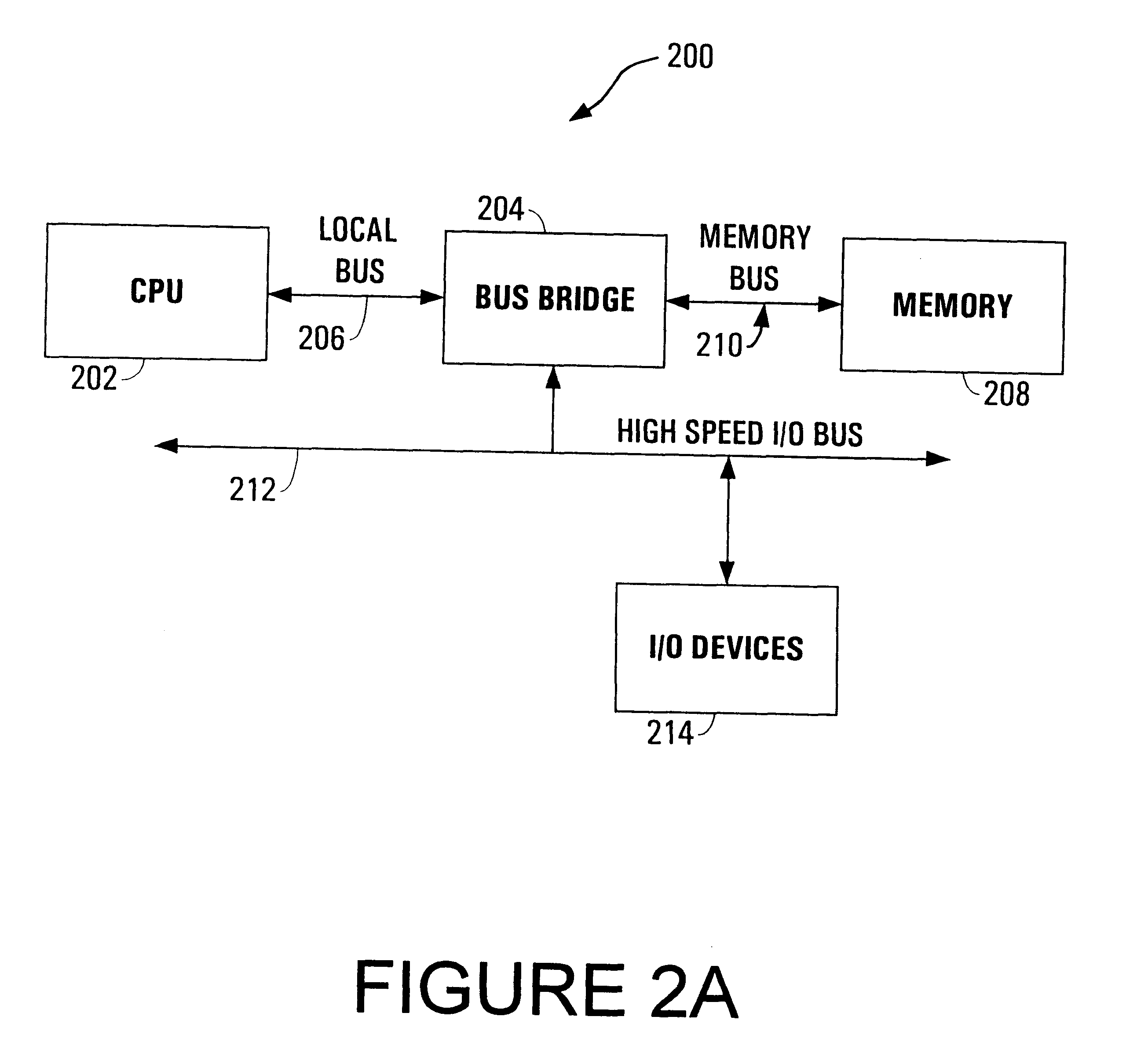

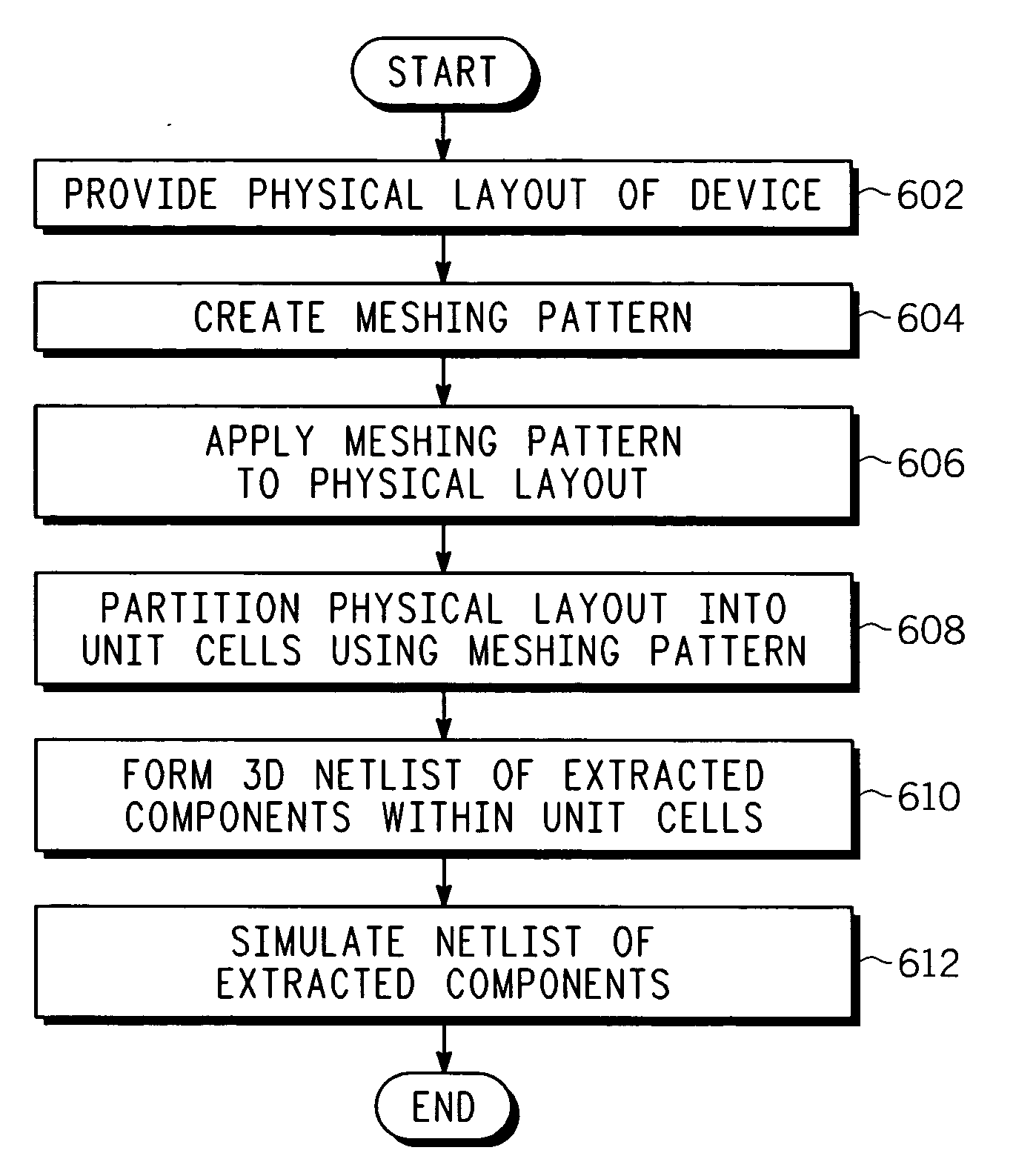

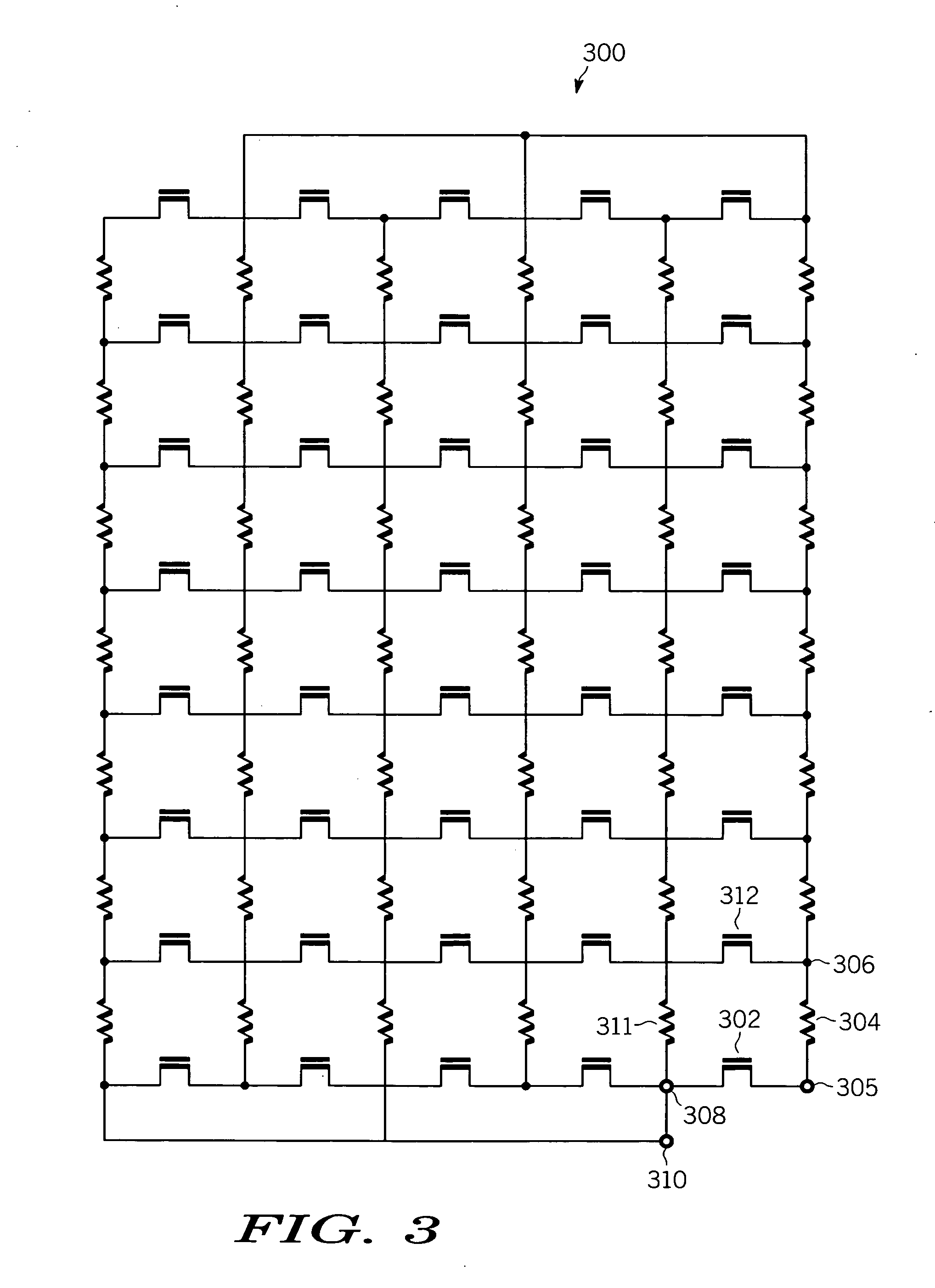

Methods and apparatus for simulating distributed effects

InactiveUS20070288882A1Detecting faulty computer hardwareComputer aided designComputer scienceNetlist

In general, various embodiments of the present invention relate to systems and methods for simulating distributed effects by providing a meshing pattern (200) (e.g., a two-dimensional meshing pattern that is part of a recognition layer), applying that meshing pattern to the physical layout (100), and partitioning the physical layout into a three-dimensional netlist (300) of components derived from the unit cells defined by the meshing pattern (200), thereby modeling the parasitics within the design.

Owner:NXP USA INC

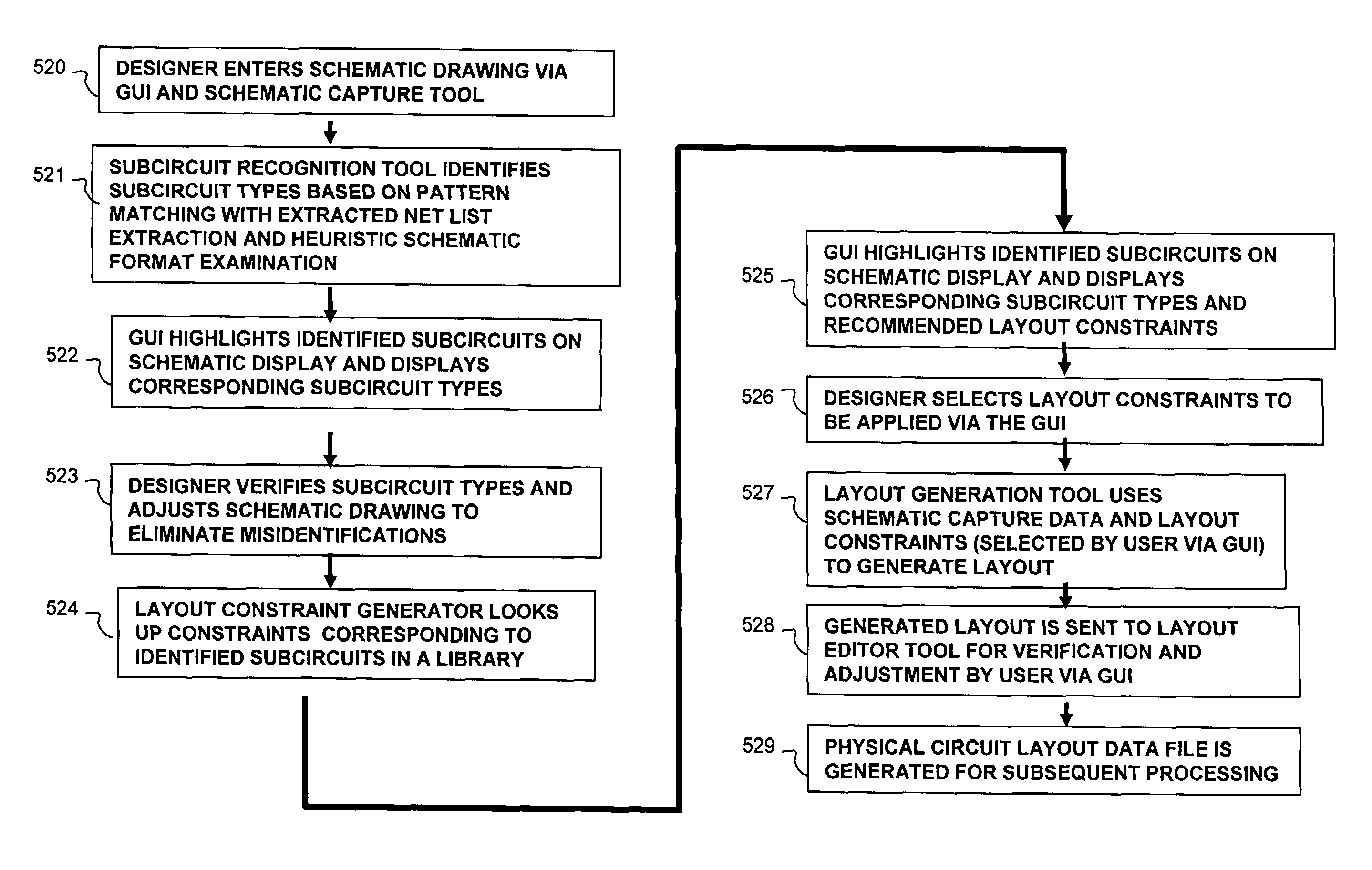

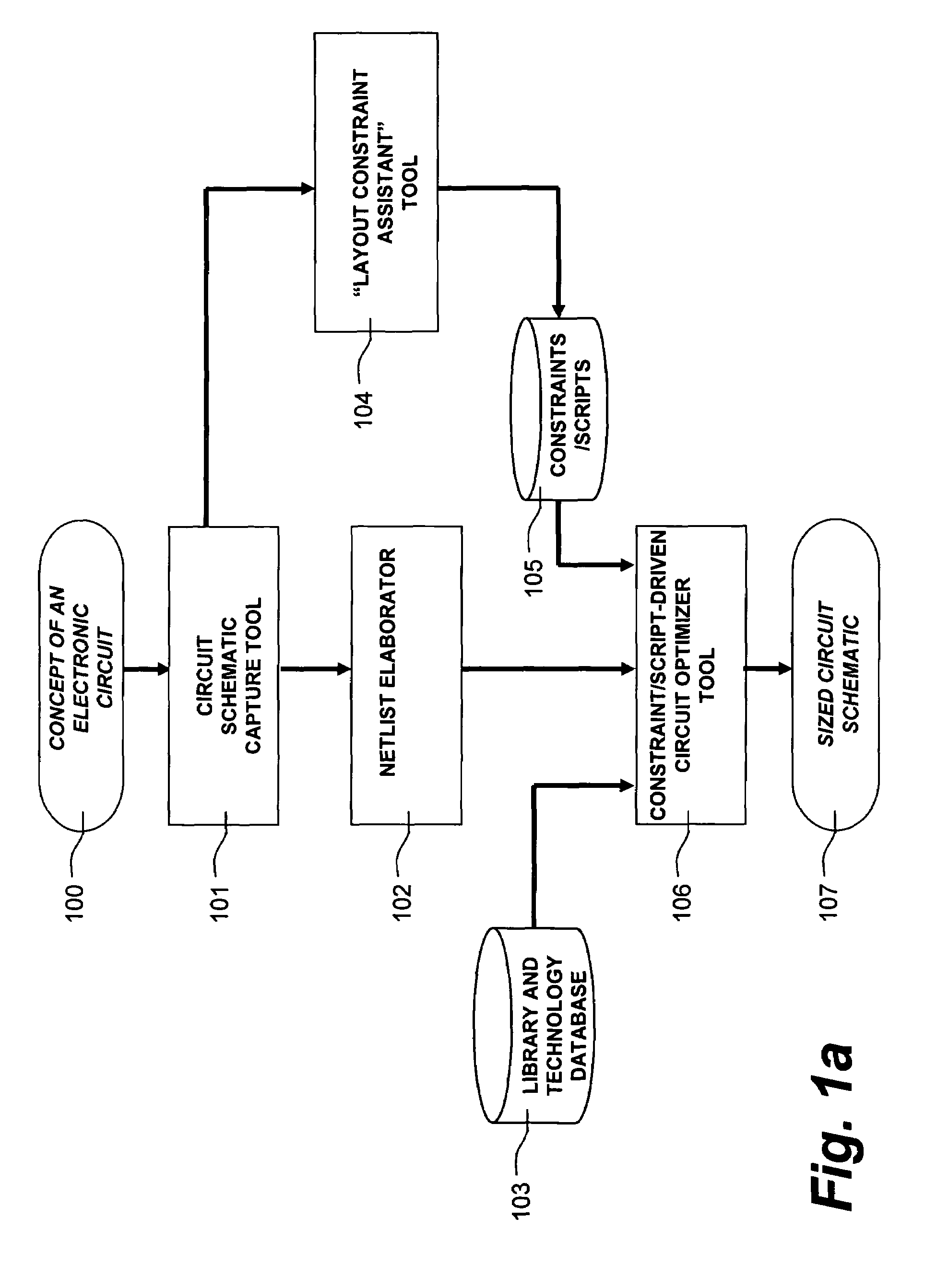

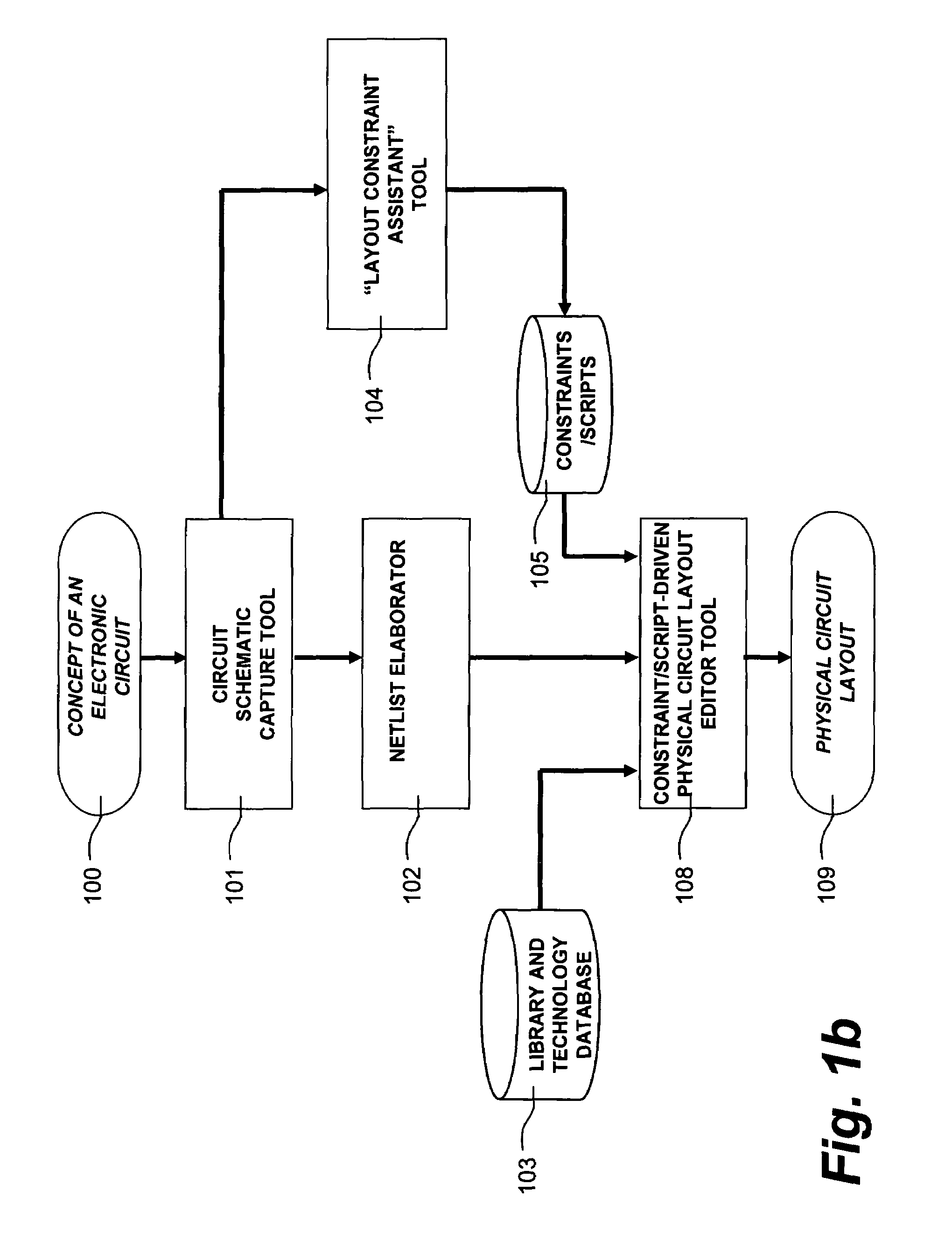

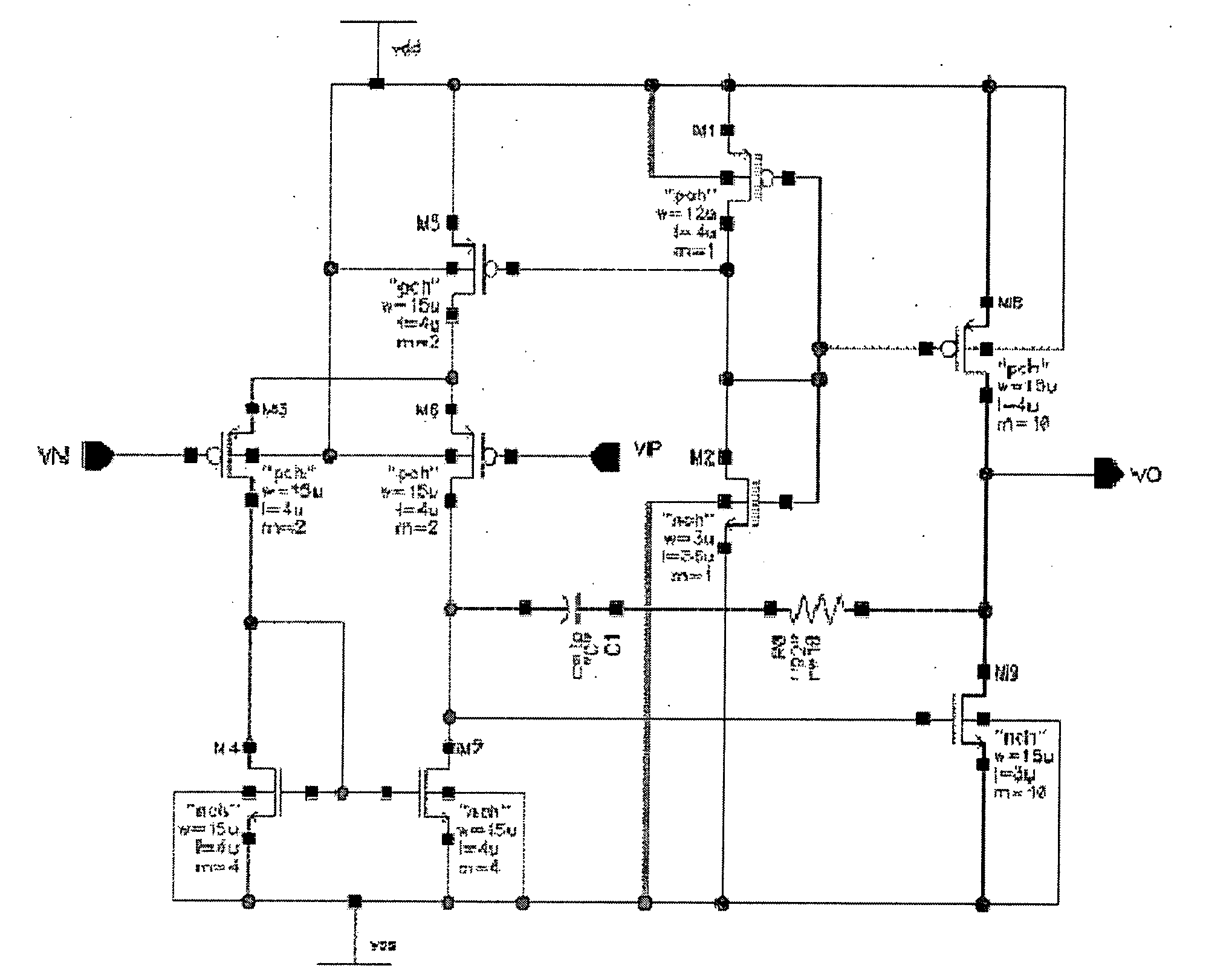

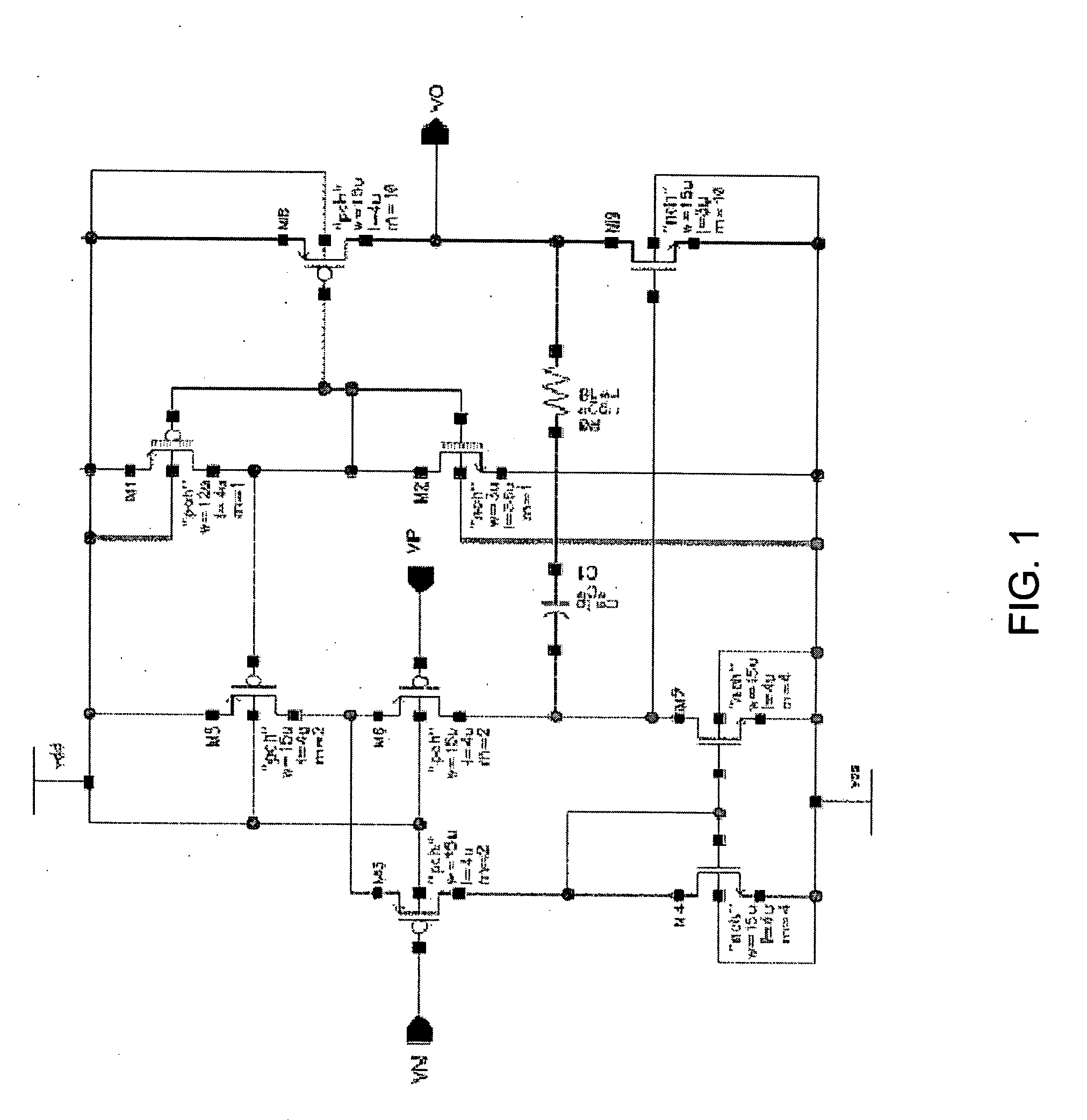

Constraint assistant for circuit design

InactiveUS7418683B1Less likelyAvoid wasting timeSpecial data processing applicationsSymbolic schematicsComputer Aided DesignEngineering

A computer aided design tool and method for designing IC layouts by recommending subcircuit layout constraints based upon an automated identification from a circuit schematic of subcircuit types requiring special IC layout constraints. Subcircuit types are identified on the basis of netlist examination, as well as cues from the layout of the circuit schematic.

Owner:CADENCE DESIGN SYST INC

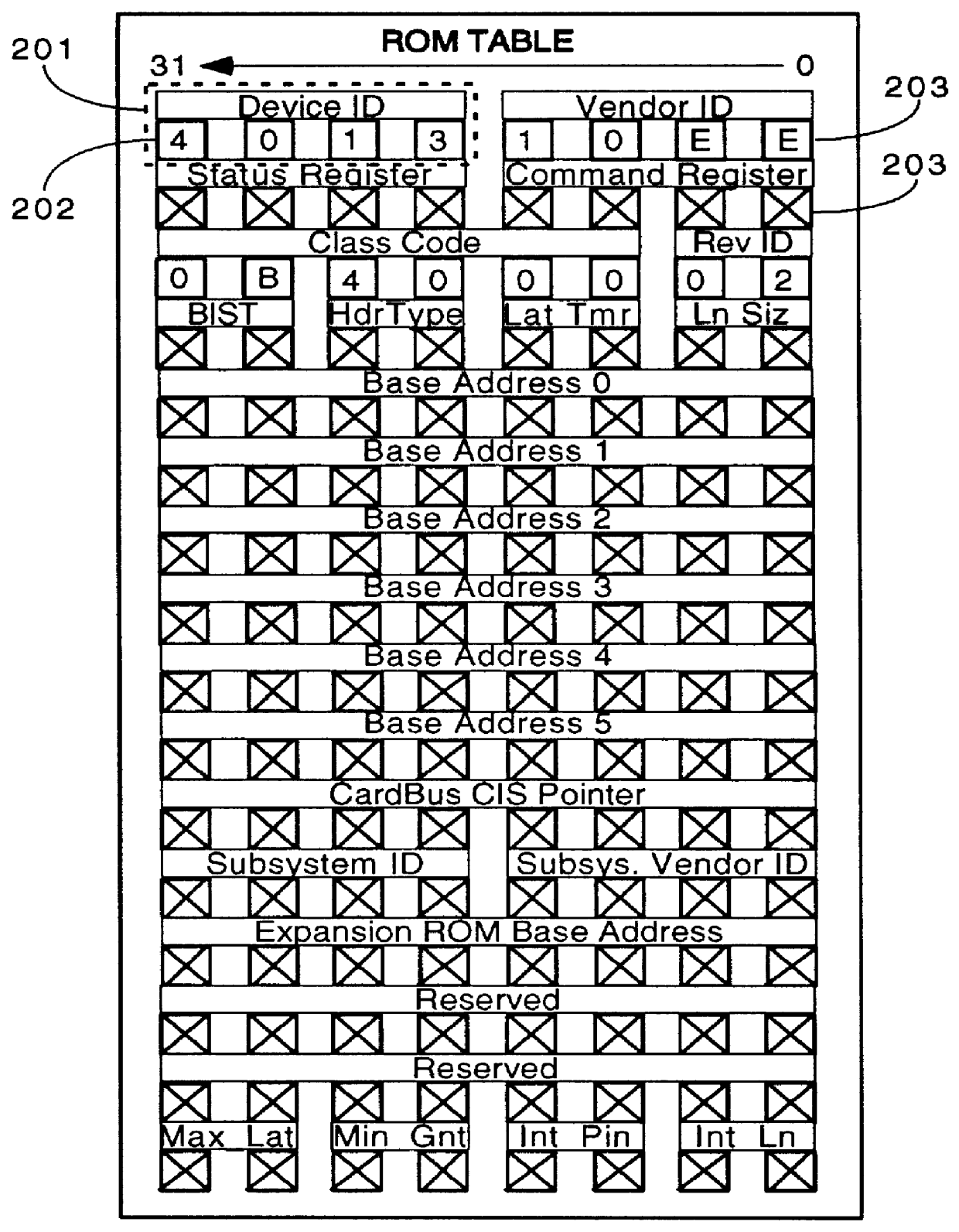

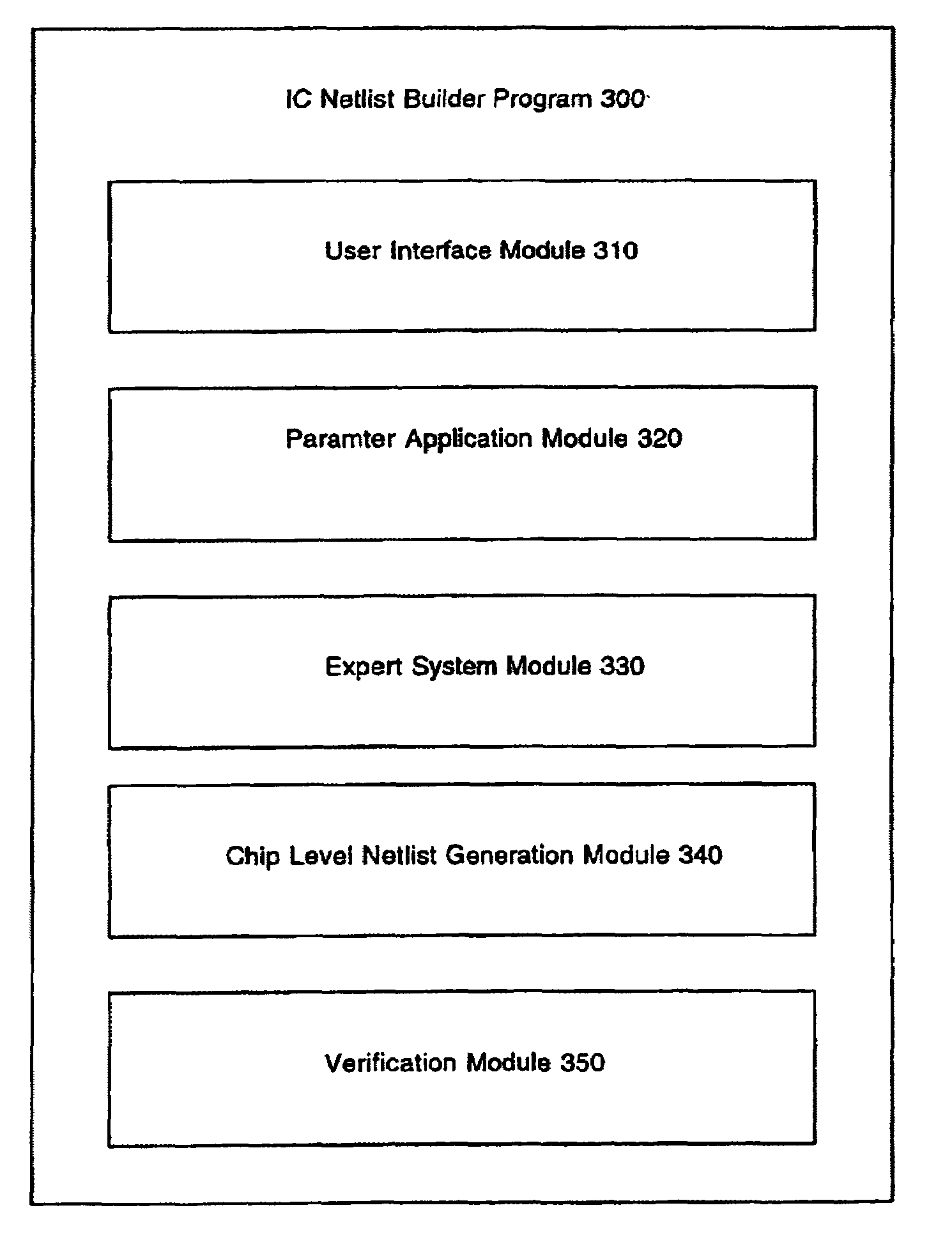

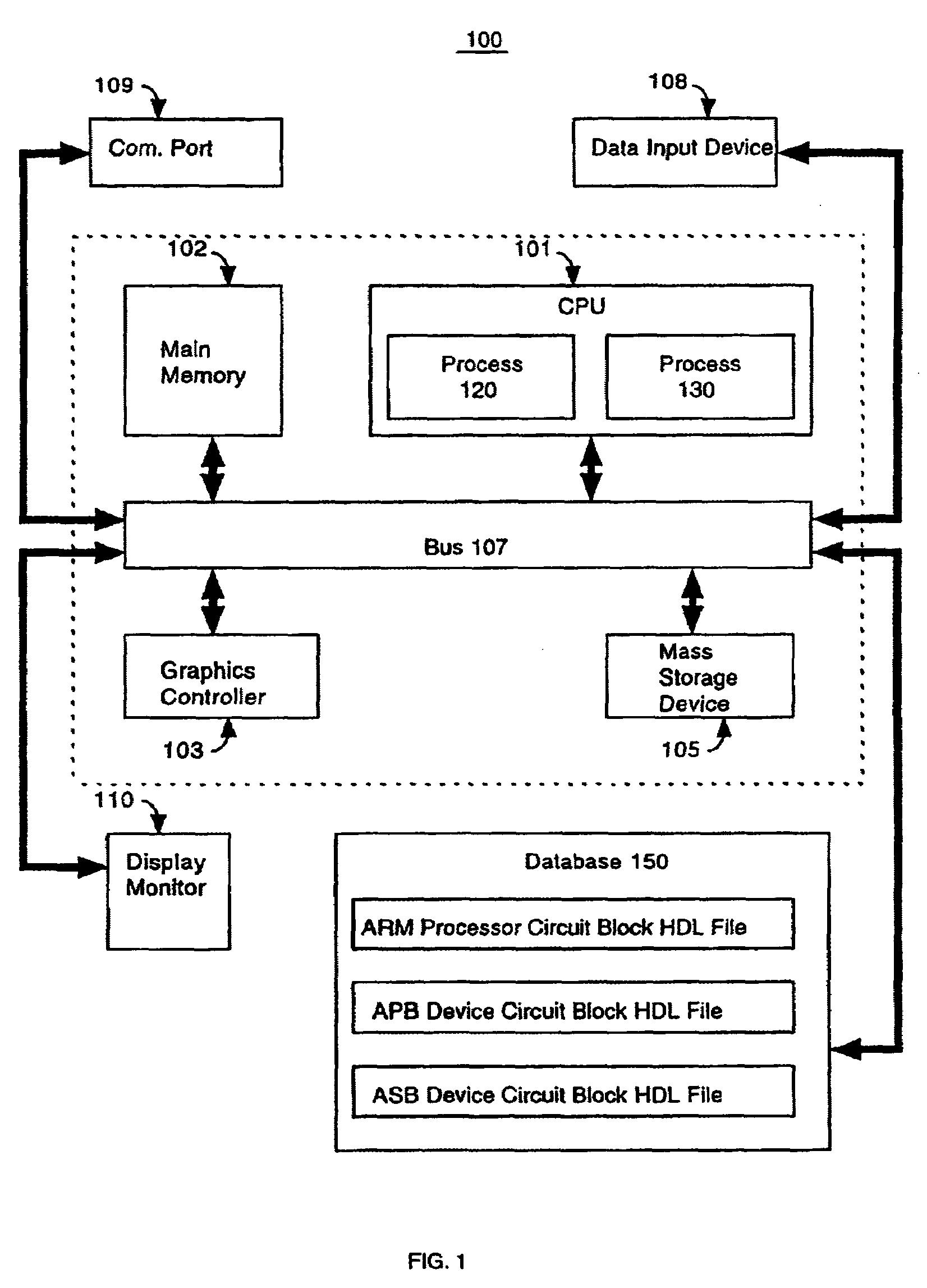

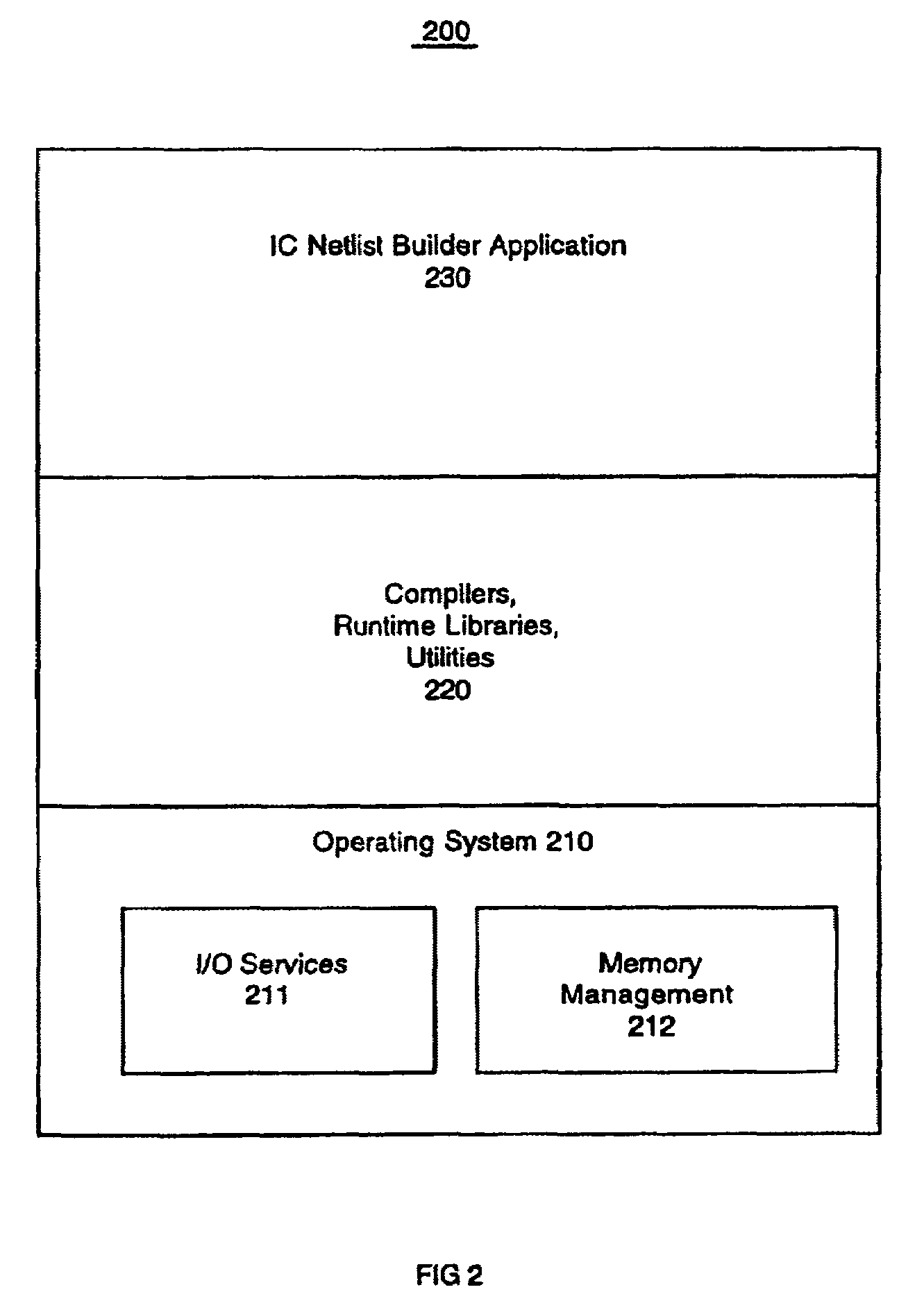

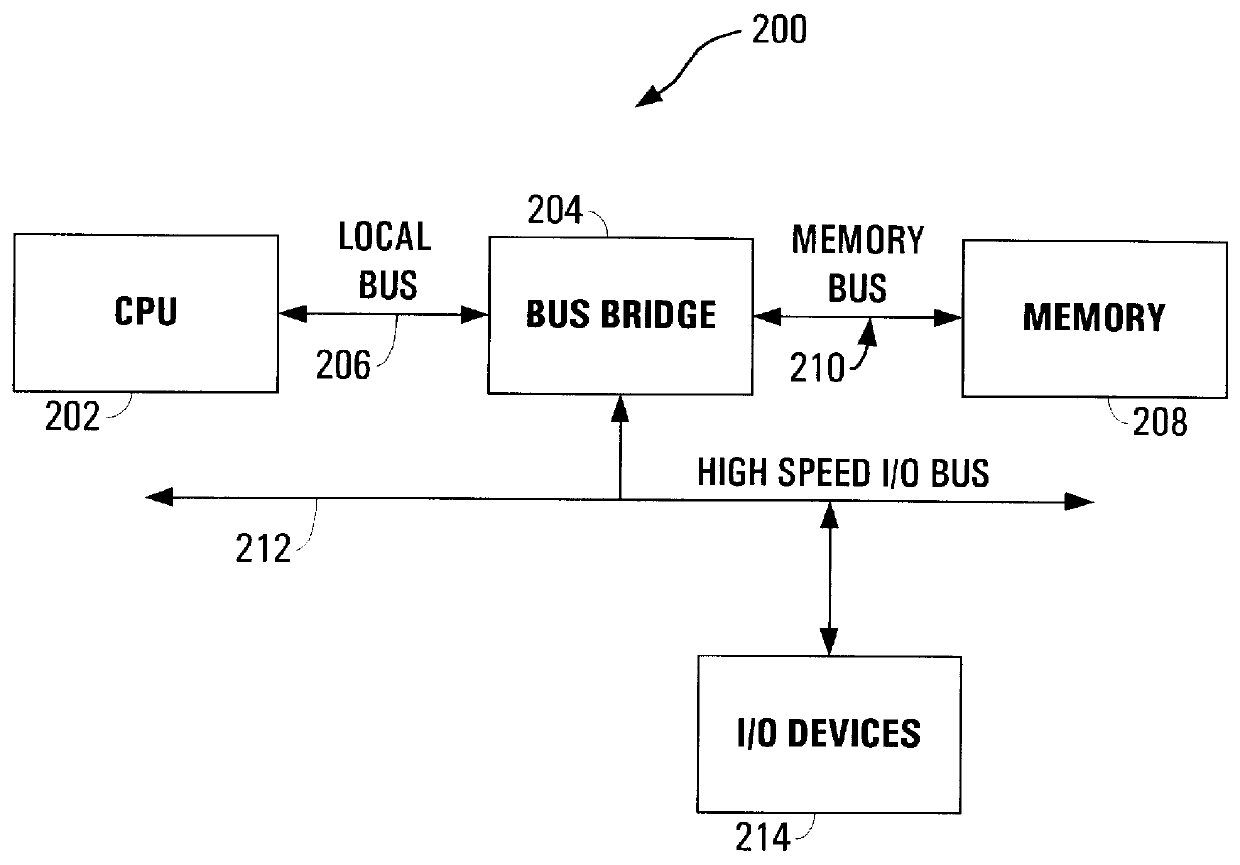

Computer system and method to dynamically generate system on a chip description files and verification information

InactiveUS7100133B1Facilitates efficient and effective creation and modification and verificationConvenience to mergeCAD circuit designSoftware simulation/interpretation/emulationComputer architectureTest platform

The present invention facilitates automation of system on a chip (SoC) design, manufacture and verification in a convenient and efficient manner. In one embodiment, a SoC netlist builder and verification computer system of the present invention includes a user interface module, a parameter application module, an expert system module and a chip level netlist generation module. The user interface module provides user friendly and convenient interfaces that facilitate easy entry and modification of user selections and parameters. The parameter application module interprets information supplied by the user module and the expert system module and creates directions (e.g., command lines) passed to other modules for execution. The expert system module analyzes information and automatically provides SoC building and verification data including automated addition of default architectural features, automated insertion of default parameters, and automated input of information to the verification module. The chip level netlist generation module automatically generates a chip level netlist, including the instantiation of internal IC devices and connections between the circuit blocks for internal signals. The verification module automatically generates a test bench and a logical verification environment including simulation models (e.g., a chip model and a system level model).

Owner:NXP BV

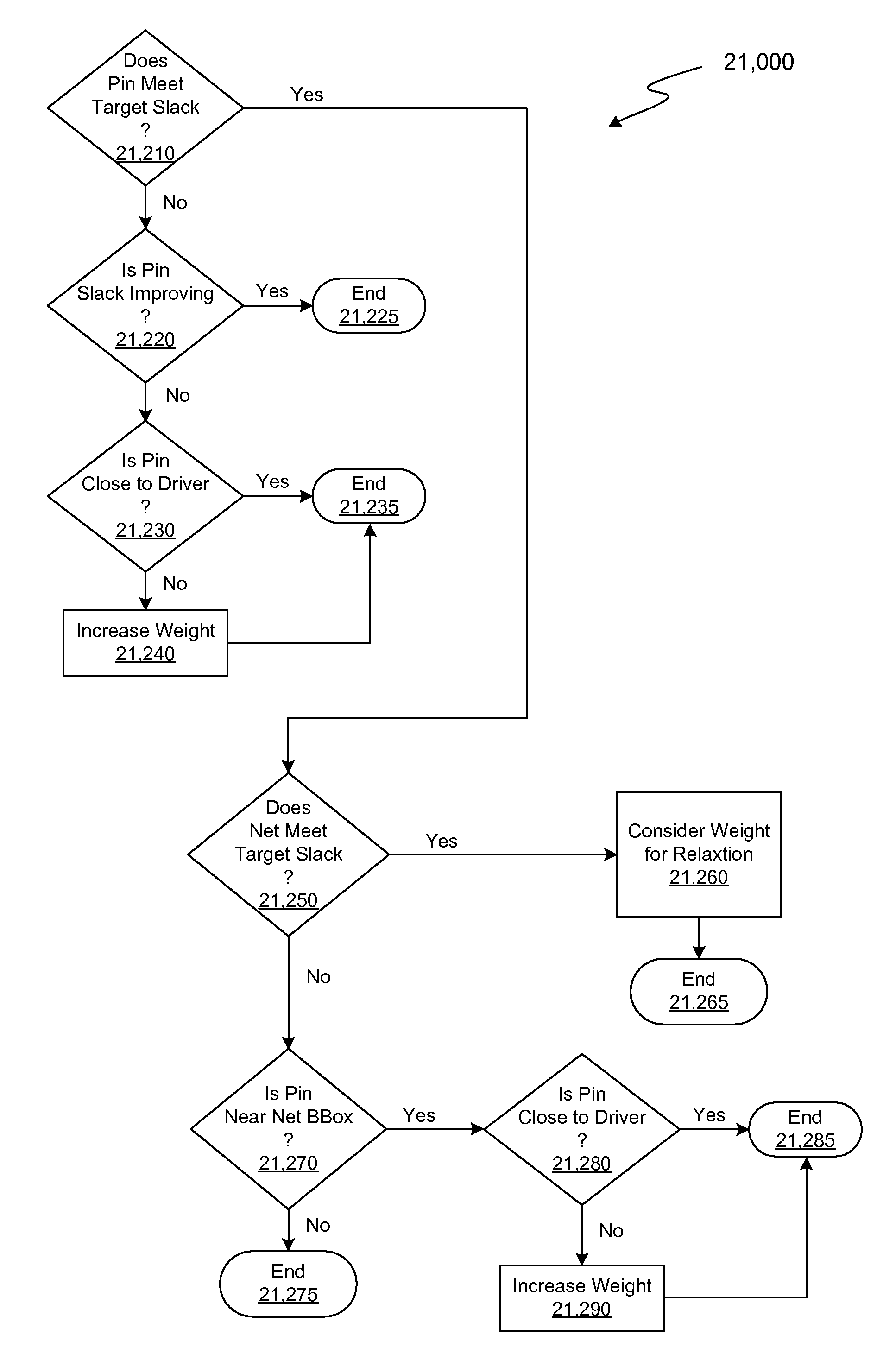

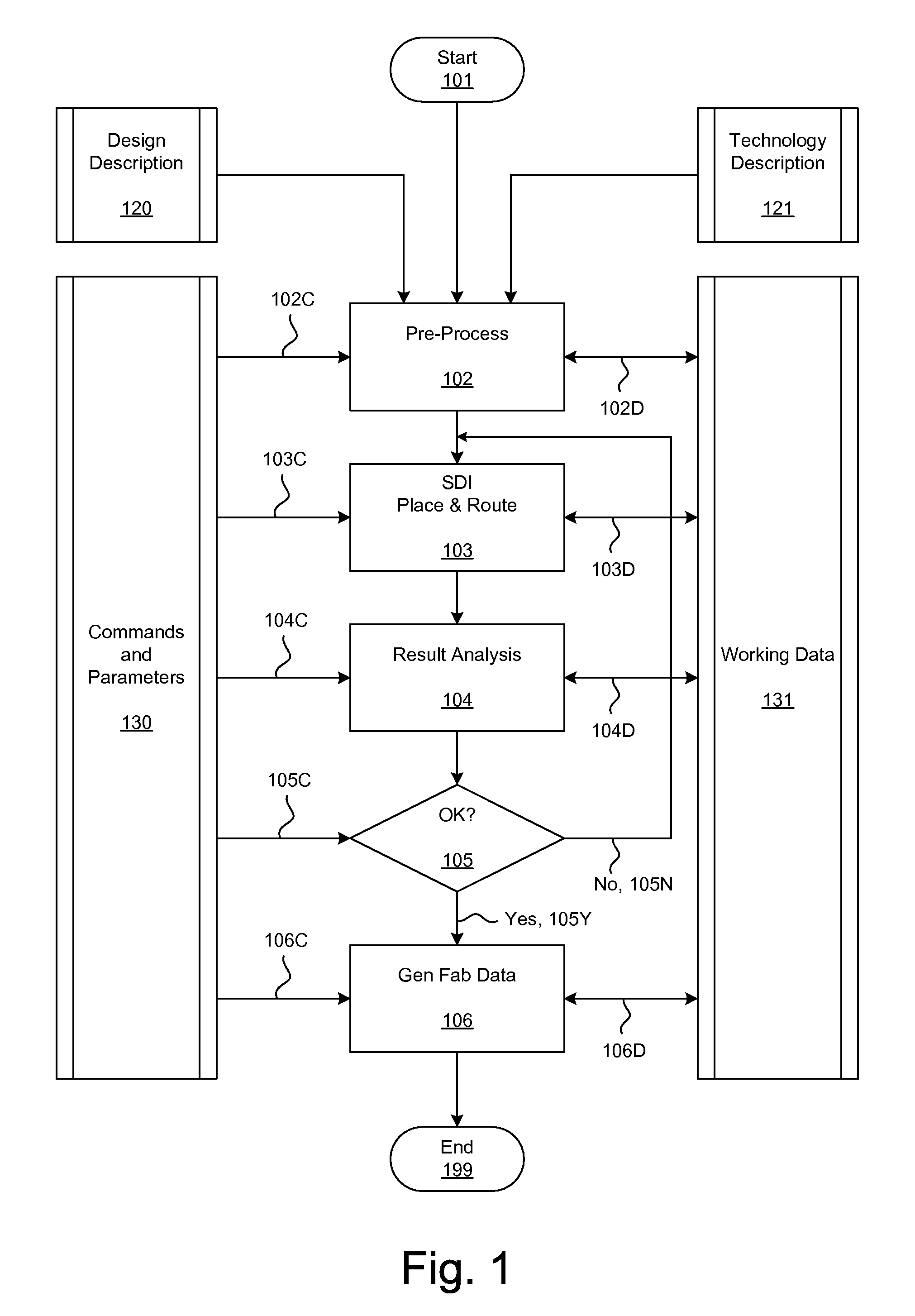

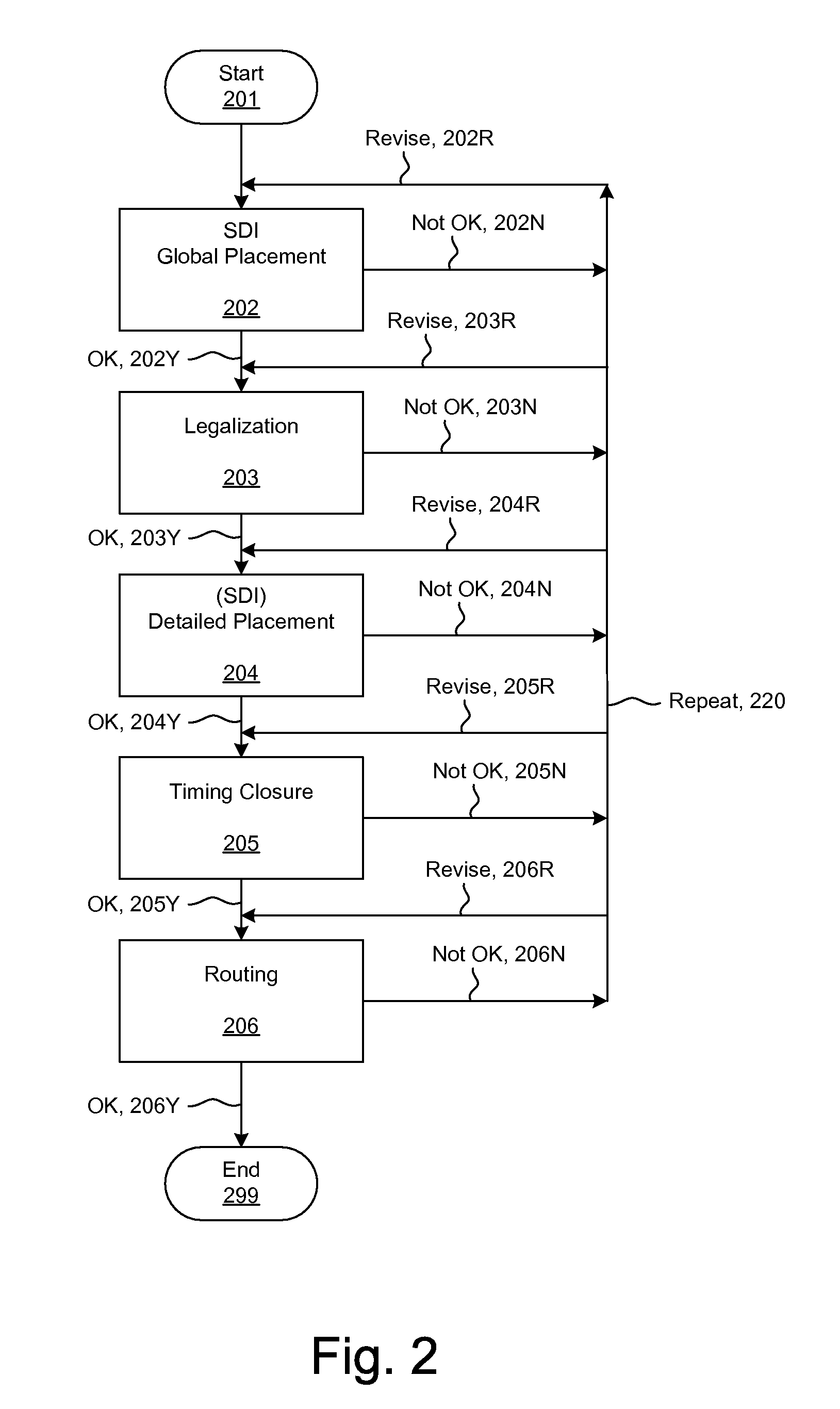

Incremental Relative Slack Timing Force Model

InactiveUS20080216040A1Influence optimizeImprove performanceCAD circuit designSpecial data processing applicationsInterconnectionComputer science

Simultaneous Dynamical Integration modeling techniques are applied to global placement of elements of integrated circuits as described by netlists specifying interconnection of morphable-devices. Solutions to a system of coupled ordinary differential equations in accordance with Newtonian mechanics are approximated by numerical integration. A resultant time-evolving system of nodes moves through a continuous location space in continuous time, and is used to derive placements of the morphable-devices having one-to-one correspondences with the nodes. Nodes under the influence of net attractive forces, computed based on the interconnections between the morphable devices, tend to coalesce into well-organized topologies. Nodes are also affected by spreading forces determined by density fields that are developed based on local spatial node populations.

Owner:CALLAHAN CELLULAR L L C

Method and apparatus for estimating internal power consumption of an electronic circuit represented as netlist

InactiveUS6075932AGreat likelihoodReduce running timeElectric devicesCAD circuit designEngineeringTransition time

This is a method of quickly computing the power dissipated by a digital circuit using information available at the gate library level. It estimates the short-circuit power by modeling the energy dissipated by the cell per input transition as a function of the transition time or edge rate, and multiplying that value by the number of transitions per second for that input.

Owner:SYNOPSYS INC

Defect location identification for microdevice manufacturing and test

InactiveUS20060069958A1Error detection/correctionElectrical testingManufacturing technologyEngineering

A defect identification tool is disclosed that predicts locations at which defects in a microdevice are most likely to occur. The tool may identify both a type of defect and the particular netlists in which that defect is likely to occur. A test circuit generation tool can then subsequently use this defect information to generate a test circuit that tests for the defect in the identified portions of the microcircuit. Similarly, an automatic test pattern generation tool may use the defect location information to generate test data custom-tailored to check for faults corresponding to the identified defect in the specified portions of the microcircuit. Various implementations of the tool may be used both to identify the locations at which defects caused by systematic errors, such as manufacturing process deficiencies or flaws, are most likely to occur and the locations at which randomly-created defects are most likely to occur.

Owner:MENTOR GRAPHICS CORP

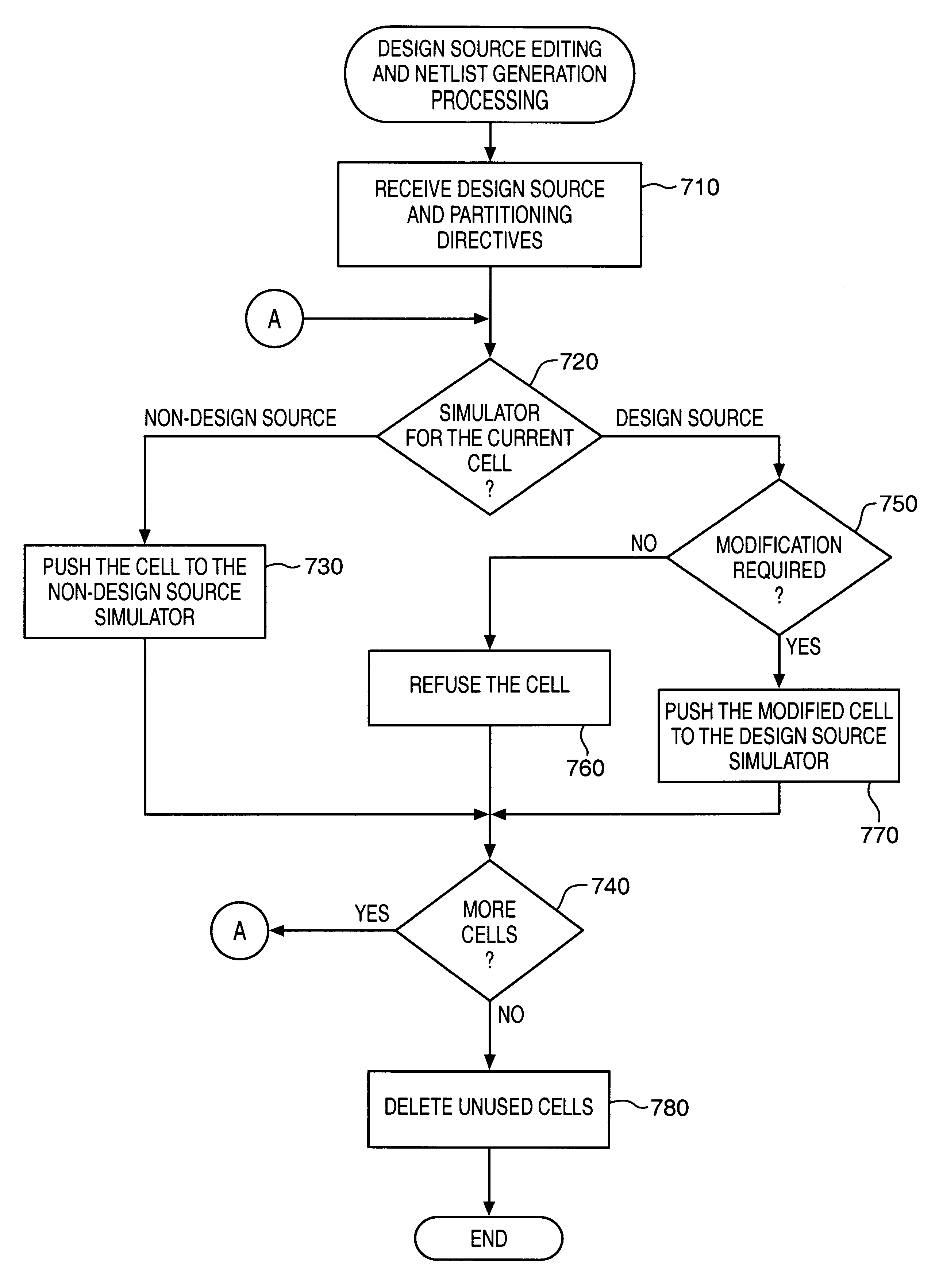

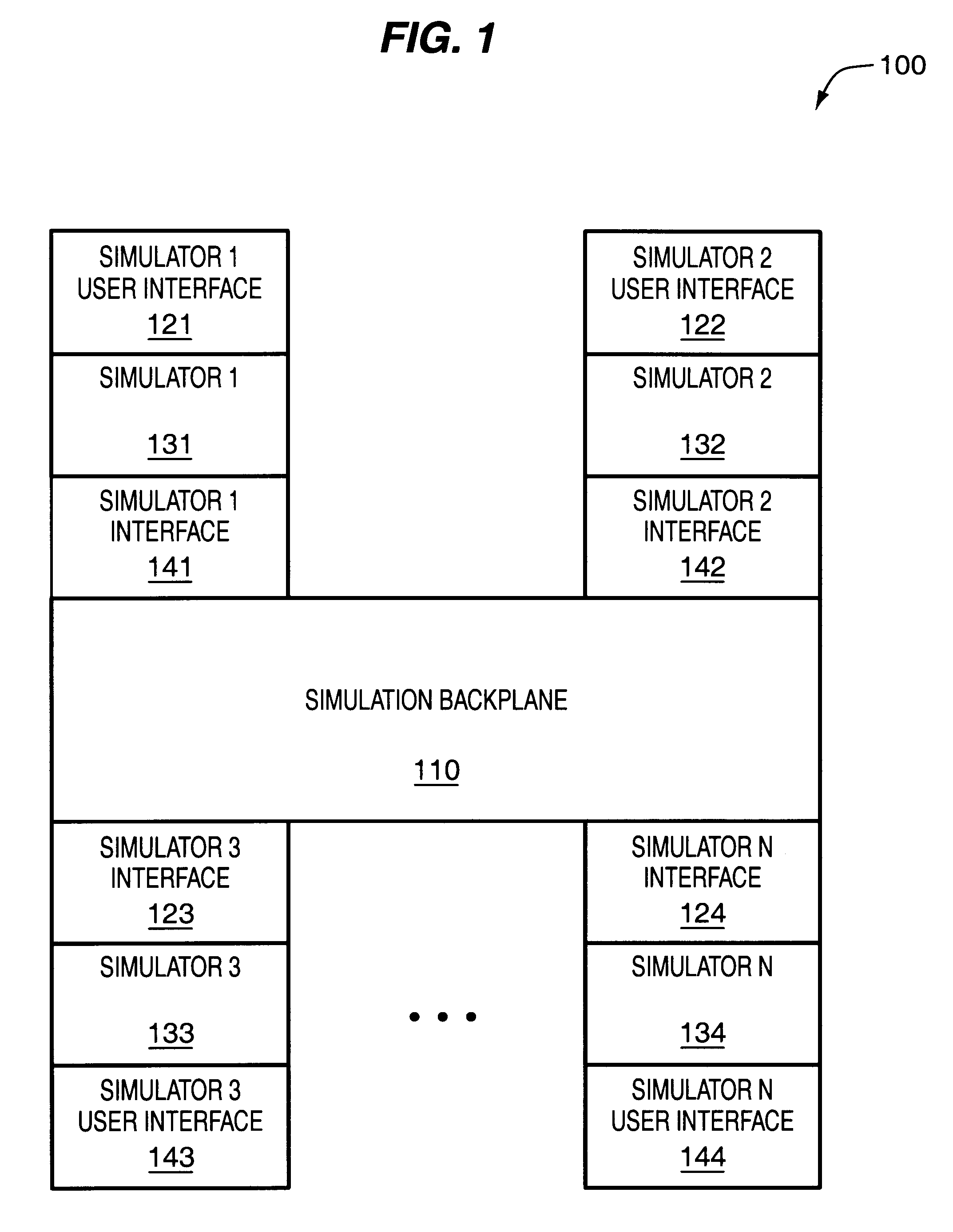

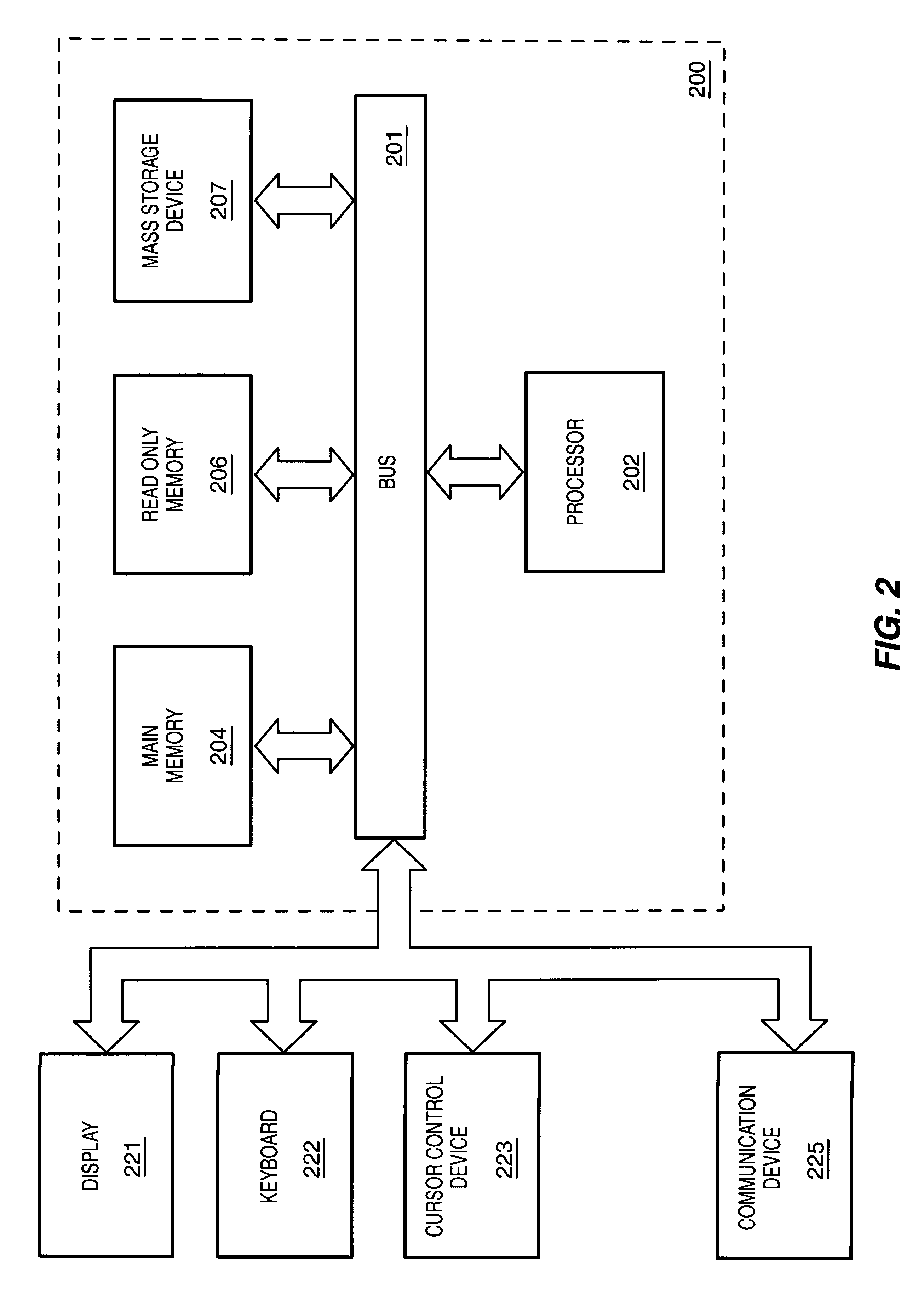

Automated design partitioning

InactiveUS6339836B1Detecting faulty computer hardwareCAD circuit designTheoretical computer scienceNetlist

A flexible and extensible automated design partitioning mechanism that facilitates simulation sessions employing two or more simulators is provided. A simulation backplane includes partitioning logic that identifies the design blocks of an overall design pertaining to each of a plurality of simulators. Once the partitions have been identified, nets that cross simulator boundaries (e.g., mixed nets) are determined and inter-simulator connectivity information is generated for the simulators. According to one aspect of the present invention, the partitioning logic is able to accomodate arbitrary (e.g., instance-based) partitioning. A design source expressed in a design representation upon which a first simulator may operate is received. Design blocks to be partitioned to each of a plurality of solvers are identified based upon one or more partitioning directives and the design source. A first instance of a cell is assigned to a first solver and a second instance of the cell is assigned to a second solver. Netlist like information is generated for those of the design blocks that are partitioned to a non-design source solver. To accomodate a folded representation of a design block containing the first or second instance of the cell, one or more additional cells are created. According to another aspect of the present invention, name space mapping is retained across all simulators. A design source upon which a first simulator may operate is read. Based upon a set of rules, a primary partition that is to be simulated by a first solver is identified. The primary partition includes a top cell of the design representation. Additionally, a secondary partition that is to be simulated by a second solver is identified. Subsequently, netlist information is generated for the second solver while retaining name space mapping in the secondary partition by adding one or more levels of hierarchy so as to include information about the top cell in the secondary partition.

Owner:MENTOR GRAPHICS CORP

Hierarchical layout method for integrated circuits

InactiveUS6574779B2Easy to modifyIncrease production capacityCAD circuit designProgram controlComputer architectureGenerative Design

Owner:INT BUSINESS MASCH CORP

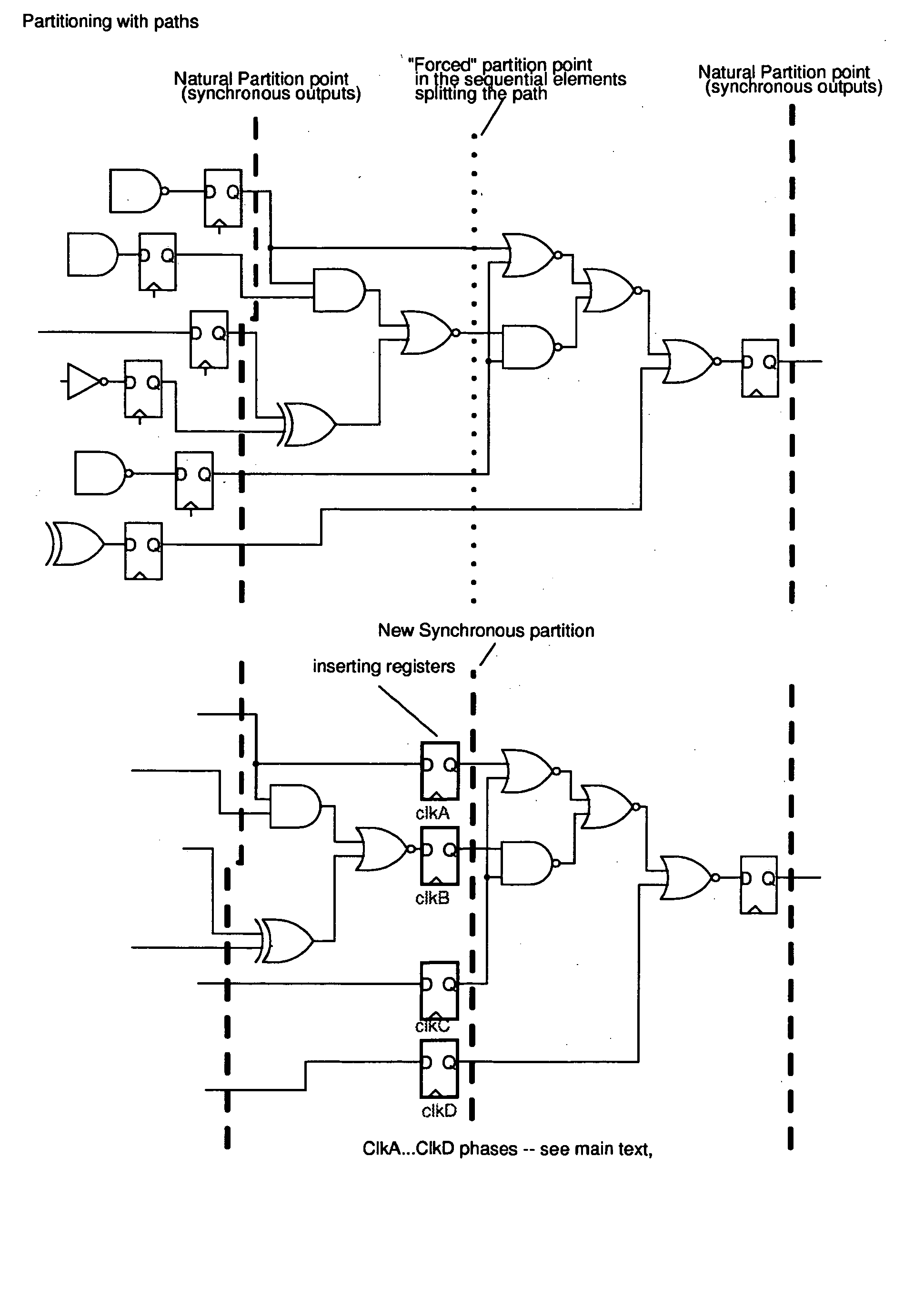

Rotary clock synchronous fabric

InactiveUS20050251775A1Minimize the numberComputer aided designSoftware simulation/interpretation/emulationEngineeringArray element

Methods for generating a design for logic circuitry using rotary traveling wave oscillators (RTWOs) are described. A plurality of RTWOs are is arranged into an array of rows and columns. Adjacent elements in the array are interconnected so that the clocks in adjacent element are phase synchronous. Clocked devices are placed along the signal path of each array element and each is connected to one of the multiple phases provided by the RTWO element. The logic circuitry, described by a netlist, is divided into a number of partitions and each of these partitions is mapped to one of the array elements. The logic circuitry of the partition is then placed within or about the element of the array to which the partition is mapped and the circuitry in the partition is connected between the clocked devices in the element of the array, according to the net list.

Owner:ANALOG DEVICES INC

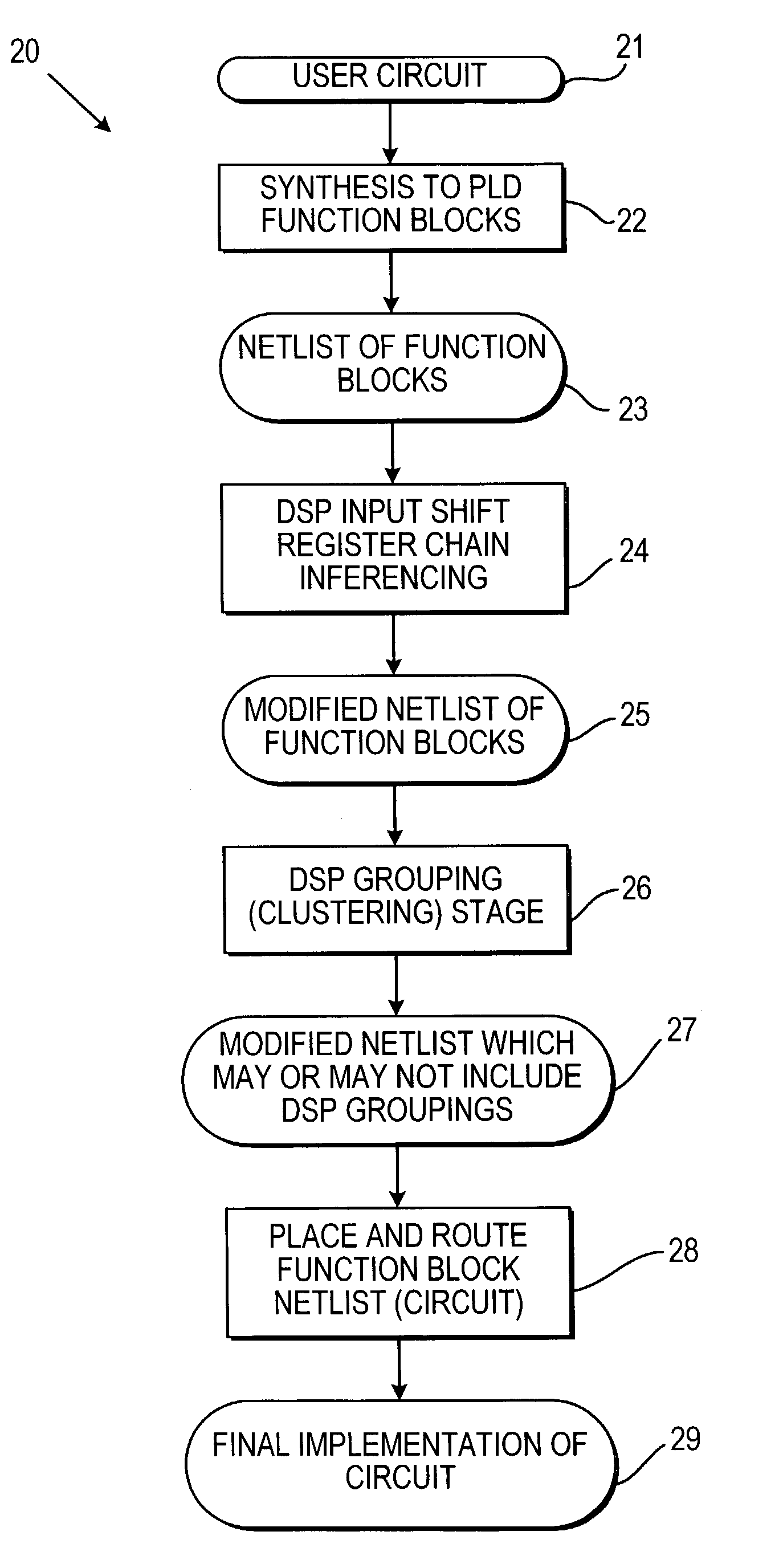

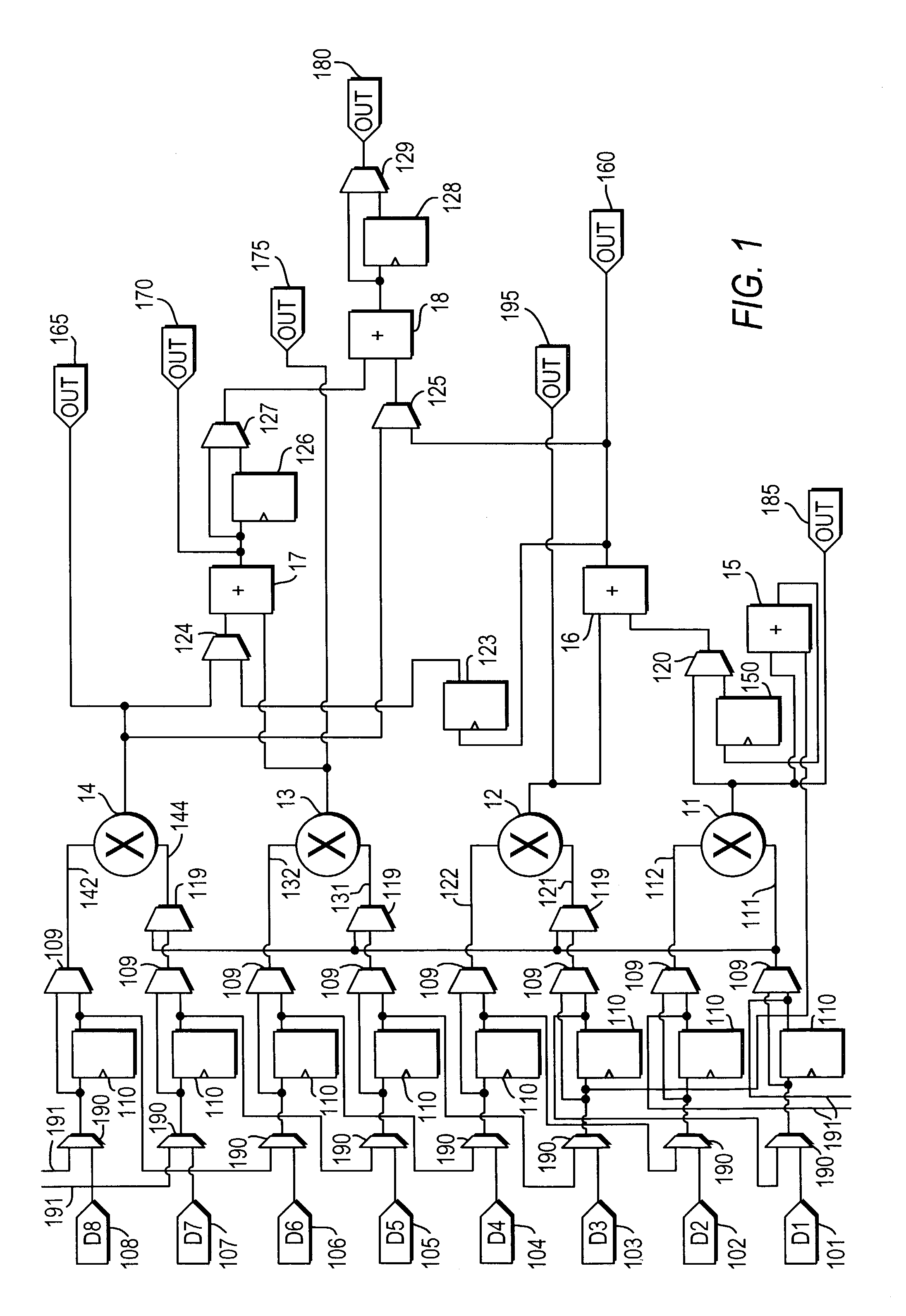

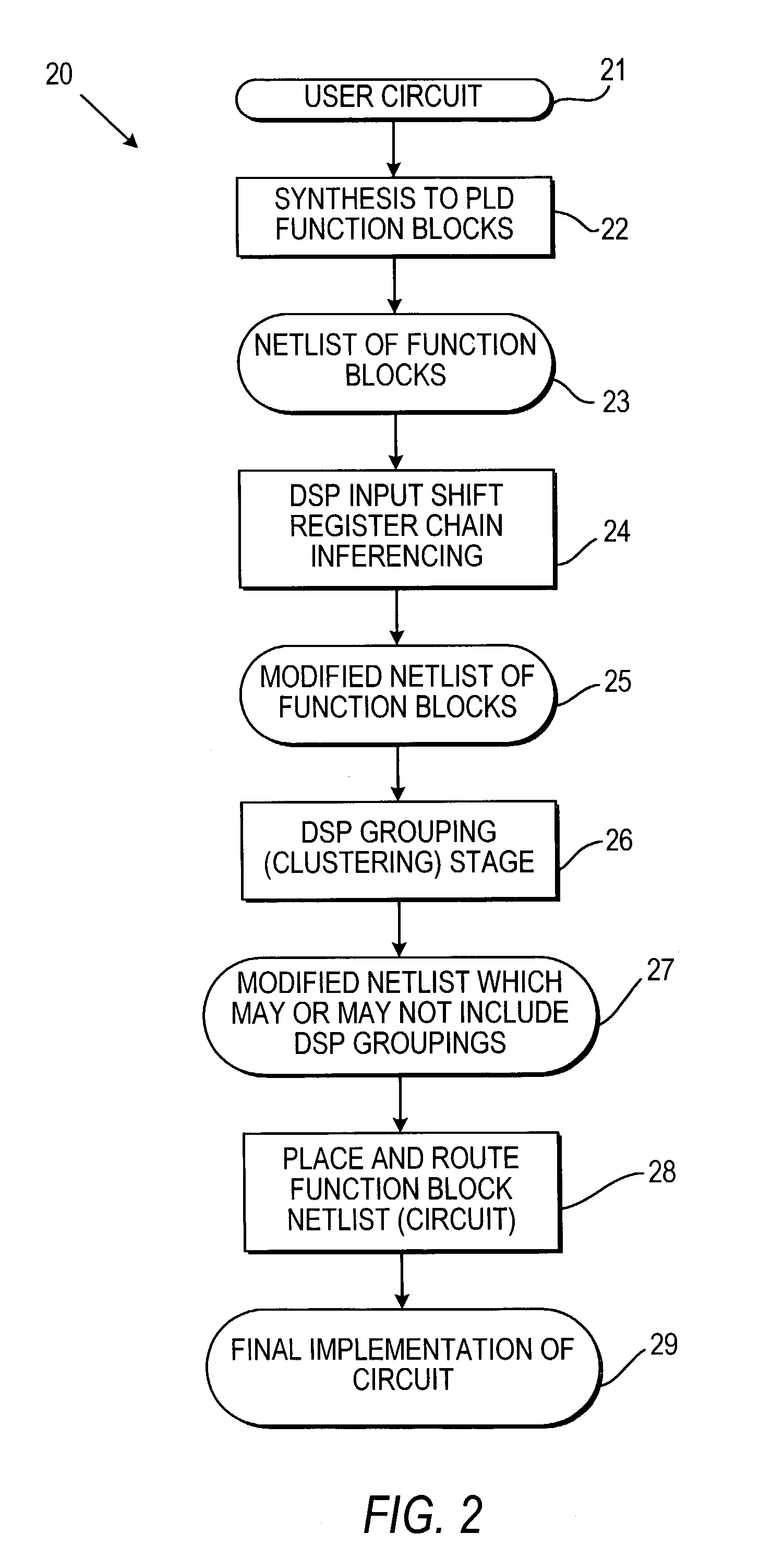

Method for programming programmable logic device with blocks that perform multiplication and other arithmetic functions

InactiveUS6971083B1CAD circuit designSpecial data processing applicationsGeneral purposeBinary multiplier

A programming method efficiently programs programmable logic devices of the type having specialized multiplier blocks that include multipliers and other arithmetic function elements. Such blocks can be used to perform certain multiplication and multiplication-related functions more efficiently than general-purpose programmable logic. In order to efficiently program devices having such specialized multiplier blocks, so that they are used to their full potential and so that the maximum number of multiplier-related functions can be accommodated on a single programmable logic device, the programming method pre-processes the netlist of function blocks in a user's programmable logic design, grouping multiplication and multiplication-related functions efficiently. The method takes into account limitations imposed by the structure of the specialized multiplier blocks, in addition to location constraints imposed by the user and location constraints dictated by the need for certain functions be carried out near where certain other functions are carried out.

Owner:ALTERA CORP

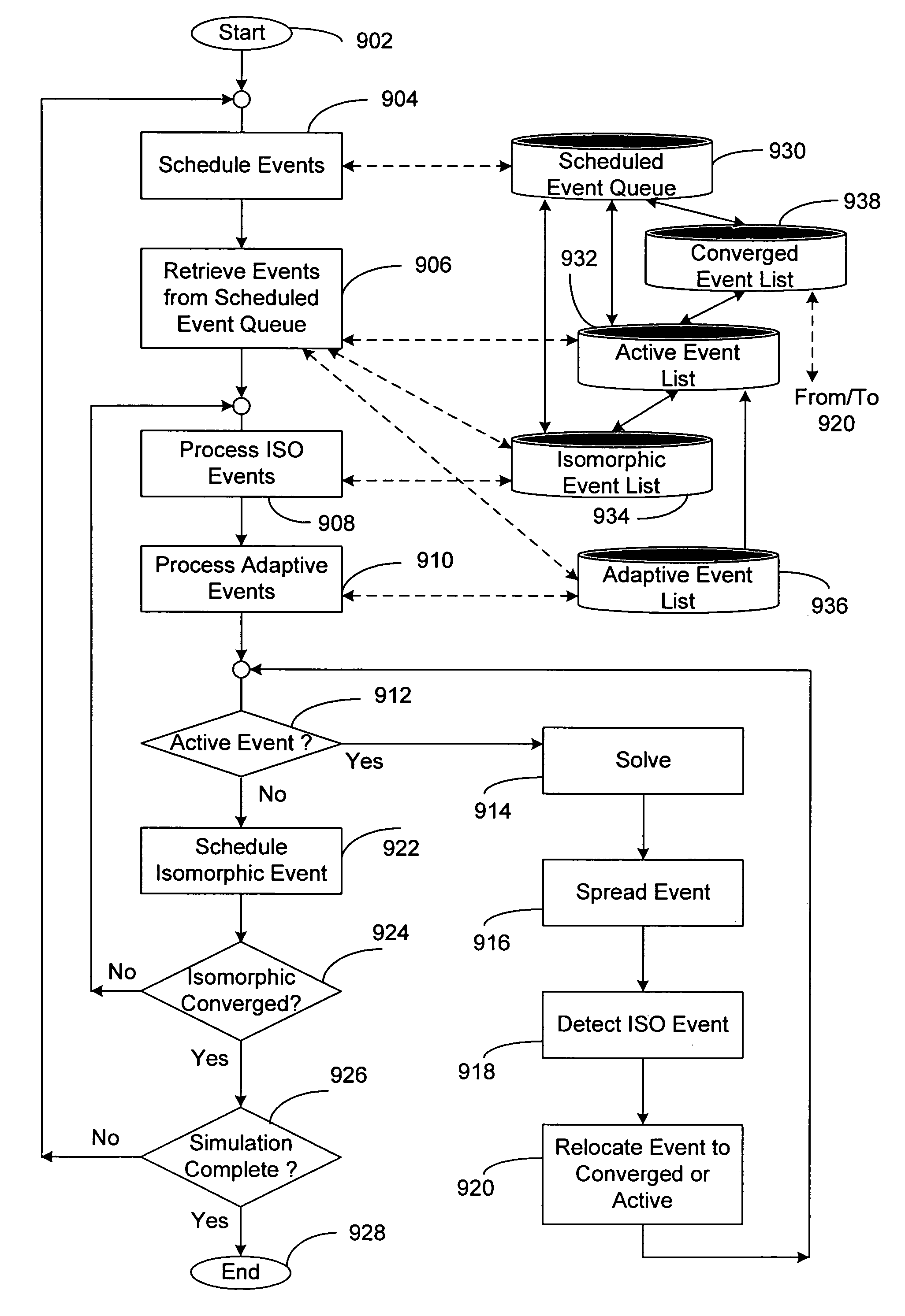

System and method for simulating a circuit having hierarchical structure

InactiveUS7181383B1Less memoryImprove performanceAnalogue computers for electric apparatusDetecting faulty computer hardwareTopology informationComputer architecture

A system for simulating a circuit having hierarchical data structure includes a simulator module having one or more computer programs for 1) creating a static database in accordance with a netlist description of the circuit, where the static database contains topology information of the circuit; 2) selecting a group circuit for simulation, where the group circuit contains one or more leaf circuits selected from the first branch and the second branch; 3) creating a dynamic database for representing the group circuit, where the dynamic database includes references to the static database for fetching topology information dynamically during simulation; and 4) simulating the group circuit in accordance with the dynamic database. Since the system duplicates and reproduces only the relevant dynamic information when necessary, the disclosed circuit simulator uses less memory and produces better performance.

Owner:CADENCE DESIGN SYST INC

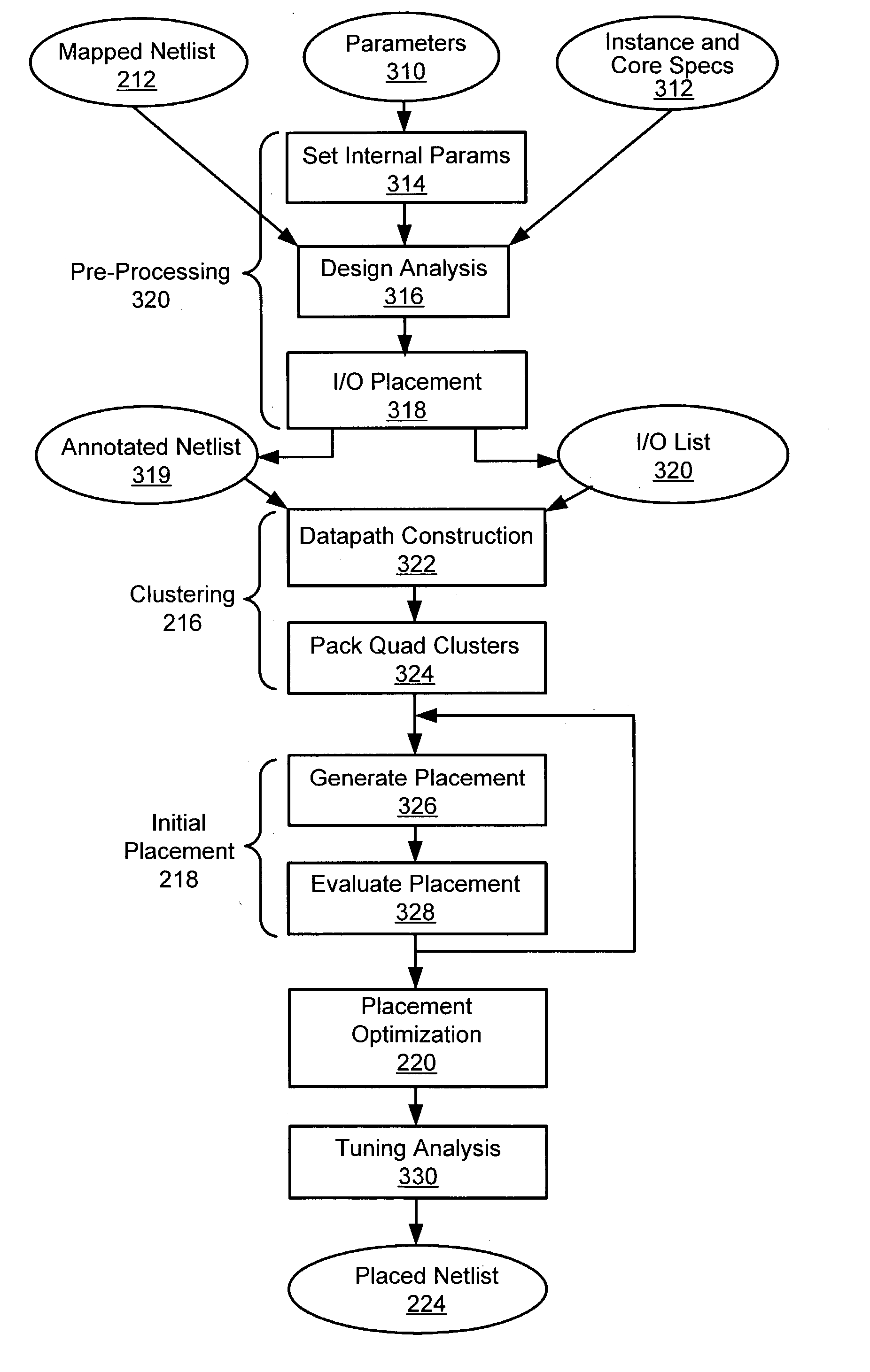

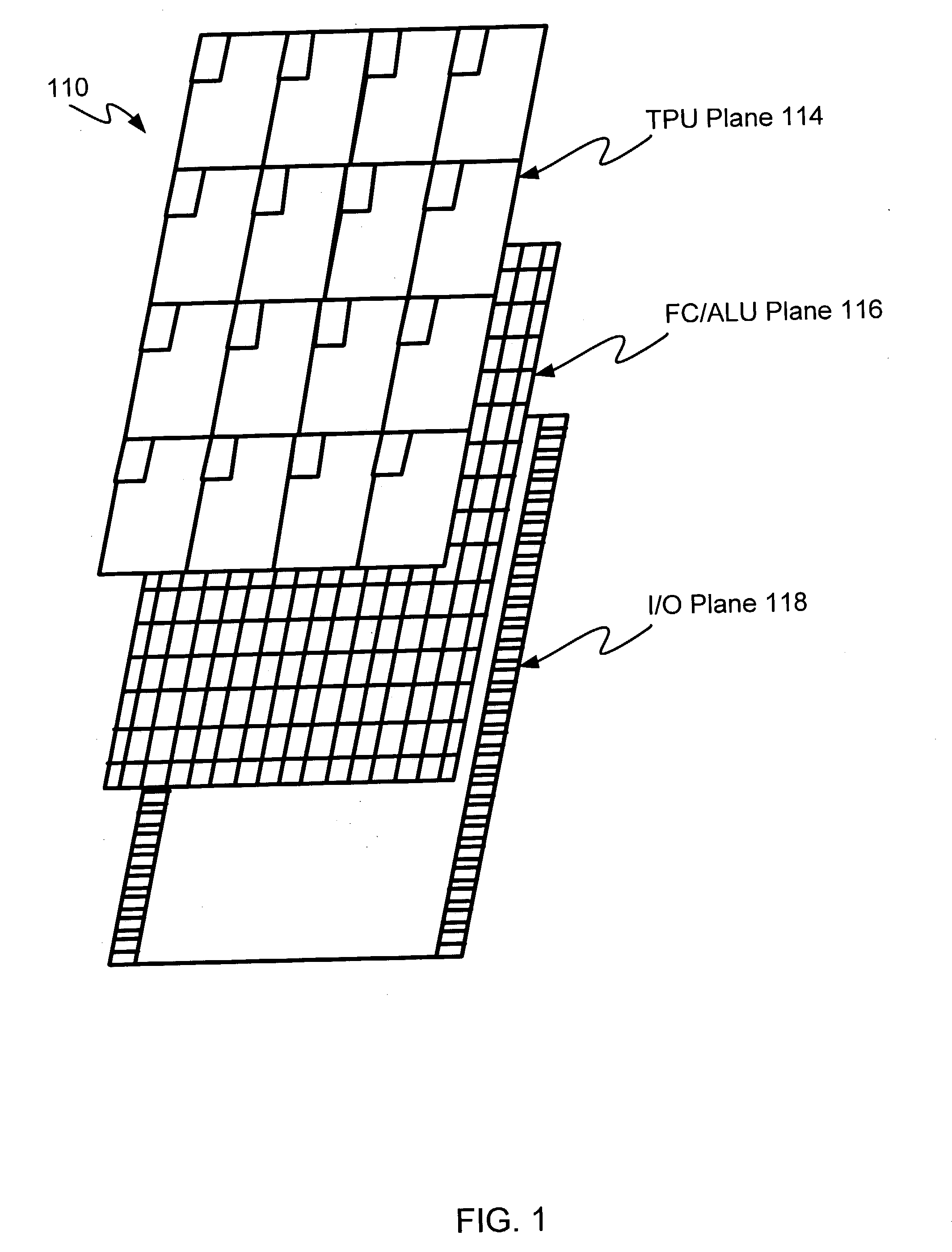

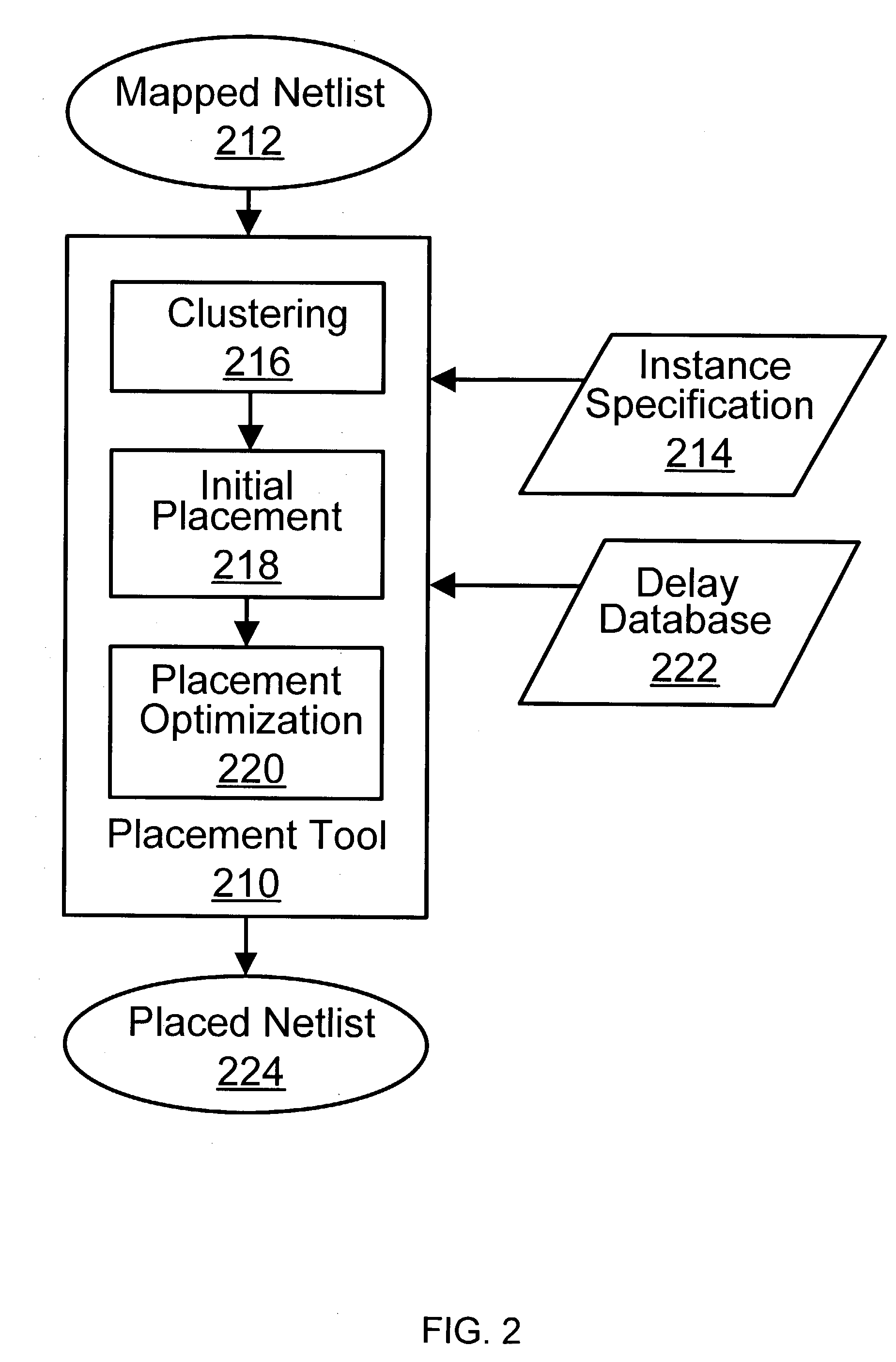

System and method for efficiently mapping heterogeneous objects onto an array of heterogeneous programmable logic resources

ActiveUS20040194048A1Computer aided designSpecial data processing applicationsInto-structureComputer module

A system and method of mapping heterogeneous objects onto an array of heterogeneous programmable logic resources. The method comprises clustering to identify datapath modules from a netlist. The method further comprises aggregating the datapath modules into higher level modules. The method also comprises clustering random logic into structures.

Owner:XILINX INC

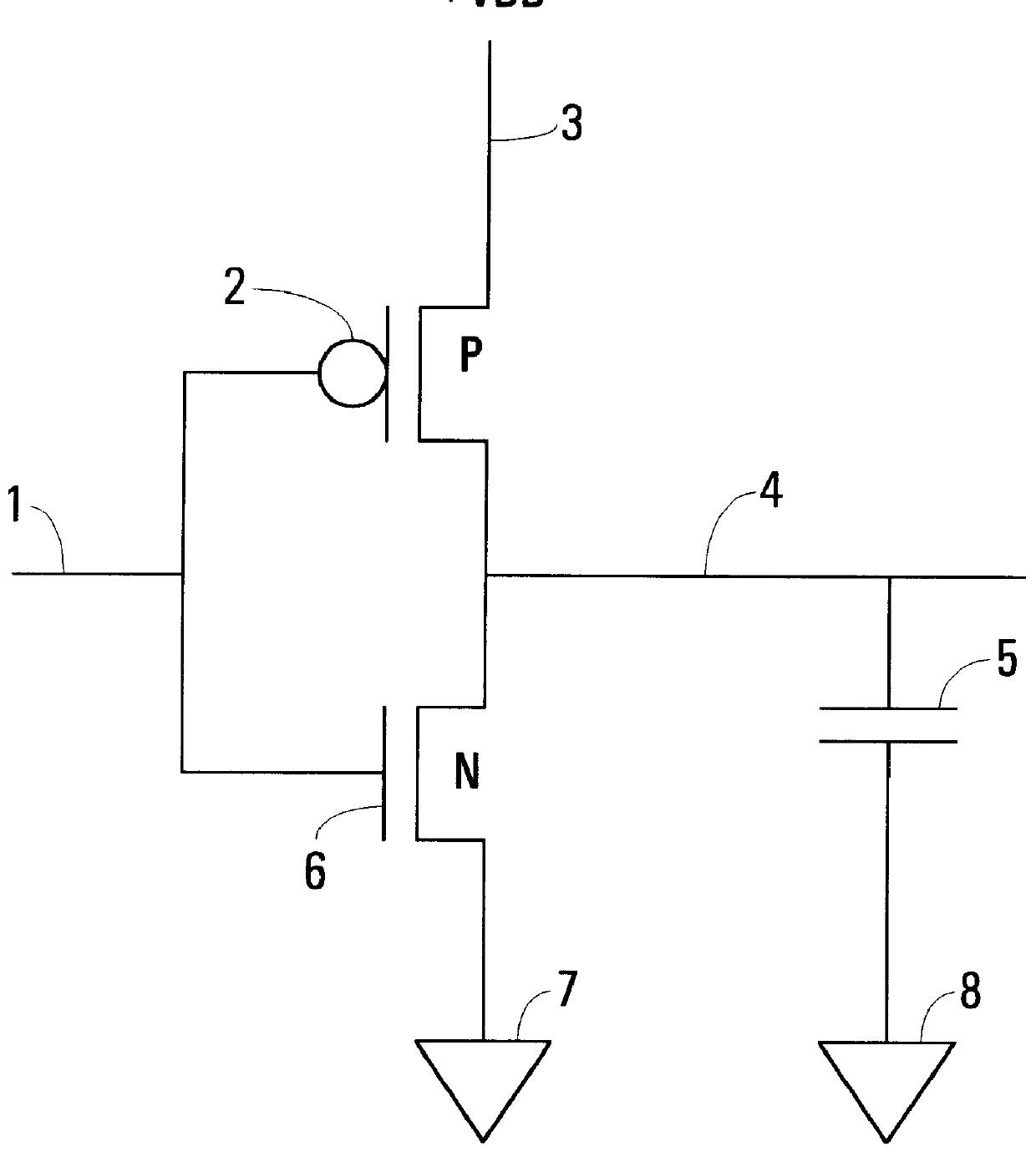

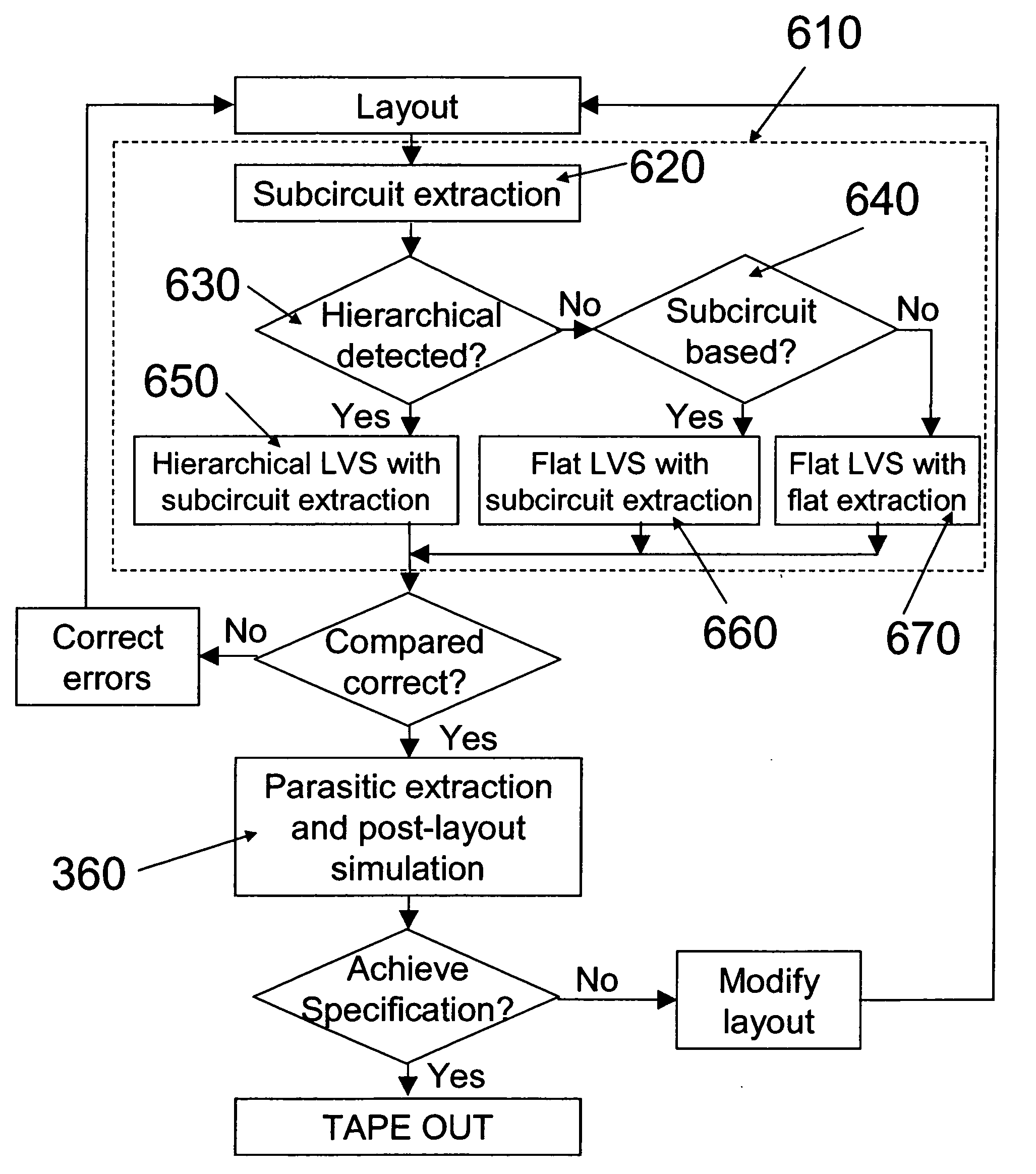

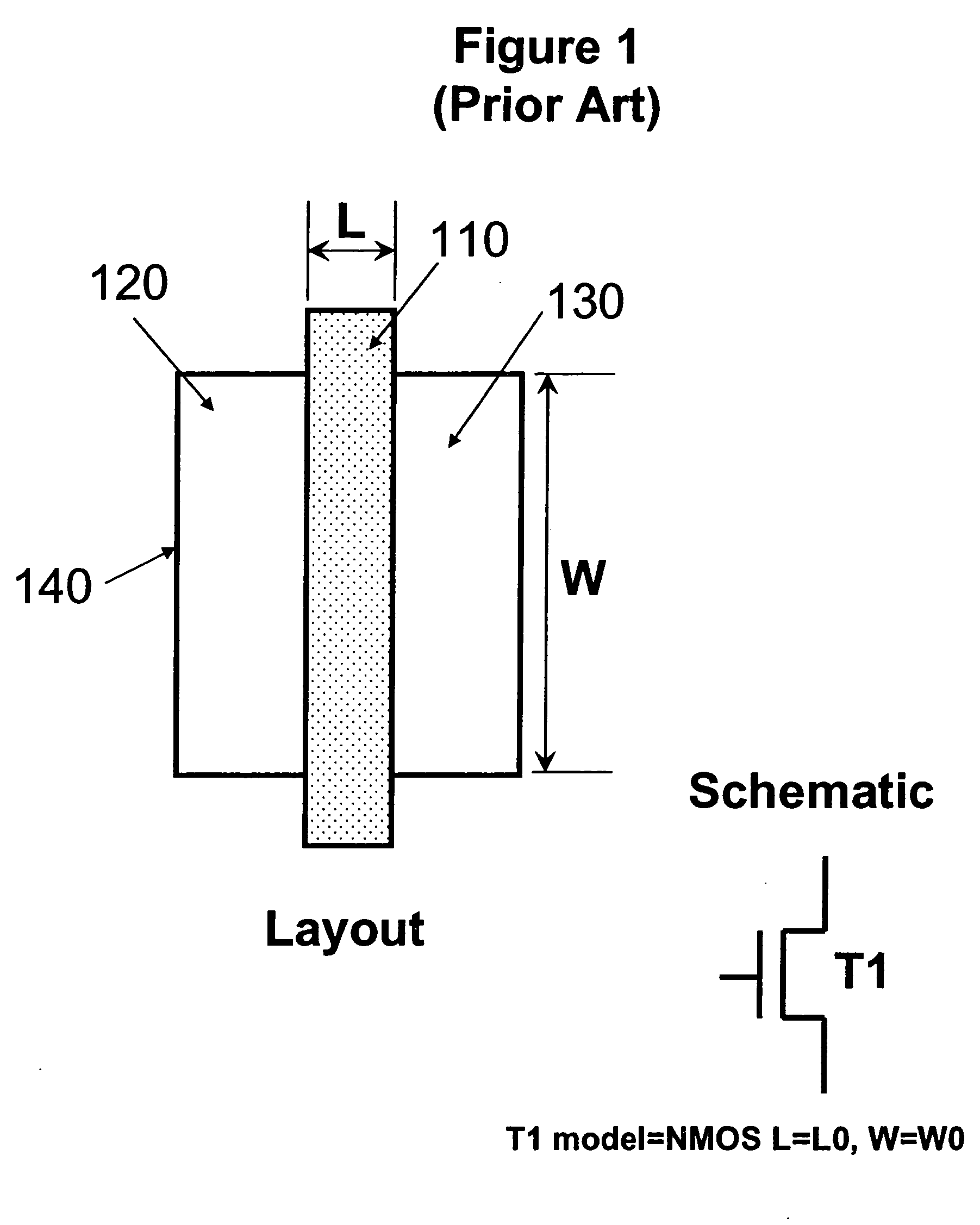

Method of checking the layout versus the schematic of multi-fingered MOS transistor layouts using a sub-circuit based extraction

InactiveUS20050216873A1Improve trustEasy to identifyCAD circuit designSoftware simulation/interpretation/emulationDevice PropertiesComputer architecture

A sub-circuit based extraction method which extracts a multi-finger MOS transistor directly as a sub-circuit is described. By adding three marking layers, the method provides the layout extracted netlist with a complete list of device geometric parameters corresponding to the device properties as presented in the sub-circuit model based schematic netlist. By performing a layout-versus-schematic comparison based on all geometric parameters extracted, the layout checking is performed in a complete and accurate way where each device parameter is checked against the corresponding design schematic. This complete and accurate geometric parameter comparison enhances the confidence level of the layout physical verification.

Owner:IBM CORP

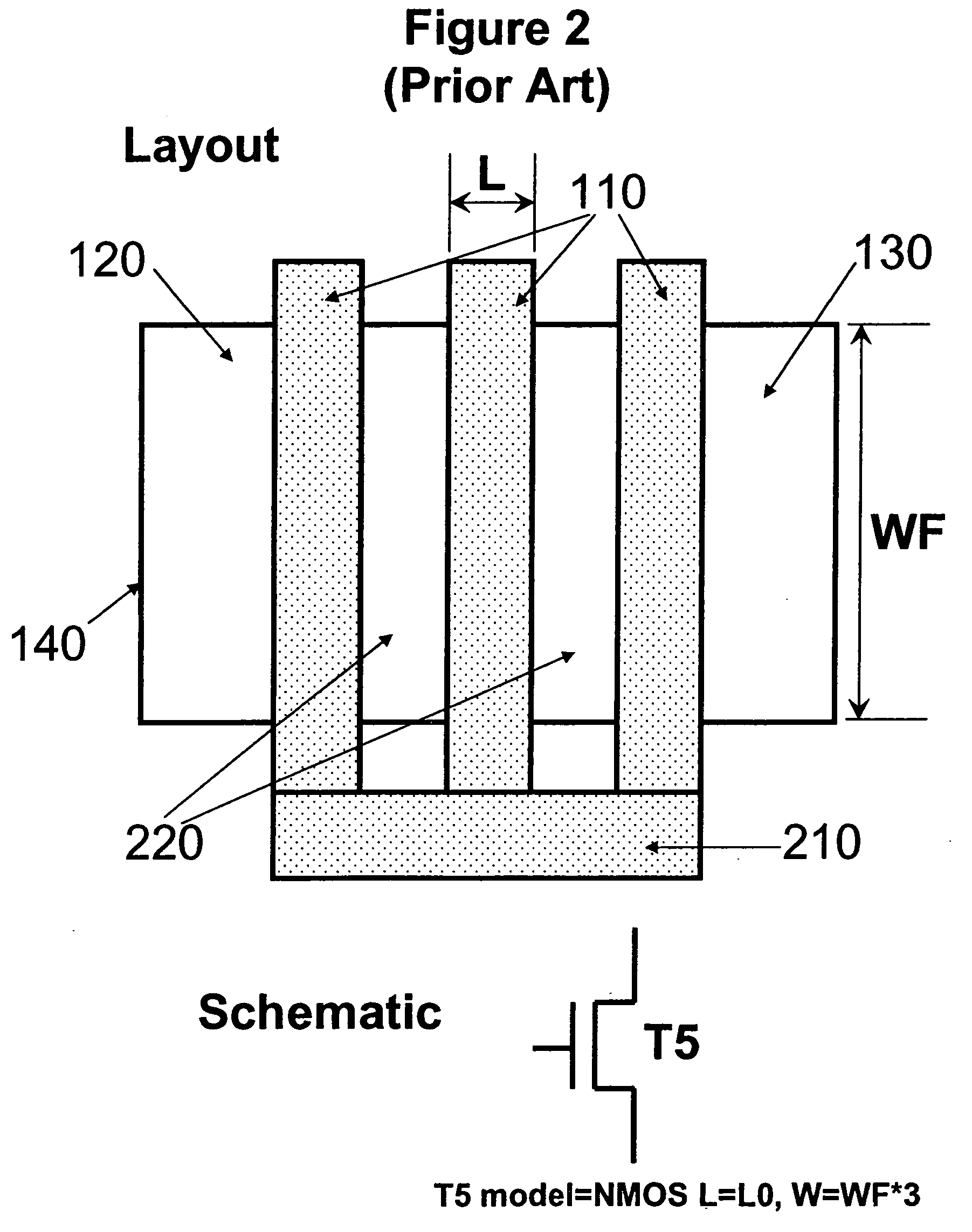

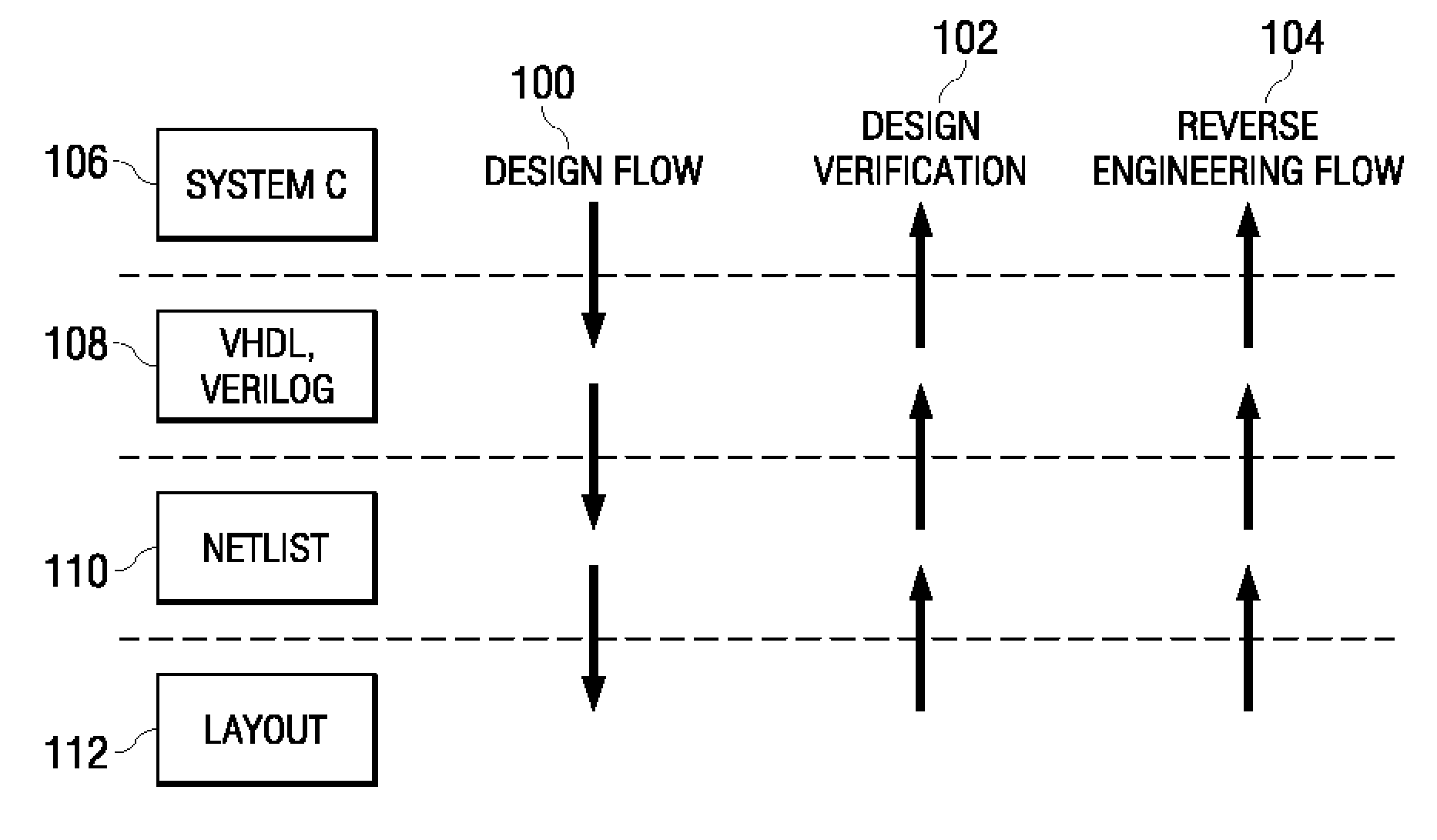

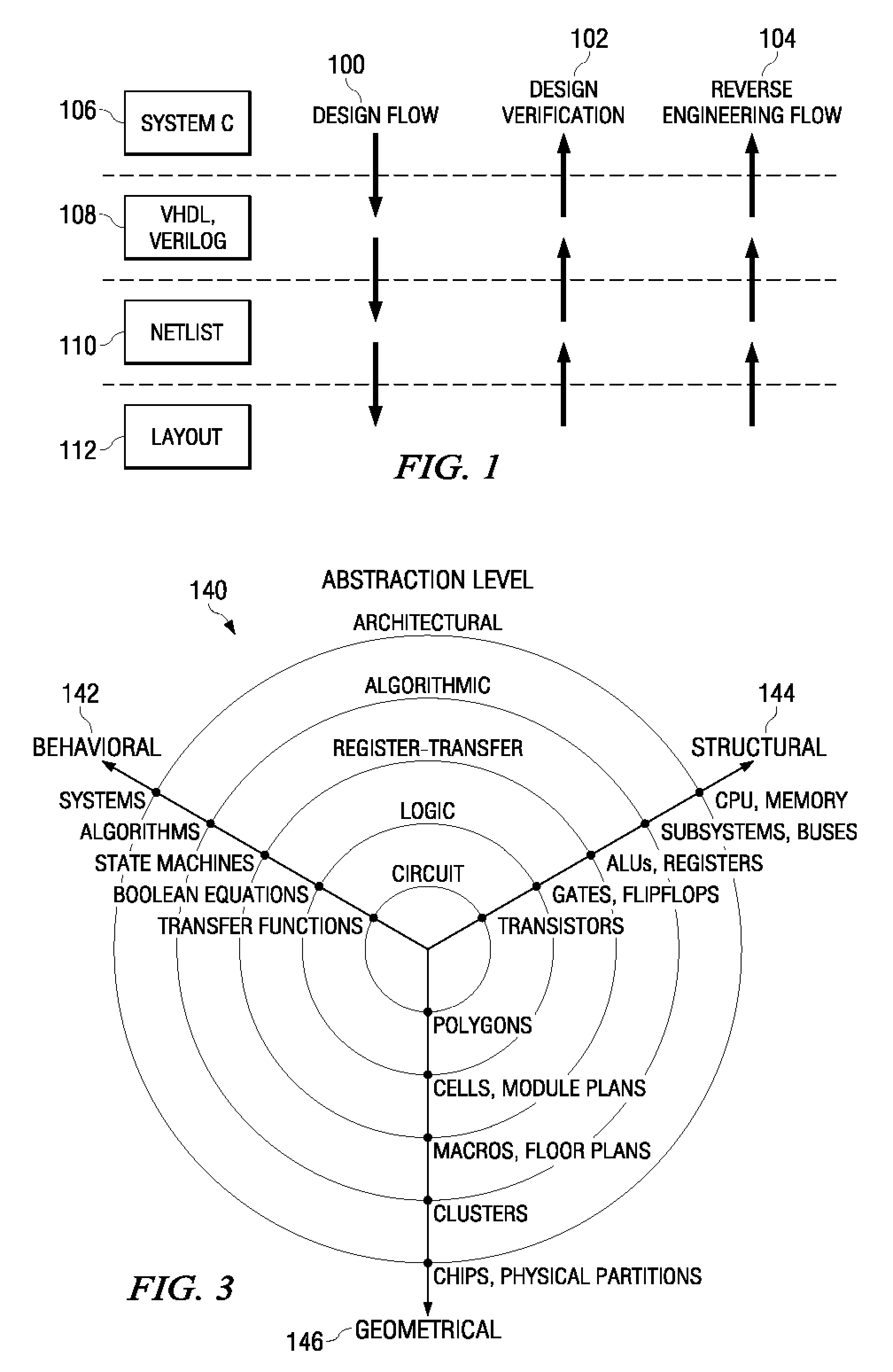

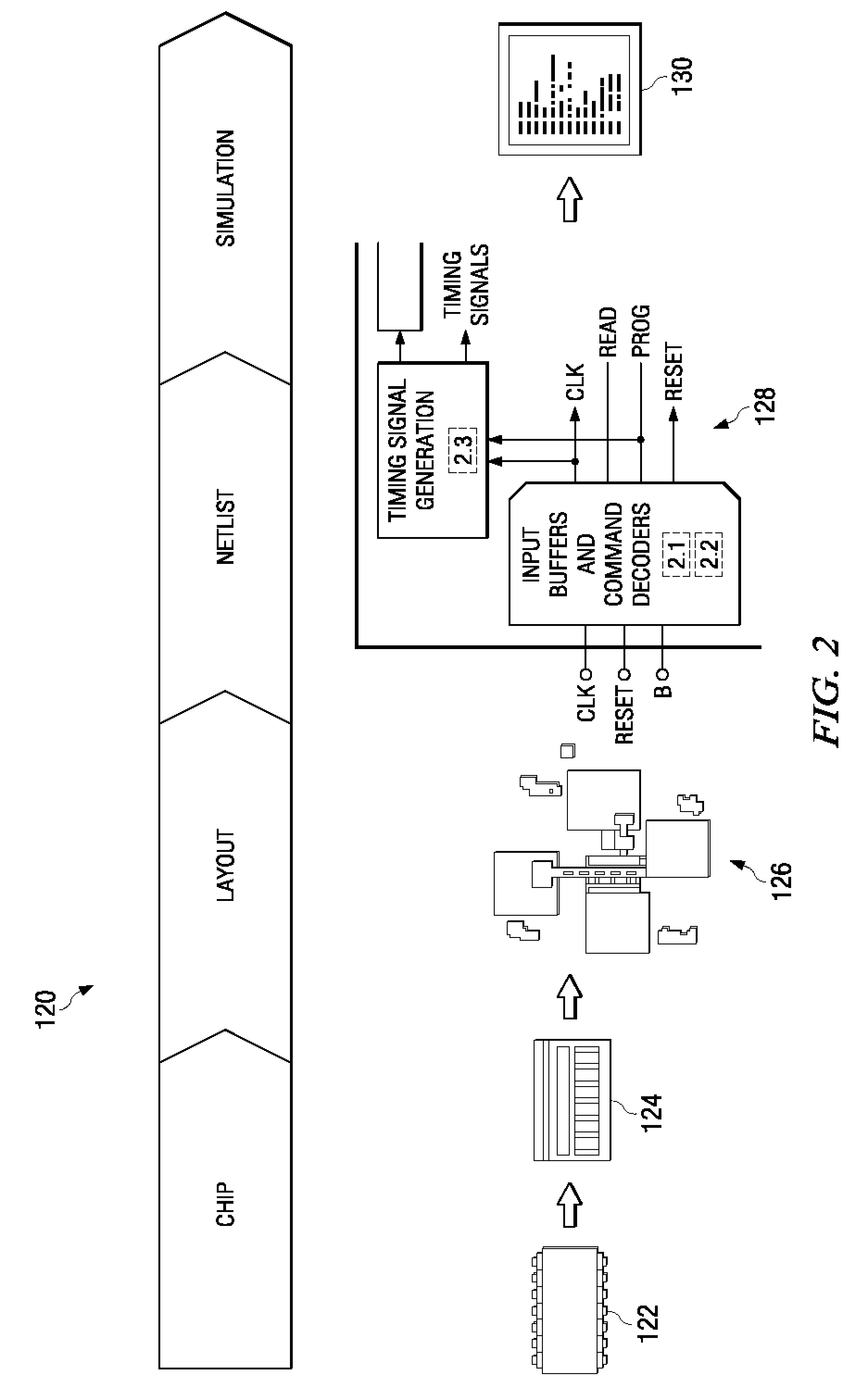

System and Method for Integrated Circuit Planar Netlist Interpretation

Systems and methods for integrated circuit planar netlist interpretation are disclosed. In one embodiment, higher abstraction level descriptions of an integrated circuit are generated from a planar netlist and layout data of the integrated circuit. Various embodiments may derive the higher abstraction levels through, for example, netlist compression and netlist partitioning. Other embodiments may derive the higher abstraction levels using, for example, device and module hypothesis search functions based on device properties and design constraints derived from netlist and layout data.

Owner:INFINEON TECH AG

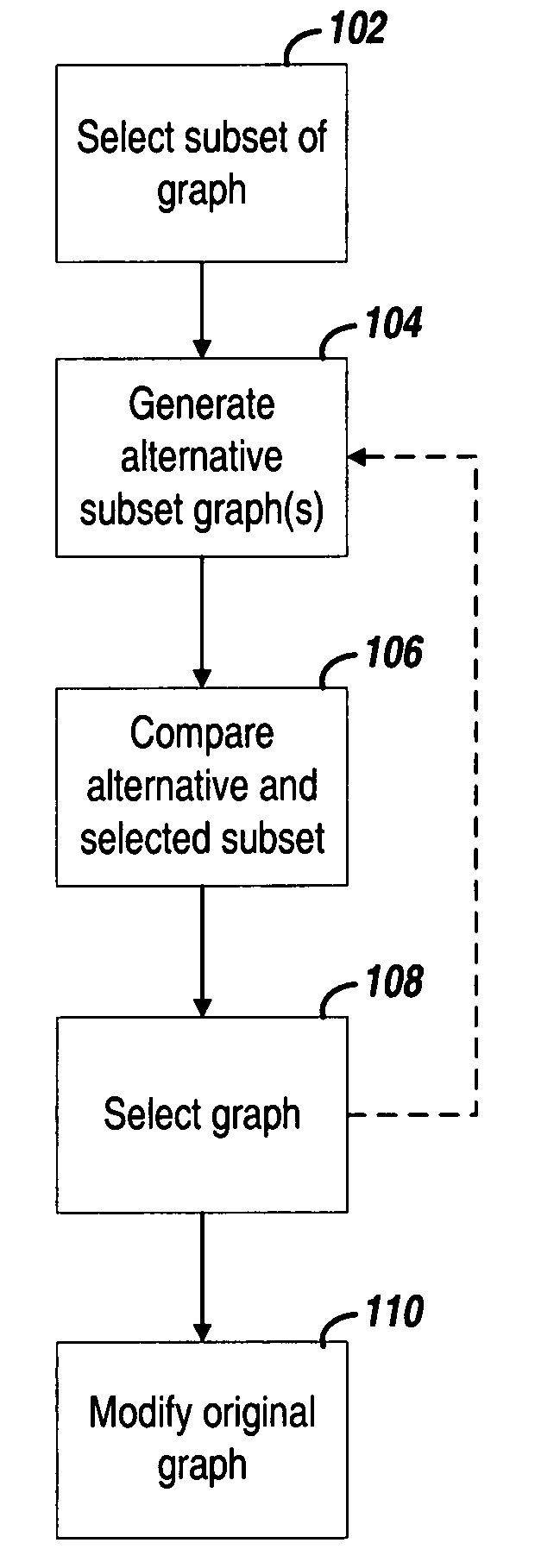

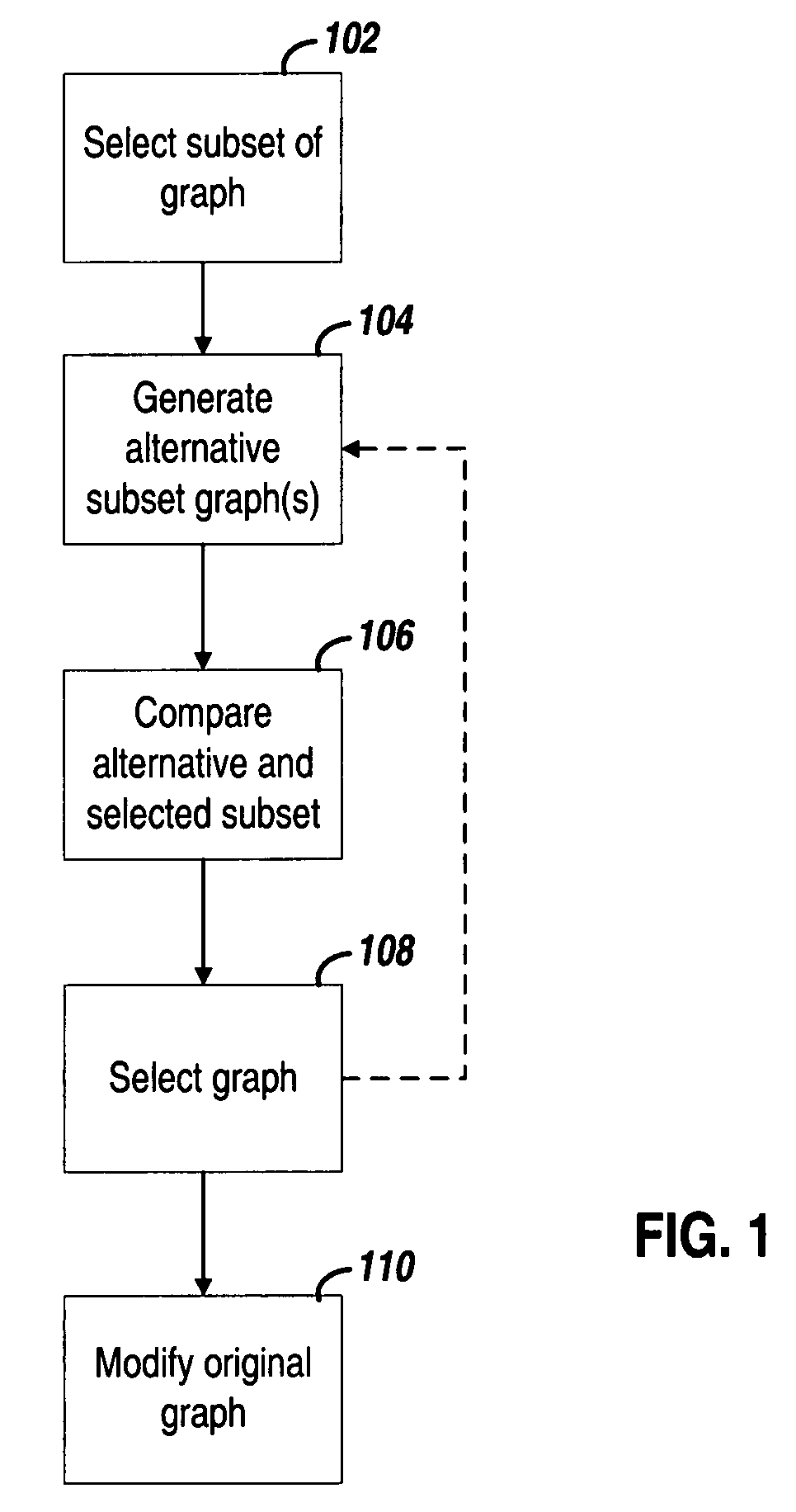

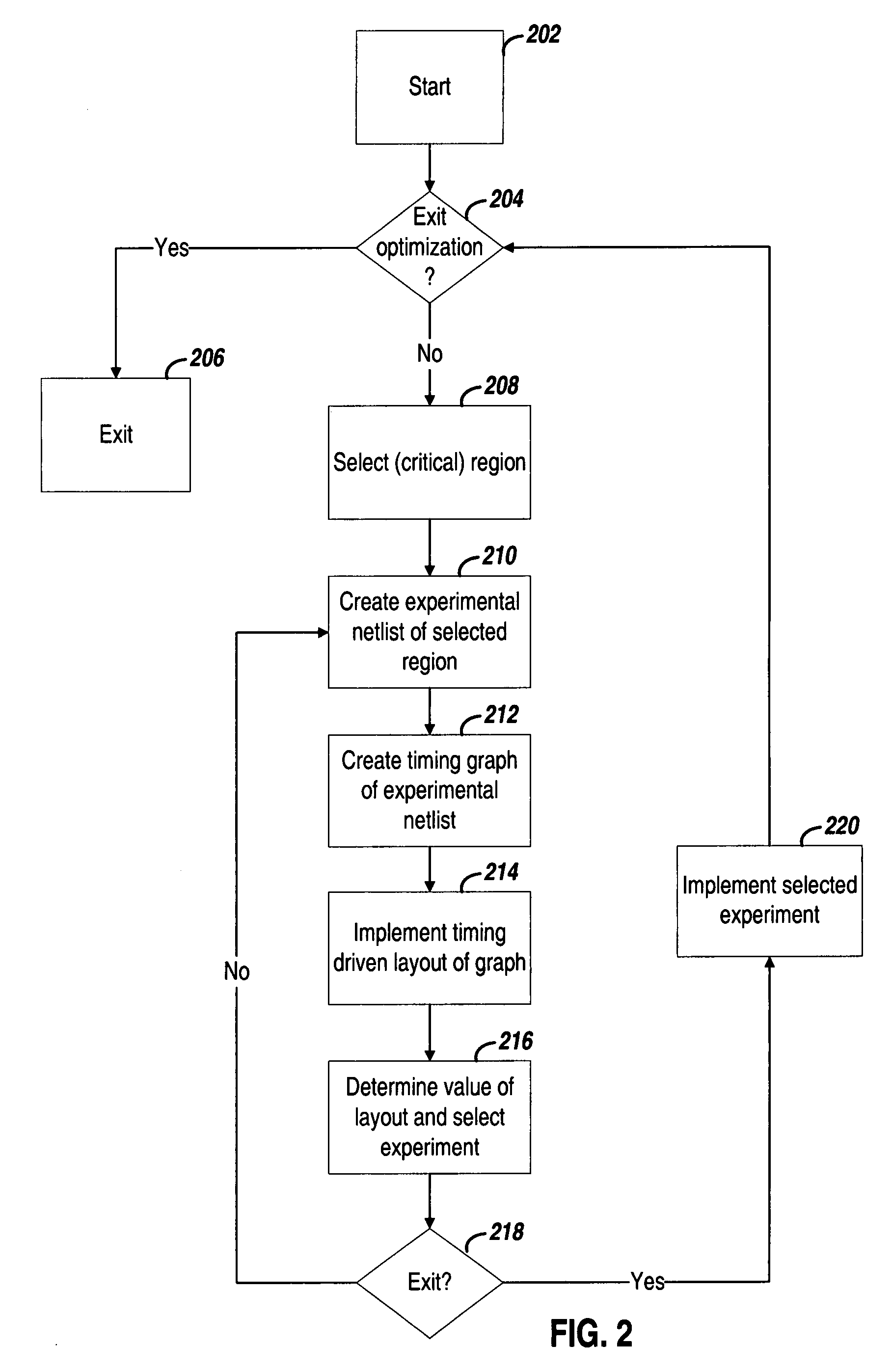

Efficient timing graph update for dynamic netlist changes

ActiveUS7657855B1Computer aided designSoftware simulation/interpretation/emulationAlgorithmElectronic circuit design

Various approaches for incrementally updating the timing of an implementation of an electronic circuit design are disclosed. In one approach, a subset timing graph is selected from a primary timing graph. Alternative subset timing graphs are generated that are functionally equivalent and structurally different with respect to the selected subset timing graph. For each of the alternative timing graphs, a respective timing metric is determined. The determined timing metrics and a timing metric for the selected subset timing graph are compared. An alternative timing graph is selected in response to the comparison. Structurally different portions of the selected one of the one or more alternative timing graphs are verified with regard to the design constraints. The structurally different portions are stored to the primary timing graph.

Owner:XILINX INC

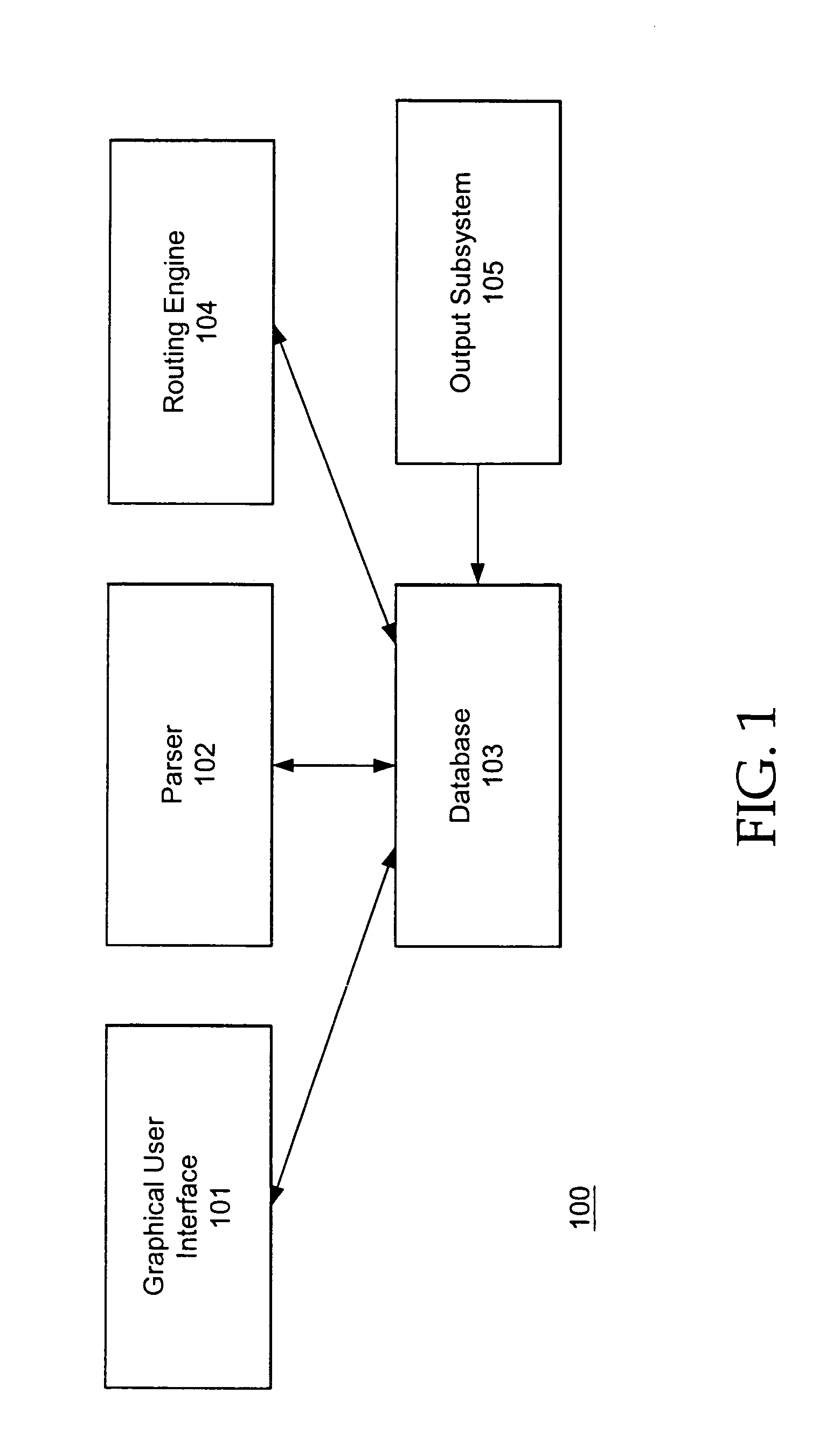

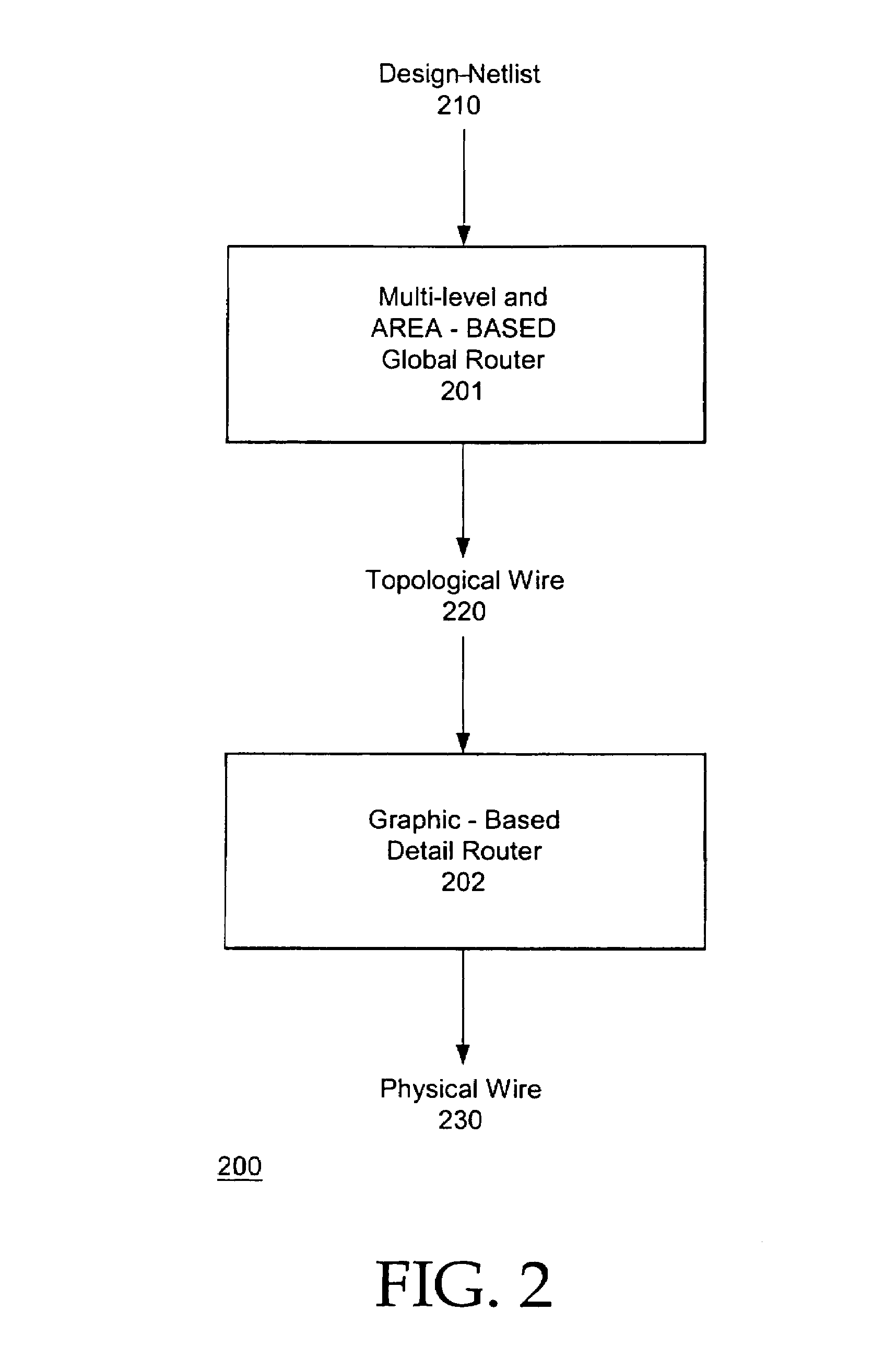

Method and apparatus for scalable interconnect solution

InactiveUS7036101B2Low costBulky designSemiconductor/solid-state device manufacturingProgram controlGraphicsComputer architecture

An innovative routing method for an integrated circuit design layout. The layout can include design netlists and library cells. A multiple-level global routing can generate topological wire for each net. An area oriented graph-based detail routing on the design can be performed. A post route optimization after the detail routing can be performed to further improve the routing quality. Some methods can be single threaded all or some of the time, and / or multi-threaded some or all of the time.

Owner:CADENCE DESIGN SYST INC

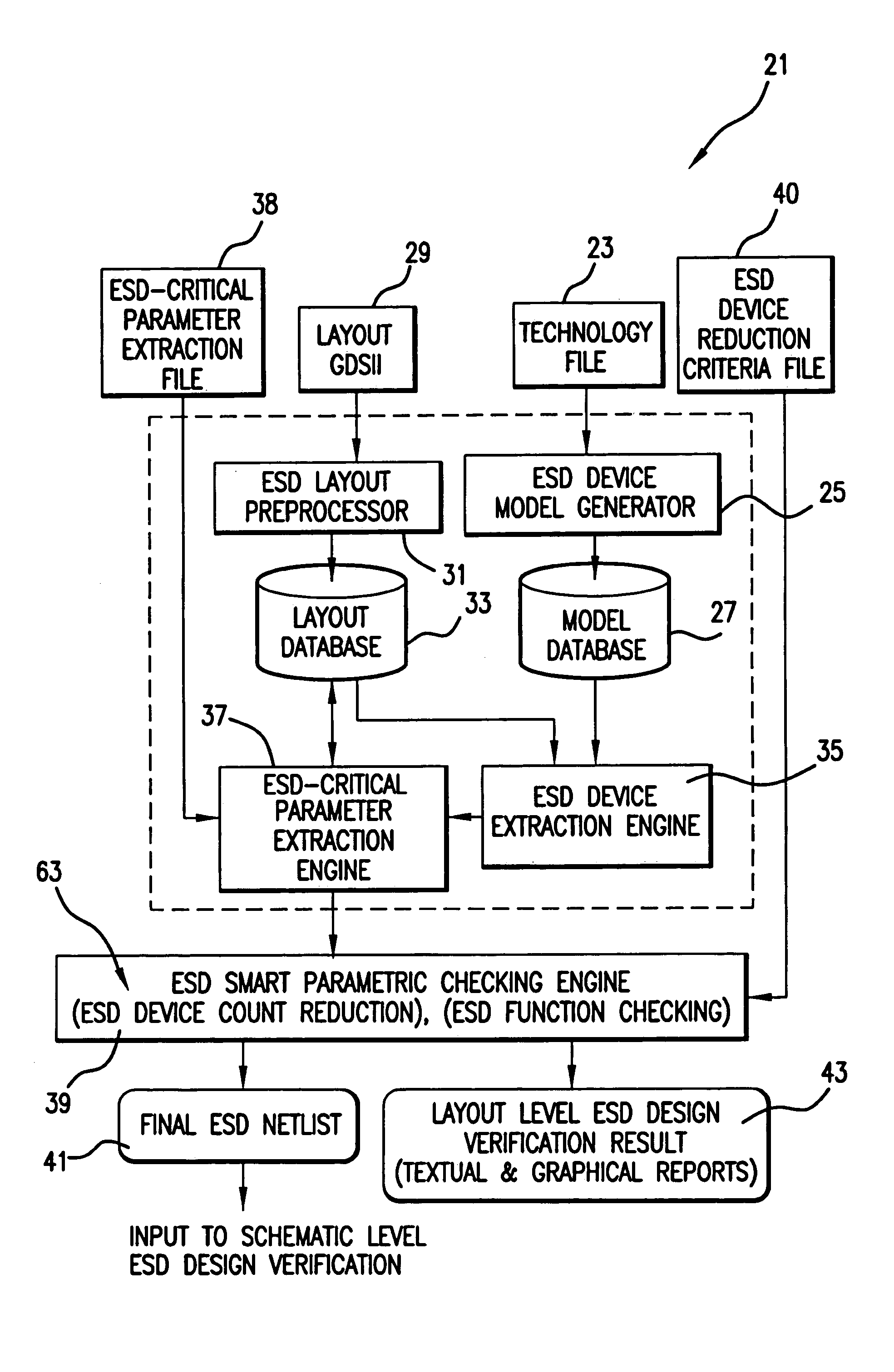

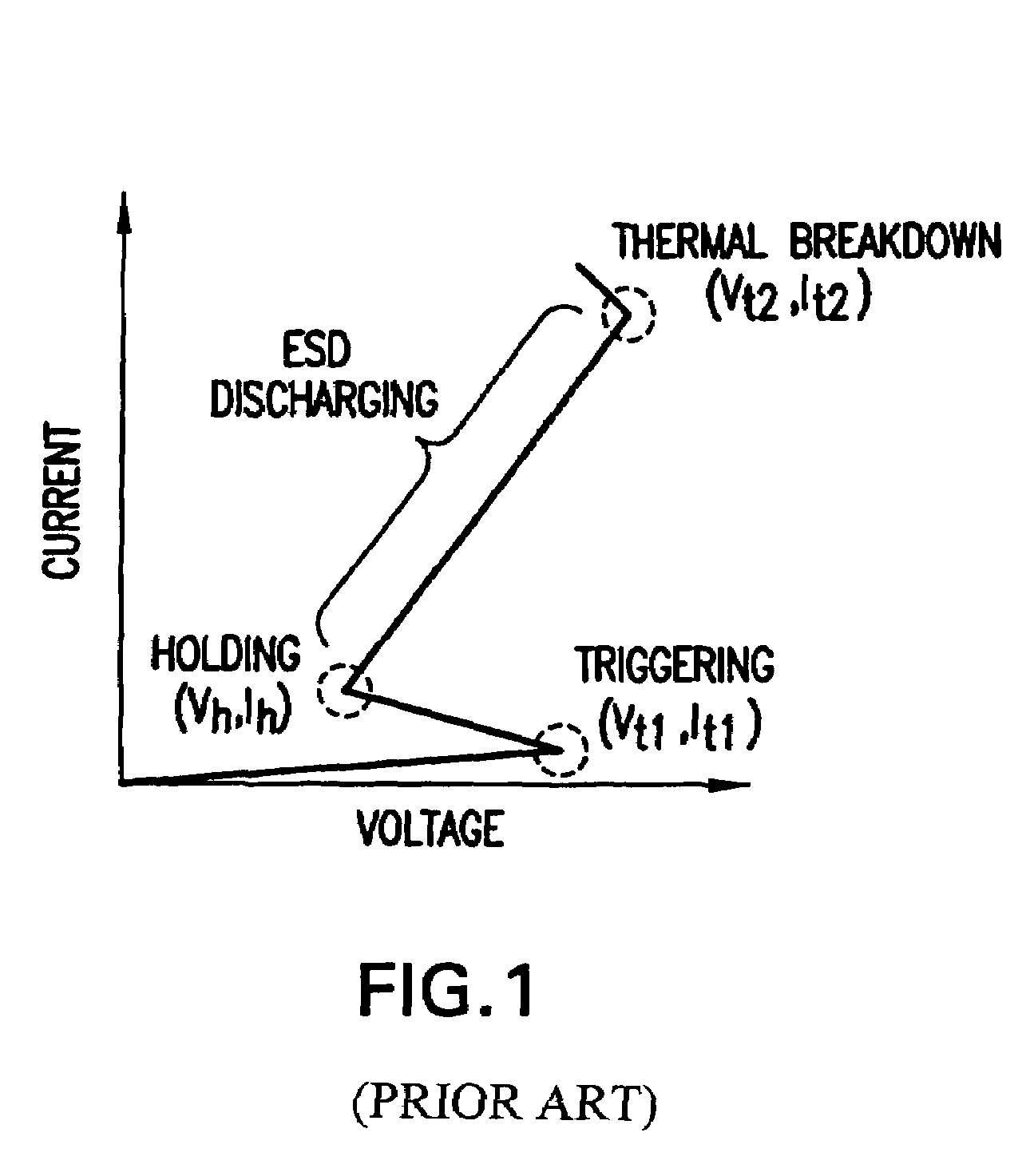

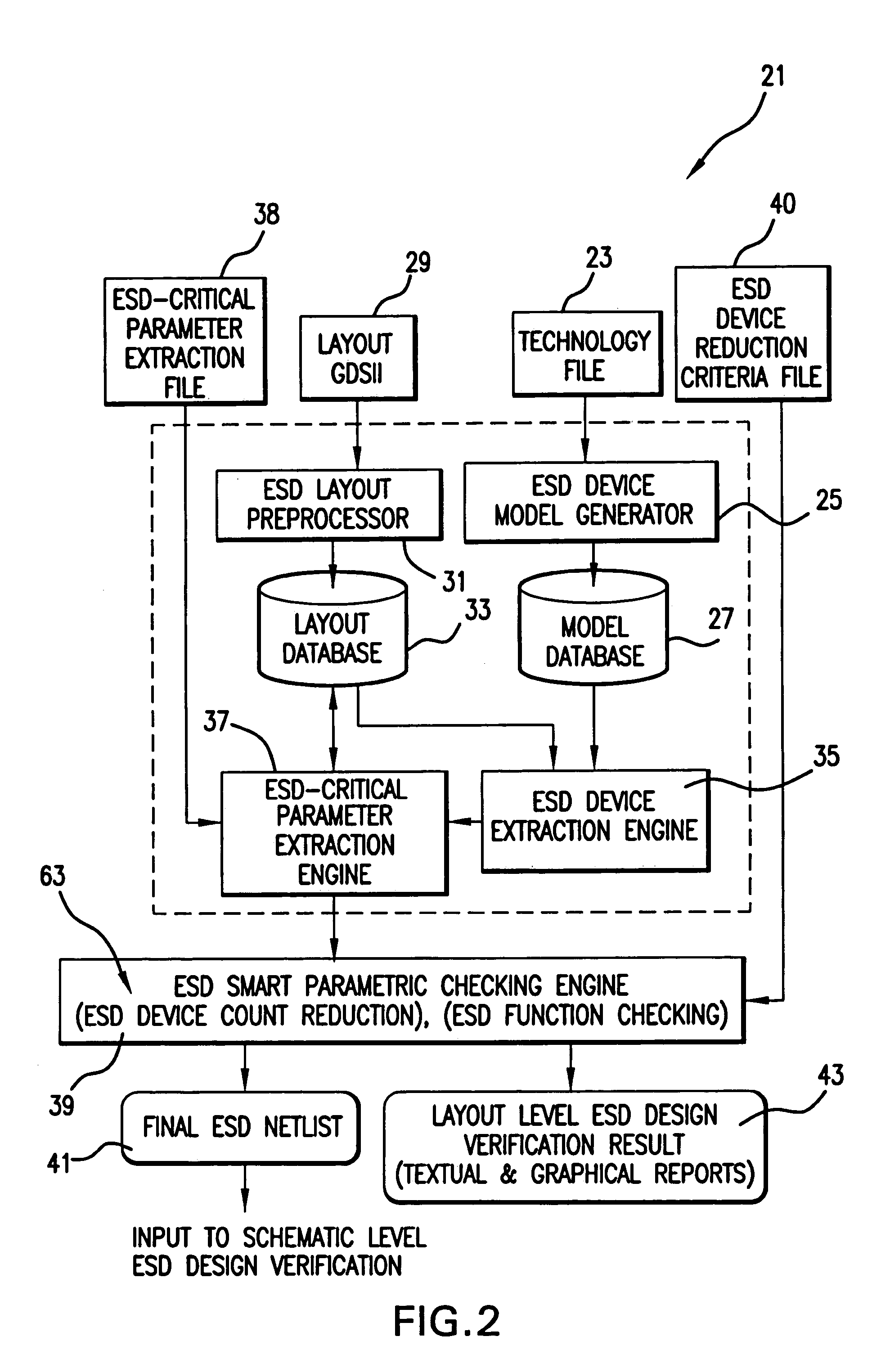

Parameter checking method for on-chip ESD protection circuit physical design layout verification

ActiveUS7243317B2Precise designEasy to disassembleComputer aided designSoftware simulation/interpretation/emulationEngineeringNetlist

A checking mechanism for complete full-chip ESD protection circuit design and layout verification at layout level identifies all of both intentional and parasitic ESD devices contained in the design layout file and compiles a netlist. The checking mechanism then determines the critical operating parameters of the identified ESD devices and determines if the parasitic devices will negatively effect ESD protection performance. The checking mechanism then determines if the intentional devices meet design specifications; eliminates parasitic devices which will not negatively effect ESD protection from the netlist, and retains those parasitic devices which may lead to ESD protection malfunction. Design layout verification and faults are then reported.

Owner:TRUSTCHIP TECH