Patents

Literature

760 results about "Design tool" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Design tools are objects, media, or computer programs, which can be used to design. They may influence the process of production, expression and perception of design ideas and therefore need to be applied skillfully.

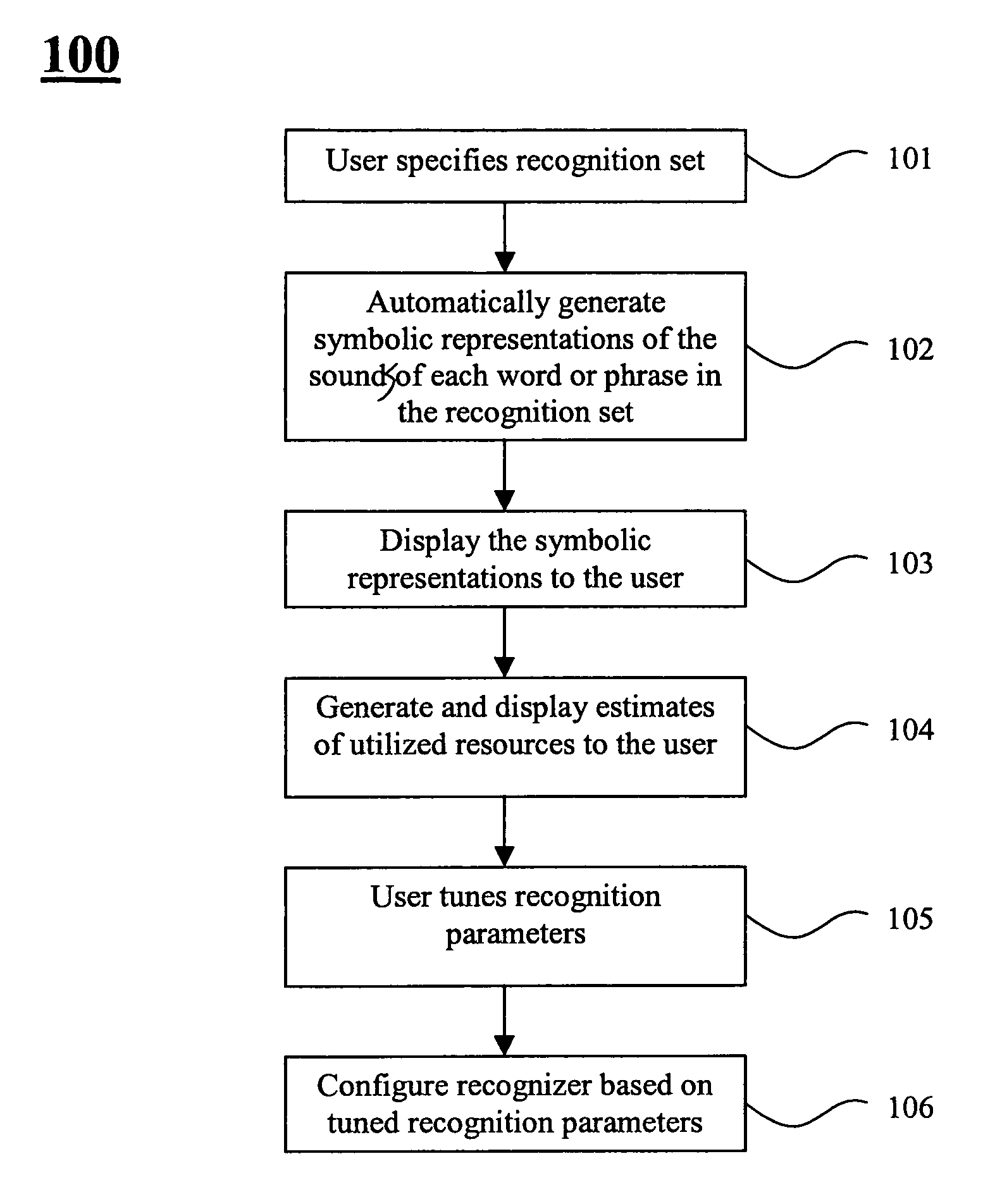

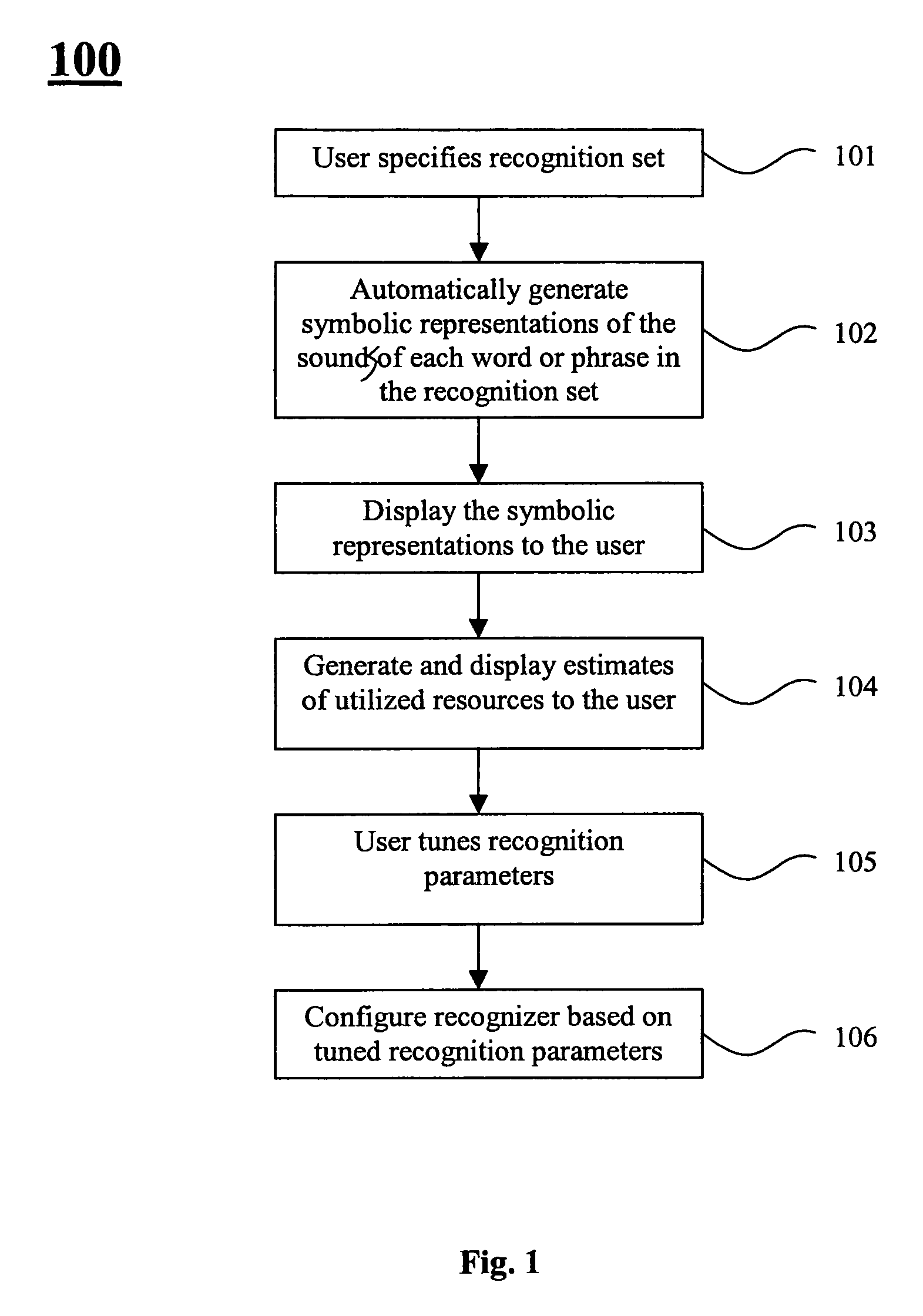

Method and apparatus of specifying and performing speech recognition operations

ActiveUS7720683B1Efficient executionShorten cycle timeSpeech recognitionSpeech identificationSpeech sound

A speech recognition technique is described that has the dual benefits of not requiring collection of recordings for training while using computational resources that are cost-compatible with consumer electronic products. Methods are described for improving the recognition accuracy of a recognizer by developer interaction with a design tool that iterates the recognition data during development of a recognition set of utterances and that allows controlling and minimizing the computational resources required to implement the recognizer in hardware.

Owner:SENSORY

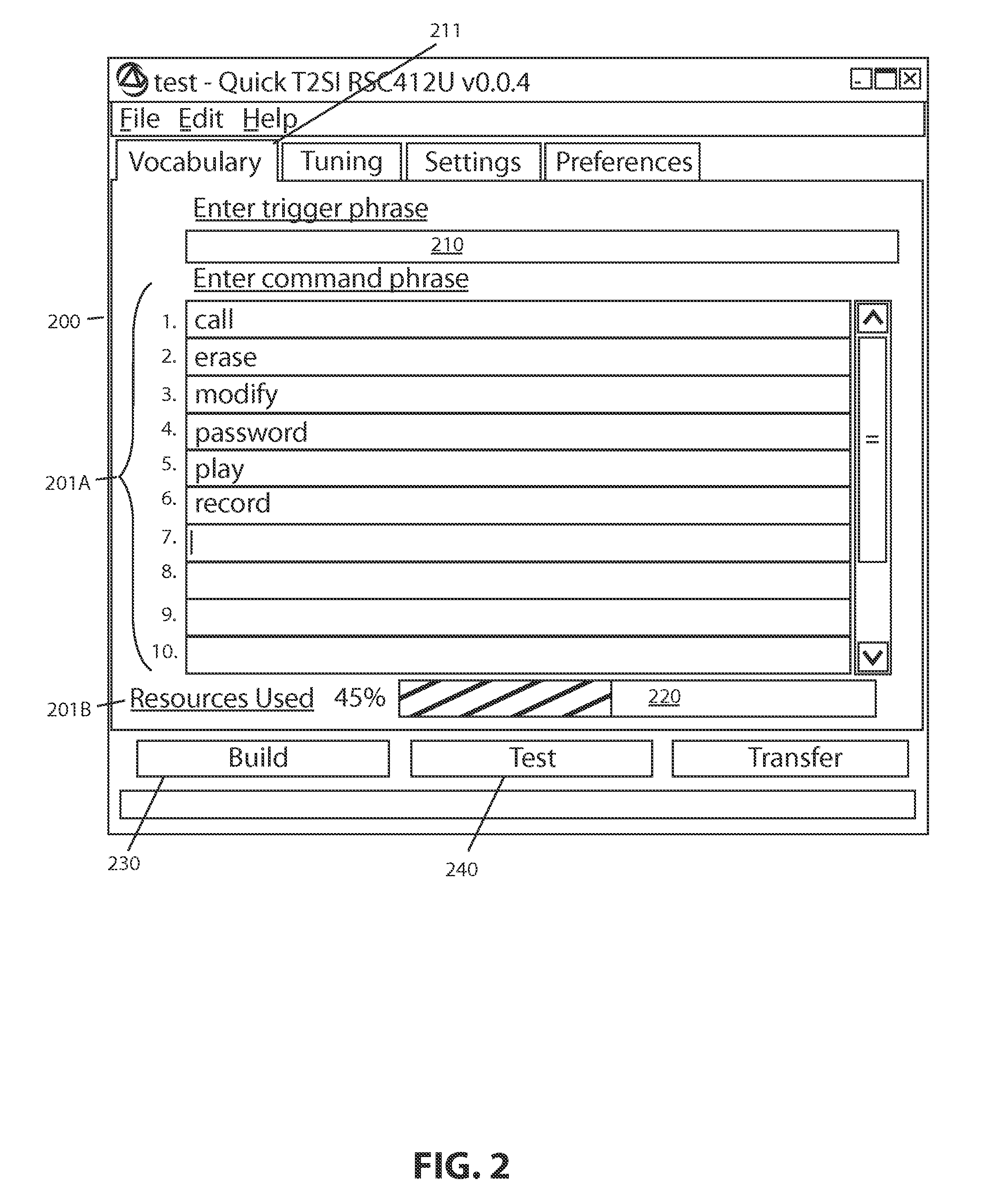

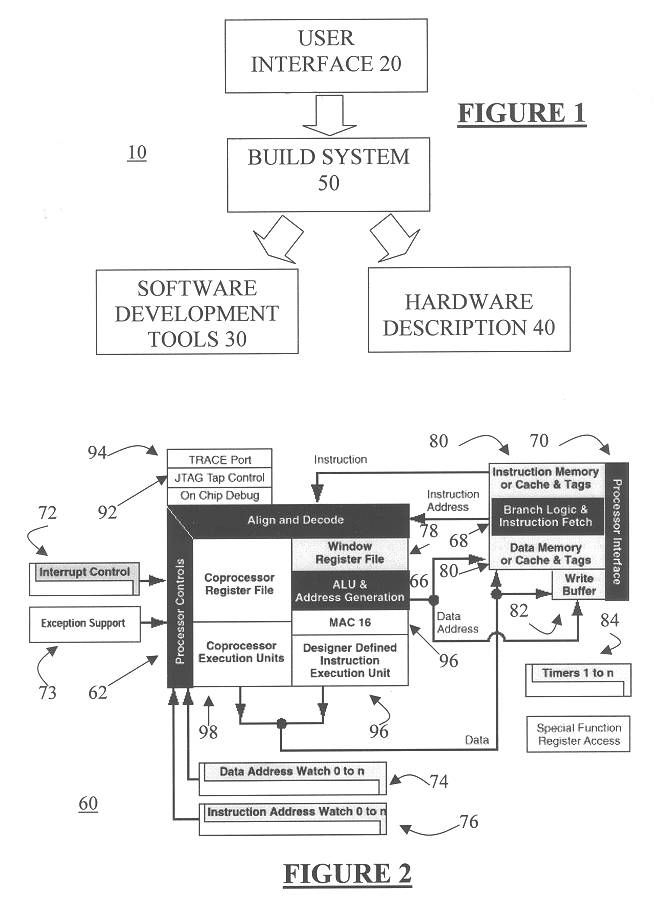

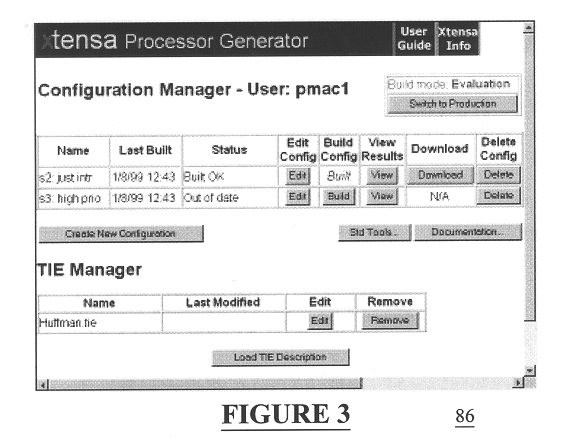

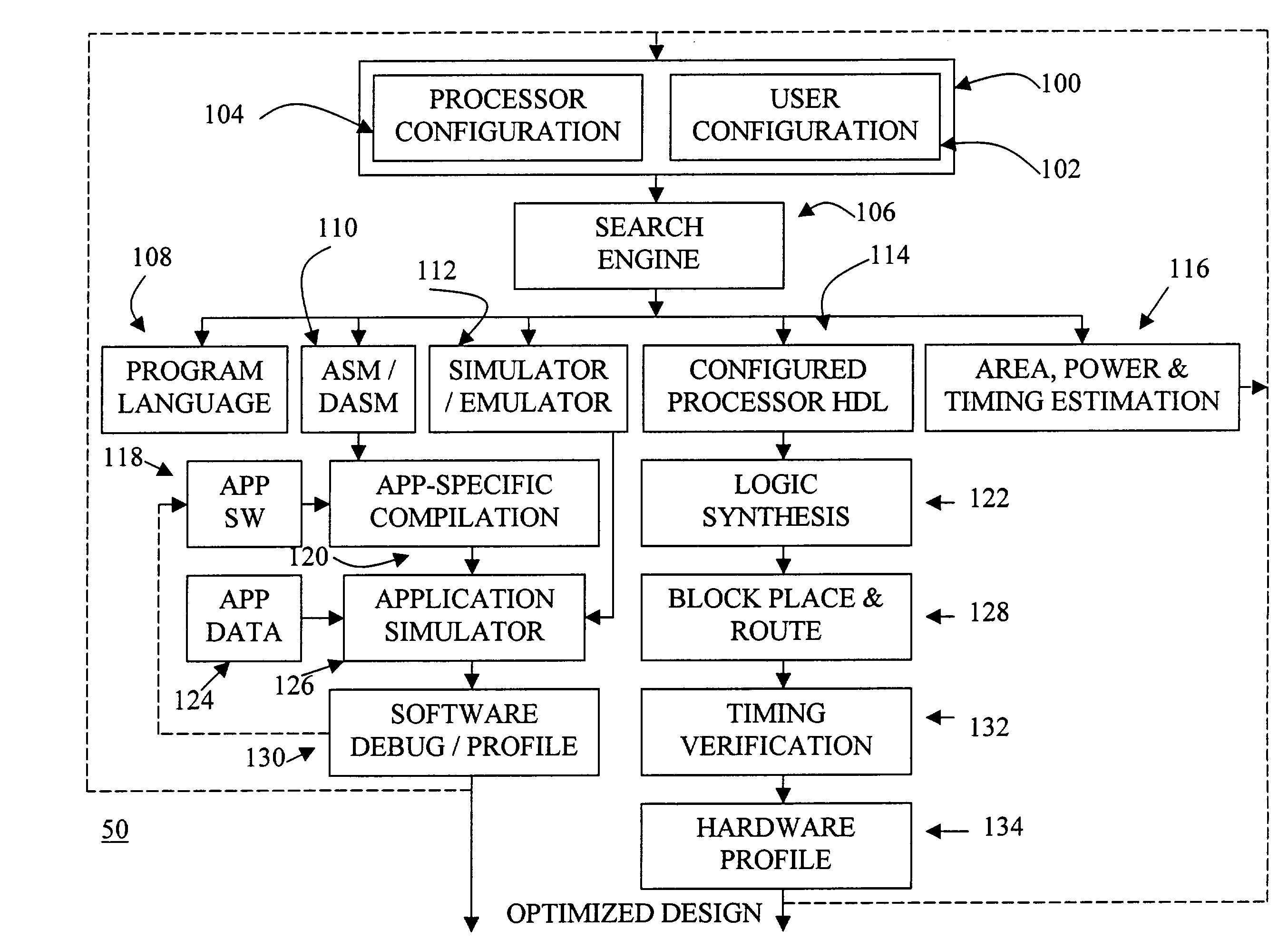

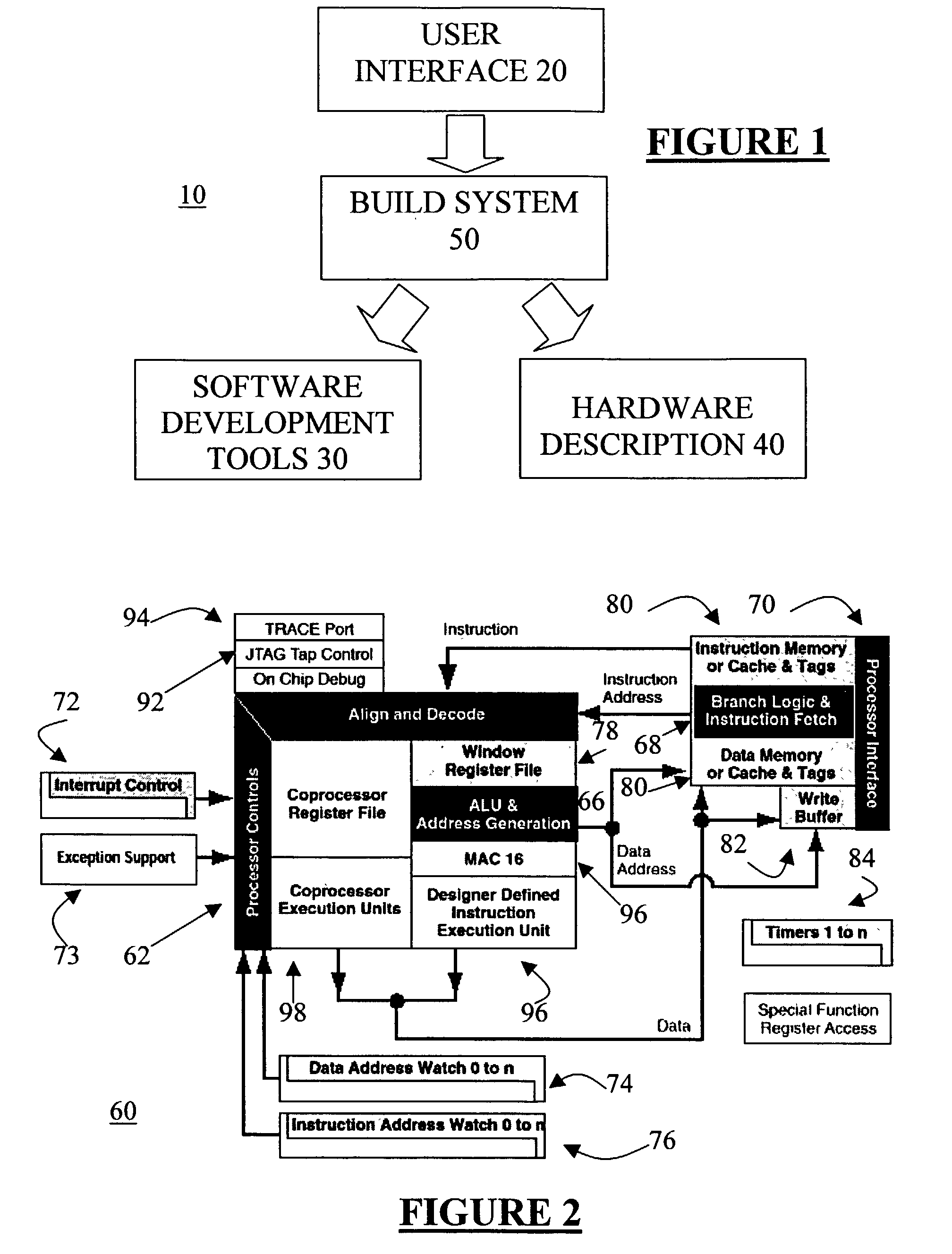

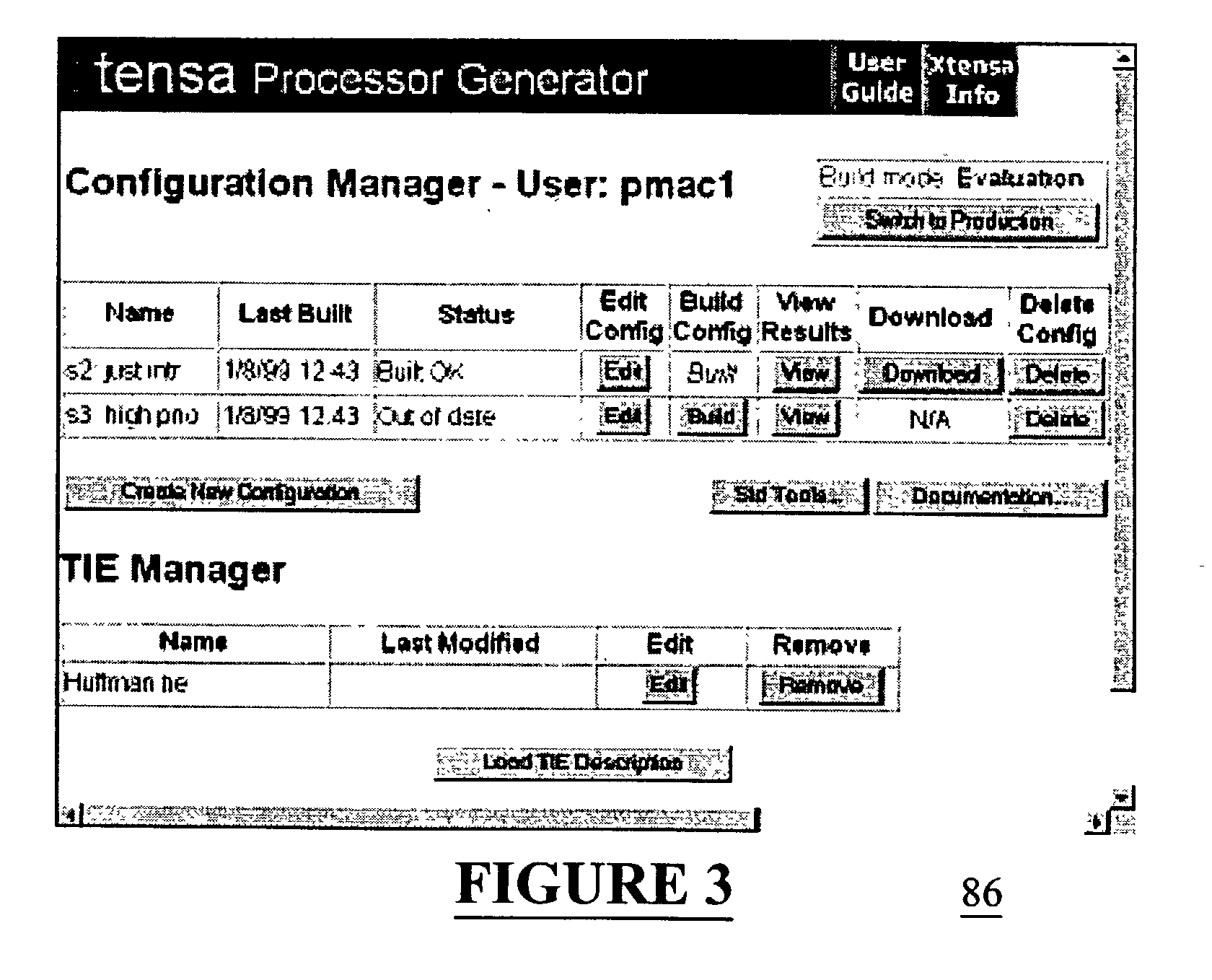

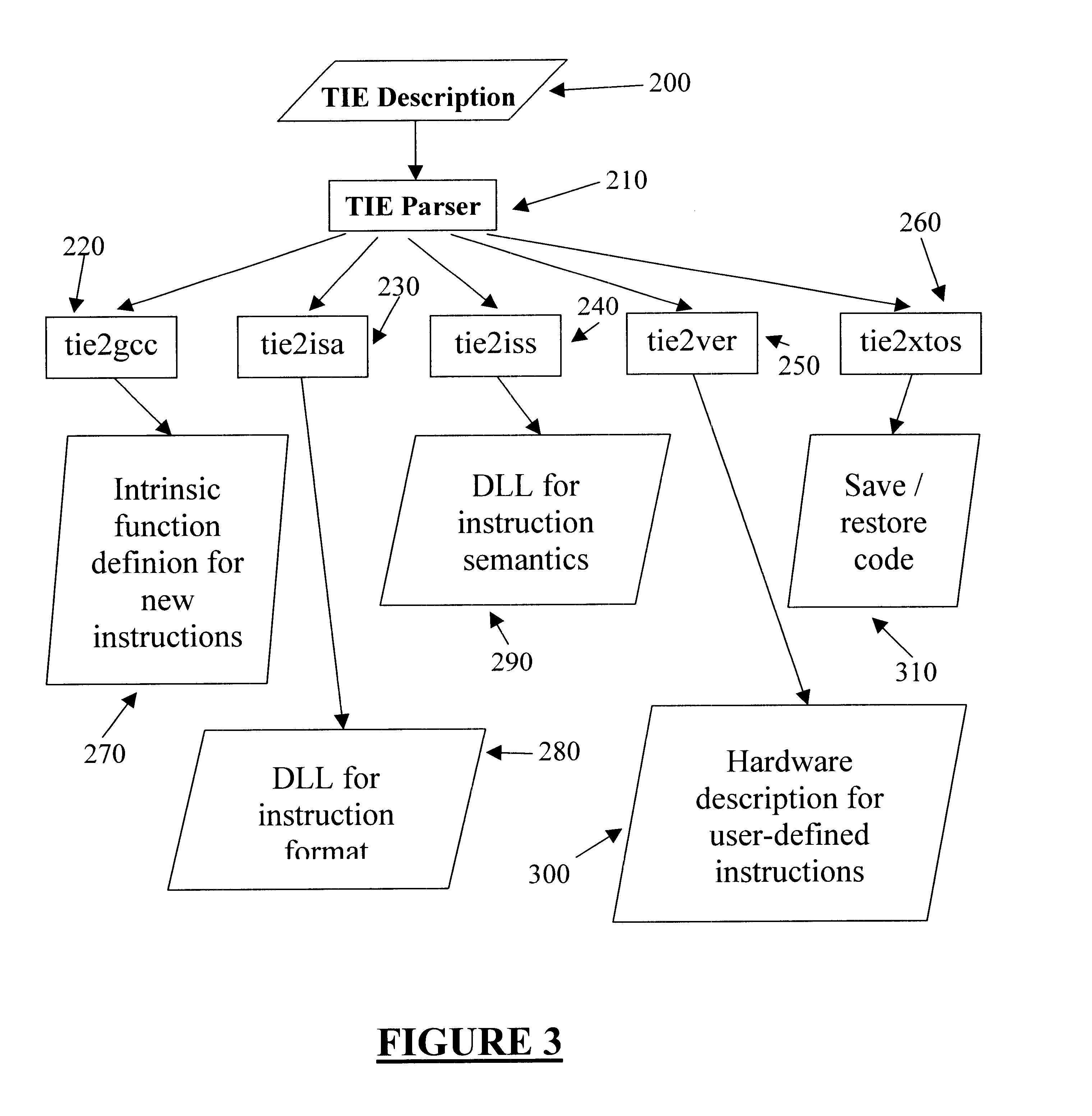

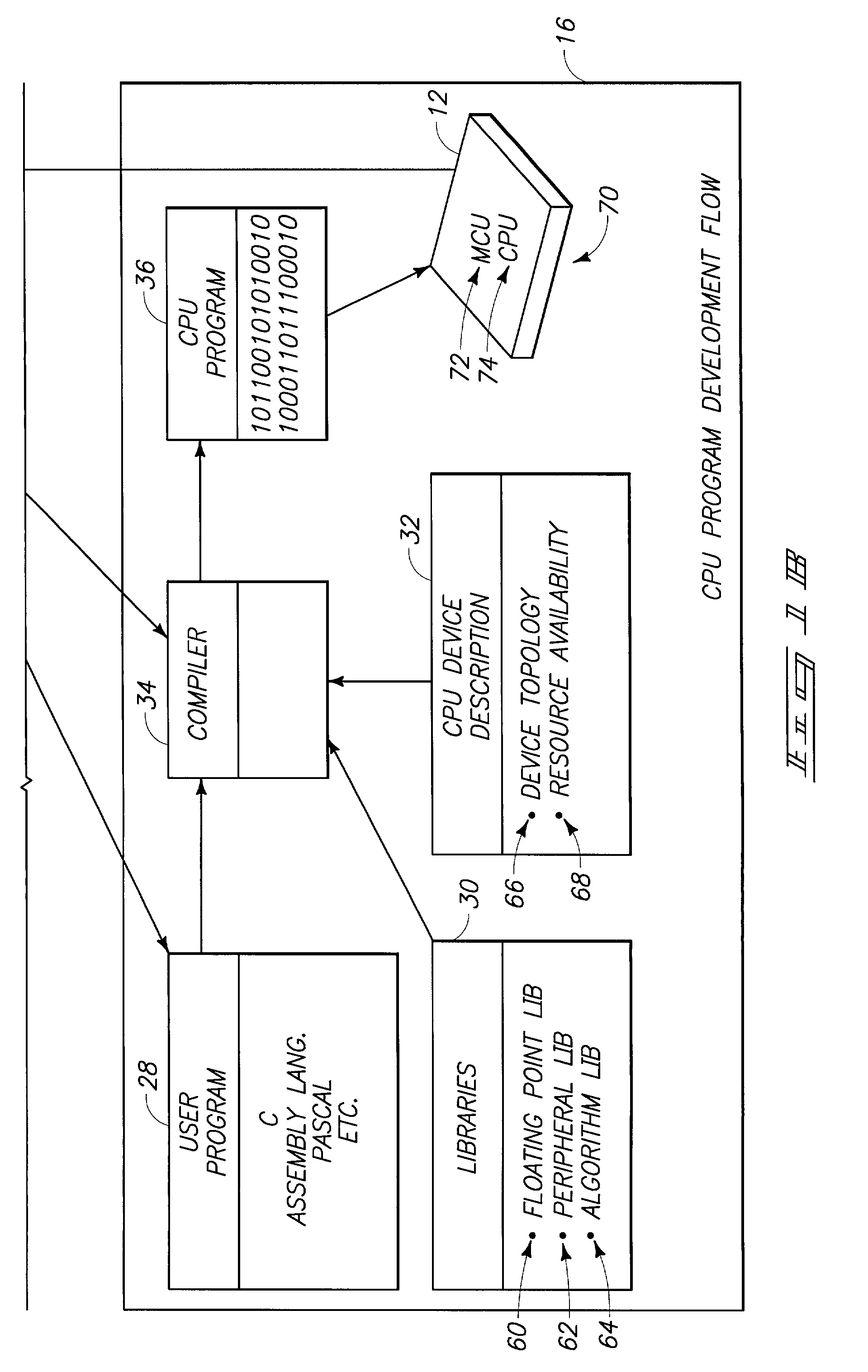

Automated processor generation system for designing a configurable processor and method for the same

InactiveUS6477683B1Decompilation/disassemblyCAD network environmentApplication softwareProcessor design

An automated processor design tool uses a description of customized processor instruction set extensions in a standardized language to develop a configurable definition of a target instruction set, a Hardware Description Language description of circuitry necessary to implement the instruction set, and development tools such as a compiler, assembler, debugger and simulator which can be used to develop applications for the processor and to verify it. Implementation of the processor circuitry can be optimized for various criteria such as area, power consumption, speed and the like. Once a processor configuration is developed, it can be tested and inputs to the system modified to iteratively optimize the processor implementation. By providing a constrained domain of extensions and optimizations, the process can be automated to a high degree, thereby facilitating fast and reliable development.

Owner:TENSILICA

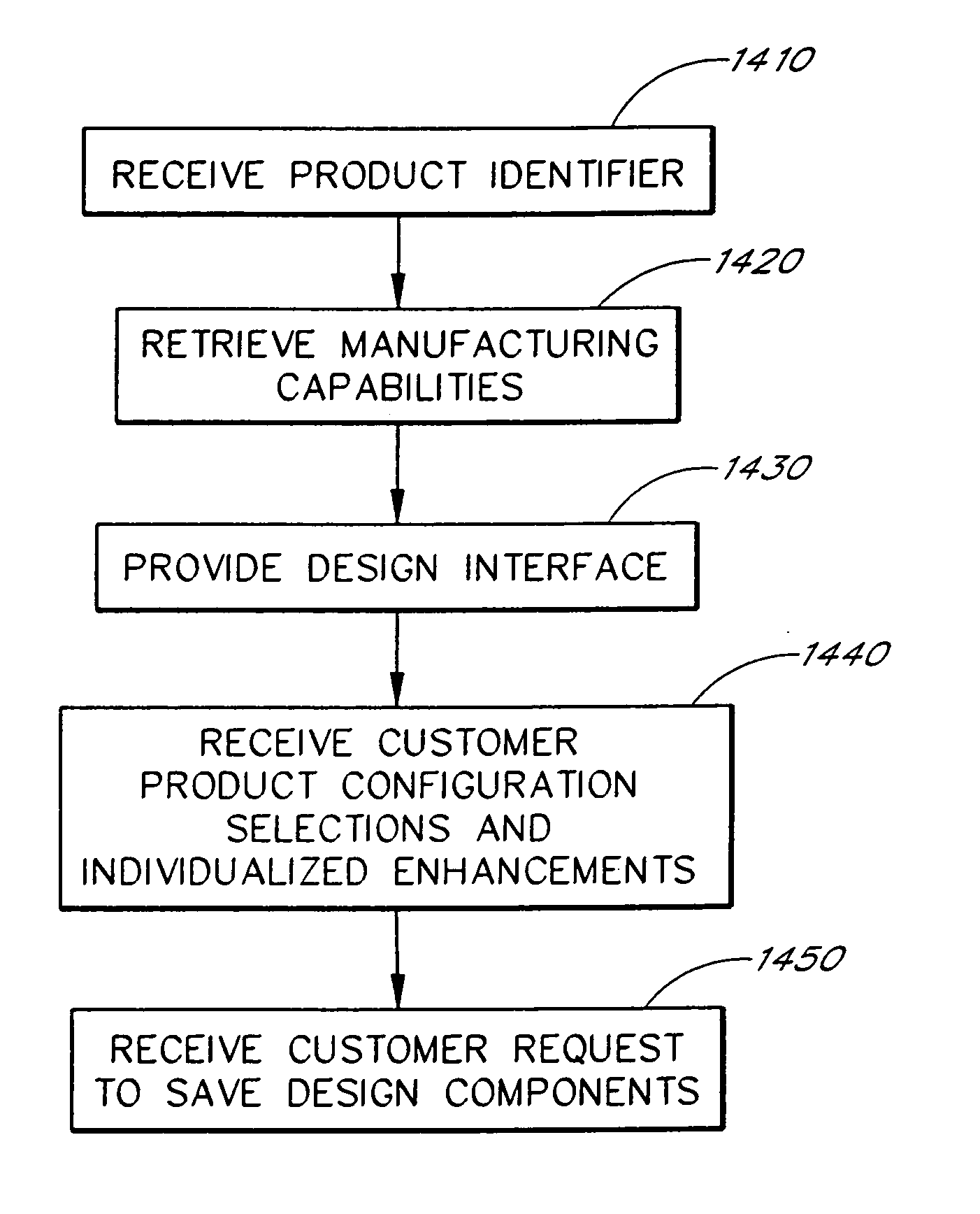

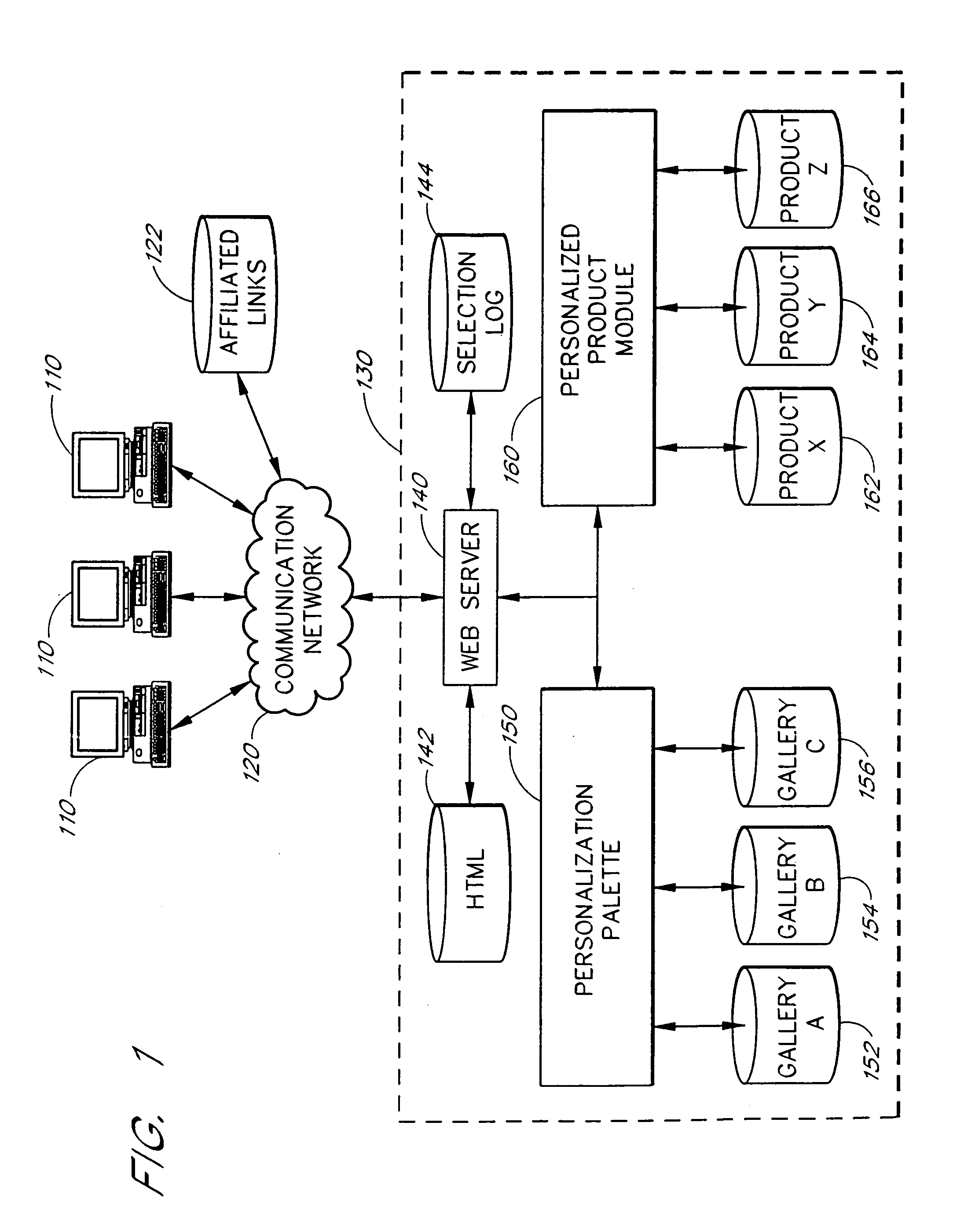

Intelligent personalization system and method

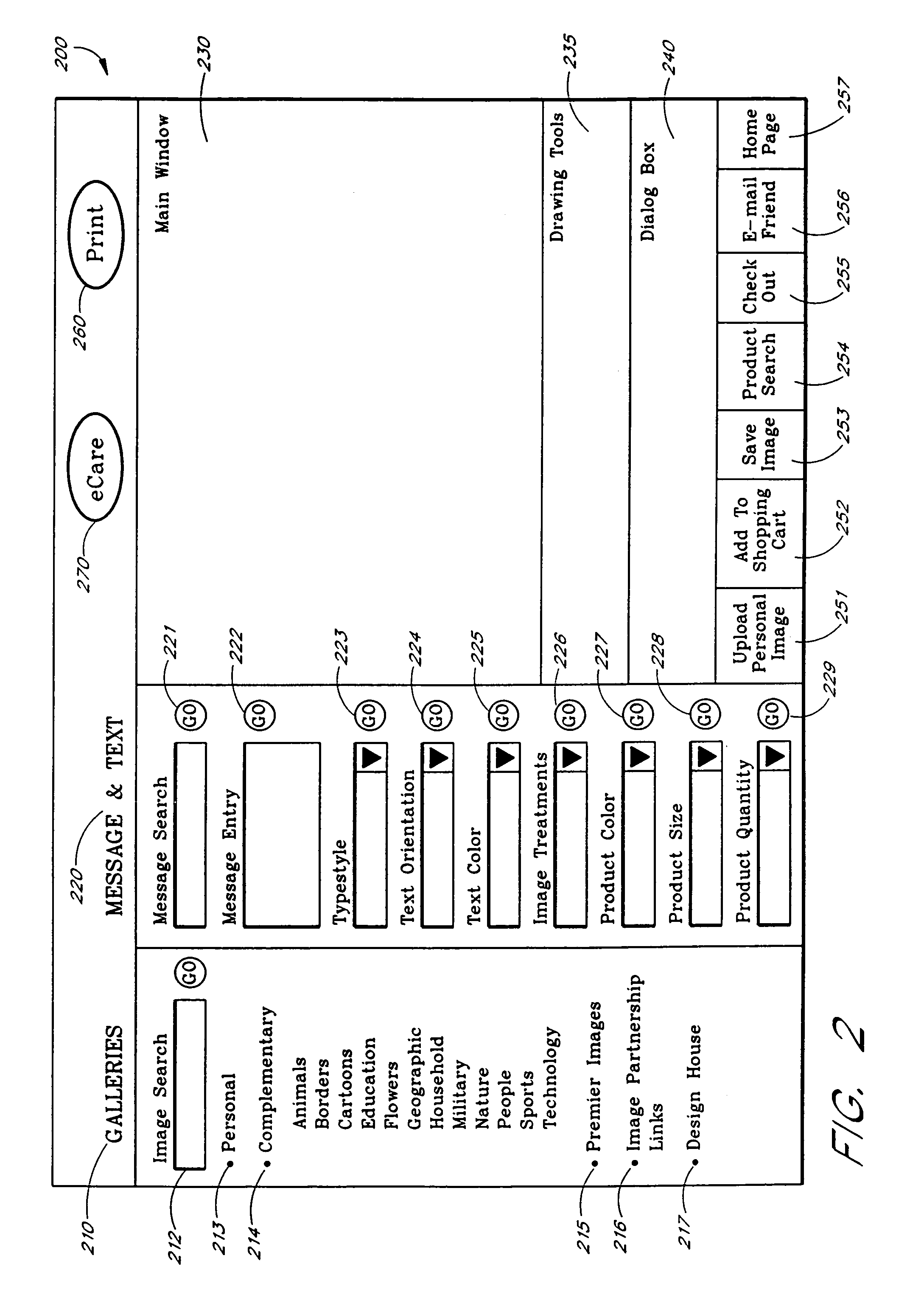

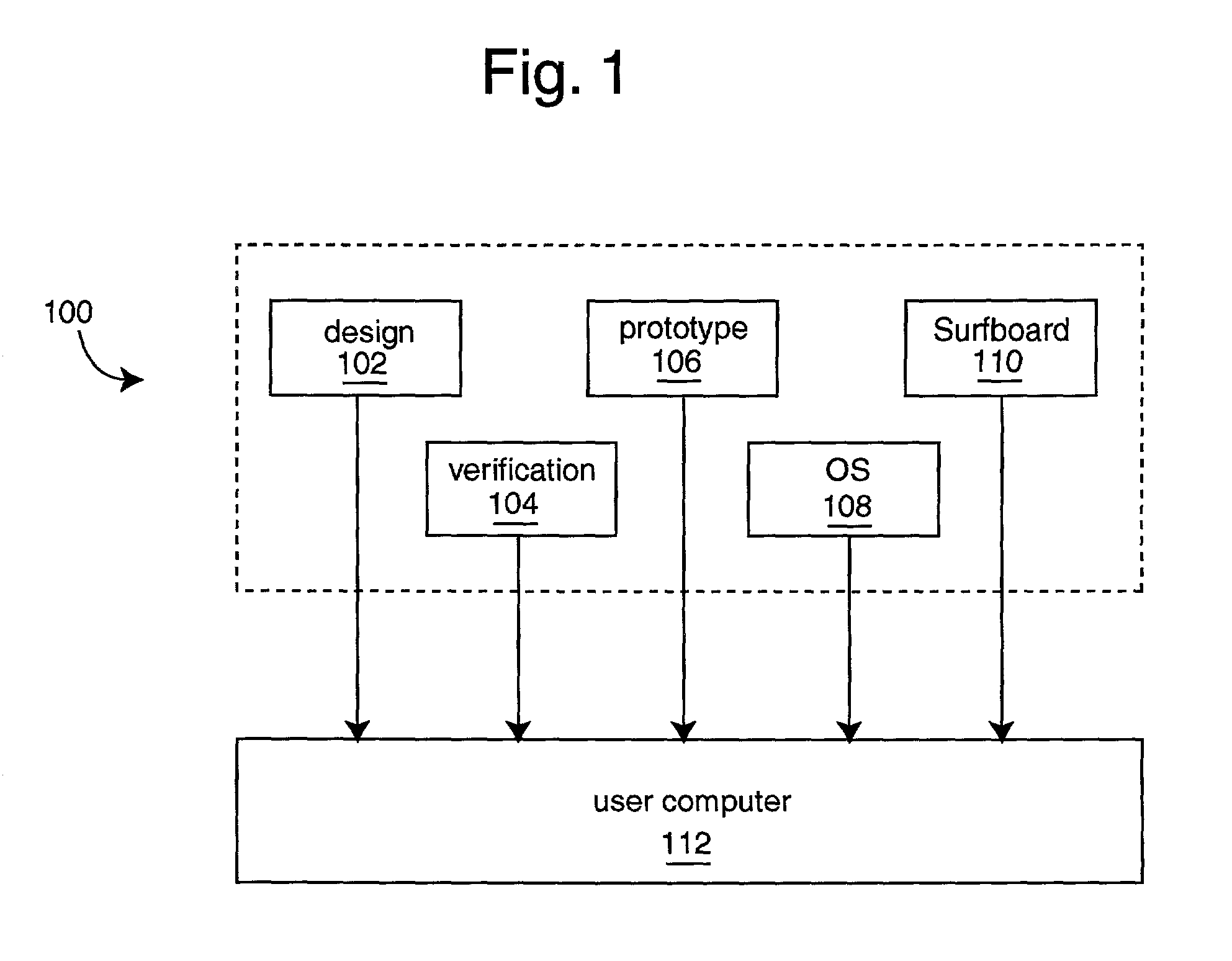

A system and method for facilitating the creation of personalized products is disclosed, wherein a user on a user computer can access a host merchant computer via a communication network, such as the Internet. The host merchant computer communicates with a products database containing information on products available for personalization and further contains manufacturing capabilities for the products. The method includes providing to the user via the communication network an assortment of product selections available in the products database, receiving a message from the user via the communication network indicating a selection of a product from the assortment, retrieving a set of manufacturing capabilities for the selected product from the products database, and providing to the user via the communication network a design interface including design tools which allow the user to select product configuration options and to create individualized enhancements, wherein the design tool is conformed to only allow configuration options and enhancements that satisfy the manufacturing capabilities.

Owner:DELUXE CORPORATION

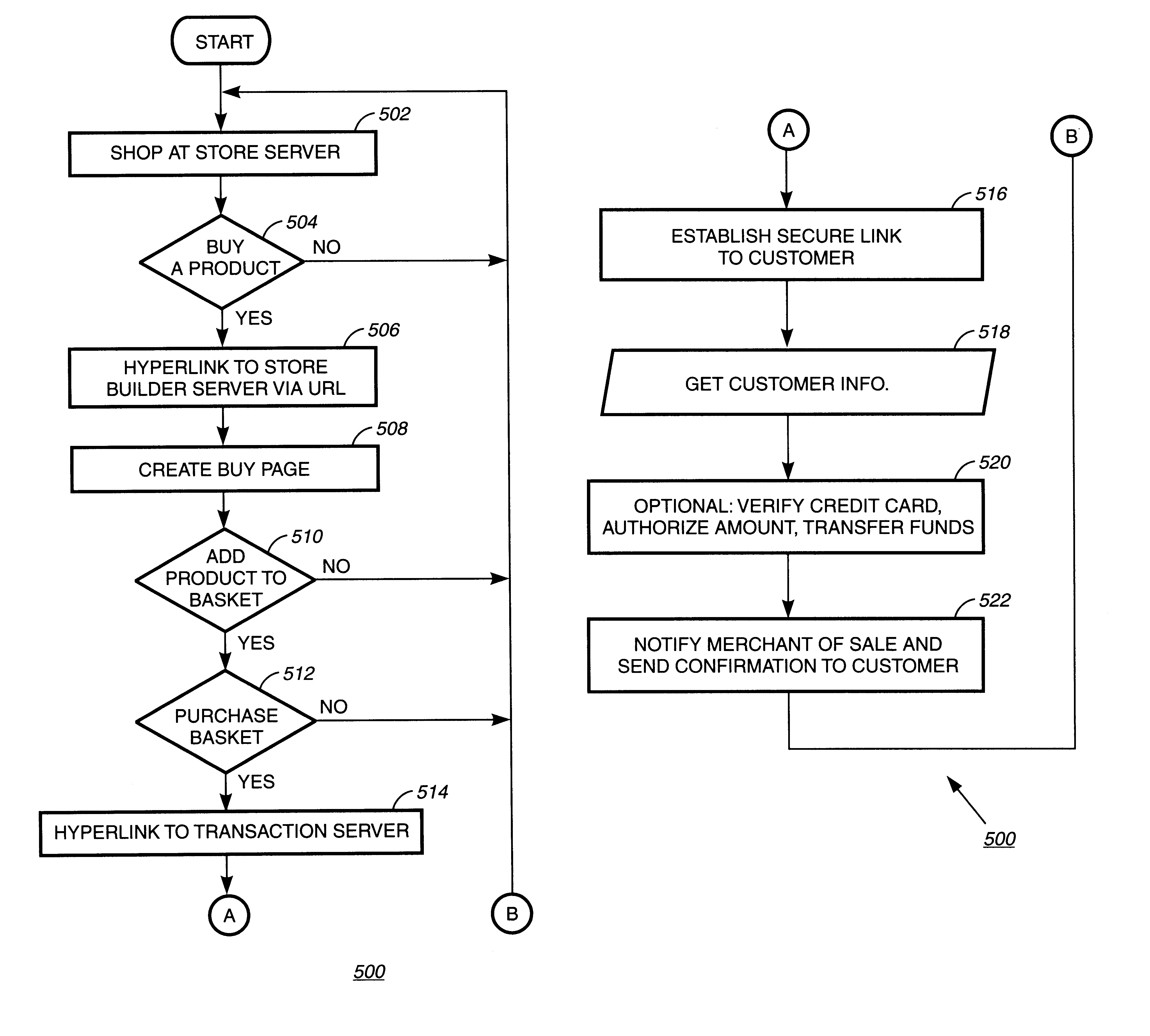

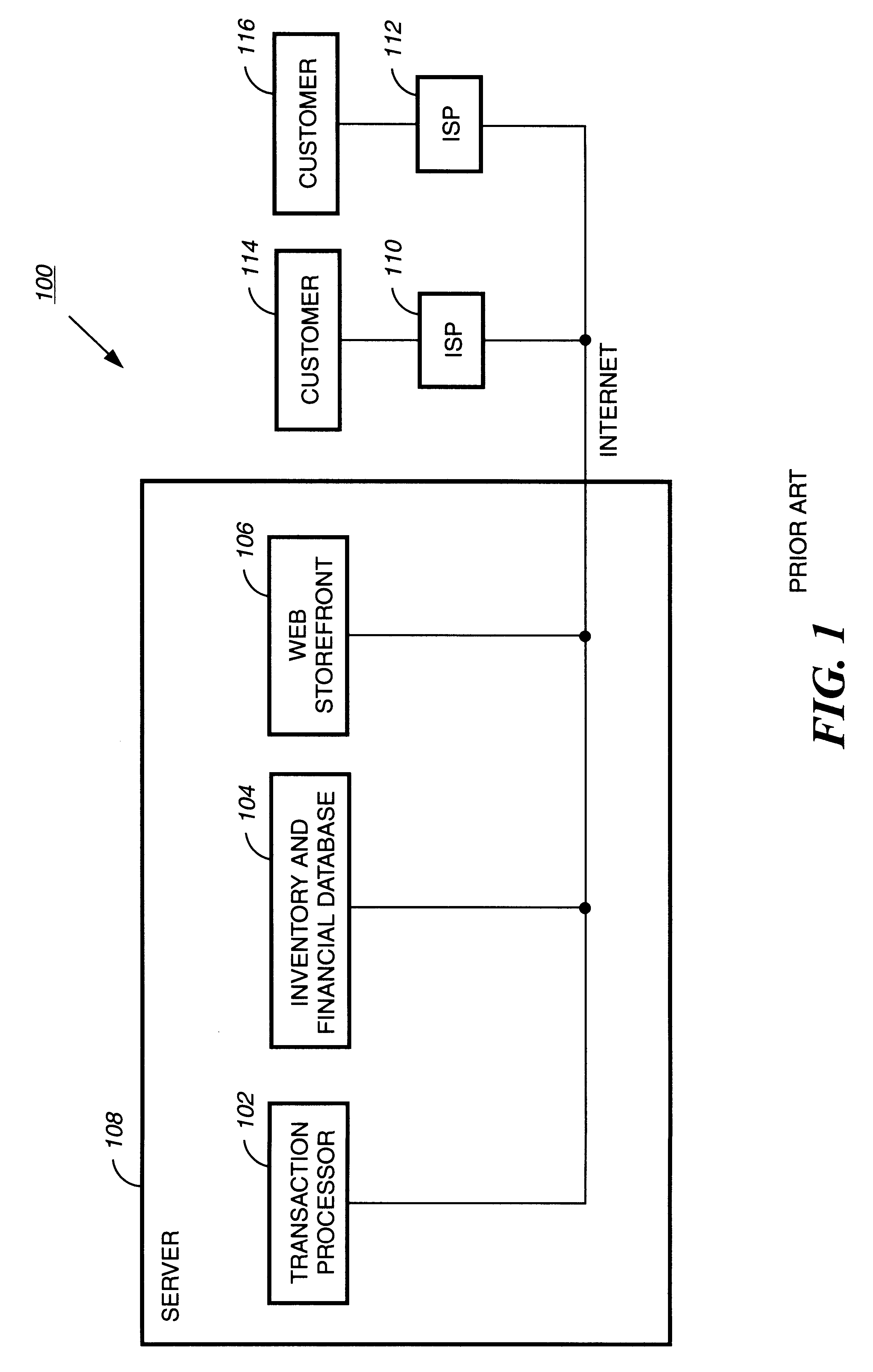

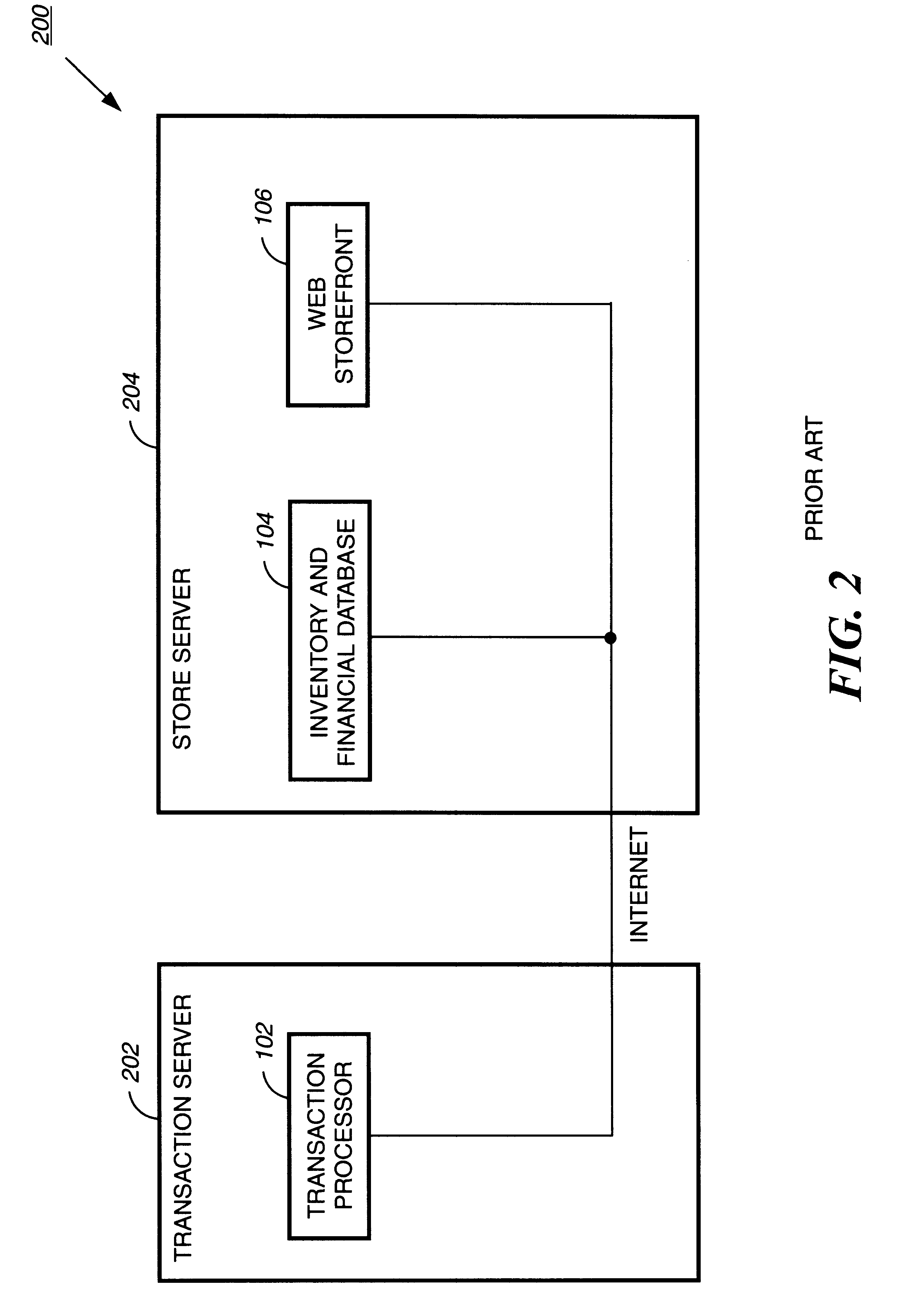

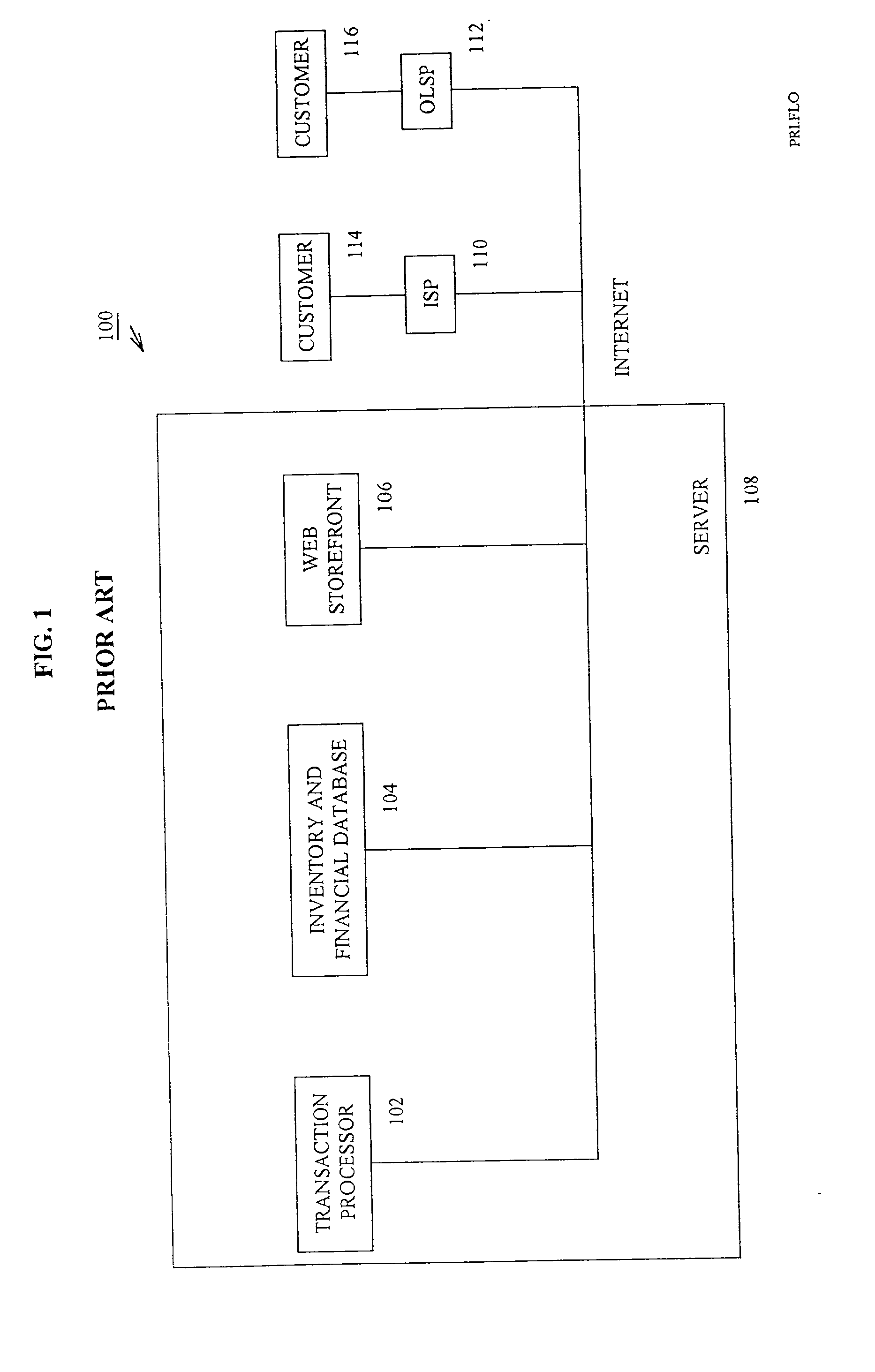

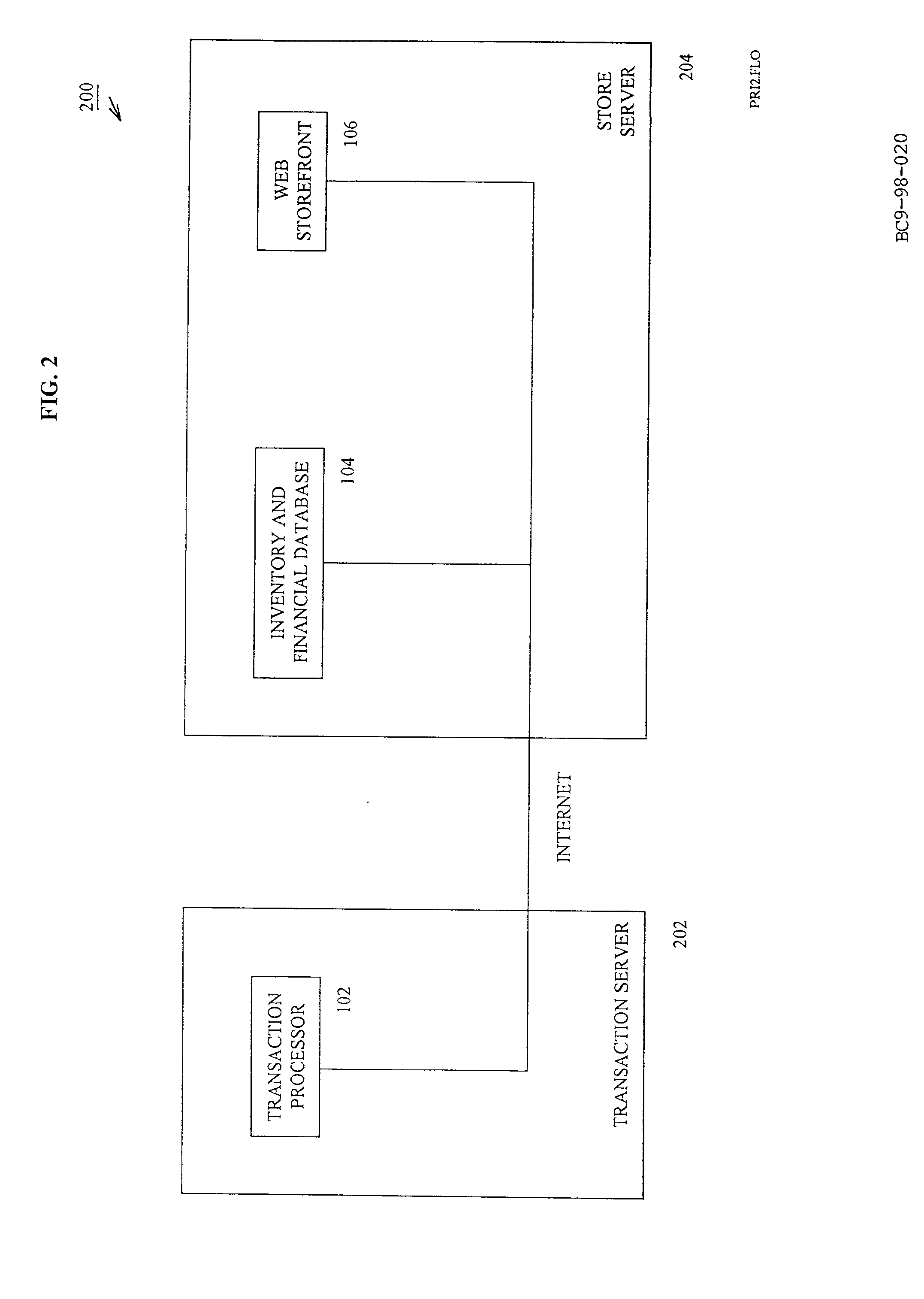

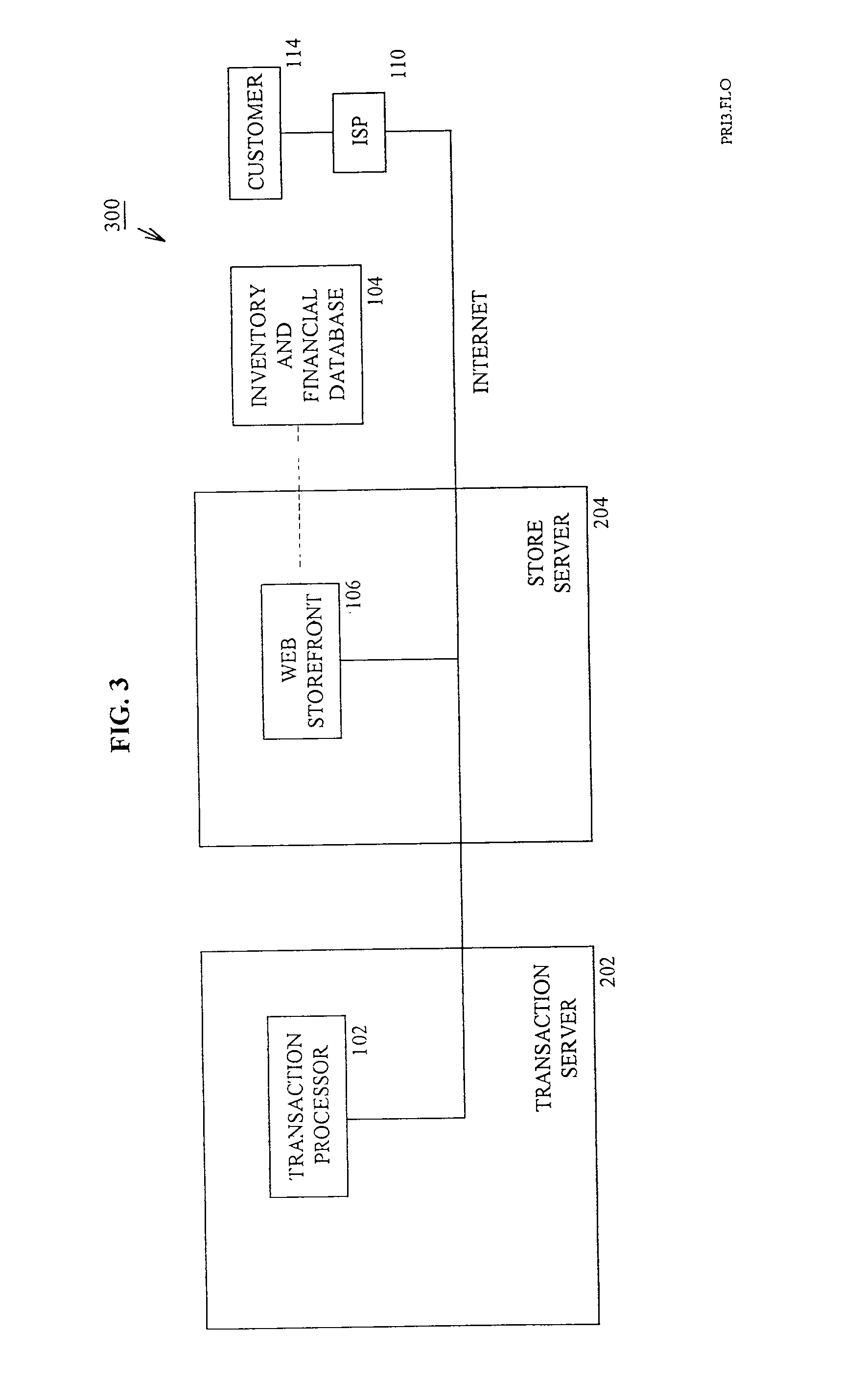

Web commerce tool kit for distributed payment processing

Methods and systems for designing a Web page, to be hosted on a Web page server. The development applications provide an object-oriented, template-driven interface for a customer or merchant to utilize in the design of a Web page or a complete Web site. The Web site produced allows the merchant to become a part of a distributed electronic commerce system or Internet commerce system for doing business on the World Wide Web. The design tool can be implemented in a Java application or applet.

Owner:IBM CORP

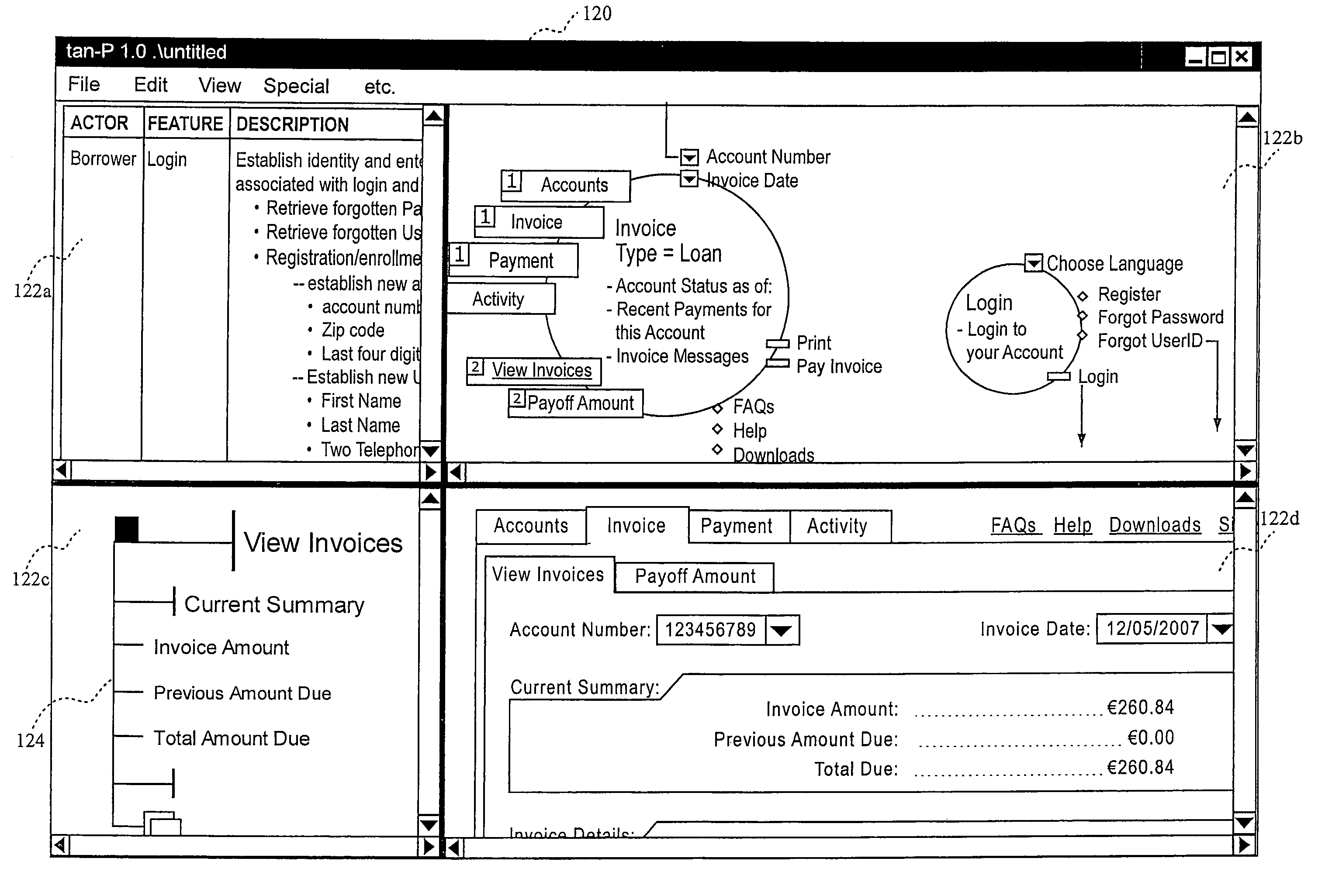

Design tool and methodology for enterprise software applications

ActiveUS7644390B2Easy to createEfficient communicationProgram documentationDesign optimisation/simulationProject managementApplication software

A system for creating and viewing simulation models that are used for managing requirements and design specifications for complex systems. Users simultaneously collaborate on the description of a complex system such as an enterprise software project throughout its life cycle. User interfaces, designed to assist in the visualization of a particular form of knowledge, allow users to describe the complex system with simple interactive elements. Information in all perspectives is presented so that it is legible and discernable to a non-technical audience. Multi-dimensional data structures record all the resulting information, creating a simulation model of the complex system, and the tasks required for construction and maintenance. Tasks are driven from the specifications not as a separate activity, but as part of the same activity to facilitate project management by allowing decisions to be tracked virtually throughout the simulation model.

Owner:KHODABANDEHLOO PAYMAN +1

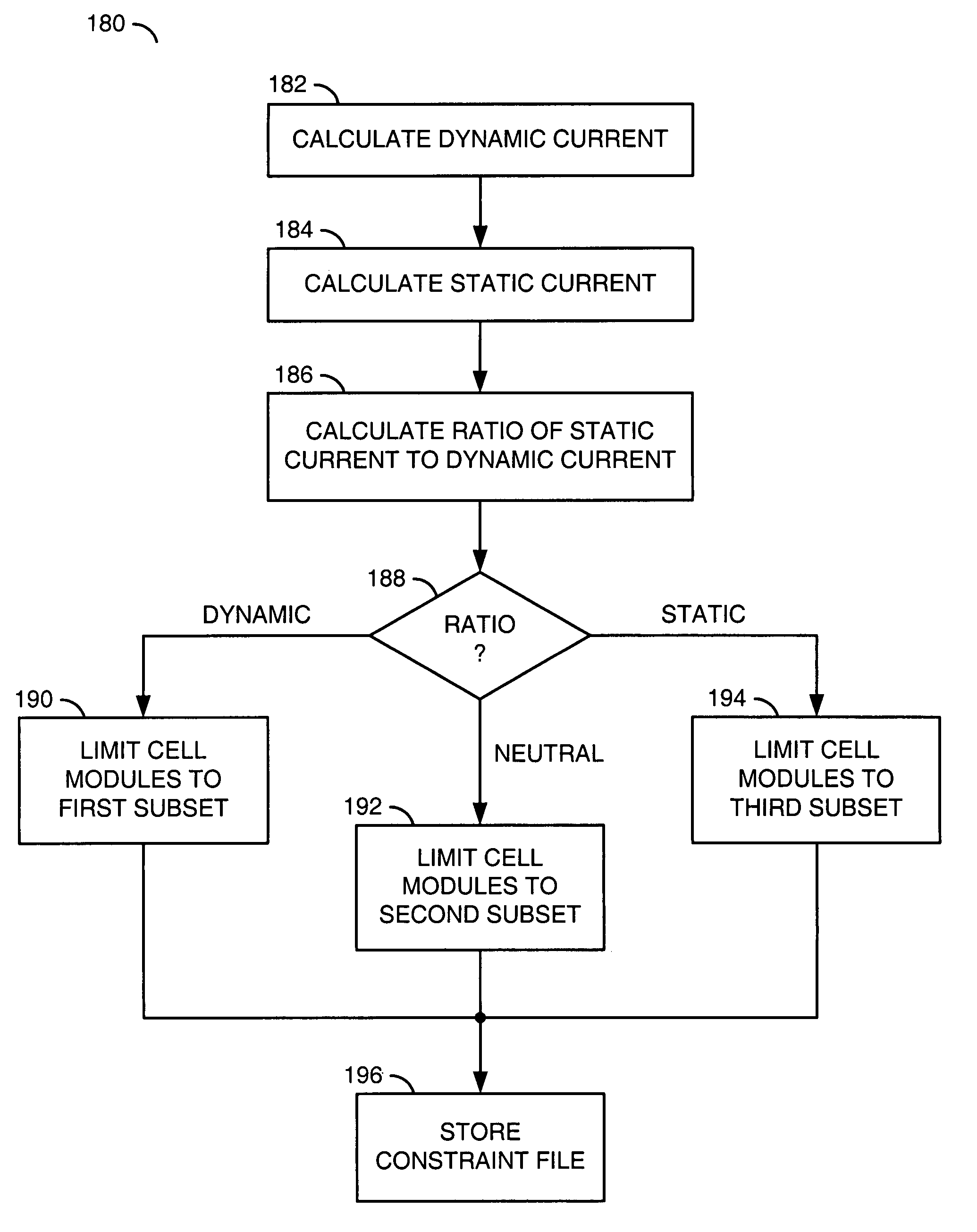

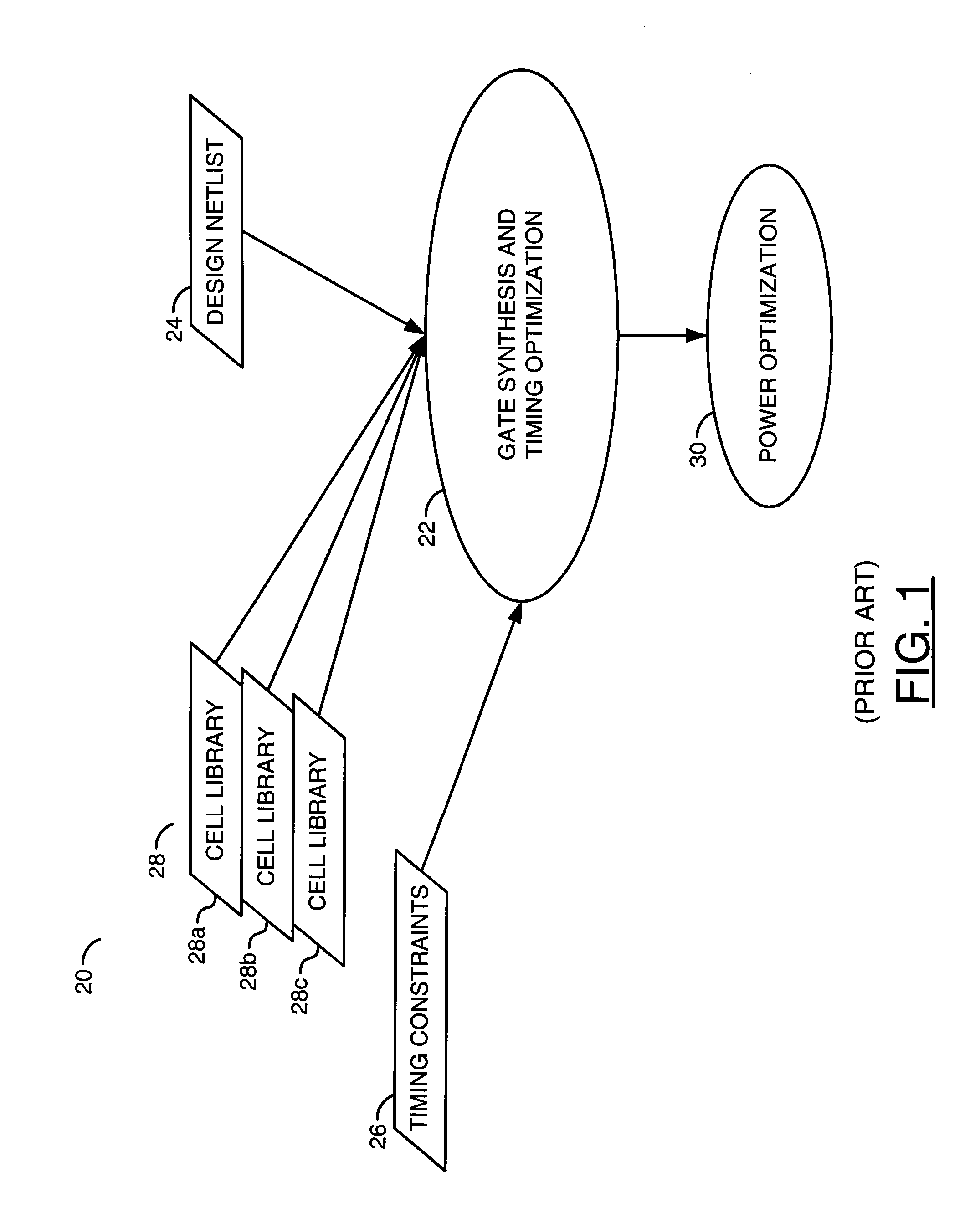

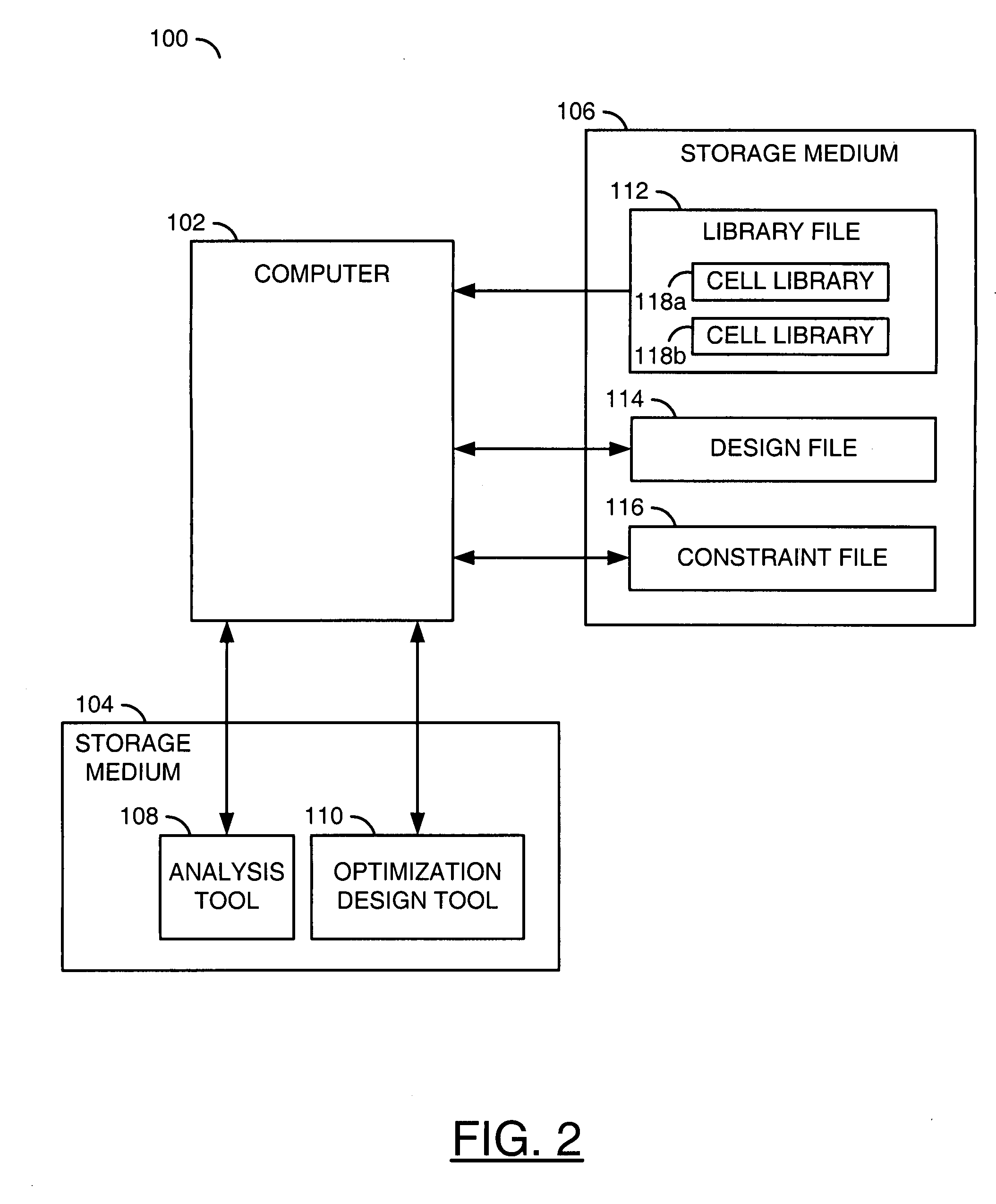

Cell library management for power optimization

InactiveUS7496867B2CAD circuit designSoftware simulation/interpretation/emulationPower optimizationOperating system

A method of managing a cell library regarding power optimization is disclosed. The method generally includes the steps of (A) reading a plurality of first modules within a first region of a circuit design stored in a design file, (B) calculating a first merit value indicating a relative sensitivity of the first region to a power consumption, the first merit value having a range from a static power dominated value to a dynamic power dominated value and (C) creating a constraint file configured to limit a design tool to a first subset of a plurality of replacement modules based on the first merit value such that the design tool automatically optimizes the power consumption of the first region by replacing at least one of the first modules with at least one of the replacement modules within the first subset, the replacement modules residing in a library file.

Owner:BELL SEMICON LLC

Web commerce tool kit for distributed payment processing

Methods and systems for designing a Web page, to be hosted on a Web page server. The development applications provide an object-oriented, template-driven interface for a customer or merchant to utilize in the design of a Web page or a complete Web site. The Web site produced allows the merchant to become a part of a distributed electronic commerce system or Internet commerce system for doing business on the World Wide Web. The design tool can be implemented in a Java application or applet.

Owner:IBM CORP

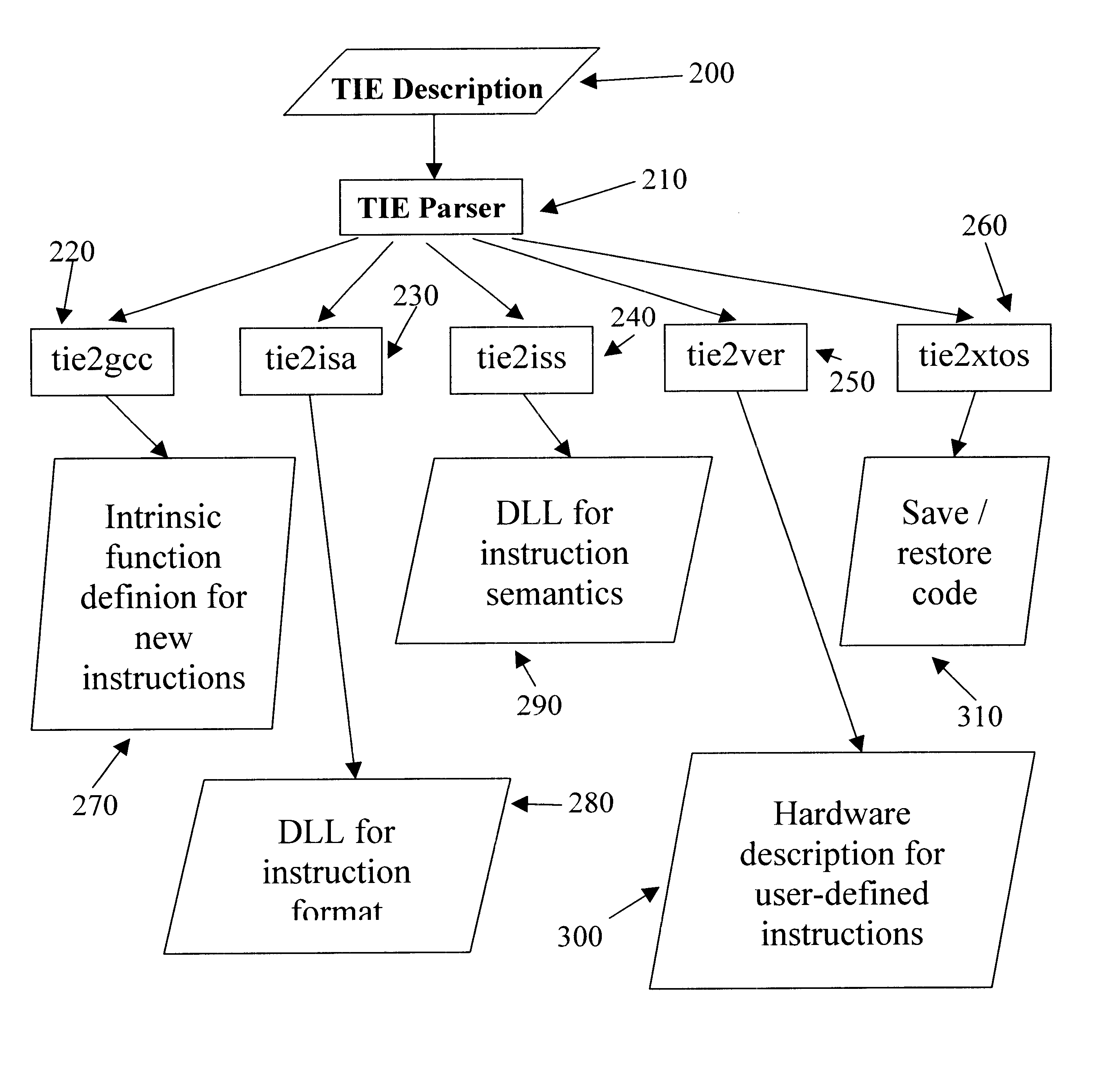

Automated processor generation system for designing a configurable processor and method for the same

InactiveUS20030208723A1Decompilation/disassemblyGeneral purpose stored program computerApplication softwareProcessor design

An automated processor design tool uses a description of customized processor instruction set extensions in a standardized language to develop a configurable definition of a target instruction set, a Hardware Description Language description of circuitry necessary to implement the instruction set, and development tools such as a compiler, assembler, debugger and simulator which can be used to develop applications for the processor and to verify it. Implementation of the processor circuitry can be optimized for various criteria such as area, power consumption, speed and the like. Once a processor configuration is developed, it can be tested and inputs to the system modified to iteratively optimize the processor implementation. By providing a constrained domain of extensions and optimizations, the process can be automated to a high degree, thereby facilitating fast and reliable development.

Owner:TENSILICA

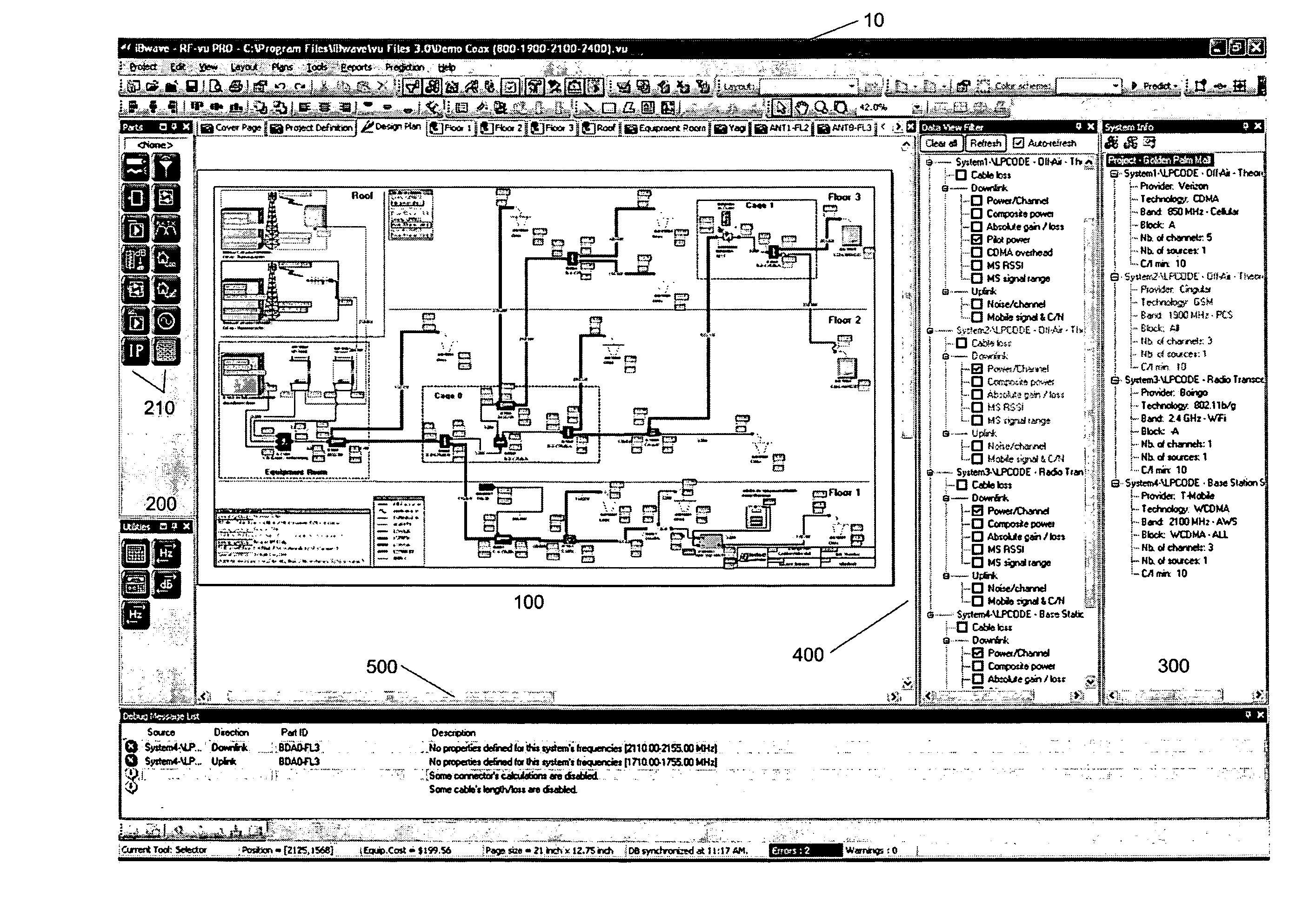

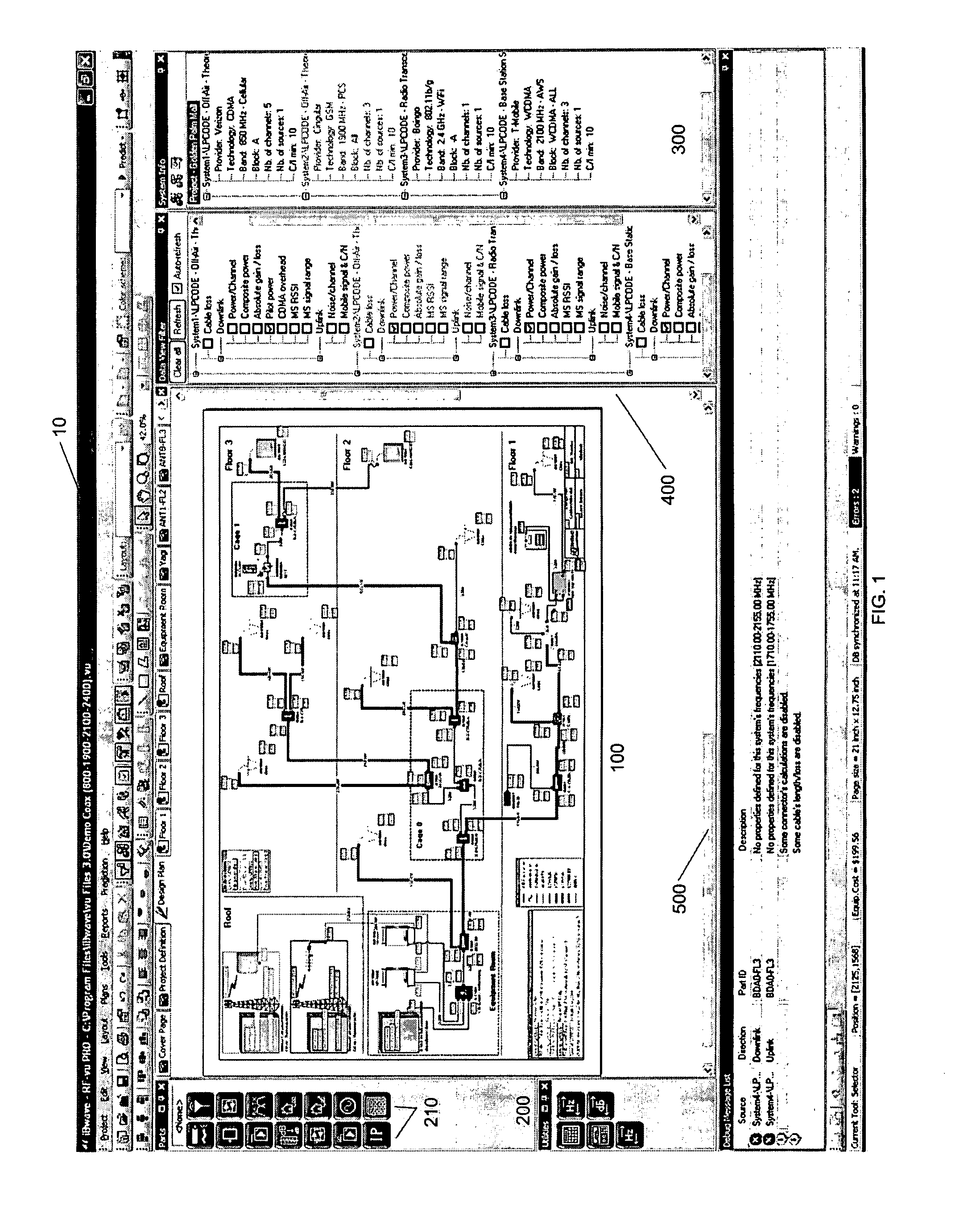

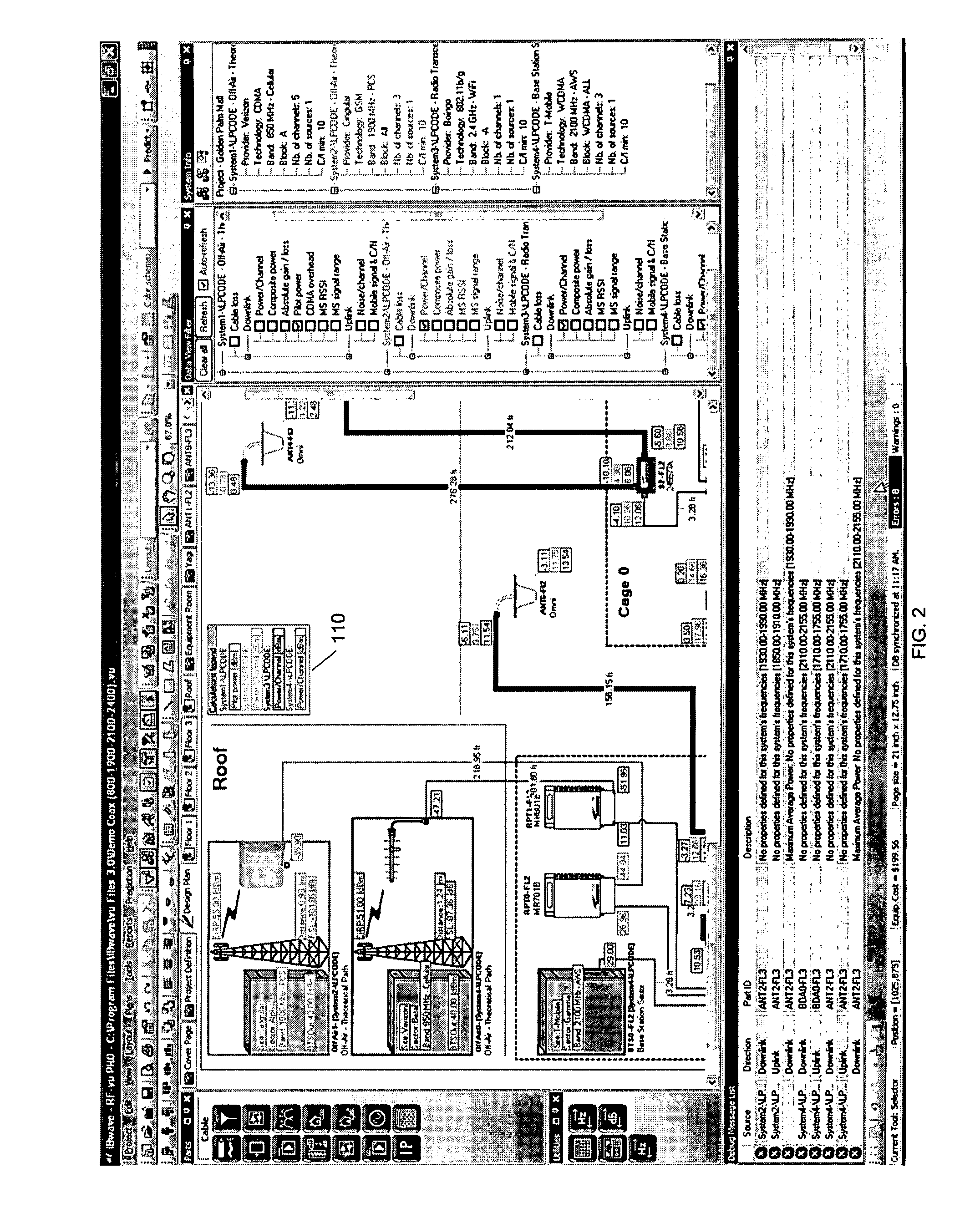

Tool for Multi-Technology Distributed Antenna Systems

InactiveUS20080026765A1Reduce difficultyReduce disadvantagesRadio/inductive link selection arrangementsNetwork planningDistributed antenna systemInterconnection

A computer-implemented design tool is disclosed for designing a multi-technology wireless Distributed Antenna Systems (DAS) network. The design tool allows a wireless designer to select antennas, network components, cable elements and signal sources from one or more databases and to place them on a design screen. The design tool is particularly configured to create DAS network adapted to support several signal sources, each signal source generally using a different band of frequencies and / or a different wireless network communication technology. In addition, the design tool performs multiple simultaneous complex RF calculations in uplink and / or downlink direction for each signal source and further displays the results of these calculations at each interconnection of the DAS network. The design tool also updates all the RF calculations when the network design is modified by the designer. Hence, by performing and updating RF calculations for several bands of frequencies and several communication technologies, the design tool allows the designer to rapidly correct the flaws in his design in order to rapidly obtain an adequate network design.

Owner:IBWAVE SOLUTIONS

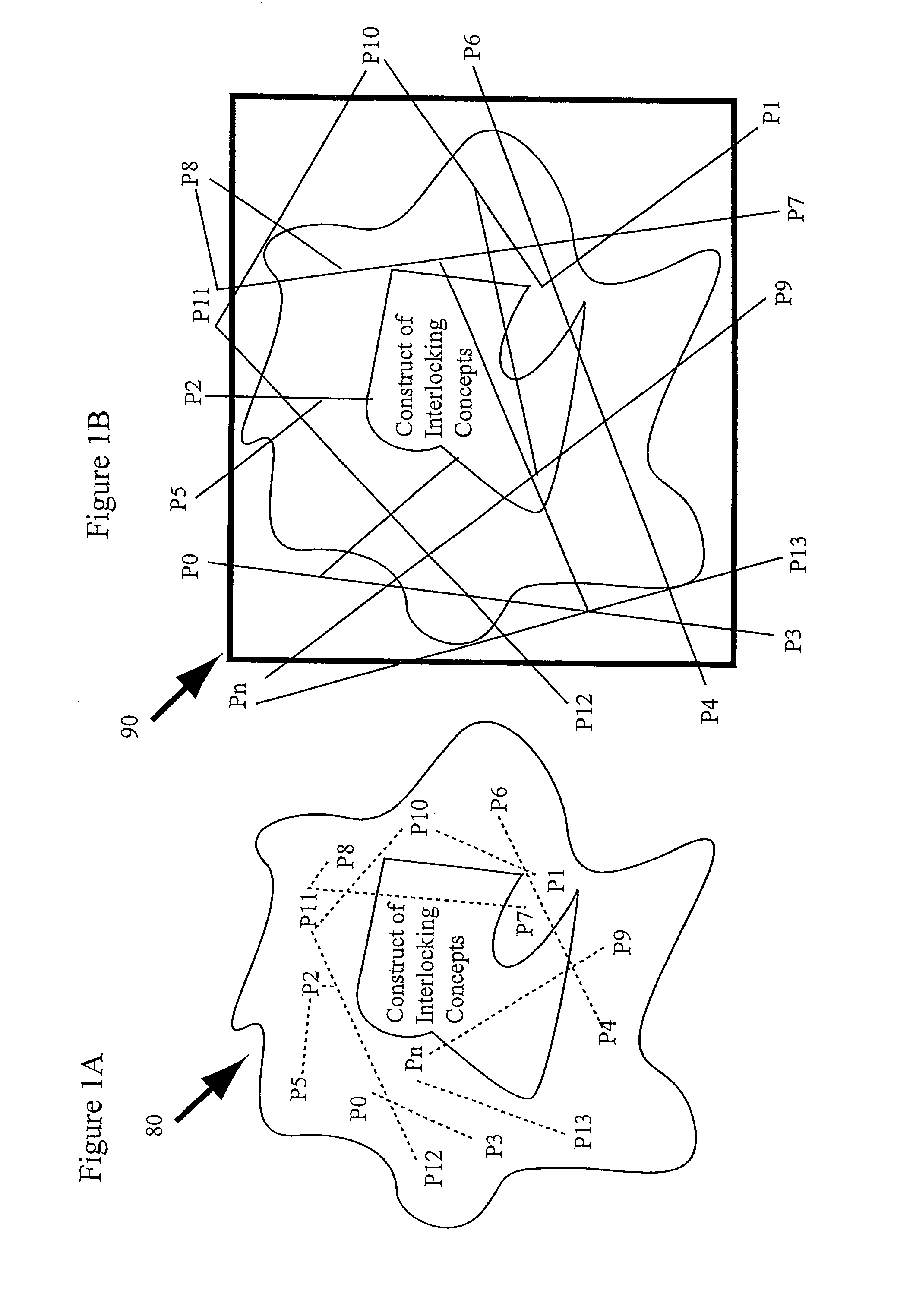

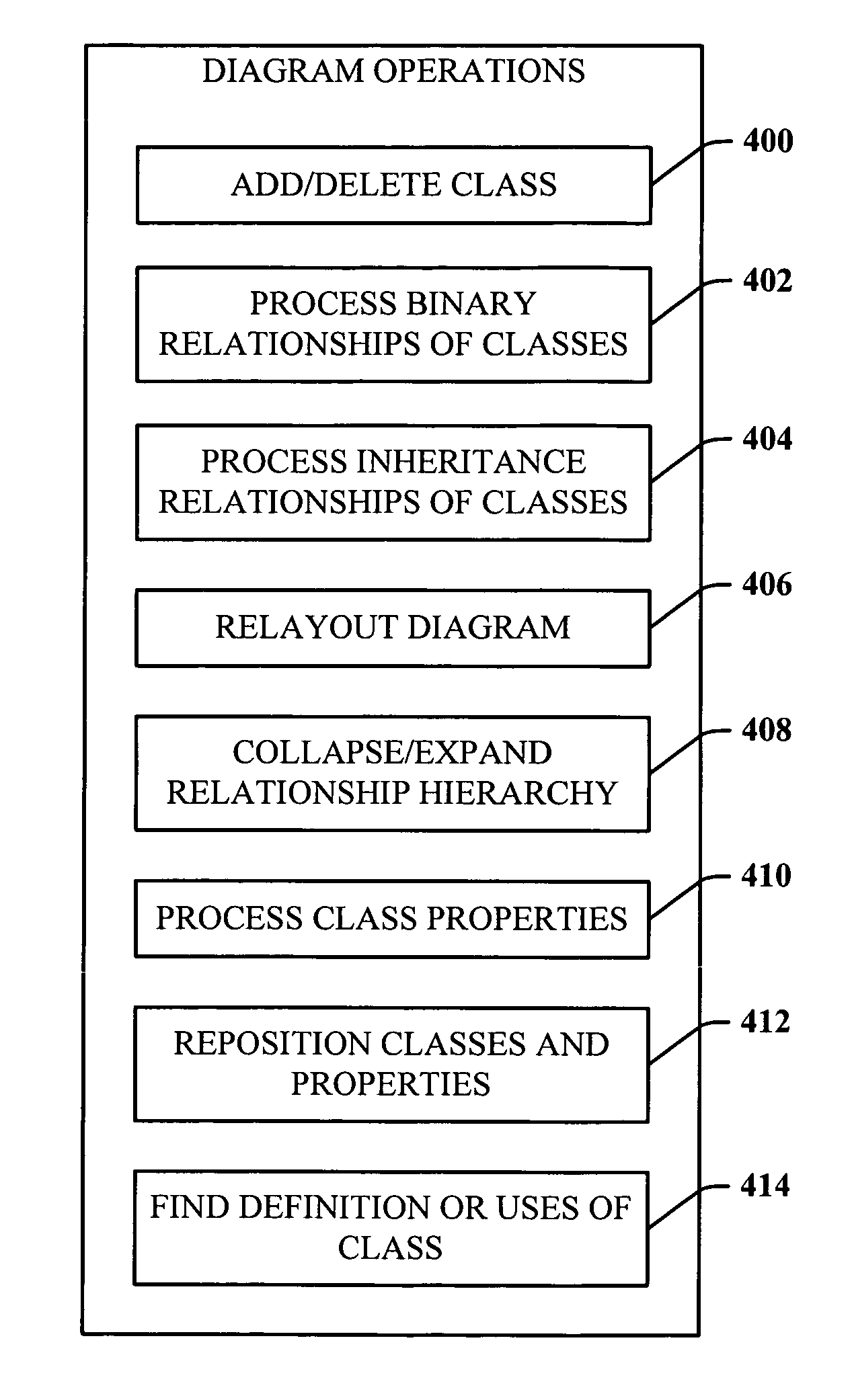

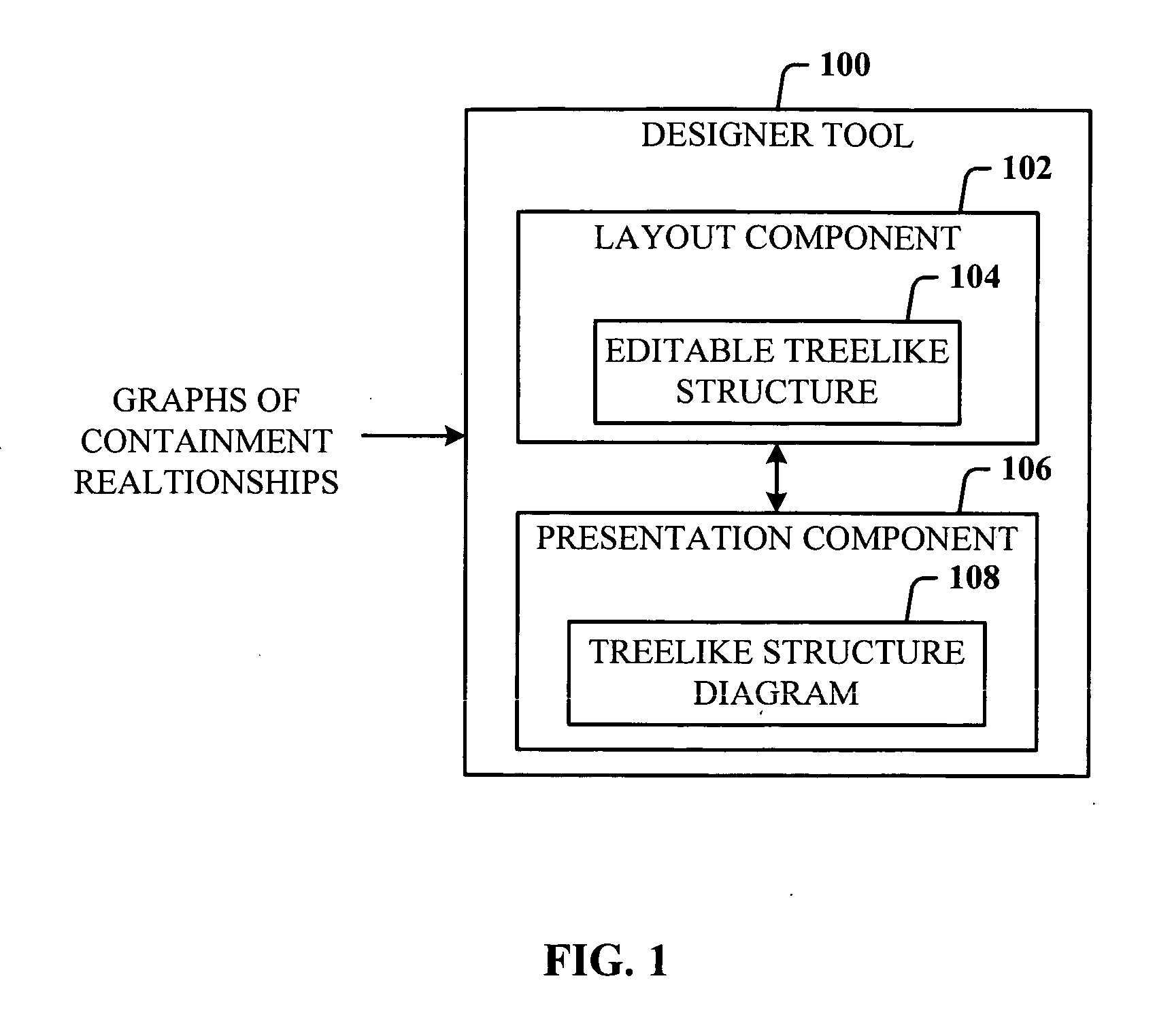

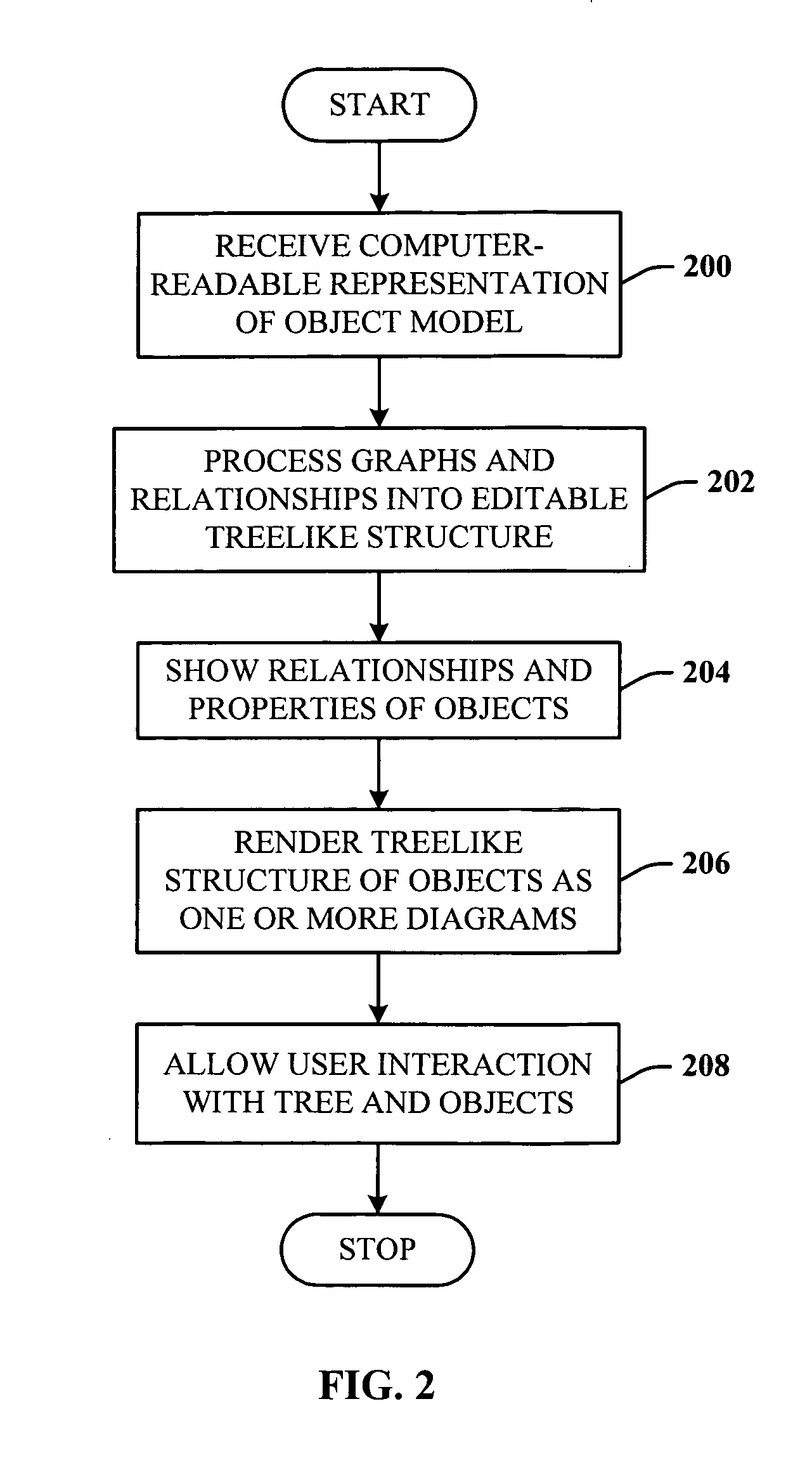

Object model tree diagram

ActiveUS20060150169A1Compact and efficient in their useSimple designVisual/graphical programmingRequirement analysisGraphicsComputer science

A designer tool that facilitates design of an object model. The tool takes as input a computer-readable representation of a graph of objects (e.g., classes), and creates automatically one or more diagrams that depict these classes as editable trees showing their relationships and properties. These graphs naturally have a tree-like structure which is exploited by the approach. The design tool system includes a layout component that receives as input one or more of the graphs, and converts the one or more graphs into the editable treelike structure. The system further comprises a presentation component that presents the editable treelike structure as a treelike structure diagram, and facilitates user interaction therewith. The tool can be used for opening, editing and saving existing object model files or to create new ones.

Owner:MICROSOFT TECH LICENSING LLC

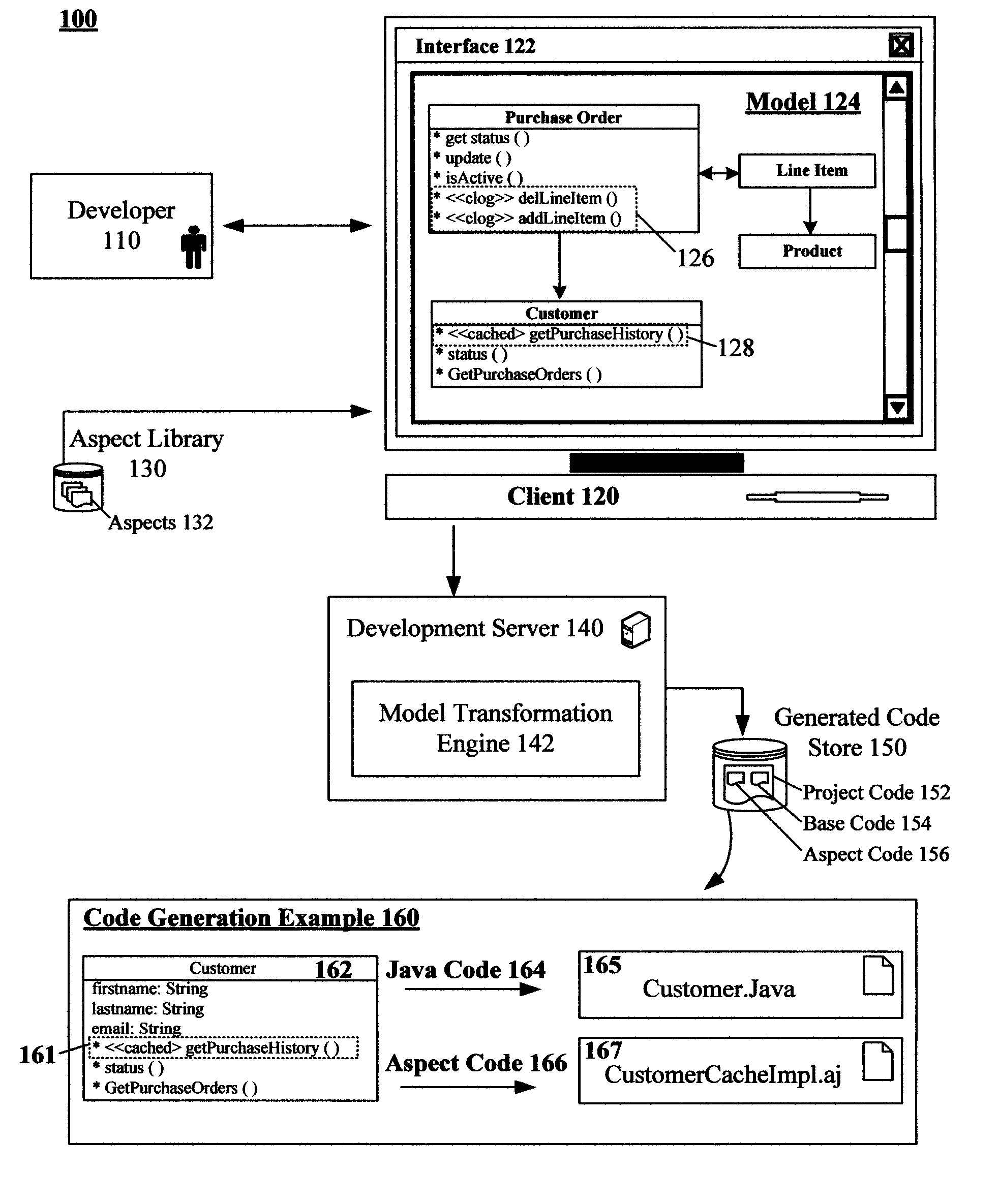

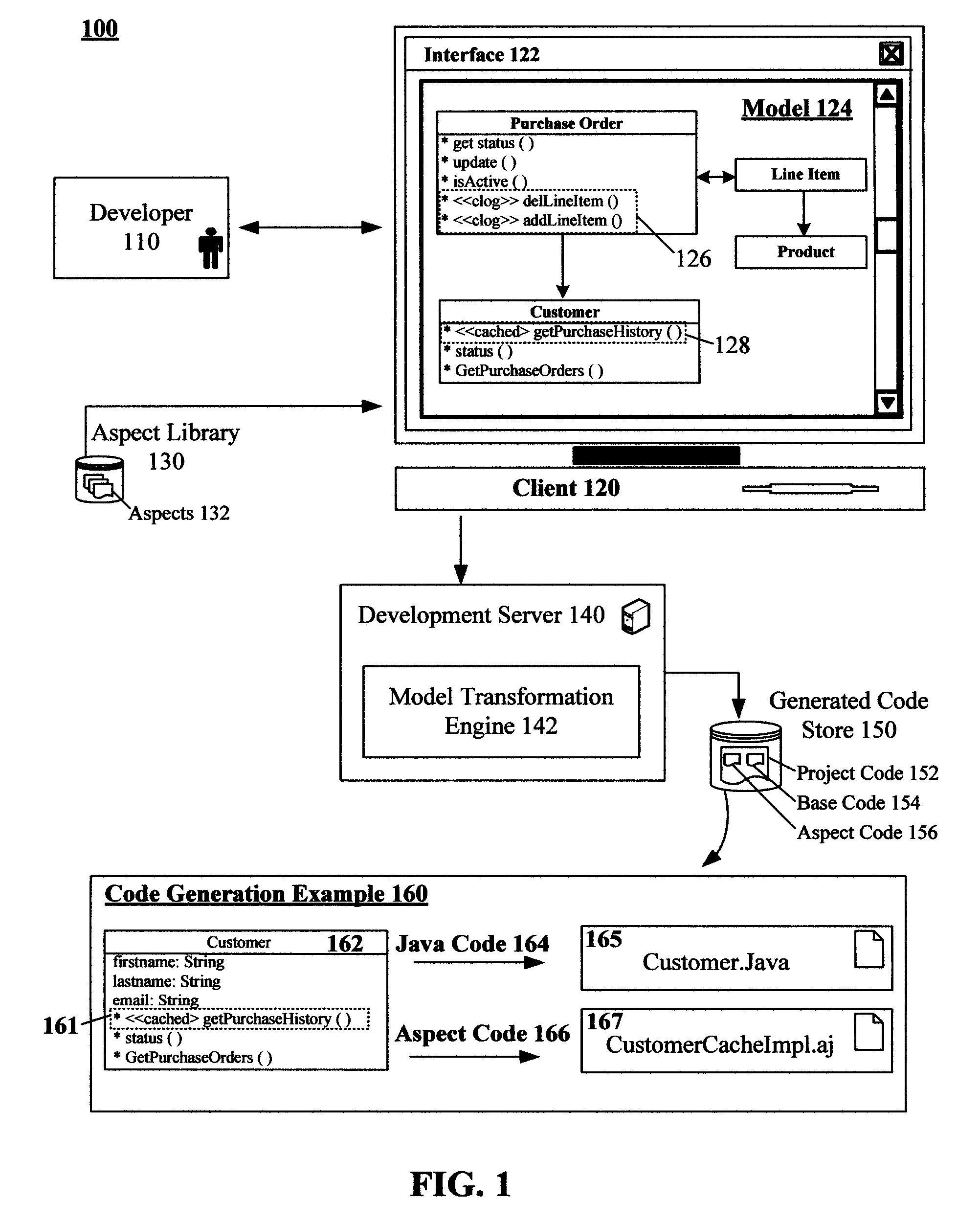

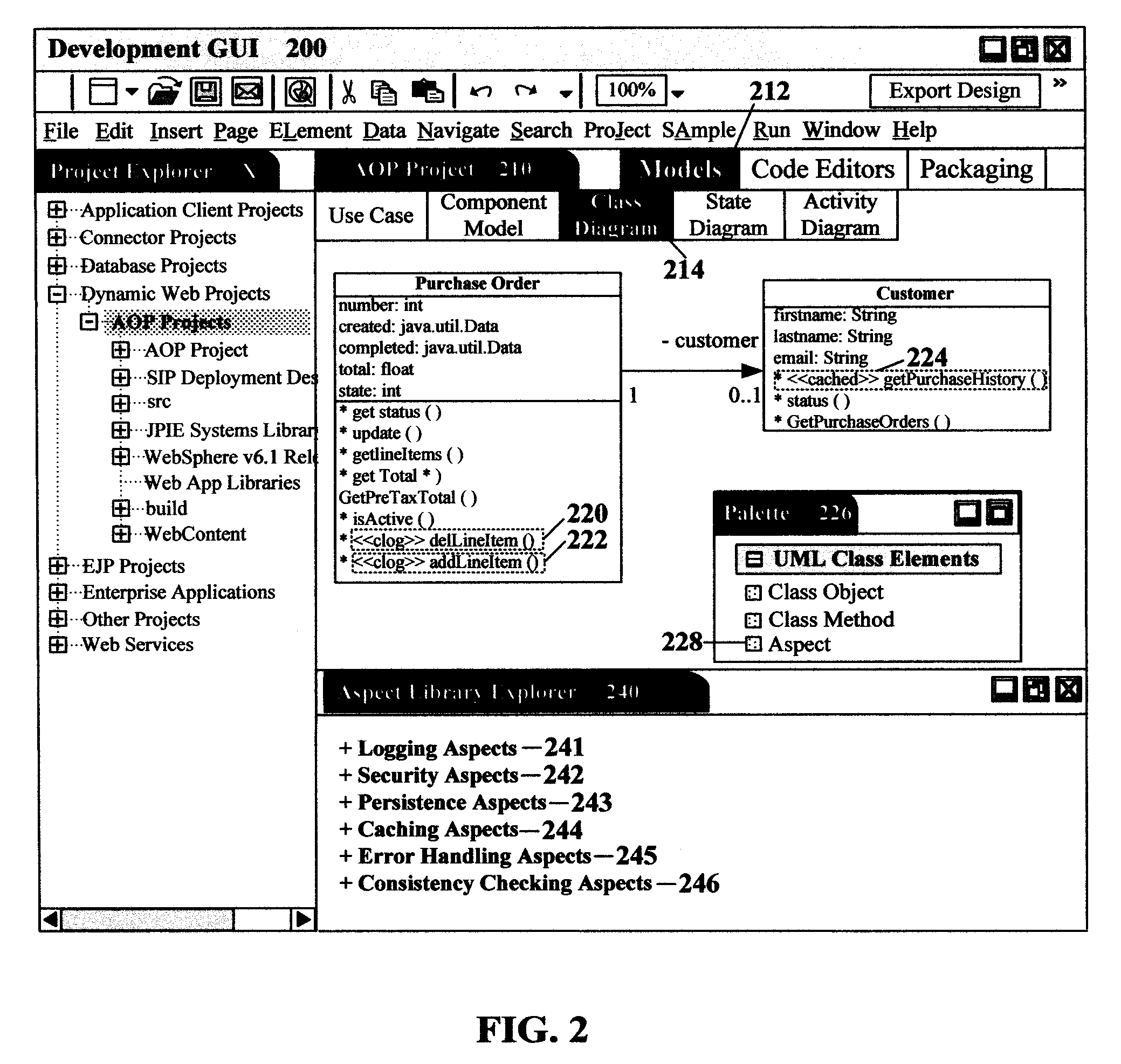

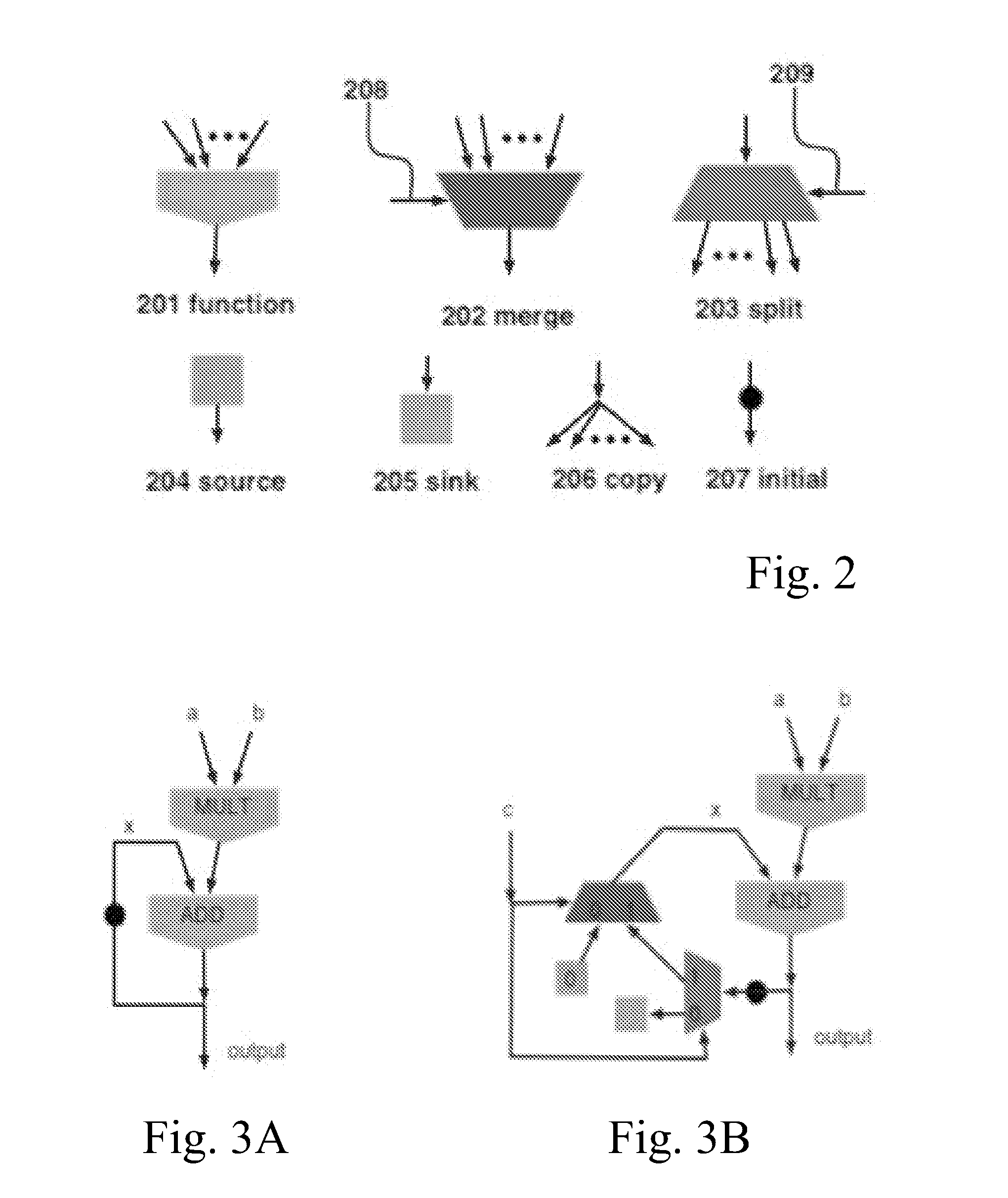

Model driven development including aspect integration tool

InactiveUS8001519B2Model driven codeSpecific program execution arrangementsGraphicsModel driven development

The present invention discloses a software development tool that includes a model development interface, an aspect design tool, and a model transformation engine. The model development interface can permit a developer to graphically design at least one software model. The aspect design tool for the model development interface can be configured to permit a user to specify at least one aspect to be applied to a model of the model development interface. The model transformation engine can transform a model of the model development interface having at least one aspect defined via the aspect design tool into automatically generated aspect code integrated with base language code.

Owner:INT BUSINESS MASCH CORP

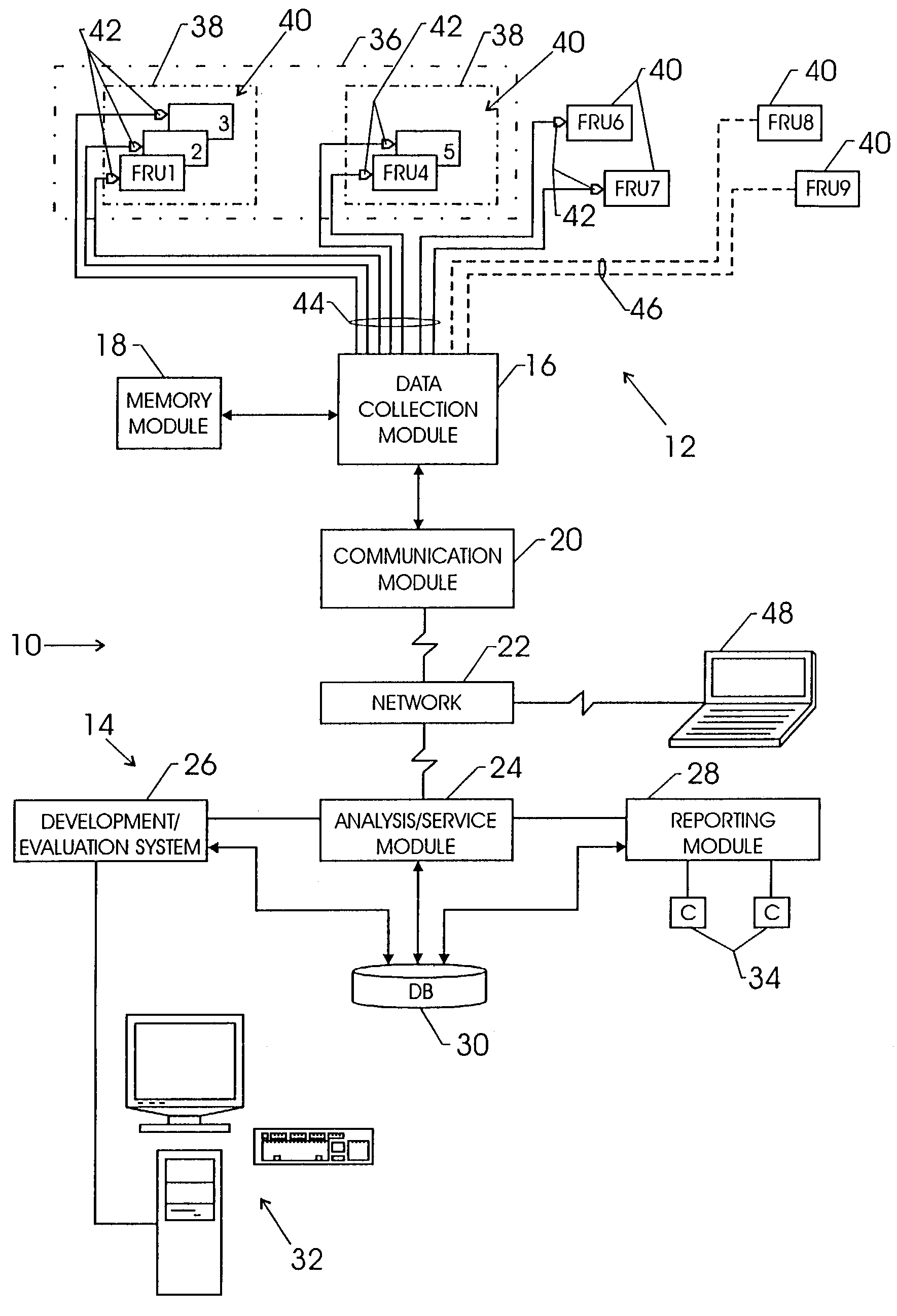

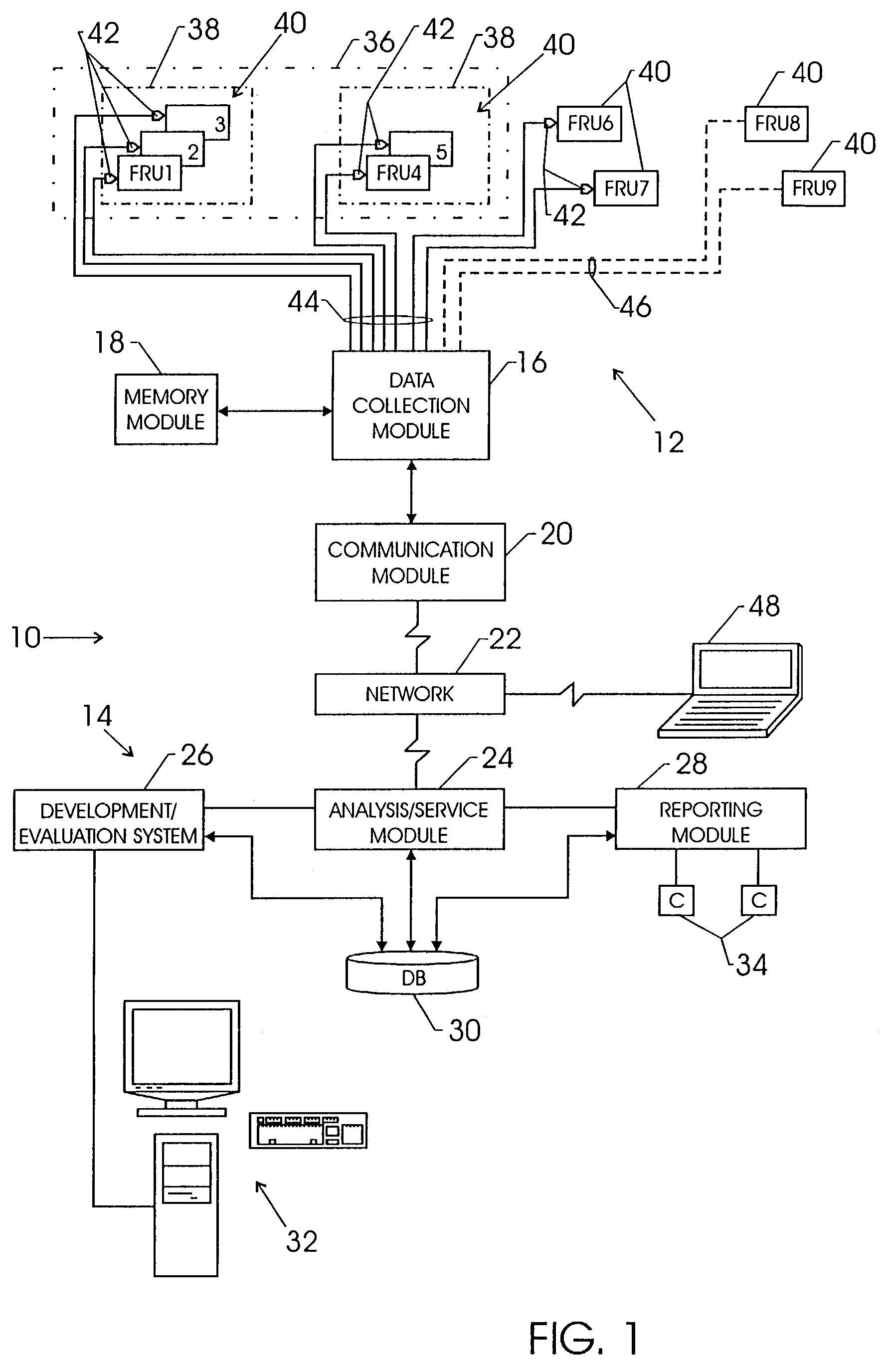

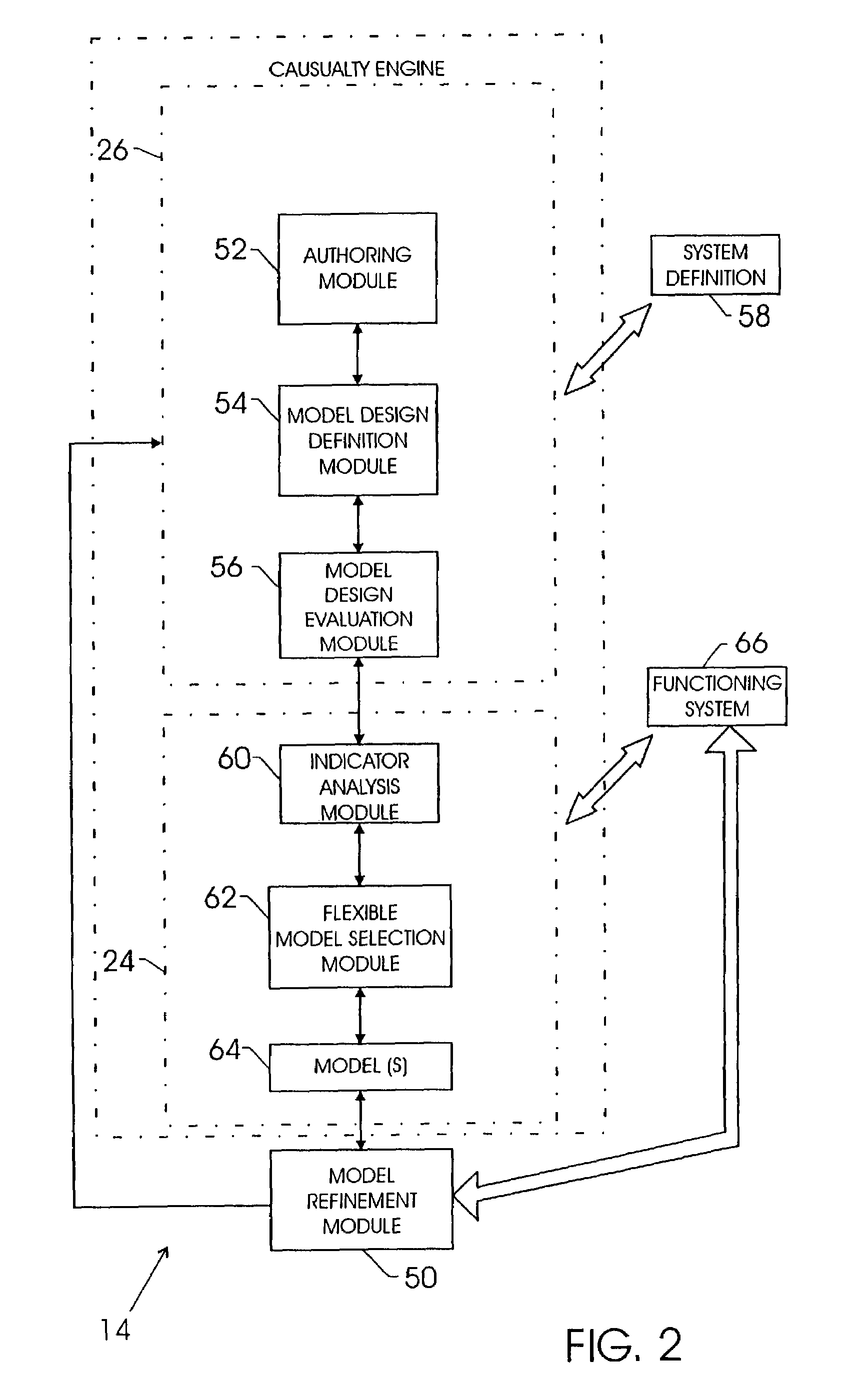

Complex system serviceability design evaluation method and apparatus

InactiveUS7249284B2Facilitate establishingEase of evaluationFault responseRegistering/indicating quality control systemsService modelField replaceable unit

A technique is provided for designing and evaluating service models for components, functions, subsystems and field replaceable units in a complex machine system. At a component or item level, each model identifies various items, failure modes, and so forth which may be the root cause of anticipated serviceable events or faults. The design tools permit numerous interfaces to be used in the design of service models, and in the evaluation of the degree to which the models address detectability and isolation capabilities for the root causes of serviceable events and faults.

Owner:GE MEDICAL SYSTEMS INC

Adding complex instruction extensions defined in a standardized language to a microprocessor design to produce a configurable definition of a target instruction set, and hdl description of circuitry necessary to implement the instruction set, and development and verification tools for the instruction set

InactiveUS6477697B1Fast and reliable developmentGeneral purpose stored program computerCAD network environmentApplication softwareProcessor design

An automated processor design tool uses a description of customized processor instruction set extensions in a standardized language to develop a configurable definition of a target instruction set, a Hardware Description Language description of circuitry necessary to implement the instruction set, and development tools such as a compiler, assembler, debugger and simulator which can be used to develop applications for the processor and to verify it. The standardized language is capable of handling instruction set extensions which modify processor state or use configurable processors. By providing a constrained domain of extensions and optimizations, the process can be automated to a high degree, thereby facilitating fast and reliable development.

Owner:TENSILICA

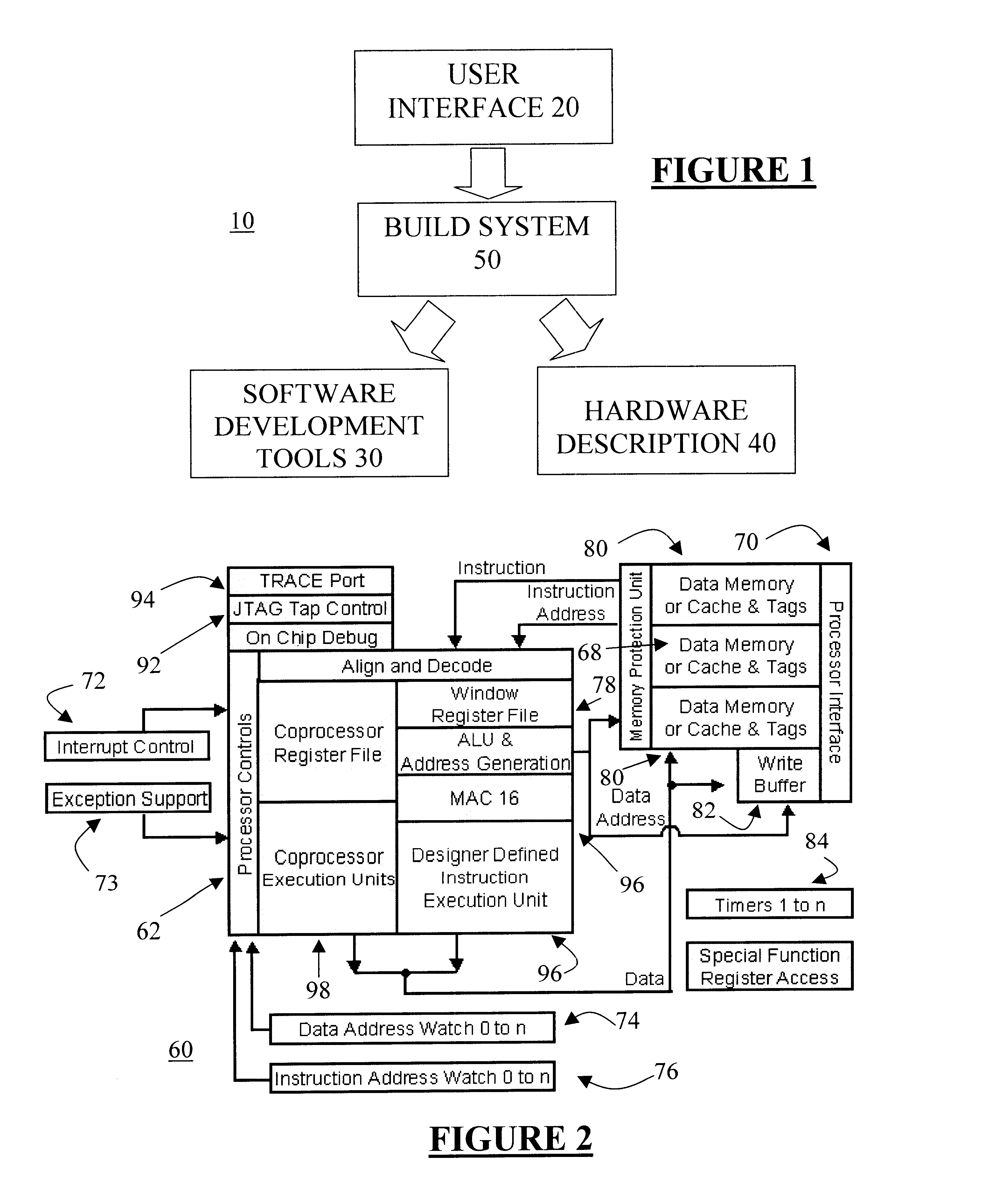

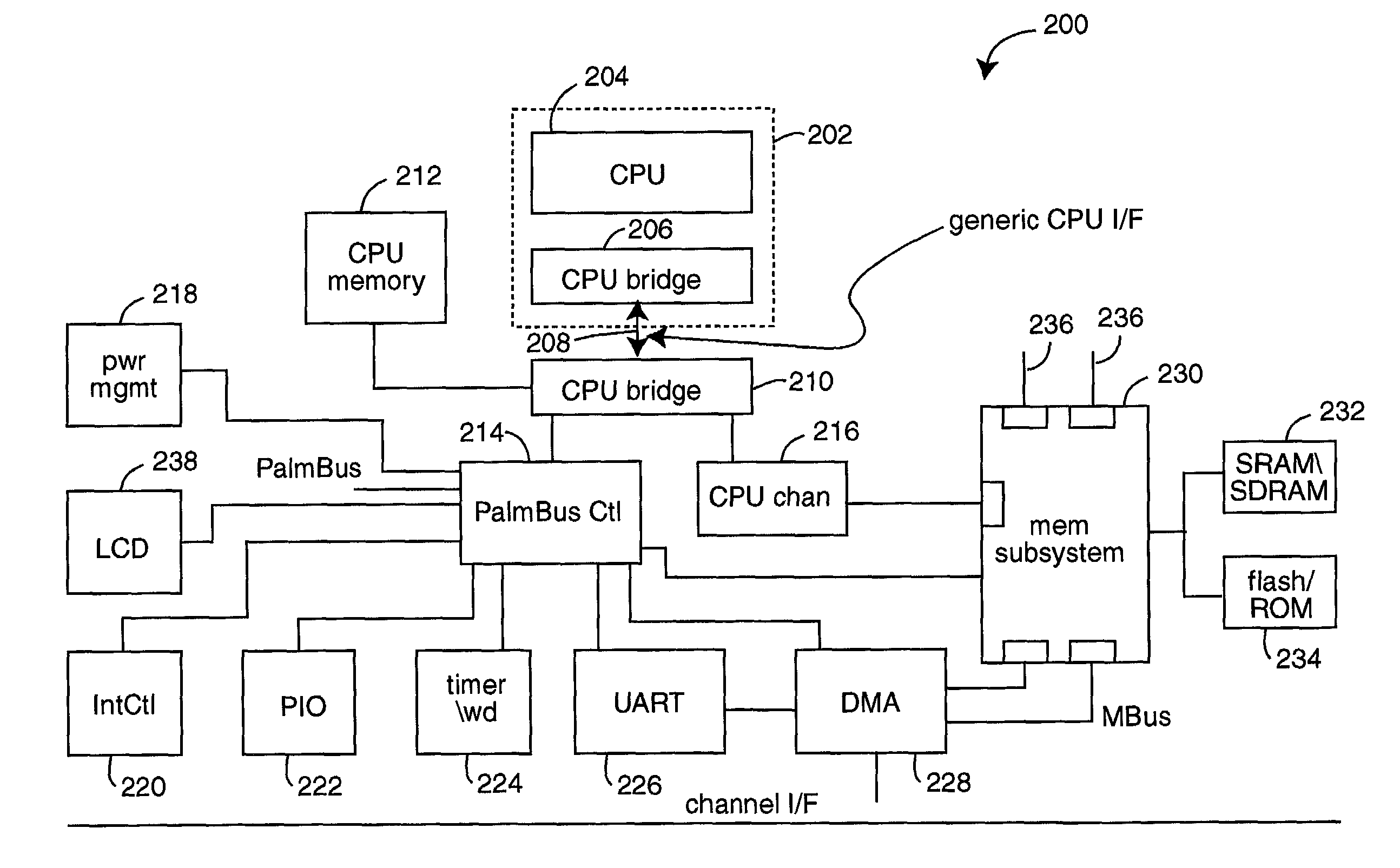

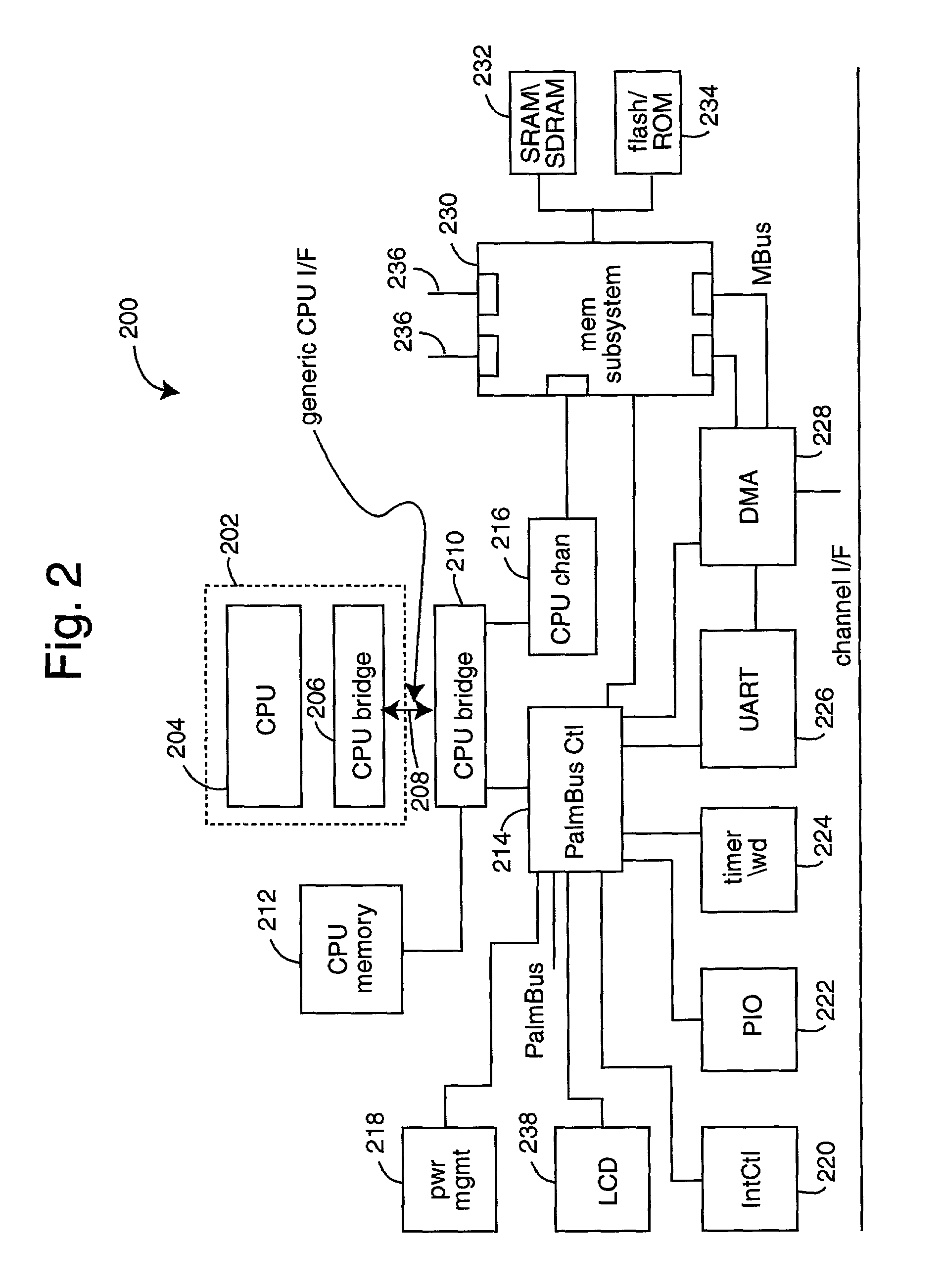

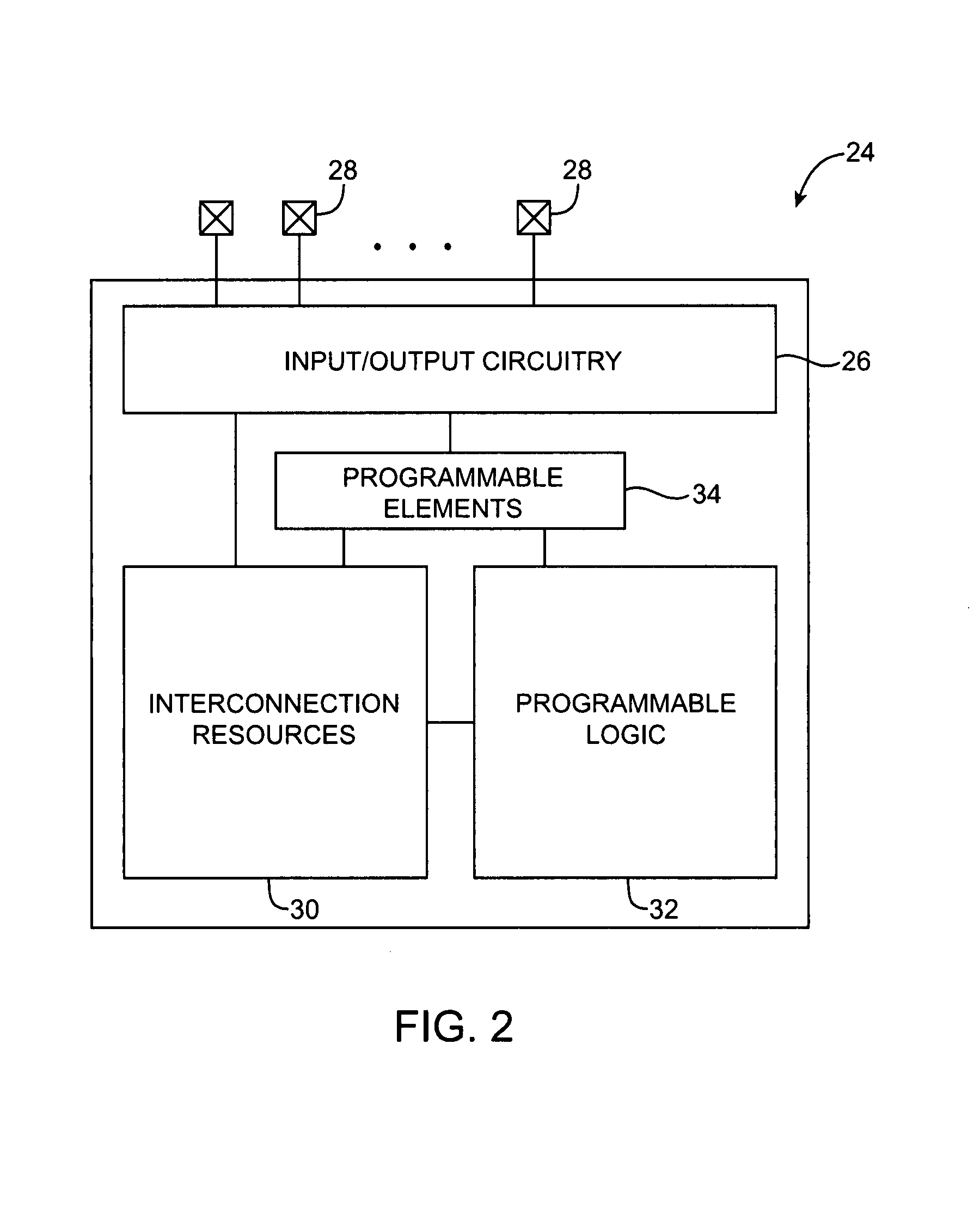

Design tool for systems-on-a-chip

InactiveUS7124376B2Promote rapid developmentReduce a user's time-to-marketCAD circuit designSoftware simulation/interpretation/emulationTest suiteMakefile

A pre-designed system-on-chip architecture and method includes several standard library devices, HDL source code, simulation environment and regression, synthesis scripts, software header files, software libraries, ASIC verification test suites, and makefiles. The standard library devices comprise an integrated CPU, a shared memory controller, a peripheral controller, system peripherals, a DMA controller, embedded memory, and general system control. CPU bridges are used to accommodate a variety of processor types and to insulate users from the complexities of interfacing to different kinds of processors. Such CPU bridges further allow the latest processors to be rapidly integrated into existing integration platforms and designs.

Owner:NETVINCI

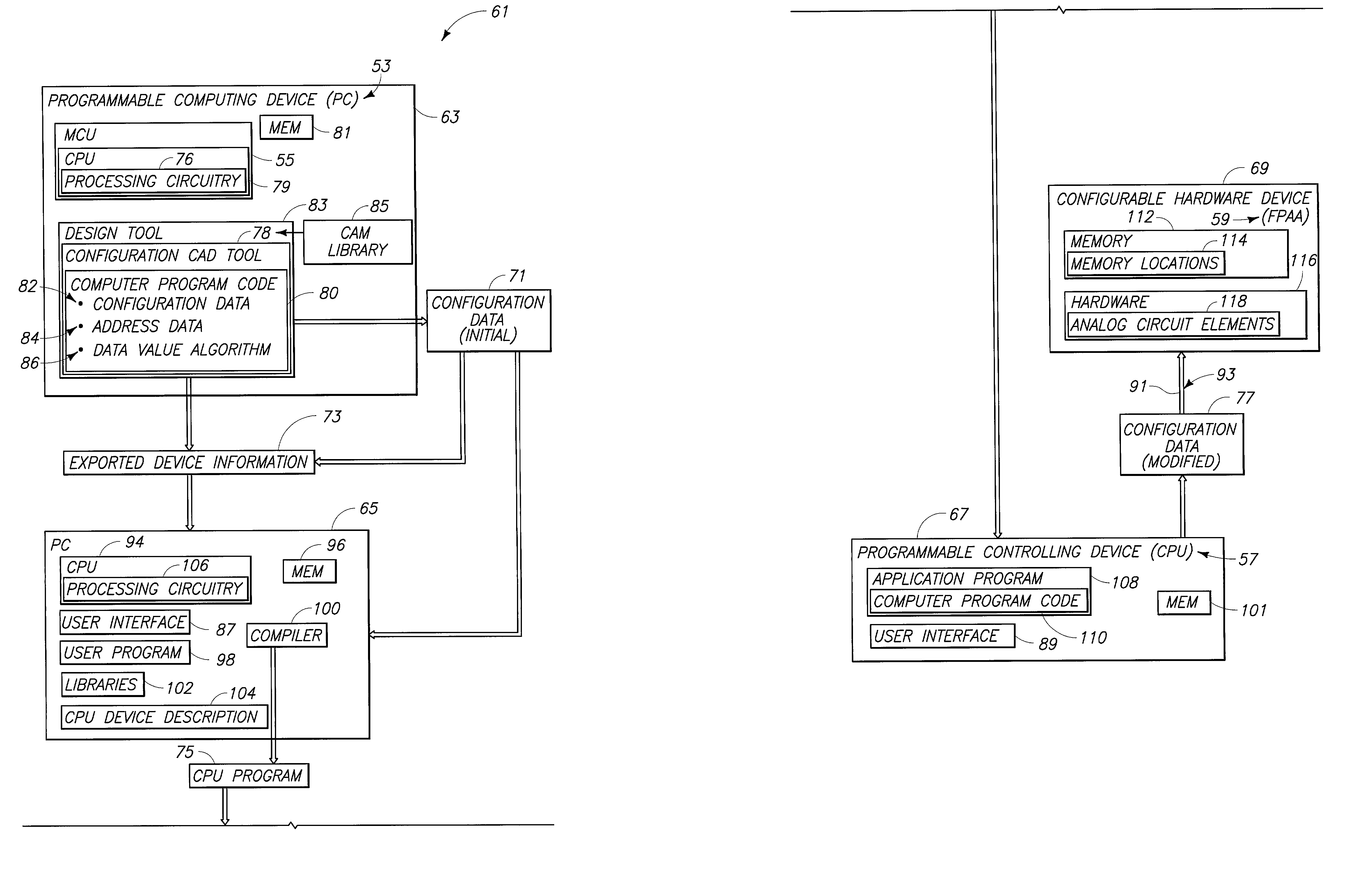

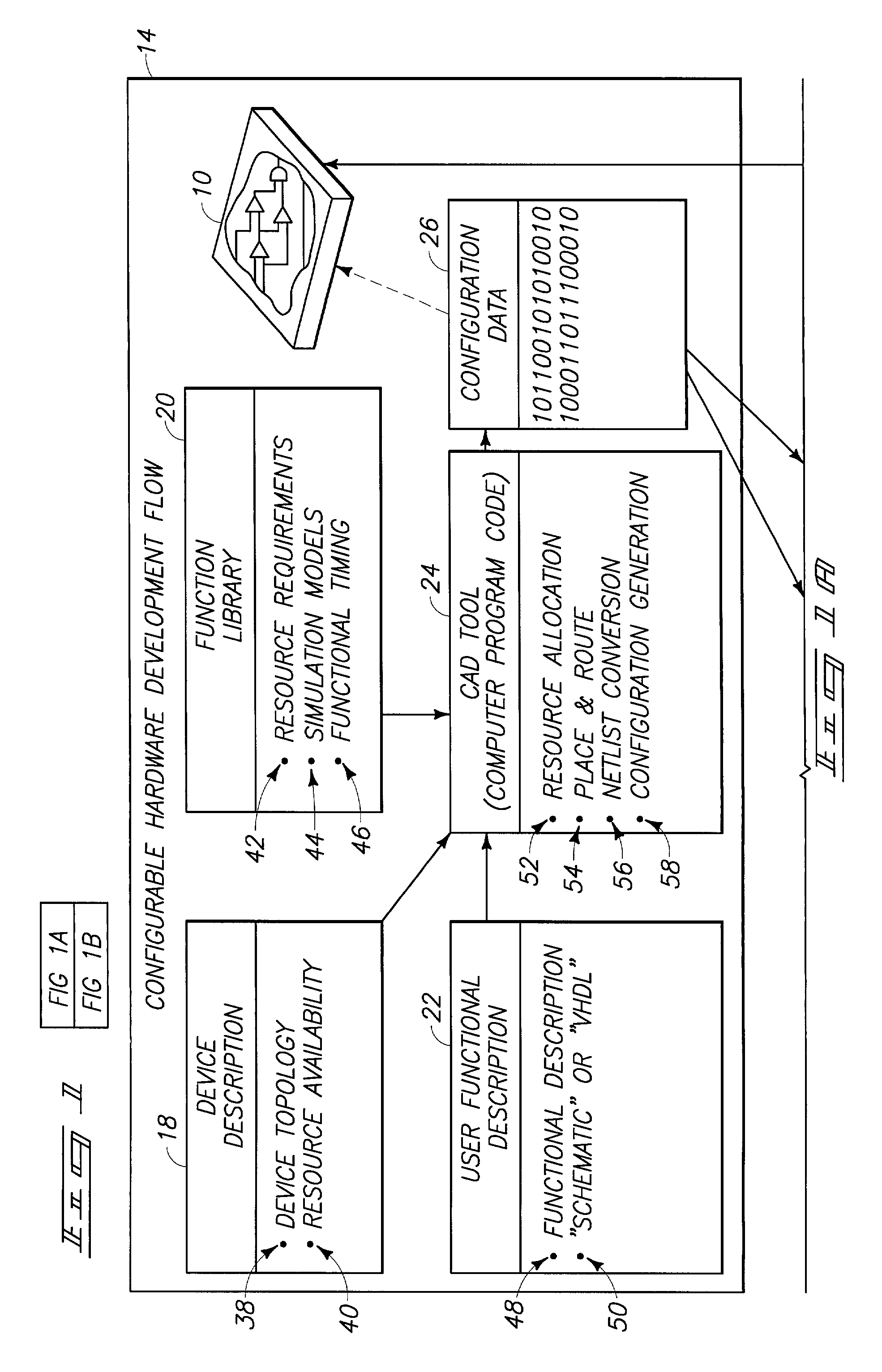

System and method for configuring analog elements in a configurable hardware device

InactiveUS7024654B2CAD circuit designSpecial data processing applicationsComputer hardwareCode generation

A system is provided for programming a configurable semiconductor device. The system includes a programmable controlling device, a programmable computing device, a communication link, a configurable hardware device, a design tool with first computer program code, and second computer program code. The configurable hardware device has memory with a plurality of memory locations and coupled with the programmable controlling device via the communication link. The design tool includes first computer program code embodied in a programmable computing device. The second computer program code is generated at least in part by the first computer program code and is embodied in the programmable controlling device for: a) applying configuration data to selected memory locations within the configurable hardware device to configure the configurable hardware device; b) determining a location of a subset of at least one of (i) the programmable memory locations in the configurable hardware device and (ii) the configuration data to be modified; and c) determining a new data value to be applied to the subset of at least one of (i) the memory locations in the configurable hardware device and (ii) the configuration data. The design tool provides at least one of configuration data, address data, and a data value algorithm usable in performing at least one of a), b), and c). A method is also provided.

Owner:F POSZAT HU

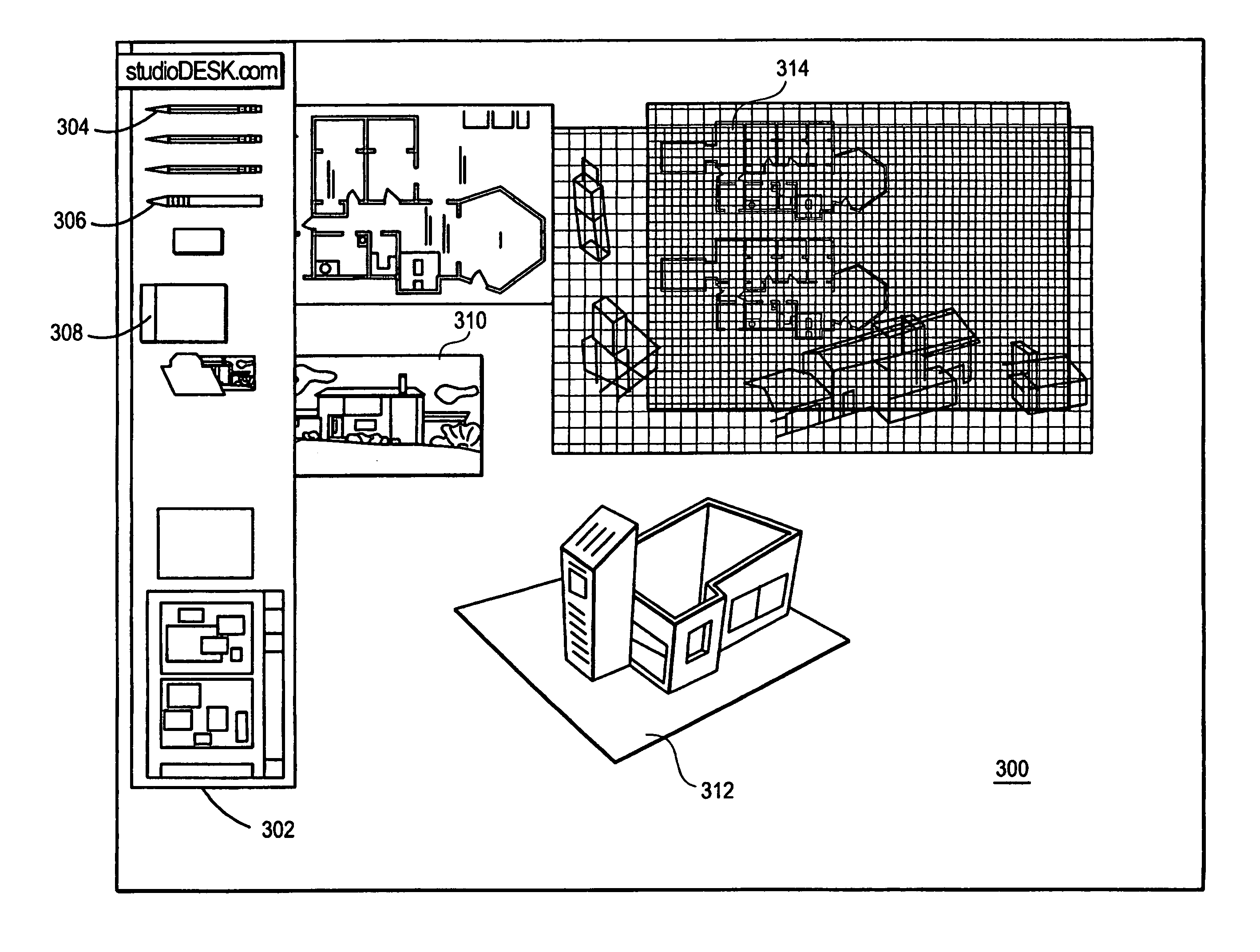

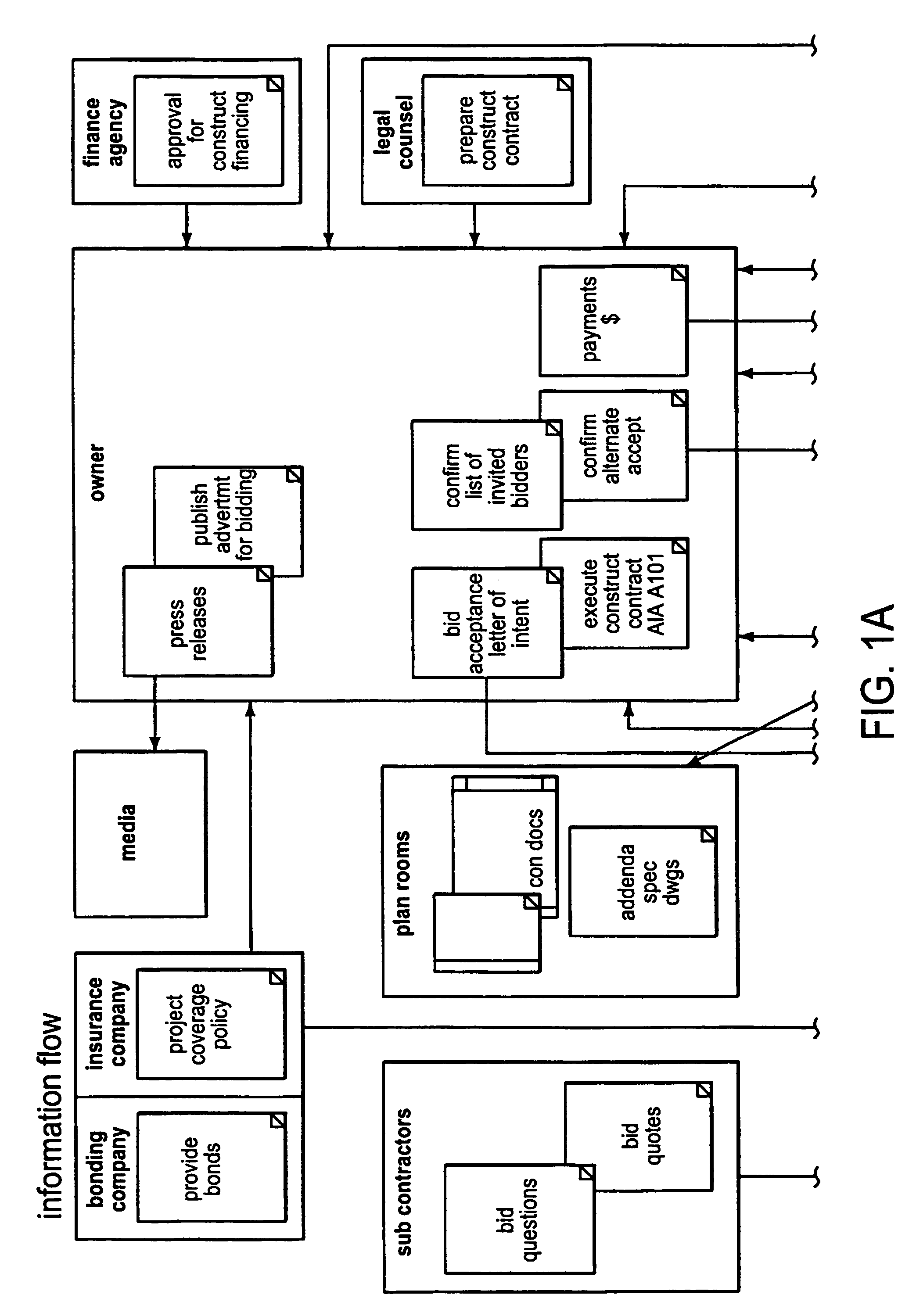

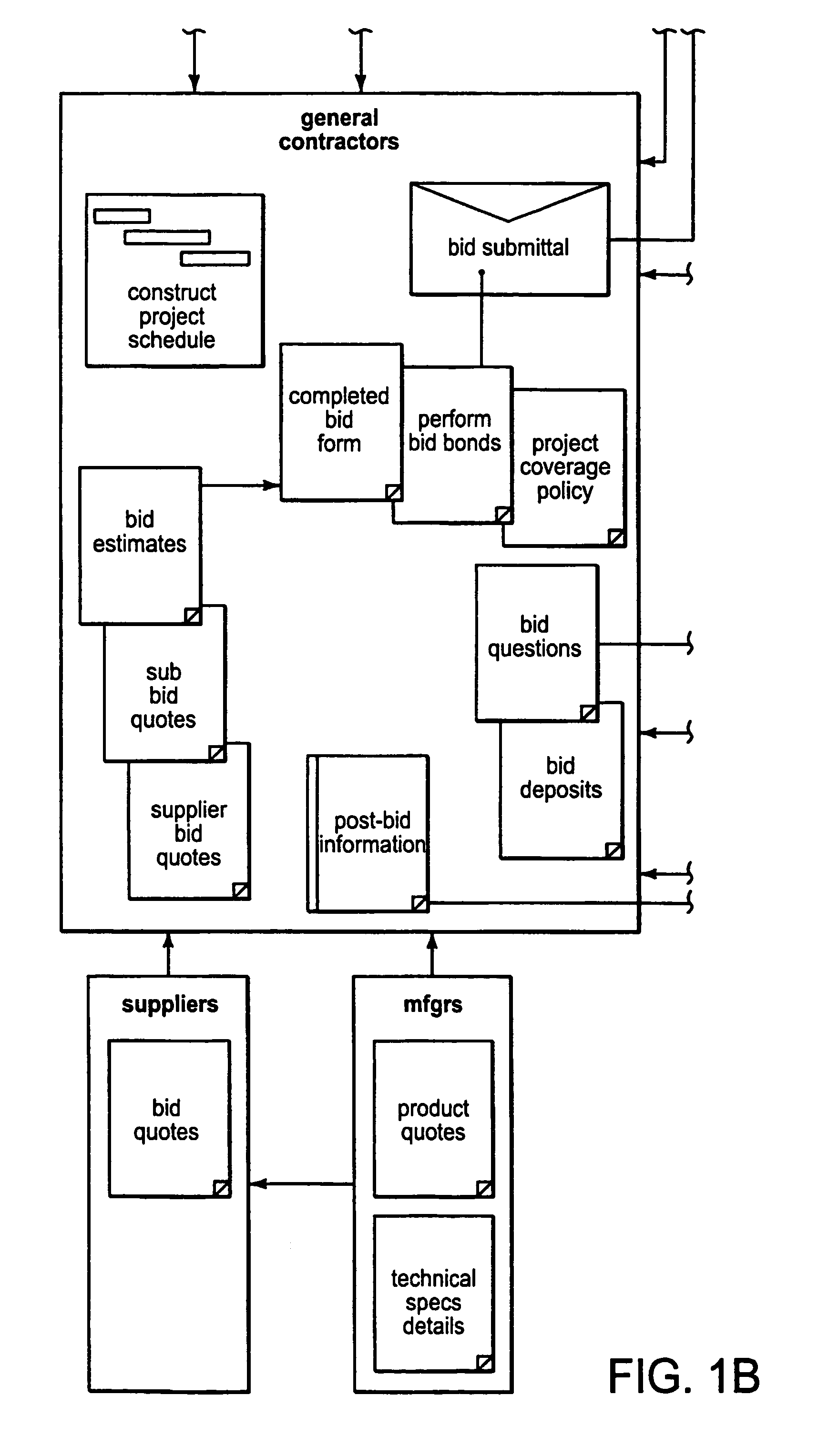

Method and apparatus for providing access to and working with architectural drawings on the internet

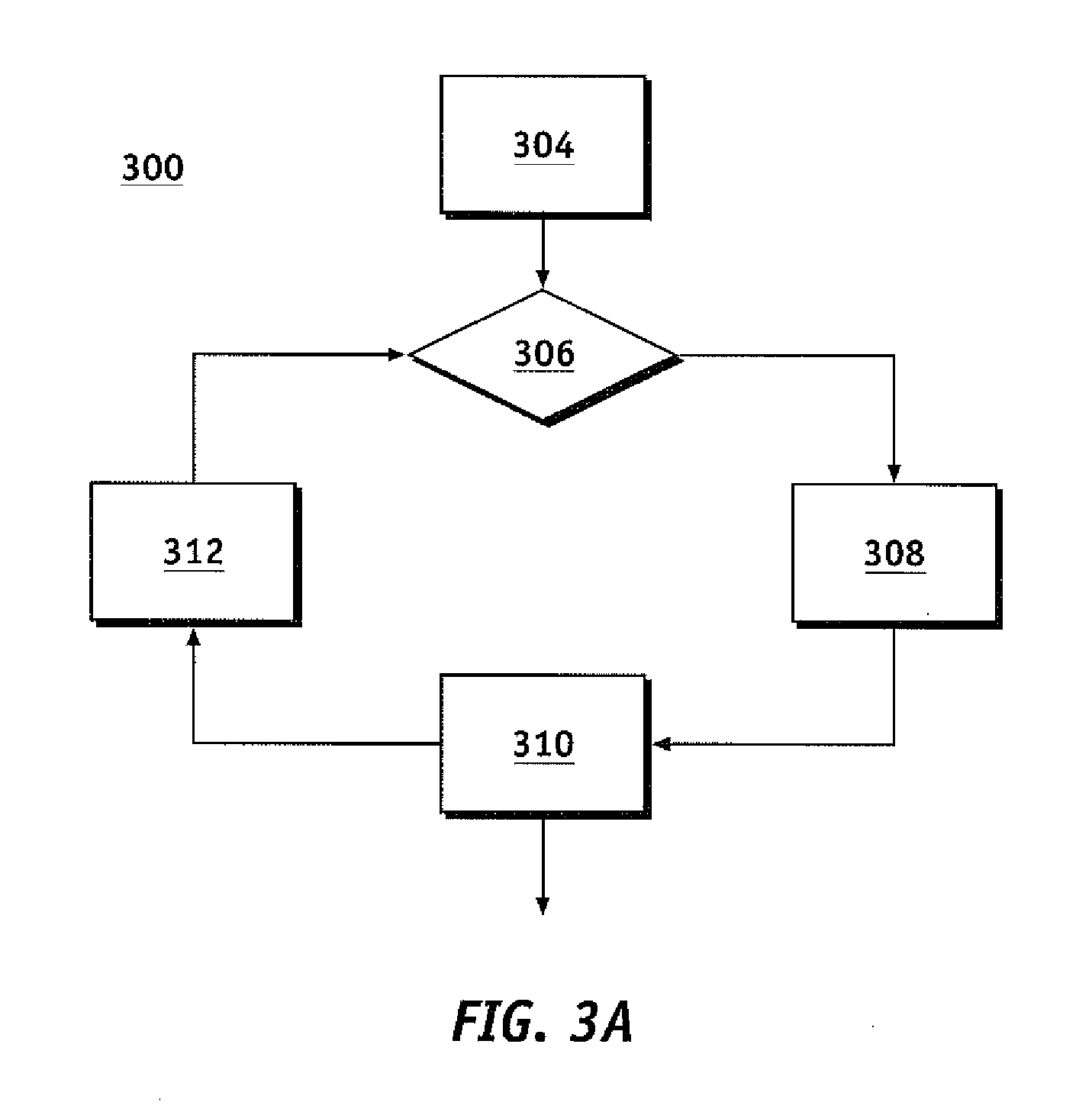

An Internet-based design environment, implemented on a web server, for use by building, design, architectural, engineering, and construction personnel, wherein the design environment provides a graphical user interface having a virtual desktop (300) that resembles an architect's desk, wherein the virtual desktop provides a virtual workspace for storing design documents and a set of basic virtual design tools (304, 306) for use in sketching, drawing, modeling, creating, and editing the stored design documents in the virtual workspace. The design documents may comprise different media types (314) and are persistently maintained on the web server. The virtual design tools comprise graphical icons that resemble physical objects with similar virtual functionality to the resembled physical objects and may be moved around the virtual workspace. The design environment supports multi-modal input, side-by-side layout of the stored documents, access permissions for users of the design environment, and the ability to interact with applications on the virtual desktop.

Owner:AUTODESK INC

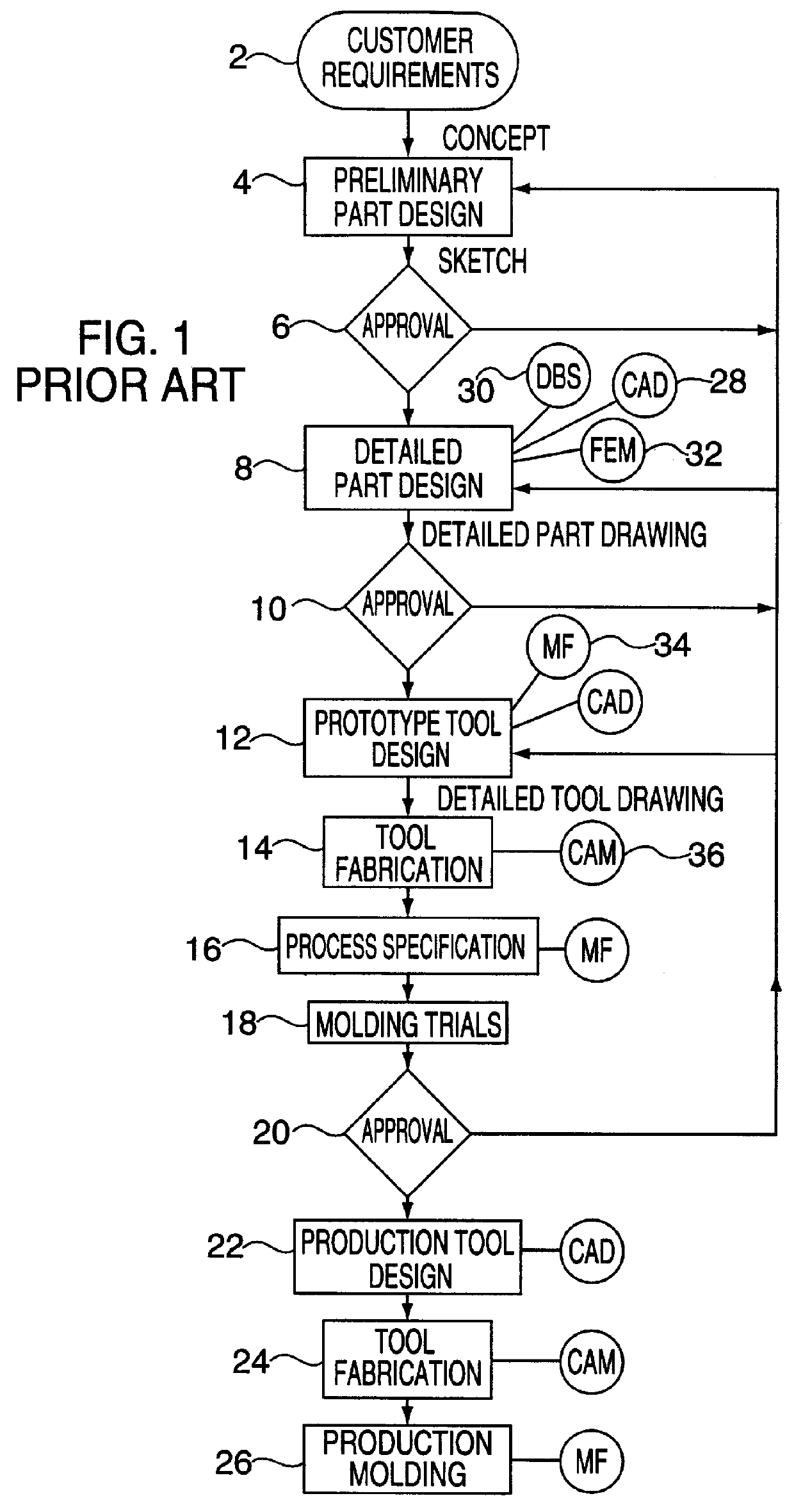

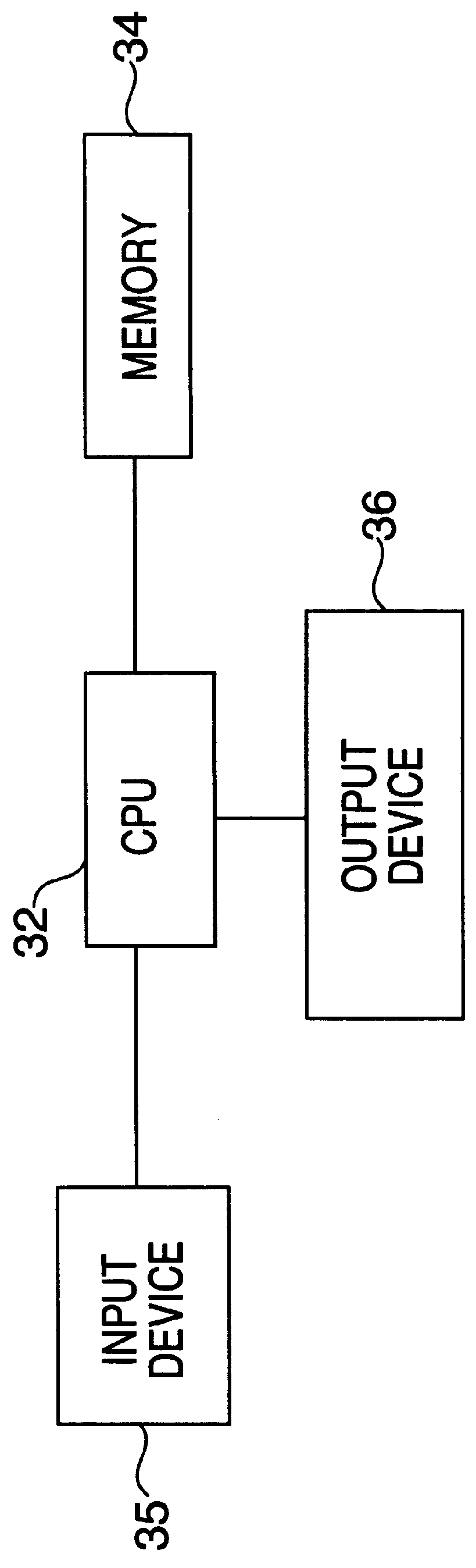

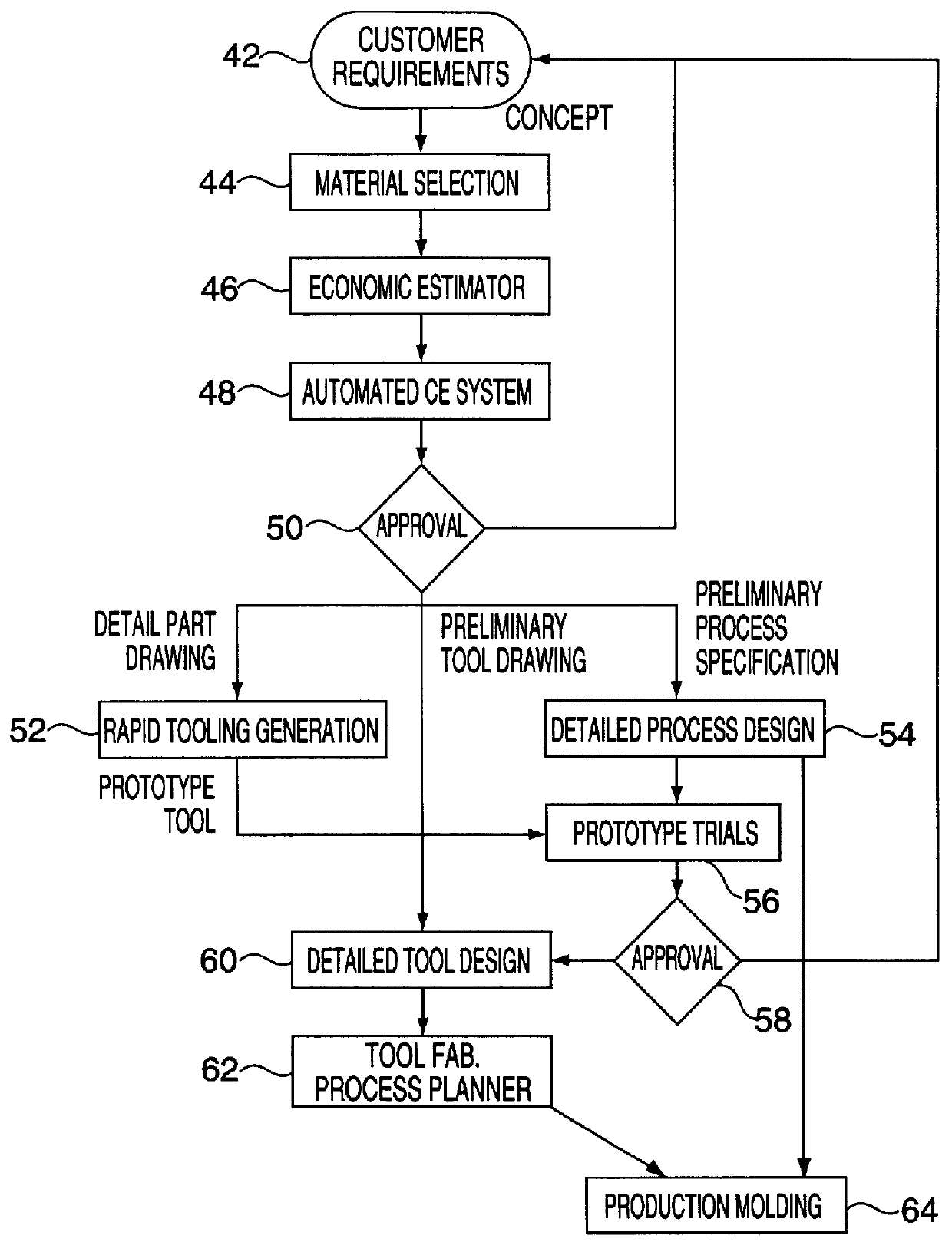

Concurrent engineering design tool and method

InactiveUSRE36602E1Shorten the time to marketGood choiceProgramme controlComputer controlProgramming languageConcurrent engineering

A computer-based engineering design system to design a part, a tool to make the part, and the process to make the part. The design system has a processor and a memory. The memory stores feature templates, each feature template being a representation of a primitive object having a form and a function. Each feature template is indexed by the function of the primitive object and includes a representation of a primitive geometric entity having the form of the primitive object. Each feature template can include information relating to a tool to make the primitive object and a process to make the primitive object. The design system also includes an input device for receiving a request to design the part. This request includes one or more predetermined functions that the part performs. A core design module, executable by the processor, designs the part, the tool to make the part and process to make the part by accessing the plurality of feature templates in the memory to locate one or more primitive objects that perform the one or more predetermined functions.

Owner:STEVENS INSTITUTE OF TECHNOLOGY

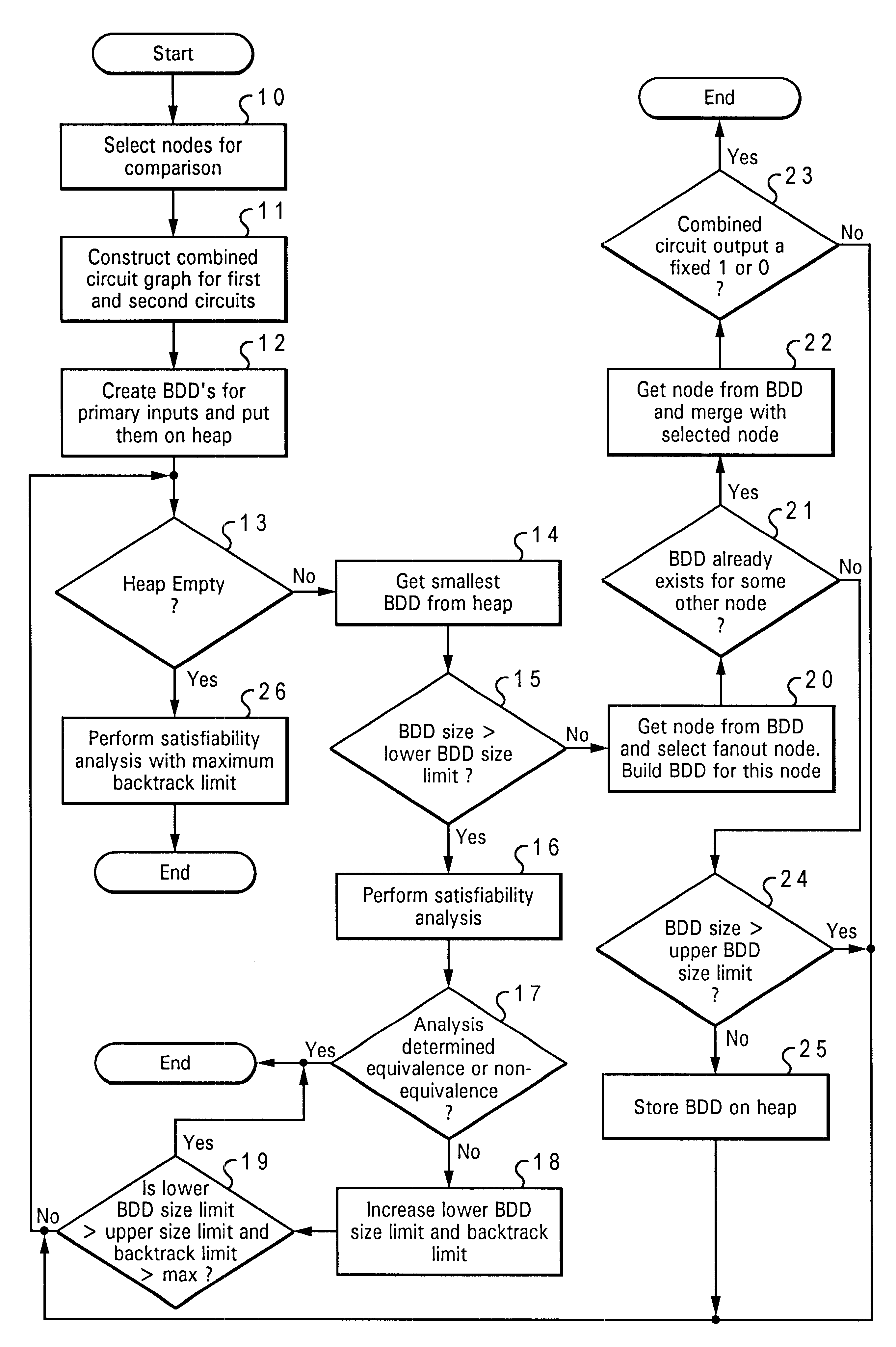

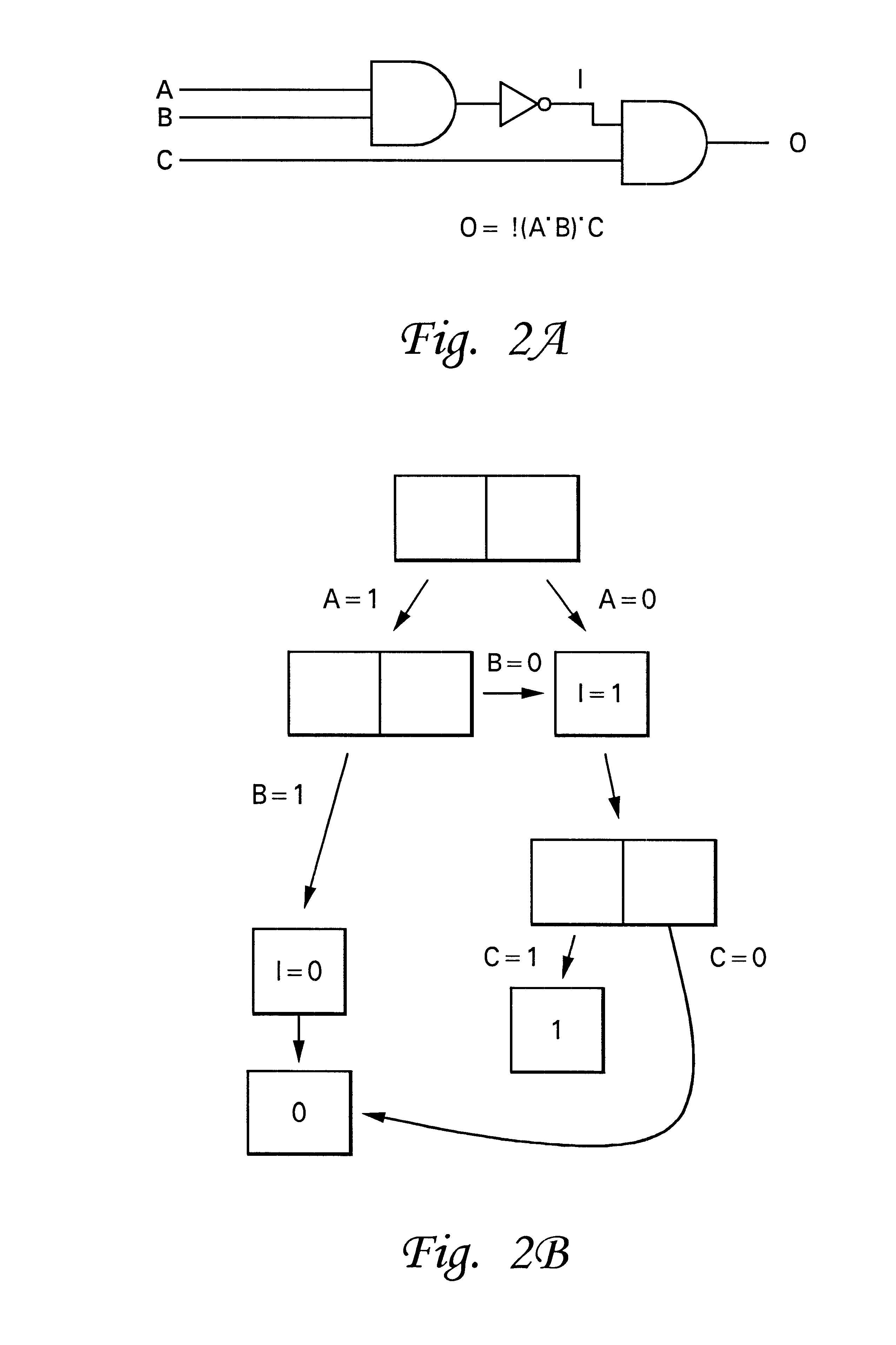

Method and system for equivalence-checking combinatorial circuits using interative binary-decision-diagram sweeping and structural satisfiability analysis

InactiveUS6473884B1Computer aided designSoftware simulation/interpretation/emulationBinary decision diagramLogical network

A method and system for equivalence checking of logical circuits using iterative circuit reduction and satisfiability techniques provide improved performance in computer-based verification and design tools. By intertwining a structural satisfiability solver and binary decision diagram functional circuit reduction method, computer-based tools can make more efficient use of memory and decrease computation time required to equivalence check large logical networks. Using the circuit reduction technique back-to-back with the simulation technique, optimum local and global circuit reduction are simultaneously achieved. By iterating between the structural and functional techniques, and adjusting the size of sub-networks being analyzed within a larger network, sub-networks can be reduced or eliminated, decreasing the amount of memory required to represent the next larger inclusive network.

Owner:IBM CORP

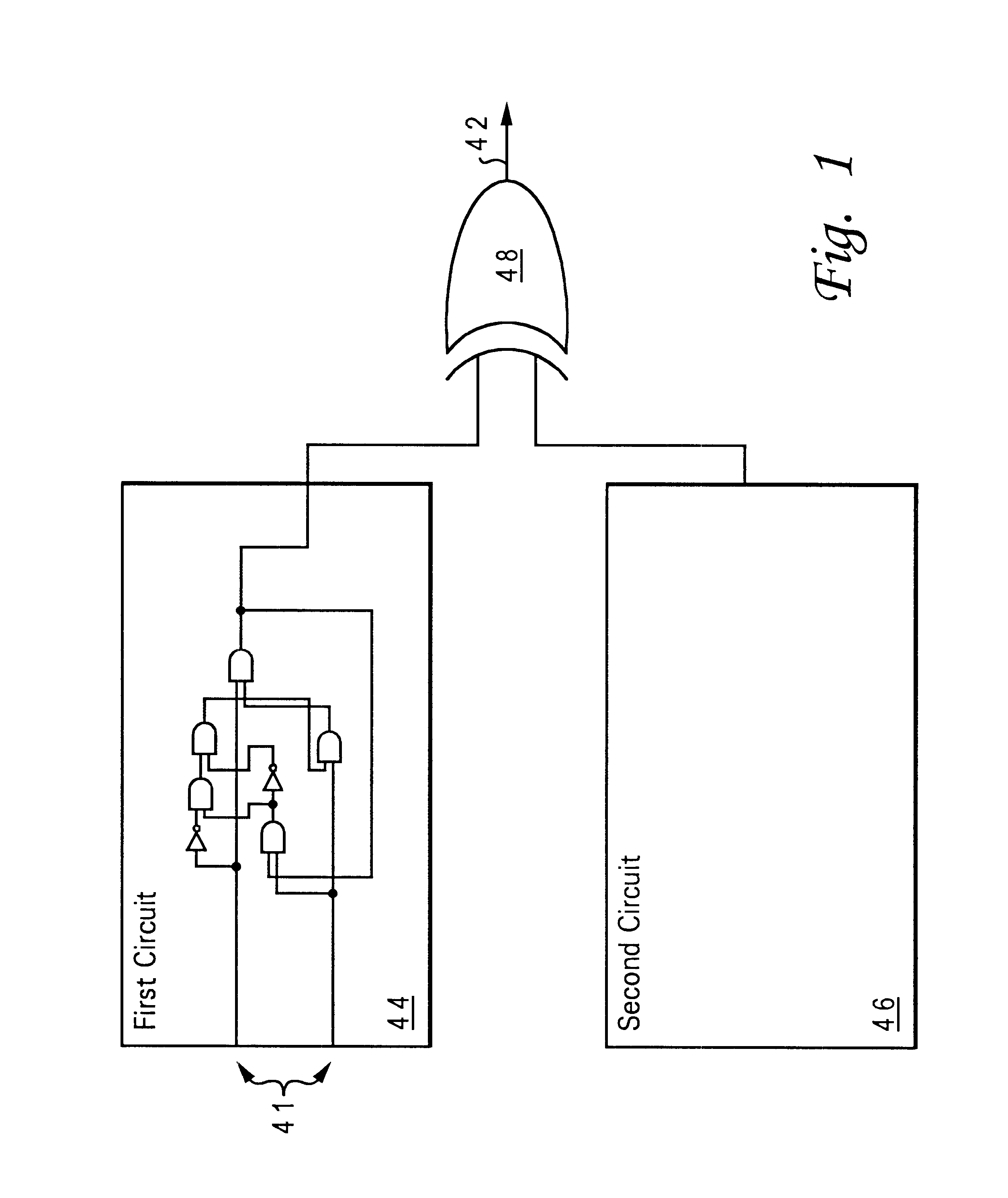

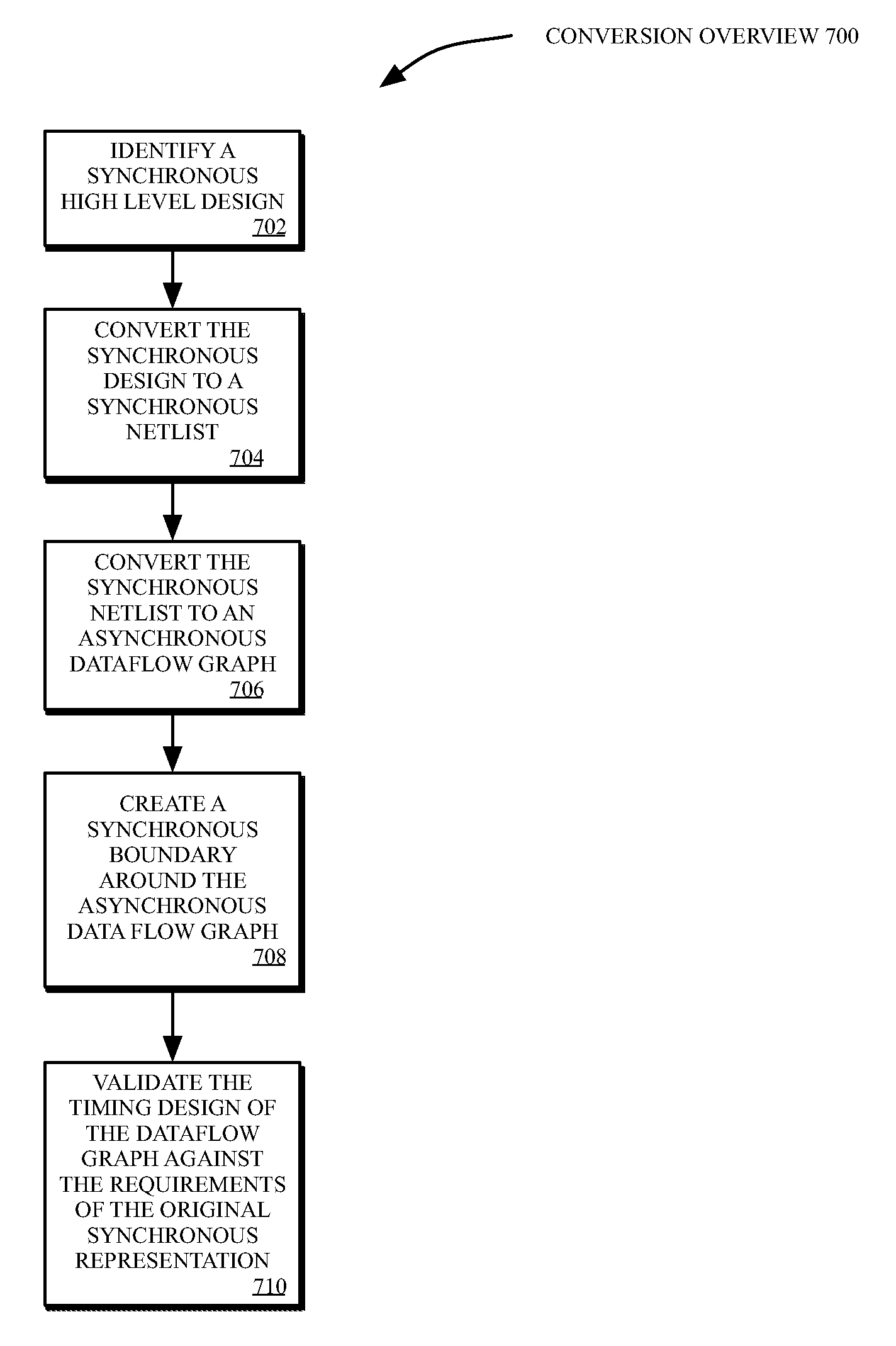

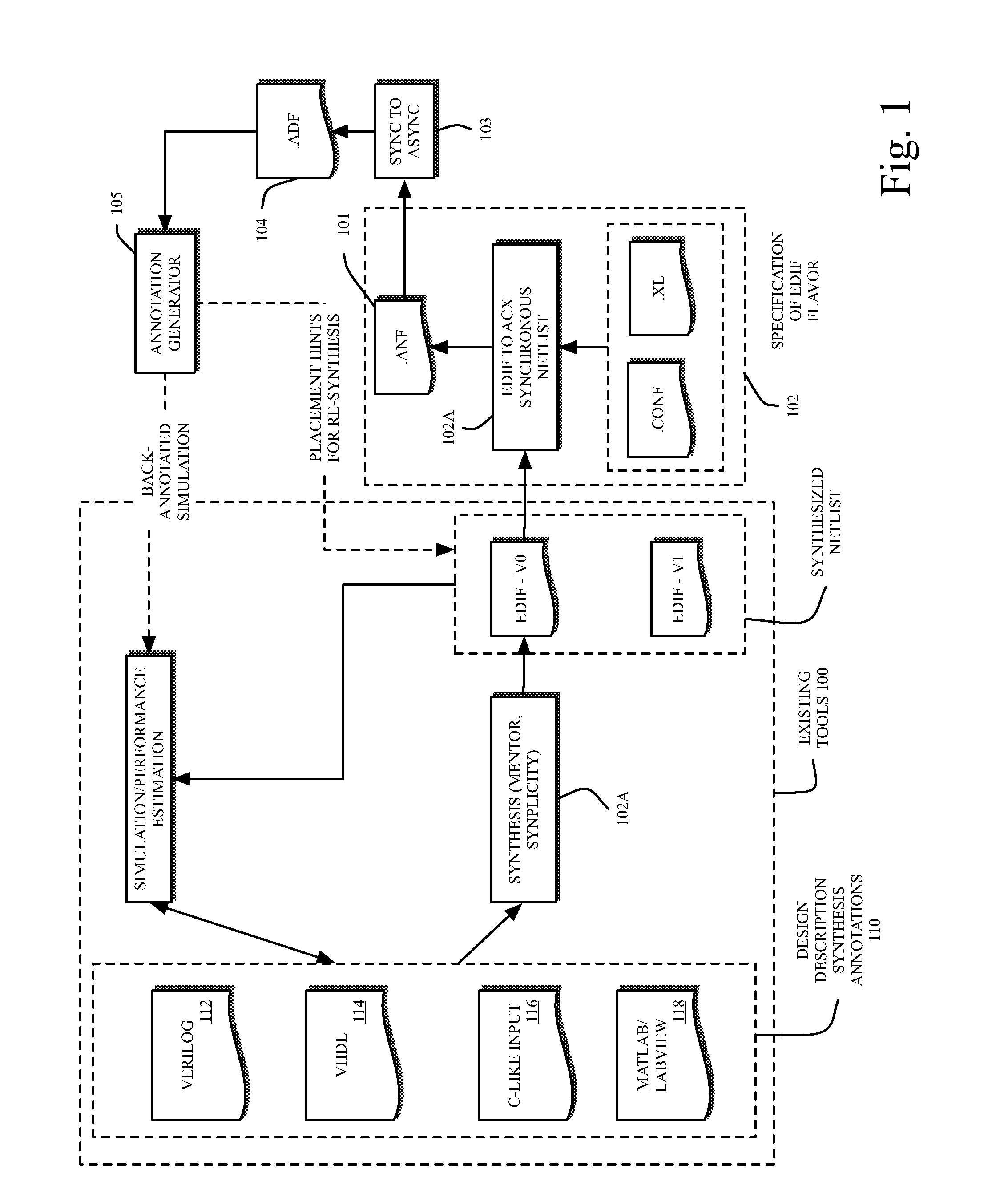

Systems and methods for performing automated conversion of representations of synchronous circuit designs to and from representations of asynchronous circuit designs

ActiveUS20070256038A1Easy to FeedbackCAD circuit designSoftware simulation/interpretation/emulationComputer architectureAsynchronous circuit design

Methods and systems automate an approach to provide a way to convert a circuit design from a synchronous representation to an asynchronous representation without any designer or user interaction or redesign of the synchronous circuit. An optimized, automated, non-Interactive conversion of representations of synchronous circuit designs to and from representations of asynchronous circuit designs, facilitating traditional electronic design automation (EDA) tools to process and manipulate asynchronous designs while allowing synchronous designs to be implemented using asynchronous hardware solutions. The invention also facilitates feedback to synchronous design tools in synchronous representation for optimization and iteration of the design process by engineers, eliminating the need for engineers to be aware of the underlying asynchronous architecture of the underlying hardware implementation.

Owner:ACHRONIX SEMICON CORP

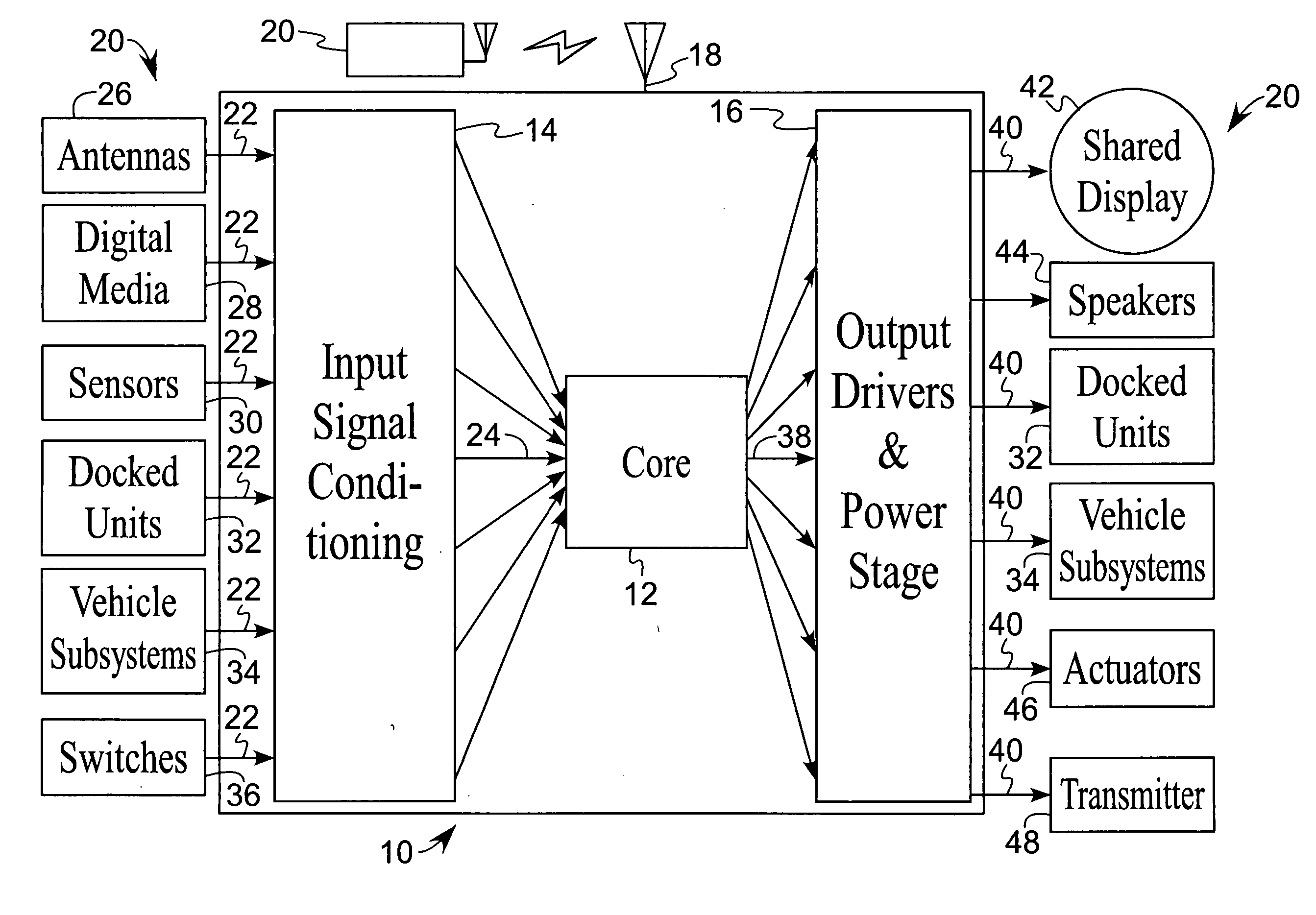

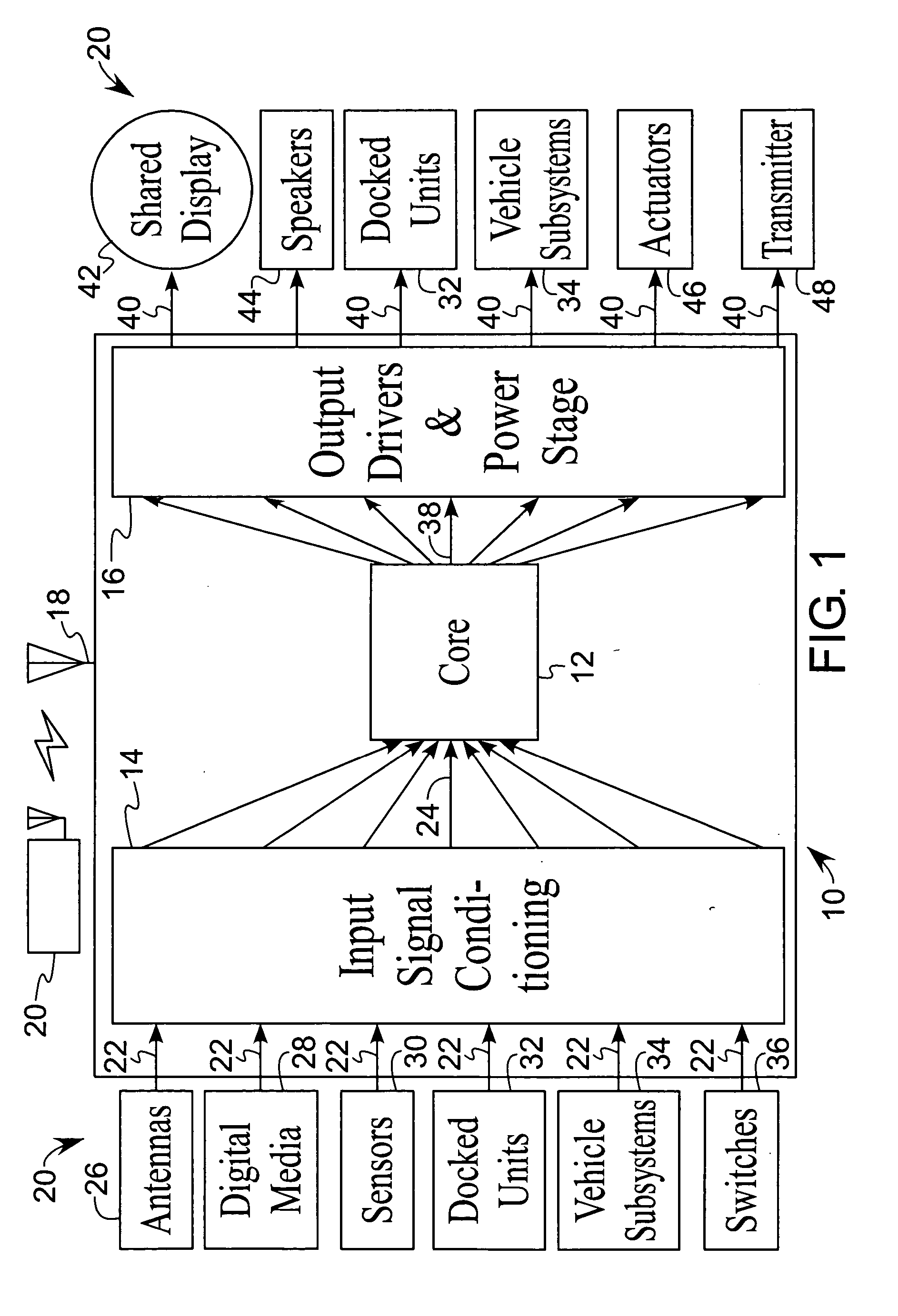

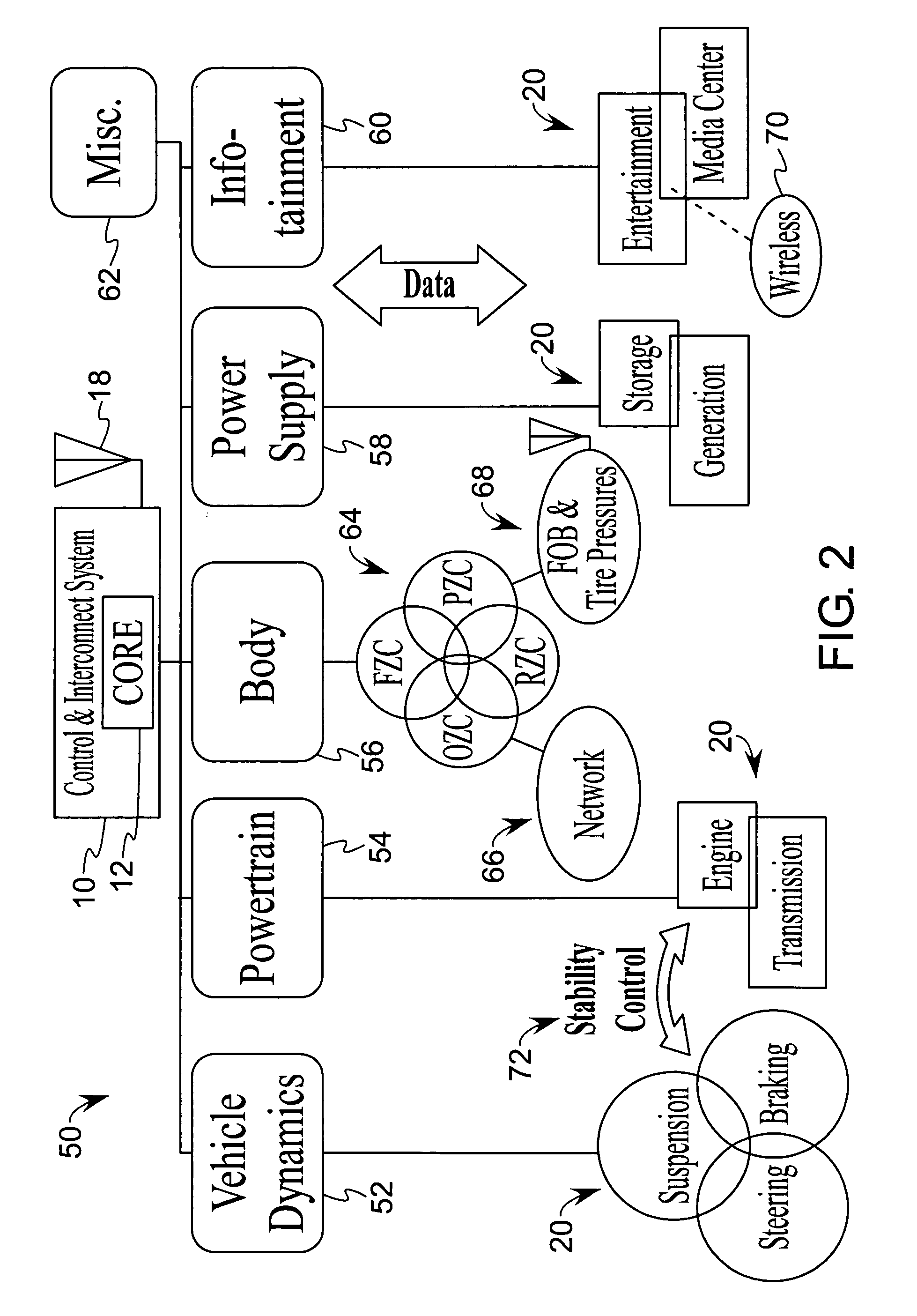

Systems and methods for implementing a vehicle control and interconnection system

ActiveUS20070073944A1Electric/fluid circuitInput/output processes for data processingInformation processingControl system

A method of developing peripherals for integration with a vehicle control system comprises providing a vehicle control and interconnection system that includes a system core for processing data, an input module and an output module. The system core includes a reconfigurable space having reconfigurable hardware, memory and a supervising processor that is customized to the order. The supervising processor is configured to provide control information to identified peripherals and control the allocation and configuration of the reconfigurable space into a plurality of independent information processing workspaces. The associated information processing workspace for the peripherals is configured if required, a verifying operation of the peripherals with the control and interconnection system is performed and the peripherals are authorized as approved peripherals. To integrate the peripherals into the system, design tools assist the developer in configuring an associated information processing workspace, setting up operating conditions or performing other integration tasks.

Owner:JOSEPH GORMLEY AS TRUSTEE UNDER THE JOSEPH GORMLEY TRUST DATED AUGUST 16 2010

System and method for automated real-time design checking

Owner:CADENCE DESIGN SYST INC

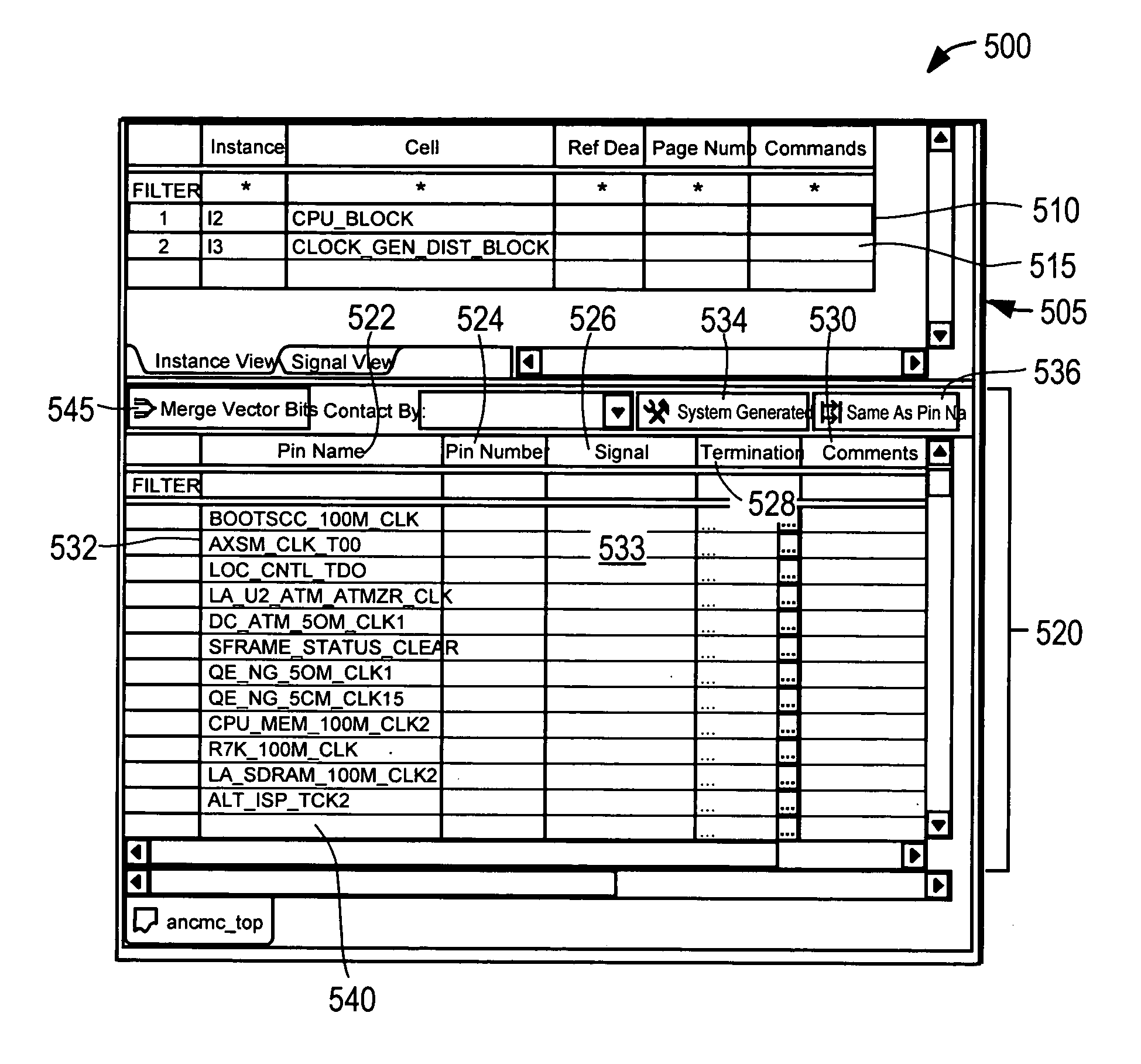

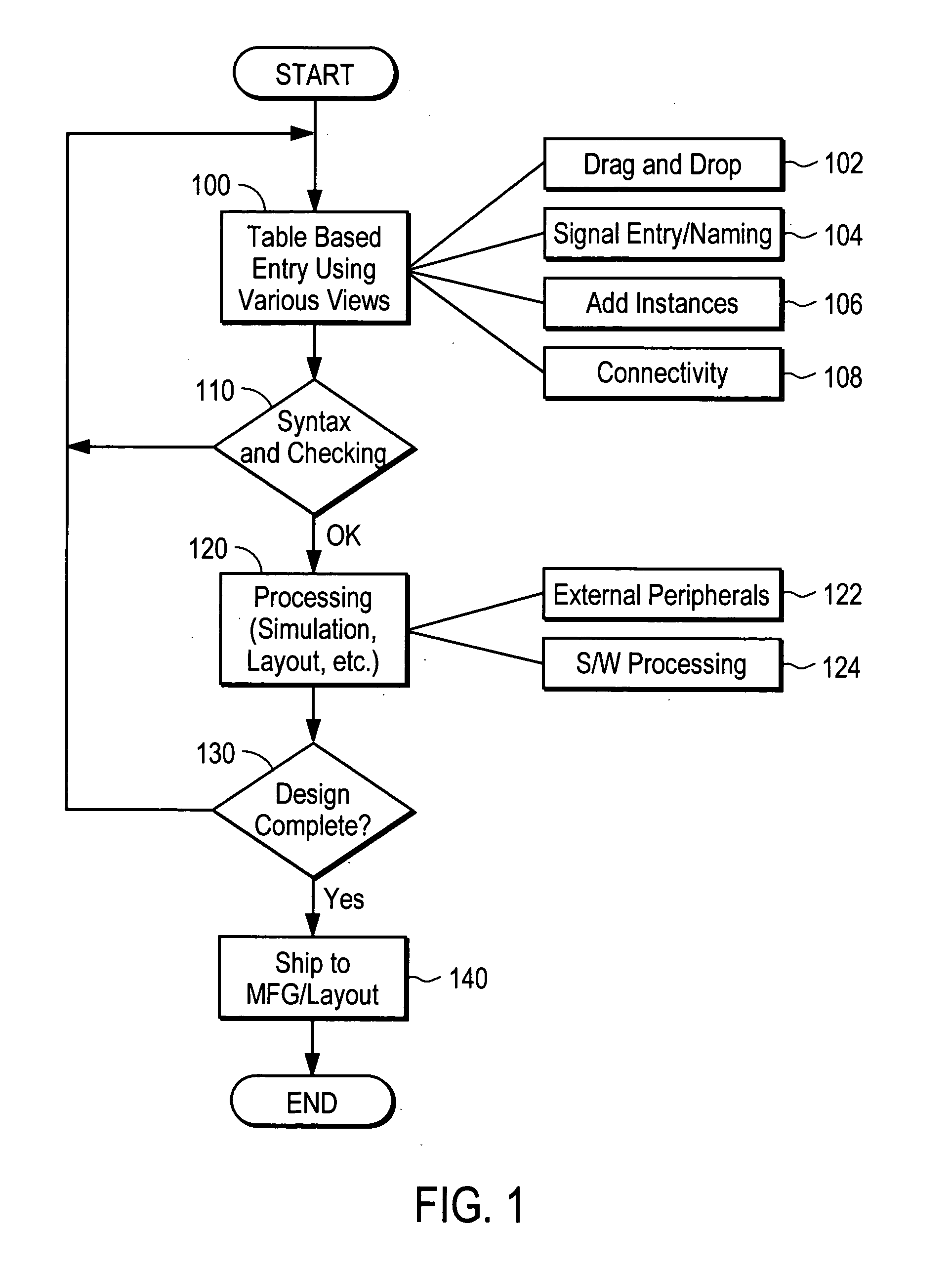

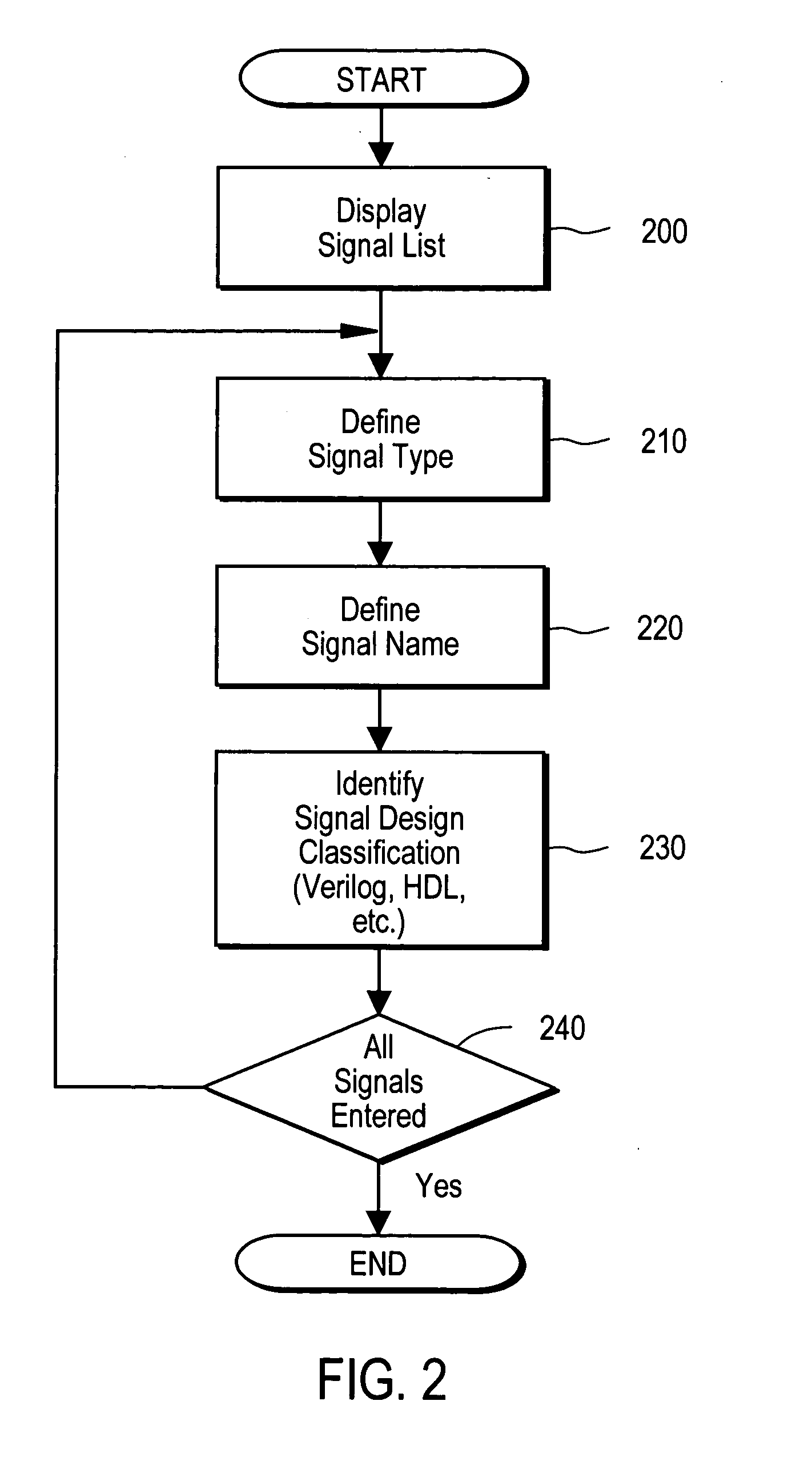

Method and apparatus for table and HDL based design entry

InactiveUS7168041B1Computer programmed simultaneously with data introductionCAD circuit designComputer architectureGrammaticality

Views for signals and instances are provided in a table based design entry system. The signal view allows a designer to enter signals to be used in a design. The signals may be individually entered or imported from pre-defined or external packages of signals. The instance view allows the designer to enter components and to define connectivity of pins of the components to signals. The components may be entered individually or imported from predefined or external packages. An naming routines provides signal name generation and copying names of other components (e.g., pin names) to name the signals. Data entered into the table based entry system is checked for errors (duplicate names, syntax, etc.), and exported to other design tools for processes such as simulation, layout, etc.

Owner:CADENCE DESIGN SYST INC

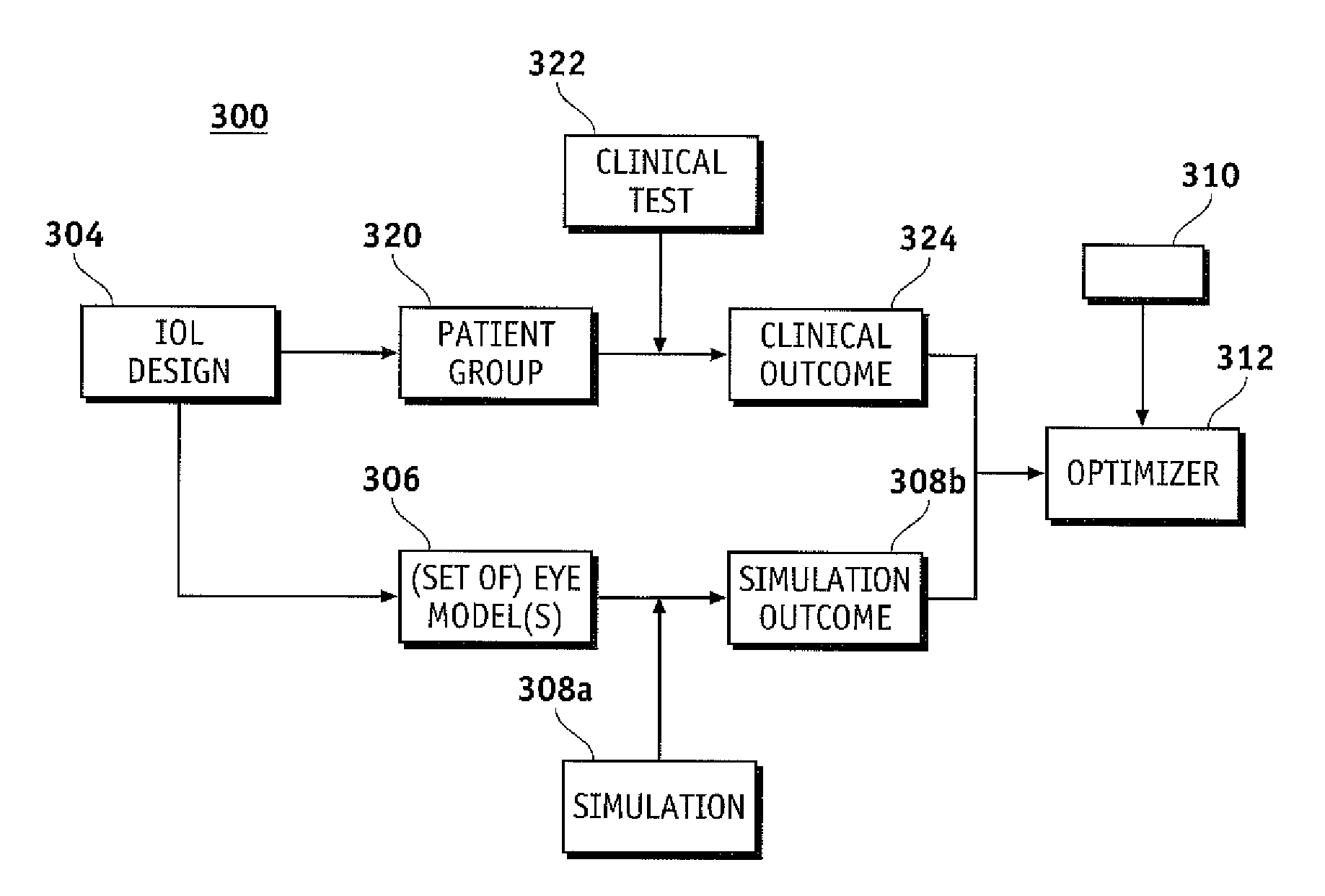

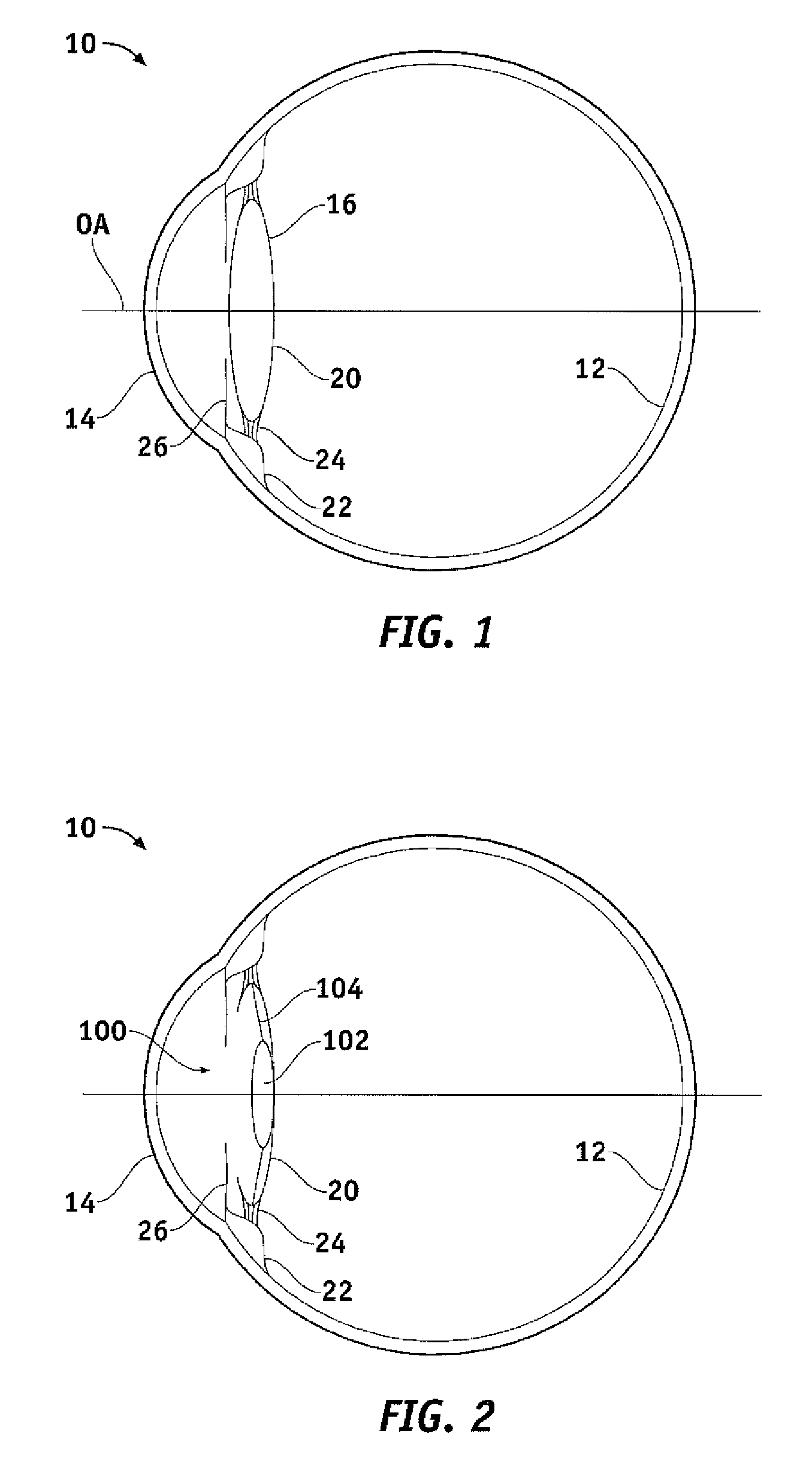

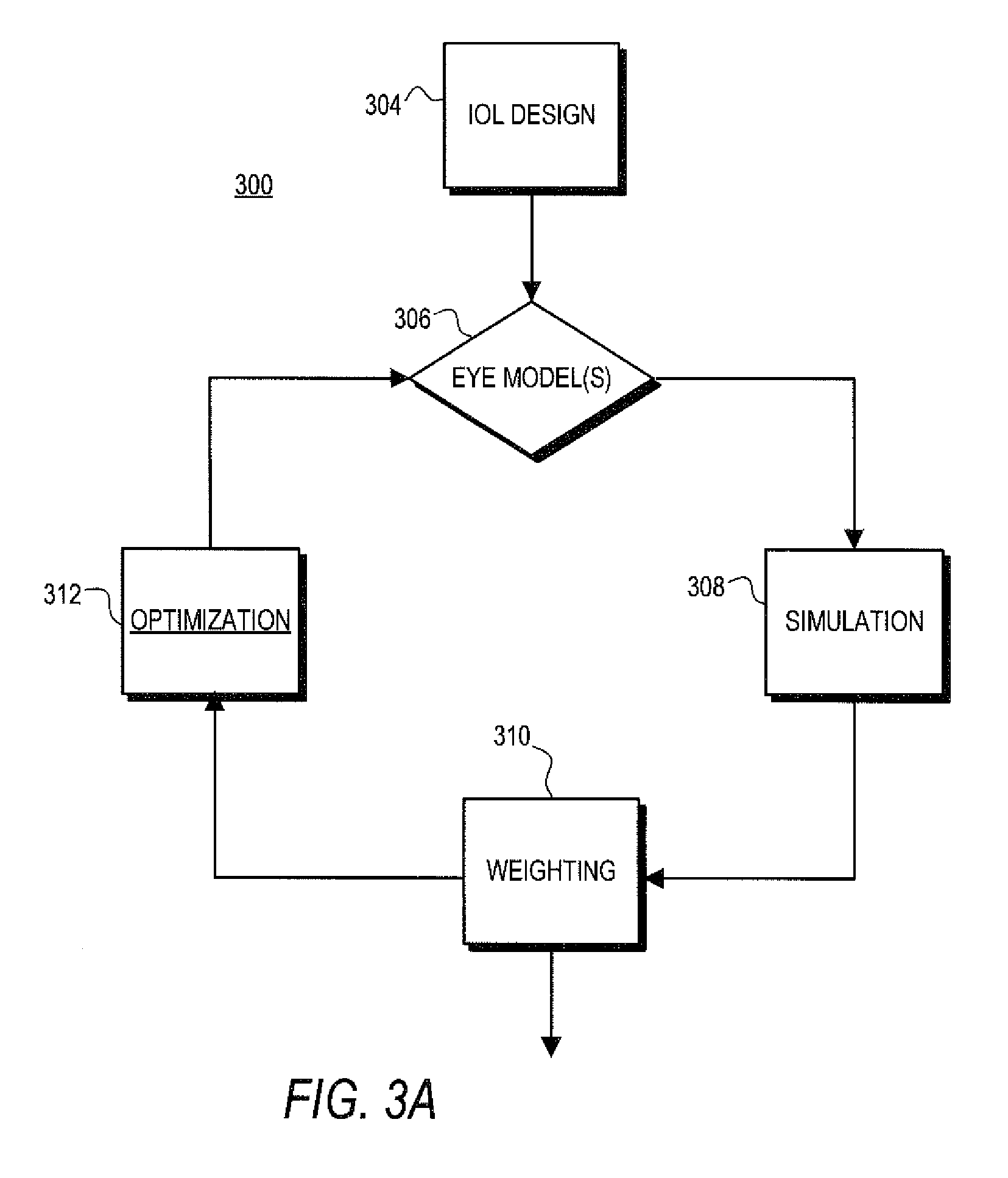

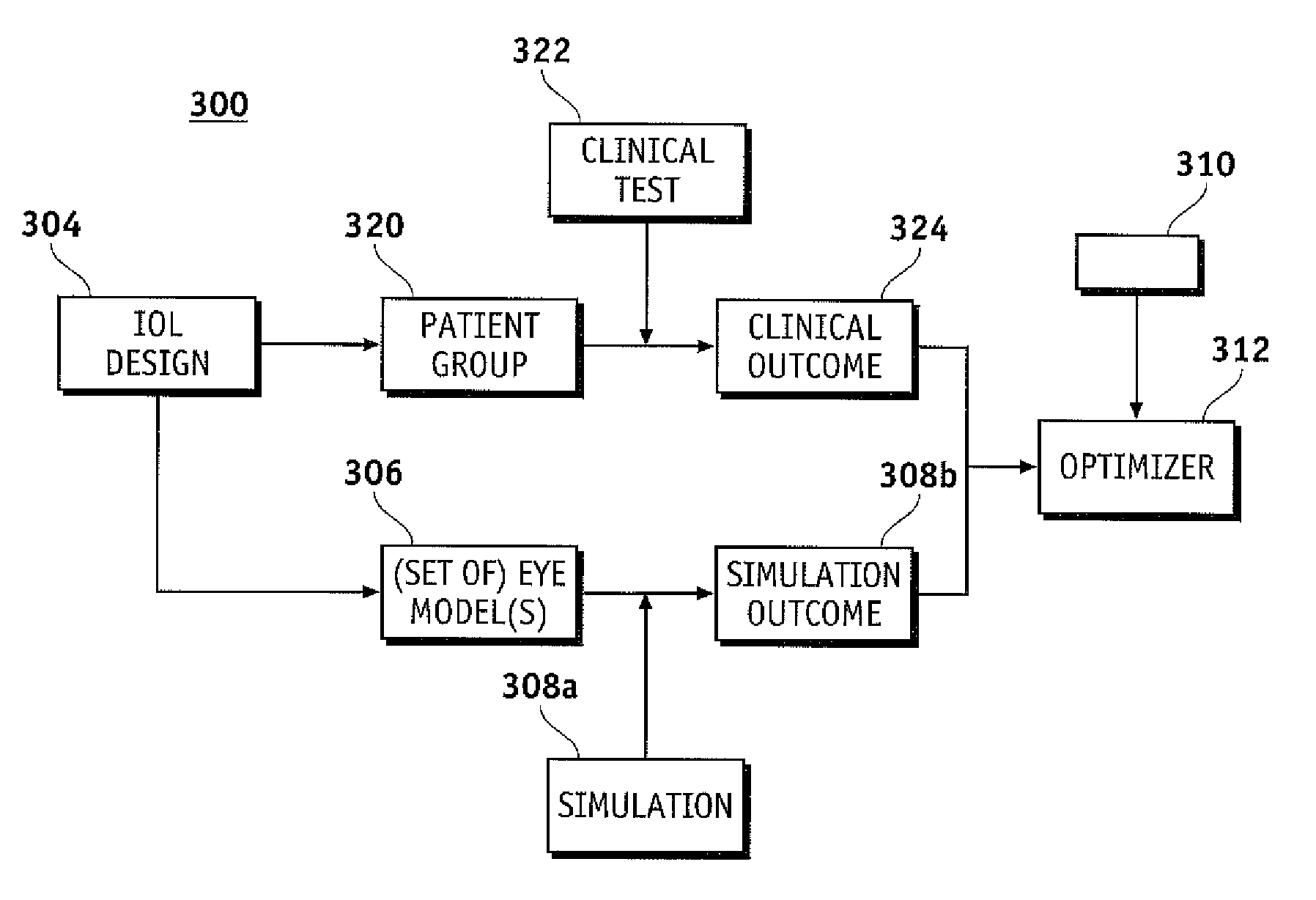

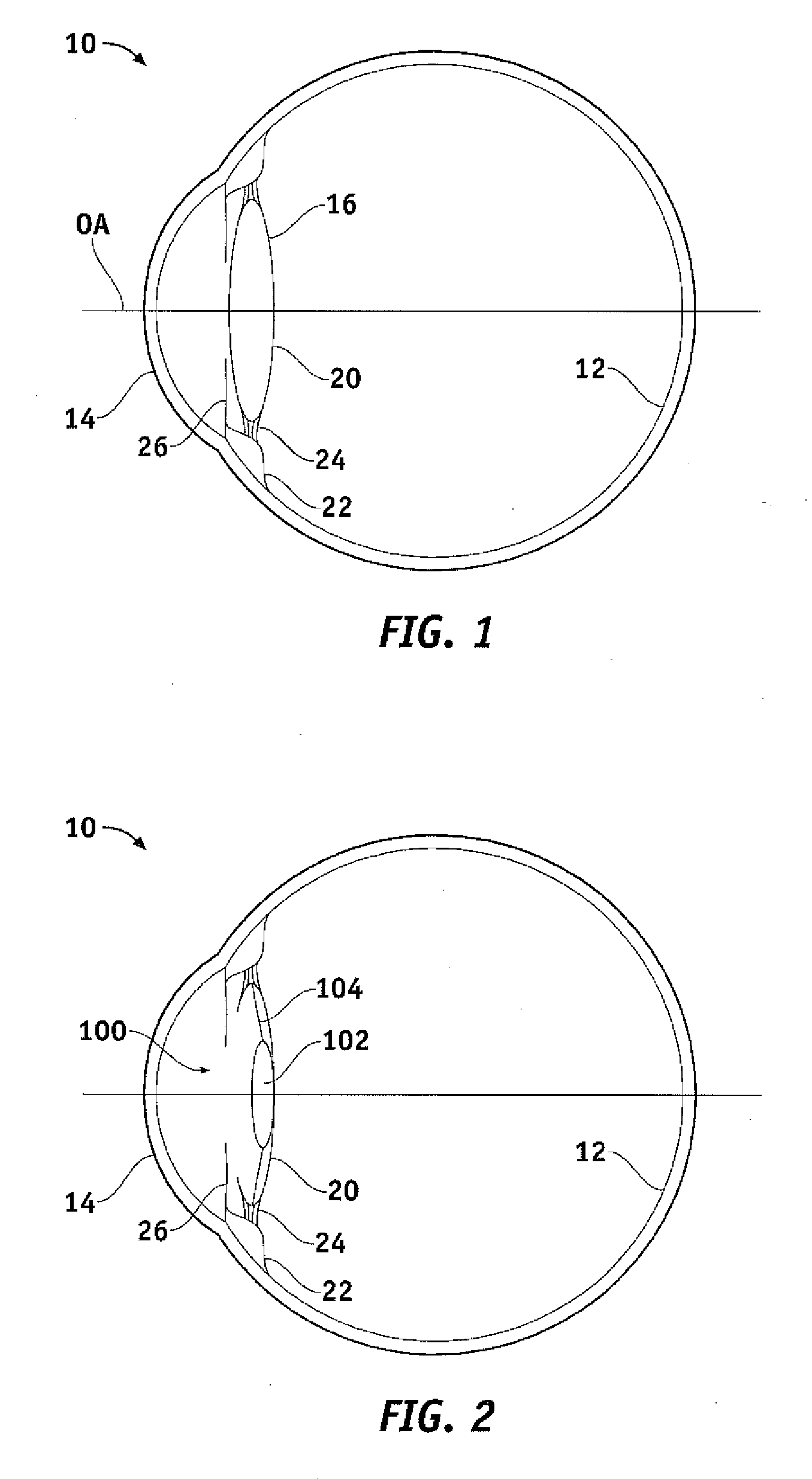

Apparatus, system and method for predictive modeling to design, evaluate and optimize ophthalmic lenses

ActiveUS8862447B2Analogue computers for chemical processesComputation using non-denominational number representationEye lensComparator

An apparatus, system and method for predictive modeling to design, evaluate and optimize ophthalmic lenses is disclosed. Ophthalmic lenses may include, for example, contacts, glasses or intraocular lenses (IOLs). The apparatus, system and method may include a design tool for designing a lens for implantation in an eye having a plurality of characteristics, a simulator for simulating performance of the lens in at least one modeled eye having the plurality of characteristics, at least one input for receiving clinical performance of the lens in the eye having the plurality of characteristics, a comparator for comparing outcomes of the clinical performance and the simulated performance, and an optimizer for optimizing a subsequent one of the outcome of the clinical performance responsive to modification of the lens in accordance with modification to the simulated performance.

Owner:AMO GRONINGEN

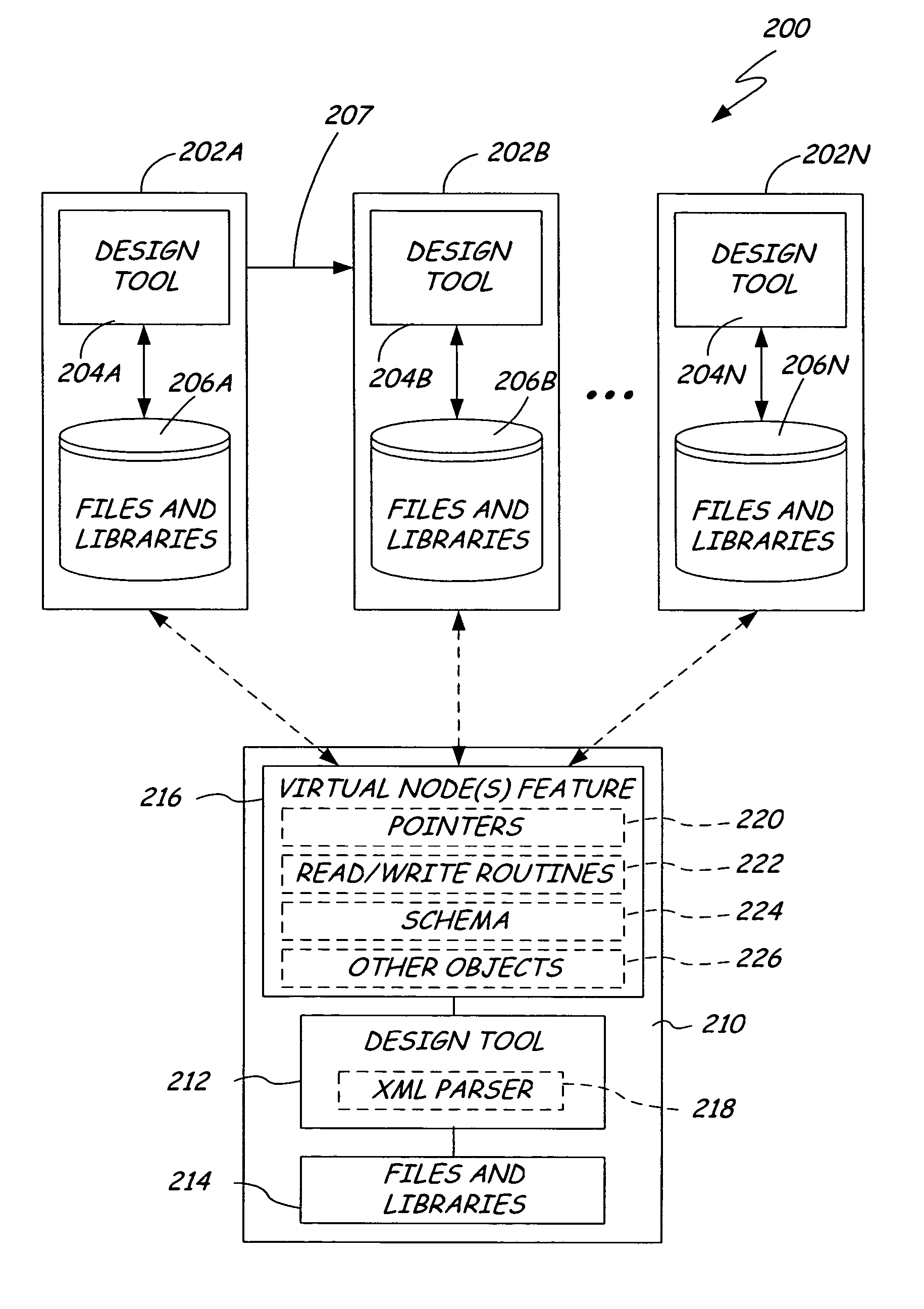

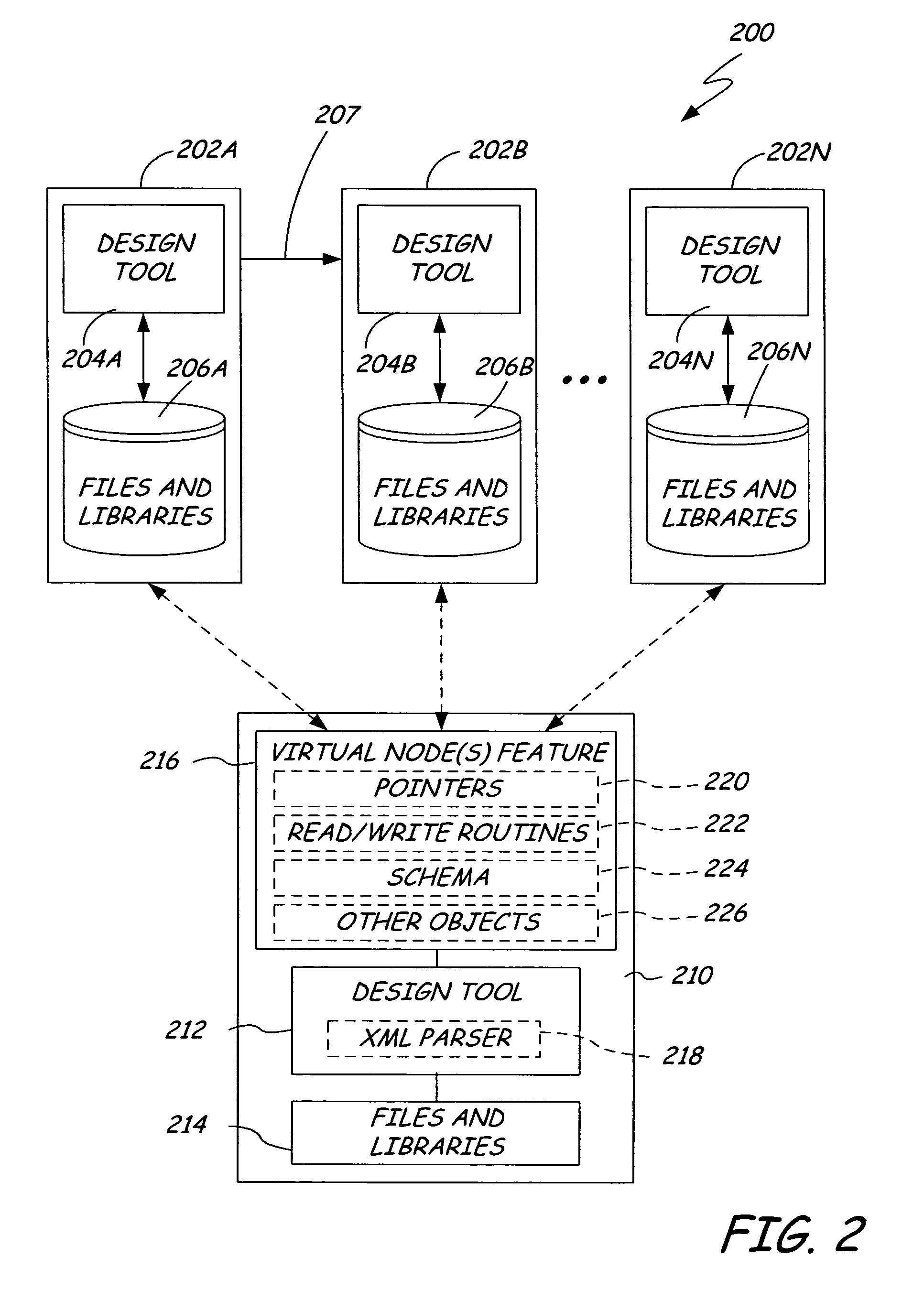

Virtual data representation through selective bidirectional translation

InactiveUS20060112376A1Software designProgram controlComputer architectureComputer aided circuit design

A computer-aided circuit design application has a virtual node feature and a design tool. The virtual node feature is adapted to access design specification information in a first data format and to represent the accessed design specification information as a virtual data node object within a list of node objects in a second data format. The design tool is operable on the list of node objects and the virtual data node object.

Owner:BELL SEMICON LLC

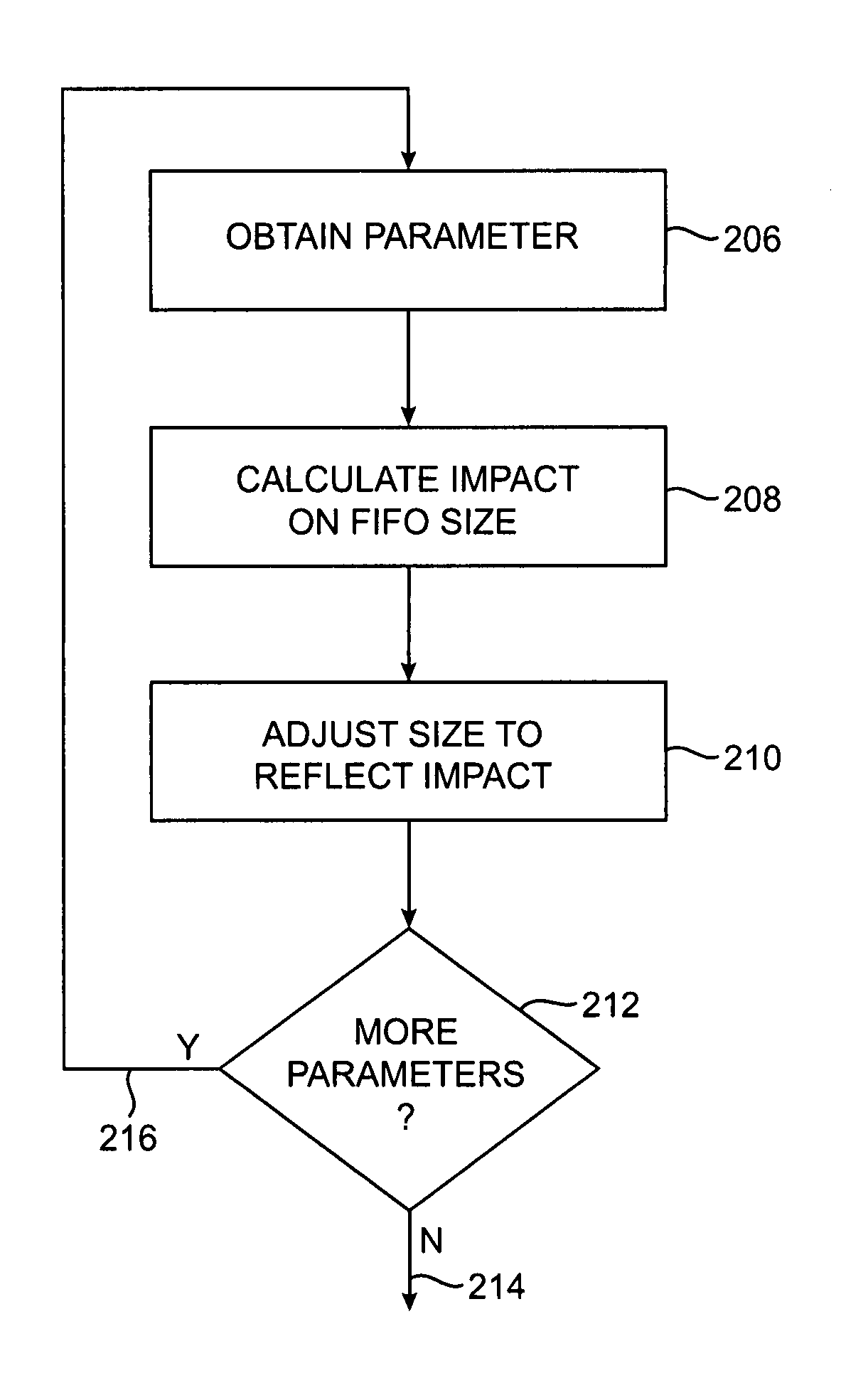

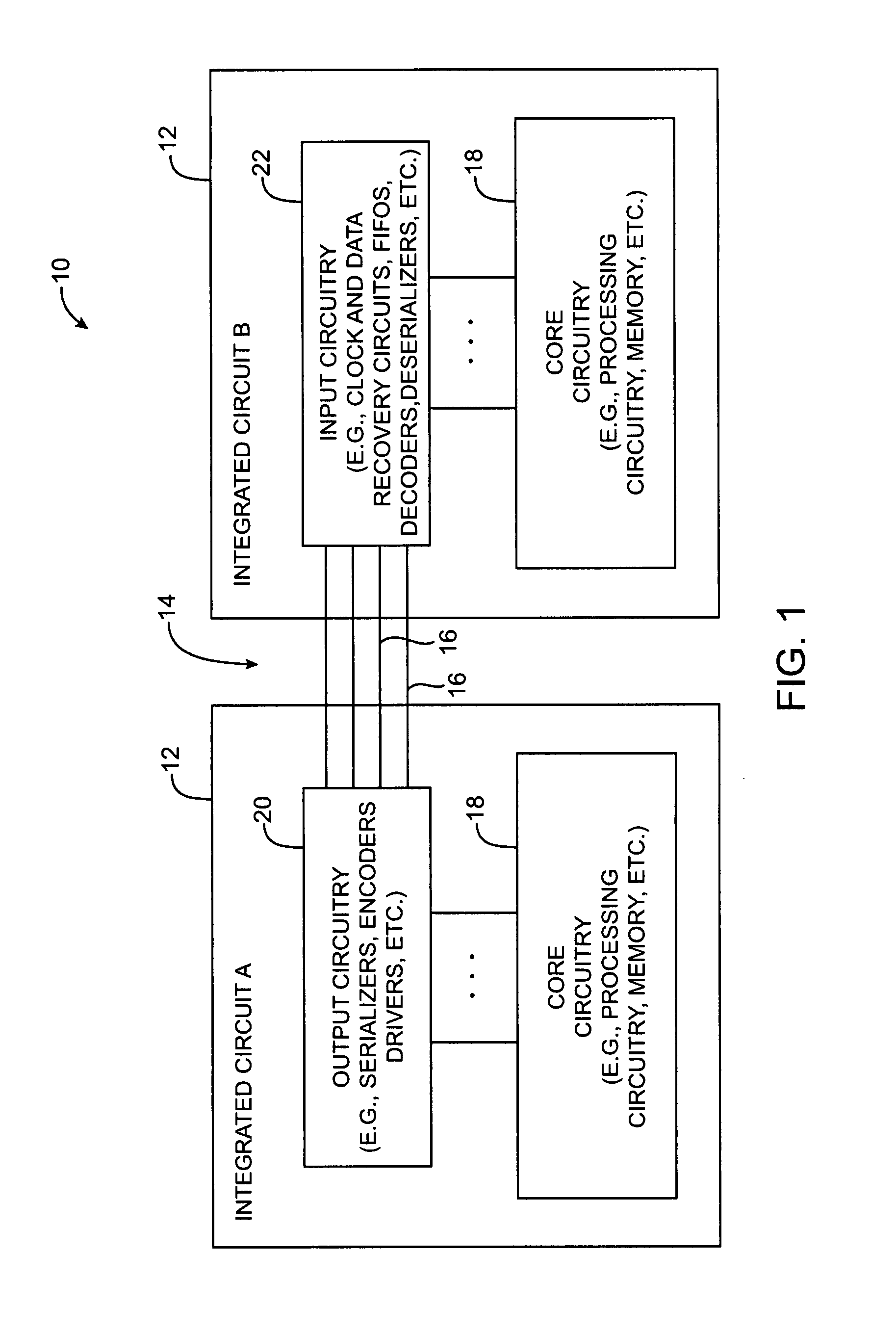

Design tools for configurable serial communications protocols

InactiveUS7228509B1TransmissionComputer aided designComputer architectureNetwork Communication Protocols

A serial communications protocol with optional and adjustable data link layer and physical layer features is provided. A logic design tool for designing circuits compliant with the protocol is also provided. Using the logic design tool, desired optional protocol features may be included to enhance circuit functionality and undesired optional protocol features may be omitted to conserve circuit resources. The logic design tool may include design aids related to retry-on-error timeout calculations, FIFO sizing, transmitter and receiver circuit parameters, and other design parameters. A user of the logic design tool can view information provided by the logic design tool's design aids and can make design selections.

Owner:ALTERA CORP

Apparatus, System and Method for Predictive Modeling to Design, Evaluate and Optimize Ophthalmic Lenses

ActiveUS20110270596A1Analogue computers for chemical processesEye diagnosticsPredictive modellingEye lens

An apparatus, system and method for predictive modeling to design, evaluate and optimize ophthalmic lenses is disclosed. Ophthalmic lenses may include, for example, contacts, glasses or intraocular lenses (IOLs). The apparatus, system and method may include a design tool for designing a lens for implantation in an eye having a plurality of characteristics, a simulator for simulating performance of the lens in at least one modeled eye having the plurality of characteristics, at least one input for receiving clinical performance of the lens in the eye having the plurality of characteristics, a comparator for comparing outcomes of the clinical performance and the simulated performance, and an optimizer for optimizing a subsequent one of the outcome of the clinical performance responsive to modification of the lens in accordance with modification to the simulated performance.

Owner:AMO GRONINGEN

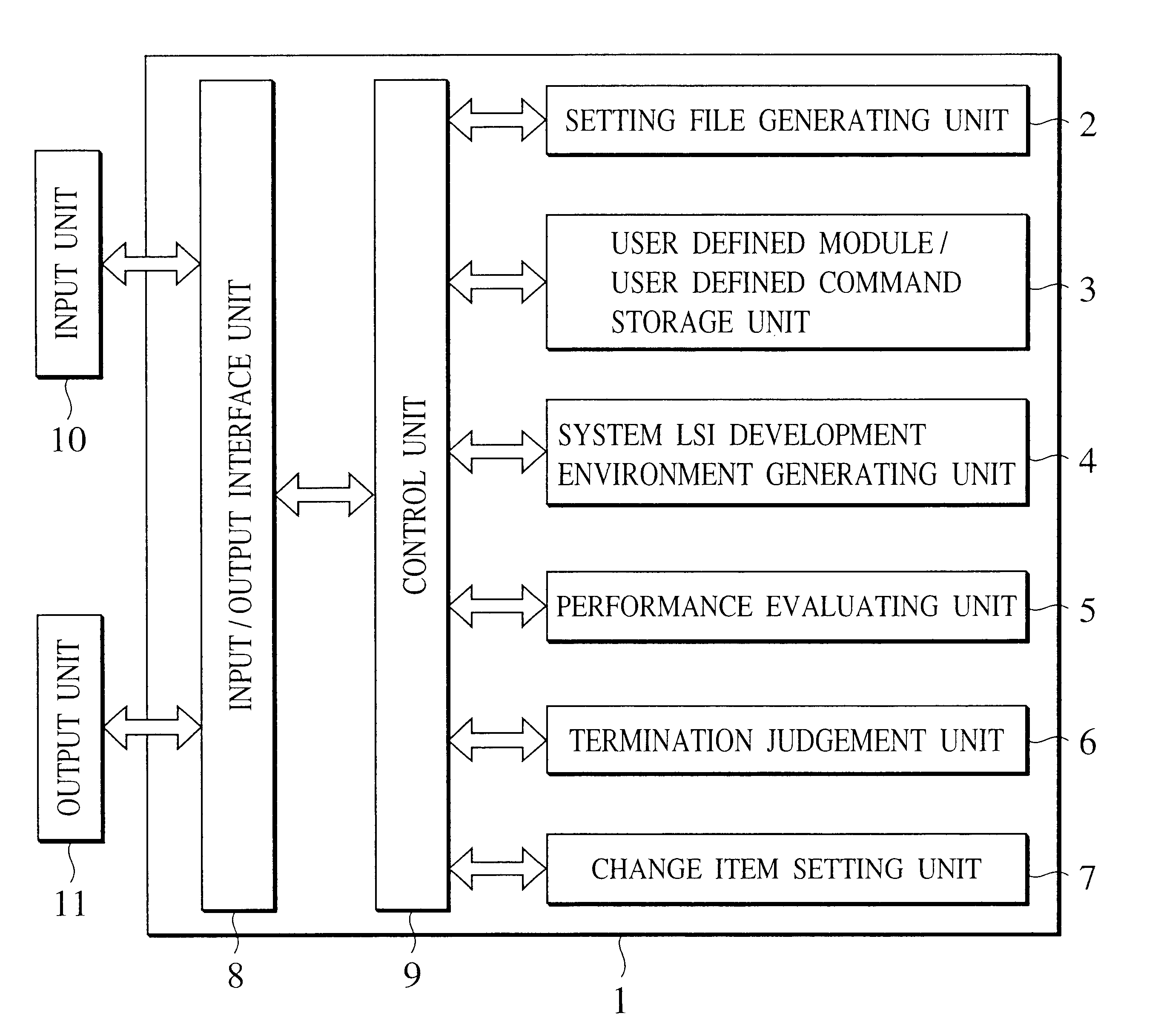

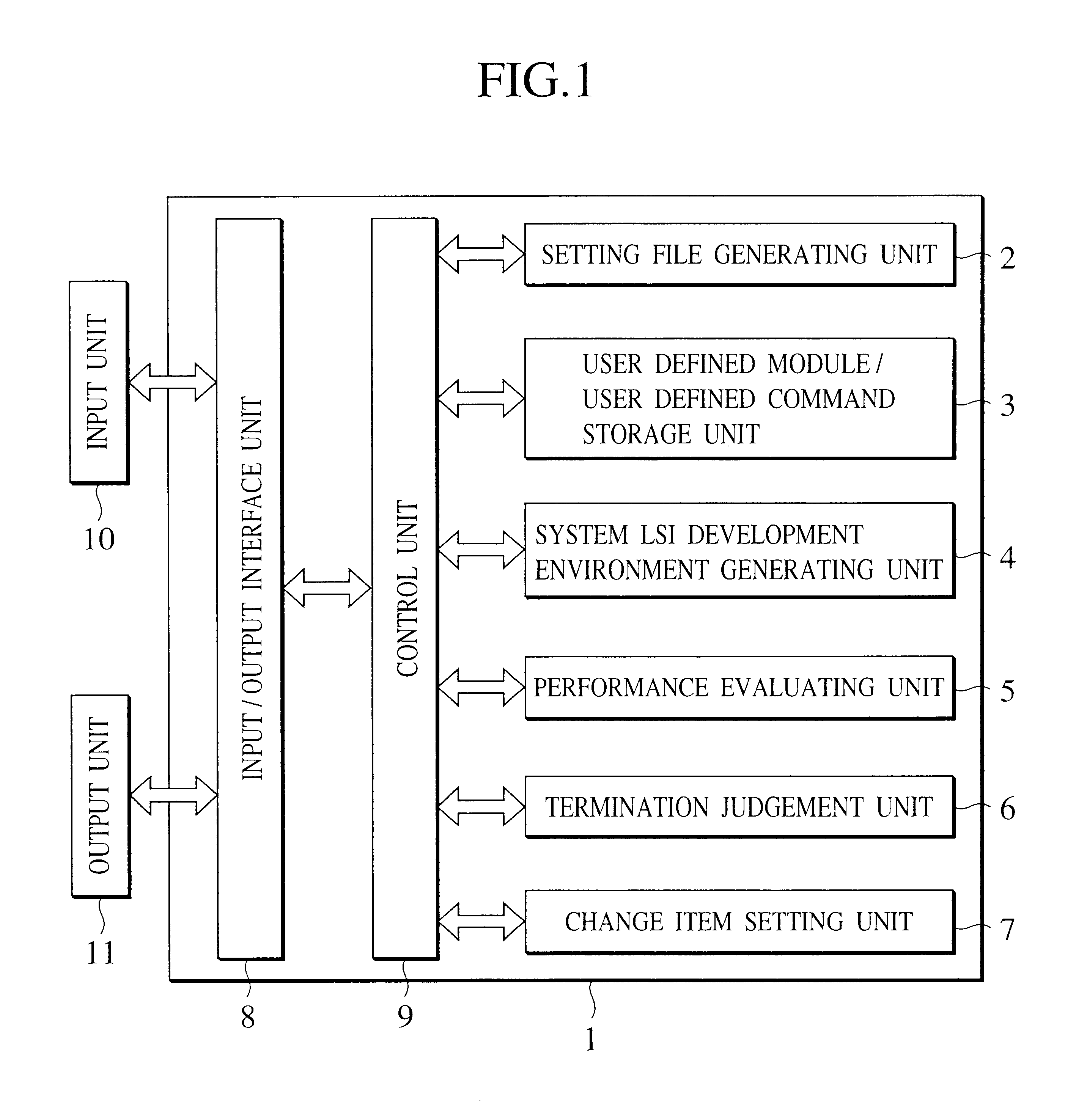

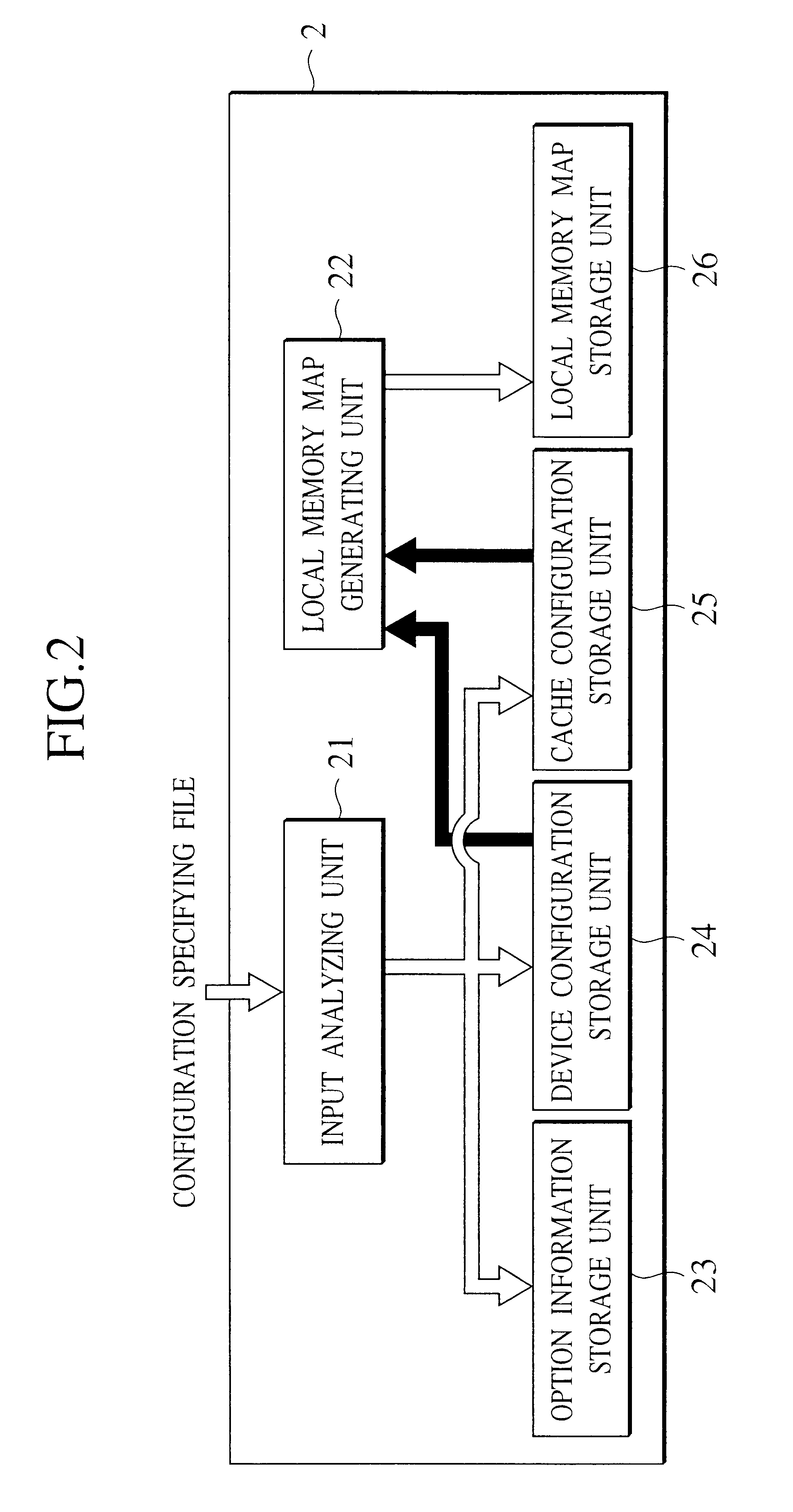

System LSI development apparatus and the method thereof for developing a system optimal to an application

In this disclosure, based on change item definition information concerning system LSI development and design, software used for development and design of a system LSI that contains a processor having optional instructions defined therein is operated, and system LSI hardware description, verification environment and a development and design tools are generated, thus making it possible to develop a system LSI optimal to an application within a short period.< / PTEXT>

Owner:KK TOSHIBA

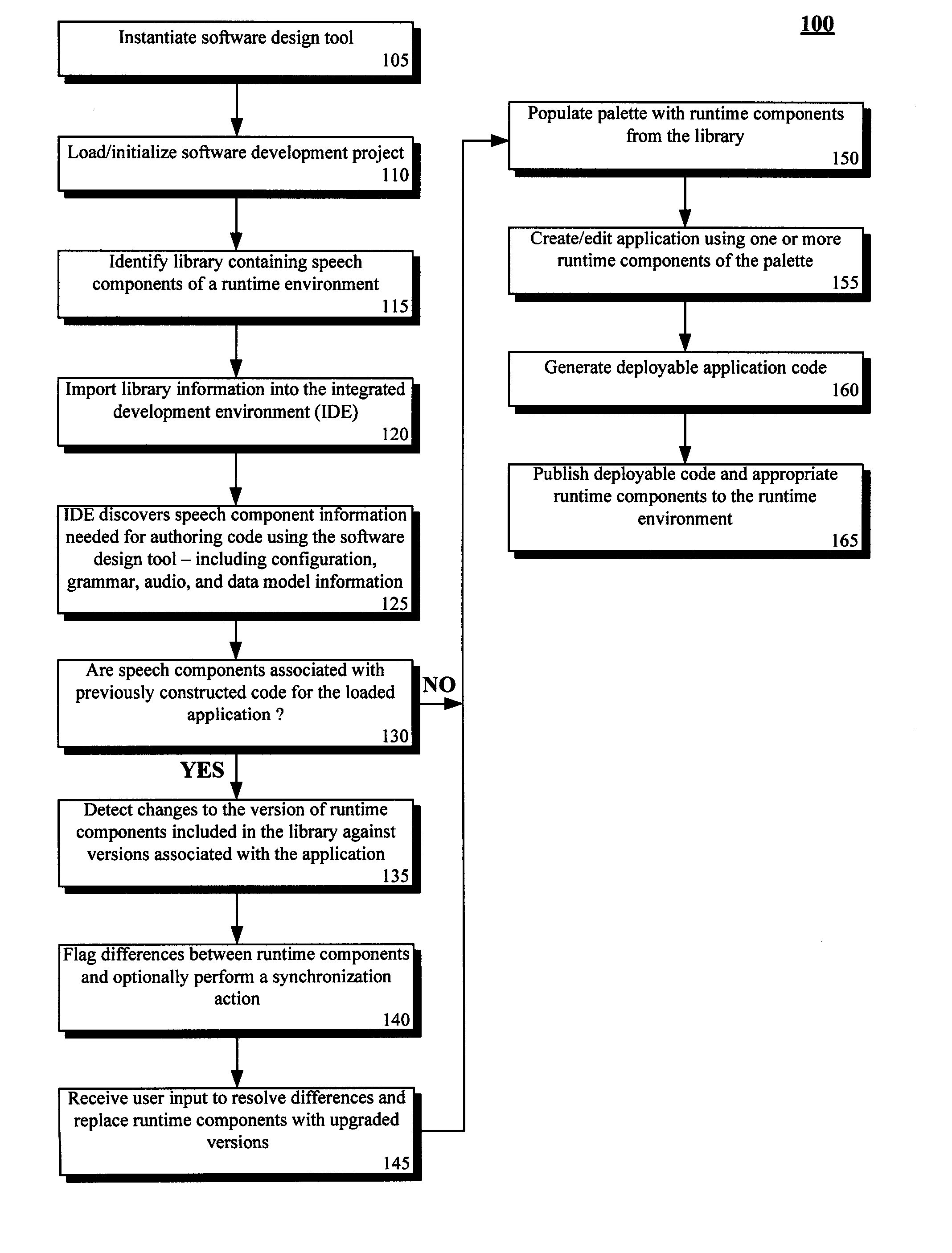

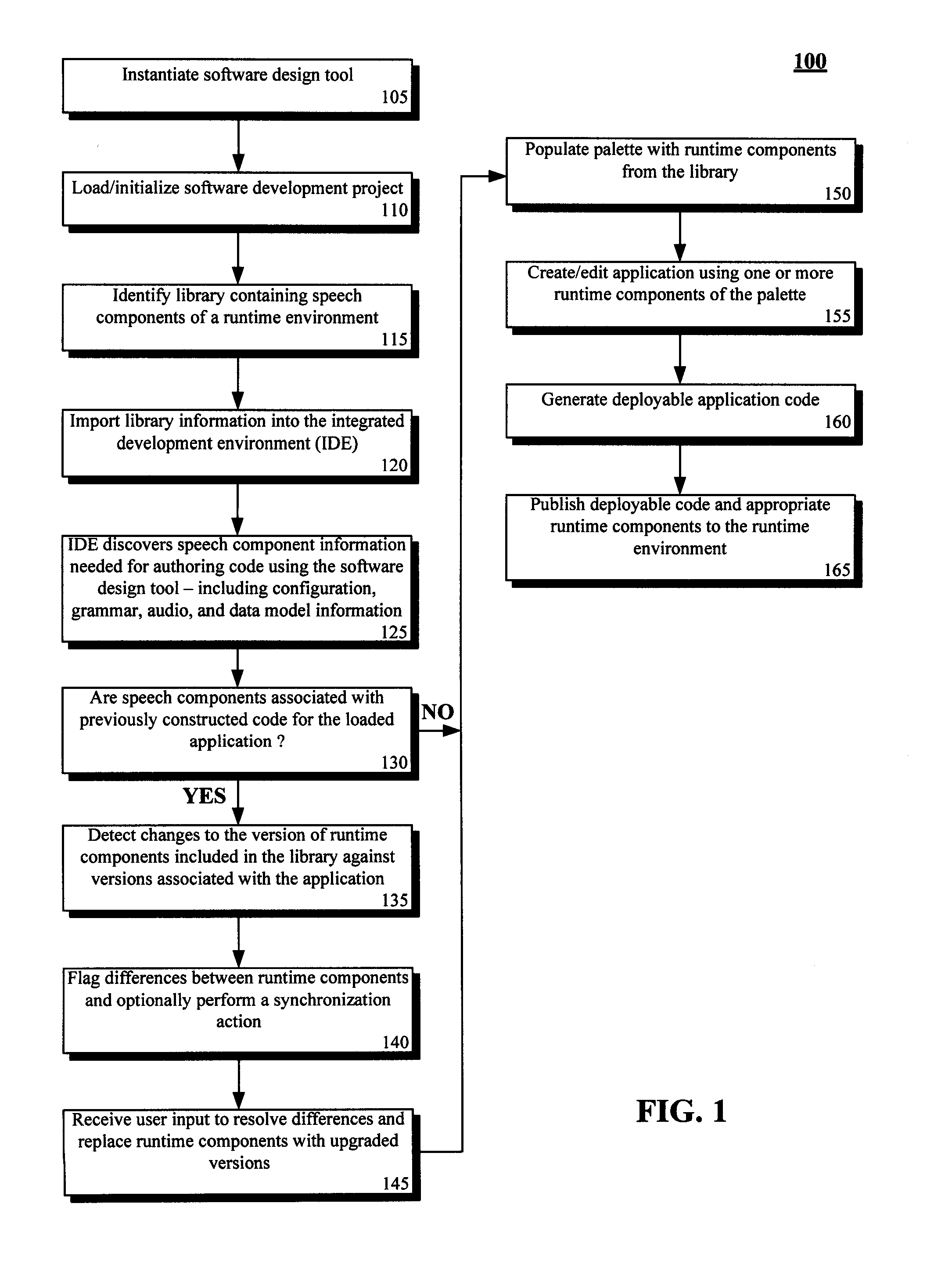

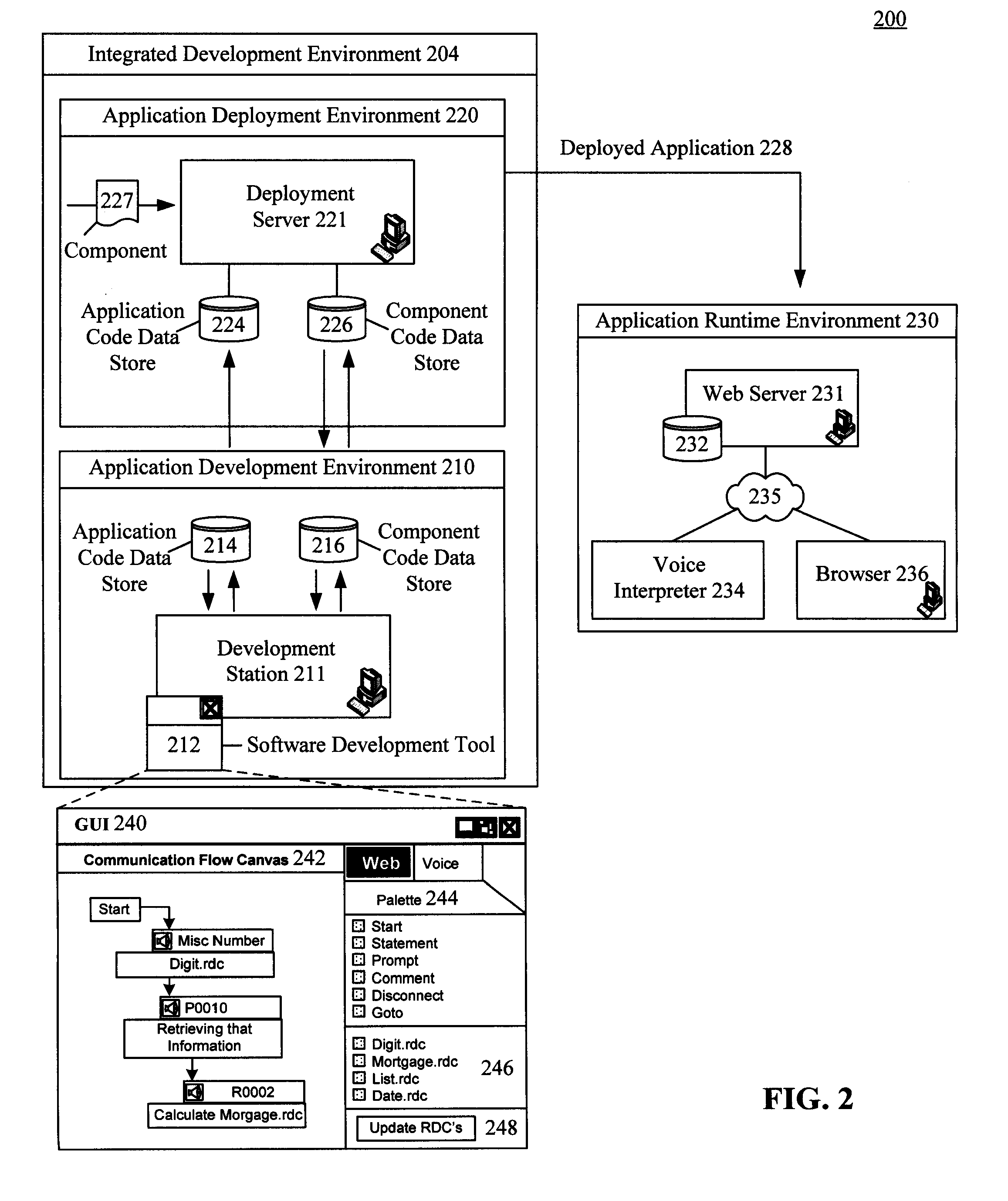

Method and system for automatically discovering and populating a palette of reusable dialog components

InactiveUS20070261027A1Easy to upgradeVisual/graphical programmingSoftware reuseSoftware designSoftware engineering

The present invention permits a speech application design tool to dynamically acquire information for runtime components, such as Reusable Dialog Components (RDCs). More specifically, a user can identify a library available to the runtime environment that includes runtime speech components. Runtime components can be imported into an integrated development environment (IDE) that includes the software design tool. The tool can discover configuration grammars, audio, and data models associated with the imported components. When previously developed application code has been loaded into the tool, versions of components associated with the previously developed application will be compared and synchronized with the library components. Differences can be flagged by the tool, which facilitates a component upgrading process. Otherwise, a palette within the tool will be populated with the imparted components, which can be used when authoring a new application.

Owner:IBM CORP

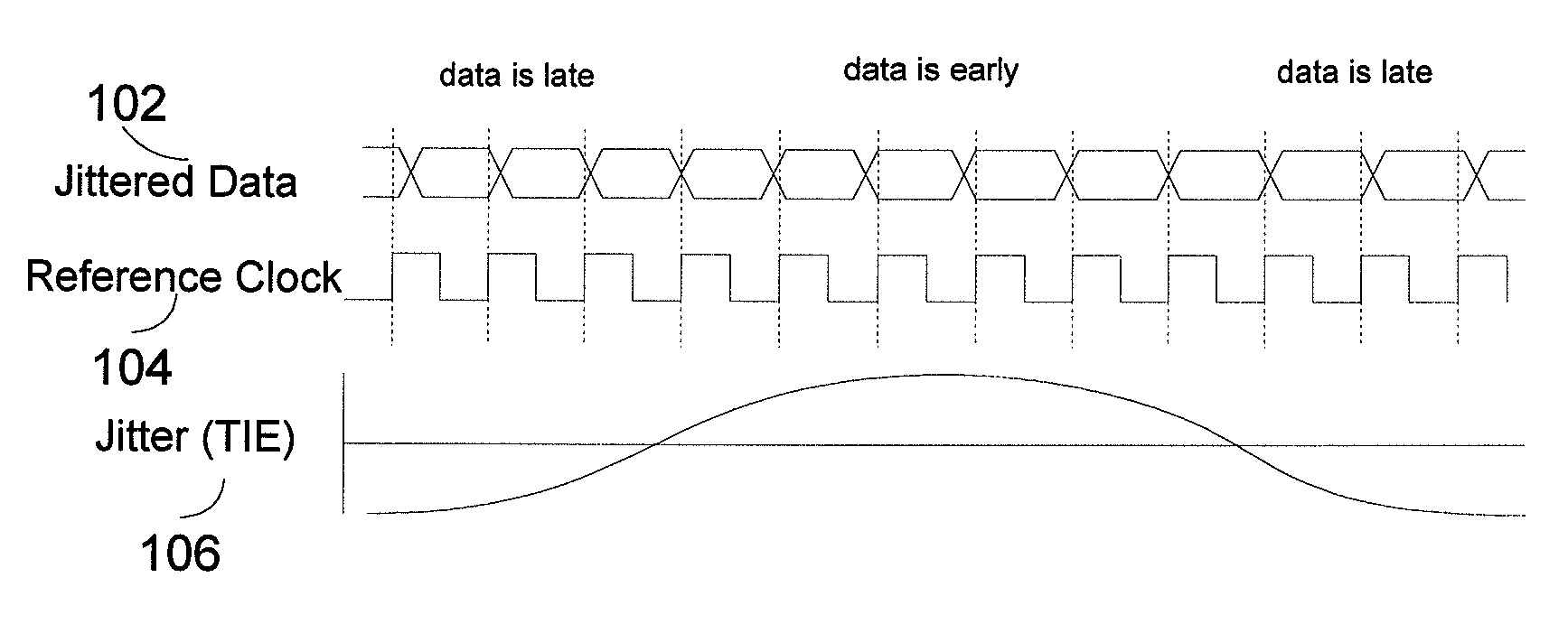

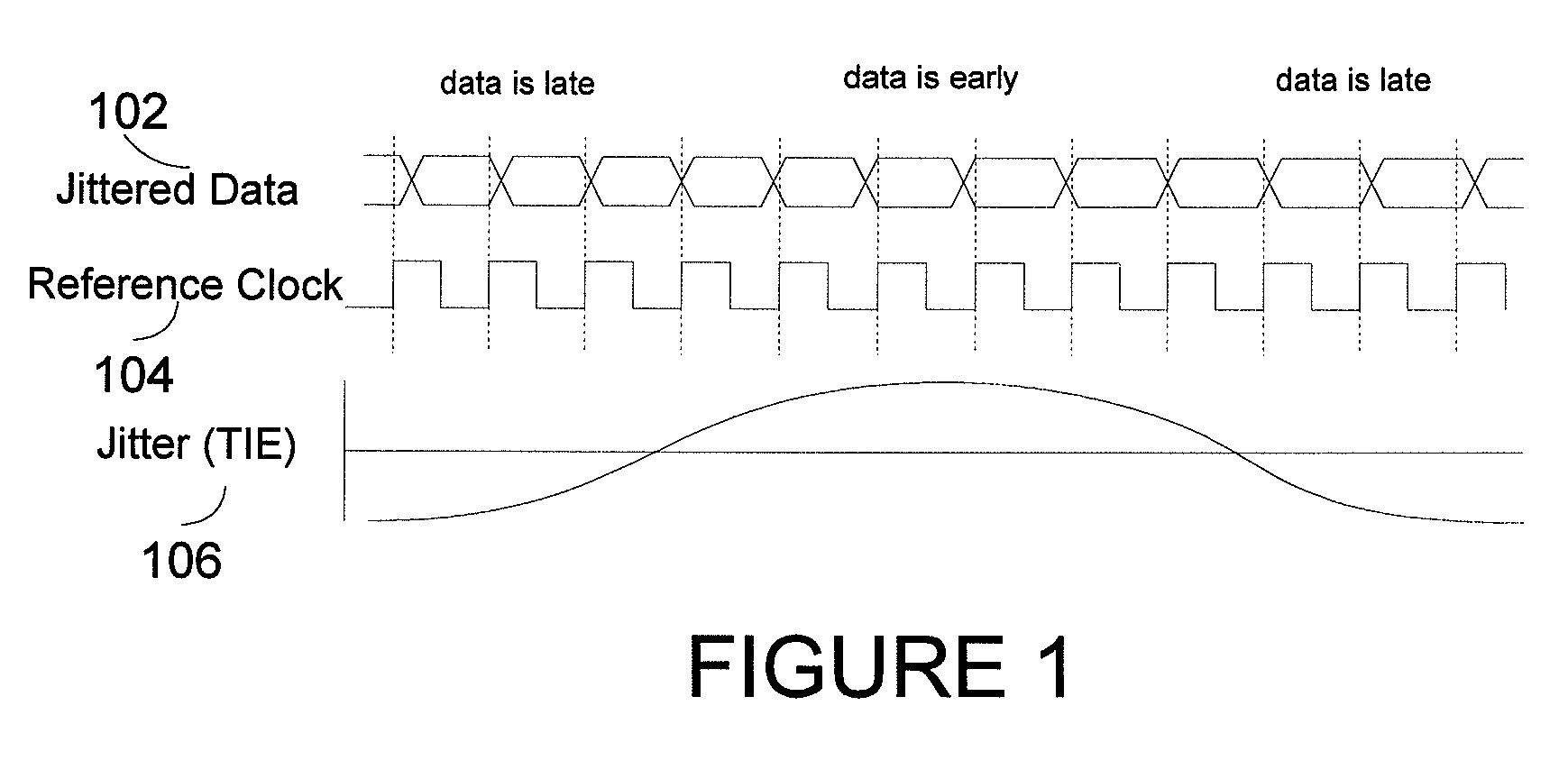

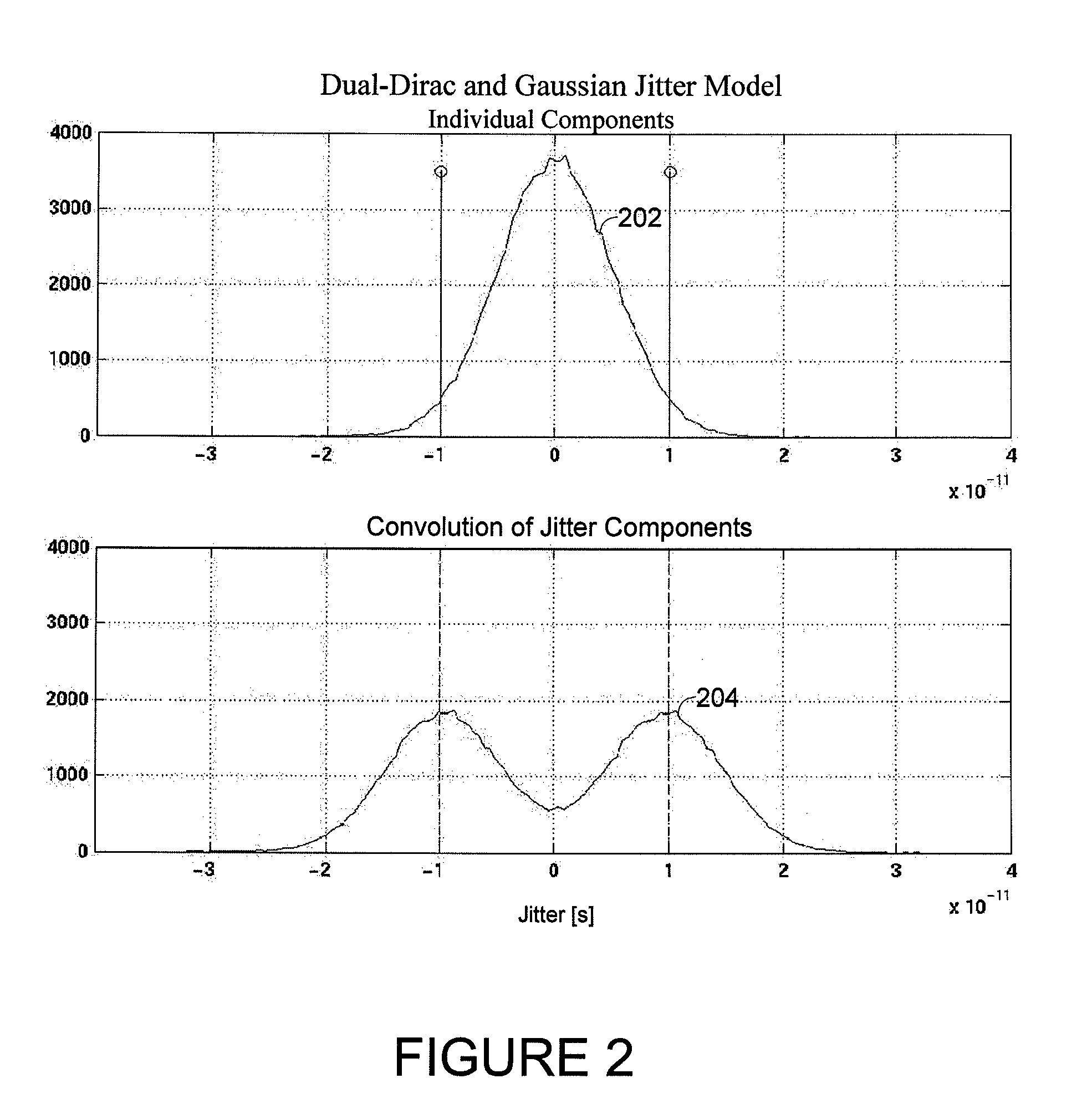

Systems and methods for jitter analysis of digital signals

InactiveUS7388937B1Accurate identificationFacilitates decomposition and quantificationError preventionLine-faulsts/interference reductionState dependentData dependent

Systems and methods for analyzing the jitter content of an oversampled digital communication signal are disclosed. Advantageously, the communication signal can correspond to an arbitrary data sequence, rather than only to a repeating test sequence. For example, the systems and methods can be embodied in test equipment and in simulation equipment as design tools and / or validation tools. The systems and methods disclosed advantageously facilitate the decomposition and quantification of the main jitter components (random and deterministic), as well as its various subcomponents (periodic jitter, data-dependent jitter, inter-symbol interference, device-state-dependent jitter, other bounded uncorrelated jitter, and data-dependent-random jitter).

Owner:MICROSEMI STORAGE SOLUTIONS

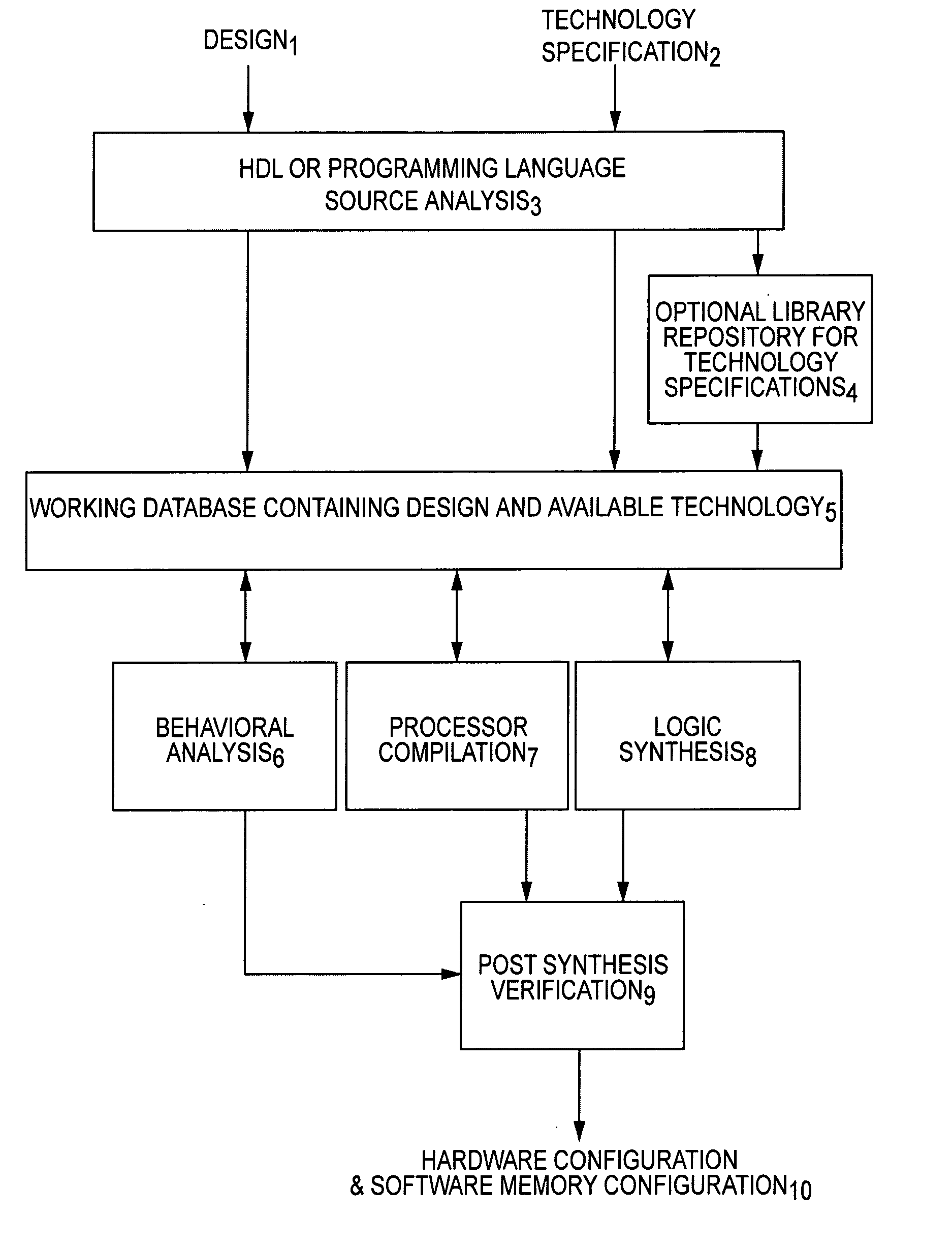

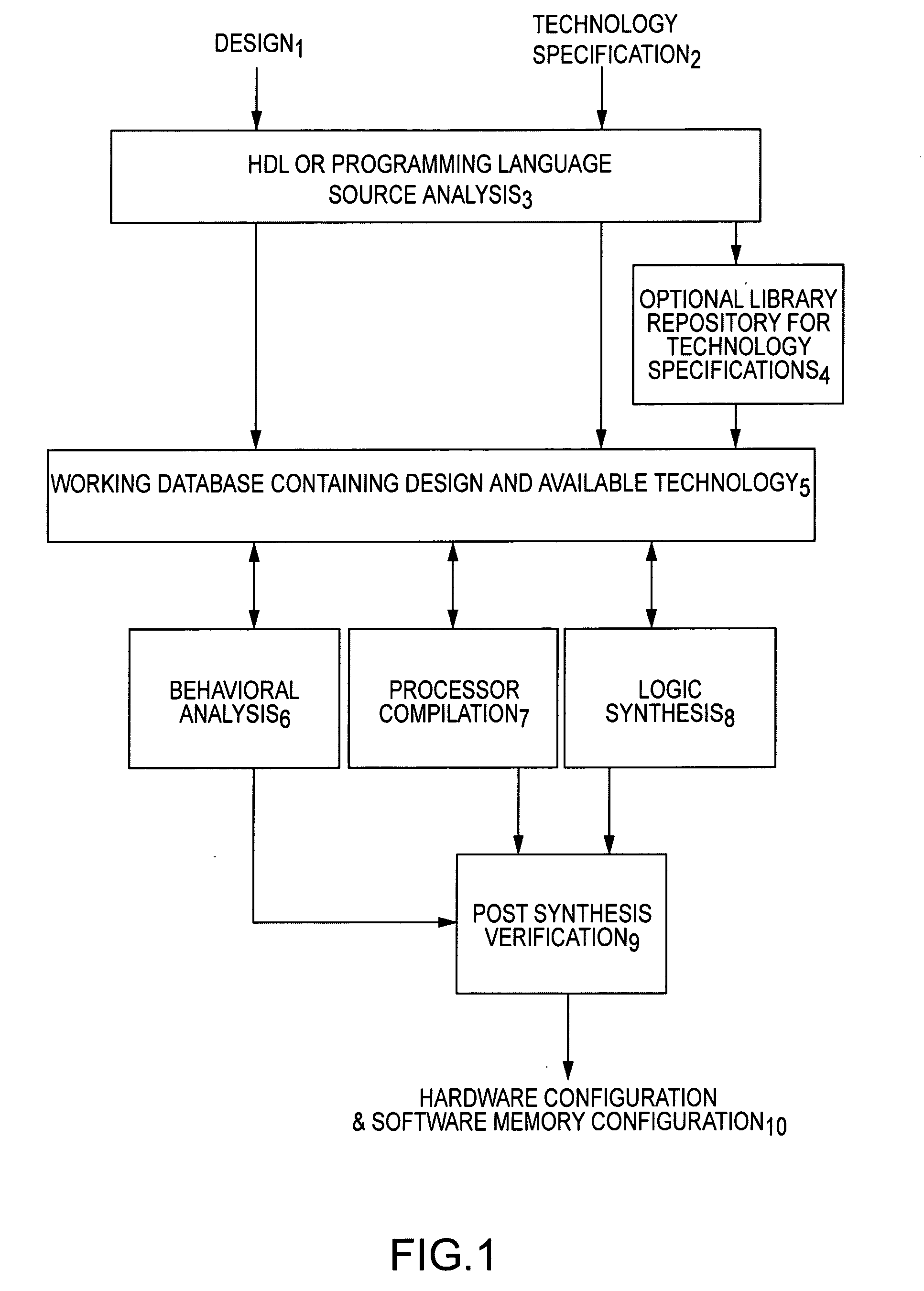

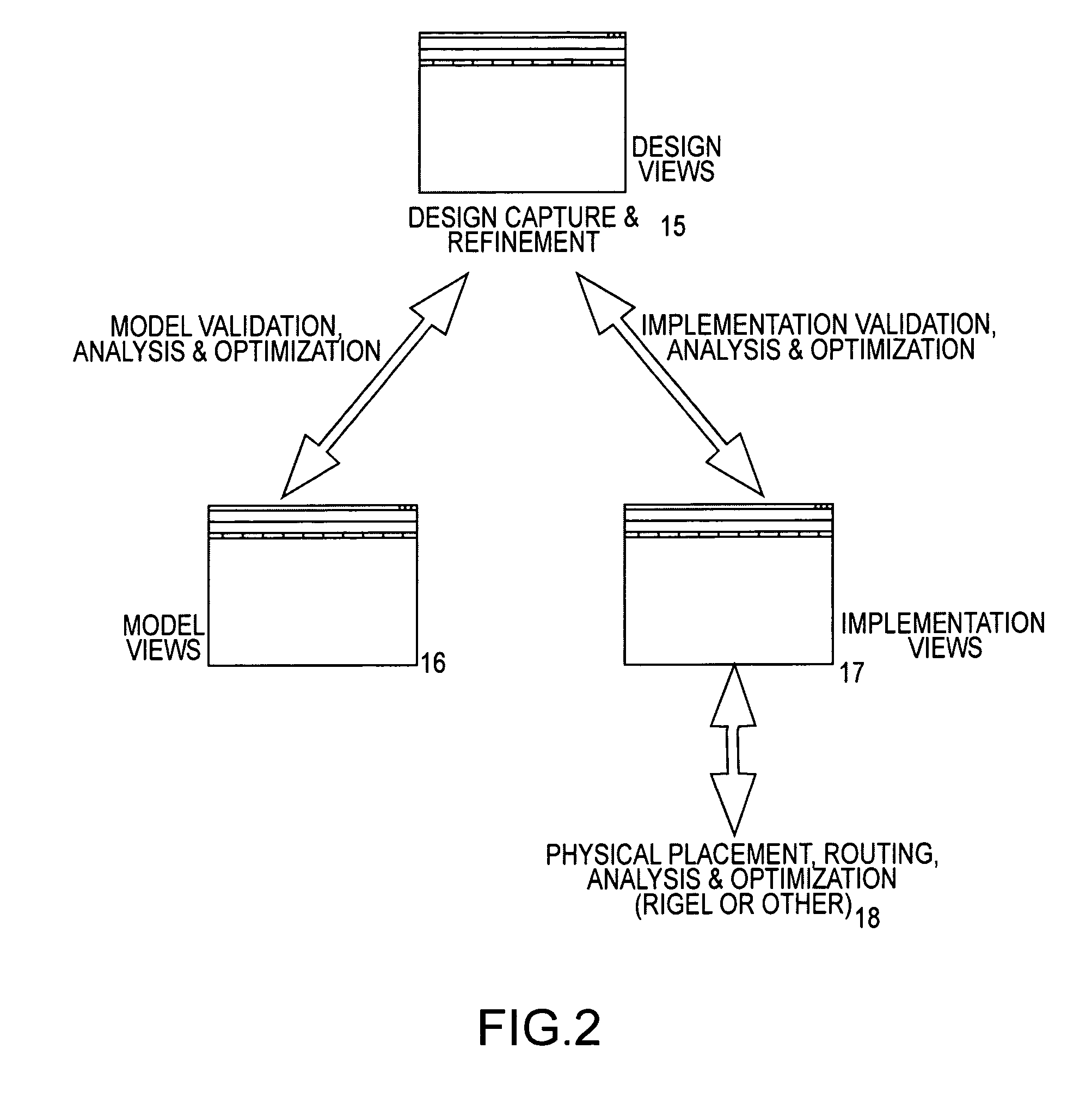

Hardware/software design tool and language specification mechanism enabling efficient technology retargeting and optimization

InactiveUS20050289485A1More compactEfficient designElectrical testingDigital computer detailsComputer architectureSoftware system

An innovative hardware / software design tool provides four modes of operation for converting an electronic design specification and zero or more technology specifications into realization of the electronic design in computer hardware, software and firmware. The first mode of operation compiles design and logic technology specifications into a model which can be utilized for behavioral analysis (such as simulation or formal verification) of logical characteristics (the model). The second mode of operation translates (compiles) partitions of the design and one or more logic technologies into one or more processor intermediates or binaries (embedded binary) suitable for execution on multi-purpose processing units (embedded or general purpose processors). The third mode of operation translates (synthesizes) partitions of the design and logic technology into a collection of cells and interconnects (net-list implementation) suitable for input to physical design processes such as is required to target a field-programmable logic array (FPGA), application specific integrated circuit (ASIC), system-on-a-chip (SOC) or custom logic). The fourth mode of operation analyzes (verifies) behavior of the embedded binaries running on processing units and implementations augmented by additional physical technology and parameters, yielding a more detailed (accurate) prediction of the resulting hardware / software system behavior when realized through manufacturing. Critically, the design specification, logic specifications, physical specifications and definition of each multi-purpose processing unit may be defined external to the hardware / software design tool using an innovative augmentation of standard hardware description or programming languages taught in this patent application. In the prior art, specification of the logic technology, physical technology and embedded or general purpose processor architecture are either incorporated directly into the design tool by the tool developer or are maintained entirely external to the design tool (such as an encapsulated component model or intermediate code interpreter). The present invention is an innovative and valuable improvement over prior art in that design specifications are combined by the tool from distinct specification(s) of generalized logic, physical and processor technology, leading to more efficient behavioral design, opportunities for third parties to add functionality by incorporating generalized logic and physical technology modules into the analysis and synthesis process and opportunities for semi-automatic, goal-directed optimization through application of various logic, physical and processor technologies by the design tool.

Owner:FTL SYST