Patents

Literature

97 results about "Configurable hardware" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

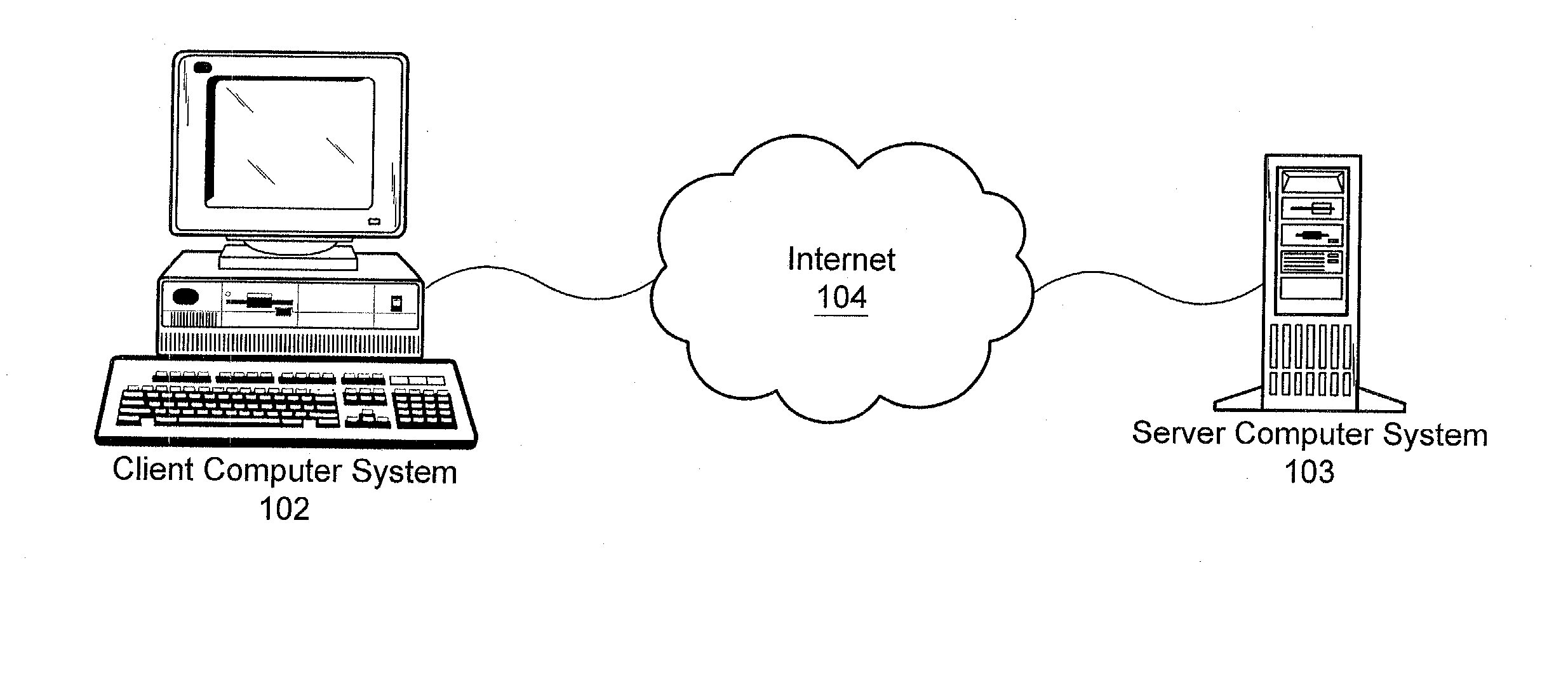

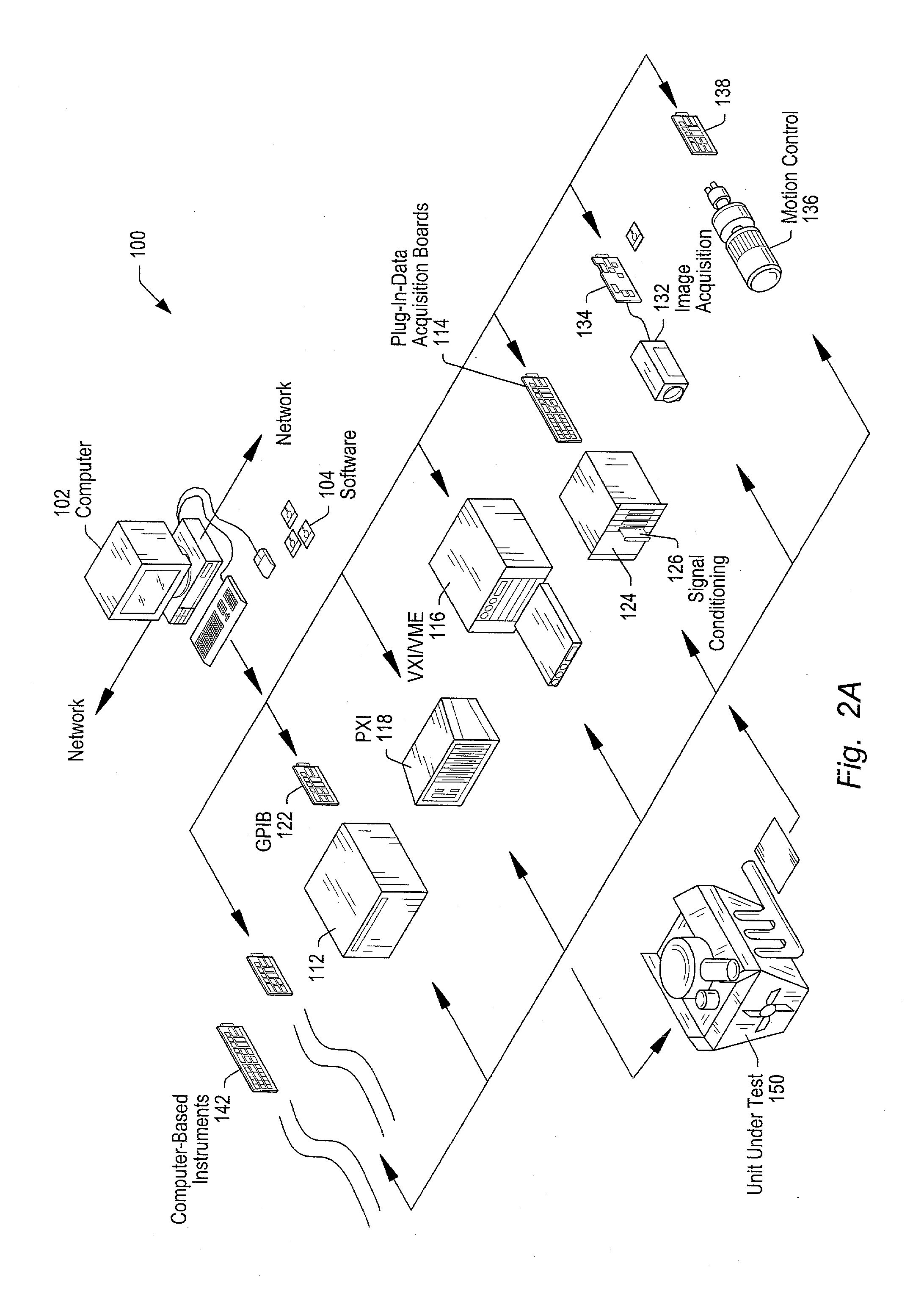

Network-based system for configuring a measurement system using configuration information generated based on a user specification

InactiveUS20030036876A1Measurement arrangements for variableStructural/machines measurementComputer hardwareAuto-configuration

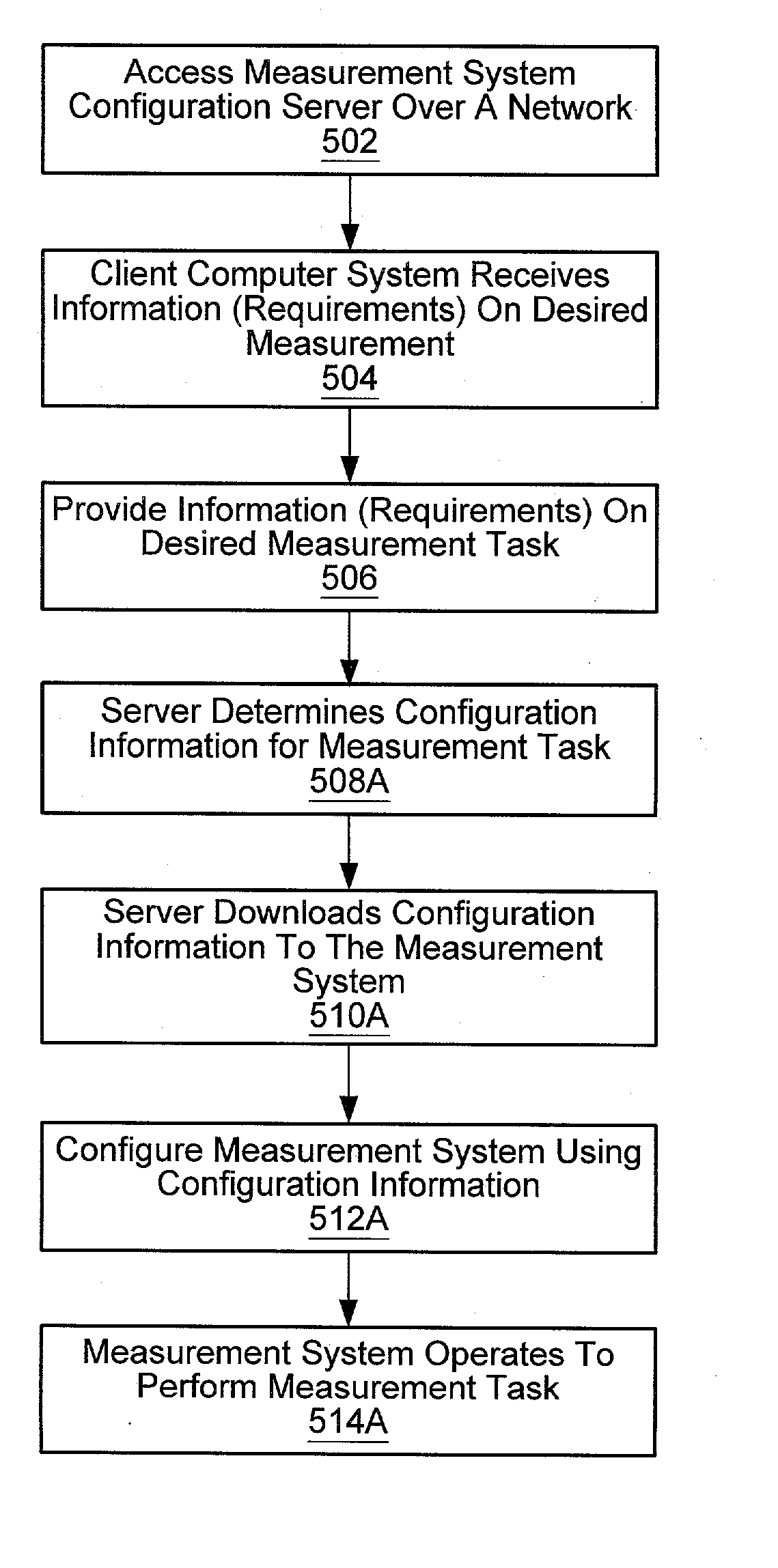

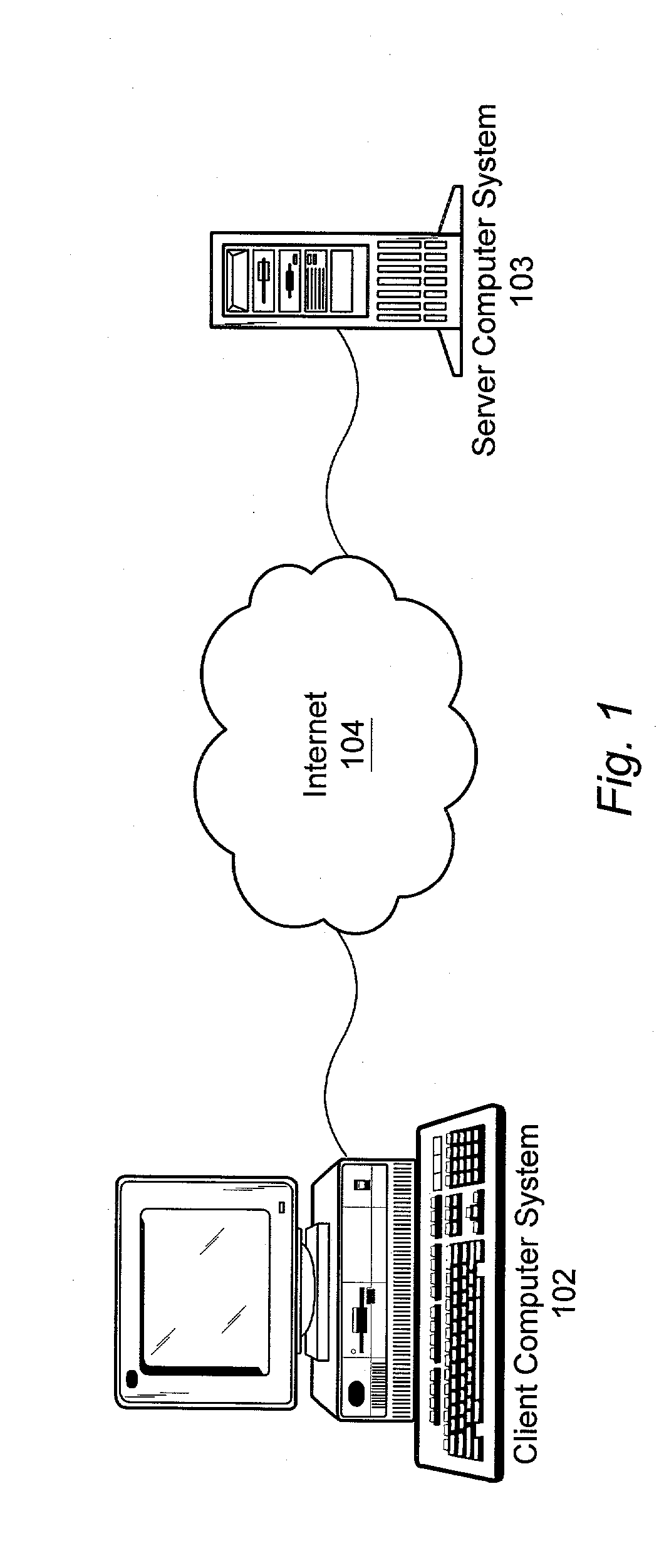

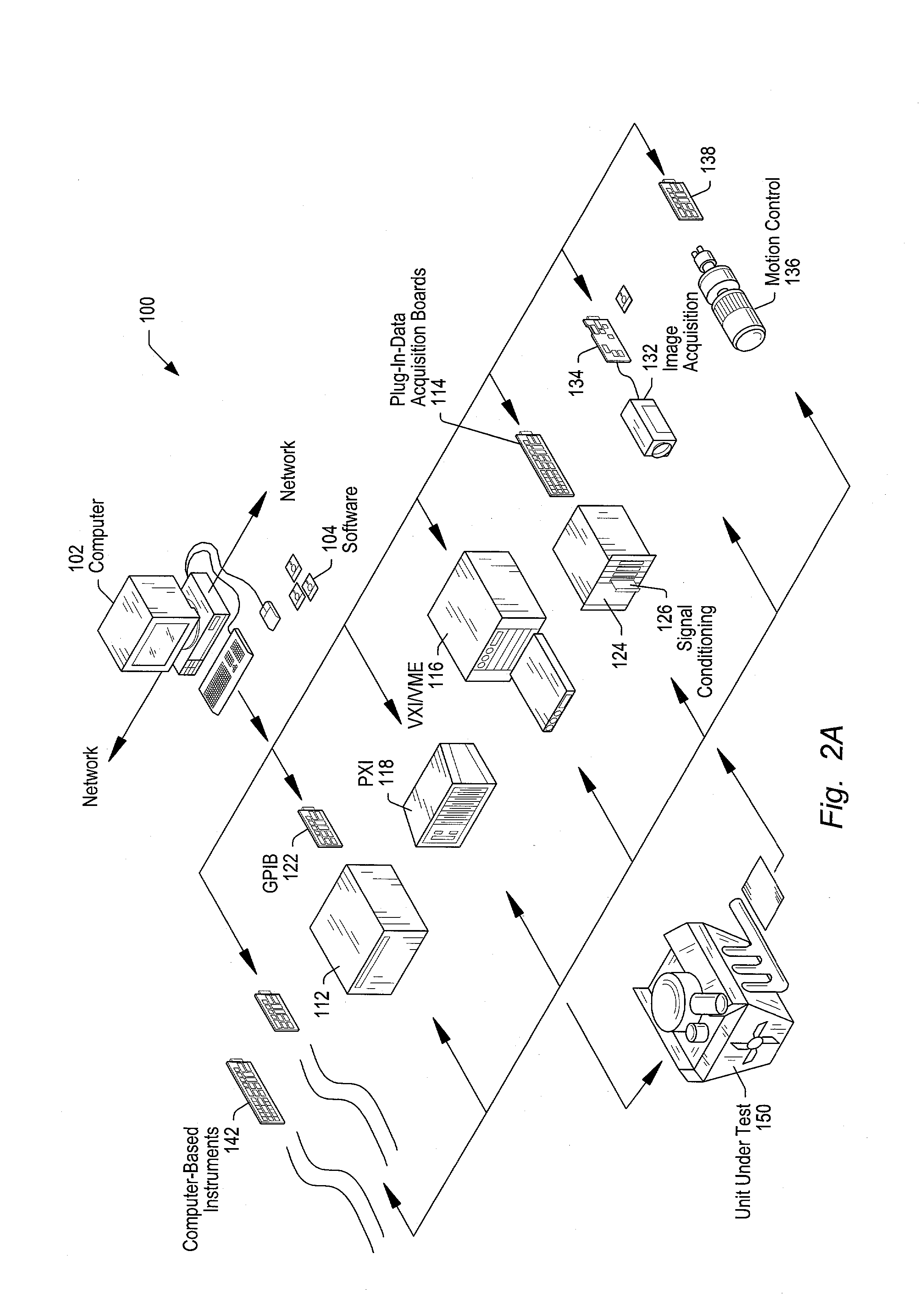

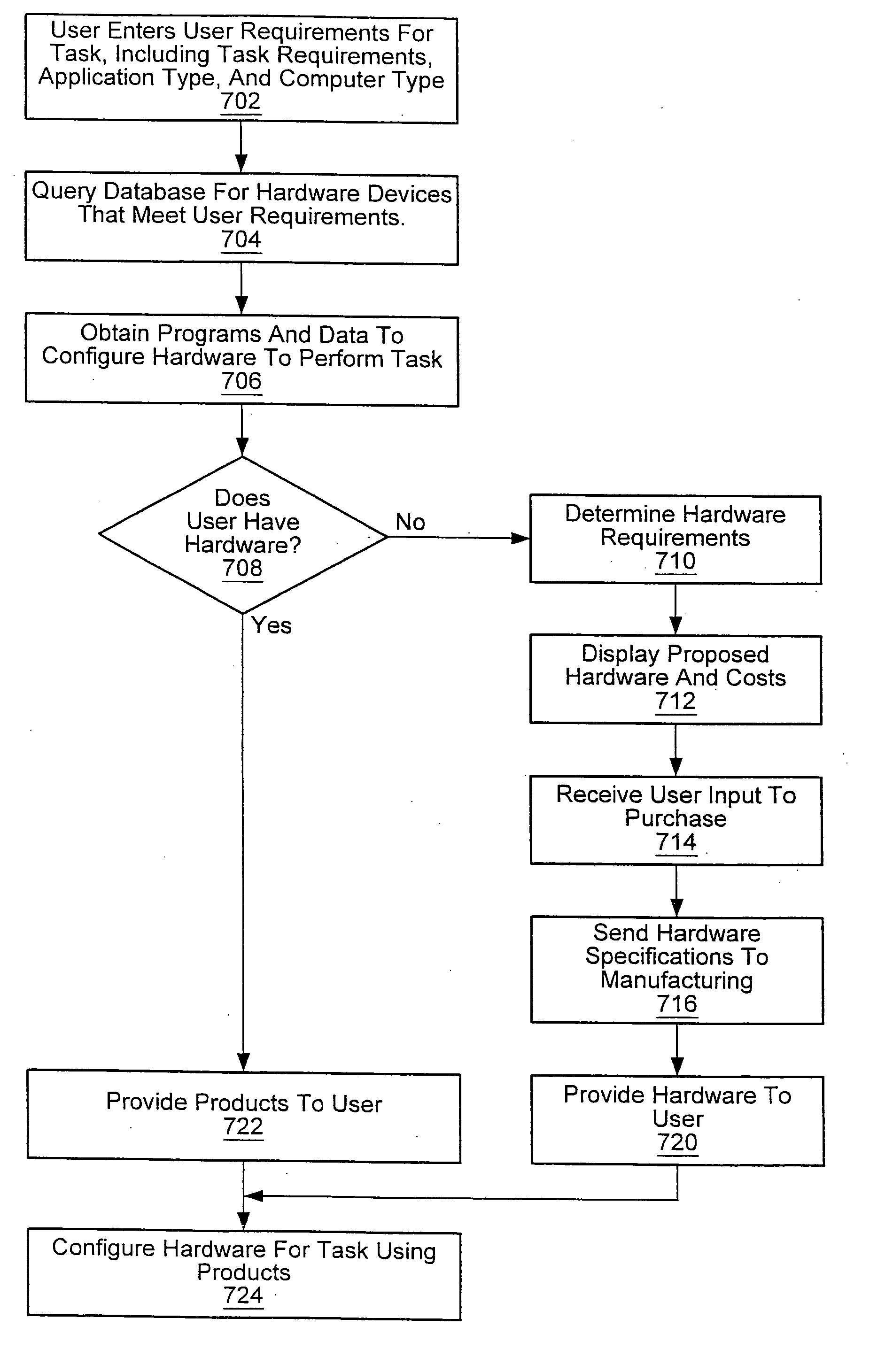

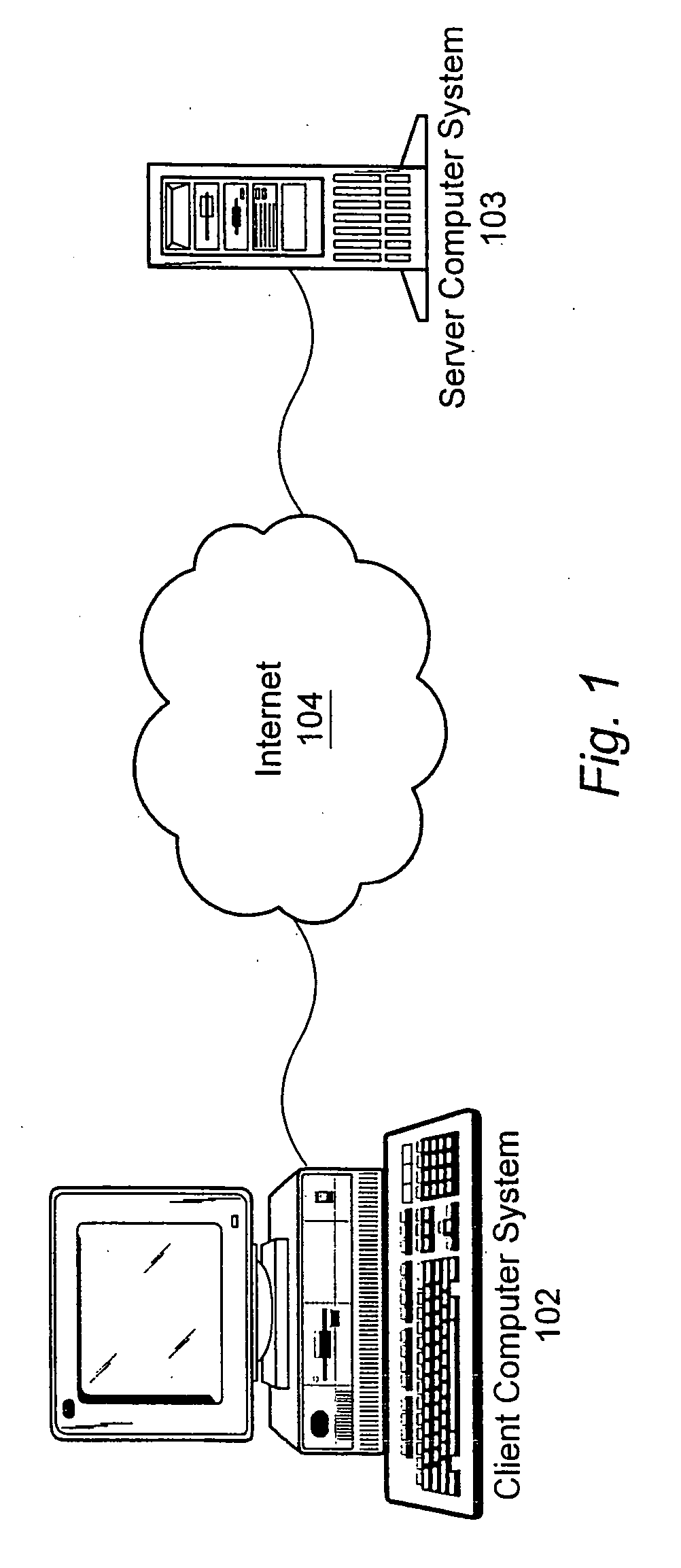

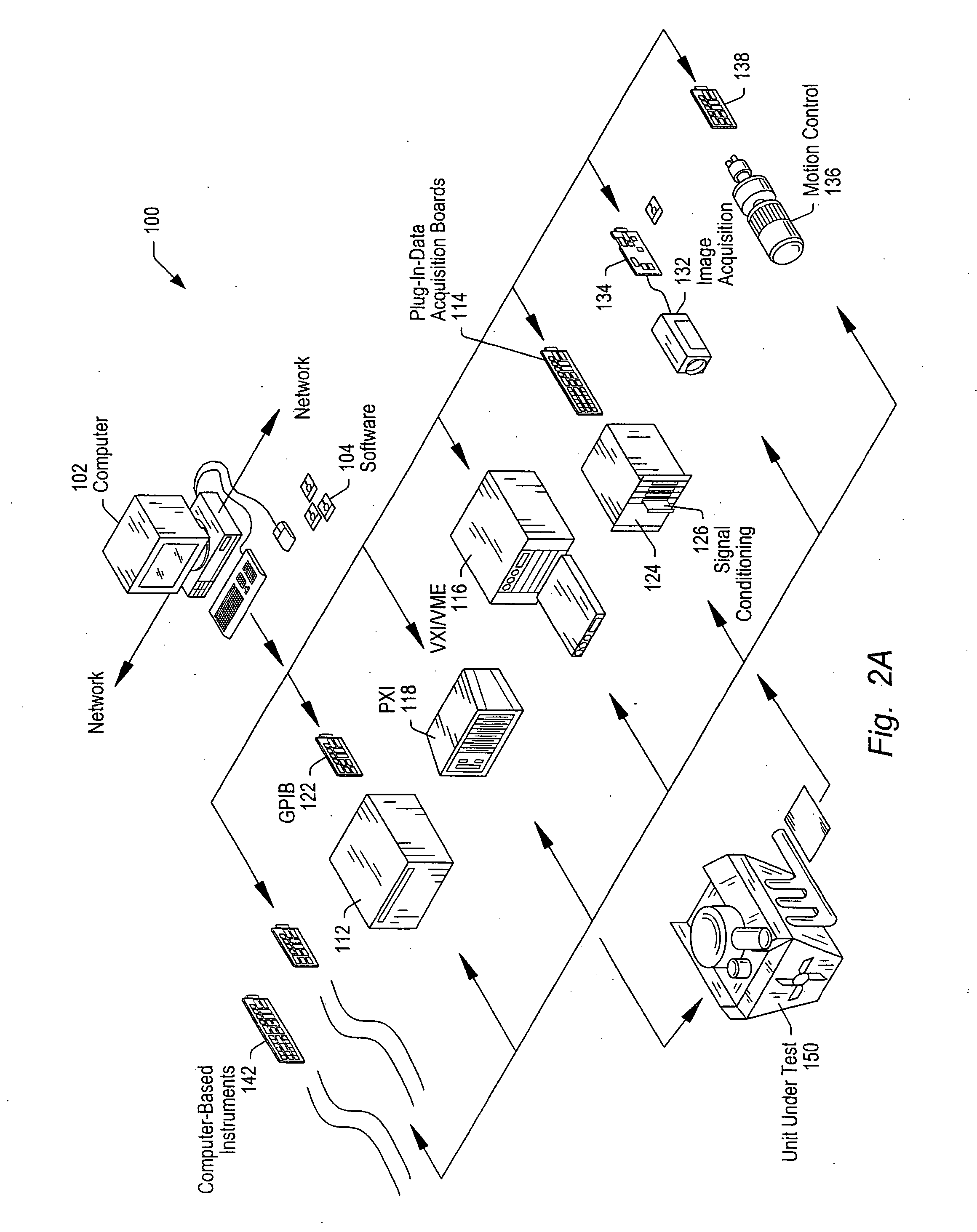

System and method for online configuration of a device for a measurement system. The user accesses a server with a client computer over a network and specifies a task. If the user lacks the hardware to perform the task, hardware specifications are sent to a manufacturer, who sends the hardware to the user. The hardware may be re-configurable hardware (a programmable hardware element or processor / memory based device). Software products (programs and / or data) for configuring measurement system hardware (and / or software) to perform the task may be sent to the user. The hardware may be configured automatically or by the user. The software products may include programs usable by the measurement system to perform the task, configuration information for configuring the client computer or other measurement device, and / or hardware configuration program(s) for configuring a programmable hardware element. Thus, hardware and / or software specific to the user's application are be provided to the user.

Owner:NATIONAL INSTRUMENTS

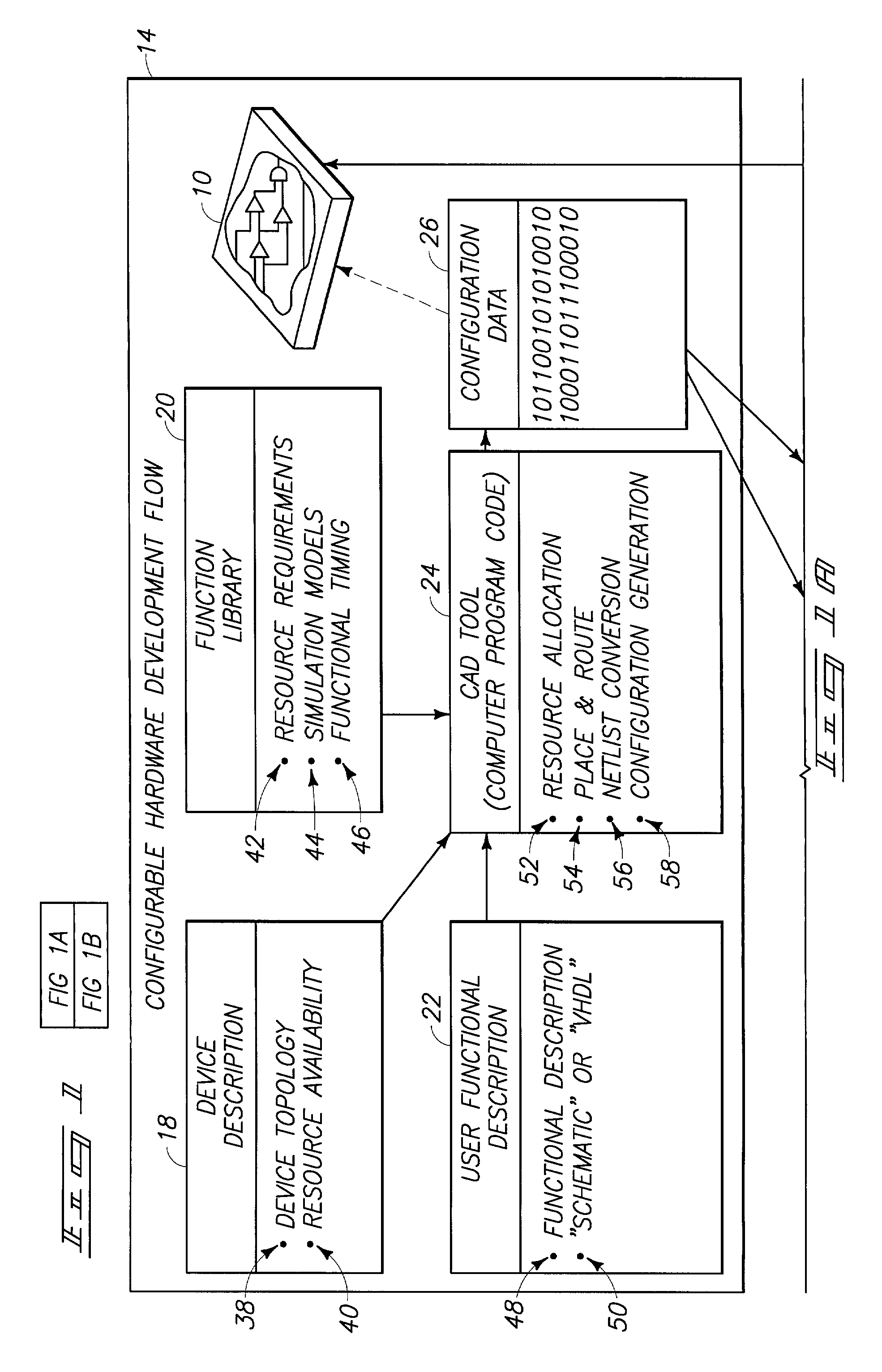

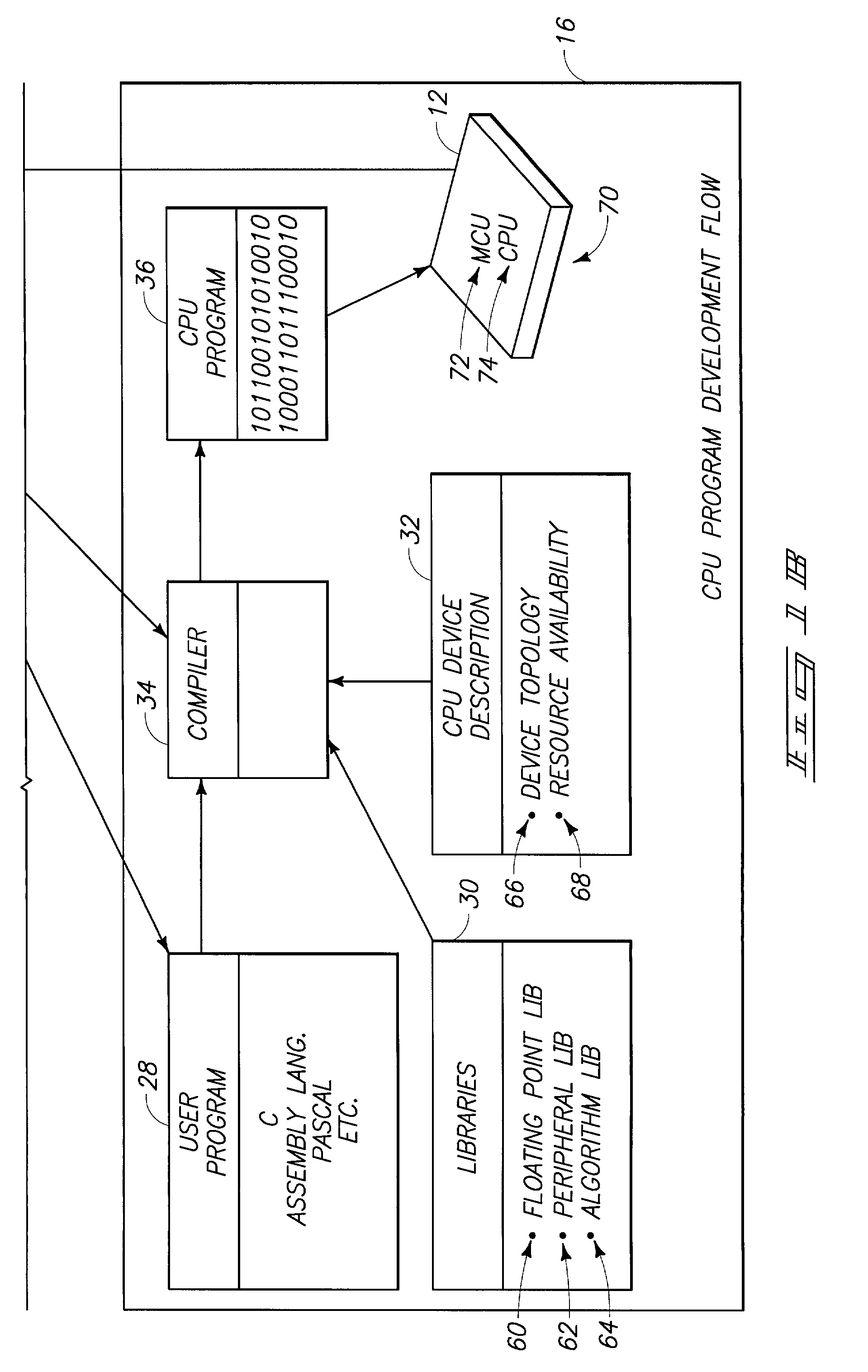

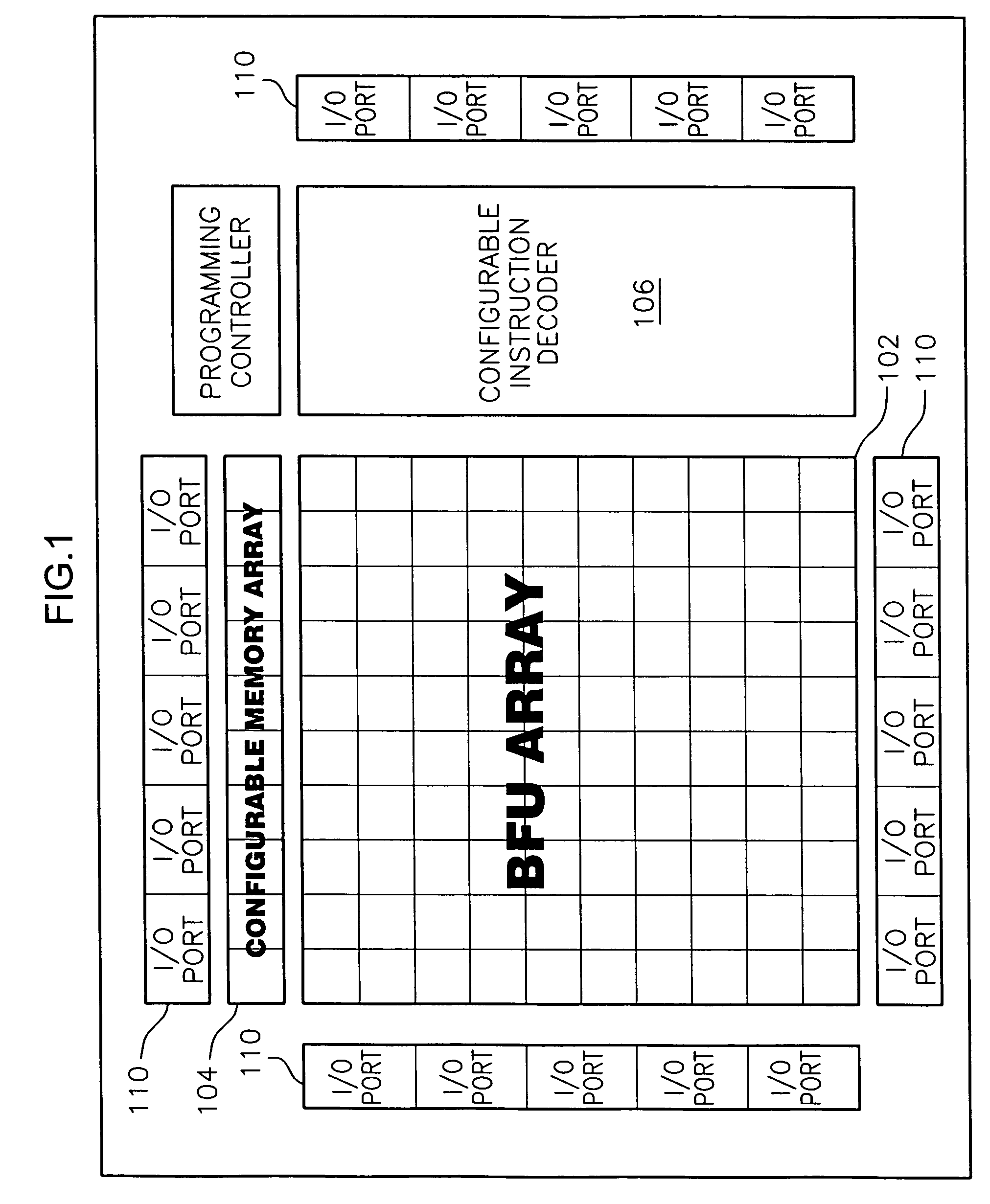

System and method for configuring analog elements in a configurable hardware device

InactiveUS7024654B2CAD circuit designSpecial data processing applicationsComputer hardwareCode generation

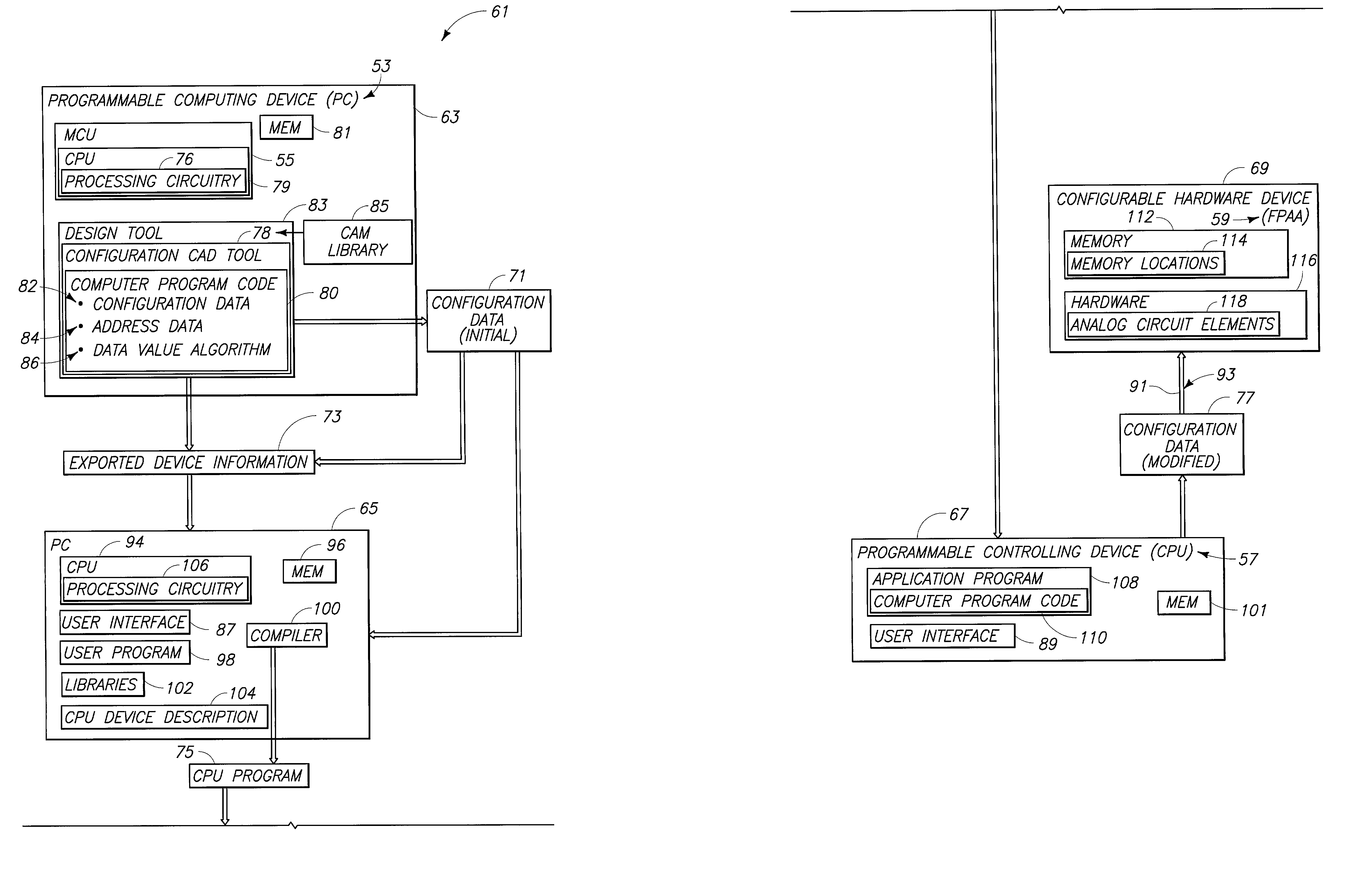

A system is provided for programming a configurable semiconductor device. The system includes a programmable controlling device, a programmable computing device, a communication link, a configurable hardware device, a design tool with first computer program code, and second computer program code. The configurable hardware device has memory with a plurality of memory locations and coupled with the programmable controlling device via the communication link. The design tool includes first computer program code embodied in a programmable computing device. The second computer program code is generated at least in part by the first computer program code and is embodied in the programmable controlling device for: a) applying configuration data to selected memory locations within the configurable hardware device to configure the configurable hardware device; b) determining a location of a subset of at least one of (i) the programmable memory locations in the configurable hardware device and (ii) the configuration data to be modified; and c) determining a new data value to be applied to the subset of at least one of (i) the memory locations in the configurable hardware device and (ii) the configuration data. The design tool provides at least one of configuration data, address data, and a data value algorithm usable in performing at least one of a), b), and c). A method is also provided.

Owner:F POSZAT HU

System and method for online specification of measurement hardware

InactiveUS20030036871A1Error preventionFrequency-division multiplex detailsComputer hardwareGraphics

A system and method for online configuration of a measurement device for a measurement system. The user accesses a server with a client computer over a network and specifies a desired measurement task. If the user lacks the hardware required to perform the task, hardware specifications and configuration software and / or data specific to the user's application, i.e., to perform the task, are sent to a manufacturer, who pre-configures the hardware with the configuration software and / or data to perform the task and sends the pre-configured hardware to the user. The hardware may be re-configurable hardware, such as a programmable hardware element or processor / memory based device. Configuration software and / or data for configuring the user's measurement system hardware (and / or software) to perform the desired task may also be sent to the user. The configuration software sent to the user may comprise a graphical program usable by the measurement system to perform the task.

Owner:NATIONAL INSTRUMENTS

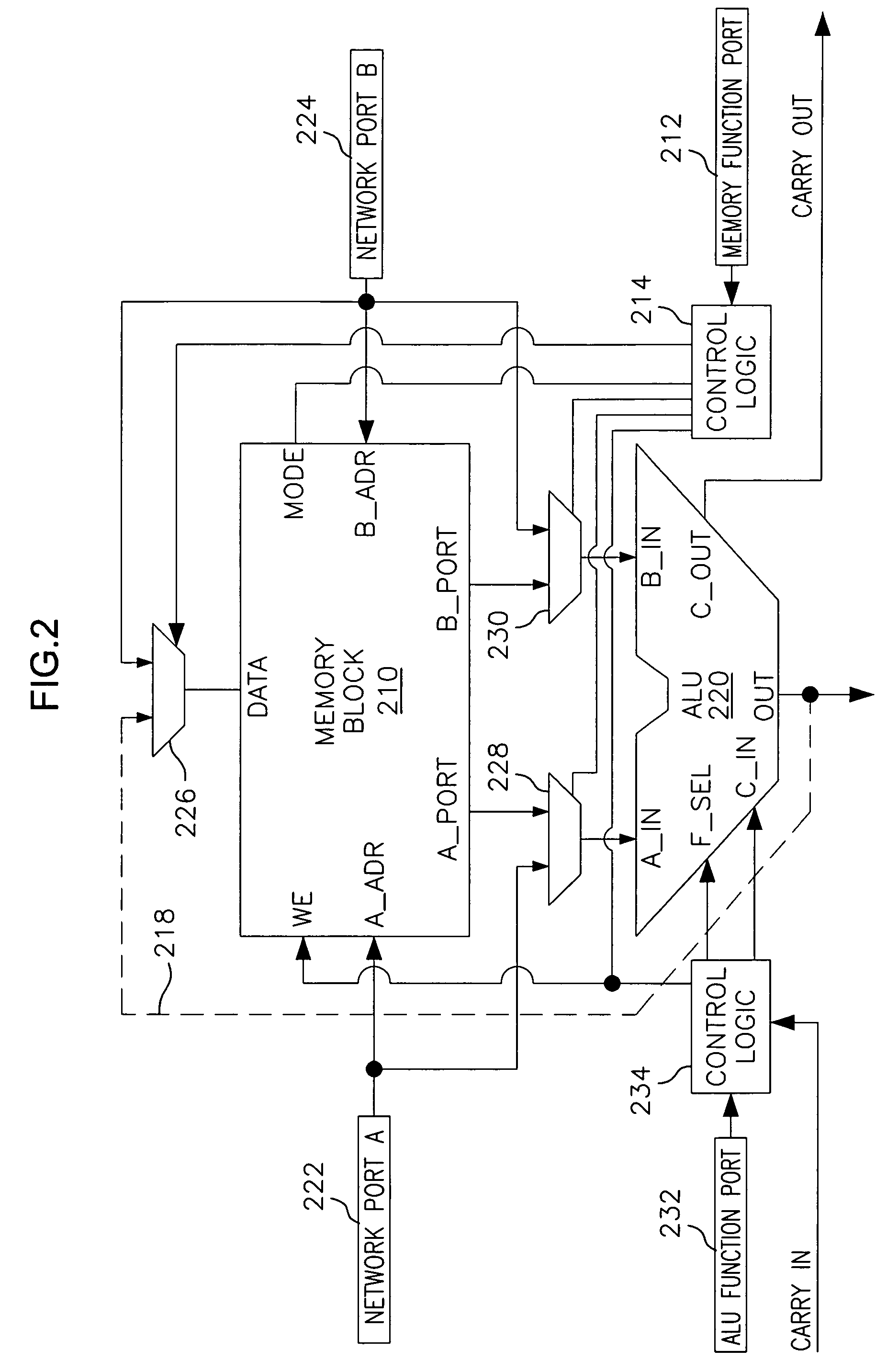

System and method for preparing software for execution in a dynamically configurable hardware environment

A system and method for creating run time executables in a configurable processing element array is disclosed. This system and method includes the step of partitioning a processing element array into a number of defined sets of hardware accelerators, which in one embodiment are processing elements called “bins”. The system and method then involves decomposing a program description in object code form into a plurality of “kernel sections”, where the kernel sections are defined as those sections of object code which are candidates for hardware acceleration. Next, mapping the identified kernel sections into a number of hardware dependent designs is performed. Finally, a matrix of the bins and the designs is formed for use by the run time system.

Owner:QUALCOMM INC

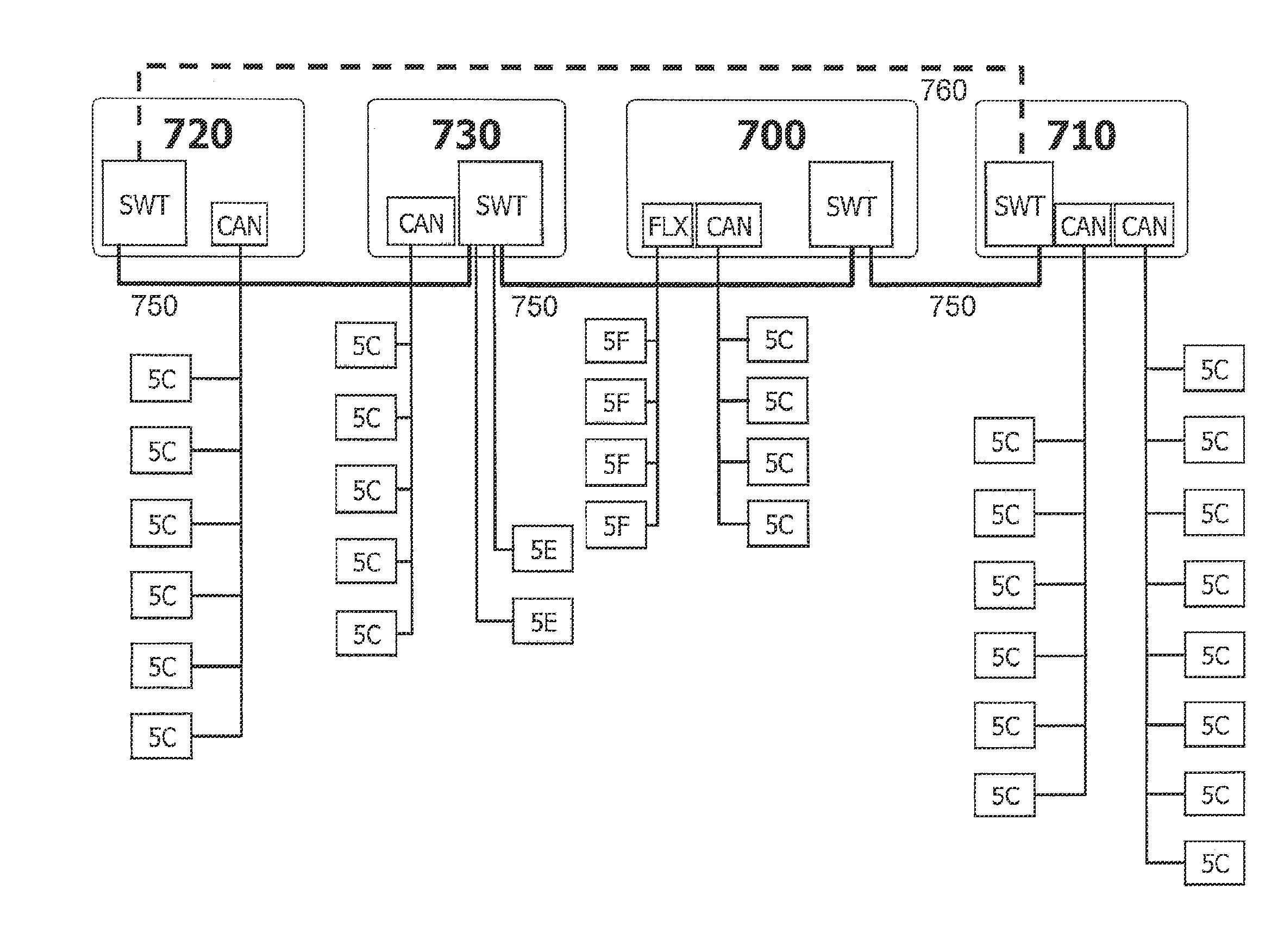

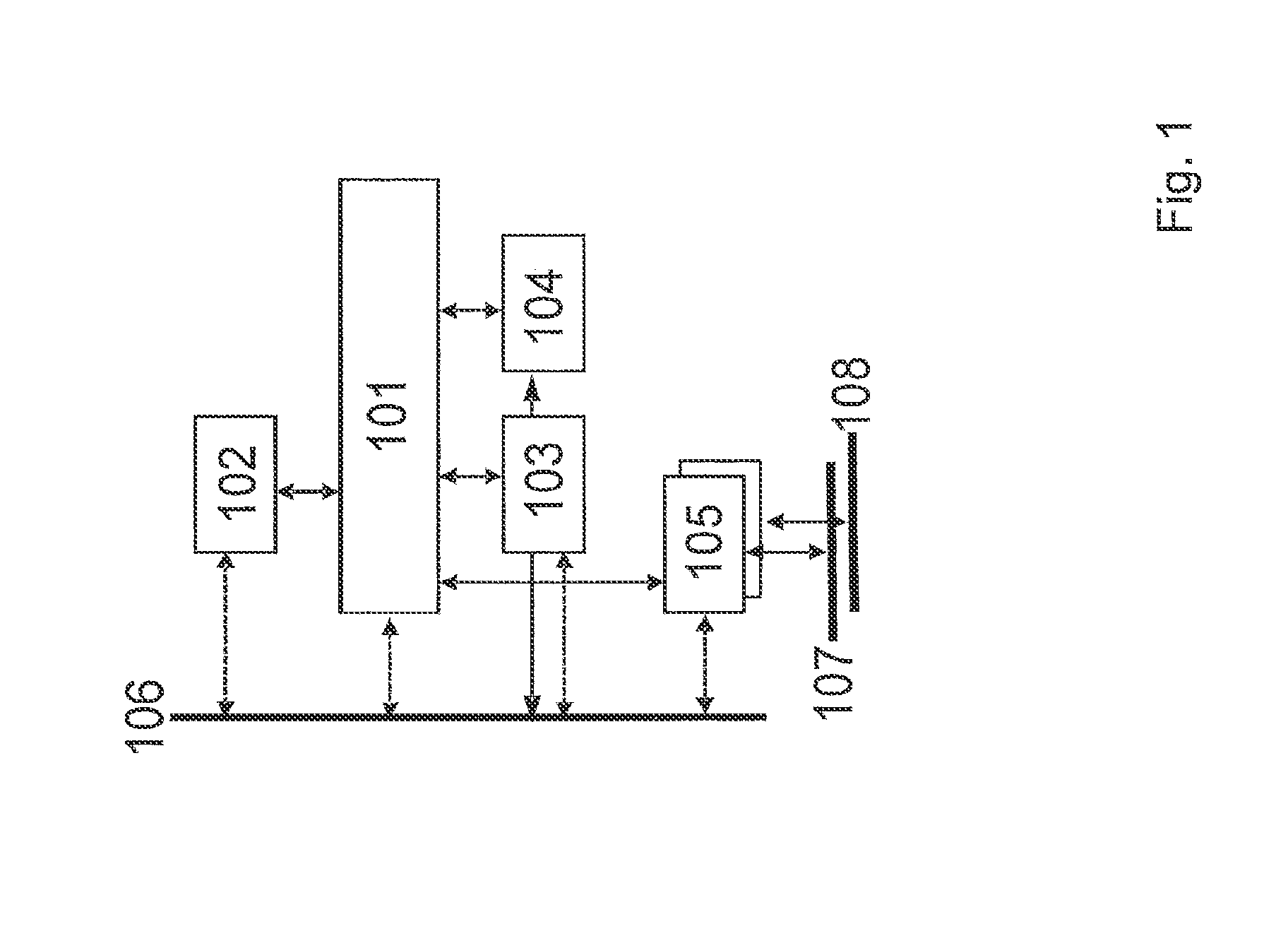

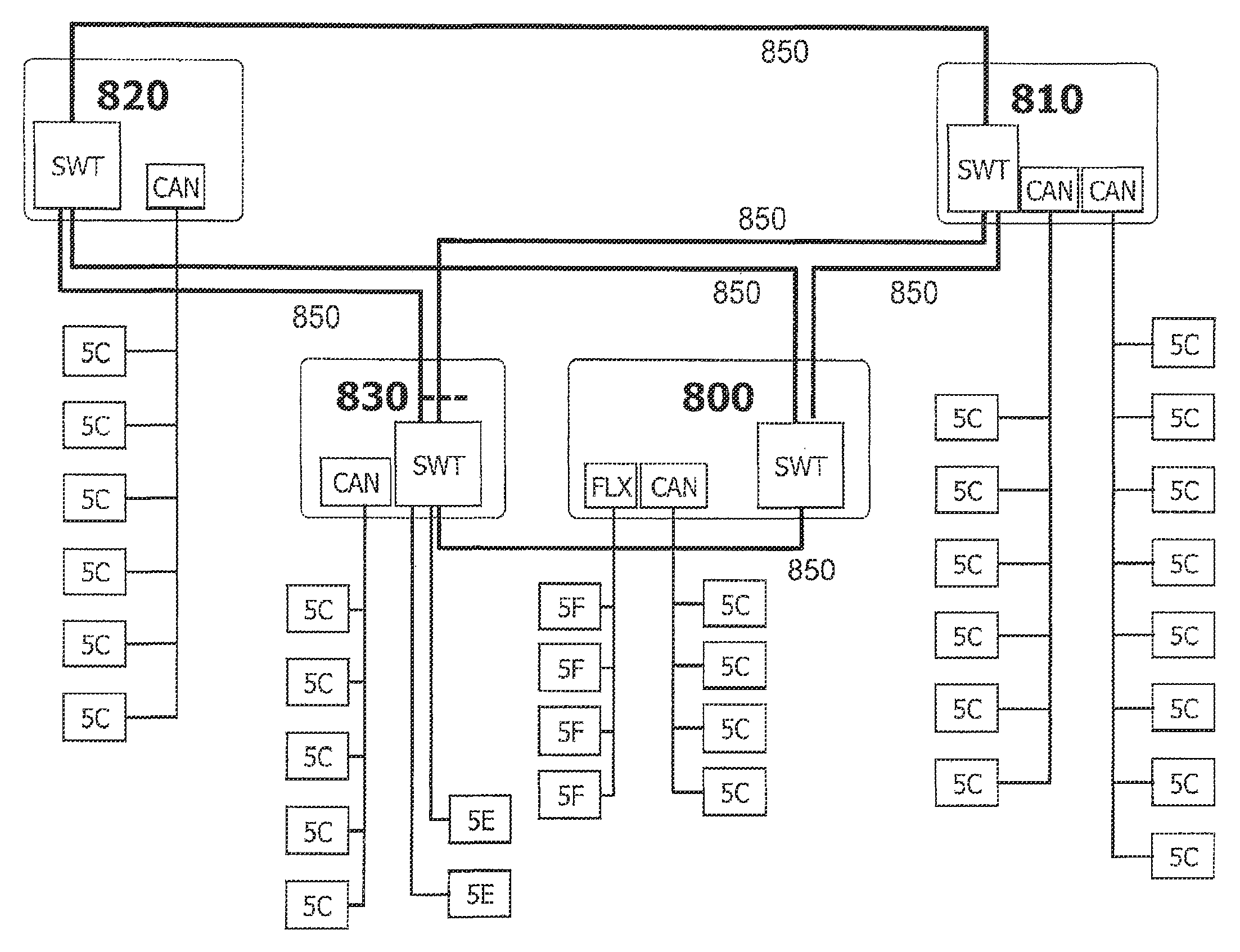

Gateway module for a communications system, communications system, and method for transmitting data between users of a communications system

ActiveUS20140133350A1Save powerShorten the timeData switching by path configurationEnergy efficient computingCommunications systemNetwork Communication Protocols

A gateway module for connection of at least two sub-networks is described. A first sub-network of the at least two sub-networks supports a data transmission in accordance with a first communications protocol, especially CAN, FlexRay, LIN, MOST or Ethernet, and a second sub-network of the at least two sub-networks supports a data transmission in accordance with a second communications protocol, especially CAN, FlexRay, LIN, MOST or Ethernet. The gateway module has a configurable hardware circuit which is adapted to manipulate and forward data from the first sub-network and to the second sub-network taking into consideration the first communications protocol and the second communications protocol.

Owner:ROBERT BOSCH GMBH

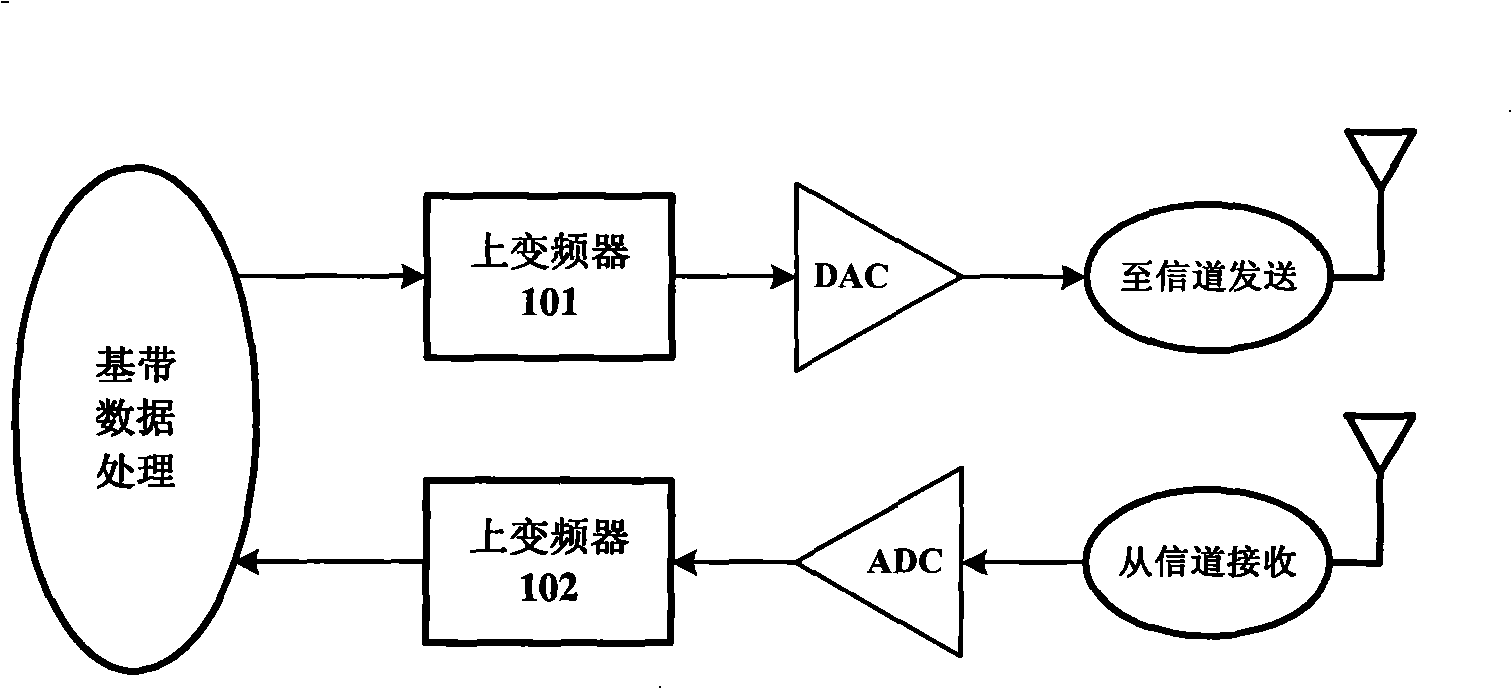

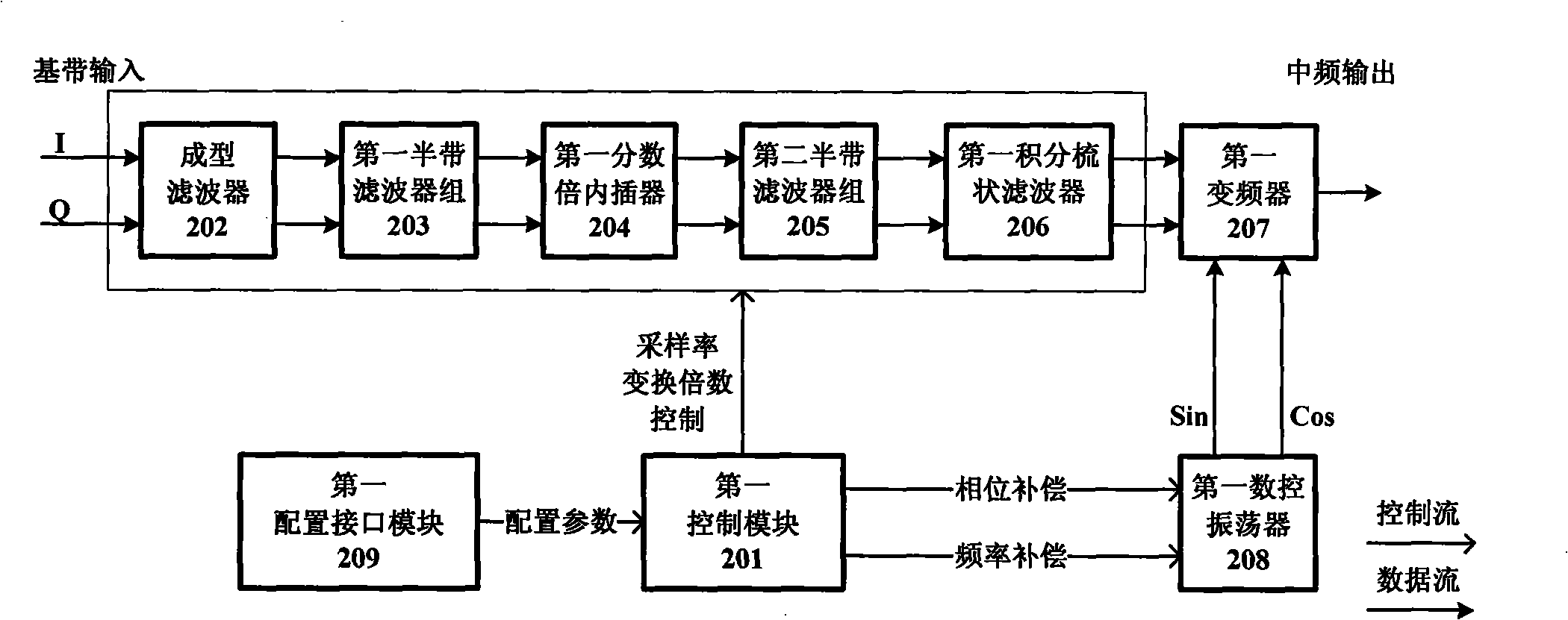

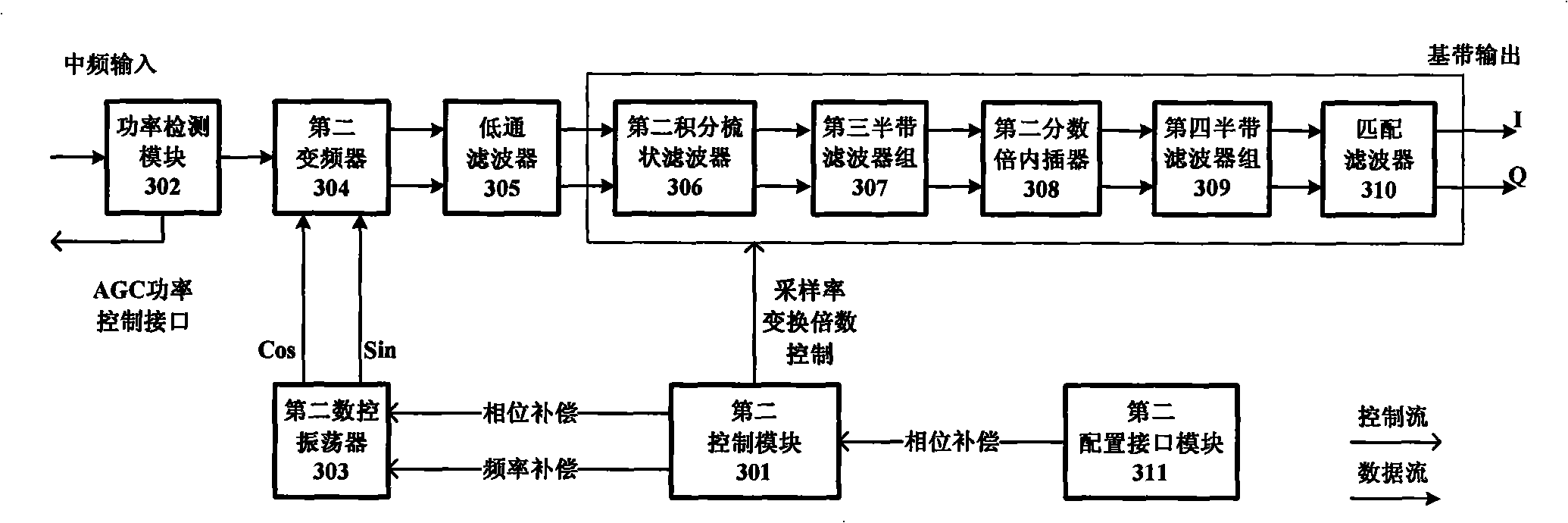

An easy-to-realize method and device for full digital frequency conversion

InactiveCN101262240AImprove versatilityIncrease working frequencyModulation transferenceTransmissionControl signalIntermediate frequency

The invention discloses an all digital frequency converting method and a device thereof, being easily realized for hardware. The method and the device are essentially used for sample rate convertion of rational number-times of baseband signals and the convertion of the baseband signals and the intermediate frequency signals in digital communication. Under the coordination of control signals and enabling signals, the convertion of signal sample rate can be finished and the convertion of the baseband signals and the intermediate signals can be finished through the reasonable matching of variable integral number-times wave filtering and fraction-times interpolation. The system of the invention essentially comprises a frequency mixer, a cascade connection integral comb filter, a fraction-time interpolating device, a half-band filter, a signal shaping filter, a power detection module and a control interface. The configurable hardware implemented structure of the invention is applicable to a plurality of modulation methods, has the advantages of low resource consumption and good portability, and is used for various wireless communication systems such as multilevel phase shift keying (MPSK), orthogonal frequency division multiplex (OFDM), direct sequence spread spectrum (DSSS) and continuous phase modulation (CPM), etc.

Owner:ZHEJIANG UNIV

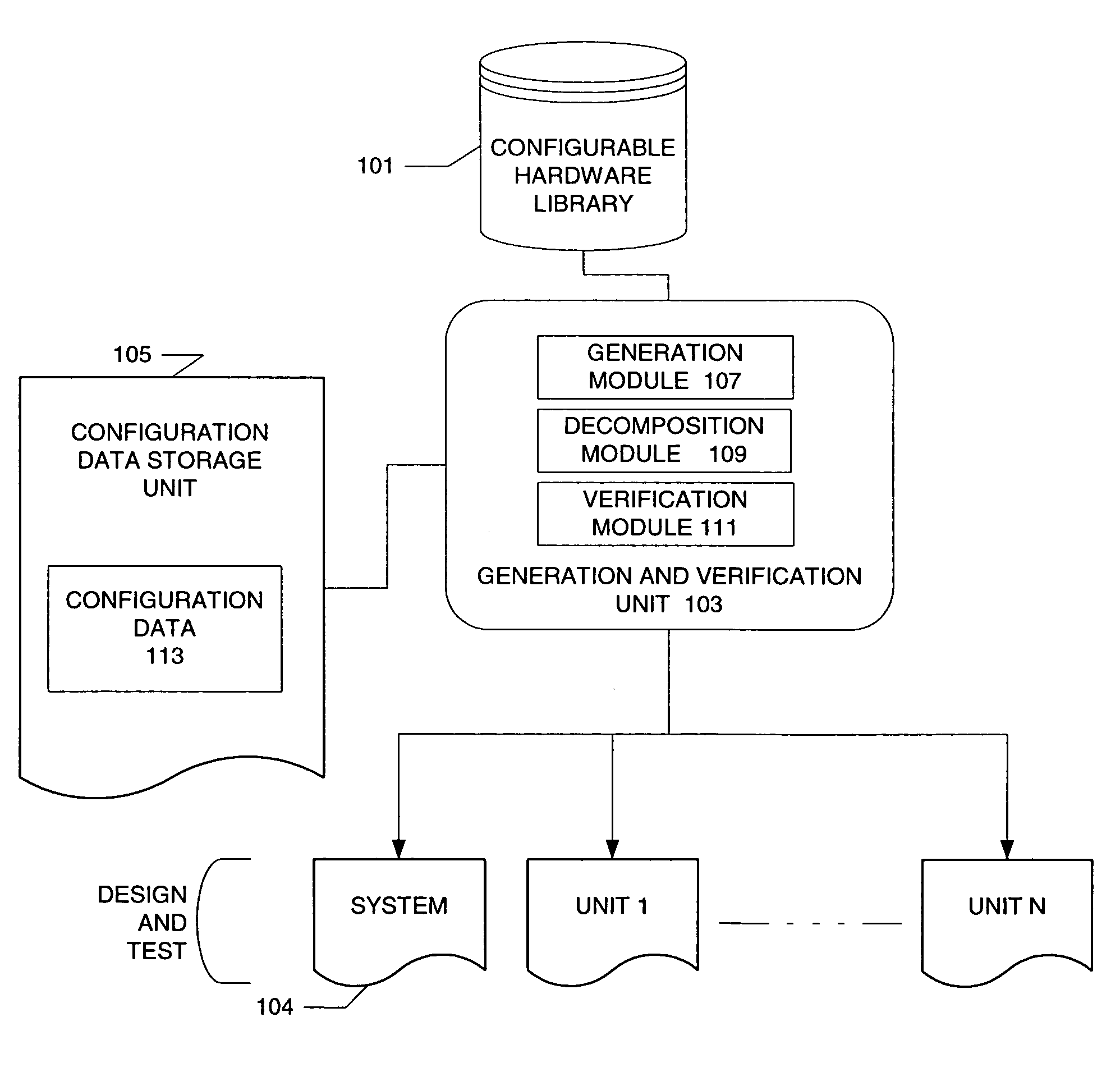

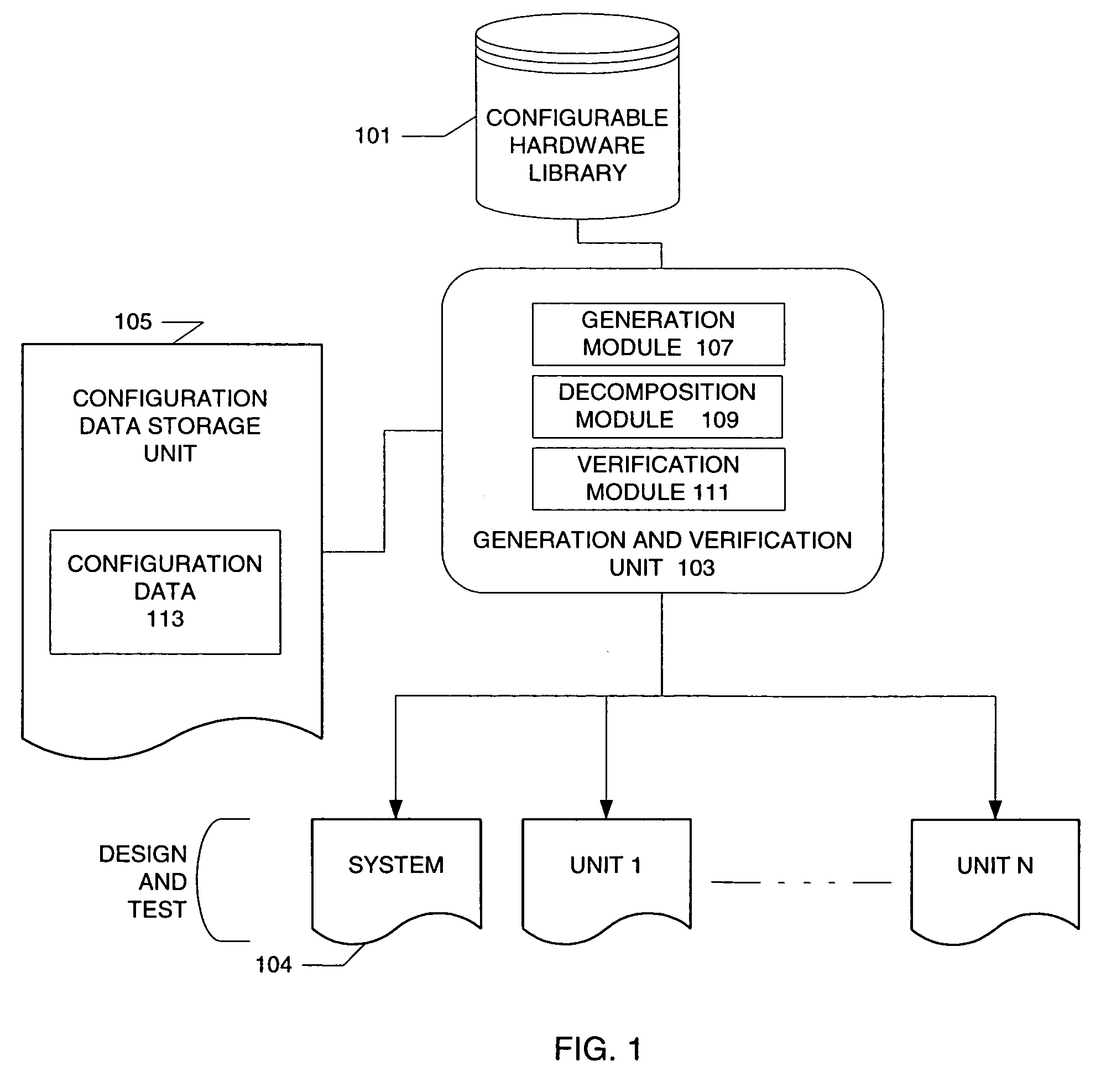

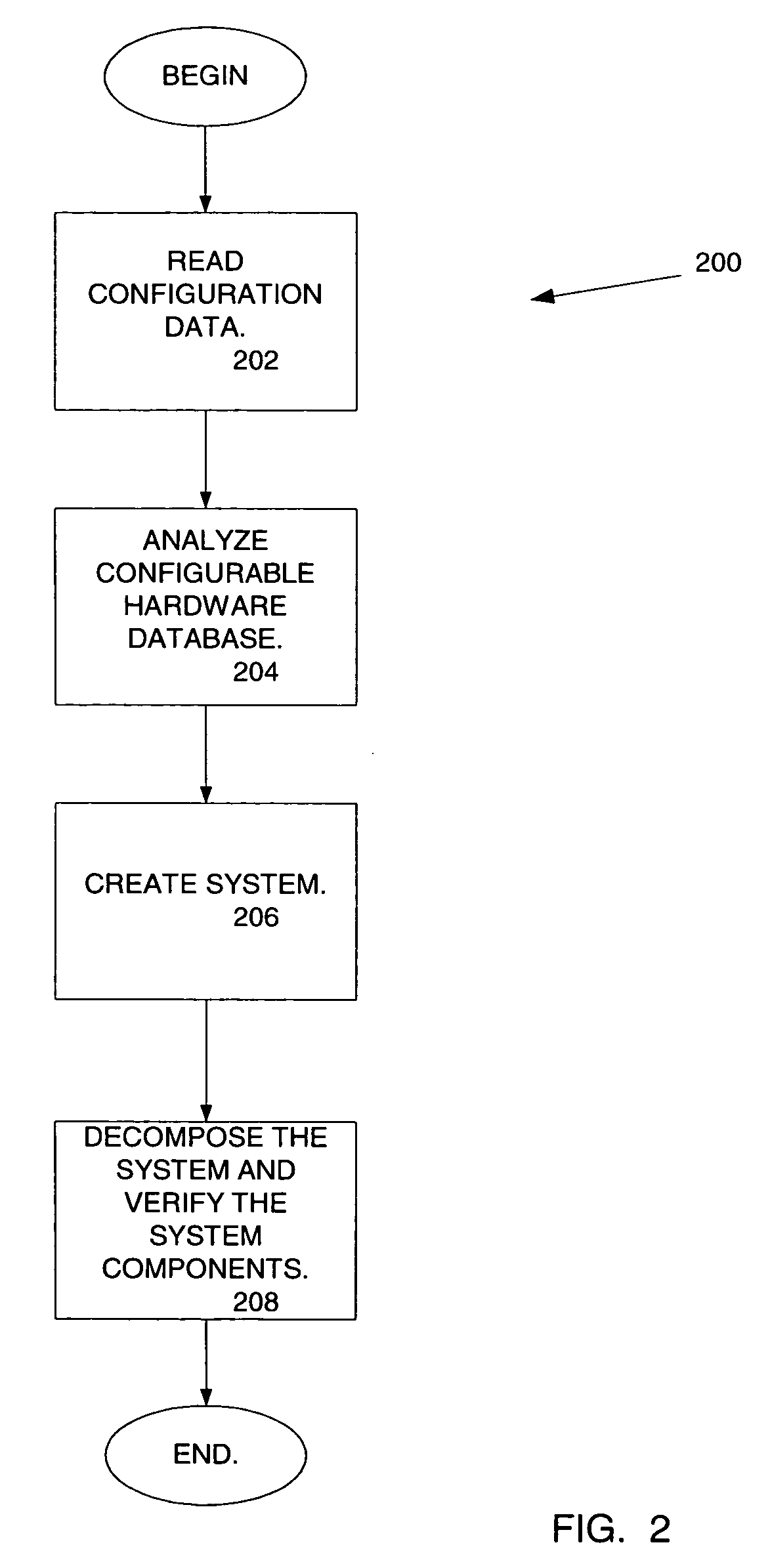

Method and apparatus for decomposing and verifying configurable hardware

The present invention includes a method and apparatus for decomposing and verifying configurable hardware. In one embodiment, the method includes automatically decomposing a set of one or more units at a first level of a configurable hardware system design hierarchy into a set of two or more units of a lower level of the hardware system design hierarchy. The set of one or more units at a first level includes one or more units dynamically instantiated at design creation time as well as at least a first unit composed of a previously instantiated hardware system composed with two or more levels of units within the hardware system design hierarchy of the previously instantiated hardware system.

Owner:META PLATFORMS TECH LLC

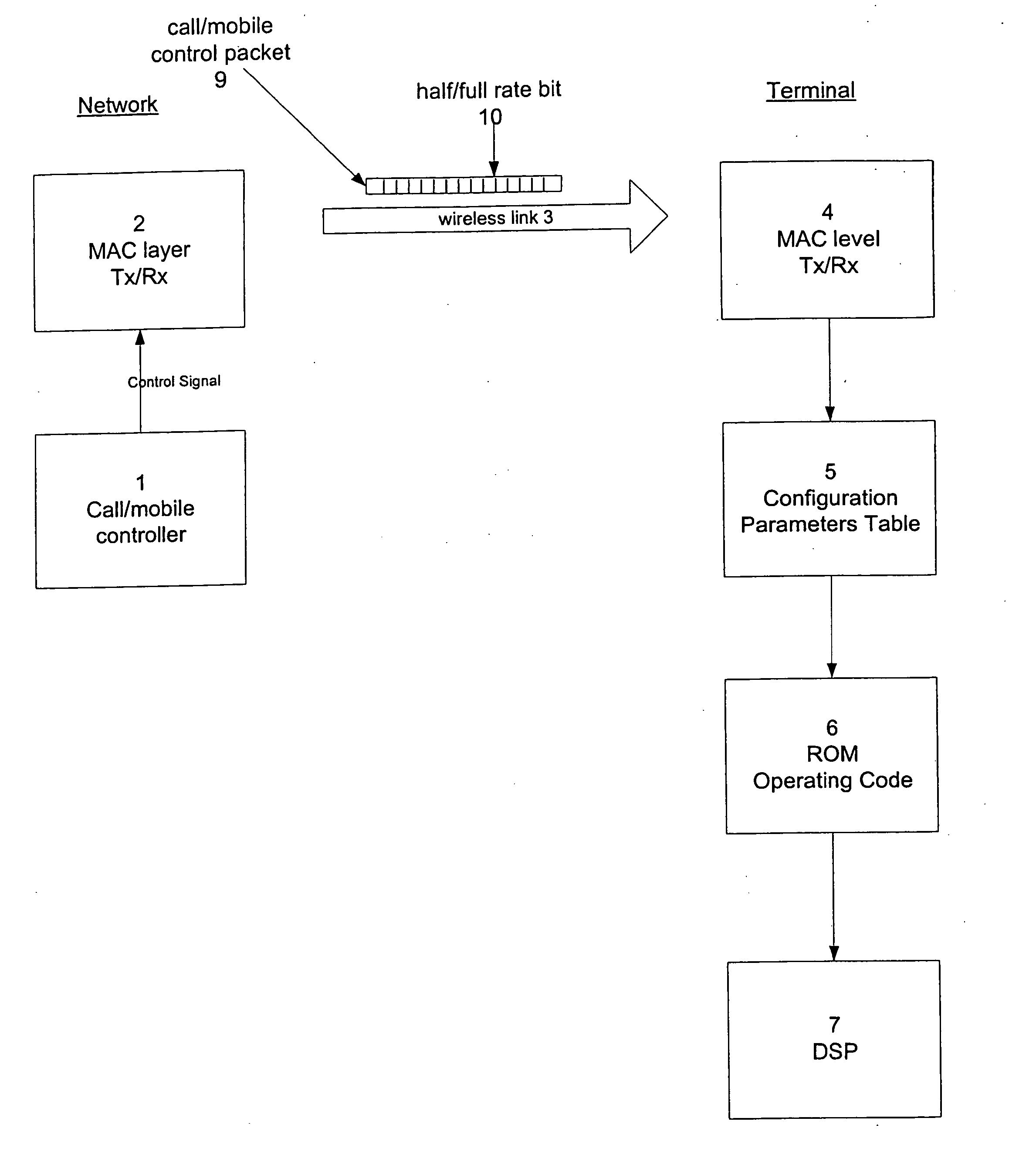

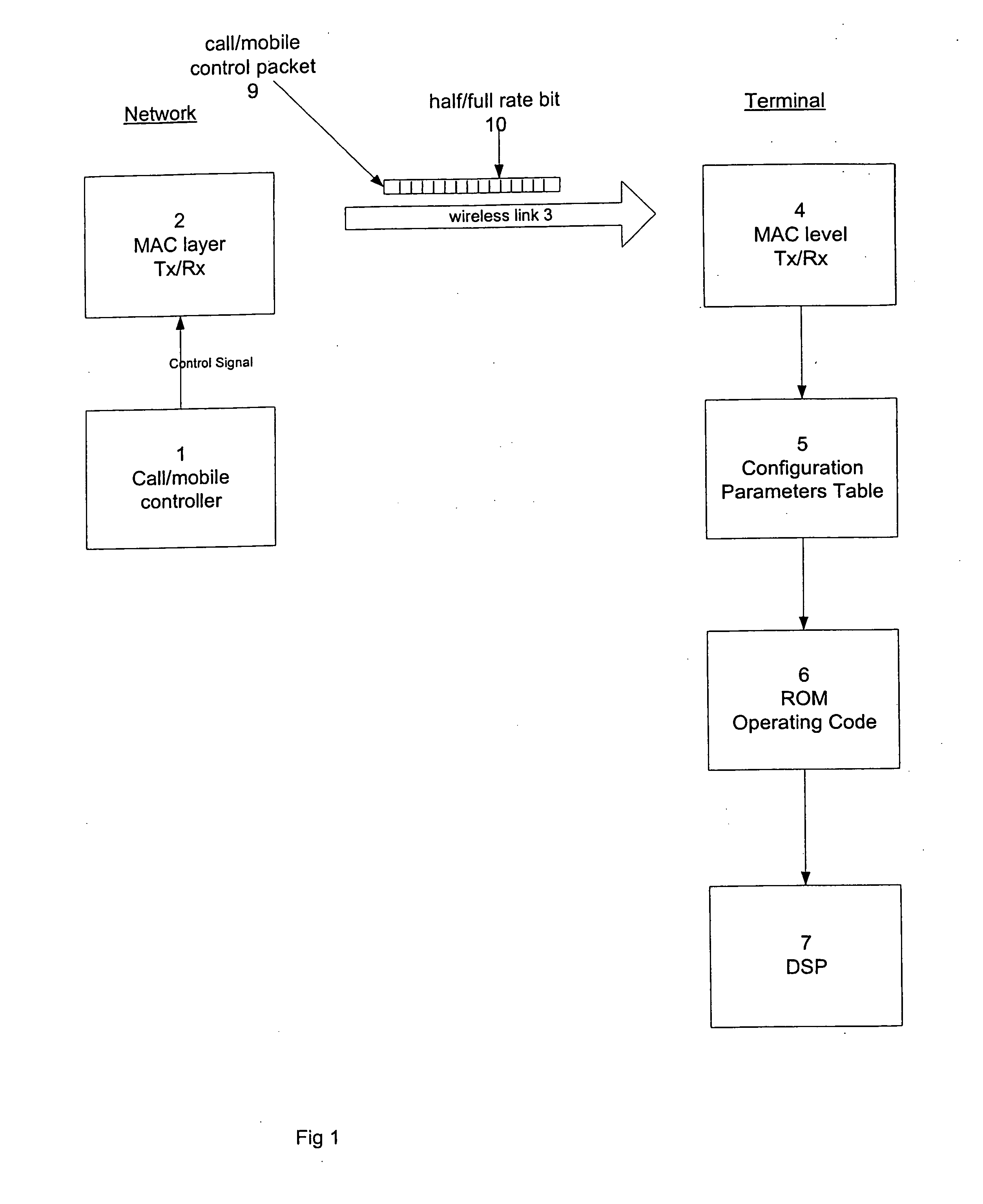

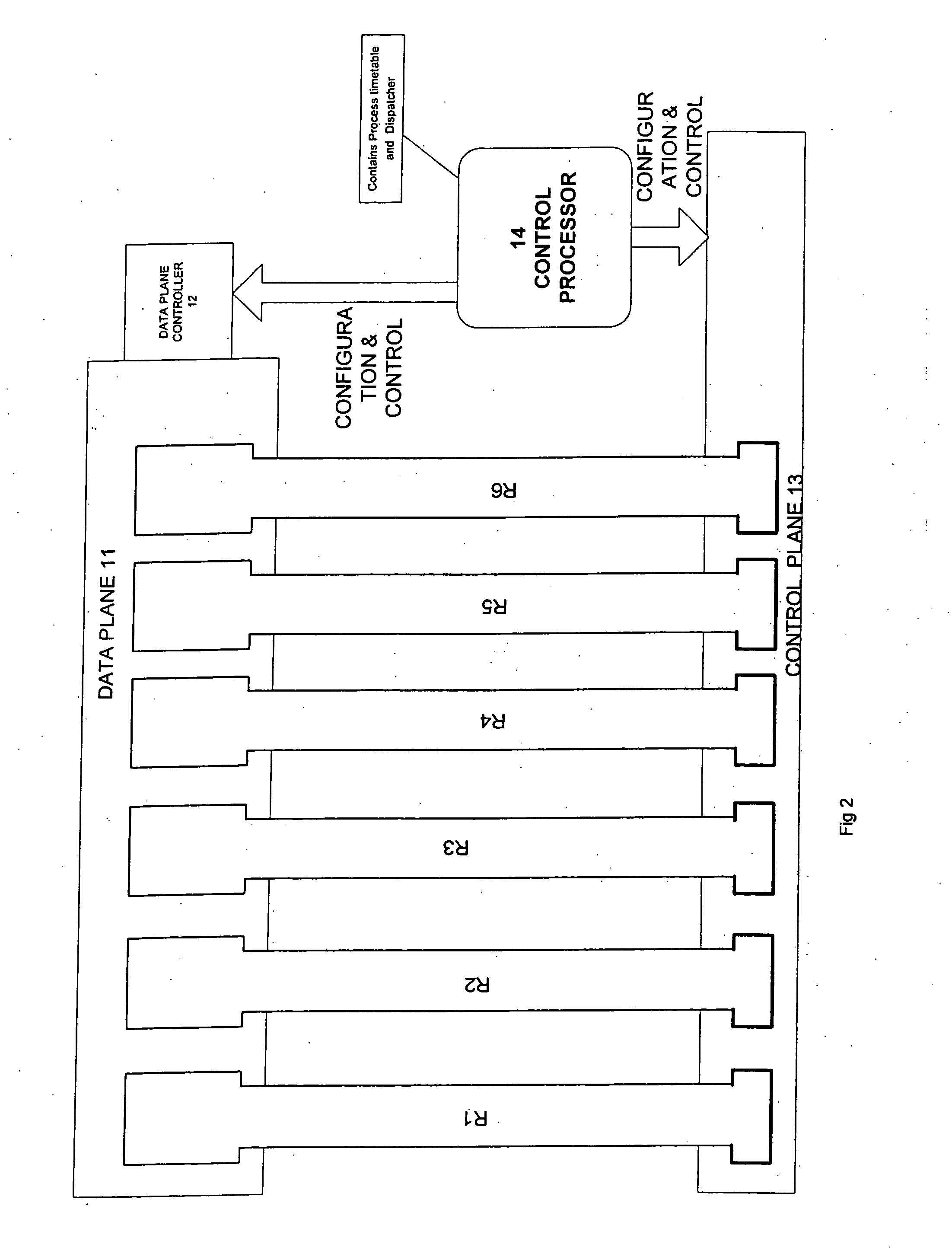

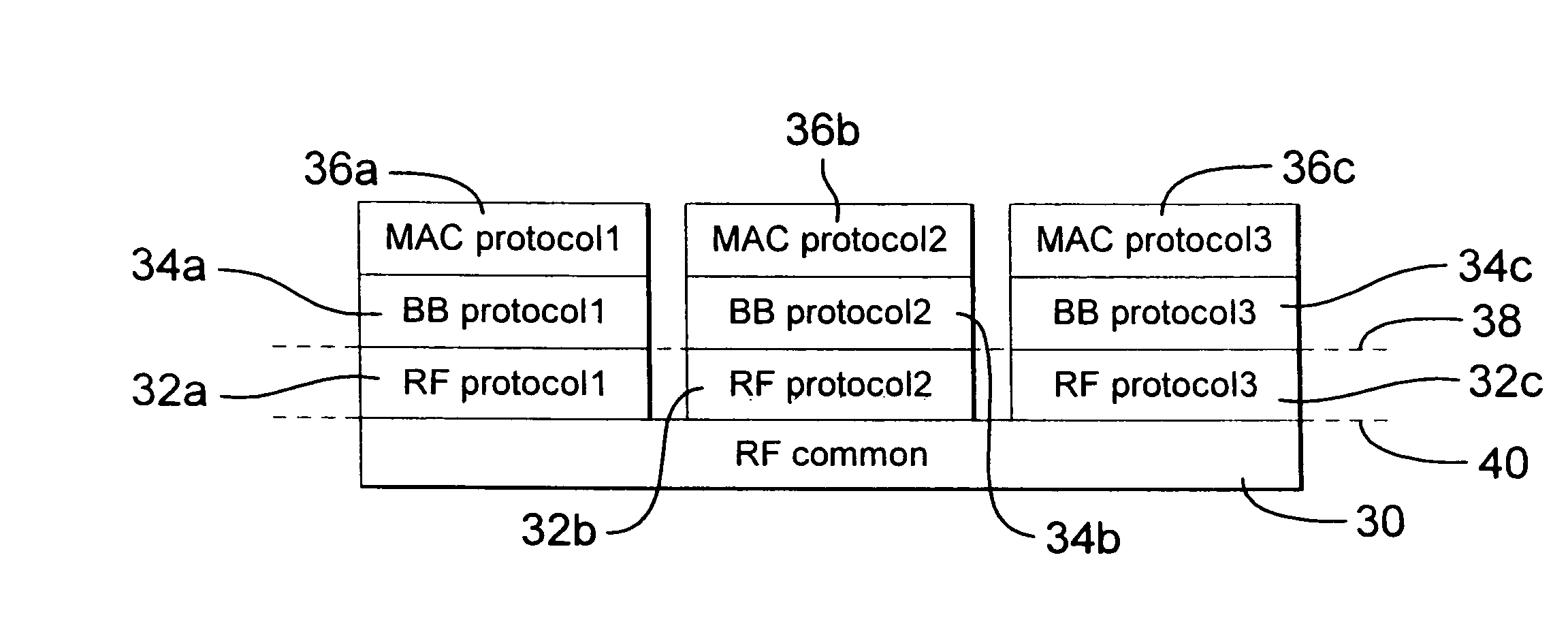

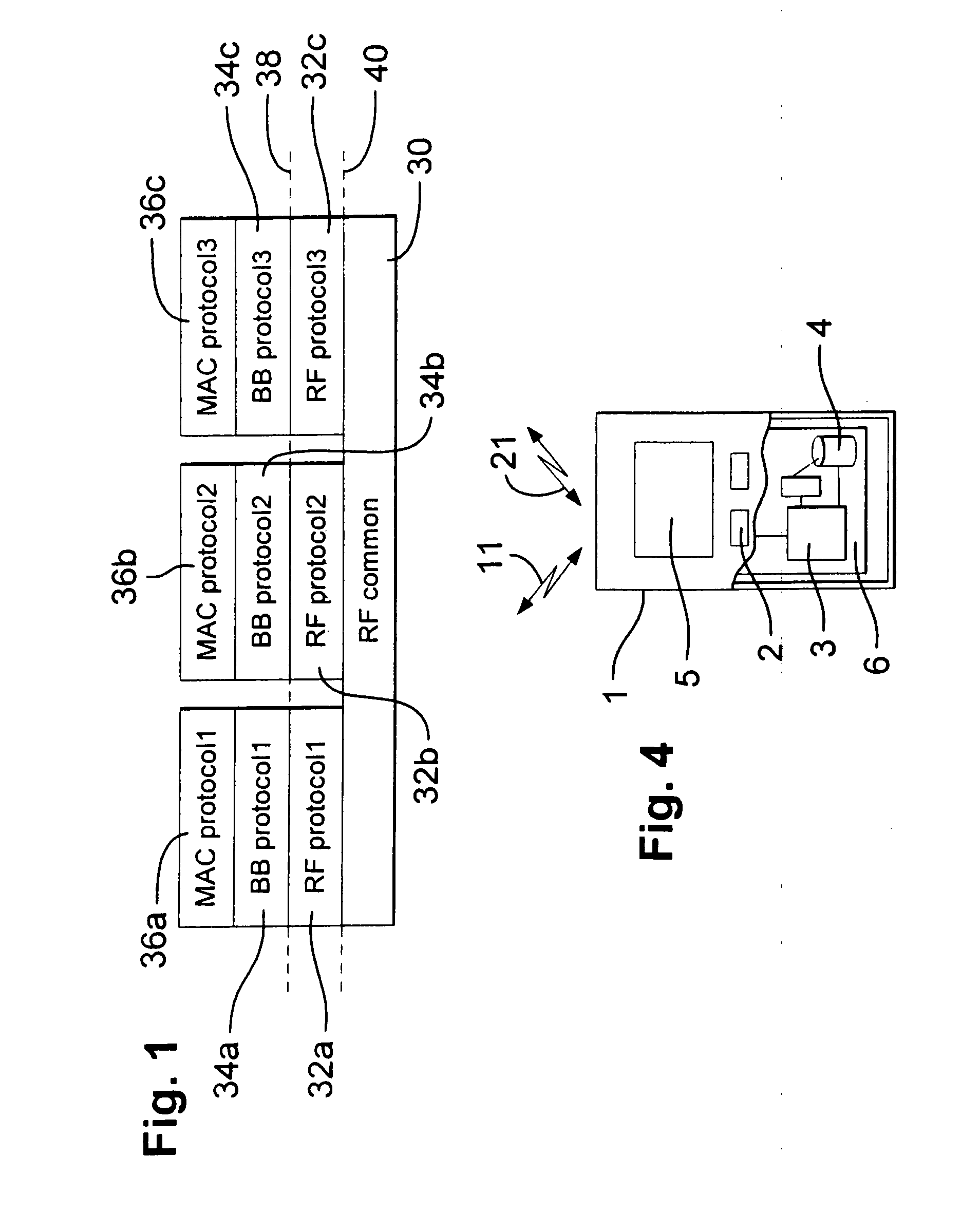

Reconfigurable signal processing module

InactiveUS20050152322A1Good flexibilityRadio/inductive link selection arrangementsAutomatic exchangesCommunications systemConfigurable hardware

The present invention relates to re-configurable signal processing modules in particular, although not exclusively, for wireless communications terminals. In general terms in one aspect the present invention provides a system for reconfiguring a signal processing module having a number of re-configurable resources such as re-configurable hardware blocks including ASIC's and field programmable logic gate arrays (FPGA's), as well as software modules for implementing different functions and which can be run on a DSP or other processing platform within the signal processing module. The module may be a mobile terminal or a base station in a wireless communications system for example. The system comprises means for generating a commands data structure comprising configuration commands for the resources, and may further comprise means for communicating this data structure to the signal processing module. The module has means for reconfiguring itself using this data structure. Typically the data structure will be a process timetable having time stamped configuration and run-time commands suitable for being dispatched to the appropriate resource.

Owner:KK TOSHIBA

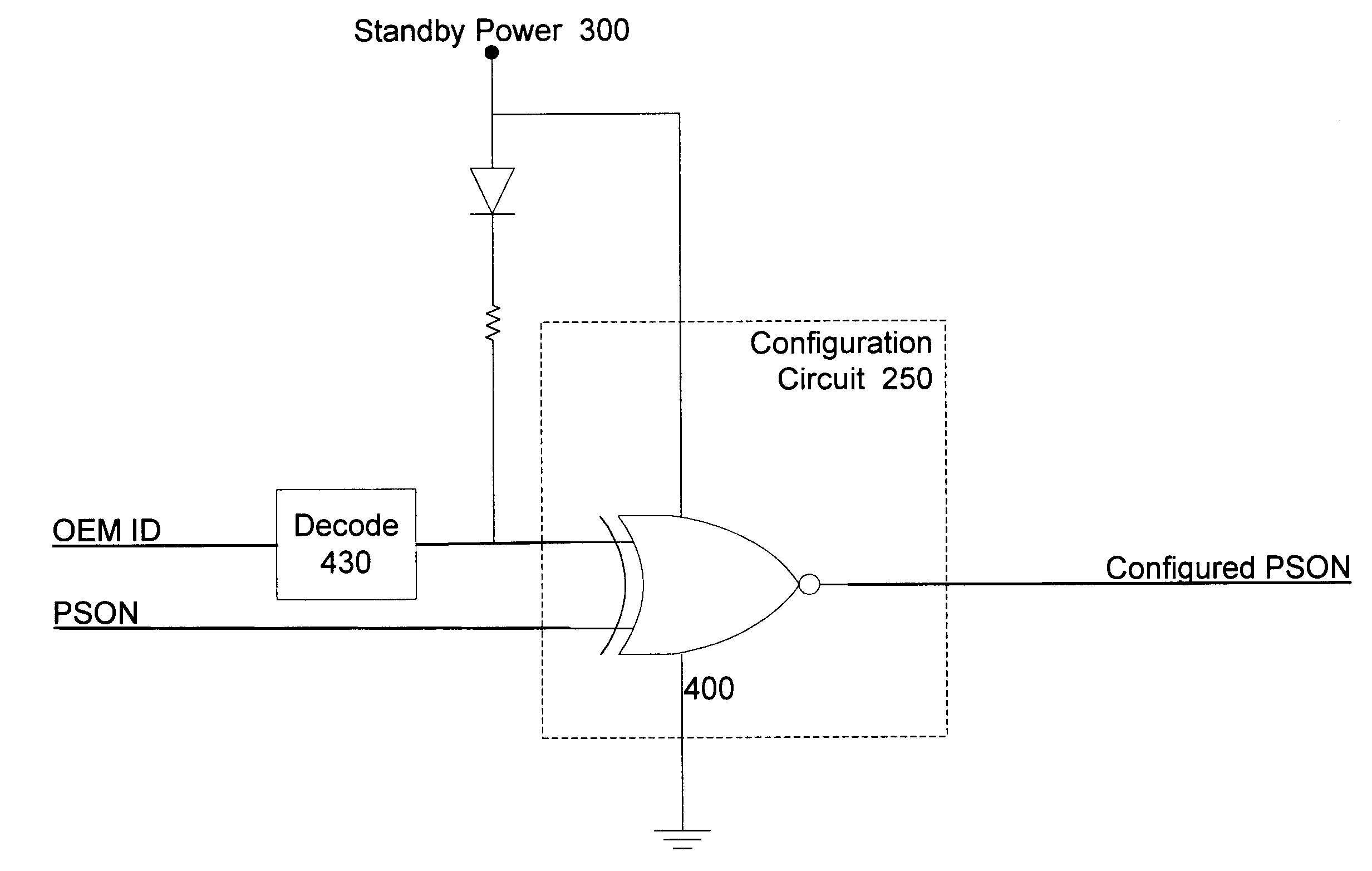

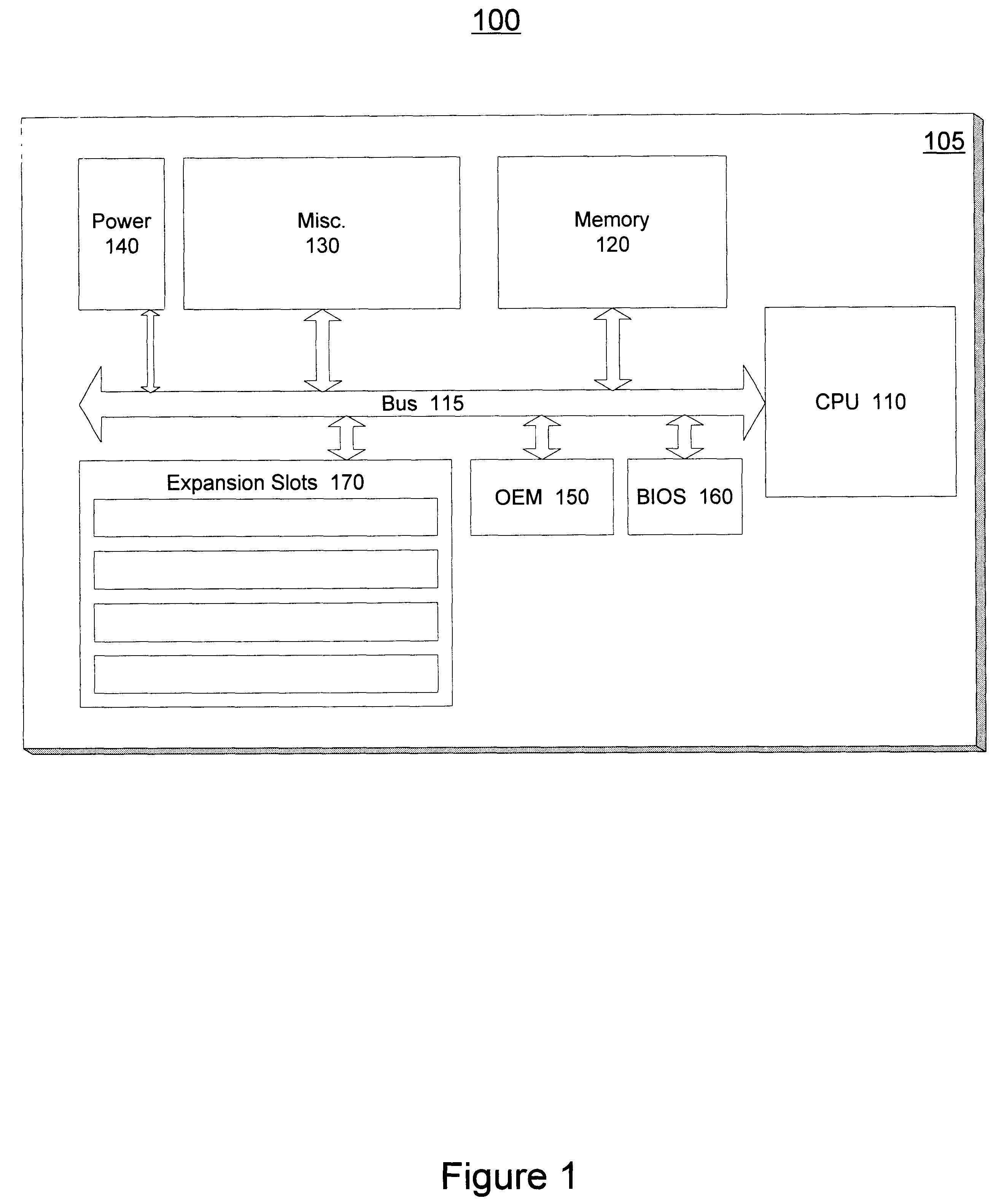

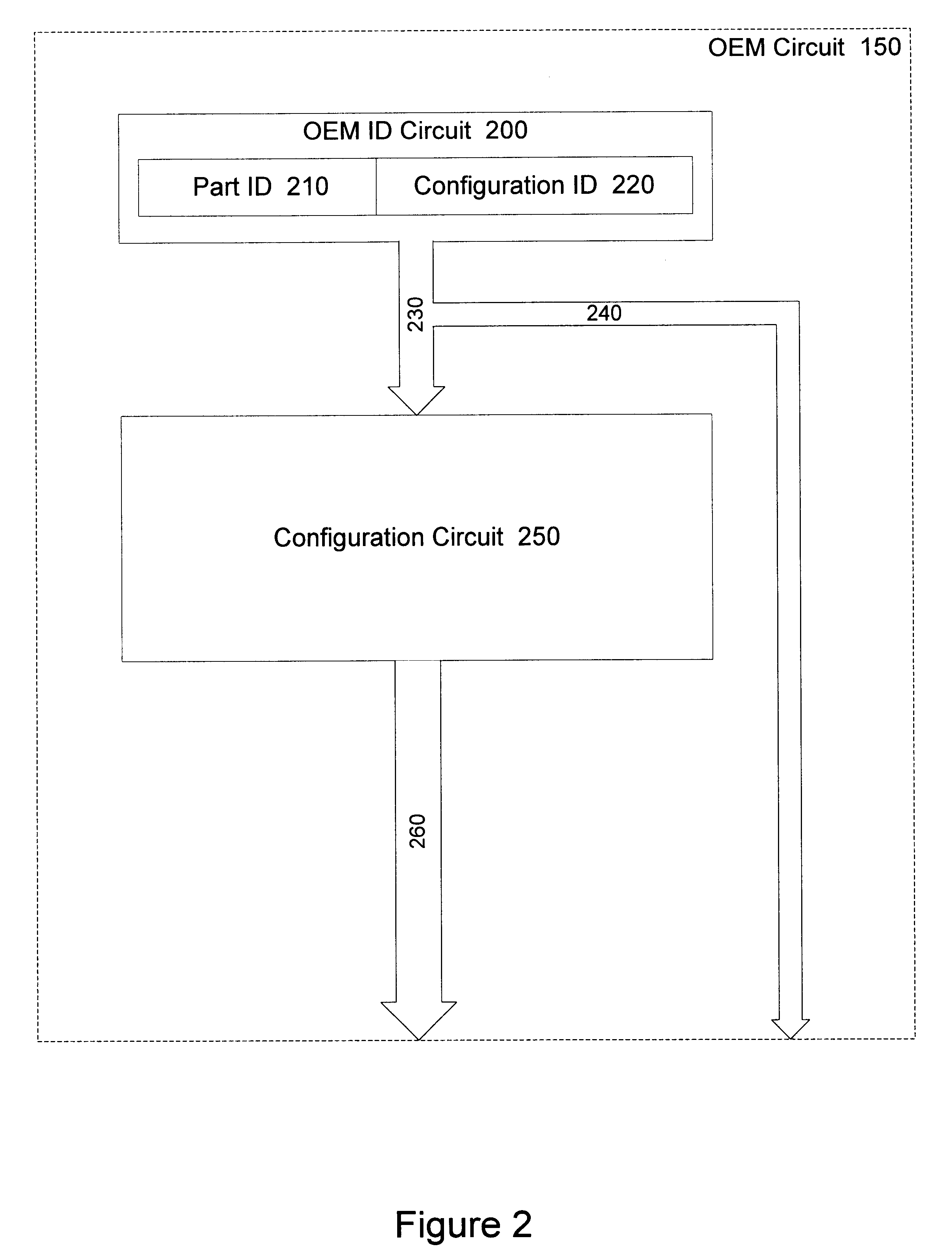

Original equipment manufacturer identification for configurable electronic hardware

InactiveUS6721817B1Input/output processes for data processingComputer hardwareOriginal equipment manufacturer

A configurable hardware for coupling to one of a plurality of hardware. Each of the plurality of hardware has a type. The configurable hardware includes a memory for storing an ID. The ID identifies the type of the hardware coupled to the configurable hardware.

Owner:DELL U SA

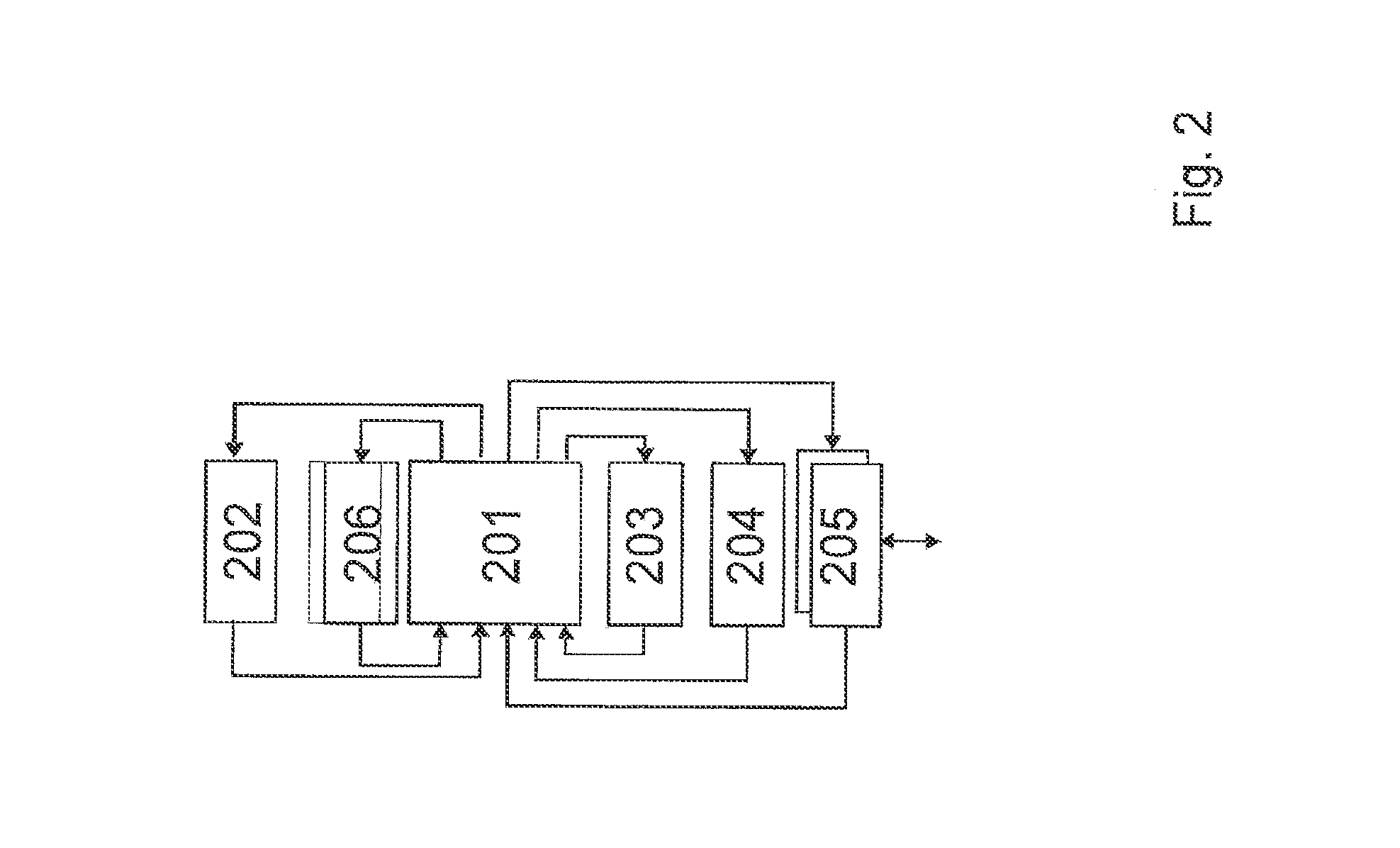

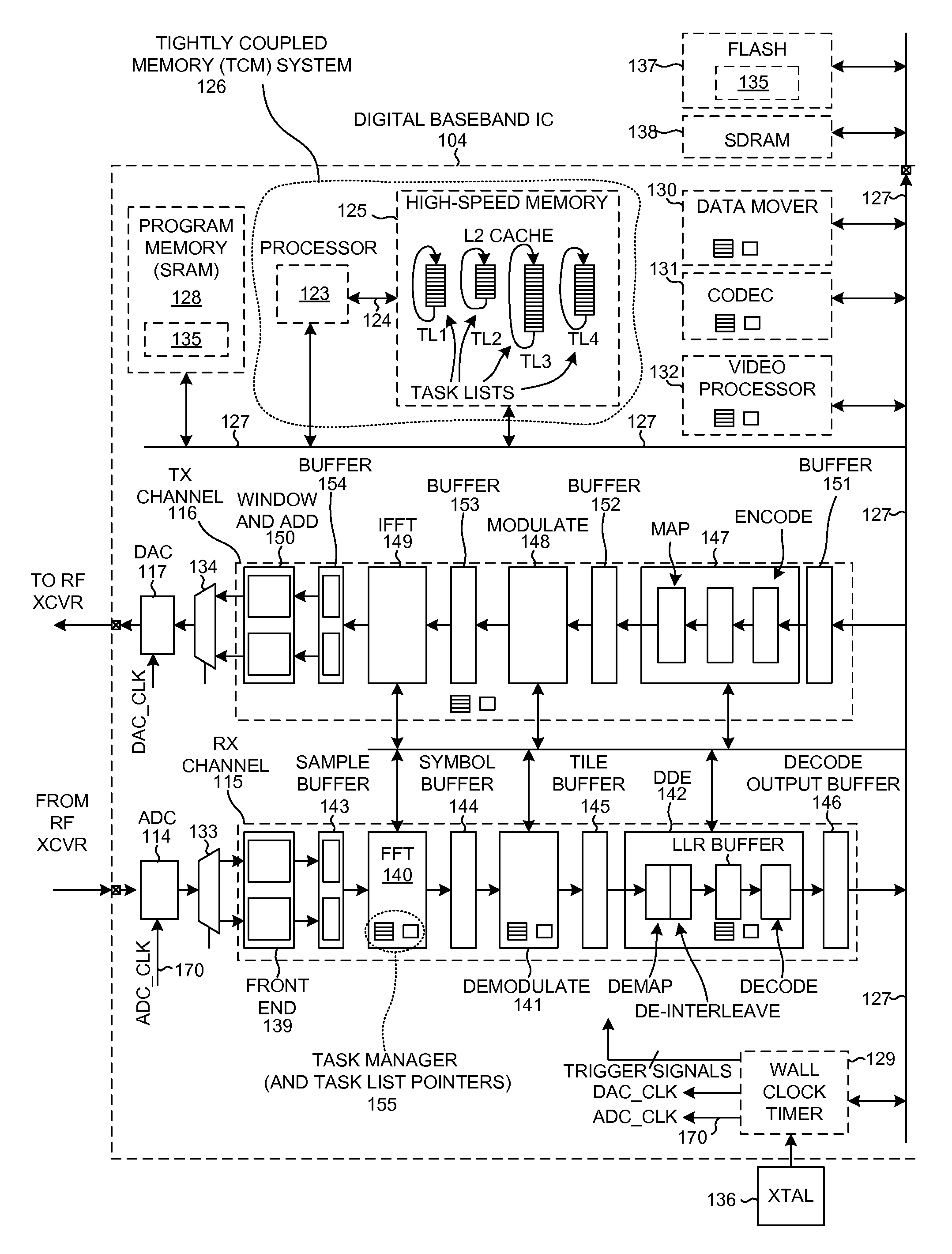

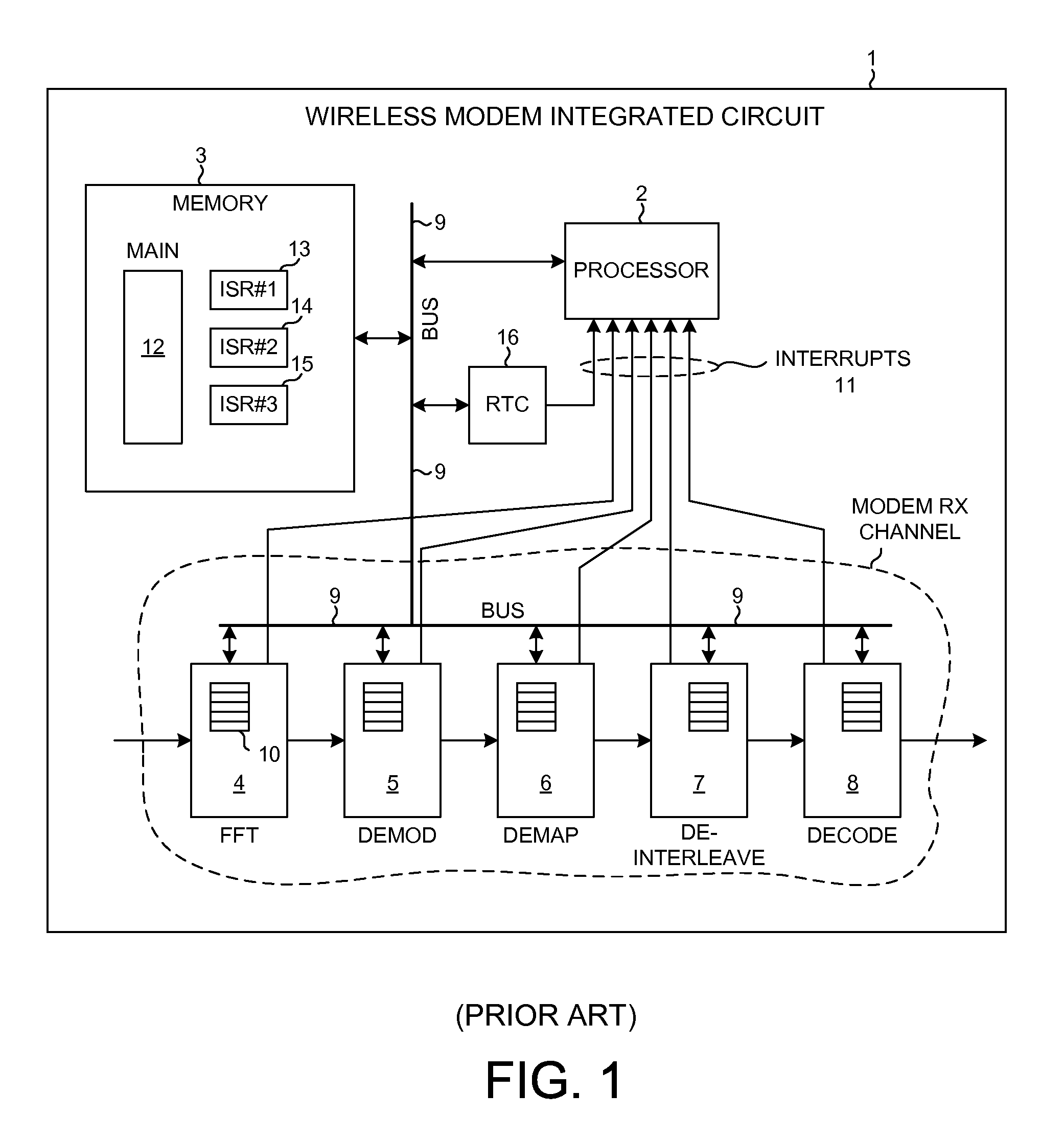

Off-Line Task List Architecture

InactiveUS20090248920A1High memory access latencySoftware execution delaysProgram initiation/switchingMemory adressing/allocation/relocationTimestampModem device

A flexible and reconfigurable digital system (for example, a wireless modem) includes a set of sub-circuits. Each sub-circuit includes a task manager and an amount of configurable hardware circuitry for performing a type of operation on a data stream. The task manager of a sub-circuit can configure and control the configurable hardware of the sub-circuit. A central processor configures and orchestrates operation of the sub-circuits by maintaining a set of task lists in a tightly coupled memory. Each task list includes task instructions for a corresponding sub-circuit. The task manager of a sub-circuit reads task instructions from its task list and controls its associated hardware circuitry as directed by the instructions. A timestamp task instruction and a push task instruction and the task list architecture allow modem sub-circuits to be easily reconfigured to operate in accordance with either a first air interface standard or a second air interface standard.

Owner:QUALCOMM INC

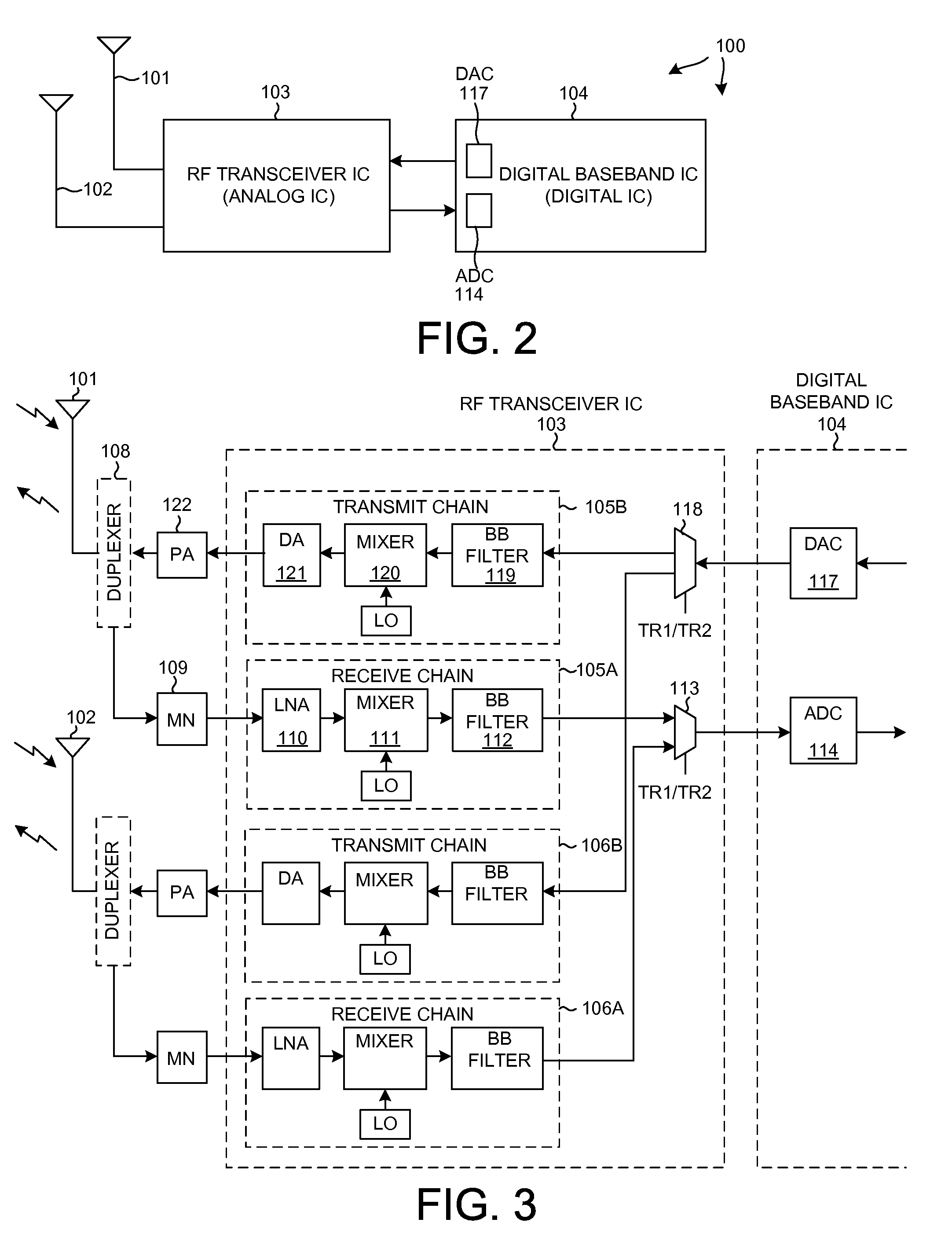

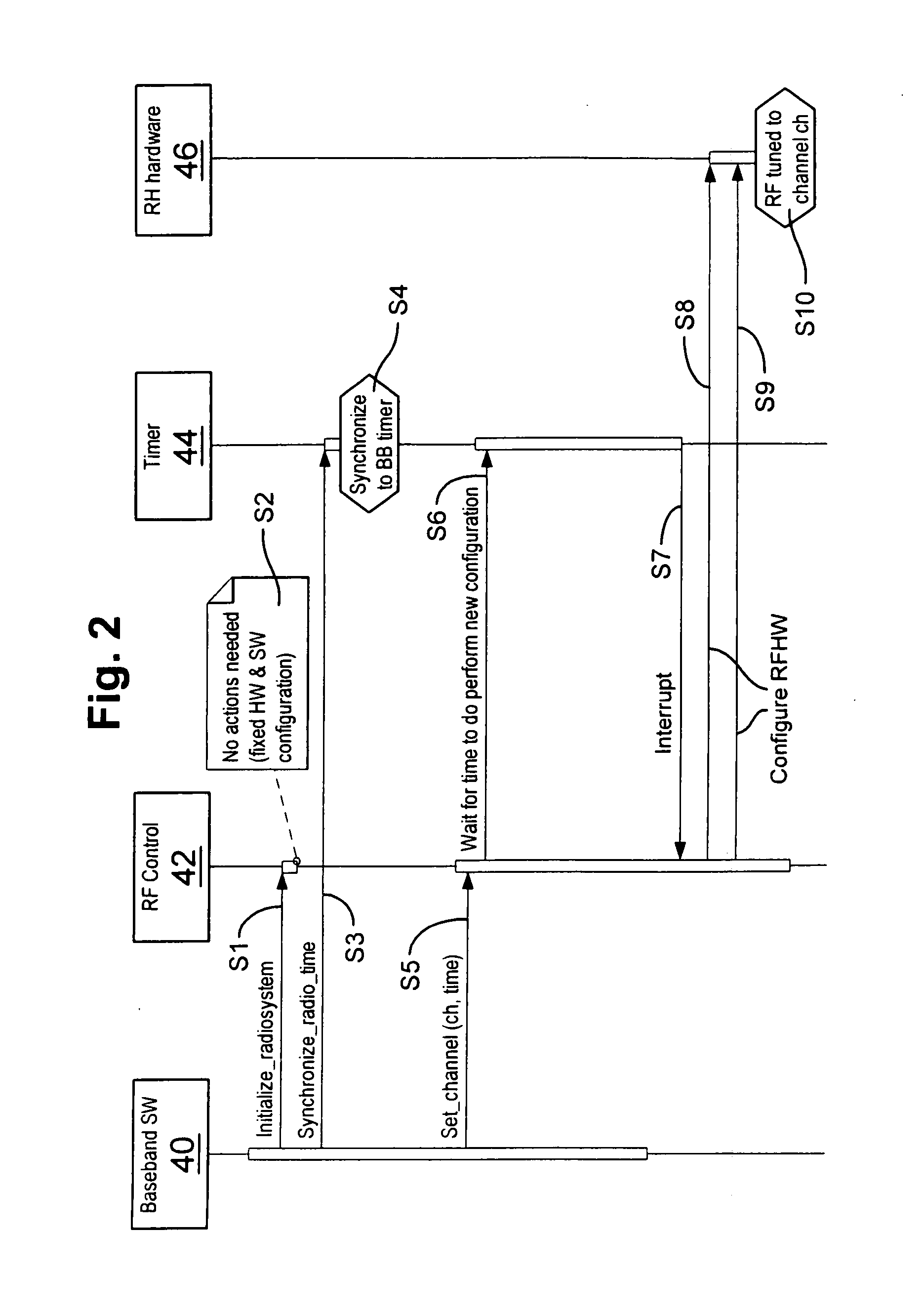

Radio frequency apparatus

A radio frequency apparatus comprising an interface configured to receive a command from a radio protocol stack. A command generator configured to generate a plurality of commands from said received command is provided. The apparatus also has configurable hardware, said hardware having a configuration which is controlled in dependence on said generated commands and being arranged to at least one of transmit and receive a radio frequency signal.

Owner:NOKIA TECHNOLOGLES OY

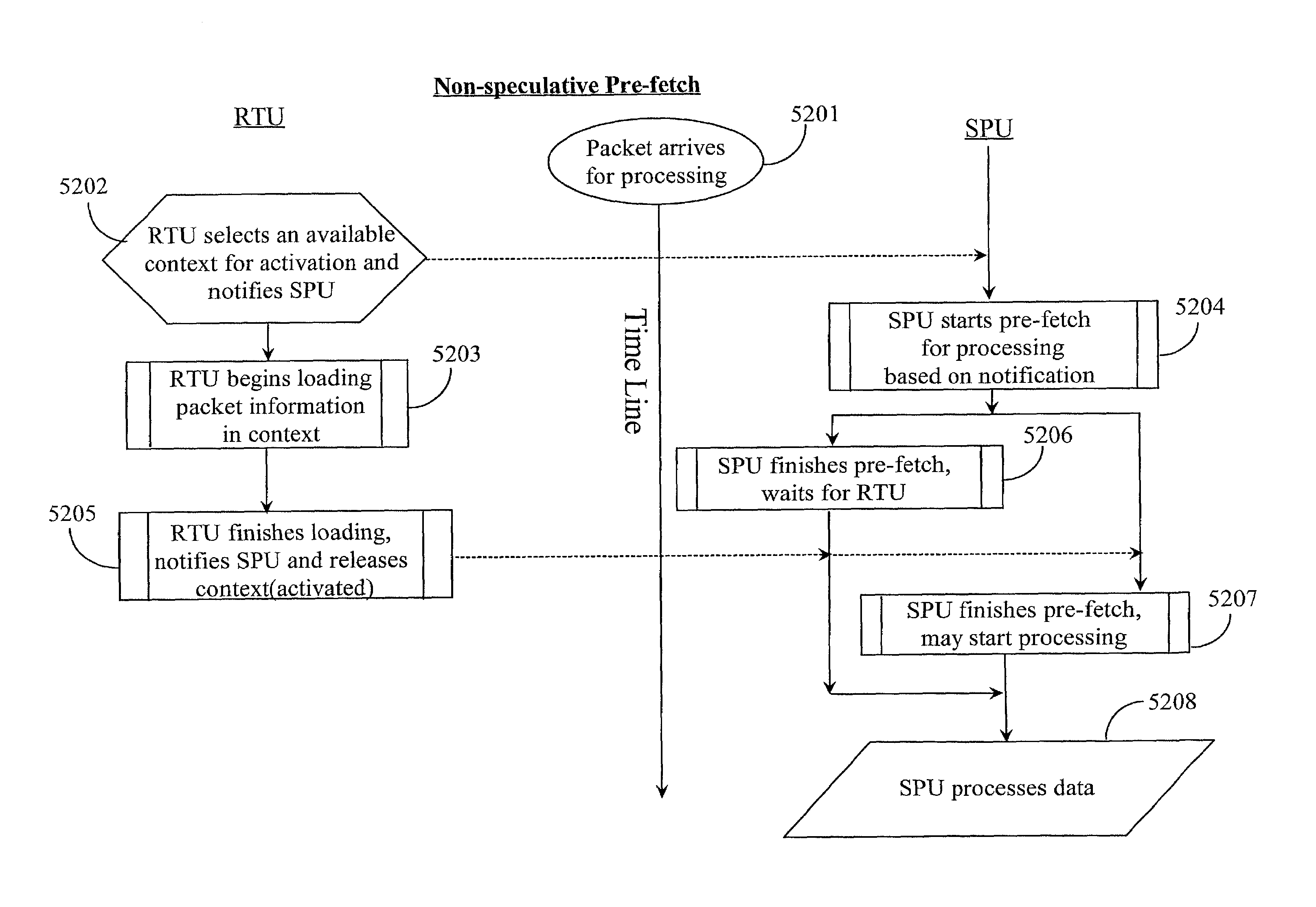

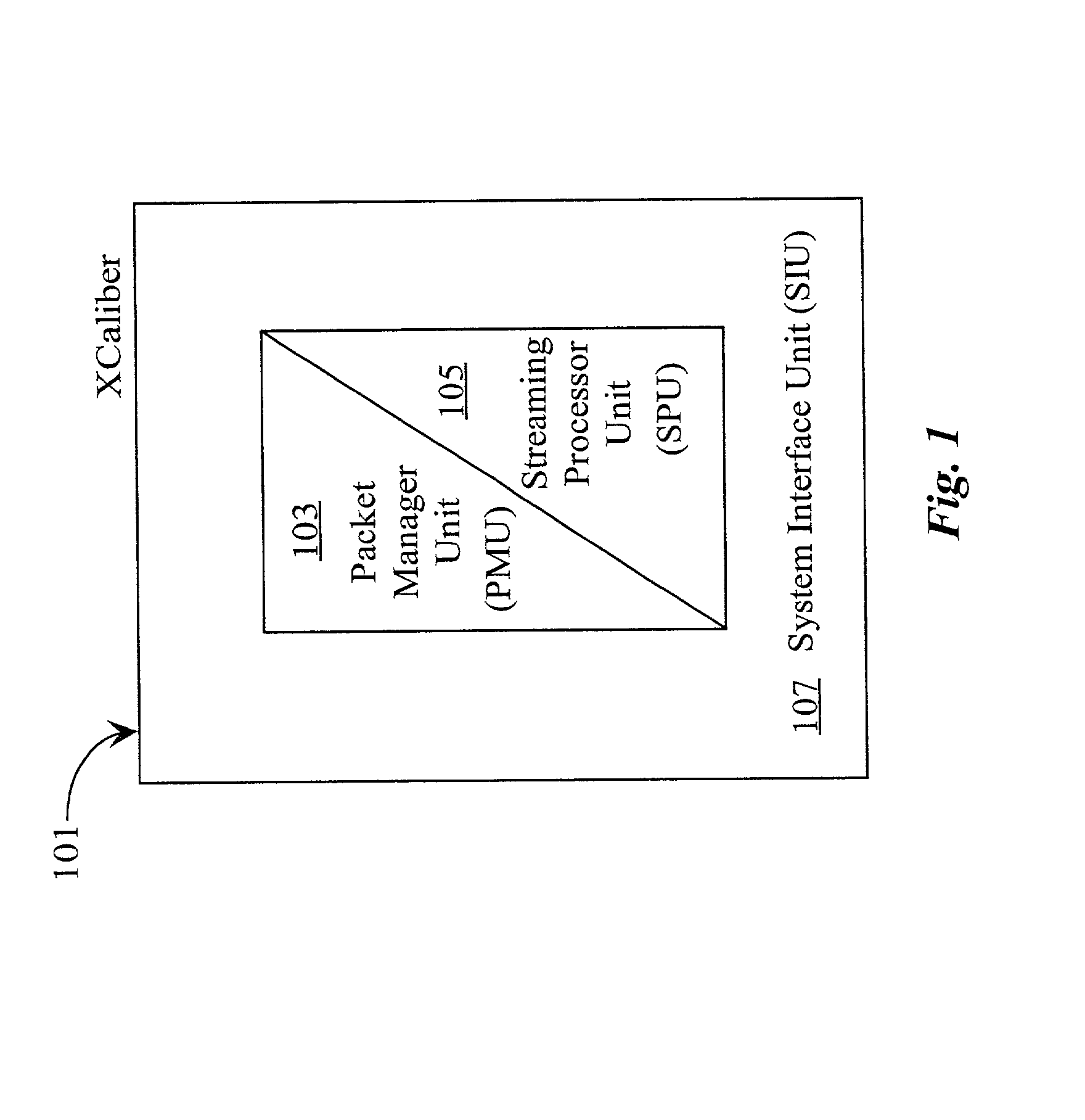

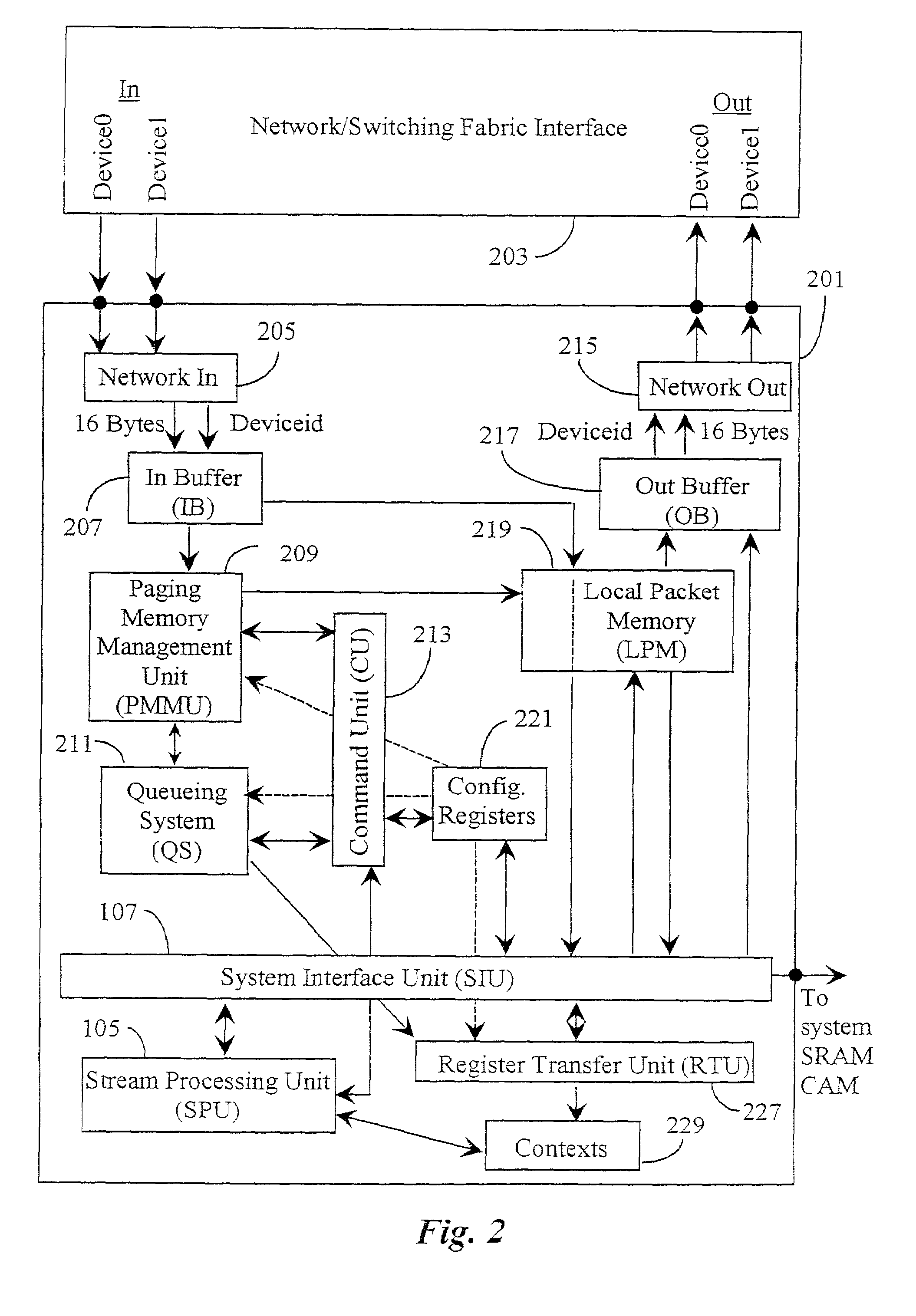

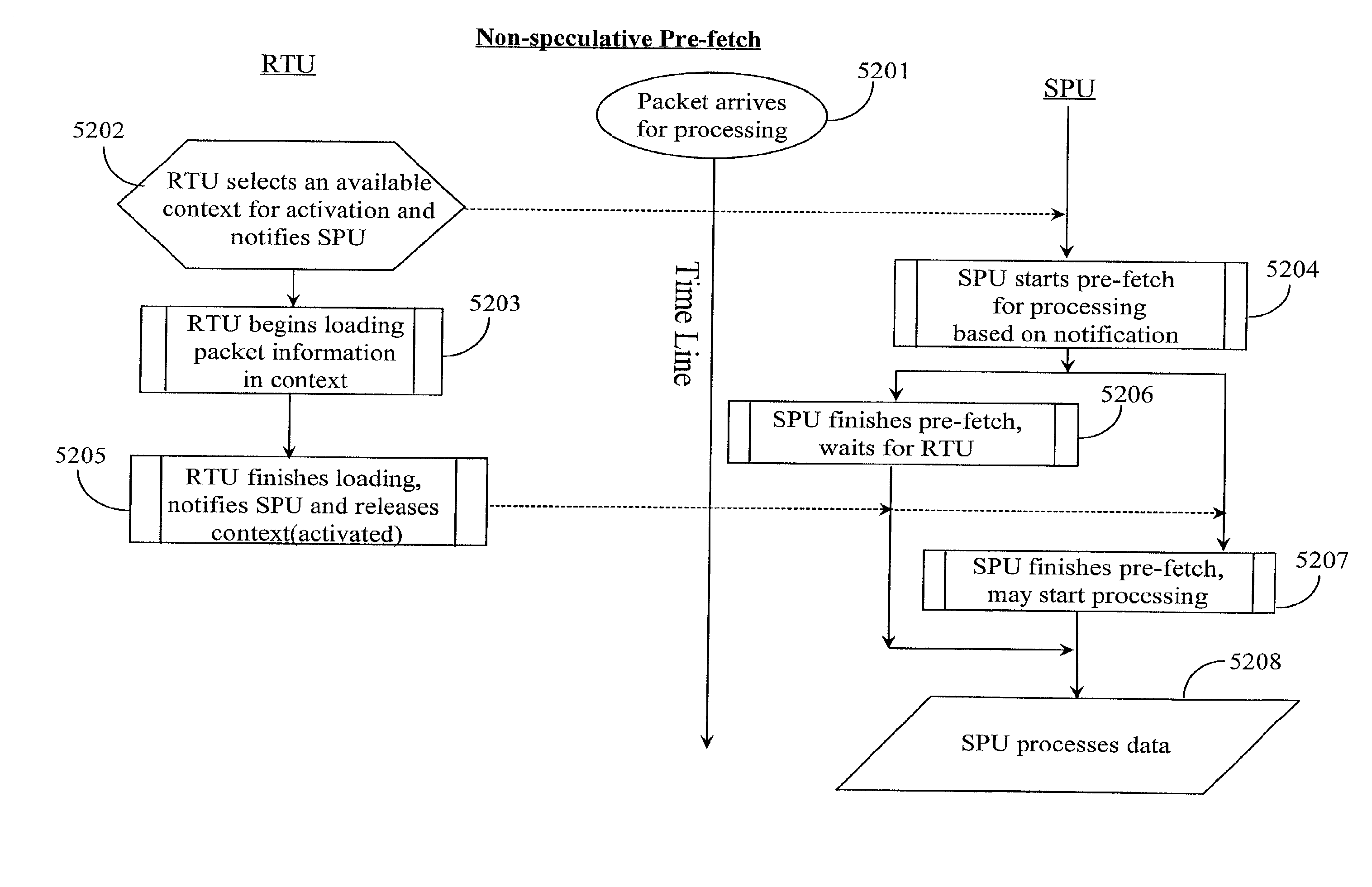

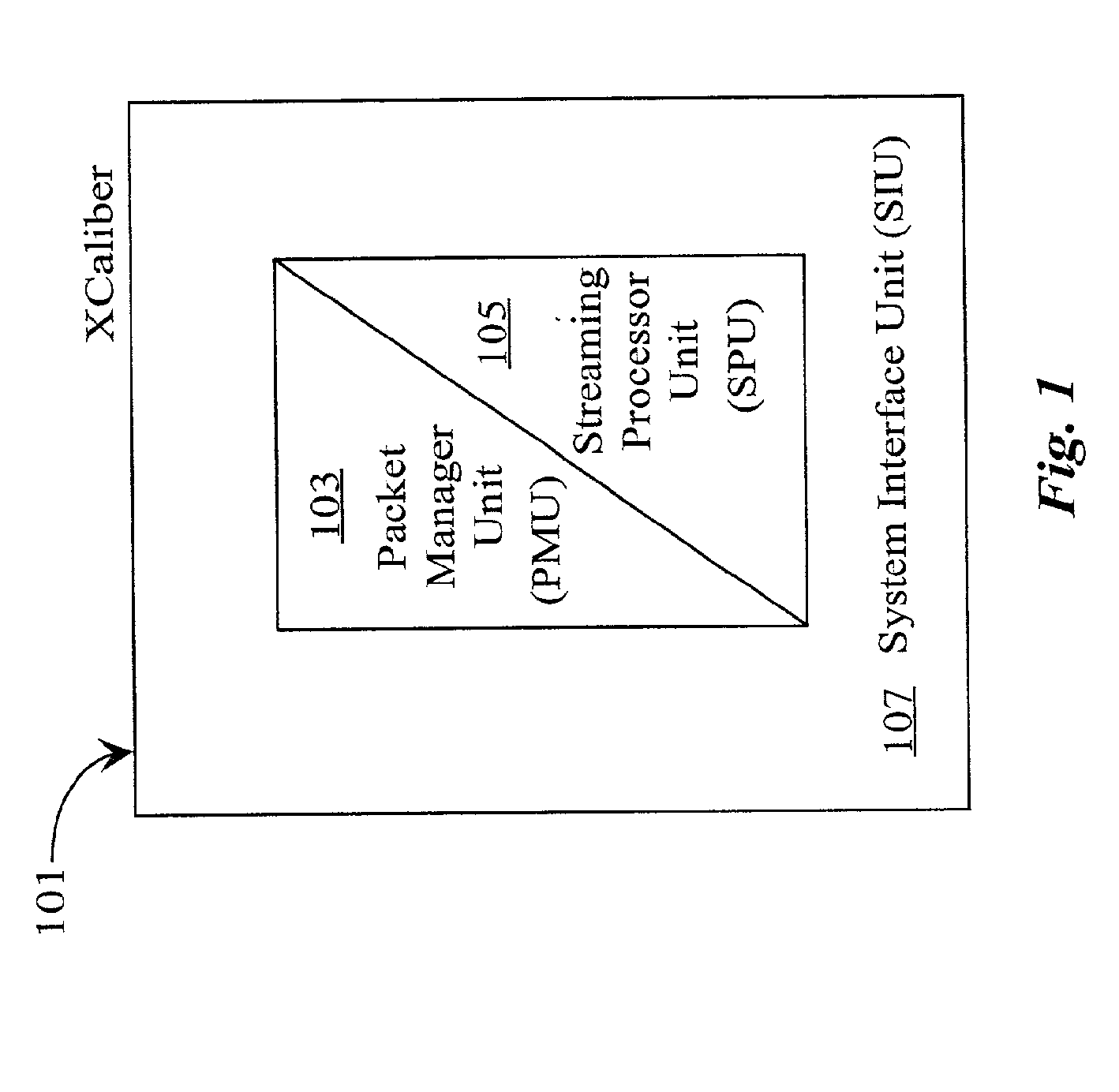

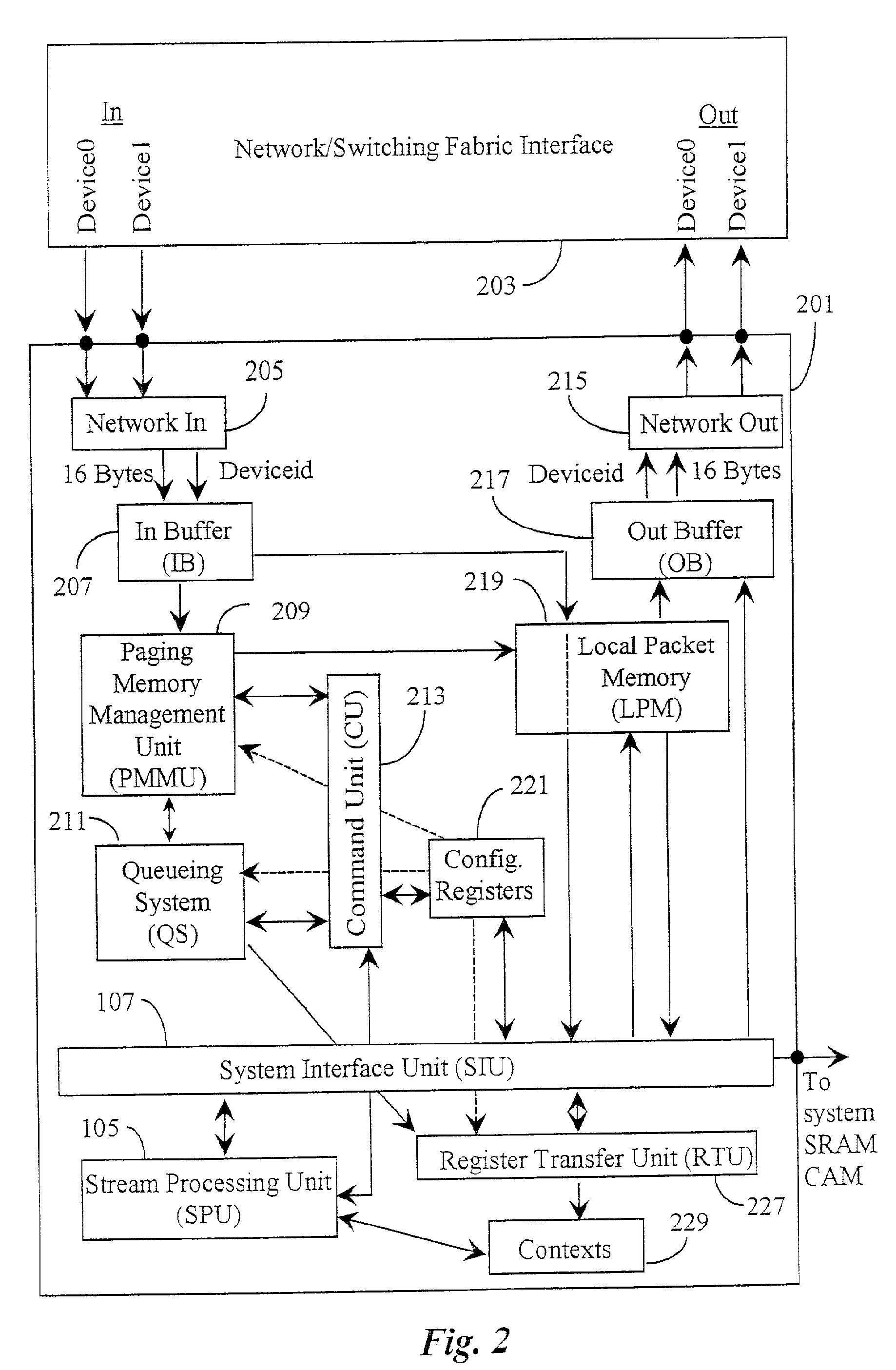

Method and apparatus for non-speculative pre-fetch operation in data packet processing

InactiveUS7042887B2Digital computer detailsMultiprogramming arrangementsManagement unitParallel computing

A system is provided for enabling a non-speculative pre-fetch operation for processing instructions to be performed in the background ahead of immediate packet processing by a packet processor. The system comprises a packet-management unit for accepting data packets and en-queuing them for processing, a processor unit for processing the data packets, a processor core memory for holding context registers and functional units for processing, a memory for holding a plurality of instruction threads and a software-configurable hardware table for relating queues to pointers to beginnings of instruction threads. The packet-management unit selects an available context in the processor core for processing of a data packet, consults the table, and communicates the pointer to the processor, enabling the processor to perform the non-speculative pre-fetch for instructions.

Owner:ARM FINANCE OVERSEAS LTD

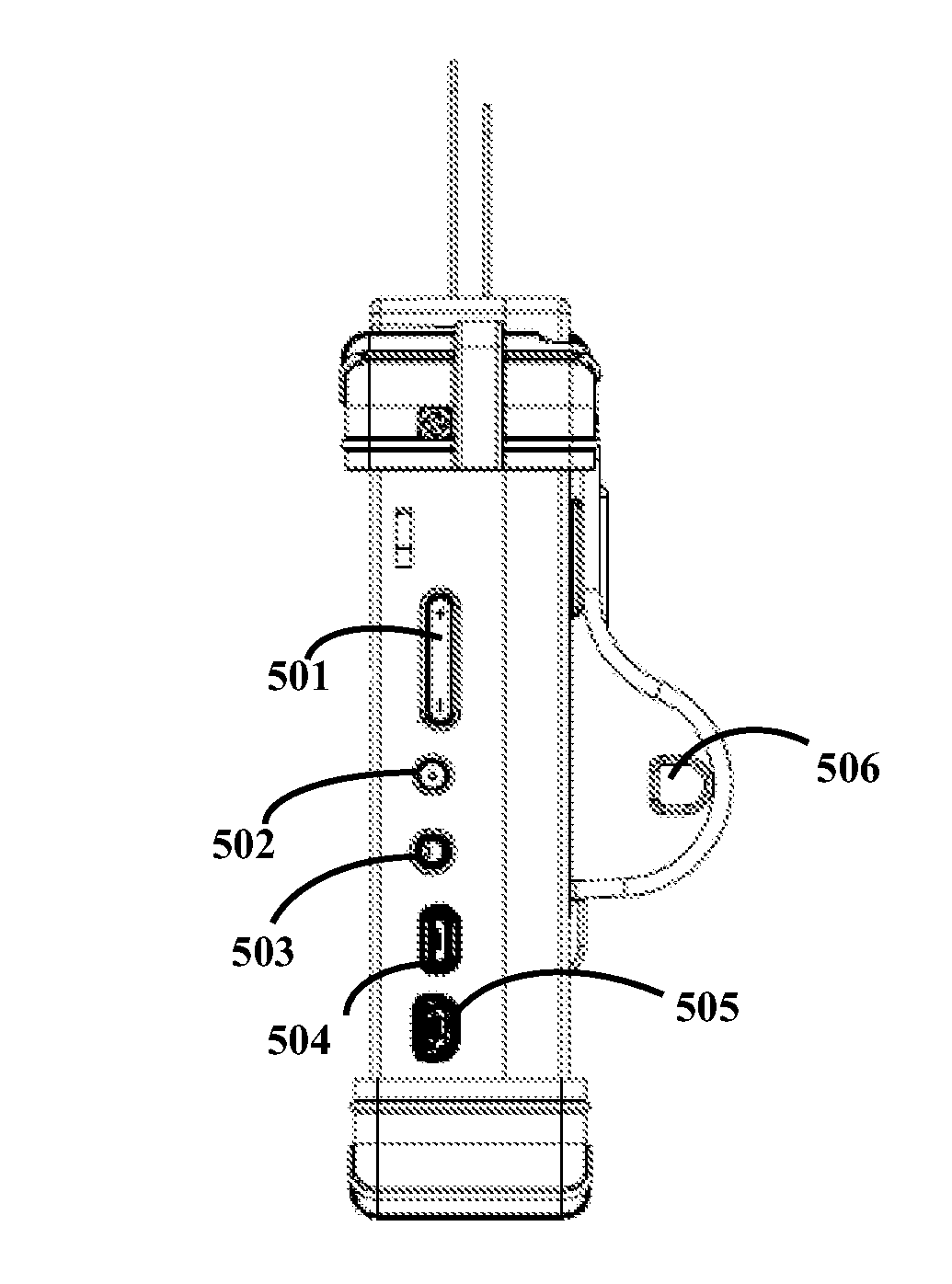

Intelligent casing for smart devices

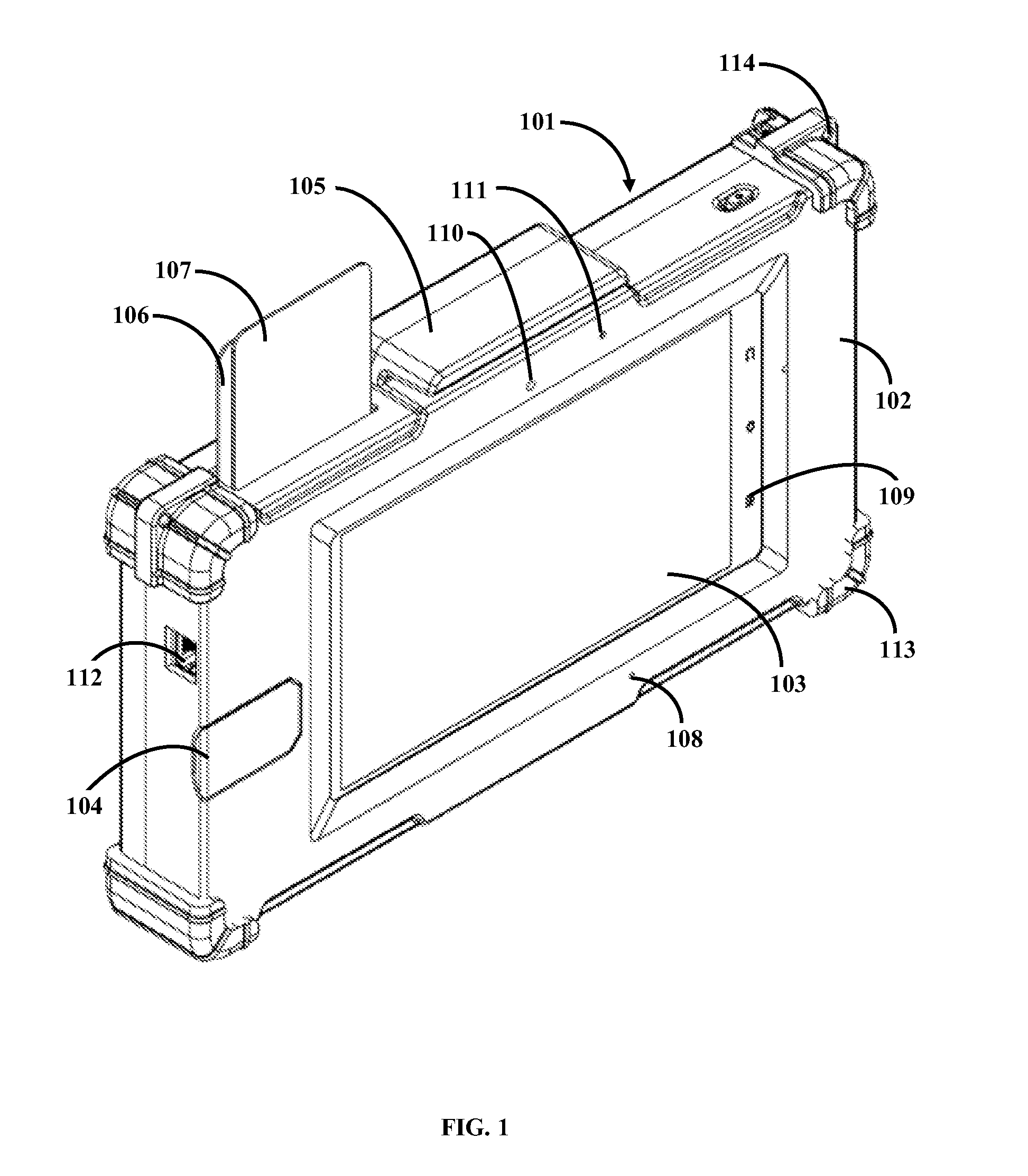

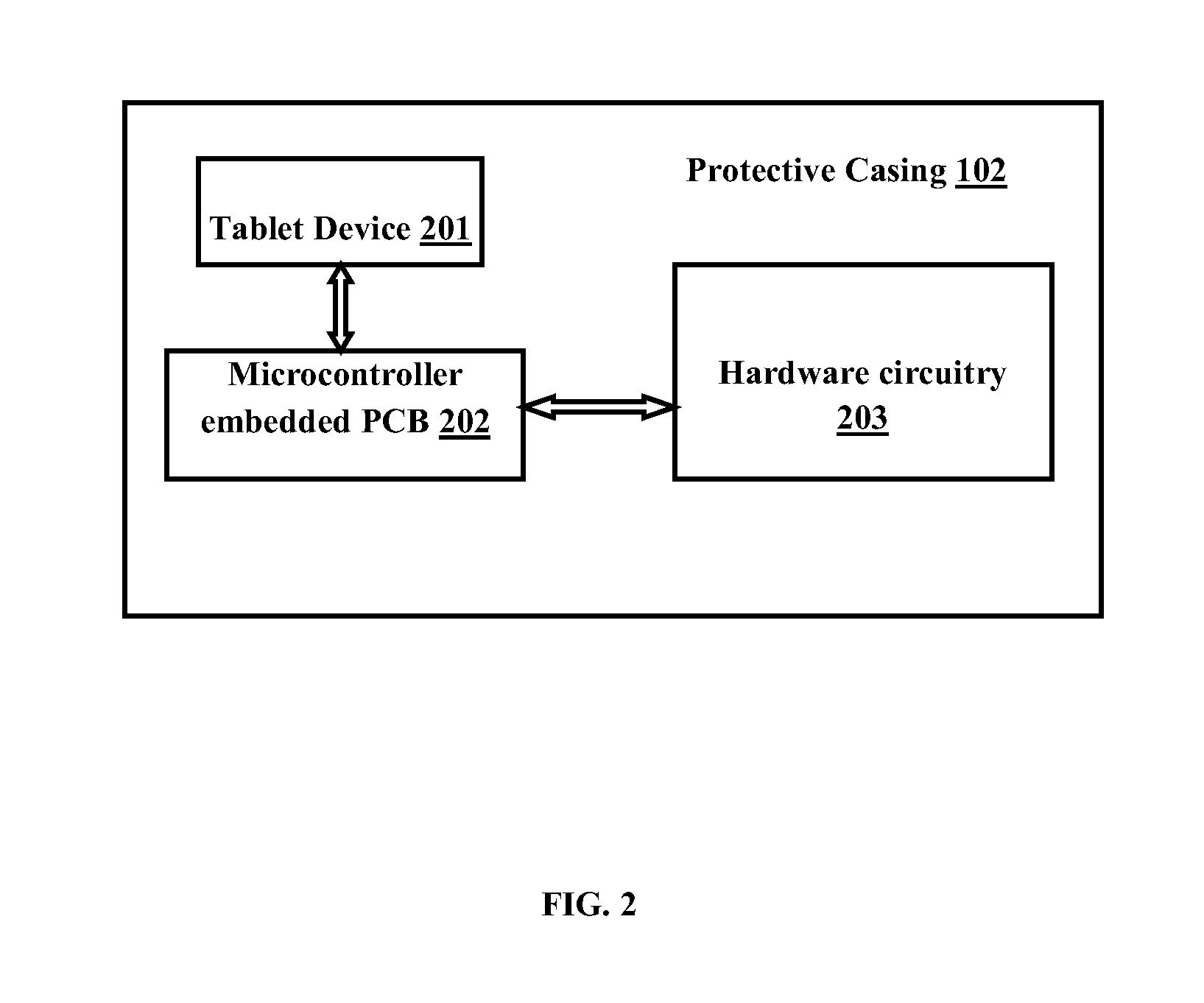

InactiveUS20130077235A1Provide compatibilityDigital data processing detailsElectrical apparatus contructional detailsMicrocontrollerGround noise

The various embodiments herein provide an intelligent protective casing for smart devices. The casing comprises a frame to releasably engage and hold a tablet device. The frame comprises an opening provided on the center for exposing a display panel of the tablet device, a printed circuit board (PCB), a microcontroller embedded in the PCB and a hardware circuitry interface for providing functional compatibility between the tablet device and the frame. The hardware circuitry includes a plurality of user configurable hardware features which are enabled according to user preferences. The user configurable hardware features comprises a fingerprint scanner, a thermal printer, one or more smart card readers, a magnetic swipe card reader, high amplitude speakers, a barcode scanner, an iris scanner, a projector, a solar panel, a back ground noise cancellation circuit, one or more noise cancellation microphones and at least one swappable battery to drive the circuitry.

Owner:BEWO TECH PVT

Multiple channel digital subscriber line framer/deframer system and method

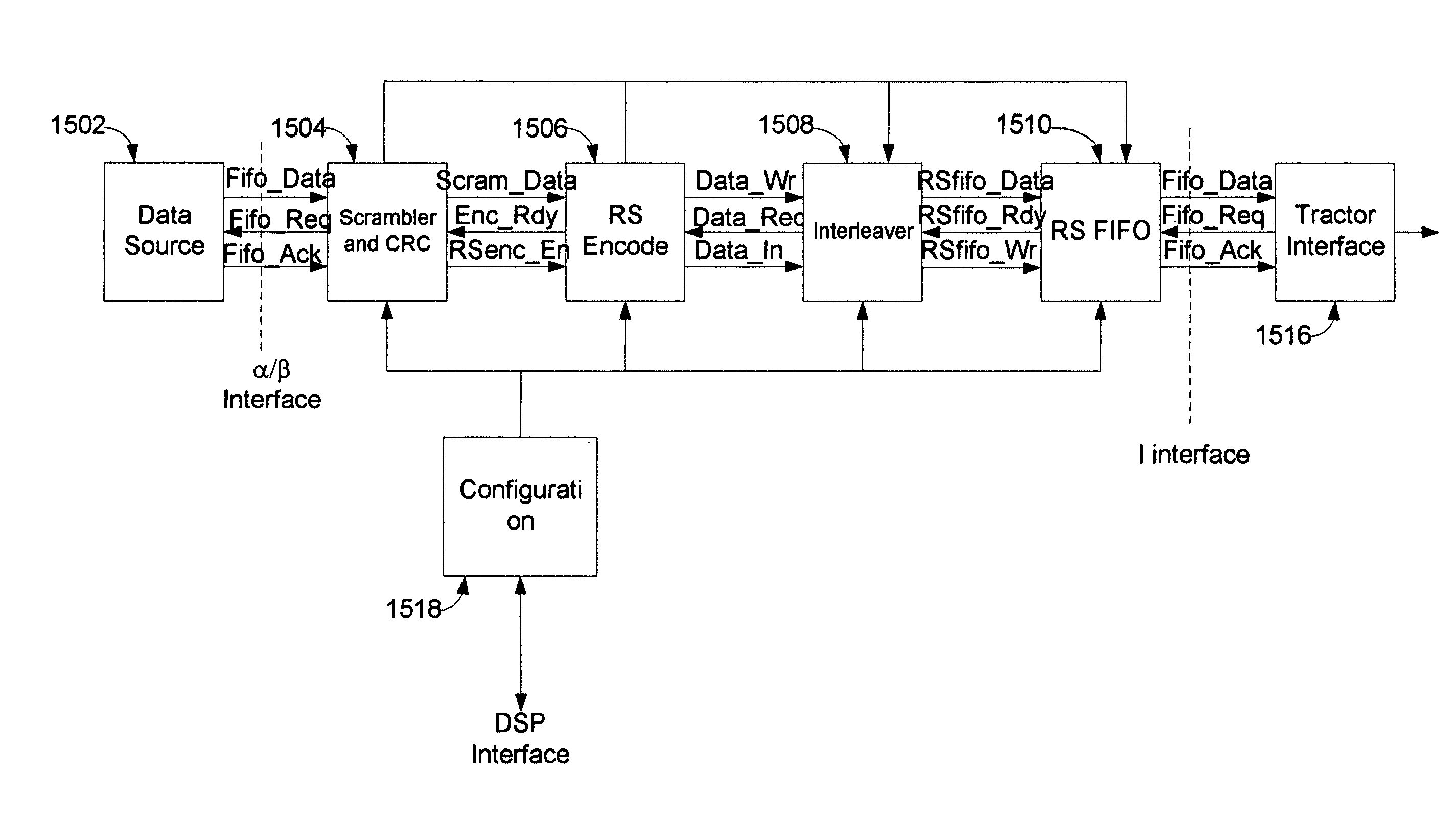

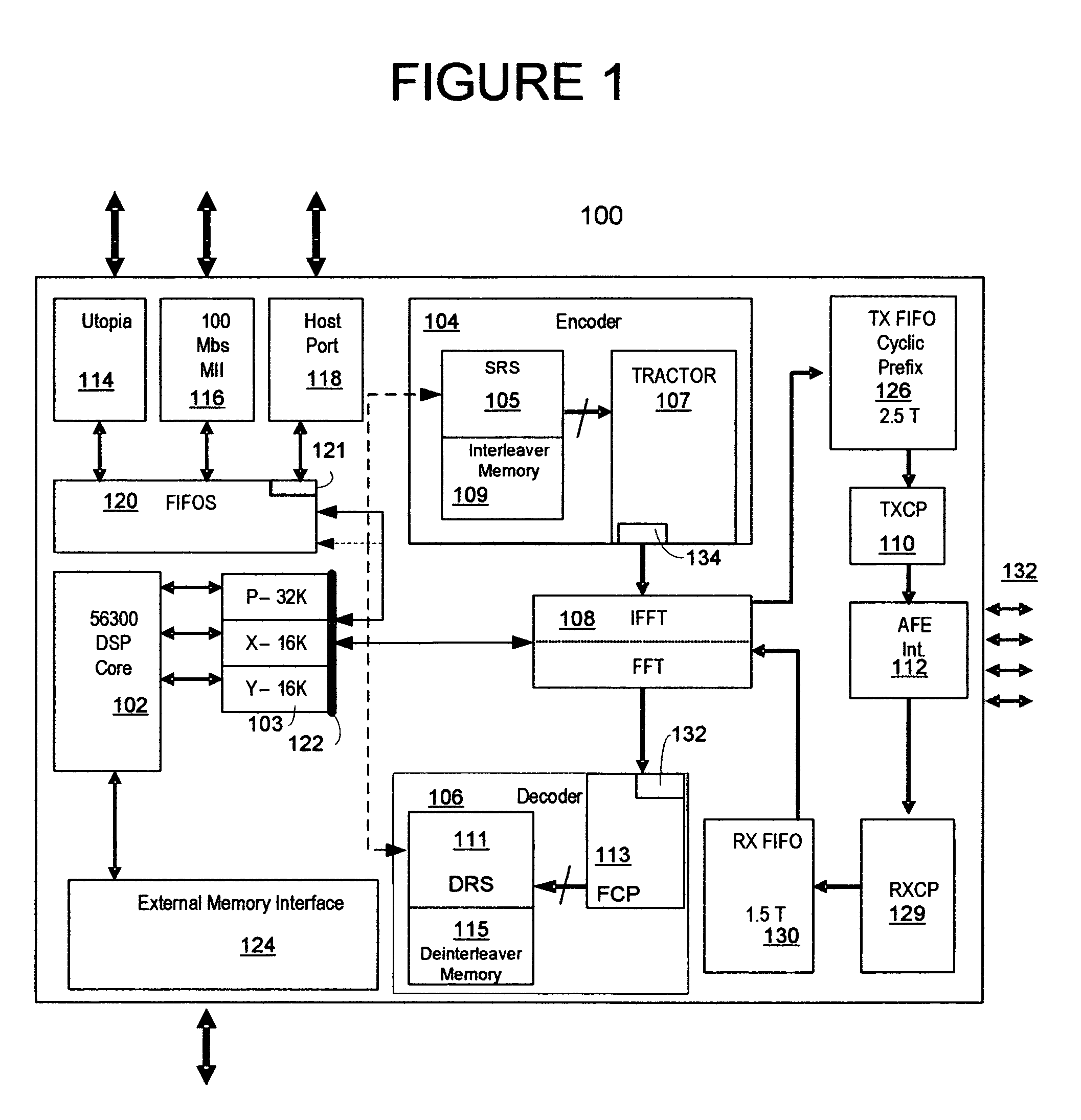

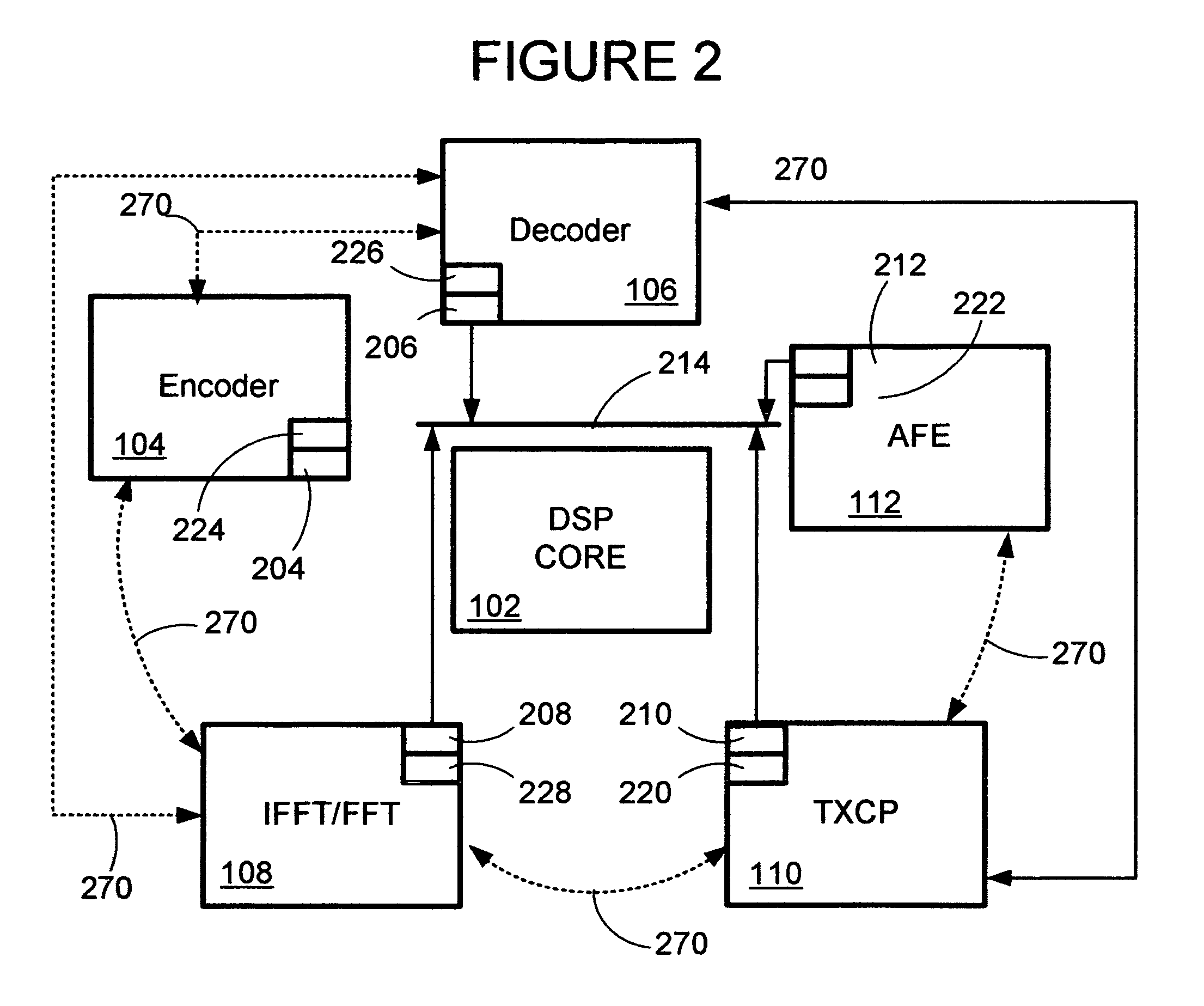

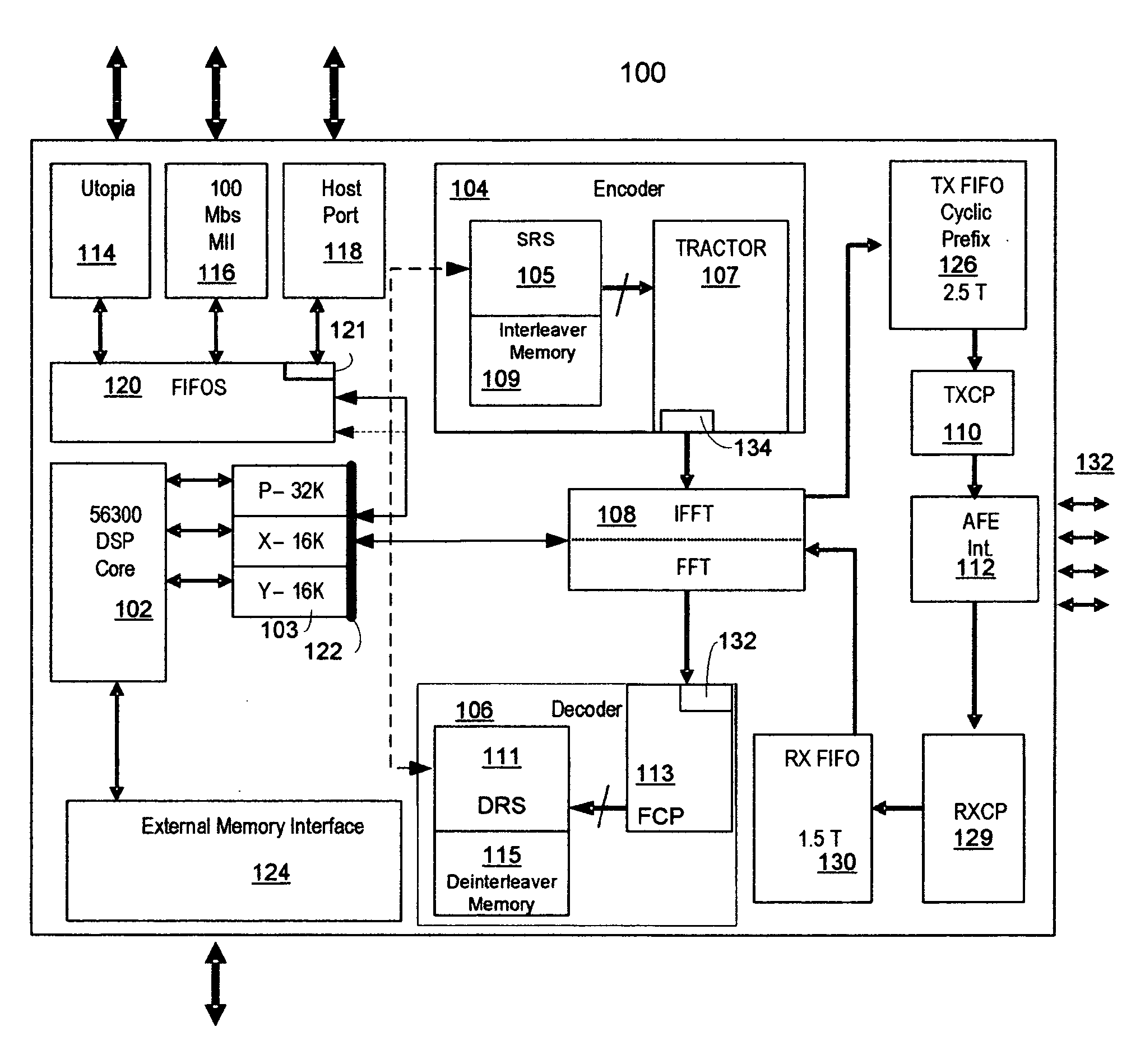

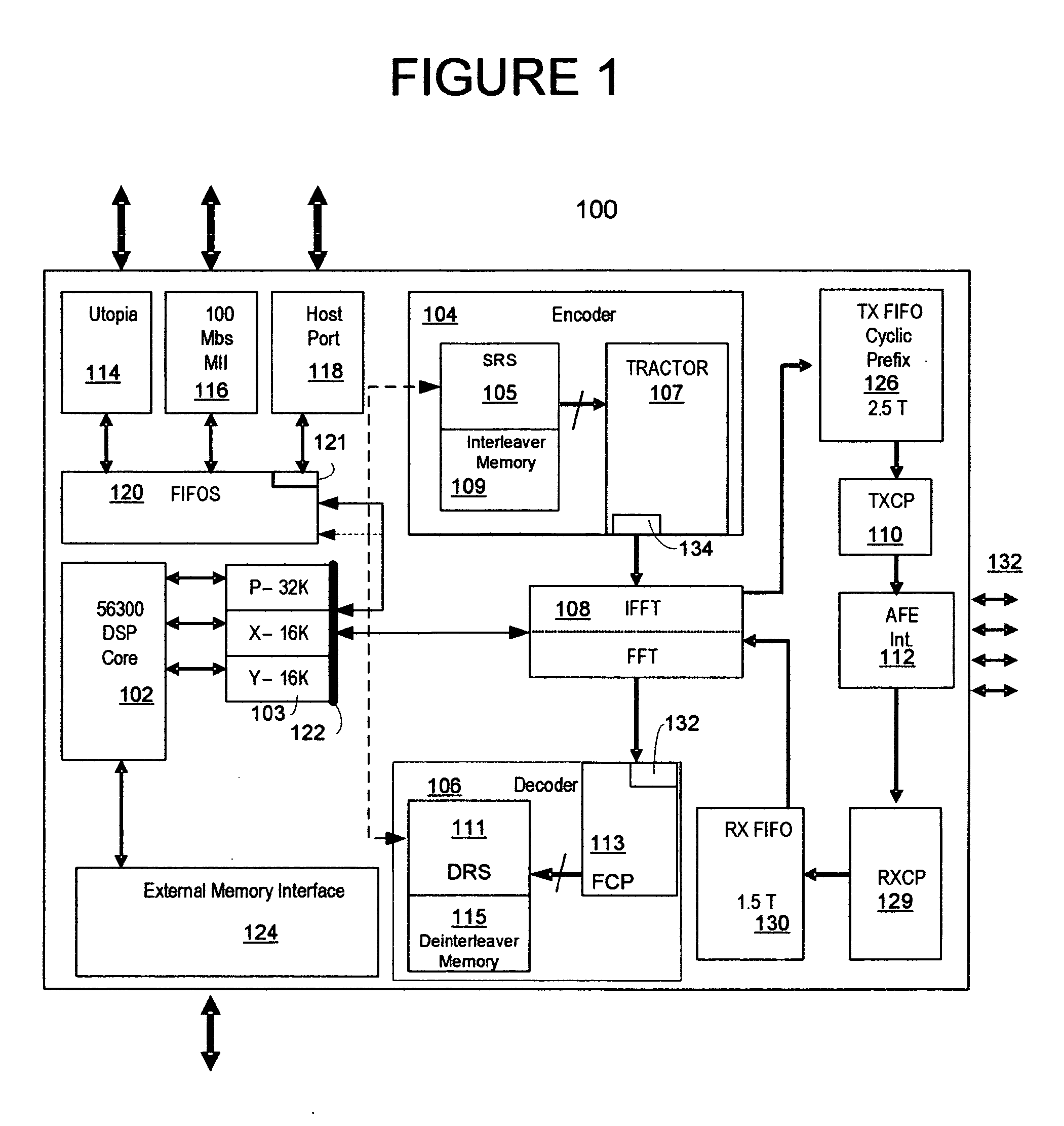

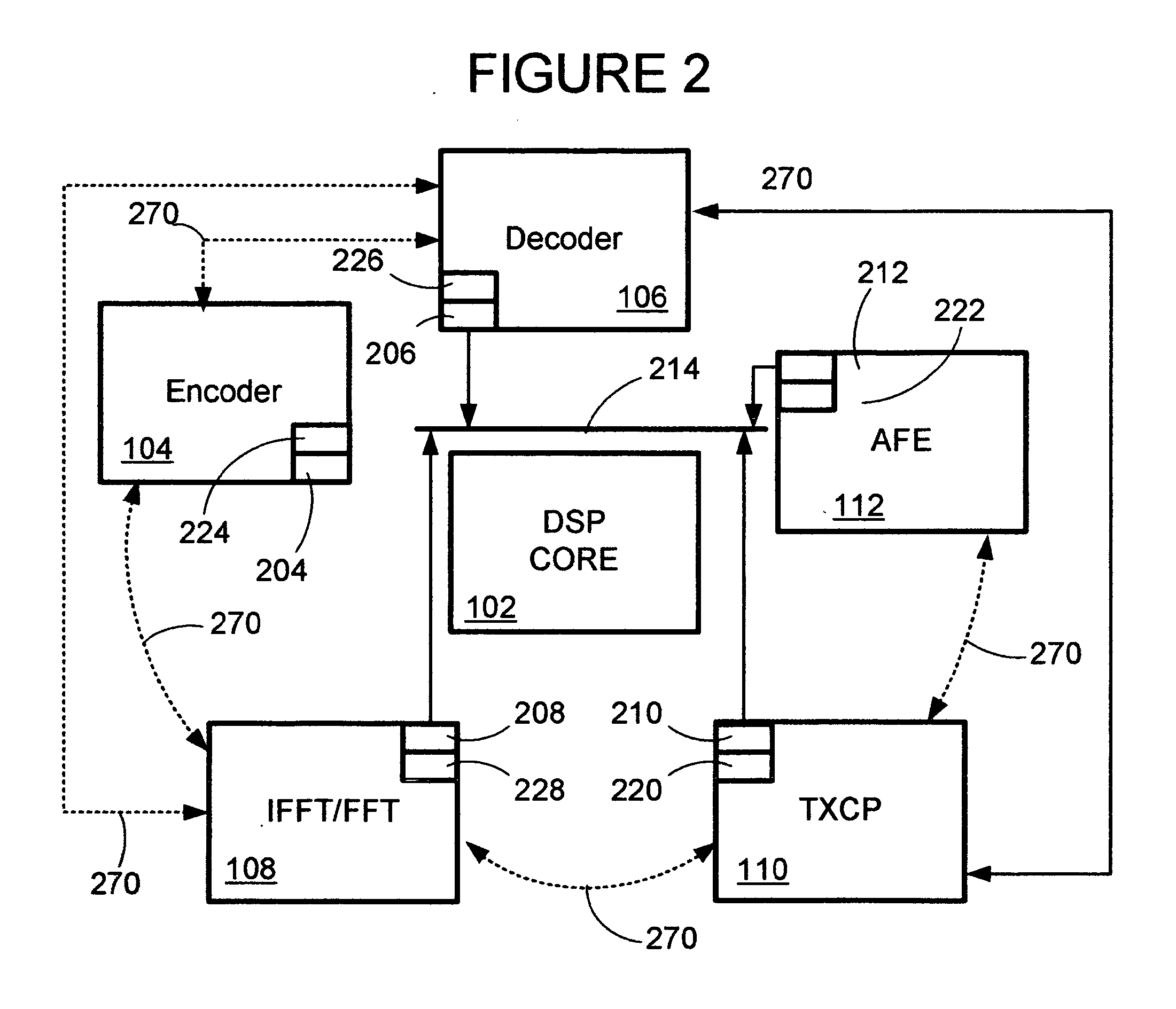

The framer, also referred to as the scrambler / Reed-Solomon encoder (SRS), is a part of the transmitter and accepts user and control data in the form of one or more logical channels, partitions this data into frames, adds error correction codes, randomizes the data through a scrambler, and multiplexes logical channels into a single data stream. The multiplexed data is then passed to the constellation encoder as the next step in the formation of the VDSL symbol. The deframer, also referred as the descrambler / Reed-Solomon decoder (DRS), is part of the receiver and performs the inverse function of the framer. Disclosed is a highly configurable hardware framer / deframer that includes a digital signal processor interface configured to provide high level control, a FIFO coupled to data interfaces, a scrambler and CRC generator, a Reed-Solomon encoder, an interleaver, a data interface coupled to a constellation encoder, a data interface coupled to a constellation decoder, a deinterleaver, a Reed-Solomon decoder, descrambler and CRC check, an interface to external data sync, methods for control of configuration of data paths between hardware blocks, and methods for control and configuration of the individual hardware blocks in a manner that provides compliance with VDSL and many related standards.

Owner:METANOIA TECH

Multiple Channel Digital Subscriber Line Framer/Deframer System and Method

InactiveUS20100246585A1Code conversionData switching by path configurationData streamReed solomon decoder

Owner:METANOIA TECH

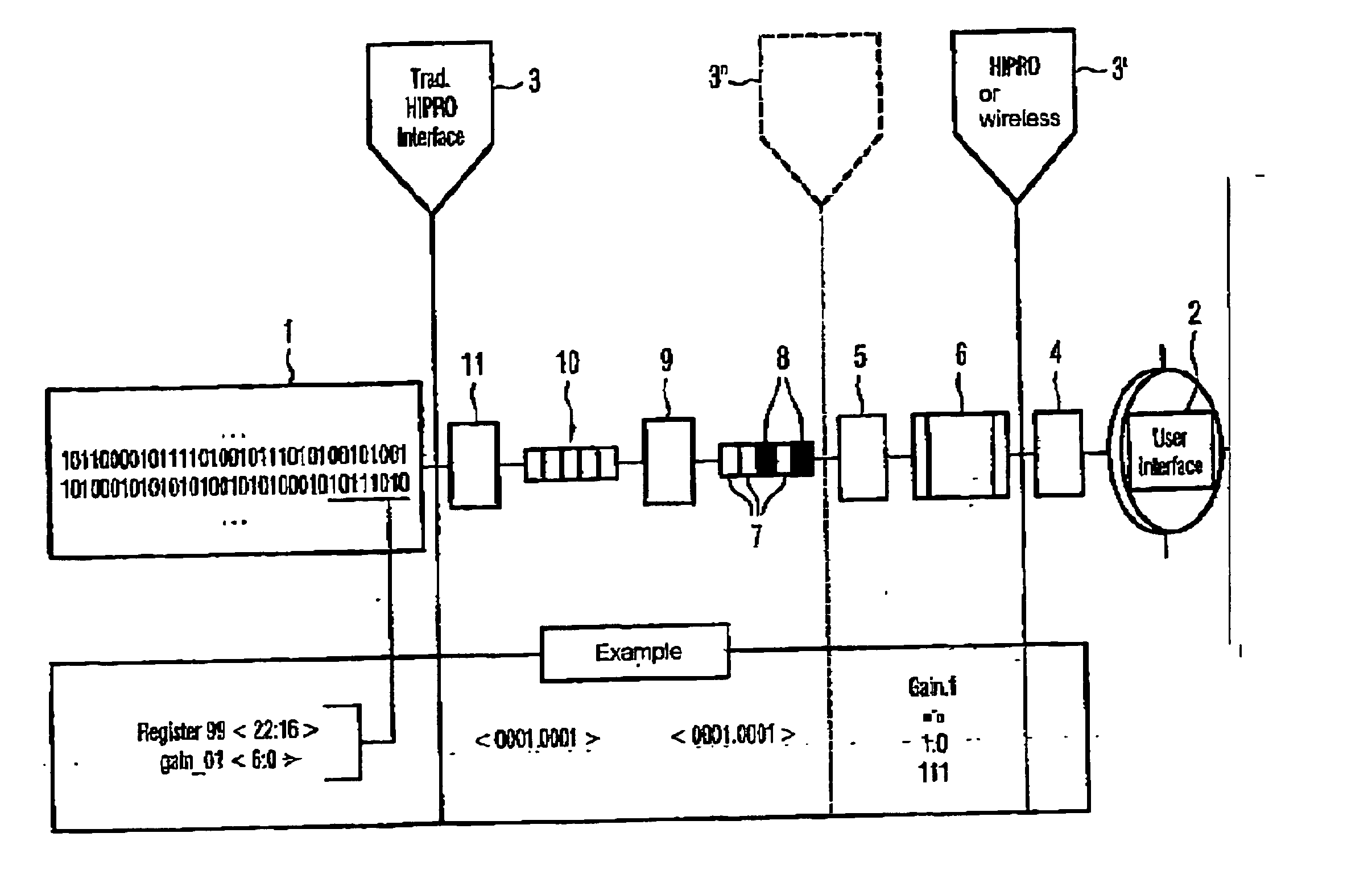

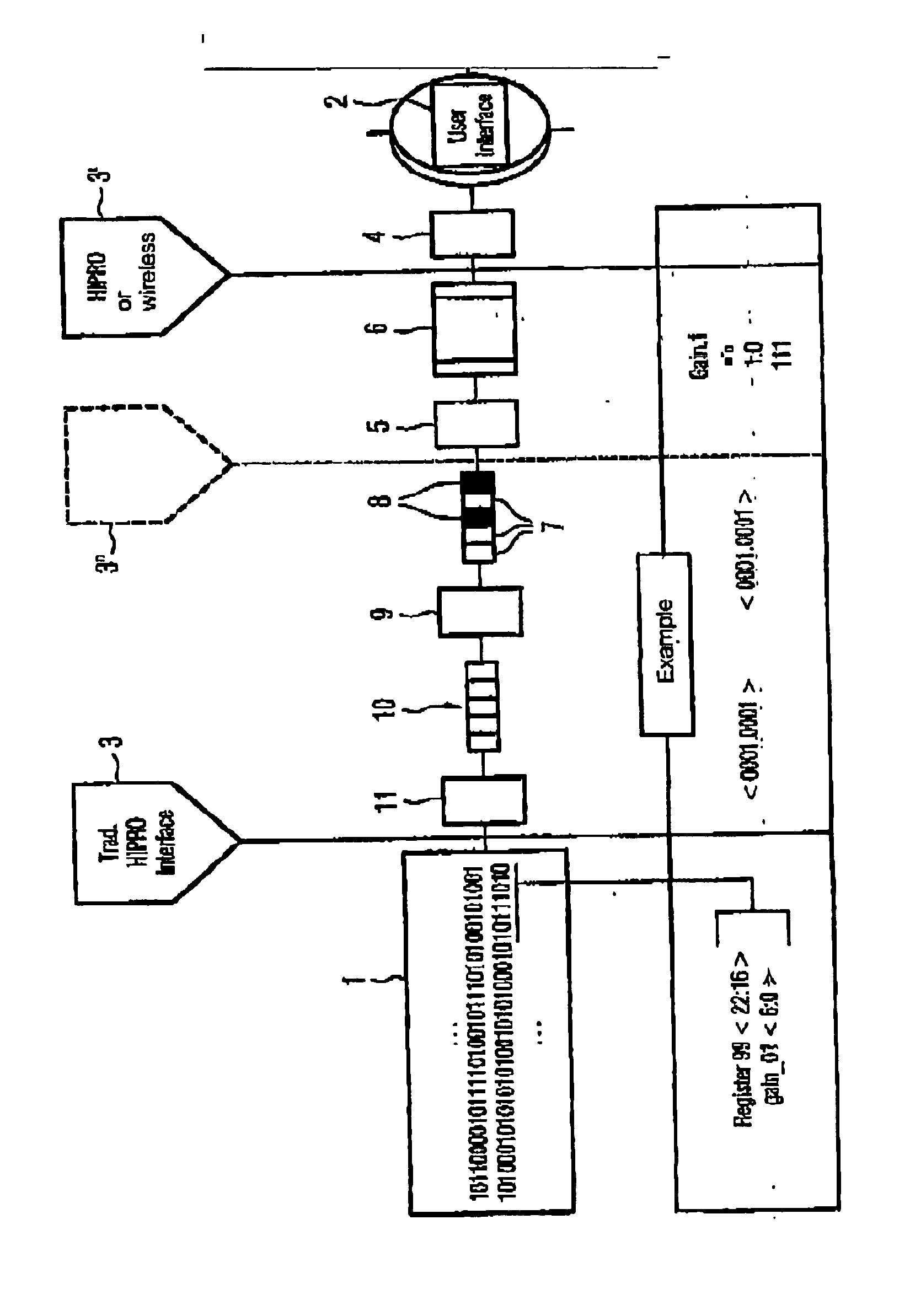

Hearing device with individually configurable hardware interface

InactiveUS20050078845A1Satisfies requirementEar supported setsTelephonic communicationCommunication interfaceHearing apparatus

To assist in the standardization of communication protocols and individual register models of various hearing devices, the register in the DSP / ASIC of a hearing device has a standardized interface in the DSP / ASIC. An application-specific, universal generic command set that is transferred via the communication interface can be used therewith. Thus command set can be standardized over hearing device families, IC generations and across manufacturers, such that a universal software for adaptation of hearing devices can be achieved.

Owner:SIVANTOS PTE LTD

Gateway module for a communications system, communications system, and method for transmitting data between users of a communications system

ActiveUS9191467B2Improve jitter characteristicsImprove throughputData switching by path configurationNetwork connectionsCommunications systemNetwork Communication Protocols

A gateway module for connection of at least two sub-networks is described. A first sub-network of the at least two sub-networks supports a data transmission in accordance with a first communications protocol, especially CAN, FlexRay, LIN, MOST or Ethernet, and a second sub-network of the at least two sub-networks supports a data transmission in accordance with a second communications protocol, especially CAN, FlexRay, LIN, MOST or Ethernet. The gateway module has a configurable hardware circuit which is adapted to manipulate and forward data from the first sub-network and to the second sub-network taking into consideration the first communications protocol and the second communications protocol.

Owner:ROBERT BOSCH GMBH

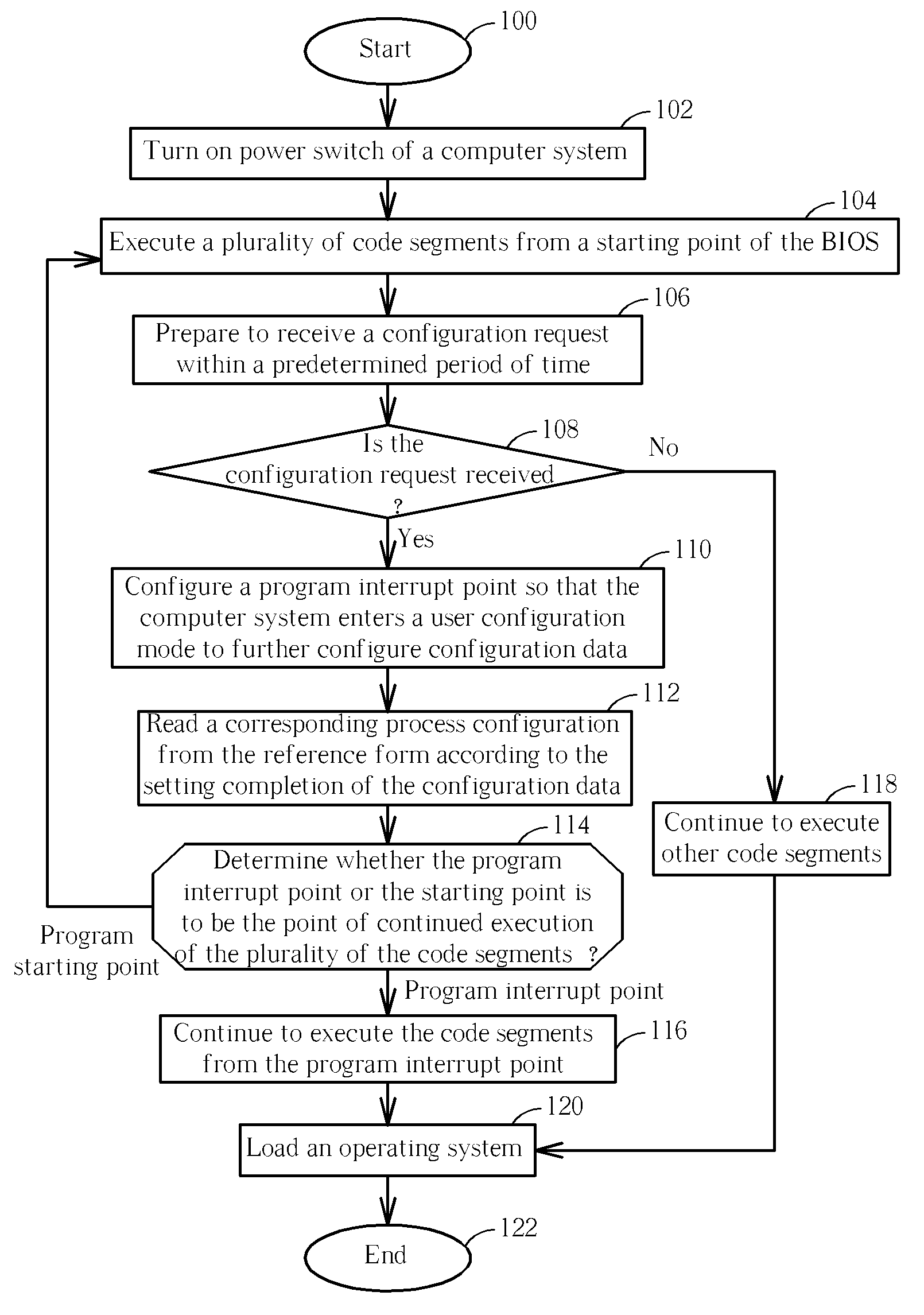

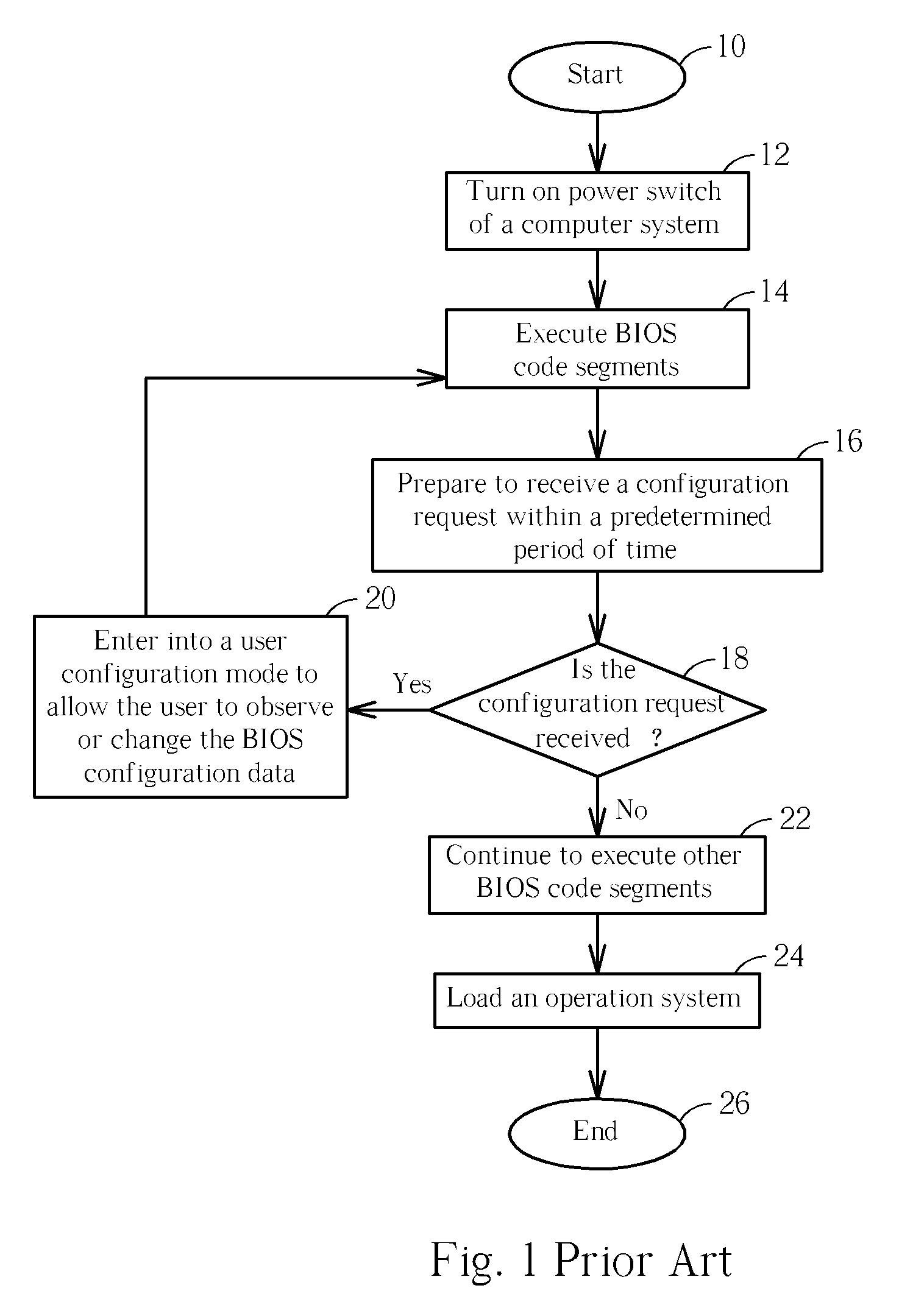

Method for Booting a Computer System

A computer system has a processor, a basic input and output system (BIOS), a plurality of configurable hardware components, configuration data and an operating system (OS). The method includes executing the plurality of code segments from a starting point of the BIOS for initializing the plurality of hardware components, preparing to receive a configuration request, setting a program interrupt point, switching the computer into a user configuration mode for configuration request, continuing to execute the code segments by the program interrupt point, and loading the operating system.

Owner:VIA TECH INC

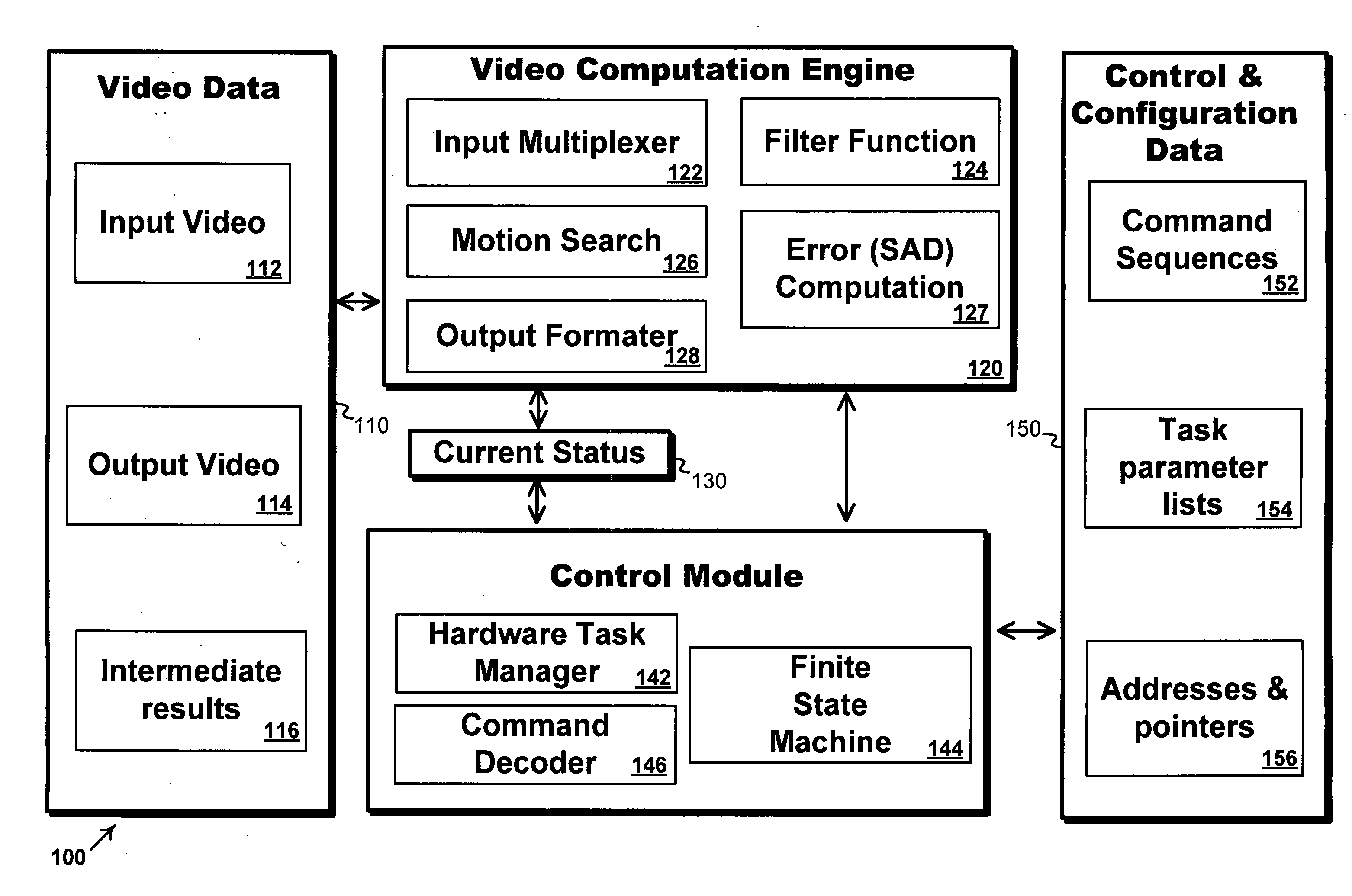

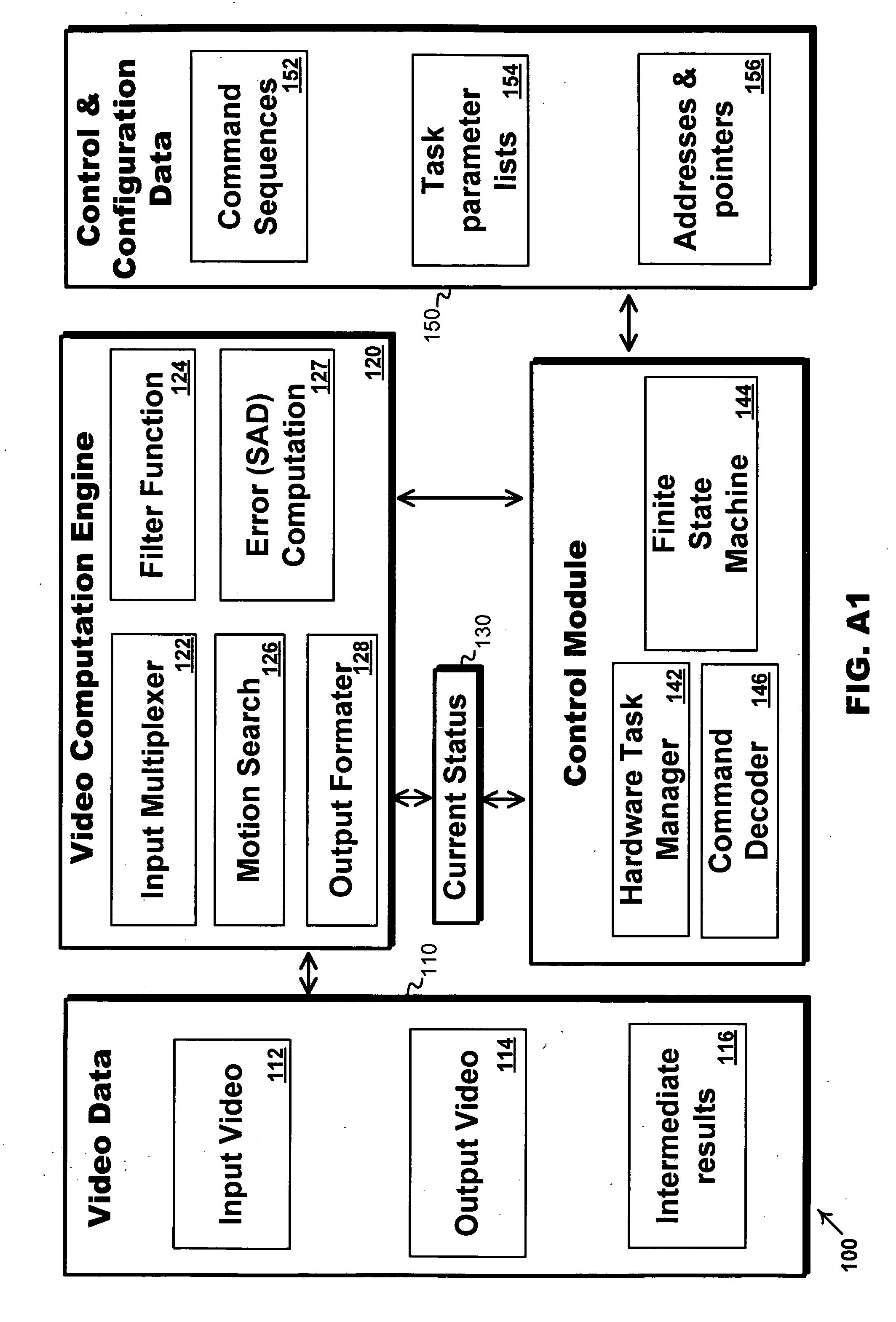

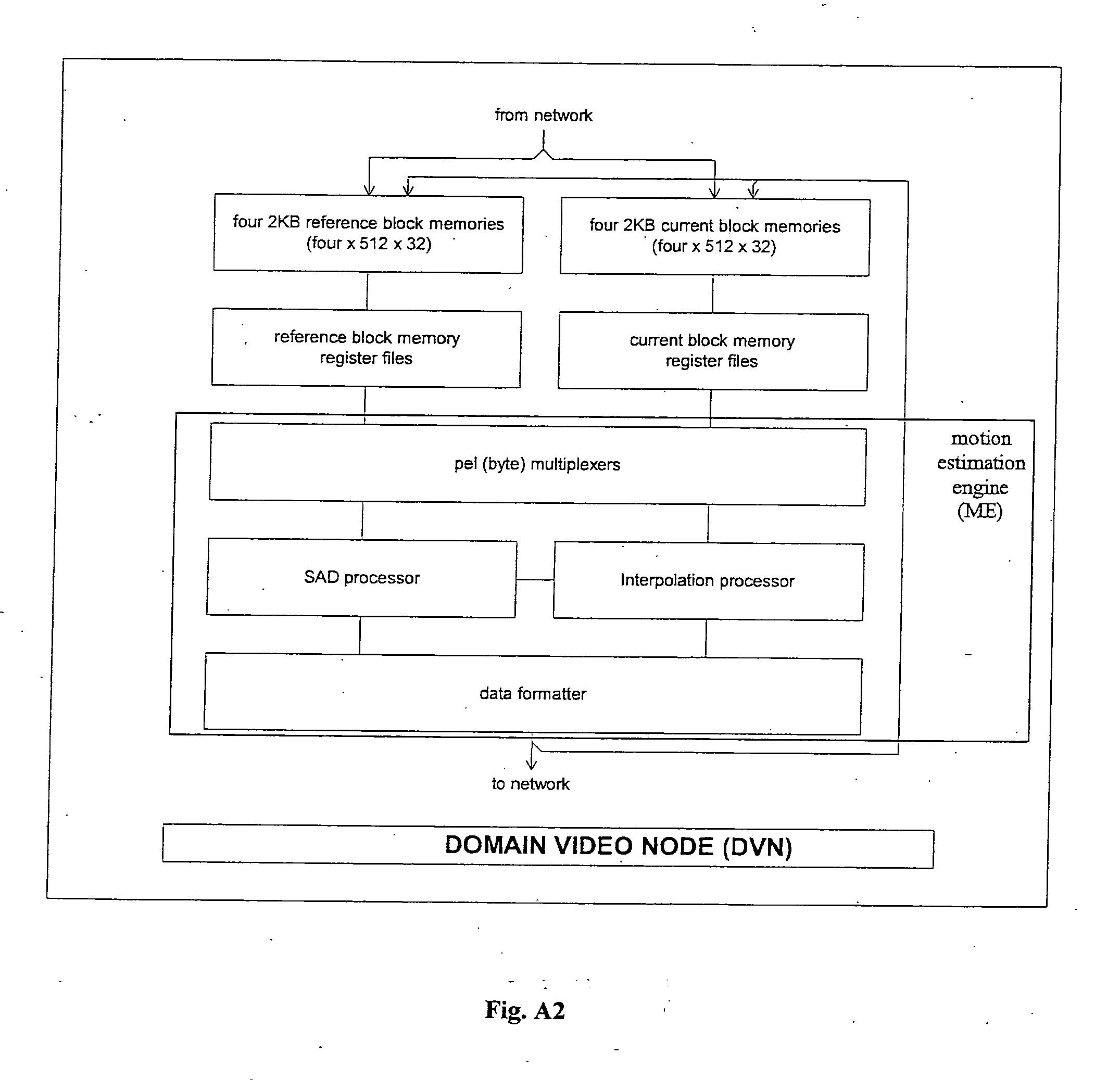

Processor for video data encoding/decoding

ActiveUS20080130742A1Improve accuracyImprove perceived qualityColor television with pulse code modulationColor television with bandwidth reductionComputer architectureVideo processing

A video processor uses attributes of video data to perform encoding and decoding. Some embodiments dynamically configure the processor via a sequence of instructions, where the instructions include information on the attributes of the current video data. Some embodiments include a dynamically configurable adder array that computes difference functions thereby generating error vectors. Some embodiments include a dynamically configurable adder array that computes filtering functions applied to the video data, e.g. interpolation or decimation of the incoming video prior to motion detection. Some embodiments of the invention provide dynamically configurable hardware searches, for example, for detecting motion. Some embodiments of the invention are implemented using an adaptive computing machines (ACMs). An ACM includes a plurality of heterogeneous computational elements, each coupled to an interconnection network.

Owner:NVIDIA CORP

Method and apparatus for non-speculative pre-fetch operation in data packet processing

InactiveUS20060215670A1Digital computer detailsMultiprogramming arrangementsProcessing InstructionManagement unit

Owner:ARM FINANCE OVERSEAS LTD

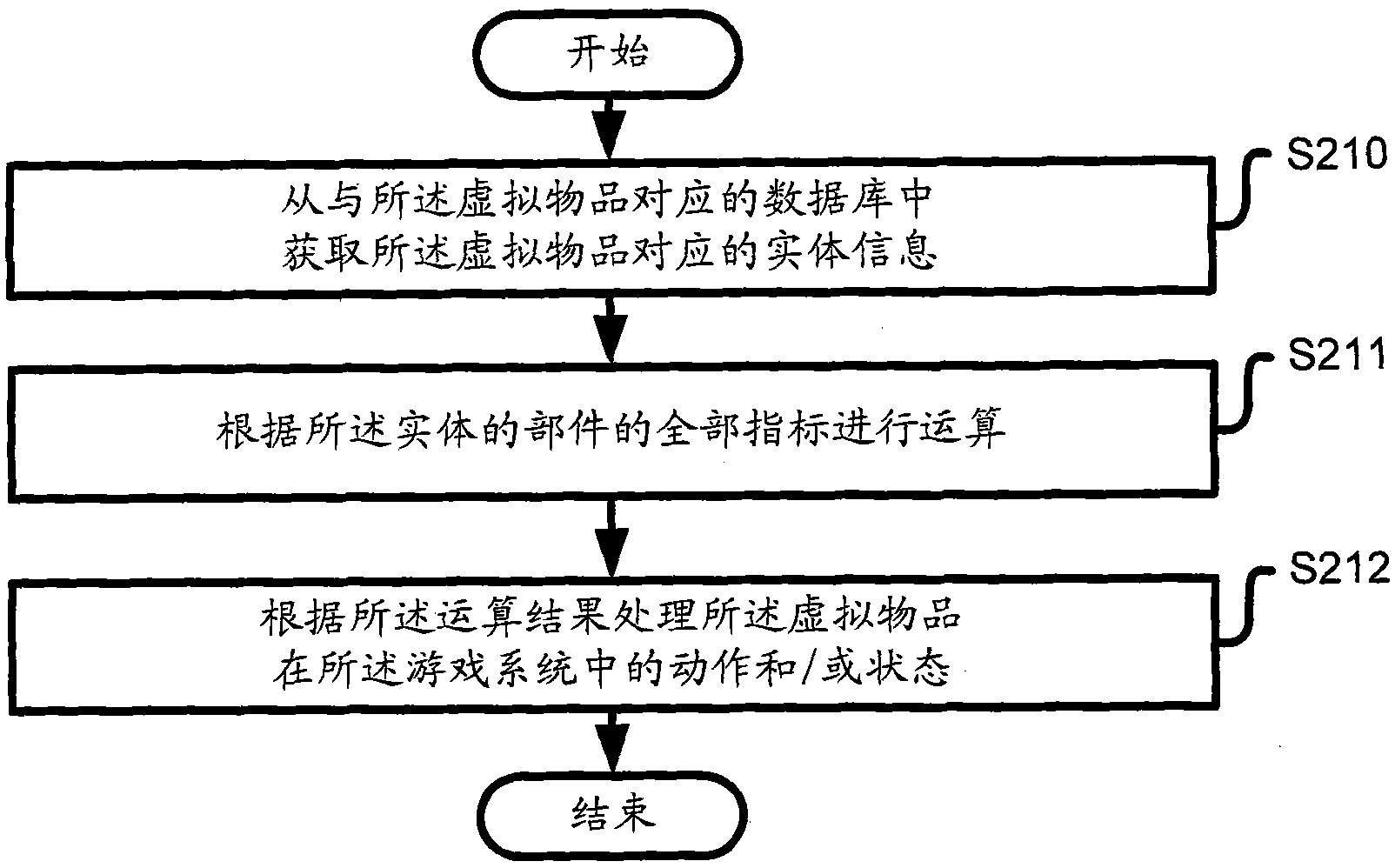

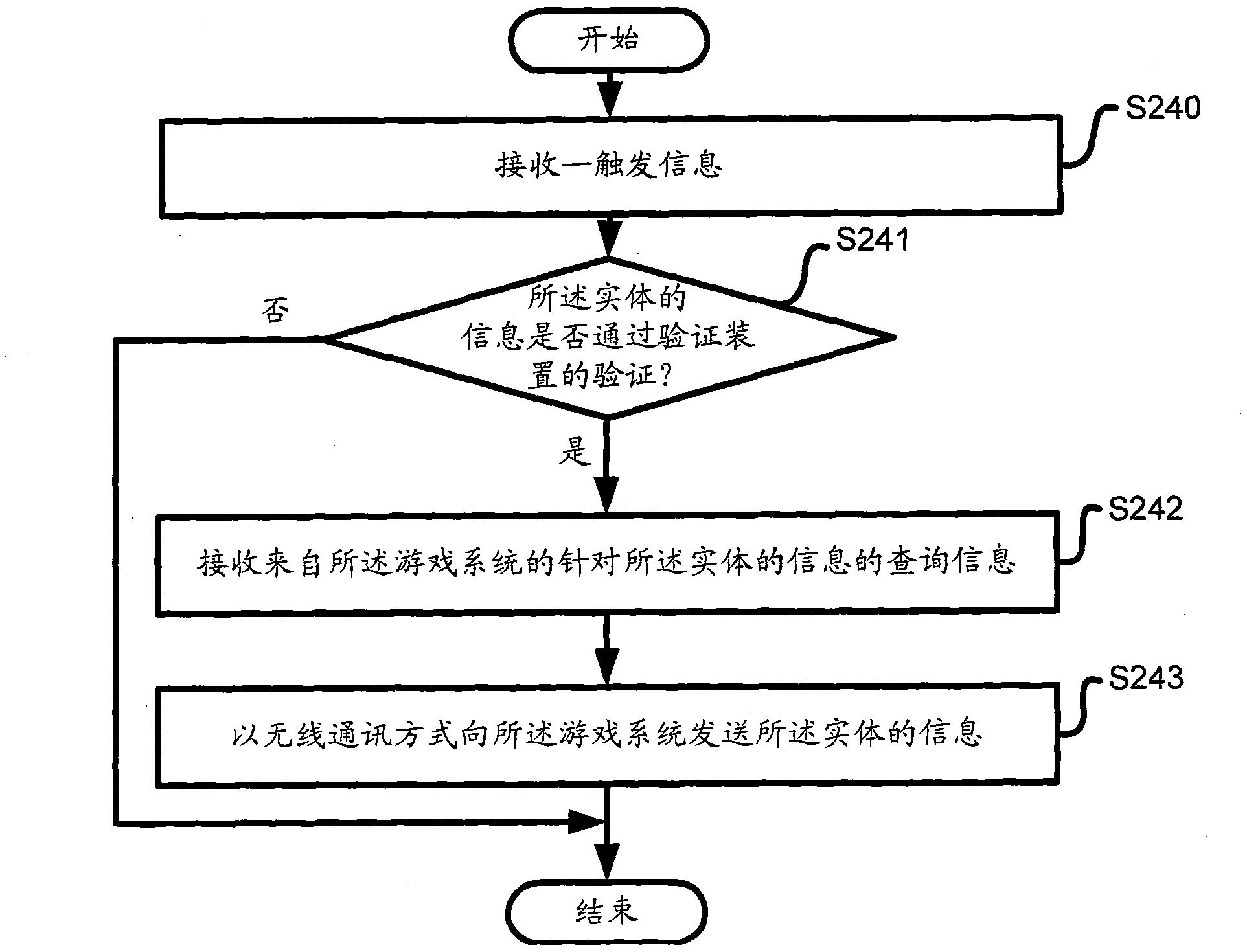

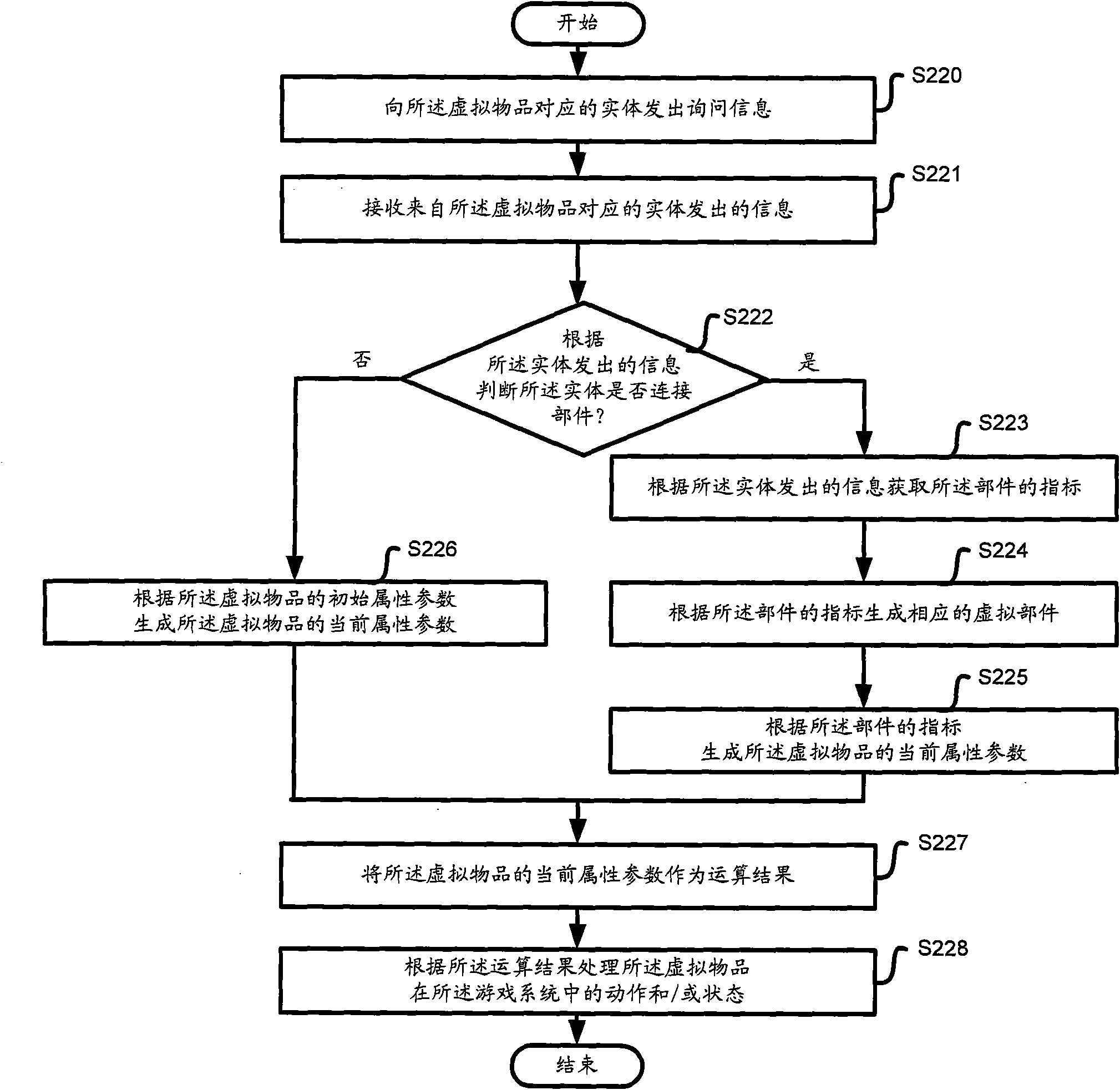

Control platform for correlating entity with virtual article and corresponding control method

InactiveCN102043890ARich experienceHow realisticSpecial data processing applicationsConfigurable hardwareHuman–computer interaction

The invention provides a control method for correlating an entity with a virtual article in a game system, wherein the virtual article is a virtual object in the game system, and the entity is an object correlated with the game system. The control method is characterized by comprising the following steps of: a. acquiring entity information corresponding to the virtual article; and b. processing the action and / or the state of the virtual article in the game system according to the entity information. The invention also provides a control device for correlating the entity with the virtual article in the game system as well as an auxiliary control method and device for correlating the entity with the virtual article in the entity and the entity correlated with the game system. The invention realizes the effect of the synchronization of entity operation and virtual article operation by correlating real entities, such as toys, articles, and the like, with the virtual article in the game system, thereby enriching the experience of players, bringing more reality sense to the players and providing sufficient market conditions for factories during marketing highly-configurable hardware.

Owner:马天龙

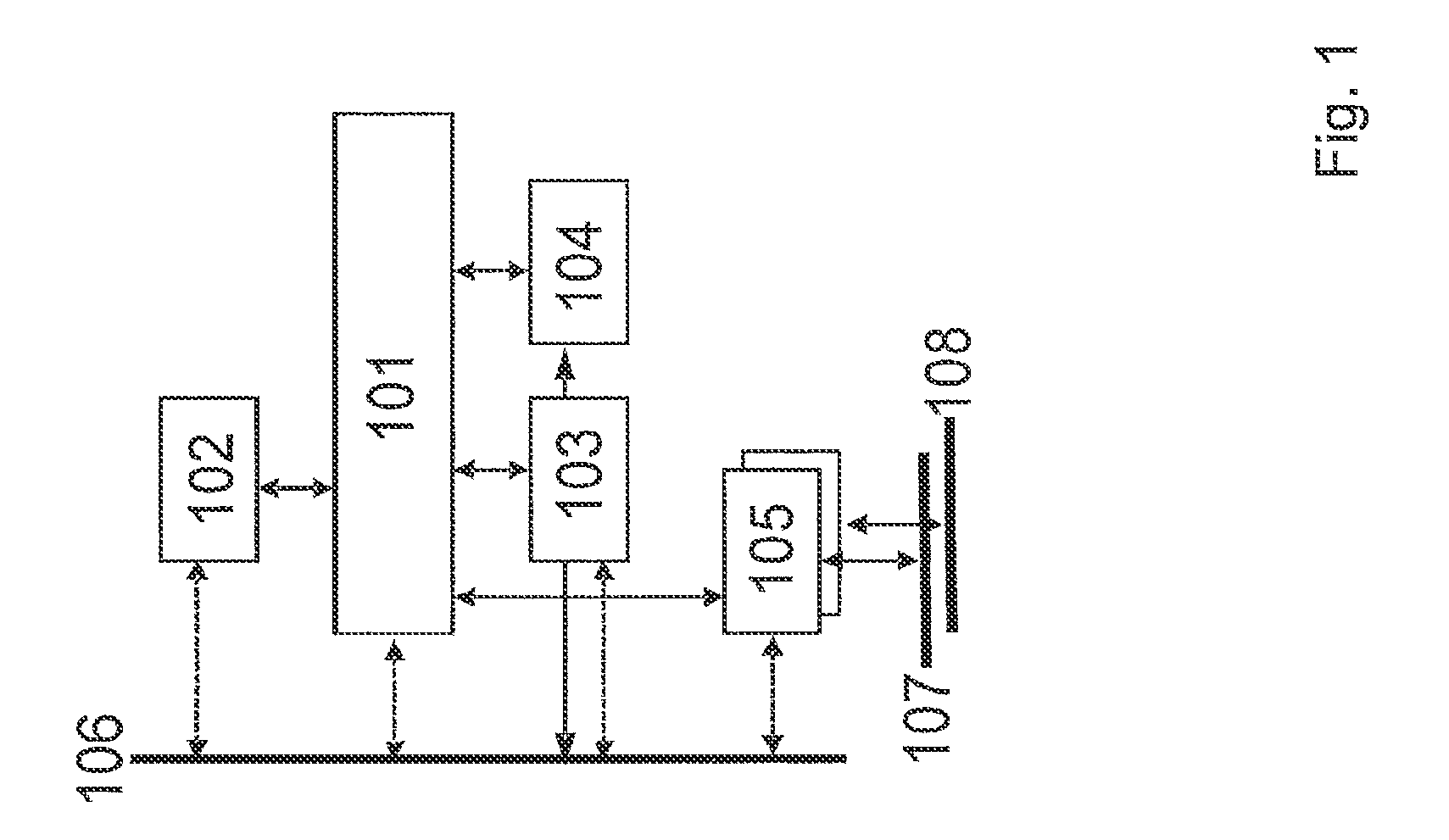

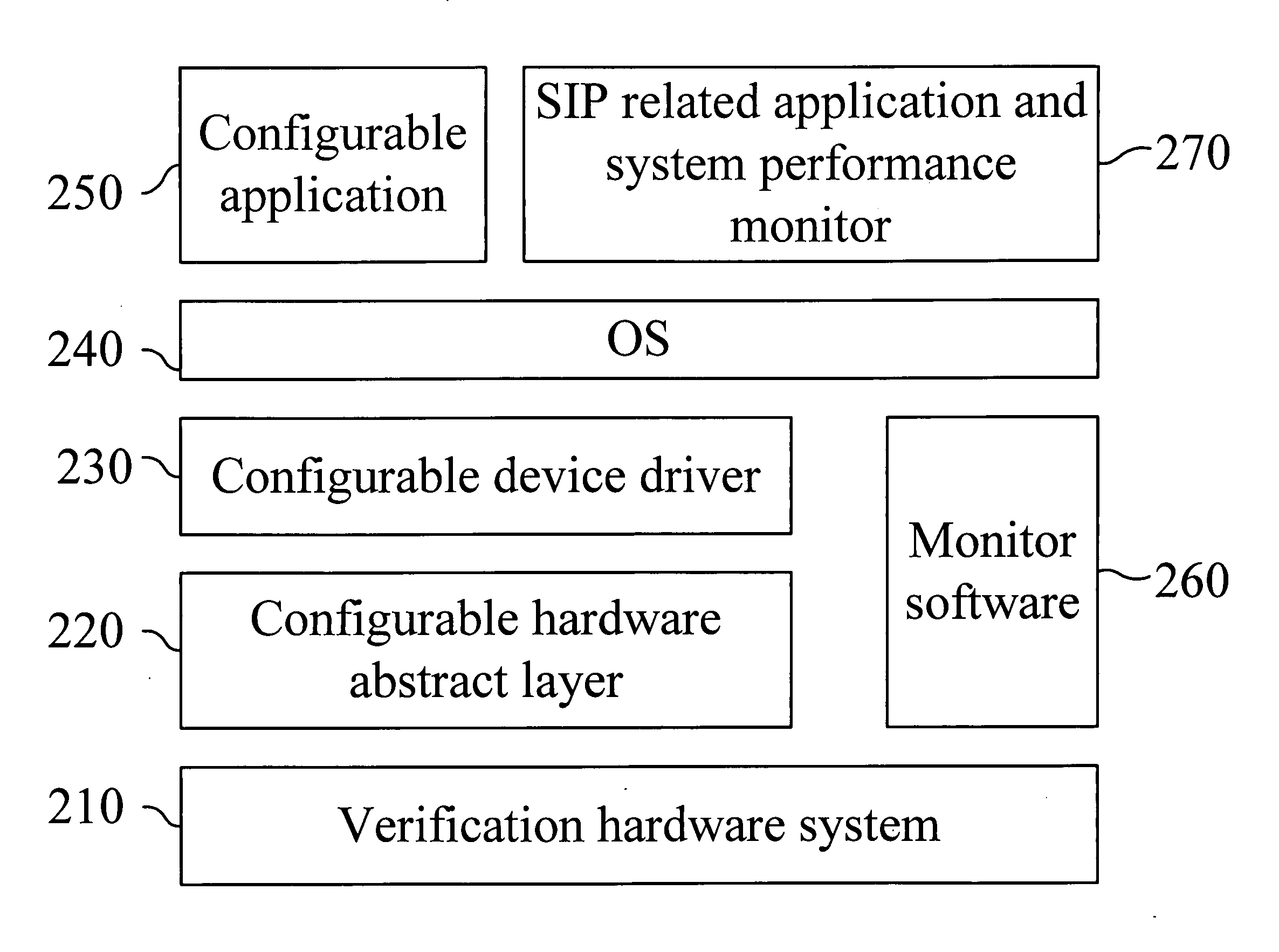

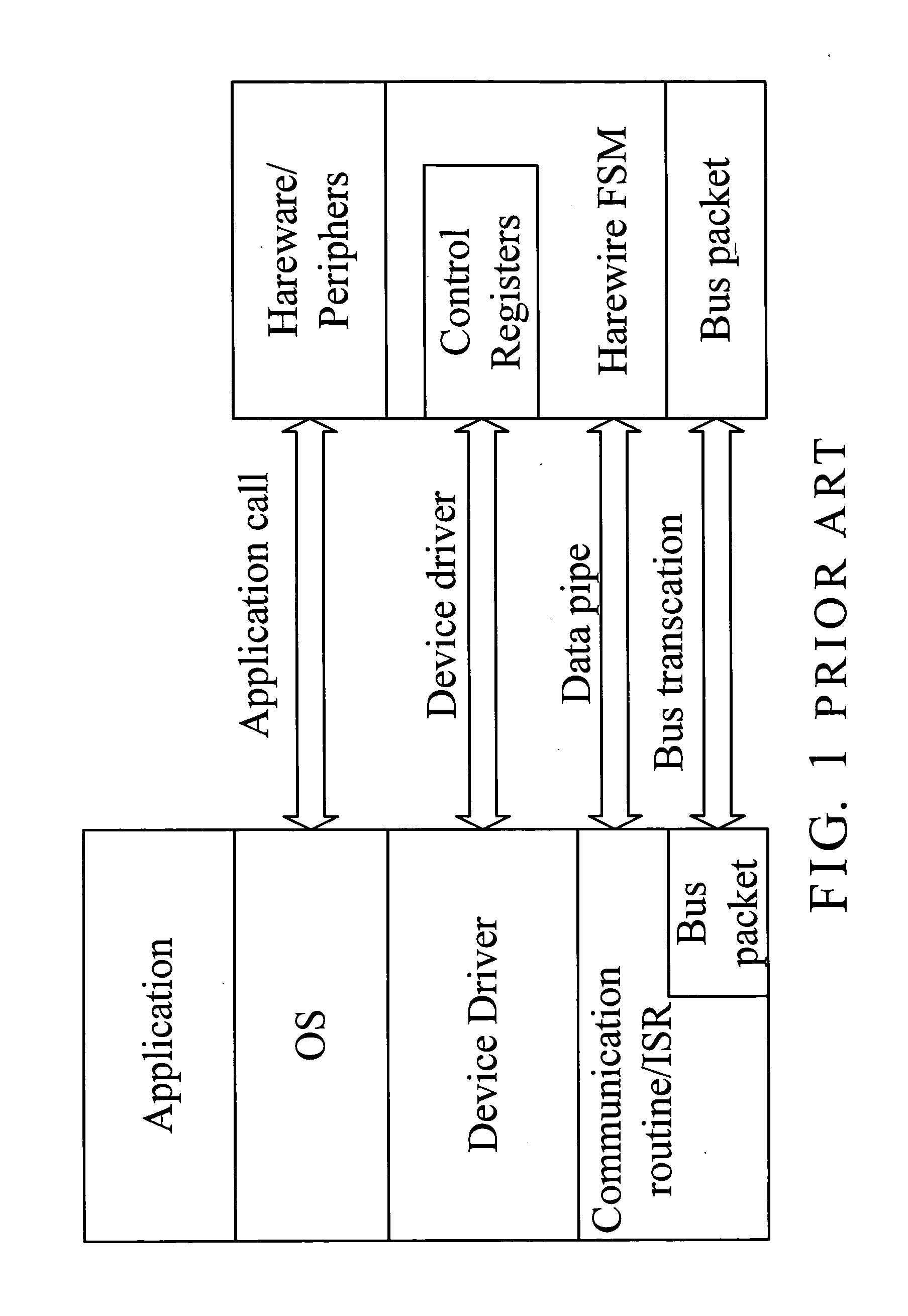

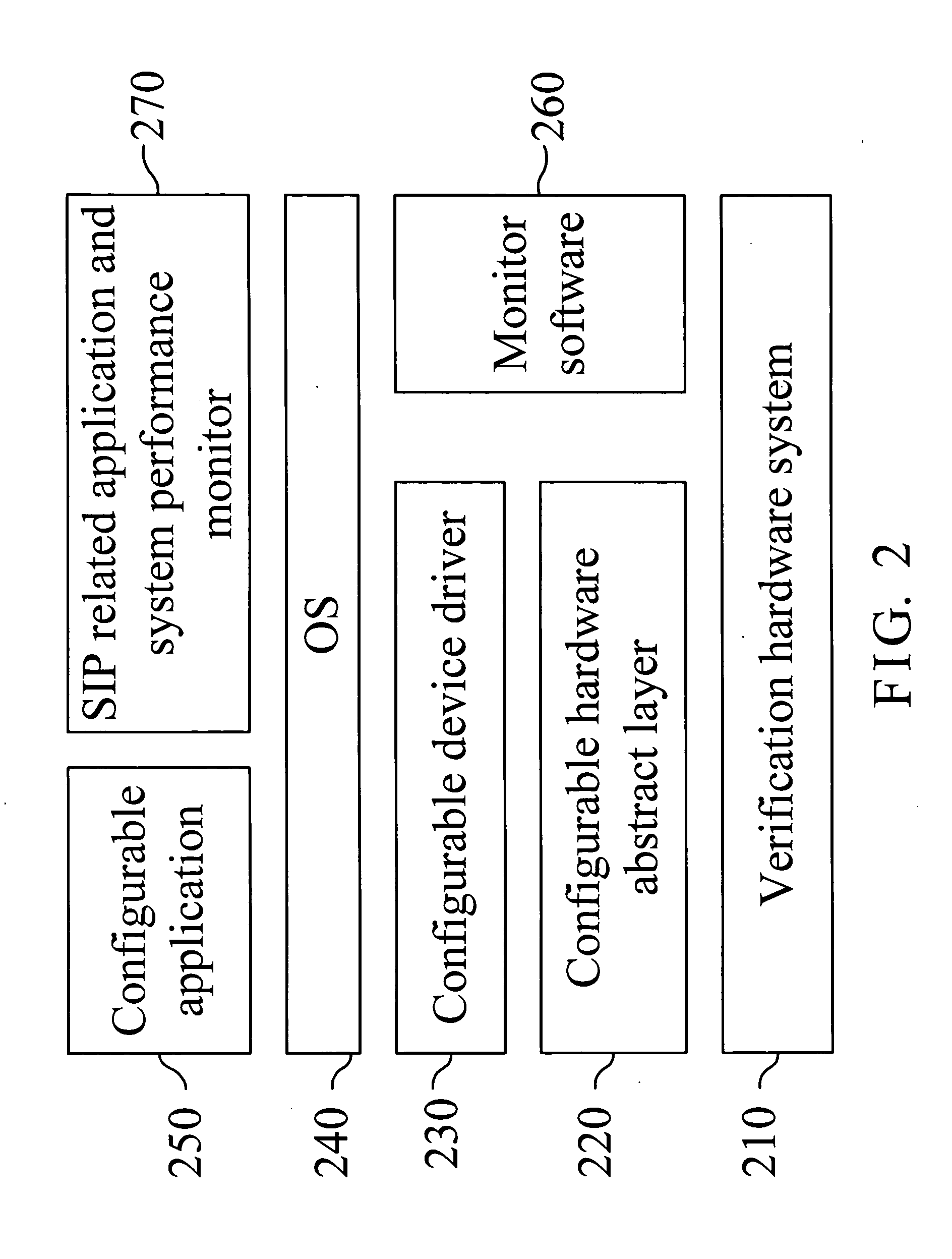

Multitasking system level platform for HW/SW co-verification

InactiveUS20050144436A1Error detection/correctionUser identity/authority verificationComputer hardwareOperational system

A multi-tasking system level Hw / Sw co-verification platform is disclosed. The platform comprises a verification hardware system including a replaceable processor core, a peripheral device required by an OS, a programming logic unit, and a SIP for implementing a complete system, a configurable hardware abstract layer for lowering a coupling with the verification hardware system in a lower level by means of an abstract description of hardware, a configurable device driver for driving hardware of the verification hardware system by means of the configurable hardware abstract layer, an OS for running on the verification hardware system so as to provide an environment and allowing applications to run thereon, and a configurable application for running functions of the verification hardware system.

Owner:INSTITUTE FOR INFORMATION INDUSTRY

System and method for online specification of a system

InactiveUS20060009945A1Facilitating native executionDigital data processing detailsElectrical testingComputer hardwareGraphics

A system and method for online configuration of a measurement device for a measurement system. The user accesses a server with a client computer over a network and specifies a desired measurement task. If the user lacks the hardware required to perform the task, hardware specifications and configuration software and / or data specific to the user's application, i.e., to perform the task, are sent to a manufacturer, who pre-configures the hardware with the configuration software and / or data to perform the task and sends the pre-configured hardware to the user. The hardware may be re-configurable hardware, such as a programmable hardware element or processor / memory based device. Configuration software and / or data for configuring the user's measurement system hardware (and / or software) to perform the desired task may also be sent to the user. The configuration software sent to the user may comprise a graphical program usable by the measurement system to perform the task.

Owner:NATIONAL INSTRUMENTS

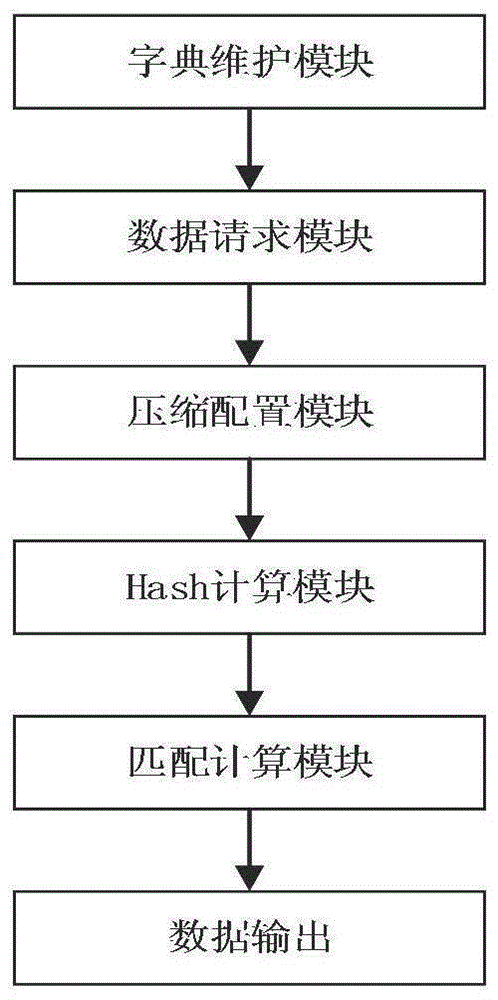

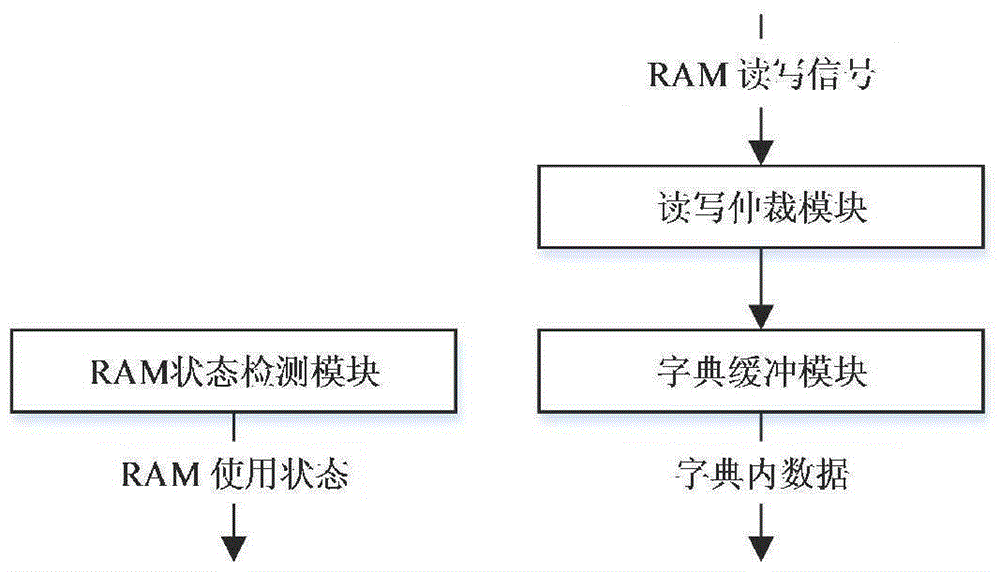

Configurable data compression system based on hardware

ActiveCN105183557AImprove the efficiency of data compression processingGuaranteed continuous readResource allocationCode conversionLossless compression algorithmProgrammable logic device

The present invention discloses a configurable data compression system based on hardware. The configurable data compression system comprises a dictionary maintenance module, a data request module, a data compression module and a data output module. By using the configurable data compression system disclosed by the present invention, a data compression function is realized by using a field programmable gate array (FPGA), the data compression system is realized by adding related modules communicated with a PC, and the efficiency of data compression process is greatly improved by adopting a LZ77 lossless compression algorithm and designing a reasonable hardware circuit structure according to the algorithm. In addition, the degree of preference to compression ratio and compression rate in an LZ77 compression process can be adjusted according to different compression levels. Further, the result of data compression can be coded differently to form compressed files with different formats, thereby realizing compatibility between hardware and software.

Owner:SOUTHEAST UNIV

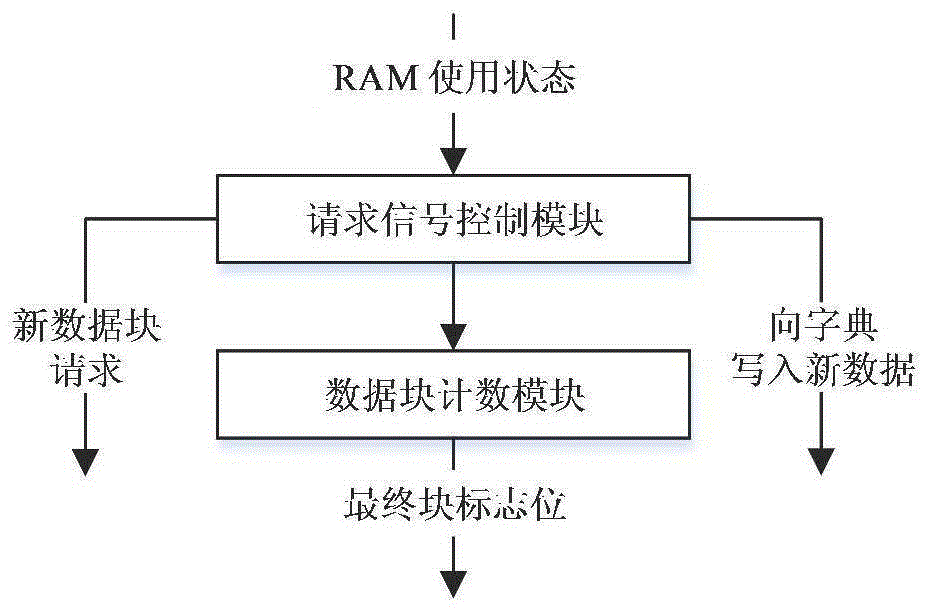

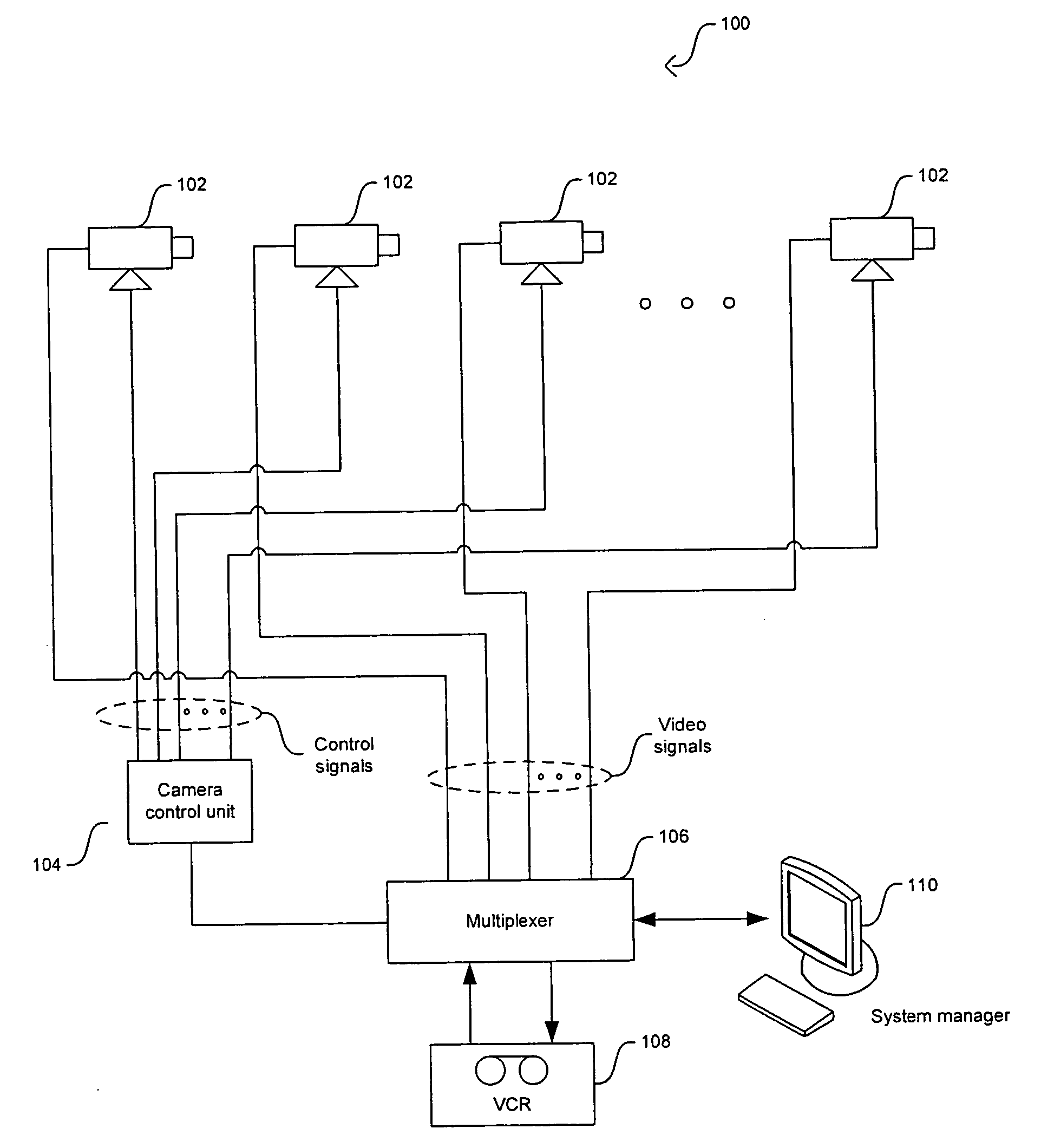

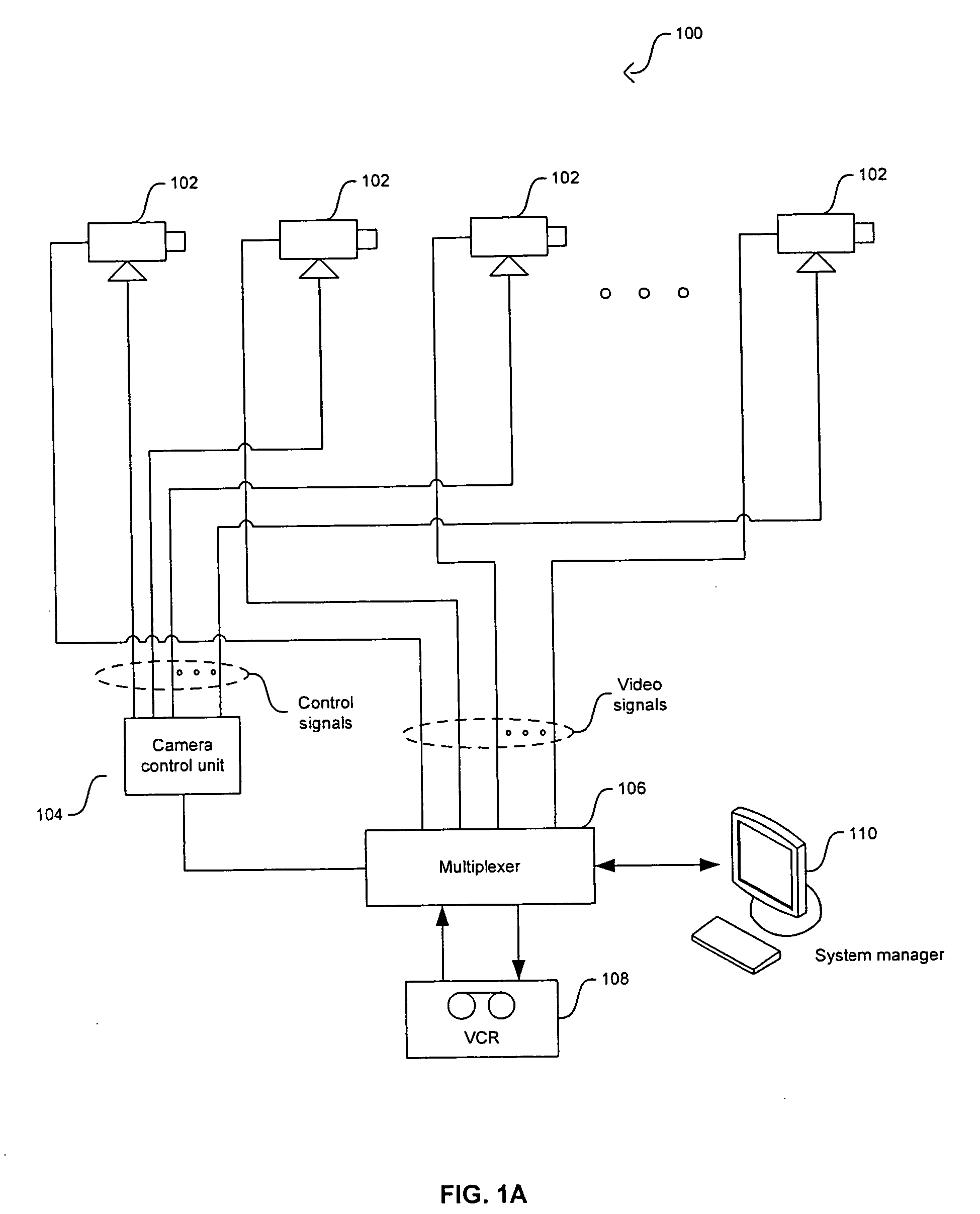

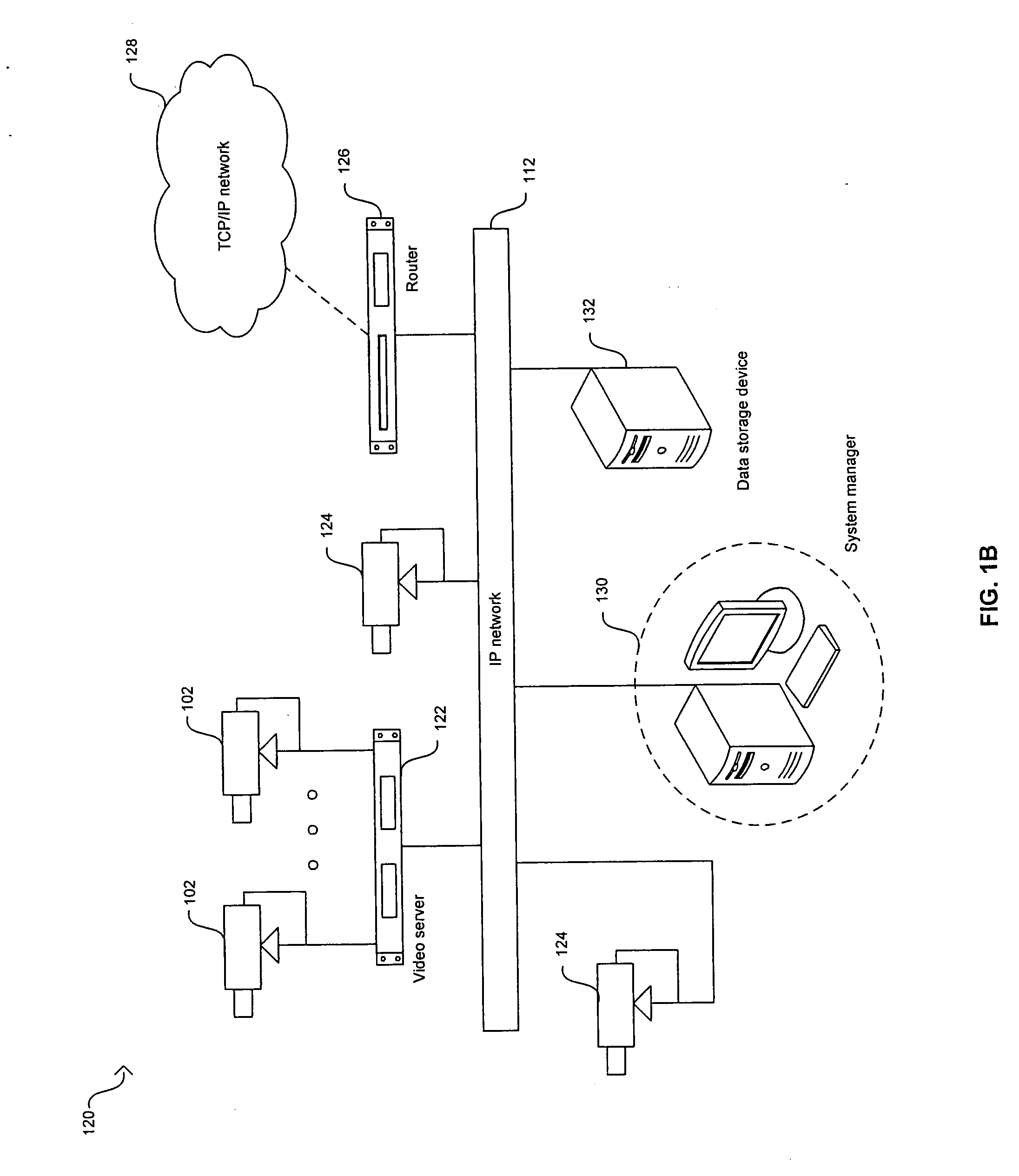

Method and system for configurable security and surveillance systems

InactiveUS20060236375A1Digital data processing detailsUser identity/authority verificationMonitoring systemE-commerce

A method and system for a configurable security and surveillance system are provided. A configurable security and surveillance system may comprise at least one programmable sensor agent and / or at least one programmable content analysis agent. A plurality of processing features may be offered by the configurable security and surveillance system by programming configurable hardware devices in the programmable sensor agents and / or the programmable content analysis agents via a system manager. Device programming files may be utilized to program the configurable hardware devices. The device programming files may be encrypted and decryption keys may be requested to enable the programming of different processing features into the programmable sensor agents and / or the programmable content analysis agents. The device programming files and / or the decryption keys may be received via a network transfer and / or via a machine-readable media from an e-commerce vendor.

Owner:9051147 CANADA

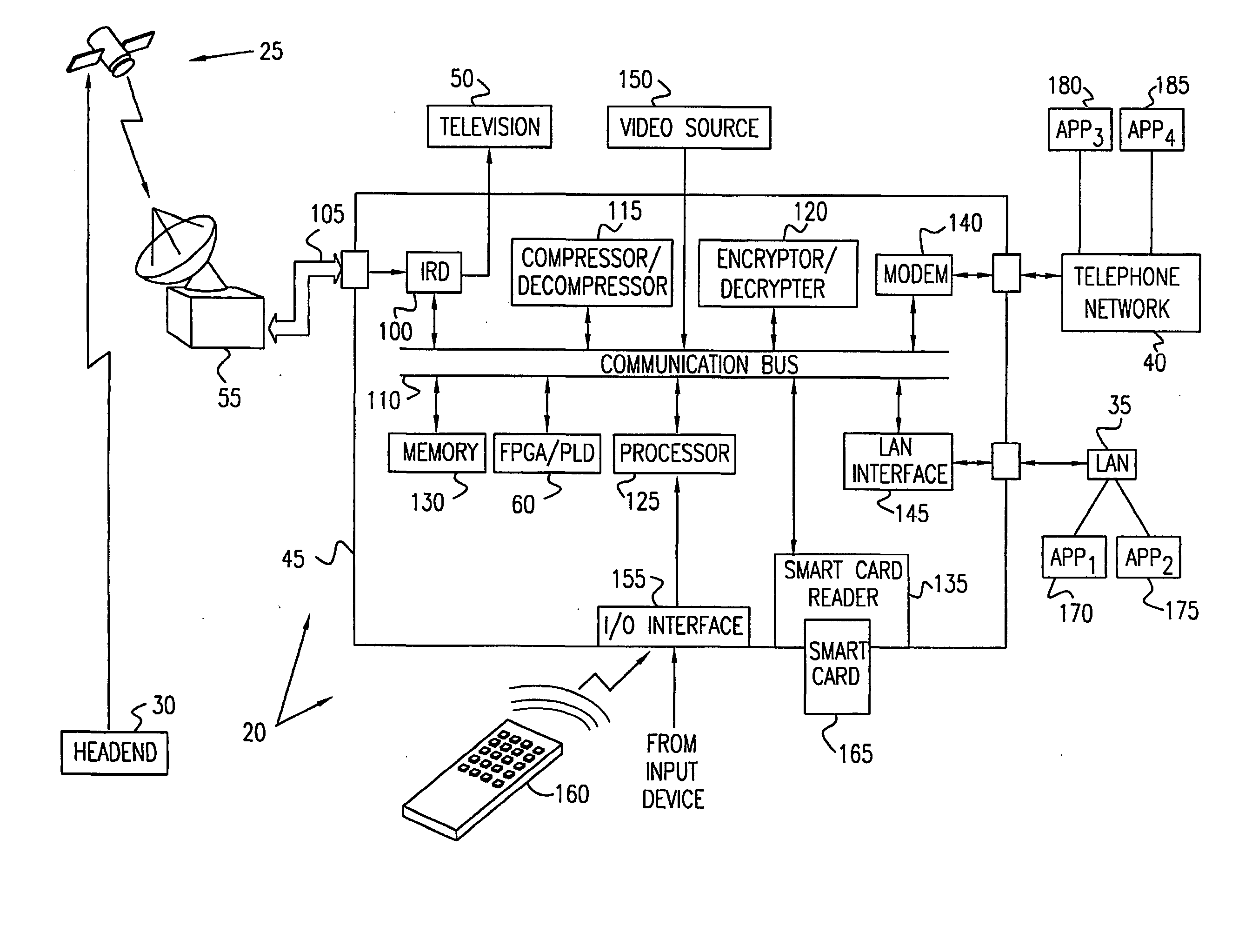

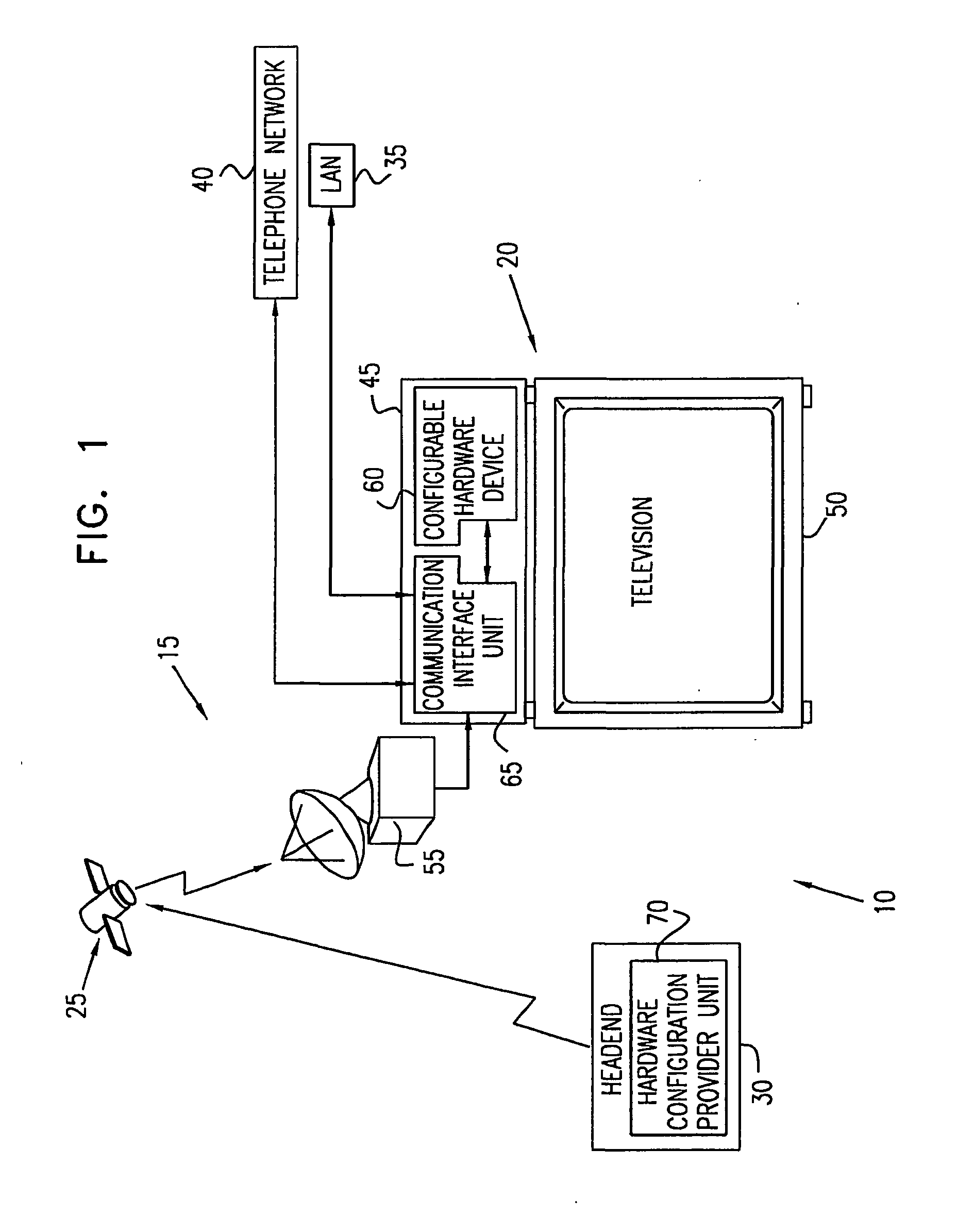

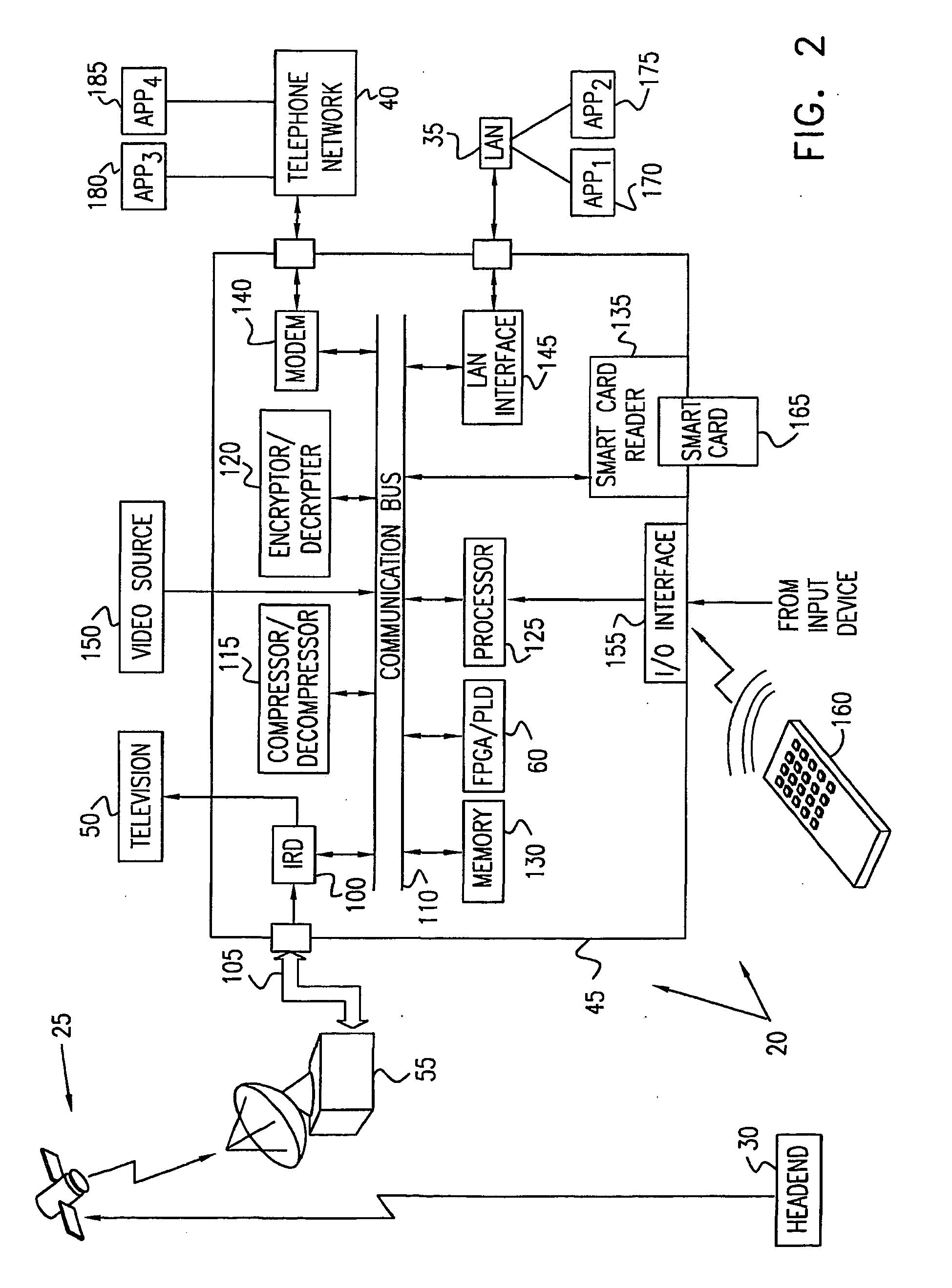

Configuring field programmable devices

InactiveUS20100121748A1Complete banking machinesTelephonic communicationComputer hardwareConfigurable hardware

A method for reconfiguring a circuit configuration of a configurable hardware device via a communication network. The method includes transmitting via the communication network from a hardware configuration provider unit to the configurable hardware device a circuit reconfiguration of the configurable hardware device in response to a request from a user of the configurable hardware device to reconfigure the configurable hardware device, implementing the circuit reconfiguration of the configurable hardware device thereby reconfiguring the configurable hardware device and providing a reconfigured hardware device and billing the user in response to a determination of correct operation of the reconfigured hardware device. A user unit in a communication network is also disclosed.

Owner:NDS

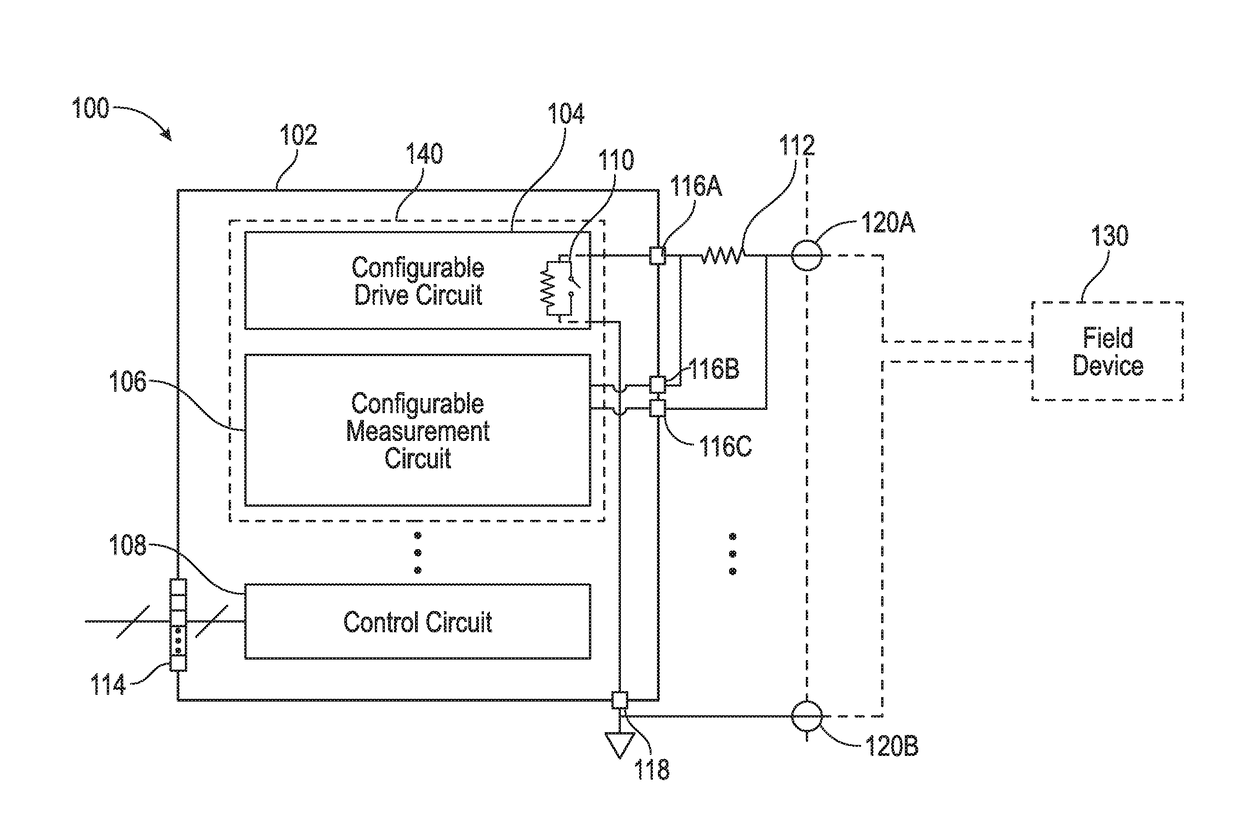

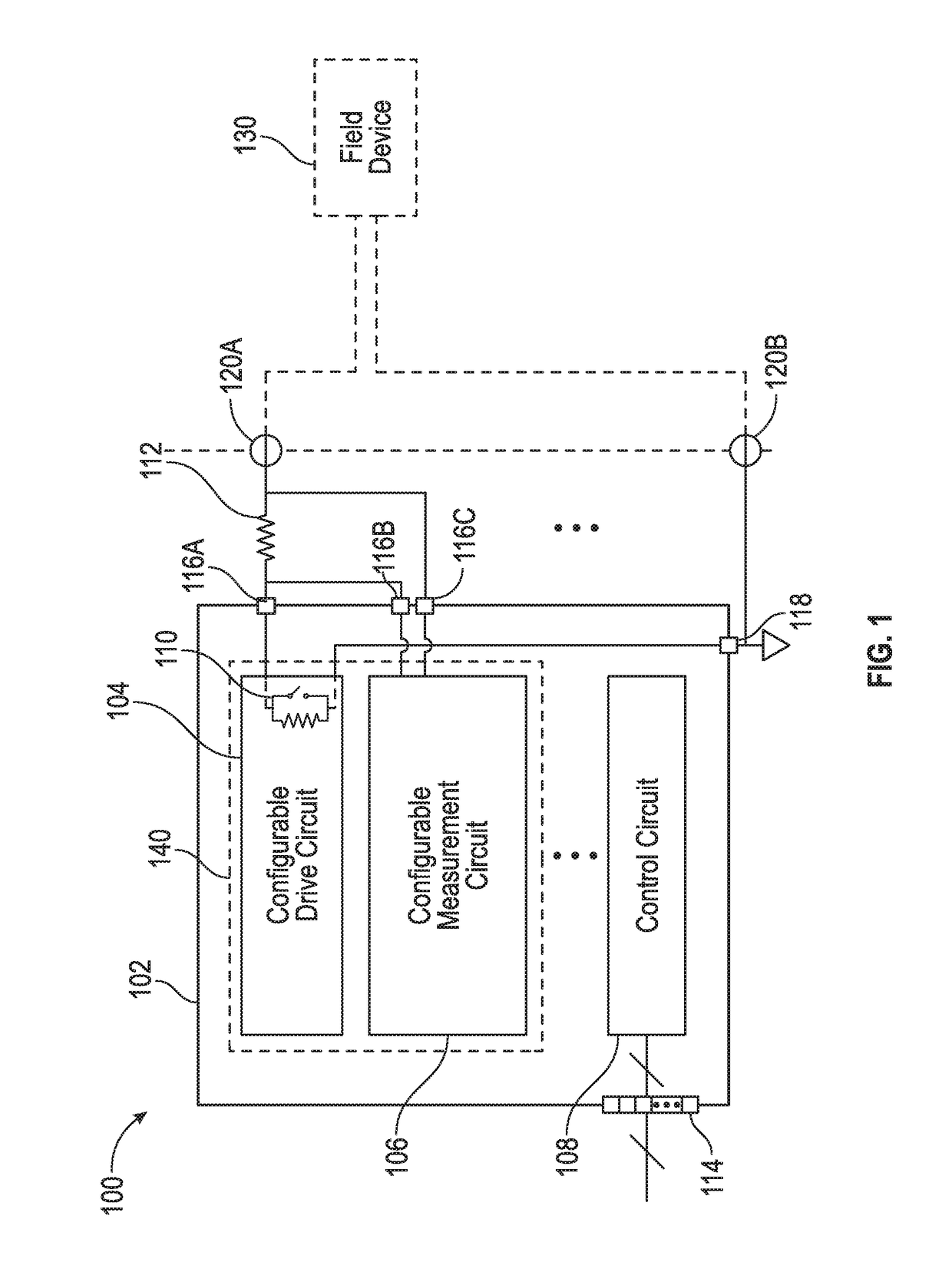

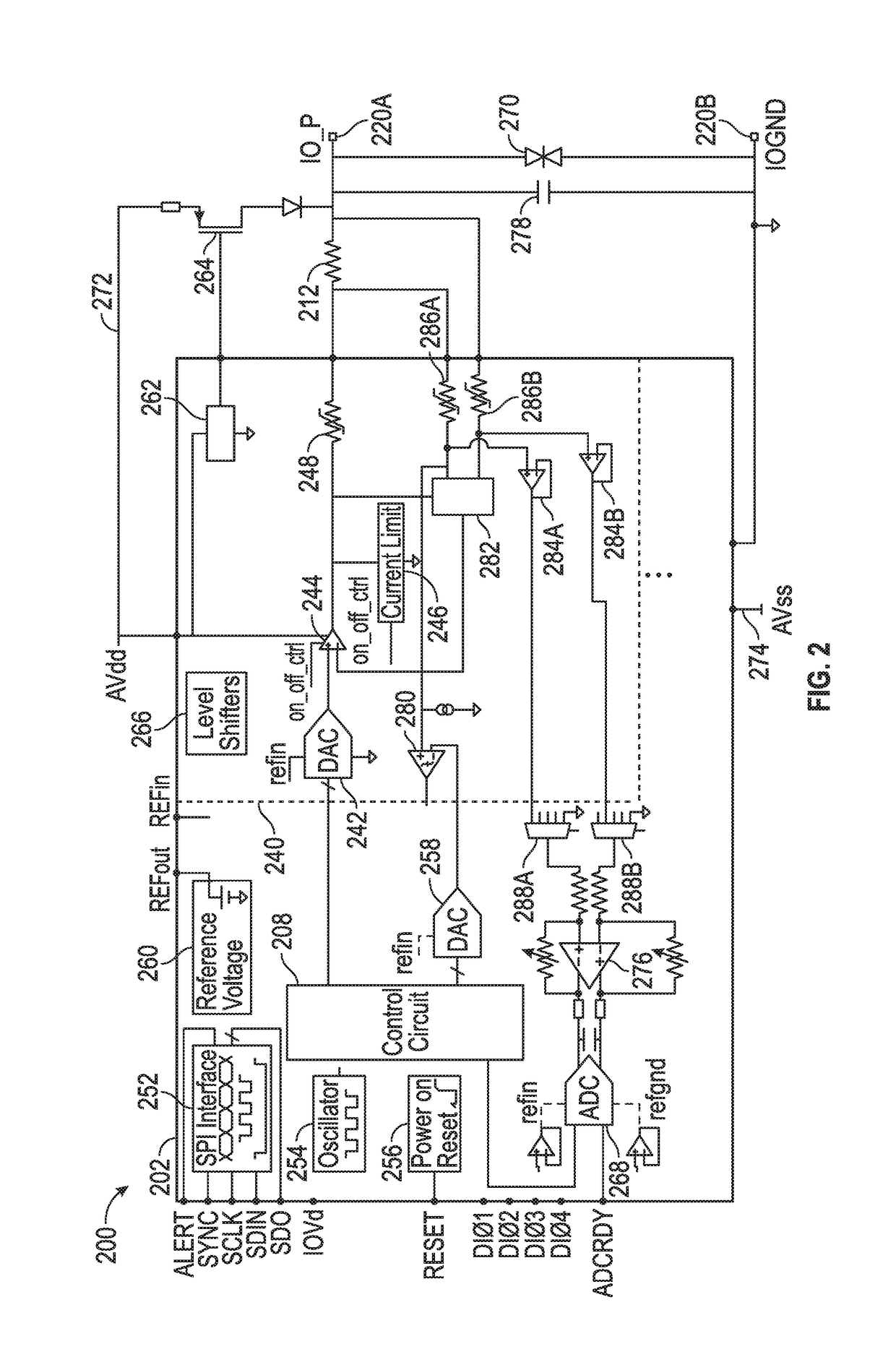

Configurable hardware platform for measurement or control

ActiveUS20170264295A1Complexity of interfaceShorten the counting processProgrammable logic circuit arrangementsSolid-state devicesControl systemConfigurable hardware

Systems for monitoring or control can include reconfigurable input and output channels. Such reconfigurable channels can include as few as a single terminal and a ground pin, or such channels can include three or four terminal configuration such as for use in four-terminal resistance measurements. Channel reconfiguration can be accomplished such as using software-enabled or firmware-enabled control of channel hardware. Such channel hardware can include analog-to-digital and digital-to-analog conversion capability, including use of a digital-to-analog converter to provide field power or biasing. In an example, the interface circuit can provide a selectable impedance.

Owner:ANALOG DEVICES INT UNLTD

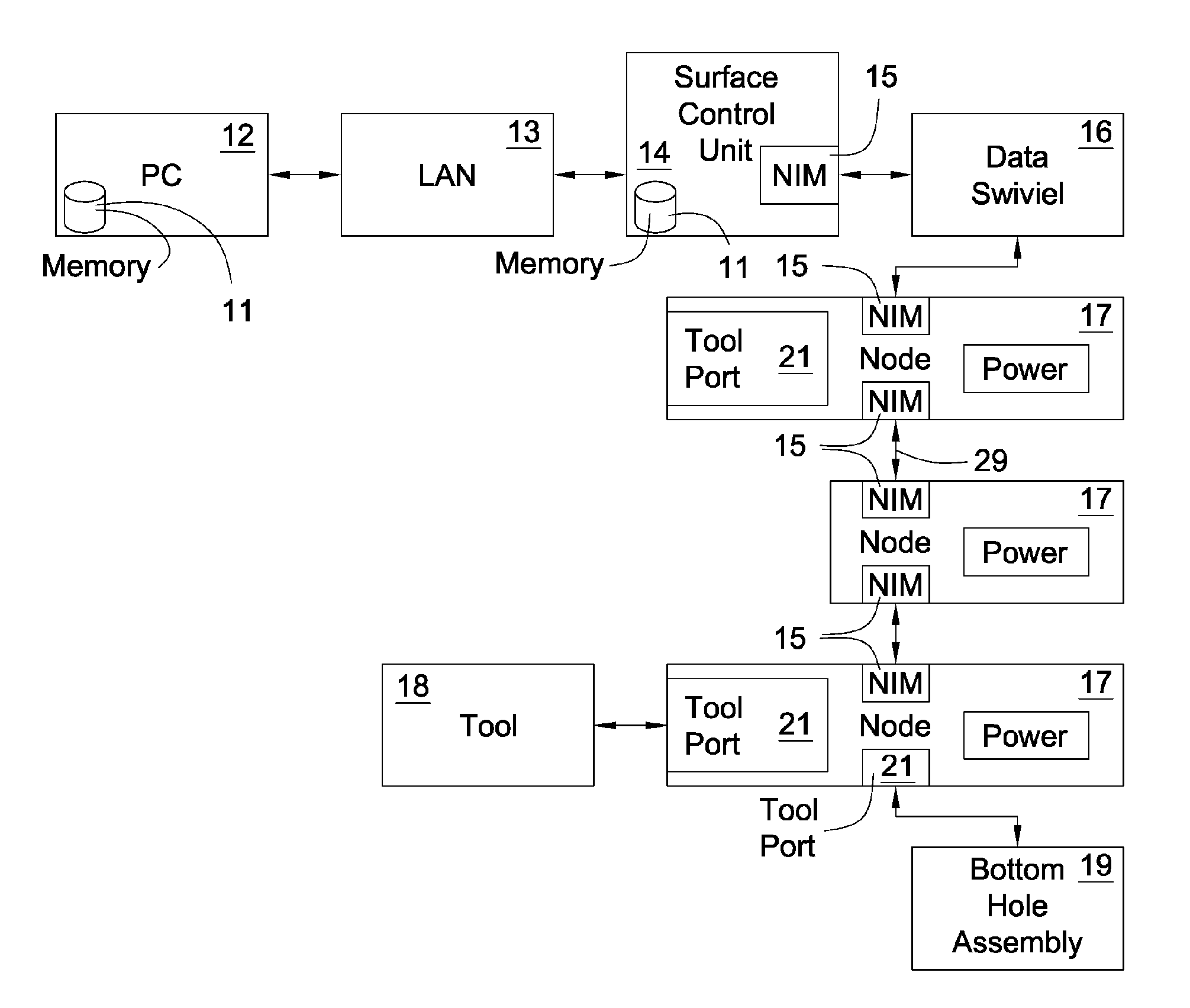

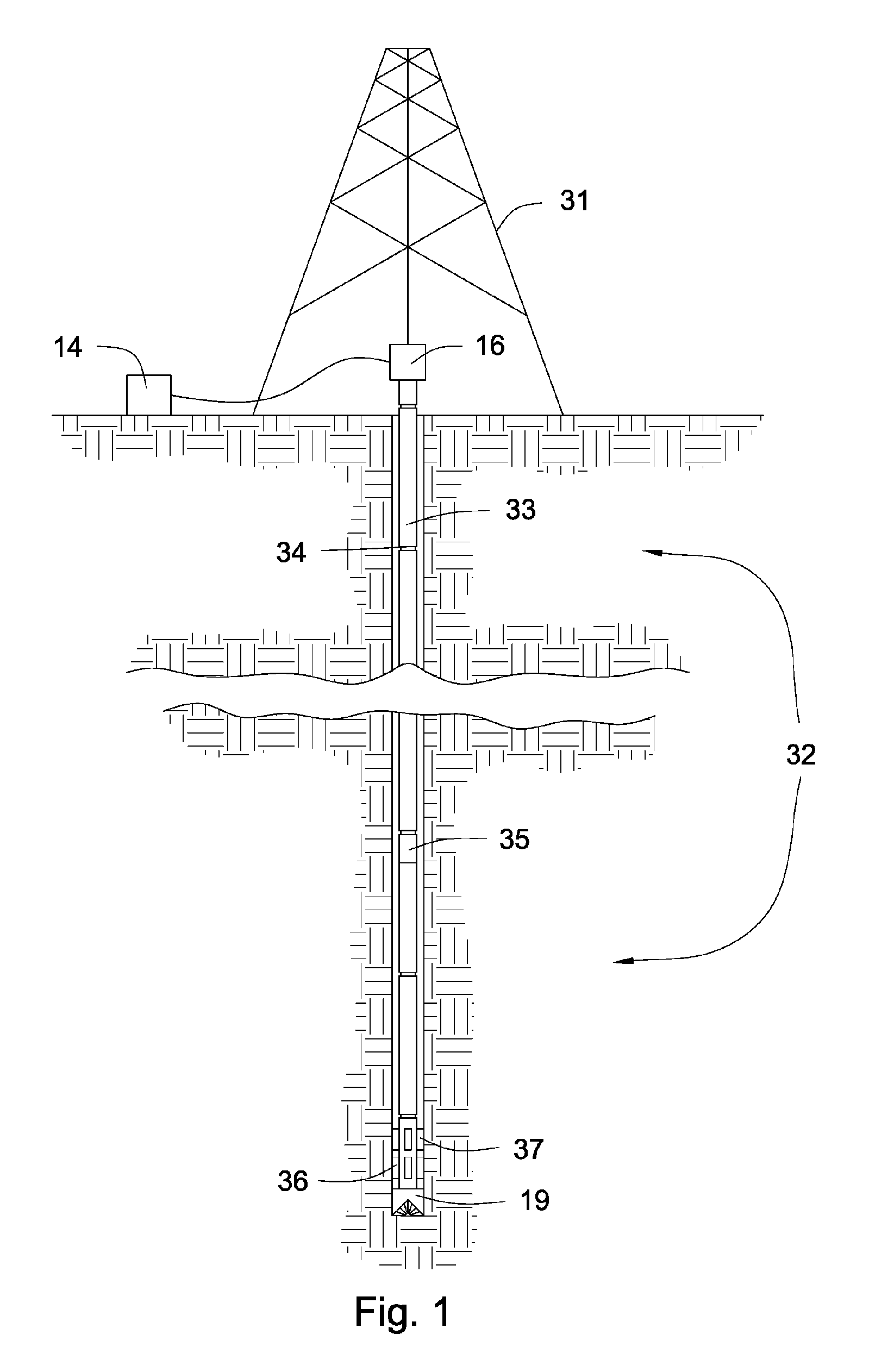

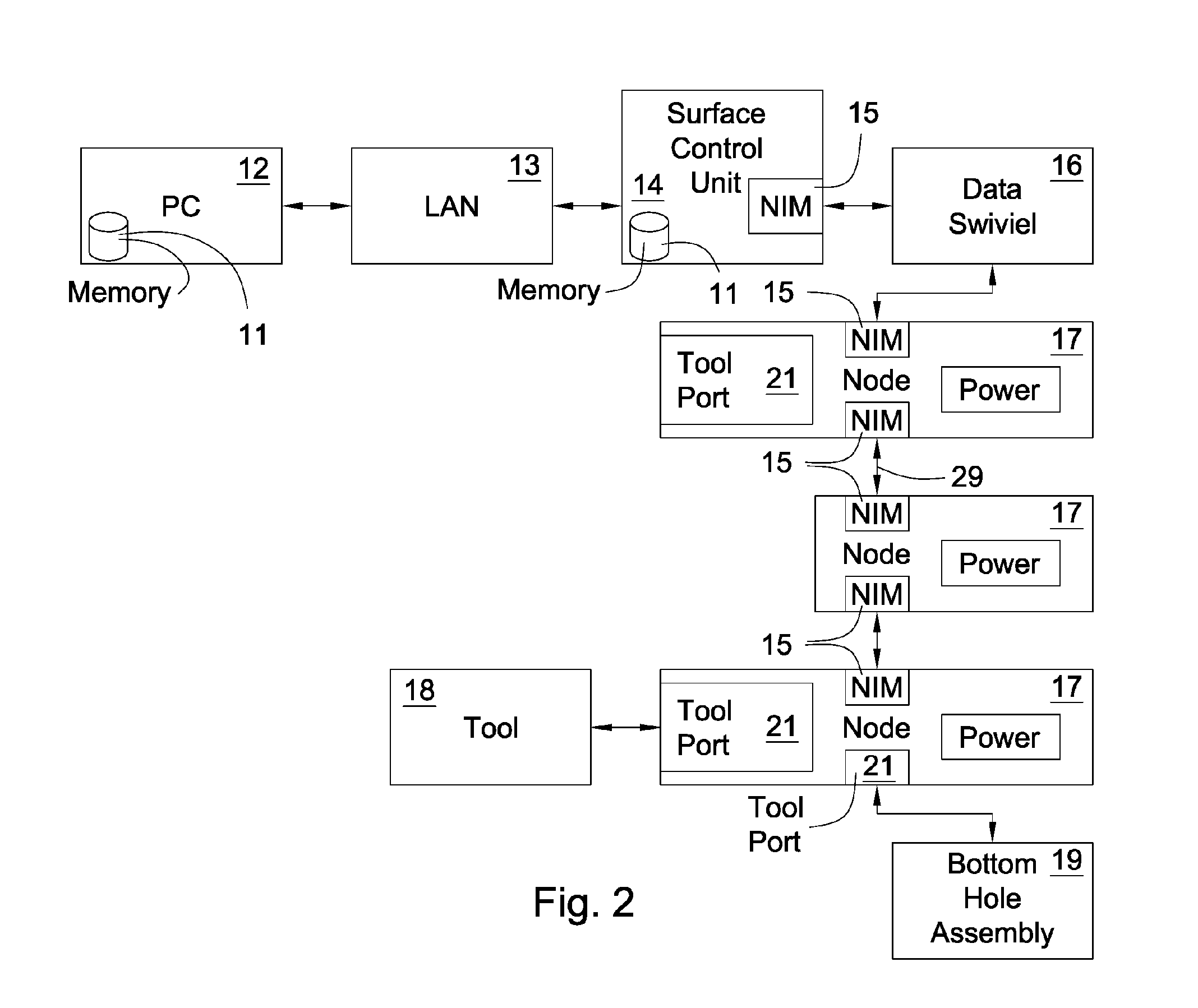

System for Configuring Hardware in a Downhole Tool

A system for loading a hardware configuration into downhole configurable hardware includes a surface control unit in communication with a downhole tool string component over a downhole network. The surface control unit initially has the hardware configuration and transmits it through the downhole network to the configurable hardware. The hardware configuration is implemented in the configurable hardware. The configurable hardware is preferably an FPGA.

Owner:INTELLISERV

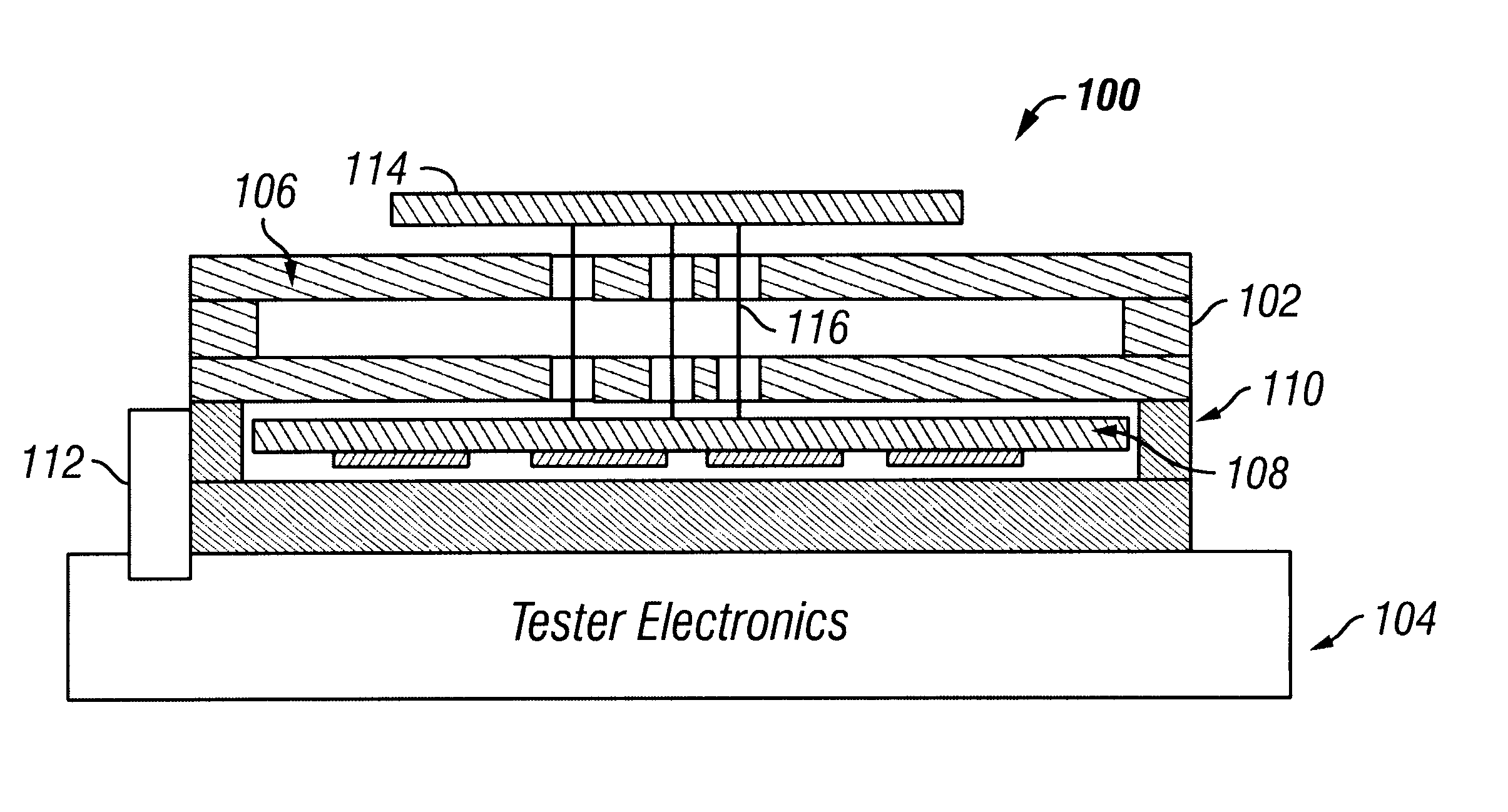

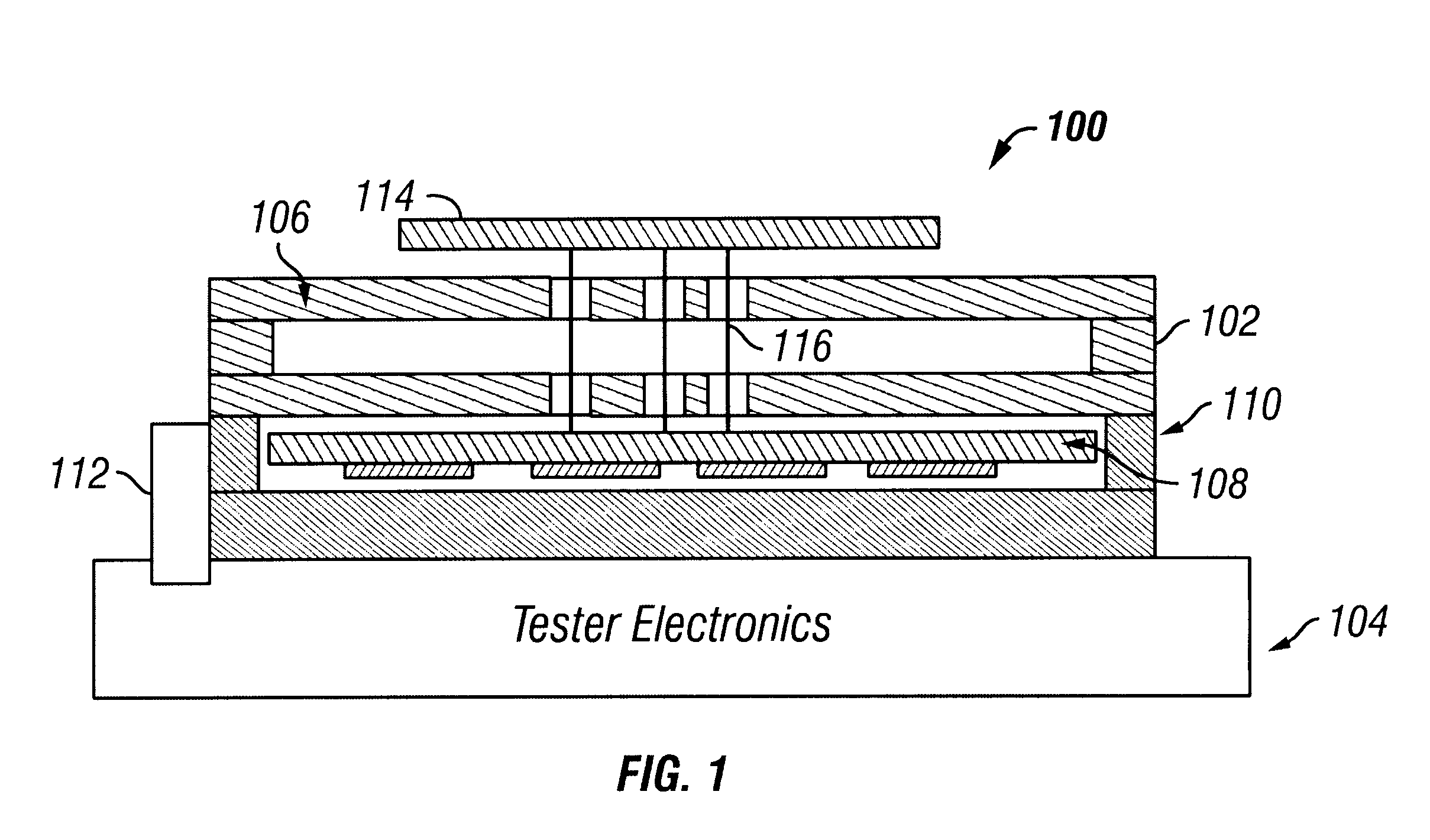

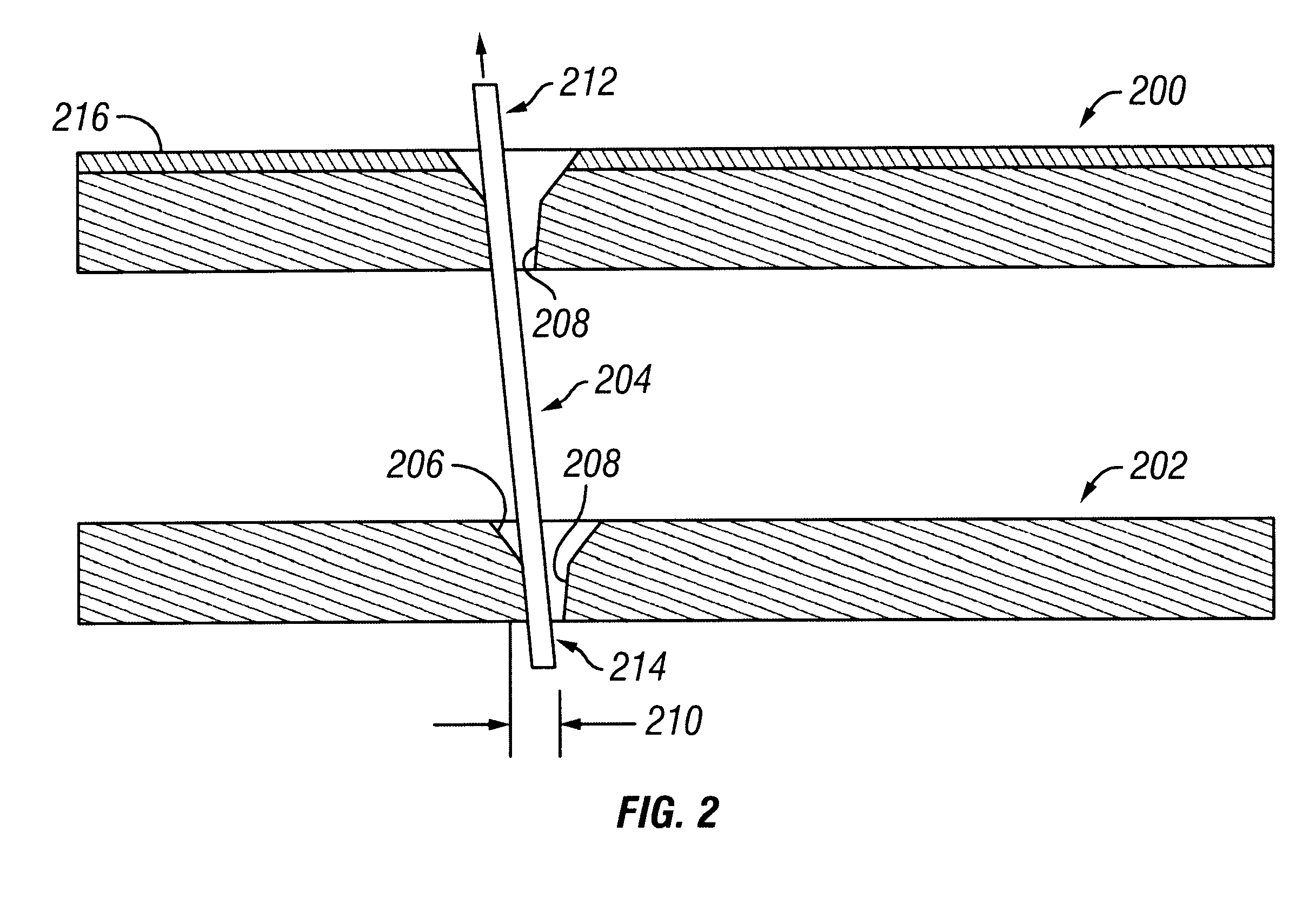

Method and apparatus for configurable hardware augmented program generation

InactiveUS6636061B1Electrical measurement instrument detailsElectrical testingEngineeringConfigurable hardware

A method and apparatus are disclosed for enabling reconfiguration of a test system. The test system includes an adapter assembly and a tester electronics assembly. The adapter assembly includes two probe plates, which hold a probe field. The two probe plates include a plurality of holes extending through each probe plate. Each hole includes a flange area for accommodating deflection of the probes, inserted in the holes extending through the probe plates. The flange area and the use of flexible probes facilitate a deflection and an offset of the probes in the probe plates. A tester assembly includes a plurality of wear pads on the topside of a printed circuit board. The wear pads positioned to engage the bottom end of the probes. Configurable logic elements located on the underside of the printed circuit board are used to generating and receive test-signals, depending on where the probes make contact with the wear pads on the printed circuit board.

Owner:KEYSIGHT TECH

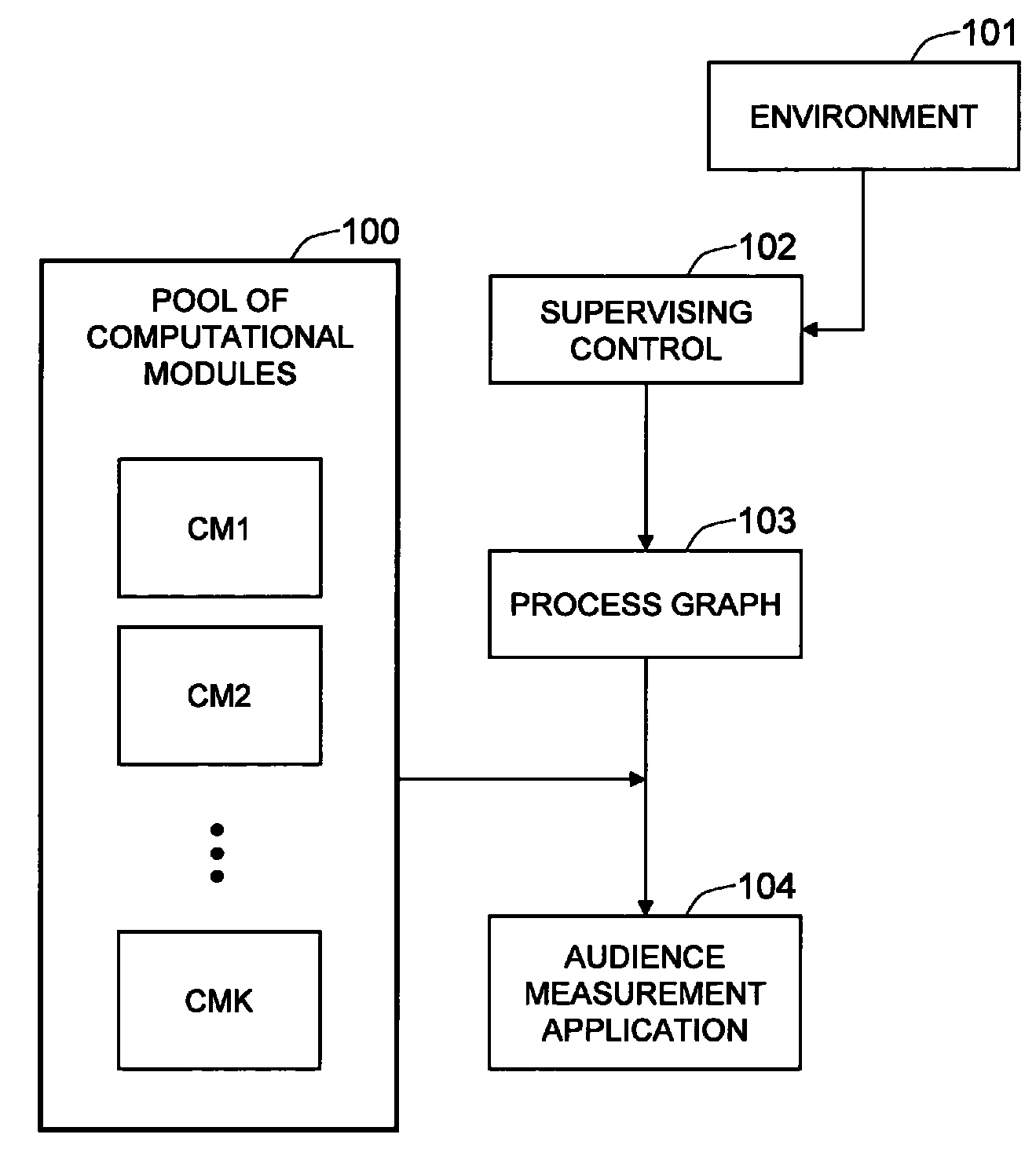

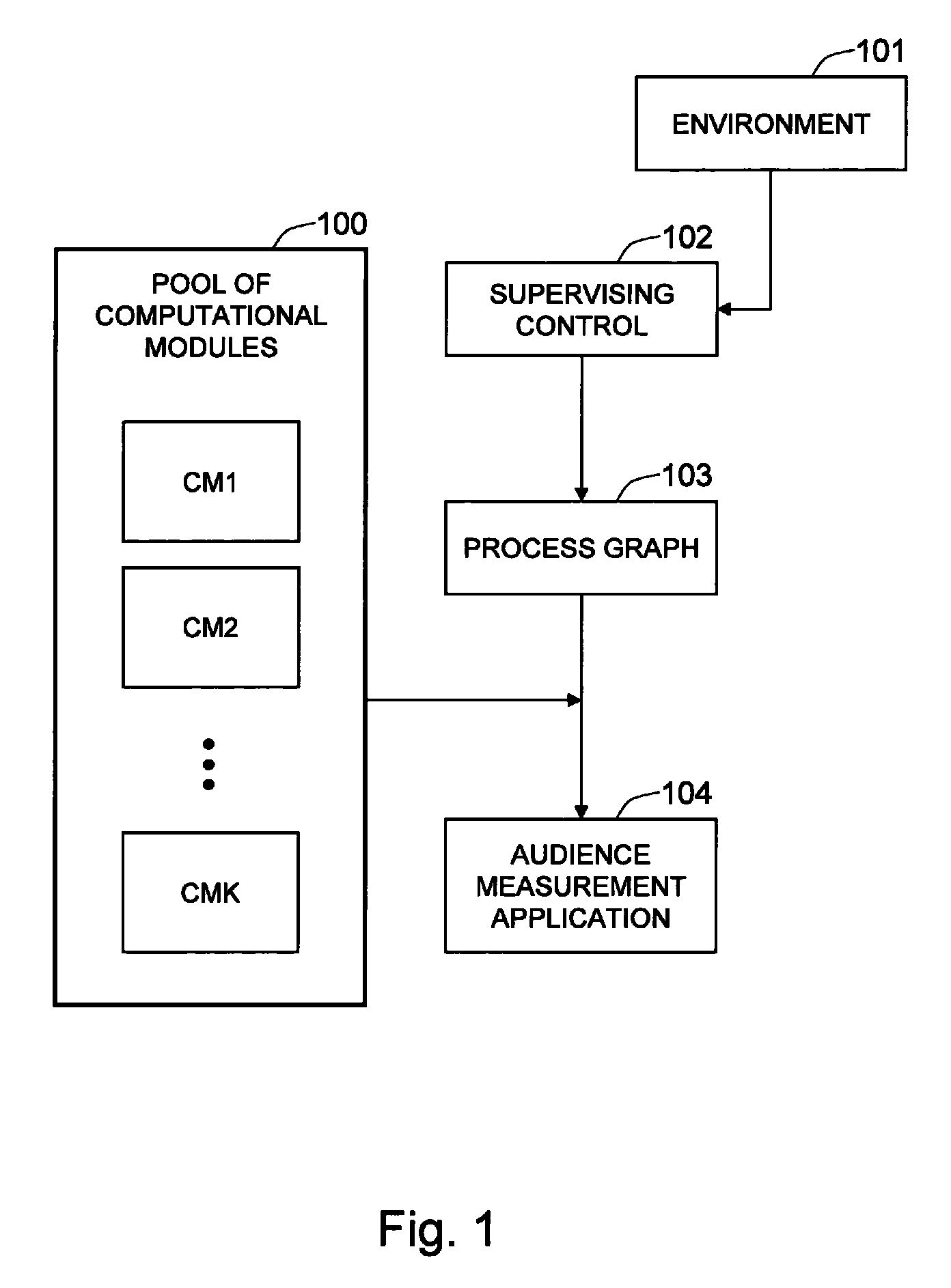

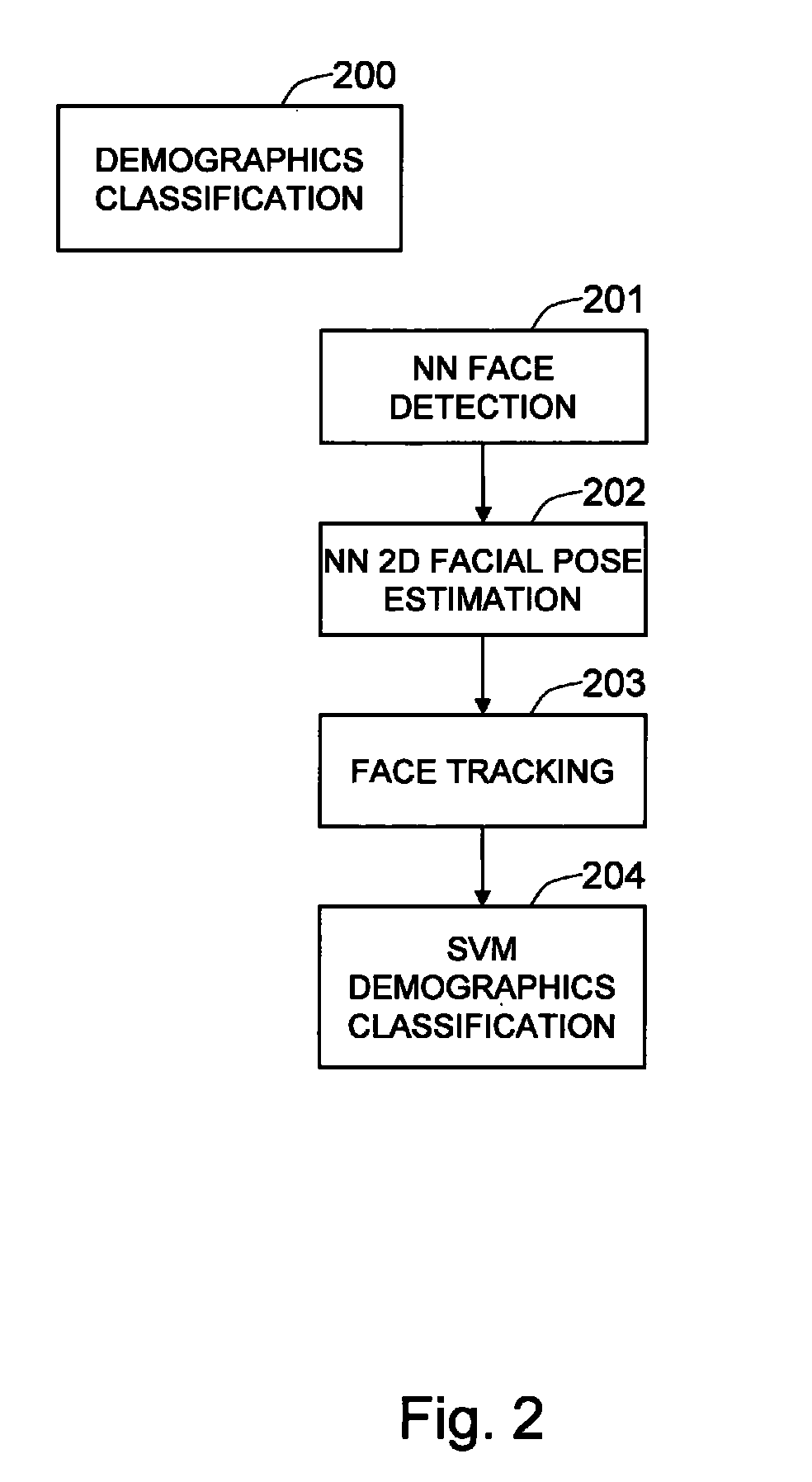

Apparatus and method for measuring audience data from image stream using dynamically-configurable hardware architecture

ActiveUS8165386B1Easy to changeReduce loadDigital computer detailsBiological neural network modelsHardware architectureComputer module

The present invention is an embedded audience measurement platform, which is called HAM. The HAM includes hardware, apparatus, and method for measuring audience data from image stream using dynamically-configurable hardware architecture. The HAM provides an end-to-end solution for audience measurement, wherein reconfigurable computational modules are used as engines per node to power the complete solution implemented in a flexible hardware architecture. The HAM is also a complete system for broad audience measurement, which has various components built into the system. Examples of the components comprise demographics classification, gaze estimation, emotion recognition, behavior analysis, and impression measurement.

Owner:MOTOROLA SOLUTIONS INC