Patents

Literature

12291results about "Electrical measurement instrument details" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

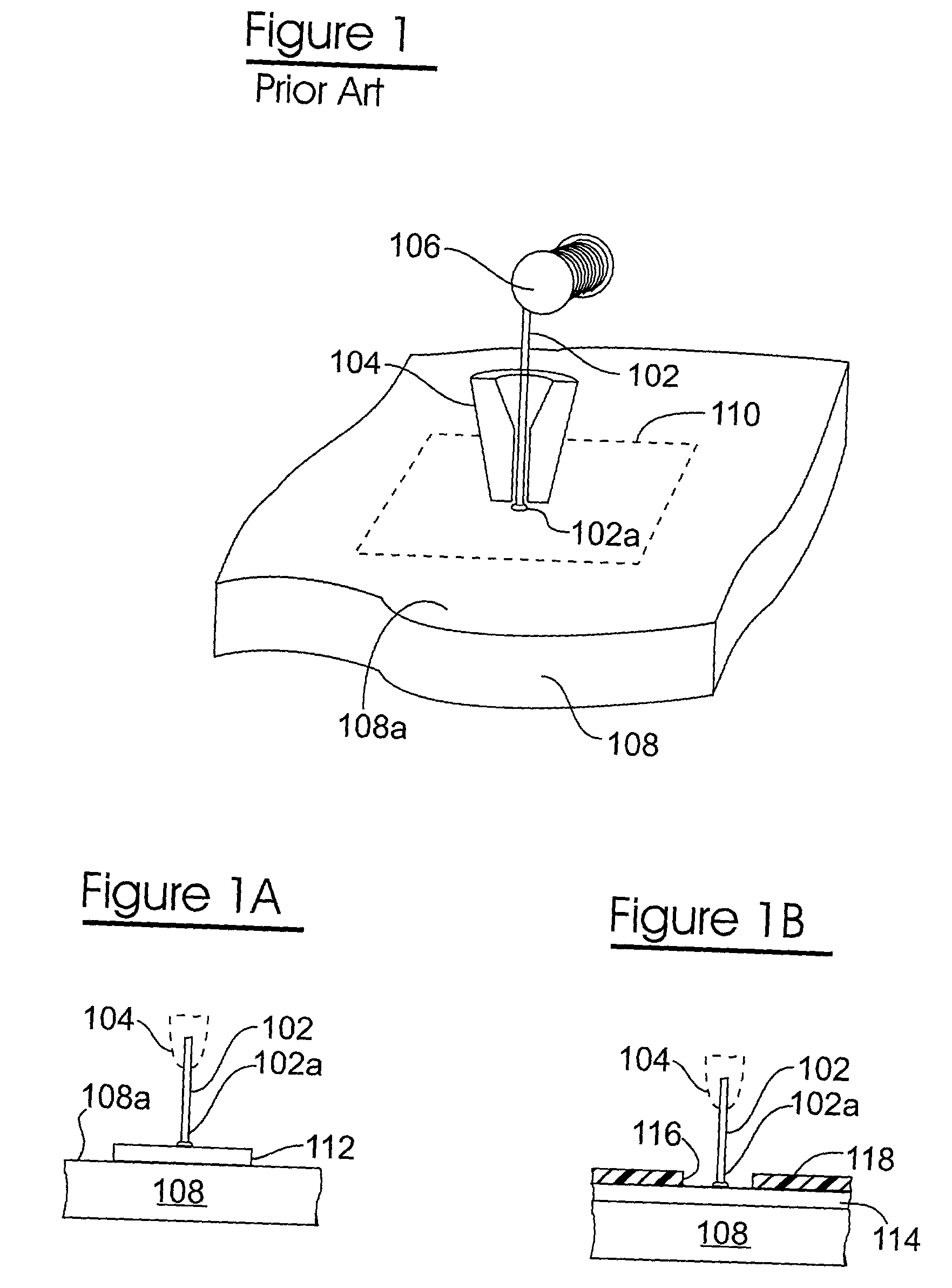

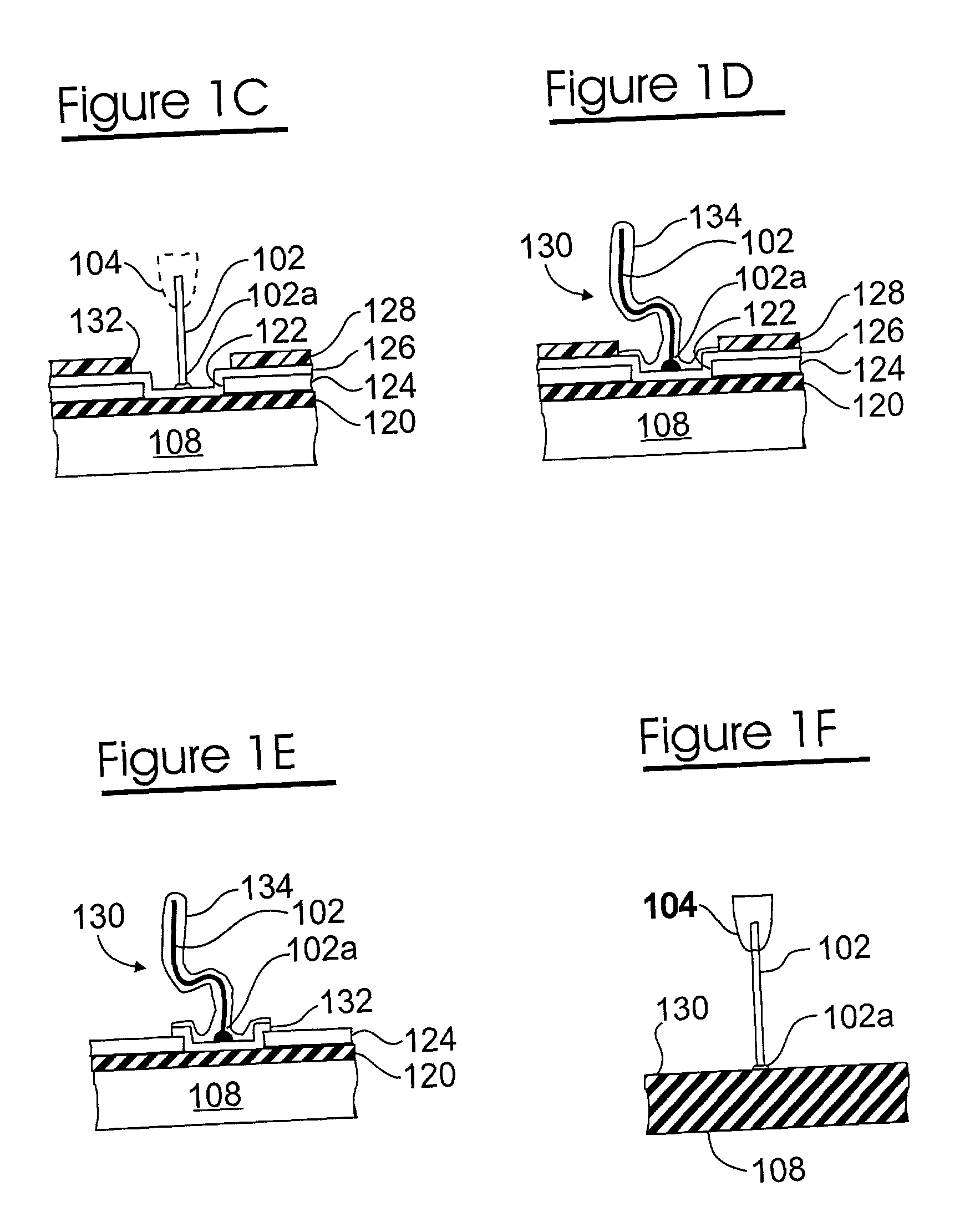

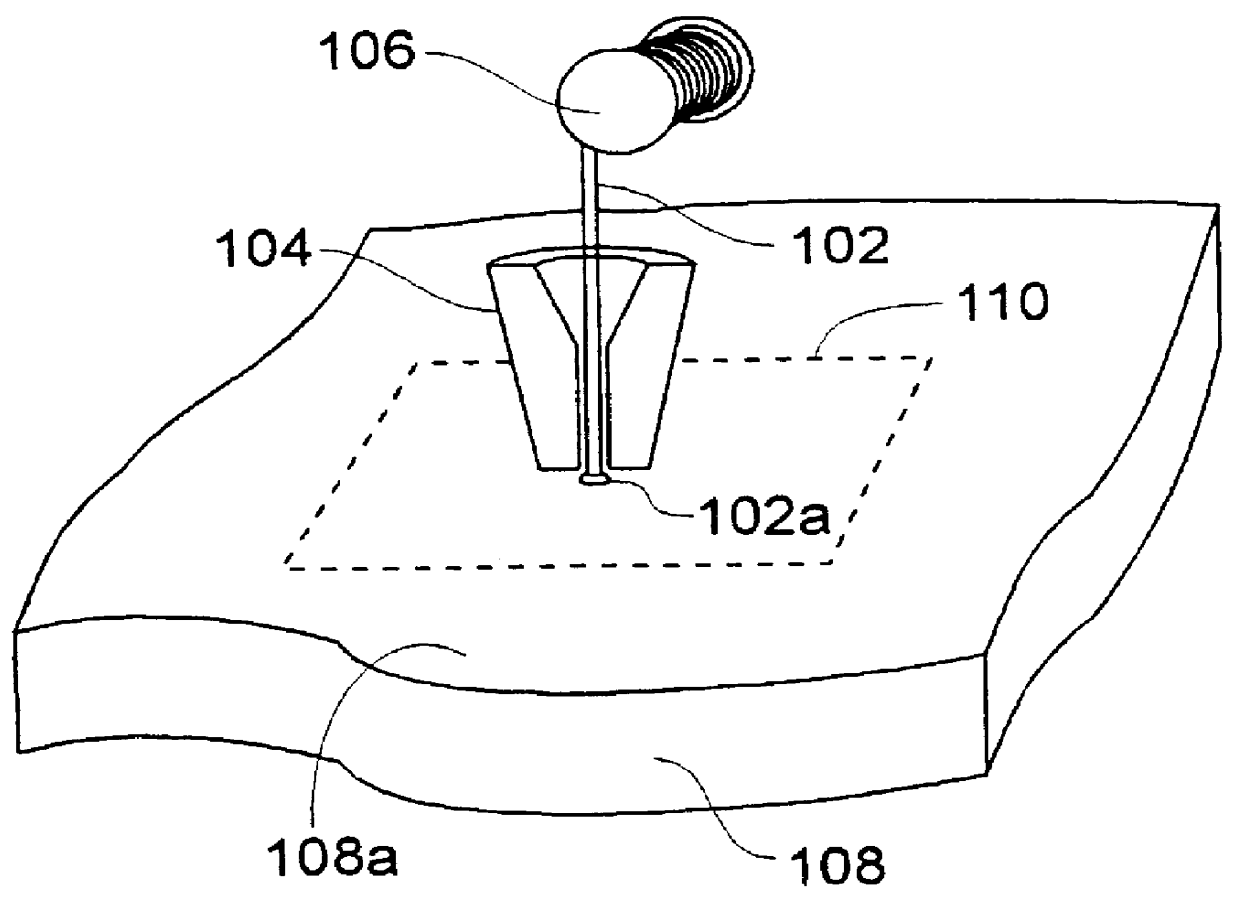

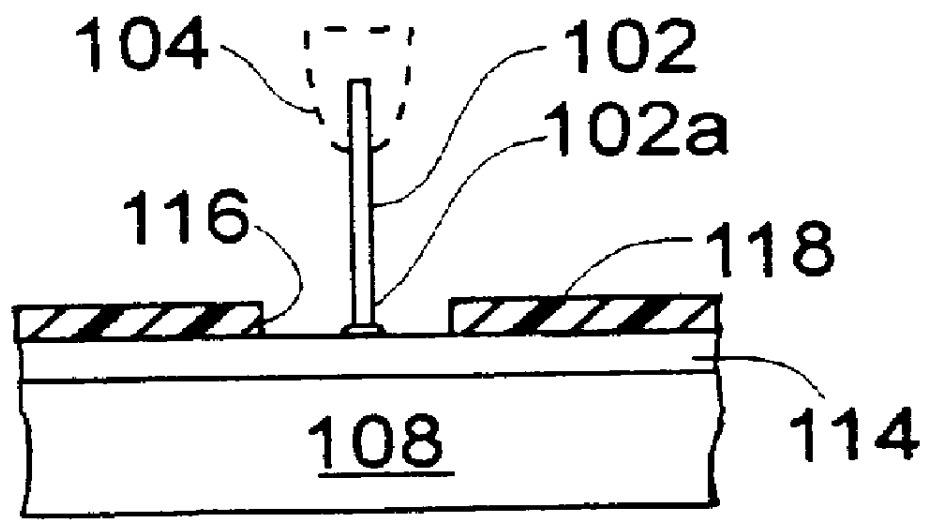

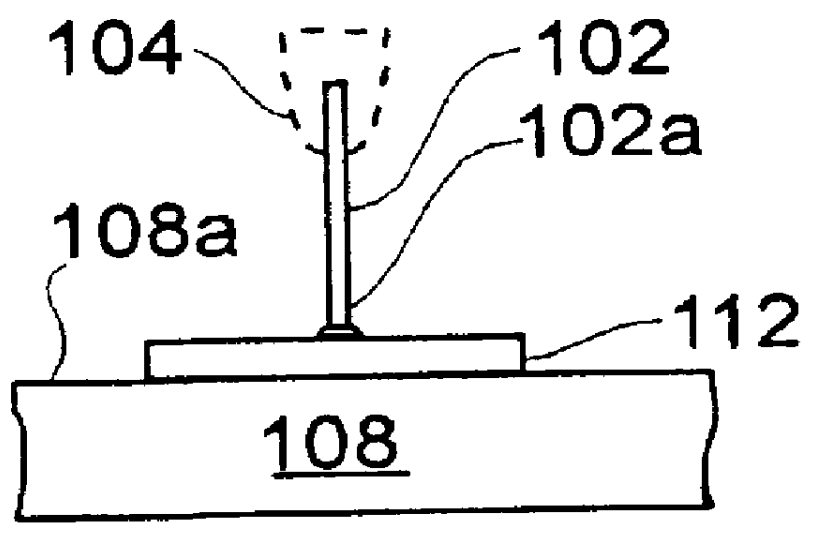

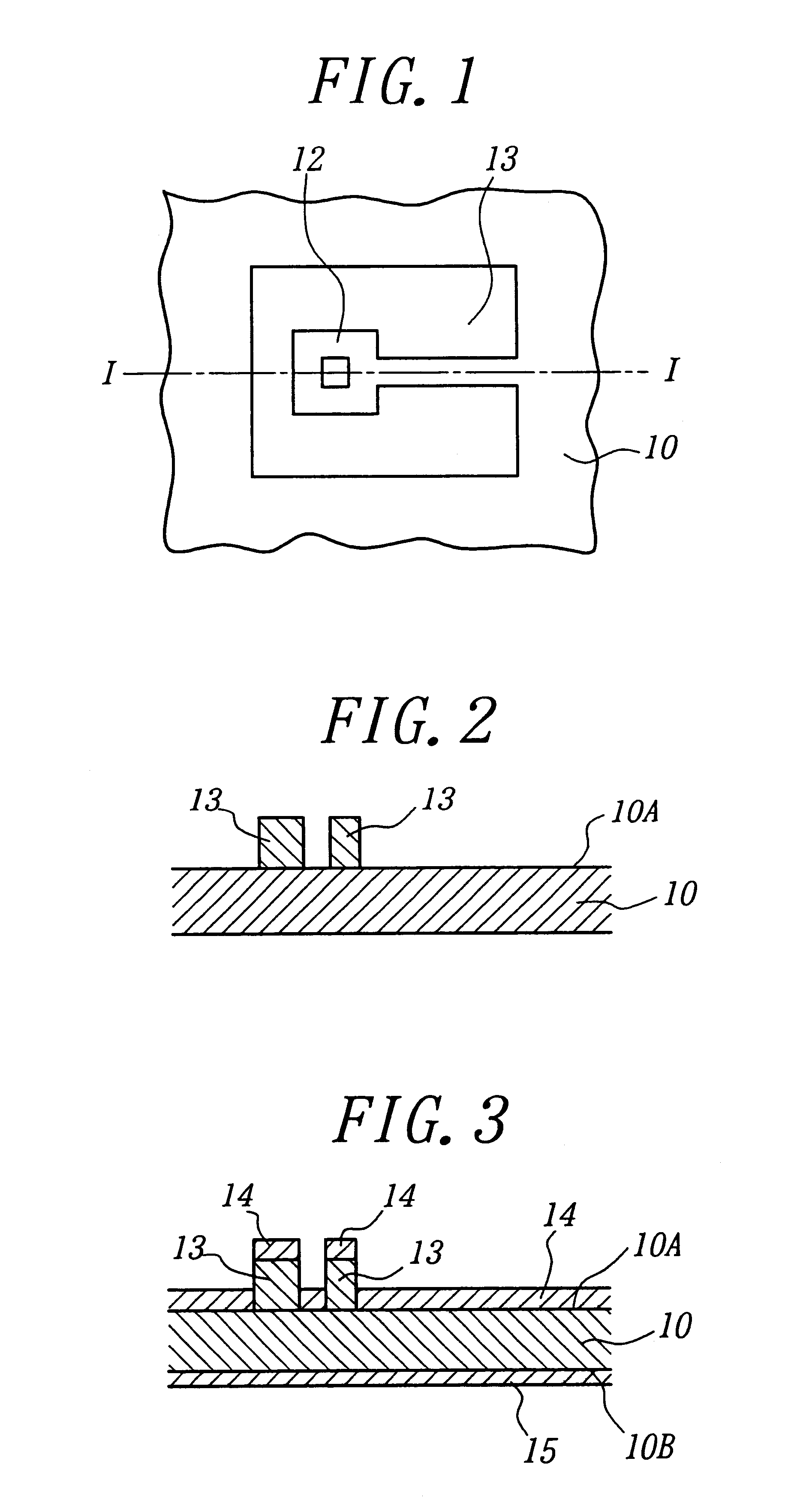

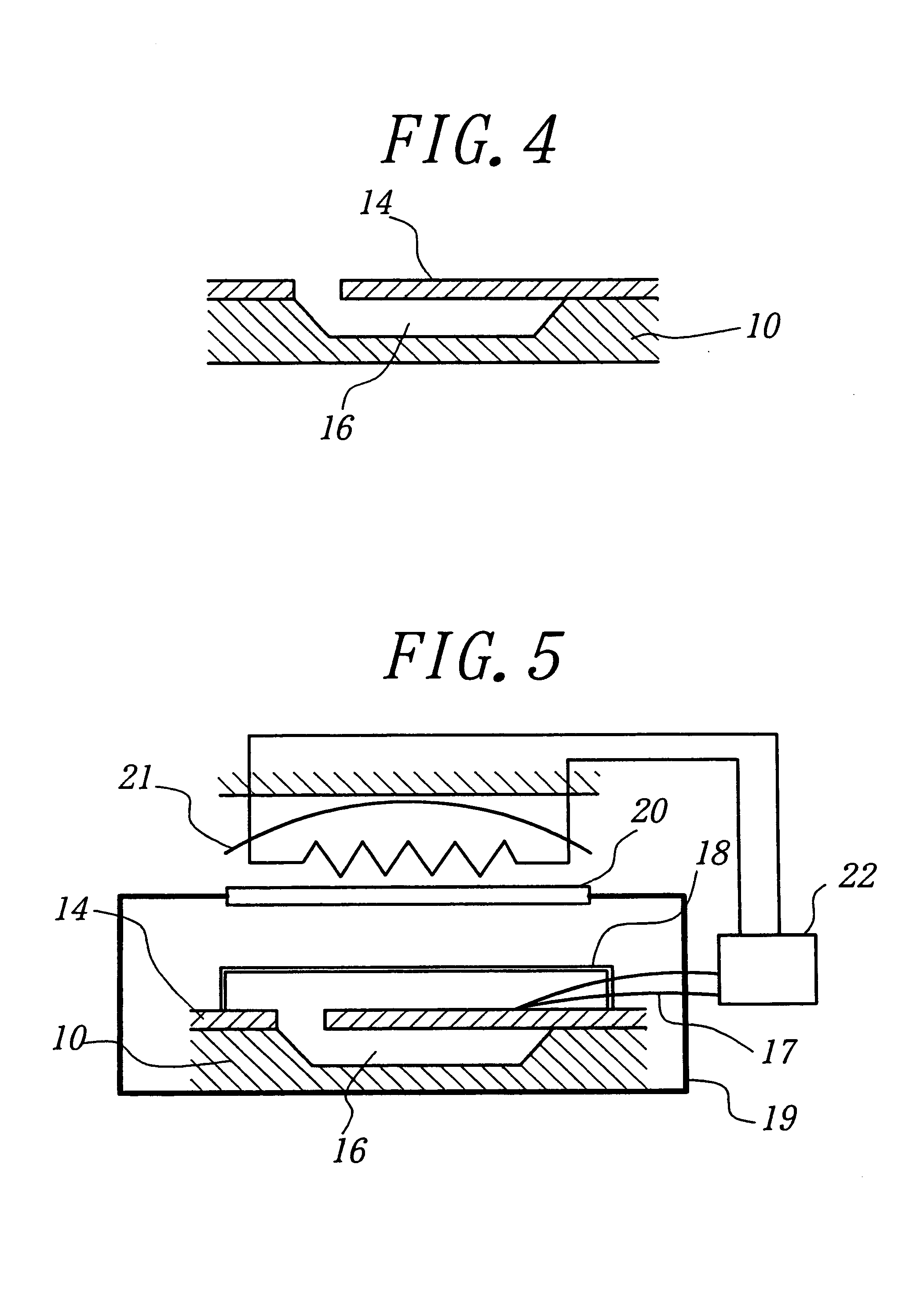

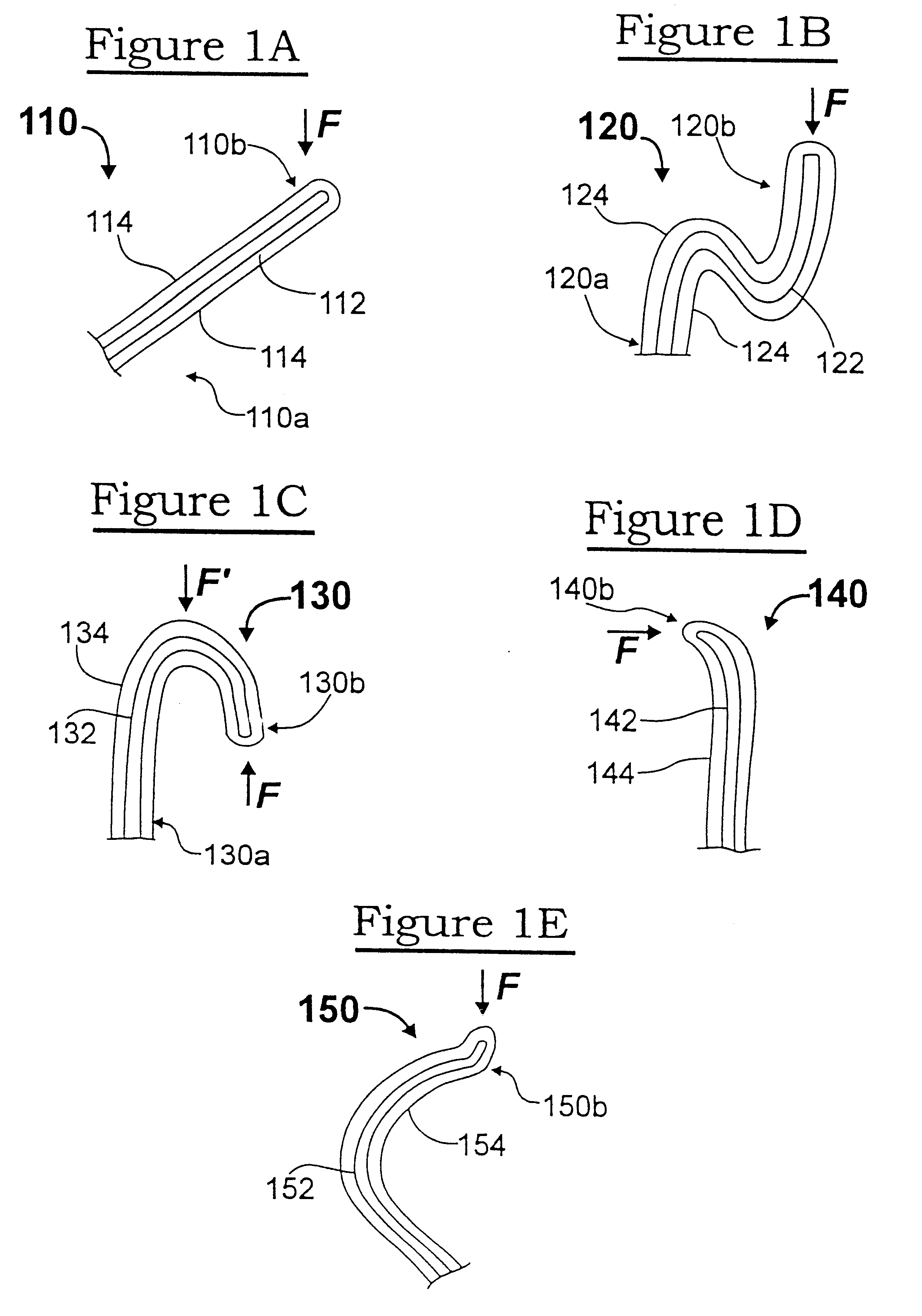

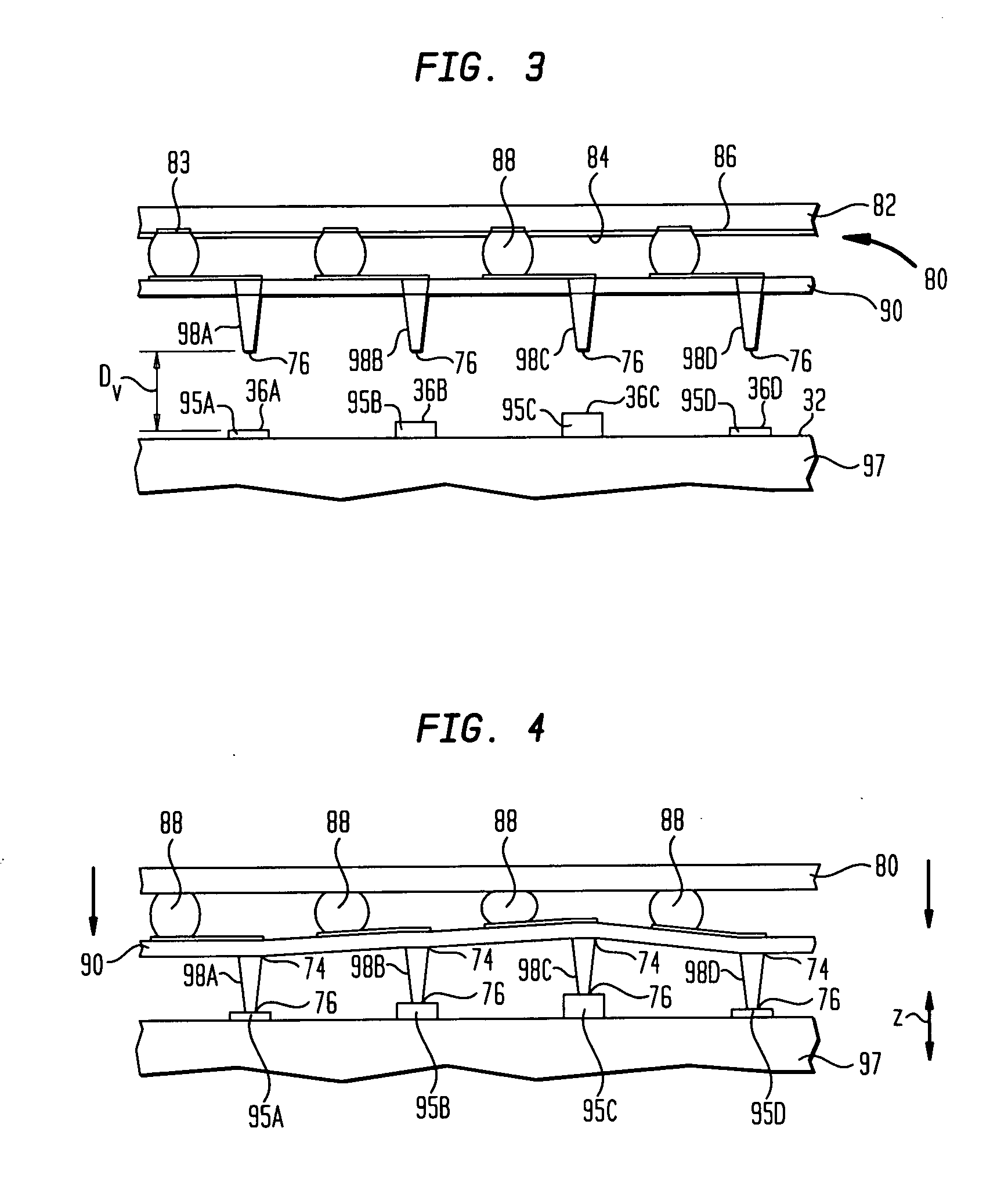

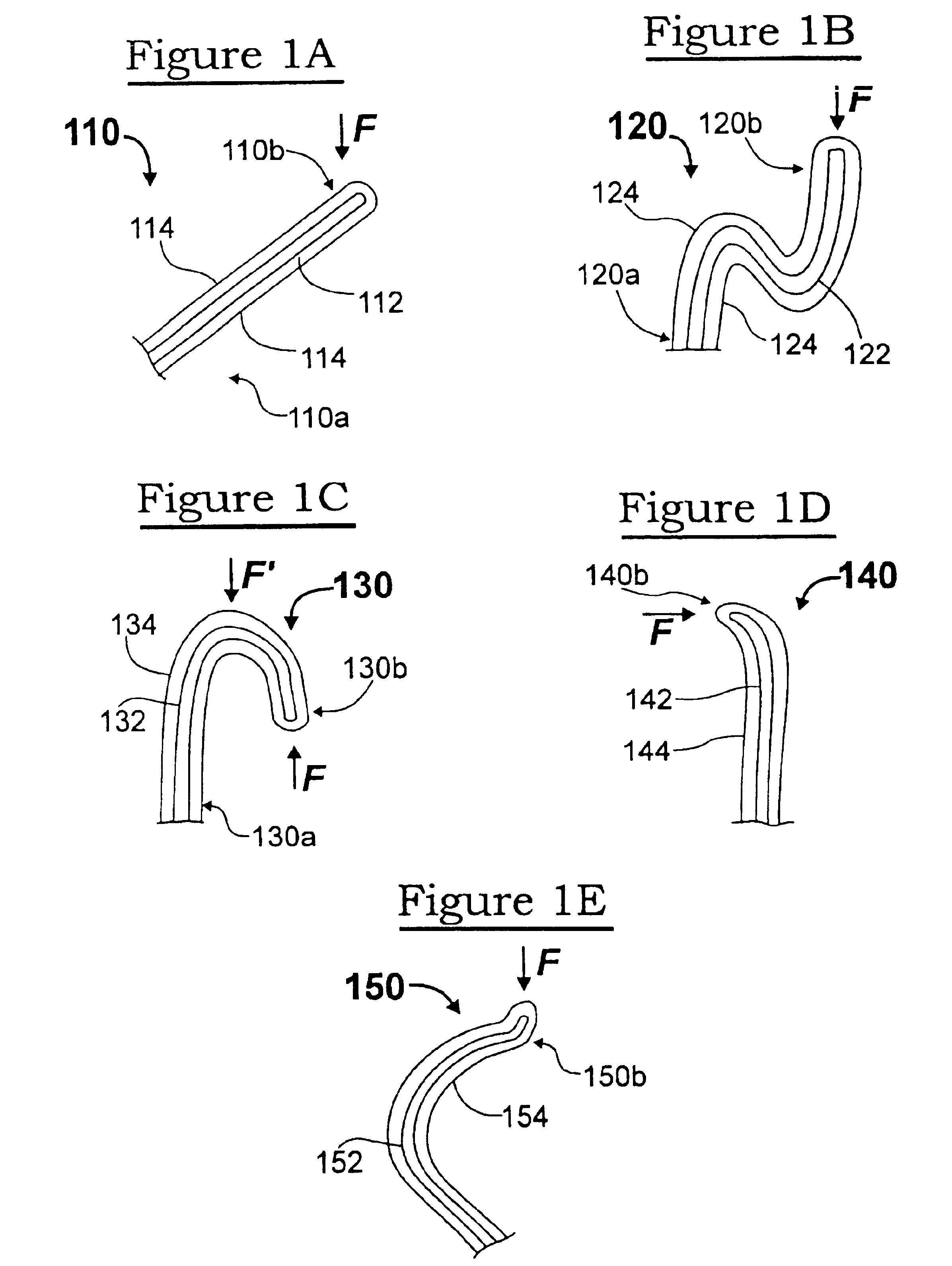

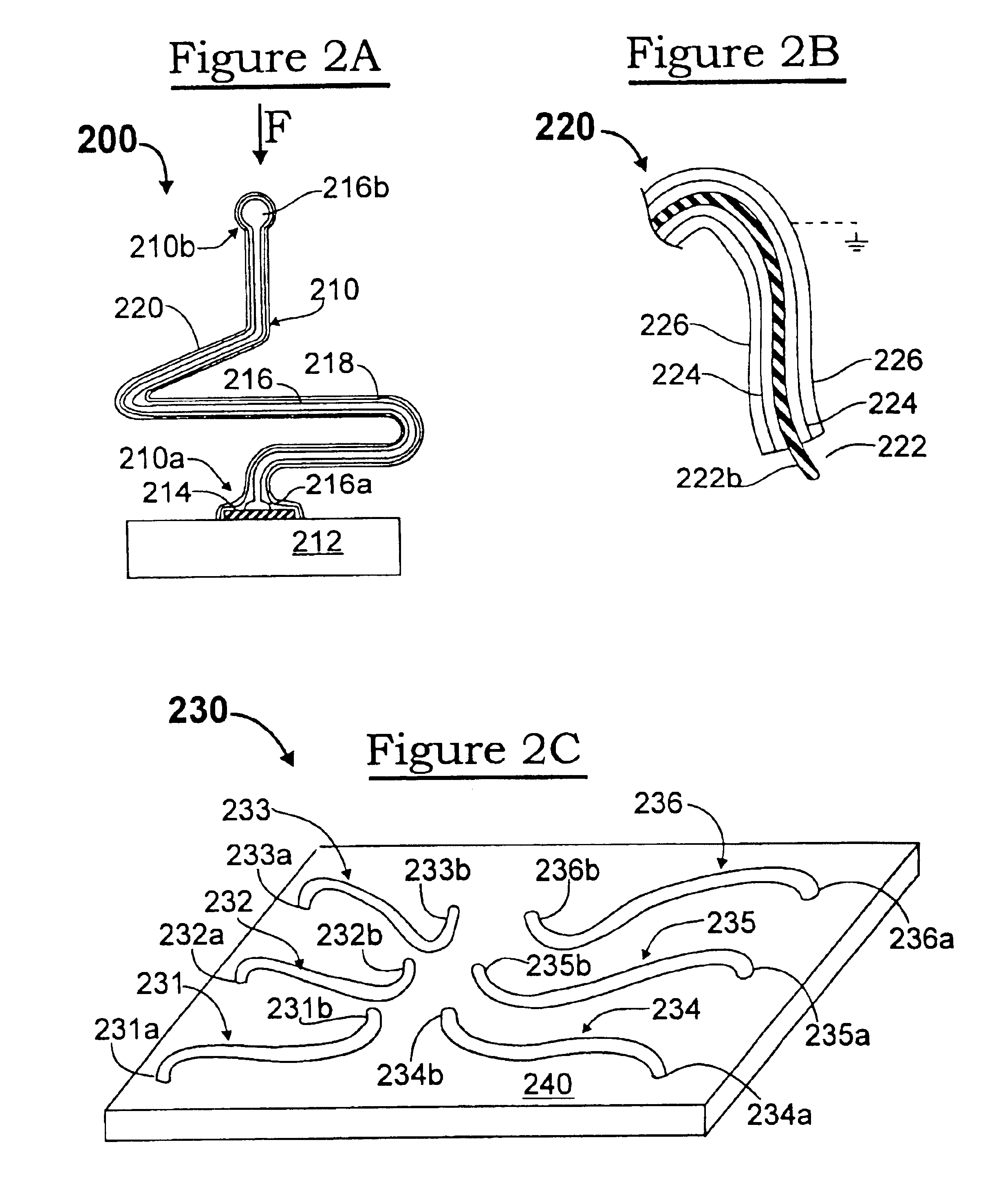

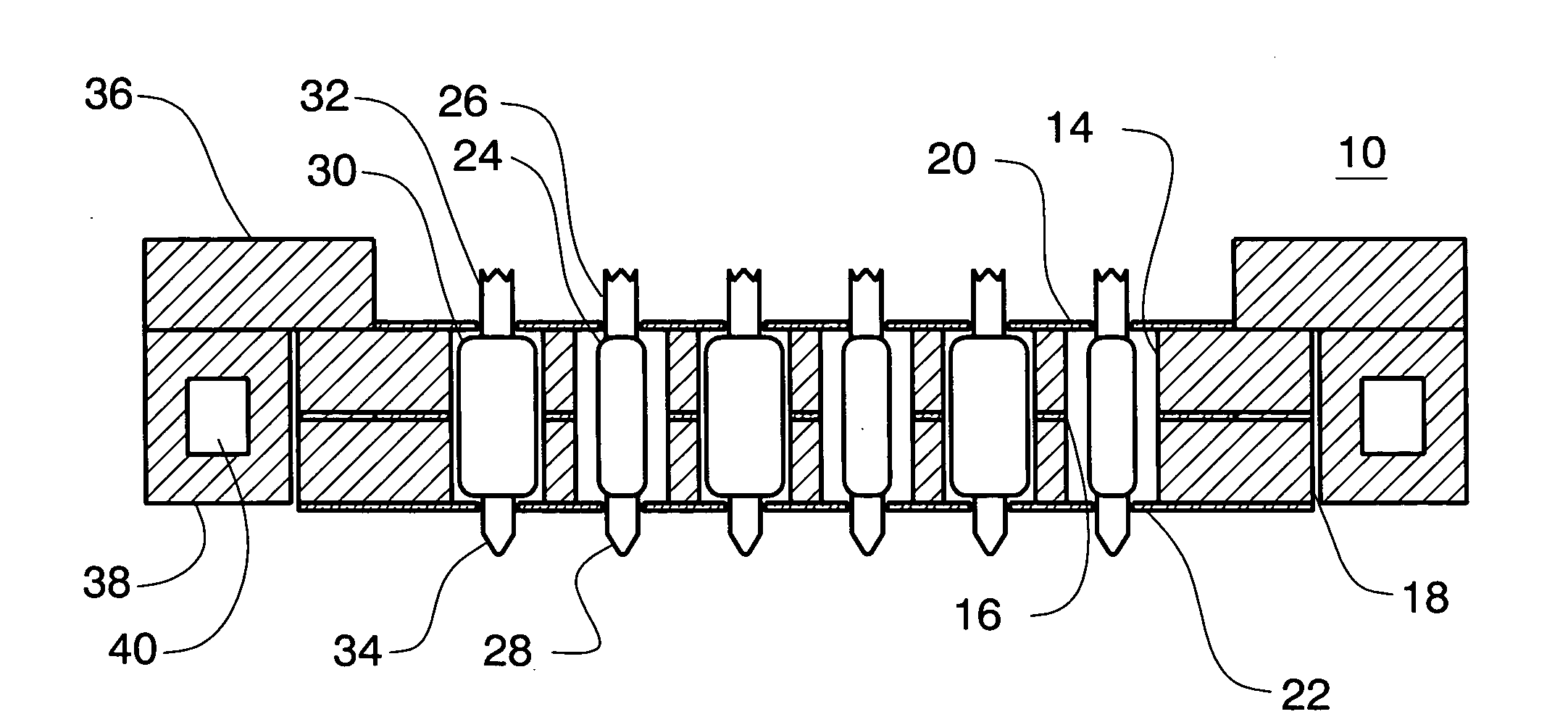

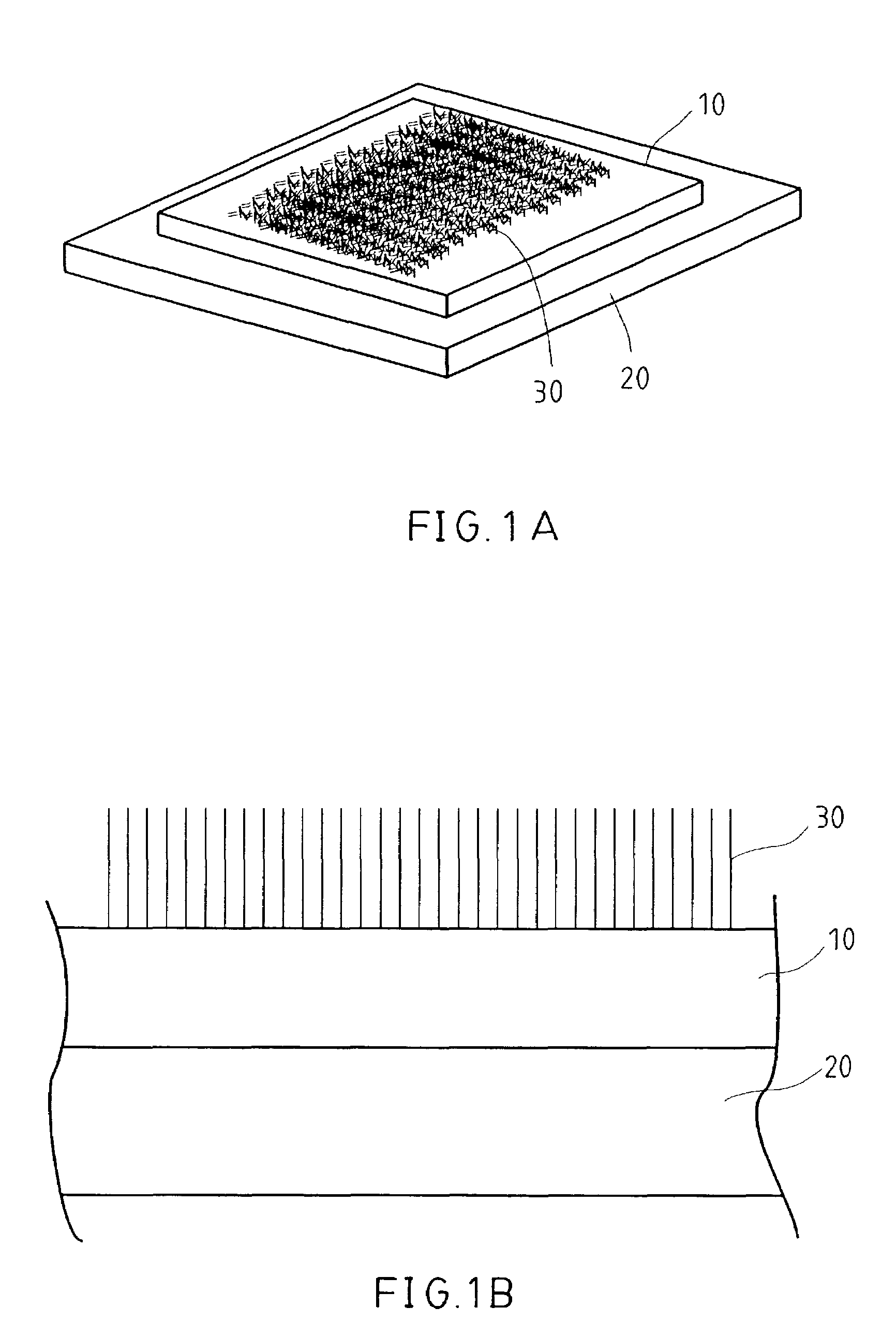

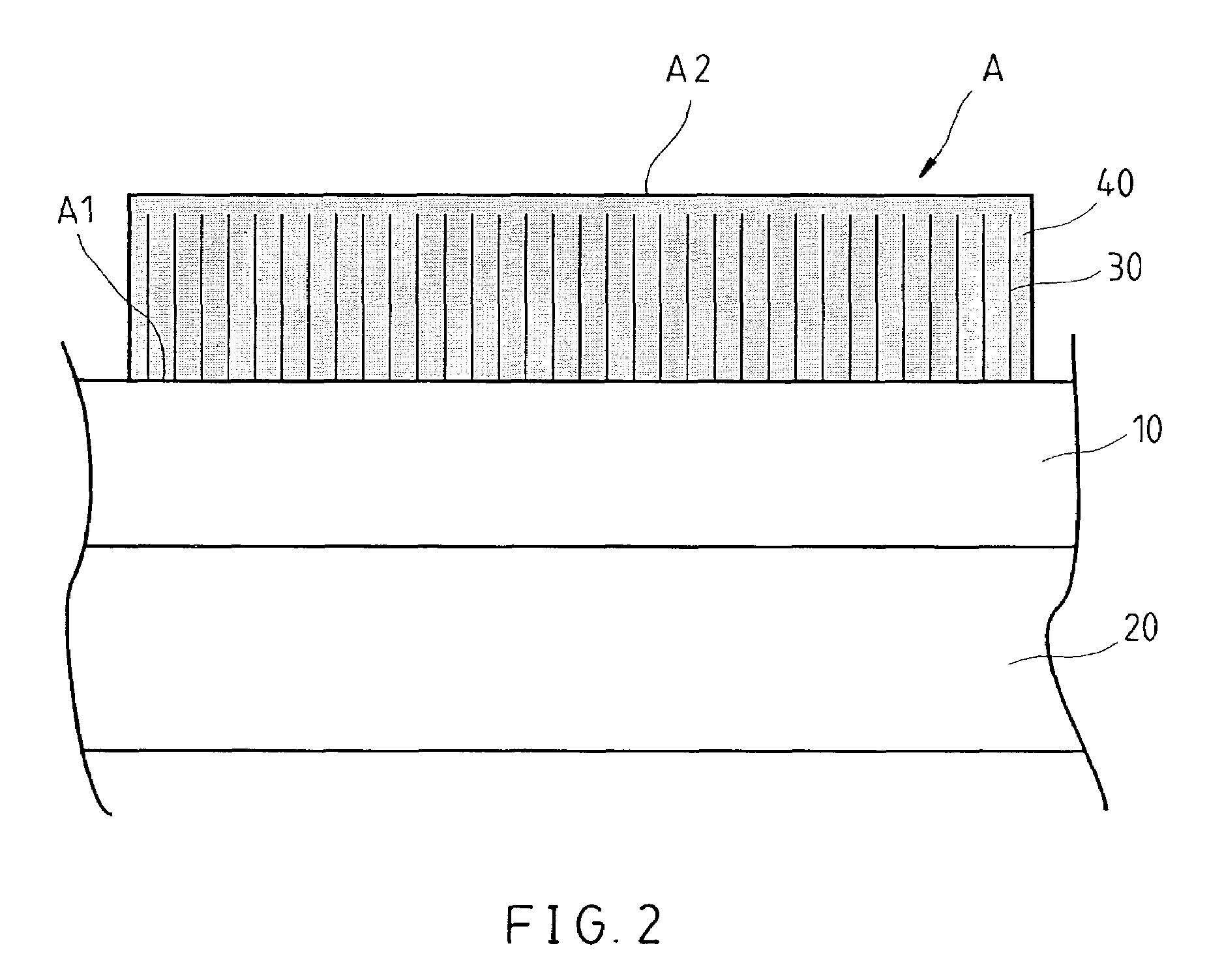

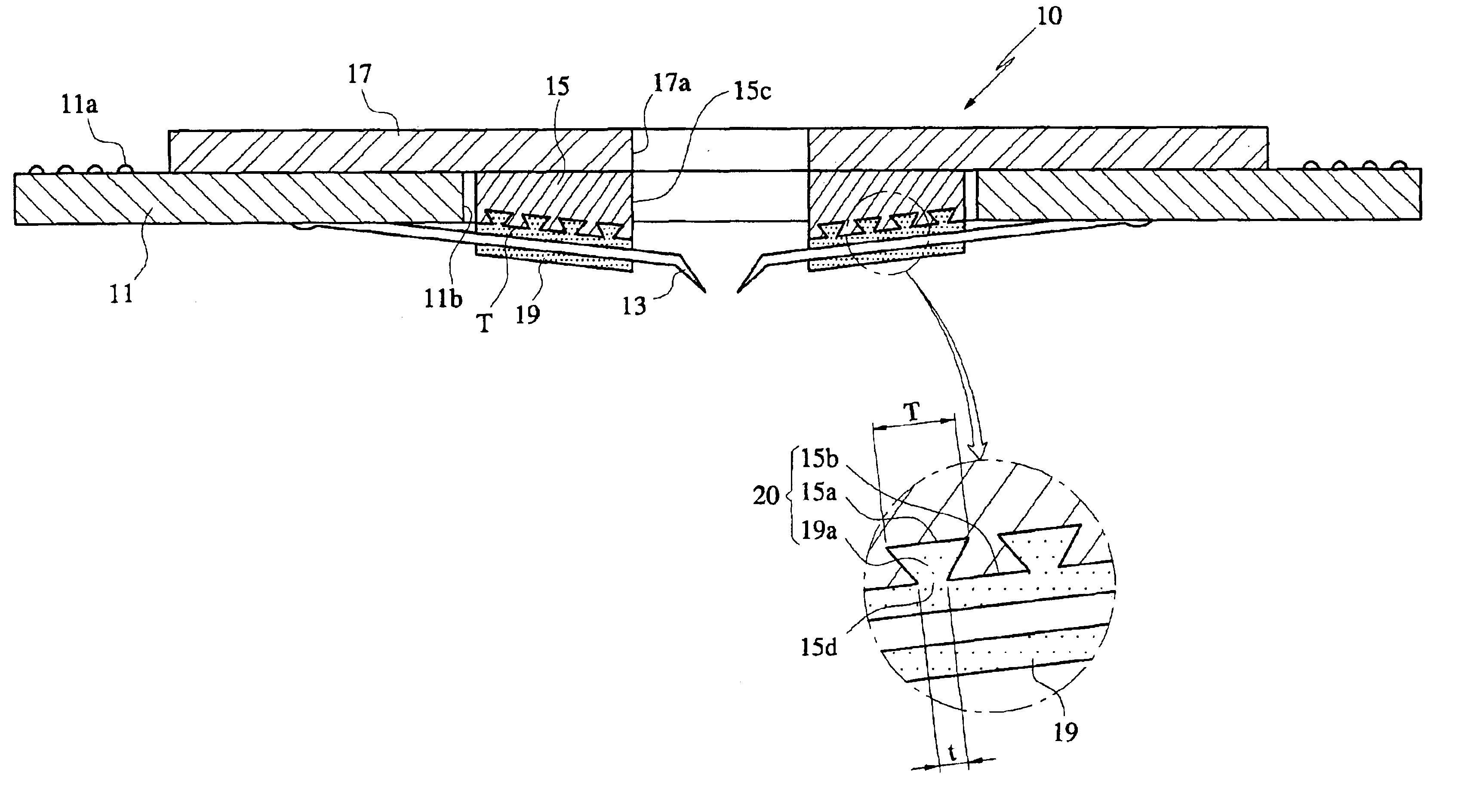

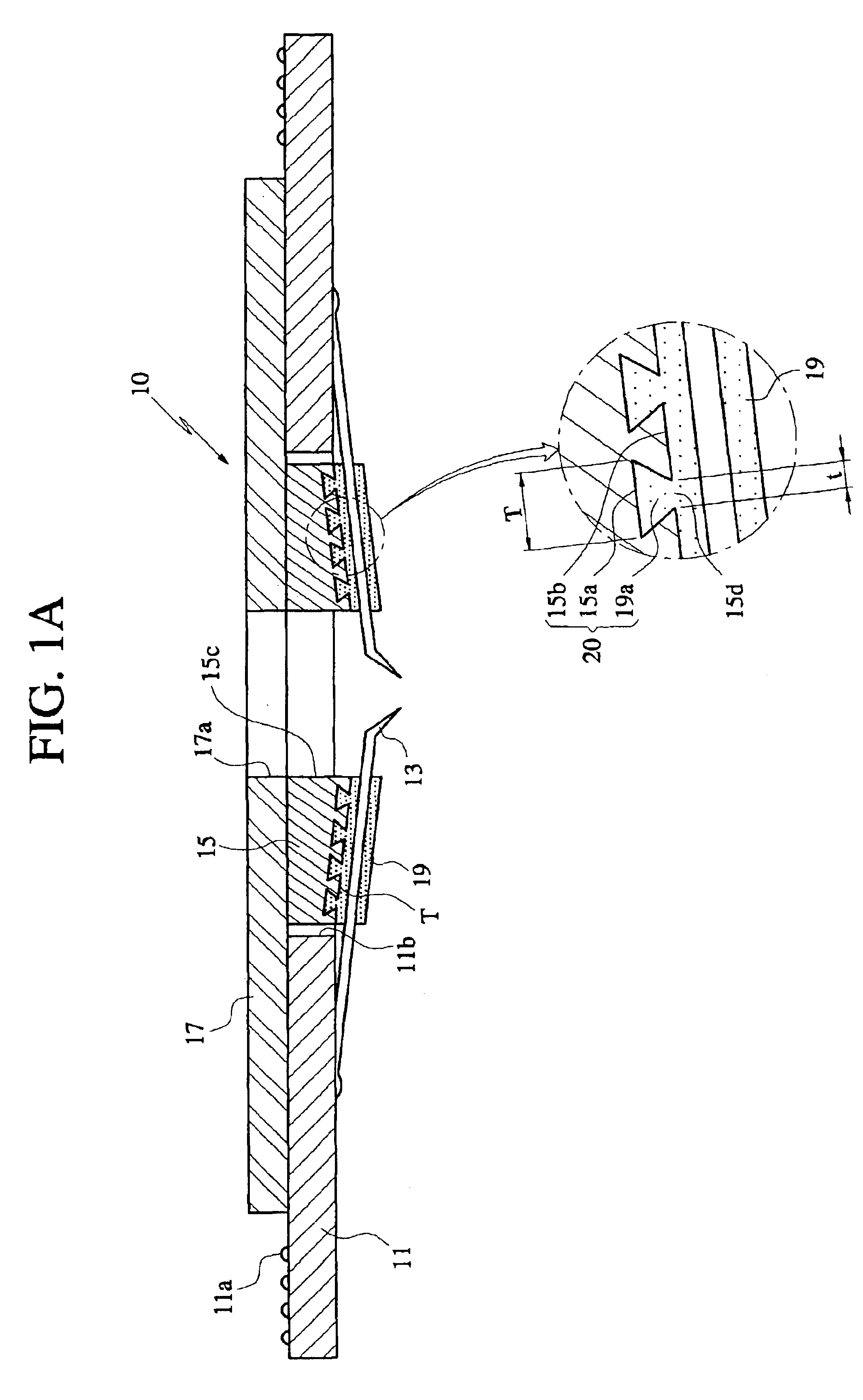

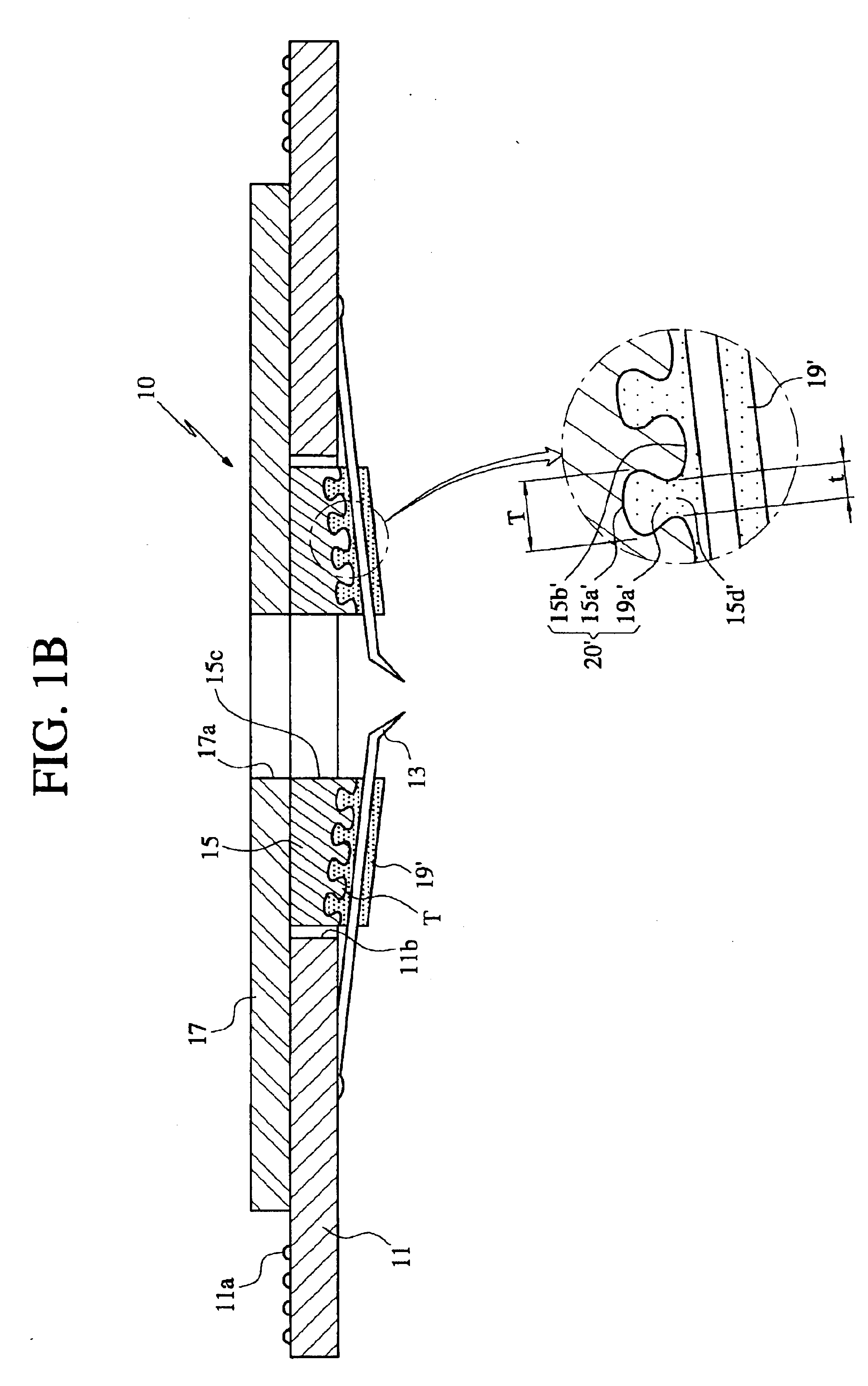

Resilient contact structures formed and then attached to a substrate

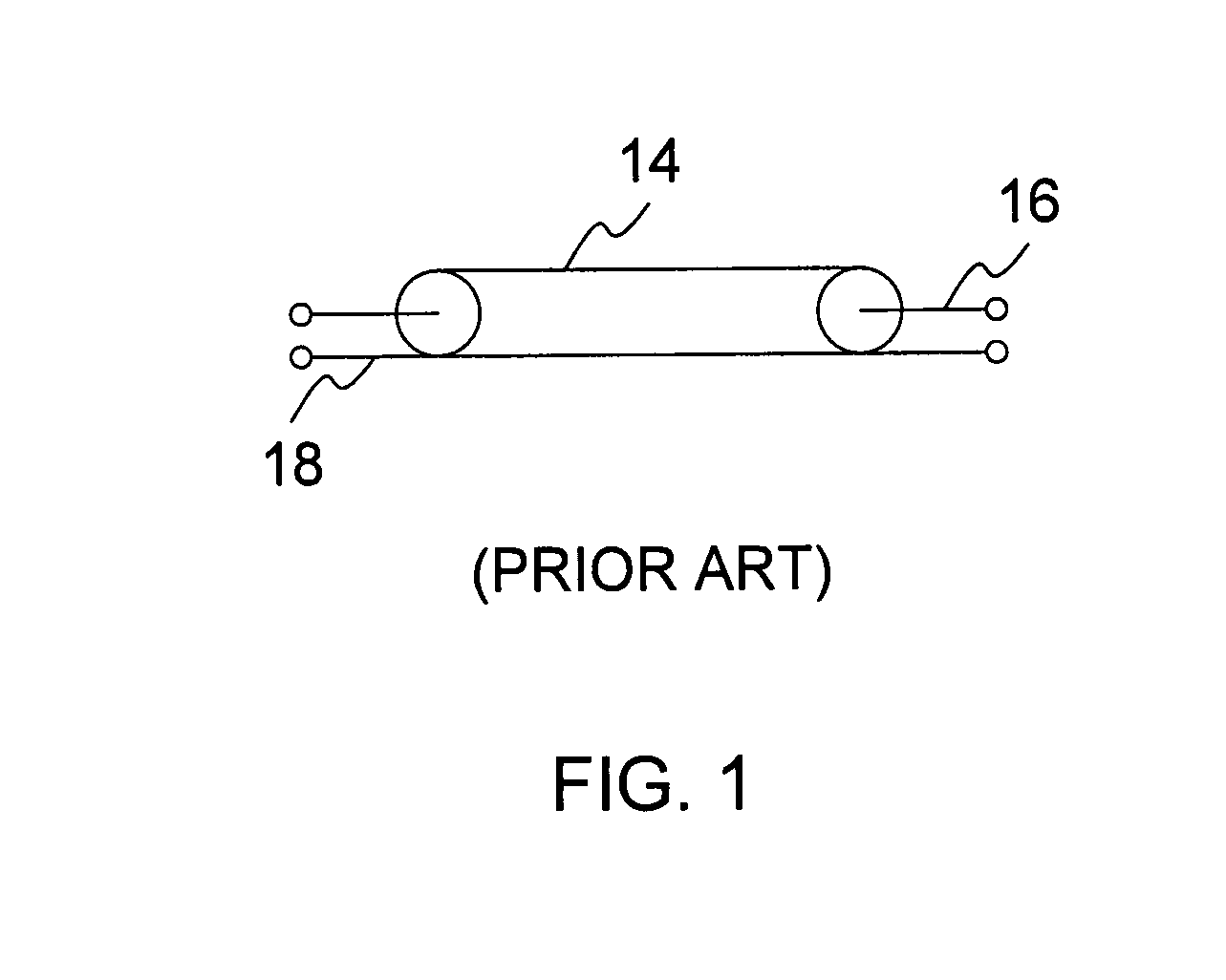

InactiveUS20020117330A1Simple technologyCoupling device connectionsSemiconductor/solid-state device testing/measurementEngineeringTopography

Owner:FORMFACTOR INC

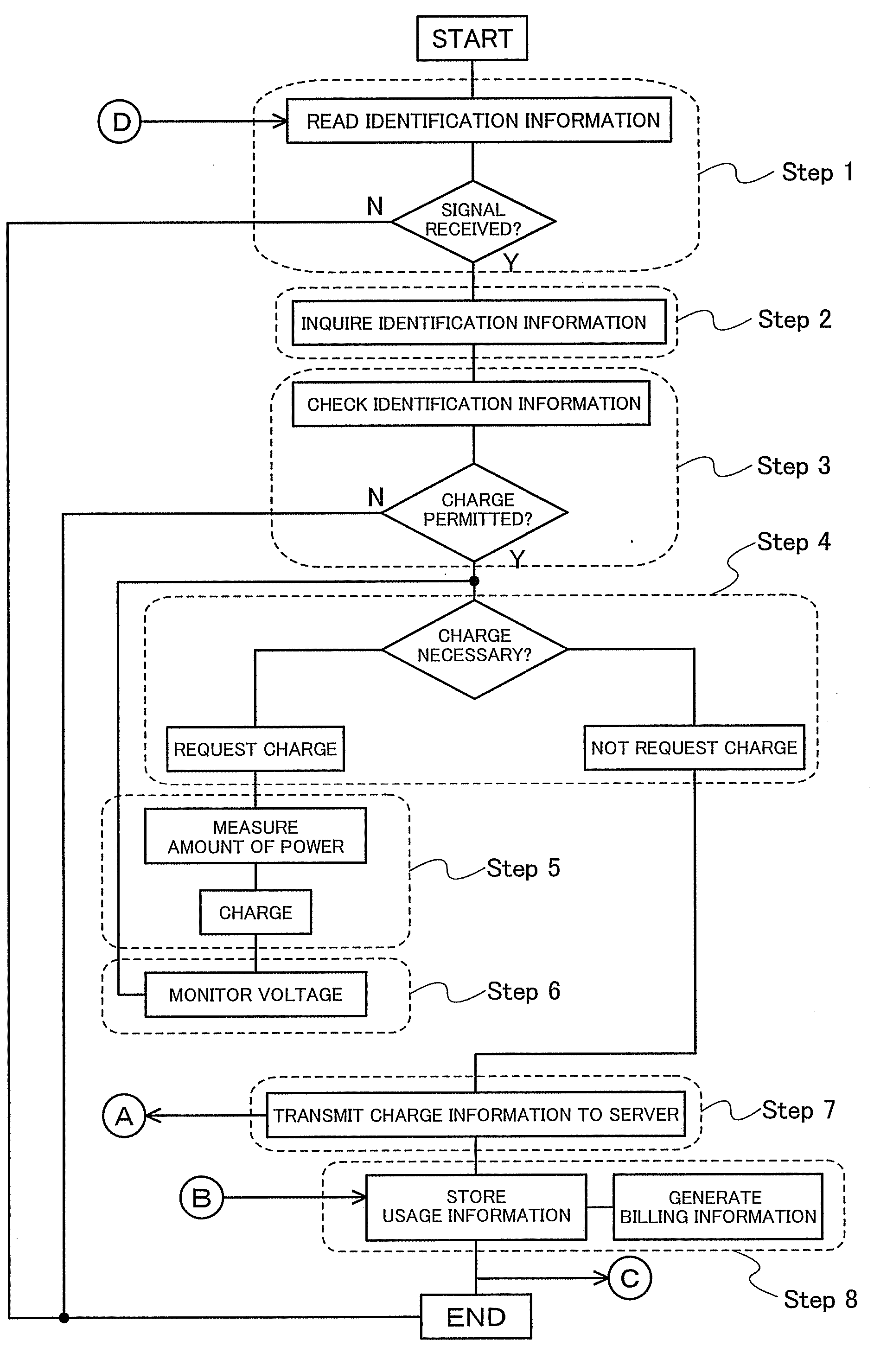

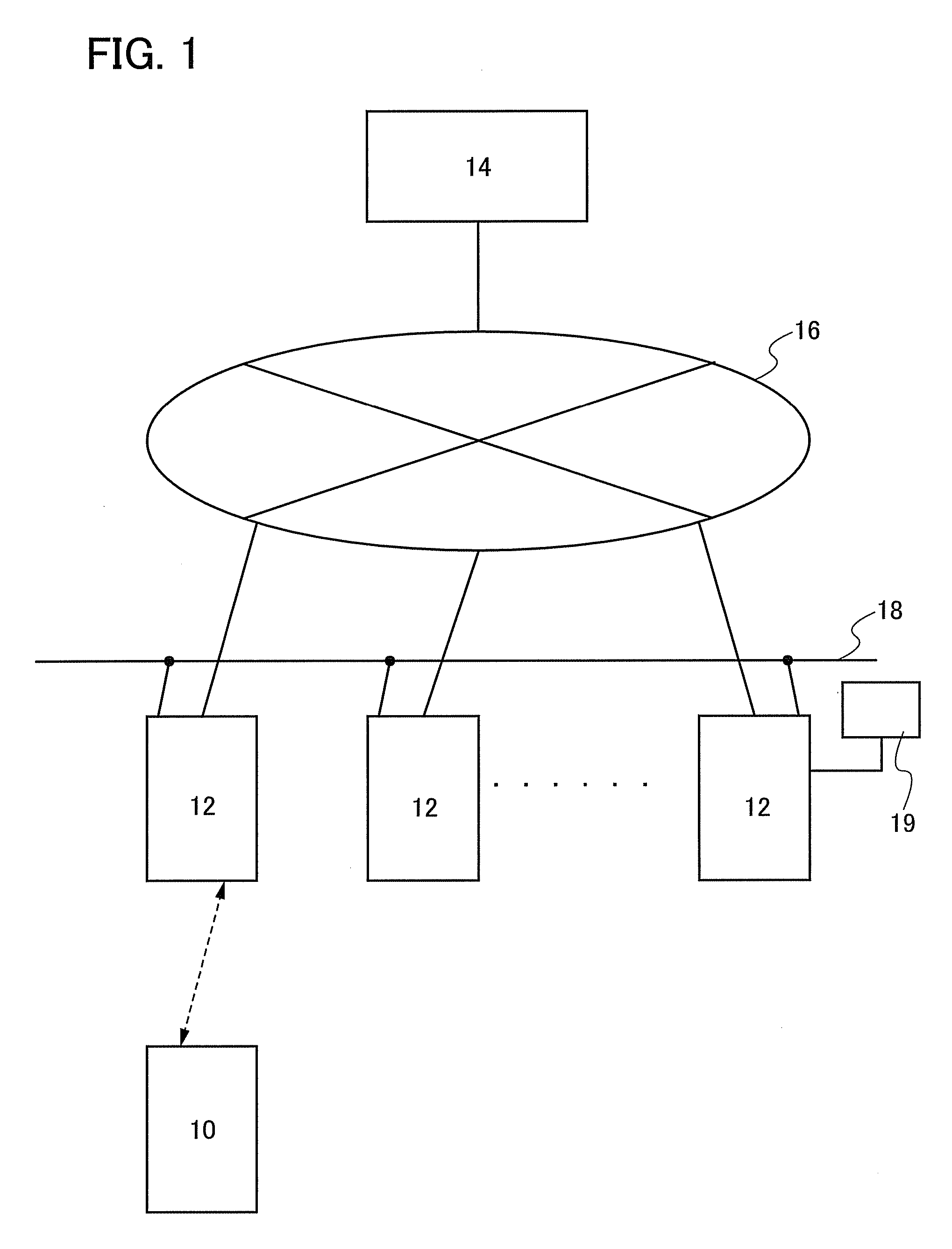

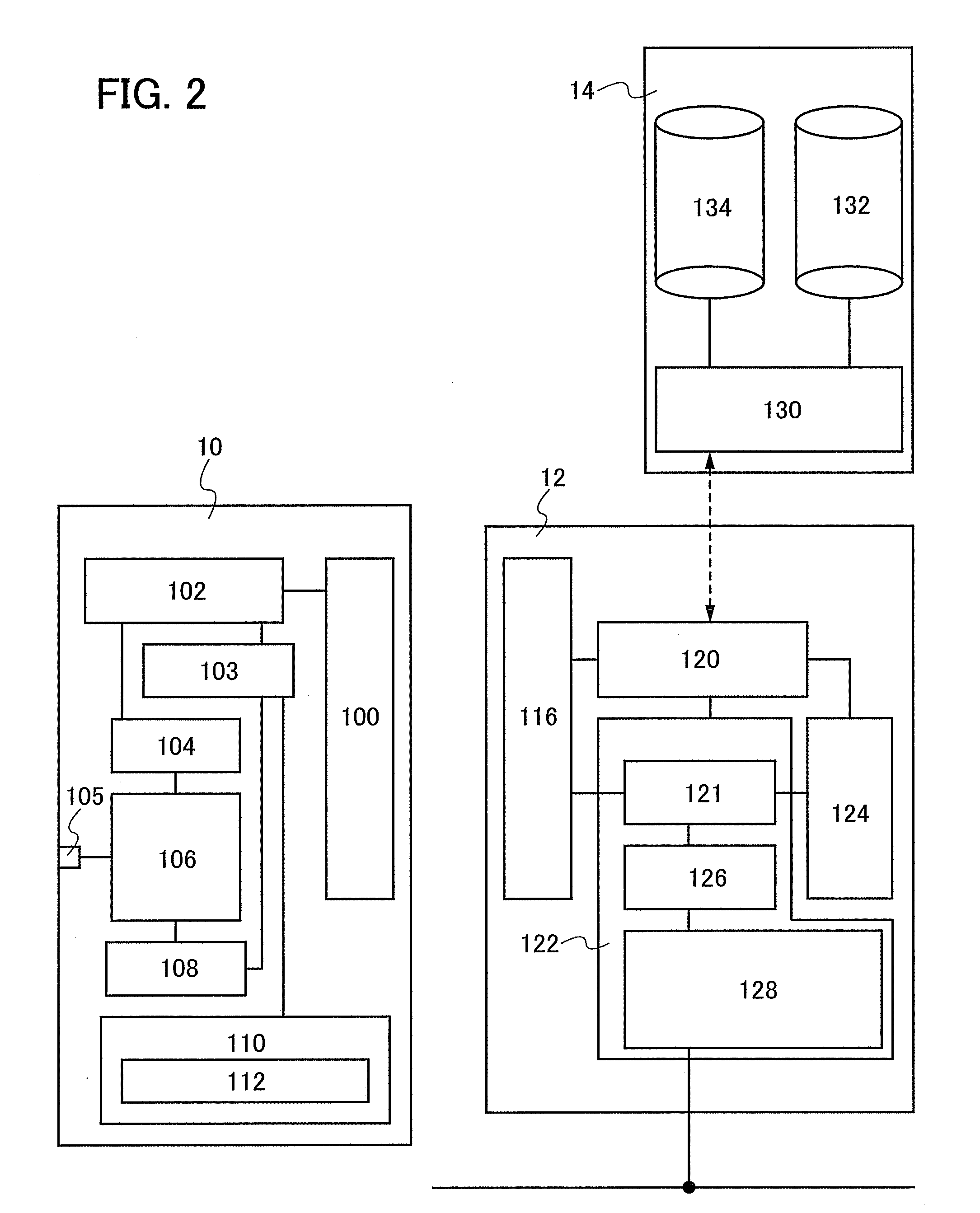

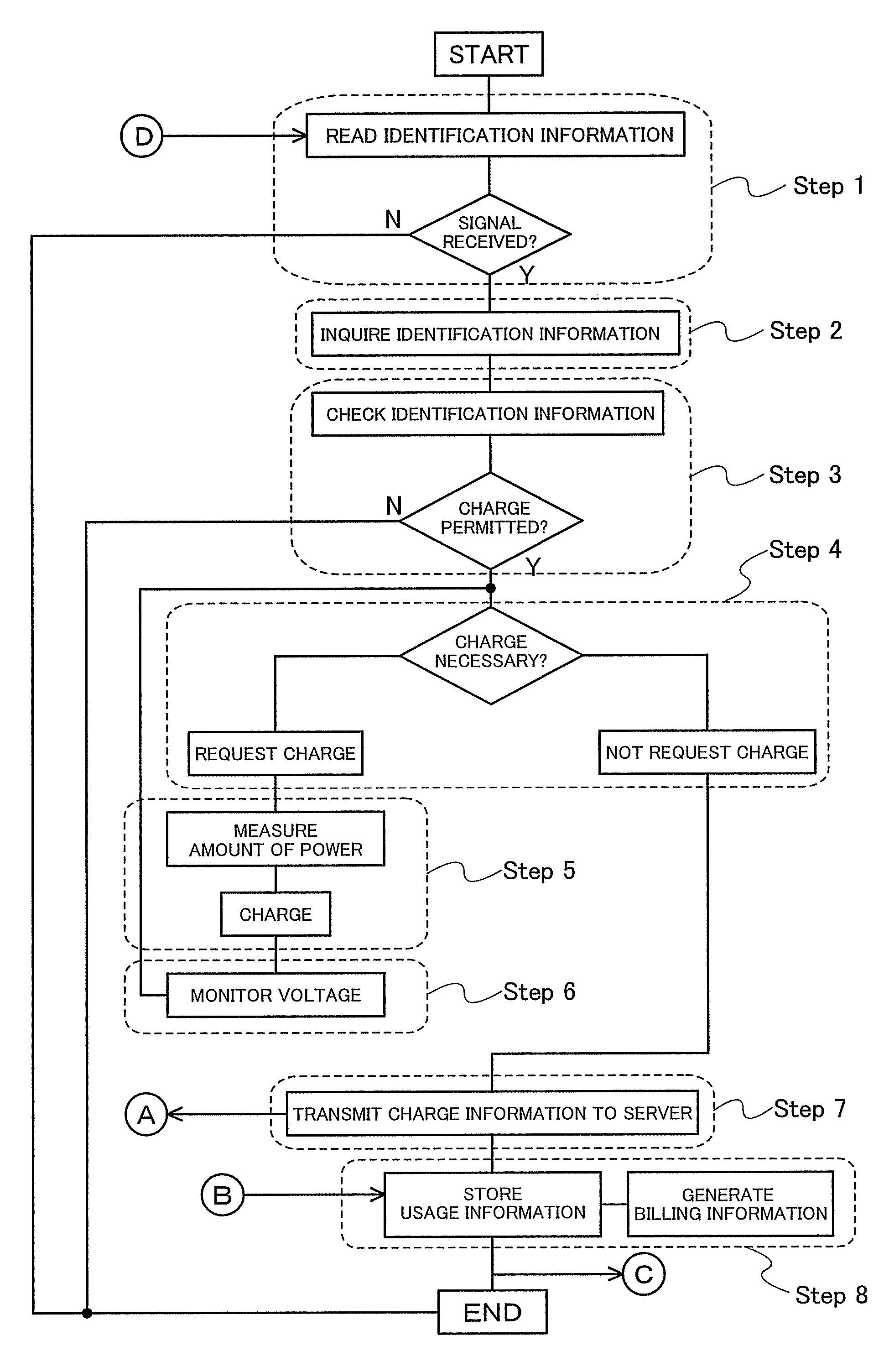

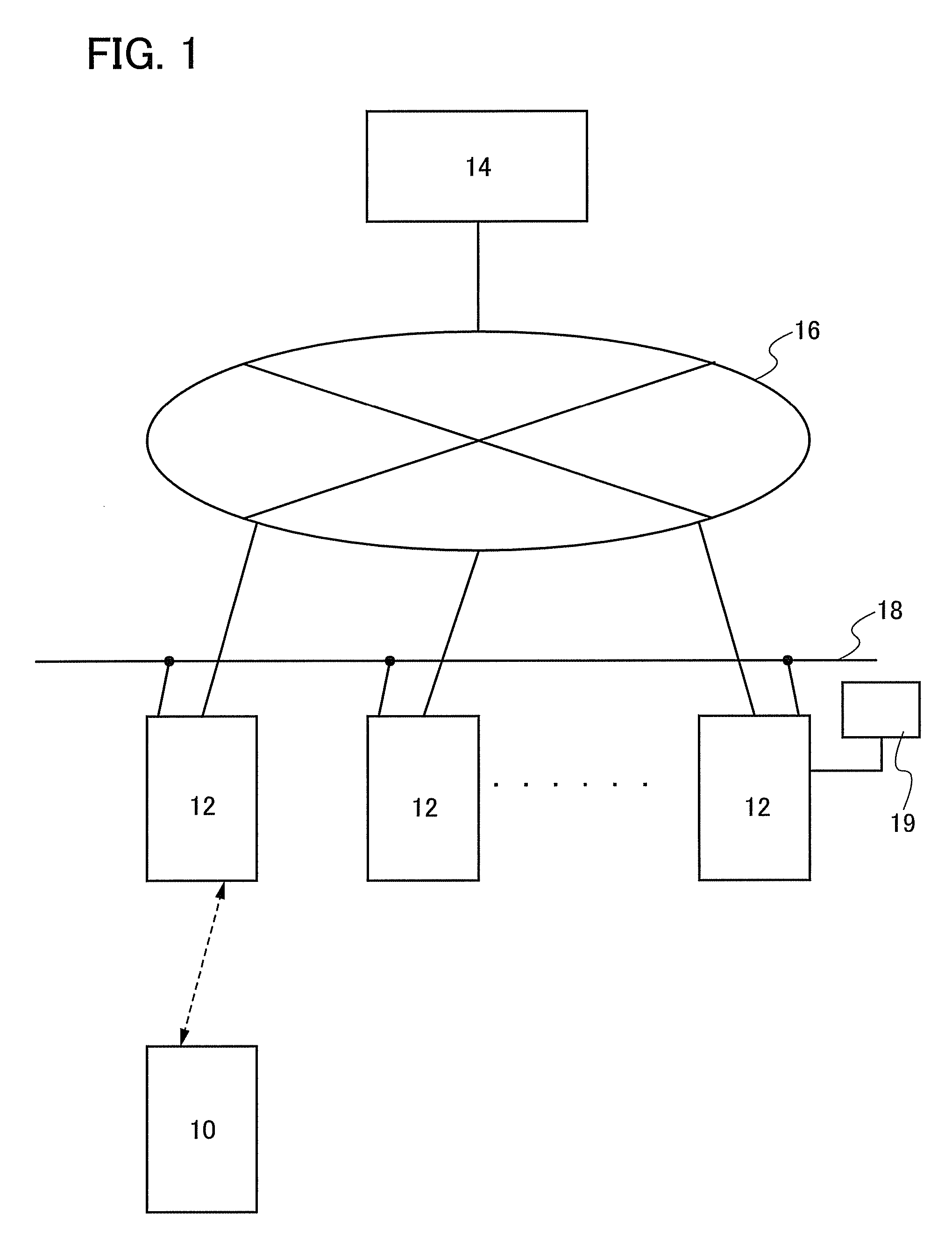

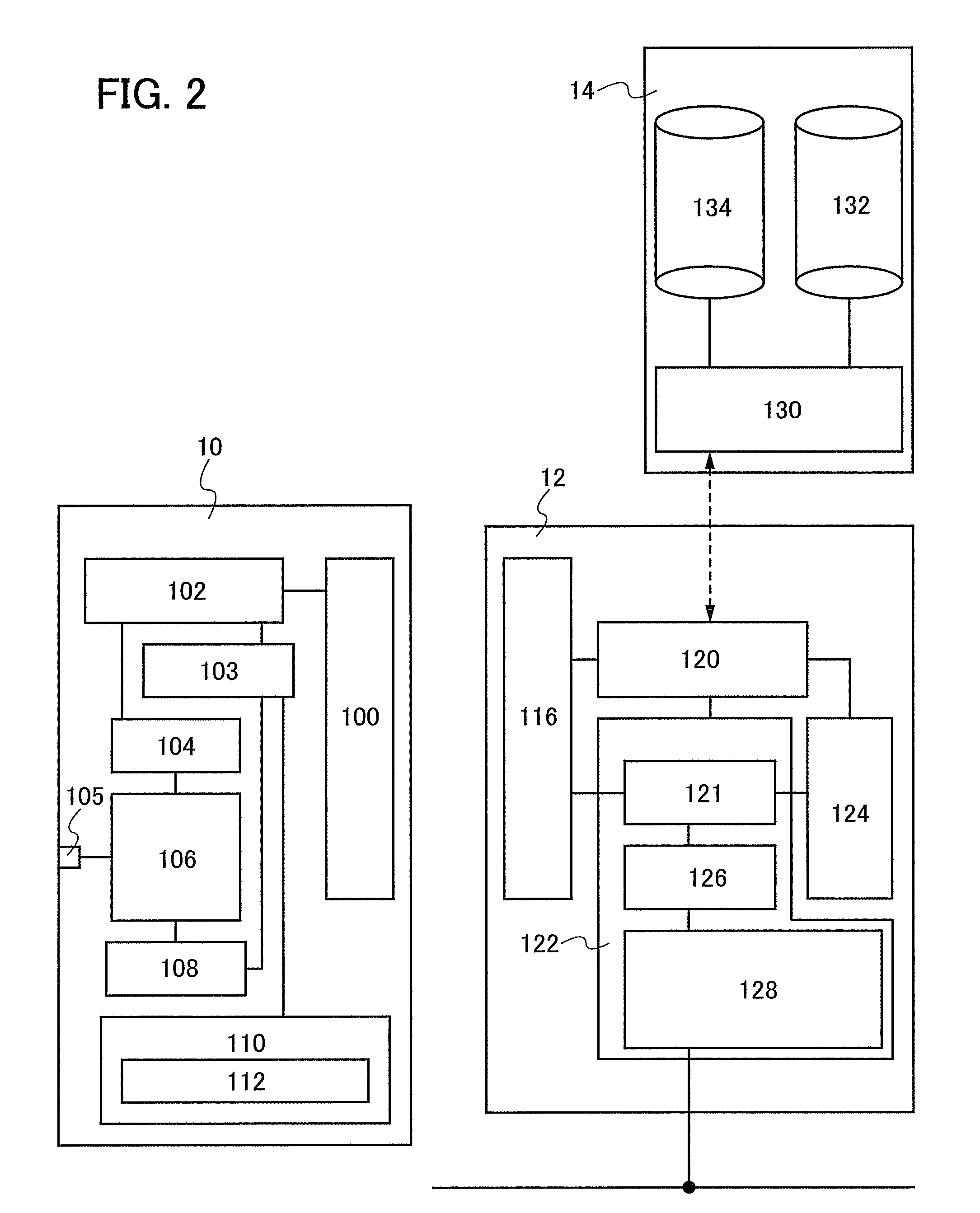

Wireless Power Supply System and Wireless Power Supply Method

ActiveUS20080122297A1Improve convenienceMeet needsElectrical testingLoop antennasElectric power systemComputer terminal

An object is to provide a system for improving convenience for users, by which a portable electronic device or the like can be charged even in a place where utility power is not available. Another object is to provide a system which allows a service provider to easily perform customer management. A wireless power supply system includes a power storage device having a power storage portion, a terminal charging device for wirelessly supplying electric power to the power storage device, and a management server having user information. Electric power can be supplied to specified users by intercommunication of user information between the power storage device and the terminal charging device and between the terminal charging device and the management server.

Owner:SEMICON ENERGY LAB CO LTD

Method of modifying the thickness of a plating on a member by creating a temperature gradient on the member, applications for employing such a method, and structures resulting from such a method

InactiveUS6110823ASimple technologyTrend downSemiconductor/solid-state device testing/measurementFinal product manufactureEngineeringElectronic component

Contact structures exhibiting resilience or compliance for a variety of electronic components are formed by bonding a free end of a wire to a substrate, configuring thw wire into a wire stem having a springable shape, serving thw wire stem, and overcoating the wire stem with at least one layer of a material chosen primarily for its structural (resiliency, compliance) characteristics. A variety of techniques for configuring, serving, and overcoating the wire stem are disclosed. In an exemplary embodiment, a free end of a wire stem is bonded to a contact area on a substrate, the wire stem is configured to ahve a springable shape, the wire stem is served to be free-standing by an electrical discharge, and the free-standing wire stem is overcoating by plating.

Owner:FORMFACTOR INC

Wireless power supply system and wireless power supply method

ActiveUS8099140B2Improve convenienceEasy to implementElectrical testingLoop antennasElectric power systemComputer terminal

An object is to provide a system for improving convenience for users, by which a portable electronic device or the like can be charged even in a place where utility power is not available. Another object is to provide a system which allows a service provider to easily perform customer management. A wireless power supply system includes a power storage device having a power storage portion, a terminal charging device for wirelessly supplying electric power to the power storage device, and a management server having user information. Electric power can be supplied to specified users by intercommunication of user information between the power storage device and the terminal charging device and between the terminal charging device and the management server.

Owner:SEMICON ENERGY LAB CO LTD

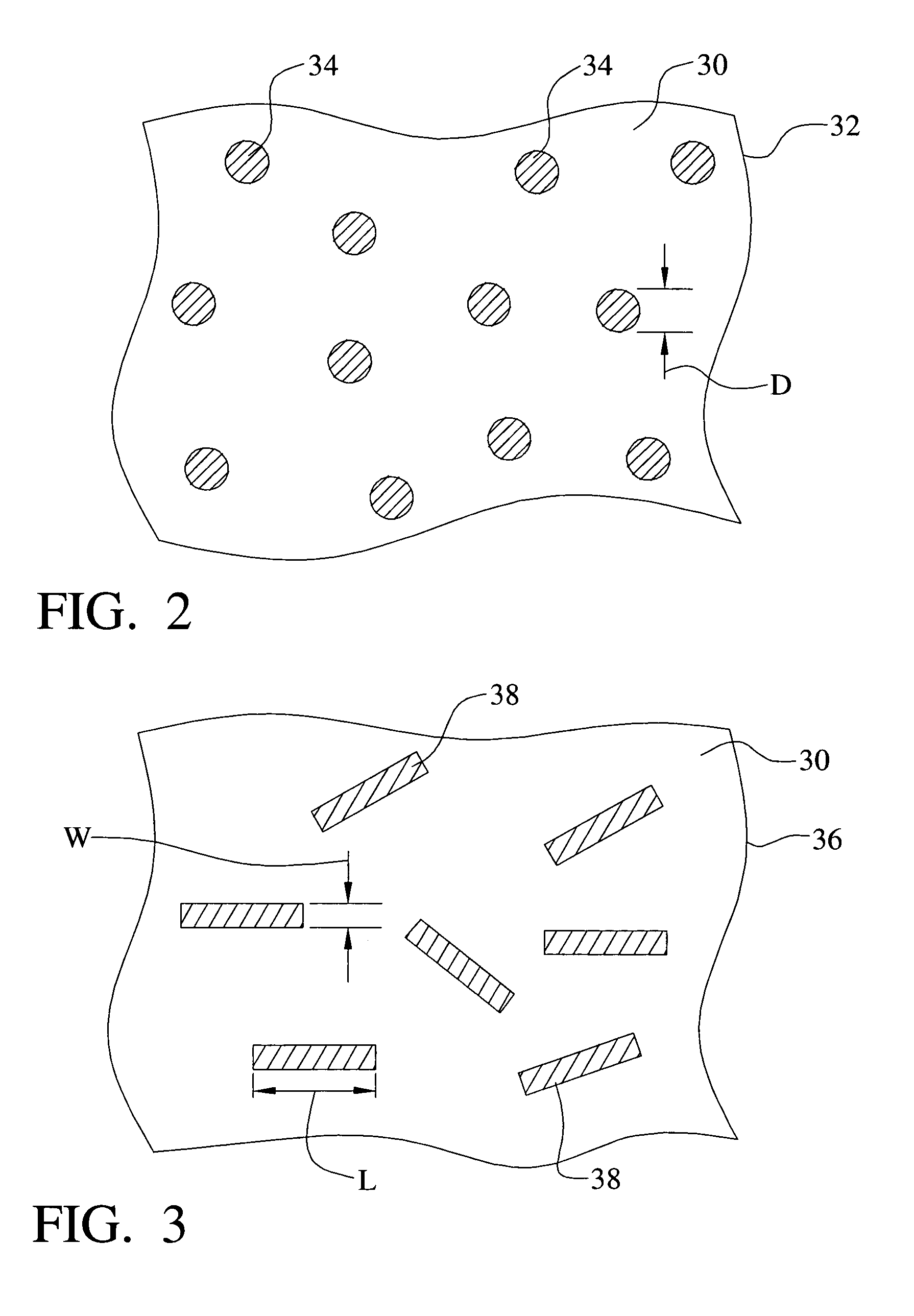

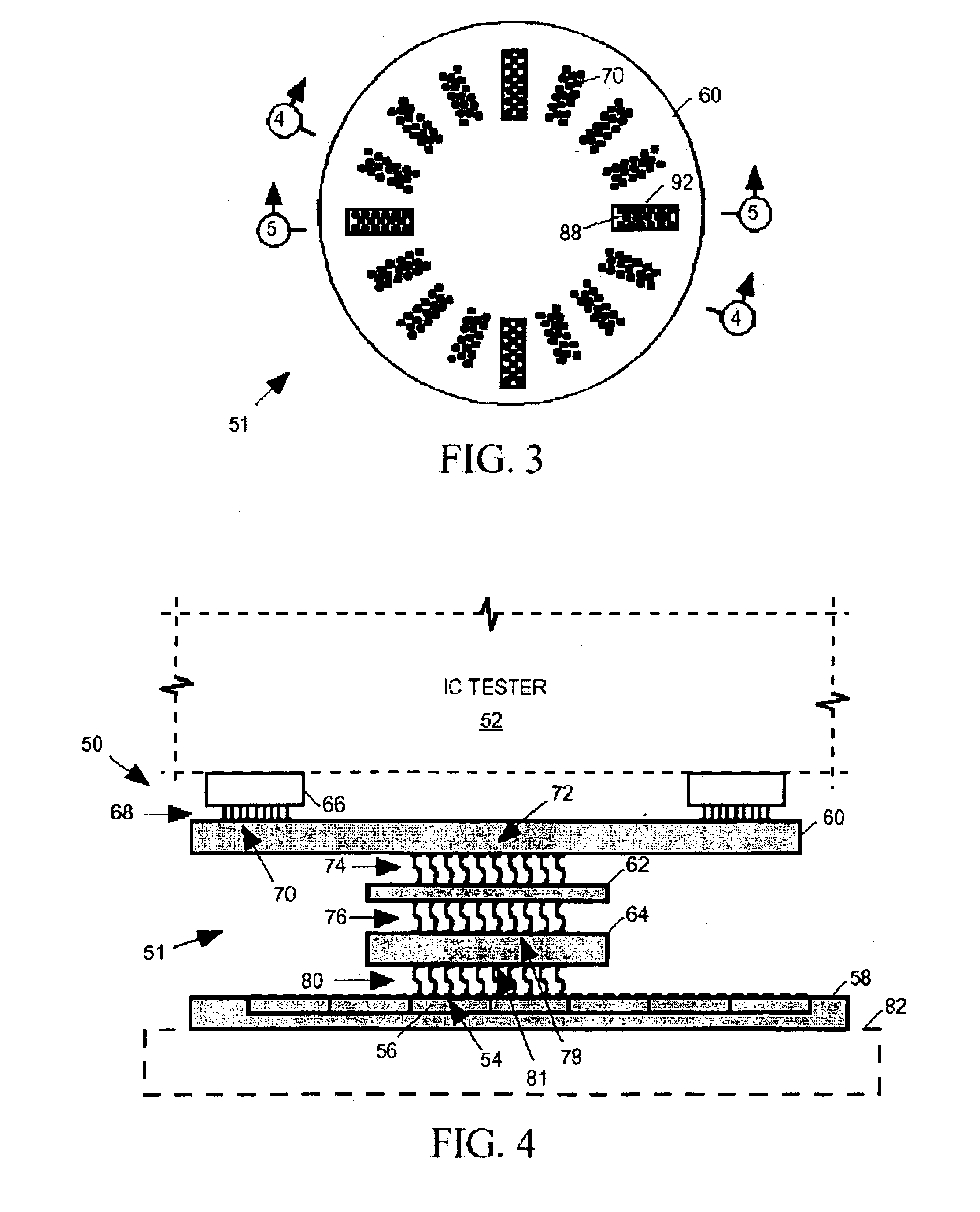

Reprogrammable circuit board with alignment-insensitive support for multiple component contact types

InactiveUS20080143379A1Semiconductor/solid-state device testing/measurementWave amplification devicesSignal conditioningContact type

The present invention is directed to a system that programmably interconnects integrated circuit chips and other components at near-intra-chip density. The system's contact structure allows it to adapt to components with a wide variety of contact spacings and interconnection requirements, the use of releasable attachment means allows component placement to be modified as needed, the system identifies the contacts and the components to facilitate specifying the inter-component connections, and the system provides signal conditioning and retiming to minimize issues with signal integrity and signal skew.

Owner:NORMAN RICHARD

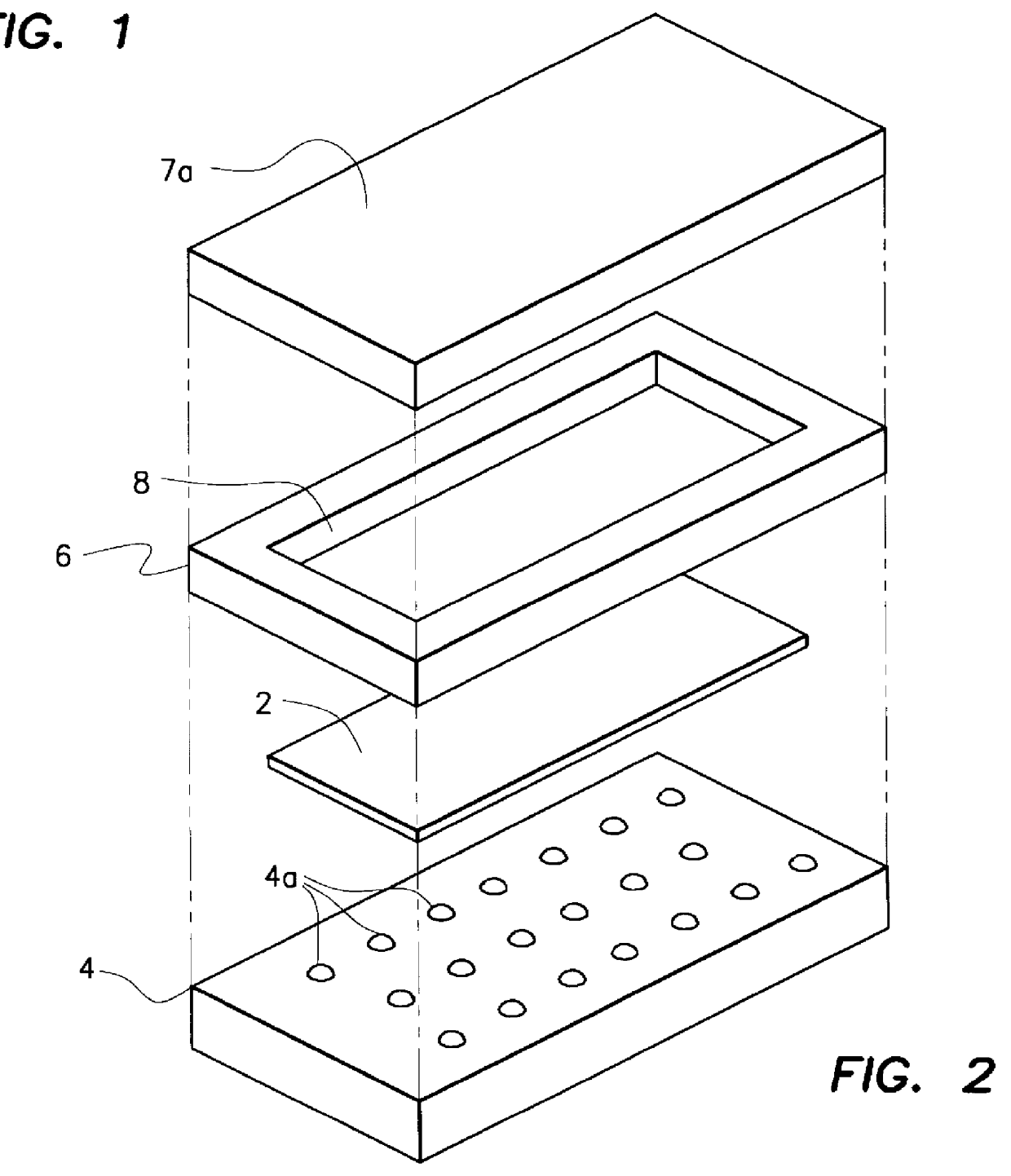

Thin film-structure and a method for producing the same

InactiveUS6759261B2Increase productivityGood reproducibilityLiquid-phase epitaxial-layer growthElectrical measurement instrument detailsRoom temperatureCooling down

A thin film made of an amorphous material having supercooled liquid phase region is formed on a substrate. Then, the thin film is heated to a temperature within the supercooled liquid phase region and is deformed by its weight, mechanical external force, electrostatic external force or the like, thereby to form a thin film-structure. Thereafter, the thin film-structure is cooled down to room temperature, which results in the prevention of the thin film's deformation.

Owner:TOKYO INST OF TECH

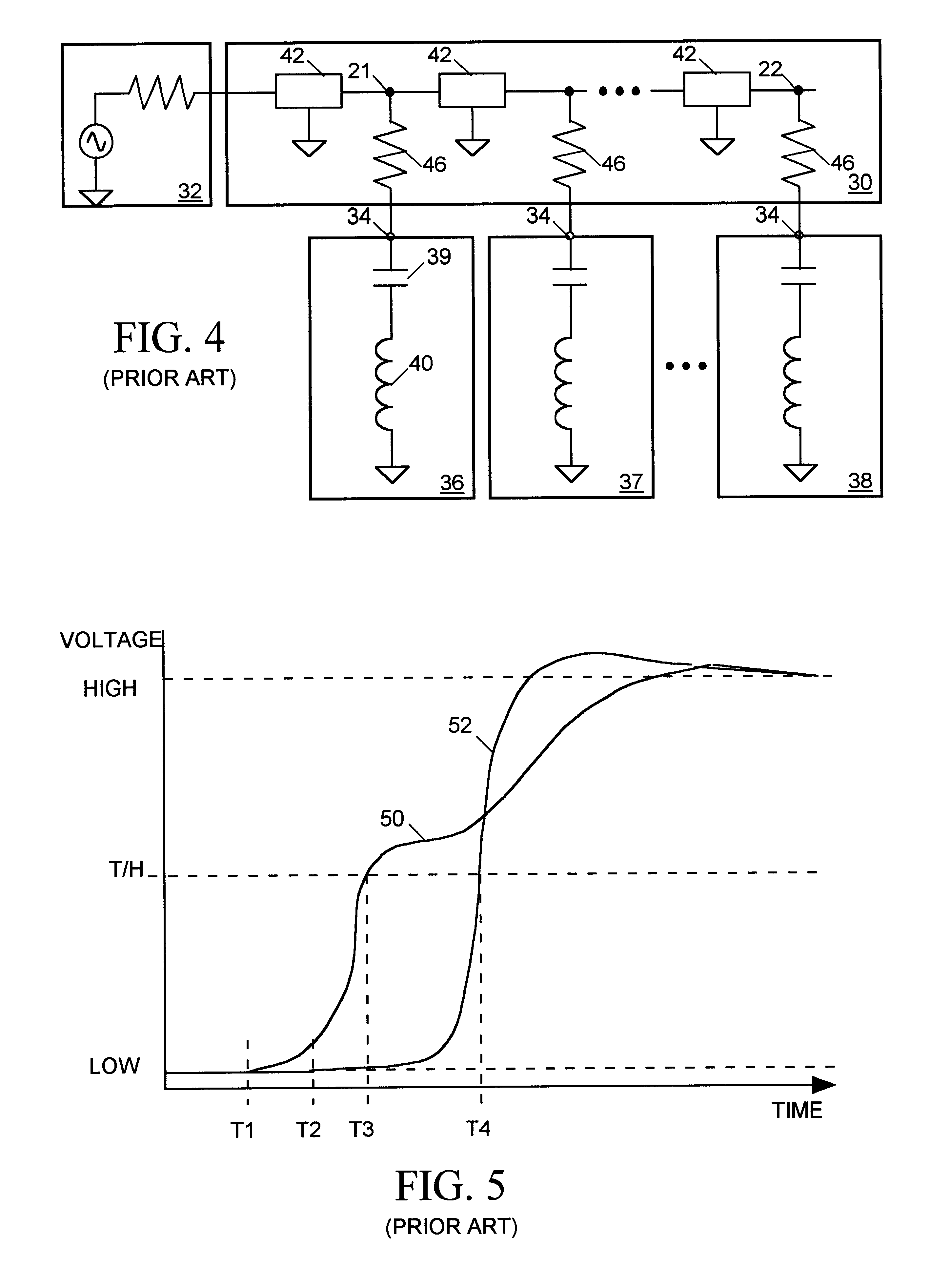

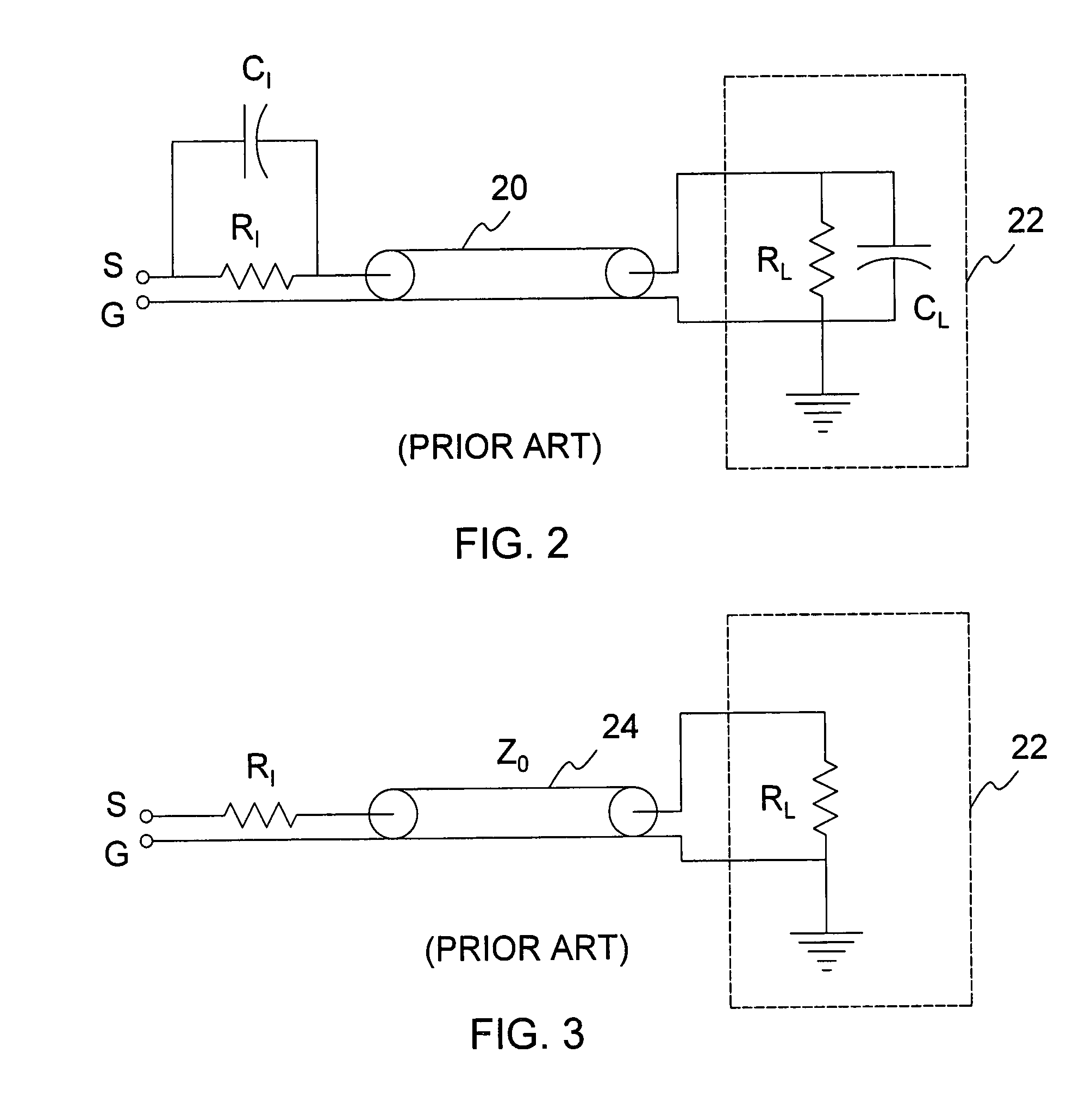

High bandwidth passive integrated circuit tester probe card assembly

InactiveUS6218910B1Multiple-port networksElectrical measurement instrument detailsCapacitanceProbe card

Described herein is a probe card assembly providing signal paths for conveying high frequency signals between bond pads of an integrated circuit (IC) and an IC tester. The frequency response of the probe card assembly is optimized by appropriately distributing, adjusting and impedance matching resistive, capacitive and inductive impedance values along the signal paths so that the interconnect system behaves as an appropriately tuned Butterworth or Chebyshev filter.

Owner:FORMFACTOR INC

Method for forming conductive bumps for the purpose of contrructing a fine pitch test device

InactiveUS20020011859A1Semiconductor/solid-state device testing/measurementElectrical measurement instrument detailsElectricityEngineering

A system is described for using with fine pitch devices including singulated bare die, semiconductor wafers, chip sized packages, printed circuit boards, and the like to determine that the fine pitch device is not faulty. The system is also usable for transfer of data, energy, for collecting data measurements or measurement-related data between two pieces, and for effecting at least part of an identification process. The disclosed embodiment includes a substrate having a circuit pad pattern in the mirror image of the pattern of contact points, usually bond pads of the fine pitch device to be connected. A conductive elastomeric probe is permanently formed on the circuit pads of the substrate such that the probe is malleable and allows repetitive electrical contact. The system may also contain an alignment template for orienting the fine pitch device onto the elastomeric probes of the contact point pattern of the substrate.

Owner:EPITECH +1

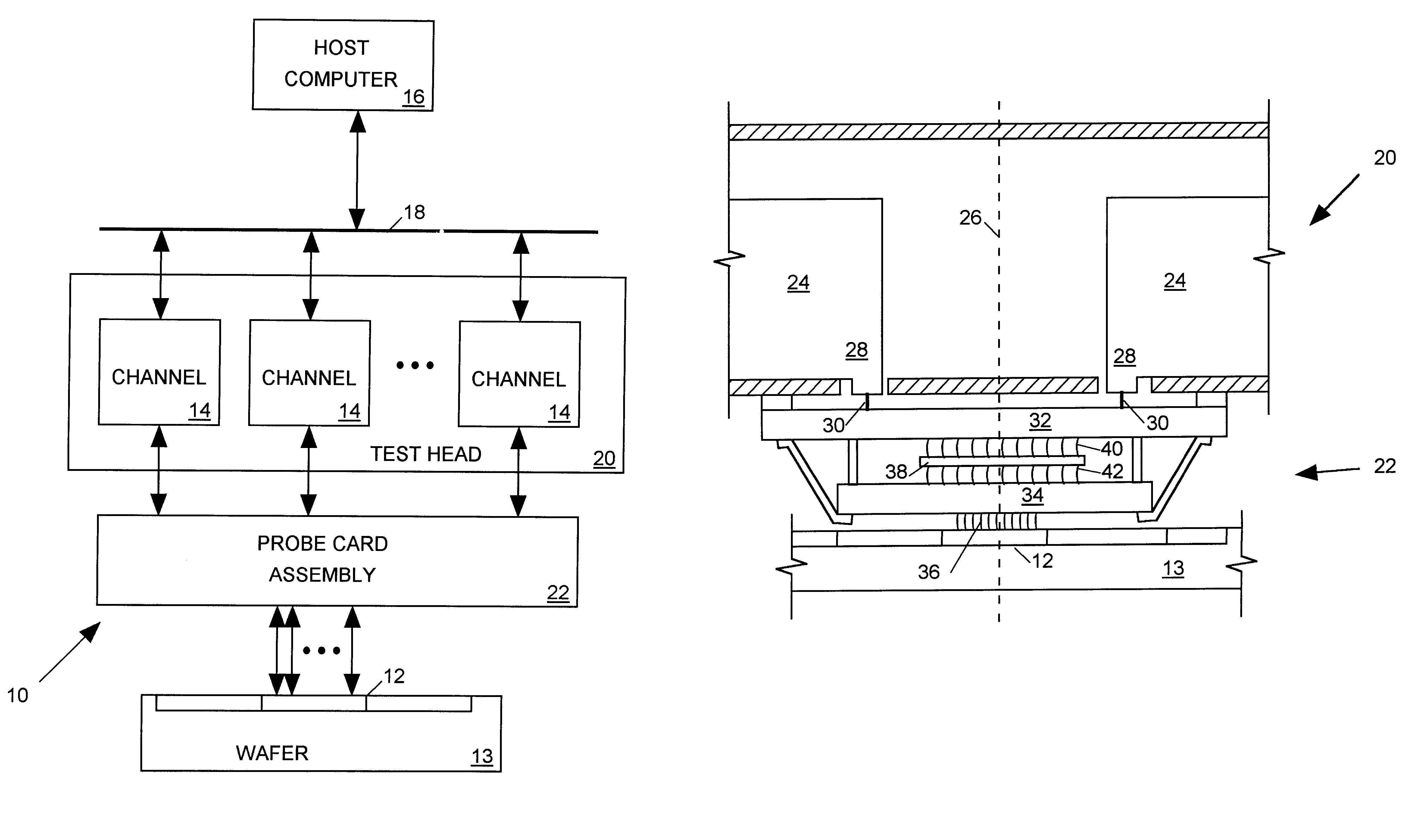

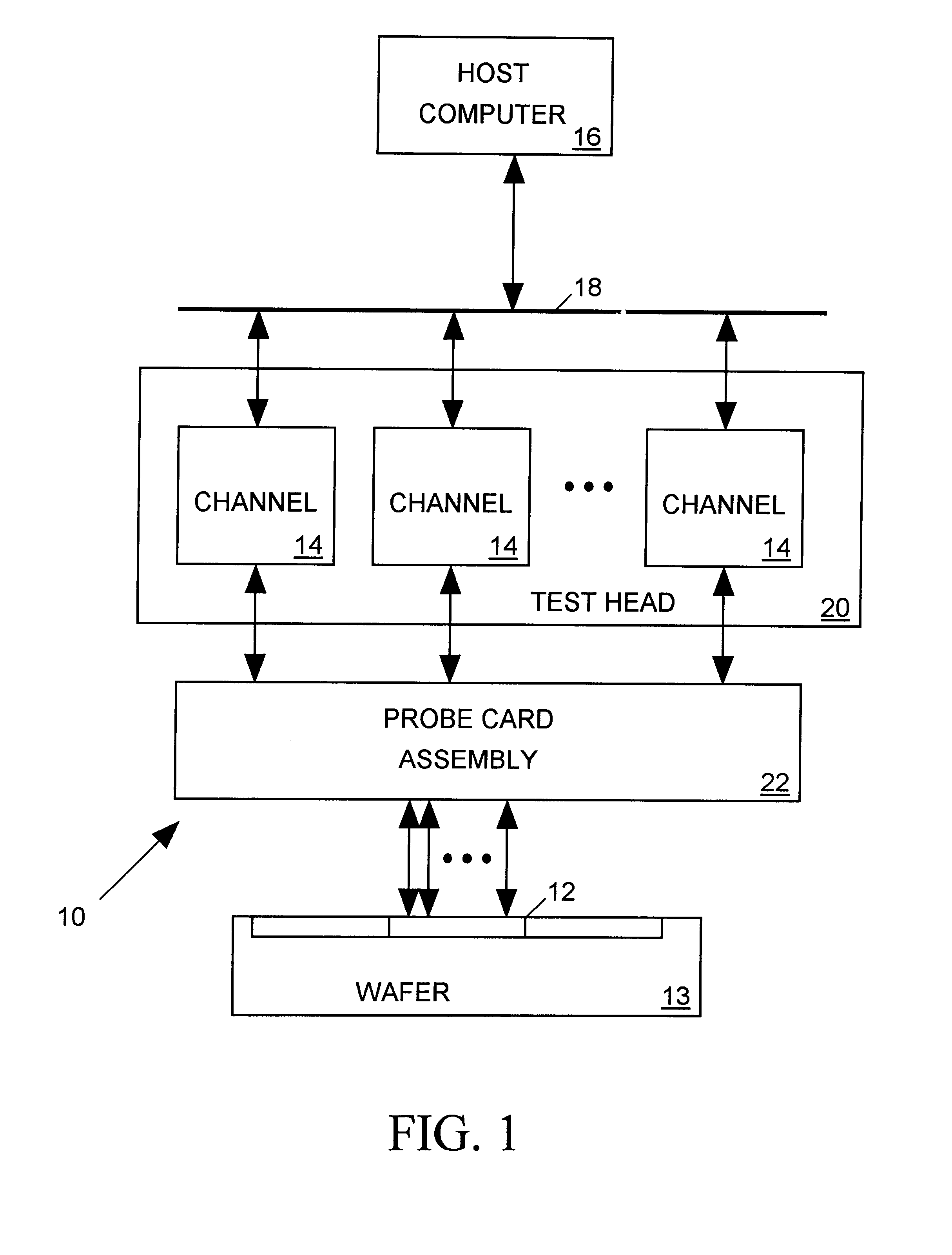

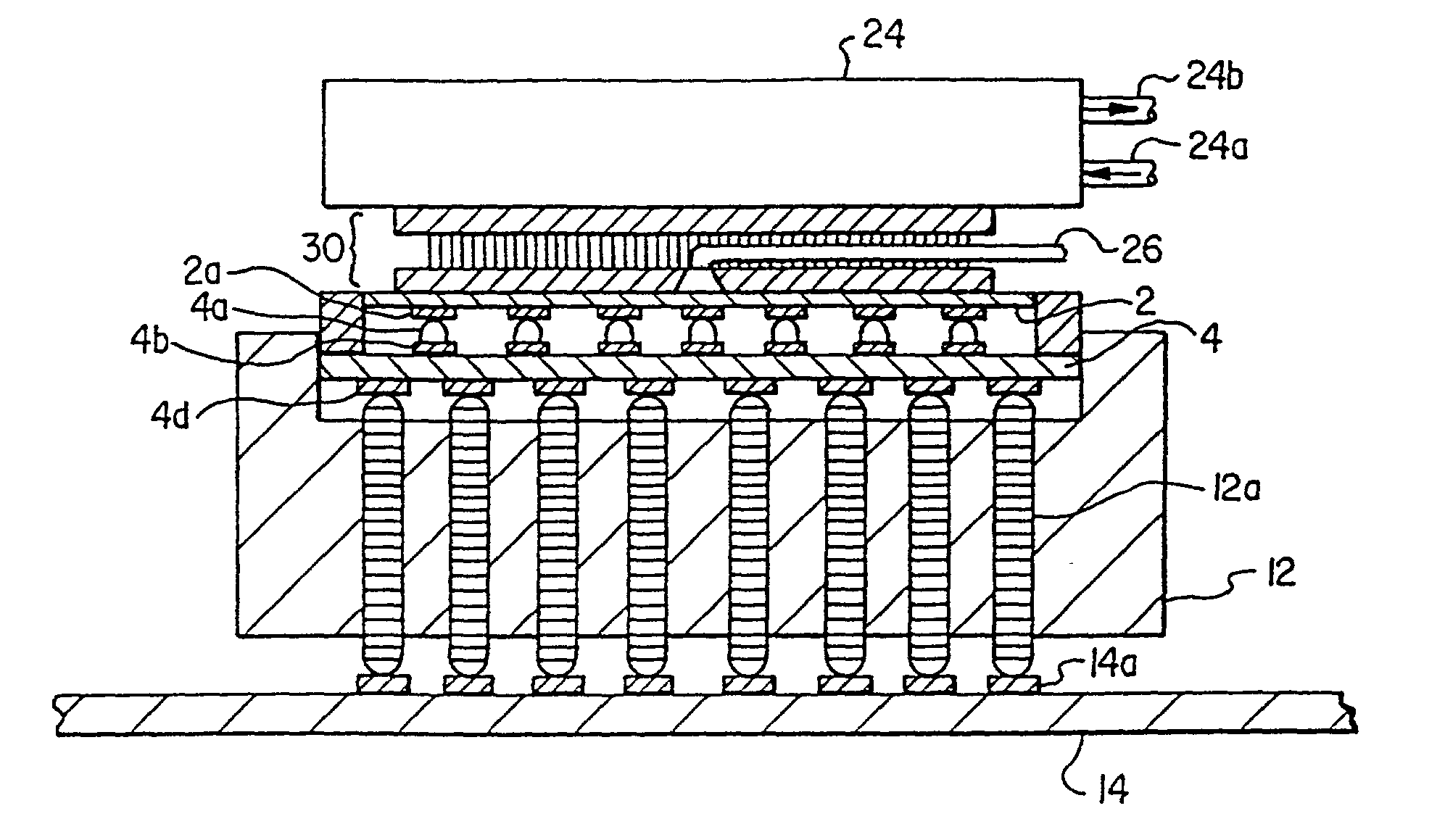

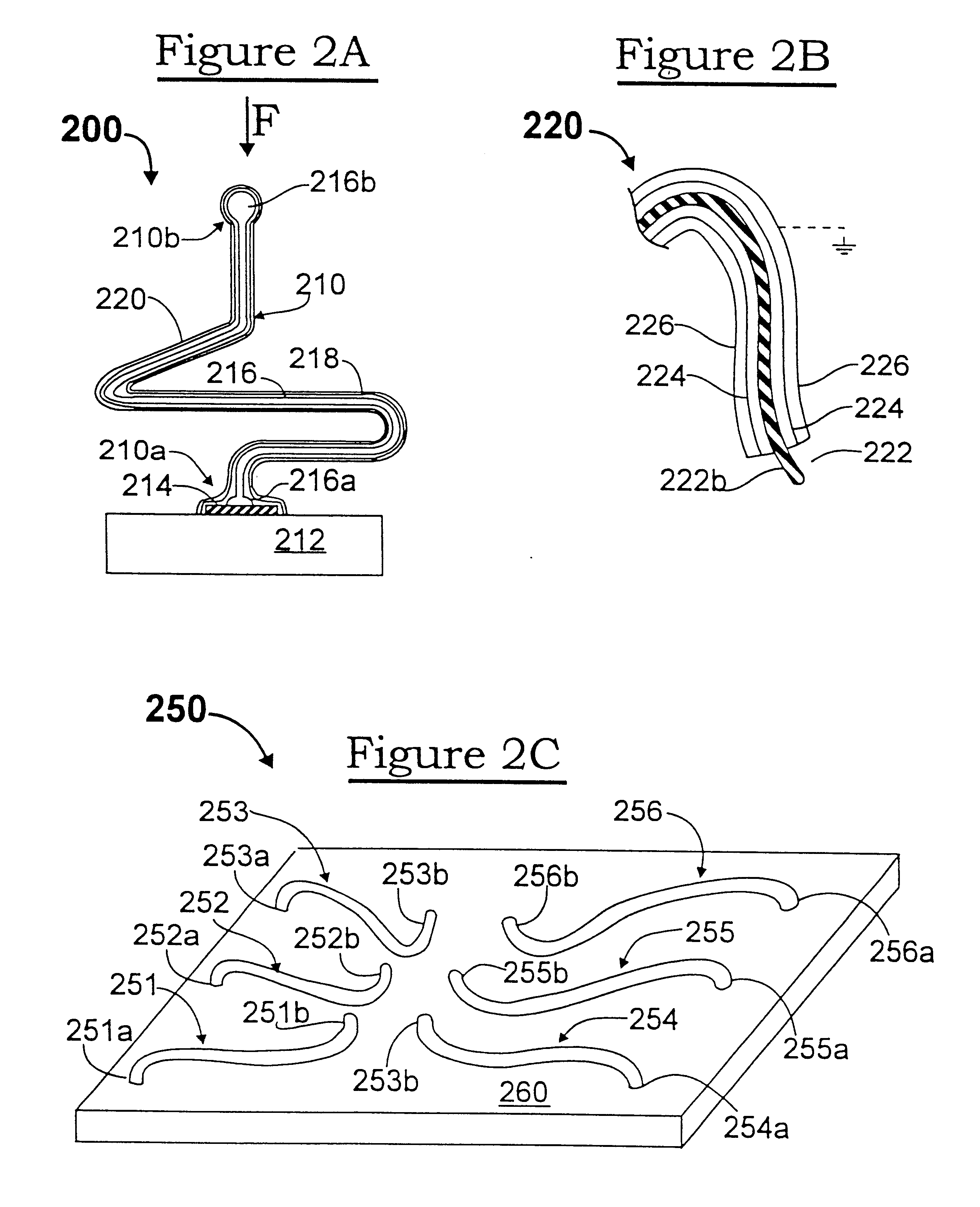

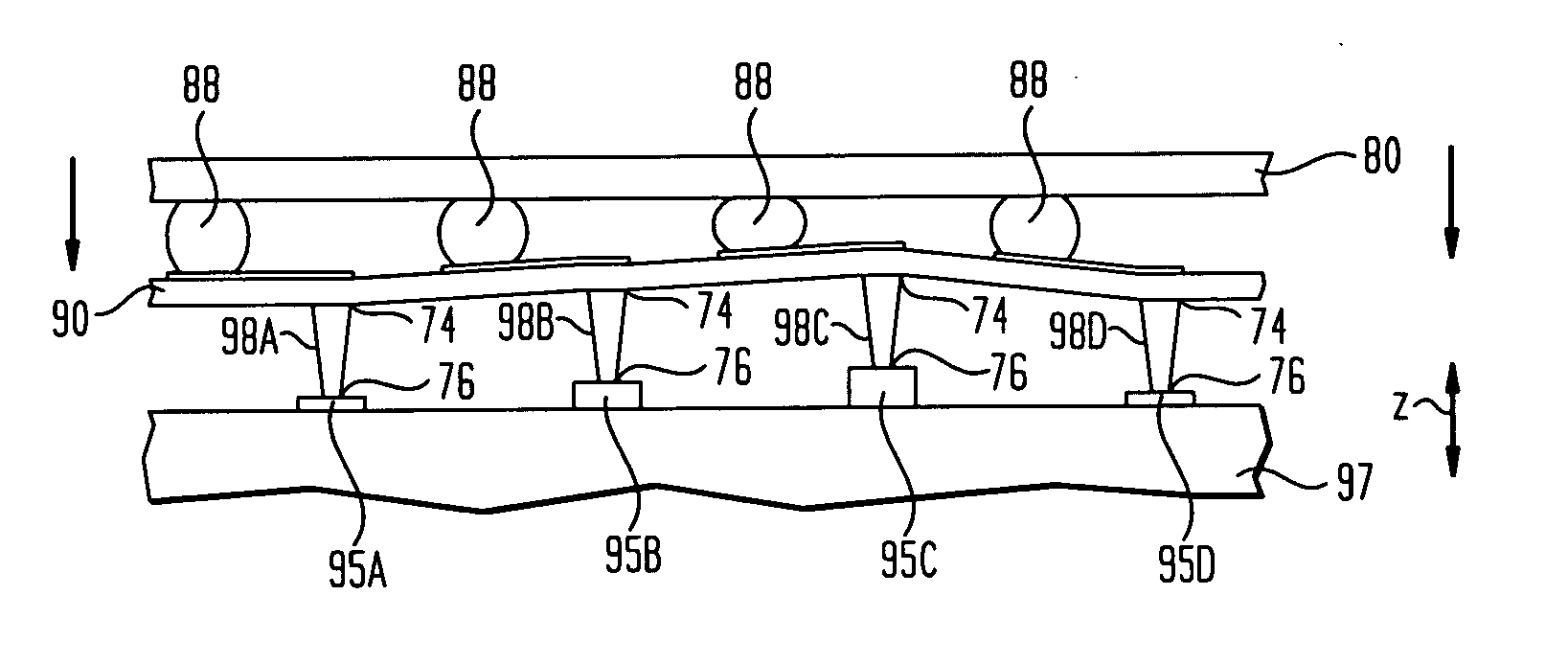

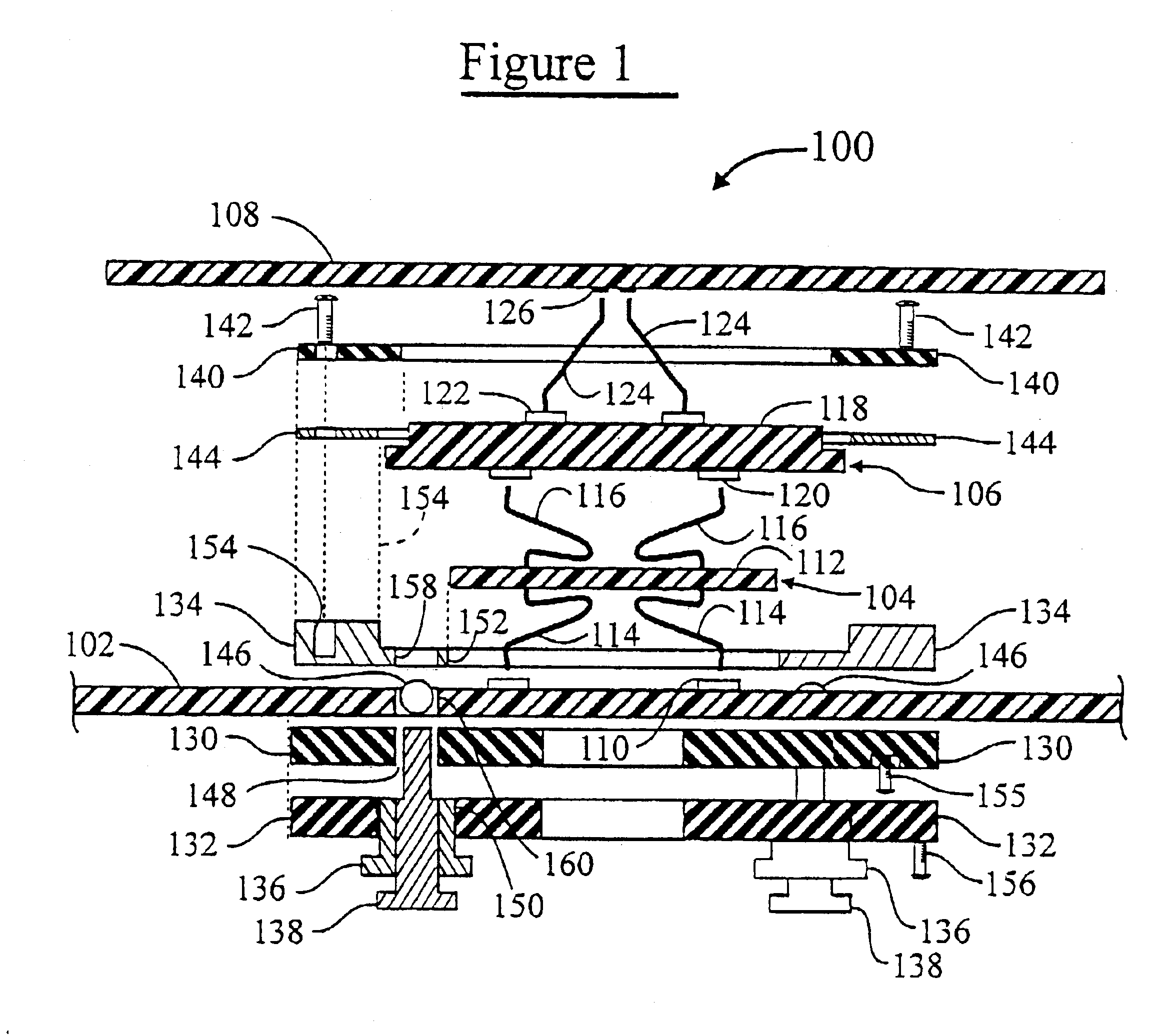

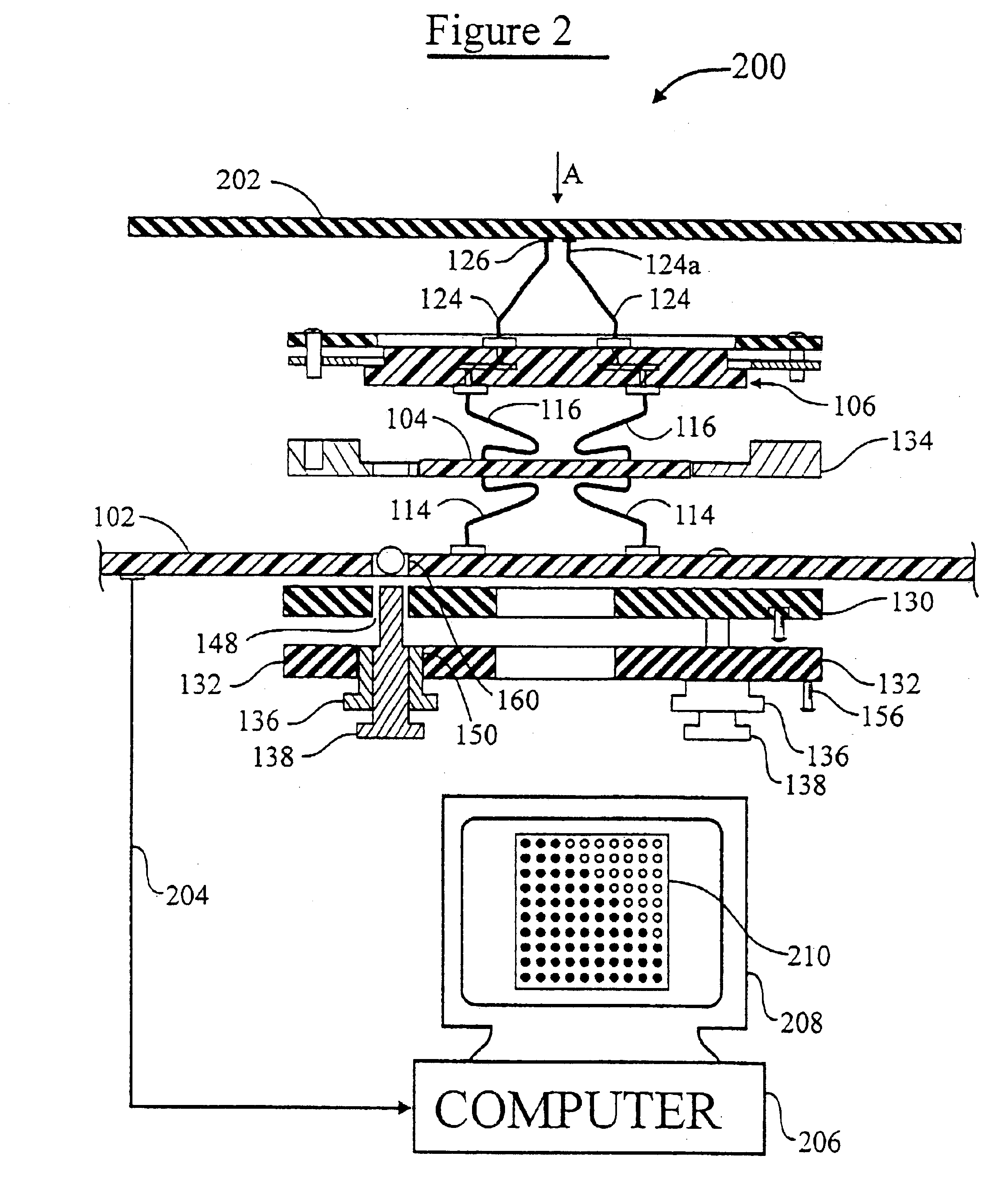

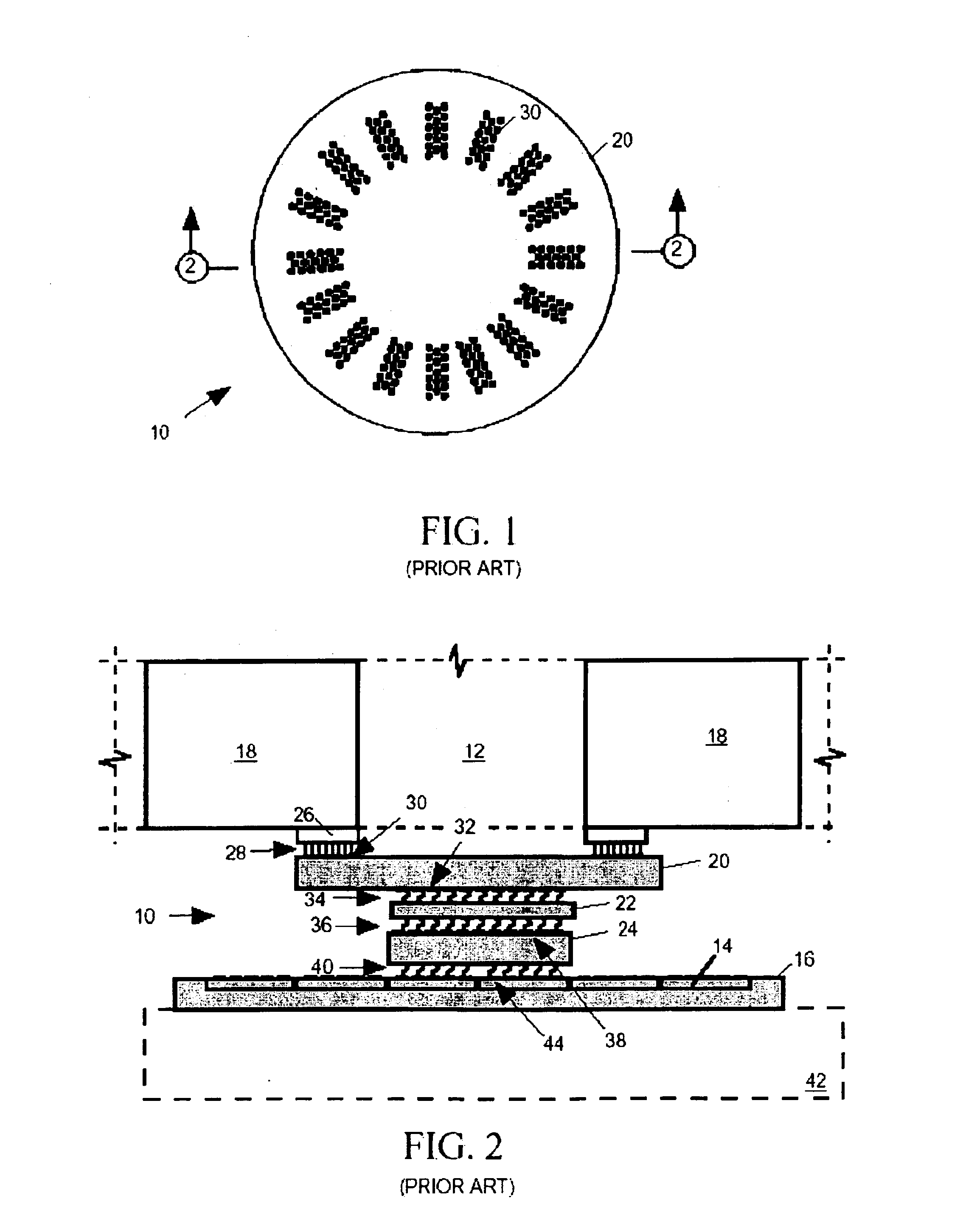

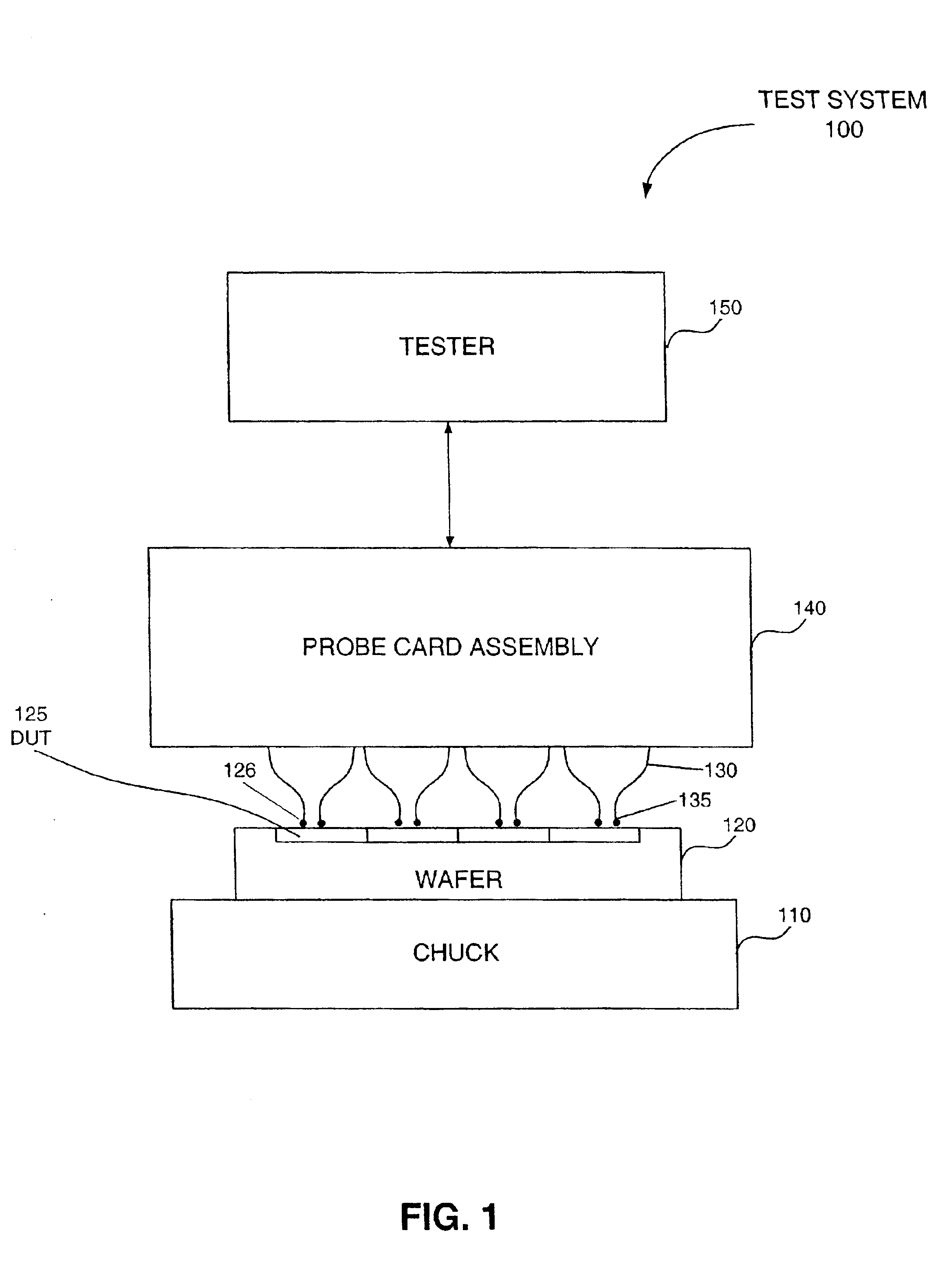

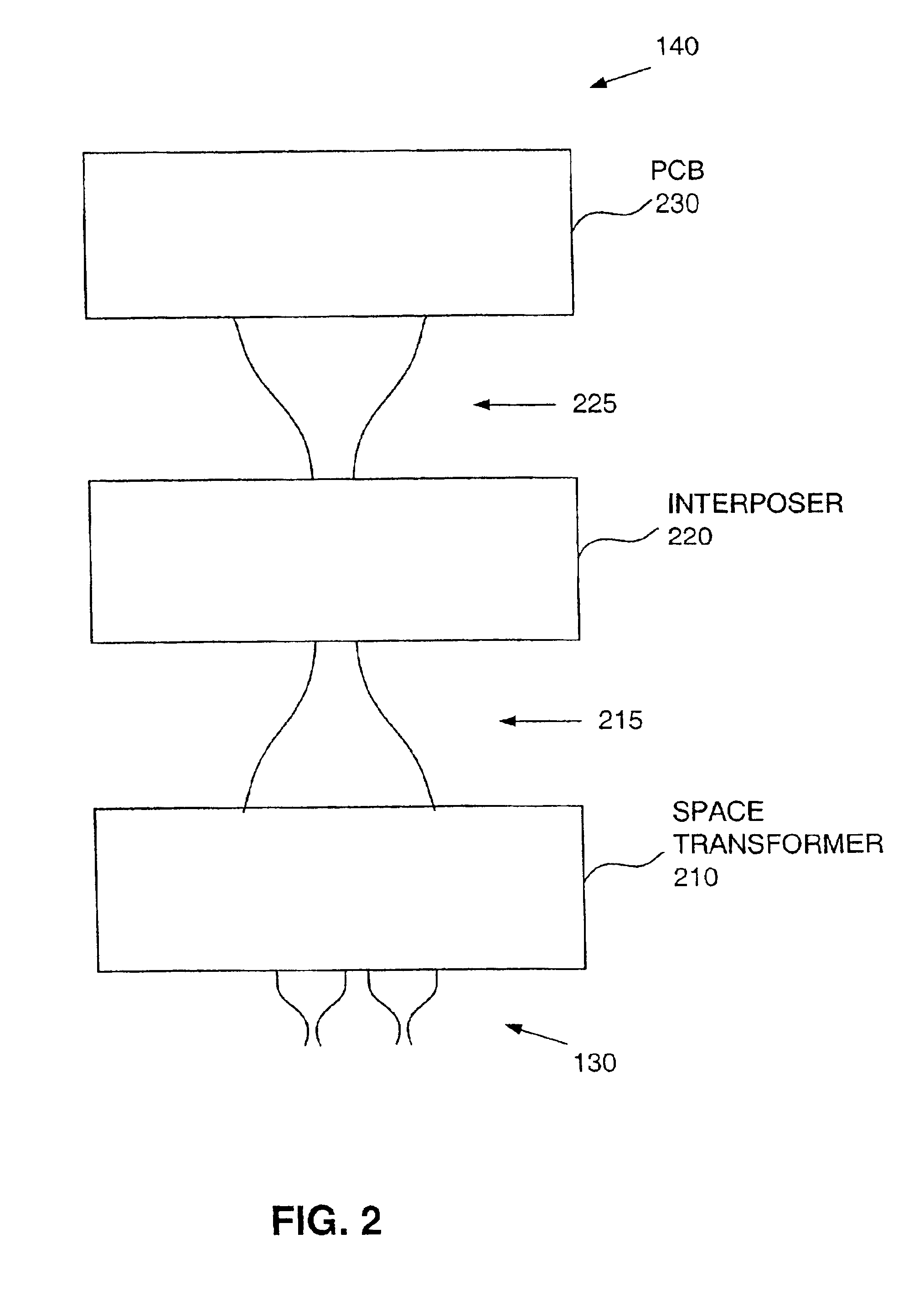

Probe card assembly and kit, and methods of using same

InactiveUS6246247B1Easy to disassembleEffective shieldingSemiconductor/solid-state device testing/measurementFinal product manufactureElectricityProbe card

A probe card assembly includes a probe card, a space transformer having resilient contact structures (probe elements) mounted directly thereto (i.e., without the need for additional connecting wires or the like) and extending from terminals on a surface thereof, and an interposer disposed between the space transformer and the probe card. The space transformer and interposer are "stacked up" so that the orientation of the space transformer, hence the orientation of the tips of the probe elements, can be adjusted without changing the orientation of the probe card. Suitable mechanisms for adjusting the orientation of the space transformer, and for determining what adjustments to make, are disclosed. The interposer has resilient contact structures extending from both the top and bottom surfaces thereof, and ensures that electrical connections are maintained between the space transformer and the probe card throughout the space transformer's range of adjustment, by virtue of the interposer's inherent compliance. Multiple die sites on a semiconductor wafer are readily probed using the disclosed techniques, and the probe elements can be arranged to optimize probing of an entire wafer. Composite interconnection elements having a relatively soft core overcoated by a relatively hard shell, as the resilient contact structures are described.

Owner:FORMFACTOR INC

Fine pitch contact device employing a compliant conductive polymer bump

InactiveUS6064217ALow costElectrical measurement instrument detailsElectrical testingElectricityEngineering

A reusable test socket is described for testing fine pitch devices including singulated bare die, semiconductor wafers, chip sized packages, printed circuit boards, and the like to determine that the fine pitch device is not faulty. The socket contains a circuit pad pattern in the mirror image of the pattern of contact points, usually bond pads of the fine pitch device to be tested. Each pad of the socket contains a conductive elastomeric probe which has been "screened" onto the bond pad. The socket also contains an alignment template for orienting the fine pitch device onto the elastomeric probes of the contact point pattern of the test socket. Additionally, the socket can be a singular piece or it can be made of two main pieces; the first being a socket, and the second being a test board designed to mate with the socket. The disclosed invention also includes a method of using the reusable test socket which includes the steps of placing the fine pitch device onto the test socket, placing the socket into electrical continuity with test equipment and conducting electrical tests at ambient as well as elevated temperatures.

Owner:EPITECH +1

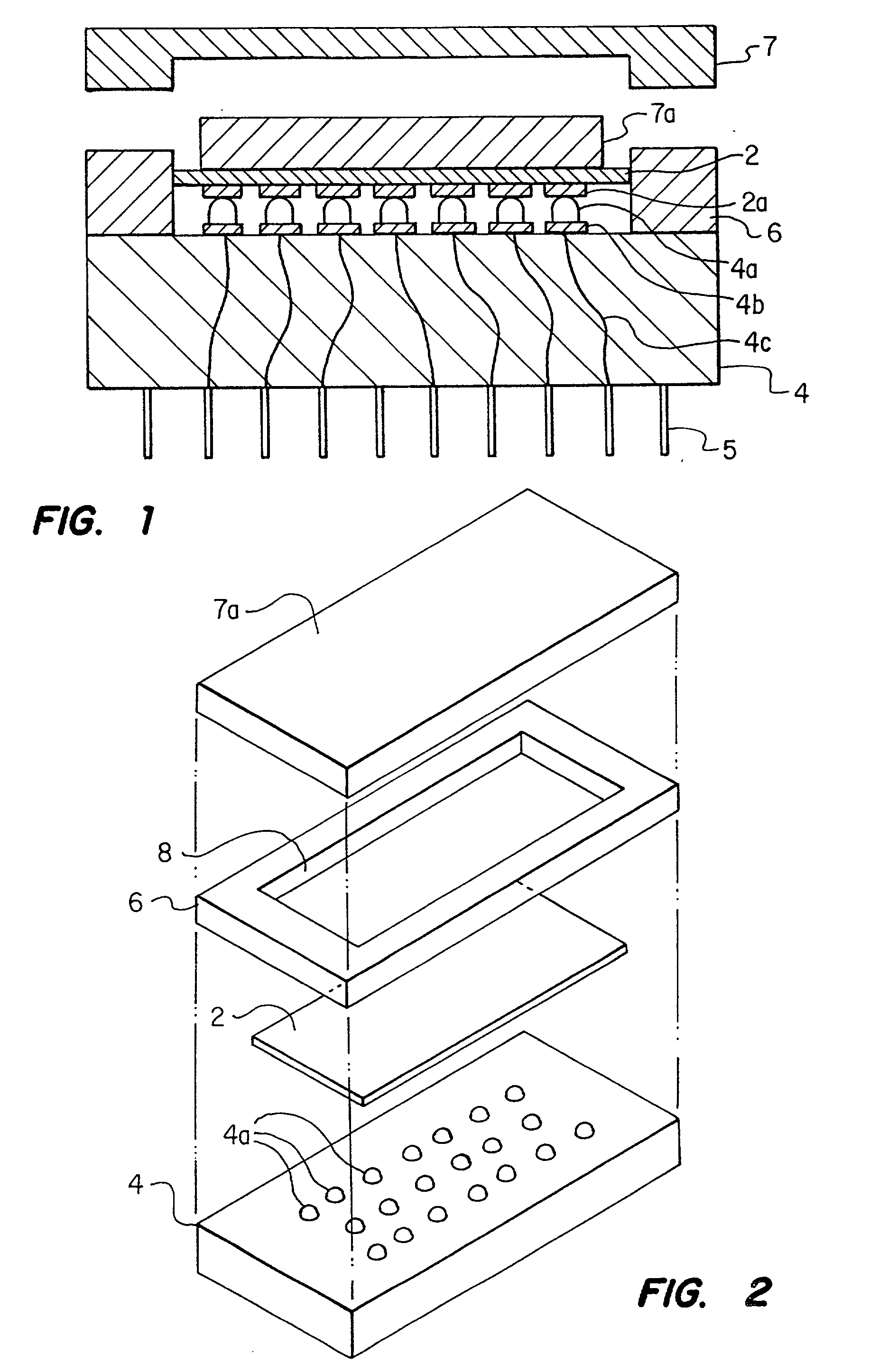

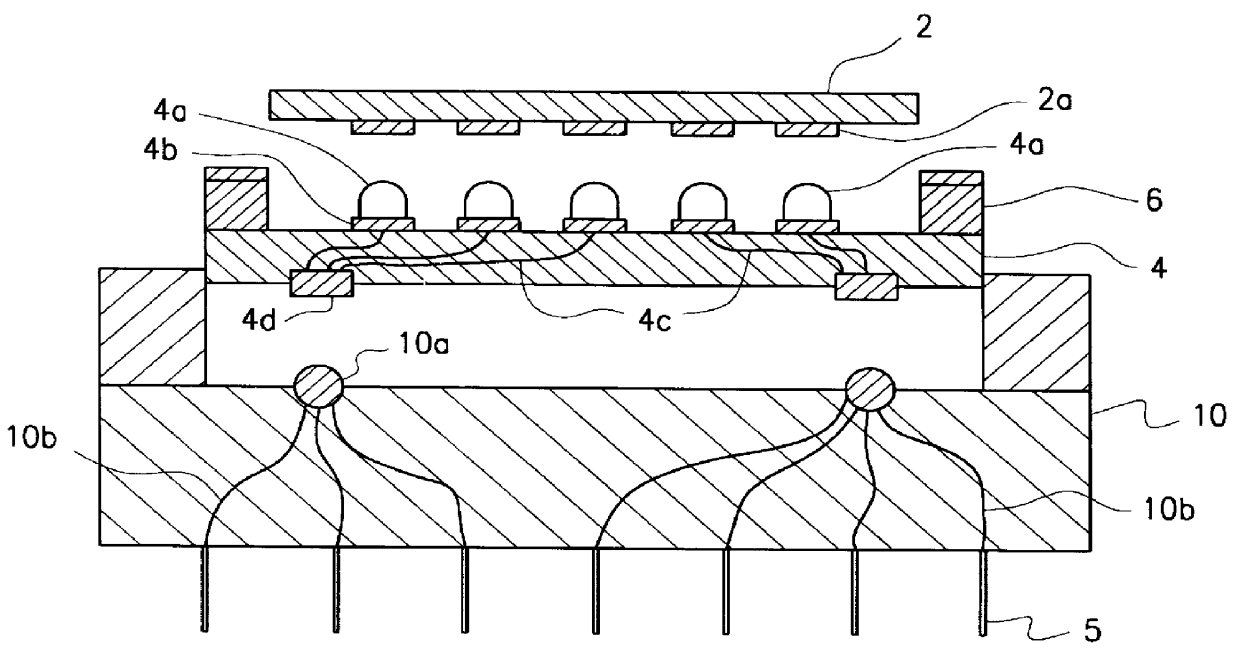

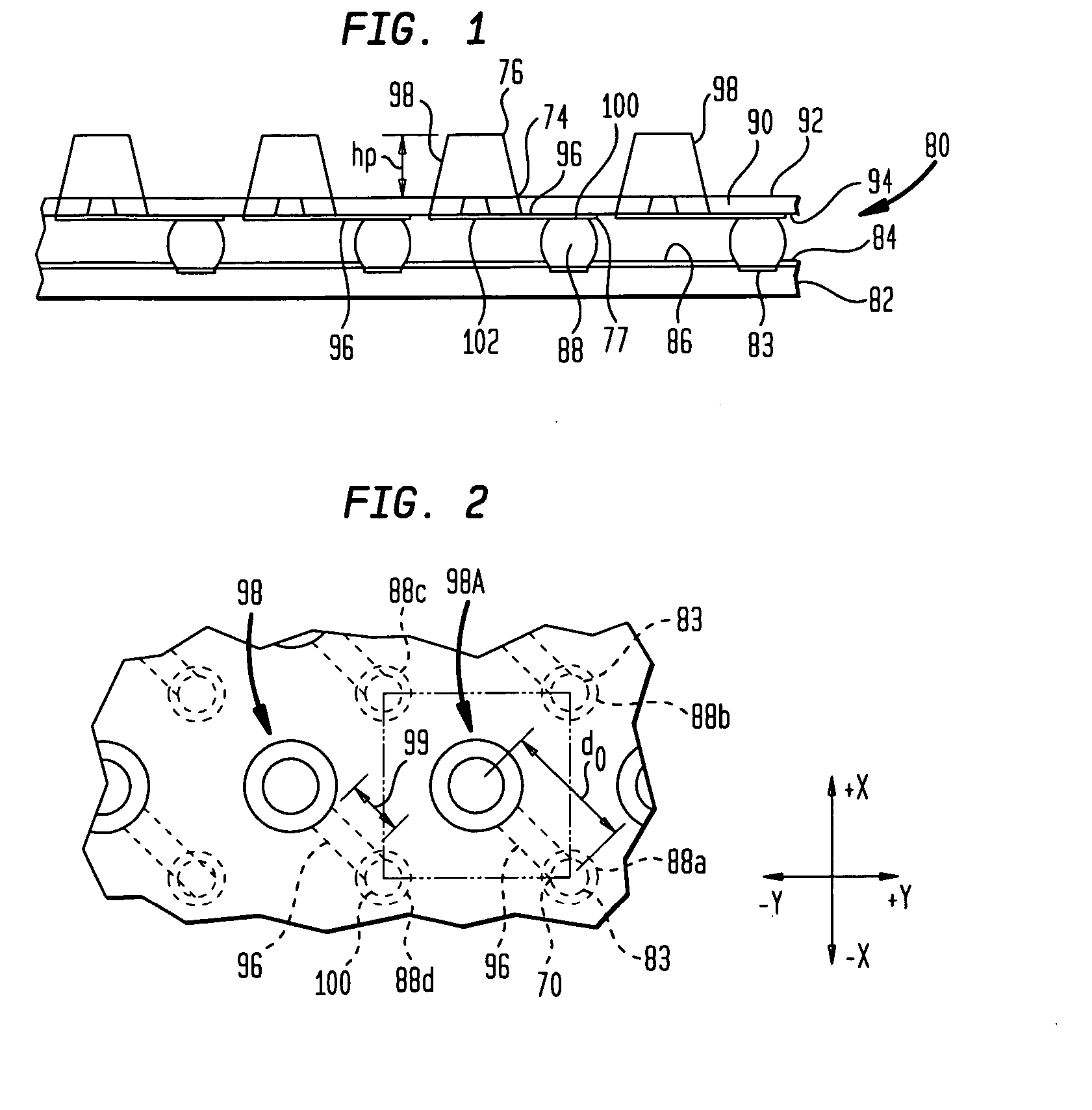

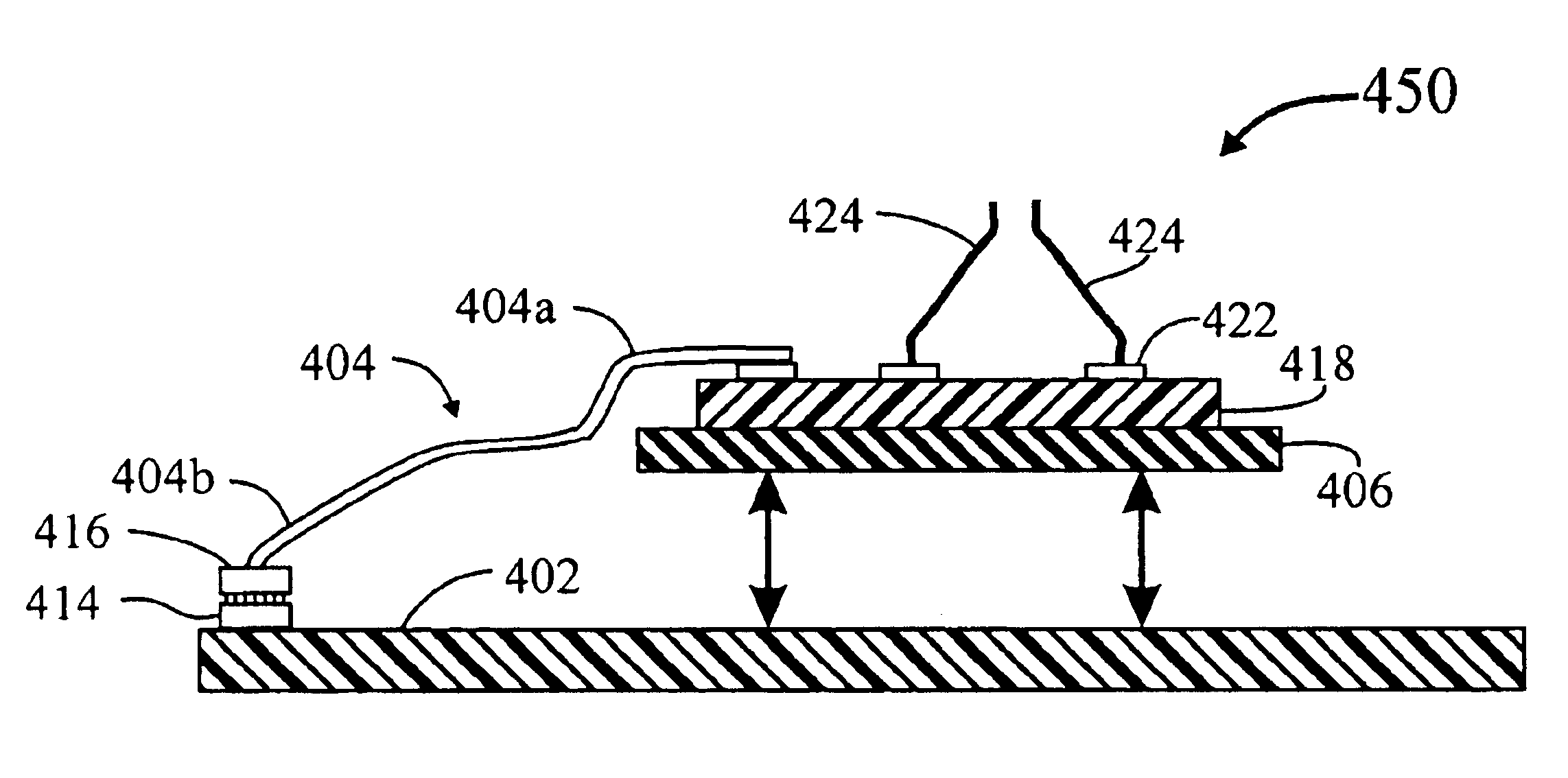

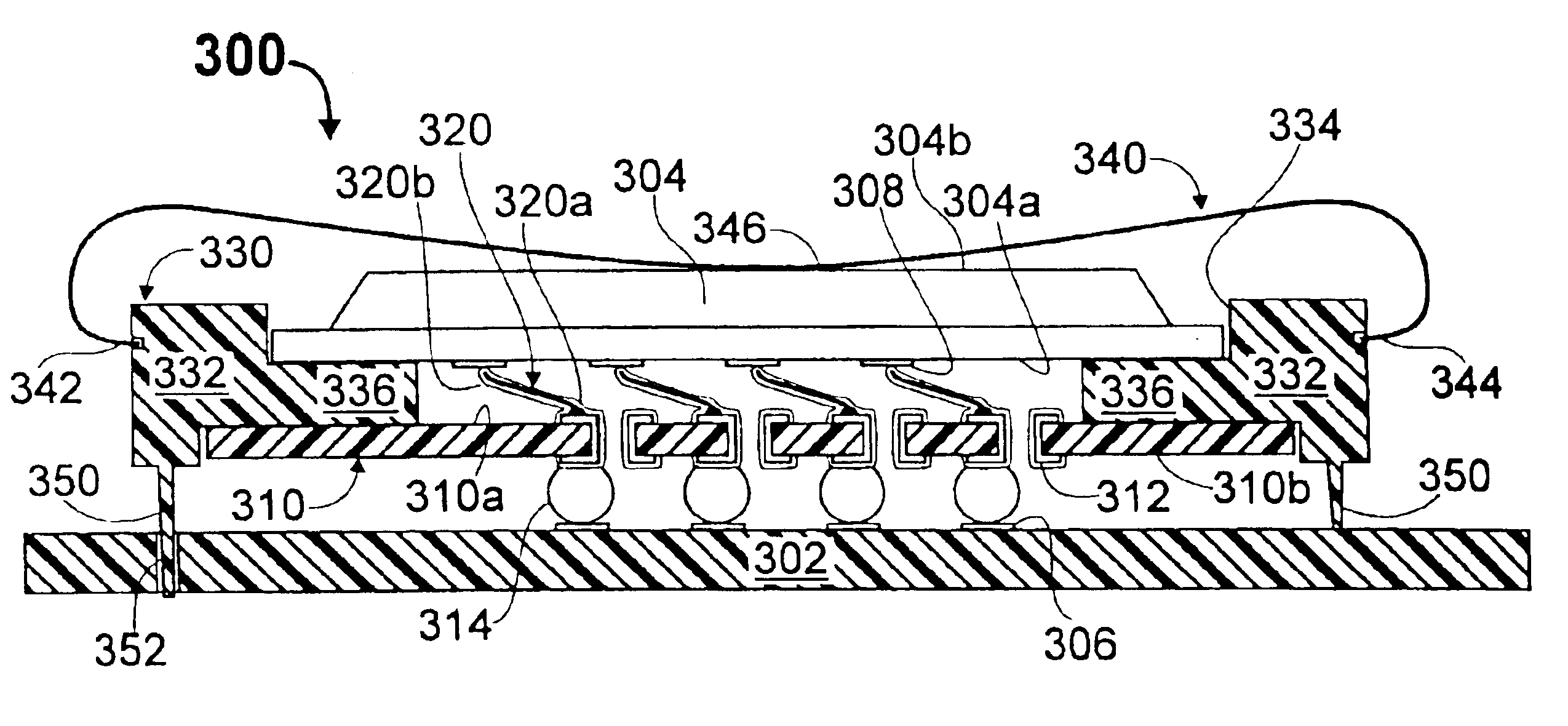

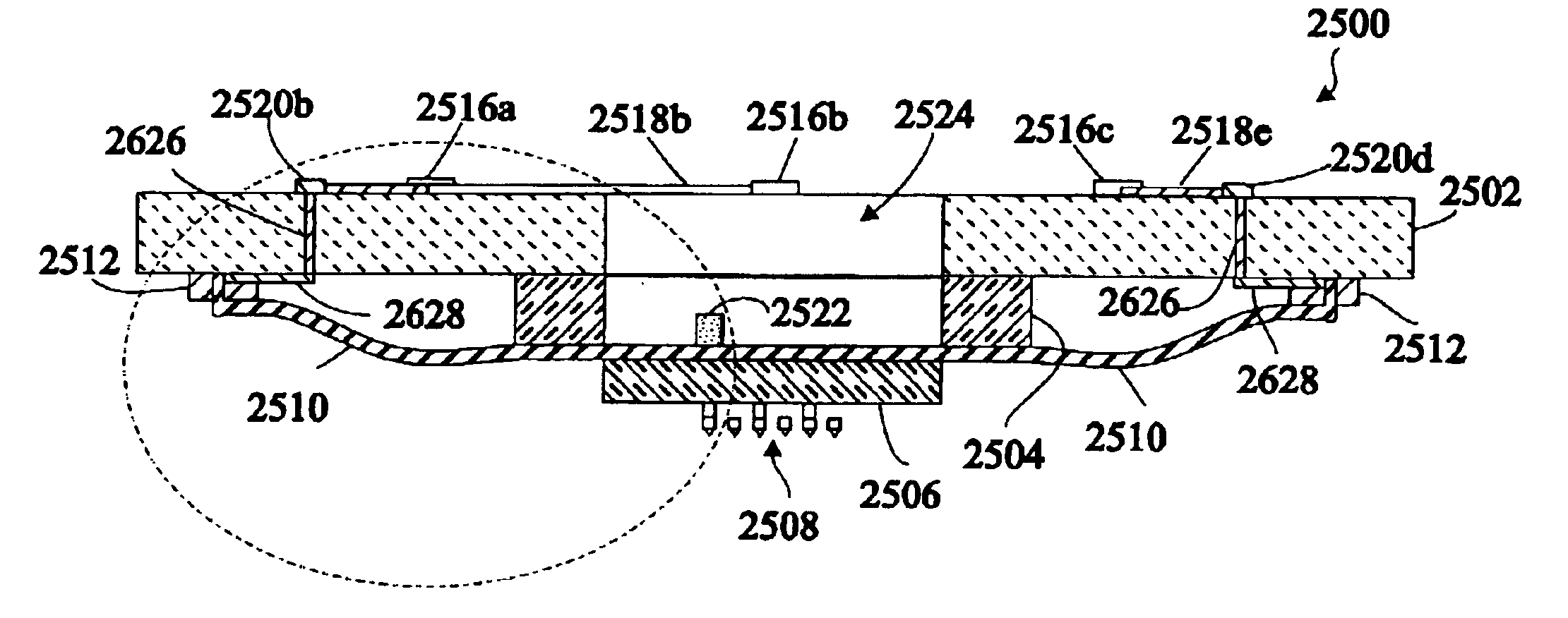

Microelectronic packages and methods therefor

ActiveUS20050181544A1Easy to testAvoid the needSemiconductor/solid-state device testing/measurementElectrical measurement instrument detailsEngineeringElectronic component

A microelectronic package includes a microelectronic element having faces and contacts and a flexible substrate spaced from and overlying a first face of the microelectronic element. The package also includes a plurality of conductive posts extending from the flexible substrate and projecting away from the first face of the microelectronic element, wherein at least some of the conductive posts are electrically interconnected with the microelectronic element, and a plurality of support elements supporting the flexible substrate over the microelectronic element. The conductive posts are offset from the support elements to facilitate flexure of the substrate and movement of the posts relative to the microelectronic element.

Owner:TESSERA INC

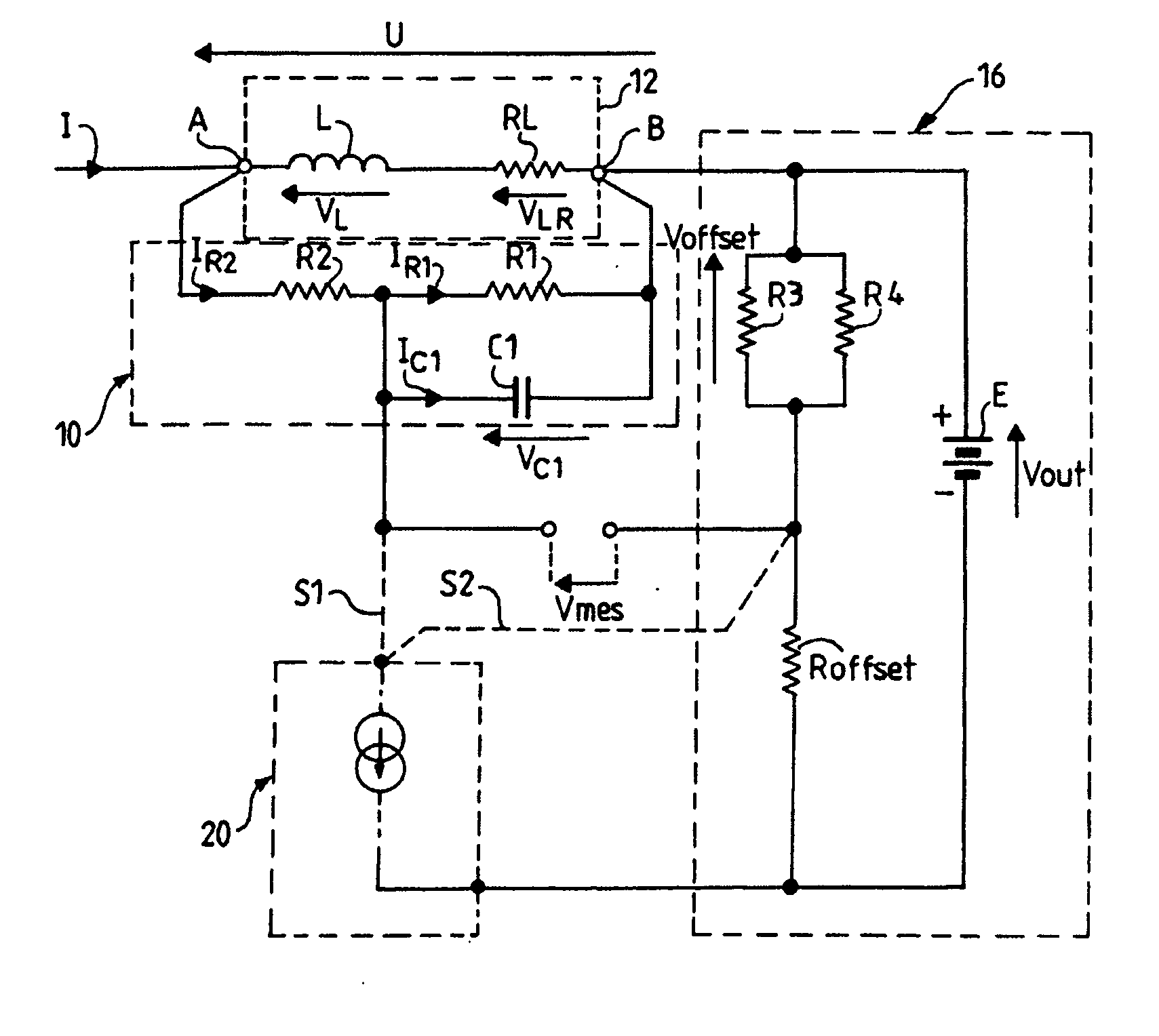

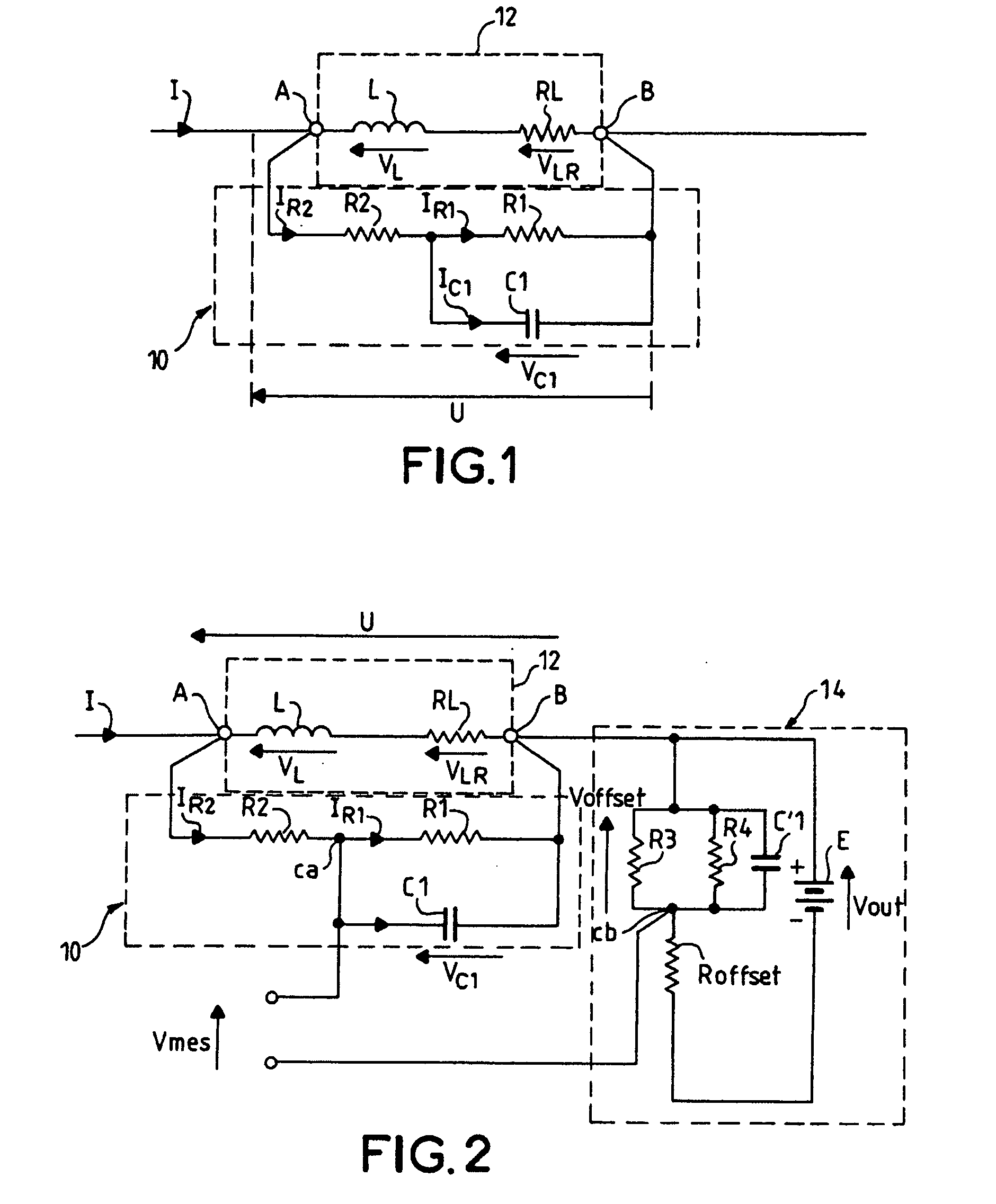

Device for non-dissipative measurement of the current in an inductor

ActiveUS20070075711A1The equipment is easy to operateHigh precisionResistance/reactance/impedenceElectrical measurement instrument detailsMeasurement deviceInductor

The invention relates to a device for measuring current in an inductor, which device is intended to be connected in parallel with said inductor, comprising two terminals A and B. The device comprises: a network in parallel with the inductor and connected to the terminals A and B having a resistor R2 in series with a resistor R1 in parallel with a capacitor C1; a voltage offset circuit having a DC voltage generator E connected in parallel with an offset resistor (Roffset) in series with two resistors in parallel R3 and R4, the positive pole of this voltage source being connected to terminal B of the inductor; a temperature compensation circuit comprising a current source controlled as a function of the temperature, one of the two terminals of the current source being connected to the negative pole of the generator E, the other terminal of the current source being connected to different points of the measurement device according to the direction of variation of the current of the source as a function of the temperature. The measurement of voltage Vmes, the image of the current I in the inductor 12, is performed between the common point between the resistors R1, R2 of the network and the common point between the offset resistor and the two resistors R3 and R4.

Owner:THALES SA

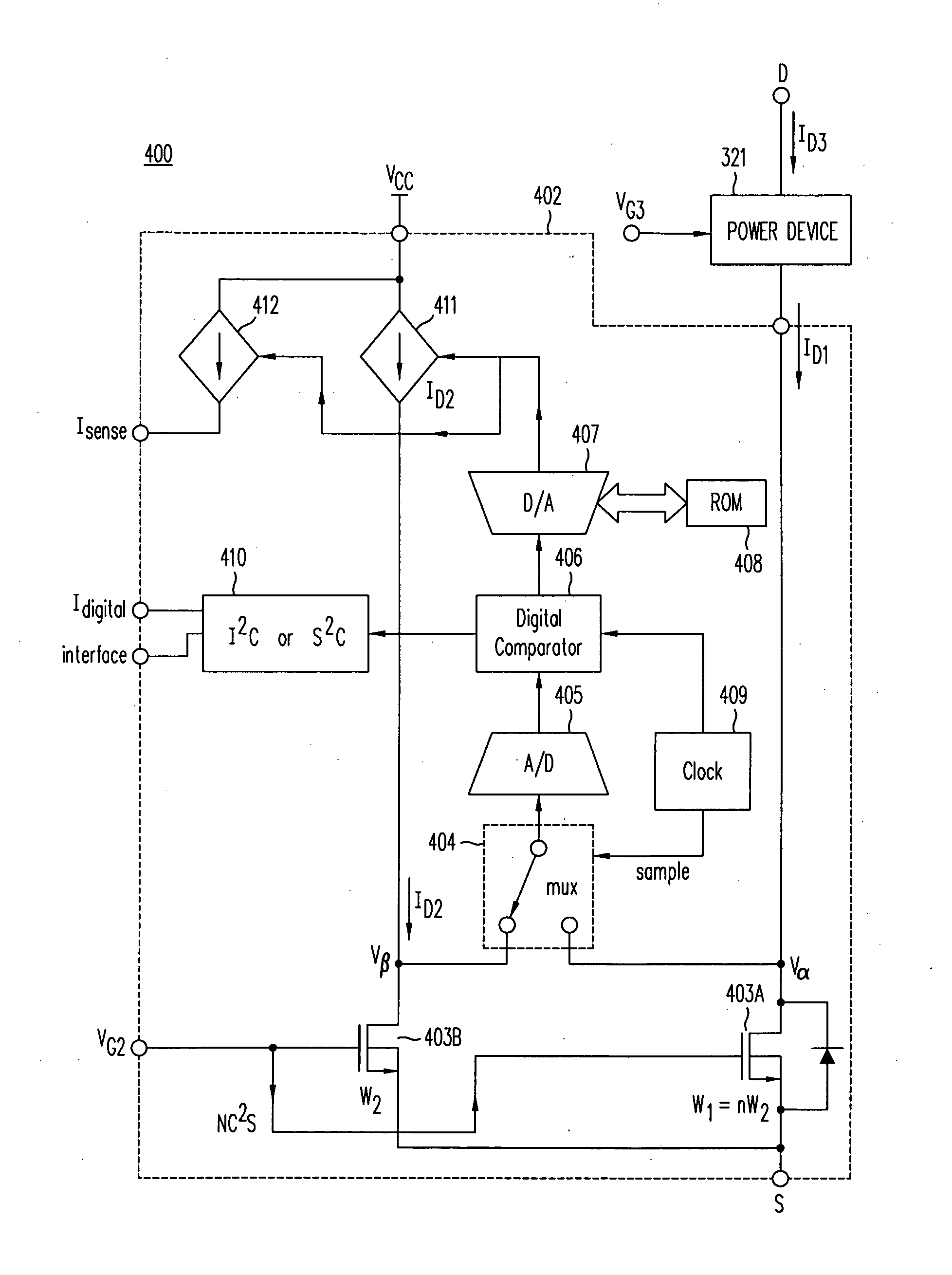

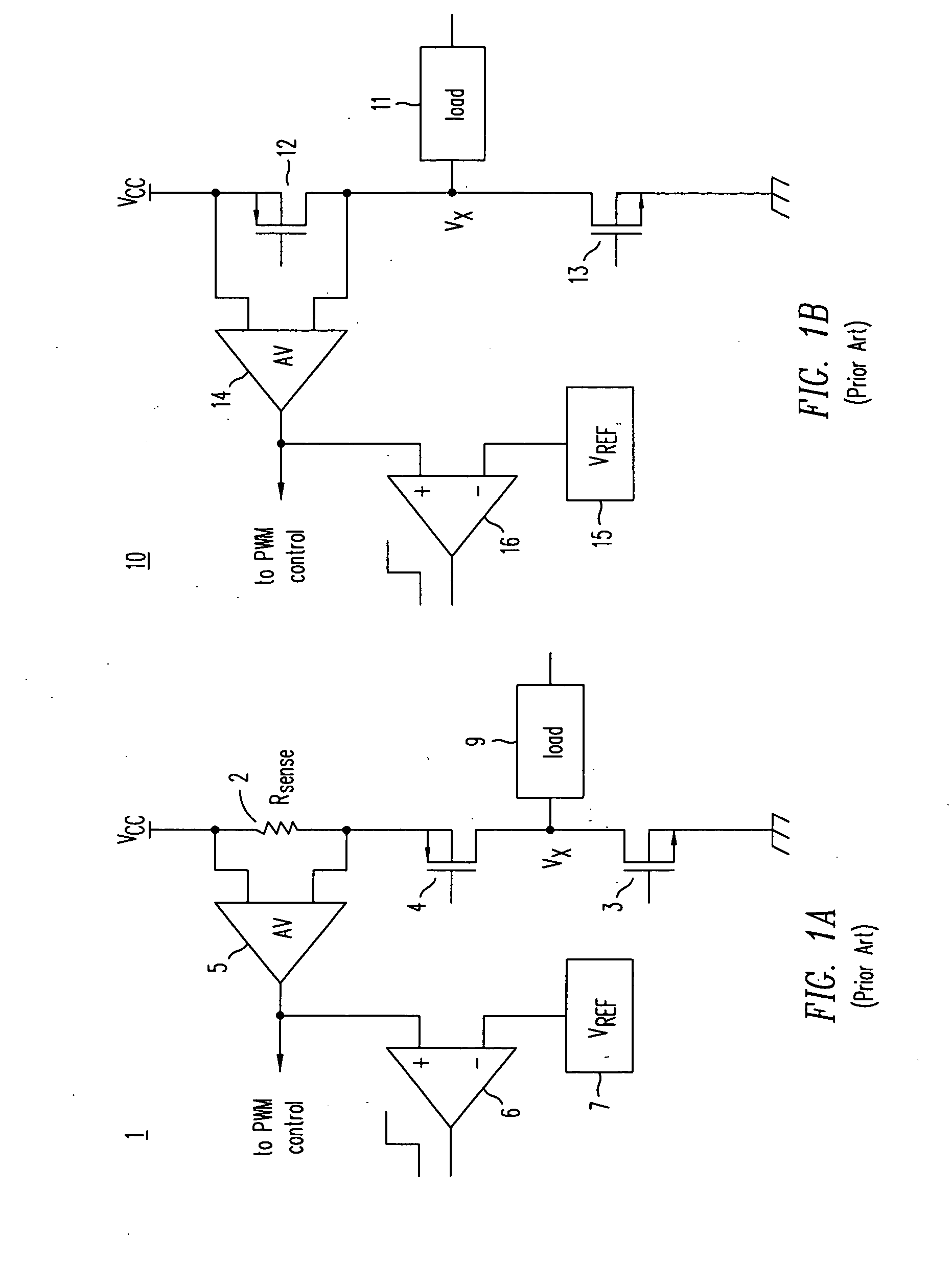

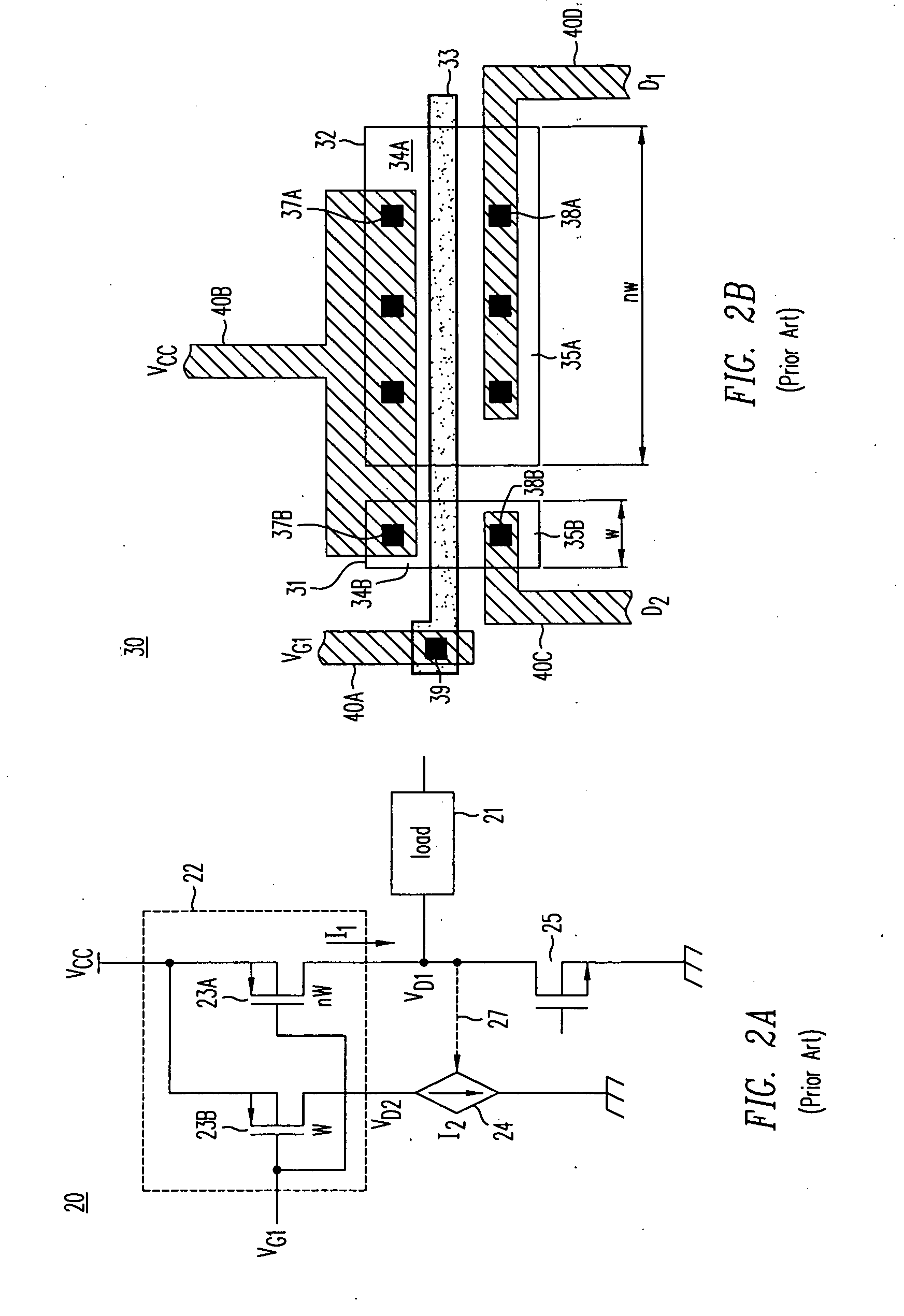

Cascode Current Sensor For Discrete Power Semiconductor Devices

InactiveUS20090039869A1Accurate detectionTransistorElectrical measurement instrument detailsMOSFETCascode

A cascode current sensor includes a main MOSFET and a sense MOSFET. The drain terminal of the main MOSFET is connected to a power device whose current is to be monitored, and the source and gate terminals of the main MOSFET are connected to the source and gate terminals, respectively, of the sense MOSFET. The drain voltages of the main and sense MOSFETs are equalized, in one embodiment by using a variable current source and negative feedback. The gate width of the main MOSFET is typically larger than the gate width of the sense MOSFET. Using the size ratio of the gate widths, the current in the main MOSFET is measured by sensing the magnitude of the current in the sense MOSFET. Inserting the relatively large MOSFET in the power circuit minimizes power loss.

Owner:ADVANCED ANALOGIC TECHNOLOGIES INCORPORATED

Method of making a product with improved material properties by moderate heat-treatment of a metal incorporating a dilute additive

InactiveUS6150186AStable mechanical propertiesImprove conductivitySemiconductor/solid-state device testing/measurementFinal product manufactureUltimate tensile strengthMechanical property

Deposition of metal in a preferred shape, including coatings on parts, or stand-alone materials, and subsequent heat treatment to provide improved mechanical properties. In particular, the method gives products with relatively high yield strength. The products often have relatively high elastic modulus, and are thermally stable, maintaining the high yield strength at temperatures considerably above 25 DEG C. This technique involves depositing a material in the presence of a selected additive, and then subjecting the deposited material to a moderate heat treatment. This moderate heat treatment differs from other commonly employed "stress relief" heat treatments in using lower temperatures and / or shorter times, preferably just enough to reorganize the material to the new, desired form. Coating a shape and heat treating provides a shaped deposit with improved material properties. Coating a shape with a portion connected to a base and a portion detached therefrom can provide a resilient, conductive contact useful for electronic applications.

Owner:FORMFACTOR INC

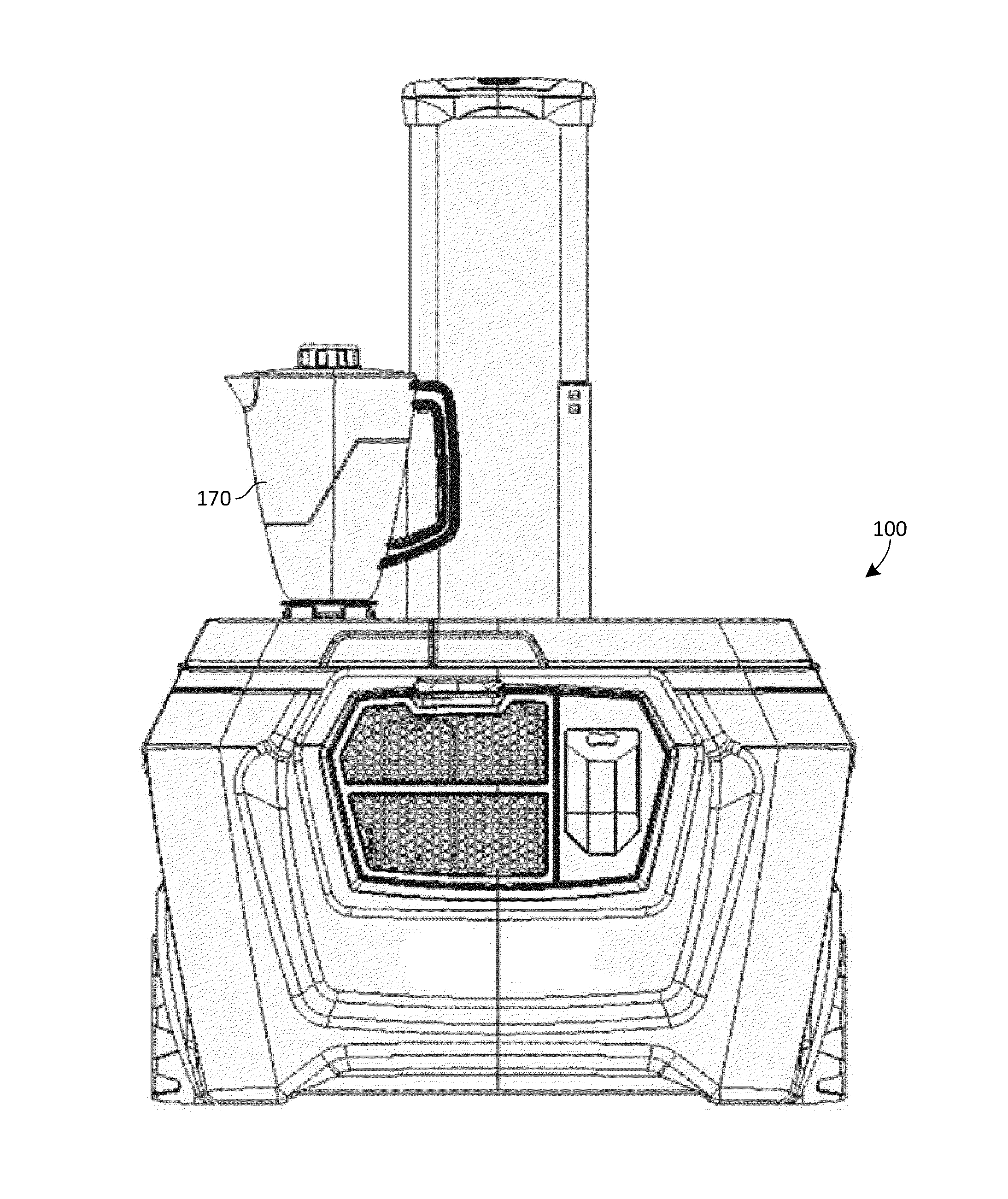

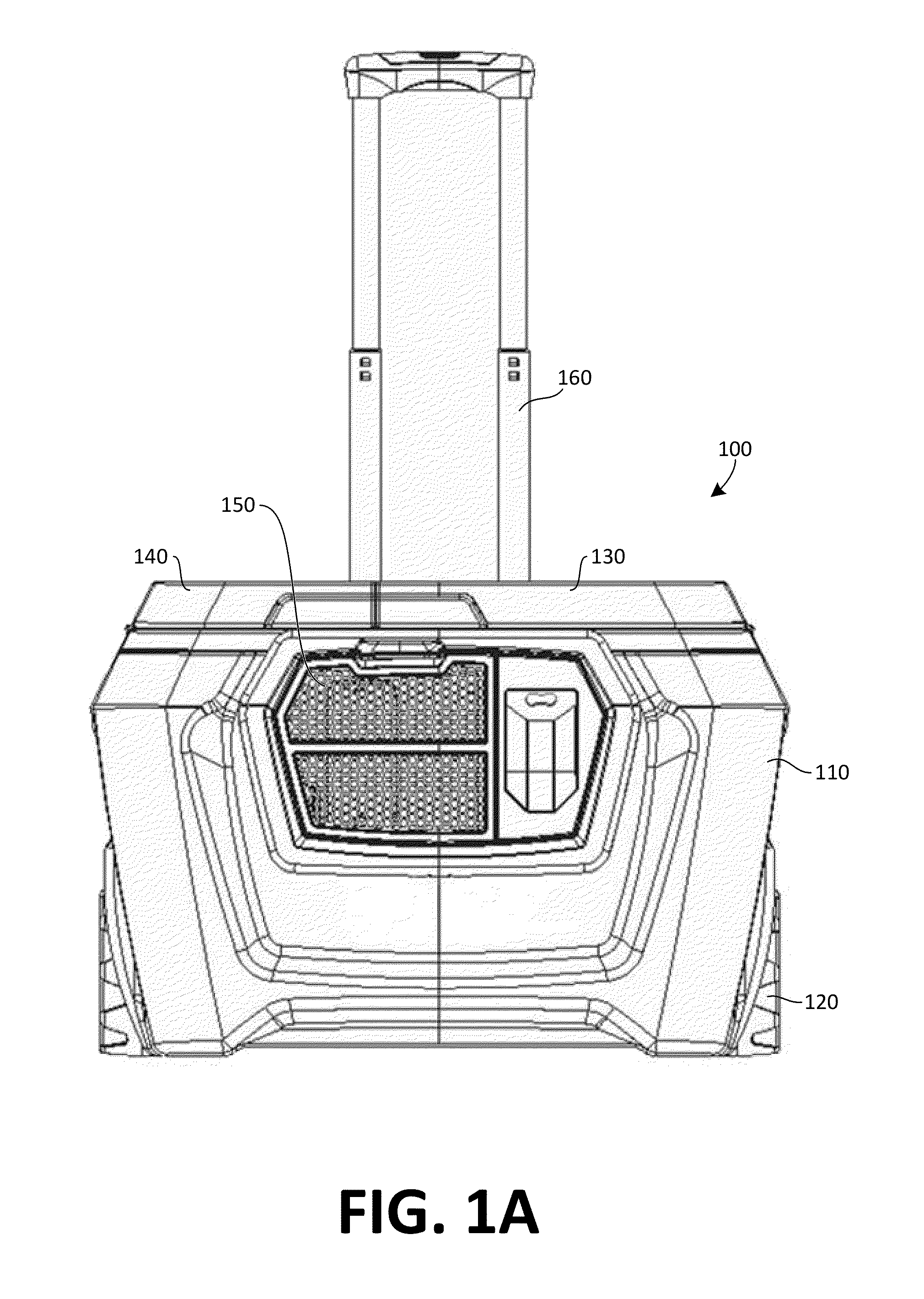

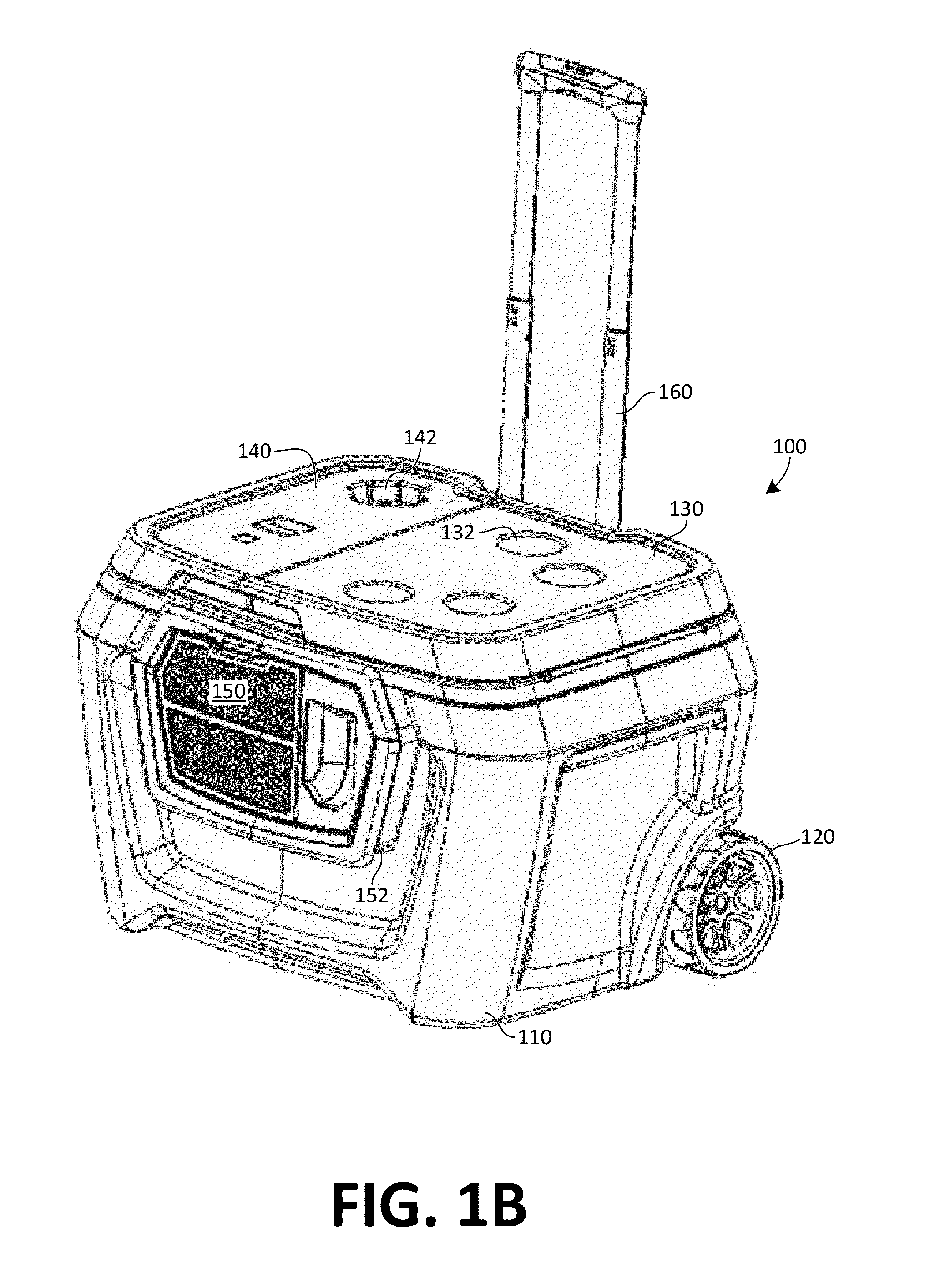

Cooler having integrated blender and accessories

A portable cooler includes an insulated body that defines a main interior storage space, and a lid structured to at least partially cover the main interior storage space. The lid includes an integrated blender or an integrated blender drive. Components of the blender may include a source of electrical power, an electric motor, and a blender spindle mounted through a surface of the lid and coupled to the electric motor. The integrated blender may also include a blender jar structured to hold food items for blending and one or more blending blades. The lid may further include a blender recess shaped in a negative mold of a collar of the blender jar to prevent the blender jar from rotating during operation.

Owner:GREPPER RYAN

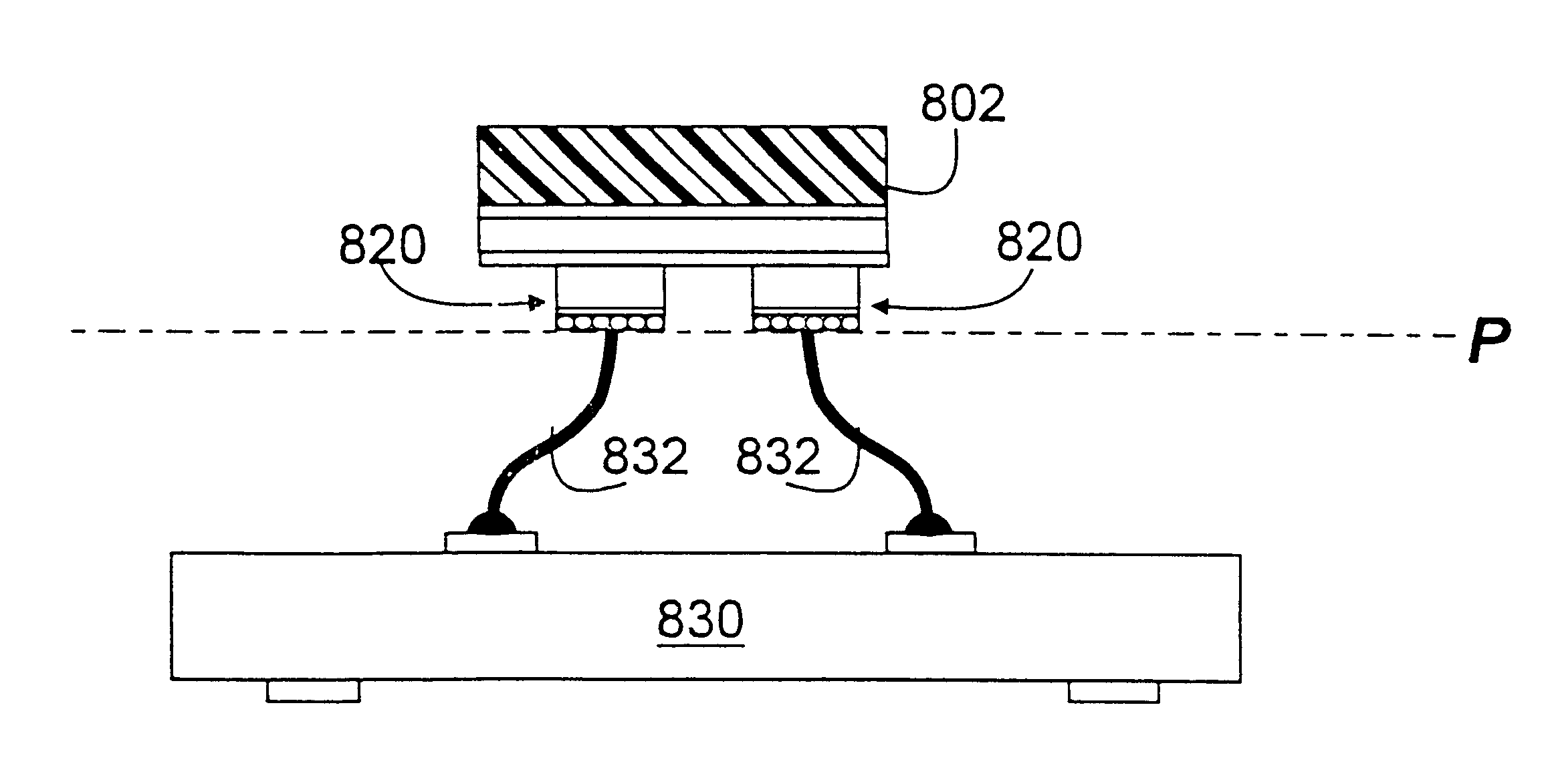

Probe card assembly

InactiveUS6838893B2Easy to disassembleEffective shieldingSemiconductor/solid-state device testing/measurementFinal product manufactureProbe cardTransformer

In a probe card assembly, a series of probe elements can be arrayed on a silicon space transformer. The silicon space transformer can be fabricated with an array of primary contacts in a very tight pitch, comparable to the pitch of a semiconductor device. One preferred primary contact is a resilient spring contact. Conductive elements in the space transformer are routed to second contacts at a more relaxed pitch. In one preferred embodiment, the second contacts are suitable for directly attaching a ribbon cable, which in turn can be connected to provide selective connection to each primary contact. The silicon space transformer is mounted in a fixture that provides for resilient connection to a wafer or device to be tested. This fixture can be adjusted to planarize the primary contacts with the plane of a support probe card board.

Owner:FORMFACTOR INC

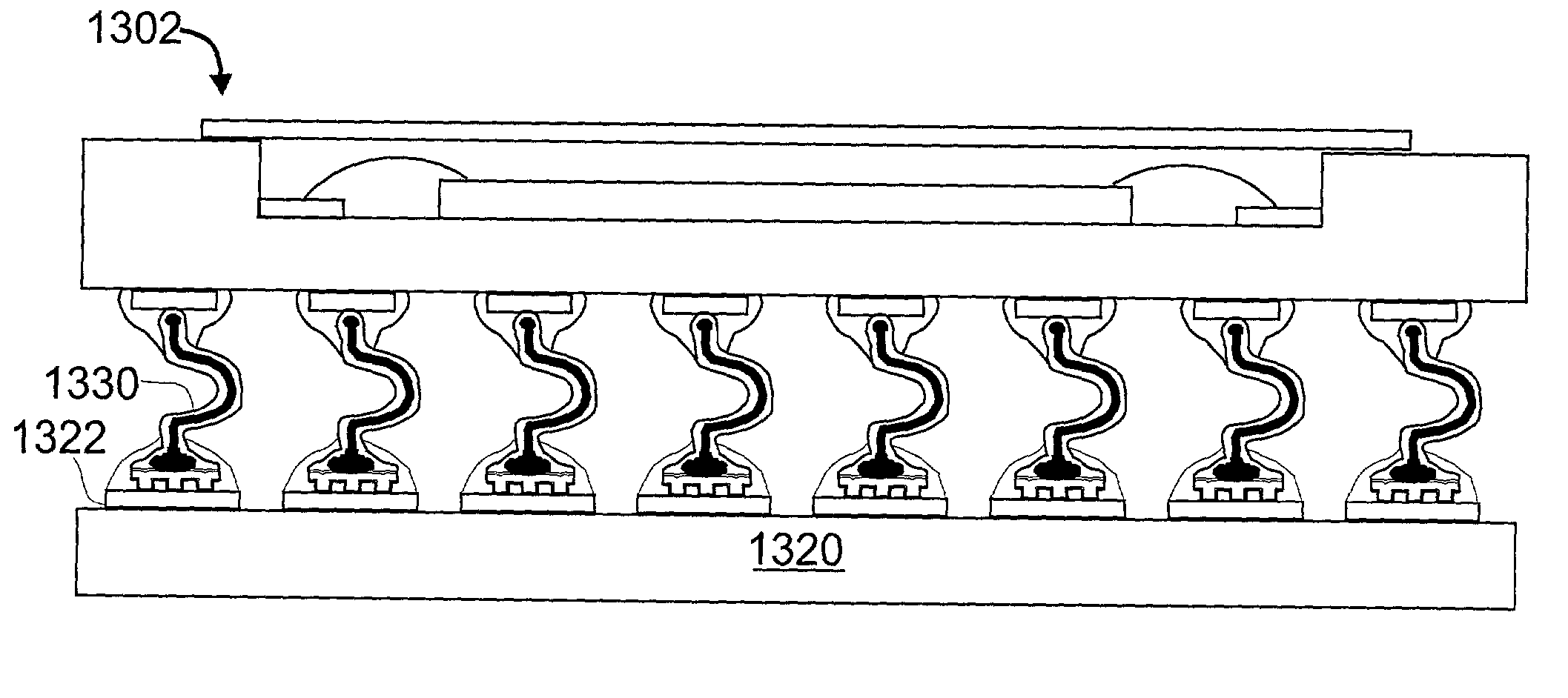

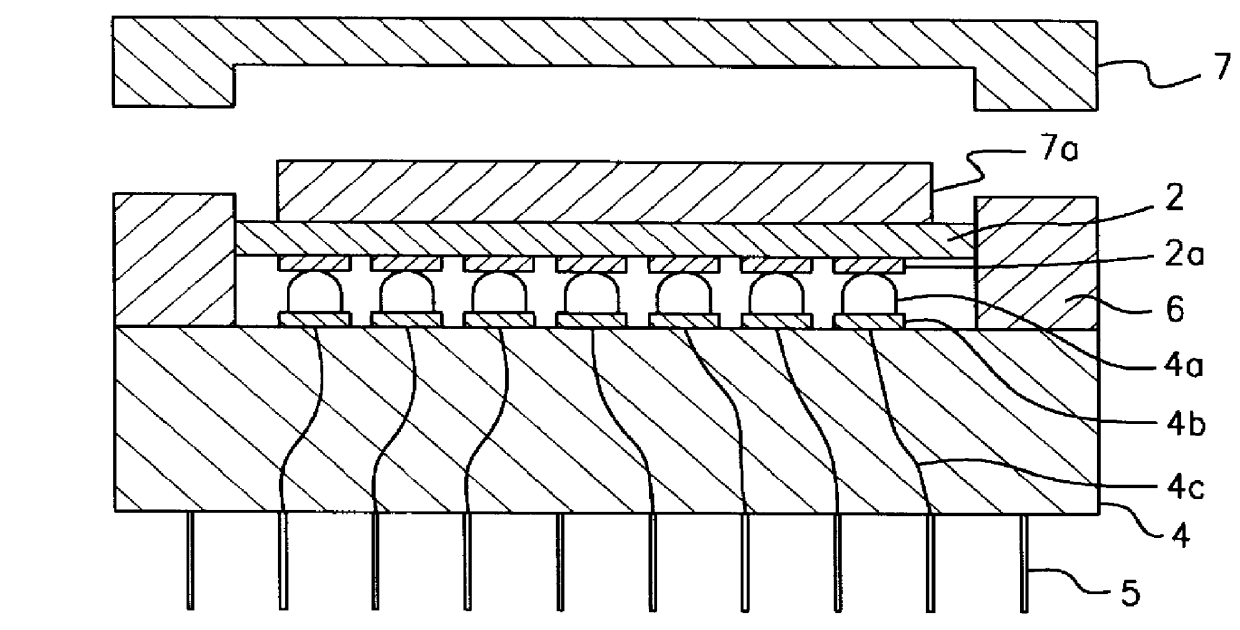

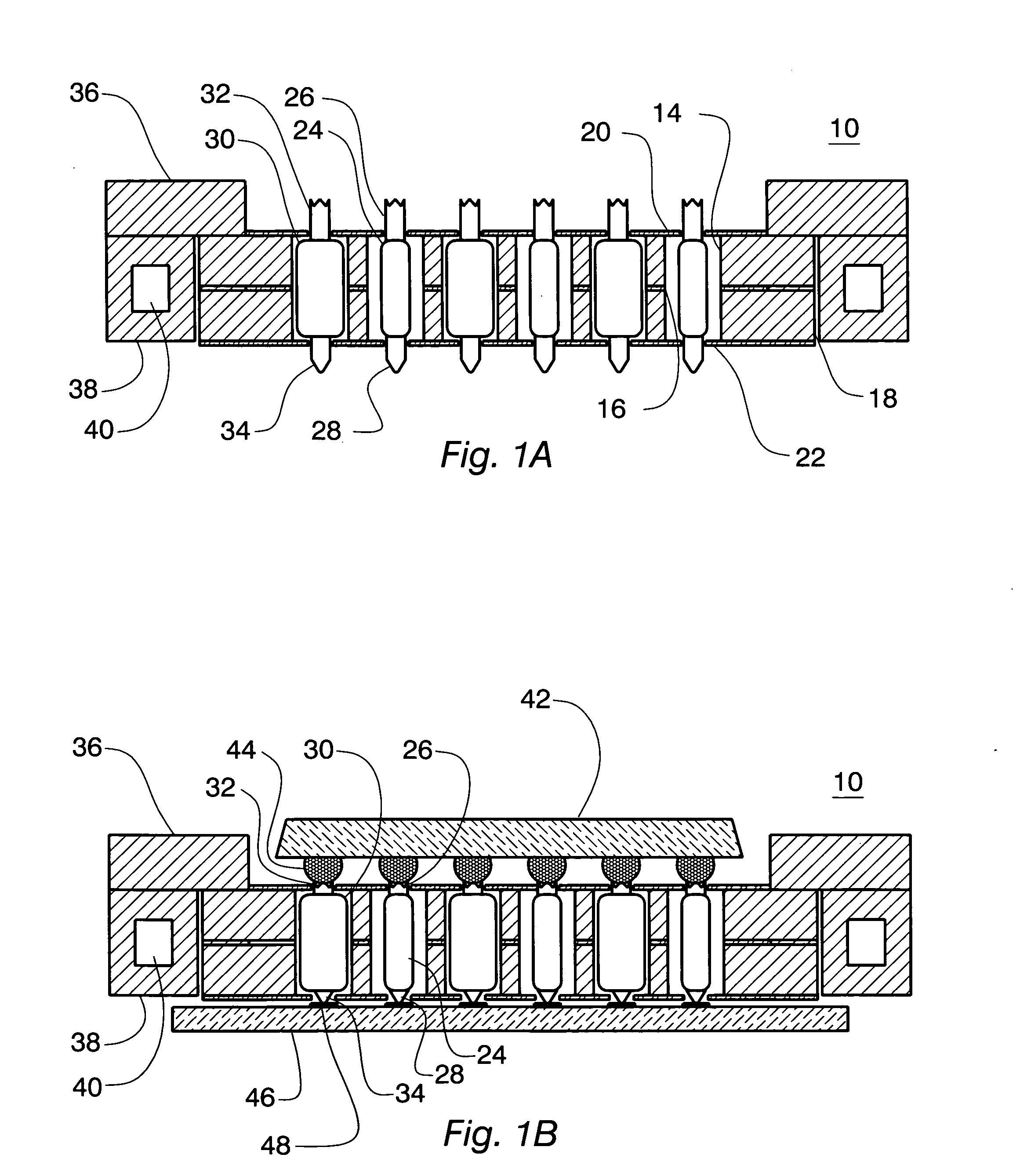

Methods of removably mounting electronic components to a circuit board, and sockets formed by the methods

InactiveUS6913468B2Easy to disassembleEffective shieldingSemiconductor/solid-state device testing/measurementFinal product manufactureSurface mountingSolder ball

Surface-mount, solder-down sockets are described which permit electronic components such as semiconductor packages to be releasably mounted to a circuit board. Generally, the socket includes resilient contact structures extending from a top surface of a support substrate, and solder-ball (or other suitable) contact structures disposed on a bottom surface of the support substrate. Composite interconnection elements are described for use as the resilient contact structures disposed atop the support substrate. In use, the support substrate is soldered down onto the circuit board, the contact structures on the bottom surface of the support substrate contacting corresponding contact areas on the circuit board. In any suitable manner, selected ones of the resilient contact structures atop the support substrate are connected, via the support substrate, to corresponding ones of the contact structures on the bottom surface of the support substrate.

Owner:FORMFACTOR INC

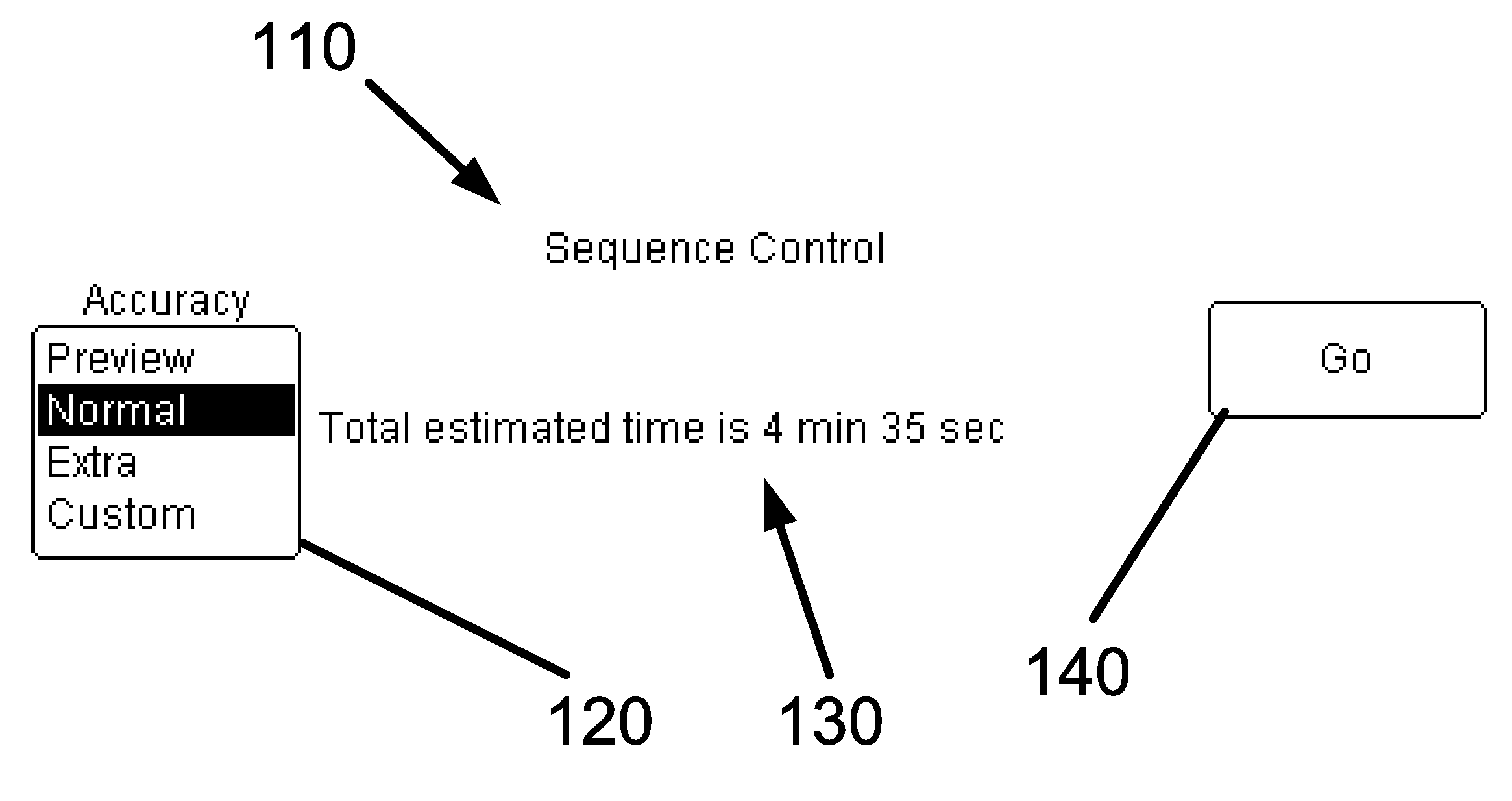

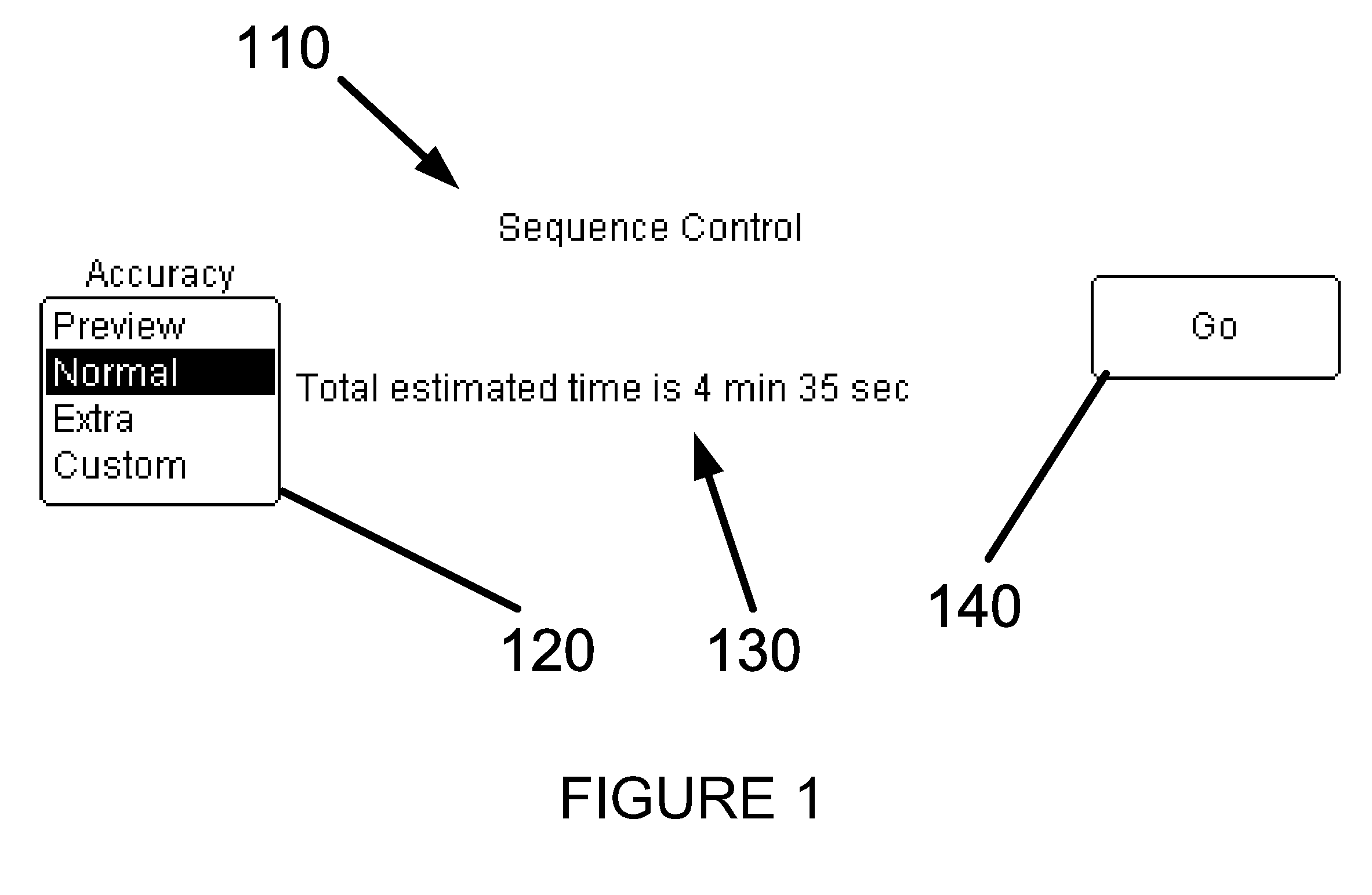

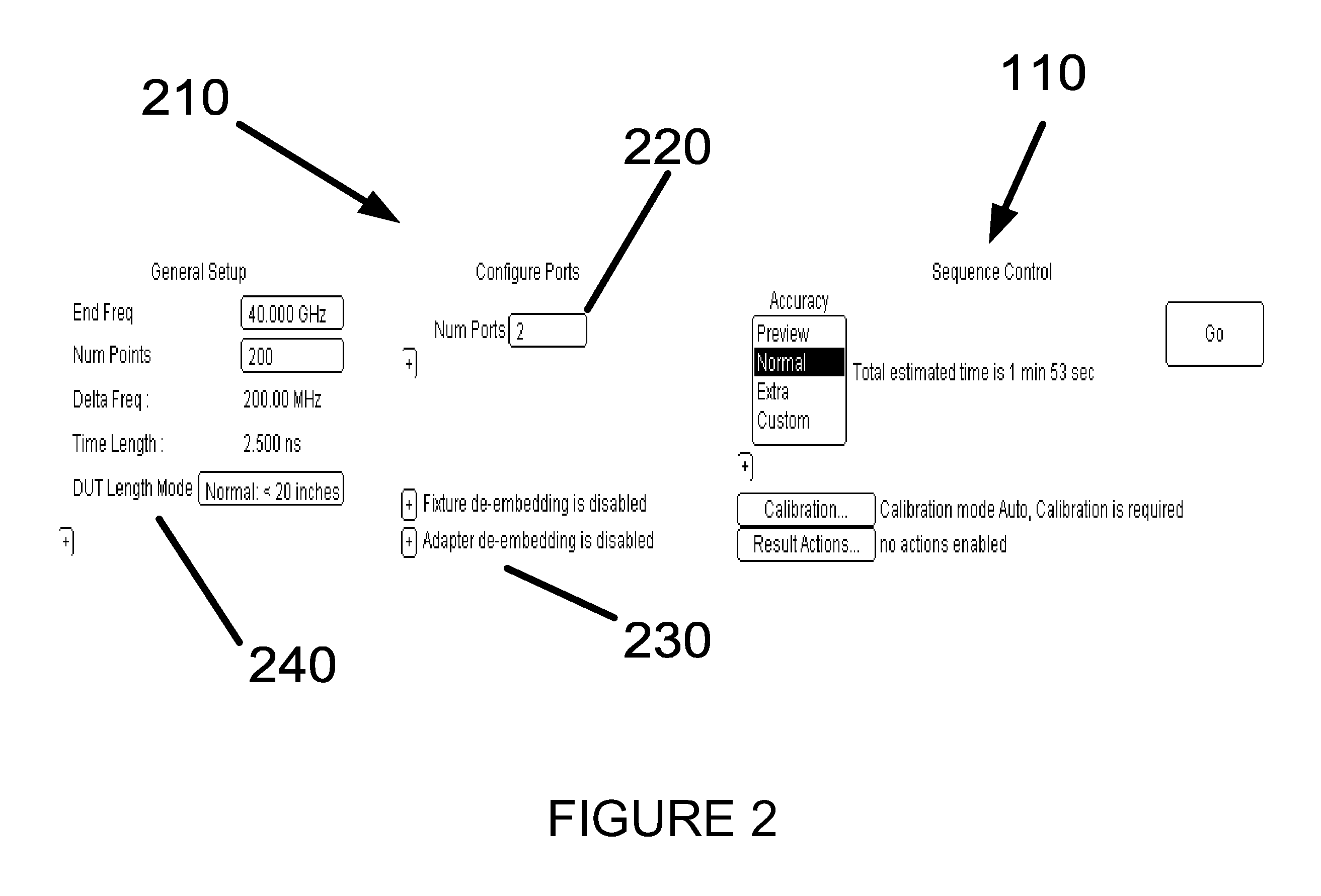

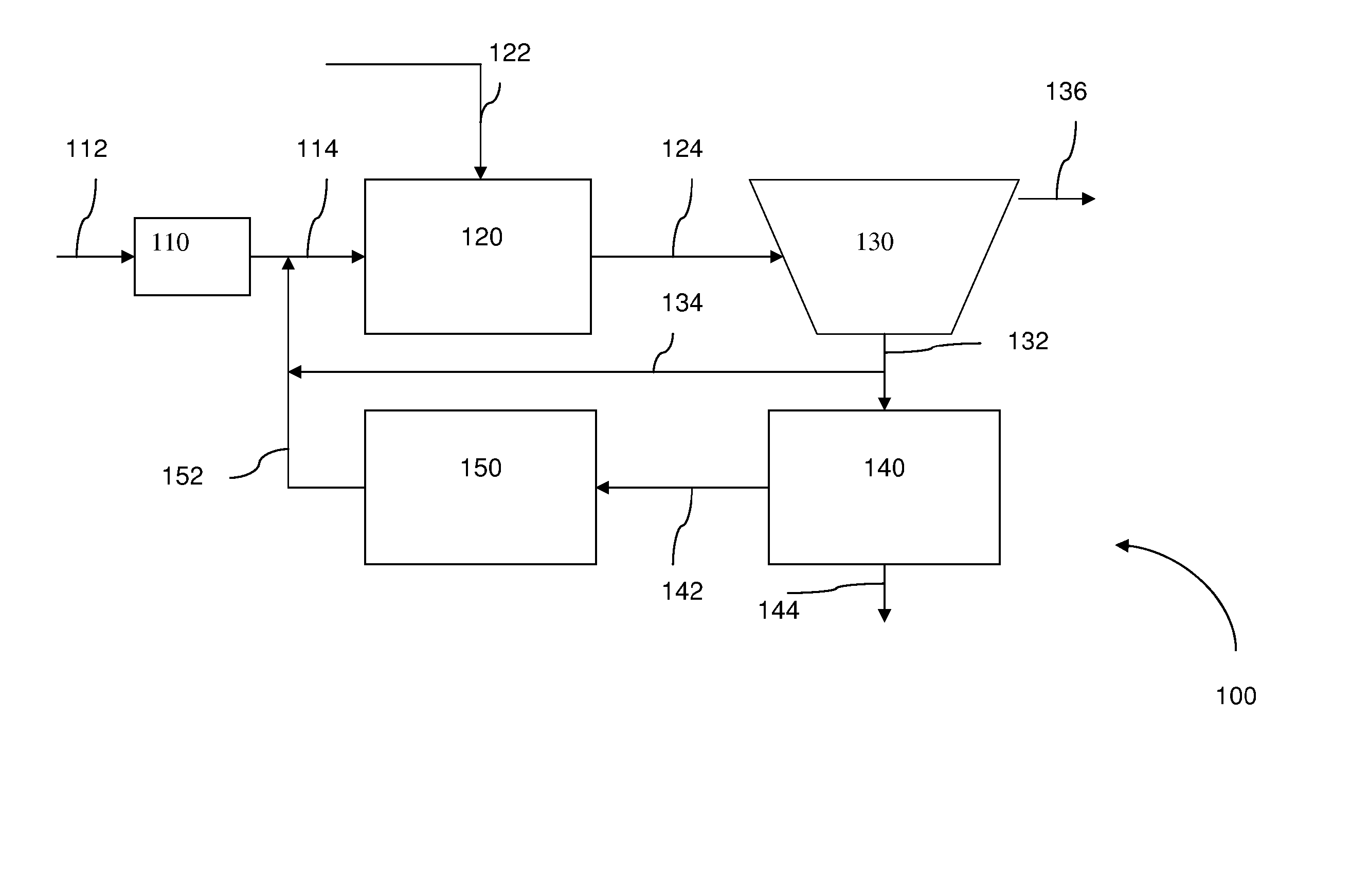

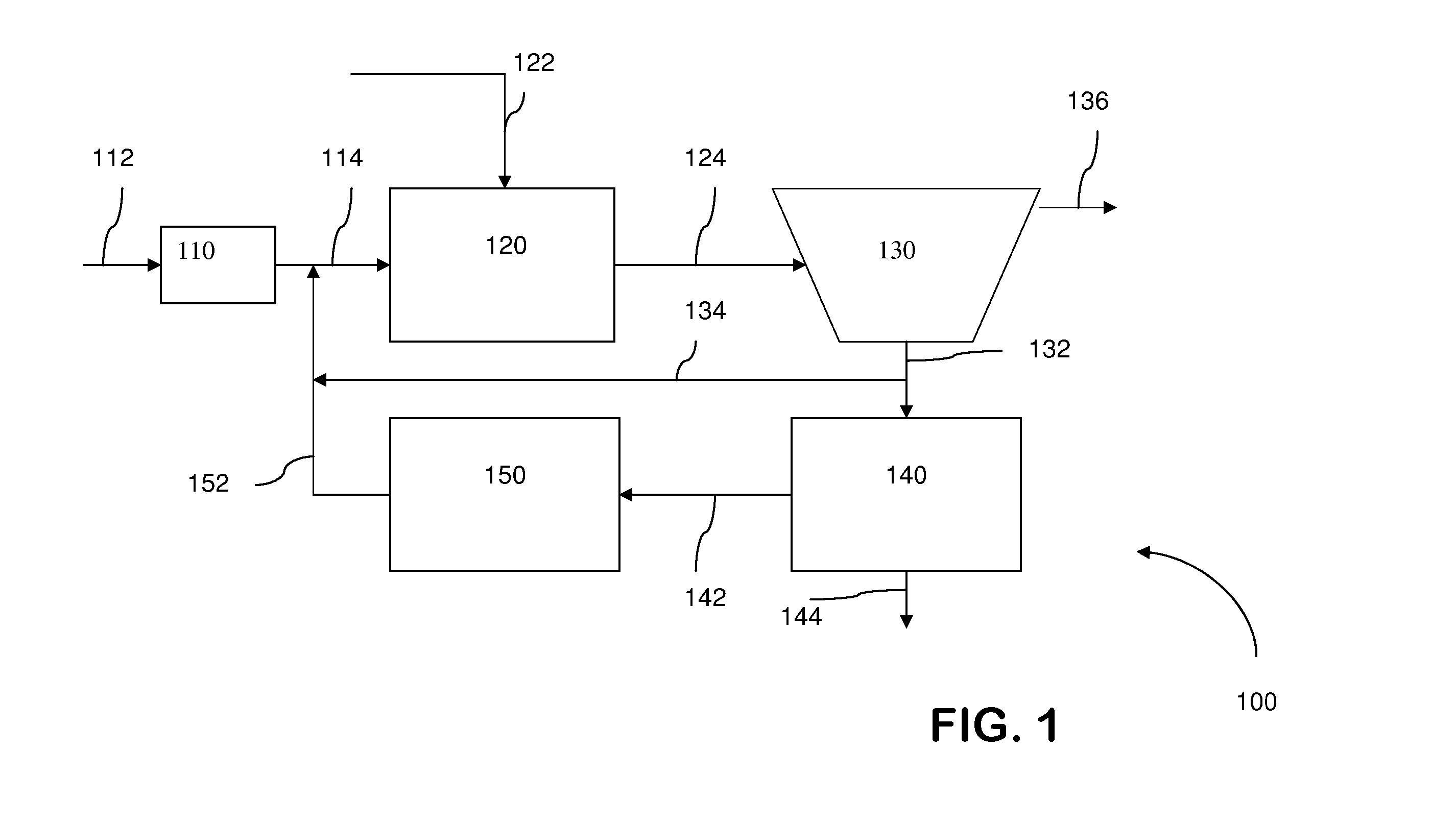

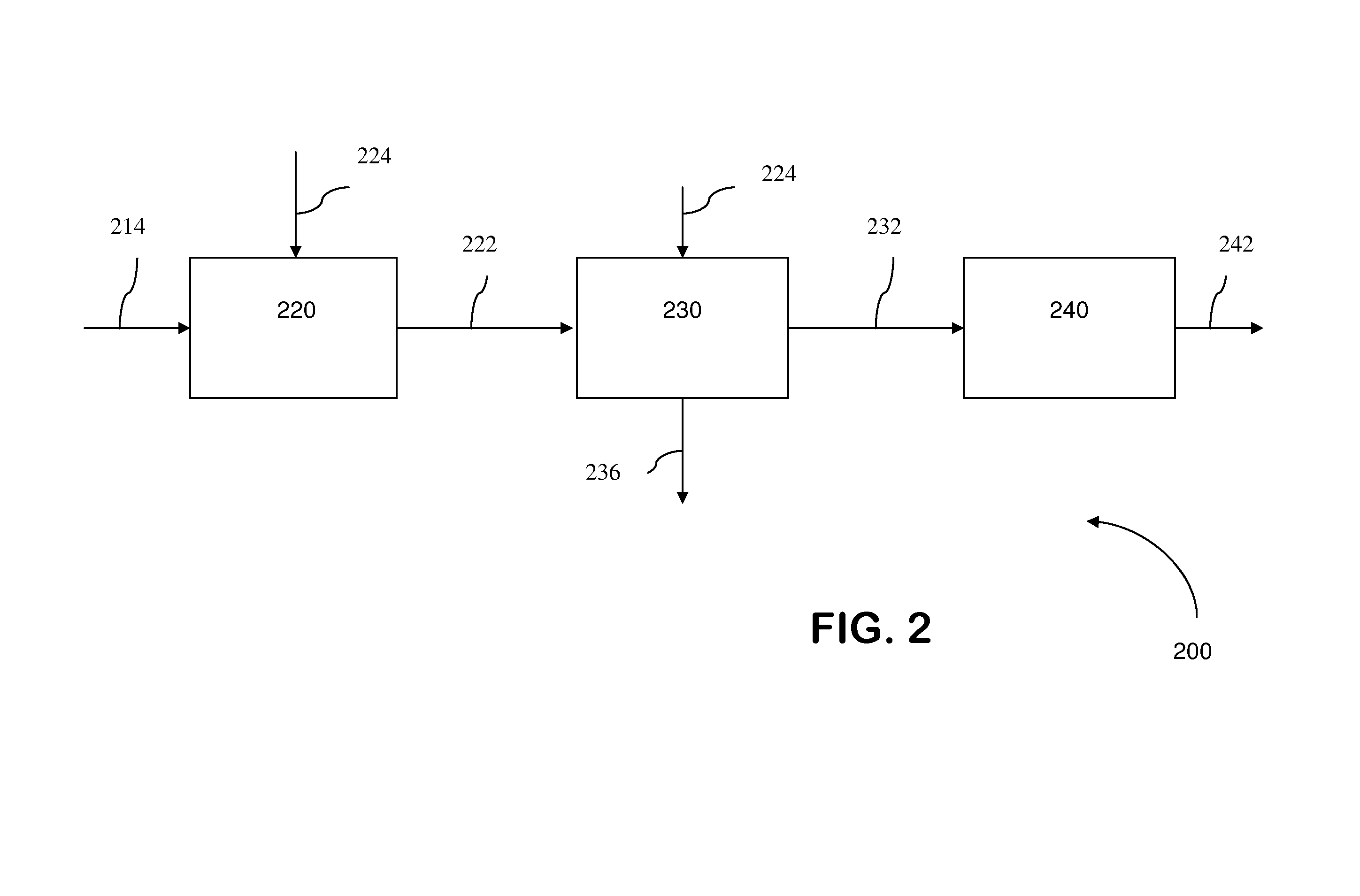

User Interface for Signal Integrity Network Analyzer

InactiveUS20110286506A1Easy to implementImprove user experienceResistance/reactance/impedenceElectrical measurement instrument detailsComputer scienceUser interface

A signal integrity network analyzer is provided. The analyzer preferably includes a characterization module for characterizing a device under test, an acquisition module for acquiring a waveform, a de-embedding module for selectively embedding and de-embedding on or more system fixtures, and an analysis module for performing analysis on the acquired waveform, with one or more system features selectively embedded or de-embedded. A single user interface is provided and is adapted to control the characterization module, the acquisition module, the de-embedding module and the analysis module.

Owner:TELEDYNE LECROY

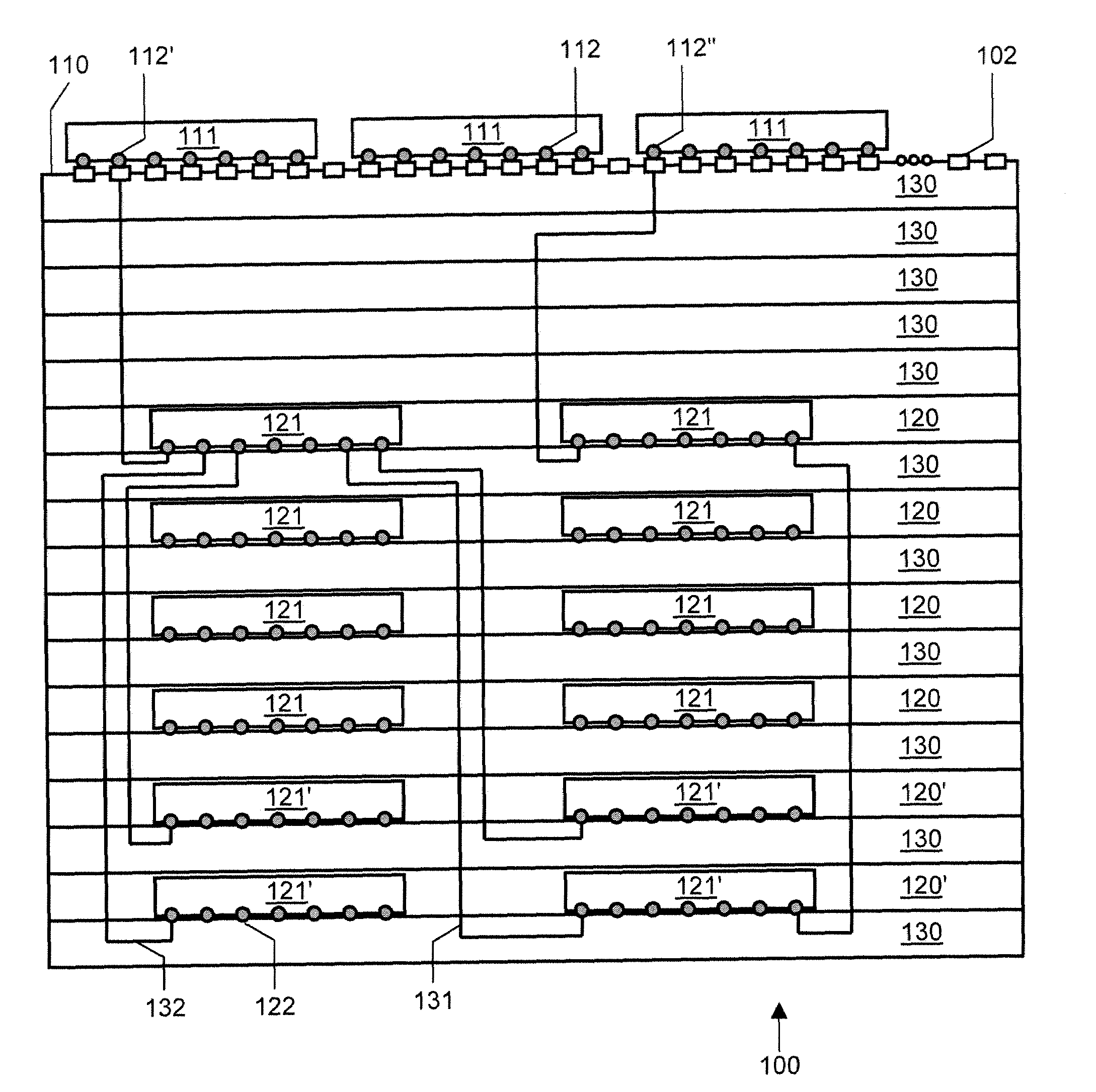

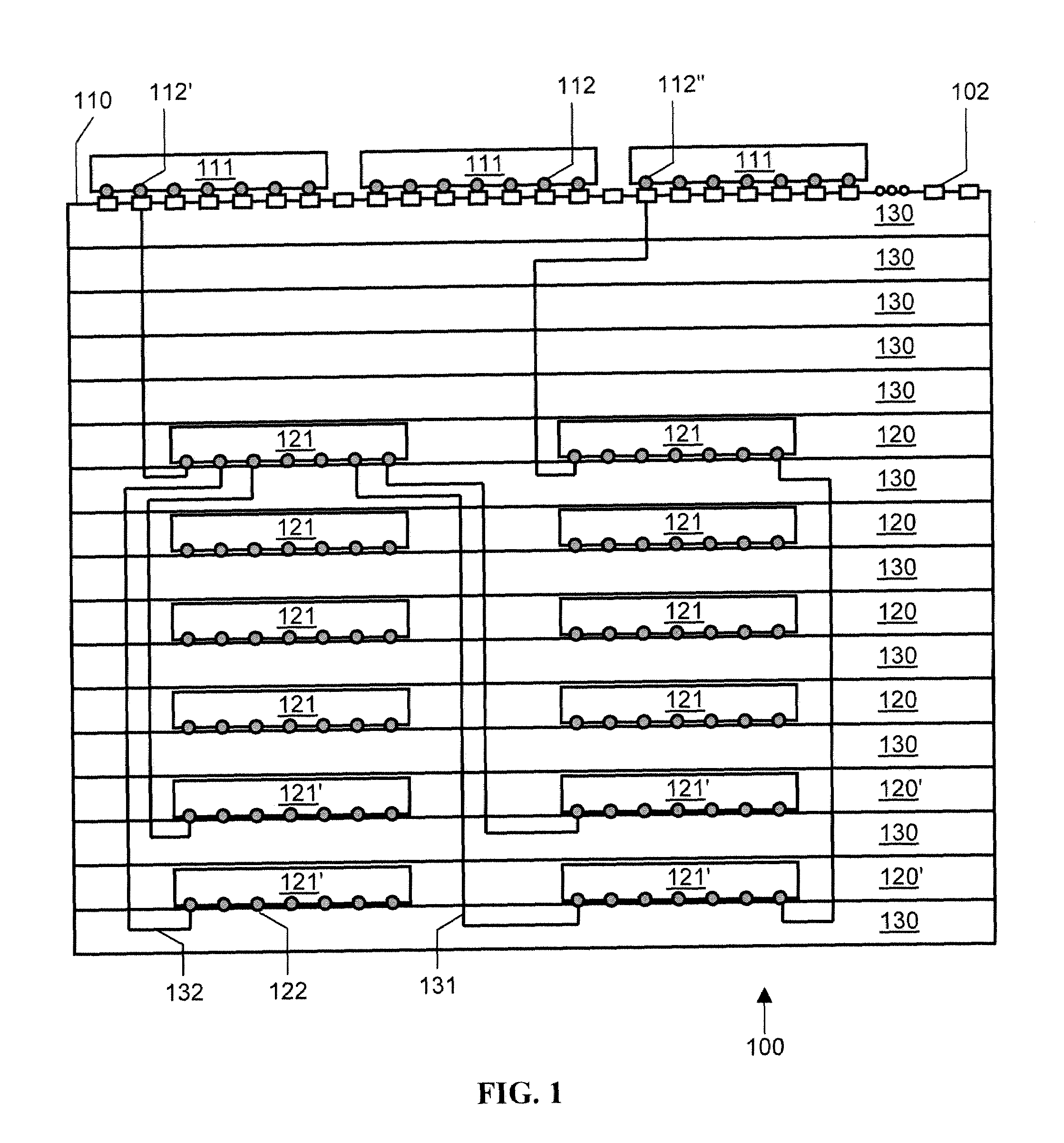

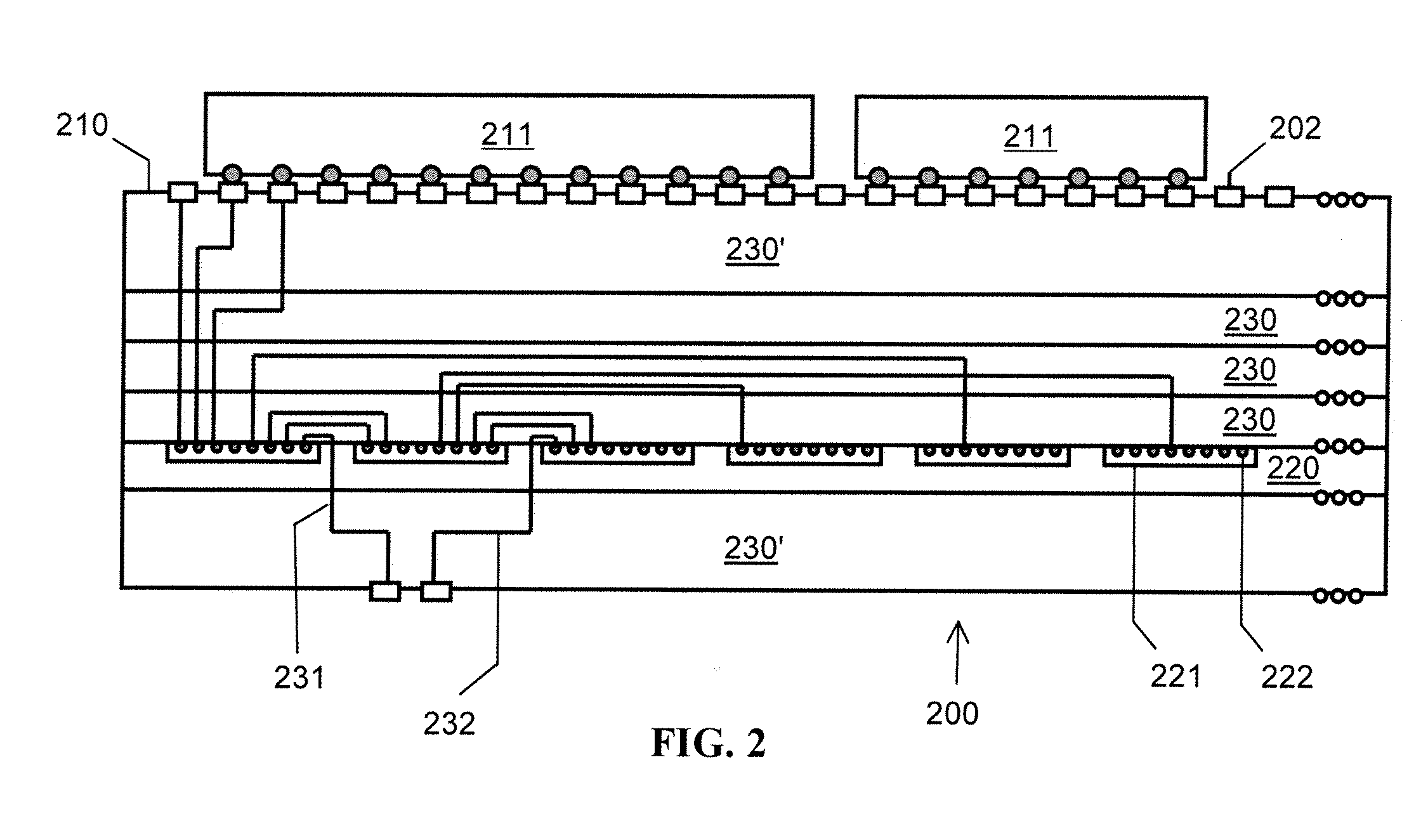

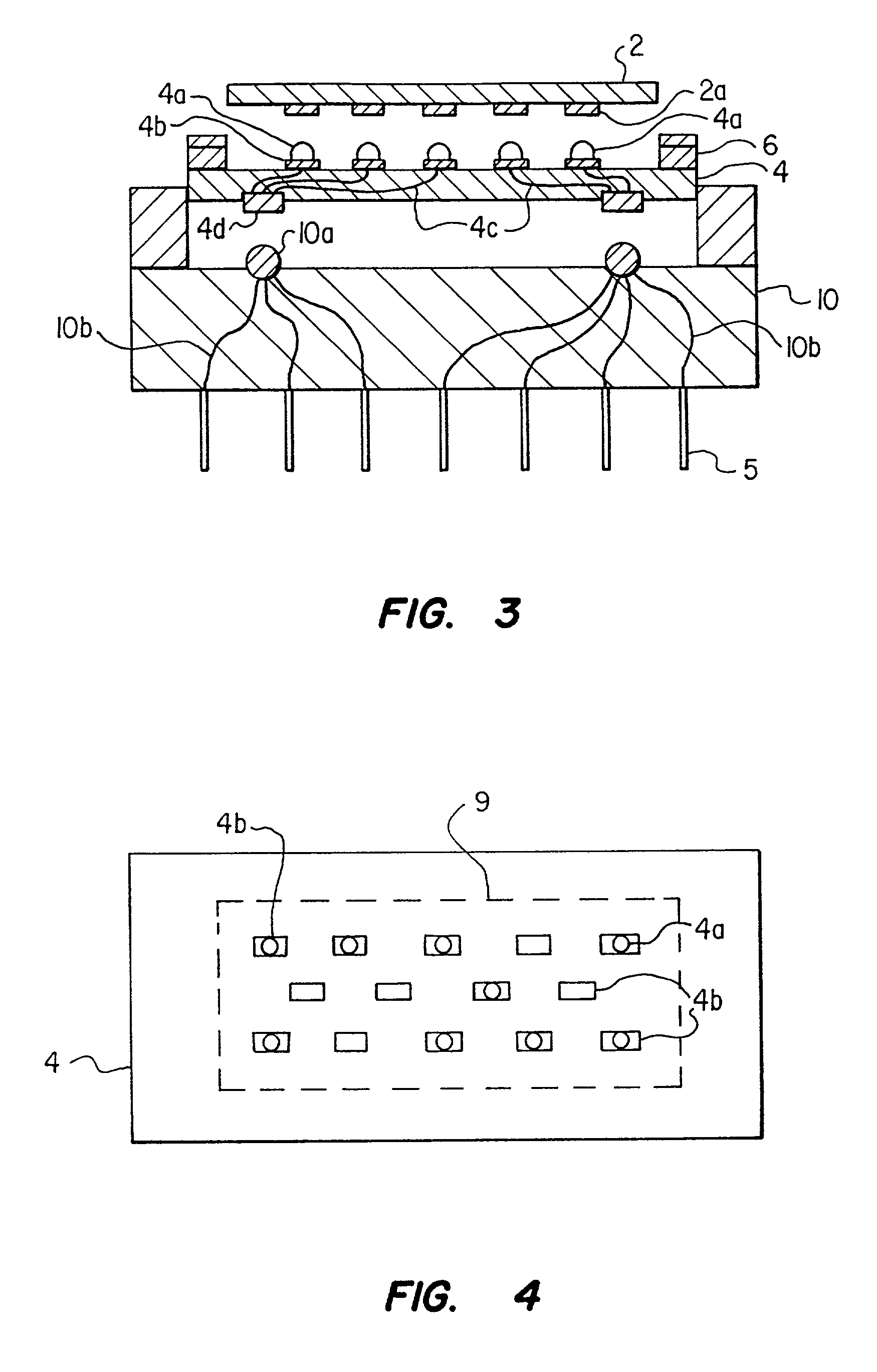

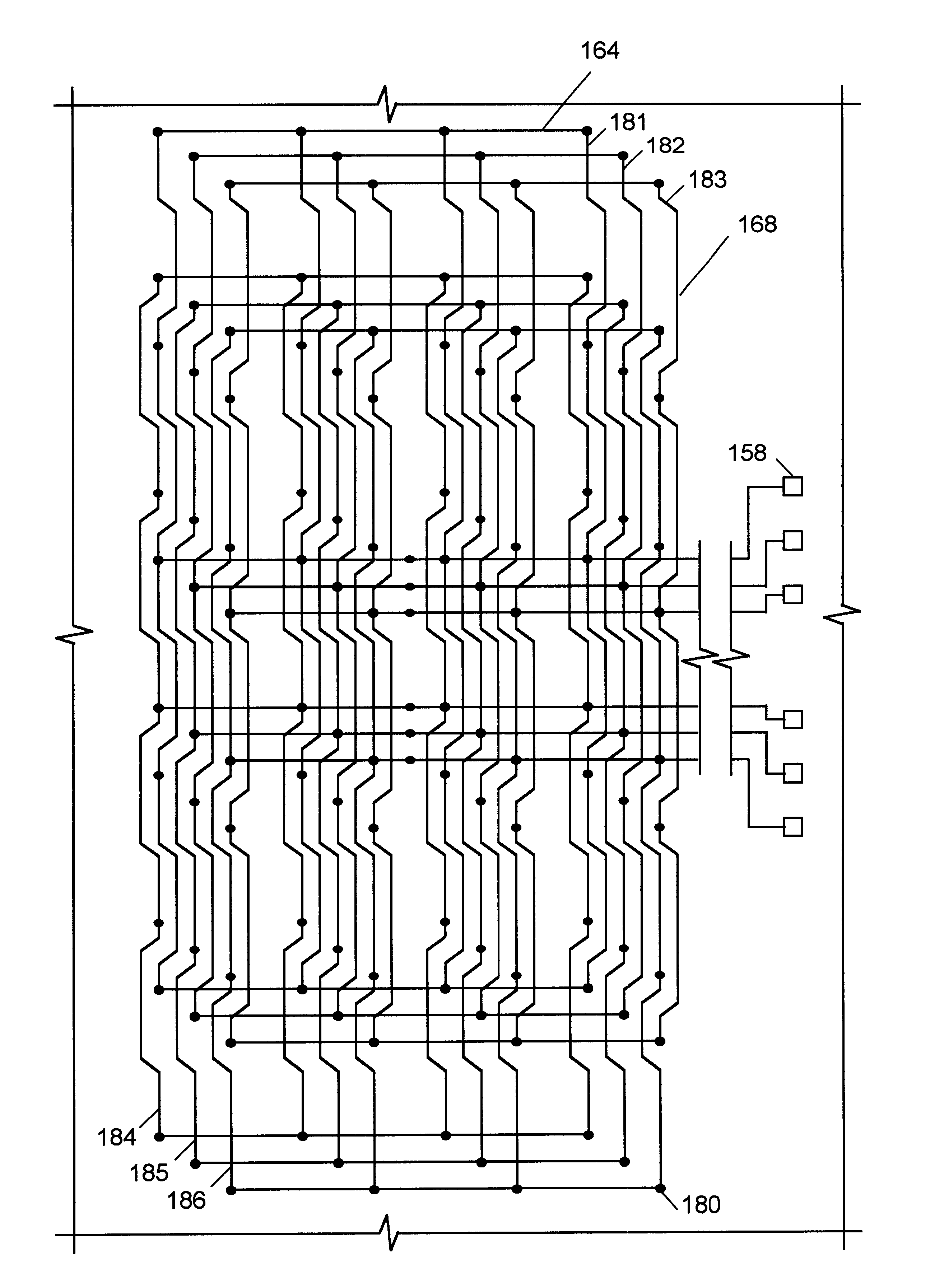

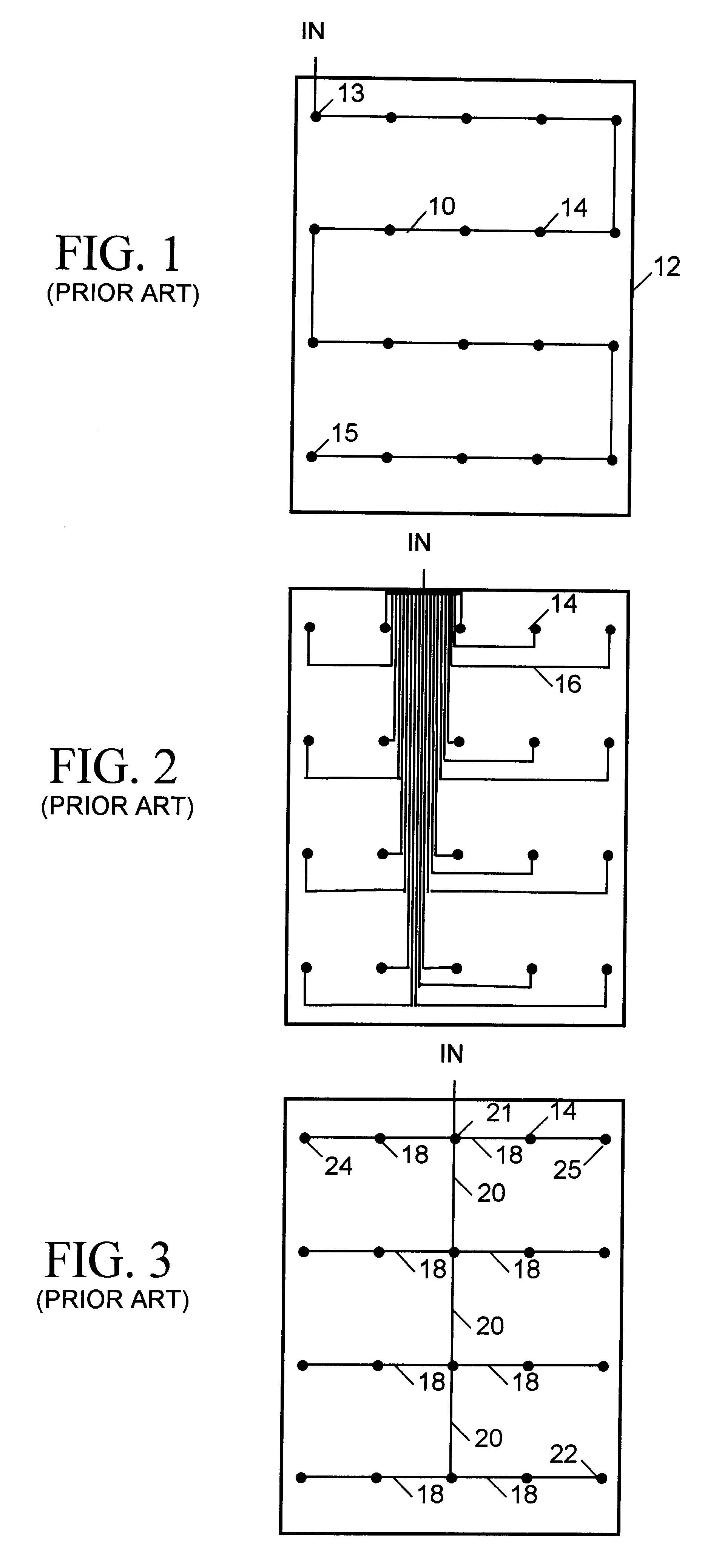

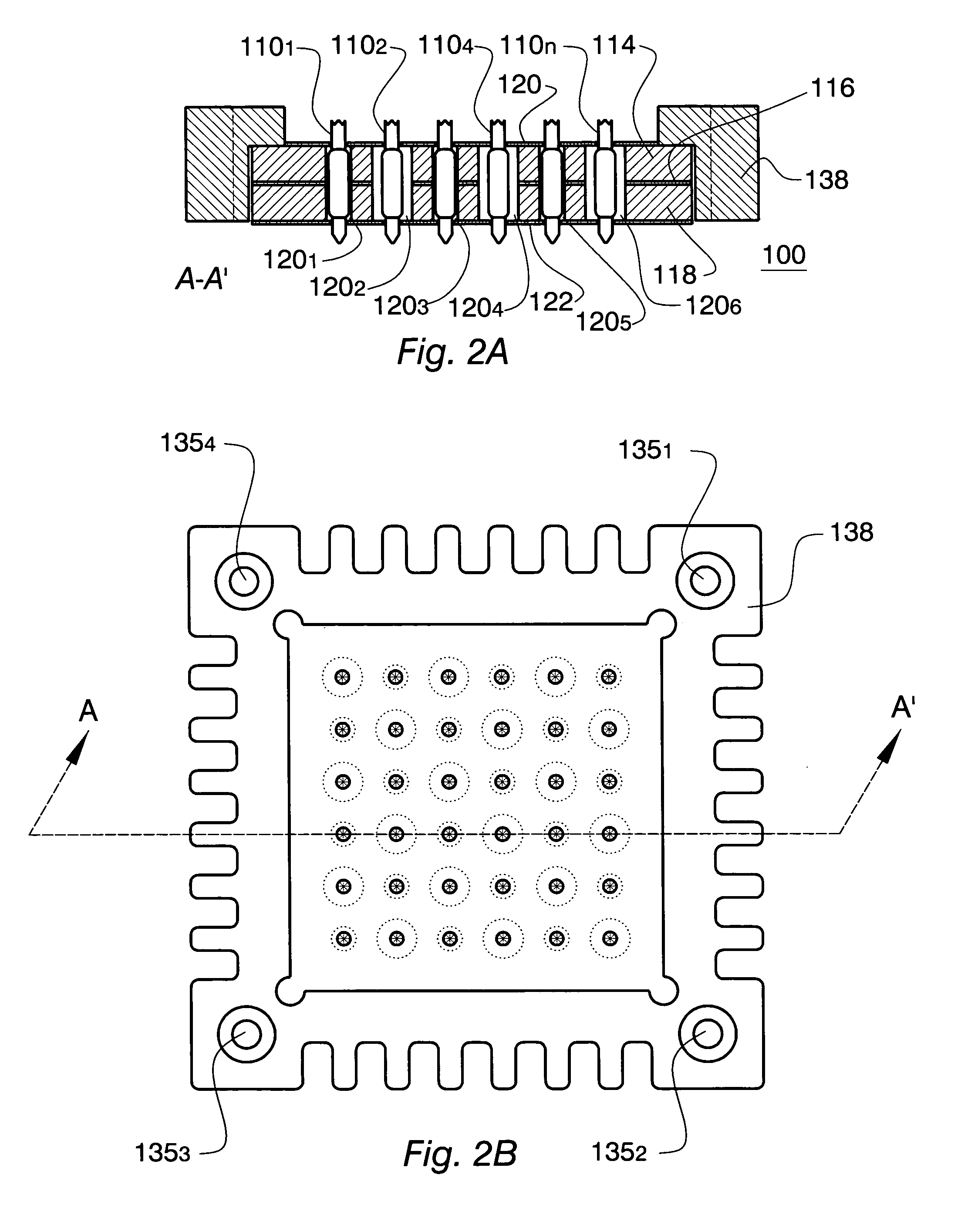

Closed-grid bus architecture for wafer interconnect structure

InactiveUS6603323B1Electrical measurement instrument detailsCross-talk/noise/interference reductionContact padSemiconductor

An interconnect structure employs a closed-grid bus to link an integrated circuit tester channel to an array of input / output (I / O) pads on a semiconductor wafer so that the tester channel can concurrently communicate with all of the I / O pads. The interconnect structure includes a circuit board implementing an array of bus nodes, each corresponding to a separate one of the I / O pads. The circuit board includes at least two layers. Traces mounted on a first layer form a set of first daisy-chain buses, each linking all bus nodes of a separate row of the bus node array. Traces mounted on a second circuit board layer form a set of second daisy-chain buses, each linking all bus nodes of a separate column of the bus node array. Vias and other circuit board interconnect ends of the first and second daisy-chain buses so that they form the closed-grid bus. Each bus node is connected though a separate isolation resistor to a separate contact pad mounted on a surface of the circuit board. A set of spring contacts or probes link each contact pad to a separate one of the I / O pads on the wafer.

Owner:FORMFACTOR INC

Wastewater treatment system and method

ActiveUS20070209999A1Treatment using aerobic processesTreatment involving filtrationActivated carbonWater treatment system

The invention is directed to a method and apparatus for treating wastewater. The wastewater treatment system includes a bioreactor including activated carbon and a first biological population. The wastewater treatment system may also include a membrane bioreactor and / or a wet oxidation unit.

Owner:SIEMENS ENERGY INC

Socket for an electronic device

InactiveUS20070269999A1Electrical measurement instrument detailsCoupling device detailsEngineeringThermal contact

One embodiment of the present invention is a socket useful to contact an electronic device, the socket including: (a) one or more contactor holder plates including one or more first through holes having a first hole cross sectional area, and one or more second through holes having a second hole cross sectional area; (b) one or more first contactors having a body with a first body cross sectional area disposed in the first through holes; (c) one or more second contactors having a body with a second body cross sectional area disposed in the second through holes; and (d) a heat sink in thermal contact with one or more of the one or more contactor holder plates; wherein a first ratio of the first hole cross sectional area to the first body cross sectional area is different from a second ratio of the second hole cross sectional area to the second body cross sectional area.

Owner:CENTIPEDE SYST

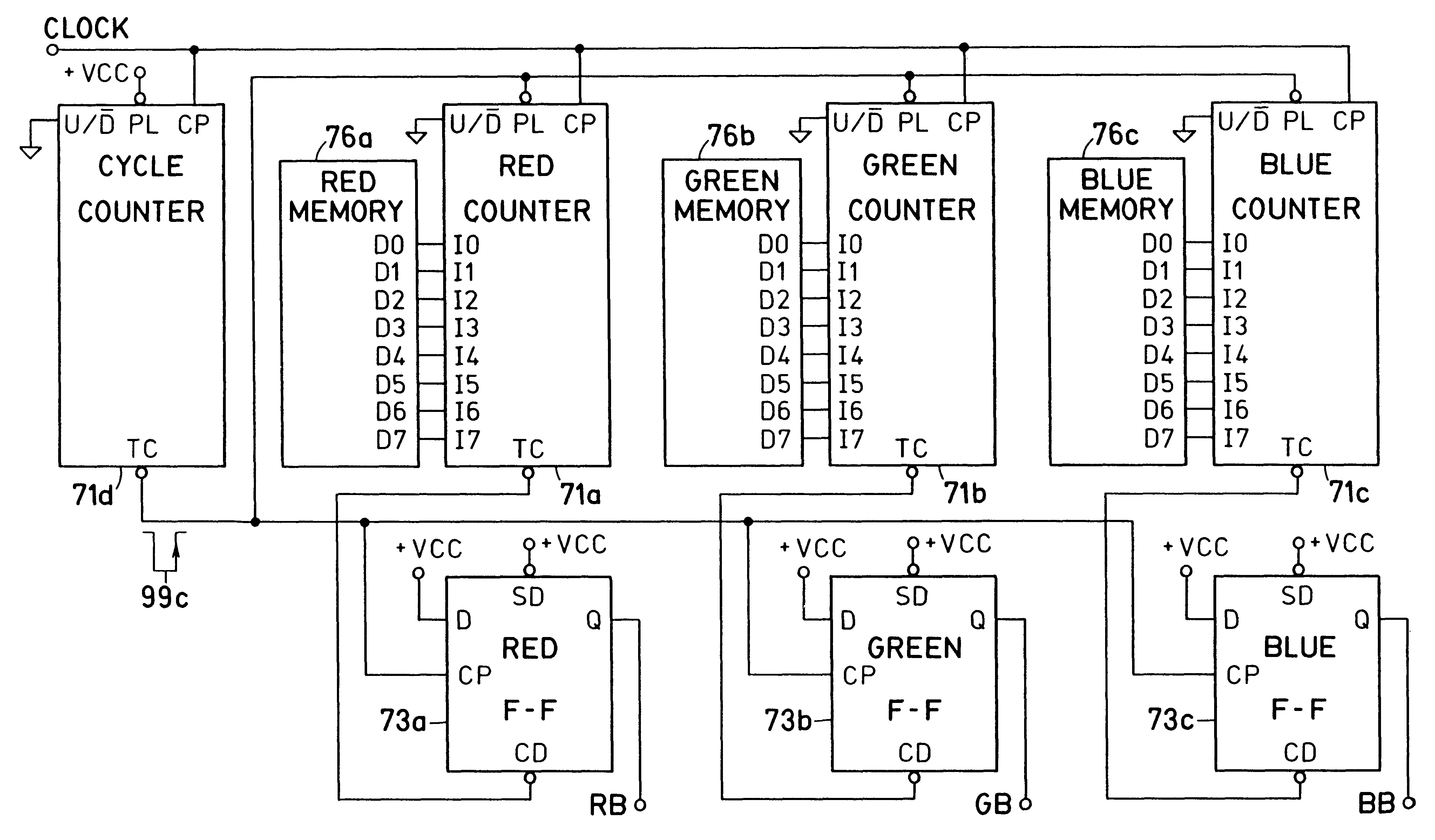

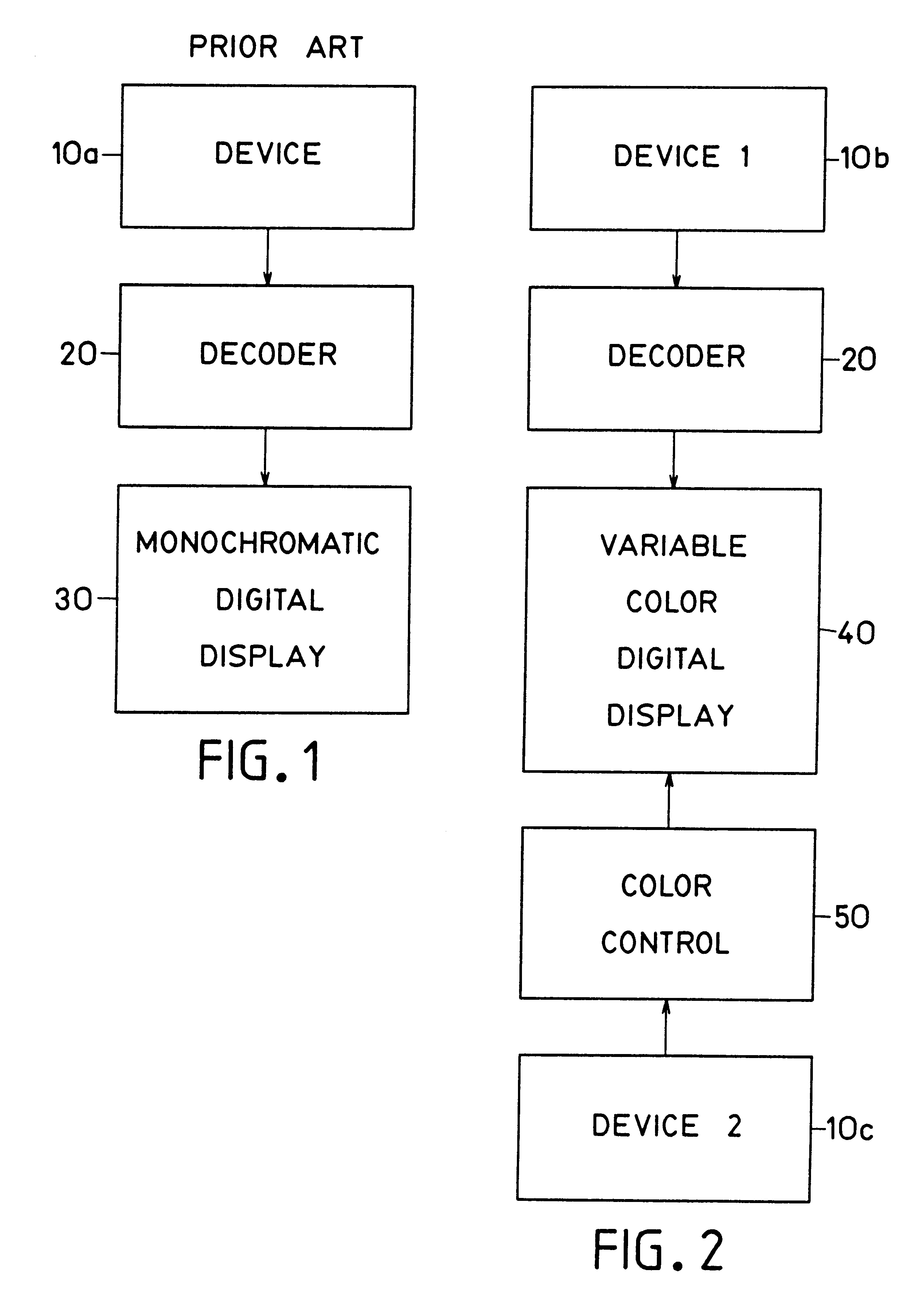

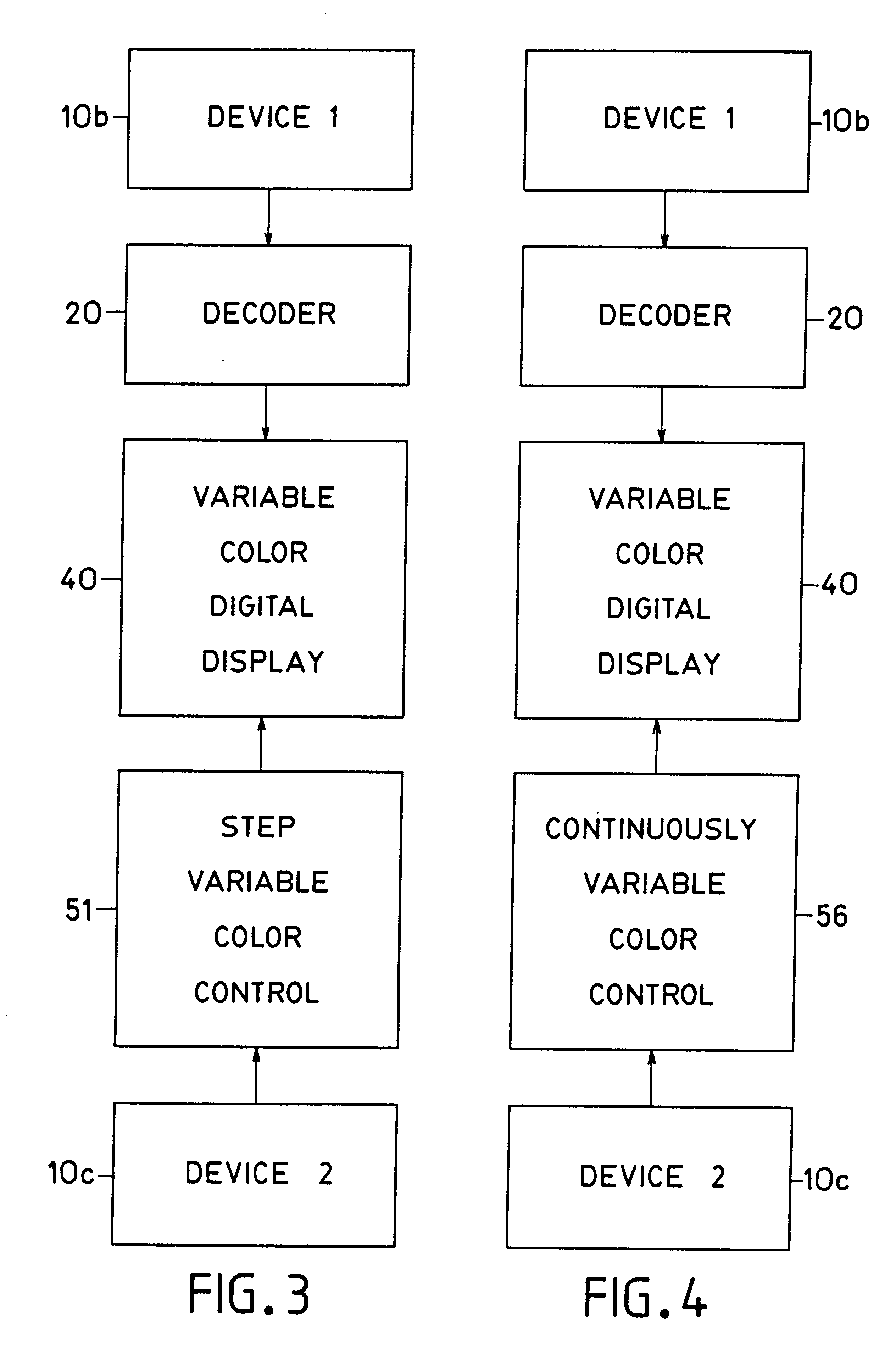

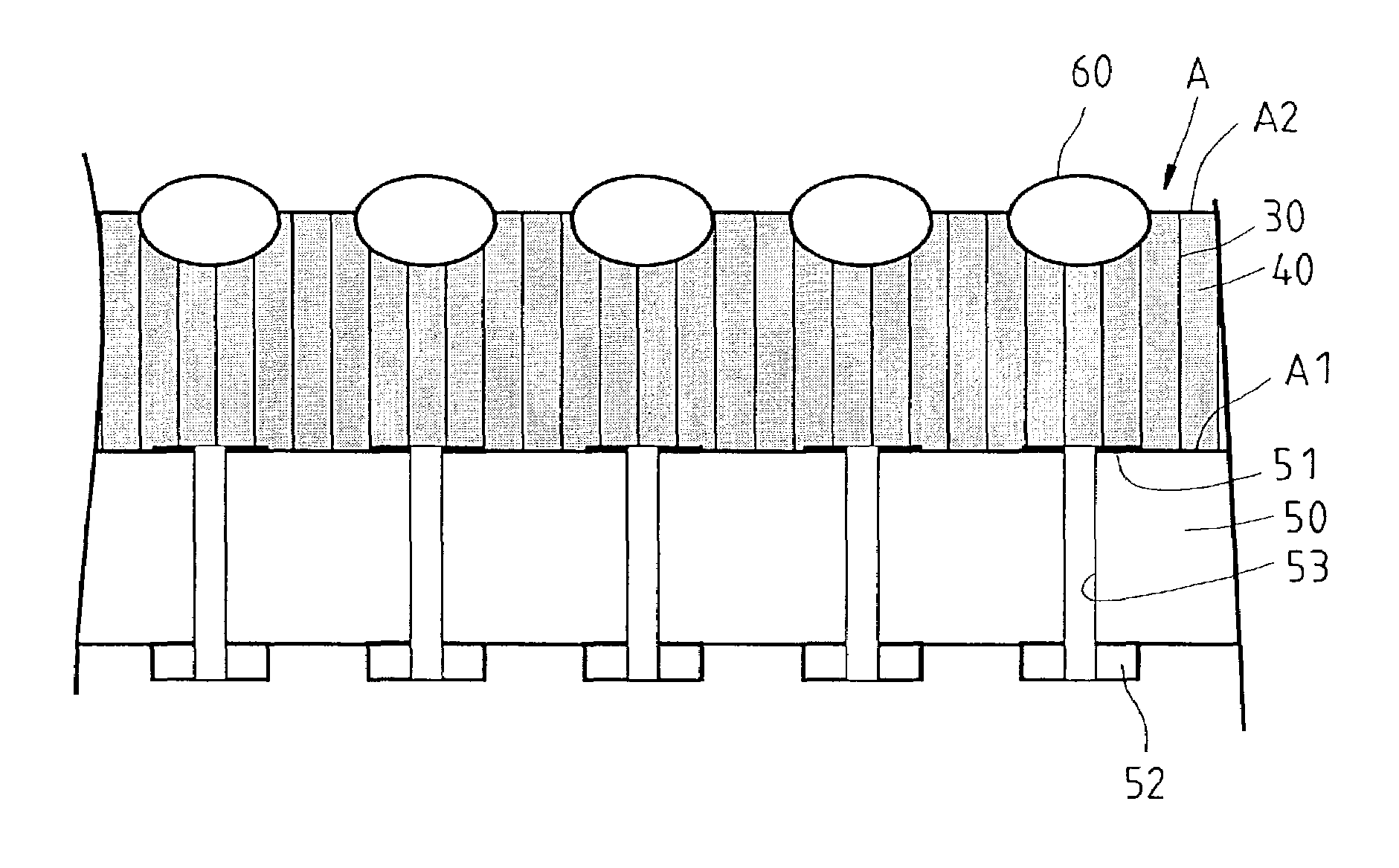

Method for continuously controlling color of display device

A method for continuously controlling color of a display device comprises the steps of receiving three sets of data respectively representing the portions of three primary colors, accumulating three counts in accordance with the data, respectively, and setting three bistable devices for the respective durations of the accumulating. The outputs of the three bistable devices are coupled for respectively energizing three buses, to which the light emitting diodes of three primary colors are connected in accordance with their colors, for controlling the portions of the light signals of the primary colors emitted therefrom.

Owner:TEXAS DIGITAL SYST

High conducting thin-film nanoprobe card and its fabrication method

InactiveUS7012441B2Compensating for such errorLine/current collector detailsElectrically conductive connectionsPolymer resinNanotube

A conducting thin-film nanoprobe card fabrication method includes the steps of: (a) arranging nanotubes on a substrate in vertical; (b) covering the nanotubes with a liquid polymeric resin and then hardening the polymeric resin to form a conducting nanomembrane; (c) removing a part of the polymeric resin from the conducting nanomembrane to expose one end of each nanotube to outside; (d) removing the substrate and preparing a ceramic substrate having contacts at one side and metal bumps at the other side and plated through holes electrically respectively connected with the contacts and the metal bumps; (e) mounting the nanomembrane on the ceramic substrate to hold the nanotubes in contact with the contacts of the ceramic substrate, and (f) forming recessed holes in the nanomembrane by etching and inserting a metal rod in each recessed hole to form a respective probe.

Owner:IND TECH RES INST

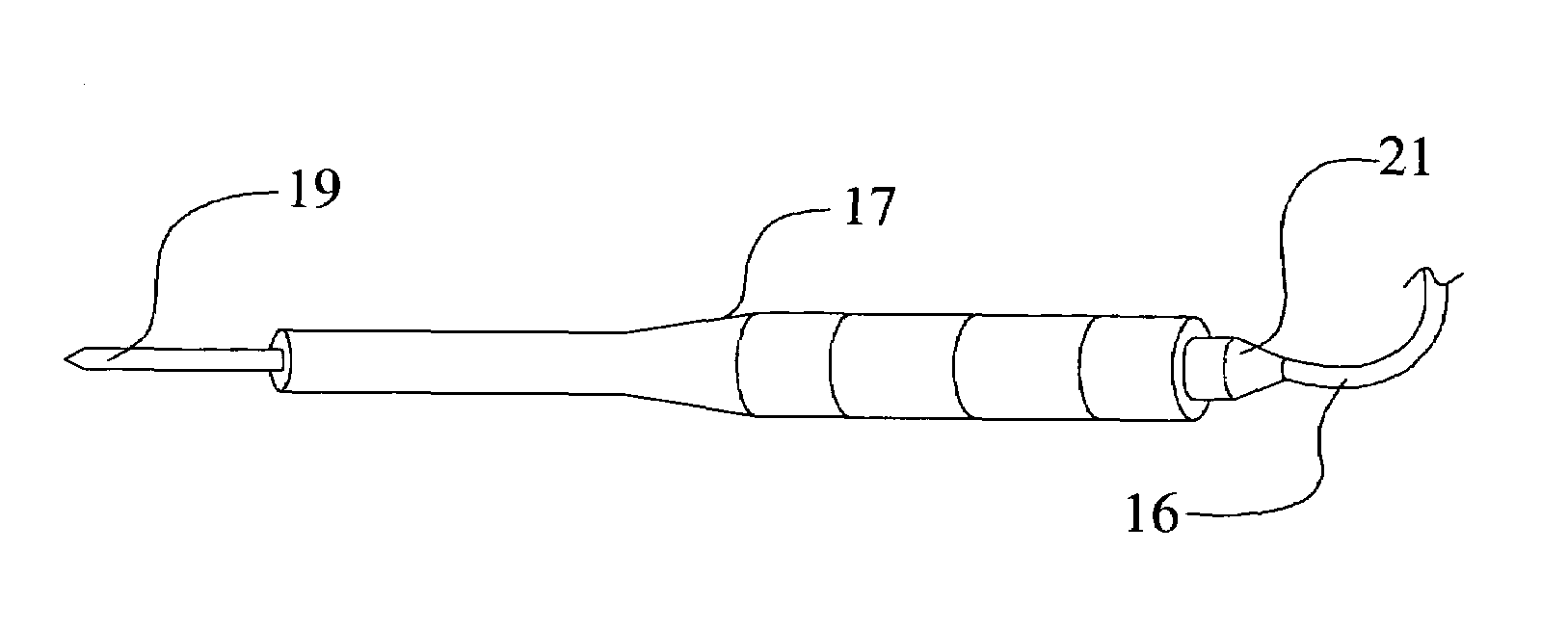

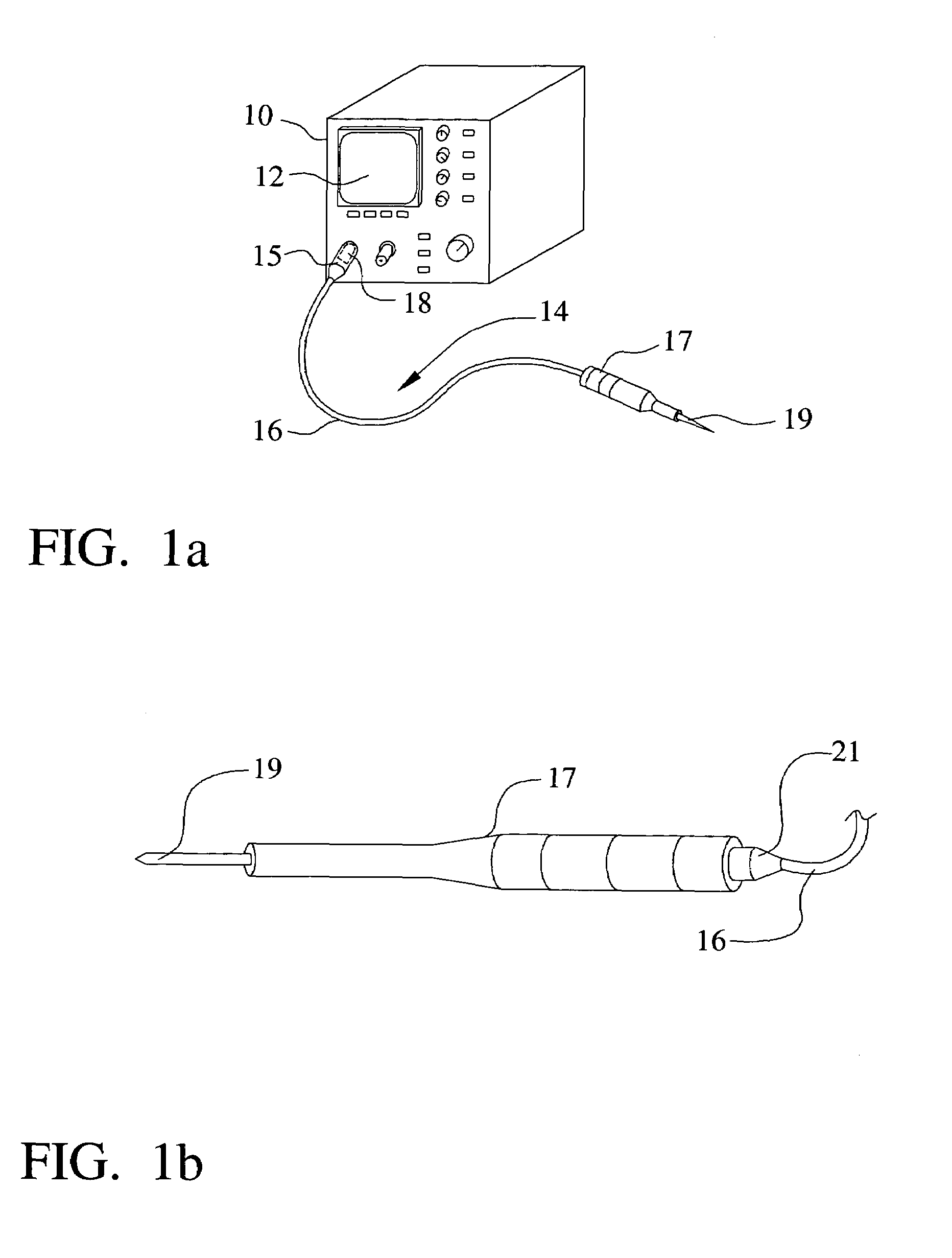

Low cost electronic probe devices manufactured from conductive loaded resin-based materials

InactiveUS7006046B2EffectiveImprove Noise CancellationElectrical measurement instrument detailsAntenna supports/mountingsOptoelectronicsNickel plate

Electronic probe devices are formed of a conductive loaded resin-based material. The conductive loaded resin-based material comprises micron conductive powder(s), conductive fiber(s), or a combination of conductive powder and conductive fibers in a base resin host. The ratio of the weight of the conductive powder(s), conductive fiber(s), or a combination of conductive powder and conductive fibers to the weight of the base resin host is between about 0.20 and 0.40. The micron conductive powders are formed from non-metals, such as carbon, graphite, that may also be metallic plated, or the like, or from metals such as stainless steel, nickel, copper, silver, that may also be metallic plated, or the like, or from a combination of non-metal, plated, or in combination with, metal powders. The micron conductor fibers preferably are of nickel plated carbon fiber, stainless steel fiber, copper fiber, silver fiber, or the like.

Owner:INTEGRAL TECHNOLOGY INC

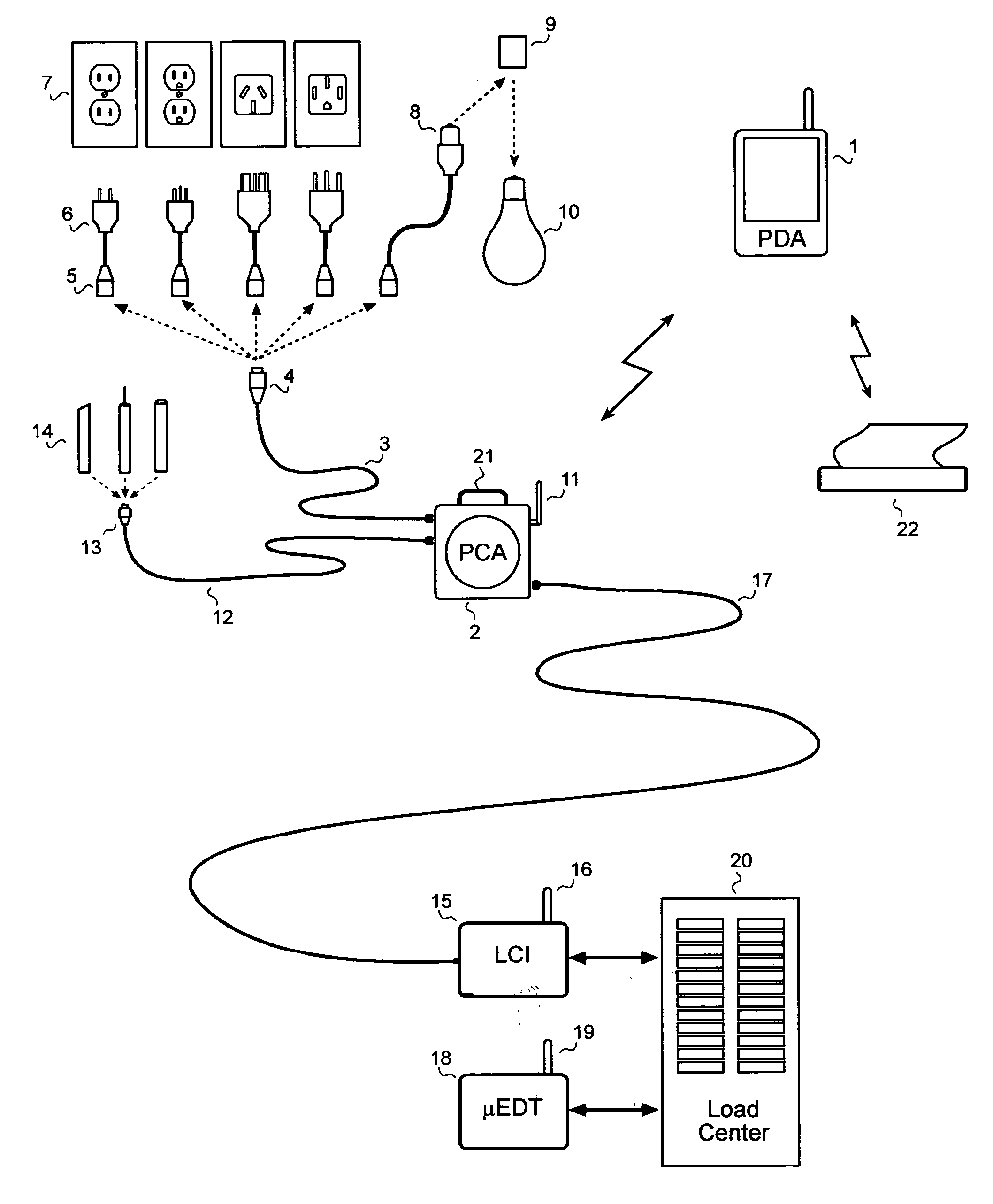

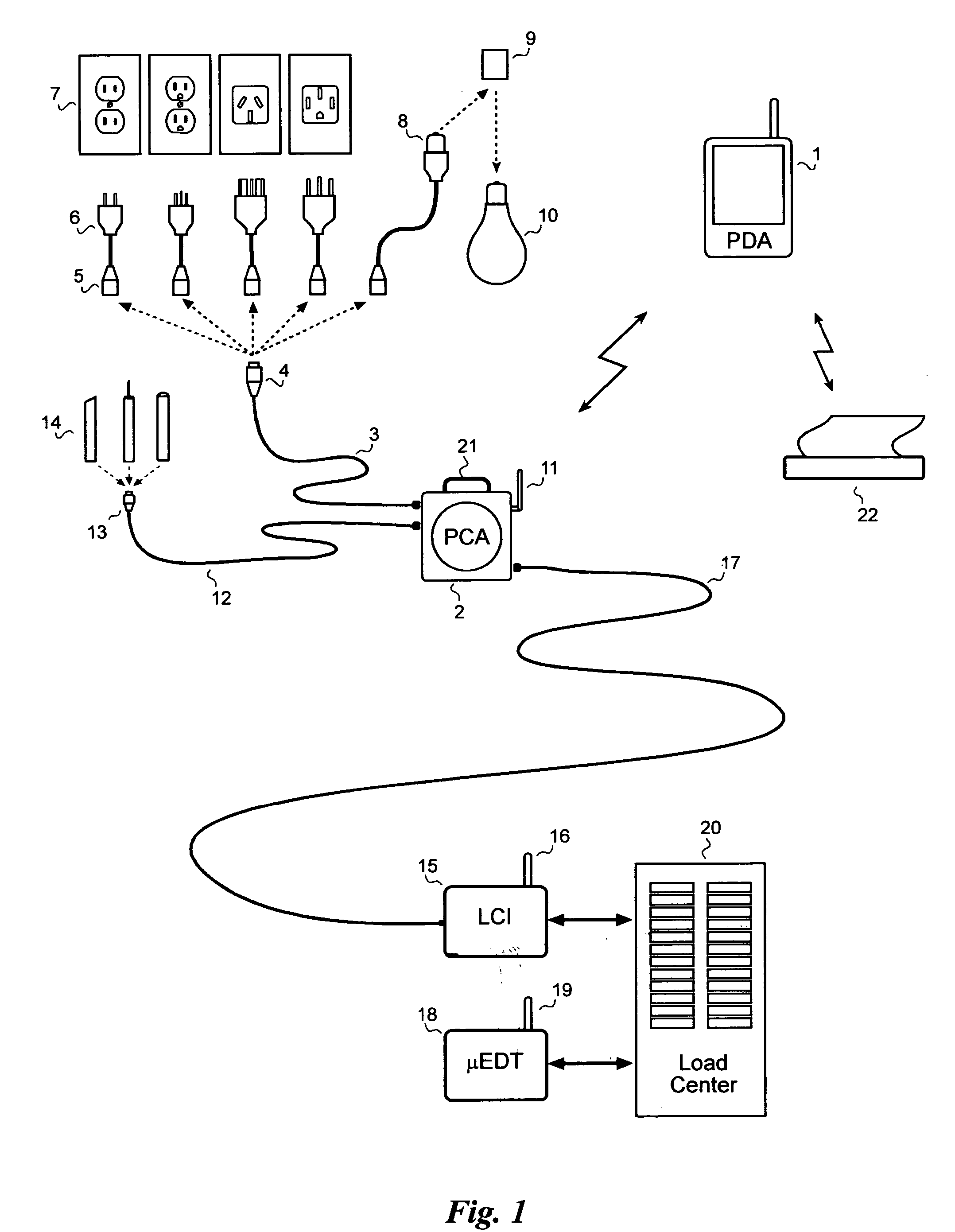

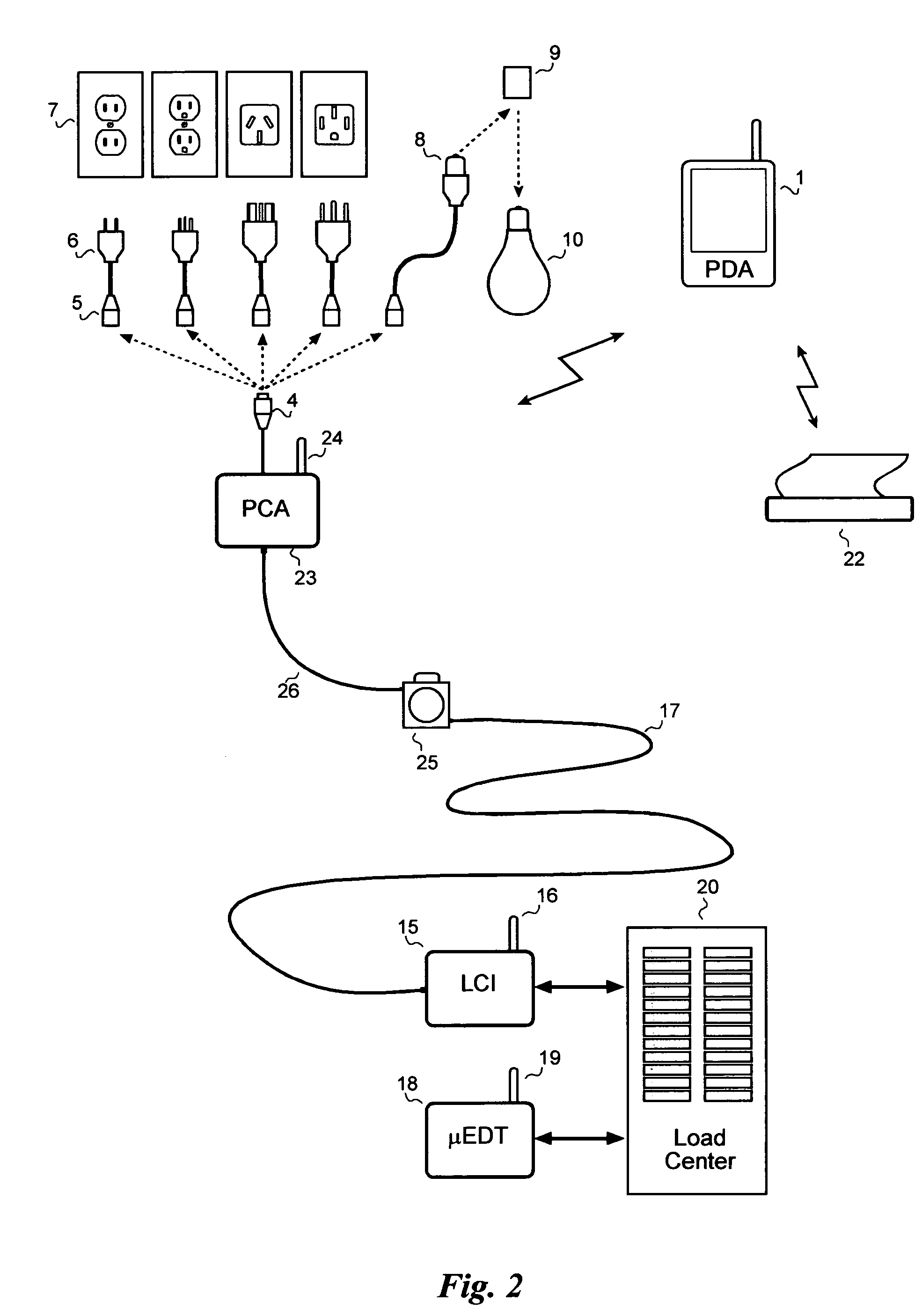

Electrical wiring inspection system

InactiveUS20050212526A1Electrical measurement instrument detailsElectric connection testingElectrical resistance and conductanceOperating energy

A system for testing and documenting the electrical wiring in a building, for example, comprises a Portable Circuit Analyzer (PCA) that is connected to the building's Load Center through an umbilical cord. The PCA is in wireless communication with a hand-held computer device, such as a personal digital assistant (PDA) as now widely available, provided with custom software according to the invention. The electrician connects the PCA in succession to each circuit in the building, operating each switch, and each fixture or appliance, while recording the test results of the circuit element on the PDA. The PCA measures the resistance and length of each circuit thus established. When the test process is completed, the PDA is enabled to generate a complete schematic diagram of the building, including, for example, an identification of the branch circuit to which each fixture, outlet, appliance, or other load or connection point is connected.

Owner:BLADES FREDERICK K

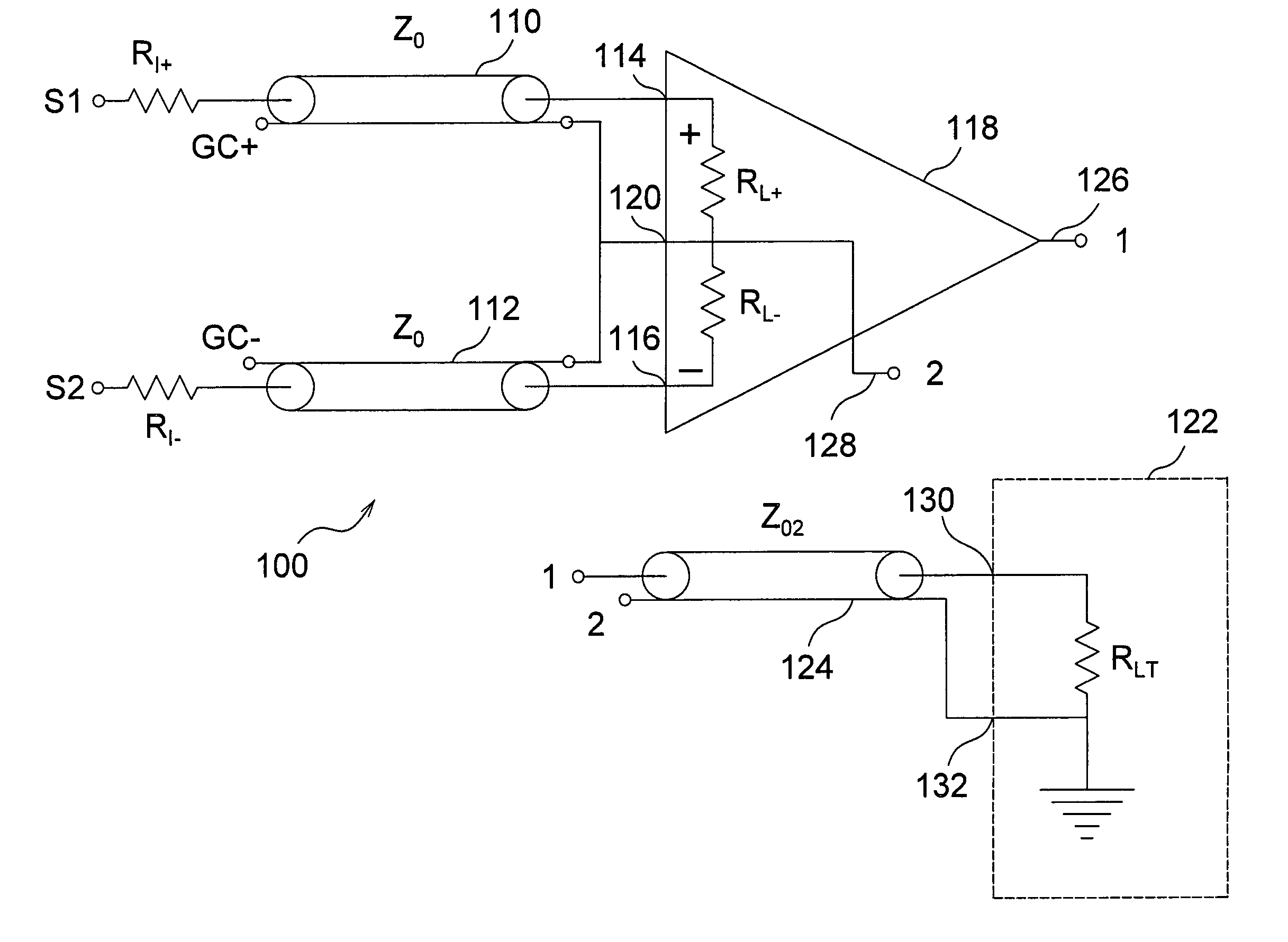

High performance probe system

InactiveUS6911835B2Semiconductor/solid-state device testing/measurementElectrical measurement instrument detailsHigh bandwidthΠ pad

A probe system for providing signal paths between an integrated circuit (IC) tester and input / output, power and ground pads on the surfaces of ICs to be tested includes a probe board assembly, a flex cable and a set of probes arranged to contact the IC's I / O pads. The probe board assembly includes one or more rigid substrate layers with traces and vias formed on or within the substrate layers providing relatively low bandwidth signal paths linking the tester to probes accessing some of the IC's pads. The flex cable provides relatively high bandwidth signal paths linking the tester to probes accessing others of the IC's pads. A flex strip may alternatively be disposed behind a substrate with probes.

Owner:FORMFACTOR INC

Transmission line input structure test probe

InactiveUS7019544B1Resistance/reactance/impedenceElectrical measurement instrument detailsDifferential signalingCharacteristic impedance

A differential electrical test probe tip for sensing a plurality of electric signals and generating a differential signal including an elongate common substrate having a two signal test points at one end and a differential amplifier at the second end. Two transmission lines are on the common substrate, each connecting a respective signal test point a signal input of the differential amplifier. The characteristic impedances of the two transmission lines are substantially equal. In one preferred embodiment, the common substrate is a flexible substrate. In one preferred embodiment an over-mold, which may have gaps therein, at least partially encloses the common substrate, the first transmission line, and the second transmission line.

Owner:TELEDYNE LECROY

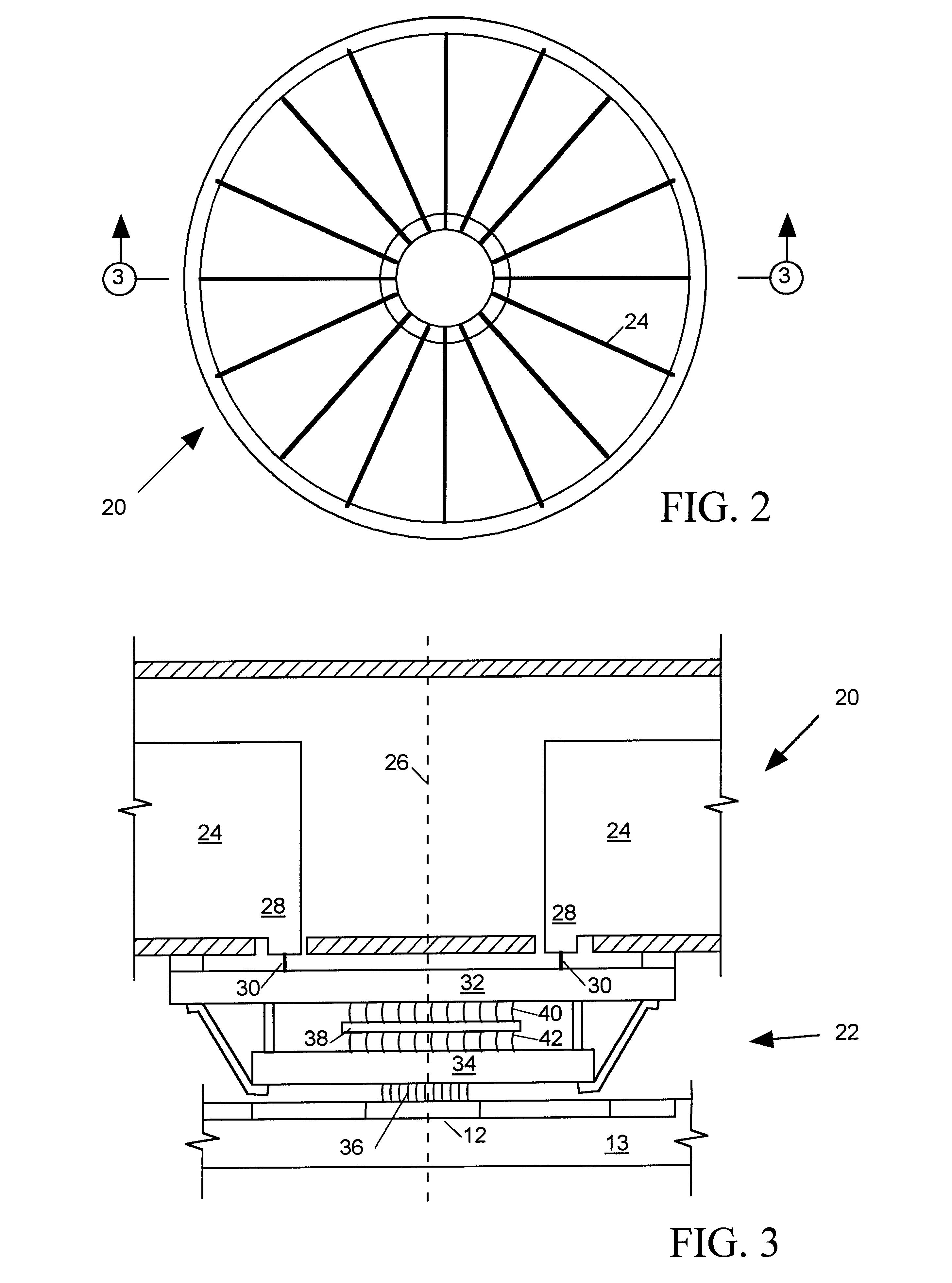

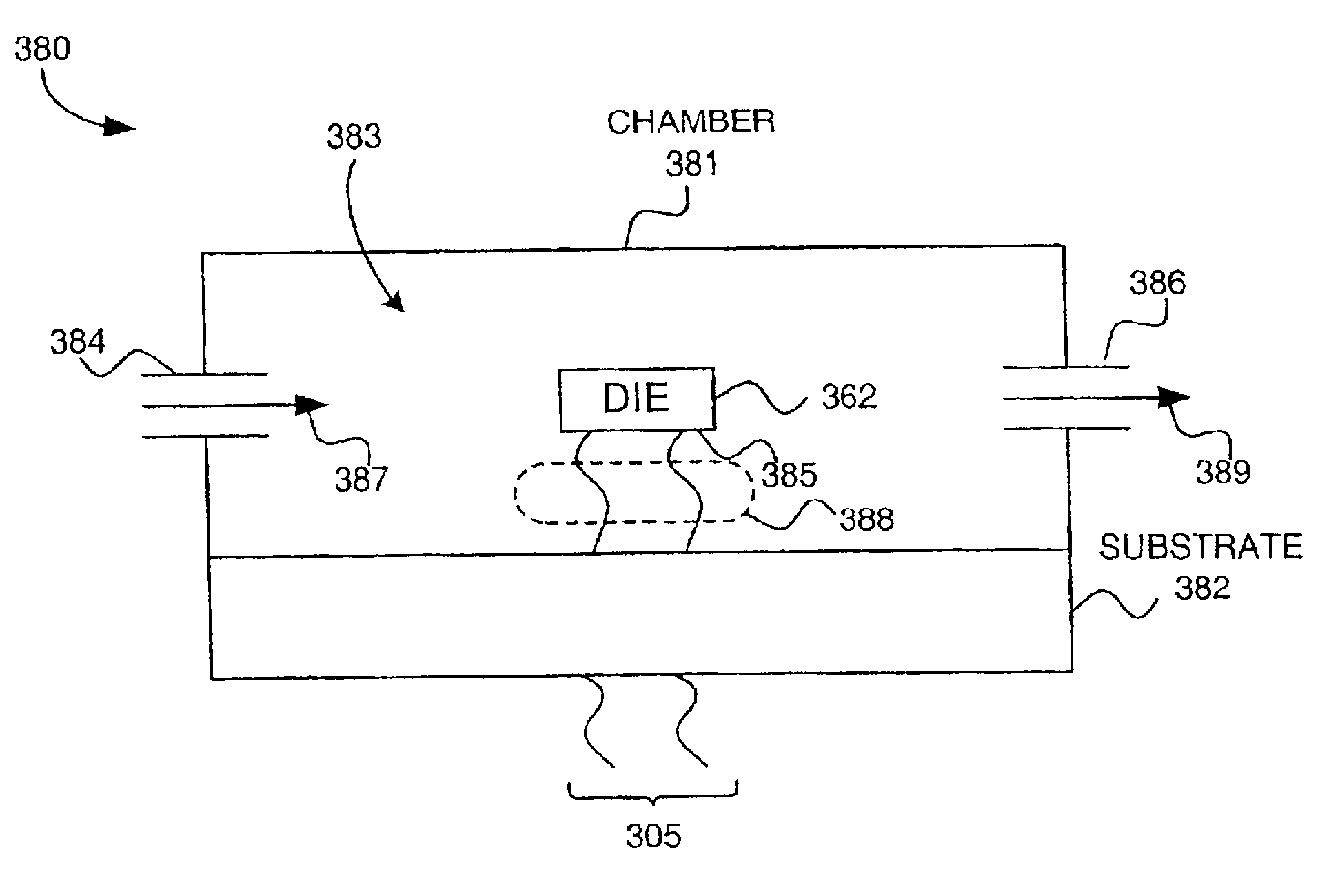

Probe card cooling assembly with direct cooling of active electronic components

InactiveUS6891385B2Shorten the conduction pathImprove performanceElectronic circuit testingElectrical measurement instrument detailsProbe cardHigh density

A probe card cooling assembly for use in a test system includes a package with one or more dies cooled by direct cooling. The cooled package includes one or more dies with active electronic components and at least one coolant port that allows a coolant to enter the high-density package and directly cool the active electronic components of the dies during a testing operation.

Owner:FORMFACTOR INC

Needle fixture of a probe card in semiconductor inspection equipment and needle fixing method thereof

InactiveUS6900653B2Improve adhesion performanceAvoid crackingSemiconductor/solid-state device testing/measurementElectrical measurement instrument detailsProbe cardAdhesive

A needle fixture of a probe card and a needle fixing method in semiconductor inspection equipment include a needle fixture of a probe card in semiconductor inspection equipment including a printed circuit board; a needle fixture installed in the printed circuit board; a resin unit affixing a probe needle to the needle fixture using an adhesive; and a separation preventer for preventing separation of the resin unit from the needle fixture, wherein the separation preventer includes: a plurality of notches formed along a bottom surface of the needle fixture; and the adhesive filling the plurality of notches.

Owner:SAMSUNG ELECTRONICS CO LTD

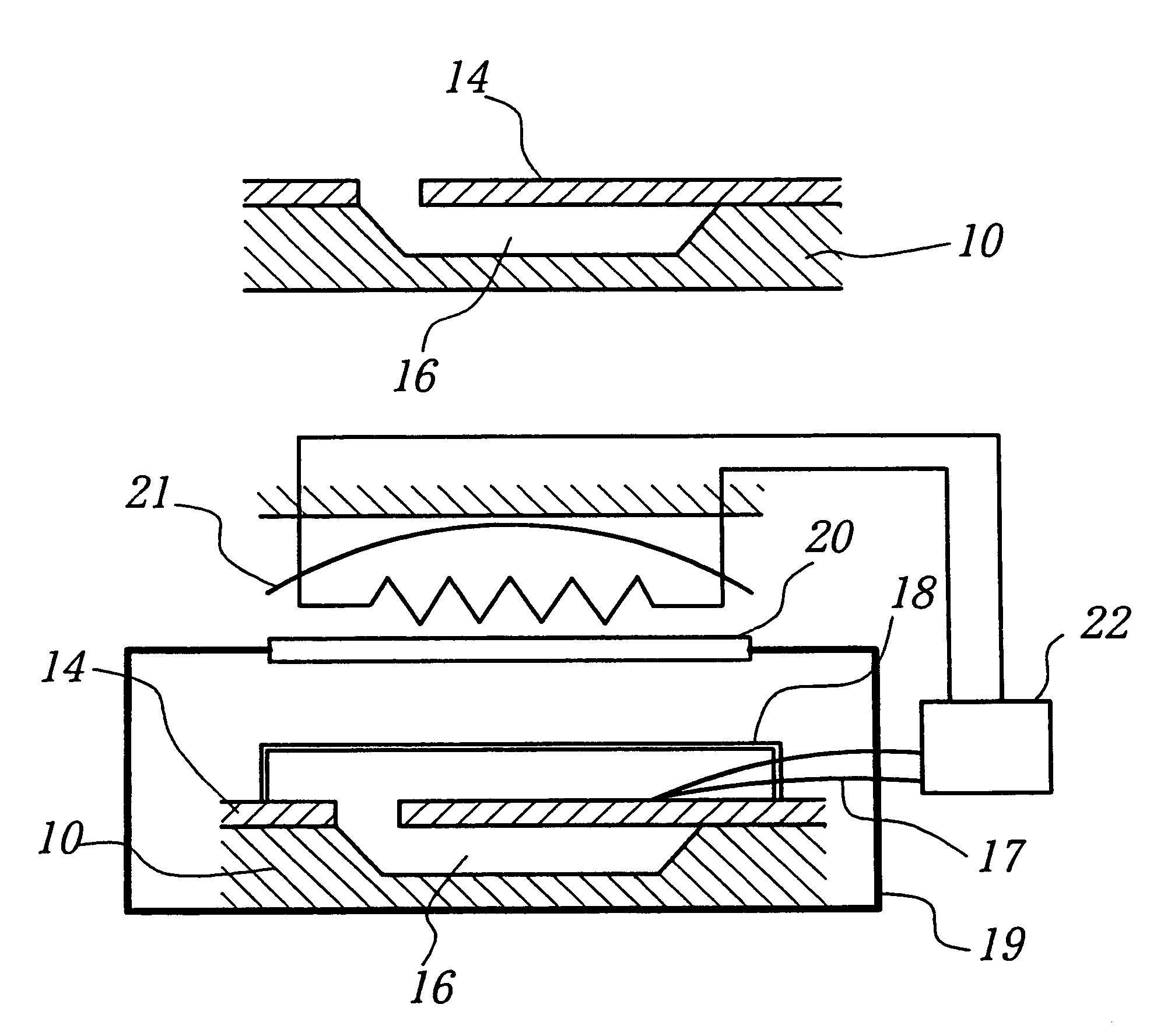

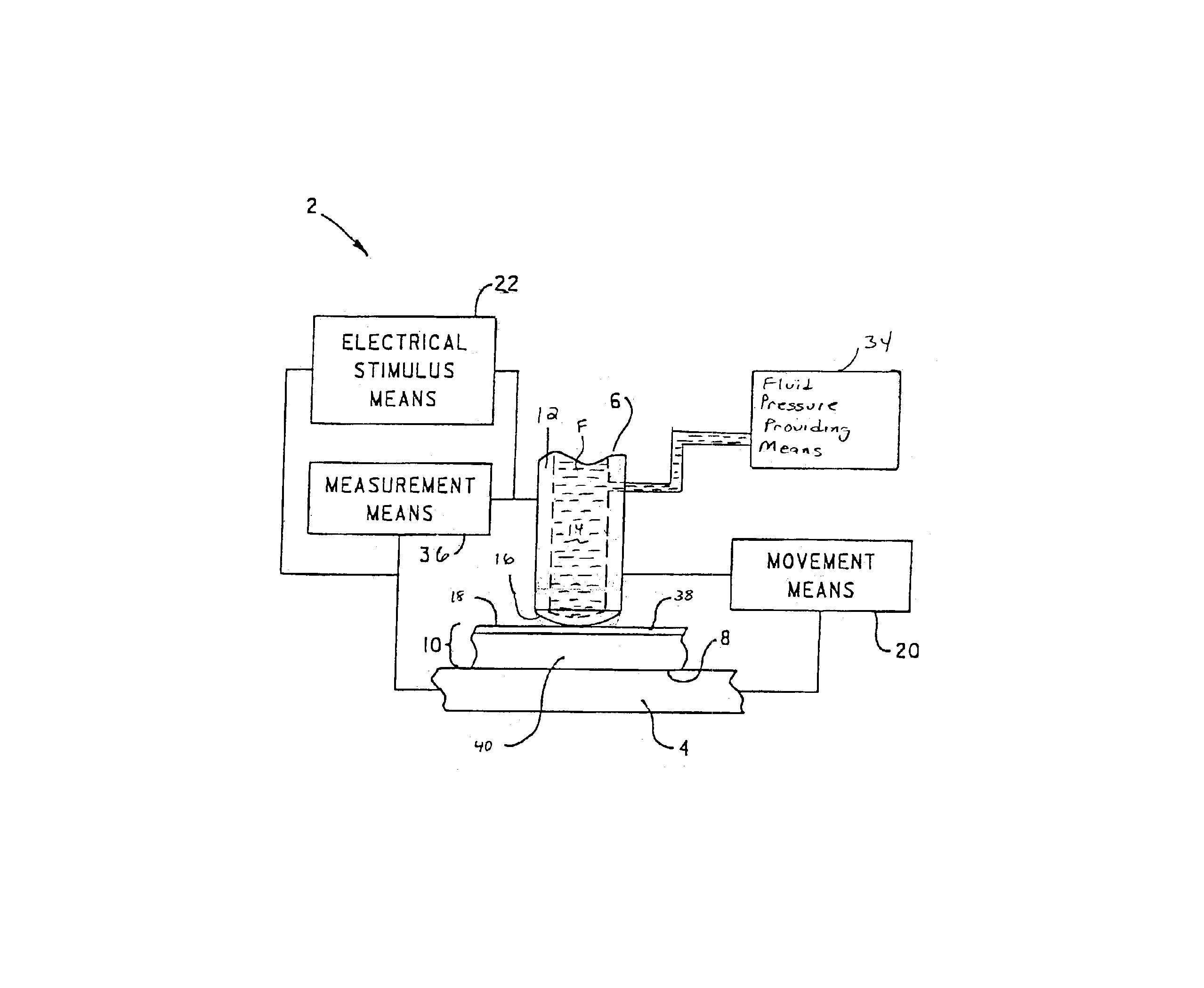

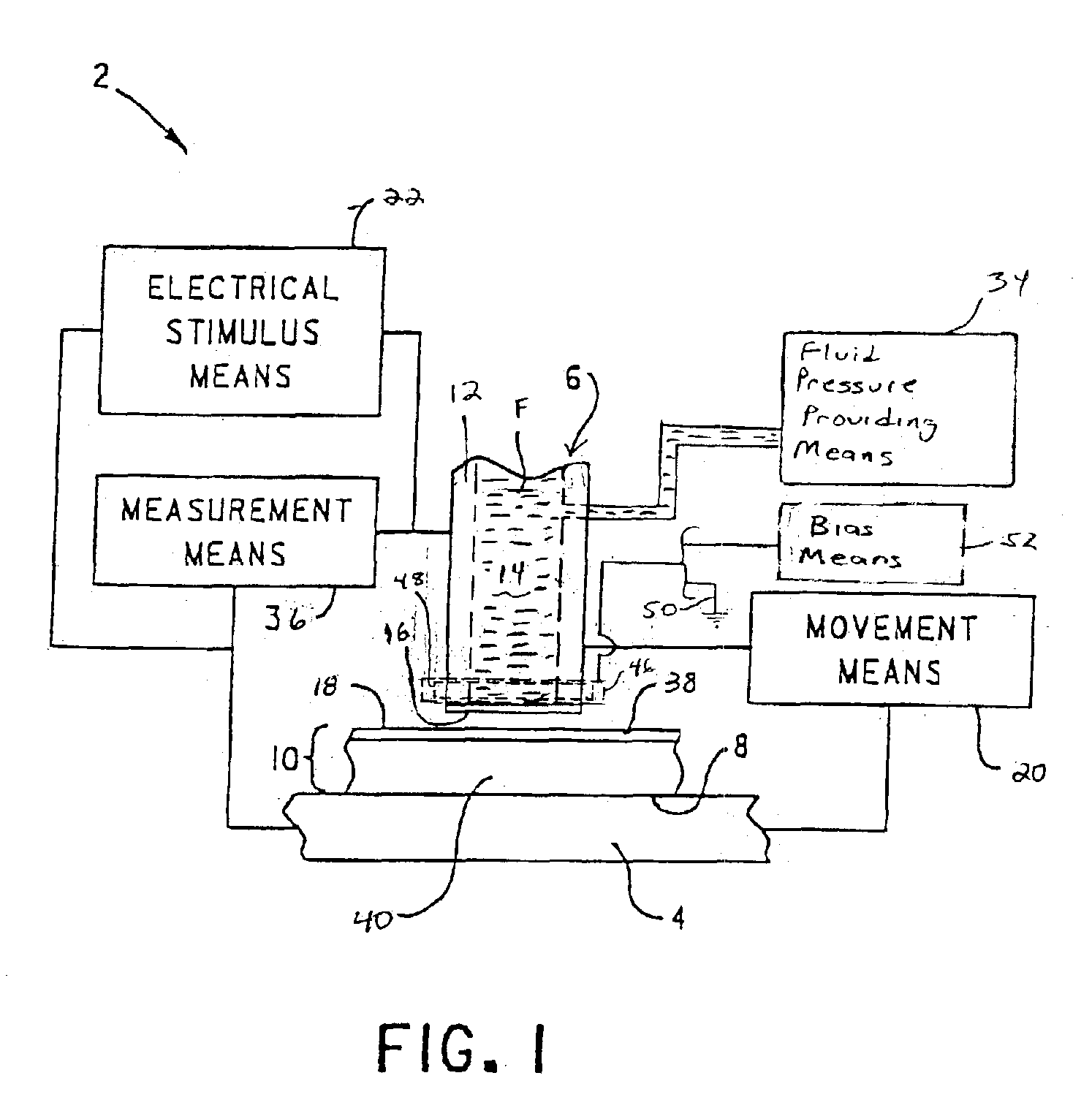

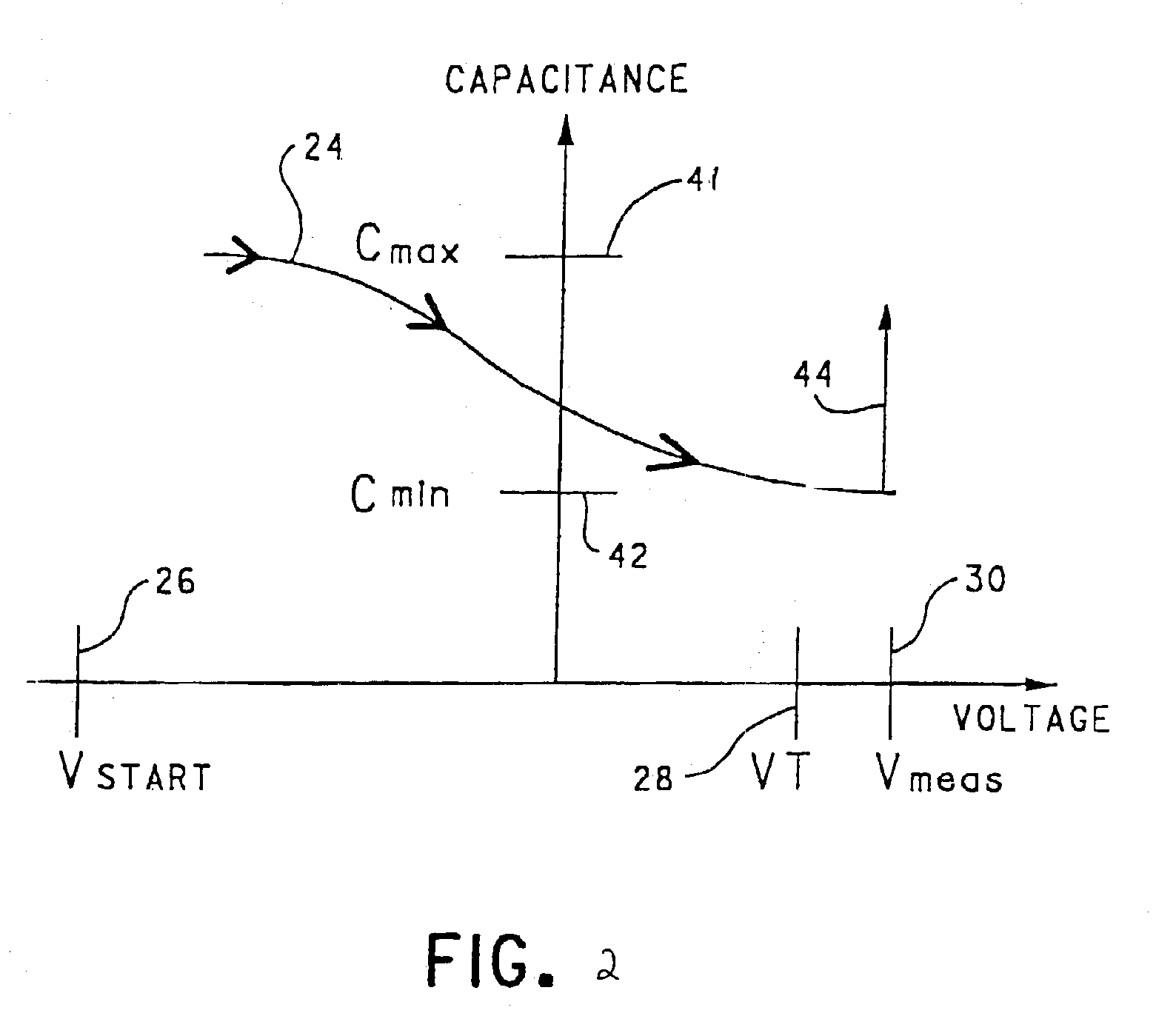

Flexible membrane probe and method of use thereof

InactiveUS6900652B2Reduce fluid pressureSemiconductor/solid-state device testing/measurementResistance/reactance/impedenceEngineeringSemiconductor

A measuring apparatus for measuring a semiconductor wafer, or a film or coating thereon, includes an electrically conductive wafer chuck and a probe having a probe body defining an internal cavity in fluid communication with an electrically conductive and elastic or resilient membrane. The membrane and a topside of the semiconductor wafer are moved into spaced relation when the semiconductor wafer is supported by the wafer chuck. A pressure of fluid supplied to the internal cavity of the probe body is selectively controlled whereupon the membrane expands into contact with the topside of the semiconductor wafer. A suitable test stimulus is applied to the membrane and the semiconductor wafer and the response of the semiconductor wafer to the test stimulus is measured.

Owner:SOLID STATE MEASUREMENTS

Popular searches

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com