Patents

Literature

436 results about "Soft core" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

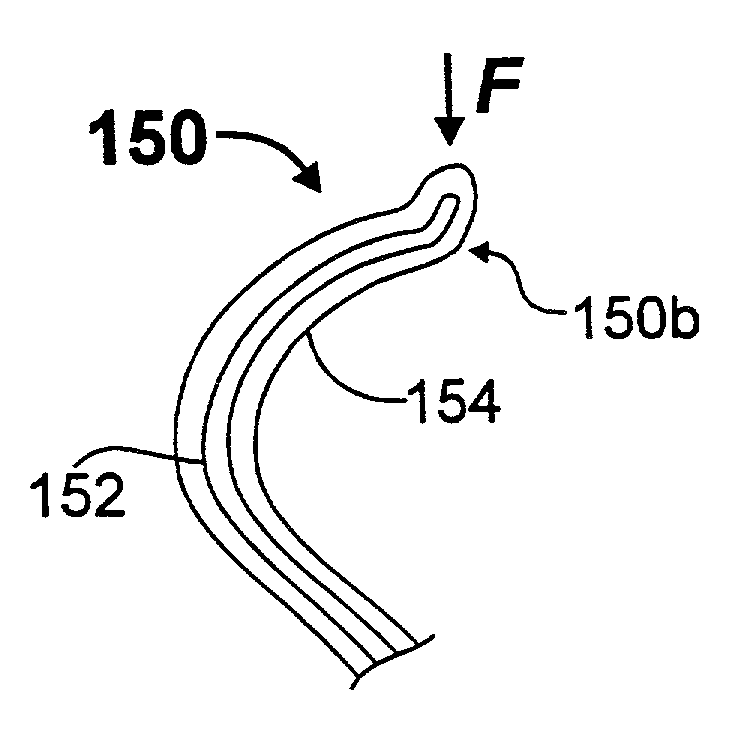

Probe card assembly and kit, and methods of using same

InactiveUS6246247B1Easy to disassembleEffective shieldingSemiconductor/solid-state device testing/measurementFinal product manufactureElectricityProbe card

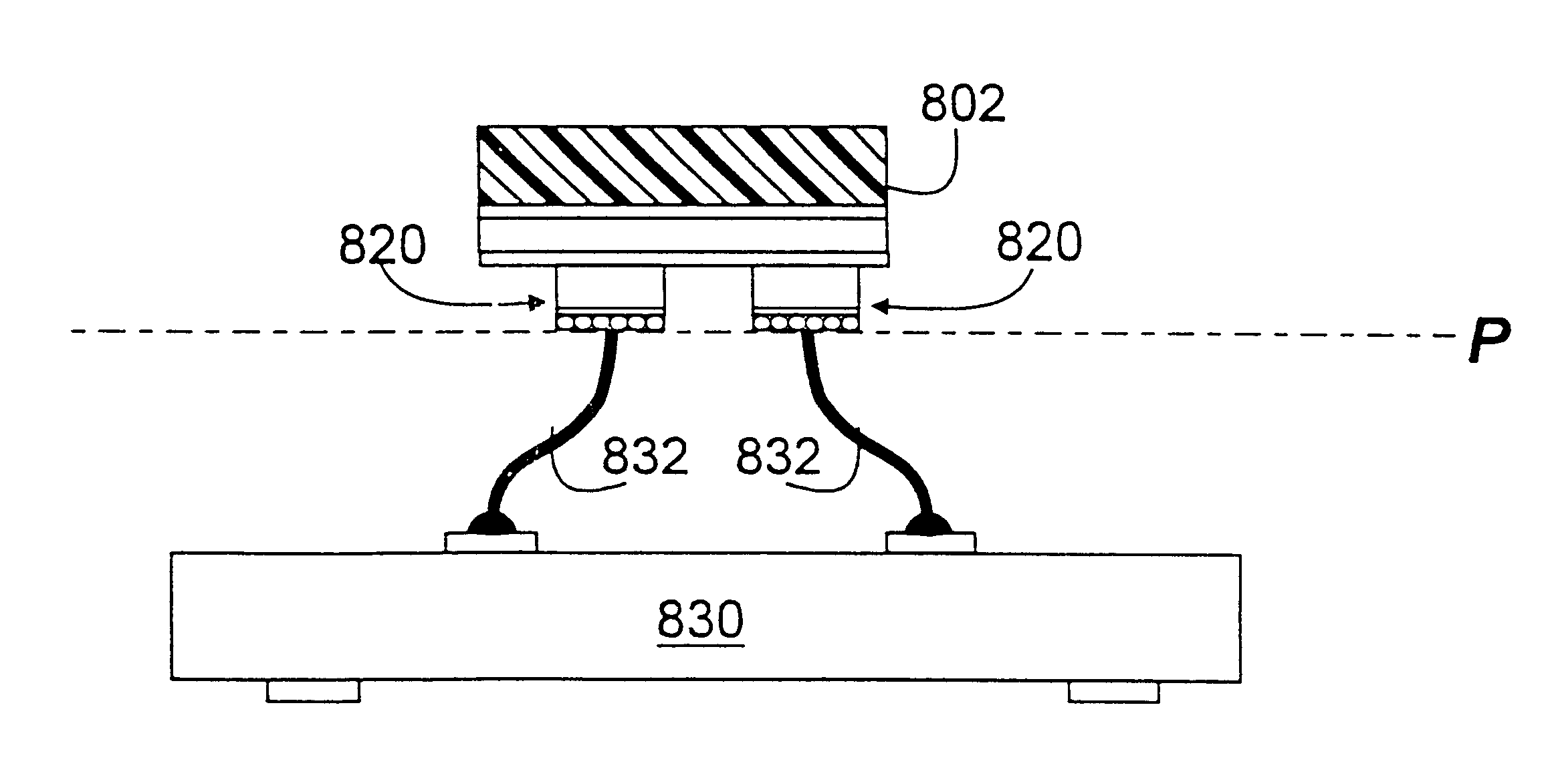

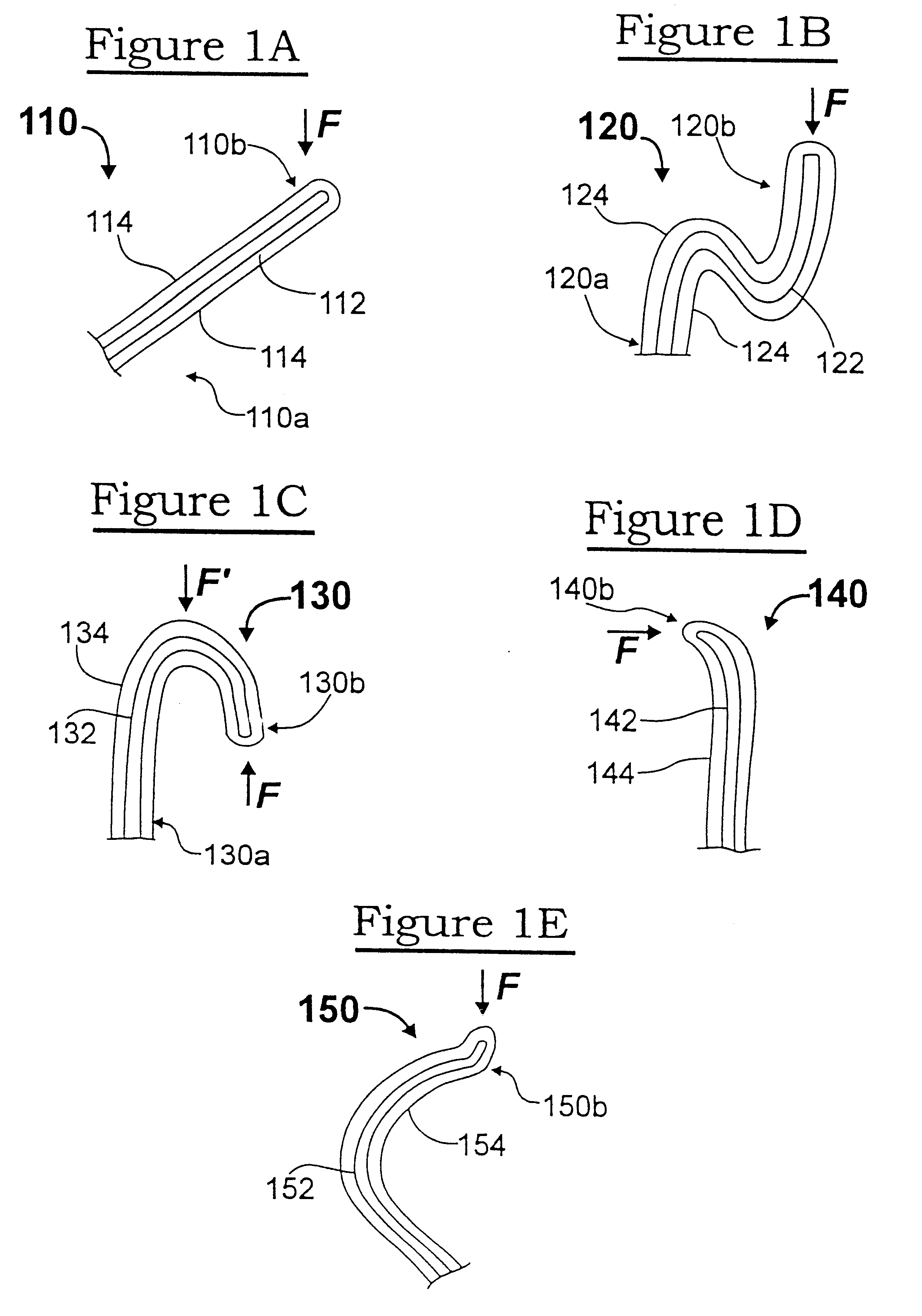

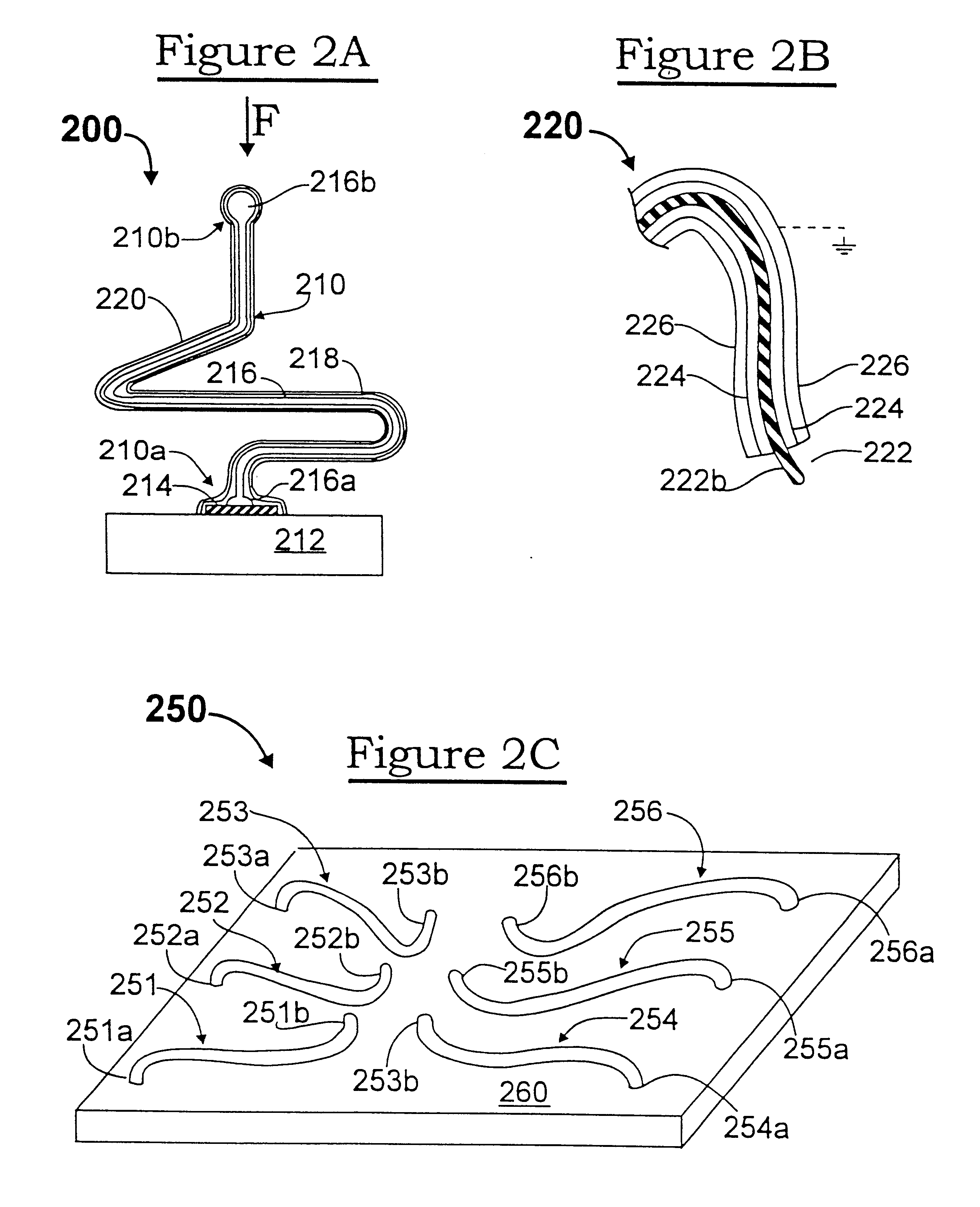

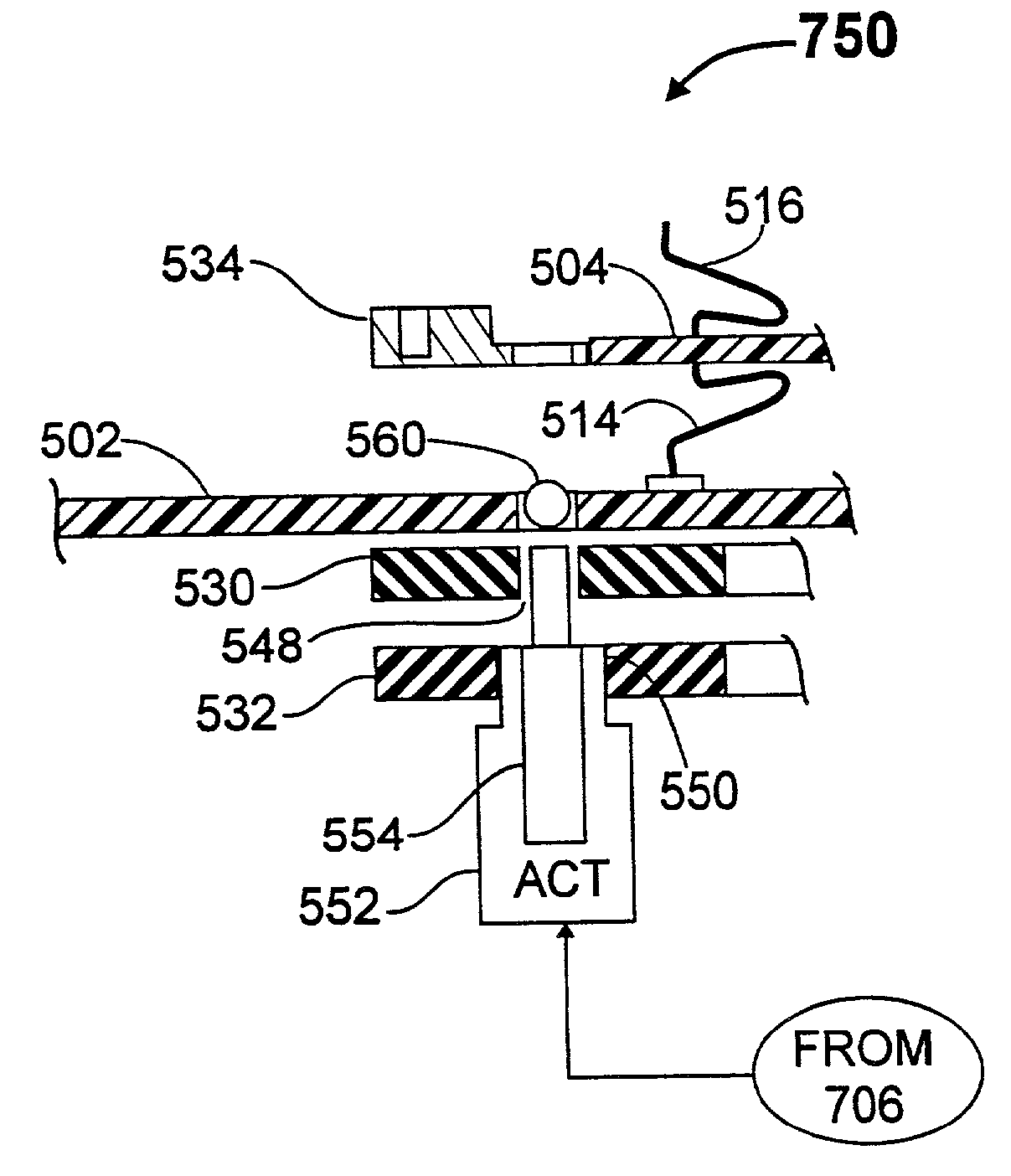

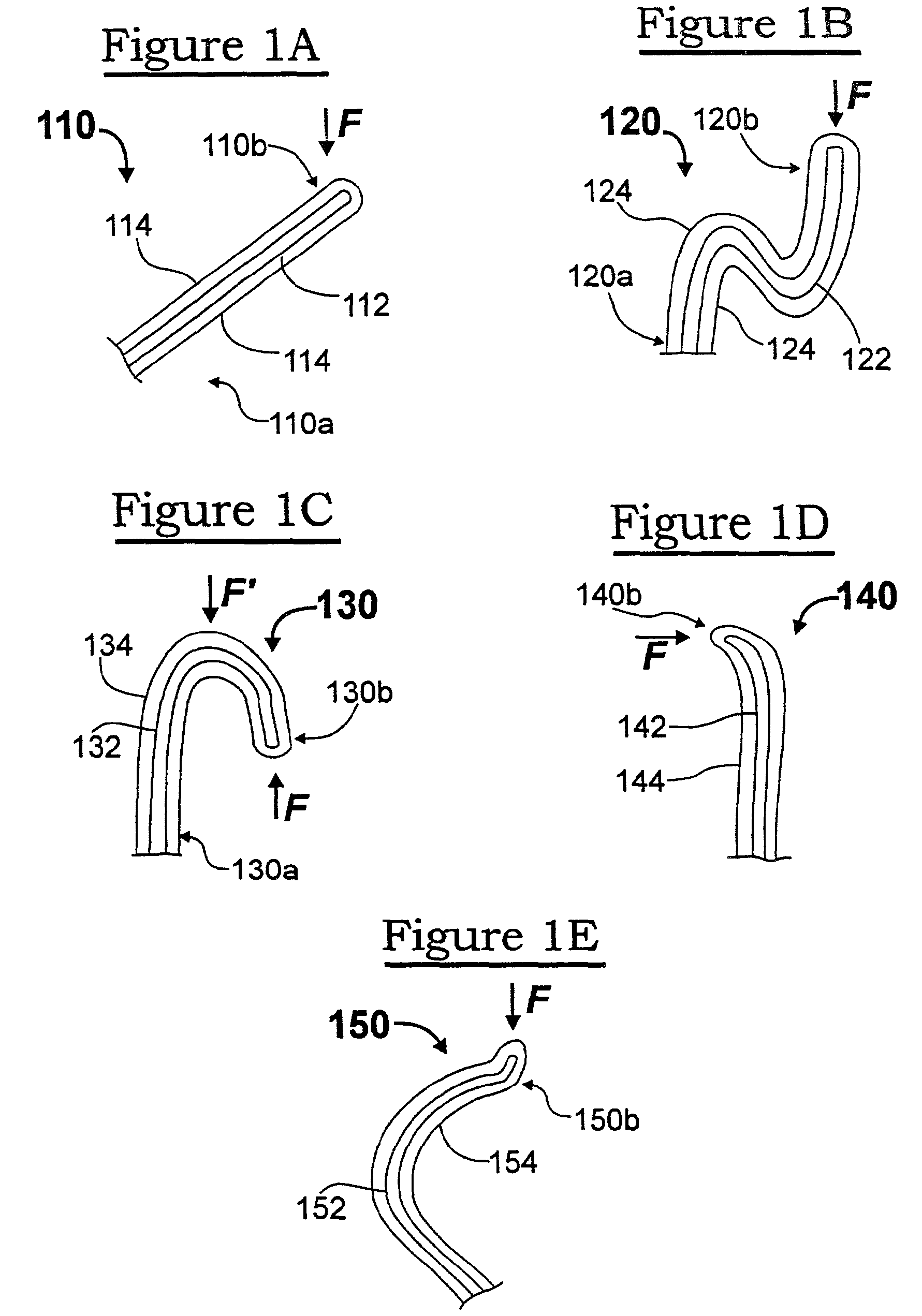

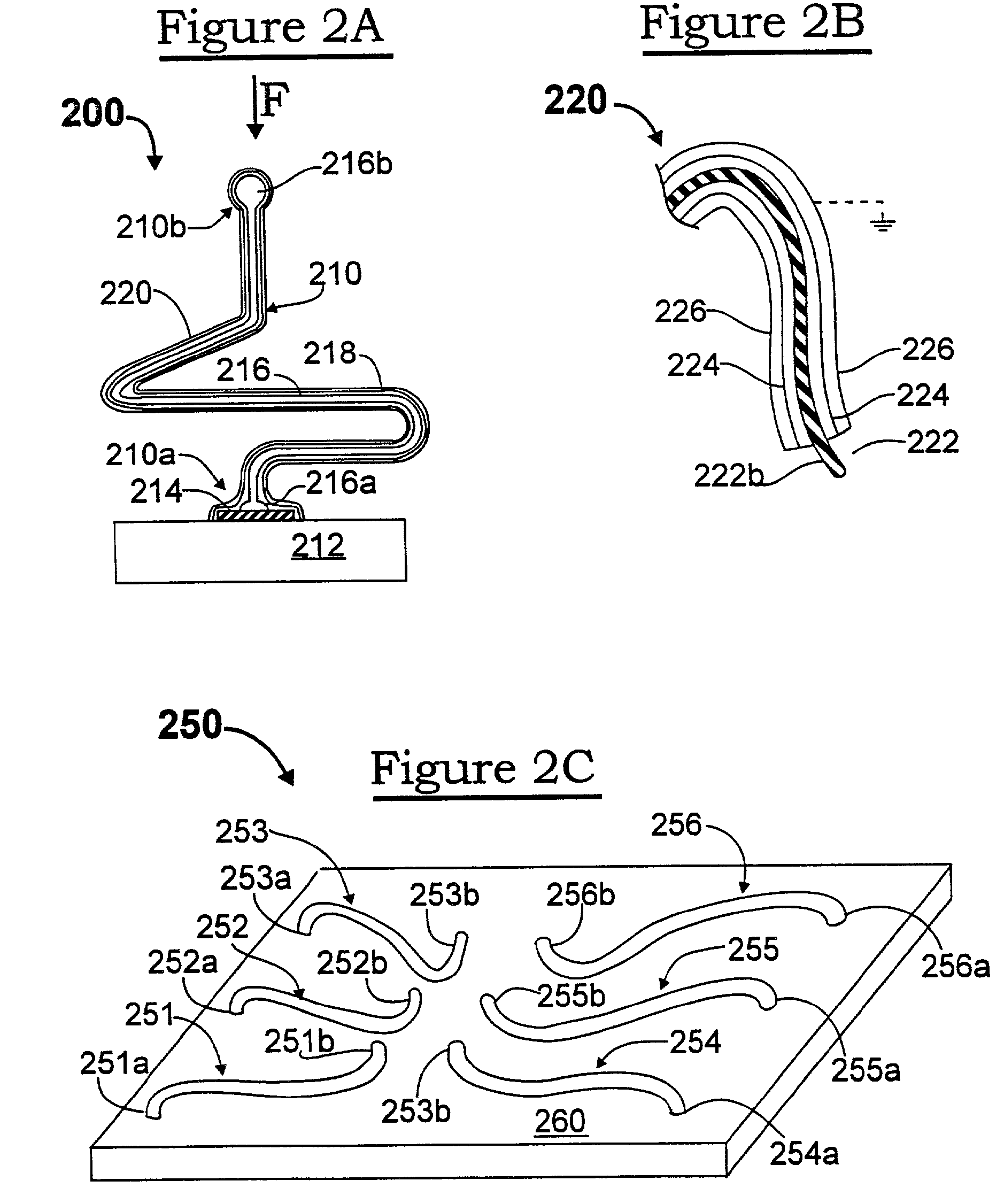

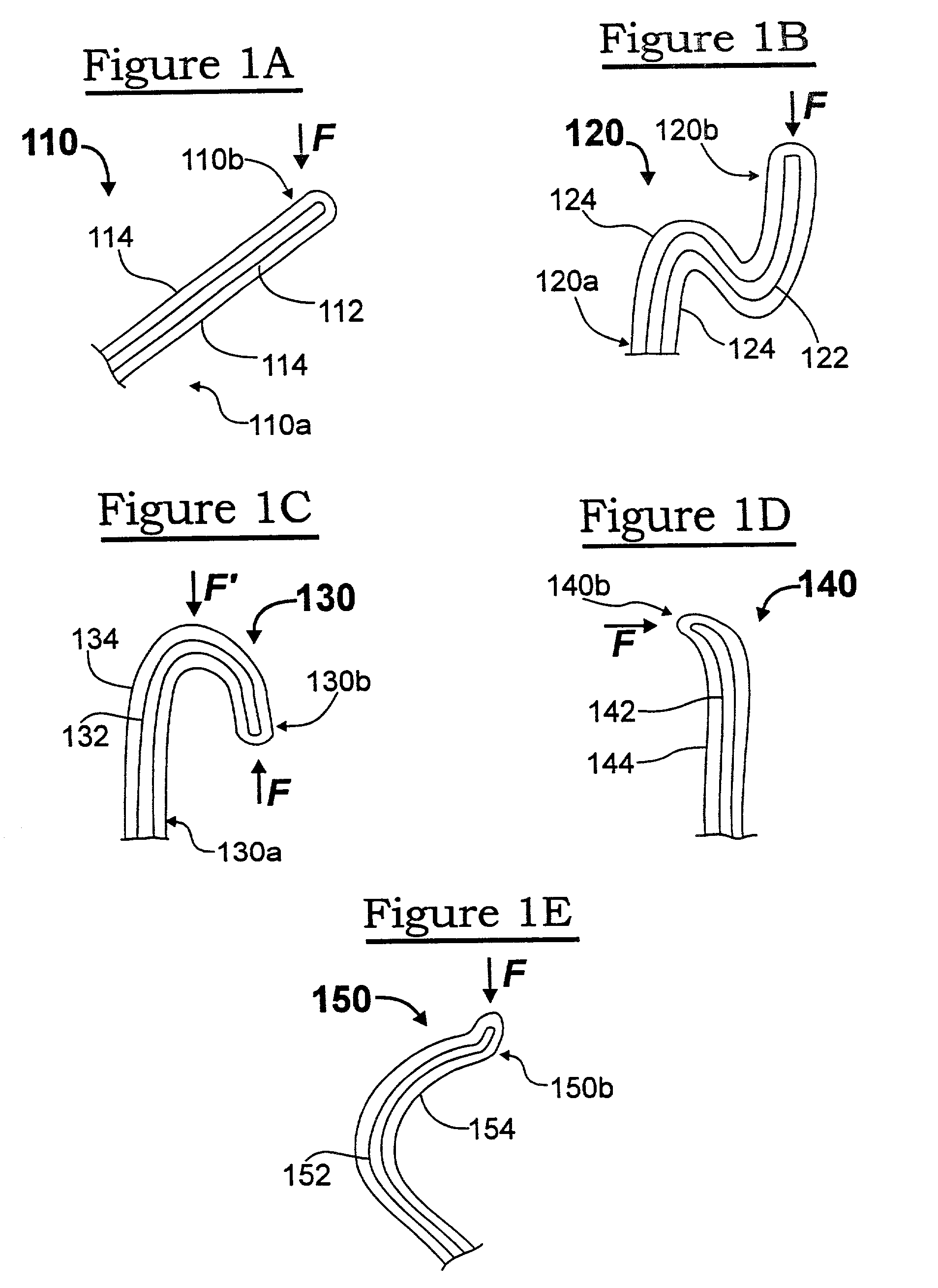

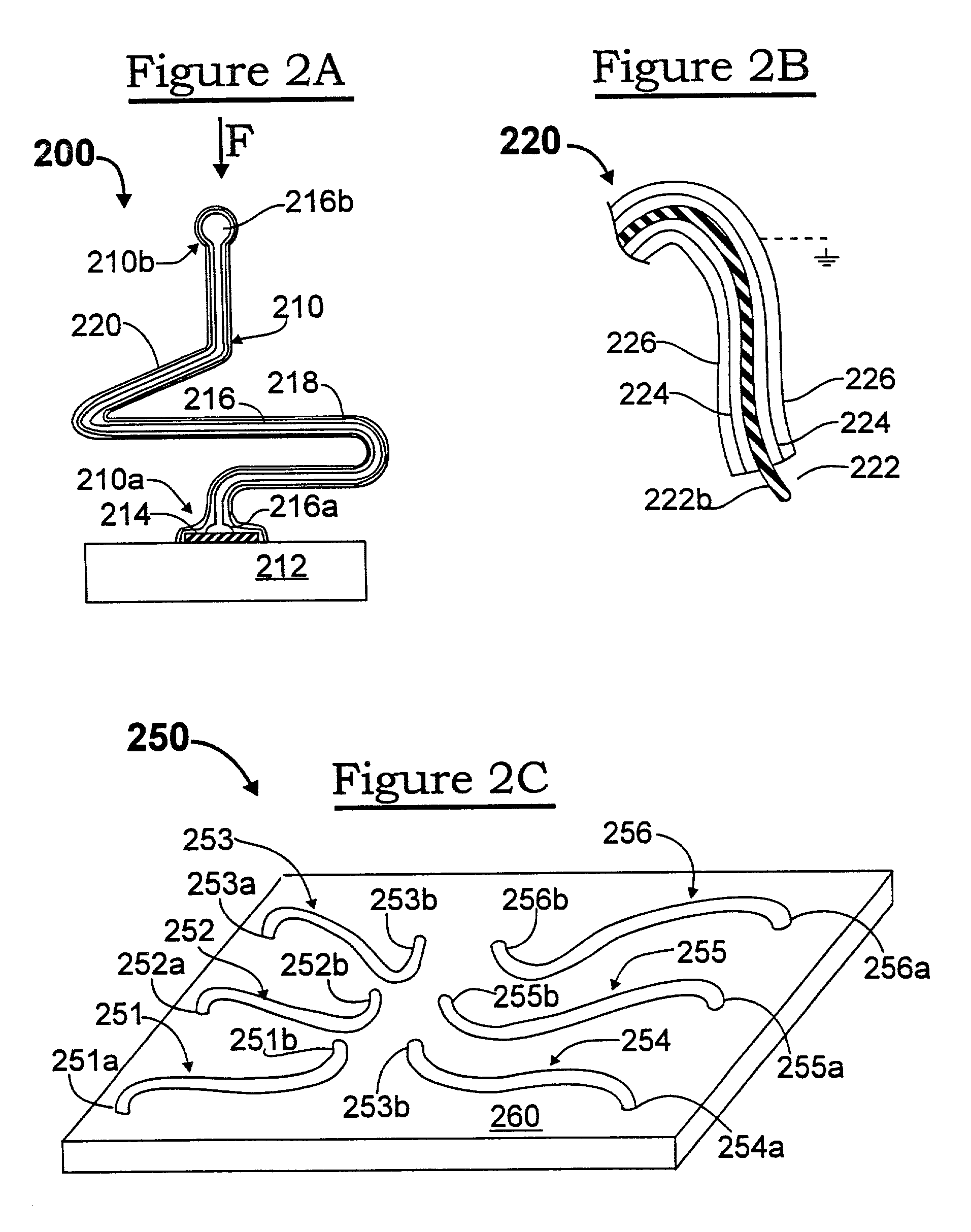

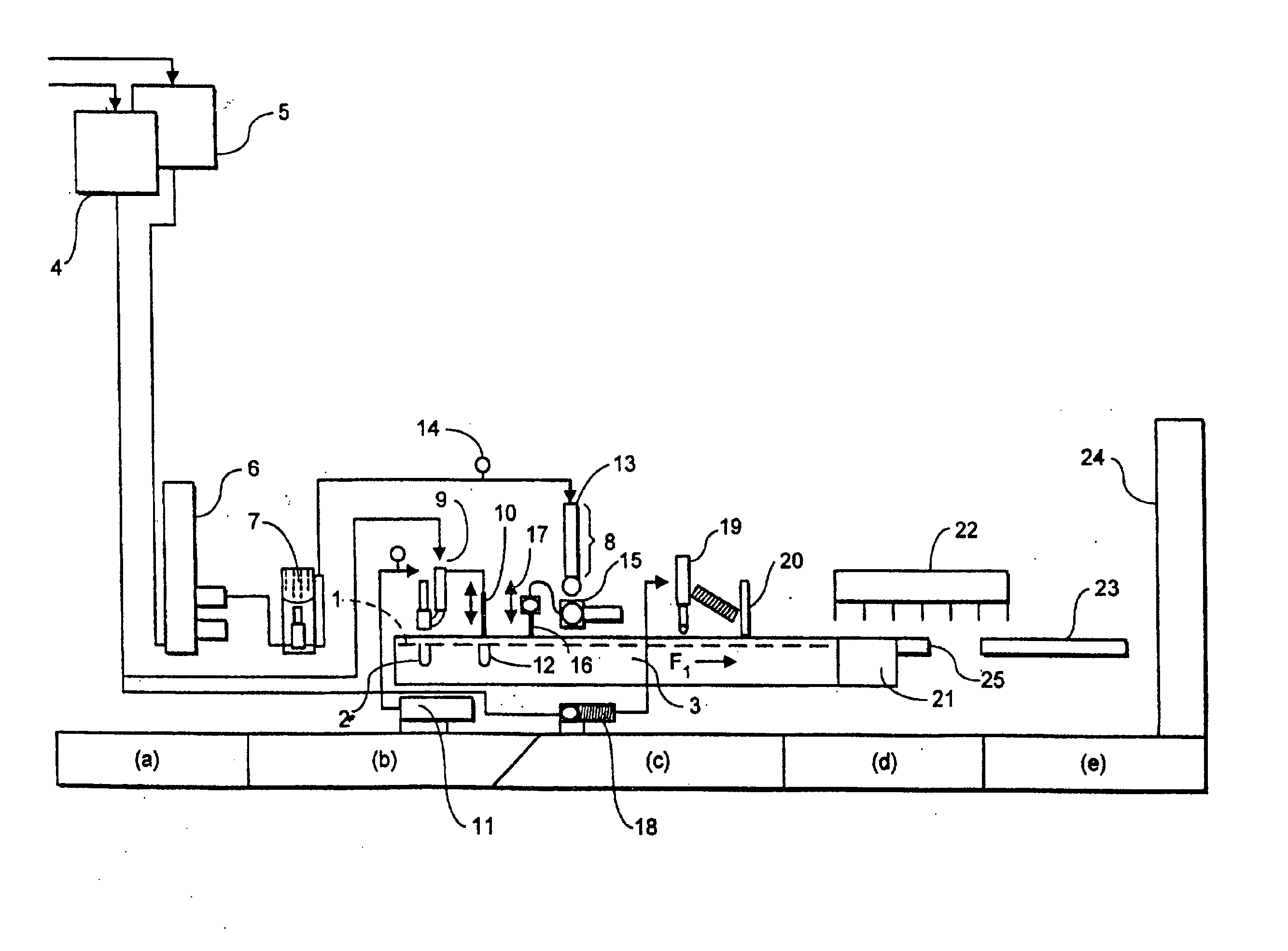

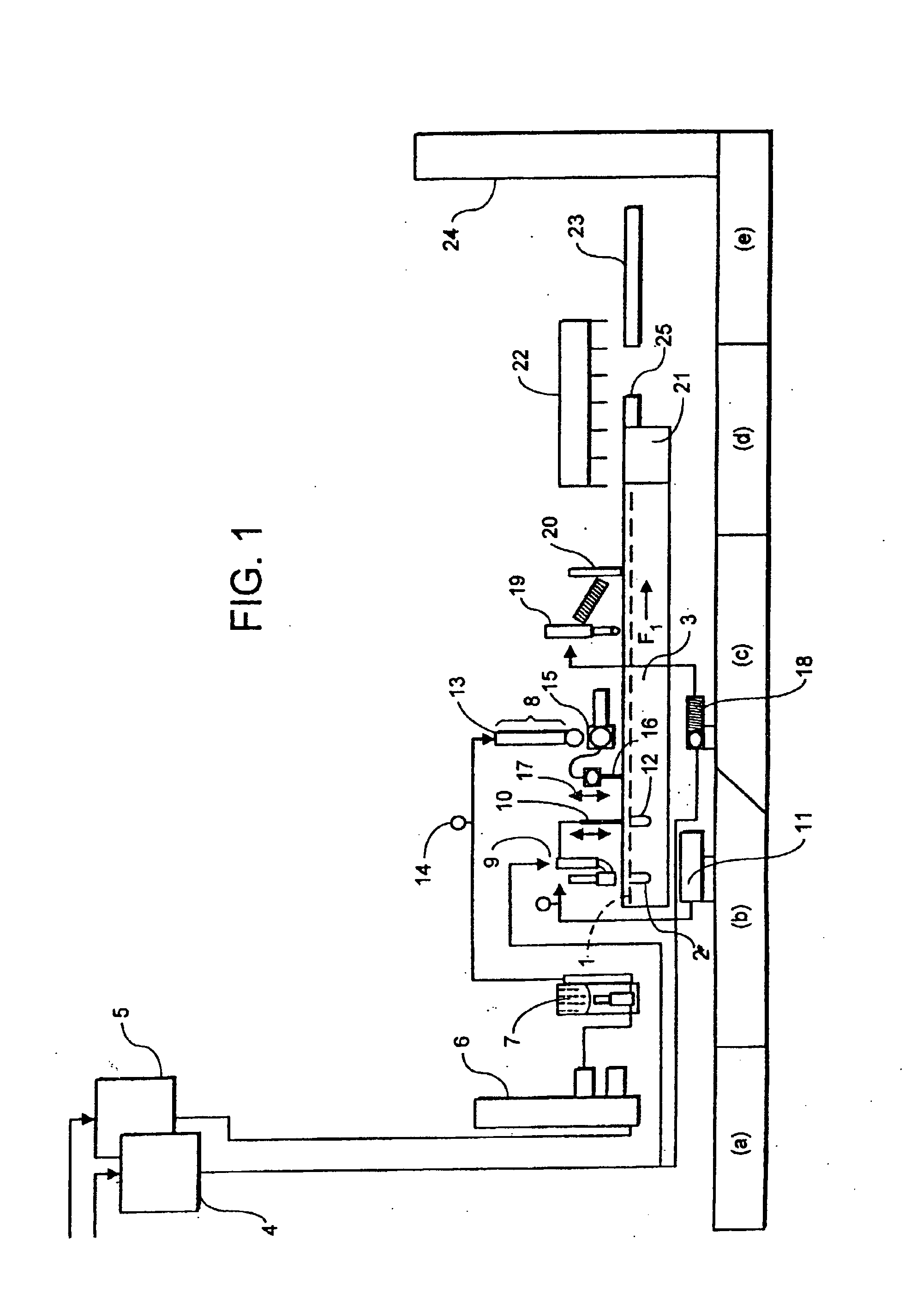

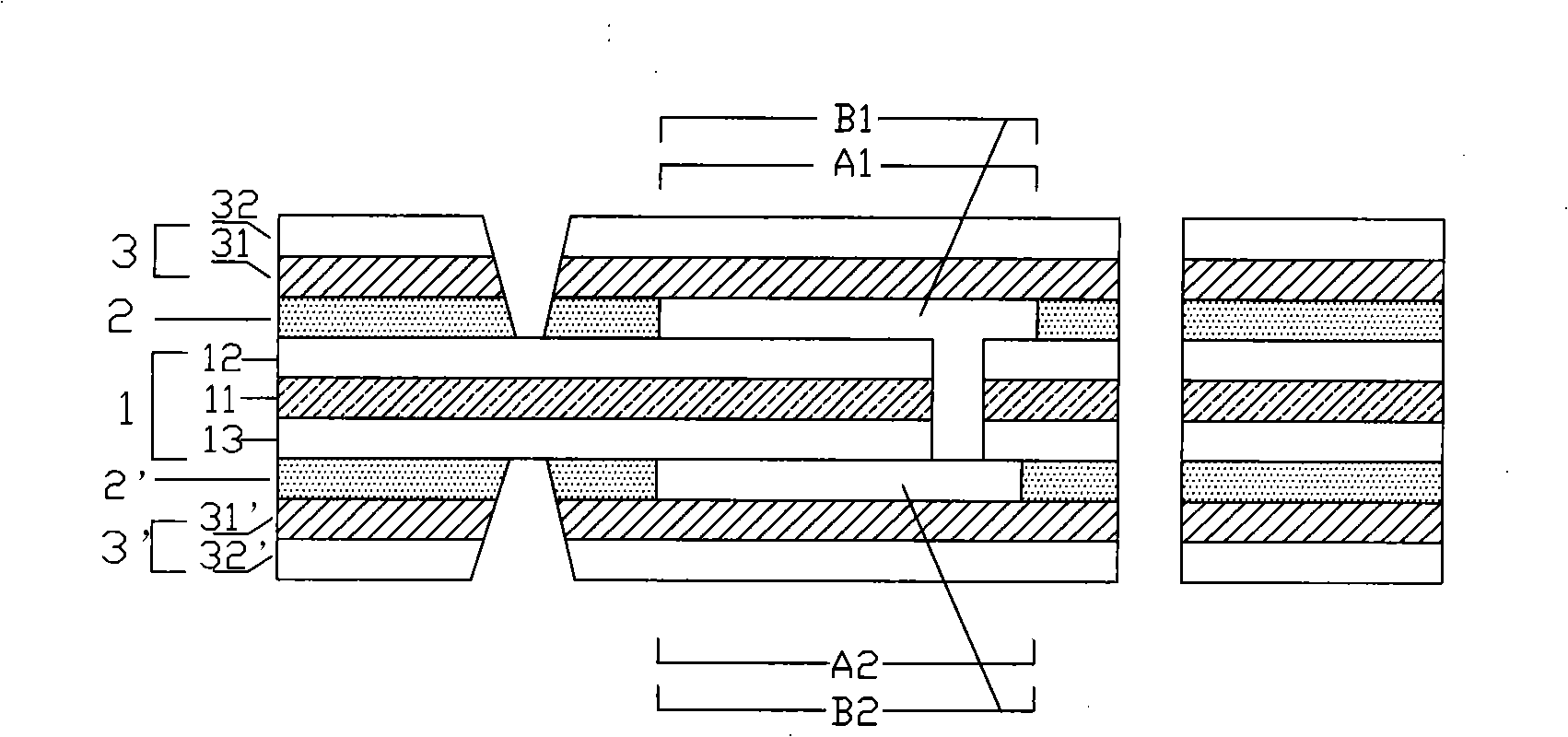

A probe card assembly includes a probe card, a space transformer having resilient contact structures (probe elements) mounted directly thereto (i.e., without the need for additional connecting wires or the like) and extending from terminals on a surface thereof, and an interposer disposed between the space transformer and the probe card. The space transformer and interposer are "stacked up" so that the orientation of the space transformer, hence the orientation of the tips of the probe elements, can be adjusted without changing the orientation of the probe card. Suitable mechanisms for adjusting the orientation of the space transformer, and for determining what adjustments to make, are disclosed. The interposer has resilient contact structures extending from both the top and bottom surfaces thereof, and ensures that electrical connections are maintained between the space transformer and the probe card throughout the space transformer's range of adjustment, by virtue of the interposer's inherent compliance. Multiple die sites on a semiconductor wafer are readily probed using the disclosed techniques, and the probe elements can be arranged to optimize probing of an entire wafer. Composite interconnection elements having a relatively soft core overcoated by a relatively hard shell, as the resilient contact structures are described.

Owner:FORMFACTOR INC

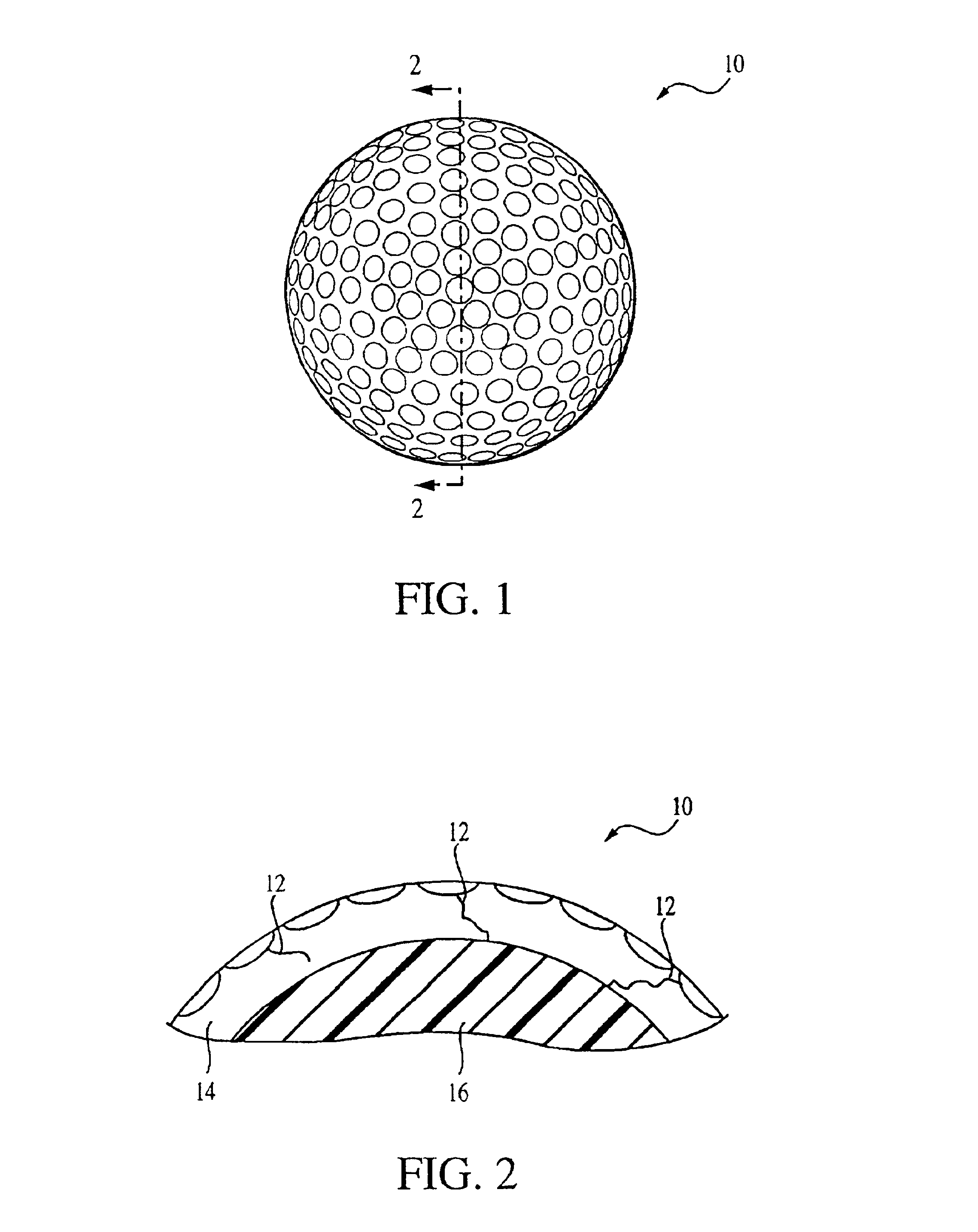

Floor Panel

ActiveUS20110296780A1Improve noise characteristicsThe process is simple and fastConstruction materialLamination ancillary operationsLacquerEngineering

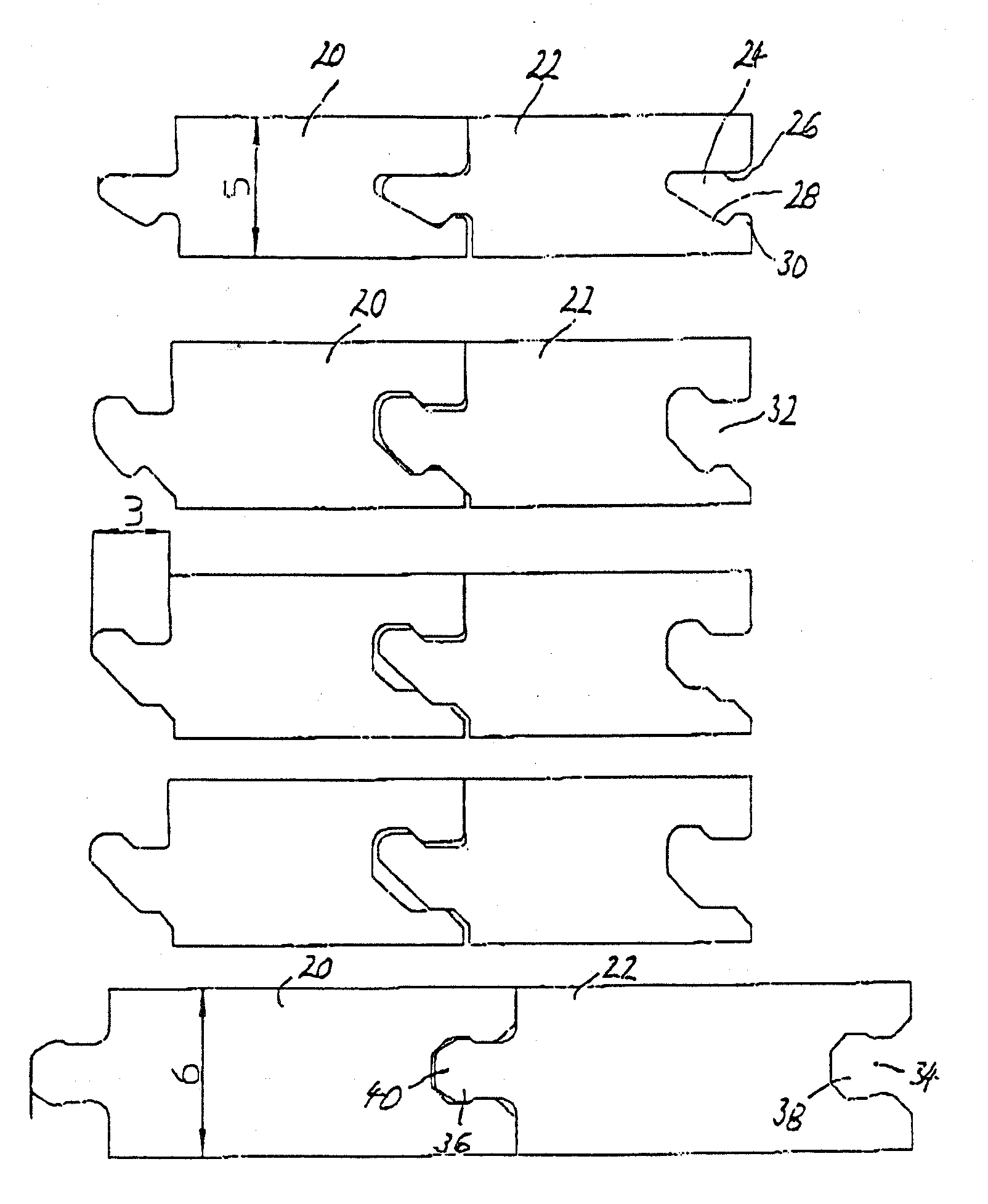

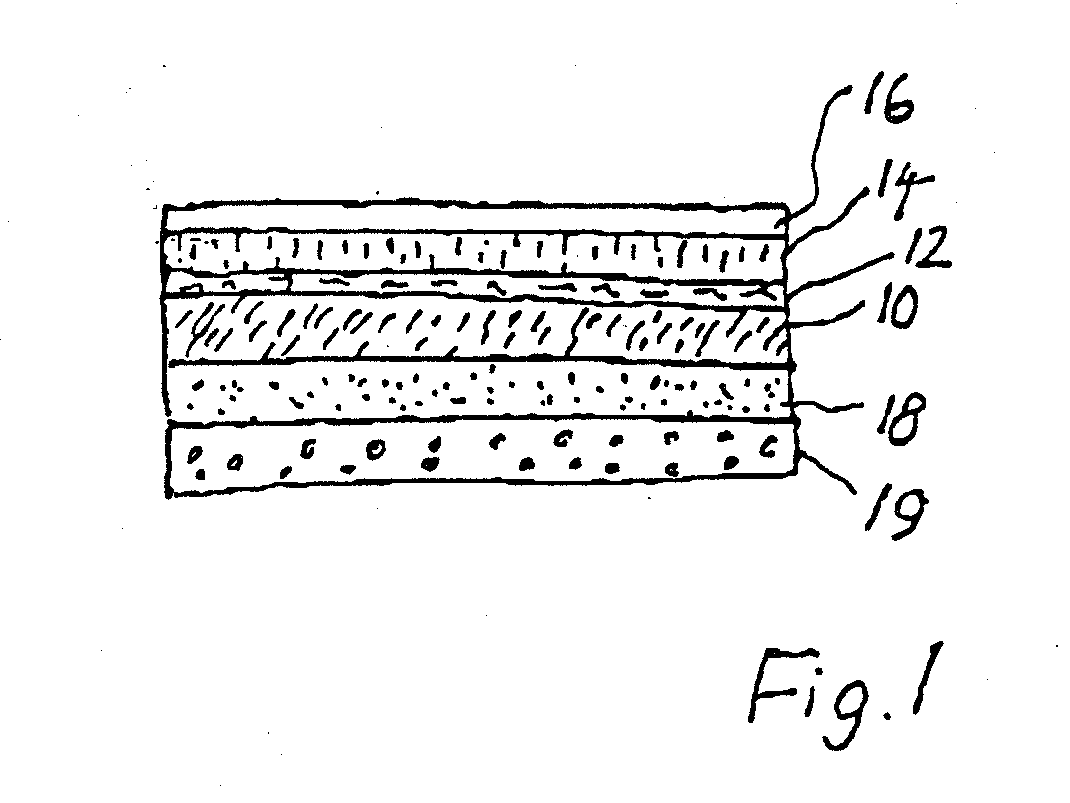

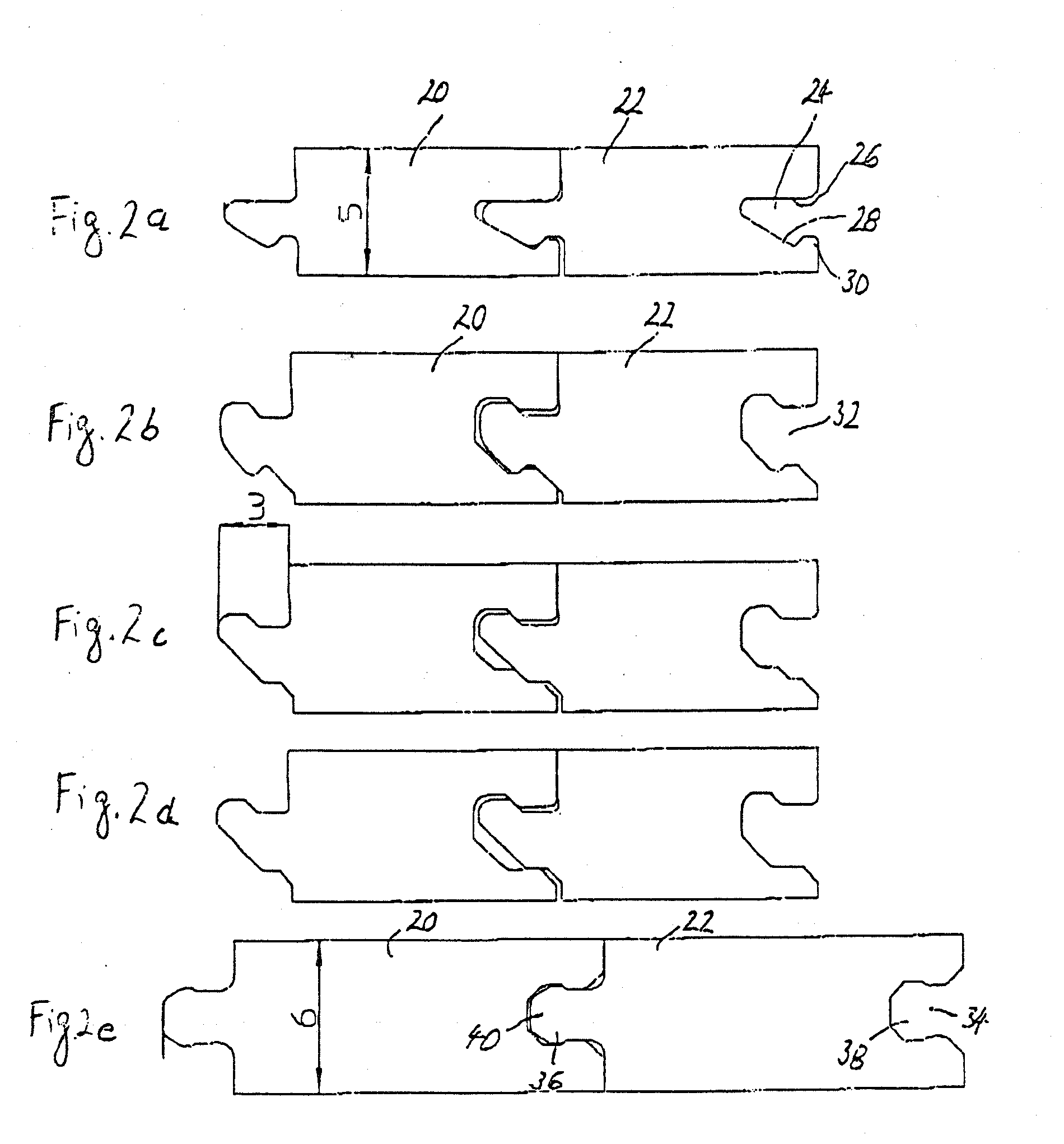

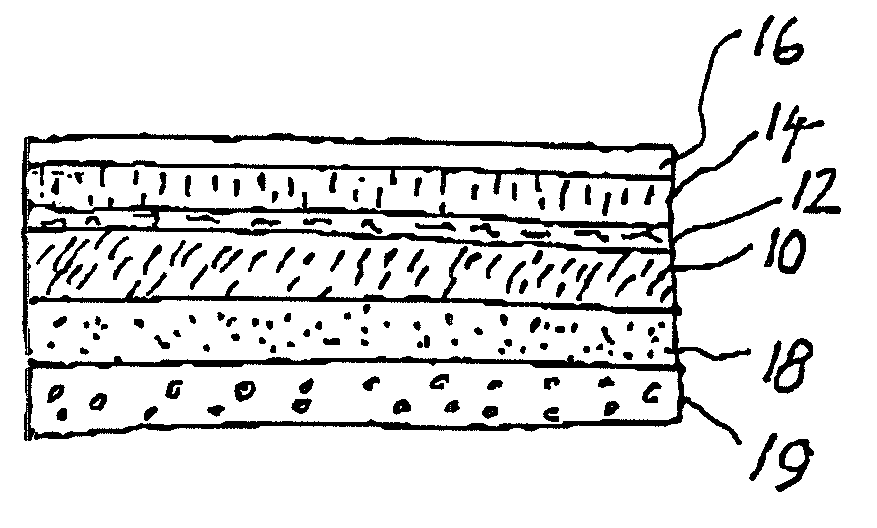

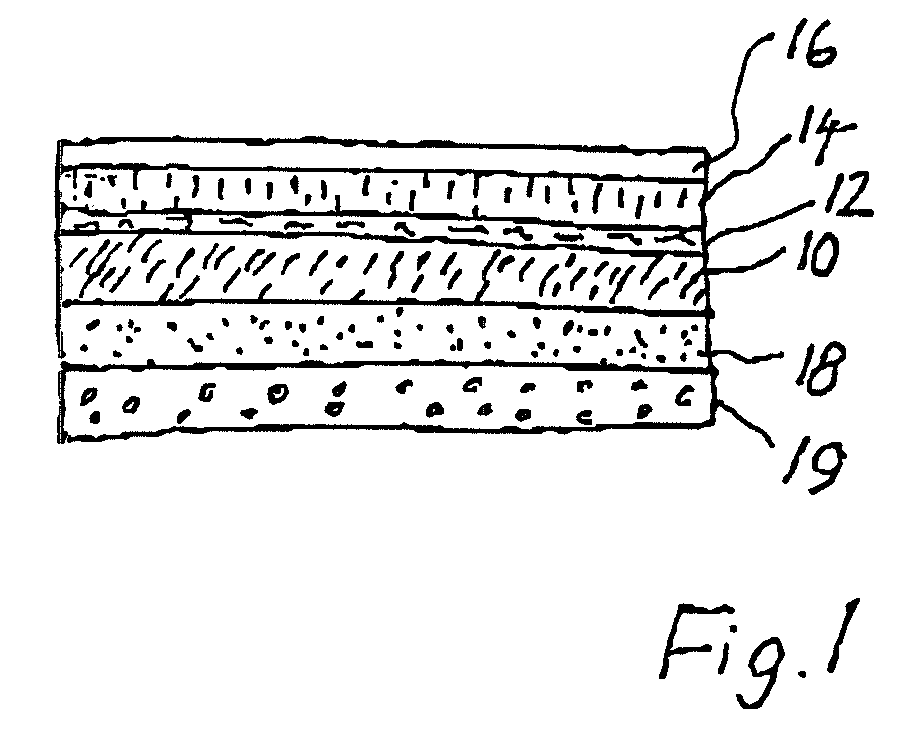

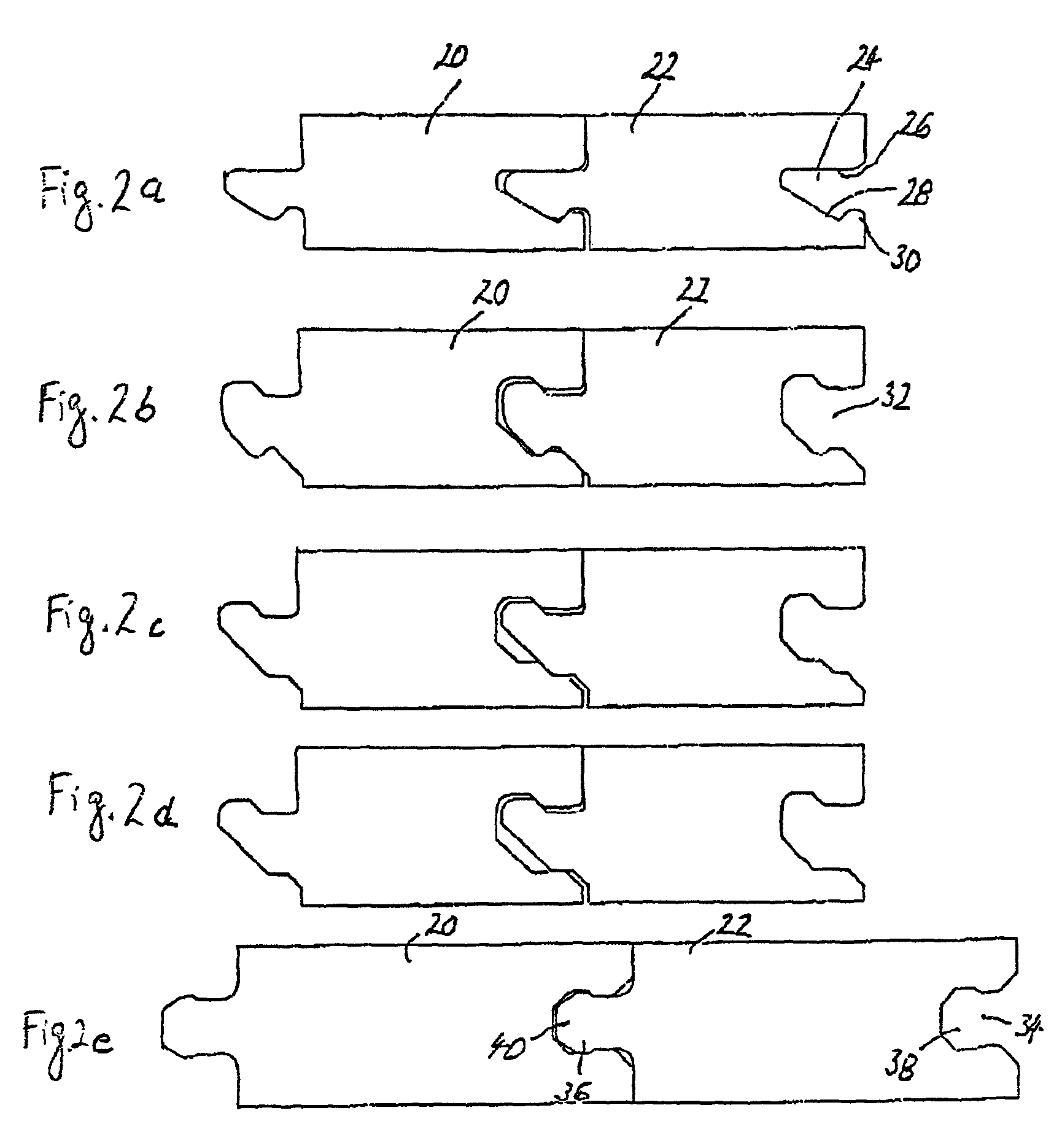

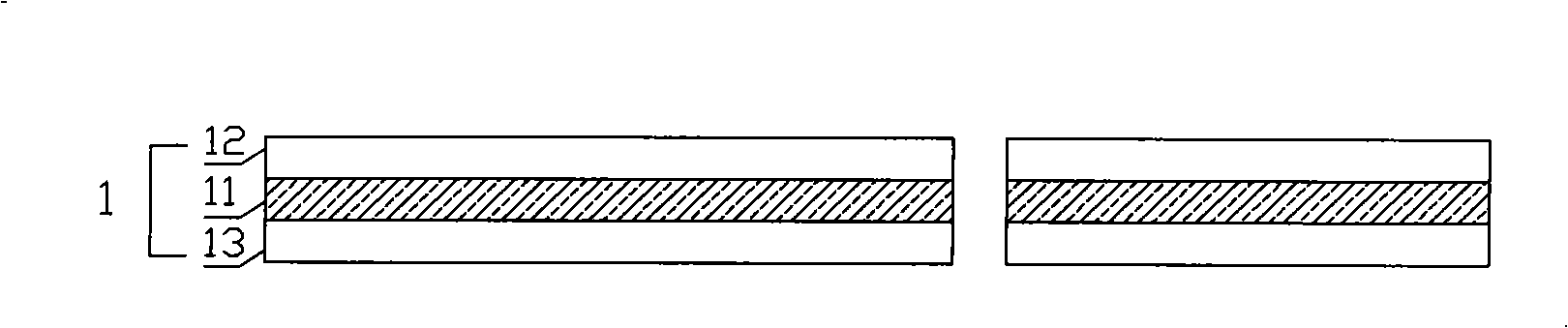

A floor panel in the form of a multilayer, rectangular laminate with a soft core (10) of plastic, a décor film (12) on the upper side of the core (10), a transparent finishing layer (14) and a transparent lacquer layer (16) applied on the finishing layer (16), as well as a back-pull layer (18) on the back of the core (10), with a lockable tongue and groove connection at least at two mutually opposite edges of the panel (20, 22).

Owner:I4F LICENSING NV +2

Floor panel

ActiveUS8071193B2Improve noise characteristicsThe process is simple and fastCeilingsWallsLacquerEngineering

The invention relates to a floor panel in the form of a multilayer, rectangular laminate with a soft core (10) of plastic, a décor film (12) on the upper side of the core (10), a transparent finishing layer (14) and a transparent lacquer layer (16) applied on the finishing layer (16), as well as a back-pull layer (18) on the back of the core (10), with a lockable tongue and groove connection at least at two mutually opposite edges of the panel (20, 22).

Owner:I4F LICENSING NV +2

Probe card assembly and kit, and methods of making same

InactiveUS8373428B2Easy to disassembleEffective shieldingSemiconductor/solid-state device testing/measurementElectronic circuit testingElectricityProbe card

A probe card assembly includes a probe card, a space transformer having resilient contact structures (probe elements) mounted directly to (i.e., without the need for additional connecting wires or the like) and extending from terminals on a surface thereof, and an interposer disposed between the space transformer and the probe card. The space transformer and interposer are “stacked up” so that the orientation of the space transformer, hence the orientation of the tips of the probe elements, can be adjusted without changing the orientation of the probe card. Suitable mechanisms for adjusting the orientation of the space transformer, and for determining what adjustments to make, are disclosed. The interposer has resilient contact structures extending from both the top and bottom surfaces thereof, and ensures that electrical connections are maintained between the space transformer and the probe card throughout the space transformer's range of adjustment, by virtue of the interposer's inherent compliance. Multiple die sites on a semiconductor wafer are readily probed using the disclosed techniques, and the probe elements can be arranged to optimize probing of an entire wafer. Composite interconnection elements having a relatively soft core overcoated by a relatively hard shell, as the resilient contact structures are described.

Owner:FORMFACTOR INC

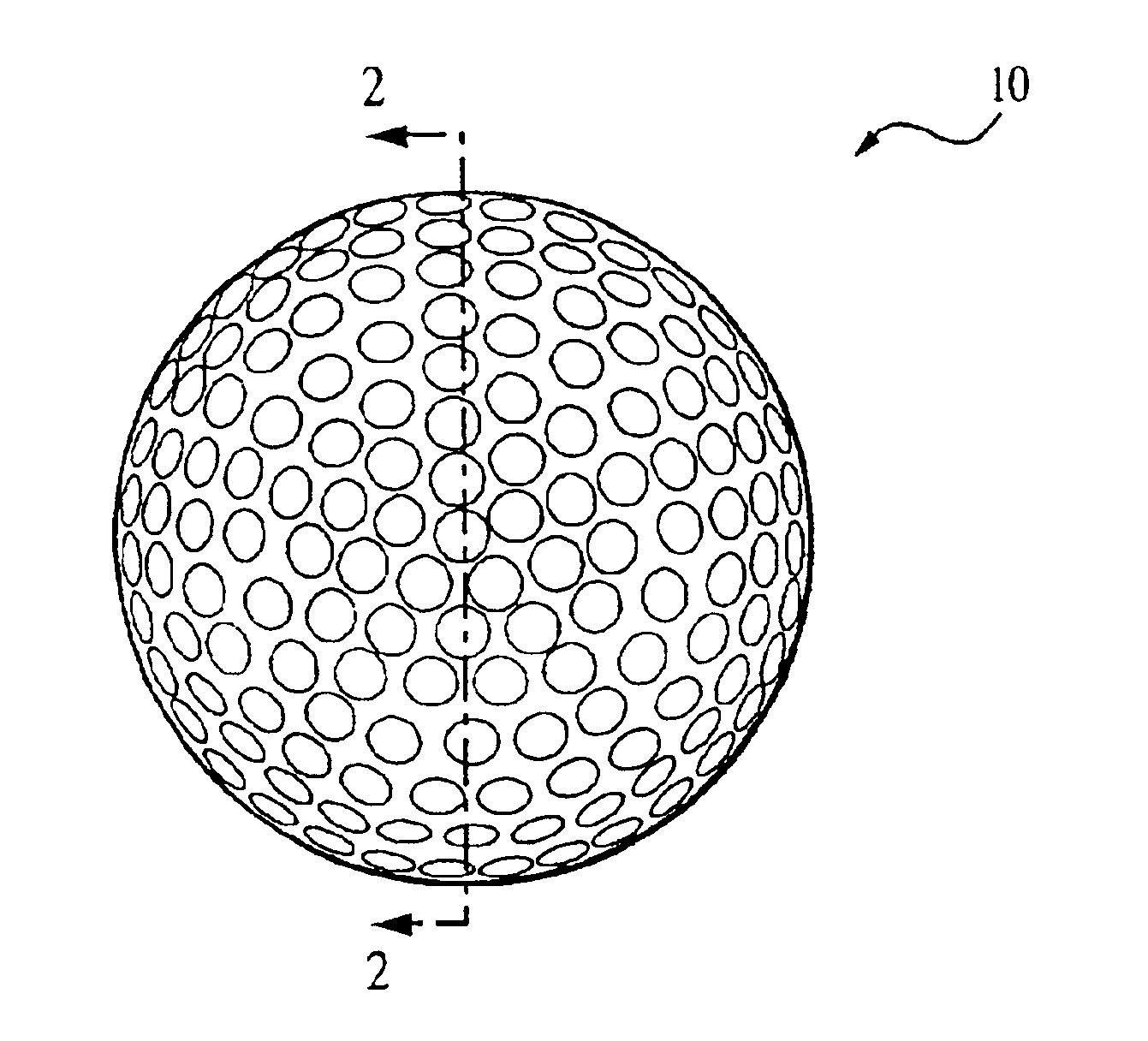

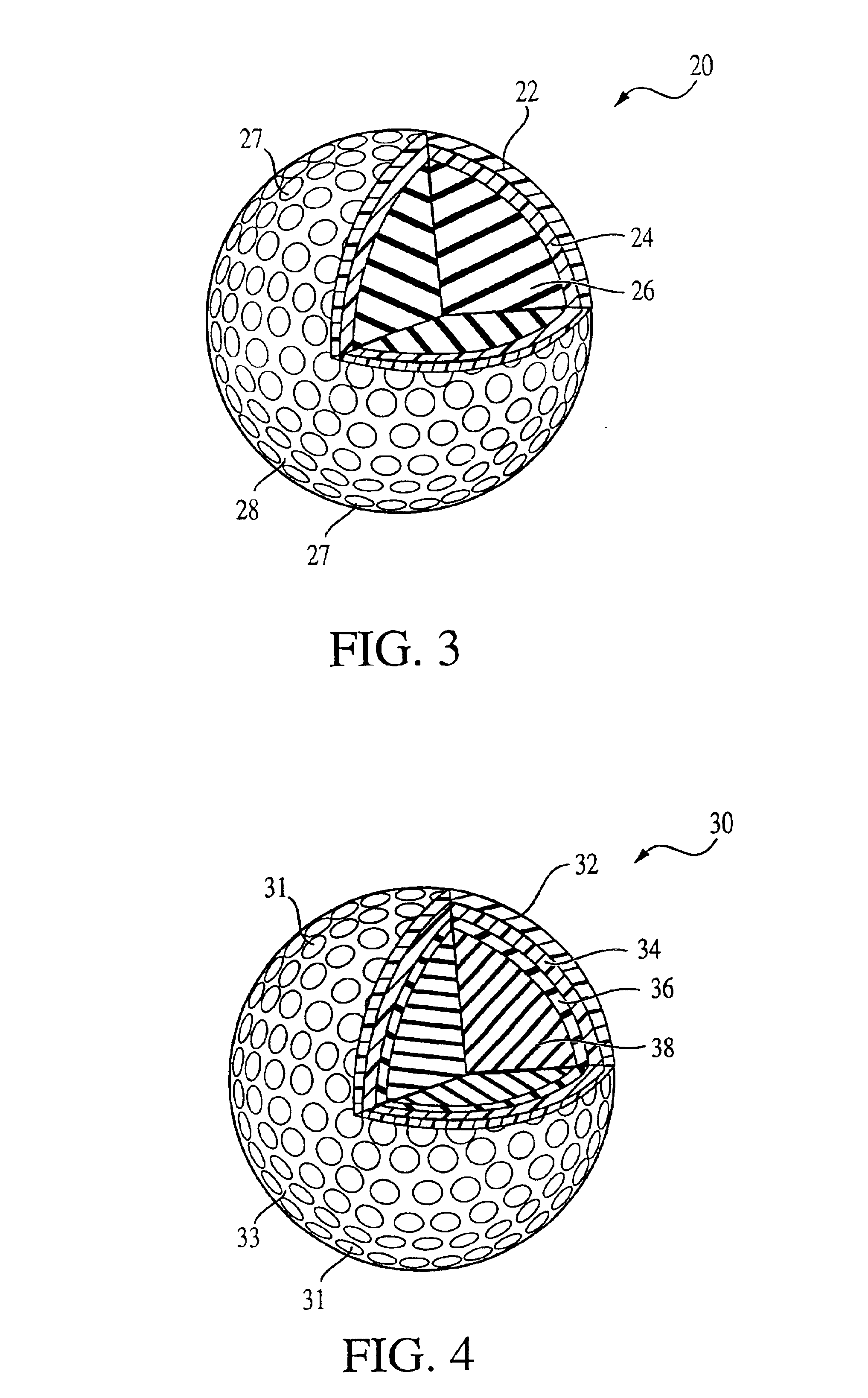

Golf ball with multi-layer cover

InactiveUS6837805B2Increased durabilityLow densityGolf ballsSolid ballsCoefficient of restitutionEngineering

A golf ball is described having a core with a multi-layer cover with a thickness of at least 3.6 mm (0.142 inches) and a Shore D hardness of at least 60. The combination of a core, preferably soft core, with a thick, relatively hard multi-layer cover results in a ball having better distance than conventional golf balls having a comparable coefficient of restitution.

Owner:TOPGOLF CALLAWAY BRANDS CORP

Method of making a contact structure with a distinctly formed tip structure

InactiveUS7086149B2Easy to disassembleEffective shieldingSemiconductor/solid-state device testing/measurementFinal product manufactureElectricityProbe card

Owner:FORMFACTOR INC

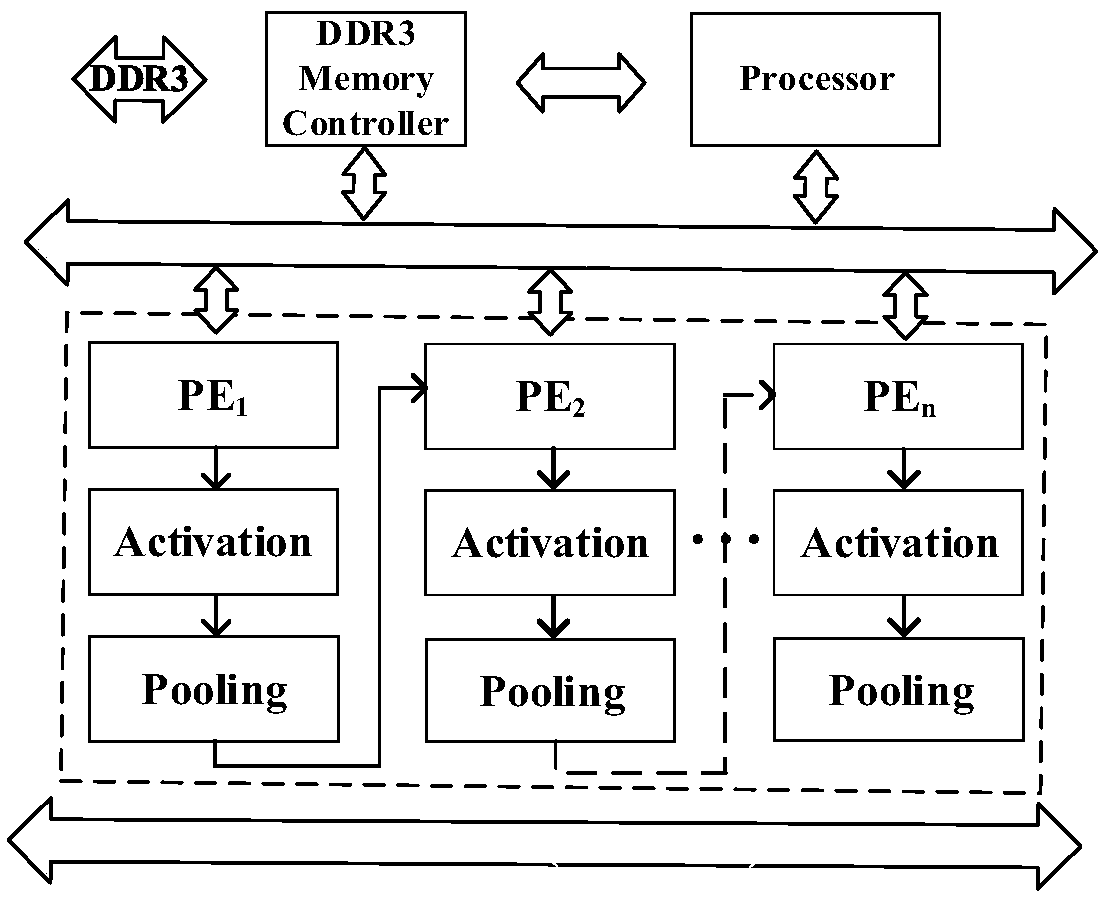

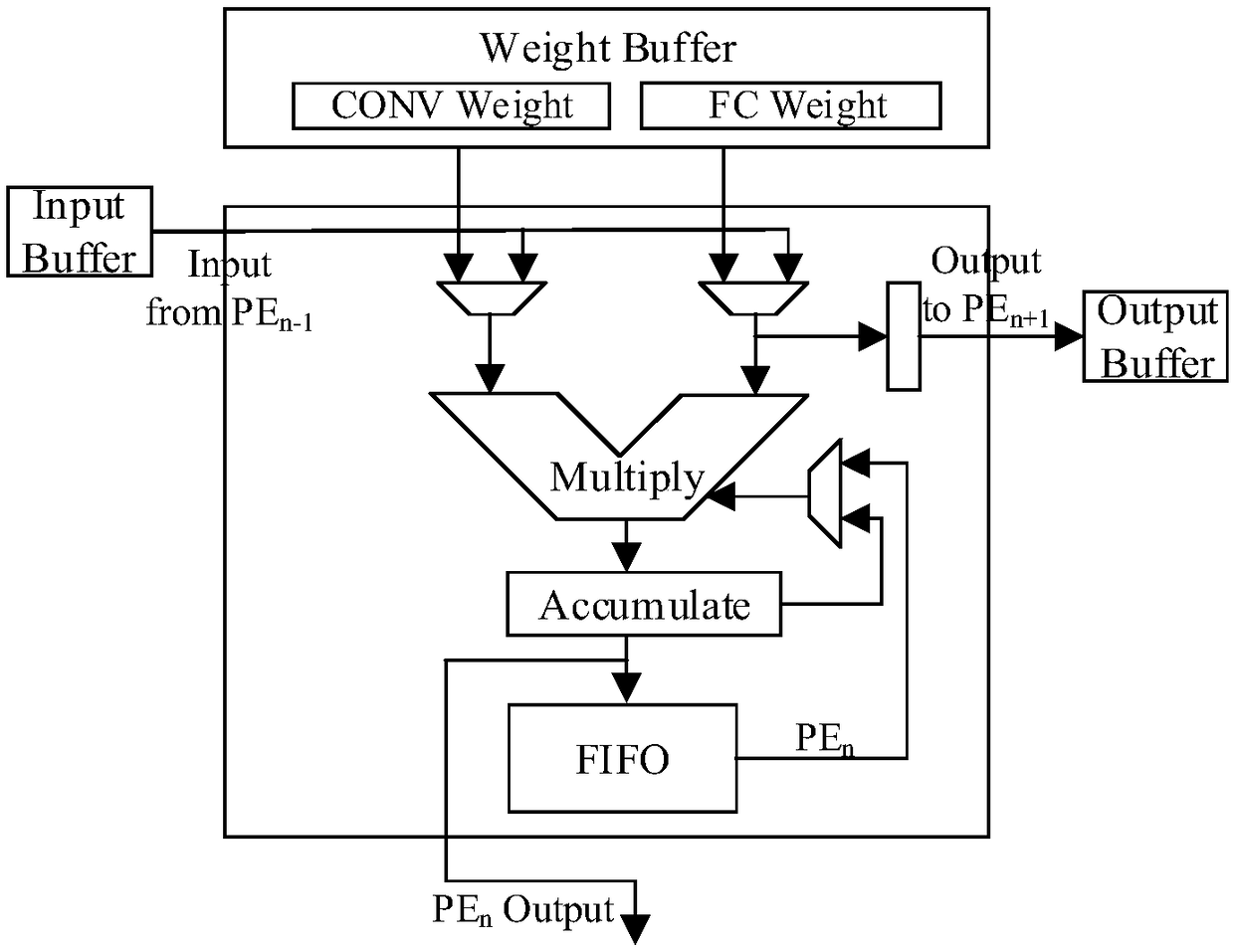

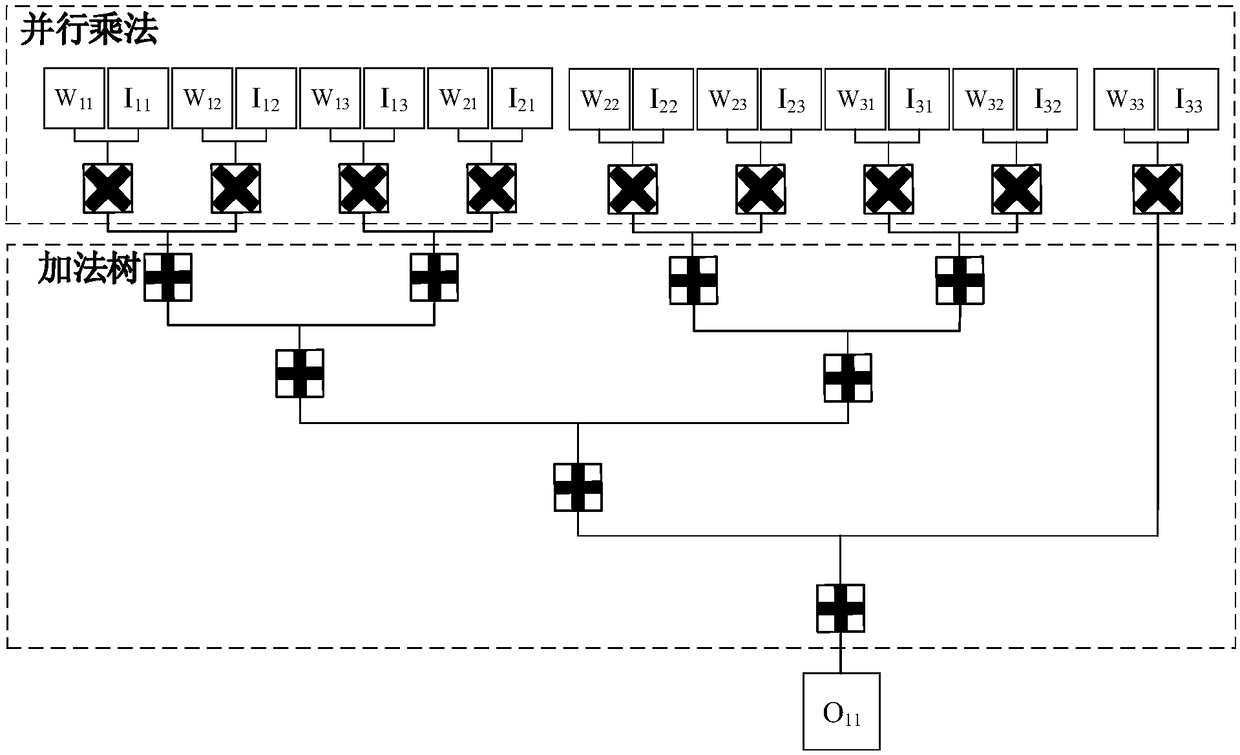

Convolutional-neural-network accelerating system based on field-programmable gate array

InactiveCN108665059AImprove resource utilizationImprove performanceNeural architecturesProduction lineExternal storage

The invention discloses a convolutional-neural-network accelerating system based on a field-programmable gate array. The convolutional-neural-network accelerating system comprises a general processor,the field-programmable gate array, a storage module, a data bus and a control bus, wherein the general processor is a soft core of a reduced instruction set, and is responsible for starting an accelerator, being in communication with a host terminal, conducting time measurement and the like; a DDR3 DRAM serves as an external storage of the accelerator system; an AXI4-Lite bus is used for demand transmission, and an AXI4 bus is used for data transmission; the field-programmable gate array comprises multiple processing engines (PE), and each processing engine adopts a most-suitable fragment unfolding strategy to correspond to calculation of one layer in the convolutional neural network; all the processing engines are mapped onto a same FPGA chip, and therefore different layers can simultaneously work in a production line mode. Compared with an existing convolutional-neural-network accelerating system, the convolutional-neural-network accelerating system based on the field-programmable gate array can obtain higher energy efficiency benefit.

Owner:SUZHOU INST FOR ADVANCED STUDY USTC

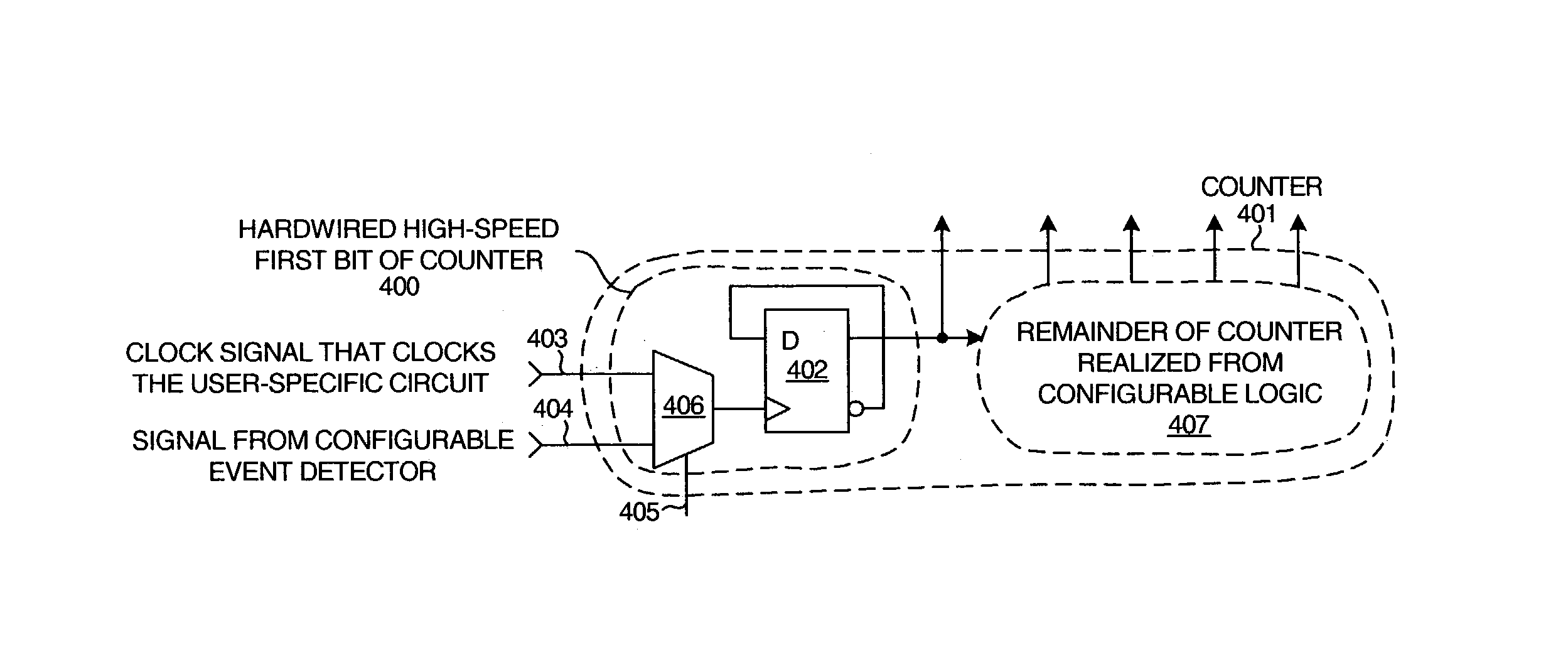

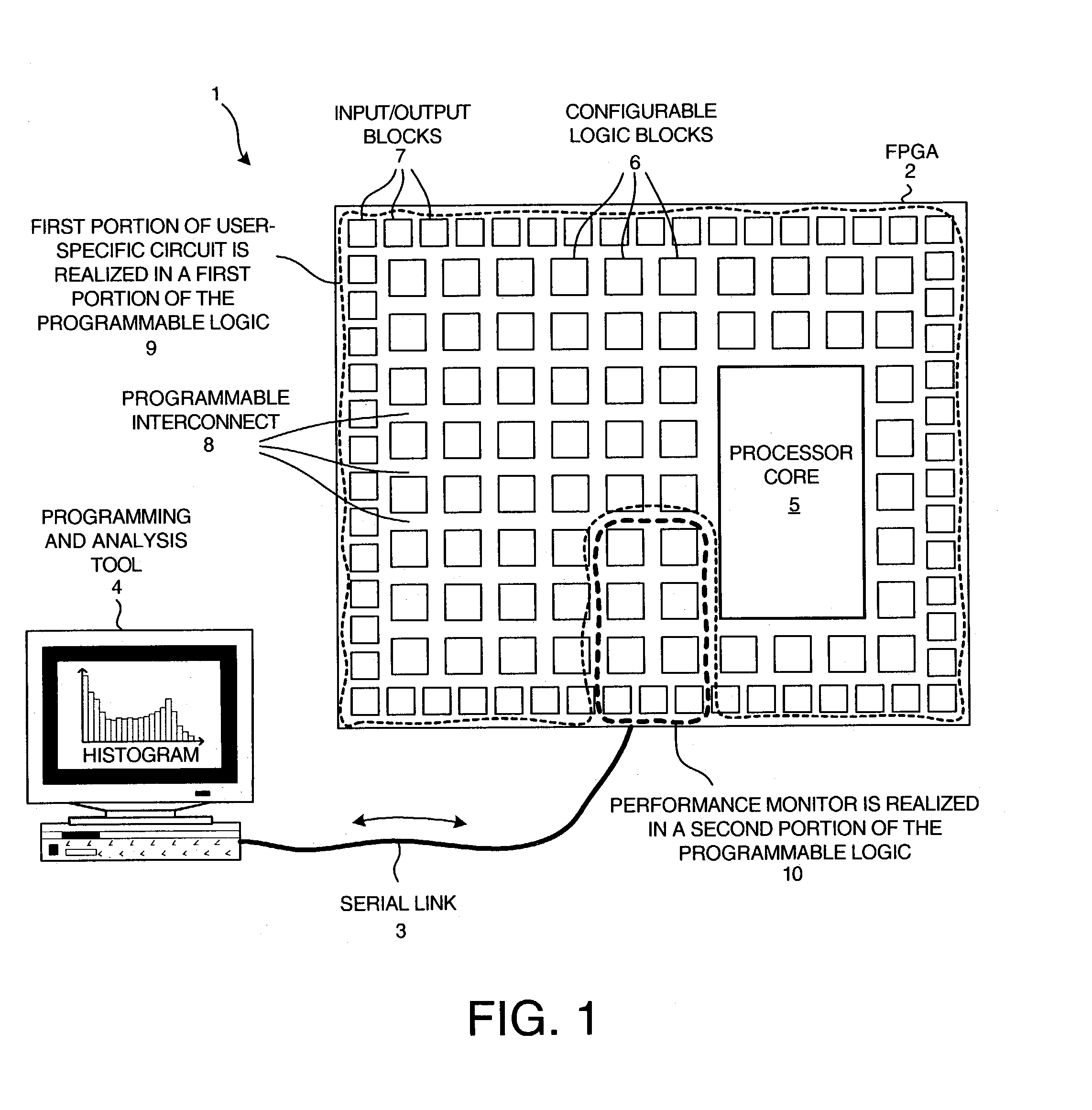

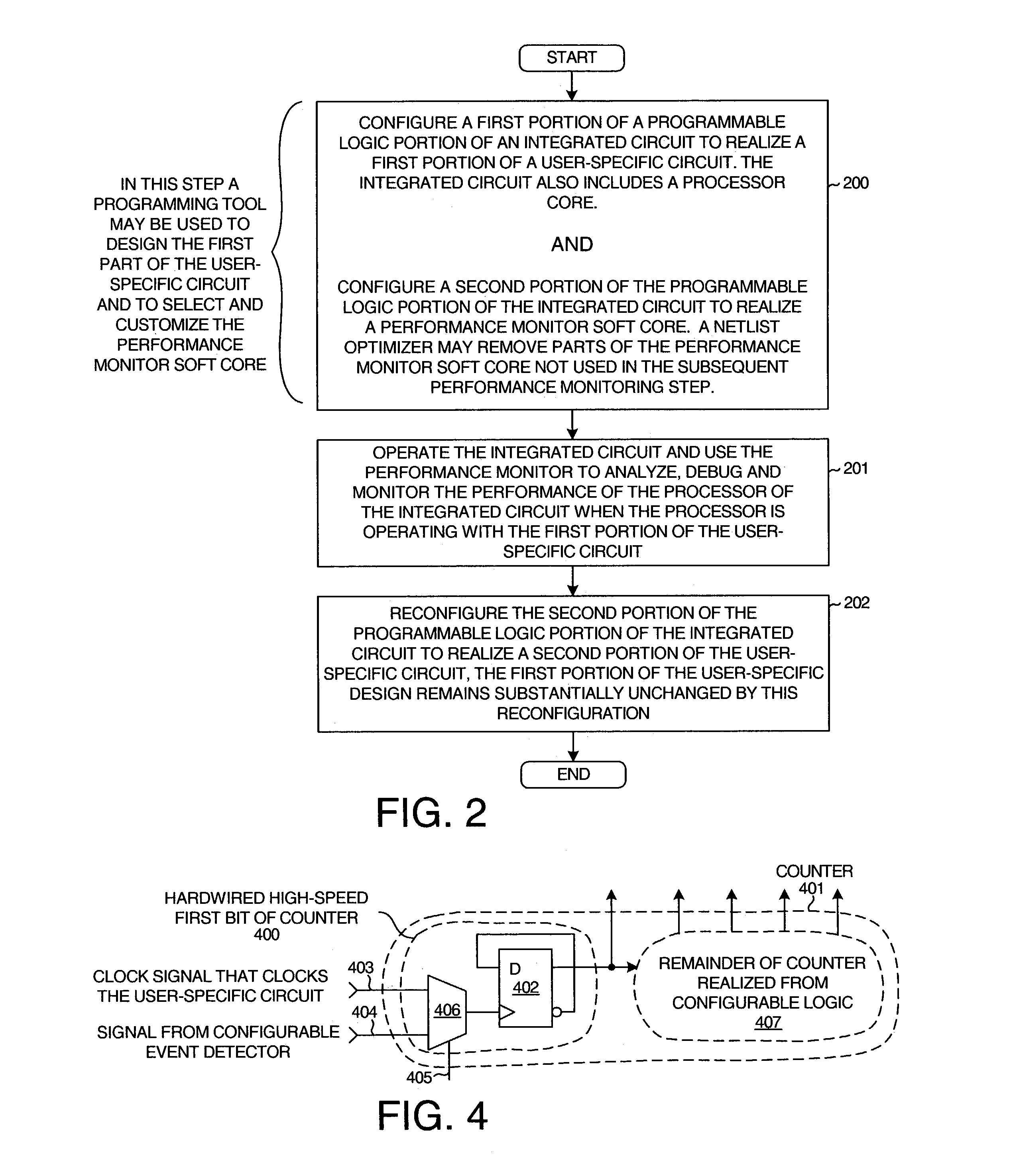

Methods and circuits for realizing a performance monitor for a processor from programmable logic

ActiveUS7308564B1Low costDigital computer detailsHardware monitoringProgrammable logic deviceLogical part

A performance monitor is realized from programmable logic on the same integrated circuit as a processor. A user may use a programming and analysis tool to select a performance monitor soft core and to program it into the integrated circuit. The performance monitor is used to debug and / or monitor operation of the processor. After the debugging and / or performance monitoring, the portion of the programmable logic used to realize the performance monitor can be reconfigured and used to realize another portion of the user-specific circuit. Because the portion of the integrated circuit used to realize the performance monitor can be later used in the user-specific design, the cost of having to provide a no-longer-desired performance monitor in each integrated circuit used in the user's design is avoided. Because the performance monitor is realized from programmable logic, the performance monitor is more flexible than a conventional hardwired configurable performance monitor.

Owner:XILINX INC

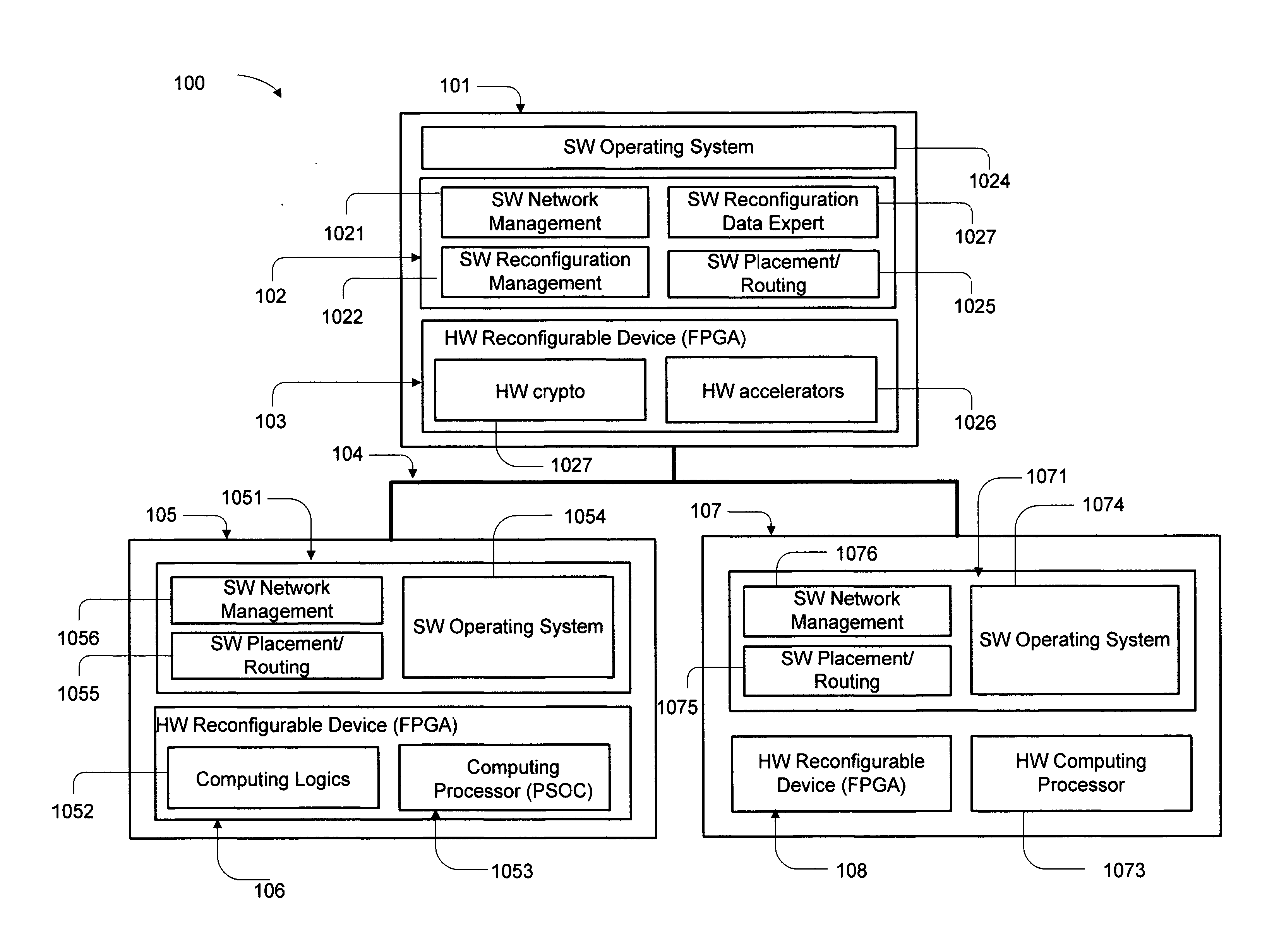

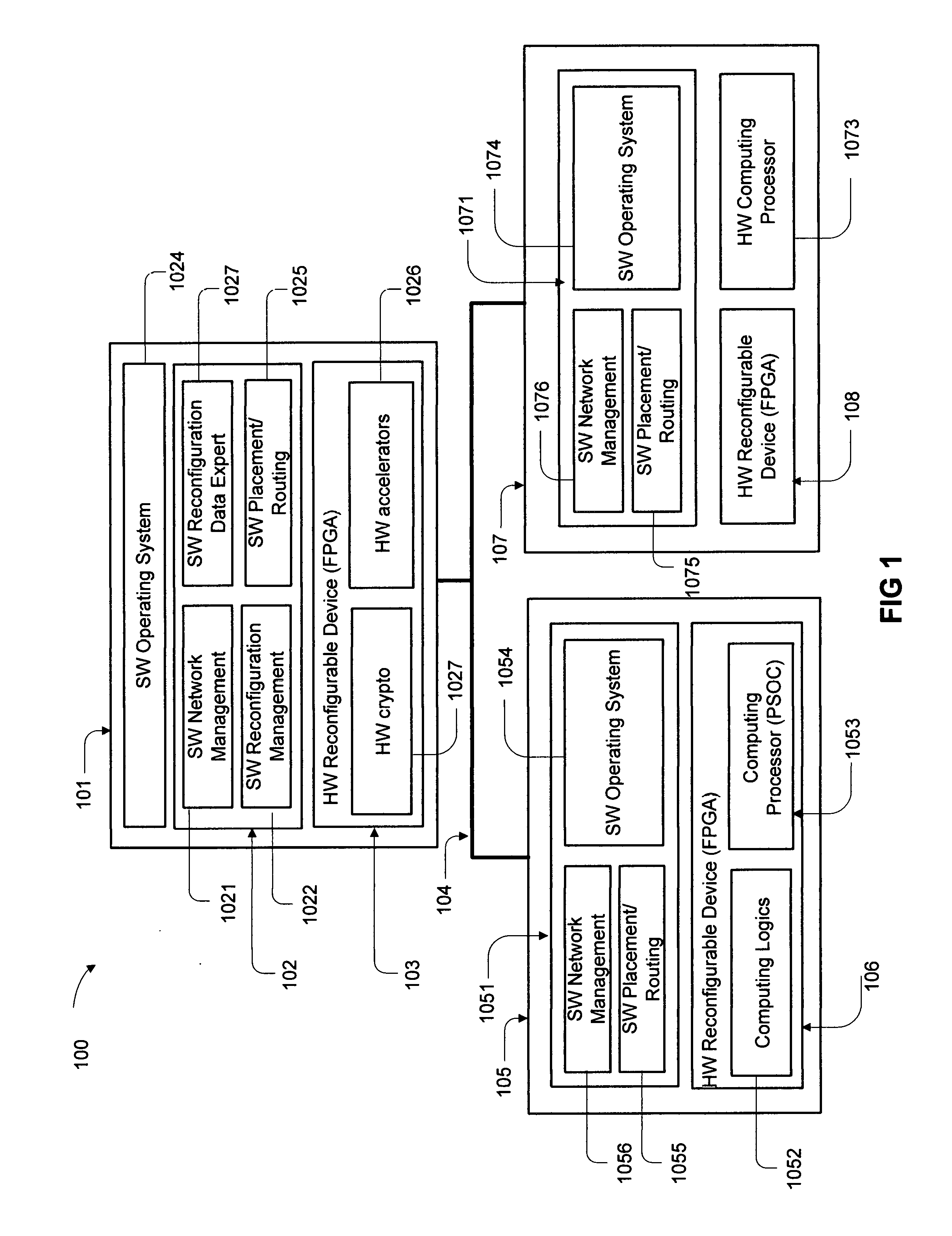

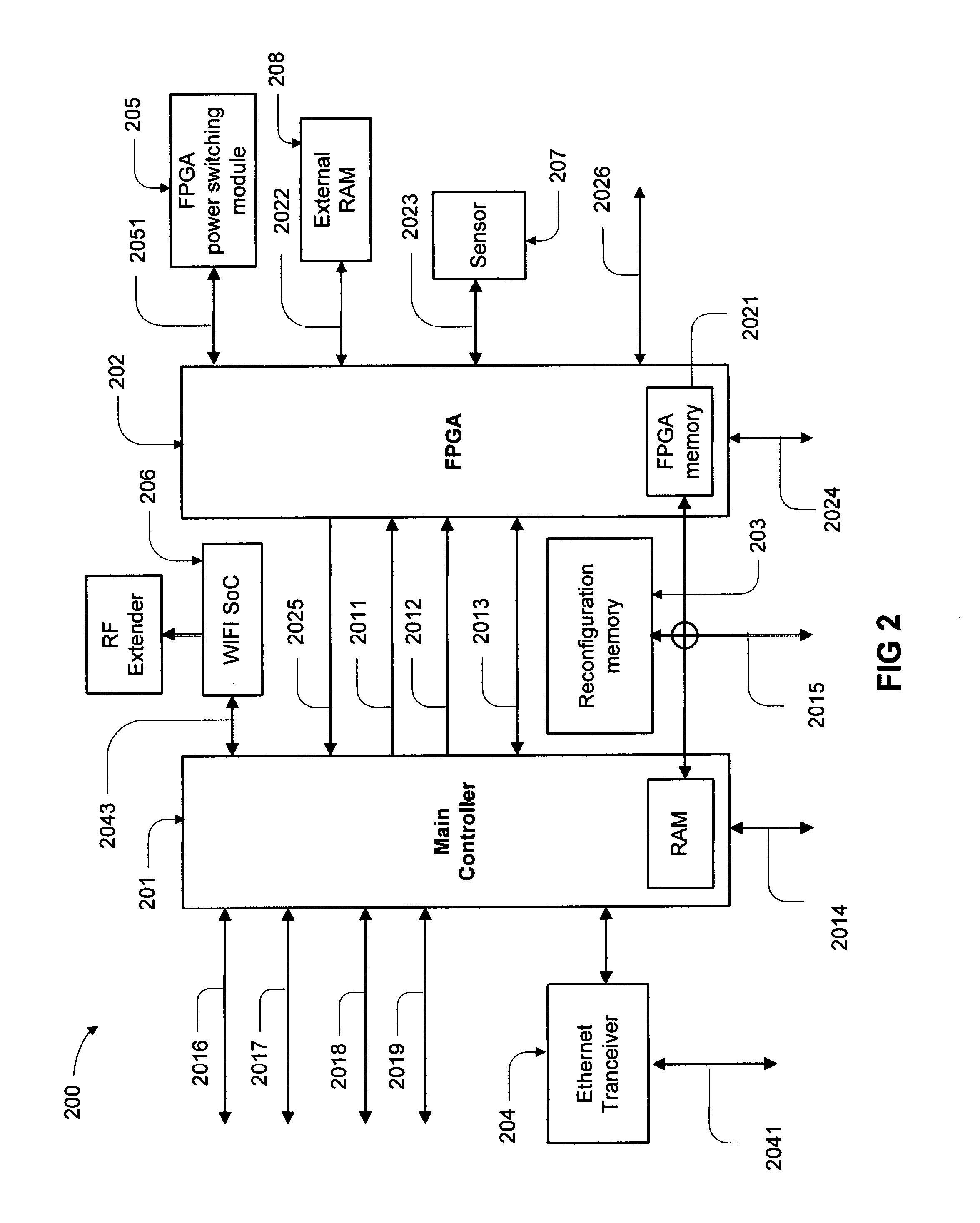

Embedded systems of internet-of-things incorporating a cloud computing service of FPGA reconfiguration

InactiveUS20160321081A1Improve performanceMemory architecture accessing/allocationData resettingHardware architectureSecure by design

IoT embedded systems as well as cloud computing infrastructure may merge processor soft cores with programmable logic (FPGAs) to yield a heterogeneous hardware-software processing ecosystem through which the embedded systems and infrastructure customize and adapt their computational power to the specific application in use. The embedded systems and cloud computing infrastructure with dynamic reconfiguration will bring neuroplasticity to the interconnected space of IoT embedded systems, enabling high-performance, customized, secure-by-design cloud computing services. A cloud server of IaaS is employed to evaluate the performances and efficiencies of embedded systems according to its hardware architectures, so that the computing service allow one reconfigurable system download its hardware architecture file or bitstream into other embedded systems via the cloud server.

Owner:KIM HYEUNG YUN +1

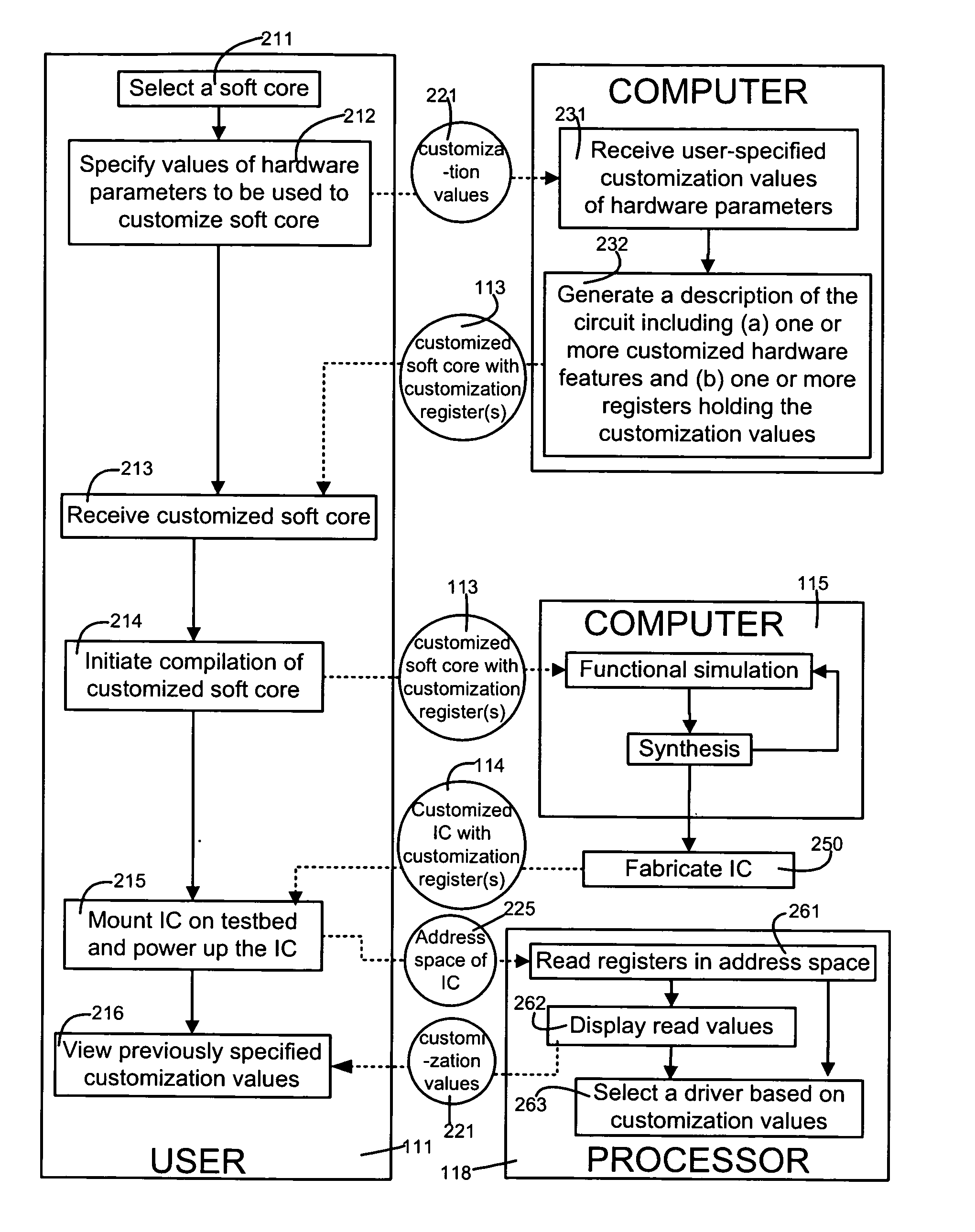

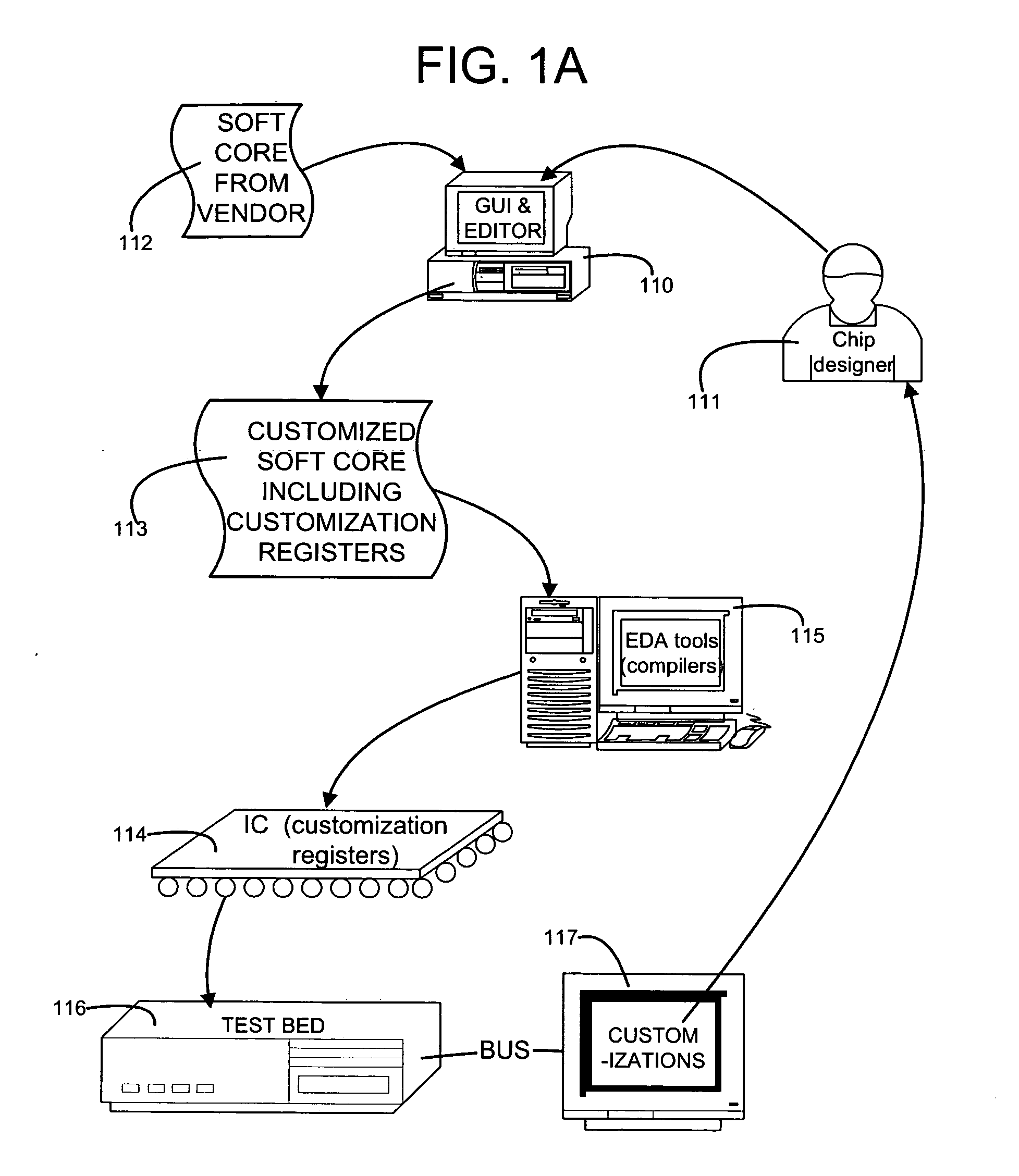

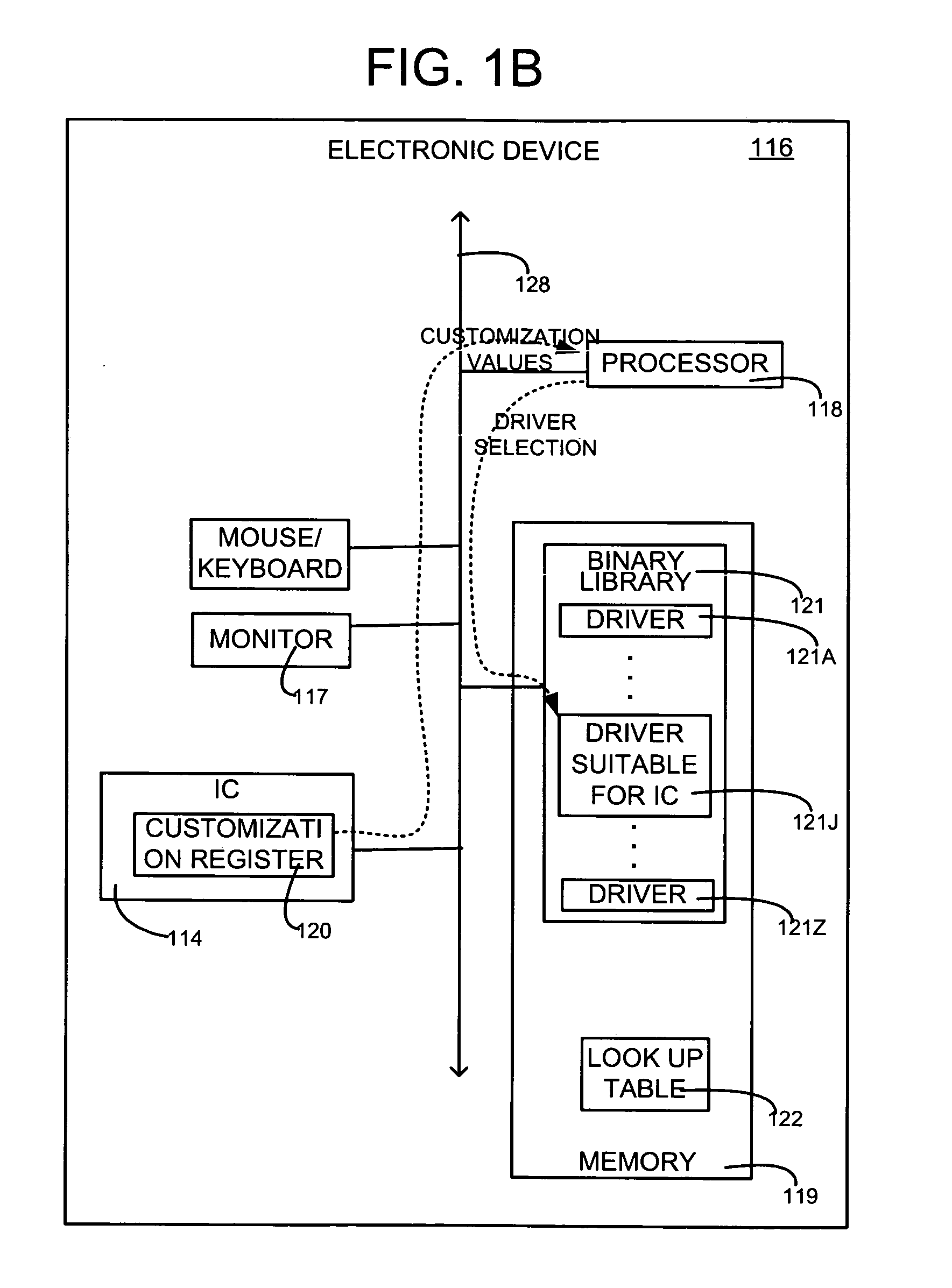

Determining hardware parameters specified when configurable IP is synthesized

ActiveUS20050278682A1Digital computer detailsCAD circuit designComputer hardwareComputer architecture

An attribute of a hardware feature to be customized in a soft core is parameterized so that a value received from a user can be used to generate a description of a circuit containing the customized hardware feature. The generated description also describes, in accordance with the invention, a register that is indicative of the customization. For example, the generated (customized) description may describe the register as containing the value. After the circuit is created, the register may be read (at any time) to identify the customization. Hence, access to such a register eliminates the need for a user to maintain documentation on values specified during customization. Such a register may additionally be used to identify a device driver that is appropriate for use with the customized hardware feature. Additional registers may be included in the generated description, e.g. to identify the function of the circuit, and the version number.

Owner:SYNOPSYS INC

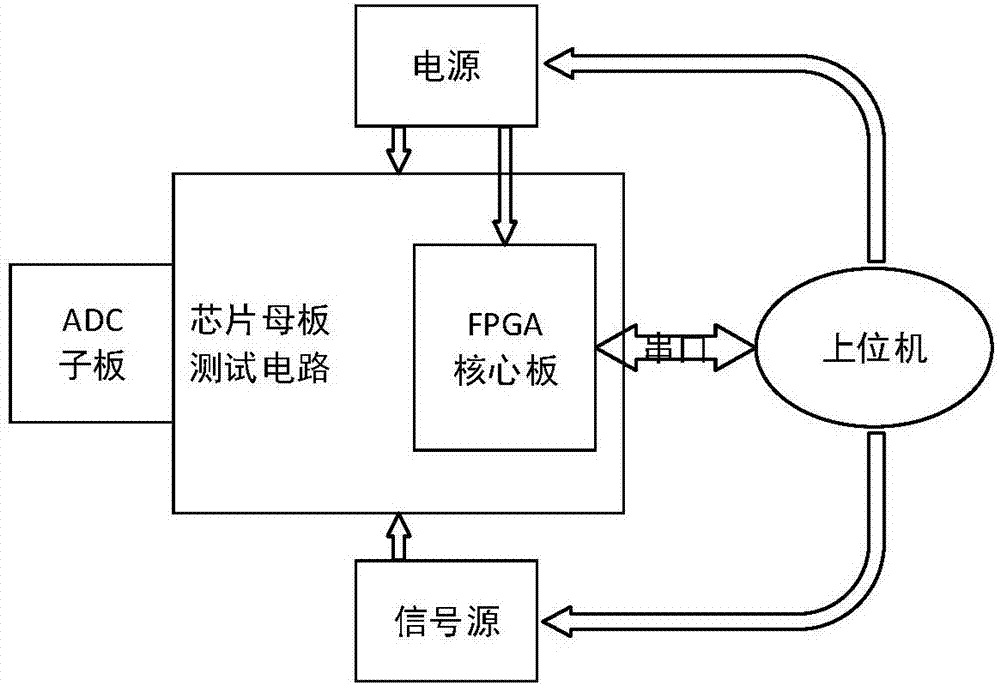

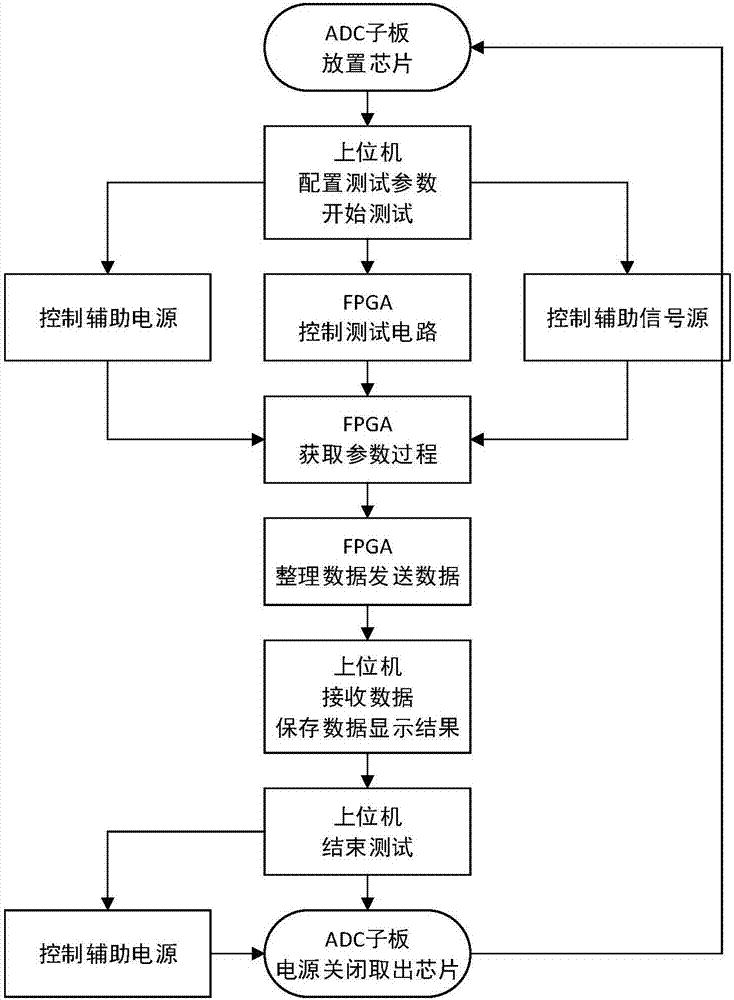

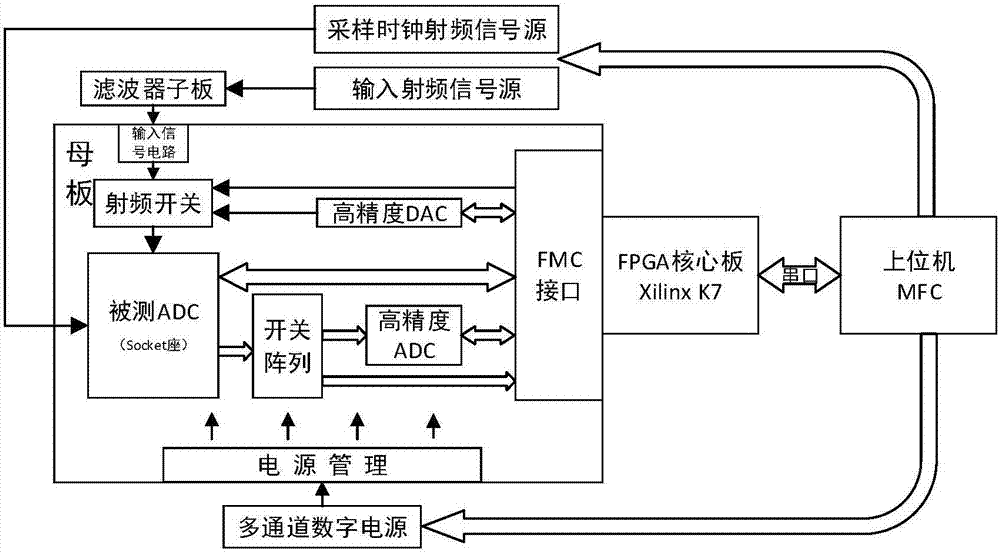

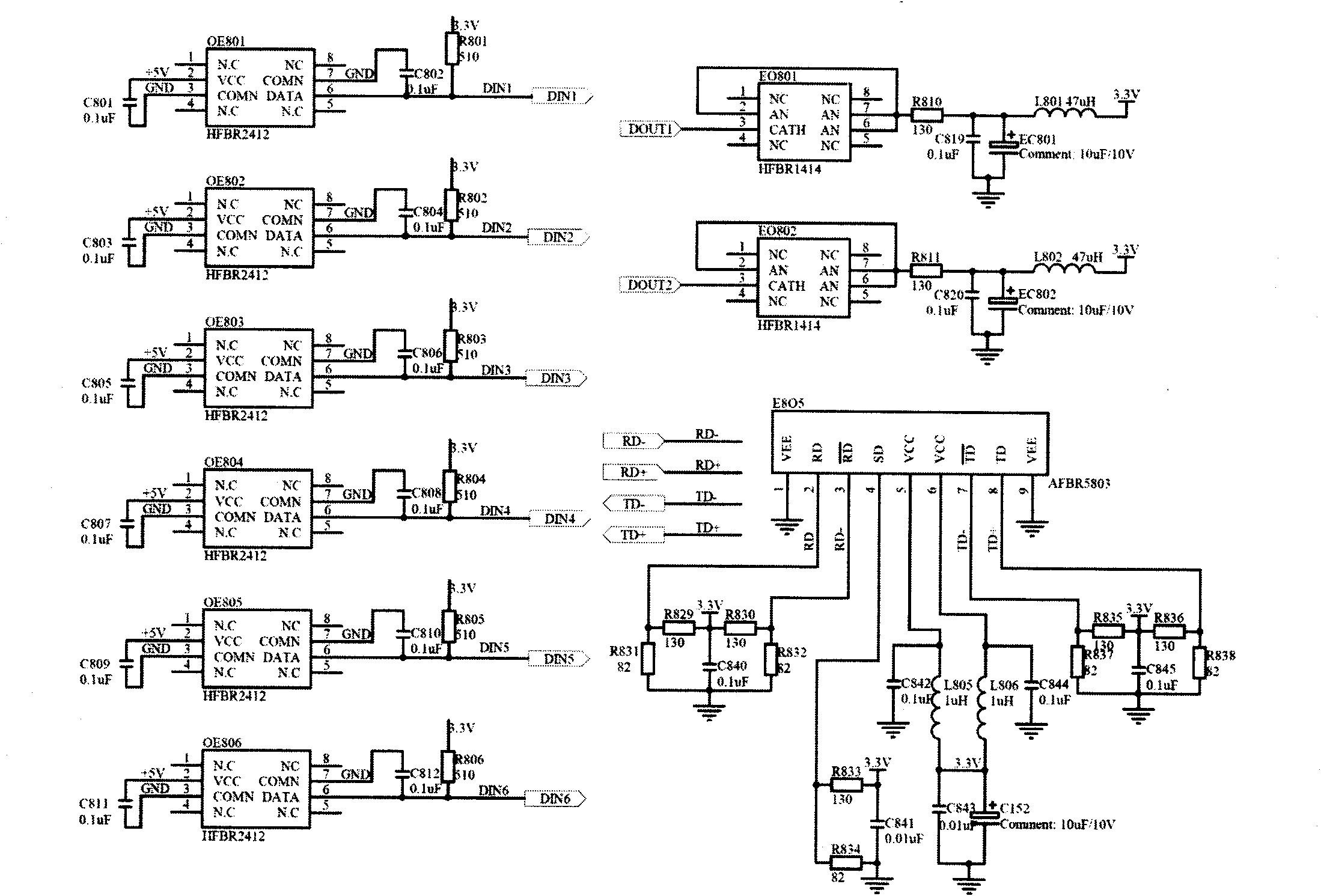

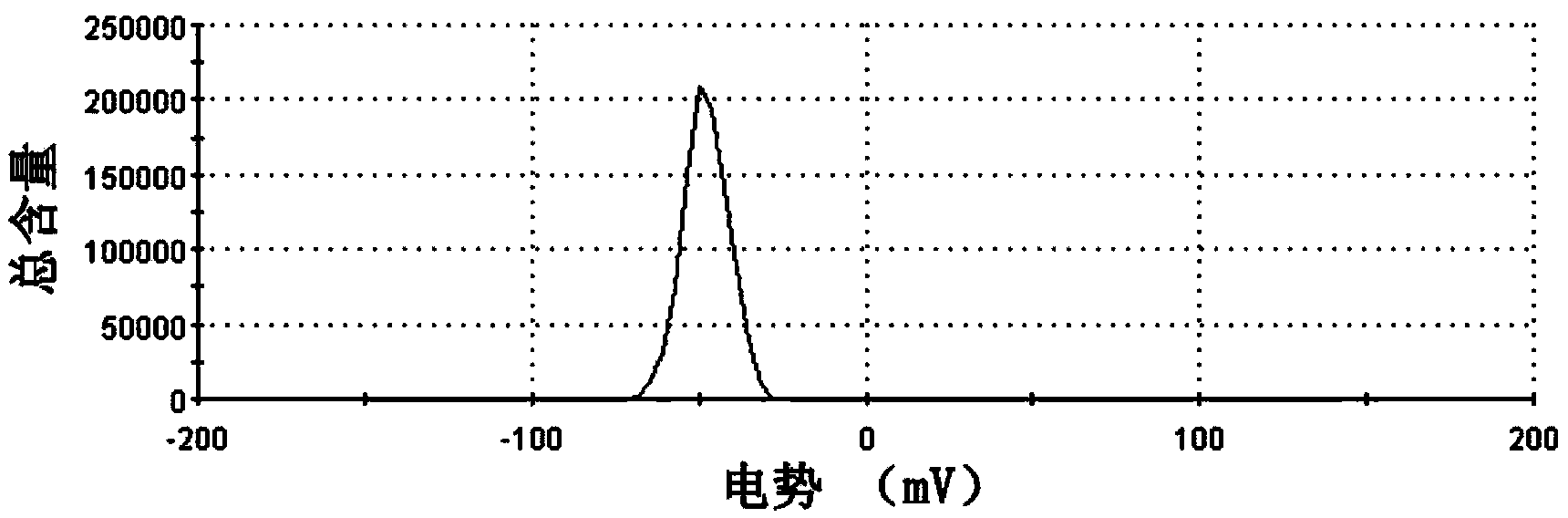

Automatic test platform of high-speed ADC chip and software framework design method thereof

ActiveCN107390109AIncrease test rateReliable high-speed data signal transmissionElectronic circuit testingTest platformAlgorithm design

The invention discloses an automatic test platform of a high-speed ADC chip and a software framework design method thereof. The design method comprises the steps of step 1, FPGA underlying logic drive design: the FPGA underlying logic part completes construction of the hardware foundation, including realizing underlying logic control, foundation computation and soft core hardware configuration of the hardware module; and synchronous drive algorithm design including the tested high-speed ADC, calibration algorithm design, hardware drive design of the onboard high-precision ADC / DAC and register array and hardware FFT operation; step 2, test parameter acquisition: the FPGA soft core receives an upper computer command to control the test process and transmits the command to the FPGA hardware program to drive an external circuit to acquire data so as to obtain the test parameter value by applying the processing algorithm, wherein the test parameters are mainly divided into static parameters and dynamic parameters; and step 3, upper computer program design. The high-precision level characteristic and the high-speed data characteristic of the chip can be simultaneously measured, and "one-key acquisition" can be realized through programming control.

Owner:苏州迅芯微电子有限公司

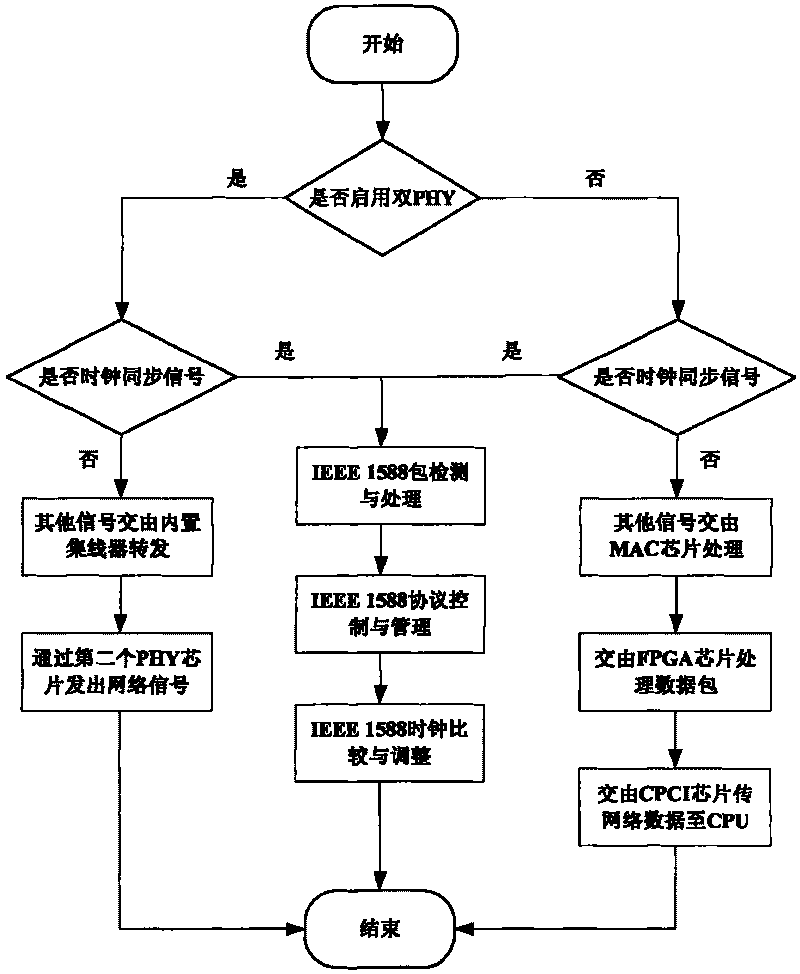

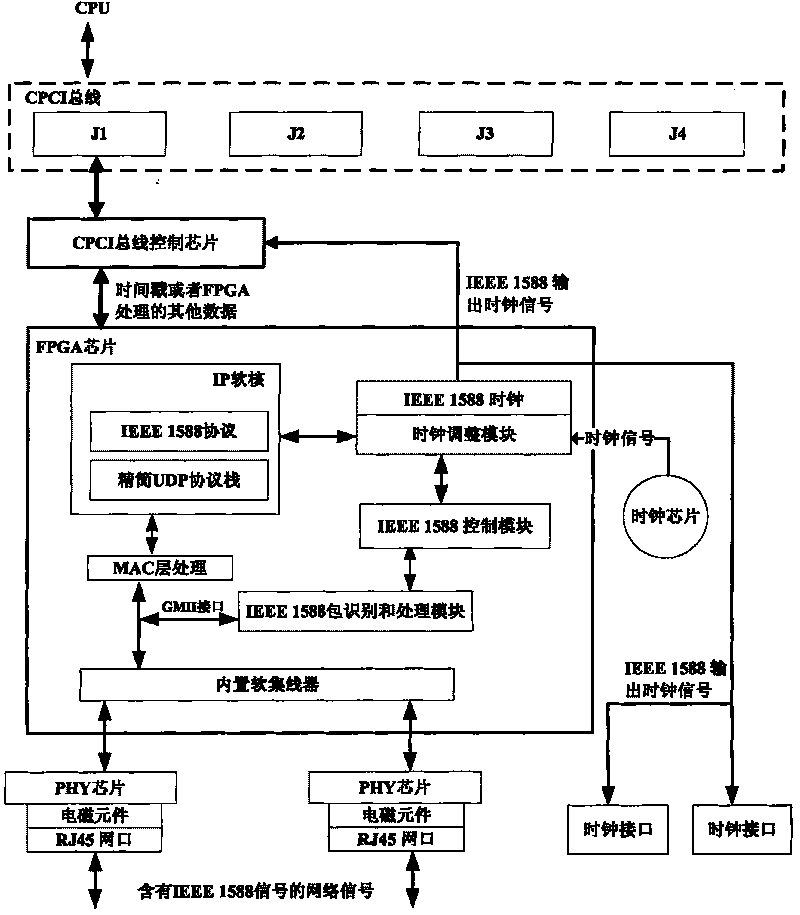

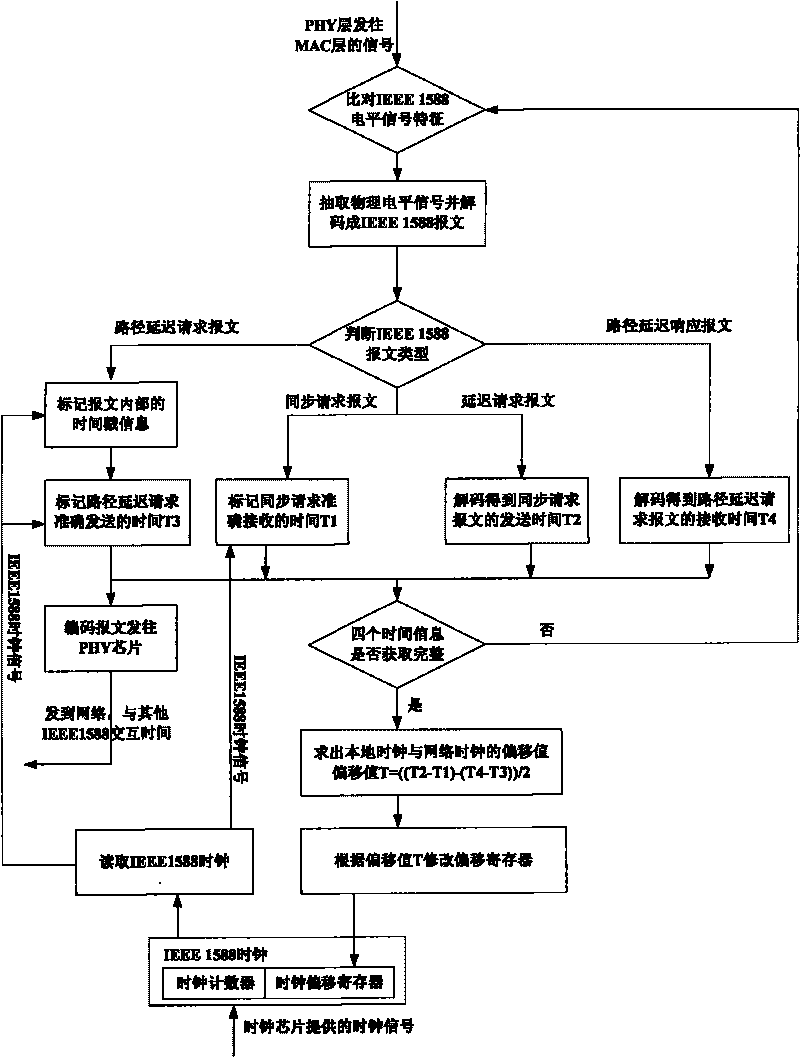

CPCI bus-based high-accuracy clock synchronization method and system thereof

InactiveCN101739011AHigh precisionMeet the requirements of high compatibilityTotal factory controlProgramme total factory controlPhysical layerFpga chip

The invention discloses a CPCI bus-based high-accuracy clock synchronization method. The method provides a plurality of high-accuracy clock synchronization signals for industrial control equipment based on an IEEE1588 protocol and comprises the following steps of: monitoring a level signal of a physical layer, judging whether the level signal is an IEEE1588 clock synchronization signal or not and triggering a processing mechanism of IEEE1588 if the level signal is a message of the IEEE1588 clock synchronization signal; performing packet processing on the message of the received IEEE1588 clock synchronization signal, controlling the message and adjusting the output clock synchronization signal by an FPGA chip; and providing the IEEE1588 clock synchronization signal to an industrial control system. An IP soft core is adopted to encapsulate the IEEE1588 protocol and a FPGA hardware processing time stamp to improve the accuracy of a local time stamp mark, so that the synchronization accuracy of the system becomes higher and the independence on the system or the equipment can be ensured.

Owner:INST OF ACOUSTICS CHINESE ACAD OF SCI

Iced confectionery article and process for preparing it

An iced confectionery article, which is in particular a molded iced confectionery article based on water ice with a soft-core texture. This article includes i) a core of water ice containing 20 to 40% by weight of solids, having a degree of overrun of 20 to 80% and a texture which is similar to that of an extruded ice-cream, which contains, where appropriate, pieces, and ii) a shell of water ice with no overrun, containing 20 to 35% by weight of solids. In another embodiment, the core contains inclusions ranging in size from 1 to 10 mm. The invention also relates to processes for preparing these molded iced confectionery articles.

Owner:NESTEC SA

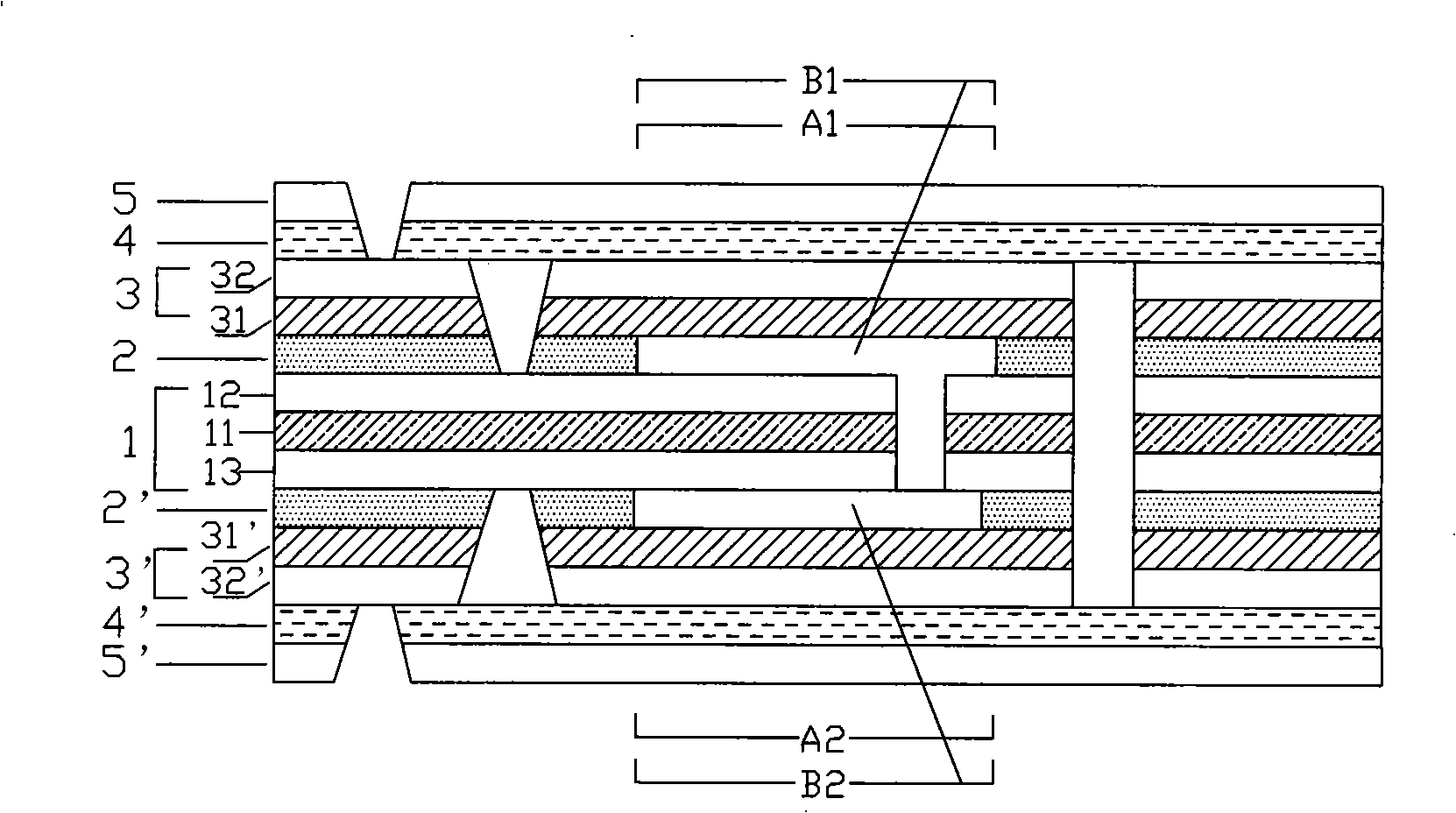

Soft and hard combined printed wiring board production method

InactiveCN101272660AAvoid crackingFacilitate post-processing operationMultilayer circuit manufactureHigh densityInsulation layer

The invention discloses a manufacturing method for a rigid-flex printed circuit board. A single-side flexible substrate (SSFCCL) or a resin coated copper foil (RCC) is adopted for replacing a copper foil and then is added with a prepreg or a signal-side rigid substrate or a two-side rigid substrate and then is directly laminated for preparing an internal layer on one side or two sides of a soft core plate (FPC) together with the non-flowing or lower flowing prepreg. The rigid substrate, the copper foil and the prepreg are laminated for preparing an external layer. In the invention, the single-side flexible substrate (SSFCCL) or a resin coated copper foil (RCC) is used for laminating and the toughness of the SSFCCL or the RCC substrate is used for supporting the copper foil over the exposure part of the soft plate in the rigid-flex plate; therefore, the copper foil breaking can be remarkably reduced when preparing the internal layer. The operation treatment of the late procedure is convenient and the product yield rate can be remarkably improved; the thickness of an insulation layer can be easily controlled, thus facilitating the preparation of a multilayer rigid-flex printed circuit board with characteristics of multistage and thinness and an interconnection printed circuit board (HDI) with high density.

Owner:SHANGHAI MEADVILLE ELECTRONICS

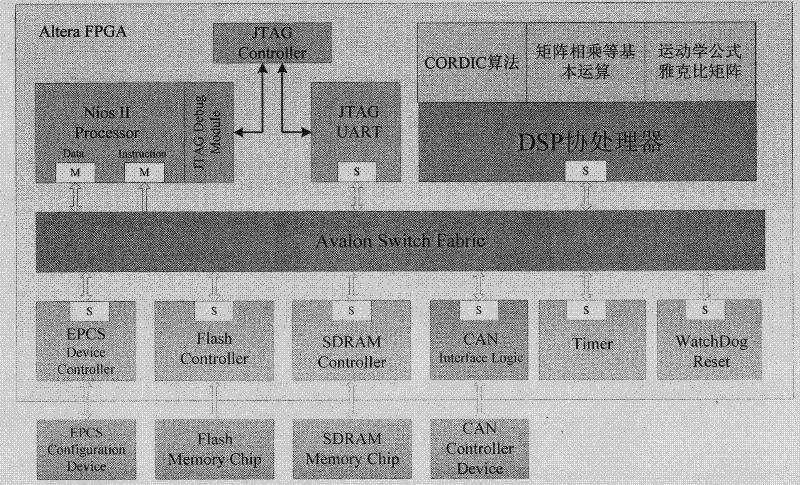

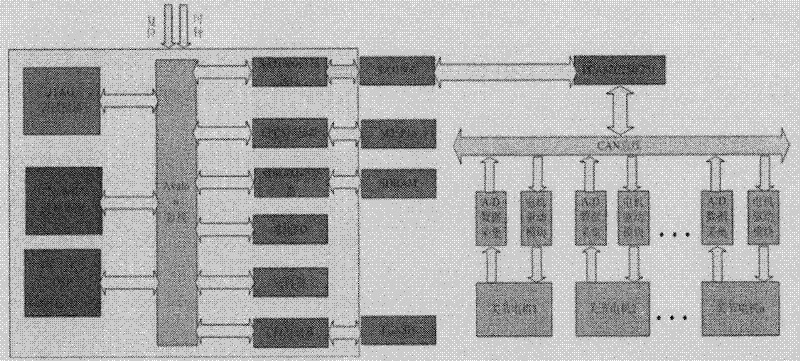

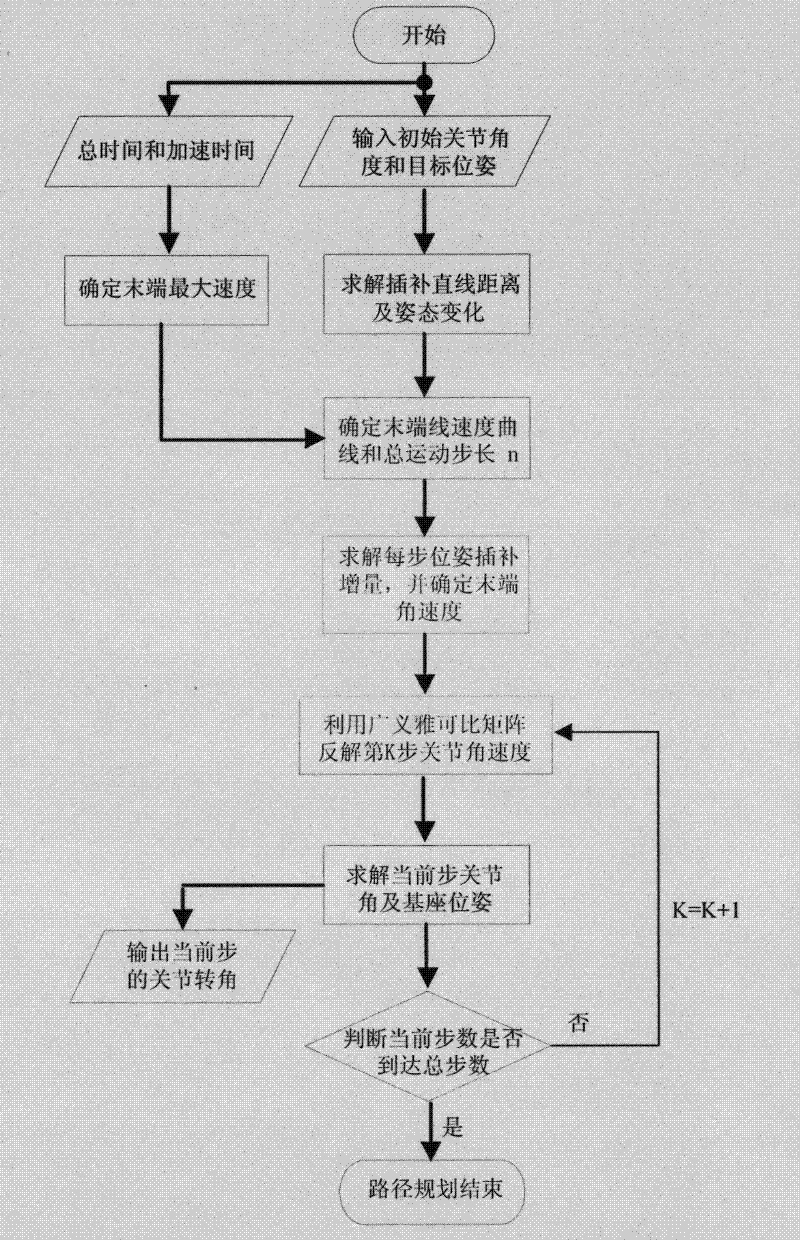

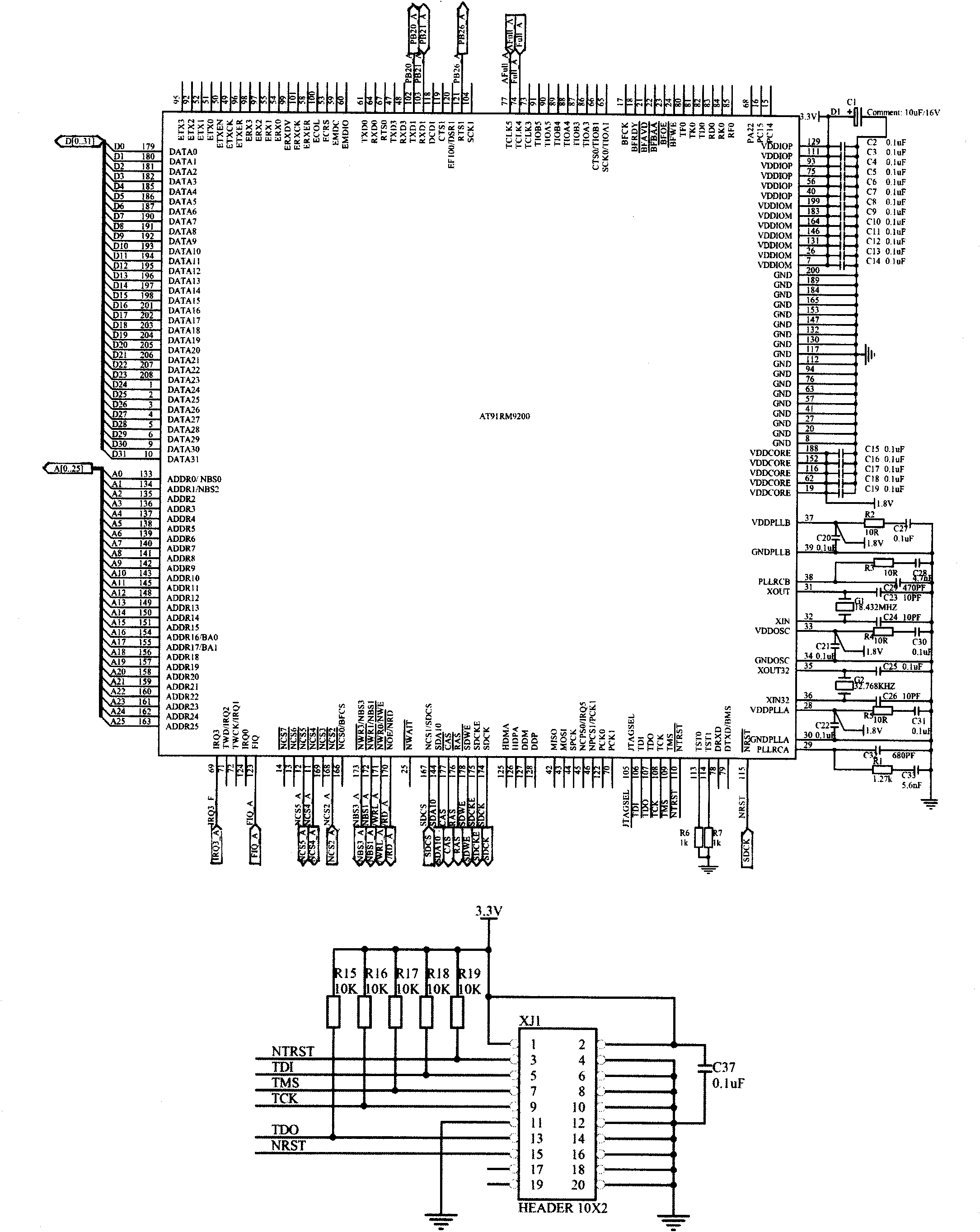

Embedded multinuclear main controller of modular robot based on FPGA (Field Programmable Gata Array)

InactiveCN102393656AReduce volumeReduce energy consumptionProgramme control in sequence/logic controllersDigital signal processingJoint Test Action Group

The invention discloses an embedded multinuclear main controller based on an FPGA (Field Programmable Gata Array) chip in the technical field of robot control. The main controller integrates two main modules, namely a Nios II soft core processor and a DSP (Digital Signal Processing) coprocessor, wherein the Nios II soft core processor communicates with a system clock module, a watchdog and resetting system module, a JTAG interface module, a CAN serial bus control module and a memorizer control module by an Avalon bus module; as a hardware computing core, the DSP coprocessor communicates with a Nios II soft core by the Avalon bus module; and the Nios II soft core is responsible for the movement planning of a robot and the communication of each controller at each joint, and the coprocessor is responsible for kinetic resolving. The embedded multinuclear main controller adopts the Nios II soft core as a communication core and the coprocessor as a computing core to realize the rapid and stable control and reduce energy consumption and the volume.

Owner:BEIJING UNIV OF POSTS & TELECOMM

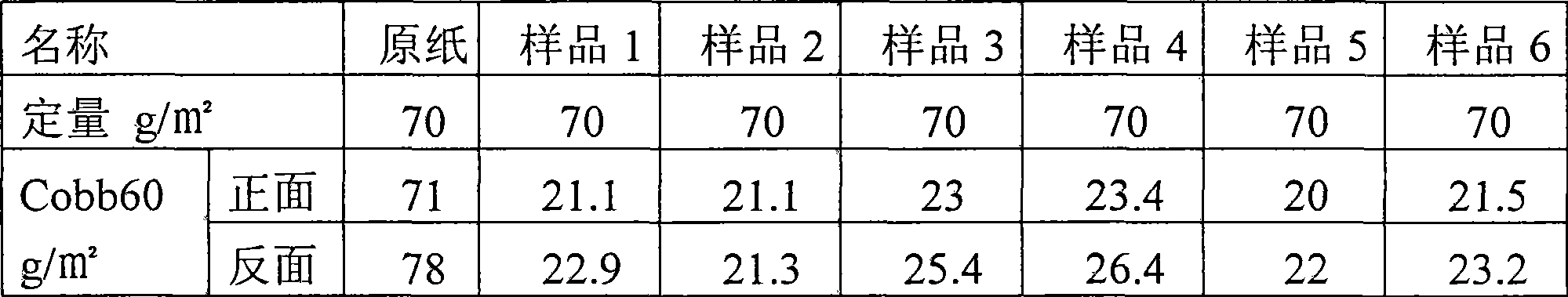

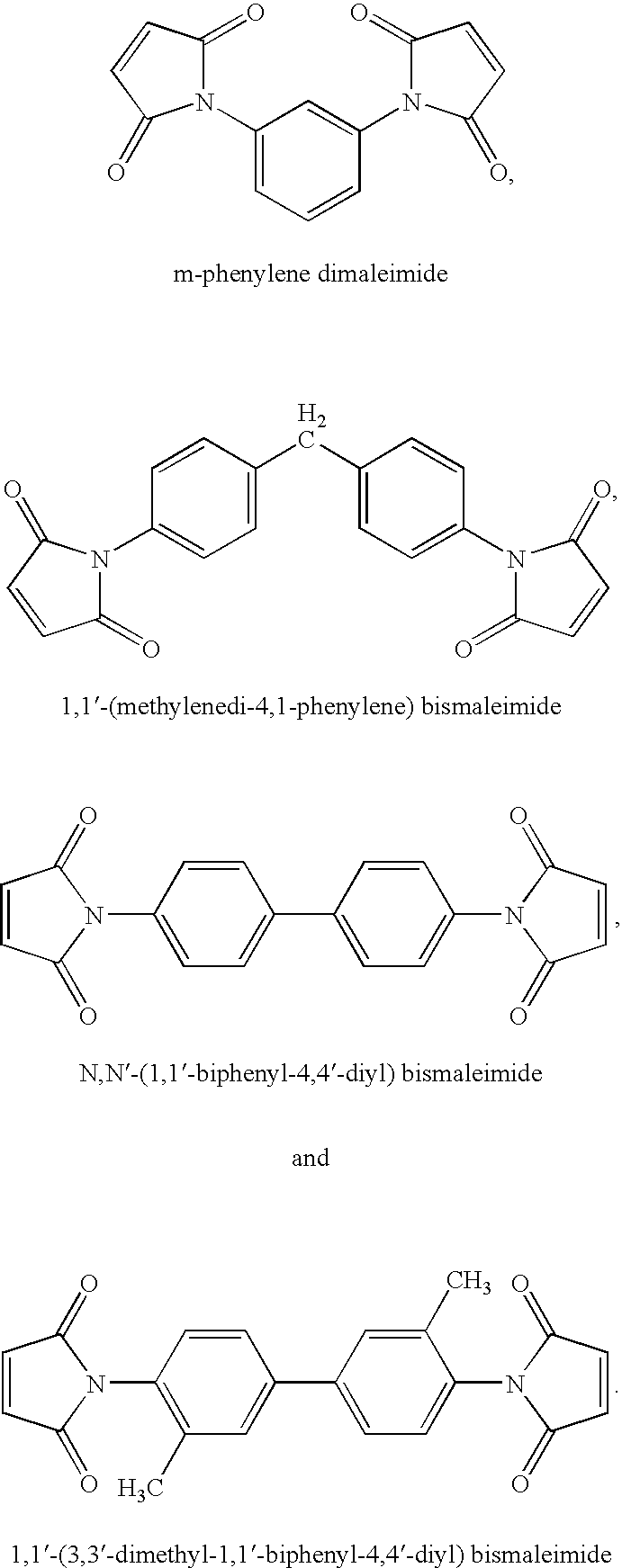

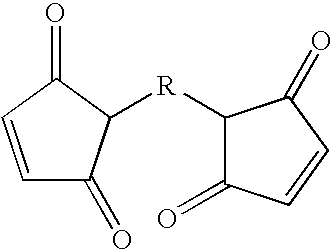

Styrene-acrylic microemulsion surface sizing agent with high solid content and core shell structure and preparation method and application thereof

InactiveCN101544717AImprove water resistanceLarge particle sizeWater-repelling agents additionPaper/cardboardEmulsionOxidation-Reduction Agent

The invention discloses a styrene-acrylic microemulsion surface sizing agent with high solid content and core shell structure and a preparation method and an application thereof. The preparation method comprises the following steps: adopting a seed emulsion method to synthesize core emulsion, dropping core pre-emulsified monomer solution and redox initiator into core the emulsion, controlling the dropping time, filtering the product of reaction by using a 250 mesh or 300 mesh sieve, discharging, and obtaining the microemulsion with hard core and soft core shell structure, wherein the microemulsion has a grain diameter of 20-100nm and the solid content of 40-48 percent. The surface sizing agent has the base characteristics of styrene-acrylic emulsion, good stability, core shell structure, small grain diameter, high solid content, and better gluing effect and can endow paper with better water resisting property and improve the surface property of the paper.

Owner:SOUTH CHINA UNIV OF TECH

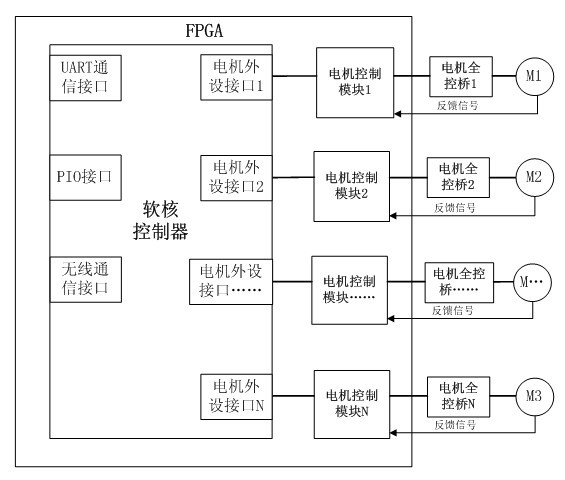

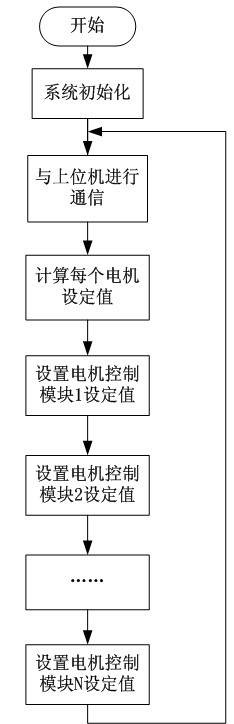

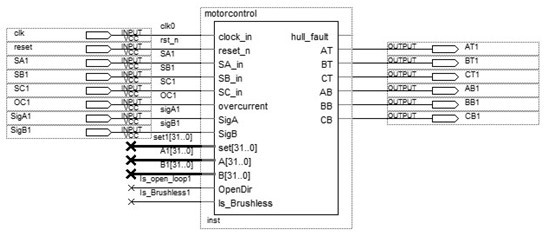

A fpga-based high-precision multi-motor control method

InactiveCN102291062AFast operationImprove performanceMultiple motor speed/torque controlControl systemMiniaturization

The invention belongs to the field of motor control, and in particular relates to a high-precision multi-motor control method. The present invention is a high-precision multi-motor control method based on FPGA. The control system includes an embedded CPU soft core and a motor control module implemented by hardware logic. , A motor control peripheral driver interface that connects the CPU and the motor control module in accordance with the avalon bus protocol. The present invention provides a multi-motor control method capable of accurate measurement, real-time control and miniaturization. The method can adjust the number of motor control modules according to the number of motors required; configure the parameters of the motor control modules according to the types and characteristics of the motors; Configure the peripheral modules of the embedded CPU according to the additional functions of the system, and all the control functions of the system will be realized on one FPGA chip.

Owner:ZHEJIANG UNIV

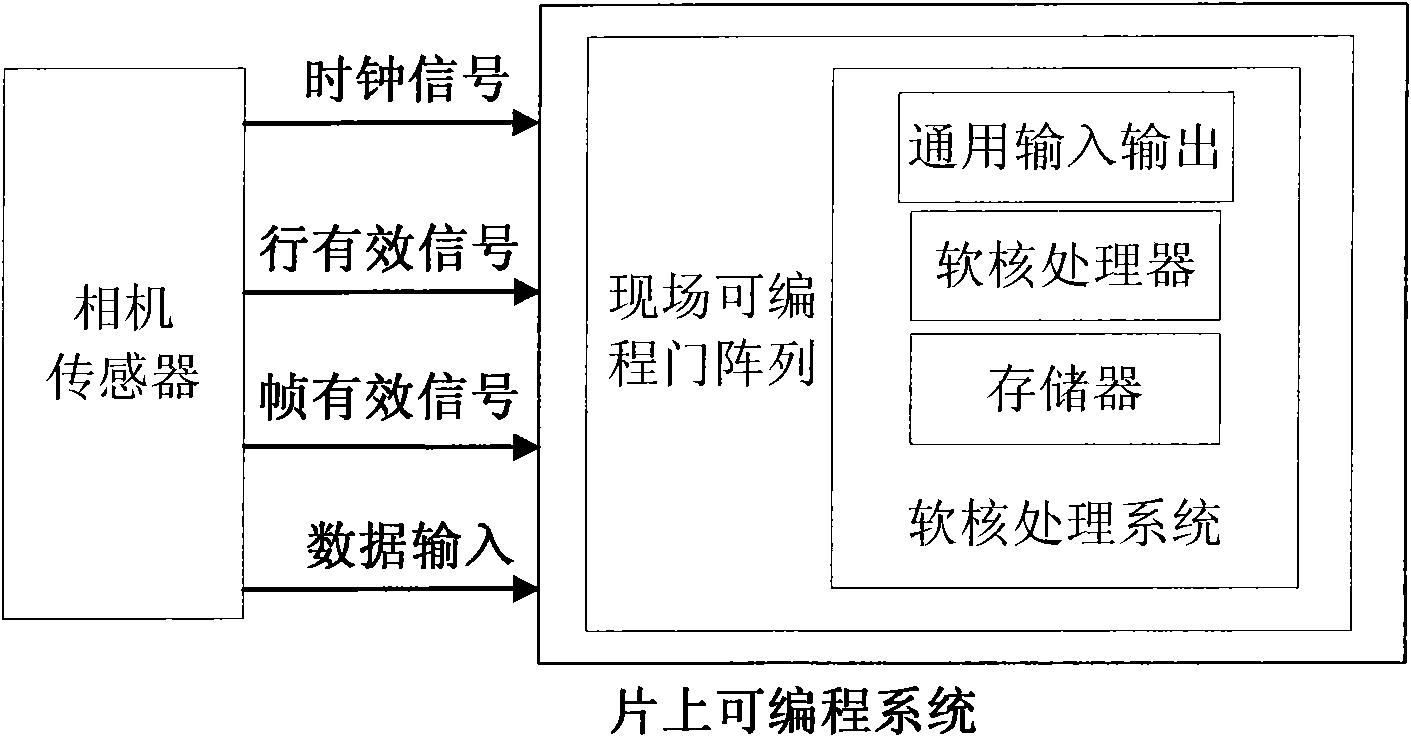

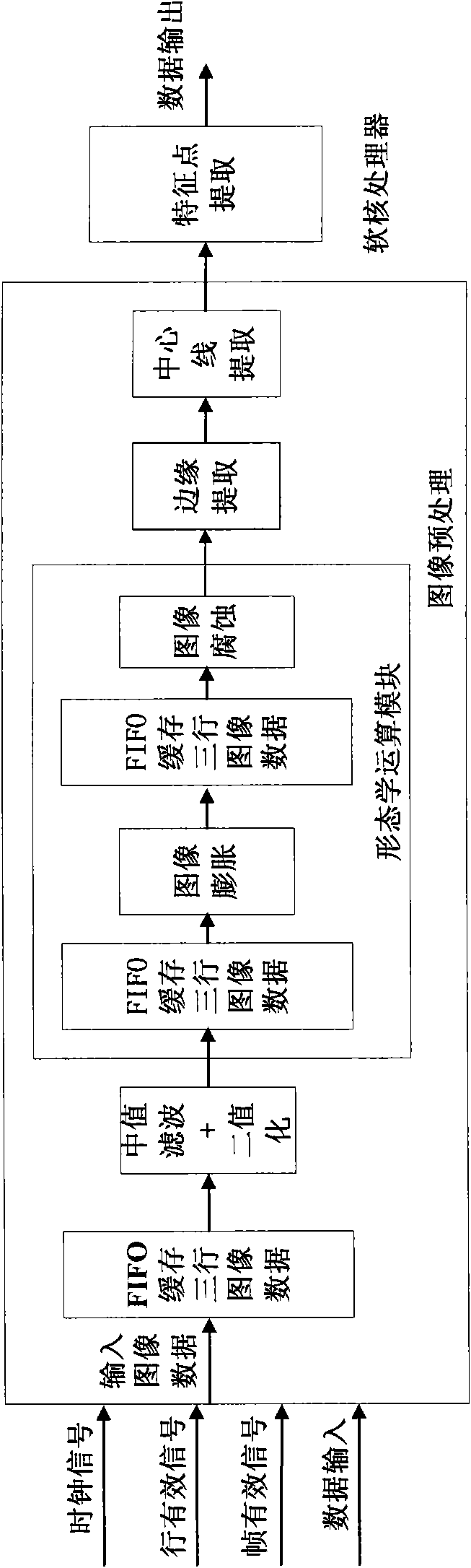

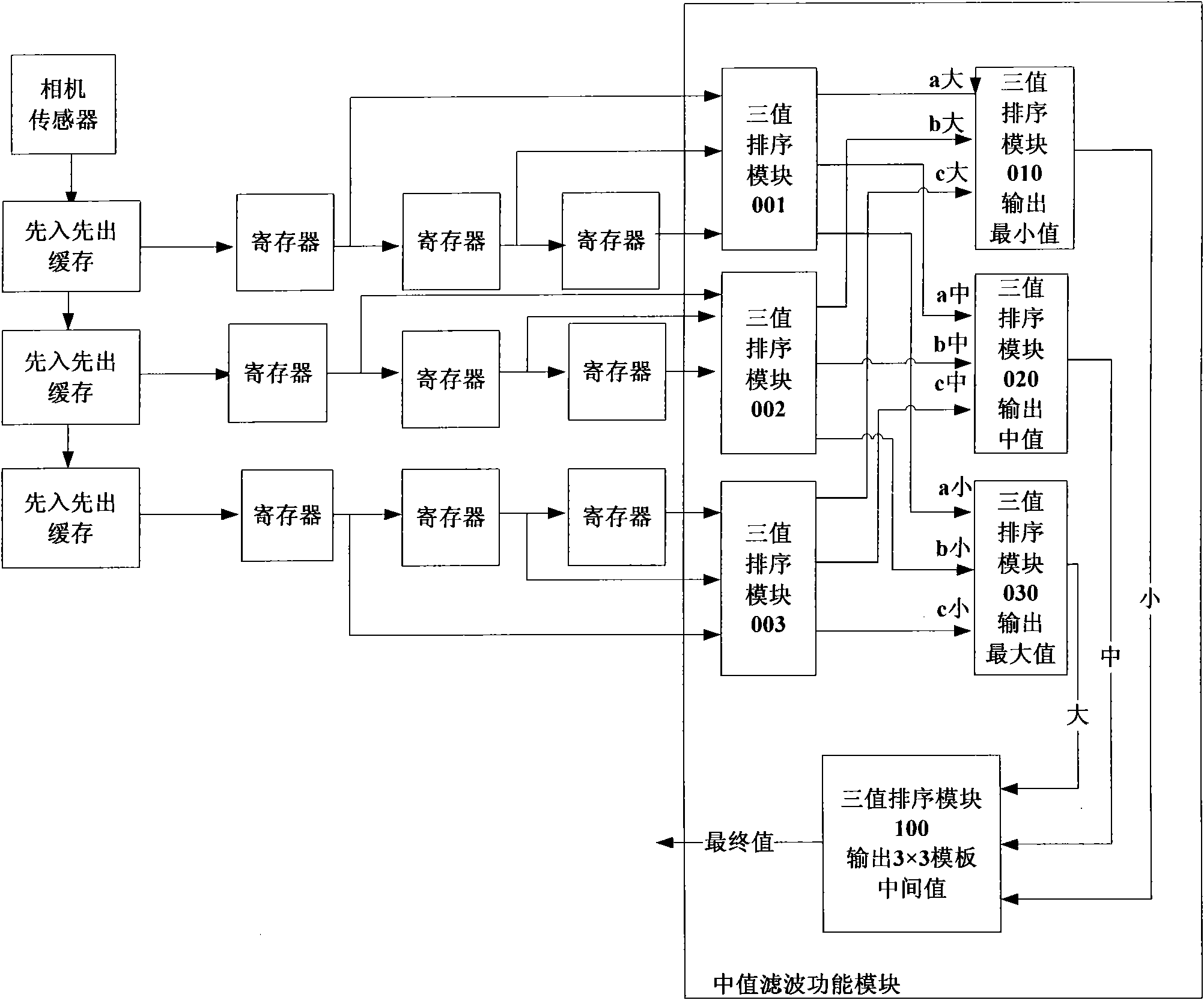

Rapid extracting method for structure light welding seam image characteristic points

InactiveCN101770641AFast and accurate extractionReduce power consumptionImage analysisCharacter and pattern recognitionGate arrayEdge extraction

The invention relates to a structure light vision detection technology, in particular to a rapid extracting method for structure light welding seam image characteristic points. In the invention, an on-site programmable gate array and a soft-core processing system are used together for improving processing speed and reducing power consumption; and the rapid extracting task for structure light welding seam image characteristic points is divided by software and hardware to extract characteristic points by software and hardware cooperation. The invention comprises the following steps: building a Programmable System-on-Chip (PSoC); carrying out mathematical morphology processing and image preprocessing on structure light stripe-containing image which is acquired by a camera sensor by the on-site programmable gate array, wherein the mathematical morphology processing comprises filtering, image enhancement, dilation and erosion, and the image preprocessing comprises edge extraction and centre line extraction; and extracting characteristic points by the soft-core processing system. In the invention, production-line working way is used among steps, thereby improving image processing speed and meeting real-time requirement of seam tracking. The invention can be widely used in the field of laser automatic welding.

Owner:SHENYANG INST OF AUTOMATION - CHINESE ACAD OF SCI

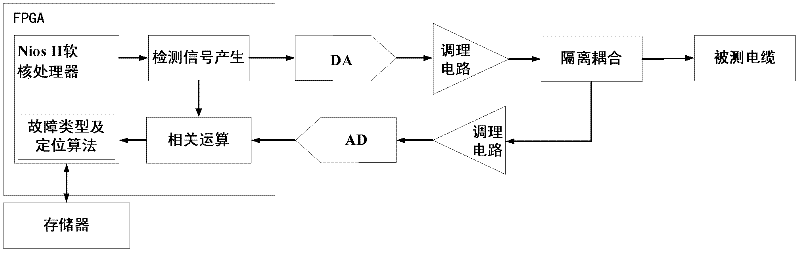

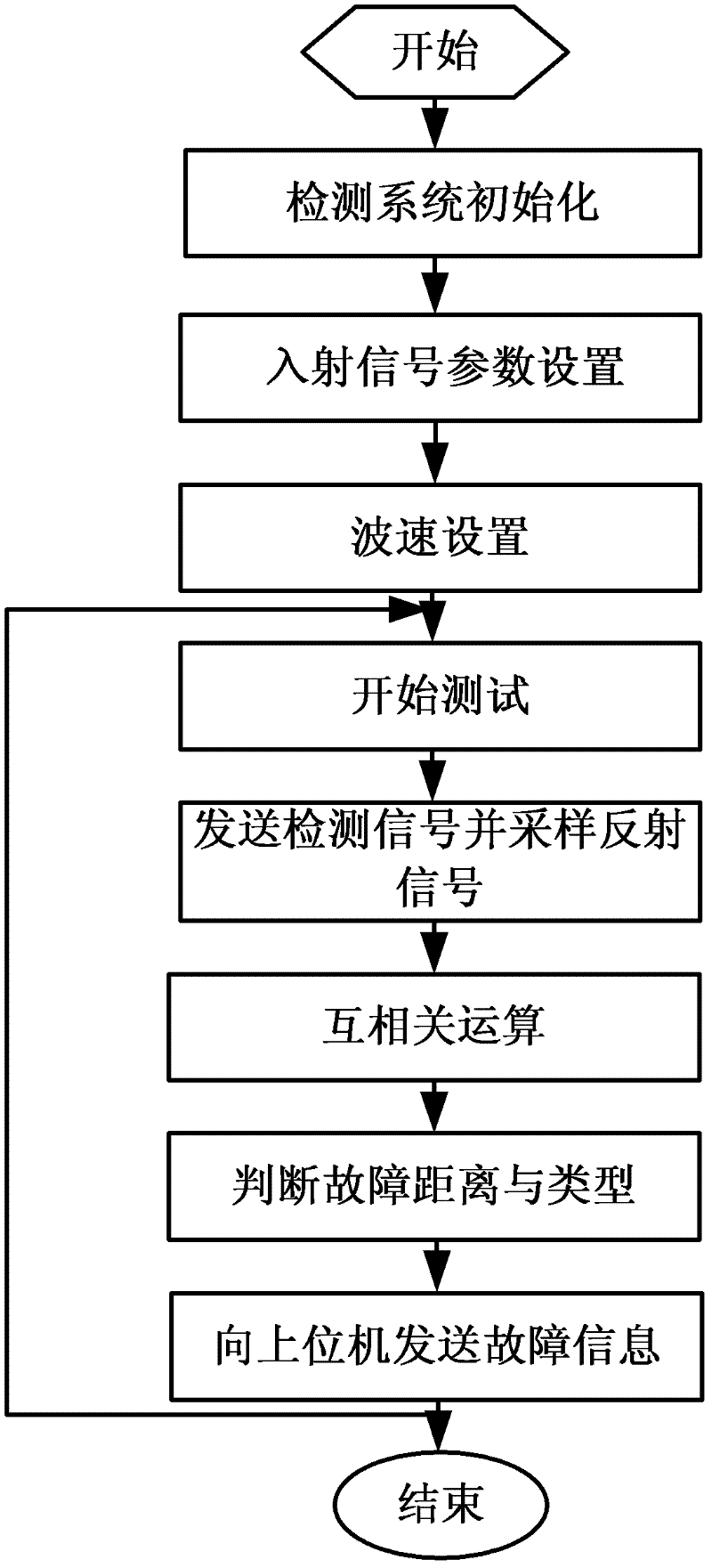

Device for online detecting and locating cable fault based on SOPC (System On Programmable Chip) technology

InactiveCN102435916AWith programmableIncrease flexibilityFault location by pulse reflection methodsInterference resistanceSignal conditioning

The invention discloses a device for online detecting and locating cable fault based on SOPC (System On Programmable Chip) technology, which comprises an FPGA (Field Programmable Gate Array) module with a NIOS II soft core, a high-speed DA module, a signal conditioning module, a separating coupling module and a high-speed AD module, wherein the FPGA (Field Programmable Gate Array) module generates detecting signals for detecting cable faults; the detecting signals are converted into analog signals by the high-speed DA module; then the analog signals are converted into detecting signals with proper amplitude by the signal conditioning module; the detecting signals are coupled into the detected cable in working state by the separating coupling module; meanwhile, the feedback signals from the cable fault points are received from the separating coupling module; the feedback signals are converted into digital signals by the high-speed AD module and the digital signals are sent to the FPGA (Field Programmable Gate Array) module with NIOS II soft core; and the fault type and fault distance information of the tested cable is acquired by the digital signals through relative calculation and fault detecting and locating algorithm. The cable fault can be detected and located in real time by the device. In addition, the device has advantages of accurate test, high test precision, strong interference resistance, high integration level and the like.

Owner:NANJING UNIV OF AERONAUTICS & ASTRONAUTICS

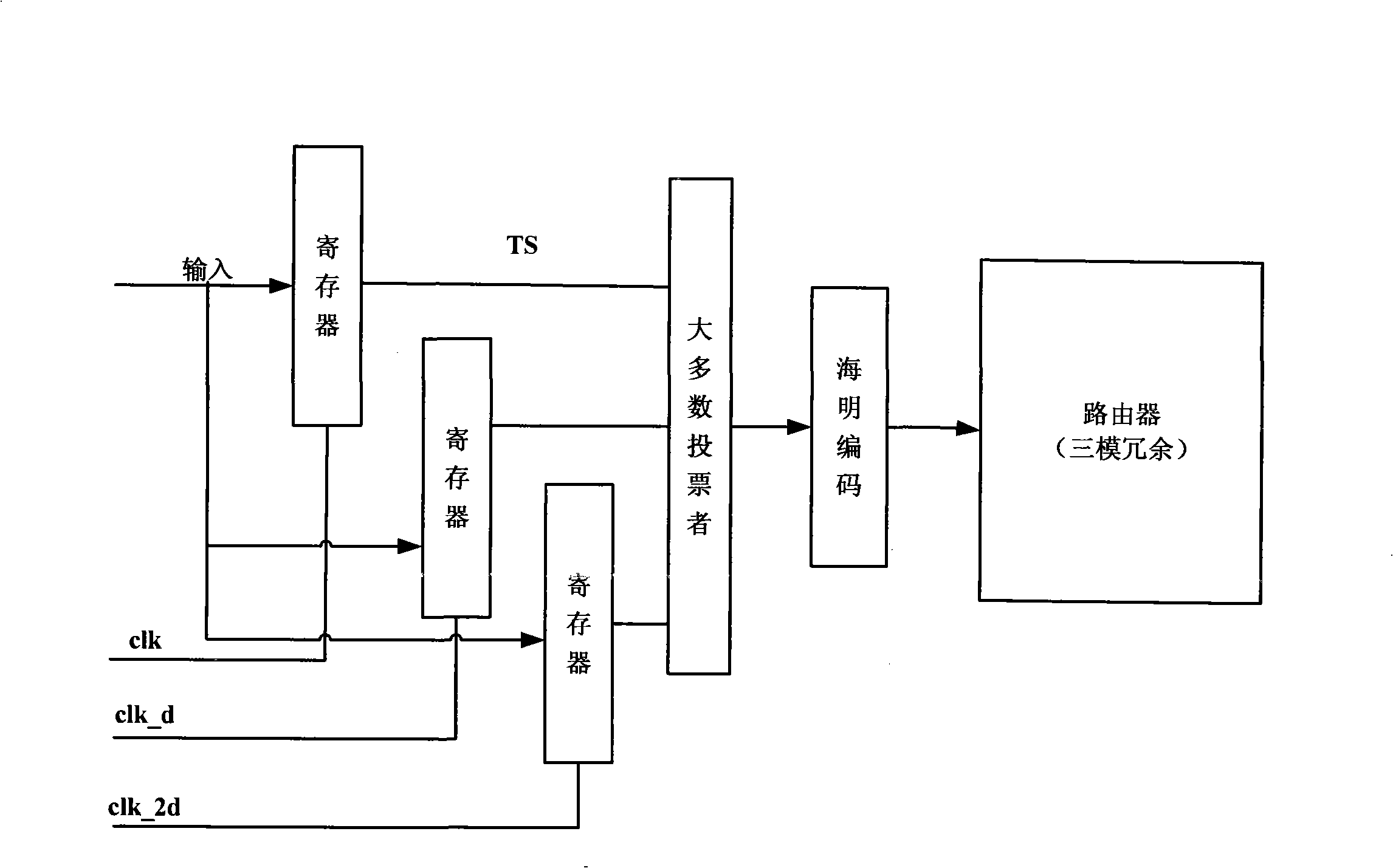

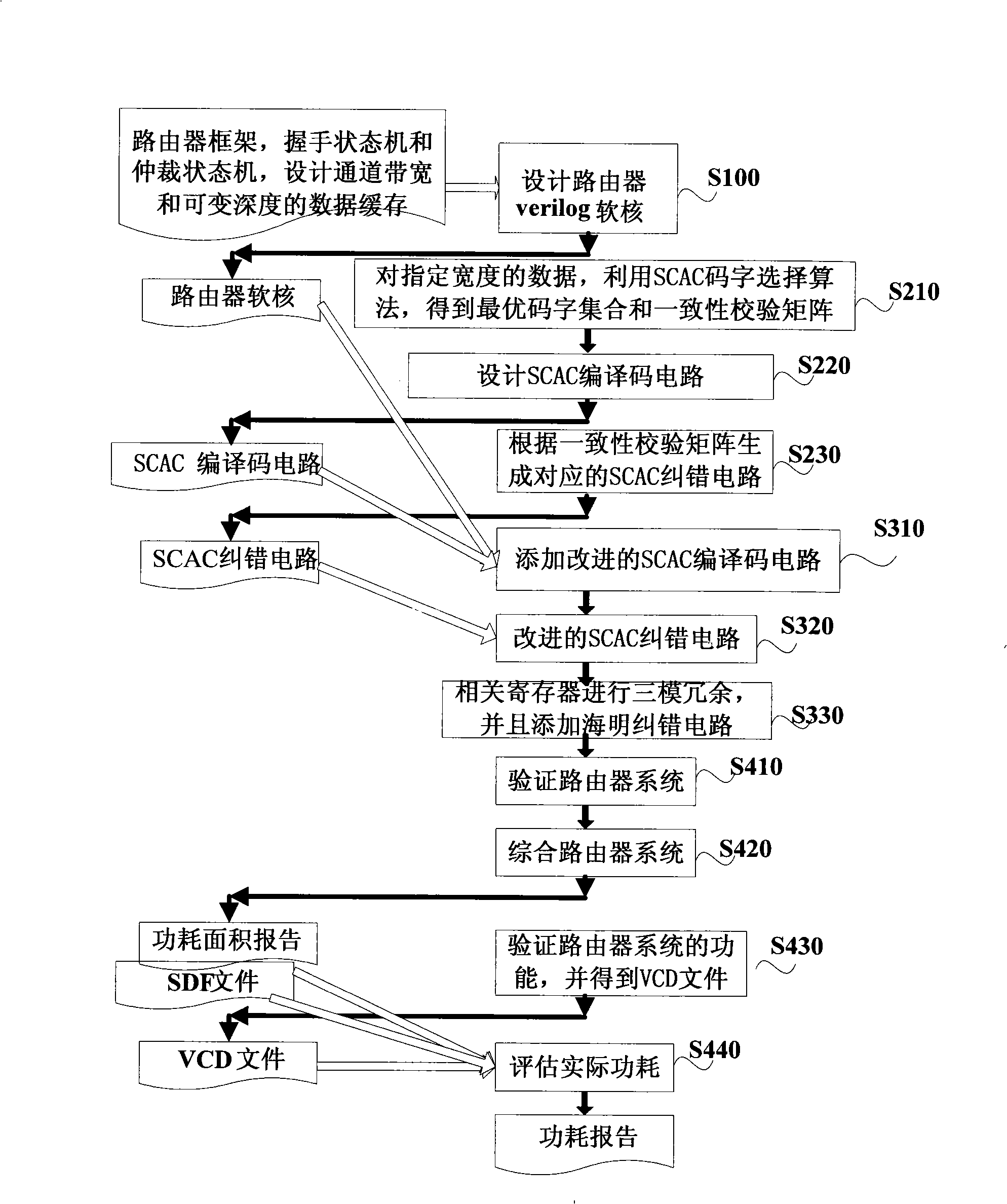

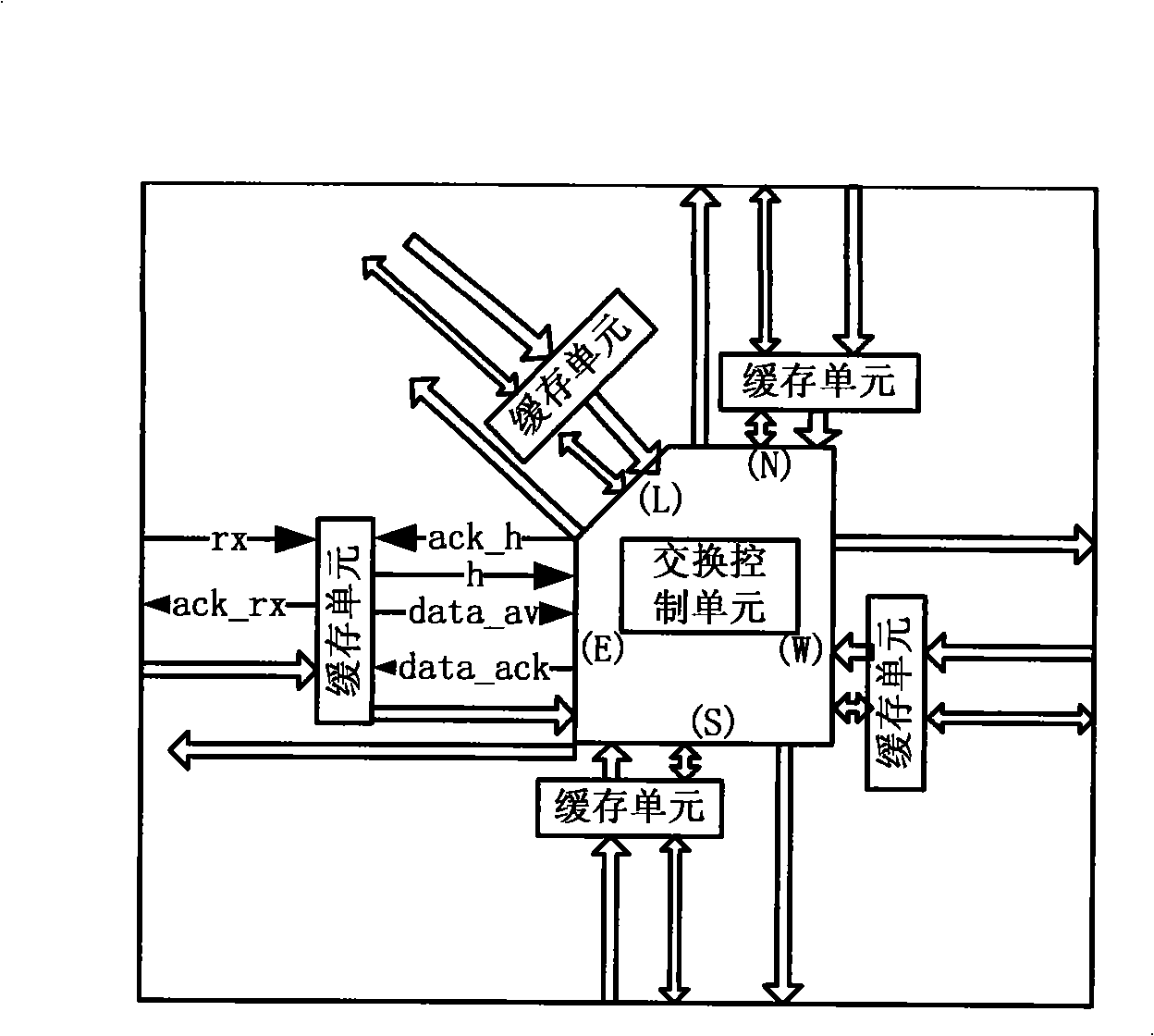

Highly reliable network server system on chip and design method thereof

ActiveCN101335606AReduce areaReduce power overheadError preventionData switching networksFault toleranceTime delays

The invention discloses an on-chip network router system with high reliability and a design method thereof, wherein, the design method of the on-chip network router system with high reliability comprises the steps that: a router soft core based on a wormhole routing swap mode and a rotation routing selection mode is designed; a corresponding SCAC coding circuit, an SCAC decoding circuit and an SCAC error correction circuit are designed for data with a specified width; and the SCAC error correction circuit is added into the router; the SCAC coding circuit and the SCAC decoding circuit are connected with the router so as to from a framework of the router system; an SCAC-TMR fault tolerance proposal is designed for the framework of the router system and the on-chip network router system with high reliability is realized; the functions of the on-chip network router system with high reliability are tested and verified and the performance of the on-chip network router system with high reliability is evaluated. The on-chip network router system with high reliability of the invention can reduce the area, the energy consumption and the expenses of the on-chip network, ensure the reliable data transmission of the on-chip network and prevent a signal jumping with a relatively long time delay from appearing on the channel, thus being more applicable to the design of fault-tolerant and multi-core processors in the future.

Owner:INST OF COMPUTING TECH CHINESE ACAD OF SCI

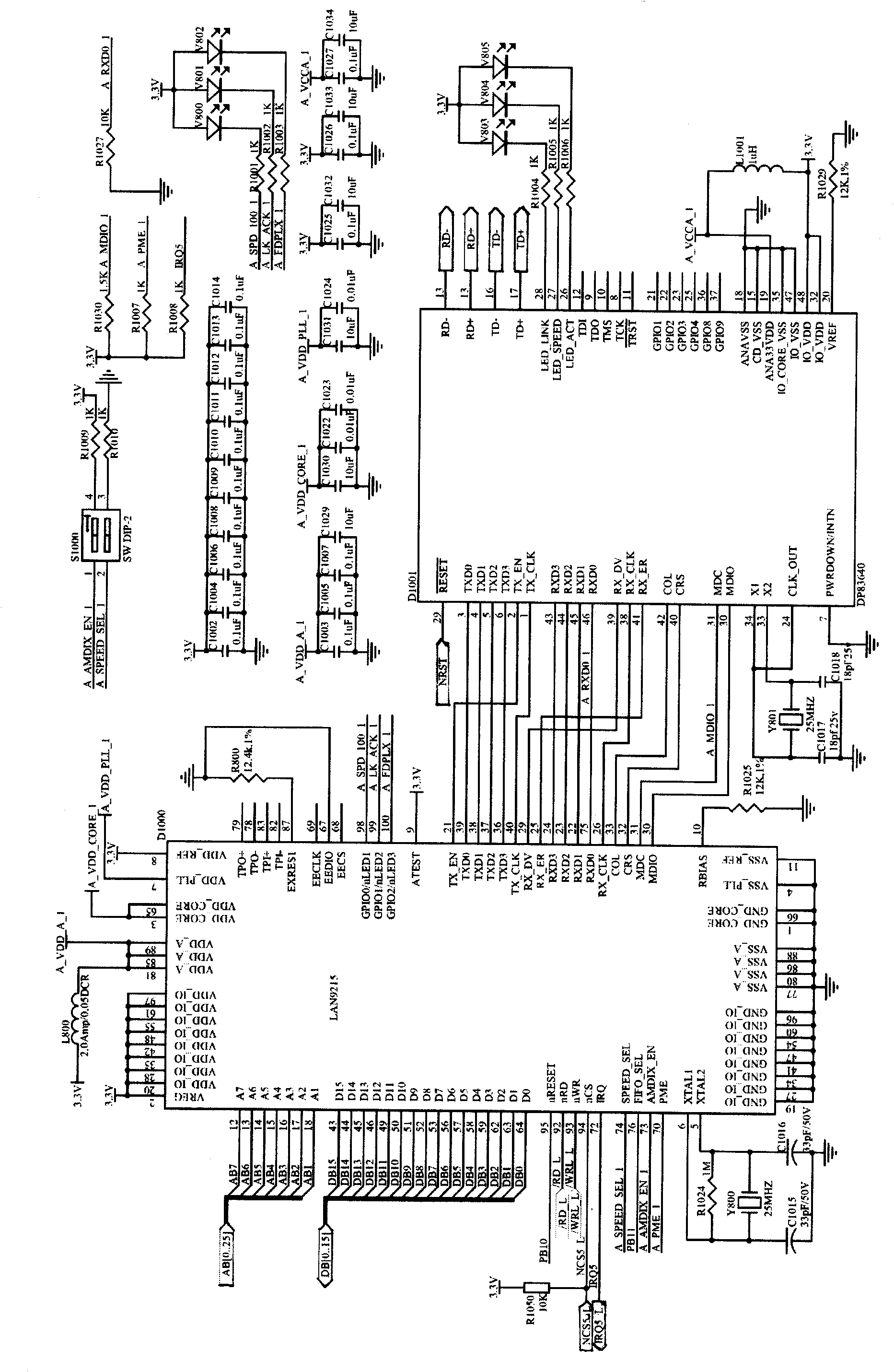

Soft core based merging unit of photoelectric current transformers

InactiveCN101795019AGuaranteed uptimeStrong real-timeCircuit arrangementsInformation technology support systemJoint Test Action GroupSoft core

The invention discloses a soft core based merging unit of photoelectric current transformers, which consists of an FPGA (Field Programmable Gate Array) chip of a main processor and a peripheral circuit. The peripheral circuit consists of a power supply module, an ARM chip, an LCD display screen, a PS2 keyboard, an EPCS16 chip, a JTAG downloading interface, a JTAG debugging interface, an FLASH chip, an SDRAM (Synchronous Dynamic Random Access Memory) chip, an Ethernet controller, an Ethernet driver, a crystal oscillator and an optical fiber interface. The FPGA chip of the main processor is used for receiving current and voltage signals transmitted through the optical fiber interface and sending the current and voltage signals with an FT3 frame format specified in the IEC 60044-8 through the optical fiber interface and with an IEC 61850-9-2 format through the optical fiber interface after interpolation calculation, digital filtering, digital integral and digital calibration operation.

Owner:SOUTHEAST UNIV +1

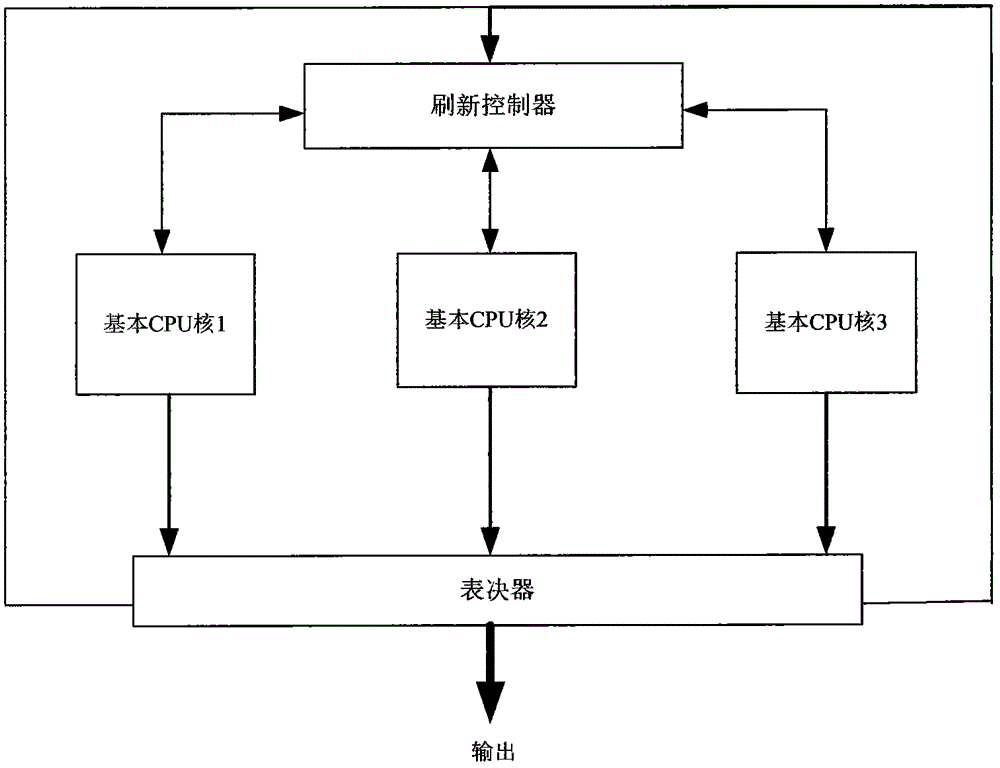

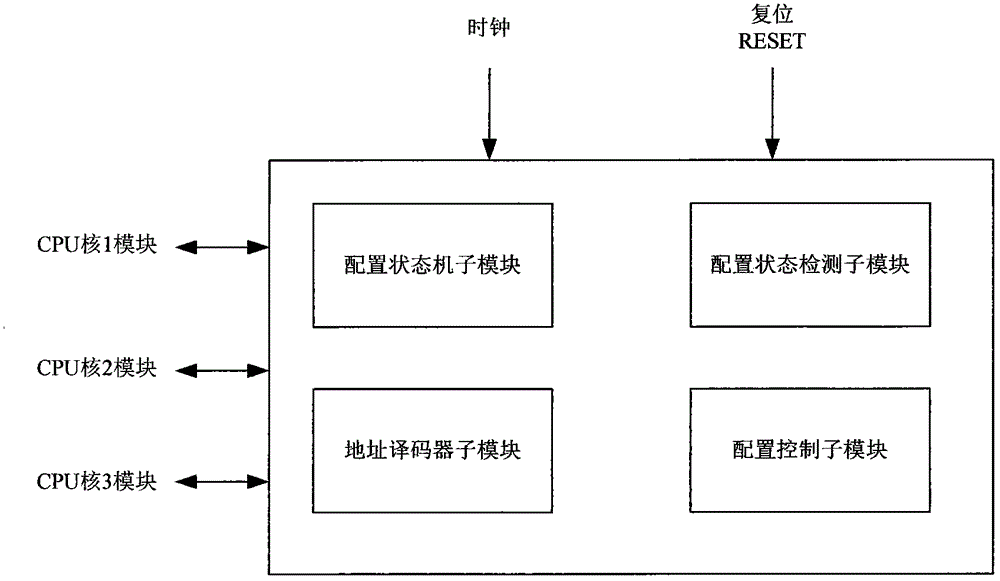

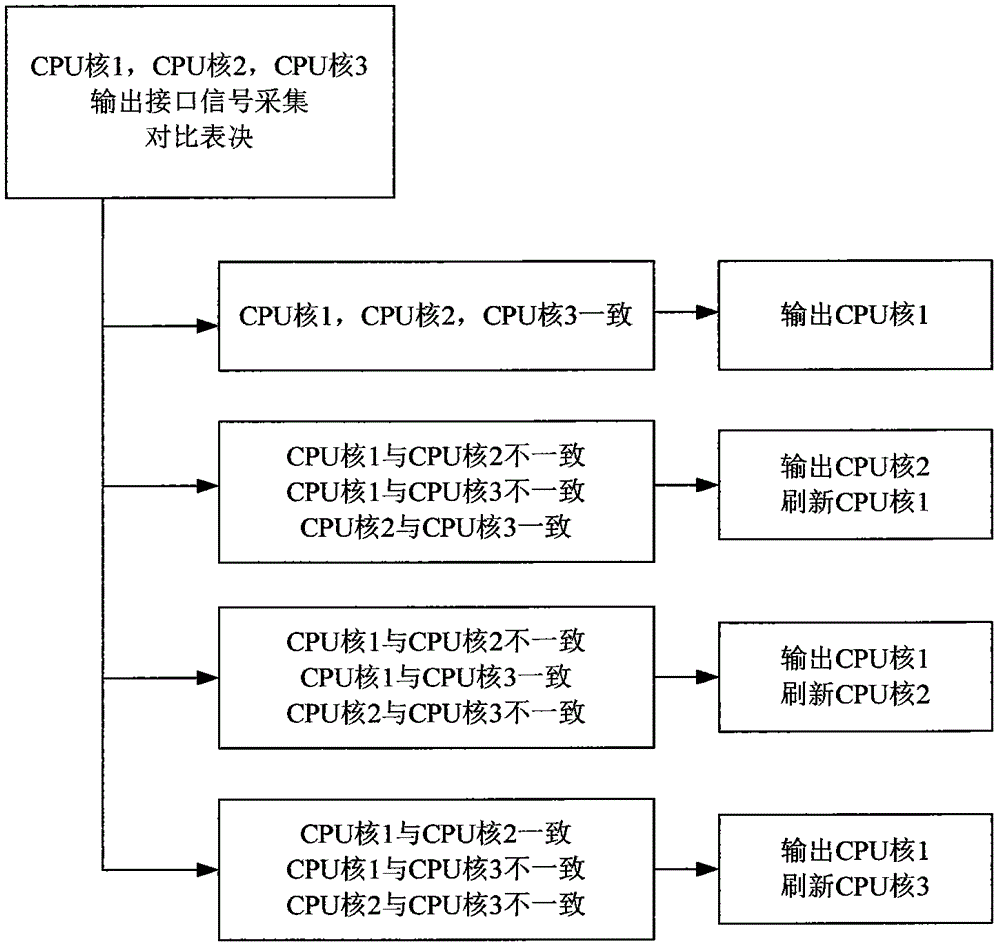

Method for designing triple-modular redundancy type fault-tolerant computer IP core with fault spontaneous restoration function

InactiveCN105279049AGuaranteed correctnessResource usage is reasonableRedundant hardware error correctionSingle point of failureComputer science

The invention designs a triple-modular redundancy type fault-tolerant computer core consisting of three basic CPU cores, namely, three same basic CPU cores are combined into one fault-tolerant computer core, a triple-modular redundancy mode is adopted, and when any one basic CPU core has a fault, the correctness of computer calculation continues to be kept and the fault is spontaneously corrected. According to the computer core, the correct basic CPU core refreshes the basic CPU core with the fault by adopting an automatic refreshing technology, so that the fault is eliminated and a normal working state is recovered. A designed IP core is an independent fault-tolerant computer core in the form of a soft core and used for automatically detecting a single-point fault caused by a single-particle effect, automatically obtaining a correct result and spontaneously correcting the fault. The technical scheme of the invention solves the problem in design of the fault-tolerant computer IP core by adopting the triple-modular redundancy technology, and can be used for FPGA application development and integrated circuit design.

Owner:KANGYUXING TECH BEIJING

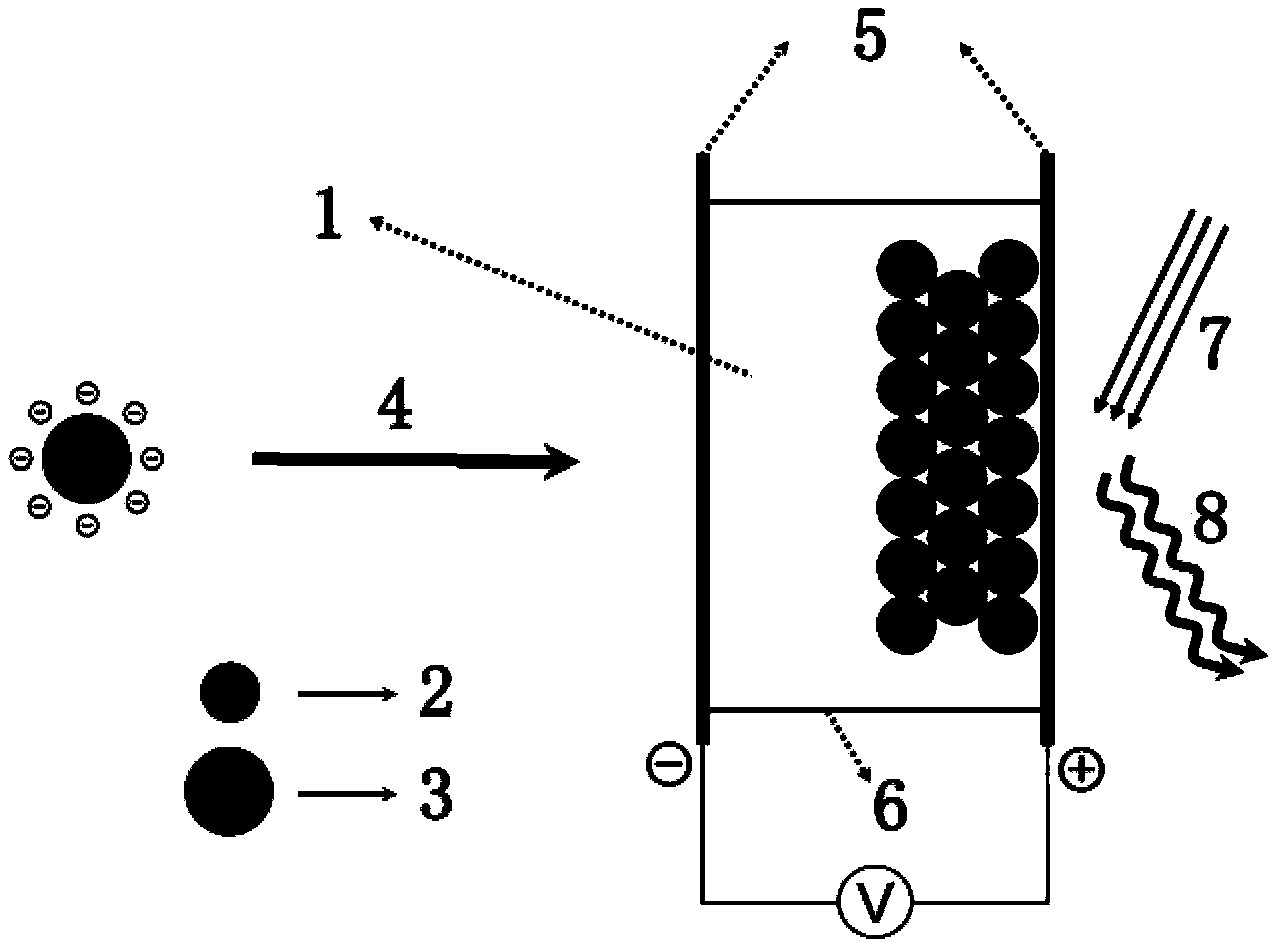

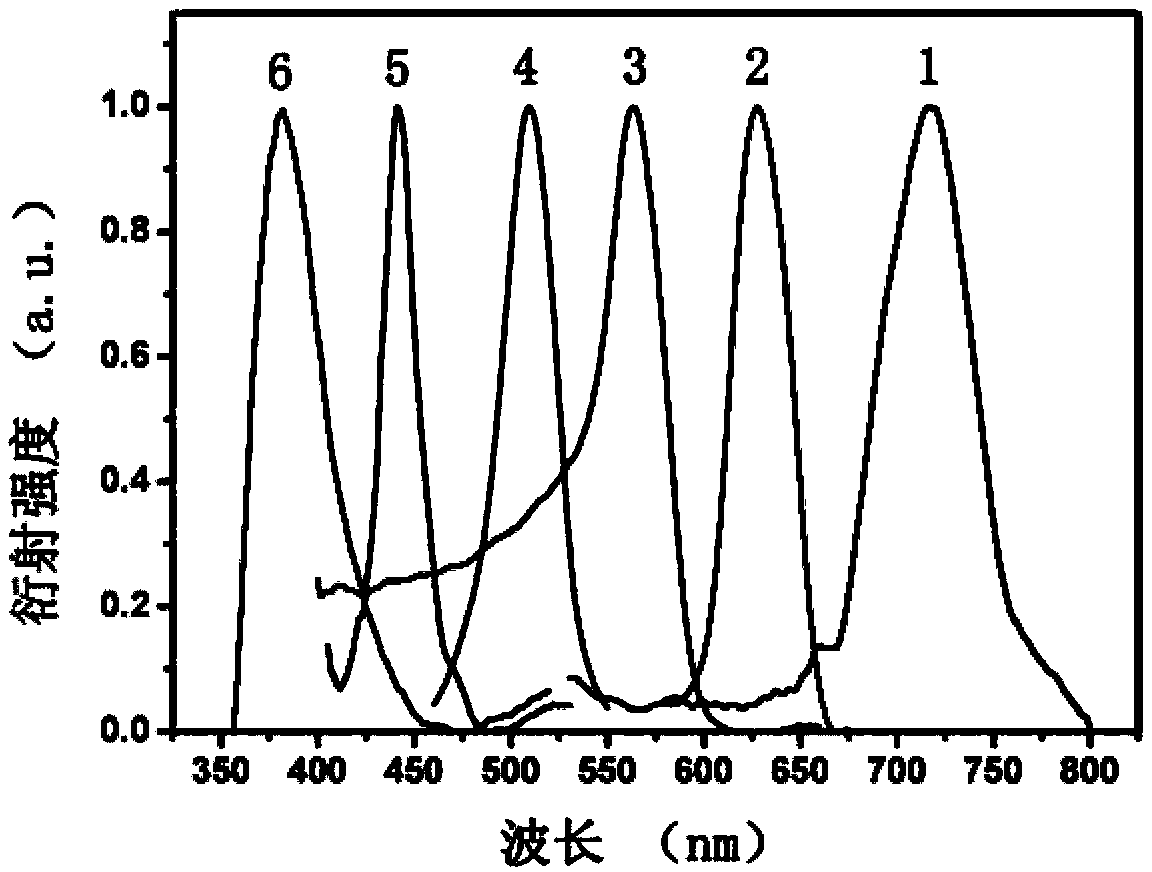

Preparation method of polymer photonic crystals with adjustable photonic band gap and presenting patterned color display

ActiveCN103436965ARapid depositionEasy electrodeposition assemblyFrom gel statePolycrystalline material growthMicrosphereLoad time

The invention discloses a preparation method of polymer photonic crystals with an adjustable photonic band gap and presenting patterned color display, and belongs to the field of polymer materials. The method comprises the steps: hydrogel polymer microspheres having a soft core-shell structure and having a relatively high surface potential and monodisperse size are selected as building base elements, the hydrogel polymer microspheres are allowed to rapidly form a large area ordered structure by electric field deposition and other ways, and the electric field induced assembled polymer photonic crystals having the photonic band gap property and presenting bright structural colors are obtained. According to different load voltages or load times, the hydrogel polymer microspheres on an electrode plate generates different close packing degrees, the soft hydrogel polymer microspheres have different degrees of volume changes, so that a lattice period of the formed photonic crystals can be adjusted, movement of a reflection spectrum peak position (i.e. the photonic band gap) happens, and thus regulation and control of the photonic crystal material structural colors on a macro level is realized.

Owner:JILIN UNIV

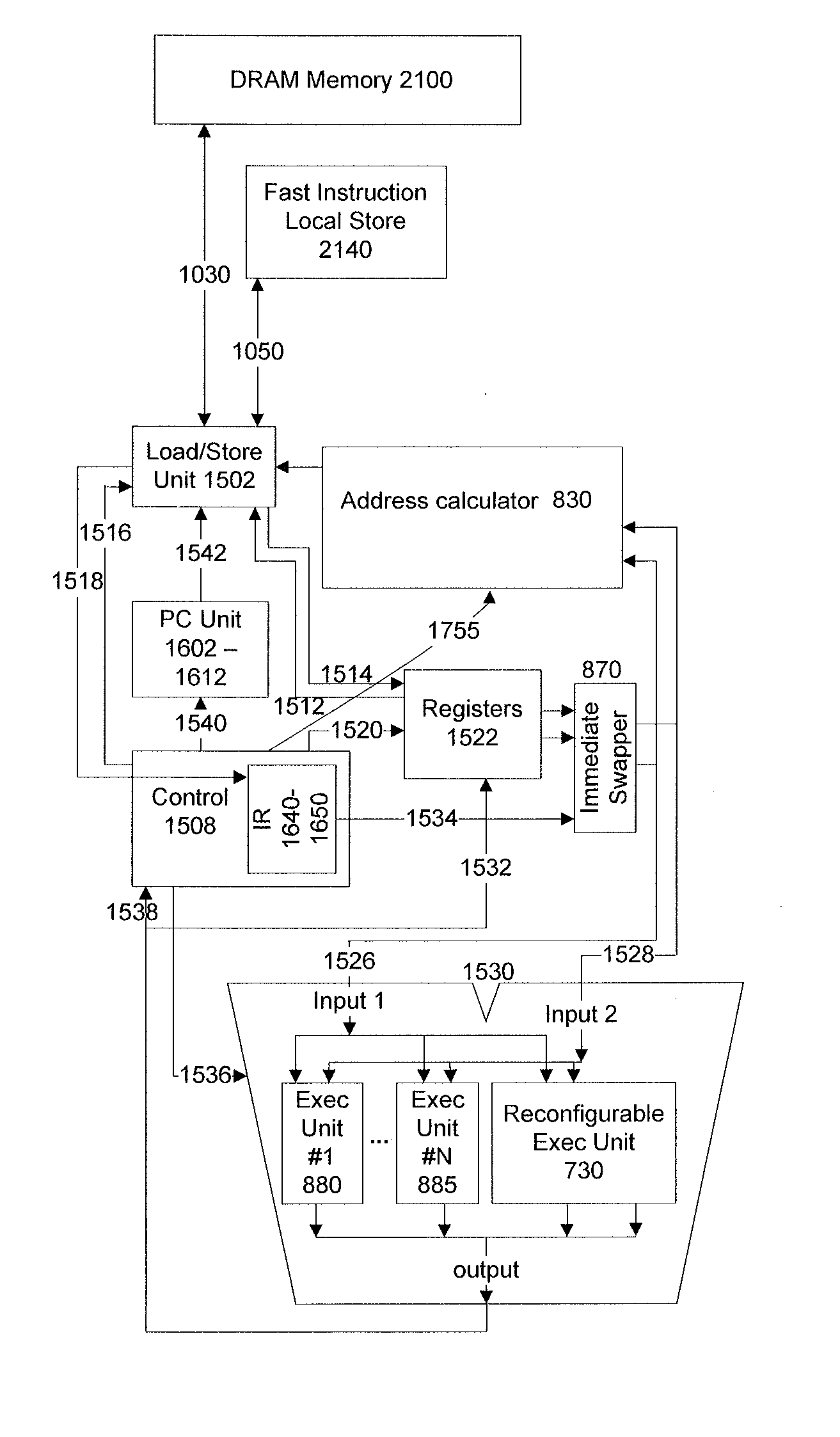

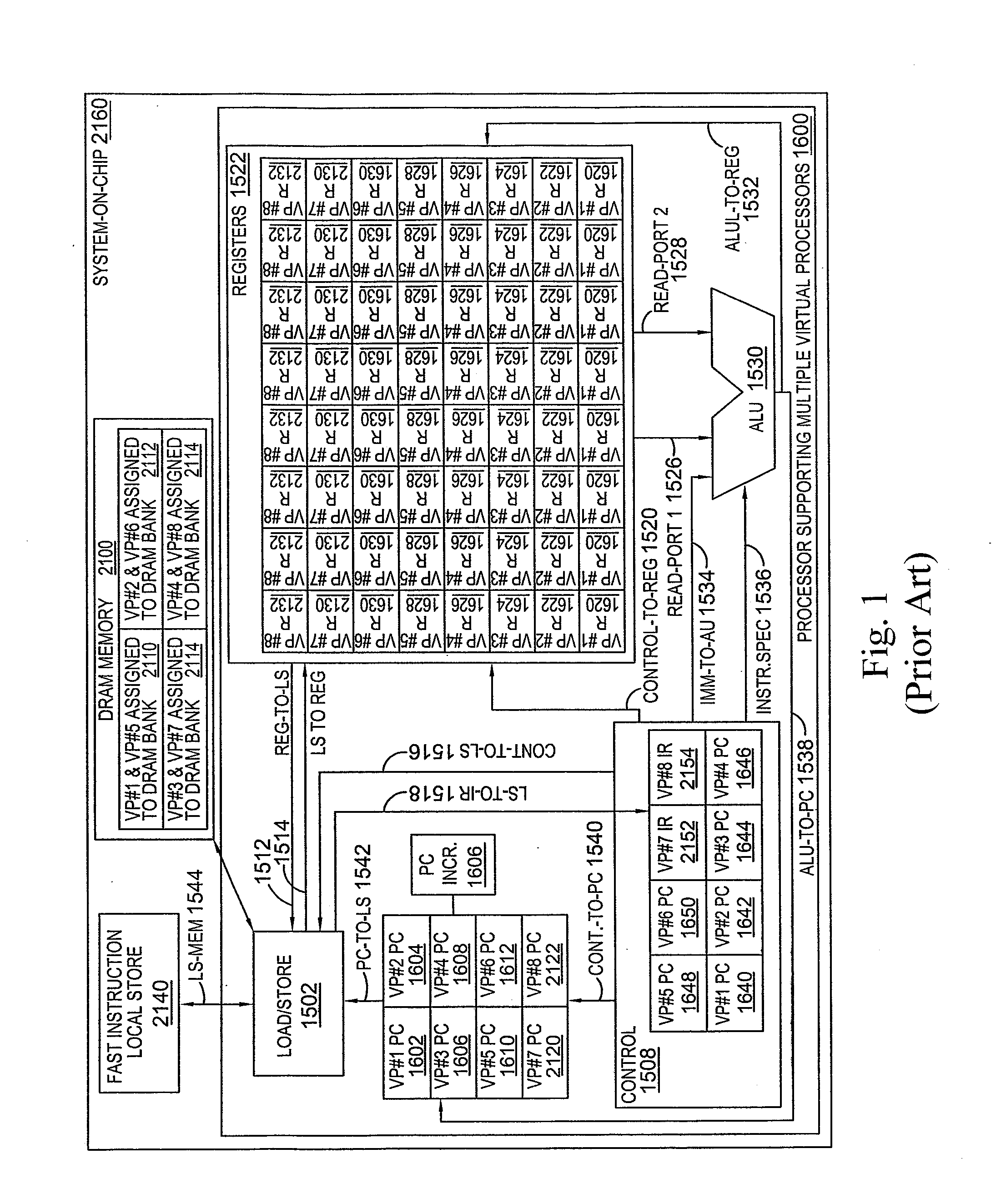

Integrated circuit having a hard core and a soft core

An integrated circuit (IC) is disclosed. The integrated circuit includes a non-reconfigurable multi-threaded processor core that implements a pipeline having n ordered stages, wherein n is an integer greater than 1. The multi-threaded processor core implements a default instruction set. The integrated circuit also includes reconfigurable hardware that implements n discrete pipeline stages of a reconfigurable execution unit. The n discrete pipeline stages of the reconfigurable execution unit are pipeline stages of the pipeline that is implemented by the multi-threaded processor core.

Owner:COGNITIVE ELECTRONICS INC

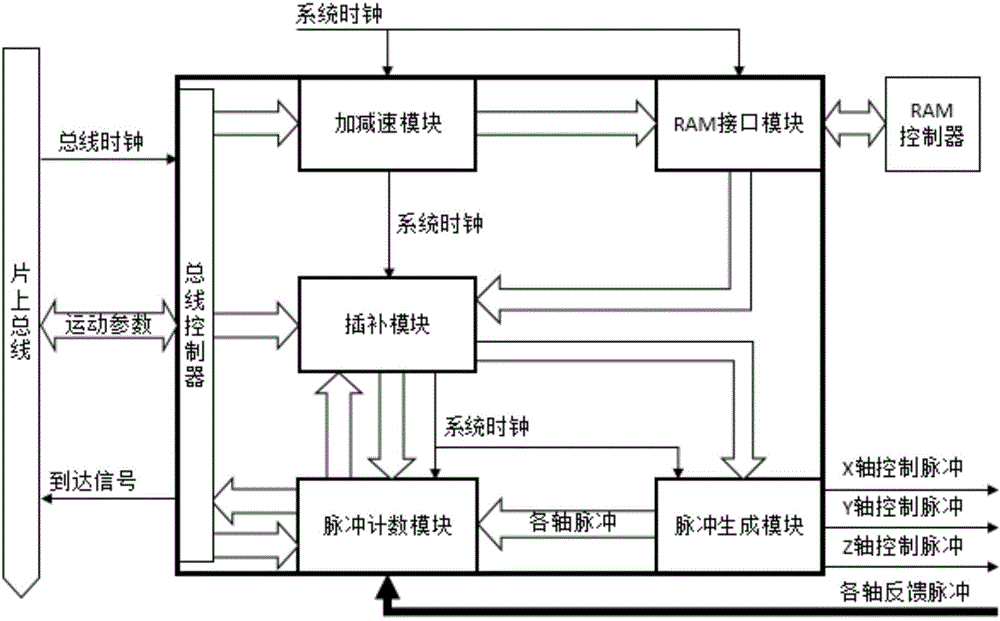

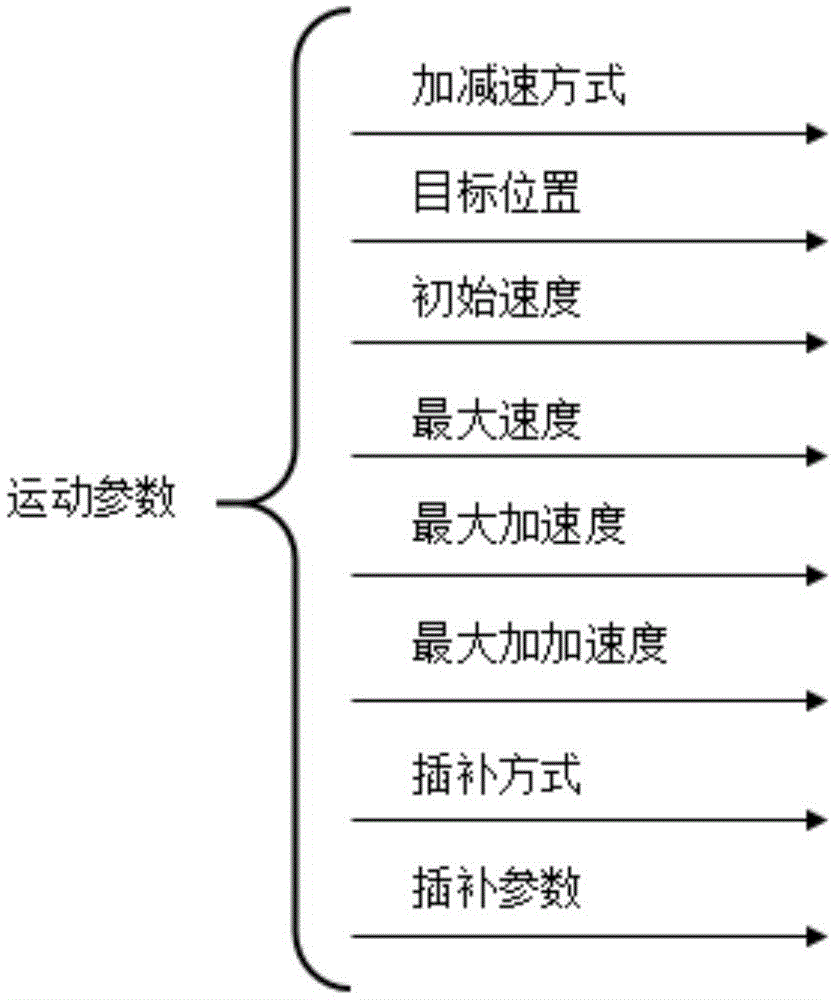

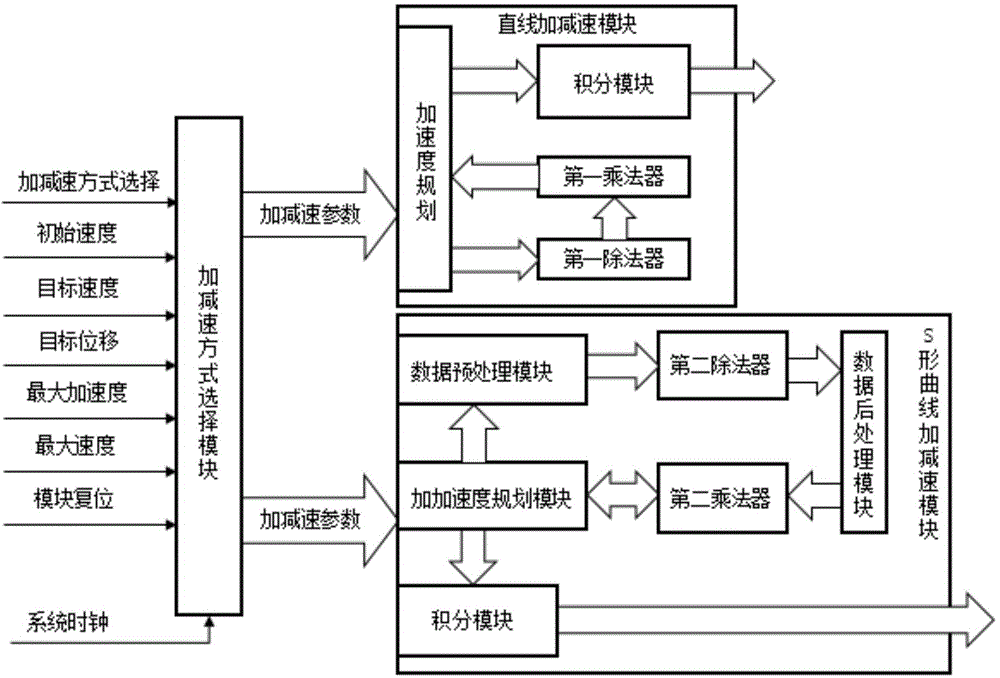

Flexibility motion control IP (Intellectual Property) core and implementation method thereof

ActiveCN104135212AFast operationShorten the control cycleElectric motor controlIntellectual propertyOperating frequency

The invention discloses a flexibility motion control IP (Intellectual Property) core and an implementation method thereof, belonging to the field of motion control. The IP core comprises a acceleration / deceleration module, an interpolation module, a pulse counting module, a pulse generation module, a bus controller and an RAM (Random Access Memory) interface module. The flexibility motion control IP core and the implementation method thereof aim to solve the problems that high speed and high precision cannot be achieved due to incapability of further reducing a control period since a motion control algorithm has a long running period in a general MCU (Micro Controller Unit) or DSP (Digital Signal Processor). The IP core has the characteristics of short control period and high output pulse precision, non-symmetrical linear acceleration and deceleration can be achieved, non-symmetrical S-shaped curve acceleration and deceleration can be achieved, two-axis or three-axis linear interpolation with the linear or the S-shaped curve acceleration and deceleration can be achieved, and two-axis arc interpolation at an uniform speed also can be achieved. Through the adoption of the IP core, motion control relevant algorithm is realized in a Verilog hardware description language soft core mode, the motion control relevant algorithm can be implemented in an FPGA (Field Programmable Gate Array), can be implemented in an ASIC (Application Specific Integrated Circuit) mode, and can be integrated into SoC (System On Chip), the typical working frequency is 100MHz, and feasibility is provided for building a flexibility motion control system.

Owner:SOUTH CHINA UNIV OF TECH

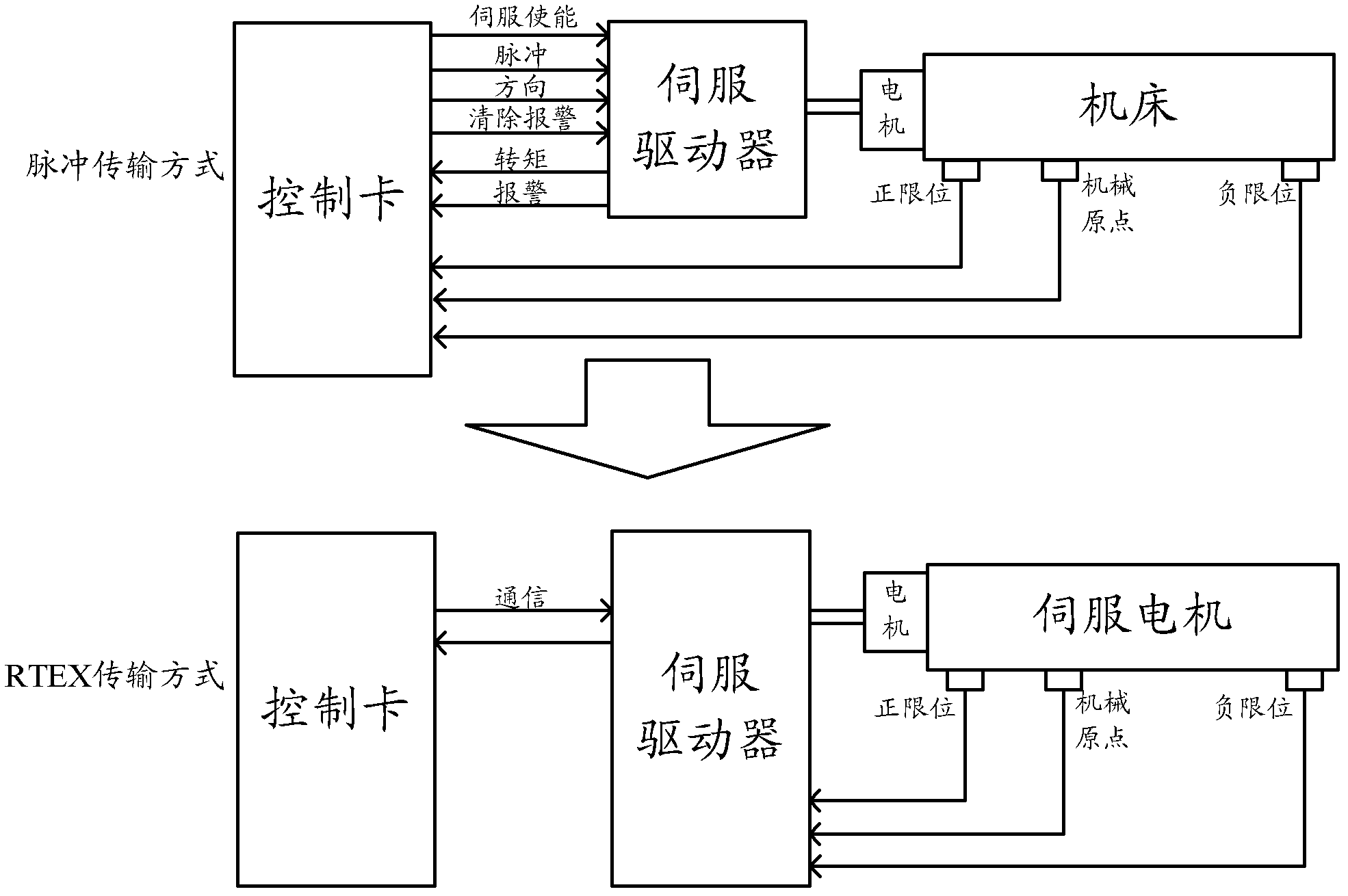

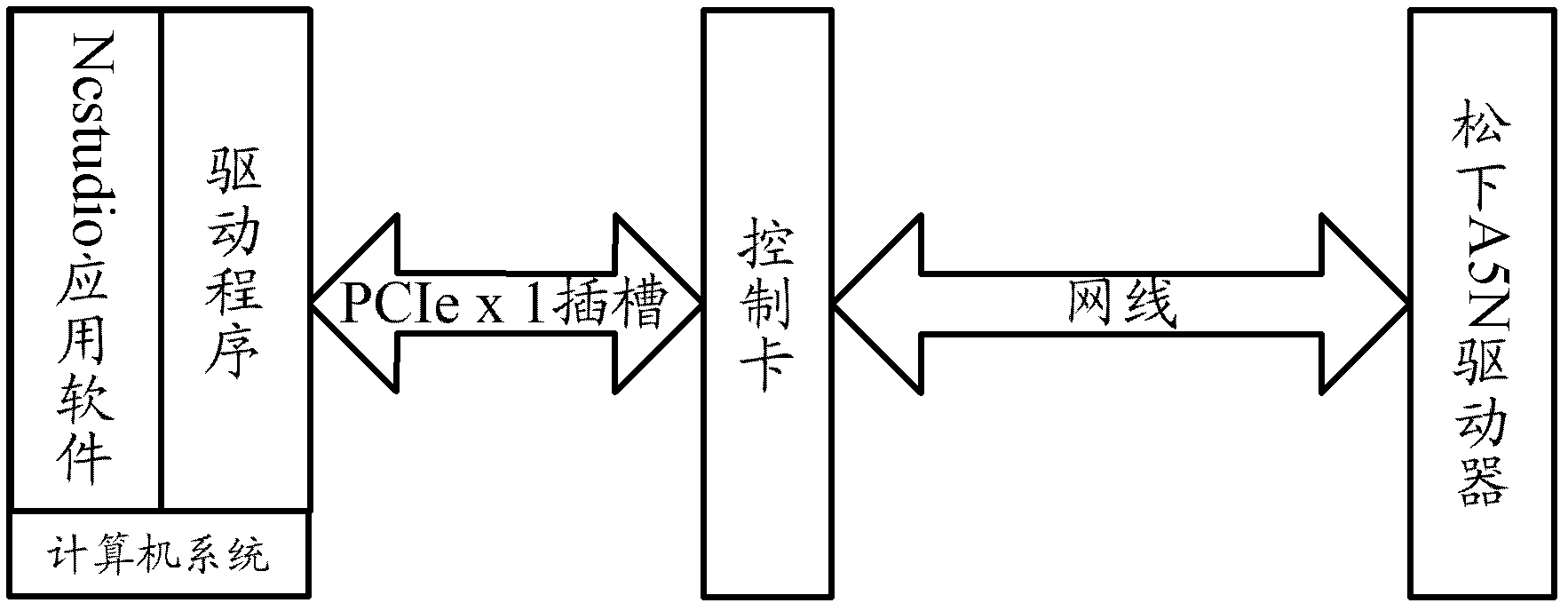

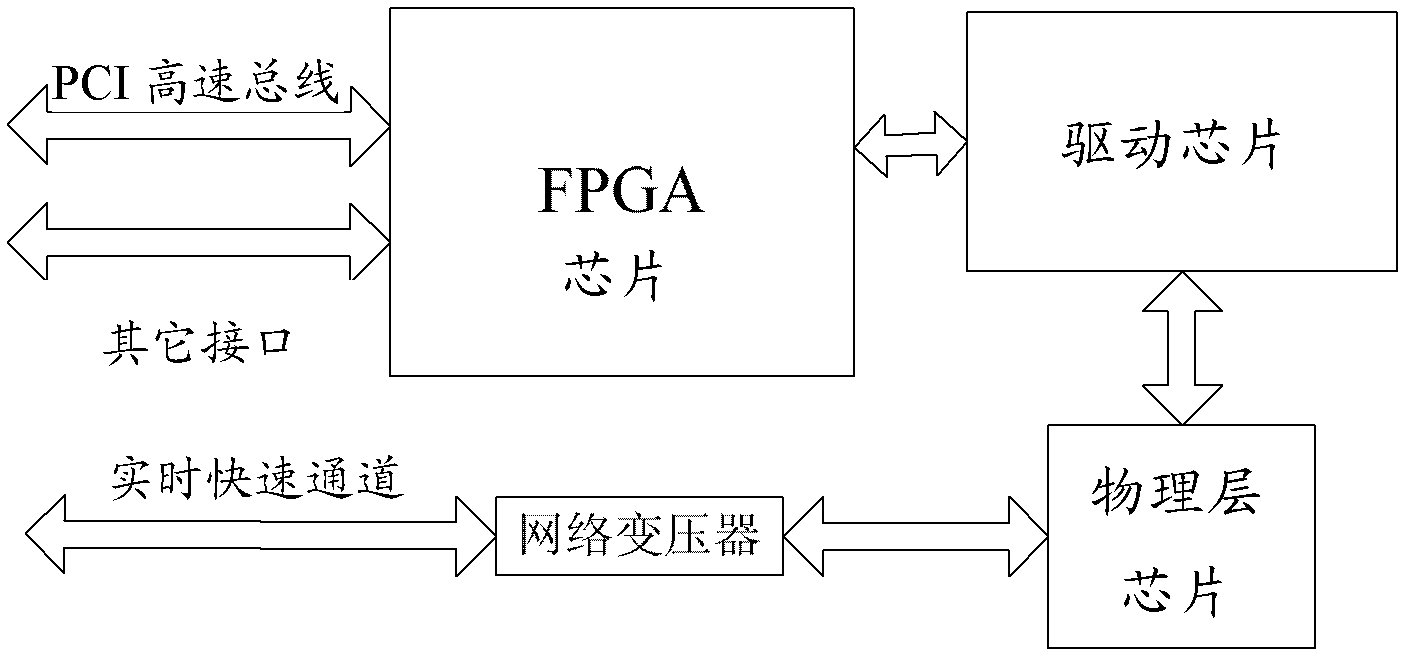

Industrial automatic real-time control device and method based on communication bus

ActiveCN102621974AImprove scalabilityProcessing speedTotal factory controlProgramme total factory controlNetwork packetPhysical layer

The invention relates to an industrial automatic real-time control device based on a communication bus. The industrial automatic real-time control device comprises an FPGA (Field Programmable Gata Array) chip, a driving chip and a physical layer chip, wherein the FPGA chip is connected with the physical layer chip through the driving chip; the physical layer chip is connected with a real-time communication bus; and the FPGA chip comprises a PCI-E (Peripheral Component Interconnect-E) bus interface, an embedded soft core module, a driving controller module, an FIFO (First In First Out) buffer module and a PCI-E data pack resolving module. The invention further relates to a method for implementing industrial automatic real-time control based on a communication bus by using the device. In the device and the method disclosed by the invention, the FPGA chip is adopted, so that appropriate resources can be selected flexibly according to user requirements in comparison to a DSP (Digital Signal Processor) chip in the prior art; meanwhile, the device and the method have the advantages of high expandability, high processing speed, high integration degree, easiness for updating and the like; the industrial automatic real-time control device based on the communication bus has a simple structure and low cost; and the method is easy and convenient to apply, and has a wide application range.

Owner:SHANGHAI WEIHONG ELECTRONICS TECH

Thick-covered, soft core golf ball

A golf ball comprising a core comprising a halogenated thiophenol and having a diameter of from about 1.30 inches to about 1.40 inches, a compression of about 45 or less; and a coefficient of restitution of about 0.780 or greater at about 125 feet per second; and a cover having a thickness of from about 0.14 inches to about 0.16 inches and being formed from a composition comprising a Na-ionomer and a Li-ionomer blend having a Shore D hardness of about 60 to about 70; wherein a combination of the core and the cover results in the golf ball having a compression of from about 85 to about 95, and a coefficient of restitution of from about 0.815 to about 0.825 at about 125 feet per second.

Owner:ACUSHNET CO

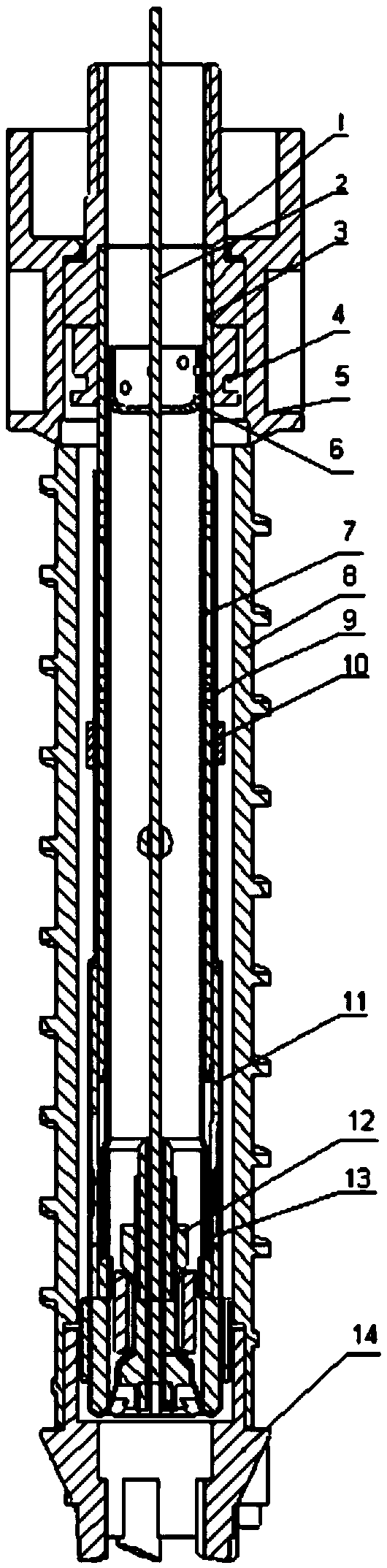

Built-in soft lunar soil sample sampling mechanism

ActiveCN105510078AGet raw scientific valueSave recycling spaceWithdrawing sample devicesLunar soilEngineering

The invention discloses a built-in soft lunar soil sample sampling mechanism. A core tube top joint, a core lifting stay rope, a core taking tube, a fixed ring, a drill rod sub, a spacing ring, a soft core-taking bag, a drill rod, a core taking belt, a guide ring, a core tube base joint, a pull head assembly, a sealer and a drill. The drill rod sub, the drill rod and the drill are fixedly connected to form a hollow drilling tool. The core tube top joint, the core taking tube and the core tube base joint form a hard core taking tube. The core tube base joint has an inner annular cavity structure. The soft core-taking bag is connected on the sealer, which is preplaced in the annular cavity of the core tube base joint. The spacing ring is installed on the soft core taking bag. The core taking belt passes through the guide ring to be fixedly connected on the pull head assembly. The sampling mechanism of the invention is simple and operates reliably, and can keep sequence information of deep lunar soil samples. The soft core taking bag for wrapping lunar soil samples can be used to realize in situ packaging, winding and recovering of deep lunar soil samples 2 m deep below the lunar surface, and recovery space is saved.

Owner:BEIJING SATELLITE MFG FACTORY

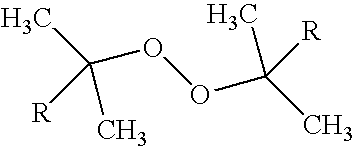

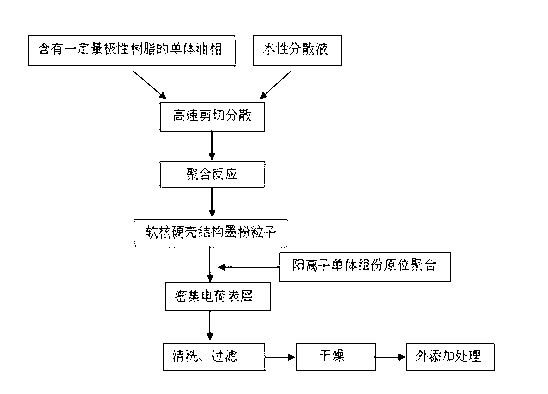

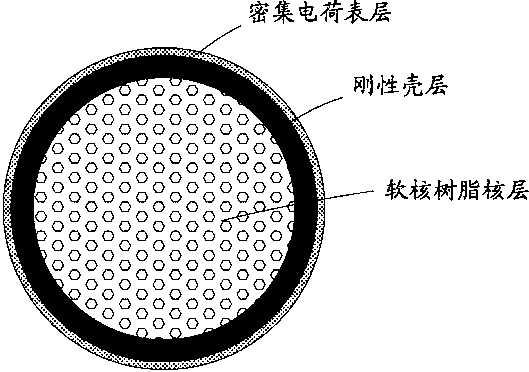

Preparation method of suspension polymerization powdered ink with core-shell structure

ActiveCN103105751AExcellent low temperature fixabilityGood environmental stabilityDevelopersOil phaseSilicon dioxide

The invention provides a preparation method of suspension polymerization powdered ink with a core-shell structure. The preparation method comprises the following steps of: (1) respectively preparing monomer oil phase which contains a certain amount of polar resin and forms into powdered ink soft core resin, and aqueous dispersion liquid; (2) adding the monomer oil phase into the aqueous dispersion liquid, shearing, suspending and pelleting at high speed, transferring into a reactor, and carrying out first warming polymerization reaction to obtain the powdered ink particles with a soft core-hard shell structure; (3) taking the powdered ink with the soft core-hard shell structure as a core layer, adding positive ion monomer components, and carrying out second polymerization reaction by a water-soluble initiator to obtain soft core-hard shell powdered ink particles of which the outer surfaces are evenly distributed with intensive charge surface layers; and (4) cleaning and filtering products, sufficiently drying, and adding silicon dioxide. According to the preparation method, the shell layer which is evenly distributed with the intensive charges can be obtained according to the characteristics of the polar resin and the cation monomer component, so that the electrification evenness of the surface of the powdered ink particles can be improved, and the preparation method is good in low-temperature fixation characteristics and environmental stability.

Owner:SHENZHEN LEPUTAI TECH CO LTD

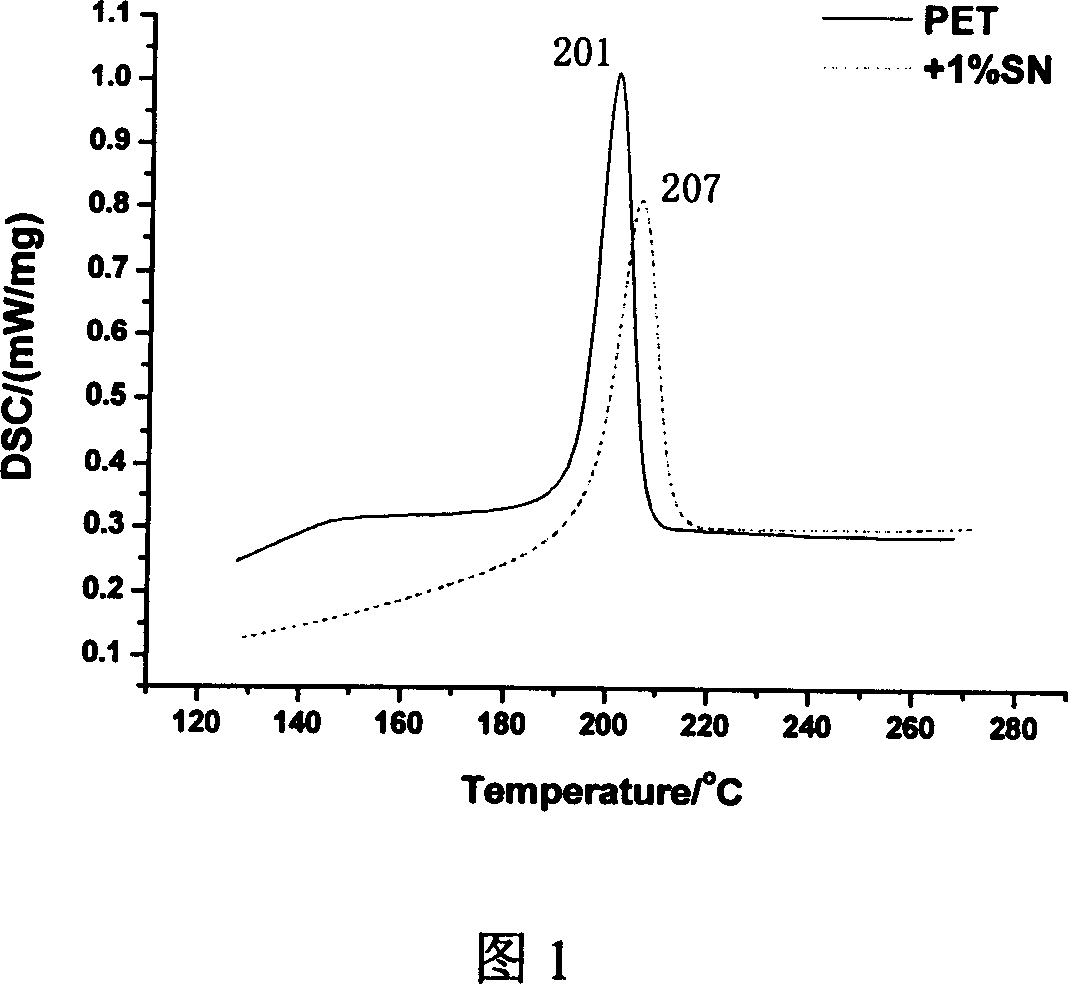

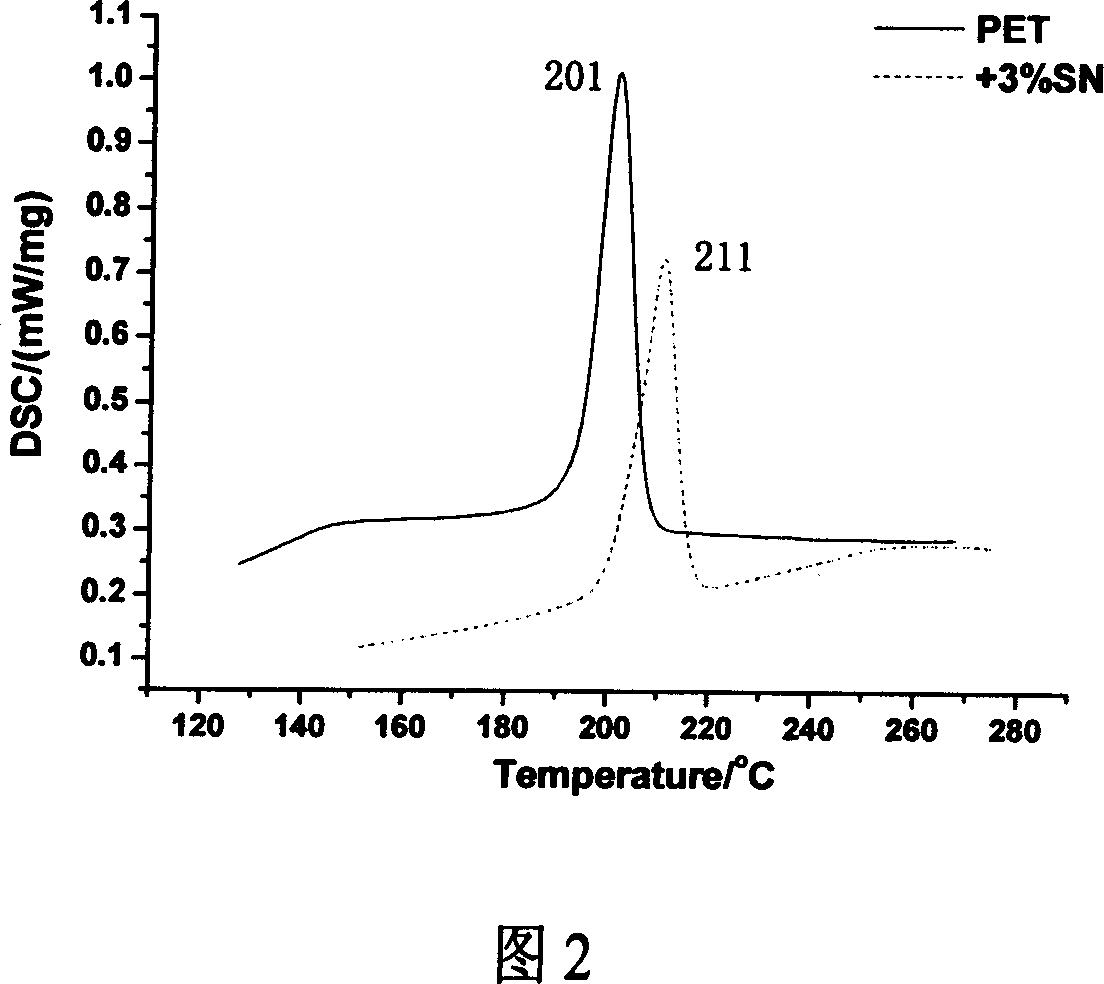

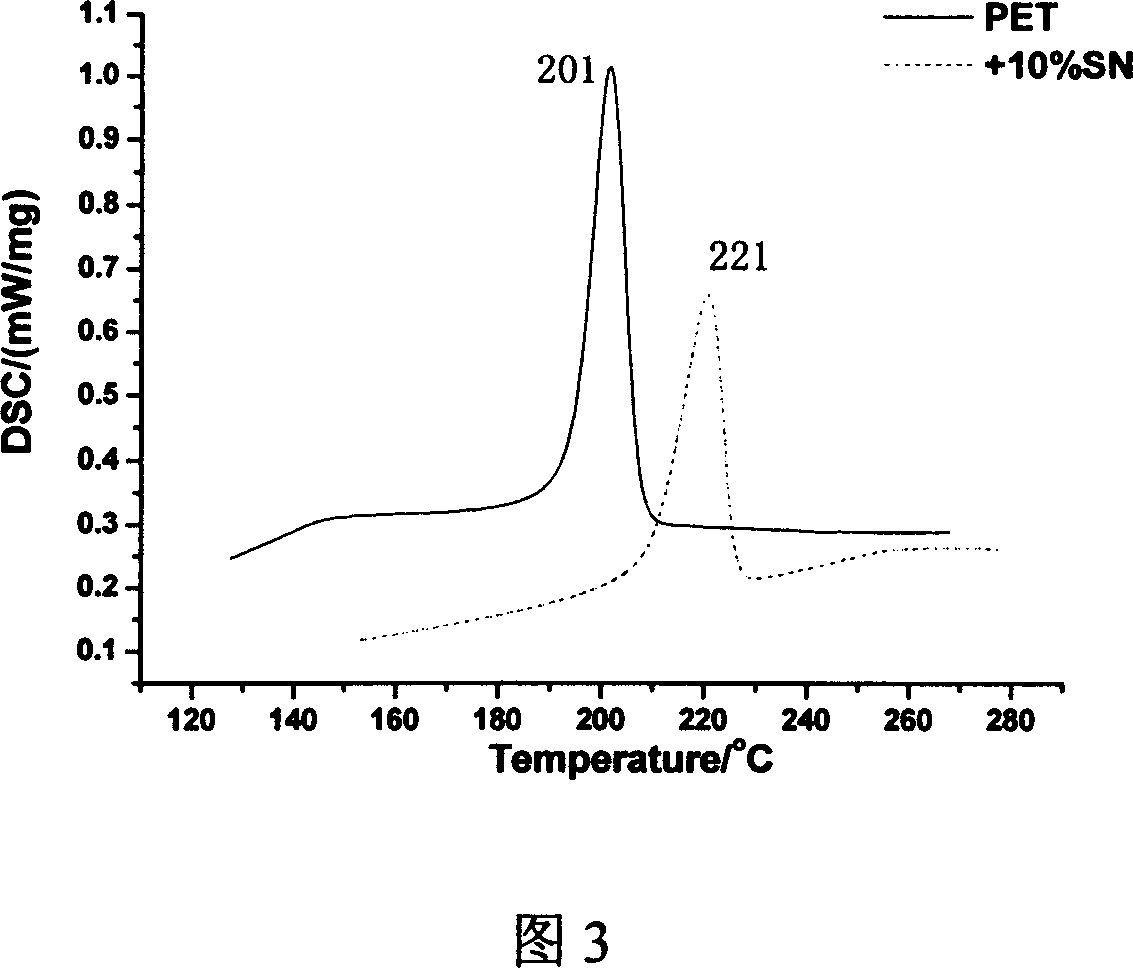

Core-shell structure ionomer for PET resin toughening crystallization and method for making same

InactiveCN1990514AGuaranteed price advantageSignificantly toughenedEngineering plasticPolymer chemistry

The invention relates to a core-shell ionomer that is used to intensify the crystallization for PET resin and the method for preparing the same. In the beginning, the ionomer employs (methyl) acrylic acid monomer with glass- transition temperature of contained butyl acrylate far lower than room temperature for part polymerization and nucleation, employs monomer with glass- transition temperature of contained methyl methacrylate higher than room temperature and a plurality of unstaratured aliphatic acids containing methacrylic acid for polymerization and nucleation, then forms soft core / hard shell core-shell construction; then, neutralizing with base liquid to establish core-shell ionomer. The invention employs cheap monomer and substance, forms core-shell ionomer through emulsion polymerization, and applies it to the forming and extrusion for PET resin, which toughes and promotes the crystallization for PET, and widens its application in engineering plastic field with lower cost.

Owner:SHANGHAI GENIUS ADVANCED MATERIAL (GRP) CO LTD