Patents

Literature

695 results about "Hardware description language" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In computer engineering, a hardware description language (HDL) is a specialized computer language used to describe the structure and behavior of electronic circuits, and most commonly, digital logic circuits.

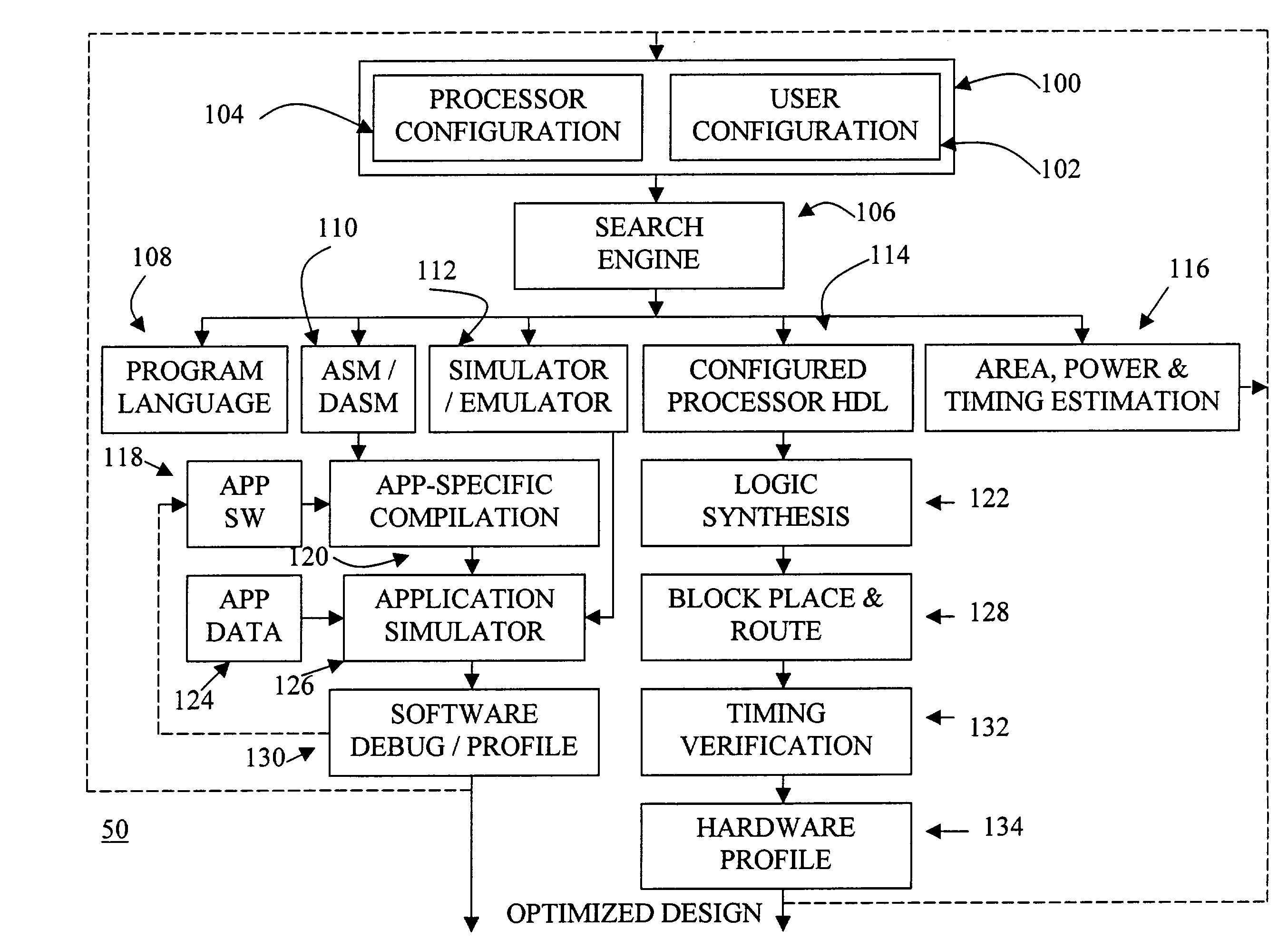

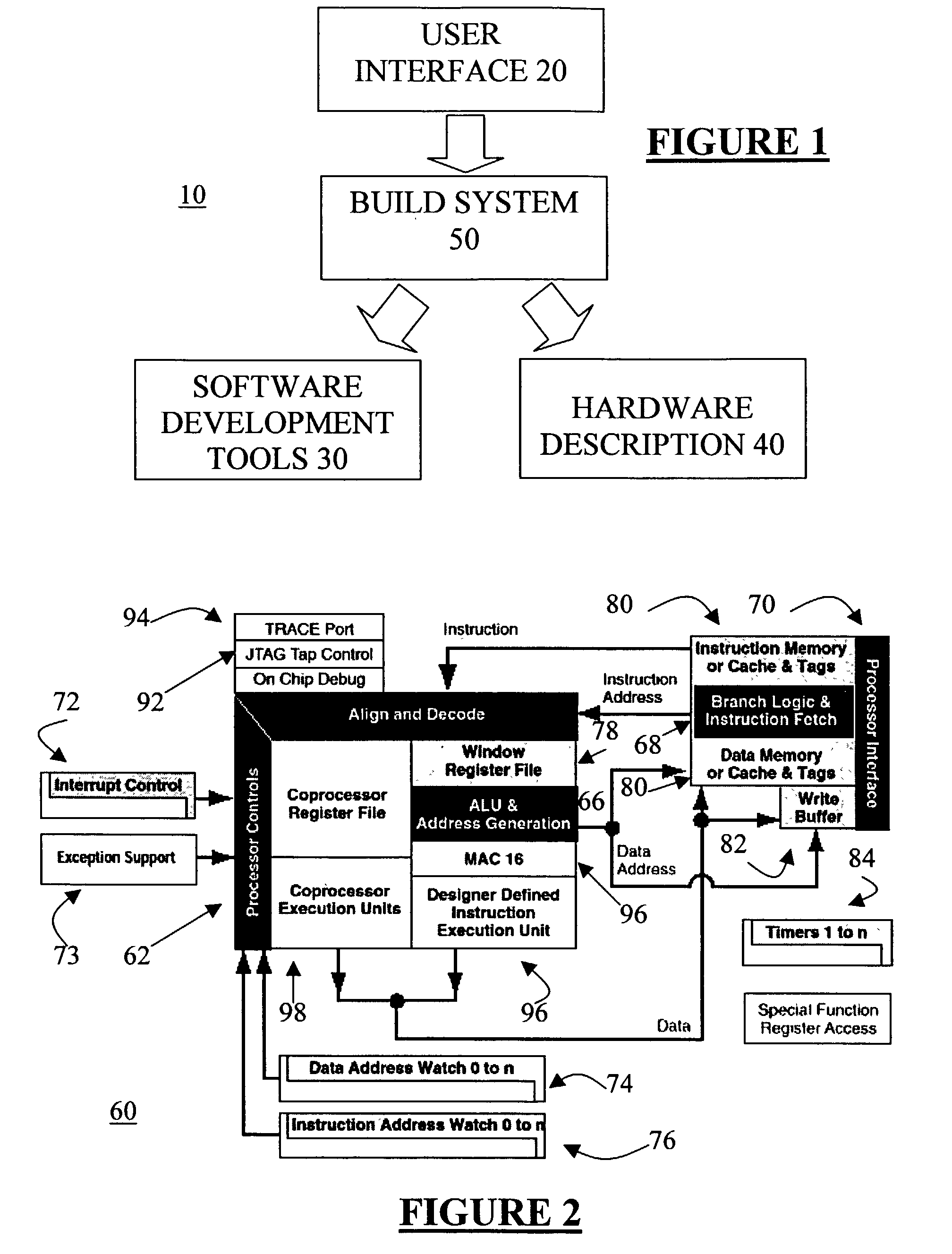

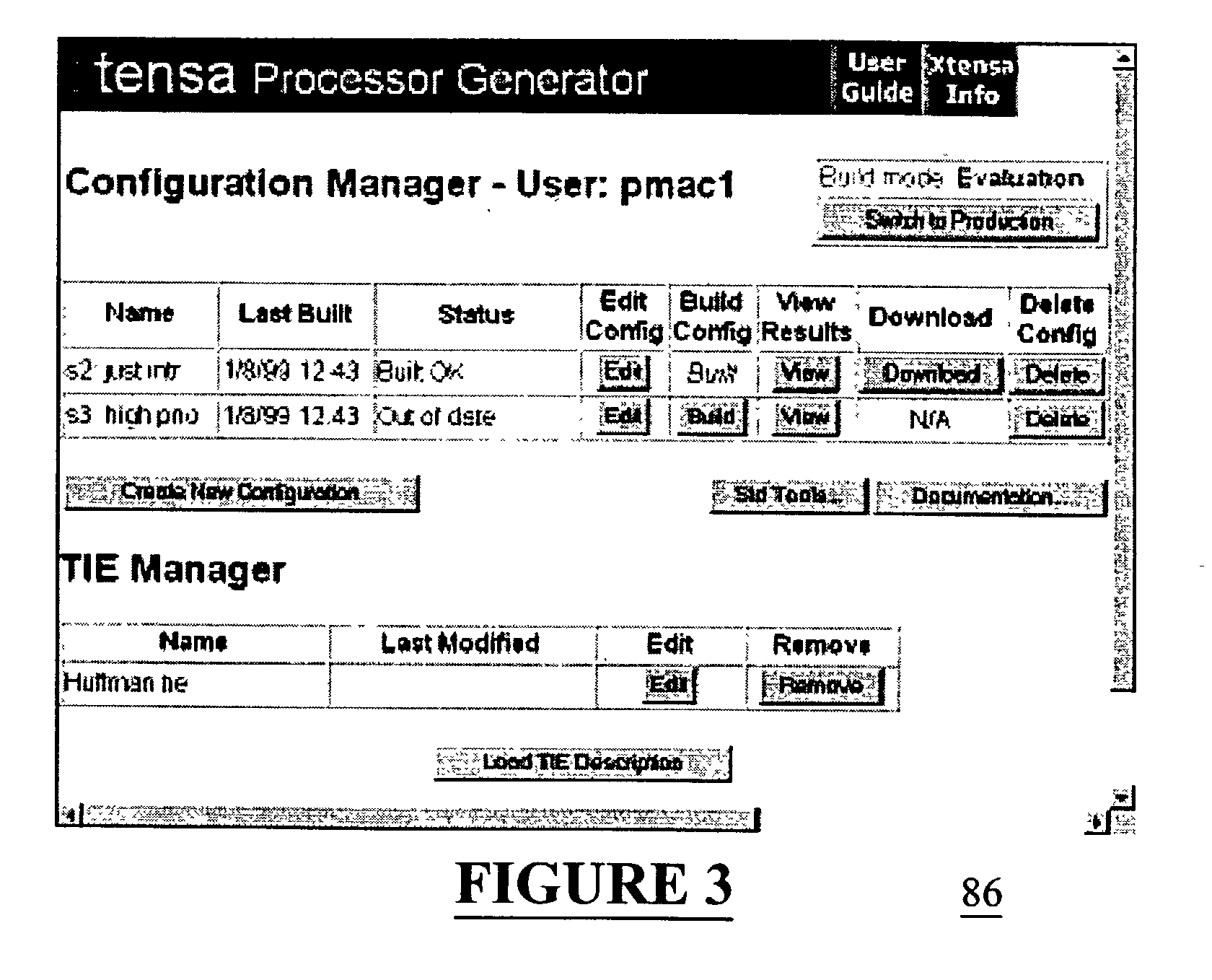

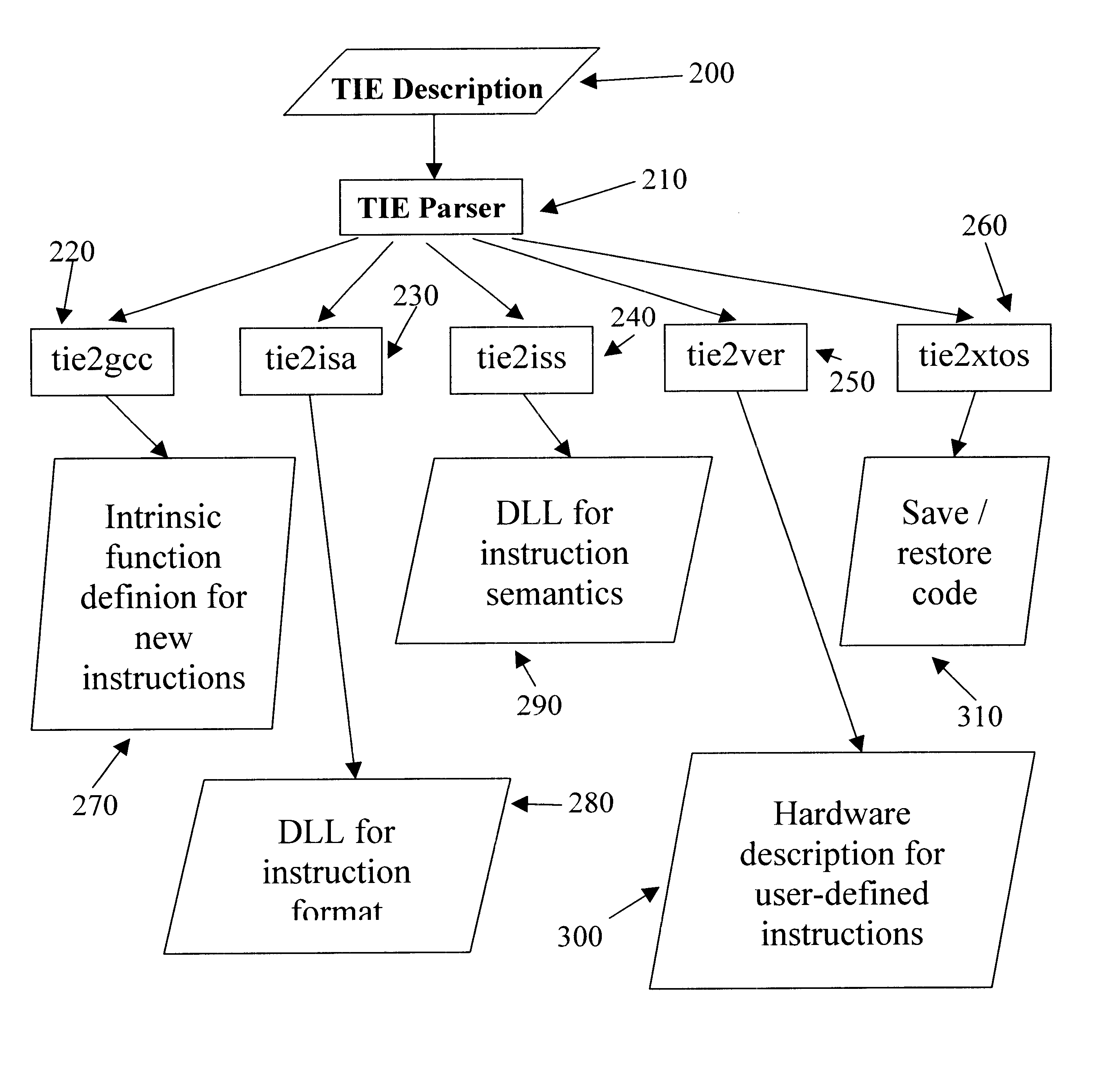

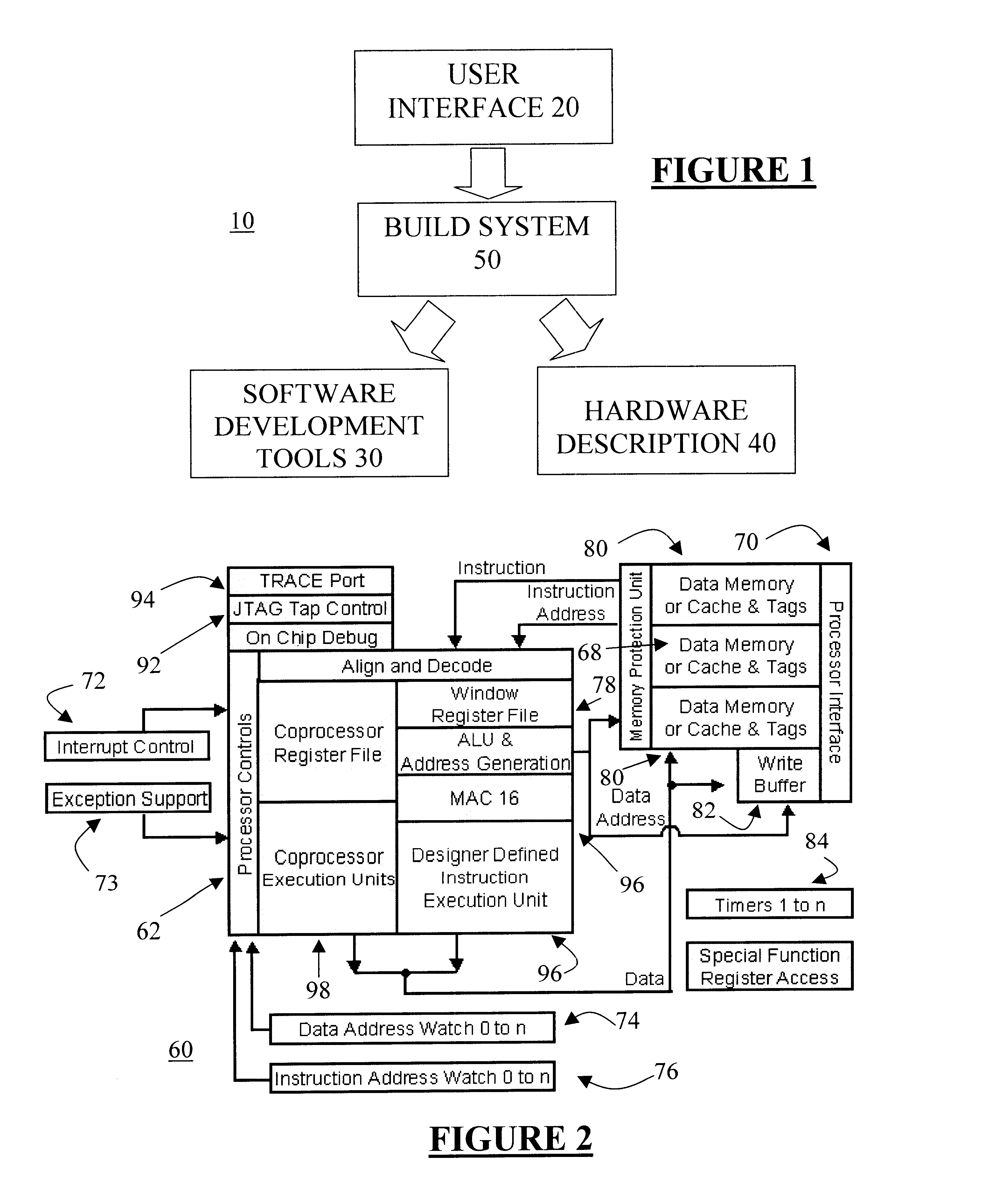

Automated processor generation system for designing a configurable processor and method for the same

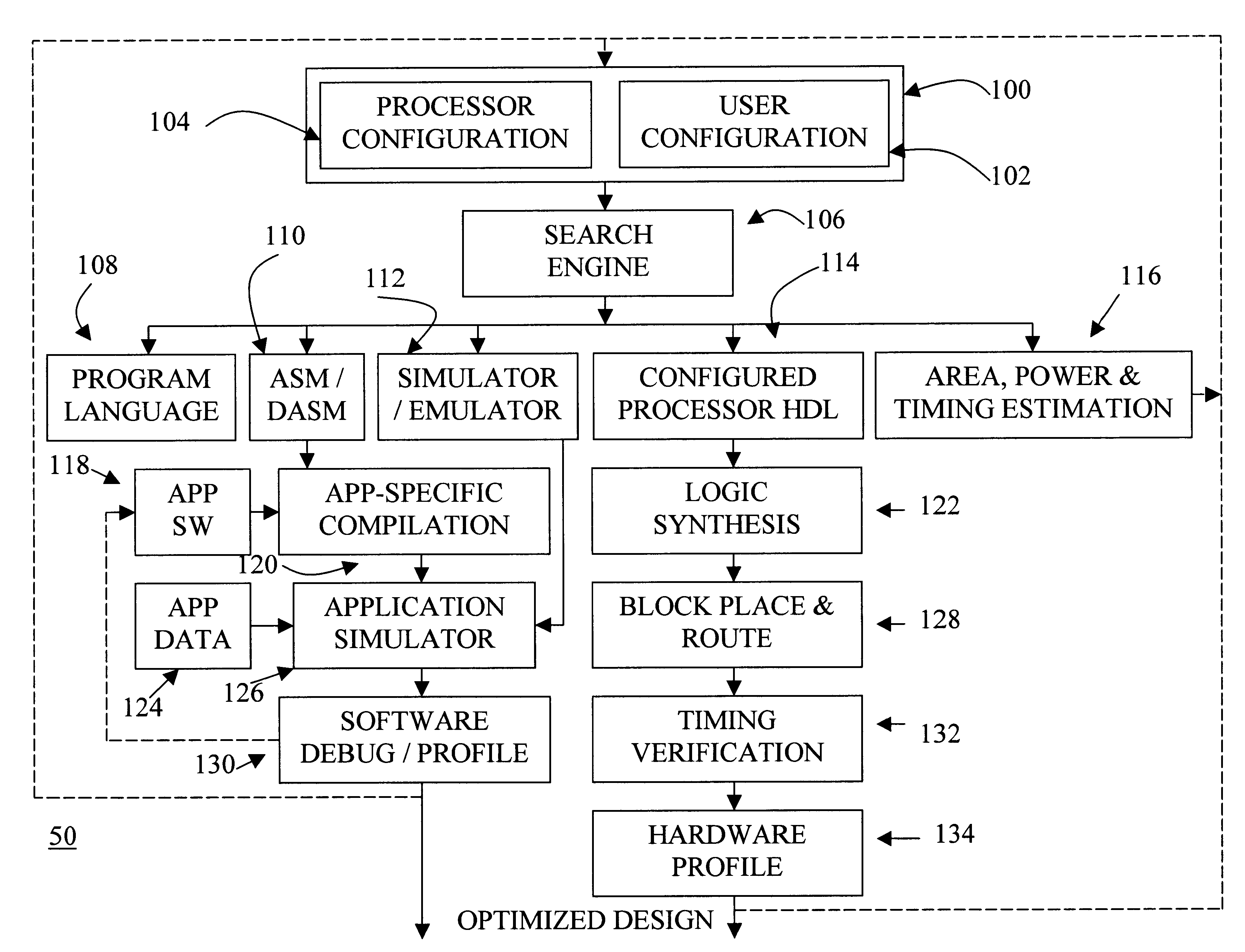

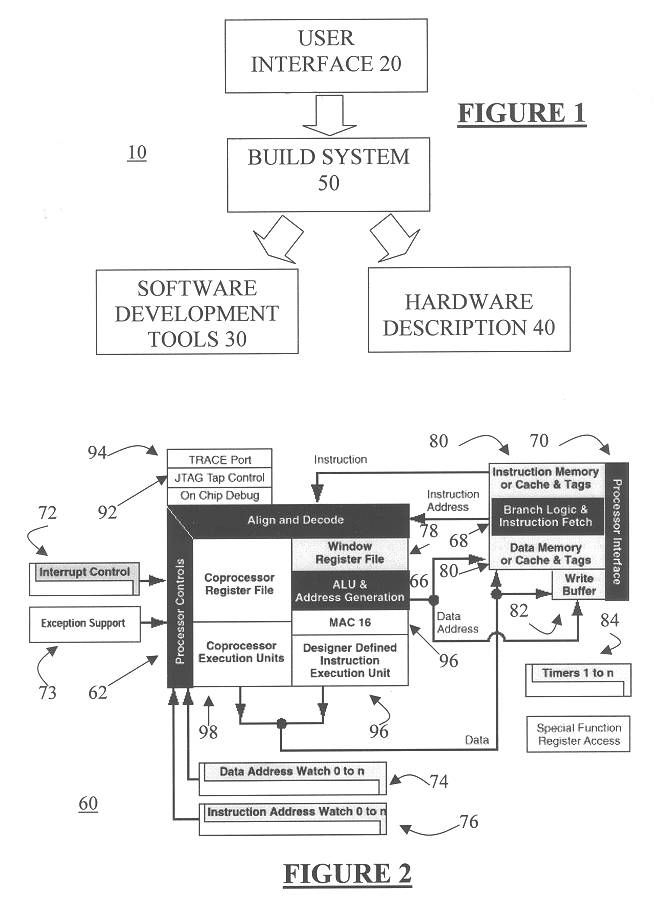

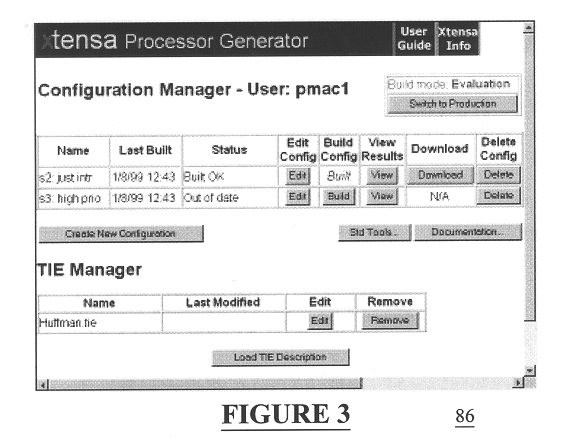

InactiveUS6477683B1Decompilation/disassemblyCAD network environmentApplication softwareProcessor design

An automated processor design tool uses a description of customized processor instruction set extensions in a standardized language to develop a configurable definition of a target instruction set, a Hardware Description Language description of circuitry necessary to implement the instruction set, and development tools such as a compiler, assembler, debugger and simulator which can be used to develop applications for the processor and to verify it. Implementation of the processor circuitry can be optimized for various criteria such as area, power consumption, speed and the like. Once a processor configuration is developed, it can be tested and inputs to the system modified to iteratively optimize the processor implementation. By providing a constrained domain of extensions and optimizations, the process can be automated to a high degree, thereby facilitating fast and reliable development.

Owner:TENSILICA

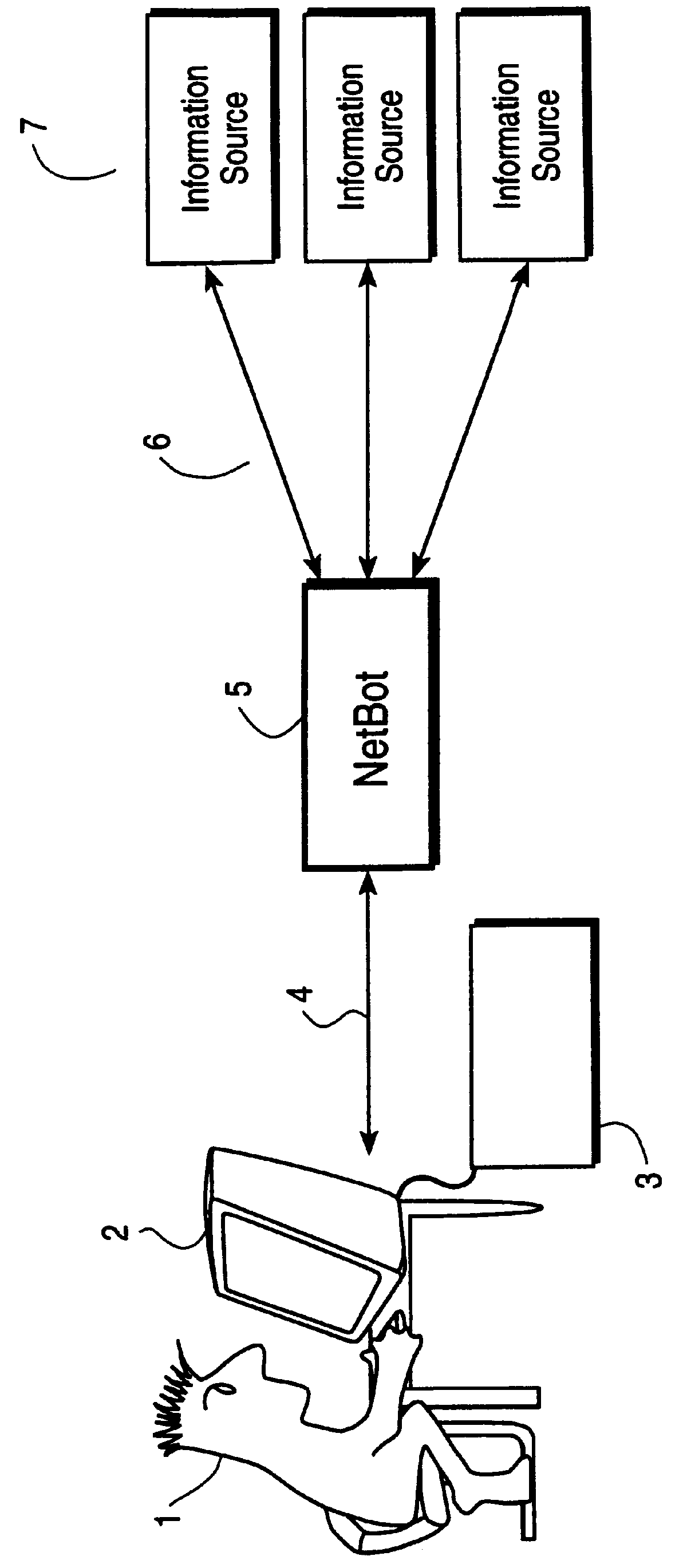

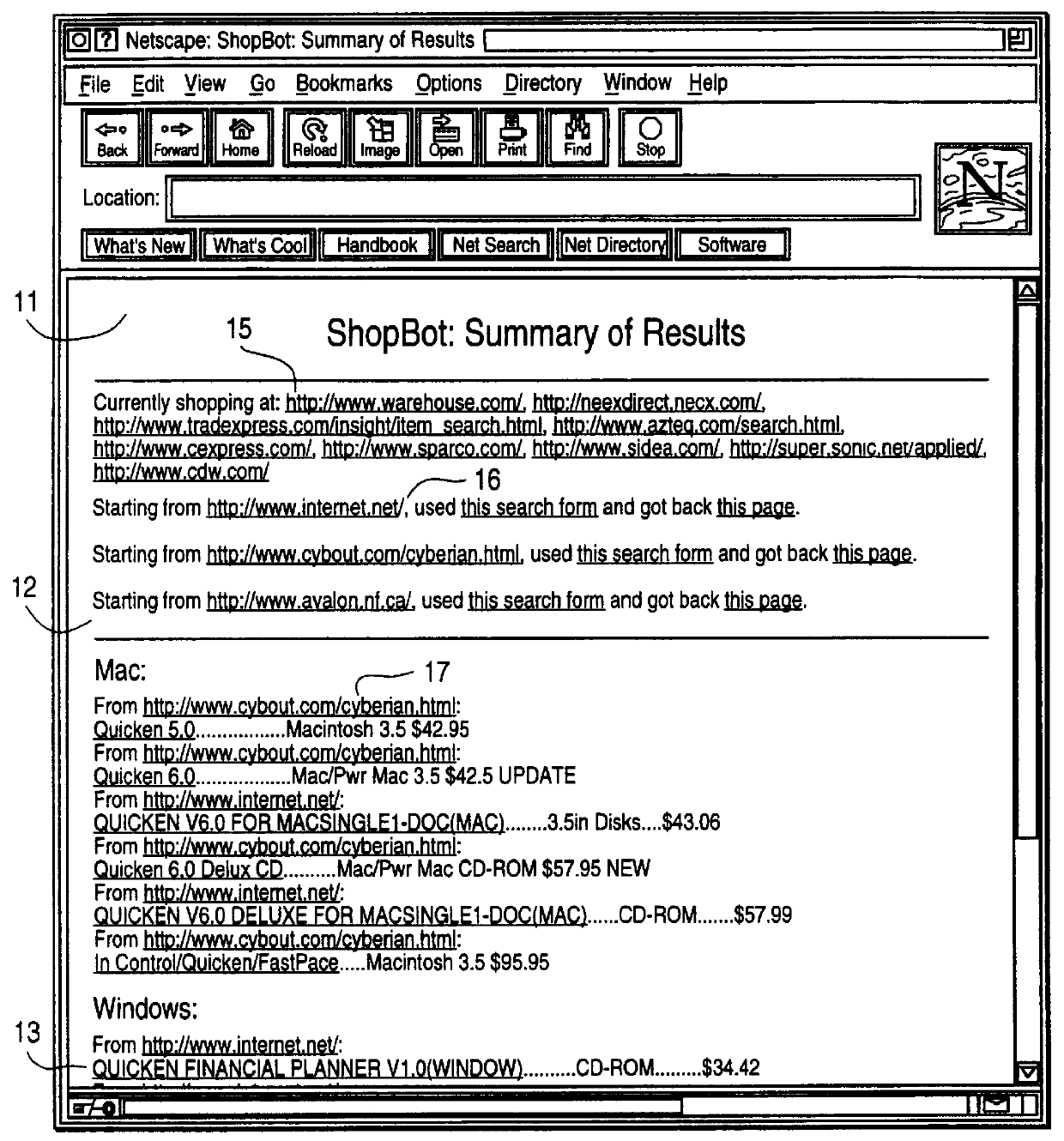

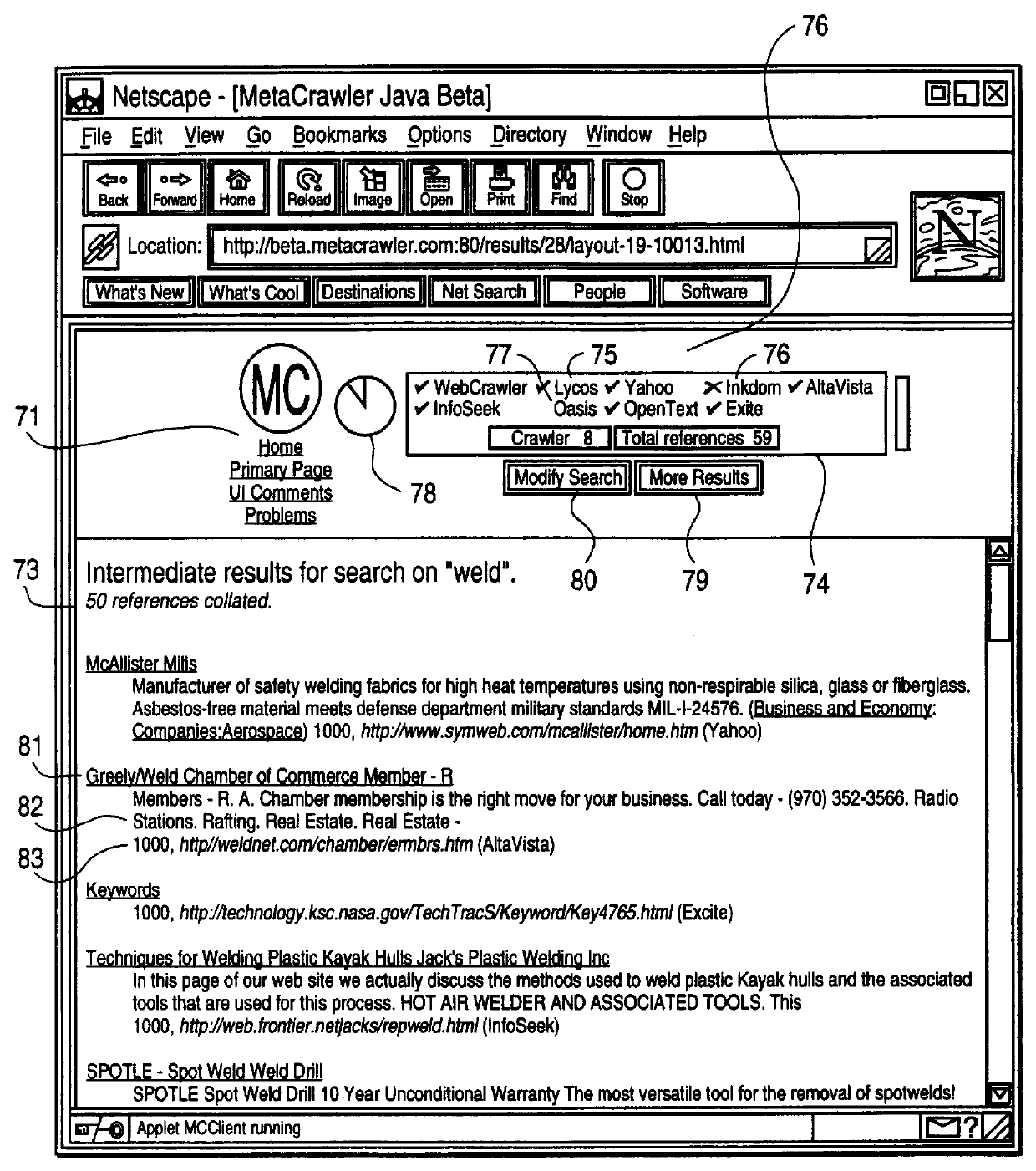

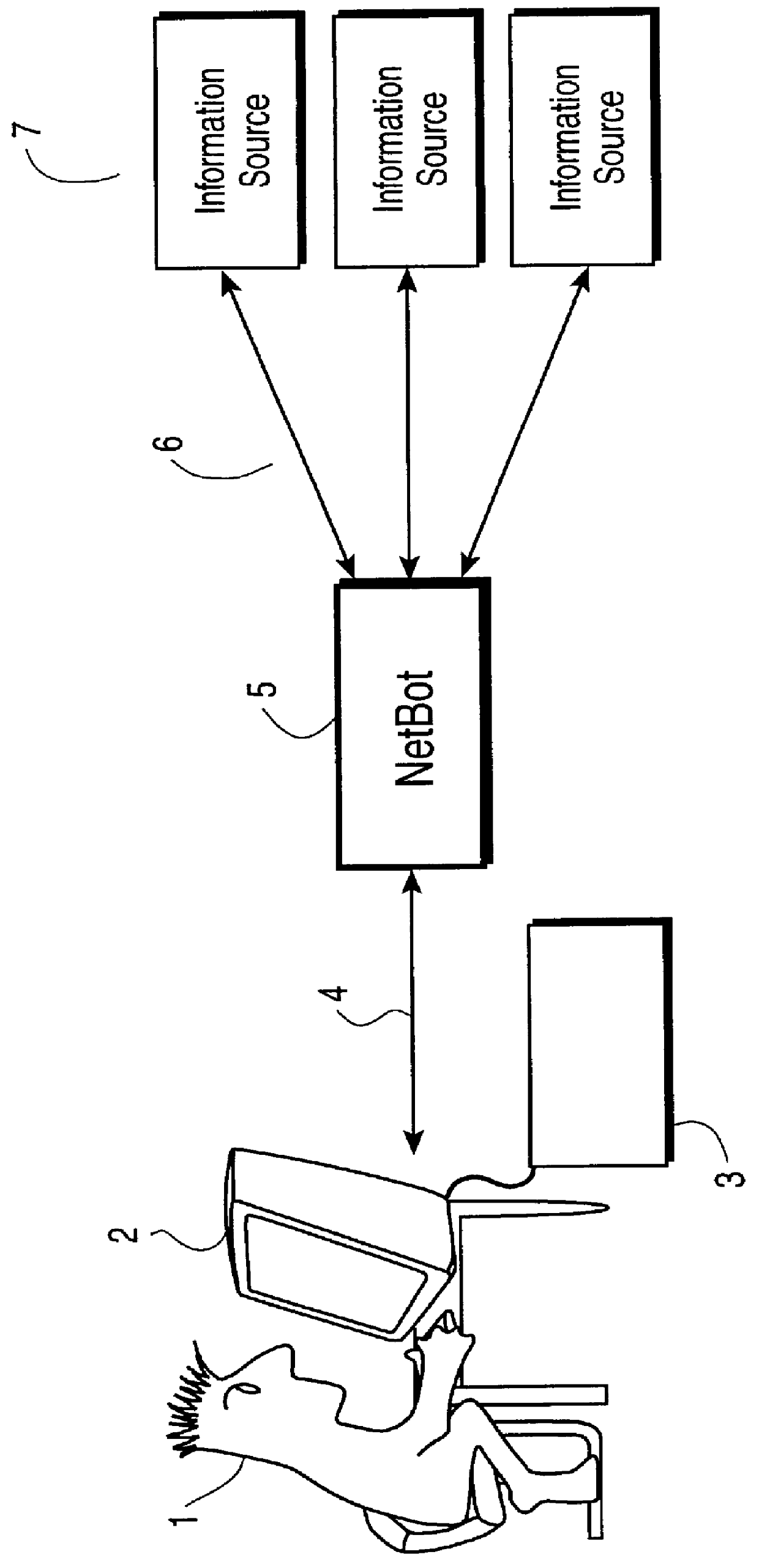

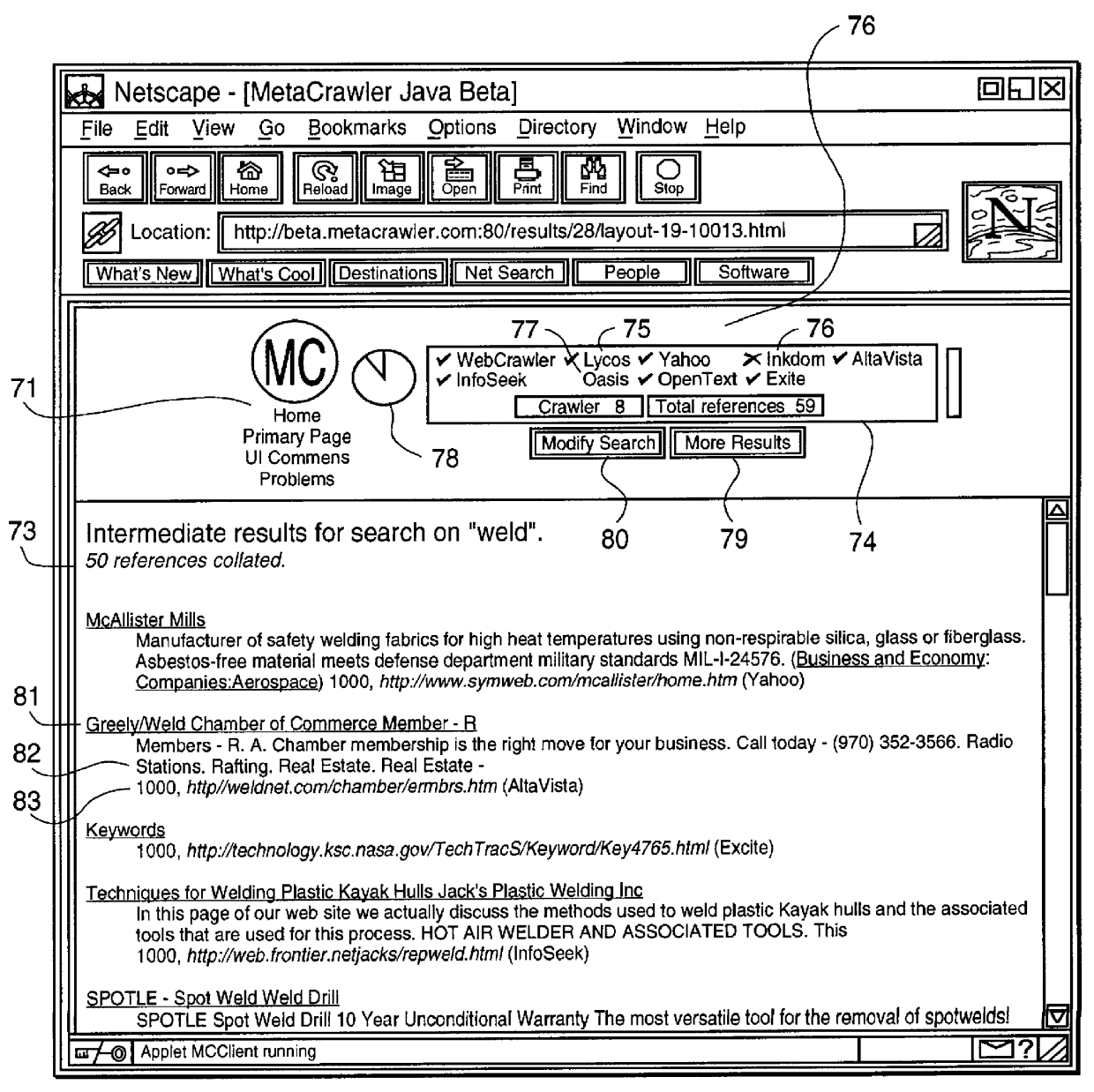

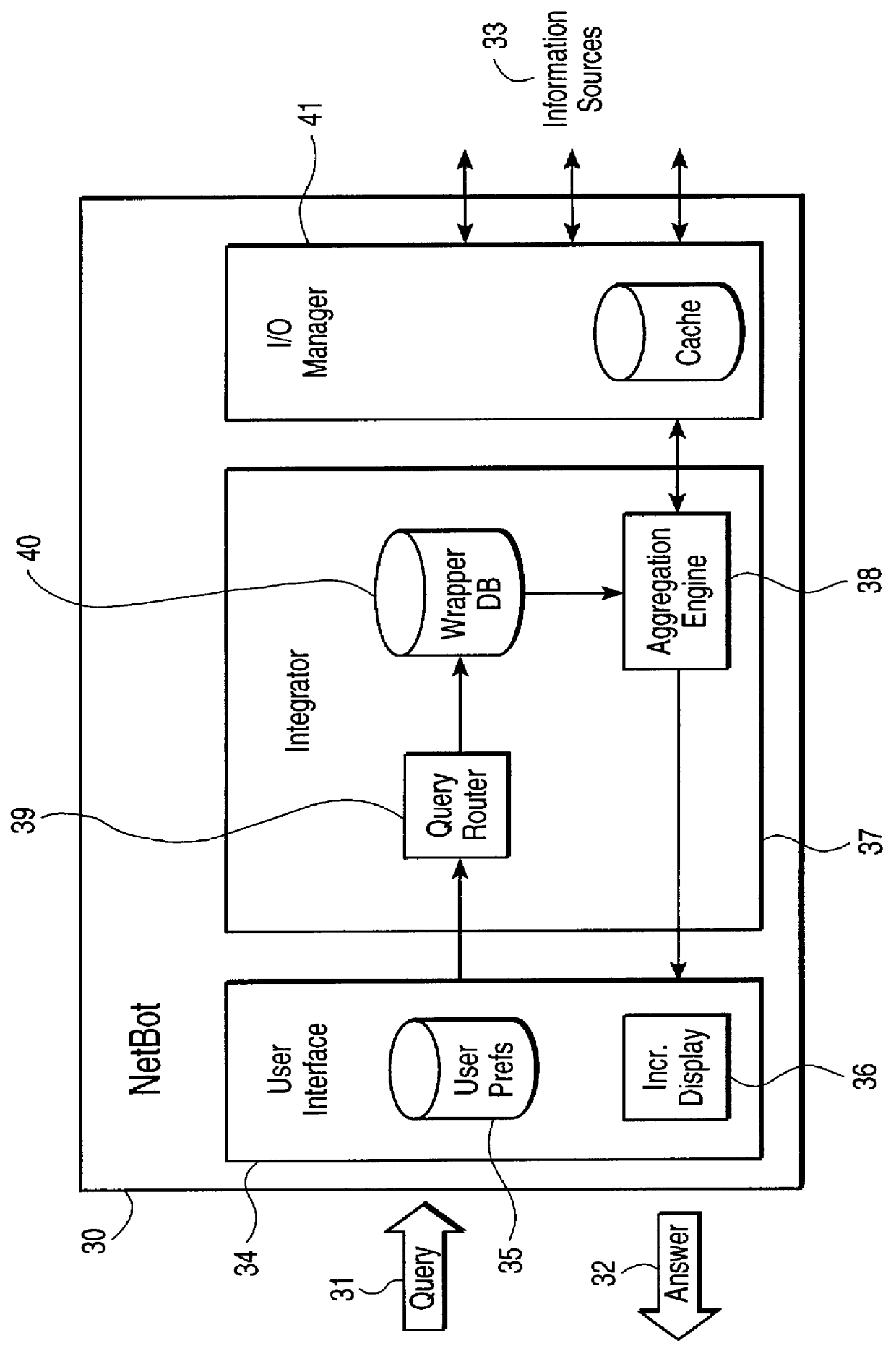

Method and system using information written in a wrapper description language to execute query on a network

InactiveUS6085186AEasy to understandEasy maintenanceData processing applicationsWeb data indexingAccess networkNetwork connection

This invention provides assistance to a user in accessing network attached information sources. In one aspect, the invention is a method for intelligently routing a user query to information sources relevant to that query, extracting relevant data fields from received responses, and intelligently presenting the extracted data in order of estimated relevance. The system of this invention implements one or more steps of the method in a centralized or distributed manner on one or more network attached computers. Further, this invention provides a novel language and implementation that facilitates easily written and maintained descriptions of information source query and response formats.

Owner:AT HOME BONDHOLDERS LIQUIDATING TRUST

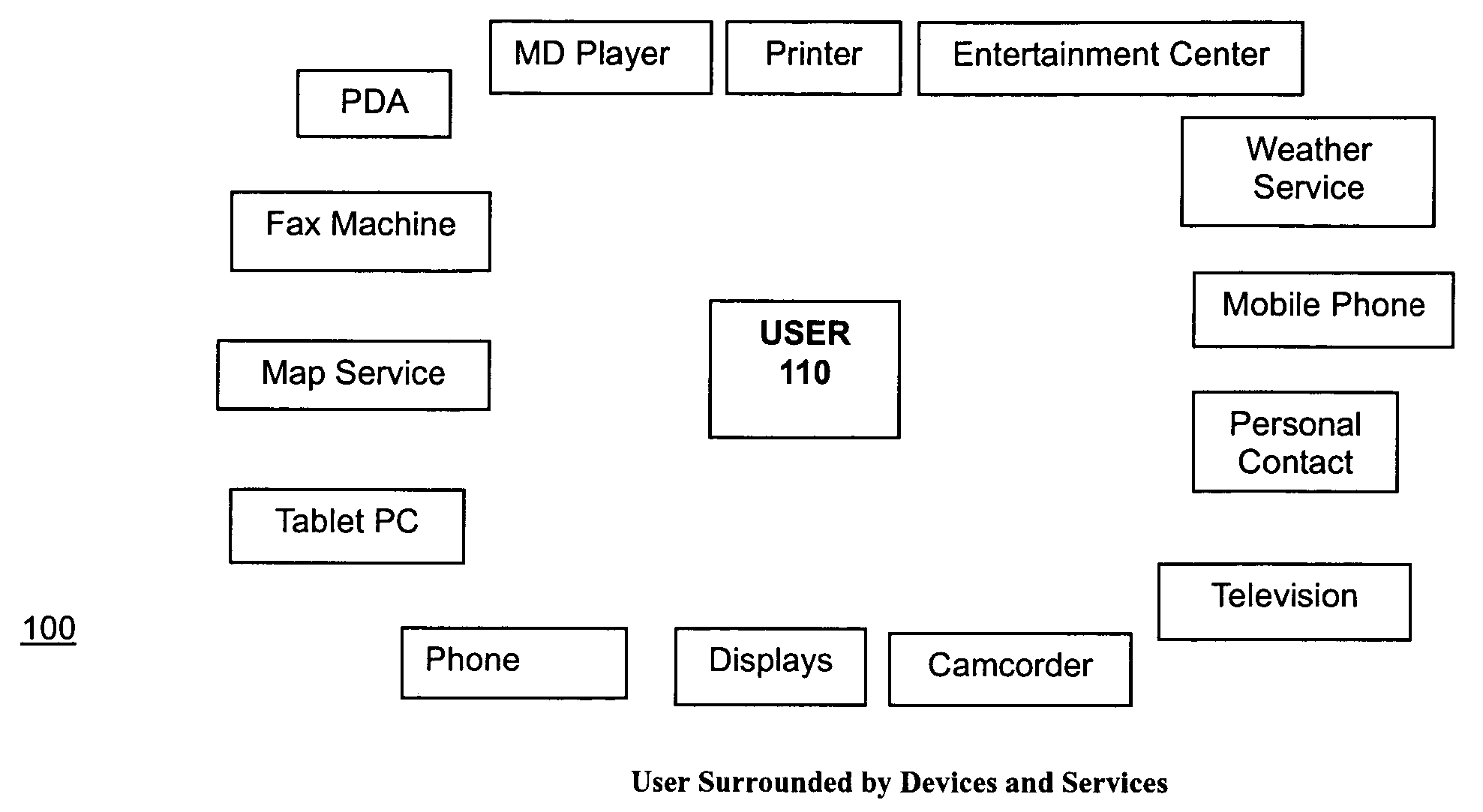

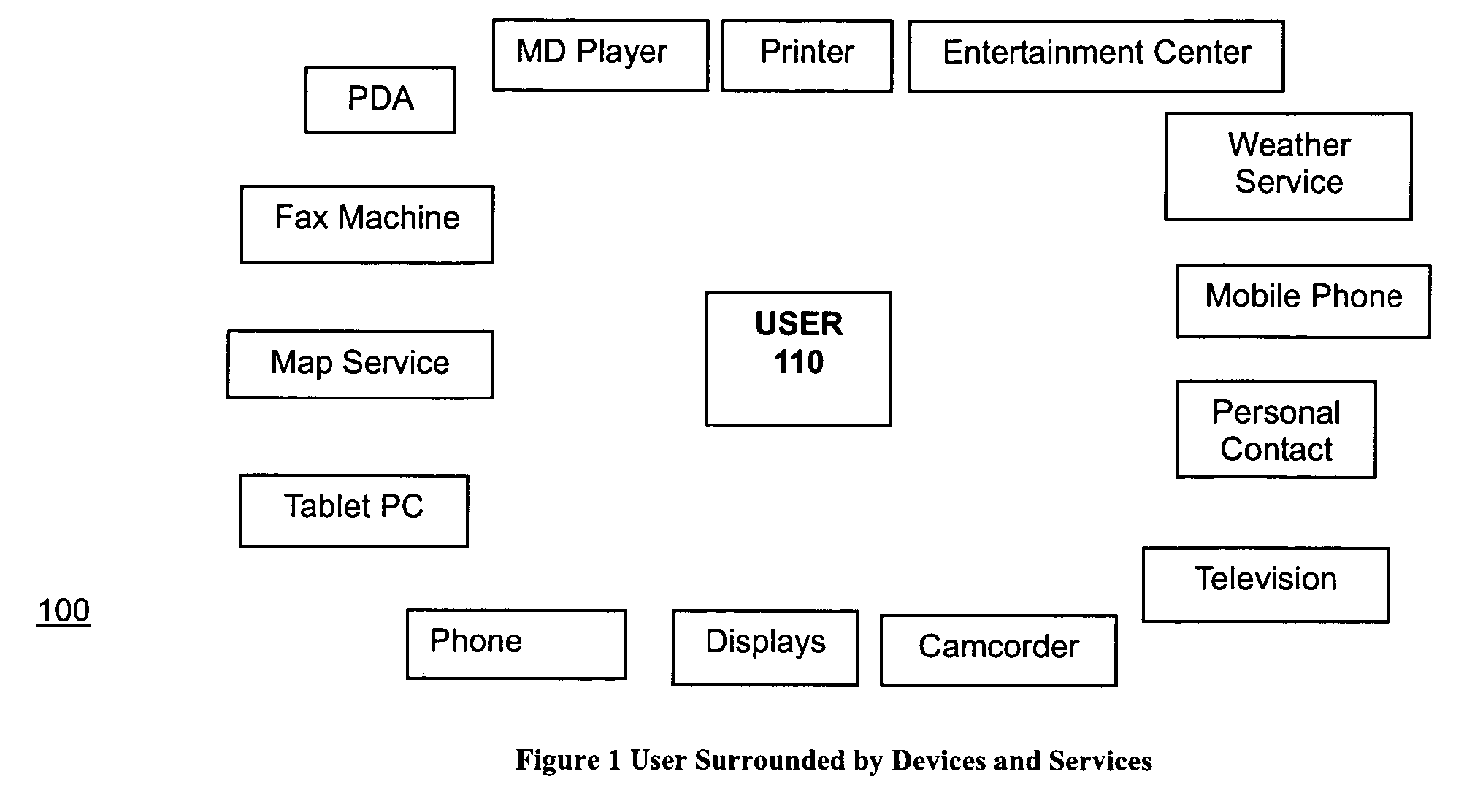

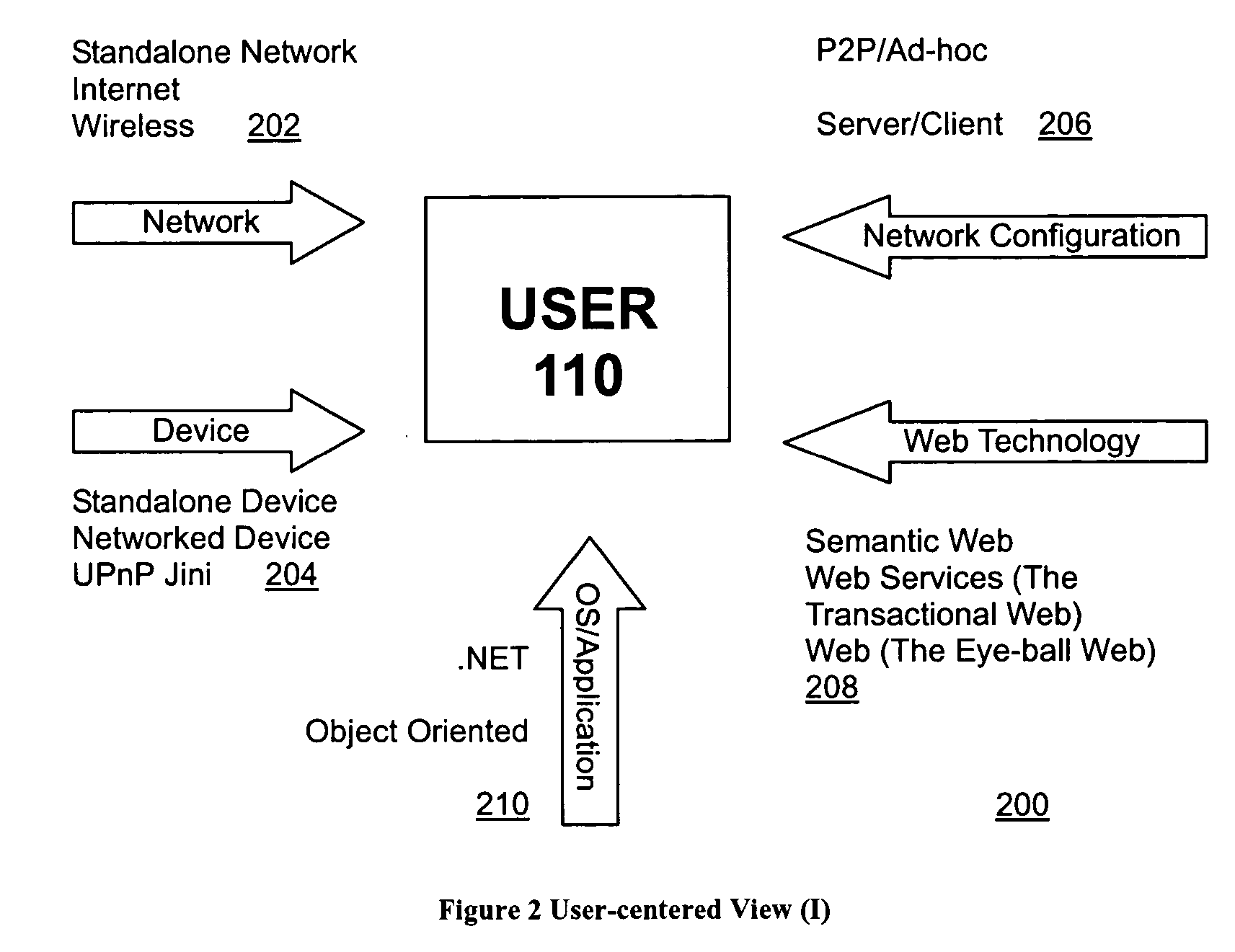

Task computing

InactiveUS20040230636A1General purpose stored program computerMultiprogramming arrangementsProcedure callsWeb service

A computer-based system includes task computing enabling users to define tasks by combining available functionality and to execute such tasks. The computer-based system of includes available functionality which originates in devices, computing applications and electronic services available through local and remote procedure calls including Web Services, UPnP, CORBA, RMI, RPC, DCE, DCOM or comprises previously defined tasks. All available functionality is abstracted to the user as a service and each service is expressed in a service description language, and the services have a semantic description associated with them.

Owner:FUJITSU LTD

Method and system using information written in a wrapper description language to execute query on a network

InactiveUS6102969AEasy to understandEasy maintenanceData processing applicationsWeb data indexingAccess networkNetwork connection

This invention provides assistance to a user in accessing network attached information sources. In one aspect, the invention is a method for intelligently routing a user query to information sources relevant to that query, extracting relevant data fields from received responses, and intelligently presenting the extracted data in order of estimated relevance. The system of this invention implements one or more steps of the method in a centralized or distributed manner on one or more network attached computers. Further, this invention provides a novel language and implementation that facilitates easily written and maintained descriptions of information source query and response formats.

Owner:AT HOME BONDHOLDERS LIQUIDATING TRUST

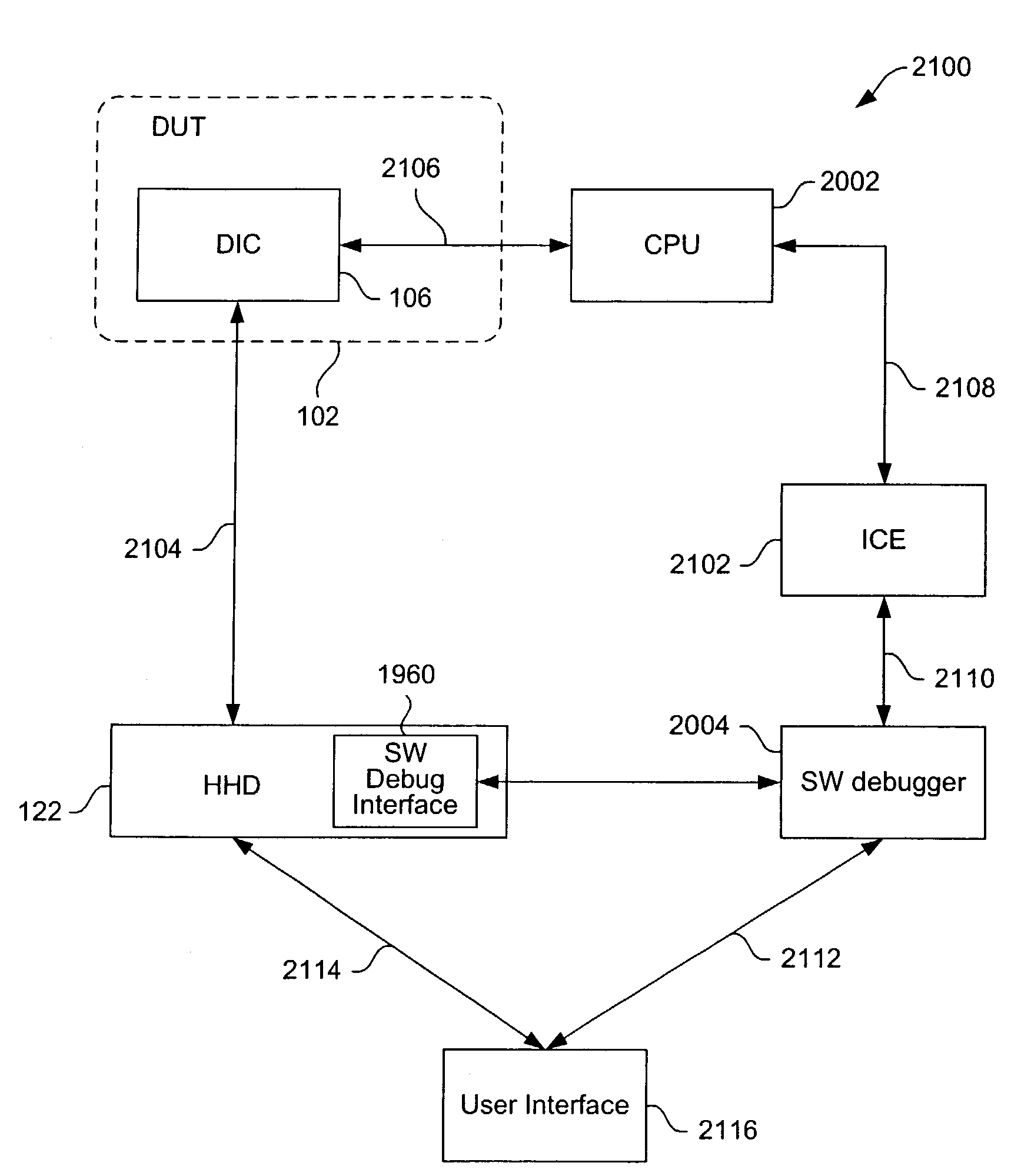

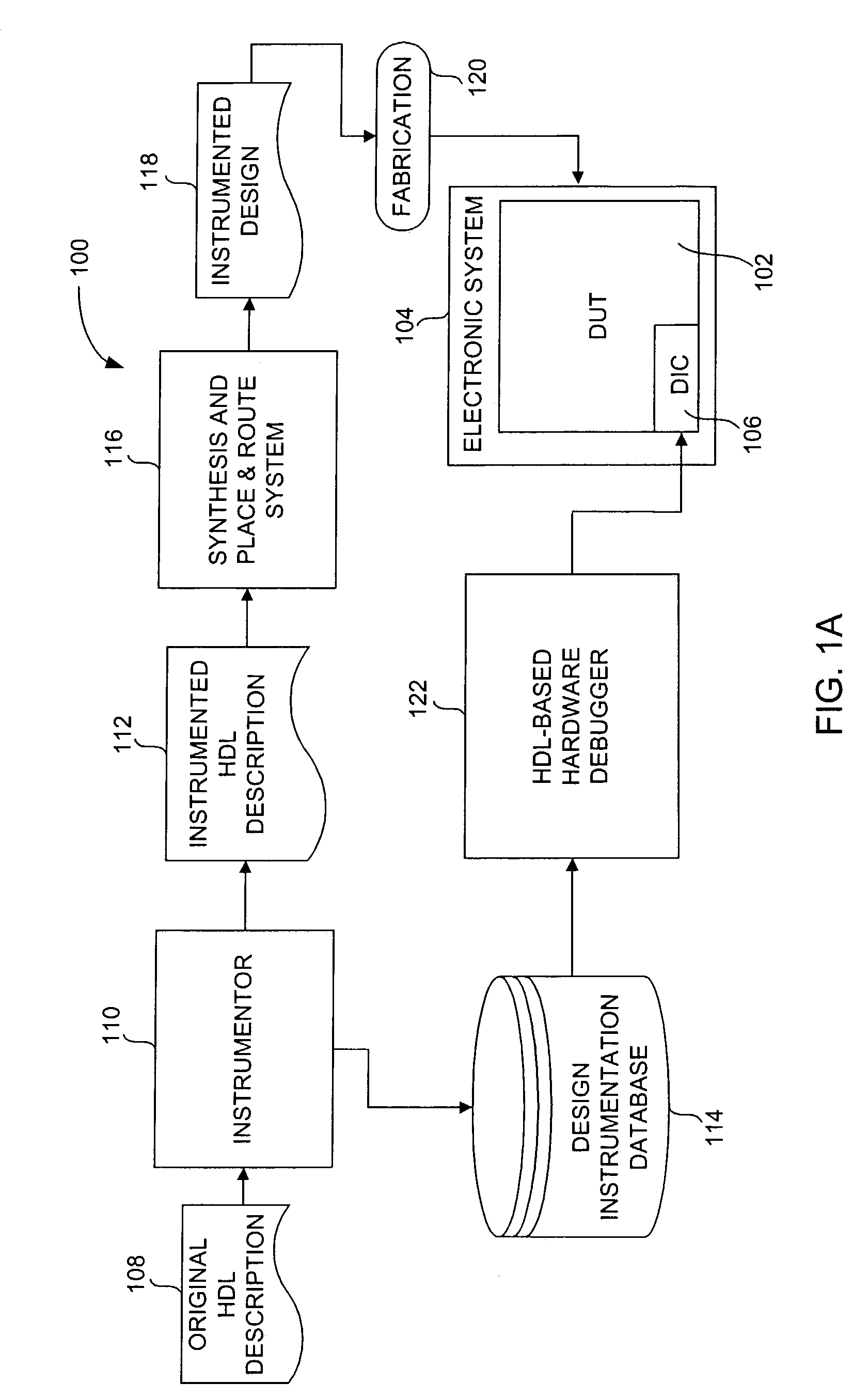

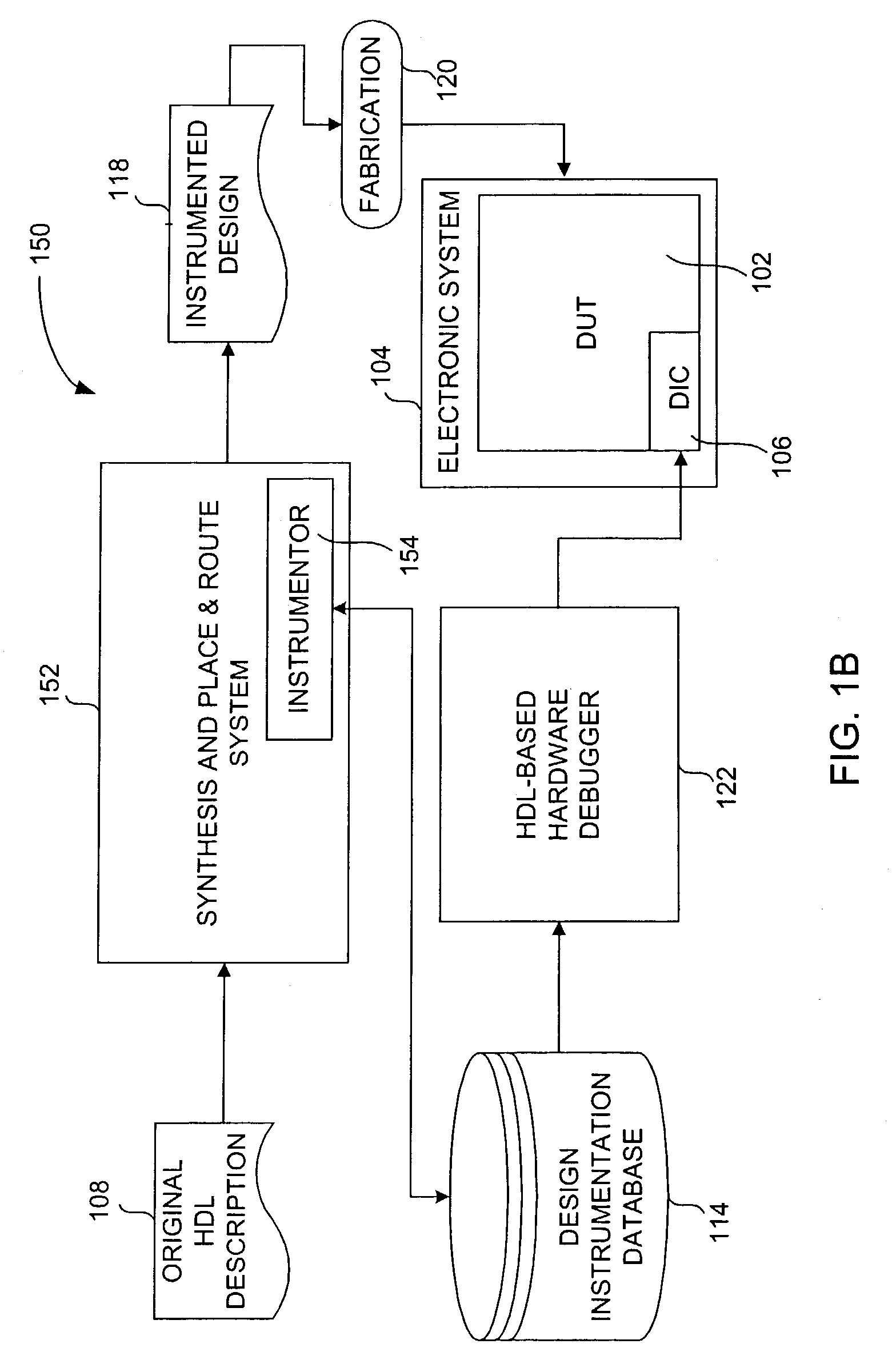

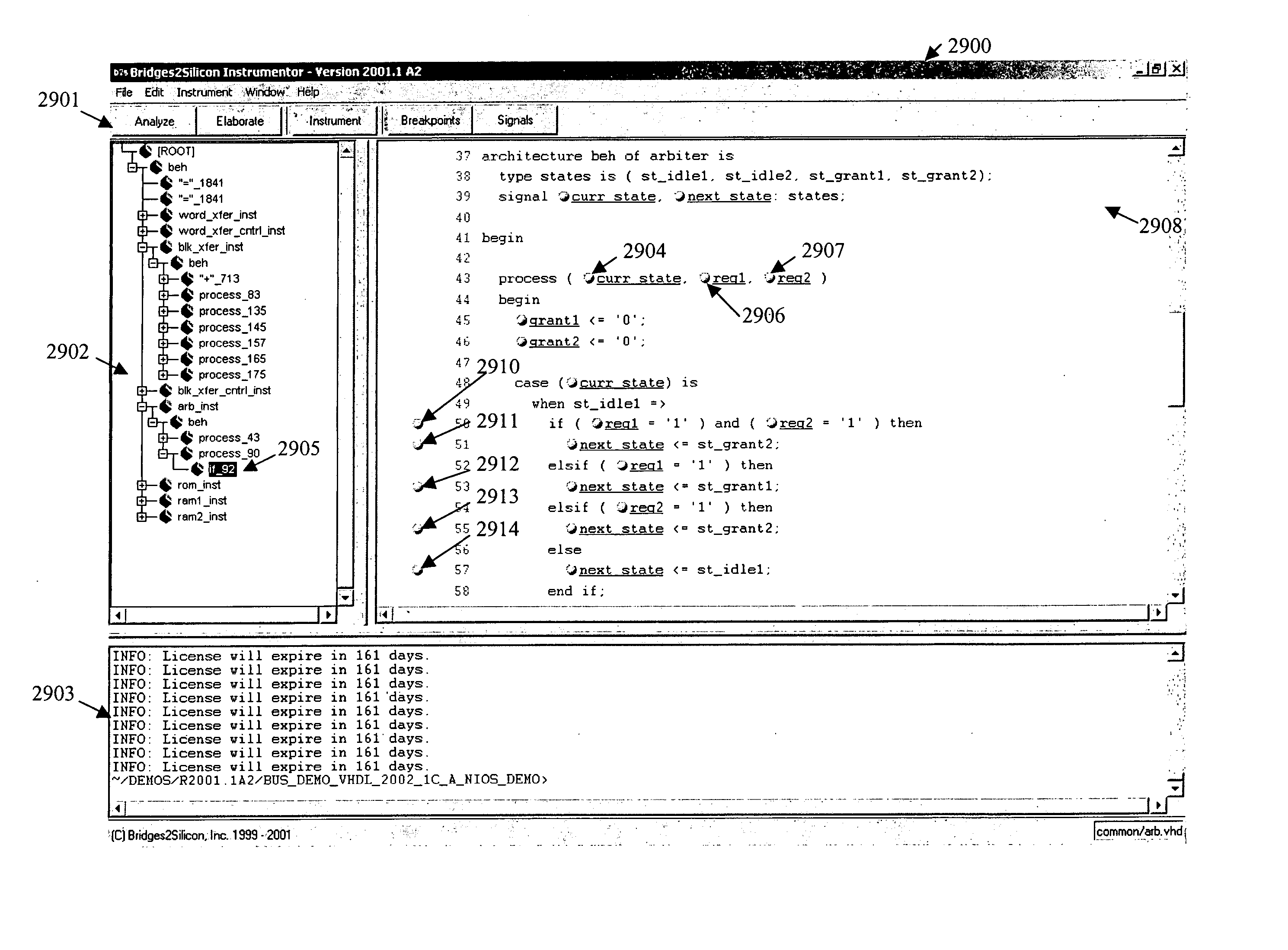

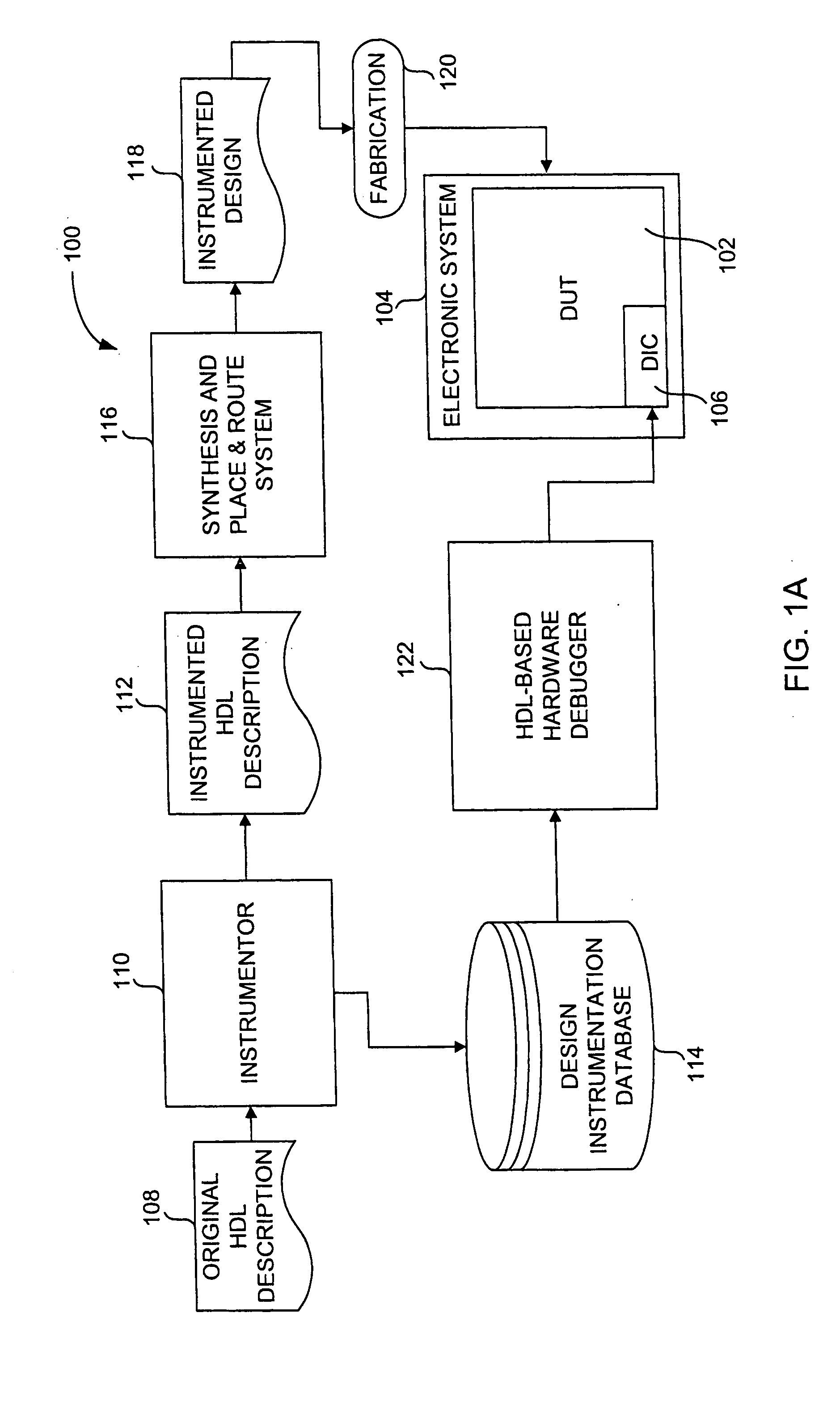

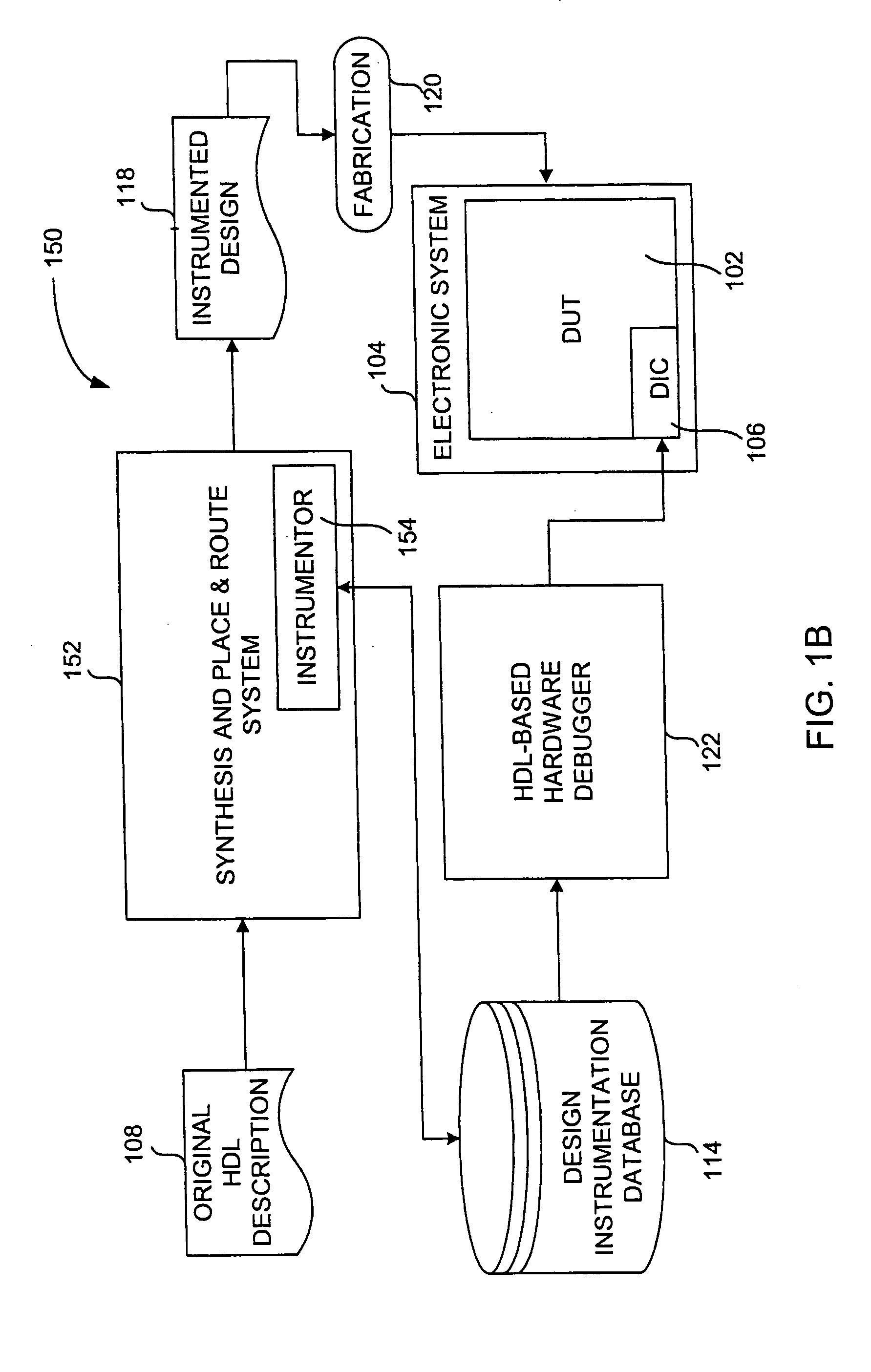

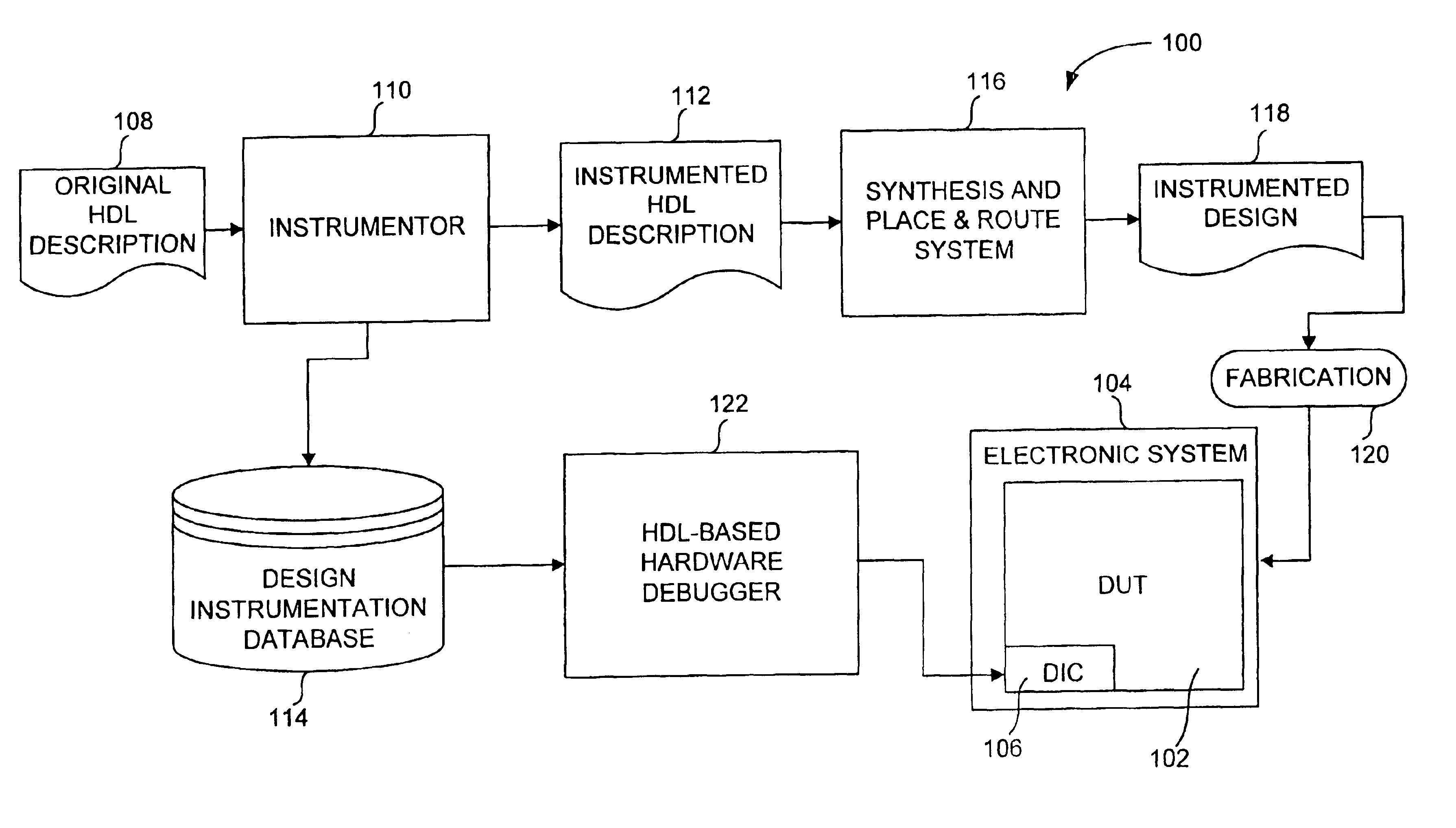

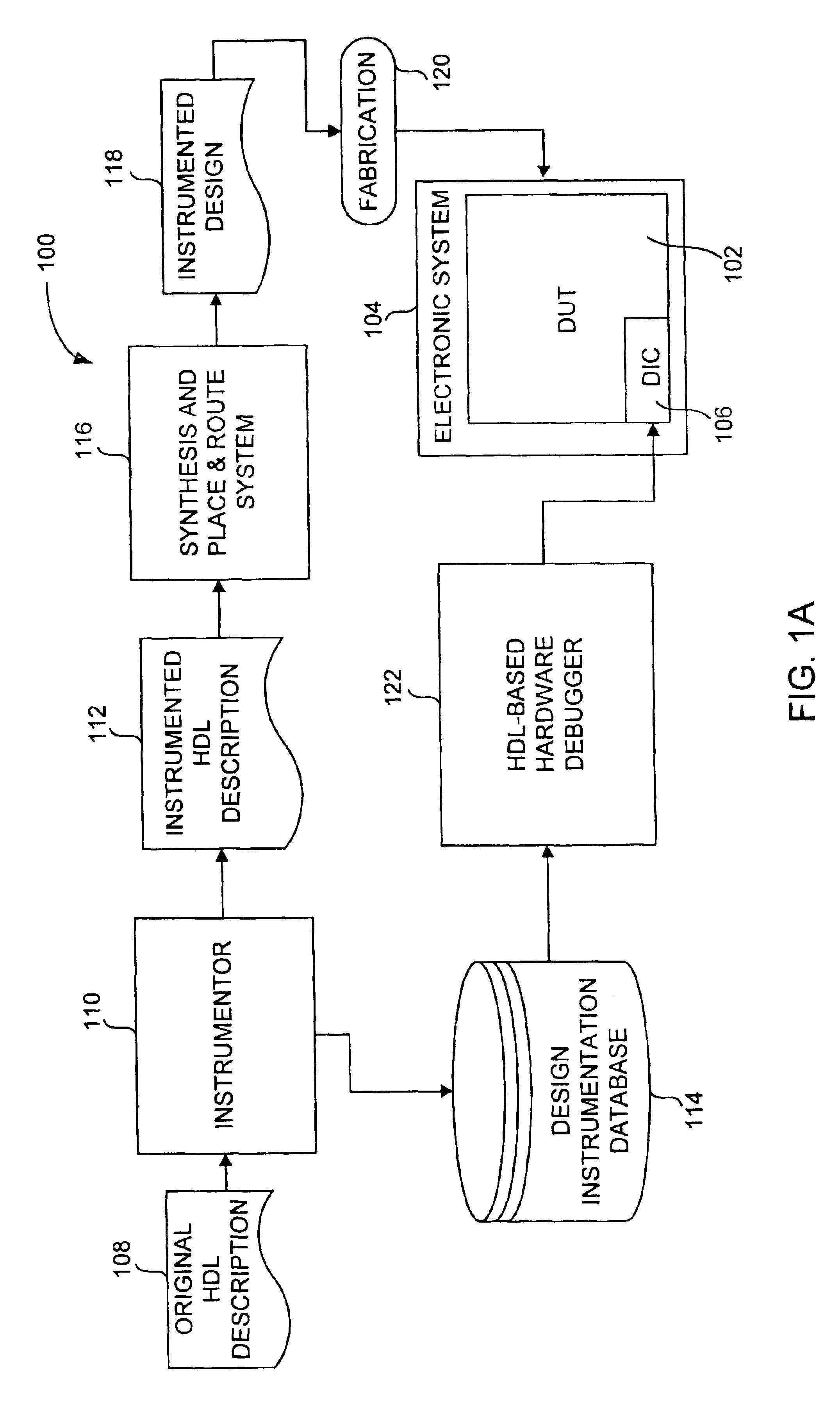

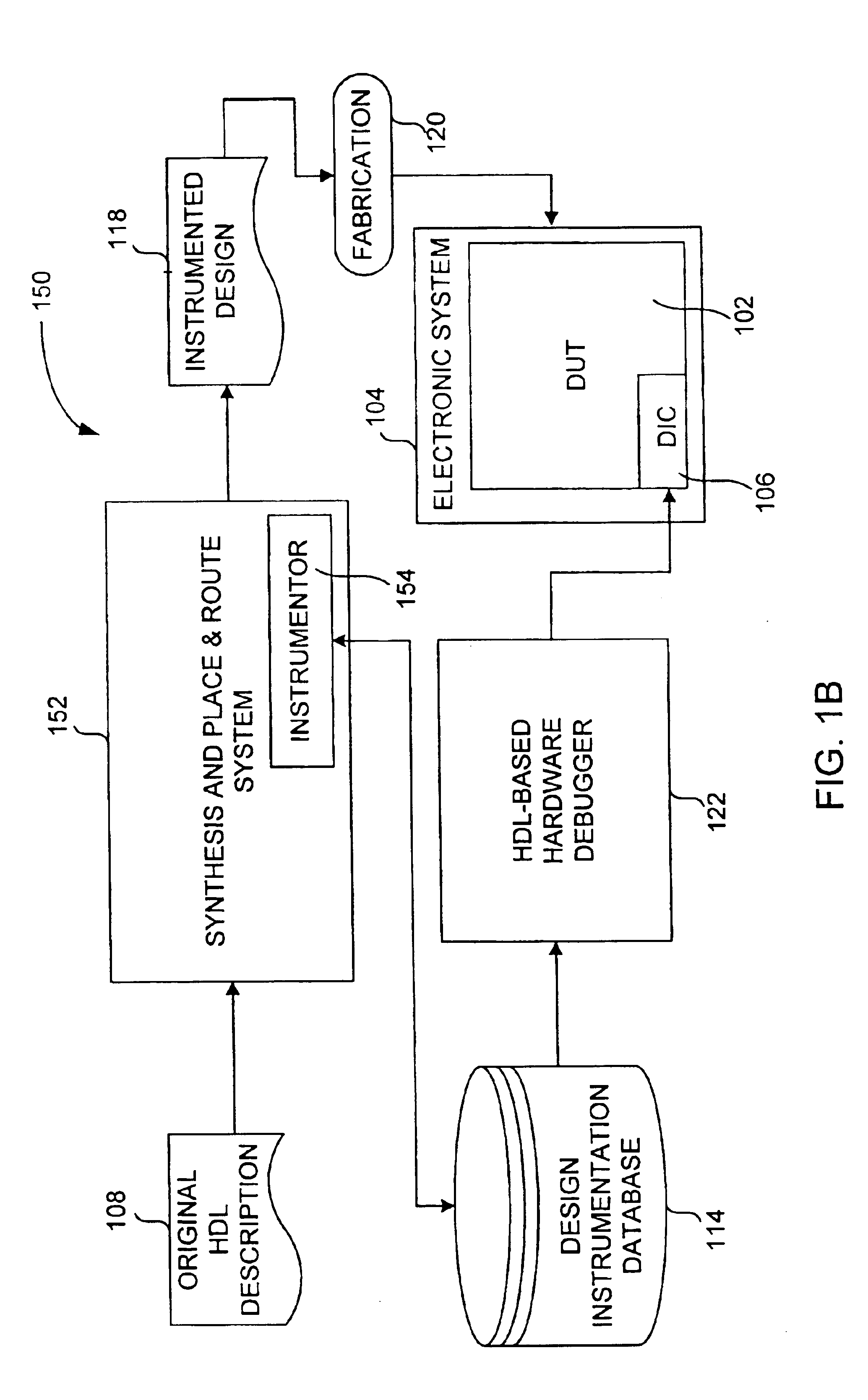

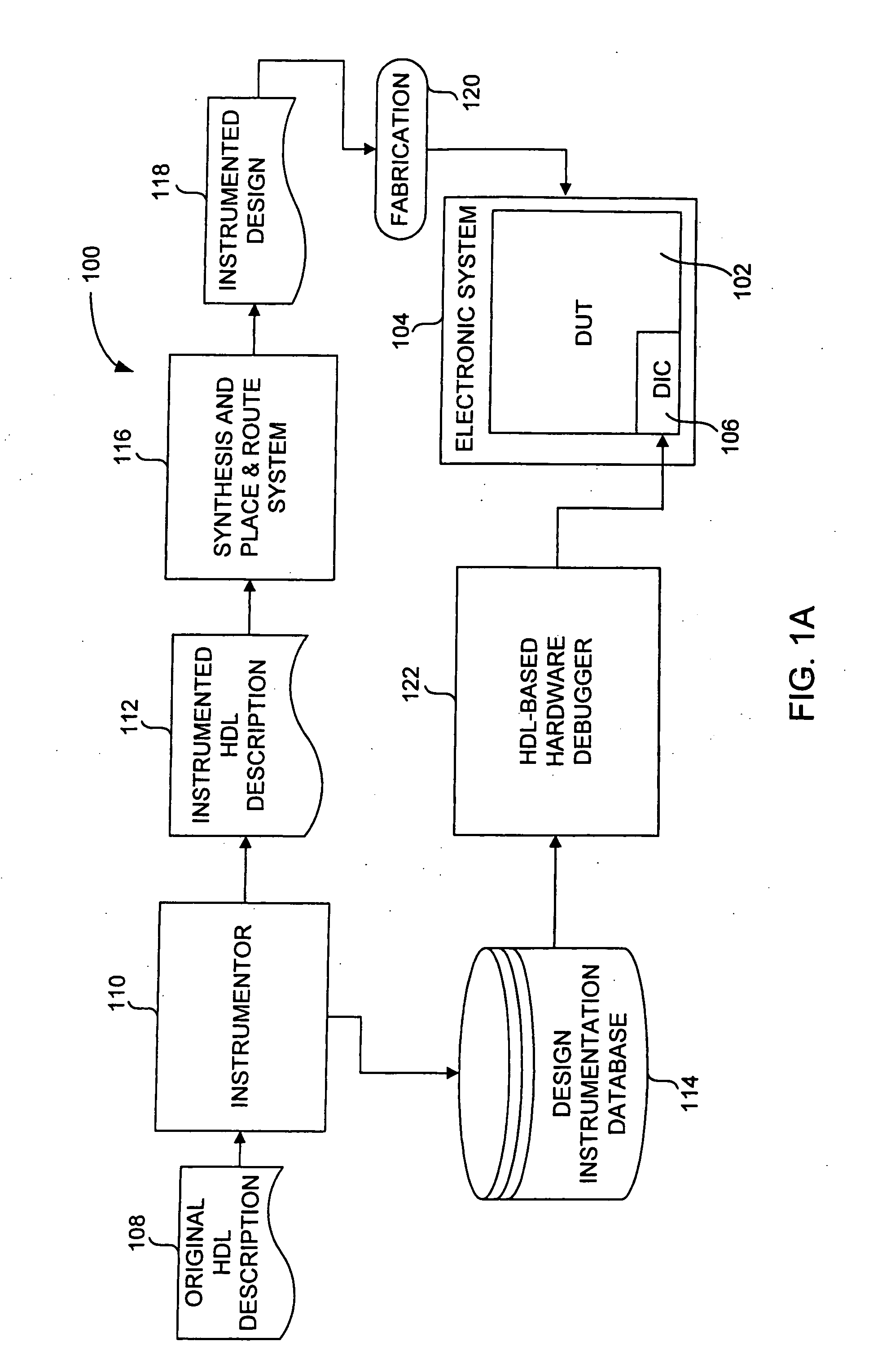

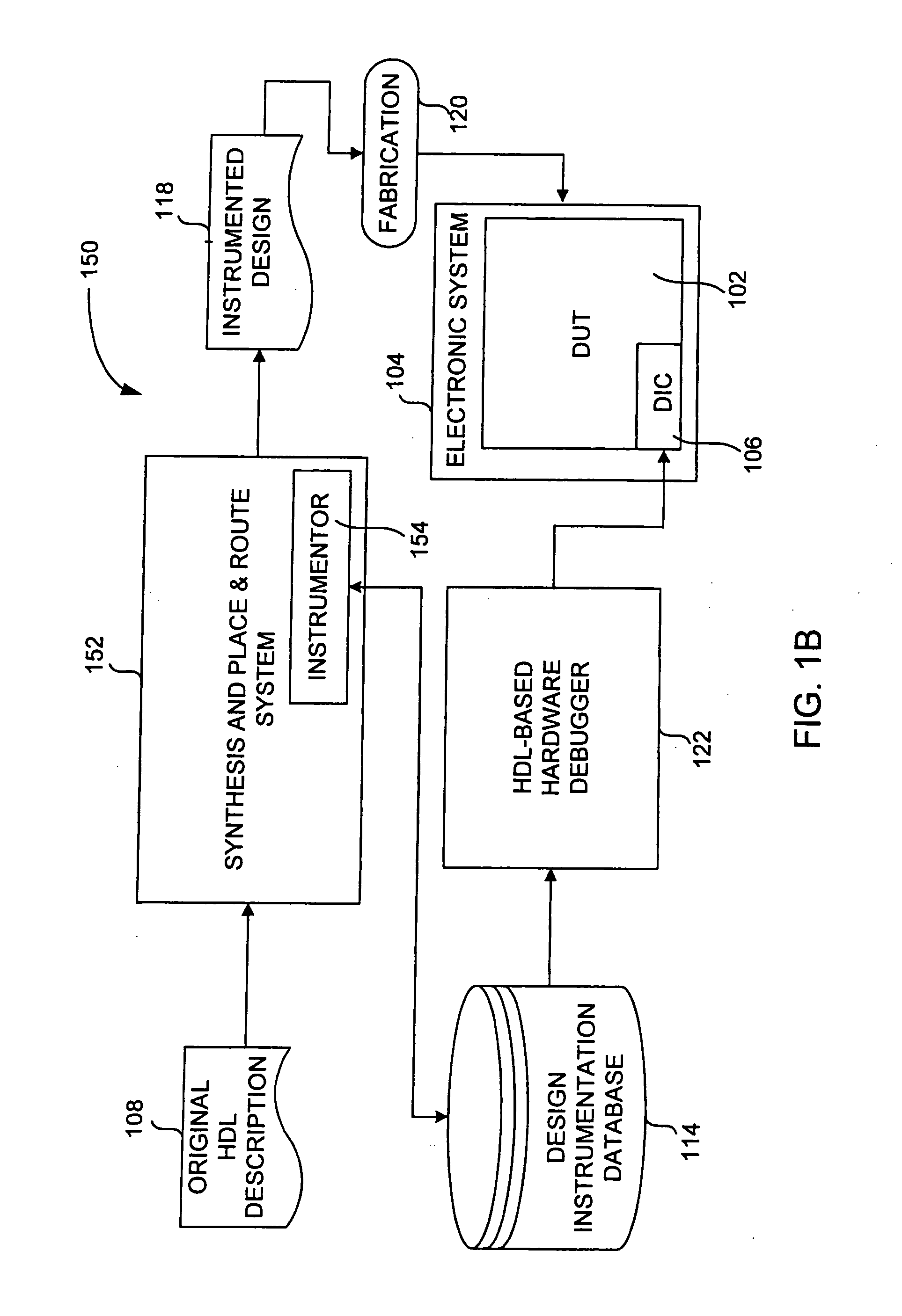

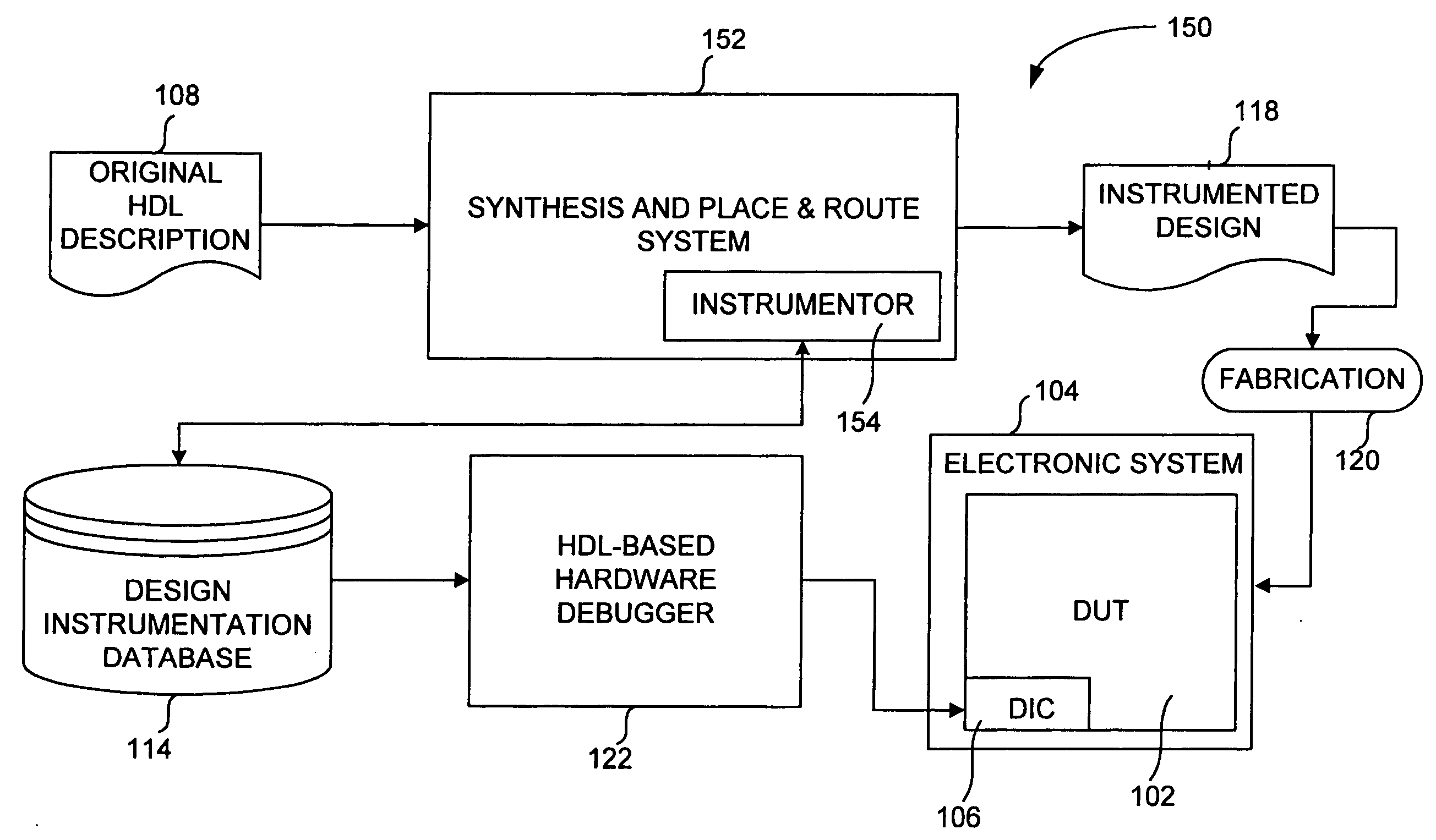

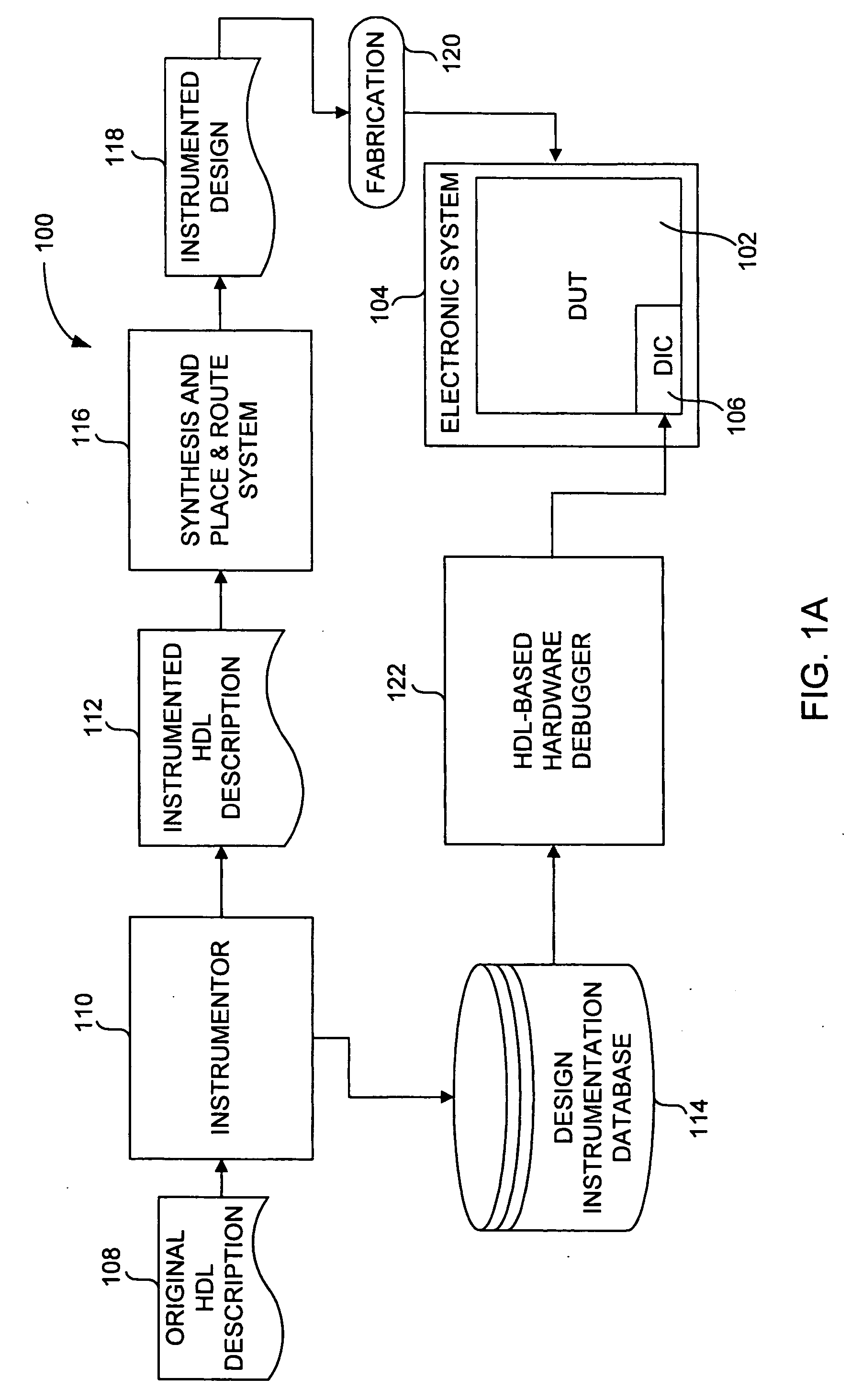

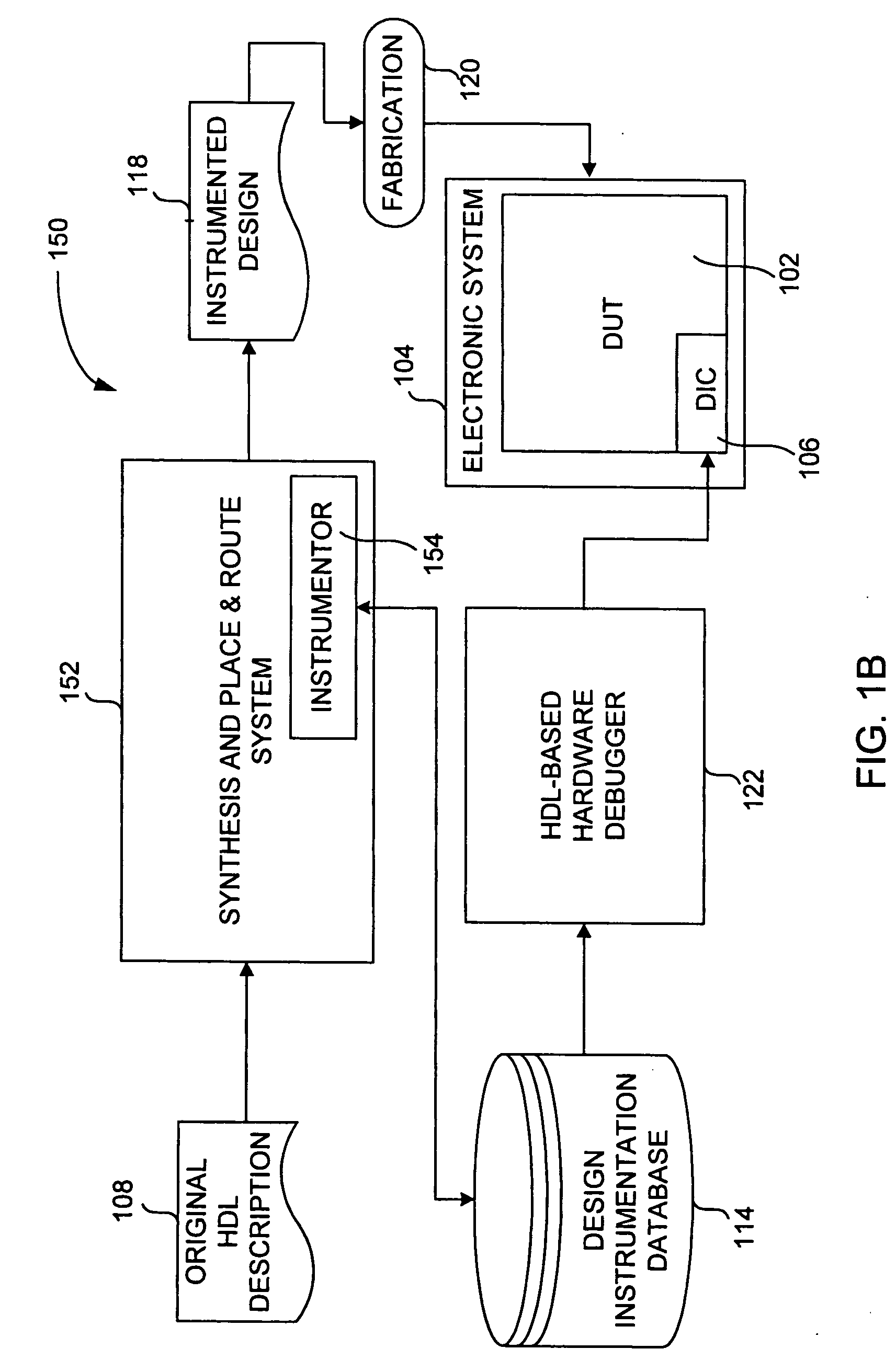

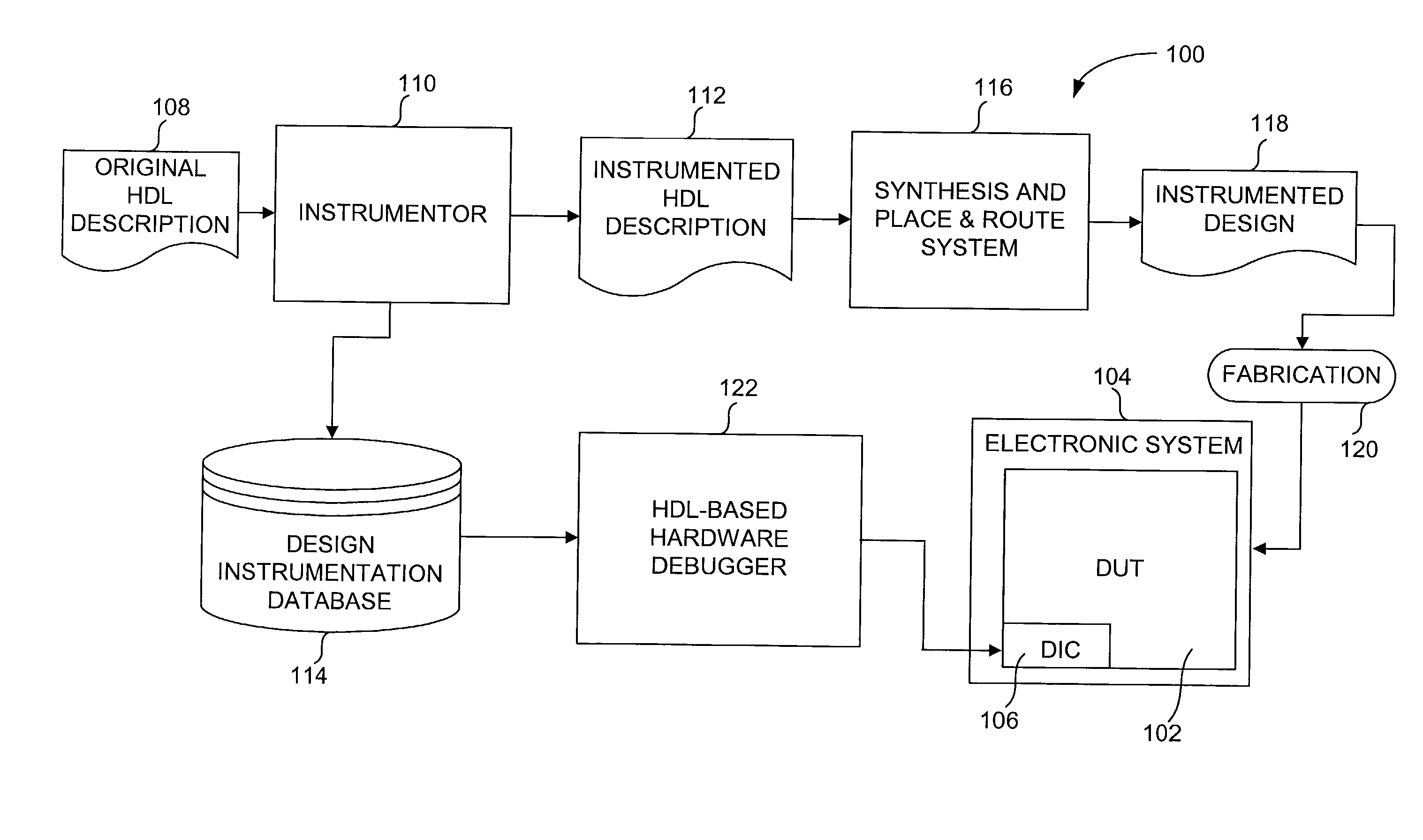

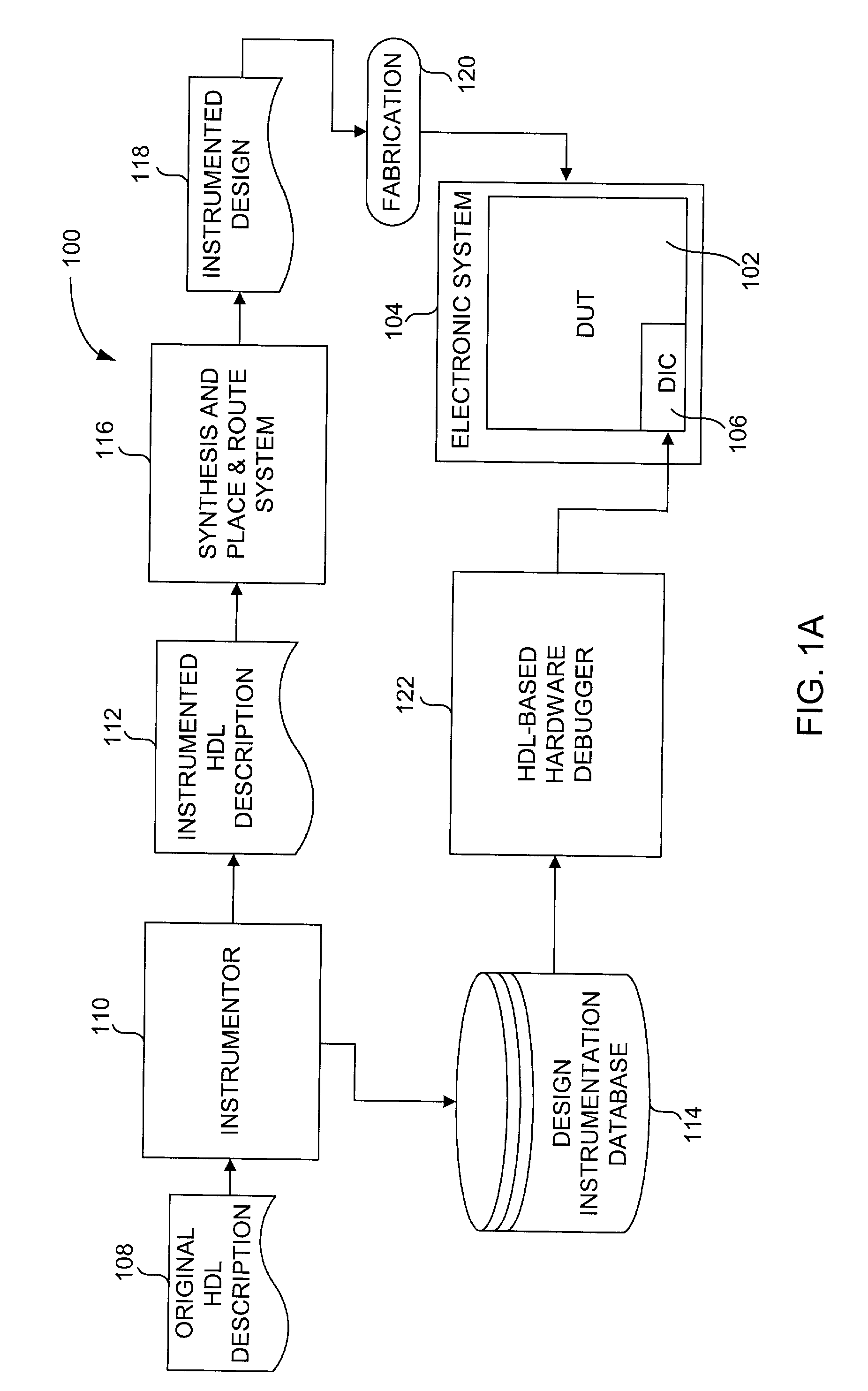

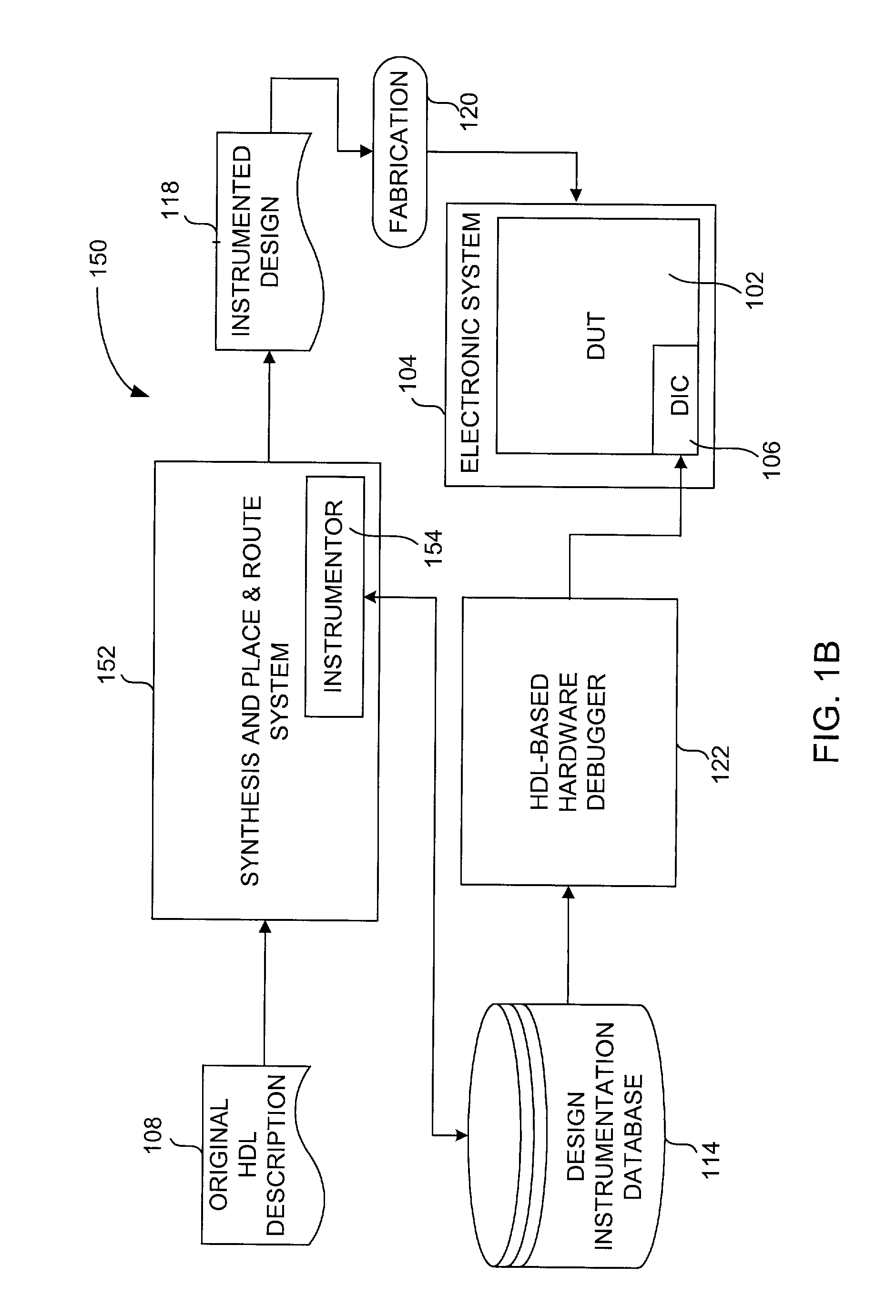

Hardware/software co-debugging in a hardware description language

InactiveUS7240303B1Error detection/correctionAnalogue computers for electric apparatusComputer scienceEmbedded system

Techniques and systems for analysis, diagnosis and debugging fabricated hardware designs at a Hardware Description Language (HDL) level are described. Although the hardware designs (which were designed in HDL) have been fabricated in integrated circuit products with limited input / output pins, the techniques and systems enable the hardware designs within the integrated circuit products to be comprehensively analyzed, diagnosed, and debugged at the HDL level at speed. The ability to debug hardware designs at the HDL level facilitates correction or adjustment of the HDL description of the hardware designs.

Owner:SYNOPSYS INC

Method and user interface for debugging an electronic system

InactiveUS20050010880A1Easy to correctEasy to adjustDigital circuit testingCAD circuit designElectronic systemsEmbedded system

Techniques and systems for analysis, diagnosis and debugging fabricated hardware designs at a Hardware Description Language (HDL) level are described. Although the hardware designs (which were designed in HDL) have been fabricated in integrated circuit products with limited input / output pins, the techniques and systems enable the hardware designs within the integrated circuit products to be comprehensively analyzed, diagnosed, and debugged at the HDL level at speed. The ability to debug hardware designs at the HDL level facilitates correction or adjustment of the HDL description of the hardware designs.

Owner:SYNOPSYS INC

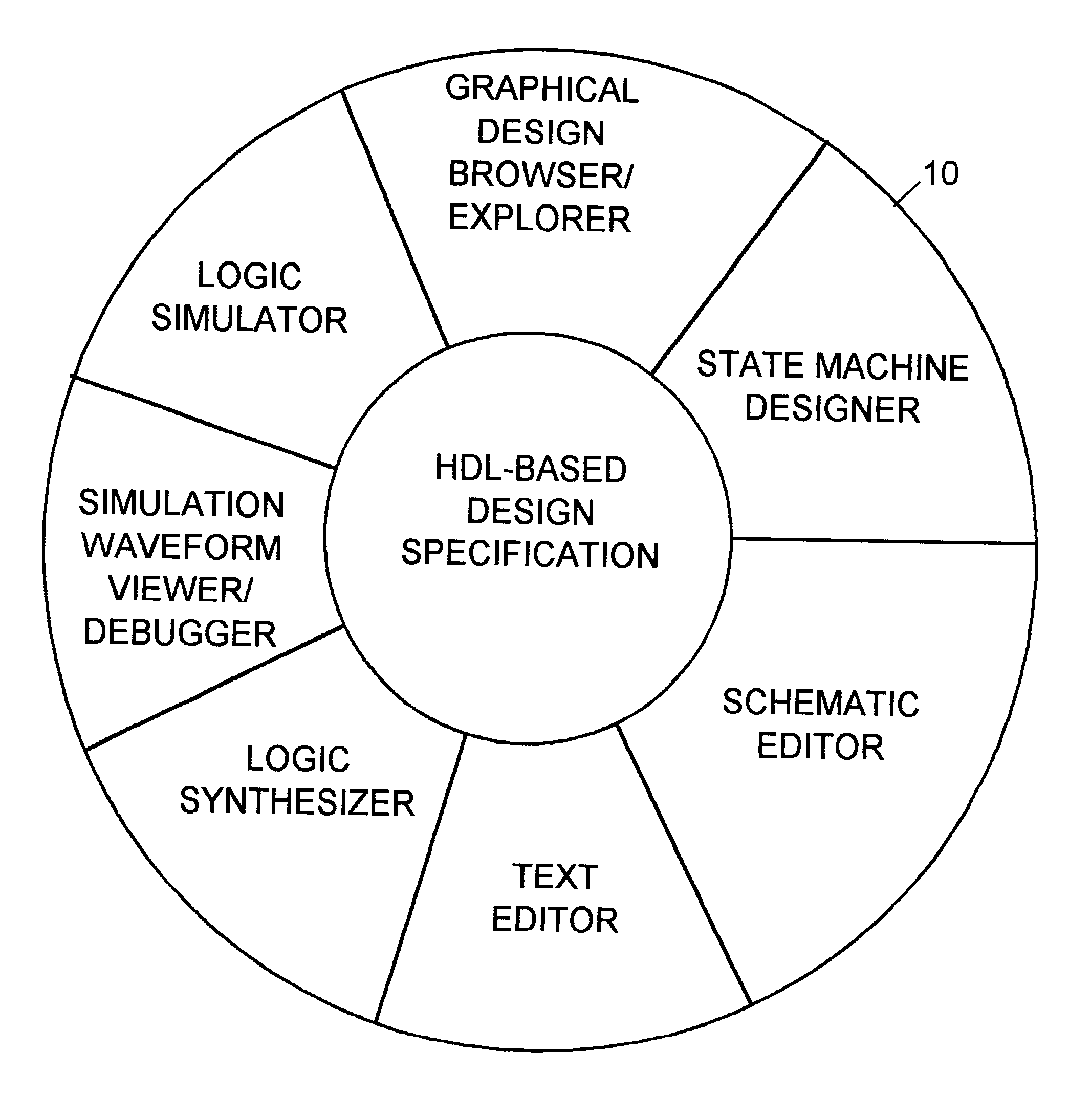

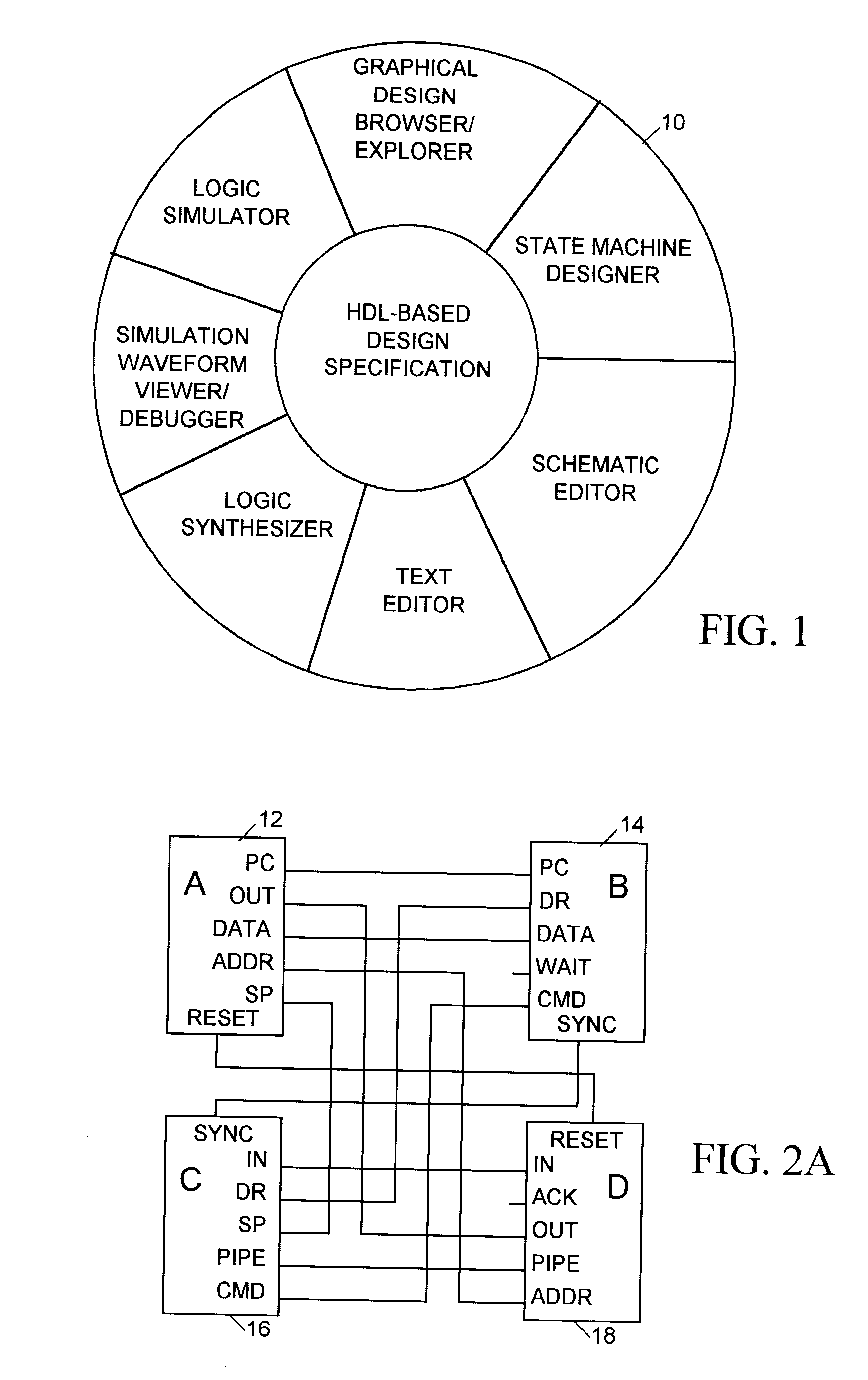

System and method for browsing graphically an electronic design based on a hardware description language specification

InactiveUS6366874B1CAD circuit designSoftware simulation/interpretation/emulationGraphicsProgramming language

Hardware description language (HDL)-centered design system and methodology uses HDL specification effectively as master depository for design intent or knowledge. Through network browser, designers conveniently navigate or explore design graphically. Designers selectively review or save design in entirety or portions. Design capture, analysis, and manipulation are based on HDL specification, either directly through text file editing, or indirectly through use of graphical tools.

Owner:SYNOPSYS INC

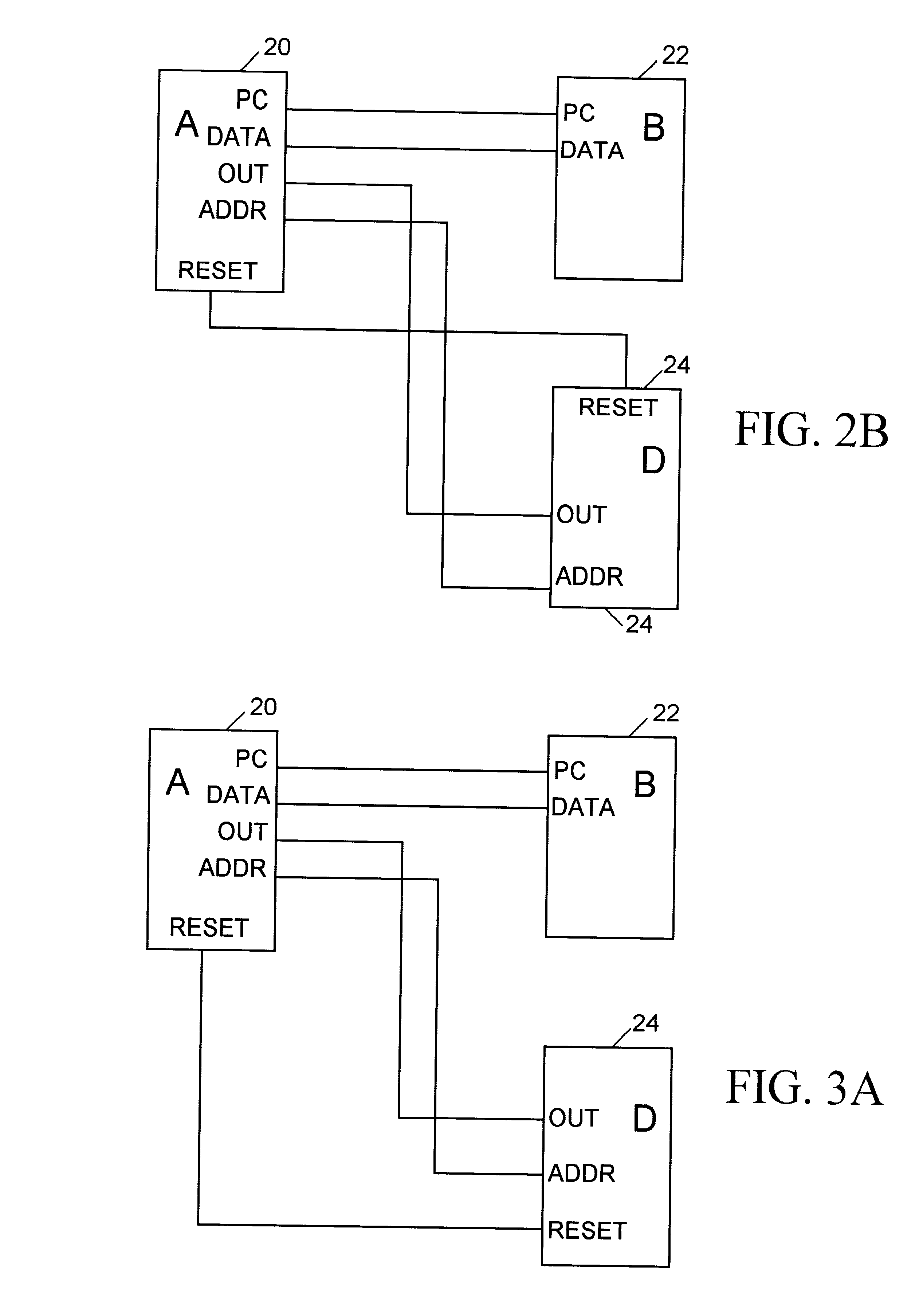

Automated processor generation system for designing a configurable processor and method for the same

InactiveUS20030208723A1Decompilation/disassemblyGeneral purpose stored program computerApplication softwareProcessor design

An automated processor design tool uses a description of customized processor instruction set extensions in a standardized language to develop a configurable definition of a target instruction set, a Hardware Description Language description of circuitry necessary to implement the instruction set, and development tools such as a compiler, assembler, debugger and simulator which can be used to develop applications for the processor and to verify it. Implementation of the processor circuitry can be optimized for various criteria such as area, power consumption, speed and the like. Once a processor configuration is developed, it can be tested and inputs to the system modified to iteratively optimize the processor implementation. By providing a constrained domain of extensions and optimizations, the process can be automated to a high degree, thereby facilitating fast and reliable development.

Owner:TENSILICA

Method and system for counting events within a simulation model

InactiveUS6470478B1Monitor performanceDigital circuit testingDetecting faulty computer hardwareTheoretical computer scienceLinear feedback shift register

A method and system that utilize the expressiveness of hardware description languages for efficiently and comprehensively monitoring performance characteristics of a digital circuit design during simulation. According to the present invention, a design entity that is part of a digital circuit design is first described utilizing a hardware description language. Next, a counting instrument is described utilizing the same hardware description language. The counting instrument is designed to detect occurrences of a count event within the design entity during simulation of the digital circuit design. The counting instrument is associated with the design entity utilizing a non-conventional call, such that the counting instrument may be utilized to monitor each instantiation of the design entity within the simulation model without the instrumentation entity becoming incorporated into the digital circuit design. In association with the counting instrument, a linear feedback shift register is automatically generated for recording the number of occurrences of the count event within the design entity.

Owner:GLOBALFOUNDRIES INC

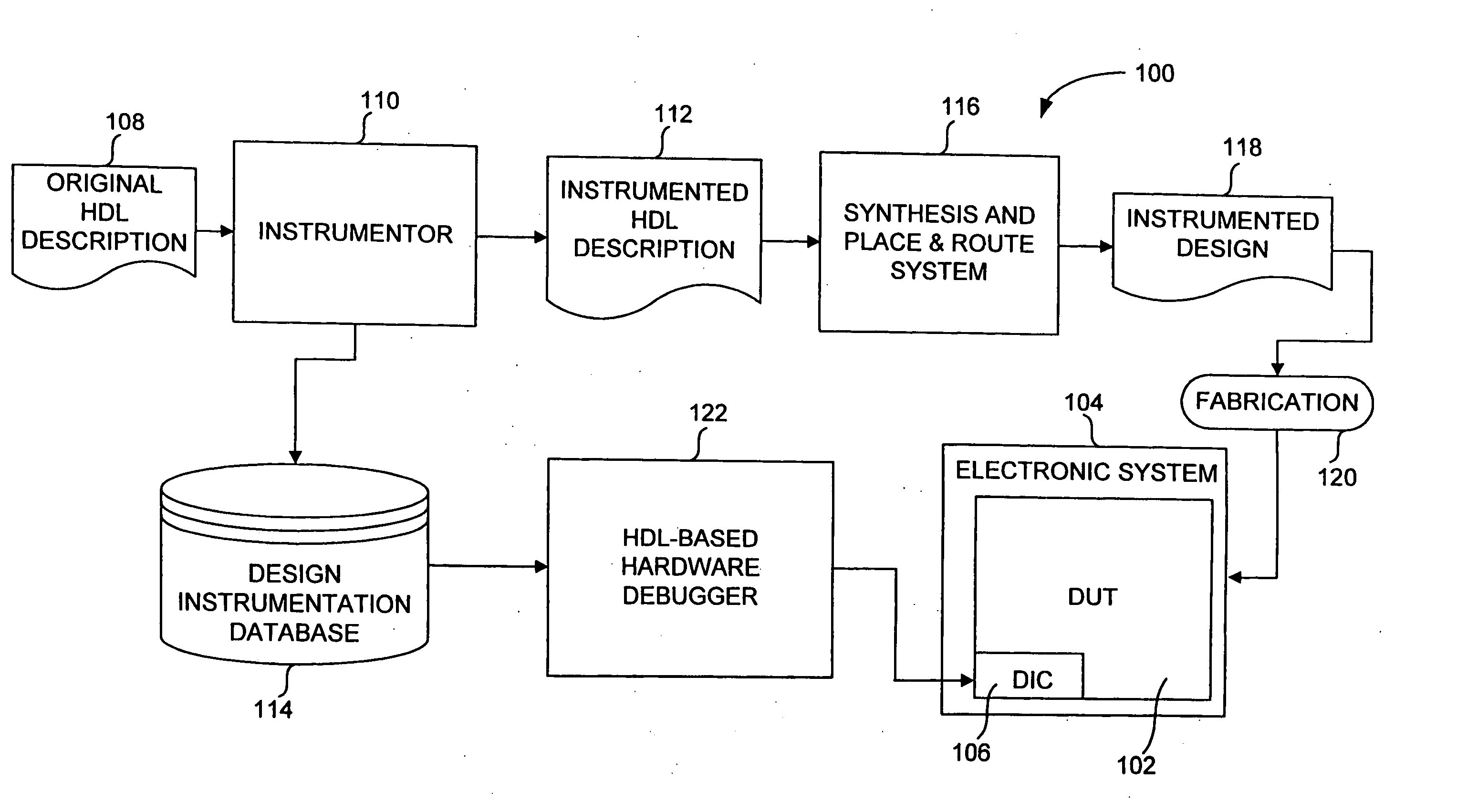

Method and system for debugging an electronic system

InactiveUS7072818B1Easy to analyzeEasy diagnosisElectrical testingCAD circuit designElectronic systemsEmbedded system

Techniques and systems for debugging an electronic system having instrumentation circuitry included therein are disclosed. The techniques and systems facilitate analysis, diagnosis and debugging fabricated hardware designs at a Hardware Description Language (HDL) level. Although the hardware designs (which were designed in HDL) have been fabricated in integrated circuit products with limited input / output pins, the invention enables the hardware designs within the integrated circuit products to be comprehensively analyzed, diagnosed, and debugged at the HDL level at speed. The ability to debug hardware designs at the HDL level facilitates correction or adjustment of the HDL description of the hardware designs.

Owner:SYNOPSYS INC

Adding complex instruction extensions defined in a standardized language to a microprocessor design to produce a configurable definition of a target instruction set, and hdl description of circuitry necessary to implement the instruction set, and development and verification tools for the instruction set

InactiveUS6477697B1Fast and reliable developmentGeneral purpose stored program computerCAD network environmentApplication softwareProcessor design

An automated processor design tool uses a description of customized processor instruction set extensions in a standardized language to develop a configurable definition of a target instruction set, a Hardware Description Language description of circuitry necessary to implement the instruction set, and development tools such as a compiler, assembler, debugger and simulator which can be used to develop applications for the processor and to verify it. The standardized language is capable of handling instruction set extensions which modify processor state or use configurable processors. By providing a constrained domain of extensions and optimizations, the process can be automated to a high degree, thereby facilitating fast and reliable development.

Owner:TENSILICA

Neural network processor oriented automatic design method, device and optimization method

ActiveCN107103113AAutomate collaborative designShorten the design cycleBiological neural network modelsCAD circuit designNerve networkAlgorithm

The invention provides a neural network processor oriented automatic design method, device and optimization method. The automatic design method includes: a first step, acquiring a neural network model description file and a hardware resource constraint parameter, wherein the hardware resource constraint parameter includes the hardware resource size and the target operation speed; a second step, searching a unit library from an established neural network assembly library according to the neural network model description file and the hardware resource constraint parameter, and generating a hardware description language code corresponding to a neural network processor of the neural network model according to the unit library; and a step 3, converting the hardware description language code into a hardware circuit of the neural network processor.

Owner:INST OF COMPUTING TECH CHINESE ACAD OF SCI

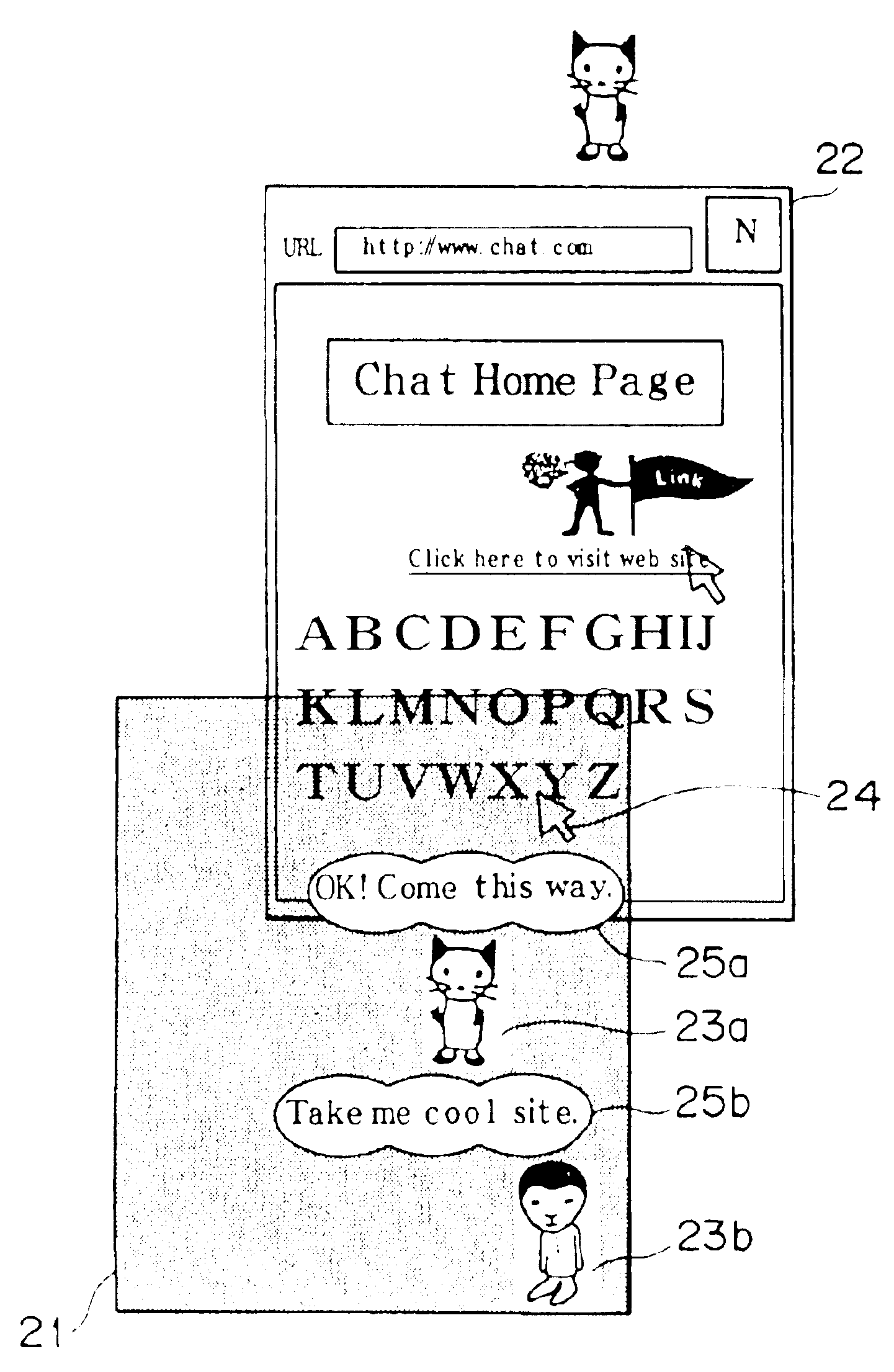

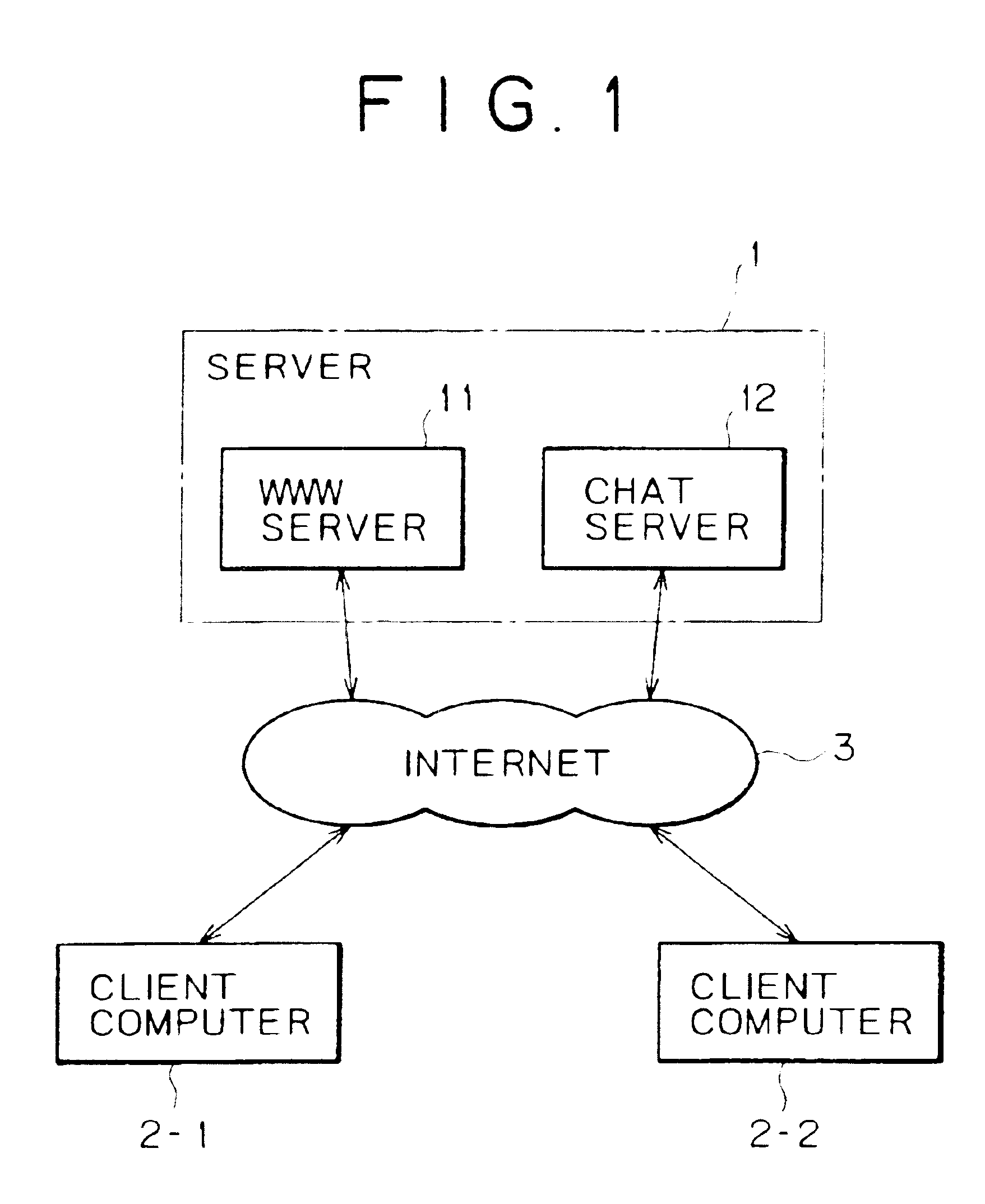

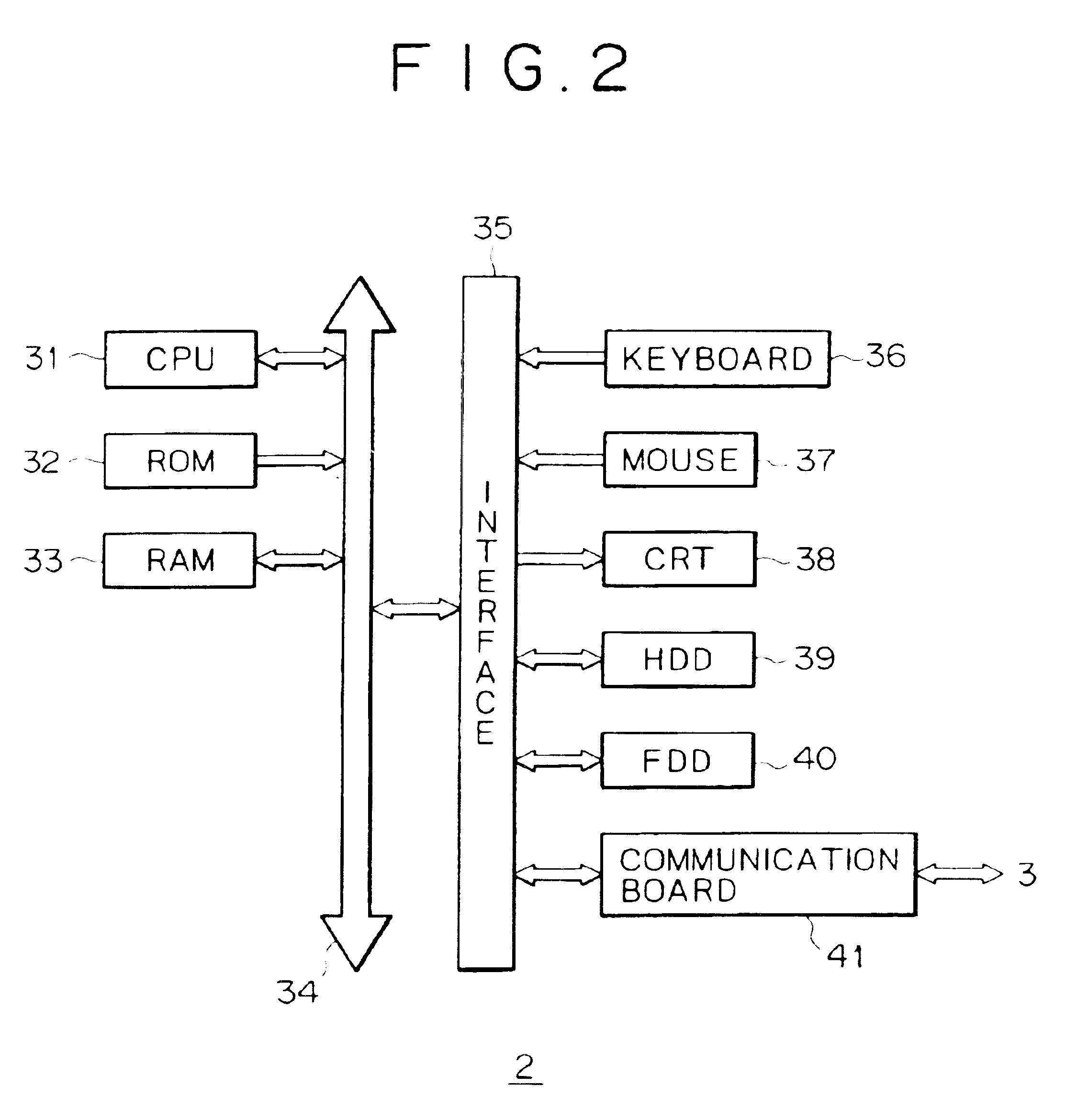

Information sharing processing method, information sharing processing program storage medium, information sharing processing apparatus, and information sharing processing system

InactiveUS6954902B2Easy to manufactureEasy accessCathode-ray tube indicatorsWeb data navigationInformation processingInformation sharing

There is provided an information sharing processing method comprising the steps of a page display processing step for acquiring a file from a predetermined server on a network and displaying the file as a page, wherein the file is described in a predetermined page description language and includes a description of link information to another file on the network; a common-screen display processing step for displaying an icon representing a user at a position on a common screen shared with the user and displaying a message issued by the user making an access to the same page as the page displayed at the page display processing step, wherein information on the position and the message are specified by the user in shared data transmitted by the user by way of a shared server on the network; and a screen superposition processing step for superposing the common screen displayed at the common-screen display processing step on the page displayed at the page display processing step. Accordingly, it is possible to make an access to the web page with ease while participating a chat. In addition, any one of the users is capable of immediately knowing whether the other user is making an access to the same web page.

Owner:SONY CORP

Hardware debugging in a hardware description language

InactiveUS20050125754A1Facilitates correction and adjustmentElectrical testingFunctional testingEmbedded systemIntegrated circuit

Owner:SYNOPSYS INC

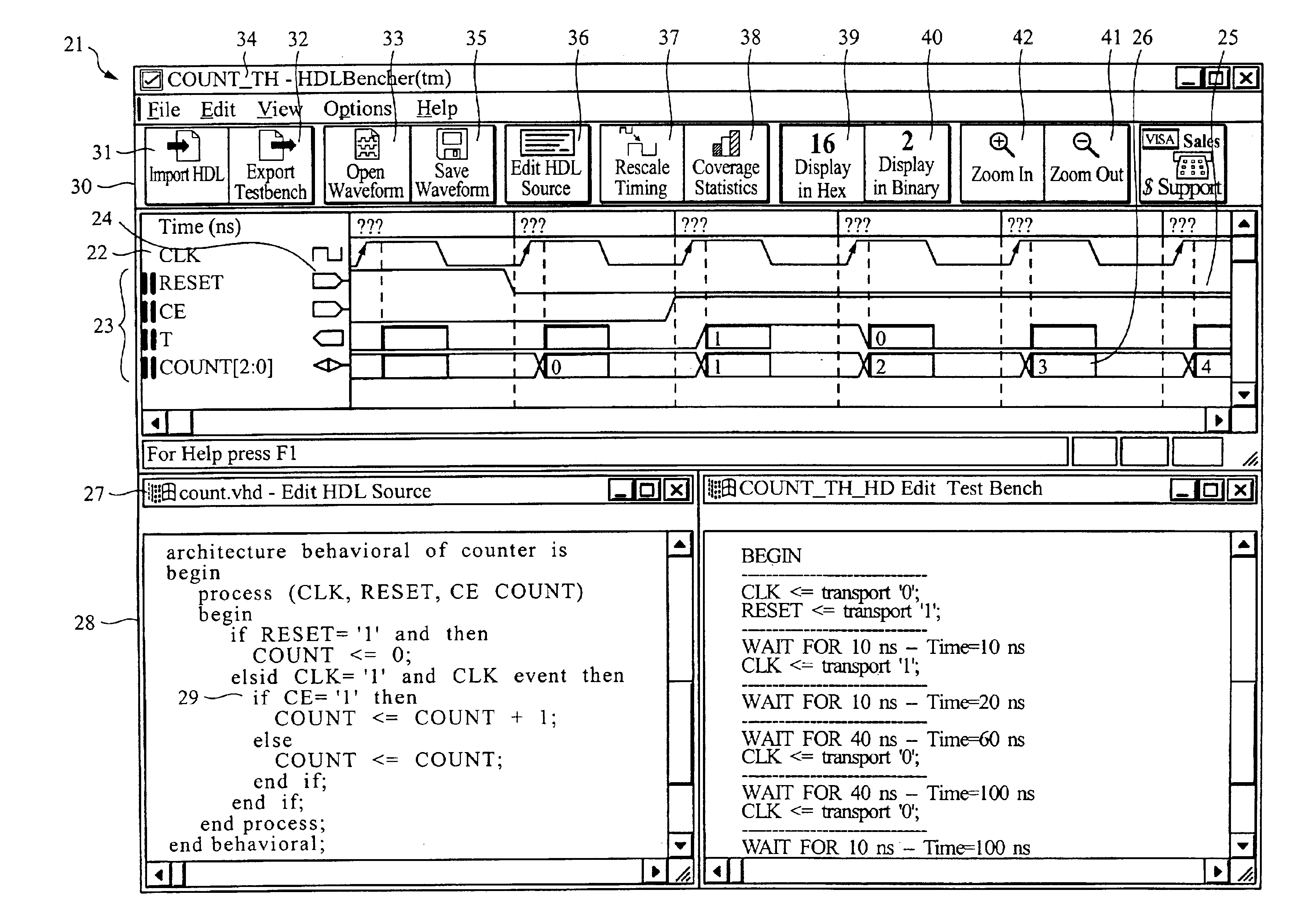

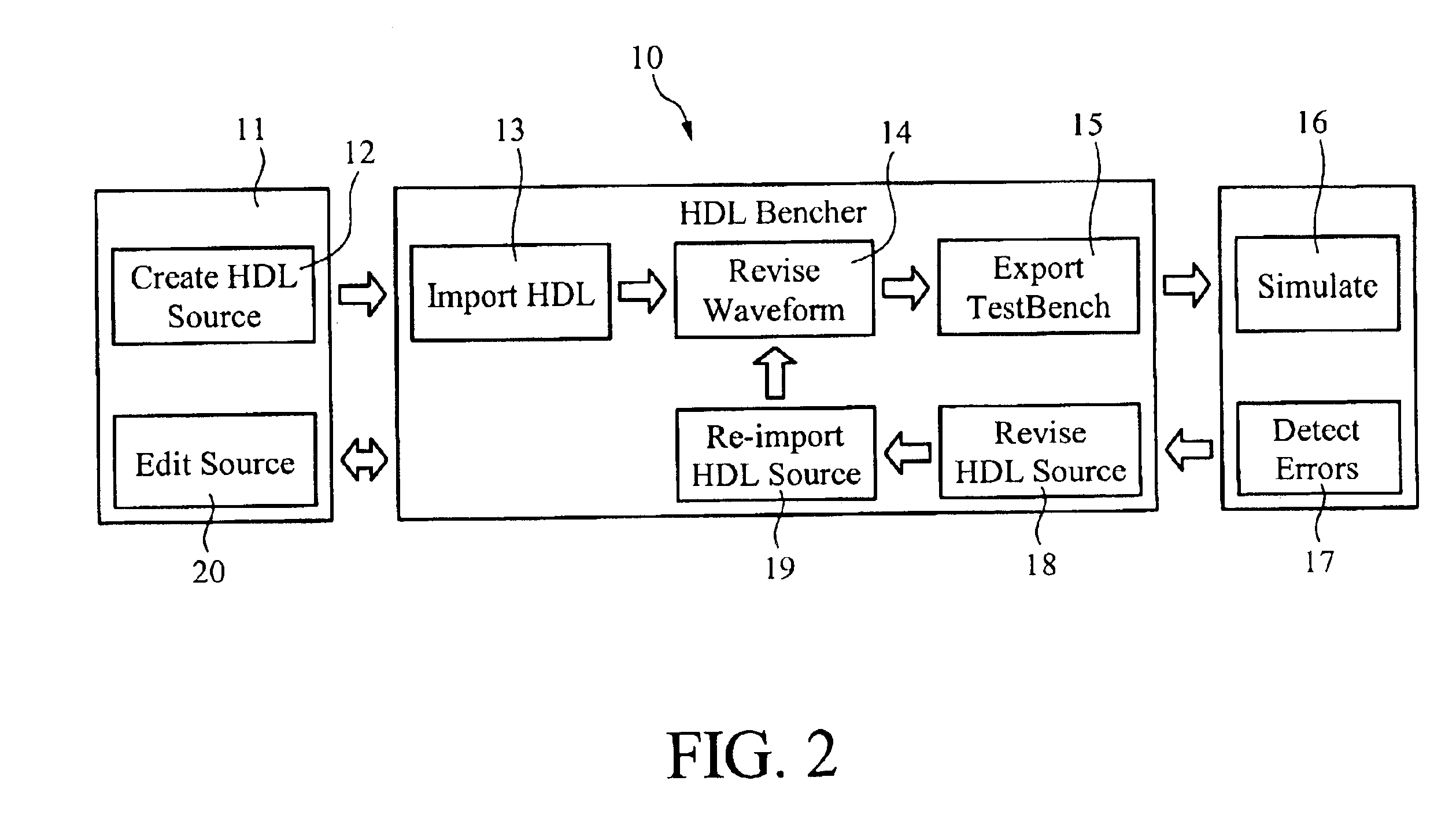

Combined waveform and data entry apparatus and method for facilitating fast behavioral verification of digital hardware designs

InactiveUS6871331B1Easy to analyzePromote generationCAD circuit designSoftware simulation/interpretation/emulationComputer scienceTest bench

A computer implemented apparatus and method that automates the entry, modification, analysis, and generation of test benches from electrical circuits, both of which are specified as hardware description language (HDL) files. The computer implemented-method and apparatus also provides a unique mechanism that blends entry and display of timing requirements that must be met by the electric circuit.

Owner:XILINX INC

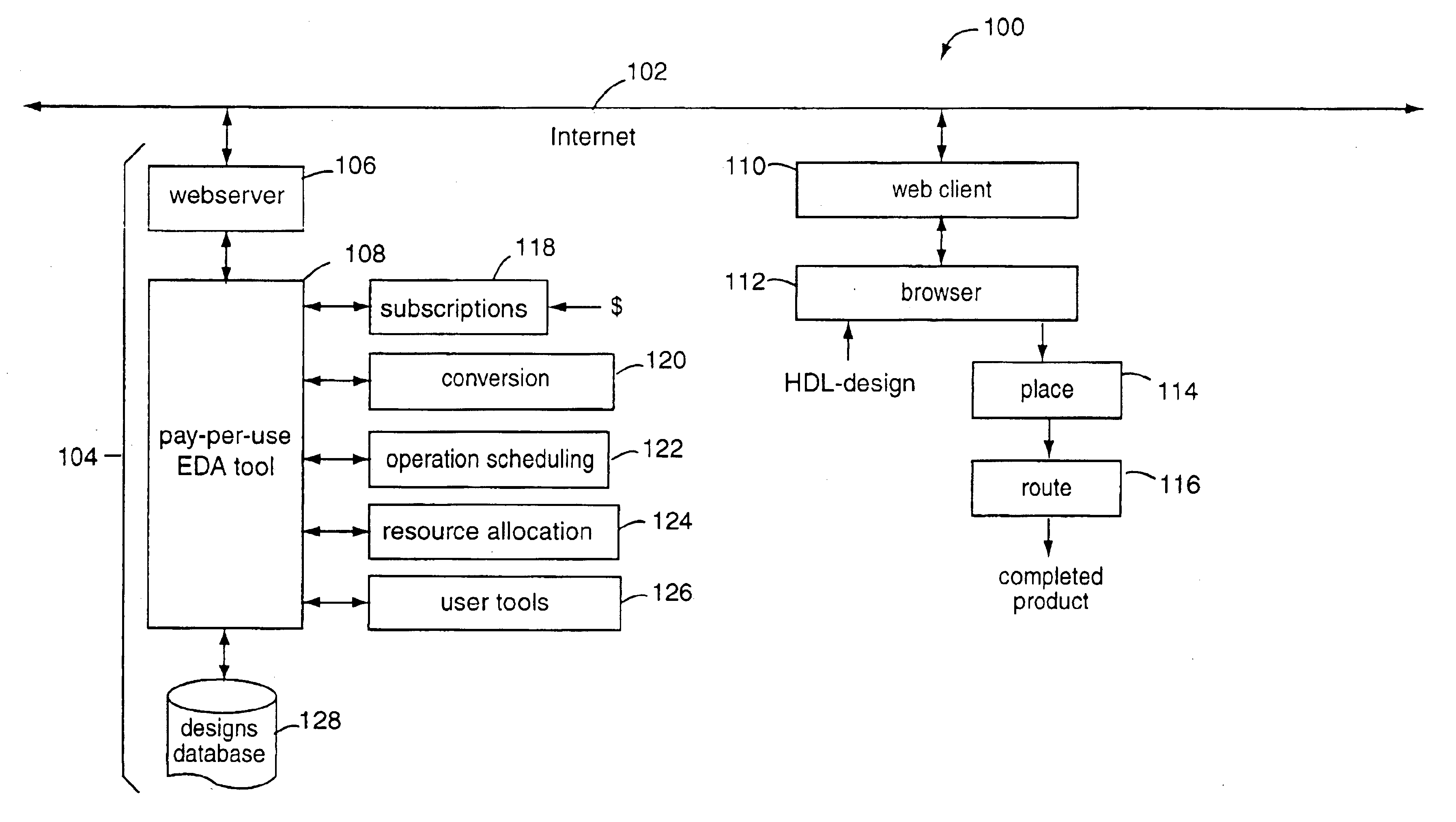

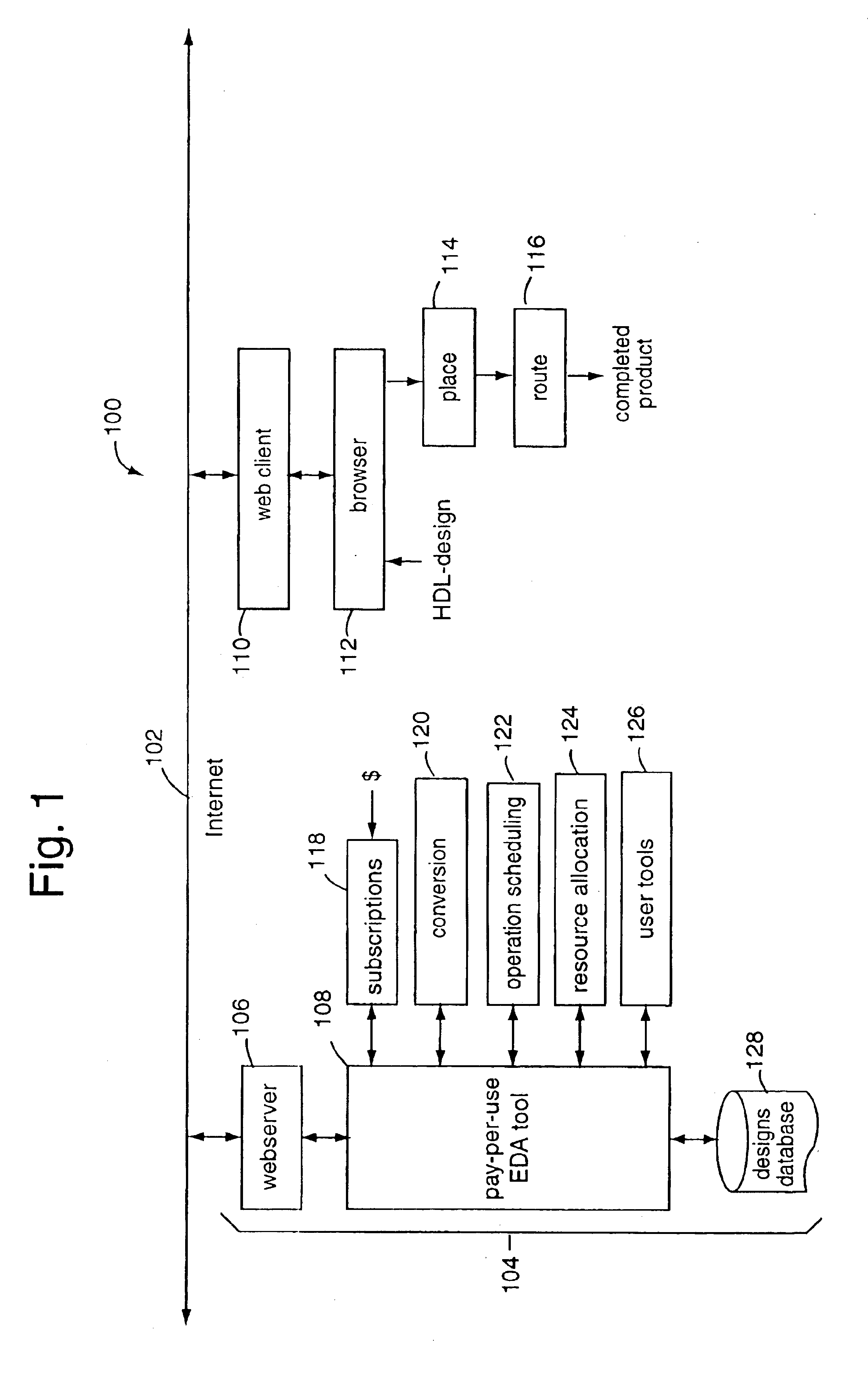

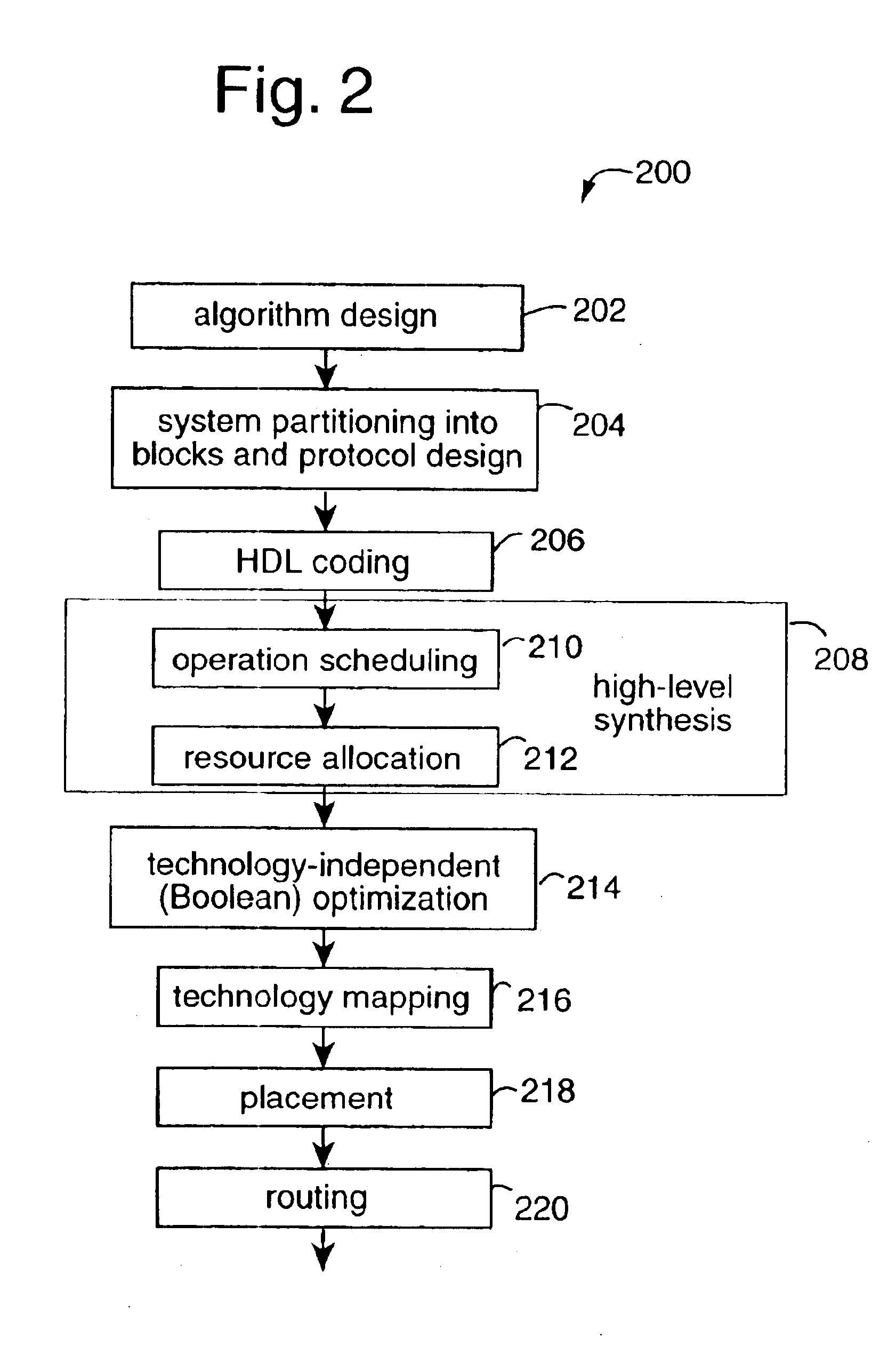

Behavioral-synthesis electronic design automation tool business-to-business application service provider

InactiveUS6782511B1Distributed efficiently and easilyCAD circuit designSoftware simulation/interpretation/emulationWeb serviceIntellectual property

A business-to-business application service provider includes an Internet website and webserver with EDA-on-demand solutions for system-on-a-chip designers. Such website allows electronic designs in hardware description language to be uploaded into a front-end EDA design environment. A behavioral model simulation tool hosted privately on the webserver tests and validates the design. Such tool executes only in the secure environment of the business-to-business application service provider. The validated solution is then downloaded back over the Internet for a pay-per-use fee to the customer, and in a form ready to be placed and routed by a back-end EDA tool. Such validated design solutions are also downloadable to others in exchange for other designs, or available in technology libraries. The intellectual property created can be re-used, sold, shared, exchanged, and otherwise distributed efficiently and easily from a central for-profit clearinghouse.

Owner:CADENCE DESIGN SYST INC

Method and system for debugging an electronic system

InactiveUS20060195822A1Facilitates analysis and diagnosis and debuggingFacilitates correction and adjustmentDetecting faulty computer hardwareElectrical testingElectronic systemsEmbedded system

Techniques and systems for debugging an electronic system having instrumentation circuitry included therein are disclosed. The techniques and systems facilitate analysis, diagnosis and debugging fabricated hardware designs at a Hardware Description Language (HDL) level. Although the hardware designs (which were designed in HDL) have been fabricated in integrated circuit products with limited input / output pins, the invention enables the hardware designs within the integrated circuit products to be comprehensively analyzed, diagnosed, and debugged at the HDL level at speed. The ability to debug hardware designs at the HDL level facilitates correction or adjustment of the HDL description of the hardware designs.

Owner:SYNOPSYS INC

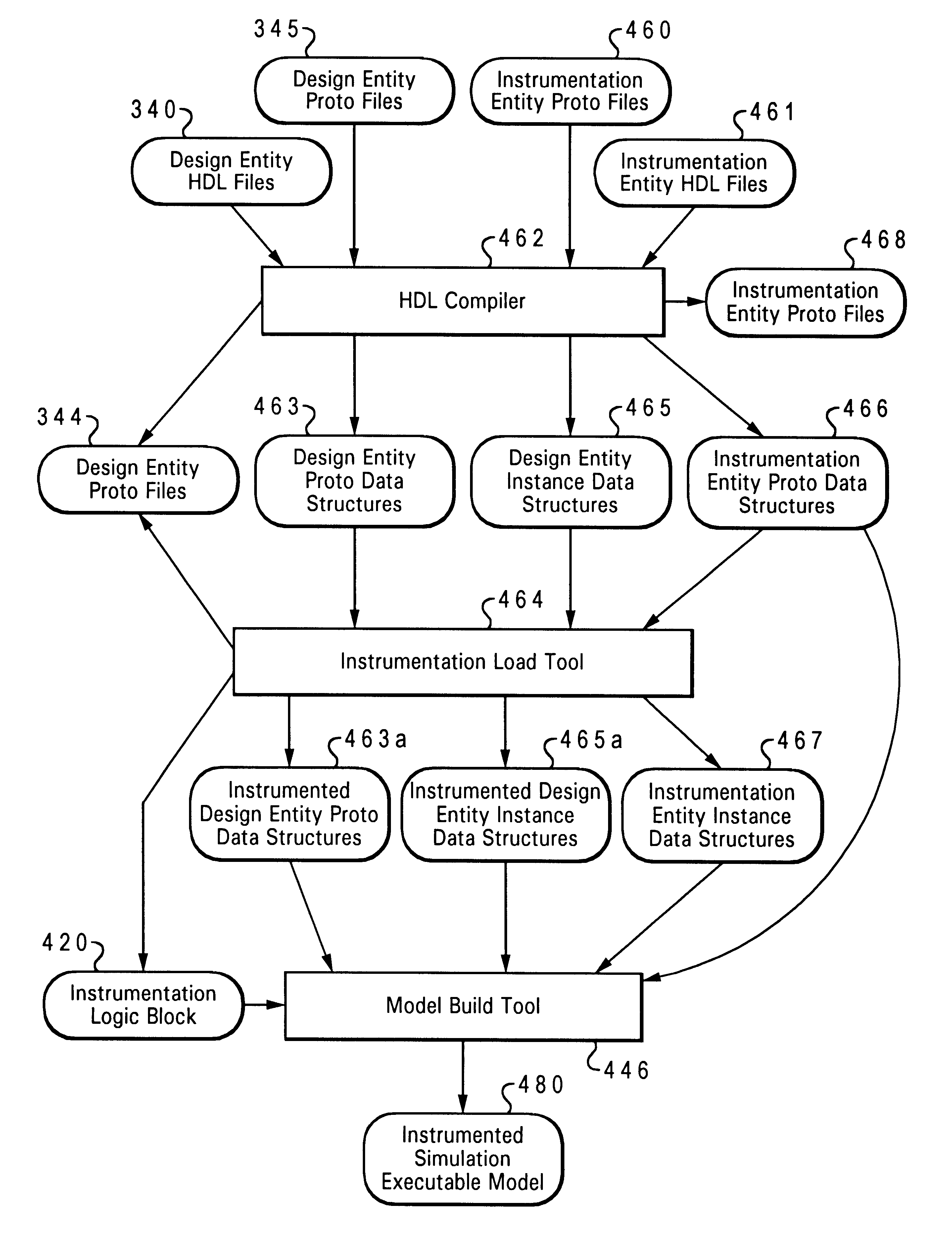

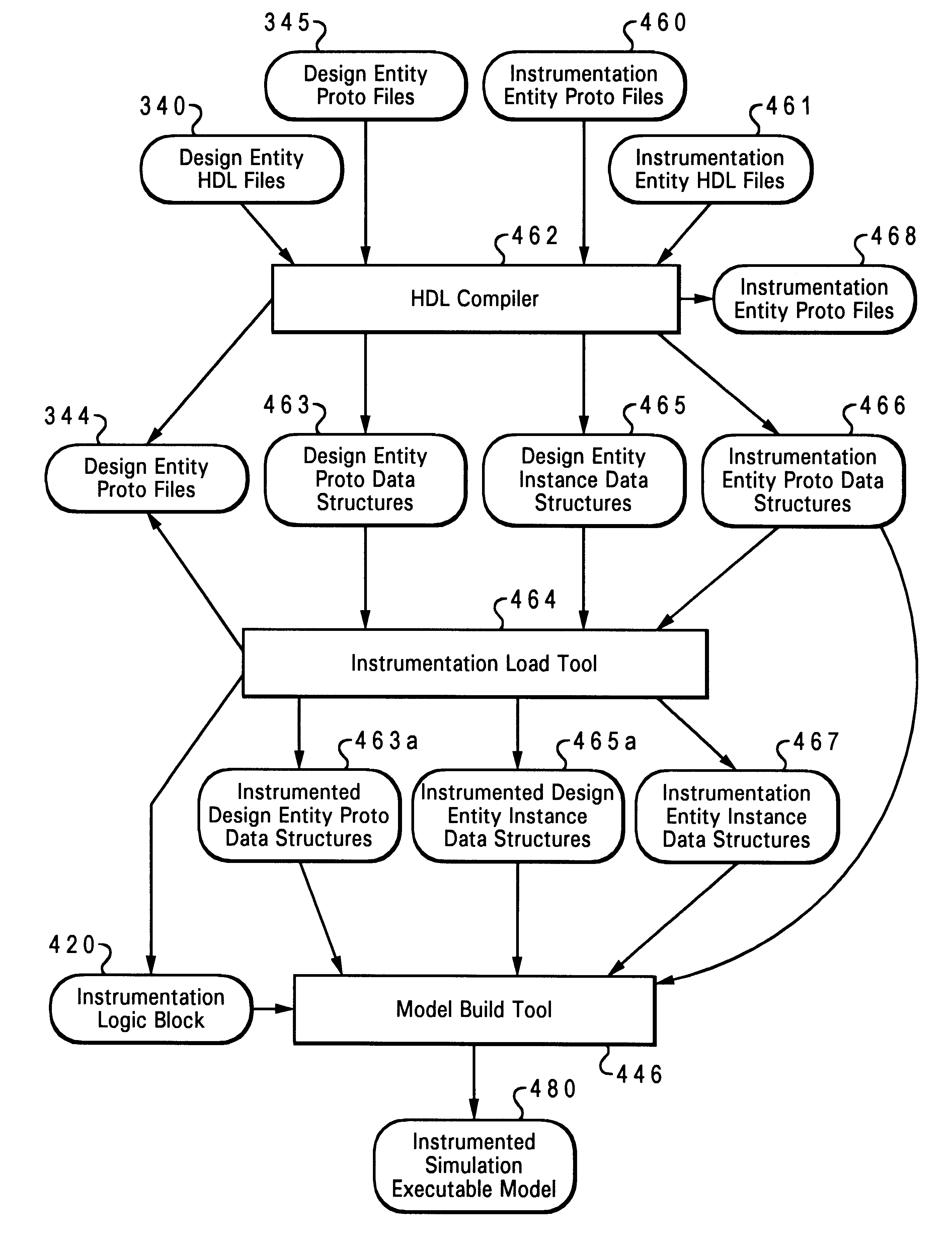

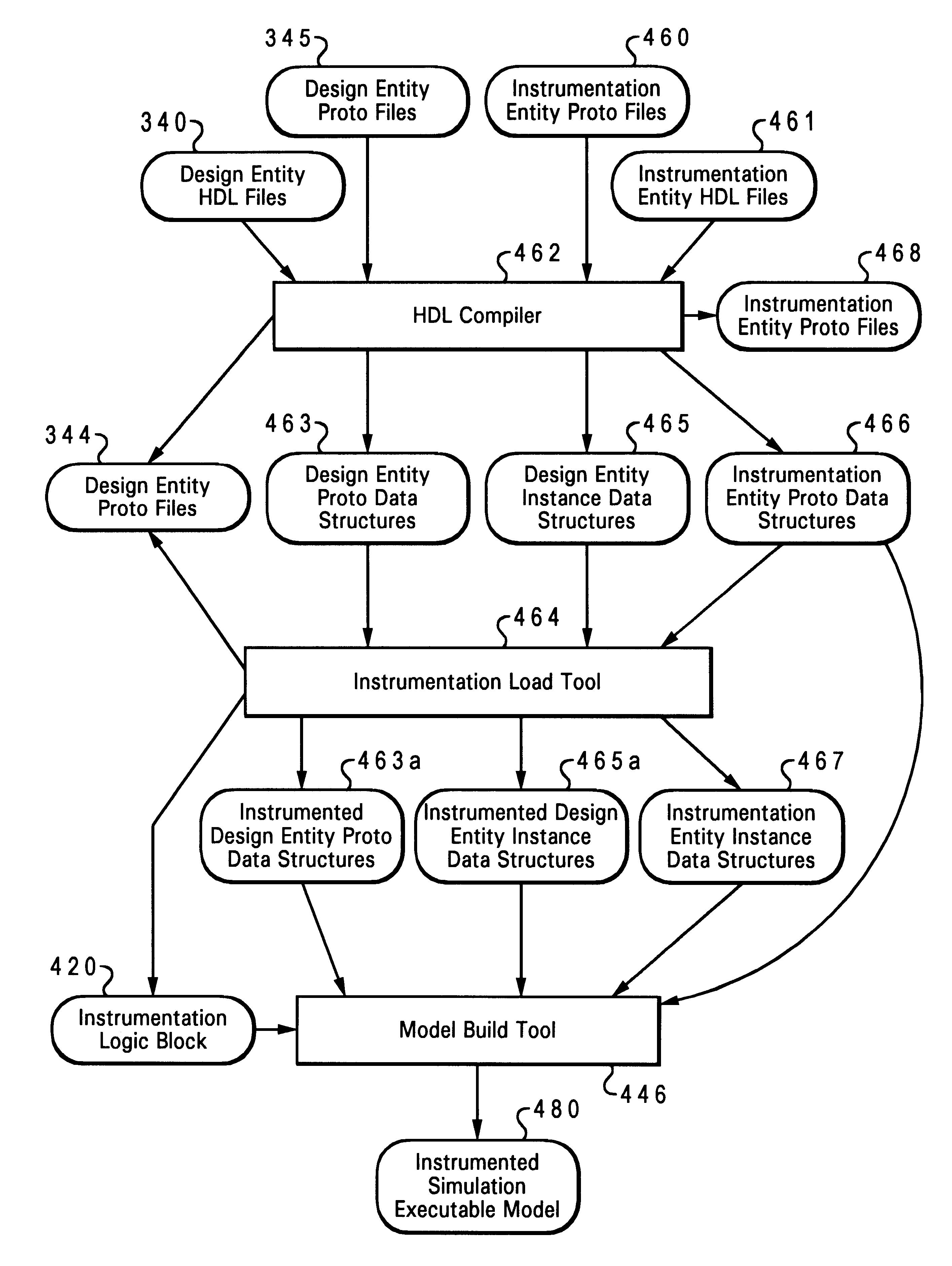

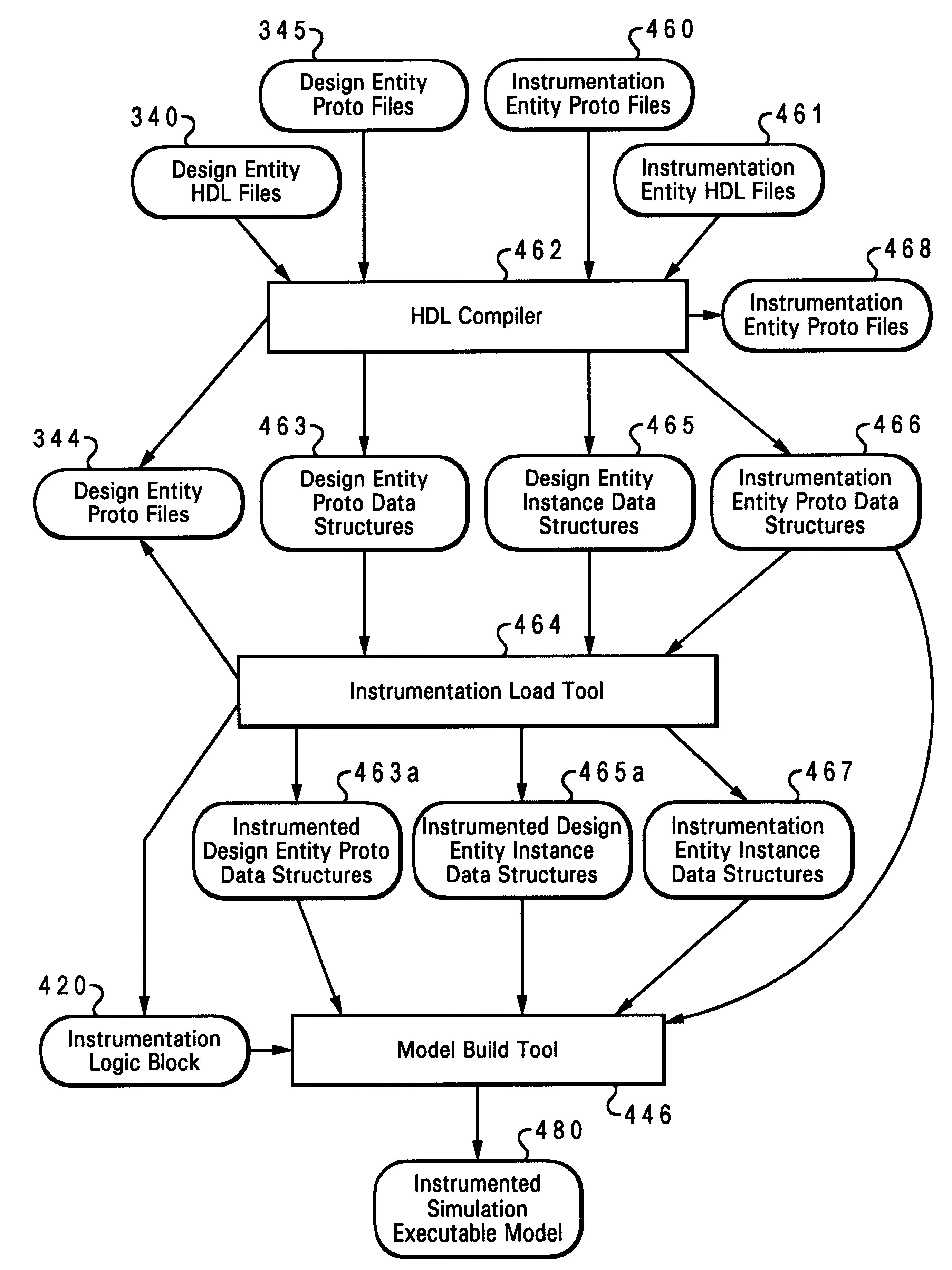

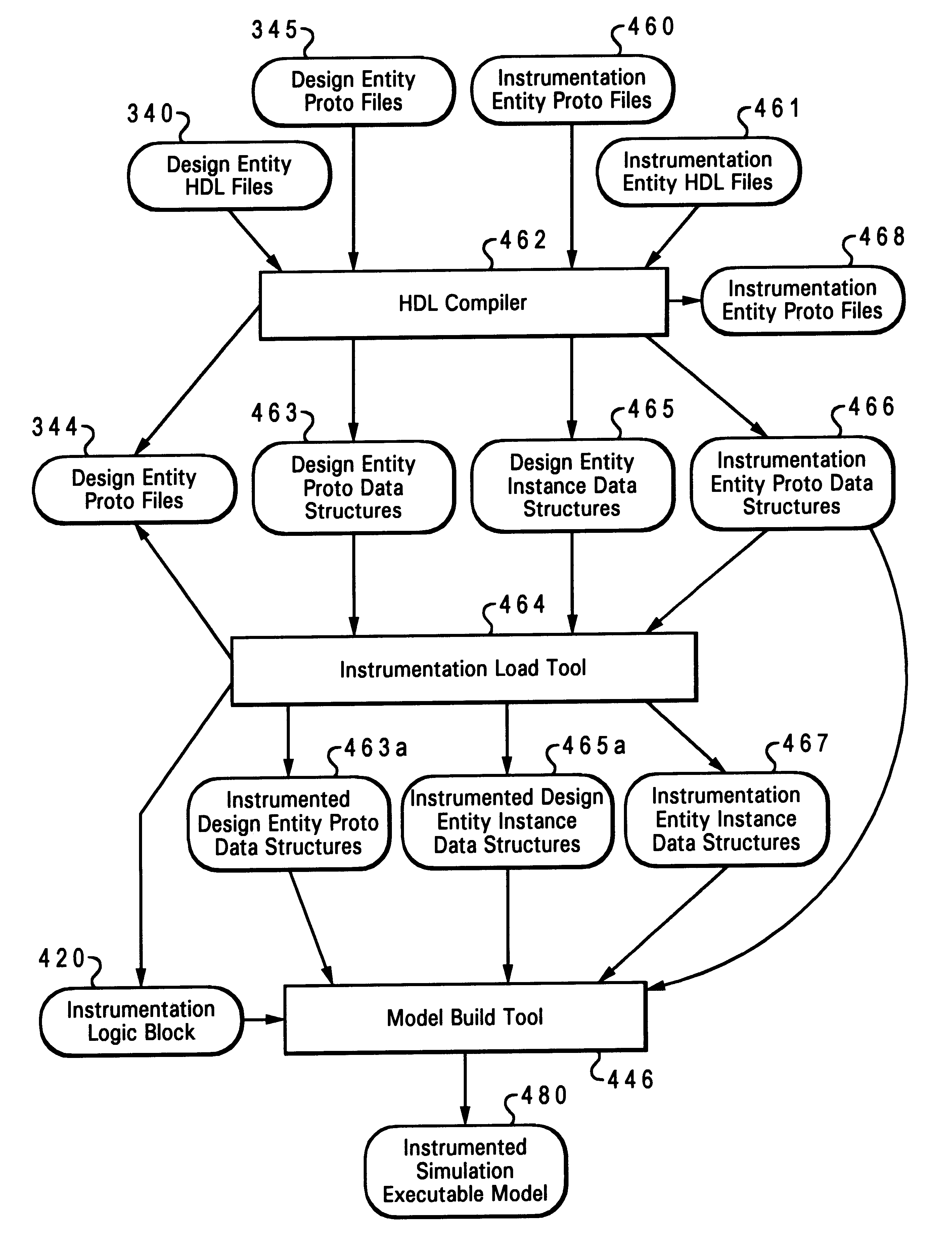

Method and system for instrumenting simulation models

InactiveUS6195627B1Complex designEasy to instrumentAnalogue computers for electric apparatusCAD circuit designTheoretical computer scienceCircuit design

A method and system are disclosed that utilize the expressiveness of hardware description languages for efficiently and comprehensively monitoring performance characteristics of a digital circuit design during simulation. According to the present invention, a design entity that is part of a digital circuit design is first described utilizing a hardware description language. Next, an instrumentation entity is described utilizing the same hardware description language. Thereafter, the design entity is instantiated in at least one instance within a simulation model of a digital circuit design. Finally, the instrumentation entity is associated with the design entity utilizing a non-conventional call, such that the instrumentation entity may be utilized to monitor each instantiation of the design entity within the simulation model without the instrumentation entity becoming incorporated into the digital circuit design.

Owner:GLOBALFOUNDRIES INC

Method and system for selectively disabling simulation model instrumentation

InactiveUS6195629B1Complex designEasy to instrumentAnalogue computers for electric apparatusCAD circuit designComputer architectureSimulation testing

A method and system are disclosed that utilize the expressiveness of hardware description languages for selectively disabling instrumentation during simulation of a digital circuit design. According to the present invention, an instrumentation entity, described utilizing a hardware description language to include an output signal to indicate an occurrence of an event during simulation, is implemented into a simulation model of a digital circuit design. Next, the output signal is associated with a unique output storage element. Finally, a disable mechanism uniquely associated with said output signal is provided, such that the output signal may be selectively masked by disabling the storage element during simulation testing of the digital circuit design.

Owner:GLOBALFOUNDRIES INC

Method and system for debugging an electronic system using instrumentation circuitry and a logic analyzer

InactiveUS7065481B2Facilitates correction and adjustmentSemiconductor/solid-state device testing/measurementAnalogue computers for electric apparatusElectronic systemsLogic analyzer

Techniques and systems for analysis, diagnosis and debugging fabricated hardware designs at a Hardware Description Language (HDL) level are described. Although the hardware designs (which were designed in HDL) have been fabricated in integrated circuit products with limited input / output pins, the techniques and systems enable the hardware designs within the integrated circuit products to be comprehensively analyzed, diagnosed, and debugged at the HDL level at speed. The ability to debug hardware designs at the HDL level facilitates correction or adjustment of the HDL description of the hardware designs.

Owner:SYNOPSYS INC

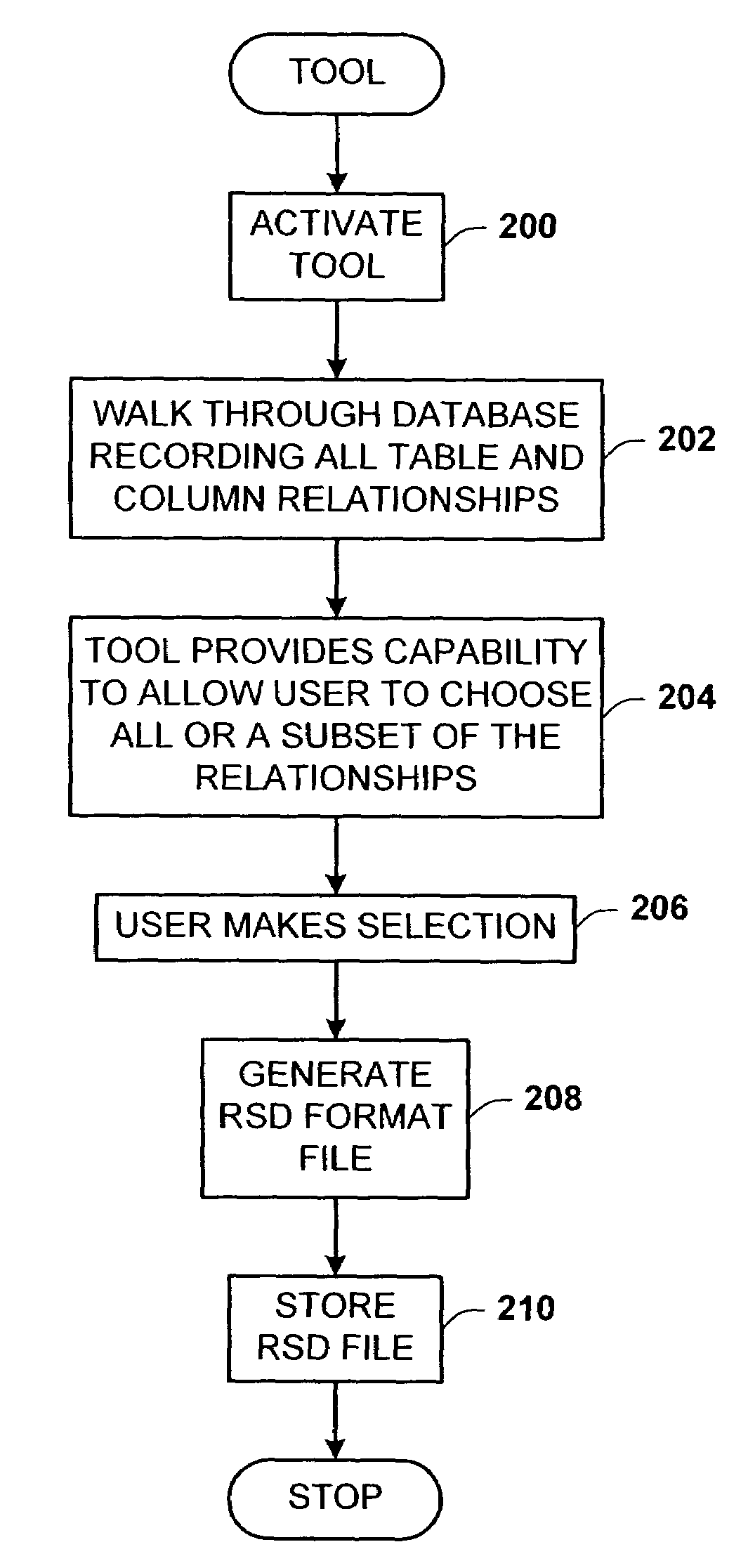

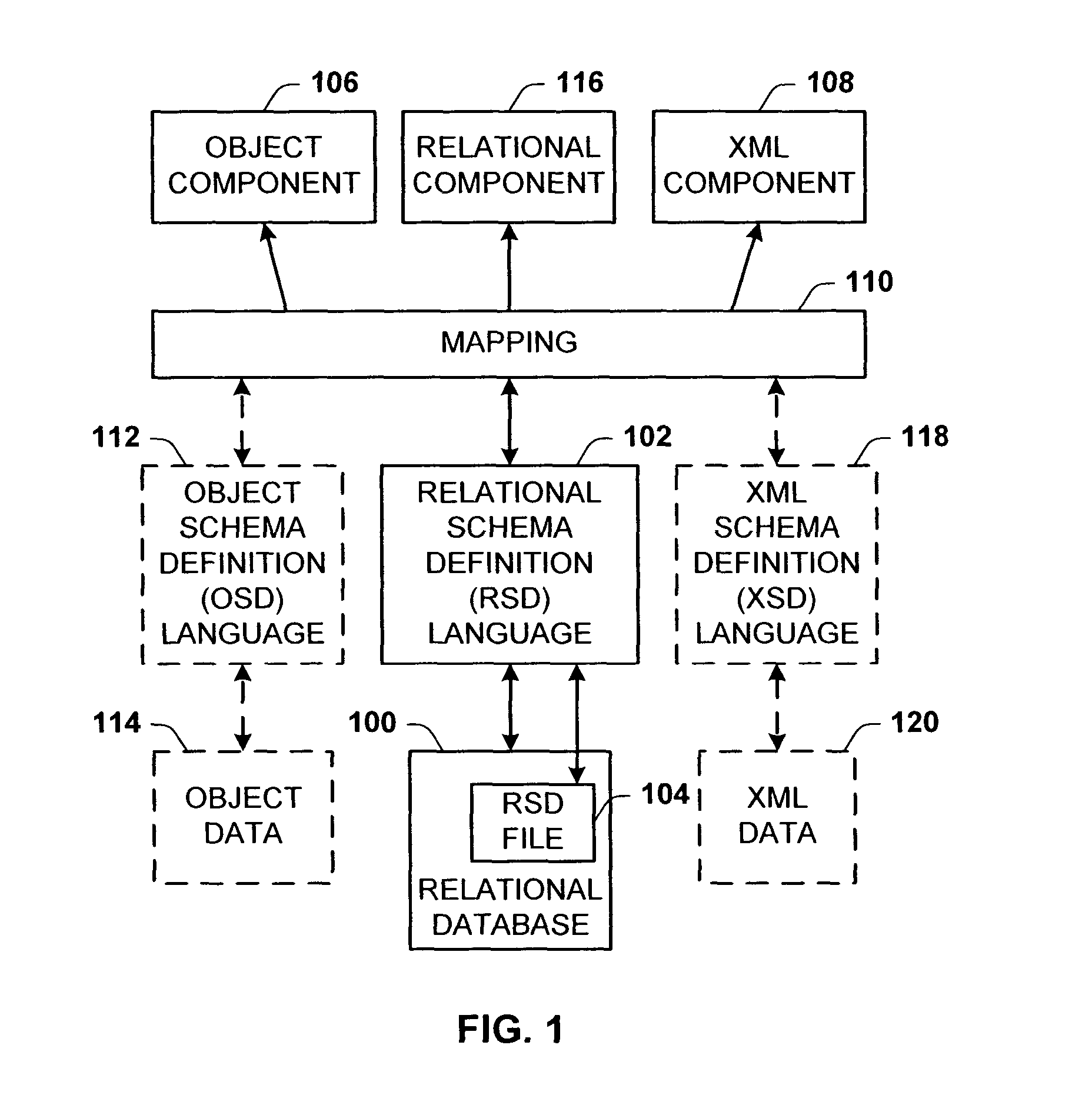

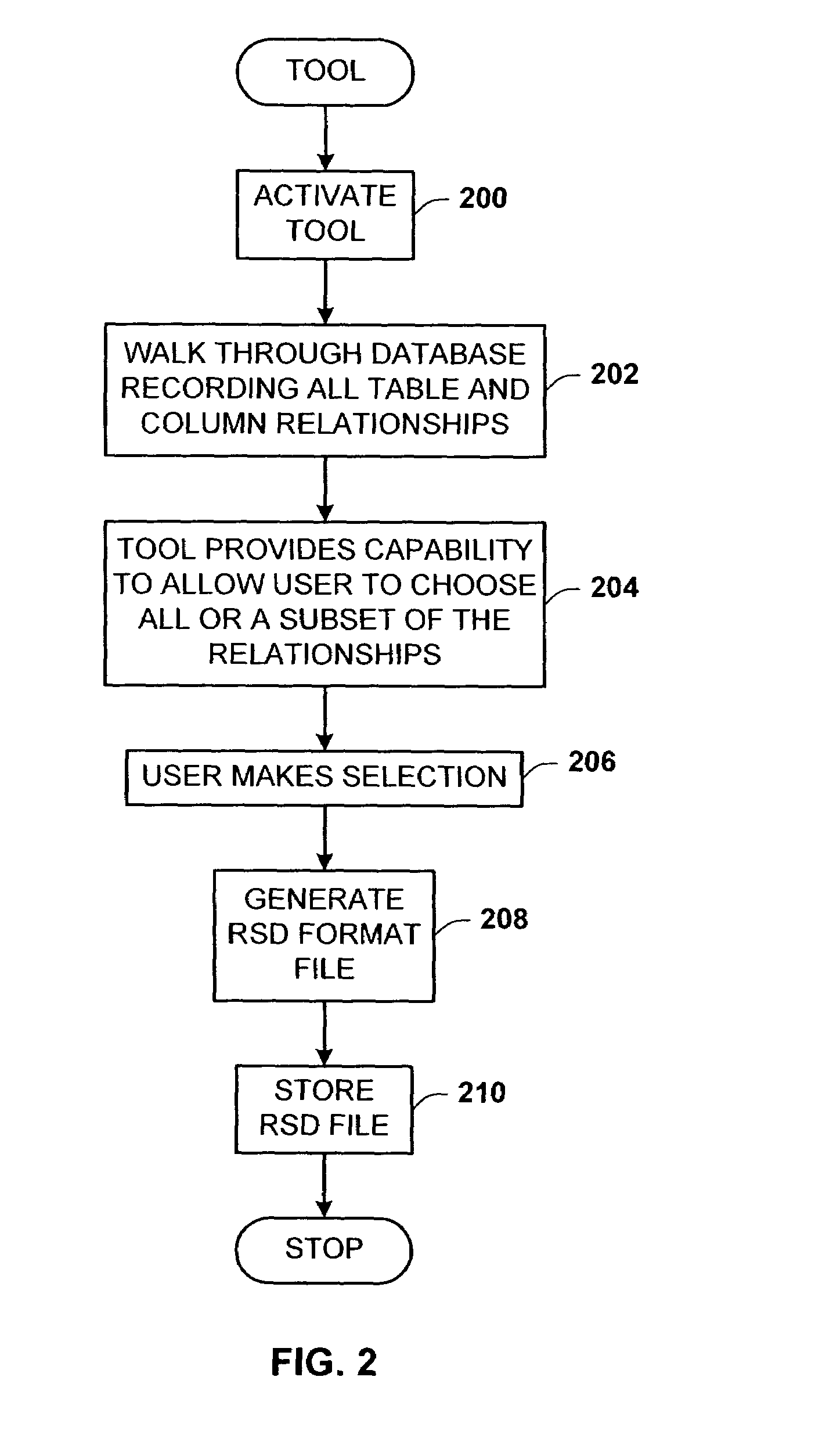

Relational schema format

InactiveUS7403956B2Easy mappingEasy to processData processing applicationsDigital data processing detailsRelational databaseInterface description language

A Relational Schema Definition (RSD) language that uses metadata of the relational database to generate an implementation-neutral or implementation-specific format that represents the precise database structure and data. The RSD language is a declarative description language such that an RSD file can then be used offline in a disconnected environment to reconstruct and use the database.

Owner:MICROSOFT TECH LICENSING LLC

Method and system for incrementally compiling instrumentation into a simulation model

InactiveUS6223142B1Complex designEasy to instrumentAnalogue computers for electric apparatusCAD circuit designParallel computingInstrumentation

A method and system are disclosed that utilize the expressiveness of hardware description languages for incrementally compiling instrumentation logic into a simulation model of a digital circuit design. According to the present invention, a simulation model that includes a design entity file of a digital circuit design is generated. Next, an instrumentation entity file is associated with the design entity file, thereby producing an instrumented design entity file. Finally, and during the process of compiling the simulation model, for the instrumented design entity file: searching for a consistent and previously compiled version of said instrumented design entity file. In response to finding a consistent and previously compiled version, loading the consistent and previously compiled version into the simulation model. In response to finding no consistent and previously compiled version, loading and compiling the instrumented design entity file.

Owner:IBM CORP

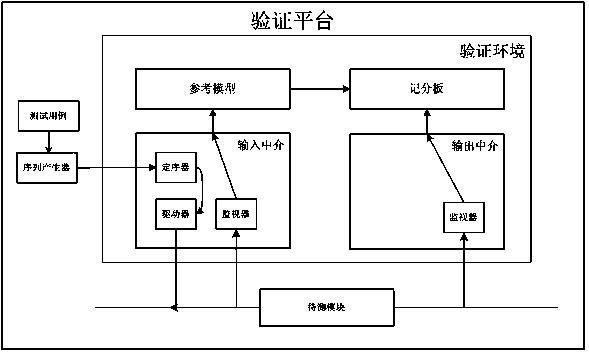

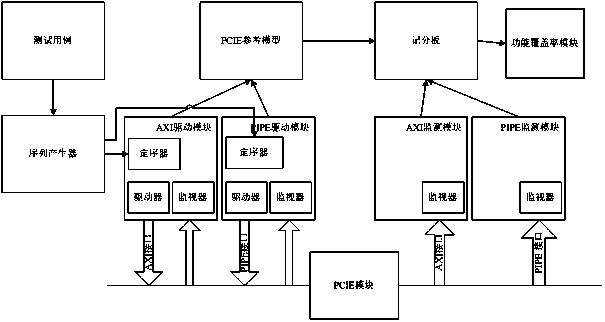

PCIE verification method based on UVM

ActiveCN103530216ASimple migration and verificationCoverage collection and monitoringError detection/correctionReference modelValidation methods

The invention relates to a PCIE verification method based on the UVM. The PCIE verification method is characterized in that the UVM and a system-level hardware descriptive language are adopted, a verification environment platform is set up through a high-level extensible interface bus behavior model, functional verification is implemented on a PCIE module, and the verification environment platform comprises a test case, a sequence generator, an AXI drive module, a PIPE drive module, an AXI monitoring module, a PIPE monitoring module, a PCIE reference model, a scoreboard and a functional coverage rate module. Due to the fact that the UVM is implemented, a stratified verification structure can be obtained, the PCIE with different types of configuration can be easily transplanted and verified, random data packet excitation can be generated through constraints, all instructions and addresses can be traversed, and the functional coverage rate module can also collect and monitor the coverage rate.

Owner:丁贤根

Hardware simulator instrumentation

InactiveUS6202042B1Complex designEasy to instrumentCAD circuit designSoftware simulation/interpretation/emulationComputer hardwareHardware simulator

A method and system are disclosed that utilize the expressiveness of hardware description languages for providing comprehensive runtime monitoring during hardware accelerated simulation of a digital circuit design. According to the present invention a design entity forming part of a digital circuit design that will be translated and assembled into a simulation executable model, is described utilizing a hardware description language. Next, an instrumentation entity designed to send a failure signal in response to detecting an occurrence of a failure event within the simulation executable model is described utilizing the same hardware description language. Thereafter, a simulation test is initiated on the simulation executable model utilizing a hardware simulator. Finally, during the simulation test, and in response to receiving a failure signal from the instrumentation entity, the simulation test is terminated such that the failure event may be efficiently identified and diagnosed.

Owner:IBM CORP

Randomized simulation model instrumentation

InactiveUS20020128809A1Analogue computers for electric apparatusCAD circuit designSource code fileTheoretical computer science

A method, system, and data structure for incorporating random instrumentation logic within a simulation model. The data structure of the present invention includes a first field containing data representing an assigned target and a second field containing data representing a logic value to be assigned to the assigned target. The first field and the second field are incorporated within a comment line of a design target entity source code file. A pre-pended comment identifier field identifies the data structure as a hardware description language comment.

Owner:IBM CORP

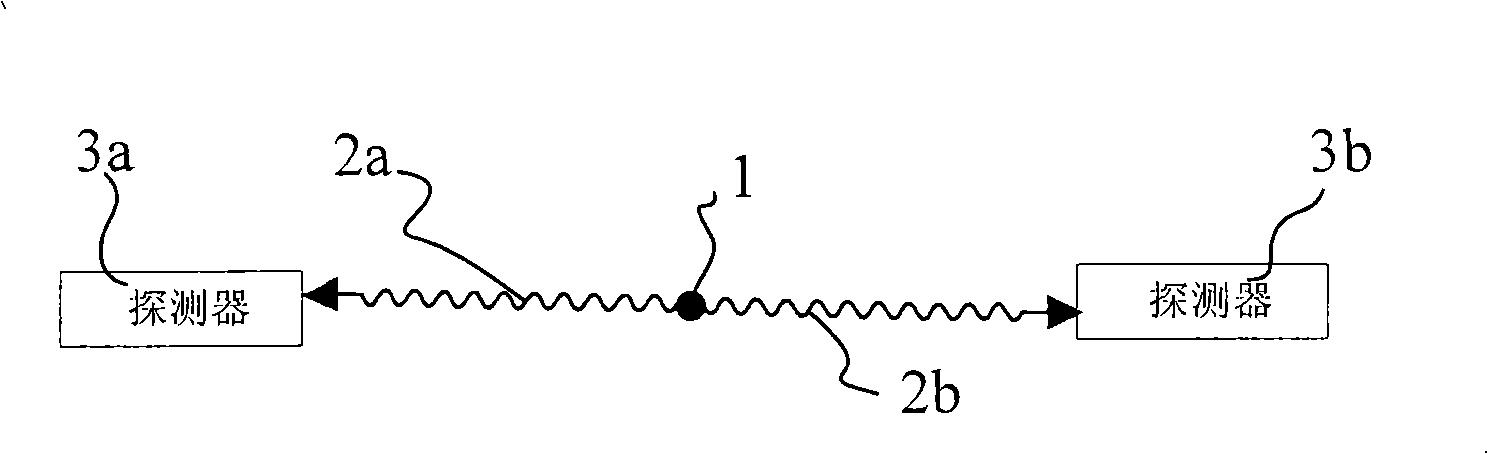

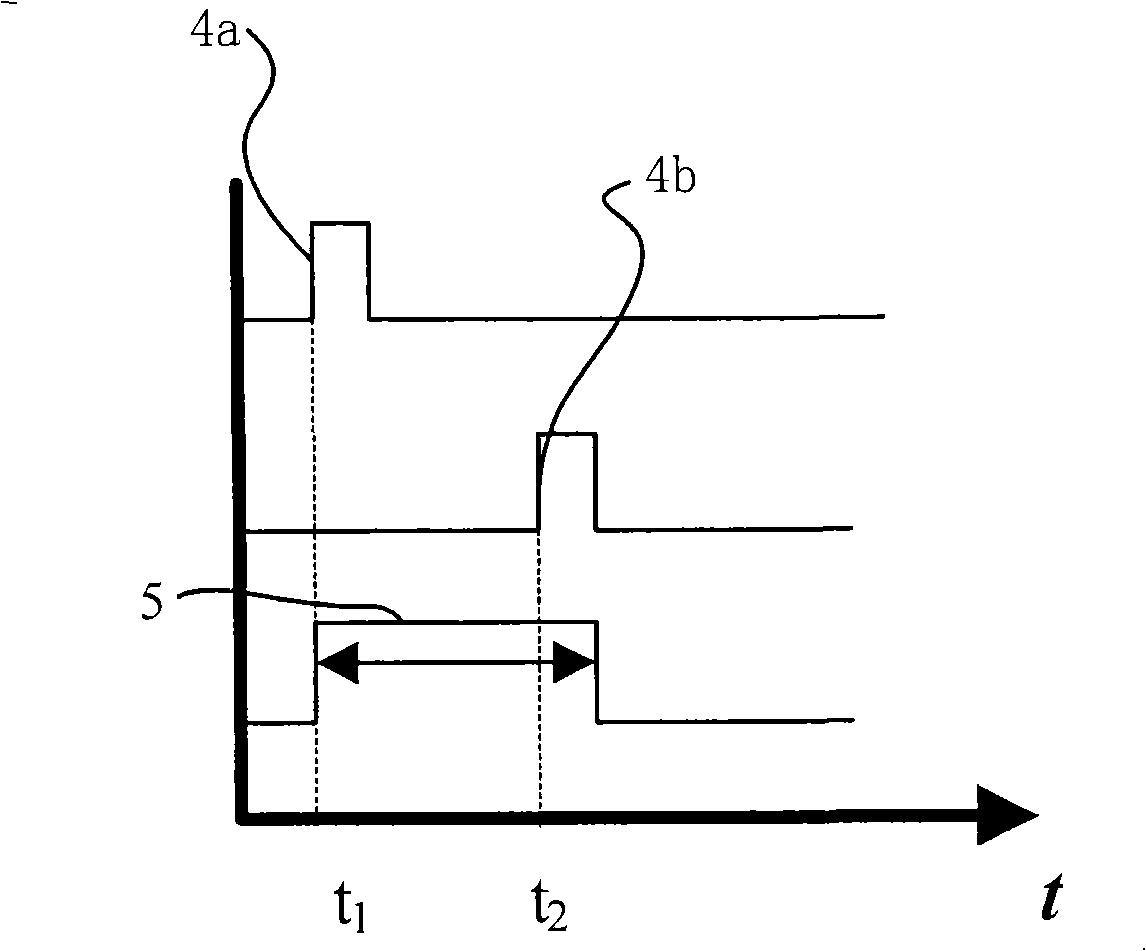

Coincidence system and method in positive electron dislocation scan

InactiveCN101268949AAvoid introducing dead timeEasy to implementData processing applicationsComputerised tomographsDead timeGate array

The invention relates to the medical slice imaging and nuclear-imaging field, in particular to a first-group board card, a signal buffering unit, a second-group receiving board card, a data buffering unit, a reference clock 17, a clock adjusting unit and an on-site programmable gate array that are used for a conforming system in a positron slice scanning device; the method is characterized in that the on-site programmable gate array is utilized to judge the time, the position and the energy among all matters, and two matters that pass through the judging and selecting regulations form a conforming case. By inducting the on-site programmable gate array, the case information captured by a front-end detector module of a PET apparatus can be processed fast and high-efficiently by compiling hardware description language, so as to ensure whether the conforming matters happen or not. The method is an improvement of the process of the prior PET conforming system. The method can finish the process of the conforming system high-efficiently and fast by using a piece of FPGA and can lead the system not to be inducted into the dead time while the high system sensitivity is obtained.

Owner:INST OF HIGH ENERGY PHYSICS CHINESE ACADEMY OF SCI

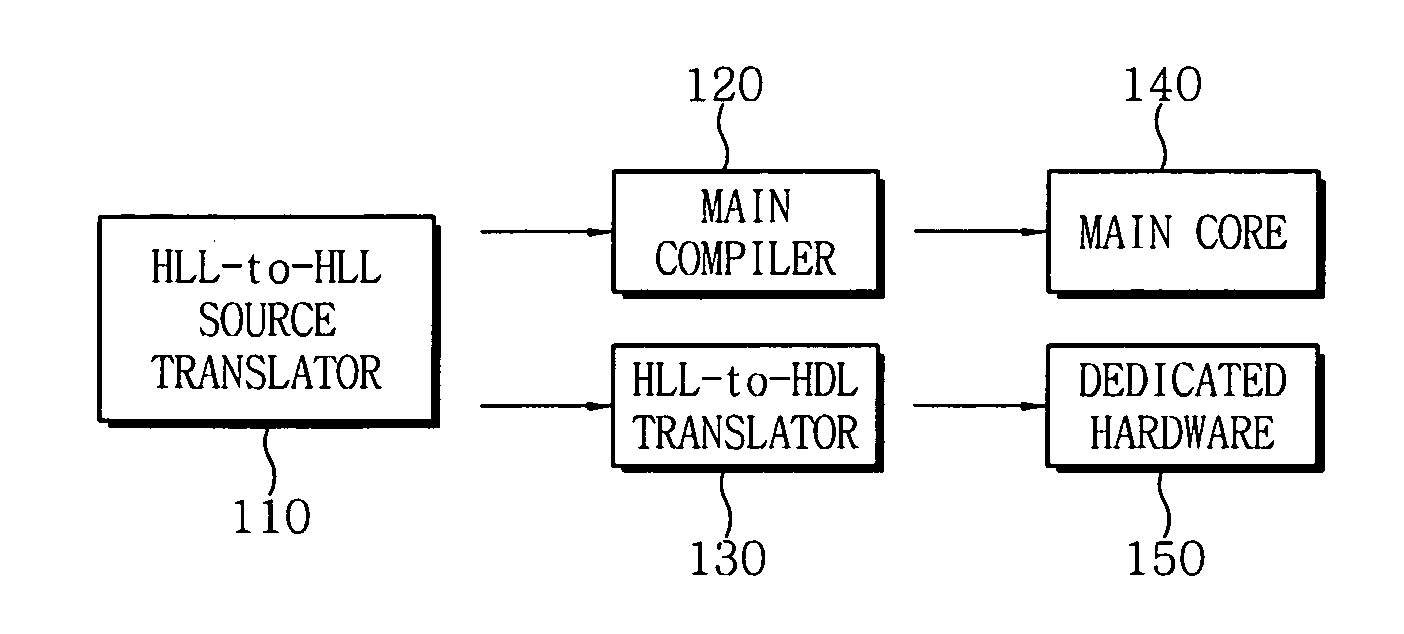

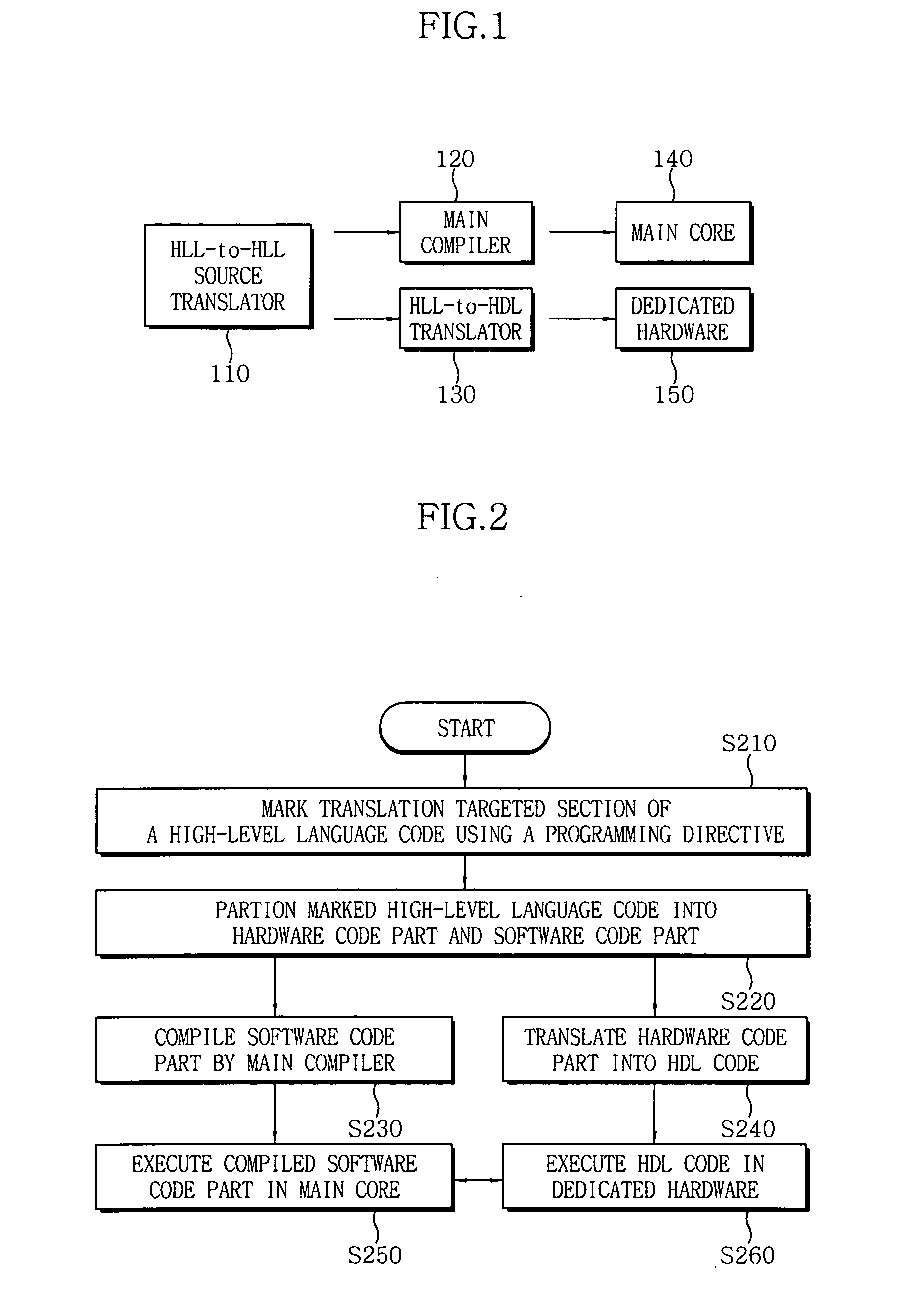

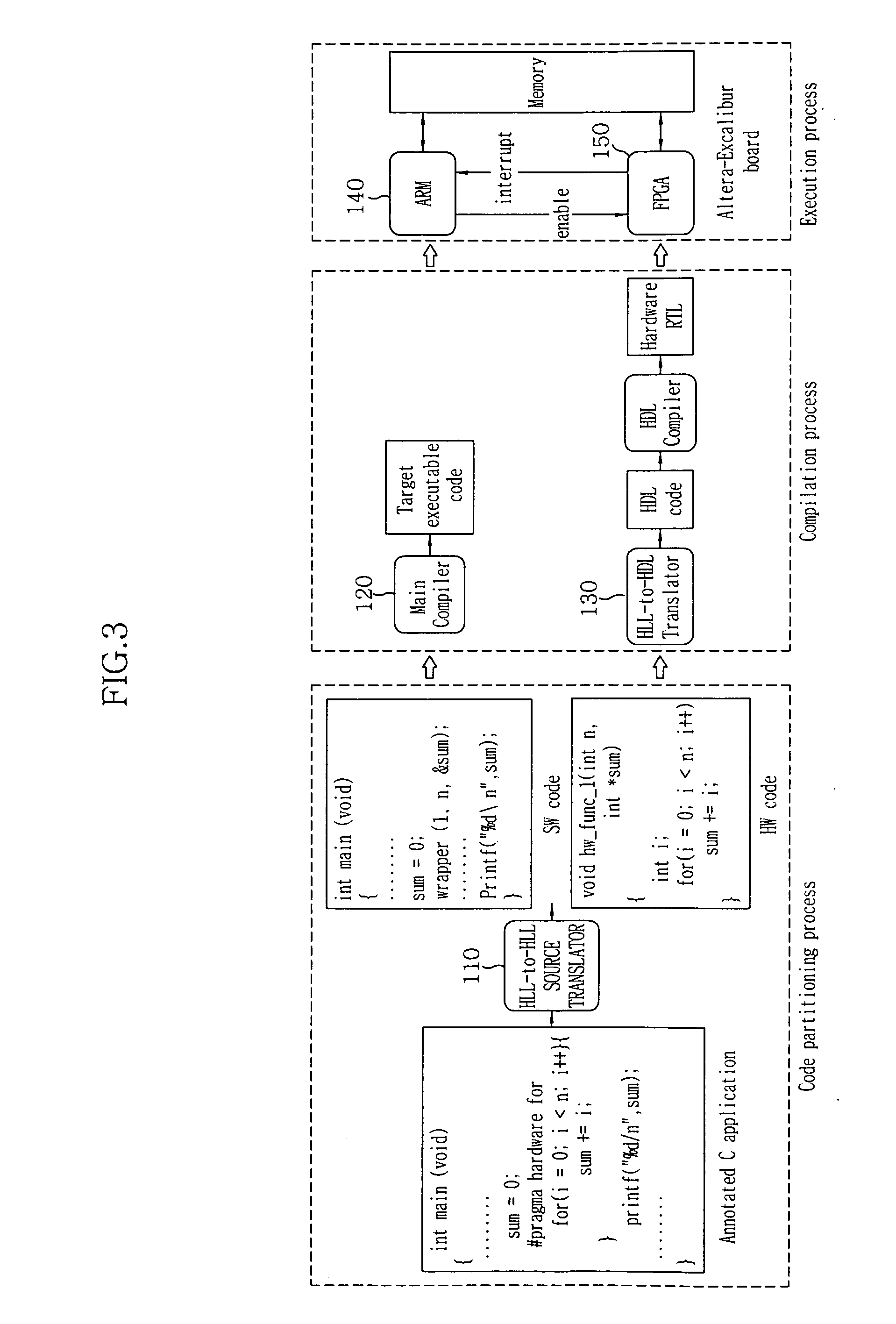

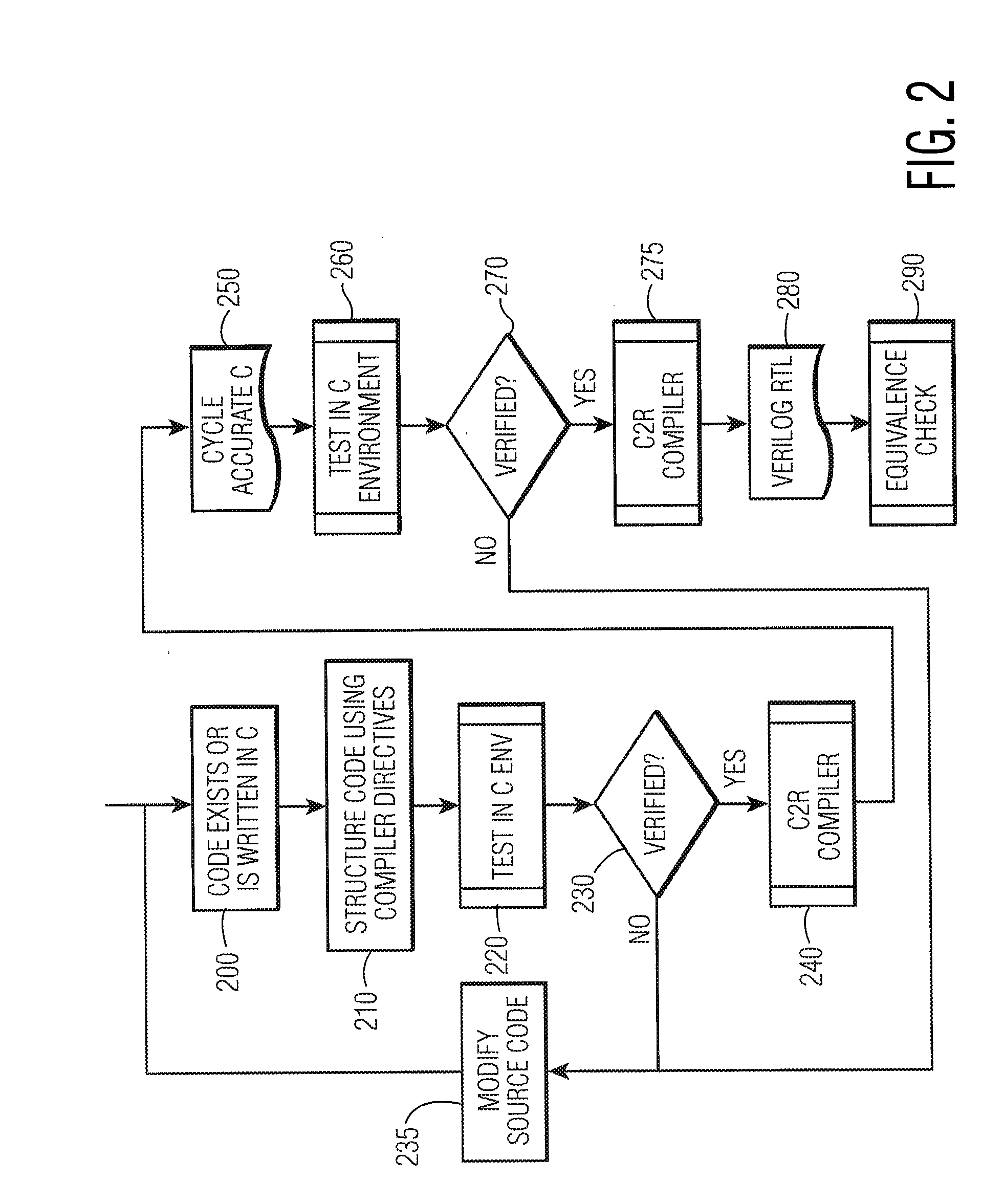

System and method for translating high-level programming language code into hardware description language code

The present invention is directed to a method and system for translating a high-level language (HLL) code such as C, C++, Fortran, Java or the like into a HDL code such as Verilog or VHDL which requires no modification in the original HLL source code, while supporting a cross call between software and hardware, and even recursive calls in hardware. The system includes: a HLL-to-HLL source translator which reads user programming directive from a translation-targeted high-level language code marked with the user directive, and separates the translation-targeted high-level language code into a hardware code part and a software code part; a main compiler which compiles the software code part; a HLL-to-HDL translator which includes the front-end and middle-end of the main compiler and a HDL backend; a main core which executes the compiled software code part; and a dedicated hardware which executes the HDL code.

Owner:KOREA UNIV IND & ACADEMIC CALLABORATION FOUND

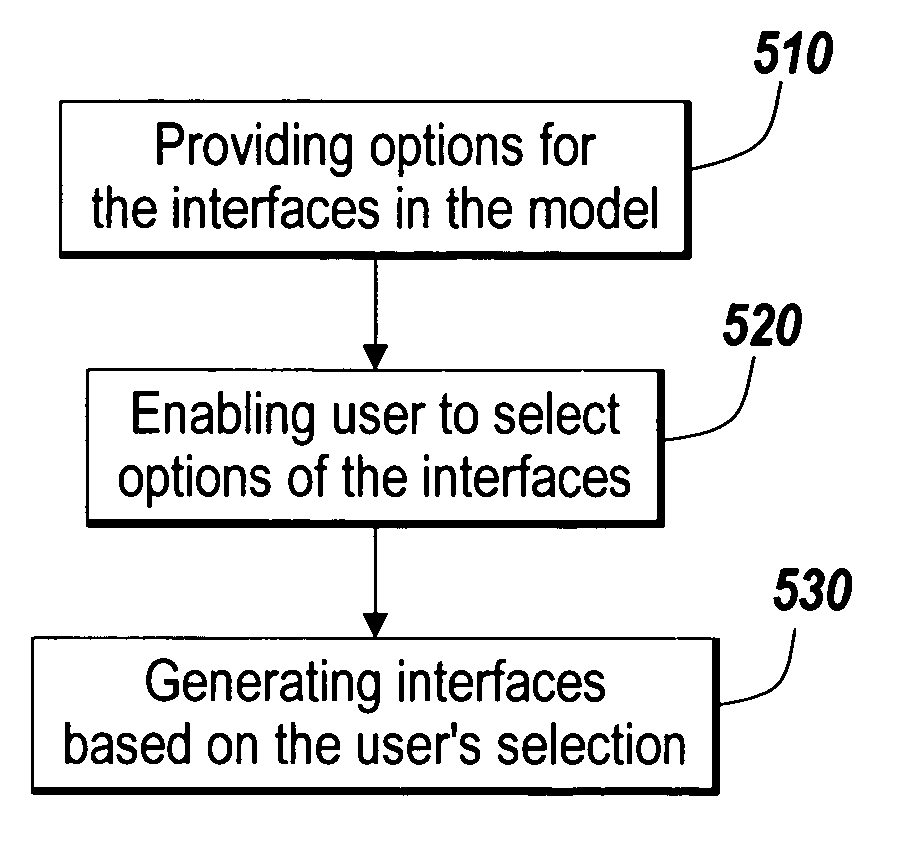

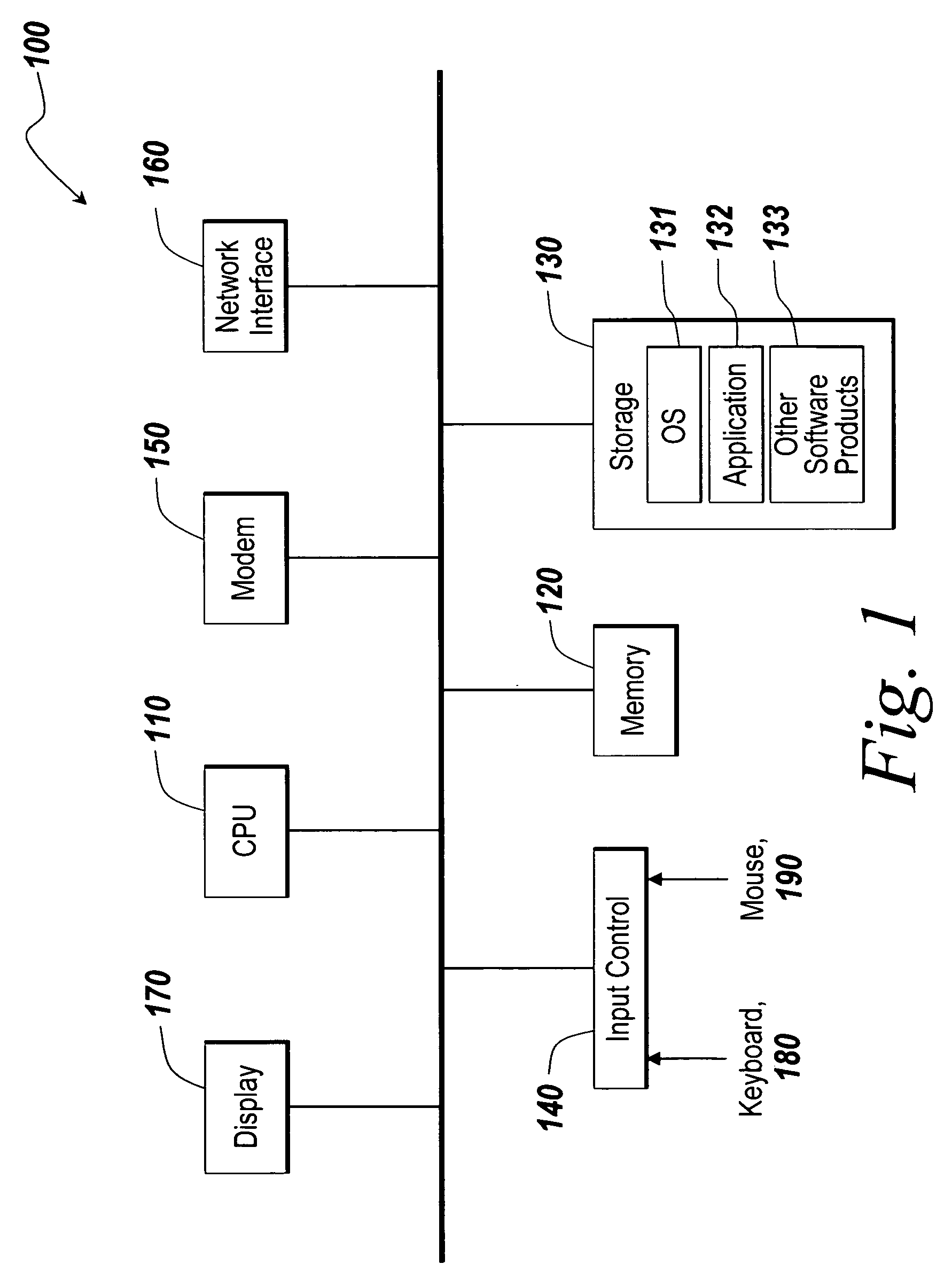

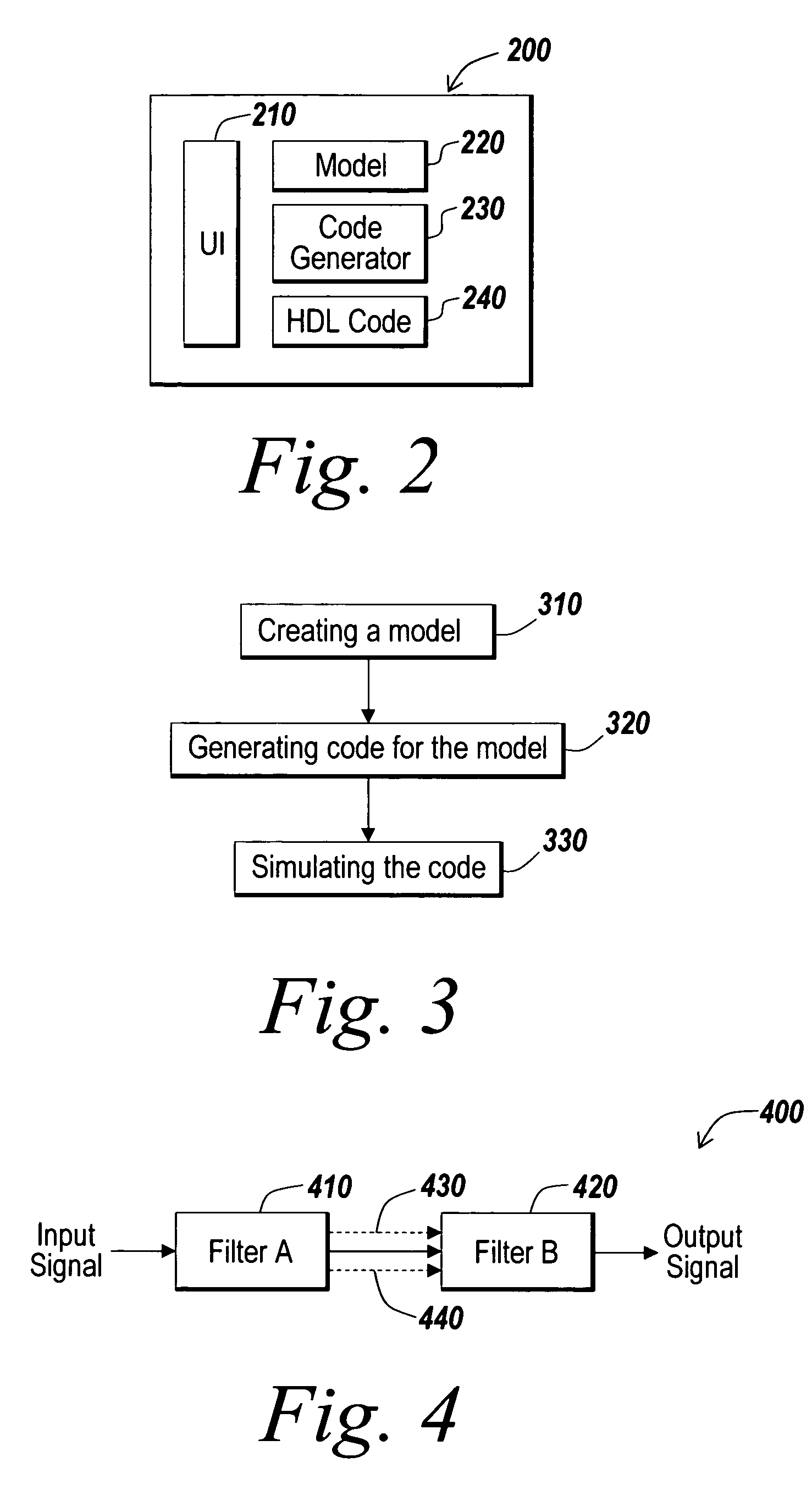

Automatic generation of code for component interfaces in models

ActiveUS20060064669A1Analogue computers for electric apparatusCAD circuit designGraphicsModel method

Methods, systems and computer program products are disclosed for automatically generating hardware description language code from a model. The hardware description language code may be generated from a graphical program / model, such as a block diagram model. The hardware description language code may also be generated from a text-based program / model, such as a model created using MATLAB® tools. In particular, the present invention provides for the automatic code generation of an interface between components in the model. The present invention may provide options for selecting at least one of multiple types or styles of the component interfaces in the model. The selection of the interface types or styles may be controlled by the user or inferred by other parameters, such as implementation parameters.

Owner:THE MATHWORKS INC

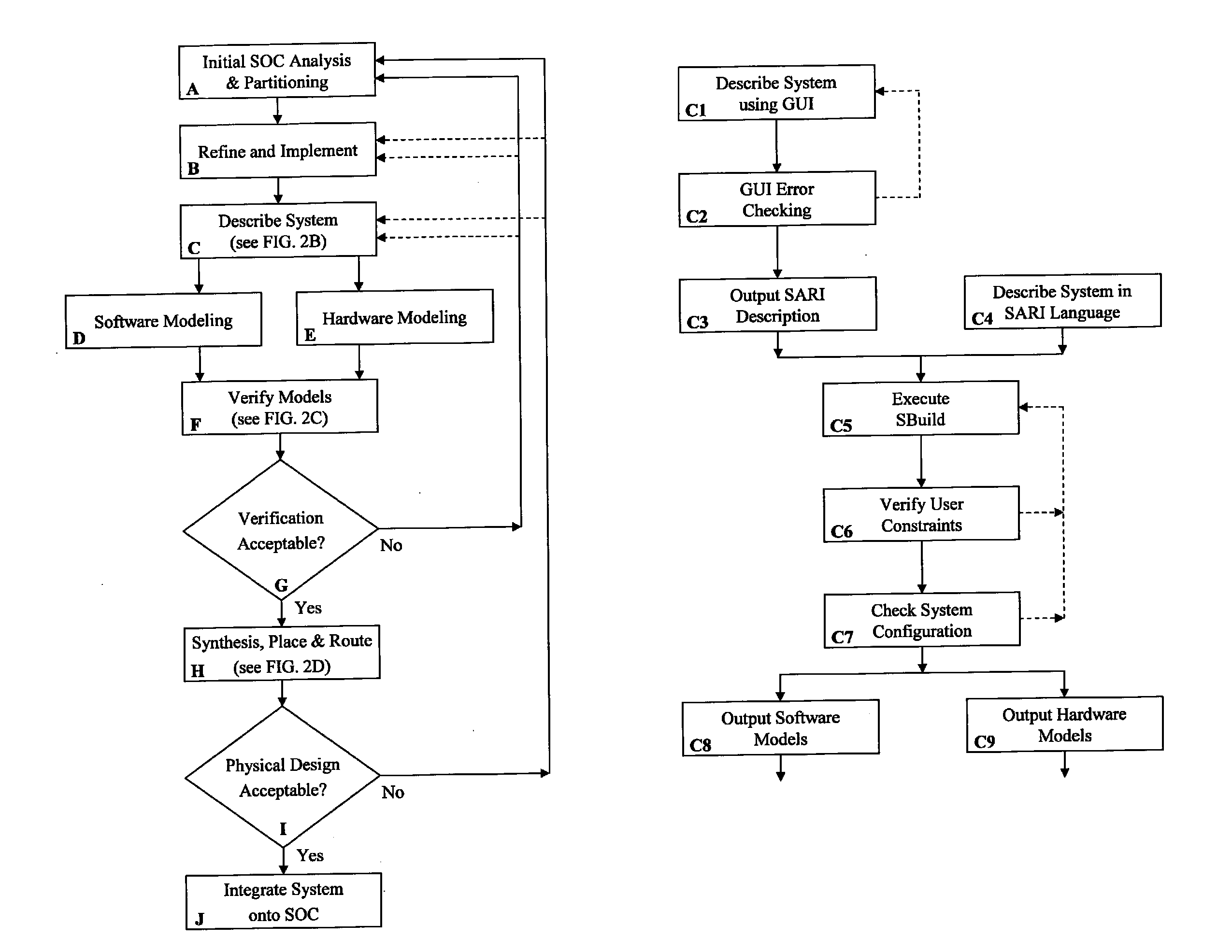

Method for multiple processor system-on-a-chip hardware and software cogeneration

ActiveUS8639487B1Analogue computers for electric apparatusCAD circuit designComputer architectureMulti processor

An automated system-on-chip (SOC) hardware and software cogeneration design flow allows an SOC designer, using a single source description for any platform-independent combination of reused or new IP blocks, to produce a configured hardware description language (HDL) description of the circuitry necessary to implement the SOC, while at the same time producing the development tools (e.g., compilers, assemblers, debuggers, simulator, software support libraries, reset sequences, etc.) used to generate the SOC software and the diagnostics environment used to verify the SOC.

Owner:CADENCE DESIGN SYST INC

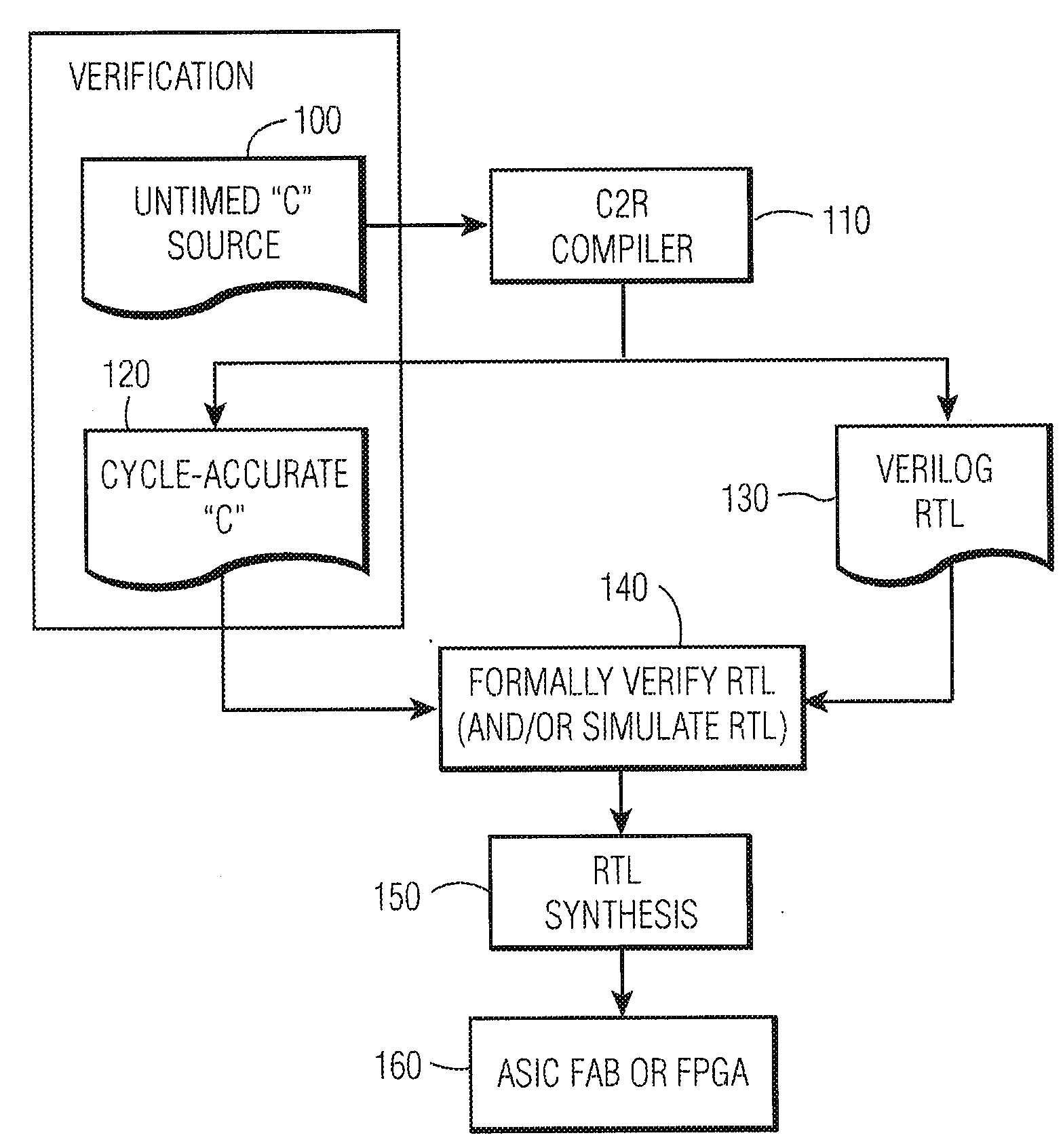

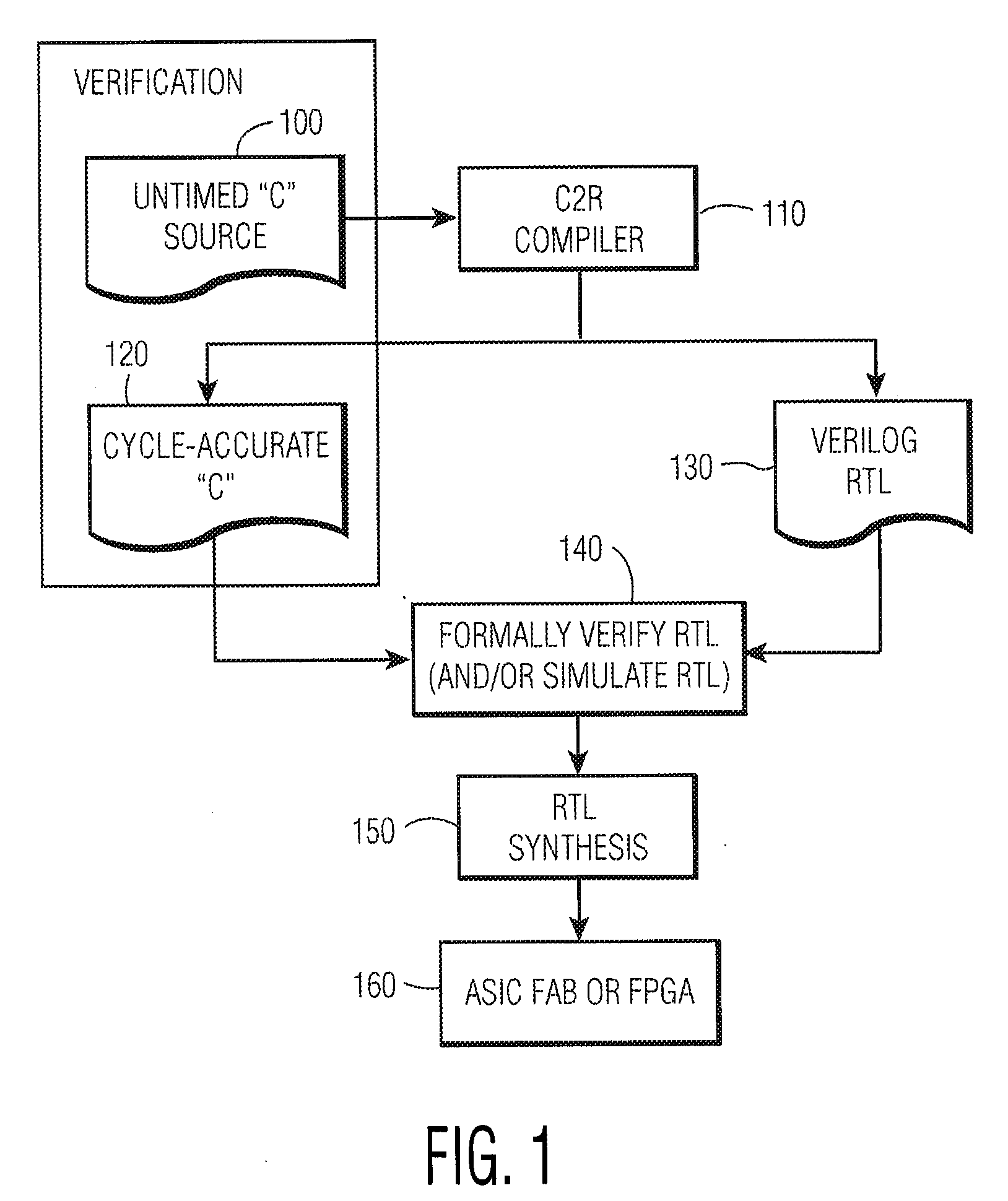

System and method for converting software to a register transfer (RTL) design

ActiveUS20090144690A1Analogue computers for electric apparatusCAD circuit designComputer architectureProcessor register

A method for converting a C-type programming language program to a hardware design, where the said program is an algorithmic representation of one or more processes. The C-type programming language program is compiled into a hardware description language (HDL) synthesizable design. The compiler categorizes variables as using either implicit memory or custom memory. Different accessor functions are used depending on which type of memory is used. The programming language may use ANSI C and the HDL may be Verilog Register Transfer Level (RTL). The hardware device generated from the HDL synthesizable design may be an Application-Specific Integrated Circuit (ASIC) or a Field Programmable Gate Array (FPGA).

Owner:EXAR CORP