Patents

Literature

1027 results about "Debugger" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A debugger or debugging tool is a computer program that is used to test and debug other programs (the "target" program). The code to be examined might alternatively be running on an instruction set simulator (ISS), a technique that allows great power in its ability to halt when specific conditions are encountered, but which will typically be somewhat slower than executing the code directly on the appropriate (or the same) processor. Some debuggers offer two modes of operation, full or partial simulation, to limit this impact.

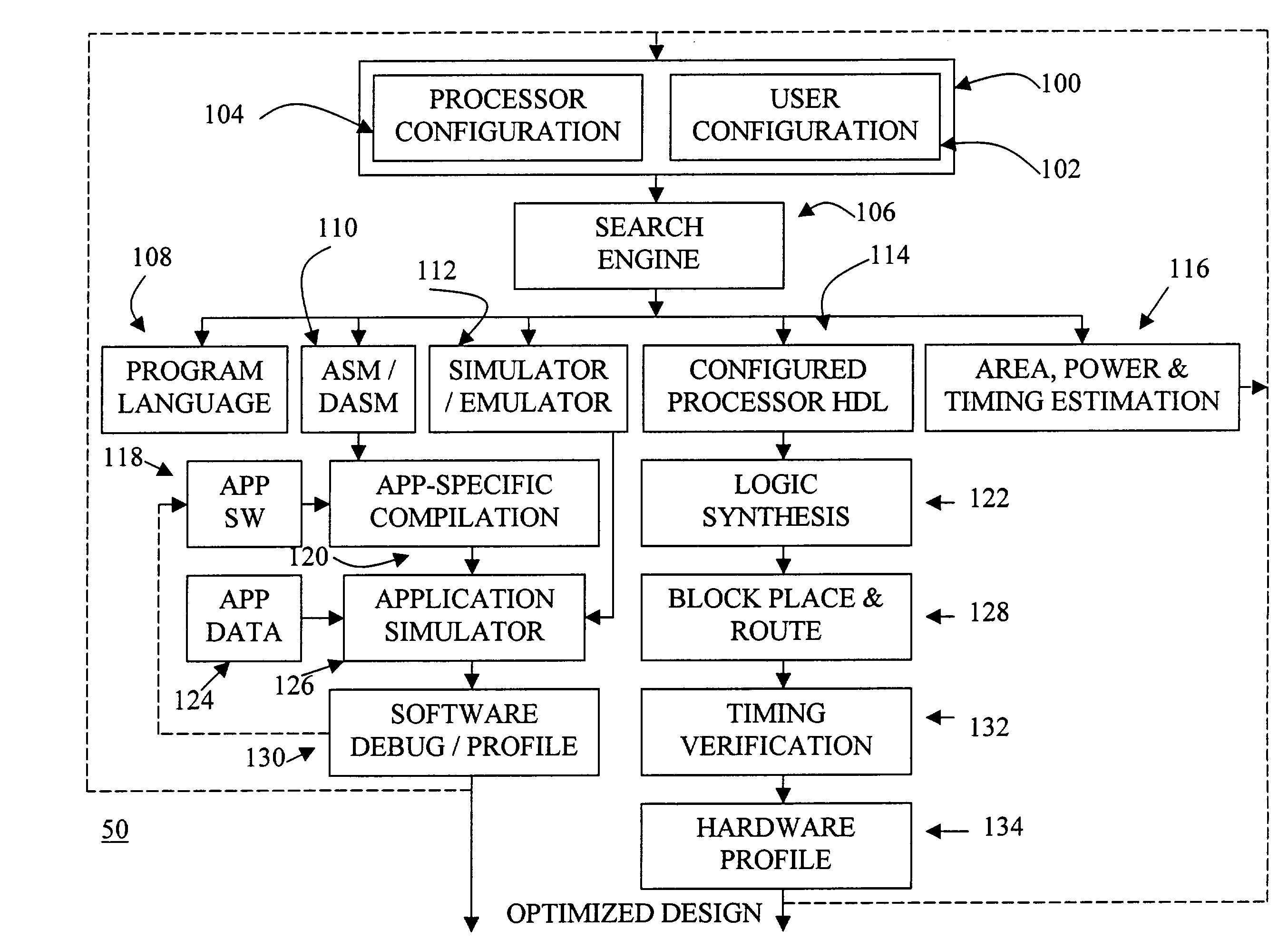

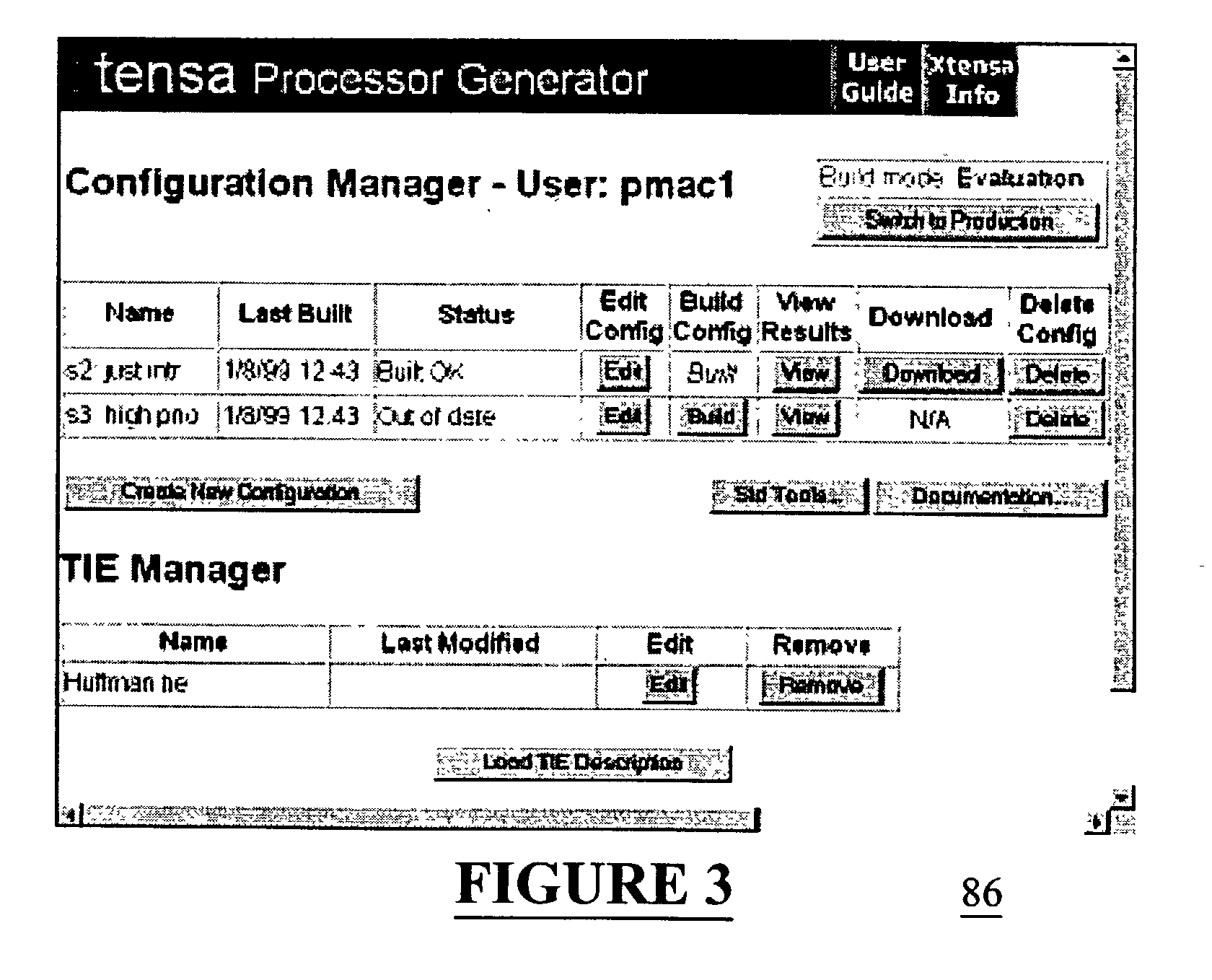

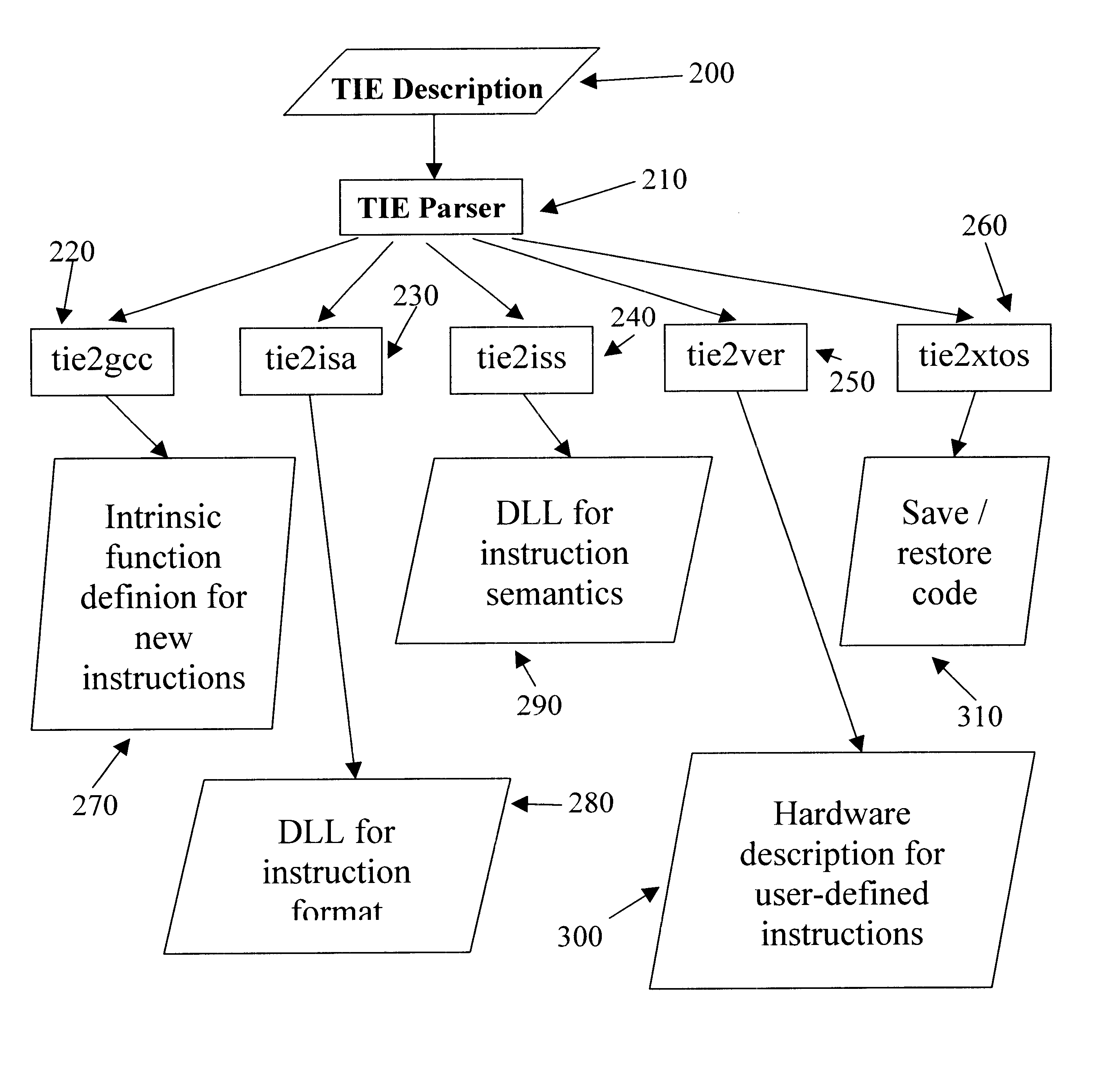

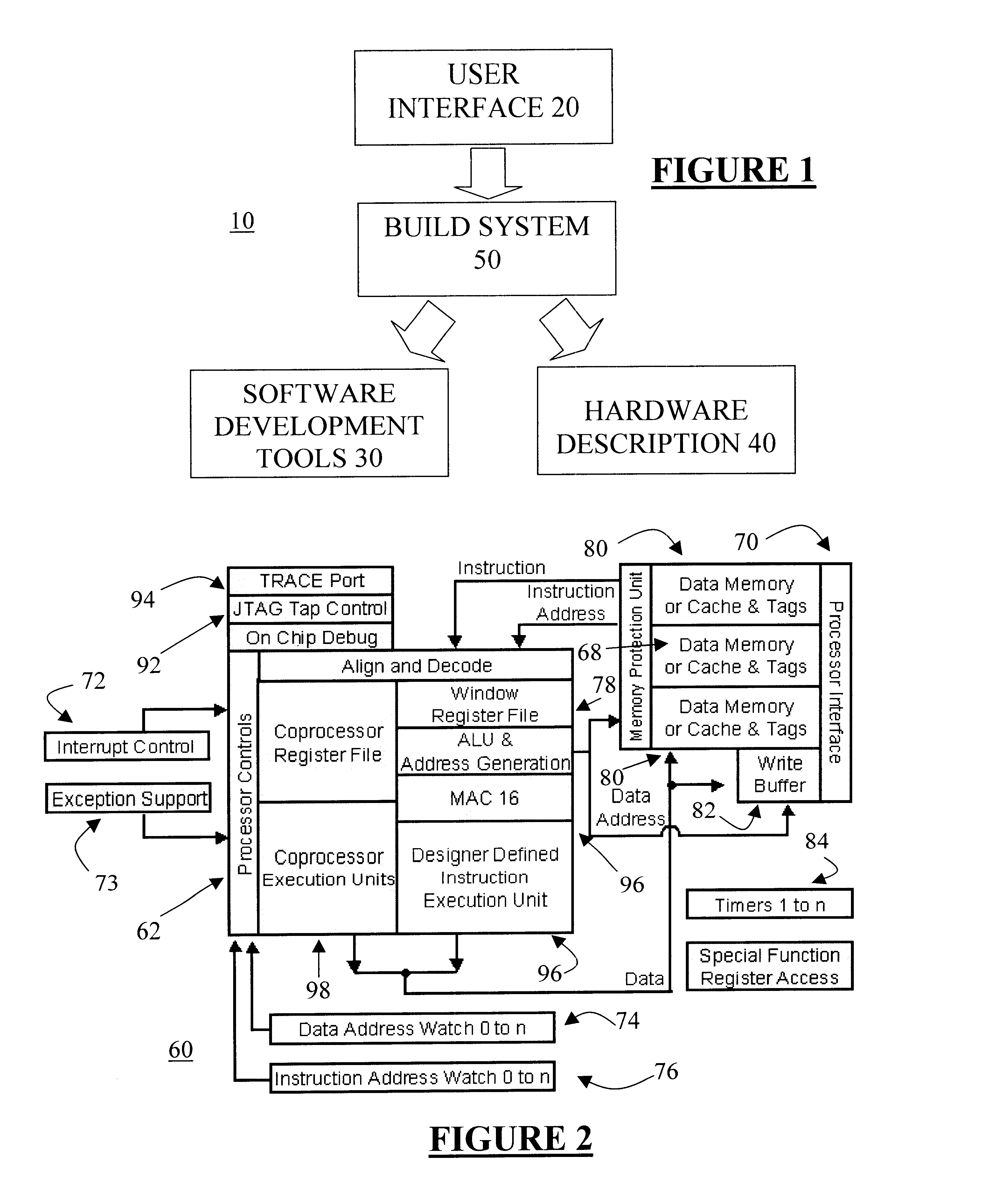

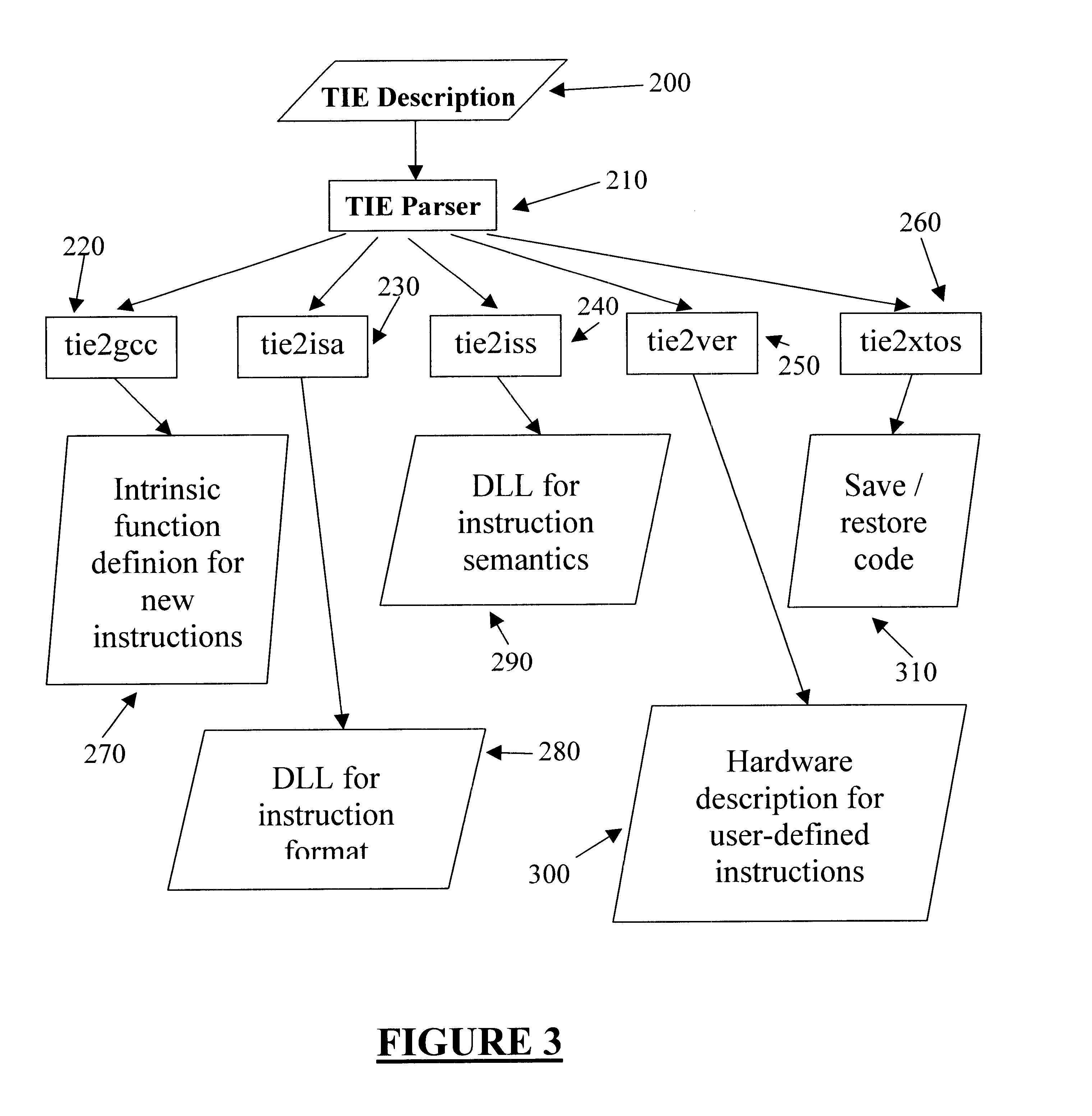

Automated processor generation system for designing a configurable processor and method for the same

InactiveUS6477683B1Decompilation/disassemblyCAD network environmentApplication softwareProcessor design

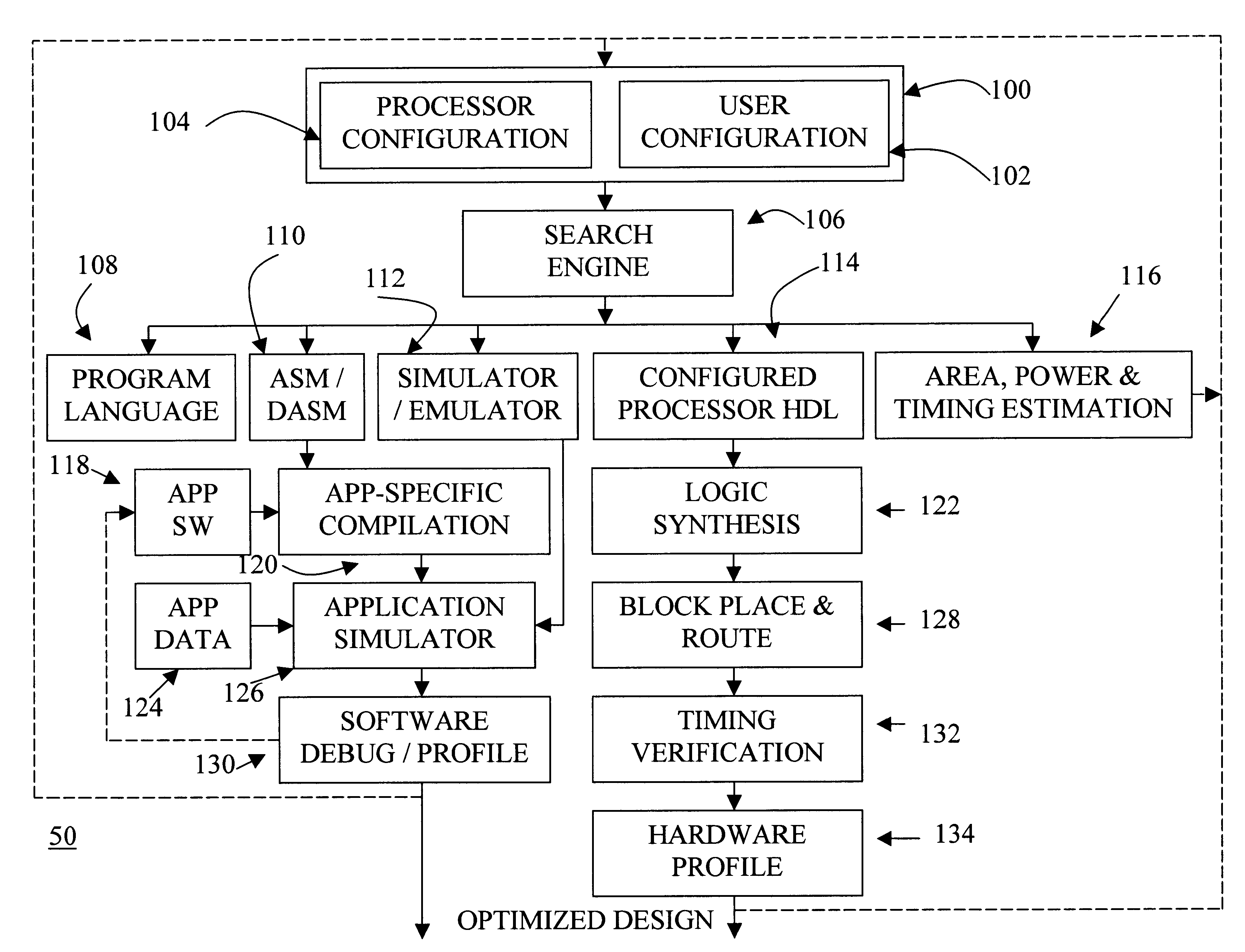

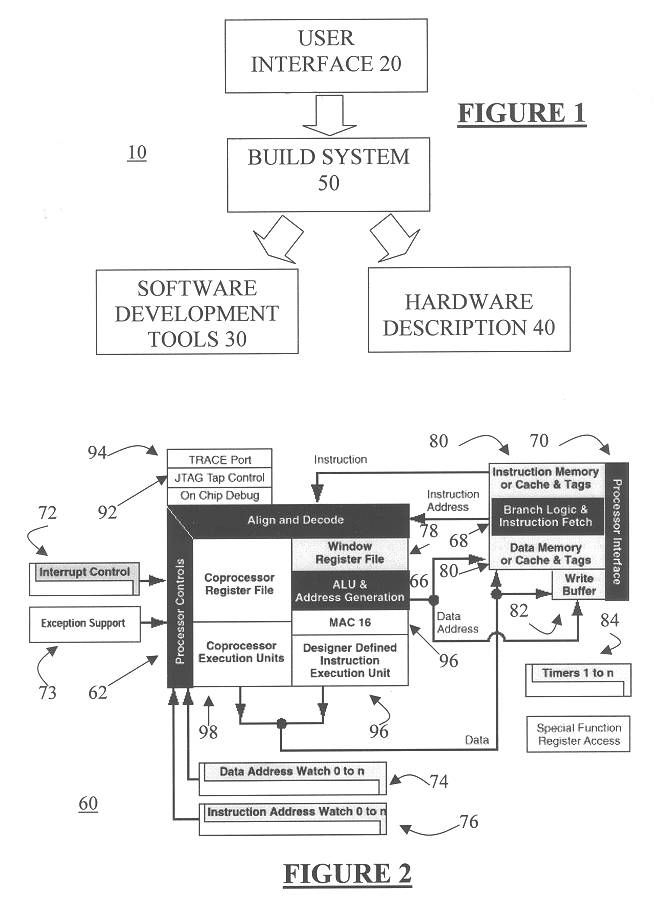

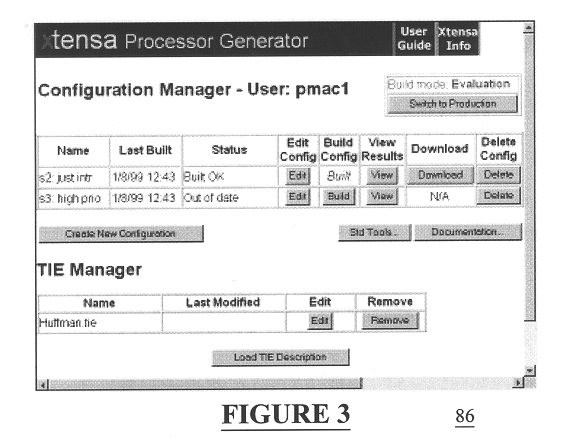

An automated processor design tool uses a description of customized processor instruction set extensions in a standardized language to develop a configurable definition of a target instruction set, a Hardware Description Language description of circuitry necessary to implement the instruction set, and development tools such as a compiler, assembler, debugger and simulator which can be used to develop applications for the processor and to verify it. Implementation of the processor circuitry can be optimized for various criteria such as area, power consumption, speed and the like. Once a processor configuration is developed, it can be tested and inputs to the system modified to iteratively optimize the processor implementation. By providing a constrained domain of extensions and optimizations, the process can be automated to a high degree, thereby facilitating fast and reliable development.

Owner:TENSILICA

Systems and methods for the prevention of unauthorized use and manipulation of digital content

InactiveUS7328453B2Overwhelm usefulnessHigh normal sclerosisMemory loss protectionDigital data processing detailsTime domainThird party

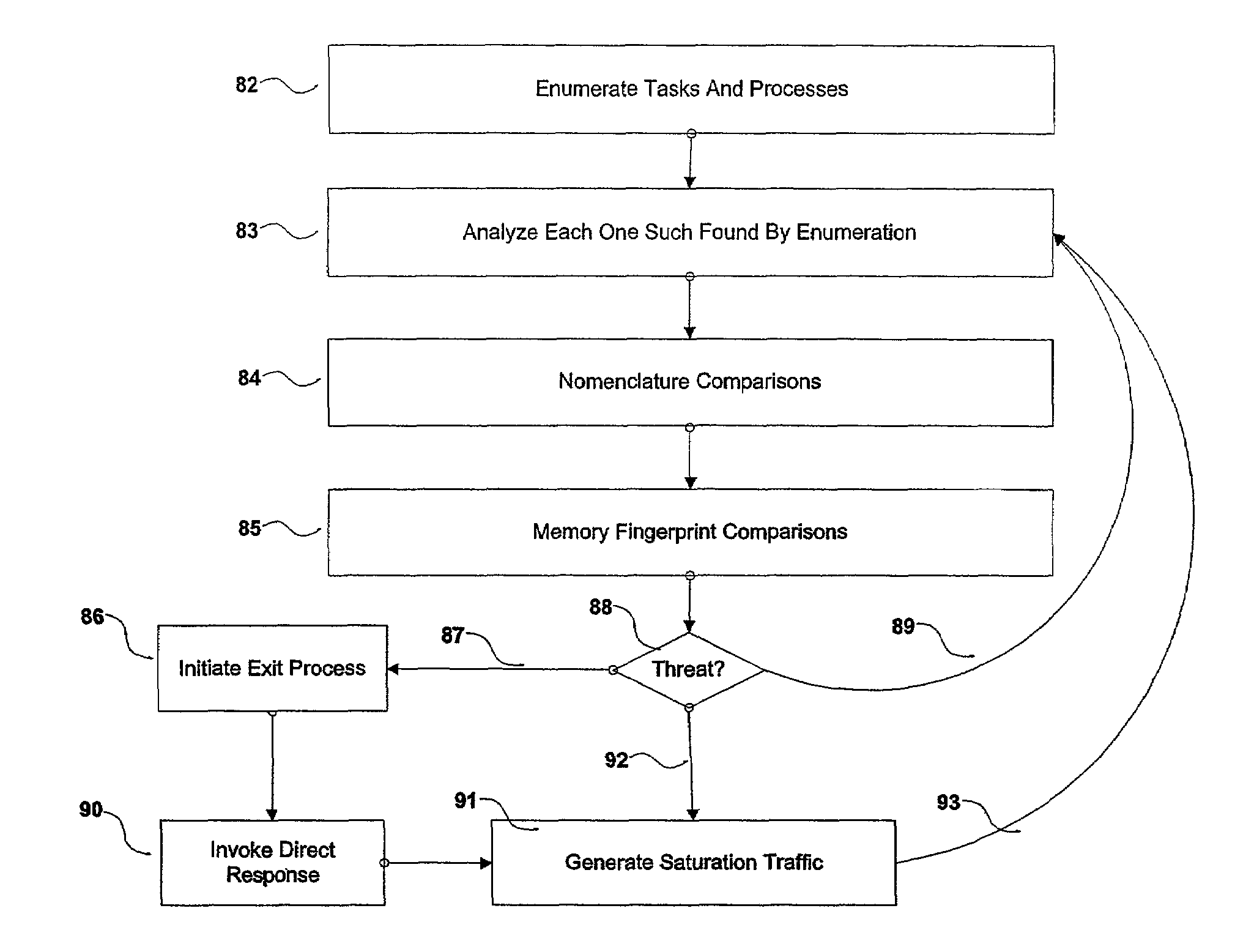

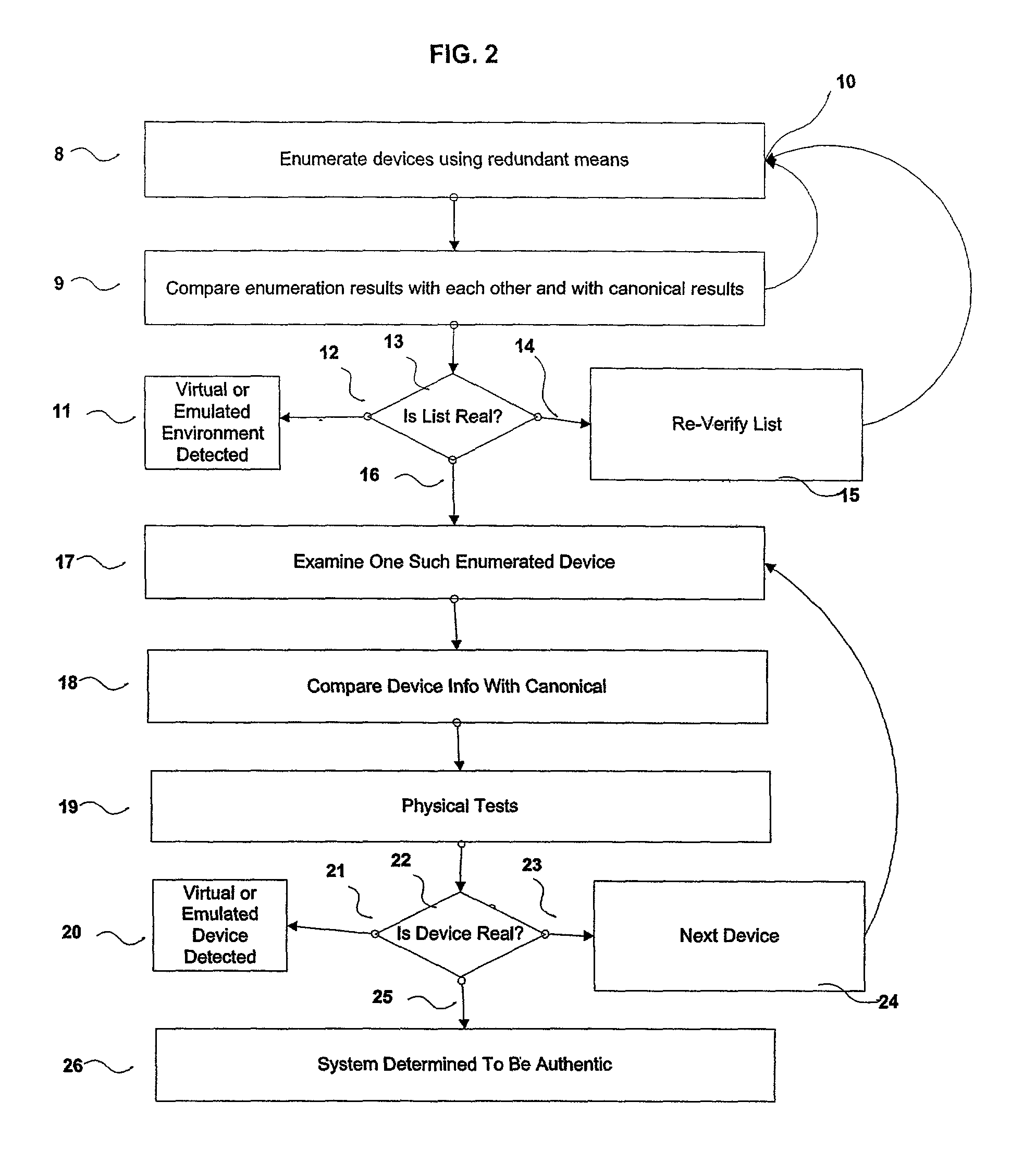

A number of systems and methods, alone, or in combination, achieve various levels of protection against unauthorized modification and distribution of digital content. This encompasses at least unauthorized study, modification, monitoring, reconstruction, and any other means for subversion from the originally intended purpose and license model of the digital content. The invention combines a number of techniques that in whole, or in part, serve to protect such content from unauthorized modification, reconstructive engineering, or monitoring by third parties. This is accomplished by means of methods which protect against subversion by specific tools operating on specific platforms as well as general tools operating on general platforms. Specific time domain attacks are identified, code modification can be identified and reversed, and virtual and emulated systems are identified. In addition, identification of in-circuit emulator tools (both software and hardware), debuggers, and security threats to running programs can be achieved.

Owner:IPLA HLDG

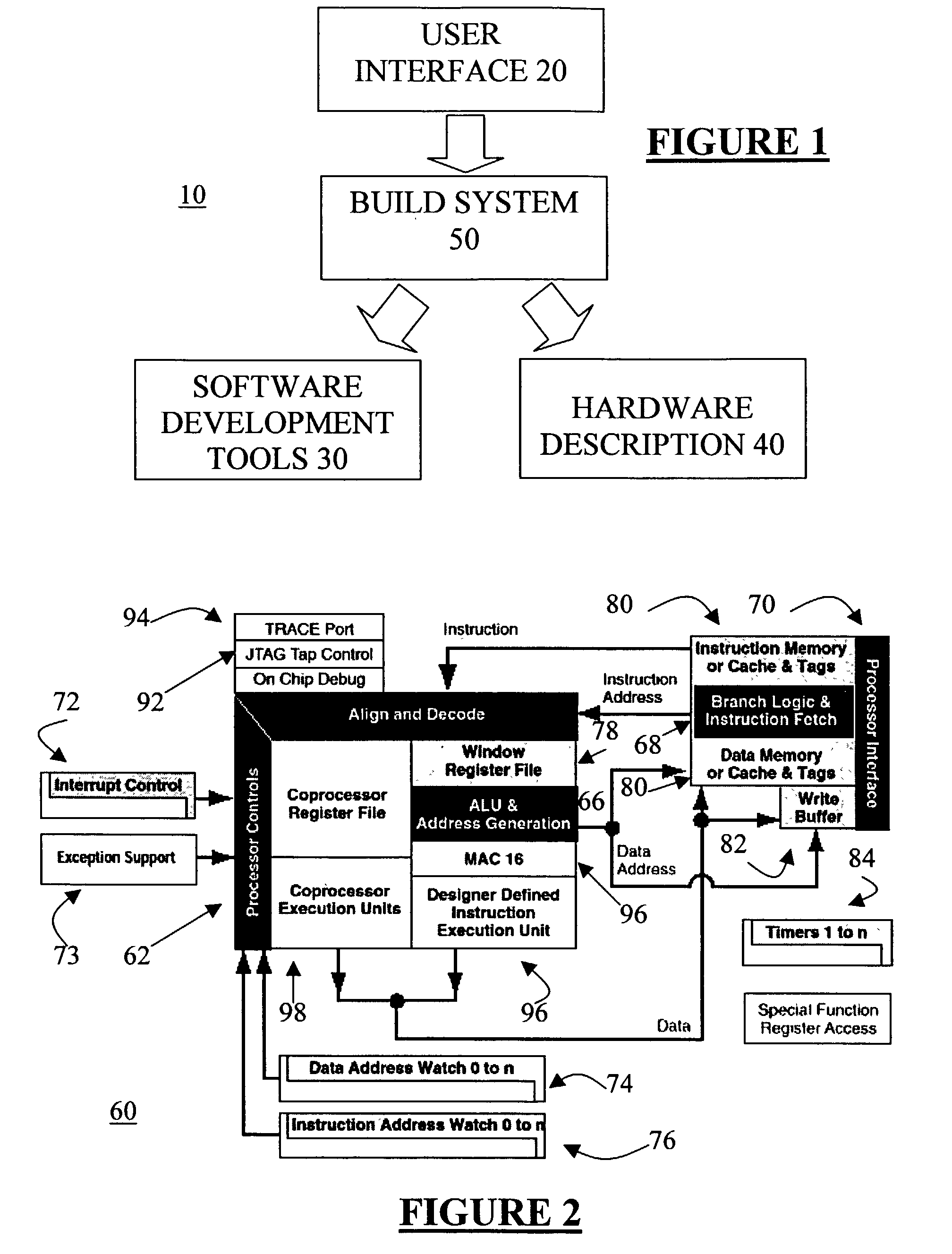

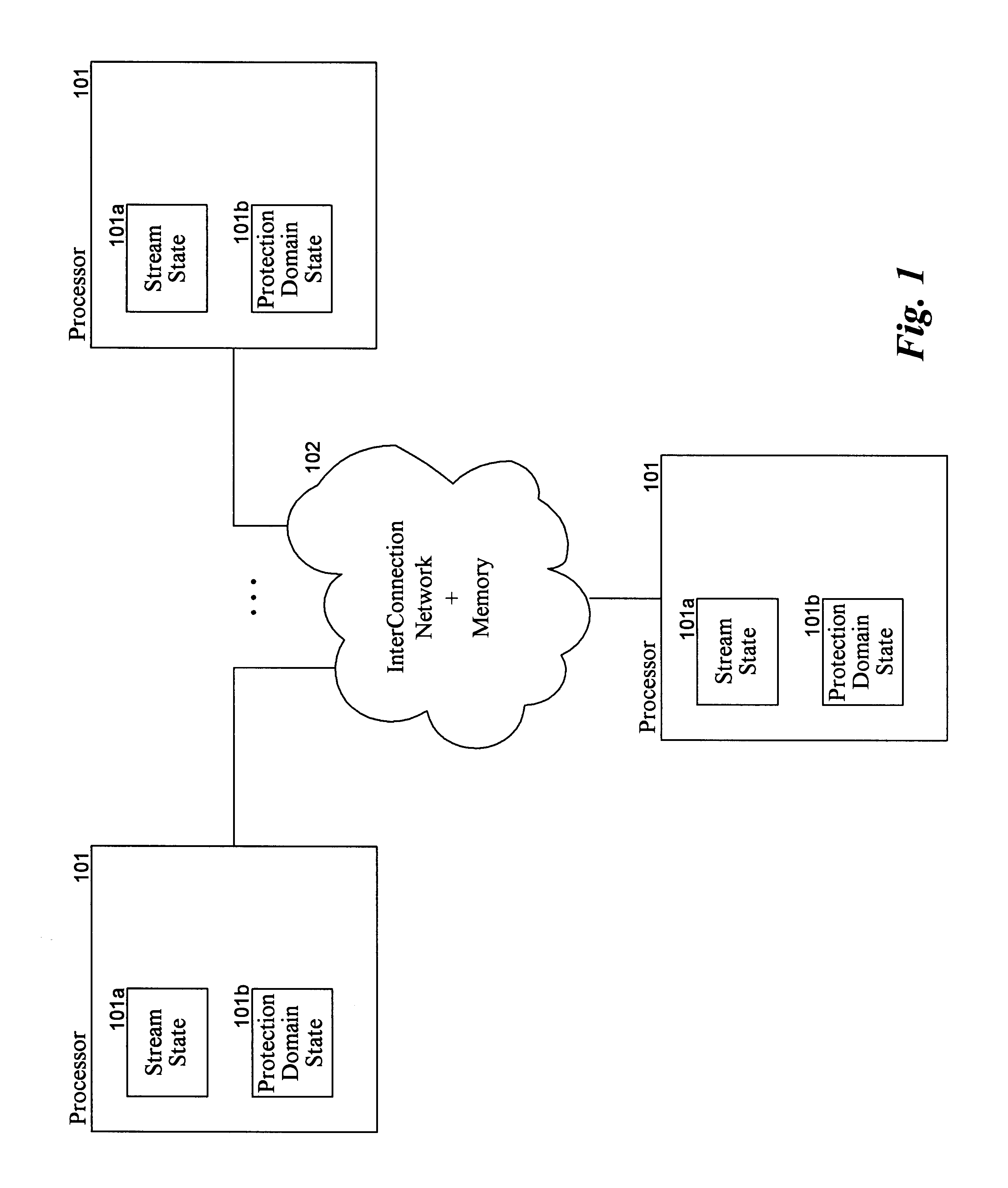

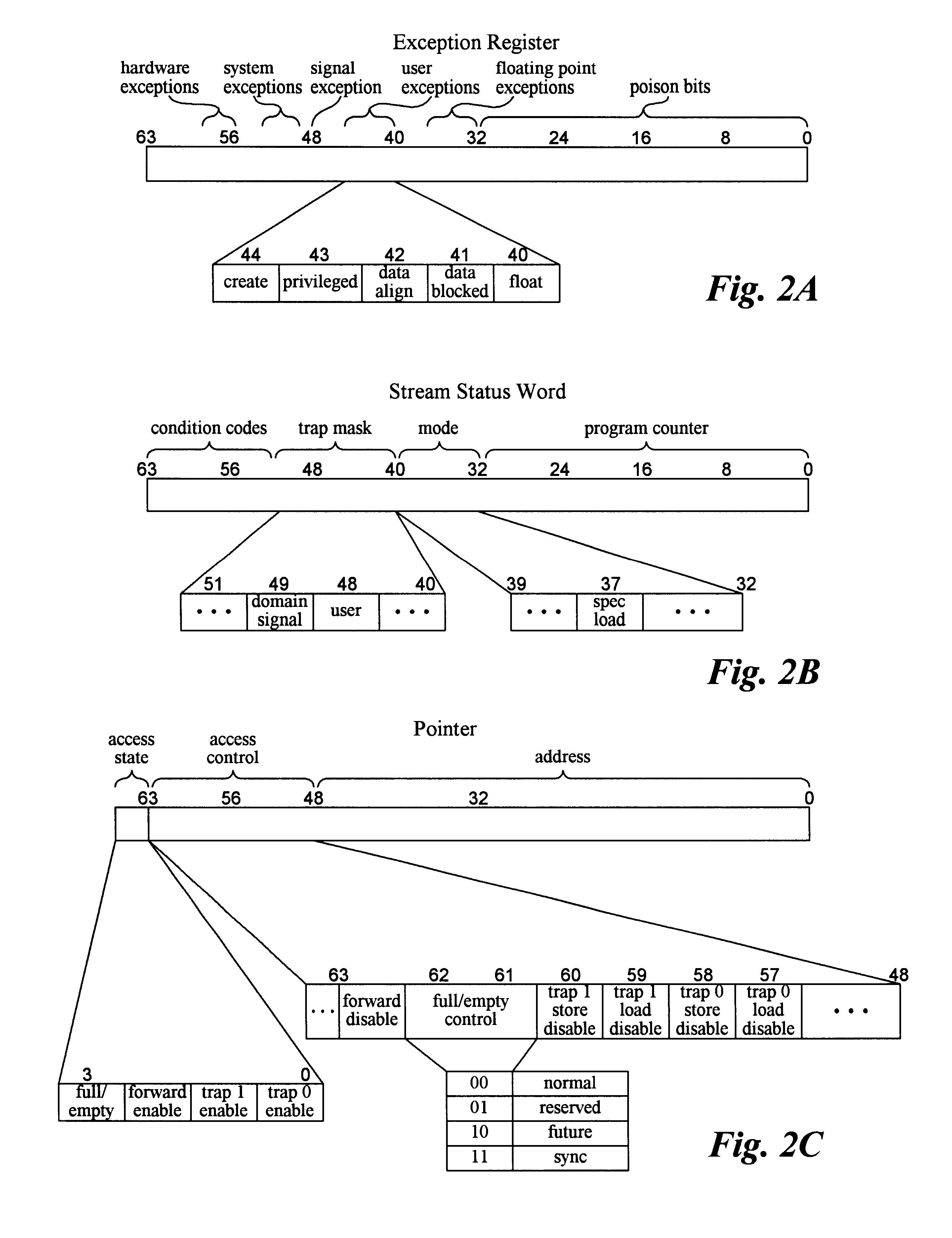

Microprocessors

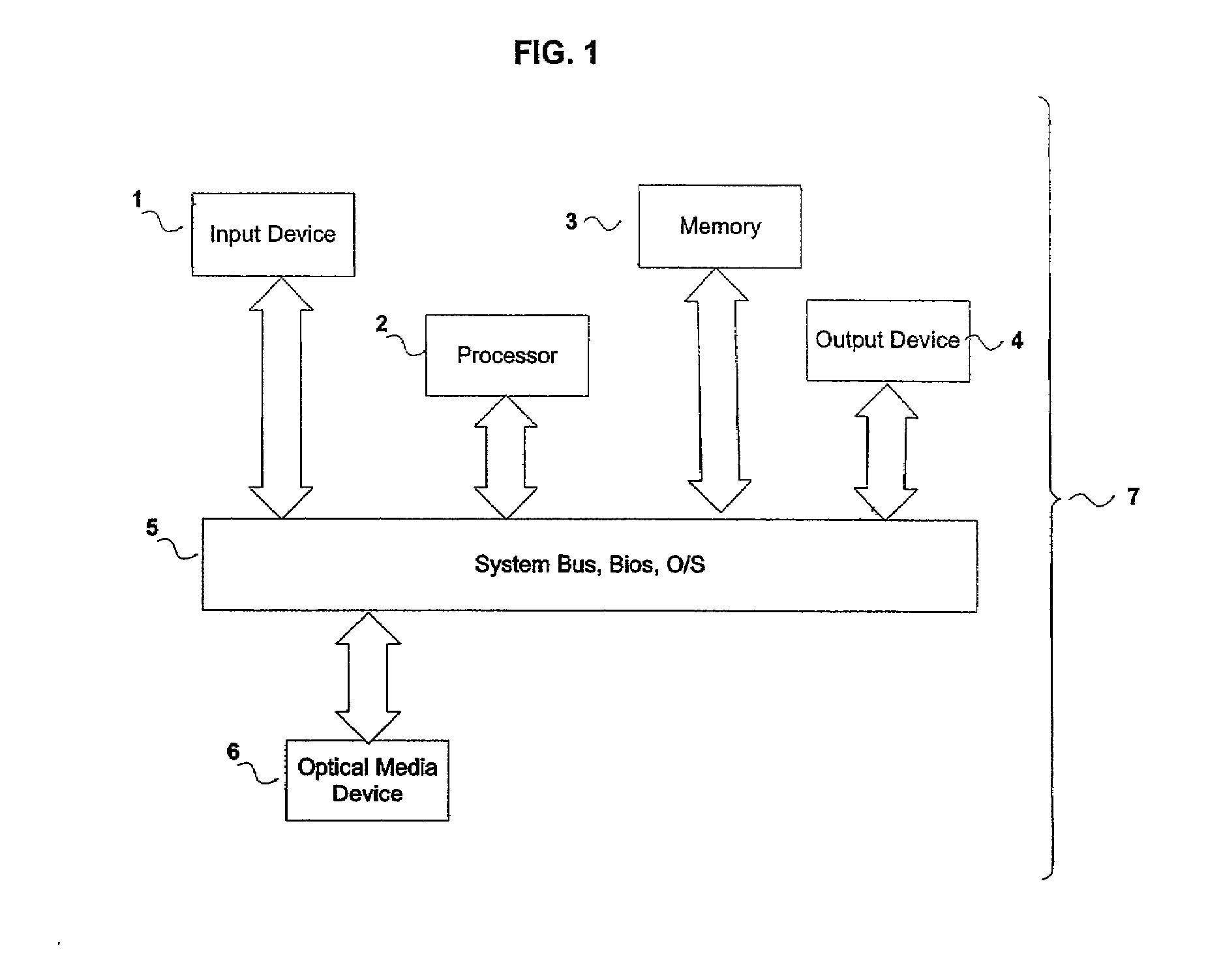

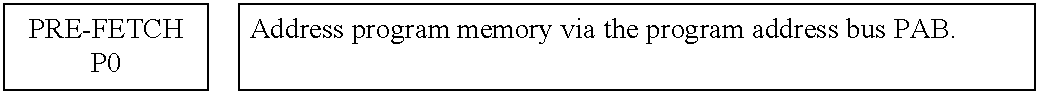

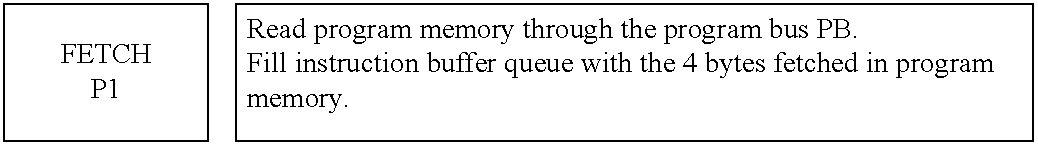

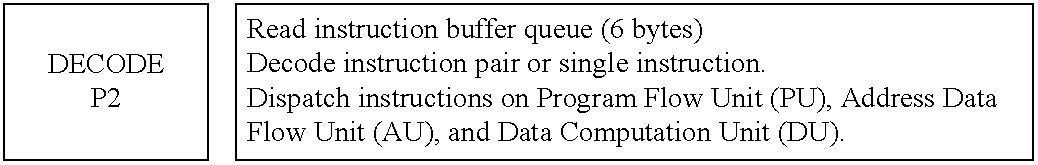

A processor (100) is provided that is a programmable fixed point digital signal processor (DSP) with variable instruction length, offering both high code density and easy programming. Architecture and instruction set are optimized for low power consumption and high efficiency execution of DSP algorithms, such as for wireless telephones, as well as pure control tasks. The processor includes an instruction buffer unit (106), a program flow control unit (108), an address / data flow unit (110), a data computation unit (112), and multiple interconnecting busses. Dual multiply-accumulate blocks improve processing performance. A memory interface unit (104) provides parallel access to data and instruction memories. The instruction buffer is operable to buffer single and compound instructions pending execution thereof. A decode mechanism is configured to decode instructions from the instruction buffer. The use of compound instructions enables effective use of the bandwidth available within the processor. A soft dual memory instruction can be compiled from separate first and second programmed memory instructions. Instructions can be conditionally executed or repeatedly executed. Bit field processing and various addressing modes, such as circular buffer addressing, further support execution of DSP algorithms. The processor includes a multistage execution pipeline with pipeline protection features. Various functional modules can be separately powered down to conserve power. The processor includes emulation and code debugging facilities with support for cache analysis.

Owner:TEXAS INSTR INC

Multi-core debugger

InactiveUS20060059286A1Avoid interferenceMemory architecture accessing/allocationError detection/correctionMulti-core processorEmbedded system

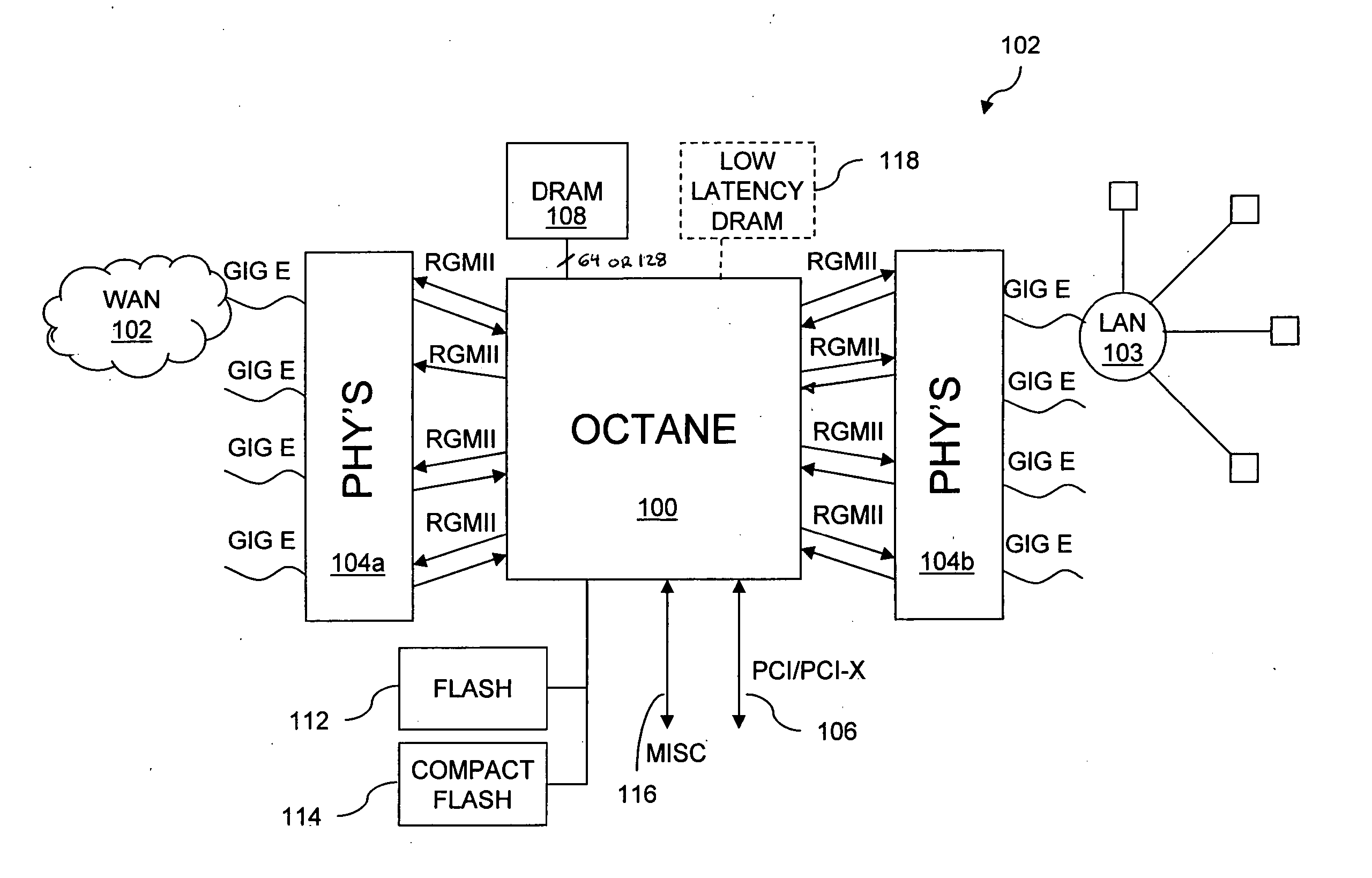

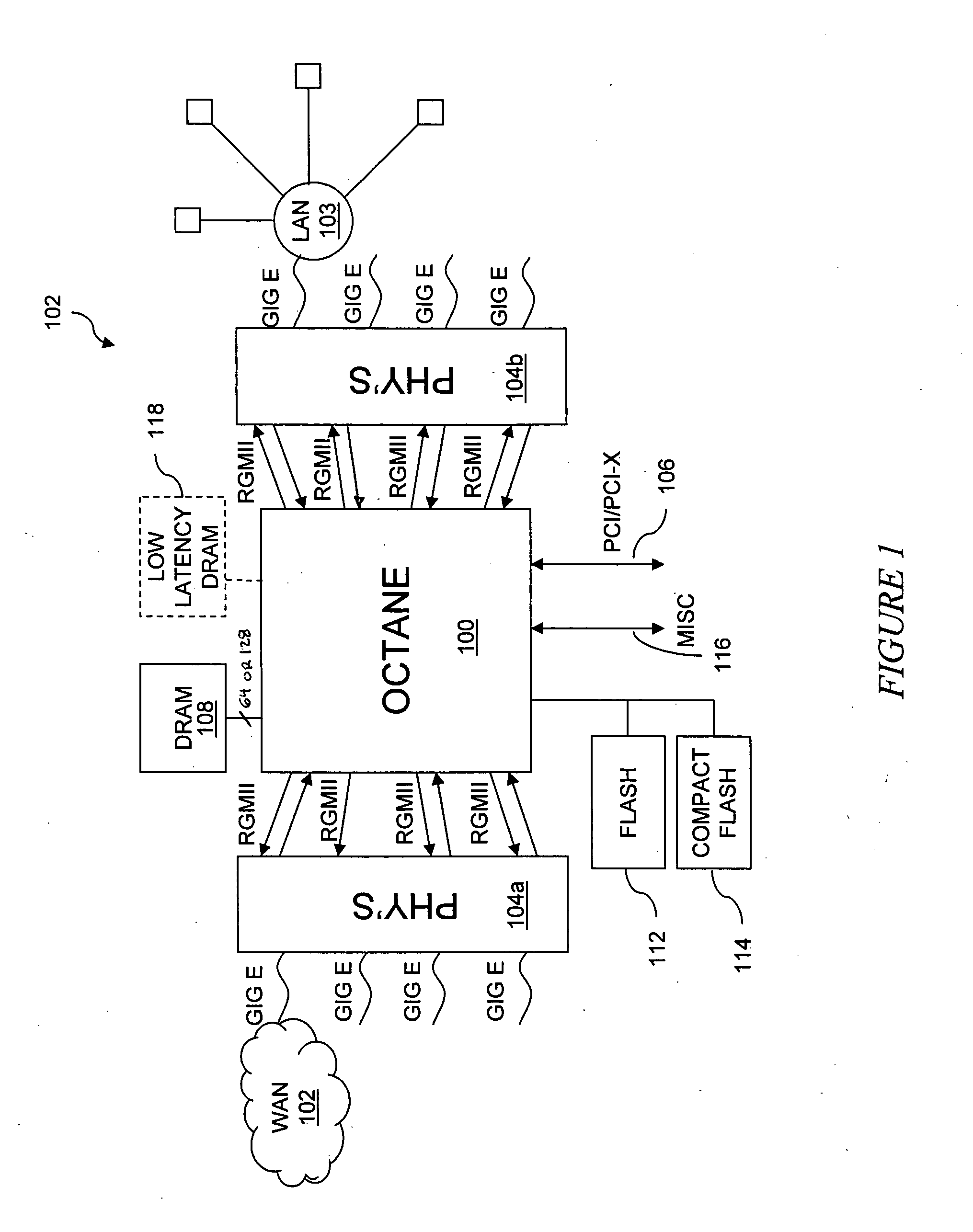

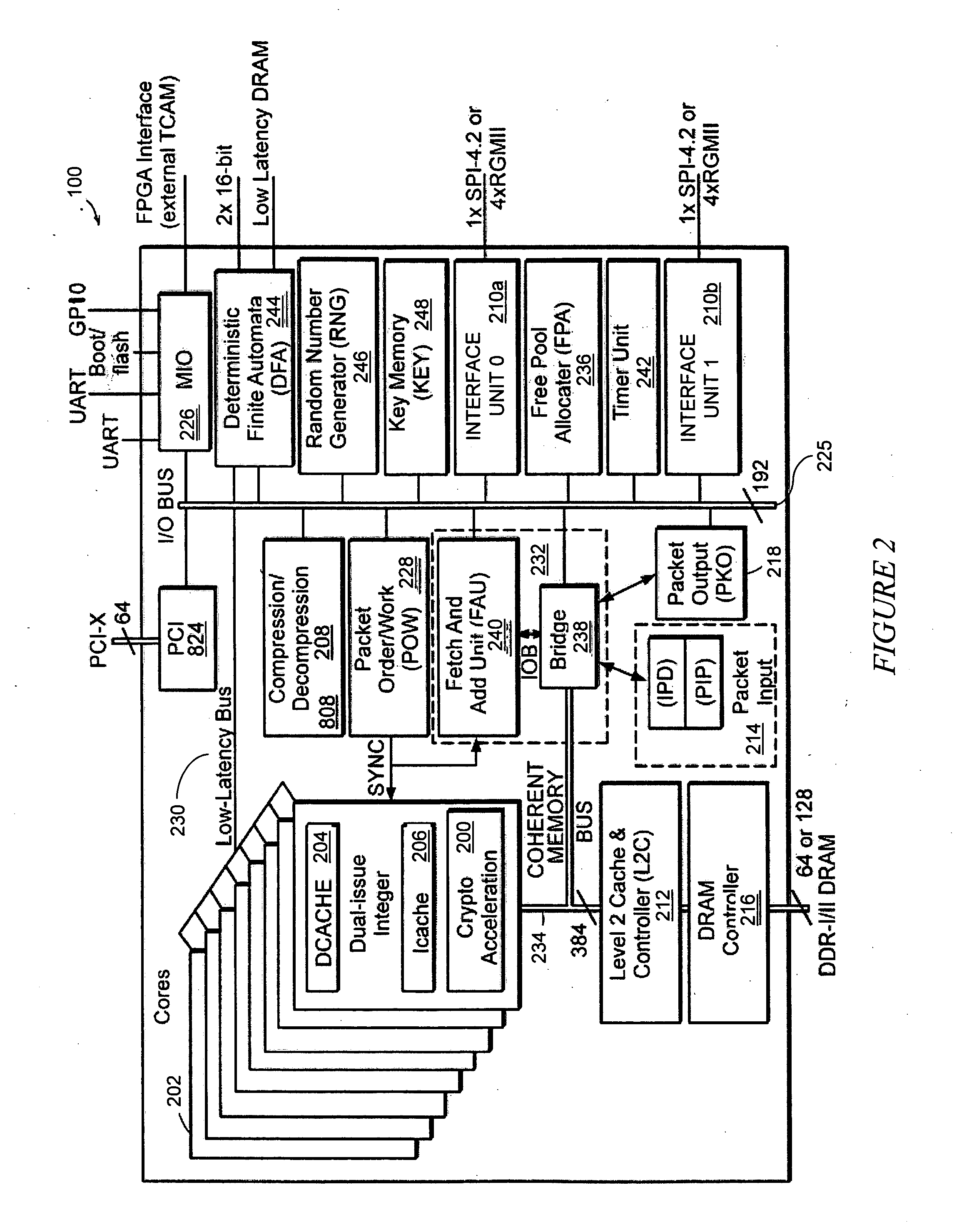

In a multi-core processor, a high-speed interrupt-signal interconnect allows more than one of the processors to be interrupted at substantially the same time. For example, a global signal interconnect is coupled to each of the multiple processors, each processor being configured to selectively provide an interrupt signal, or pulse thereon. Preferably, each of the processor cores is capable of pulsing the global signal interconnect during every clock cycle to minimize delay between a triggering event and its respective interrupt signal. Each of the multiple processors also senses, or samples the global signal interconnect, preferably during the same cycle within which the pulse was provided, to determine the existence of an interrupt signal. Upon sensing an interrupt signal, each of the multiple processors responds to it substantially simultaneously. For example, an interrupt signal sampled by each of the multiple processors causes each processor to invoke a debug handler routine.

Owner:CAVIUM NETWORKS

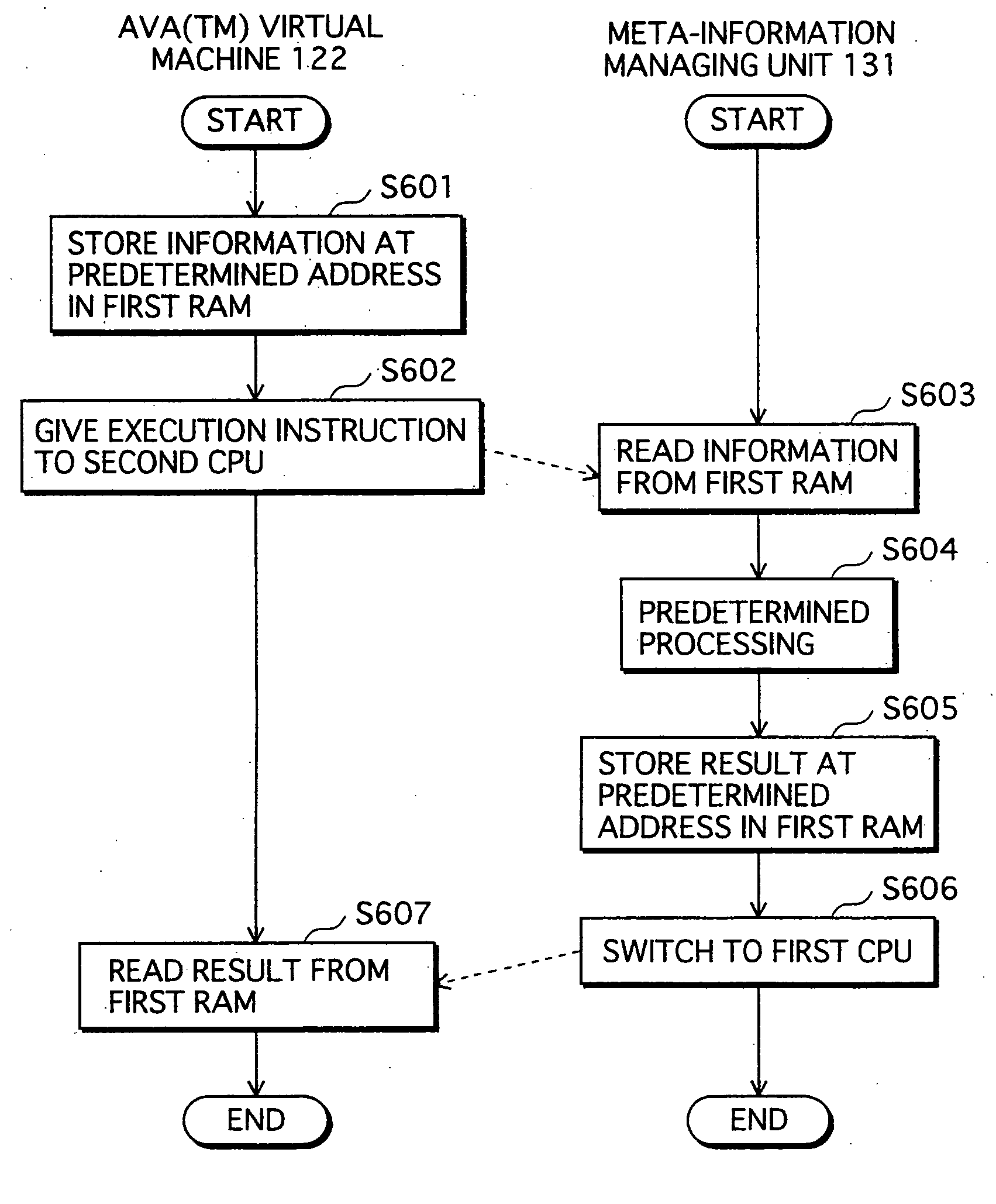

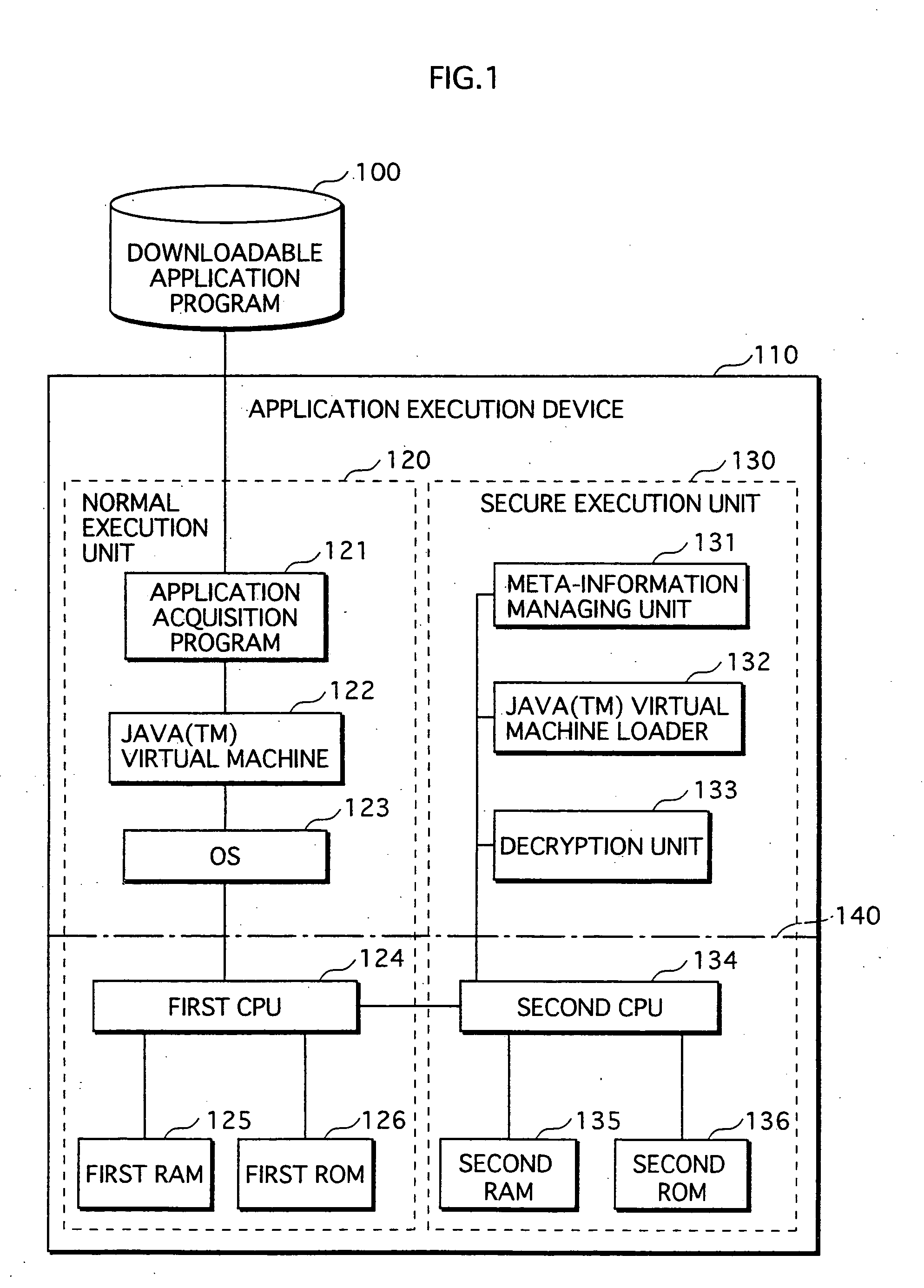

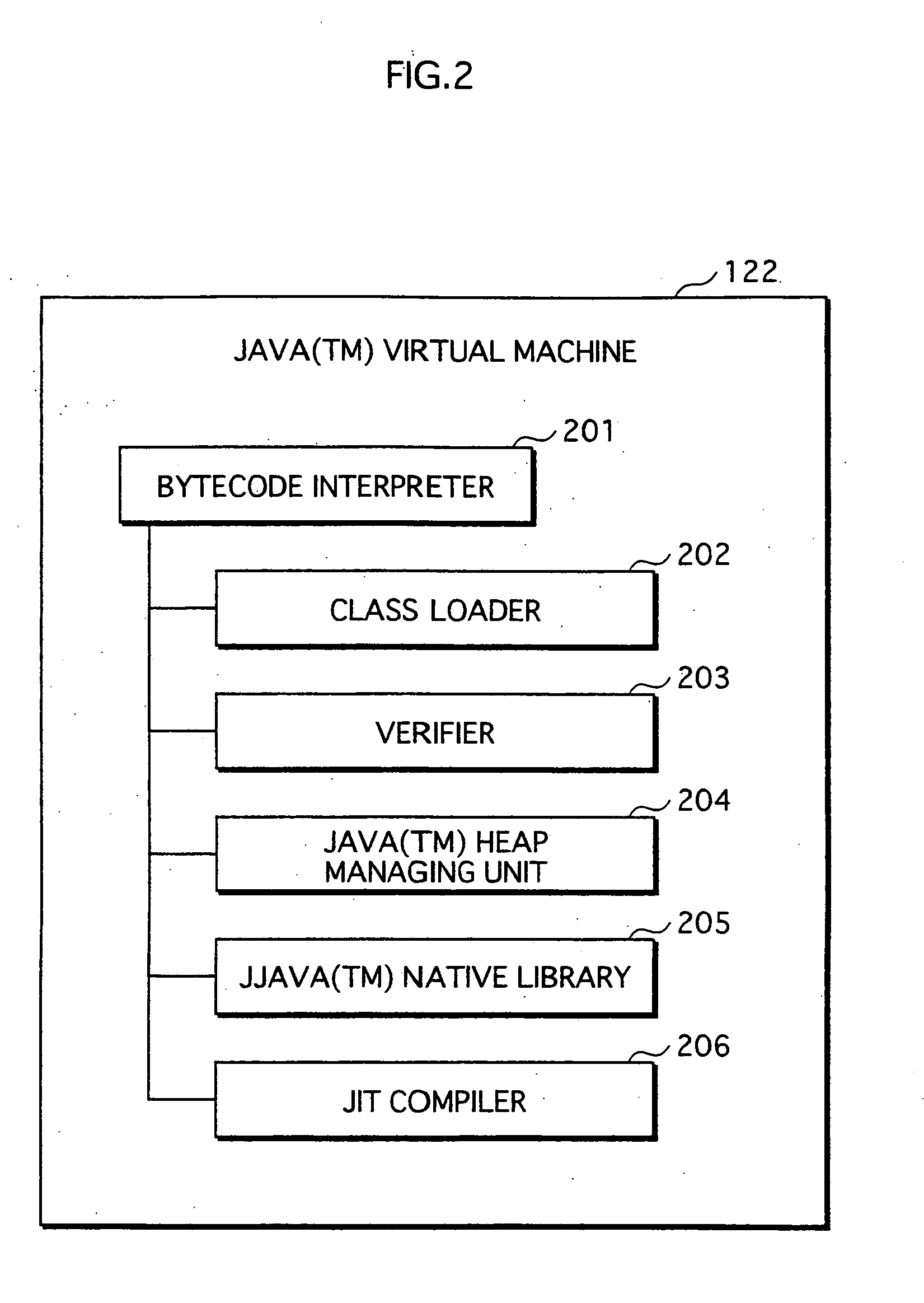

Application Execution Device and Application Execution Device Application Execution Method

InactiveUS20070271446A1High protection levelDigital computer detailsPlatform integrity maintainanceExecution unitOperating system

The conventional application protection technique complicates an application to make it difficult to analyze the application. However, with such a complication method, the complicate program can be analyzed sooner or later by taking a lot of time no matter how the degree of the complication is high. Also, it is impossible to protect the application from unauthorized copying. The meta-information managing unit that is to be executed in the secure execution unit stores the meta-information of the application in an area that can not be accessed by a debugger. When the meta-information is required by the normal execution unit to execute the application, a result of predetermined calculation using the meta-information is notified to the normal execution unit. In this way, the meta-information of the application can be kept secret.

Owner:PANASONIC CORP

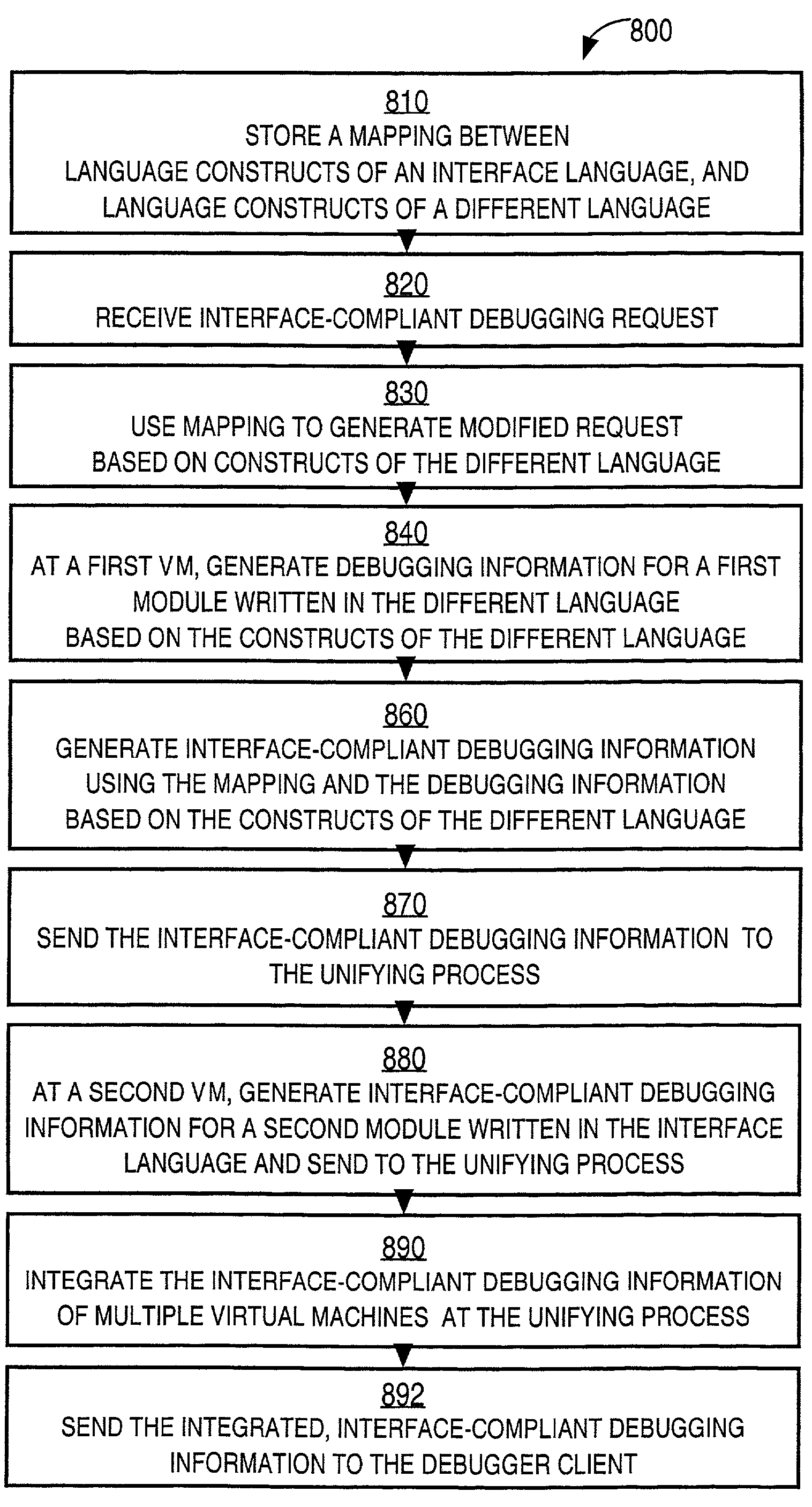

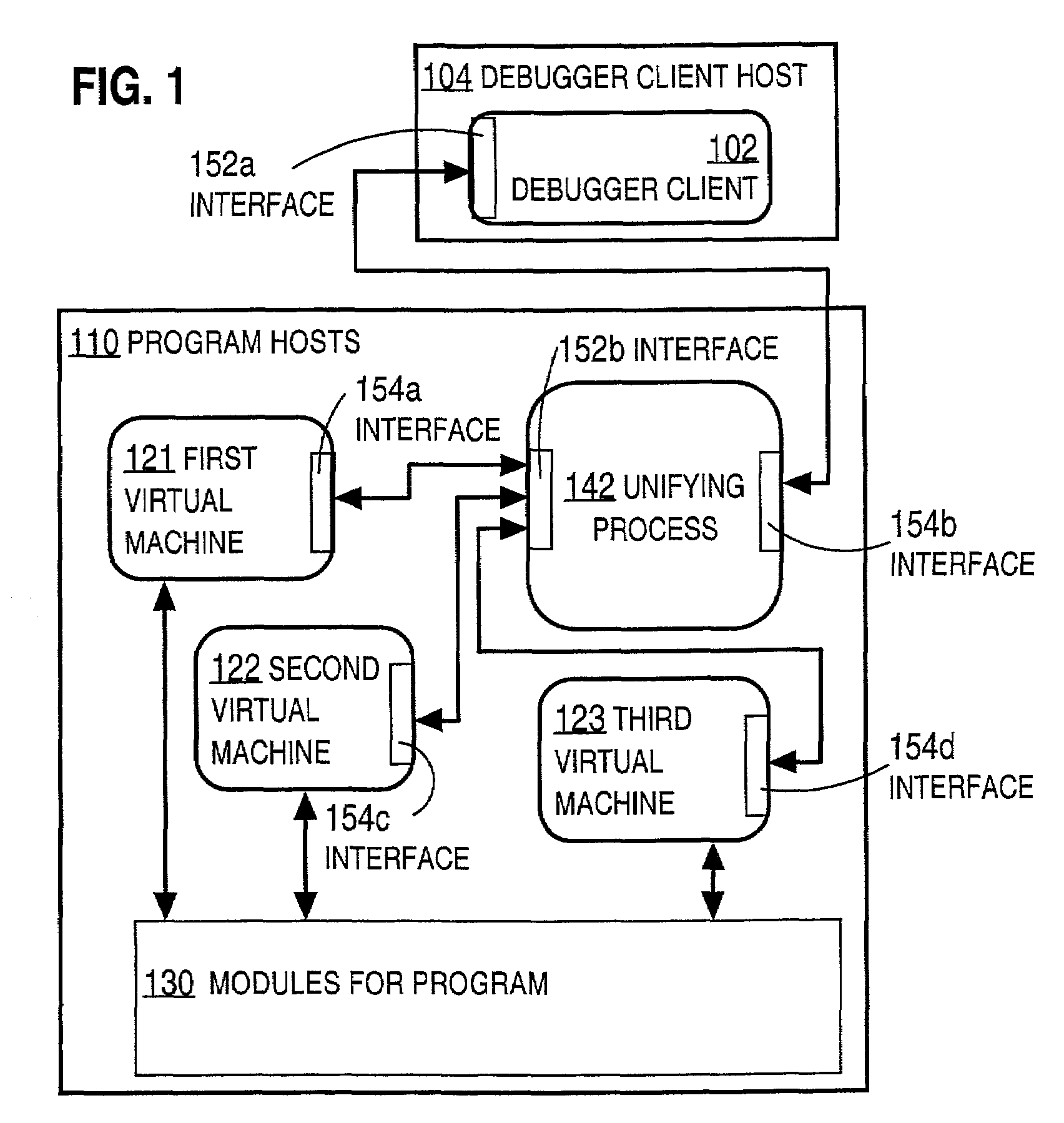

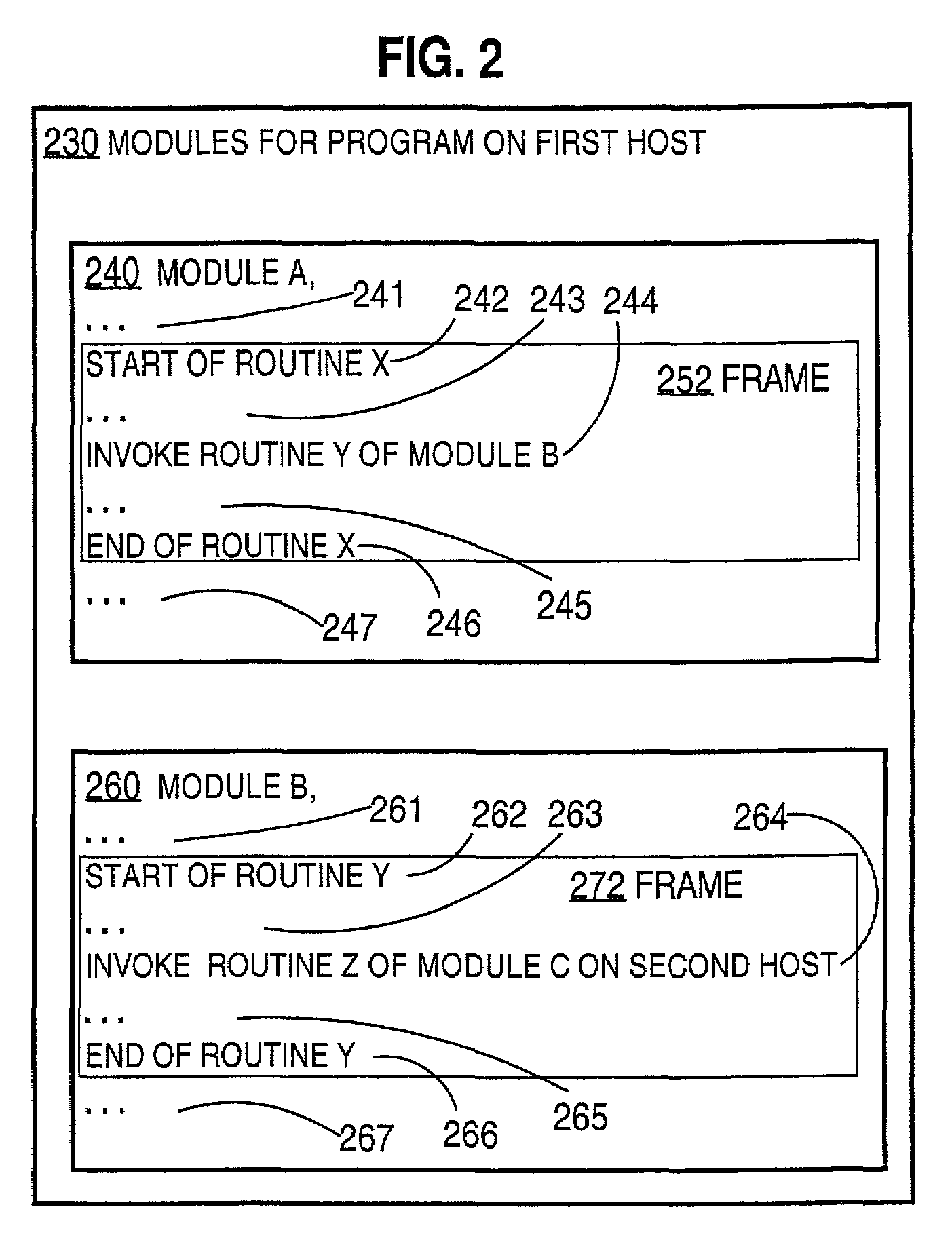

Techniques for debugging computer programs involving multiple programming languages

ActiveUS7107578B1Error detection/correctionSpecific program execution arrangementsLanguage constructProcess design

Techniques for debugging a computer program that includes multiple modules written in multiple languages allow machines for the multiple languages to interface with a single debugger client using a standard interface. The techniques include storing a mapping that maps language constructs of a first language into language constructs of a second language. While a first machine is executing a first module that is written in the first language, the mapping is used to generate debugging information based on language constructs of the second language. The debugging information is sent to a debugger process designed for debugging programs written in the second language.

Owner:ORACLE INT CORP

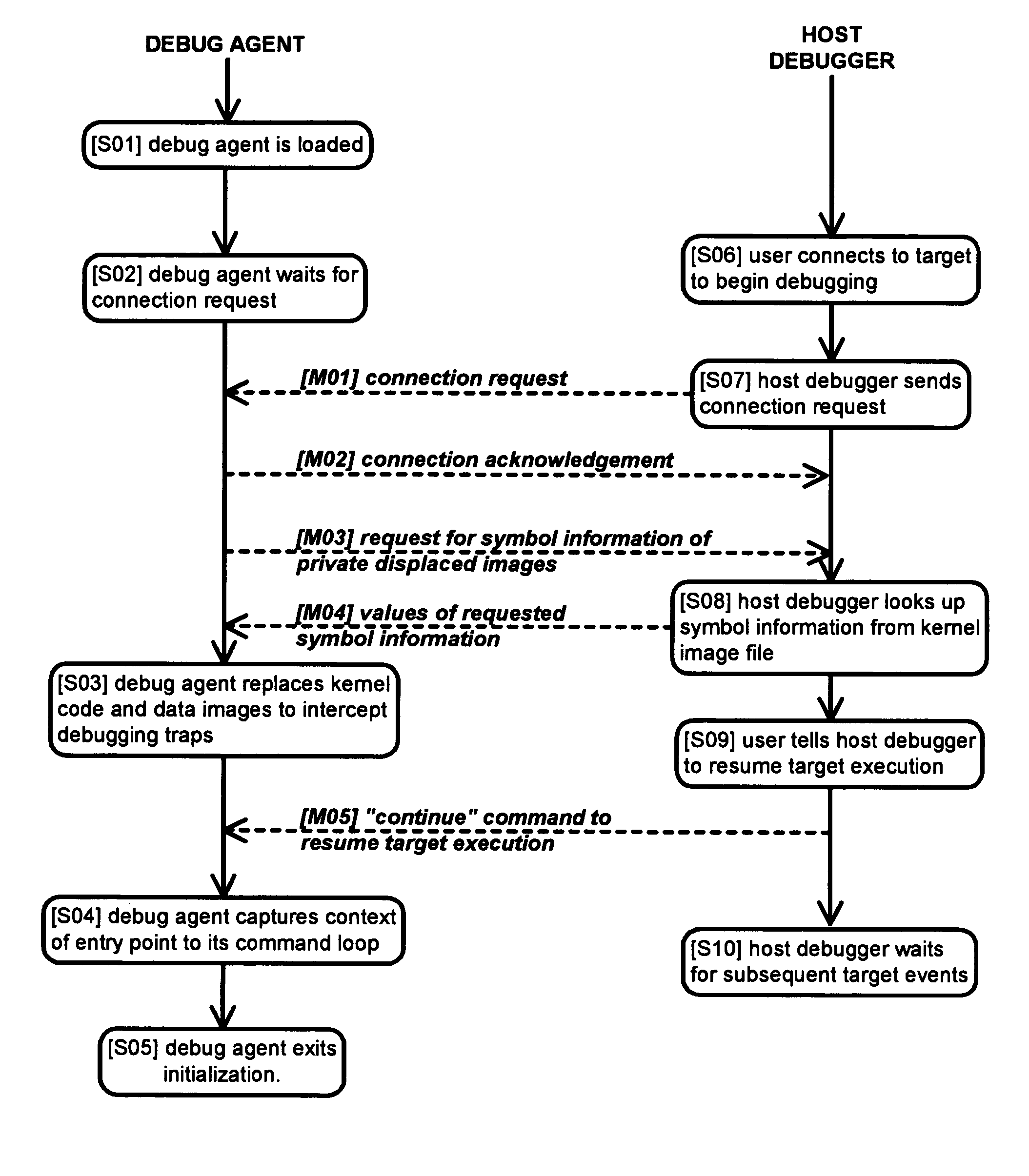

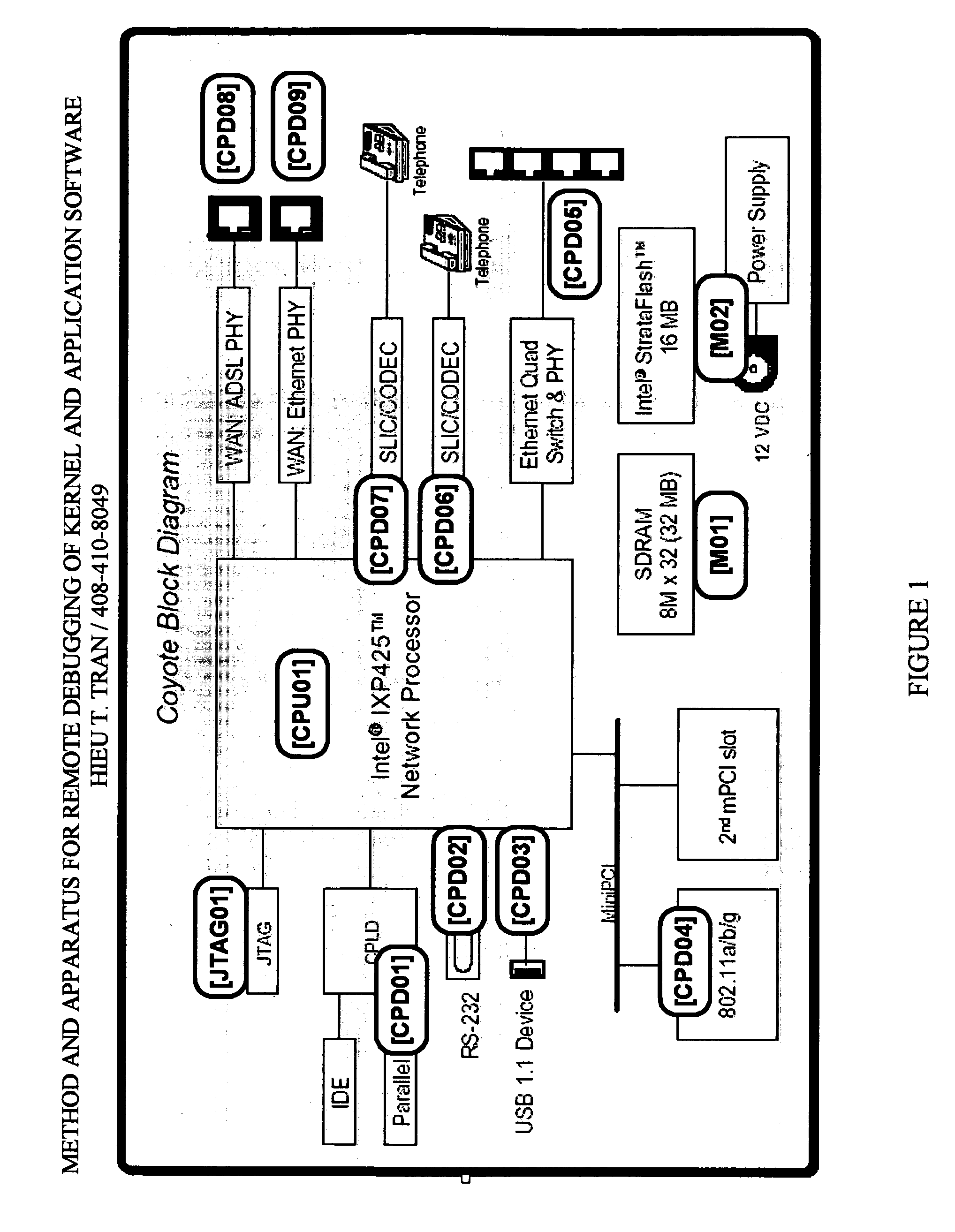

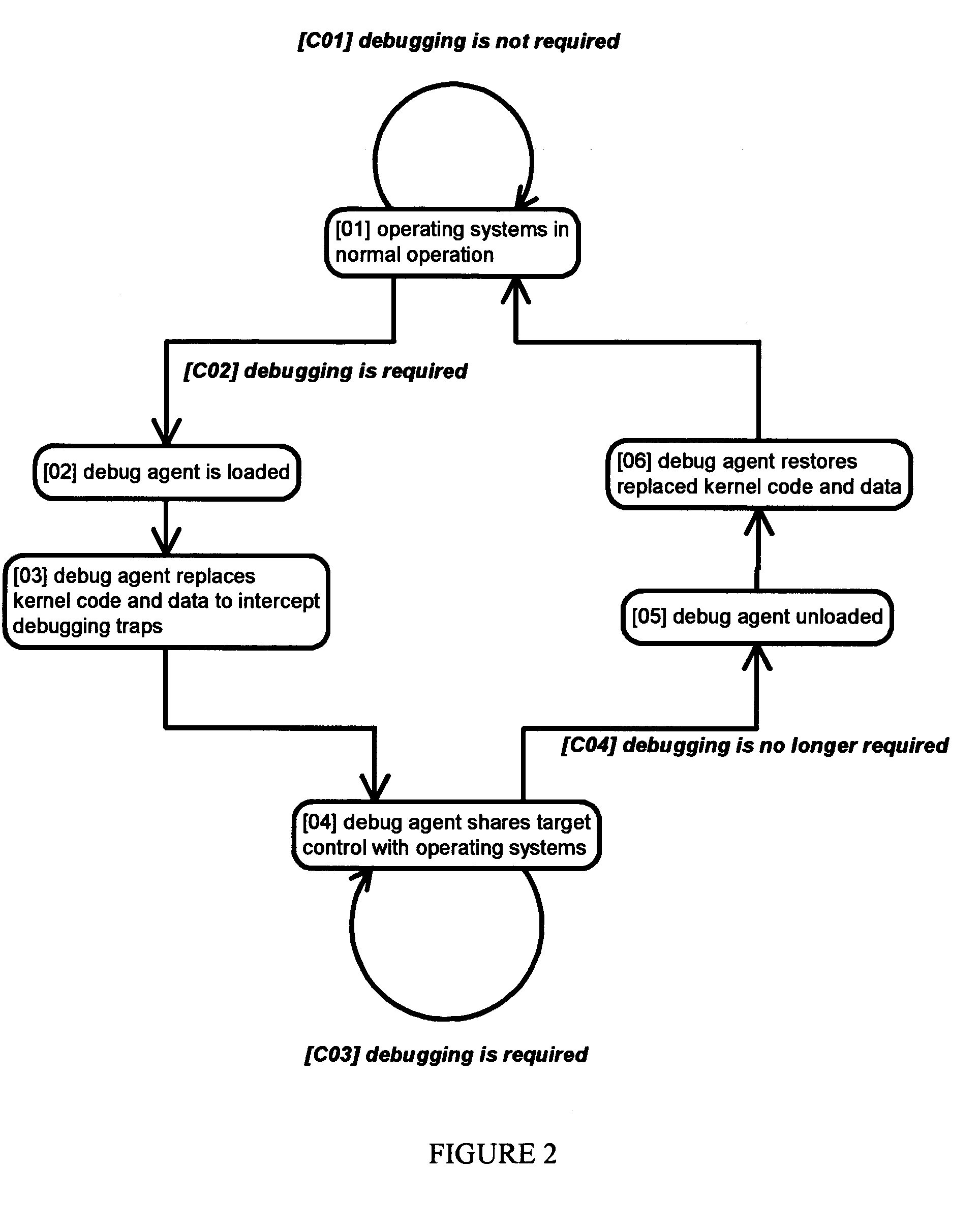

Method and apparatus for remote debugging of kernel and application software

InactiveUS20050216895A1Modified dynamicallyError detection/correctionSpecific program execution arrangementsOperational systemSystem call

A method and apparatus for debugging of OS kernel and applications software that does not require use of a hardware probe; can debug both user-mode programs and a significant body of the OS kernel code; allows the OS to continue servicing exceptions while debugging; leverages OS built-in device drivers for communicating devices to communicate with the host debugger; and can debug a production version of the OS kernel. When debugging is required, the running OS kernel dynamically loads a software-based debug agent on demand whereby such debug agent dynamically modifies the running production OS kernel code and data to intercept debugging traps and provide run-control. To provide debugging of loadable module, the debug agent implement techniques to intercept the OS module loading system call; set breakpoints in the loaded module initialization function; calculate the start address of the debugged module in memory; and asynchronously put the system under debug. By structuring command loop to execute in non-exception mode, and devising a process to transfer execution from the debug agent exception handler to the debug agent command loop and back, the debug agent can communicate with the host debugger using interrupt-driven input / output devices as well as allowing the system to service interrupts while under debug.

Owner:TRAN HIEU TRUNG

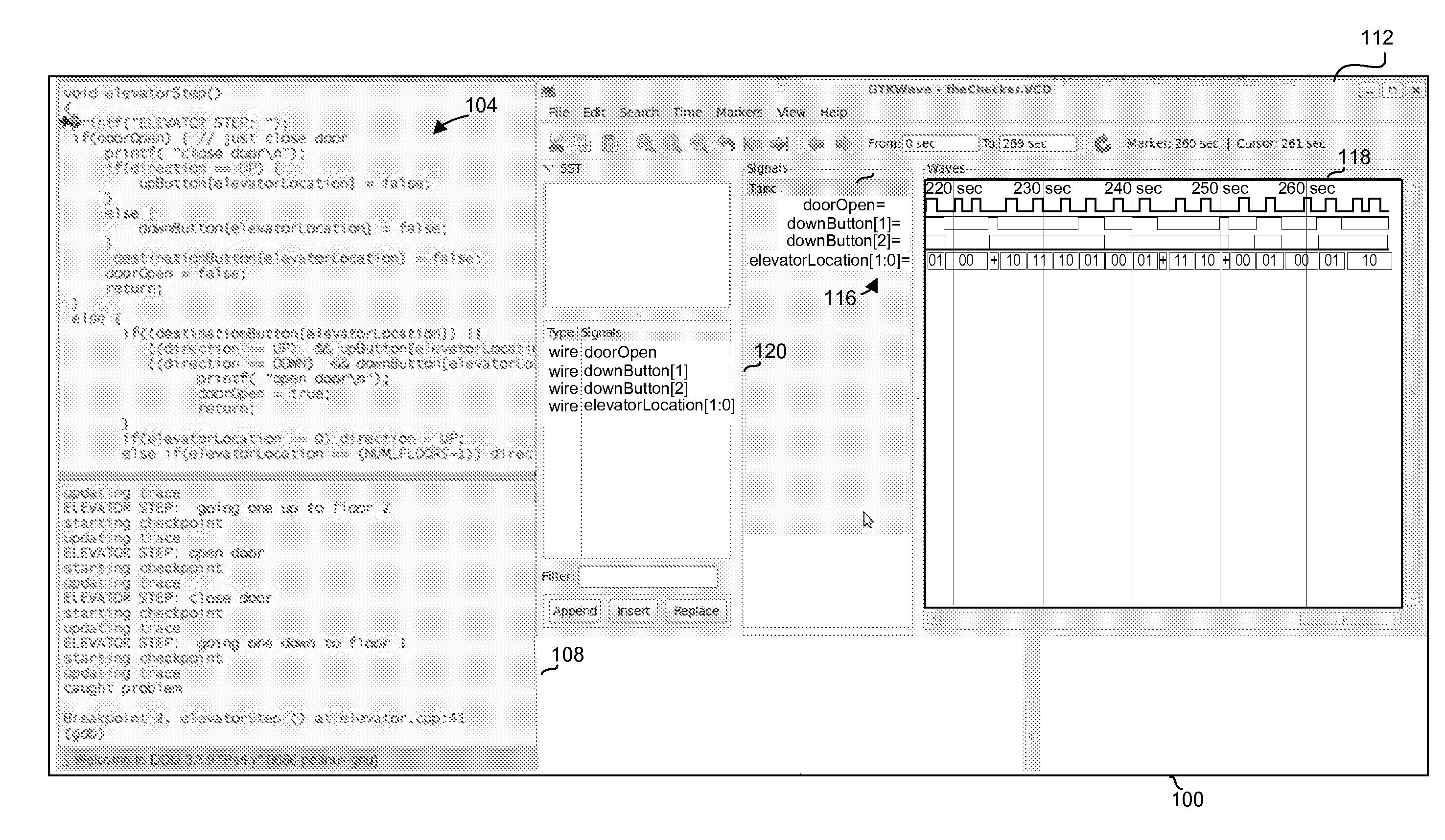

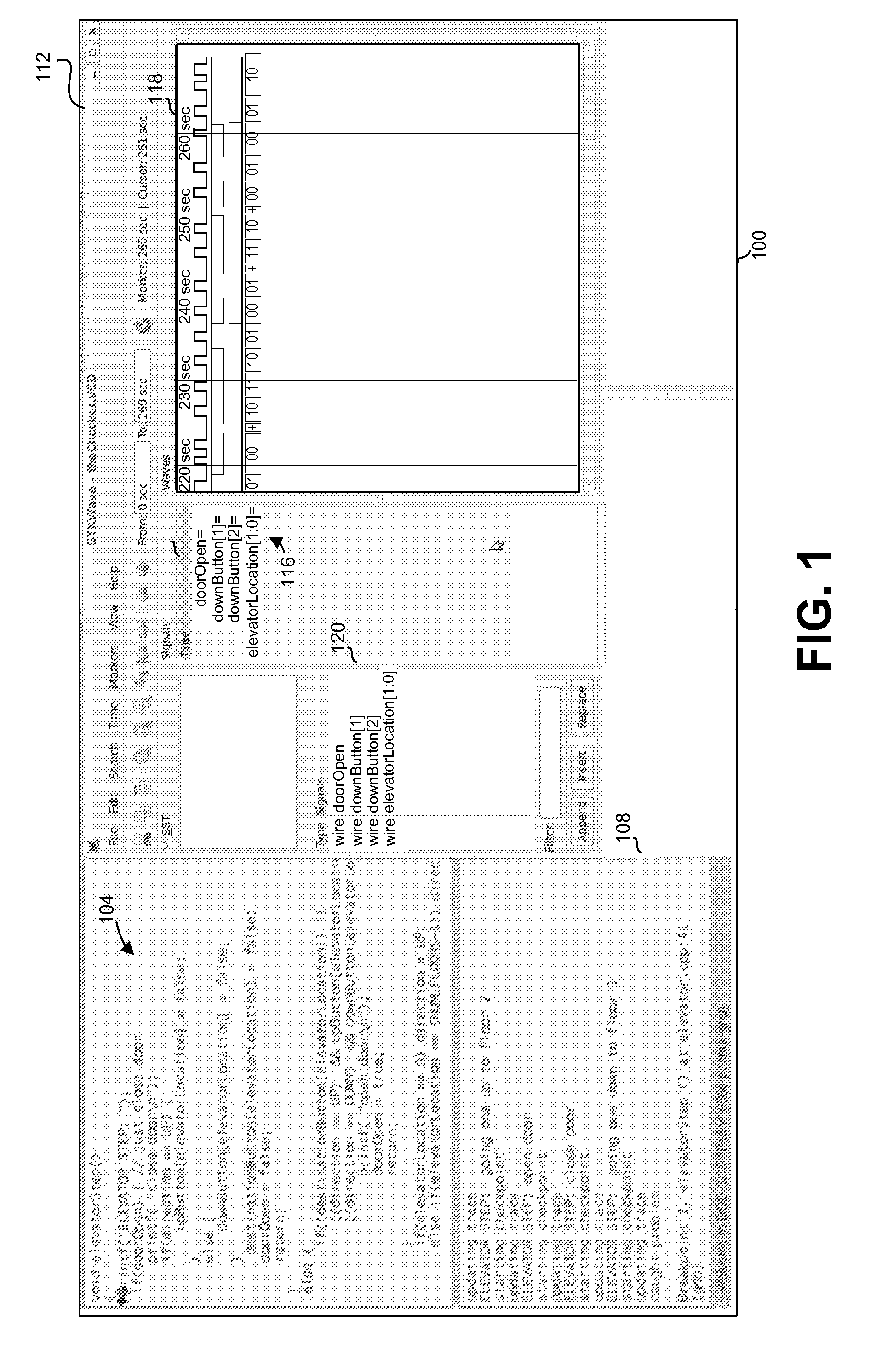

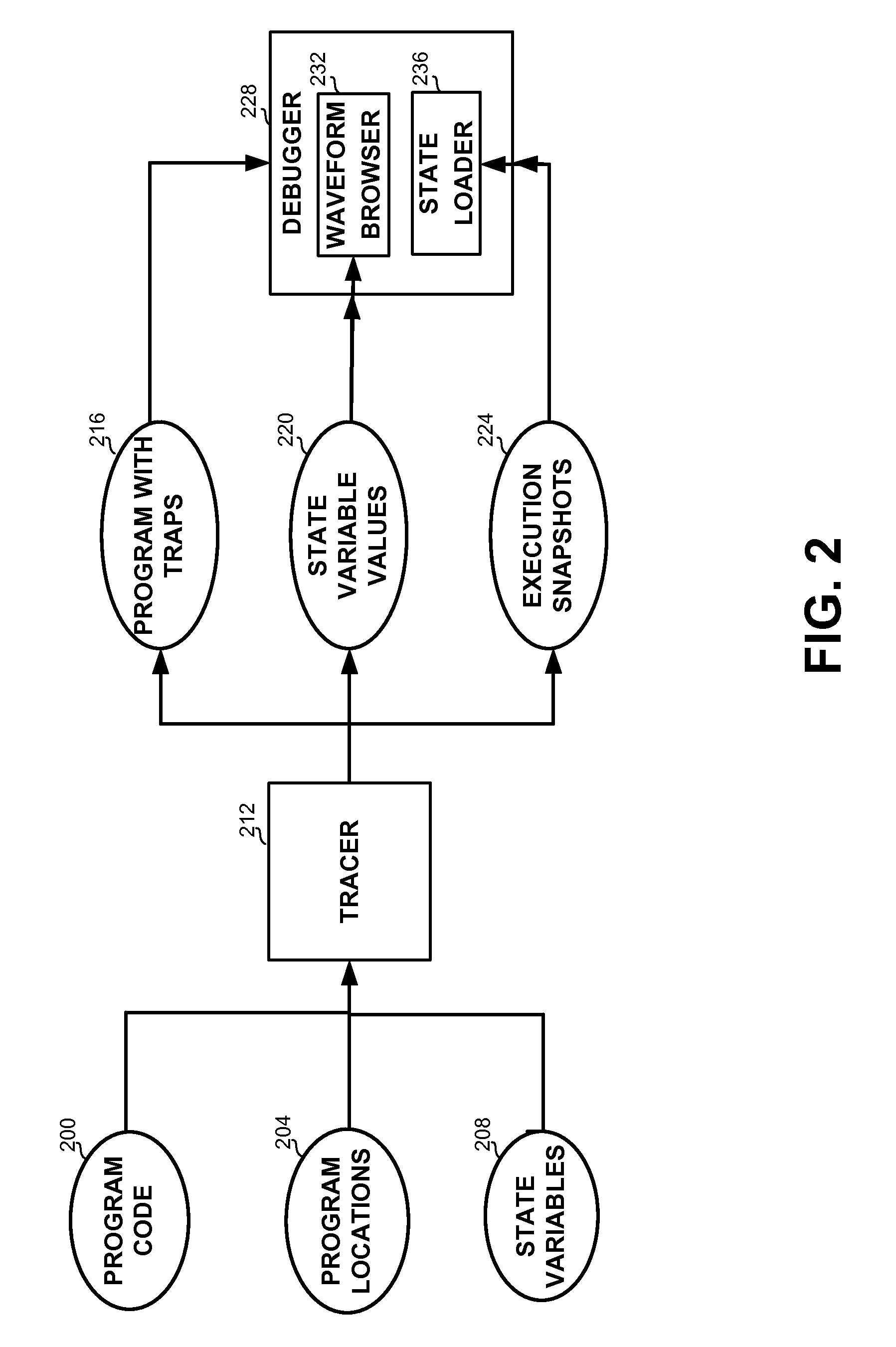

Method and apparatus for debugging programs

ActiveUS20130036403A1Software testing/debuggingSpecific program execution arrangementsGraphicsState variable

A computer-implemented method, apparatus and computer program product for debugging programs, the method comprising: displaying a graphic waveform showing values of one or more state variables of a computer program being debugged in two or more points in time; receiving a user selection from points in time, of an indication to a selected point in time in execution from the graphic waveform; and resuming within a debugger an execution state of the computer program associated with the selected point in time.

Owner:GEIST DANIEL

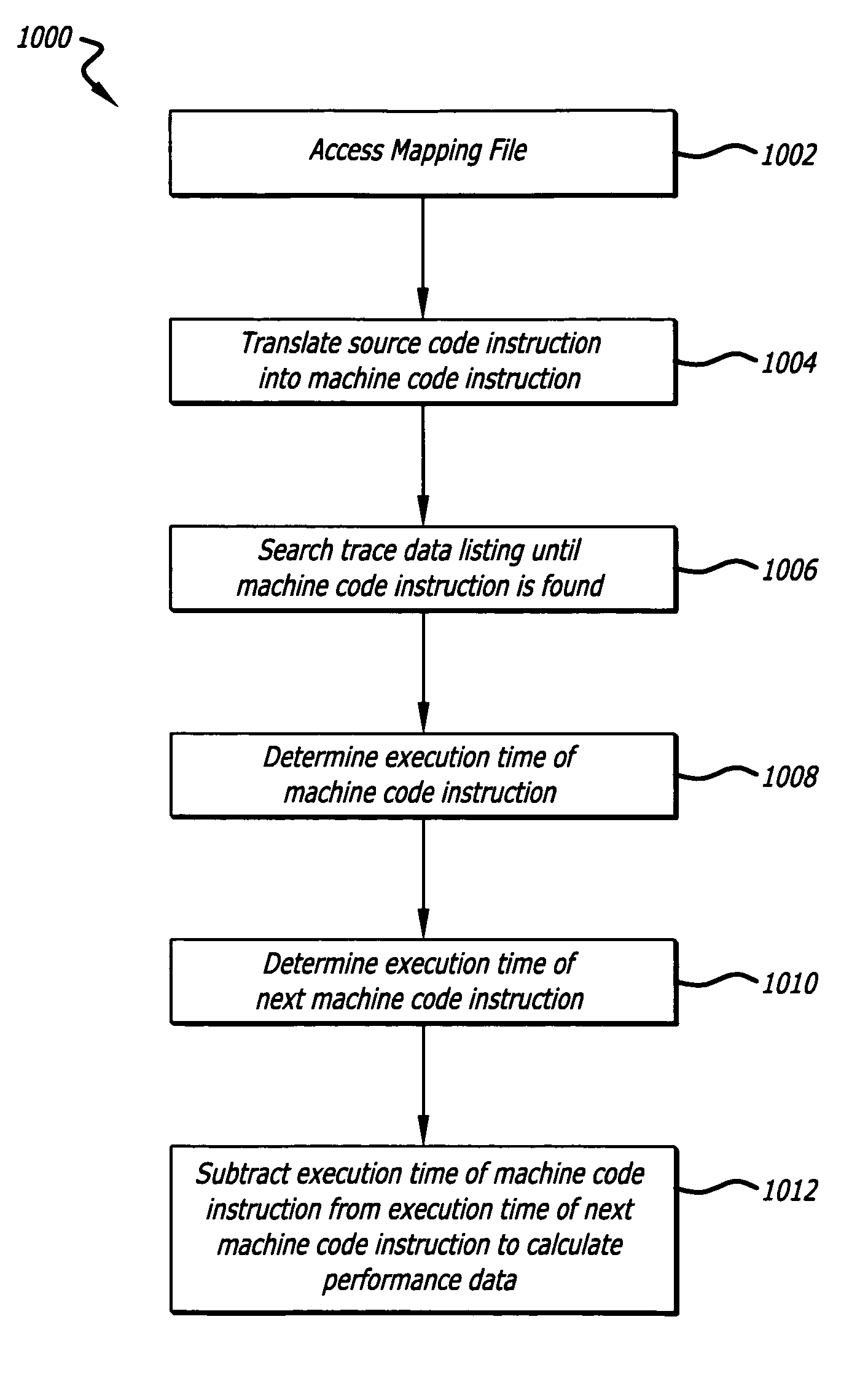

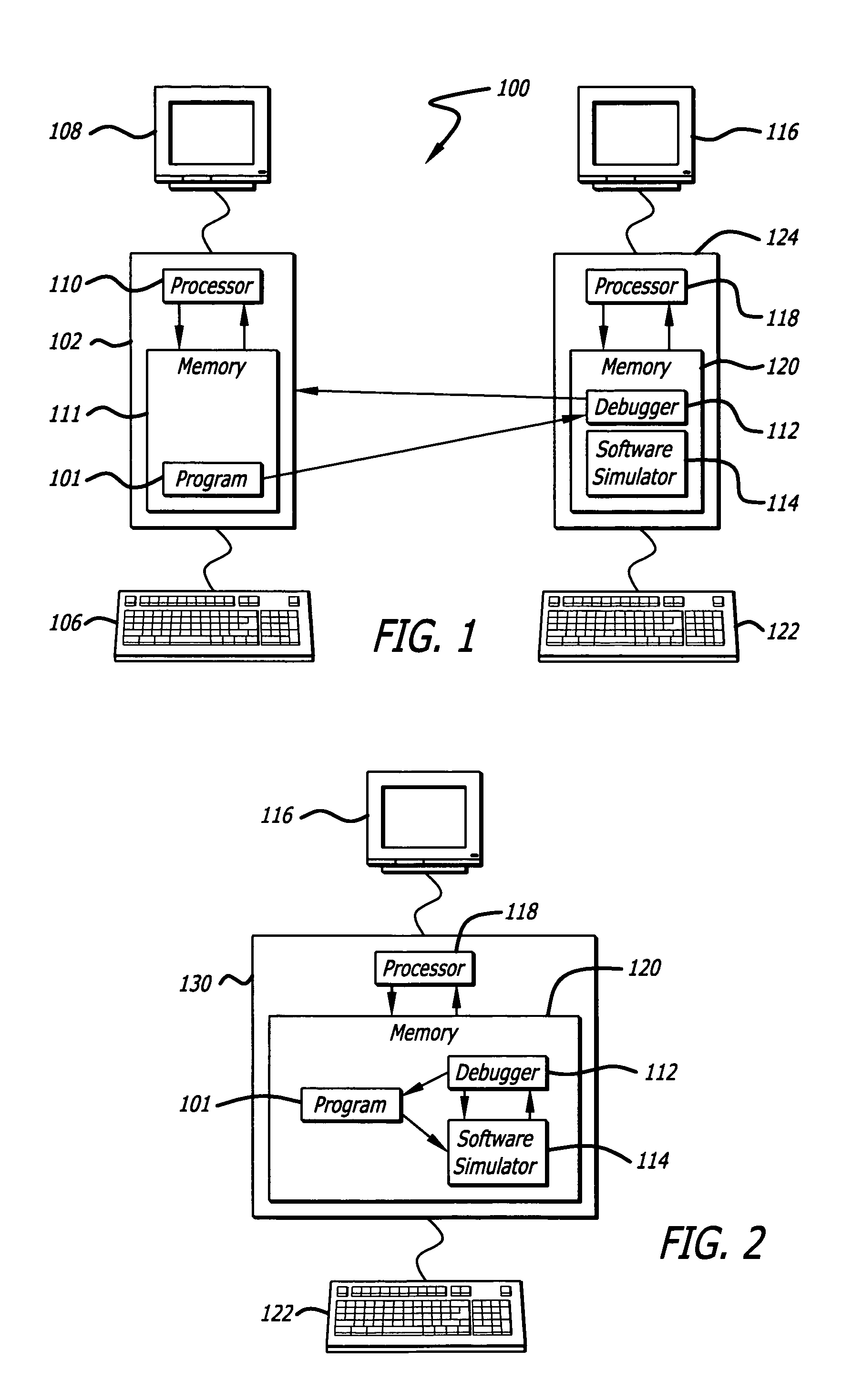

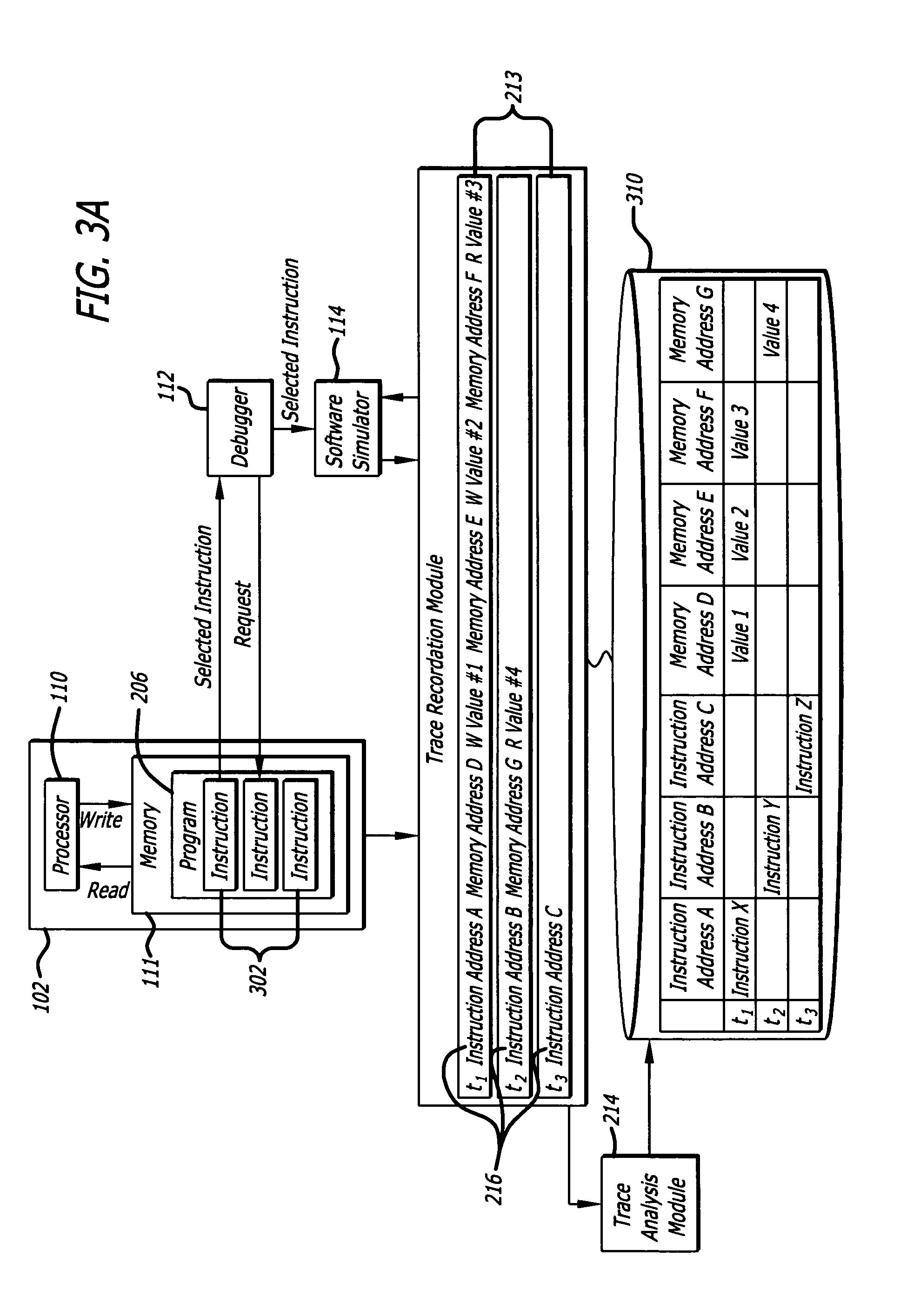

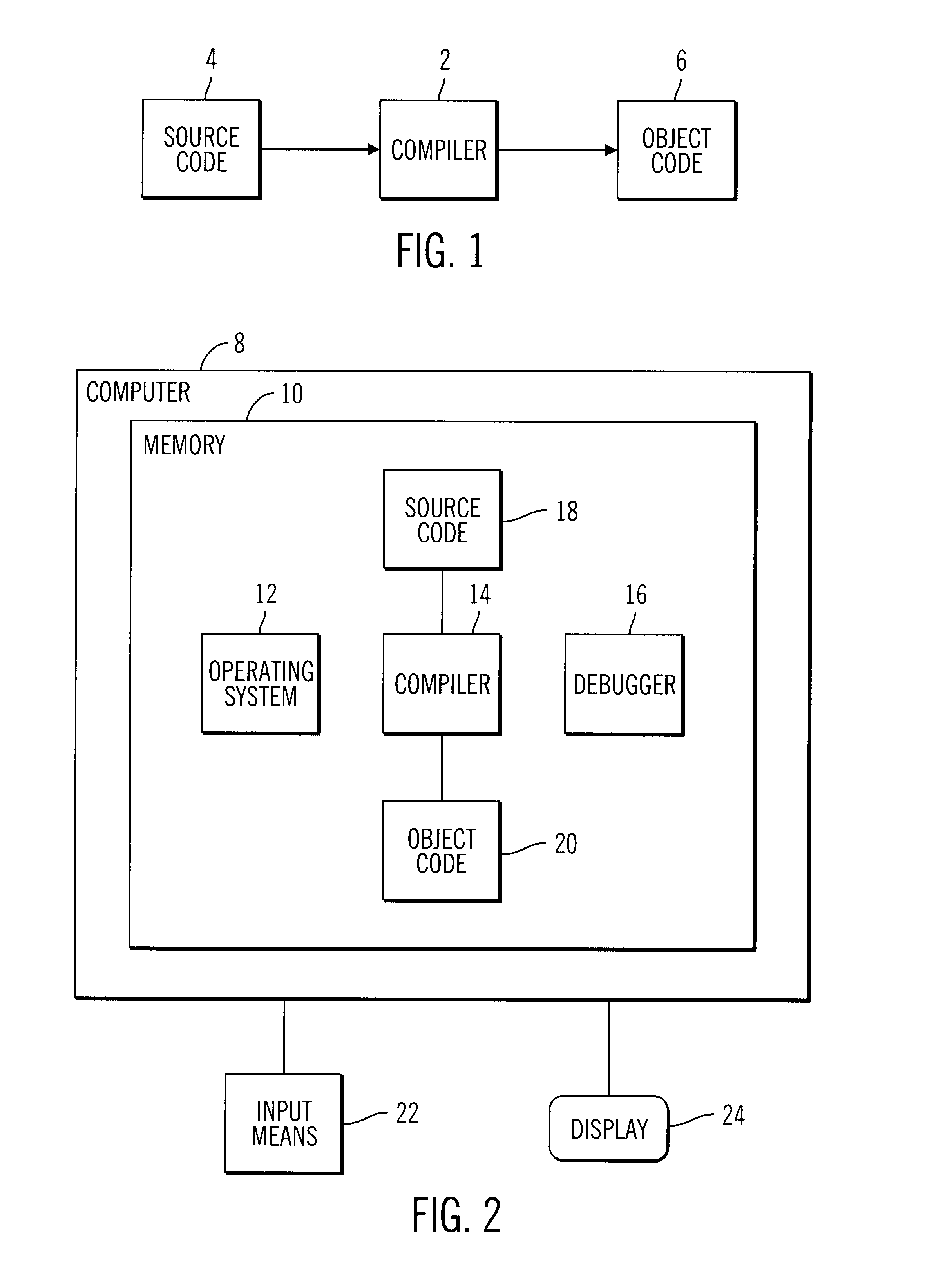

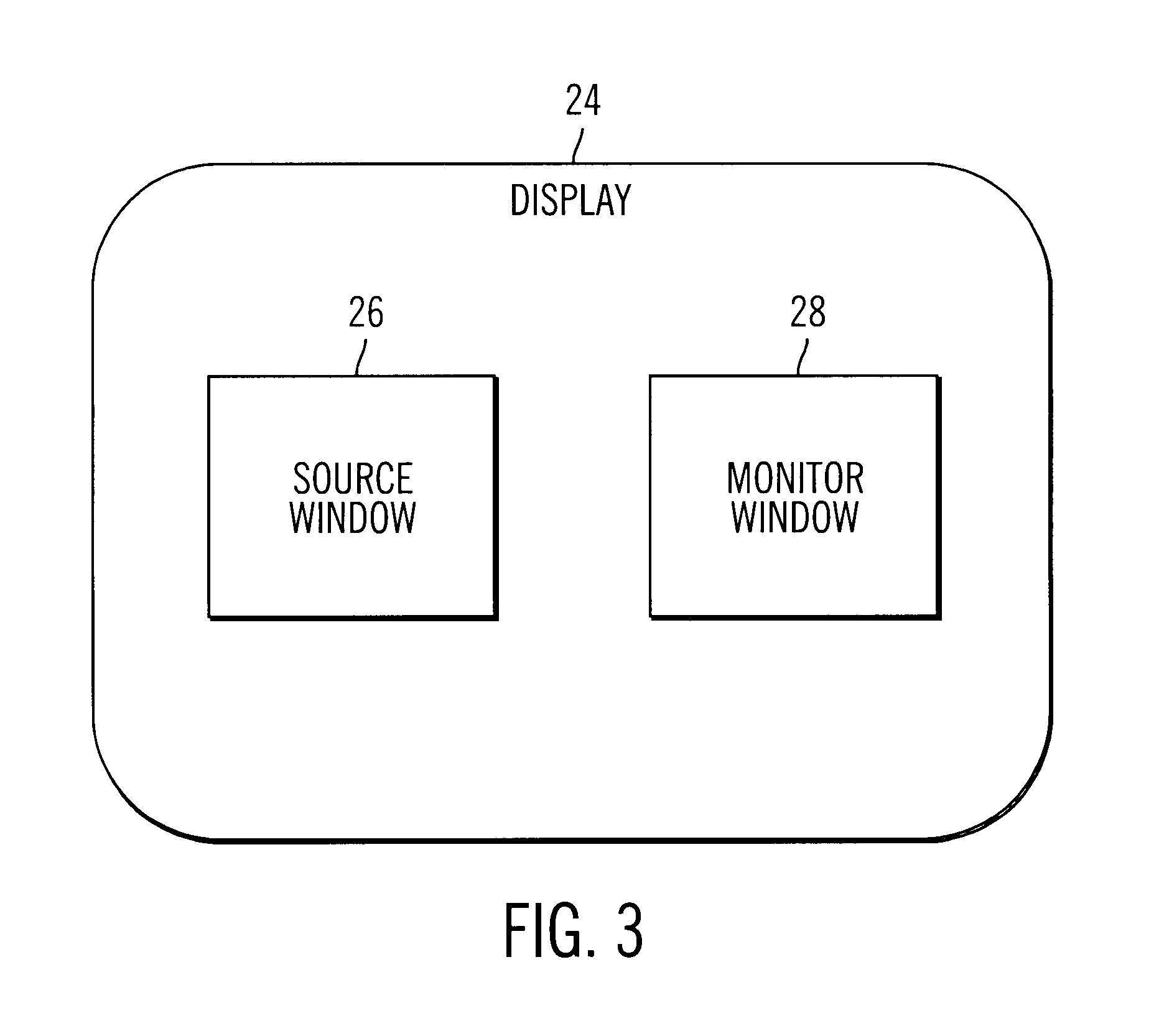

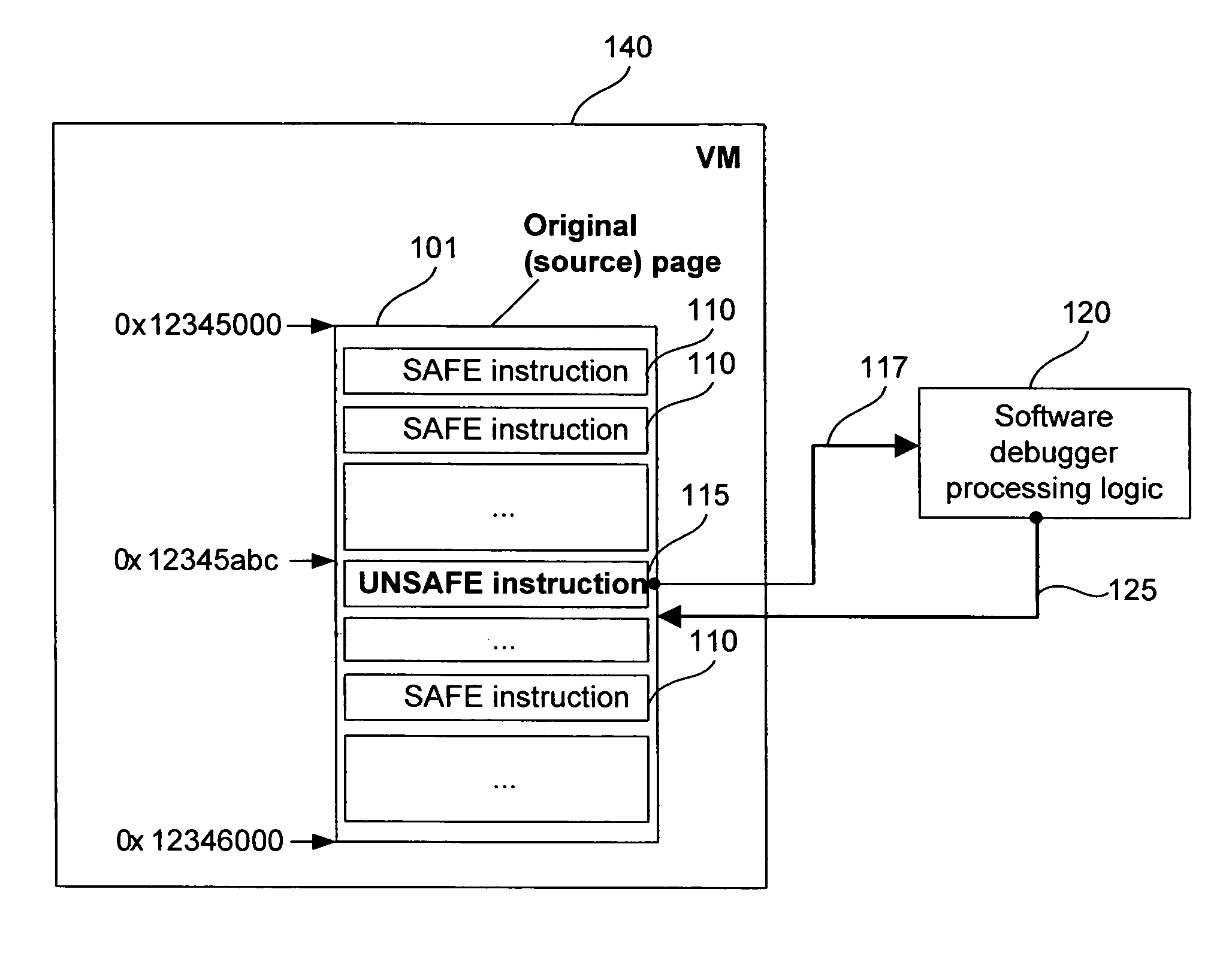

Post-execution software debugger with performance display

ActiveUS7653899B1Error detection/correctionSpecific program execution arrangementsParallel computingMachine instruction

A method for finding an error in a computer program is disclosed. A sequence of machine instructions performed by a processor is recorded as trace data. A mapping file is accessed. A source code instruction is translated into a machine code instruction according to a mapping found in the mapping file. Further, at least a portion of the trace data is searched through until the machine code instruction is found. In addition, a first execution time of the machine code instruction is determined by reviewing the trace data in a first vicinity that an address of the machine code instruction is located. Further, a second execution time of the next machine code instruction is determined by reviewing the trace data in a second vicinity that an address of the next machine code instruction is located. Accordingly, performance data is calculated by subtracting the first execution time from the second execution time. The performance data is displayed.

Owner:GREEN HILLS SOFTWARE

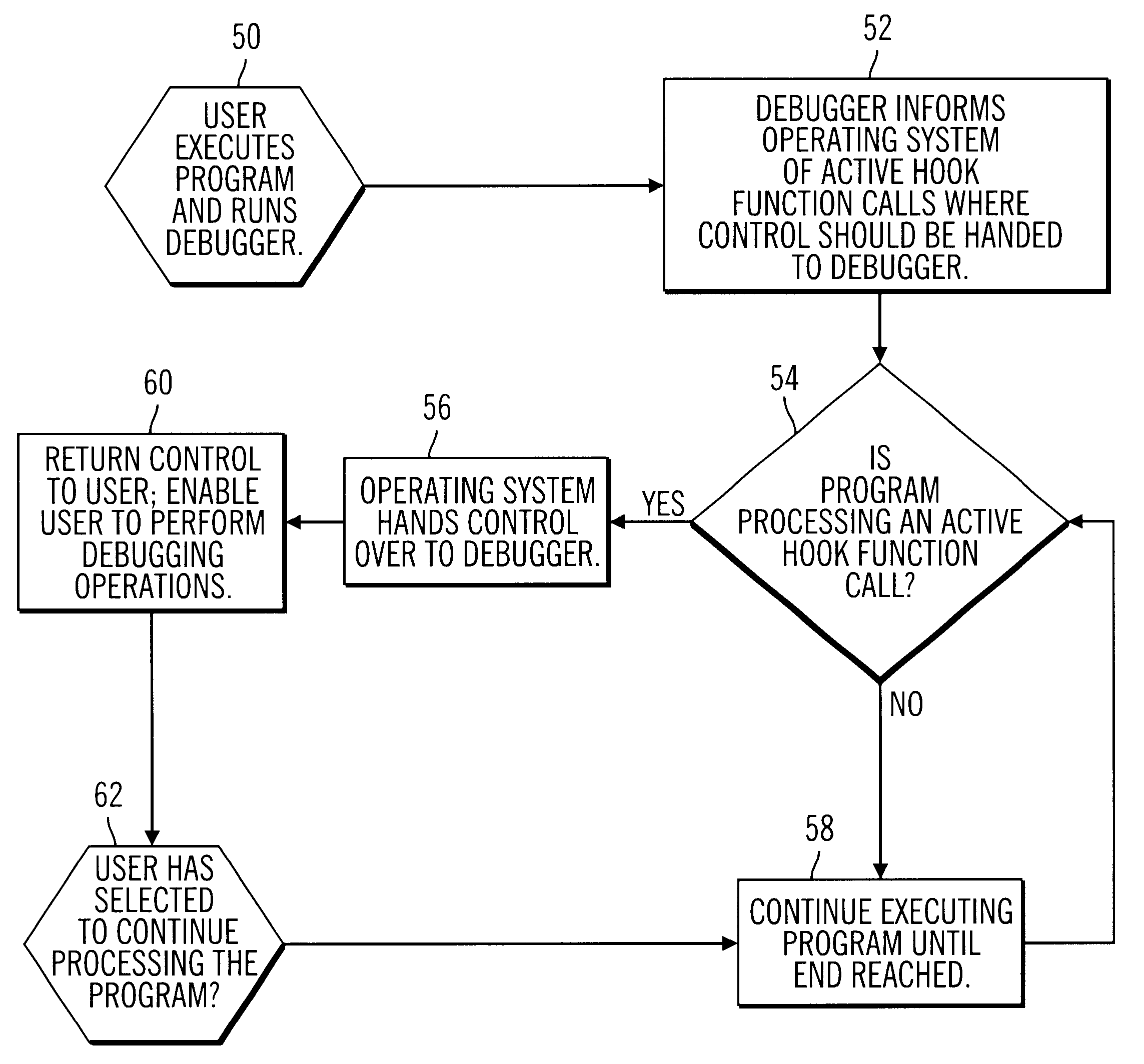

Method system and article of manufacture for debugging a computer program by encoding user specified breakpoint types at multiple locations in the computer program

InactiveUS6249907B1Efficient insertionSoftware testing/debuggingSpecific program execution arrangementsDebuggerComputer program

Disclosed is a system for debugging a computer program. A user indicates a specified breakpoint type, such as a program statement, variable reference, command, etc. The program, including program statements, is then compiled. During compilation, the compiler locates statements in the program corresponding to the breakpoint types and generates a function call into the program at instances in the program of statements corresponding to the user specified breakpoint types. During a debugging phase, a debugger may execute an executable version of the program, including the function calls. Upon processing the function calls, the debugger may stop execution of the program and pass control to the user to perform debugging operations.

Owner:IBM CORP

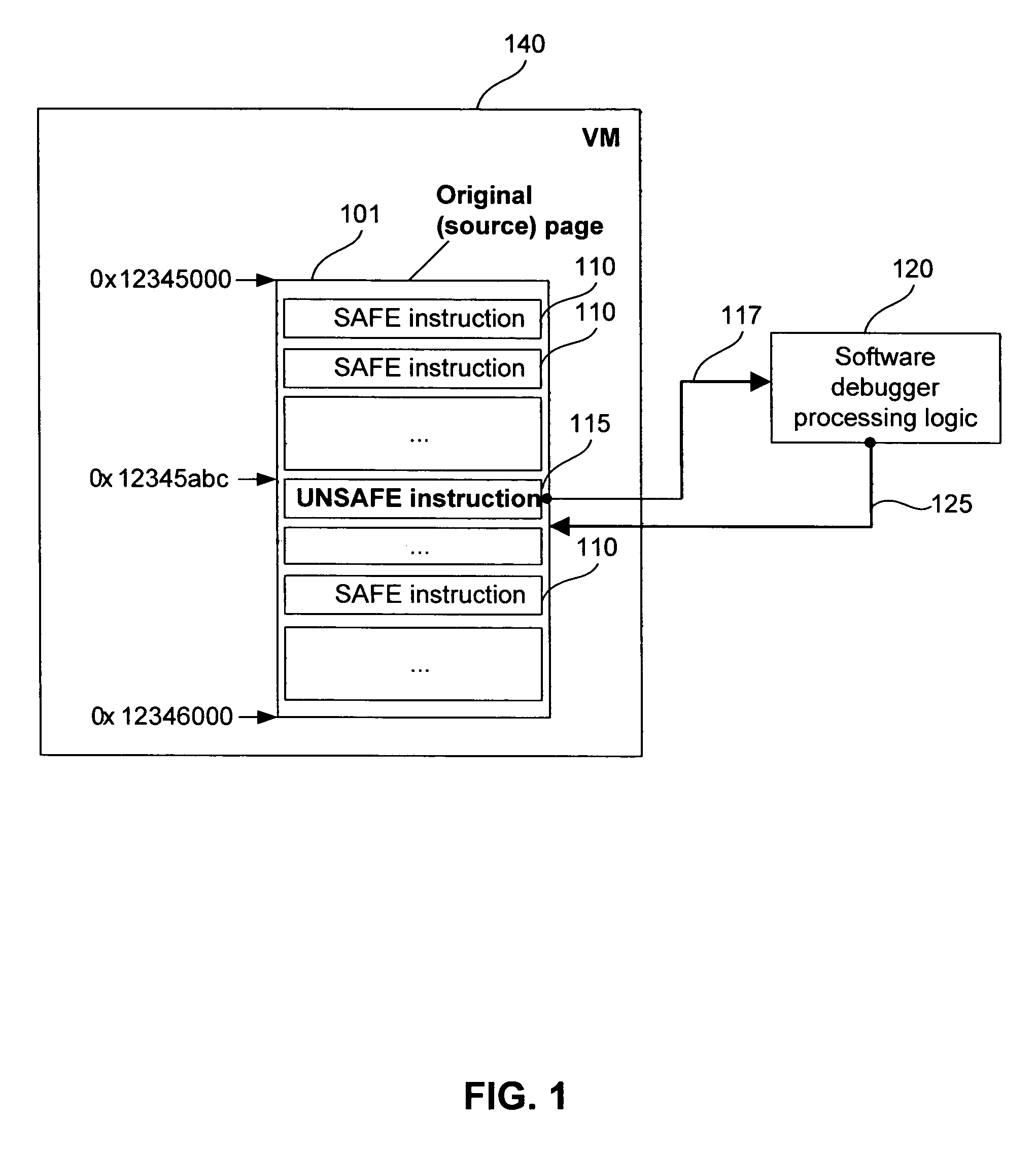

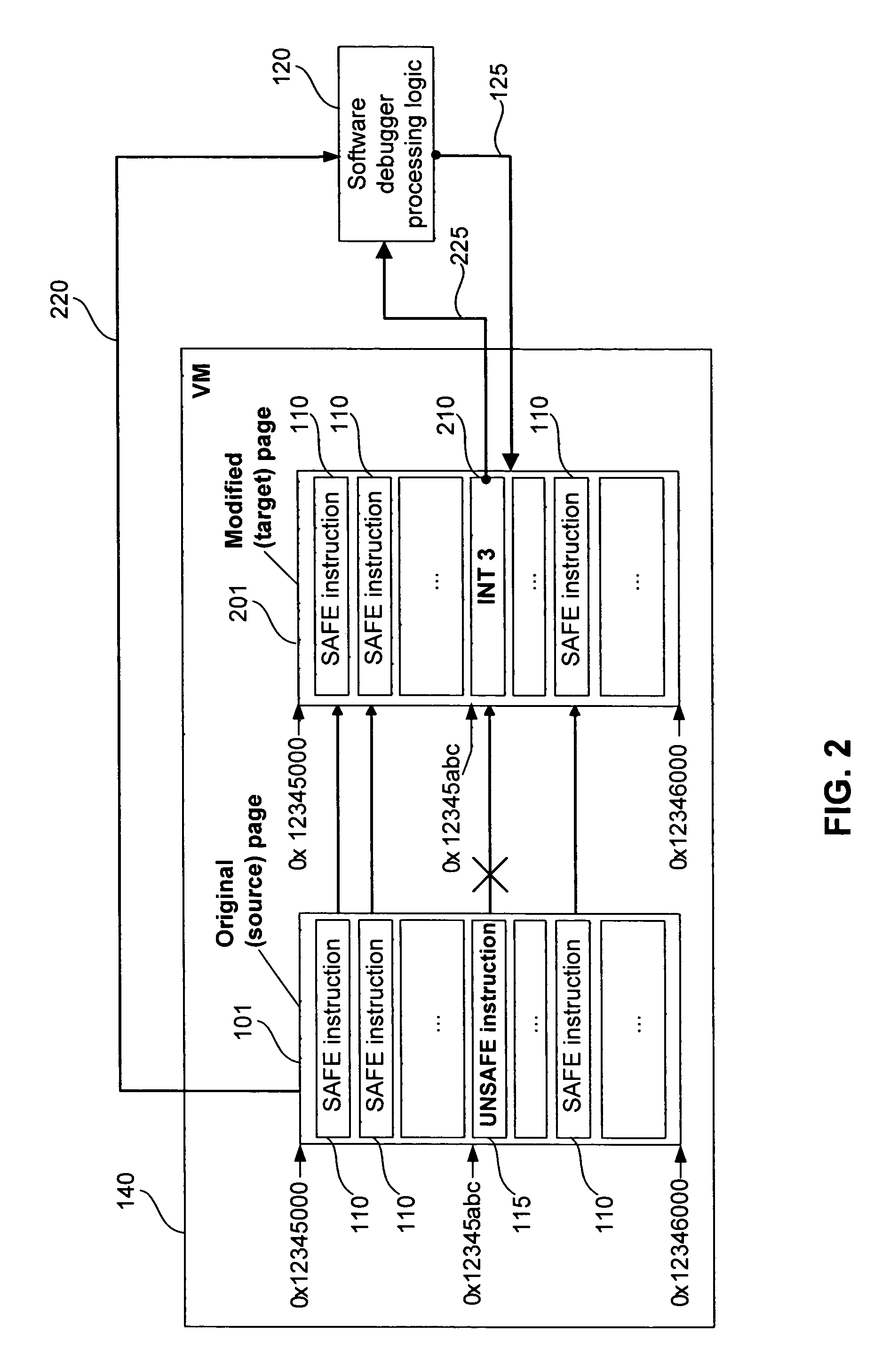

Methods and systems for safe execution of guest code in virtual machine context

ActiveUS7647589B1Ensuring Safe ExecutionError detection/correctionPlatform integrity maintainanceSoftware engineeringLogisim

Methods and systems for safe execution of guest code in virtual machine context are presented. A method for running a virtual machine in a computing system includes (a) launching a virtual machine monitor (VMM) that uses a software debugger; (b) launching a virtual machine (VM) that can natively run safe instructions; (c) determining, at runtime, if the instruction is safe or potentially unsafe; (d) executing safe instructions in a native mode; and (e) activating control logic to process potentially unsafe instructions in the software debugger. The software debugger can bypass at least one of the potentially unsafe instructions. The potentially unsafe instructions include instructions that cannot be safely executed in the context of the VM, and instructions that can cause unpredictable results in the context of the VM.

Owner:PARALLELS INT GMBH

Automated processor generation system for designing a configurable processor and method for the same

InactiveUS20030208723A1Decompilation/disassemblyGeneral purpose stored program computerApplication softwareProcessor design

An automated processor design tool uses a description of customized processor instruction set extensions in a standardized language to develop a configurable definition of a target instruction set, a Hardware Description Language description of circuitry necessary to implement the instruction set, and development tools such as a compiler, assembler, debugger and simulator which can be used to develop applications for the processor and to verify it. Implementation of the processor circuitry can be optimized for various criteria such as area, power consumption, speed and the like. Once a processor configuration is developed, it can be tested and inputs to the system modified to iteratively optimize the processor implementation. By providing a constrained domain of extensions and optimizations, the process can be automated to a high degree, thereby facilitating fast and reliable development.

Owner:TENSILICA

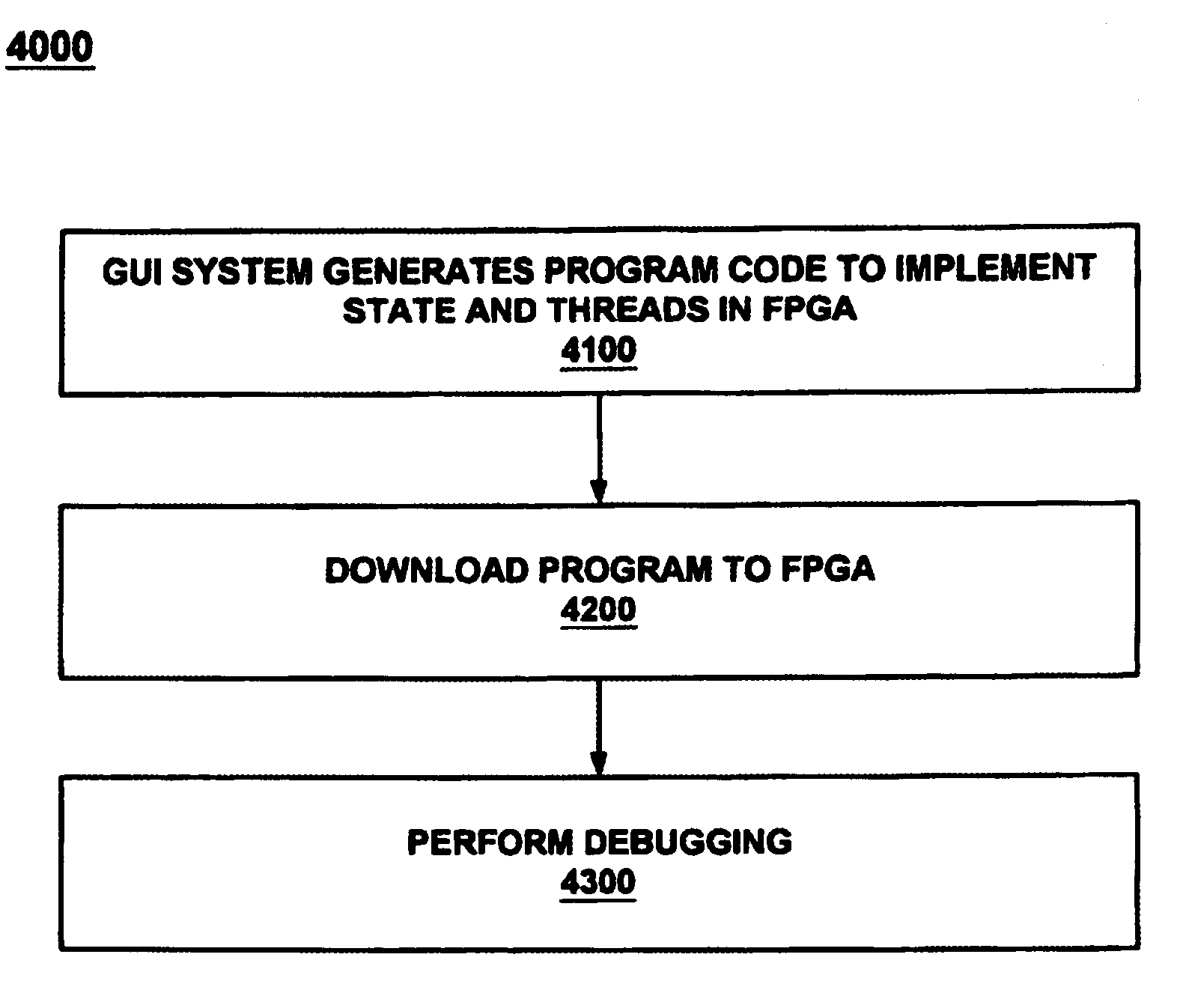

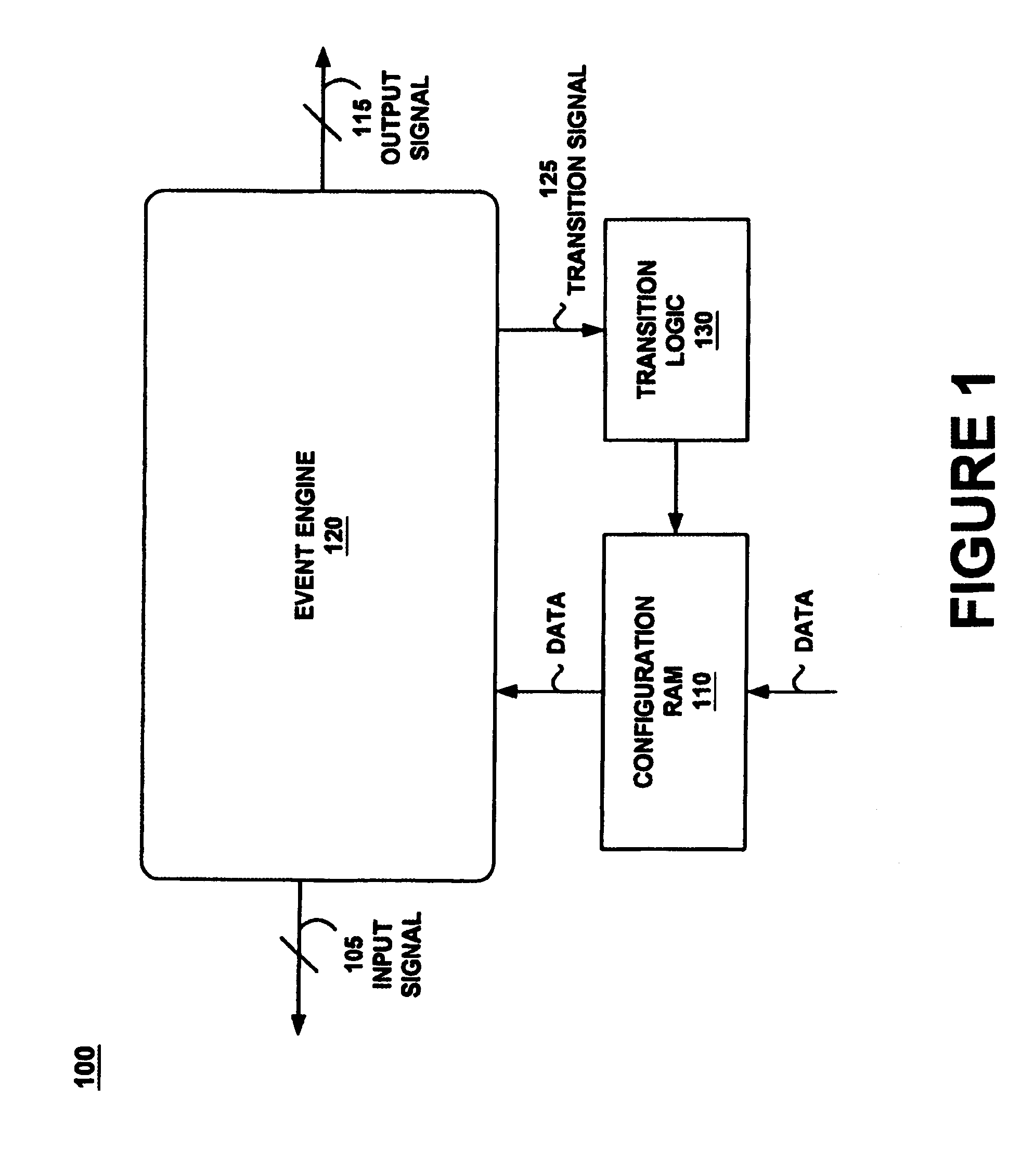

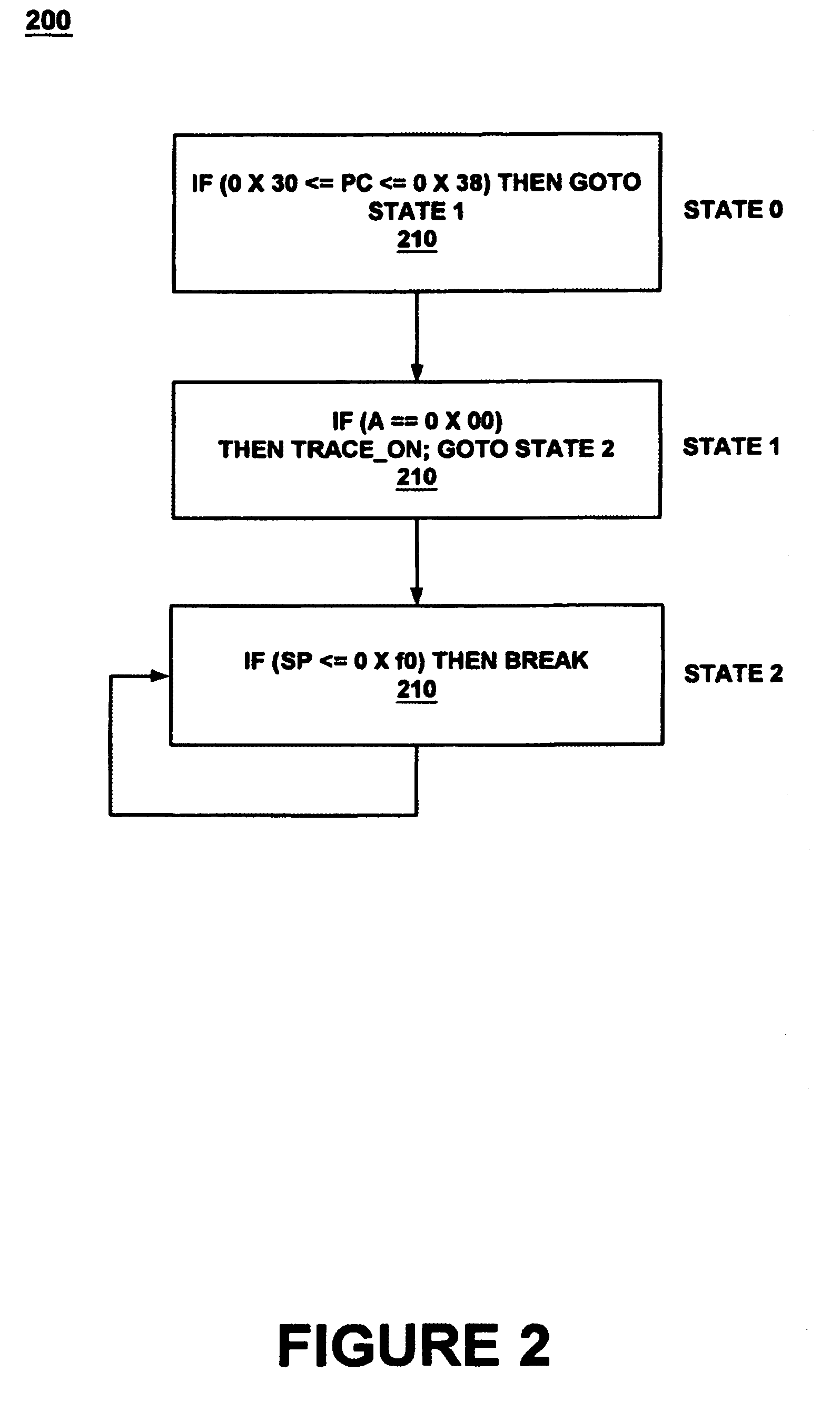

Graphical user interface with logic unifying functions

ActiveUS7150002B1Easy programmingError detection/correctionSpecific program execution arrangementsGraphical user interfaceSoftware engineering

Programming a plurality of states having respective threads is achieved by an event engine and a computer controlled GUI causing the event engine to monitor a signal and execute an action based thereon. The GUI programs an event and several states and causes the event engine to traverse between the states upon reaching the event. The GUI further programs a logic chain which unifies the threads. A method unifies several threads by selecting and executing a logic operation. The method further configures several states and causes traversing between them. The GUI may be deployed co-functionally with debuggers, logic analyzers, scopes, utilities, and software development tools. The results of the GUI are automatically transformed into program code which programs the event engine to operate during debug of a device under test by monitoring for events and taking action based thereon.

Owner:MONTEREY RES LLC

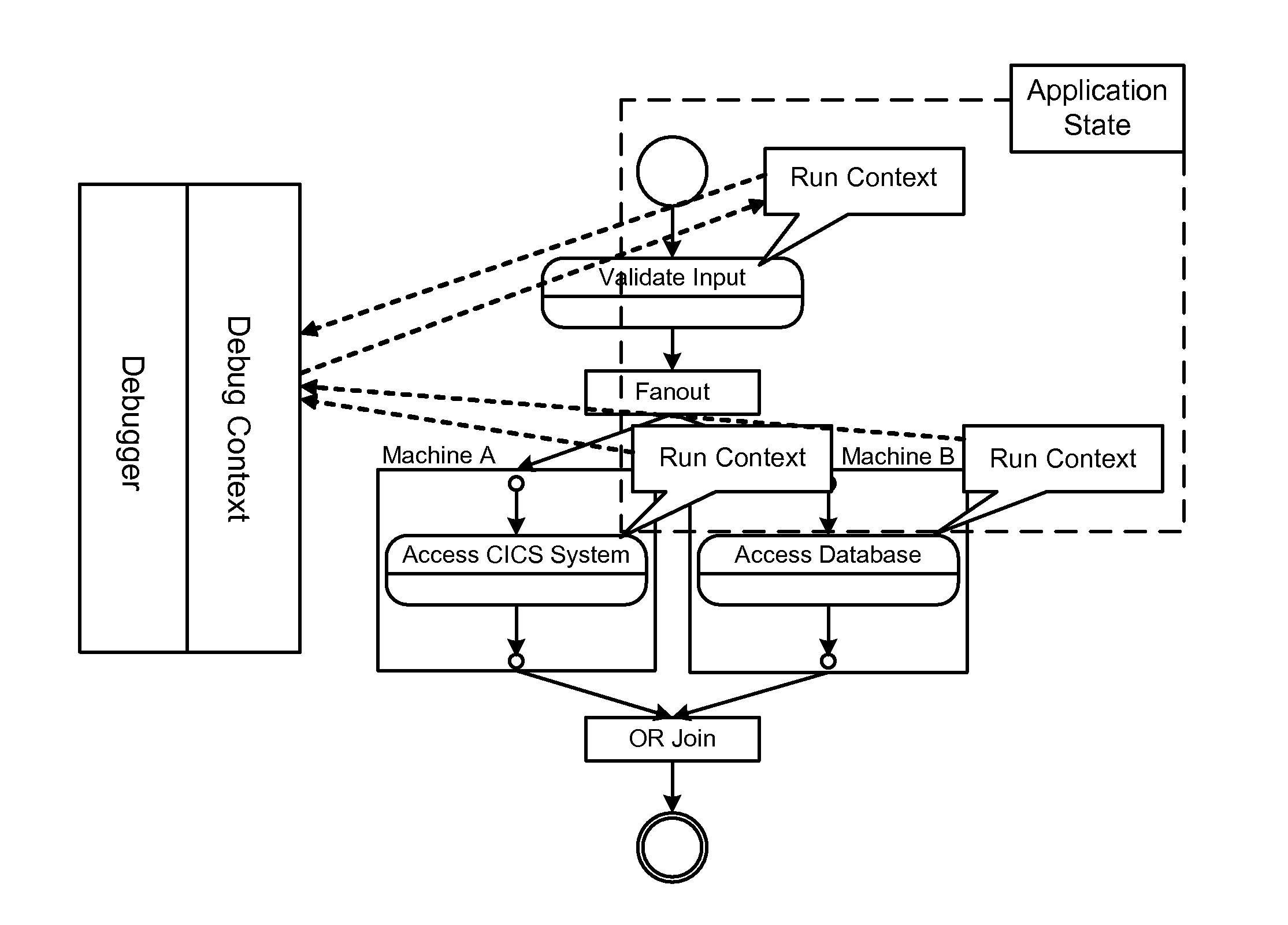

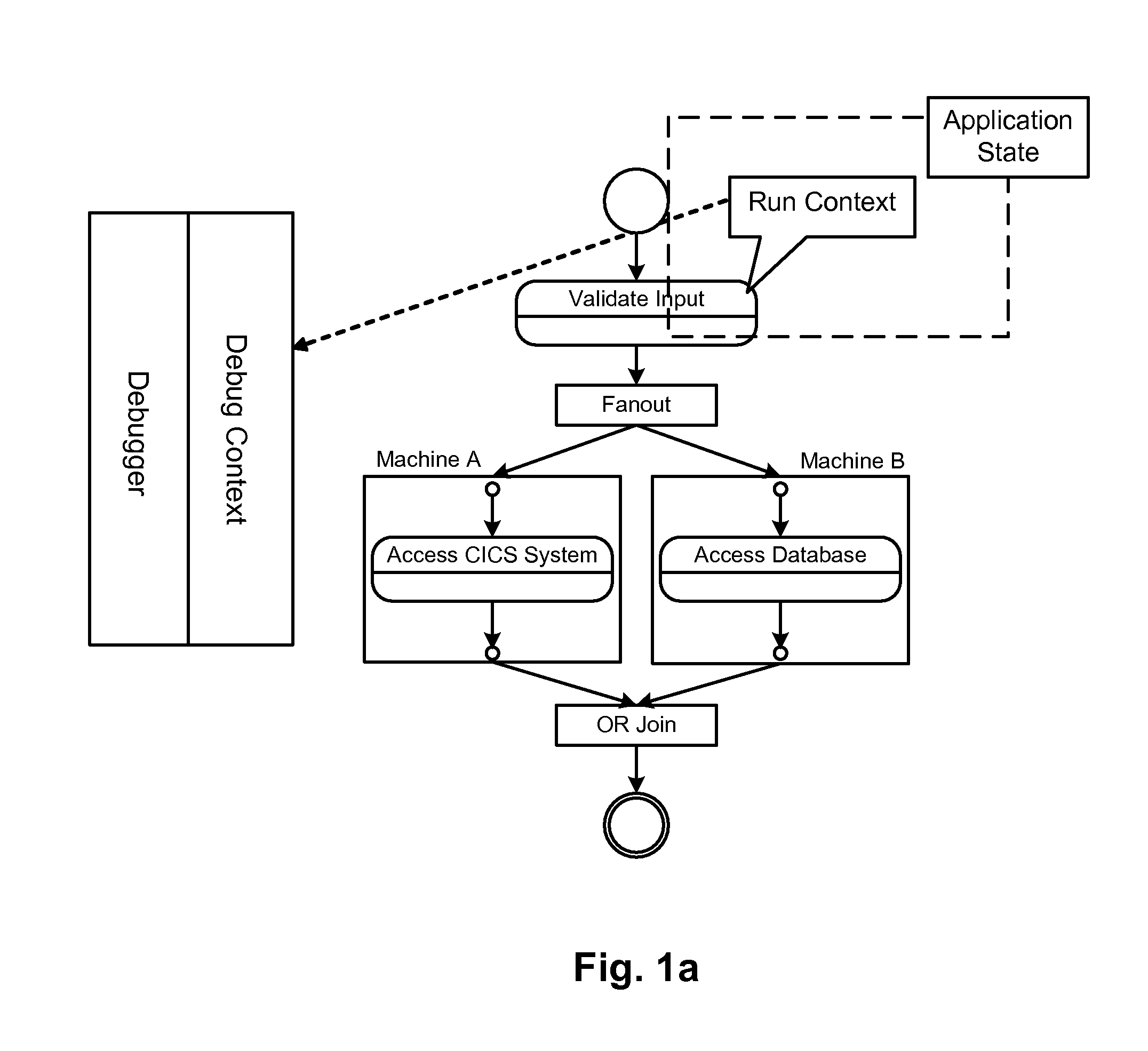

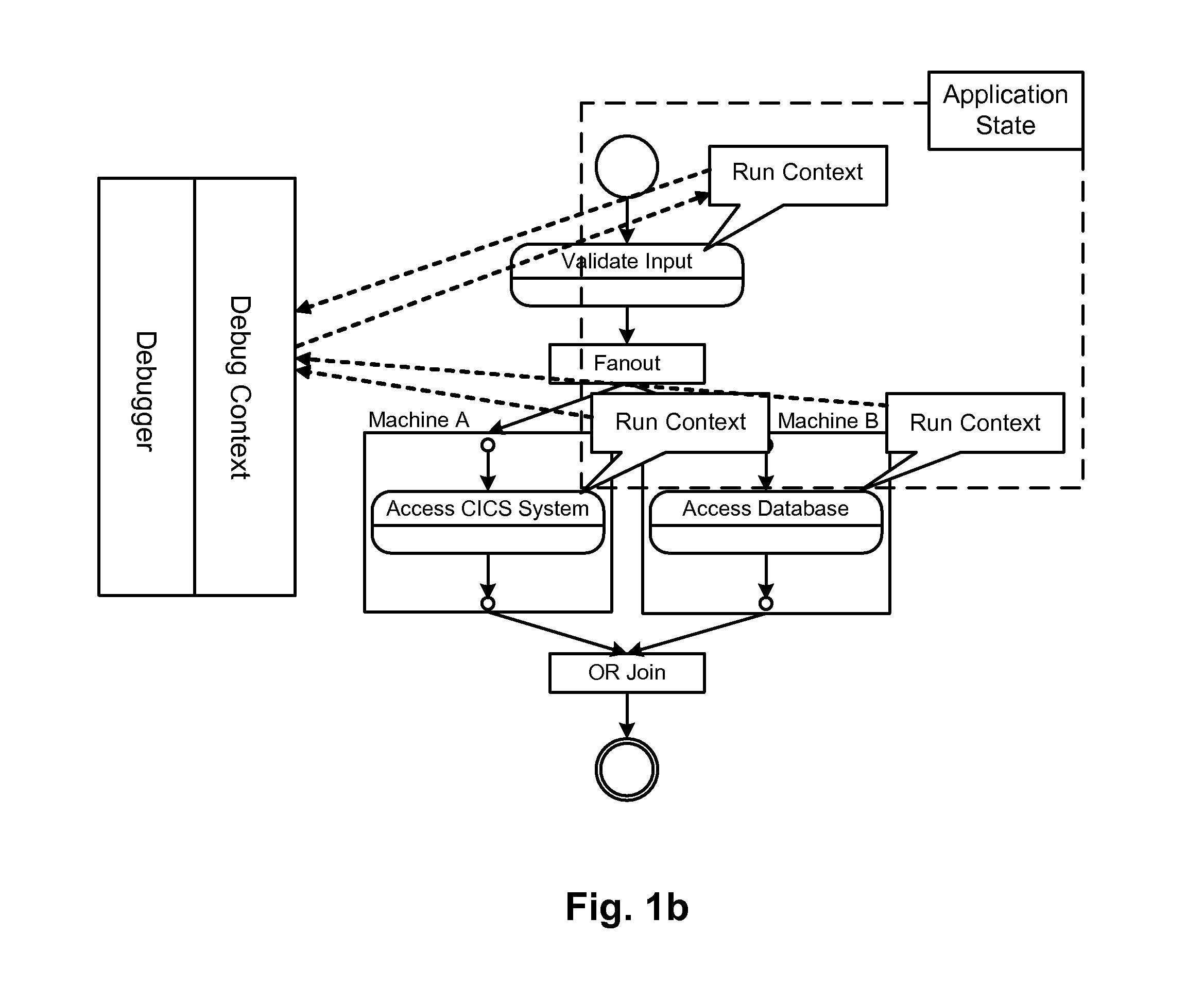

Techniques for debugging distributed applications

ActiveUS7992133B1Error detection/correctionSpecific program execution arrangementsApplication softwareRunning time

Techniques are disclosed for debugging heterogeneous applications in a distributed environment. In one embodiment, an architecture for debugging heterogeneous applications in a distributed environment is configured to enable both location transparency and dynamic exposure of service state. Regardless of where the physical application state resides, the architecture describes or otherwise provides a mechanism that allows seamless debugging and troubleshooting of distributed applications. The location of the state is transparent to the debugger and the application being debugged. In addition, the architecture enables an individual service to expose its state dynamically at run-time. It is possible for the service to expose its state in a self-describing fashion, allowing service state to be exposed in the architecture regardless of the service environment. The architecture allows for all the capabilities of debuggers running in non-distributed, homogeneous environments in a distributed heterogeneous environment.

Owner:AUREA SOFTWARE

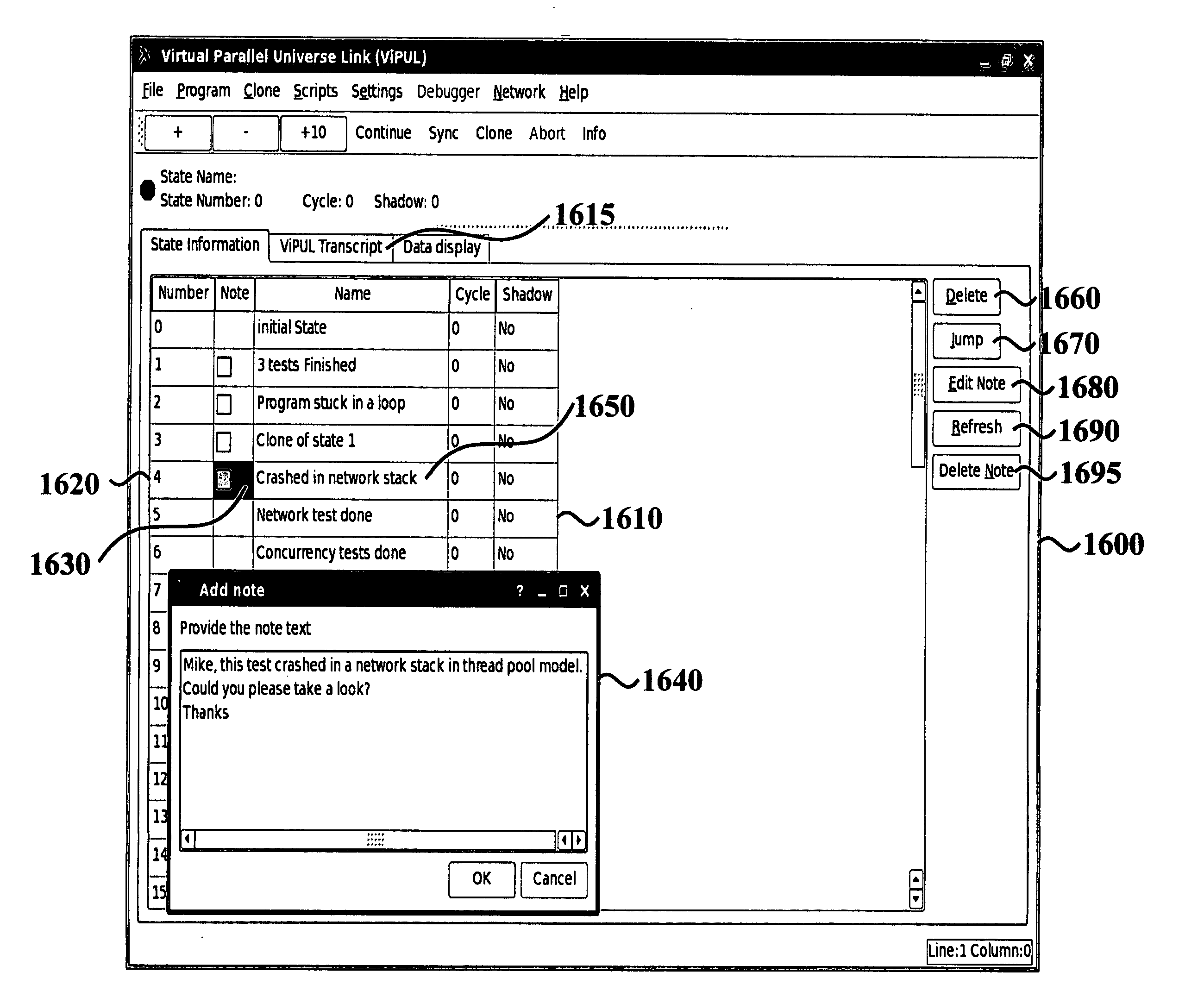

Method and apparatus for execution control of computer programs

InactiveUS20080295114A1High level of abstractionCreate illusionError detection/correctionInterprogram communicationSoftware engineeringExecution control

A method for execution control of a user application program utilizing control program and management software is provided. This execution control is provided without a need to modify or recompile the user application program. The invention provides ability to save states during the execution of an application program and provides a means to jump between them. The invention also provides a means for multiple remote users to interact with the user program and also provide means to control the user application via script and share common portions of execution among multiple execution instances of the same user application program. The invention enables attaching a debugger to a state, maintaining debug context for all the saved states, and means to jump to a state saved at an earlier point in execution to help debug user application programs.

Owner:ARGADE PRAMOD VASANT +1

Method and system for virtual prototyping

ActiveUS7613599B2Reduce simulation overheadFast executionElectronic circuit testingError detection/correctionHuman–machine interfaceComputer architecture

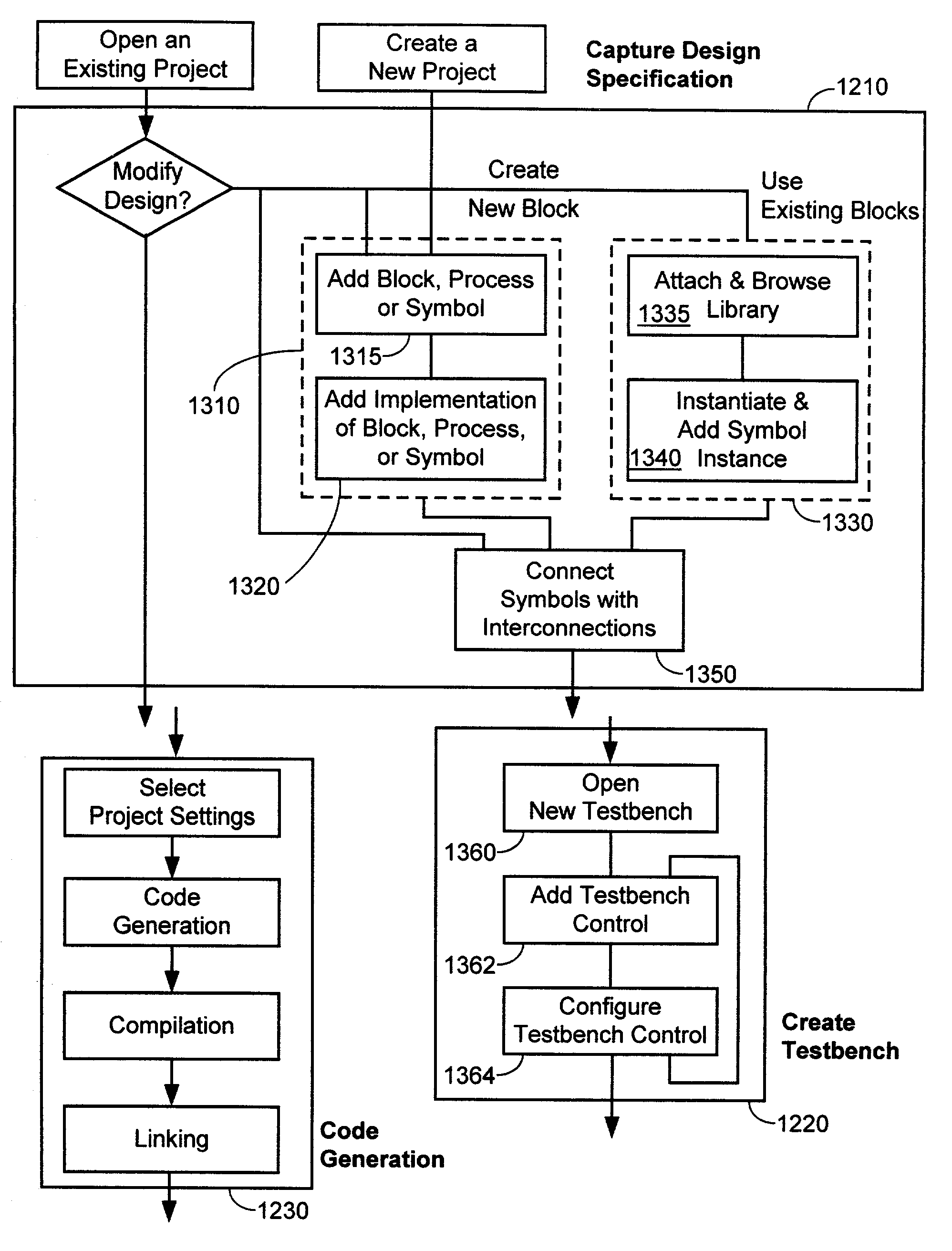

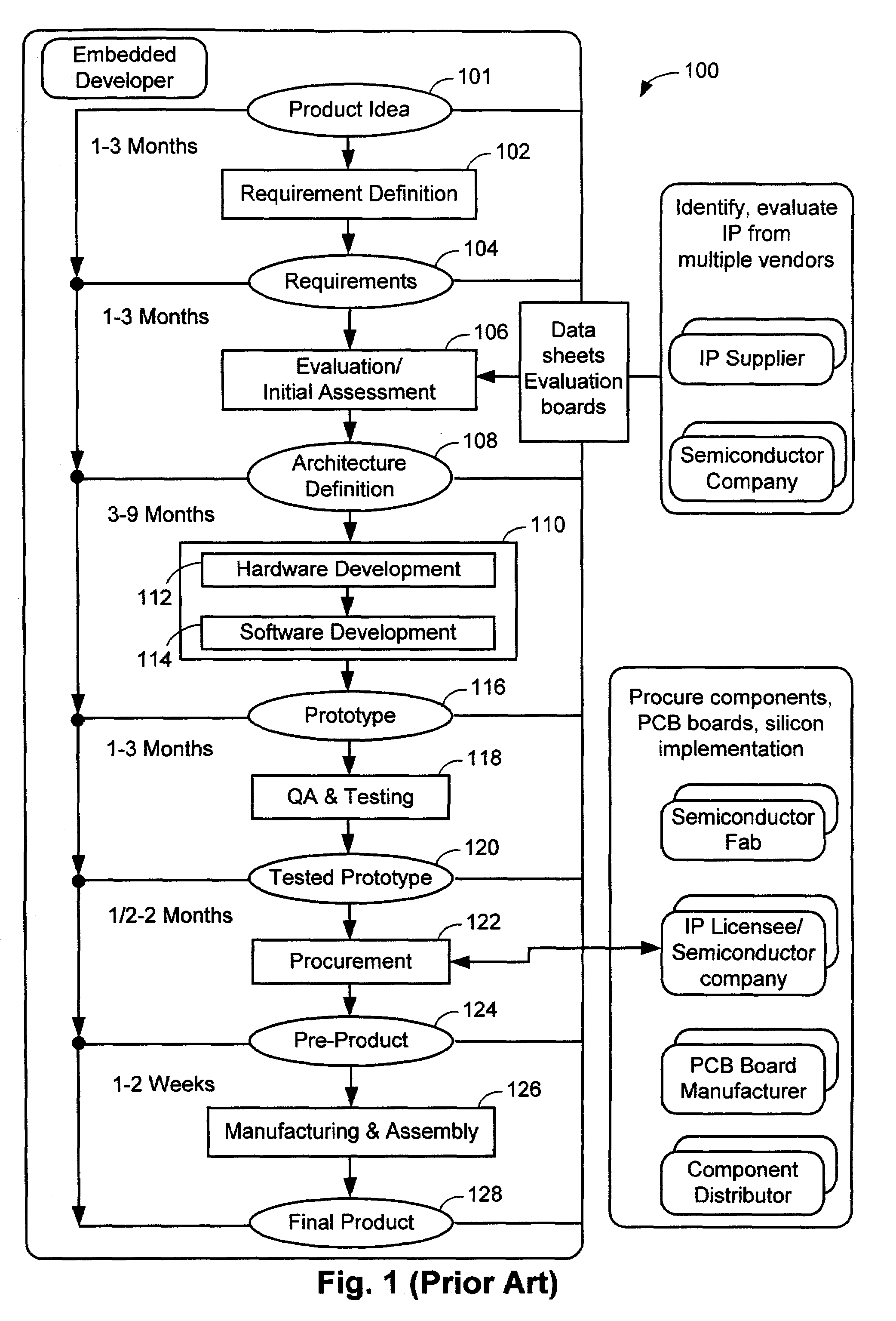

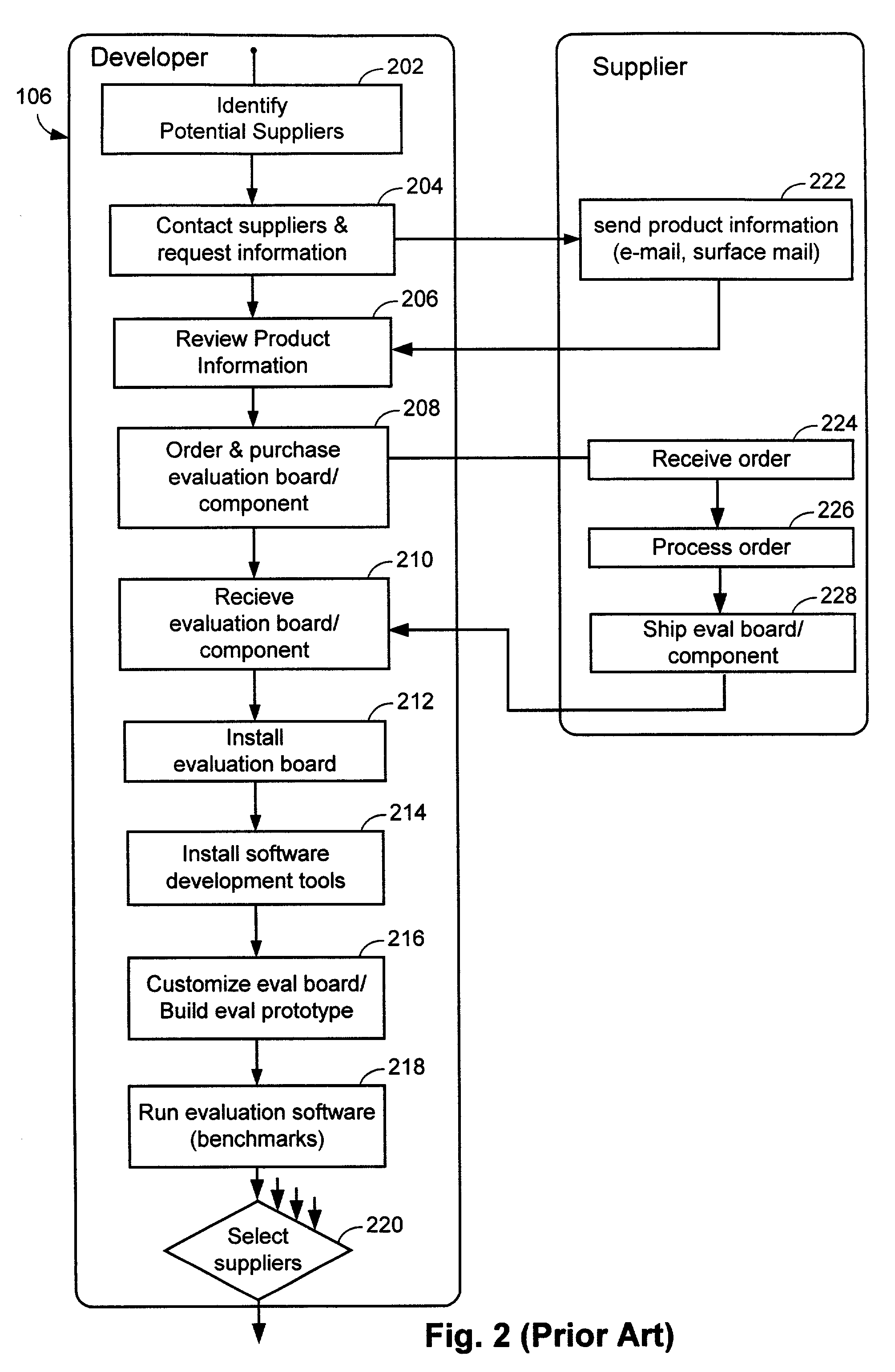

An integrated design environment (IDE) is disclosed for forming virtual embedded systems. The IDE includes a design language for forming finite state machine models of hardware components that are coupled to simulators of processor cores, preferably instruction set accurate simulators. A software debugger interface permits a software application to be loaded and executed on the virtual embedded system. A virtual test bench may be coupled to the simulation to serve as a human-machine interface. In one embodiment, the IDE is provided as a web-based service for the evaluation, development and procurement phases of an embedded system project. IP components, such as processor cores, may be evaluated using a virtual embedded system. In one embodiment, a virtual embedded system is used as an executable specification for the procurement of a good or service related to an embedded system.

Owner:SYNOPSYS INC

Adding complex instruction extensions defined in a standardized language to a microprocessor design to produce a configurable definition of a target instruction set, and hdl description of circuitry necessary to implement the instruction set, and development and verification tools for the instruction set

InactiveUS6477697B1Fast and reliable developmentGeneral purpose stored program computerCAD network environmentApplication softwareProcessor design

An automated processor design tool uses a description of customized processor instruction set extensions in a standardized language to develop a configurable definition of a target instruction set, a Hardware Description Language description of circuitry necessary to implement the instruction set, and development tools such as a compiler, assembler, debugger and simulator which can be used to develop applications for the processor and to verify it. The standardized language is capable of handling instruction set extensions which modify processor state or use configurable processors. By providing a constrained domain of extensions and optimizations, the process can be automated to a high degree, thereby facilitating fast and reliable development.

Owner:TENSILICA

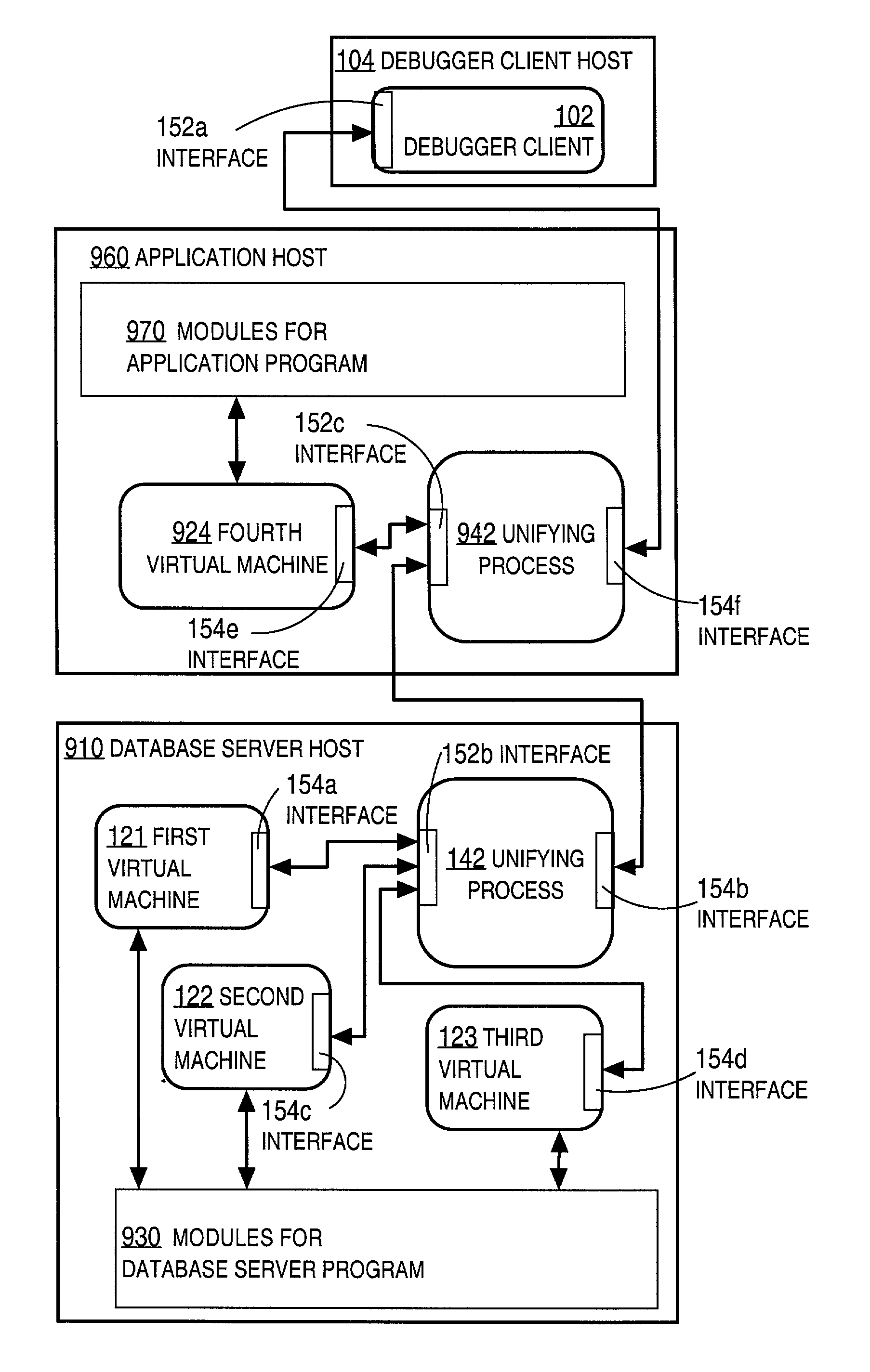

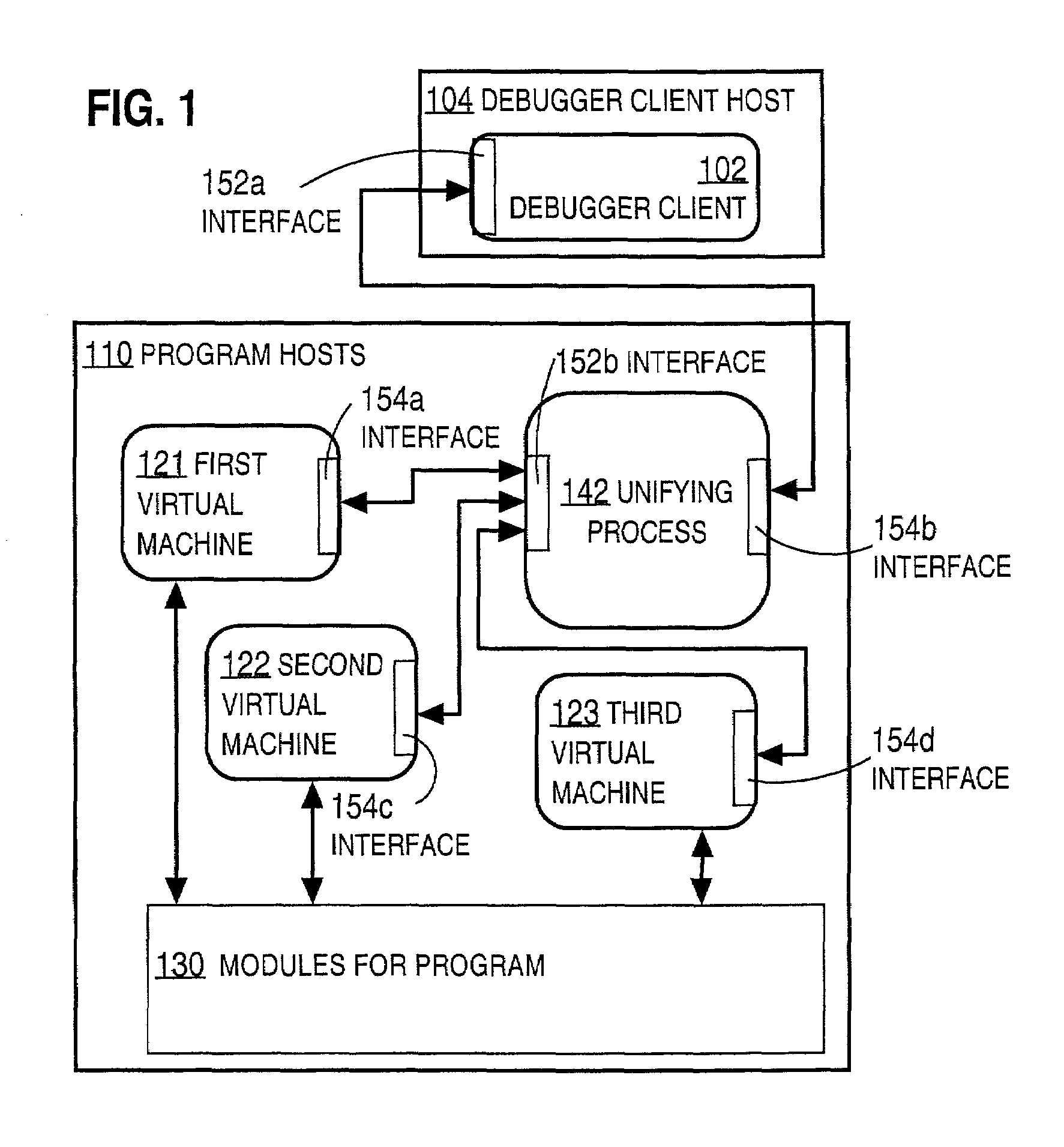

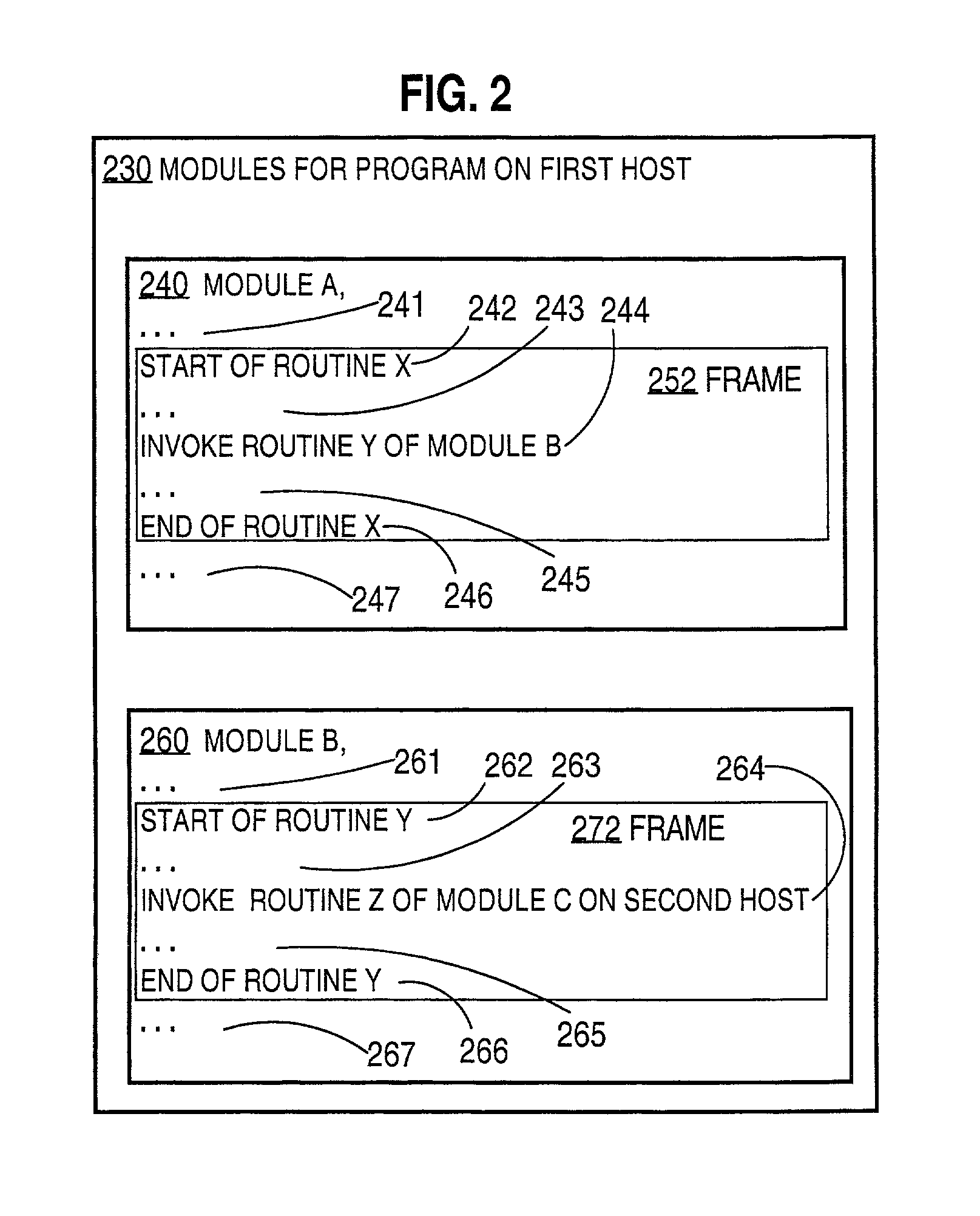

Techniques for debugging computer programs involving multiple computing machines

InactiveUS7350194B1Error detection/correctionSpecific program execution arrangementsClient-sideDebugger

Techniques for debugging a computer program that includes multiple modules executing on multiple machines include receiving, at a unifying component, first data from a first machine. The first data indicates debugging information generated by the first machine. Second data is also received at the unifying component from a second machine. The second data indicates debugging information generated by the second machine. Based on the first data and the second data, third data is formed indicating a single integrated representation of debugging information for the computer program. The unifying component allows debugging information from several machines to be integrated and then presented to a user through a single debugger client.

Owner:ORACLE INT CORP

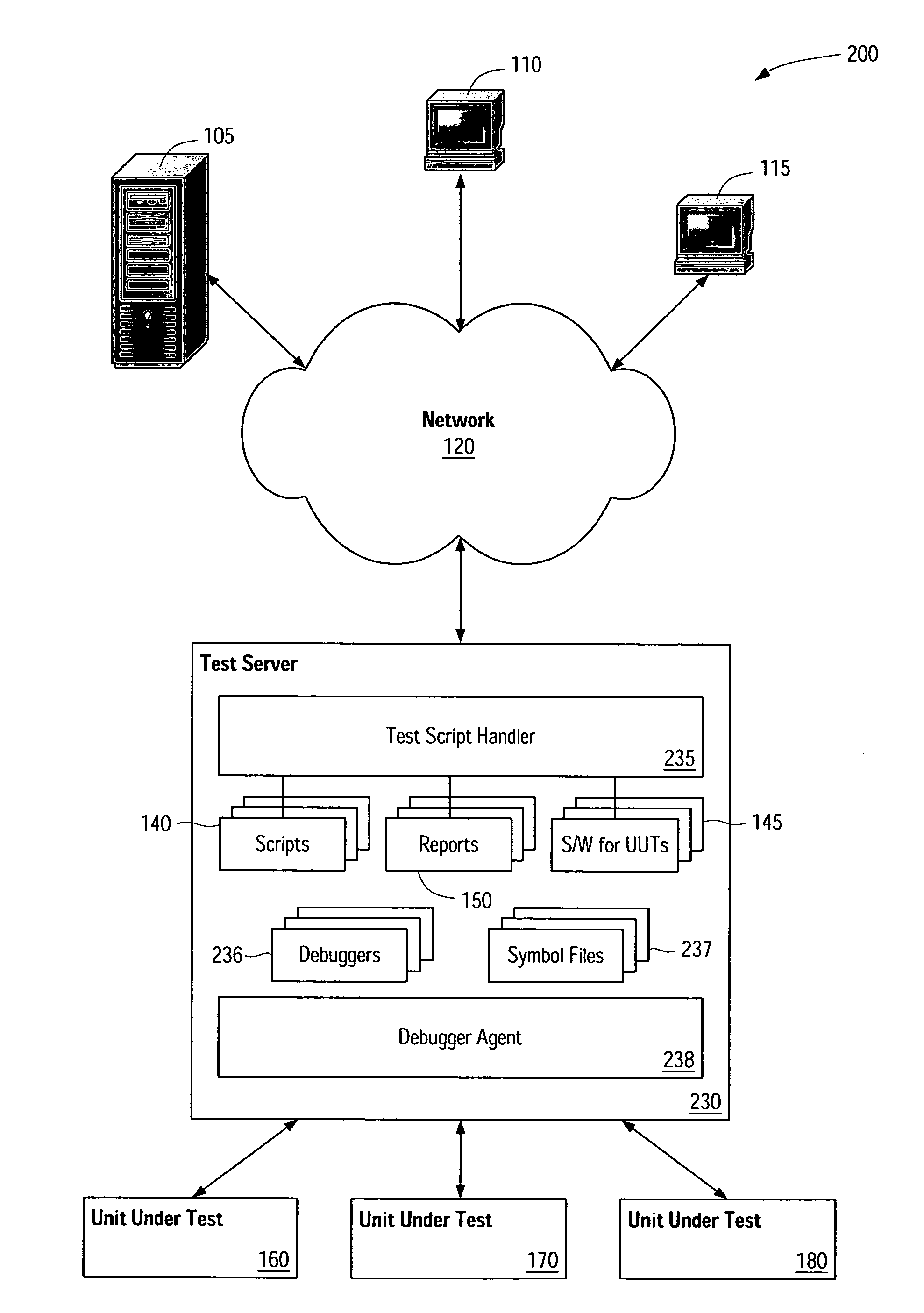

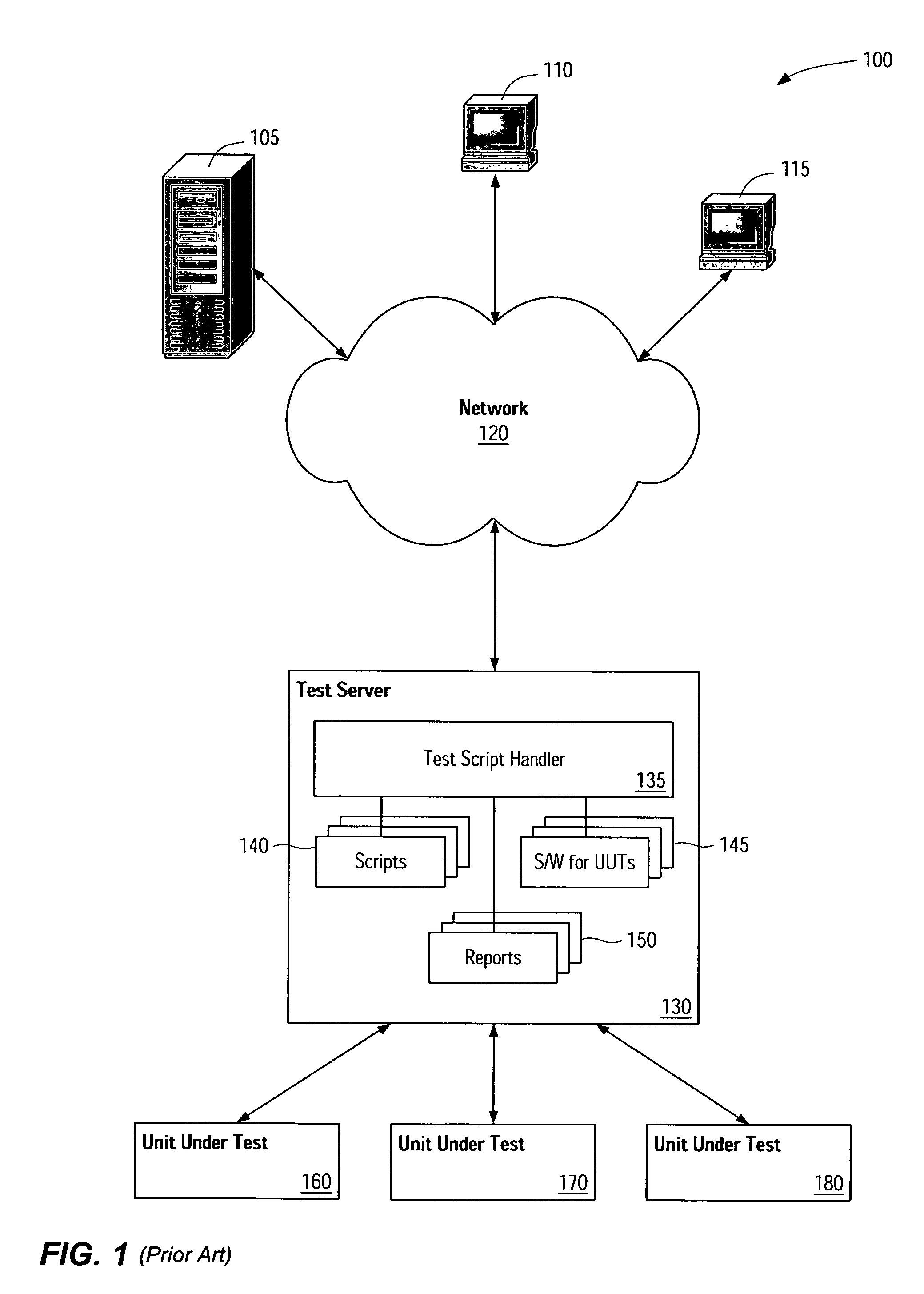

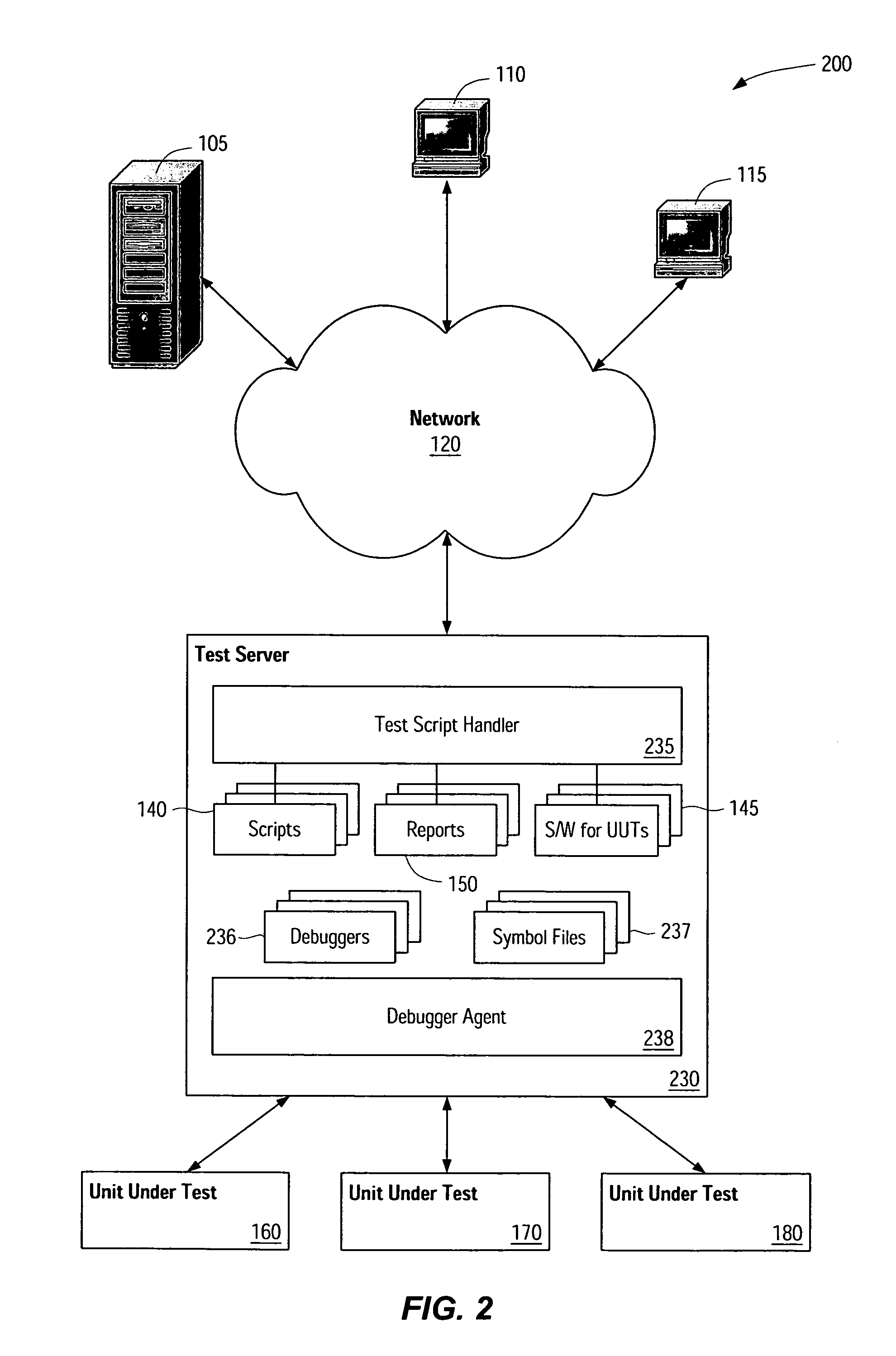

Source code debugging method and apparatus for use in script testing environment

InactiveUS7721265B1Error detection/correctionSpecific program execution arrangementsTest scriptBiological activation

Systems, methods, apparatus and software can be implemented to provide a debugger agent, either separate form or integrated into the script-based testing platform, to coordinate the selection, activation, and or / operation of debuggers suitable for a particular unit and program under test. Such a debugger agent can provide run time monitoring and debugging activities where previously not possible. The debugger agent is generally independent agent, in that it can work with a variety of types of test scripts, test script handlers, programming languages, and debuggers without customization. Moreover, implementation generally needs no code instrumentation.

Owner:CISCO TECH INC

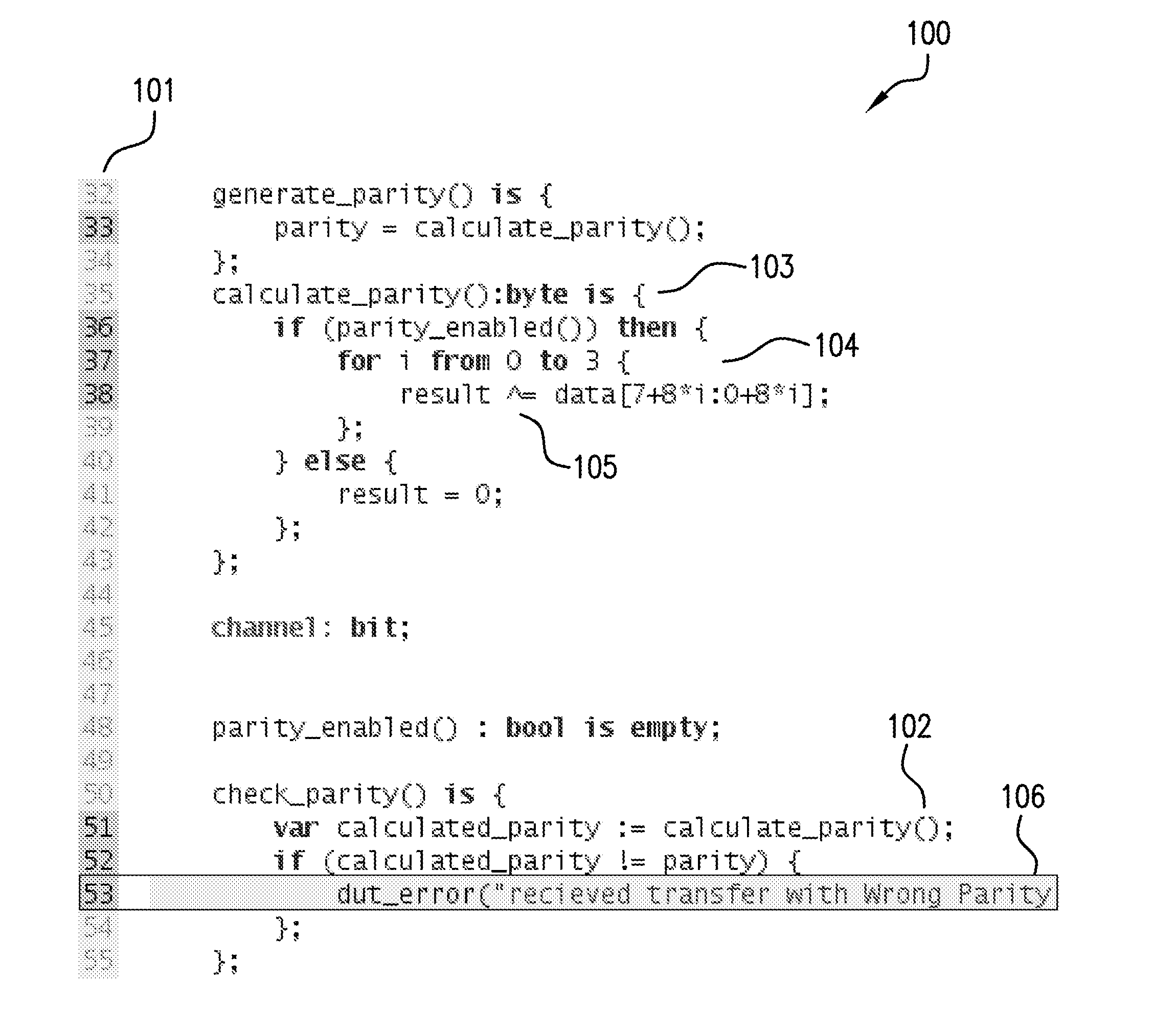

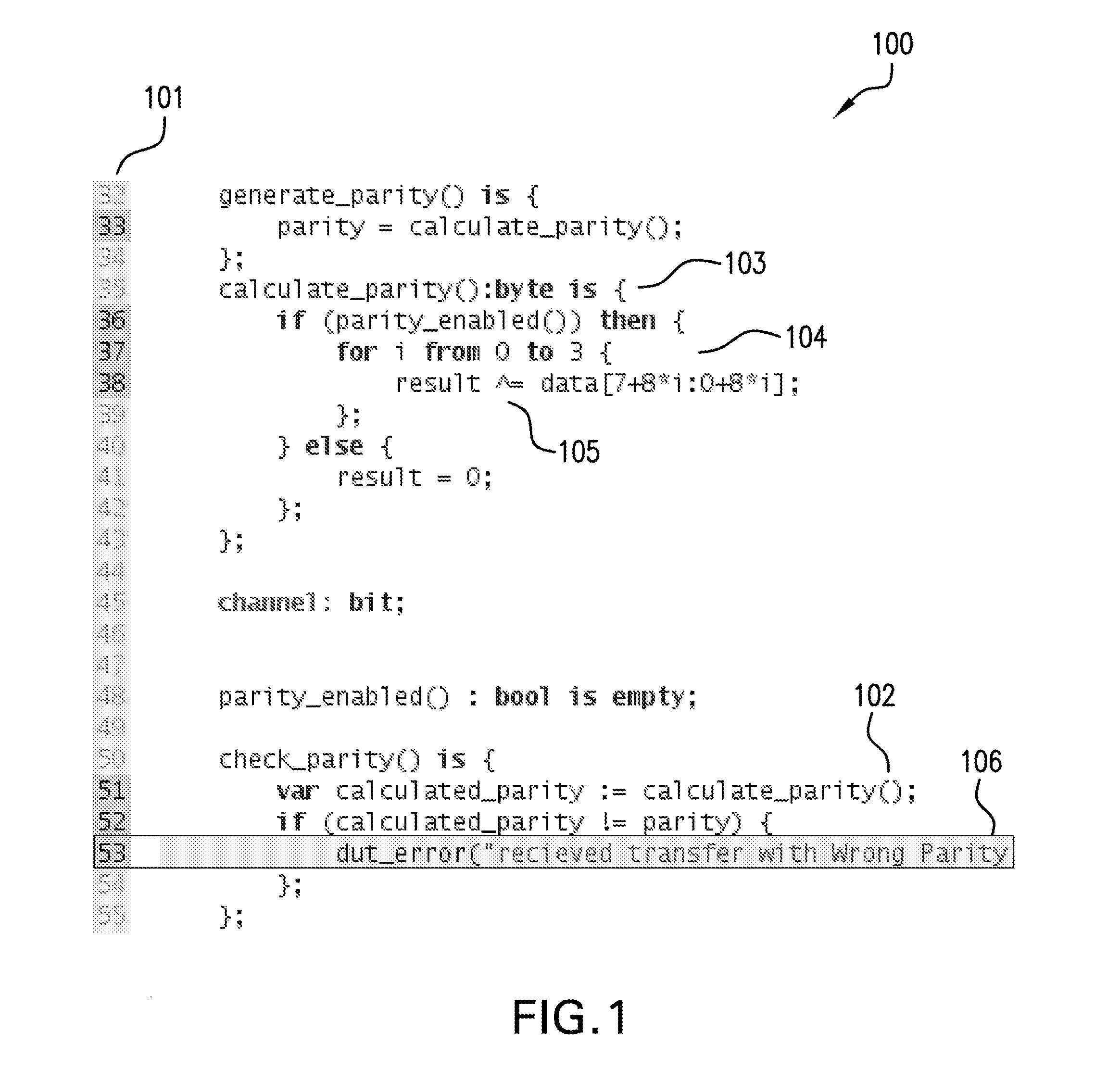

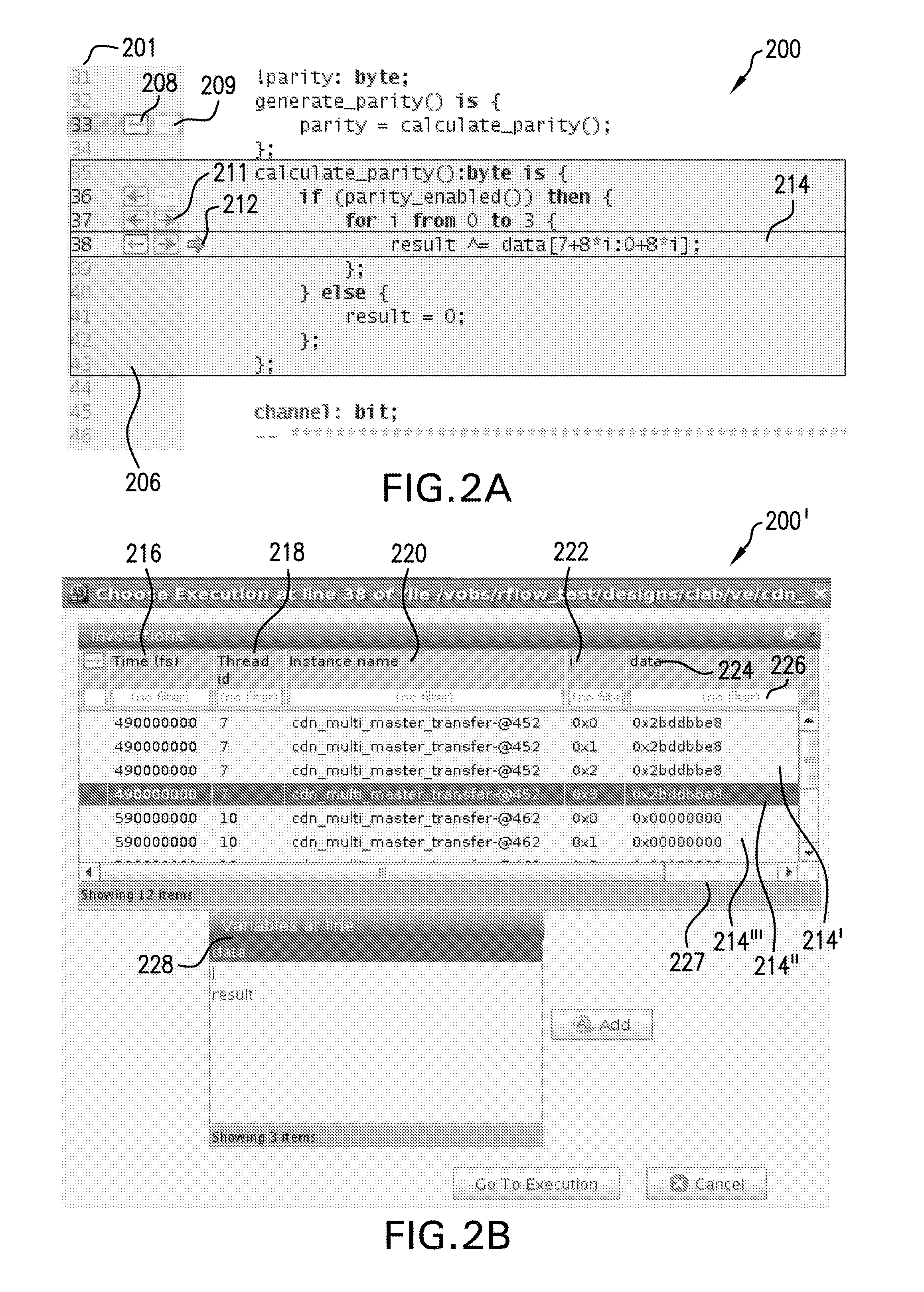

System and method for debugging computer program based on execution history

ActiveUS8935673B1Easy to debugEasy to navigateMemory loss protectionNuclear monitoringCode spaceSystem of record

A system and method are provided for enhanced navigation along execution time and code space in a debugger to assist a user in remediating errors, streamlining, or reverse engineering a computer program and the source code thereof. Snapshots of system states are recorded, a causality tree of commands is constructed through execution of the program to be debugged, and an intelligent display of system states captured during runtime and indexed or cross-referenced by time are displayed to the user in an intelligent manner to aid the user with certain debugging tasks. Additionally, further features in assisting the user to locate a root cause of an error or unexpected value and remediate that cause are also provided.

Owner:CADENCE DESIGN SYST INC

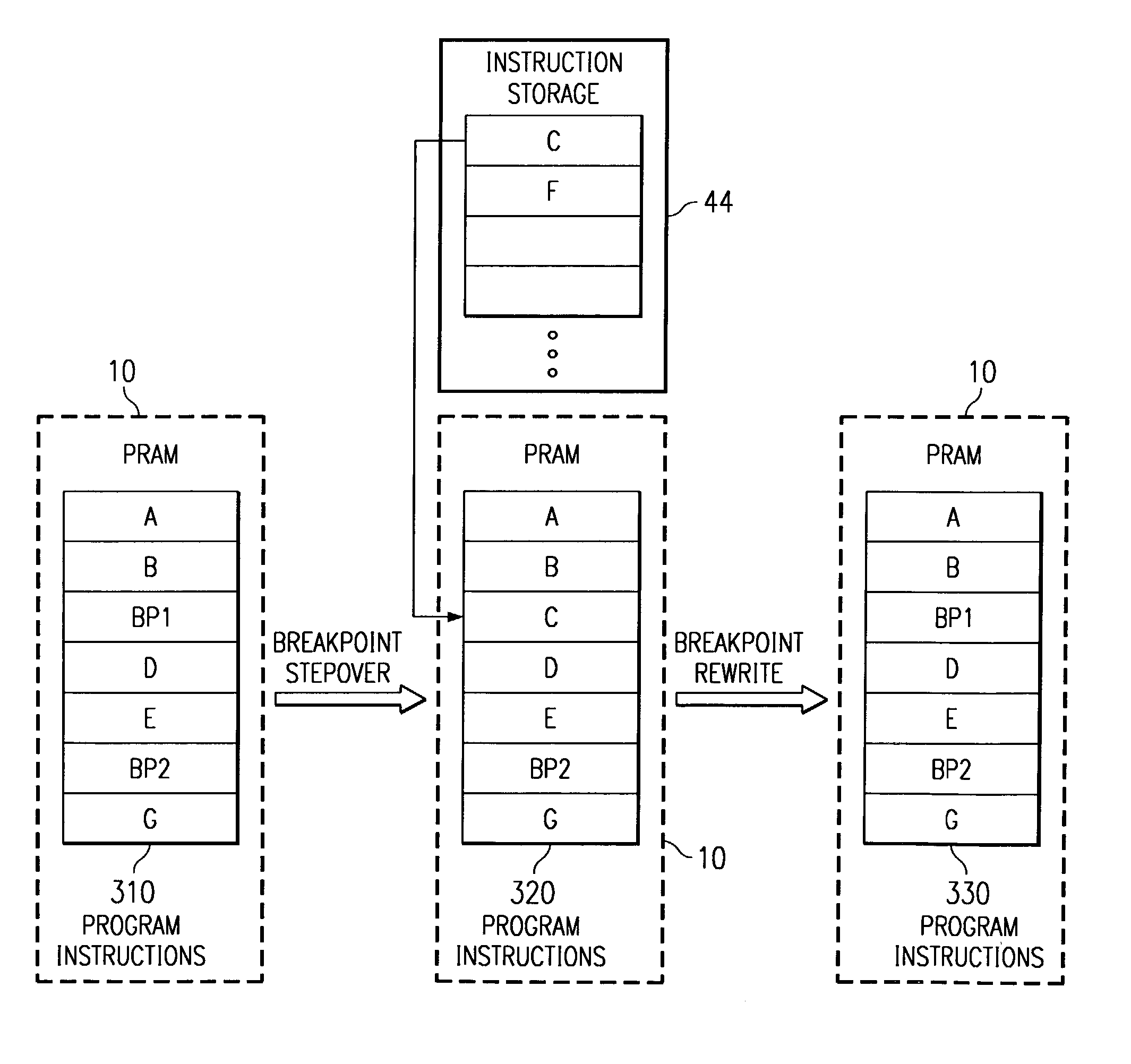

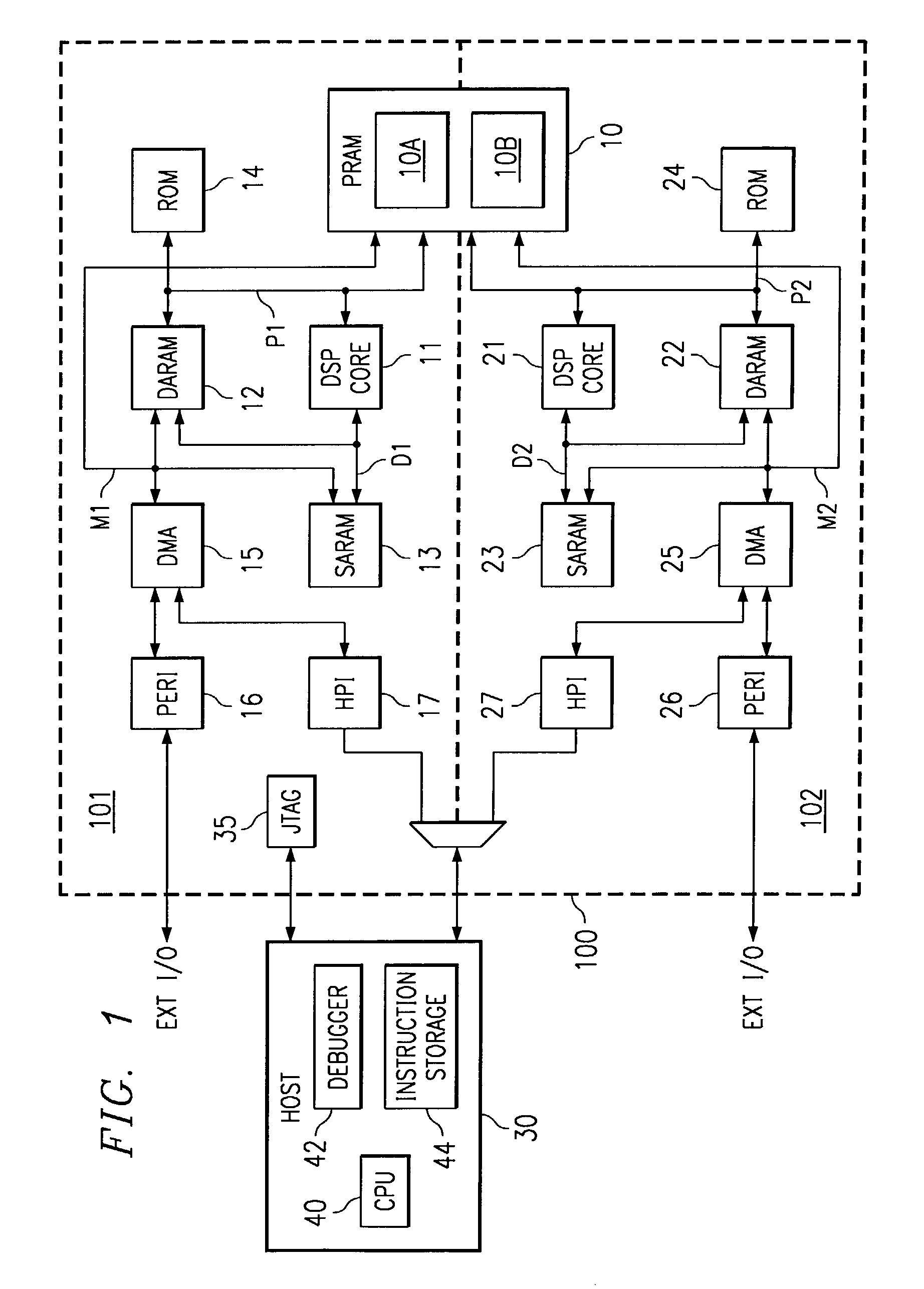

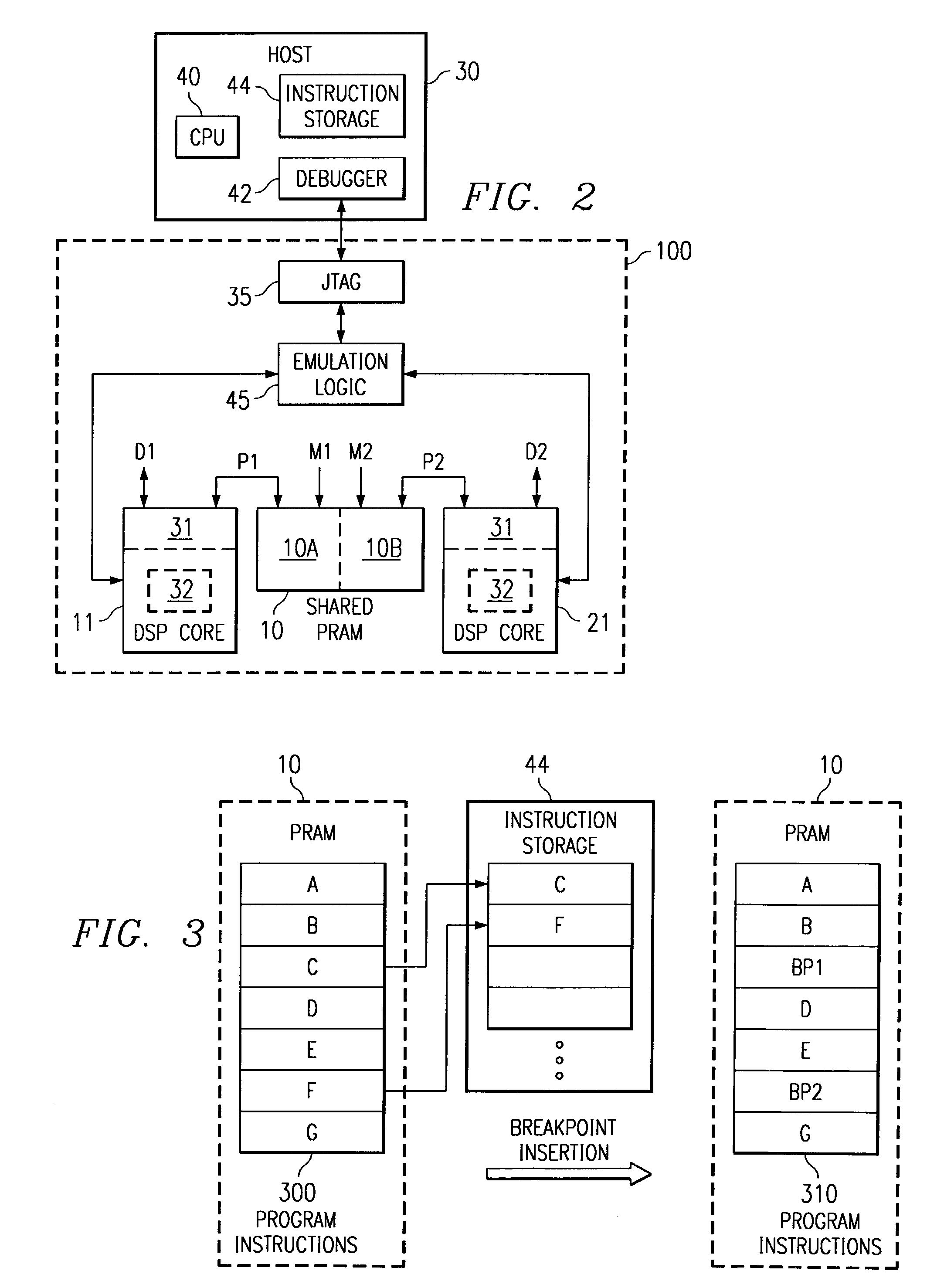

Debugger breakpoint management in a multicore DSP device having shared program memory

ActiveUS20030014736A1Software testing/debuggingSpecific program execution arrangementsProgram instructionAs Directed

A processing system comprises a digital signal processor (DSP) device and a host system on which the DSP device is implemented. The DSP device comprises a shared program memory and a plurality of processor subsystems coupled to the shared program memory to concurrently execute program instructions stored in the shared program memory. The host system is capable of independently debugging each subsystem. During debugging, the host device inserts breakpoints into the shared program memory and tracks the debug breakpoints to determine which subsystems are associated with the breakpoints. When a subsystem executes a breakpoint associated with that subsystem, the subsystem halts until the host gathers necessary debug information from the subsystem. However, when a subsystem executes a breakpoint that is not associated with that subsystem, the host system causes the subsystem to execute the original program instructions and proceed as directed.

Owner:TEXAS INSTR INC

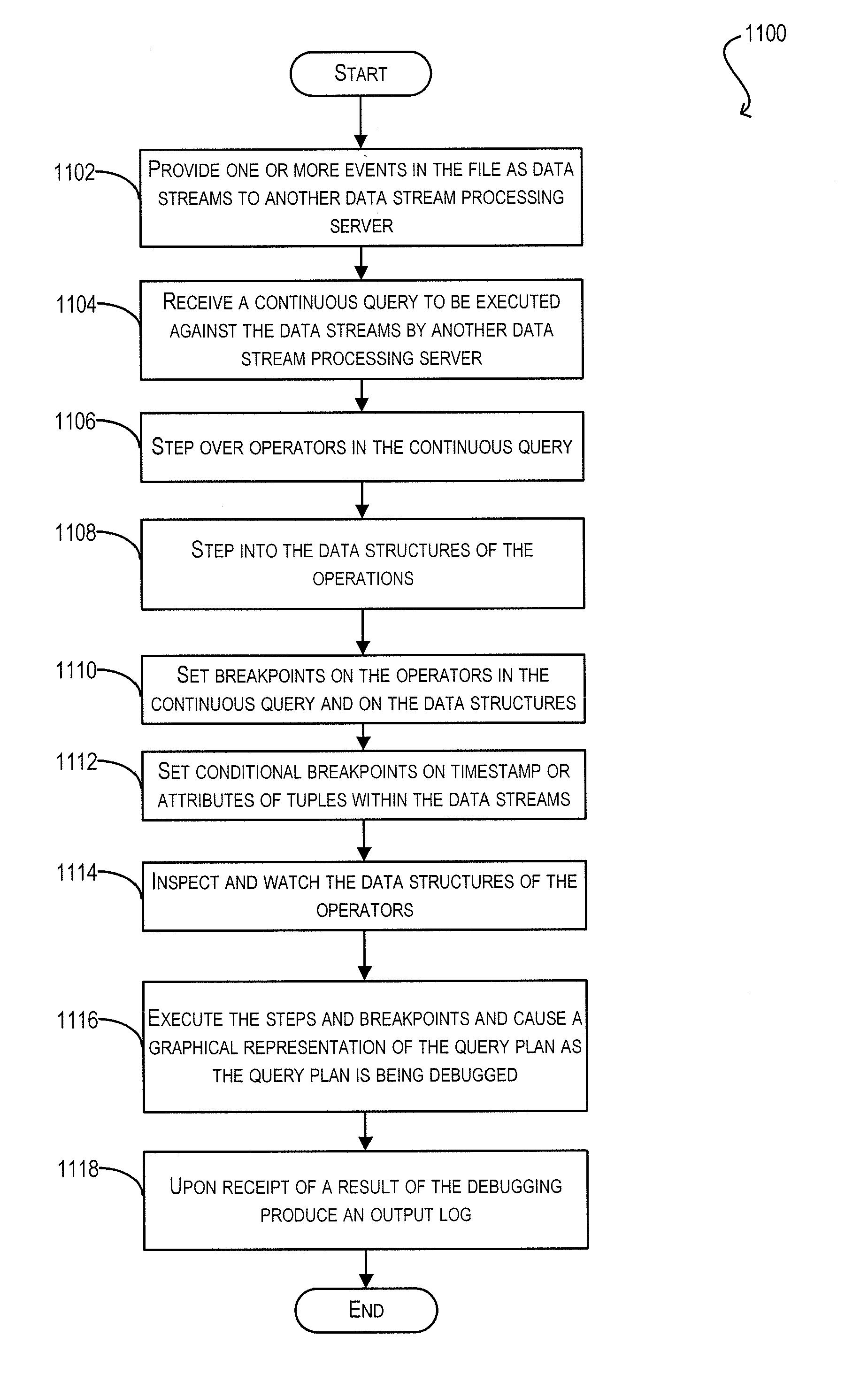

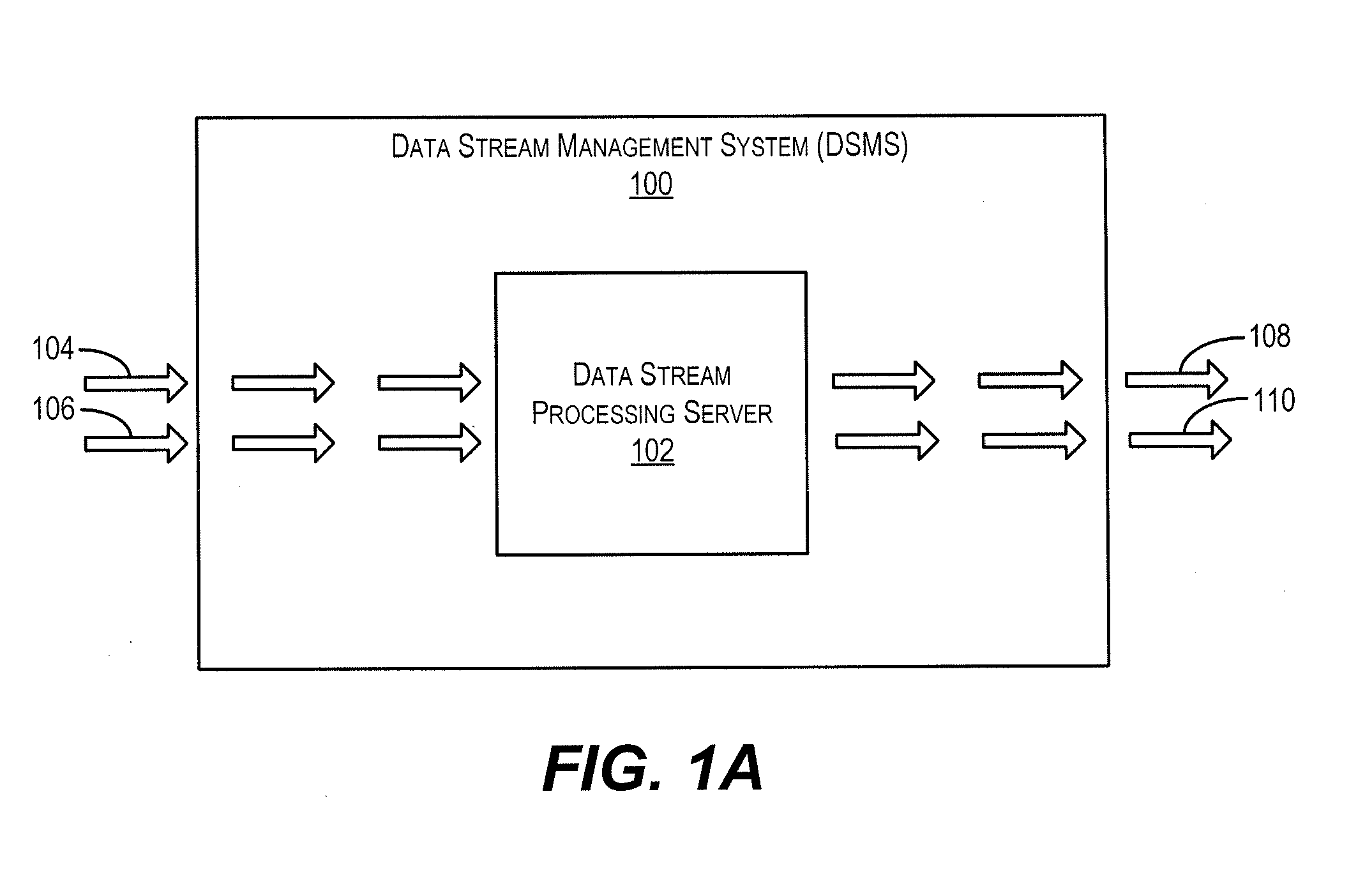

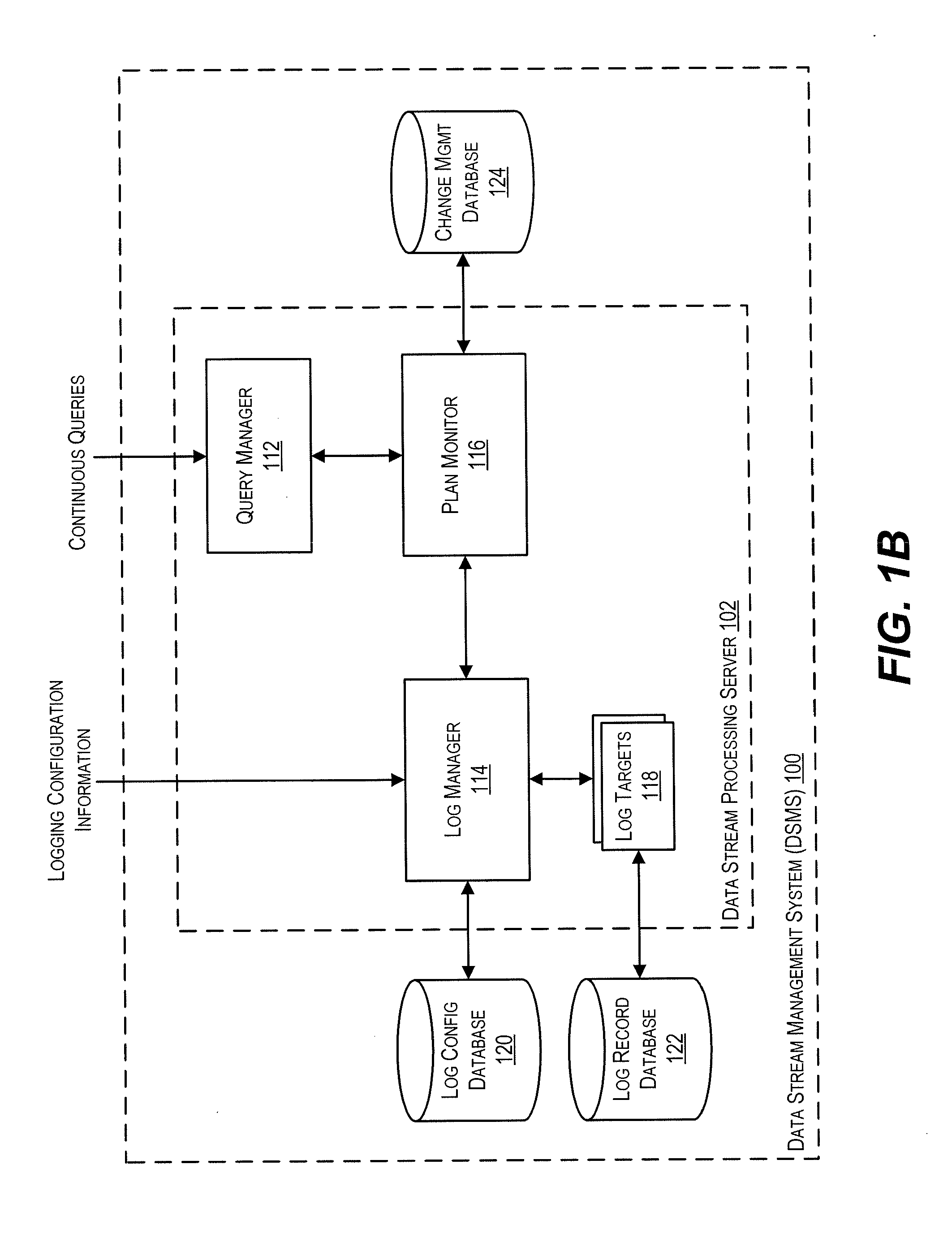

Continuous query language (CQL) debugger in complex event processing (CEP)

ActiveUS20130014088A1Software testing/debuggingSoftware designComplex event processingData stream processing

A method including receiving, at a computer system, debugging configuration information specifying a functional area of a data stream processing server to be debugged, is described. Furthermore, the method includes identifying, by the computer system, an object associated with the functional area that has been instantiated by the data stream processing server, determining, by the computer system, that tracing for the object is enabled to perform the debugging, and instantiating, by the computer system, a tracelet associated with the object. Further, the method includes stepping, by the computer system, through the tracelet associated with the object to debug the object, and displaying, by the computer system, a visual representation of debugging results associated with the object.

Owner:ORACLE INT CORP

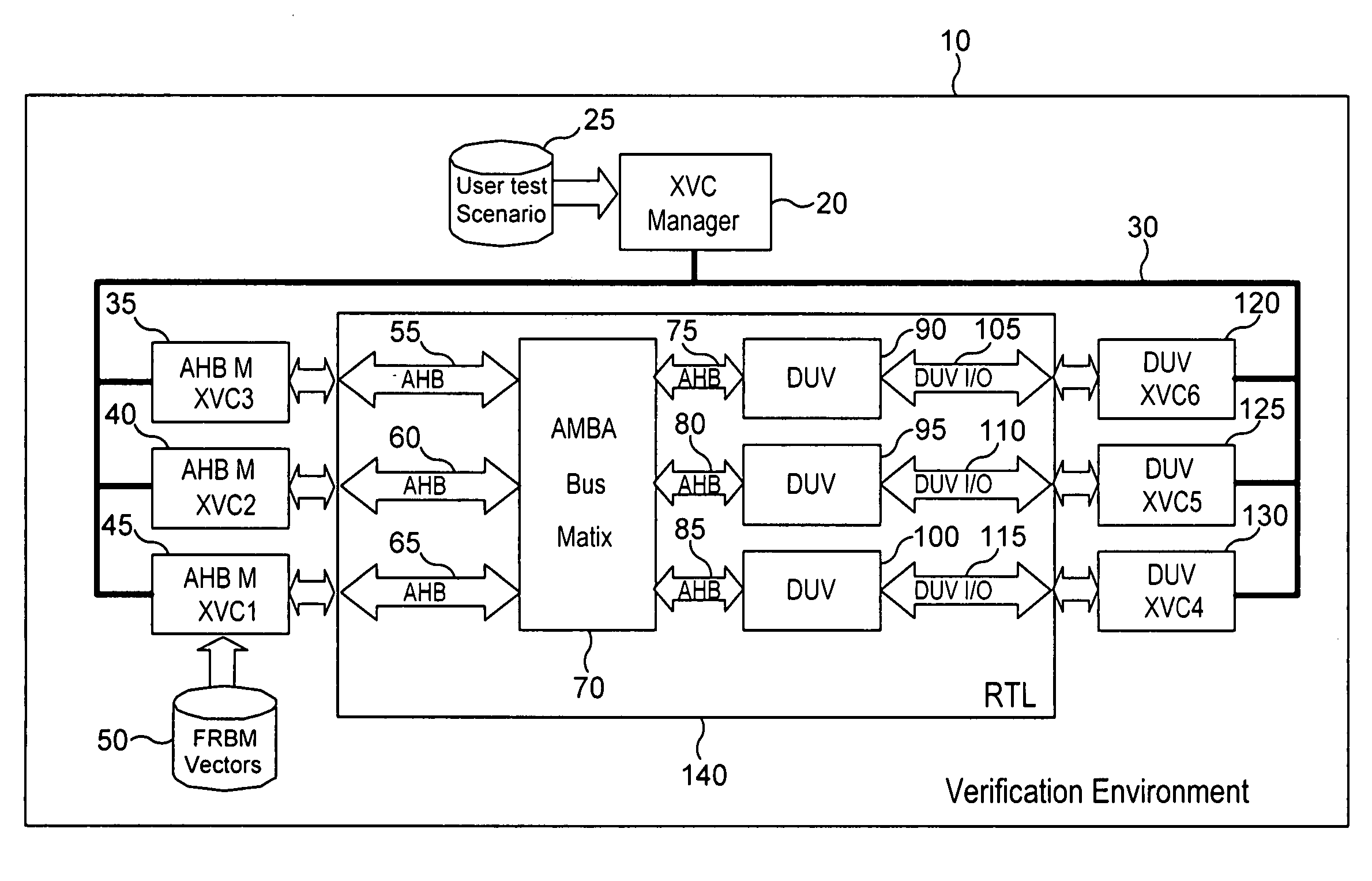

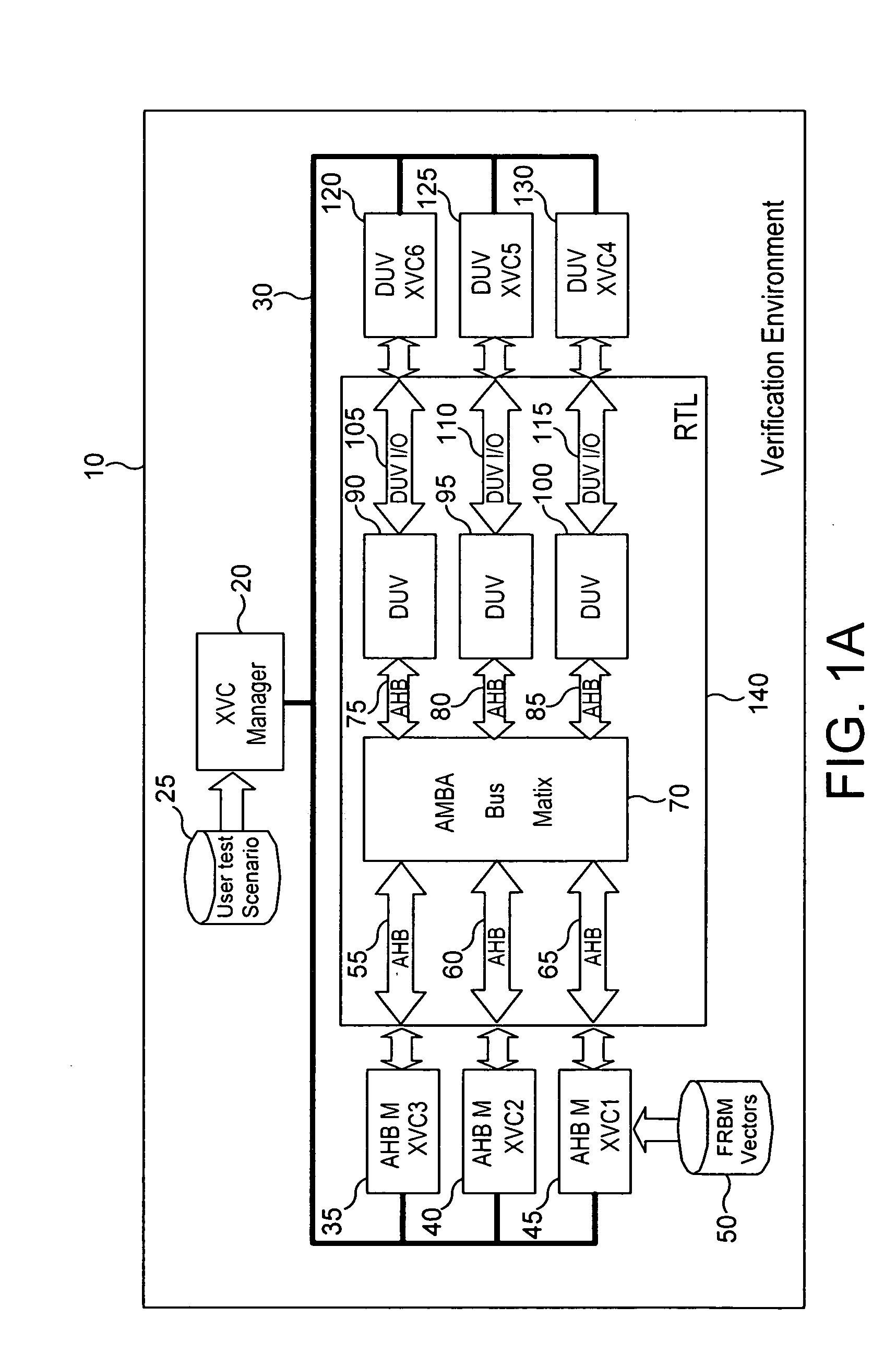

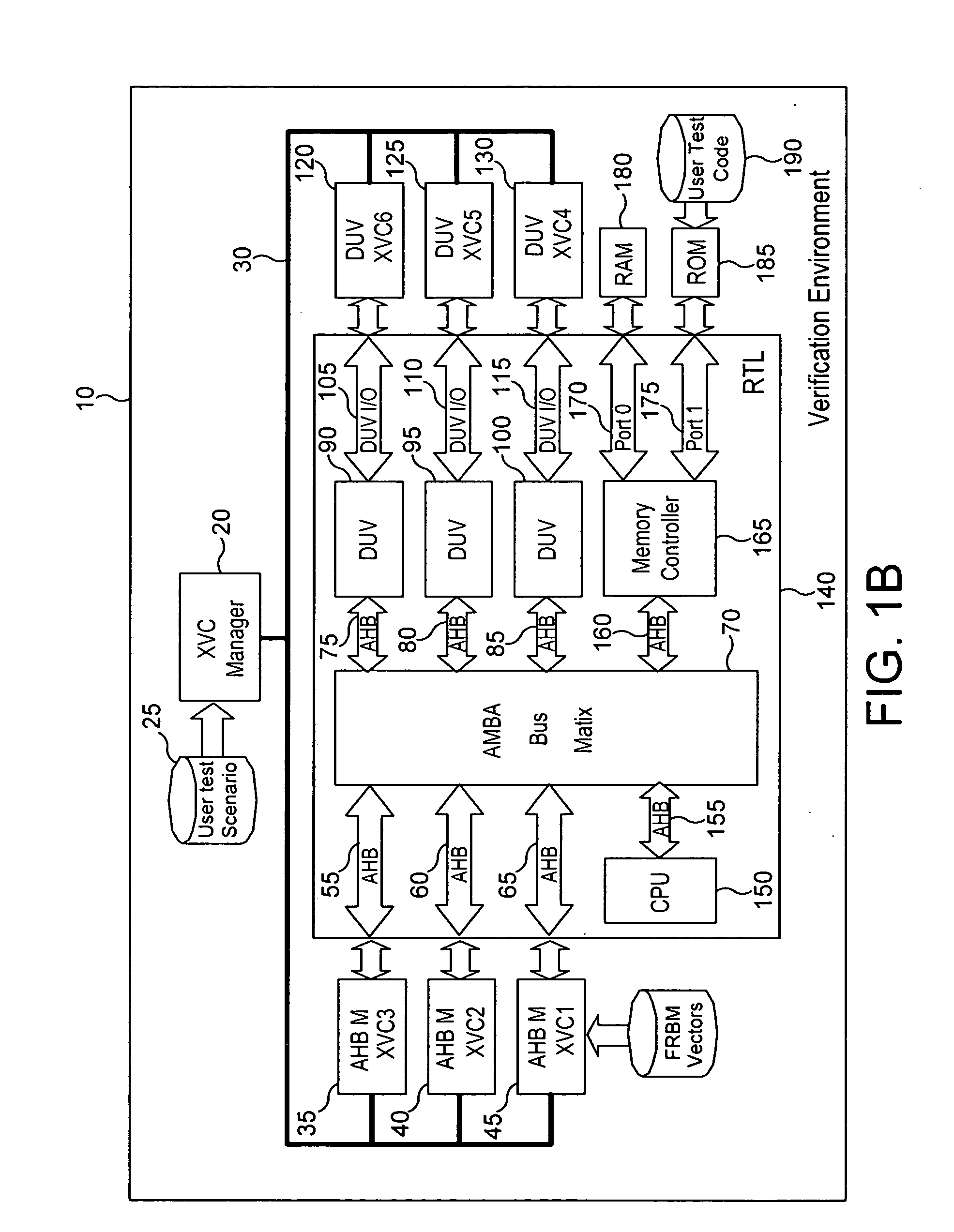

Apparatus and method for performing hardware and software co-verification testing

ActiveUS20050165597A1Flexible and efficient techniqueFlexible and efficientError detection/correctionSoftware simulation/interpretation/emulationProcessing elementTest management

An apparatus, method and computer program product are provided for performing a sequence of verification tests to perform hardware and software co-verification on a system under verification. The apparatus comprises a plurality of signal interface controllers operable to be coupled to the system under verification, with each signal interface controller being operable to perform one or more test actions transferring at least one of one or more stimulus signals and one or more response signals between a corresponding portion of the system under verification and the signal interface controller during performance of the sequence of verification tests. A debugger is also provided which is operable to control operation of a processing unit associated with the system under verification, the processing unit being operable to execute software routines. A debugger signal interface controller is arranged to interface with the debugger and to perform one or more test actions transferring at least one of one or more stimulus signals and one or more response signals between the debugger and the debugger signal interface controller during performance of the sequence of verification tests. A test manager coupled to the plurality of signal interface controllers and the debugger signal interface controller is operable to transfer test controlling messages to these interface controllers identifying the test actions to be performed. By this approach, the test manager is operable to control the operation of the processing unit via the debugger signal interface controller and the debugger in order to co-ordinate the execution of the software routines with a sequence of verification tests. This has been found to be a particularly efficient technique for performing hardware and software co-verification.

Owner:ARM LTD

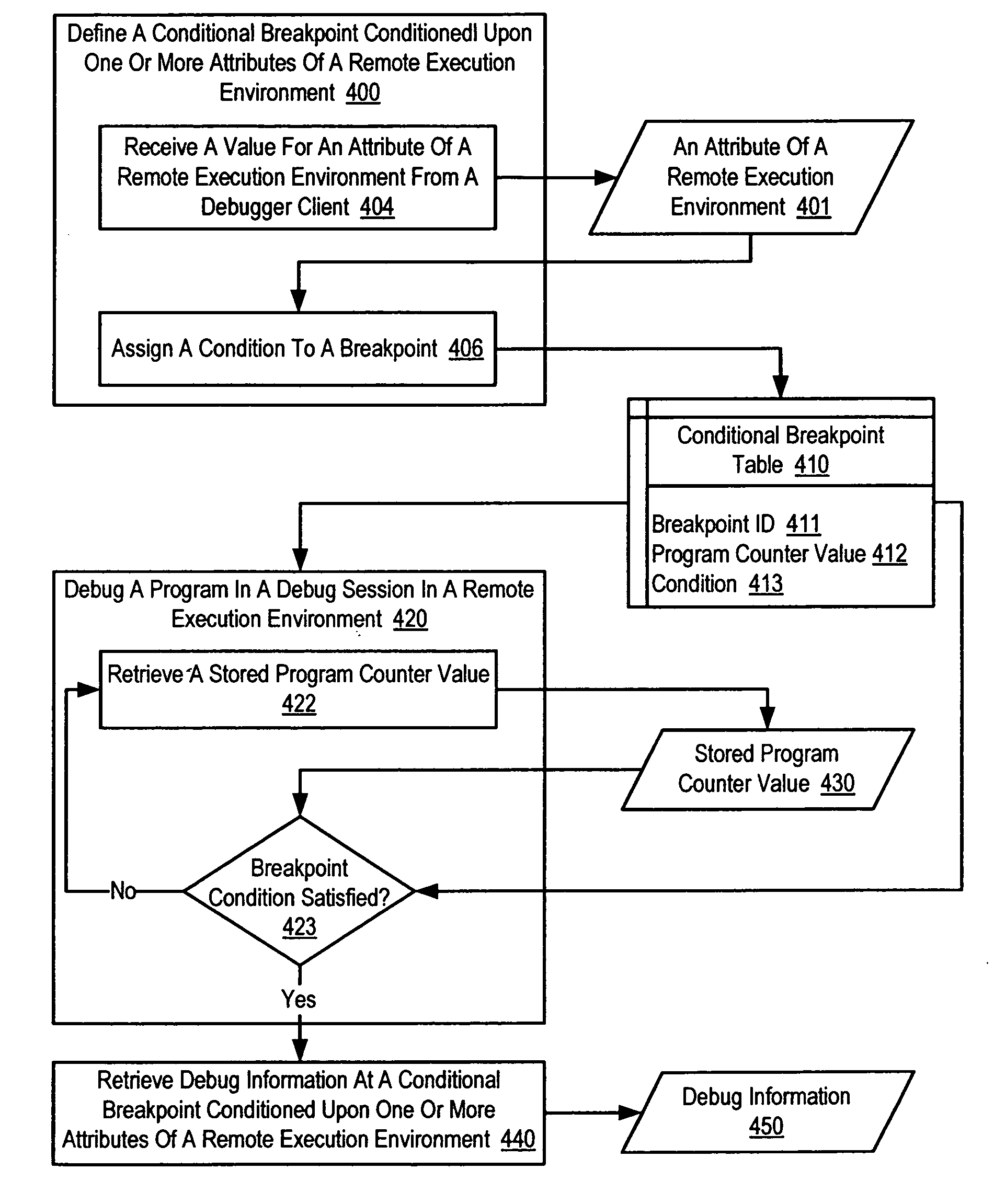

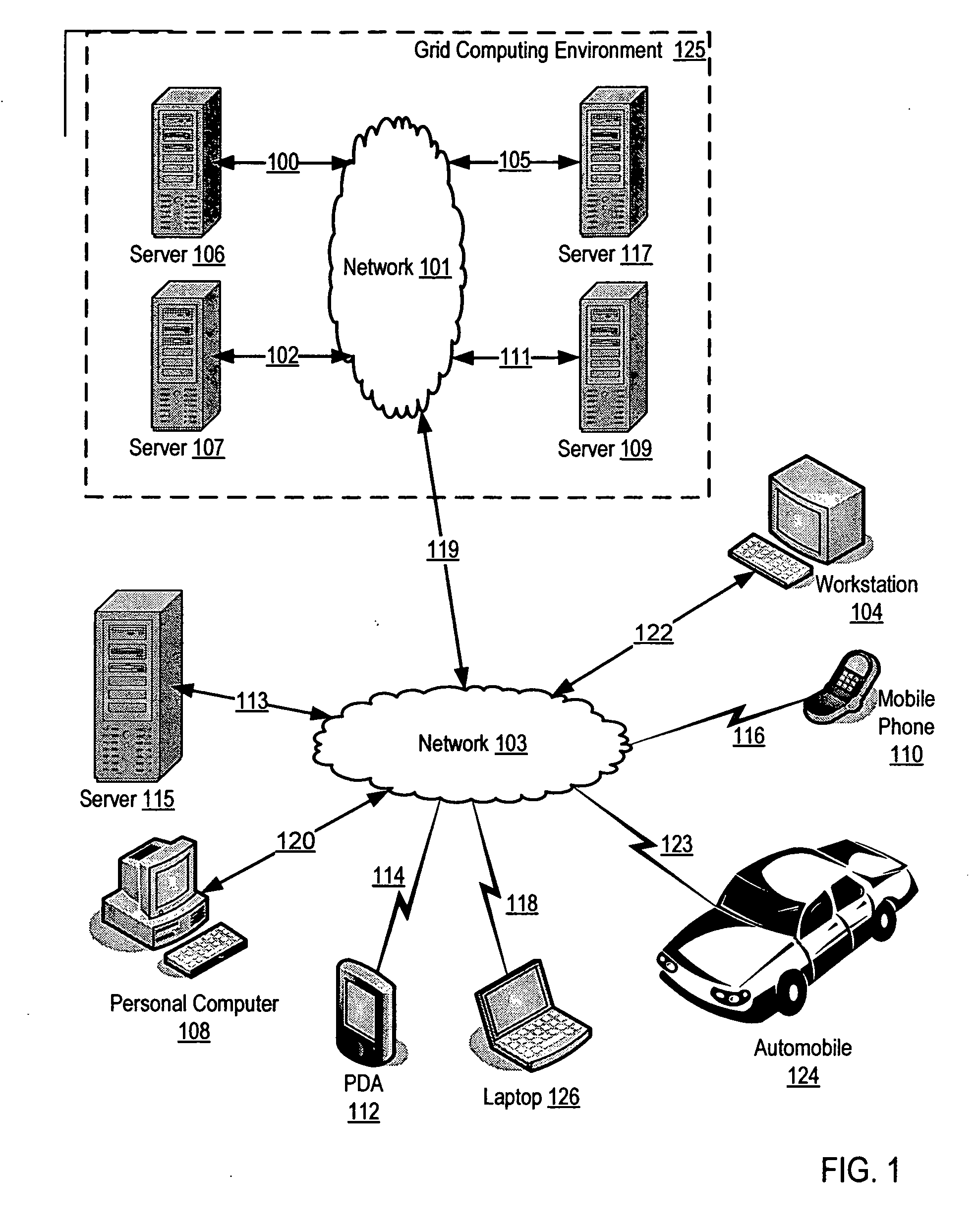

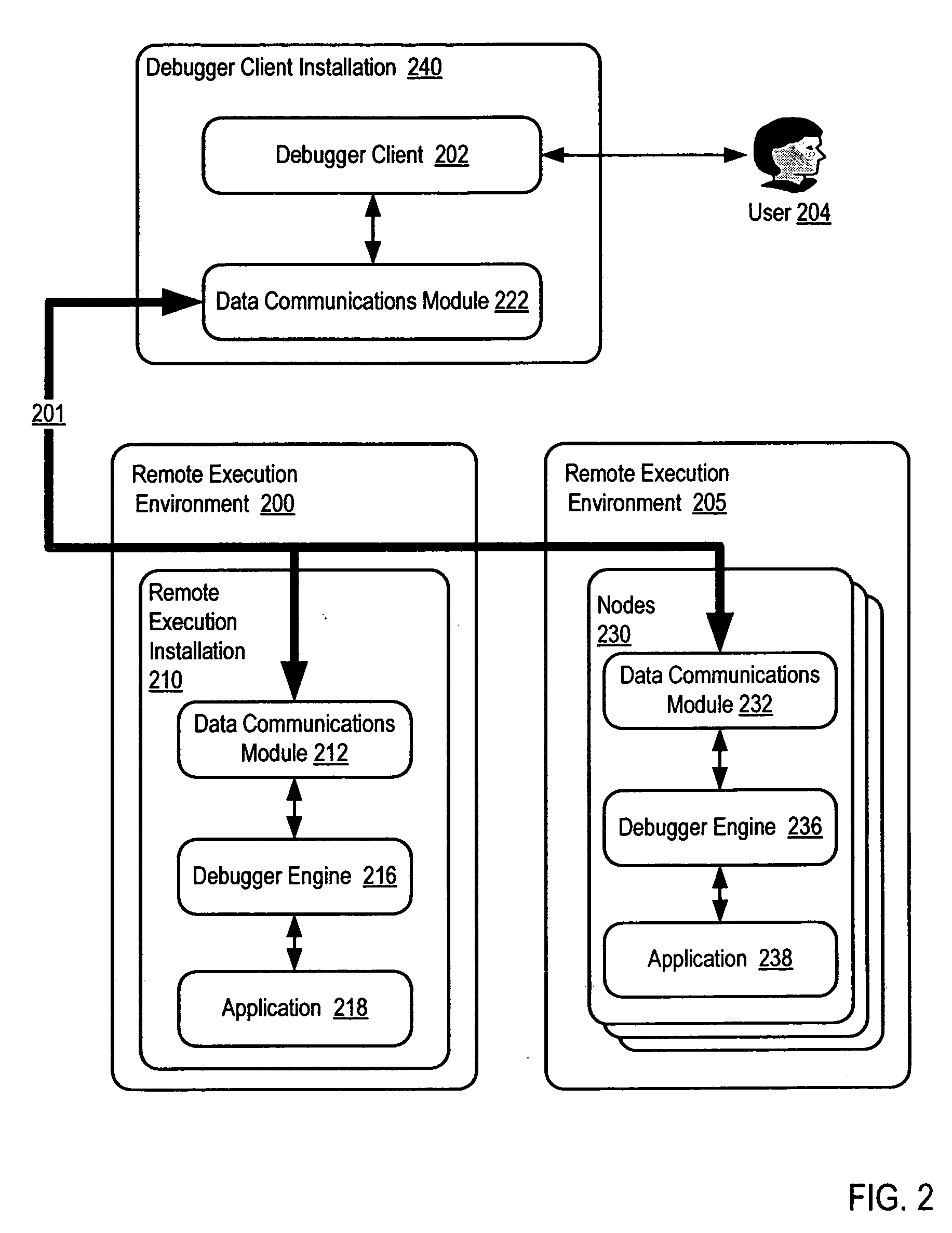

Debugging a computer program in a distributed debugger

InactiveUS20070168994A1Error detection/correctionSpecific program execution arrangementsDebuggerComputer program

Methods, apparatus, and computer program products are disclosed for debugging a computer program in a distributed debugger that include defining a conditional breakpoint conditioned upon one or more attributes of a remote execution environment, debugging the computer program in a debug session in the remote execution environment, and retrieving debug information at the breakpoint conditioned upon one or more attributes of the remote execution environment.

Owner:IBM CORP

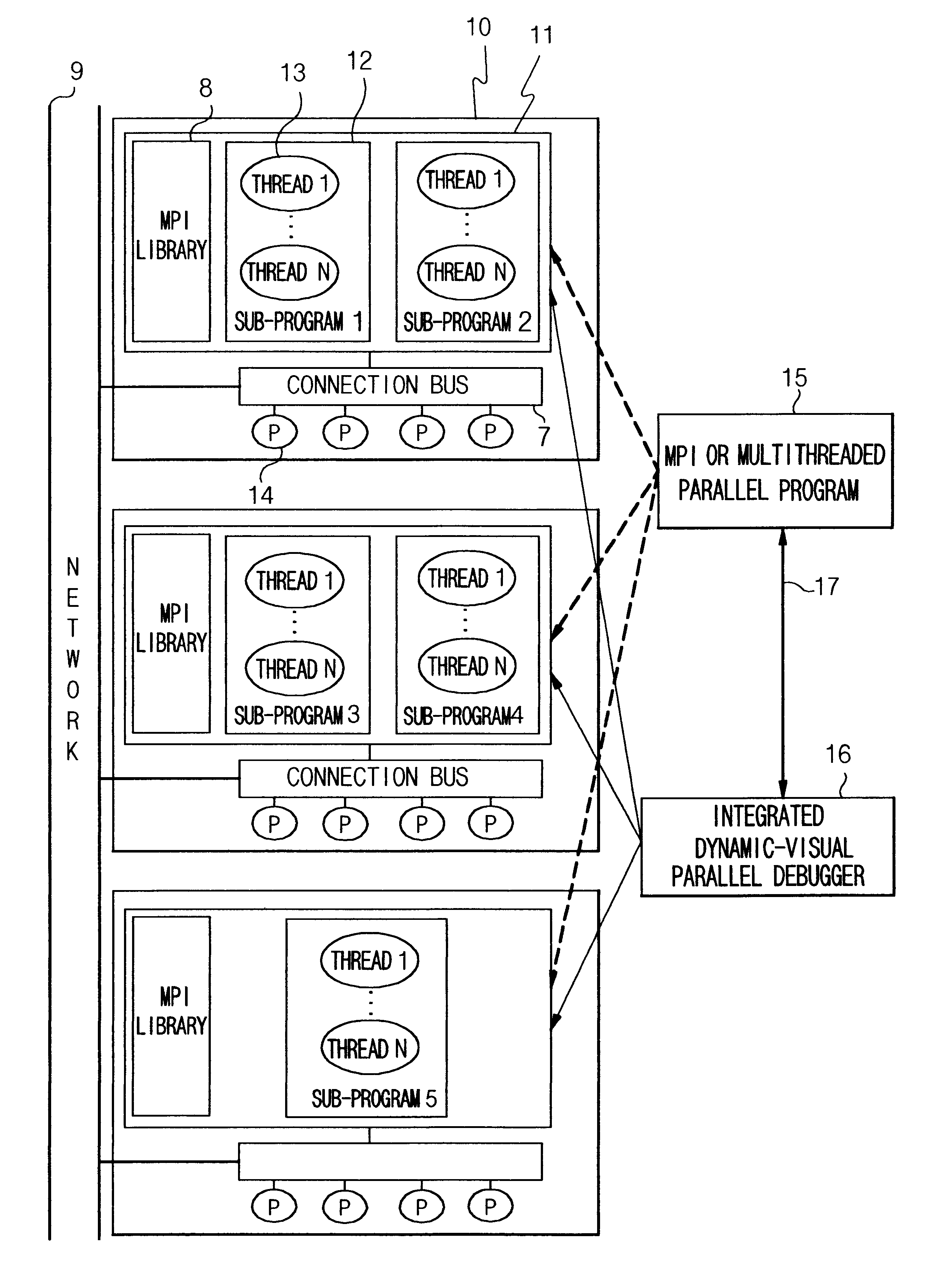

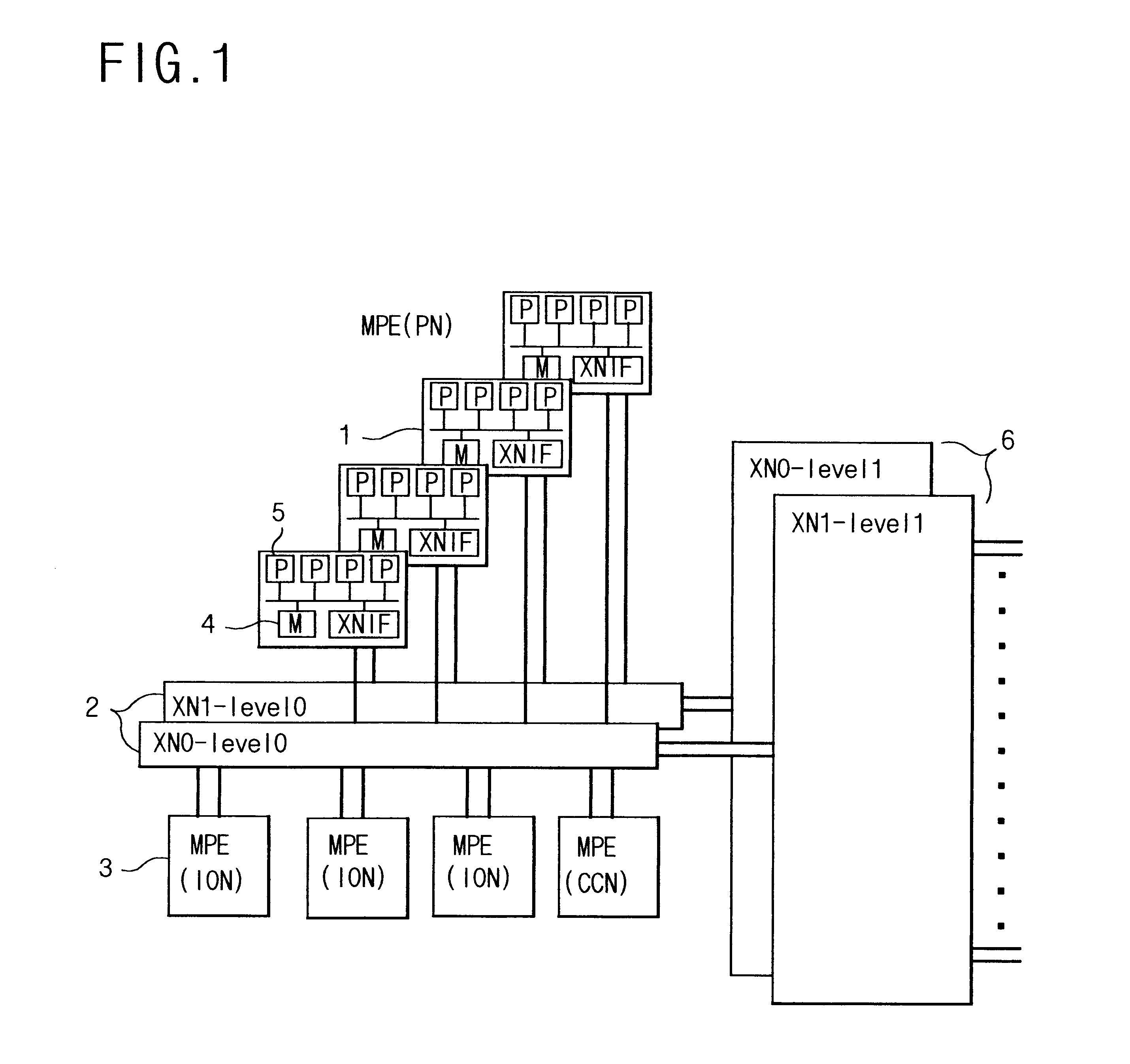

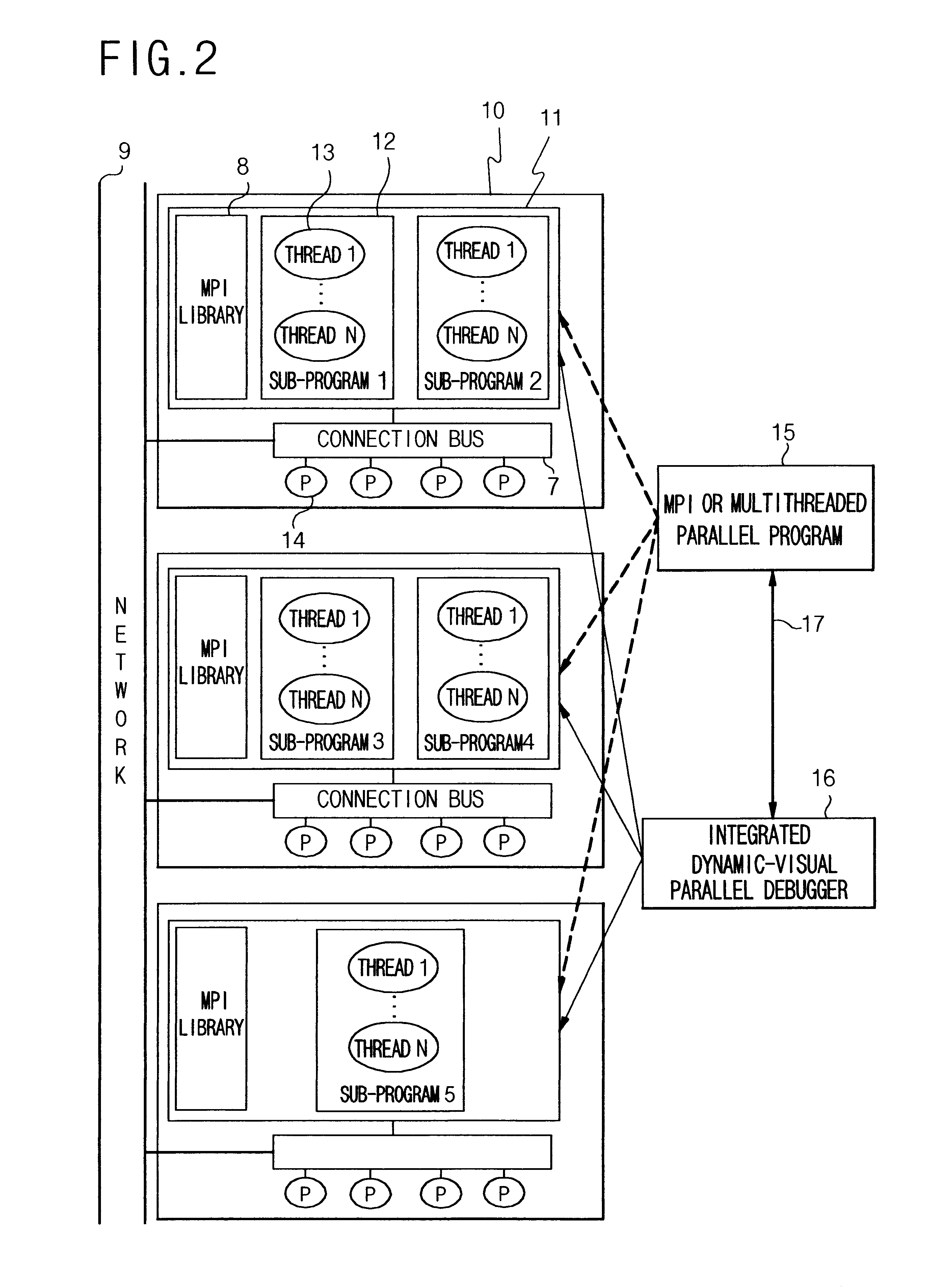

Integrated dynamic-visual parallel debugging apparatus and method thereof

InactiveUS6275956B1Software testing/debuggingSpecific program execution arrangementsGraphicsGraphical user interface

An integrated dynamic-visual parallel debugging apparatus comprising: replay drive means for receiving a program and creating program symbol table information and an execution log file through reference execution; a parallel debugger core for receiving the program symbol table information and the execution log file from the replay drive means and managing views and events; and graphical user interface means for interfacing the parallel debugger core and a user.

Owner:UNILOC 2017 LLC

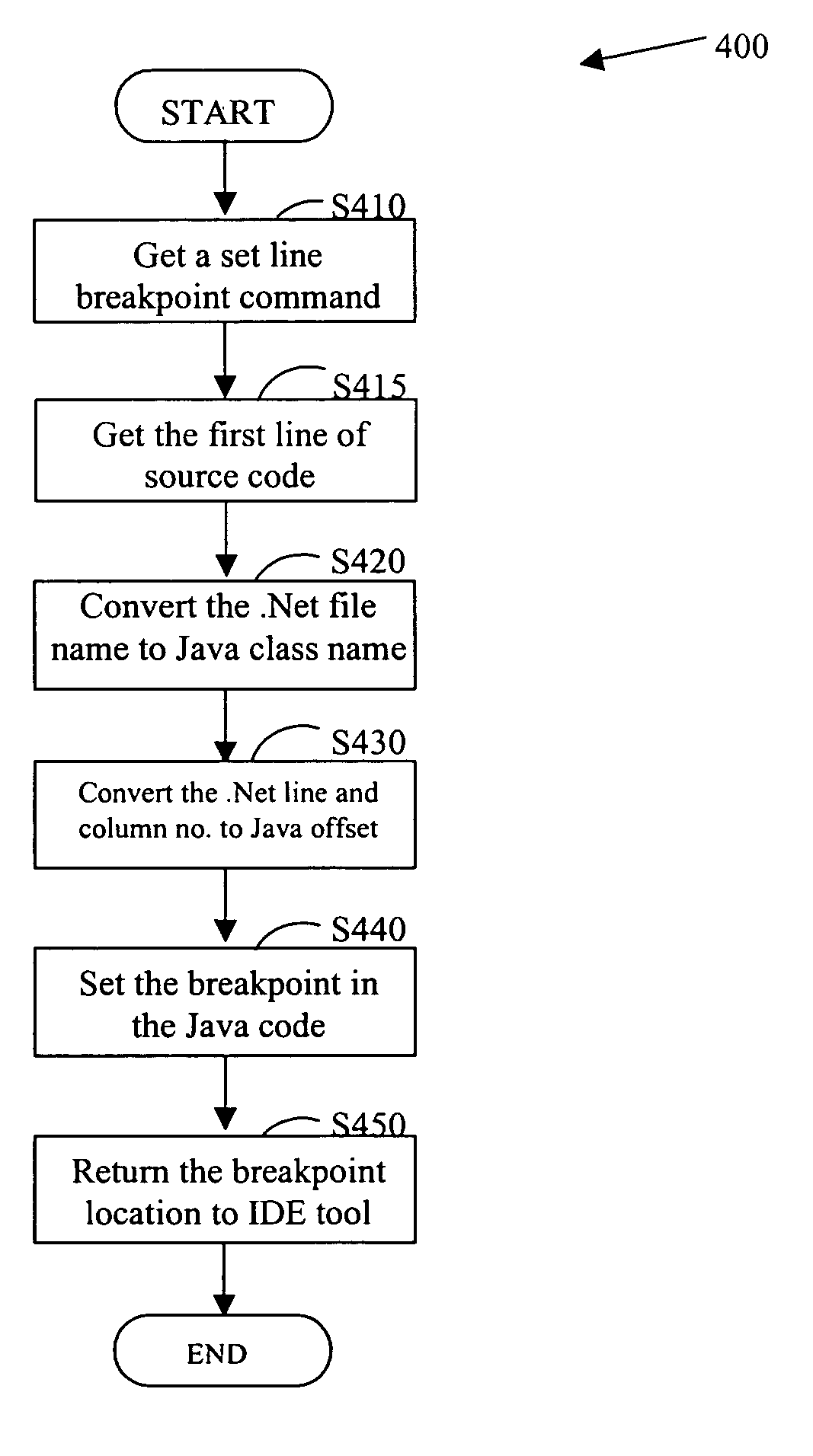

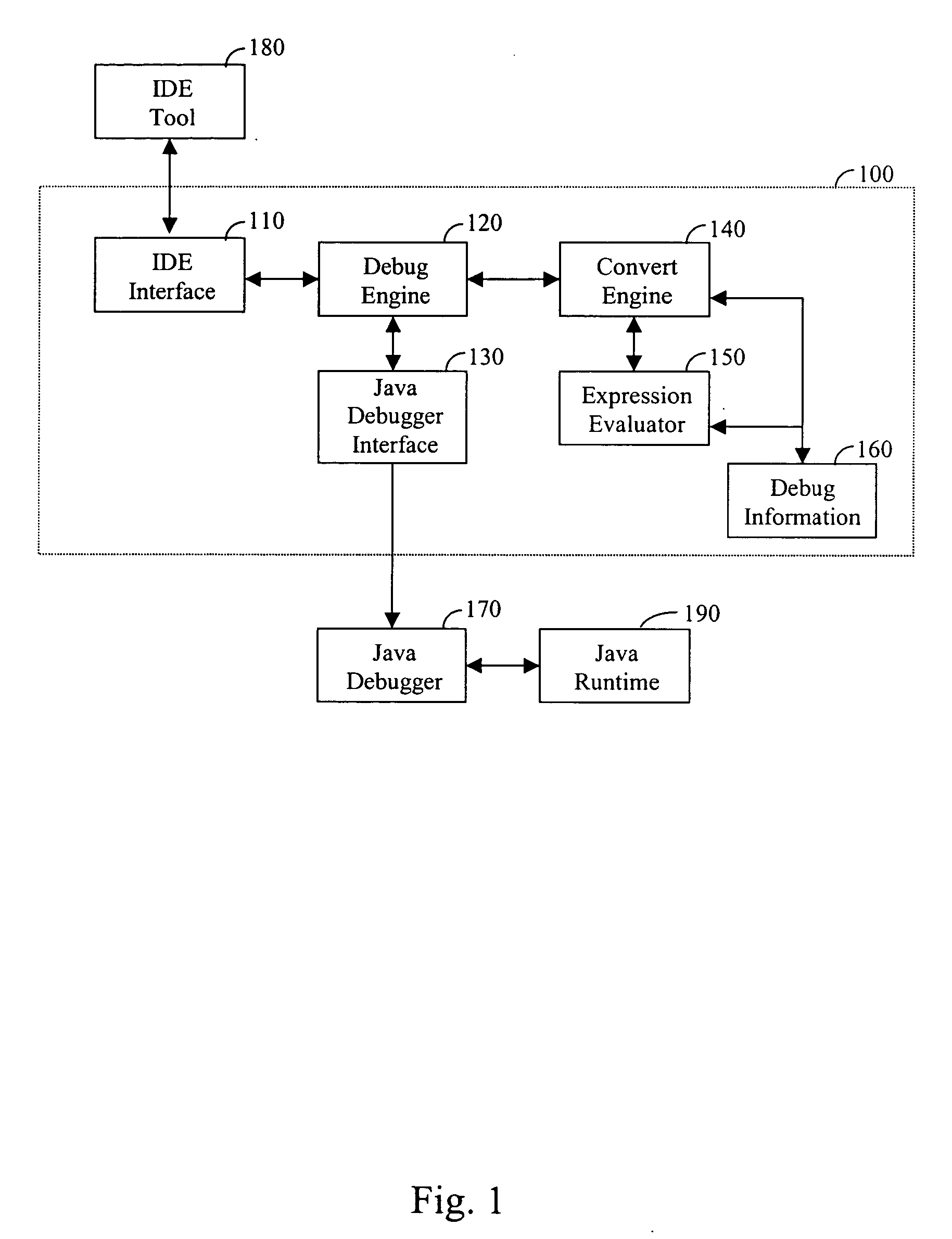

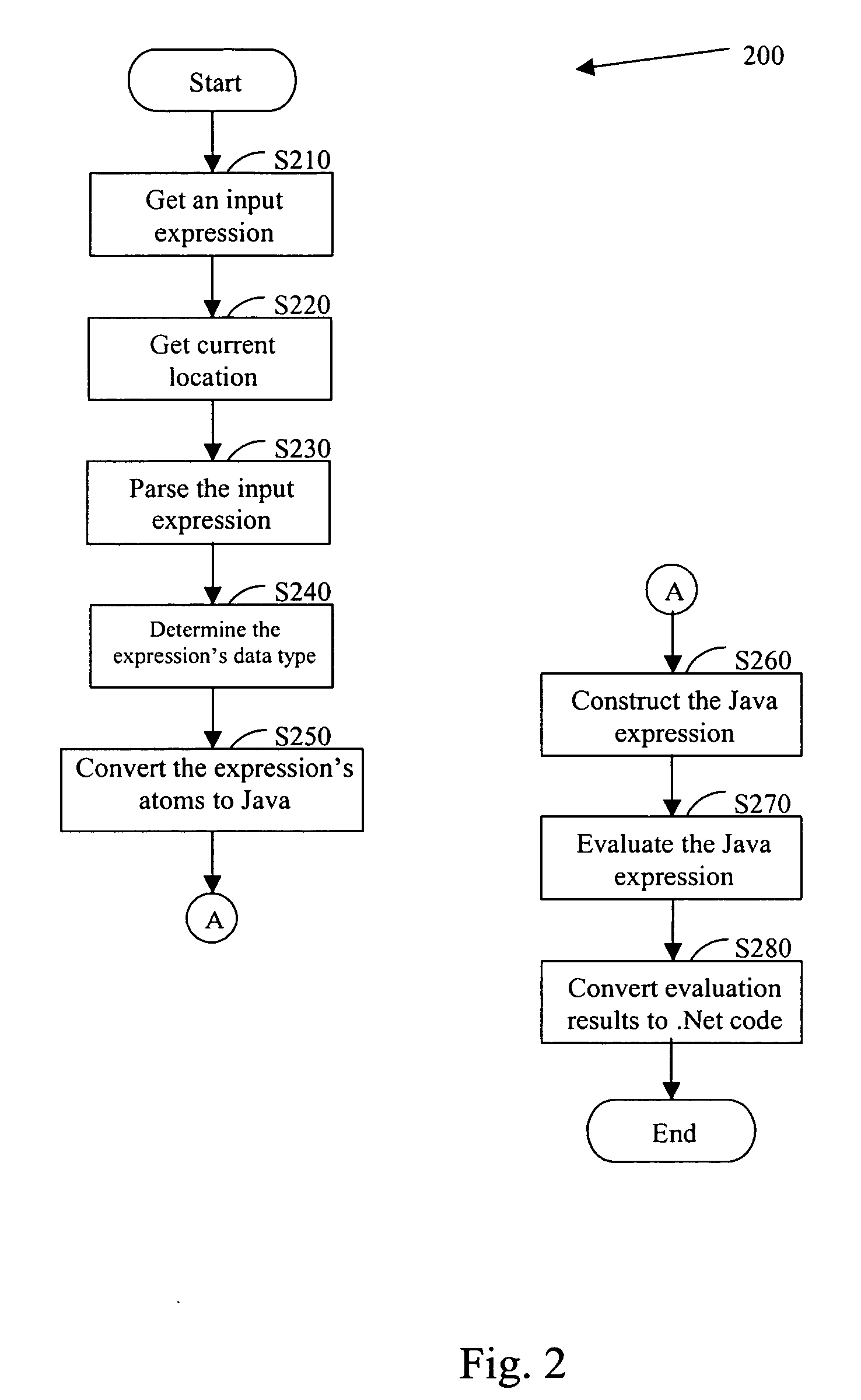

Debugger and method for debugging computer programs across multiple programming languages

InactiveUS20060064677A1Error detection/correctionSpecific program execution arrangementsCall stackSoftware development

A debugger and method for debugging computer programs across multiple programming languages are provided. The debugging is performed at a source level of a computer program written in any programming language supported by the .Net® platform, while the program is executed over a Java runtime environment. The debugger disclosed provides a call stack display and an expression evaluator. Furthermore, the debugger allows software developers to step through Java source code and follow the execution flow of the Java program. One exemplary embodiment of the disclosed debugger is an extension of the Microsoft® Visual Studio .Net®.

Owner:HARMON IE R&D

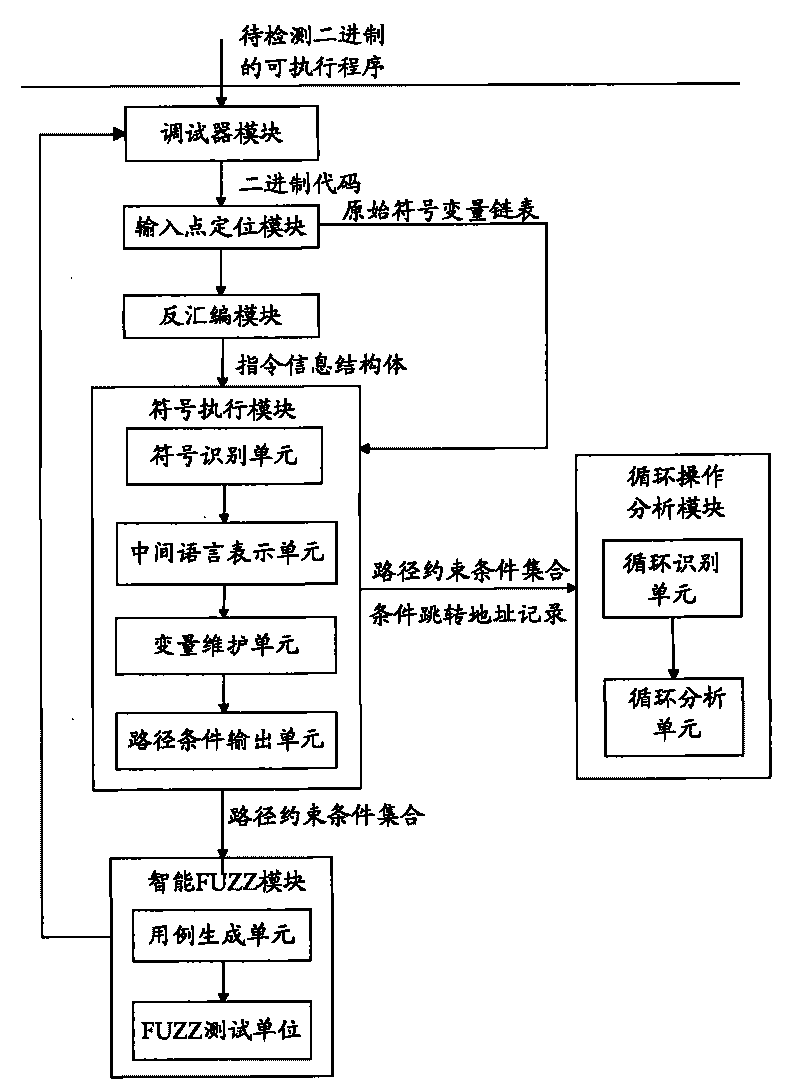

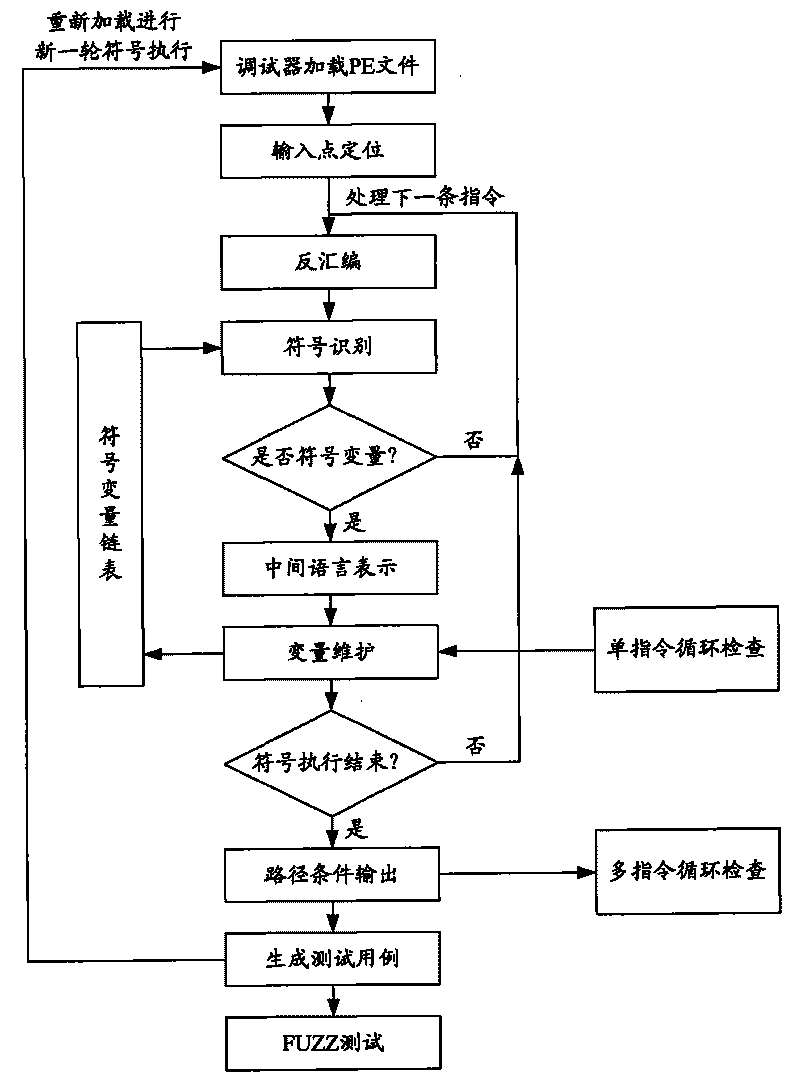

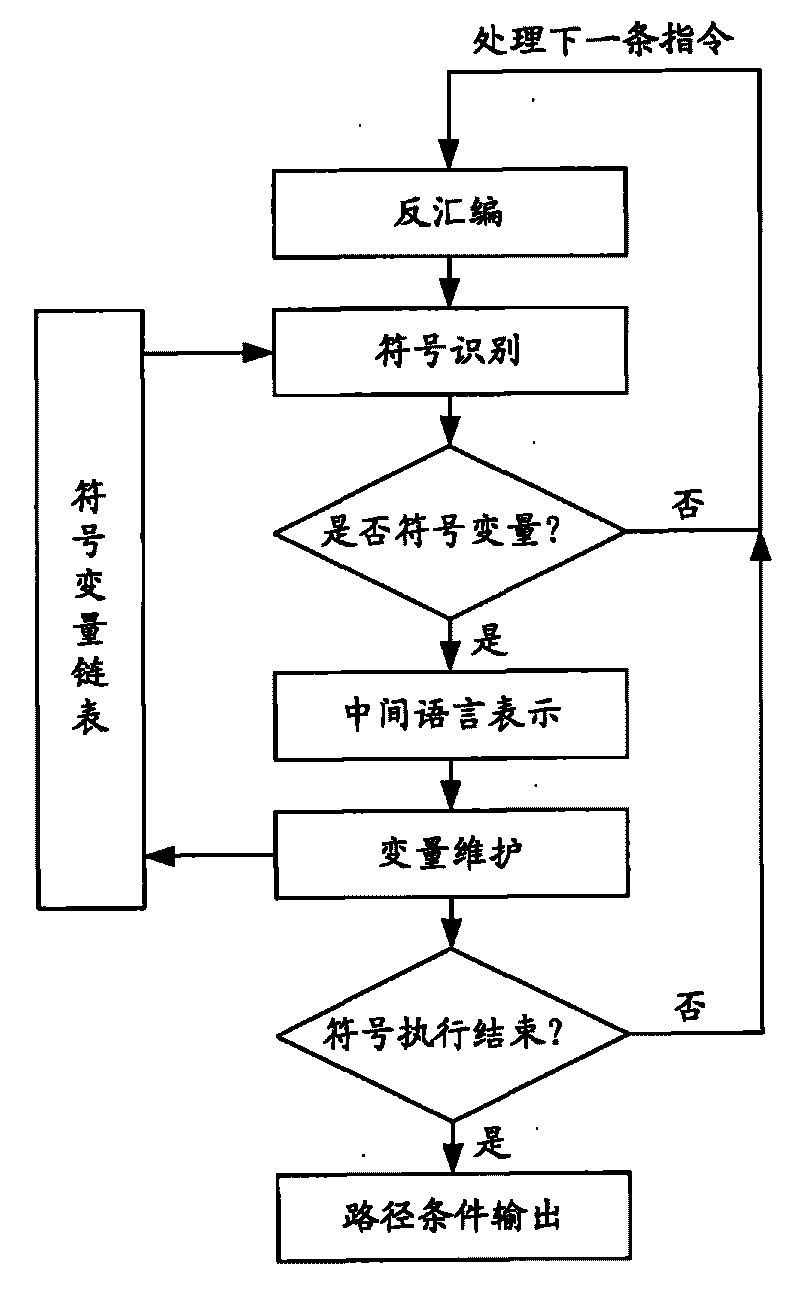

Detector for binary-code buffer-zone overflow bugs, and detection method thereof

InactiveCN101714118AGuaranteed feasibilityGuaranteed accuracyMultiprogramming arrangementsSoftware testing/debuggingBuffer overflowSource code

The invention provides a detector for binary-code buffer-zone overflow bugs, and a detection method thereof. The detector comprises six functional modules, namely a debugger module, an input point positioning module, a disassembling module, a symbolic execution module, a loop operation analysis module and an intelligent FUZZ test module. Differing from static symbolic execution, the detection method dynamically loads programs through the self-developed debugger module to synchronously performing symbolic execution and single-step practical execution, and then applies a model to solve each difficulty in binary code analysis so as to test path coverage and detect overflow bugs in accordance with all executable programs of PE format under a Windows platform. The detection can also provide propagation paths of input data and other important information related to bug formation cause while positioning the bugs, only analyzes the selves of the executable programs, needs no source codes, is unrelated to the species of source codes and development tools, and is extensive in applicable occasions, so the detection method has good prospects for popularization and application.

Owner:BEIJING UNIV OF POSTS & TELECOMM

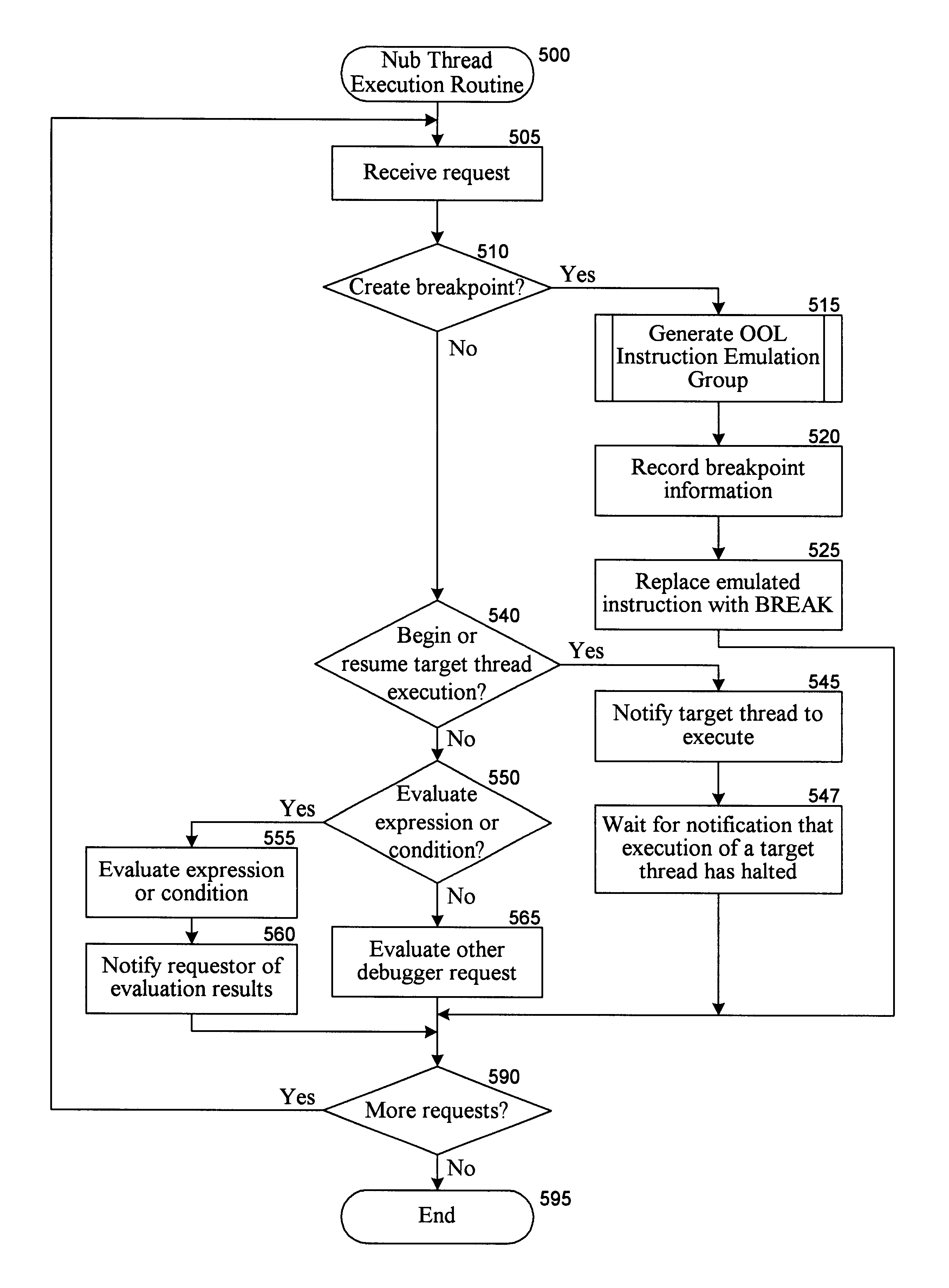

Debugging techniques in a multithreaded environment

InactiveUS6848097B1Provide immunitySoftware testing/debuggingSpecific program execution arrangementsOperating systemDebugger

A system for debugging targets using various techniques, some of which are particularly useful in a multithread environment. These techniques include implementing breakpoints using out-of-line instruction emulation so that an instruction replaced with a breakpoint instruction does not need to be returned to its original location for single-step execution, executing a debugger nub for each target as part of the target task but using a nub task thread for the nub execution that is separate from the target task threads, providing immunity from breakpoints for specified threads such as the nub thread via specialized breakpoint handlers used by those threads, and virtualizing the debugger nub such that a shared root nub provides a uniform interface between the debugger and the target while specialized nubs provide differing functionality based on the type of target being debugged.

Owner:CRAY

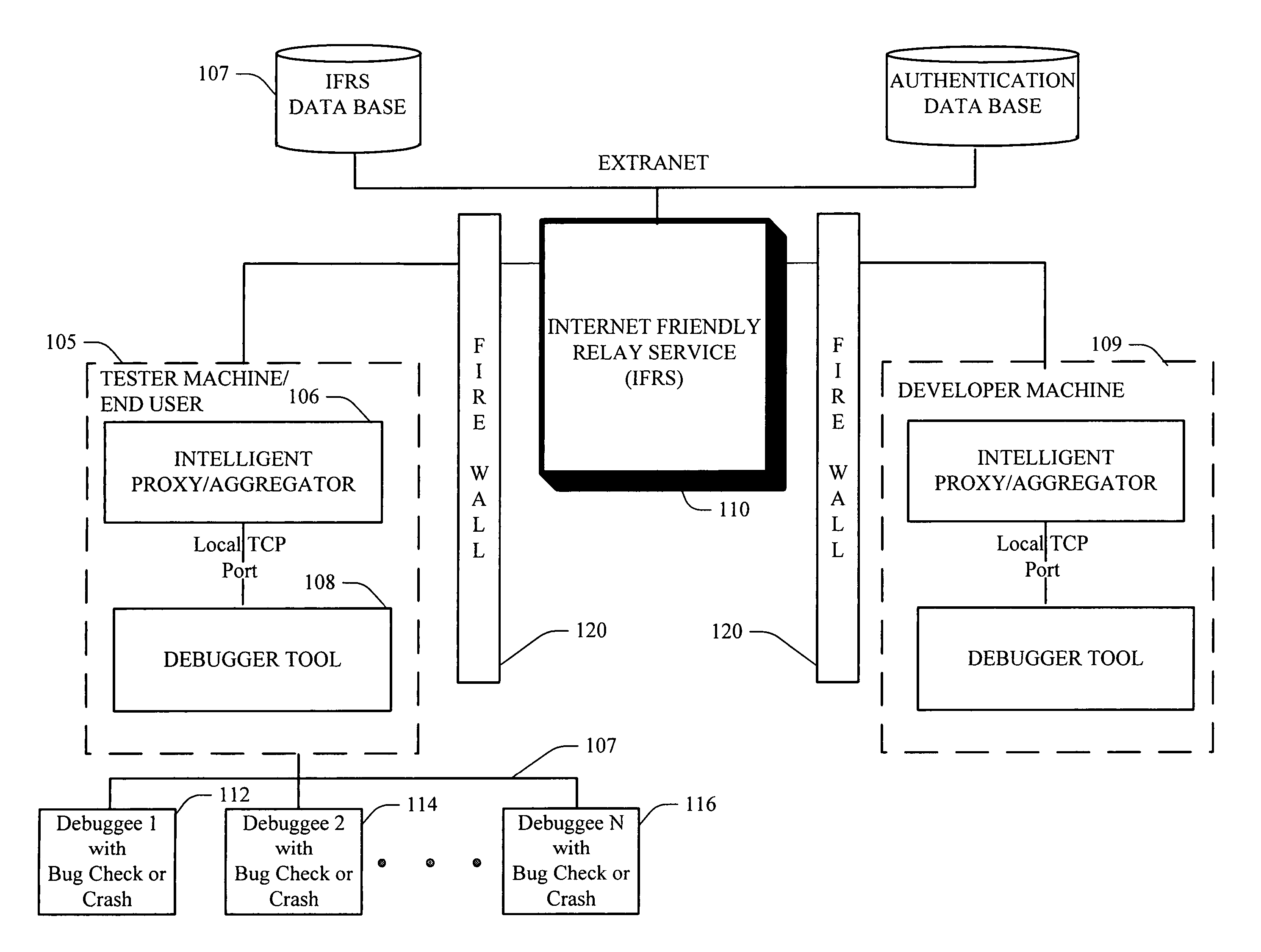

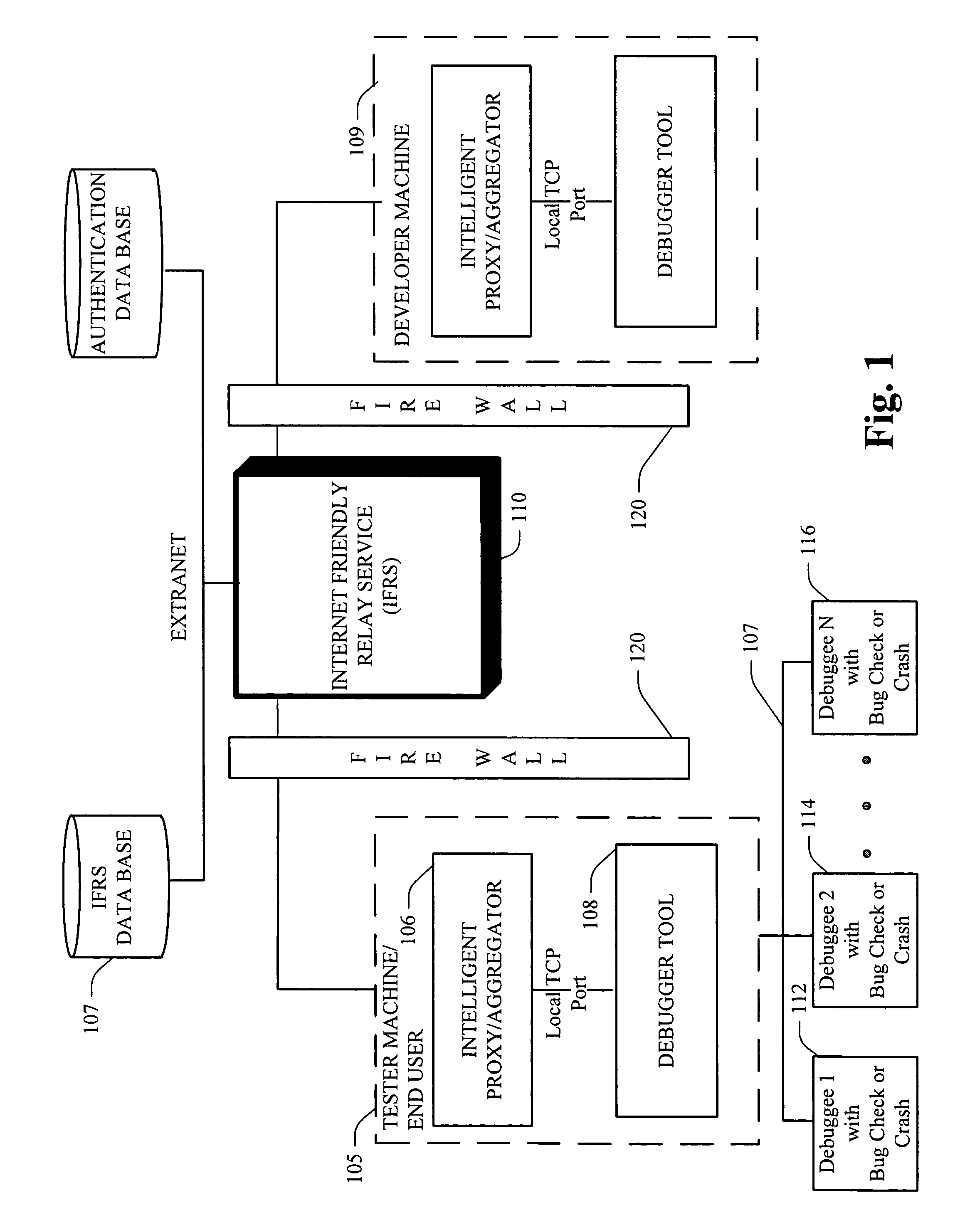

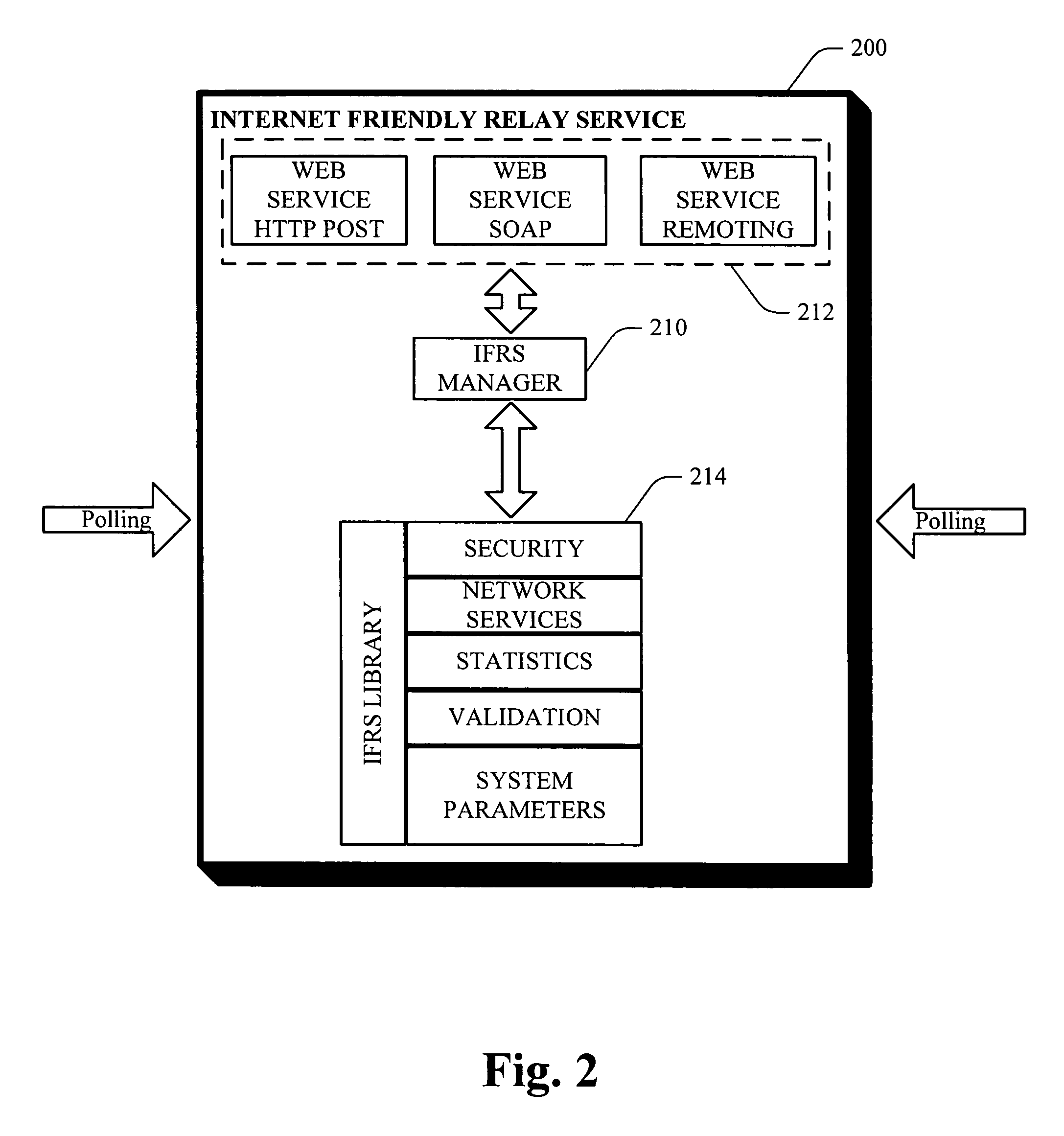

Windows remote debugger service

InactiveUS20060195894A1Improve balanceFacilitate regulationError detection/correctionMultiple digital computer combinationsClient-sideAuthorization

Systems and methodologies for a scalable remote debugging system that can debug machines positioned behind a firewall and thru the Internet, via employing an Internet Friendly Relay Service (IFRS). The IFRS can be positioned in a common reach location and provide a secure method of exchanging communication traffic over HTTP using SSL and security tokens in real time. Web server(s) of the IFRS can further employ an authorization and / or tracking system to verify connection of a client thereto, for debugging purposes.

Owner:MICROSOFT TECH LICENSING LLC

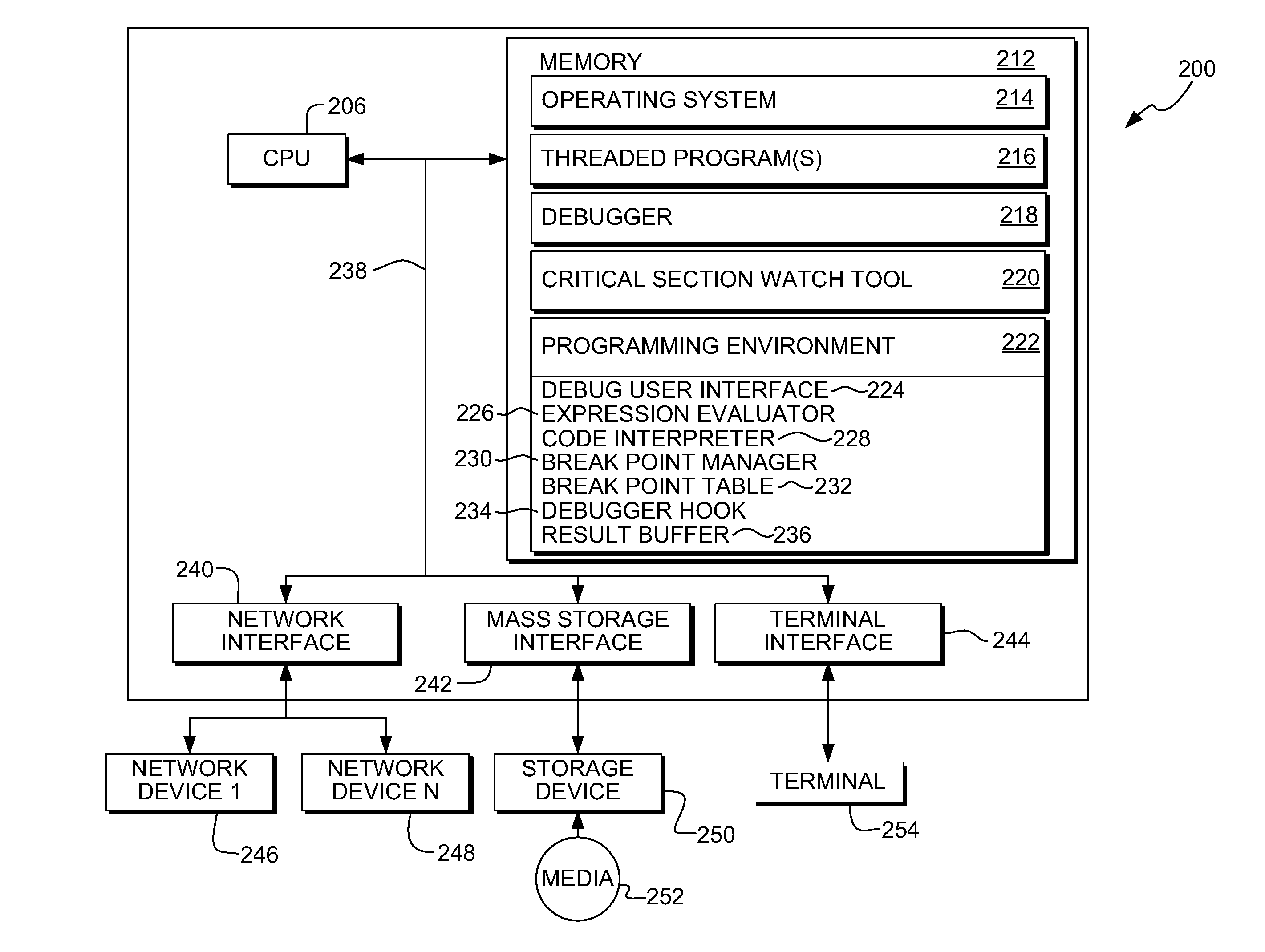

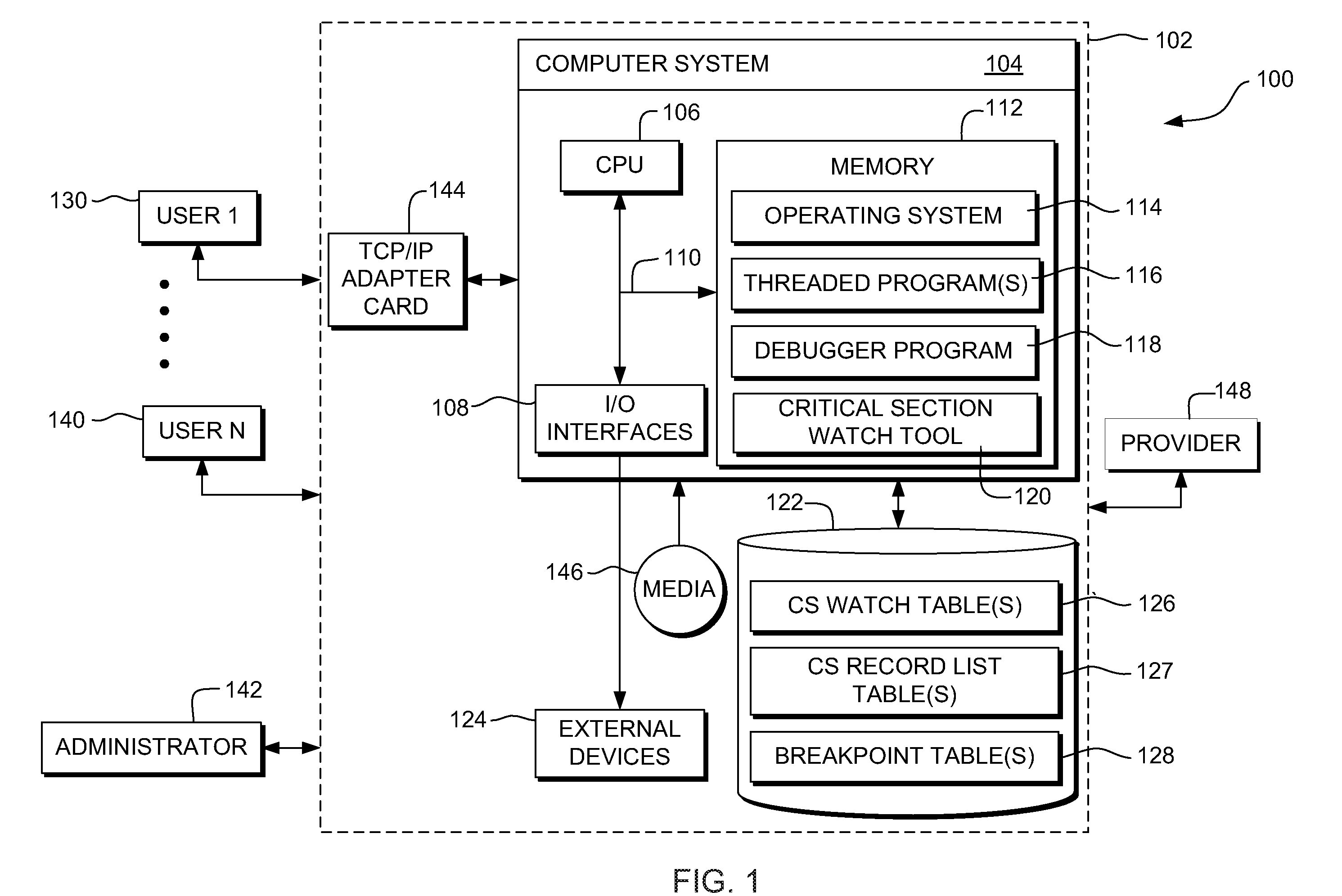

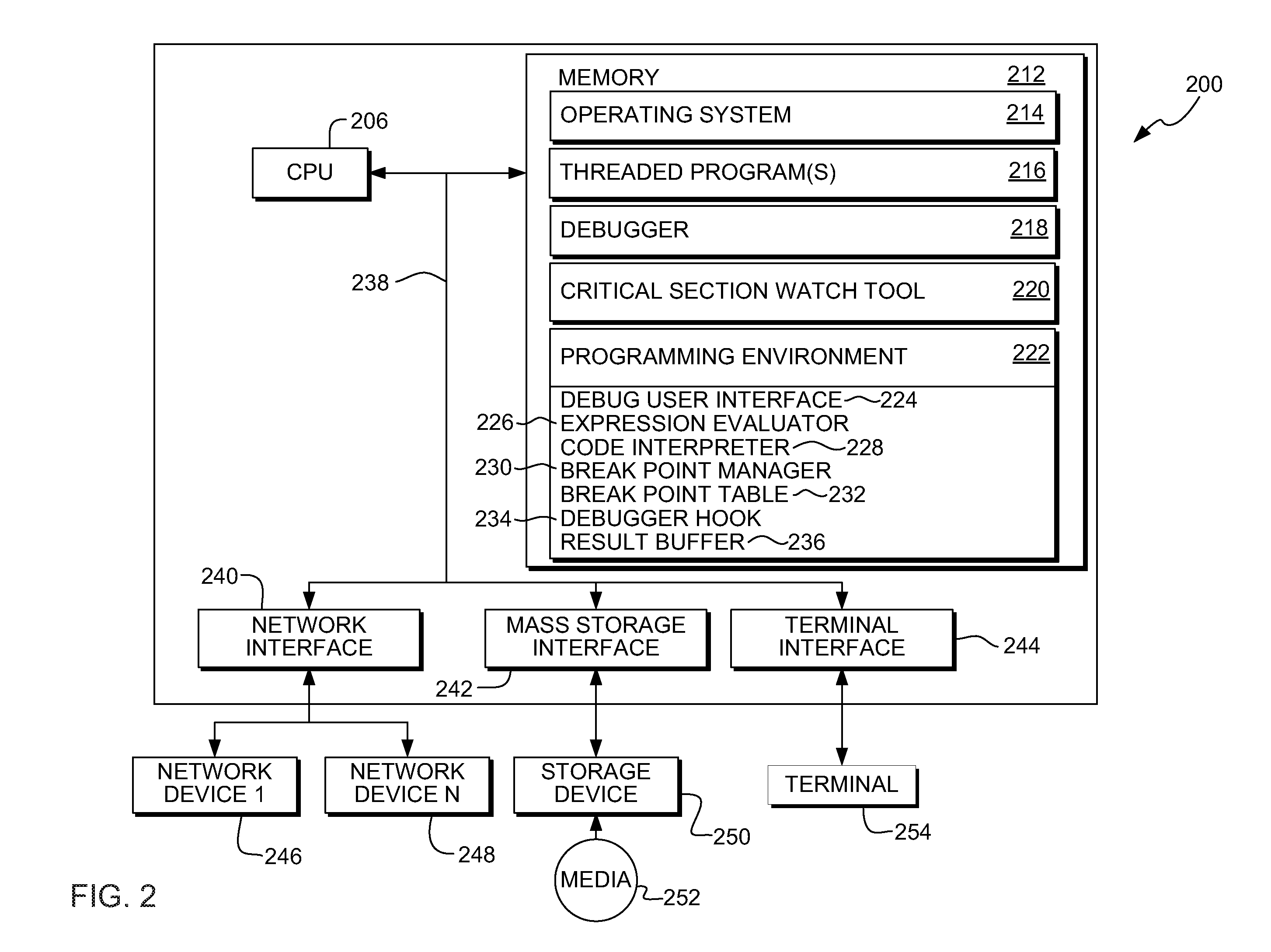

System, method and program product for monitoring changes to data within a critical section of a threaded program

InactiveUS20090320001A1Error detection/correctionSpecific program execution arrangementsCritical sectionCritical zone

A method, system and program product for monitoring changes to a variable within a critical section of a threaded program. The method includes establishing, using a debugging tool, a watch for monitoring changes to a variable that occur outside of the critical section and executing a portion of the threaded program with a debugger. Further, the method includes determining, using the tool, whether or not a thread has executed a start breakpoint set for the critical section, if the thread has executed the start breakpoint set, determining whether or not the thread has executed an end breakpoint set for the critical section, and if the thread has not executed the end breakpoint set, displaying any watches triggered responsive to updates to the variable that occur outside of the critical section, such that, only updates to the variable that occur outside of the critical section will trigger the displaying.

Owner:IBM CORP