Patents

Literature

408 results about "Assemblers" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

The Champions of Angor (also known as the Justifiers, the Assemblers and the Meta Militia) are a fictional superhero team in the DC Comics universe. They are a pastiche of the Avengers from the Marvel Comics universe. They were created by Mike Friedrich and Dick Dillin in the pages of Justice League of America #87 February (1971).

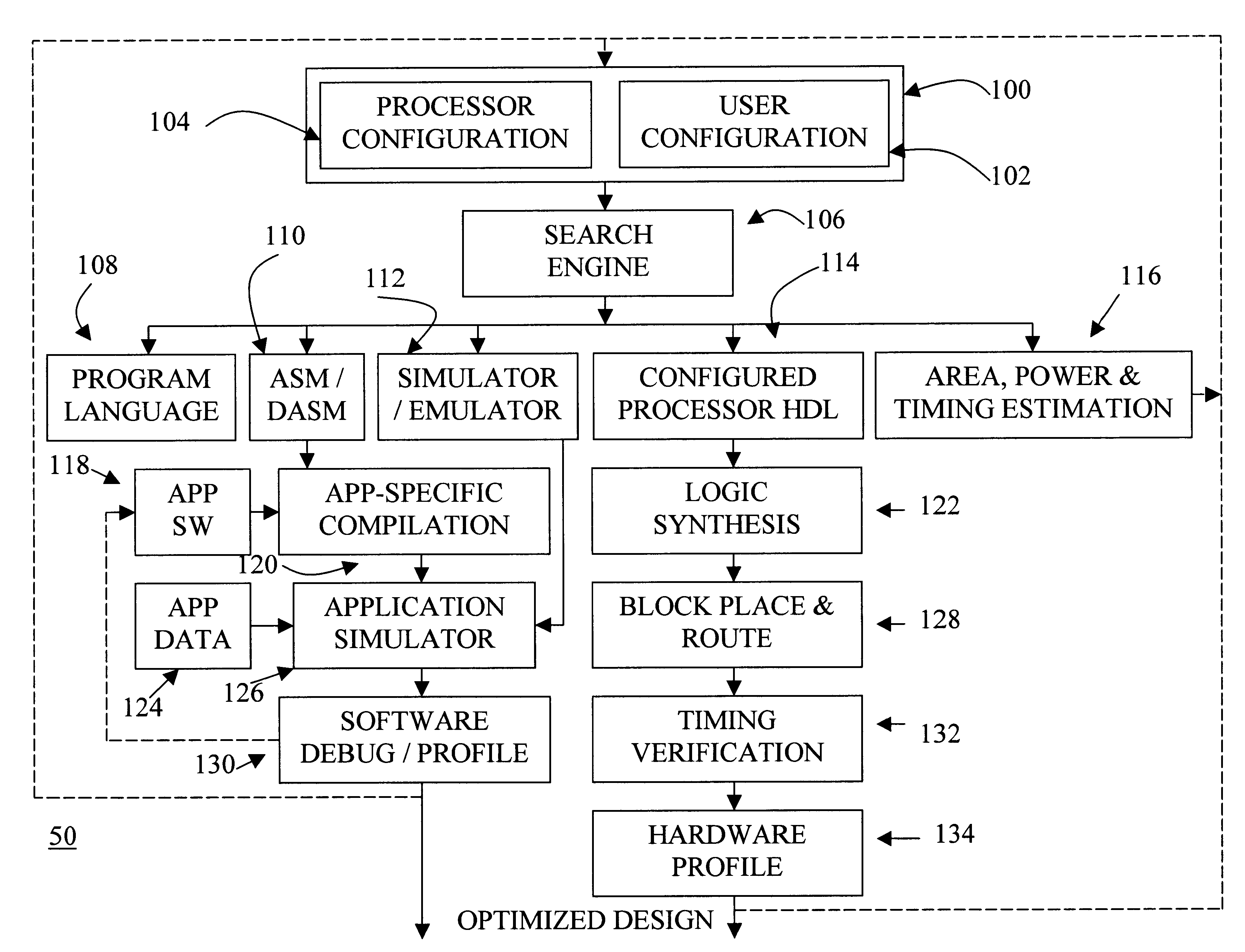

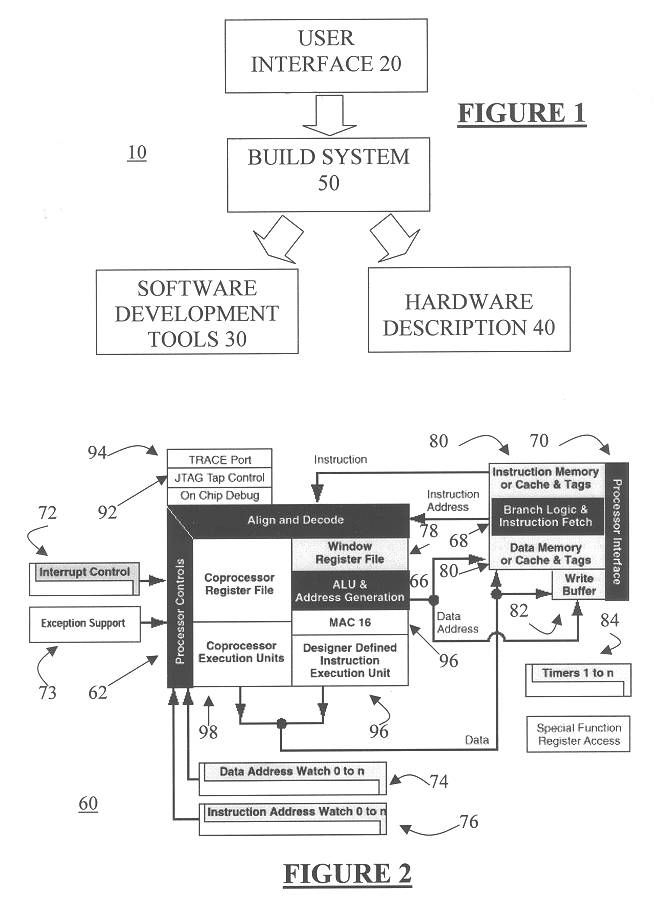

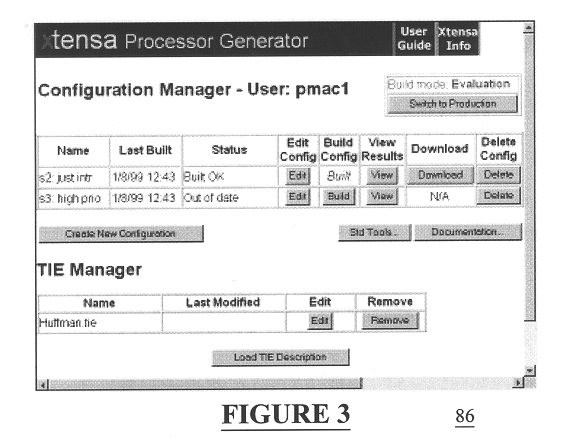

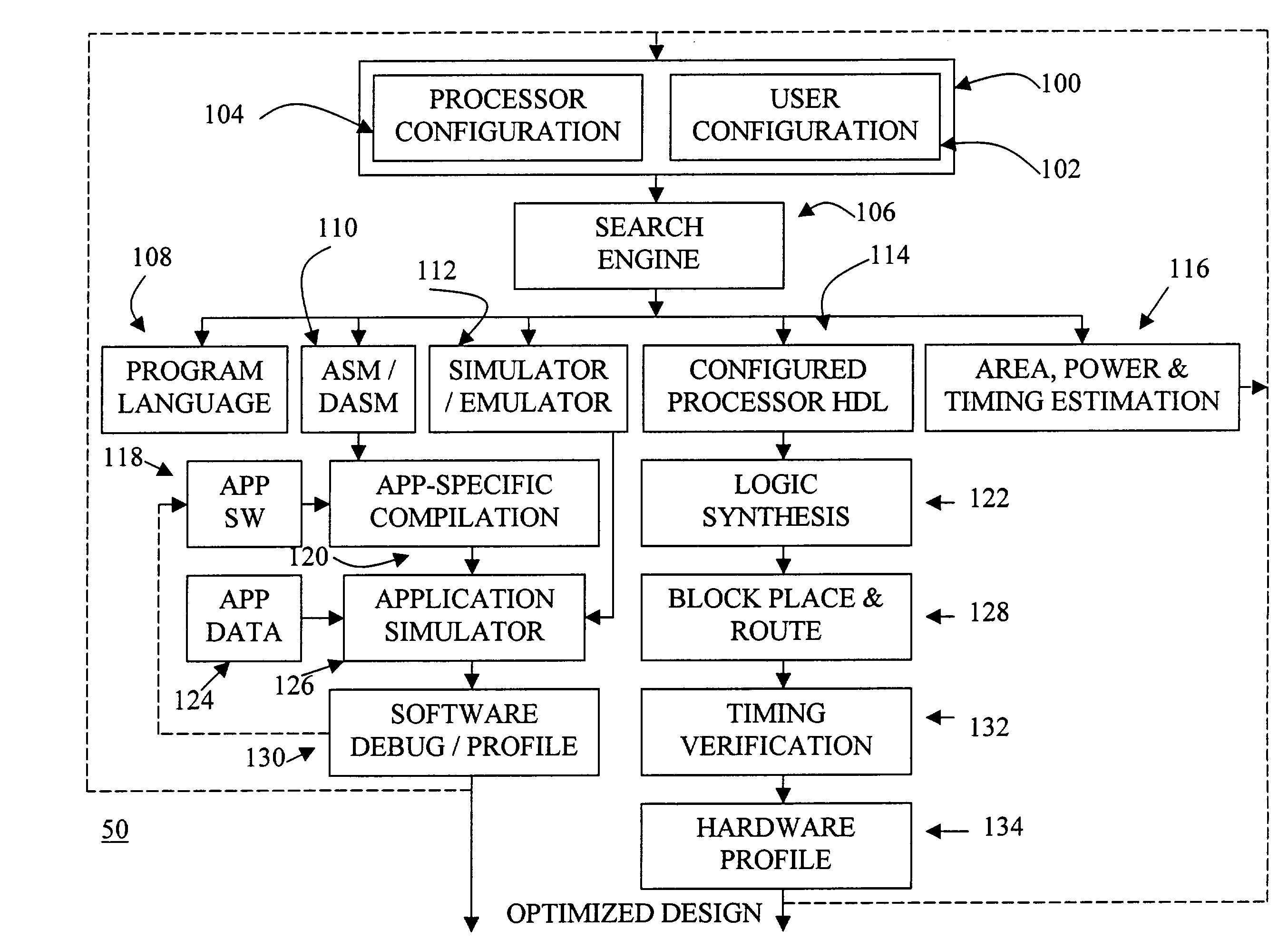

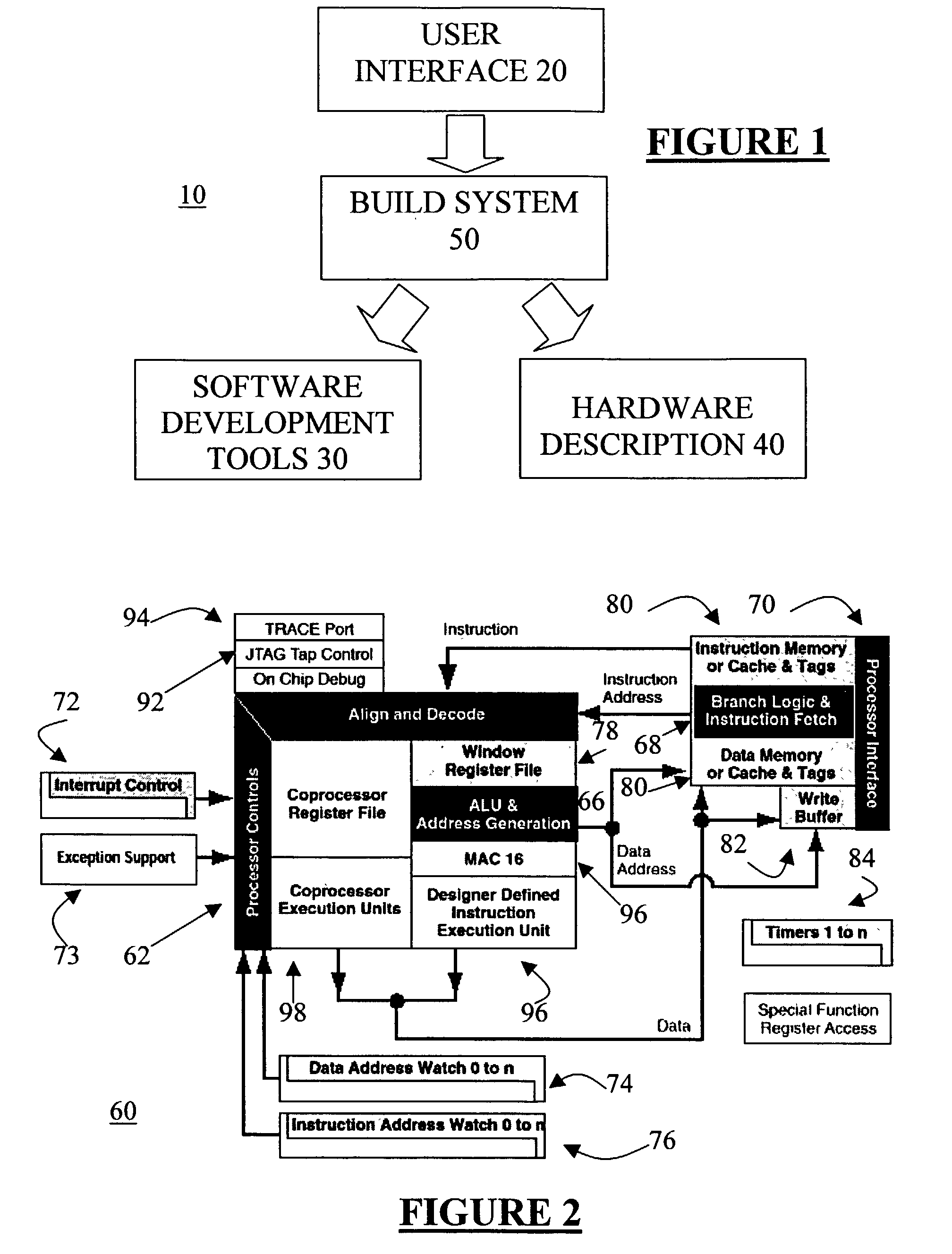

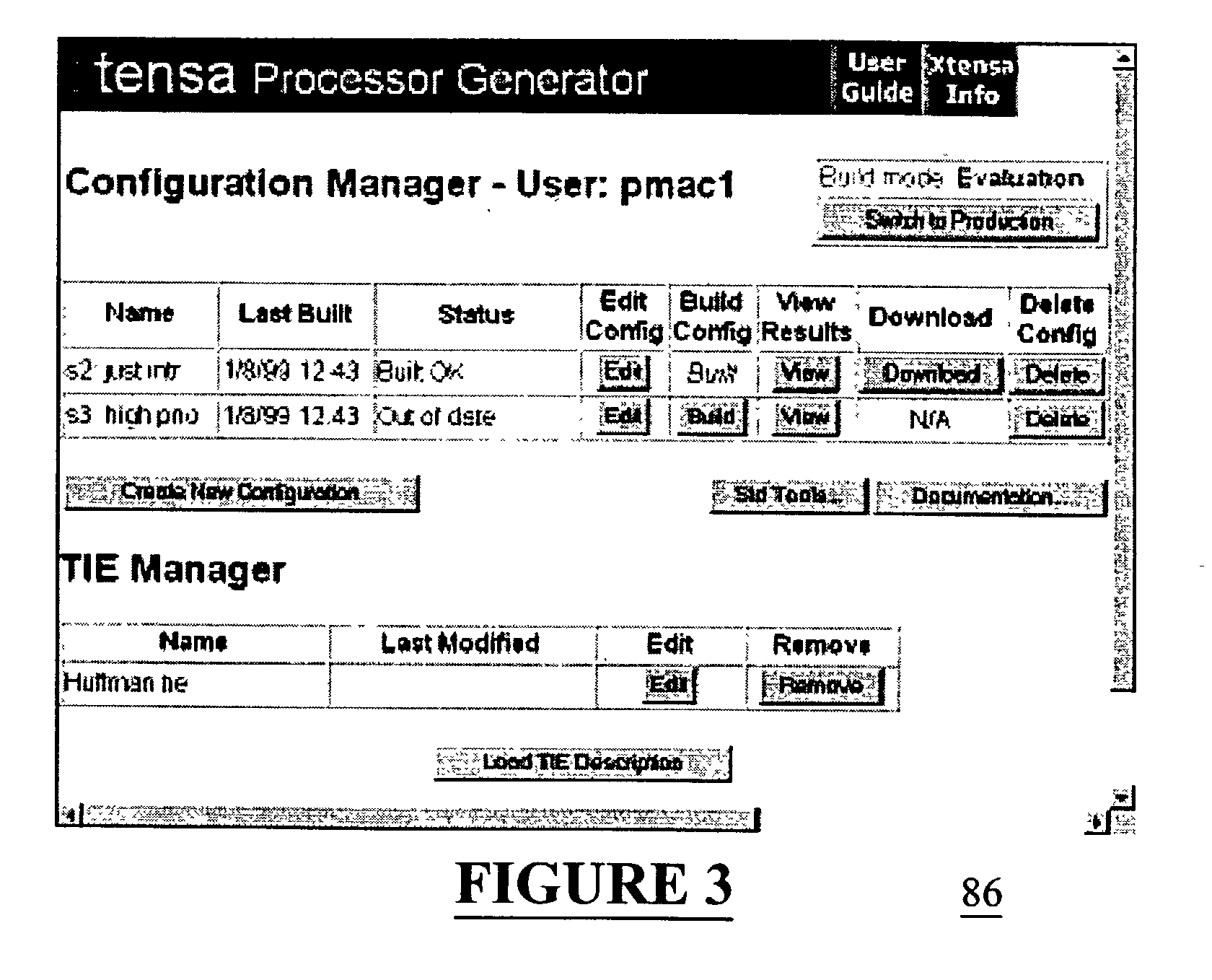

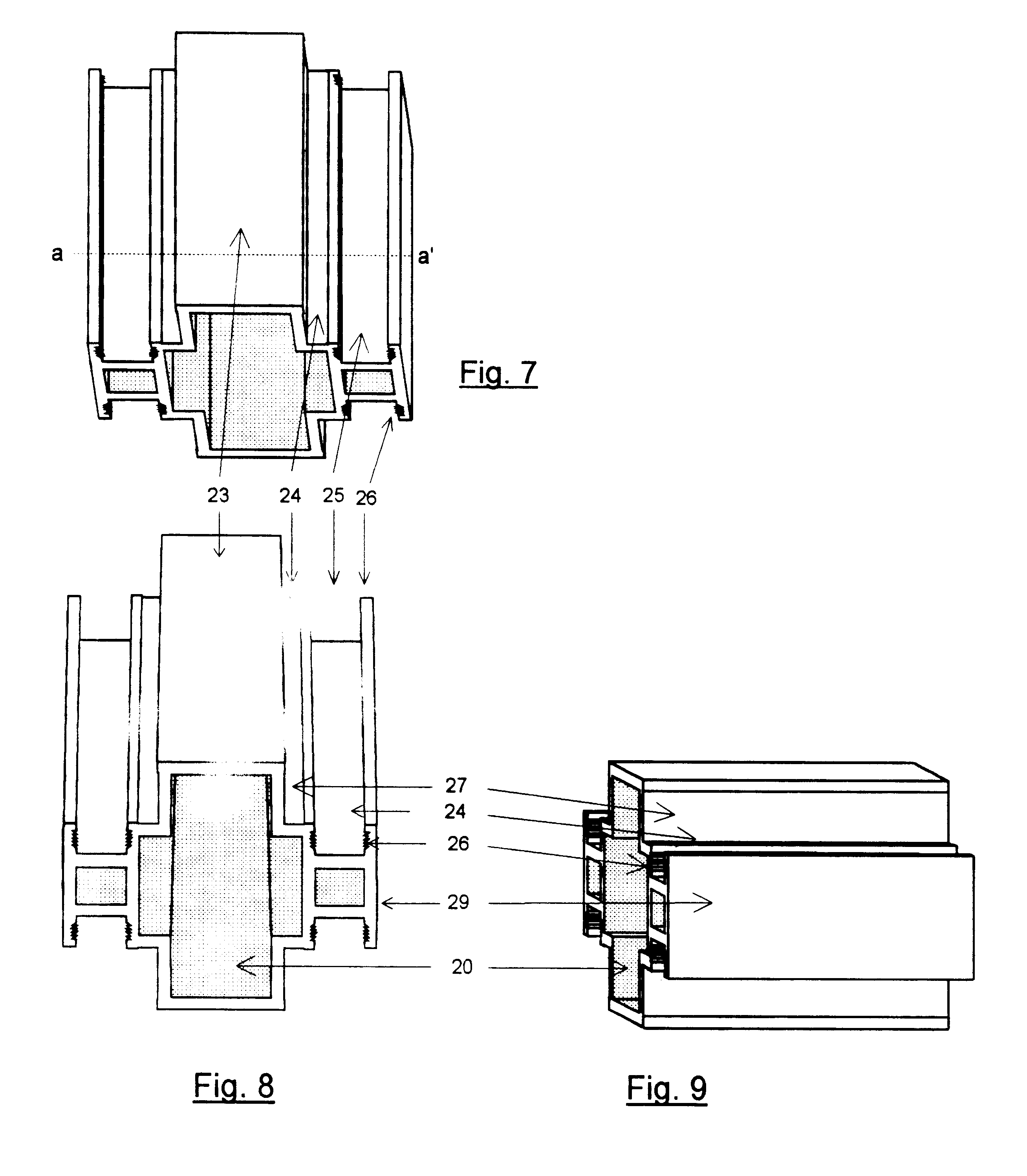

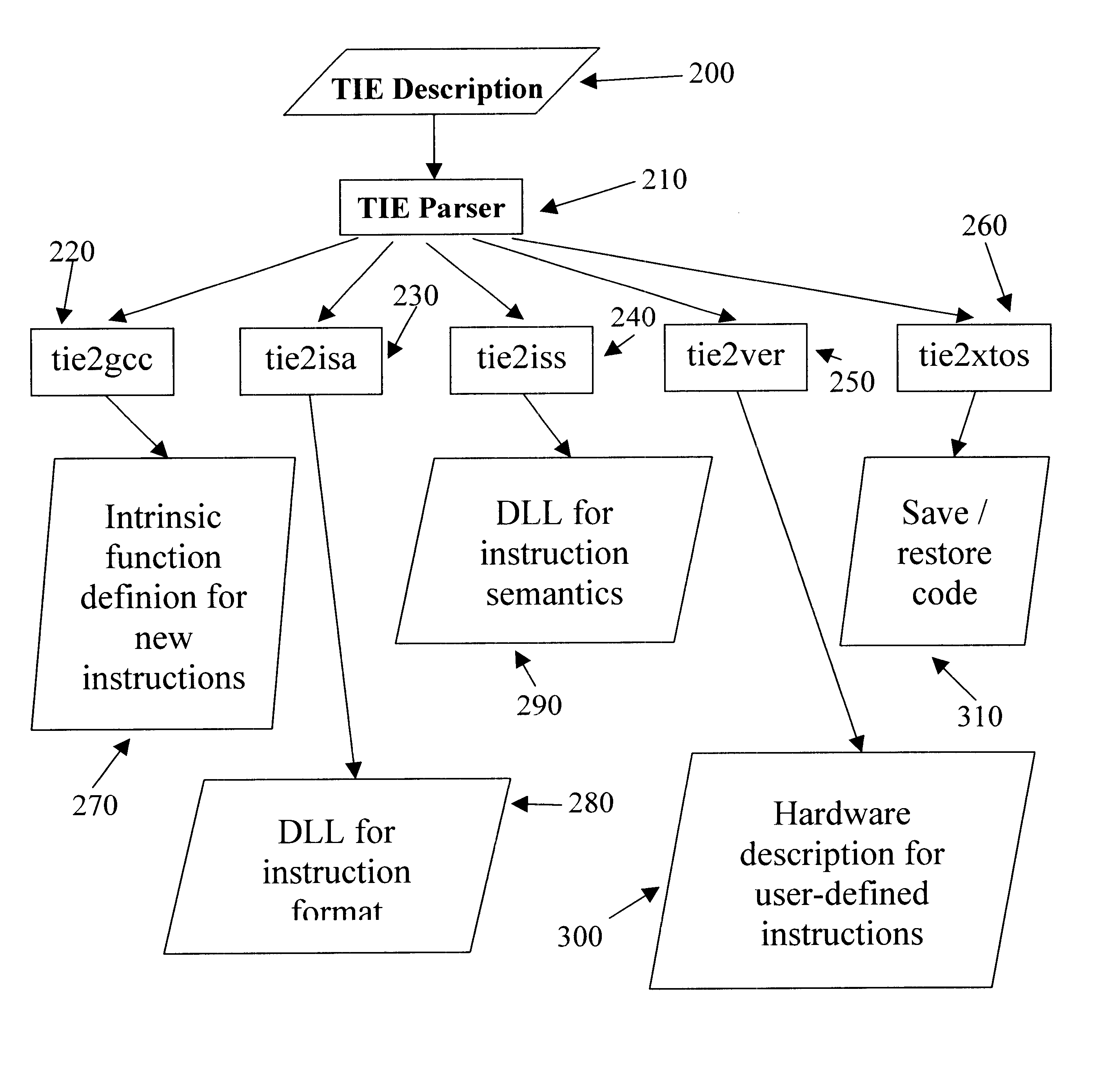

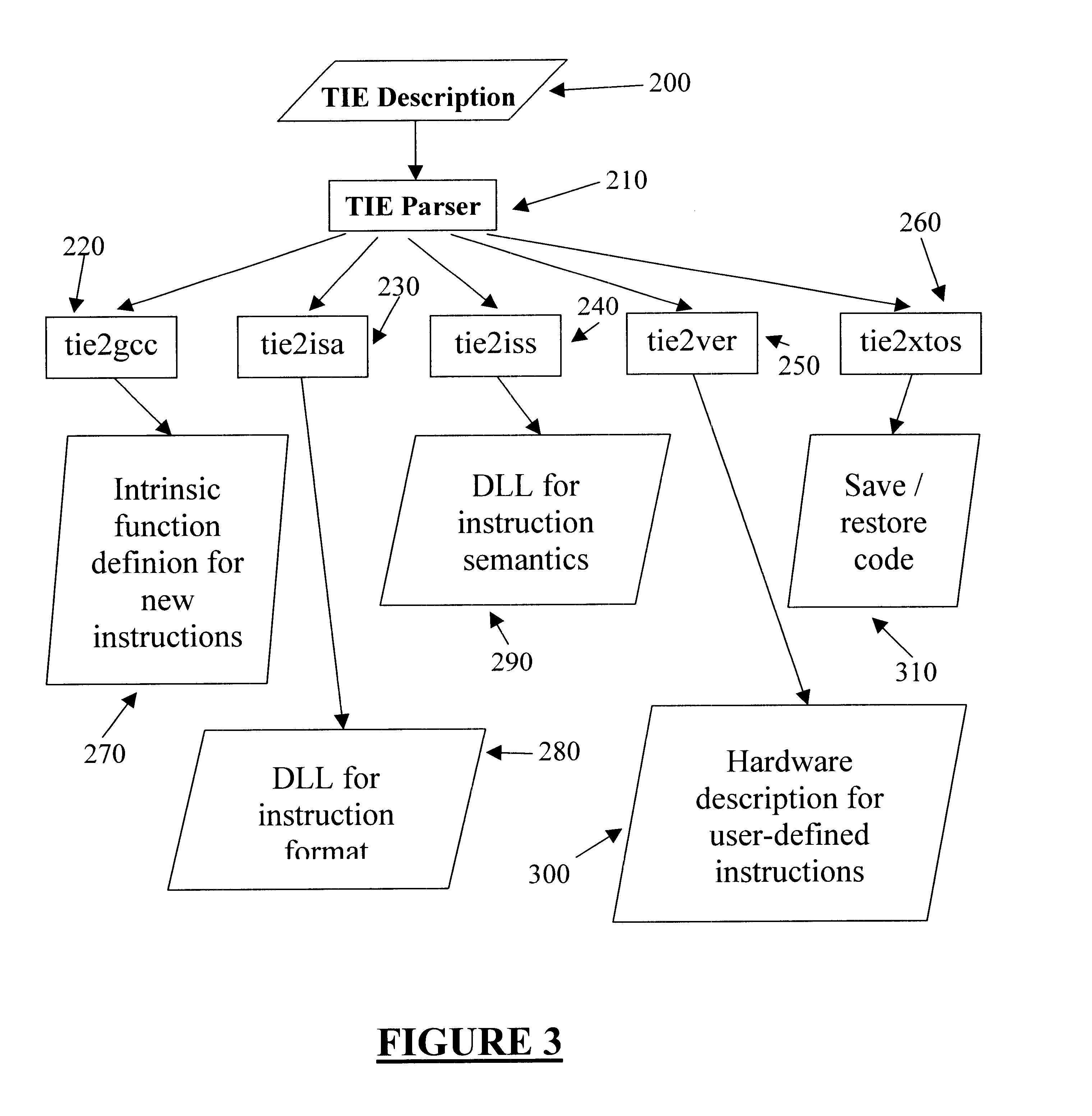

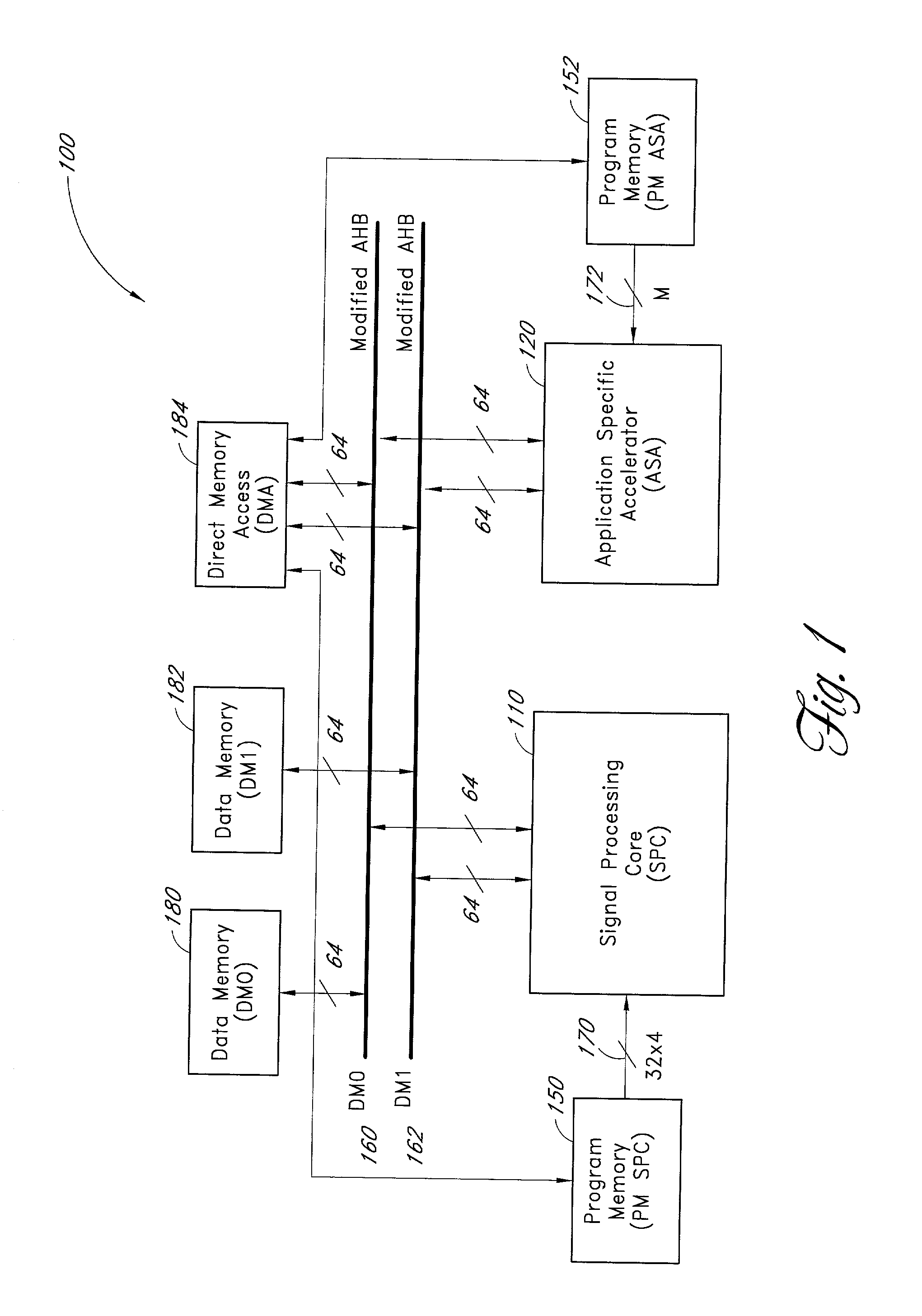

Automated processor generation system for designing a configurable processor and method for the same

InactiveUS6477683B1Decompilation/disassemblyCAD network environmentApplication softwareProcessor design

An automated processor design tool uses a description of customized processor instruction set extensions in a standardized language to develop a configurable definition of a target instruction set, a Hardware Description Language description of circuitry necessary to implement the instruction set, and development tools such as a compiler, assembler, debugger and simulator which can be used to develop applications for the processor and to verify it. Implementation of the processor circuitry can be optimized for various criteria such as area, power consumption, speed and the like. Once a processor configuration is developed, it can be tested and inputs to the system modified to iteratively optimize the processor implementation. By providing a constrained domain of extensions and optimizations, the process can be automated to a high degree, thereby facilitating fast and reliable development.

Owner:TENSILICA

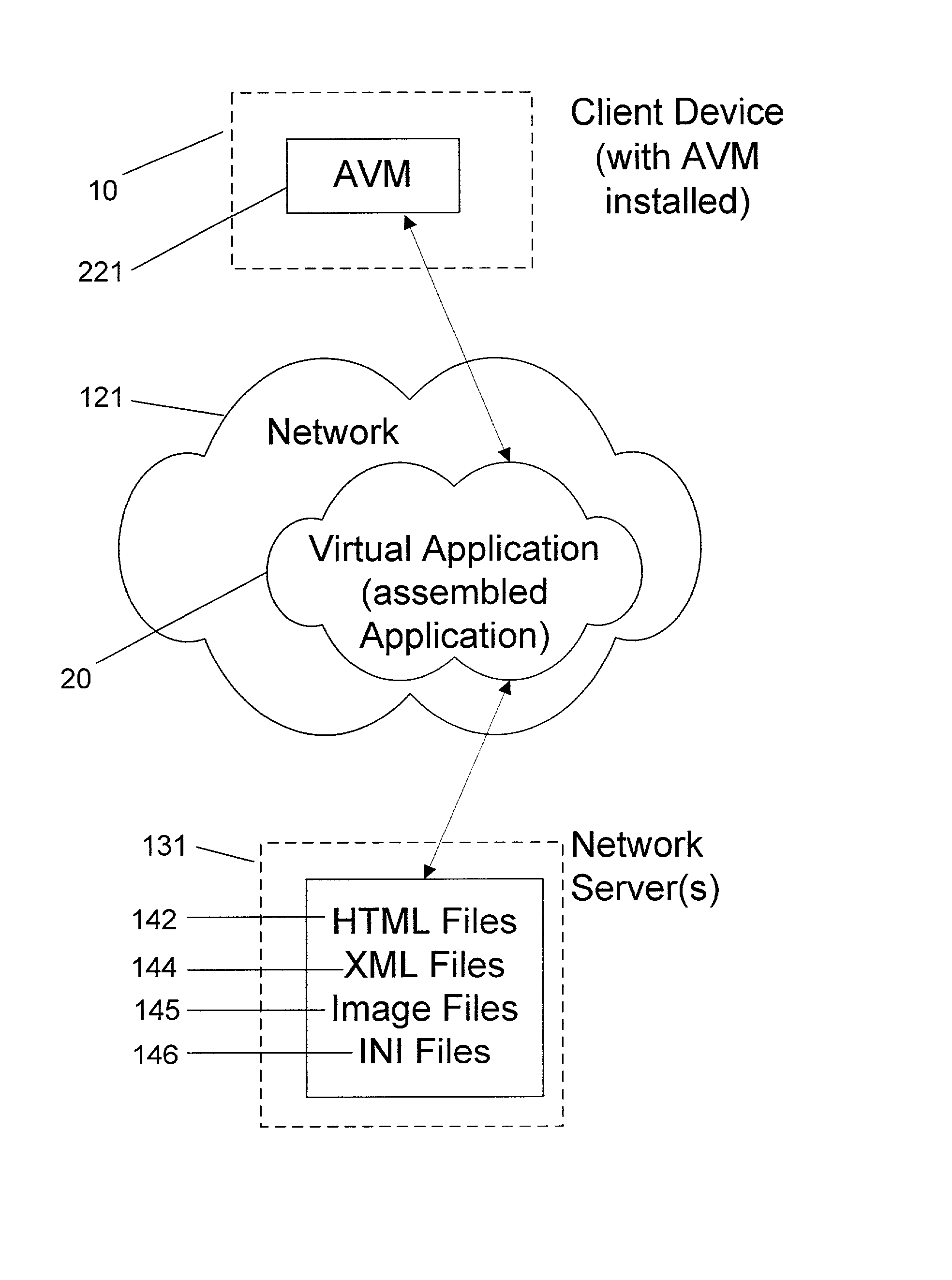

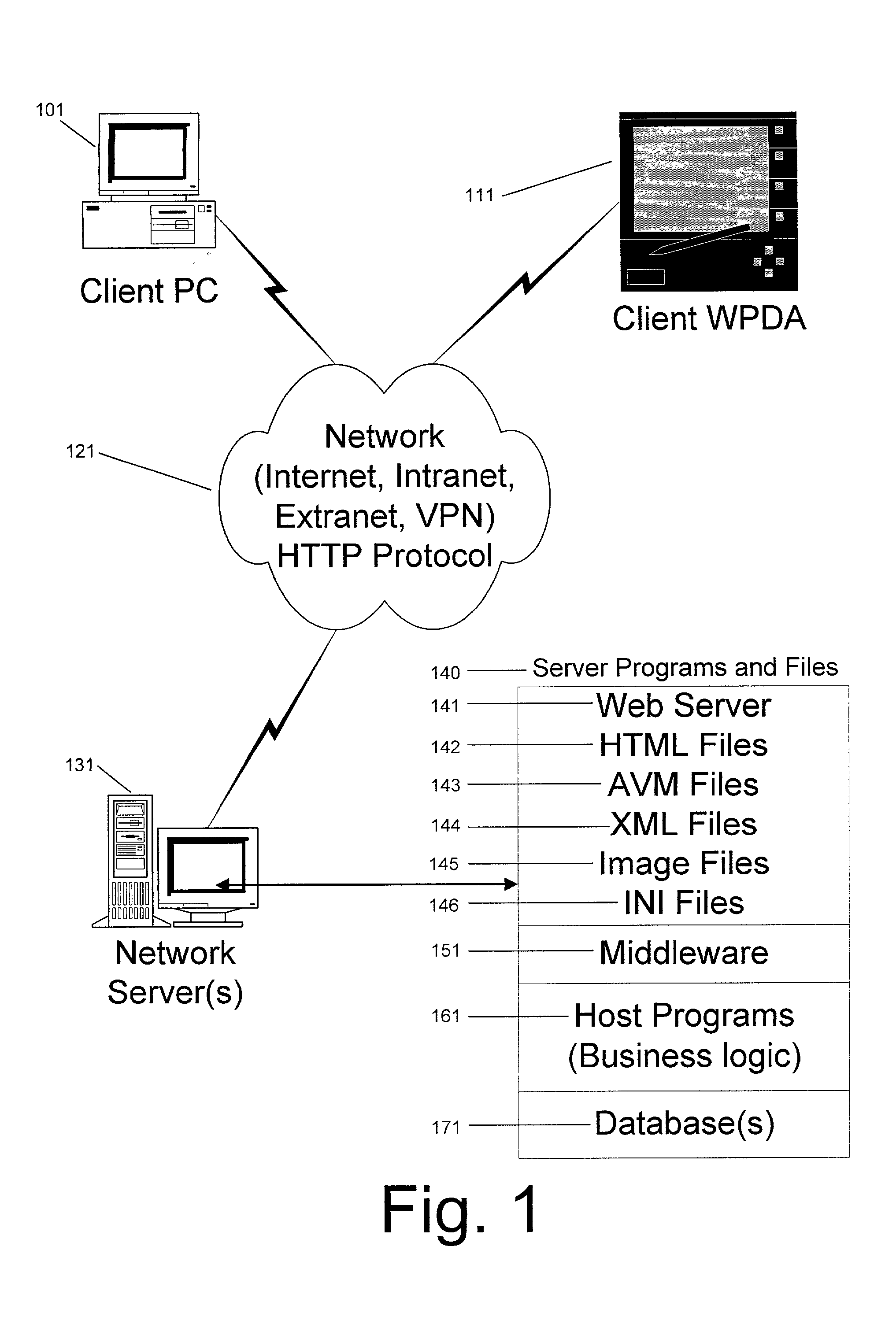

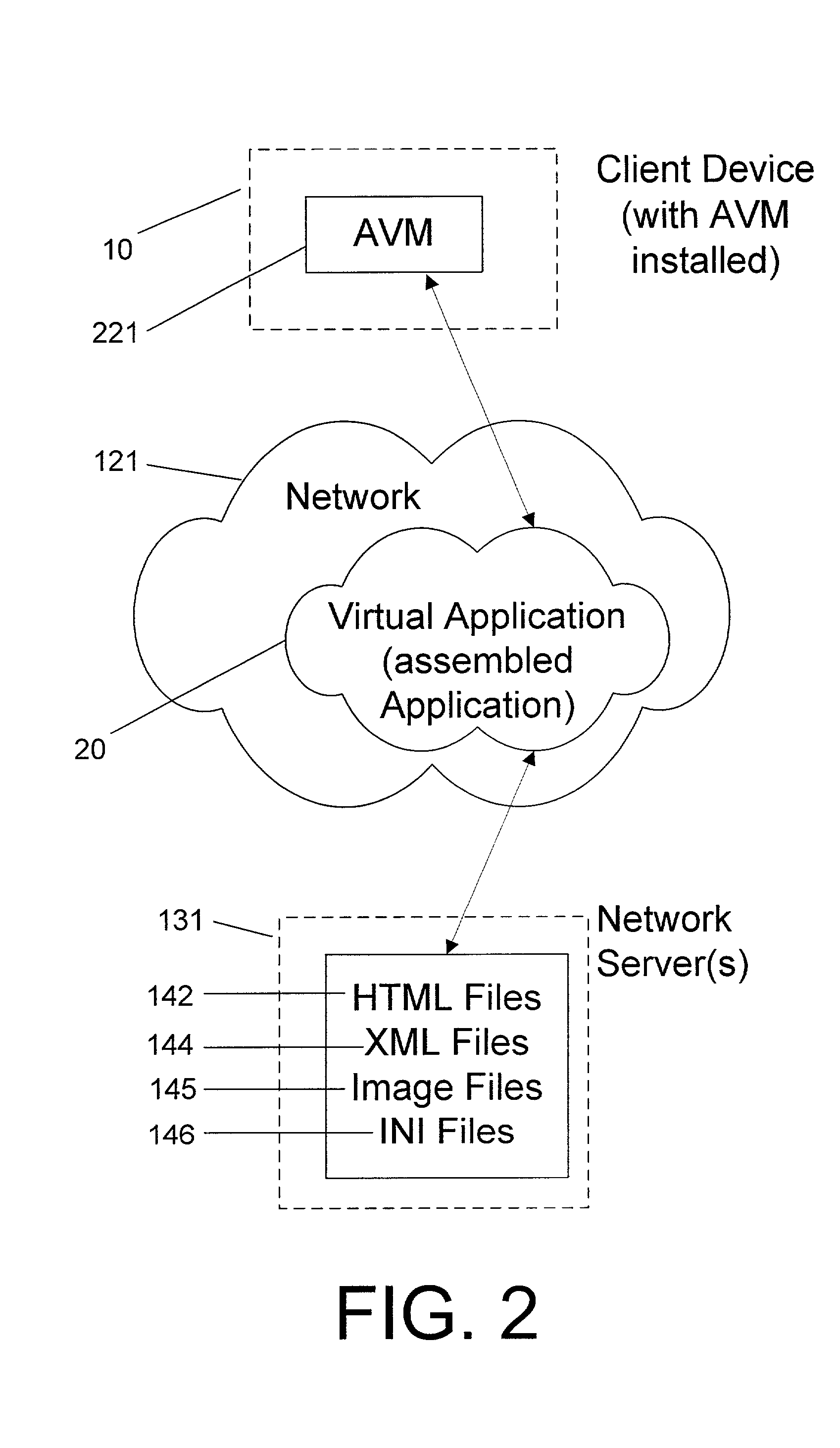

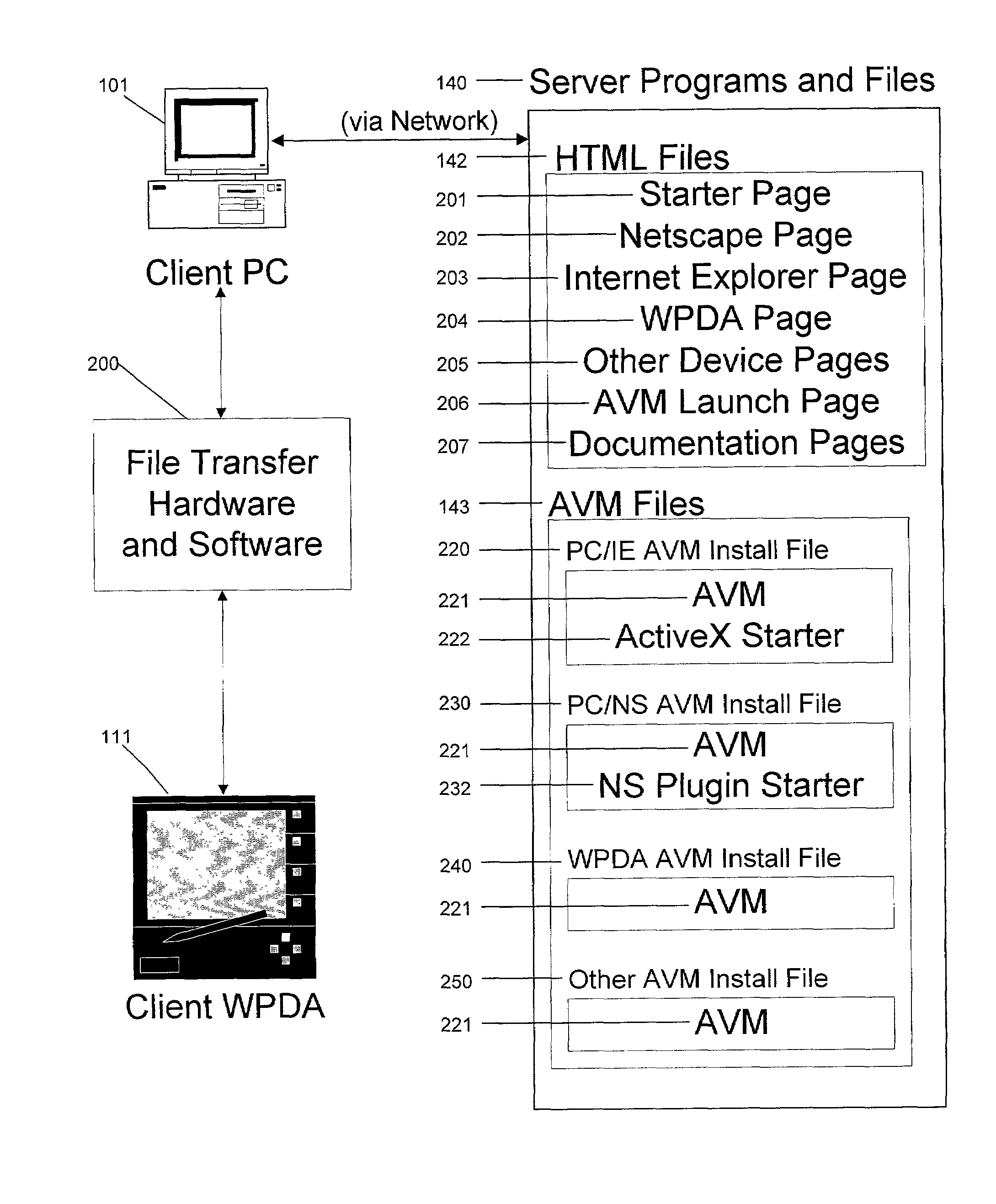

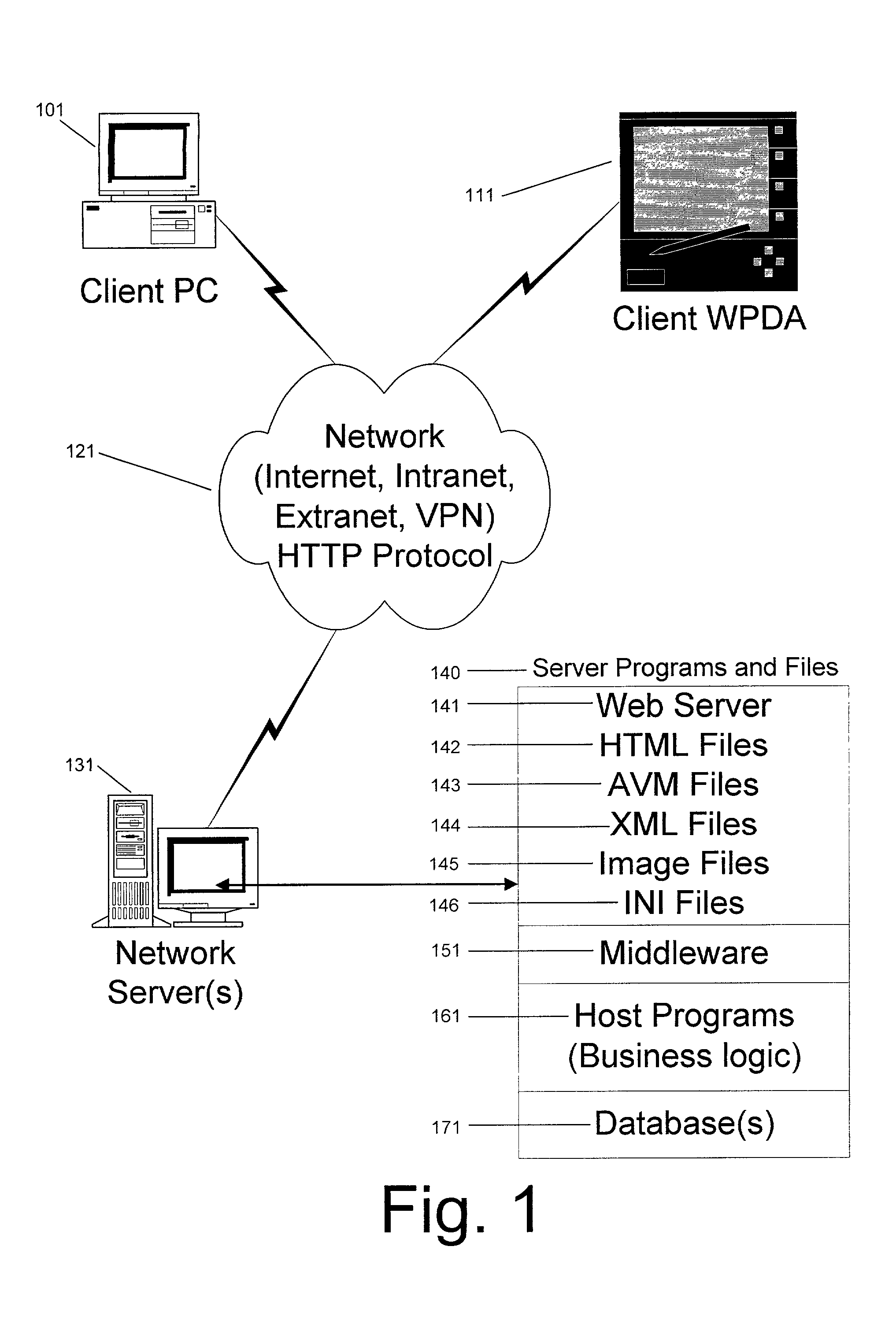

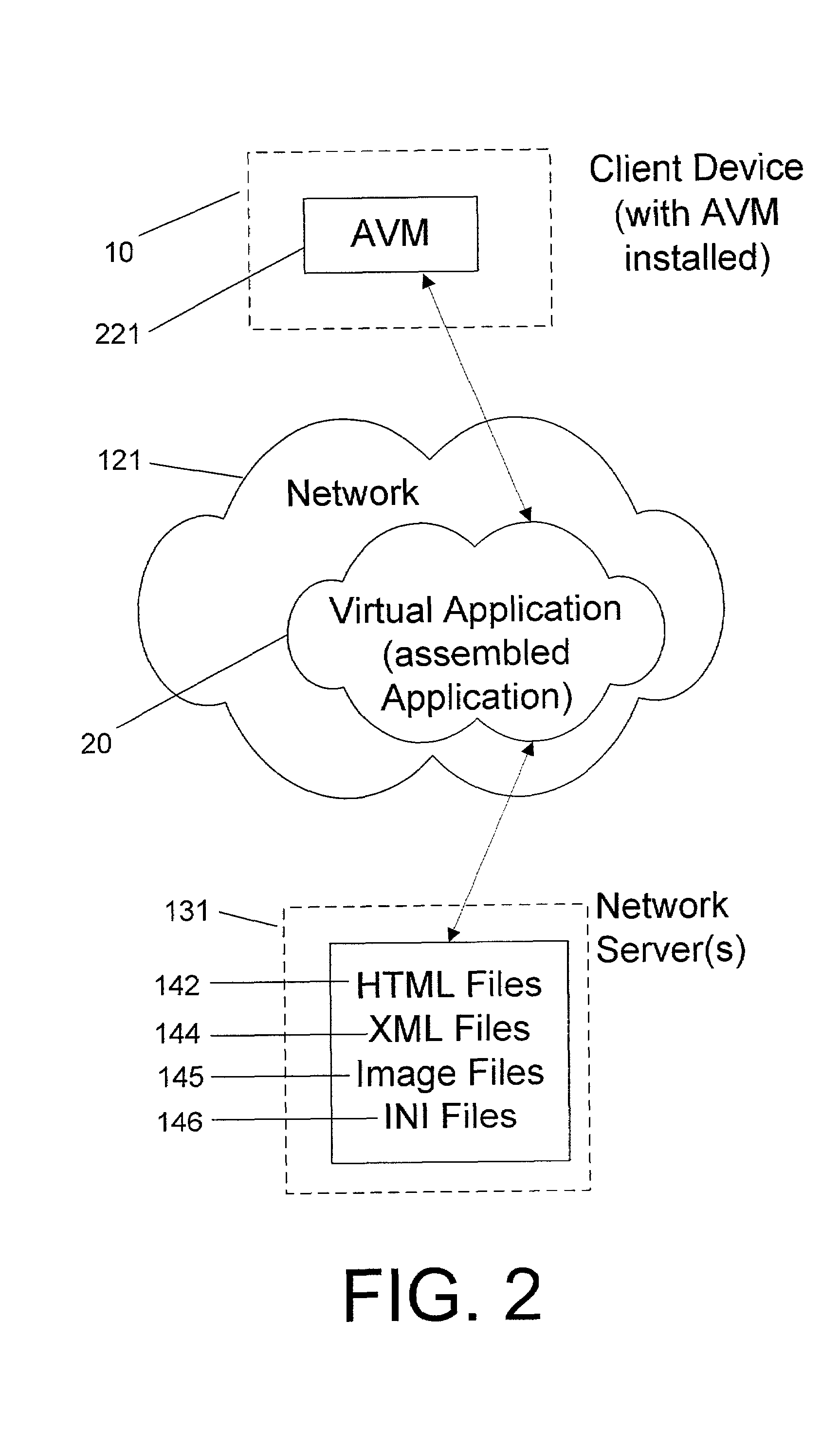

System and method for deploying and implementing software applications over a distributed network

ActiveUS20020129129A1Multiple digital computer combinationsProgram loading/initiatingApplication softwareProgram logic

A system for deploying applications over a distributed network to web-enabled devices uses a server, with stored text files containing application logic, and an application assembler. The application assembler downloads and installs on each web-enabled device. Then, the application assembler downloads one or more text files from the server, retrieves program logic from each of the downloaded text files, and assembles the retrieved program logic into a functioning application. In some instances, a plugin that is downloaded and installed on each web-enabled device is activated by web pages on the server to launch the application assembler.

Owner:DATACLOUD TECH LLC

System and method for deploying and implementing software applications over a distributed network

ActiveUS7246351B2Multiple digital computer combinationsProgram loading/initiatingSystem usageProgram logic

Owner:DATACLOUD TECH LLC

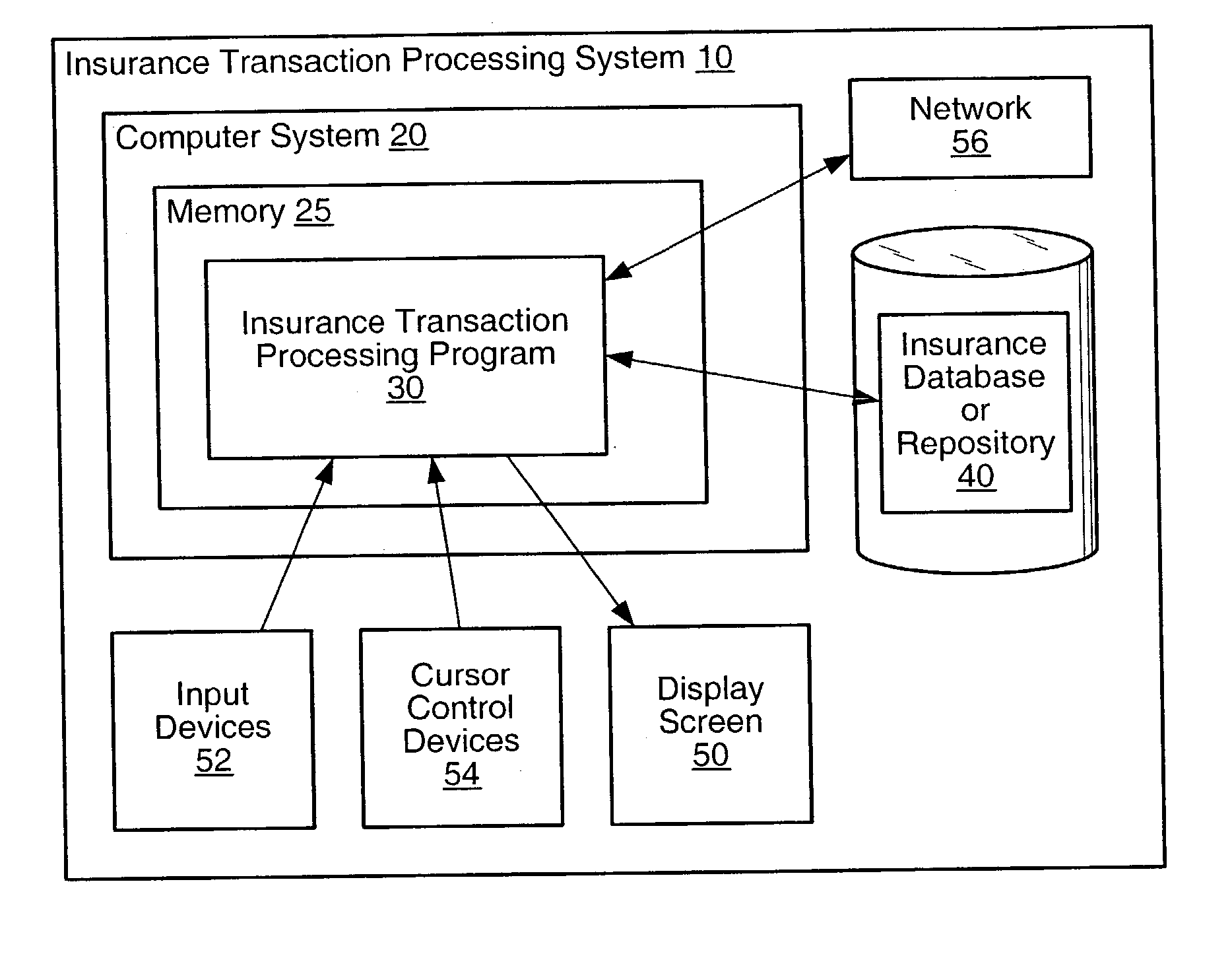

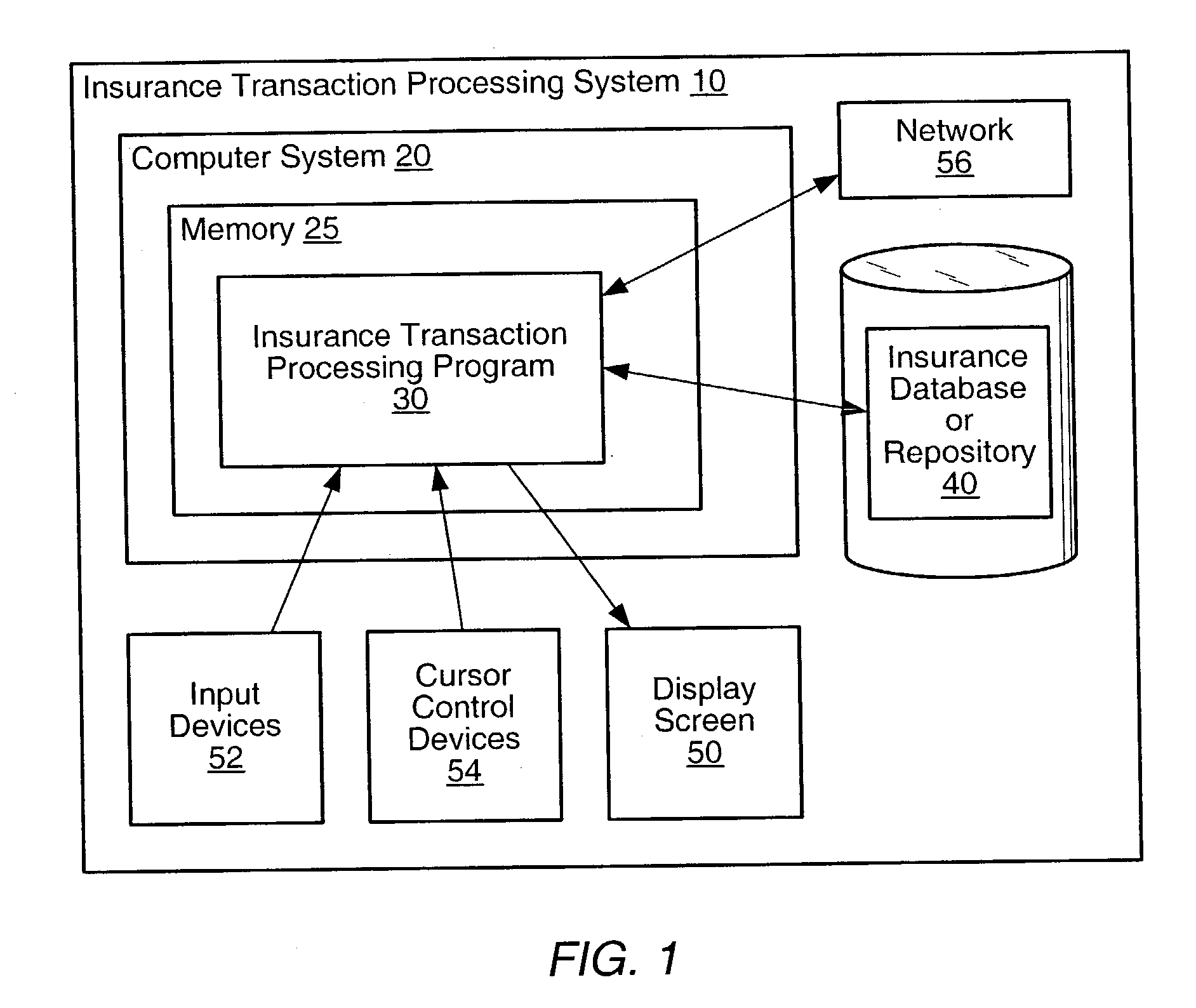

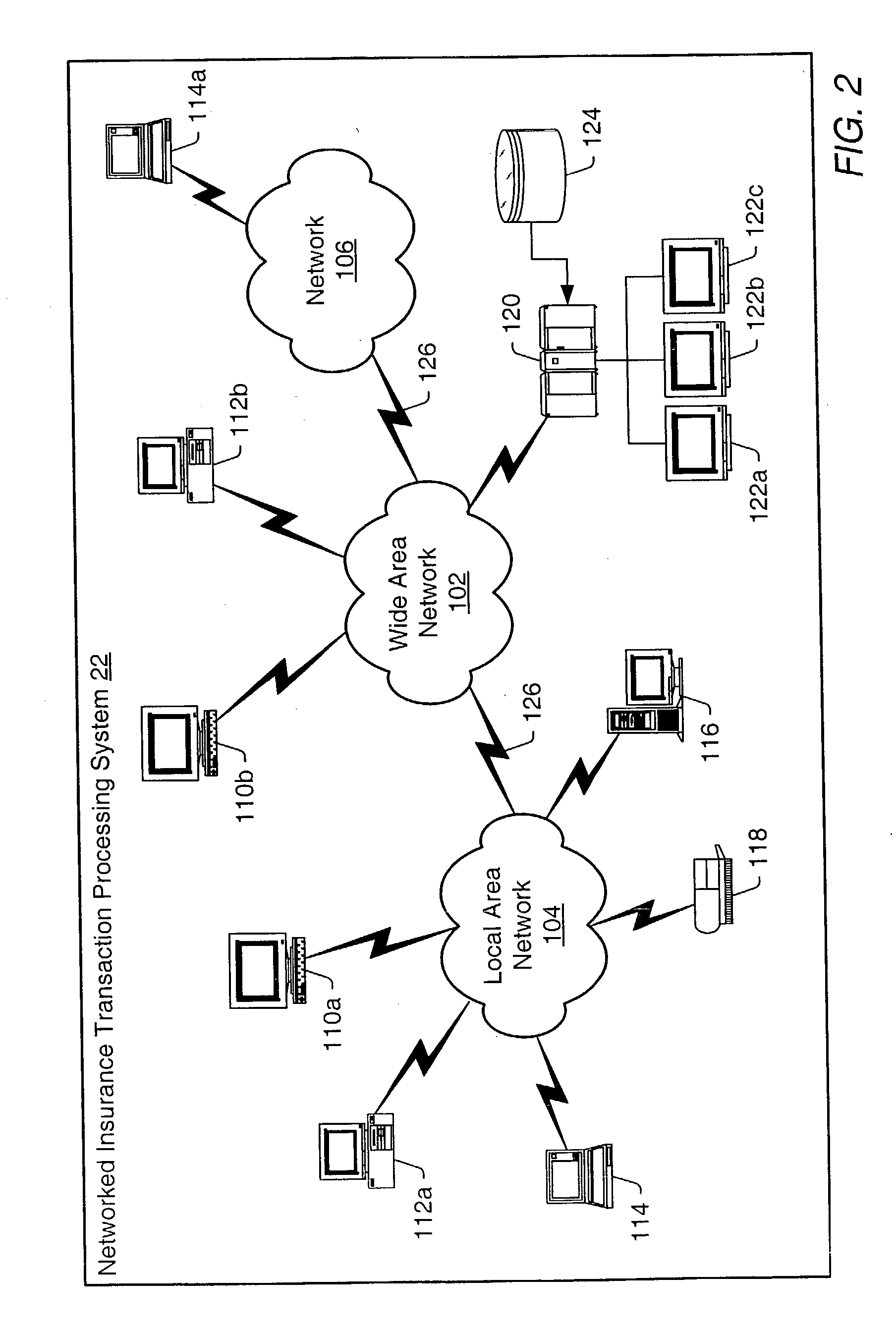

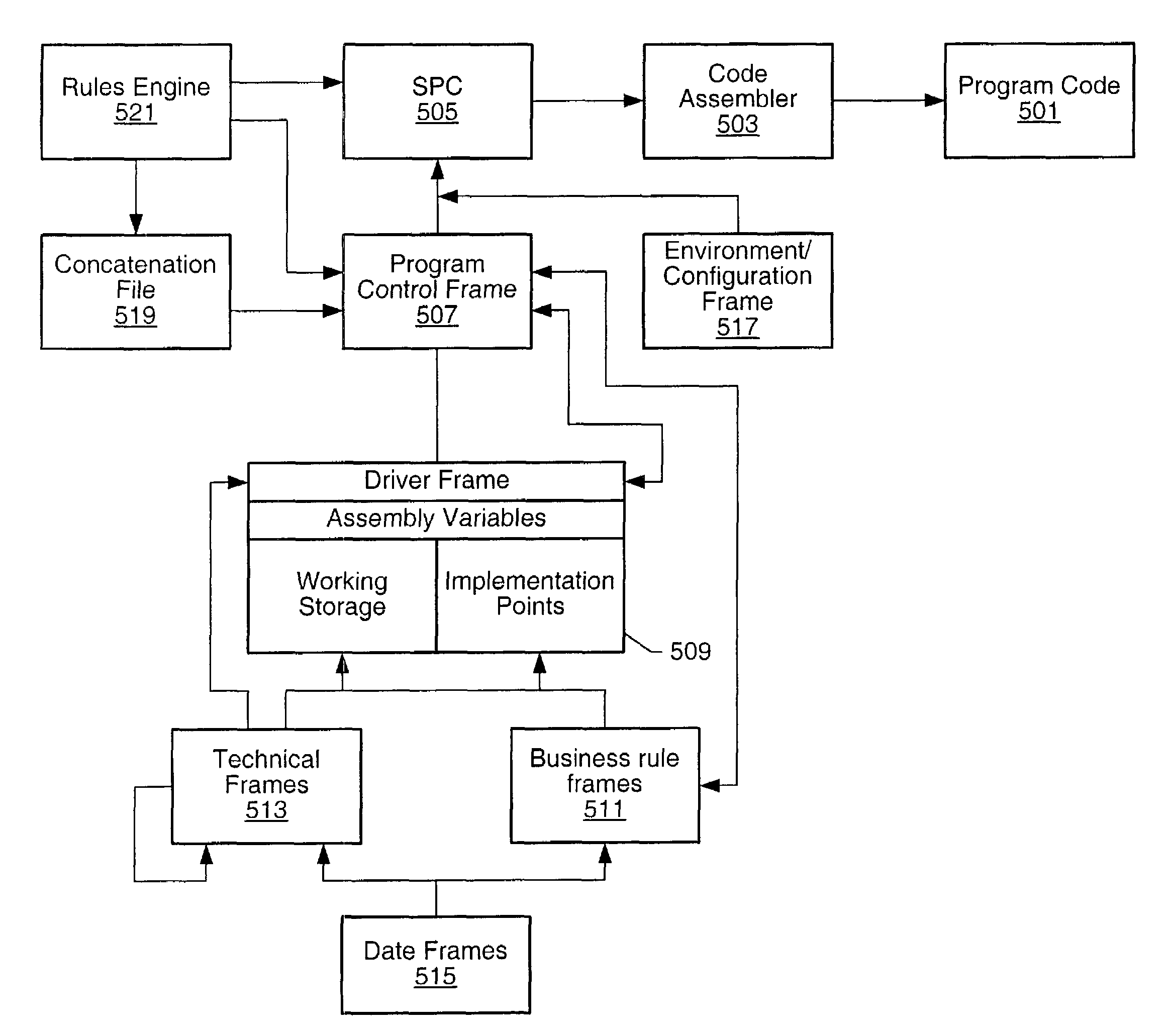

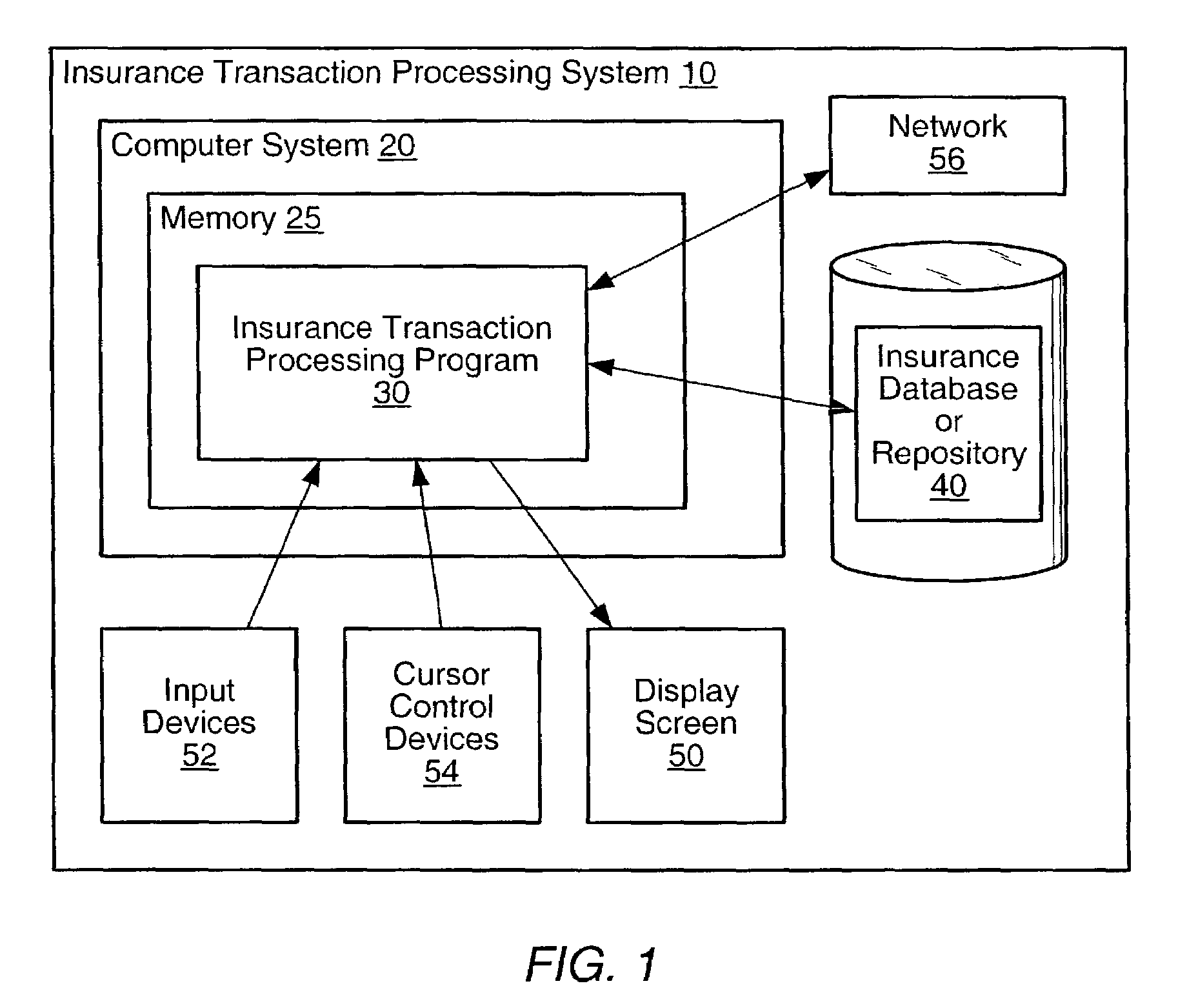

System for modifying software using reusable software components

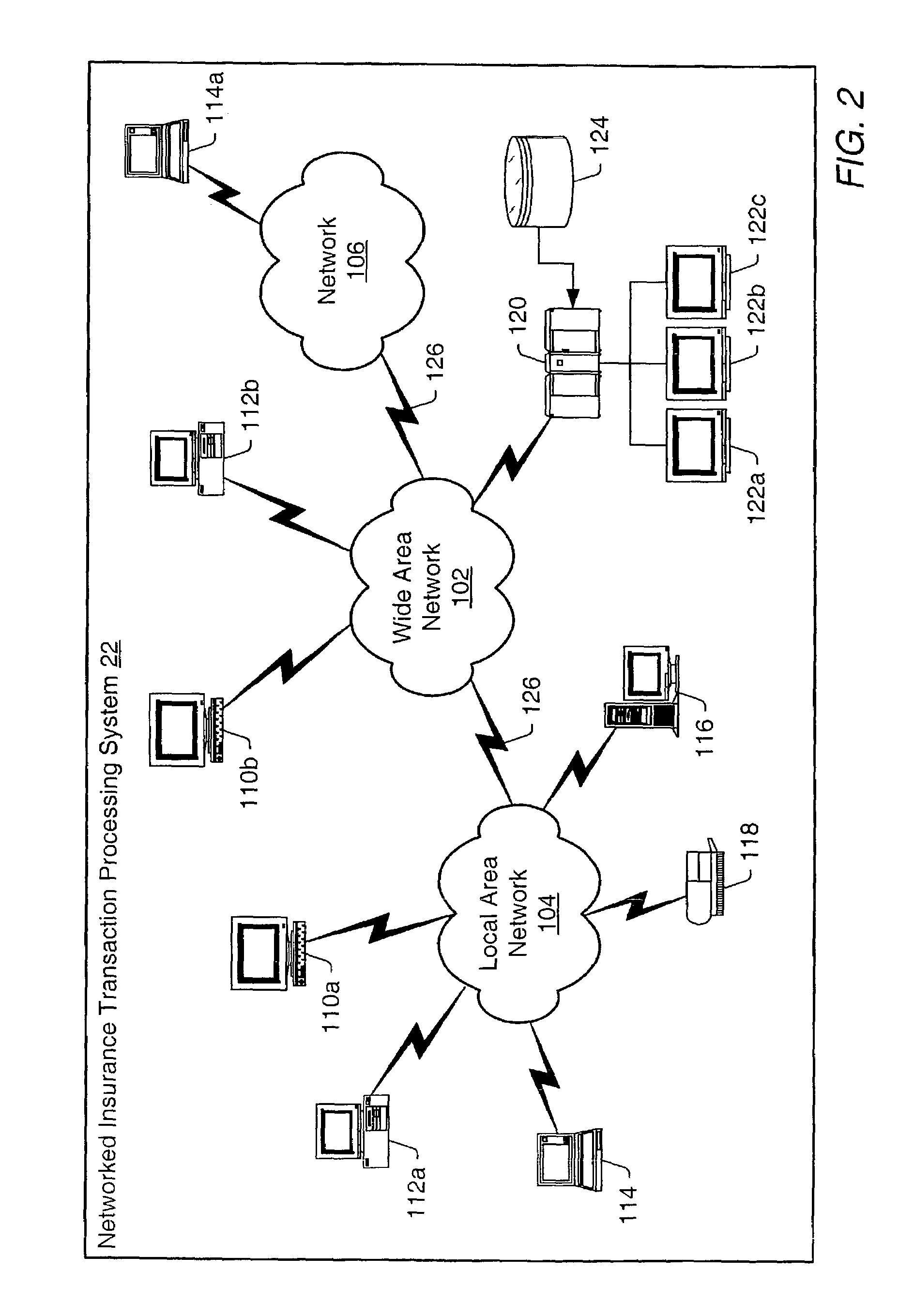

A system, method for modifying insurance transaction processing software are provided. A library of code packets may be stored in a database. One or more code packets may implement at least one business requirement of an insurance organization. If the organization changes one of the business requirements or develops a new business requirement, a user may modify an insurance transaction processing program to reflect the change via a rules engine. The rules engine may be operable to generate program code assembly instructions based on user input. The assembly instructions may be used by a code assembler to form program code for an insurance transaction processing program software module. The insurance transaction processing program may be changed by adding a formed software module.

Owner:COMP SCI A OF NV

Automated processor generation system for designing a configurable processor and method for the same

InactiveUS20030208723A1Decompilation/disassemblyGeneral purpose stored program computerApplication softwareProcessor design

An automated processor design tool uses a description of customized processor instruction set extensions in a standardized language to develop a configurable definition of a target instruction set, a Hardware Description Language description of circuitry necessary to implement the instruction set, and development tools such as a compiler, assembler, debugger and simulator which can be used to develop applications for the processor and to verify it. Implementation of the processor circuitry can be optimized for various criteria such as area, power consumption, speed and the like. Once a processor configuration is developed, it can be tested and inputs to the system modified to iteratively optimize the processor implementation. By providing a constrained domain of extensions and optimizations, the process can be automated to a high degree, thereby facilitating fast and reliable development.

Owner:TENSILICA

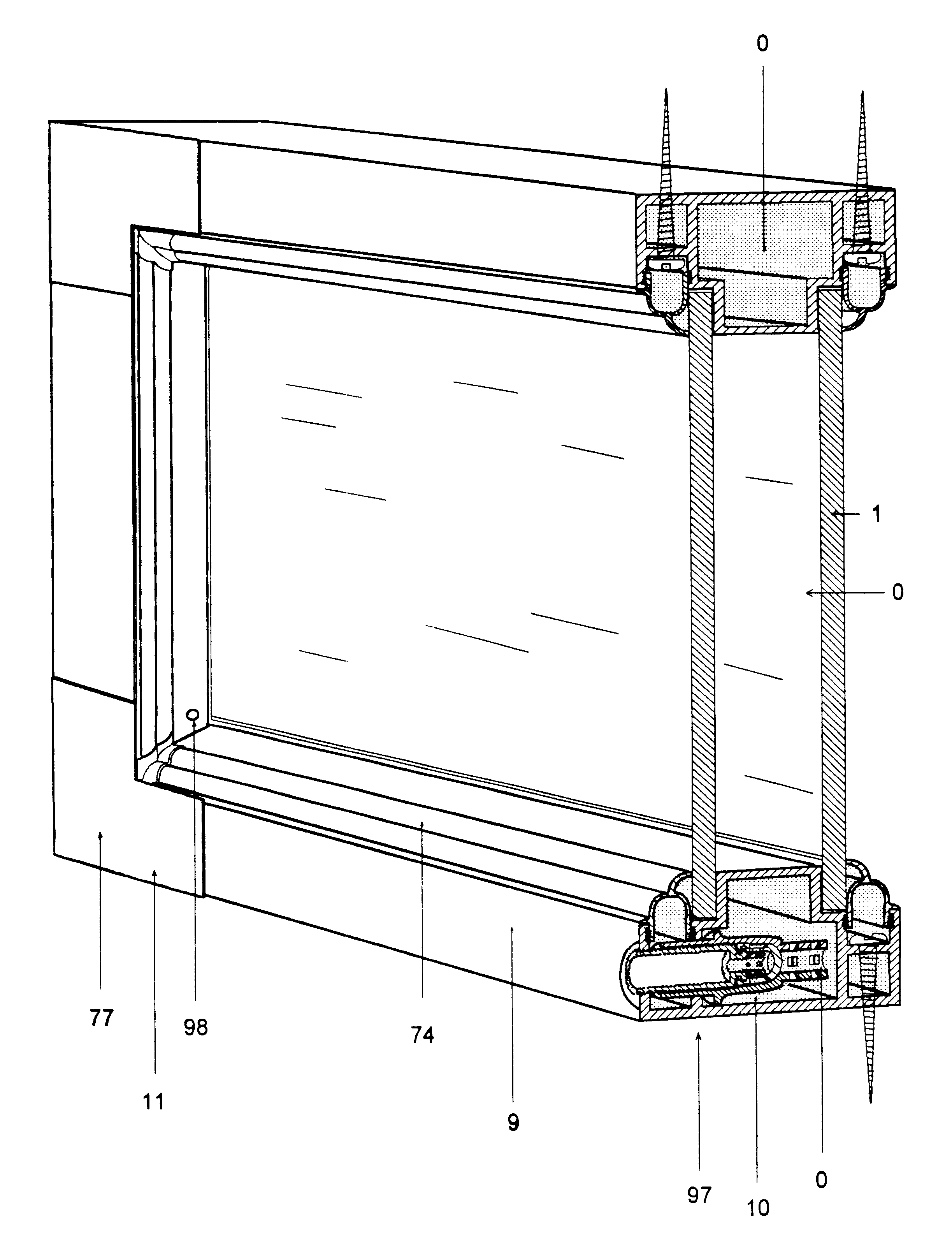

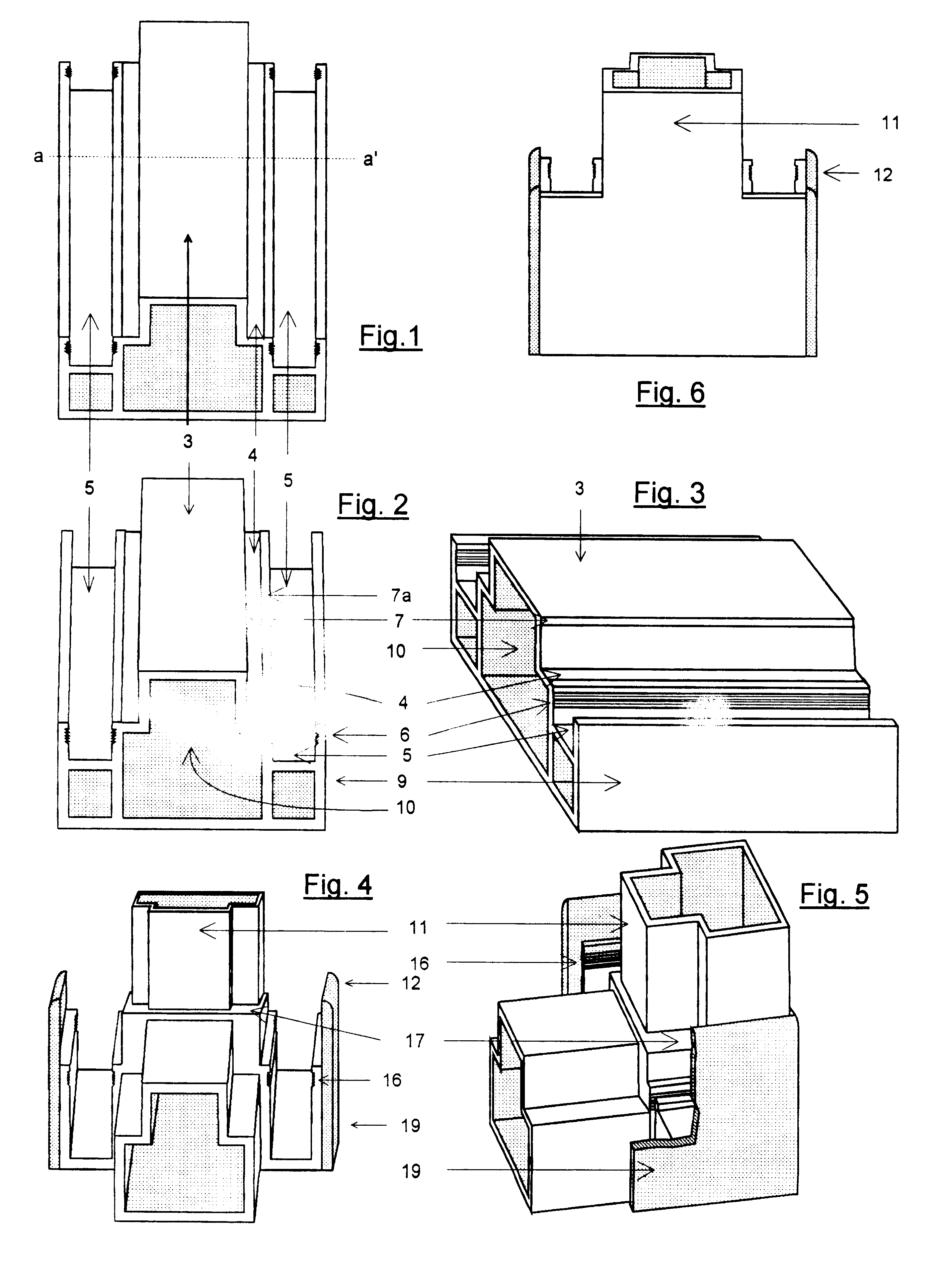

Assembly system for thermoacoustic windows

An assembly system used to build two pane thermoacoustic windows for houses and buildings is provided. The assembly system uses a set of profiles and joints and a permanently installed valve to assemble the window frame without a fusion welding machine. The system creates an airtight chamber directly on the frame. The valve allows the assembler to evacuate the air in the airtight chamber to make a vacuum, or to inflow a gas. The system improves the insulating thermal and acoustic capacity of the window, and allows a supplier to sell the components to build the window, which is then assembled by snapping together profiles and joints. The system can also be applied to assembly one pane window and for other purposes.

Owner:VALDERRAMA MARIO

Adding complex instruction extensions defined in a standardized language to a microprocessor design to produce a configurable definition of a target instruction set, and hdl description of circuitry necessary to implement the instruction set, and development and verification tools for the instruction set

InactiveUS6477697B1Fast and reliable developmentGeneral purpose stored program computerCAD network environmentApplication softwareProcessor design

An automated processor design tool uses a description of customized processor instruction set extensions in a standardized language to develop a configurable definition of a target instruction set, a Hardware Description Language description of circuitry necessary to implement the instruction set, and development tools such as a compiler, assembler, debugger and simulator which can be used to develop applications for the processor and to verify it. The standardized language is capable of handling instruction set extensions which modify processor state or use configurable processors. By providing a constrained domain of extensions and optimizations, the process can be automated to a high degree, thereby facilitating fast and reliable development.

Owner:TENSILICA

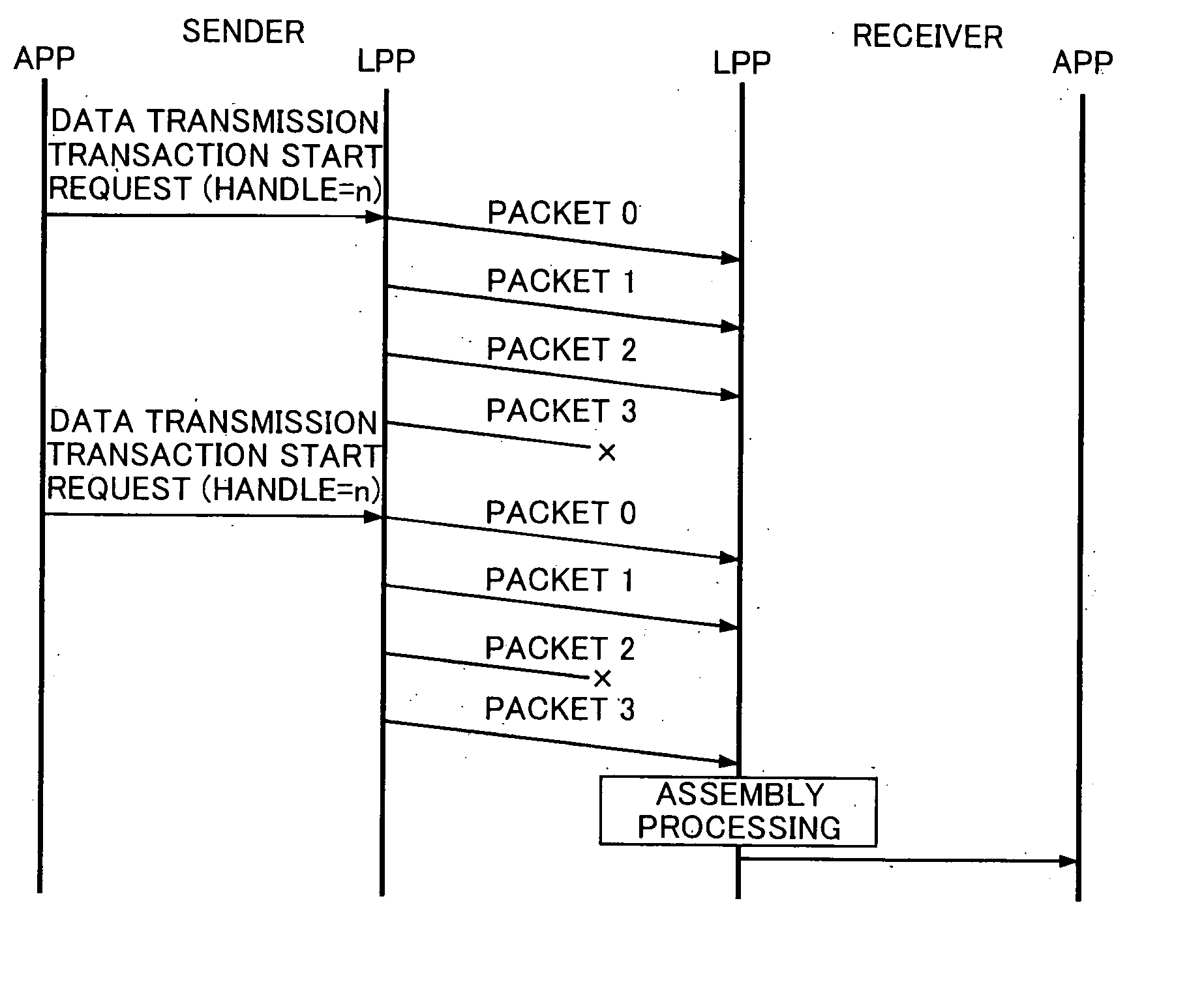

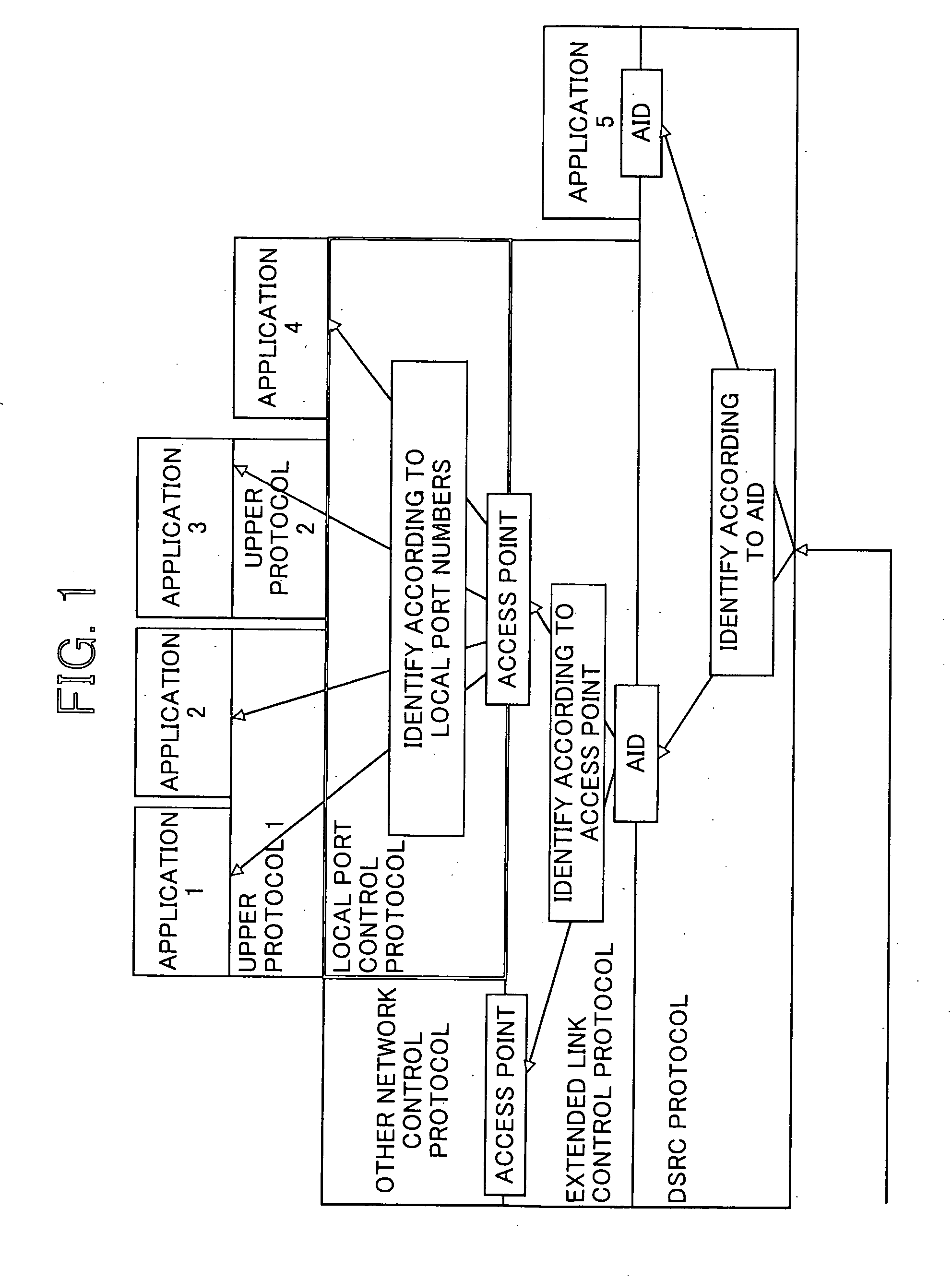

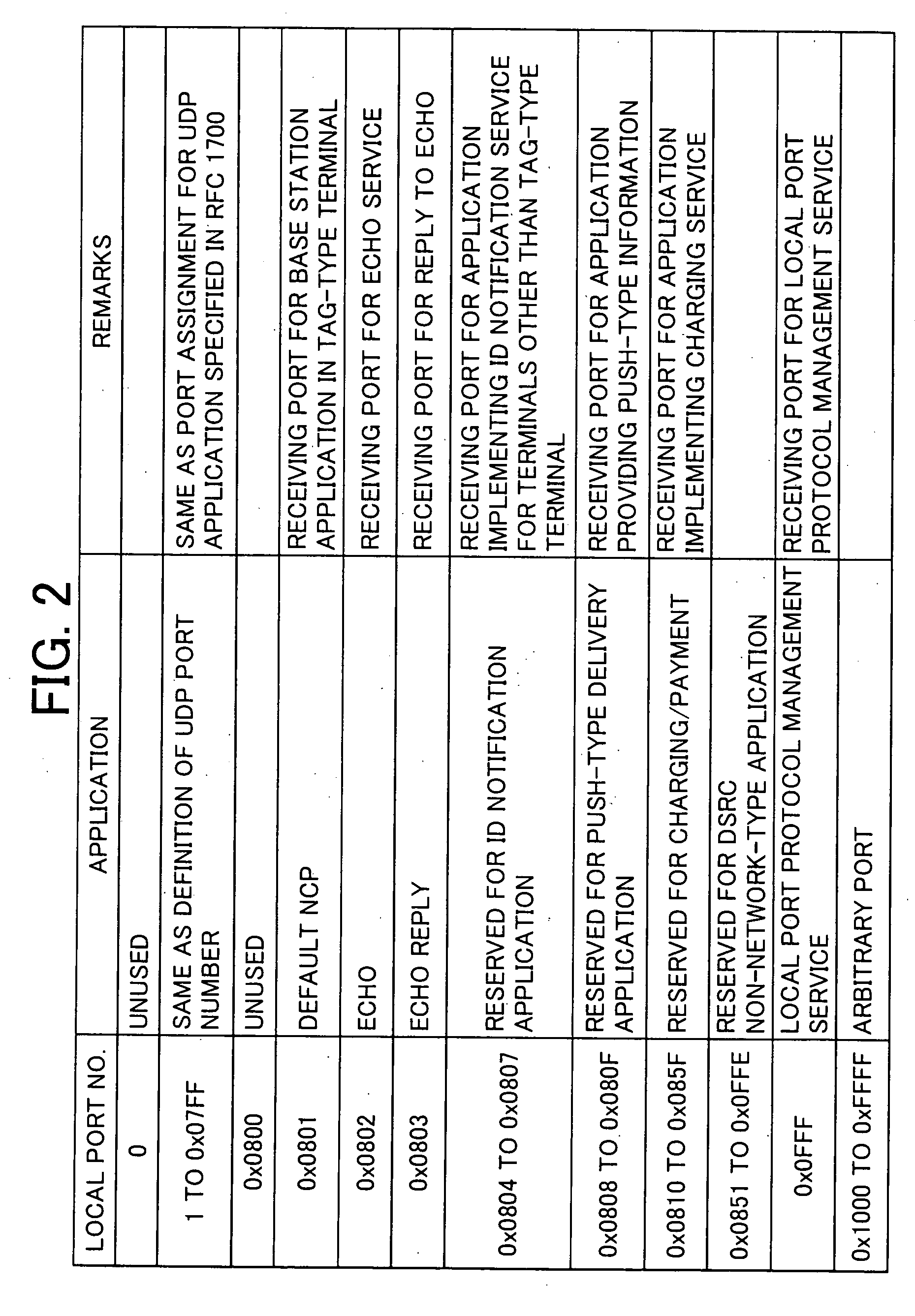

Between-load-and-vehicle communication system

InactiveUS20060193282A1High error rateReduce overheadError prevention/detection by using return channelNetwork traffic/resource managementTransaction managementTransaction service

A roadside-to-vehicle communication system for providing a mobile station with application service by utilizing roadside-to-vehicle communication implemented between the mobile station that travels on a road and a base station system installed along the road provides non-network-type communication protocols that can implement diverse application services, even when the mobile station is moving. The roadside-to-vehicle communication system includes transfer service processing entities for implementing data transfer among applications and transaction management entities have undelivered data resenders, data send / receive for each message, and a message segmenter / assembler that provides unidirectional data transmission and request-response transaction services.

Owner:MITSUBISHI ELECTRIC CORP

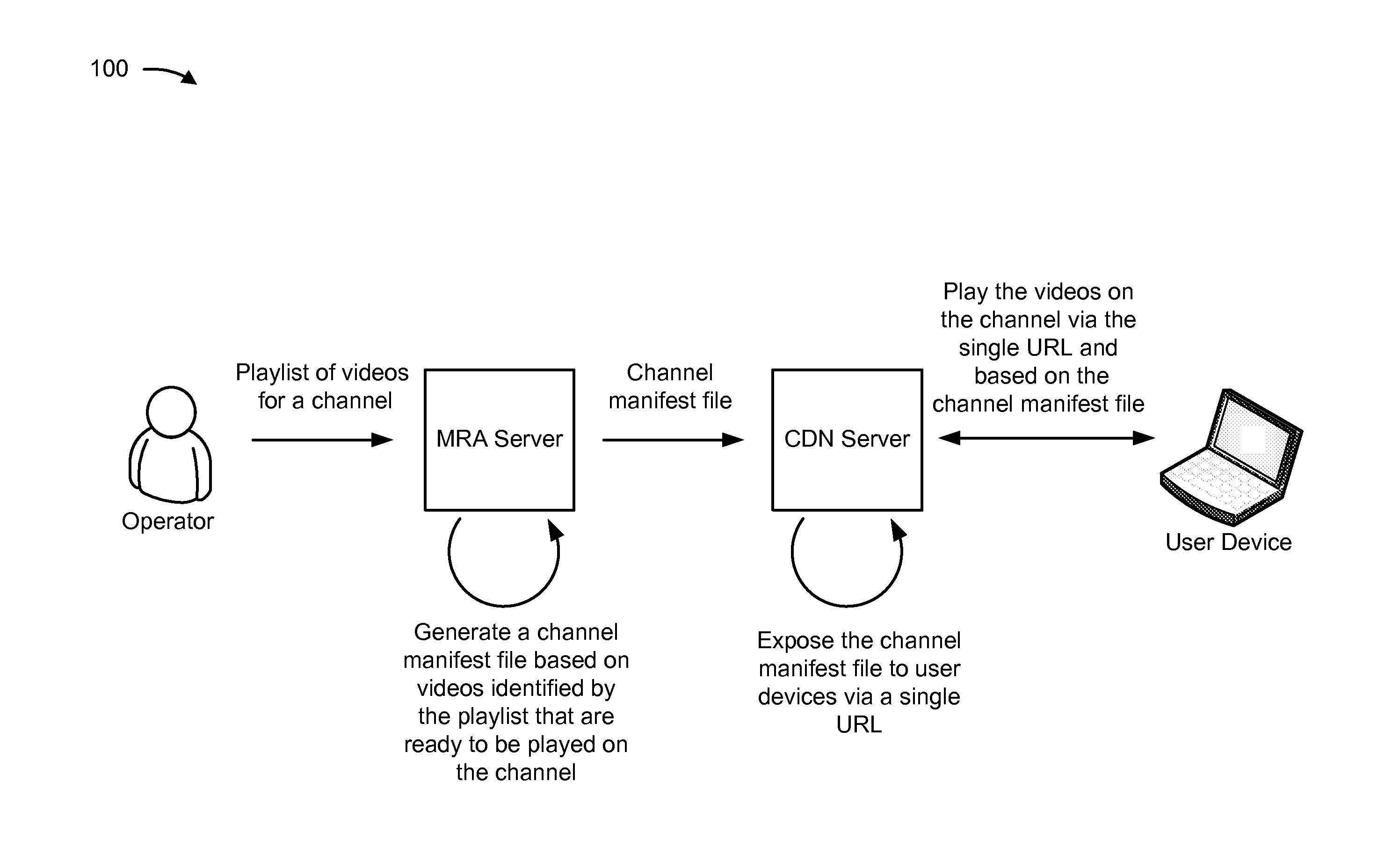

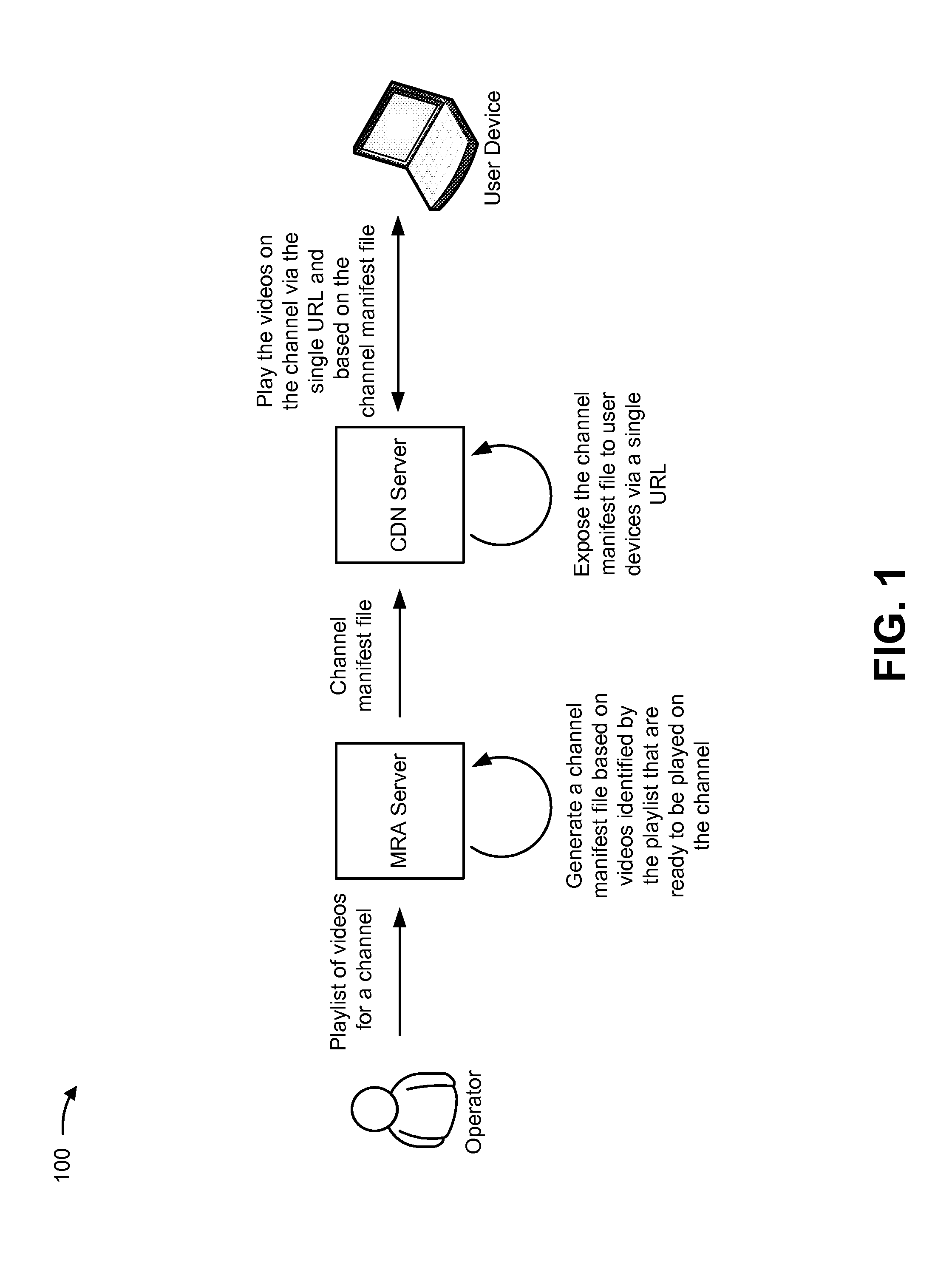

Manifest re-assembler for a streaming video channel

ActiveUS20150271234A1Multiple digital computer combinationsTransmissionNetwork addressingNetwork address

A device is configured to receive a playlist identifying content assets to be played on a streaming video channel. Each of the content assets may include segments. The device may add segment addresses associated with a content asset into a queue. The segment addresses may identify memory locations at which the segments included in the content asset are stored. However, the segments themselves may not be stored by the device or added to the queue. The device may generate a batch of segment addresses from the segment addresses in the queue. The device may publish a channel manifest for the streaming video channel including the batch of segment addresses. The content assets may be accessible via the streaming video channel through a single network address. The device may periodically update the channel manifest based on the segment addresses in the queue.

Owner:ACCENTURE GLOBAL SERVICES LTD

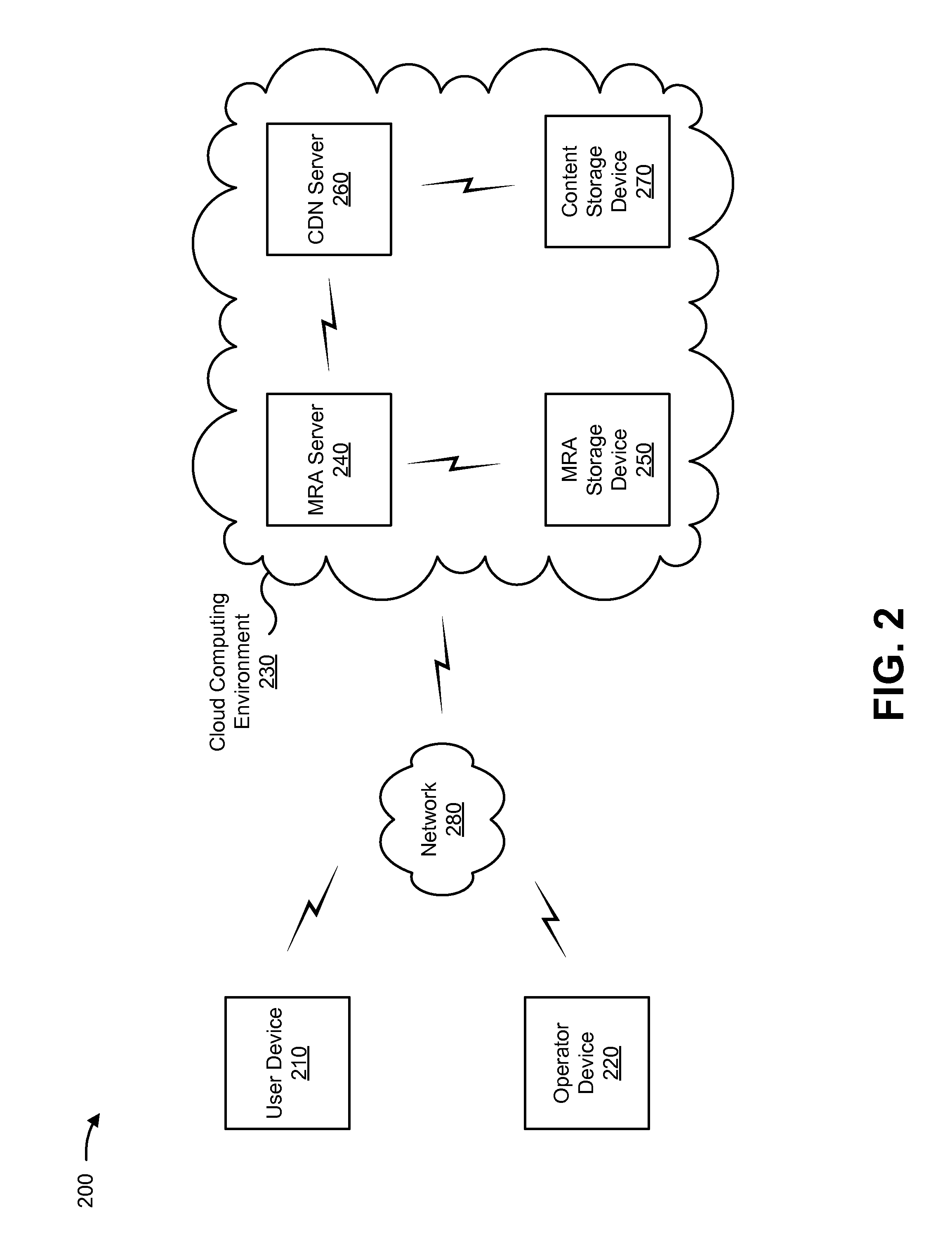

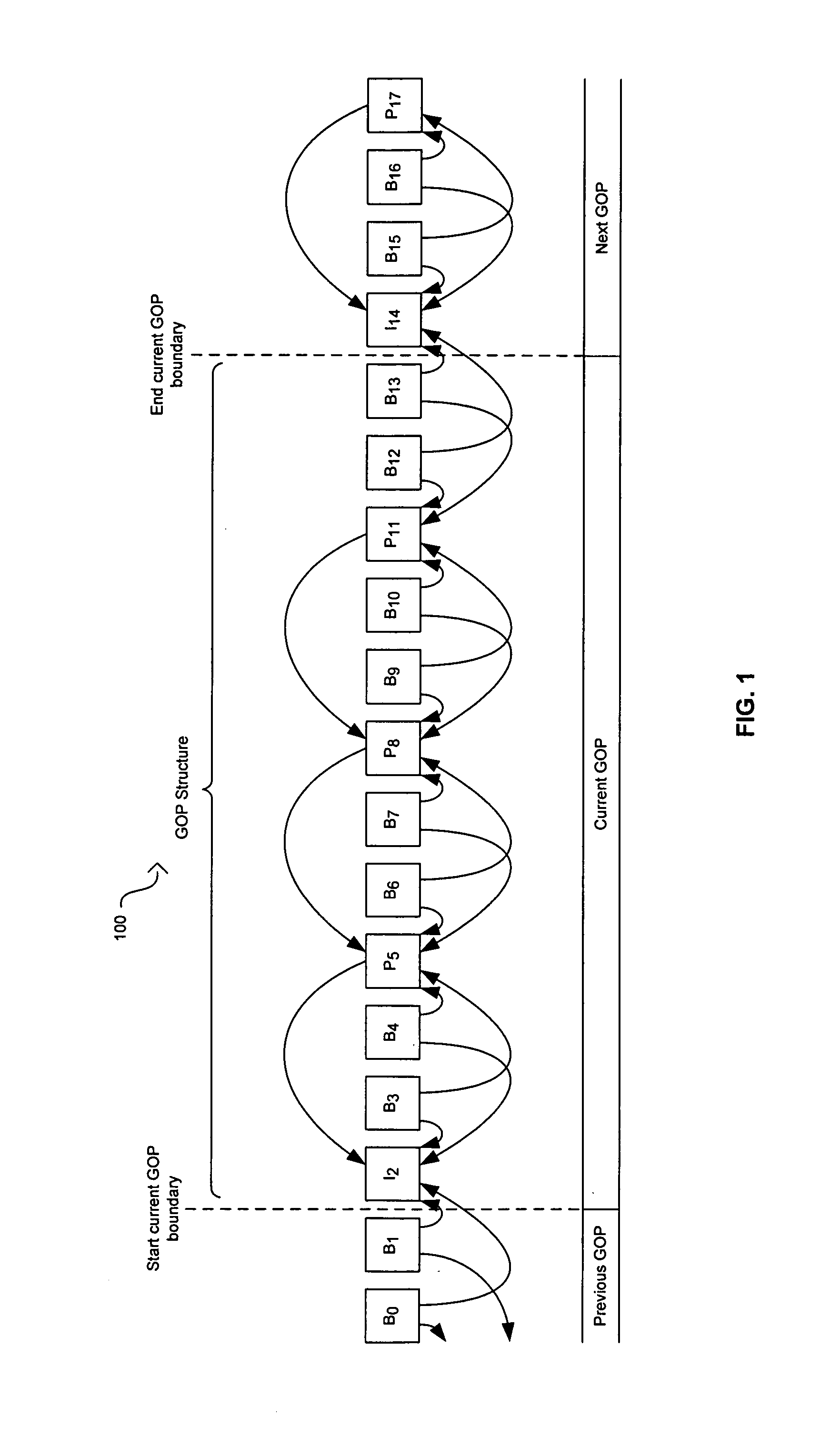

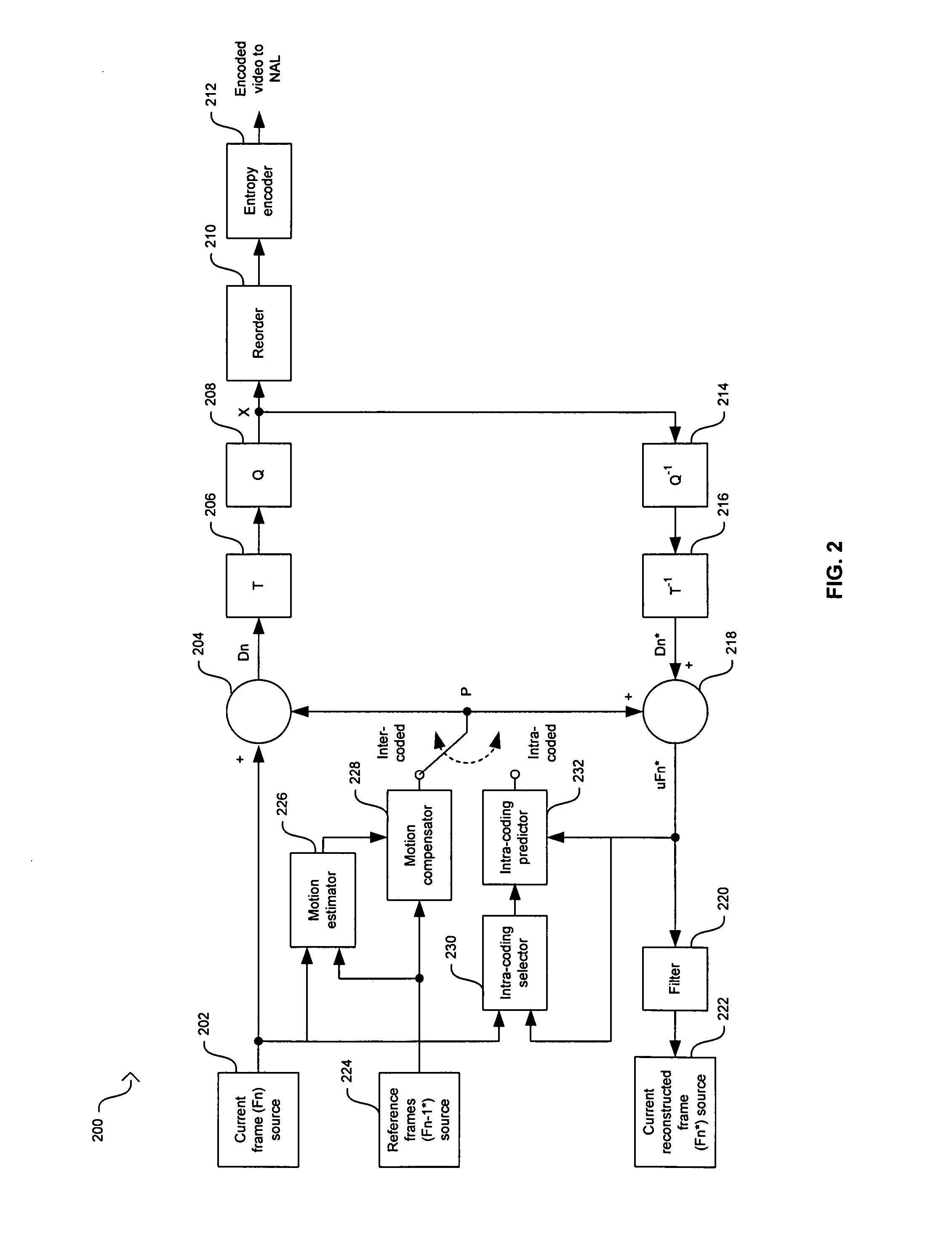

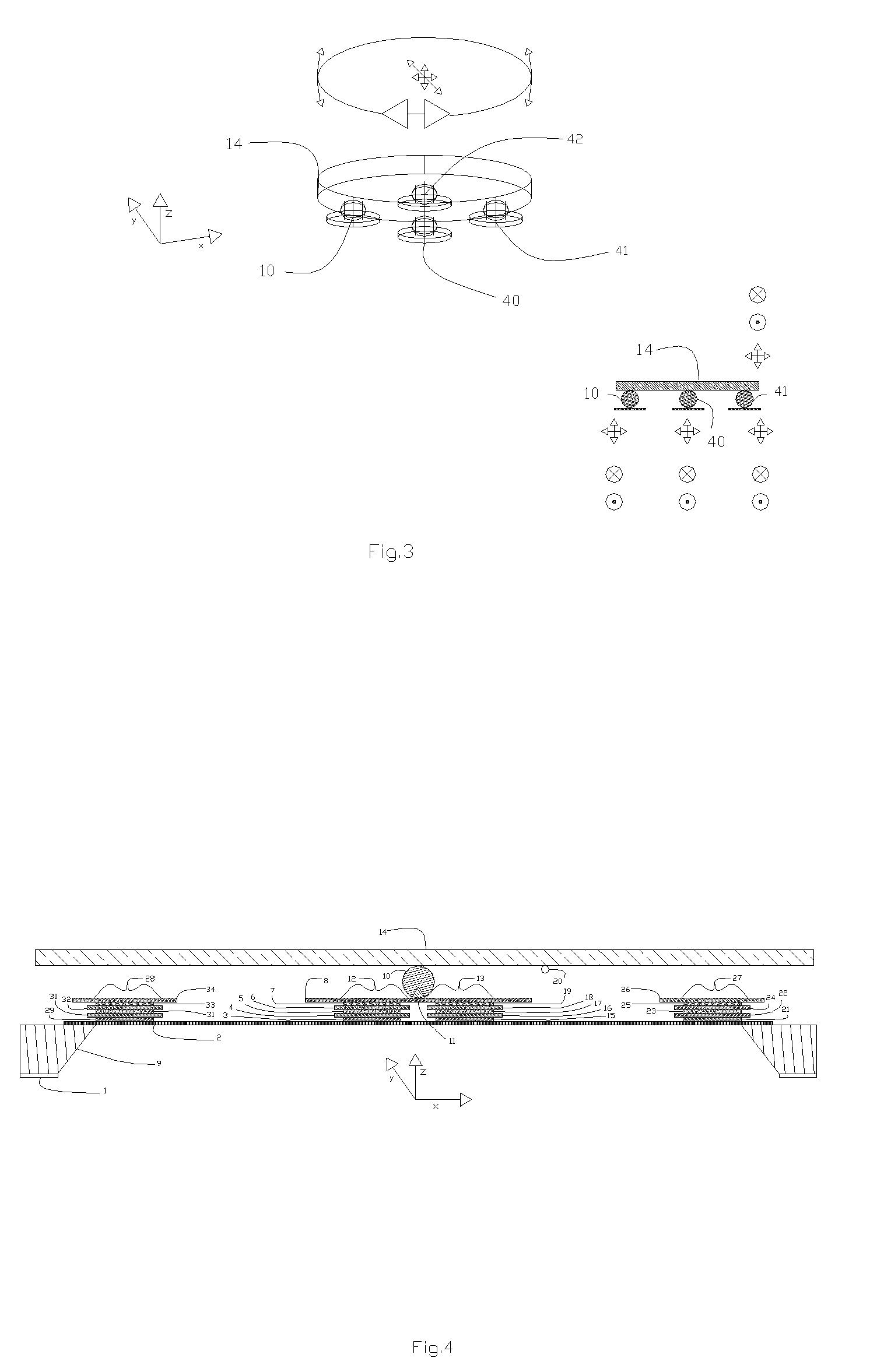

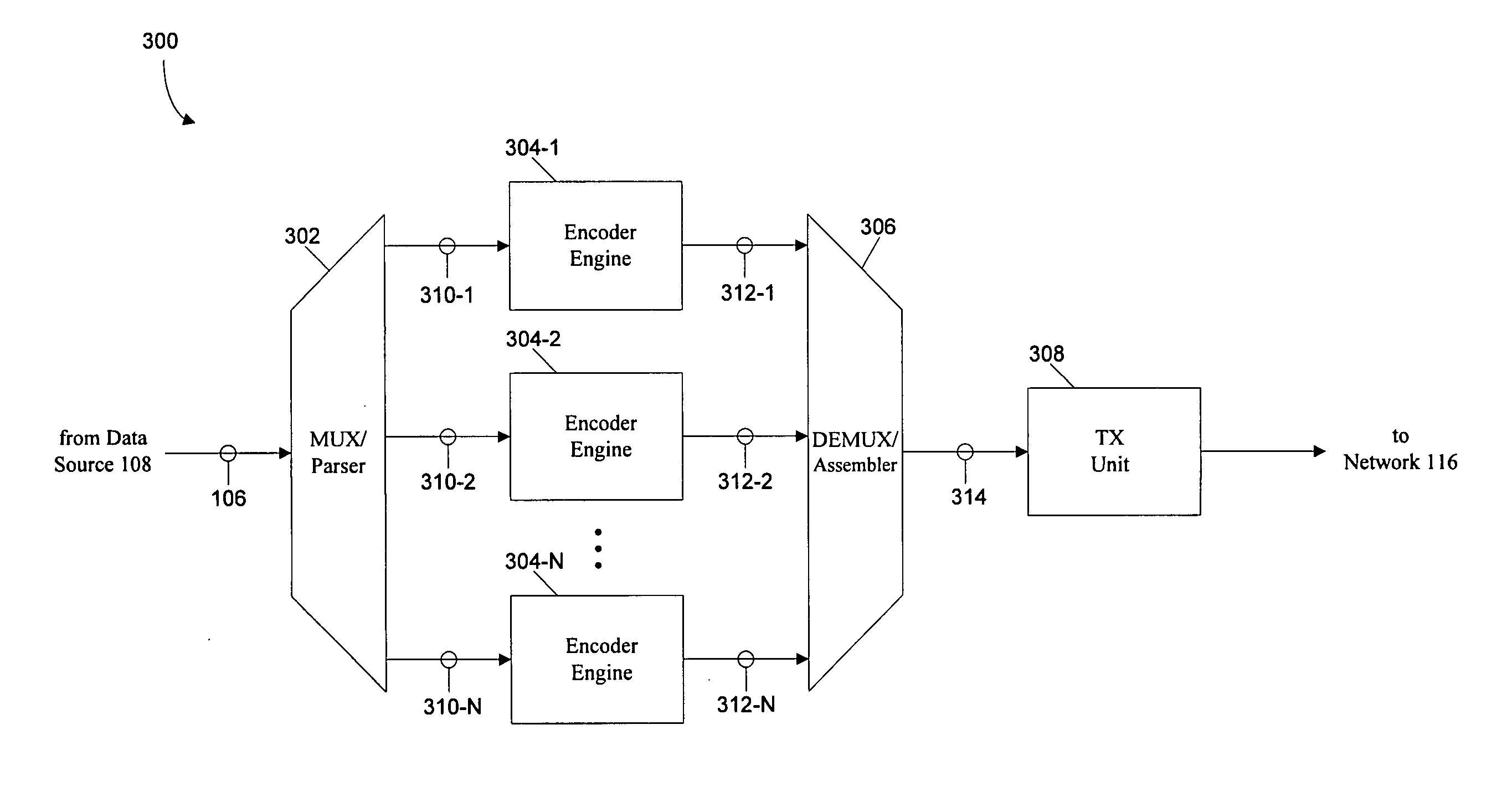

Method and system for high speed video encoding using parallel encoders

InactiveUS20060114995A1Increase speedColor television with pulse code modulationColor television with bandwidth reductionParallel computingVideo processing

In a video processing system, a method and system for high speed video encoding using parallel encoders are provided. A delimiter may break up a video sequence into encoding groups that are transferred to a plurality of parallel encoders. The parallel encoders may process and transfer intra-coded pictures in the encoding groups to previous parallel encoders or may process and transfer last predictive pictures to next parallel encoders. When intra-coded pictures are transferred, the encoding group may correspond to that of a GOP structure. When predictive pictures are transferred, the encoding group may end in at least one bidirectional-predictive picture. The parallel encoders process the transferred intra-coded pictures or transferred predictive pictures to generate a plurality of parallel outputs. An assembler assembles an encoded video output from the parallel outputs based on timing information. A controller controls the operation of the delimiter, the parallel encoders, and the assembler.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

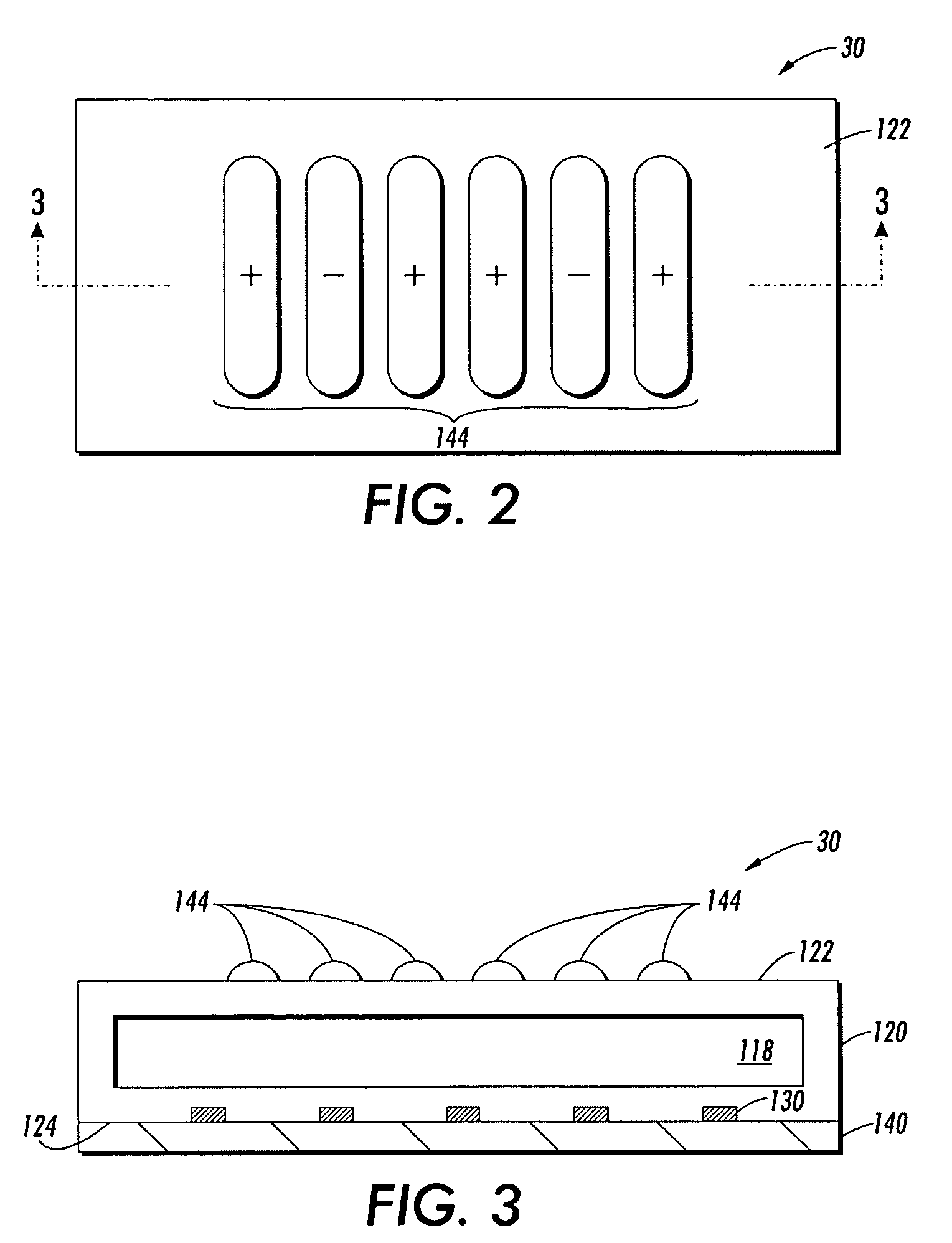

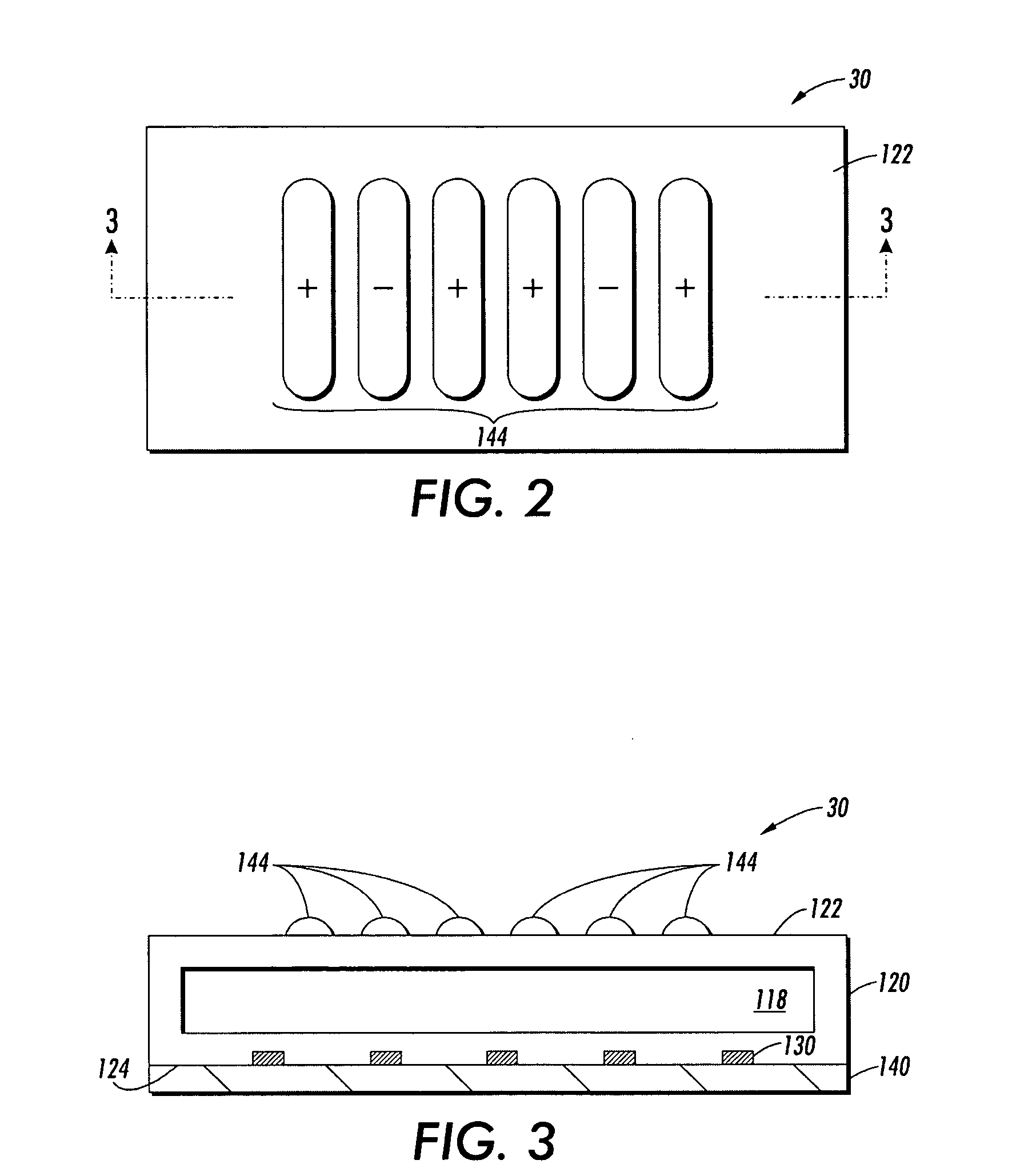

Xerographic micro-assembler

ActiveUS7332361B2Semiconductor/solid-state device testing/measurementSolid-state devicesObject basedImage transfer

Xerographic micro-assembler systems and methods are disclosed. The systems and methods involve manipulating charge-encoded micro-objects. The charge encoding identifies each micro-object and specifies its orientation for sorting. The micro-objects are sorted in a sorting unit so that they have defined positions and orientations. The sorting unit has the capability of electrostatically and magnetically manipulating the micro-objects based on their select charge encoding. The sorted micro-objects are provided to an image transfer unit. The image transfer unit is adapted to receive the sorted micro-objects, maintain them in their sorted order and orientation, and deliver them to a substrate. Maintaining the sorted order as the micro-objects are delivered to the substrate may be accomplished through the use of an electrostatic image, as is done in xerography. The substrate with the micro-objects is further processed to interconnect the micro-objects—through electrical wiring, for example—to form the final micro-assembly.

Owner:XEROX CORP

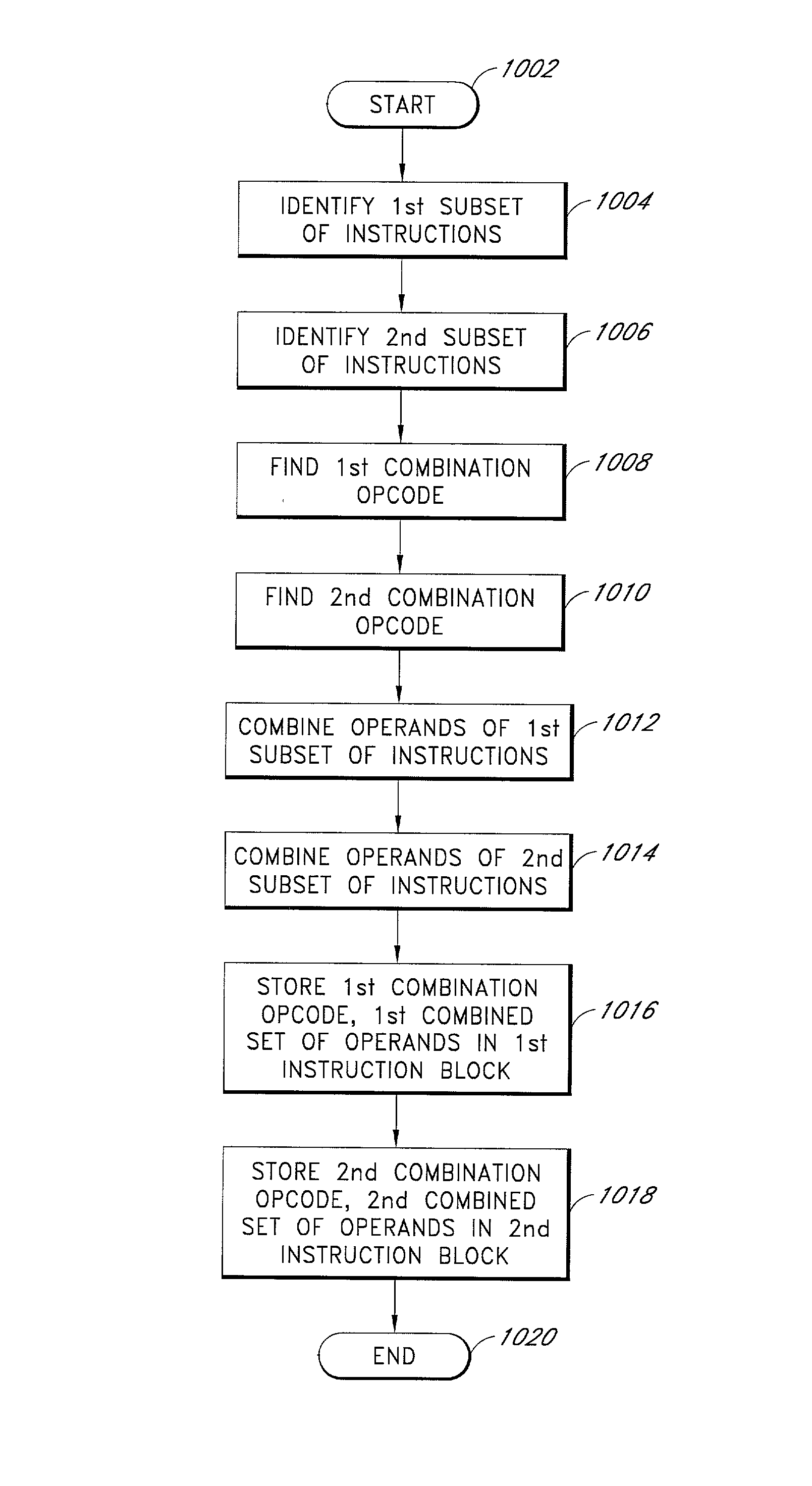

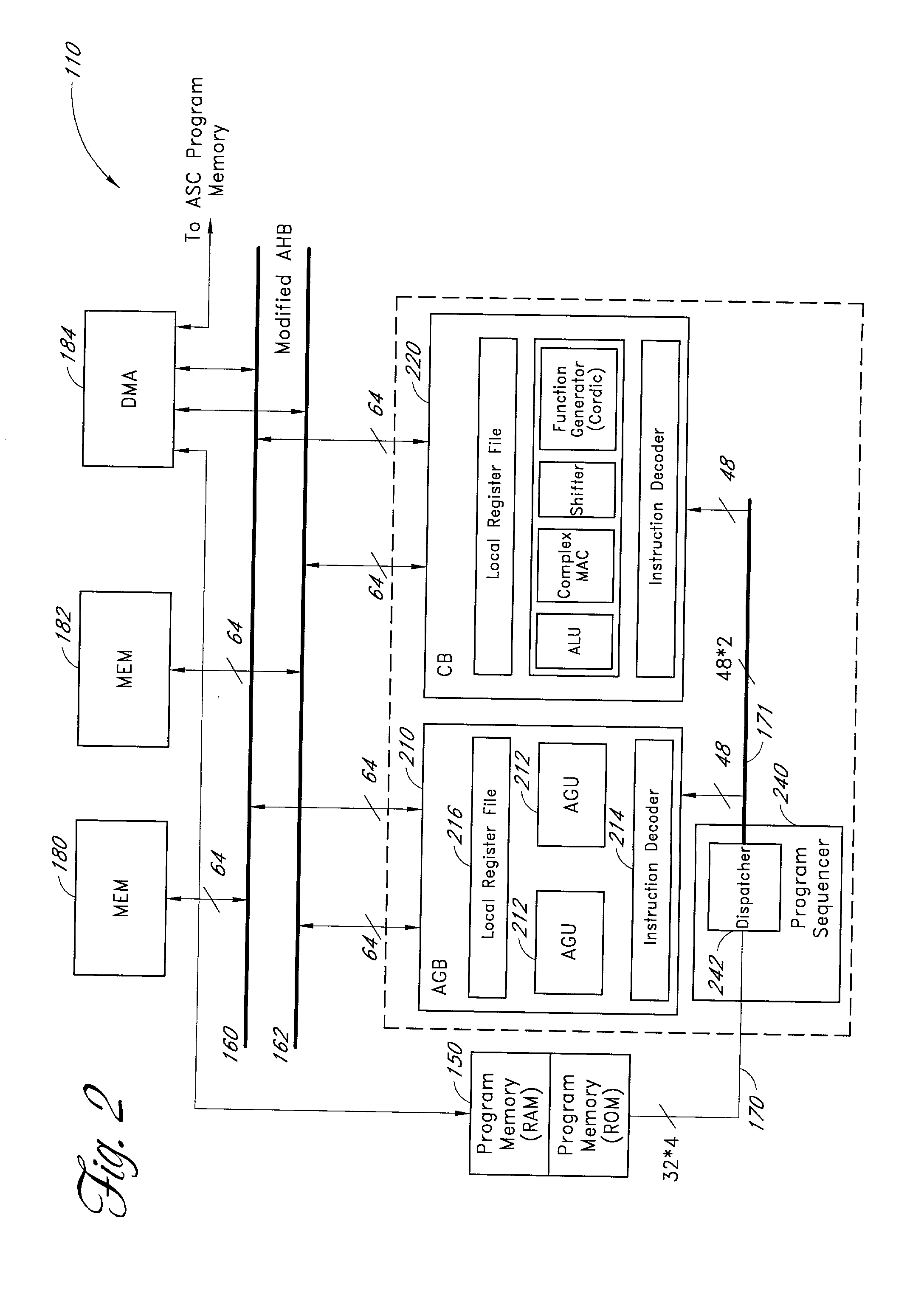

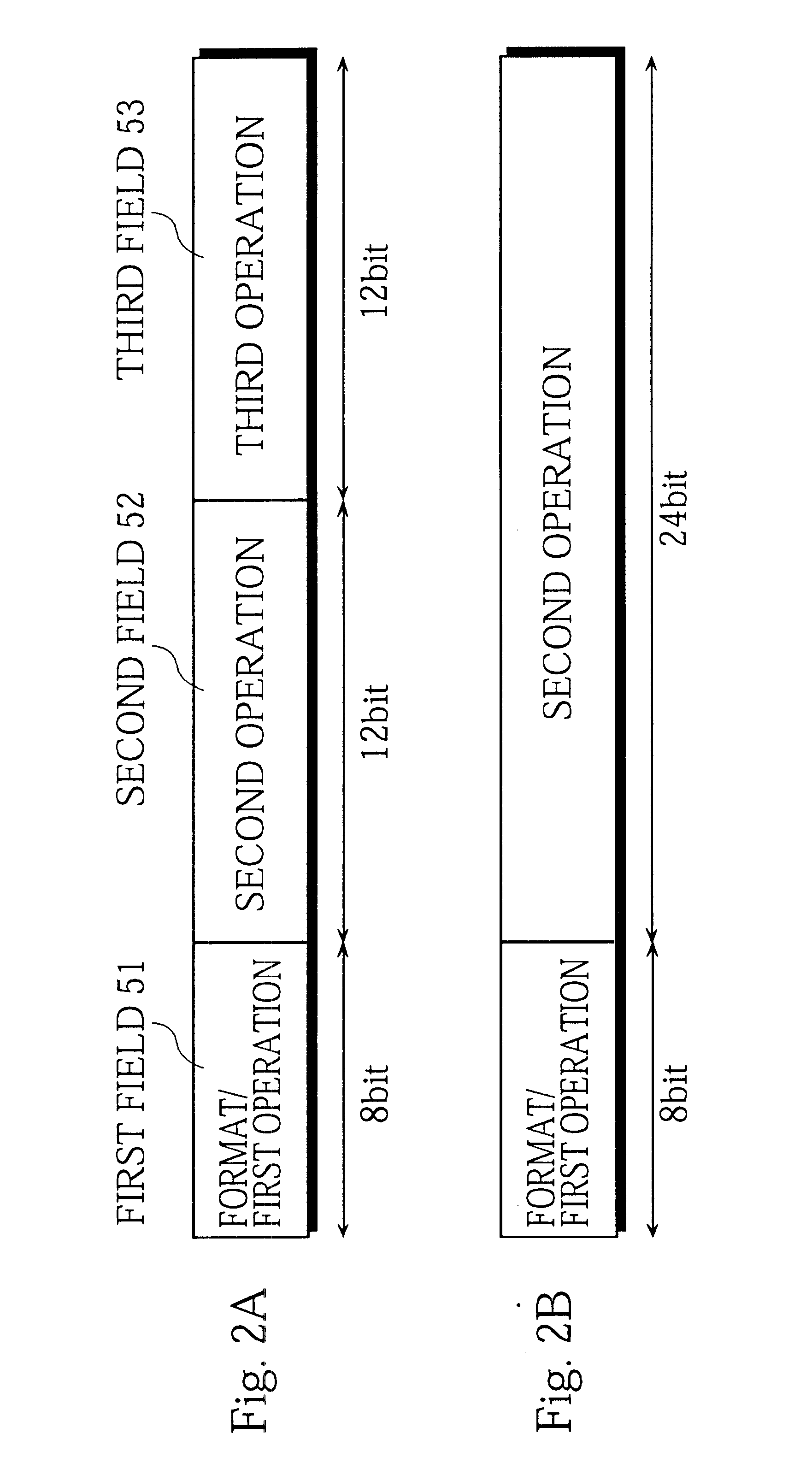

Microprocessor instruction format using combination opcodes and destination prefixes

The present application discloses an instruction format for storing multiple microprocessor instructions as one combined instruction. The instruction format includes a combination opcode field for storing a combination opcode that identifies a combination of the multiple instructions. The application also discloses an instruction format that uses prefix fields to specify the destination functional block for each combined instruction stored in an execute packet. A compiler program or an assembler program obtains from a table a combination opcode that corresponds to a combination of the multiple instructions. The table stores combination opcodes and their corresponding combinations of instructions. The compiler program or assembler program then assigns the found combination opcode to an opcode field of the combined instruction. In a trivial scenario, a single instruction can also be stored as a combined instruction. The compiler program or assembler program also uses prefix fields to identify the destination functional block of each combined instruction in an execute packet. A dispatcher identifies the prefix fields and sends each combined instruction in the execute packet to its destination functional block. An instruction decoder identifies the combination opcode of the combined instruction, separates the combined instruction into the multiple individual instructions, and sends each individual instruction to its respective functional unit for execution.

Owner:AVAZ NETWORKS

Data communication system, method and apparatus for communicating a data signal formed of successive data elements

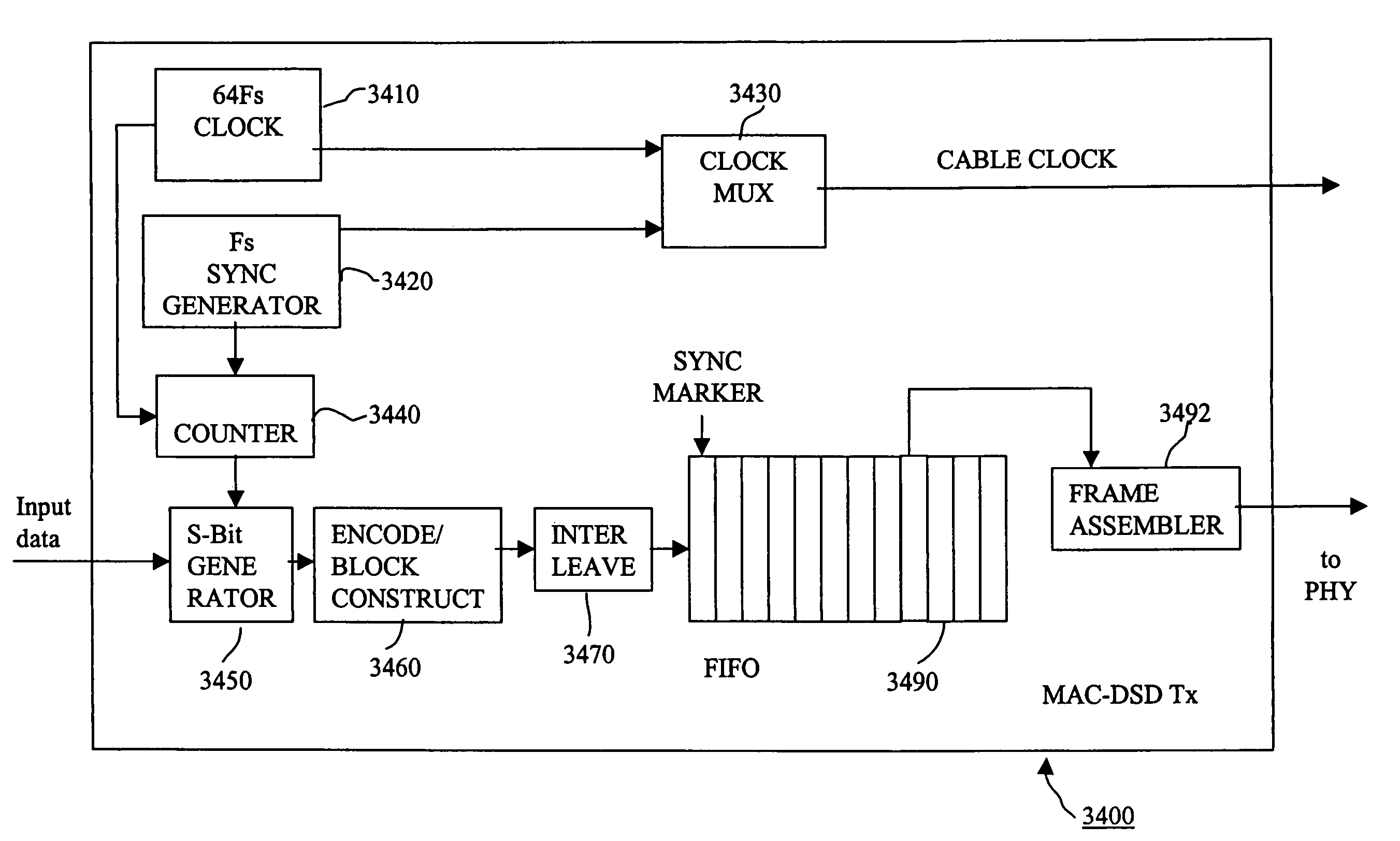

InactiveUS7499500B2Relatively large bandwidthProven electromagnetic compatibilitySynchronisation information channelsModulated-carrier systemsData connectionCommunications system

A data communications system for communicating a data signal formed of successive data elements, said system comprising a transmission node; a reception node; and a link providing a data connection from said transmission node to said reception node; in which: said transmission node comprises a clock signal transmitter for transmitting a synchronisation clocking signal to said reception node via said link, said synchronisation clocking signal having synchronising features occurring at a frequency lower than a data element rate; an assembler for assembling elements of said data signal into data frames, each data frame having a plurality of successive data elements of said data signal, for transmission to said reception node via said link, said assembler being responsive to said synchronisation clocking signal so as to set a synchronisation flag associated with a data element having a first predetermined temporal relationship with a synchronising feature of said synchronisation clocking signal; and said reception node comprises: a detector detecting a synchronising feature of said synchronisation clocking signal received from said transmission node; a disassembler for disassembling received data frames to regenerate said data signal, said disassembler being operable to detect a data element associated with a set synchronisation flag; an output unit for outputting a data element associated with a set synchronisation flag at a second predetermined temporal relationship with respect to said synchronising feature of said received synchronisation clocking signal; said first and second predetermined temporal relationships being arranged so that a predetermined system latency exists between input of a data element to said transmission node and subsequent output of that data element by said reception node.

Owner:SONY UK LTD

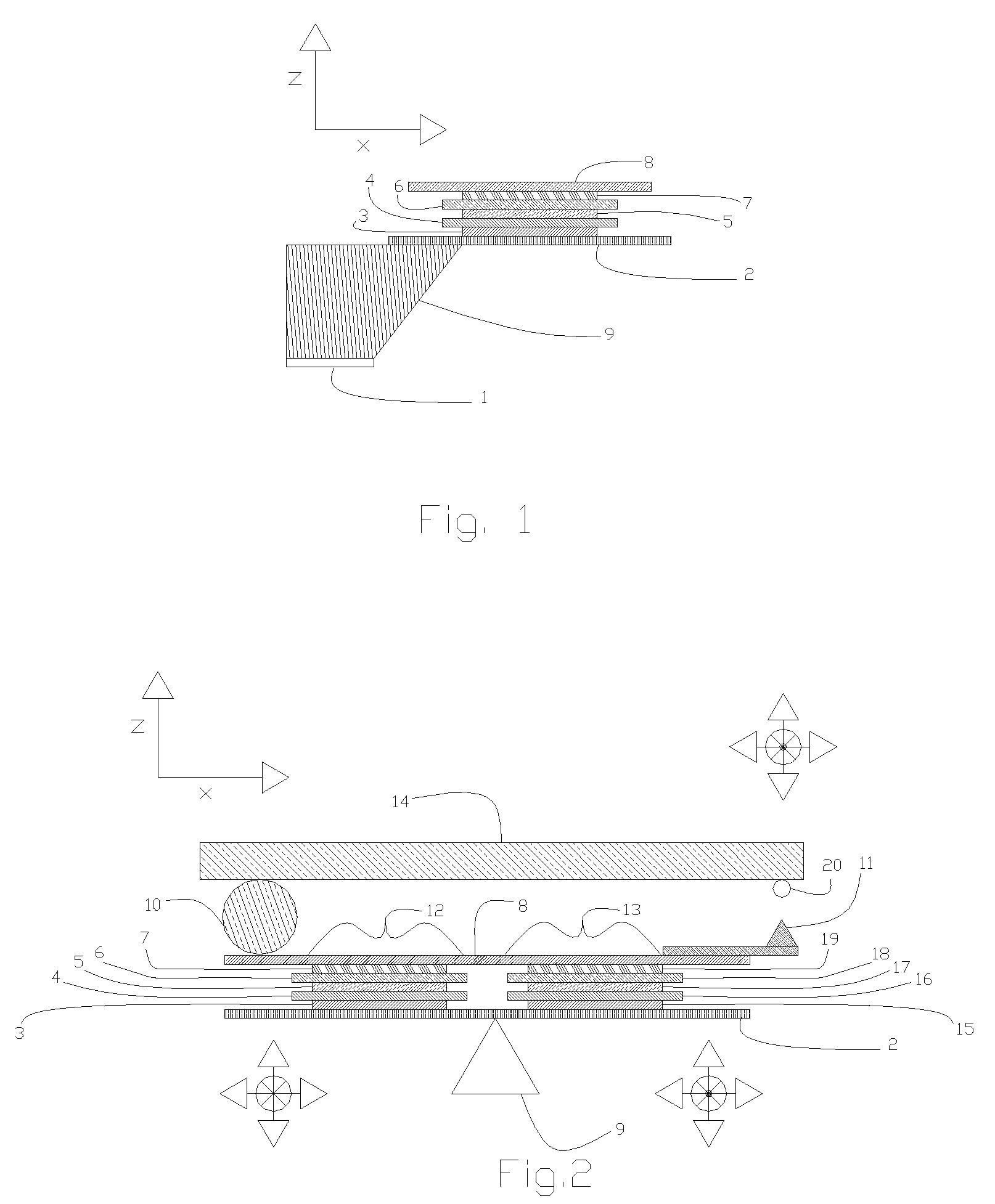

Scanning Probe Microscope, Nanomanipulator with Nanospool, Motor, nucleotide cassette and Gaming application

InactiveUS20080149832A1Material analysis using wave/particle radiationNanotechnologyNucleotideScanning probe microscopy

This invention has applications as a scanning probe microscope / nanomanipulator with consumer gaming applications. An integrated compound lever cantilever which can function simultaneously as both a sample substrate actuator and probe tip scanner actuator for modulation of one or more probe tip. In one embodiment a piezoelectric multimorph MEMS structure is fabricated which serves as a Scanning Probe Microscope cantilever probe tip scanner and allows for the substrate to be moved in more than 1 Degree of freedom with subnanometer resolution. Nanomanipulation means such as nanotweezer, nanopore and nanomachine embodiments are possible uses for the device in addition to data storage. Parallel array operation of many sets of cantilevers is a preferred embodiment which can be used as a nanoscale manipulation and fabrication means. In addition an embodiment where the actuation effects of the device are used to propel the scanner can allow for a programmable drivable MEMS / NEMS based autonomous or semi-autonomous robotic scanner, manipulator and assembler. The device has embodiments where it is essentially a planarized MEMS / NEMS derivative version of a Besocke type scanner. The invention also discloses uses for scanning probe microscopes and nanomanipulators as means for gaming systems, erector set and chemistry kit for entertainment and educational applications. Other applications include rotational actuation, linear motion and spooling of material on rotational bodies through coordination of the actuator probe or probes.

Owner:ZORN MIGUEL

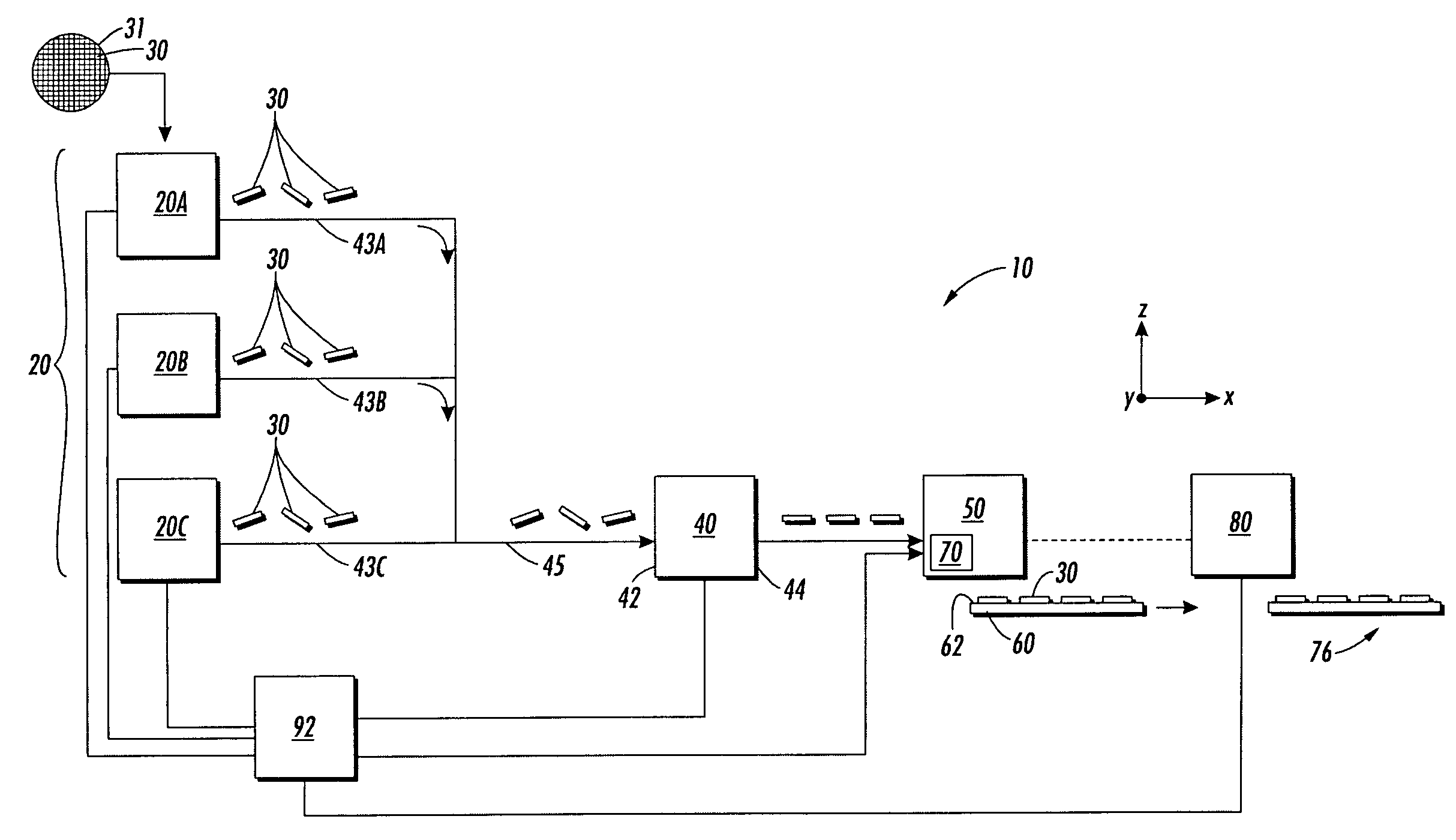

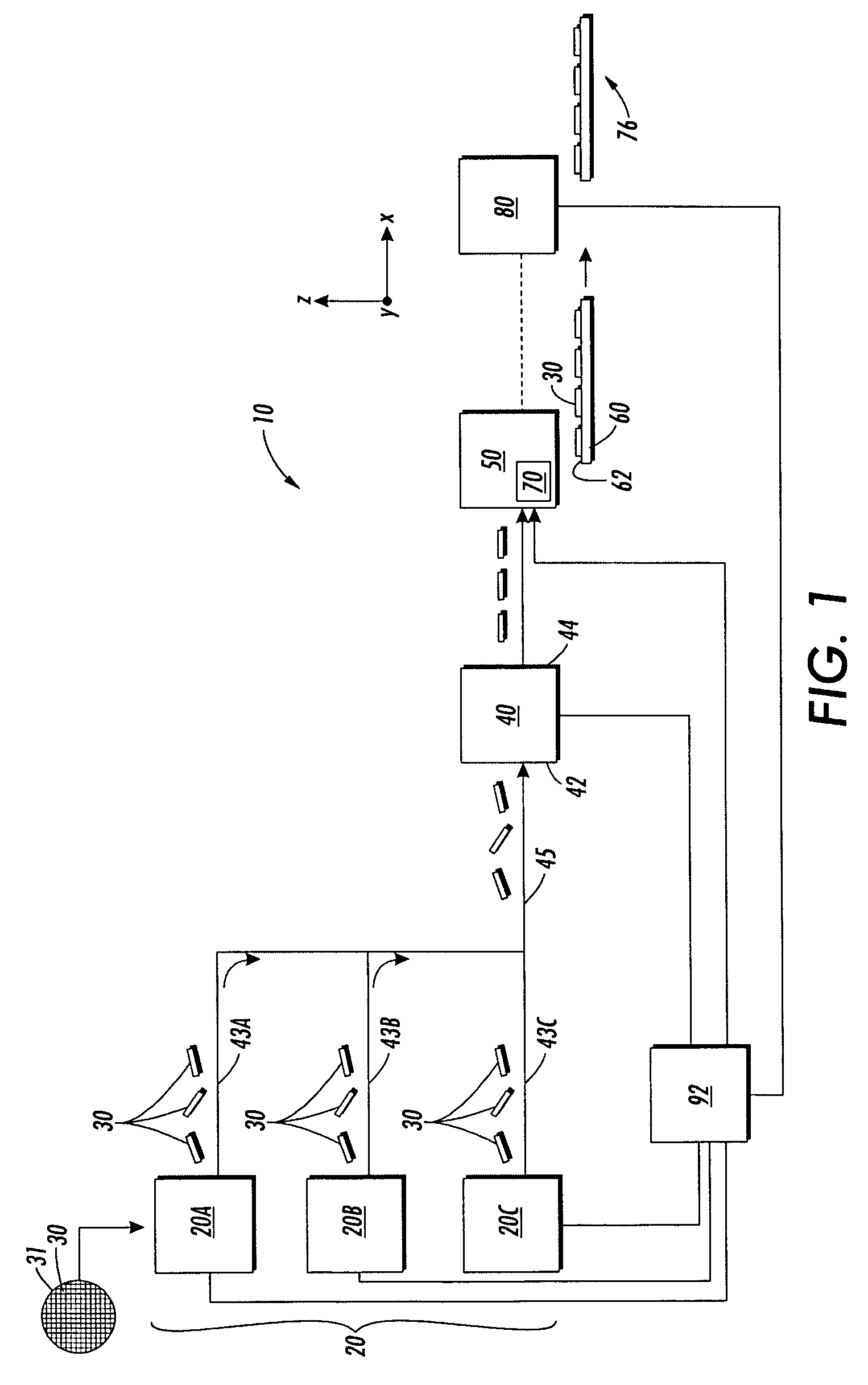

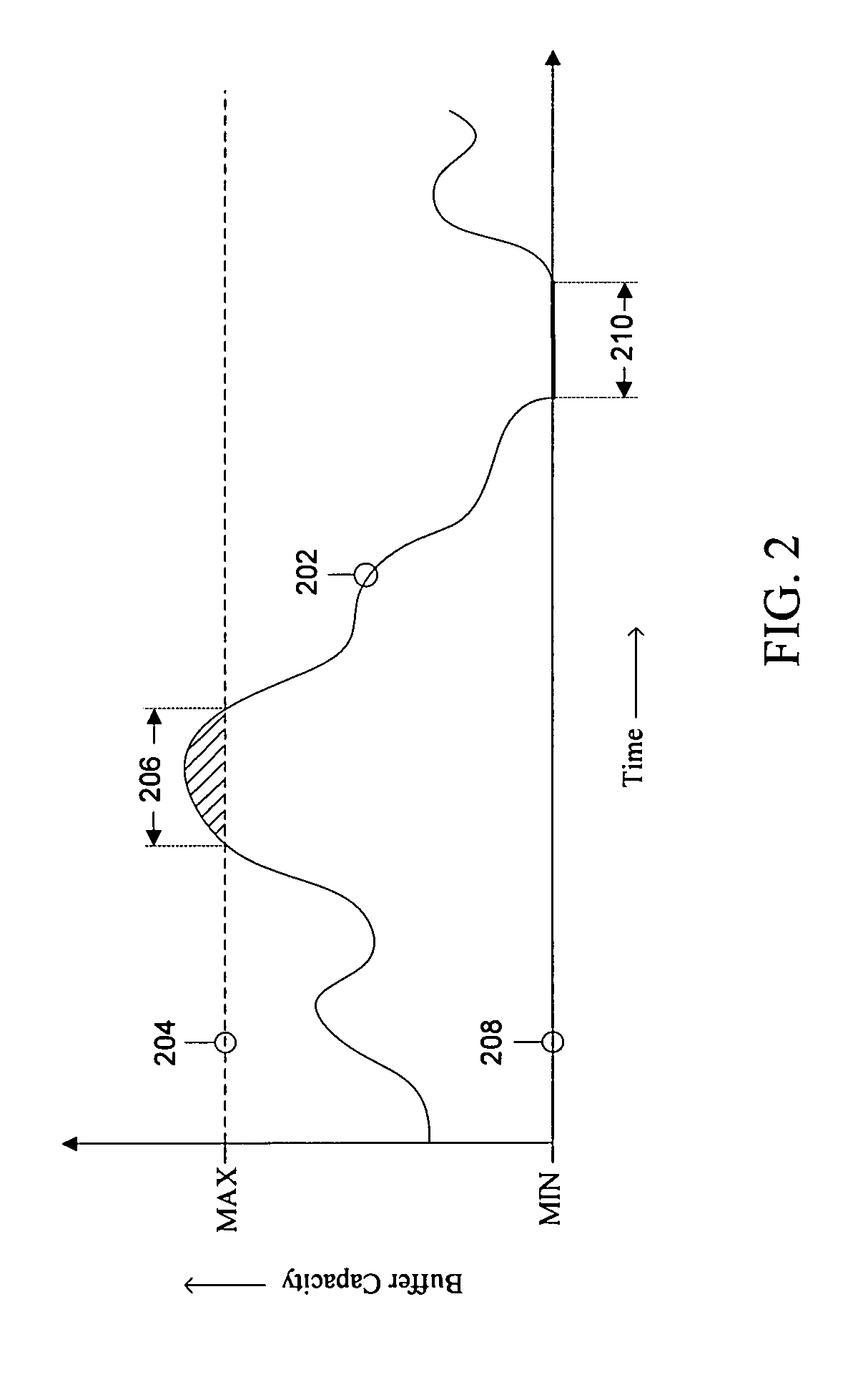

Controlling buffer states in video compression coding to enable editing and distributed encoding

InactiveUS20070116117A1Color television with pulse code modulationColor television with bandwidth reductionDigital dataComputer science

An encoder includes a parser, a plurality of encoder engines and an assembler. The parser divides a portion of a received digital data stream into a plurality of segments having a begin boundary and an end boundary. The plurality of encoder engines independently encode the plurality of segments to accommodate a begin buffer status condition corresponding to each begin boundary and an end buffer status condition corresponding to each end boundary, thereby producing a plurality of corresponding encoded segments. The assembler combines the plurality of encoded segments to form a portion of an encoded digital data stream. The encoder engines verify the begin and the end buffer status conditions are satisfied for each encoded segment and also verify each encoded segment prevents an overflow and an underflow of a modeled decoder buffer. Any violating segment is re-encoded and re-verified prior to assembly.

Owner:APPLE INC

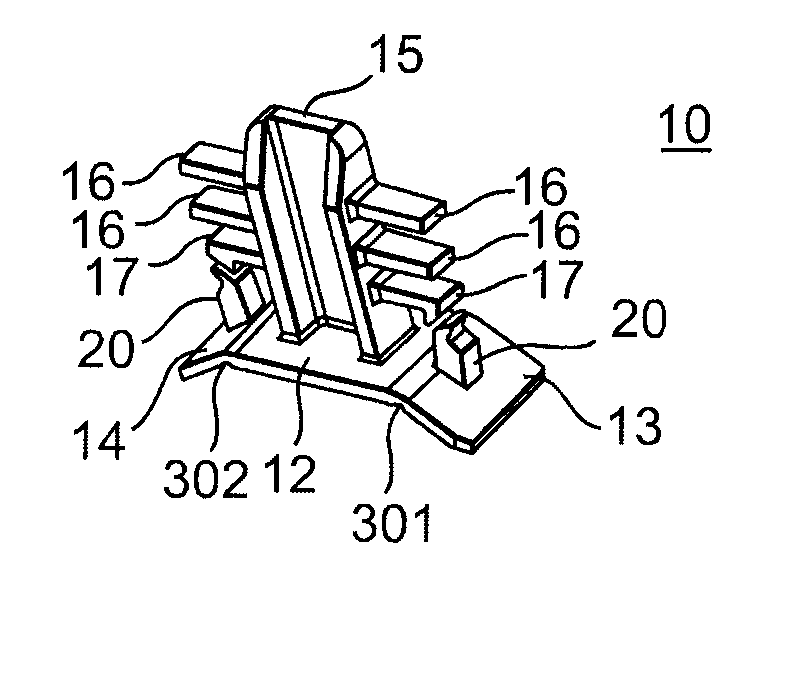

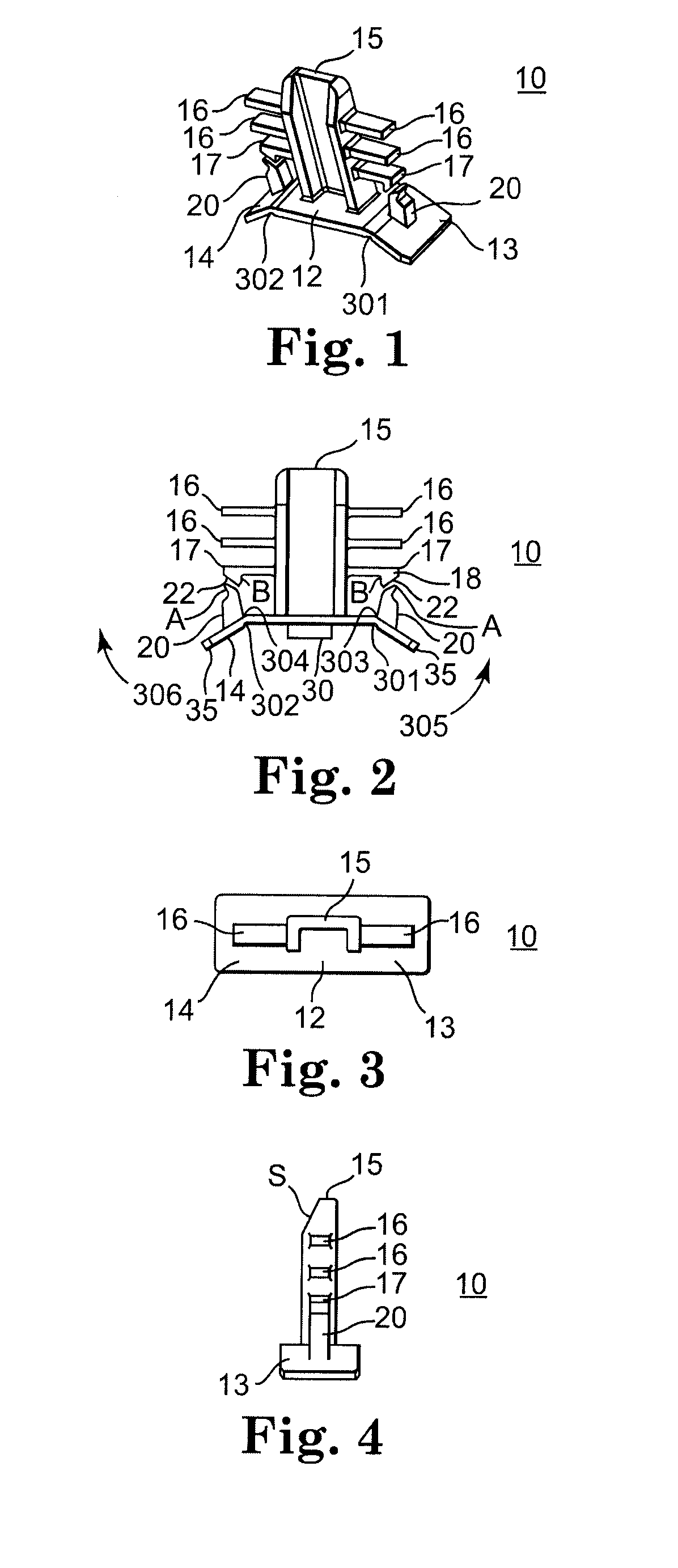

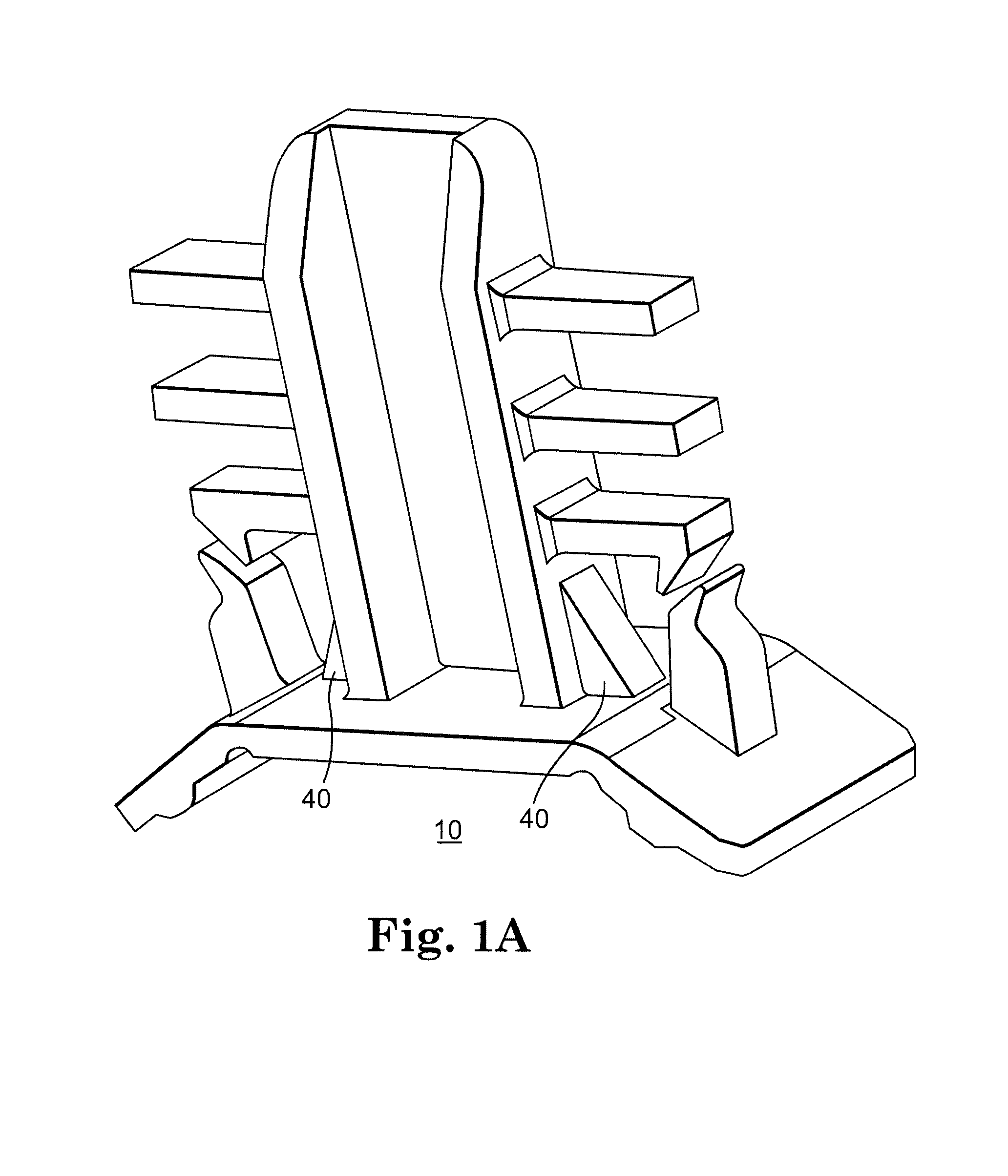

Muntin bar connector with positioning tabs

A connector for holding an internal muntin assembly away from a perimeter spacer of an insulating glass assembly until the assembler is ready to affix the muntin bar to the perimeter bar using an attachment device. The connector includes a positioning tab for holding the muntin bar away from the perimeter spacer to allow positioning of the muntin bar assembly until the positioning tab is moved relative to a baseplate so that the attachment device, such as thick double stick tape, is pressed to the perimeter spacer.

Owner:PELLA

Xerographic micro-assembler

Xerographic micro-assembler systems and methods are disclosed. The systems and methods involve manipulating charge-encoded micro-objects. The charge encoding identifies each micro-object and specifies its orientation for sorting. The micro-objects are sorted in a sorting unit so that they have defined positions and orientations. The sorting unit has the capability of electrostatically and magnetically manipulating the micro-objects based on their select charge encoding. The sorted micro-objects are provided to an image transfer unit. The image transfer unit is adapted to receive the sorted micro-objects, maintain them in their sorted order and orientation, and deliver them to a substrate. Maintaining the sorted order as the micro-objects are delivered to the substrate may be accomplished through the use of an electrostatic image, as is done in xerography. The substrate with the micro-objects is further processed to interconnect the micro-objects—through electrical wiring, for example—to form the final micro-assembly.

Owner:XEROX CORP

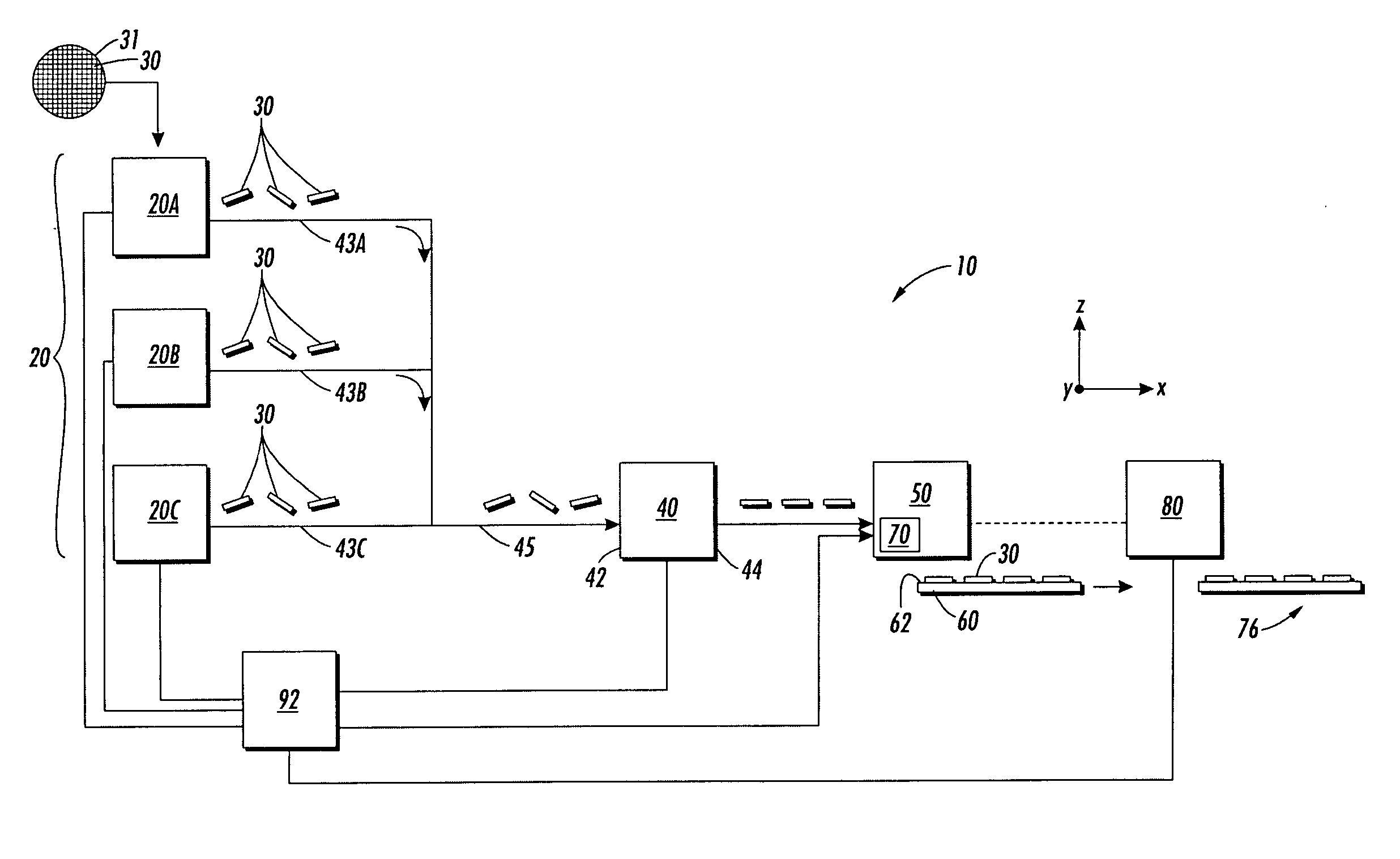

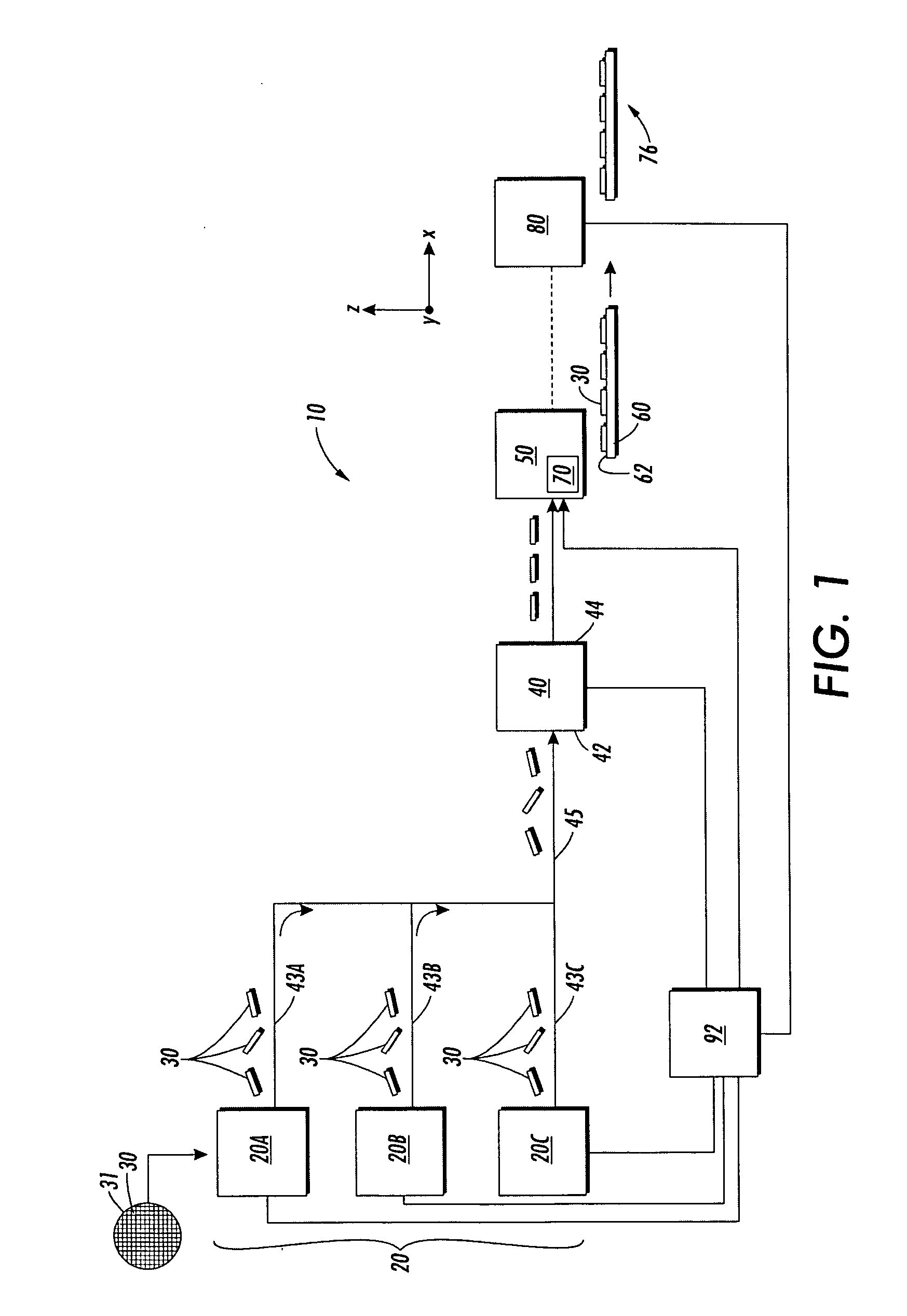

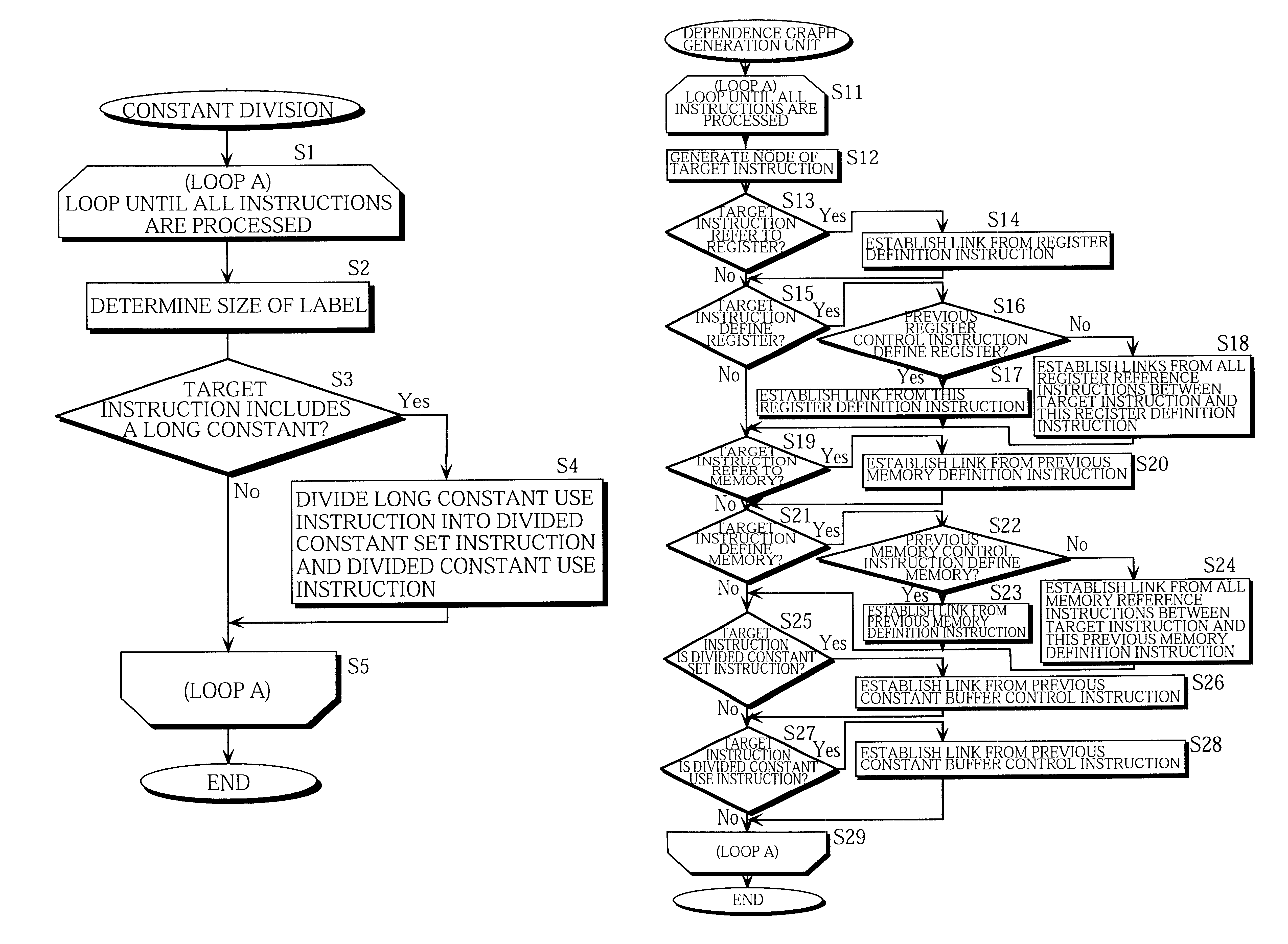

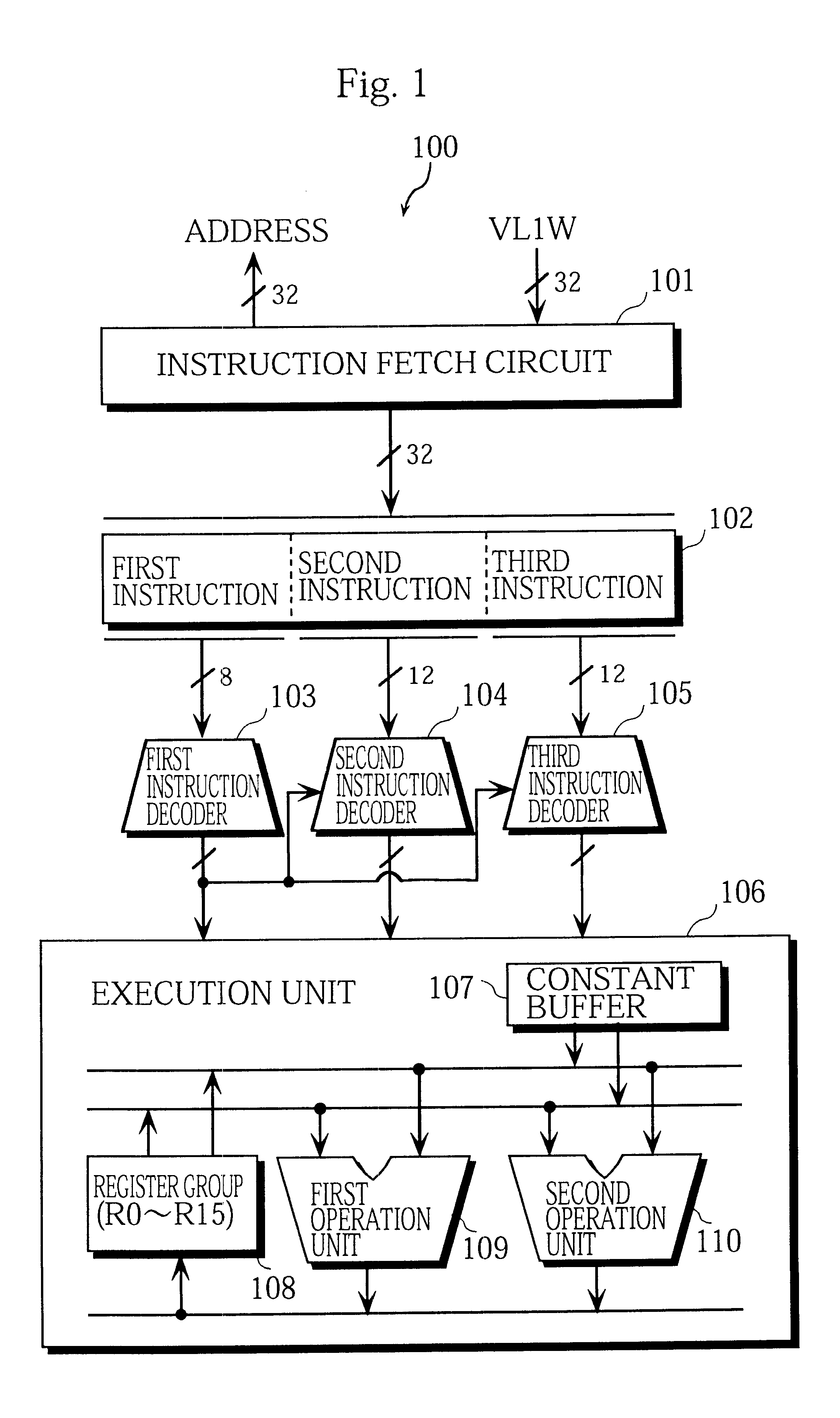

Program conversion apparatus for constant reconstructing VLIW processor

InactiveUS6367067B1Shorten the timeAvoid combiningTransformation of program codeInstruction analysisParallel computingLattice constant

A program conversion apparatus includes: the constant division unit 12 for specifying instructions in the serial assembler code 42 that use large constants which cannot be arranged within the operation fields of object VLIWs and for dividing the specified instructions into divided constant use instructions for storing pieces of the large constants into the specialized constant buffer 107 of a VLIW processor and divided constant use instructions for performing operations using the stored constants; the dependence graph generation unit 20 for generating a dependence graph based on the execution order of each instruction in the serial assembler code 42 after the division process by the constant division unit 12; and the instruction relocation unit 21 for relocating the instructions according to the dependence graph to generate parallel assembler code.

Owner:SOCIONEXT INC

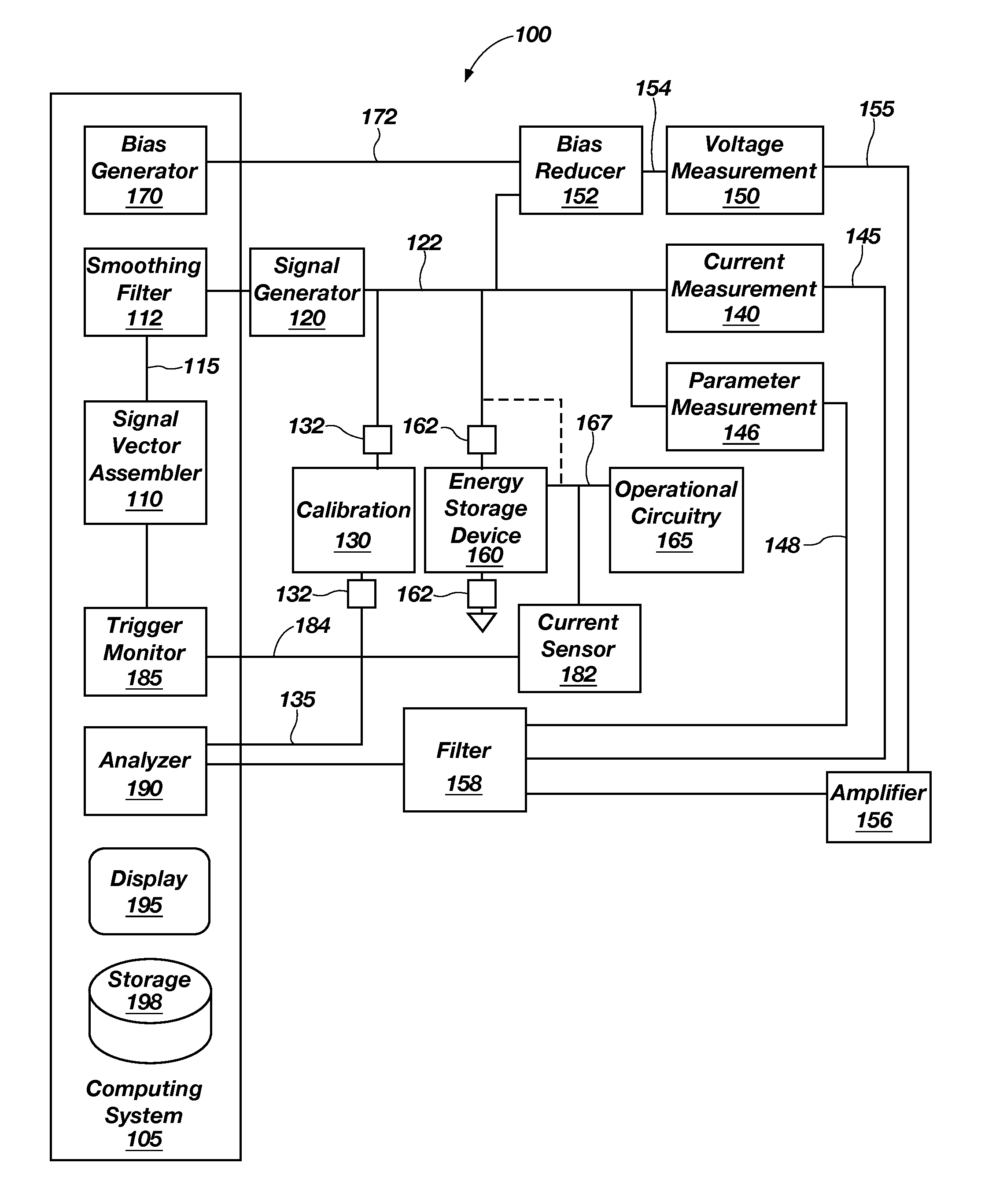

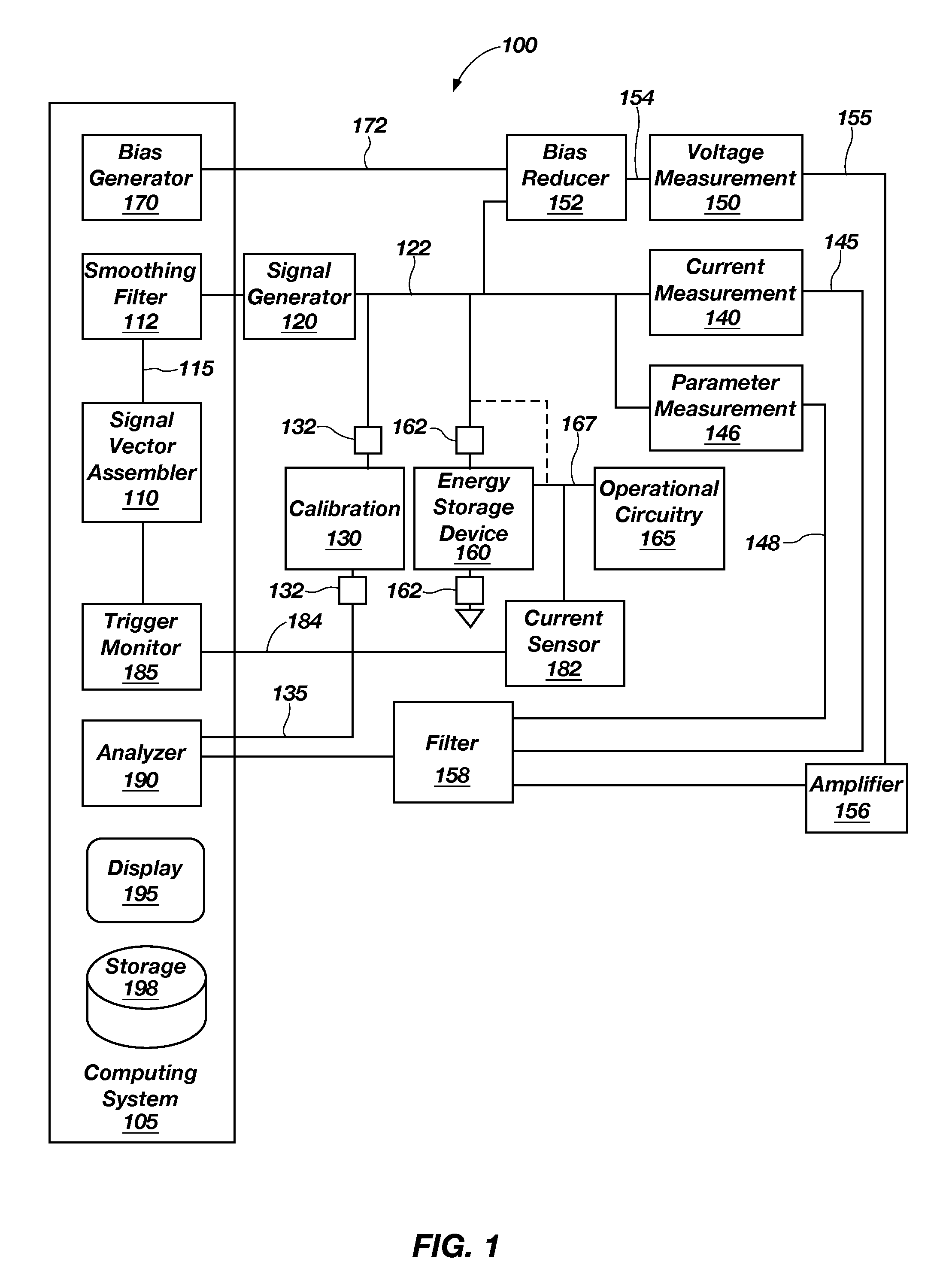

In-situ real-time energy storage device impedance identification

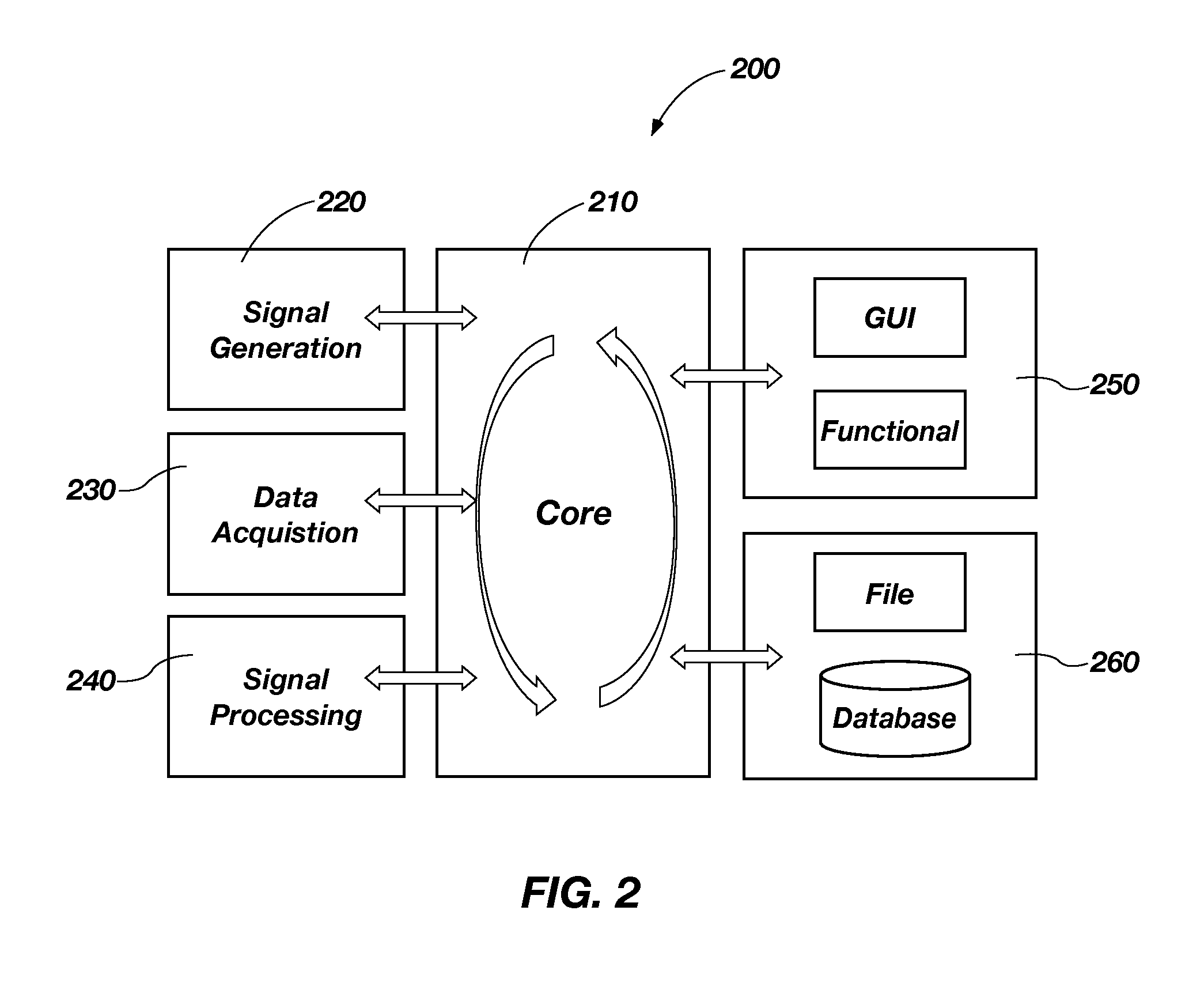

InactiveUS20110270559A1Resistance/reactance/impedenceElectrical testingStored energyMeasurement device

An impedance analysis system for characterizing an energy storage device (ESD) includes a signal vector assembler to generate a signal vector from a composition of one or more waveforms and a signal generator for generating a stimulus signal responsive to the signal vector. A signal measurement device measures a response signal indicative of a response of the ESD substantially simultaneously with when the stimulus signal is applied to the energy storage device. A load variation monitor monitors load variations on the energy storage device due to operational circuitry coupled thereto. An analyzer is operably coupled to the response signal and analyzes the response signal relative to the signal vector to determine an impedance of the energy storage device.

Owner:BATTELLE ENERGY ALLIANCE LLC

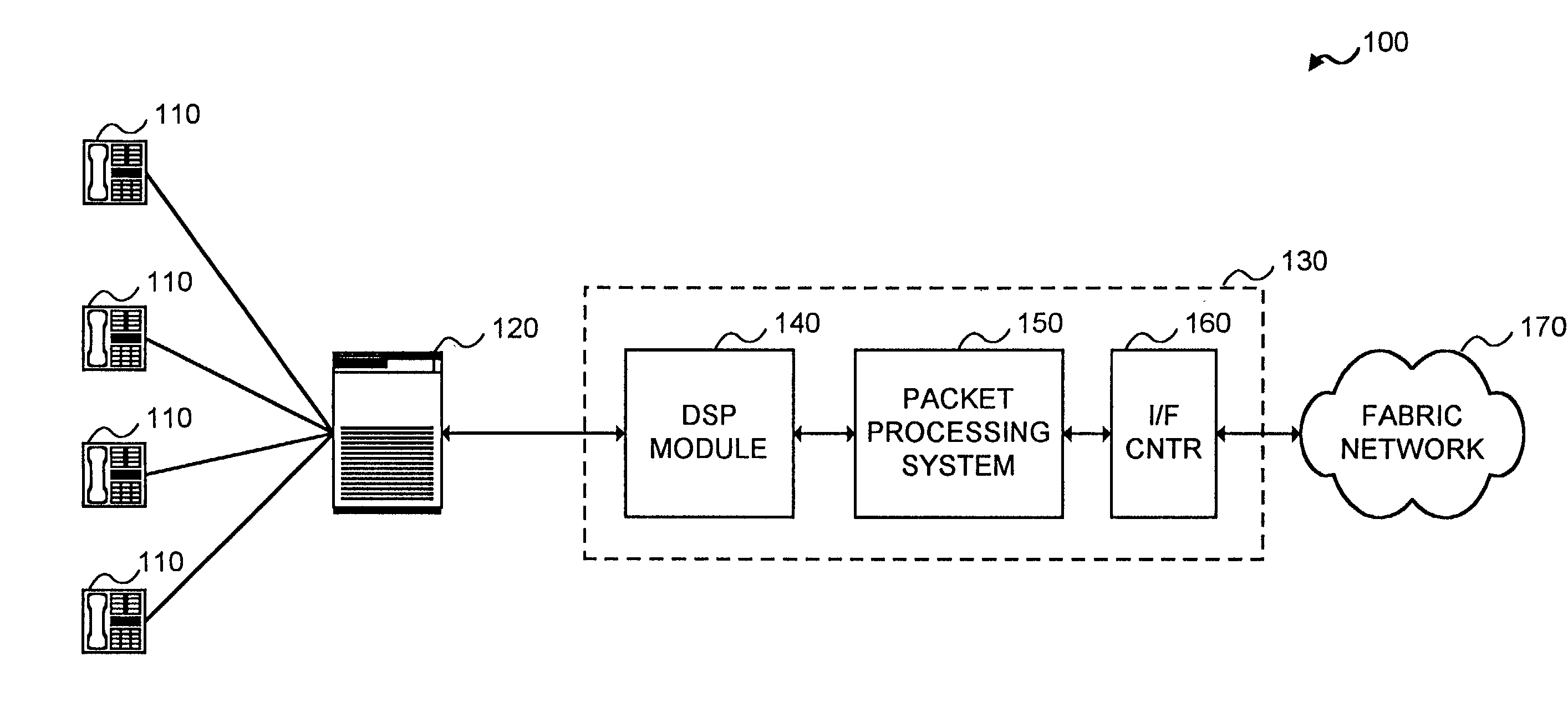

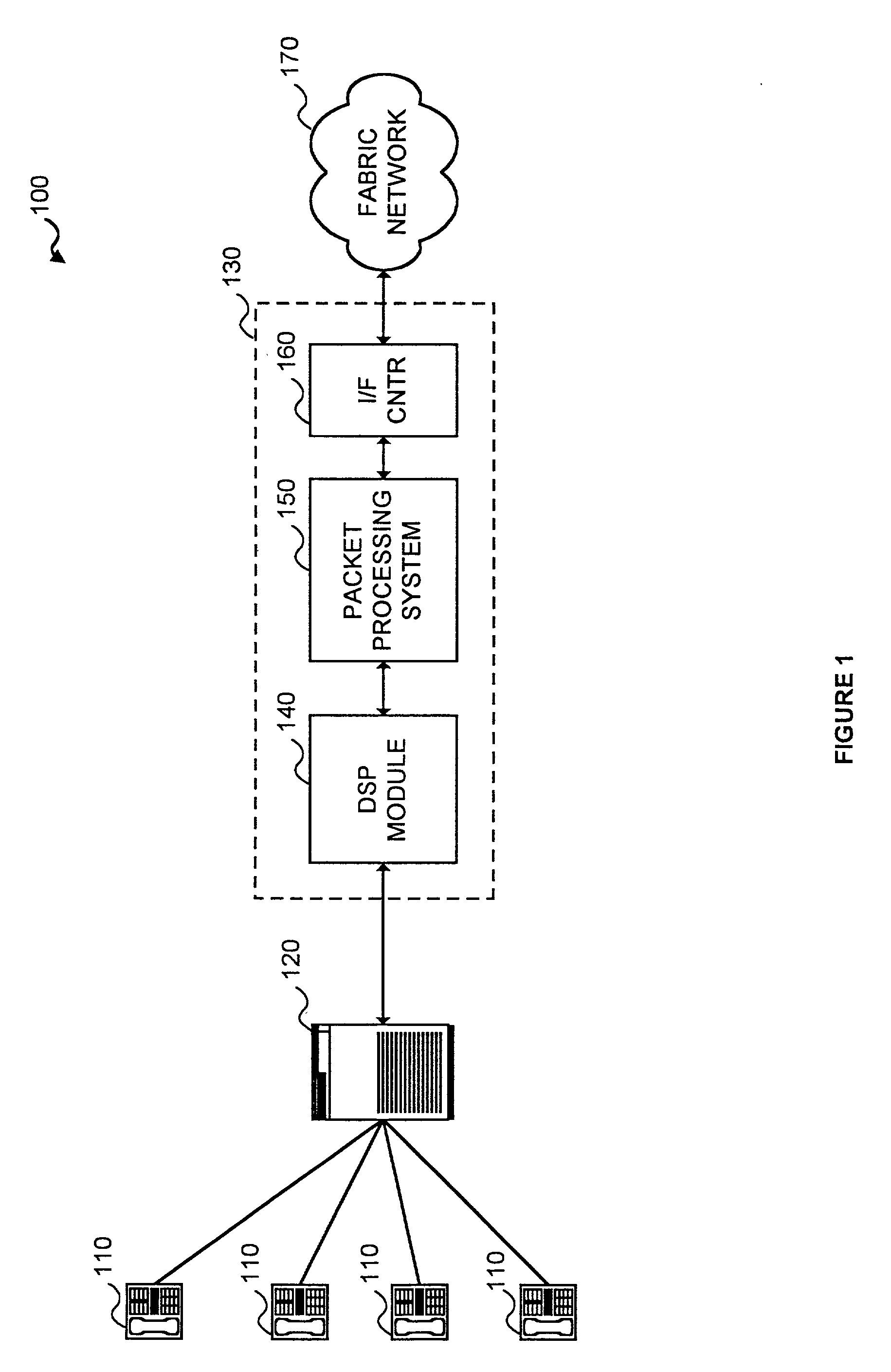

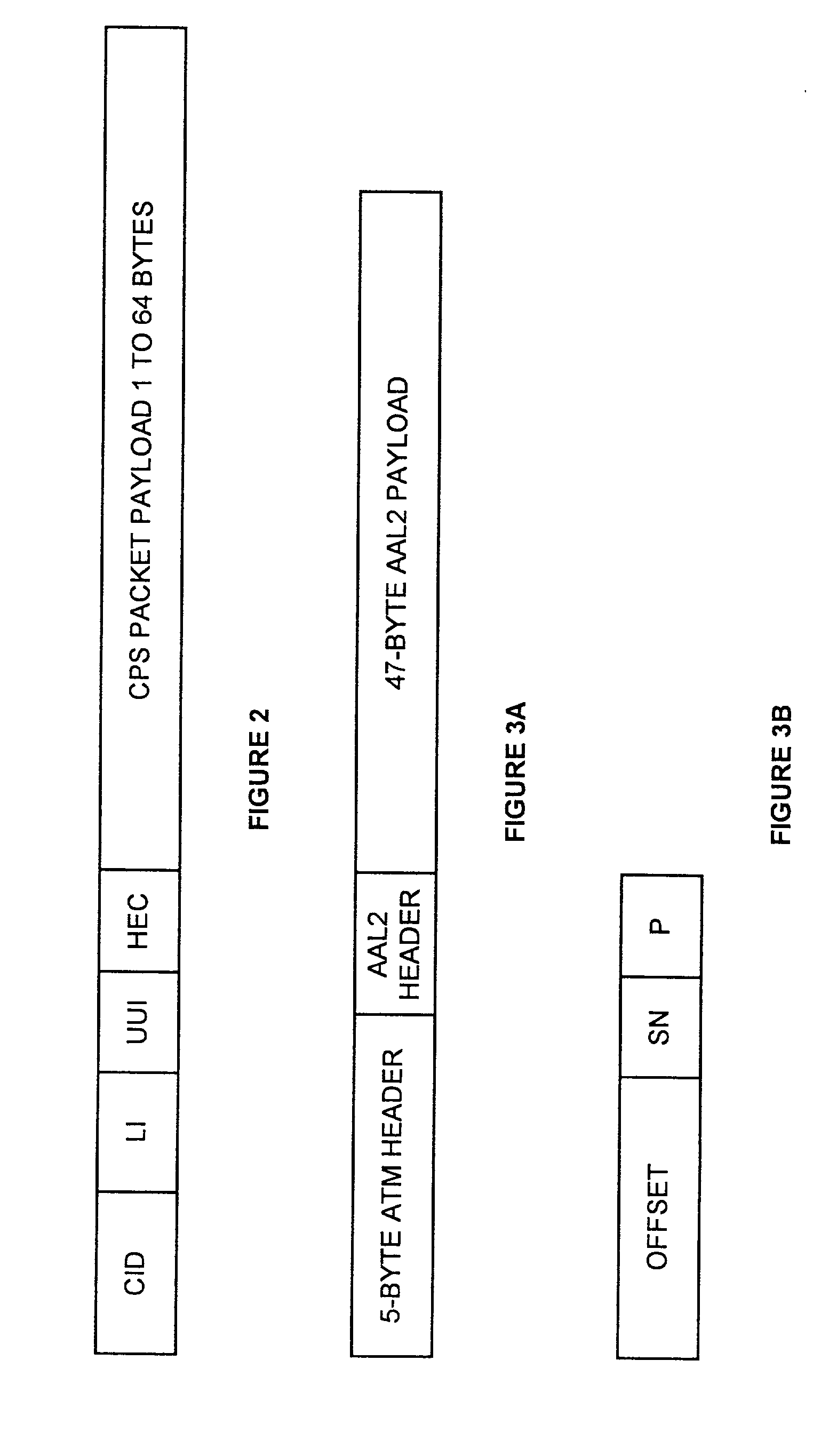

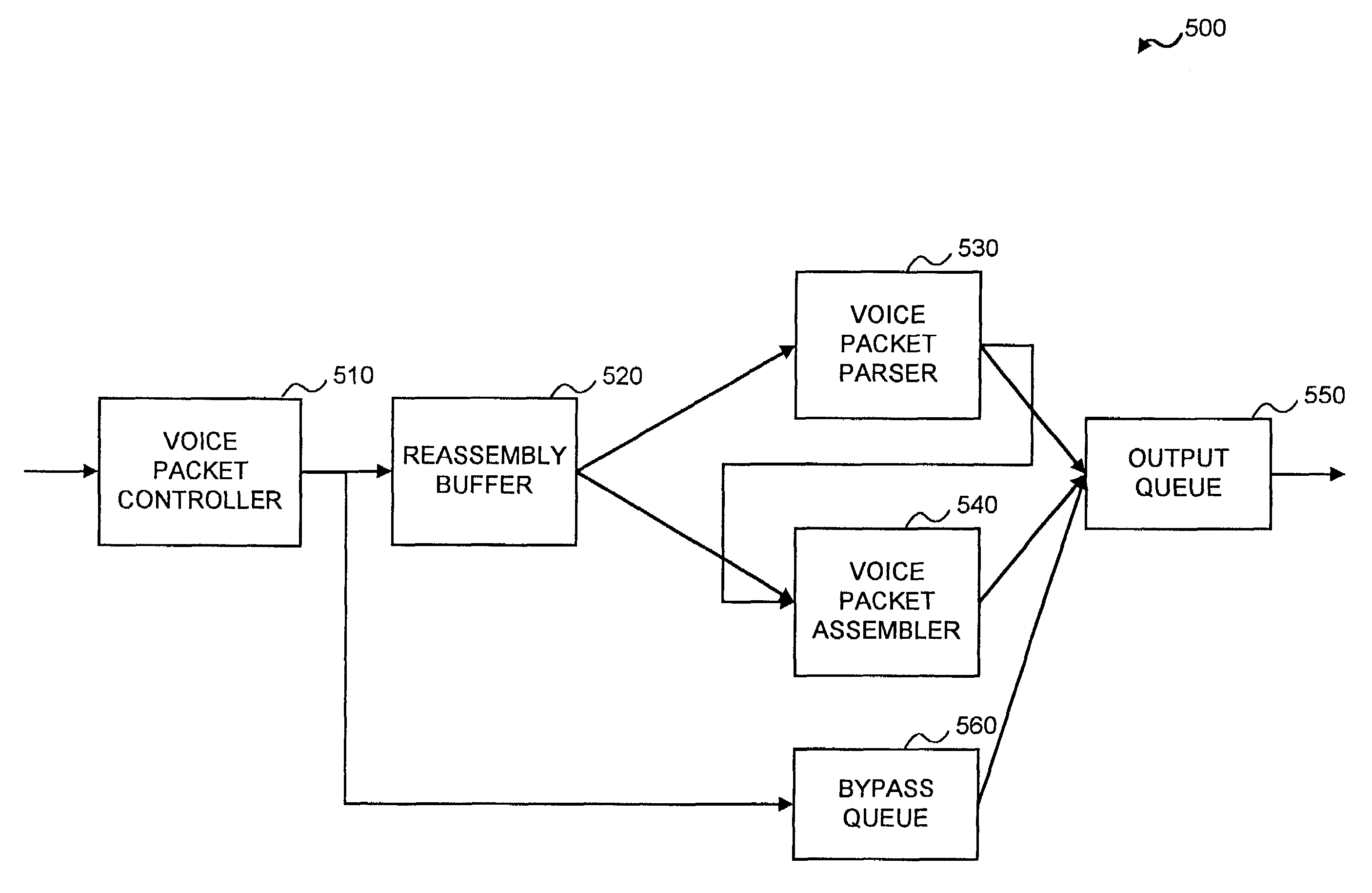

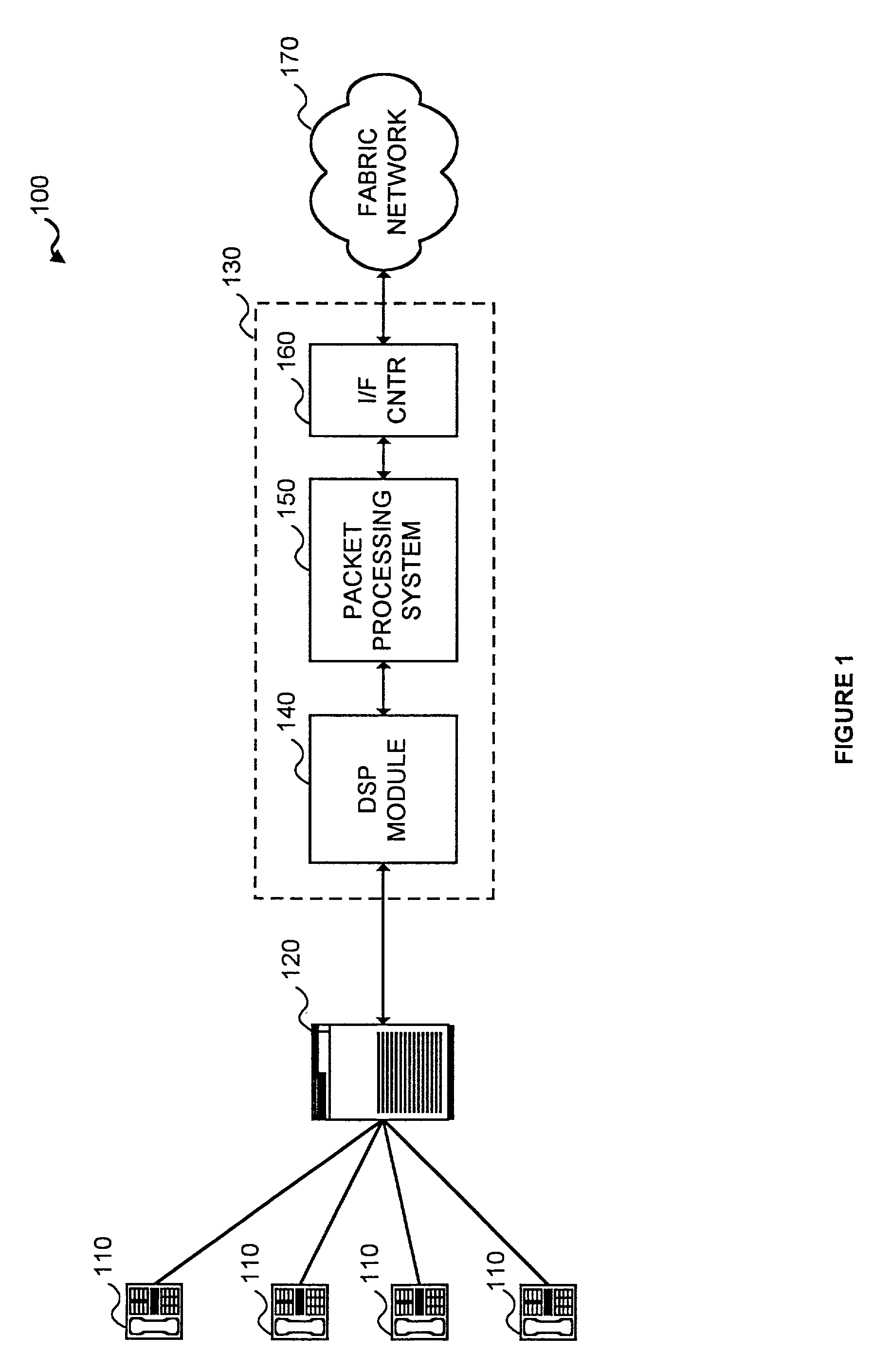

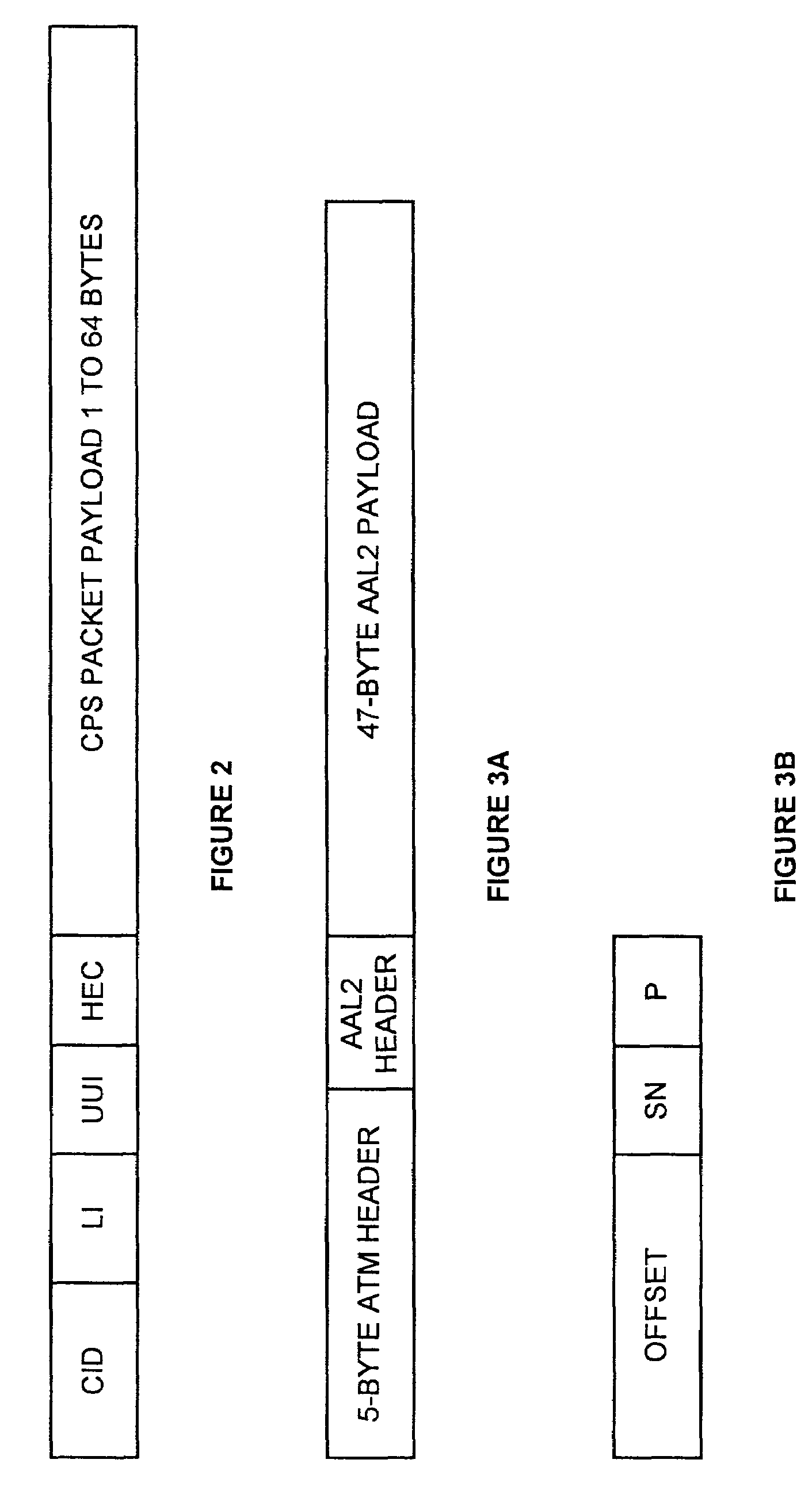

Voice packet processor and method of operation thereof

InactiveUS20020126677A1Time-division multiplexData switching by path configurationComputer hardwareVoice data

A voice packet processor for use with voice applications employing a fast pattern processor (FPP) and a routing switch processor (RSP) that receive and transmit protocol data units (PDUs) and a method of operation thereof. In one embodiment, the voice packet processor includes (1) a voice packet controller (VPC) configured to receive the PDUs from the FPP and queue the PDUs for processing, (2) a voice packet parser configured to receive the PDUs that are ATM adaptation layer 2 (AAL2) cells containing voice data from the VPC, parse the AAL2 cells into at least one Common Part Sublayer (CPS) packet and transmit the at least one CPS packet to the RSP, and (3) a voice packet assembler configured to receive the PDUs that are CPS packets from the VPC, assemble the CPS packets into at least one AAL2 Cell and transmit the at least one AAL2 cell to the RSP.

Owner:INTEL CORP

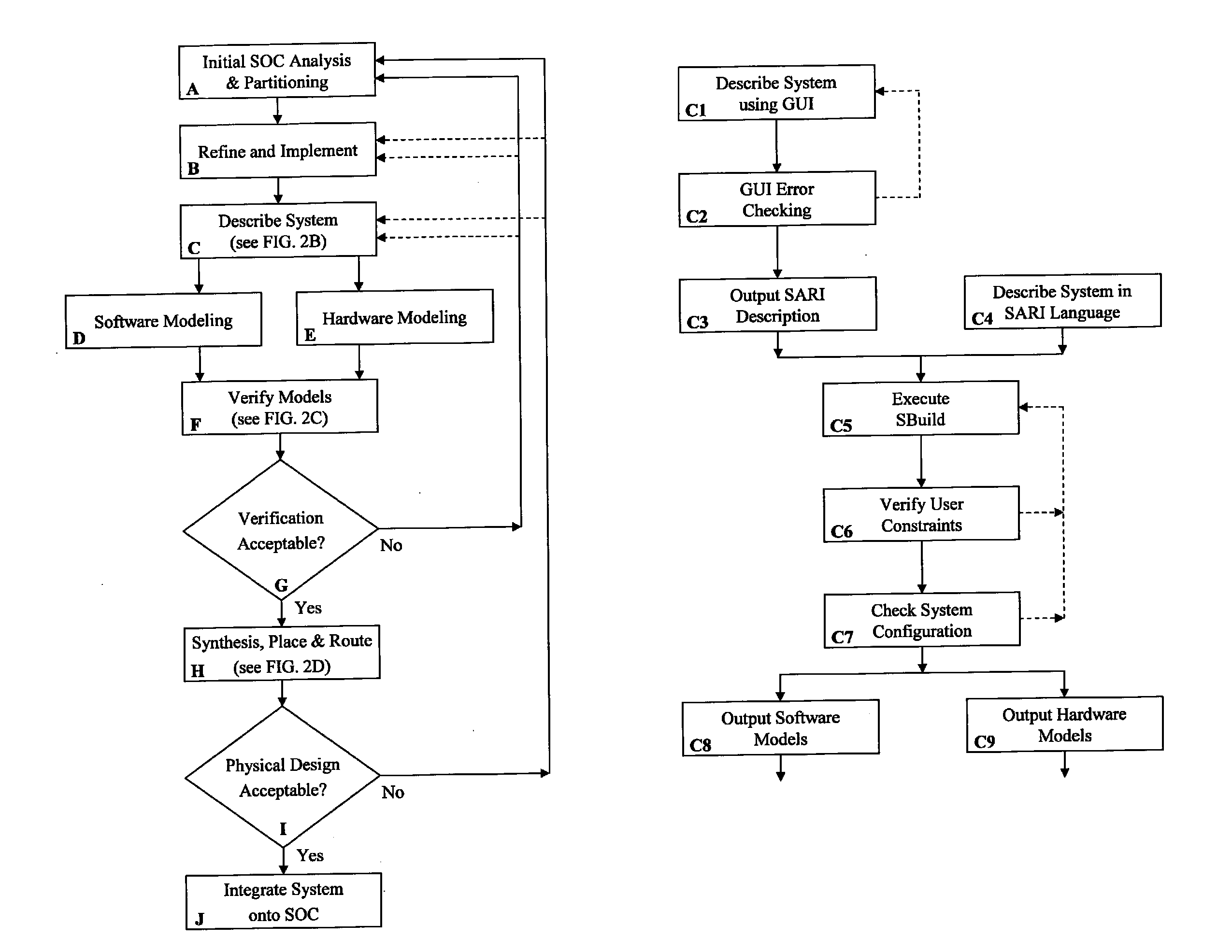

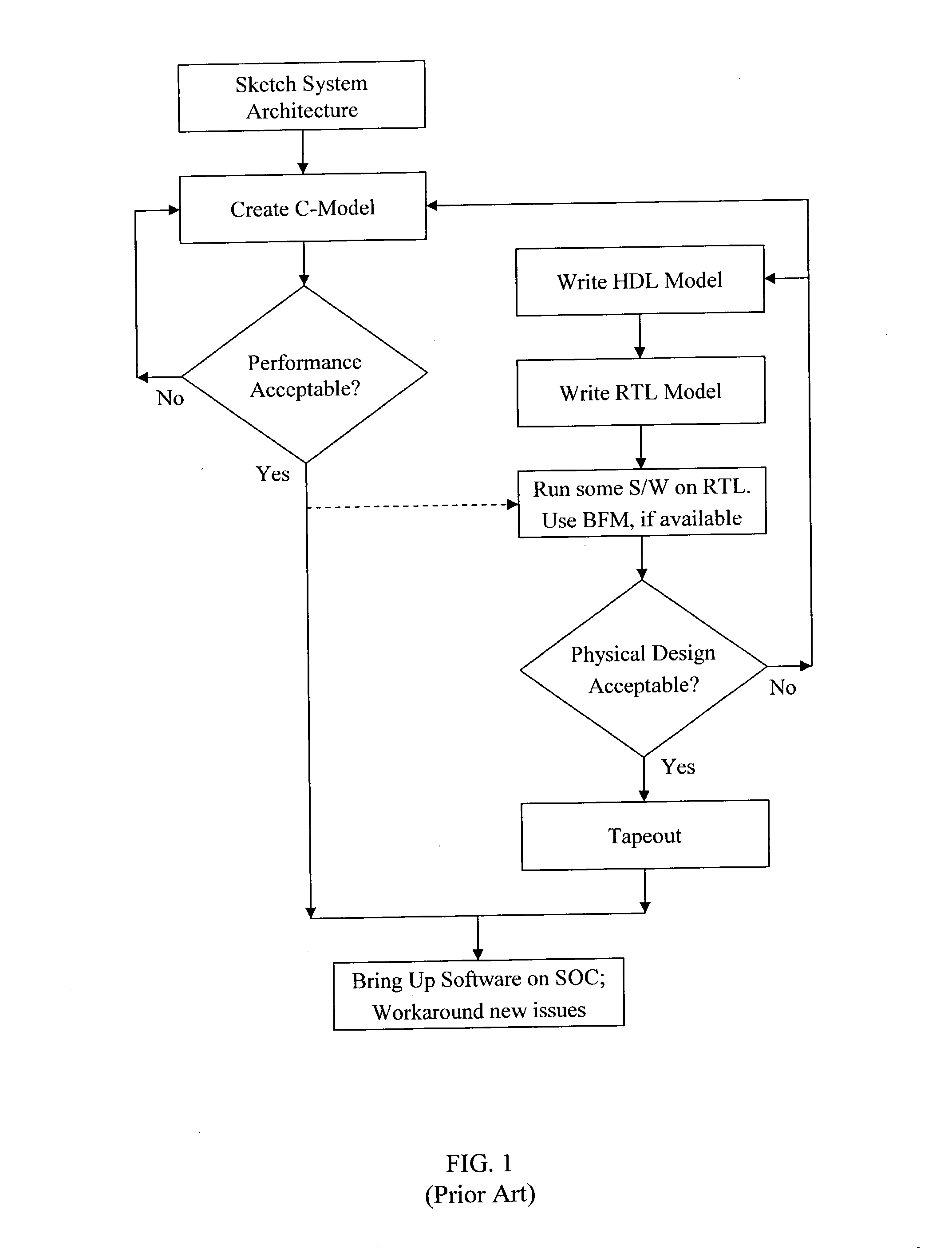

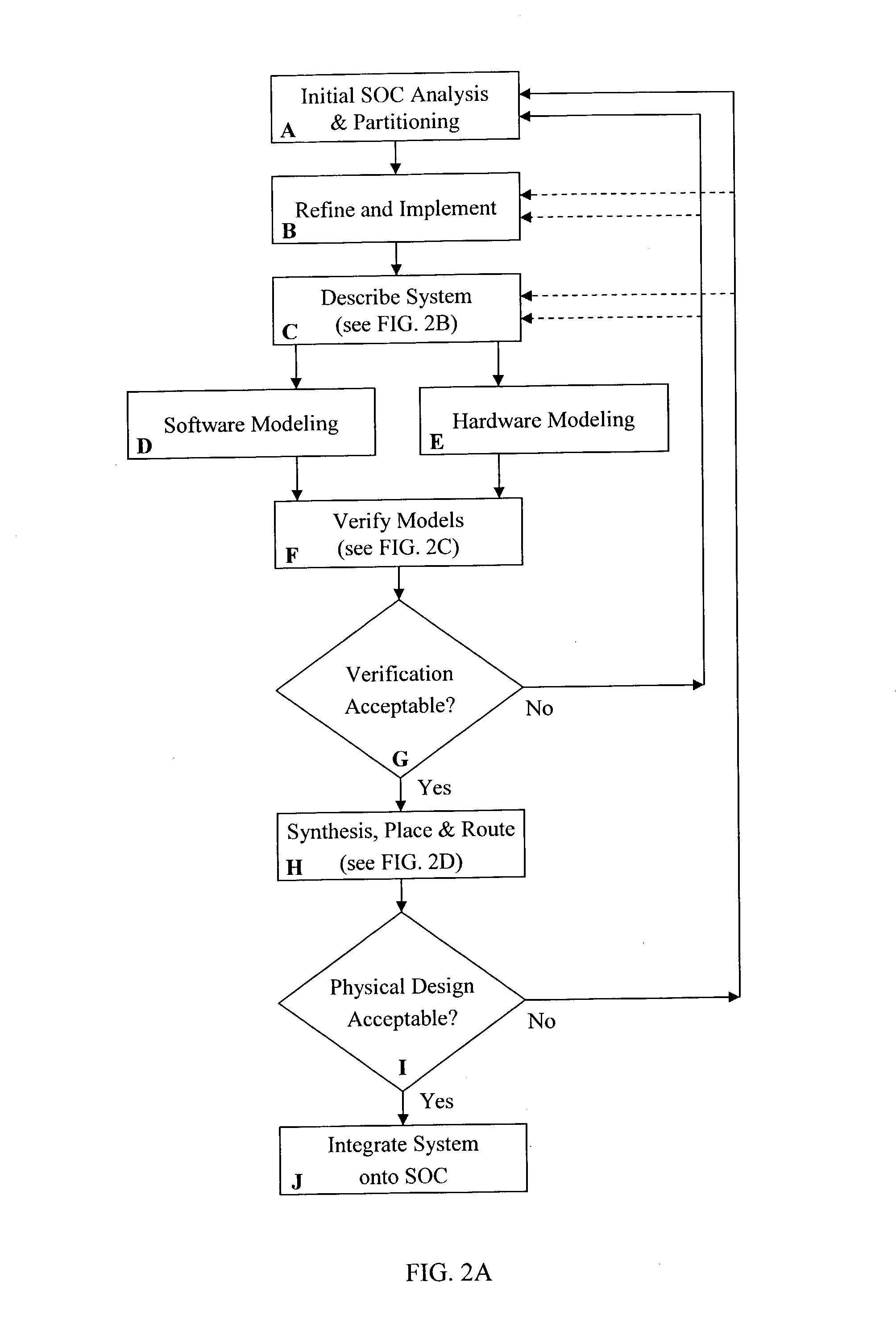

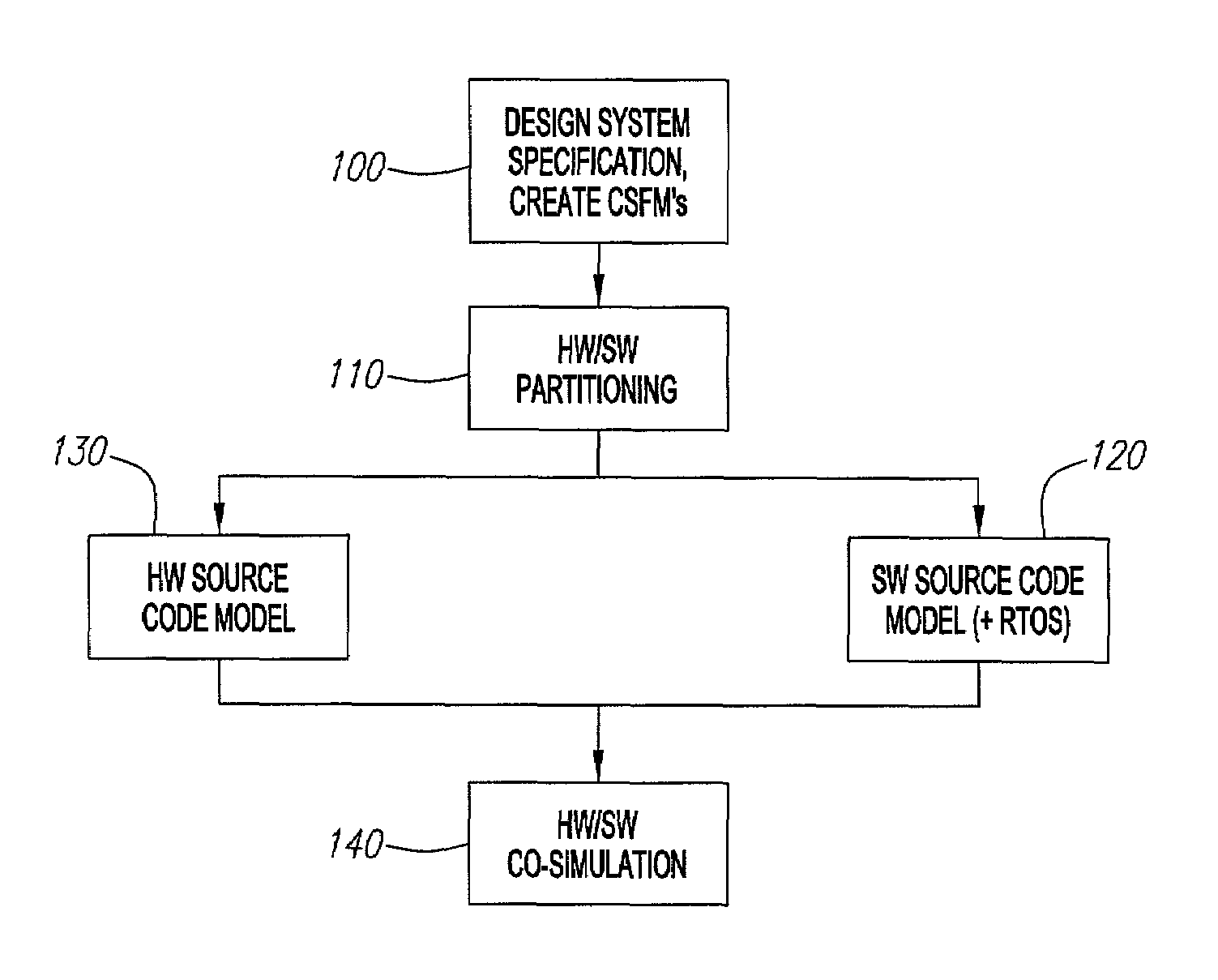

Method for multiple processor system-on-a-chip hardware and software cogeneration

ActiveUS8639487B1Analogue computers for electric apparatusCAD circuit designComputer architectureMulti processor

An automated system-on-chip (SOC) hardware and software cogeneration design flow allows an SOC designer, using a single source description for any platform-independent combination of reused or new IP blocks, to produce a configured hardware description language (HDL) description of the circuitry necessary to implement the SOC, while at the same time producing the development tools (e.g., compilers, assemblers, debuggers, simulator, software support libraries, reset sequences, etc.) used to generate the SOC software and the diagnostics environment used to verify the SOC.

Owner:CADENCE DESIGN SYST INC

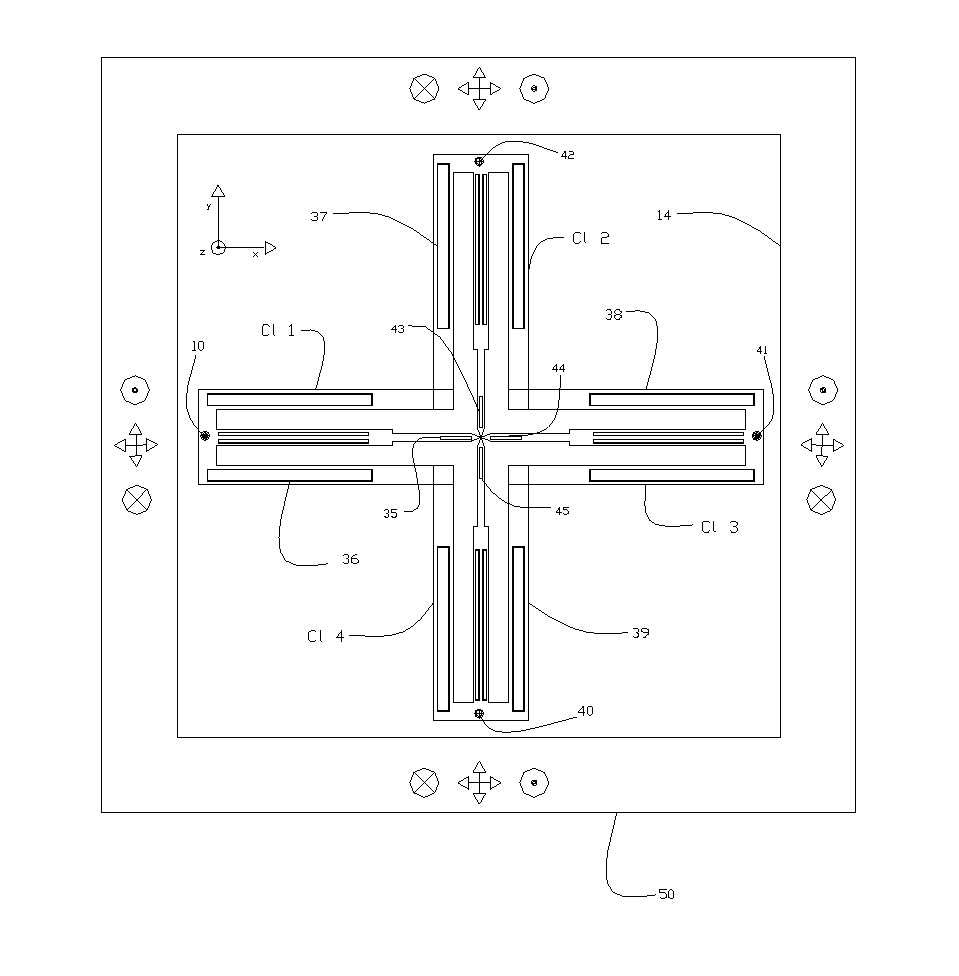

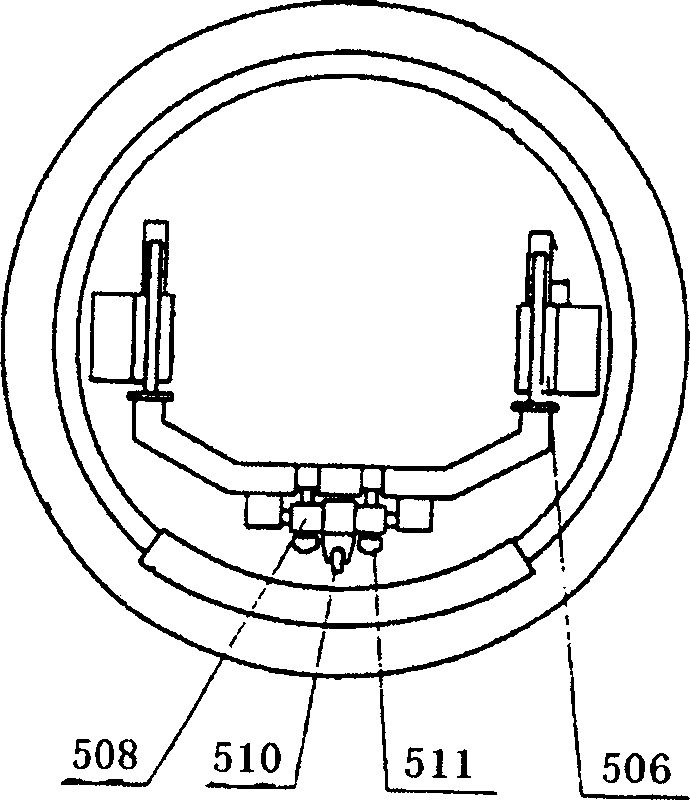

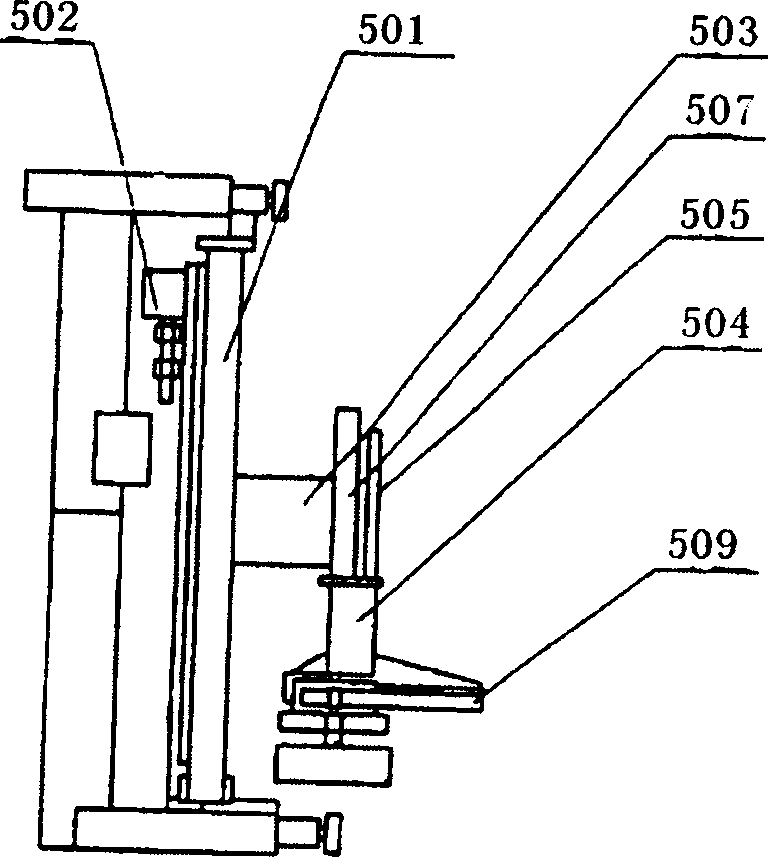

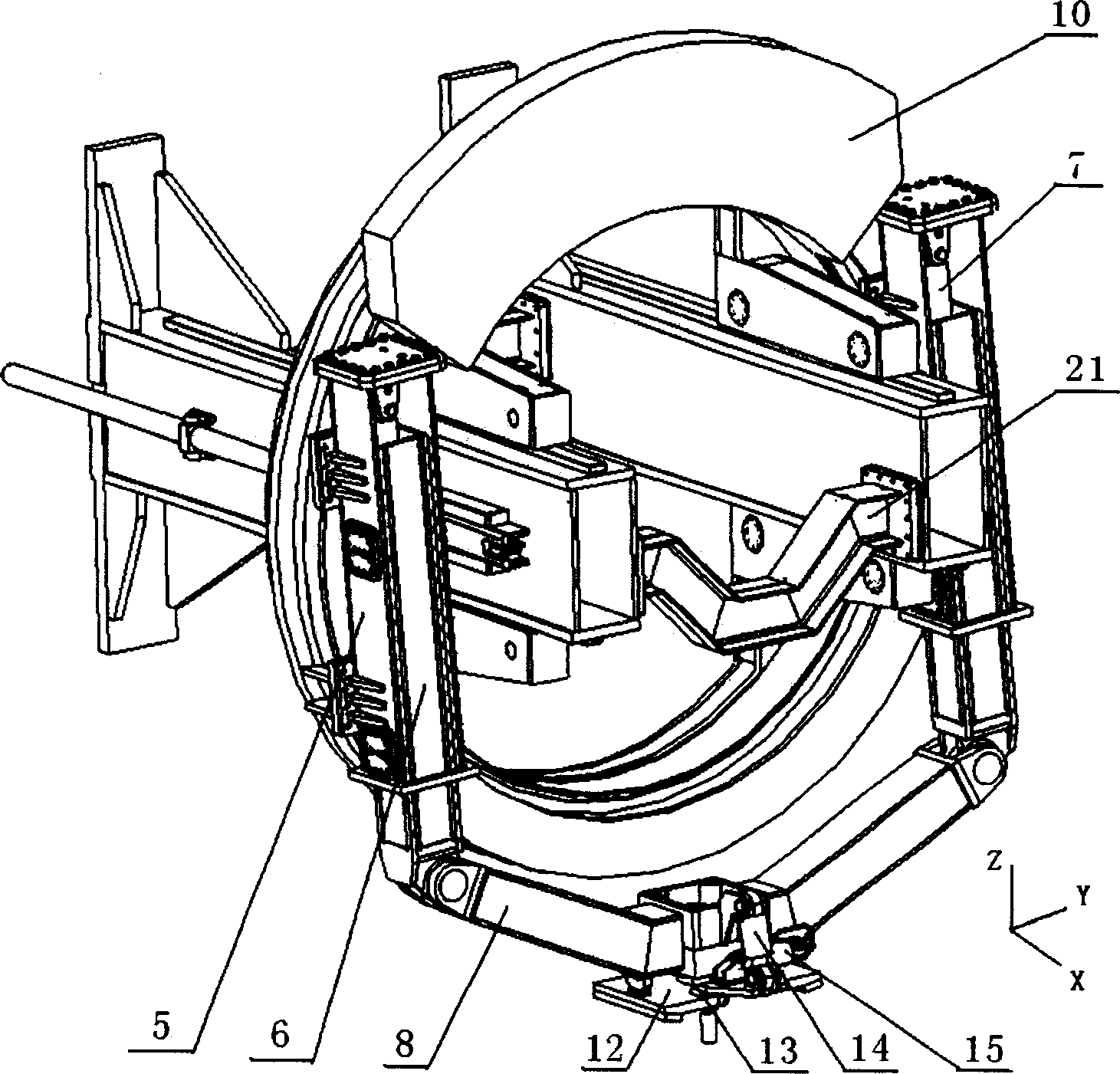

Shield segment splicing machine with six-freedom degree

InactiveCN1837578AIncrease loadReduce adverse effectsUnderground chambersTunnel liningEngineeringSystem stability

The invention relates to a shield construction tube assembler with six freedoms, which comprises a rotational disc, a driving device, two suspending beams, two translation cylinders, two guide sheathes, two guide inner sheathes, two lifting cylinders, a lifting beam, a tube clamper, a tube weight, a rotational platform, a central ball joint bearing, a tube incline cylinder, a tube rotational cylinder, a fixed disc and a rolling wheel. The invention has six freedoms to meet the demand of assemble different spatial positions; and a middle beam and a tube clamper, etc, are arranged between two suspending beams to improve the system stability.

Owner:SHANGHAI TUNNEL ENGINEERING CO. LTD.

System for modifying software using reusable software components

A system, method for modifying insurance transaction processing software are provided. A library of code packets may be stored in a database. One or more code packets may implement at least one business requirement of an insurance organization. If the organization changes one of the business requirements or develops a new business requirement, a user may modify an insurance transaction processing program to reflect the change via a rules engine. The rules engine may be operable to generate program code assembly instructions based on user input. The assembly instructions may be used by a code assembler to form program code for an insurance transaction processing program software module. The insurance transaction processing program may be changed by adding a formed software module.

Owner:COMP SCI A OF NV

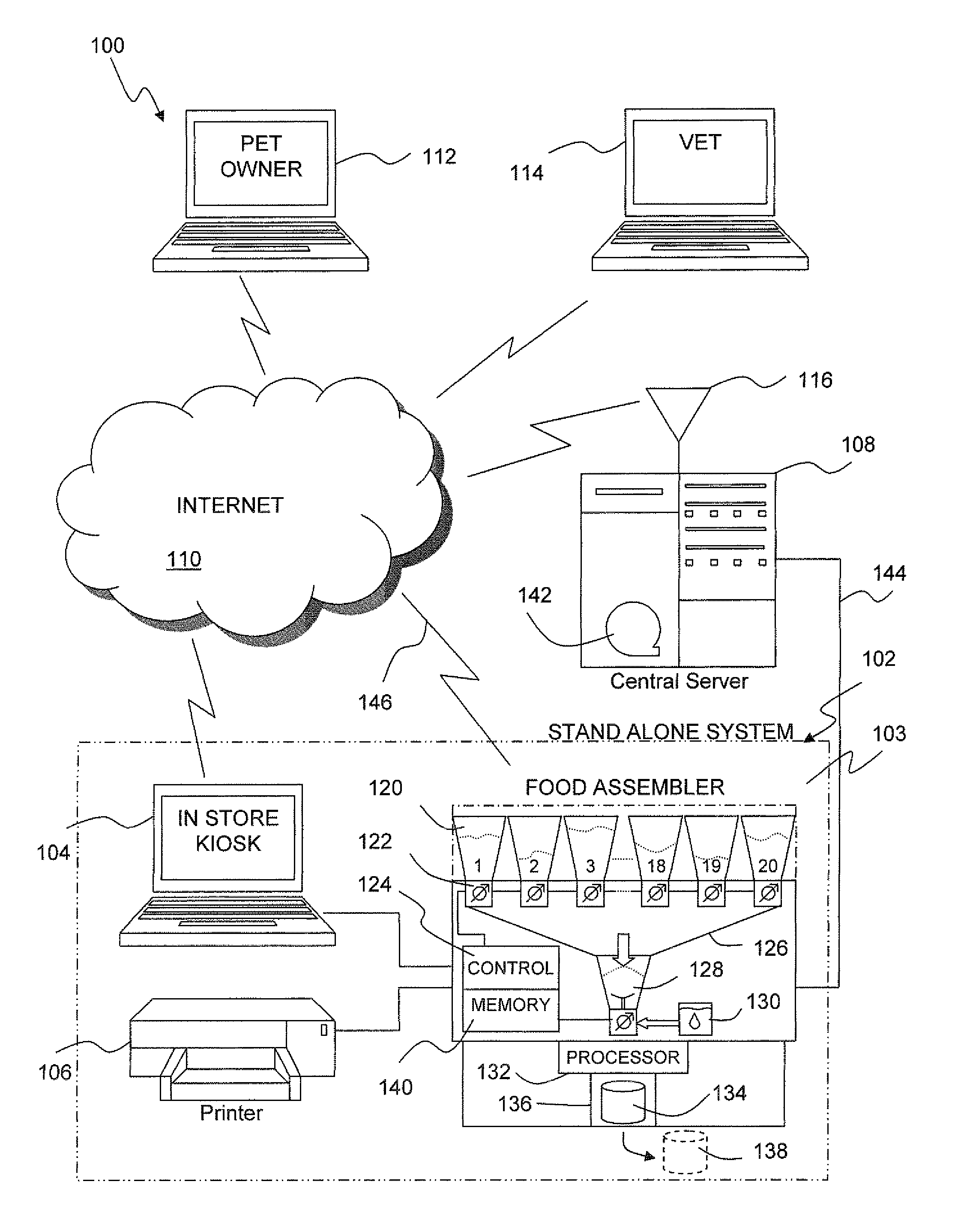

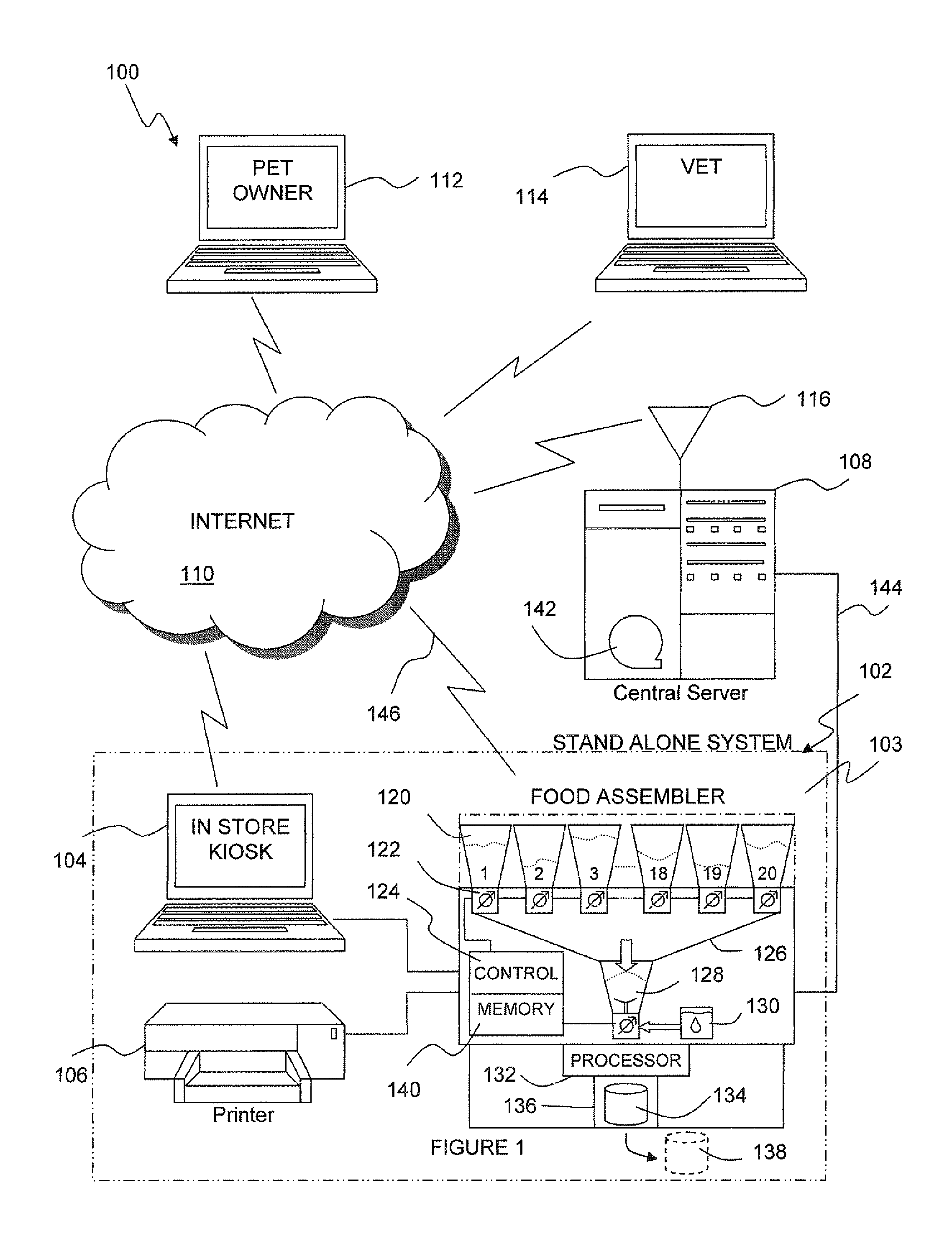

Method and apparatus for producing customized food blends for animals

InactiveUS20110160902A1Controlling ratio of multiple fluid flowsAnimal feeding stuffComputerized systemElectrical connection

A method and apparatus for producing customized food blends for animals includes a food assembler that is in electrical connection with one or more computer systems that provide instructions and specifications for the preparation of a custom food blend. The food assembler includes a number of basic food elements contained in hoppers that can be selectively combined to create a custom food blended from the basic food elements. These elements may include a selection of meats, fruits, vegetables, grains, herbs, vitamins, minerals, and other therapeutic elements.

Owner:POSTINS LUCY

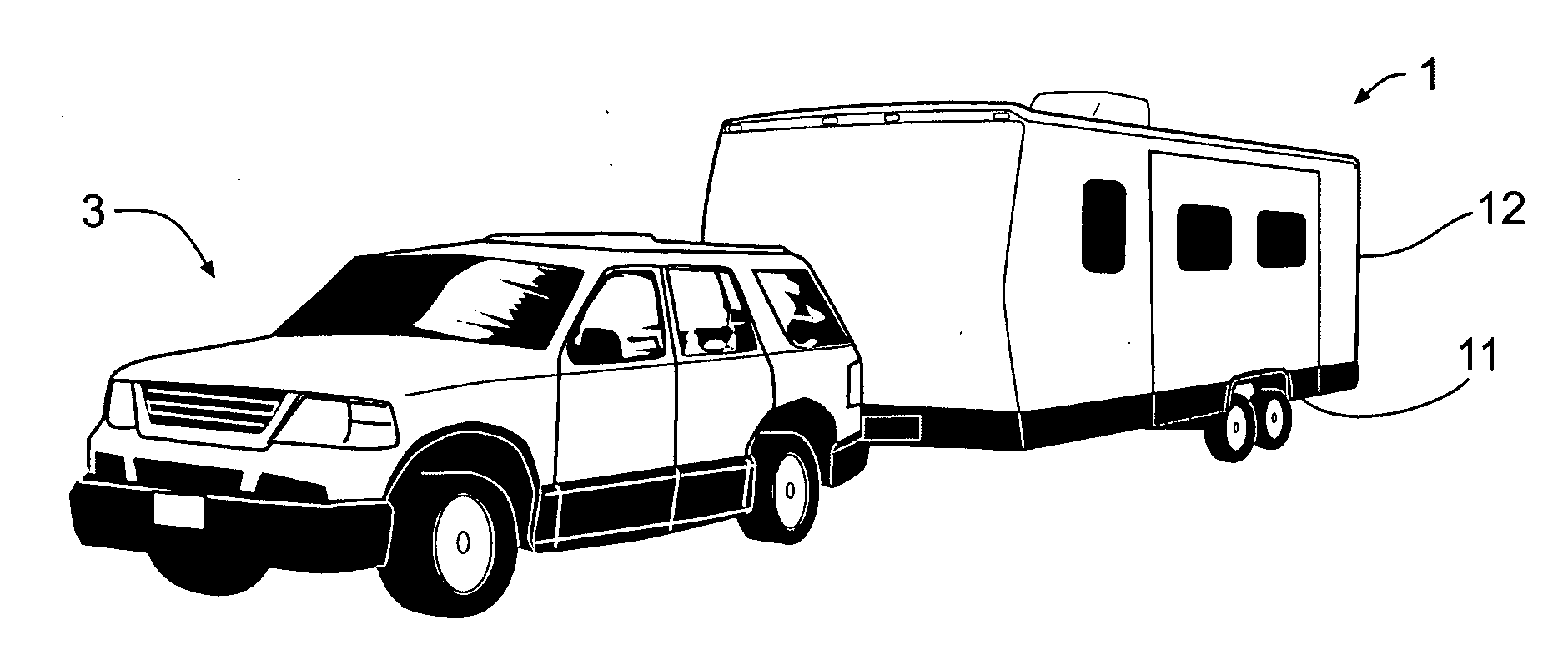

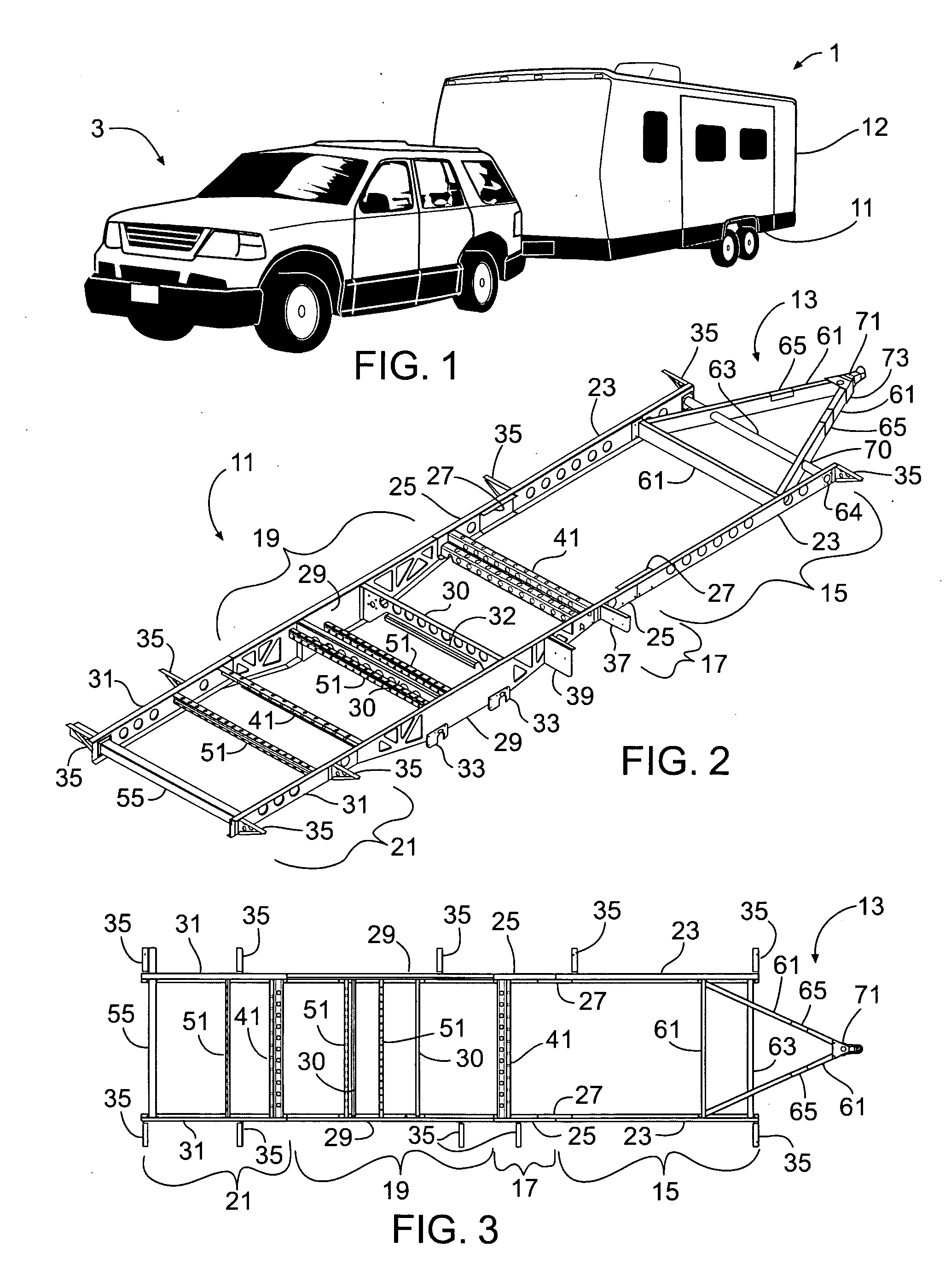

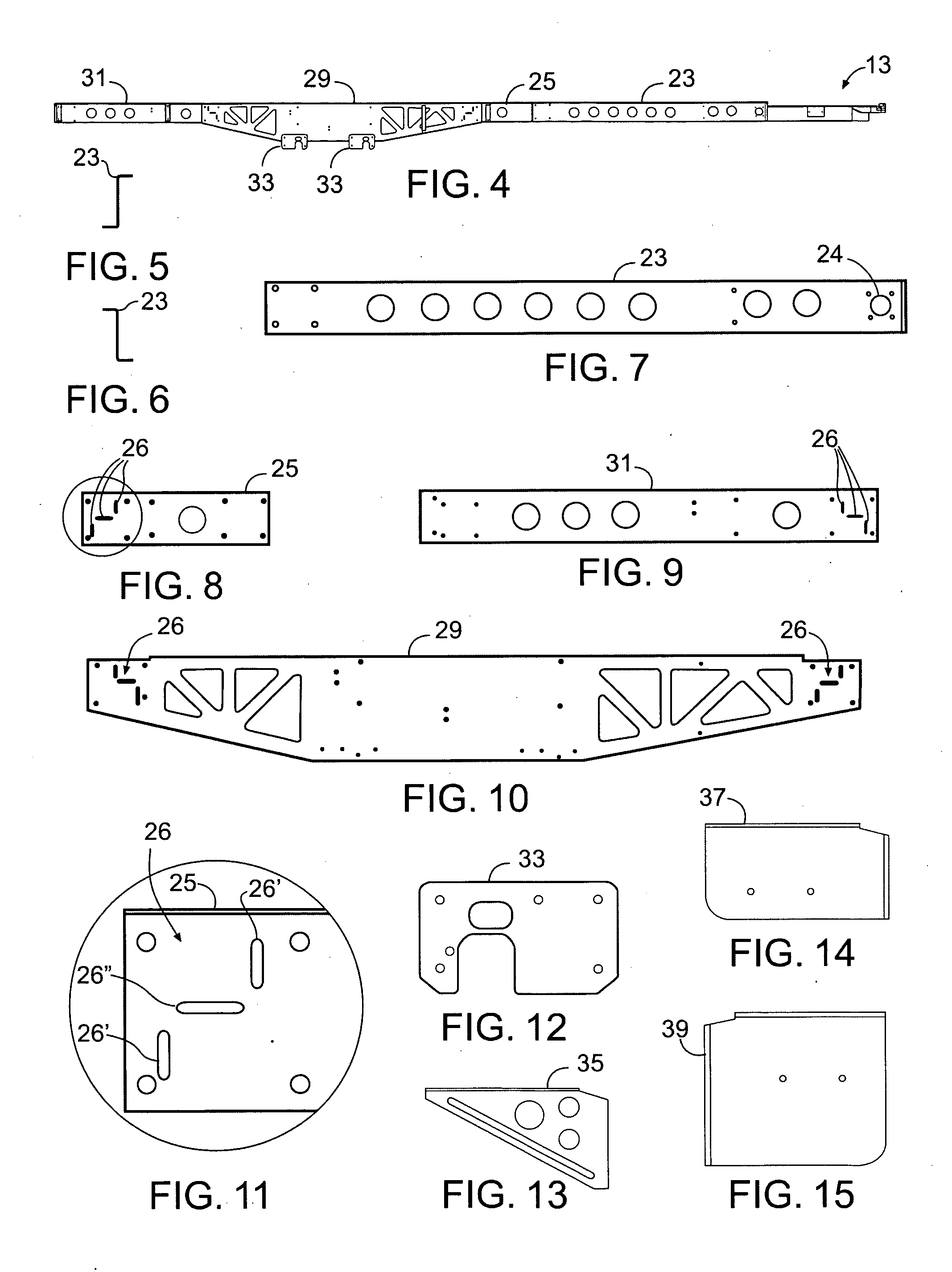

Light weight chassis and hull

InactiveUS20070007794A1Quick assemblyLower skilled assemblersVehicle seatsUnderstructuresEngineeringAssemblers

A recreational vehicle includes a hull coupled to a chassis where the hull is formed by coupling pre-formed panels together using two piece channel members, and / or the chassis is formed by mechanically coupling pre-formed segments together. In some instances, the two piece channel members will interconnect substantially perpendicular panels such as by coupling wall panels to a floor panel, to a ceiling panel, and to adjacent wall panels. Such a vehicle can be quickly assembled from space efficient pre-formed pieces by lower skilled assemblers than are typically required in manufacturing a recreational vehicle.

Owner:REV RECREATION GRP

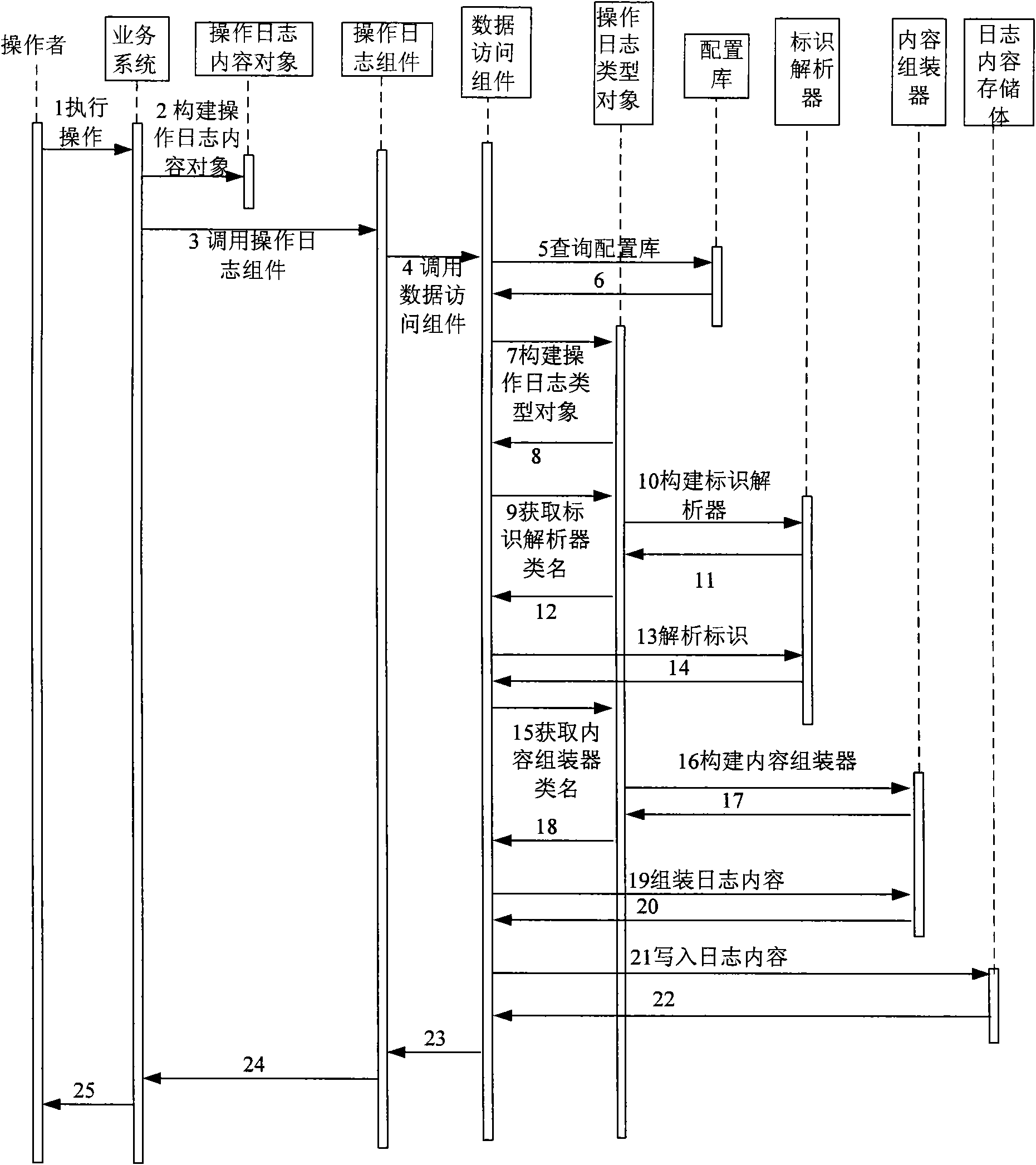

Operation log recording method and system

InactiveCN101515245AAvoid the problem of inconsistency in the operation log descriptionReduce maintenance costsHardware monitoringData accessComputer science

The invention discloses an operation log recording method, which comprises the following steps: setting a configuration library for storing the configuration information of an operation log type; acquiring the operation information comprising the operation log type, an operator and an operated object mark; calling a data access component, acquiring the configuration information of the operation log type from the configuration library, and constructing a mark analyzer and a content assembler according to the class names of the mark analyzer and the content assembler therein; analyzing the operator and the operated object mark to acquire the description of the operator and the operated object, performing mode matching according to a preset mode of the operation log type, and assembling the operation log content; and recording the operation log content, wherein the configuration information at least comprises the class names of the mark analyzer and the content assembler of the type. The invention also discloses an operation log recording system. The method and the system can avoid bring randomness recorded by the operation log into a service system, improve the consistency of the service system, and reduce maintenance cost.

Owner:卓望数码技术(深圳)有限公司

Voice packet processor and method of operation thereof

InactiveUS7075936B2Time-division multiplexData switching by path configurationComputer hardwareATM adaptation layer

A voice packet processor for use with voice applications employing a fast pattern processor (FPP) and a routing switch processor (RSP) that receive and transmit protocol data units (PDUs) and a method of operation thereof. In one embodiment, the voice packet processor includes (1) a voice packet controller (VPC) configured to receive the PDUs from the FPP and queue the PDUs for processing, (2) a voice packet parser configured to receive the PDUs that are ATM adaptation layer 2 (AAL2) cells containing voice data from the VPC, parse the AAL2 cells into at least one Common Part Sublayer (CPS) packet and transmit the at least one CPS packet to the RSP, and (3) a voice packet assembler configured to receive the PDUs that are CPS packets from the VPC, assemble the CPS packets into at least one AAL2 Cell and transmit the at least one AAL2 cell to the RSP.

Owner:INTEL CORP

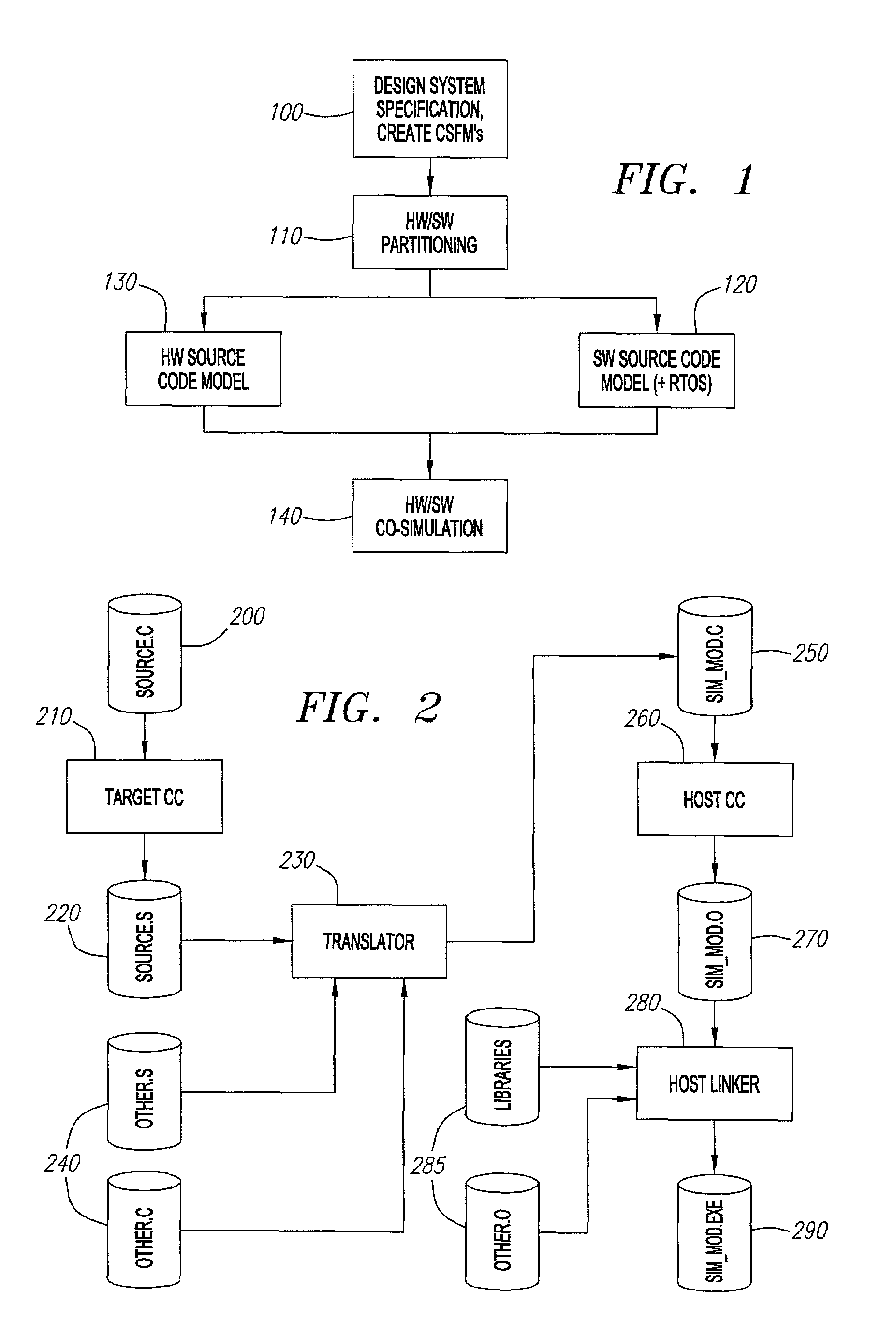

Systems and methods for performing software performance estimations

InactiveUS7702499B1Error detection/correctionSoftware simulation/interpretation/emulationParallel computingSource code

Systems and methods are provided for annotating software with performance information. The computer code is compiled into assembler code, the assembler code is translated into a simulation model, expressed in assembler-level source code. The simulation model is annotated with information for calculating various performance parameters of the software, such as timing information, or resource usage information. The simulation model is then re-compiled and executed on a simulator, optionally including a hardware simulation model, and the performance information is computed from the simulation.

Owner:CADENCE DESIGN SYST INC

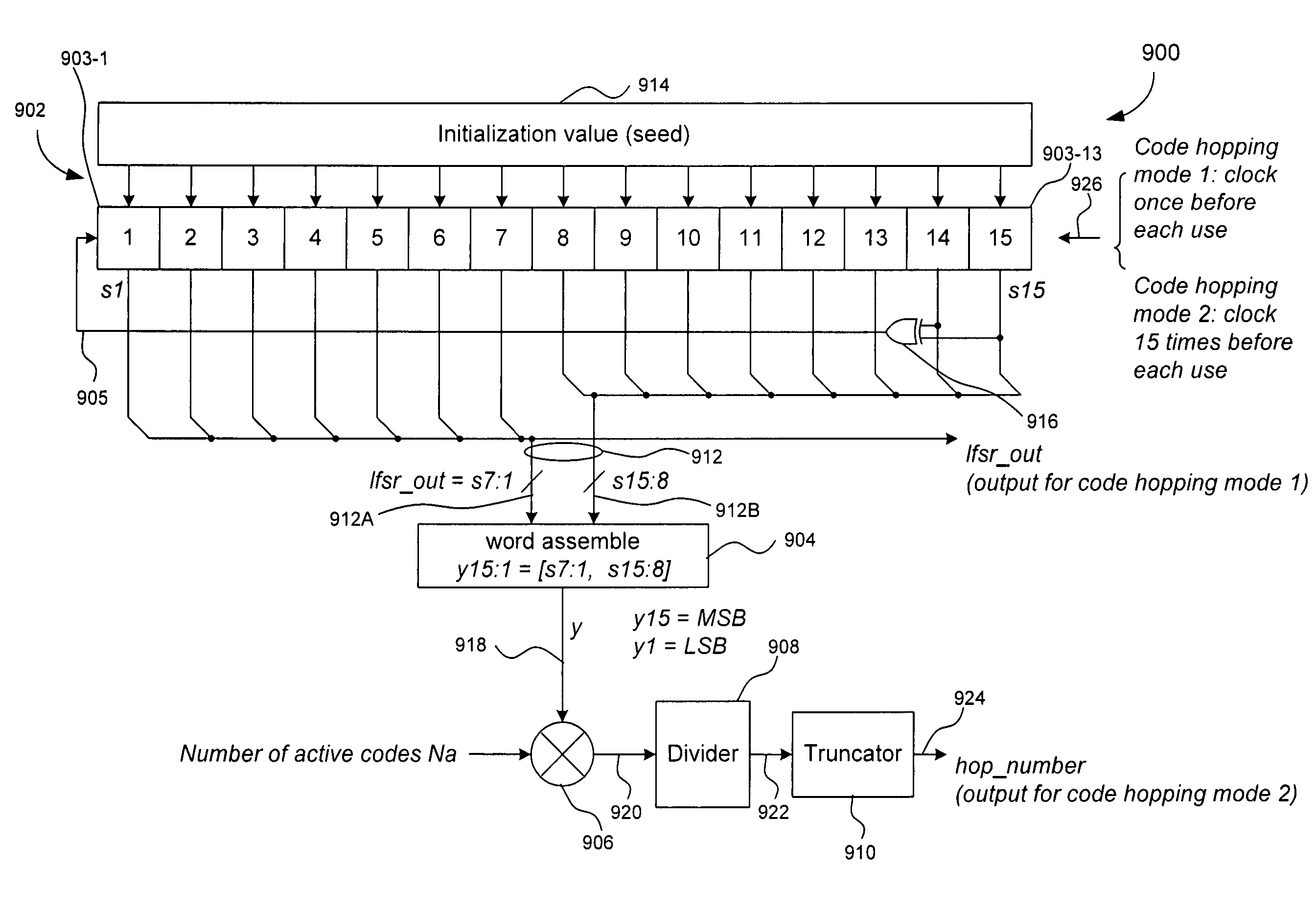

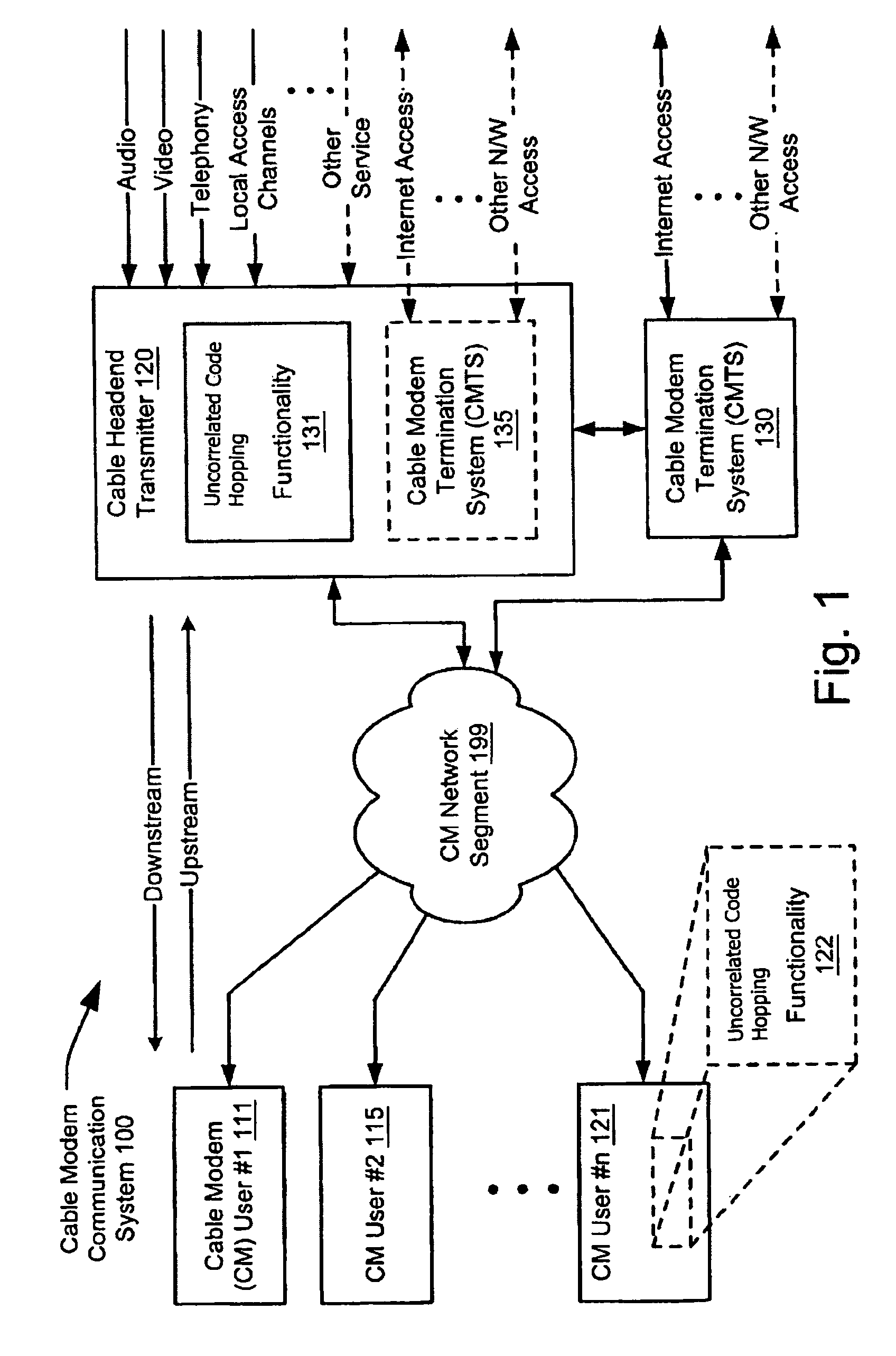

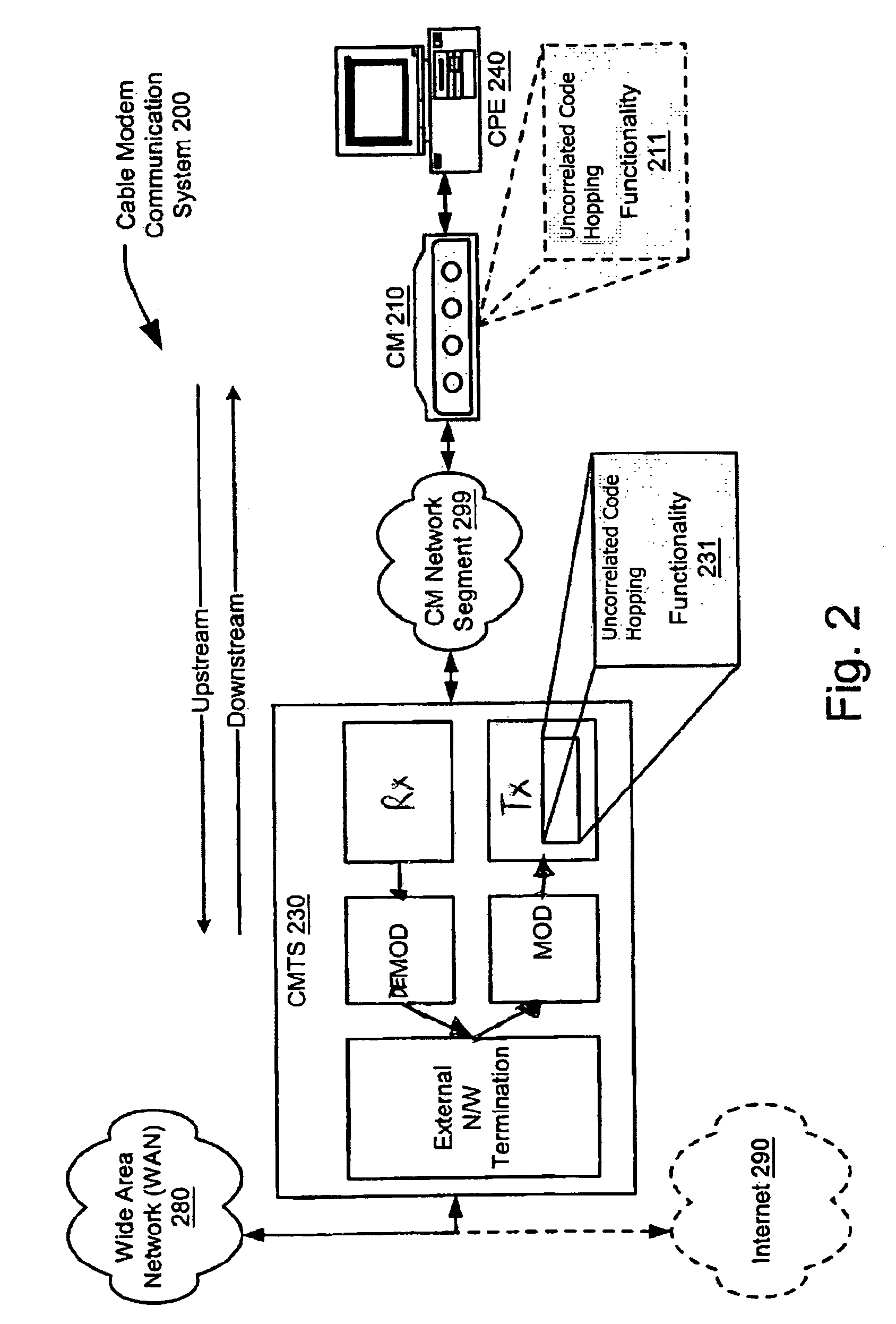

System and method of uncorrelated code hopping in a communications system

InactiveUS7673192B2Electronic circuit testingError detection/correctionShift registerCommunications system

A system and method are used to provide uncorrelated code hopping in a communications system. A multi-bit linear shift register receives data and clocks the data fifteen times. A word assembler receives the shifted data and outputs a fifteen bit word. A mixer mixes the fifteen bit word with an numerical value of active codes to generate a mixed signal. A divider divides the mixed signal to produce a divided signal. A truncator truncates the divided signal to its seven most significant bits to produce a pseudo random hop number. A code matrix shifter circularly shifts the active codes in a code matrix based on the pseudo random hop number to produce a circularly shifted code. A transmitter transmits the circularly shifted code matrix.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

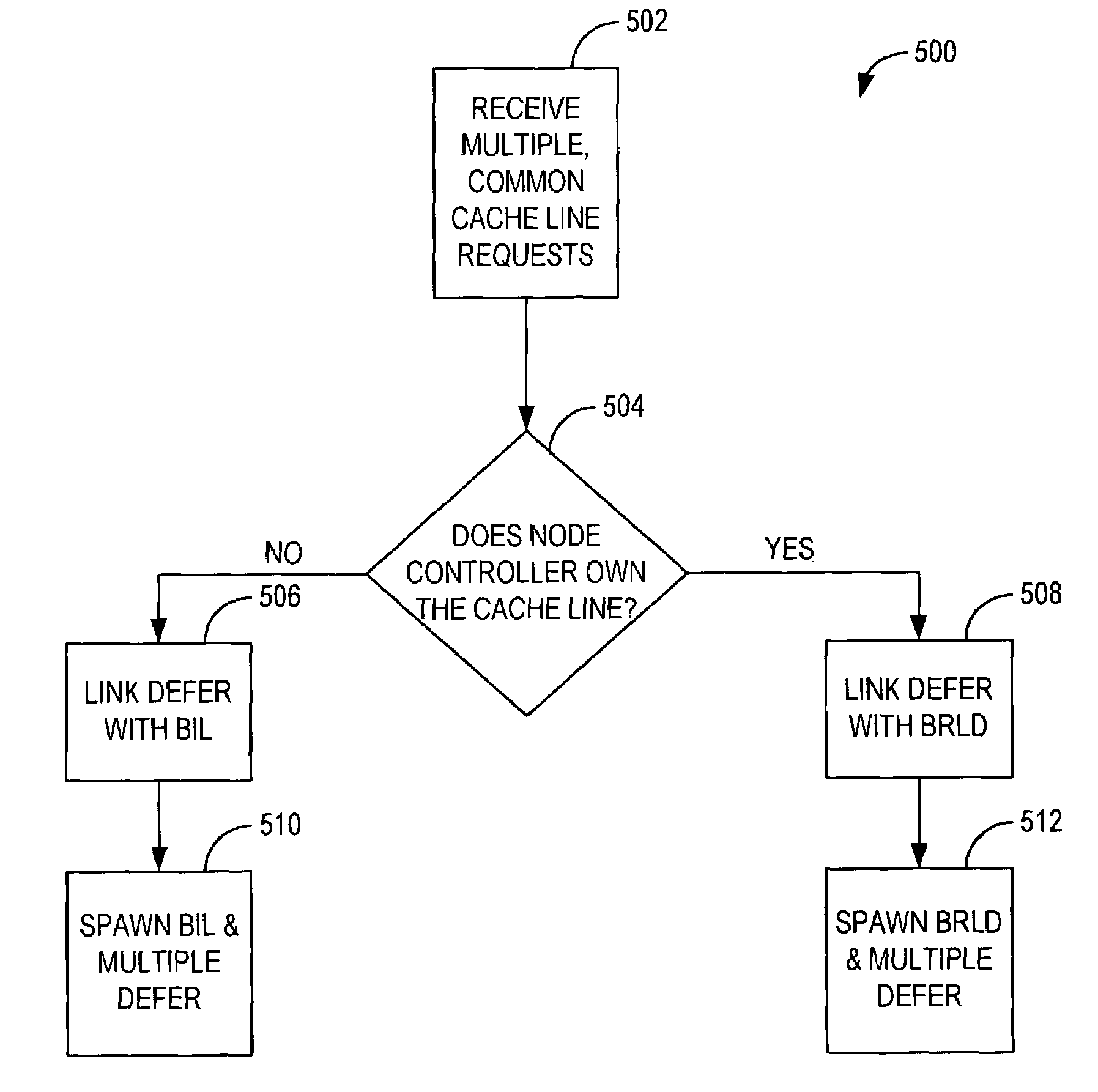

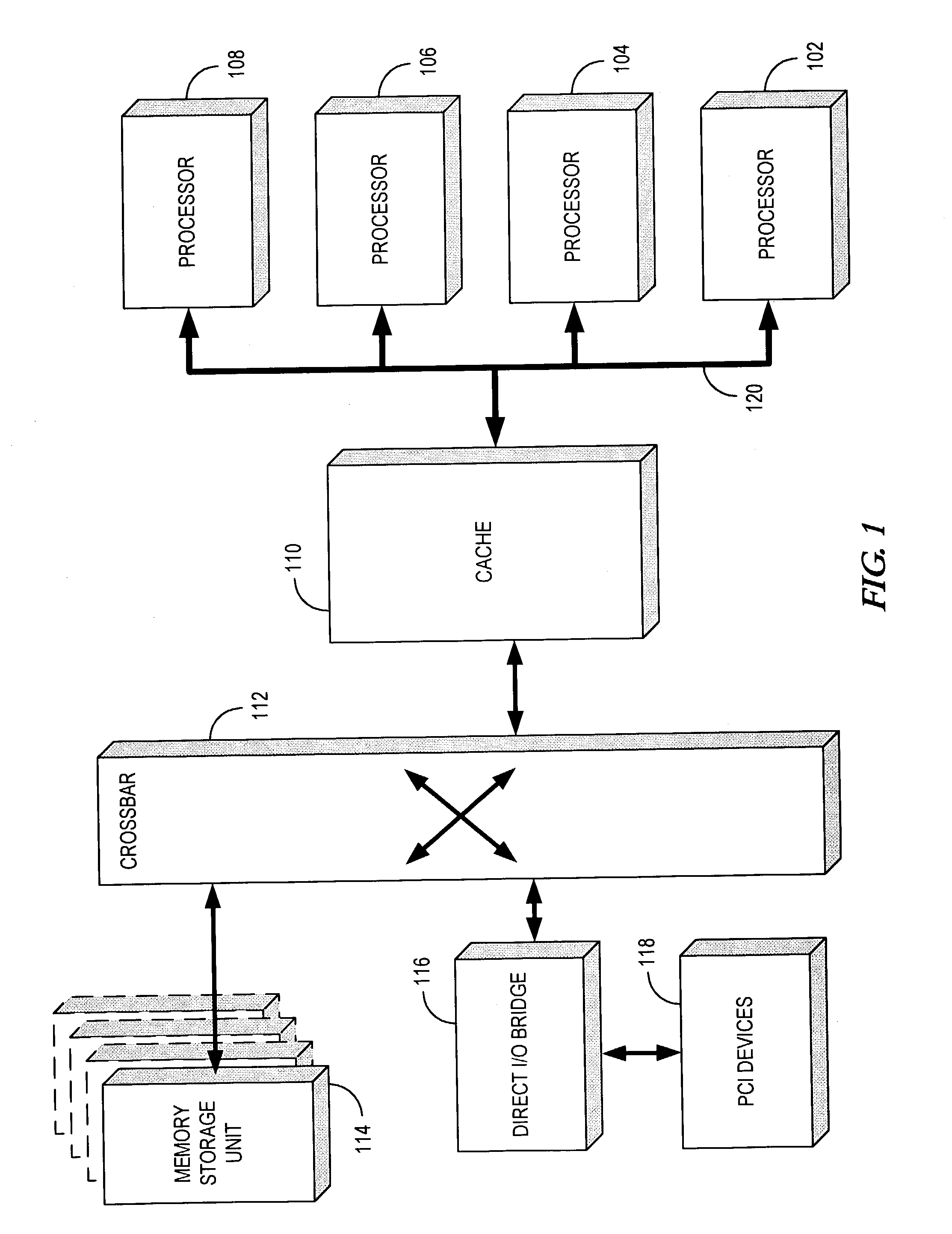

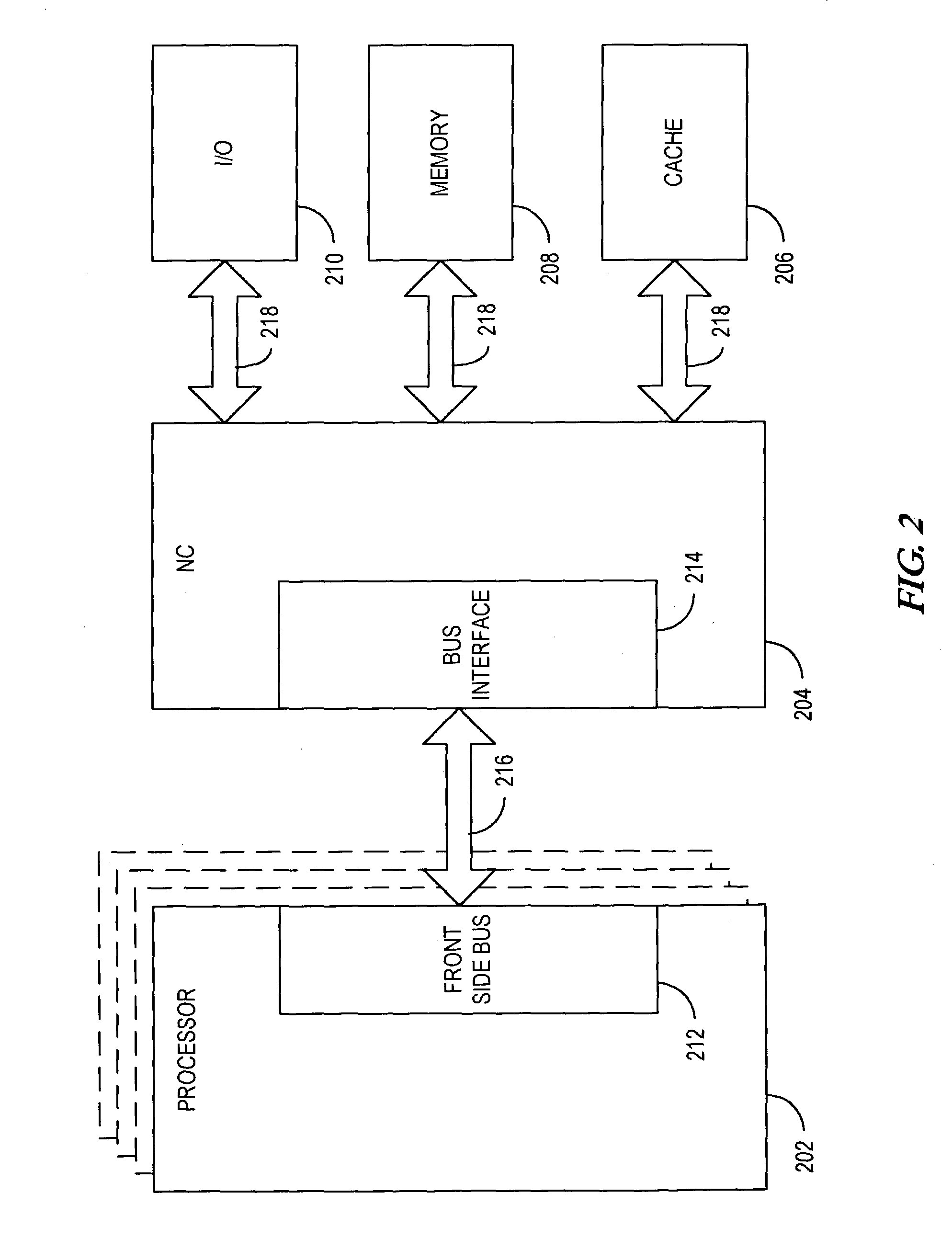

Method and apparatus for spawning multiple requests from a single entry of a queue

InactiveUS6996645B1Increase effective capacityMemory systemsInput/output processes for data processingBus interfaceDistributed computing

Coded requests are received from Memory Port Interfaces (608 and 612) and stored into Outgoing Queue (604). Coded requests are also received from Transaction Pipeline (610), some of which may be linked requests. In response to each linked request stored in Outgoing Queue (604), multiple bus requests are generated by Outgoing Queue (604) and assembled by Assembler (602) and placed onto Bus Interface (620).

Owner:UNISYS CORP