Patents

Literature

95 results about "Design flow" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

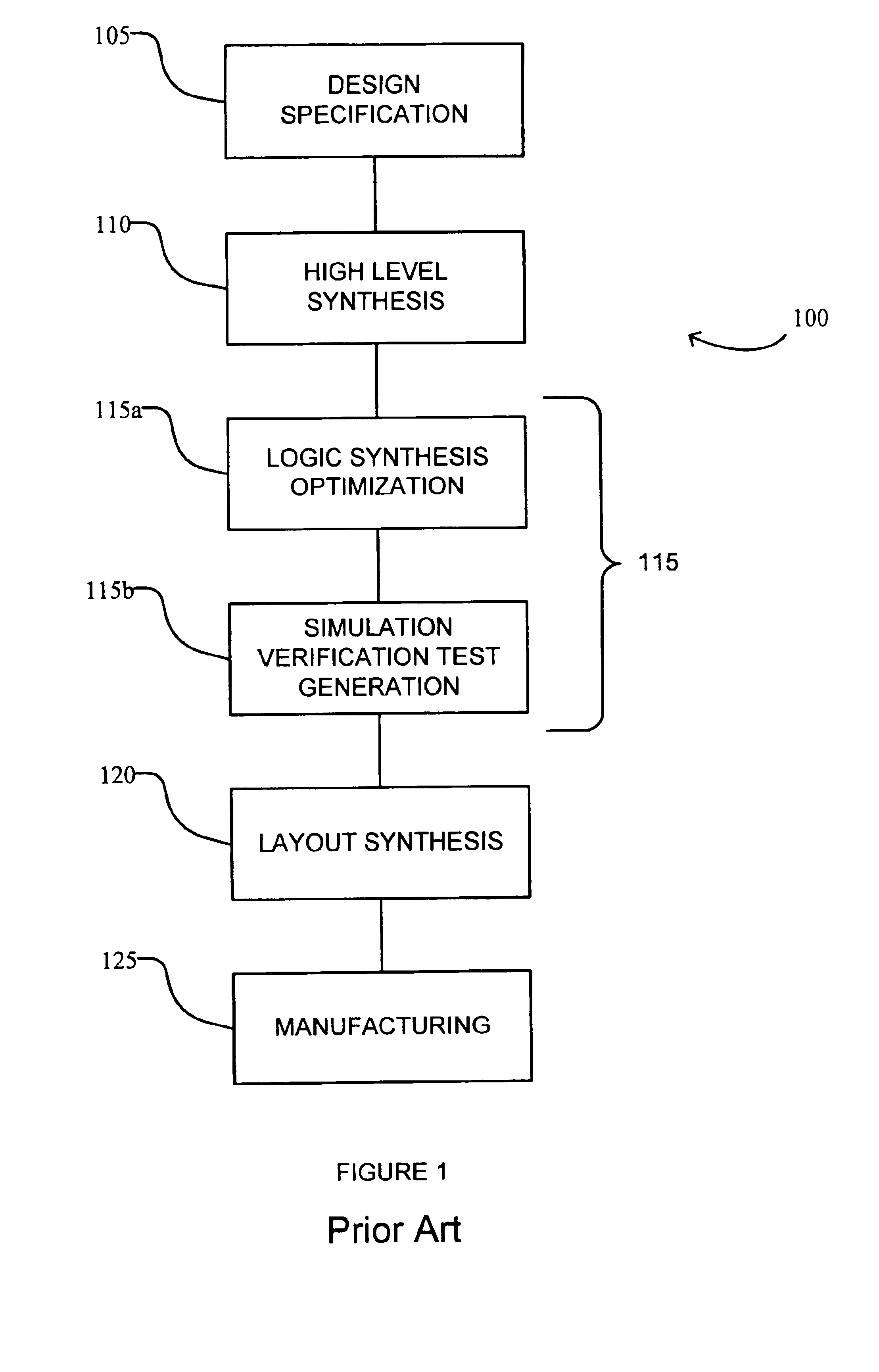

Design flows are the explicit combination of electronic design automation tools to accomplish the design of an integrated circuit. Moore's law has driven the entire IC implementation RTL to GDSII design flows from one which uses primarily stand-alone synthesis, placement, and routing algorithms to an integrated construction and analysis flows for design closure. The challenges of rising interconnect delay led to a new way of thinking about and integrating design closure tools.

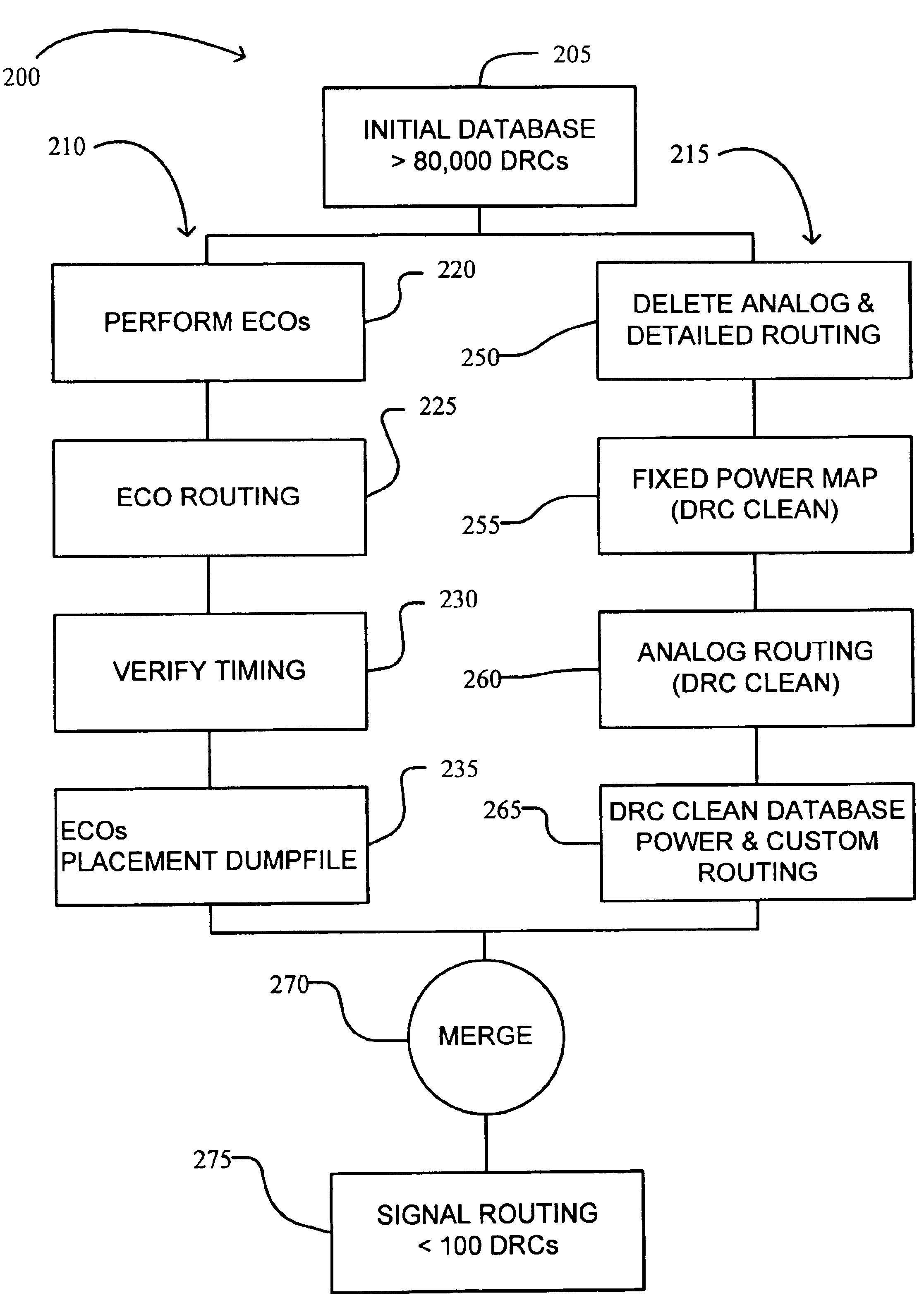

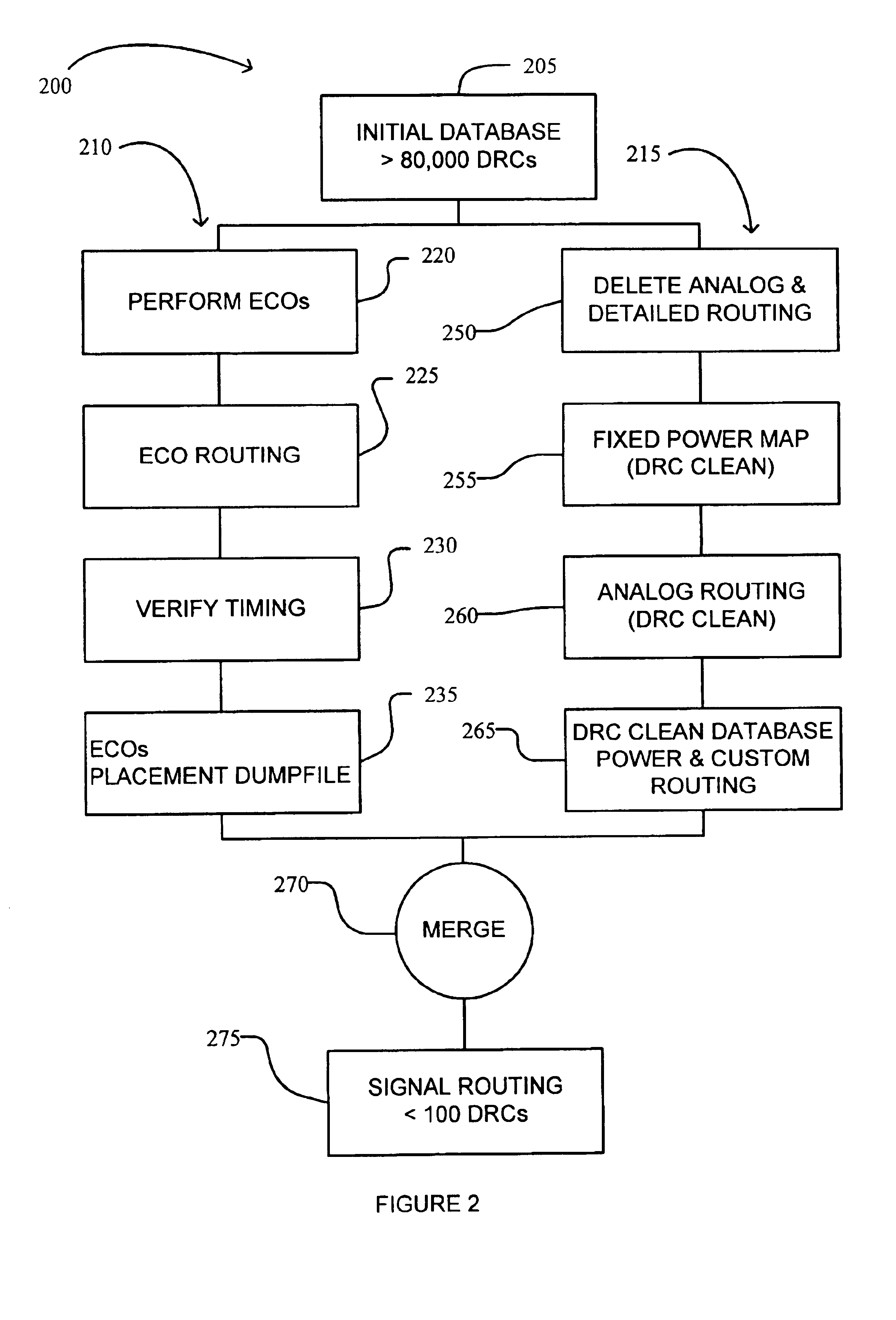

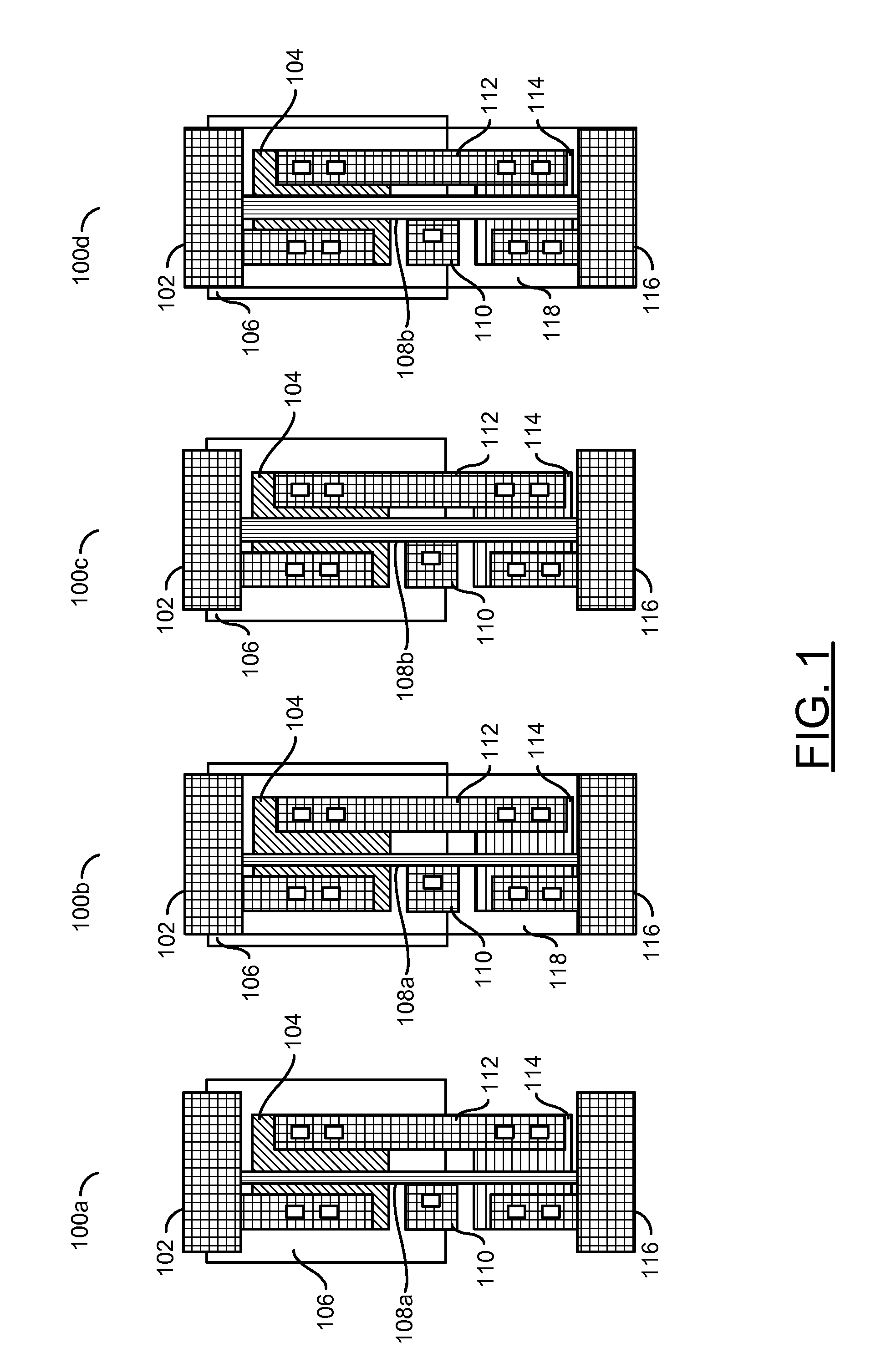

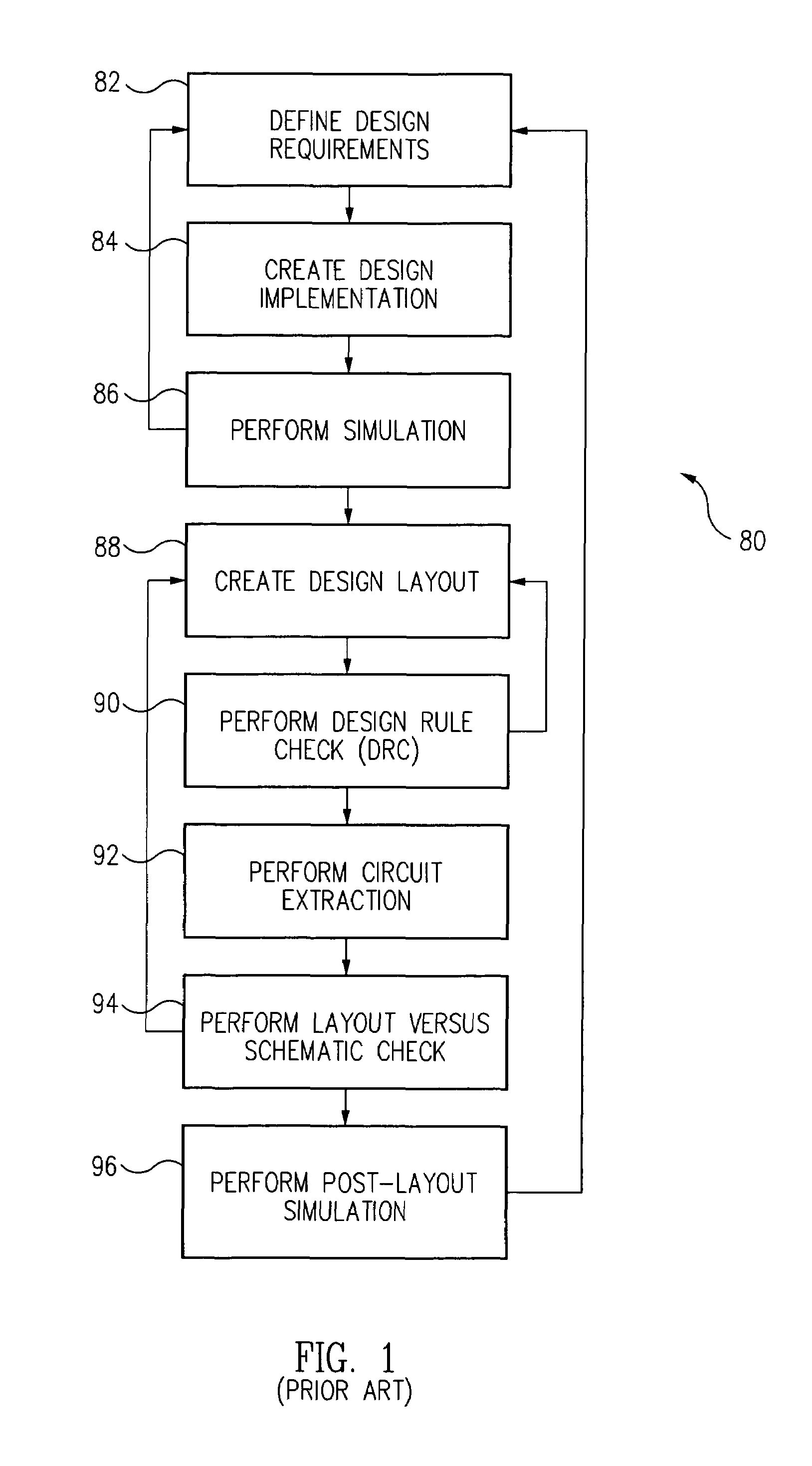

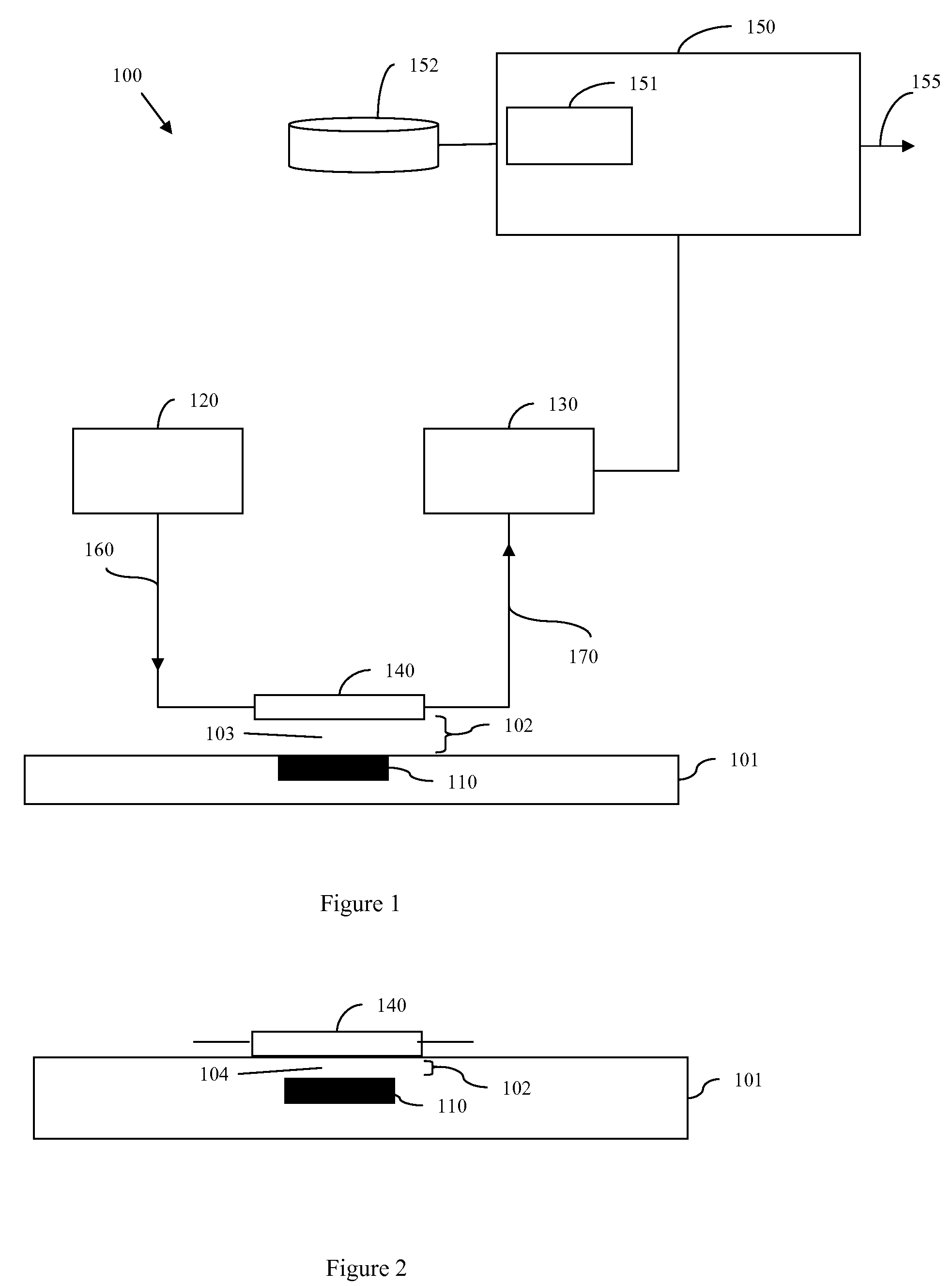

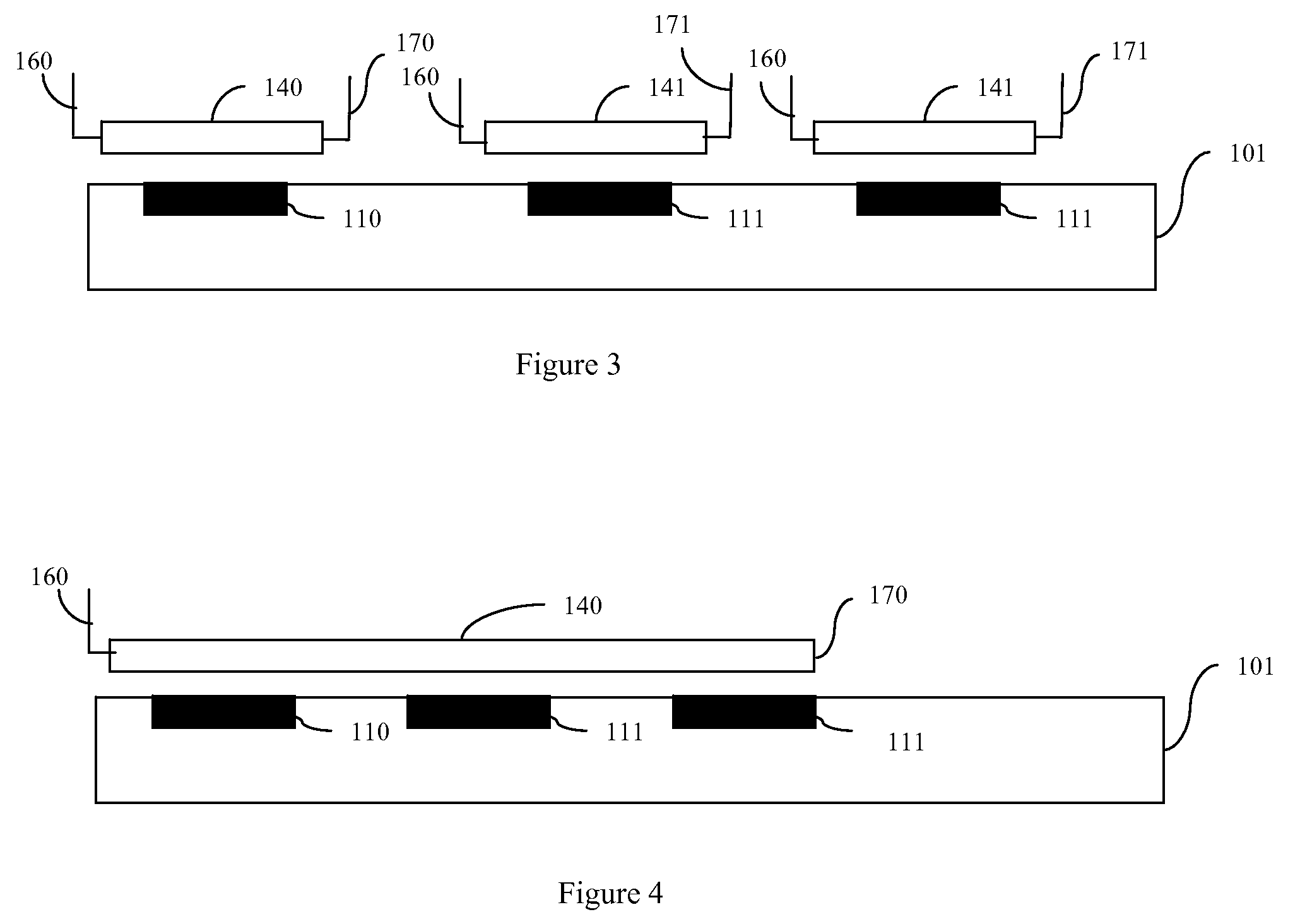

Split and merge design flow concept for fast turnaround time of circuit layout design

ActiveUS6898770B2Increase turnaround timeAccurate verificationComputer aided designSoftware simulation/interpretation/emulationSufficient timeTurnaround time

A method and system is disclosed to improve the turnaround time to provide adequate time to meet project schedules in the event that adjustments or modifications to the design are necessary. A method for improving a turnaround time for design verification of a process database representing a semiconductor design includes the steps of (a) deriving a timing database and a (DNE) database from the process database; (b) performing, using the timing database, one or more design changes and one or more timing verifications and corrections to generate a modified timing database; (c) initiating, using the process database, physical validation of the semiconductor design prior to completion of step (b) to generate a modified DNE database; (d) merging the modified timing database with the modified DNE database to form a modified process database; and (e) performing, using the modified process database, one or more design verification checks of the semiconductor design.

Owner:BELL SEMICON LLC

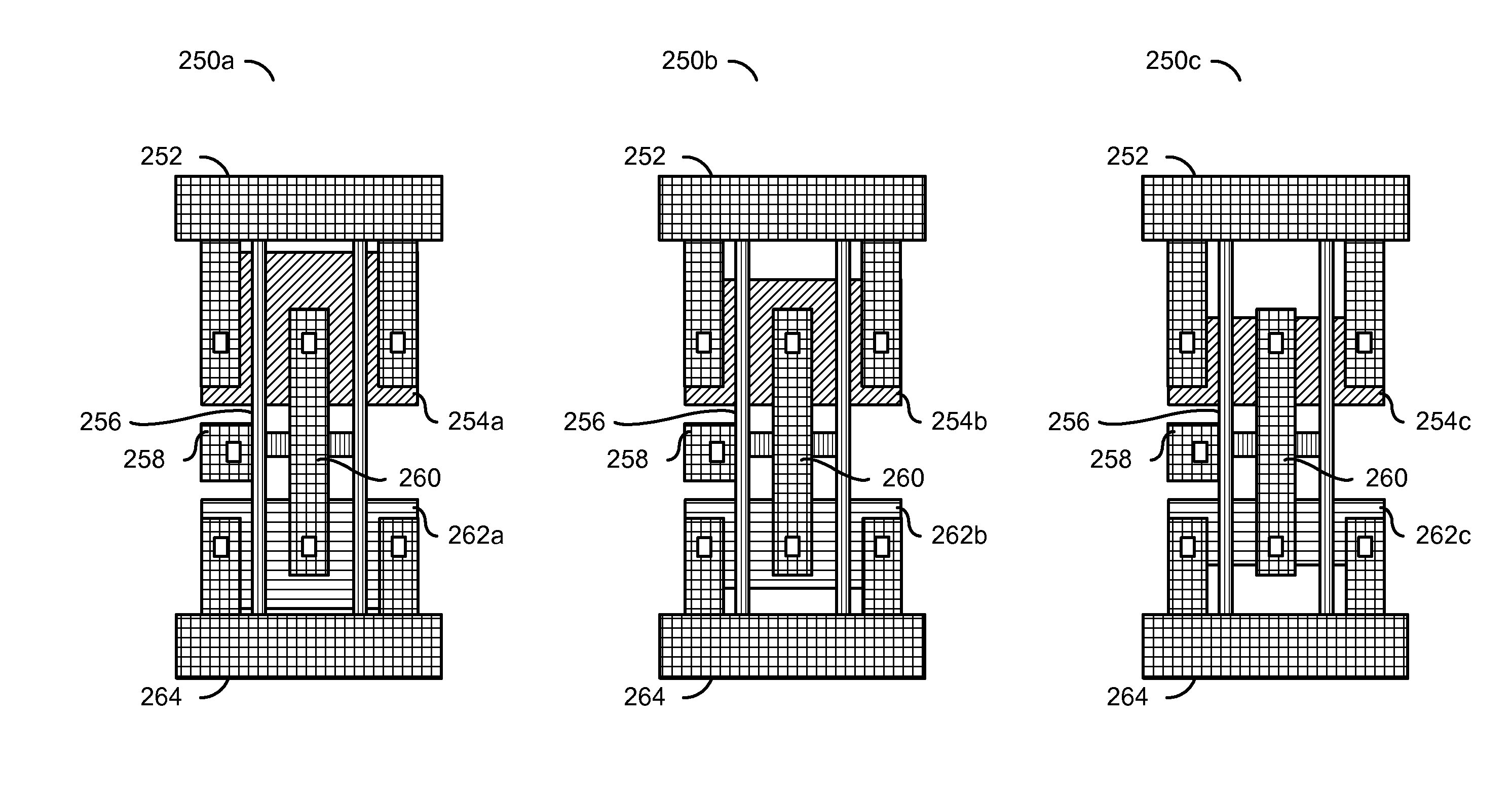

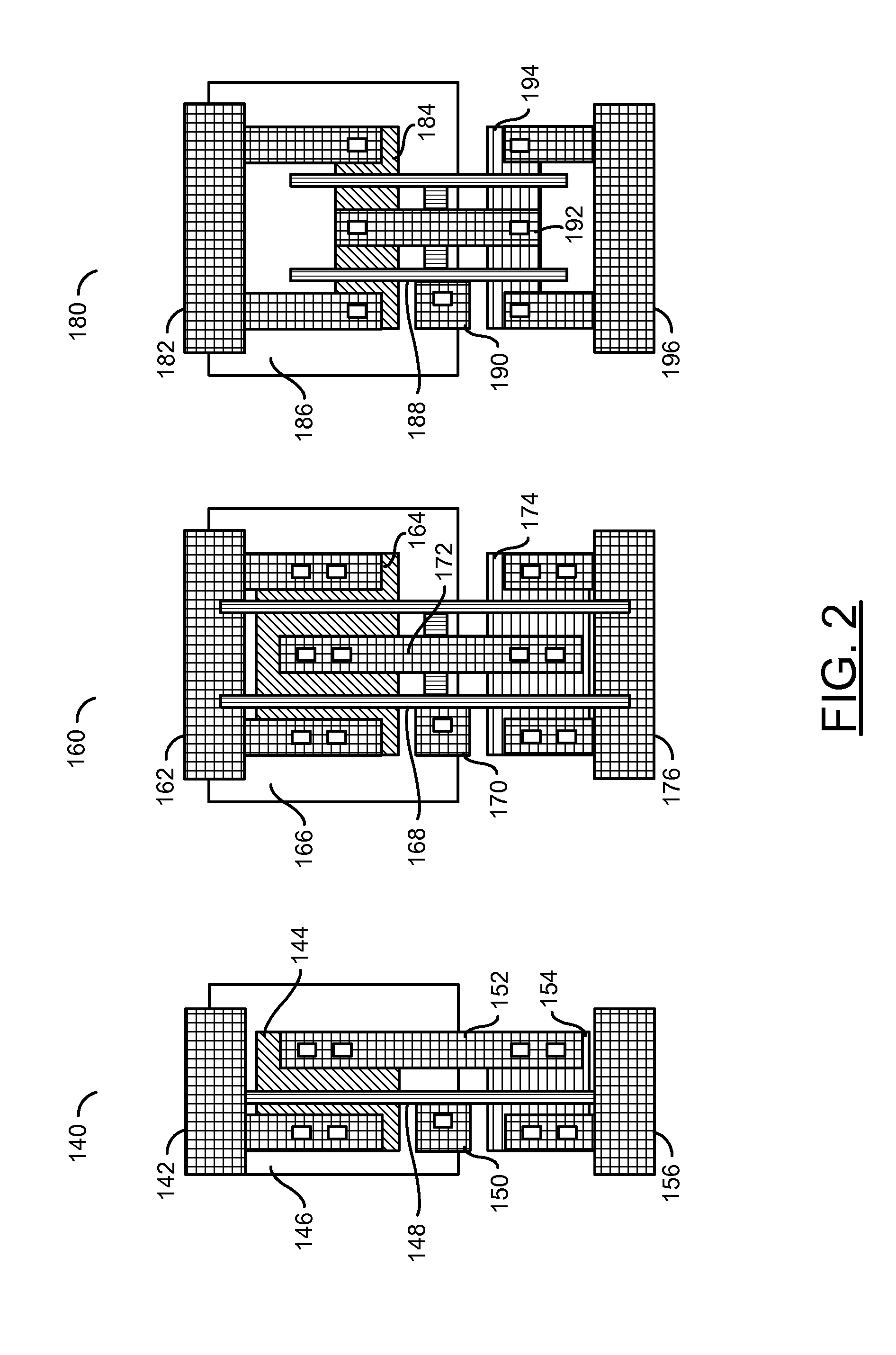

Granular channel width for power optimization

ActiveUS20120023473A1Improve performancePower optimizationDetecting faulty computer hardwarePower supply for data processingComputational sciencePower optimization

A storage medium recording a cell library having one or more cells that may be readable by a computer and may be used by the computer to design an integrated circuit. The one or more cells may have a physical dimension parameter and a channel width parameter. The physical dimension parameter may be a footprint of the one or more cells. The channel width parameter may have a minimum driver size and a maximum driver size. The channel width parameter may define a range within which a tool varies the channel width between the maximum driver size and the minimum driver size during a design flow of the integrated circuit based upon one or more power criteria without changing the footprint.

Owner:BELL SEMICON LLC

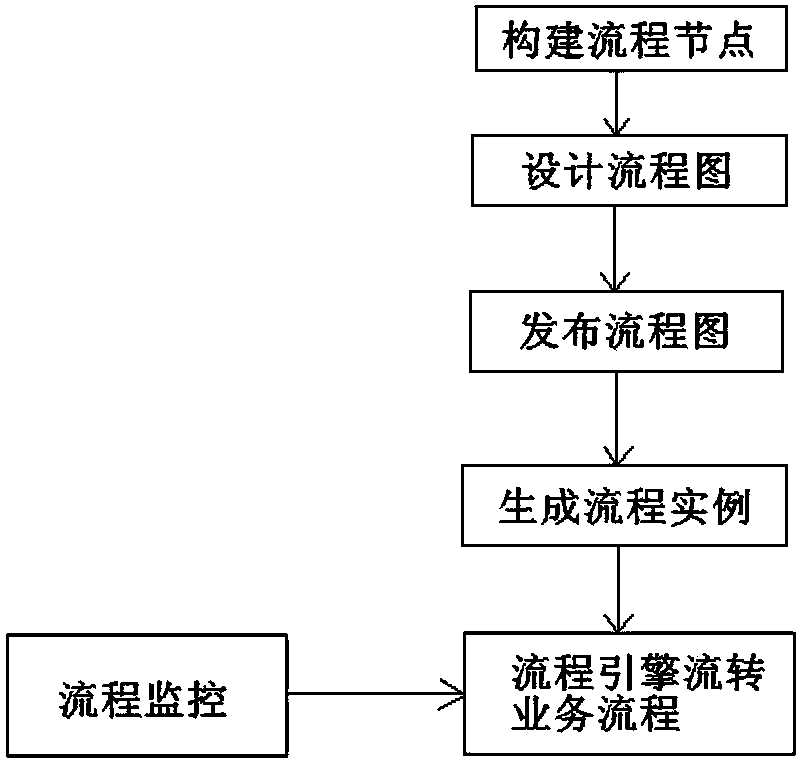

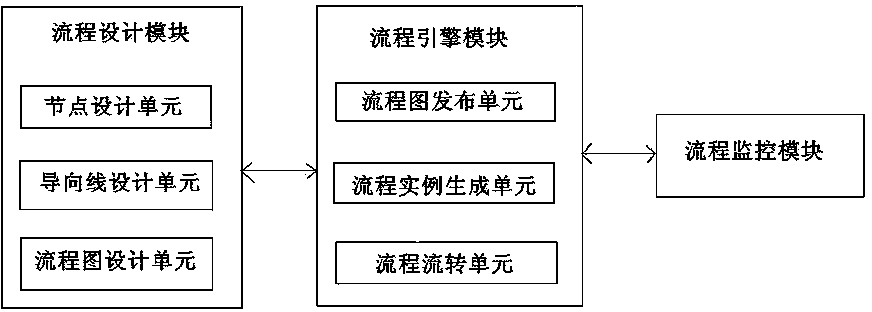

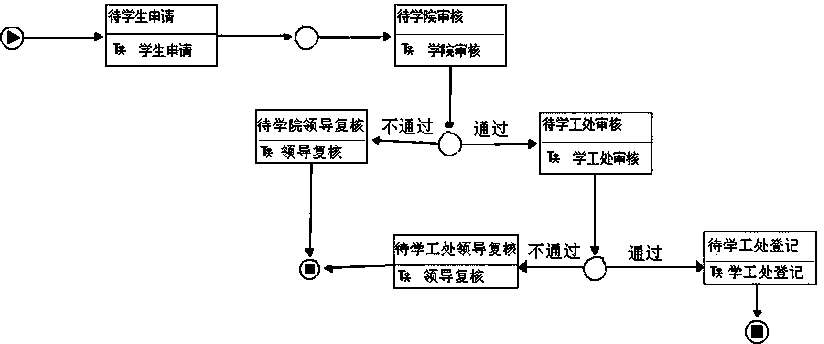

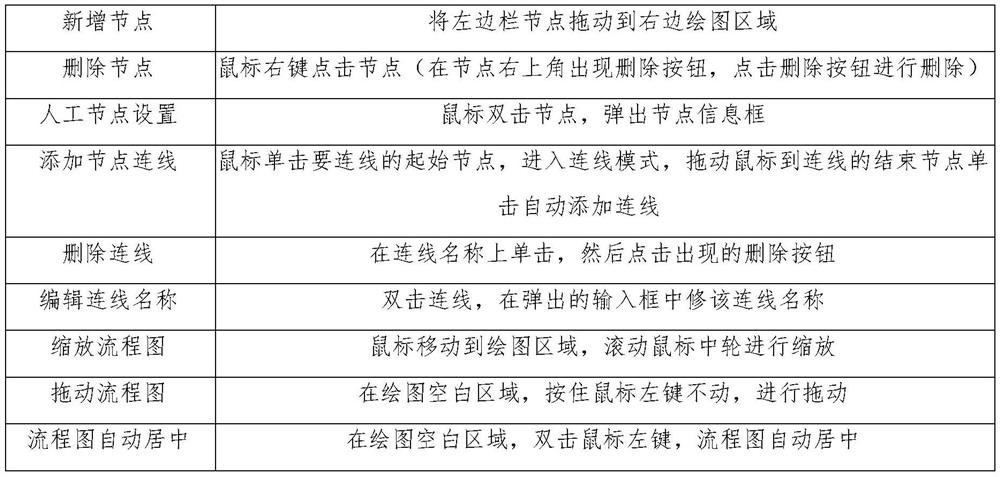

Process engine achieving method and system in service process

InactiveCN104281906ARapid deploymentEasy to createResourcesSpecific program execution arrangementsDesign flowProcess engineering

The invention discloses a process engine achieving method in a service process and belongs to the technical field of dynamic process control of the computer technology. The method includes the following steps that firstly, imaging process nodes are constructed; secondly, a process graph is designed, the process nodes are connected through a guiding line with a condition and a direction according to the service requirement, and the service process graph is formed; thirdly, the designed process graph is stored and issued to a process engine; fourthly, the process engine automatically circulates tasks to the corresponding nodes according to the operation of a service system. The invention further discloses a process engine system in the service process, and the process engine system comprises a process design module and a process engine module. The service process design and changing processes are simplified, the implementation cost is saved, and the process issuing time is shortened.

Owner:JIANGSU DATATECH INFORMATION TECH

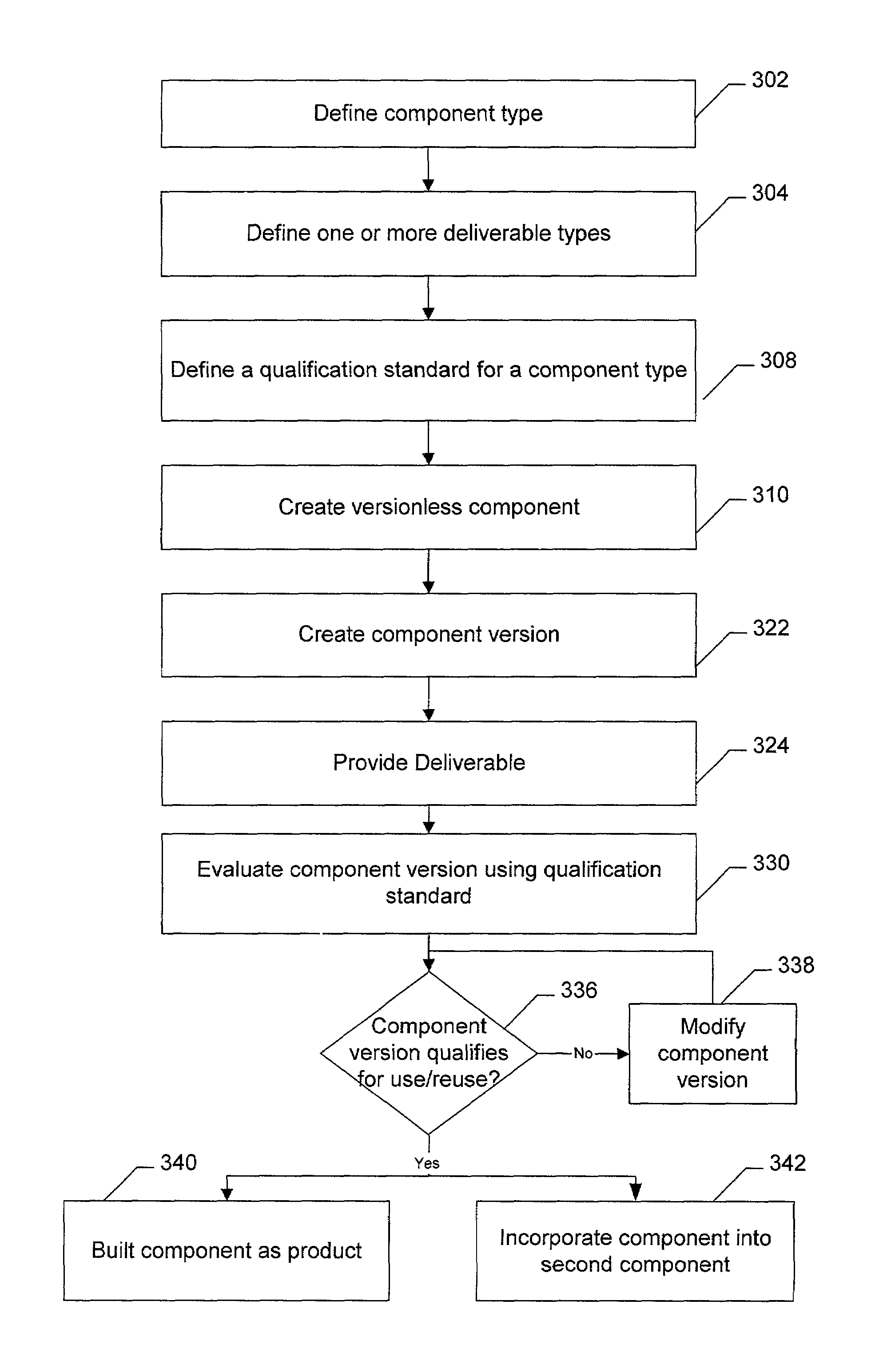

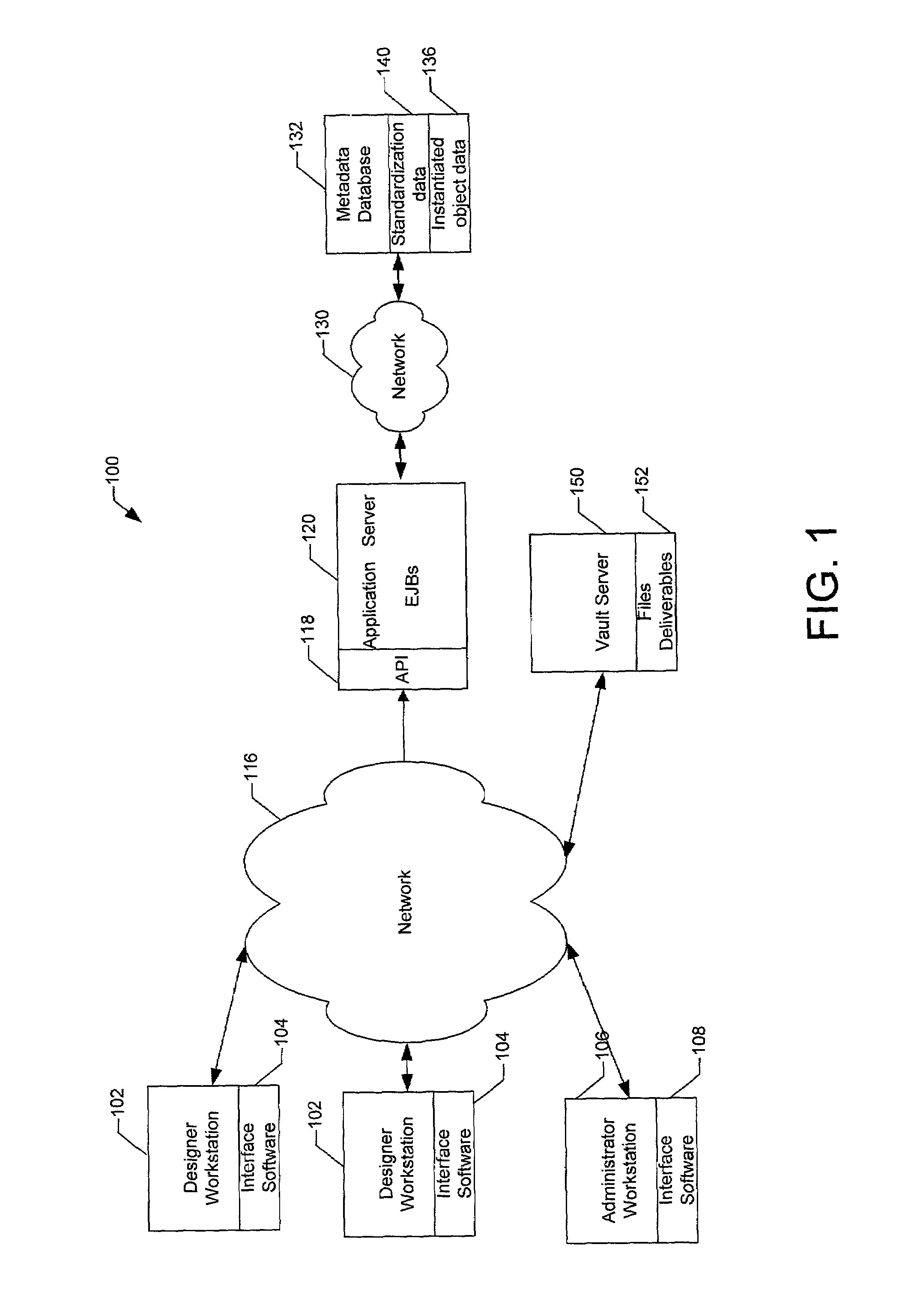

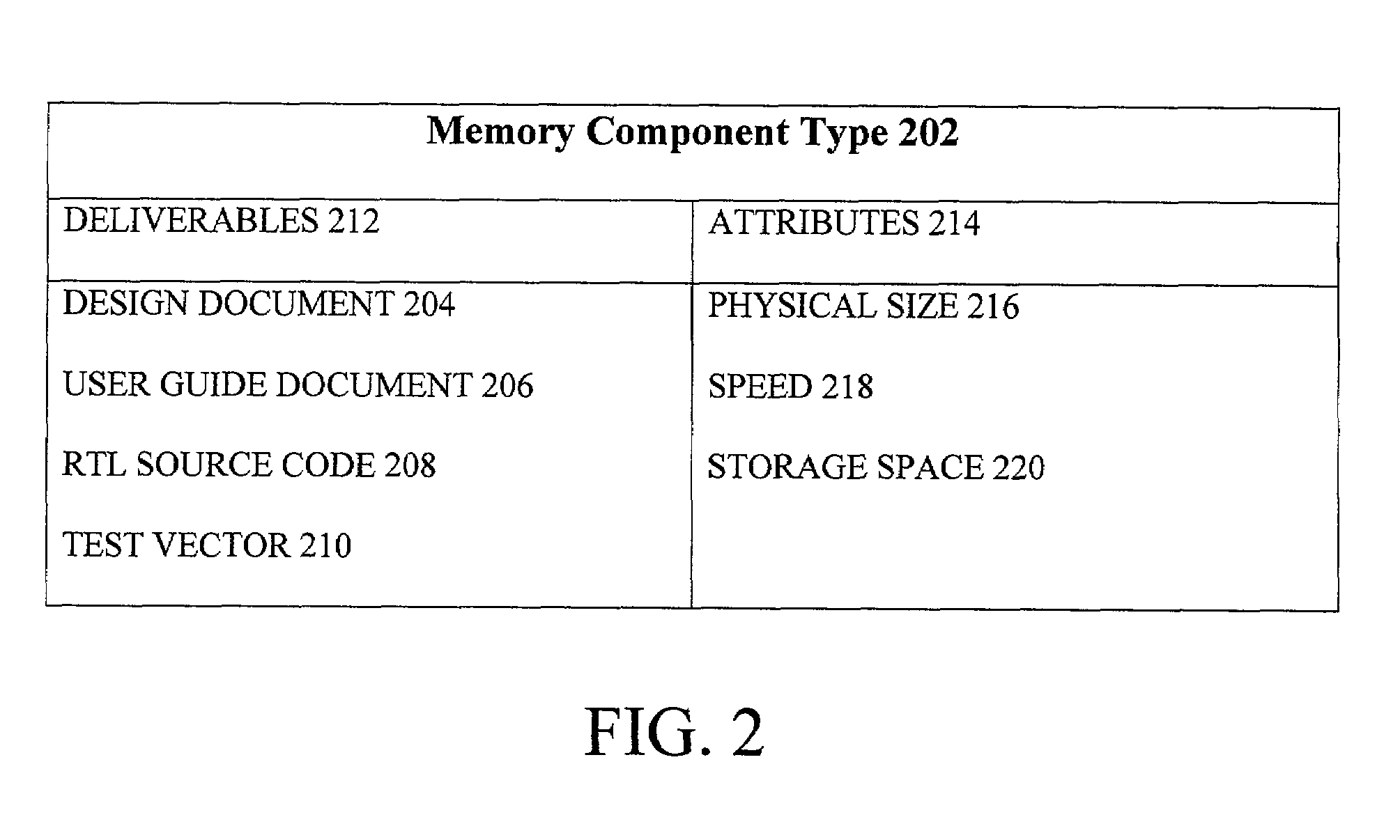

System for intellectual property reuse in integrated circuit design

InactiveUS6961918B2Uniform characteristicsEasy to createCAD network environmentComputer programmed simultaneously with data introductionIntellectual propertyApplication software

The invention provides a knowledge management system particularly suited for use in the integrated circuit design environment. The system allows administrators to define standardized component types. Instantiated components versions comprise “deliverables” and “attributes.” Deliverables comprise a file or directory of files or groups of files or directories that perform a common function and are characterized by the system in a standardized manner. Attributes comprise metadata describe the component version. By the abstraction of design files into deliverables, the systems can work with design files originating from any source and having different structures and still make those design files available by other designers in a uniform manner for efficient reuse of pre-qualified components. Tasks in the design flow can be tracked in the system. The system may also include a communications application, an issue tracking application, and an audit trail application.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

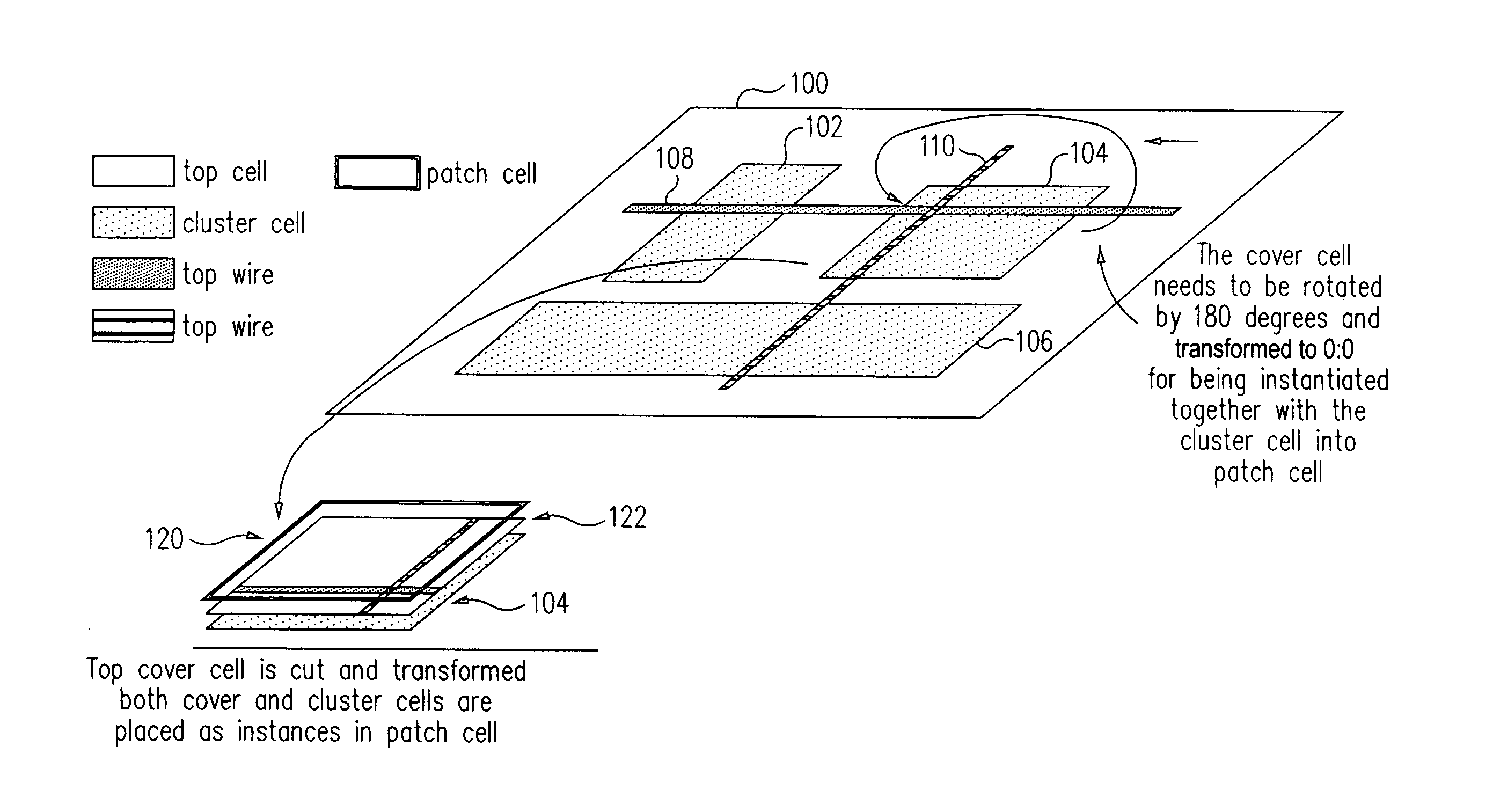

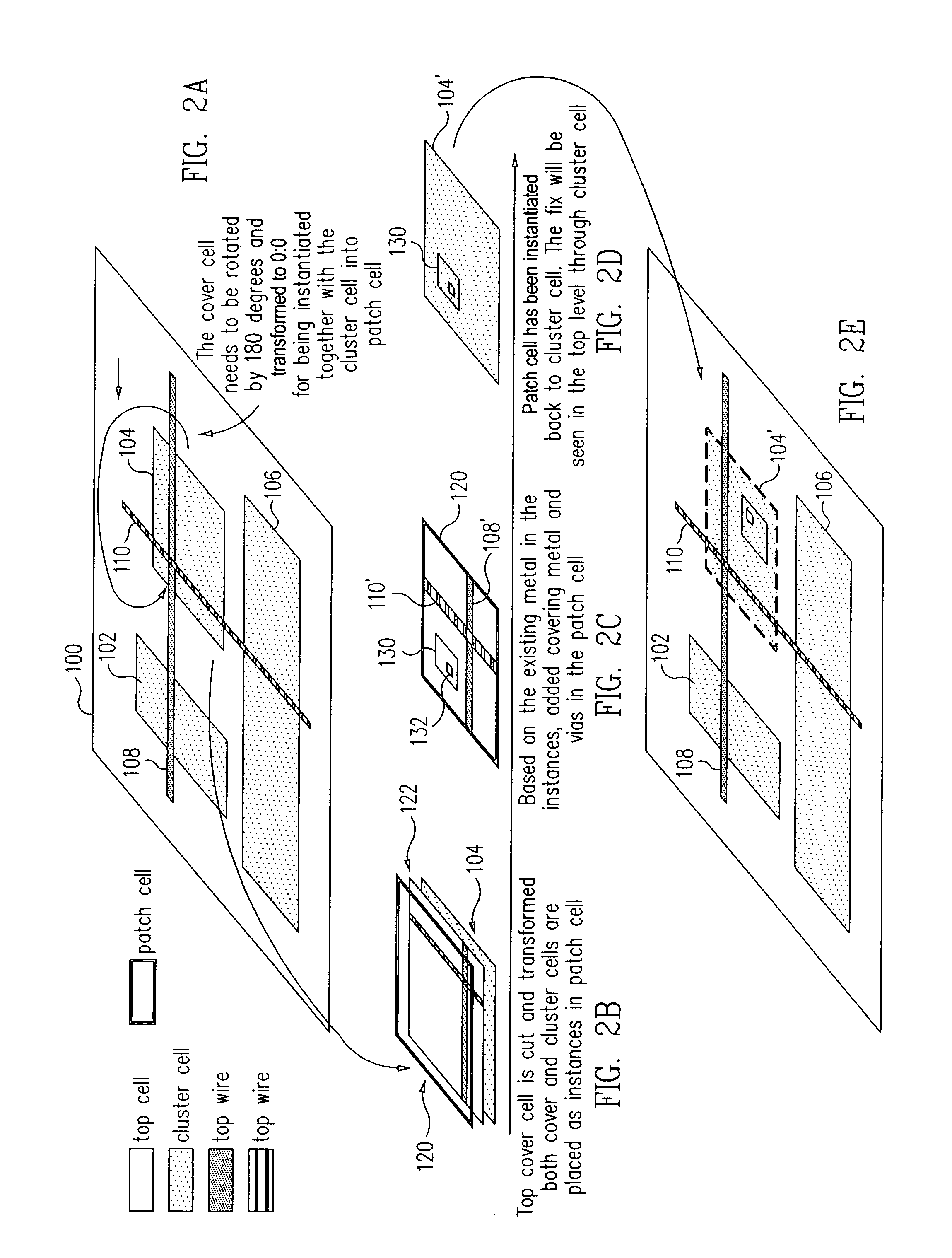

Method and apparatus for efficiently locating and automatically correcting certain violations in a complex existing circuit layout

ActiveUS7096447B1High failure rateReduce riskComputer aided designSoftware simulation/interpretation/emulationCluster cellEngineering

An exemplary CAD design flow modifies an existing large scale chip layout to reinforce the redundant via design rules to improve the yield and reliability. The flow operates on each metal-via pair from bottom up to locate and correct isolated via rule violations by adding metal features and vias in a respective patch cell associated with each cluster cell. A large complex design is thus divided into cells so that multiple processes can work concurrently as if every process were working on the top level of the design layout.

Owner:ORACLE INT CORP

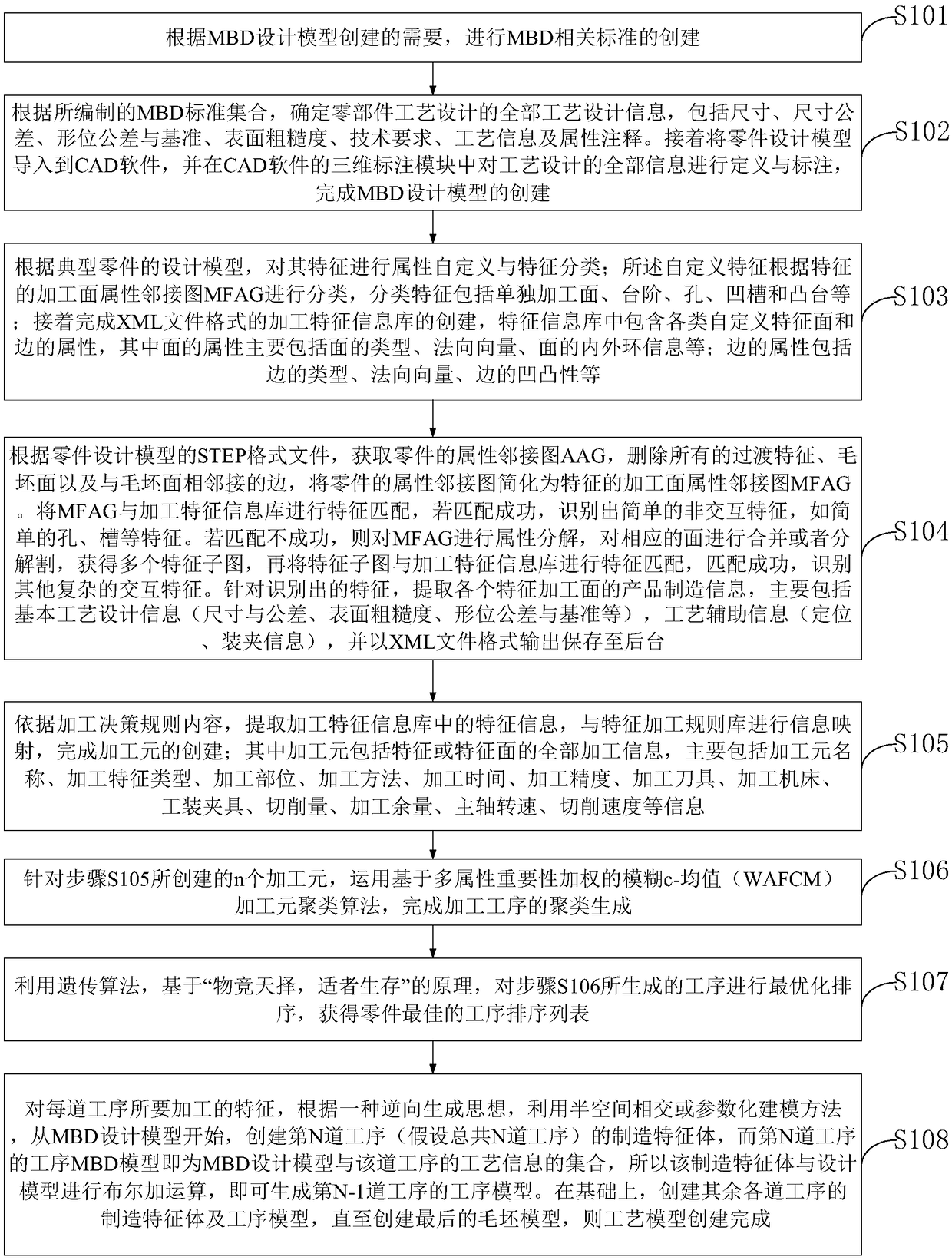

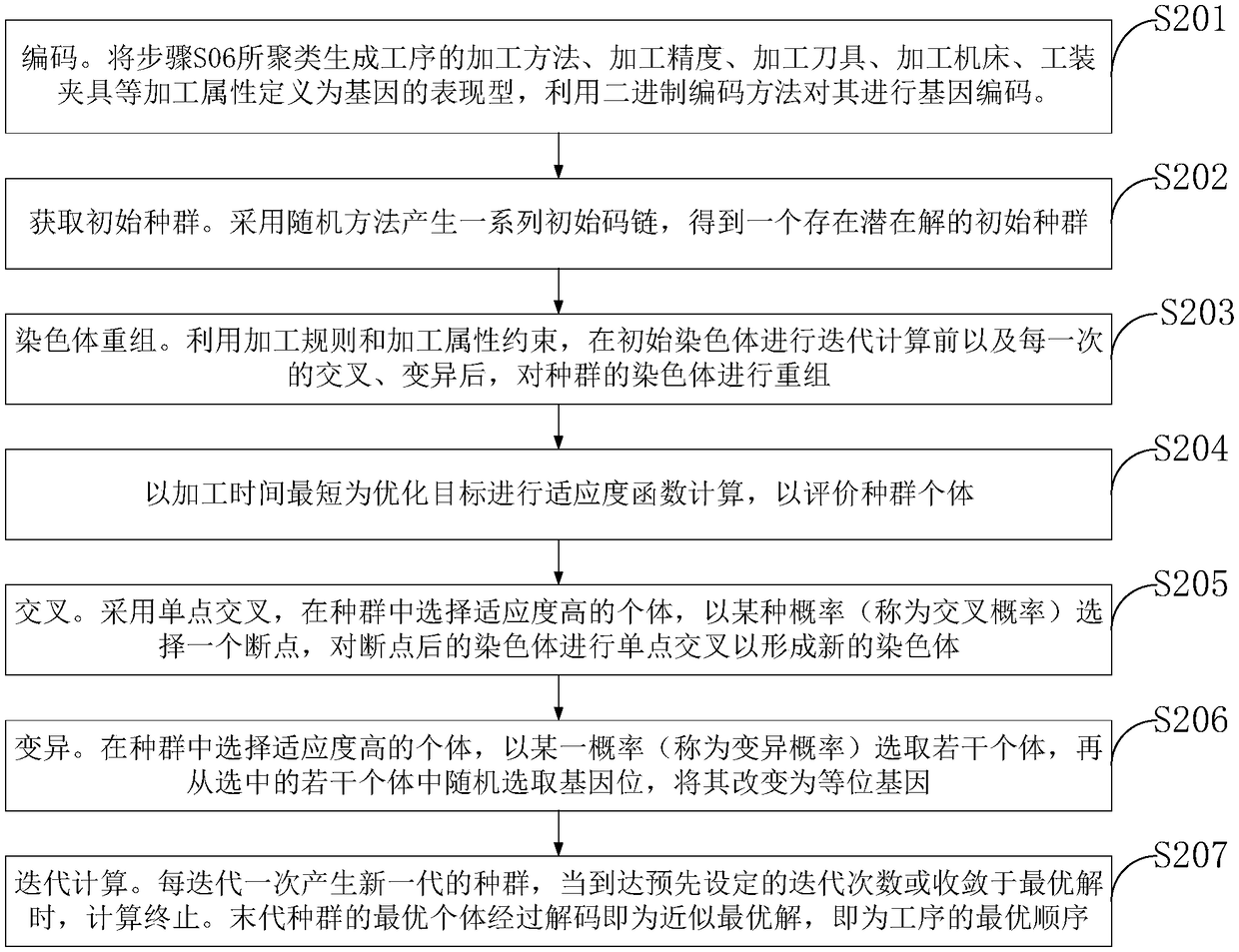

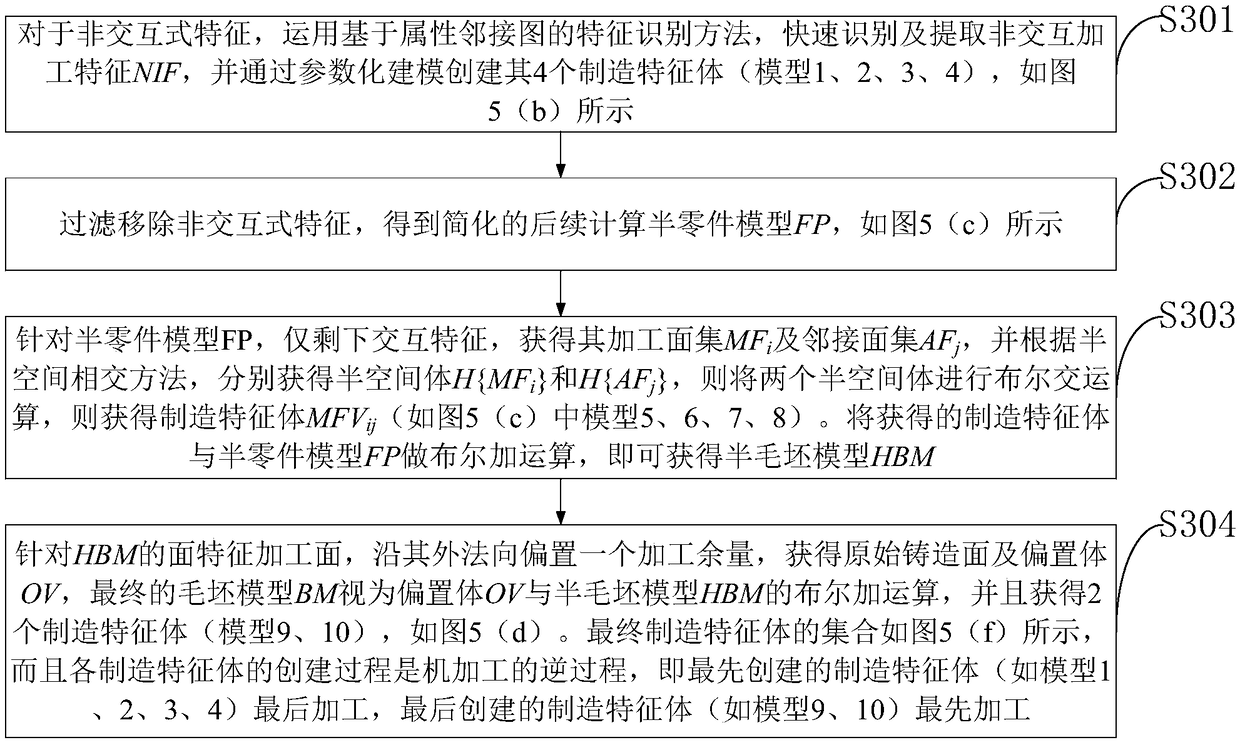

Three-dimensional process planning method and platform for typical automobile machined parts based on MBD

ActiveCN109117560ADesign specificationGuaranteed accuracyGeometric CADDesign optimisation/simulationMachine partsComputer-aided

The invention belongs to the technical field of computer-aided process planning, the invention discloses a three-dimensional process planning method and a platform for typical automobile machined parts based on MBD, based on 3D CAD software, with the MBD design model as the sole data input, the process MBD model is used as the data output, and the design process includes the establishment of MBD related standards, the creation of MBD design model, feature classification and feature database, feature recognition and information extraction, the generation of machining elements, the generation ofmachining elements clustering process, process sequencing, manufacturing features, the creation of process model and so on. The final application example of the present invention is in the case whereNX is used as a carrier, C + + and NXopen language, the invention can quickly generate a process MBD model which integrates a process model and a manufacturing feature body, can realize the visualization of the process design flow, improve the process design efficiency, and lays a foundation for the integration of CAD / CAPP / CAM. The invention can be used in the three-dimensional CAPP system developed by C + + and NXopen language.

Owner:WUHAN UNIV OF TECH

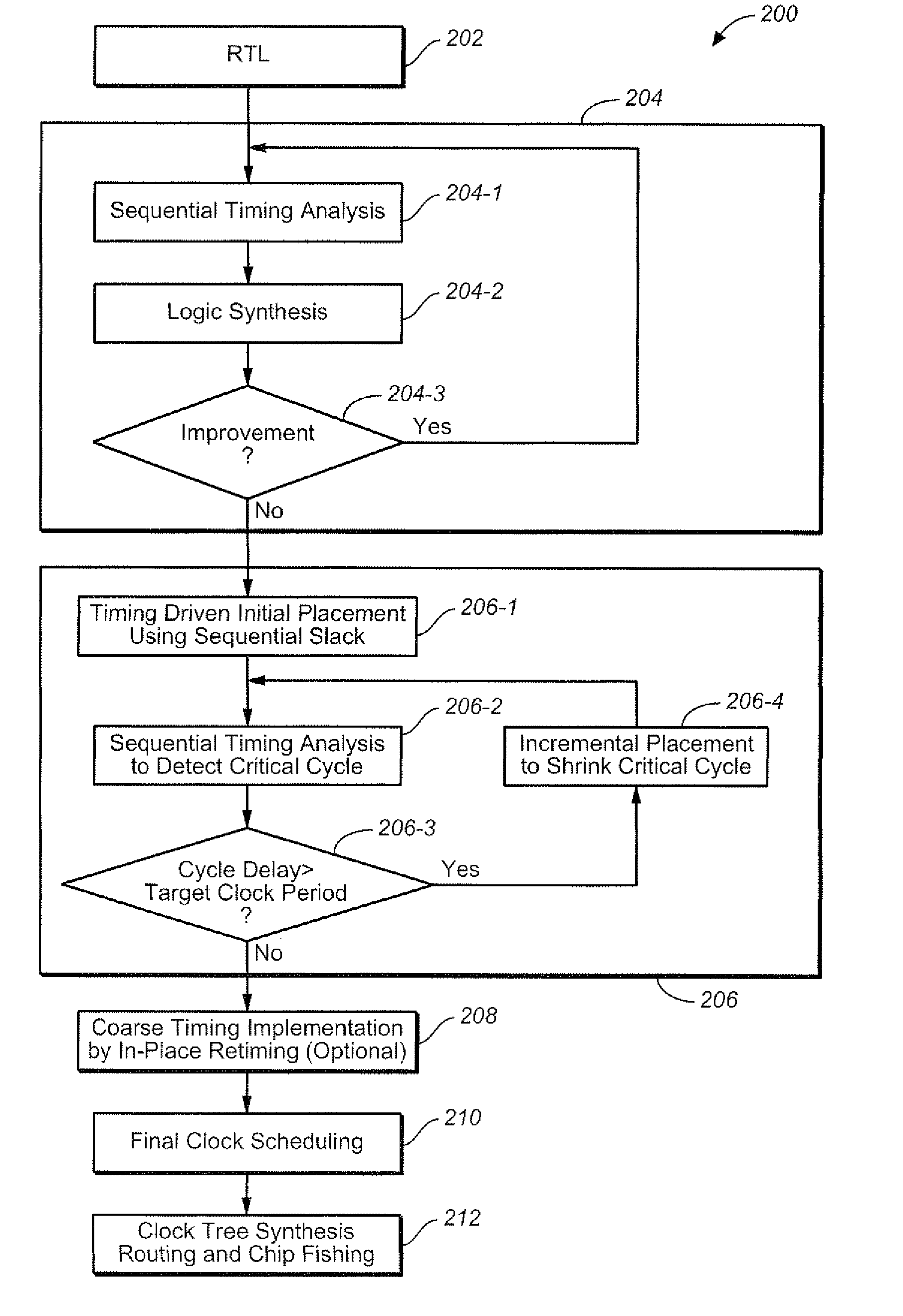

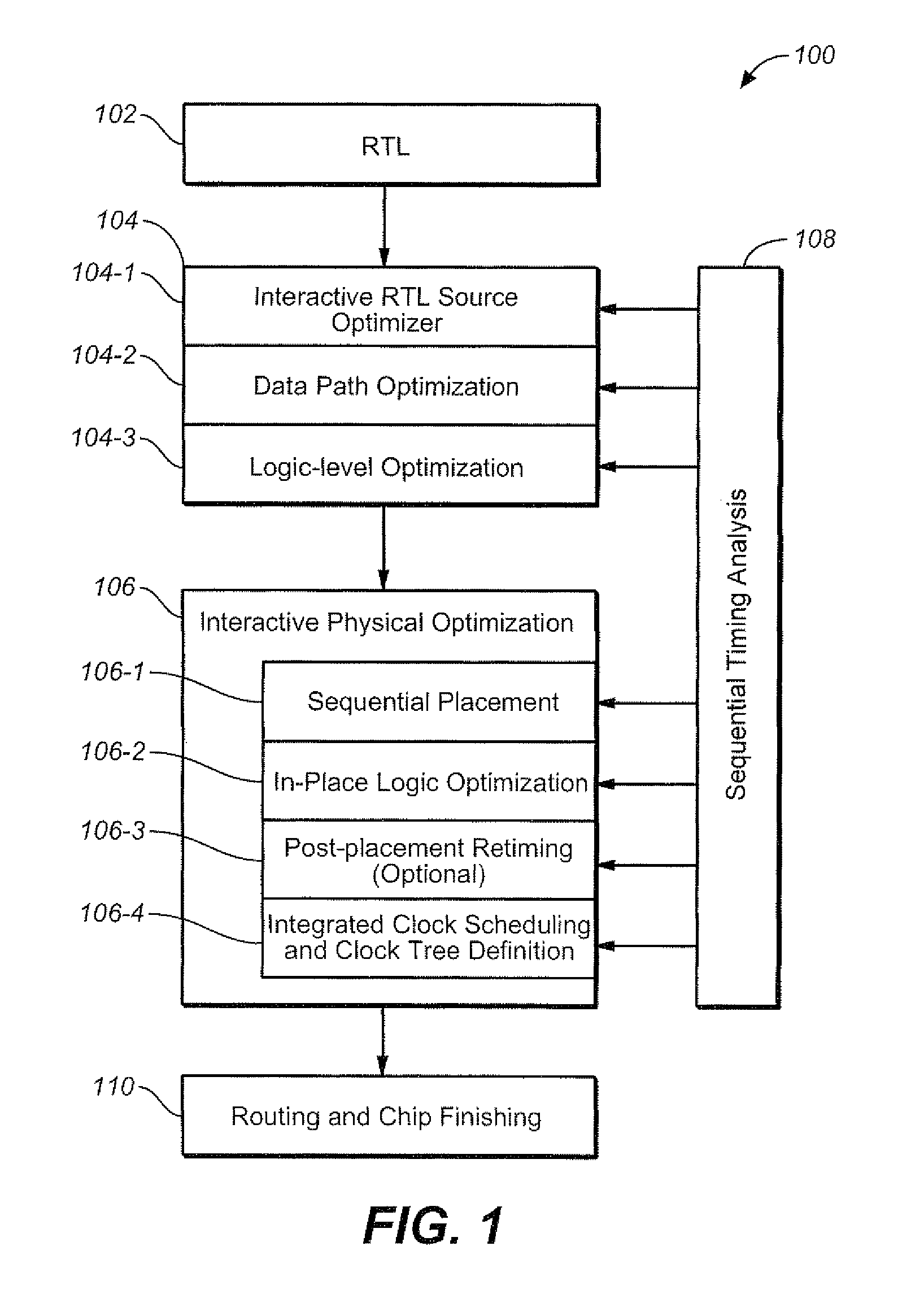

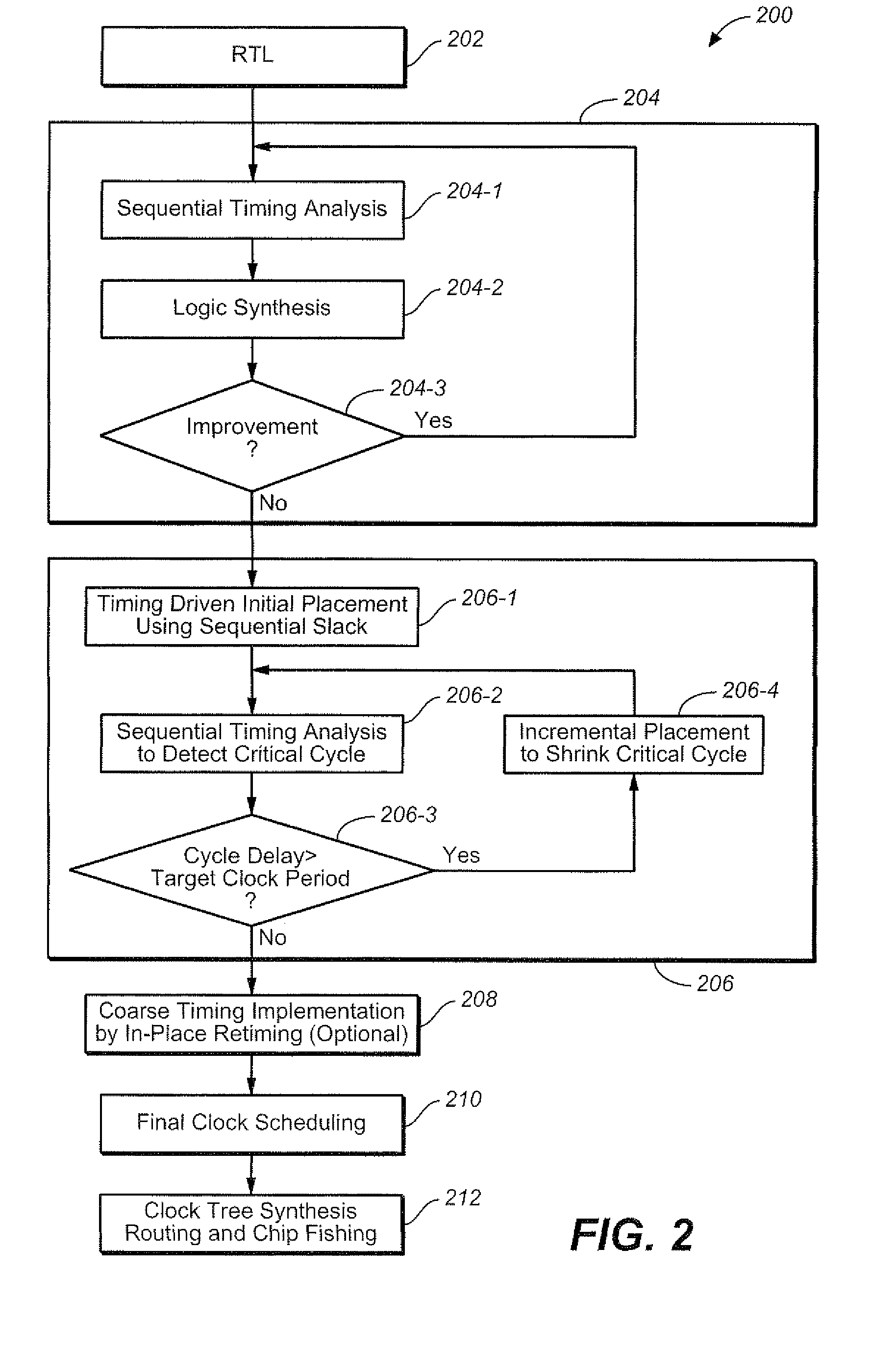

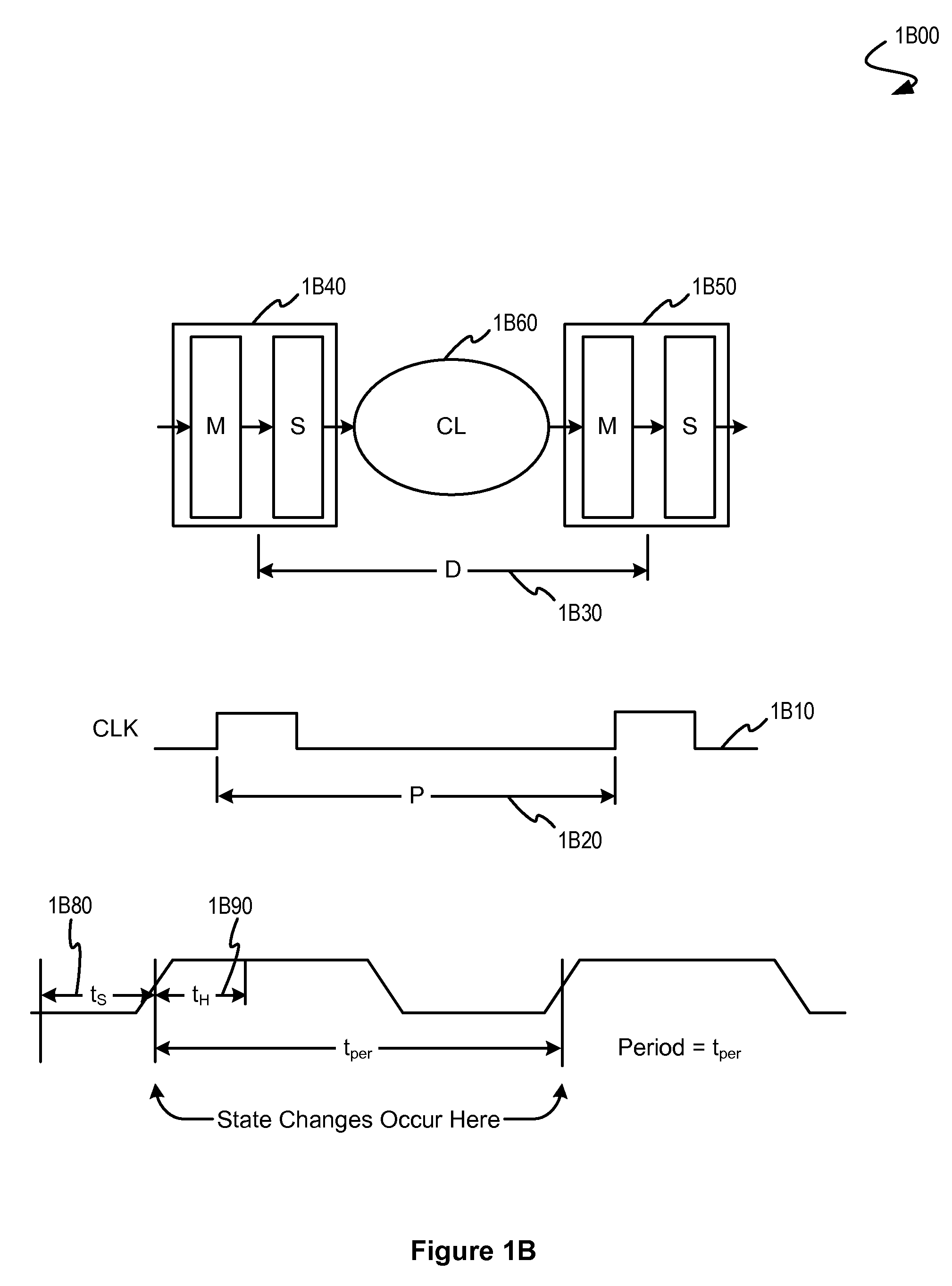

Optimizing integrated circuit design through use of sequential timing information

InactiveUS7743354B2Increase flexibilityEasy to implementCAD circuit designSoftware simulation/interpretation/emulationTiming marginMaximum latency

A method is provided that includes: determining a minimum clock cycle that can be used to propagate a signal about the critical cycle in a circuit design; wherein the critical cycle is a cycle in the design that has a highest proportionality of delay to number of registers; determining for a circuit element in the circuit design, sequential slack associated with the circuit element; wherein the sequential slack represents a minimum delay from among respective maximum delays that can be added to respective structural cycles of which the circuit element is a constituent, based upon the determined limit upon clock cycle duration; using the sequential slack to ascertain sequential optimization based design flexibility throughout multiple stages of a design flow.

Owner:CADENCE DESIGN SYST INC

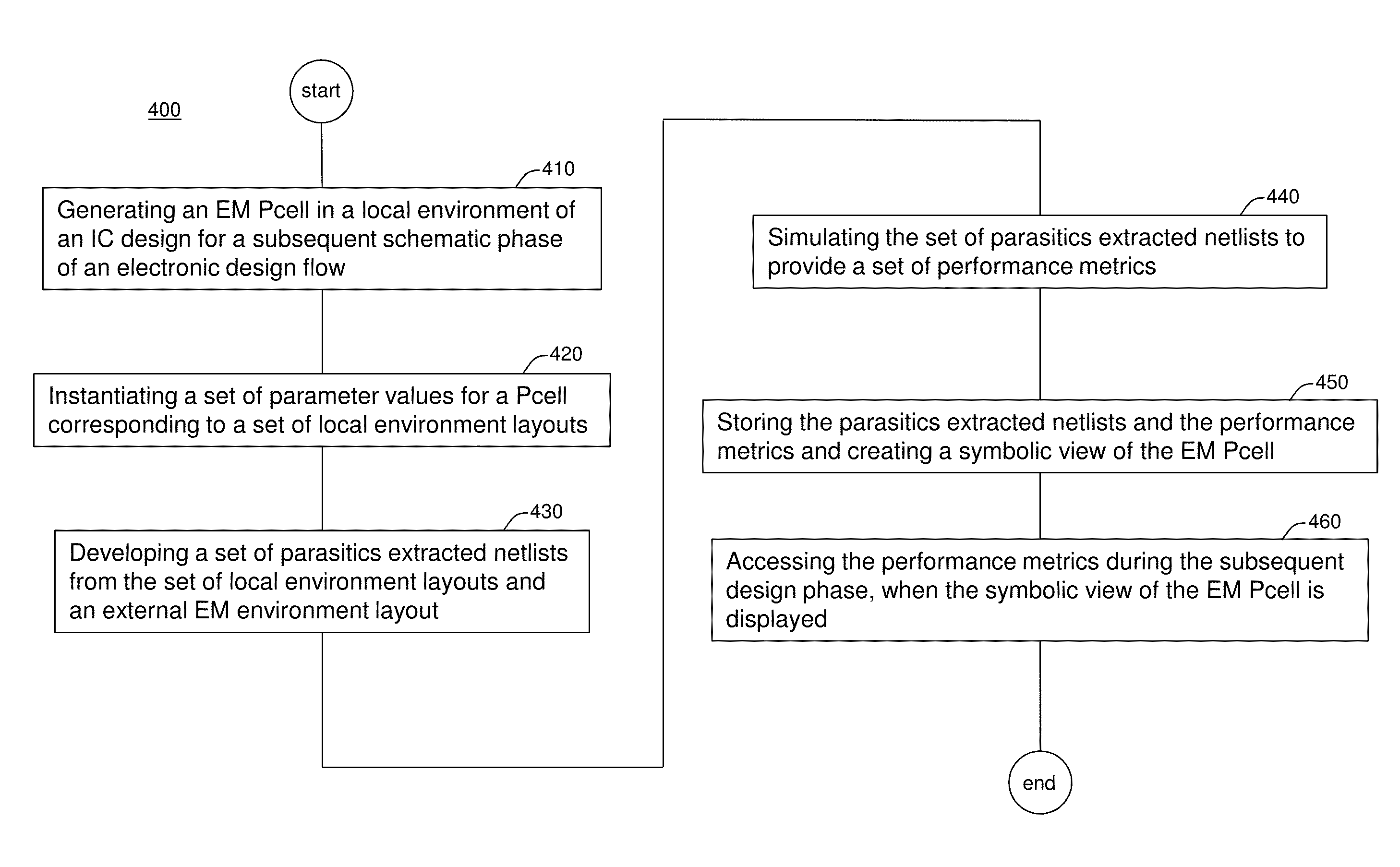

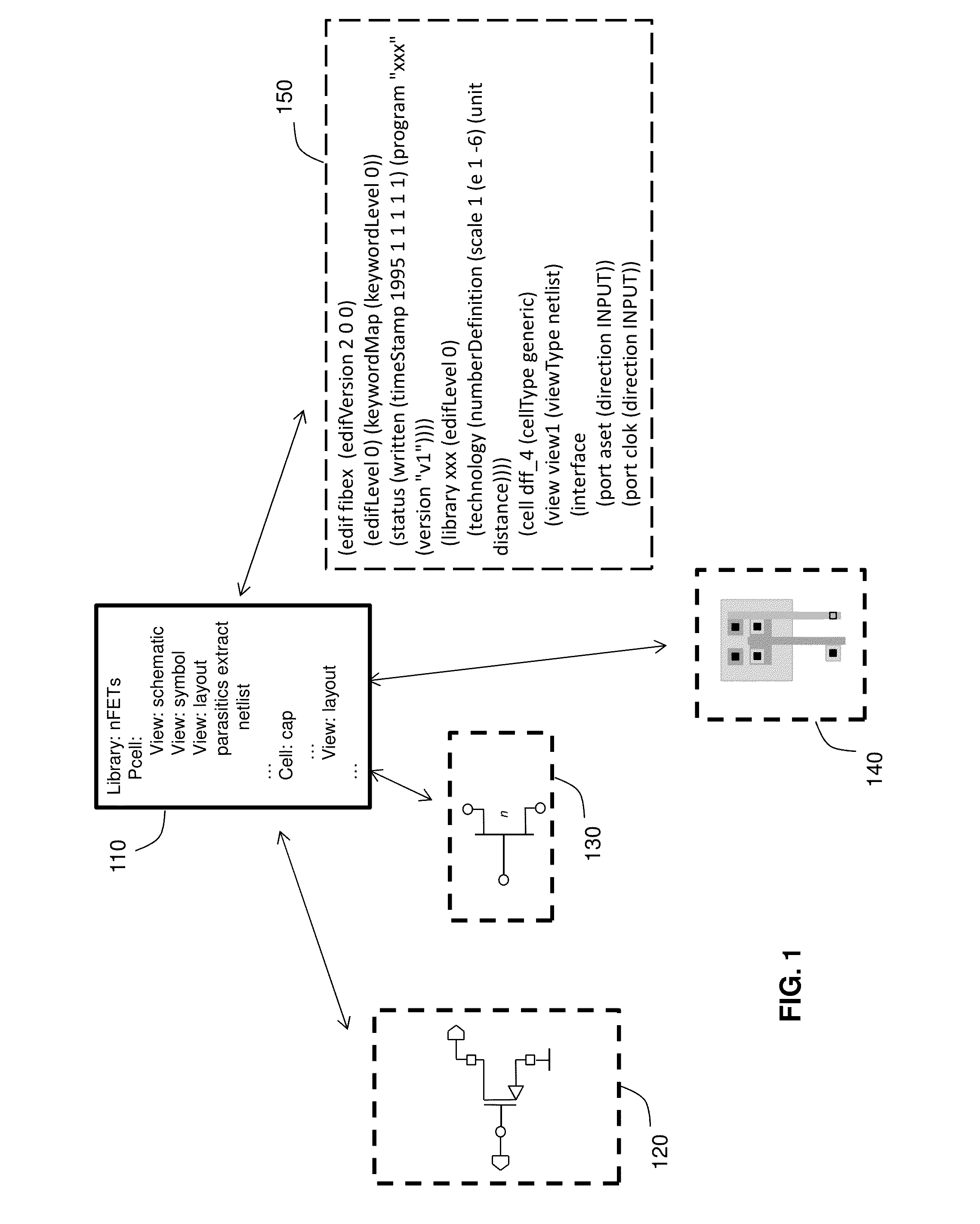

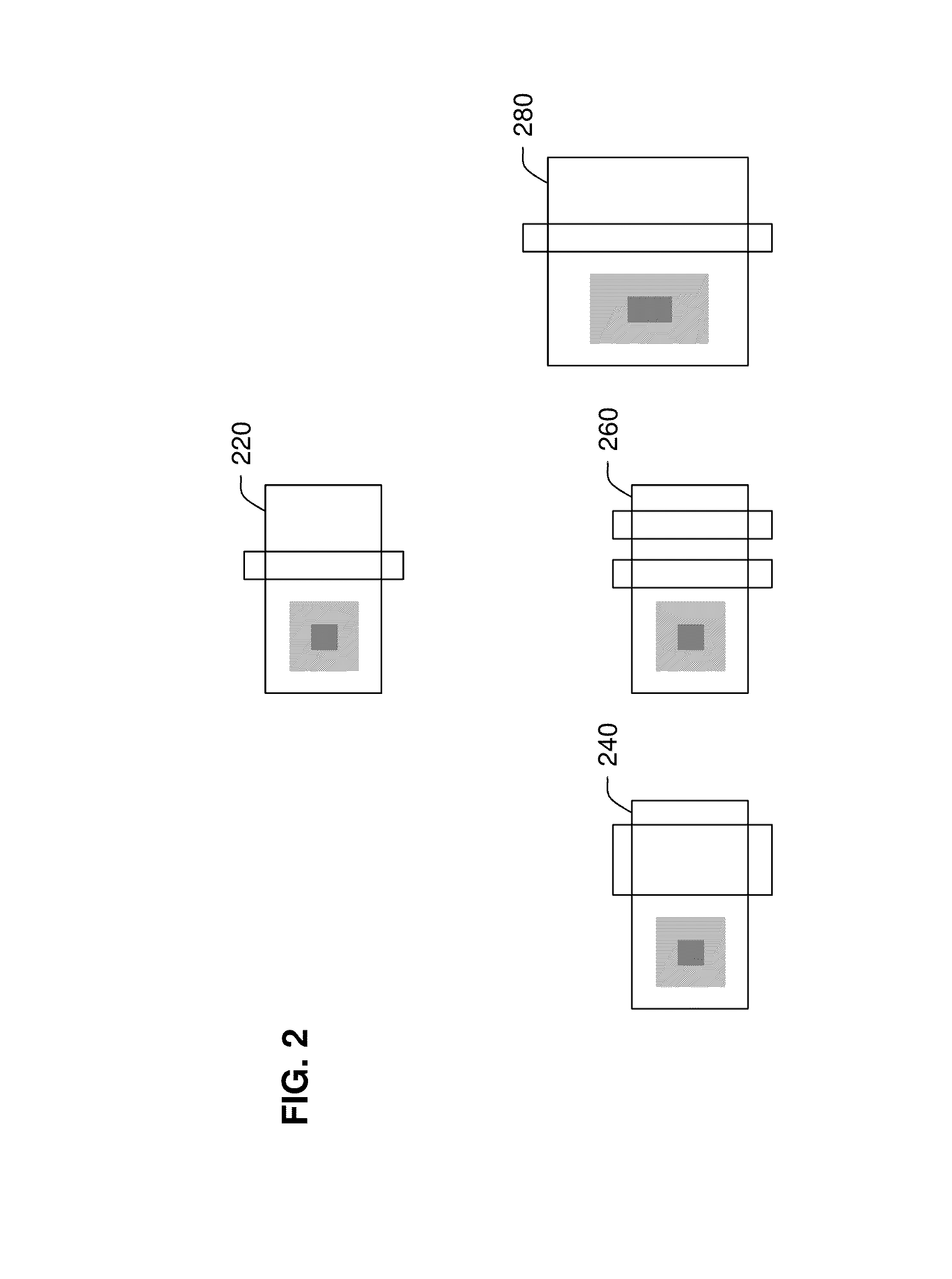

Generating an electromagnetic parameterized cell for an integrated circuit design

InactiveUS20160125115A1Improve accuracyImprove computing efficiencyDesign optimisation/simulationCAD circuit designParasitic extractionElectronic design

An electromagnetic parameterized cell (EM Pcell) is generated for a local environment of an integrated circuit (IC) design for an electronic design flow. A set of parasitics extracted netlists is developed from a set of Pcell layouts and an external EM environment. The parasitics extracted netlists are simulated to provide a set of performance metrics. When a symbolic view of the EM Pcell is displayed to a designer during a subsequent schematic phase of the design flow, the performance metrics are accessed from a design library, to increase accuracy of parameter value selection for the EM Pcell without a parasitics extraction of the physical layout and generation of a parasitics extracted netlist.

Owner:GLOBALFOUNDRIES INC

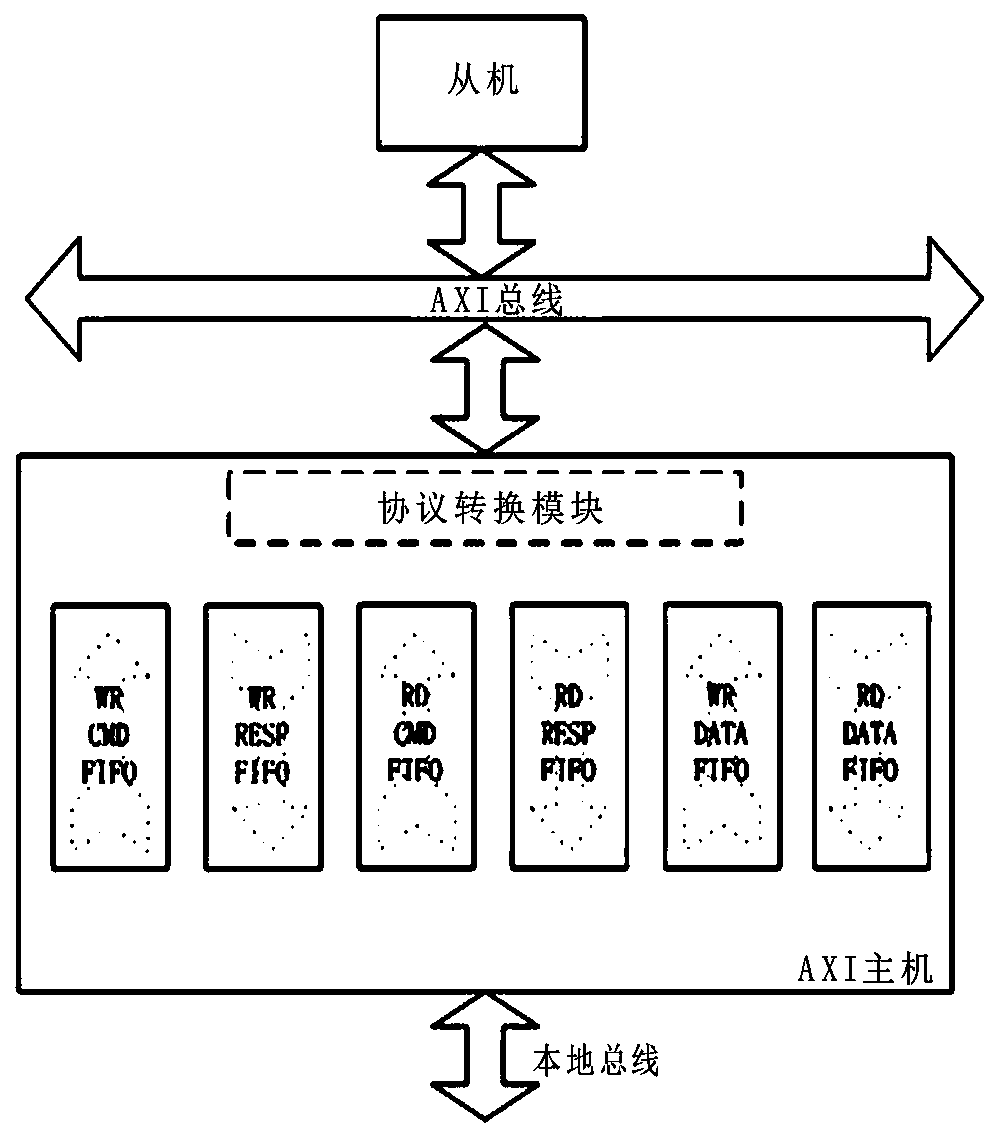

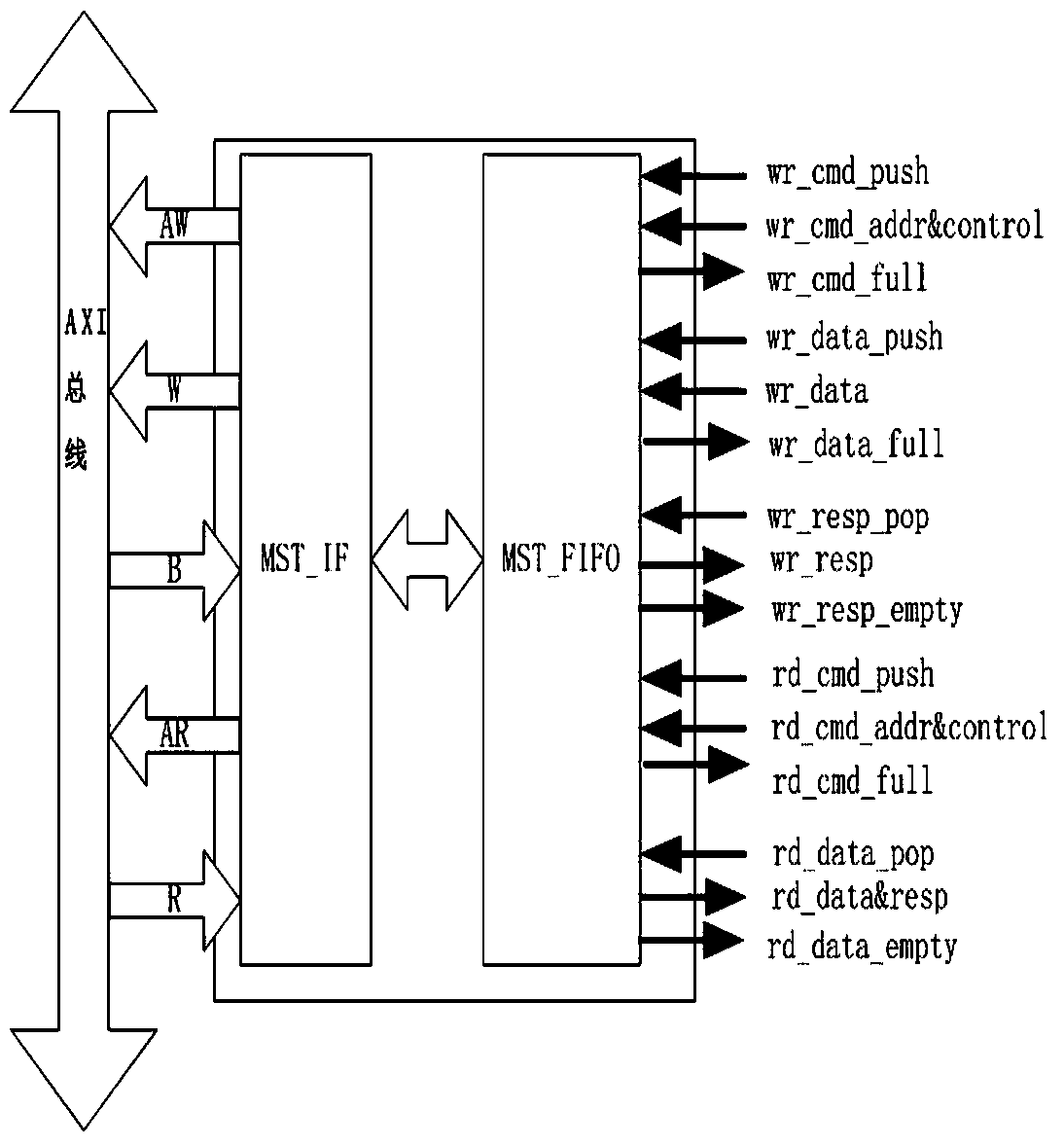

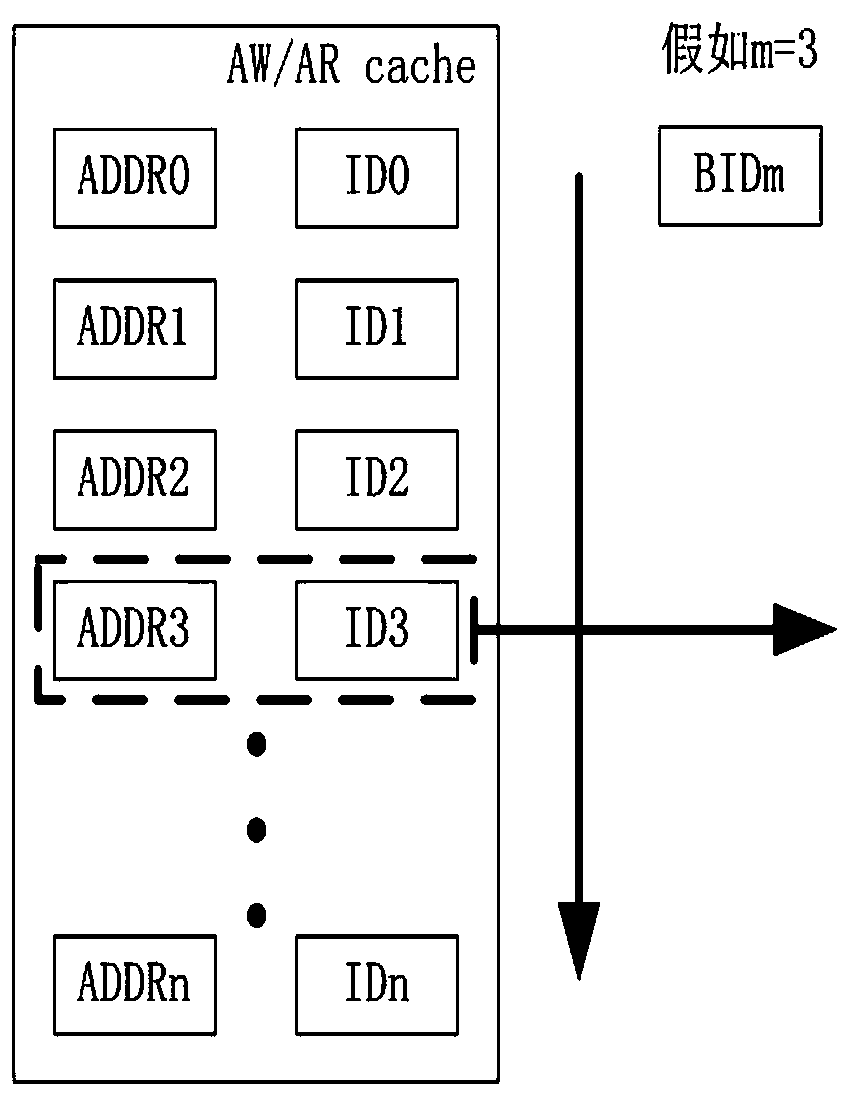

Host equipment data transmission extension method based on AXI bus

InactiveCN110704351ASimplify the design processGuaranteed independenceElectric digital data processingHigh bandwidthDesign flow

The invention discloses a host equipment data transmission extension method based on an AXI bus. The host equipment data transmission extension method is characterized in that a protocol conversion module is added between an AXI bus and an FIFO interface bus of host equipment; the protocol conversion module comprises an MST_FIFO module and an MST_IF module; the MST_IF module receives a read-writeaddress, a read-write length and a control command from the AXI interface; the MST_FIFO comprises five independent FIFOs which respectively correspond to five independent channels of a write command,a write data, a write response, a read command and a read data of an AXI bus; and the five independent FIFOs receive or send the five independent channels to host equipment. According to the host equipment data transmission extension method, the protocol conversion of the AXI signal and the FIFO signal is realized through the protocol conversion module, so that the self-research module does not need to accord with the AXI protocol any more, and the design flow of the self-research module is simplified, and the independence of each channel of the AXI protocol and the characteristics of high performance, and high bandwidth and low delay of the protocol are maintained.

Owner:SHANDONG SINOCHIP SEMICON

Integrated Circuit Chip Design Flow Methodology Including Insertion of On-Chip or Scribe Line Wireless Process Monitoring and Feedback Circuitry

ActiveUS20090239313A1Semiconductor/solid-state device testing/measurementDetecting faulty computer hardwareEngineeringFeedback circuits

Disclosed are embodiments of a design and manufacturing system and an associated method that allow for design analysis and for insertion, during wafer manufacture, of intra-process monitoring circuitry. These embodiments use a library of pre-qualified intra-process monitoring circuits and a cross-correlation table that links different monitoring circuits with different IC chip components. Specifically, these embodiments analyze integrated circuit chip design data to identify the components designed into the chip. Then, one or more intra-process monitoring circuits are selected from the library and the design data is modified to include the selected monitoring circuit(s).

Owner:MARVELL ASIA PTE LTD

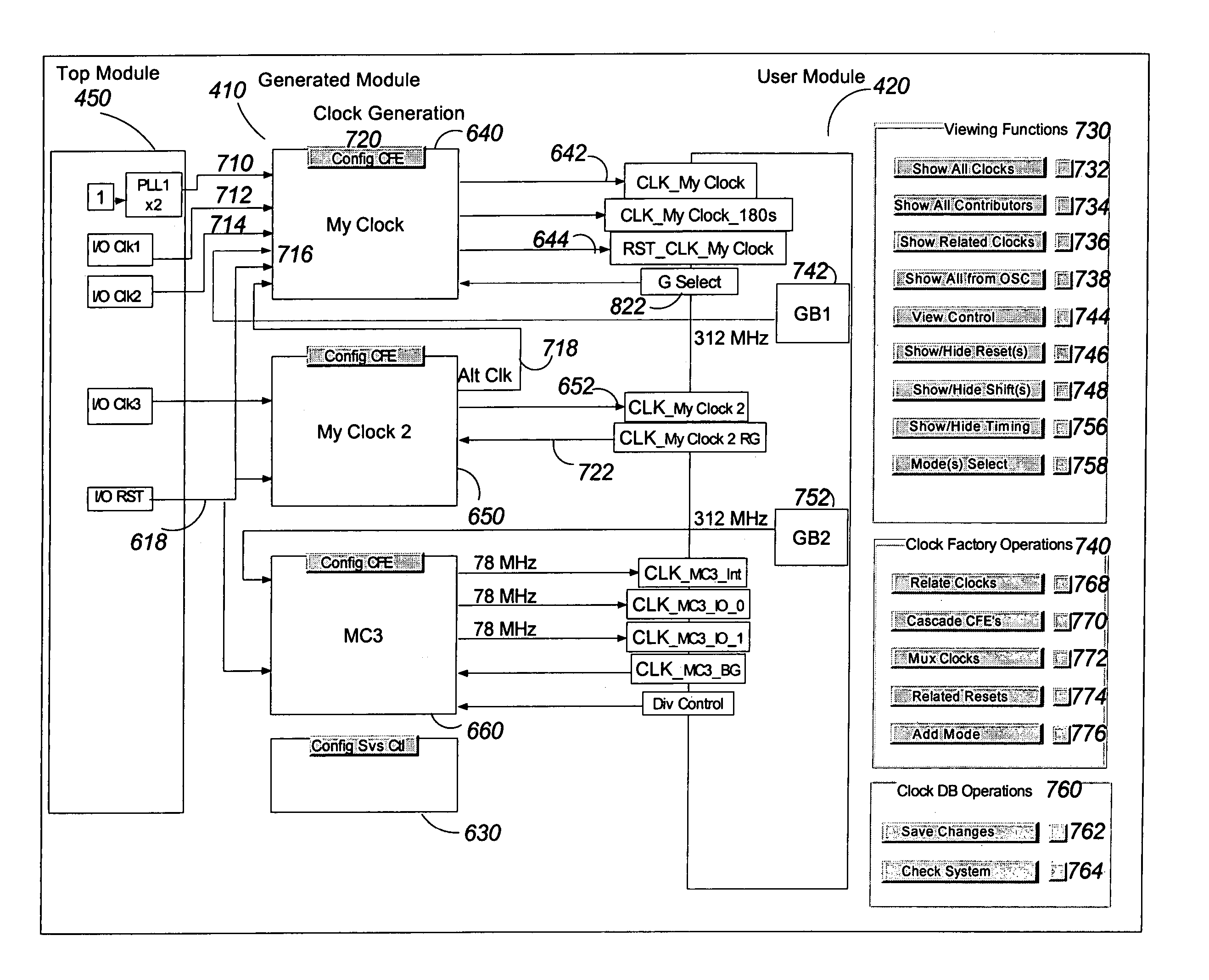

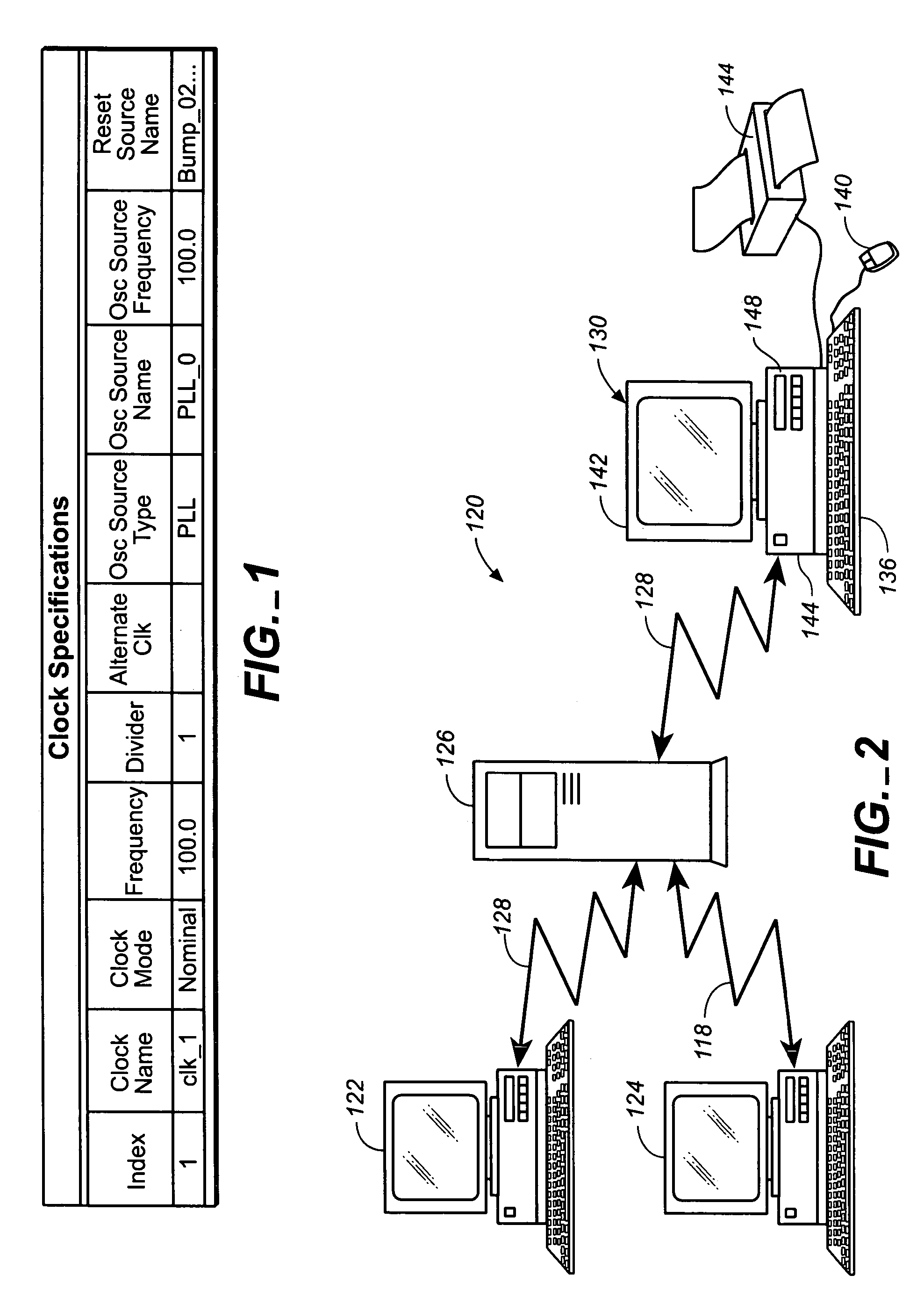

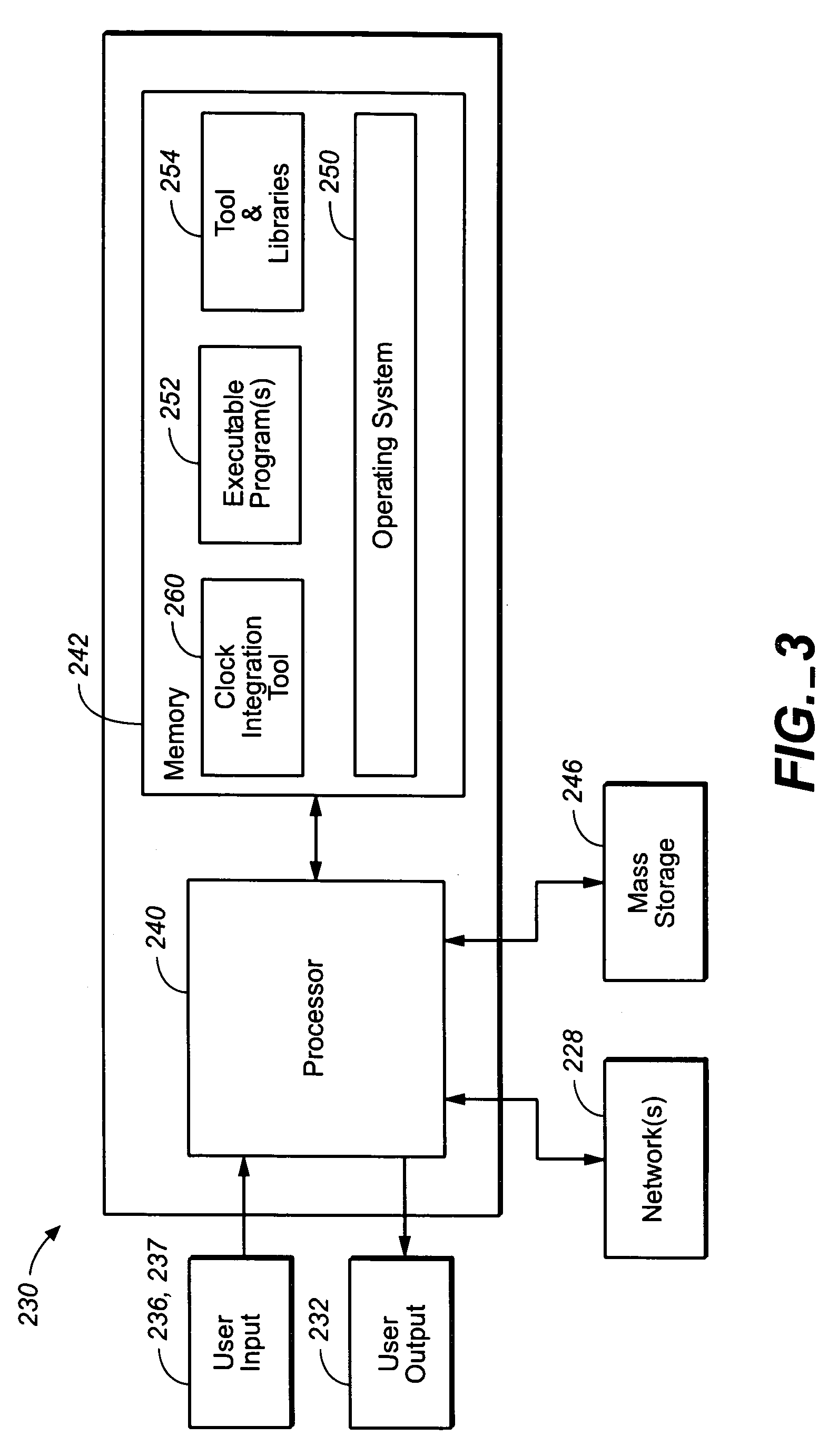

Guided capture, creation, and seamless integration with scalable complexity of a clock specification into a design flow of an integrated circuit

InactiveUS7290224B2Generating/distributing signalsExecution for user interfacesMultiple contextComputer architecture

A method and tool that capture, create, and integrate a clock specification to achieve a correct-by-construction design flow of a semiconductor product from a partially manufactured semiconductor platform. The clocking elements of the design flow are combined and displayed in a plurality of context-driven views. Within each view, details of the clock specification are presented in the context of the information. A user may zoom in / out through the plurality of views of the design flow for more or less detailed information. Each view can combine the logical, structural, architectural, cost, timing, and other features of the clock in a particular context. A user can zoom in to select and manipulate circuit elements. The user can then zoom out and the present invention determines how changes affect other clocks in the same or other modules and / or the same clock in other modules.

Owner:BELL SEMICON LLC

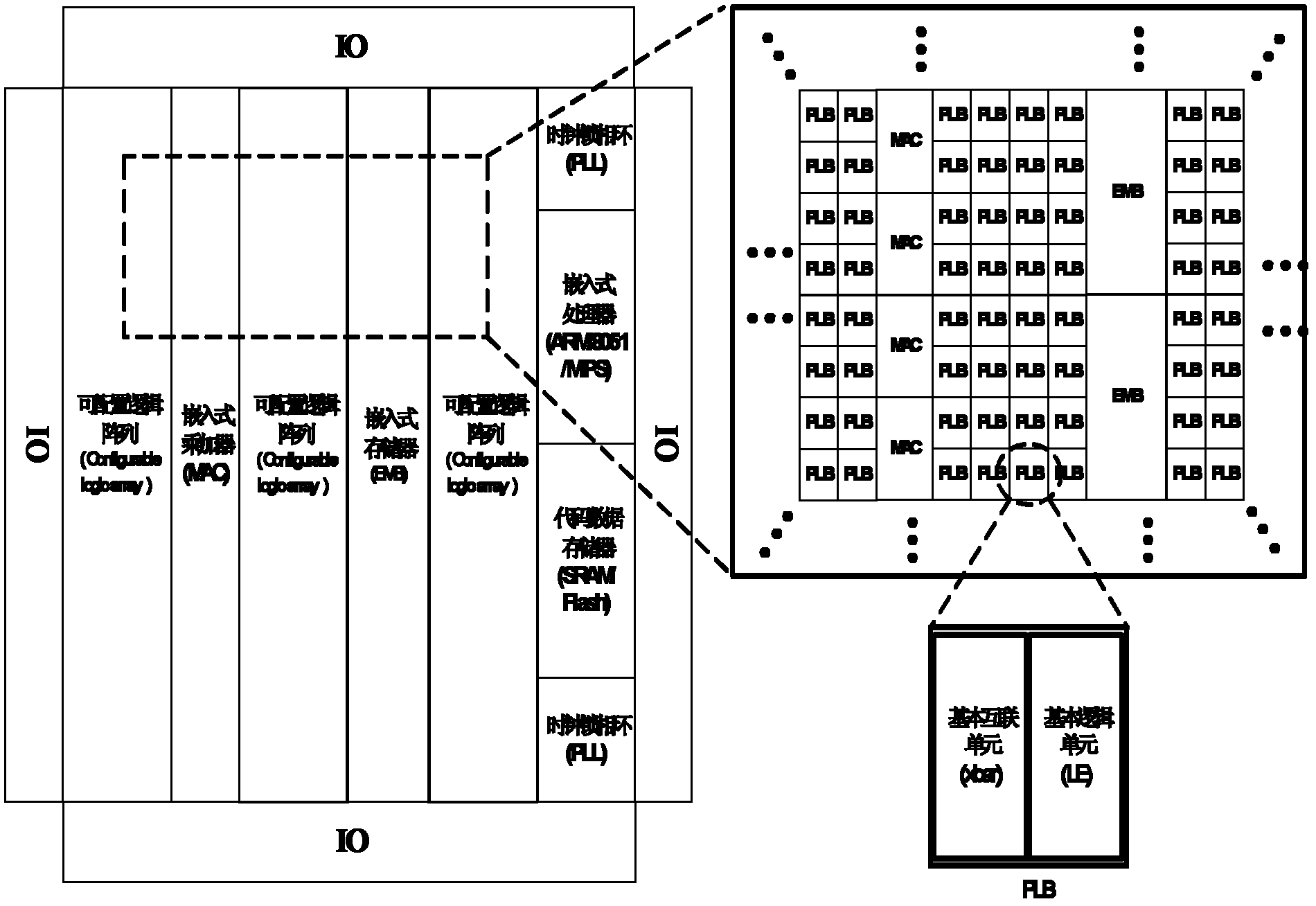

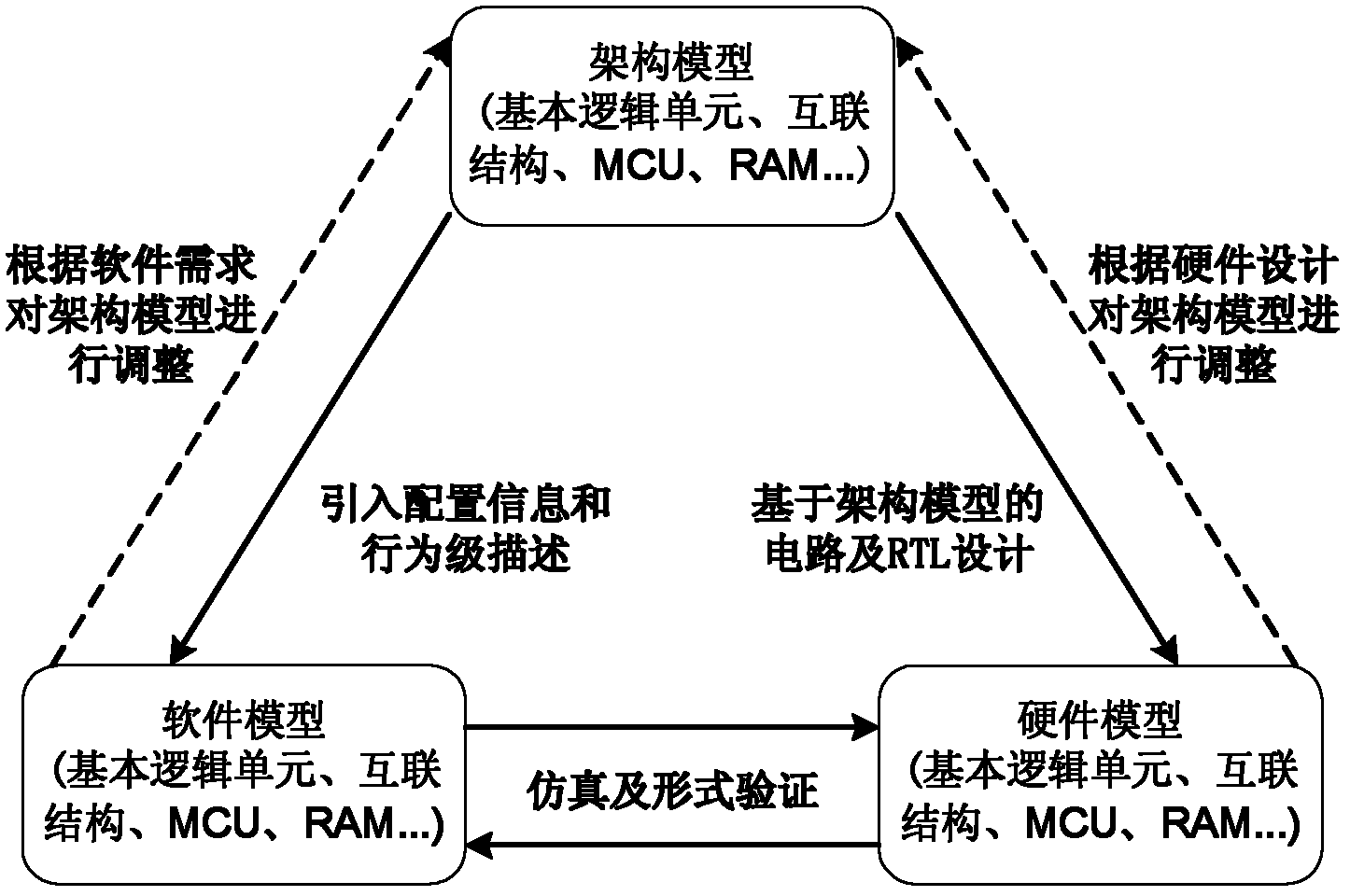

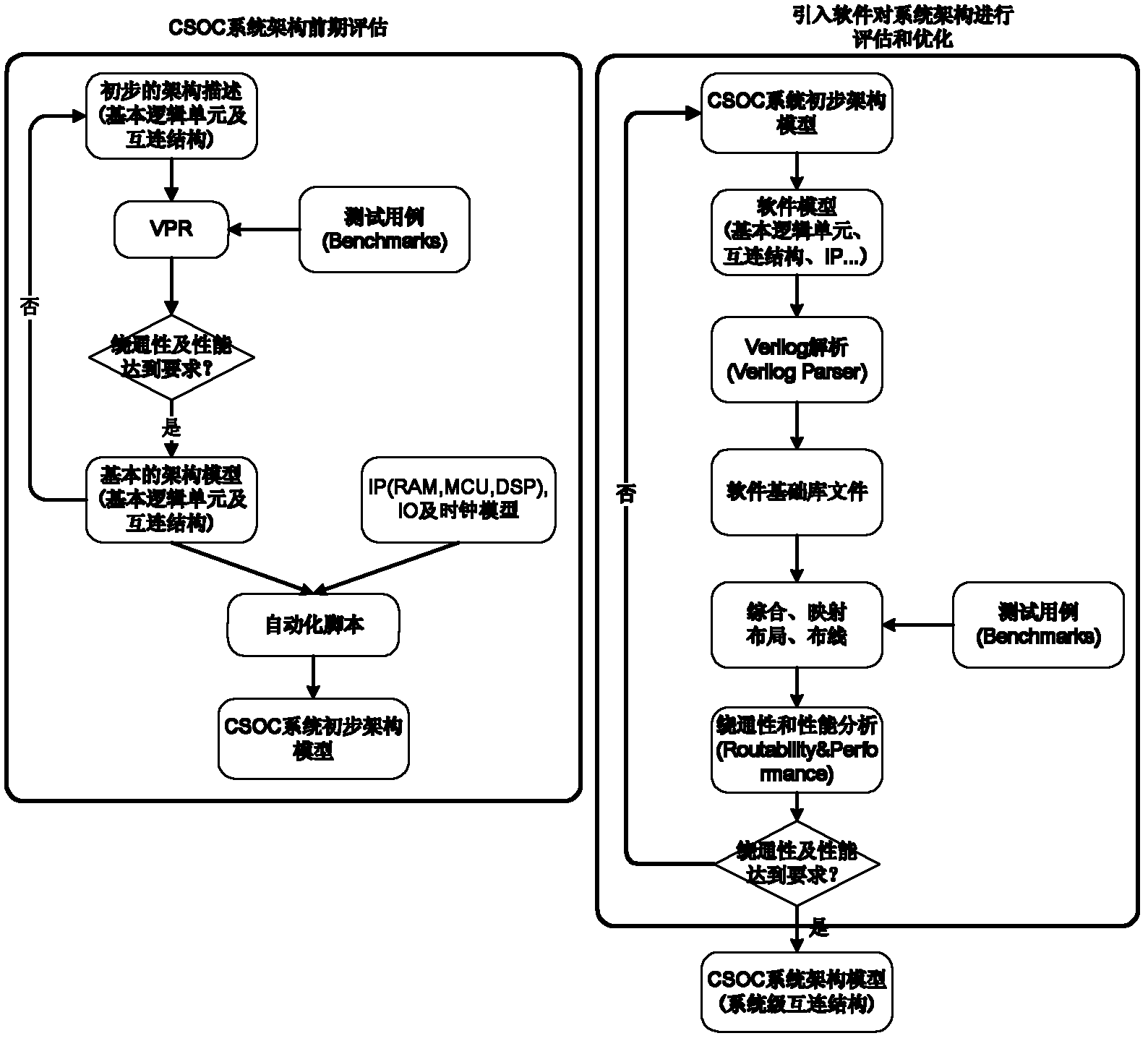

Method for keeping architecture, software and hardware conforming in configurable chip operating system

ActiveCN103258067AEnsure consistencySpecial data processing applicationsHardware description languageData architecture

The invention provides a method for keeping architecture, software and hardware conforming in a configurable chip operating system. The method includes steps of describing an architecture model of a CSOC (configurable system on chip) system by hardware description language; describing a software model on the basis of the architecture model through configuration parameters and behavioral level description by hardware description language; and describing a hardware model on the basis of the architecture model by the hardware description language. By the method for keeping architecture, software and hardware conforming in the configurable chip operating system, design process of the CSOC system can be greatly simplified, and a great quantity of repeated work can be reduced.

Owner:CAPITAL MICROELECTRONICS

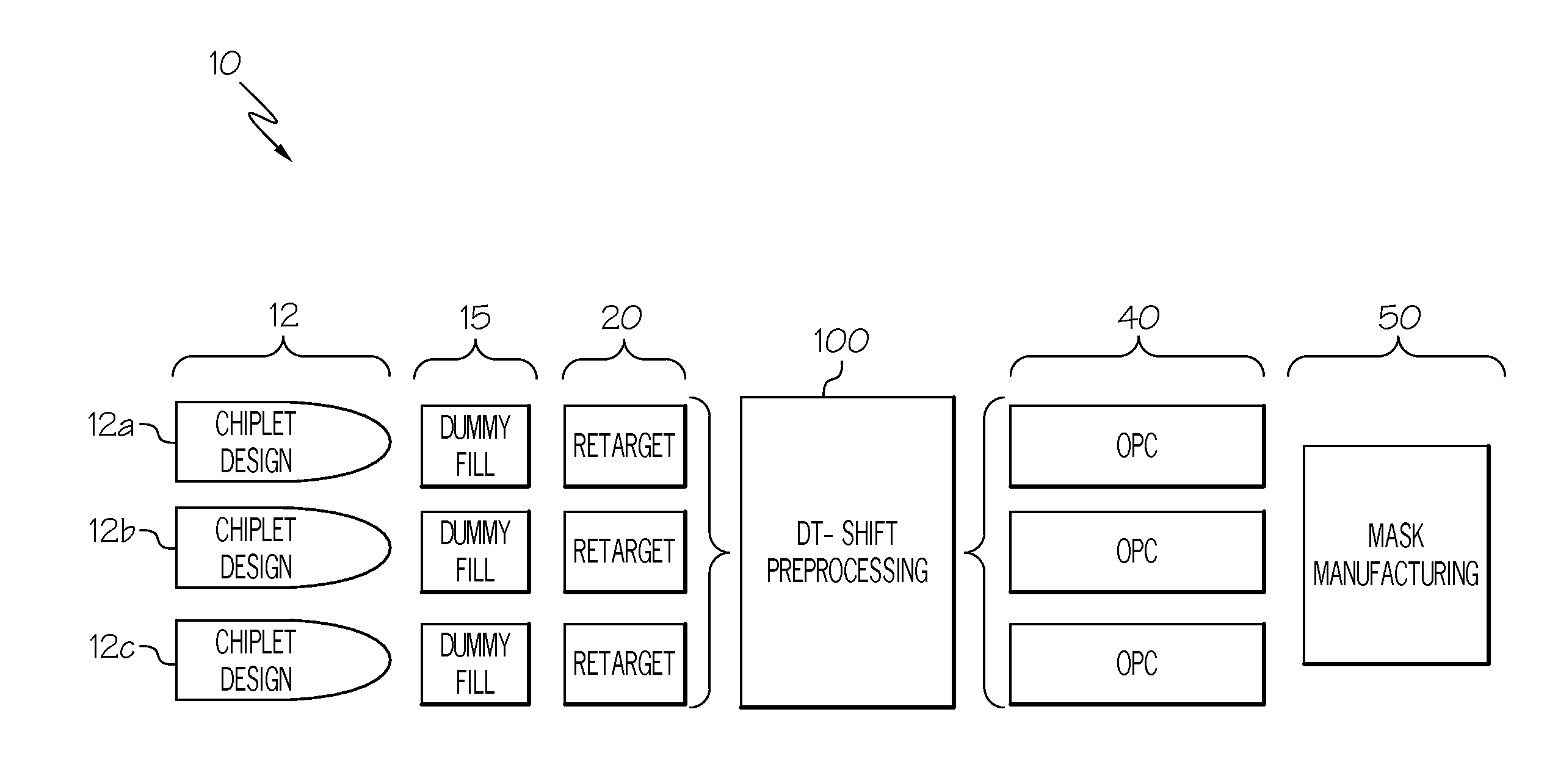

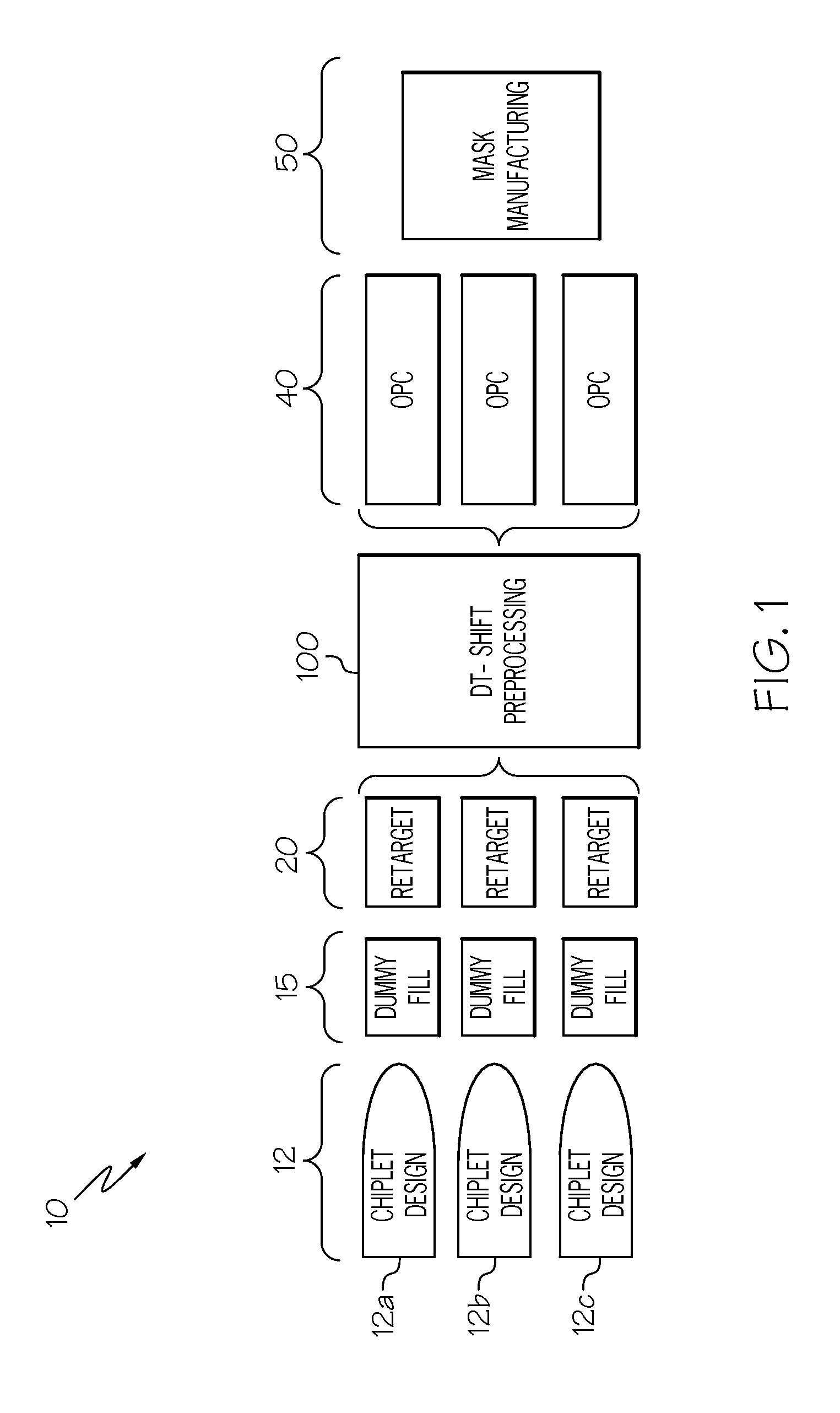

Correcting for stress induced pattern shifts in semiconductor manufacturing

ActiveUS20150363536A1Reduce overlay errorSolid-state devicesPhotomechanical apparatusData setField data

Apparatus, method and computer program product for reducing overlay errors during a semiconductor photolithographic mask design process flow. The method obtains data representing density characteristics of a photo mask layout design; predicts stress induced displacements based on said obtained density characteristics data; and corrects the mask layout design data by specifying shift movement of individual photo mask design shapes to pre-compensate for predicted displacements. To obtain data representing density characteristics, the method merges pieces of data that are combined to make a photo mask to obtain a full reticle field data set. The merge includes a merge of data representing density characteristic driven stress effects. The density characteristics data for the merged reticle data are then computed. To predict stress-induced displacements, the method inputs said density characteristics data into a programmed model that predicts displacements as a function of density, and outputs the predicted shift data.

Owner:GLOBALFOUNDRIES US INC

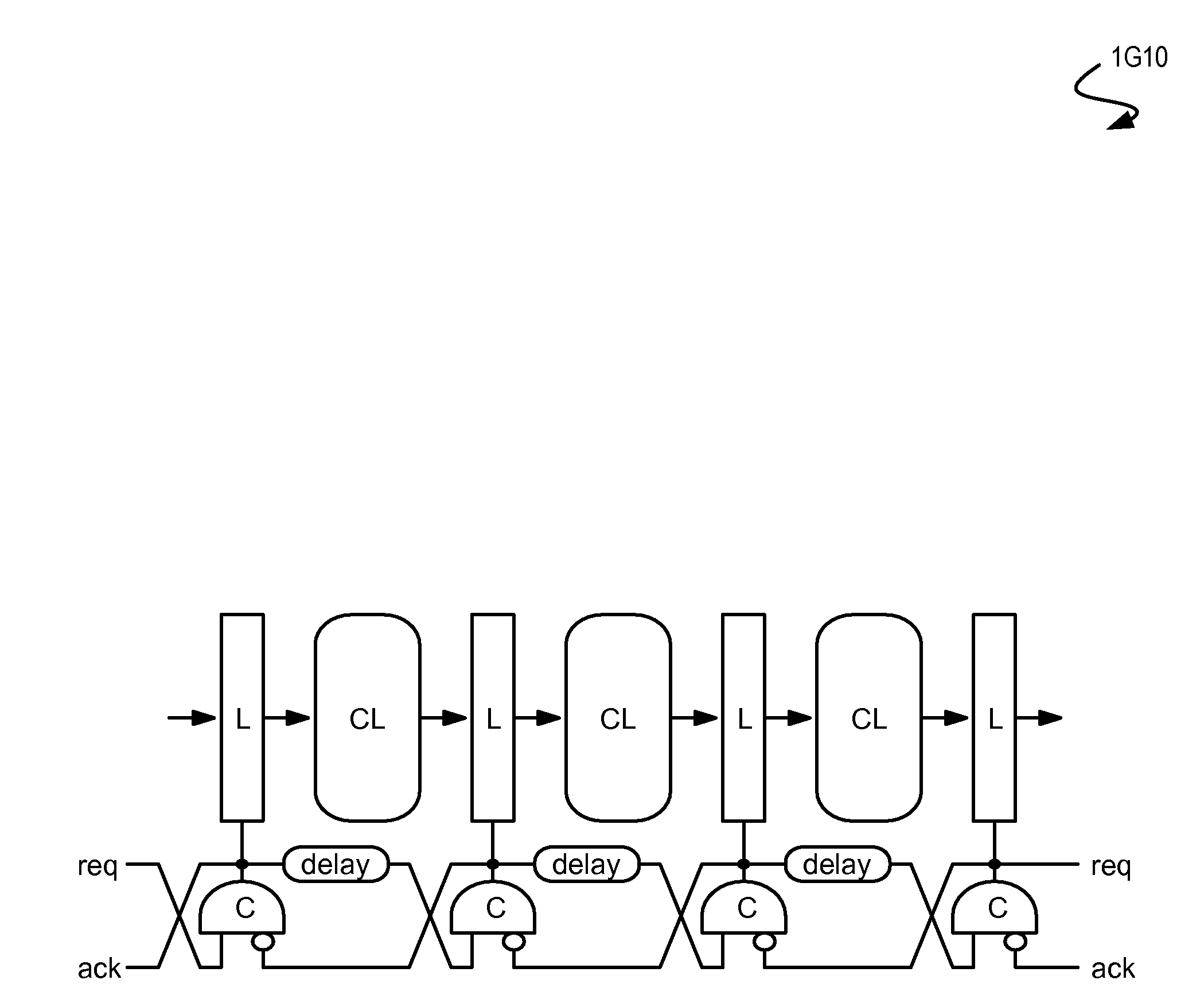

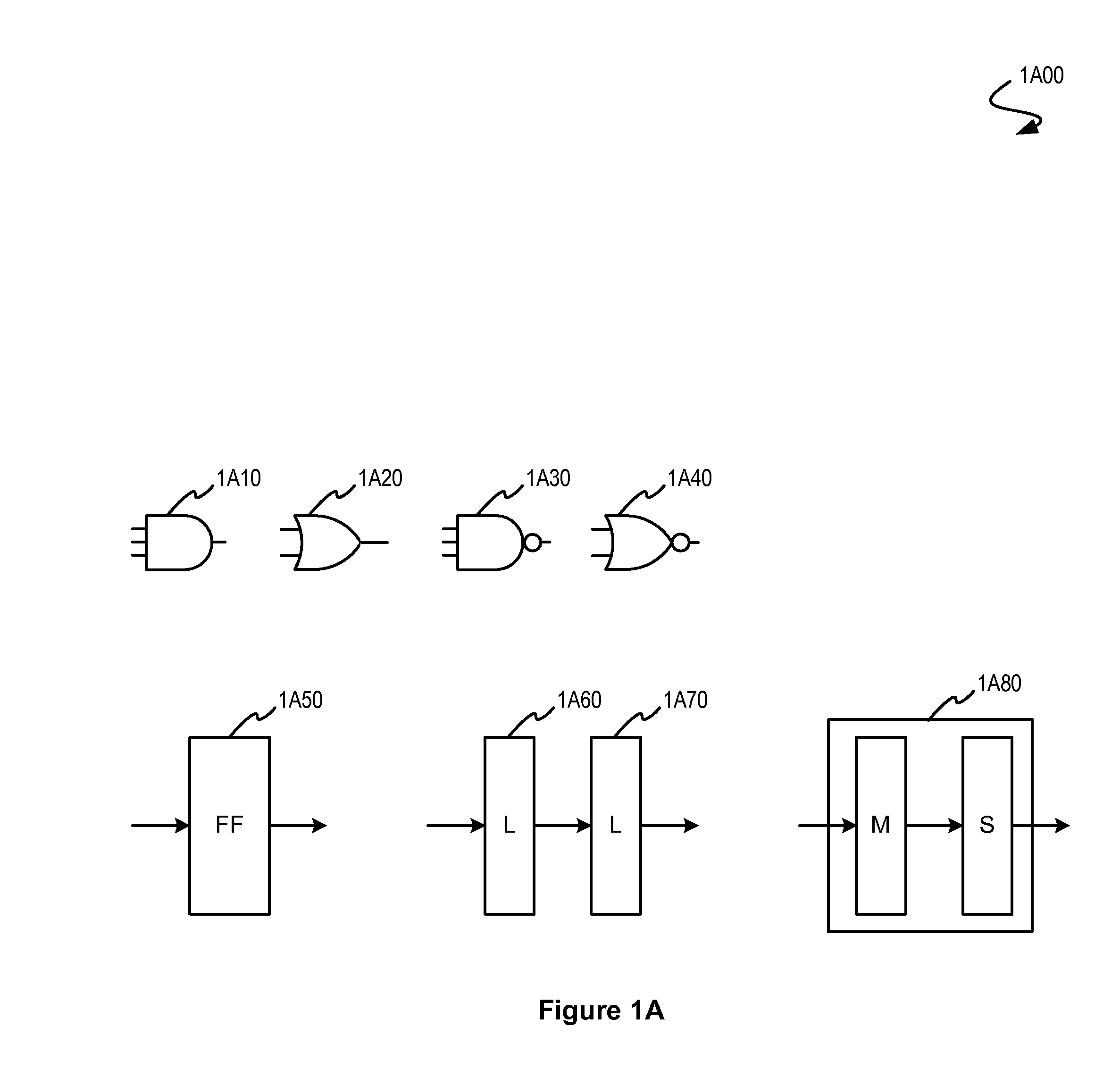

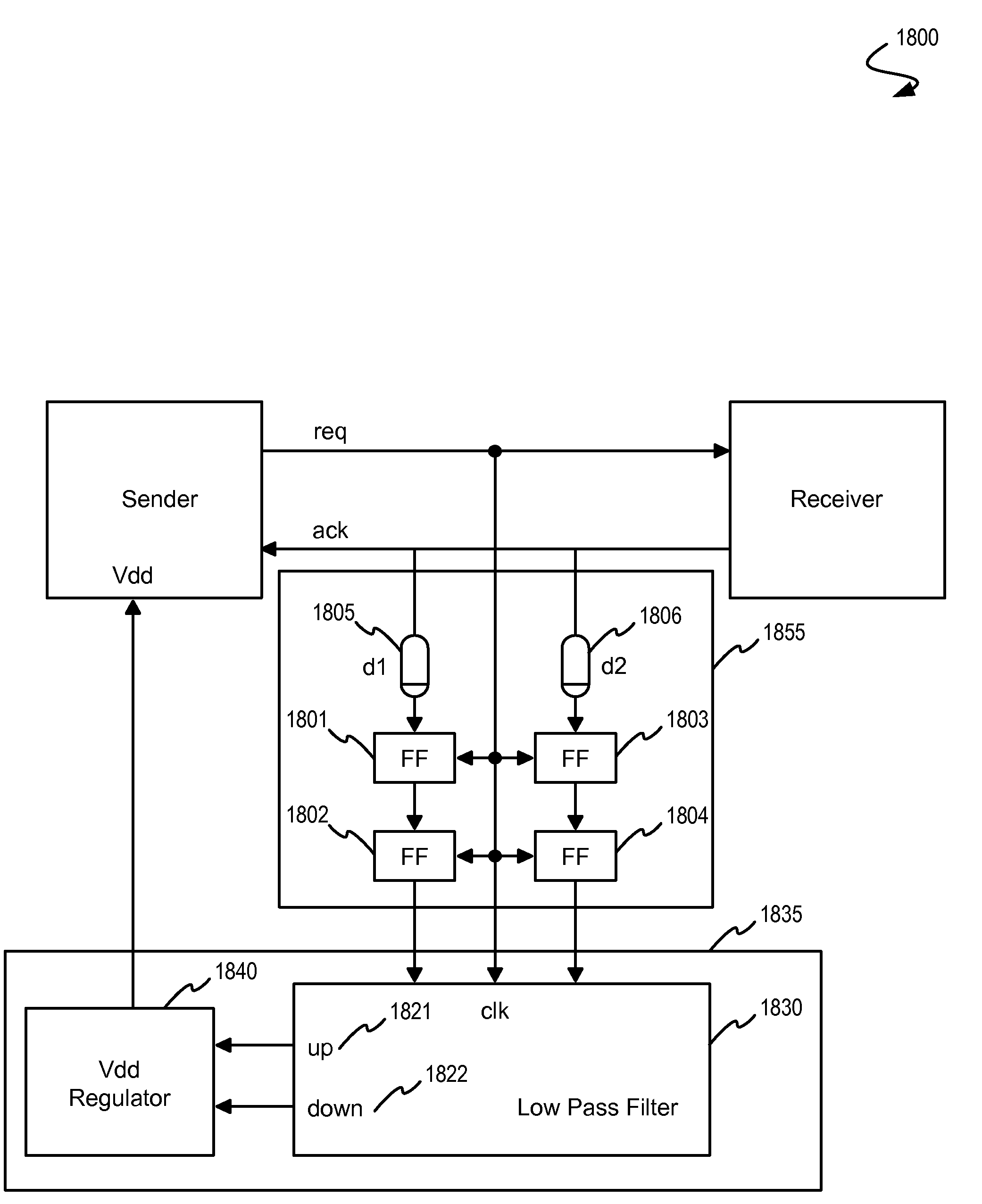

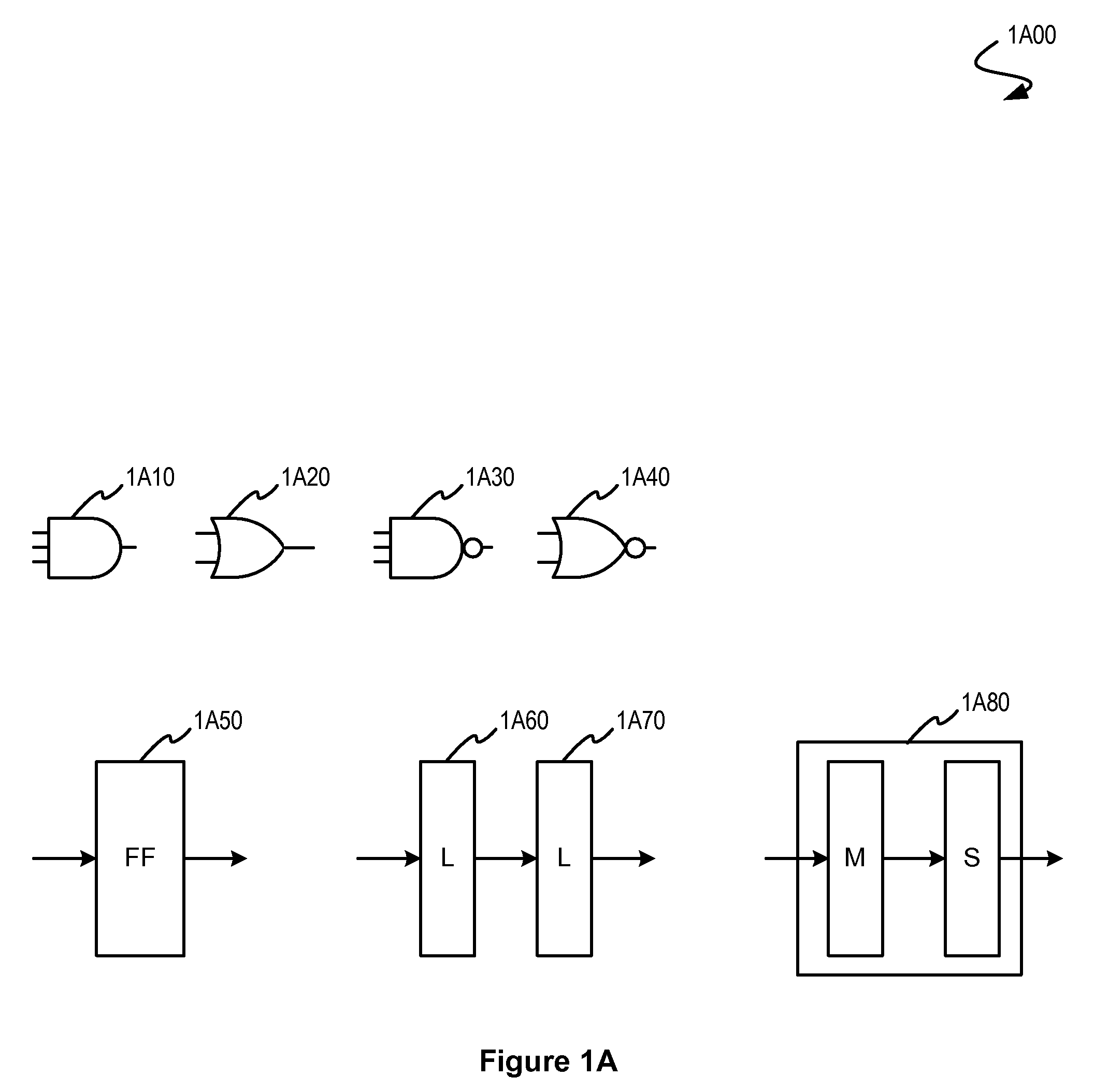

Variability-Aware Asynchronous Scheme for High-Performance Communication Between an Asynchronous Circuit and a Synchronous Circuit

InactiveUS20090116597A1Logic circuits characterised by logic functionPulse automatic controlAsynchronous circuitHigh performance communication

A system for automatically transforming a given synchronous circuit description into an equivalent and provably correct desynchronized circuit description. Included in the automated transformation are techniques for synthesizing a variability-aware controller using a two-phase protocol, techniques for synthesizing a variability-aware controller using gated clocks and testability circuits, techniques for synthesizing a variability-aware controller optimized for performance, techniques for initializing the synthesized controller, techniques for dynamically minimizing power requirements, and techniques for interfacing the desynchronized circuit with external synchronous circuits. Also disclosed are techniques for implementing a system for automatically transforming a synchronous circuit description into an equivalent and provably correct desynchronized circuit description within the context of an electronic design automation design flow. Exemplary circuits used in the application of the aforementioned techniques are provided. Application of mathematical models and techniques used for proving equivalence between the input description and the resulting desynchronized circuit are presented and explained.

Owner:CO INVERSION NEOTEC +1

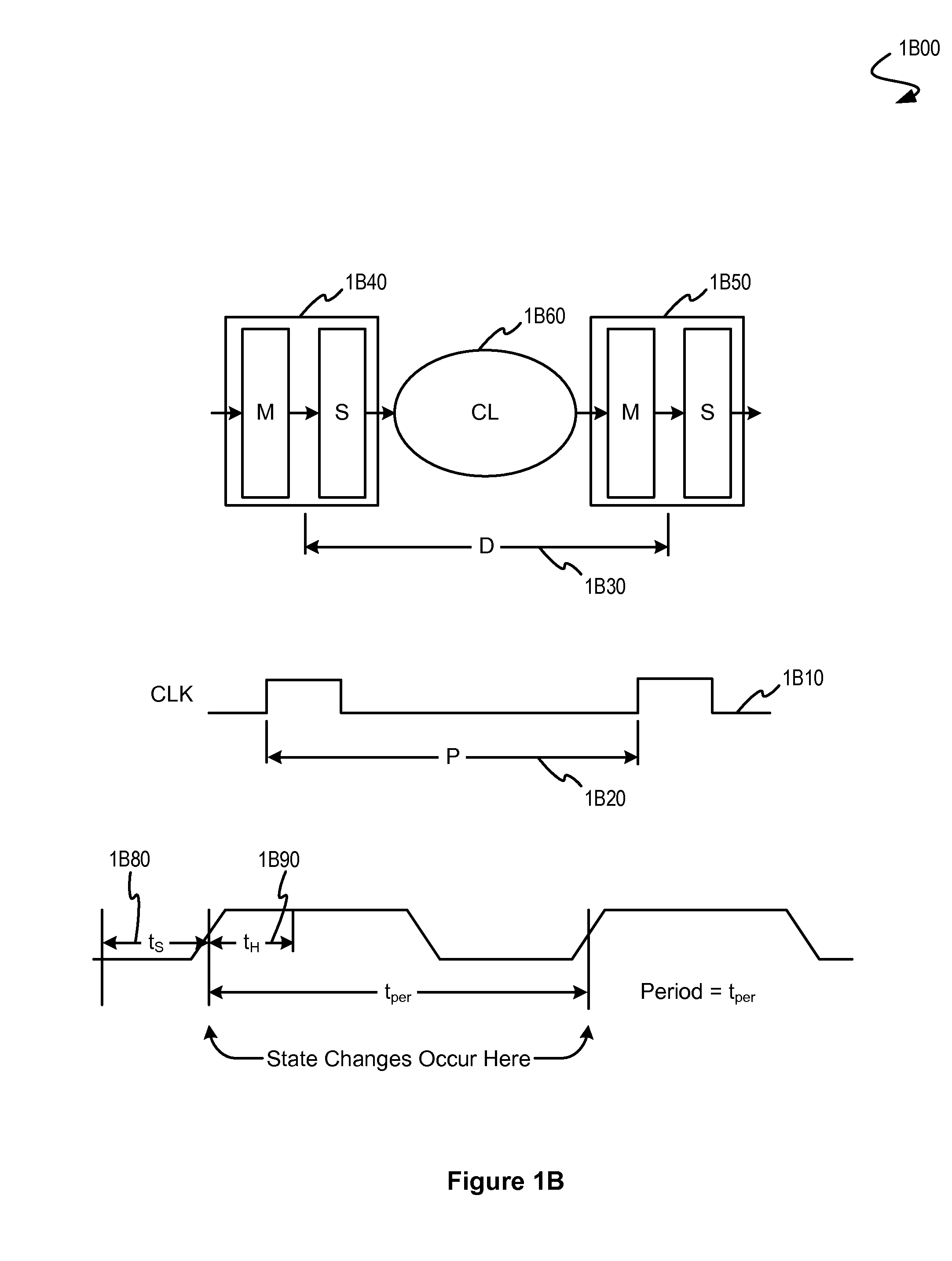

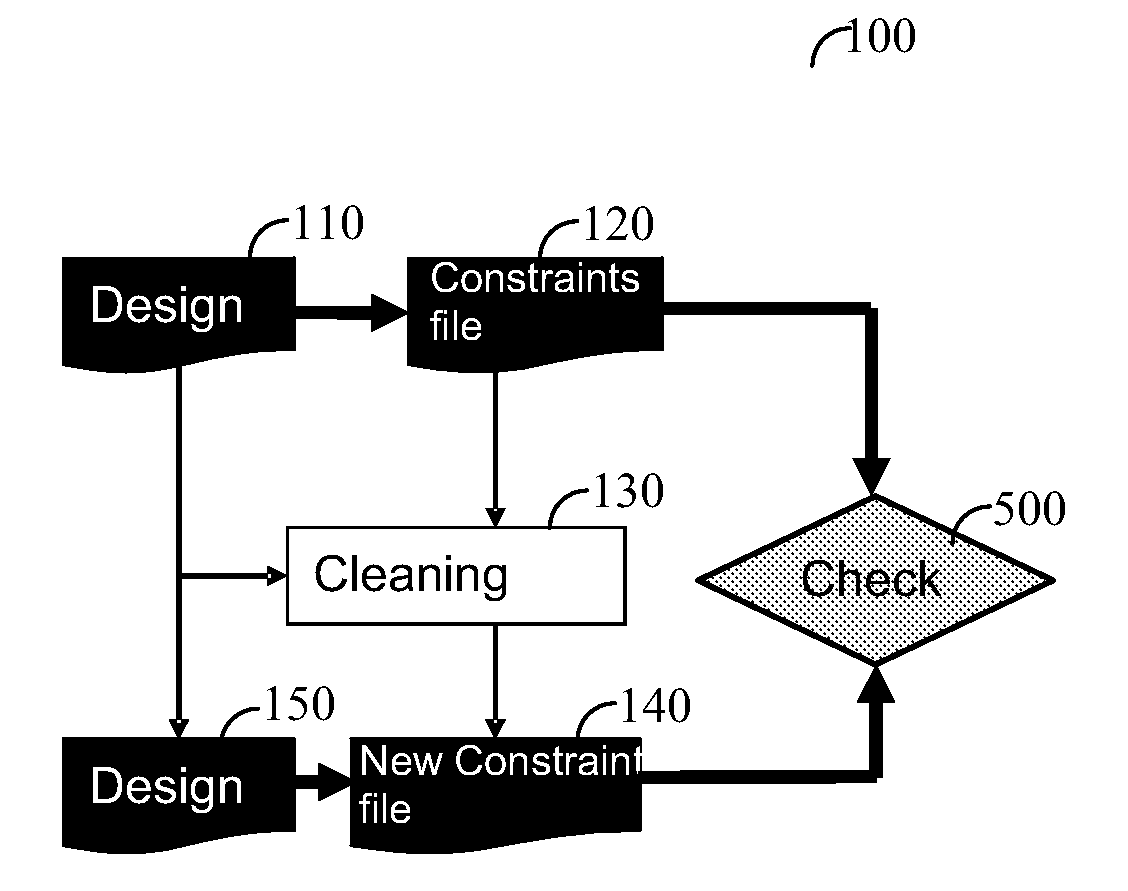

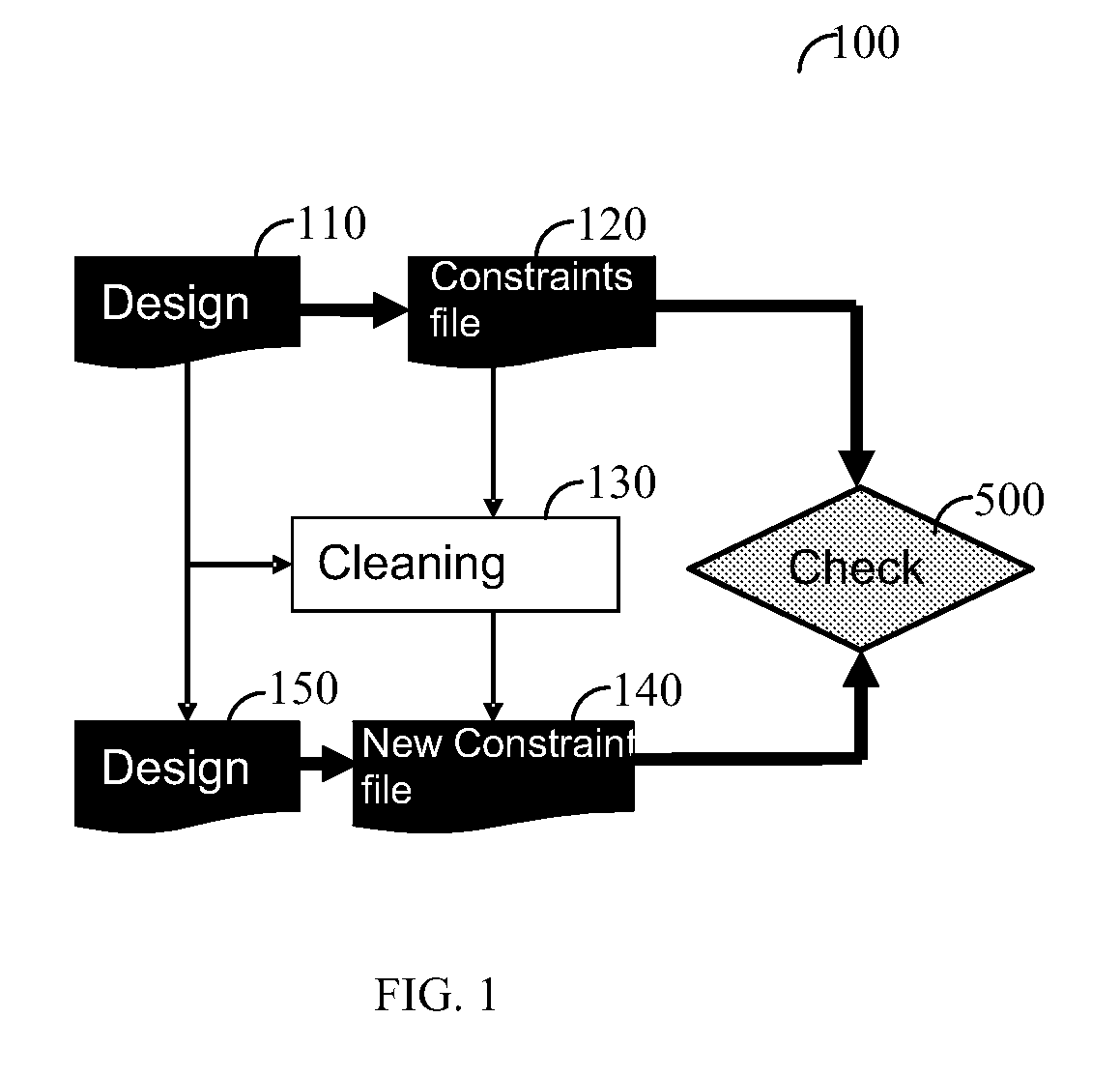

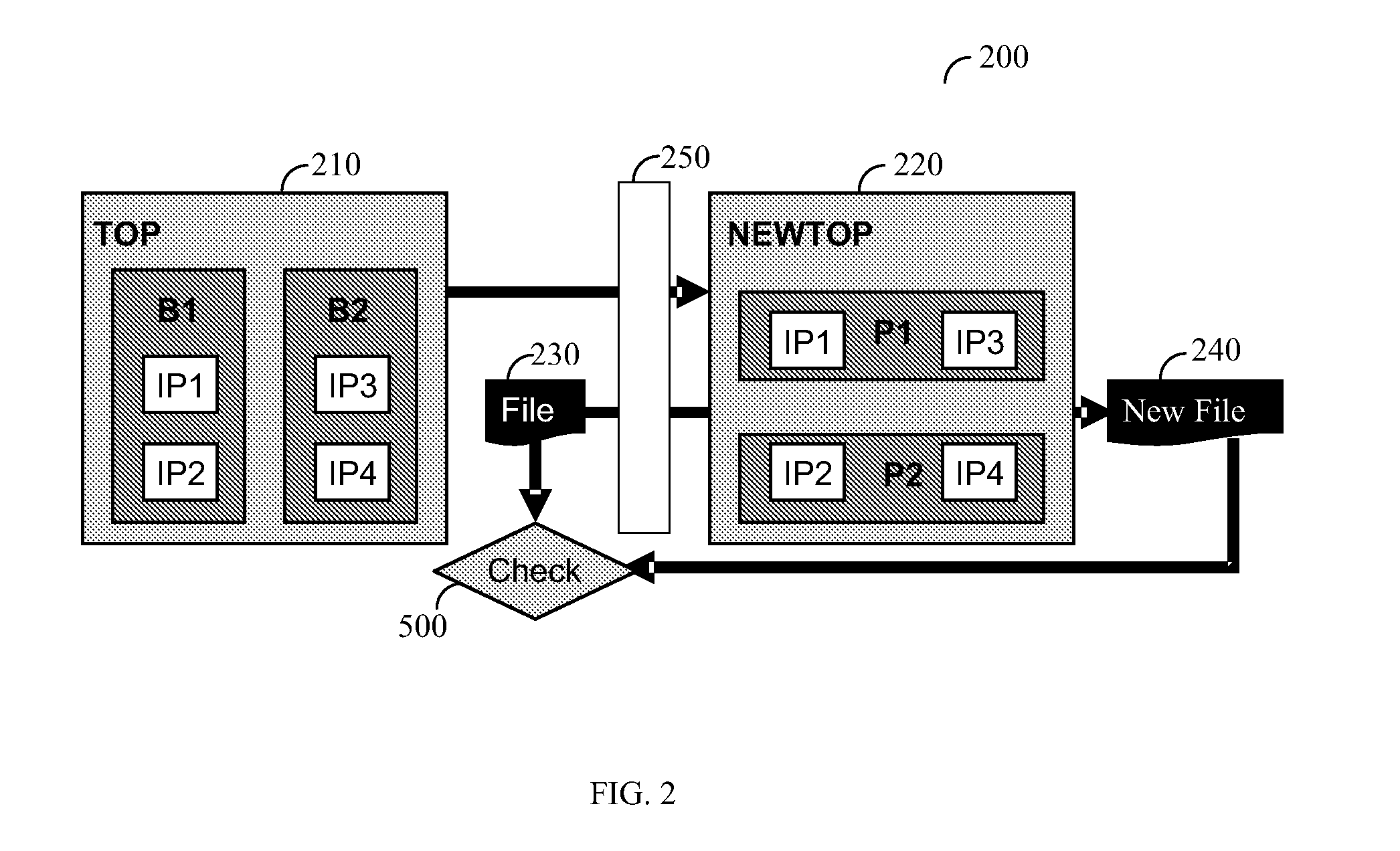

Method for checking constraints equivalence of an integrated circuit design

ActiveUS20080301598A1Computer aided designSoftware simulation/interpretation/emulationComputer architectureBlock level

The equivalence of two or more constraint files of an integrated circuit (IC) design are checked. The comparison is performed between files at the same stage of design, files that correspond to different stages of the design flow, or between top-level and block-level constraint files.

Owner:SYNOPSYS INC

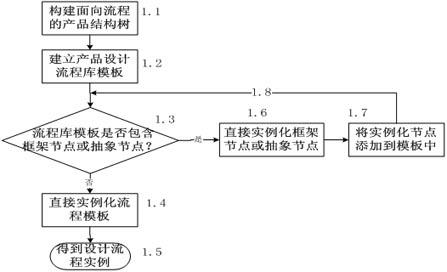

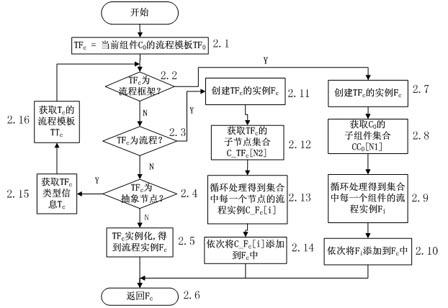

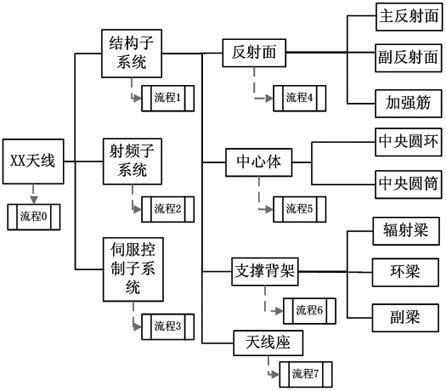

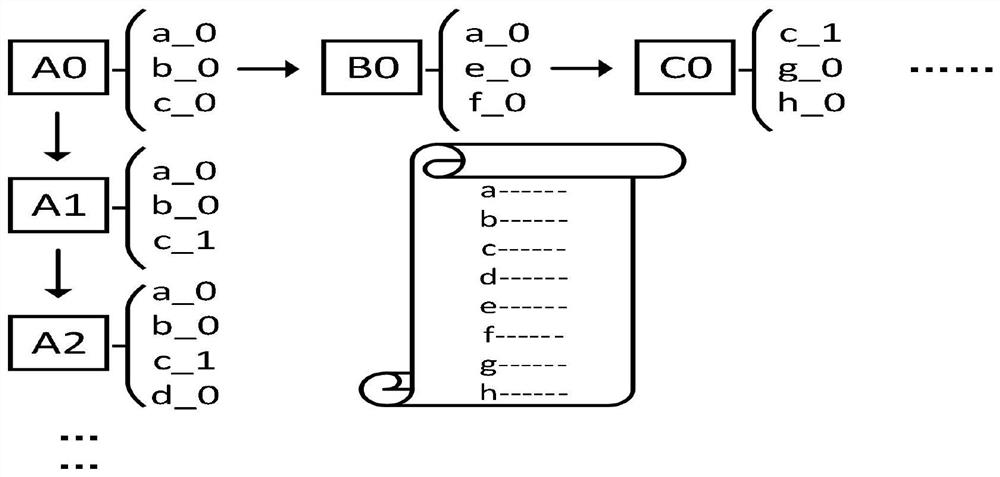

Product structure tree-based design flow dynamic modeling method

The invention relates to the field of computer product supported collaborative design, in particular to a product structure tree-based design flow dynamic modeling method. The method is characterized by at least comprising the following steps: 1.1, constructing a flow oriented product structure tree which contains structure composition information and design flow information of a product; 1.2, establishing a product design flow base template to complete mapping of the flow base template and the product structure tree; 1.3, determining whether or not the flow base template contains flow frame nodes or abstract nodes, entering step 1.6 if so, otherwise entering step 1.4; 1.4, directly generating flow instances by the nodes; 1.5 finishing and obtaining flow template design flow instances; 1.6, generating instances of the frame nodes or the abstract nodes by combining the product structure information; 1.7, adding the generated instances into the corresponding frame nodes and abstract nodes in the flow base template; and 1.8, returning to the step 1.3. In the product designing process, types of components and parts of the product structure tree and the composition information of the product structure tree are extracted in real time, and a dynamic work flow model of the whole machine of the product can be established through algorithm by combining an established component and part work flow template base.

Owner:XIDIAN UNIV

Variability-Aware Scheme for High-Performance Asynchronous Circuit Voltage Reglulation

ActiveUS20090115503A1Logic circuits characterised by logic functionPulse automatic controlAsynchronous circuitMathematical model

A system for automatically transforming a given synchronous circuit description into an equivalent and provably correct desynchronized circuit description. Included in the automated transformation are techniques for synthesizing a variability-aware controller using a two-phase protocol, techniques for synthesizing a variability-aware controller using gated clocks and testability circuits, techniques for synthesizing a variability-aware controller optimized for performance, techniques for initializing the synthesized controller, techniques for dynamically minimizing power requirements, and techniques for interfacing the desynchronized circuit with external synchronous circuits. Also disclosed are techniques for implementing a system for automatically transforming a synchronous circuit description into an equivalent and provably correct desynchronized circuit description within the context of an electronic design automation design flow. Exemplary circuits used in the application of the aforementioned techniques are provided. Application of mathematical models and techniques used for proving equivalence between the input description and the resulting desynchronized circuit are presented and explained.

Owner:CO INVERSION NEOTEC +1

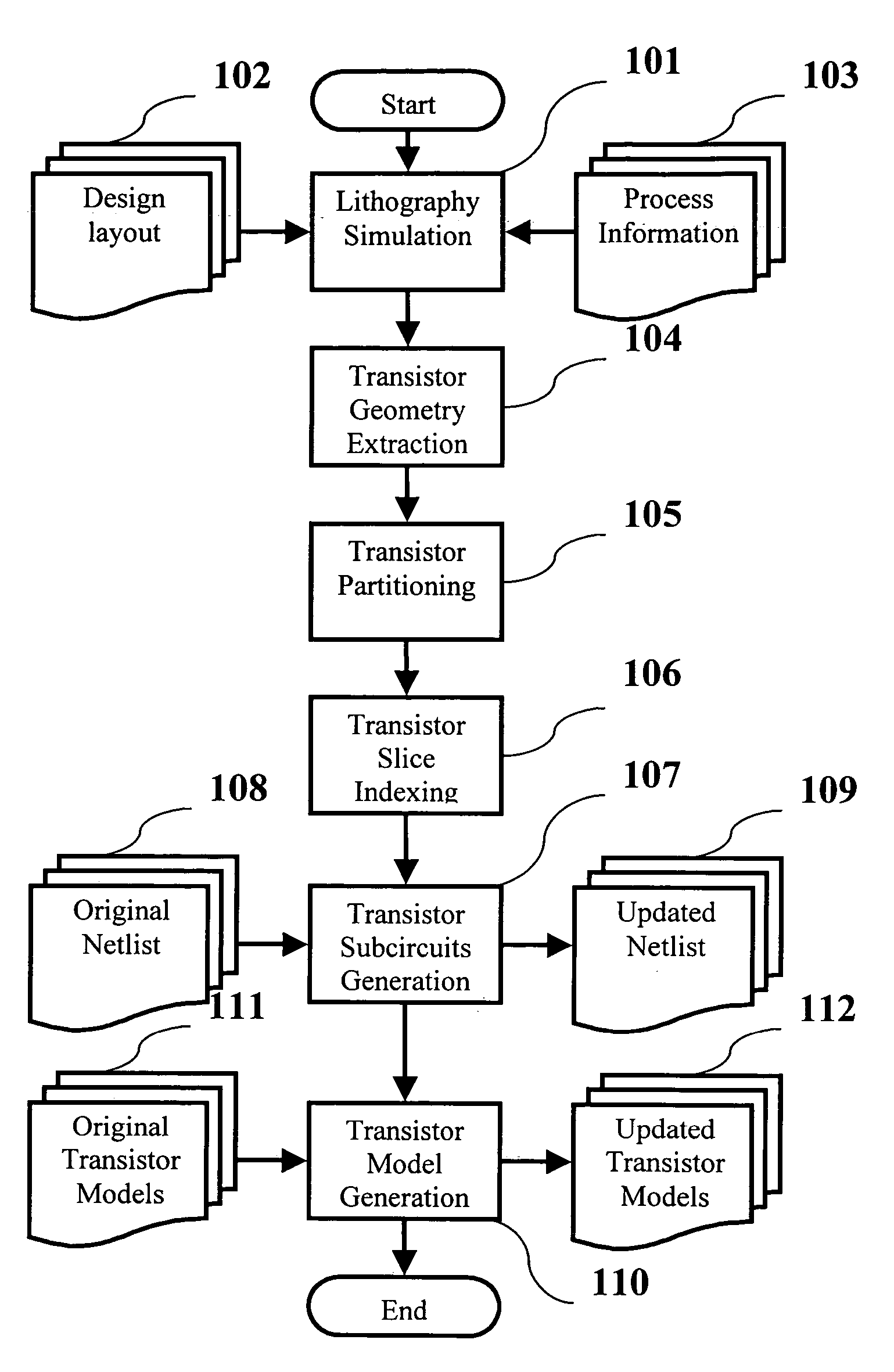

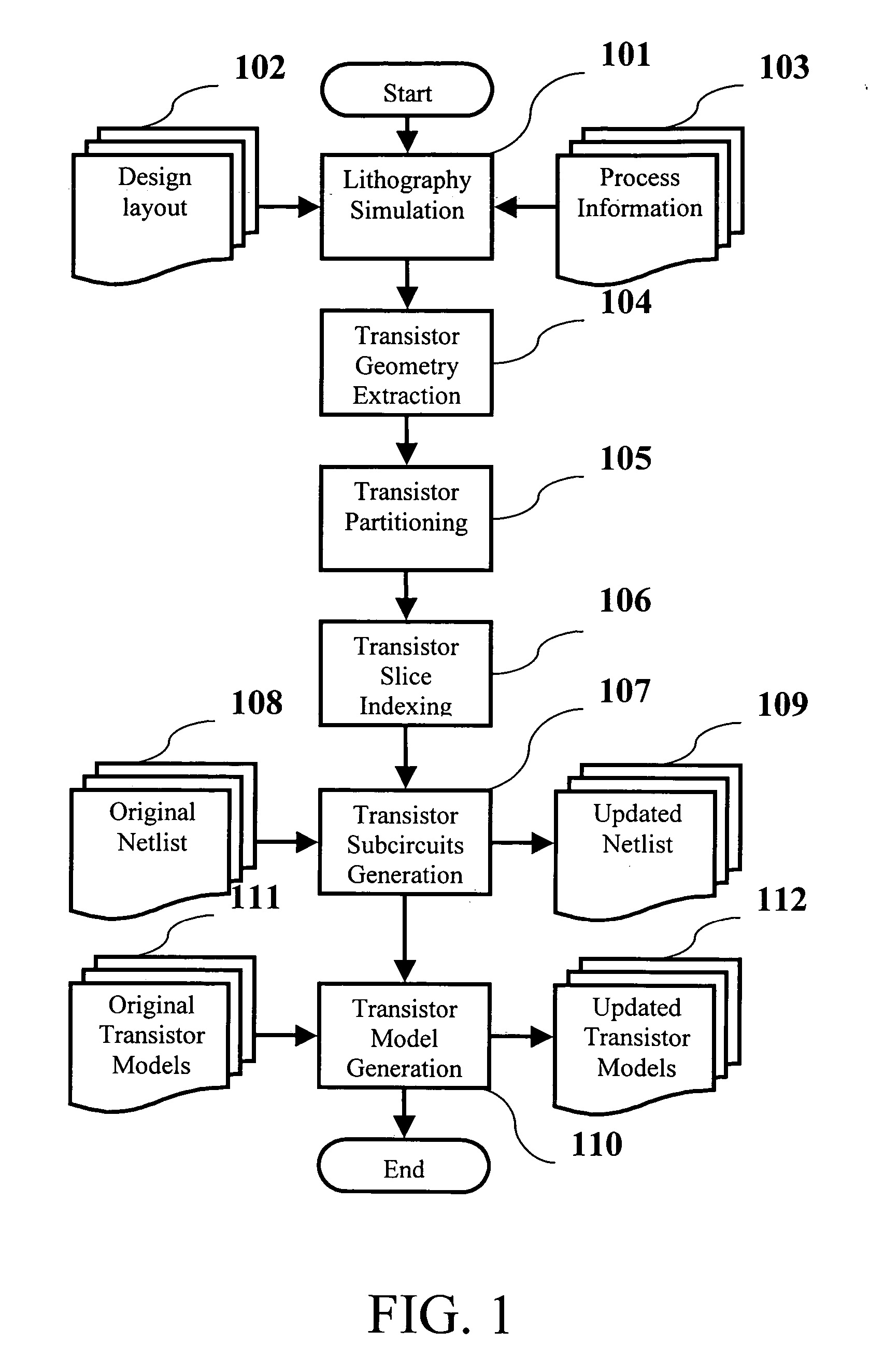

Method for improving accuracy of MOSFET models used in circuit simulation integrated circuits

InactiveUS20060190863A1Ensure correct executionEasy to implementDetecting faulty computer hardwareComputer aided designMOSFETPredicting performance

Disclosed is a method of modeling submicron MOSFETs for the purpose of circuit simulation. This invention is capable of accurately predicting performance of a MOSFET with complex geometry closely approximating the actual geometry of a device manufactured as part of an integrated circuit. Actual device geometry is predicted using physical simulation to account for process-related pattern distortion. The method constructs a sub-circuit representation of a MOSFET that is equivalent to a regular MOSFET compact model when ideal device geometry is assumed, while providing substantially better accuracy when process-related geometry distortion is considered. Models created using the disclosed method are compatible with existing circuit simulators. The method may be readily implemented using SPICE or other circuit simulators in a design flow.

Owner:AXELRAD VALERY +1

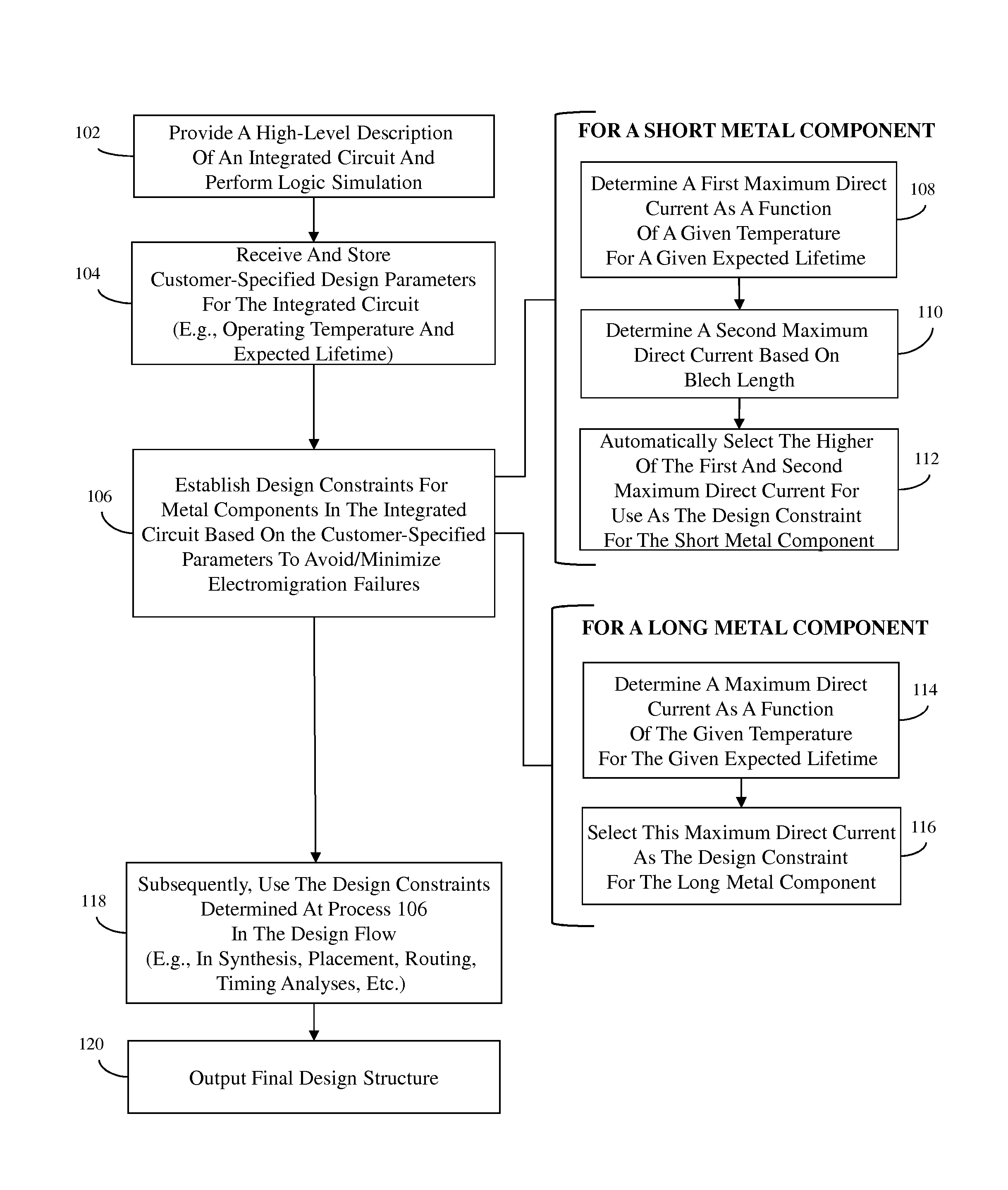

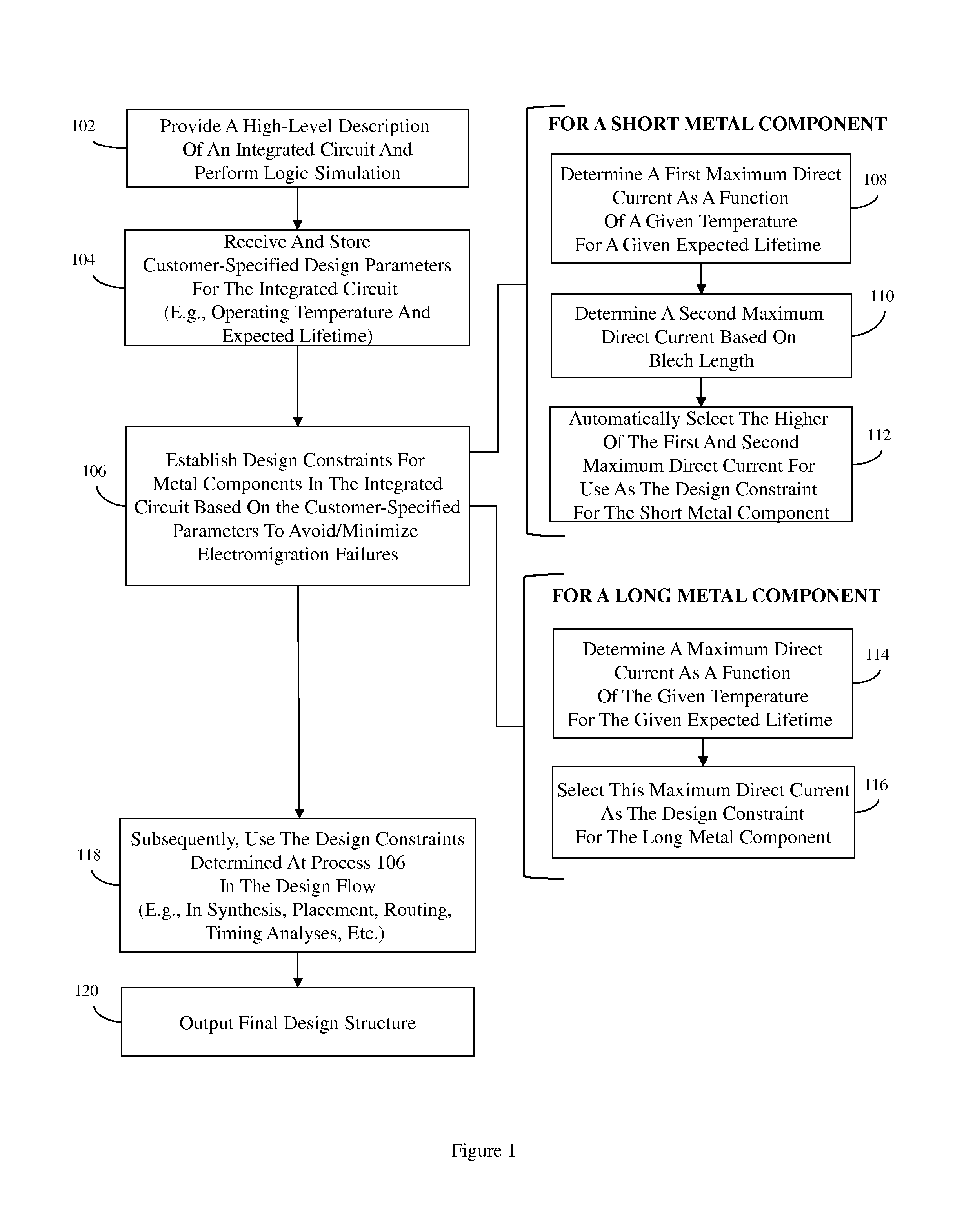

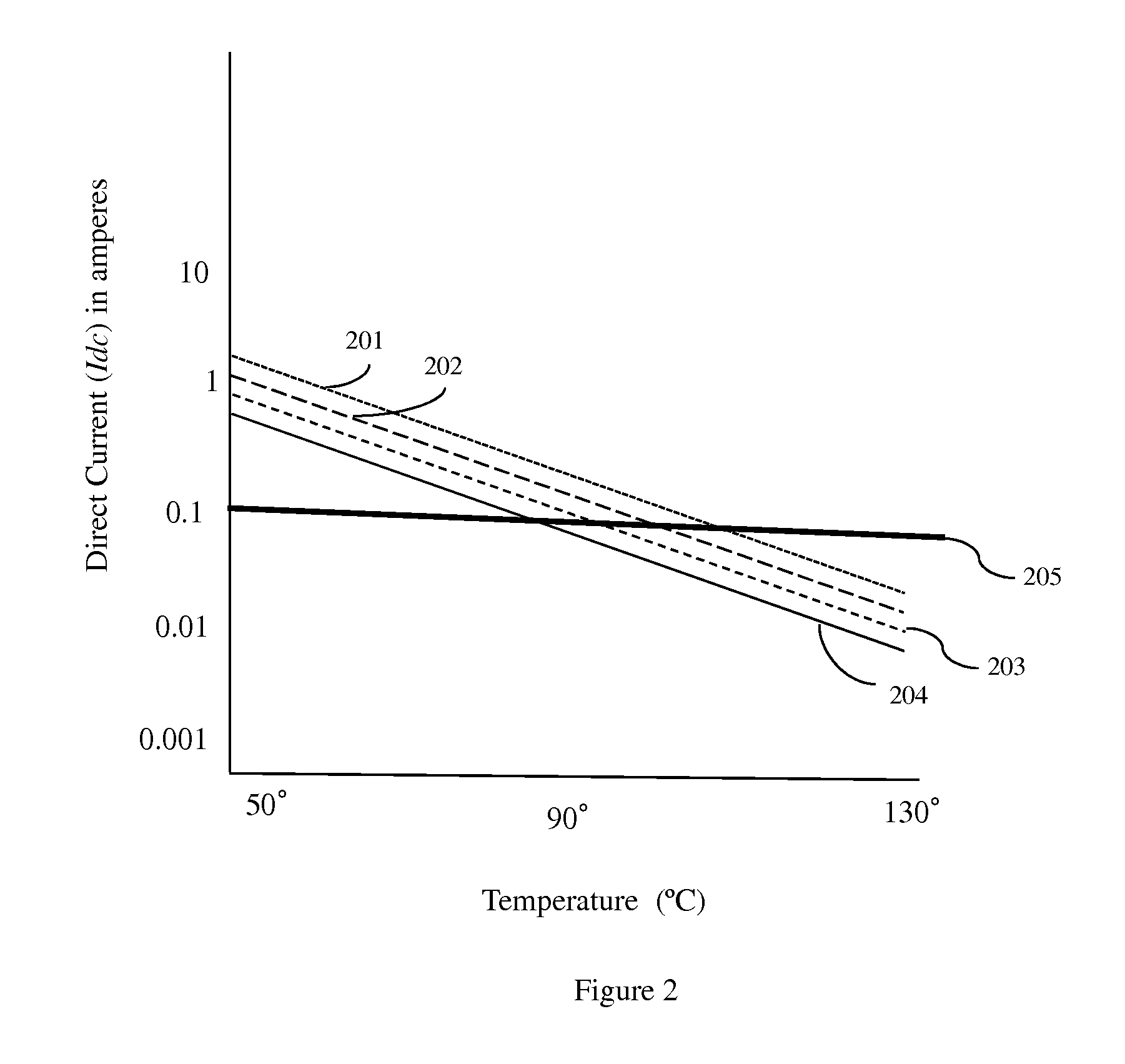

Integrated circuit design method and system

ActiveUS20130185684A1Avoid/minimize electromigration failureCAD circuit designSpecial data processing applicationsElectricityDesign methods

Disclosed is an integrated circuit design method that determines maximum direct currents for metal components and uses them as design constraints in the design flow in order to avoid / minimize electromigration failures. Short and long metal components are treated differently for purposes of establishing the design constraints. For a short metal component, the maximum direct current as a function of a given temperature for a given expected lifetime of the integrated circuit is determined, another maximum direct current is determined based on the Blech length, and the higher of these two is selected and used as the design constraint for that short metal component. For a long metal component, only the maximum direct current as a function of the given temperature for the given expected lifetime is determined and used as the design constraint. Also disclosed herein are associated system and program storage device embodiments for designing an integrated circuit.

Owner:MARVELL ASIA PTE LTD

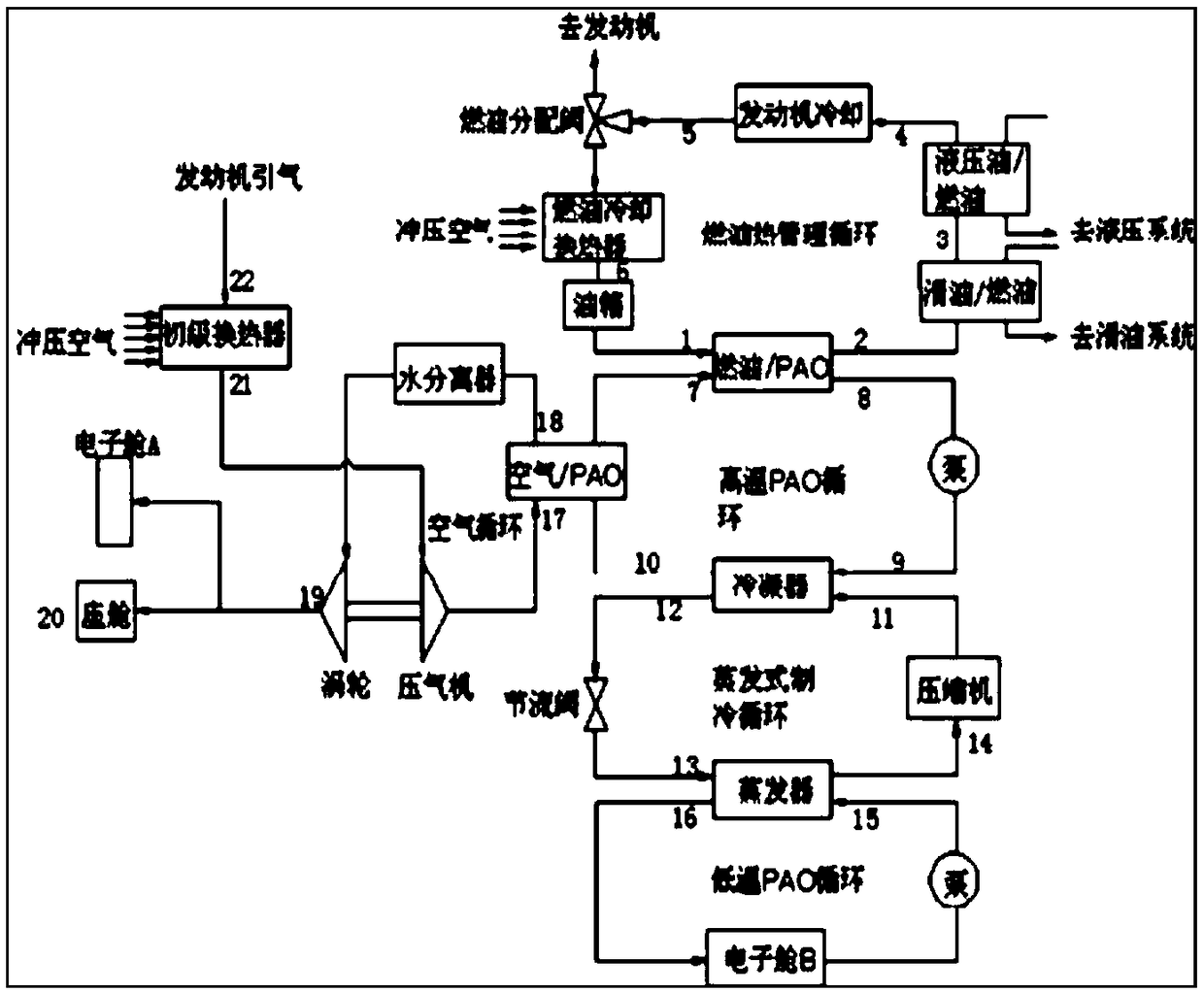

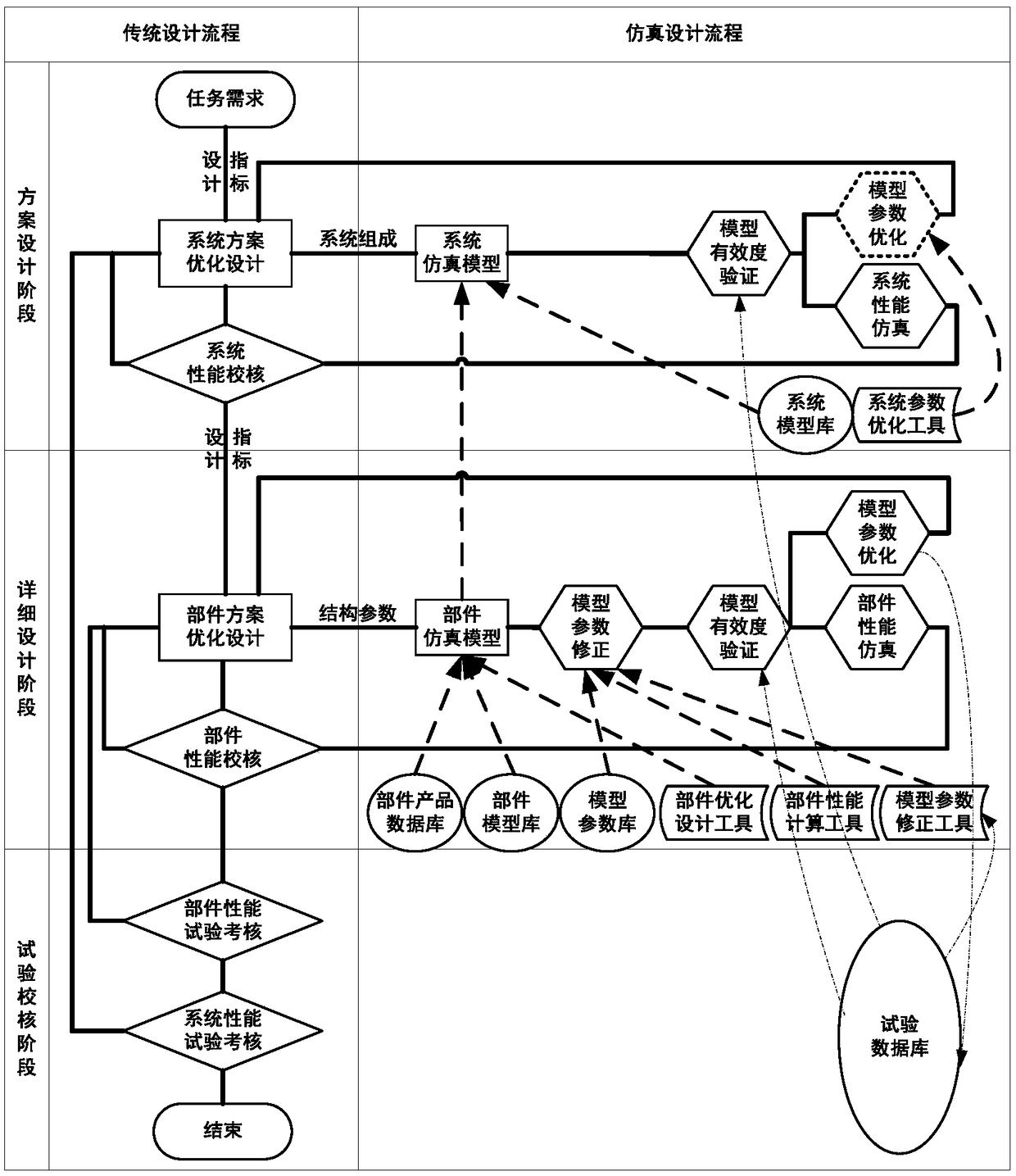

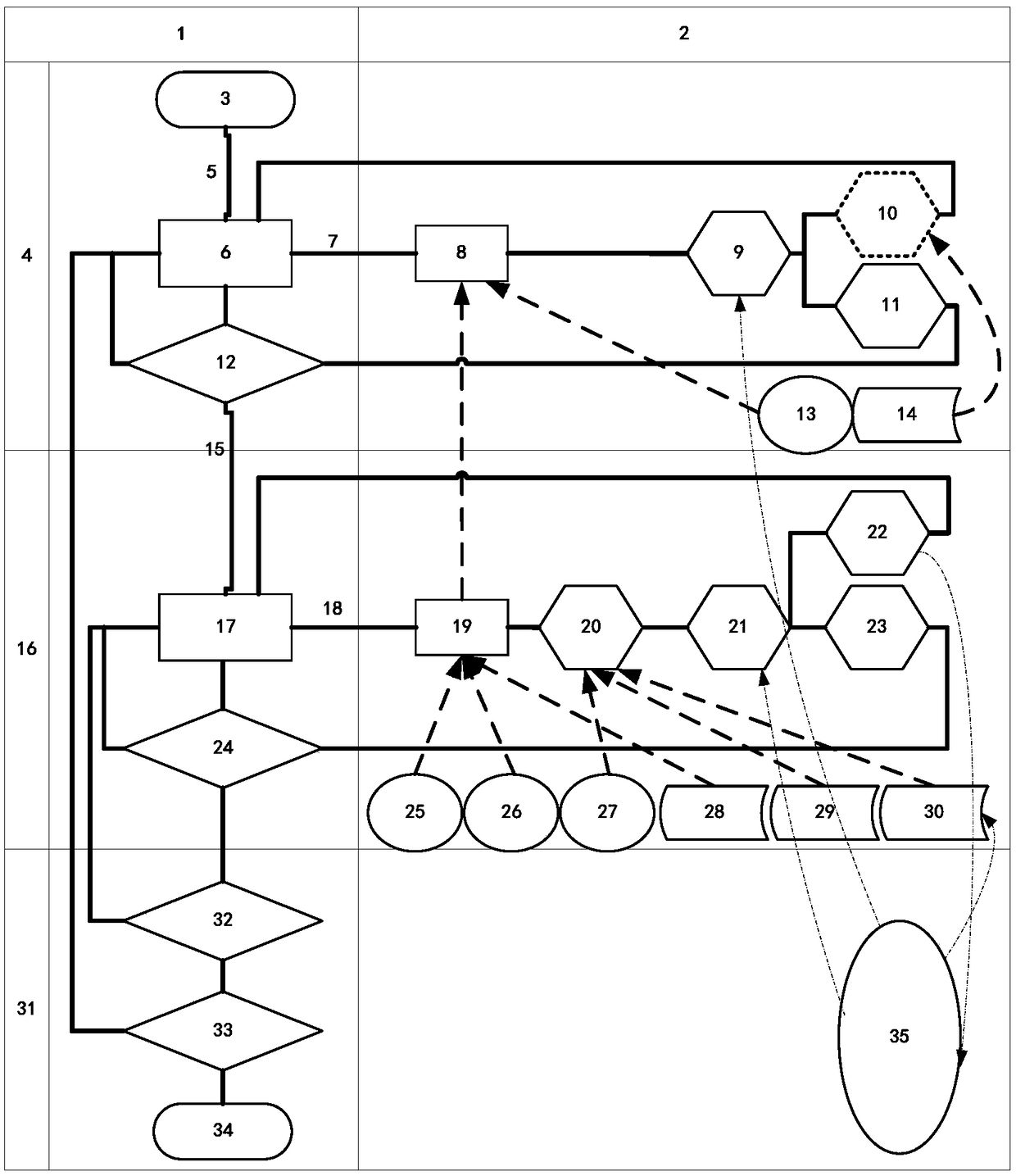

Method for model-based integrated design and simulation software architecture of airborne thermal management system

ActiveCN109446624ARealize evaluationEase of evaluationGeometric CADDesign optimisation/simulationDesign flowThermal management system

The invention belongs to the design field of airborne environmental control / heat management system, and a method for model-based integrated design and simulation software architecture of airborne thermal management system is proposed. The method comprises 1 normalizing the model-based integrated design process of the airborne thermal management system as a matrix of two columns and three rows, intersecting the columns and rows to determine the belonging of the design flow; 2 firstly building the architecture of the traditional design flow 1; 3 qualifying that scheme of the system performancecheck 12 and entering the second row of the first column of the matrix; 4 enabling the component qualified by the component performance check 24 to enter the third row of the first column of the matrix; 5 constructing the architecture of the second column simulation design flow 2 of the matrix; 6 entering that construction of the simulation design flow 2 of the second column and the second row; 7entering the third row of the second column to build the simulation design flow 2. The invention realizes the comprehensive evaluation and optimization from parameters to configurations.

Owner:JINCHENG NANJING ELECTROMECHANICAL HYDRAULIC PRESSURE ENG RES CENT AVIATION IND OF CHINA

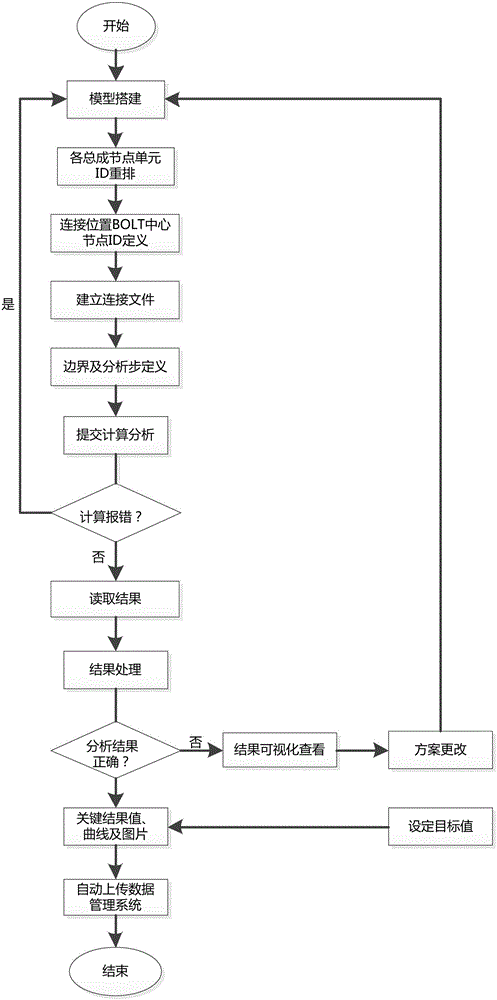

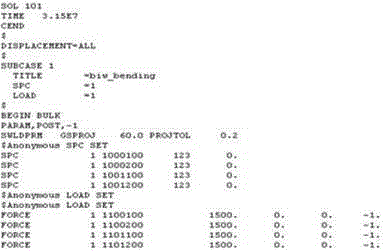

Method for establishing CAE linear analysis sub-assembly connection relation

ActiveCN104992006AEasy to operateShorten the timeSpecial data processing applicationsTrunk compartmentVehicle frame

The invention relates to a method for establishing a CAE linear analysis sub-assembly connection relation. The method is characterized by comprising the following steps of: 1) dividing an assembly: according to a design process of the whole vehicle, dividing a linear analysis model into nine parts, namely a white vehicle body (1), an engine hood (2), left and right front doors (3), left and right rear doors (4), a secondary frame (5), a trunk lid (6), a front-end module (7), an instrument board cross beam (8) and seats (9); 2) defining node and unit sections of each assembly: according to the assemblies divided in the step 1), performing node and unit section definition on a numerical model of each assembly by utilizing ANSA preprocessing software; 3) defining a connection position node number of each assembly: establishing a rigid connection at a connection position in the numerical model of each assembly, and performing redefinition on a central node of the connection position according to a node section in a format; defining the format of a node number of a connection point as follows: first two digits of the minimum value of the section 1# of a part plus first two digits of the minimum value of the section 2# of the part plus node range; and 4) establishing a connection file. ( / b)

Owner:BRILLIANCE AUTO

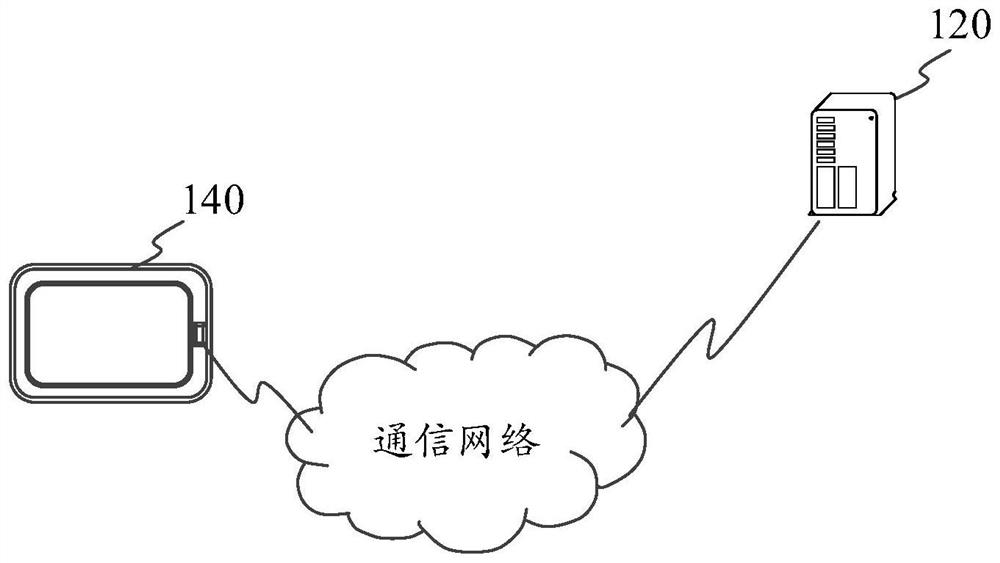

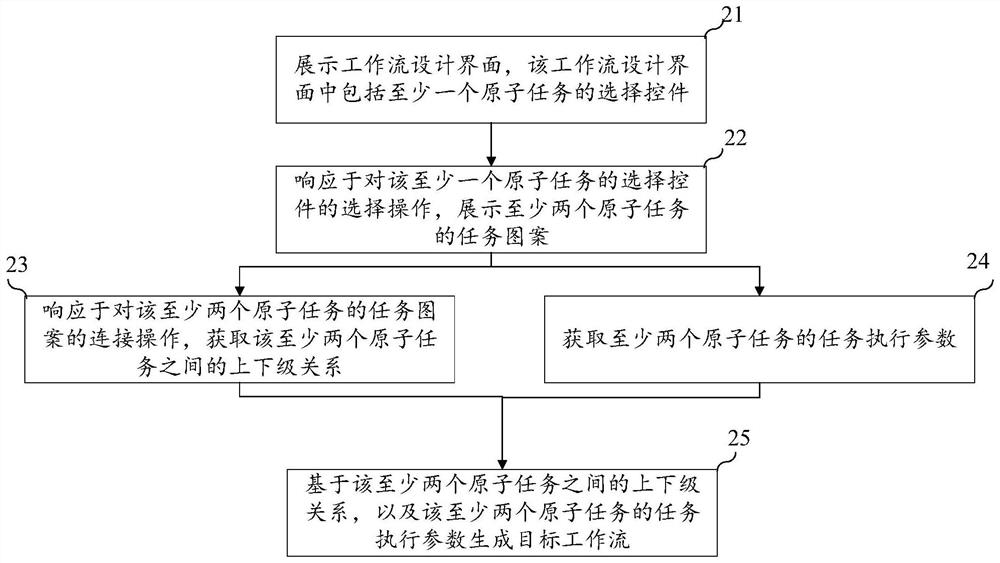

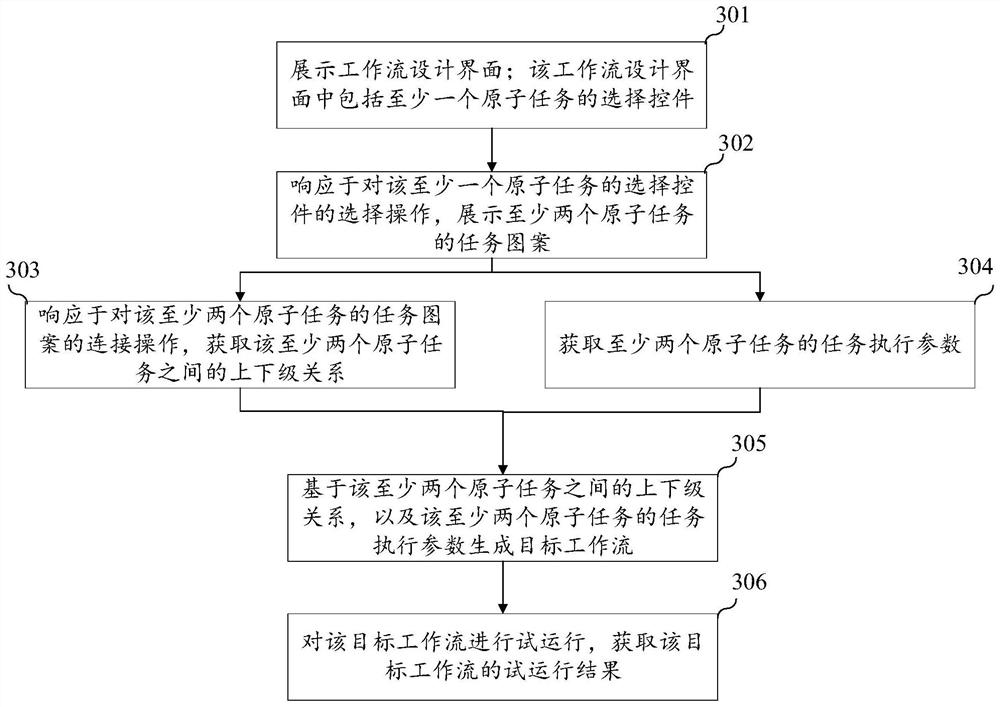

Workflow generation method and device, computer equipment and storage medium

PendingCN111813391AImprove application efficiencyShorten the timeSoftware designDesign flowCode development

The invention relates to a workflow generation method and device, computer equipment and a storage medium. The method comprises the steps of: displaying a workflow design interface which comprises a selection control of at least one atomic task; in response to the selection operation on the selection control of at least one atomic task, displaying task patterns of at least two atomic tasks; in response to a connection operation on the task patterns of the at least two atomic tasks, obtaining a superior-subordinate relationship between the at least two atomic tasks; obtaining task execution parameters of the at least two atomic tasks; generating a target workflow based on the superior-subordinate relationship between the at least two atomic tasks and the task execution parameters of the atleast two atomic tasks. According to the method, a user can design an automatically executed workflow by himself / herself through a visual design process, and does not need to develop the workflow bywriting program codes by developers, so that the code development time is saved, and the application efficiency of the workflow is improved.

Owner:TENCENT TECH (SHENZHEN) CO LTD

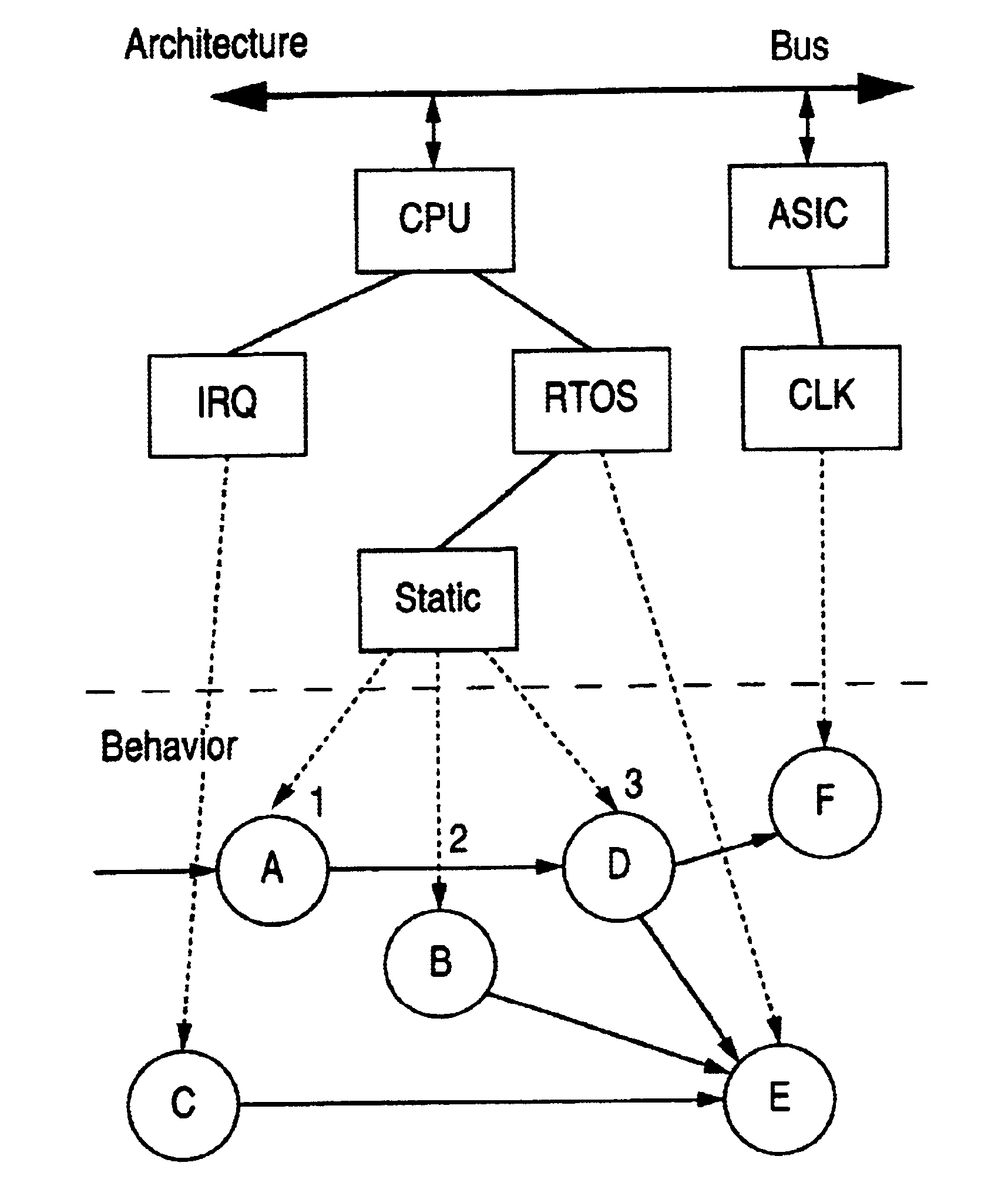

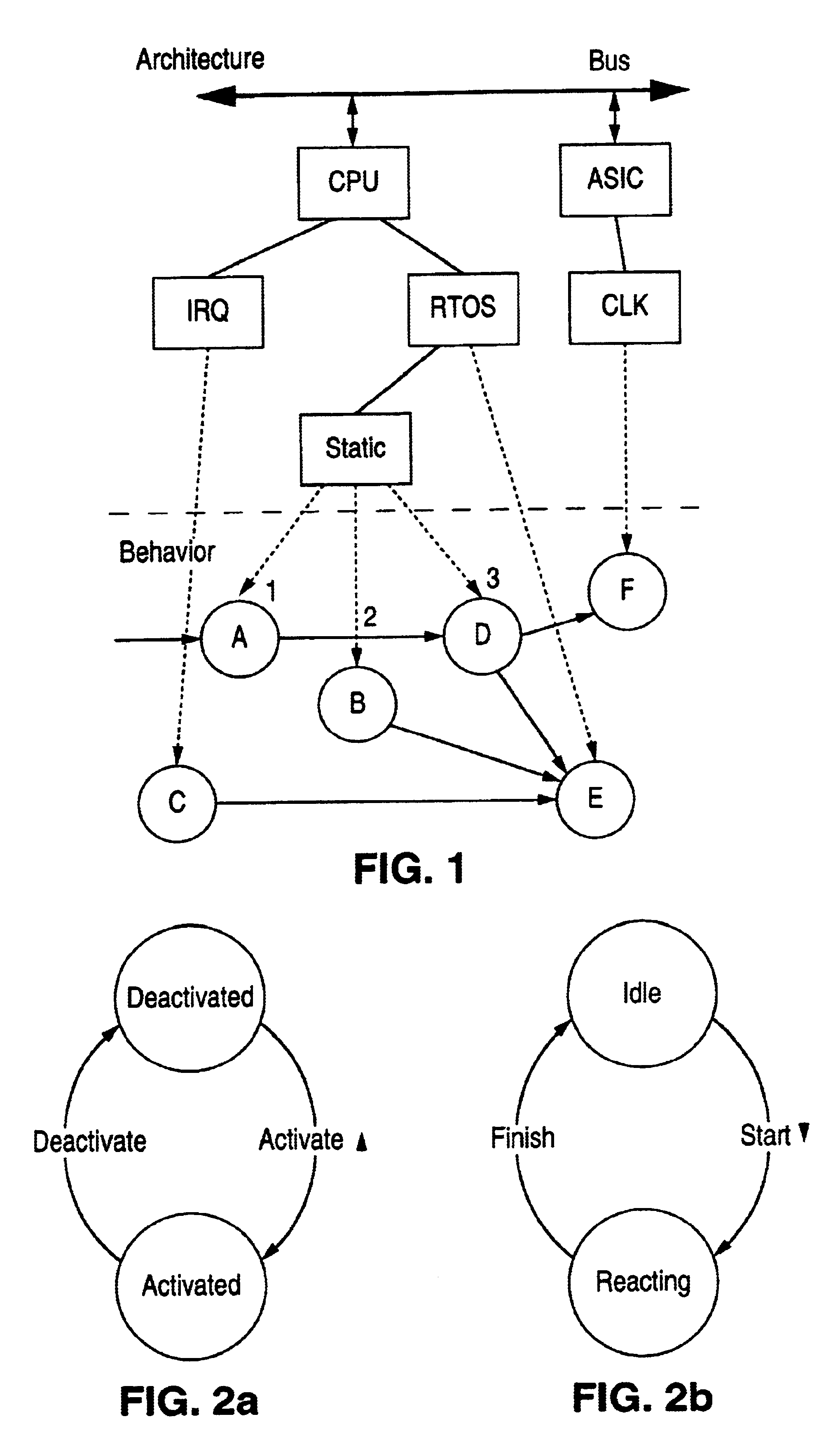

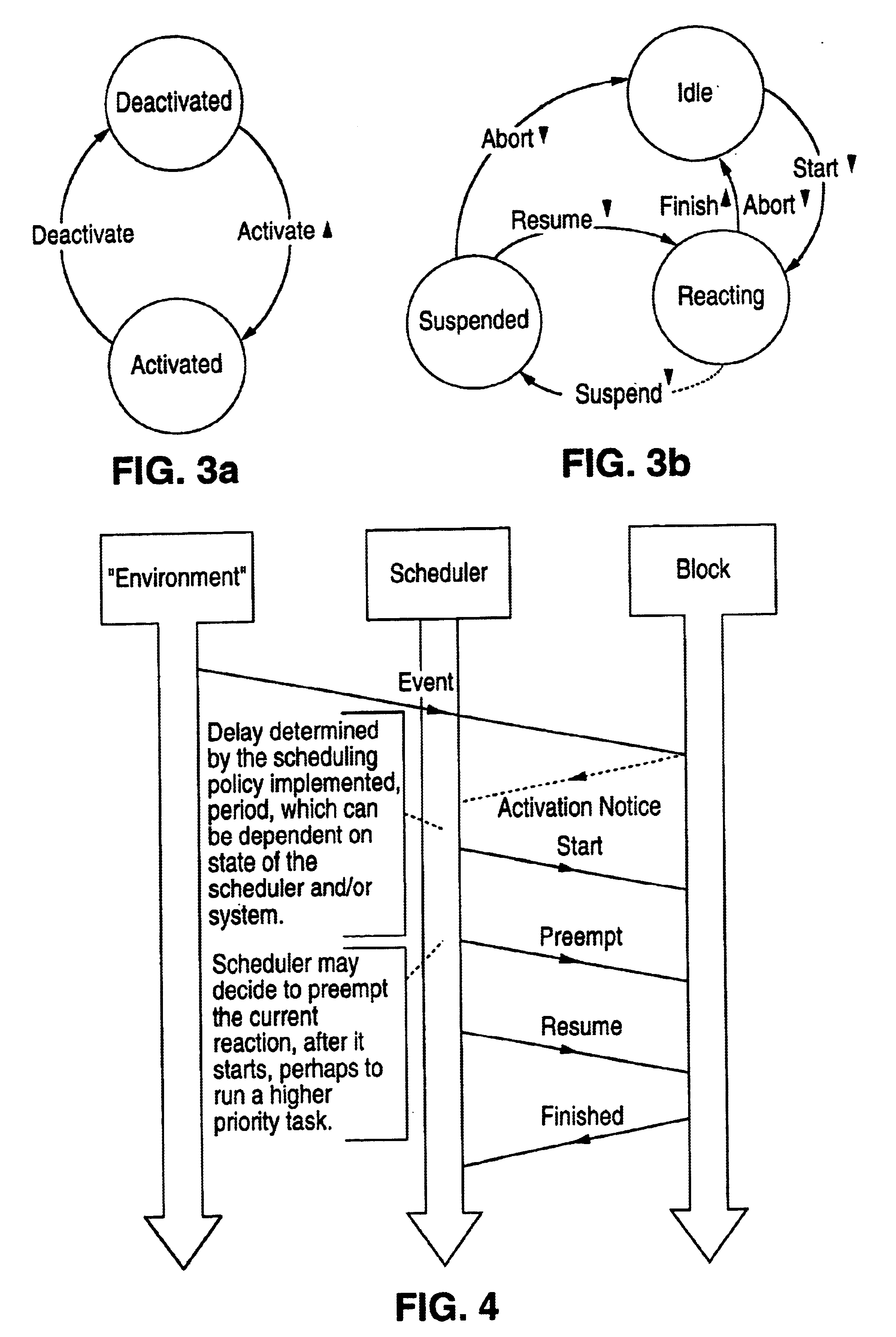

Method for hierarchical specification of scheduling in system-level simulations

InactiveUS6882965B1Multiprogramming arrangementsCAD circuit designAbstract interfaceDistributed computing

A method for hierarchical specification and modeling of scheduling in system-level simulations. The invention addresses the specification aspect by introducing an explicit notion of a scheduler that must be designed as part of the system. A scheduler effectively represents a scheduling policy for an architectural resource. A scheduling policy governs how behaviors assigned to a resource, gain access and share the resource. The invention includes a general framework for modeling a scheduling policy, which includes a simple mechanism that covers many common cases. This framework is part of a Virtual Component Codesign (VCC) process, which is targeted at consumer embedded system design. Two orthogonal models, one of a scheduler and one of a schedulable, comprise the overall modeling of scheduling in the invention. The two models interact by sending messages to each other via a simple protocol. The protocol itself is implemented by a pair of abstract interfaces, which in turn are implemented in concrete schedulable and scheduler objects in the simulator.

Owner:CADENCE DESIGN SYST INC

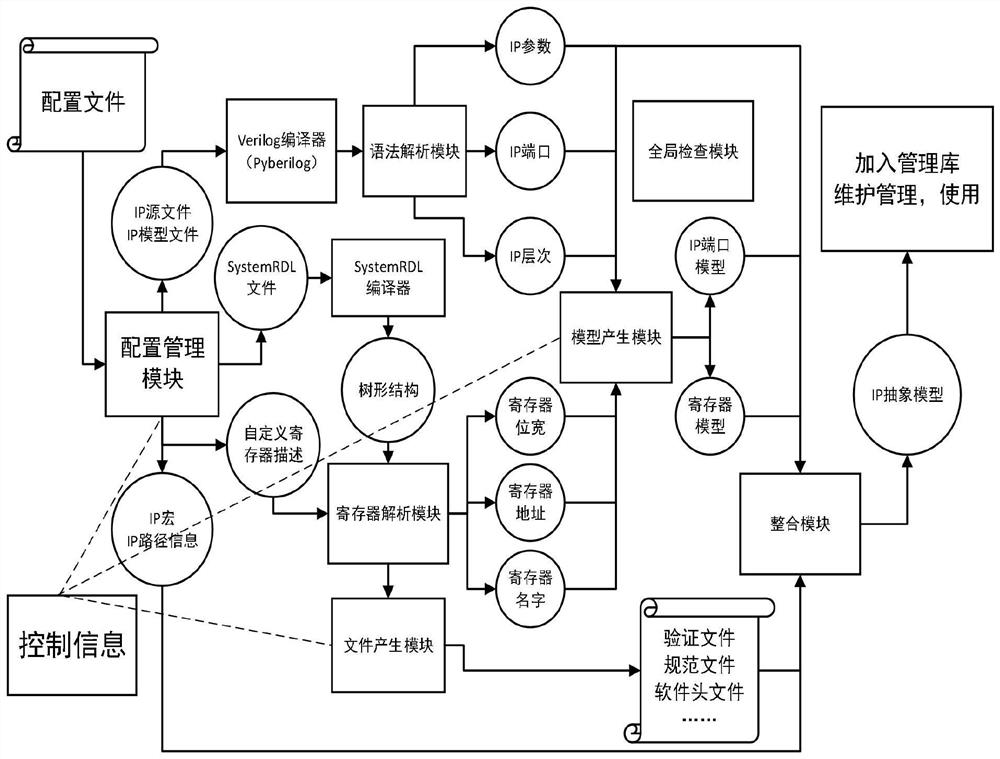

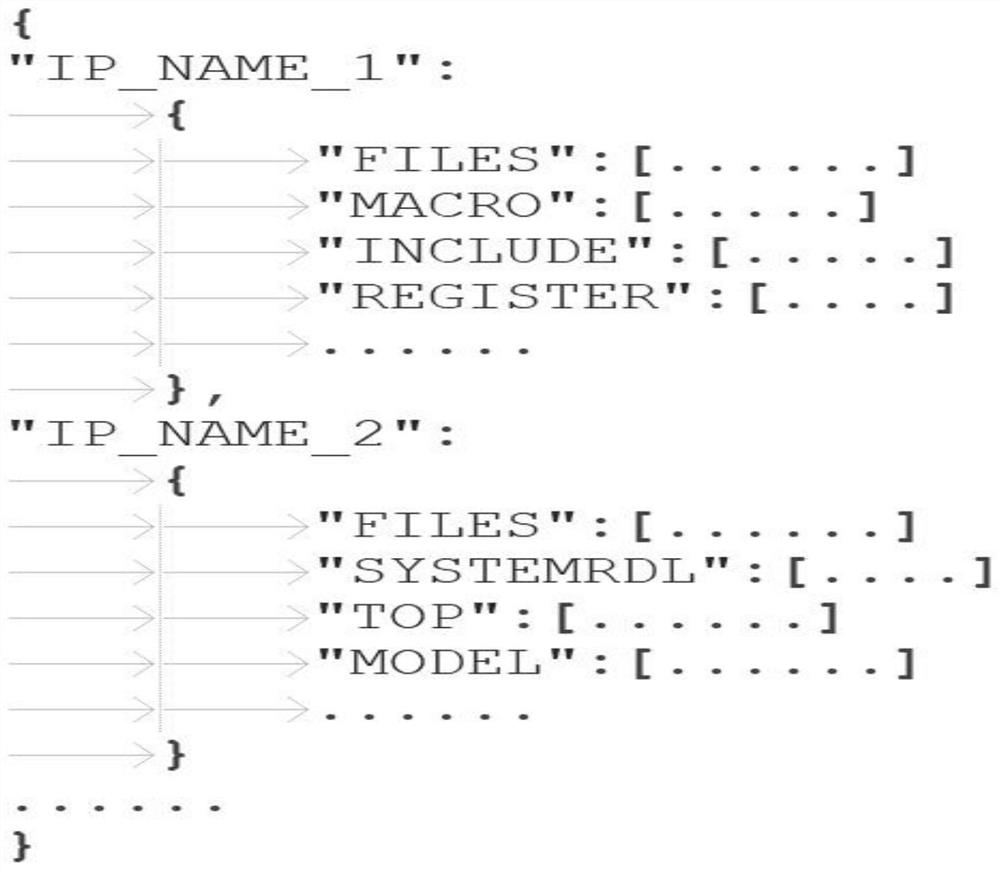

IP management system and IP management method

PendingCN111709215AWork lessImprove design efficiencyCAD circuit designSpecial data processing applicationsPathPingDesign flow

The invention discloses an IP management system and an IP management method, and relates to an IP management system and an IP management method. The invention aims to solve the problems that the existing IP-level SoC design process is complicated and lengthy and the accuracy is reduced due to excessive repetitive work along with the increase of the system. The IP management system comprises a configuration management module, a grammar analysis module, a register analysis module, a model generation module, a text generation module, a global check module and an integration module. The content ofthe configuration file comprises source file of each soft IP and hard IP or the position information of the model files of each soft IP and each hard IP, the macro information of each soft IP and each hard IP, the path information of each soft IP and each hard IP, the SystemRDL file position information corresponding to each soft IP and each hard IP or the user-defined register information description file position information. The method is applied to the field of digital chip design and EDA tools thereof.

Owner:HARBIN INST OF TECH

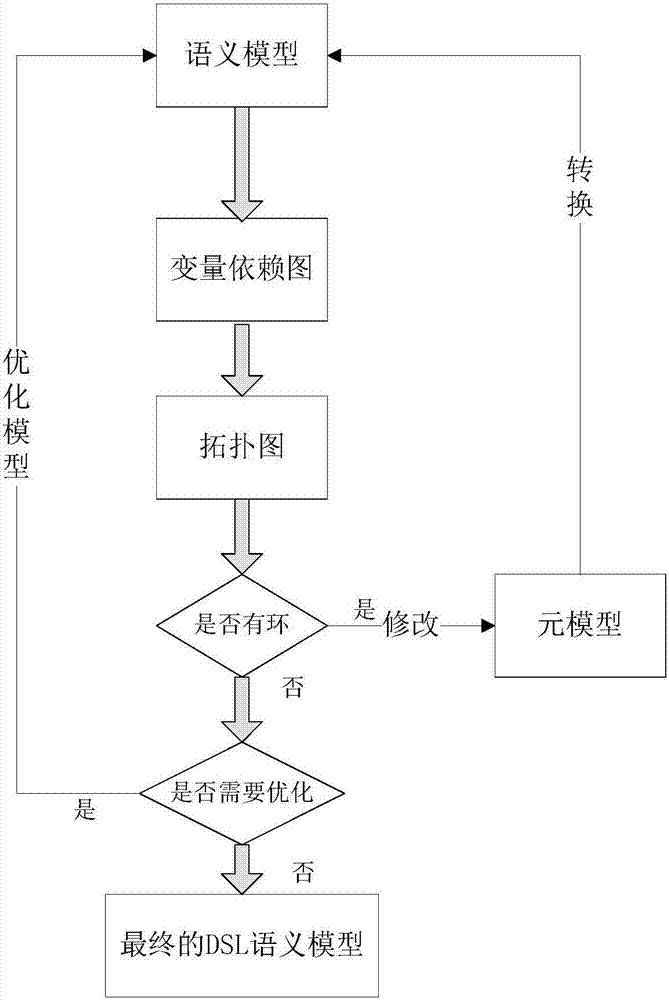

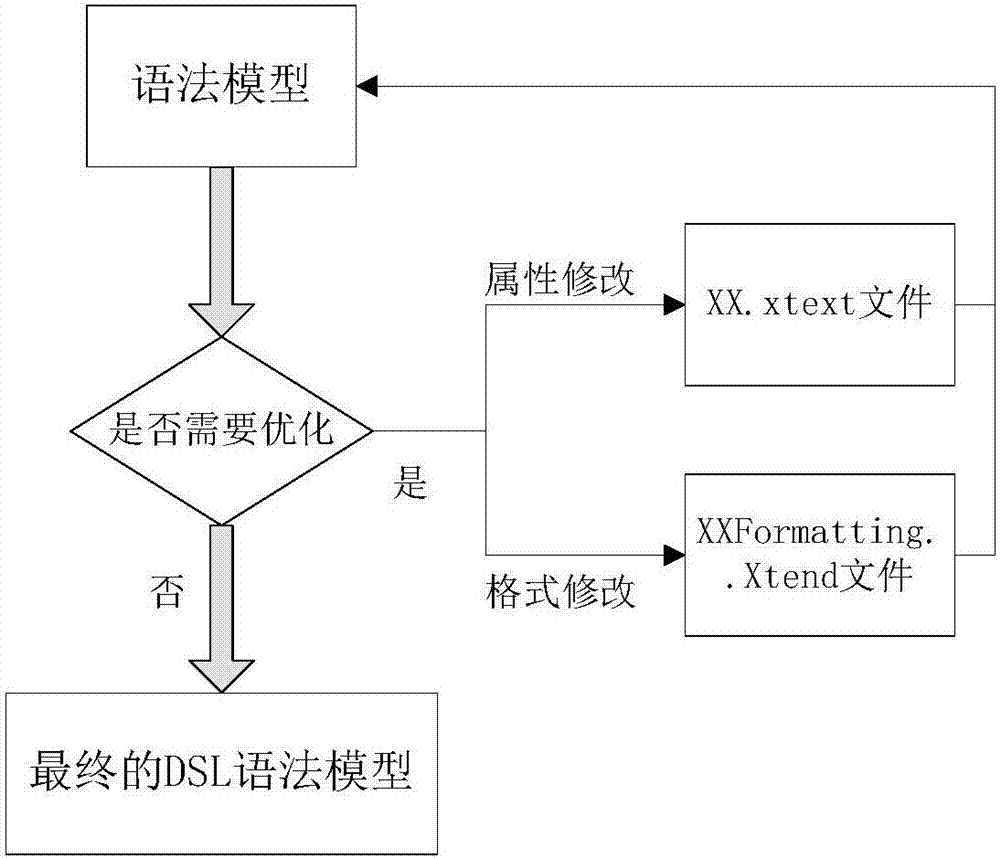

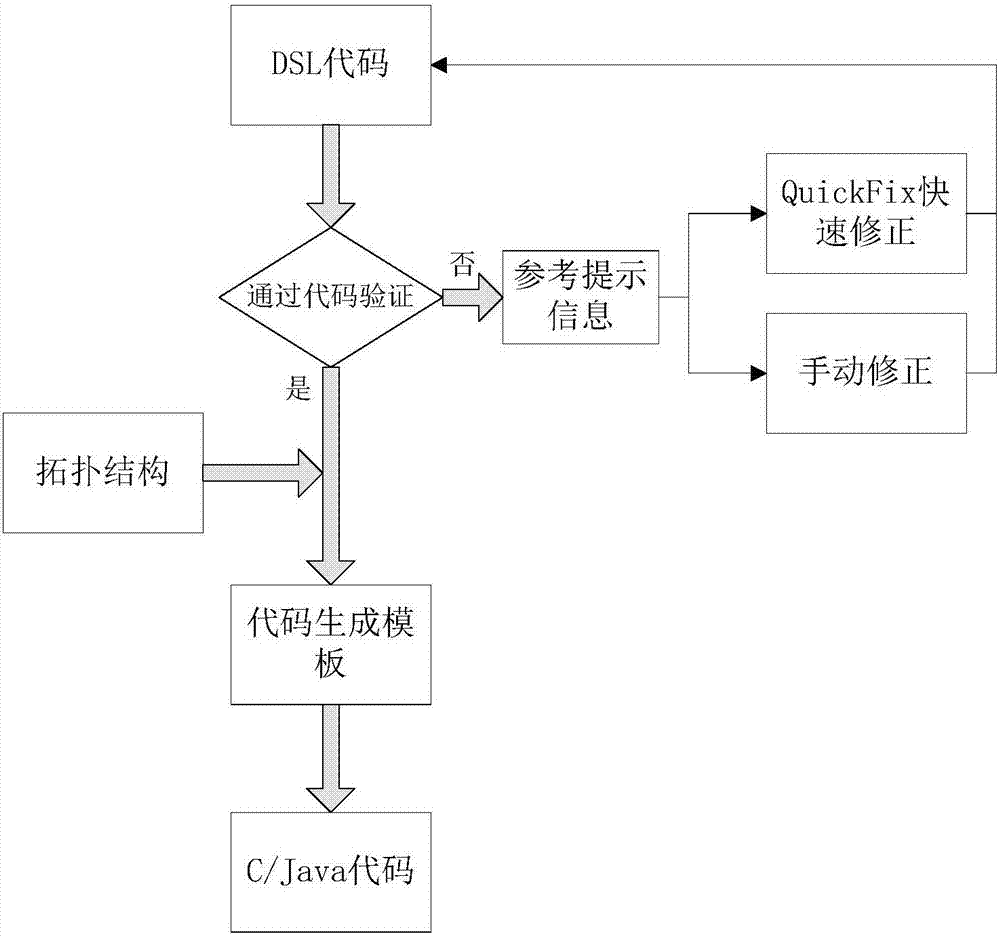

Xtext-based software engineering design method of domain specific language (DSL)

InactiveCN107273143AStandardize the design processLower build costsProgramming languages/paradigmsSoftware designDomain-specific languageSyntax

The invention discloses a Xtext-based software engineering design method of a domain specific language (DSL). The method comprises: step 1, converting an EMF meta-model to an Xtext semantics model; step 2, using a topology graph structure to validate and optimize the semantics model according to the initial DSL semantics model obtained in step 1; step 3, utilizing a method of editing validation rules at a syntax validation module of Xtext to validate code; and step 4, generating C / Java code after validation is completed. According to the Xtext-based software engineering design method of the domain specific language of the invention, a DSL design process is regulated, and DSL construction costs are reduced; at the same time, relevant personnel are helped to debug the code on the basis of the code validation module of the Xtext, and the adaptability of the DSL to a software environment is enhanced; and finally, the DSL code is enabled to be used to automatically generate the C / Java code, and language noise and language concentration camp problems are avoided.

Owner:BEIJING INST OF COMP TECH & APPL

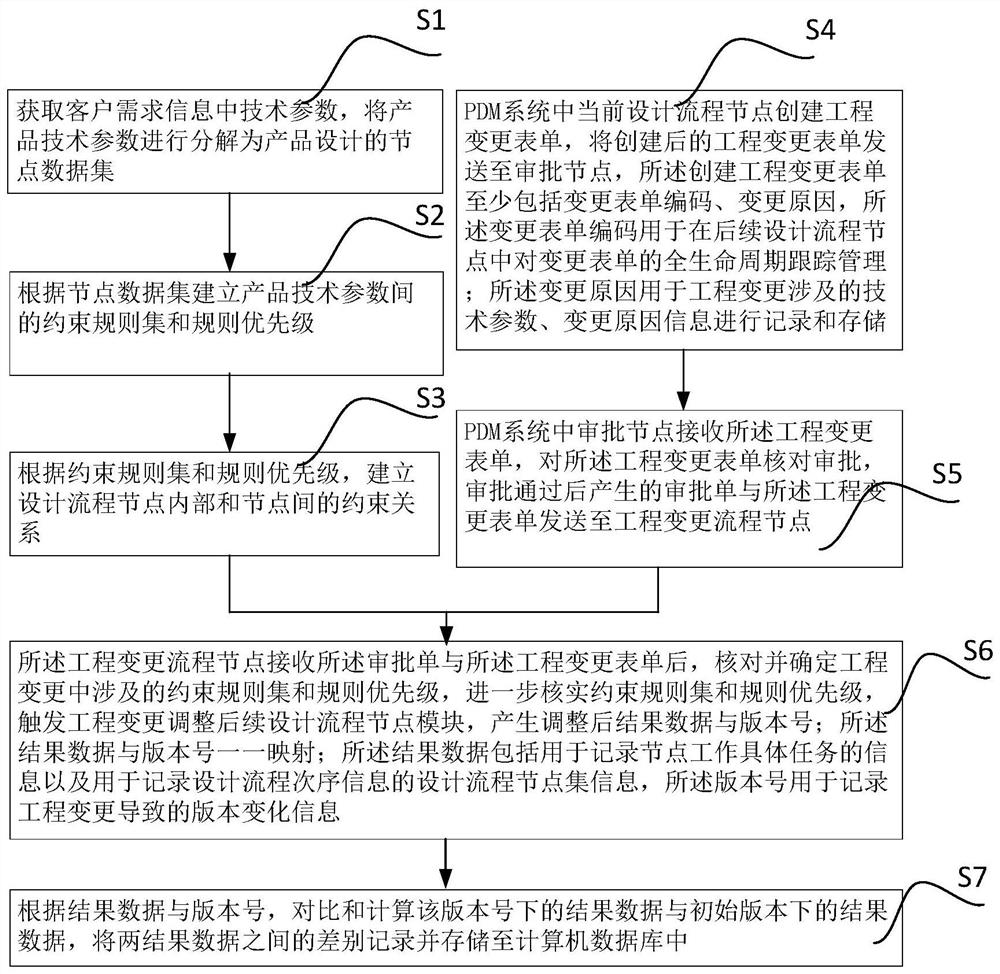

Full-life-cycle management method and system for engineering change in PDM system

PendingCN111859479ARealize associationEngineering change reductionConstraint-based CADSpecial data processing applicationsData setDesign flow

The invention relates to the field of product data management, and provides a product design process problem full-life-cycle management method and system. The method comprises the steps: obtaining technical parameters in customer demand information, and decomposing the technical parameters of a product into a node data set of product design; establishing a constraint rule set and rule priorities among the product technical parameters; establishing constraint relationship in the design process nodes and between the nodes; when an engineering change form is created in the PDM system, sending theengineering change form to an approval node, and sending the approval form generated after approval is passed and the engineering change form to an engineering change process node; and adjusting a subsequent design flow node module. According to the method, engineering changes and technical parameters can be changed, the association between the nodes is realized before the product design activityis started, and once the engineering change occurs, the repeated communication required by the data change generated by the engineering change is reduced, the full-life-cycle management of the automatic information change and the engineering change is realized, and the product collaborative design efficiency is further improved.

Owner:NINGBO ZHEDA LIANKE TECH

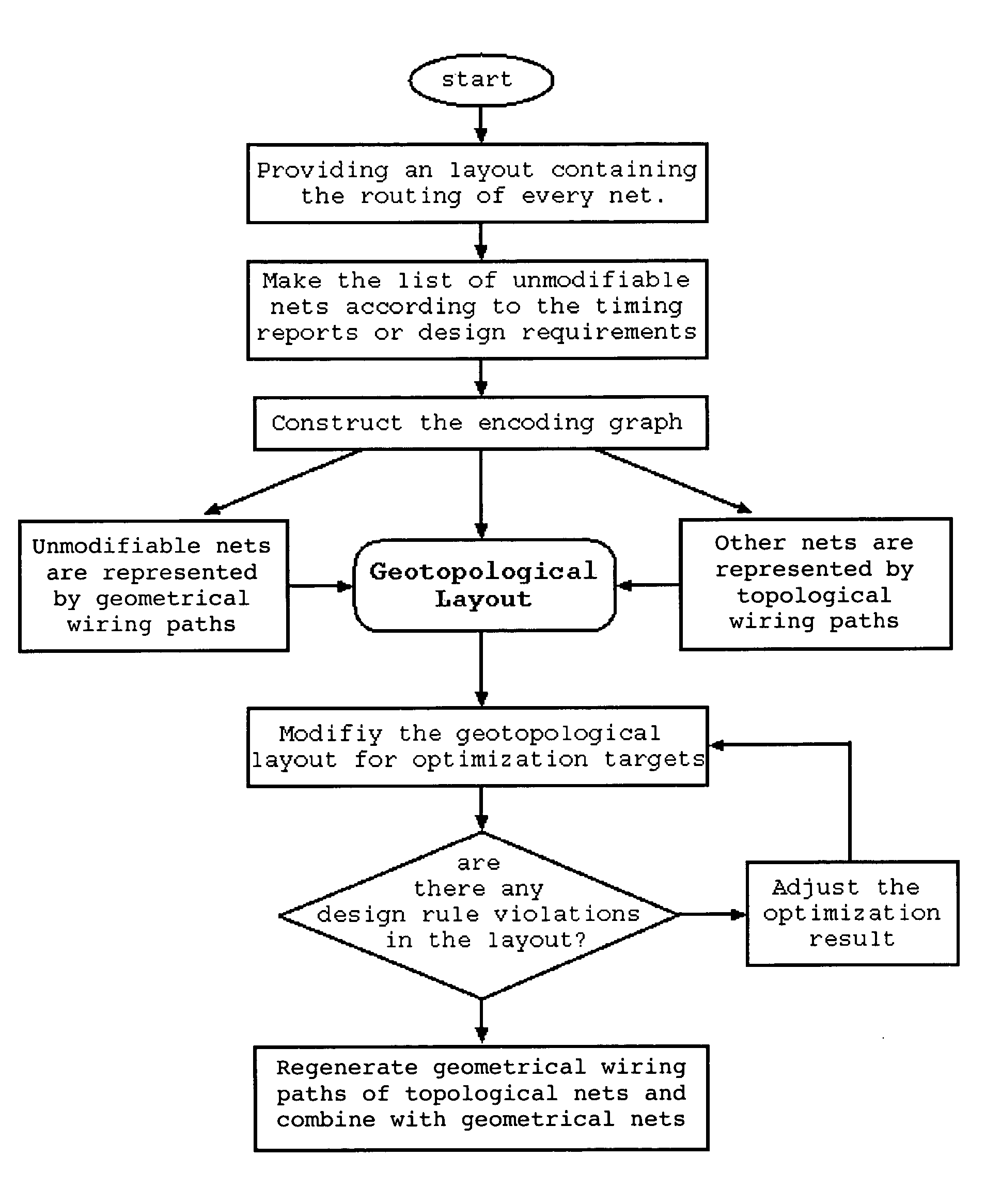

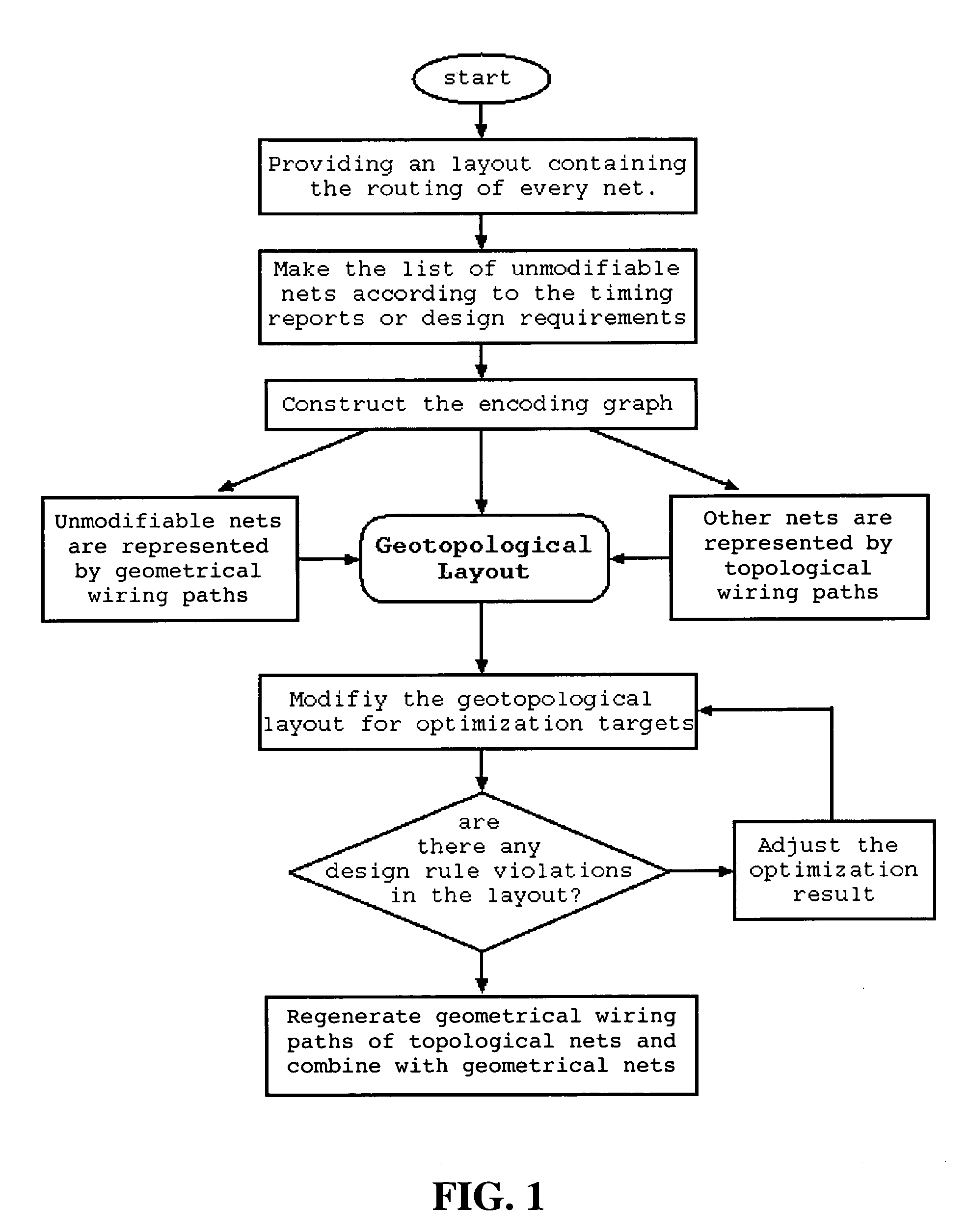

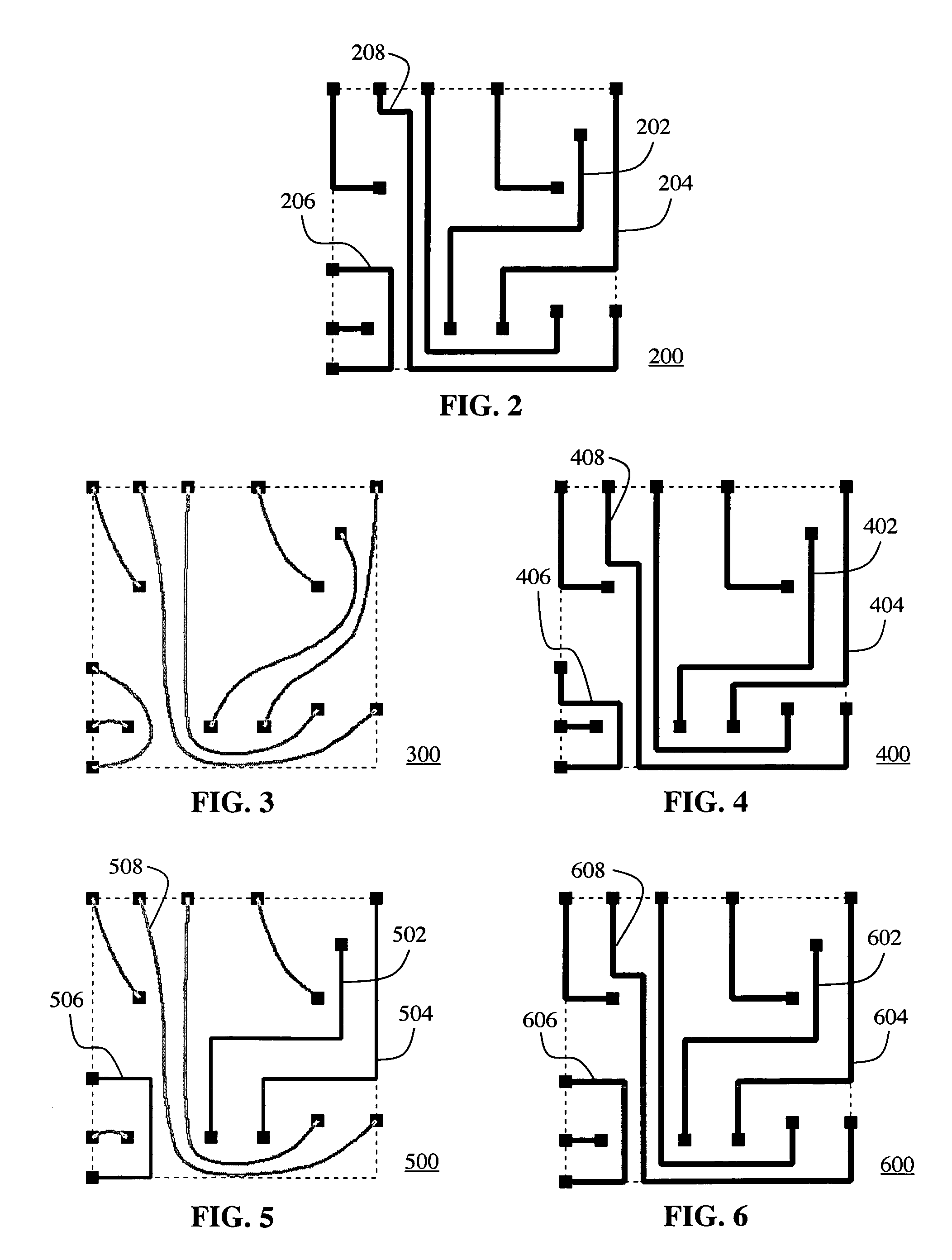

Routed layout optimization with geotopological layout encoding for integrated circuit designs

InactiveUS7131095B2Easy to modifyComputer aided designSoftware simulation/interpretation/emulationEngineeringIntegrated circuit design

Owner:NANNOR TECH

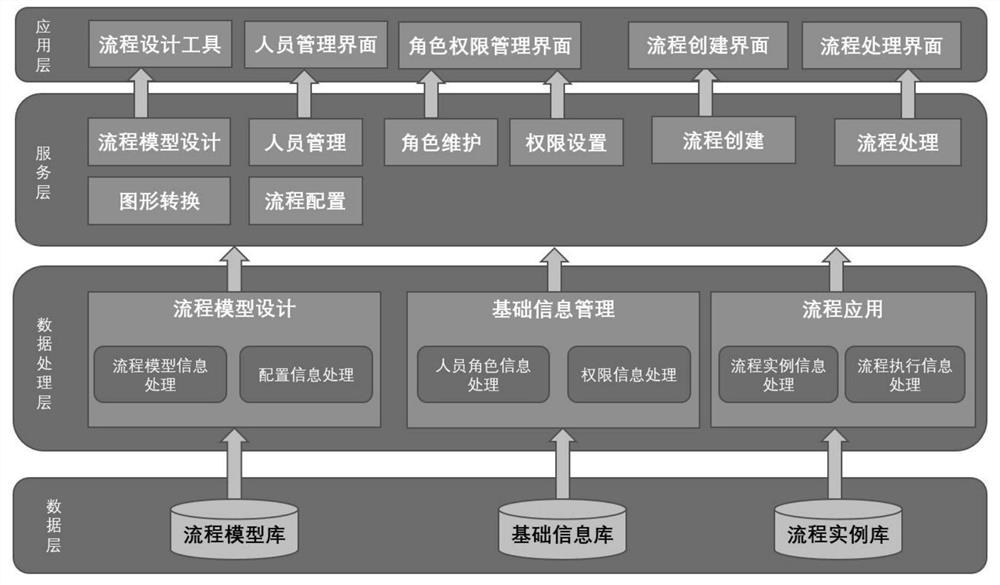

Intelligent process engine service system and method

PendingCN113535836AReduce the difficulty of writingReduce the difficulty of debuggingDatabase management systemsRelational databasesDesign flowProcessing

The invention discloses an intelligent process engine service system and method, the logic level of the system comprises an application layer, a service layer, an acquisition and data processing layer and a database, and the process management and design interface of the application layer provides a processing permission and operation type setting module for manual processing nodes in the process; and the flow engine of the service layer controls the execution of the flow by reading the settings. The system adopts a micro-service architecture, provides convenient and flexible configuration and deployment, and can be fused with an enterprise information system through a small amount of simple configuration modification, and a user can design a flow by completely operating on an interface without programming or code modification; a process design interface is simple and clear; the process storage efficiency is higher, and modification is more convenient.

Owner:成都融微软件服务有限公司

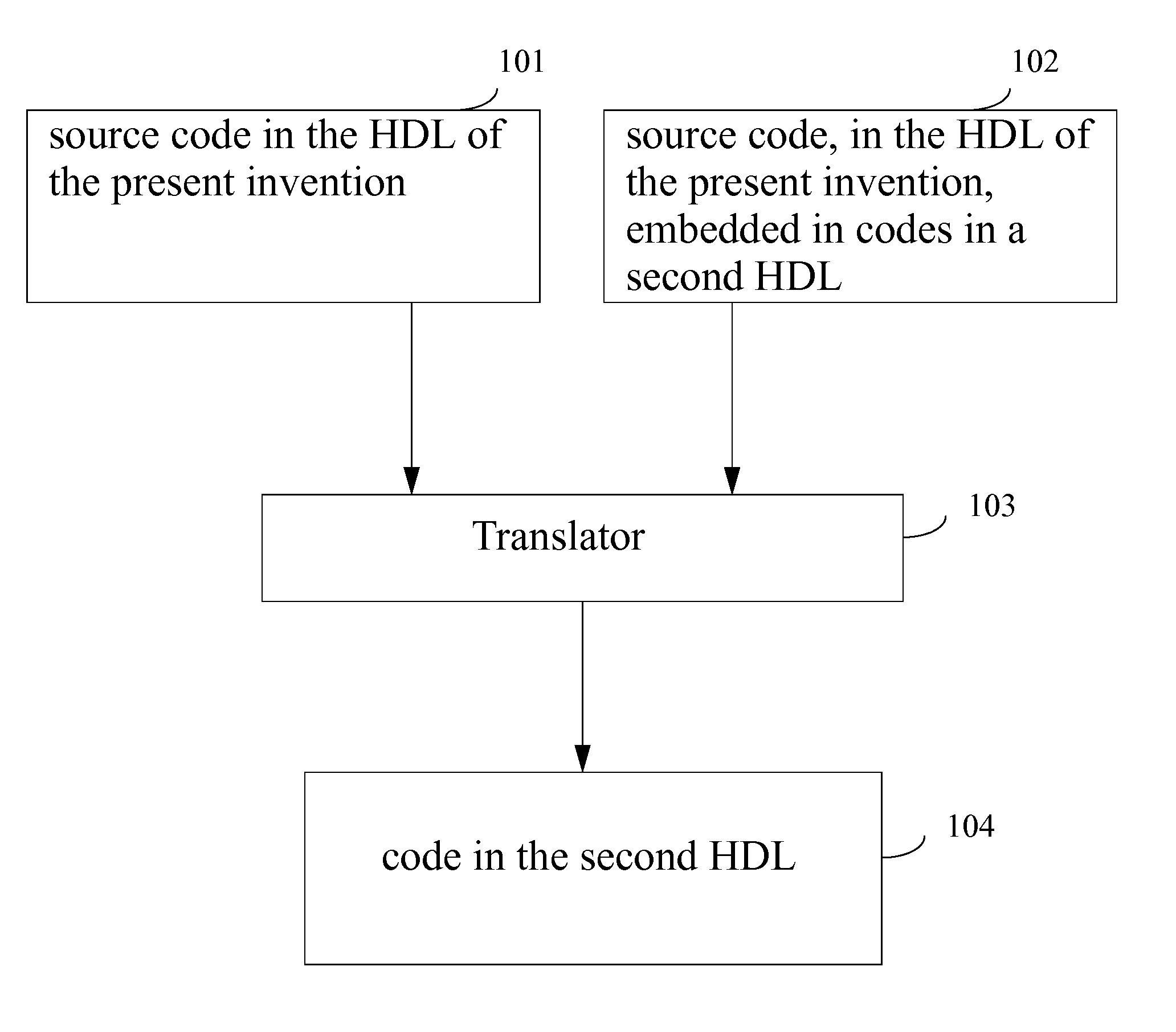

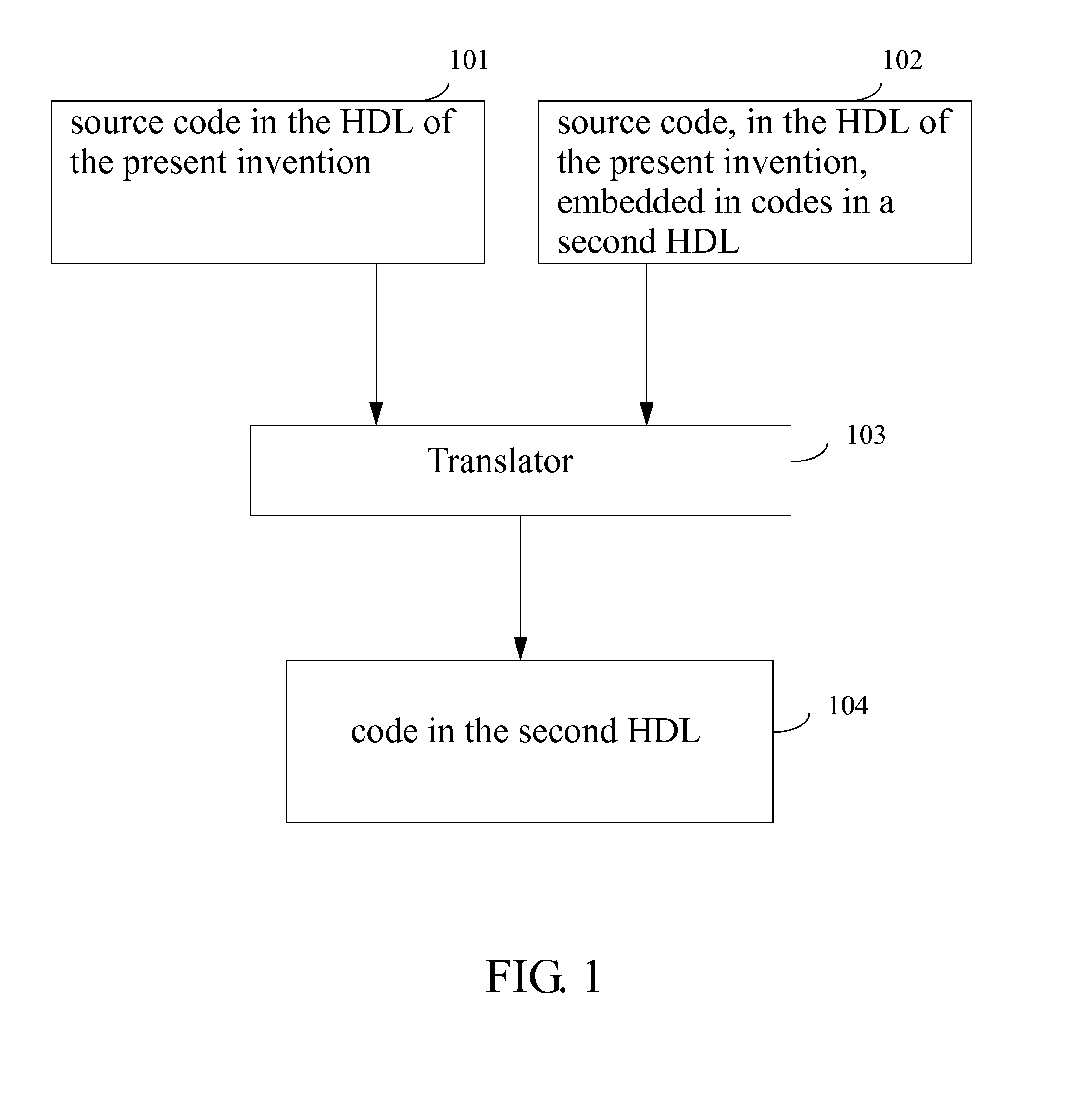

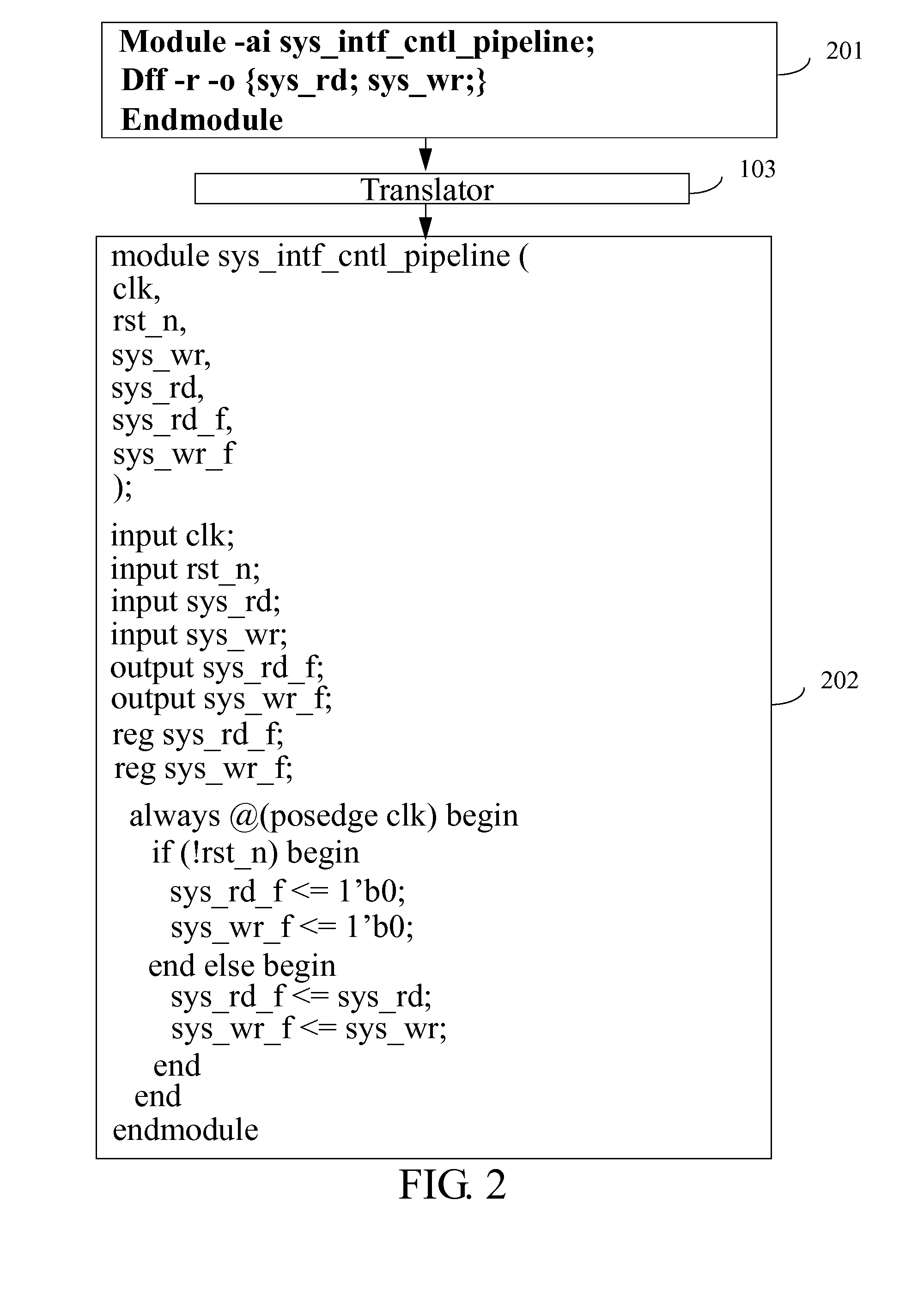

Hardware description language and a system and methods for electronic design

InactiveUS20090293036A1Commonly usedCAD circuit designSpecial data processing applicationsComputer architectureElectronic design

A Hardware Description Language (HDL) comprising of a plurality of object commands, a plurality of compile commands and a plurality of comment styles is used in methods of electronic circuit design. An object command in the HDL defines a logic object, which can be as simple as a piece of wire or as complex as a priority-encoded arbitrator with a variable number of requesters. A Register Transfer Level (RTL) design in the HDL can be translated into a set of generic gates and instantiated library modules for design verification and synthesis. The design can also be translated to a target hardware description language such as Verilog-HDL or VHDL to feed into a conventional design flow.

Owner:YAU DANIEL

Special graph avoiding method and device for optimizing manufacturability of integrated circuit

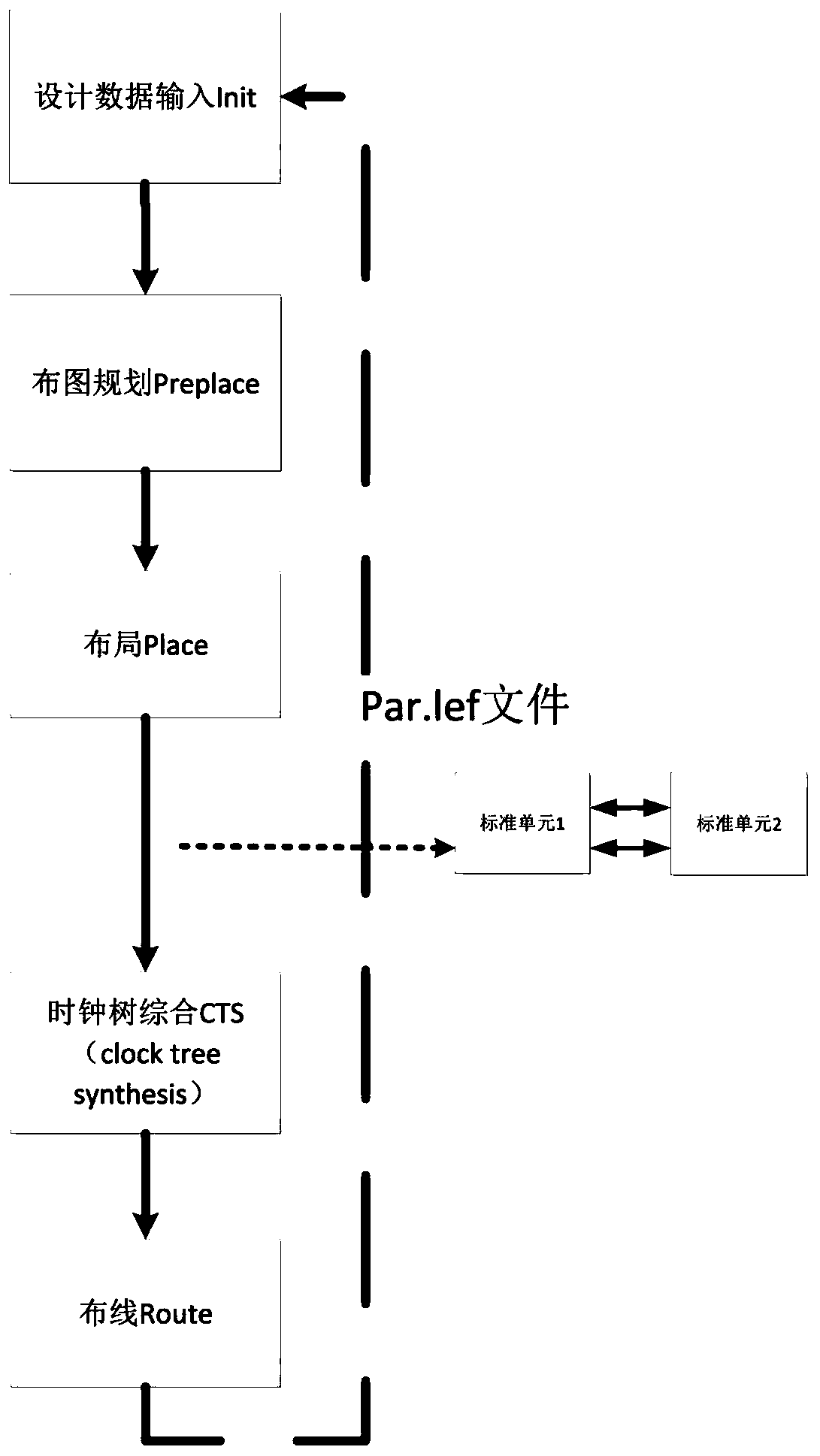

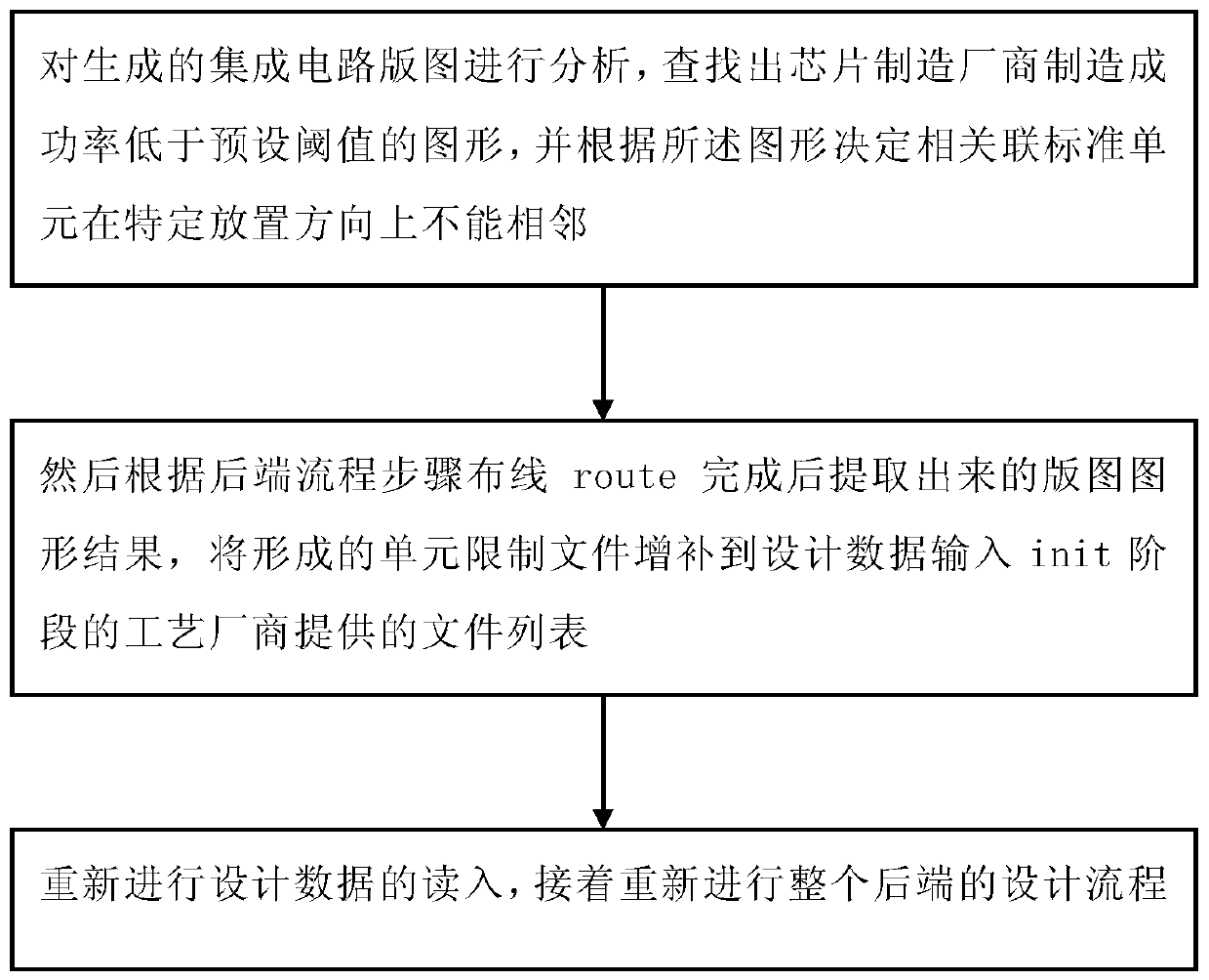

ActiveCN111177996AImprove manufacturabilityAvoid physical proximityComputer aided designSpecial data processing applicationsDesign flowIntegrated circuit layout

The invention discloses a special graph avoiding method for optimizing manufacturability of an integrated circuit. The back-end process of the integrated circuit comprises five basic steps of design data input, layout planning, layout, clock tree synthesis and wiring, after the steps are completed, a generated integrated circuit layout is analyzed, a graph with the manufacturing success rate of achip manufacturer lower than a preset threshold value is found out, and it is determined that associated standard units cannot be adjacent in the specific placement direction according to the graph; and then, according to a layout graphic result extracted after the wiring of the back-end process step is completed, the formed unit limiting file is supplemented into a file list provided by a processmanufacturer in the init stage of inputting the design data, the design data is read in again, and then, the whole back-end design process is carried out again. According to the method, files related to process manufacturing provided by process manufacturers and EDA tool manufacturers do not need to be modified, and new file formats of the EDA tool manufacturers do not need to be supplemented.

Owner:PHYTIUM TECH CO LTD