Patents

Literature

1617 results about "Low delay" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Management of uplink scheduling modes in a wireless communication system

InactiveUS20040219919A1Radio/inductive link selection arrangementsWireless commuication servicesCommunications systemMostly True

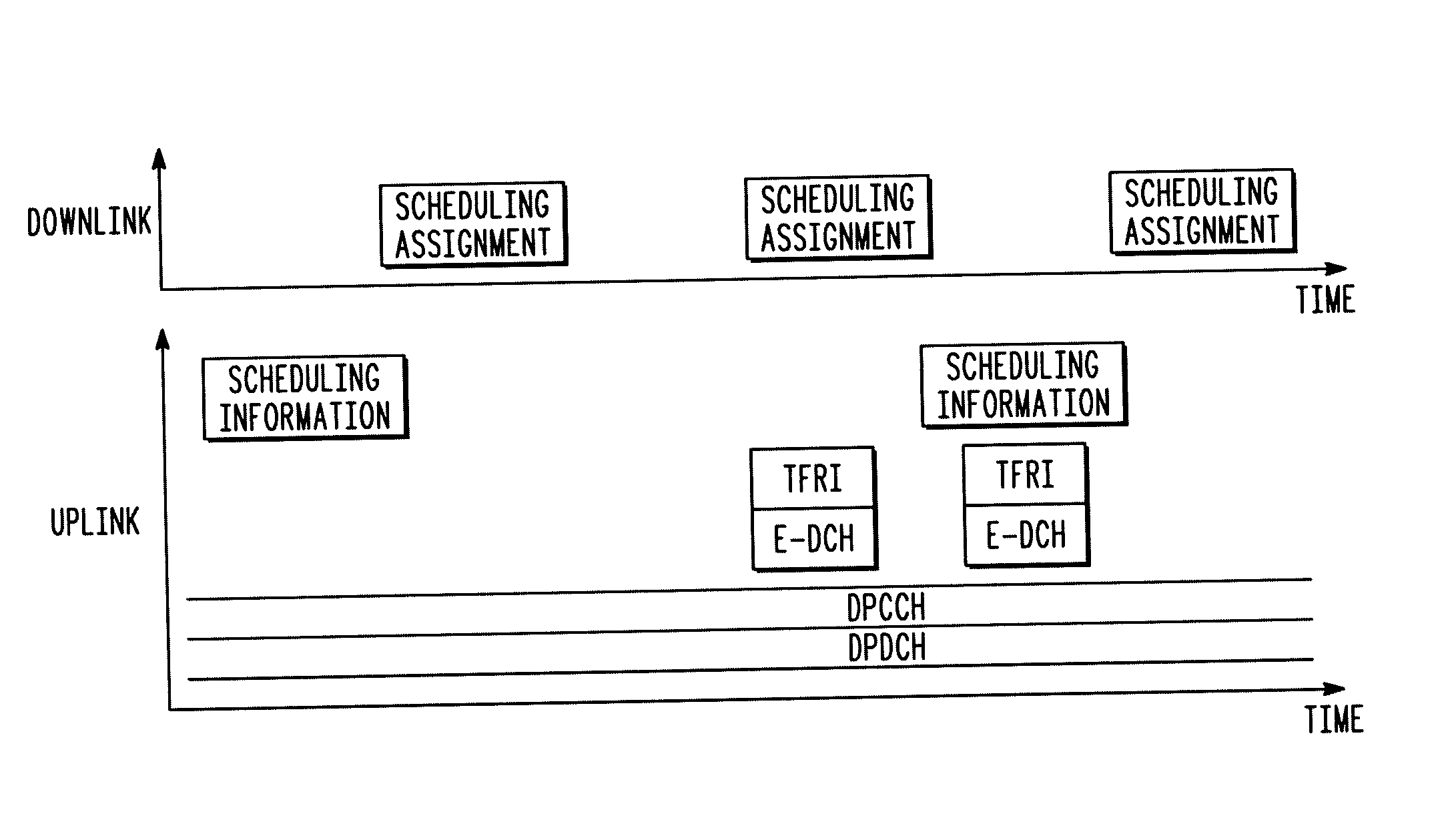

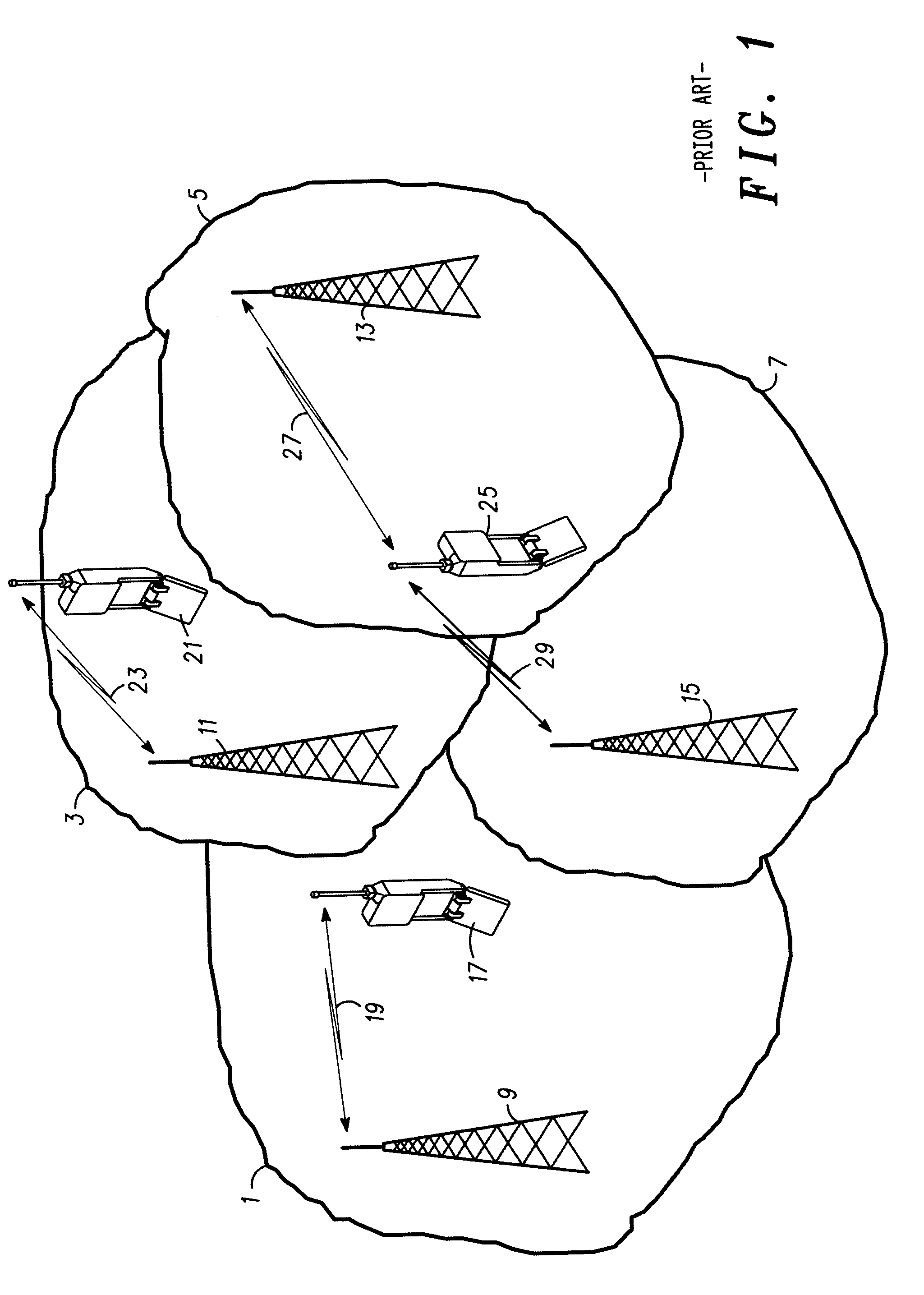

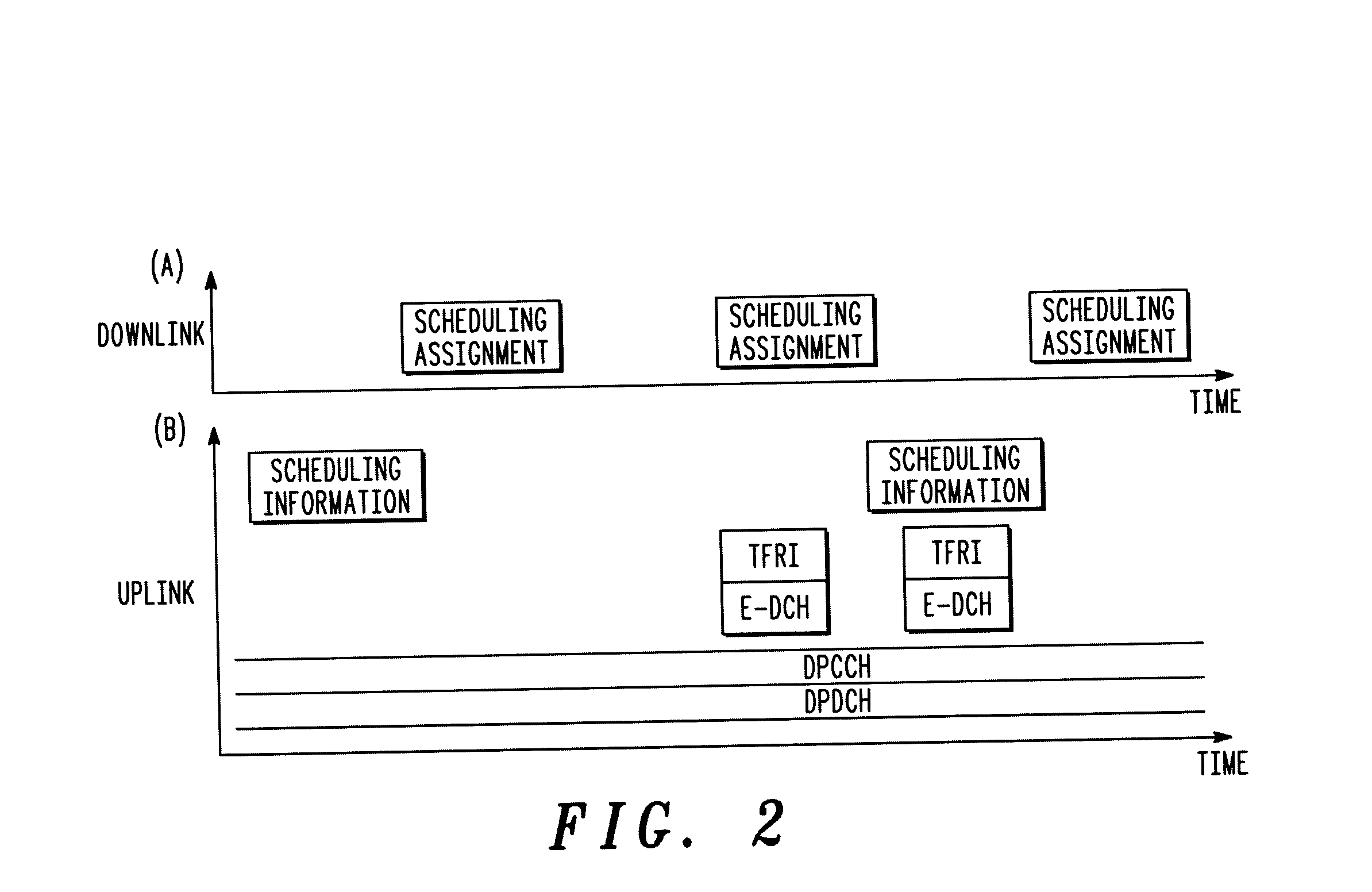

The present invention provides an advantageous method for transitioning reliably between scheduling modes on an uplink in a wireless communication system. Transitions between scheduling modes are effected as far as possible using signaling between a wireless communication device and a base station, providing low delay transitions in the majority of cases. Advantageously, signaling direct between the wireless communication device and a network control element may be employed. In addition, the method may operate effectively even when the wireless communication device is in communication with a number of base stations in a soft handoff situation because the network control element may act to ensure that all base stations correspond to the current scheduling mode employed by the wireless communication device.

Owner:GOOGLE TECH HLDG LLC +1

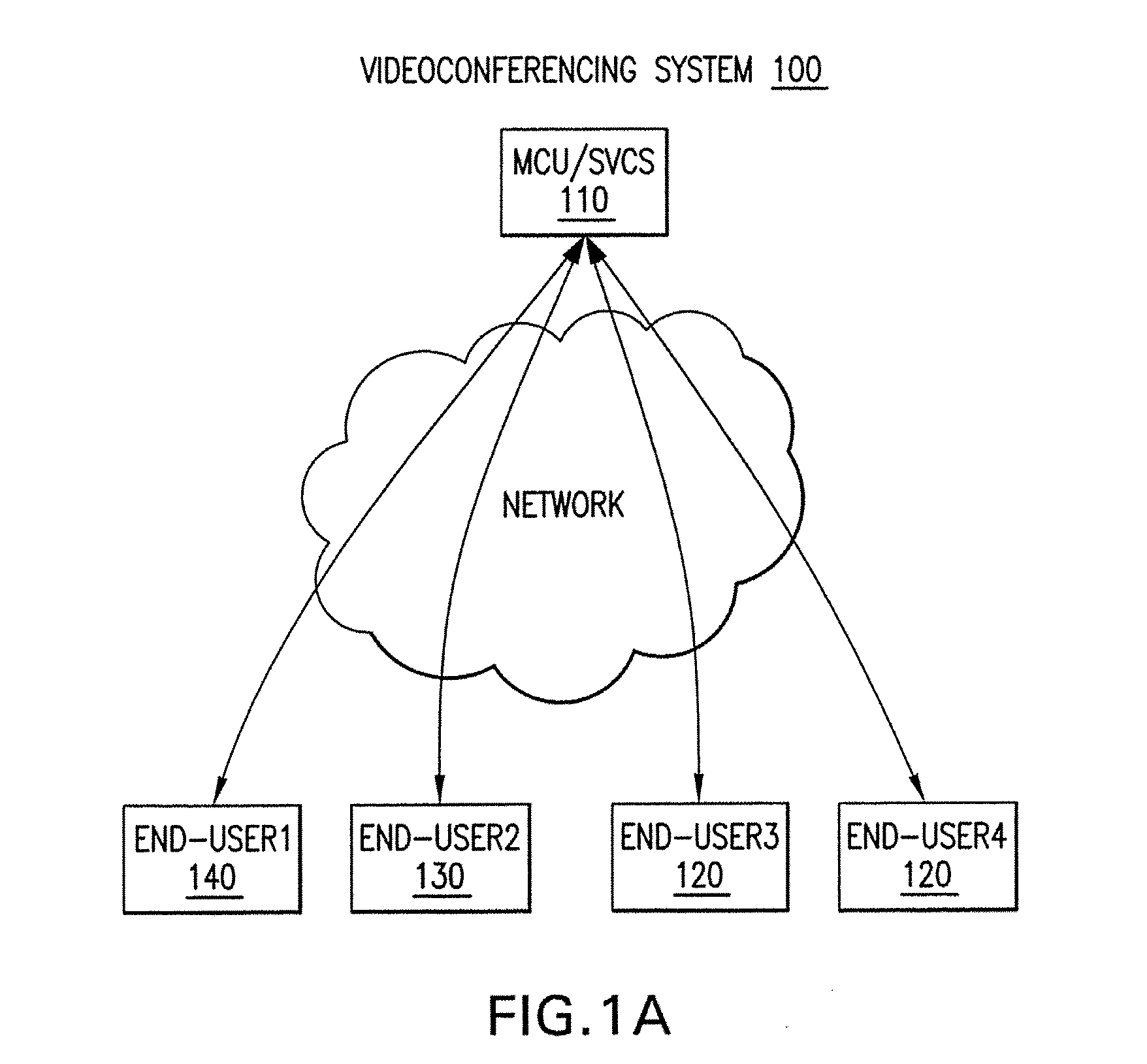

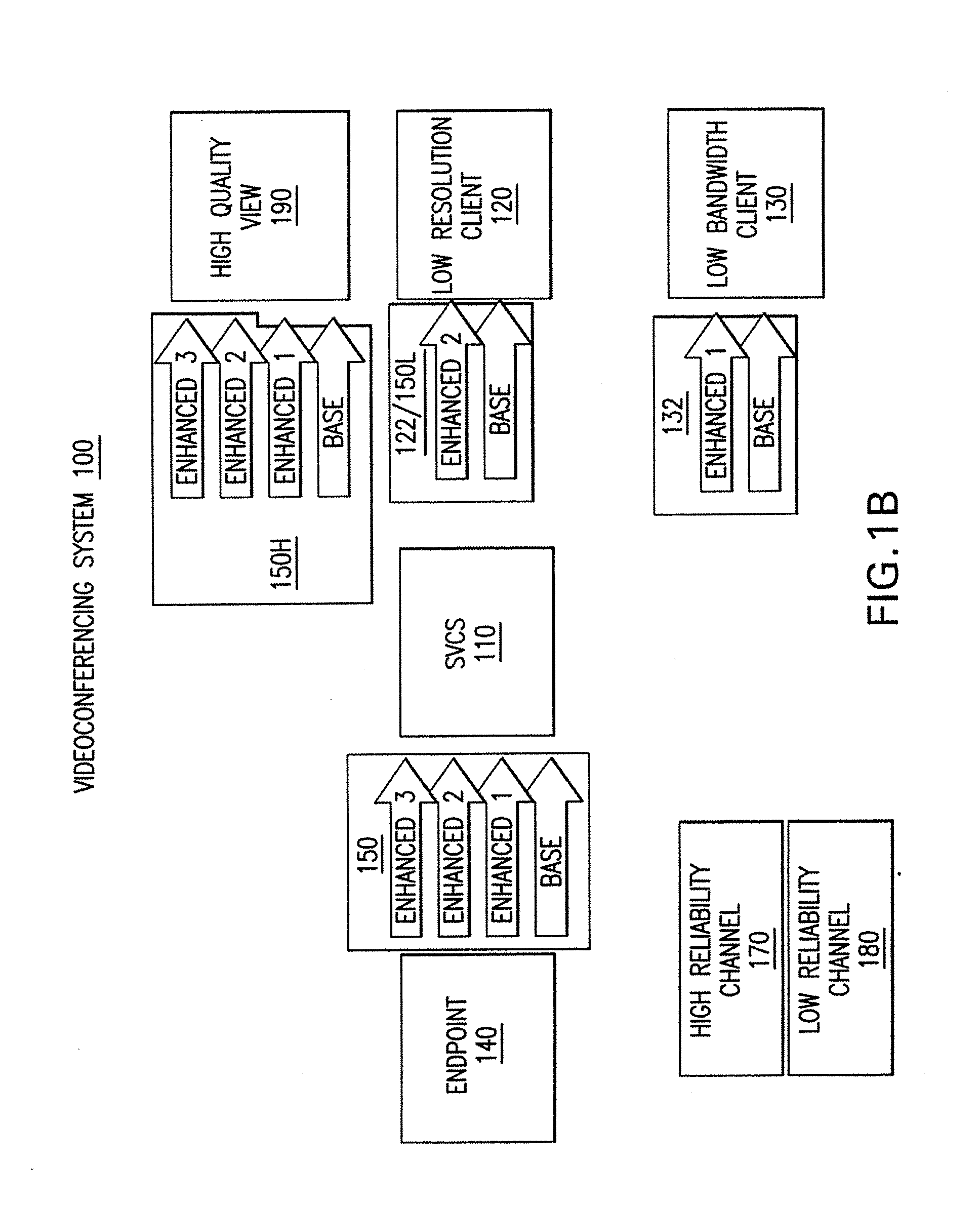

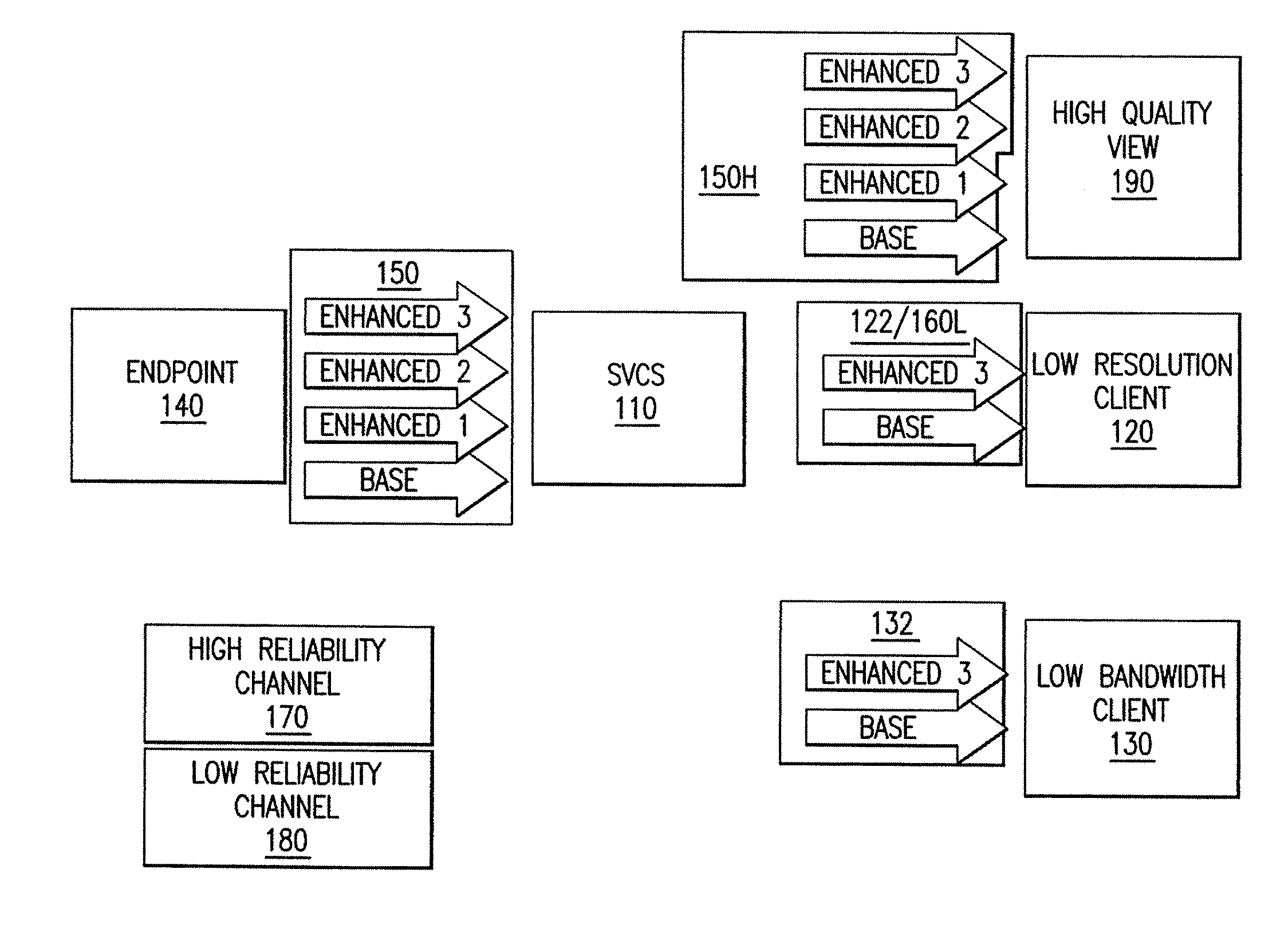

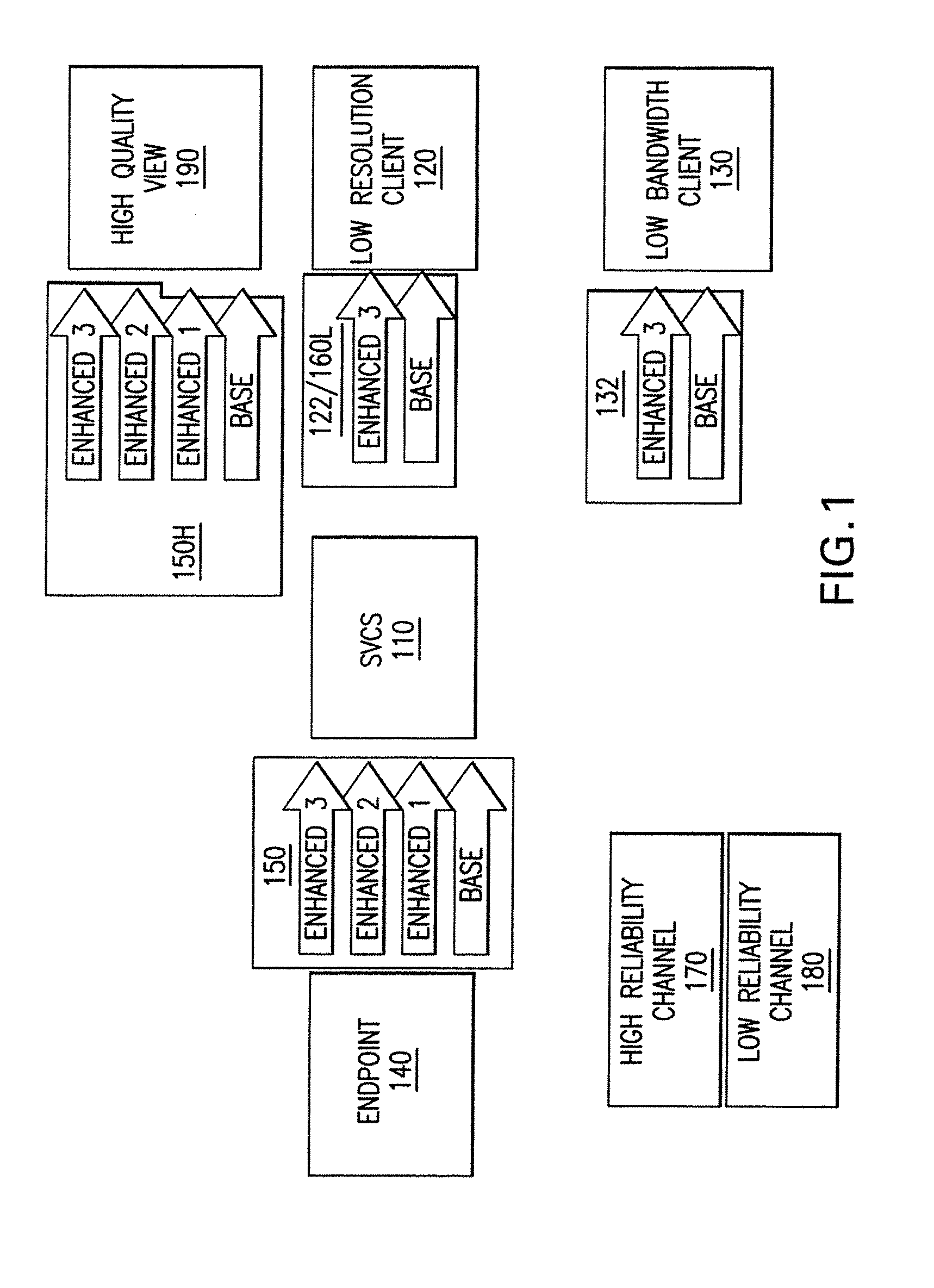

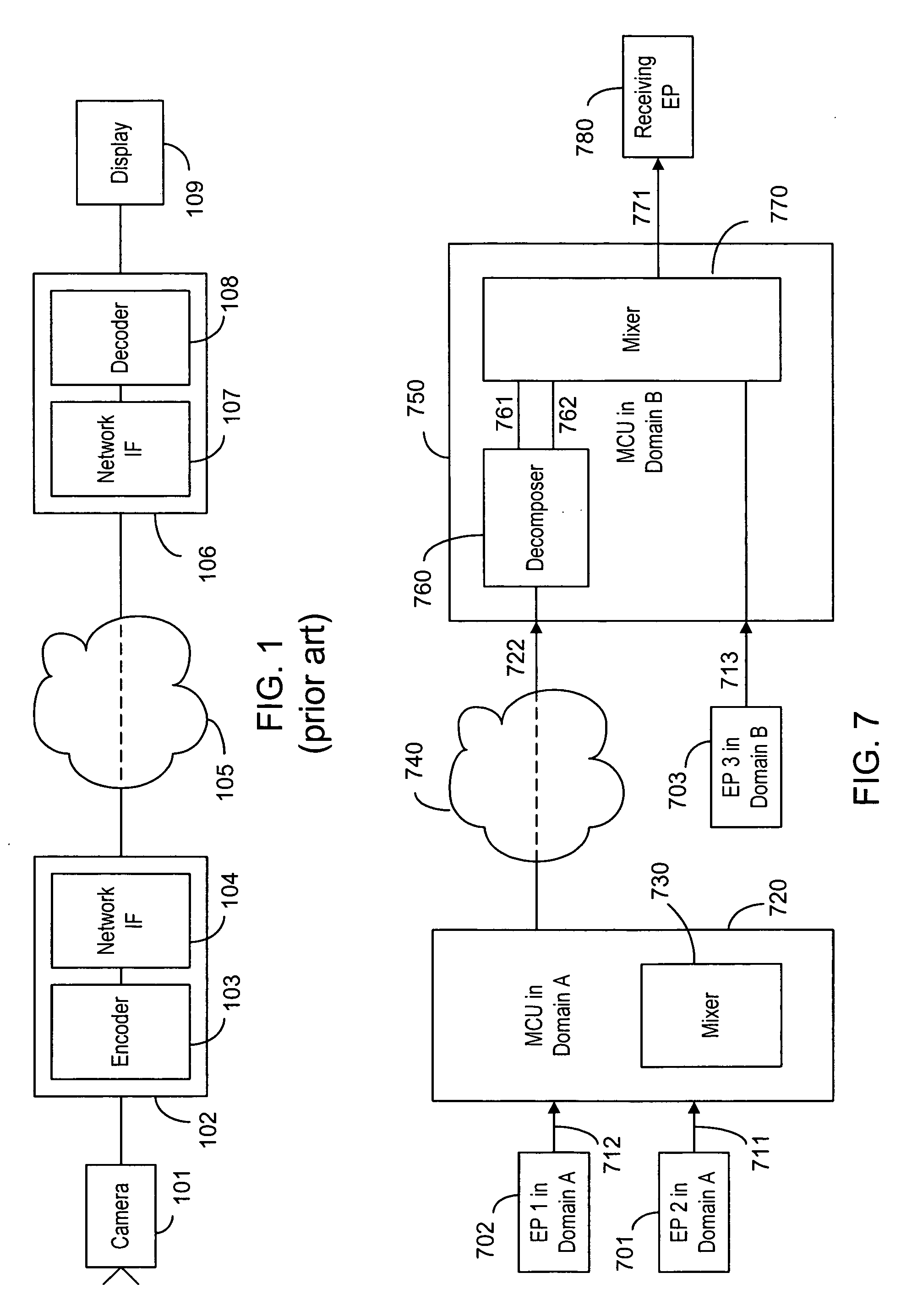

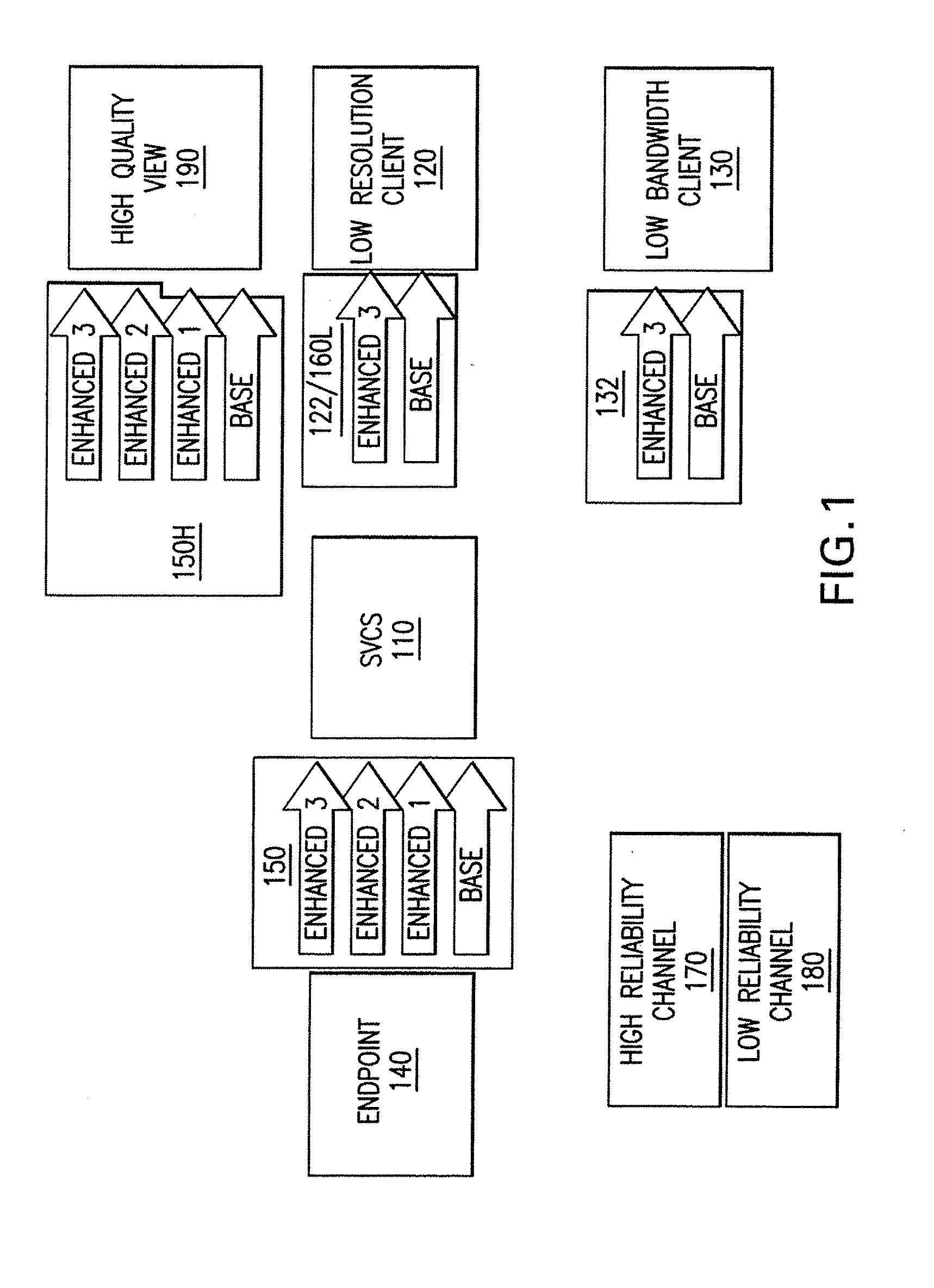

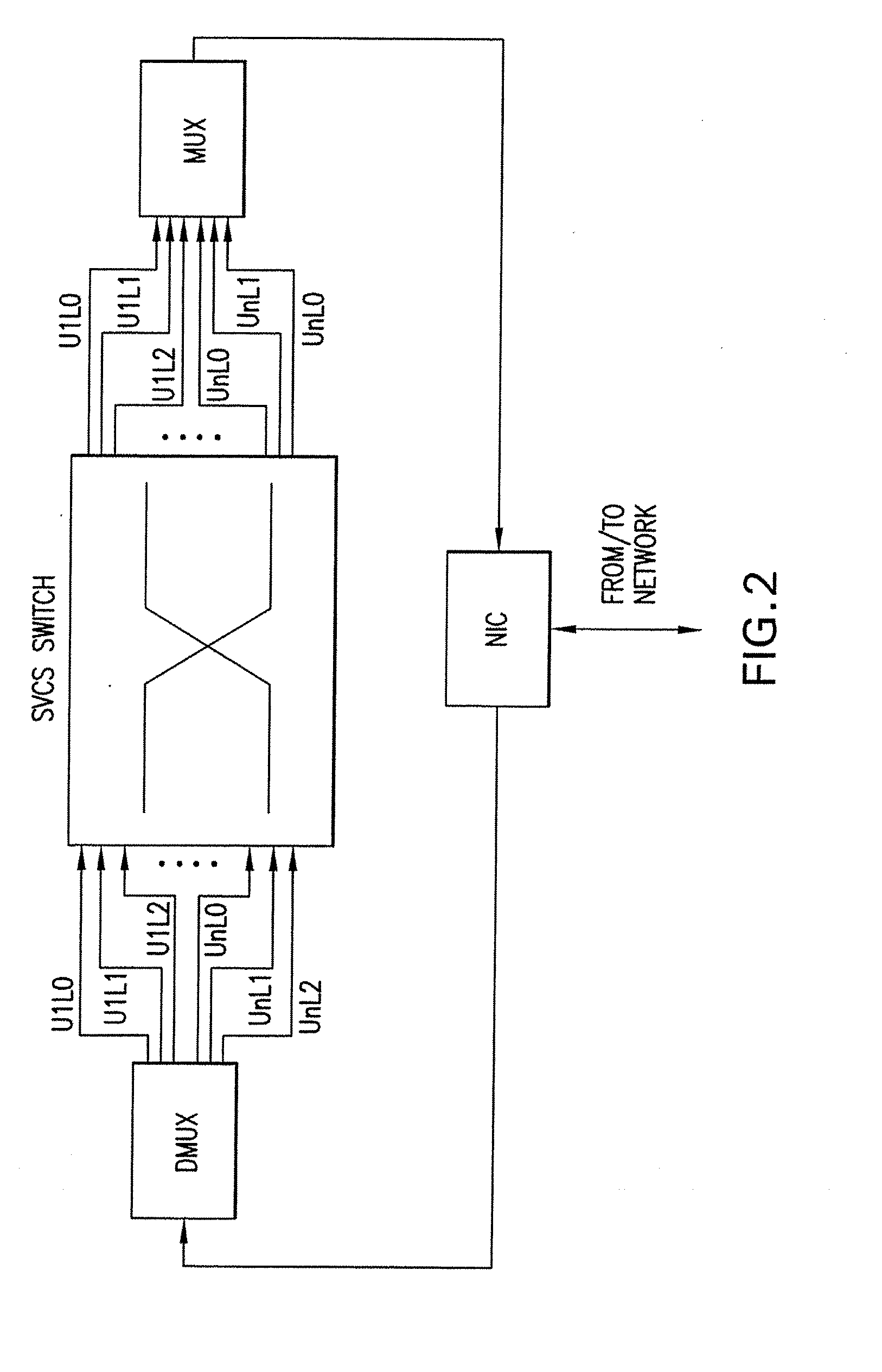

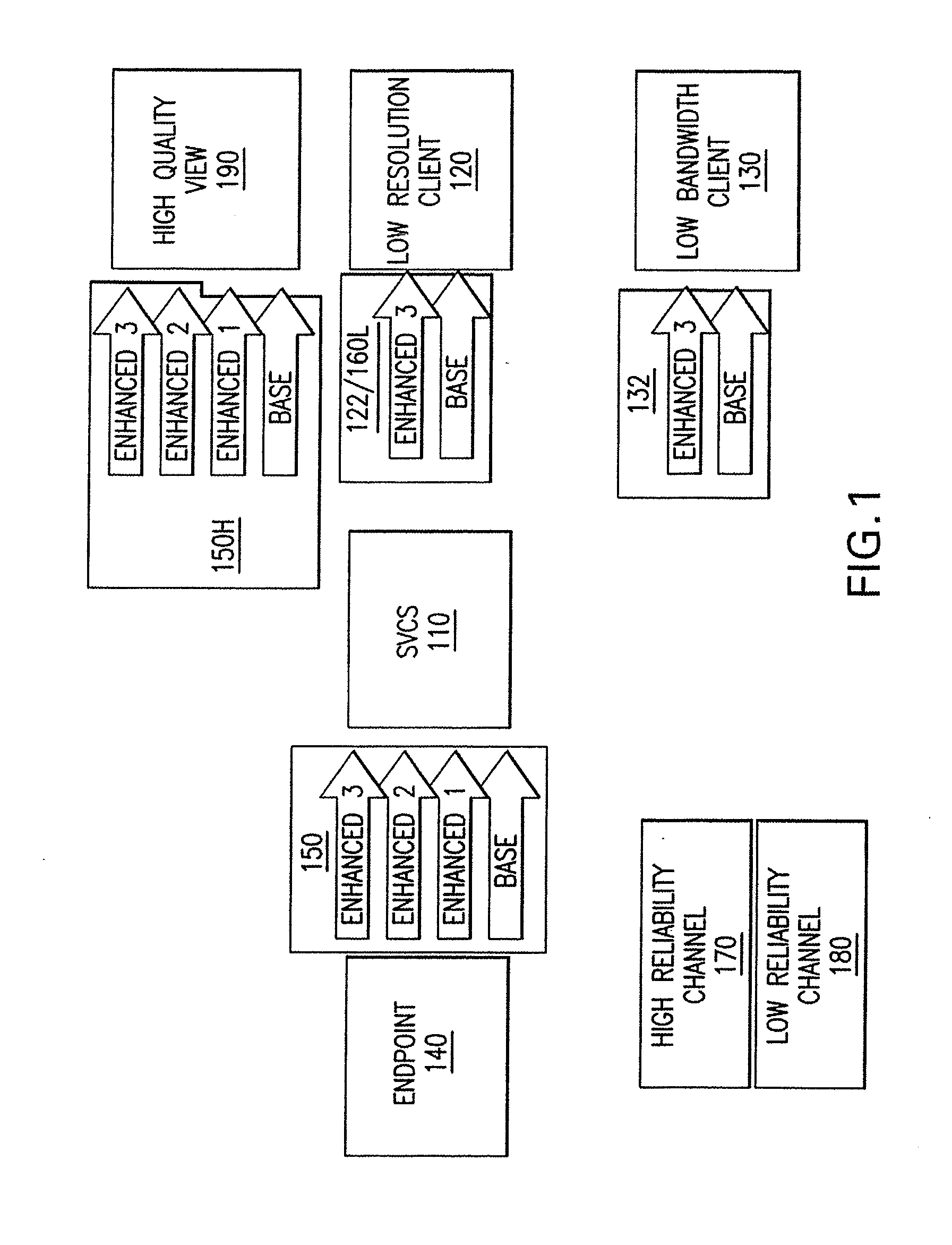

System and method for scalable and low-delay videoconferencing using scalable video coding

ActiveUS20080211901A1Decrease in error resilienceReduce reboundPicture reproducers using cathode ray tubesPicture reproducers with optical-mechanical scanningVideo encodingImage resolution

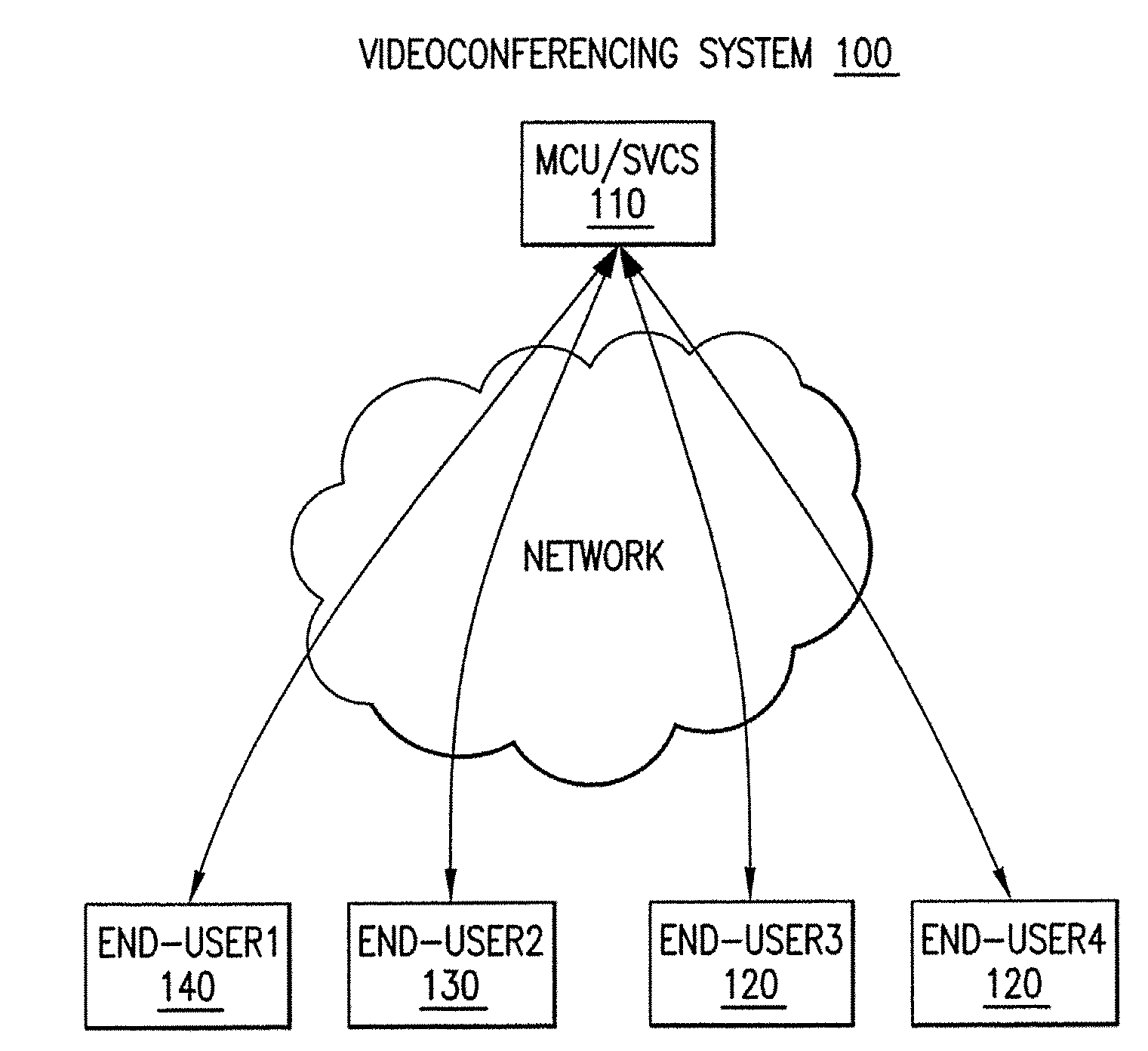

Scalable video codecs are provided for use in videoconferencing systems and applications hosted on heterogeneous endpoints / receivers and network environments. The scalable video codecs provide a coded representation of a source video signal at multiple temporal, quality, and spatial resolutions.

Owner:VIDYO

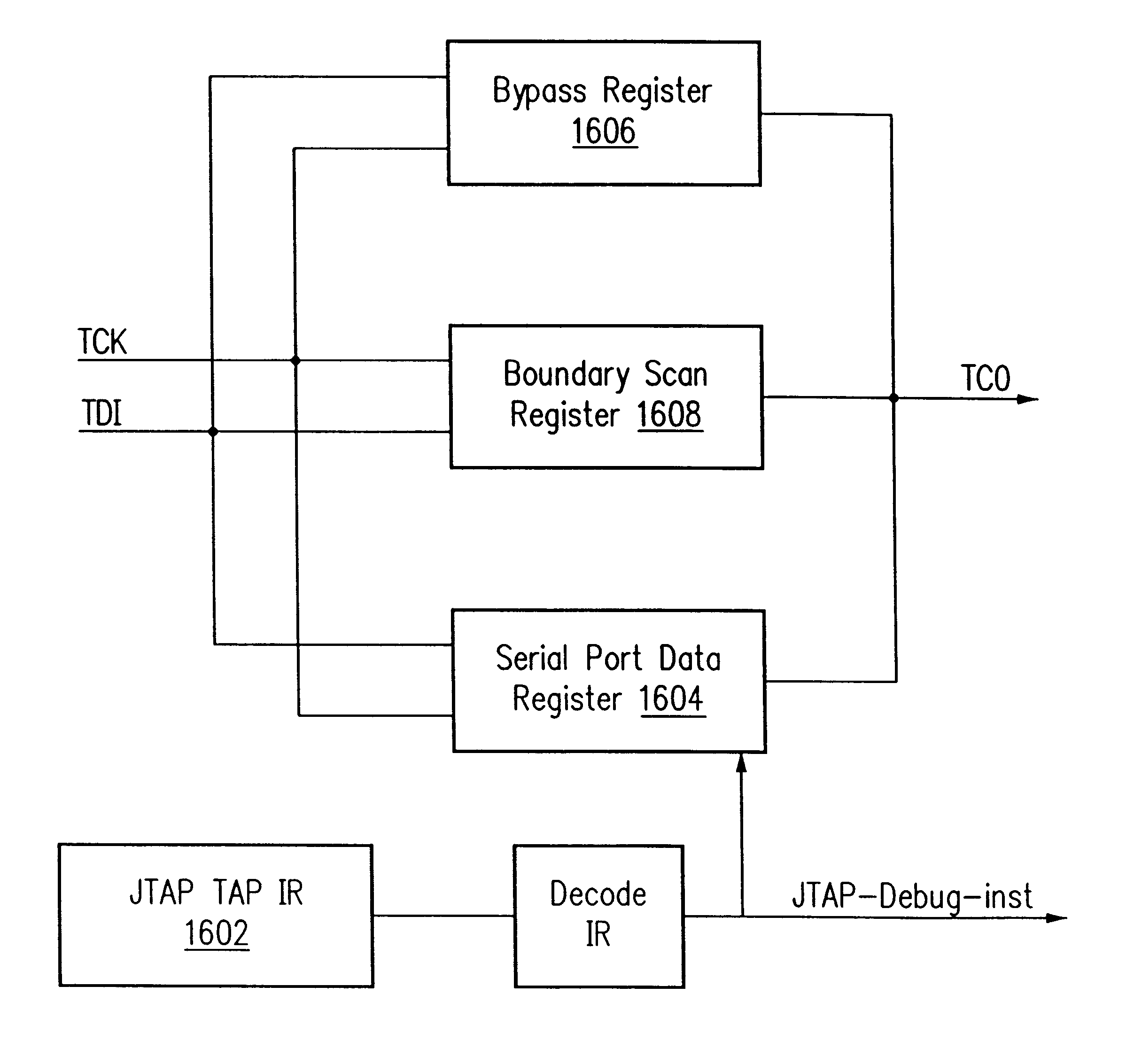

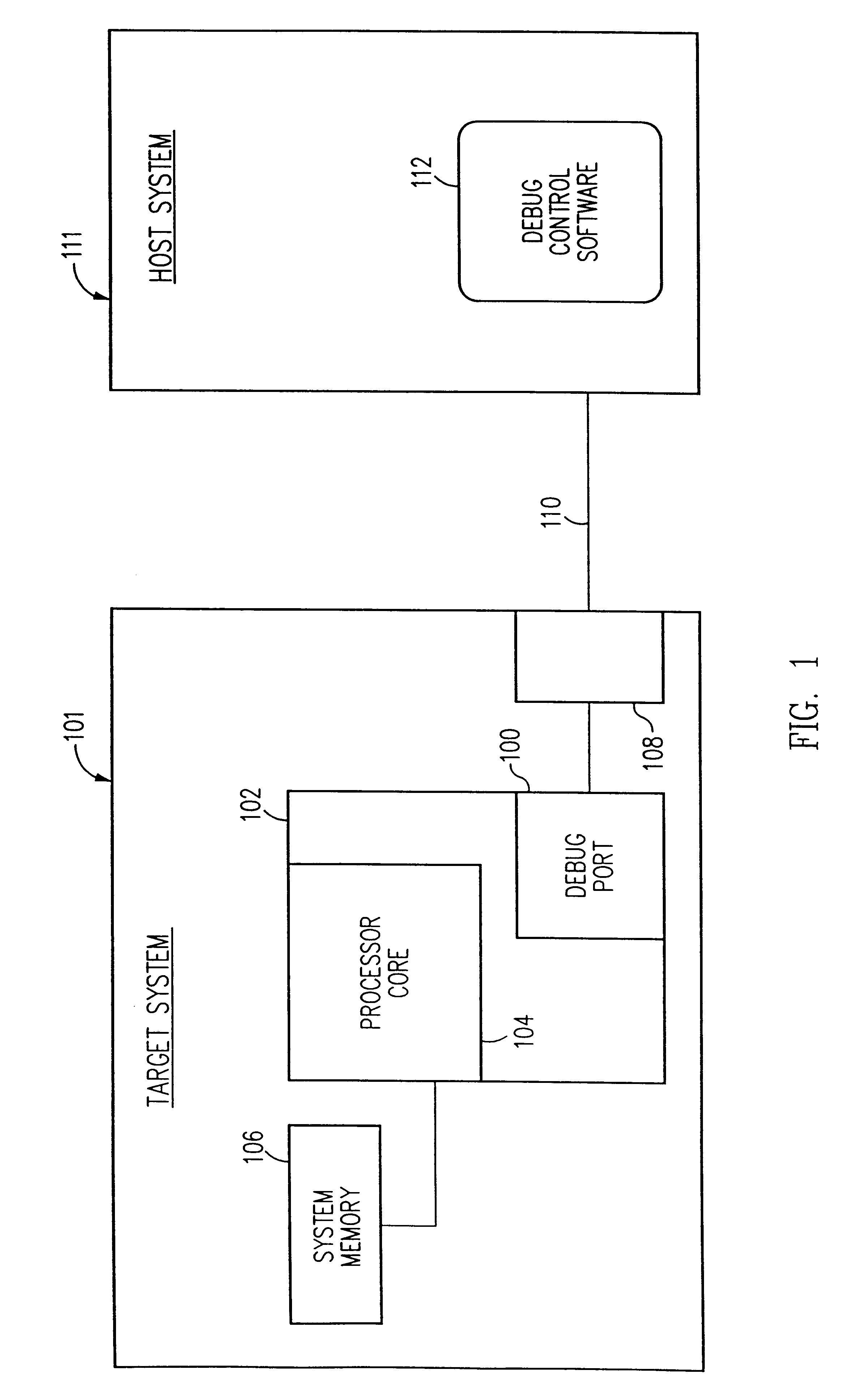

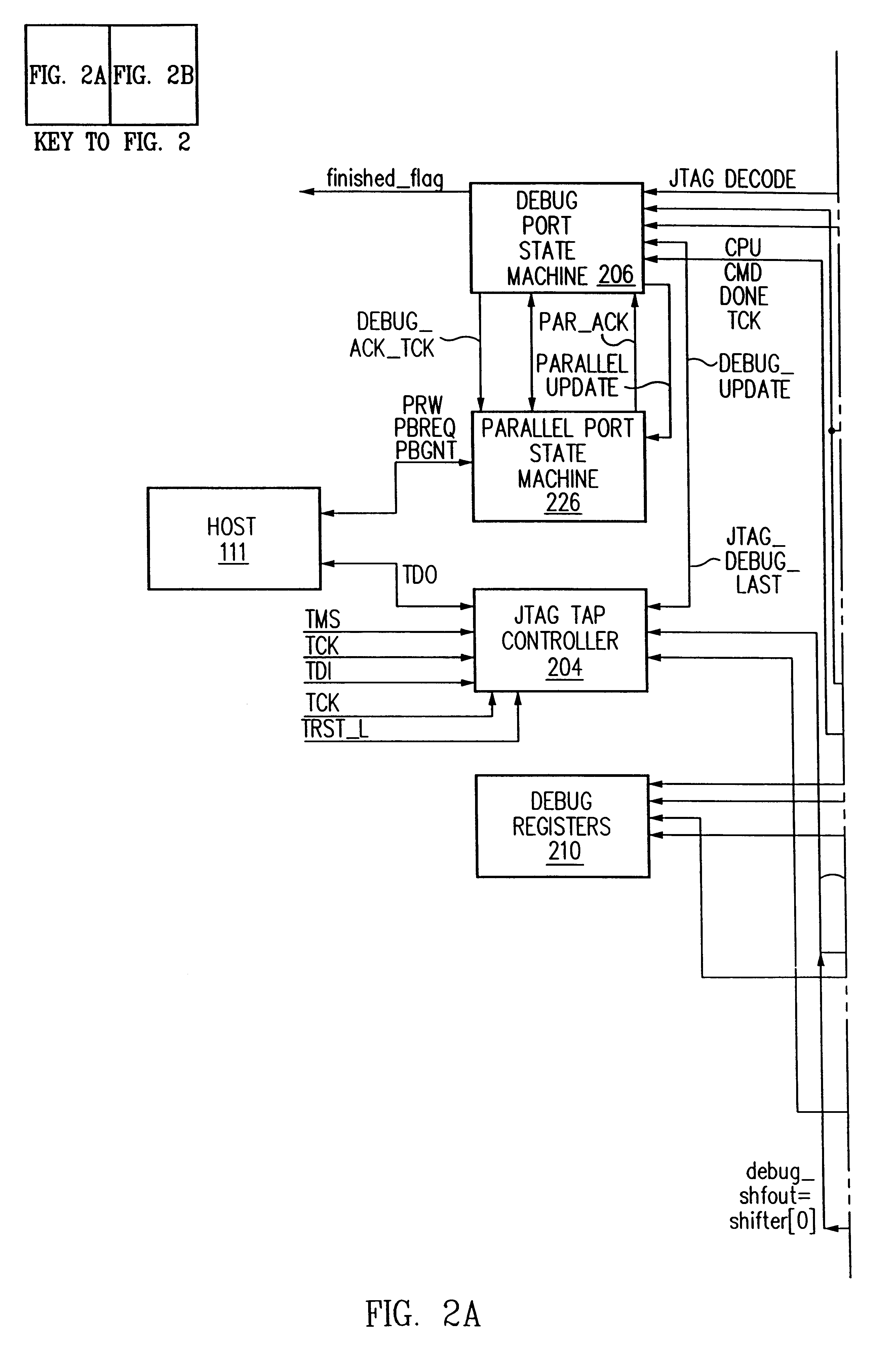

Debug interface including logic generating handshake signals between a processor, an input/output port, and a trace logic

A system for debugging a processor includes a debug interface including a handshake logic for communicating commands and data from a serial input / output port to a processor and to a trace control logic with a low delay. The handshake logic results in a low latency through the inclusion of a state machine that operates at the same speed as the processor. The state machine generates handshake signals to communicate among the serial input / output port, the processor, and the trace control logic.

Owner:ADVANCED MICRO DEVICES INC

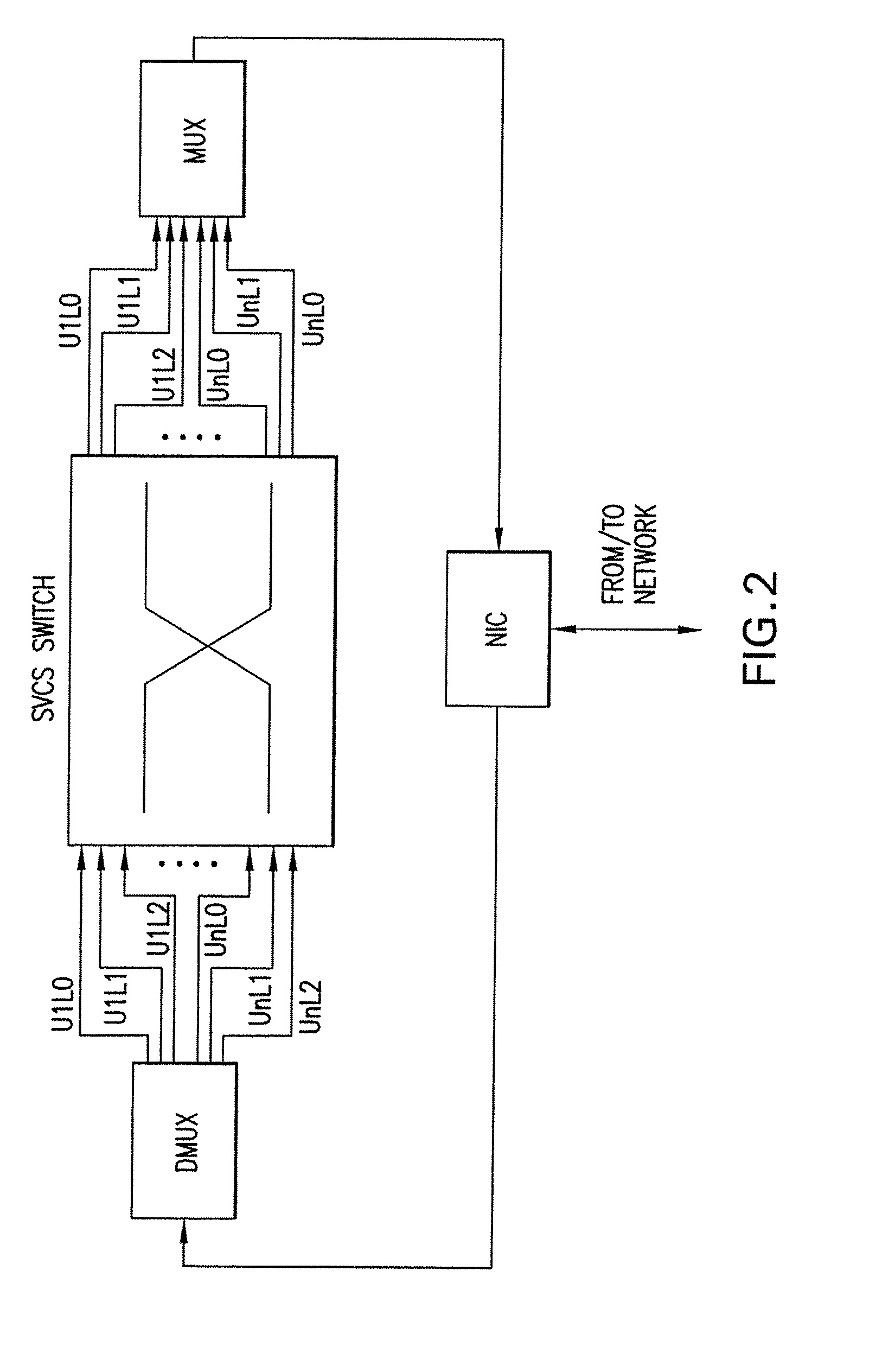

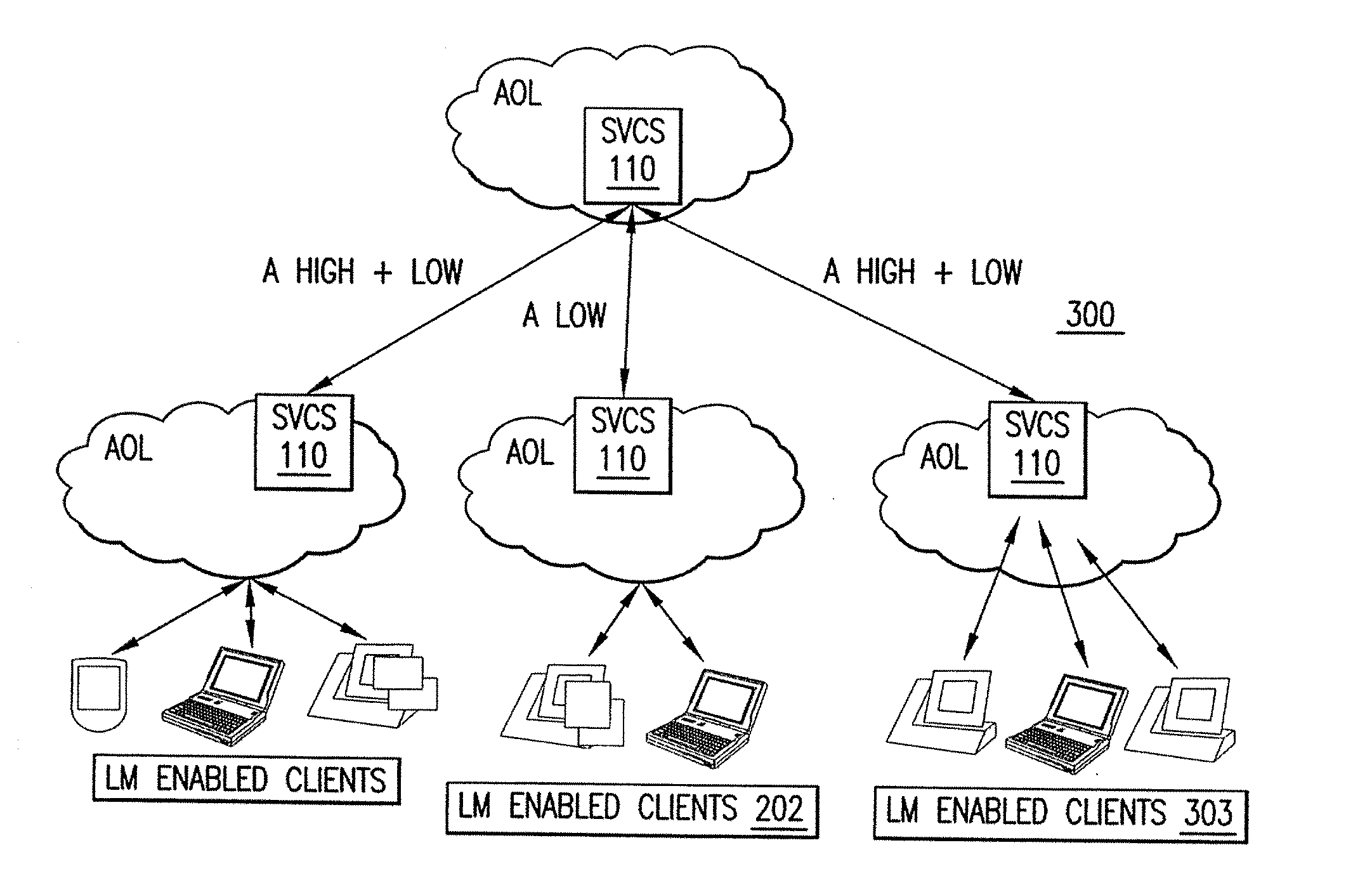

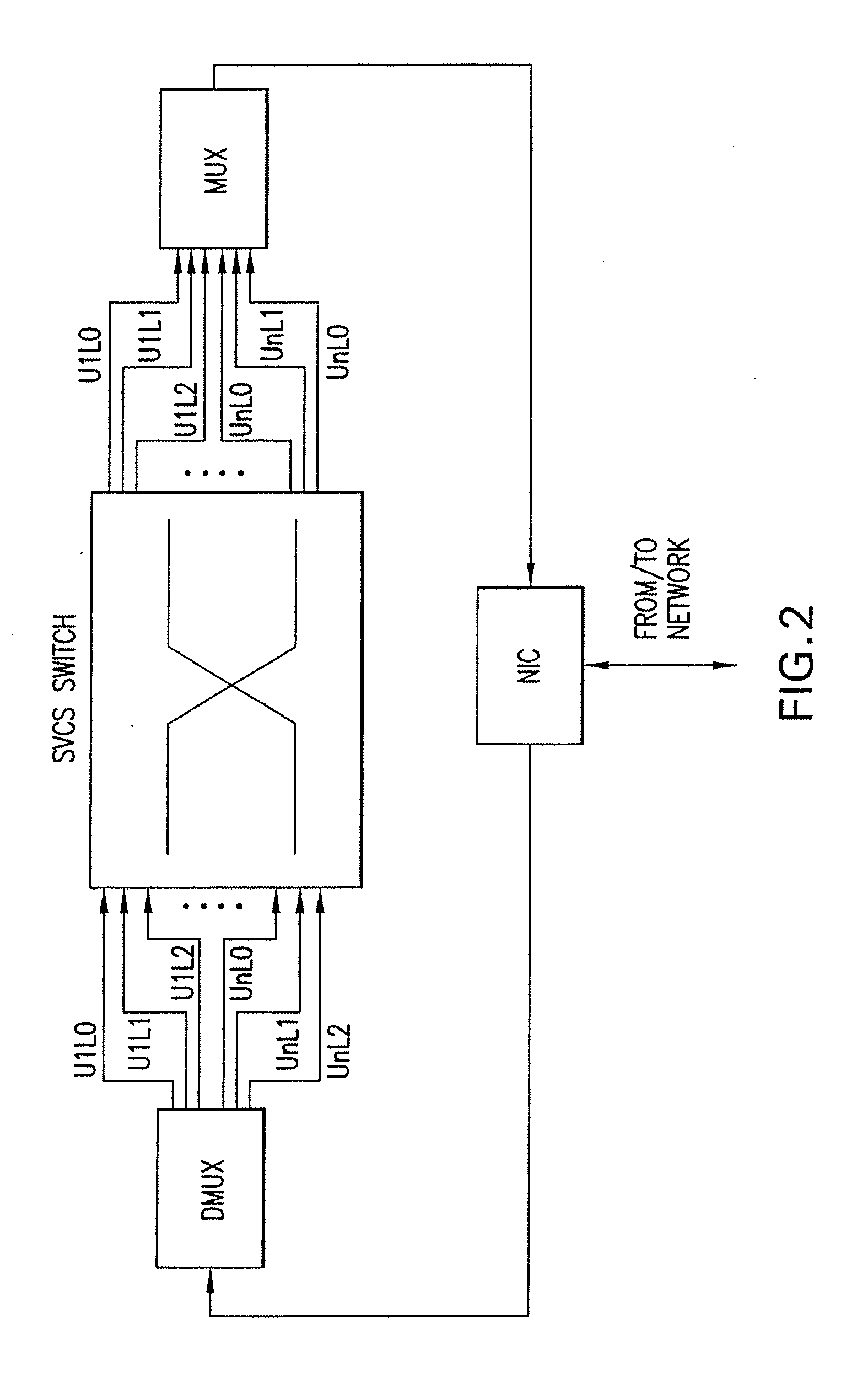

System and method for a conference server architecture for low delay and distributed conferencing applications

ActiveUS7593032B2Lower latencyImprove fault toleranceTelevision conference systemsTwo-way working systemsComputer architectureLow delay

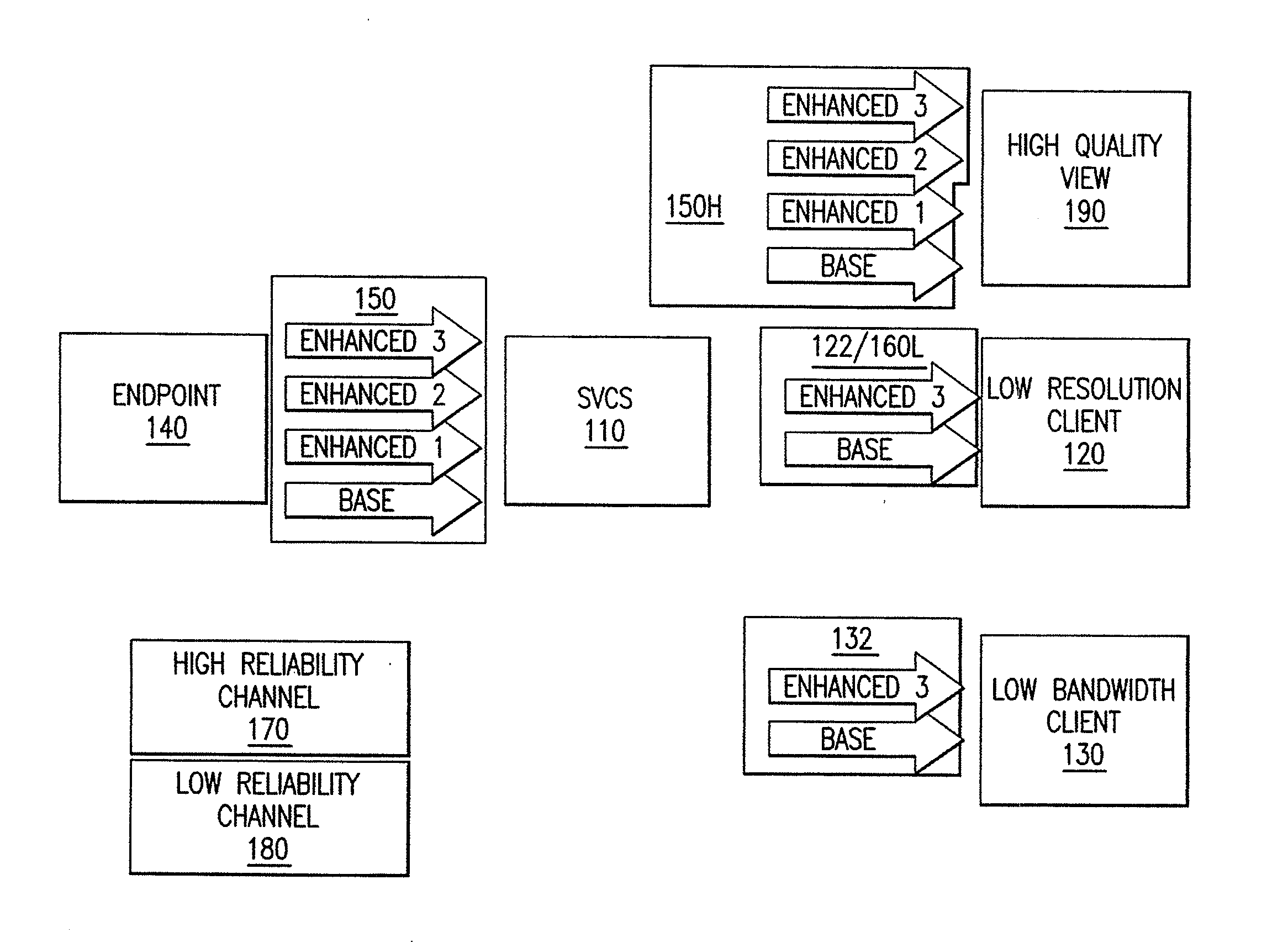

Systems and methods for conducting a multi-endpoint video signal conference are provided. Conferencing endpoints are linked by pairs of a reliable and a less reliable communication channel. Conference video signals are scaleable coded in base layer and enhancement layers format. Video signal base layers, which correspond to a minimum picture quality, are communicated over reliable channels. The video signal enhancements layers may be communicated over the less reliable channels. A conference server mediates the switching of video layer information from transmitting endpoints to receiving endpoints without any intermediate coding or re-coding operations. The video conference can be integrated with an audio conference using either scalable coded audio signals or non-scaleable coded audio signals.

Owner:VIDYO

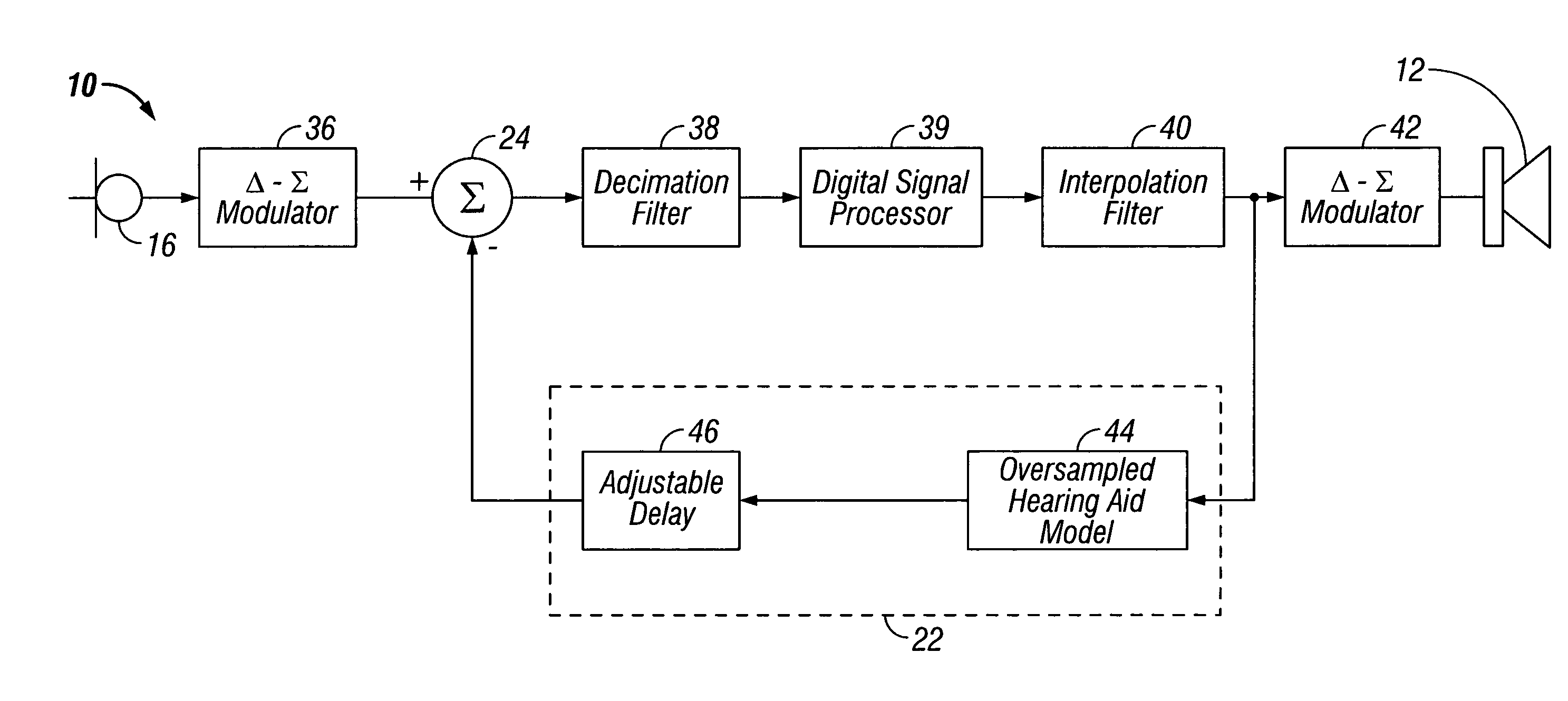

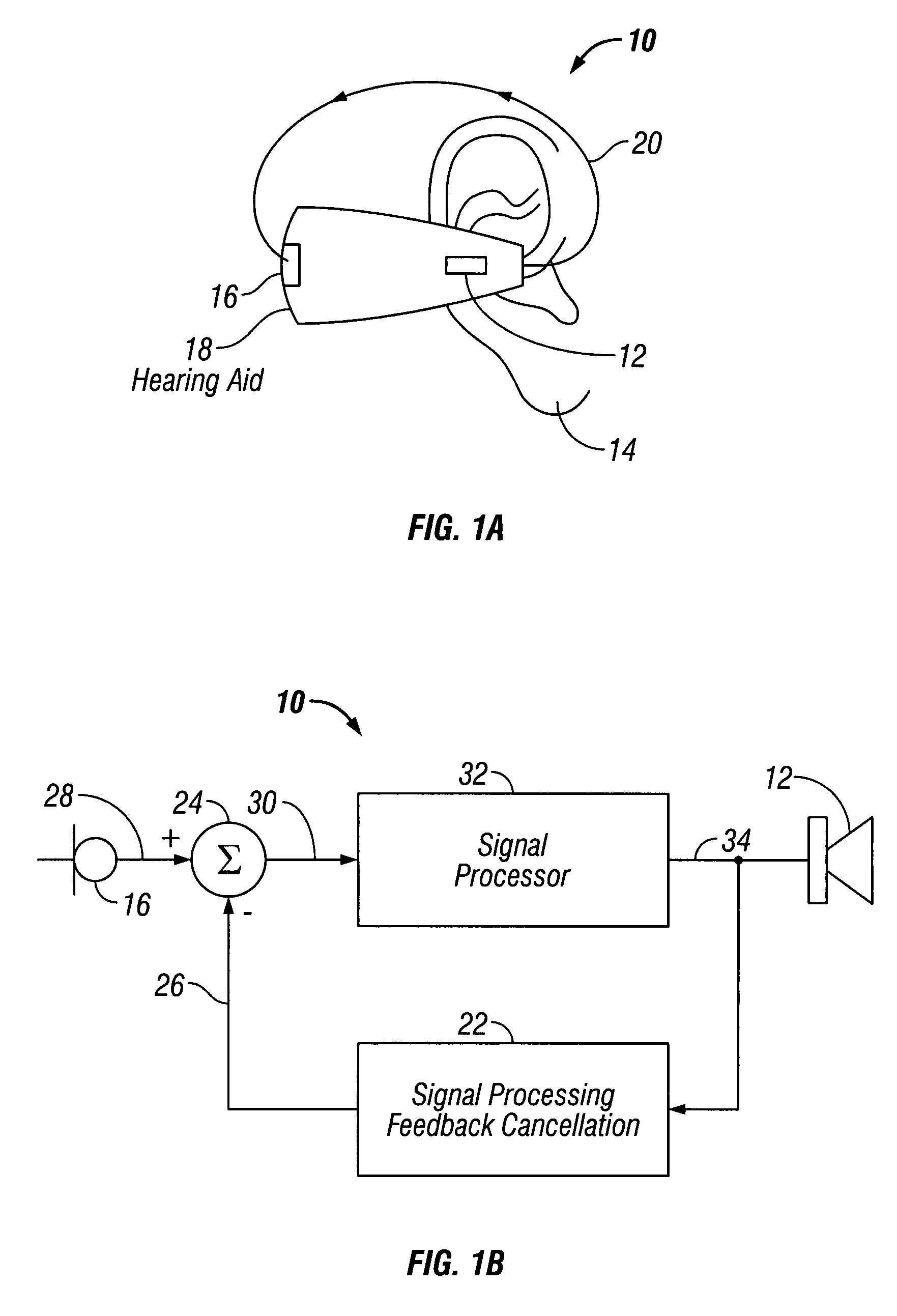

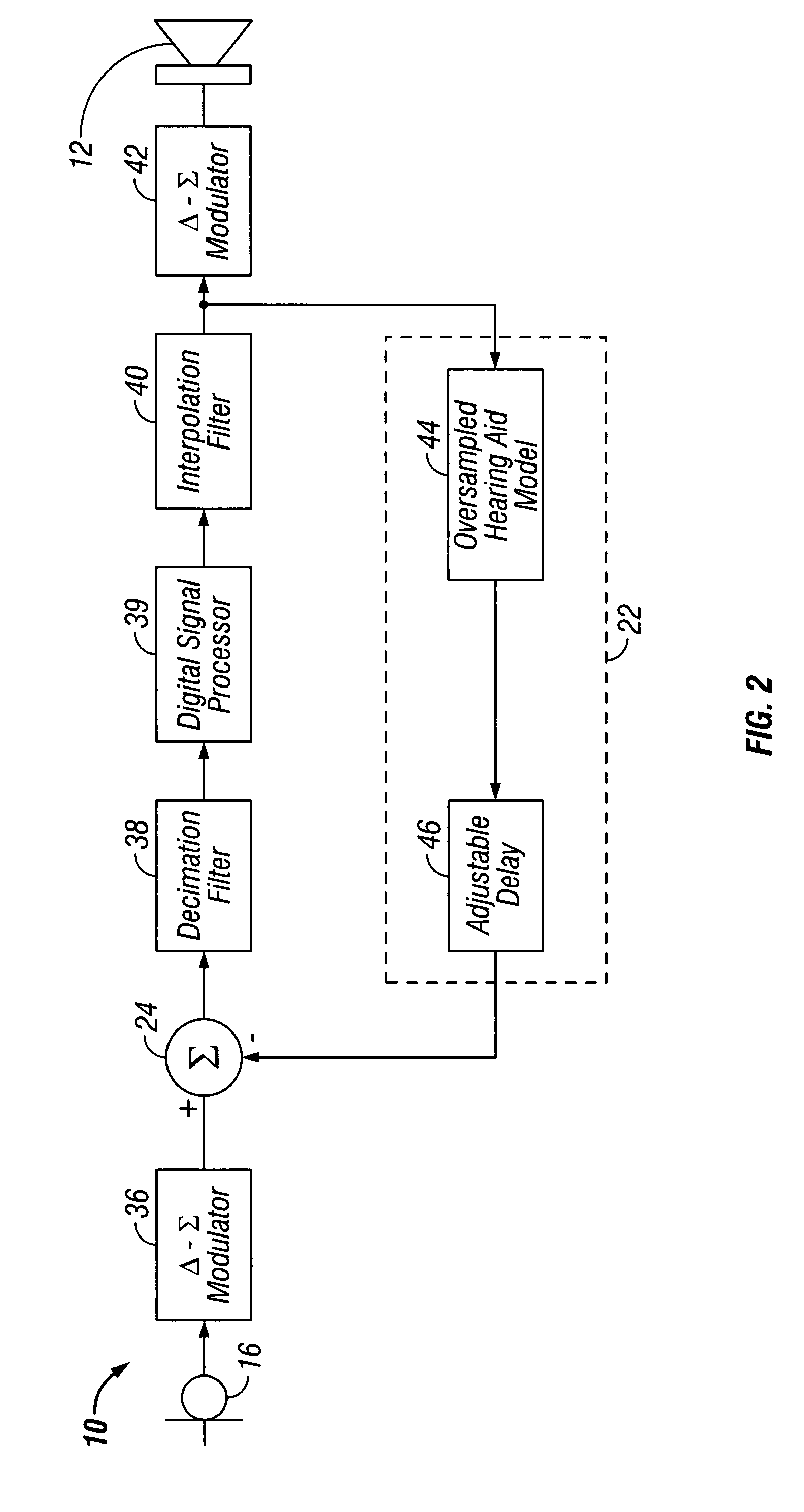

Low-delay signal processing based on highly oversampled digital processing

ActiveUS7365669B1High oversampling rateLower latencyAnalogue conversionSpeech analysisAnalog signalOversampling

A low-delay signal processing system and method are provided which includes a delta-sigma analog-to-digital converter, an oversampling processor, and a delta-sigma digital-to-analog converter. The delta-sigma analog-to-digital converter receives an input or audio signal and generates a digital sample signal at a high oversampling rate. The oversampling processor is connected to the analog-to-digital converter for processing the digital sample signal at the high oversampling rate with low-delay. The delta-sigma digital-to-analog converter is connected to the oversampling processor for receiving the digital sample signal at the high oversampling rate with low-delay for generating an analog signal. The oversampling processor includes a low-delay filter and a programmable delay element. In this manner, the analog signal is produced with a low delay and high accuracy.

Owner:CIRRUS LOGIC INC

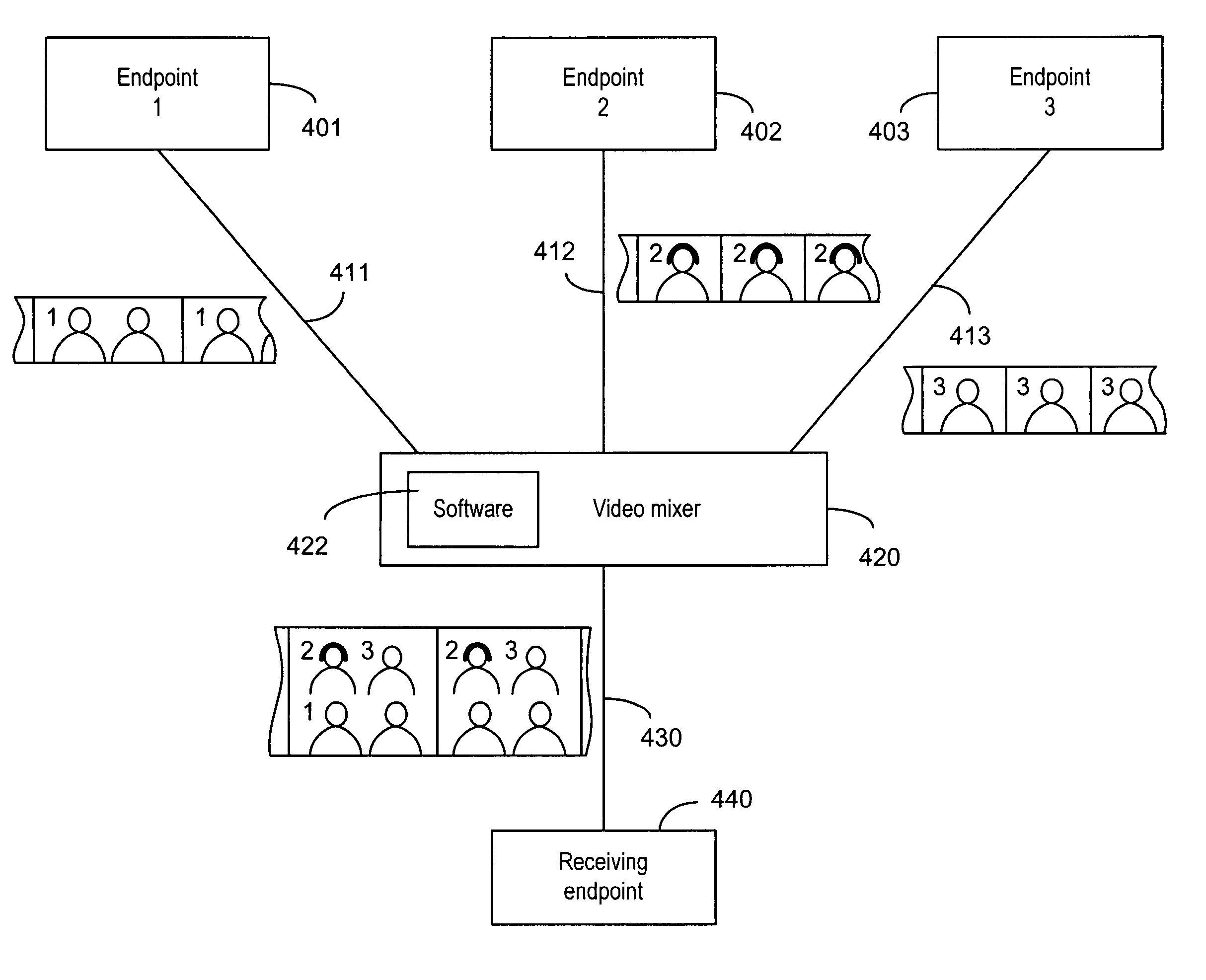

Method and system for low-delay video mixing

InactiveUS20060146734A1Multiplex system selection arrangementsSpecial service provision for substationLow delayReal-time computing

A method and system for compressed domain video mixing for spatially combining incoming video streams into an outgoing video stream. Using H.264 as an example, each incoming stream is divided into a plurality of slices, each having a plurality of header fields including a first_mb_in_slice header field. Based on the picture format in the outgoing stream, first_mb_in_slice for each incoming stream is modified such that the modified first_mb_in_slice header field is indicative of location in the spatial representation of the outgoing stream at which the slice of the incoming stream is placed. H.264's slice group mechanism is used to map the spatial positions of the second and following macroblocks of the slices to the appropriate locations. If the incoming streams are previously mixed by upstream mixers, a decomposer can be used to separate these mixed streams into component streams before combining them with other incoming streams.

Owner:NOKIA CORP

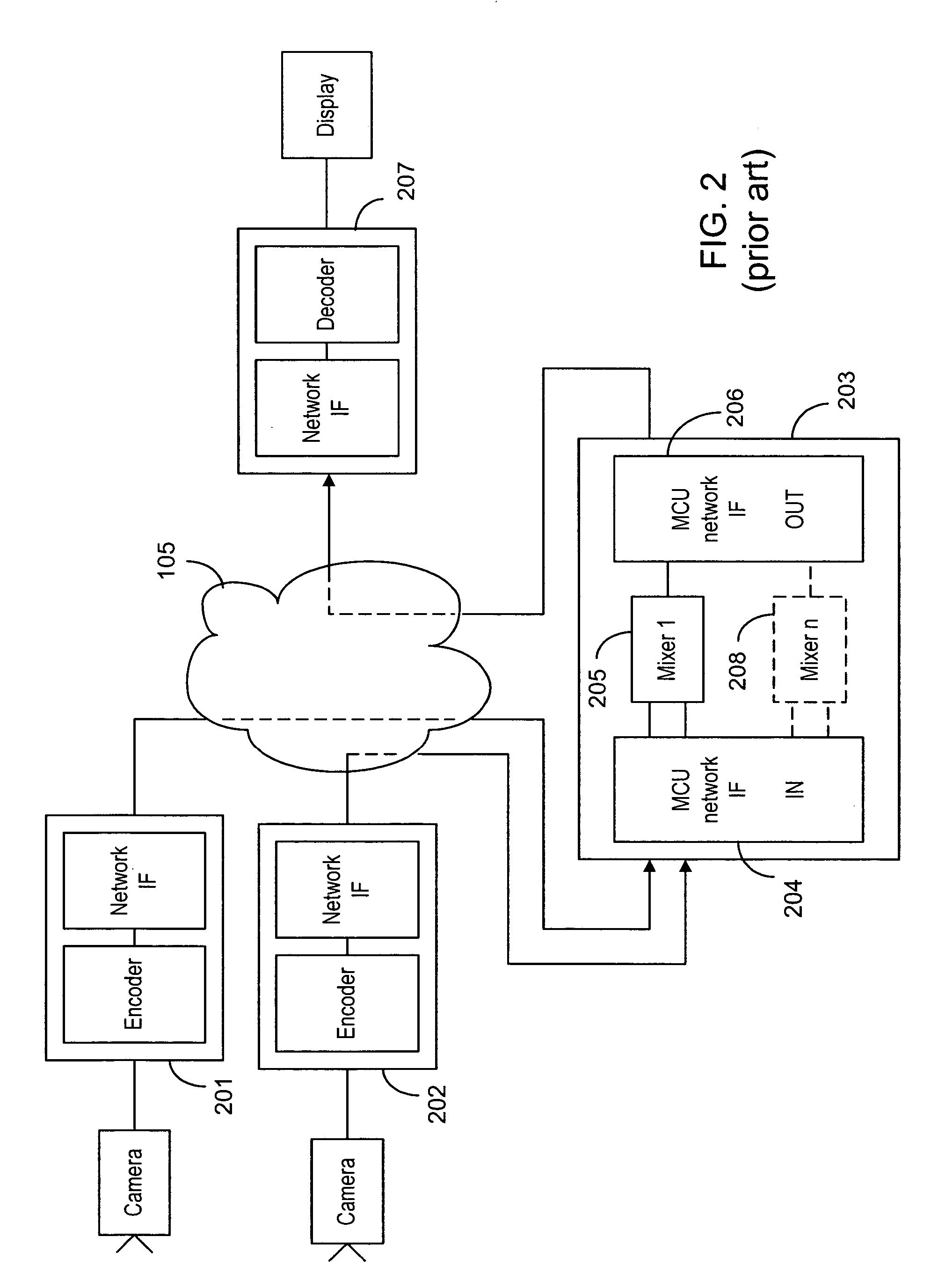

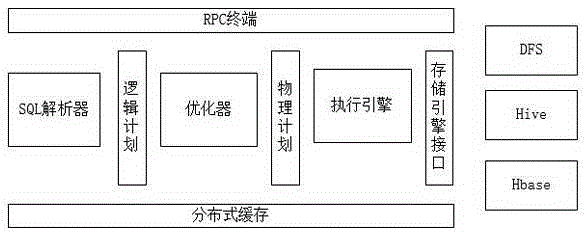

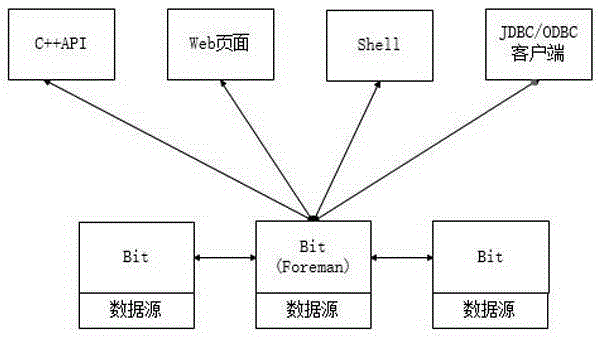

Interactive large data analysis query processing method

InactiveCN105279286AImprove query efficiencyImprove scalabilitySpecial data processing applicationsDatabase queryData set

The invention provides an interactive large data analysis query processing method. The interactive large data analysis query processing method comprises steps that, 1), a query request generated by a user or a machine is submitted to an SQL query analyzer; 2), the query quest is analyzed by the SQL query analyzer into a logic plan; 3), the logic plan is read by an optimizer and is converted into a physical plan, and interaction between a storage engine and a specific data source is realized; and 4), the physical plan is performed by a performing engine, and meta-data information is provided based on a meta-database query performing framework. For real-time interactive large data set analysis blank, P-byte data is processed under the condition of low delay response through the method according to design, multiple functions of other SQL-on-Hadoop engines are integrated, the query speed is greatly improved, and thereby Hadoop data query and enterprise-level large data analysis can be rapidly and efficiently carried out for enterprise users.

Owner:陕西艾特智慧信息技术有限公司

System and method for a conference server architecture for low delay and distributed conferencing applications

ActiveUS20080158339A1Improve fault toleranceReduce processing requirementsTwo-way working systemsComputer architectureLow delay

Owner:VIDYO

Low delay picture coding

ActiveUS20150023409A1Lower end-to-end latencyEfficient preparationColor television with pulse code modulationColor television with bandwidth reductionEntry pointLow delay

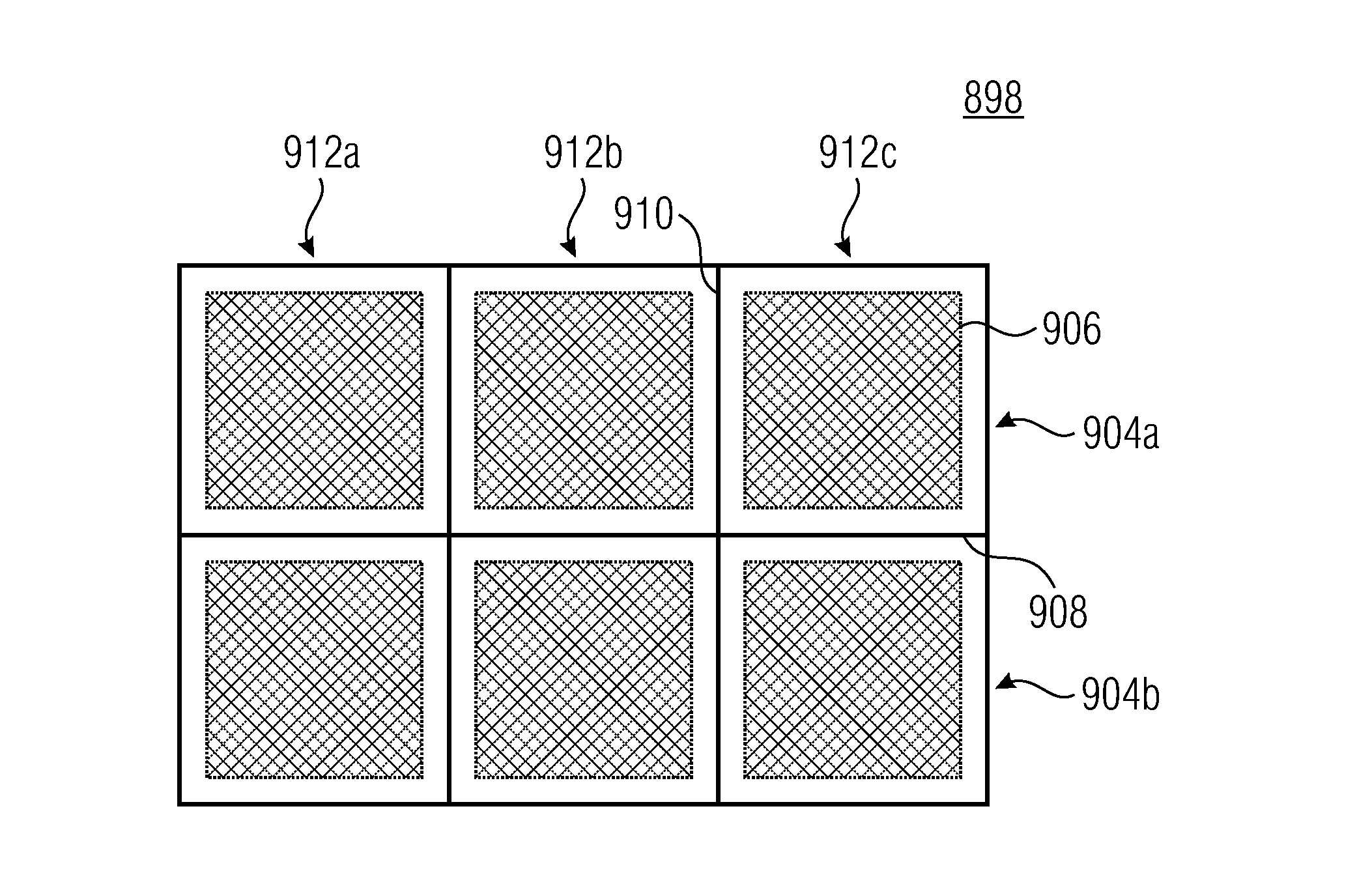

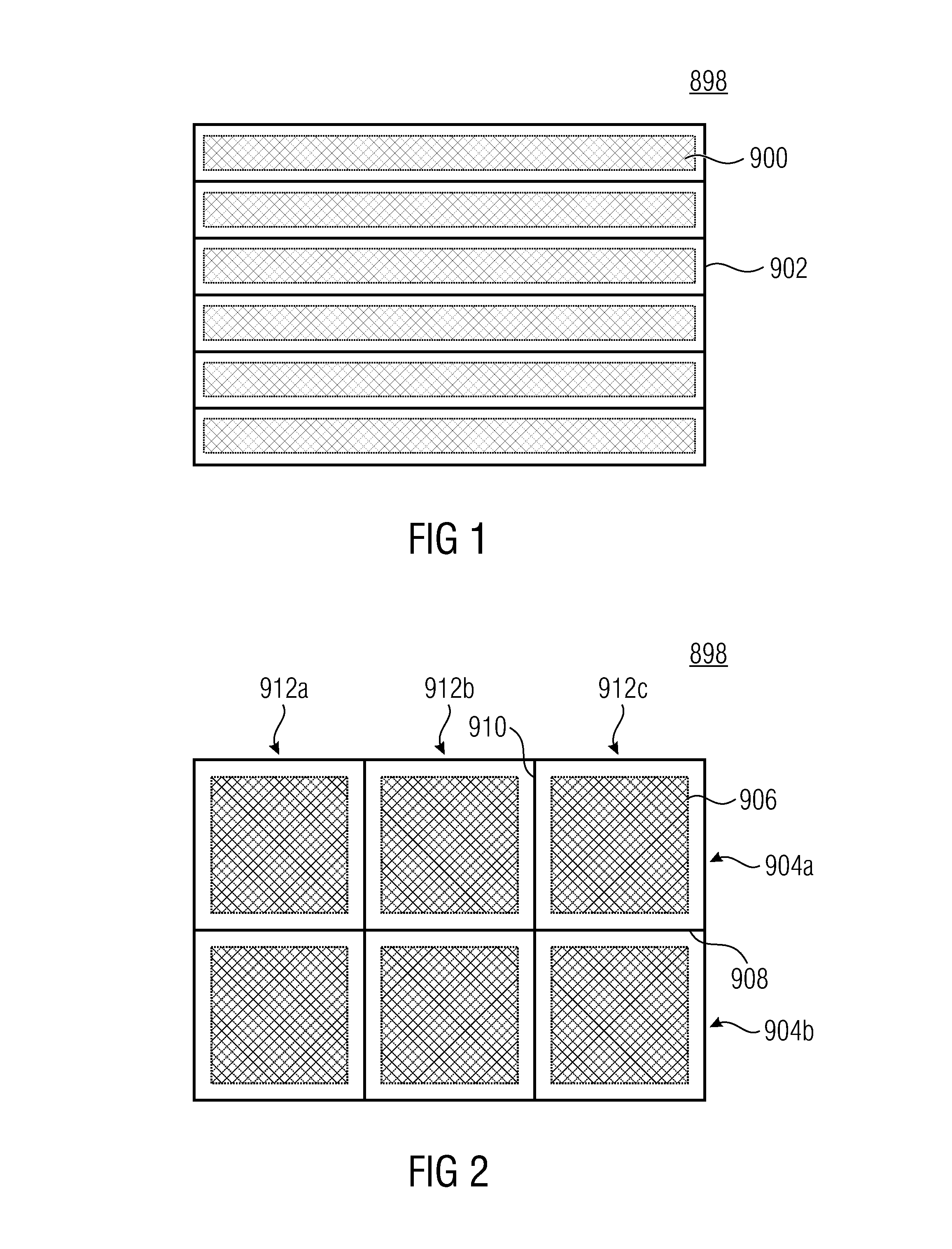

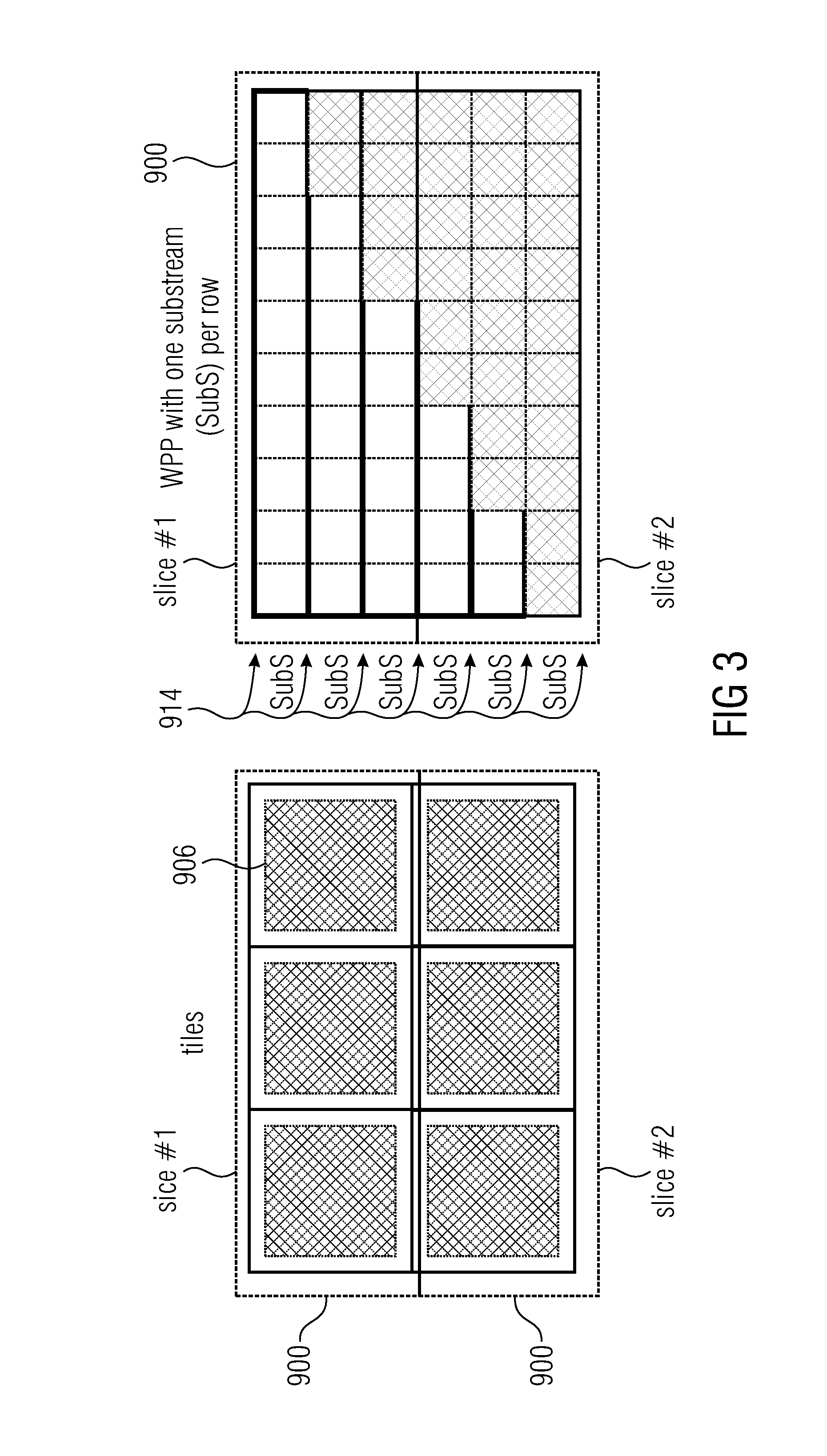

Parallel processing concepts such as wavefront parallel processing, are realized with a reduced end-to-end delay by giving up the usual slice concept according to which slices are either coded / decoded completely independent from areas of the picture outside of the respective slice, or at least independent from areas outside the respective slice as far as the entropy coding is concerned, namely in favor of slices of different modes, namely ones called dependent slices which allow for interdependencies across slice boundaries, and others which do not, called normal slices, for example. Combined with the aspect or not, WPP processing concept is made more efficiently by using the slices' start syntax portions to locate WPP entry points.

Owner:GE VIDEO COMPRESSION LLC

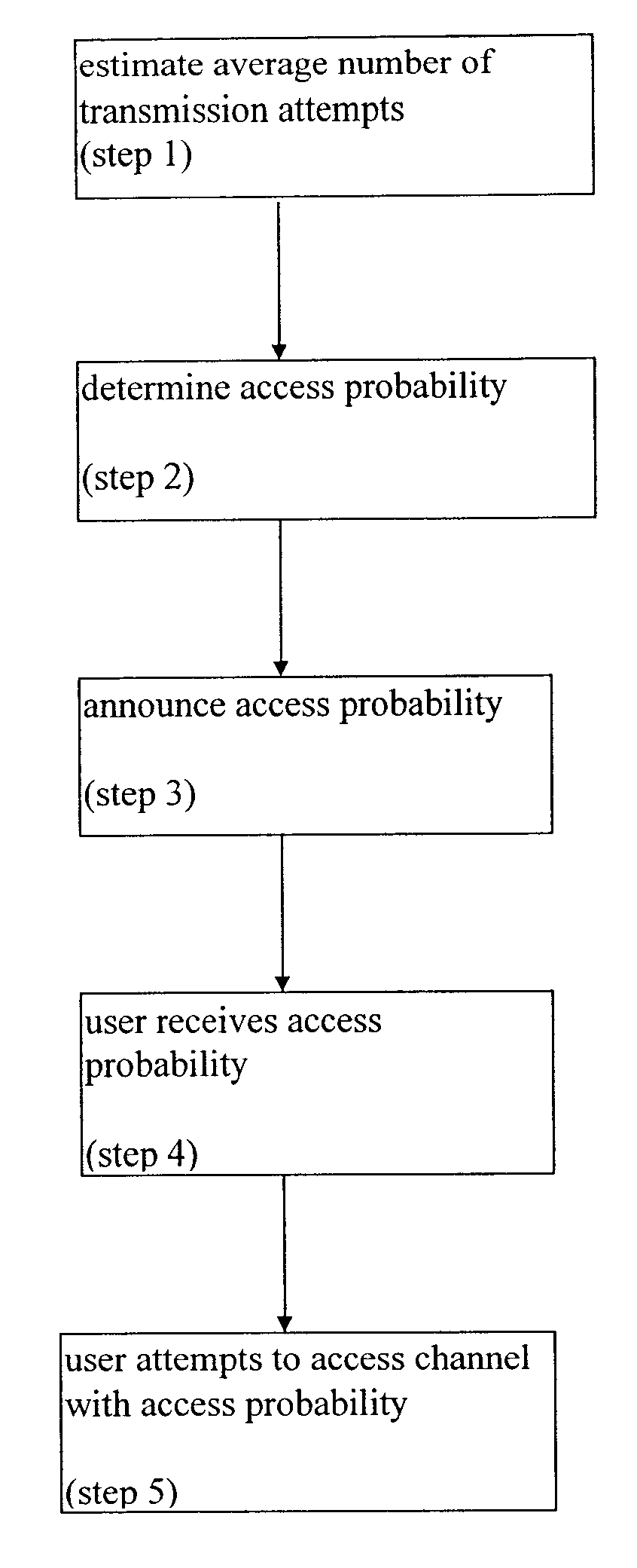

Announced dynamic access probability protocol for shared bandwidth networks

InactiveUS6418136B1Network traffic/resource managementRadio transmissionWireless mesh networkLow load

A system and a method for a dynamic probability access protocol for determining access to shared channels. Some networks have a common channel which is shared by many users. A key issue in such networks is the allocation of the shared channel among many competing users. The system and method of the present invention enable media access control in shared bandwidth networks. When the user wishes to send a message, the user transmits with a probability p, which depends on the load on the channel. The probability p is announced by the network, and transmitted to the users as a broadcast message. Under conditions of low load, the probability p approaches 1, while at high load p is relatively low. This media access control protocol guarantees high channel utilization at high load, as well as low delay at low load periods. The proposed method is applicable on wireless networks, such as cellular networks and satellite-based networks. In addition, the method and system of the present invention can be used in wired networks, for other applications such as local area networks (LAN), client / server networks, and accessing a Web site through the Internet. The method and system of the present invention are able to reduce the likelihood of collisions, without increasing the access delay at low load periods.

Owner:RAMOT UNIV AUTHORITY FOR APPLIED RES & INDAL DEVMENT

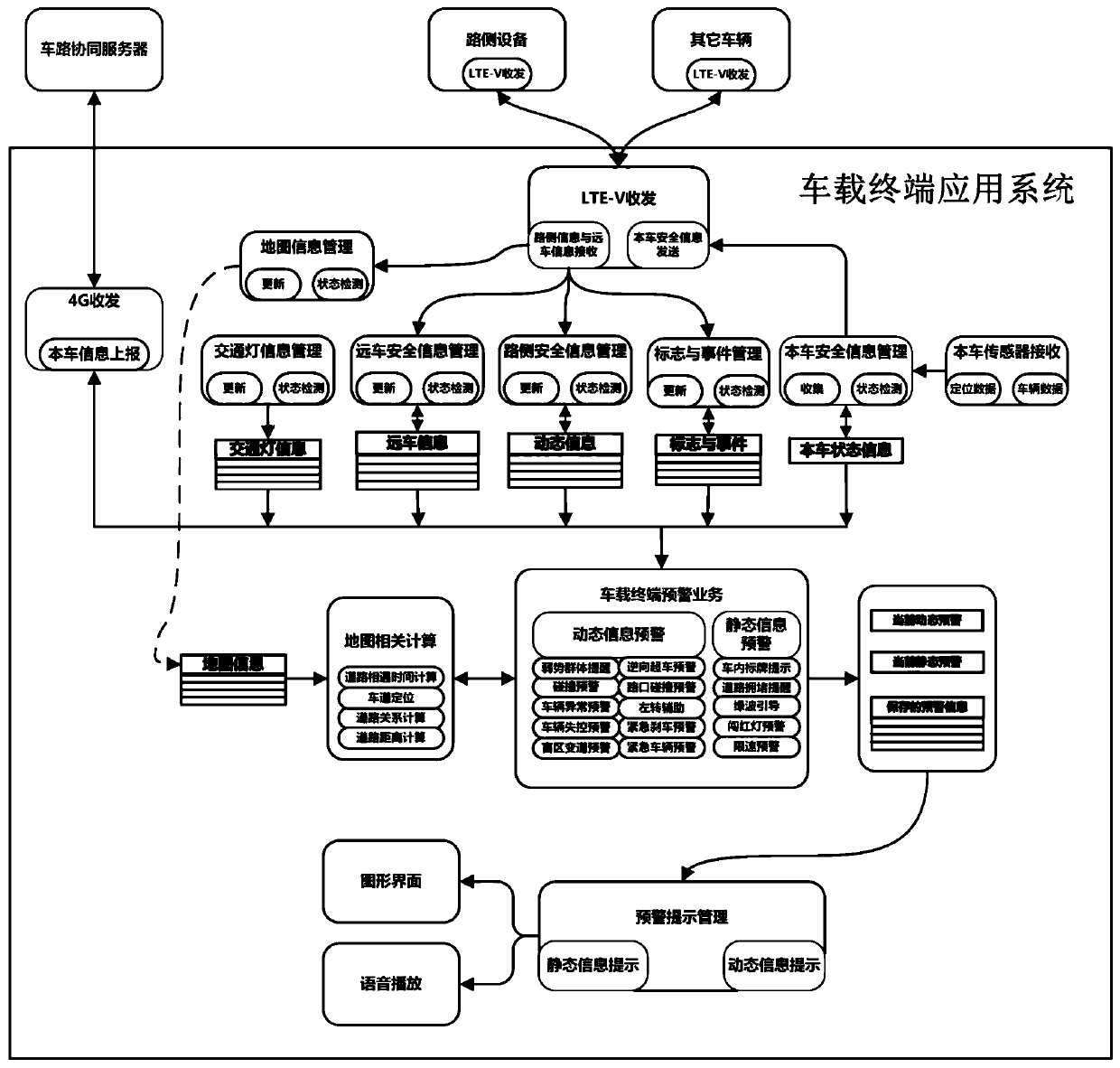

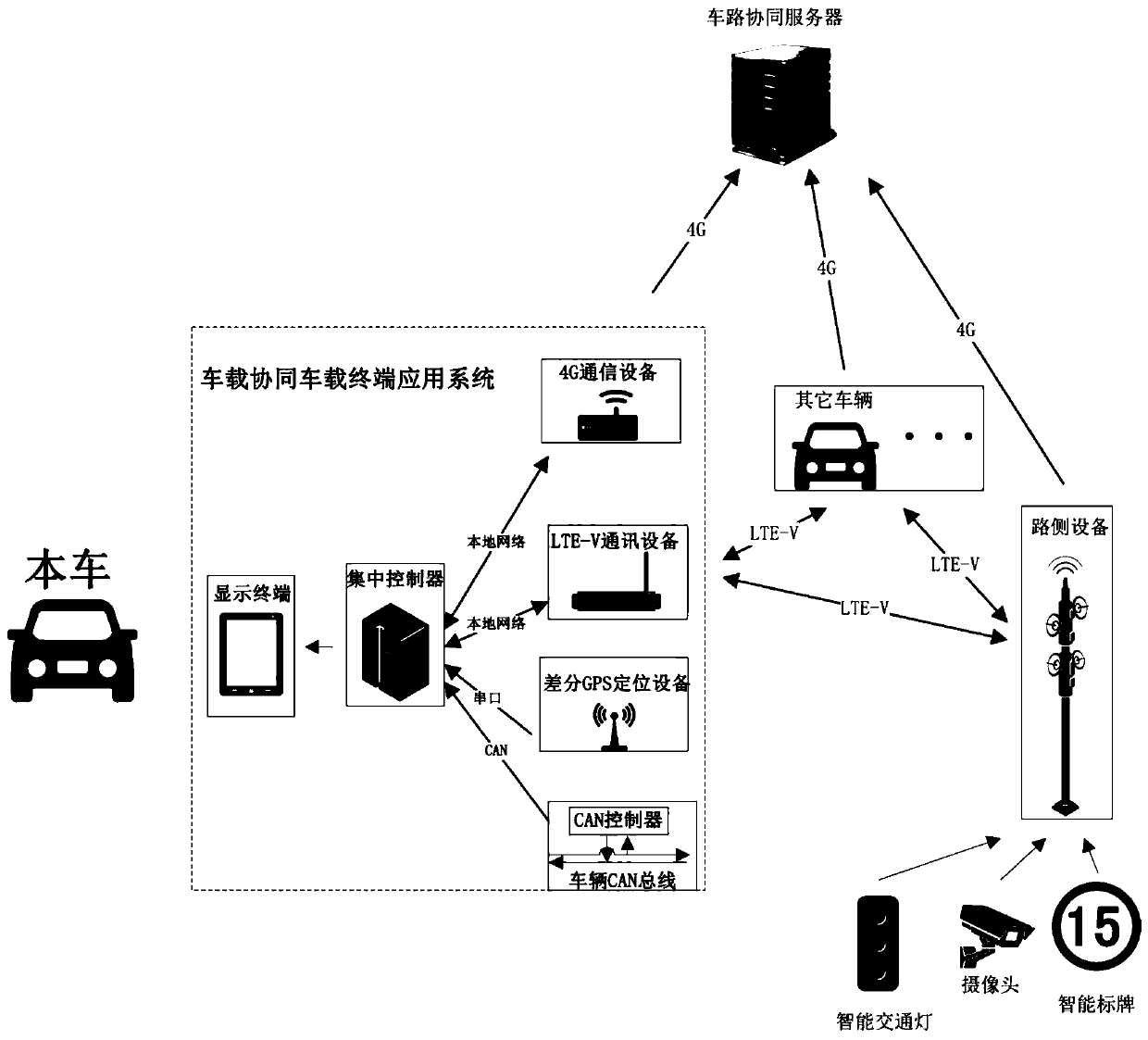

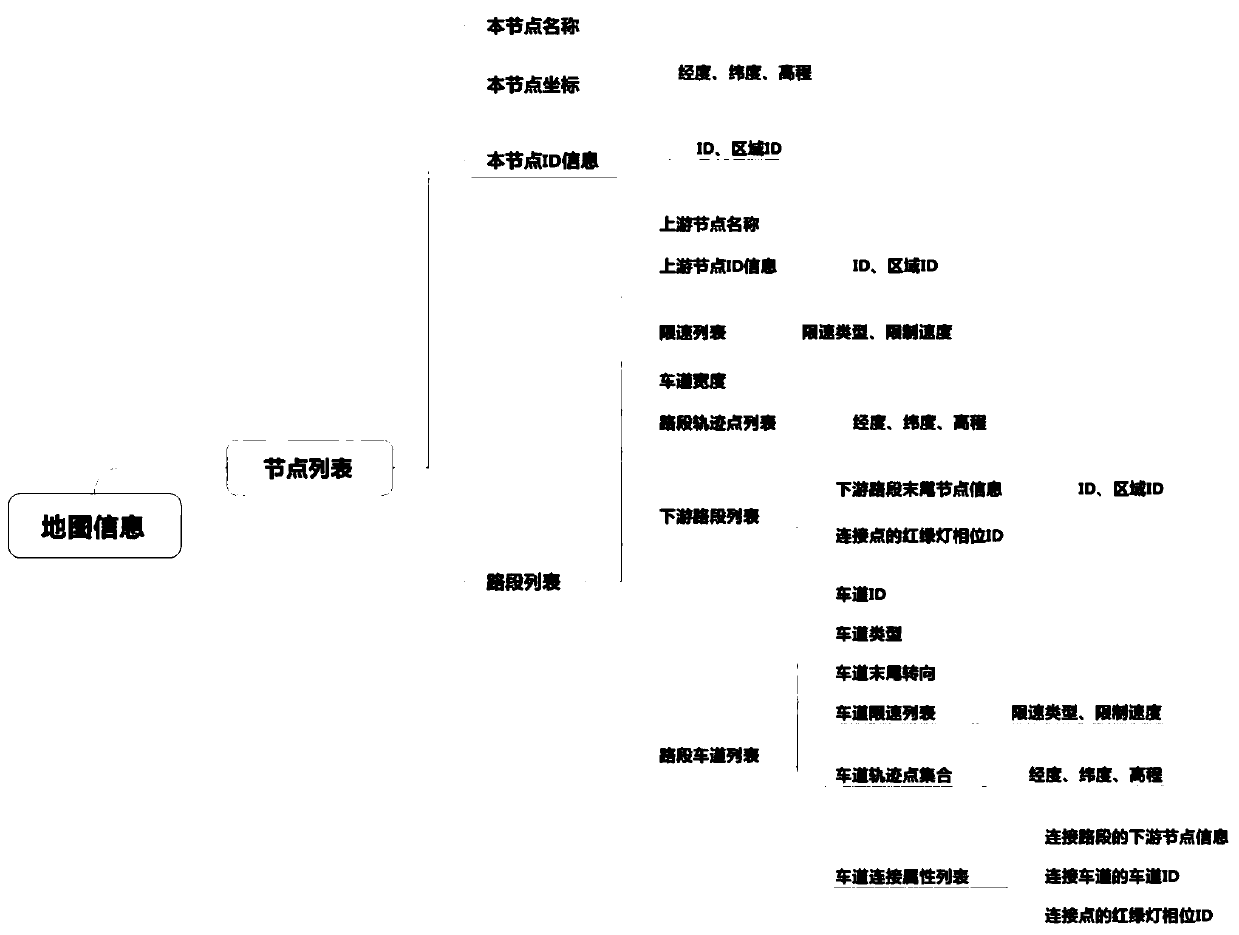

vehicle-road collaborative vehicle-mounted terminal application system based on LTE-V

ActiveCN109756867ALow costImprove real-time performanceDetection of traffic movementParticular environment based servicesTime informationDriver/operator

The invention discloses a vehicle-road collaborative vehicle-mounted terminal application system based on LTE-V. In the system, the vehicle maintains wireless short-wave communication with other vehicles and roadside equipment in real time by utilizing the characteristics of low delay and high coverage range of LTE-V communication, and interacts information with a vehicle-road collaborative background server through a 4G network. The method comprises the following steps: receiving real-time state information of other vehicles; The method comprises the following steps of: sensing surrounding traffic conditions by traffic participant real-time information sent by roadside equipment, and judging and analyzing a map road relationship, a road distance and collision time between a vehicle and other traffic participants, traffic signs or events according to the vehicle state information and local lane track point map information; According to different traffic scenes judged by the system, a driver is reminded of different traffic events and early warning information through visualization, so that the driving safety is enhanced, and meanwhile, the traffic efficiency is improved.

Owner:INST OF SOFTWARE APPL TECH GUANGZHOU & CHINESE ACAD OF SCI

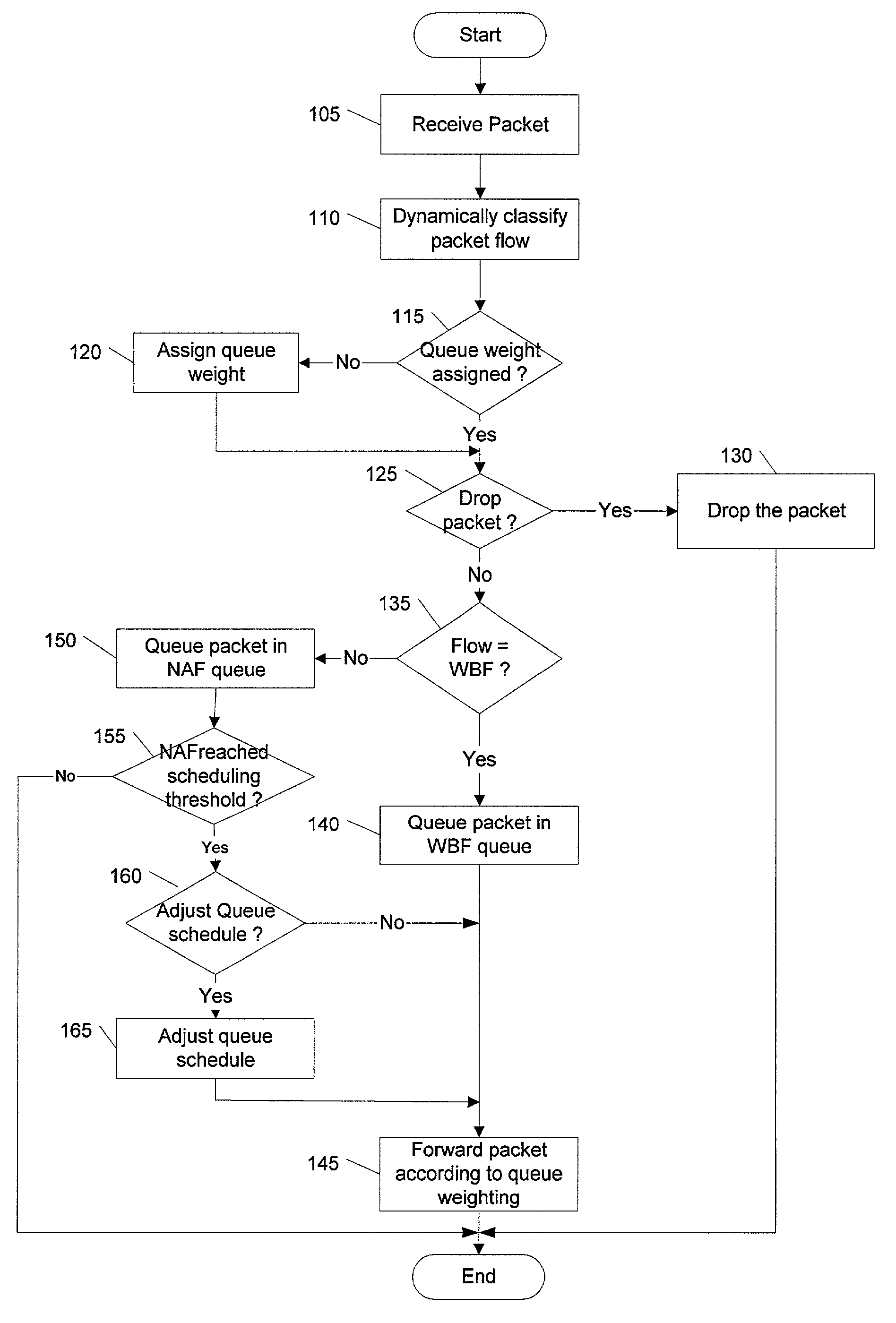

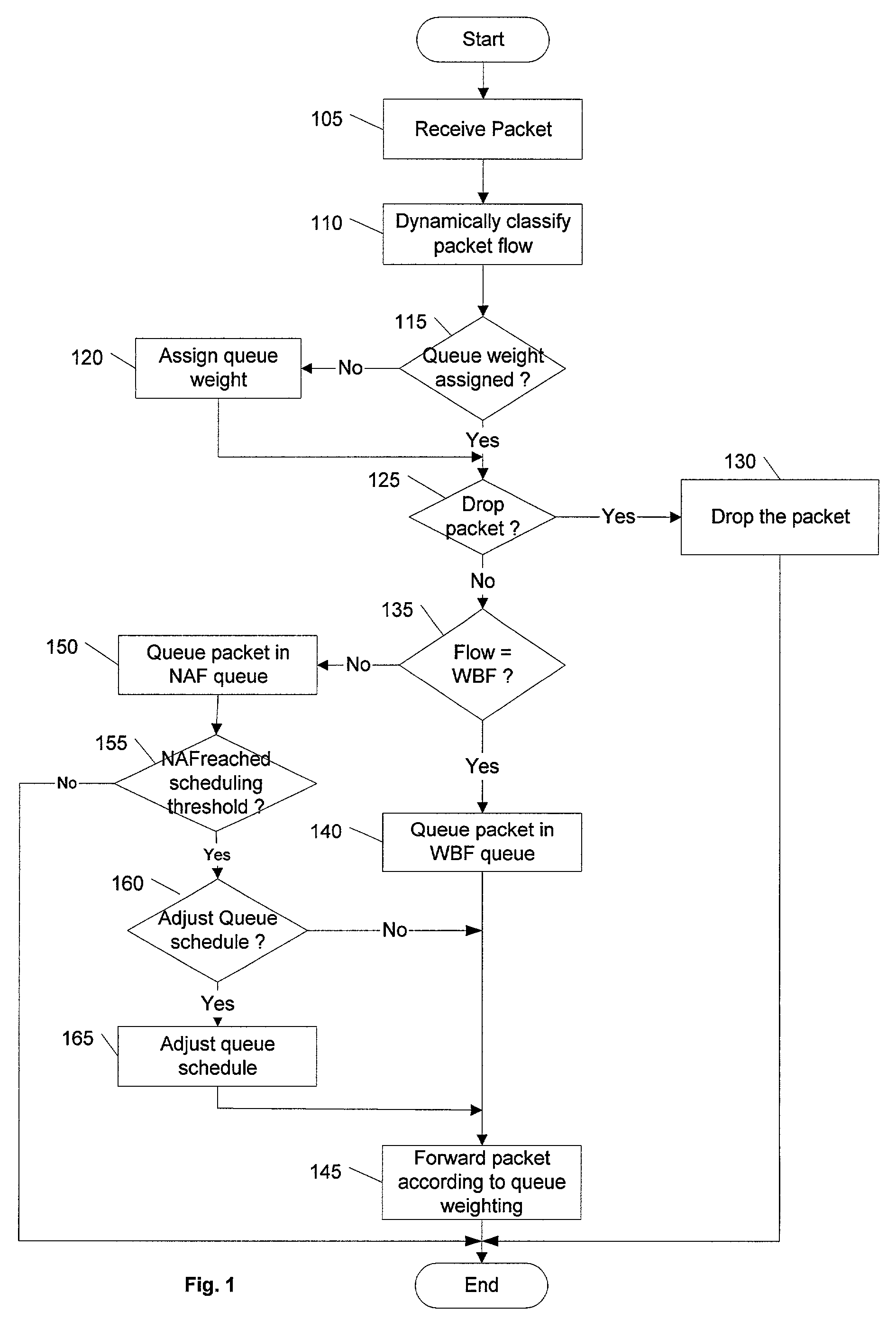

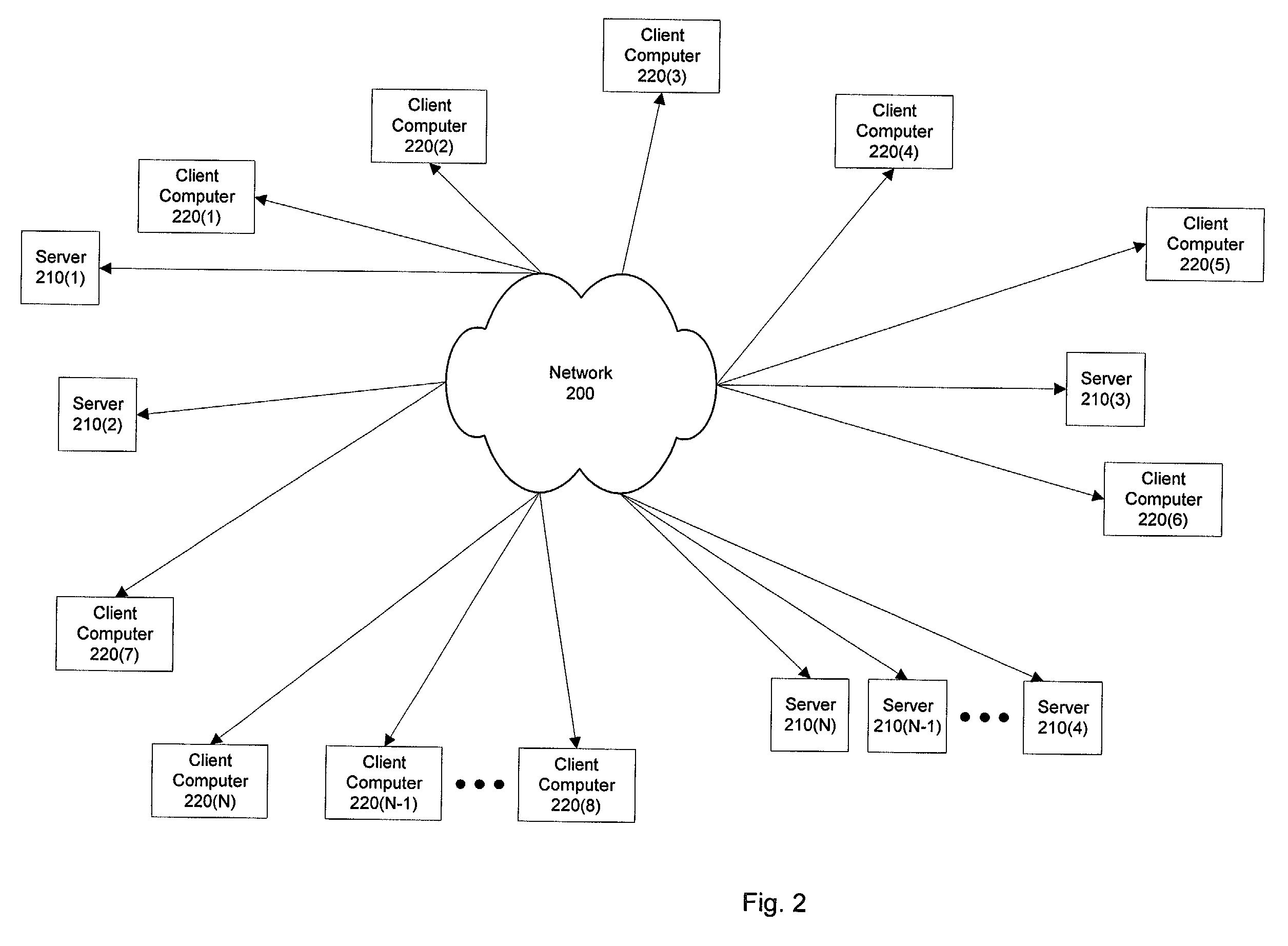

Dynamic behavioral queue classification and weighting

The present invention defines a method and apparatus to extend class-based queuing (CBQ) with multiple “behavioral” queues per class, to include a dynamic weighting mechanism between these queues. The packets are forwarded from the behavioral queues according to the weighting assigned to each queue. The weighting for packet scheduling of the queues is adjusted to account for additional flow going through the queues. The weight of a queue is controlled relative to the weight available to other queues. When a flow is reclassified, the queue weights is readjusted accordingly. Well behaved flows experience low delay and can thus achieve a fair bandwidth allocation without having to have multiple packets queued to compete with non-adaptive aggressive flows.

Owner:CISCO TECH INC

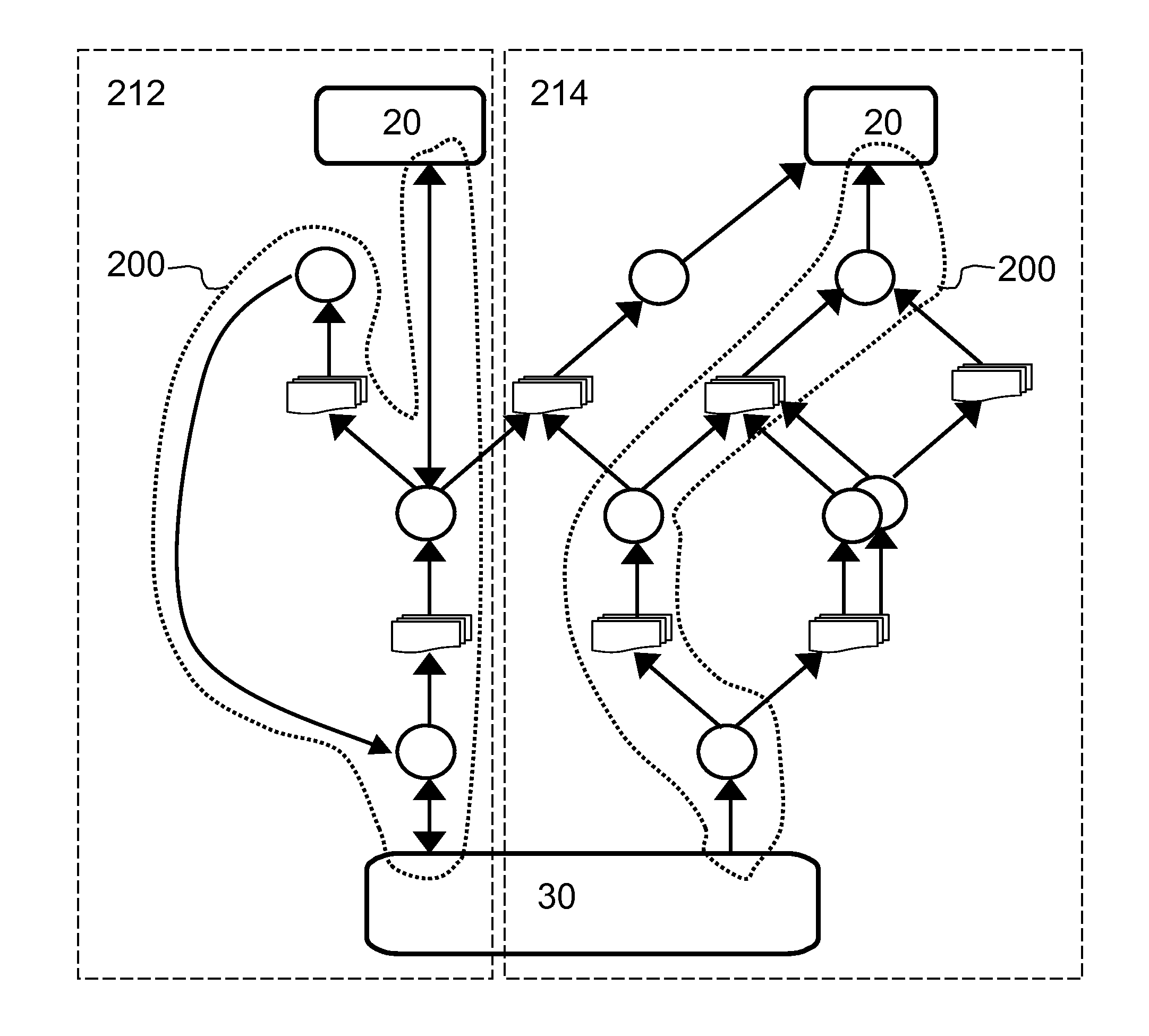

System and method for a conference server architecture for low delay and distributed conferencing applications

ActiveUS20090295905A1Improve fault toleranceReduce processing requirementsTelevision conference systemsTwo-way working systemsComputer architectureLow delay

Systems and methods for conducting a multi-endpoint video signal conference are provided. Conferencing endpoints are linked by pairs of a reliable and a less reliable communication channel. Conference video signals are scaleable coded in base layer and enhancement layers format. Video signal base layers, which correspond to a minimum picture quality, are communicated over reliable channels. The video signal enhancements layers may be communicated over the less reliable channels. A conference server mediates the switching of video layer information from transmitting endpoints to receiving endpoints without any intermediate coding or re-coding operations. The video conference can be integrated with an audio conference using either scalable coded audio signals or non-scaleable coded audio signals.

Owner:VIDYO

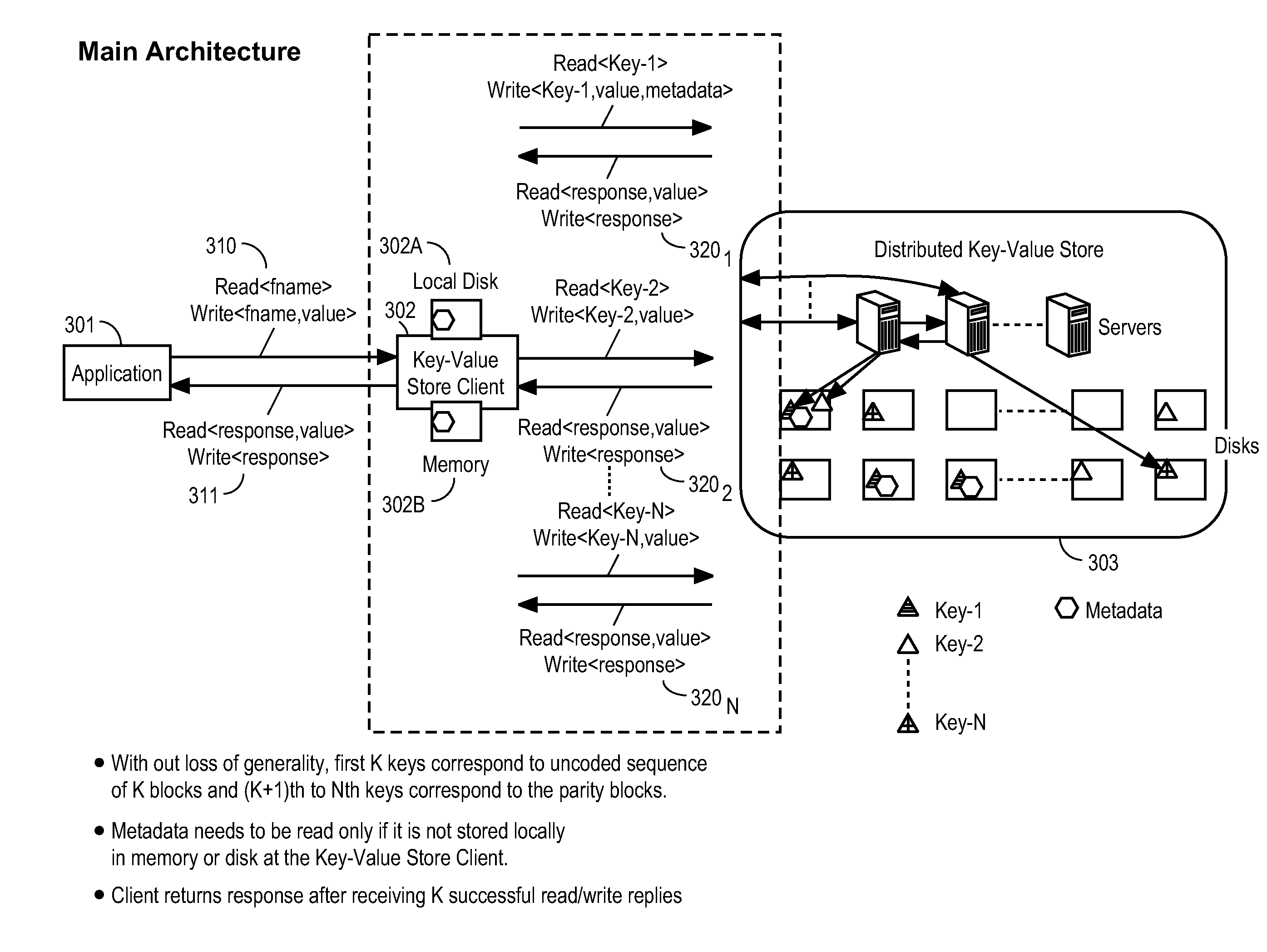

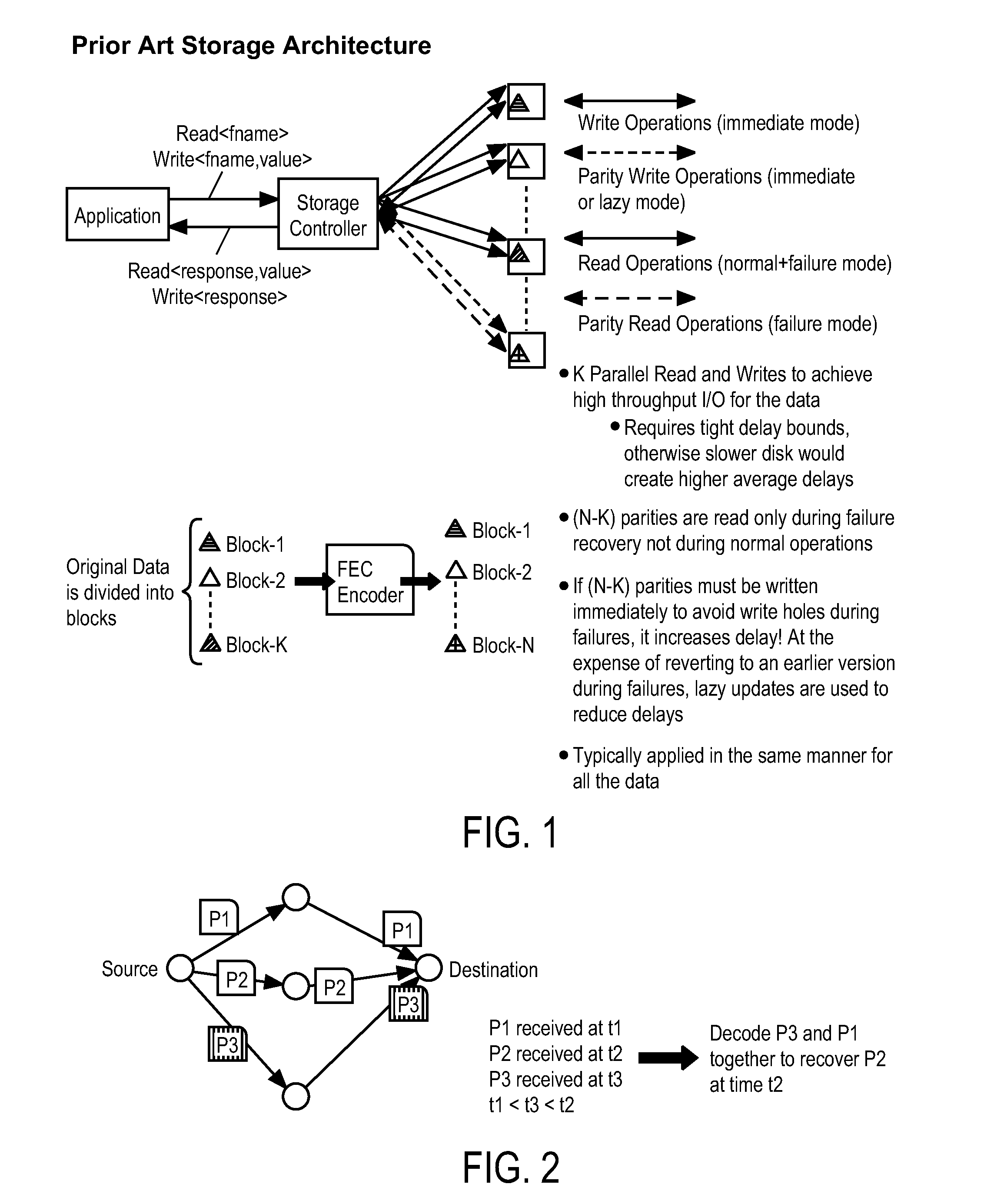

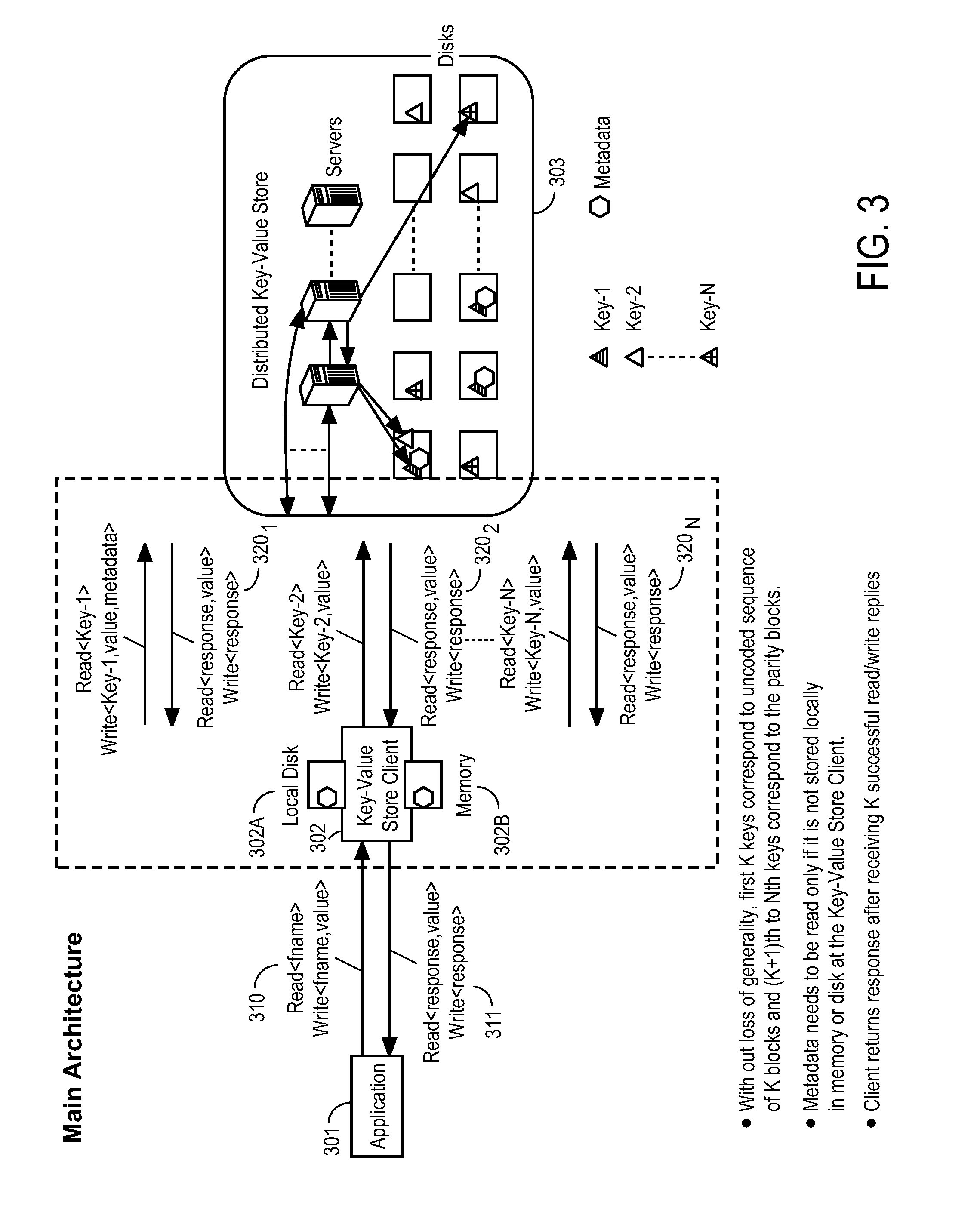

Method and apparatus for low delay access to key-value based storage systems using fec techniques

ActiveUS20150149870A1Lower latencyStatic storageForward error control useComputer architectureHybrid storage system

A method and apparatus is disclosed herein for low delay access to key-value based storage systems. In one embodiment, the method for putting data into a key-value store comprising dividing the data into K portions, where K is an integer; selecting an erasure coding to apply to the K portions as a function of delay performance of the key-value based storage system including determining a number of parity blocks to generate to satisfy one or both of a delay target of putting the object into the key-value store and a delay target of subsequent read requests based on an offline performance simulation of delay performance when different numbers of parity blocks are used given the delay distributions obtained through measurements for different request types and object sizes; applying the erasure coding to the K portions to create N blocks of data; sending the N write requests to write blocks of data to the storage system, where each block is assigned a unique key in the key-value store.

Owner:NTT DOCOMO INC

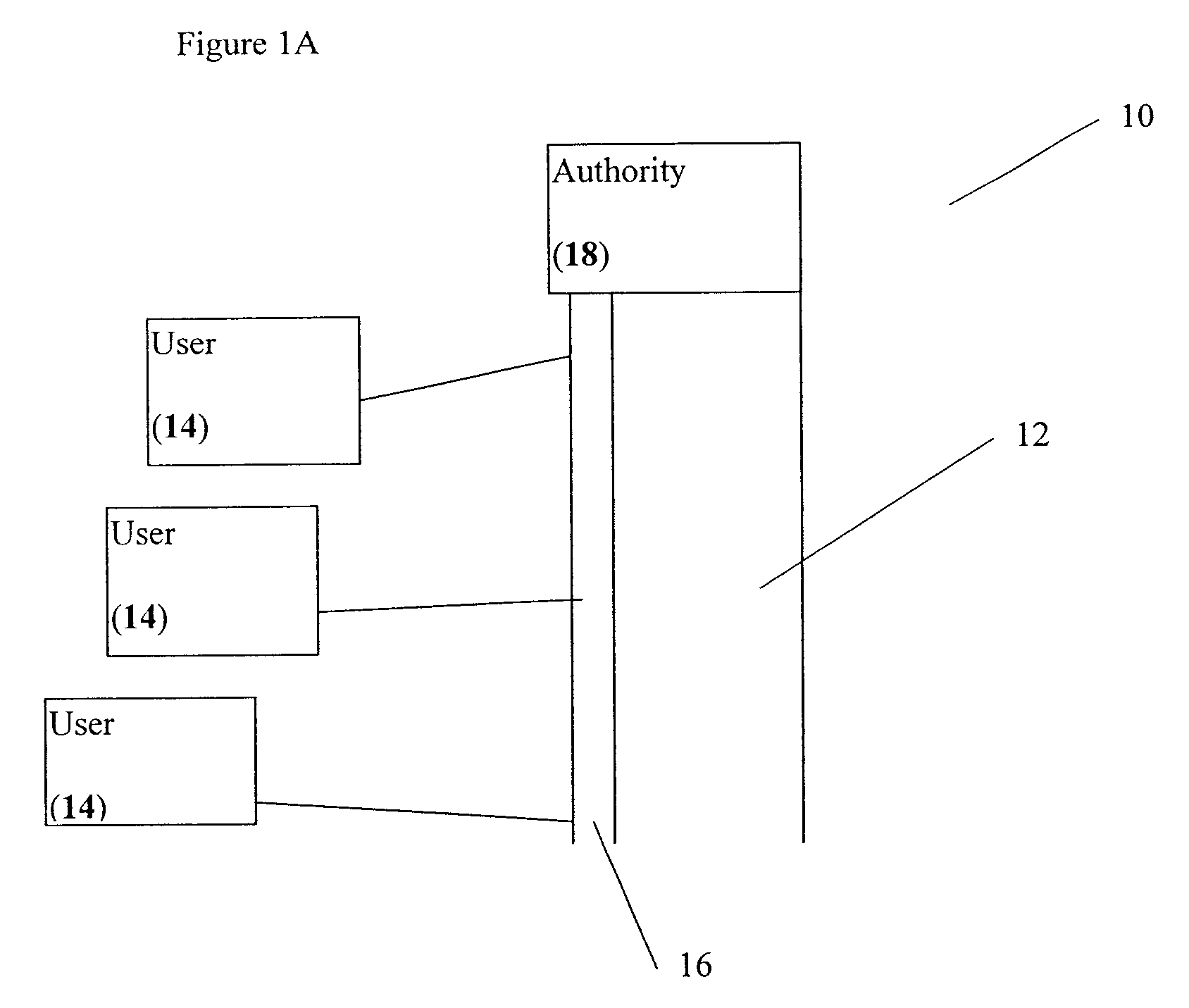

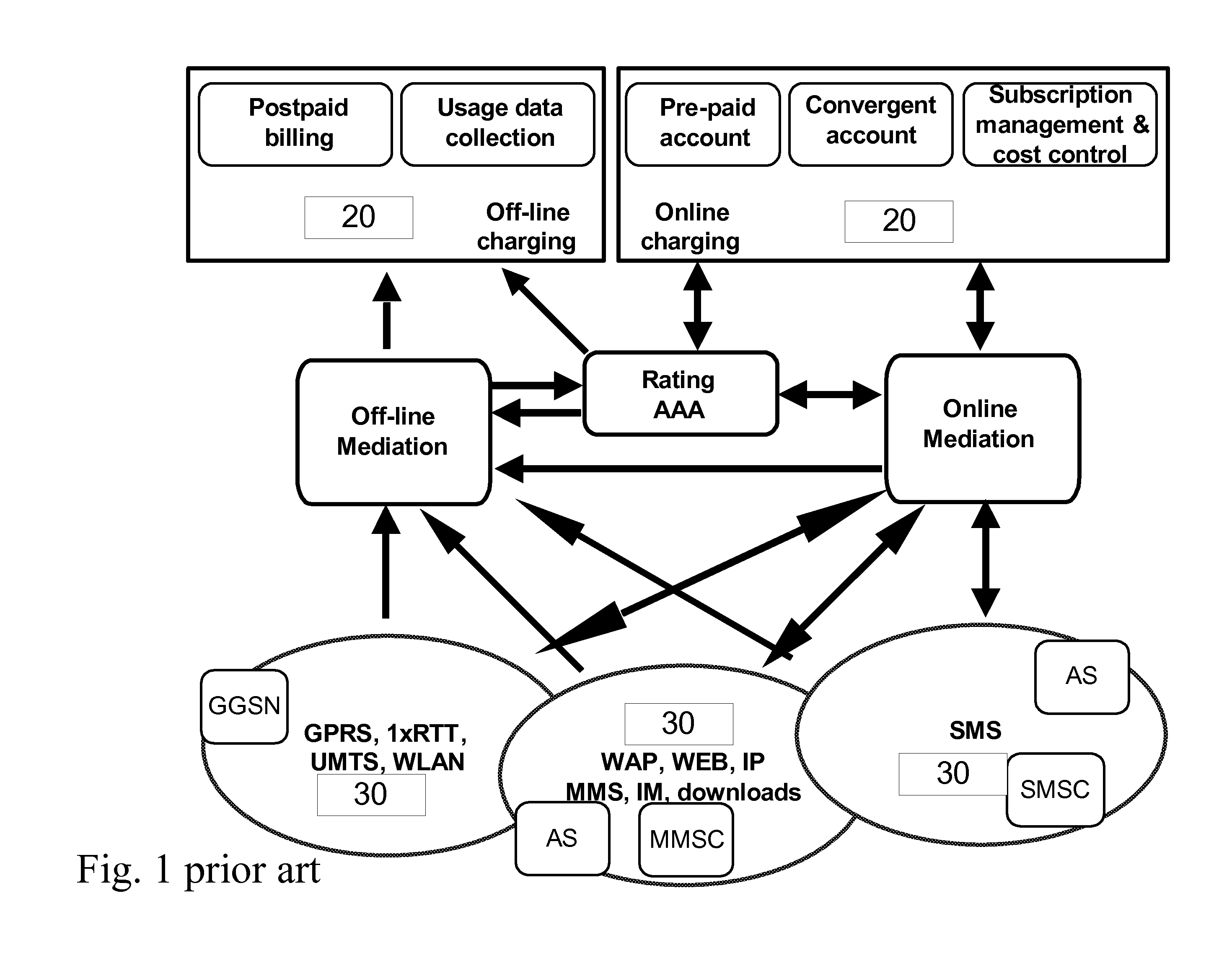

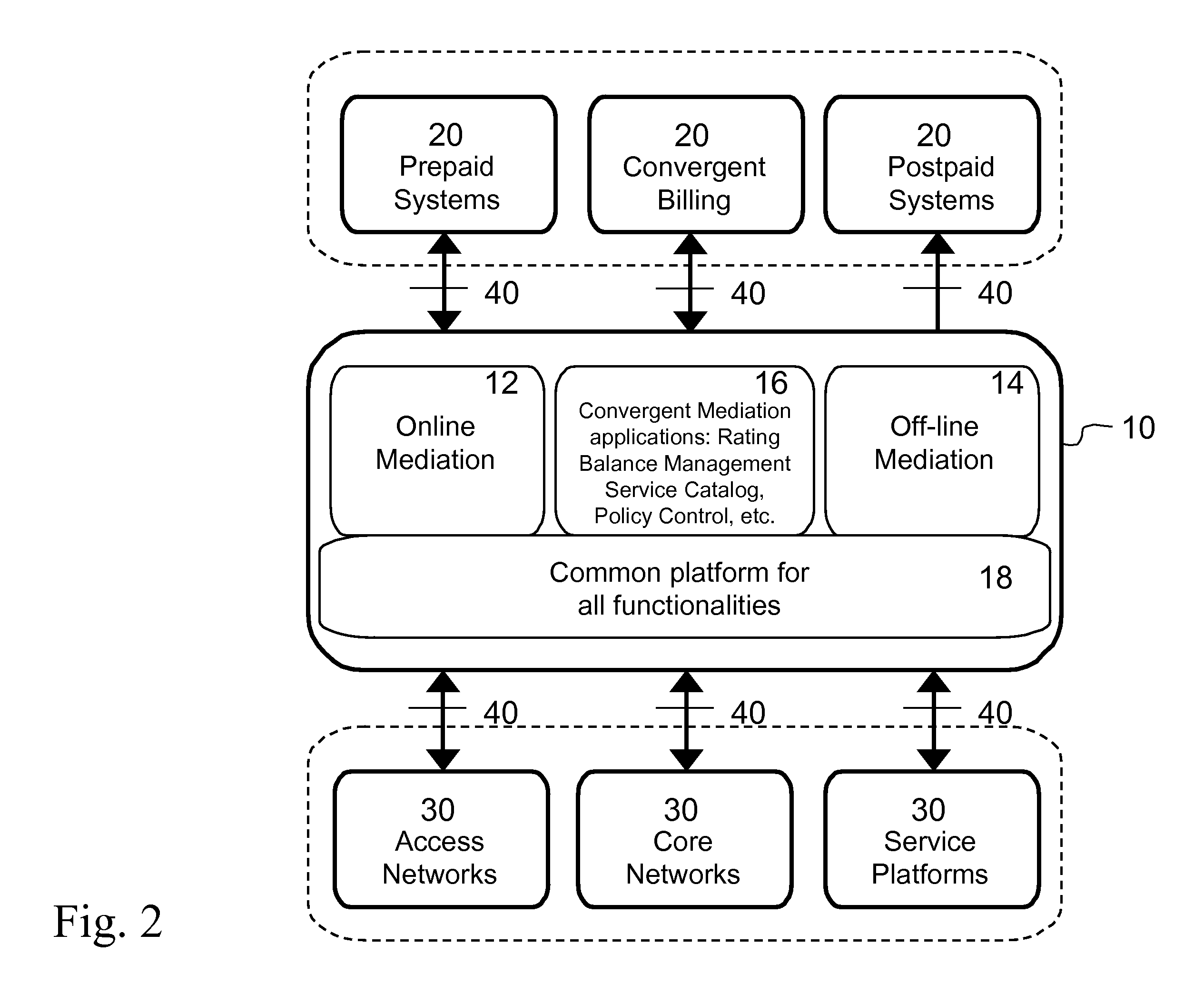

Convergent mediation system with dynamic resource allocation

InactiveUS20110010581A1Reliable and fast processHigh of administrationResource allocationTelephonic communicationDynamic resourceLatency (engineering)

An object is to create a convergent mediation system (10) and method that meet the technical requirements of low latency time and high throughput, without compromising the interoperability and ease of administration of the system. According an aspect of the invention, these objects are achieved by providing a convergent mediation system (10) that comprises a common platform (18) providing processing power for both online processing (12) and off-line processing (14) of data. The convergent mediation system (10) is also provided with a system controller (110) that is adapted to dynamically allocate the processing power of the common platform (18) for the online processing (12) and off-line processing (14) of data.

Owner:COMPTEL CORP

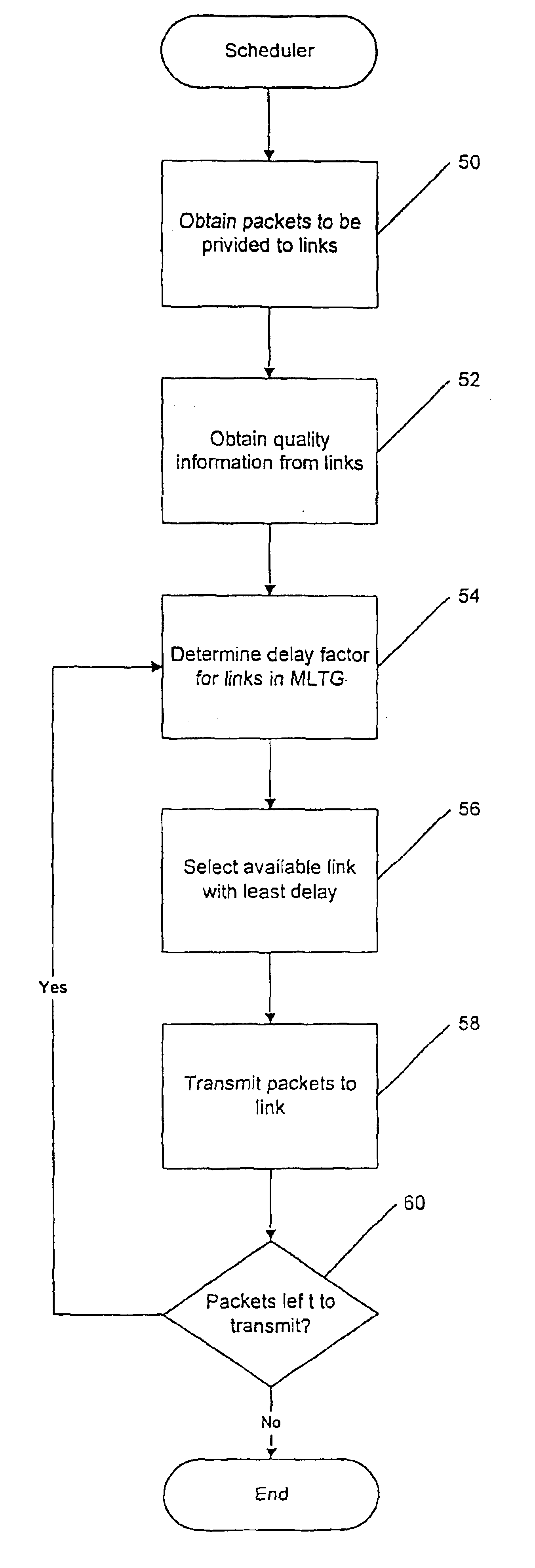

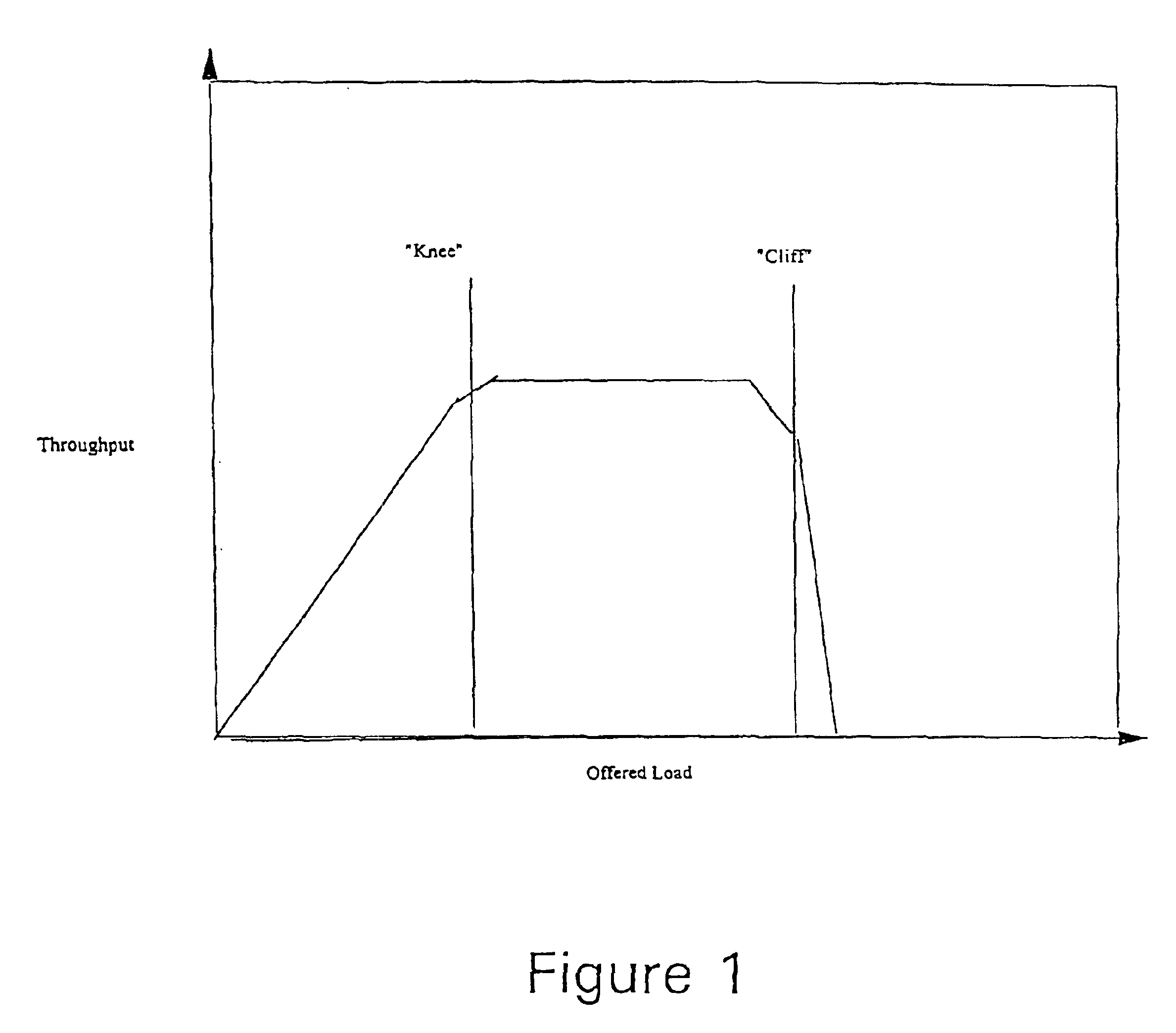

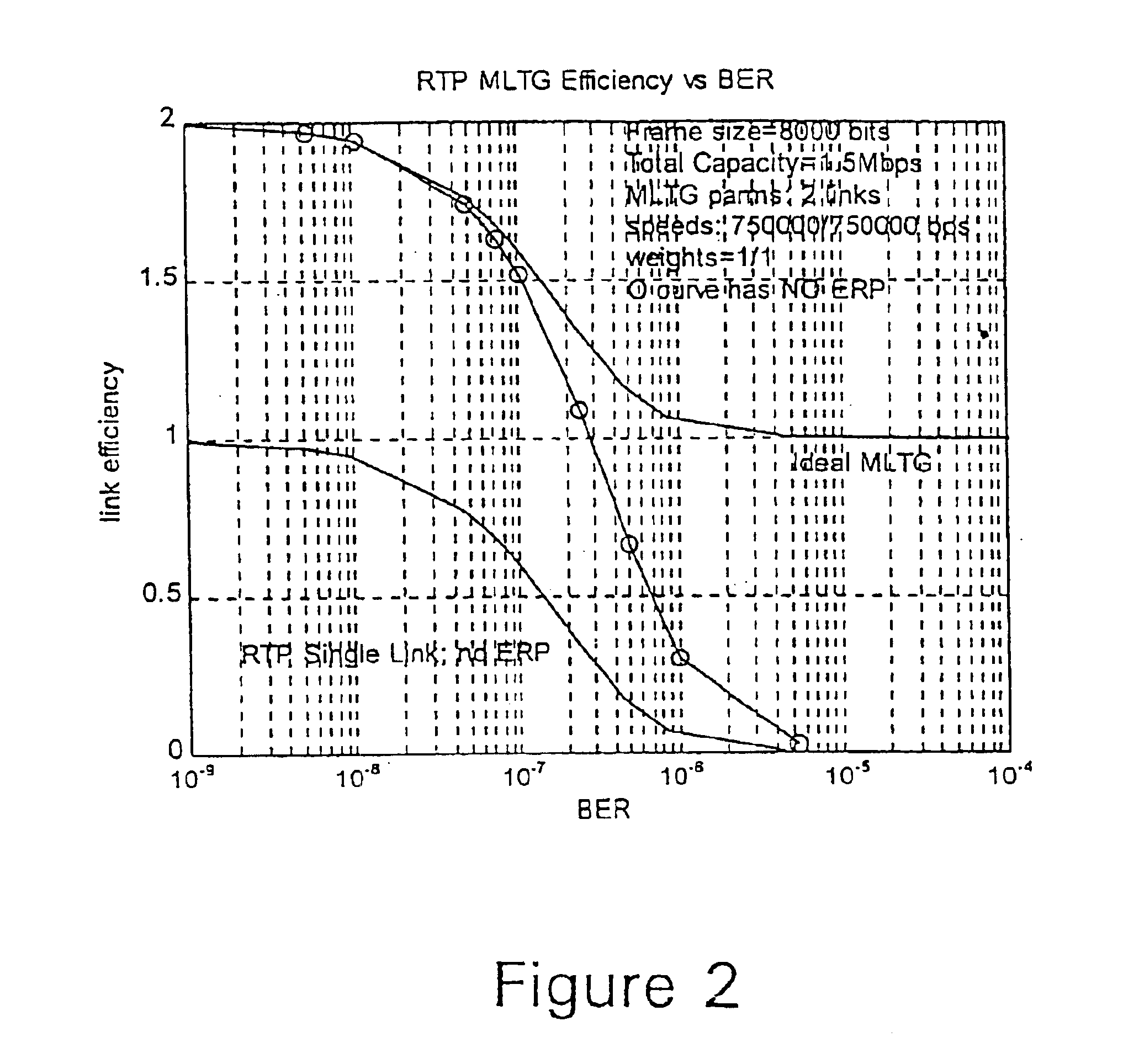

Optimal link scheduling for multiple links

InactiveUS6862618B1Easy flow controlImprove efficiencyTime-division multiplexMultiple digital computer combinationsTime delaysLow delay

Methods, apparatus and computer program products are provided for distributing communication packets over multiple concurrent parallel links between a first node and a second node in a communication network based upon link quality information for the links. By utilizing link quality information from the links, the rate at which packets are provided to the links may be made proportional to the quality of the link, and thus, the link's ability to transmit the packet. The rate at which packets are provided to links may be reduced when error rates on a link exceed a specified threshold and eliminated when error rates exceed a higher threshold. Alternatively, timing delays from errors on a link may be used to determine a delay factor for a link and packets scheduled to the links based on the link with the lowest delay. The present invention is particularly useful in High Performance Routing Multilink Transmission Groups.

Owner:IBM CORP

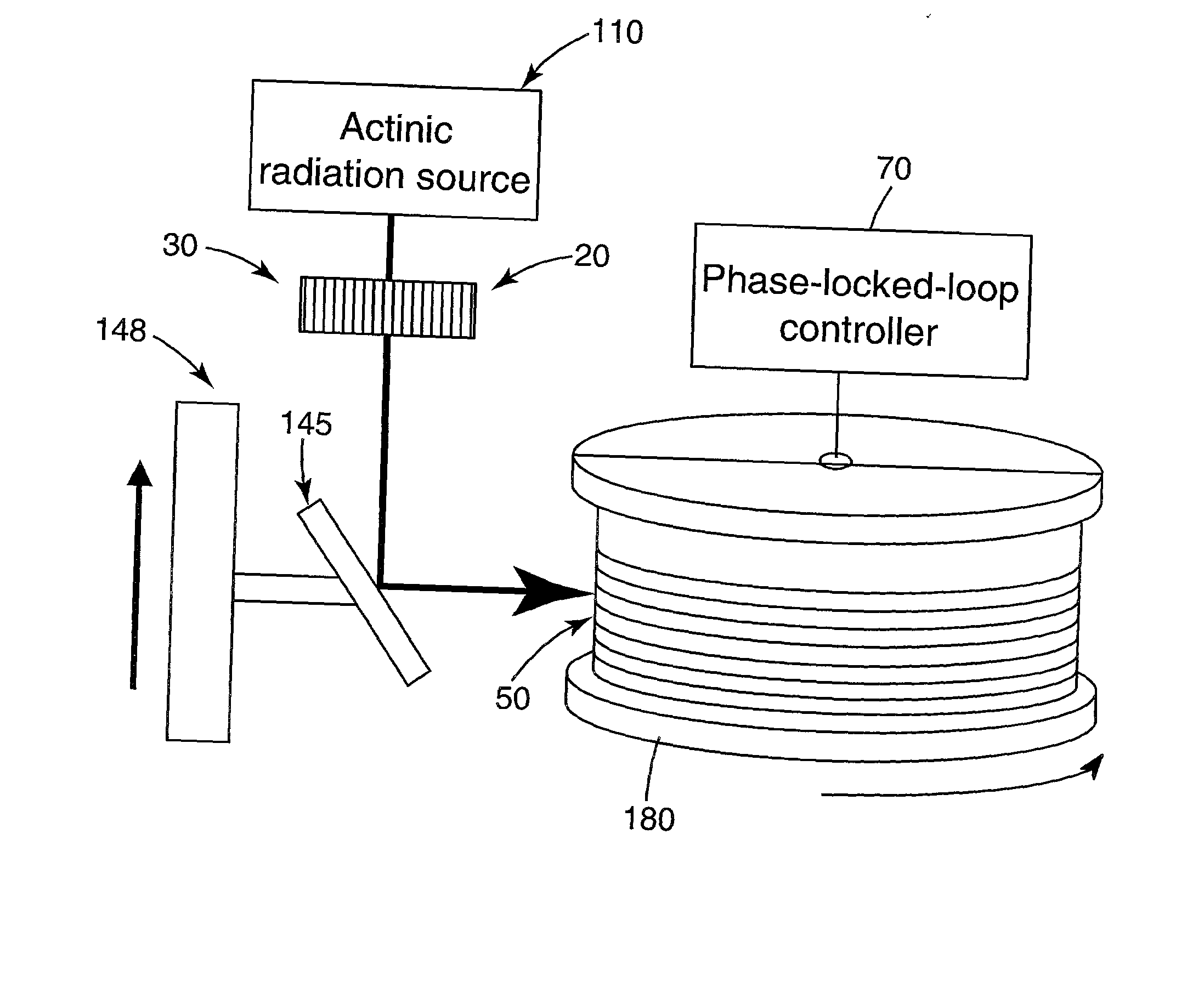

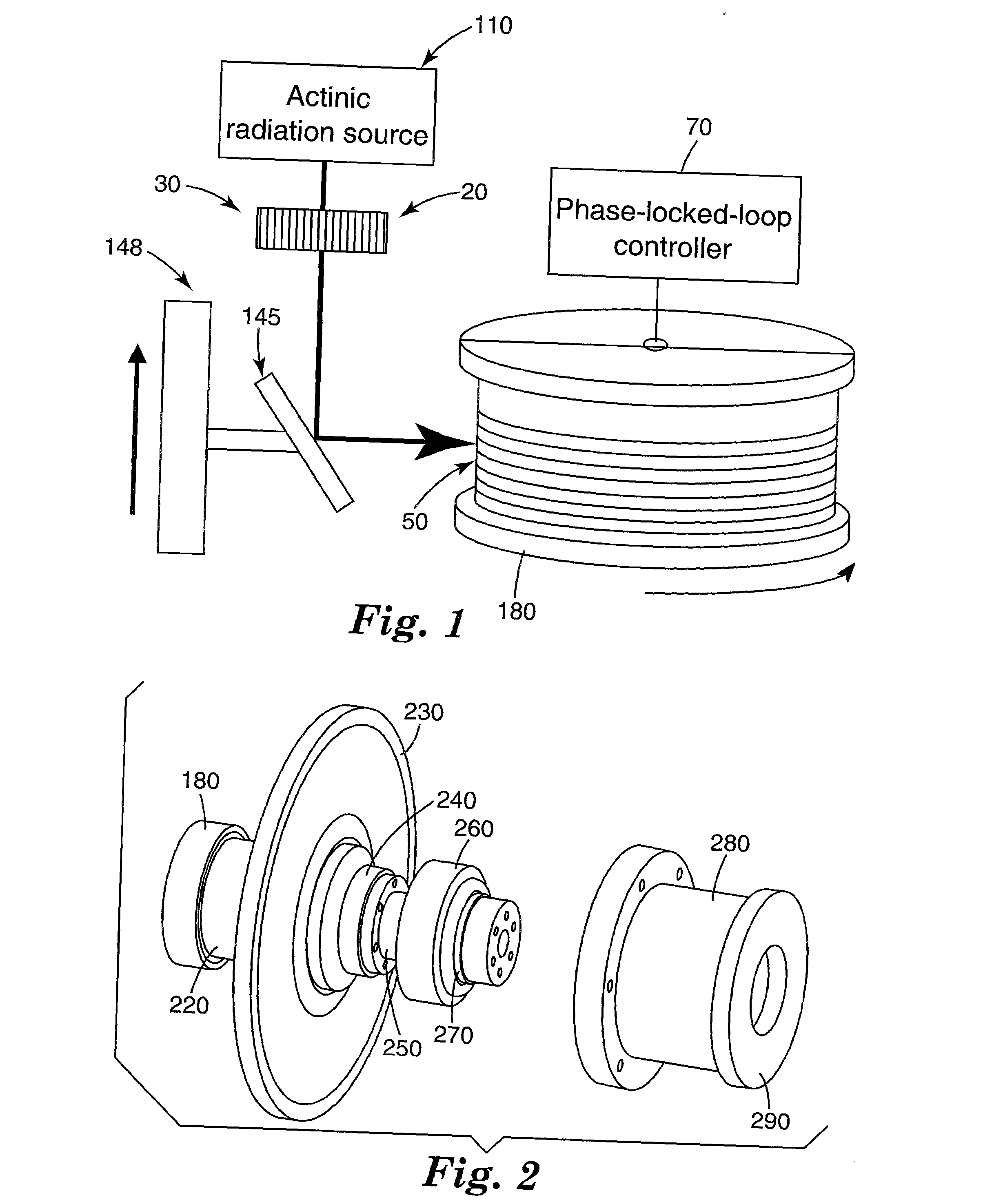

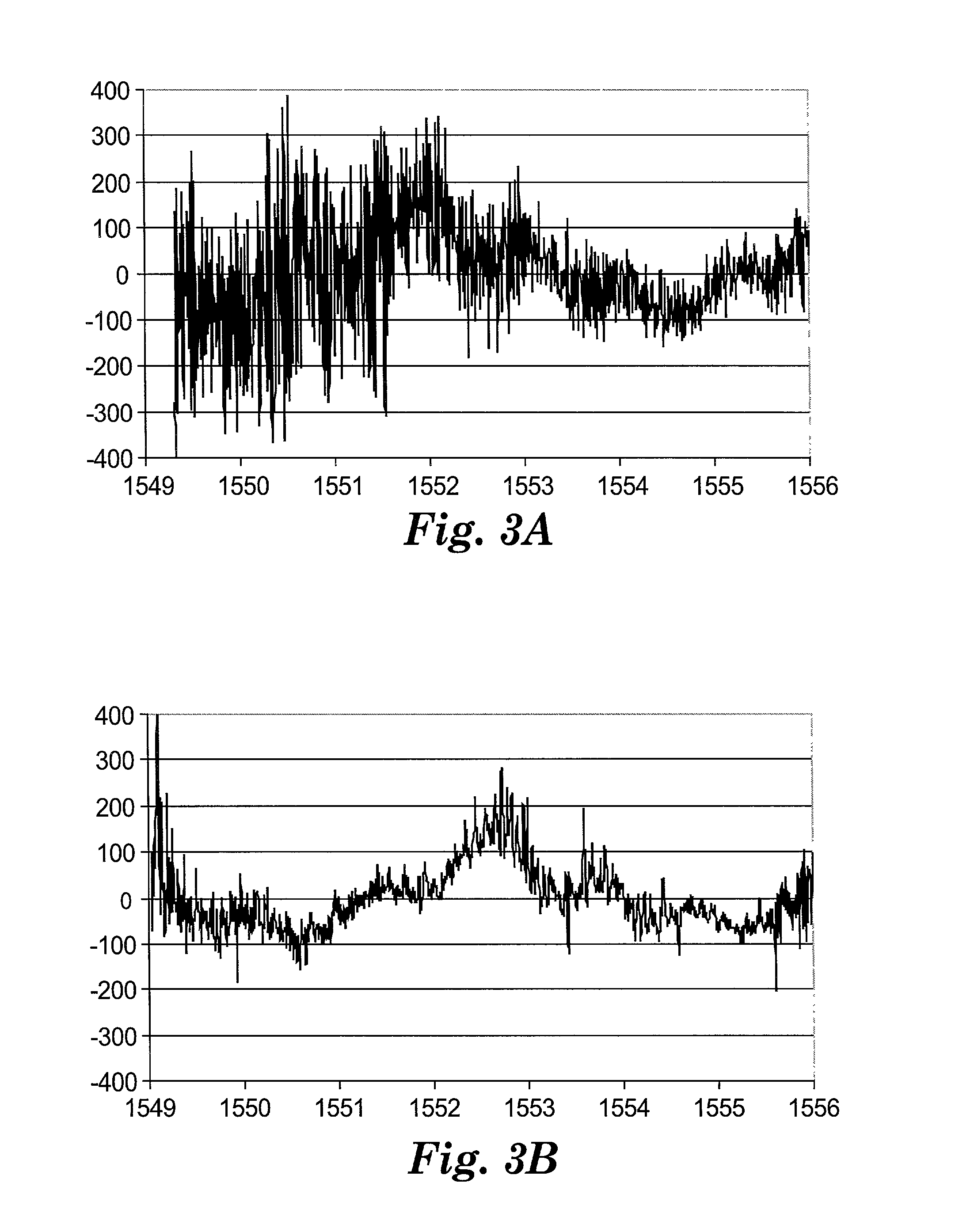

Wide-bandwidth chirped fiber bragg gratings with low delay ripple amplitude

Owner:PROXIMON FIBER SYST

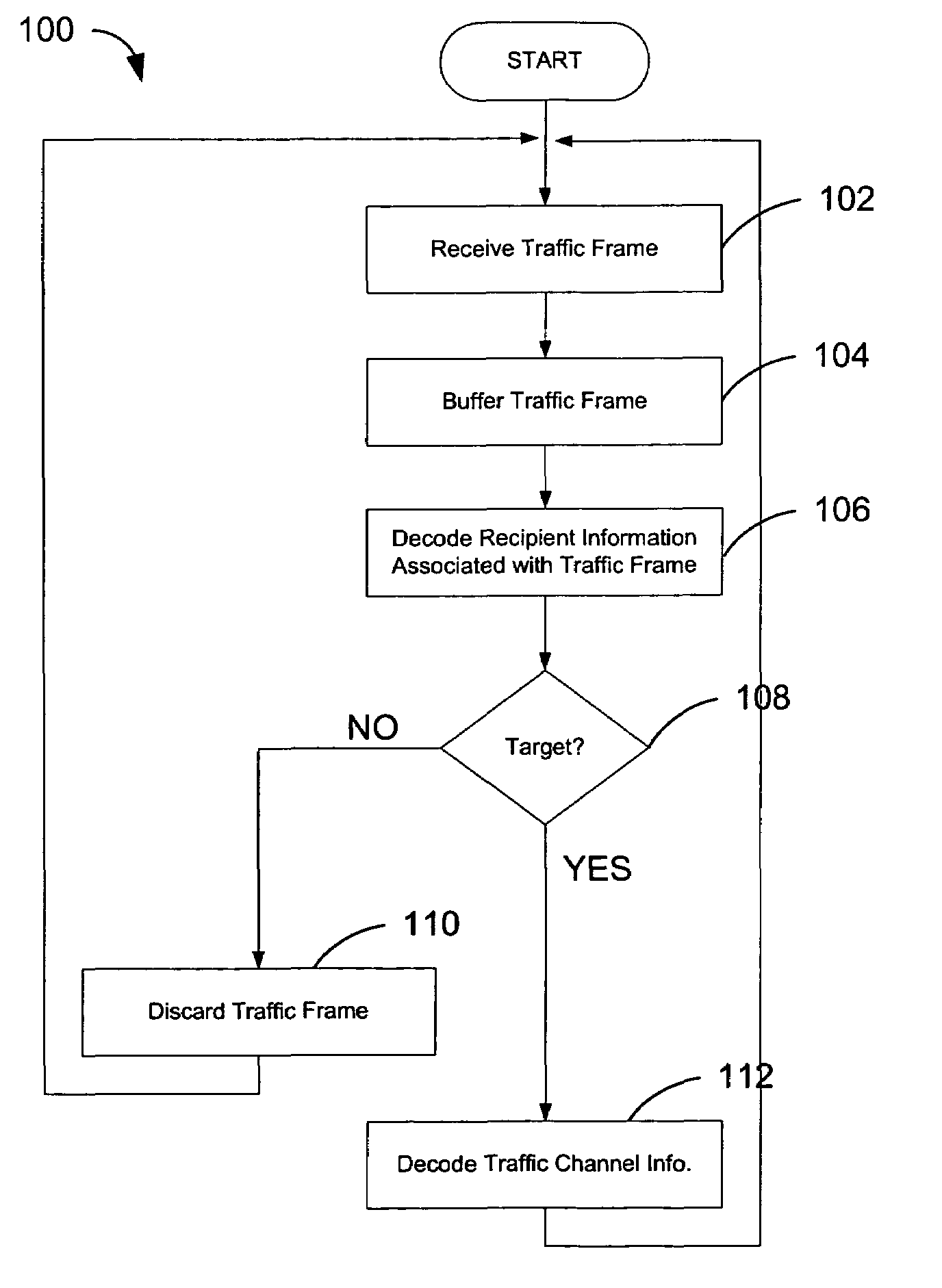

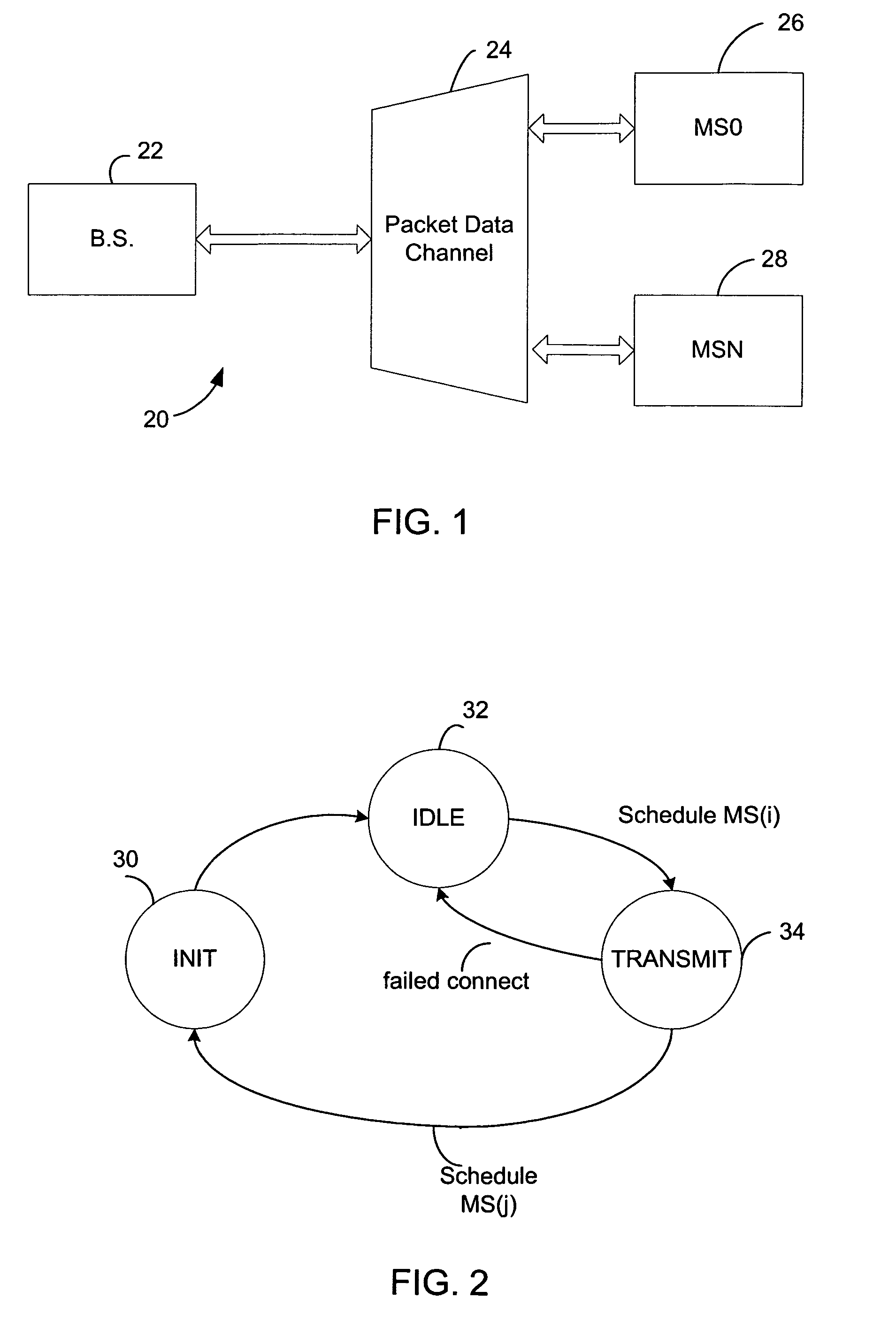

Method and apparatus for determining a data rate in a high rate packet data wireless communications system

InactiveUS6973098B1High packet data rateLower latencyPower managementTransmission control/equlisationHigh rateCommunications system

In a wireless communication system a method for combination transmission of packet data and low delay data. In one embodiment a parallel signaling channel provides a message to receivers indicating a target recipient of packet data. The message also identifies the transmission channels used for packet data transmissions. Each receiver may then selectively decode only packets where the message identifies the receiver as a target recipient. The data packets stored in a buffer are ignored if the target recipient is another mobile unit. In one embodiment, the message is sent concurrently with the data packet on a parallel channel. In one embodiment, the message is punctured into the high rate packet data transmission.

Owner:QUALCOMM INC

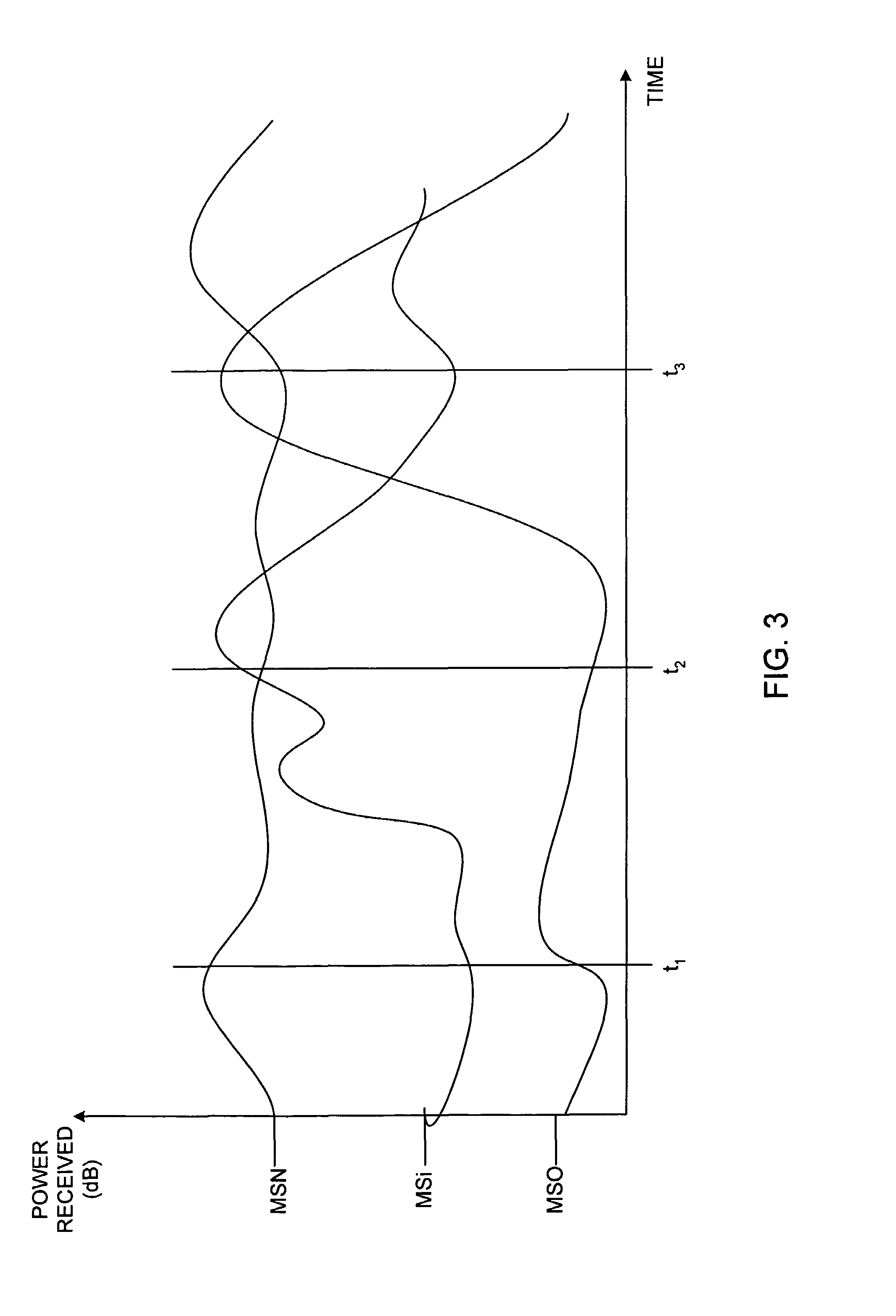

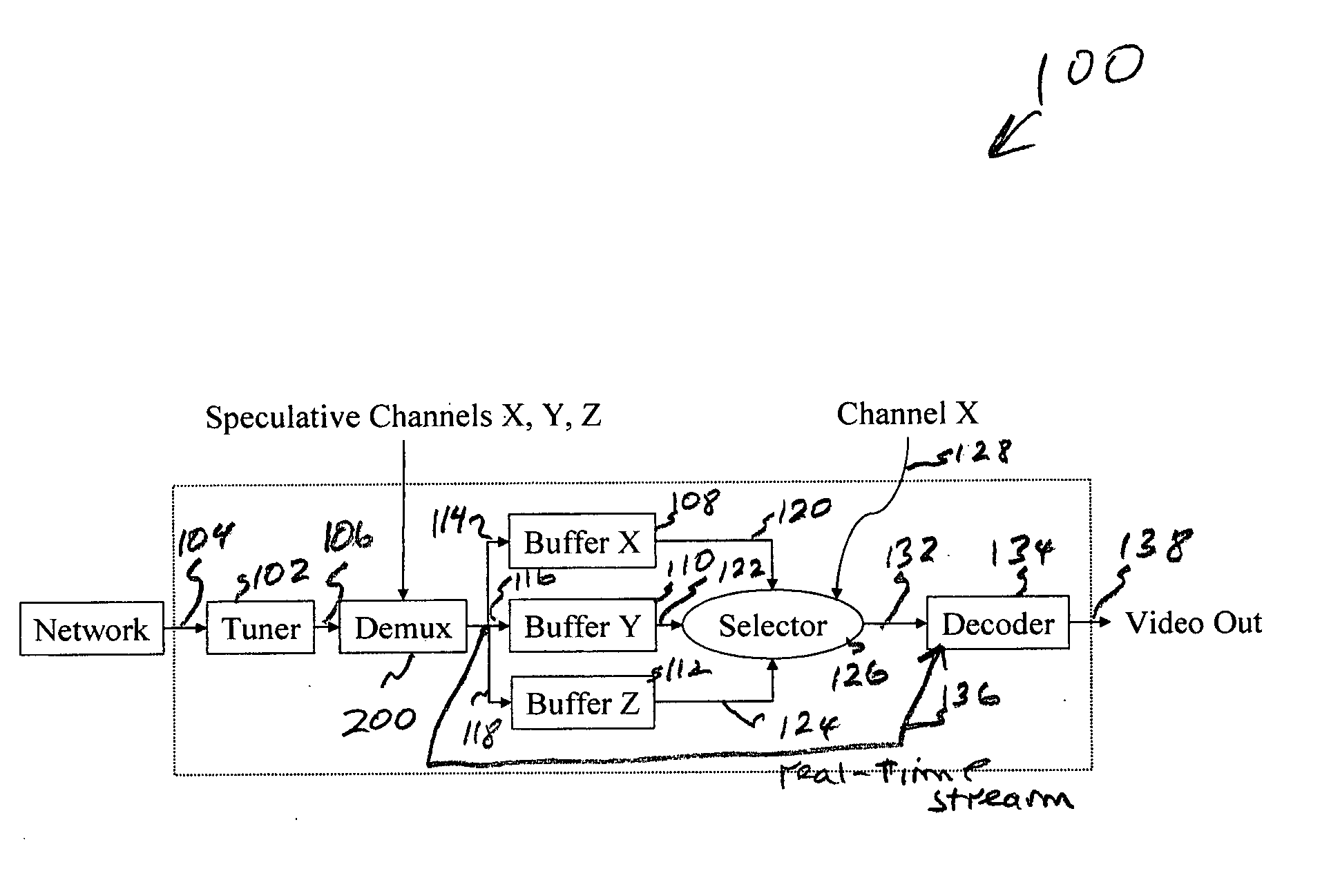

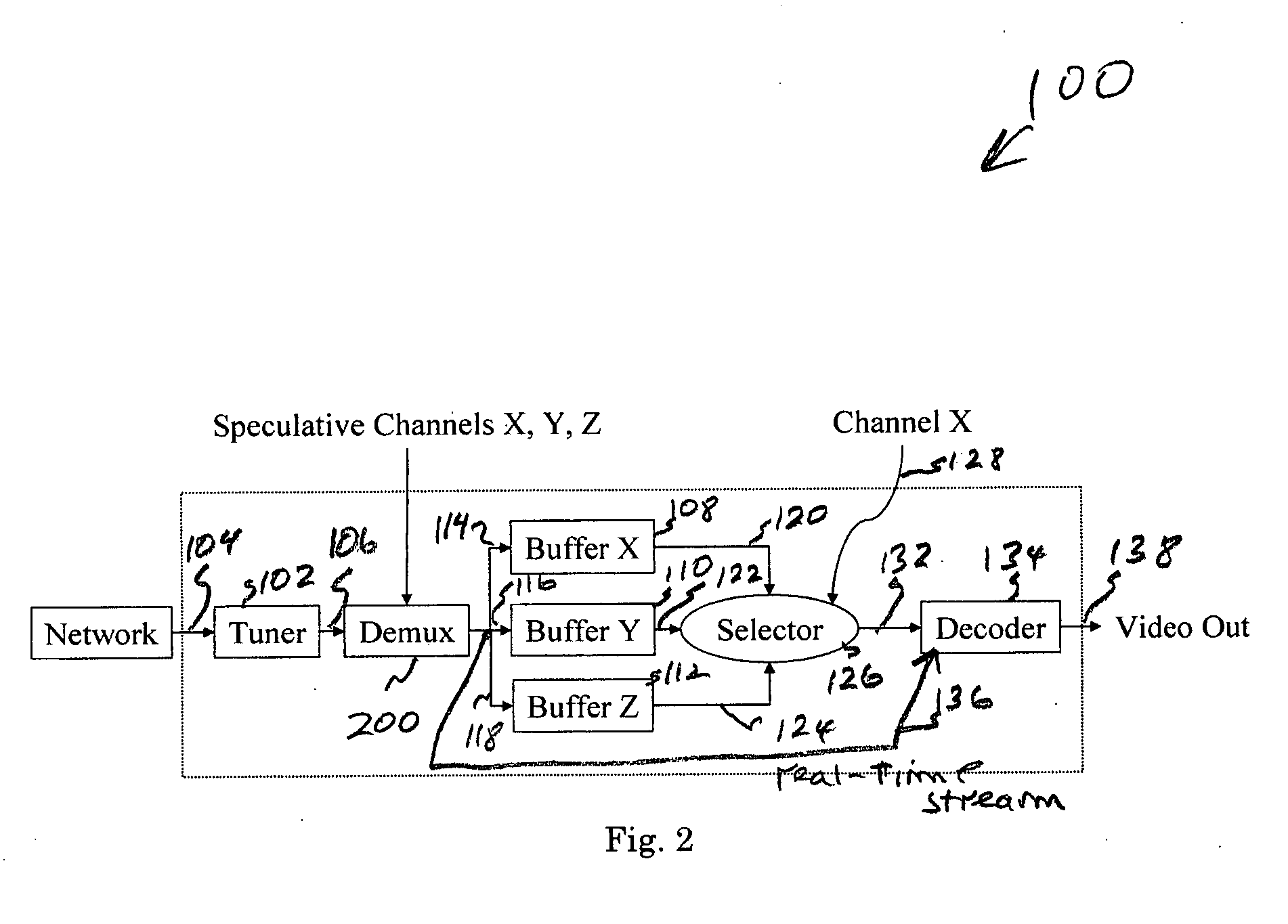

System and method for low-delay channel hopping

InactiveUS20050229221A1Reduce delaysControl complexityTelevision system detailsAnalogue secracy/subscription systemsLow delayBroadcasting

A system and method are provided for low-delay channel changes in a multicast / broadcast of compressed video. The method comprises: receiving a multicast / broadcast with a plurality of compressed video channels; buffering information from a plurality of channels; selecting a channel; and, decoding the selected channel in response to the buffered information. In some aspects, the method pre-identifies access points in the buffered information for each channel, prior to selecting the channel. Then, decoding the selected channel in response to the buffered information includes: accessing the buffered information at the pre-identified access point; and, decoding the selected channel, beginning at the access point. Alternately, access points are not pre-identified. Then, decoding the selected channel in response to the buffered information includes: discovering an access point in the information buffered for the selected channel subsequent to selecting the channel; and, decoding the selected channel, beginning at the discovered access point.

Owner:SHARP LAB OF AMERICA INC

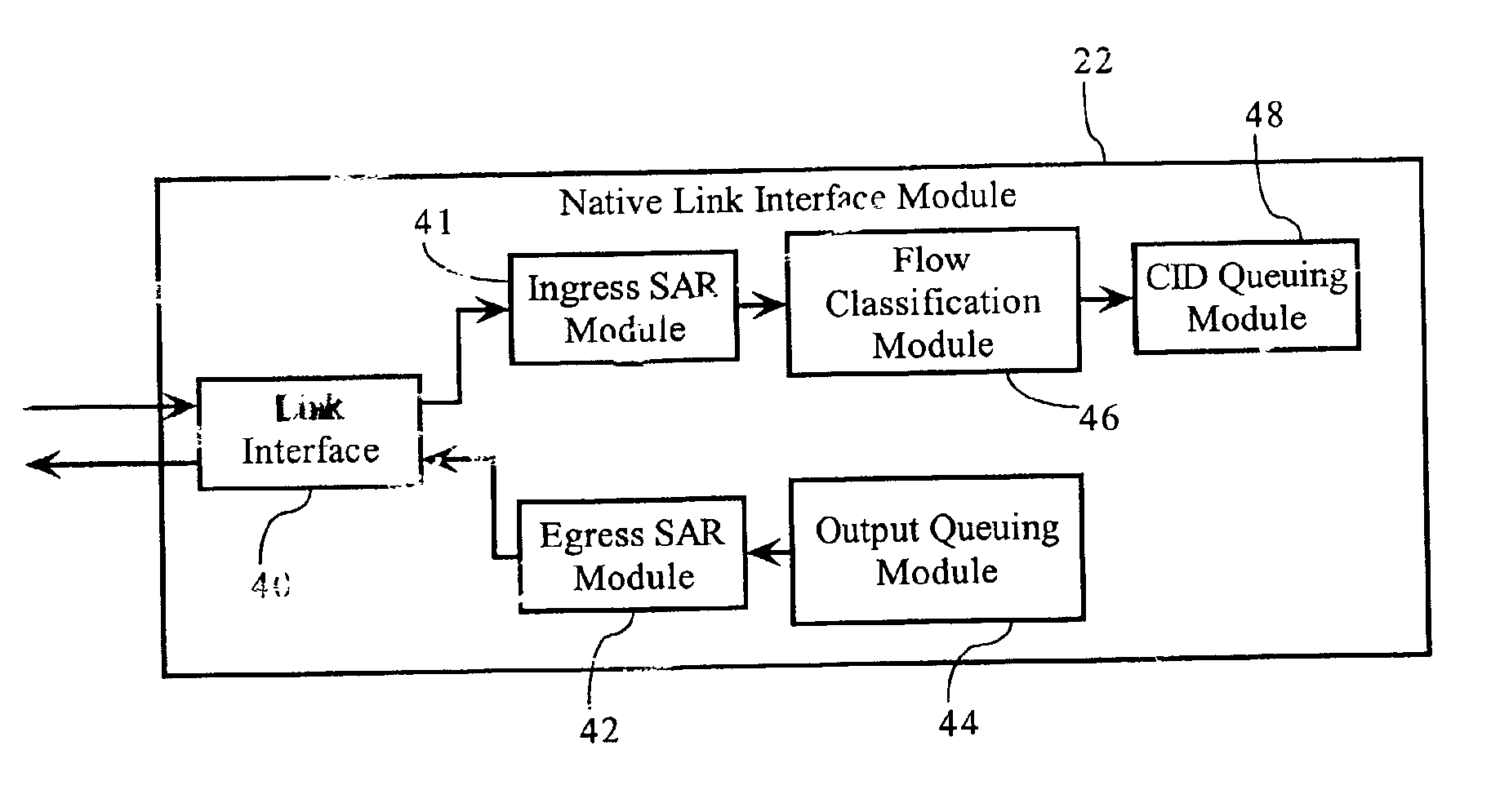

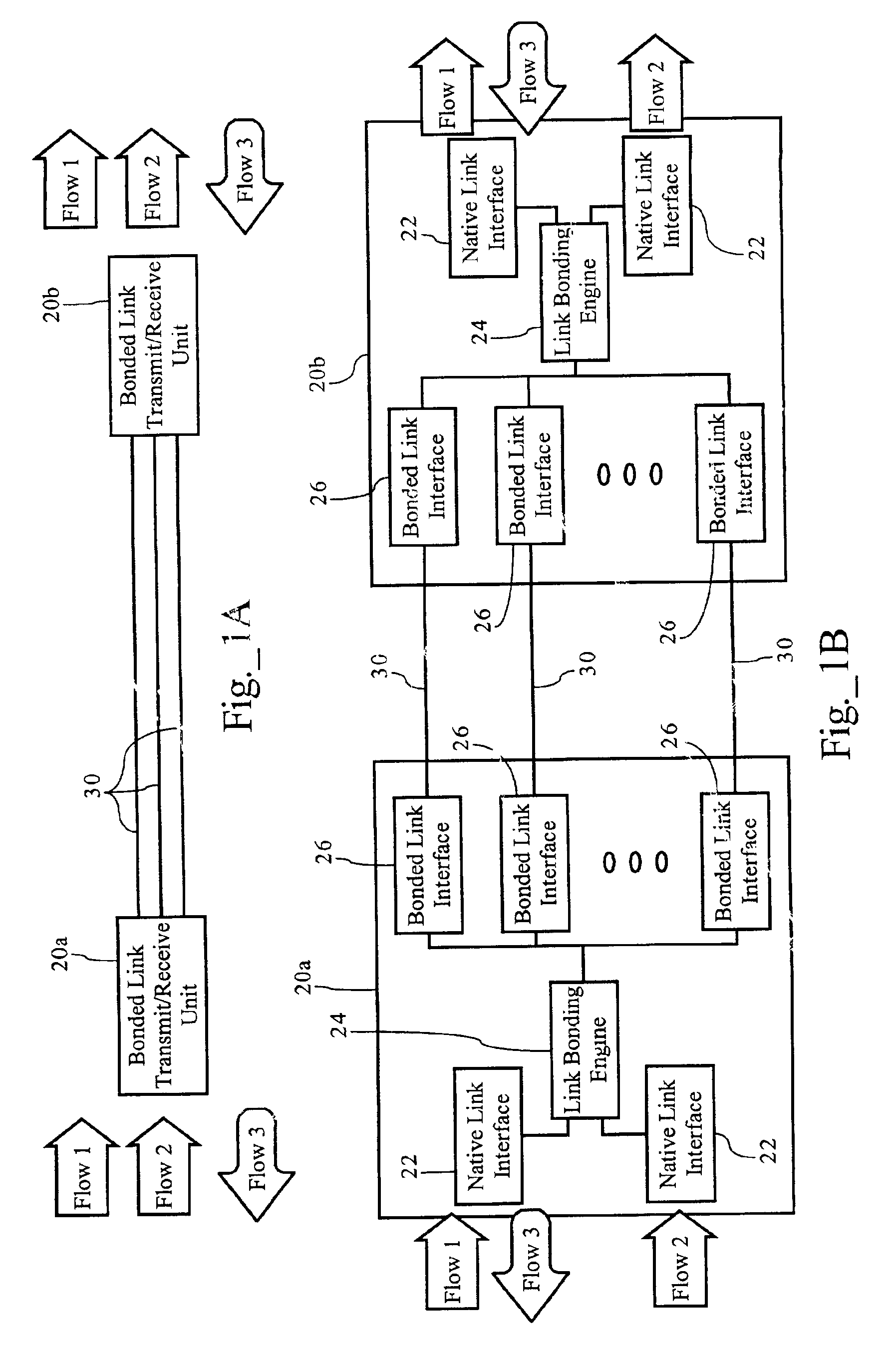

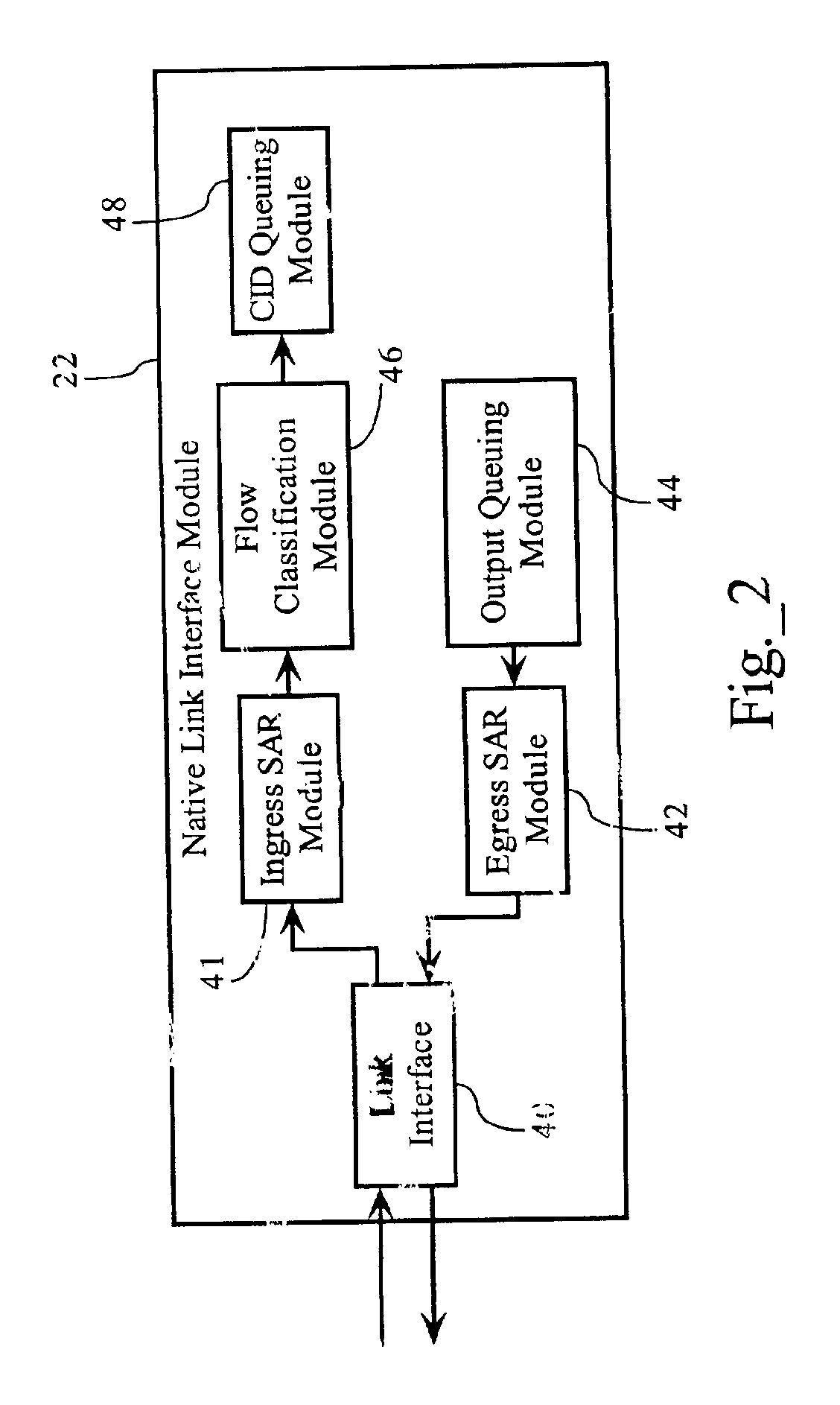

Methods, apparatuses and systems facilitating aggregation of physical links into logical link

InactiveUS6879590B2Improve data transfer efficiencyLower latencyEnergy efficient ICTTelephonic communicationQuality of serviceTraffic capacity

Methods, apparatuses and systems facilitating the aggregation or bonding of physical communications links into higher-bandwidth logical links. A novel link bonding and encapsulation protocol scheme that optimizes the efficiency of data transfer across the physical links, while still allowing for desired Quality of Service (QoS) levels to high-priority traffic, such as voice data, with low delay requirements. Data streams are divided and concurrently transported over multiple physical links that are aggregated or bonded together to form one logical link. At the receive end, the original cell streams are recovered from the bonded logical links. In one embodiment, the physical links are xDSL links transmitting and receiving signals via conventional copper twisted-pair cabling. In one embodiment, the present invention allows telecommunications service providers to leverage their investments in existing twisted pair connection technologies to deliver high-bandwidth services to customers in a fast and cost-efficient manner.

Owner:KLAMATH NETWORKS

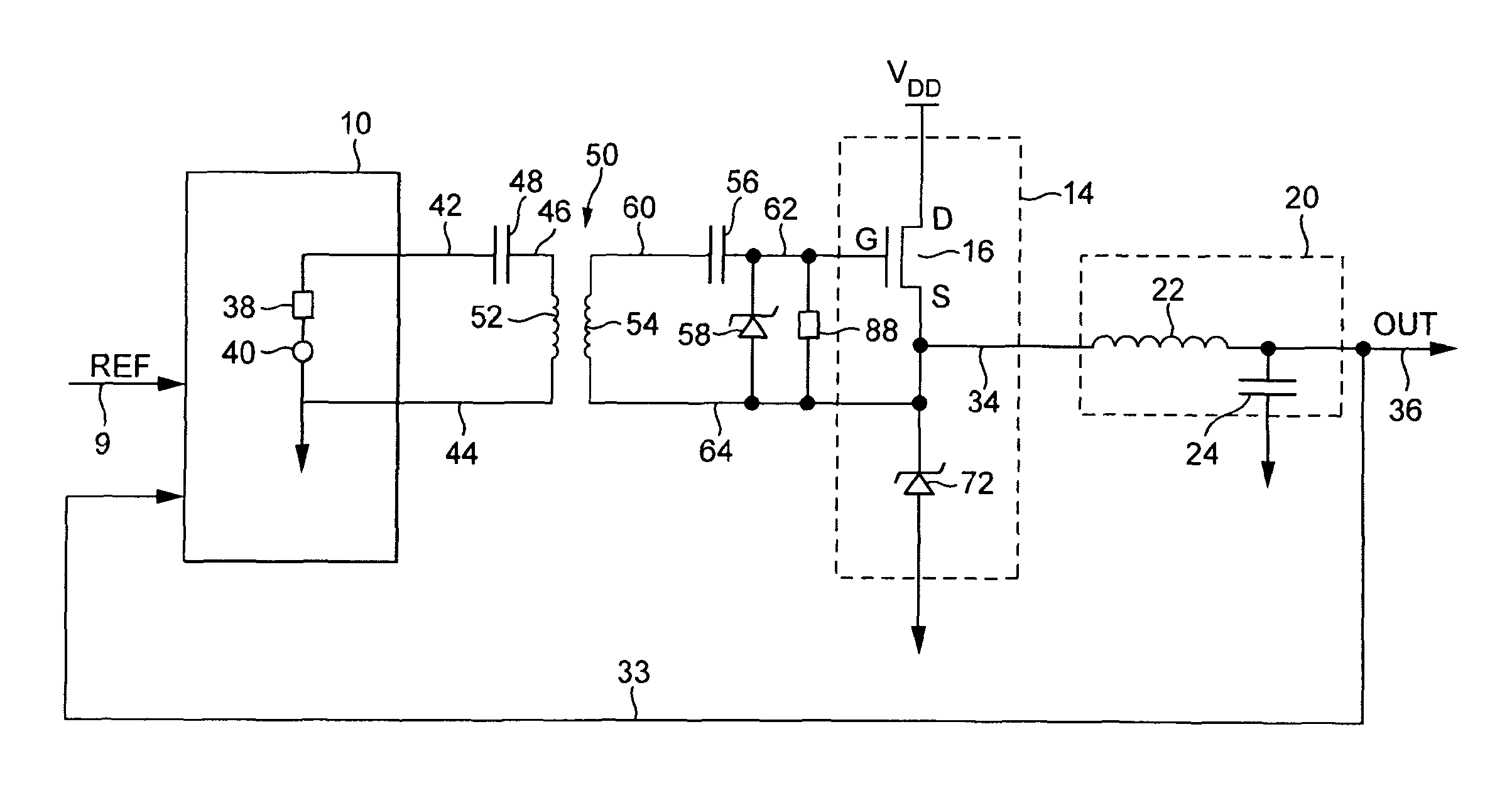

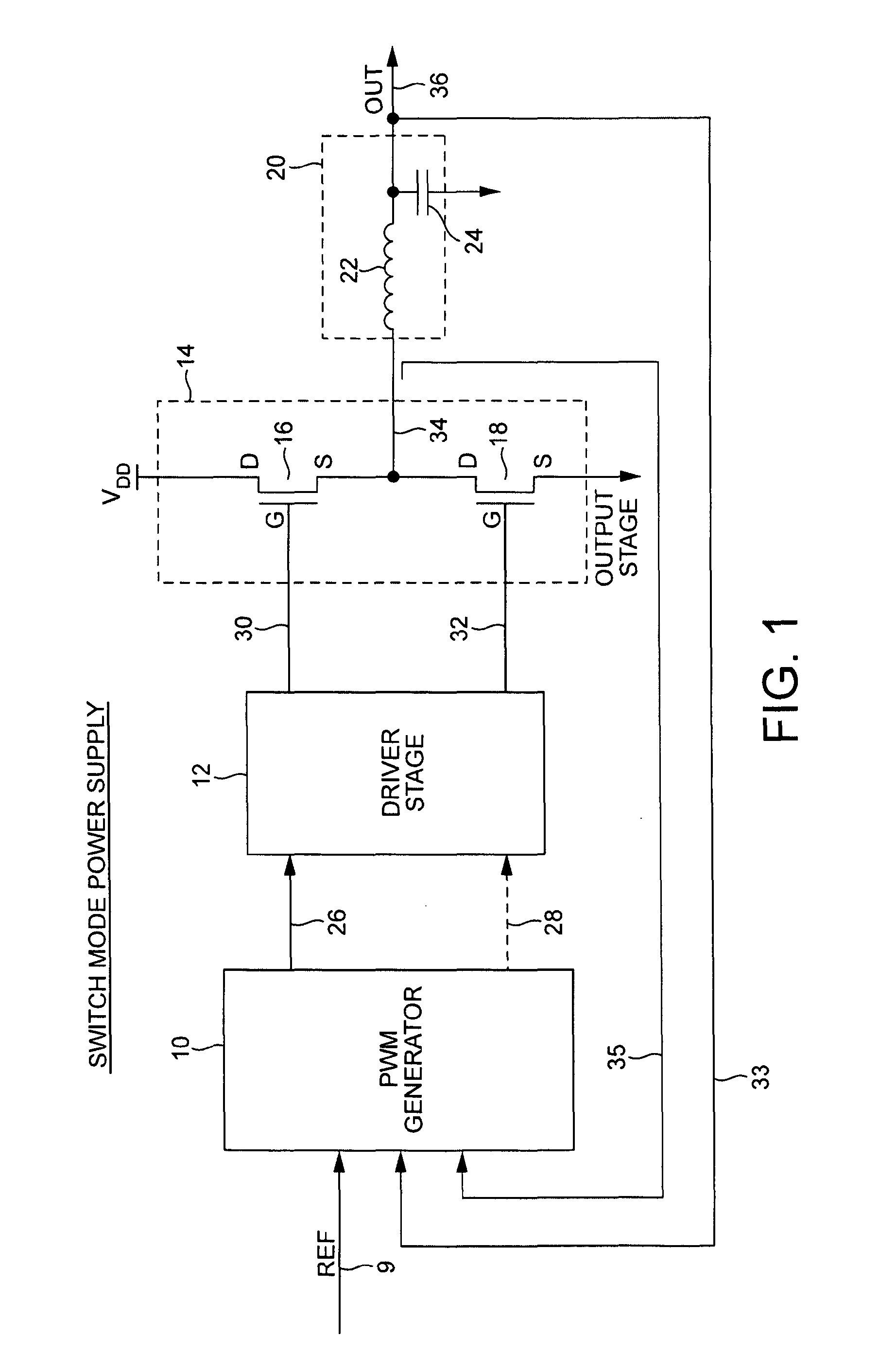

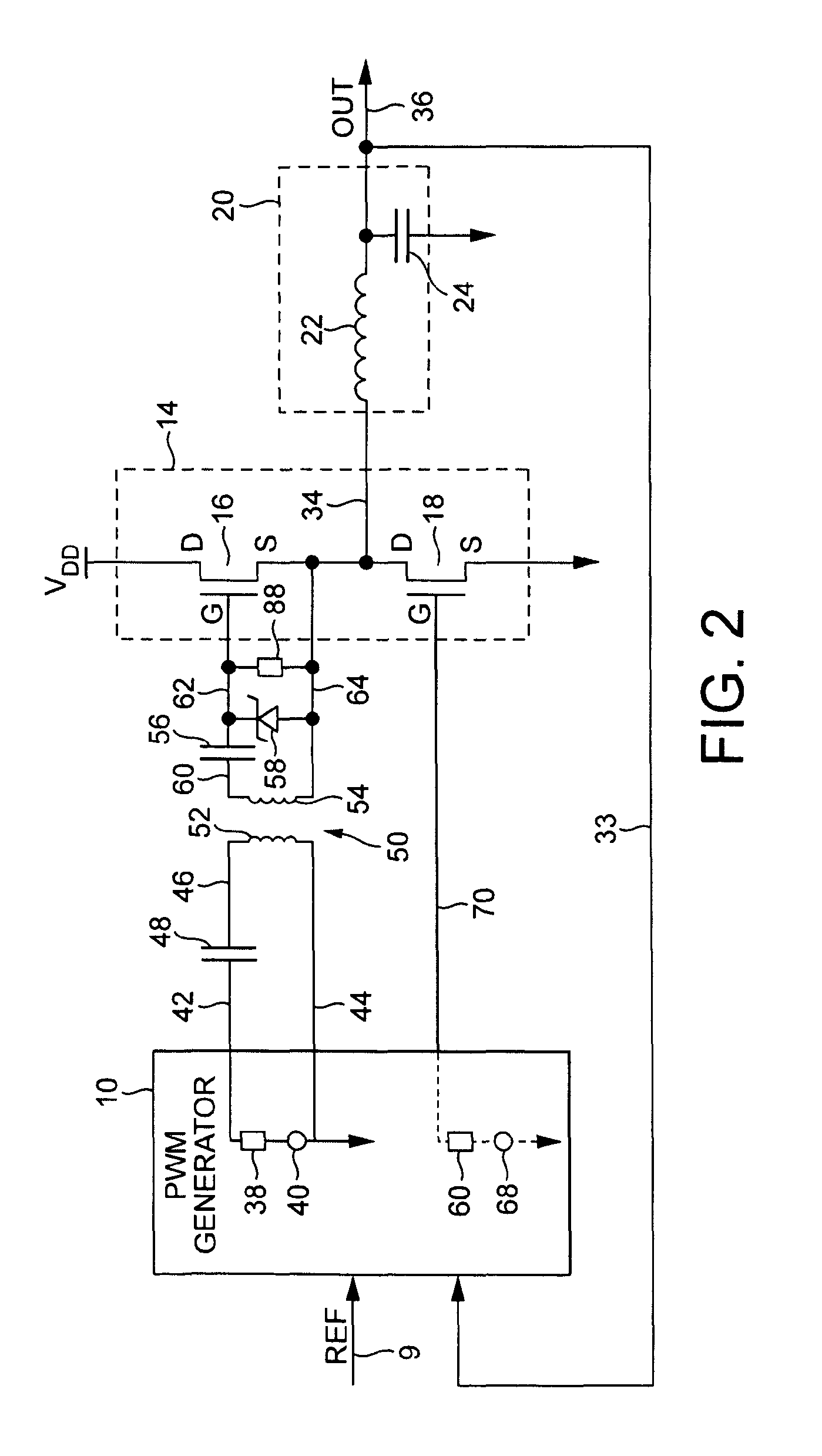

Switch mode power supply for envelope tracking

ActiveUS20130200865A1High bandwidthLower latencyEfficient power electronics conversionDc-dc conversionHigh bandwidthTransformer

There is disclosed an envelope tracked power supply comprising a high bandwidth, low delay closed loop switch mode power supply stage comprising: a pulse width modulator for generating a width modulated pulse in dependence on an input signal and an output voltage of the switch mode power supply stage; a wideband transformer, having a winding of a first side connected to receive the modulated pulse, and a winding of a second side; and an output stage connected to the winding of the second side of the transformer, and for generating the output voltage in dependence on the modulated pulse induced in the winding of the second side.

Owner:SNAPTRACK

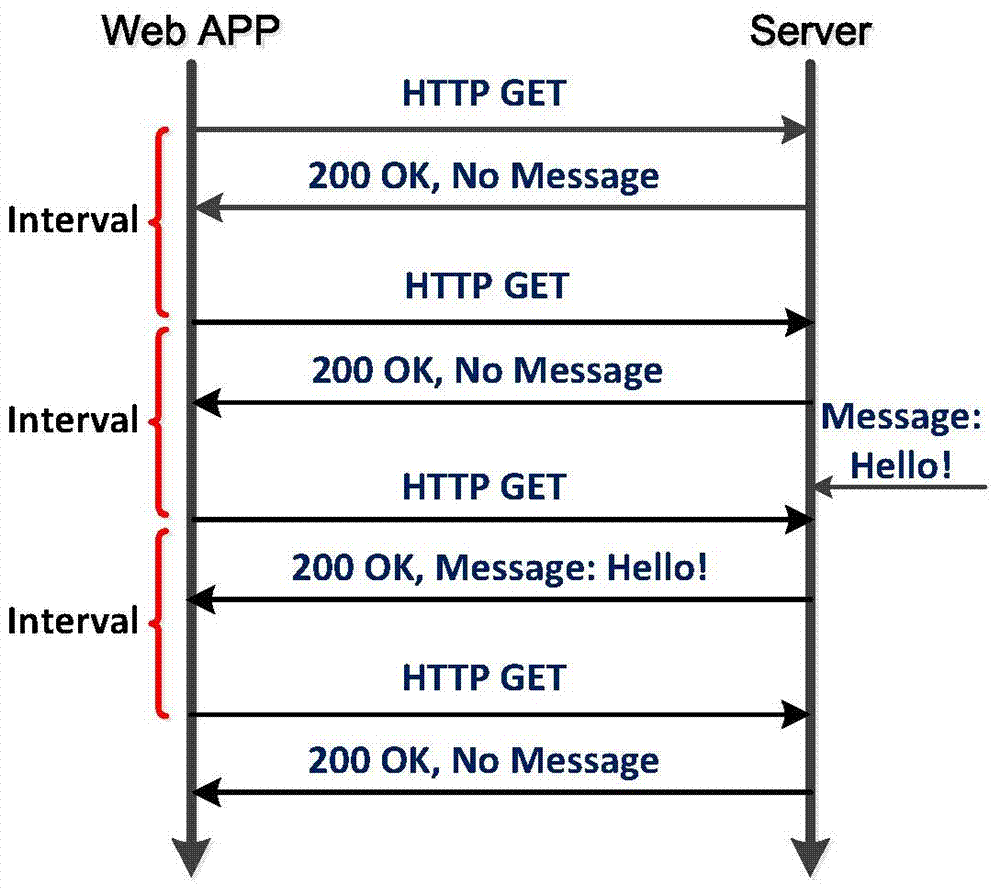

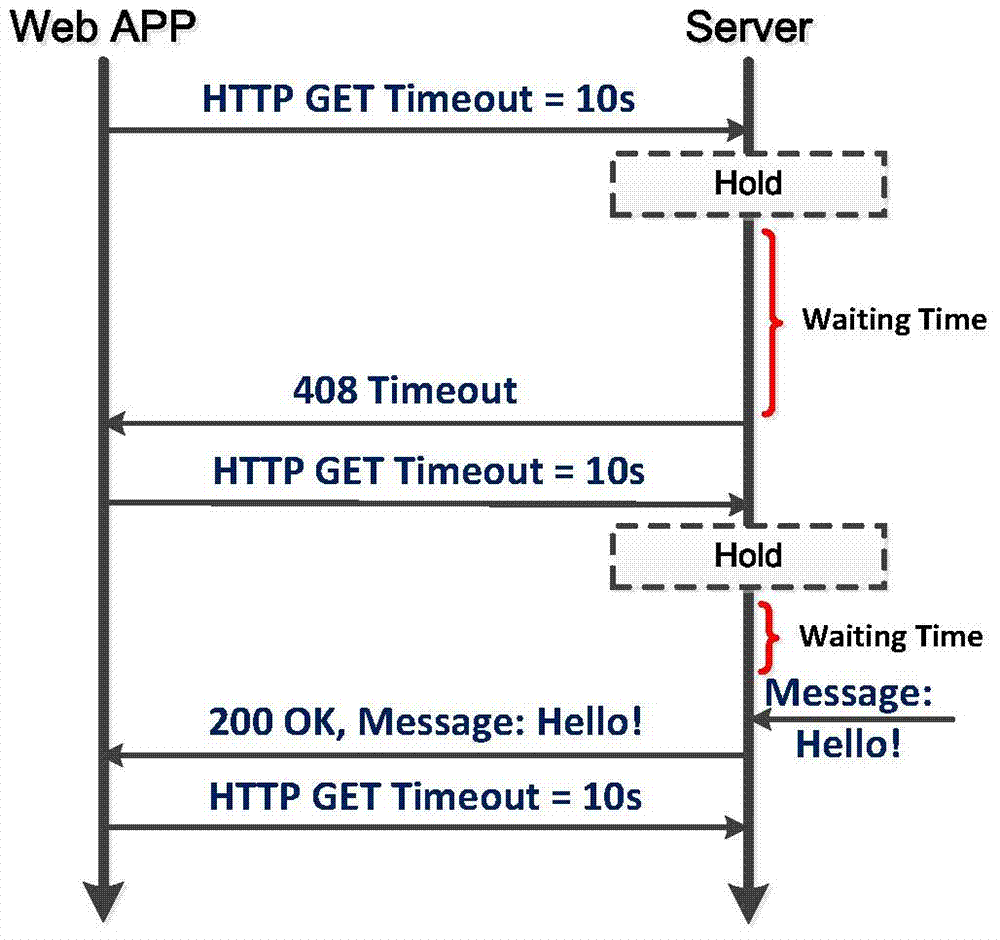

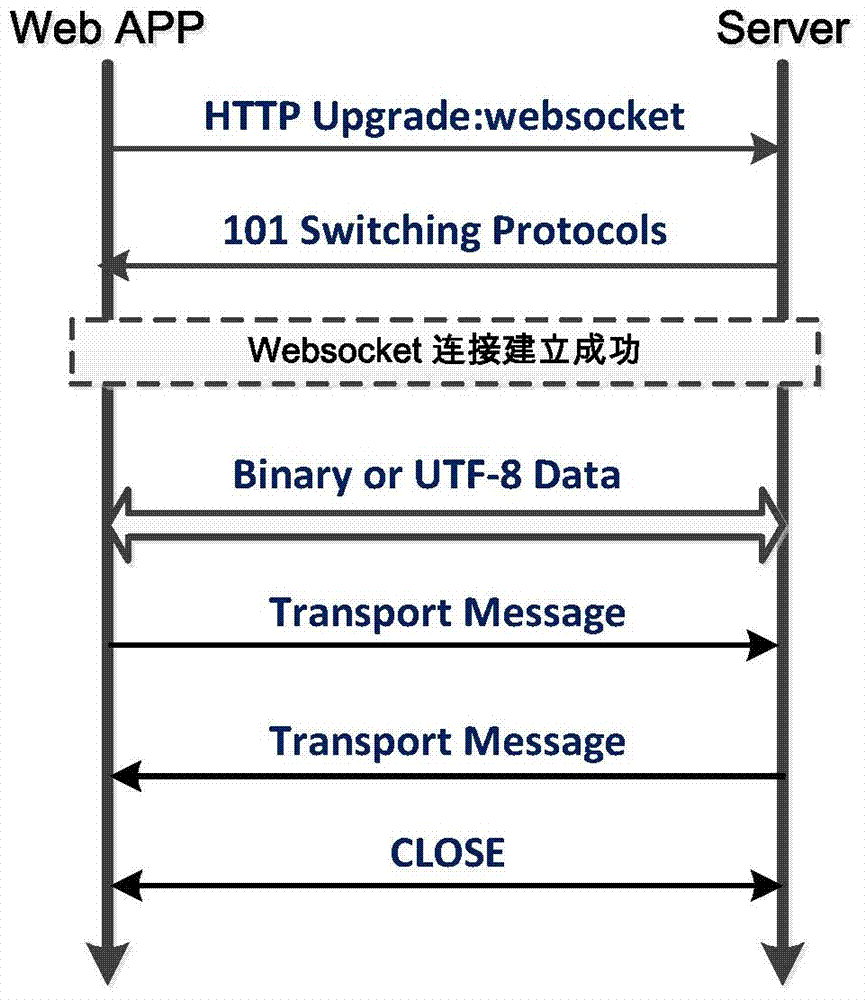

Dynamic self-adapting method for connection of Web RTC (Real Time Communication) client

ActiveCN103945003AFunction increaseImprove intelligenceTransmissionHyper text transport protocolLow delay

The invention provides a dynamic self-adapting method for the connection of a Web RTC (Real Time Communication) client, belonging to the technical fields of a Web RTC, an HTML (Hypertext Markup Language) 5 web Socket and the like. An entity related by the method comprises a Web RTC client, a browser and a real-time communication server, wherein the Web RTC client can support three connecting ways, including an HTTP (Hyper Text Transport Protocol) polling, an HTTP long connection and a Web Socket, and the HTTP long connection comprises an HTTP stream; according to the method, the connecting way with lowest delay of the HTTP polling, the HTTP long connection and the Web Socket can be optimally selected, and the Web RTC client and the real-time communication server are connected by using the connecting way with the lowest delay. Under the premise of guaranteeing timeliness, the communication delay can be reduced, the functions of the client can be enhanced, and the intelligence of the client can be improved.

Owner:BEIJING UNIV OF POSTS & TELECOMM

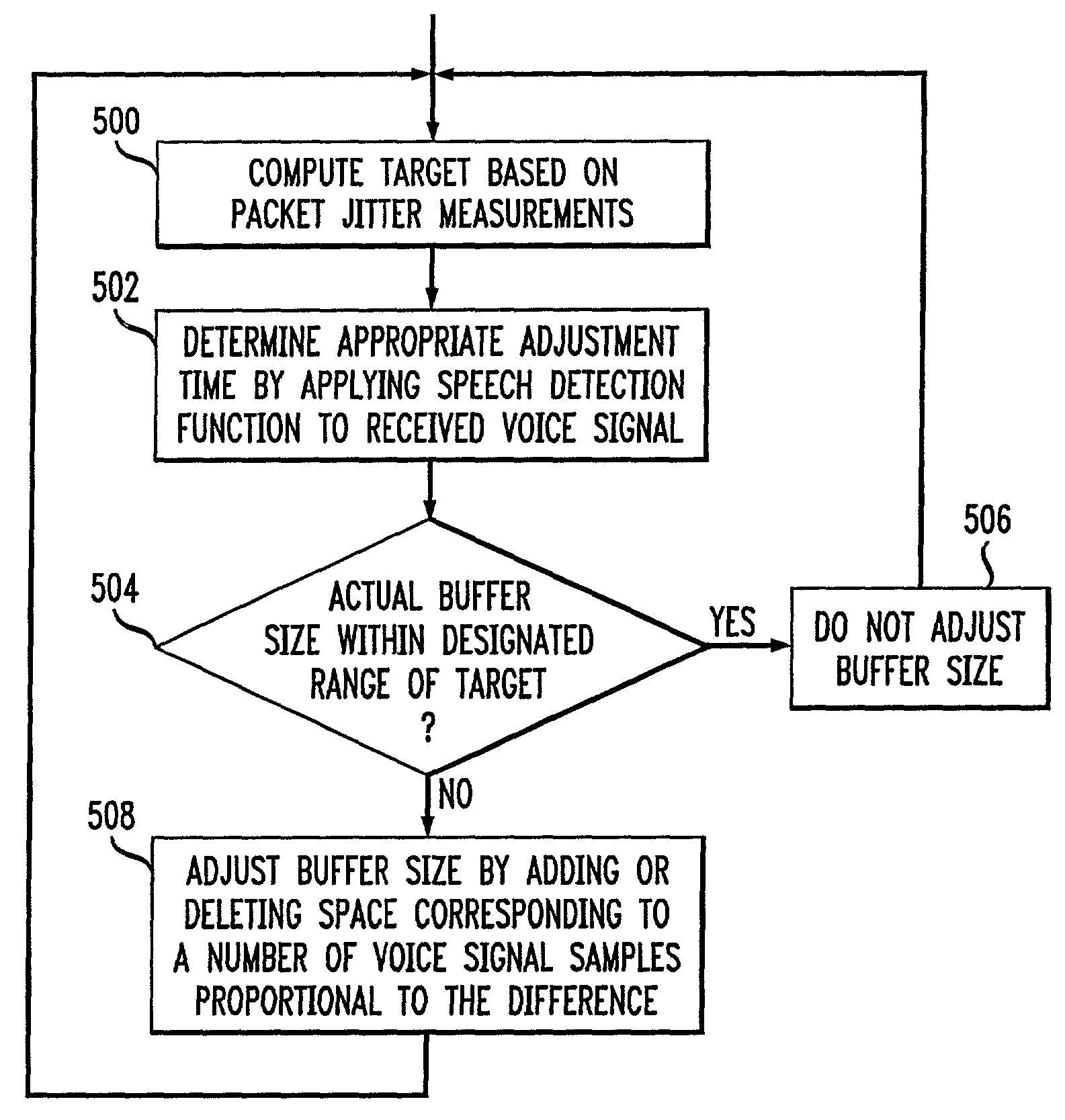

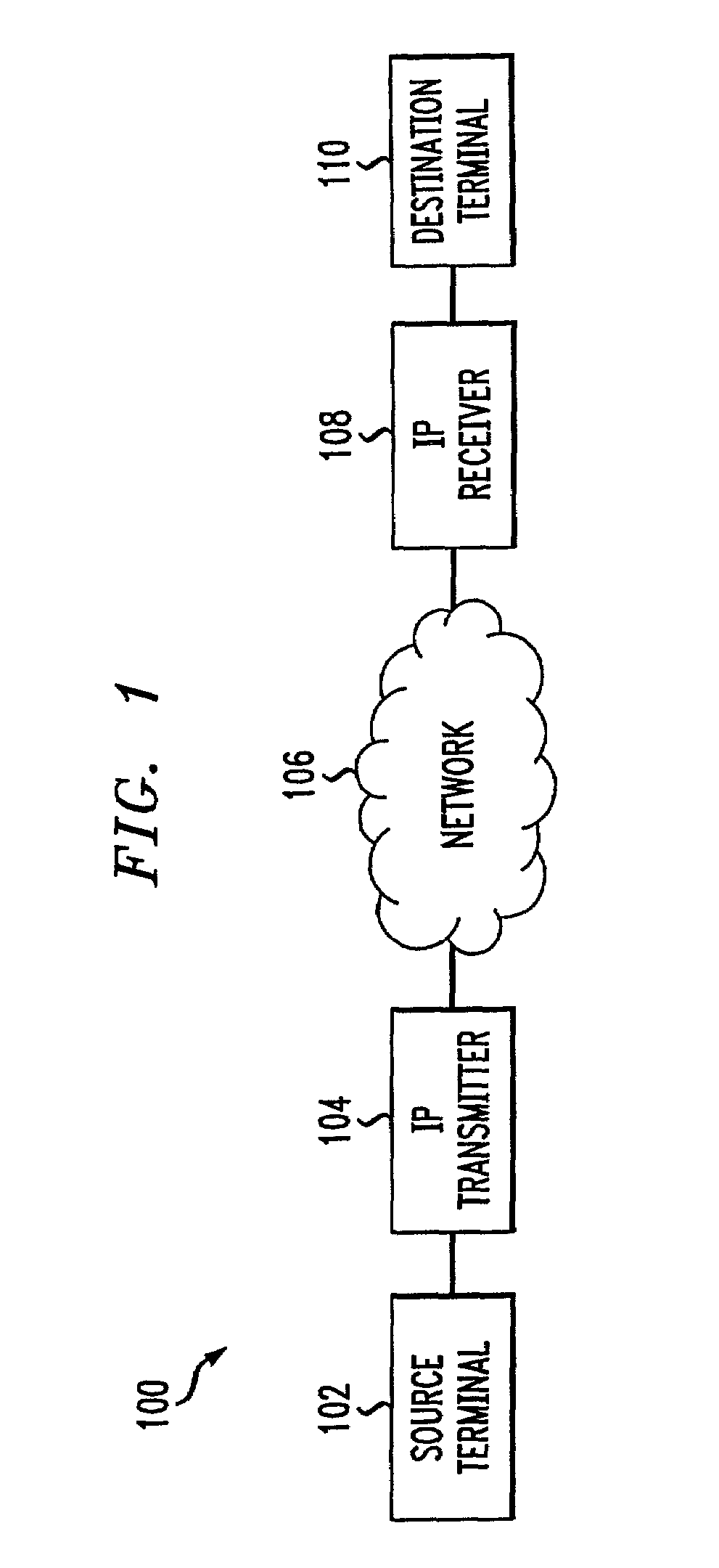

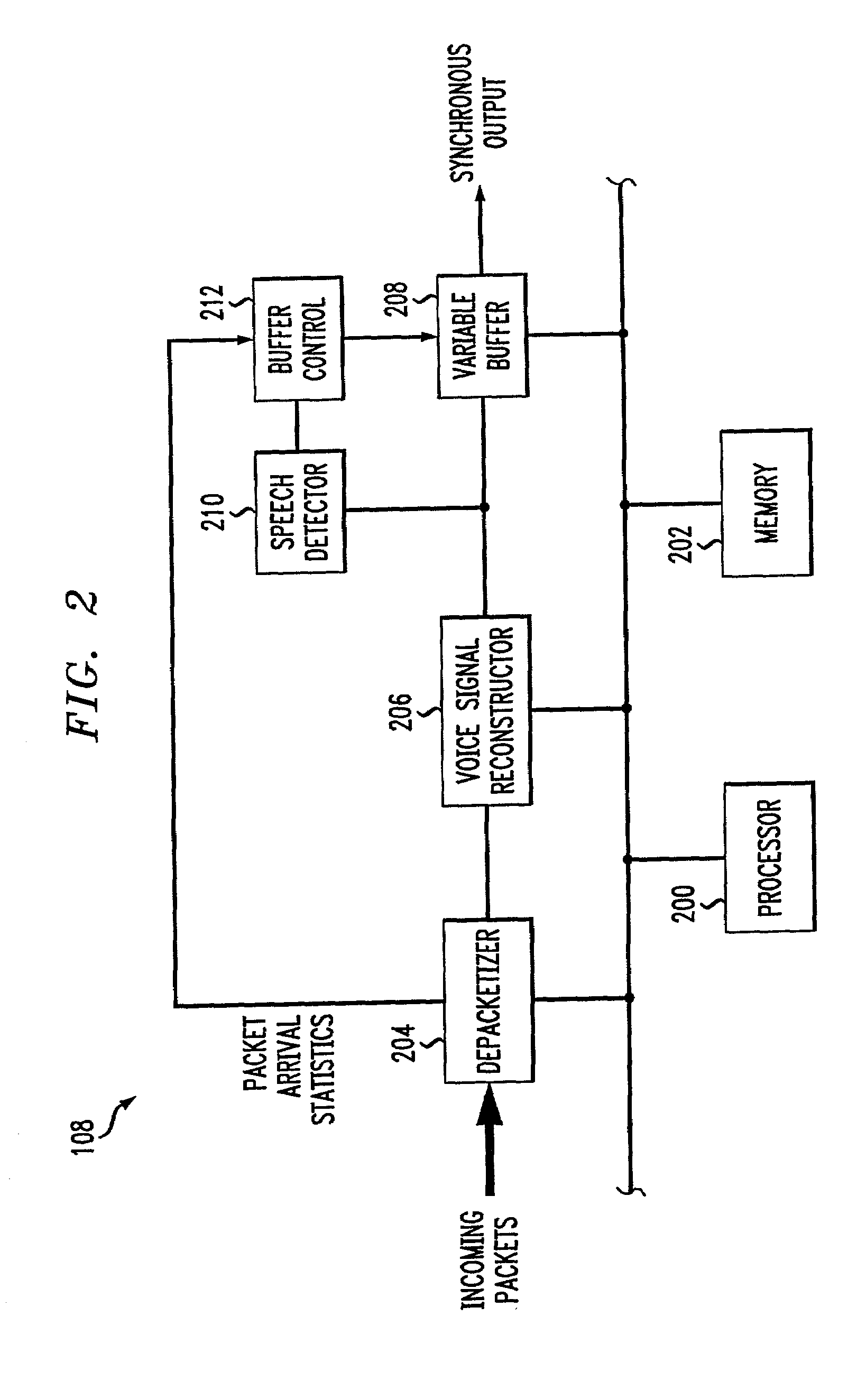

Dynamic jitter buffering for voice-over-IP and other packet-based communication systems

ActiveUS7006511B2Prevents excessively rapidLess resourcesTime-division multiplexData switching by path configurationCommunications systemSignal correlation

A variable-size jitter buffer is used to store information associated with a voice signal, facsimile signal or other received signal in a receiver of a packet-based communication system. The receiver determines an appropriate adjustment time for making an adjustment to the size of the buffer based at least in part on a result of a signal detection operation performed on the received signal. For example, in the case of a received voice signal, the determined adjustment time may be a time at which a state machine associated with a speech detector is in a “no speech” state. If the actual buffer size at the determined adjustment time is not within a designated range of a target computed at least in part based on one or more jitter measurements, the buffer size is adjusted at the determined adjustment time, e.g., by an amount representative of the difference between the actual buffer size and the target. The invention provides low-delay and low-complexity jitter buffering particularly well suited for use in an Internet Protocol (IP) receiver of a voice-over-IP system.

Owner:AVAYA INC

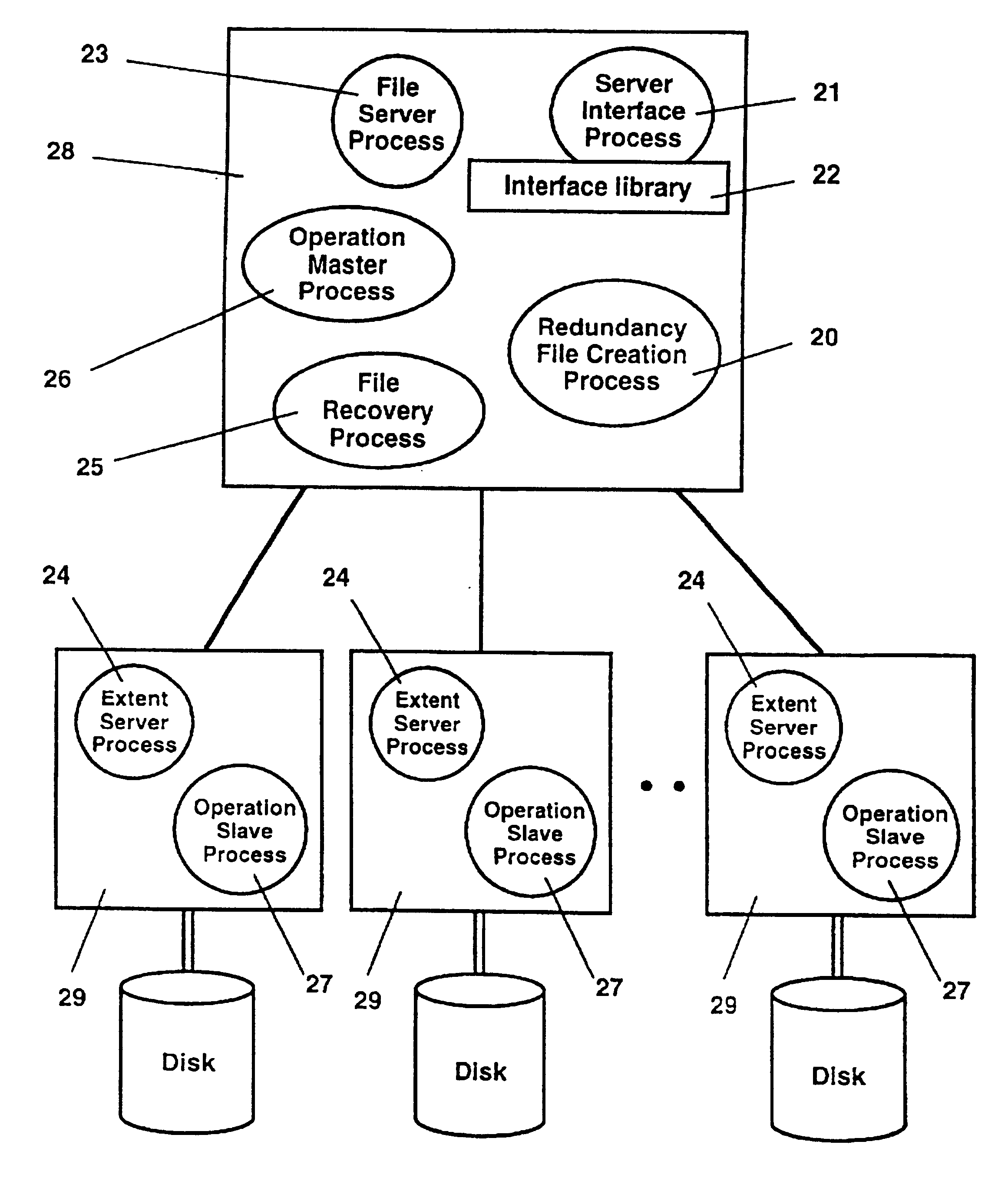

Method and apparatus for a parallel data storage and processing server

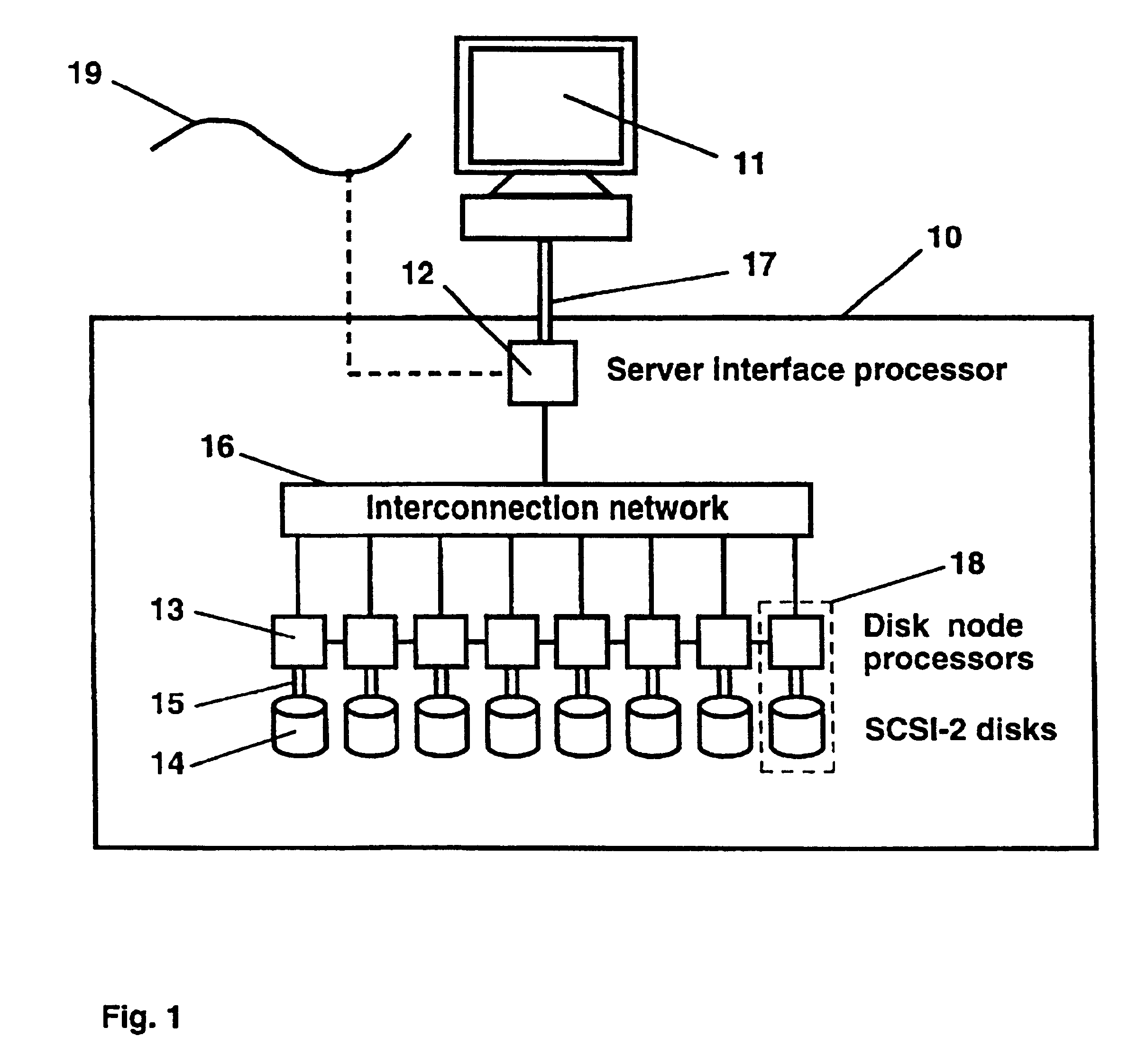

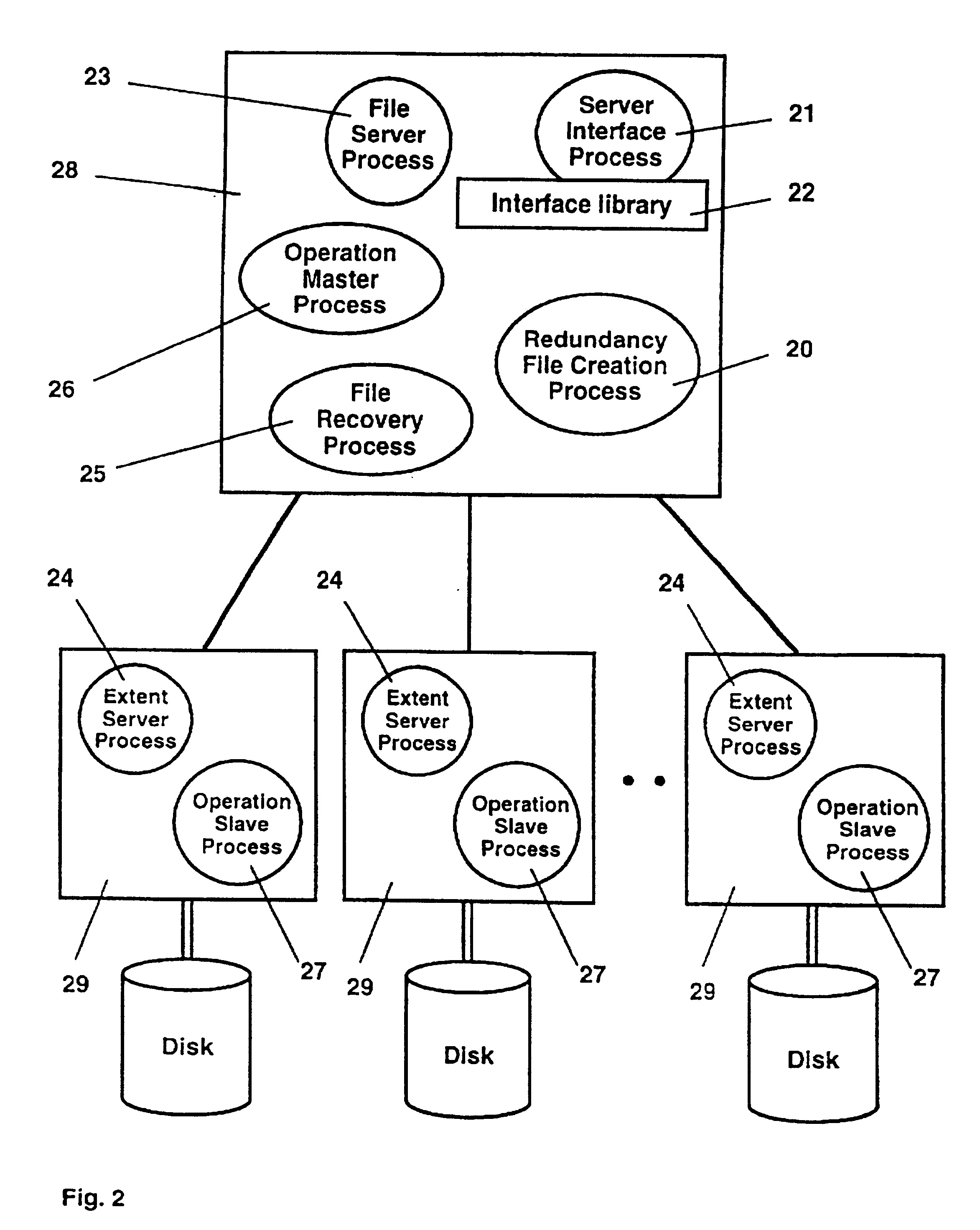

InactiveUSRE38410E1Lower latencyImprove throughputImage memory managementMultiple digital computer combinationsConcurrent computationComputer architecture

The present invention concerns a parallel multiprocessor-multidisk storage server which offers low delays and high throughputs when accessing and processing one-dimensional and multi-dimensional file data such as pixmap images, text, sound or graphics. The invented parallel multiprocessor-multidisk storage server may be used as a server offering its services to computer, to client stations residing on a network or to a parallel host system to which it is connected. The parallel storage server comprises (a) a server interface processor interfacing the storage system with a host computer, with a network or with a parallel computing system; (b) an array of disk nodes, each disk node being composed by one processor electrically connected to at least one disk and (c) an interconnection network for connecting the server interface processor with the array of disk nodes. Multi-dimensional data files such as 3-d images (for example tomographic images), respectively 2-d images (for example scanned aerial photographs) are segmented into 3-d, respectively 2-d file extents, extents being striped onto different disks. One-dimensional files are segmented into 1-d file extents. File extents of a given file may have a fixed or a variable size. The storage server is based on a parallel image and multiple media file storage system. This file storage system includes a file server process which receives from the high level storage server process file creation, file opening, file closing and file deleting commands. It further includes extent serving processes running on disk node processors, which receive from the file server process commands to update directory entries and to open existing files and from the storage interface server process commands to read data from a file or to write data into a file. It also includes operation processes responsible for applying in parallel geometric transformations and image processing operations to data read from the disks and a redundancy file creation process responsible for creating redundant parity extent files for selected data files.

Owner:AXS TECH

Voice activity detection and wake-up method and device

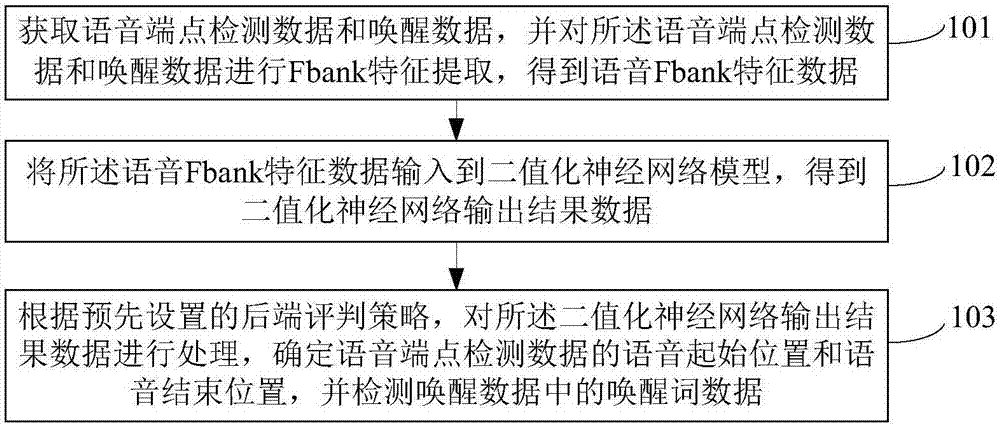

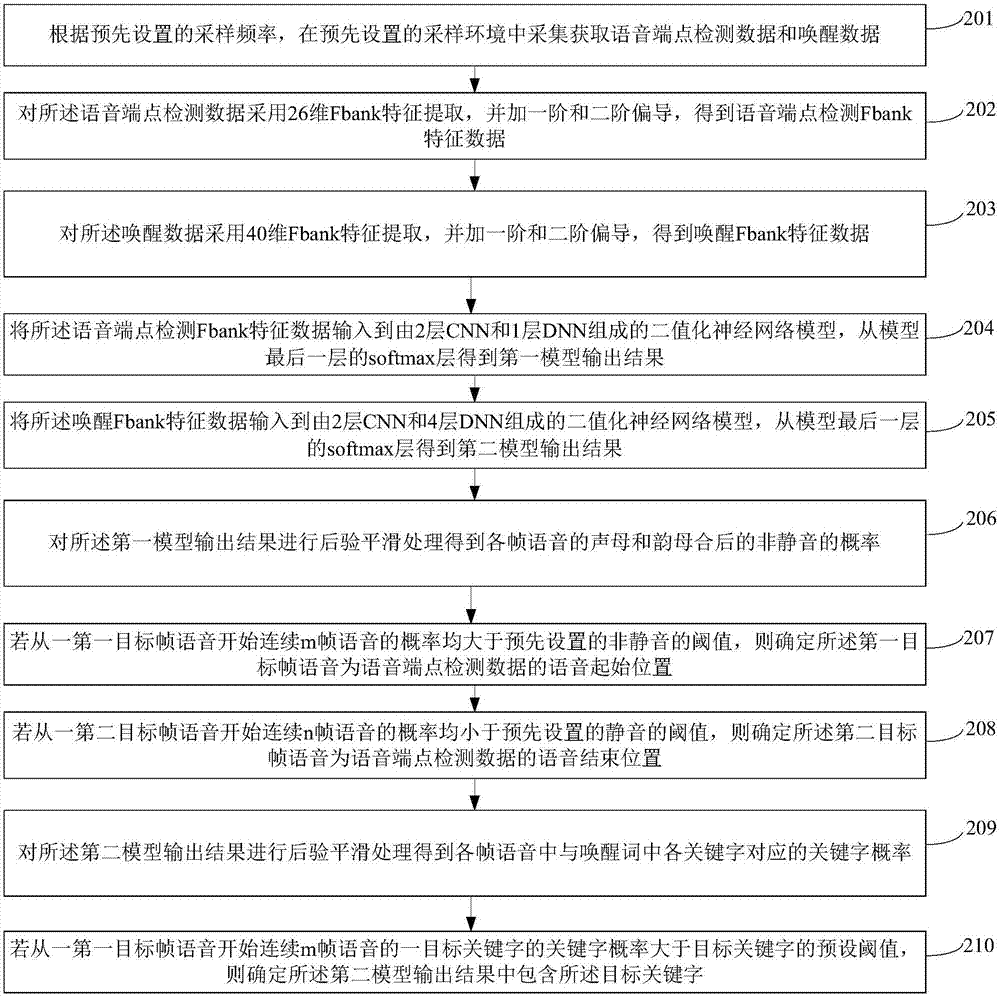

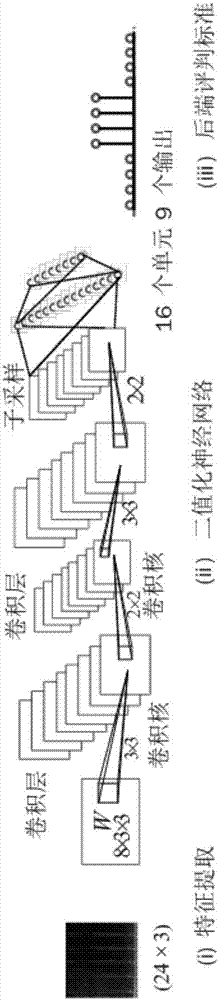

ActiveCN108010515ALower latencyReduce power consumptionSpeech recognitionFeature extractionNetwork output

The invention provides a voice activity detection and wake-up method and device, and relates to the technical field of machine learning speech recognition. The method includes the steps of acquiring voice activity detection data and wake-up data, and performing Fbank feature extraction on the voice activity detection data and wake-up data to obtain voice Fbank feature data; inputting the voice Fbank feature data to a binary neural network model to obtain binarized neural network output result data; and according to a preset backend evaluation strategy, processing the binarized neural network output result data, determining a voice start position and a voice end position of the voice activity detection data, and detecting wake-up word data in the wake-up data. The system framework of the invention can be applied to voice activity detection and voice wake-up technologies at the same time, and can implement accurate, fast, low-delay, small-model and low-power voice activity detection technologies and voice wake-up technologies.

Owner:TSINGHUA UNIV

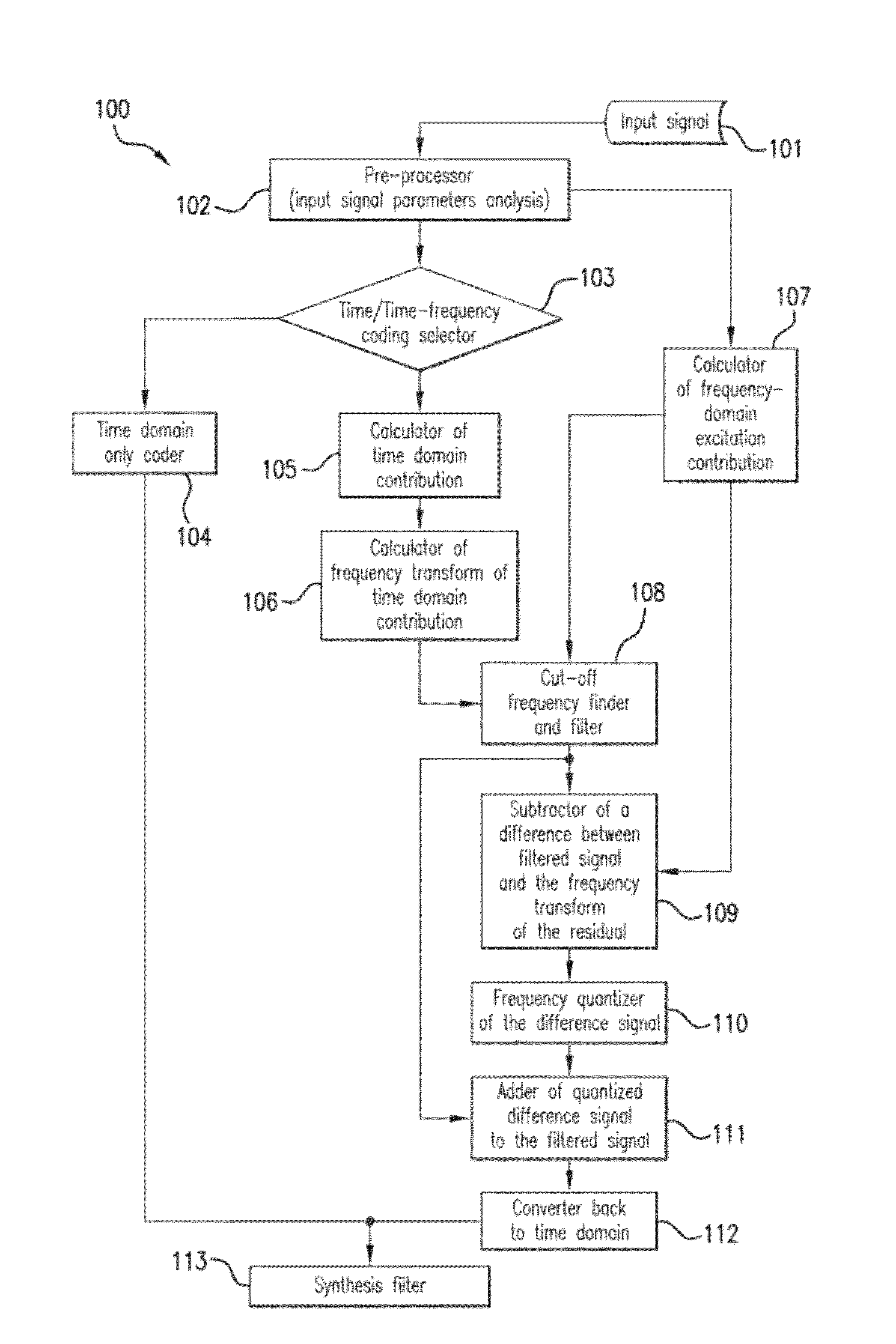

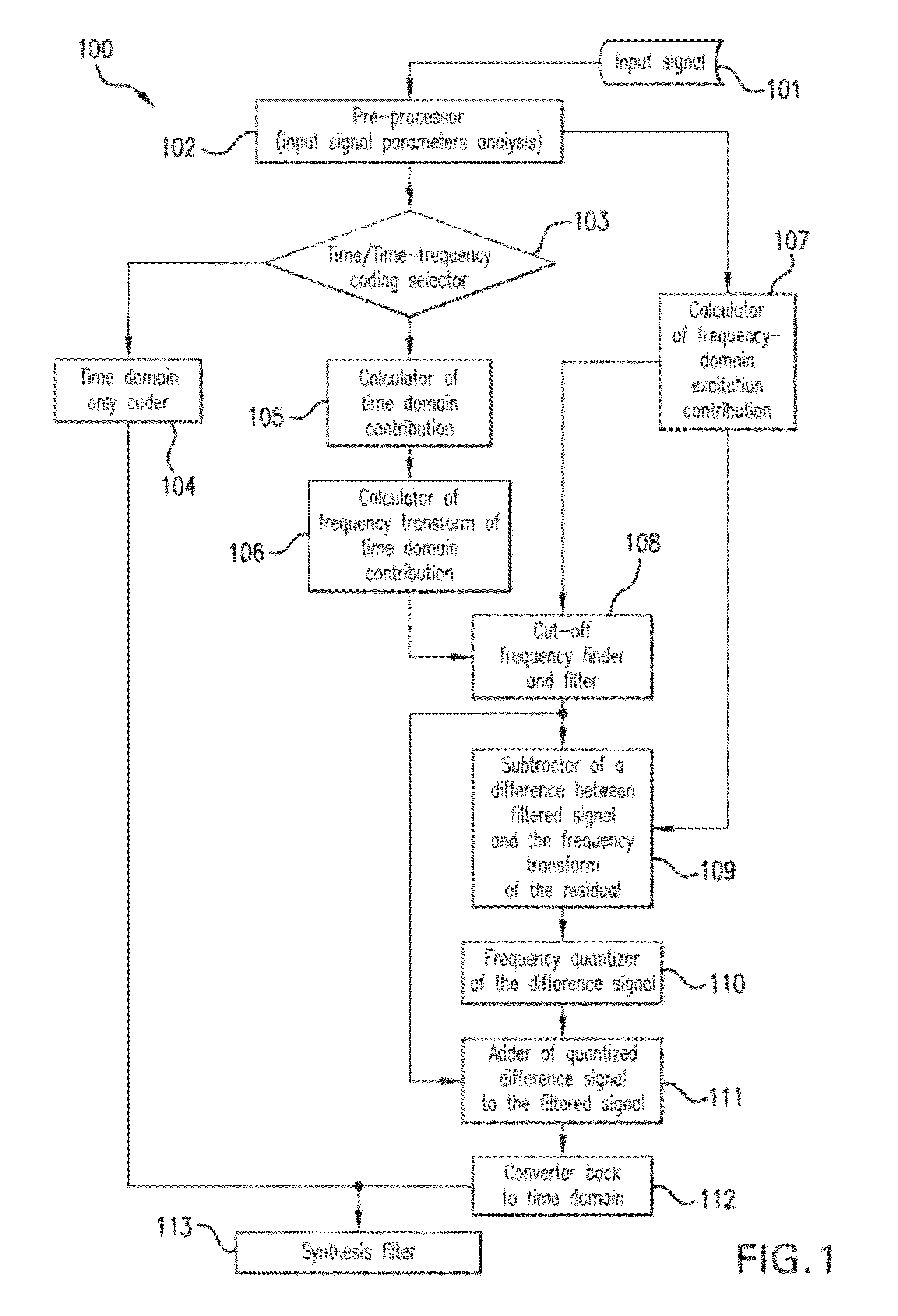

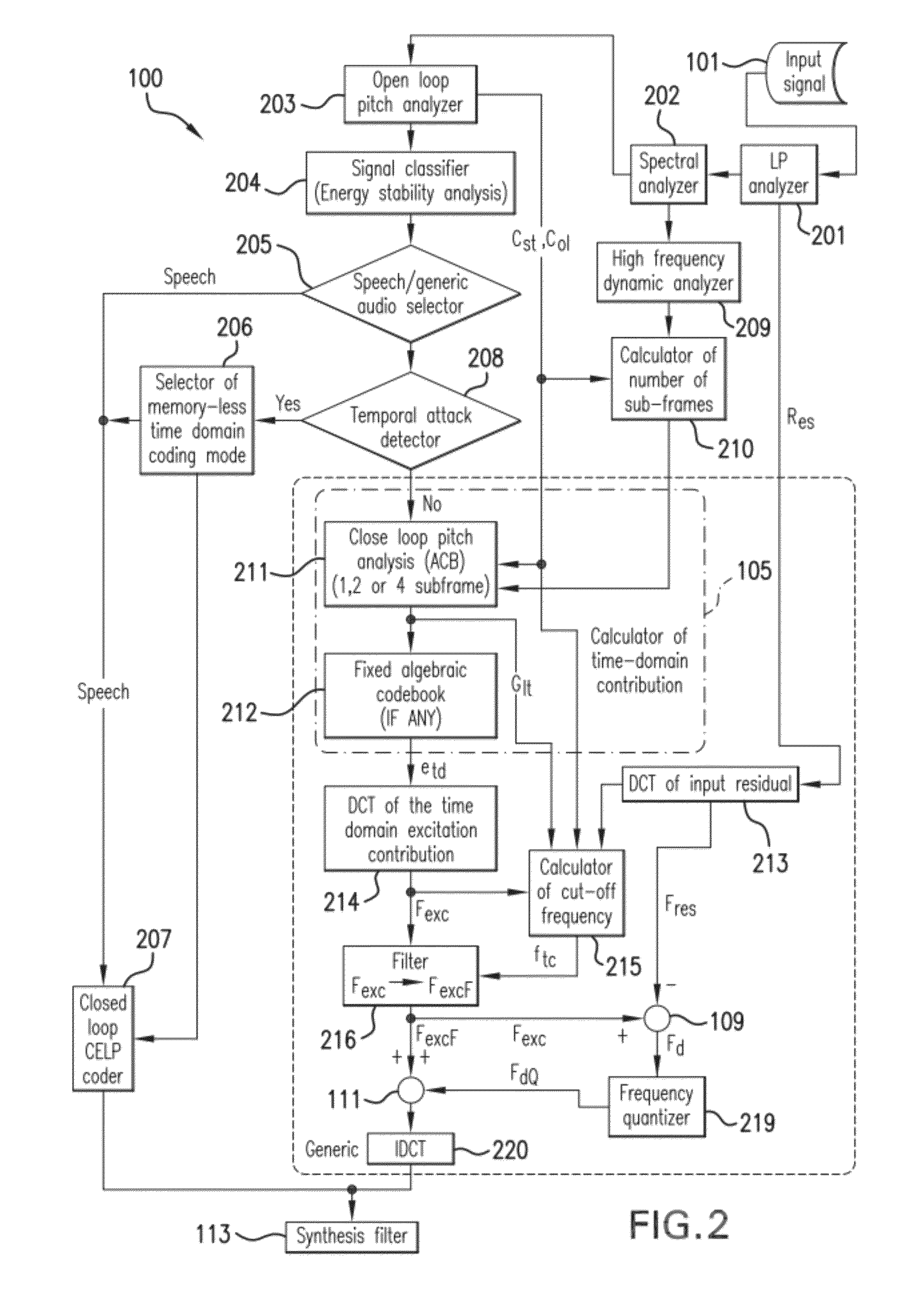

Coding Generic Audio Signals at Low Bitrates and Low Delay

A mixed time-domain / frequency-domain coding device and method for coding an input sound signal, wherein a time-domain excitation contribution is calculated in response to the input sound signal. A cut-off frequency for the time-domain excitation contribution is also calculated in response to the input sound signal, and a frequency extent of the time-domain excitation contribution is adjusted in relation to this cut-off frequency. Following calculation of a frequency-domain excitation contribution in response to the input sound signal, the adjusted time-domain excitation contribution and the frequency-domain excitation contribution are added to form a mixed time-domain / frequency-domain excitation constituting a coded version of the input sound signal. In the calculation of the time-domain excitation contribution, the input sound signal may be processed in successive frames of the input sound signal and a number of sub-frames to be used in a current frame may be calculated.

Owner:VOICEAGE EVS LLC

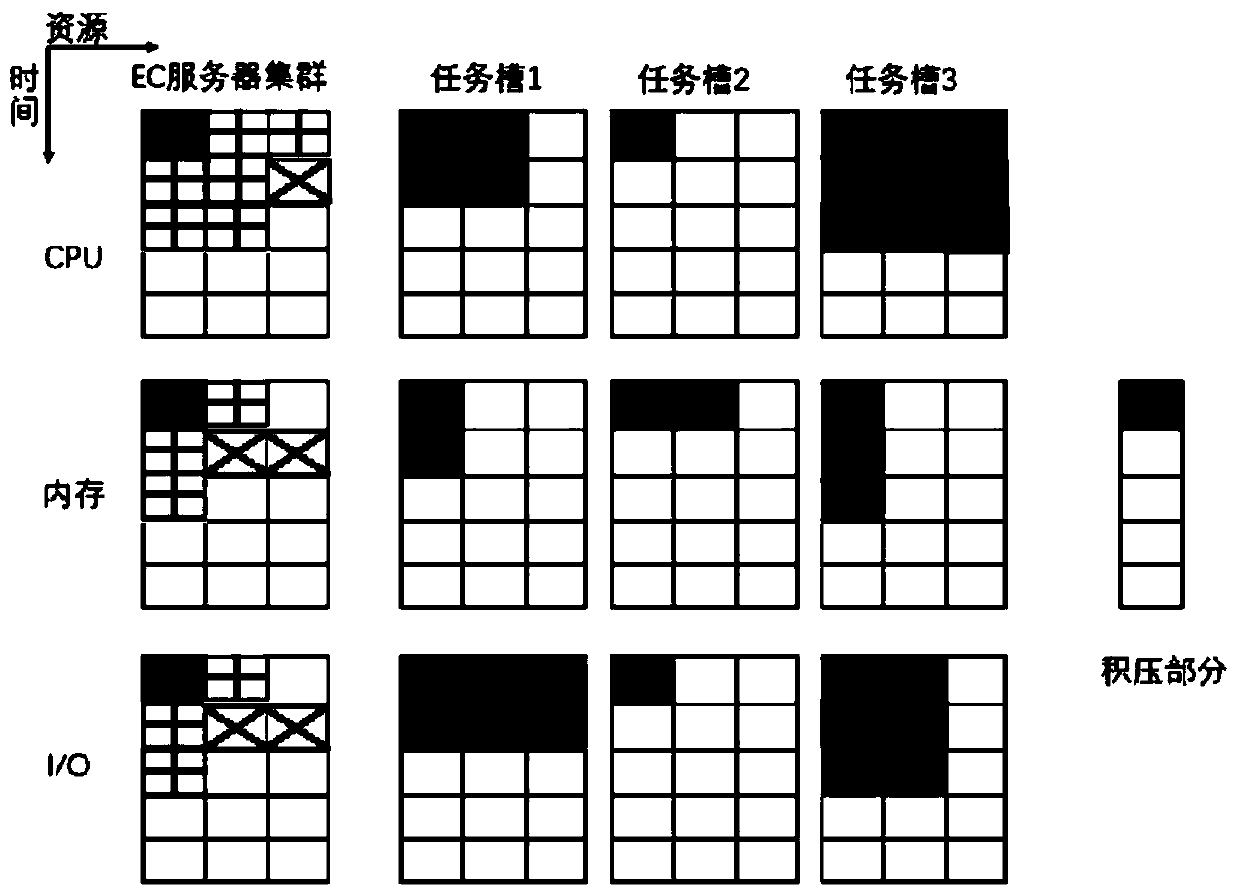

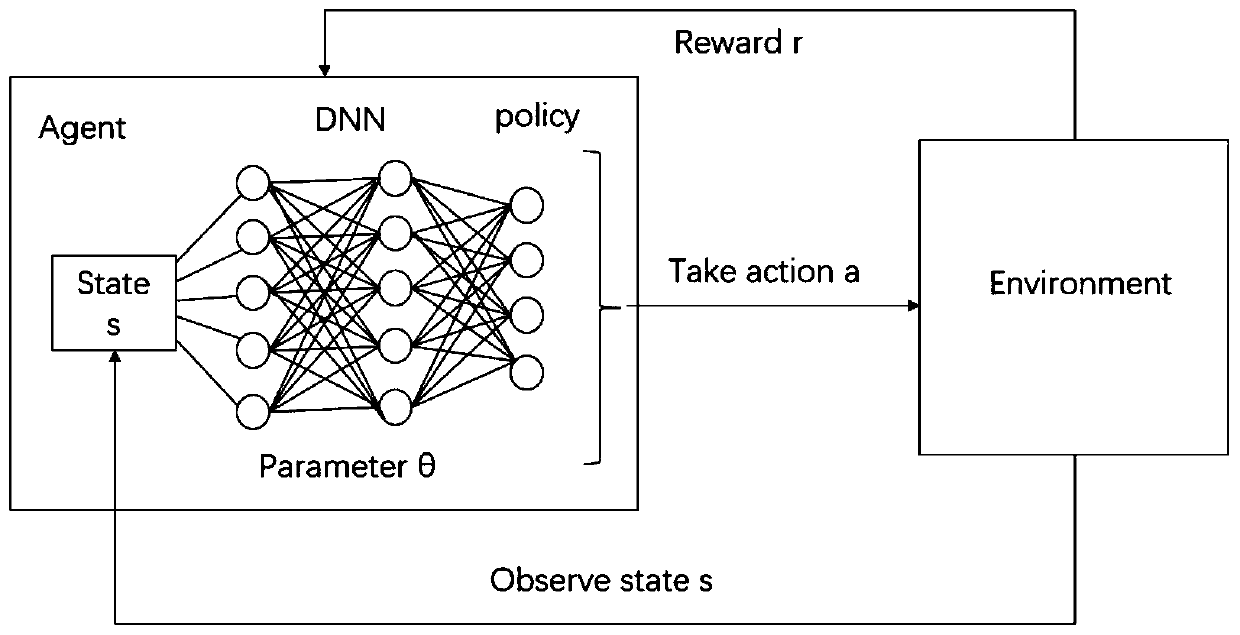

Learning-based low-delay task scheduling method in edge computing network

The invention discloses a learning-based low-delay task scheduling method in an edge computing network, and aims to solve the problem that a heuristic algorithm is easily influenced by environmental changes and is difficult to design in an existing task scheduling method, and a task scheduling scheme is designed by using a reinforcement learning technology. Decisions made by the system in resourcemanagement are generally highly repeated, so that a large amount of training data can be generated for an RL algorithm. Next, the RL may model the decision policy of the complex system into a deep neural network. And through continuous interactive learning with the environment, a specific target (minimum delay) can be optimized.

Owner:CENT SOUTH UNIV

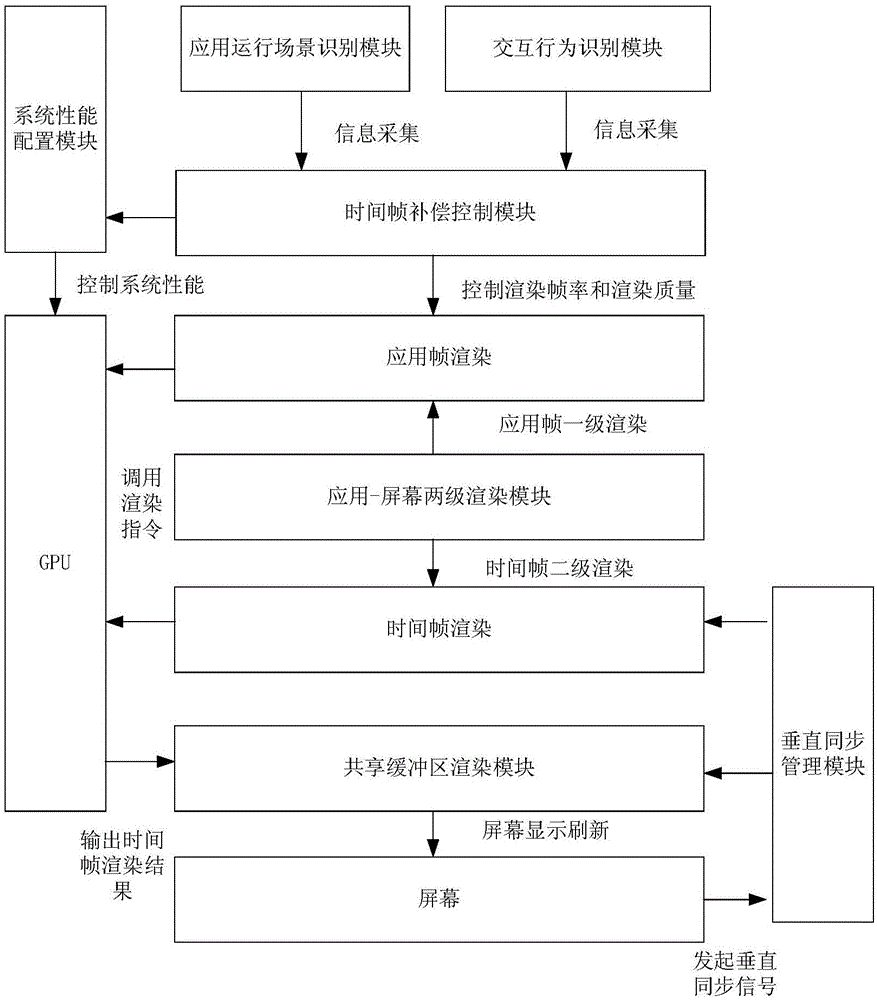

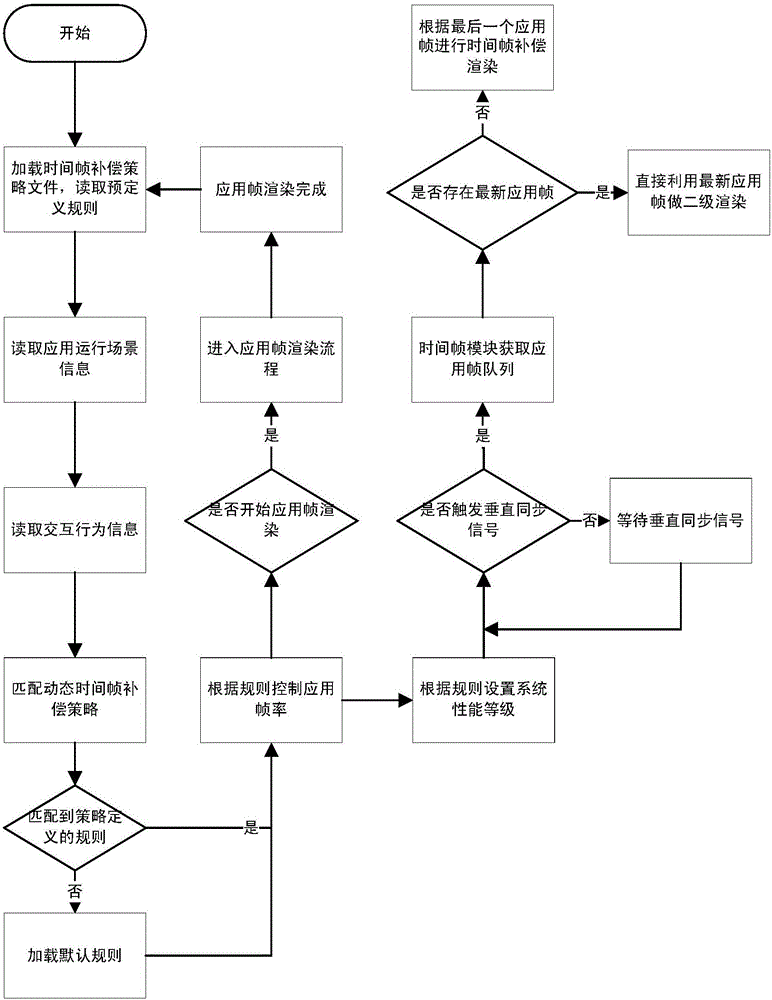

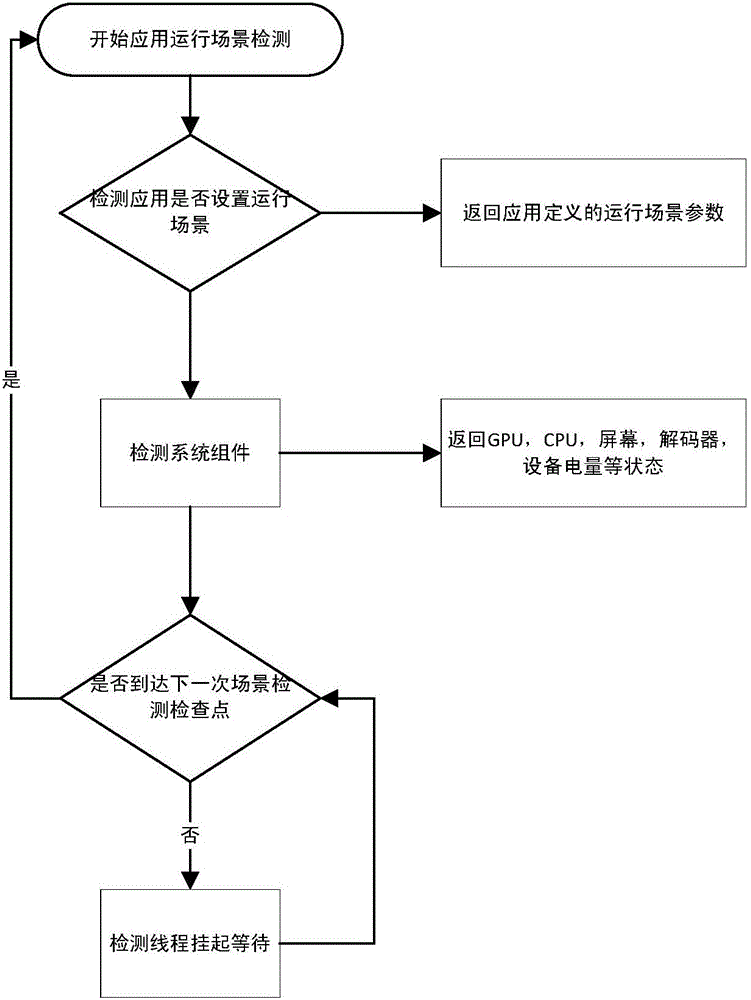

Dynamic time frame compensation rendering system and dynamic time frame compensation rendering method for virtual-reality mobile terminal

ActiveCN106296566ALower latencyControl rendering timeImage memory managementProcessor architectures/configurationSequence controlComputer graphics (images)

The invention discloses a dynamic time frame compensation rendering system and a dynamic time frame compensation rendering method for a virtual-reality mobile terminal. The method comprises the following steps of generating an application frame buffer sequence by use of frame rendering, extracting the up-to-date or latest application frame from the application frame buffer sequence, and performing secondary rendering, thereby obtaining a time frame; sending the time frame to a shared buffer; and under sequence control of a vertical synchronous management module, reading a time frame rendering result by use of a screen, and performing updating. By virtue of the design of the shared buffer, a GPU rendering result is directly stored in a cache updated by the screen, so that delay of multi-caching exchange is reduced; by virtue of vertical synchronous time management, the GPU rendering time is controlled, collision between GPU rendering writing and screen update reading is avoided, frames can be normally displayed with low delay, and no splitting is generated.

Owner:NANJING RUIYUE INFORMATION TECH

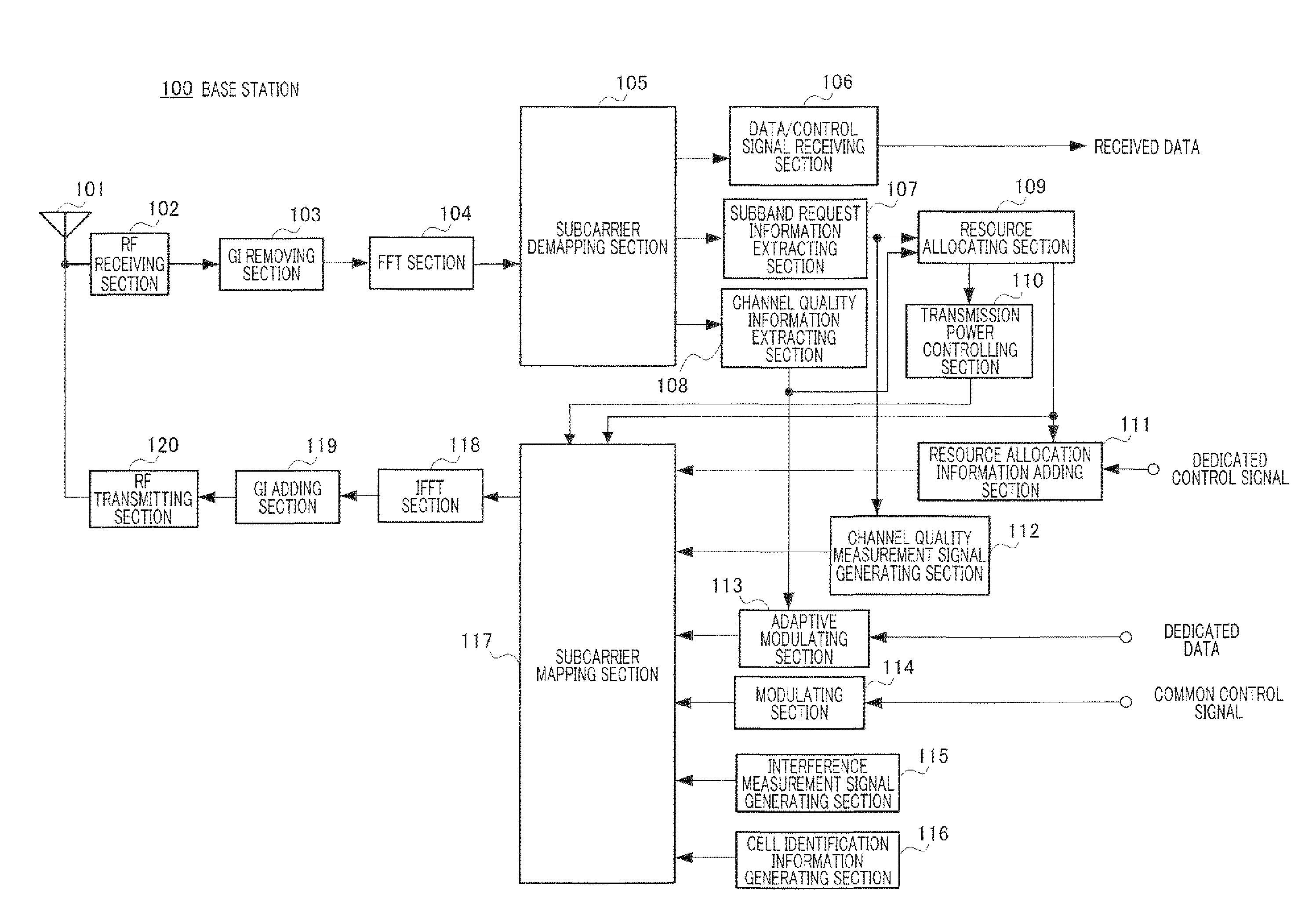

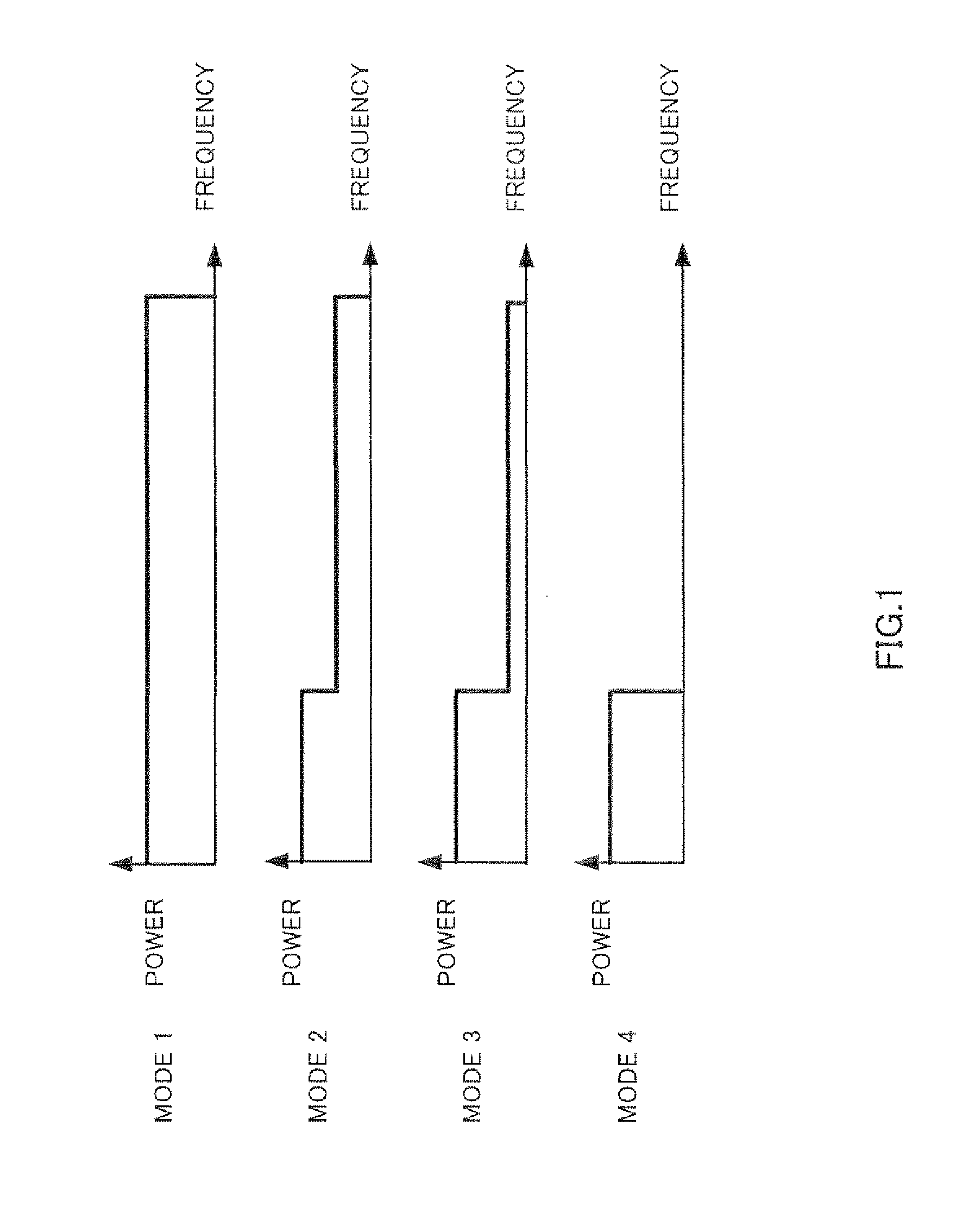

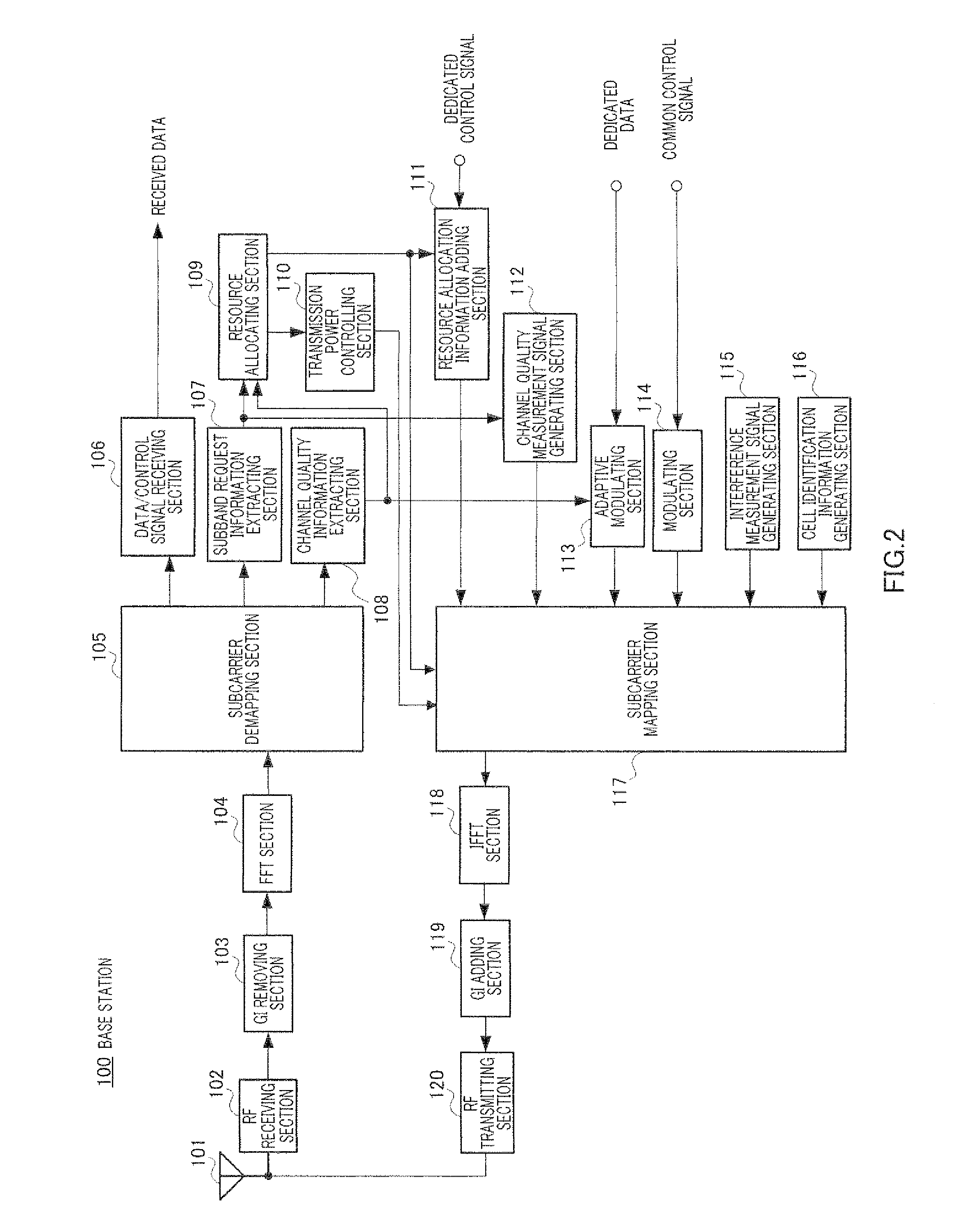

Terminal device, base station device, and frequency resource allocation method

InactiveUS20110222525A1Little overheadTransmission path divisionCriteria allocationBase station identity codeTerminal equipment

It is possible to realize reduction of inter-cell interference by an adaptive FFR with a low delay. A terminal (200) includes: an interference condition detection unit (209) which detects an interference condition of other cell to the local cell; a cell identification unit (210) which acquires signals for cell identification of each base station; and a sub-band selection unit (211) which selects a sub-band used for the downstream line transmission to the local station according to the interference condition detected by the interference condition detection unit (209) and the signals for cell identification of each base station obtained by the cell identification unit (210). Thus, the terminal (200) can autonomously select a small sub-band of inter-cell interference and to realize reduction of the inter-cell interference by the adaptive FFR with a low delay.

Owner:SOVEREIGN PEAK VENTURES LLC

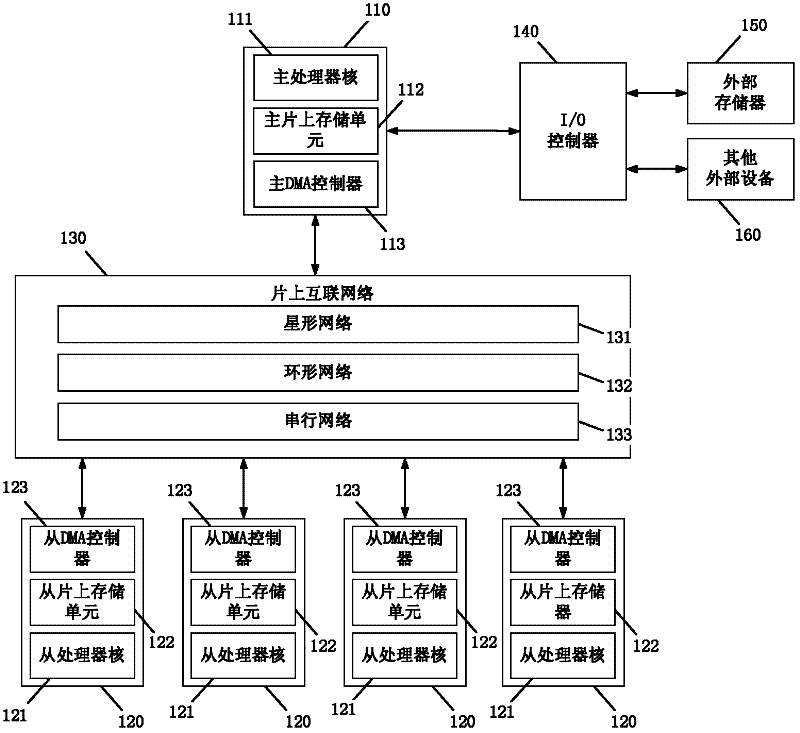

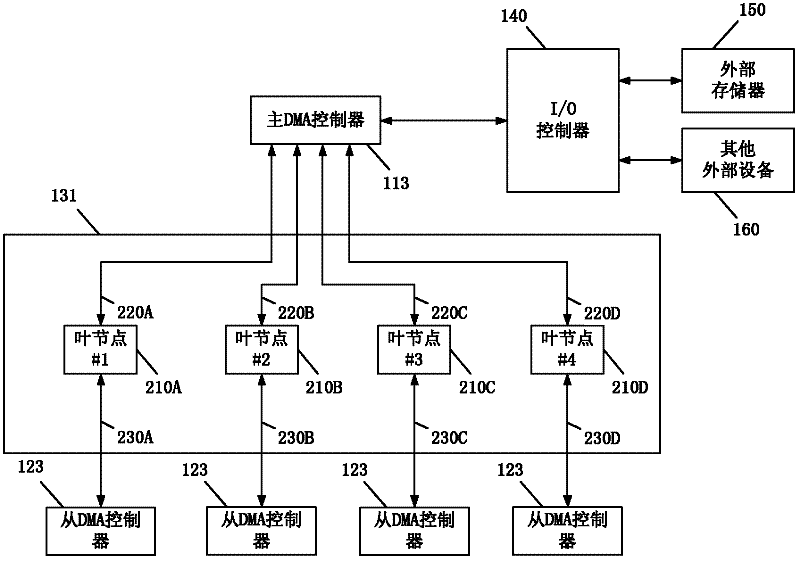

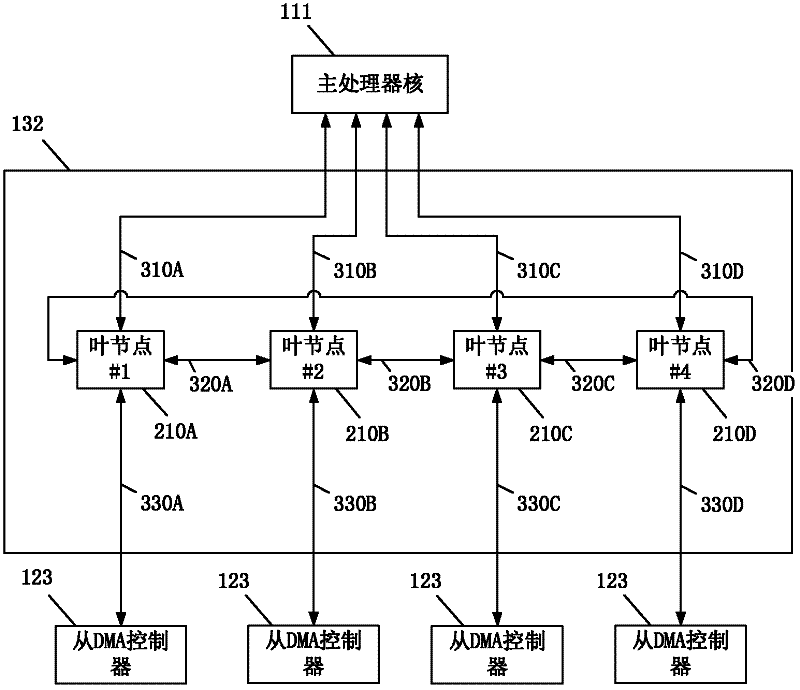

Multi-core DSP (digital signal processor) system-on-chip and data transmission method

InactiveCN102521201ASimplified Access to ArbitrationReduce synchronization operationsMemory adressing/allocation/relocationDigital computer detailsStreaming dataDigital signal processing

The embodiment of the invention provides a multi-core DSP (digital signal processor) system-on-chip and a data transmission method. The system comprises a main processor, multiple slave processors and an external memorizer, wherein each main processor and slave processor respectively comprise a processor core, a memorizer-on-chip and a direct memory access (DMA) controller, the main processor controls and accesses the external memorizer through an I / O (input / output) controller, data exchange can be realized among processors through an internet-on-chip, wherein the internet-on-chip is composed of a star network, a loop network and a serial network. The internet-on-chip provided by the embodiment of the invention combines the star network, the loop network and the serial network, so that the internet-on-chip can not only provide streaming data transmission with high bandwidth, but also provide short message transfer with low delay. Besides, the embodiment of the invention simplifies the access arbitration of the external memorizer through the software control of the main processor, reduces the synchronous operations among the multi-core processors through the network data buffer and lowers the complexity of the program design of the multi-core processors.

Owner:刘大可