Multi-core DSP (digital signal processor) system-on-chip and data transmission method

A data transmission method and digital processor technology, which are applied in digital transmission systems, electrical digital data processing, transmission systems, etc., can solve the problems of larger address space, increased hardware design overhead, and complex hardware arbiter design. Complexity, reduction of synchronous operations, effect of low-latency short message delivery

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0037] The following will clearly and completely describe the technical solutions in the embodiments of the present invention with reference to the accompanying drawings in the embodiments of the present invention. Obviously, the described embodiments are only some, not all, embodiments of the present invention. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without creative efforts fall within the protection scope of the present invention.

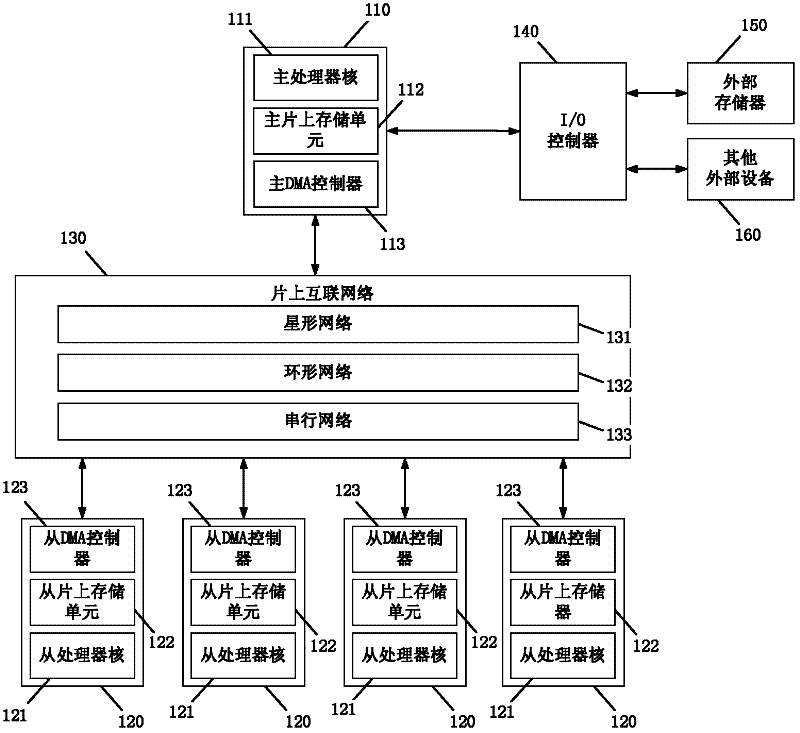

[0038] Such as figure 1 Shown is a schematic structural diagram of a multi-core digital processor system-on-chip provided by an embodiment of the present invention, the multi-core digital processor system-on-chip includes a main processor 110 and a plurality of slave processors 120, the main processor 110 and the slave processors 120 are connected through an on-chip interconnection network 130, and in this embodiment, the number of slave processors is four, but it ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More