Patents

Literature

39 results about "Global address space" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Global Address Space Programming Interface (GPI) is an application programming interface (API) for the development of scalable, asynchronous and fault tolerant parallel applications. It is an implementation of the partitioned global address space programming model.

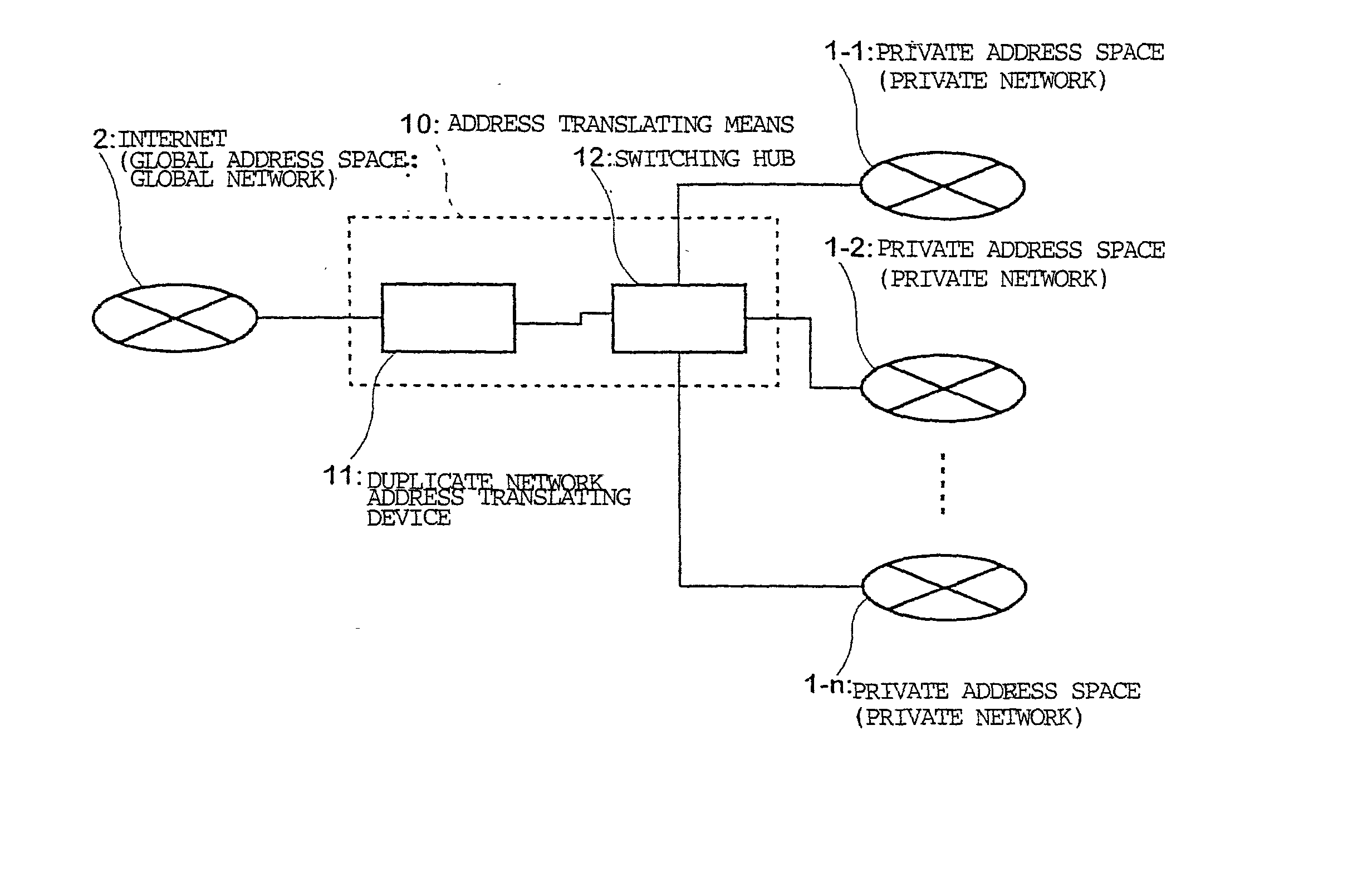

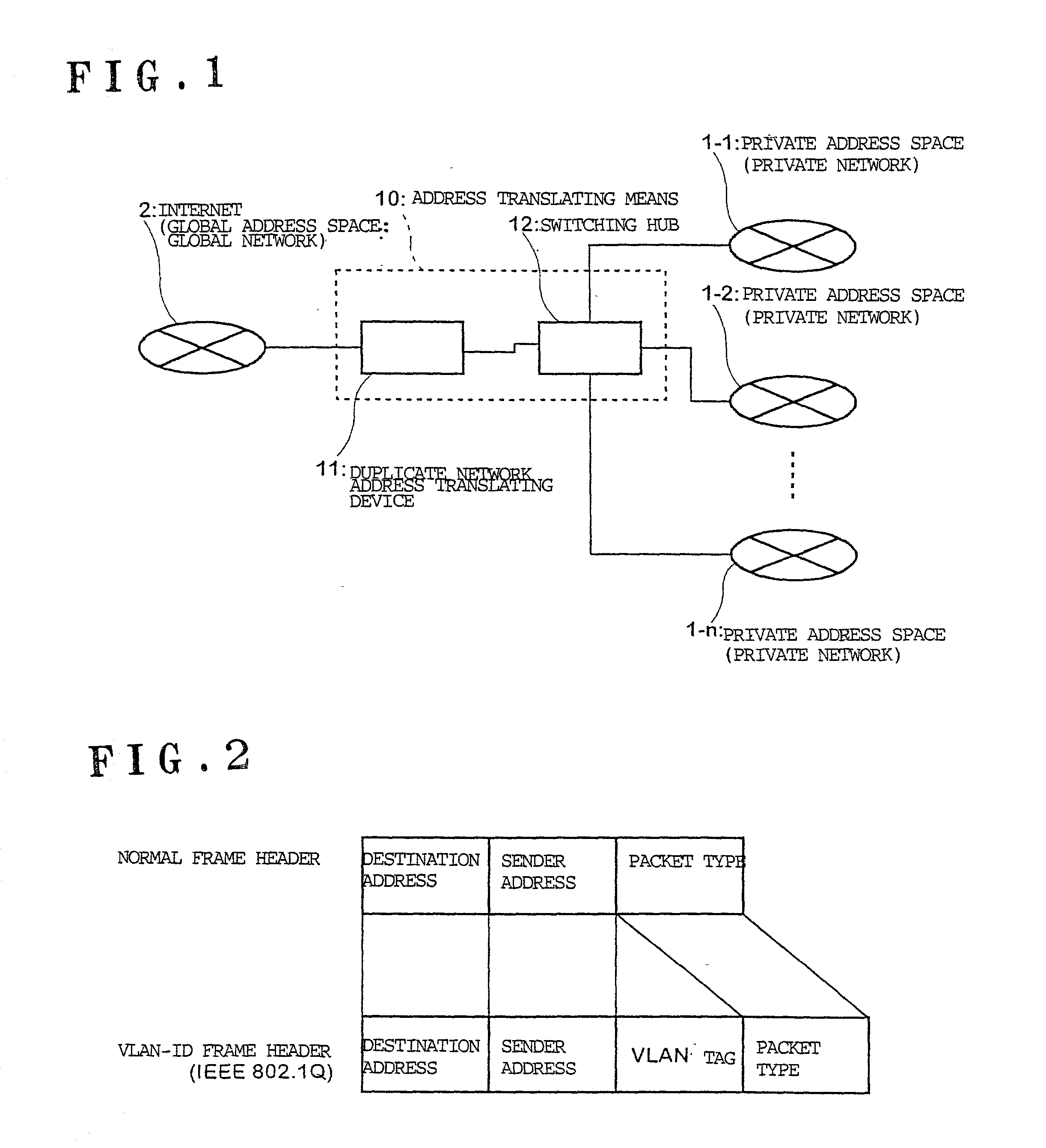

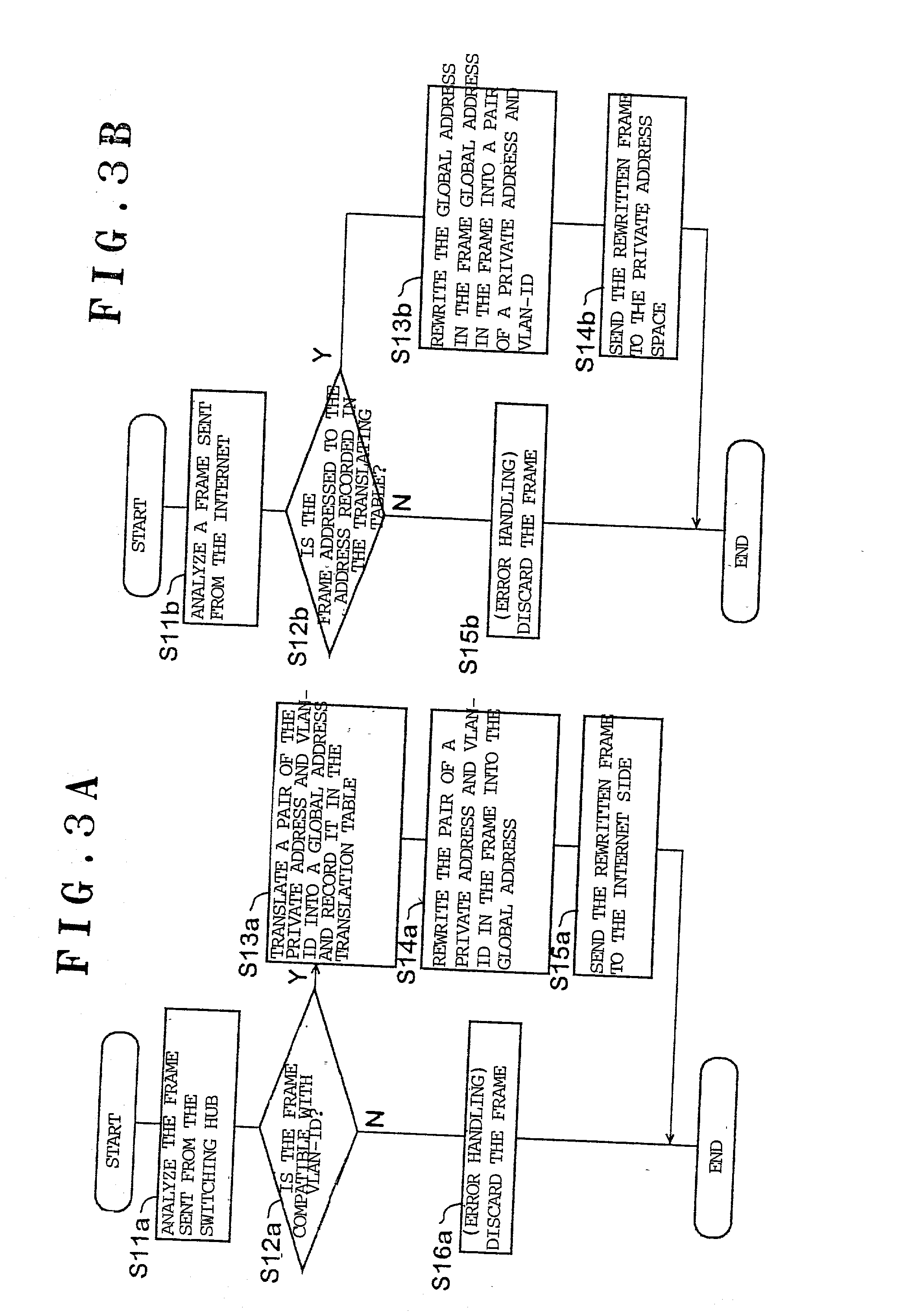

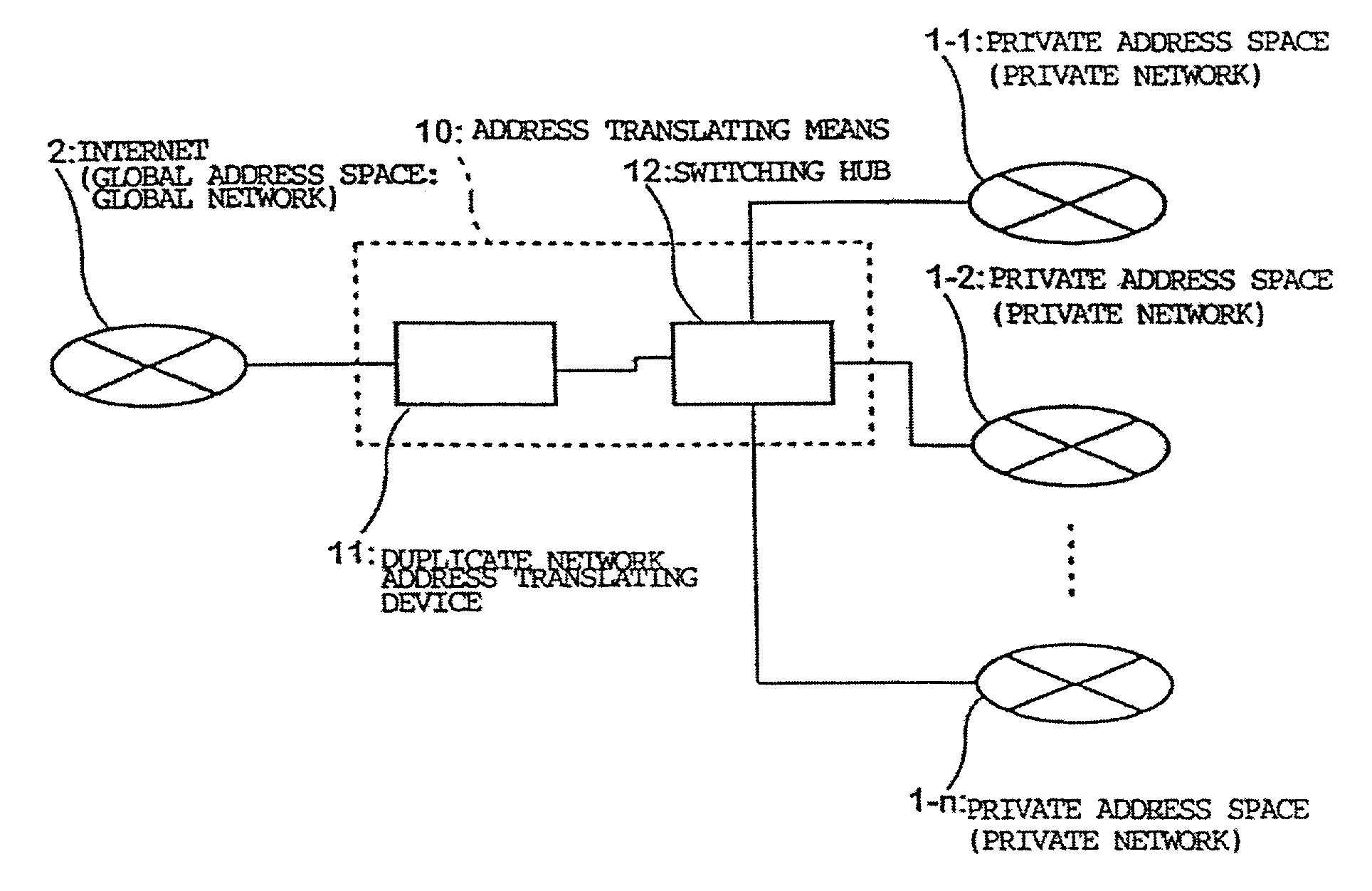

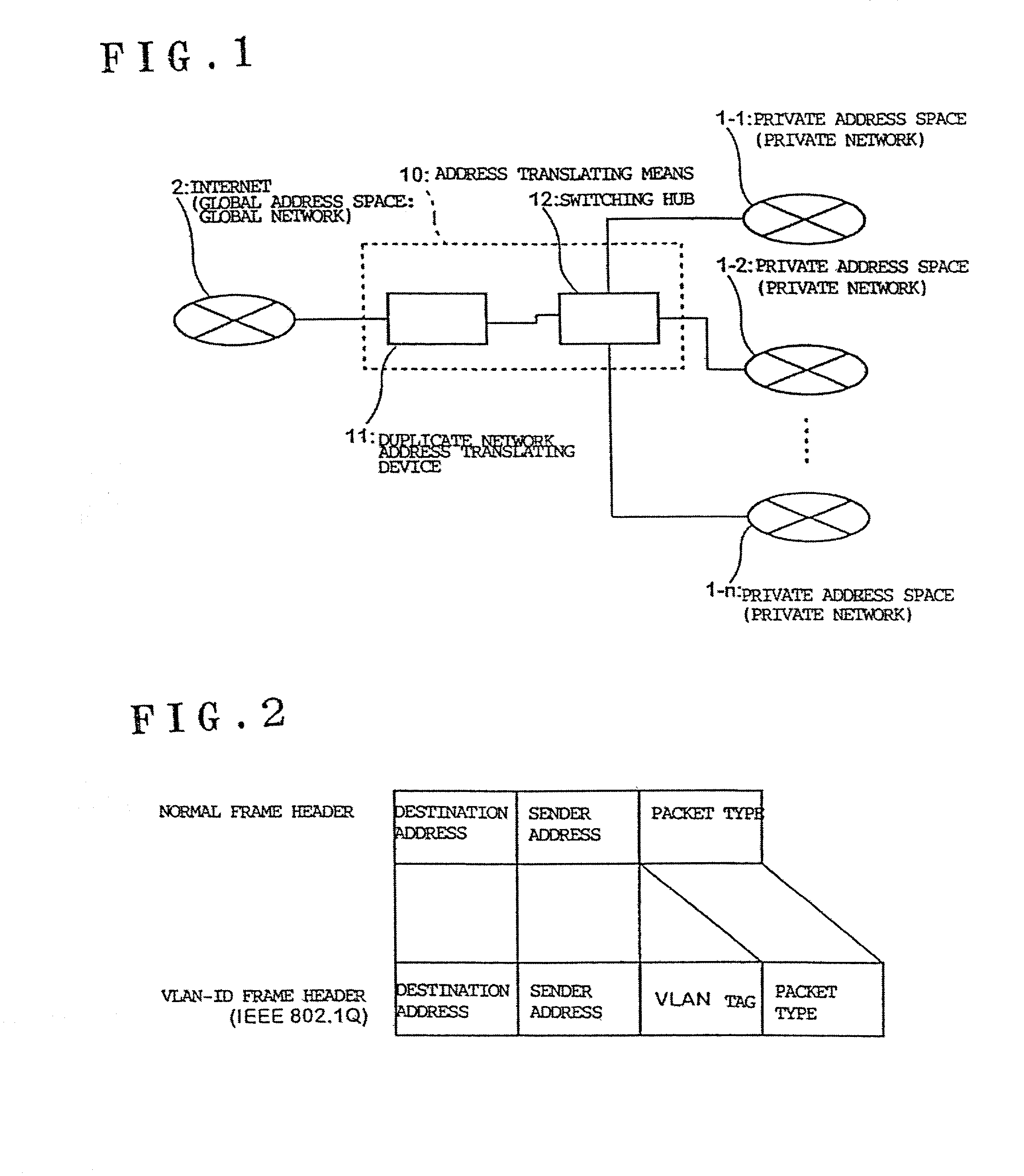

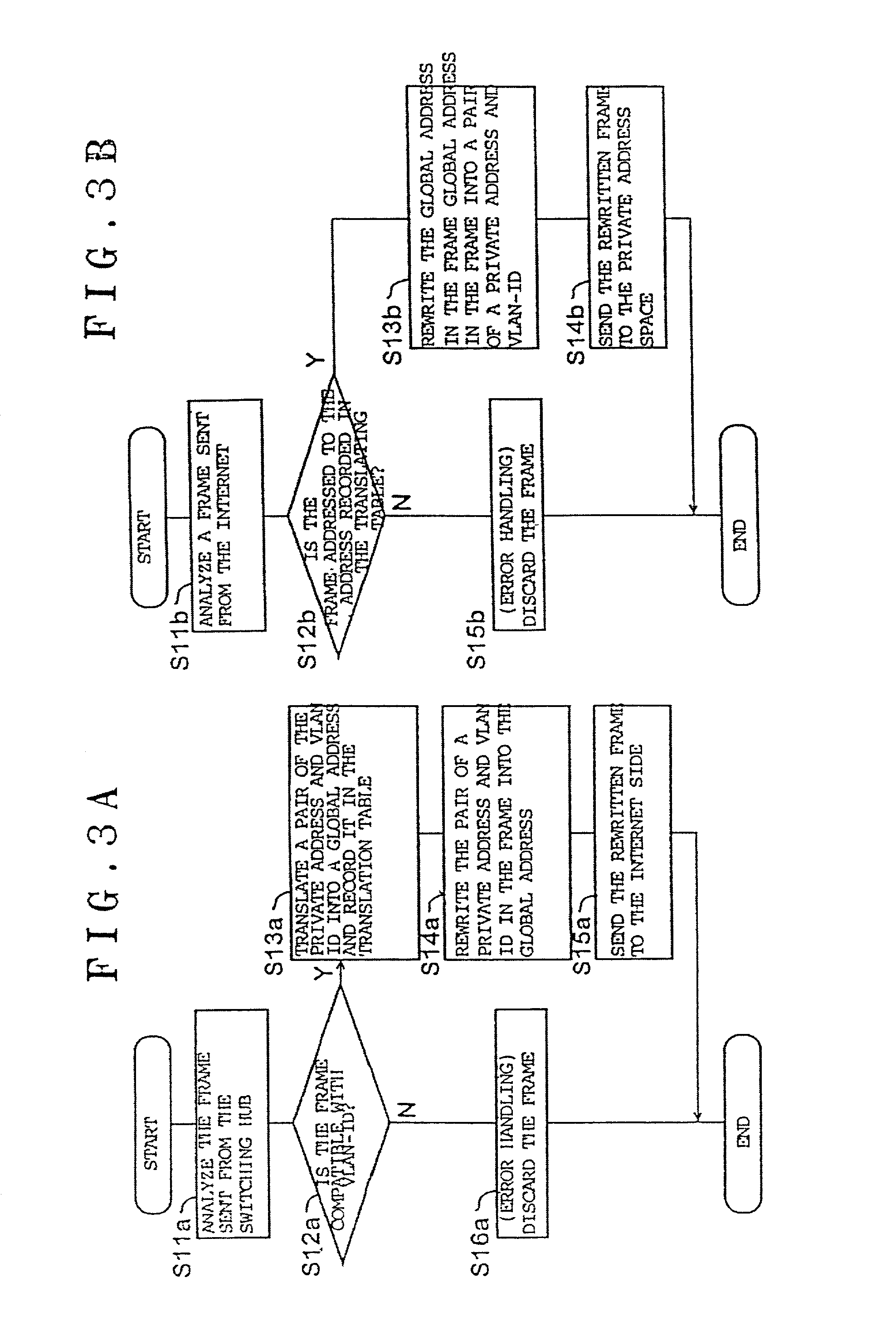

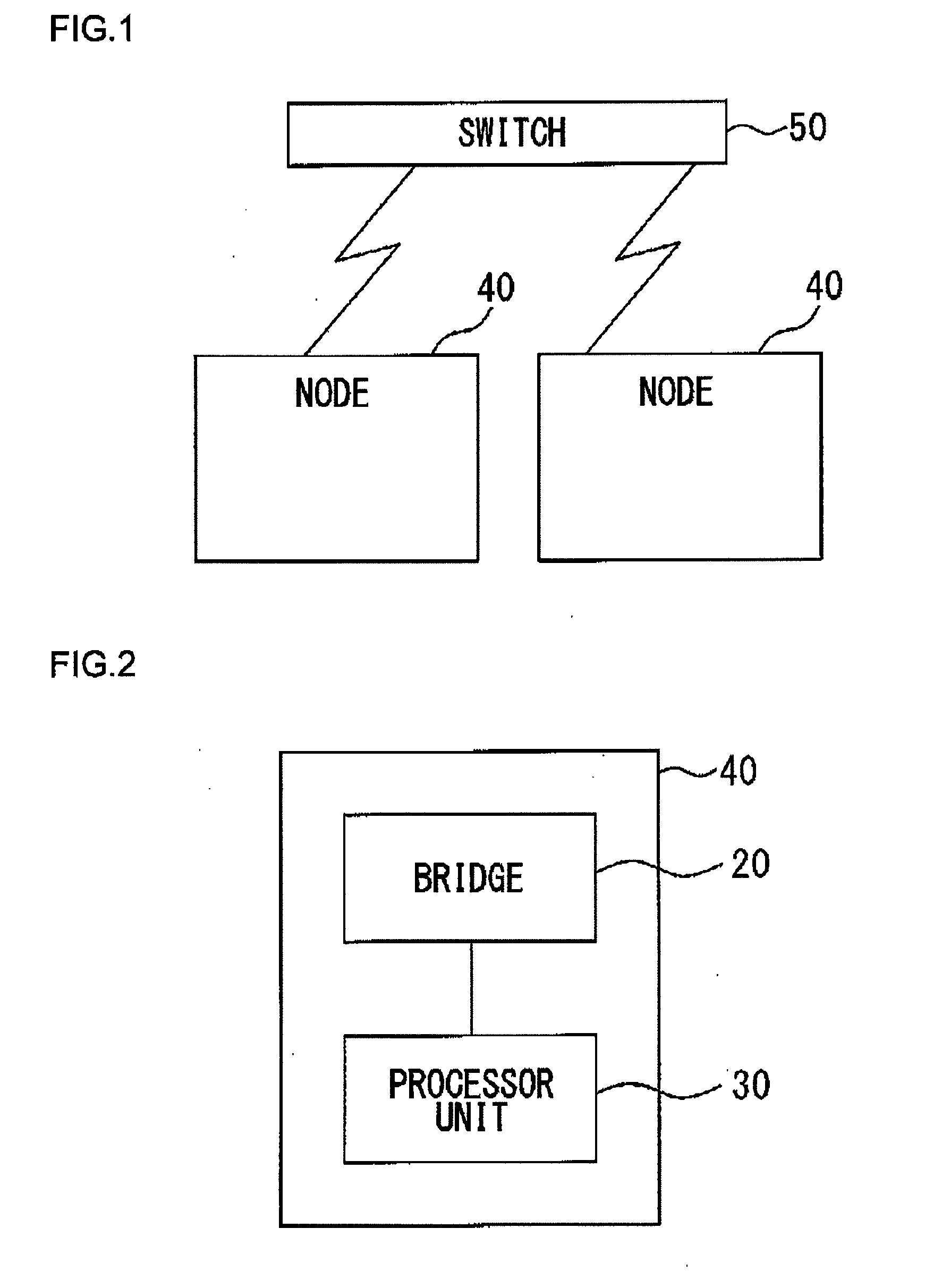

Duplicate private address translating system and duplicate address network system

ActiveUS20020087721A1Time-division multiplexData switching by path configurationGlobal address spaceRouting table

A plurality of private address spaces where private addresses may possibly overlap are connected with a global address space. Respective private address spaces possess VLAN-IDs as identification information for VLANs. When connecting the respective private address spaces with the Internet, a duplicate network address translating device performs, with VLAN-ID and the private address of the respective private address spaces in pairs, mutual translation between the private address and global address of the Internet. According to another aspect of the invention, a duplicate addresses-handling server is provided with a routing table which shows the relationship between virtual interfaces corresponding to VLAN-IDs and addresses of the respective private address spaces. A server portion of the duplicate addresses-handling server records, if a request is made from apparatuses of a private address space, the request and VLAN-ID, refers to, if making a response thereto, the routing table, selects a virtual interface which corresponds to the address of the response receiver, and makes a response. A virtual interface processing portion gives an applicable VLAN-ID and carries out an output to a switching hub.

Owner:OKI ELECTRIC IND CO LTD

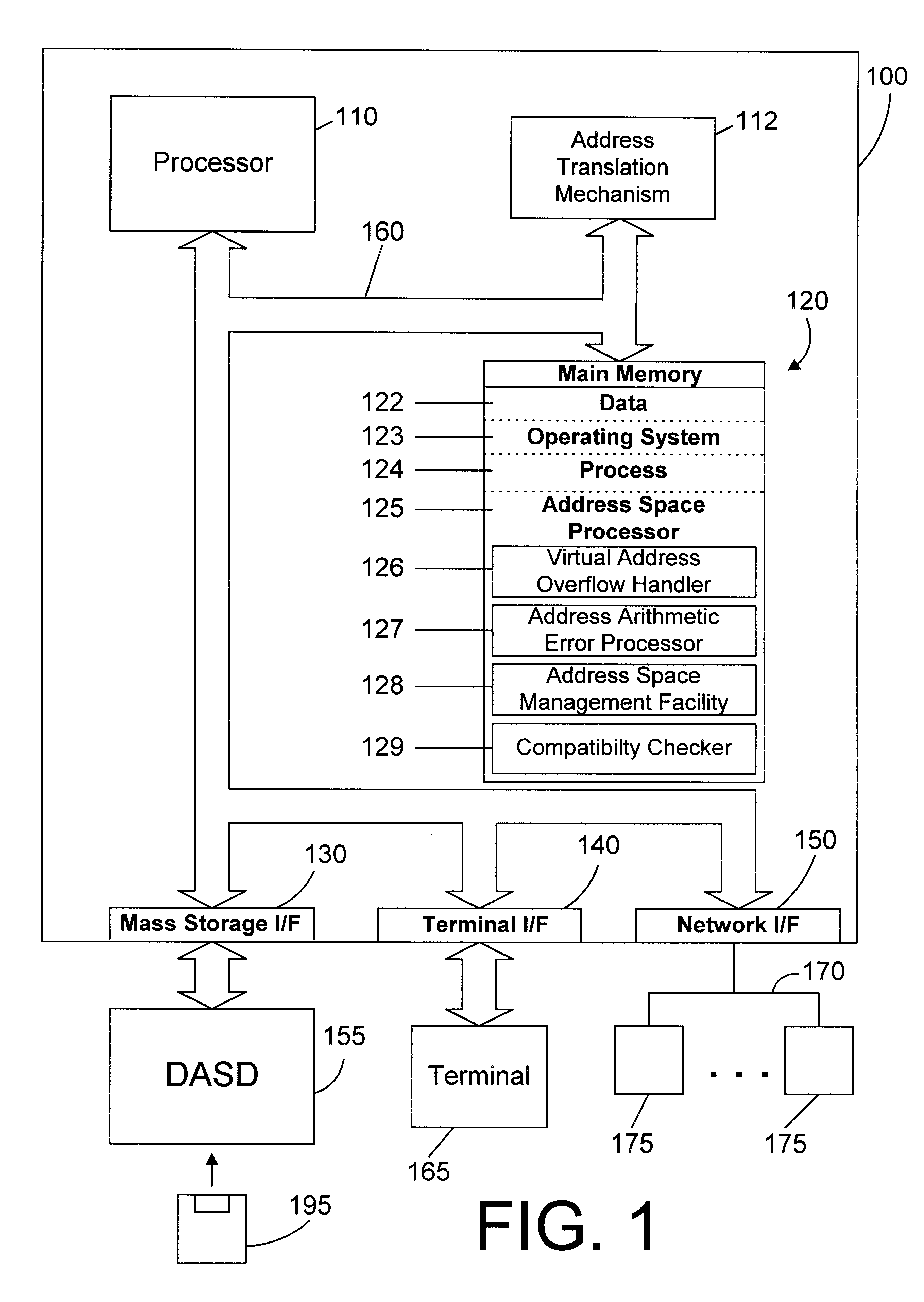

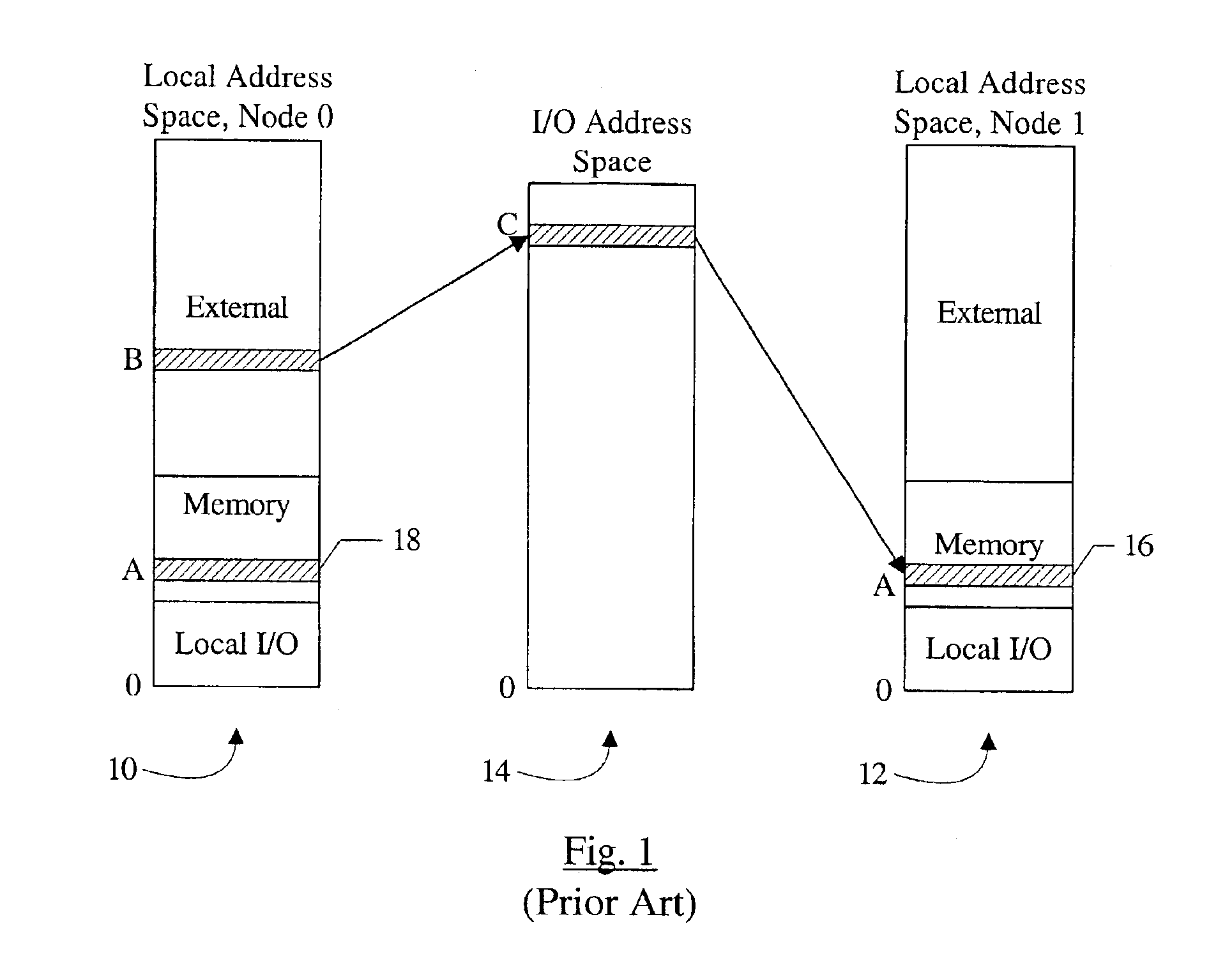

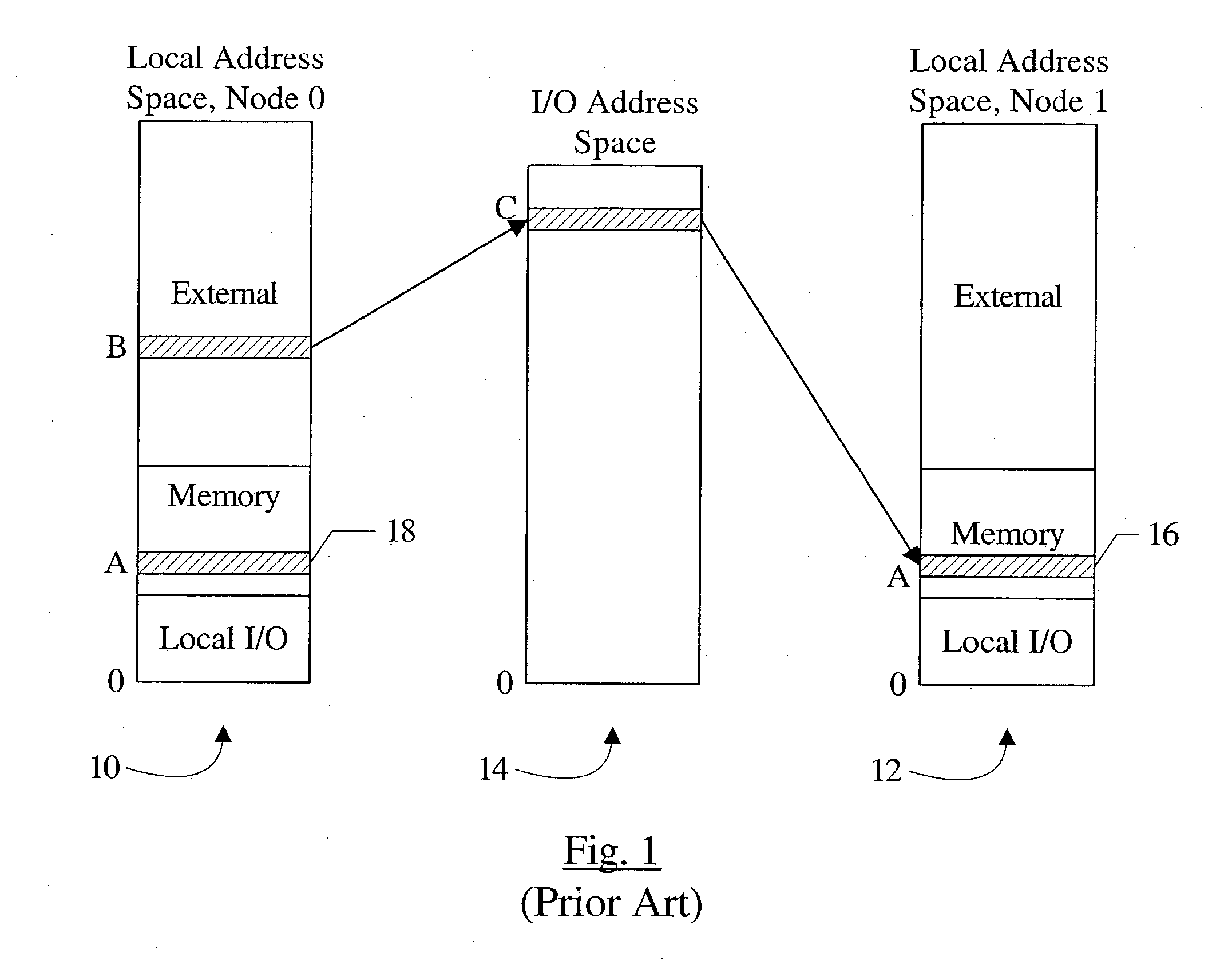

Apparatus and method for providing simultaneous local and global addressing using software to distinguish between local and global addresses

InactiveUS6574721B1Good flexibilityMemory adressing/allocation/relocationMicro-instruction address formationGlobal address spaceComputer compatibility

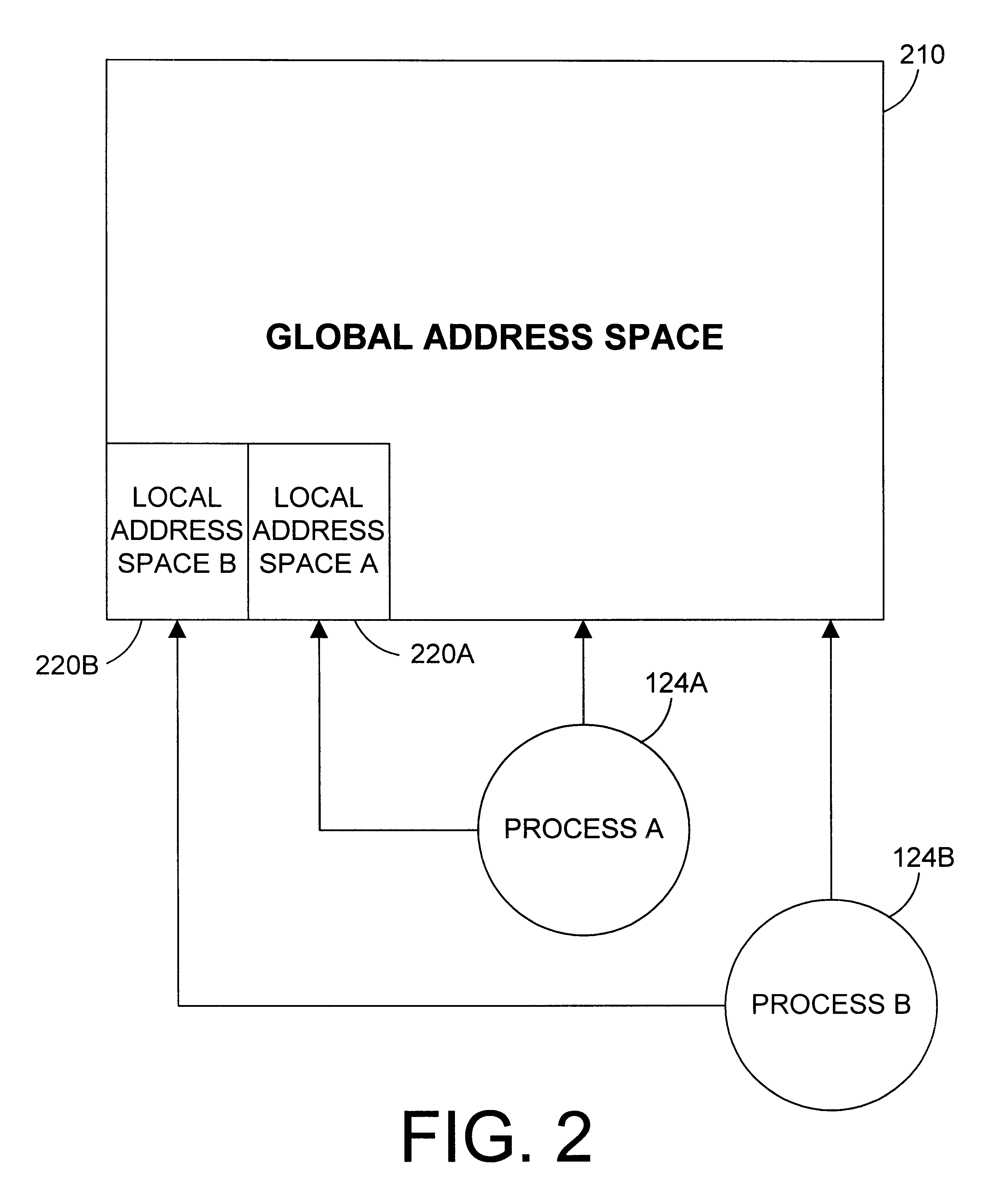

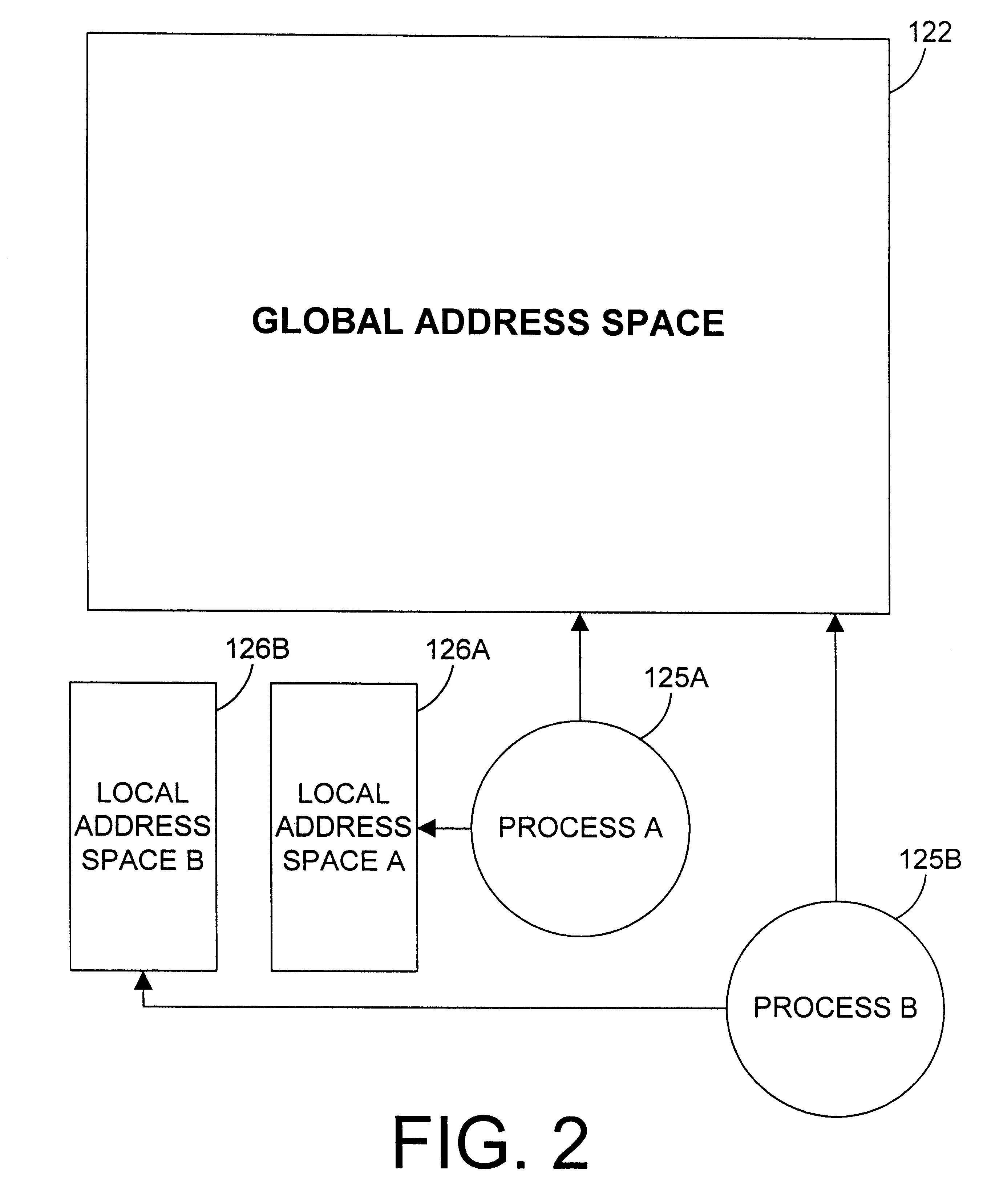

An apparatus and method provide simultaneous local and global addressing capabilities in a computer system. A global address space is defined that may be accessed by all processes. In addition, each process has a local address space that is local (and therefore available) only to that process. An address space processor is implemented in software to perform system functions that distinguish between local addresses and global addresses. In the preferred embodiments, the local address space has a size that is a multiple of the size of a segment of global address space. When the hardware indicates a page fault, the address space processor determines whether the address being translated is a local address or a global address. If the address is a local address, the address space processor uses a local directory to process the page fault. If the address is a global address, the address space processor uses a global directory to process the page fault. When the hardware indicates an addressing error because a computed address crosses a global segment boundary, the address space processor determines whether the address is a local address or a global address. If the address is a global address, the address space processor indicates an addressing error. If the address is a local address, the address space processor determines whether the address is within the process' local address space, and indicates an addressing error if the address is outside the process' local address space. Instructions are allowed to operate on both local and global addresses because the address space processor handles either type of address whenever software assistance is required, such as for servicing a page fault or checking a segment boundary crossing. In addition, the address space processor dynamically checks the addressing compatibility of called code before passing control to the called code.

Owner:IBM CORP

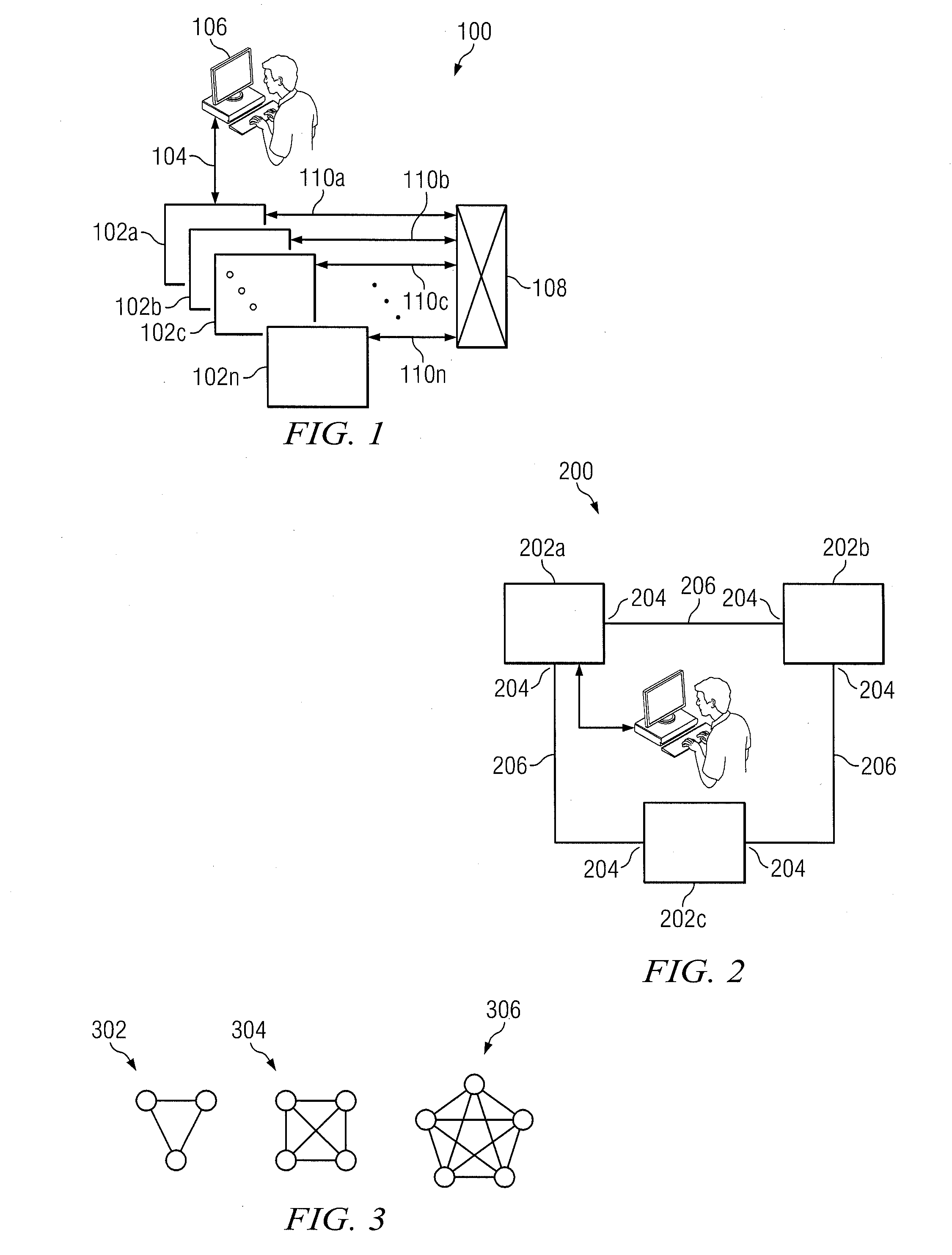

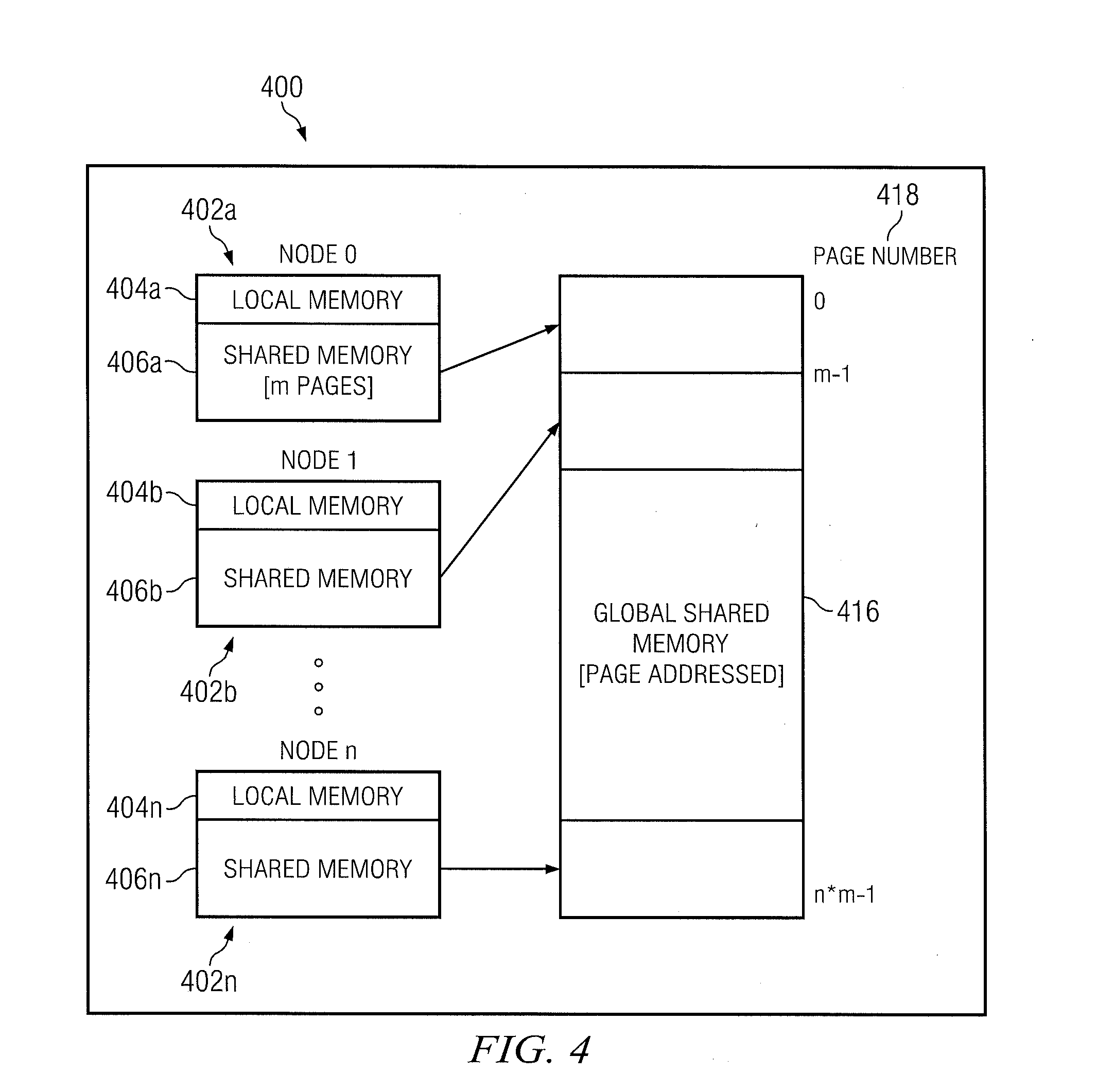

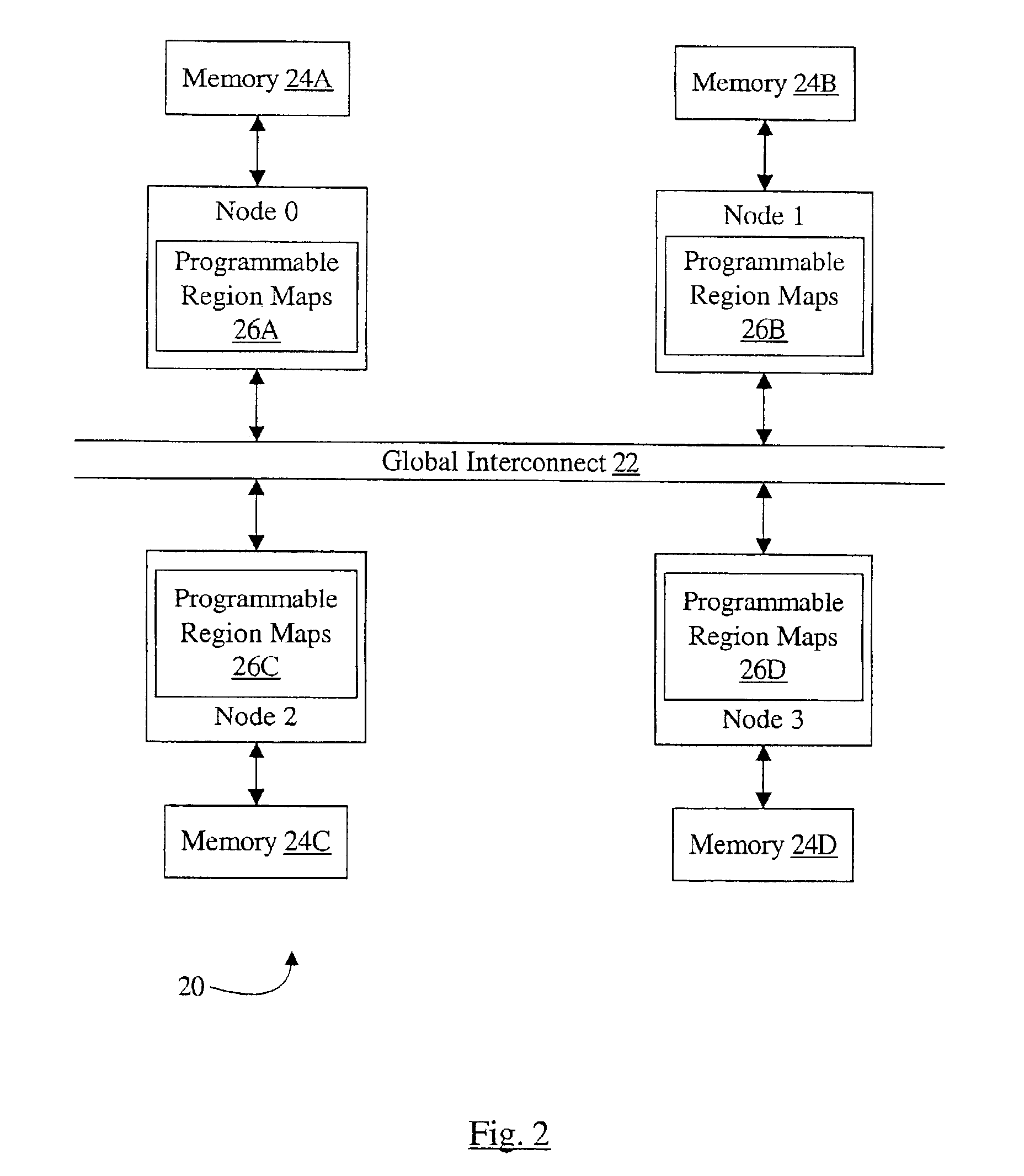

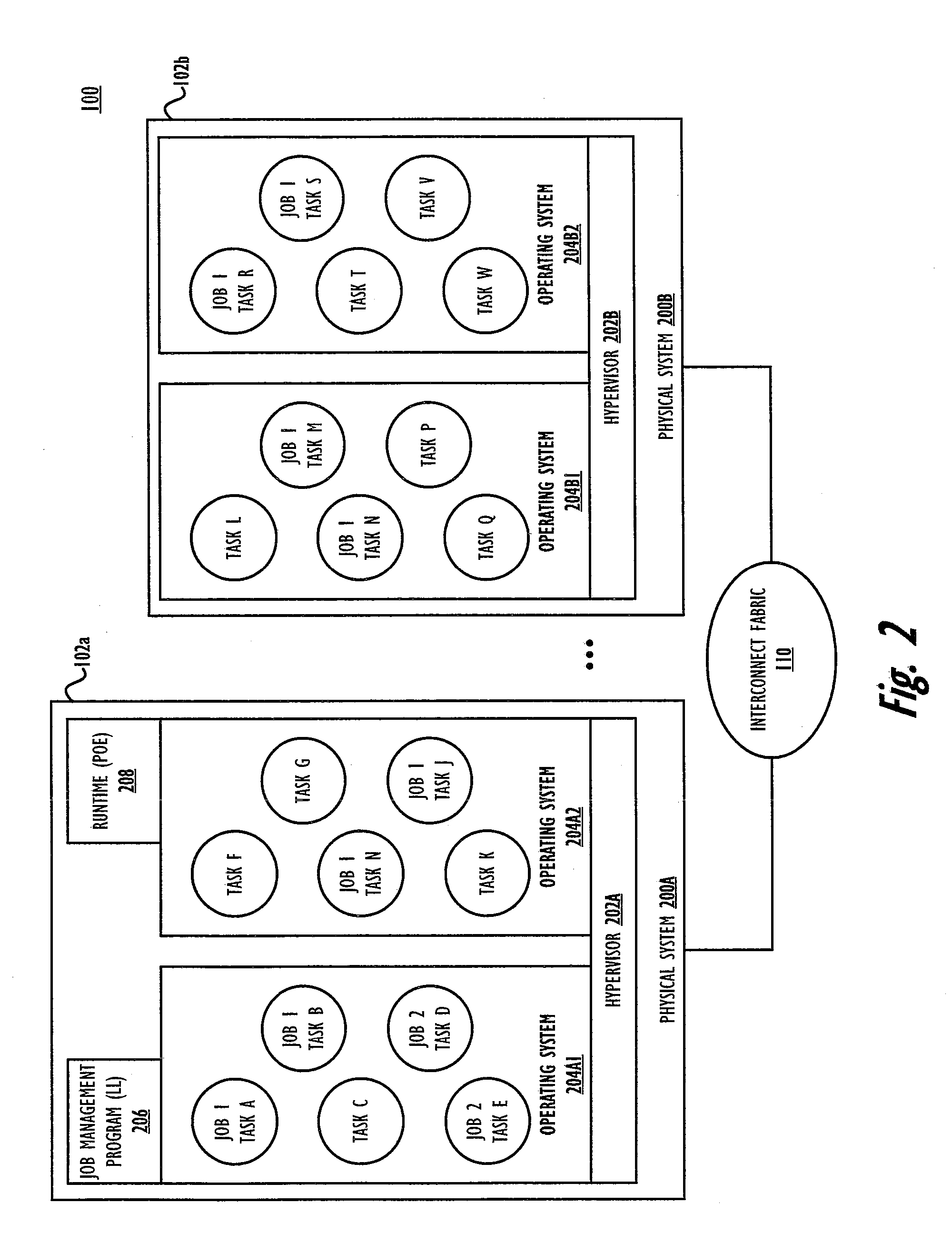

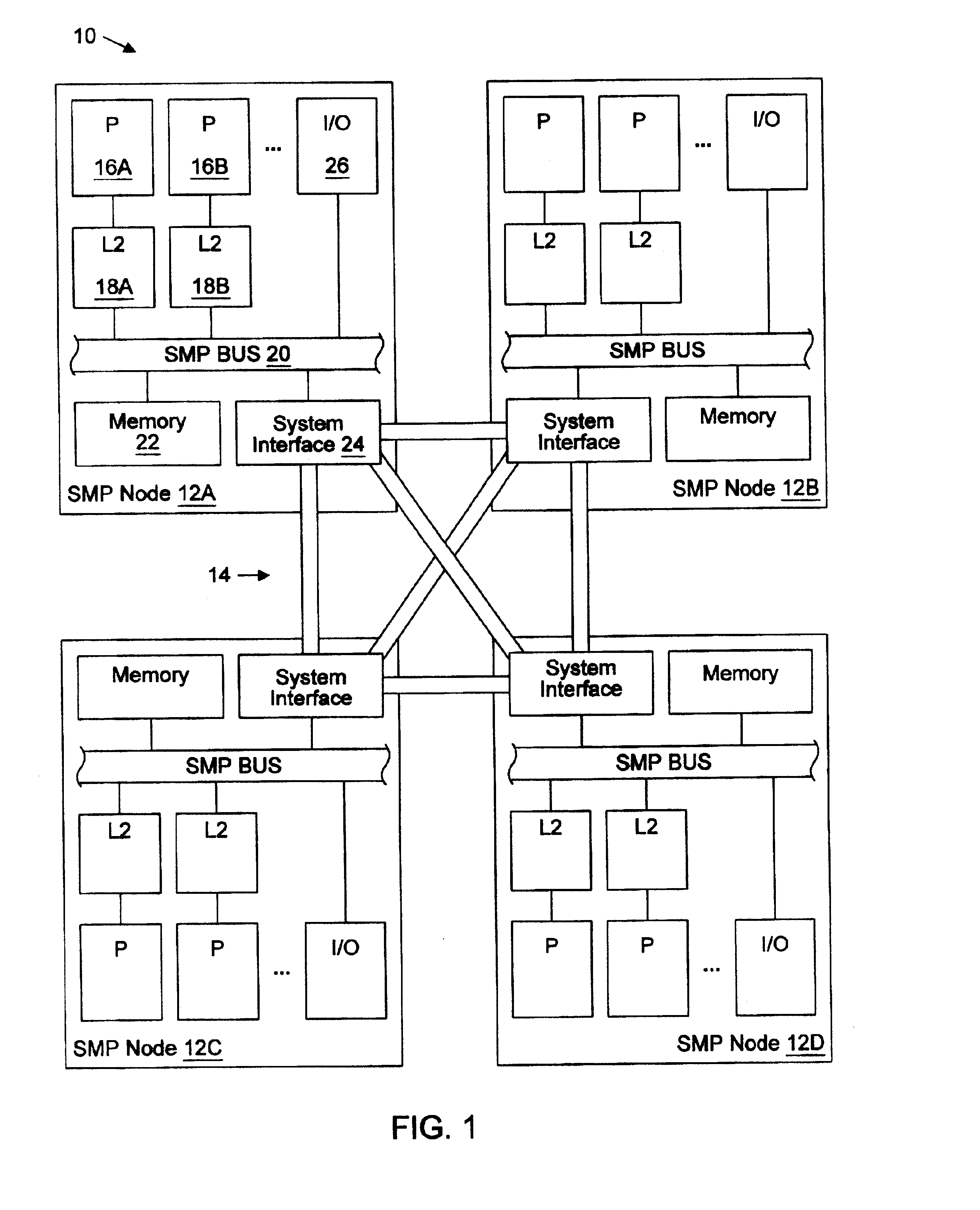

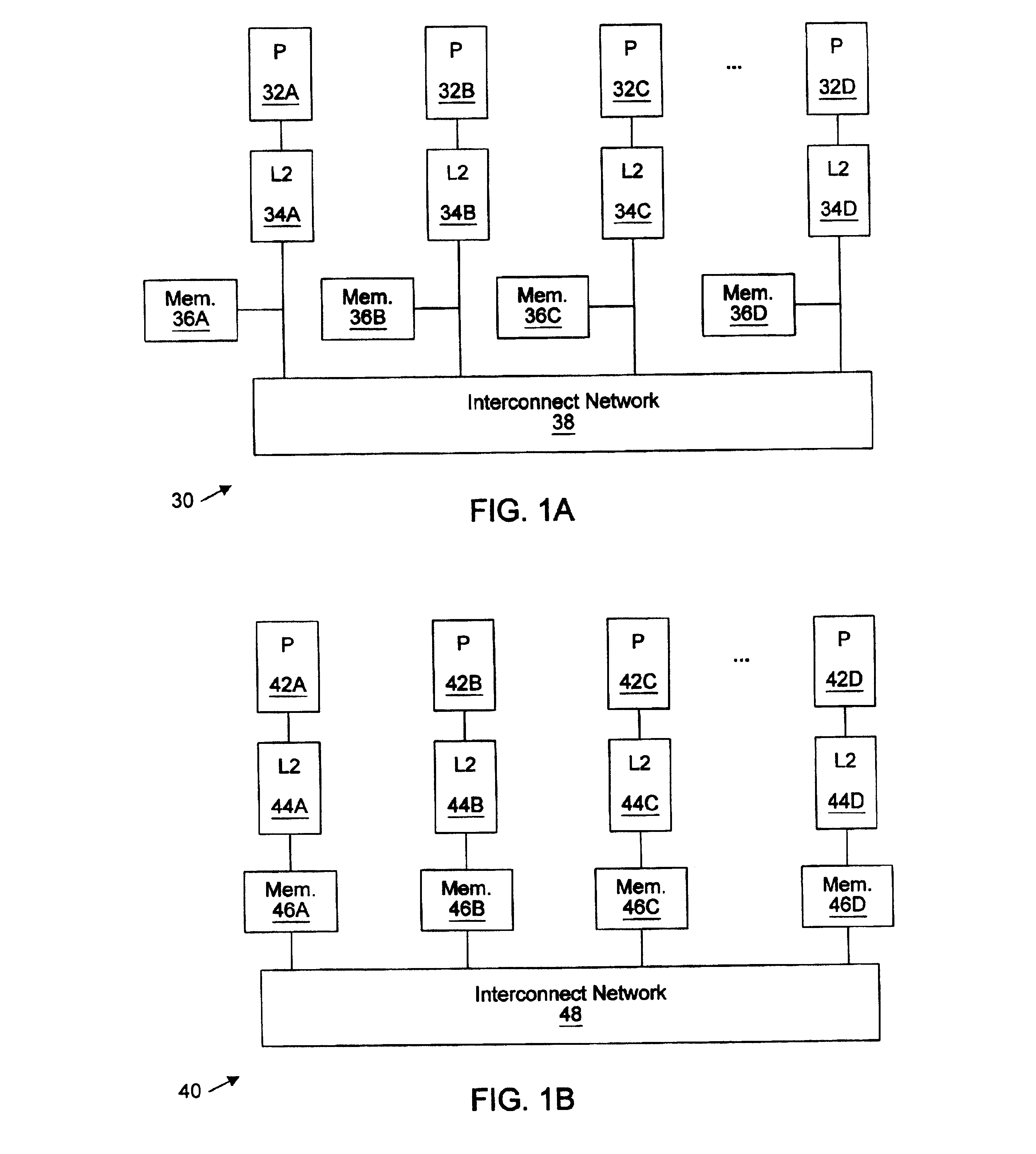

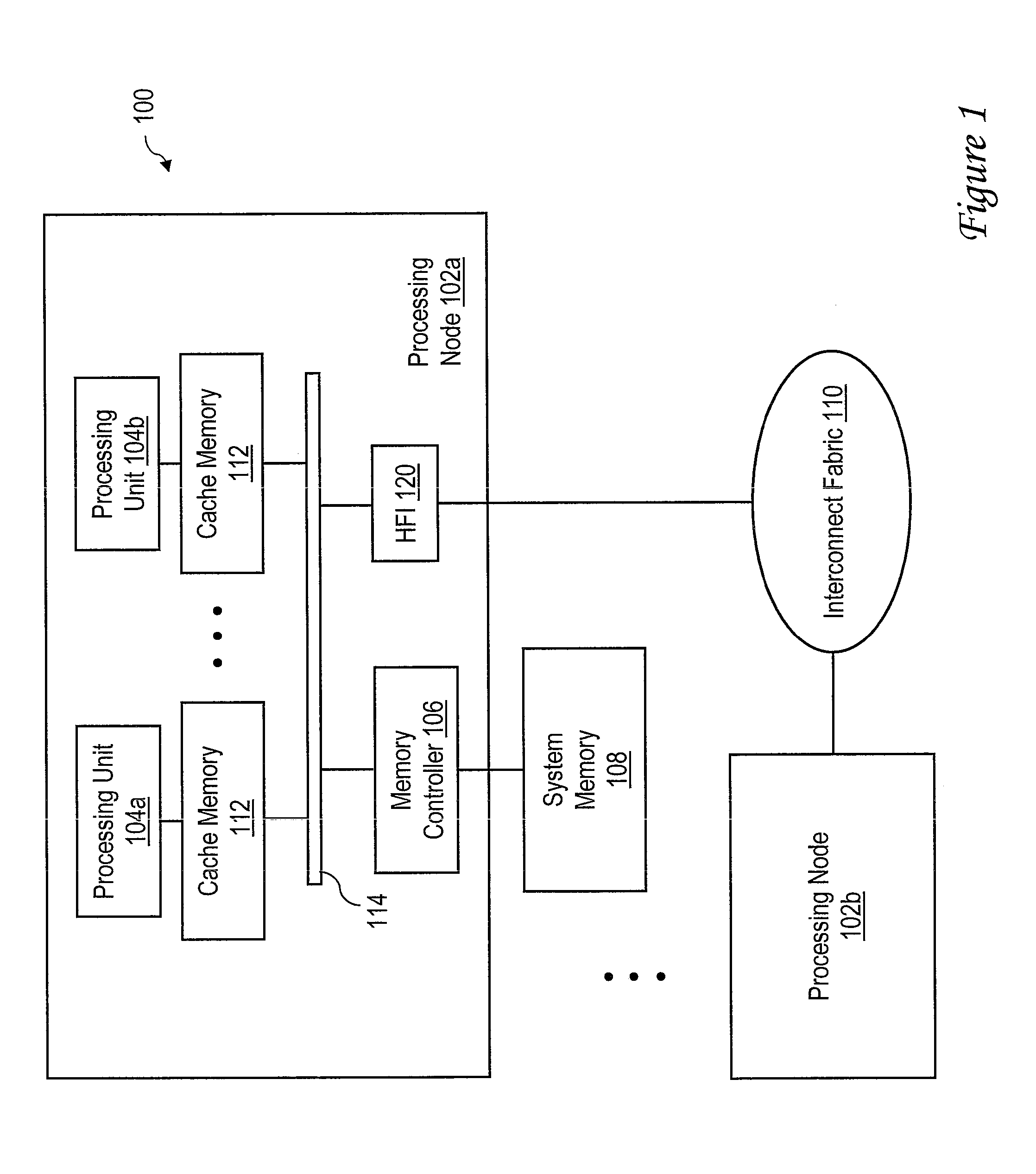

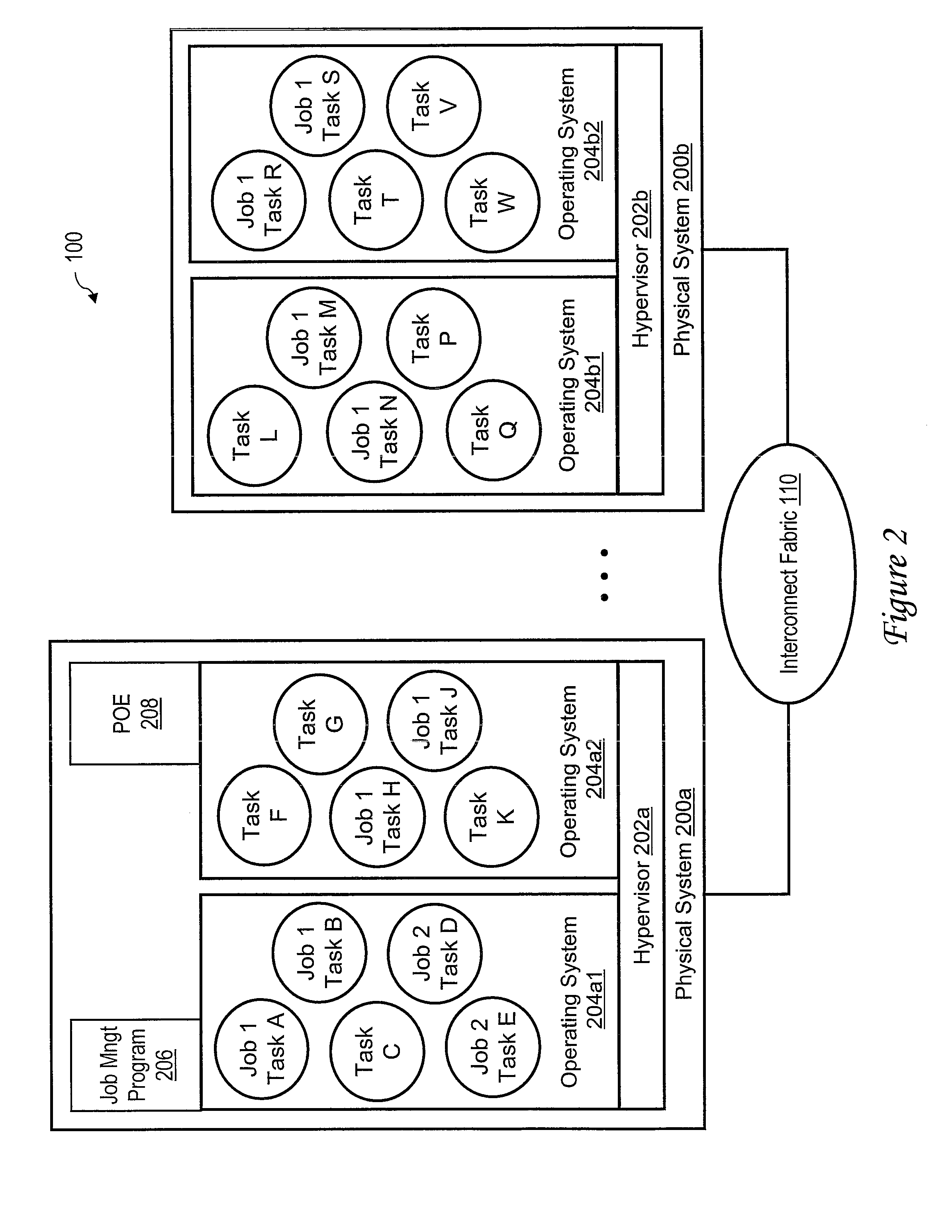

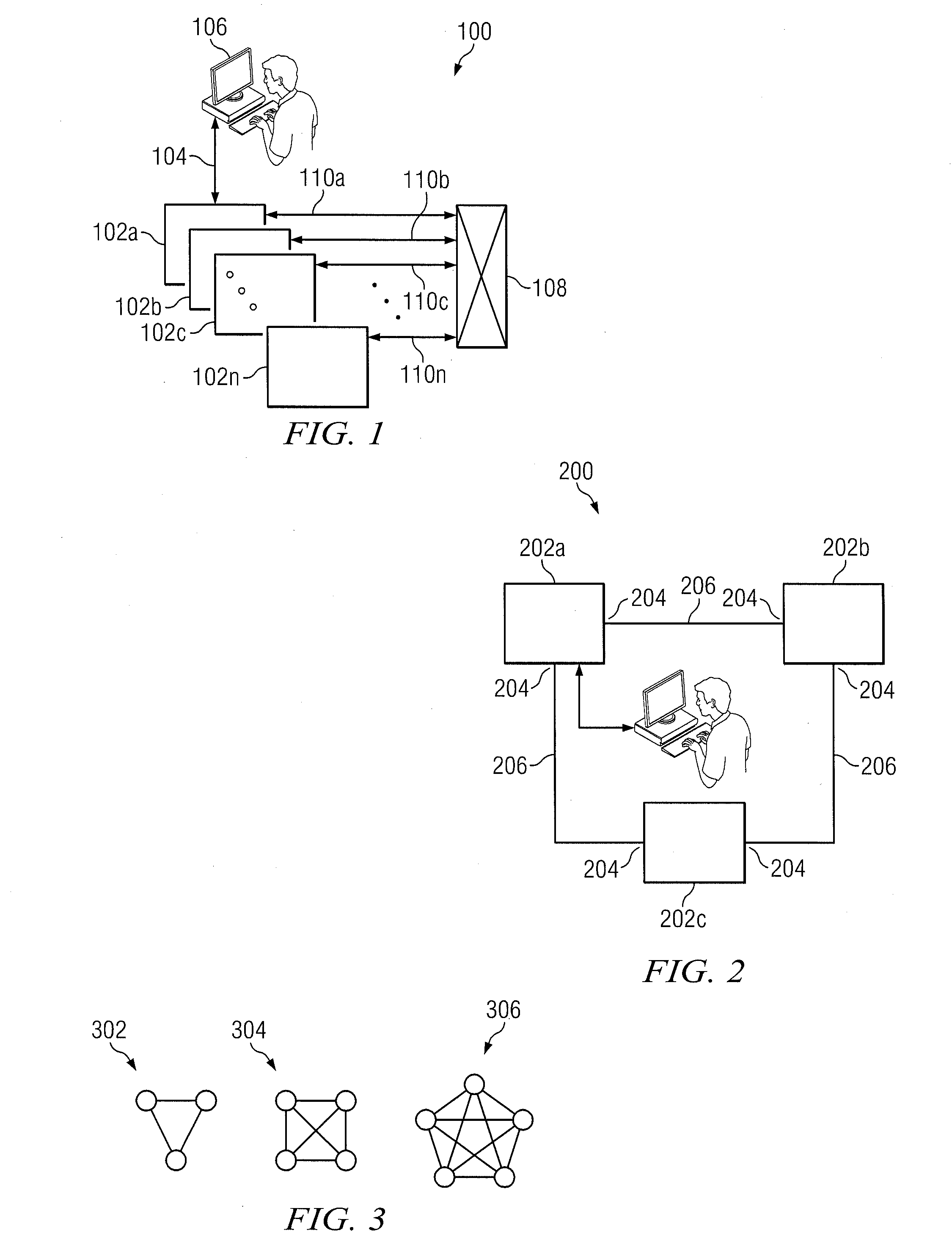

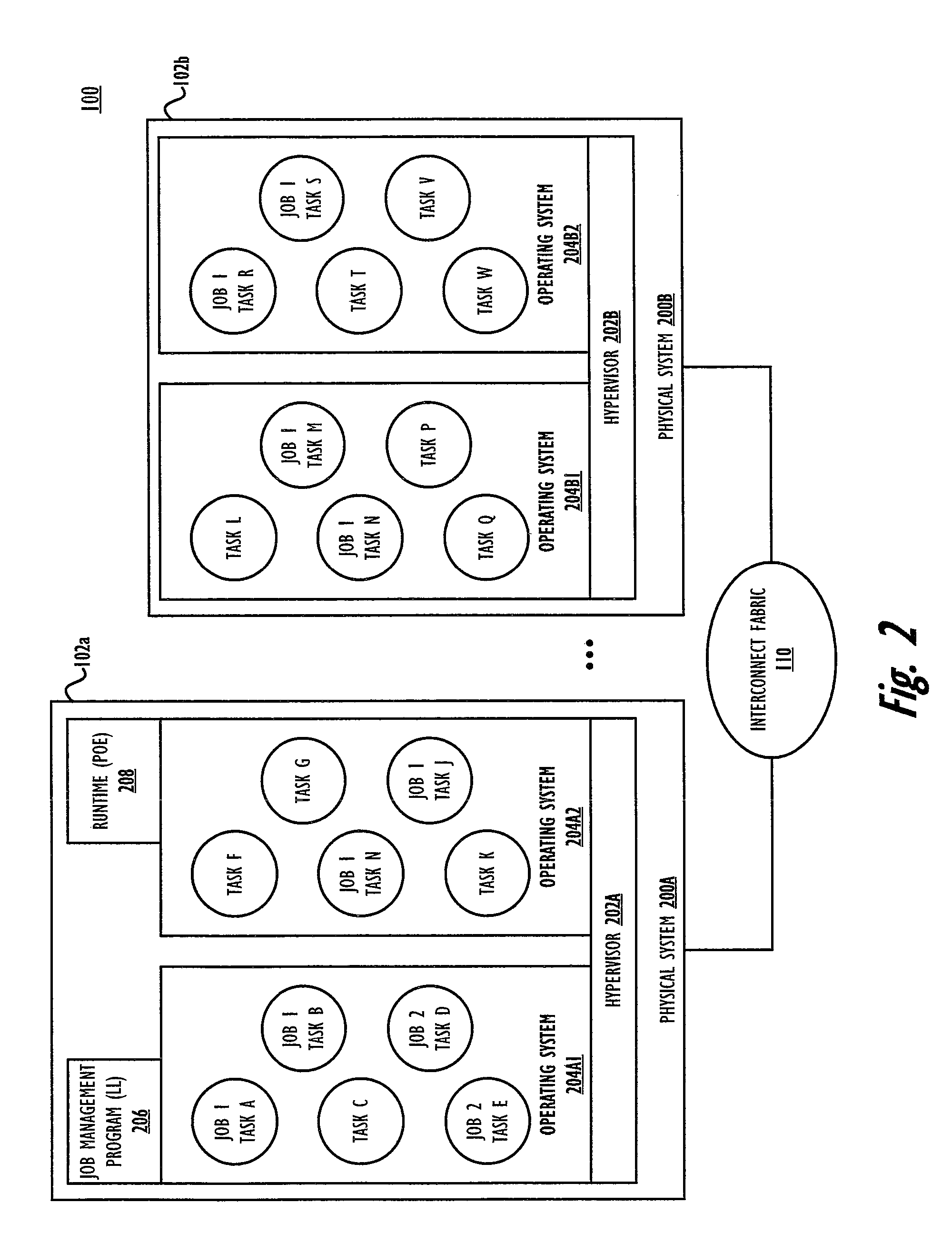

Distributed symmetric multiprocessing computing architecture

ActiveUS20110125974A1Shorten the progressMemory adressing/allocation/relocationDigital computer detailsSupercomputerGlobal address space

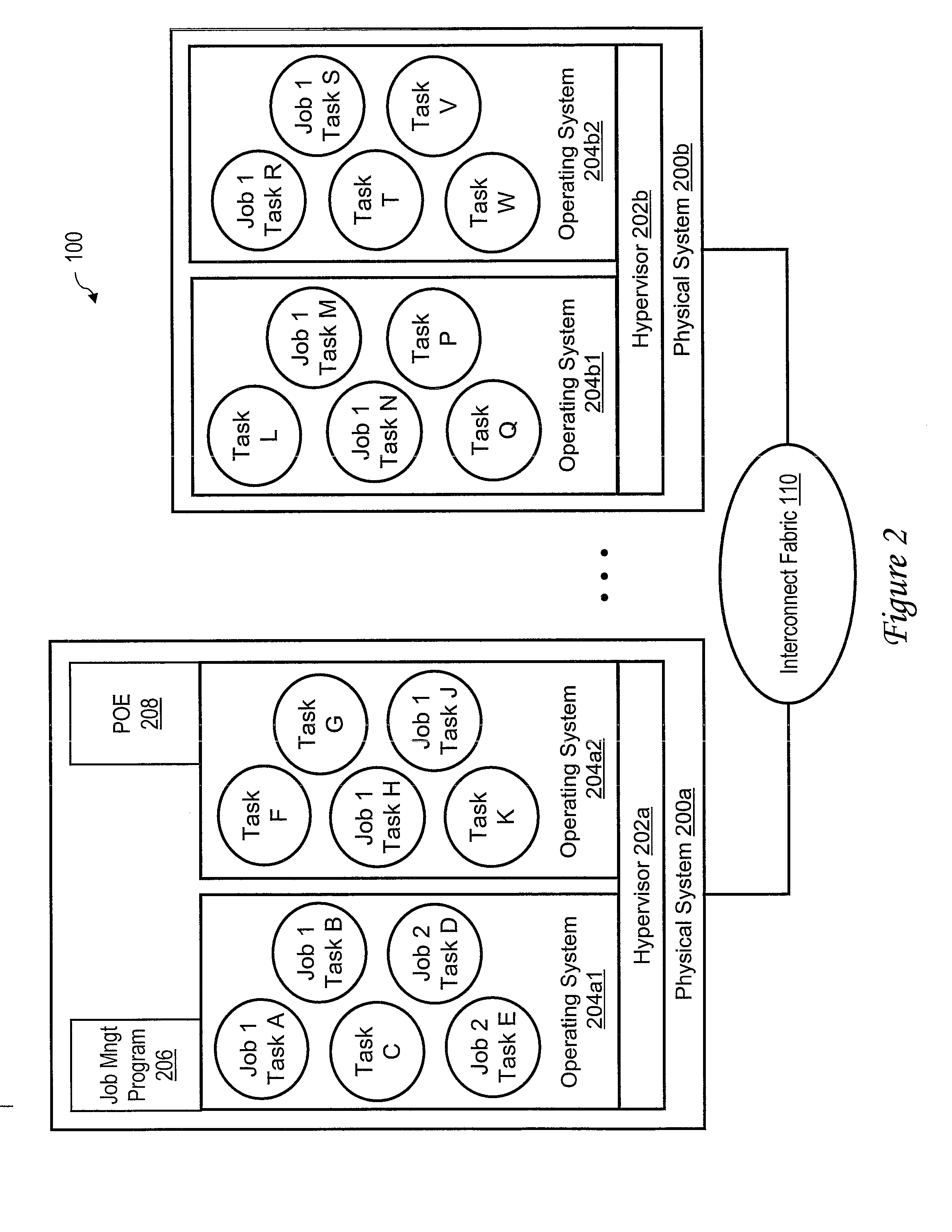

Example embodiments of the present invention includes systems and methods for implementing a scalable symmetric multiprocessing (shared memory) computer architecture using a network of homogeneous multi-core servers. The level of processor and memory performance achieved is suitable for running applications that currently require cache coherent shared memory mainframes and supercomputers. The architecture combines new operating system extensions with a high-speed network that supports remote direct memory access to achieve an effective global distributed shared memory. A distributed thread model allows a process running in a head node to fork threads in other (worker) nodes that run in the same global address space. Thread synchronization is supported by a distributed mutex implementation. A transactional memory model allows a multi-threaded program to maintain global memory page consistency across the distributed architecture. A distributed file access implementation supports non-contentious file I / O for threads. These and other functions provide a symmetric multiprocessing programming model consistent with standards such as Portable Operating System Interface for Unix (POSIX).

Owner:ANDERSON RICHARD S

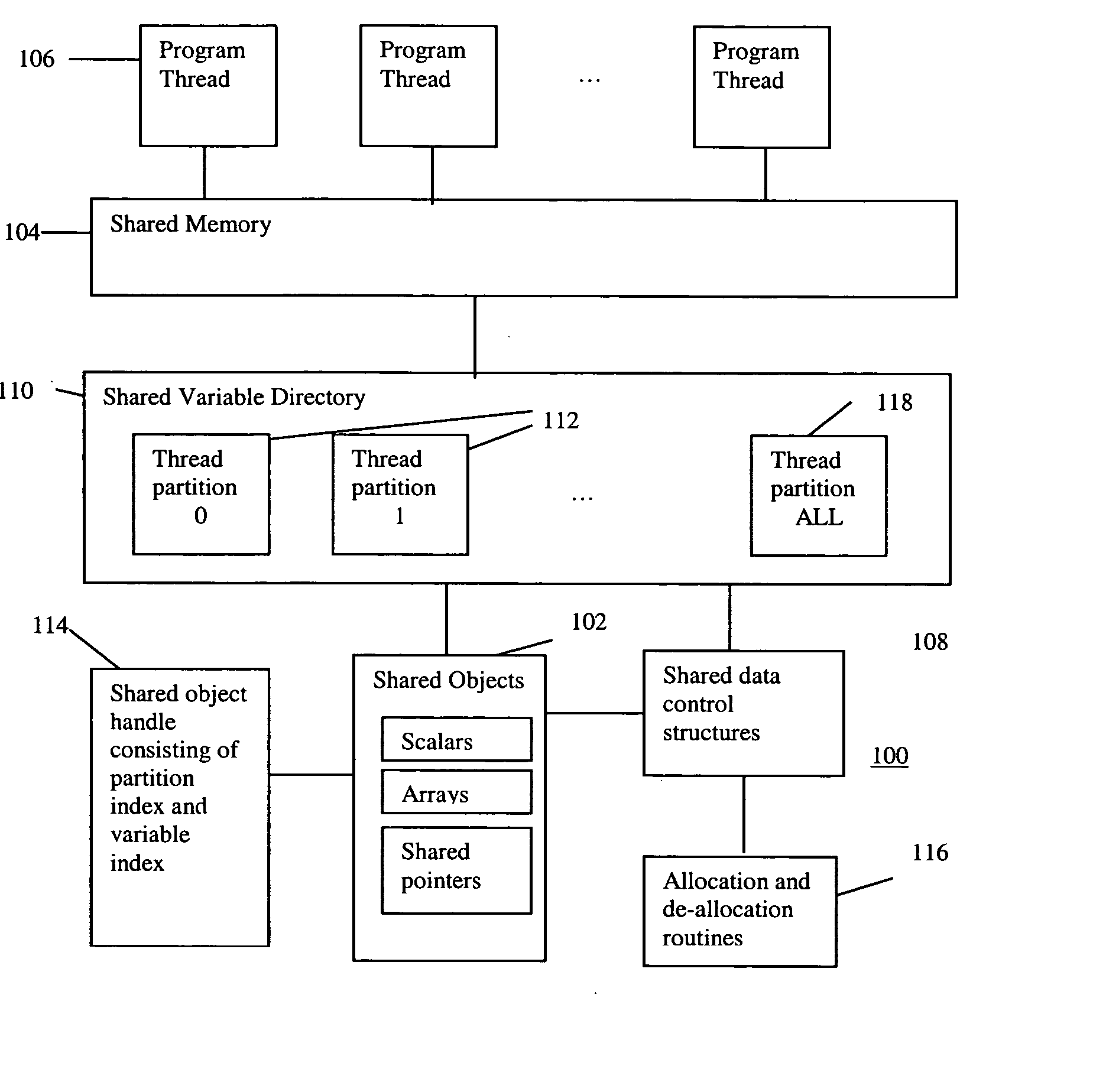

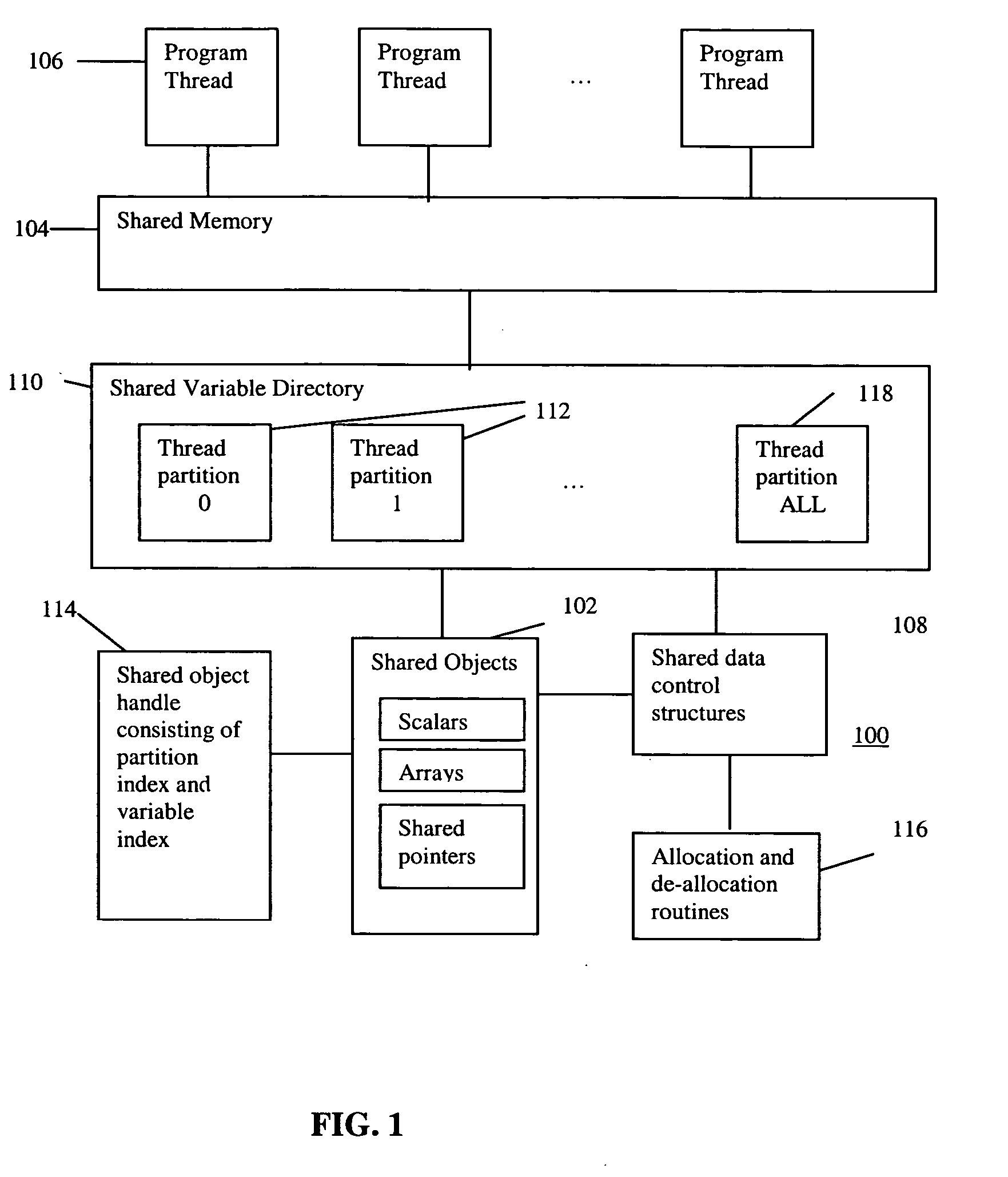

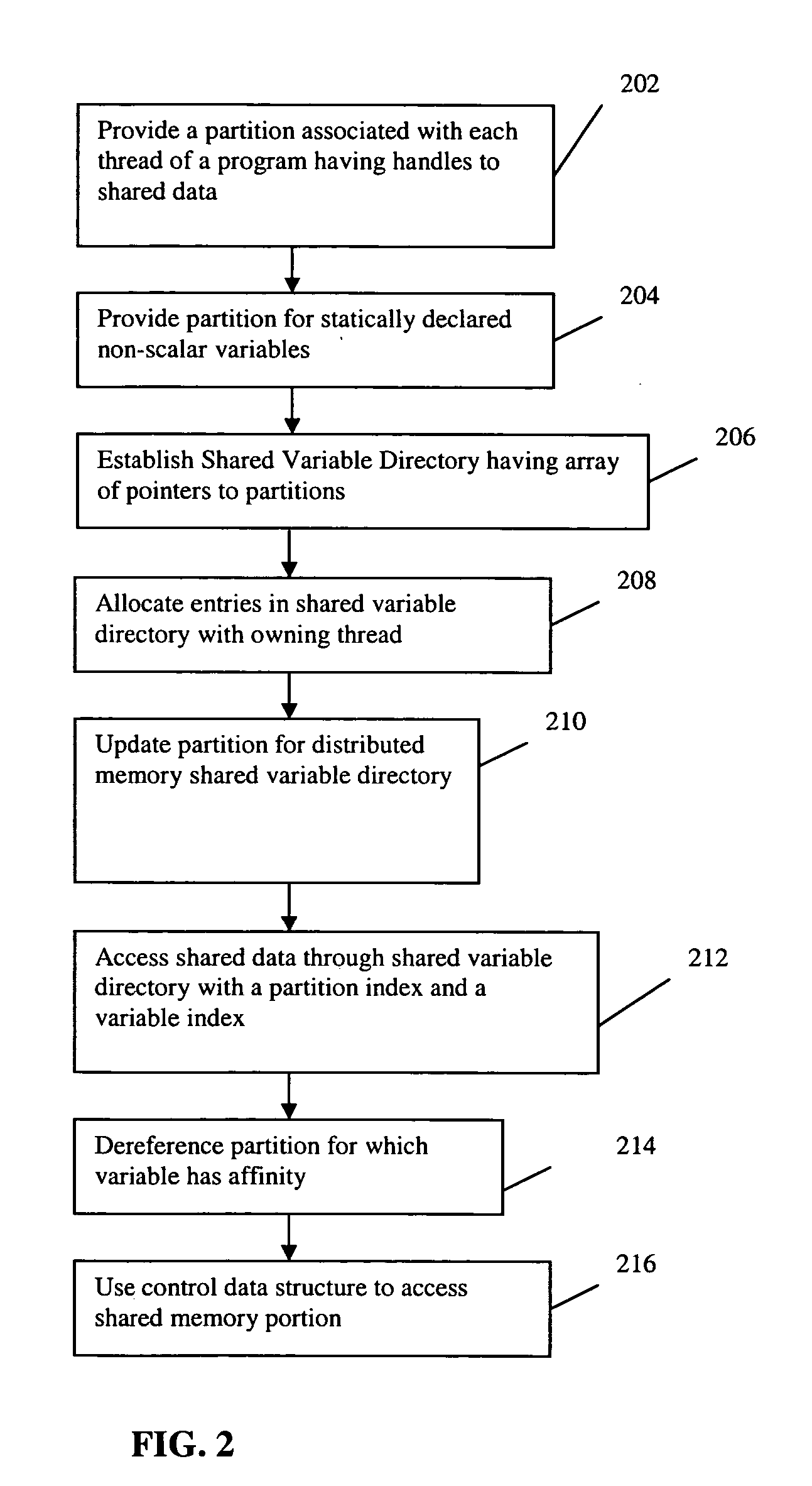

Scalable runtime system for global address space languages on shared and distributed memory machines

ActiveUS20050149903A1Improve scalabilityResource allocationSpecific program execution arrangementsExtensibilityGlobal address space

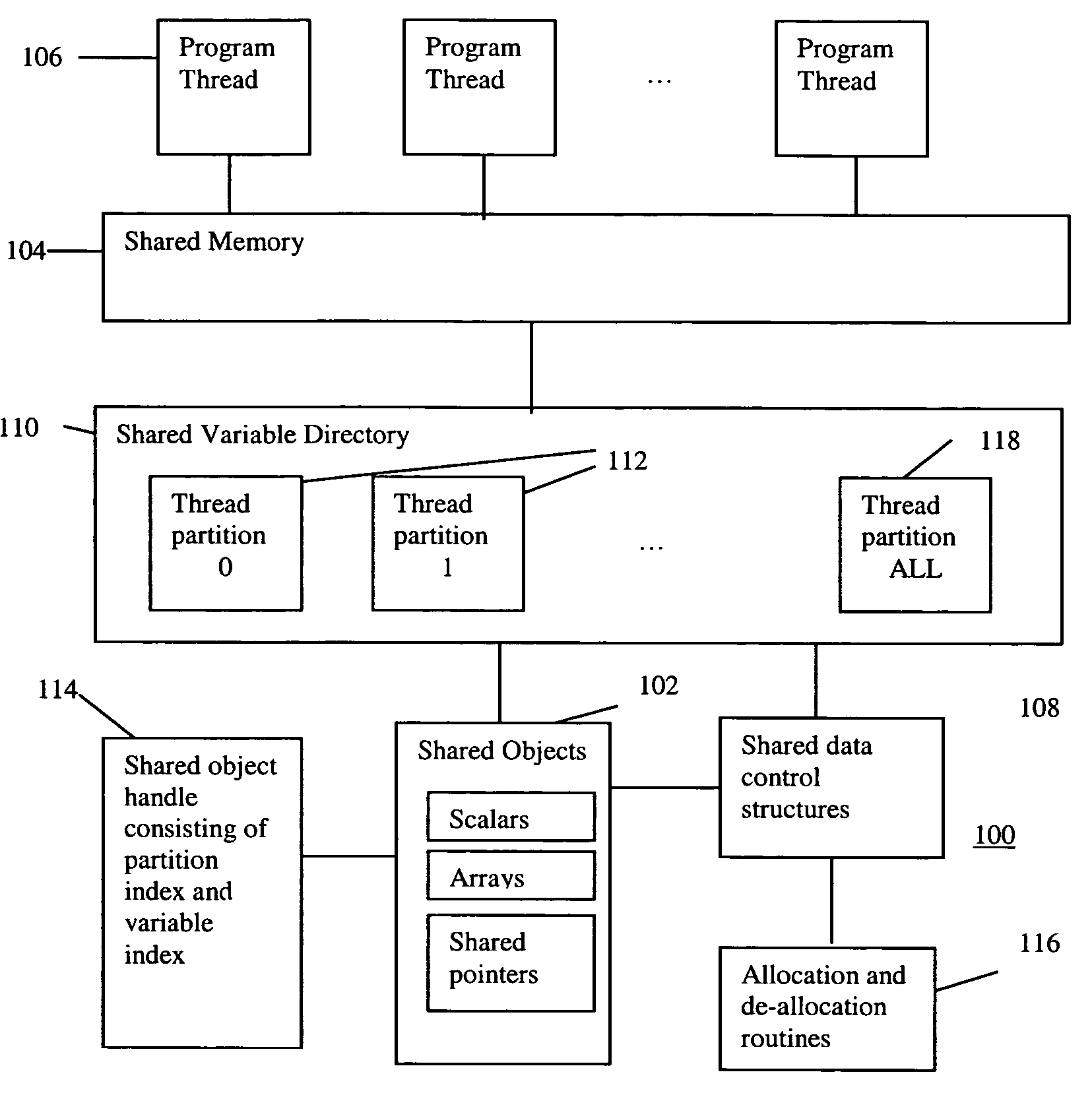

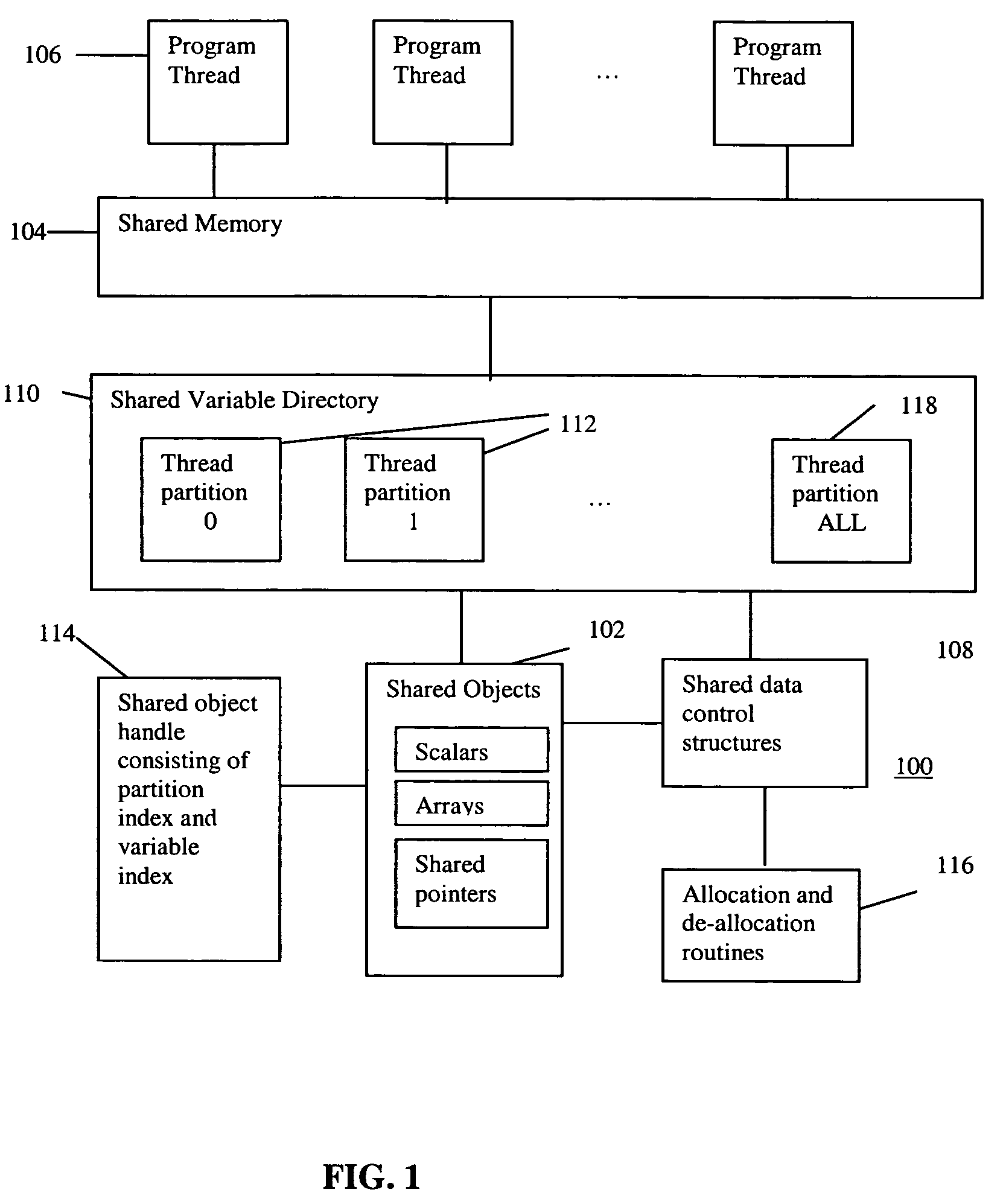

An improved scalability runtime system for a global address space language running on a distributed or shared memory machine uses a directory of shared variables having a data structure for tracking shared variable information that is shared by a plurality of program threads. Allocation and de-allocation routines are used to allocate and de-allocate shared variable entries in the directory of shared variables. Different routines can be used to access different types of shared data. A control structure is used to control access to the shared data such that all threads can access the data at any time. Since all threads see the same objects, synchronization issues are eliminated. In addition, the improved efficiency of the data sharing allows the number of program threads to be vastly increased.

Owner:DAEDALUS BLUE LLC

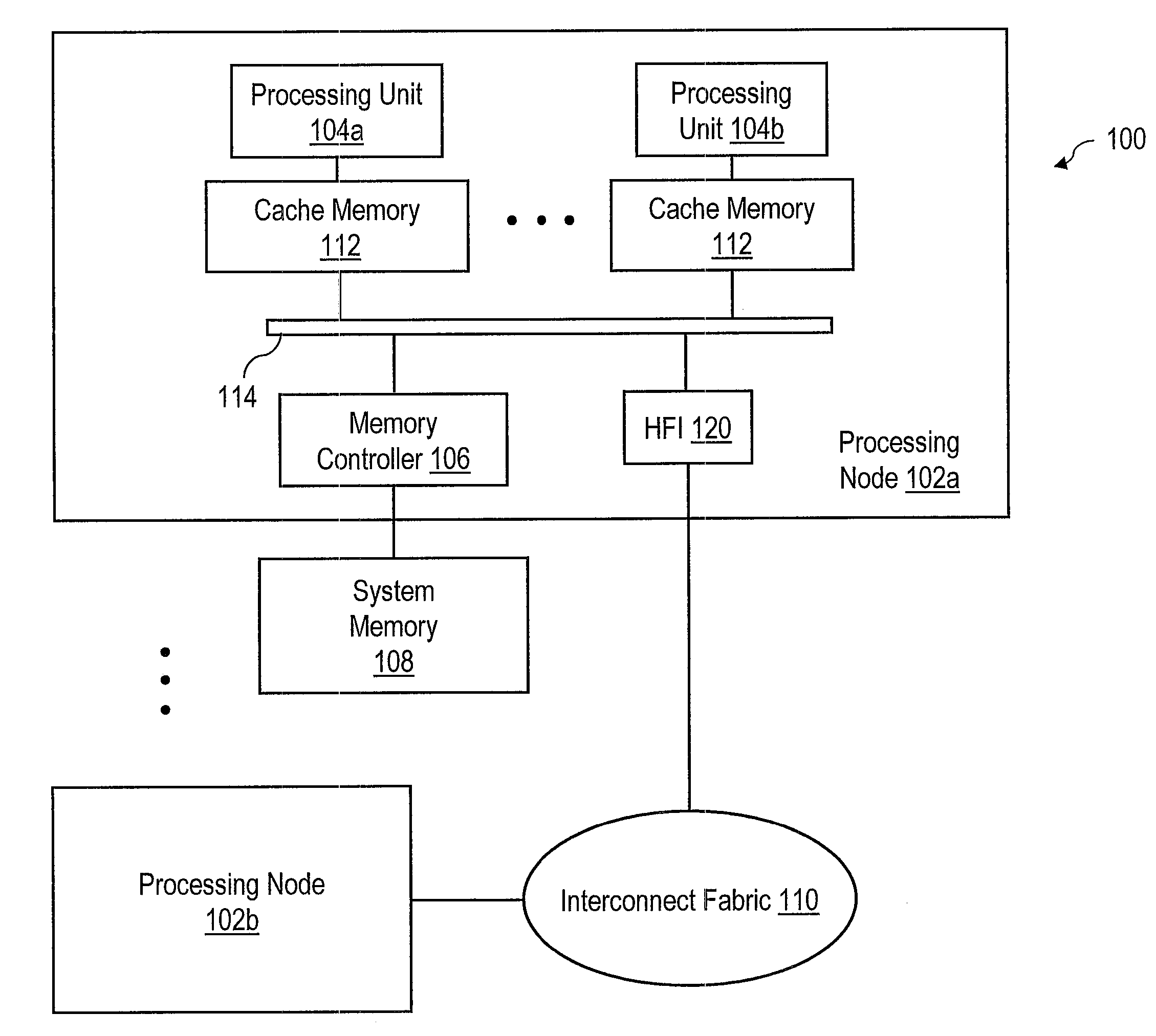

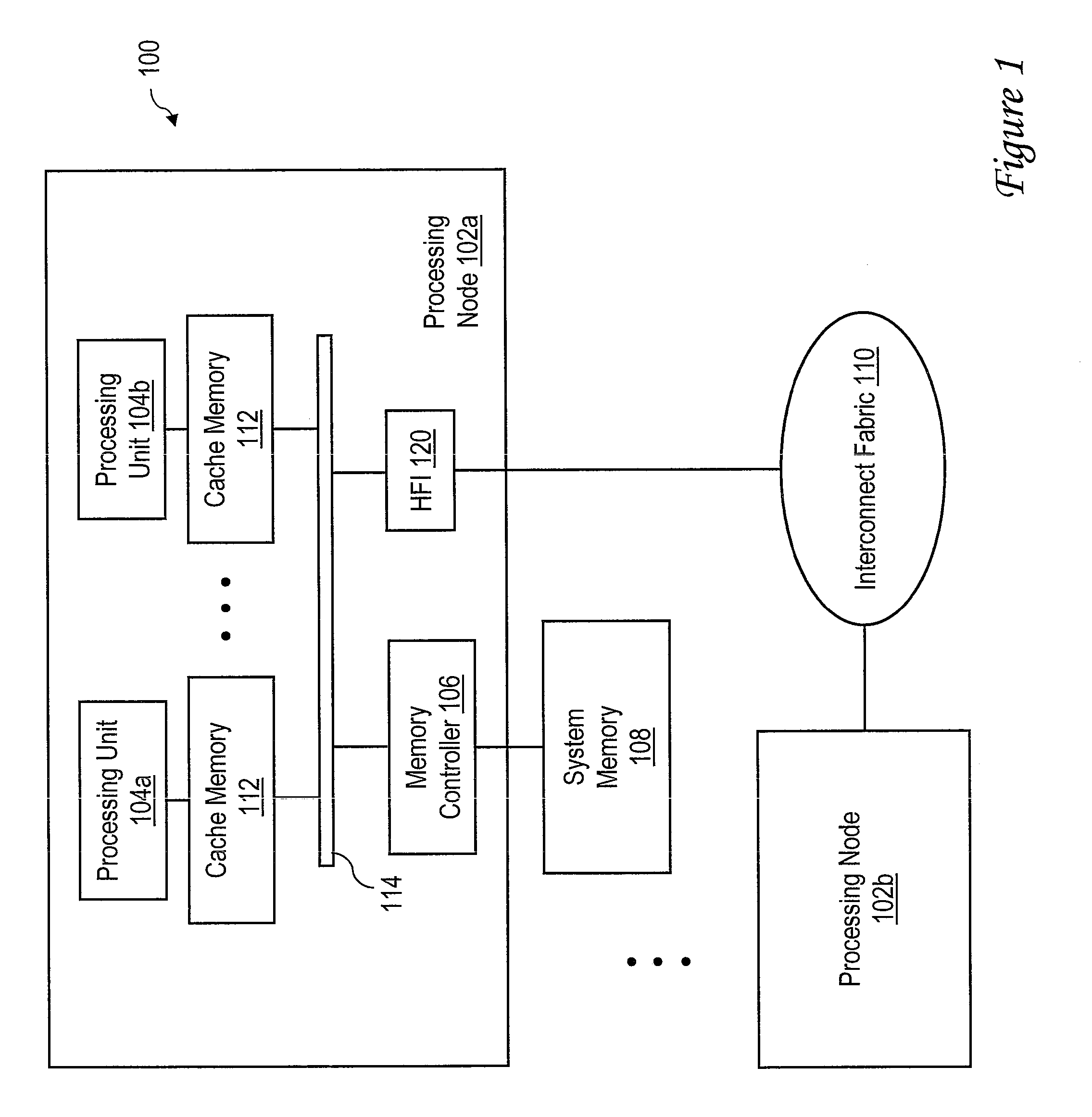

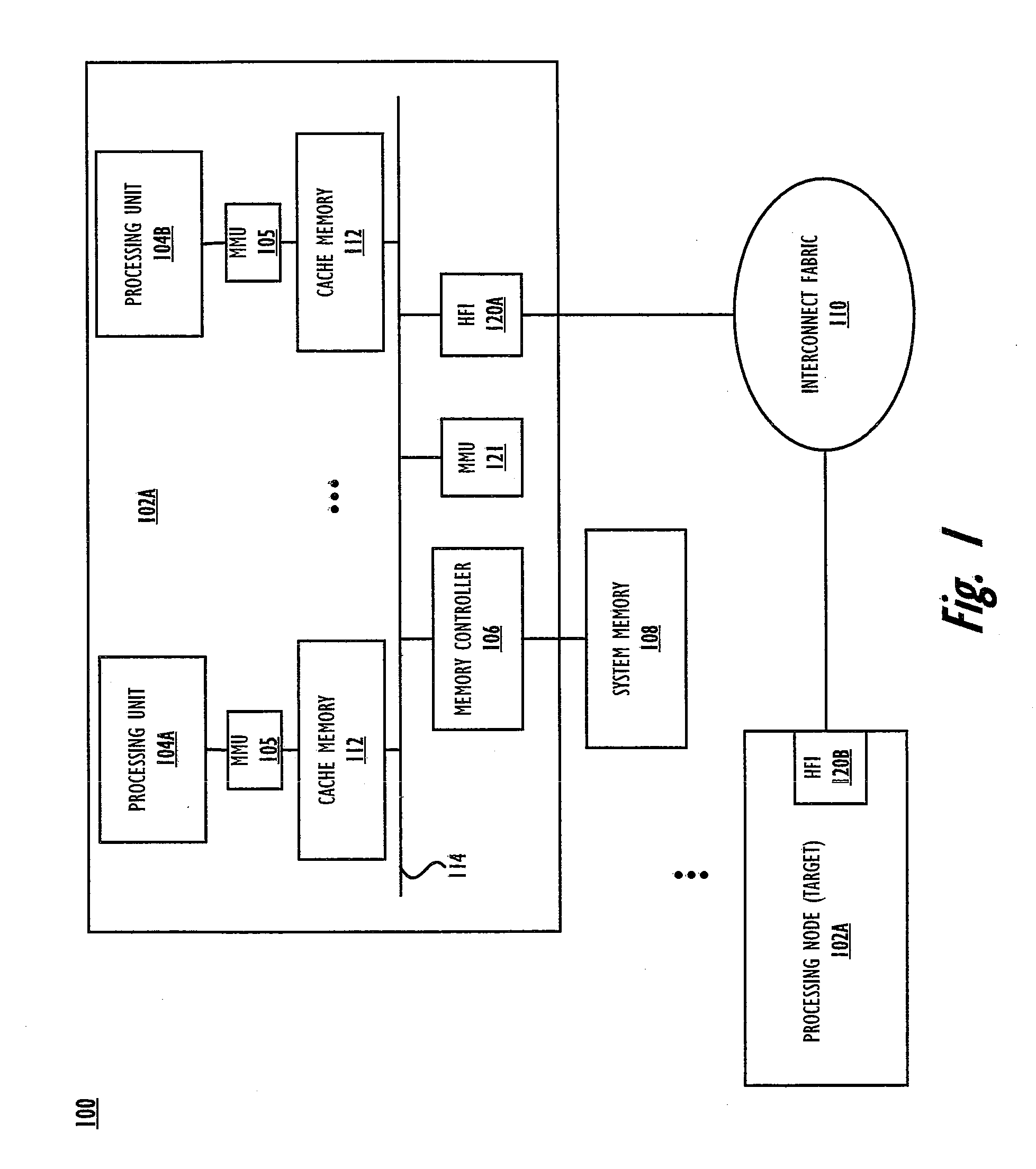

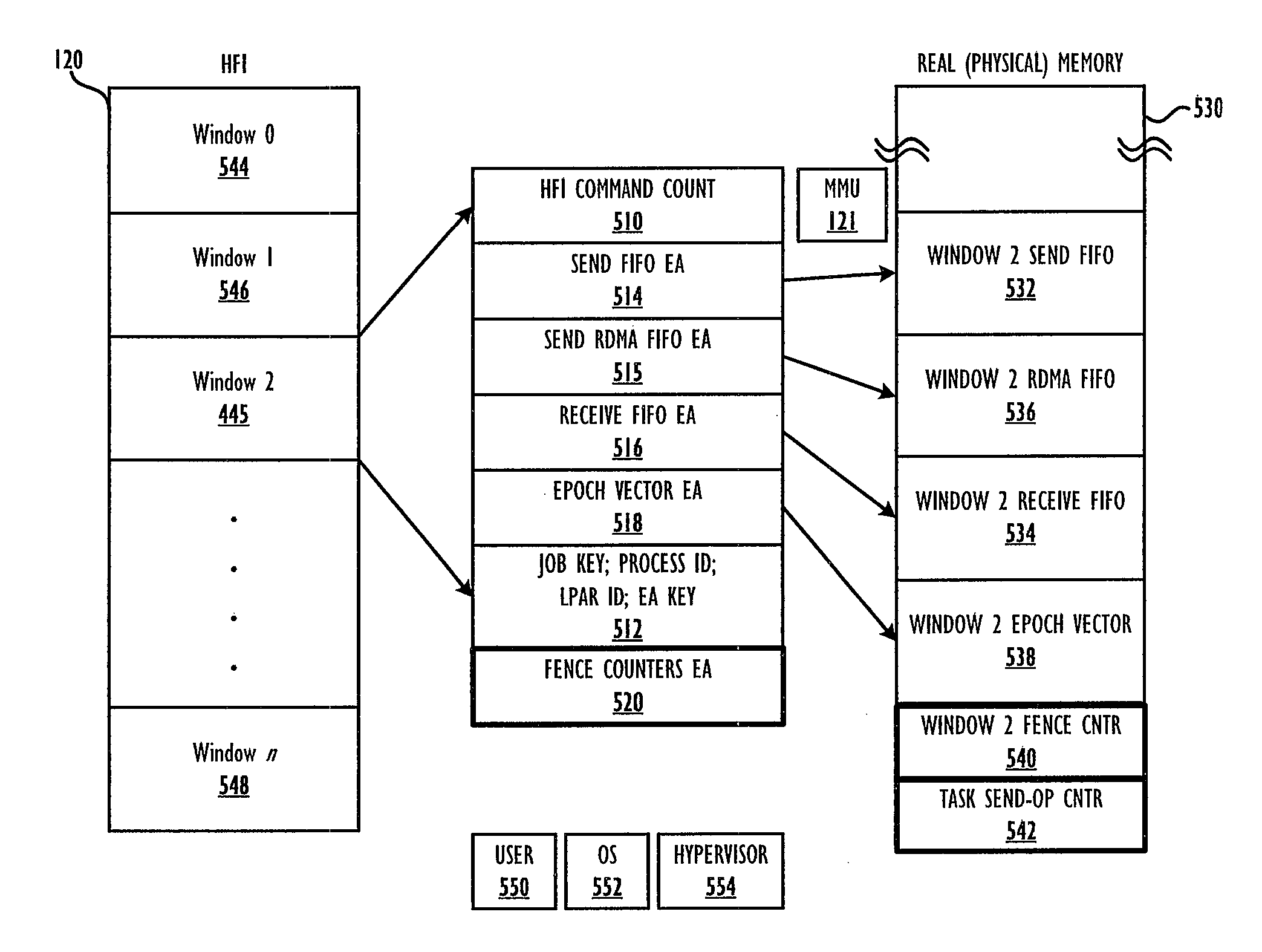

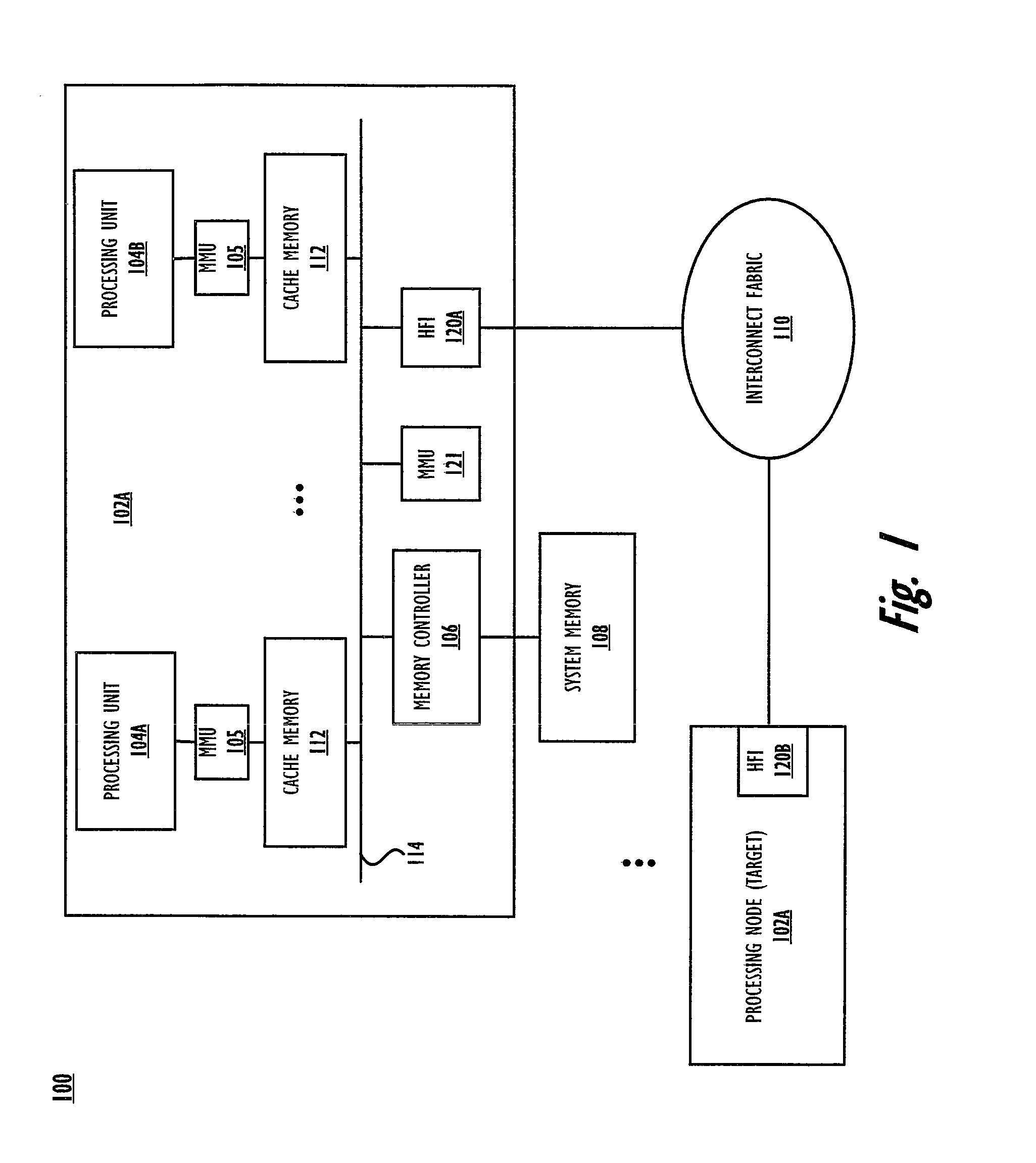

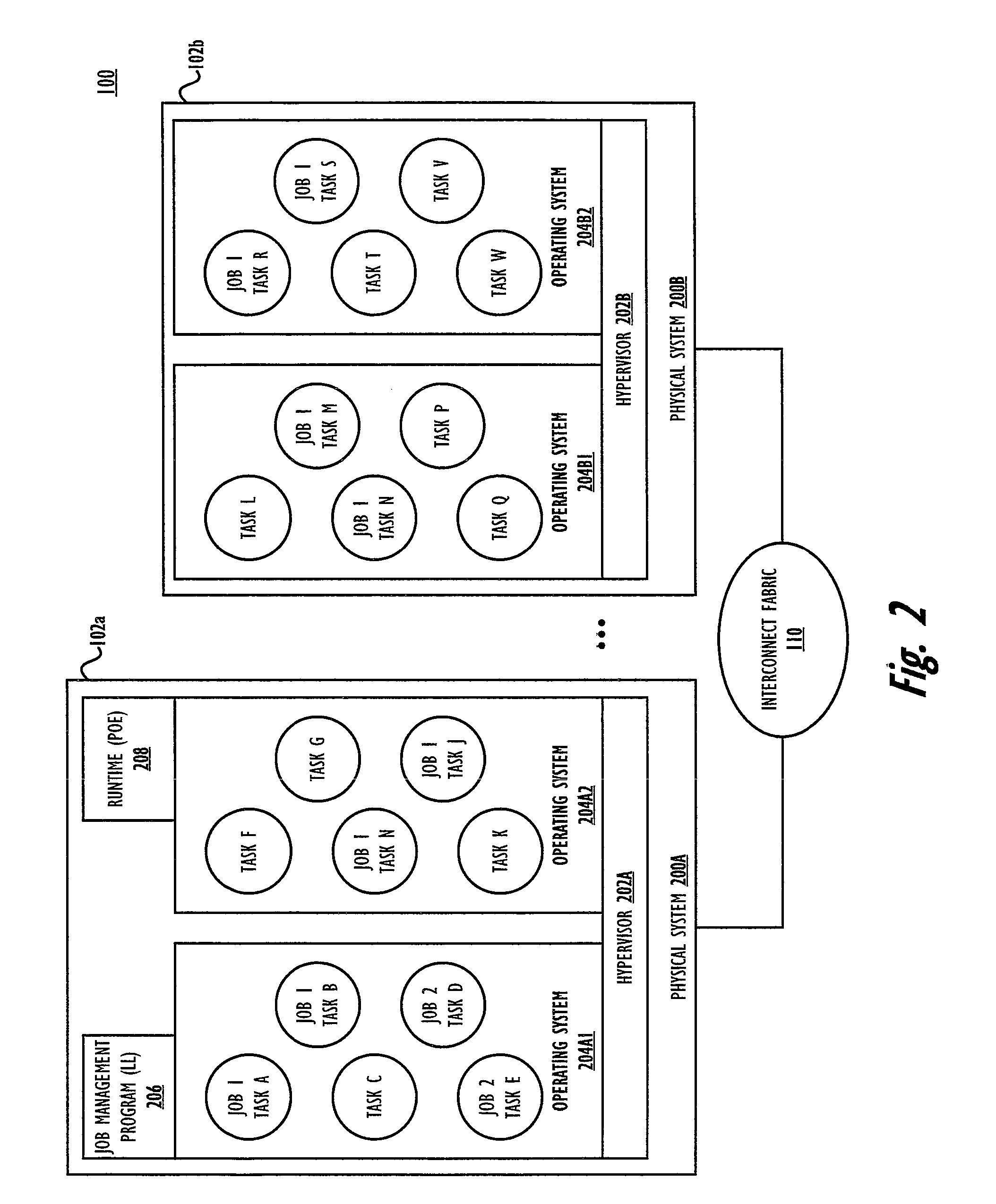

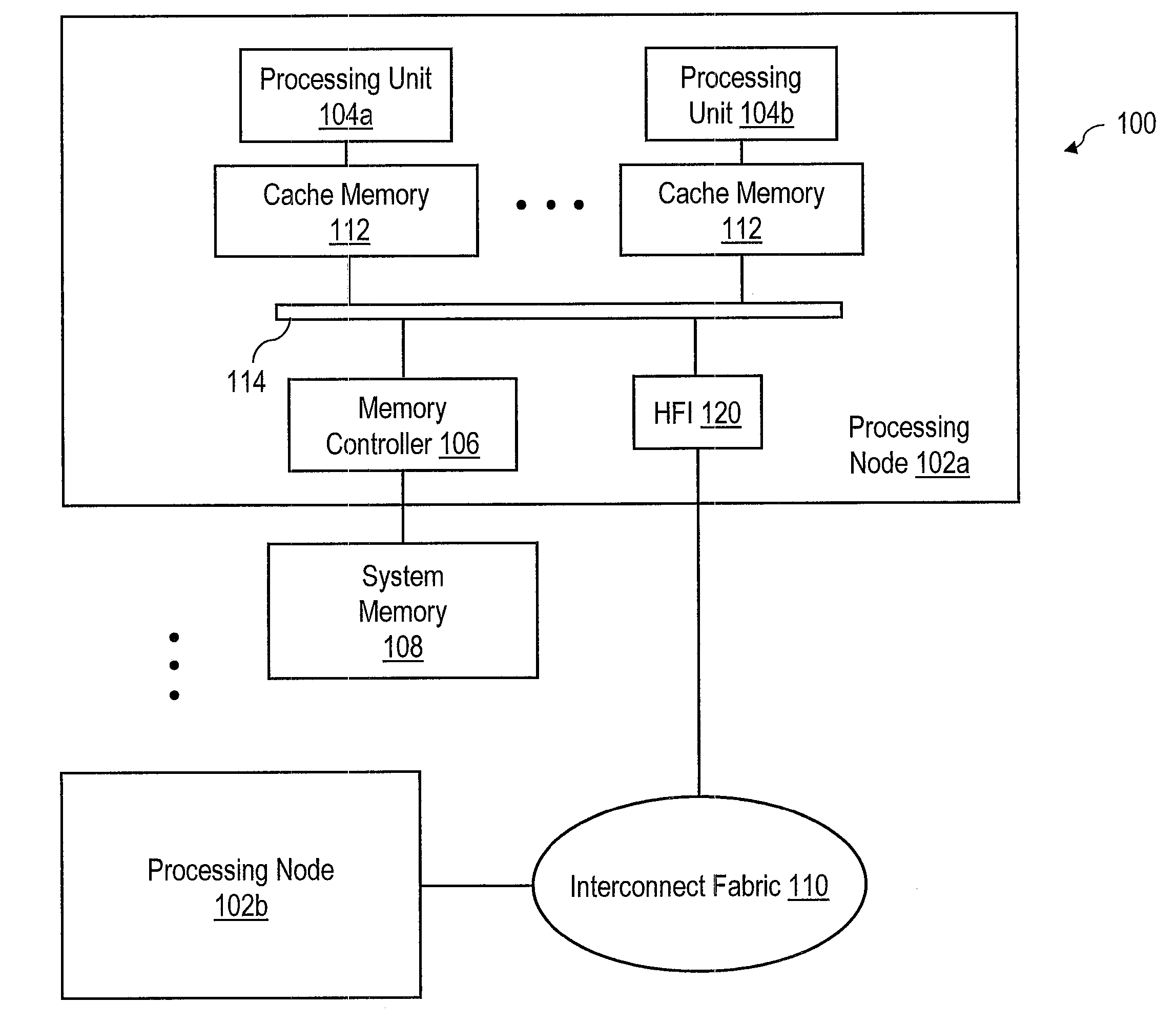

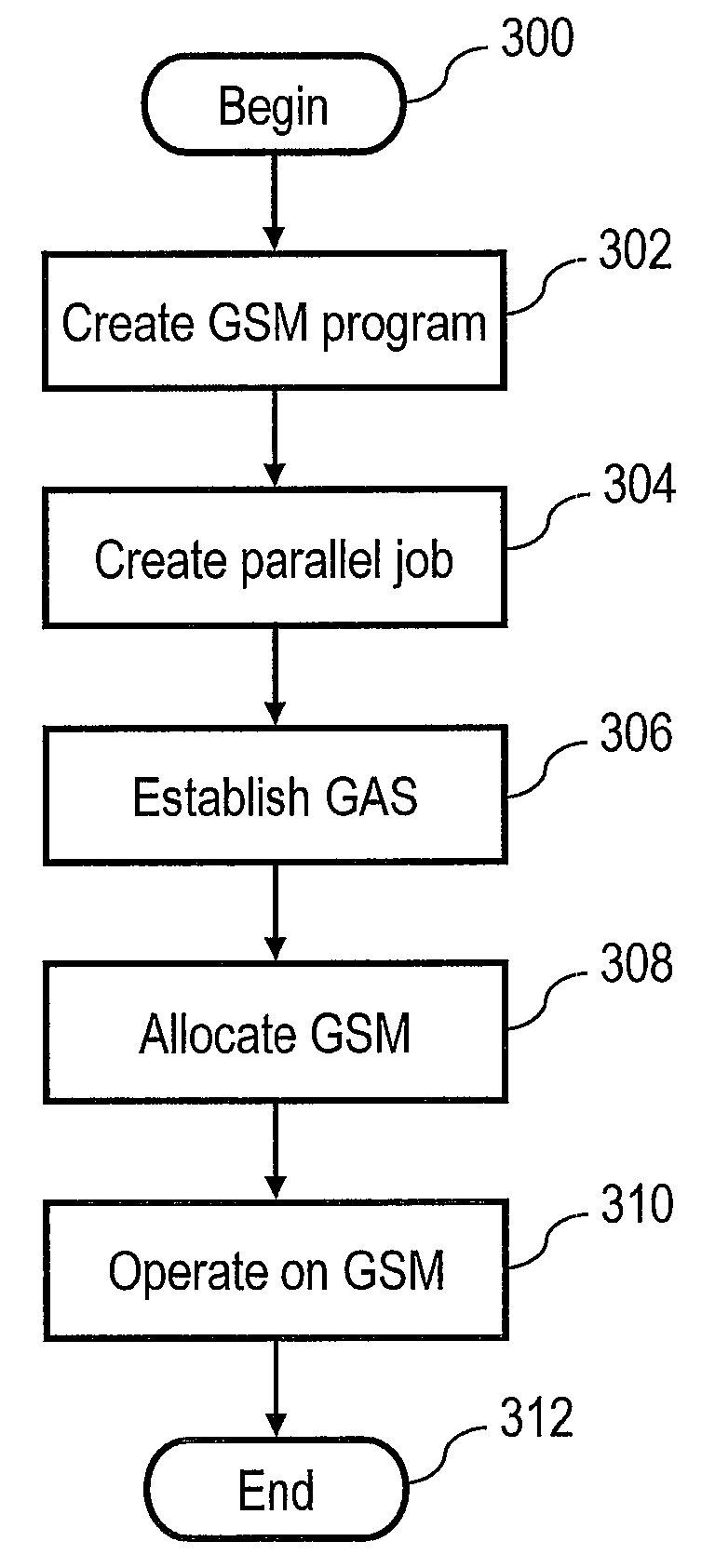

Host Fabric Interface (HFI) to Perform Global Shared Memory (GSM) Operations

InactiveUS20090198918A1Memory adressing/allocation/relocationDigital computer detailsData processing systemGlobal address space

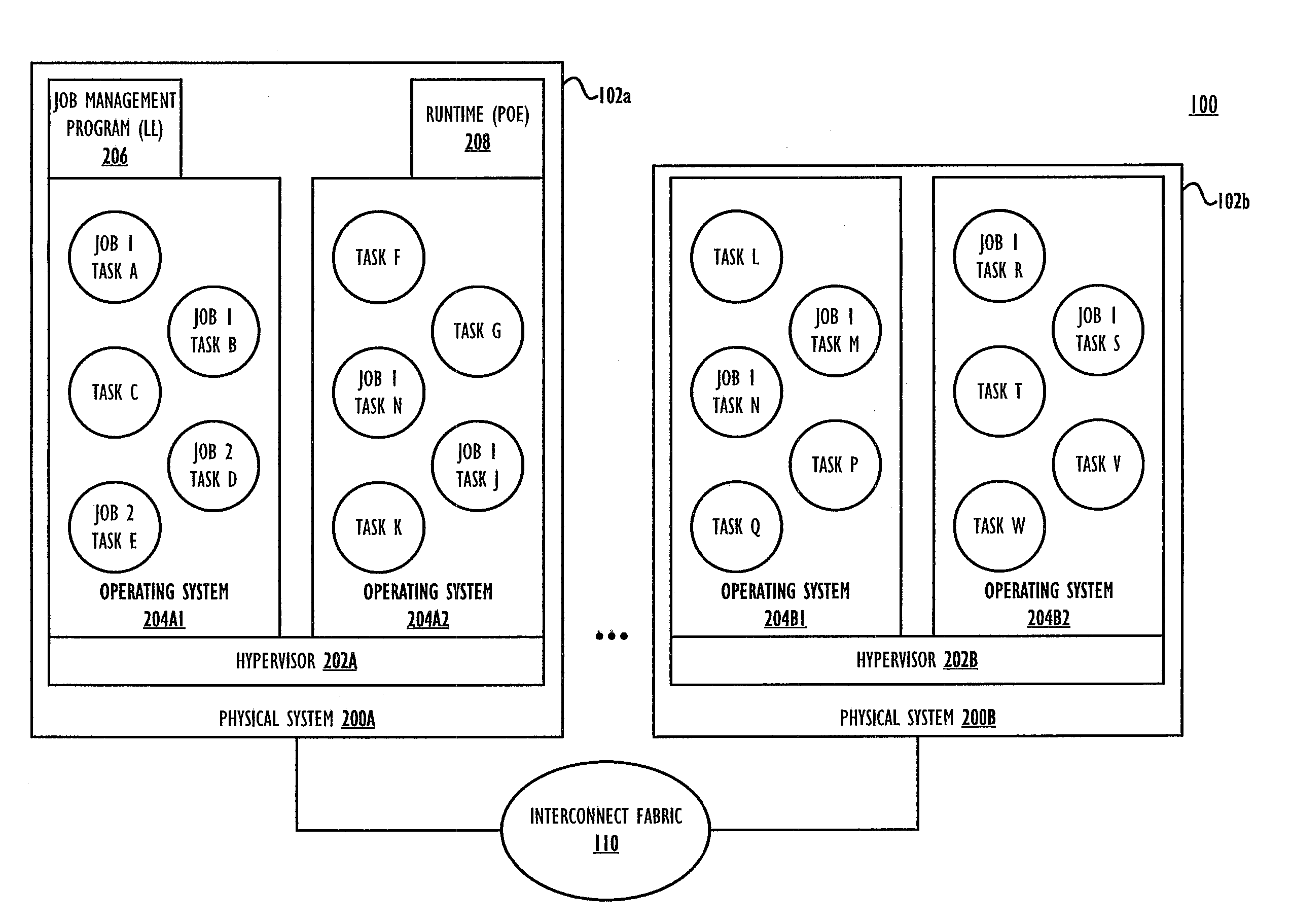

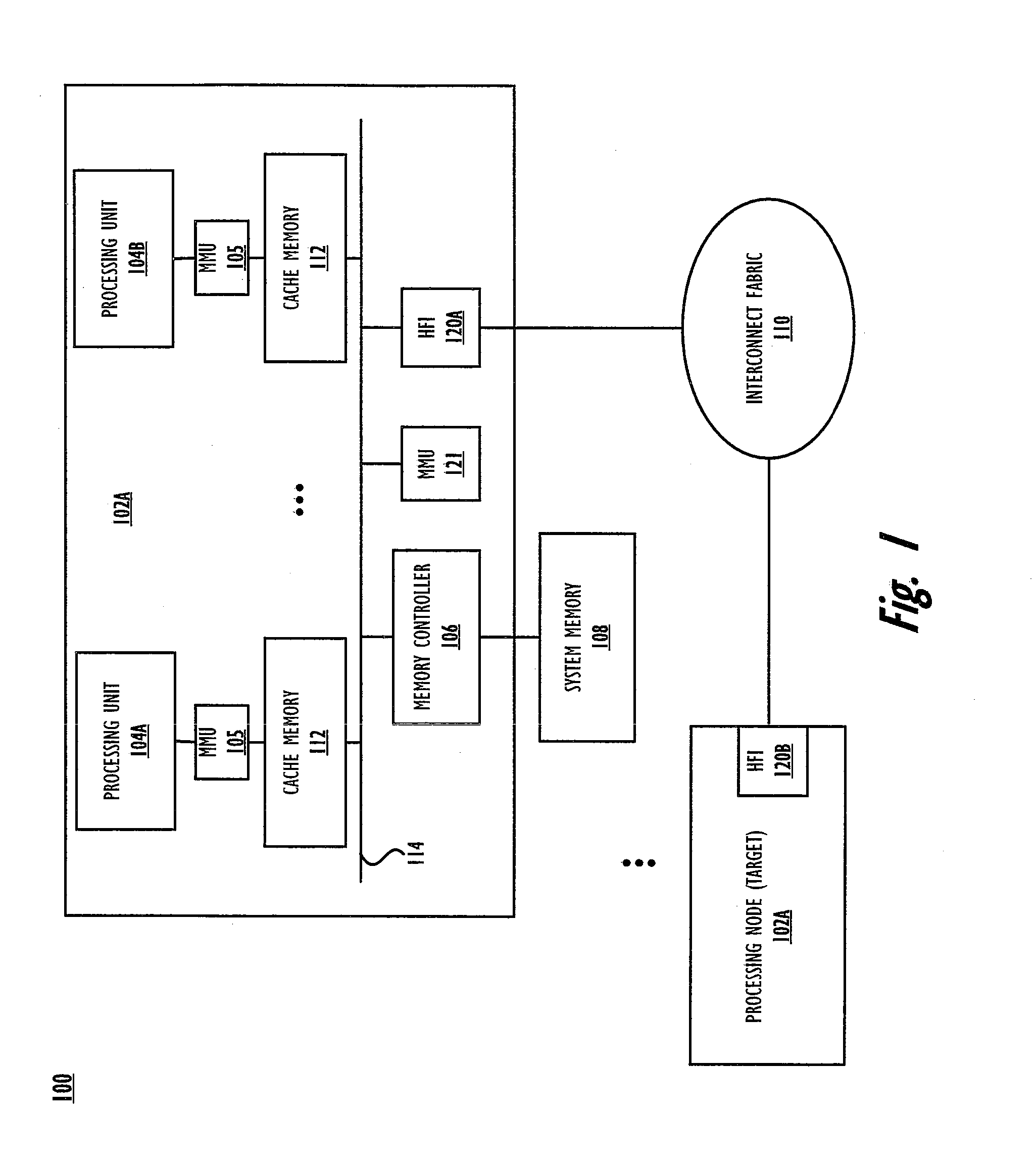

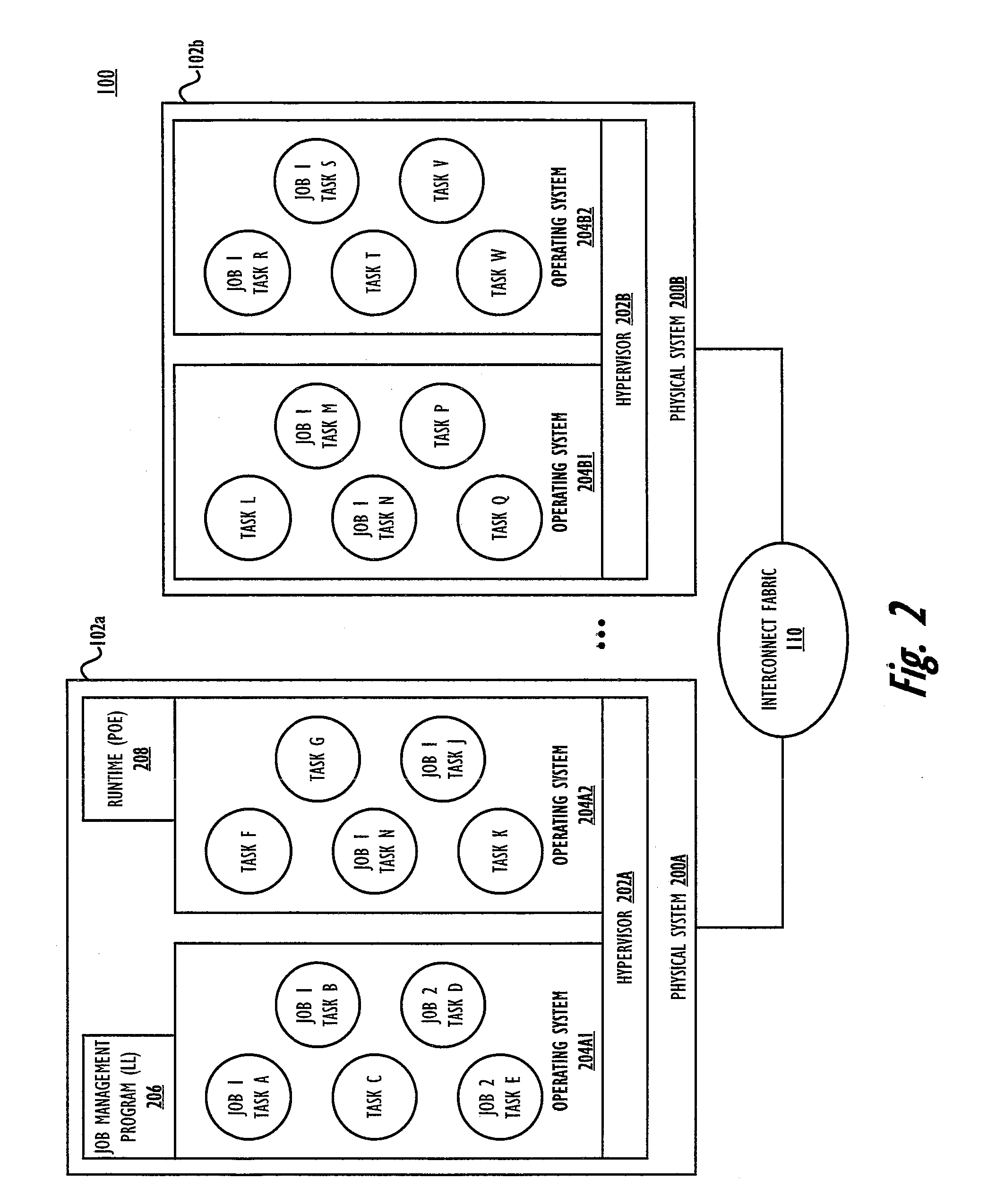

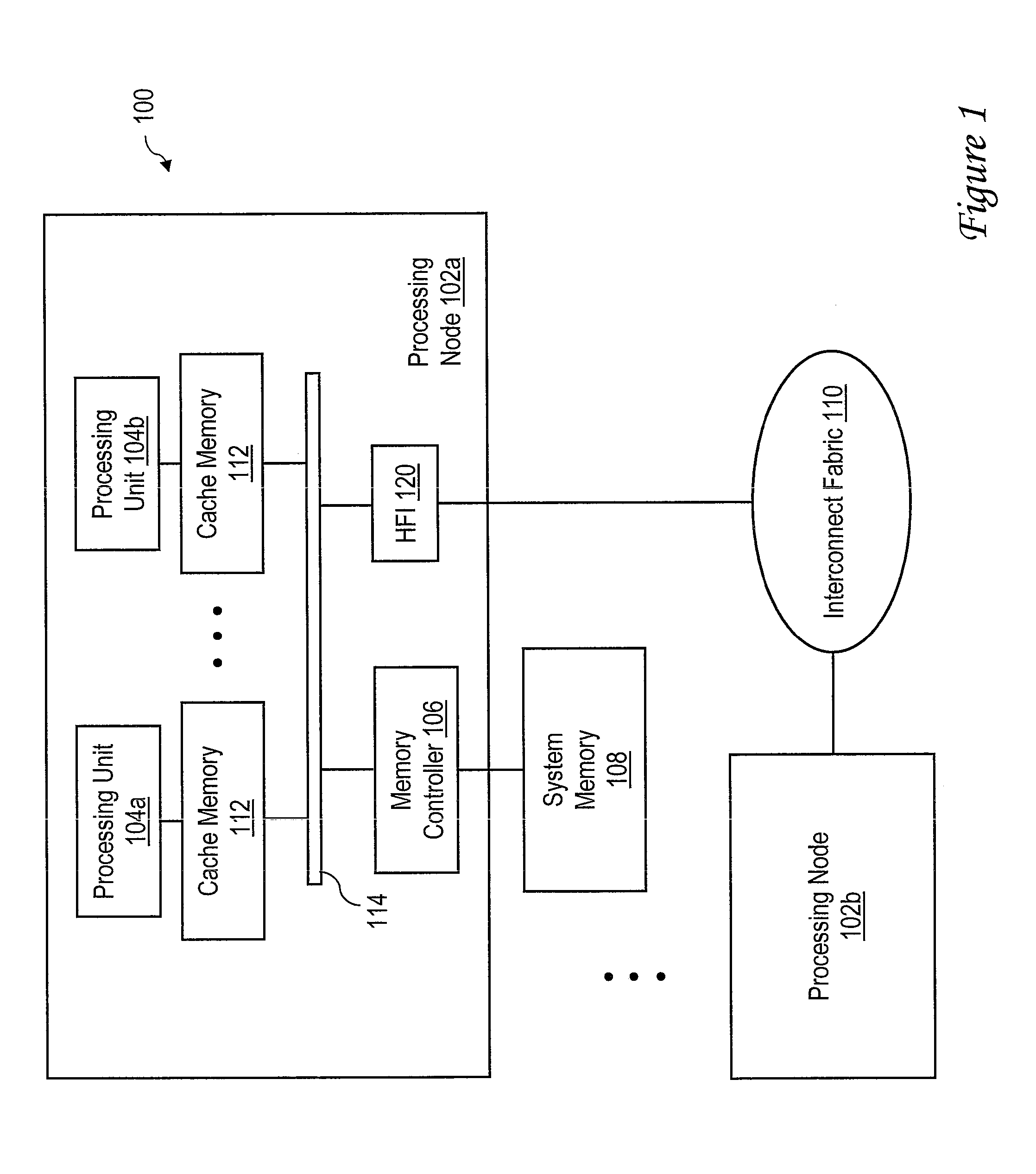

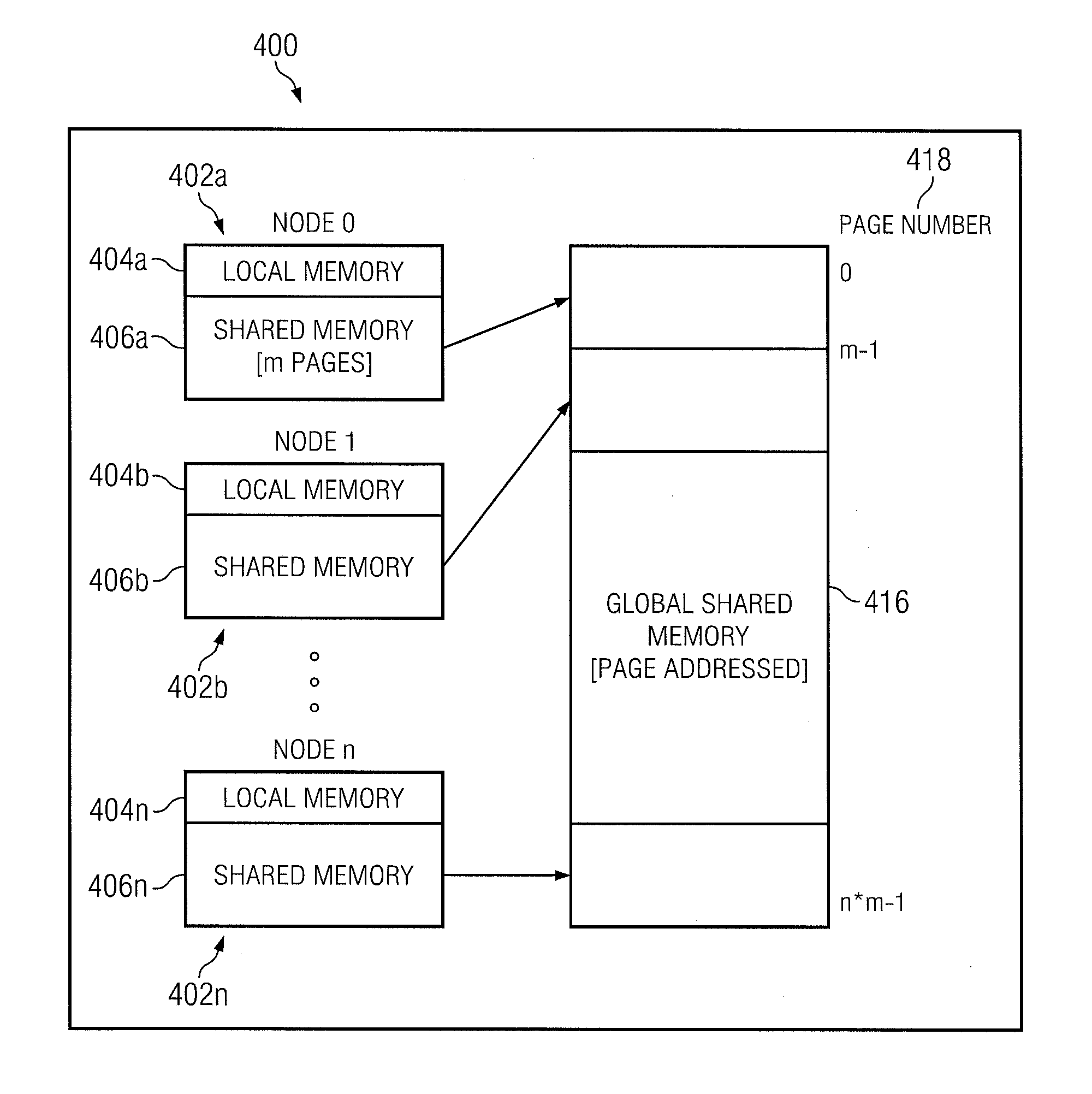

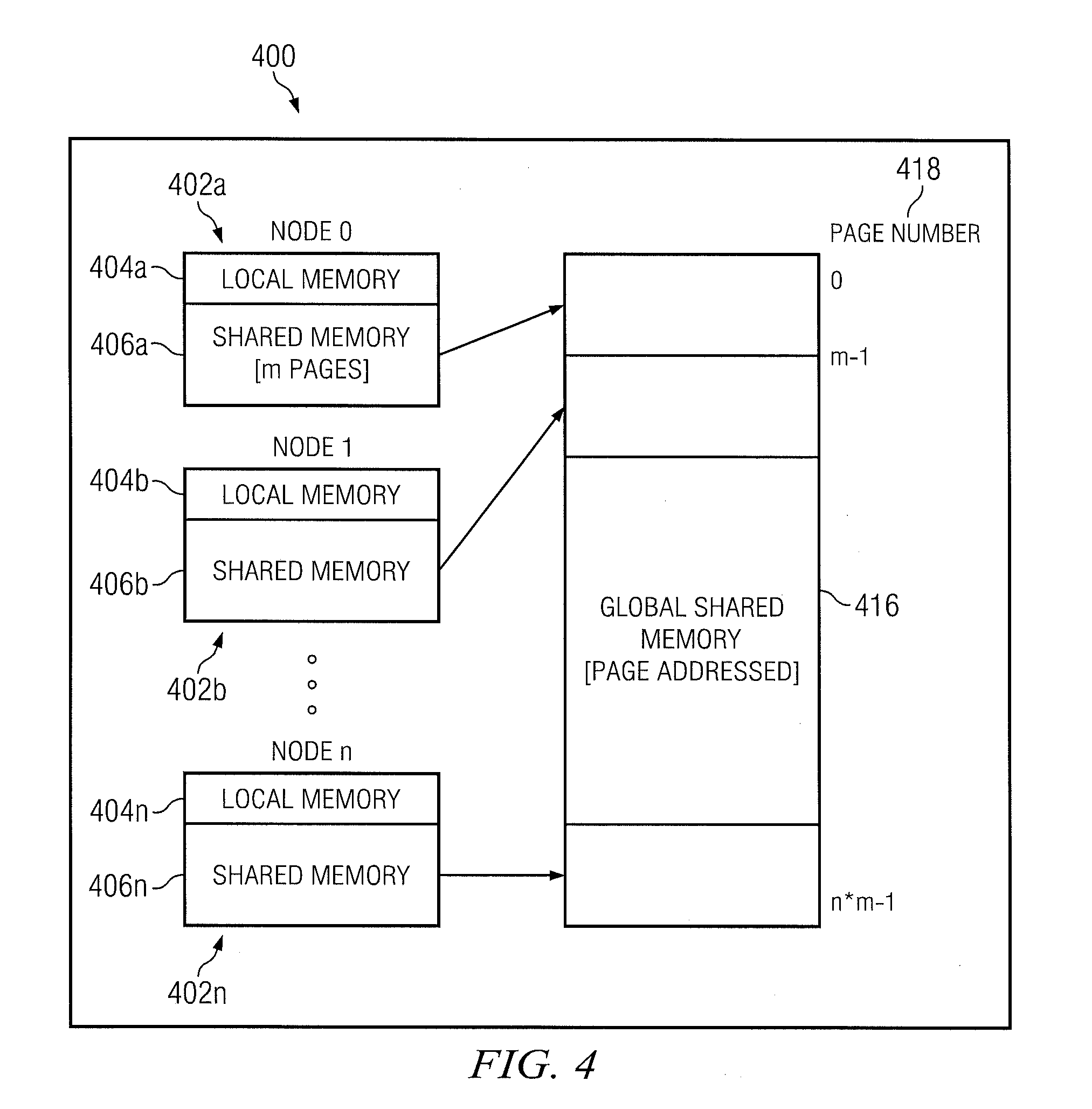

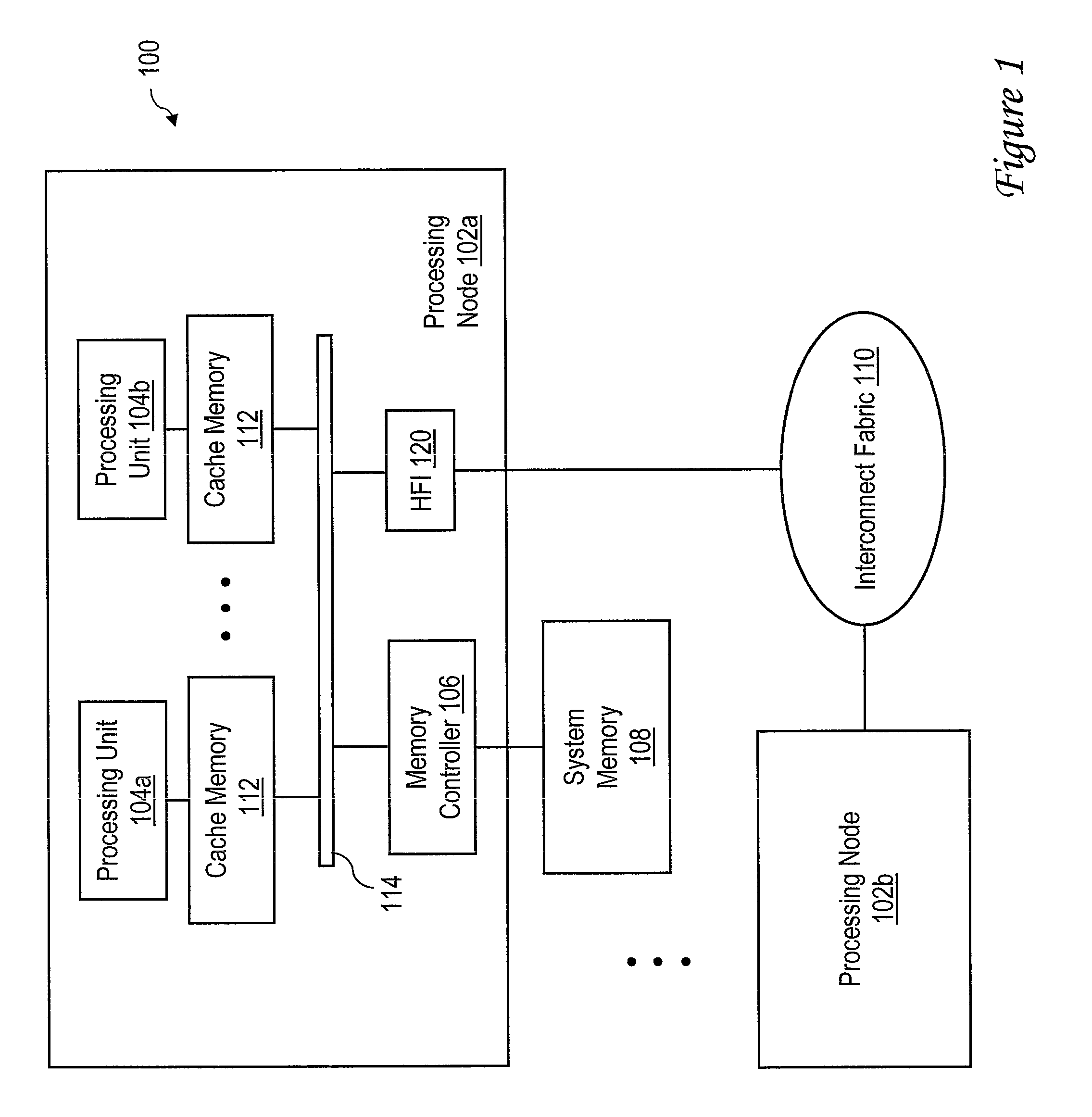

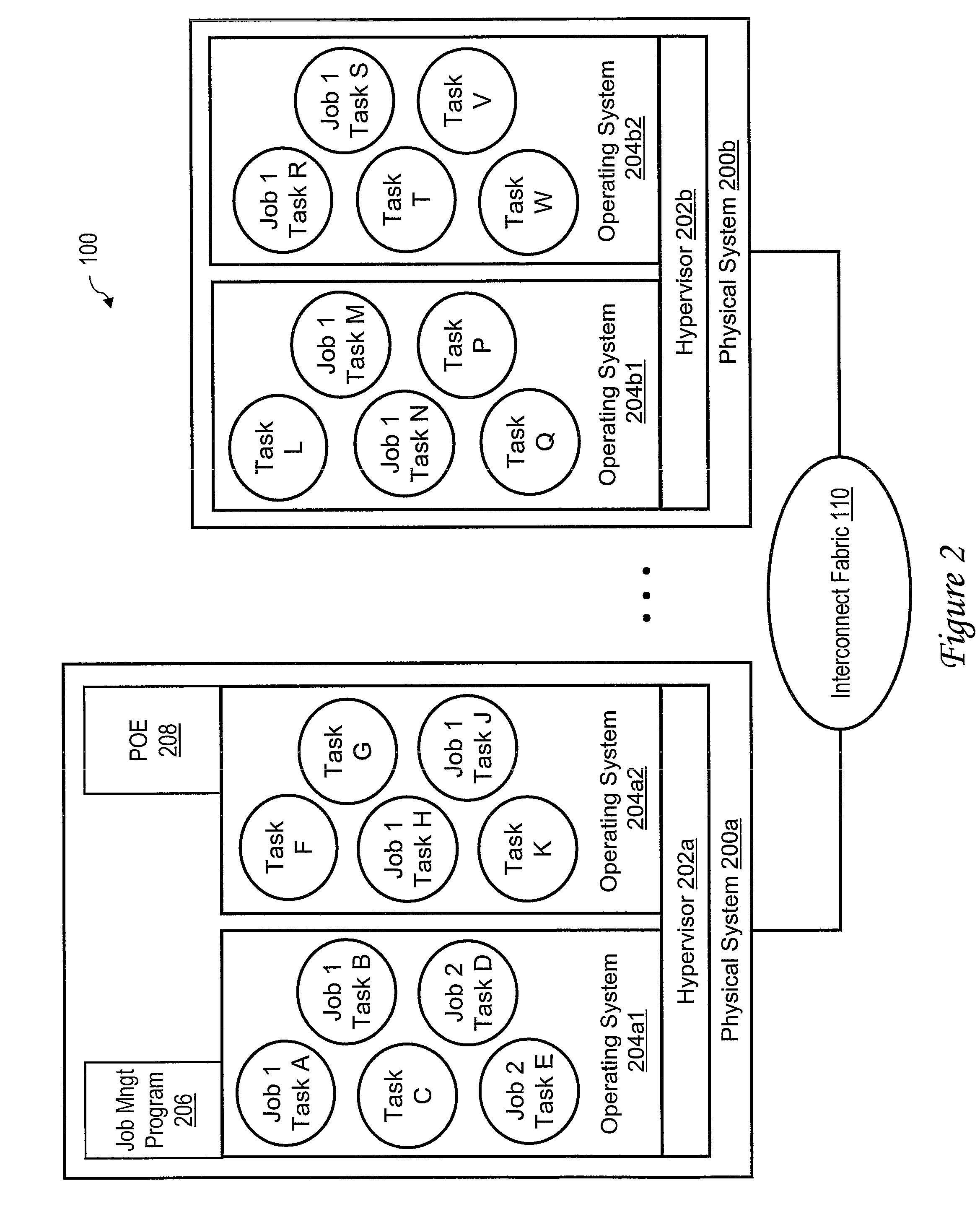

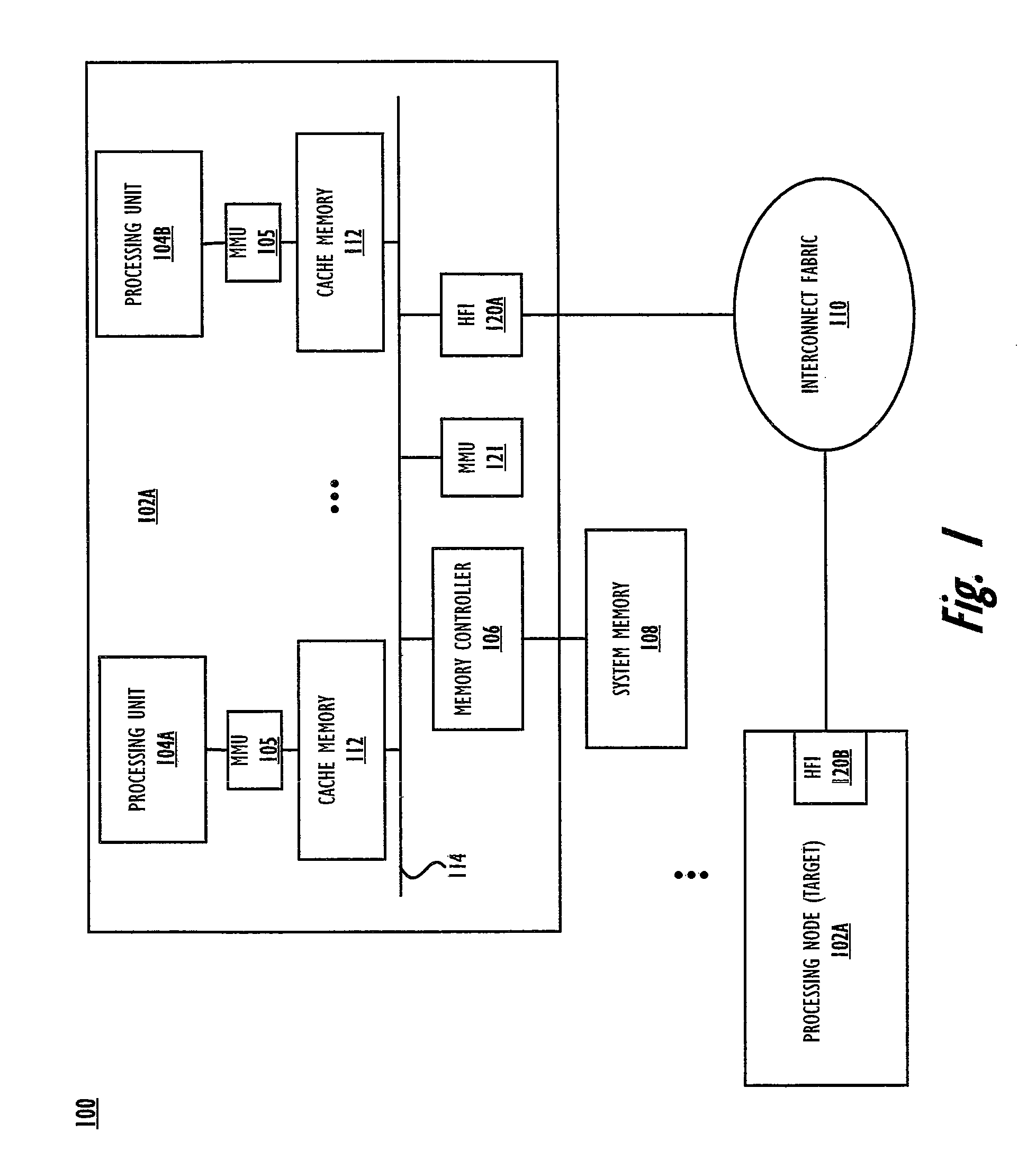

A data processing system enables global shared memory (GSM) operations across multiple nodes with a distributed EA-to-RA mapping of physical memory. Each node has a host fabric interface (HFI), which includes HFI windows that are assigned to at most one locally-executing task of a parallel job. The tasks perform parallel job execution, but map only a portion of the effective addresses (EAs) of the global address space to the local, real memory of the task's respective node. The HFI window tags all outgoing GSM operations (of the local task) with the job ID, and embeds the target node and HFI window IDs of the node at which the EA is memory mapped. The HFI window also enables processing of received GSM operations with valid EAs that are homed to the local real memory of the receiving node, while preventing processing of other received operations without a valid EA-to-RA local mapping.

Owner:IBM CORP

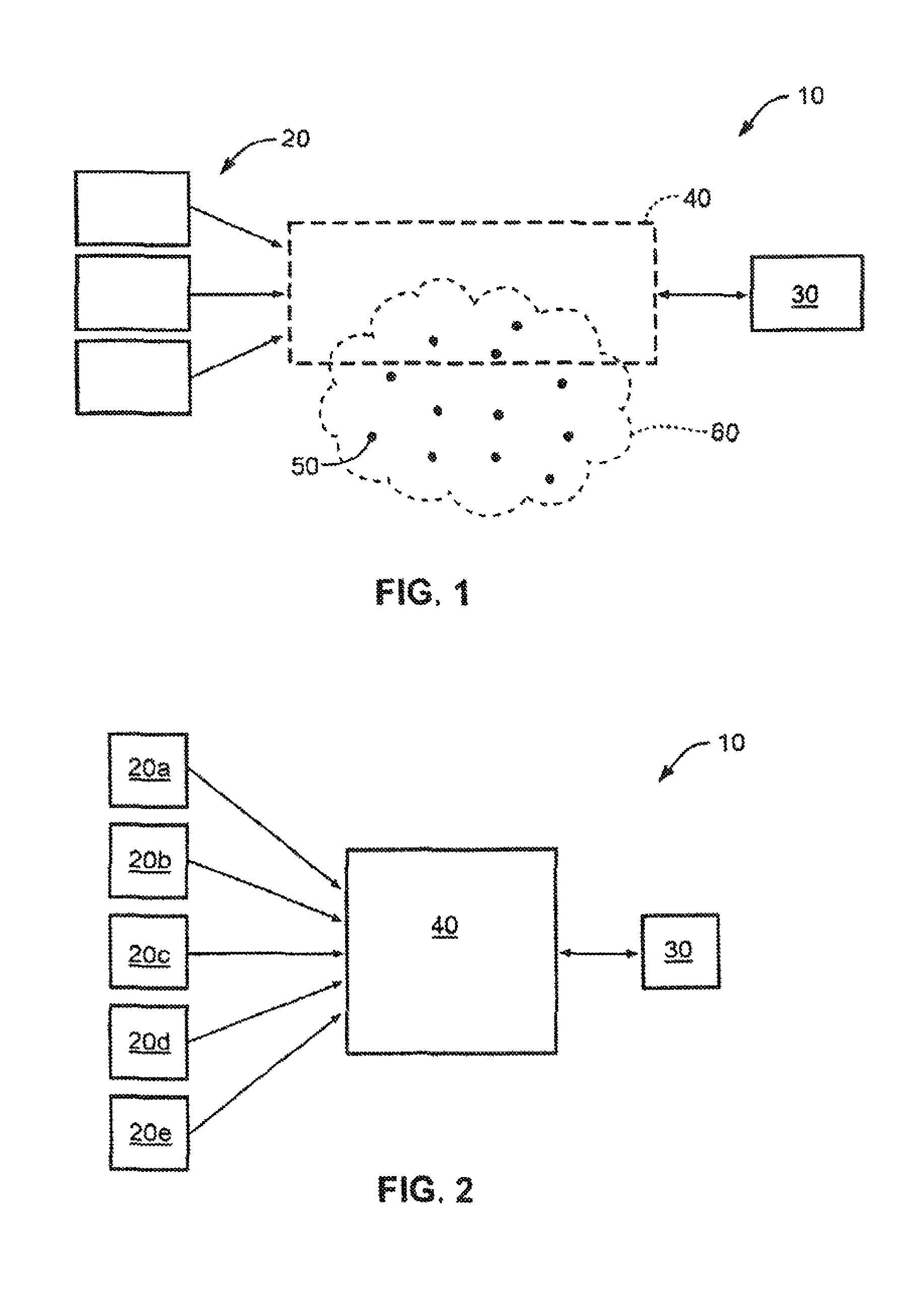

System and architecture for robust management of resources in a wide-area network

ActiveUS8572290B1Reliable actionAvoid communicationDatabase distribution/replicationMultiple digital computer combinationsGlobal address spaceArea network

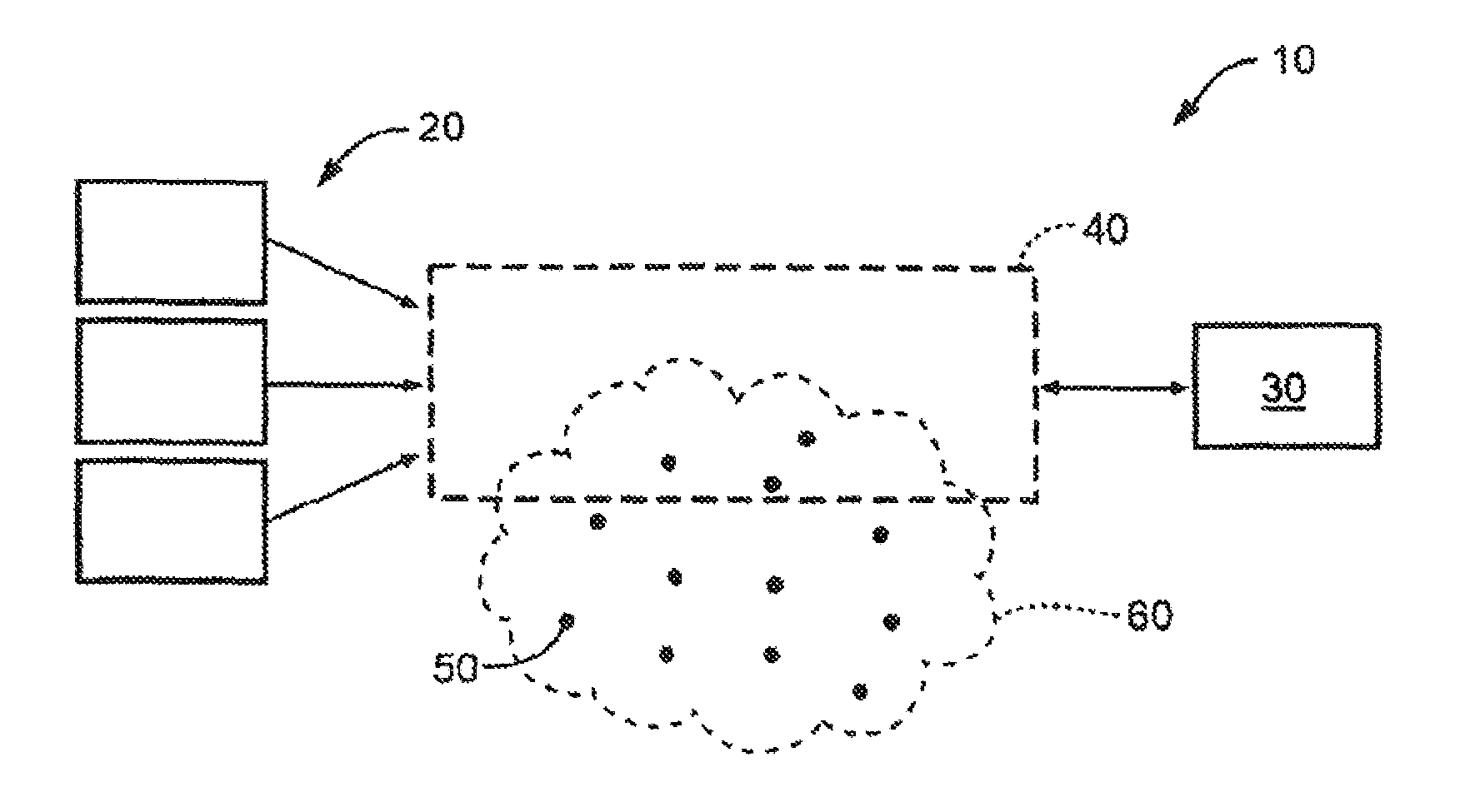

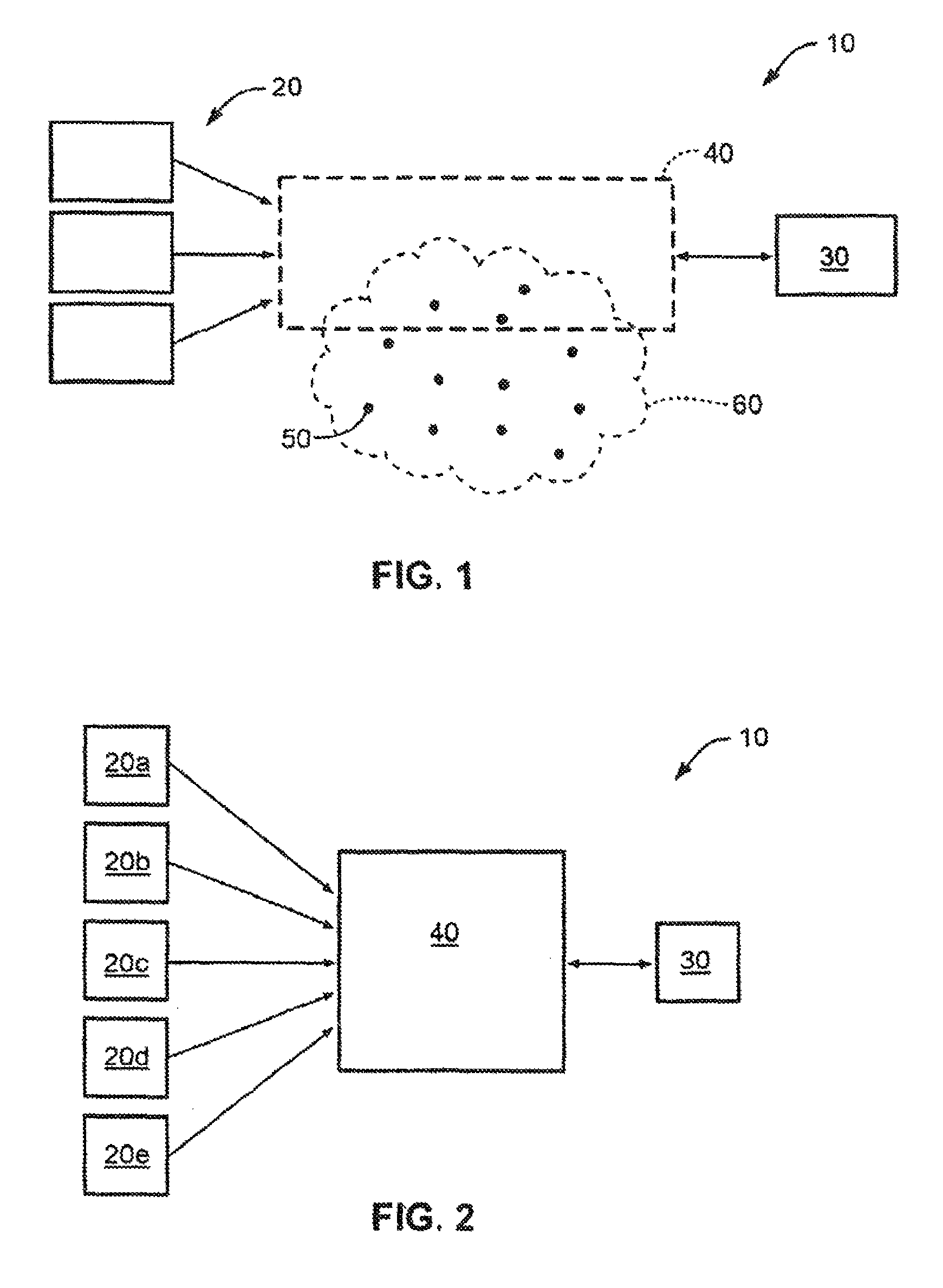

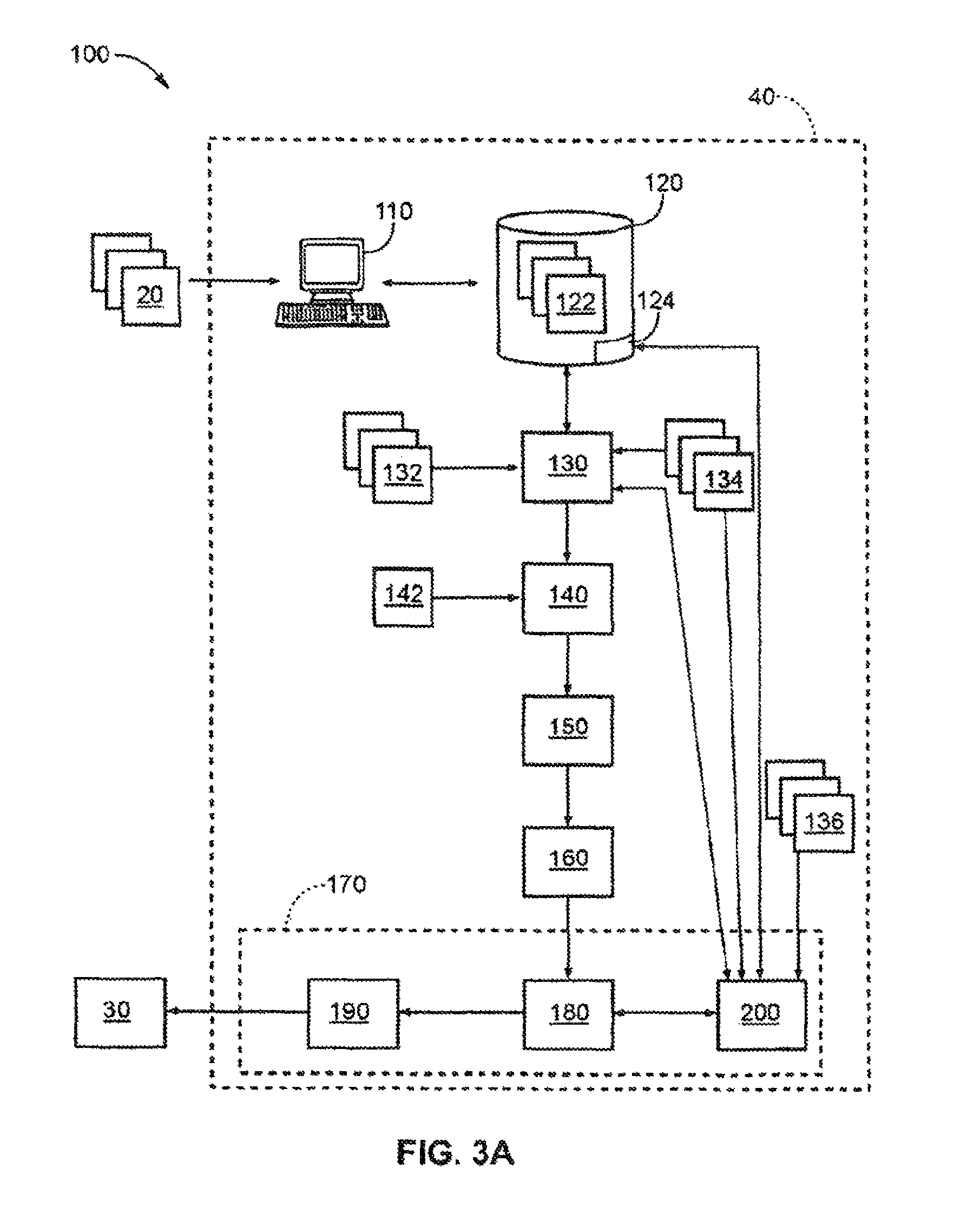

A system and method of management of communication in a potentially unreliable wide-area network that contains one or more nodes connected to said network, each potentially having access to one or more inputs and / or outputs and capable of evaluating said inputs and directing said outputs, a global address space (GAS) accessible by said nodes, and a communication system using said GAS that provides communications between said nodes.

Owner:BOARD OF SUPERVISORS OF LOUISIANA STATE UNIV & AGRI & MECHANICAL COLLEGE

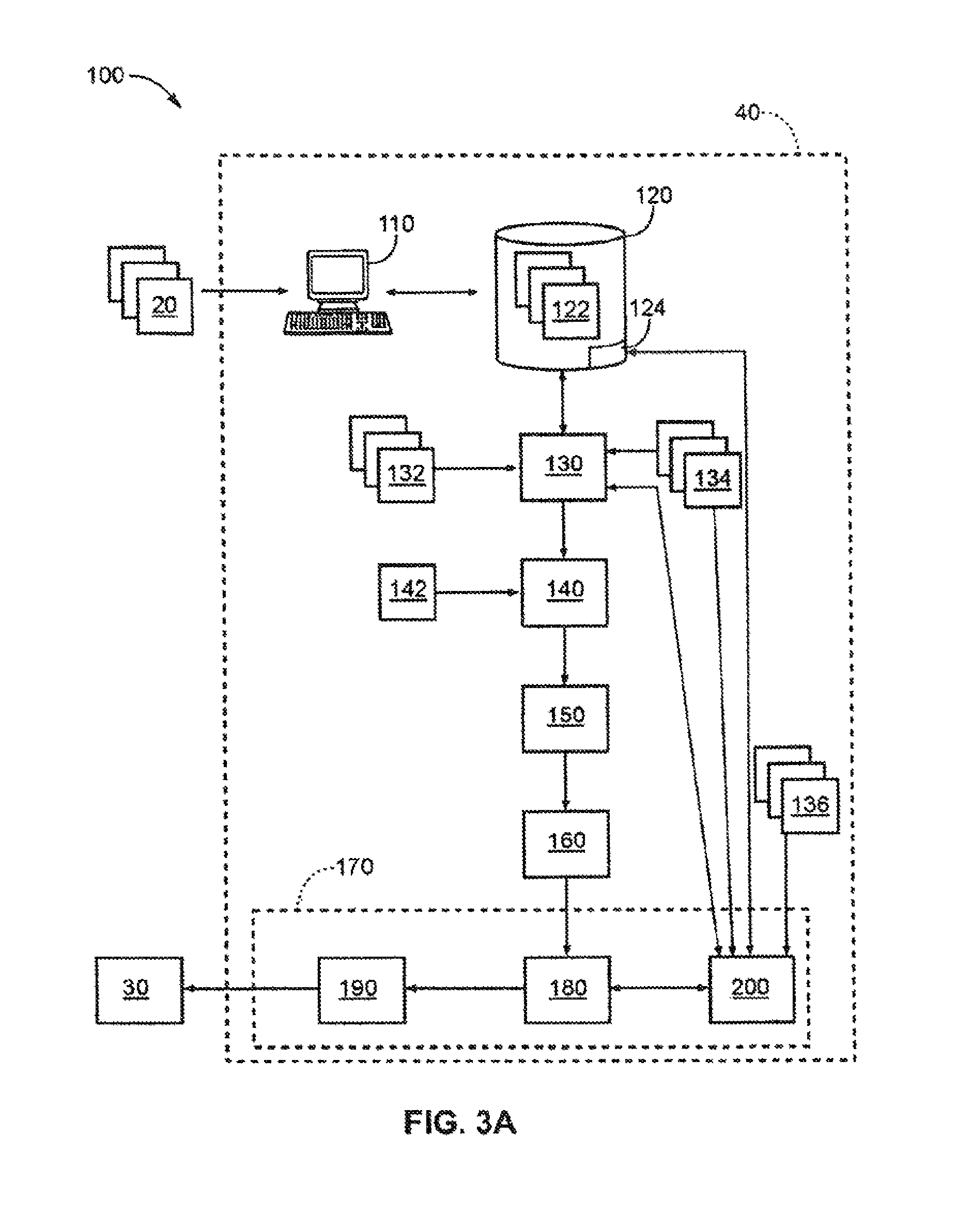

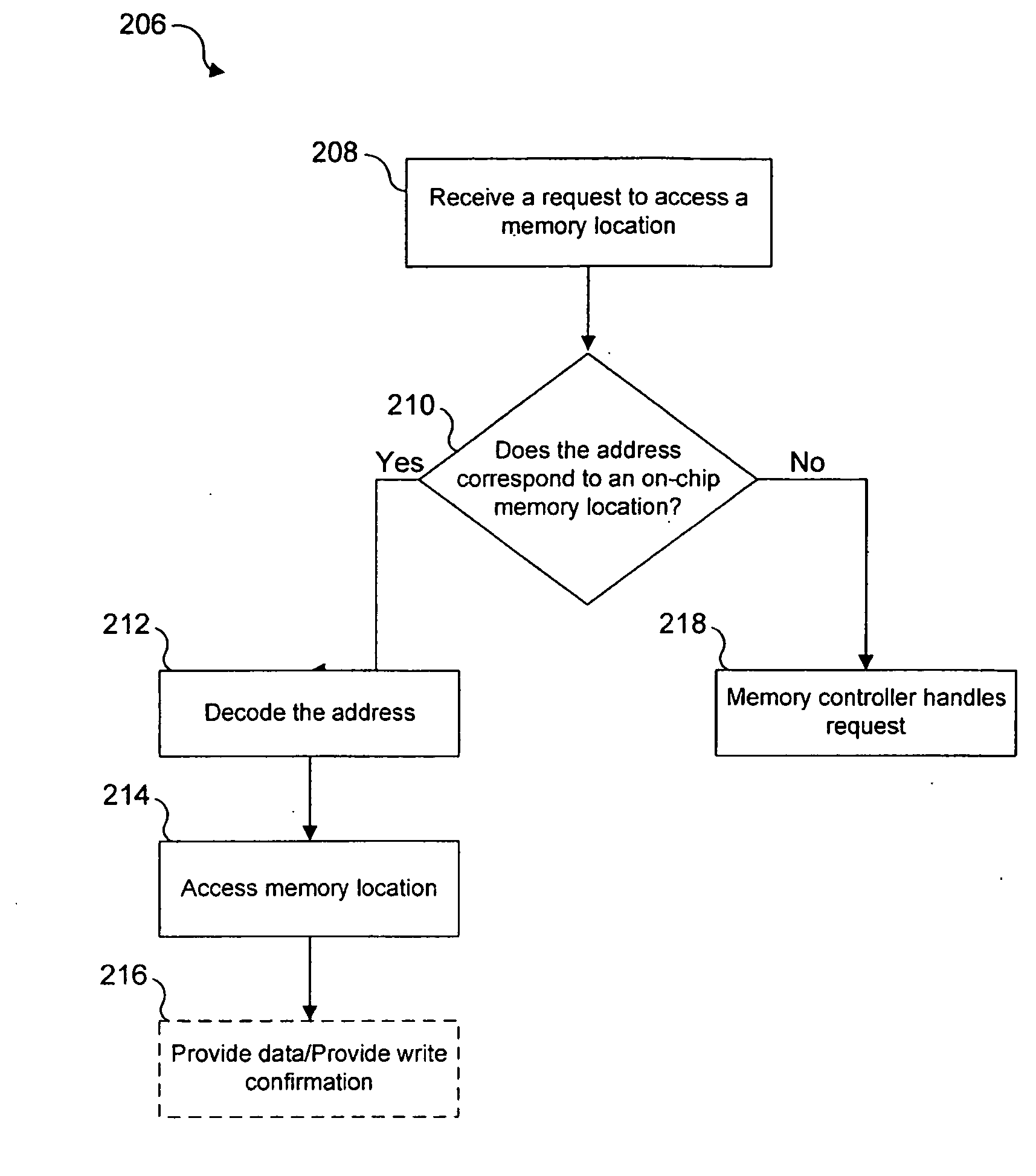

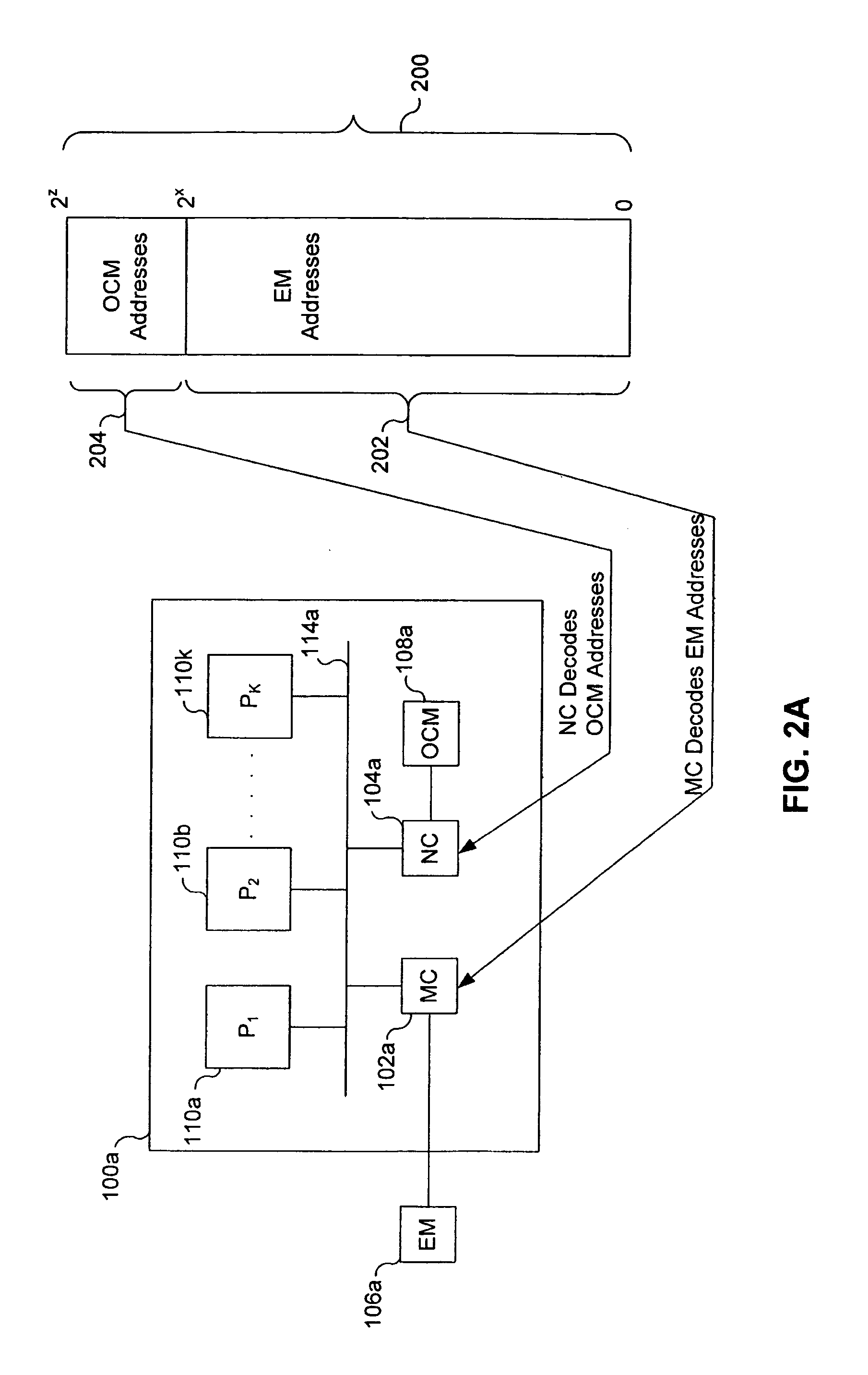

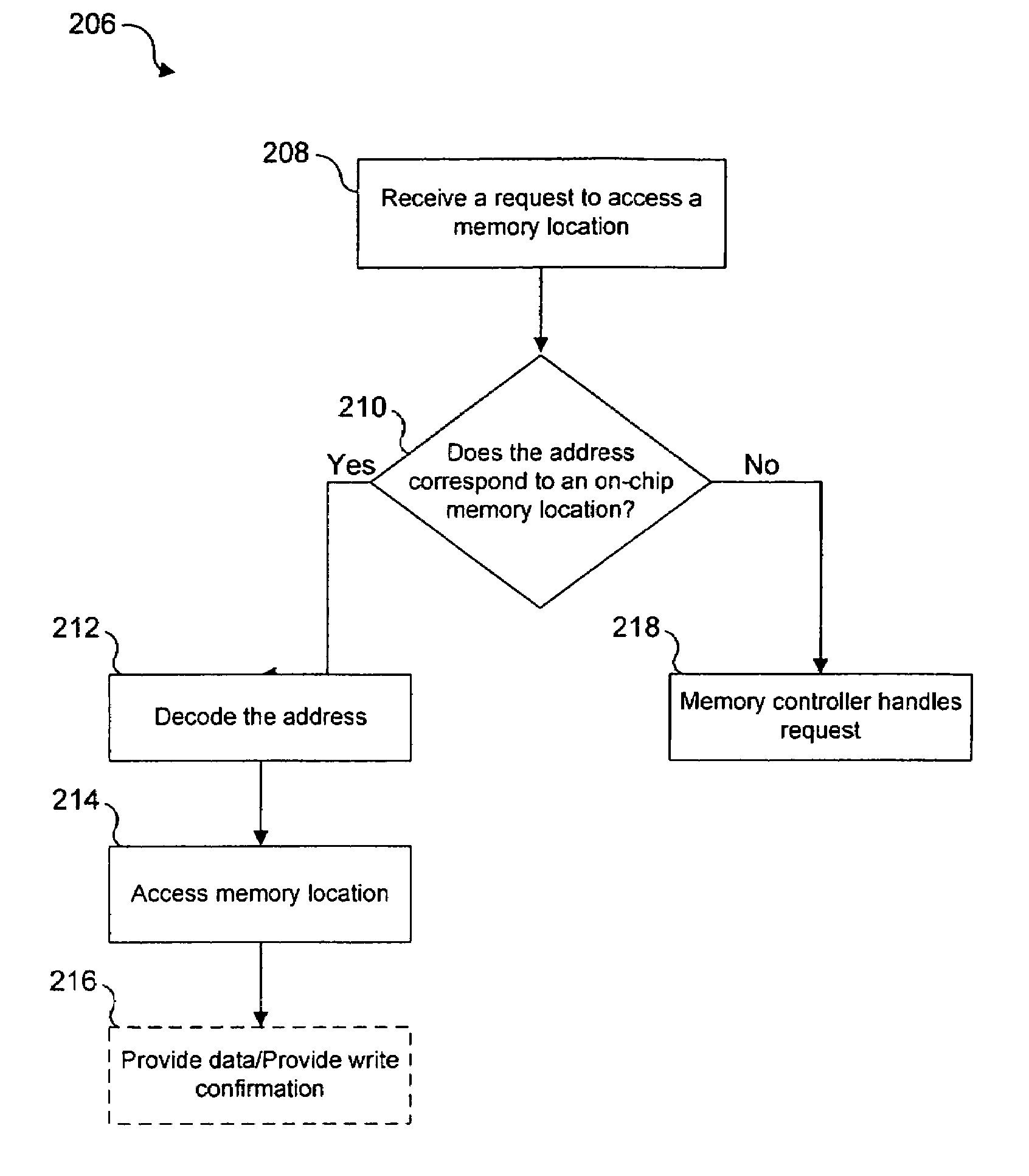

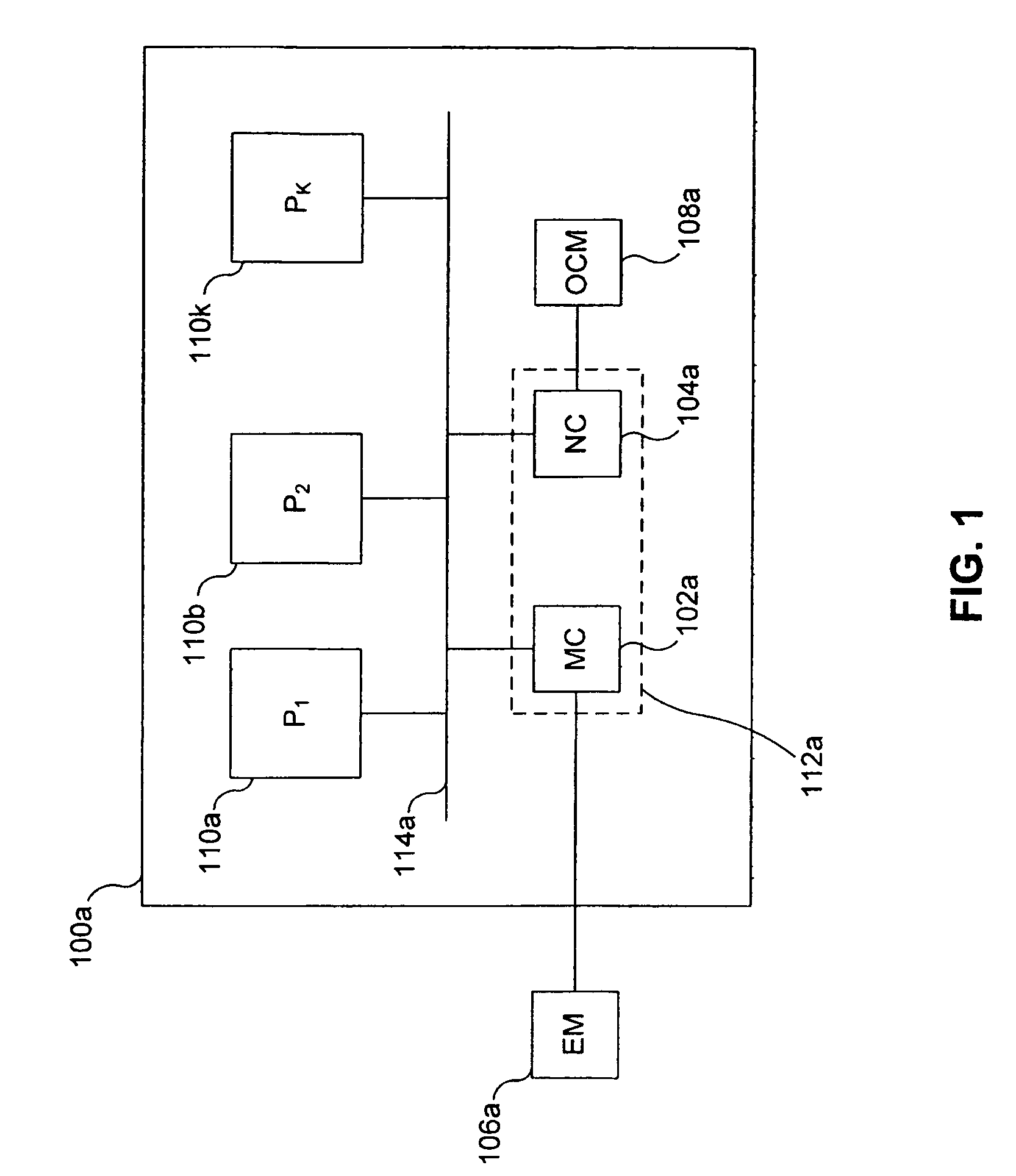

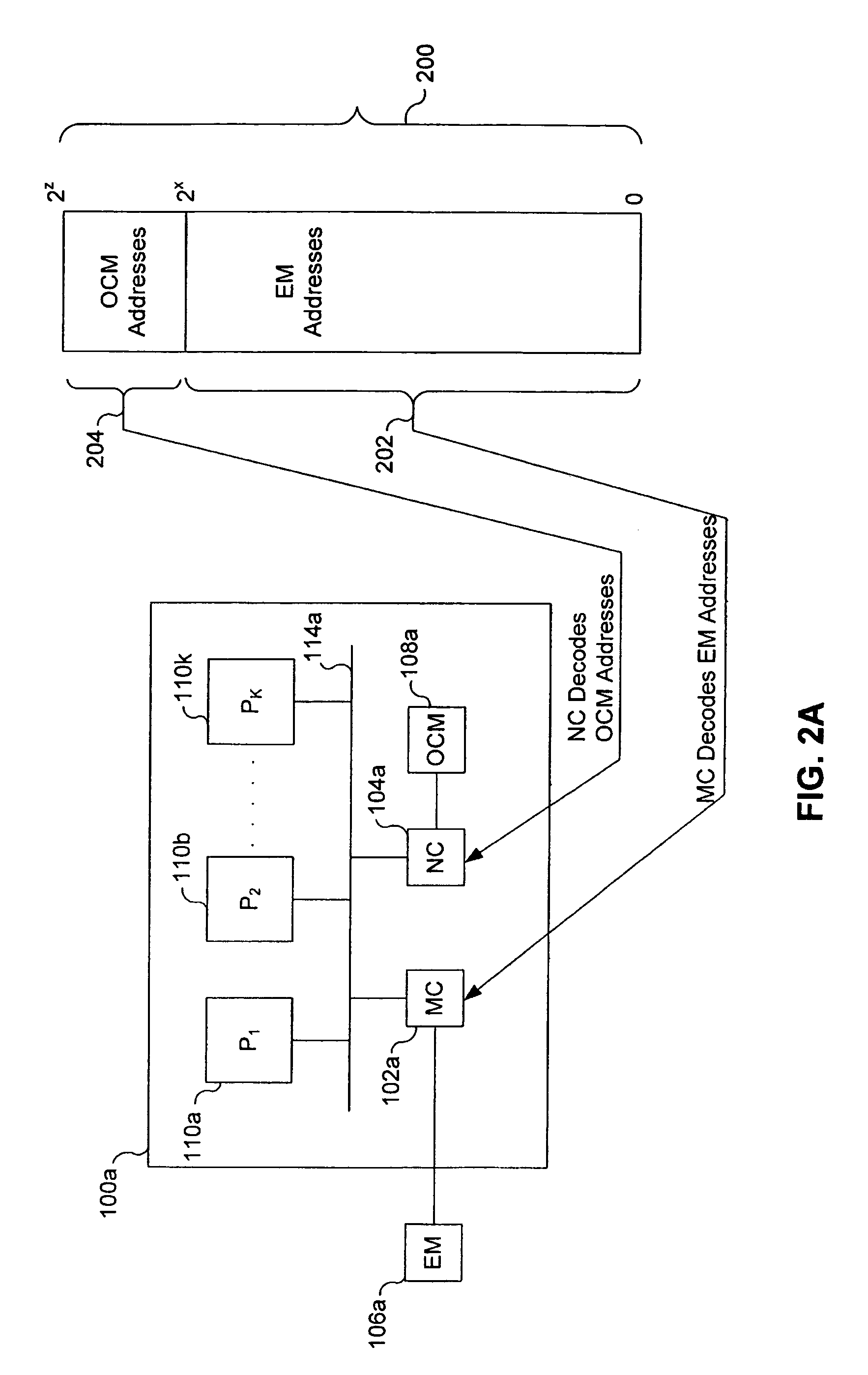

Global address space management

Methods, systems and computer program products for global address space management are described herein. A System on Chip (SOC) unit configured for a global address space is provided. The SOC includes an on-chip memory, a first controller and a second controller. The first controller is enabled to decode addresses that map to memory locations in the on-chip memory and the second controller is enabled to decode addresses that map to memory locations in an off-chip memory.

Owner:AVAGO TECH INT SALES PTE LTD

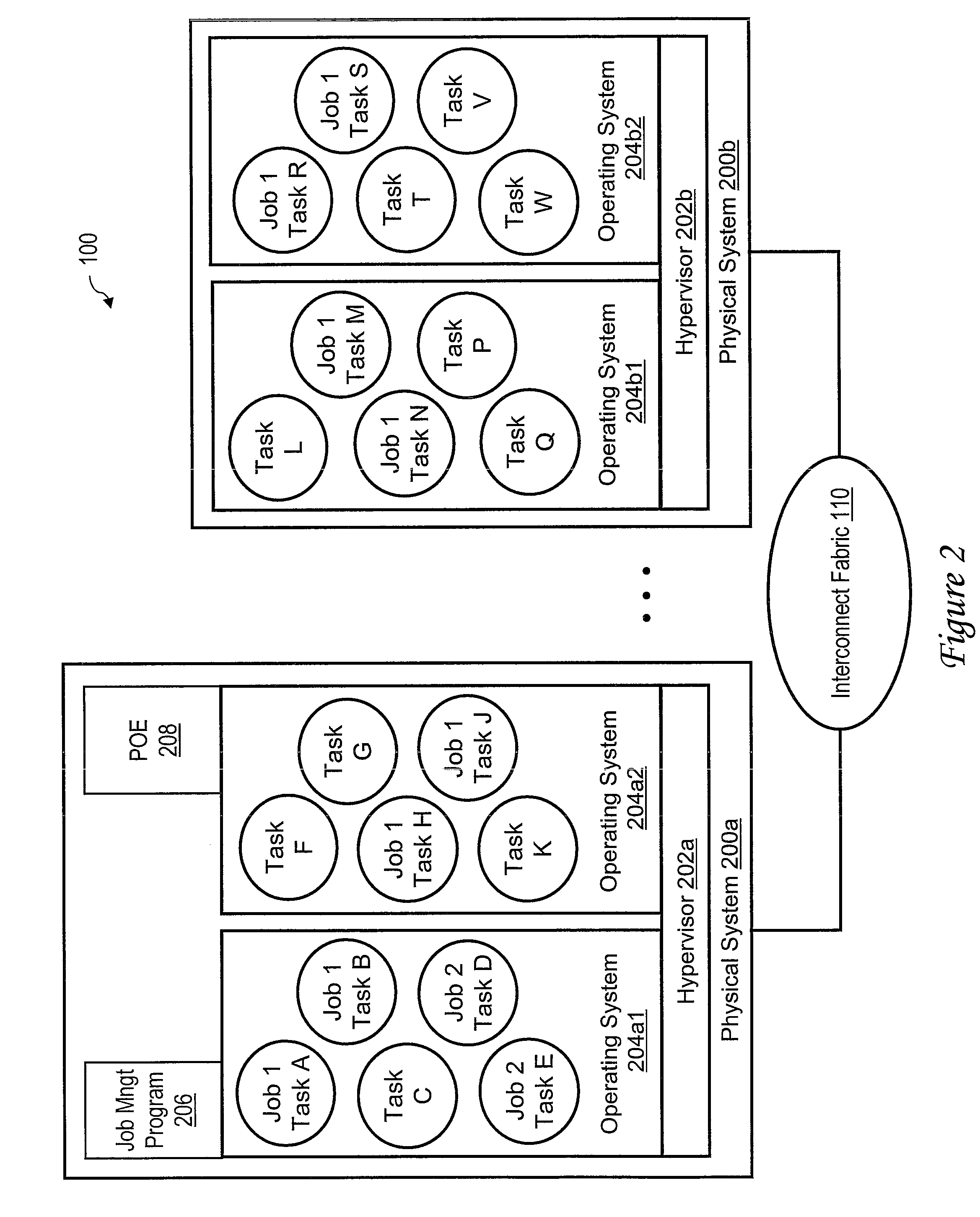

Method, System and Program Product for Reserving a Global Address Space

InactiveUS20090153897A1Memory architecture accessing/allocationProgram controlData processing systemGlobal address space

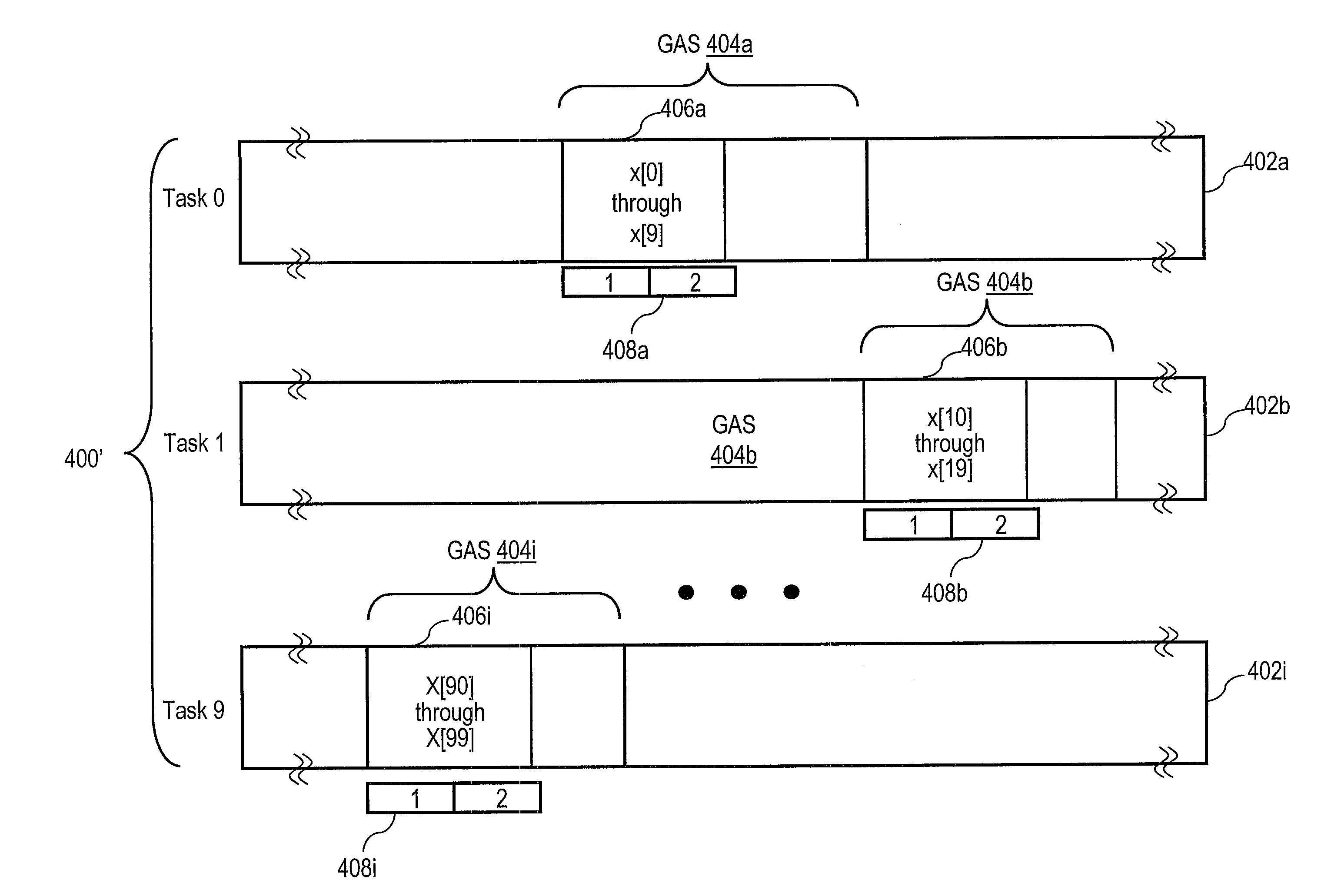

A method of operating a data processing system includes each of multiple tasks within a parallel job executing on multiple nodes of the data processing system issuing a respective system call to request reservation, without allocation of backing storage in physical memory, of a global address space defined by a range of effective addresses as global shared memory accessible to all of the multiple tasks within the parallel job. At least two of the tasks within the parallel job allocate global address spaces including a same effective address.

Owner:IBM CORP

Duplicate private address translating system and duplicate address network system

ActiveUS7047314B2Time-division multiplexData switching by path configurationGlobal address spaceRouting table

Owner:OKI ELECTRIC IND CO LTD

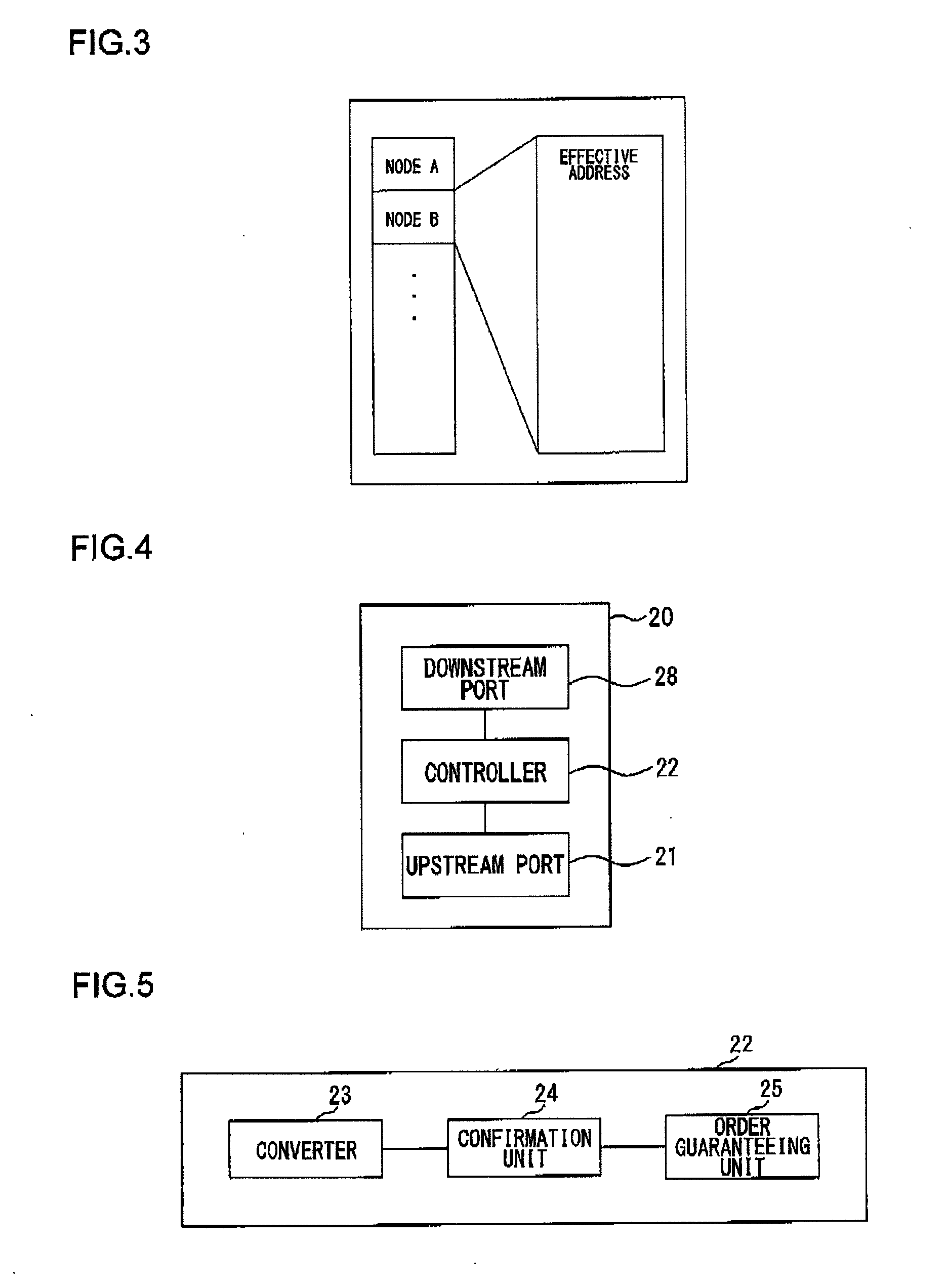

Bridge, information processing system, and access control method

InactiveUS20100070675A1Achieve transparencyData switching networksMemory systemsInformation processingGlobal address space

Owner:SONY COMPUTER ENTERTAINMENT INC +1

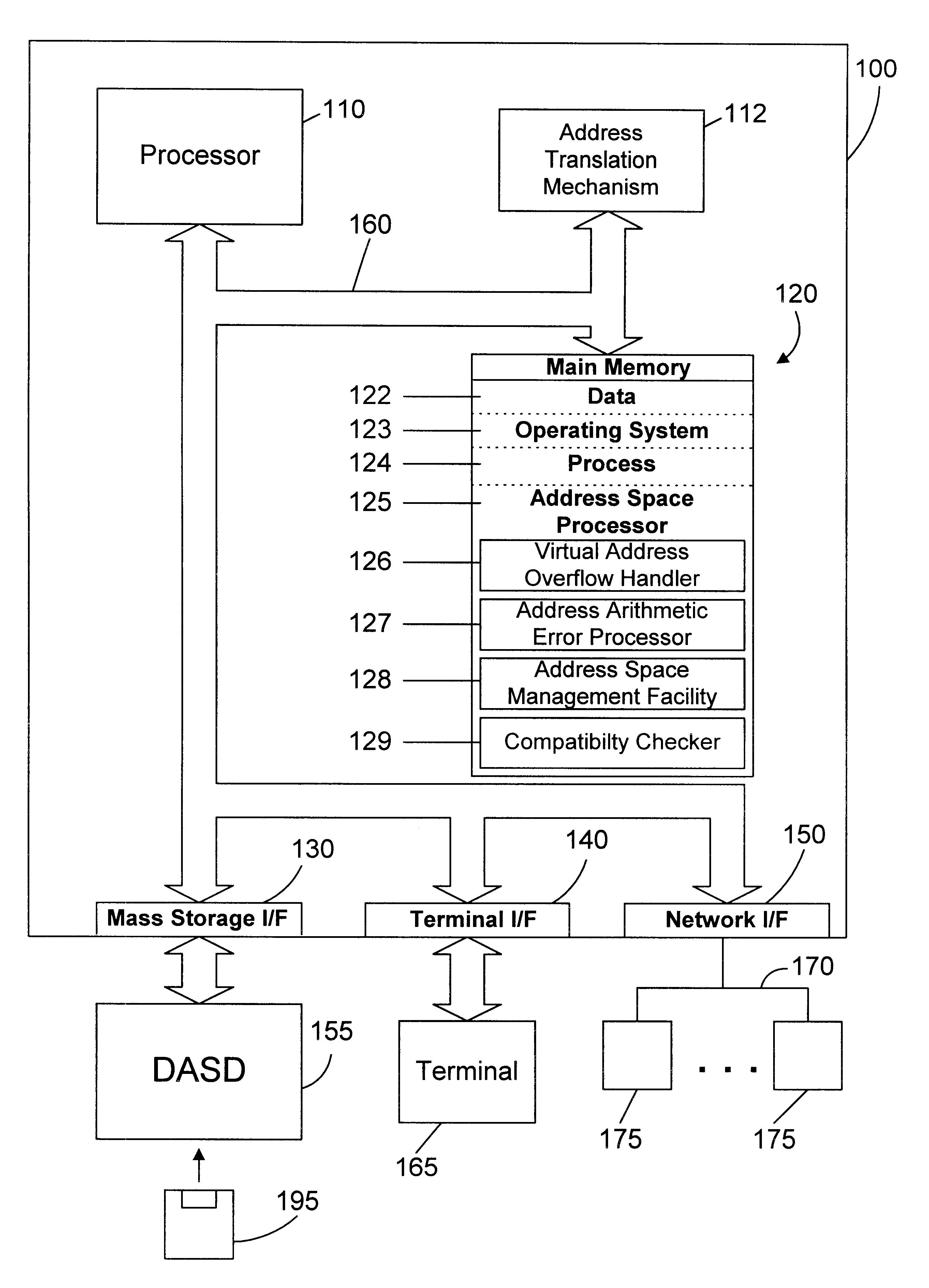

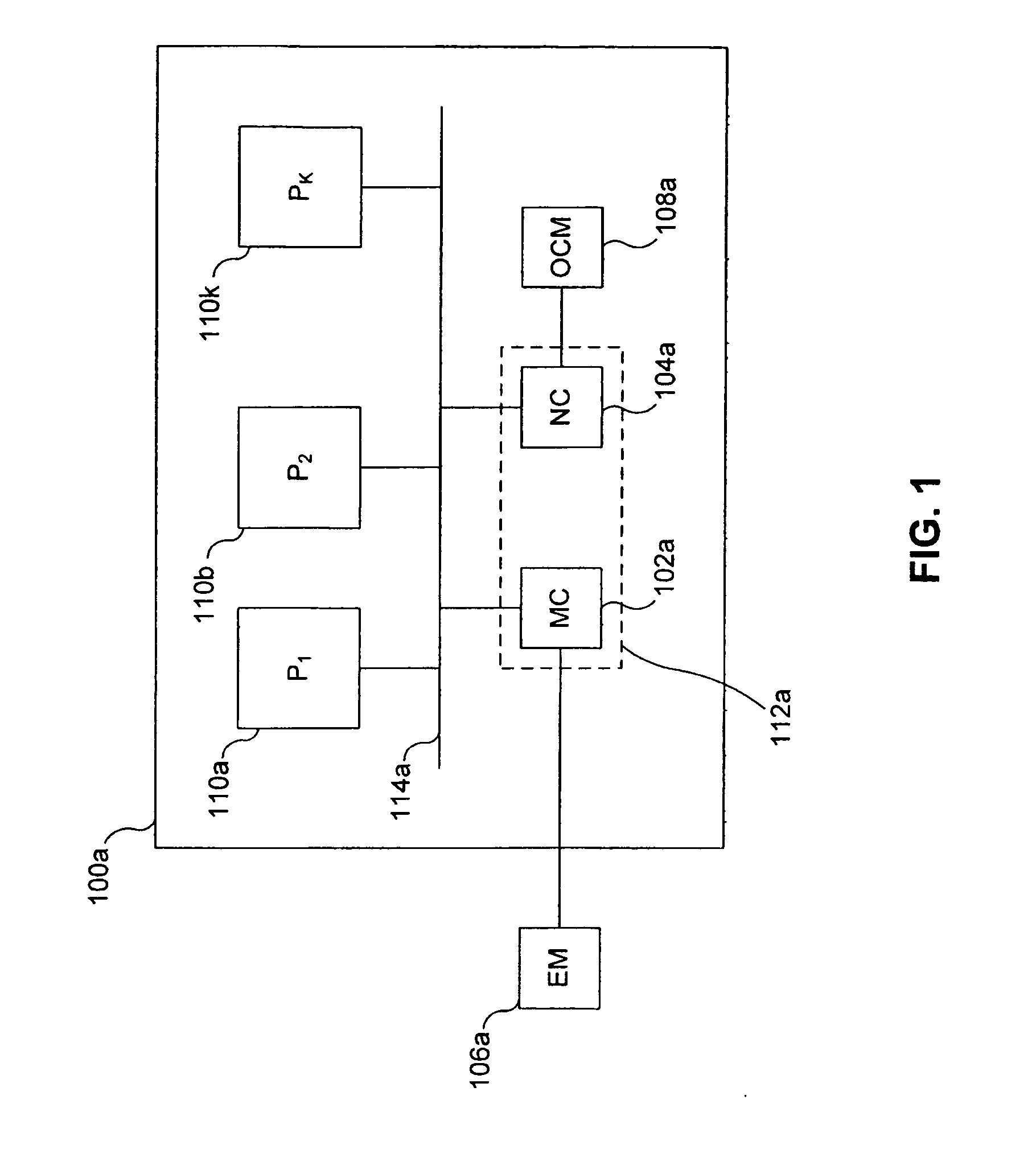

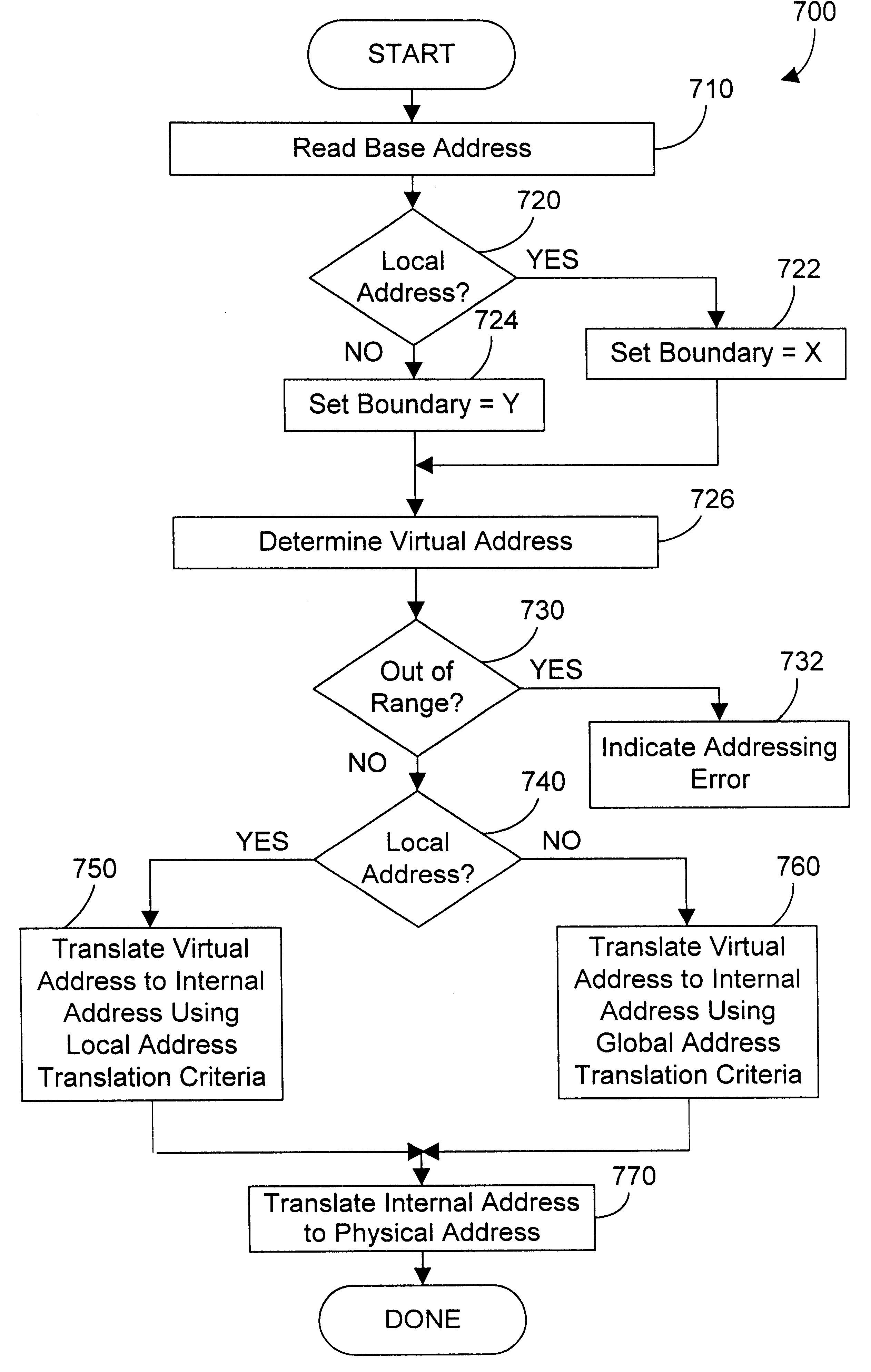

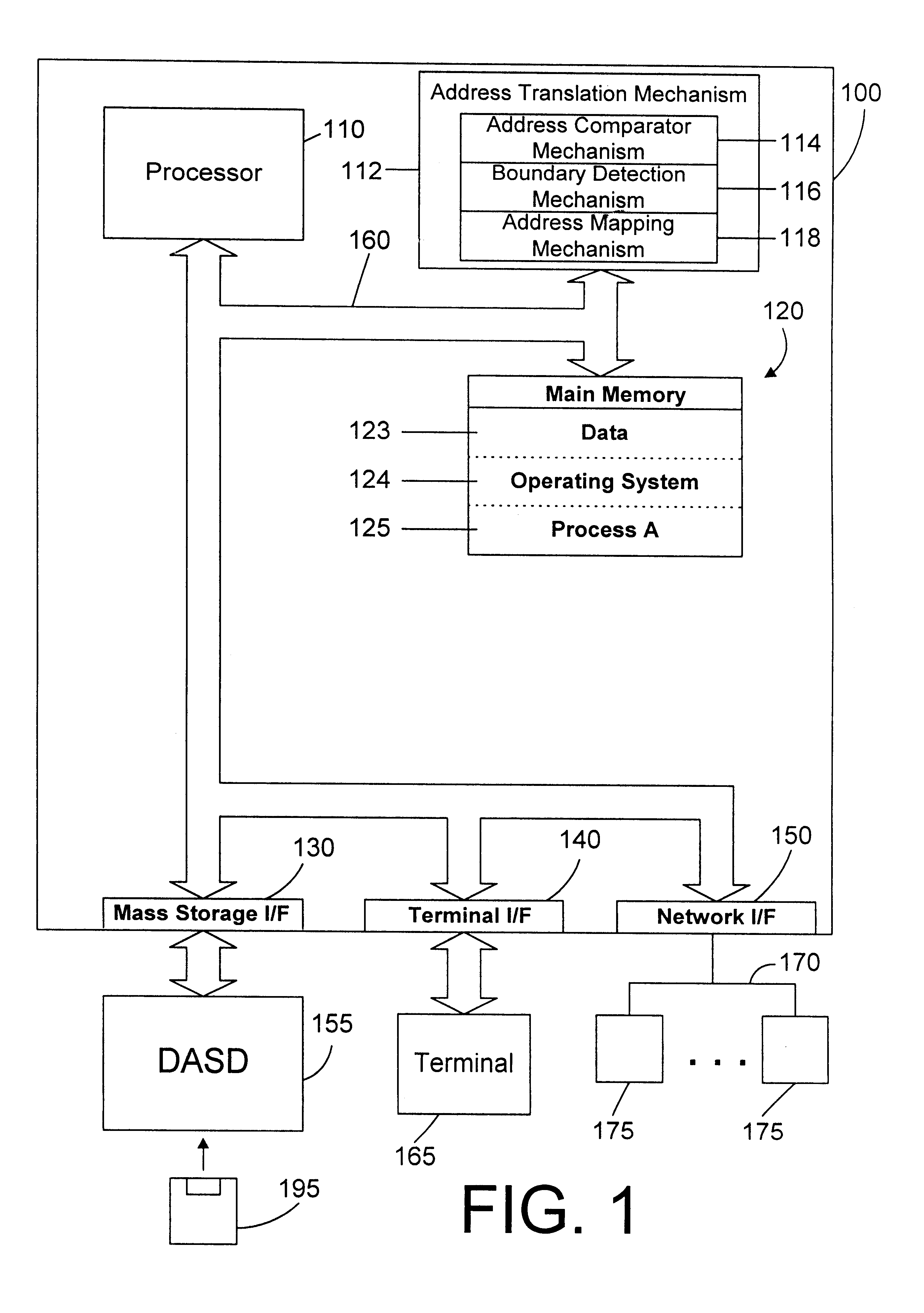

Apparatus and method for providing simultaneous local and global addressing with hardware address translation

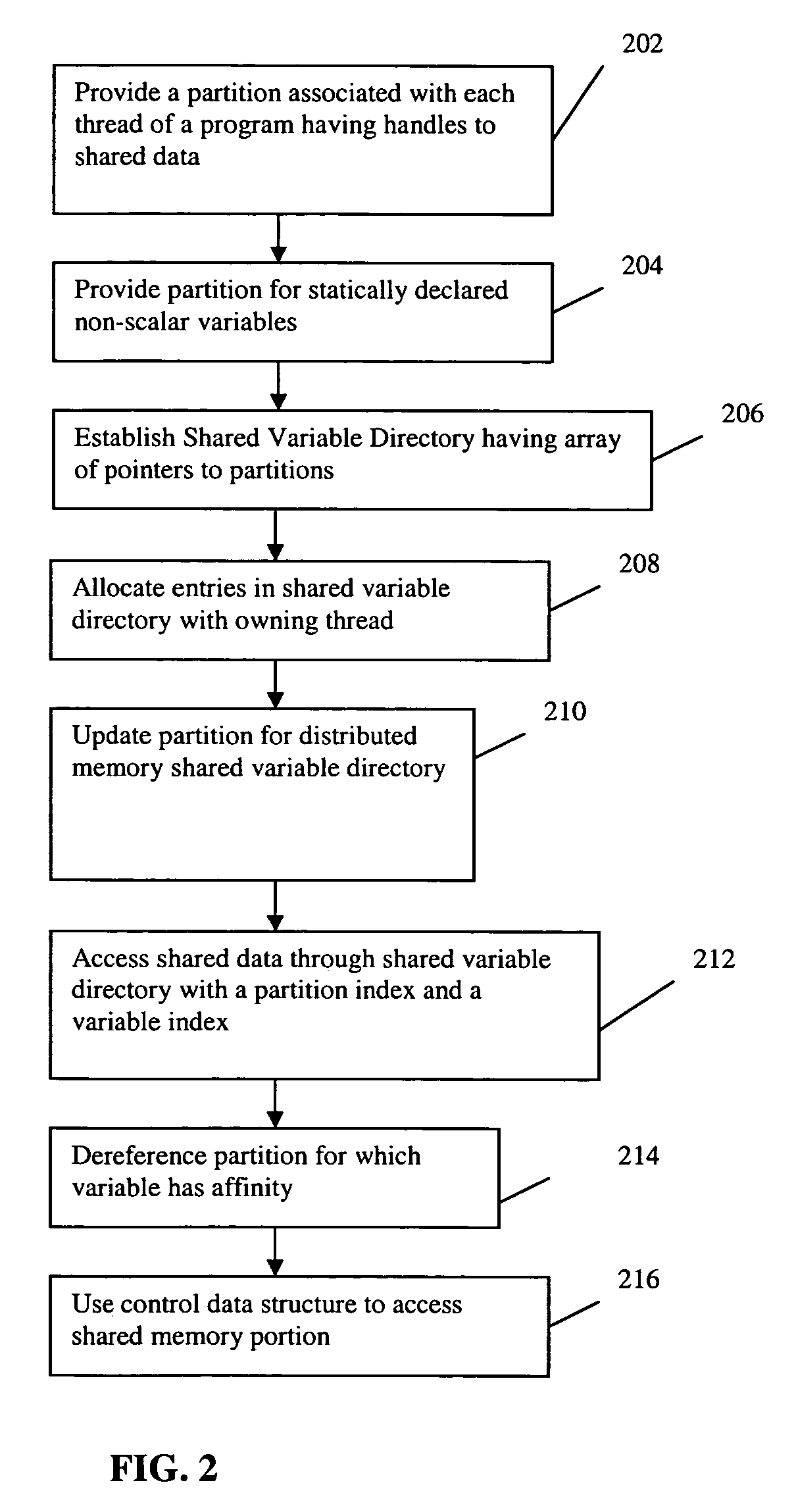

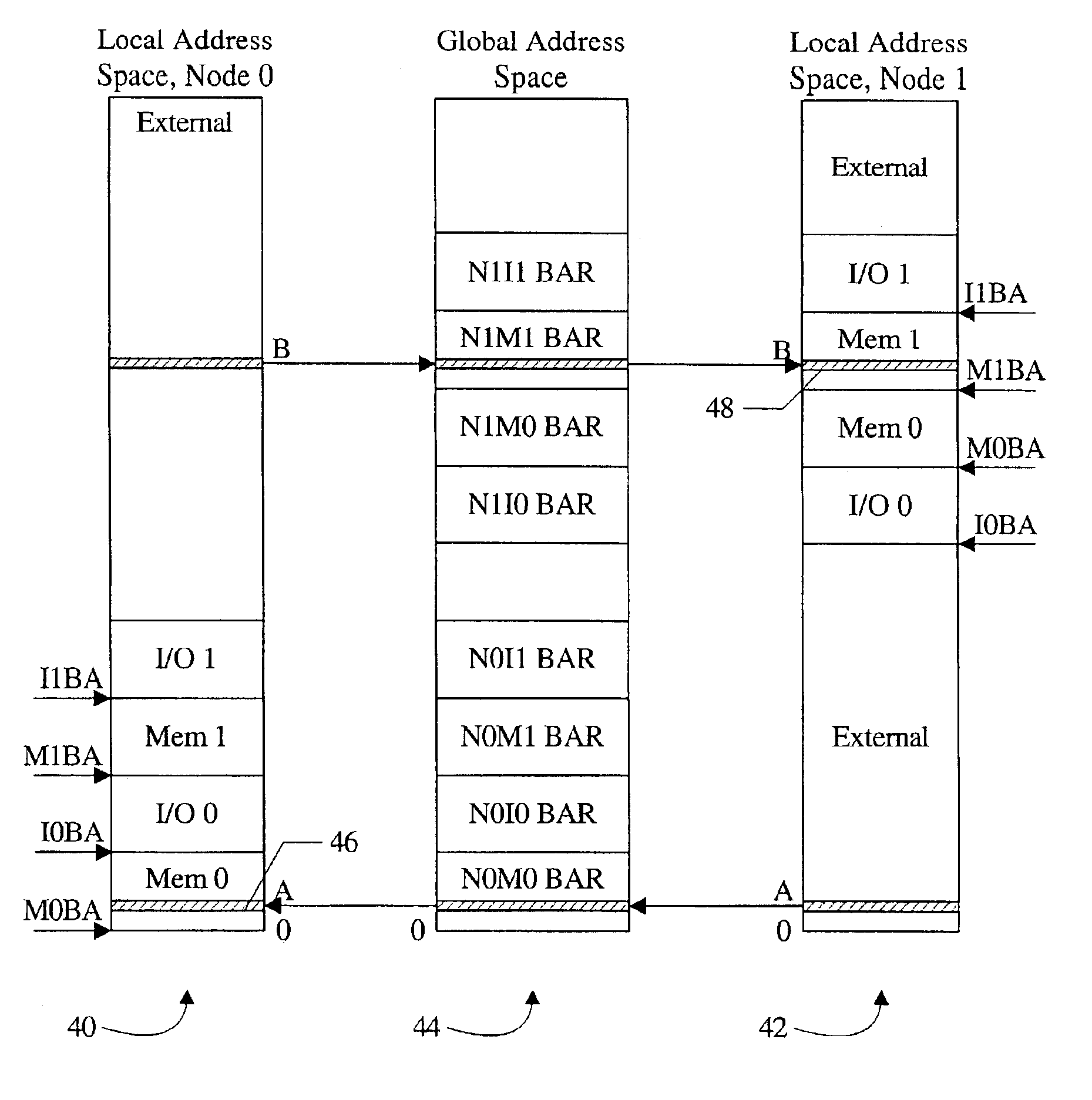

InactiveUS6738889B2Good flexibilityMemory adressing/allocation/relocationDigital computer detailsGlobal address spaceParallel computing

An apparatus and method provide simultaneous local and global addressing capabilities. A global address space is defined that may be accessed by all processes. In addition, each process has a local address space that is local (and therefore available) only to that process. An address translation mechanism is implemented, preferably in hardware, to compare an address to defined addresses for local and global addressing and to detect when a virtual address computation result would go outside a boundary for the appropriate addressing scheme. The address translation mechanism maps a virtual address to a corresponding physical address, and uses different criteria depending on whether the address is local or global. The address translation mechanism allows an instruction to operate on both local and global addresses by determining at run-time which address space is referenced, and by performing the necessary translation and boundary checking for either global or local address space, whichever is accessed by the instruction. By providing both global and local addressing for the same instructions, the apparatus and method of the present invention provide great flexibility in addressing, allowing a computer program to benefit from the advantages of both addressing modes.

Owner:GOOGLE LLC

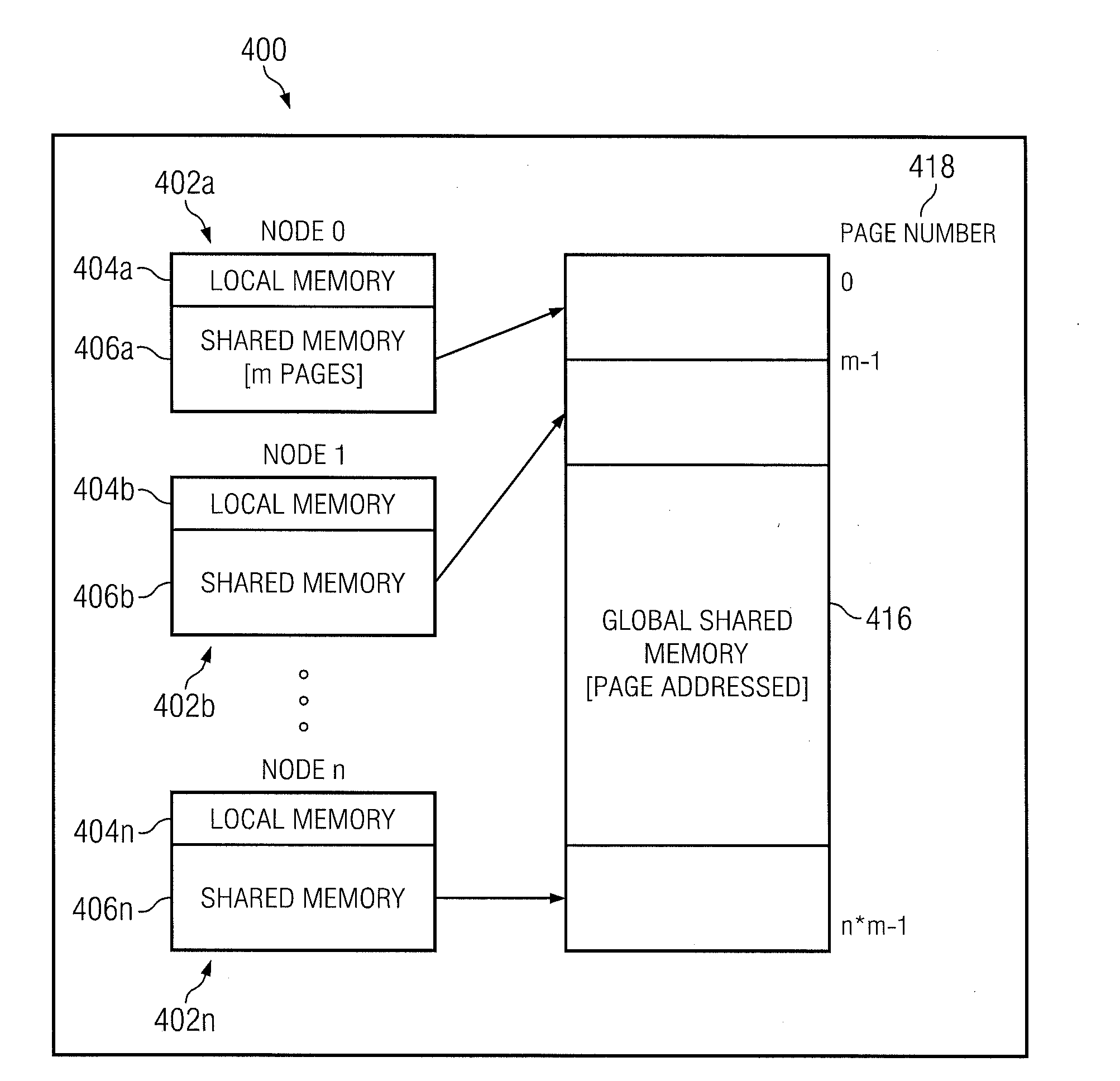

Method, System and Program Product for Allocating a Global Shared Memory

ActiveUS20090157996A1Memory architecture accessing/allocationMemory adressing/allocation/relocationData processing systemGlobal address space

A method of operating a data processing system includes each of multiple tasks within a parallel job executing on multiple nodes of the data processing system issuing a system call to request allocation of backing storage in physical memory for global shared memory accessible to all of the multiple tasks within the parallel job, where the global shared memory is in a global address space defined by a range of effective addresses. Each task among the multiple tasks receives an indication that the allocation requested by the system call was successful only if the global address space for that task was previously reserved and backing storage for the global shared memory has not already been allocated.

Owner:IBM CORP

Scalable runtime system for global address space languages on shared and distributed memory machines

ActiveUS7380086B2Improve scalabilityResource allocationSpecific program execution arrangementsGlobal address spaceDistributed memory

An improved scalability runtime system for a global address space language running on a distributed or shared memory machine uses a directory of shared variables having a data structure for tracking shared variable information that is shared by a plurality of program threads. Allocation and de-allocation routines are used to allocate and de-allocate shared variable entries in the directory of shared variables. Different routines can be used to access different types of shared data. A control structure is used to control access to the shared data such that all threads can access the data at any time. Since all threads see the same objects, synchronization issues are eliminated. In addition, the improved efficiency of the data sharing allows the number of program threads to be vastly increased.

Owner:DAEDALUS BLUE LLC

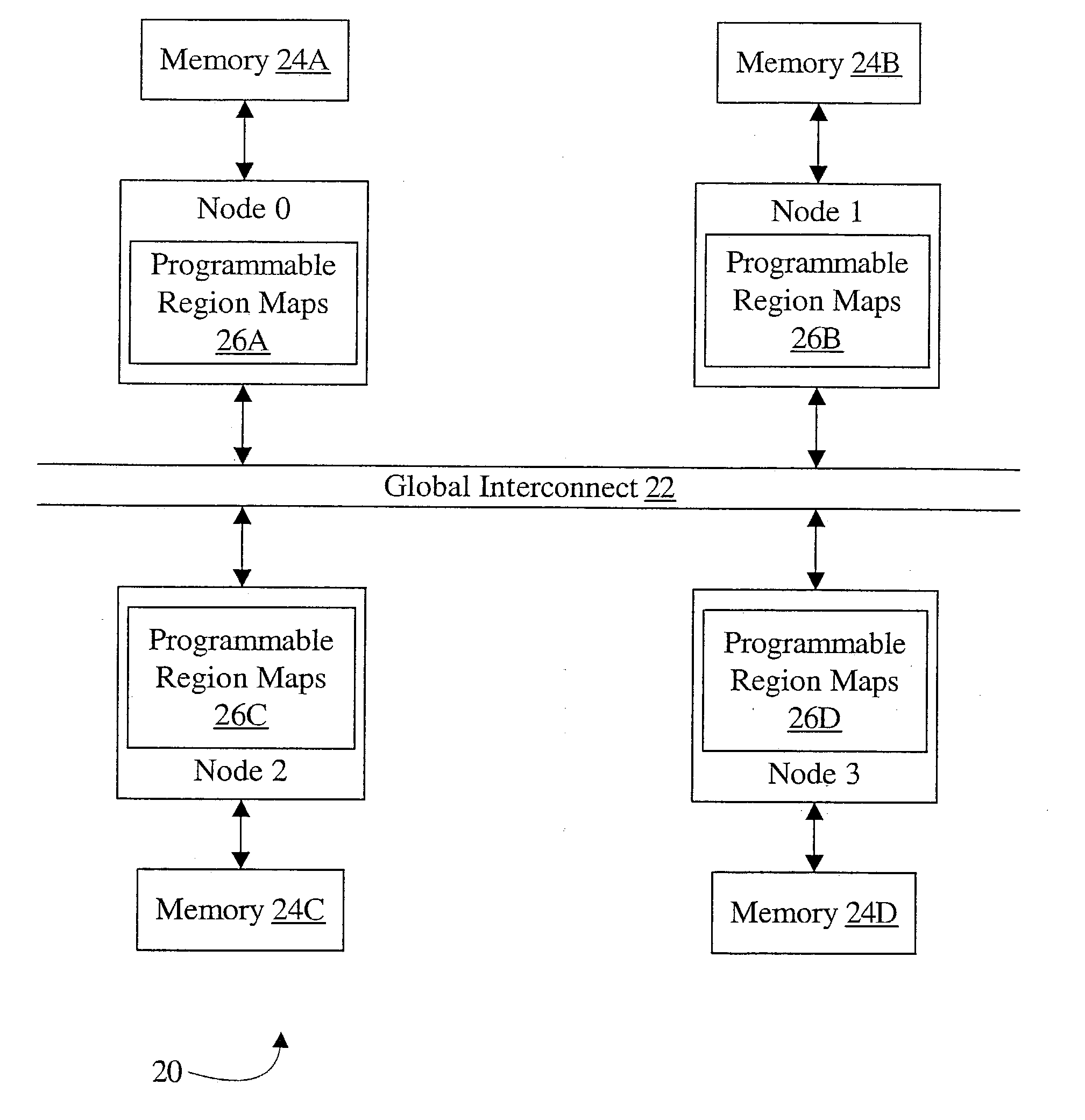

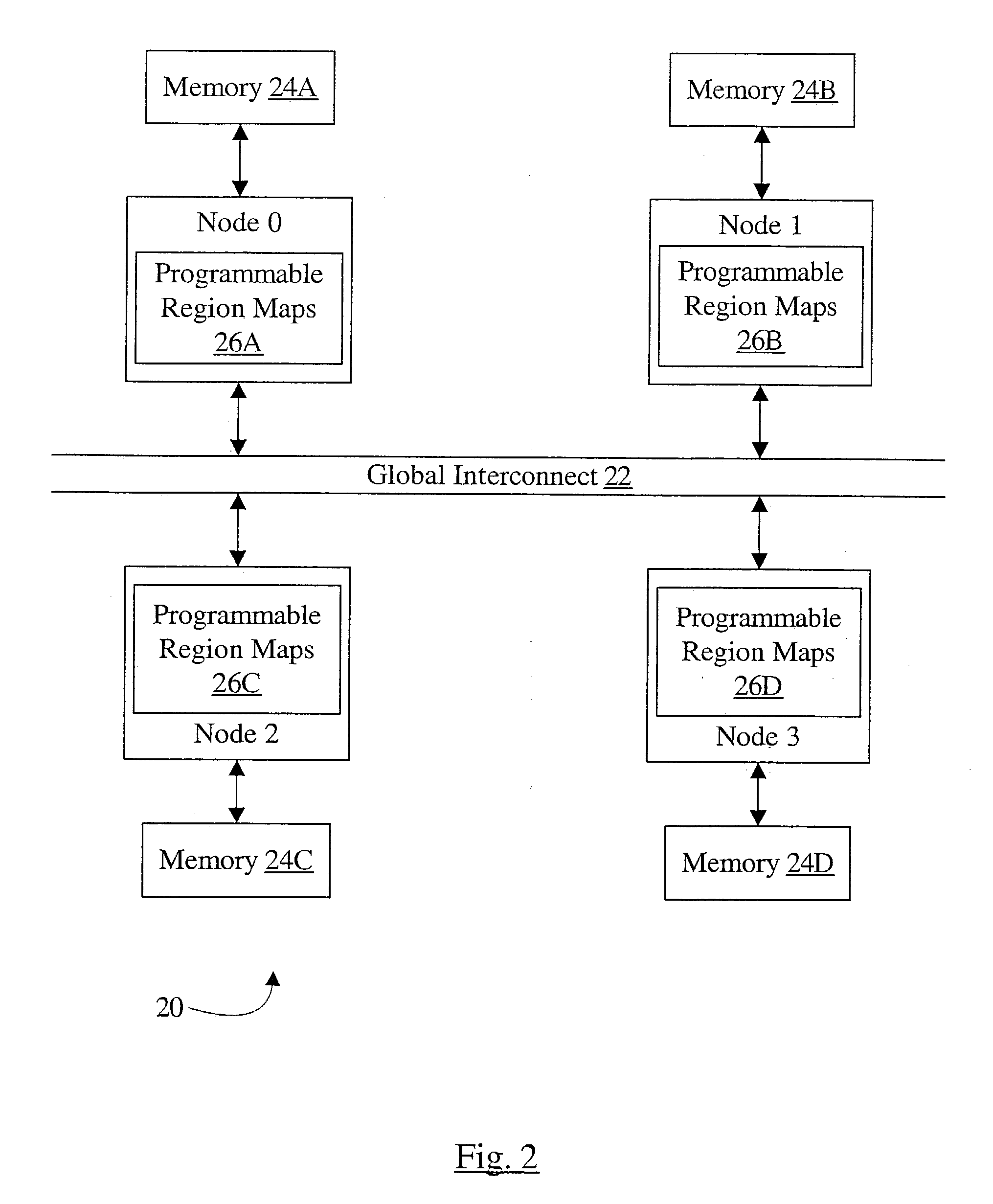

Addressing scheme supporting variable local addressing and variable global addressing

InactiveUS6941440B2Memory adressing/allocation/relocationDigital computer detailsGlobal address spaceParallel computing

A node comprises at least one agent and an input / output (I / O) circuit coupled to an interconnect within the node. The I / O circuit is configured to communicate on a global interconnect to which one or more other nodes are coupled during use. Addresses transmitted on the interconnect are in a first local address space of the node, and addresses transmitted on the global interconnect are in a global address space. The first local address space includes at least a first region used to address at least a first resource of the node. The node is programmable, during use, to relocate the first region within the first local address space, whereby a same numerical value in the first local address space and a second local address space corresponding to one of the other nodes coupled to the global interconnect refers to the first resource in the node during use.

Owner:AVAGO TECH INT SALES PTE LTD

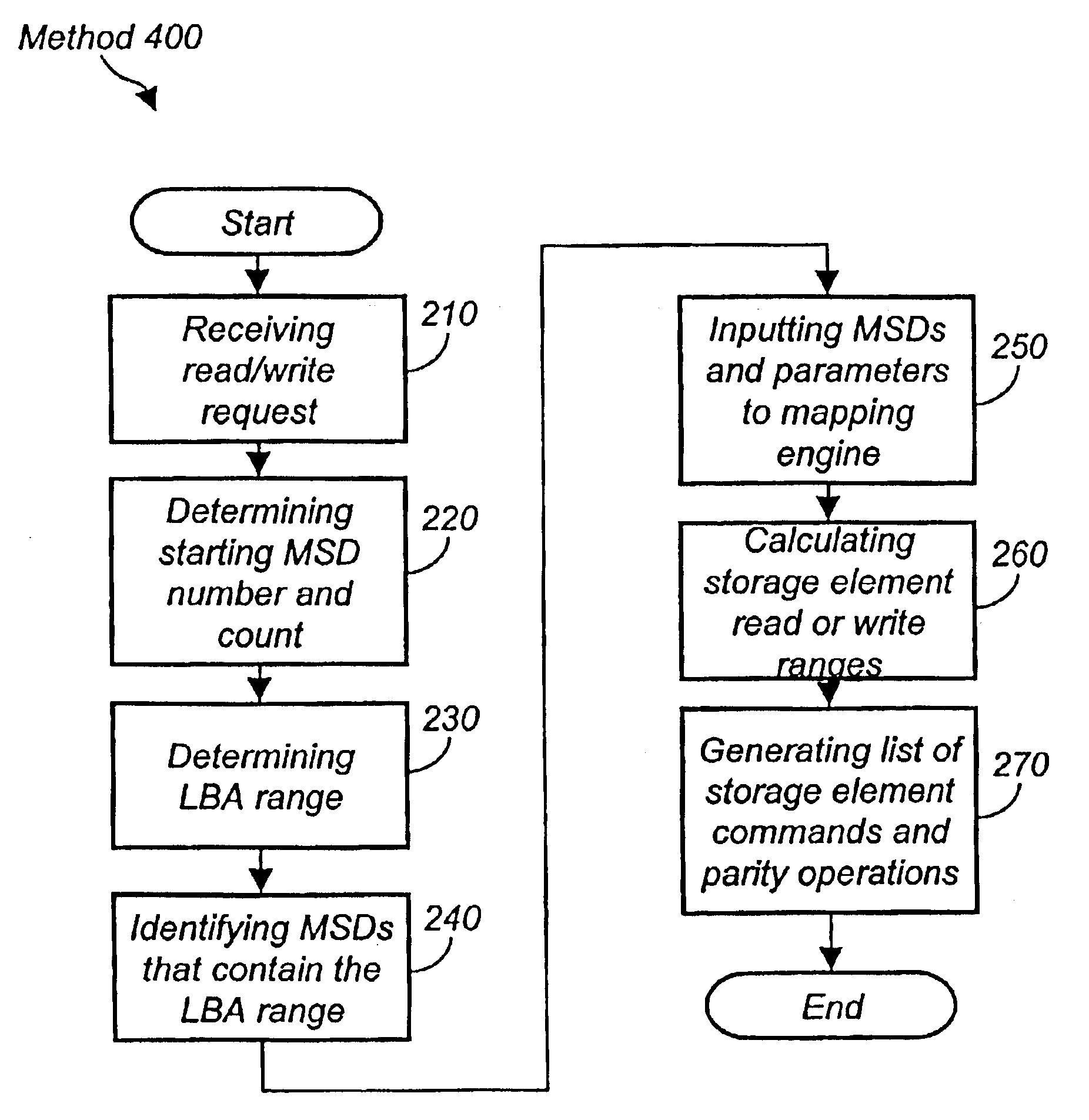

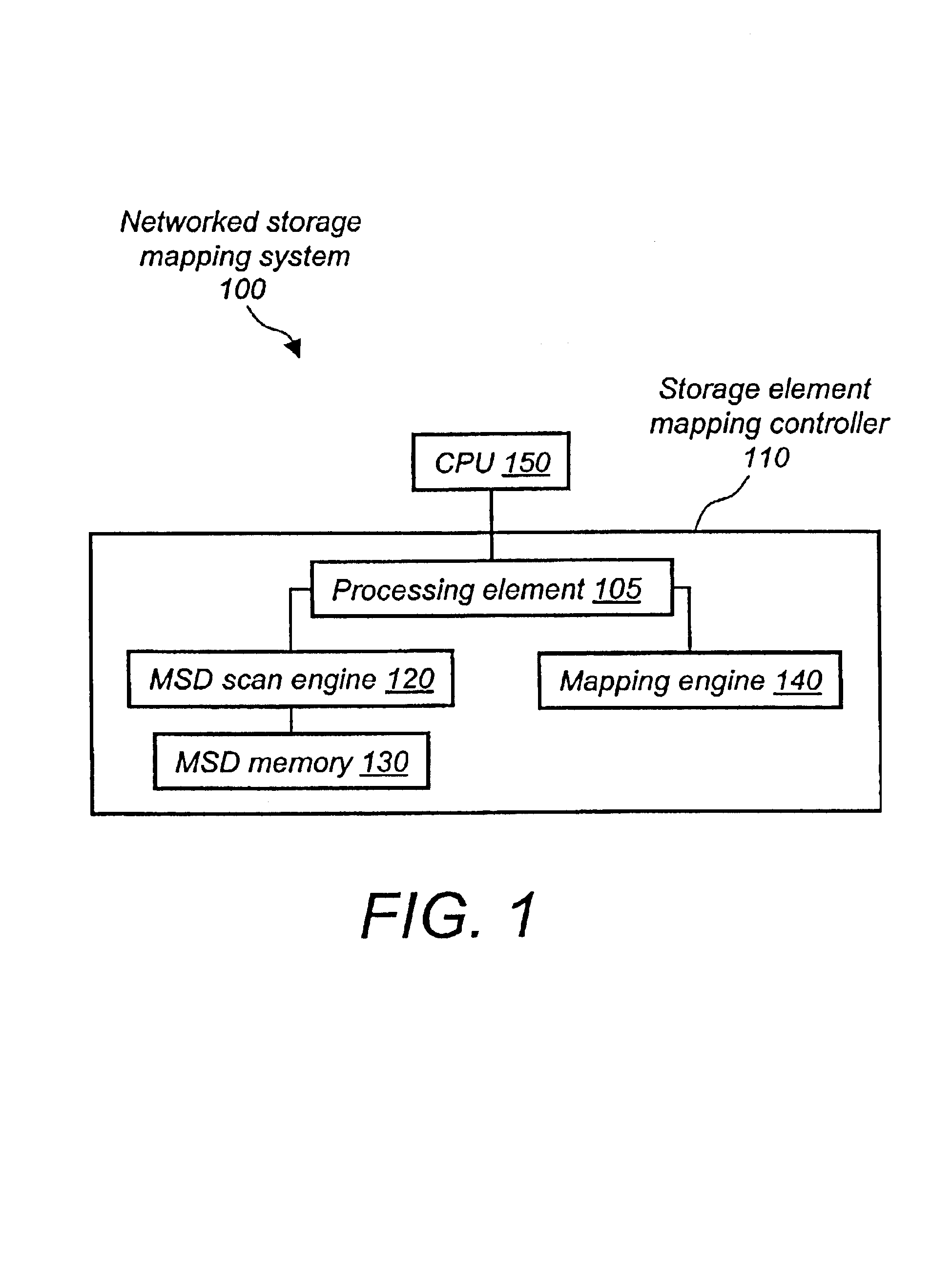

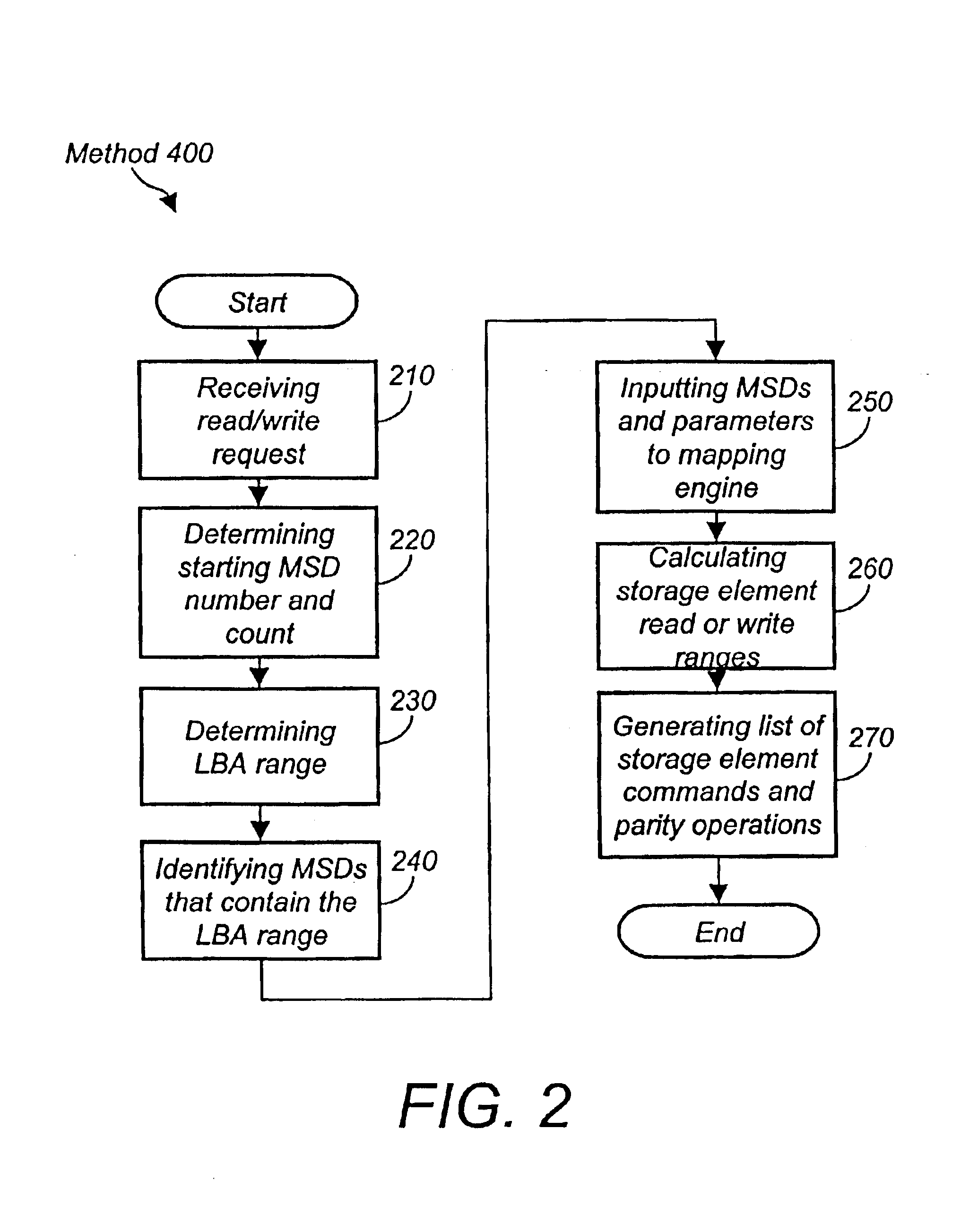

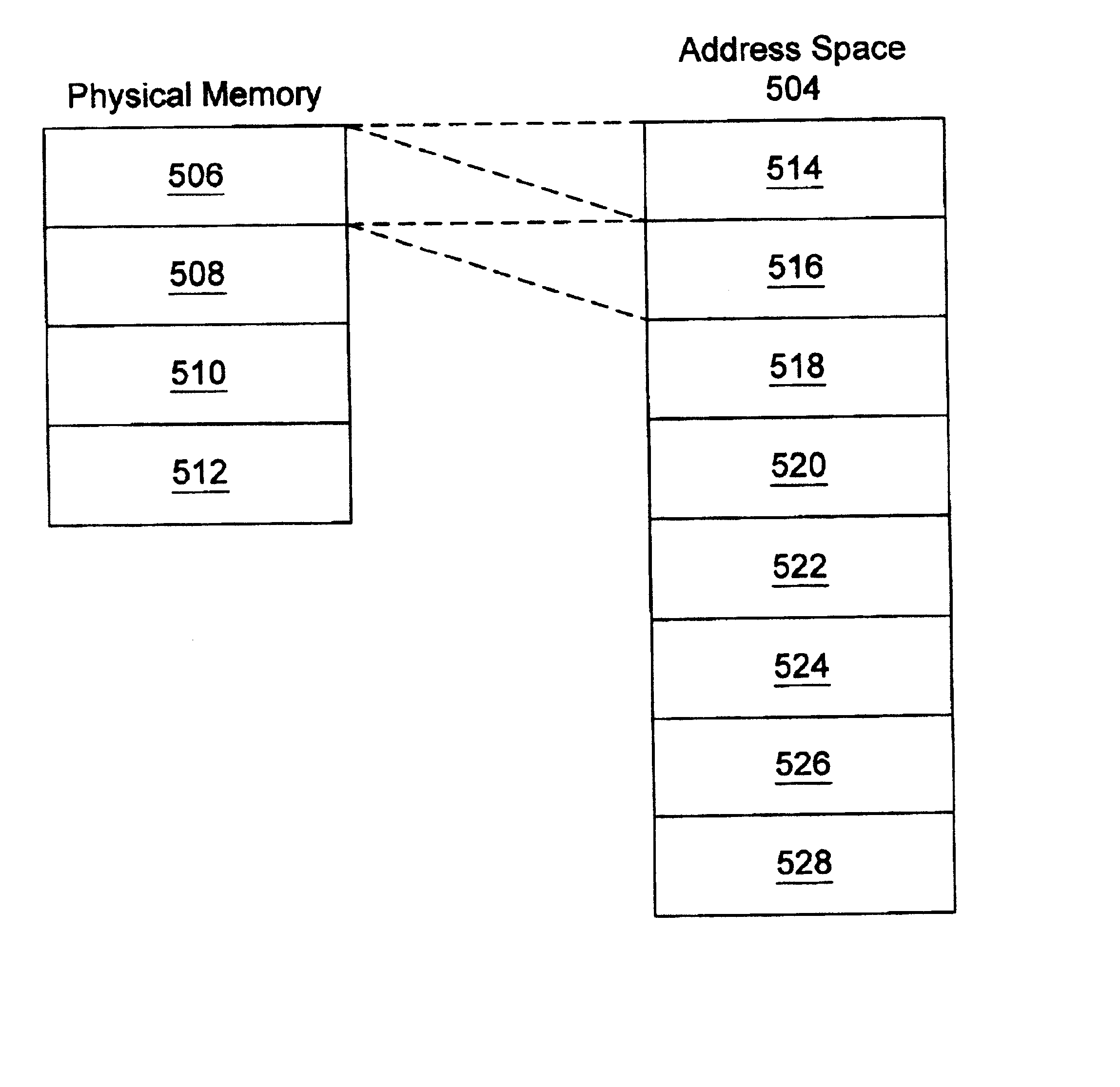

Method of flexibly mapping a number of storage elements into a virtual storage element

InactiveUS6912643B2Increase the number ofIncrease flexibilityInput/output to record carriersRedundant data error correctionGlobal address spaceSegment descriptor

The present invention provides an architecture and method for increasing the performance and resource utilization of networked storage architectures by use of hardware-based storage element mapping. The architecture utilizes a customized programmable processing element to map host read or write commands to physical storage element commands. The present invention uses a plurality of data structures, such as tables, to map host read and write commands to physical storage elements. The hardware-based storage element mapping controller uses the tables, including a mapping segment descriptor table, to map from global address space addresses to physical storage element addresses.

Owner:ADAPTEC

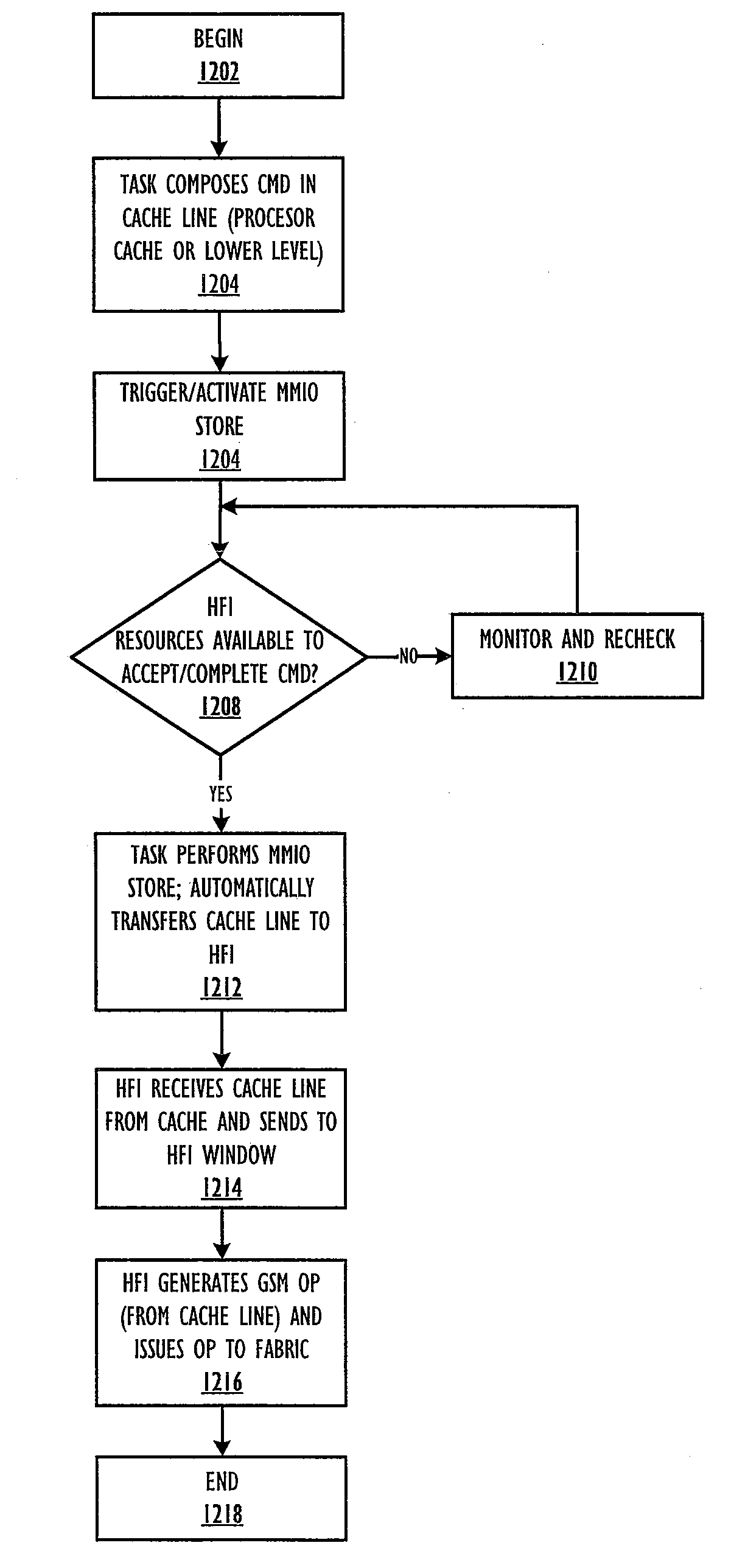

Issuing Global Shared Memory Operations Via Direct Cache Injection to a Host Fabric Interface

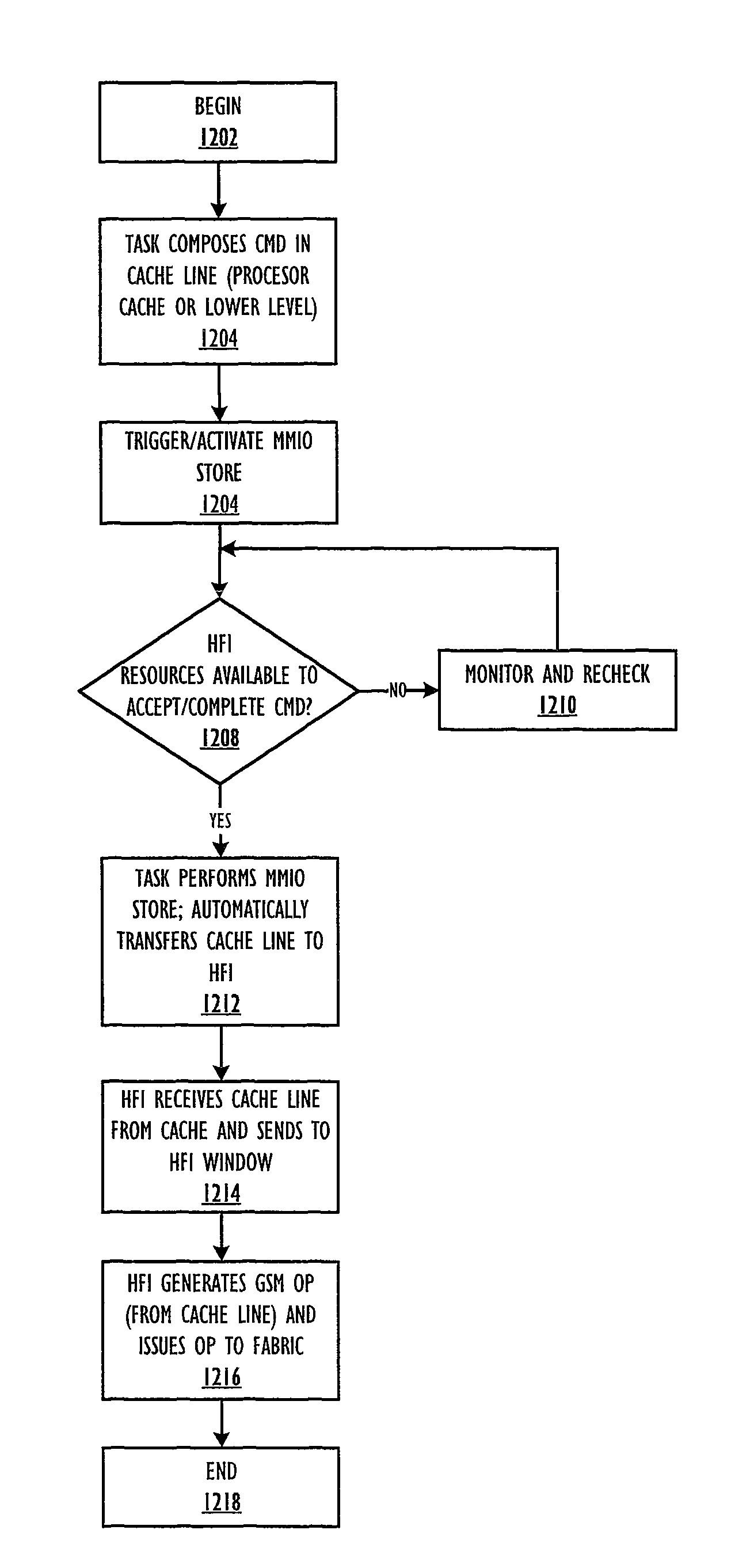

ActiveUS20090198891A1Memory adressing/allocation/relocationGeneral purpose stored program computerData processing systemGlobal address space

A data processing system enables global shared memory (GSM) operations across multiple nodes with a distributed EA-to-RA mapping of physical memory. Each node has a host fabric interface (HFI), which includes HFI windows that are assigned to at most one locally-executing task of a parallel job. The tasks perform parallel job execution, but map only a portion of the effective addresses (EAs) of the global address space to the local, real memory of the task's respective node. The HFI window tags all outgoing GSM operations (of the local task) with the job ID, and embeds the target node and HFI window IDs of the node at which the EA is memory mapped. The HFI window also enables processing of received GSM operations with valid EAs that are homed to the local real memory of the receiving node, while preventing processing of other received operations without a valid EA-to-RA local mapping.

Owner:IBM CORP

System and Architecture for Robust Management of Resources in a Wide-Area Network

ActiveUS9240955B1Avoid communicationDigital computer detailsDatabase distribution/replicationGlobal address spaceCommunications system

A system and method of management of communication in a potentially unreliable wide-area network that contains one or more nodes connected to said network, each potentially having access to one or more inputs and / or outputs and capable of evaluating said inputs and directing said outputs, a global address space (GAS) accessible by said nodes, and a communication system using said GAS that provides communications between said nodes.

Owner:BOARD OF SUPERVISORS OF LOUISIANA STATE UNIV & AGRI & MECHANICAL COLLEGE

Addressing scheme supporting variable local addressing and variable global addressing

InactiveUS20040044806A1Memory adressing/allocation/relocationDigital computer detailsGlobal address spaceParallel computing

A node comprises at least one agent and an input / output (I / O) circuit coupled to an interconnect within the node. The I / O circuit is configured to communicate on a global interconnect to which one or more other nodes are coupled during use. Addresses transmitted on the interconnect are in a first local address space of the node, and addresses transmitted on the global interconnect are in a global address space. The first local address space includes at least a first region used to address at least a first resource of the node. The node is programmable, during use, to relocate the first region within the first local address space, whereby a same numerical value in the first local address space and a second local address space corresponding to one of the other nodes coupled to the global interconnect refers to the first resource in the node during use.

Owner:AVAGO TECH INT SALES PTE LTD

Selective address translation in coherent memory replication

InactiveUS20030097539A1Memory architecture accessing/allocationMemory adressing/allocation/relocationGlobal address spaceComputerized system

A multiprocessing computer system employs local and global address spaces and multiple access modes. A portion of the global memory of the multiprocessing computer system is allocated to each node, called local memory space. Two logical address spaces are mapped to the local memory of each node. A coherent memory replication (CMR) address space stores shadow pages of data from remote nodes and a local address space stores local data. A bit within a local physical address identifies whether data is a shadow page, which is stored in CMR space, or local data, which is stored in local address space. When a transaction requiring a coherency operation is performed, the CMR bit indicates whether a local physical address to global address translation is required. In one embodiment if the CMR bit is clear, the local physical address is the same as the global address and the local physical address is used for the coherency operation. Alternatively, if the CMR bit is set, the local physical address is translated to a global address during the coherency operation.

Owner:SUN MICROSYSTEMS INC

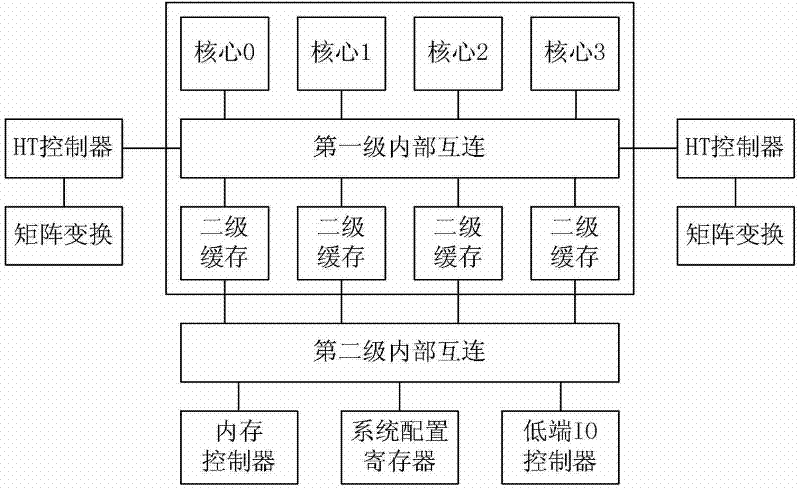

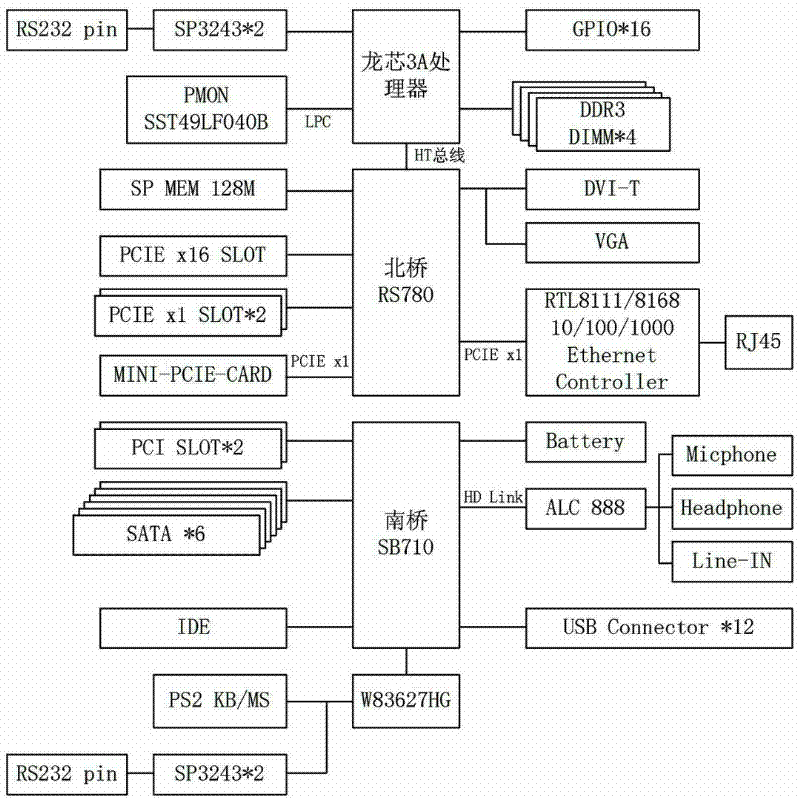

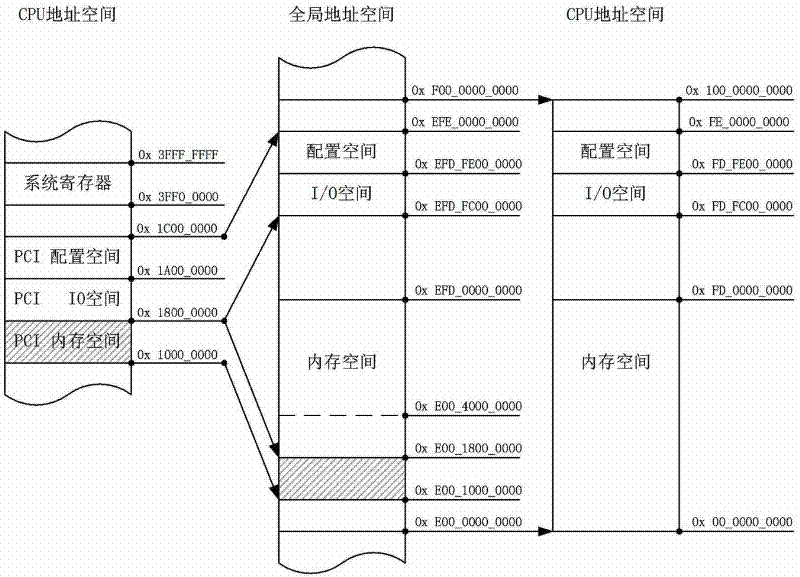

Address mapping method for large memory devices of Loongson 3A platforms

ActiveCN102646074AImplementation supportTake advantage ofMemory adressing/allocation/relocationGlobal address spaceAddress mapping

The invention discloses an address mapping method for large memory devices of Loongson 3A platforms, which comprises the implementation steps: 1) aiming at each CPU (central processing unit) core of a Loongson 3A processor, moving a PCI (peripheral component interconnect) memory space in a CPU address space out of an address range of a system register, and adjusting the size of the PCI memory space; 2) establishing a mapping relation between the PCI memory space being moved in the CPU address space and a memory space in a global address space, and establishing a mapping relation between the memory space in the global address space and a memory space in an HT (hyper transport) address space; and 3) according to the PCI memory space being moved in the CPU address space, updating a PCI memory resource structure body of an operating system. According to the invention, the large memory PCI / PCIE (peripheral component interconnect express) device support of a Loongson 3A platform can be realized, the popularization and application of the Loongson 3A platform can be promoted, and the method has the advantages of good compatibility and wide application range.

Owner:NAT UNIV OF DEFENSE TECH

Host fabric interface (HFI) to perform global shared memory (GSM) operations

InactiveUS8484307B2Digital computer detailsMultiprogramming arrangementsData processing systemGlobal address space

Owner:IBM CORP

Global address space management

Owner:AVAGO TECH INT SALES PTE LTD

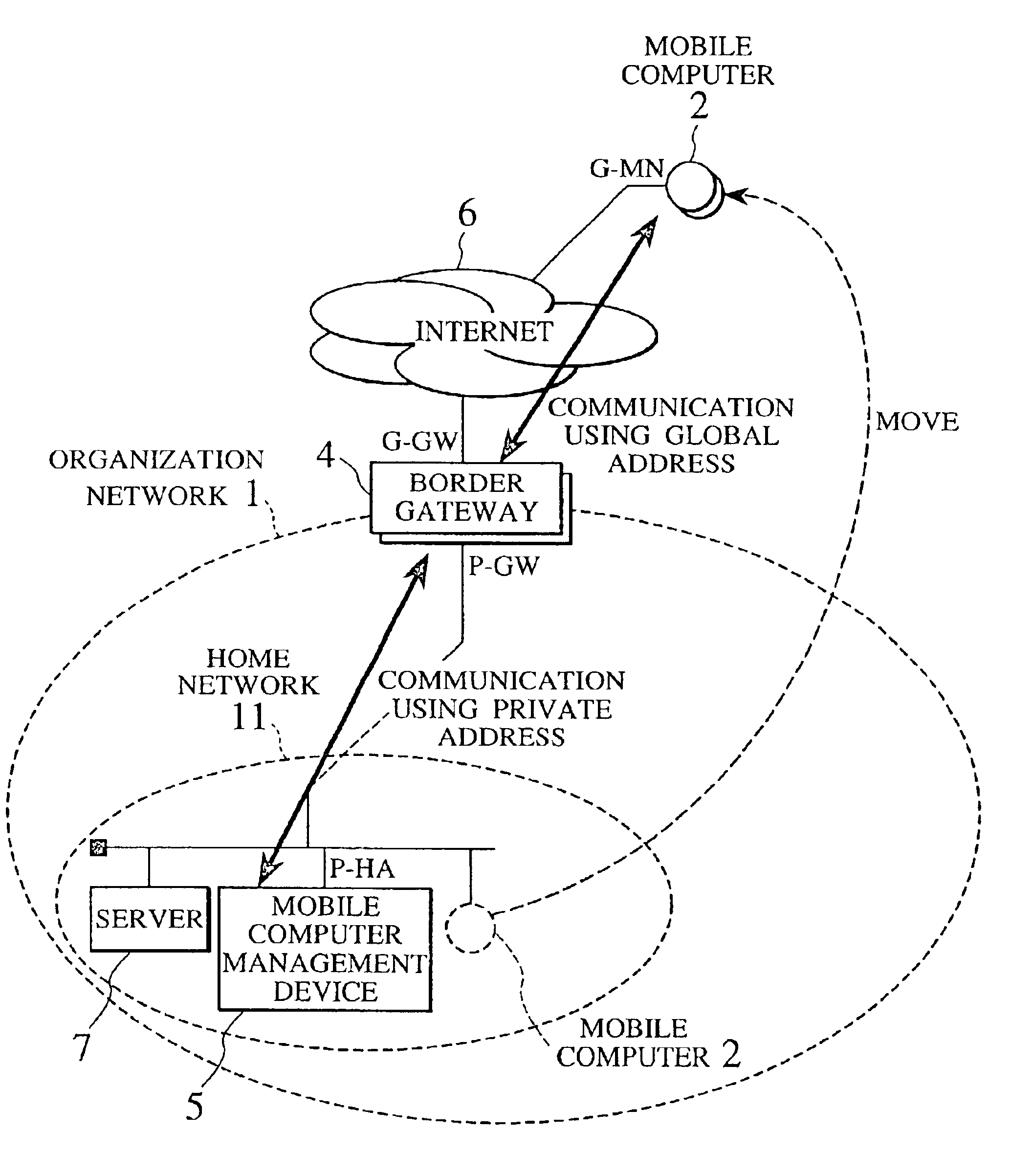

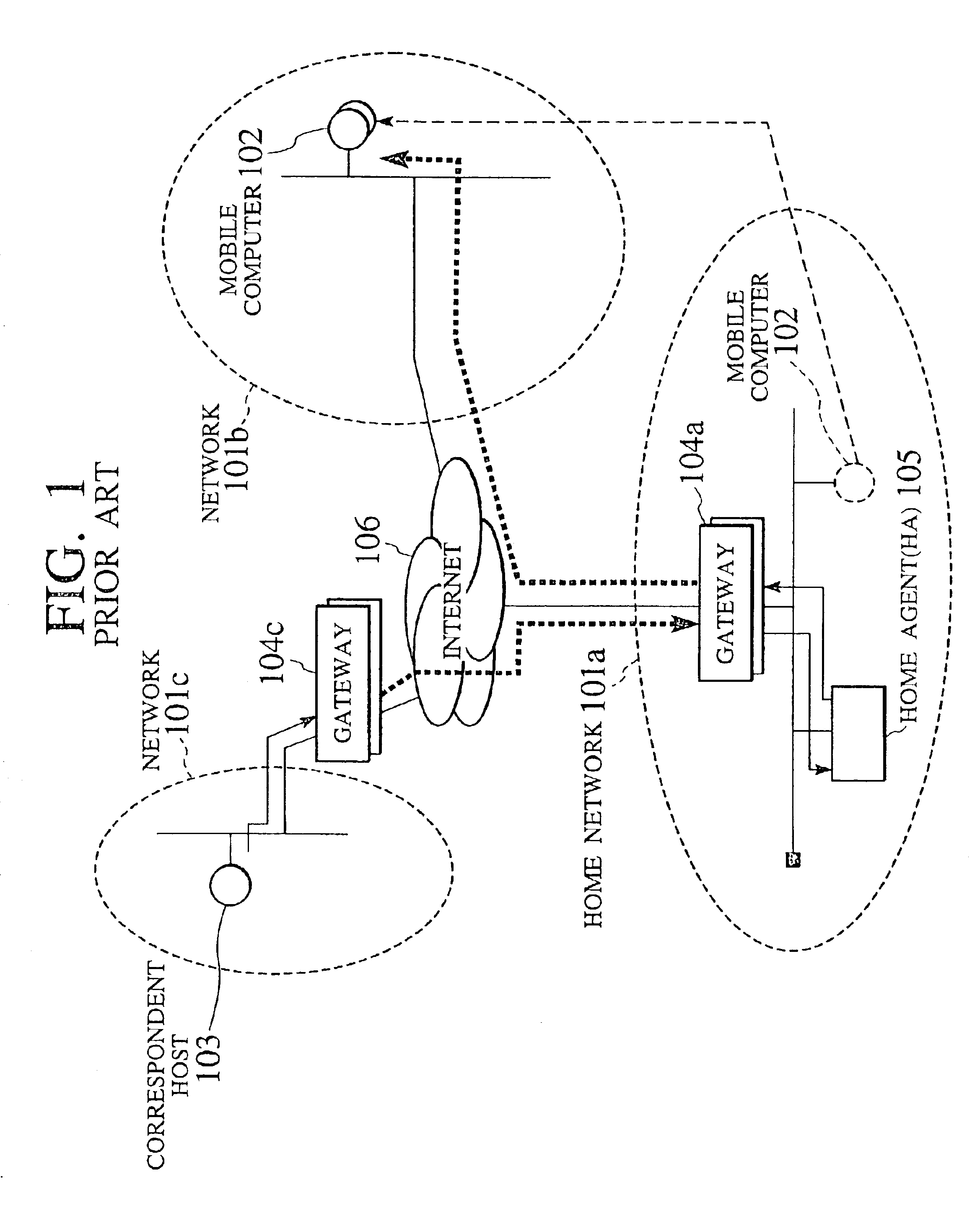

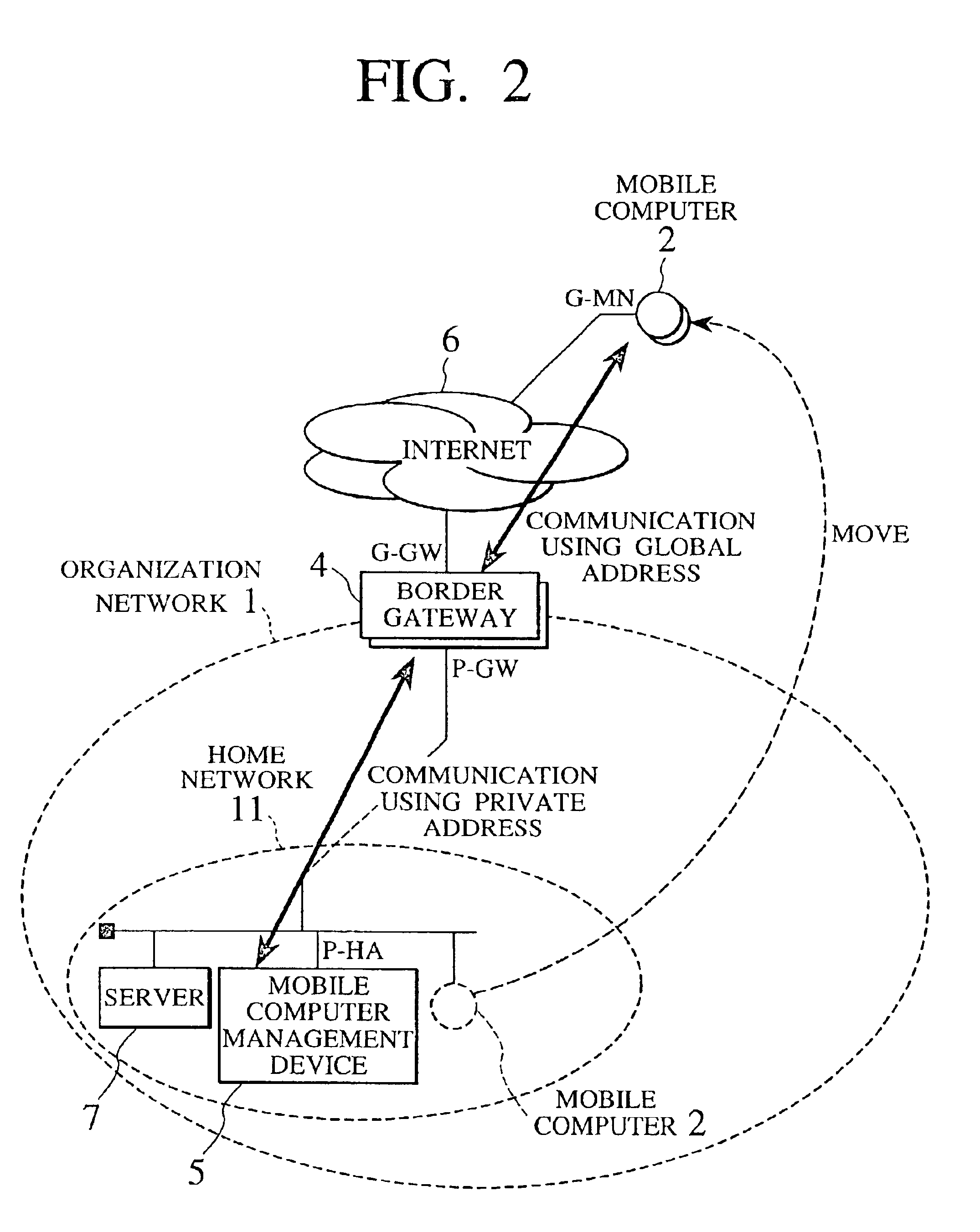

Mobile IP communication scheme for supporting mobile computer move over different address spaces

InactiveUS6944181B2Multiple keys/algorithms usageData switching by path configurationGlobal address spacePrivate address

A mobile IP communication scheme for supporting a mobile computer moving over different address spaces is disclosed. A packet relay device for relaying packets having an address of the mobile computer device as a destination or source is provided at a border between a private address space and a global address space, where the packet relay device has a packet receiving unit for receiving a packet in a first format using a global address which is transmitted by the mobile computer for a location registration from a visited site managed by a global address system, and checking a content of the packet, and a packet transfer unit for transferring the packet in a second format using a private address, to a correspondent computer in a home network of the mobile computer managed by a private address system, according to the content of the packet.

Owner:KK TOSHIBA

Allocating a global shared memory

ActiveUS7925842B2Memory architecture accessing/allocationMemory systemsData processing systemGlobal address space

A method of operating a data processing system includes each of multiple tasks within a parallel job executing on multiple nodes of the data processing system issuing a system call to request allocation of backing storage in physical memory for global shared memory accessible to all of the multiple tasks within the parallel job, where the global shared memory is in a global address space defined by a range of effective addresses. Each task among the multiple tasks receives an indication that the allocation requested by the system call was successful only if the global address space for that task was previously reserved and backing storage for the global shared memory has not already been allocated.

Owner:INT BUSINESS MASCH CORP

Distributed symmetric multiprocessing computing architecture

ActiveUS8607004B2Shorten the progressMemory adressing/allocation/relocationDigital computer detailsSupercomputerGlobal address space

Example embodiments of the present invention includes systems and methods for implementing a scalable symmetric multiprocessing (shared memory) computer architecture using a network of homogeneous multi-core servers. The level of processor and memory performance achieved is suitable for running applications that currently require cache coherent shared memory mainframes and supercomputers. The architecture combines new operating system extensions with a high-speed network that supports remote direct memory access to achieve an effective global distributed shared memory. A distributed thread model allows a process running in a head node to fork threads in other (worker) nodes that run in the same global address space. Thread synchronization is supported by a distributed mutex implementation. A transactional memory model allows a multi-threaded program to maintain global memory page consistency across the distributed architecture. A distributed file access implementation supports non-contentious file I / O for threads. These and other functions provide a symmetric multiprocessing programming model consistent with standards such as Portable Operating System Interface for Unix (POSIX).

Owner:ANDERSON RICHARD S

Reserving a global address space

InactiveUS7921261B2Memory architecture accessing/allocationProgram controlData processing systemGlobal address space

A method of operating a data processing system includes each of multiple tasks within a parallel job executing on multiple nodes of the data processing system issuing a respective system call to request reservation, without allocation of backing storage in physical memory, of a global address space defined by a range of effective addresses as global shared memory accessible to all of the multiple tasks within the parallel job. At least two of the tasks within the parallel job allocate global address spaces including a same effective address.

Owner:INT BUSINESS MASCH CORP

Issuing global shared memory operations via direct cache injection to a host fabric interface

ActiveUS7966454B2Memory adressing/allocation/relocationGeneral purpose stored program computerData processing systemGlobal address space

A data processing system enables global shared memory (GSM) operations across multiple nodes with a distributed EA-to-RA mapping of physical memory. Each node has a host fabric interface (HFI), which includes HFI windows that are assigned to at most one locally-executing task of a parallel job. The tasks perform parallel job execution, but map only a portion of the effective addresses (EAs) of the global address space to the local, real memory of the task's respective node. The HFI window tags all outgoing GSM operations (of the local task) with the job ID, and embeds the target node and HFI window IDs of the node at which the EA is memory mapped. The HFI window also enables processing of received GSM operations with valid EAs that are homed to the local real memory of the receiving node, while preventing processing of other received operations without a valid EA-to-RA local mapping.

Owner:INT BUSINESS MASCH CORP

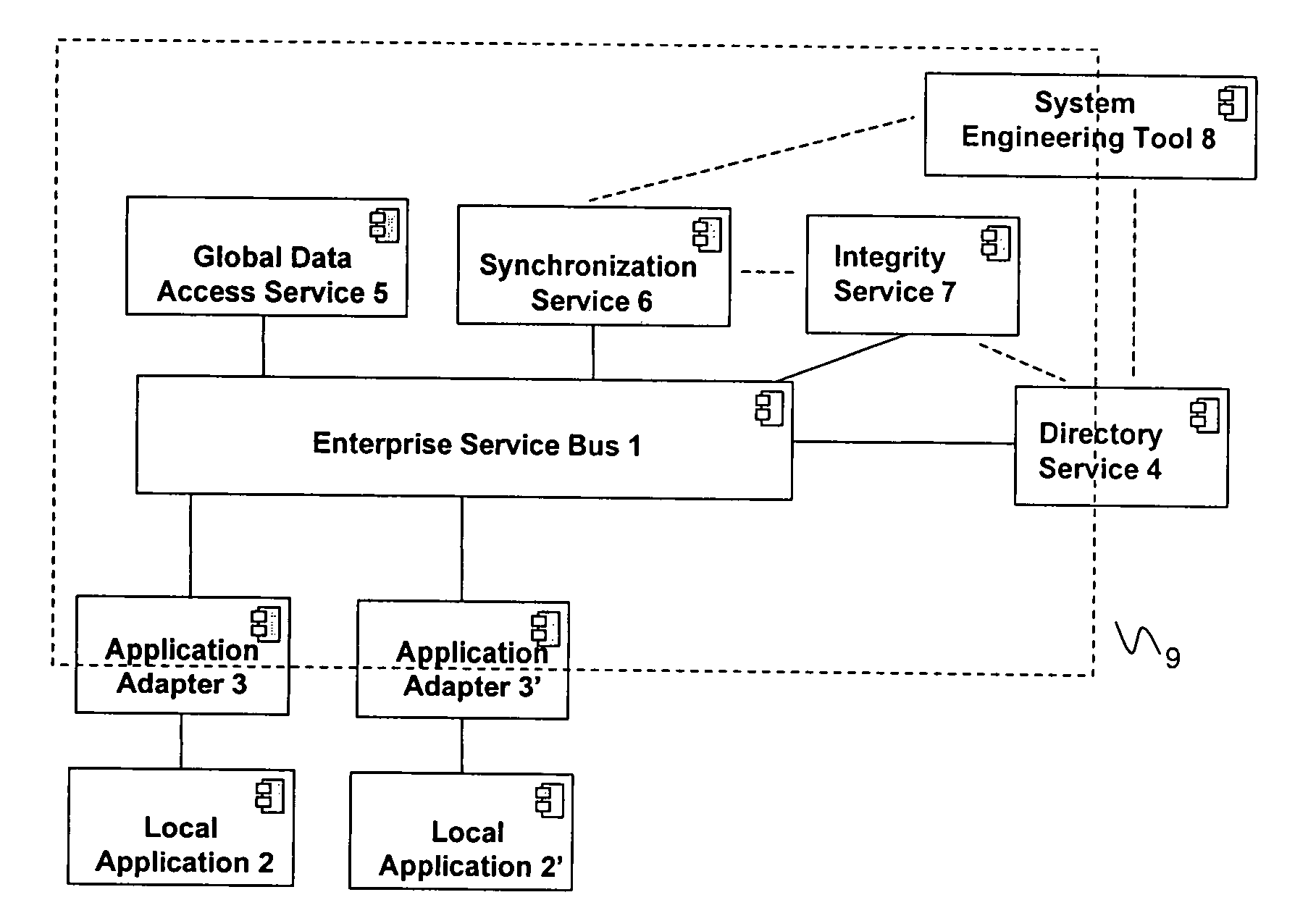

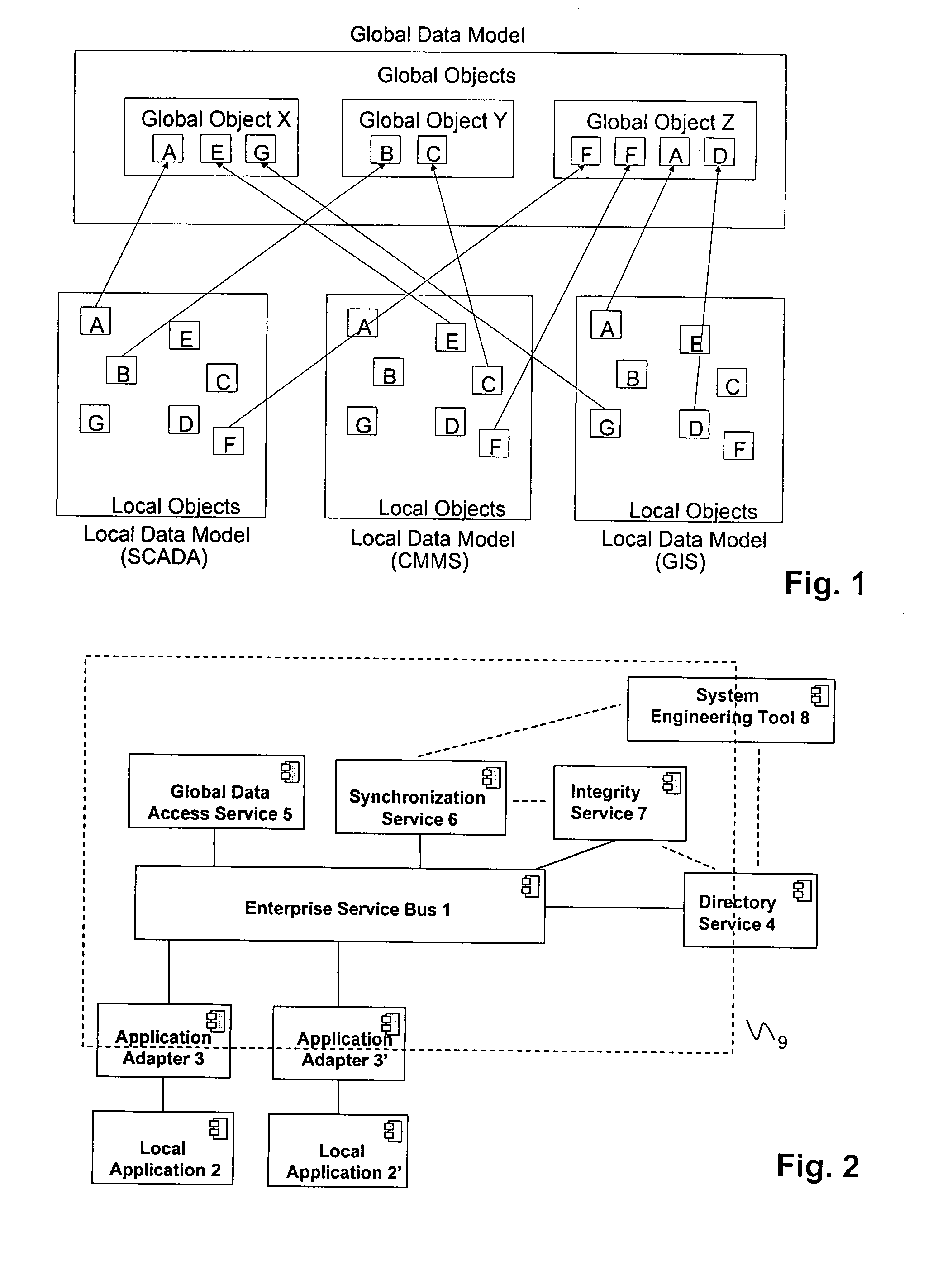

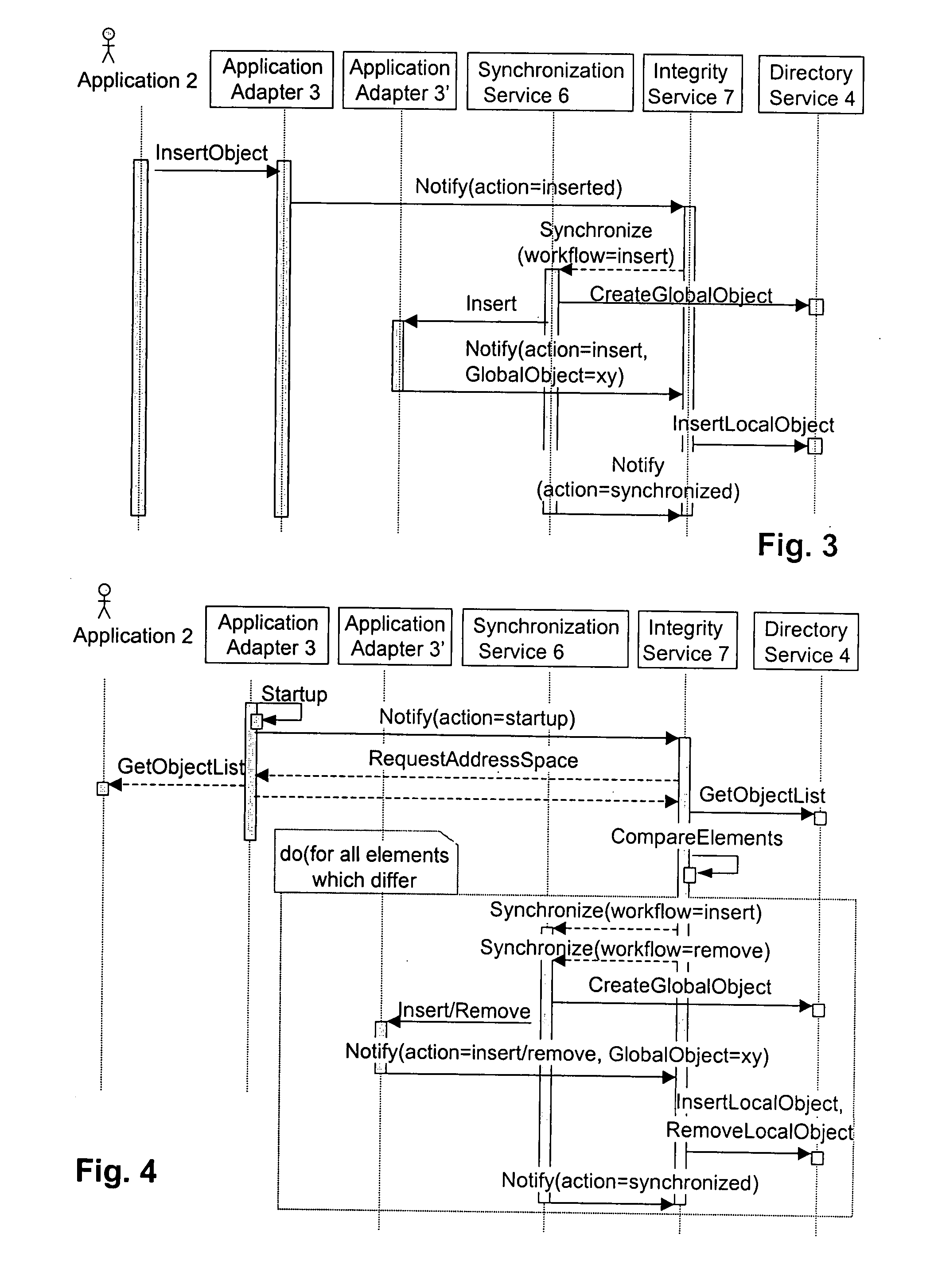

Maintaining data consistency between integrated applications

ActiveUS20080133613A1Improve interoperabilityMaintain data consistencyProgram synchronisationDigital data processing detailsGlobal address spaceApplication software

The present disclosure facilitates the interoperability between different local applications. Related local data objects are referenced via global objects or reference containers within a global data model or a global address space of an integration solution. The present disclosure assumes that the integration solution is per default in a consistent state, e.g., an engineered or initially configured global address space is regarded as consistent, and all software components that operate within this space assume that the information they access is valid and likewise consistent. The local applications are the only components that can interact with the global address space and introduce invalidations, they are continuously monitored for changes. Invalidation and subsequent synchronization or restoration of consistency is performed upon a particular triggering event related to a change in a local application object (such as an insertion or removal of an object or a modification of an attribute thereof) or related to a changing application or adapter status (component shutdown / startup).

Owner:HITACHI ENERGY SWITZERLAND AG

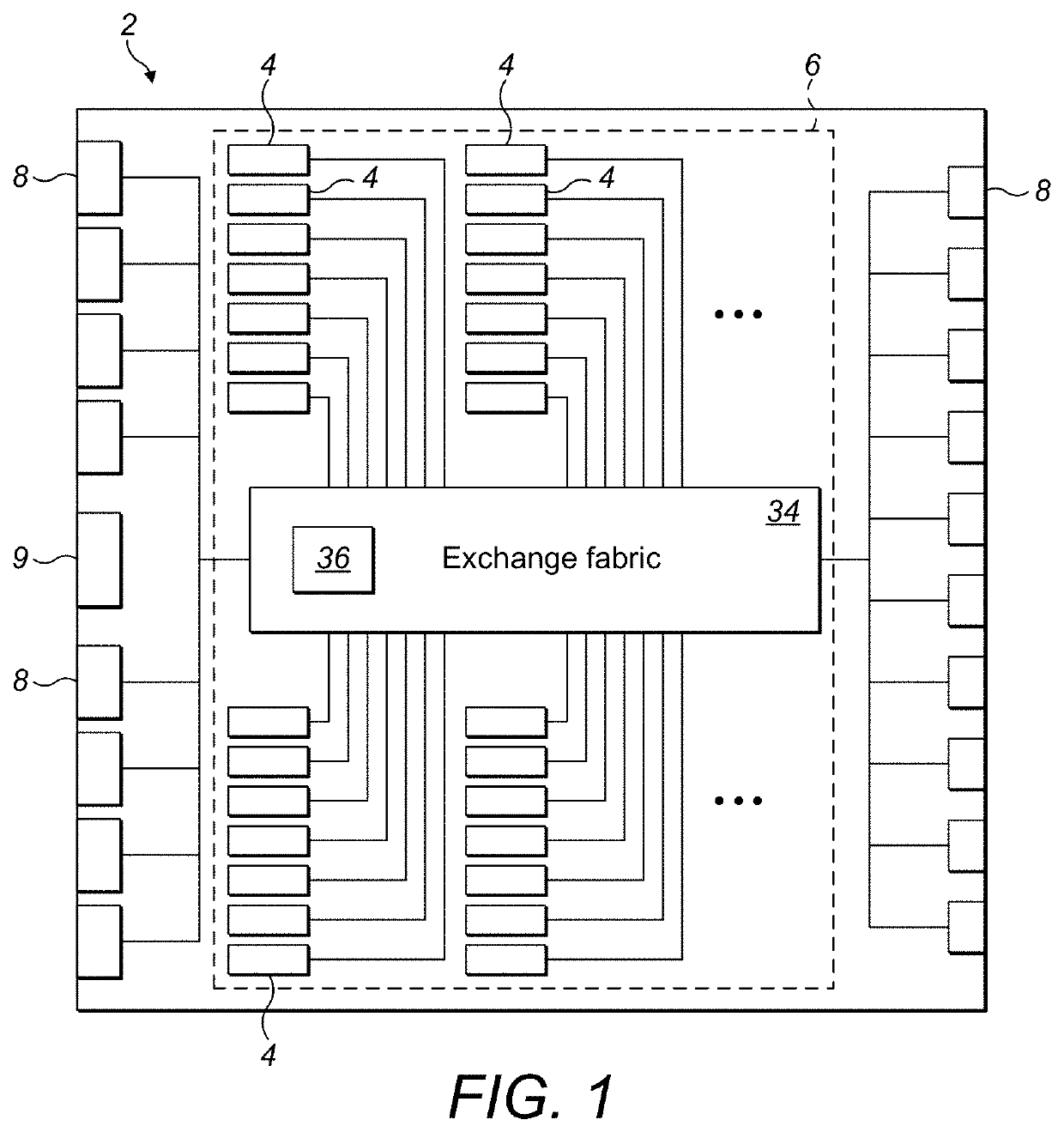

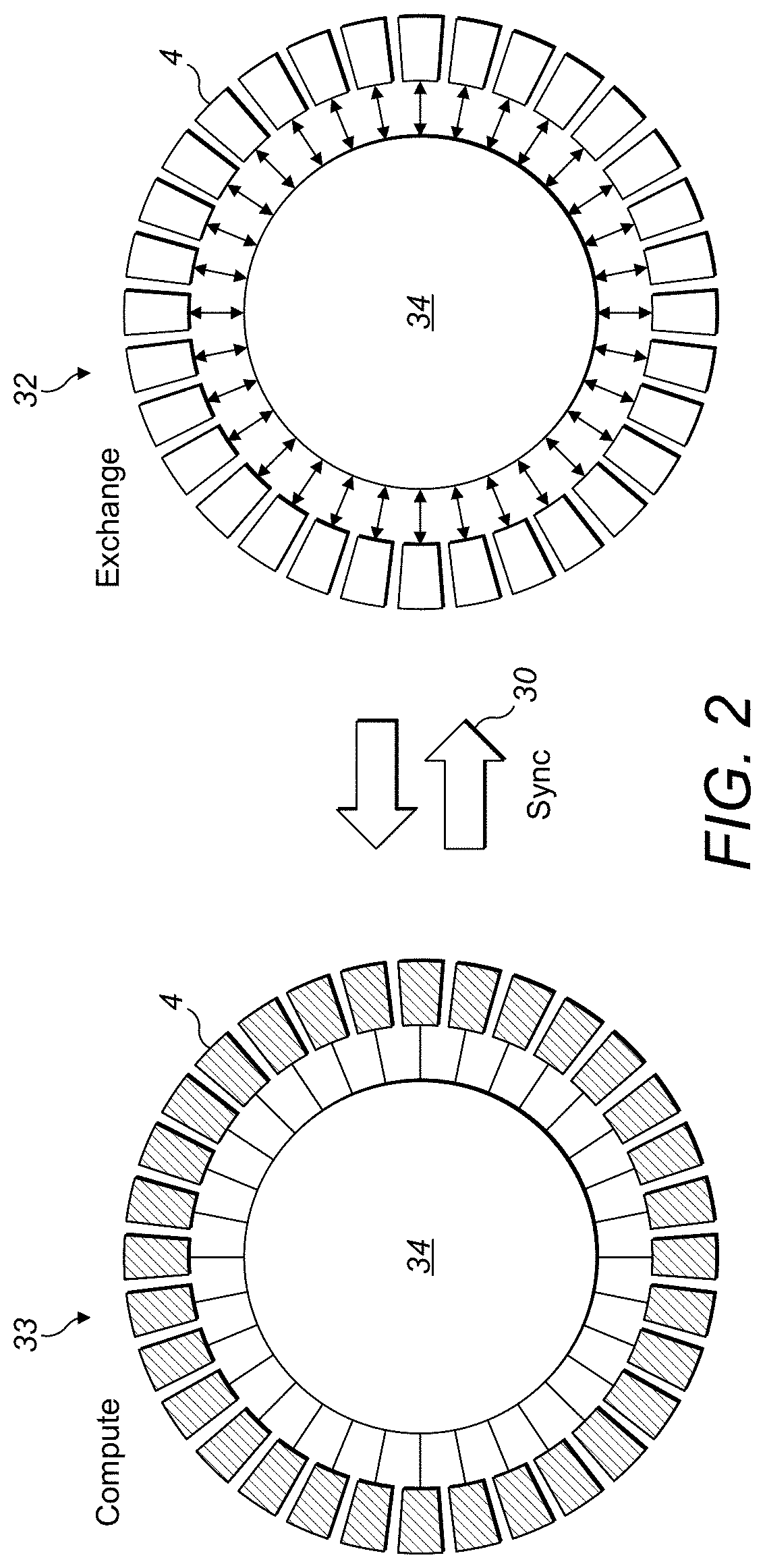

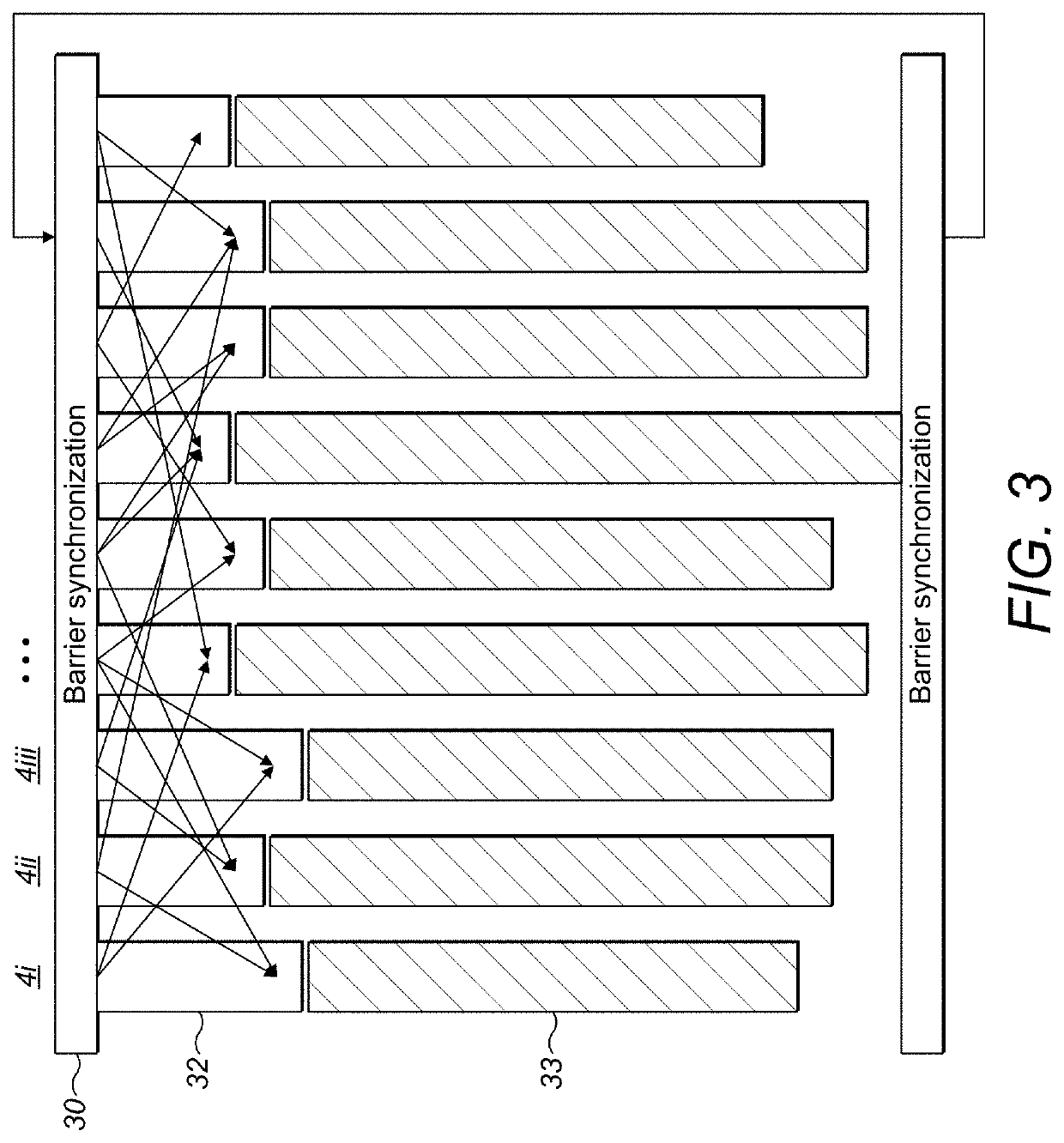

Gateway fabric ports

ActiveUS20200014560A1Digital computer detailsMicrocontrol arrangementsGlobal address spaceData transport

Owner:GRAPHCORE LTD

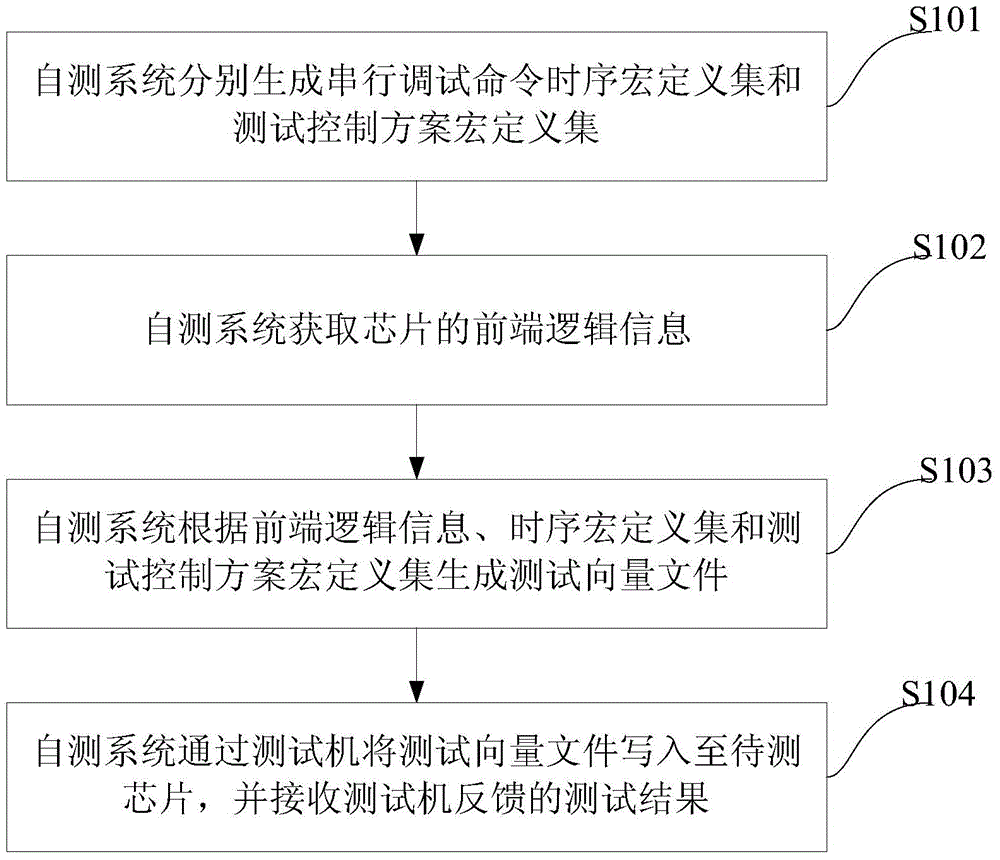

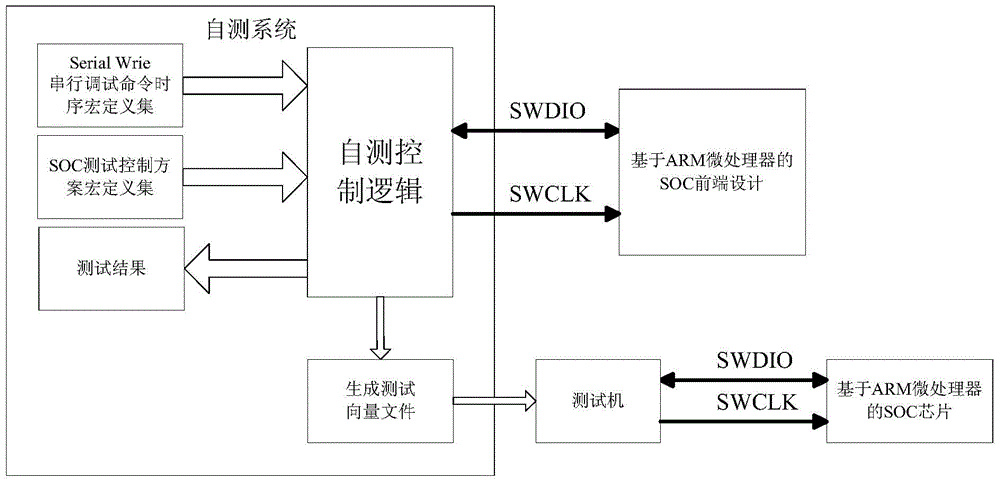

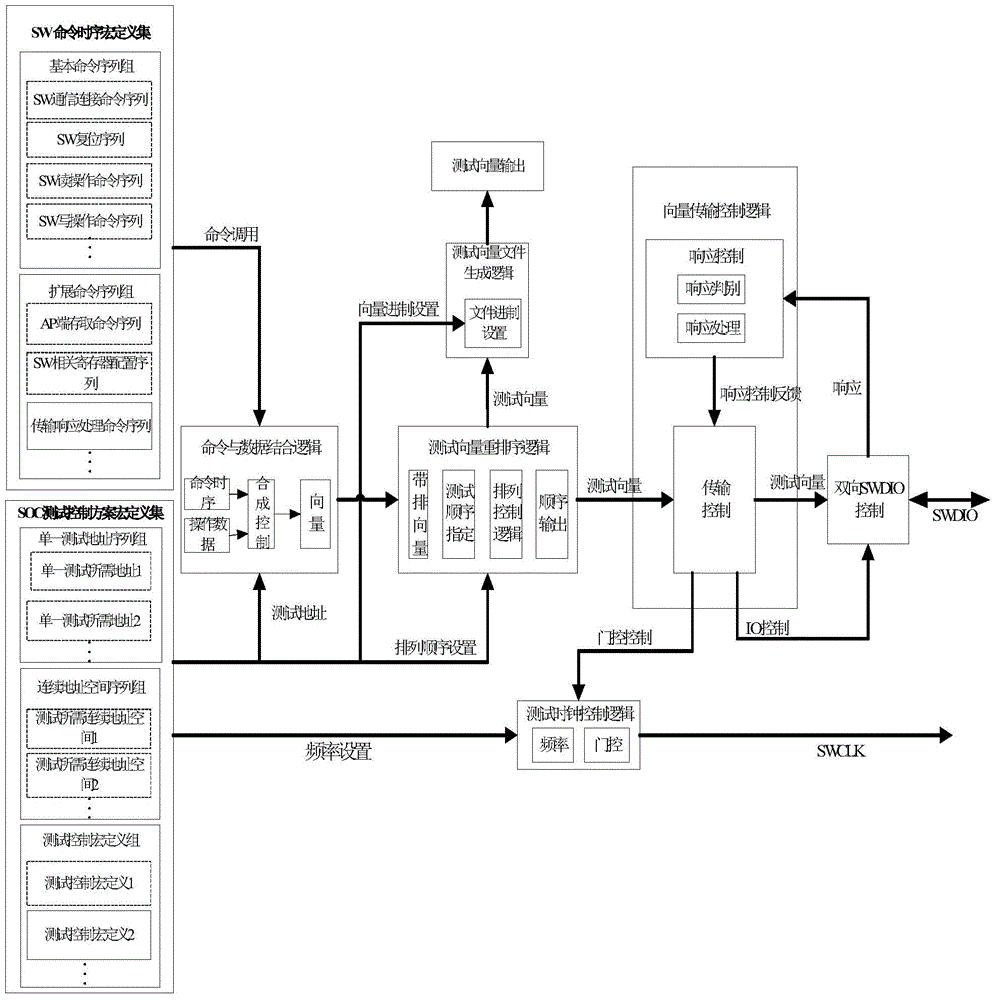

Chip self-test method and system

ActiveCN104459522AGuaranteed correctnessReduce testing costsElectrical testingGlobal address spaceEmbedded system

The invention provides a chip self-test method executed by a self-test system; the method comprises the following steps: the self-test system respectively generates a serial debug command sequential macrodefinition set and a test control scheme macrodefinition set; the self-test system obtains front end logic information of the chip; the self-test system generates a test vector file according to the front end logic information, the sequential macrodefinition set and the test control scheme macrodefinition set; the self-test system writes the test vector file into a tested chip through a test machine, and receives a test result returned by the test machine. The chip self-test method can fast and effectively verify SOC global address space, is simple in operation, easy to realize, and the method has high transplantability and connectivity; in addition, the method can save resources, and reduces test cost; the invention also provides the chip self-test system.

Owner:BYD SEMICON CO LTD