Patents

Literature

30 results about "Segment descriptor" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In memory addressing for Intel x86 computer architectures, segment descriptors are a part of the segmentation unit, used for translating a logical address to a linear address. Segment descriptors describe the memory segment referred to in the logical address.

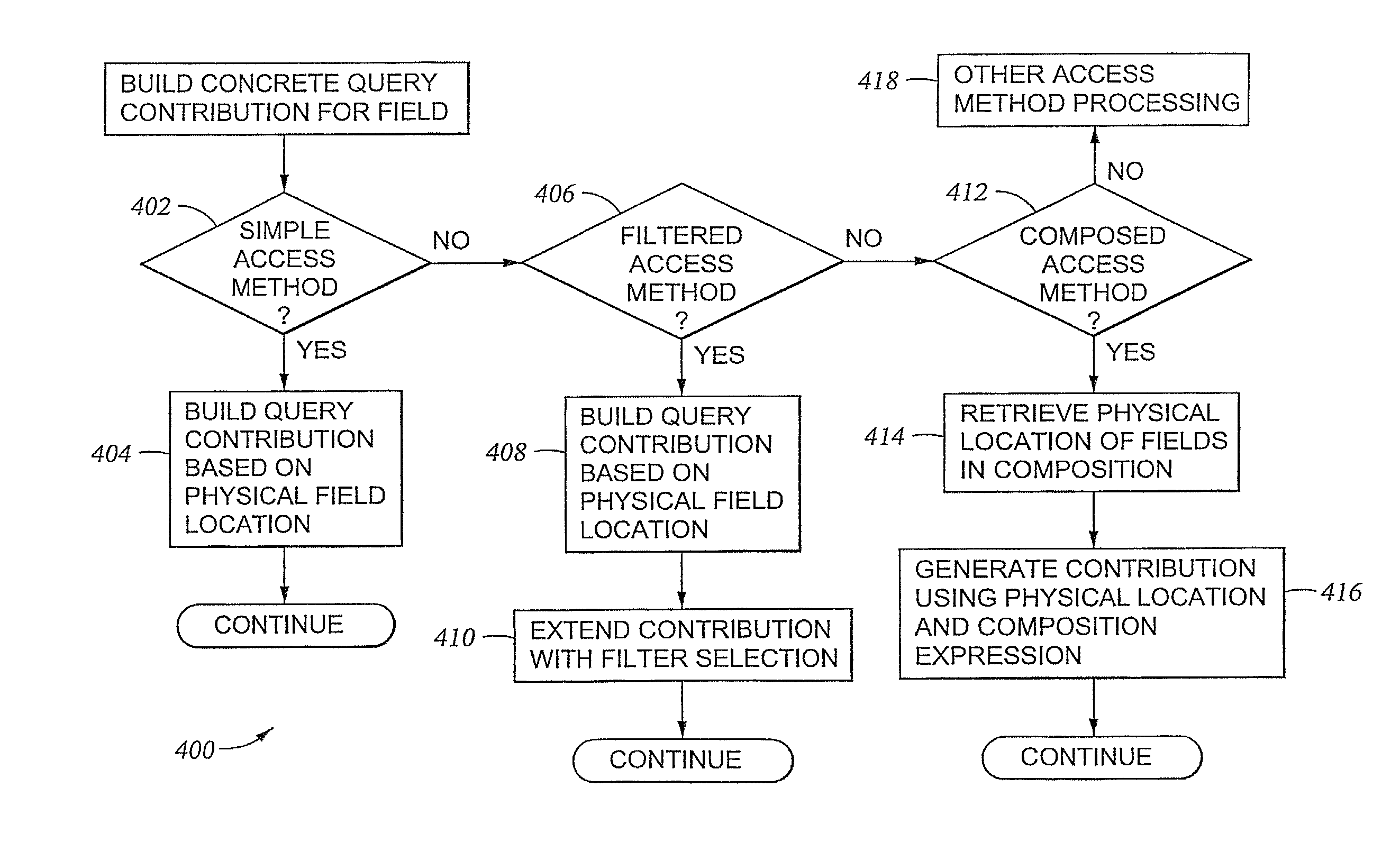

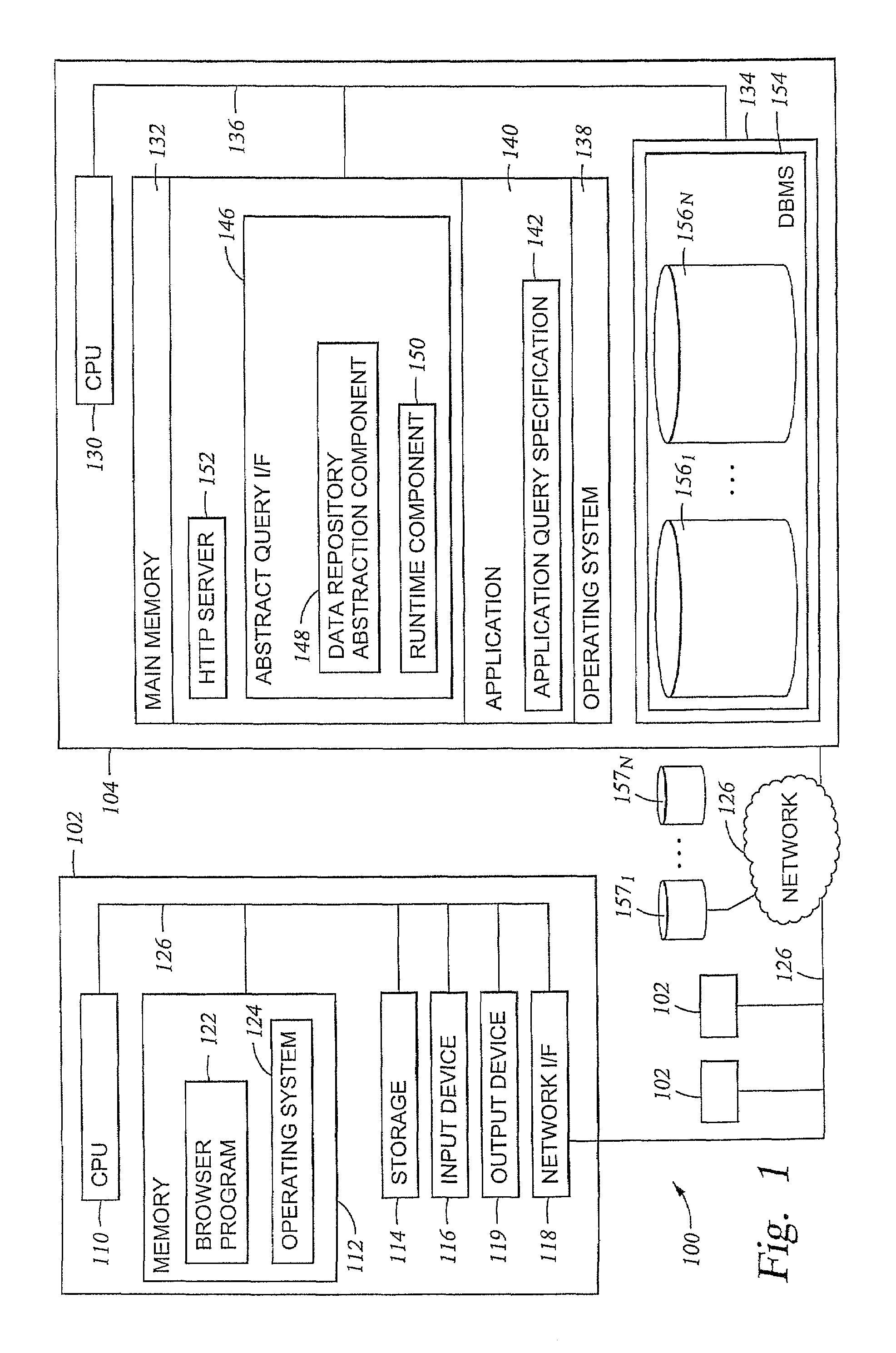

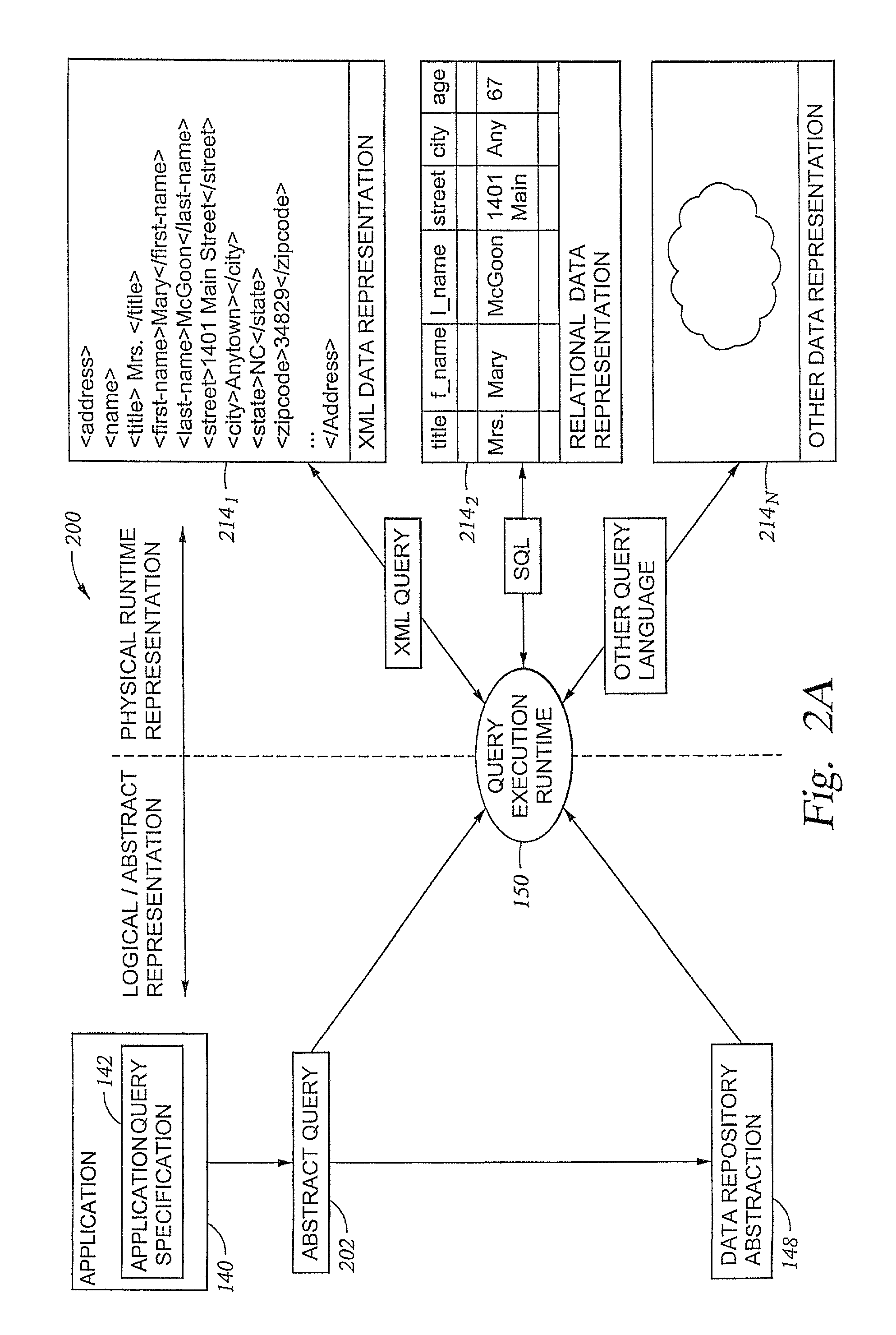

Dynamic content generation/regeneration for a database schema abstraction

InactiveUS7096229B2Data processing applicationsDatabase queryingSegment descriptorField specification

A method, system and article of manufacture for generating a logical field specification for a logical field associated with a physical entity of data in a computer system, the physical entity of data having a particular physical data representation, the method comprising: providing a logical field specification template comprising a plurality of specification sub-fields, each specification sub-field designated by a sub-field descriptor; accessing the physical entity of data to determine data items associated with the sub-field descriptors; and linking each specification sub-field to a corresponding determined data item.

Owner:IBM CORP

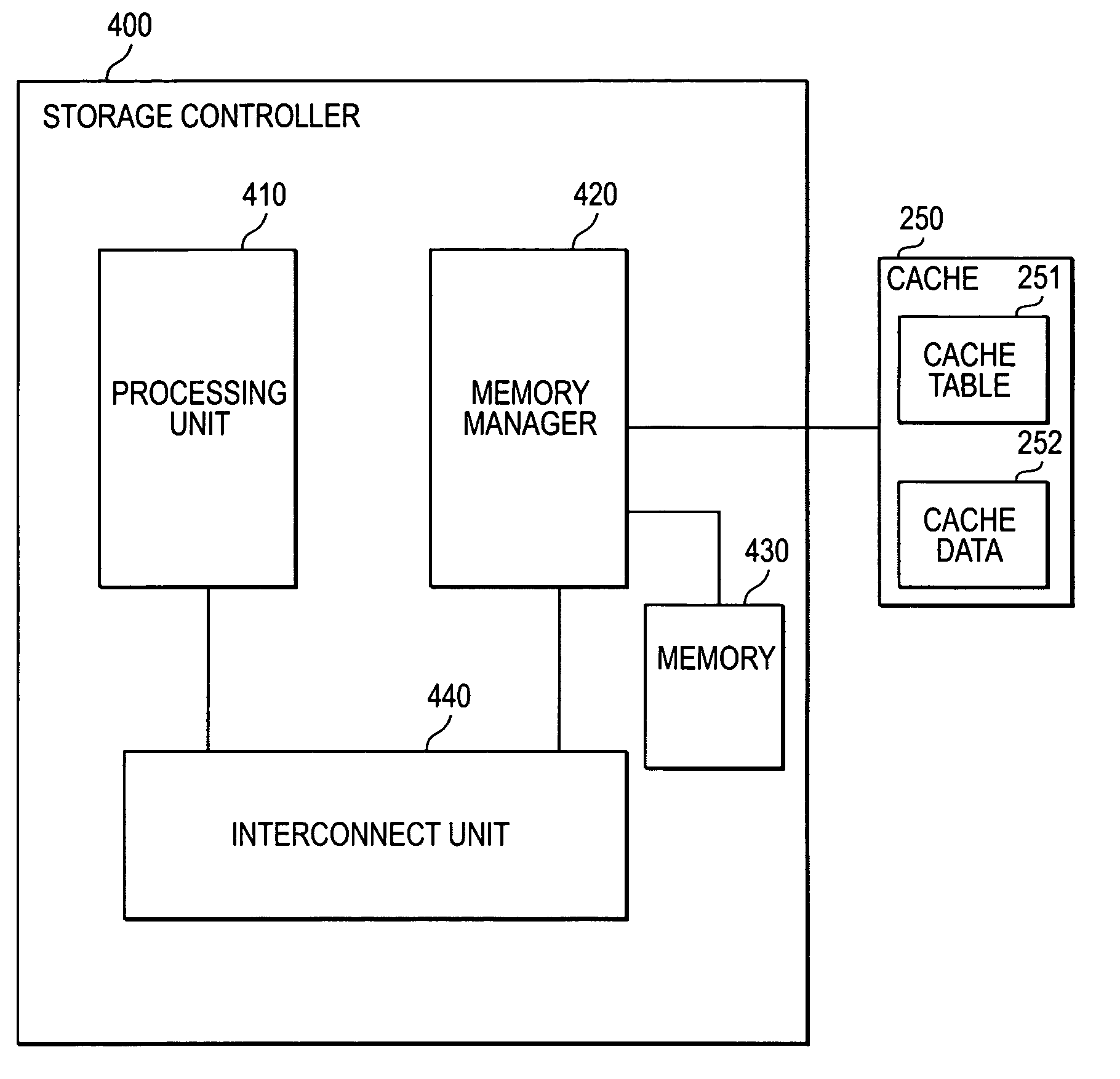

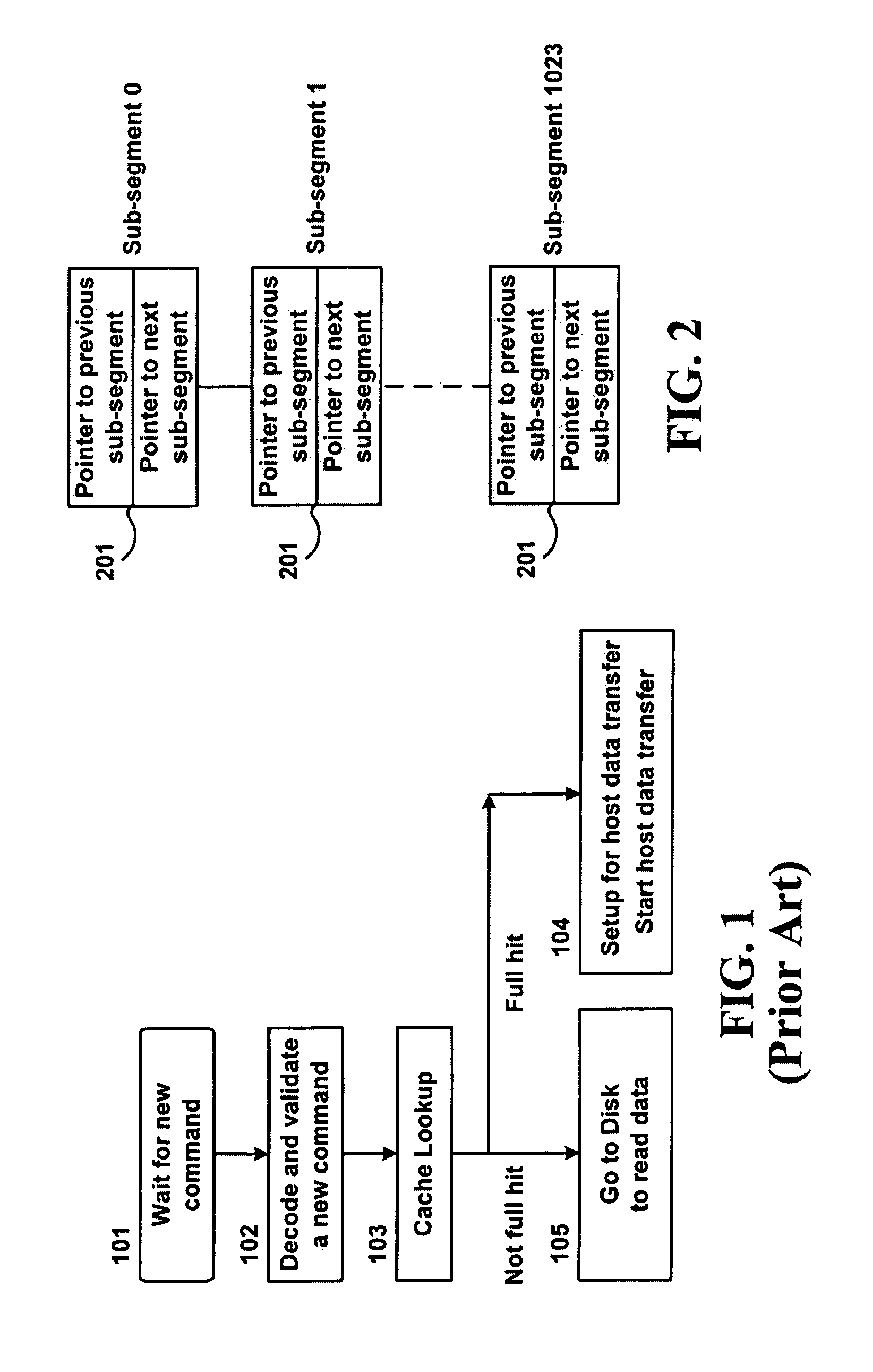

System and method for maintaining cache coherency without external controller intervention

InactiveUS7043610B2Efficiently detectsEfficiently resolveMemory adressing/allocation/relocationSegment descriptorControl store

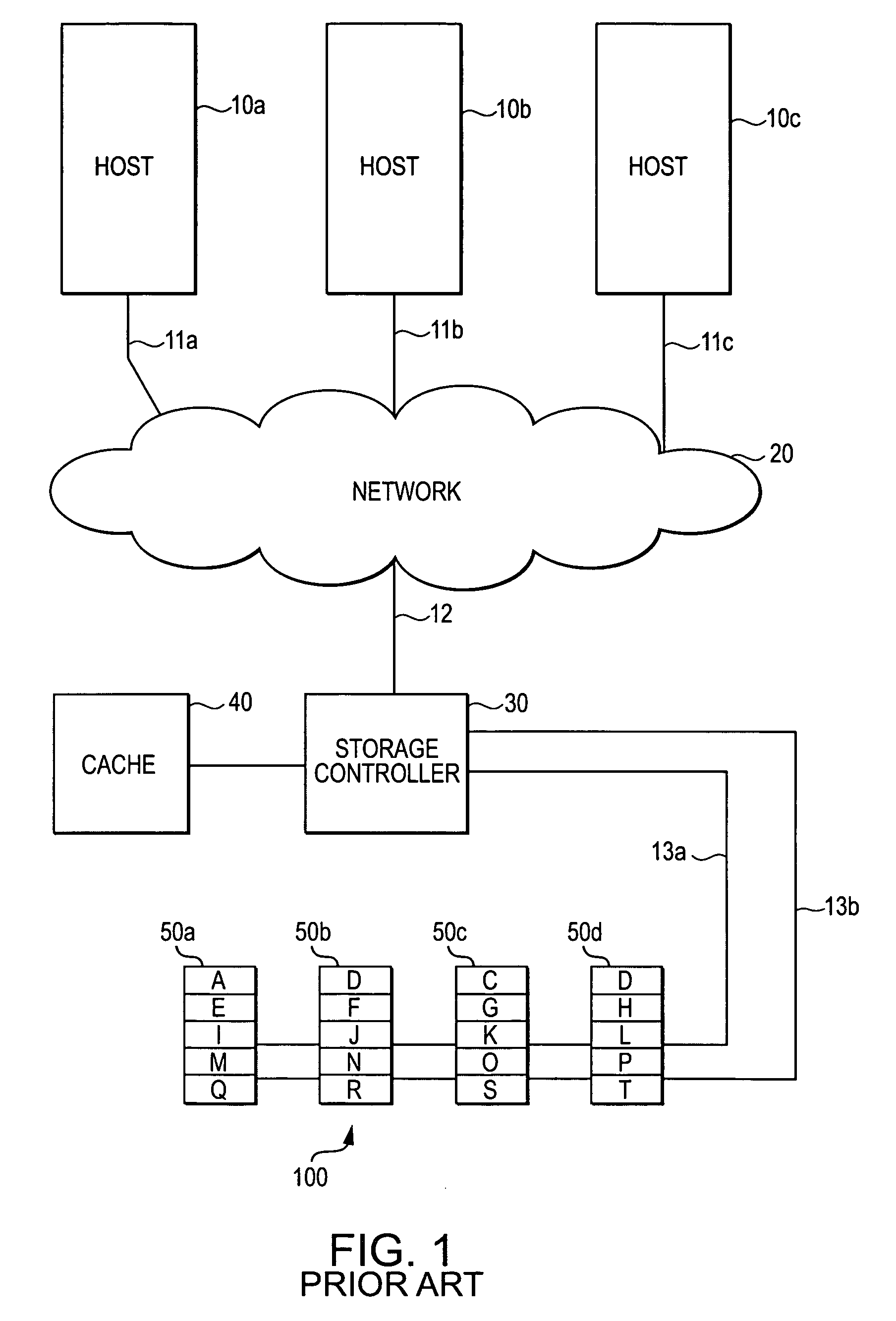

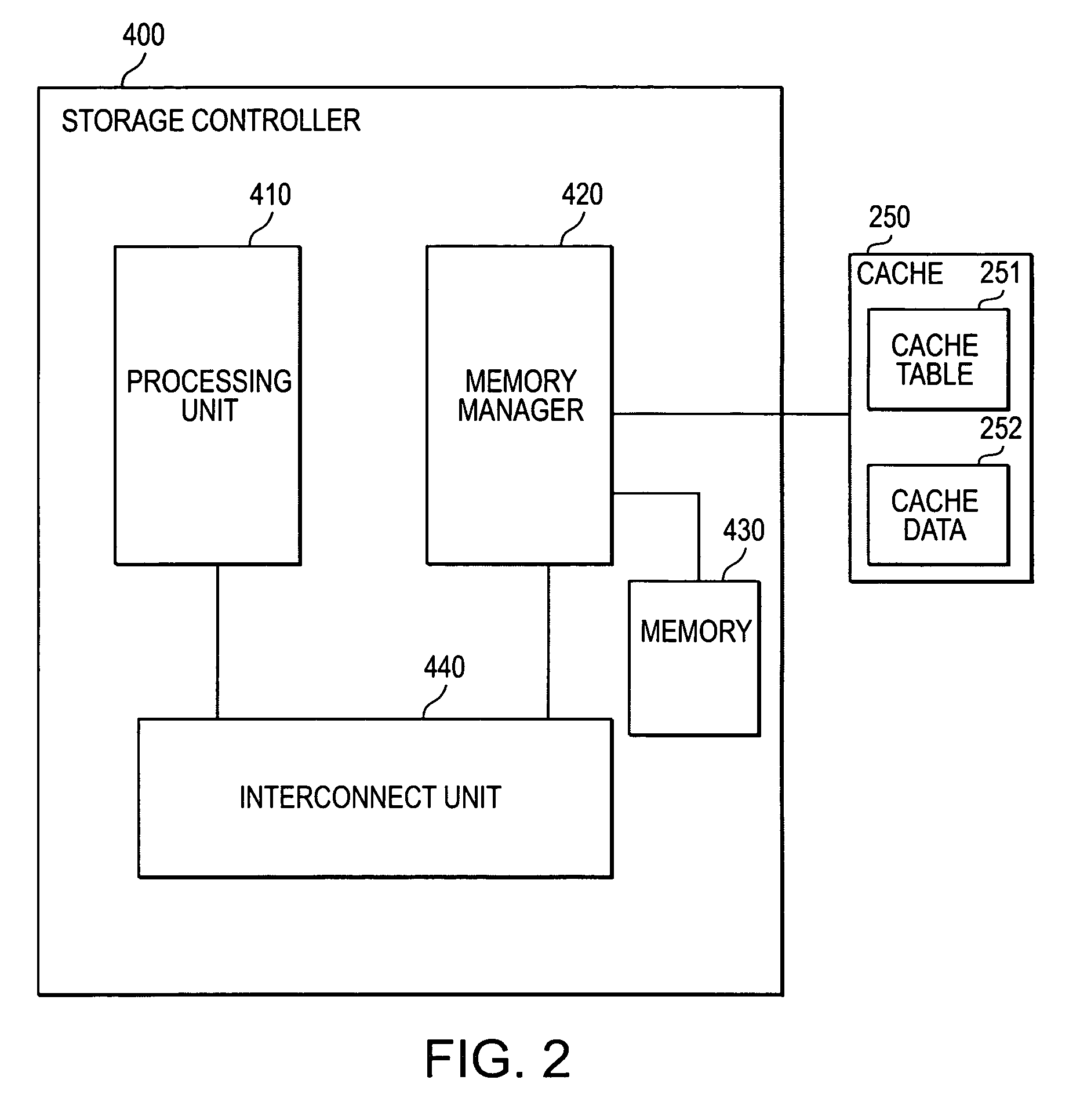

A disk array includes a system and method for cache management and conflict detection. Incoming host commands are processed by a storage controller, which identifies a set of at least one cache segment descriptor (CSD) associated with the requested address range. Command conflict detection can be quickly performed by examining the state information of each CSD associated with the command. The use of CSDs therefore permits the present invention to rapidly and efficiently perform read and write commands and detect conflicts.

Owner:ADAPTEC

Text generation and searching method and system

ActiveUS20050125435A1Data processing applicationsDigital data processing detailsSegment descriptorData field

A text-generation method and system includes receiving data records, such that each data record includes one or more data fields and a field value associated with each data field. A text-string is generated for each data record, such that each text-string includes one or more text-based data descriptors. Each data descriptor includes a field descriptor that defines a specific data field within the data record to which the text-string is related, and a value descriptor that defines the field value associated with the specific data field.

Owner:COGNIZANT TRIZETTO SOFTWARE GRP INC

Text generation and searching method and system

ActiveUS7478049B2Data processing applicationsDigital data processing detailsSegment descriptorData field

Owner:COGNIZANT TRIZETTO SOFTWARE GRP INC

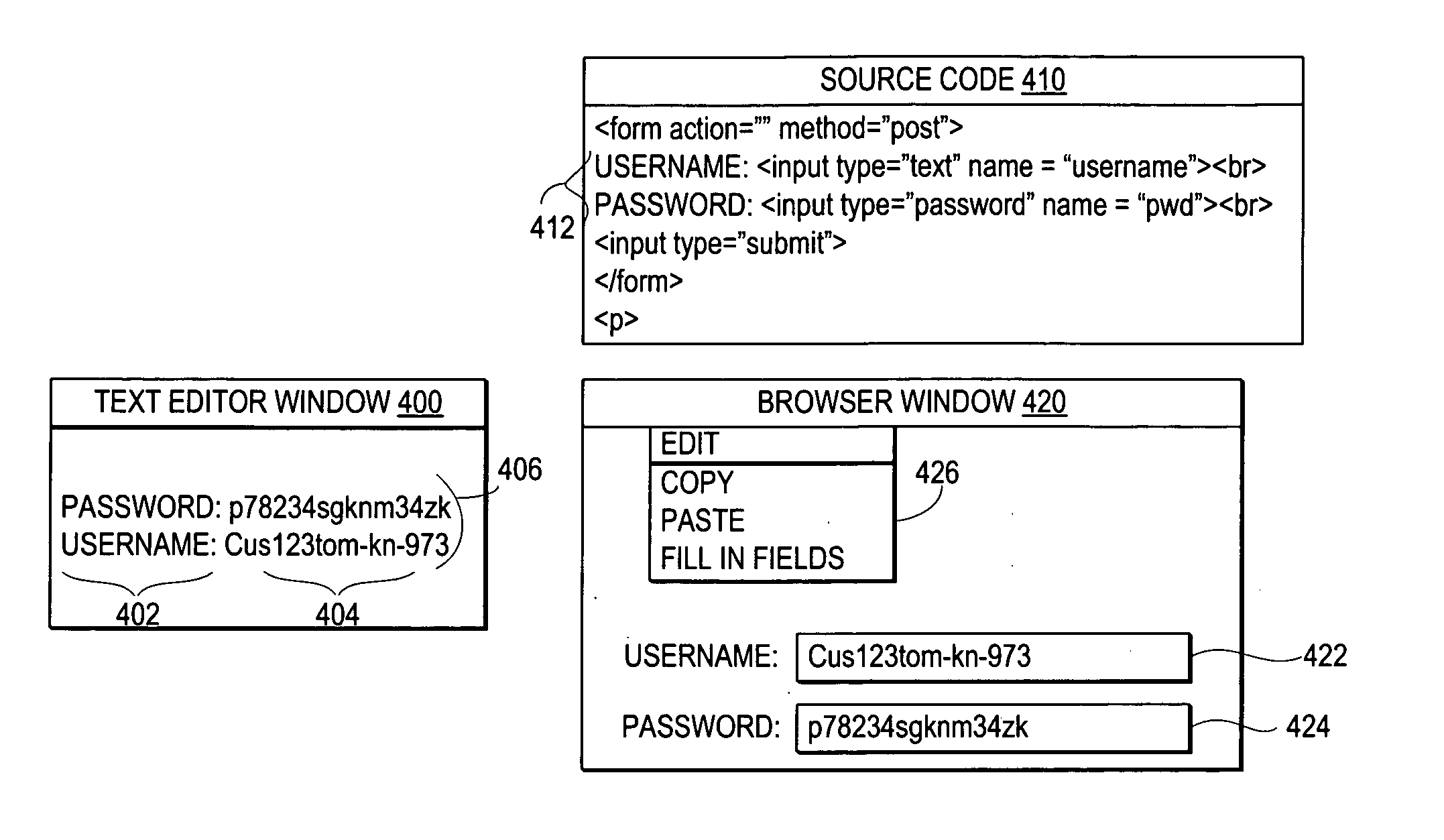

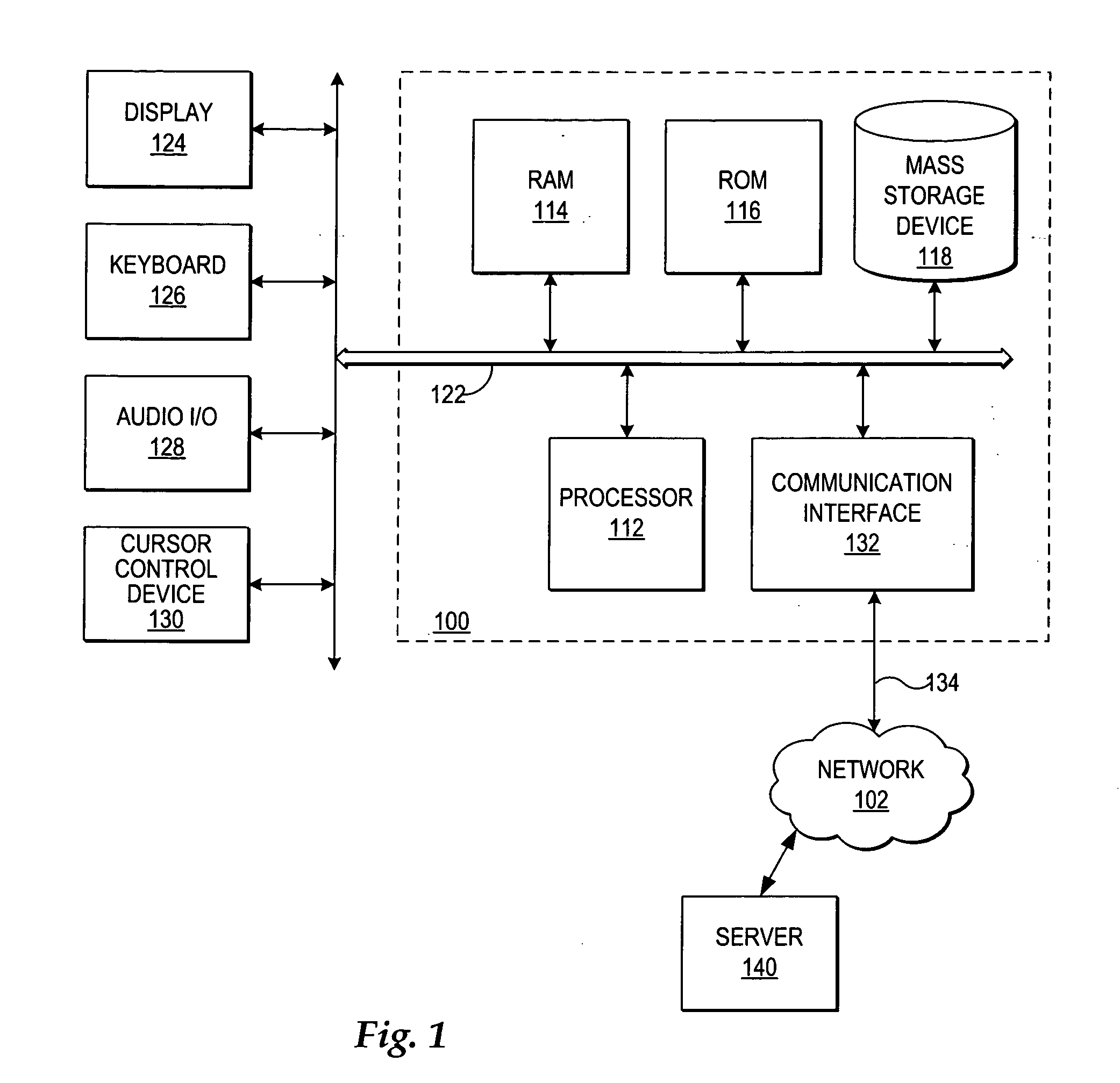

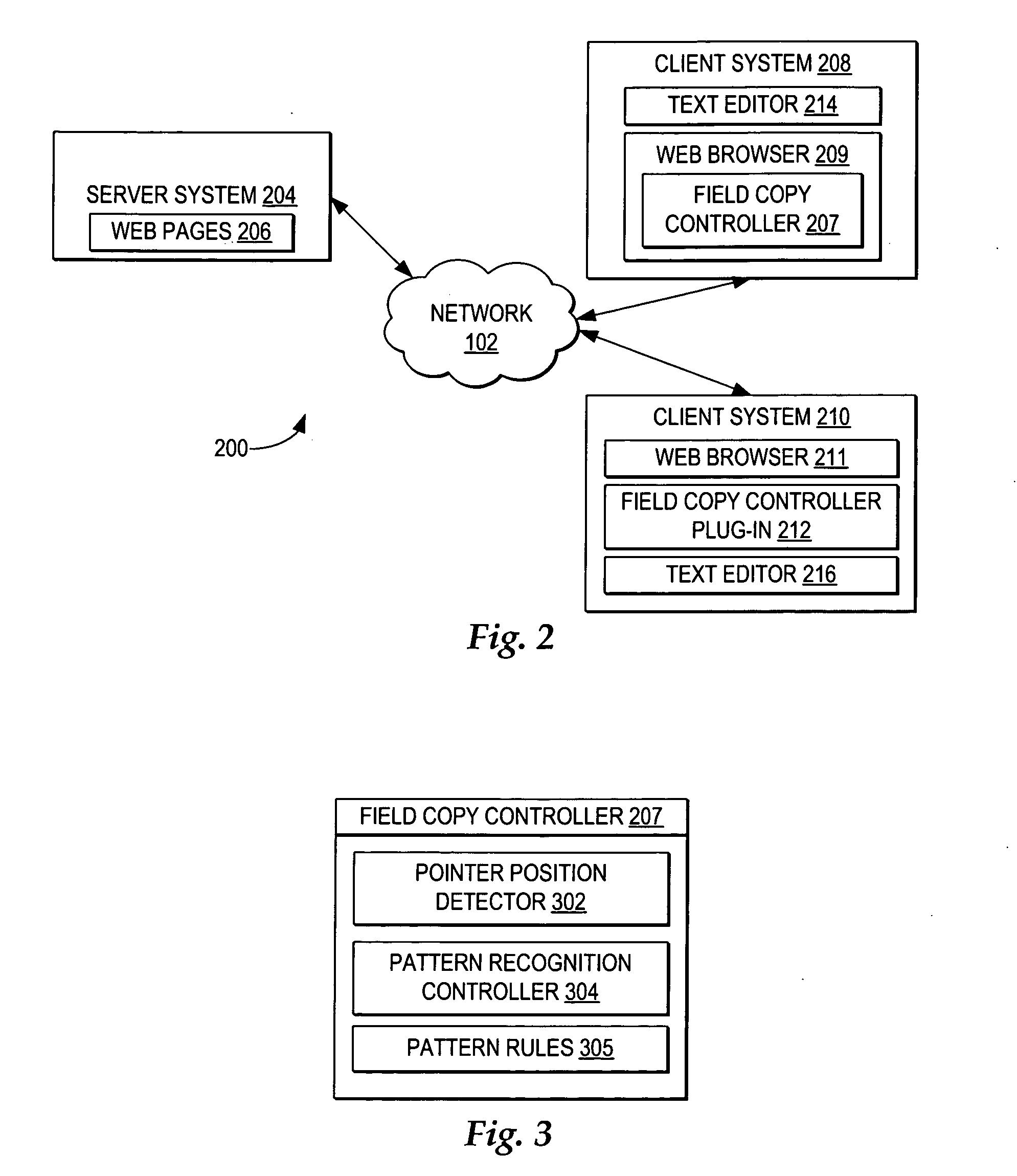

Automatic simultaneous entry of values in multiple web page fields

InactiveUS20060059247A1Improved copyingImproved pastingNatural language data processingMultiple digital computer combinationsWeb browserSegment descriptor

A method, system, and program for automatic simultaneous entry of values in multiple web page fields are provided. Responsive to detecting a single action selection by a user to fill multiple fields of a web page, wherein each of the fields is associated with one from among multiple field descriptors within a source code for the web page, a field copy controller scans multiple lines of text copied into a local memory to identify text tags that match the field descriptors. Then, the field copy controller automatically fills in the fields within the web browser with the values from the lines of text, wherein each of the values is associated with one from among multiple text tags matching the field descriptors associated with the fields, such that multiple fields of a web page are automatically filled in responsive to only a single action by a user.

Owner:IBM CORP

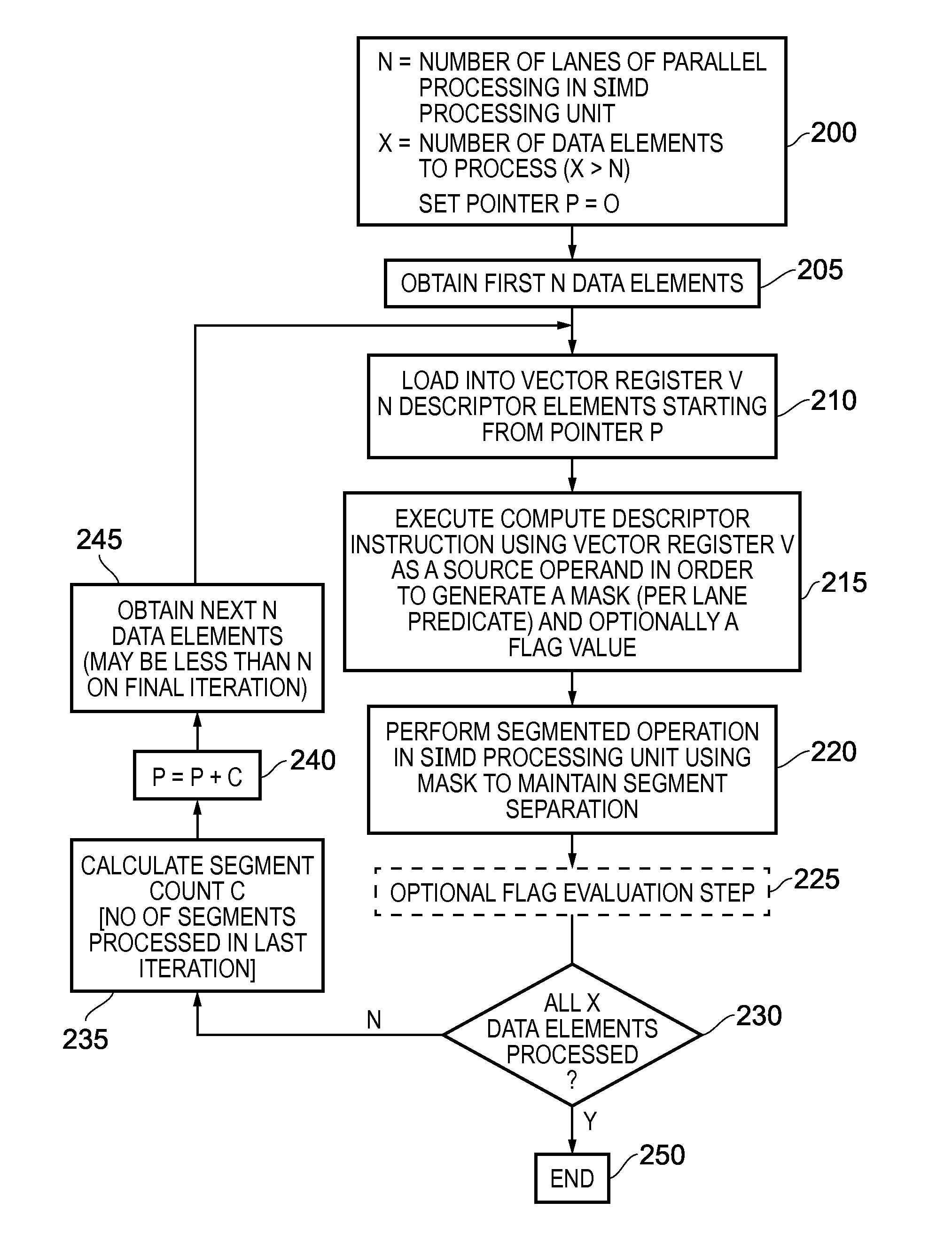

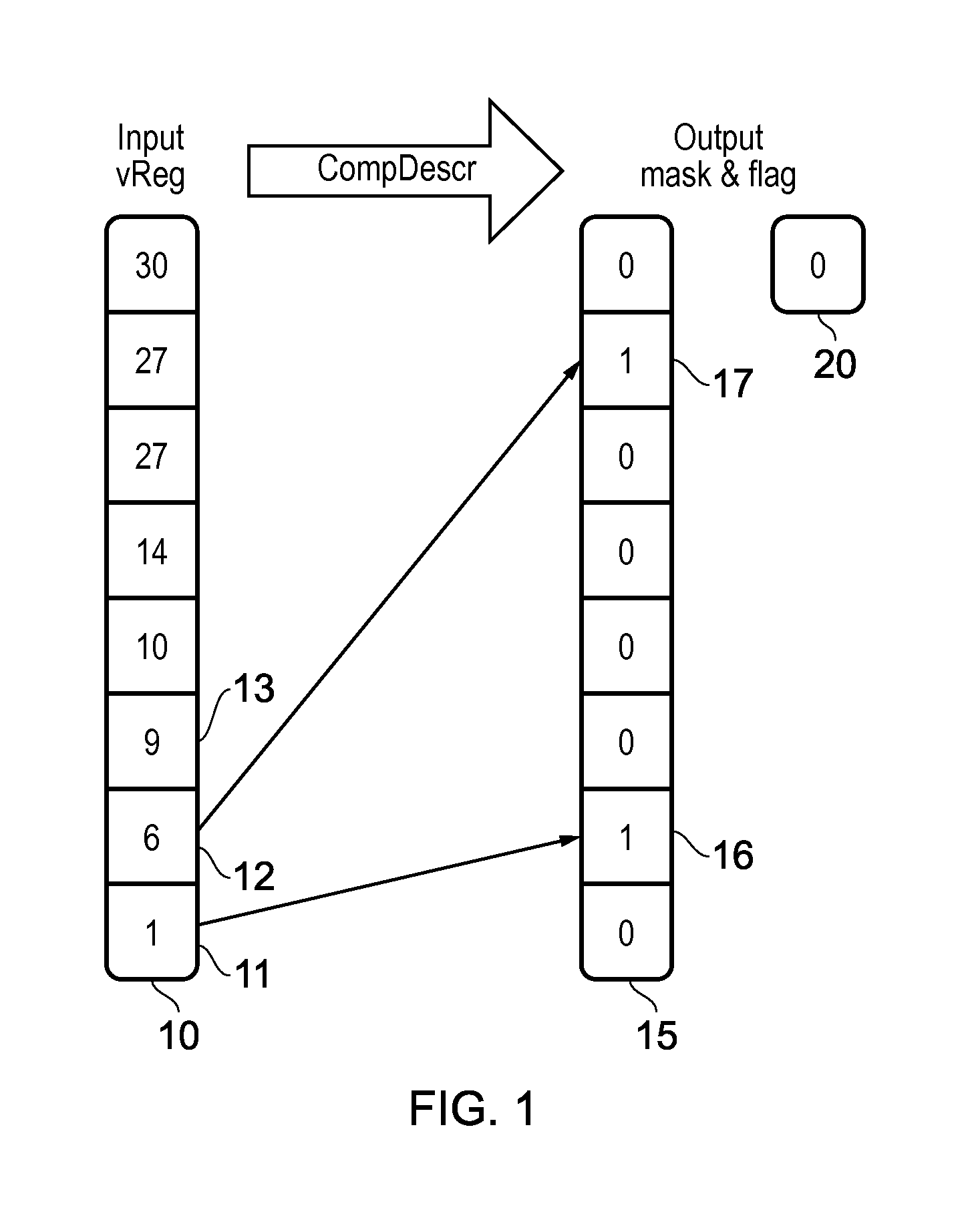

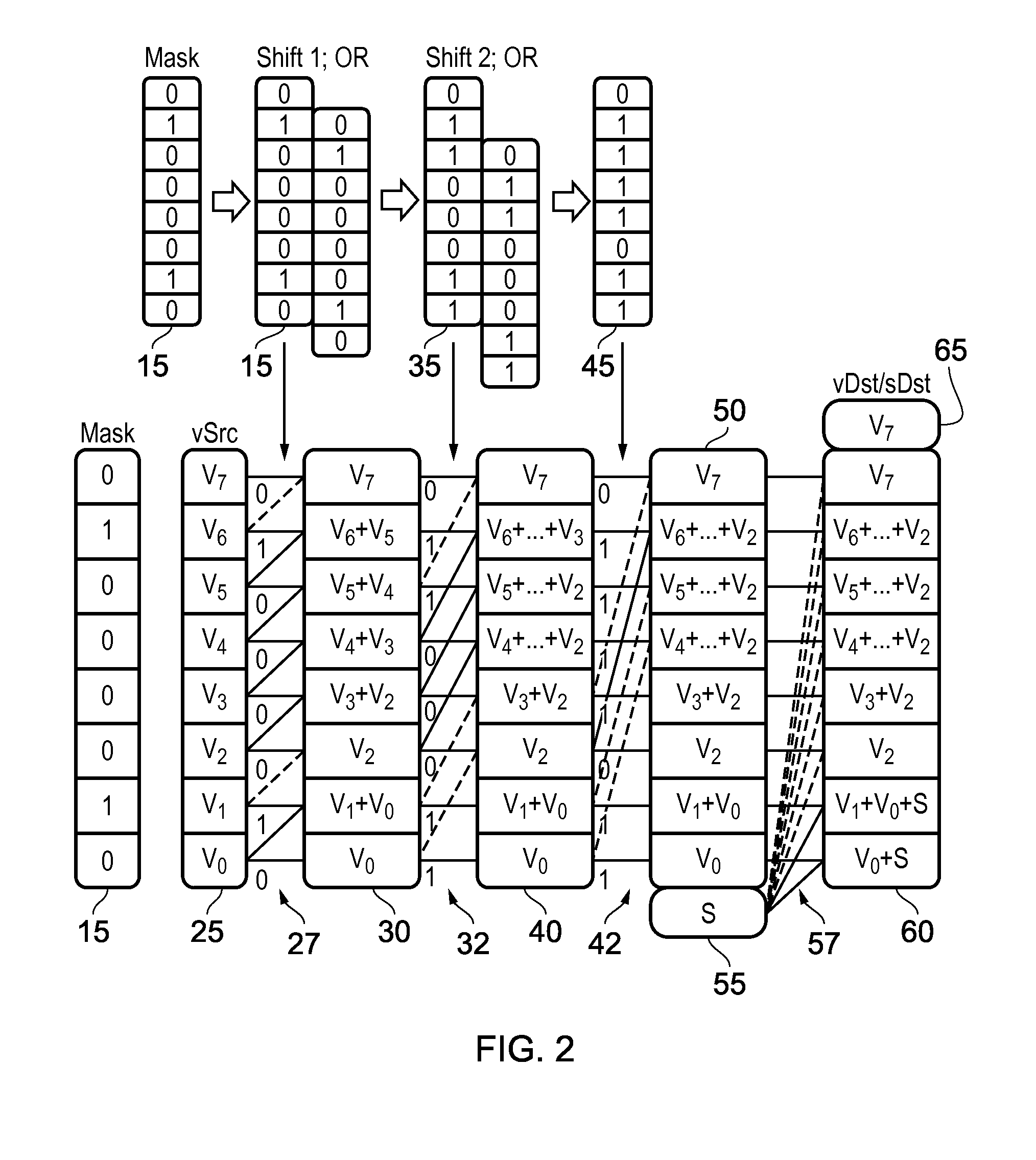

Data processing apparatus and method for performing segmented operations

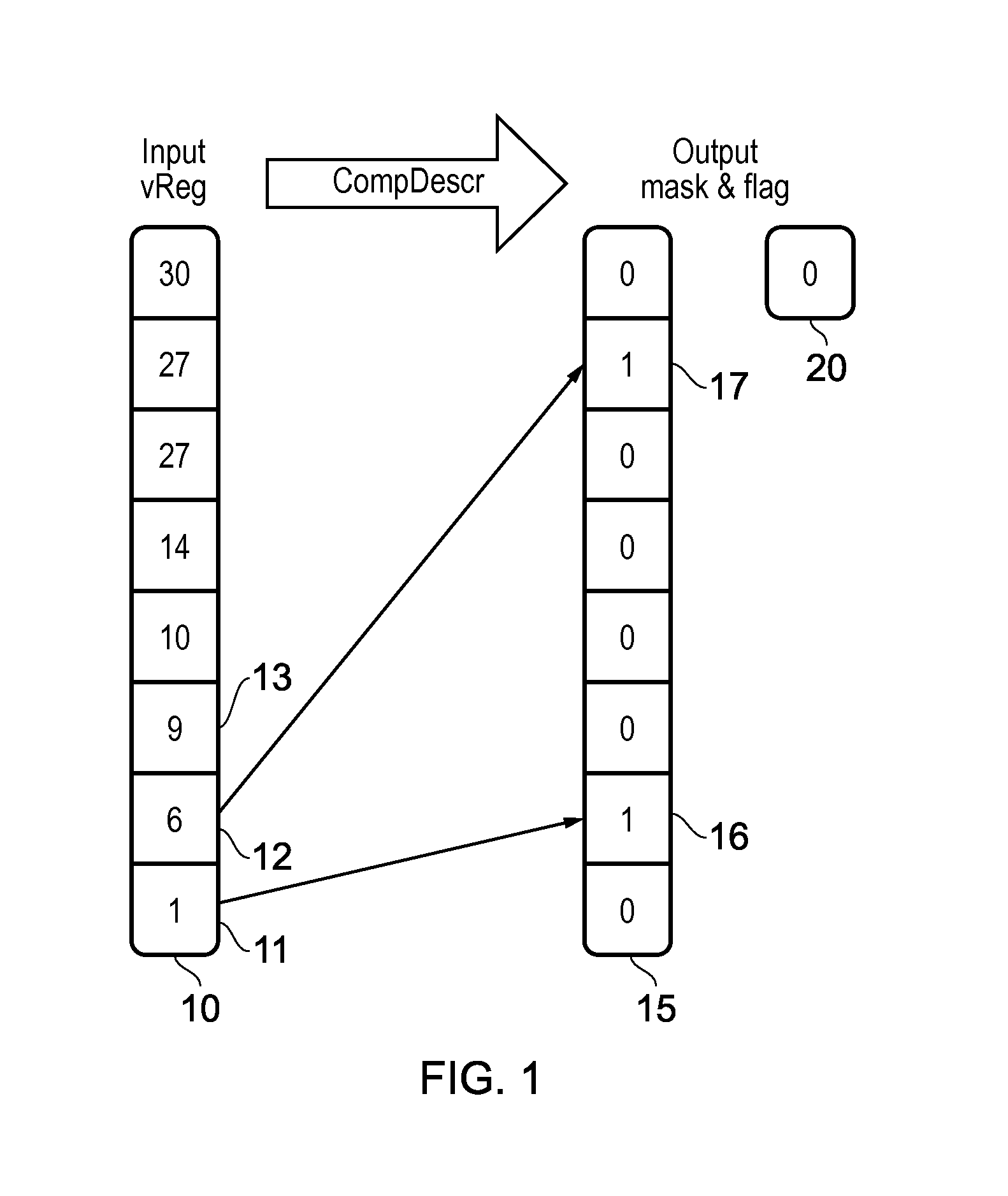

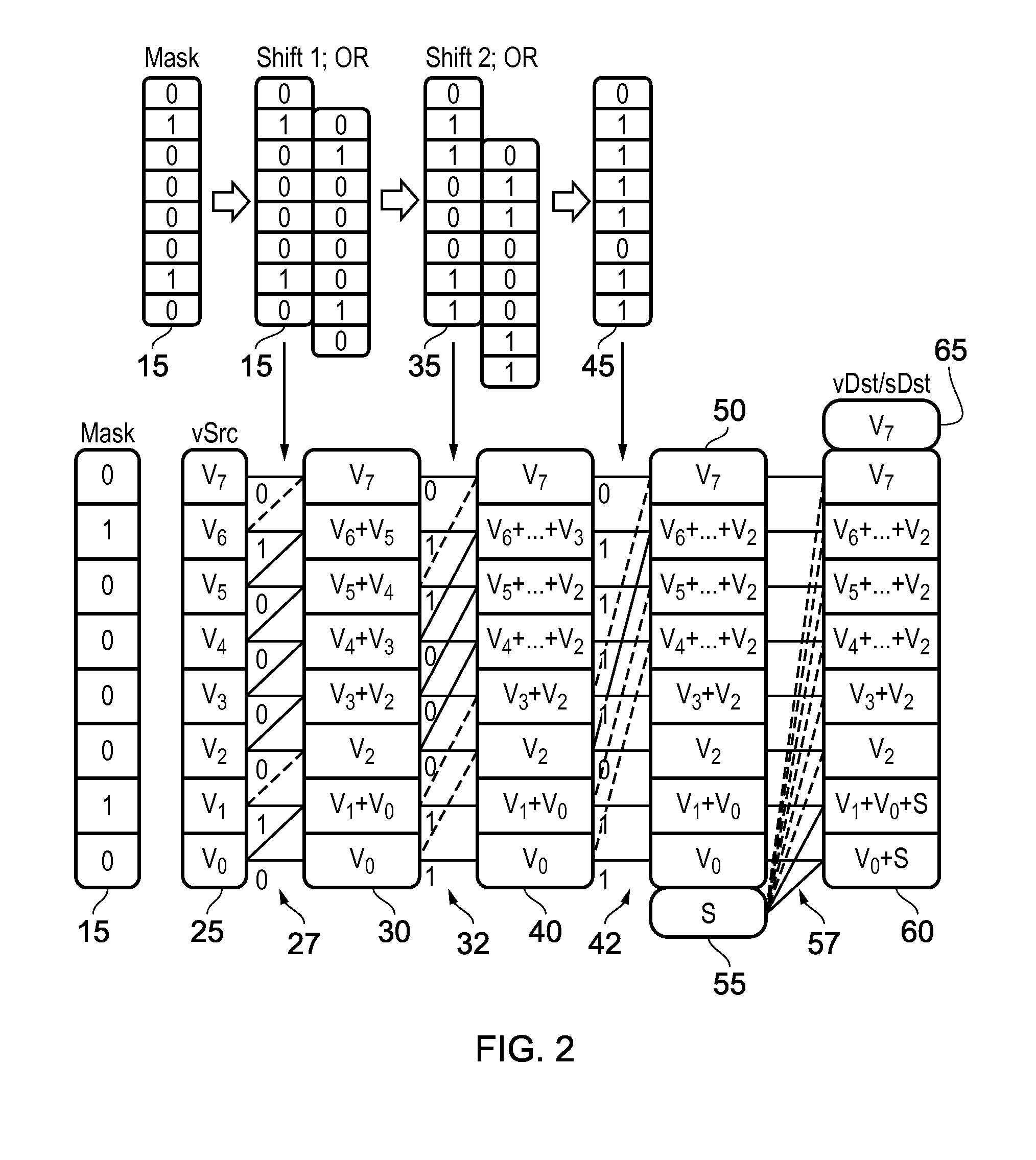

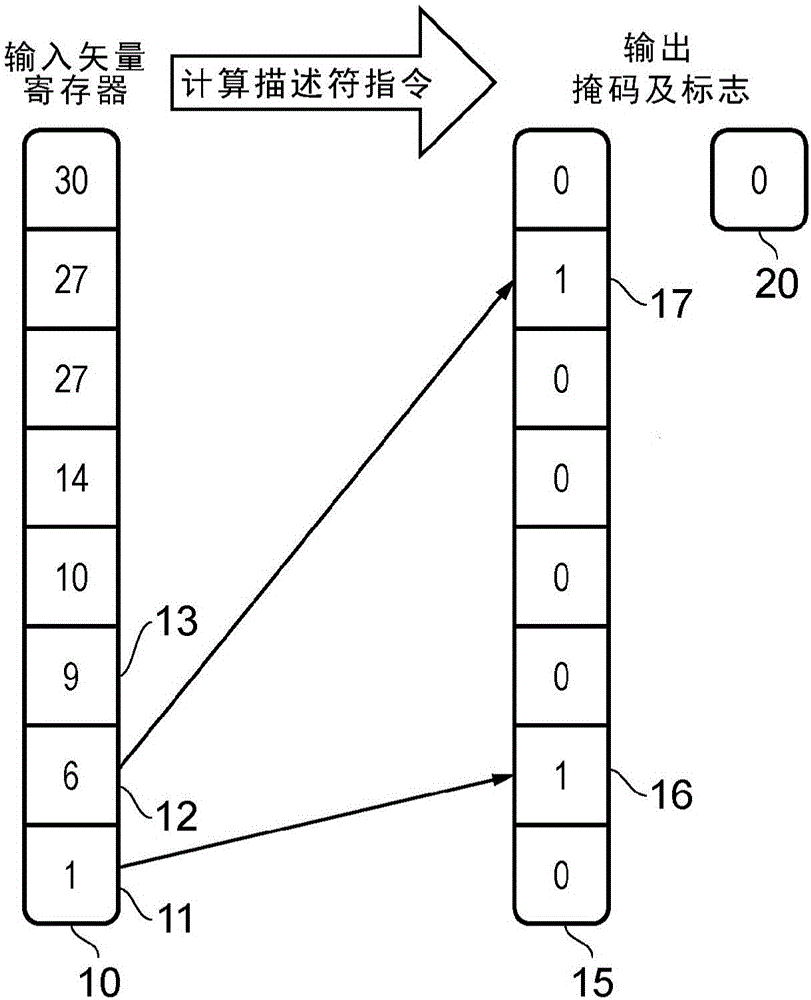

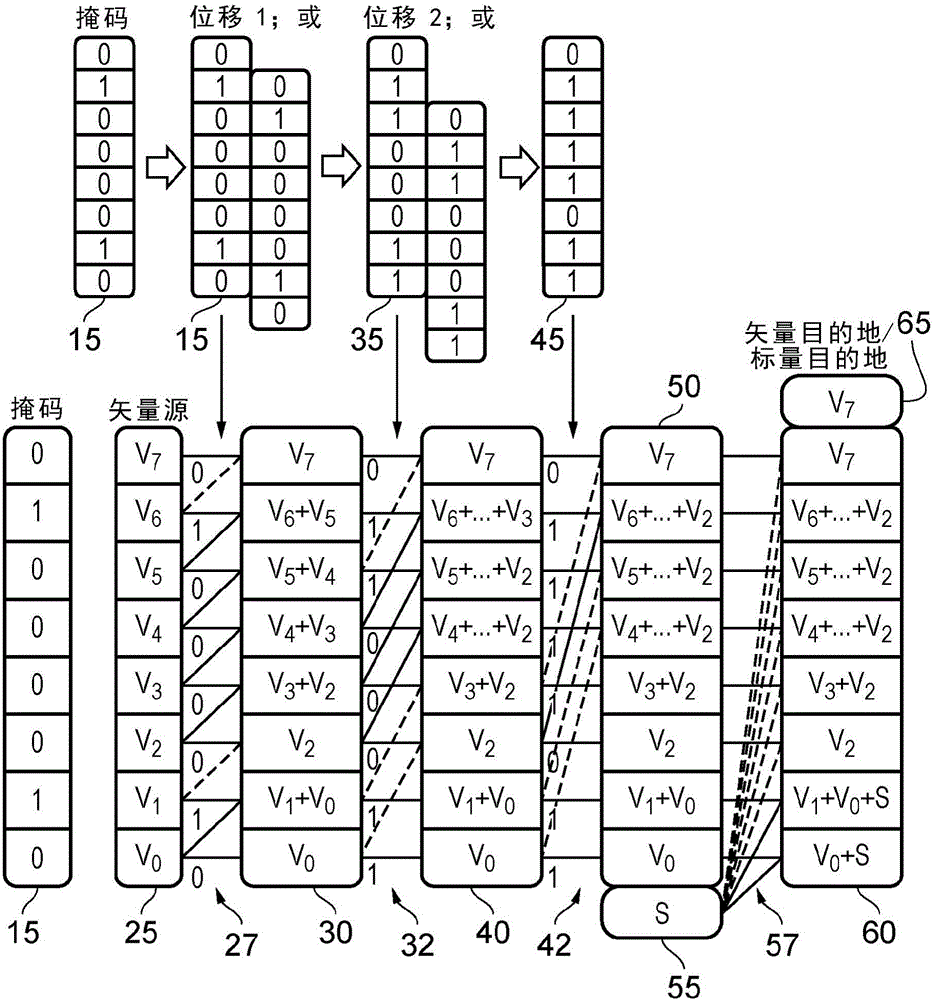

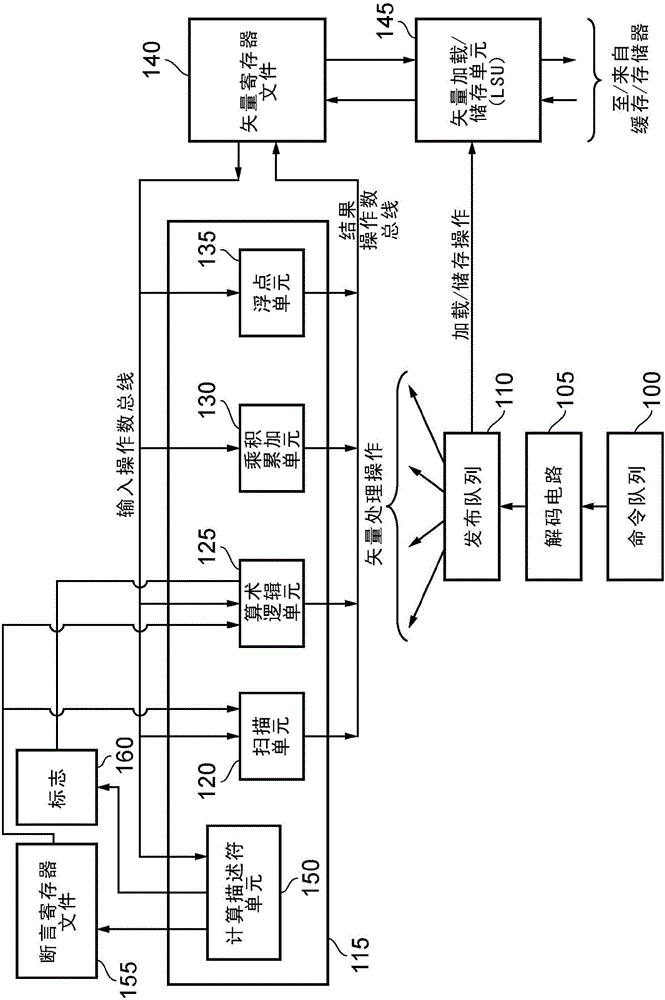

ActiveUS20150227367A1Efficient use ofSave energy consumptionRegister arrangementsGeneral purpose stored program computerSegment descriptorOperand

A data processing apparatus and method are provided for performing segmented operations. The data processing apparatus comprises a vector register store for storing vector operands, and vector processing circuitry providing N lanes of parallel processing, and arranged to perform a segmented operation on up to N data elements provided by a specified vector operand, each data element being allocated to one of the N lanes. The up to N data elements forms a plurality of segments, and performance of the segmented operation comprises performing a separate operation on the data elements of each segment, the separate operation involving interaction between the lanes containing the data elements of the associated segment. Predicate generation circuitry is responsive to a compute descriptor instruction specifying an input vector operand comprising a plurality of segment descriptors, to generate per lane predicate information used by the vector processing circuitry when performing the segmented operation to maintain a boundary between each of the plurality of segments. As a result, interaction between lanes containing data elements from different segments is prevented. This allows very effective utilisation of the lanes of parallel processing within the vector processing circuitry to be achieved.

Owner:ARM LTD

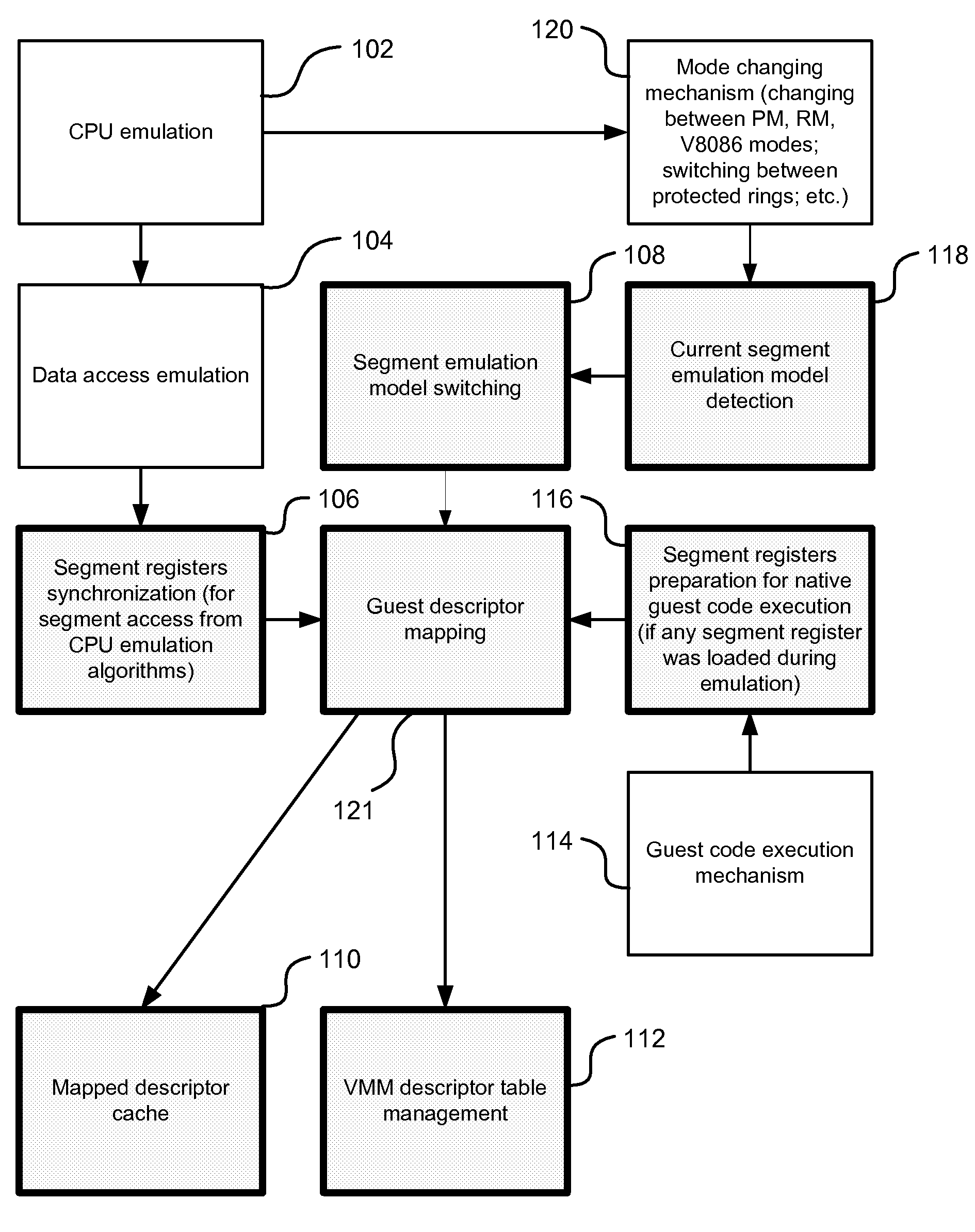

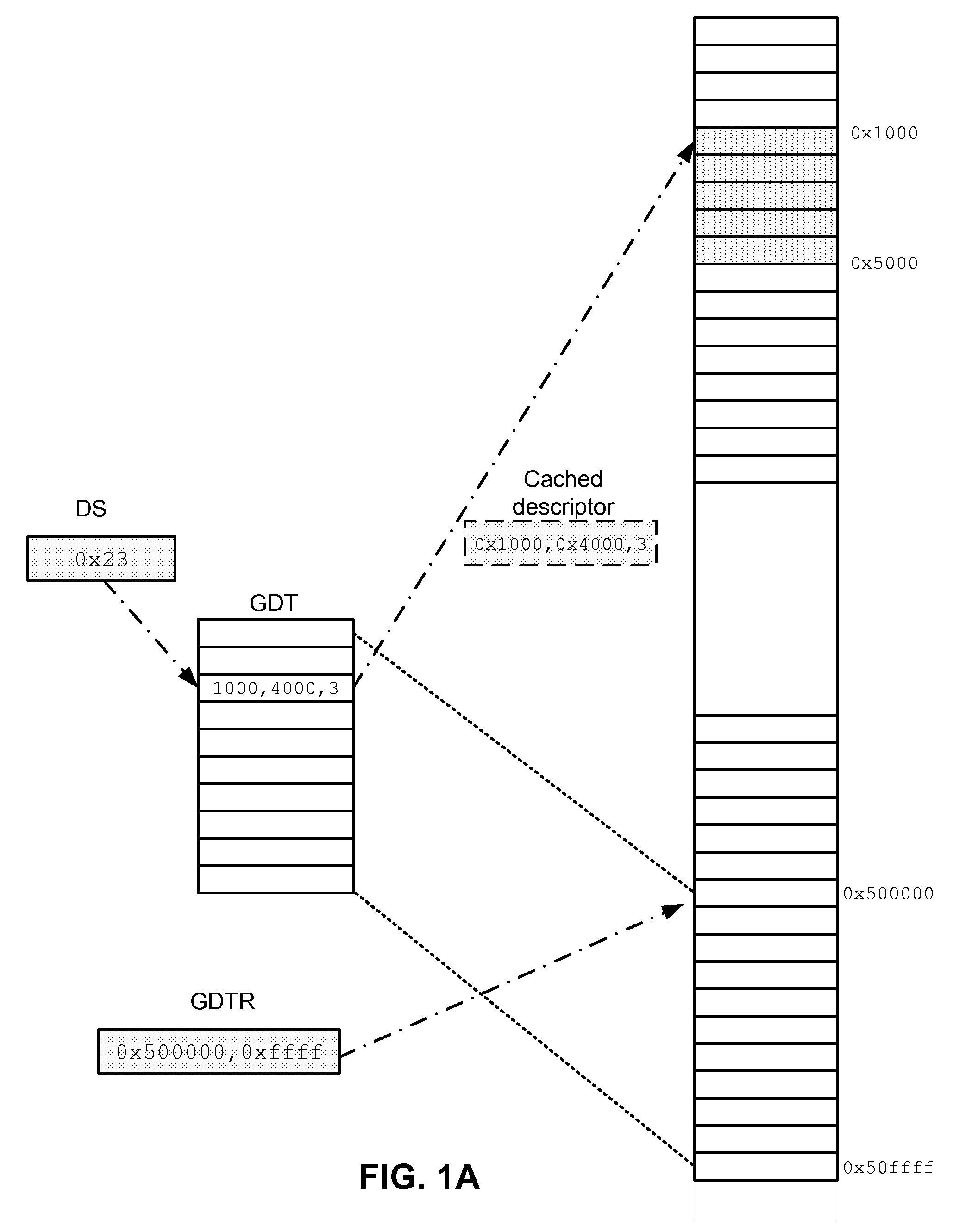

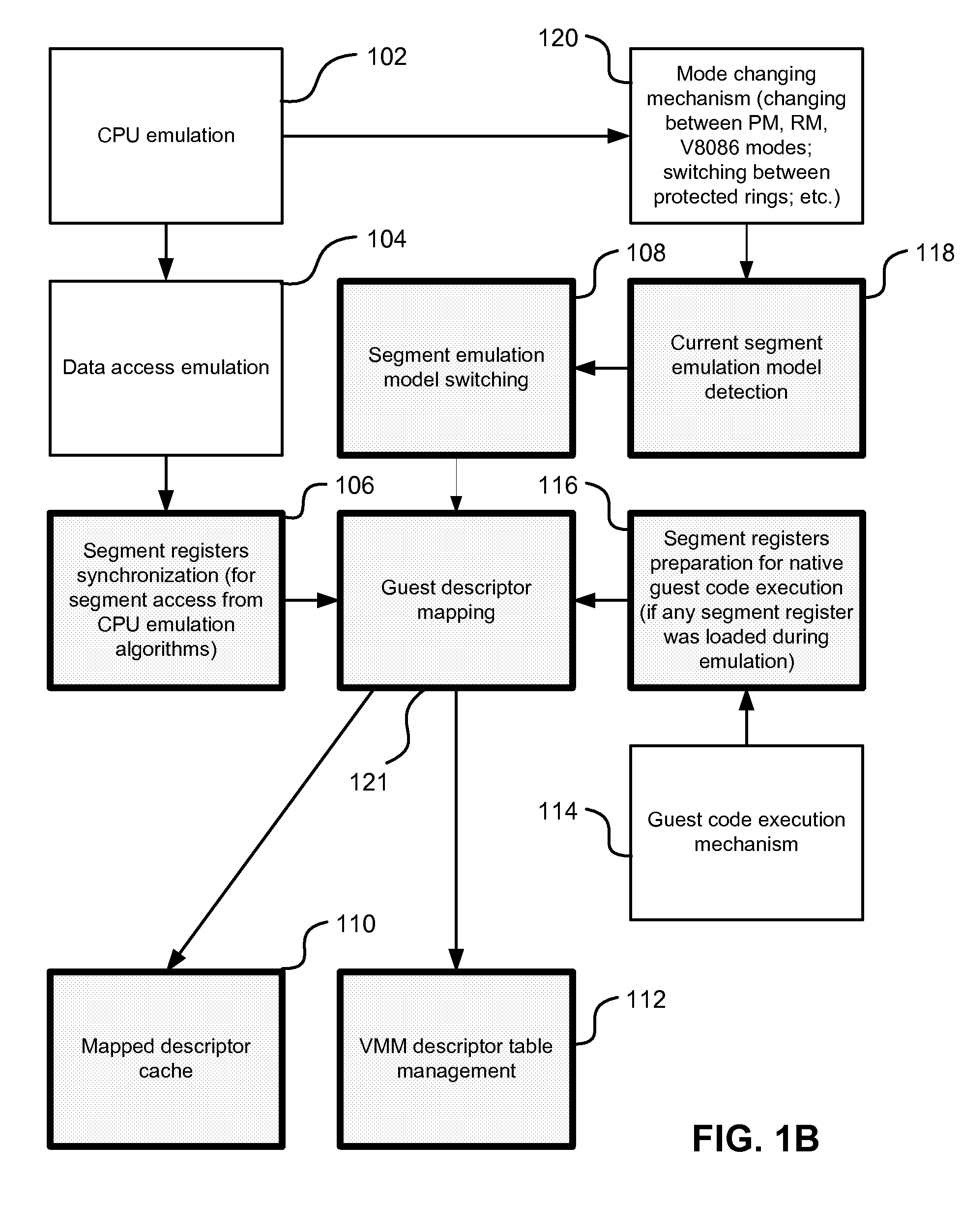

Memory segment emulation model for virtual machine

ActiveUS7506096B1Memory architecture accessing/allocationComputer security arrangementsSegment descriptorVirtual machine

A method of emulating segment addressing by a processor that includes initiating a Virtual Machine Monitor in a kernel mode; initiating a Virtual Machine in a user mode; forming a dynamically mapped table in Virtual Machine Monitor space, the dynamically mapped table corresponding to a table of segment descriptors of the Virtual Machine; populating the dynamically mapped table with descriptors that raise exceptions upon an attempt by the Virtual Machine to address a corresponding segment; and mapping a descriptor to the dynamically mapped table upon the Virtual Machine's use of that descriptor.

Owner:PARALLELS INT GMBH

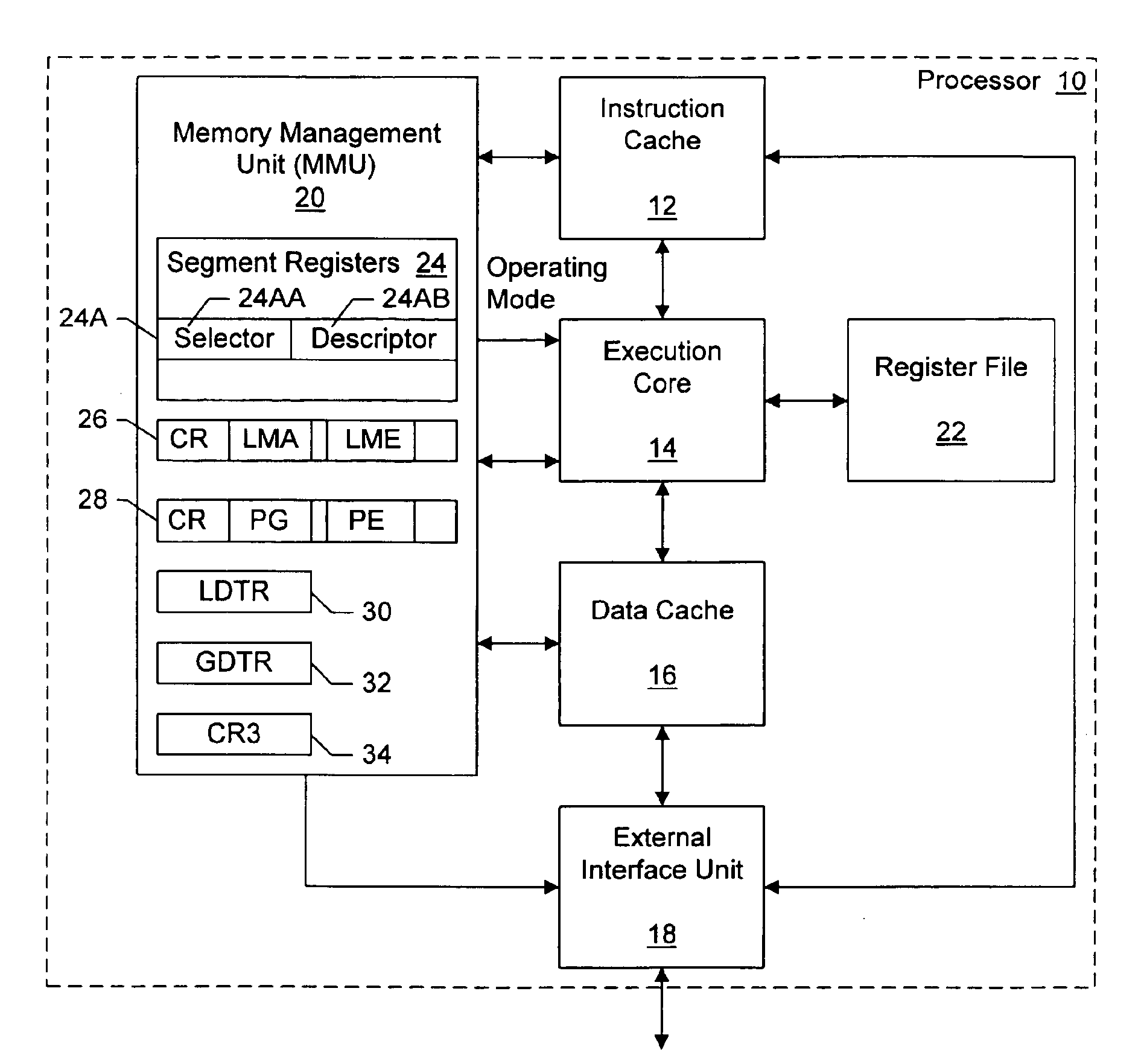

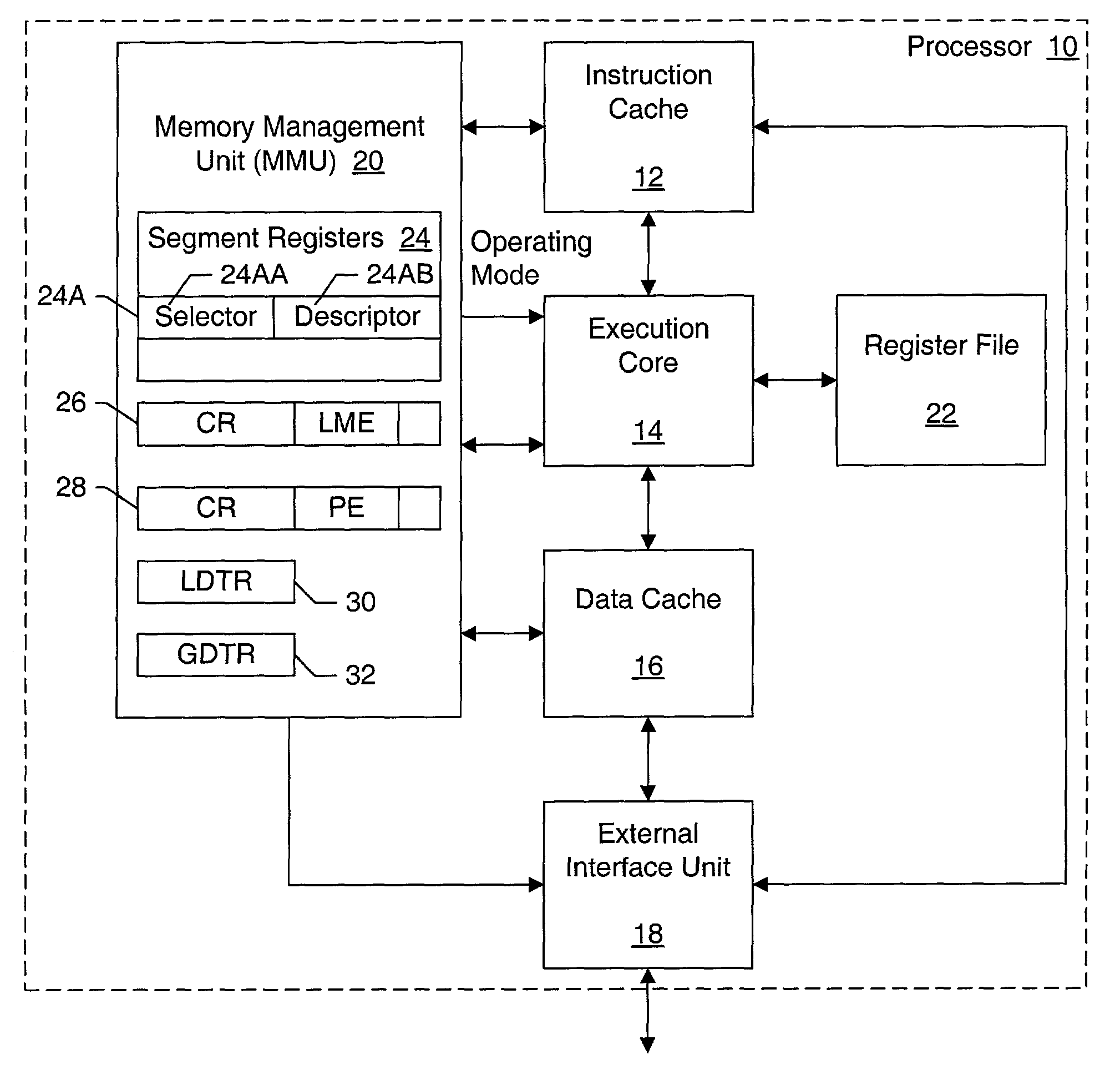

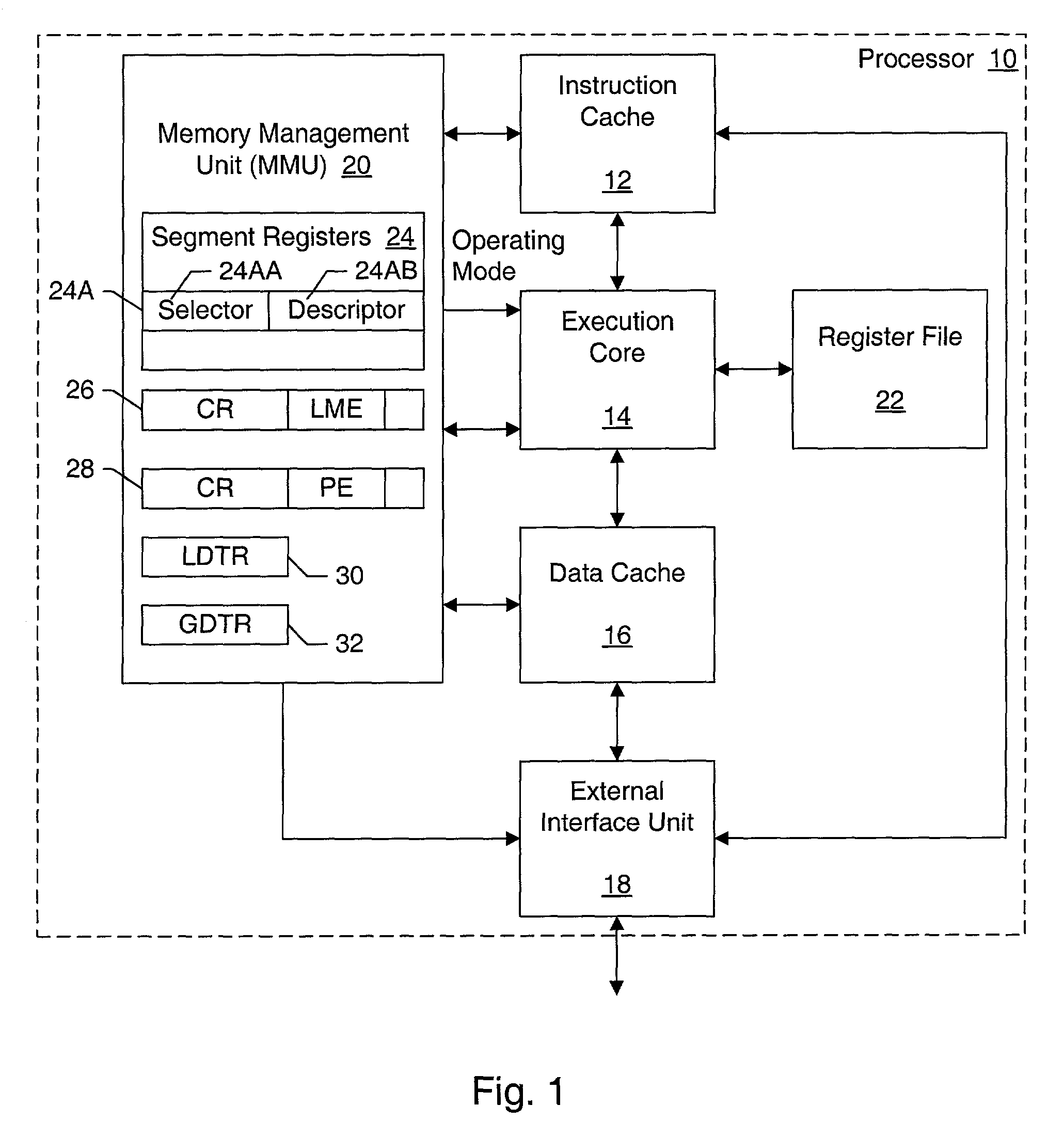

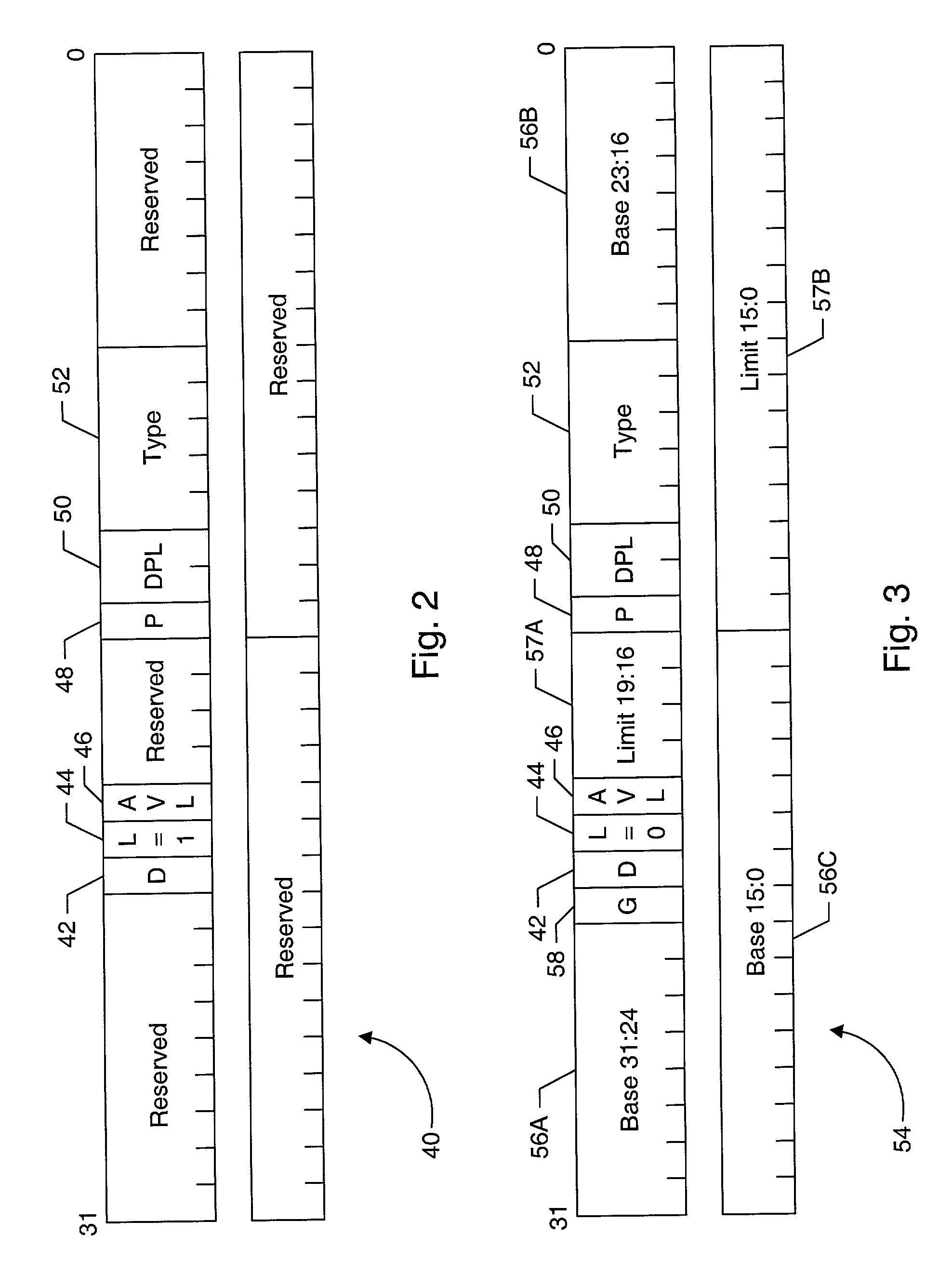

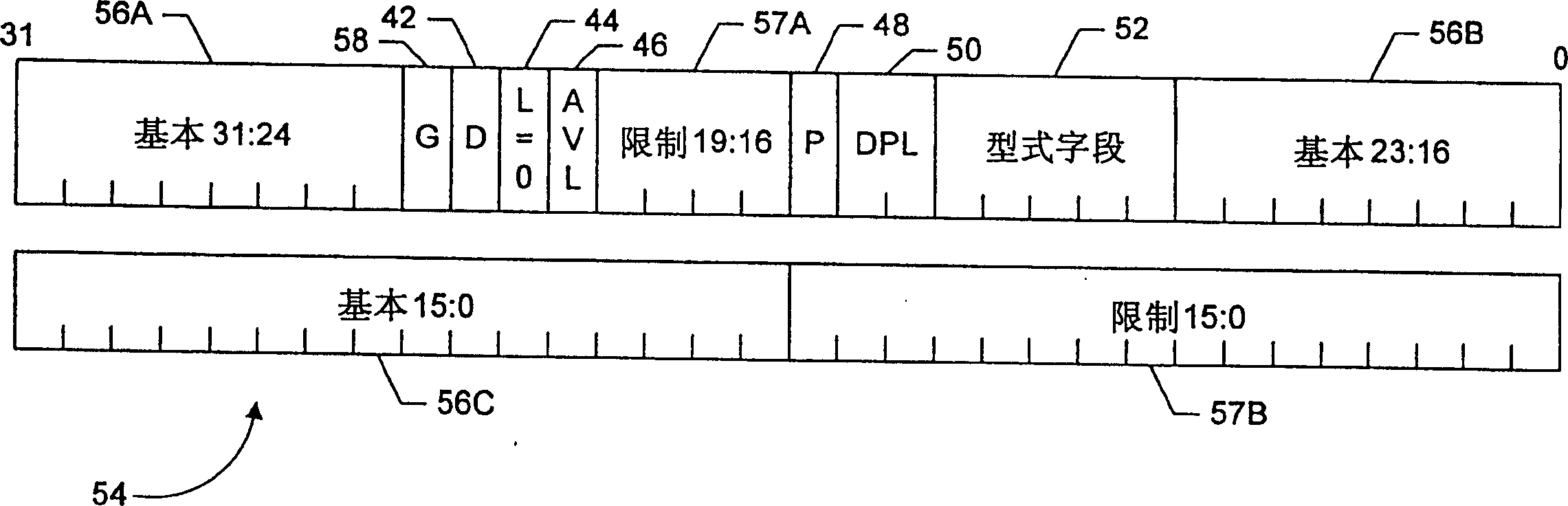

Mode dependent segment use with mode independent segment update

InactiveUS6880068B1Maintain compatibilityProtection operationMemory adressing/allocation/relocationDigital computer detailsSegment descriptorLoad instruction

A processor includes multiple protected operating modes. In at least one of the protected operating modes, segmentation is disabled or partially disabled. In other words, segment descriptor information may not affect the execution of an instruction specifying the segment register storing the segment descriptor information. In other protected operating modes, segmentation may not be disabled (e.g. segment descriptor information does affect the execution of the instruction specifying the segment register storing the segment descriptor information). However, segment load instructions may be performed in any protected operating mode (including checking segment descriptors for exception conditions during the segment load), which may allow a code sequence executing in one of the protected operating modes in which segmentation is disabled to establish segments in the segment registers for use by other code sequences executing in other protected operating modes.

Owner:ADVANCED MICRO DEVICES INC

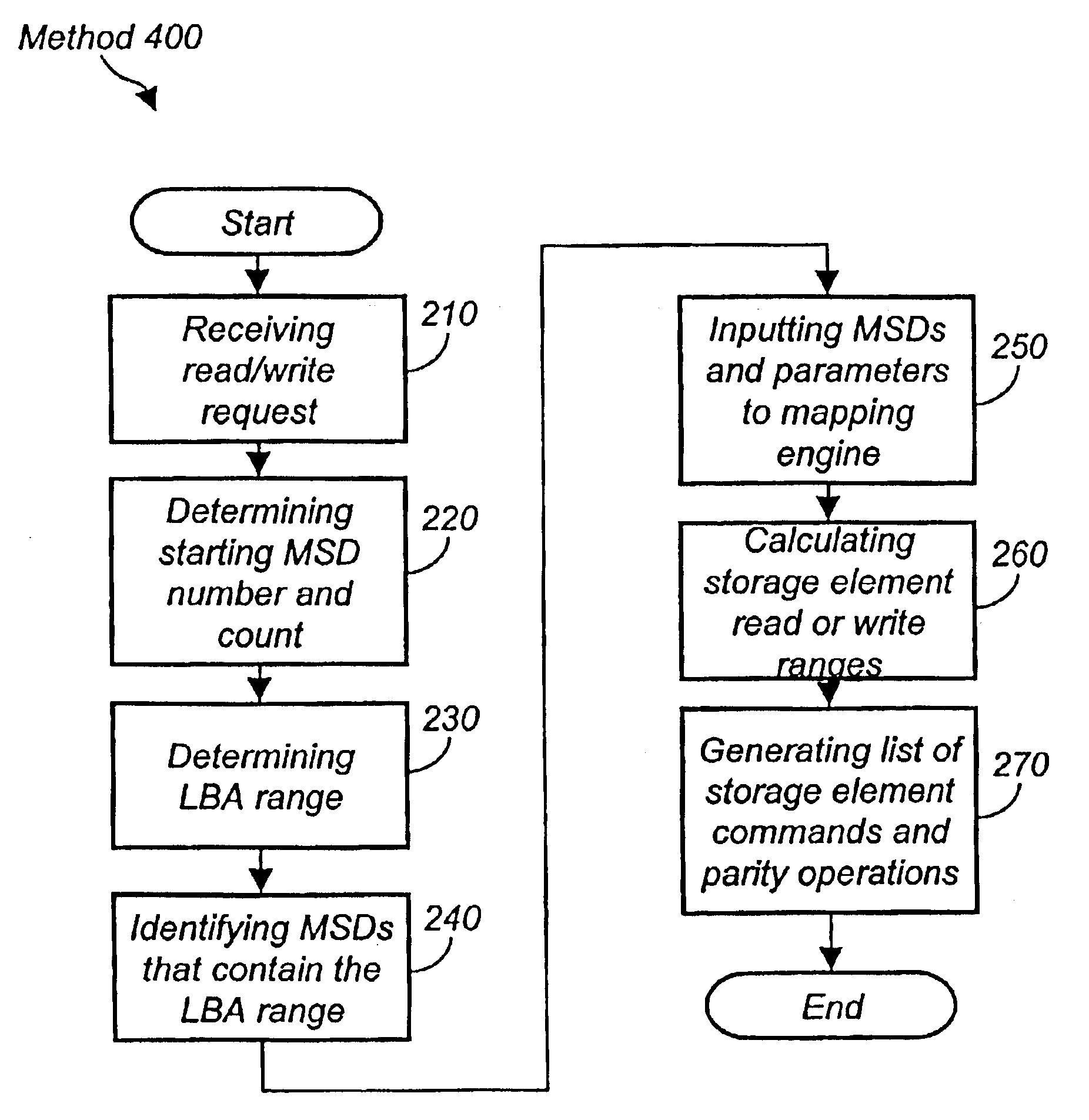

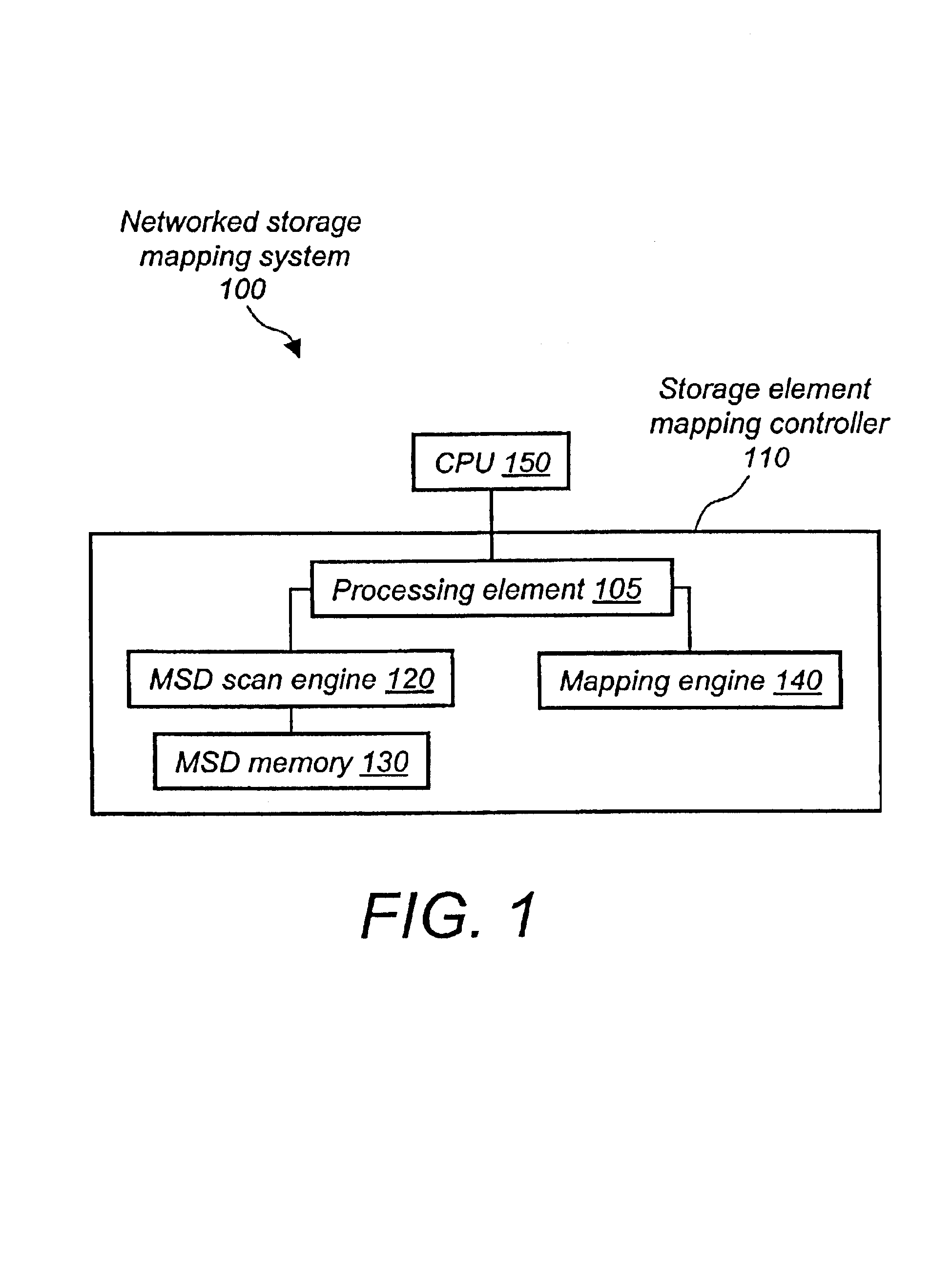

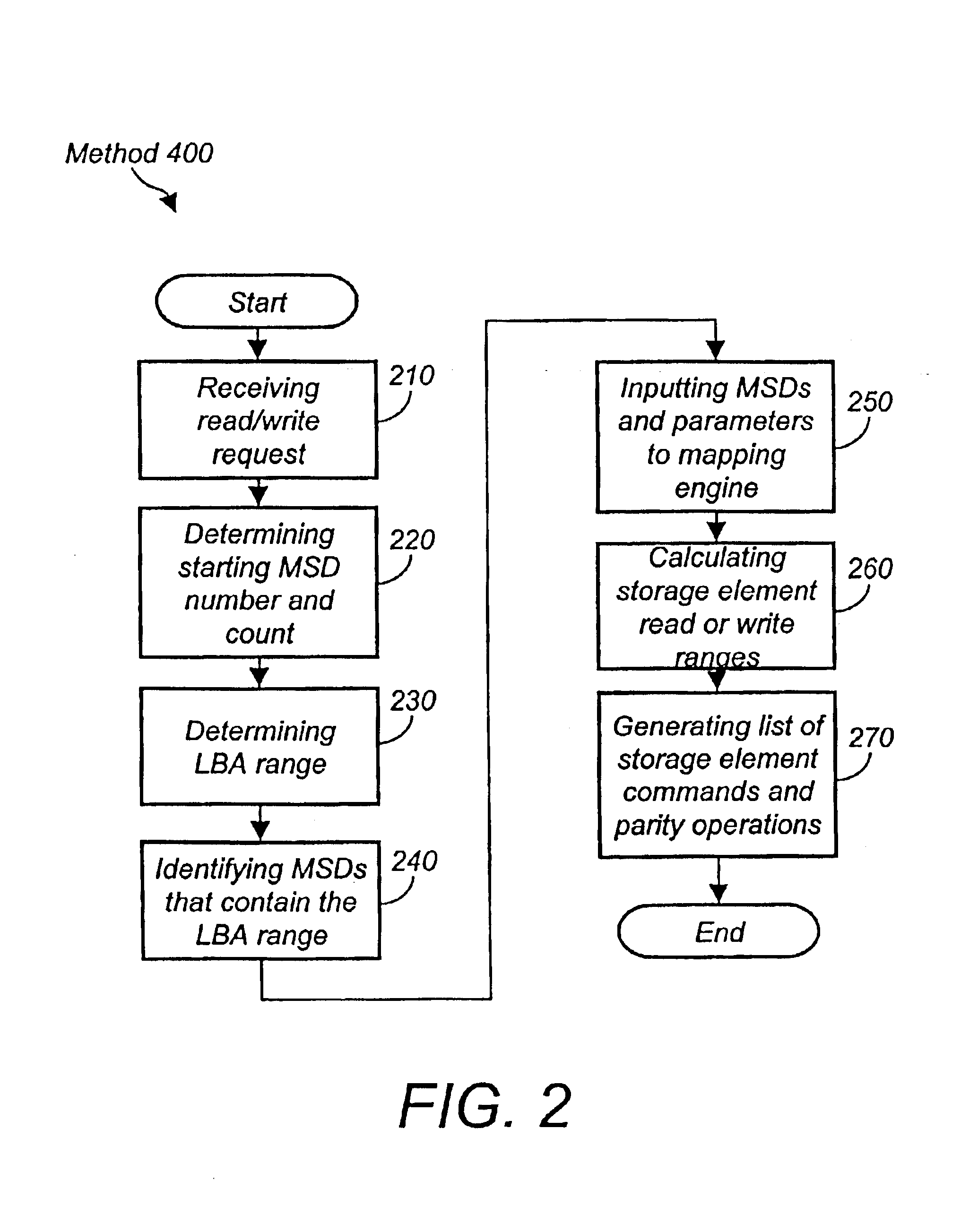

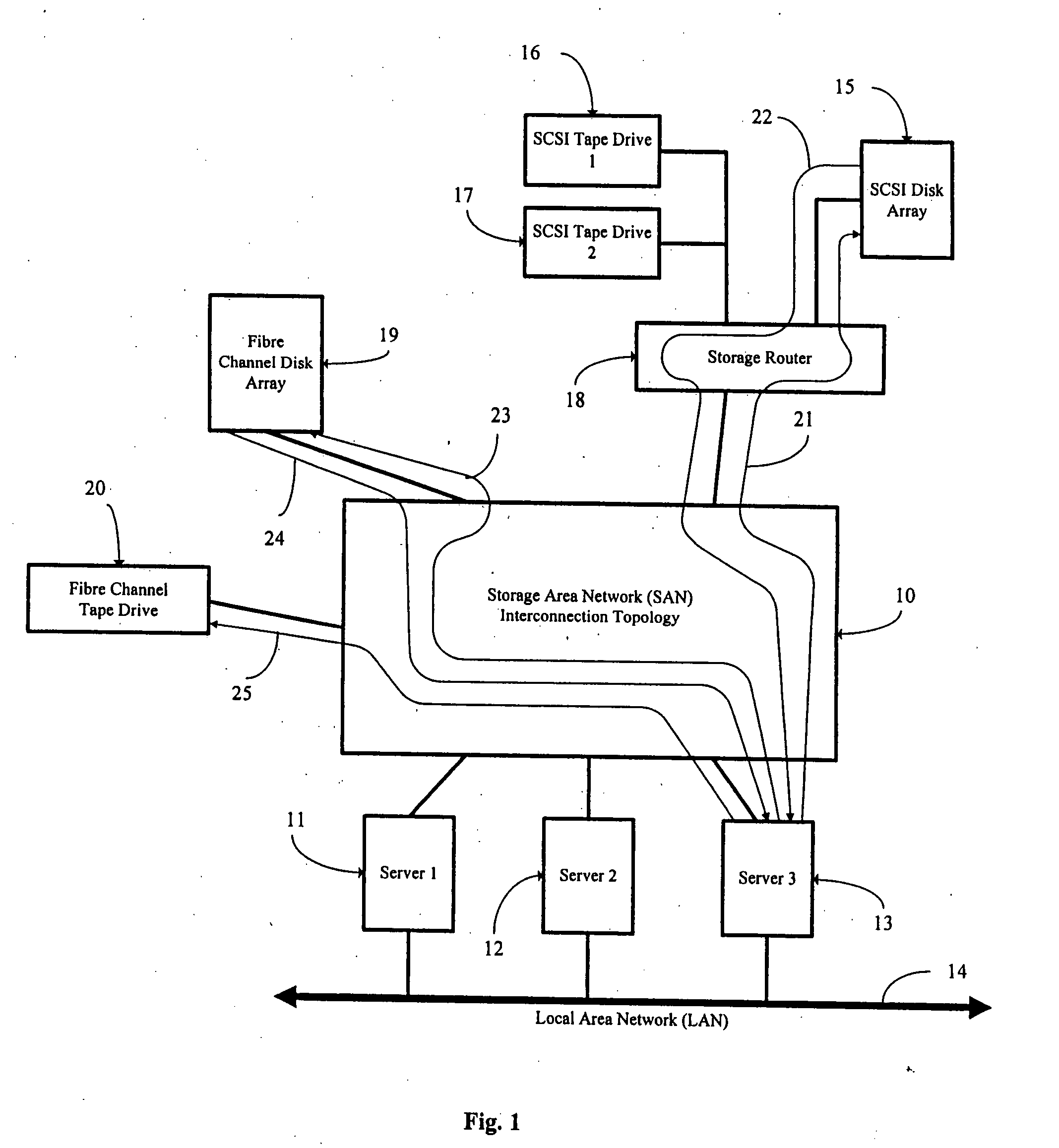

Method of flexibly mapping a number of storage elements into a virtual storage element

InactiveUS6912643B2Increase the number ofIncrease flexibilityInput/output to record carriersRedundant data error correctionGlobal address spaceSegment descriptor

The present invention provides an architecture and method for increasing the performance and resource utilization of networked storage architectures by use of hardware-based storage element mapping. The architecture utilizes a customized programmable processing element to map host read or write commands to physical storage element commands. The present invention uses a plurality of data structures, such as tables, to map host read and write commands to physical storage elements. The hardware-based storage element mapping controller uses the tables, including a mapping segment descriptor table, to map from global address space addresses to physical storage element addresses.

Owner:ADAPTEC

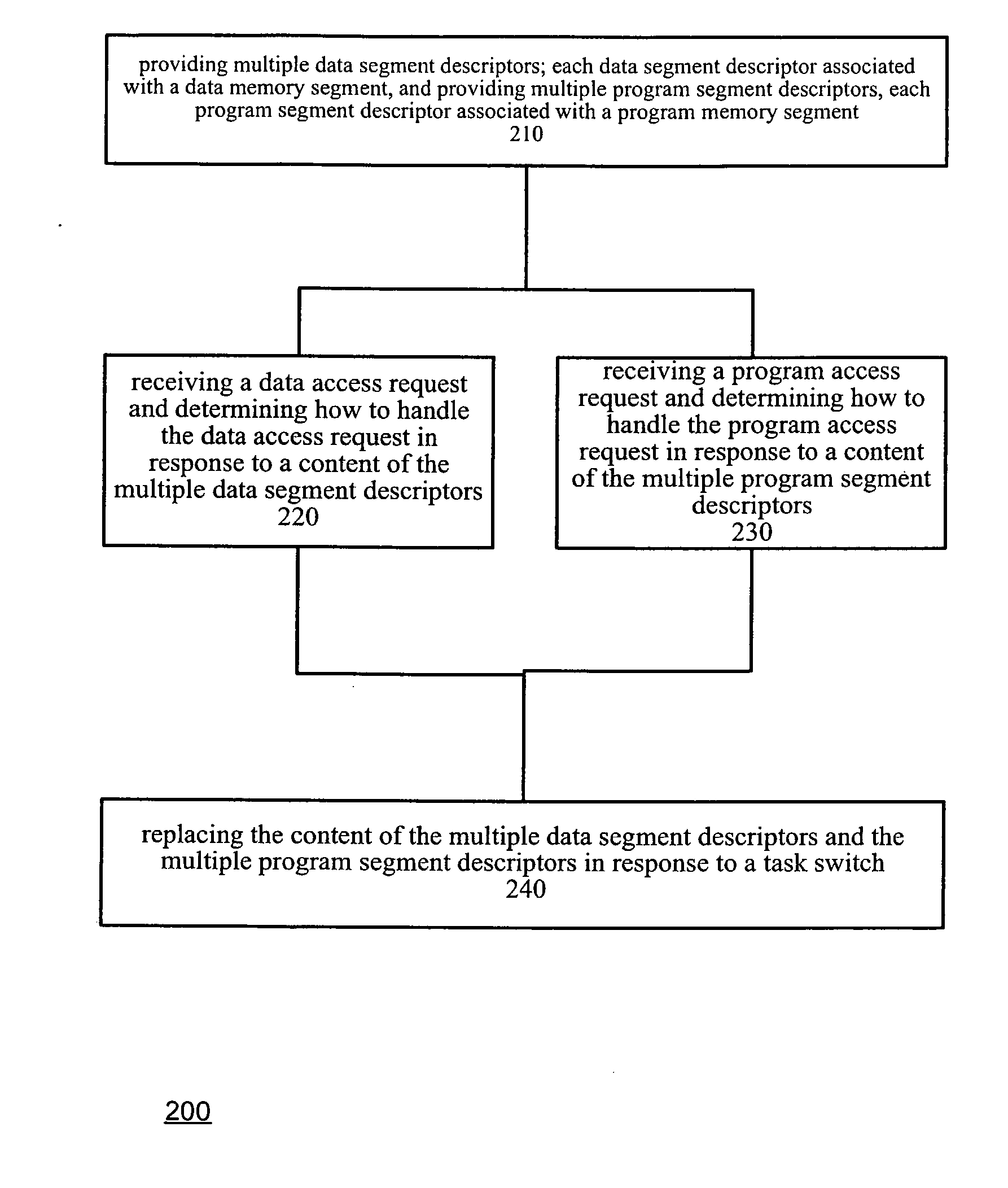

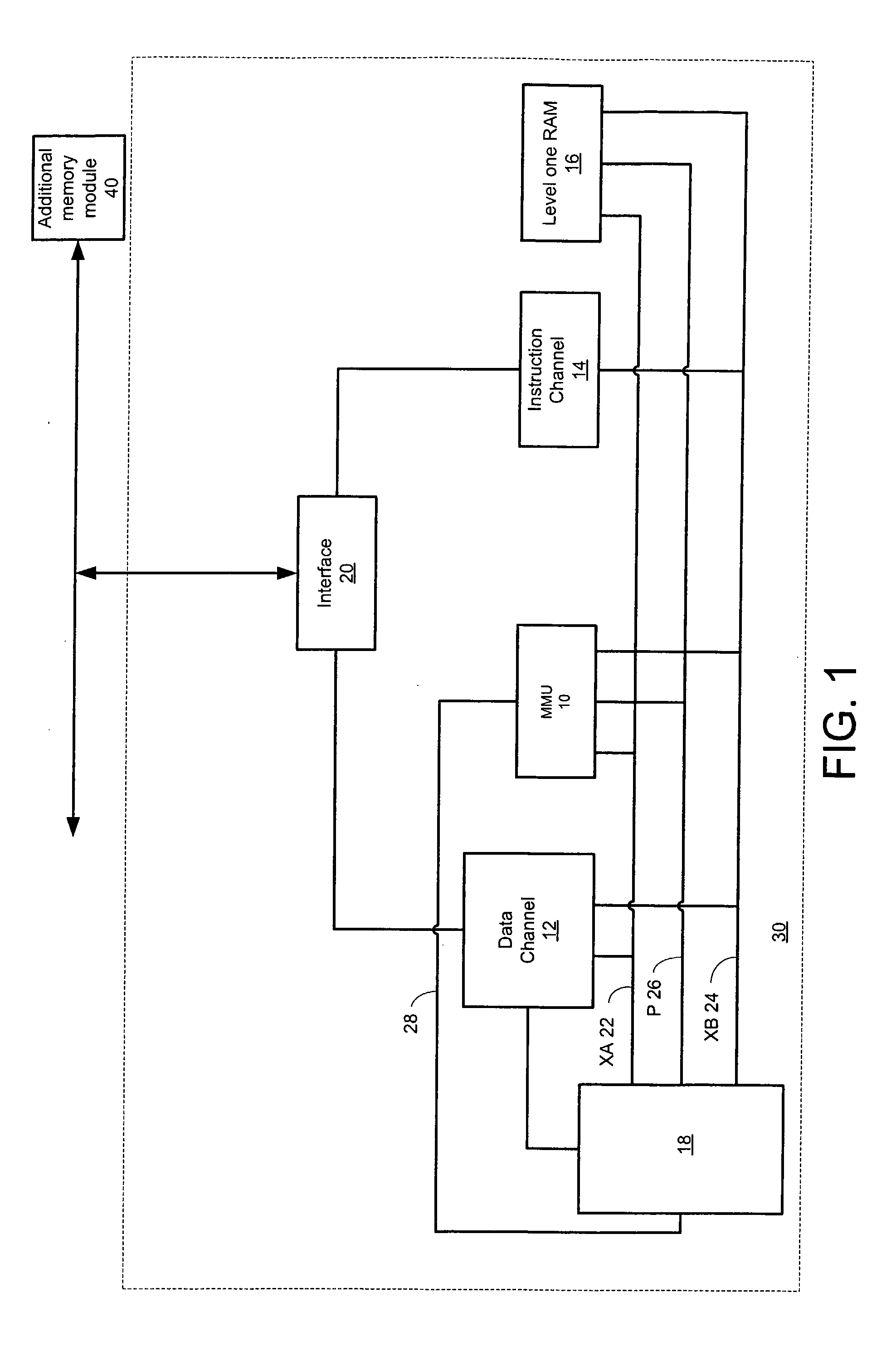

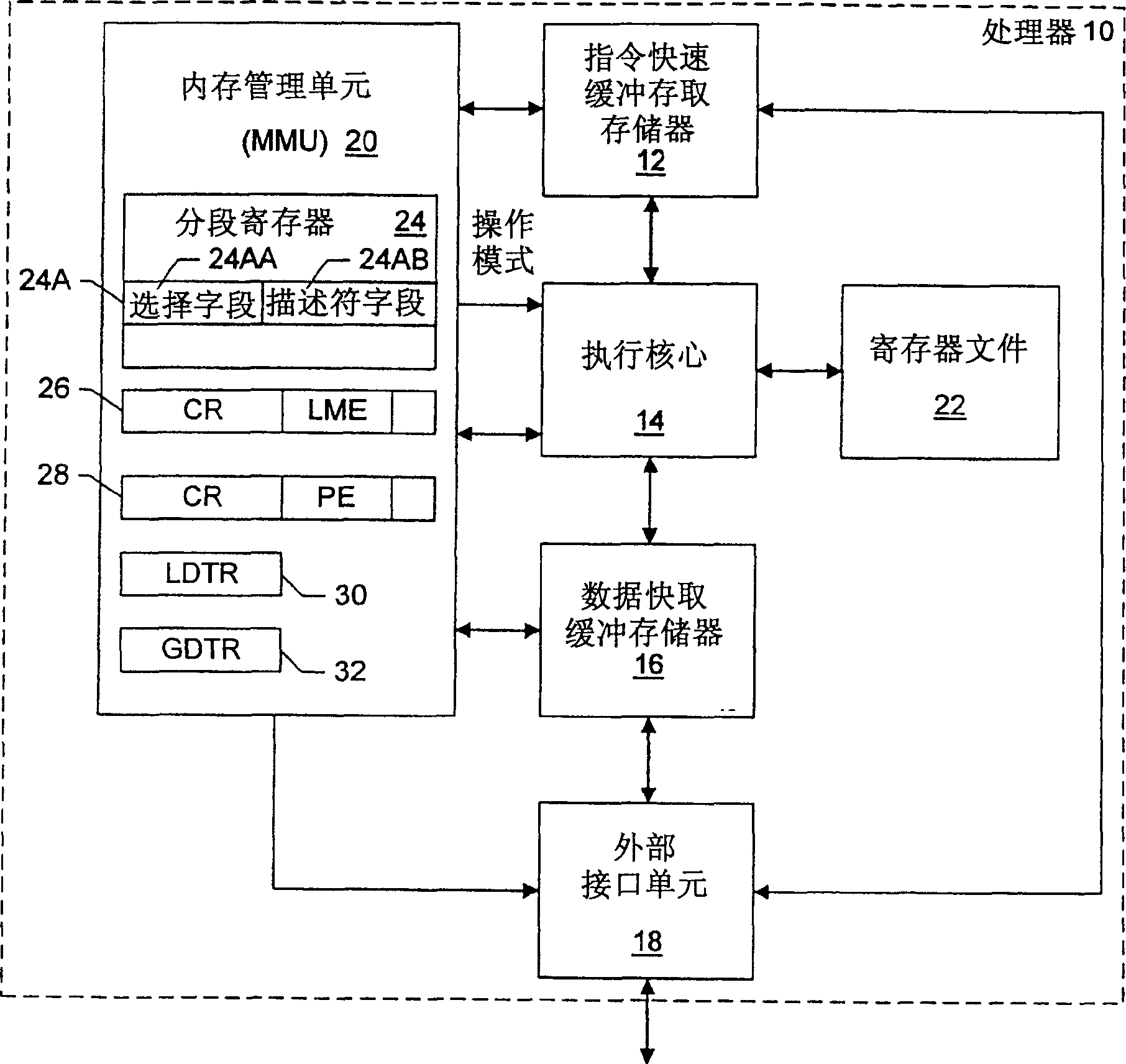

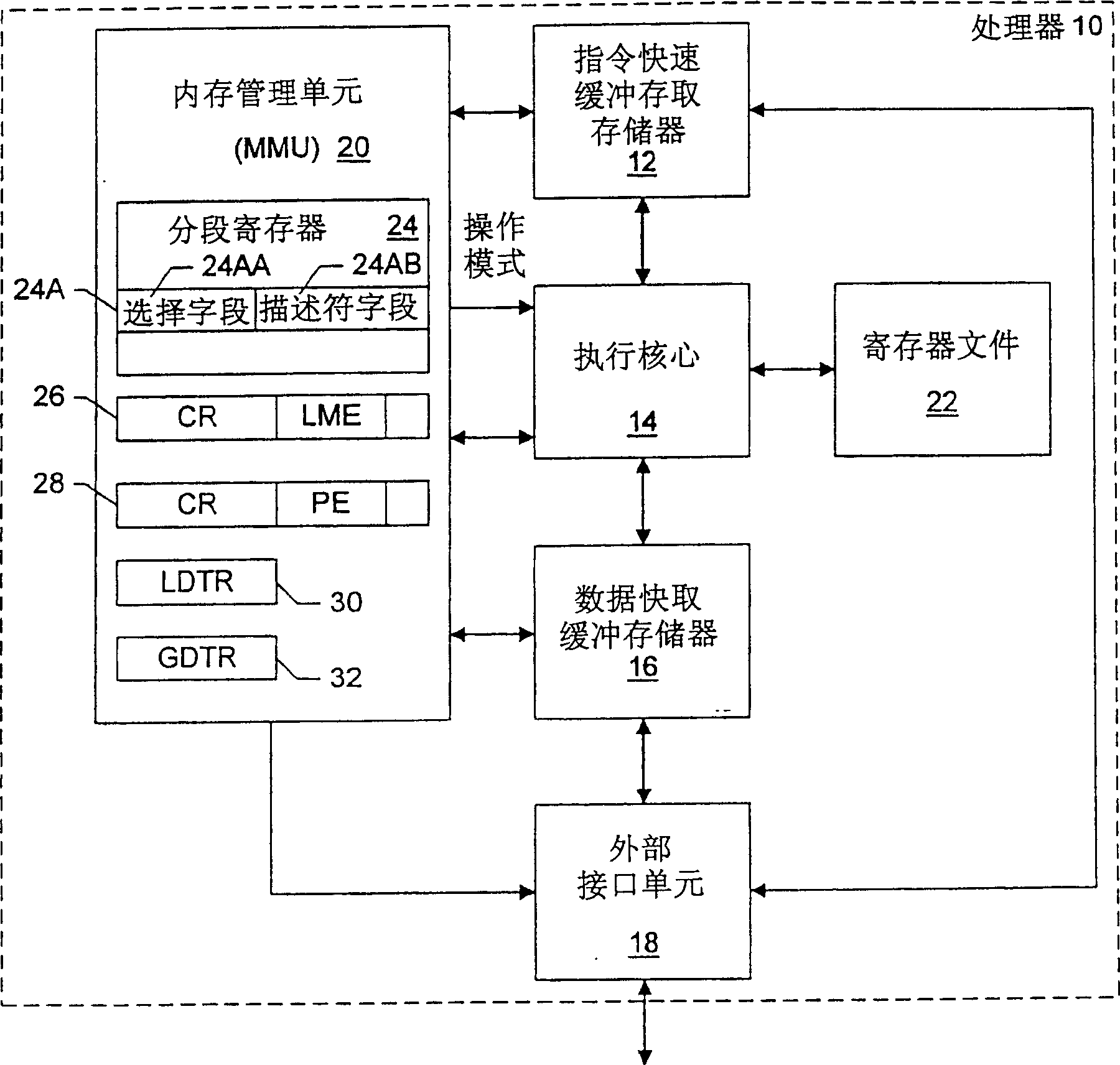

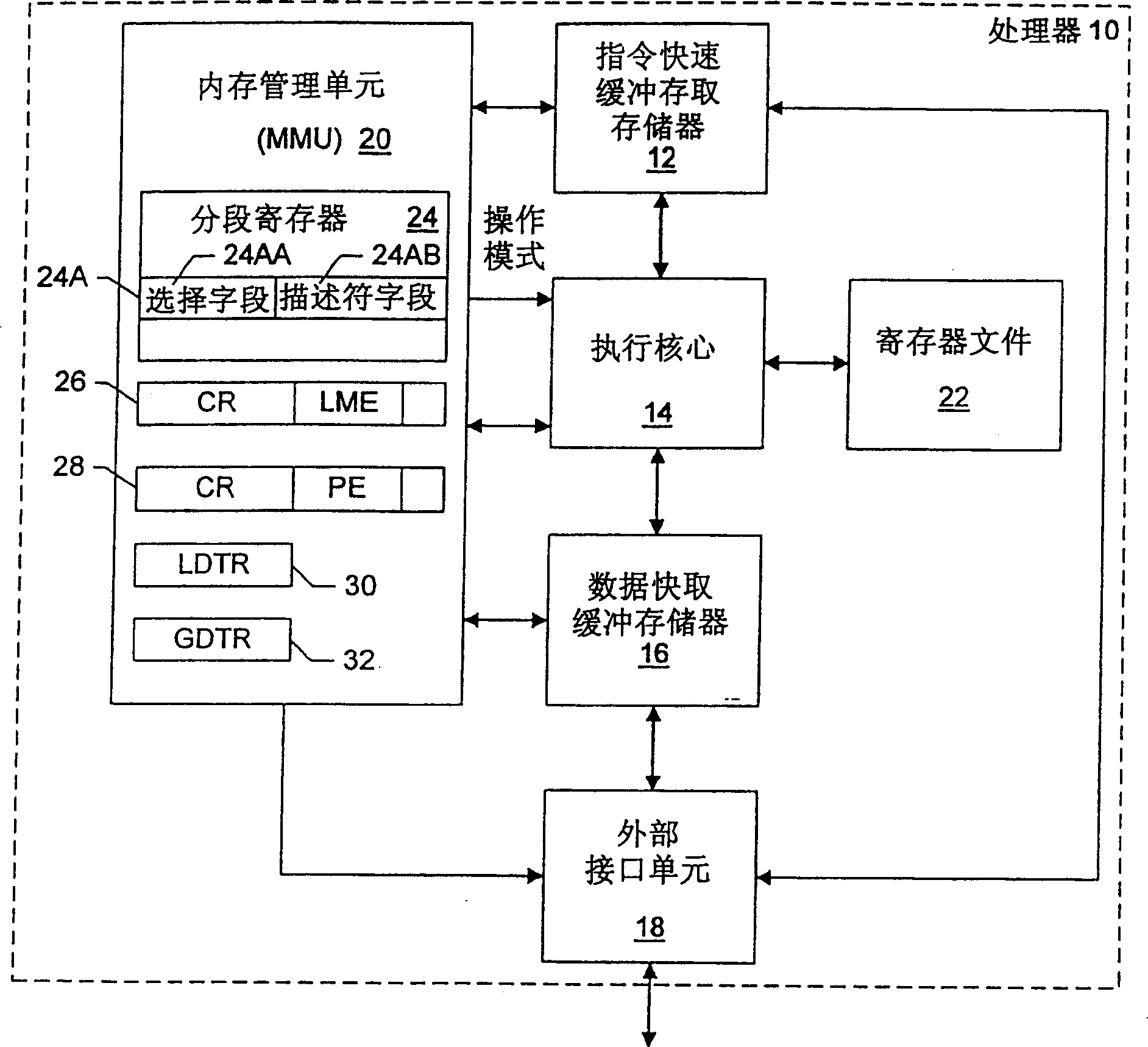

Memory Management Unit and Method for Memory Management

ActiveUS20070277009A1Save bus bandwidthFacilitates a fast hardware mechanism for translating virtual addressesMemory systemsMicro-instruction address formationProgram segmentData segment

A memory management unit that includes: (i) multiple data segment descriptors, each data segment descriptor associated with a data memory segment; (ii) multiple program segment descriptors, each program segment descriptor associated with a program memory segment; and (iii) a controller, adapted to replace the content of the multiple data segment descriptors and the multiple program segment descriptors in response to a task switch. A method for memory management, the method includes: (i) providing multiple data segment descriptors; each data segment descriptor associated with a data memory segment, and providing multiple program segment descriptors, each program segment descriptor associated with a program memory segment; (ii) receiving and storing a program task identifier and a data task identifier; (iii) receiving a data access request and determining how to handle the data access request in response to a content of the multiple data segment descriptors; and (iv) receiving a program access request and determining how to handle the program access request in response to a content of the multiple program segment descriptors.

Owner:NXP USA INC

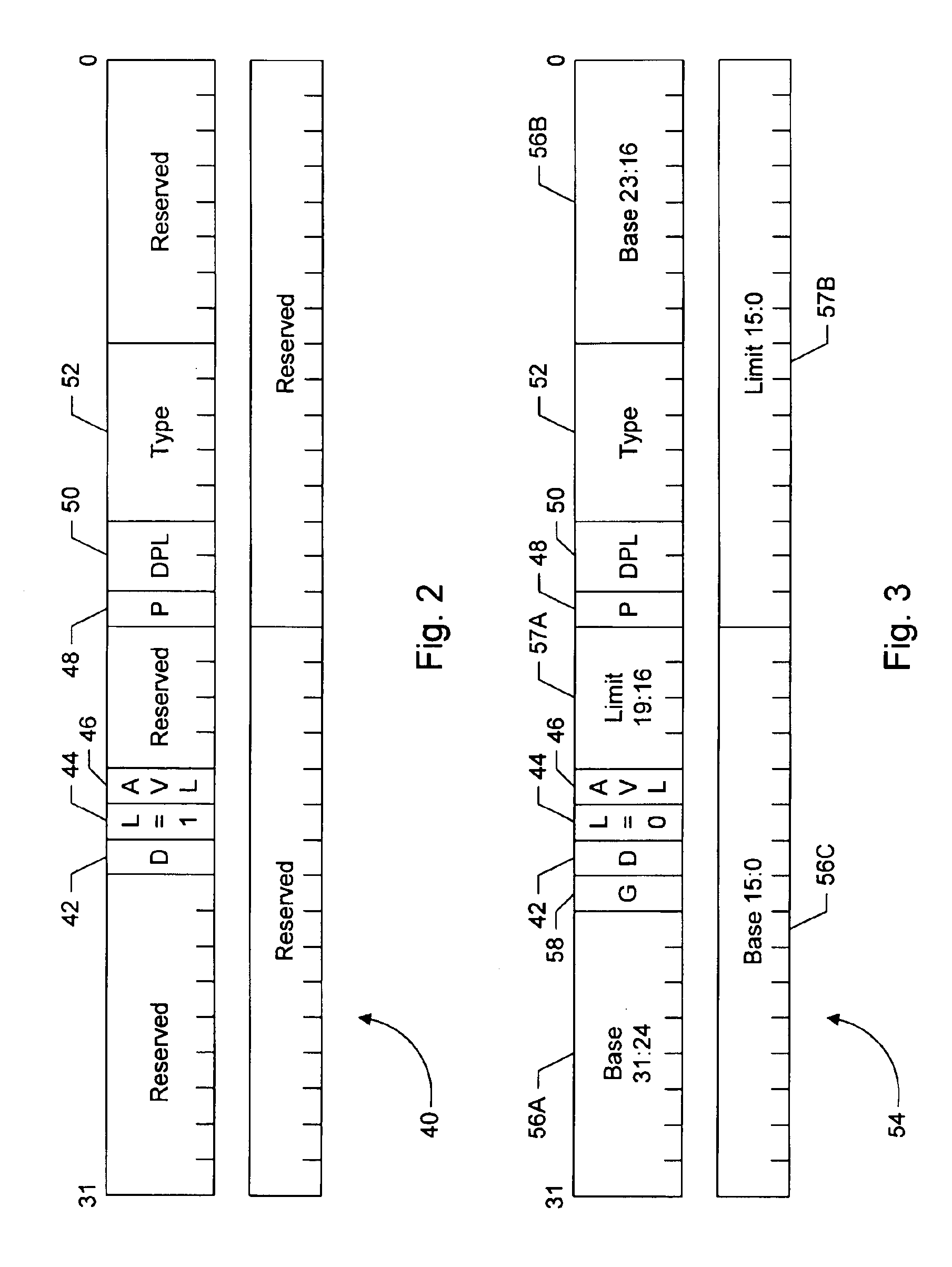

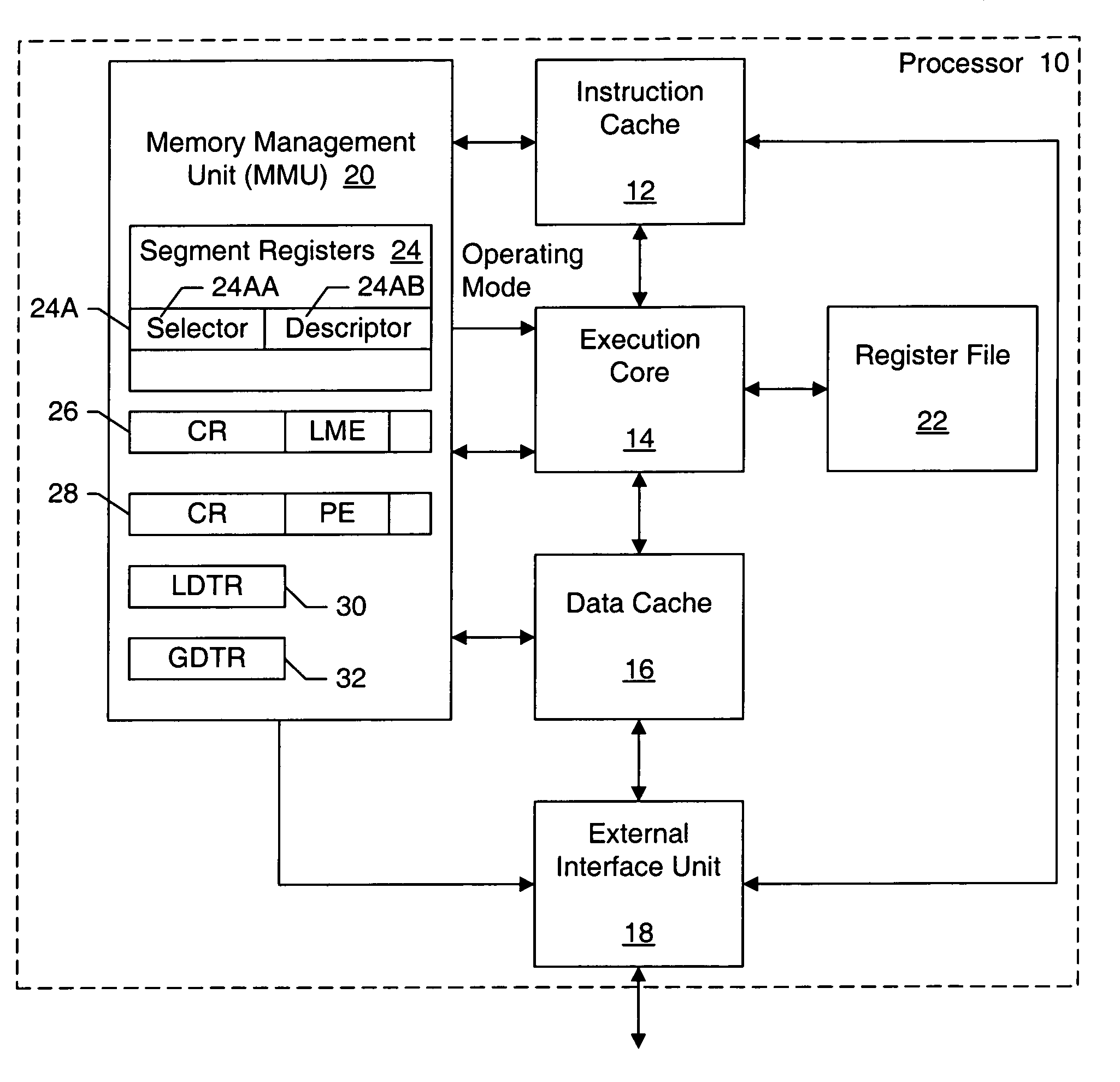

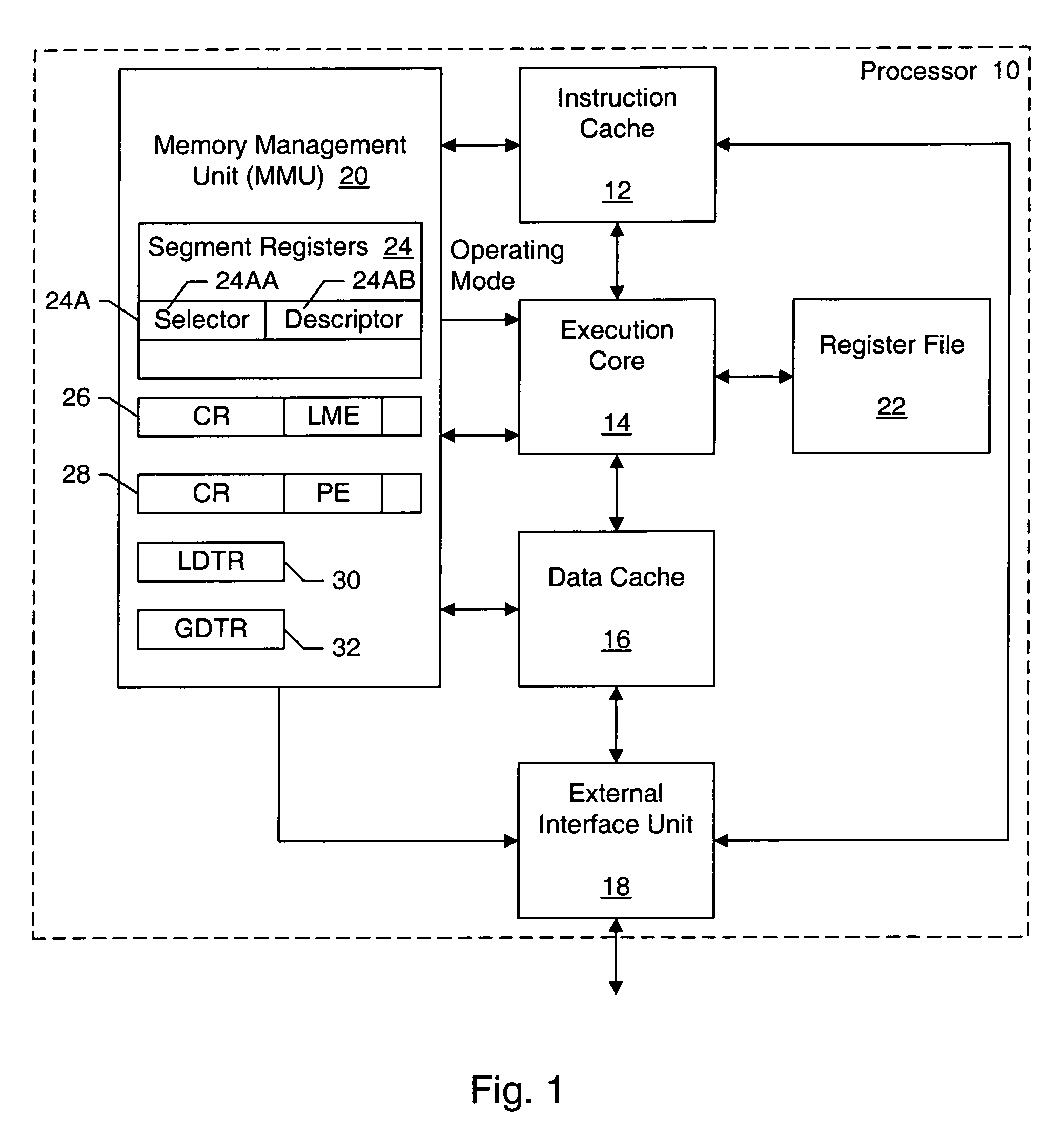

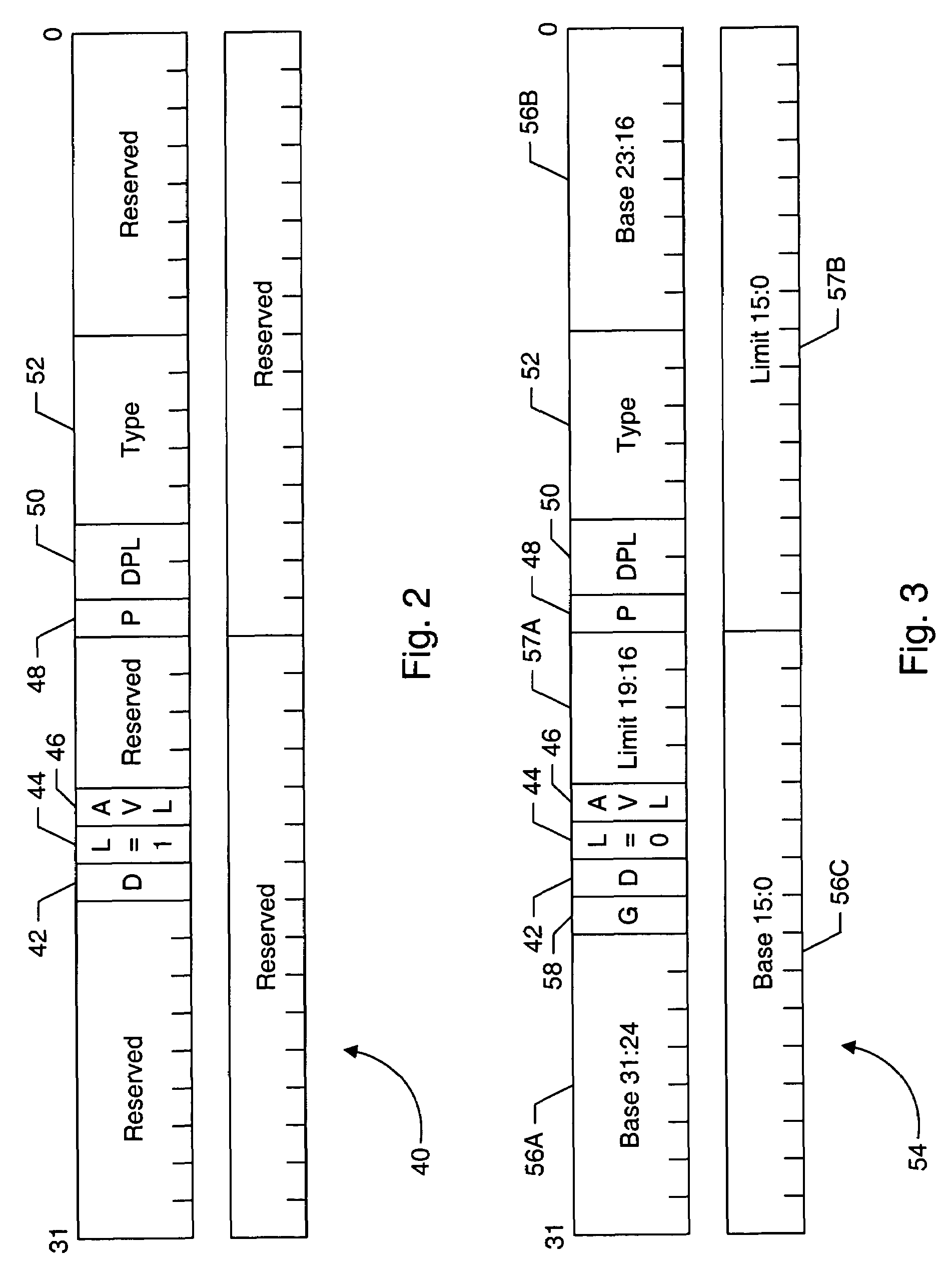

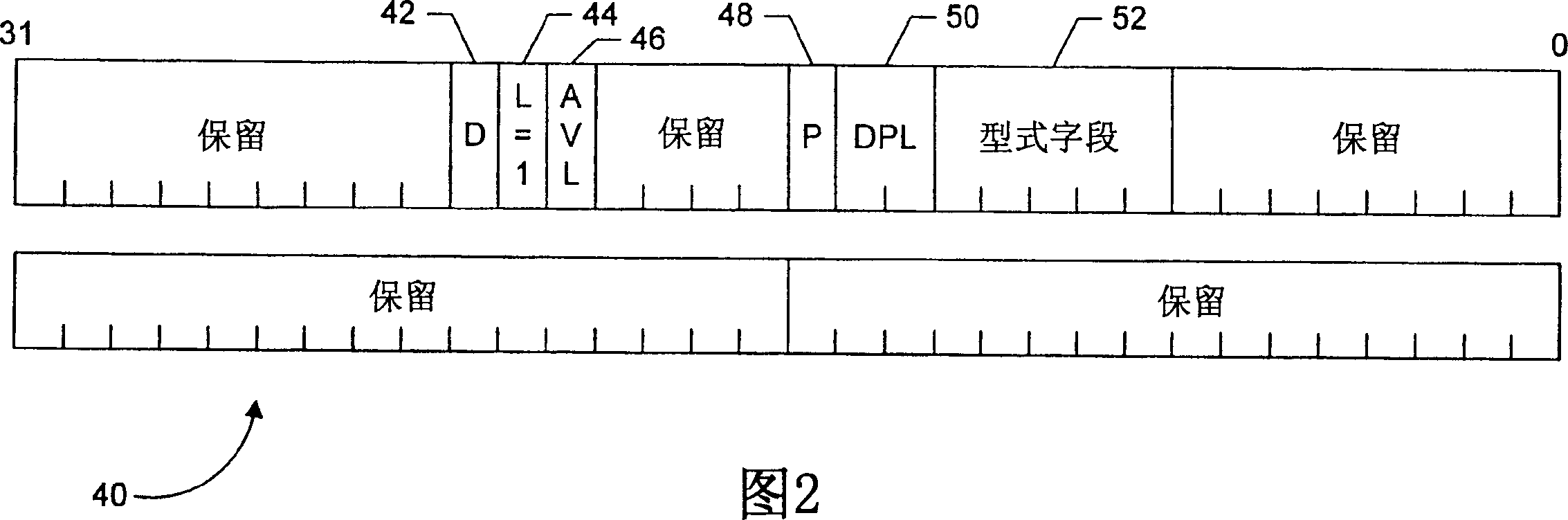

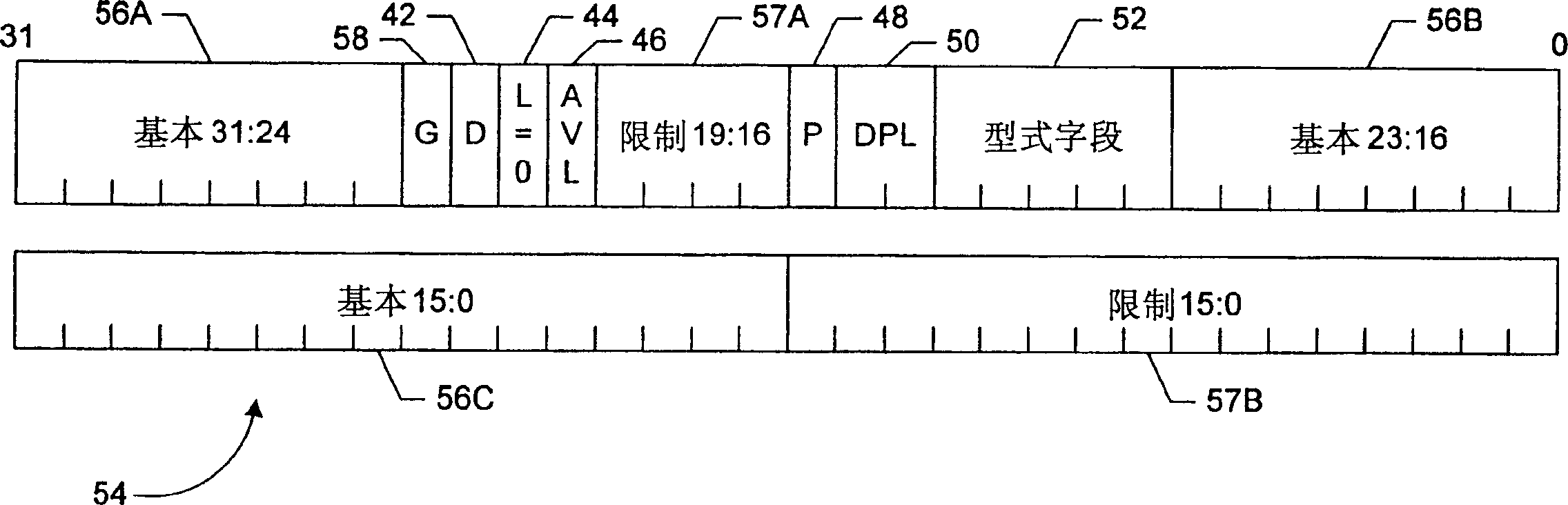

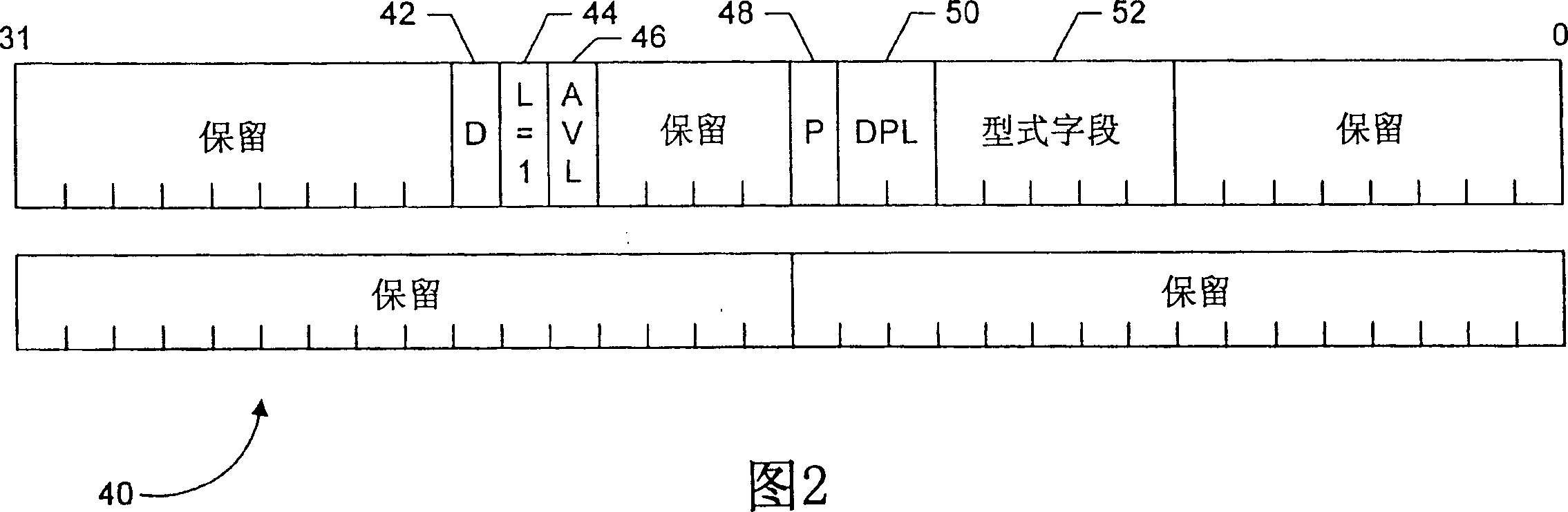

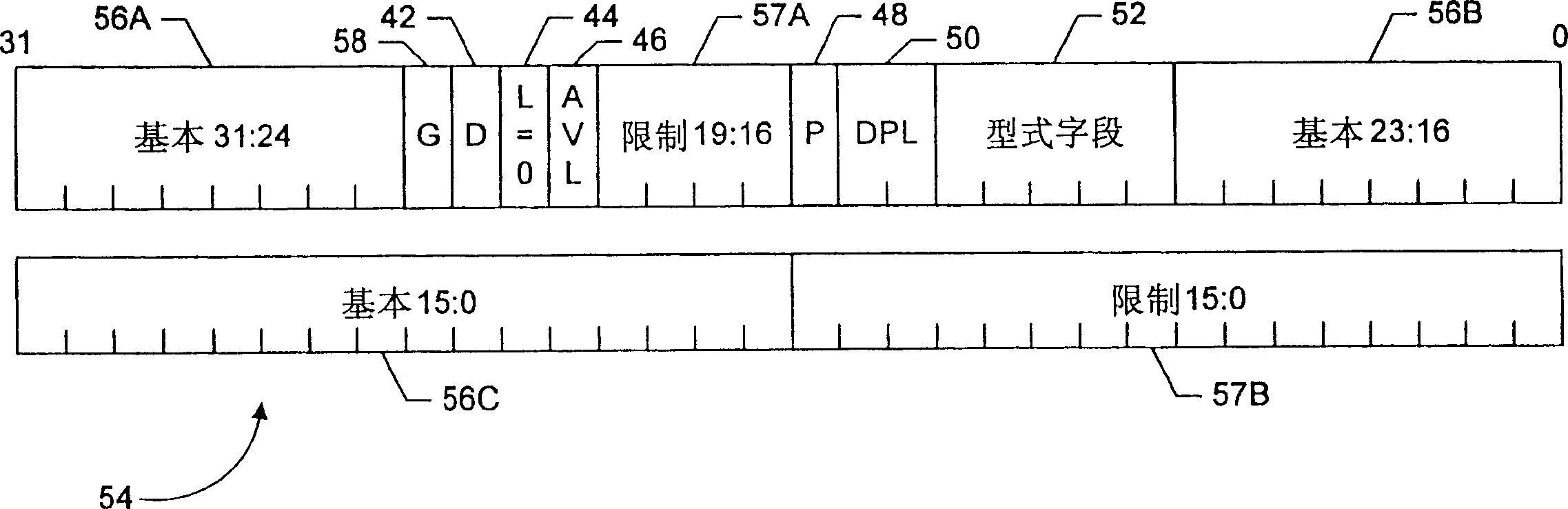

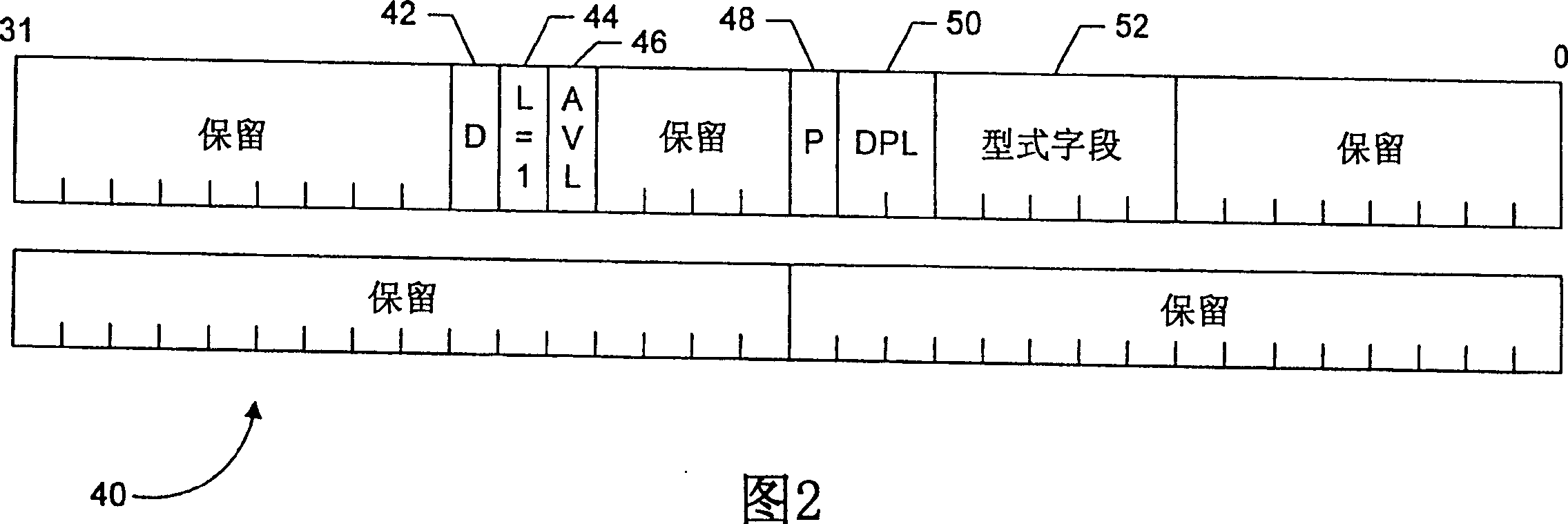

Establishing an operating mode in a processor

InactiveUS6973562B1Compatibility is simpleGeneral purpose stored program computerSpecific program execution arrangementsSegment descriptorProcessor register

A processor supports a processing mode in which the address size is greater than 32 bits and the operand size may be 32 or 64 bits. The address size may be nominally indicated as 64 bits, although various embodiments of the processor may implement any address size which exceeds 32 bits, up to and including 64 bits, in the processing mode. The processing mode may be established by placing an enable indication in a control register into an enabled state and by setting a first operating mode indication and a second operating mode indication in a segment descriptor to predefined states. Other combinations of the first operating mode indication and the second operating mode indication may be used to provide compatibility modes for 32 bit and 16 bit processing compatible with the x86 processor architecture (with the enable indication remaining in the enabled state).

Owner:ADVANCED MICRO DEVICES INC

Method and system for managing virtual memory

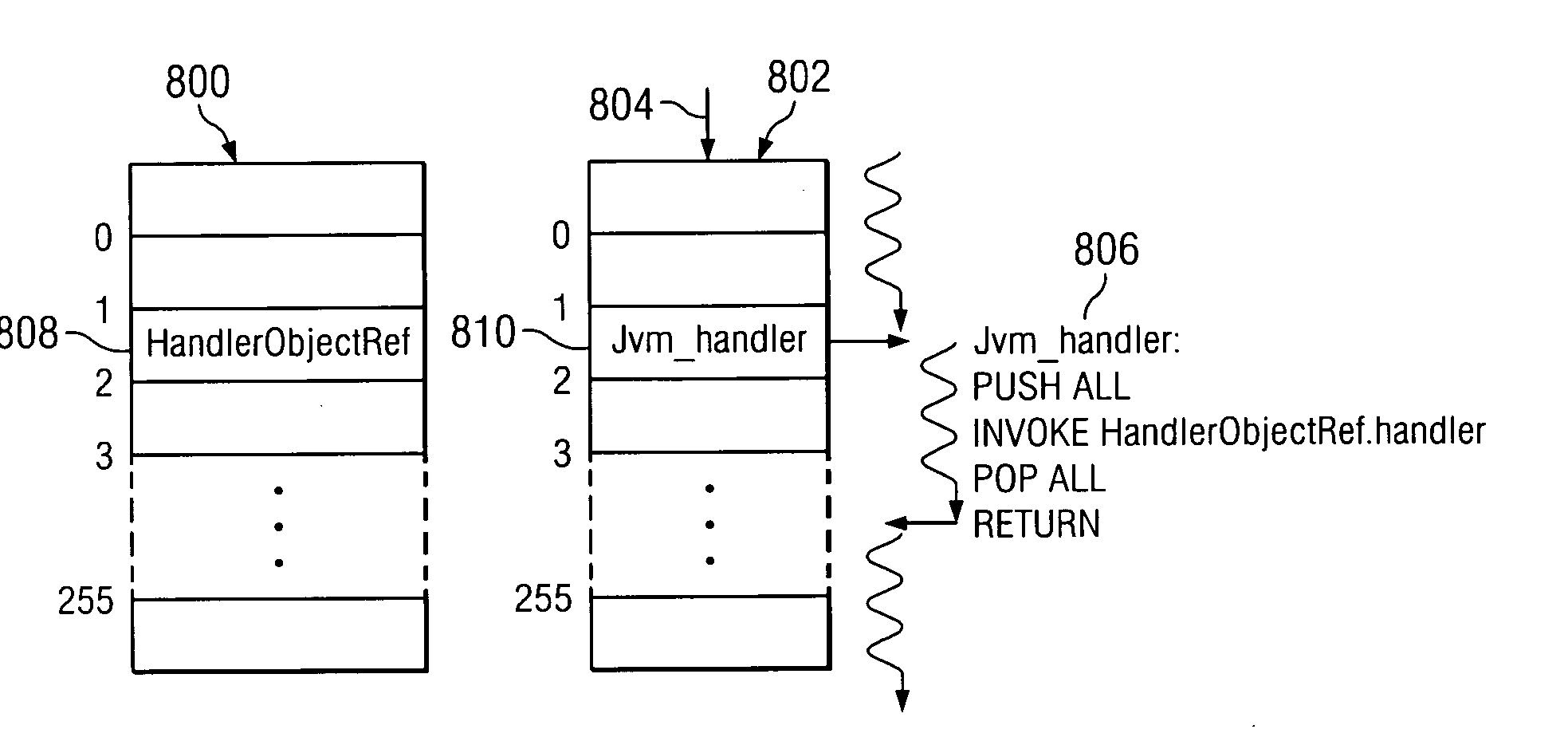

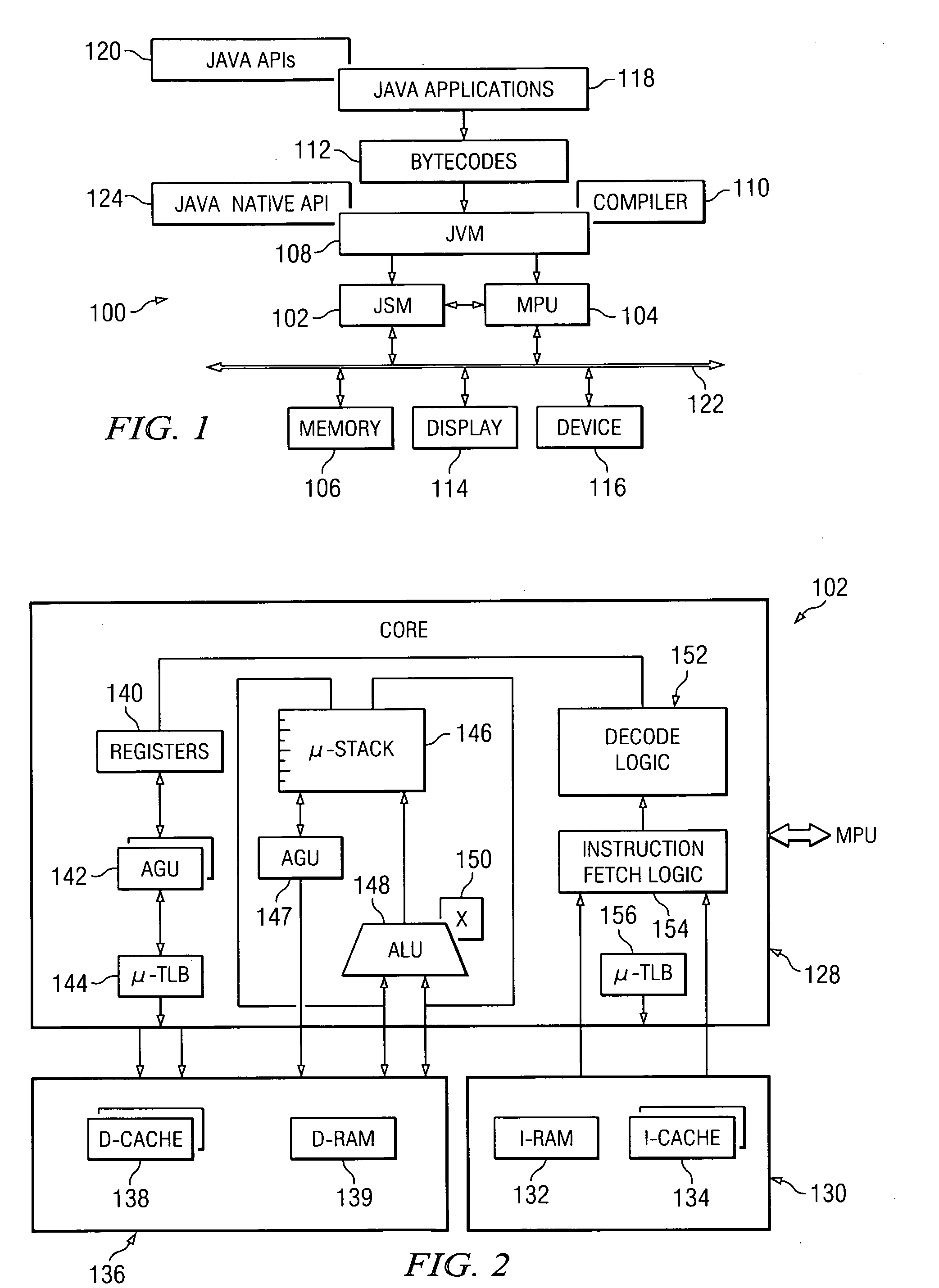

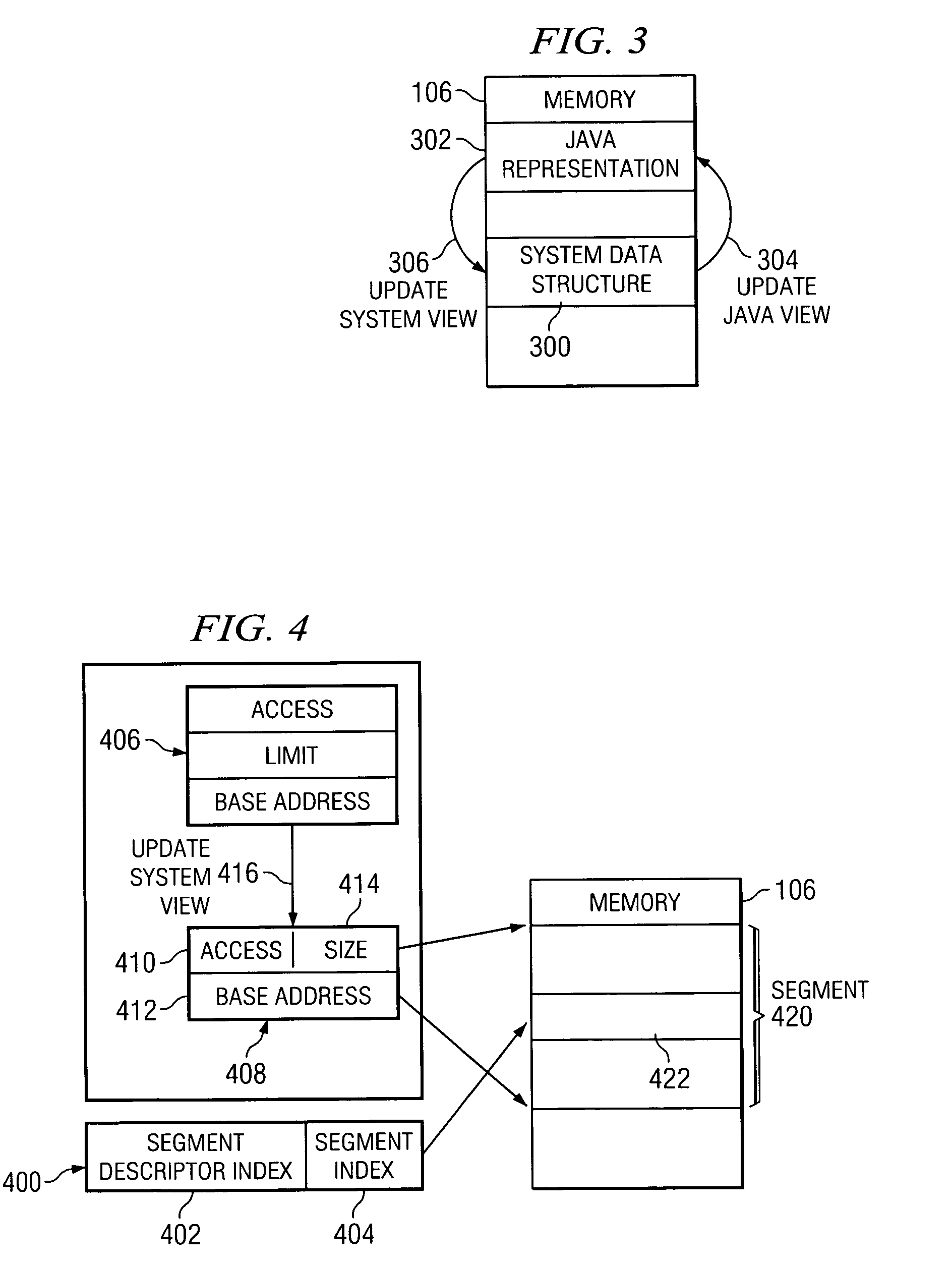

ActiveUS20060026563A1Memory architecture accessing/allocationEnergy efficient ICTSegment descriptorParallel computing

Methods, computer-readable media, and systems for virtual memory management in Java™ are provided. In some illustrative embodiments, a computer-readable medium storing a Java program that, when executed by a processor, performs a method for virtual memory management is provided. The method includes creating a Java representation of a page table, wherein each entry of the Java representation comprises a Java representation of a page descriptor, changing a field of a Java representation of a page descriptor in the Java representation of the page table, and updating a corresponding field in a page descriptor of a system level page table using the contents of the field in the Java representation of the page descriptor. Some illustrative embodiments provide a computer-readable medium storing a Java program that, when executed by a processor, performs a method for virtual memory management that includes creating a Java representation of a segment descriptor, changing a field of the Java representation of the segment descriptor, and updating a corresponding field in a system level segment descriptor using the contents of the field in the Java representation of the segment descriptor.

Owner:TEXAS INSTR INC

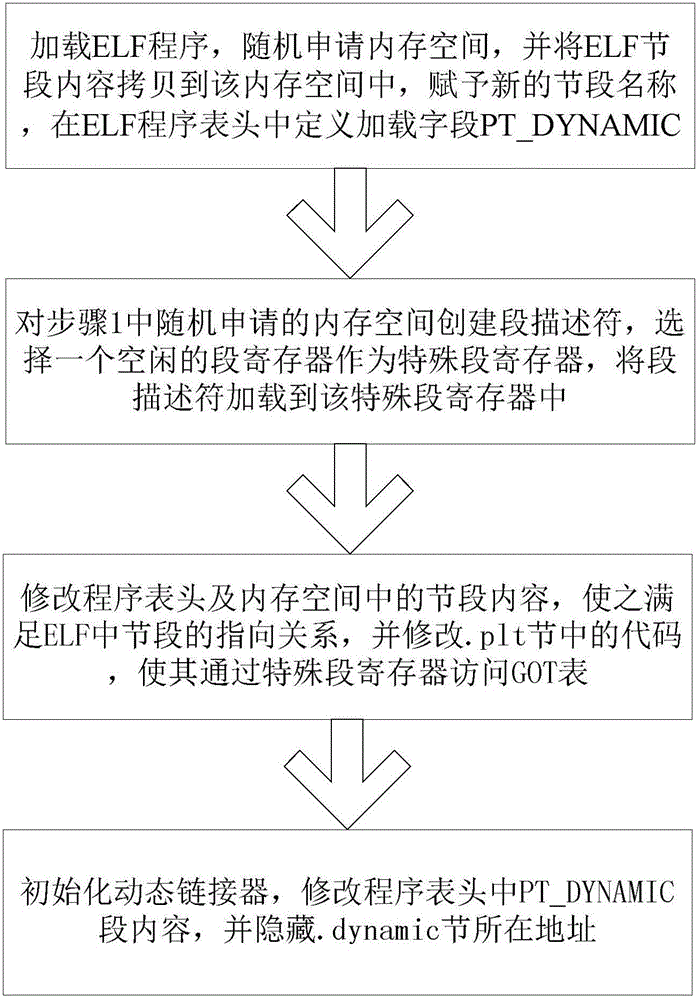

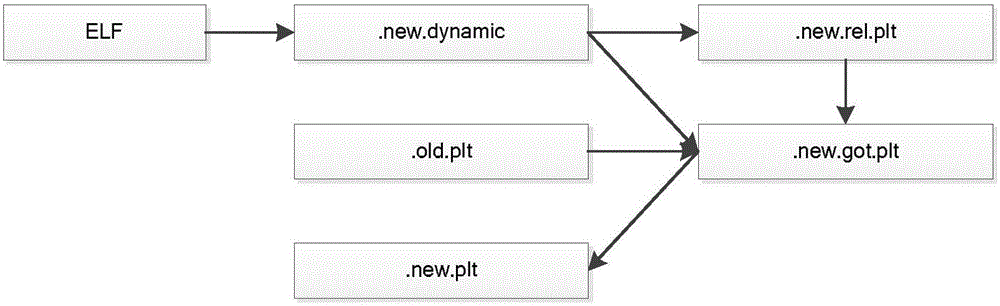

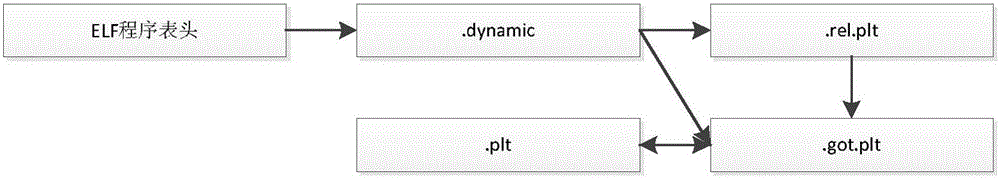

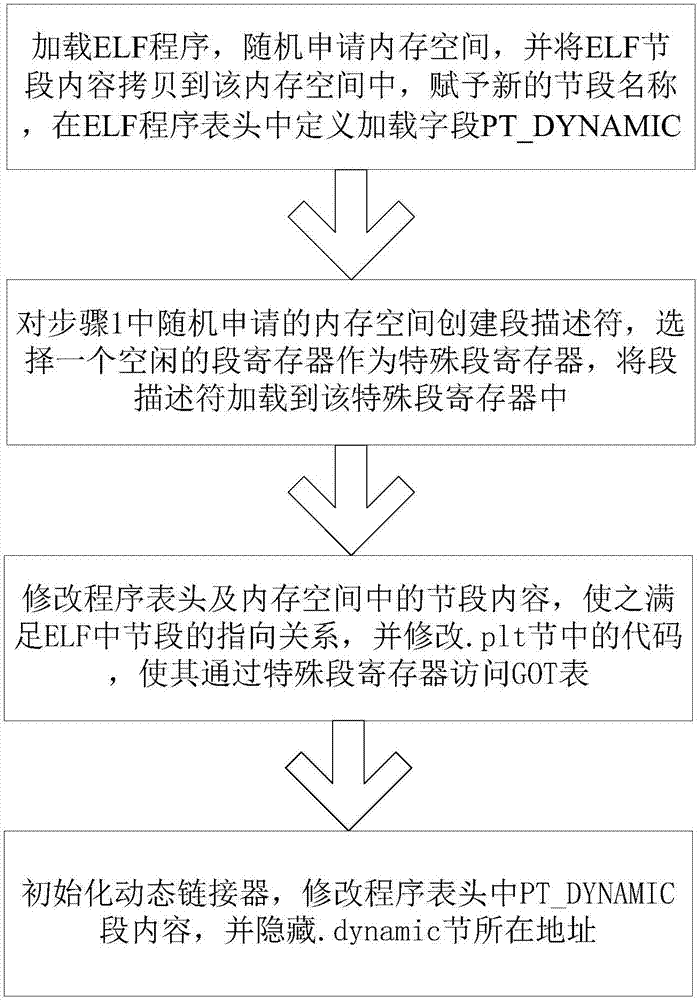

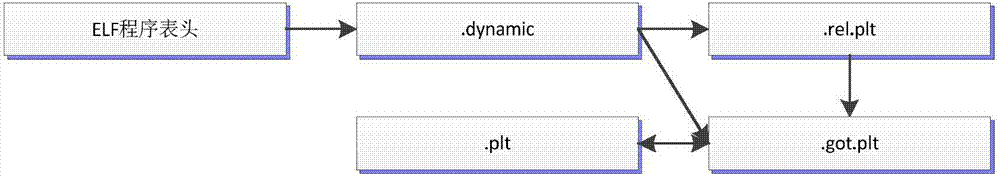

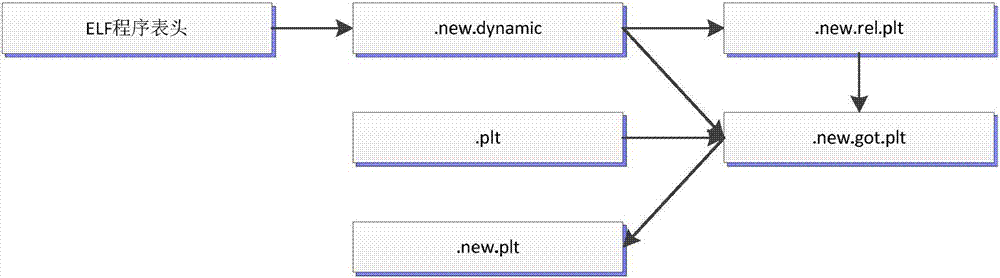

Global offset table protection method based on address randomness and segment isolation

ActiveCN105095762AOvercoming problems such as wasteAdded randomizationPlatform integrity maintainanceMemory addressSegment descriptor

The invention relates to a global offset table protection method based on address randomness and segment isolation. The global offset table protection method comprises the steps that an ELF program is loaded, a memory space is randomly applied, ELF segment content is copied and given a new segment name, and a field PT_DYNAMIC is loaded; a segment descriptor is established for the memory space, an idle segment register is selected, and the segment descriptor is loaded into the segment register; the header of the program and the segment content in the memory space are modified, and codes in a .plt segment are modified; a dynamic linker is initialized, the segment content of the header of the program is modified, and an address where a .dynamic segment is located is hidden. According to the global offset table protection method, randomization processing is added, the address of a GOT is obtained by disassembling the codes, the address of the GOT cannot be worked out under the situation that the segment base address of the segment register is not known, the malicious code hijack attack carried out on the original fixed address of the GOT fails, and the malicious attack through the method of trying to read the fixed memory address and working out the address of the GOT fails.

Owner:THE PLA INFORMATION ENG UNIV +1

A data processing apparatus and method for performing segmented operations

A data processing apparatus and method are provided for performing segmented operations. The data processing apparatus comprises a vector register store for storing vector operands, and vector processing circuitry providing N lanes of parallel processing, and arranged to perform a segmented operation on up to N data elements provided by a specified vector operand, each data element being allocated to one of the N lanes. The up to N data elements forms a plurality of segments, and performance of the segmented operation comprises performing a separate operation on the data elements of each segment, the separate operation involving interaction between the lanes containing the data elements of the associated segment. Predicate generation circuitry is responsive to a compute descriptor instruction specifying an input vector operand comprising a plurality of segment descriptors, to generate per lane predicate information used by the vector processing circuitry when performing the segmented operation to maintain a boundary between each of the plurality of segments. As a result, interaction between lanes containing data elements from different segments is prevented. This allows very effective utilisation of the lanes of parallel processing within the vector processing circuitry to be achieved.

Owner:ARM LTD

Establishing an operating mode in a processor

InactiveUS7124286B2Provide compatibilityRegister arrangementsGeneral purpose stored program computerSegment descriptorProcessor register

A processor supports a processing mode in which the address size is greater than 32 bits and the operand size may be 32 or 64 bits. The address size may be nominally indicated as 64 bits, although various embodiments of the processor may implement any address size which exceeds 32 bits, up to and including 64 bits, in the processing mode. The processing mode may be established by placing an enable indication in a control register into an enabled state and by setting a first operating mode indication and a second operating mode indication in a segment descriptor to predefined states. Other combinations of the first operating mode indication and the second operating mode indication may be used to provide compatibility modes for 32 bit and 16 bit processing compatible with the x86 processor architecture (with the enable indication remaining in the enabled state).

Owner:ADVANCED MICRO DEVICES INC

Call gate expansion for 64 bit addressing

A processor supports a first processing mode in which the address size is greater than 32 bits. The address size may be nominally indicated as 64 bits, although various embodiments of the processor may implement any address size which exceeds 32 bits, up to and including 64 bits, in the first processing mode. The first processing mode may be established by placing an enable indication in a control register into an enabled state and by setting a first operating mode indication and a second operating mode indication in a segment descriptor to predefined states. Other combinations of the first operating mode indication and the second operating mode indication may be used to provide compatibility modes for 32 bit and 16 bit processing compatible with the x86 processor architecture (with the enable indication remaining in the enabled state). To call code operating in the first processing mode from the 32 bit or 16 bit code, a call gate descriptor is defined which occupies two entries in a segment descriptor table. By occupying two entries, each of which may otherwise store a segment descriptor, the call gate descriptor may include enough space to store an address in excess of 32 bits. Thus, a calling code segment may reference a call gate descriptor, which may reference the target code semgent and may provide an address within the address space of the target code segment, even if the address exceeds the address size in the calling code segment.

Owner:ADVANCED MICRO DEVICES INC

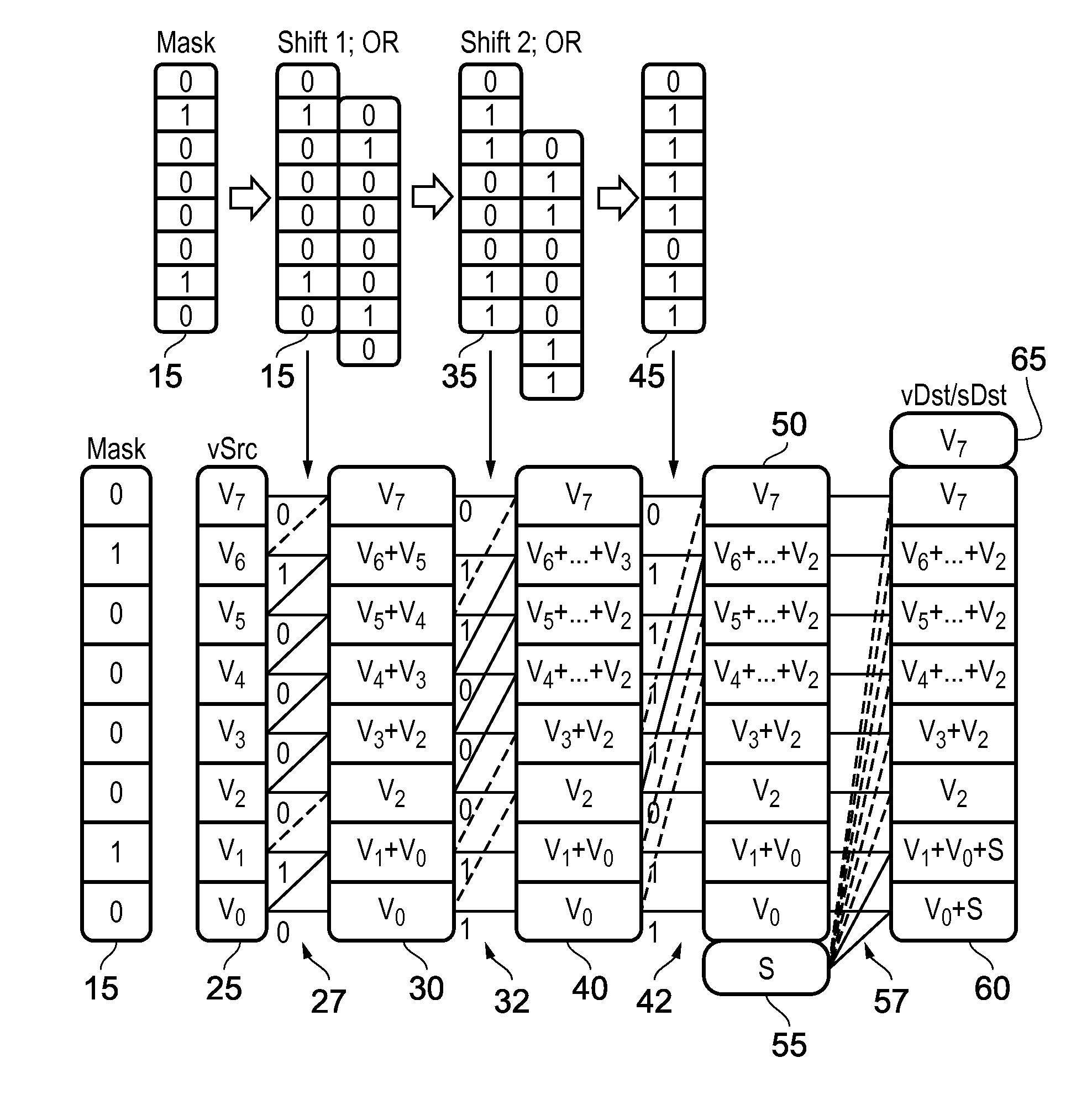

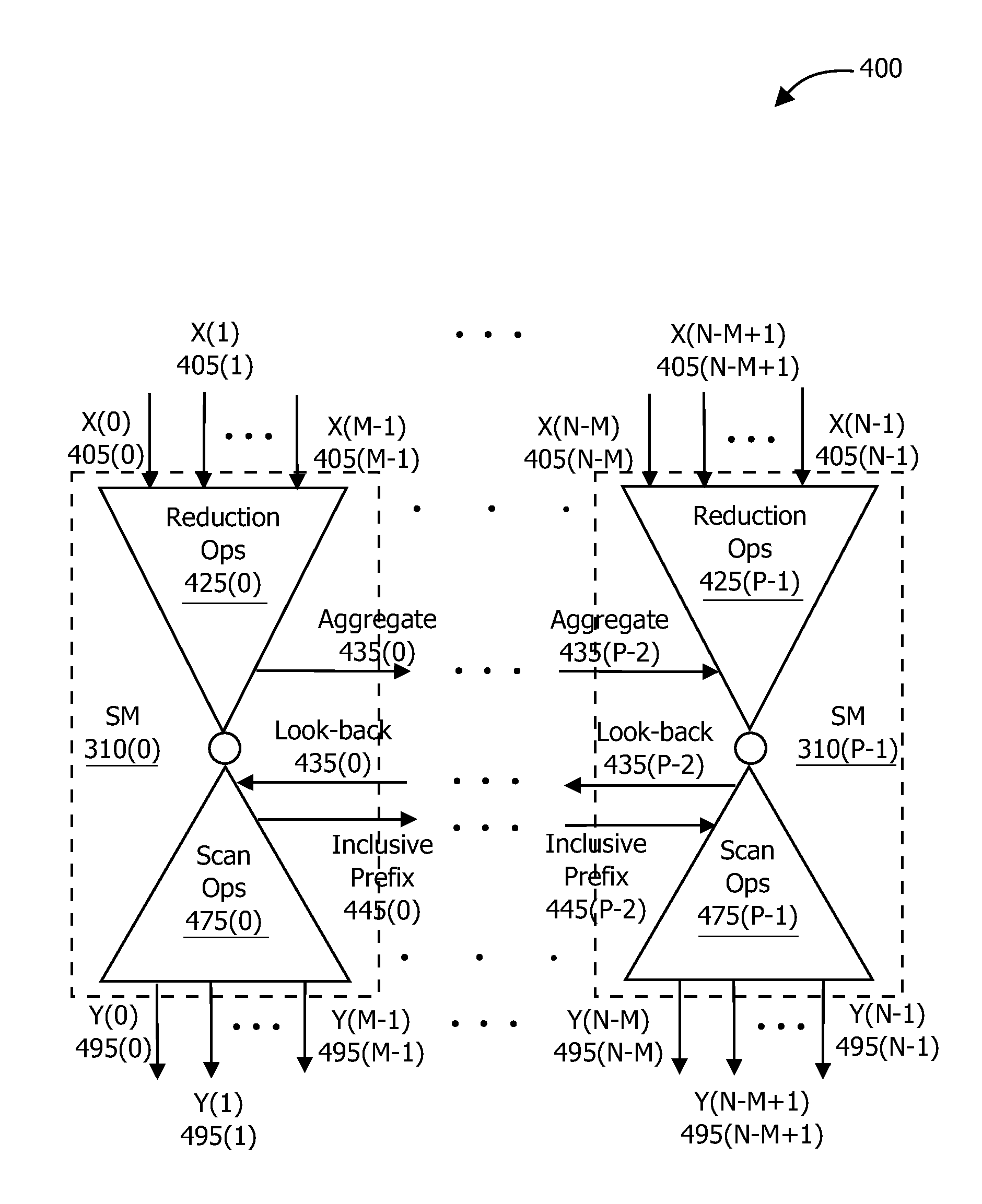

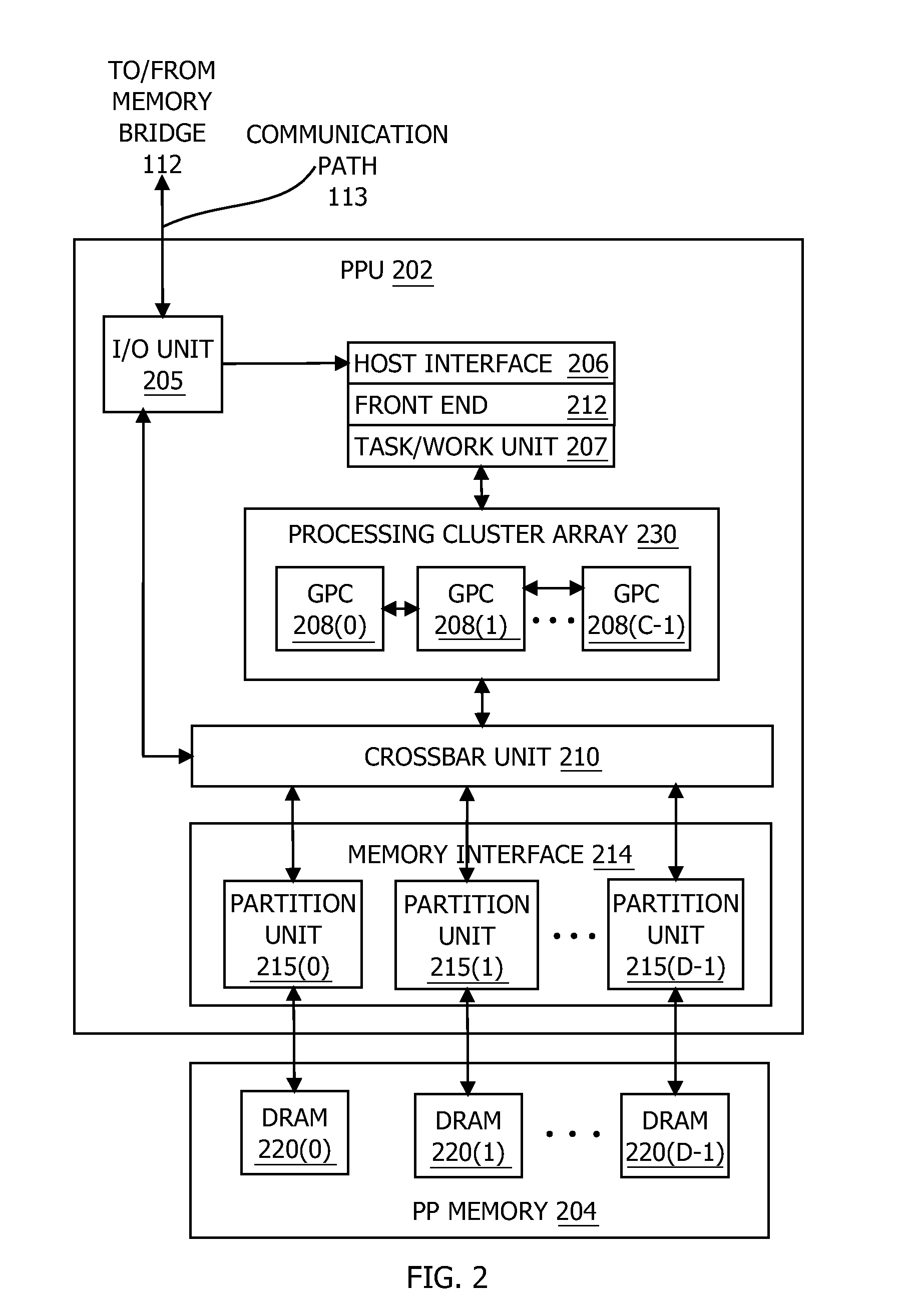

Single-pass parallel prefix scan with dynamic look back

ActiveUS20140380317A1Reduce power consumptionShorten the timeSoftware engineeringDigital data processing detailsSegment descriptorMulti processor

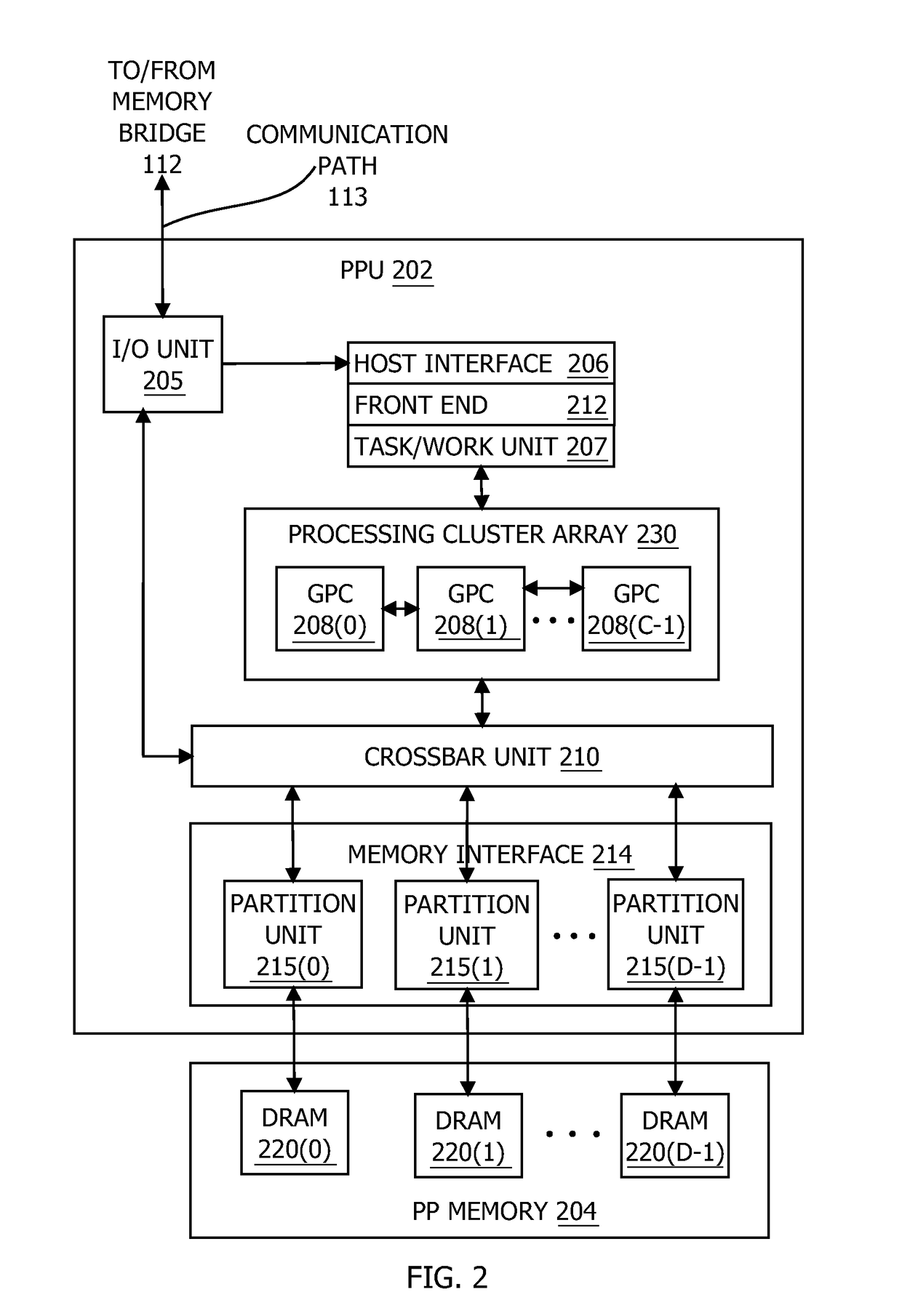

One embodiment of the present invention performs a parallel prefix scan in a single pass that incorporates variable look-back. A parallel processing unit (PPU) subdivides a list of inputs into sequentially-ordered segments and assigns each segment to a streaming multiprocessor (SM) included in the PPU. Notably, the SMs may operate in parallel. Each SM executes write operations on a segment descriptor that includes the status, aggregate, and inclusive-prefix associated with the assigned segment. Further, each SM may execute read operations on segment descriptors associated with other segments. In operation, each SM may perform reduction operations to determine a segment-wide aggregate, may perform look-back operations across multiple preceding segments to determine an exclusive-prefix, and may perform a scan seeded with the exclusive prefix to generate output data. Advantageously, the PPU performs one read operation per input, thereby reducing the time required to execute the prefix scan relative to prior-art parallel implementations.

Owner:NVIDIA CORP

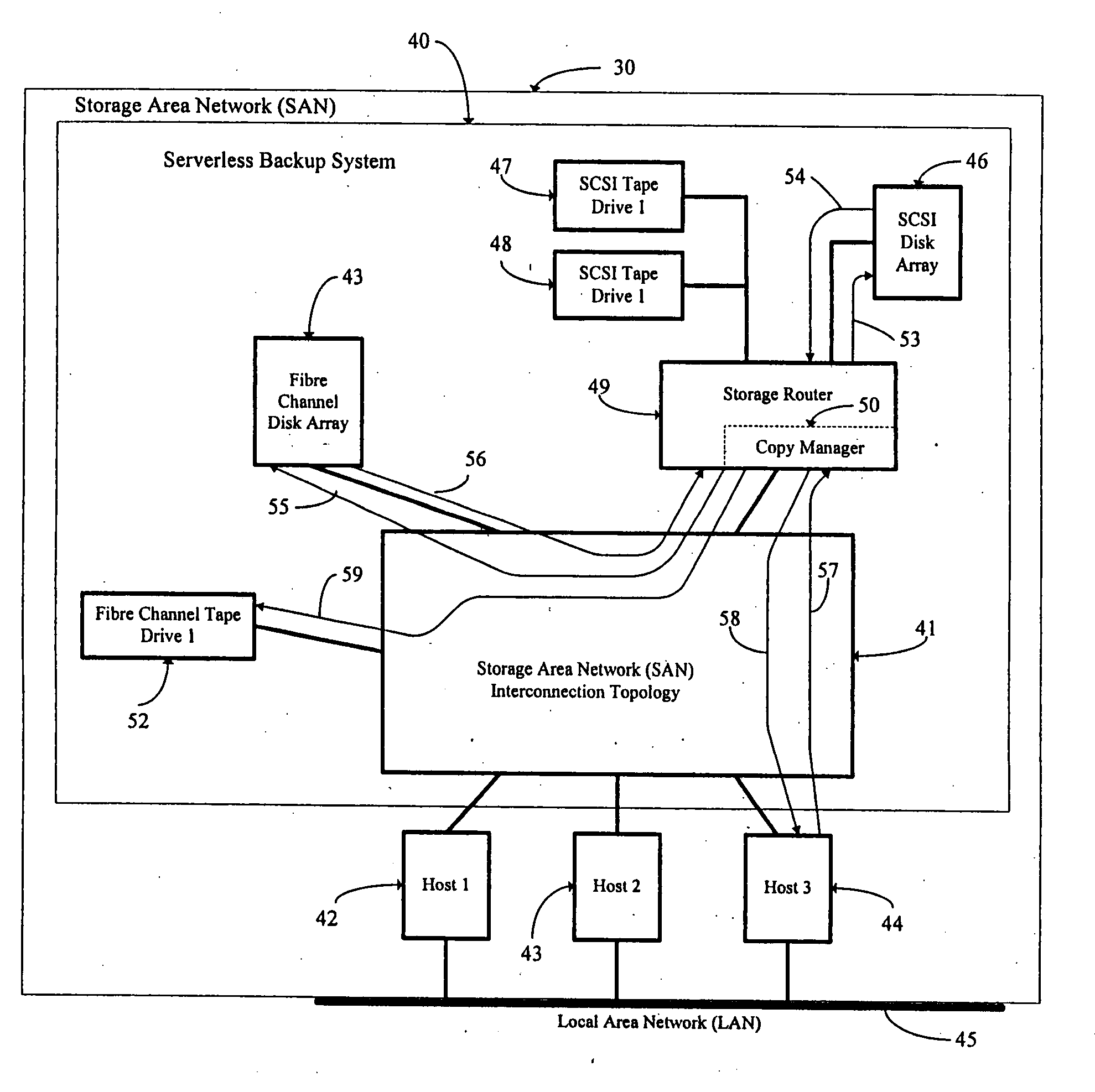

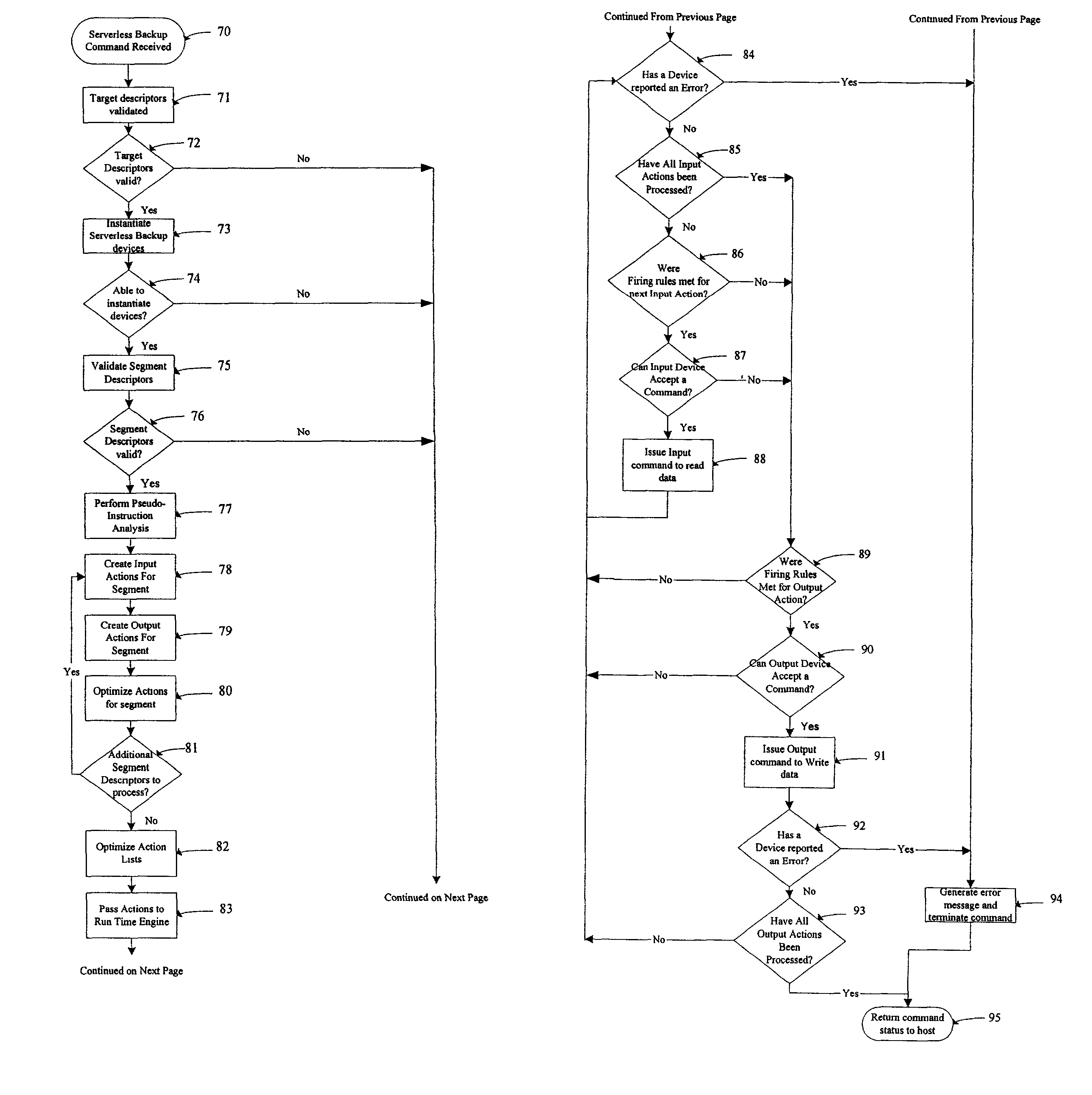

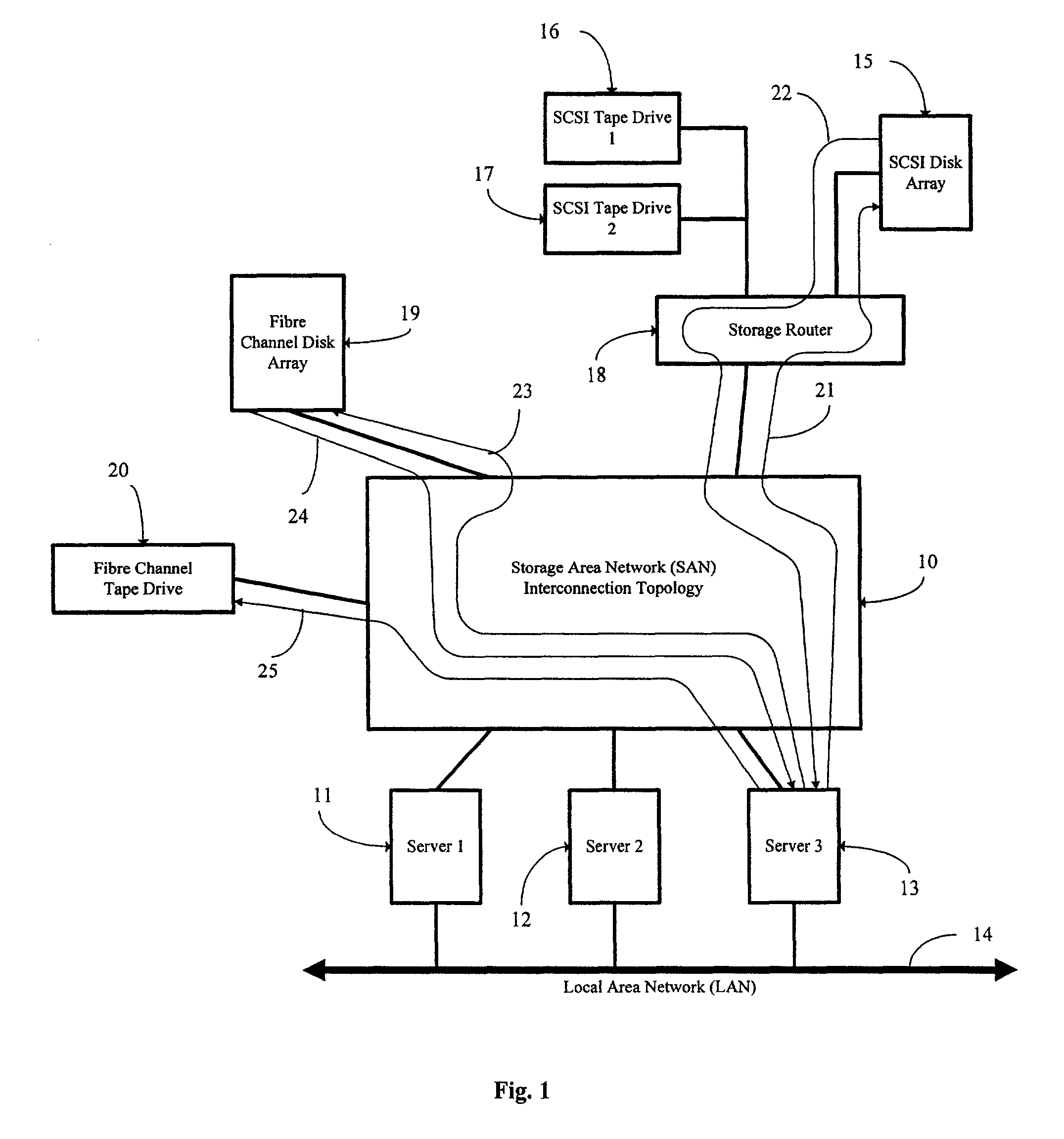

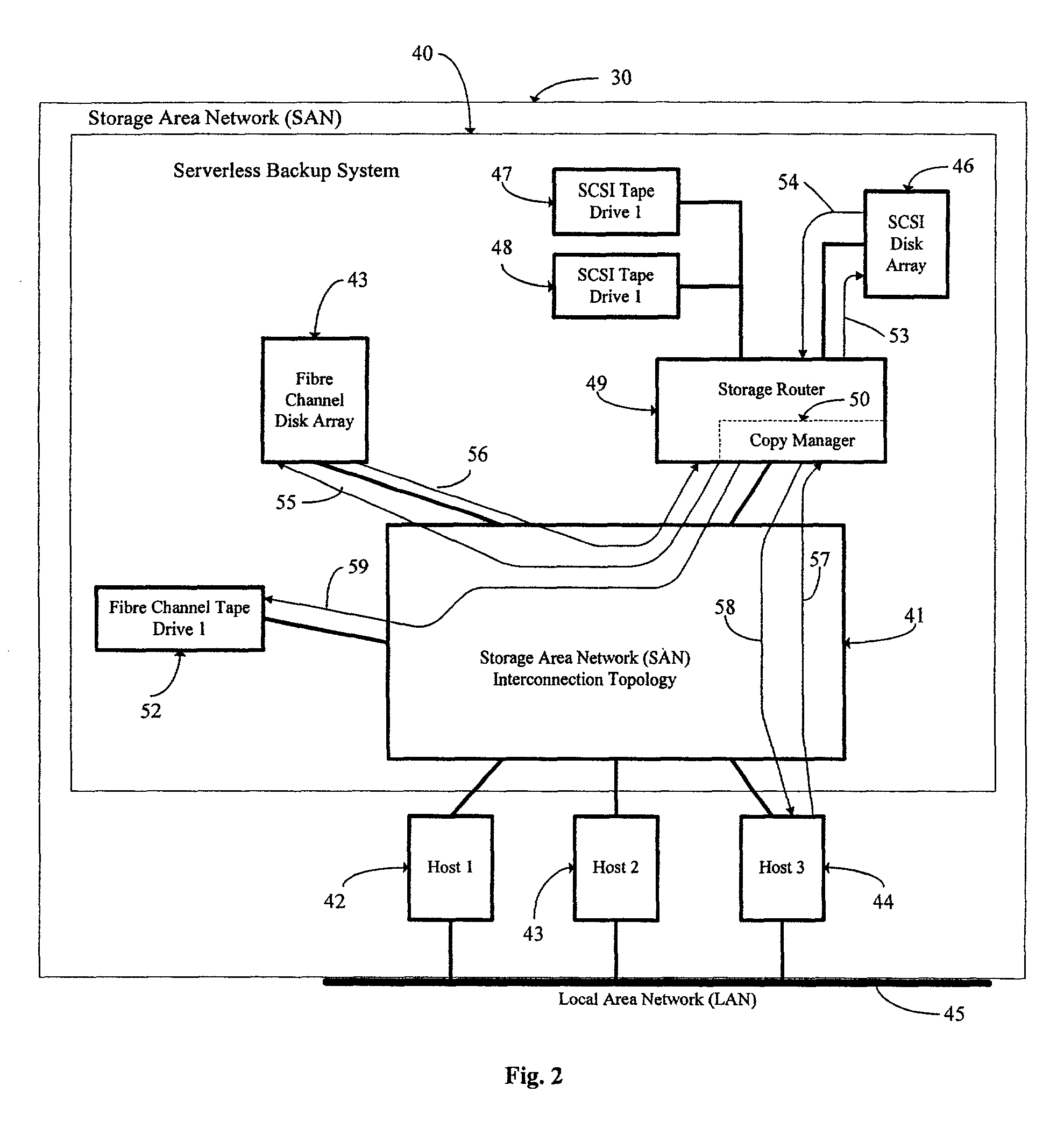

Method and system for improving the efficiency and ensuring the integrity of a data transfer

InactiveUS20070174413A1Improve efficiencyEnsure integrityMemory loss protectionDigital computer detailsThird partySegment descriptor

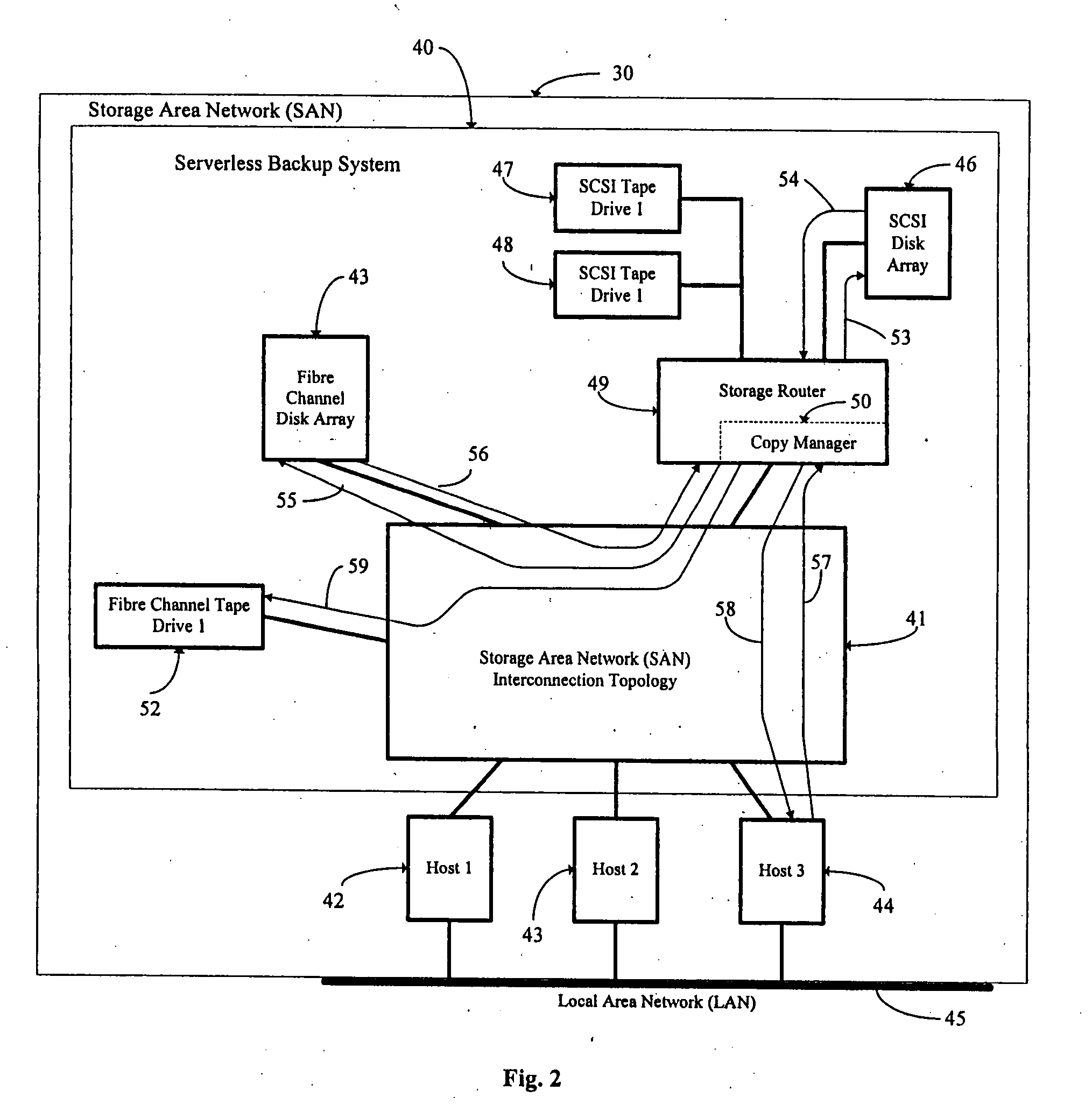

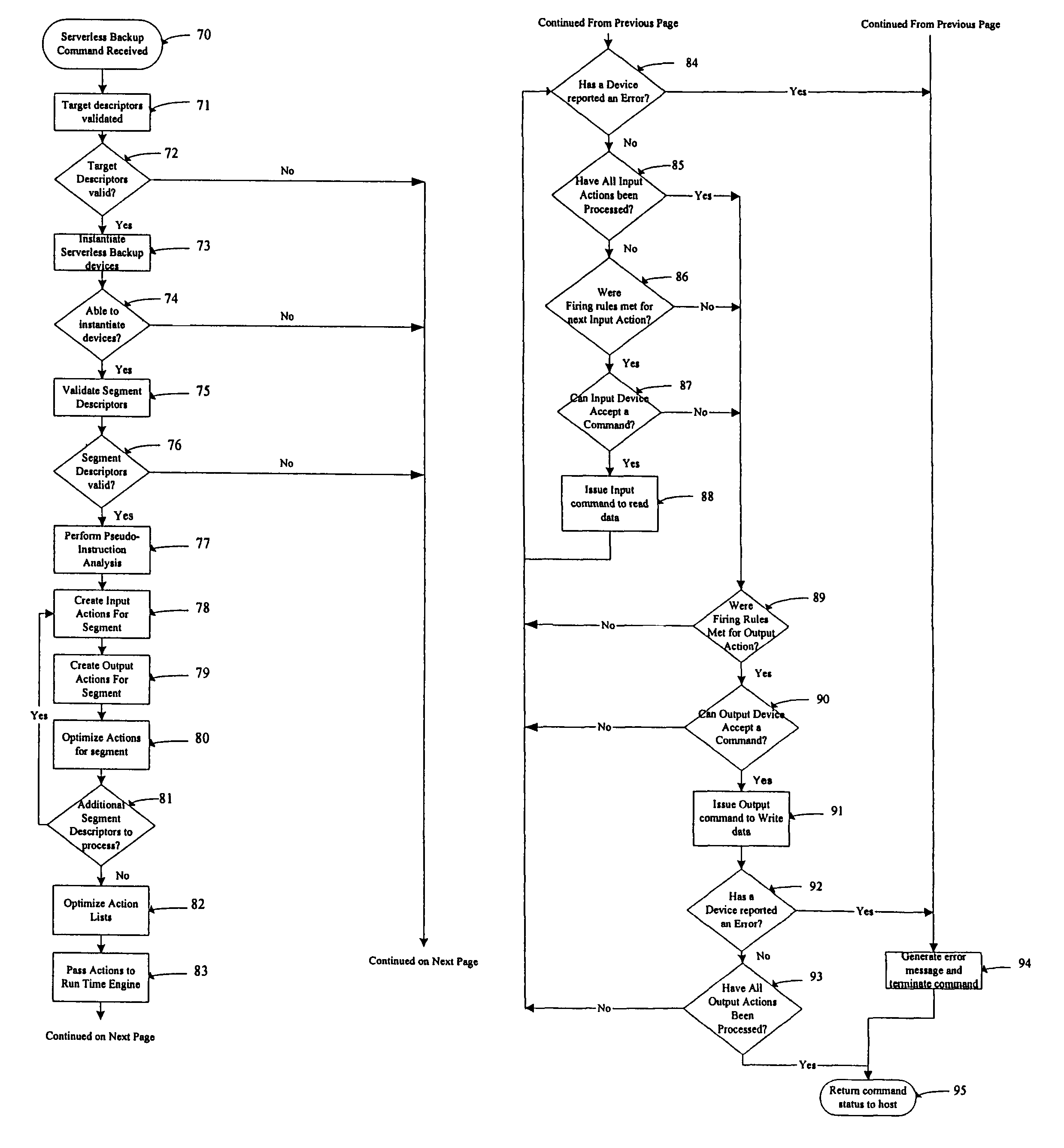

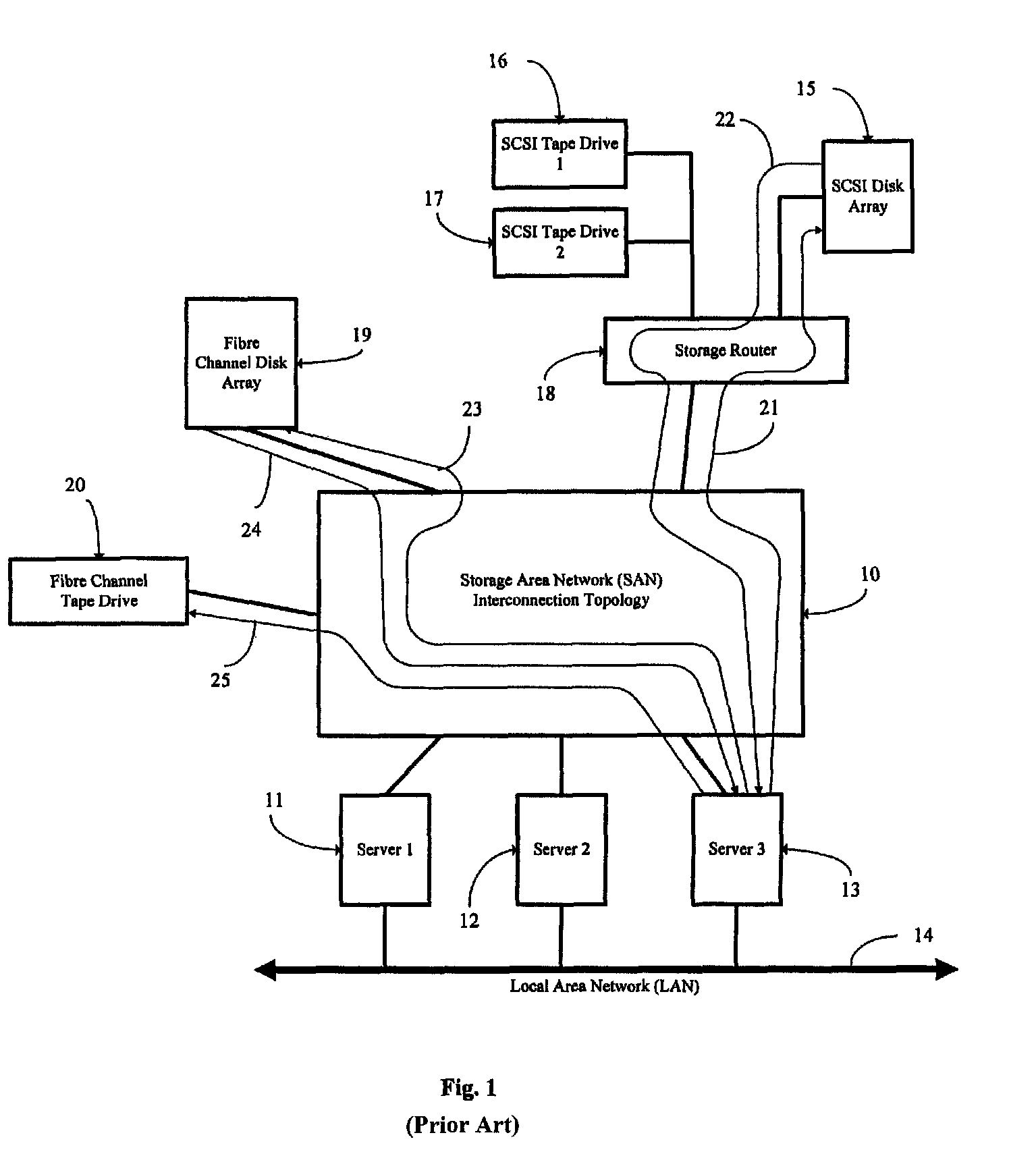

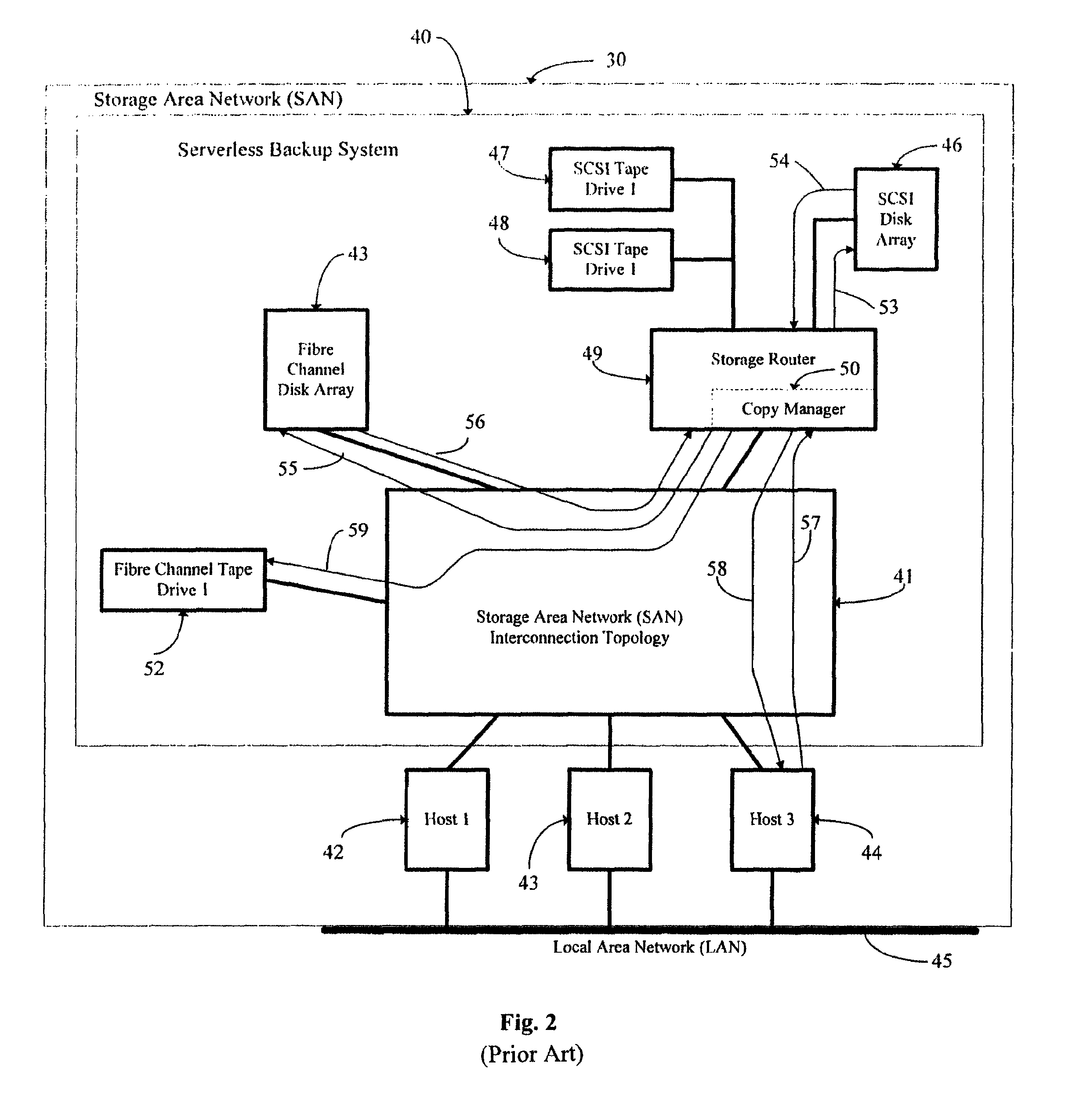

The present invention provides an improved method and system of improving the efficiency, and ensuring the integrity, of a data transfer in a serverless backup, or third party copy, system having one or more physical storage devices. The present invention provides improvements to the processing of serverless copy, or EXTENDED COPY, commands, and transfers of data associated with such commands. These improvements increase the speed at which such commands are executed and completed, and increase the capabilities of copy managers in serverless backup systems. The improvements also make better use of the storage devices involved in the data backup process. The method broadly includes determining a desired manner of execution of segment descriptors, or instructions, as a function of components of those instructions. Other aspects of the invention allow for execution of data segments of any size, and validation of segment descriptors and target descriptors prior to data transfer.

Owner:ATTO TECHNOLOGY

Establishing an operating mode in a processor

InactiveCN1423773AMemory systemsMachine execution arrangementsComputer architectureSegment descriptor

Owner:ADVANCED MICRO DEVICES INC

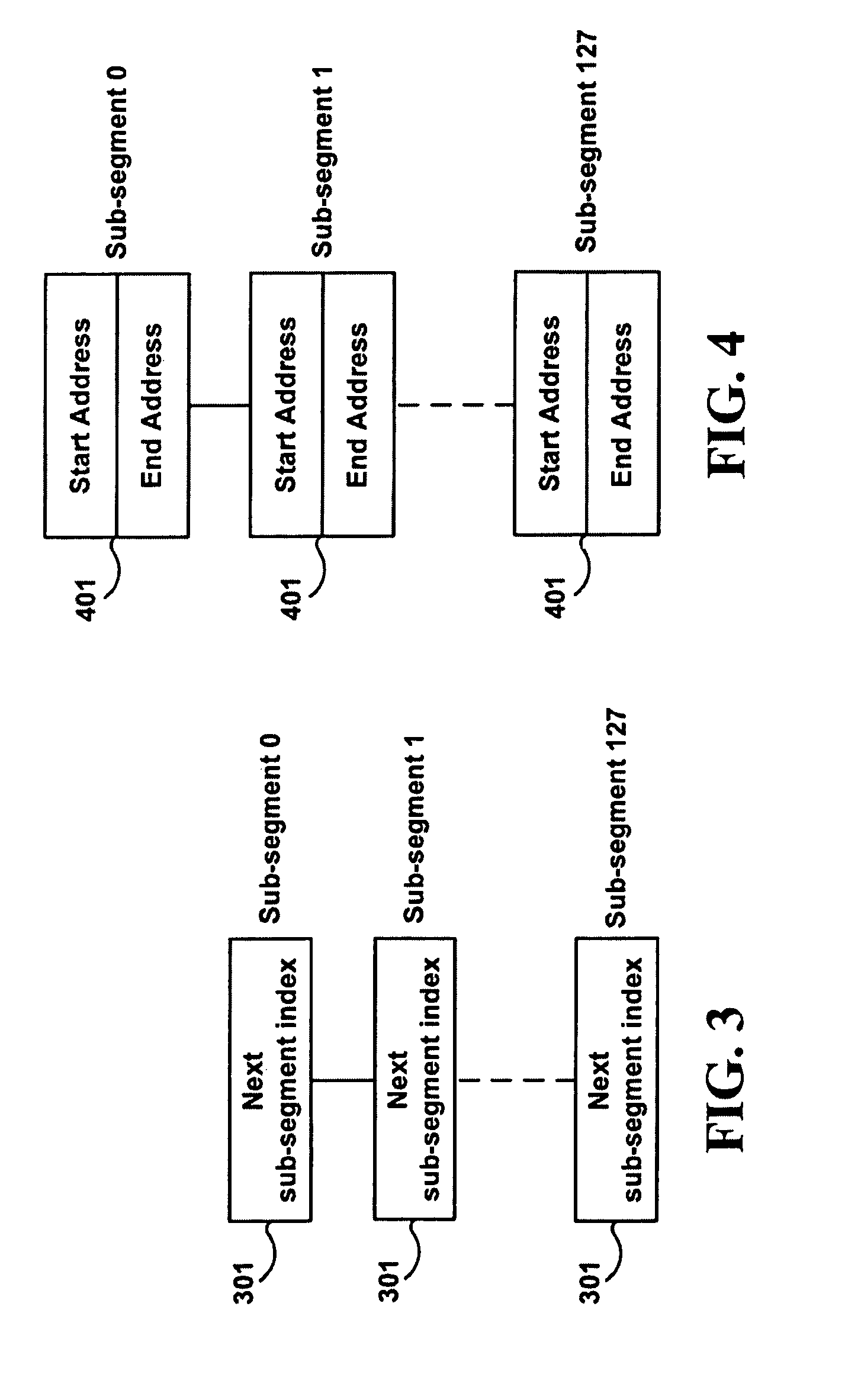

Unlimited sub-segment support in a buffer manager

InactiveUS8127100B1Reduce complexityOvercomes shortcomingMemory systemsMicro-instruction address formationExternal storageSegment descriptor

A system and method of buffer management may employ a common data structure that is recognizable by both hardware and firmware. In some implementations, hardware register settings may be programmed independent of firmware updates to an internal sub-segment description table maintained in an ASIC or other buffer manager logic. Implementation of such a common data structure in external memory may substantially reduce hardware real estate and complexity of a buffer manager ASIC by minimizing the number of required registers and eliminating the need for an internal sub-segment descriptor table. In addition, by eliminating the internal sub-segment descriptor table and allowing buffer manager logic to recognize a common data structure in external memory, the number of buffer sub-segments recognized by the buffer manager may be readily expanded, and may be limited only by the size of the external memory.

Owner:MARVELL ASIA PTE LTD

Method and system for improving the efficiency and ensuring the integrity of a data transfer

ActiveUS7788324B2Improve efficiencyEnsure integrityMultiple digital computer combinationsTransmissionThird partyData segment

The present invention provides an improved method and system of improving the efficiency, and ensuring the integrity, of a data transfer in a serverless backup, or third party copy, system having one or more physical storage devices. The present invention provides improvements to the processing of serverless copy, or EXTENDED COPY, commands, and transfers of data associated with such commands. These improvements increase the speed at which such commands are executed and completed, and increase the capabilities of copy managers in serverless backup systems. The improvements also make better use of the storage devices involved in the data backup process. The method broadly includes determining a desired manner of execution of segment descriptors, or instructions, as a function of components of those instructions. Other aspects of the invention allow for execution of data segments of any size, and validation of segment descriptors and target descriptors prior to data transfer.

Owner:ATTO TECHNOLOGY

Data processing apparatus and method for performing segmented operations

ActiveUS9557995B2Avoid interactionRegister arrangementsConcurrent instruction executionSegment descriptorProcessor register

A data processing apparatus and method are provided for performing segmented operations. The data processing apparatus comprises a vector register store for storing vector operands, and vector processing circuitry providing N lanes of parallel processing, and arranged to perform a segmented operation on up to N data elements provided by a specified vector operand, each data element being allocated to one of the N lanes. The up to N data elements forms a plurality of segments, and performance of the segmented operation comprises performing a separate operation on the data elements of each segment, the separate operation involving interaction between the lanes containing the data elements of the associated segment. Predicate generation circuitry is responsive to a compute descriptor instruction specifying an input vector operand comprising a plurality of segment descriptors, to generate per lane predicate information used by the vector processing circuitry when performing the segmented operation to maintain a boundary between each of the plurality of segments. As a result, interaction between lanes containing data elements from different segments is prevented. This allows very effective utilisation of the lanes of parallel processing within the vector processing circuitry to be achieved.

Owner:ARM LTD

Method and system for improving the efficiency and ensuring the integrity of a data transfer

InactiveUS7836225B2Improve efficiencyEnsure integrityDigital computer detailsTransmissionThird partyData segment

The present invention provides an improved method and system of improving the efficiency, and ensuring the integrity, of a data transfer in a serverless backup, or third party copy, system having one or more physical storage devices. The present invention provides improvements to the processing of serverless copy, or EXTENDED COPY, commands, and transfers of data associated with such commands. These improvements increase the speed at which such commands are executed and completed, and increase the capabilities of copy managers in serverless backup systems. The improvements also make better use of the storage devices involved in the data backup process. The method broadly includes determining a desired manner of execution of segment descriptors, or instructions, as a function of components of those instructions. Other aspects of the invention allow for execution of data segments of any size, and validation of segment descriptors and target descriptors prior to data transfer.

Owner:ATTO TECHNOLOGY

Single-pass parallel prefix scan with dynamic look back

ActiveUS9928033B2Available memory bandwidth may be more fullyReduce power consumptionDigital data processing detailsSoftware engineeringSegment descriptorMulti processor

One embodiment of the present invention performs a parallel prefix scan in a single pass that incorporates variable look-back. A parallel processing unit (PPU) subdivides a list of inputs into sequentially-ordered segments and assigns each segment to a streaming multiprocessor (SM) included in the PPU. Notably, the SMs may operate in parallel. Each SM executes write operations on a segment descriptor that includes the status, aggregate, and inclusive-prefix associated with the assigned segment. Further, each SM may execute read operations on segment descriptors associated with other segments. In operation, each SM may perform reduction operations to determine a segment-wide aggregate, may perform look-back operations across multiple preceding segments to determine an exclusive-prefix, and may perform a scan seeded with the exclusive prefix to generate output data. Advantageously, the PPU performs one read operation per input, thereby reducing the time required to execute the prefix scan relative to prior-art parallel implementations.

Owner:NVIDIA CORP

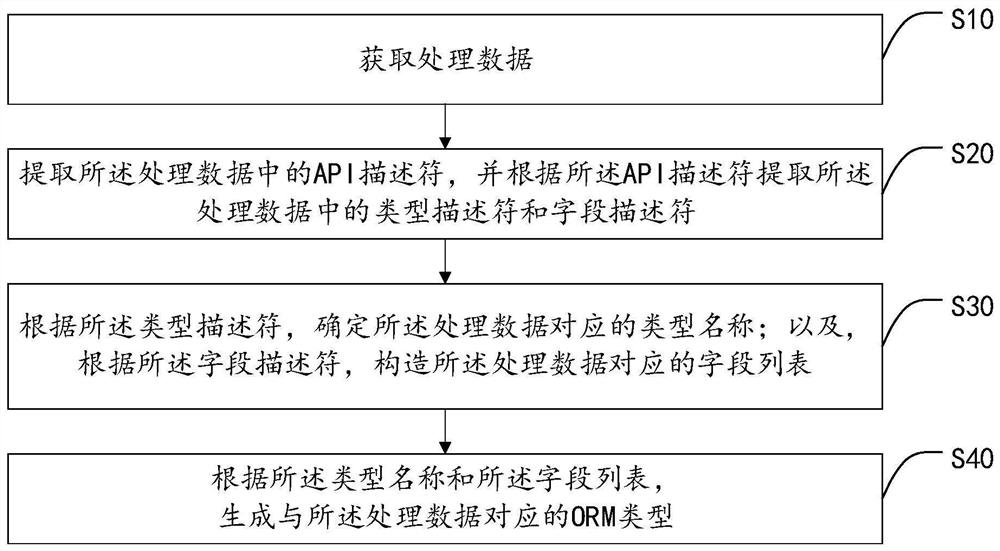

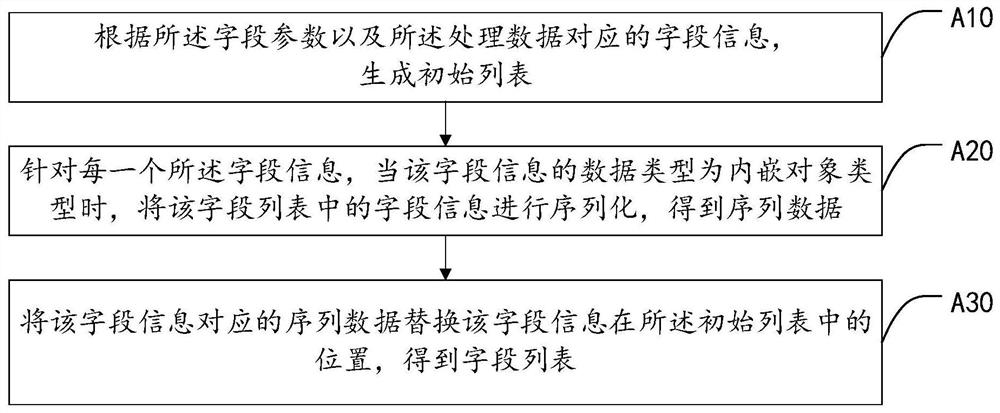

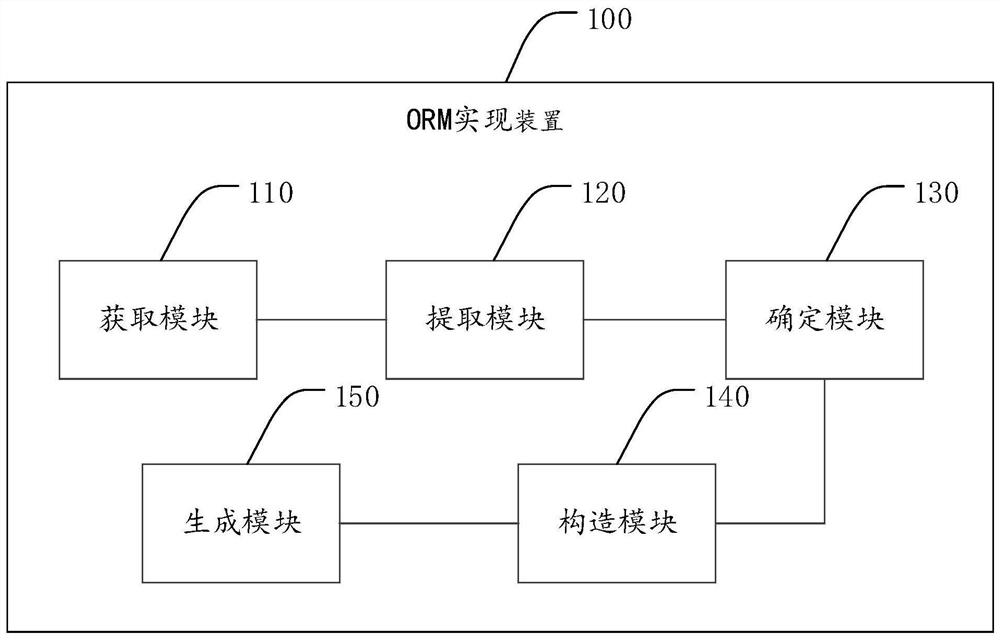

ORM implementation method and related equipment

PendingCN113485684AImprove processing efficiencyProgram documentationCreation/generation of source codeData classSegment descriptor

The invention discloses an ORM implementation method and related equipment, and the method comprises the steps: obtaining processing data, wherein the type of the processing data is a Protobuf type; extracting an API descriptor in the processing data, and extracting a type descriptor and a field descriptor in the processing data according to the API descriptor; determining a type name corresponding to the processing data according to the type descriptor; according to the field descriptor, constructing a field list corresponding to the processing data; and according to the type name and the field list, generating an ORM type corresponding to the processing data. According to the method, the Protobuf data type is directly used for the ORM type, and the data processing efficiency is improved.

Owner:深圳市观麦网络科技有限公司

A Global Offset Table Protection Method Based on Address Randomization and Segment Isolation

ActiveCN105095762BOvercoming problems such as wasteAdded randomizationPlatform integrity maintainanceMemory addressSegment descriptor

Owner:THE PLA INFORMATION ENG UNIV +1

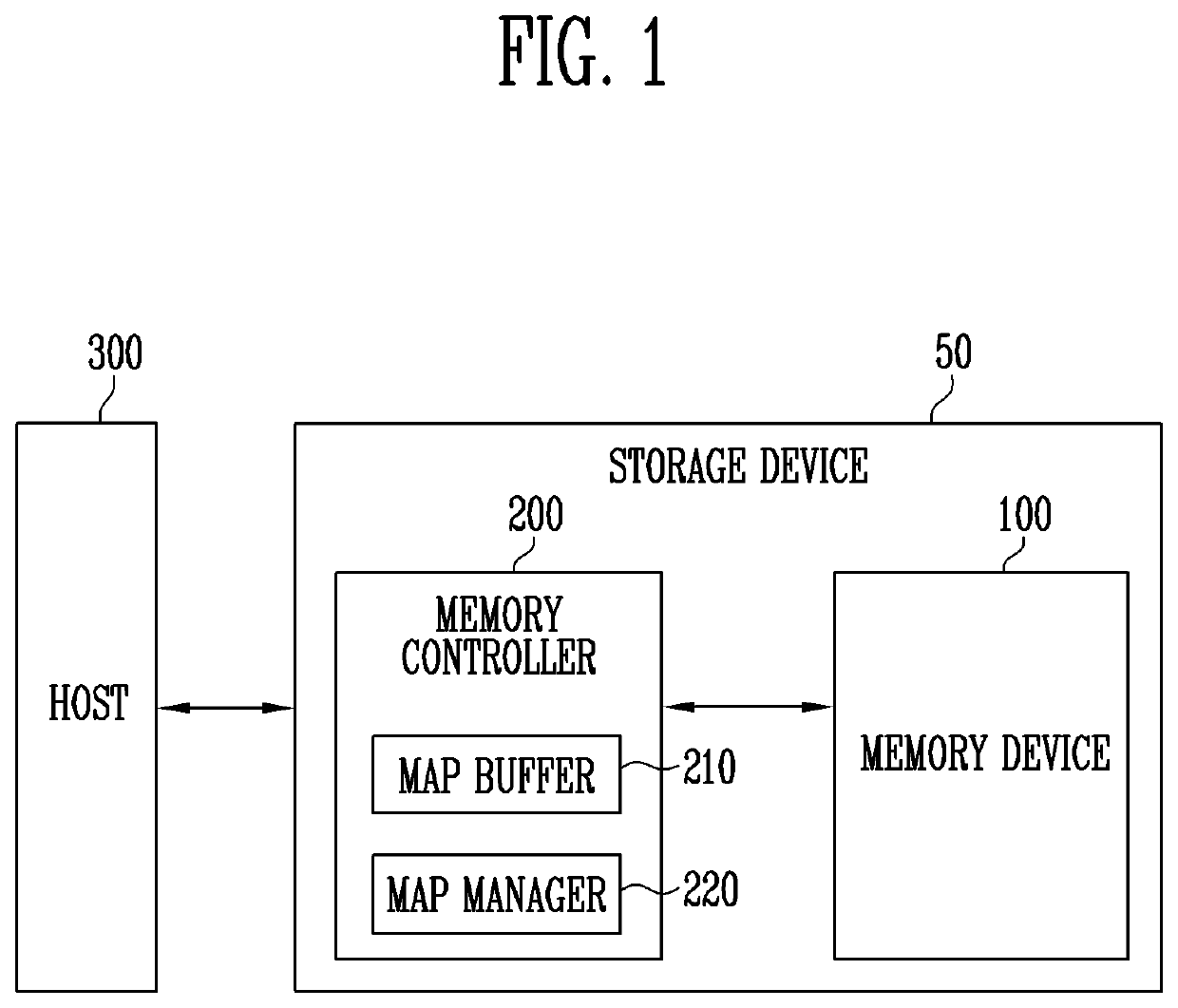

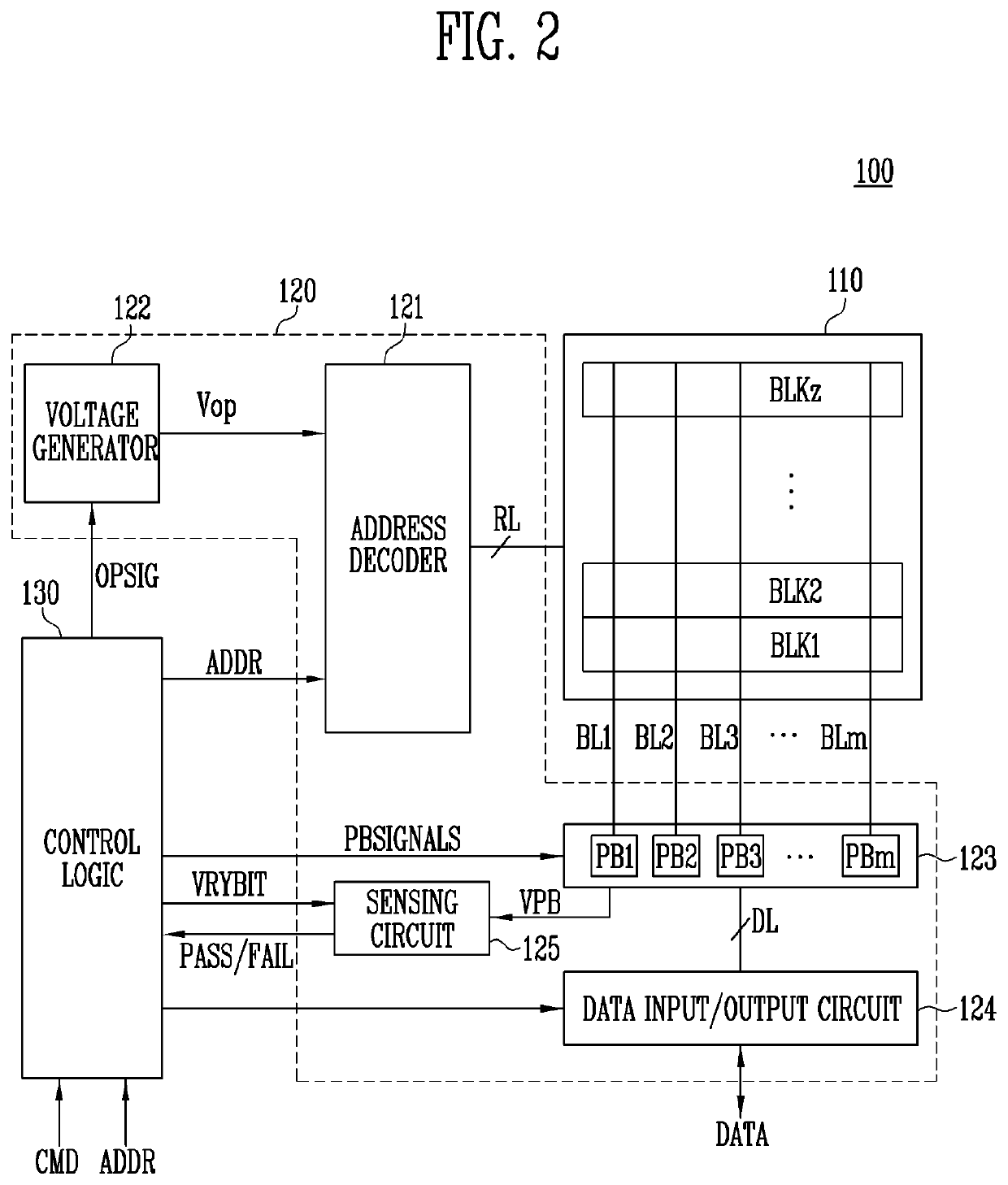

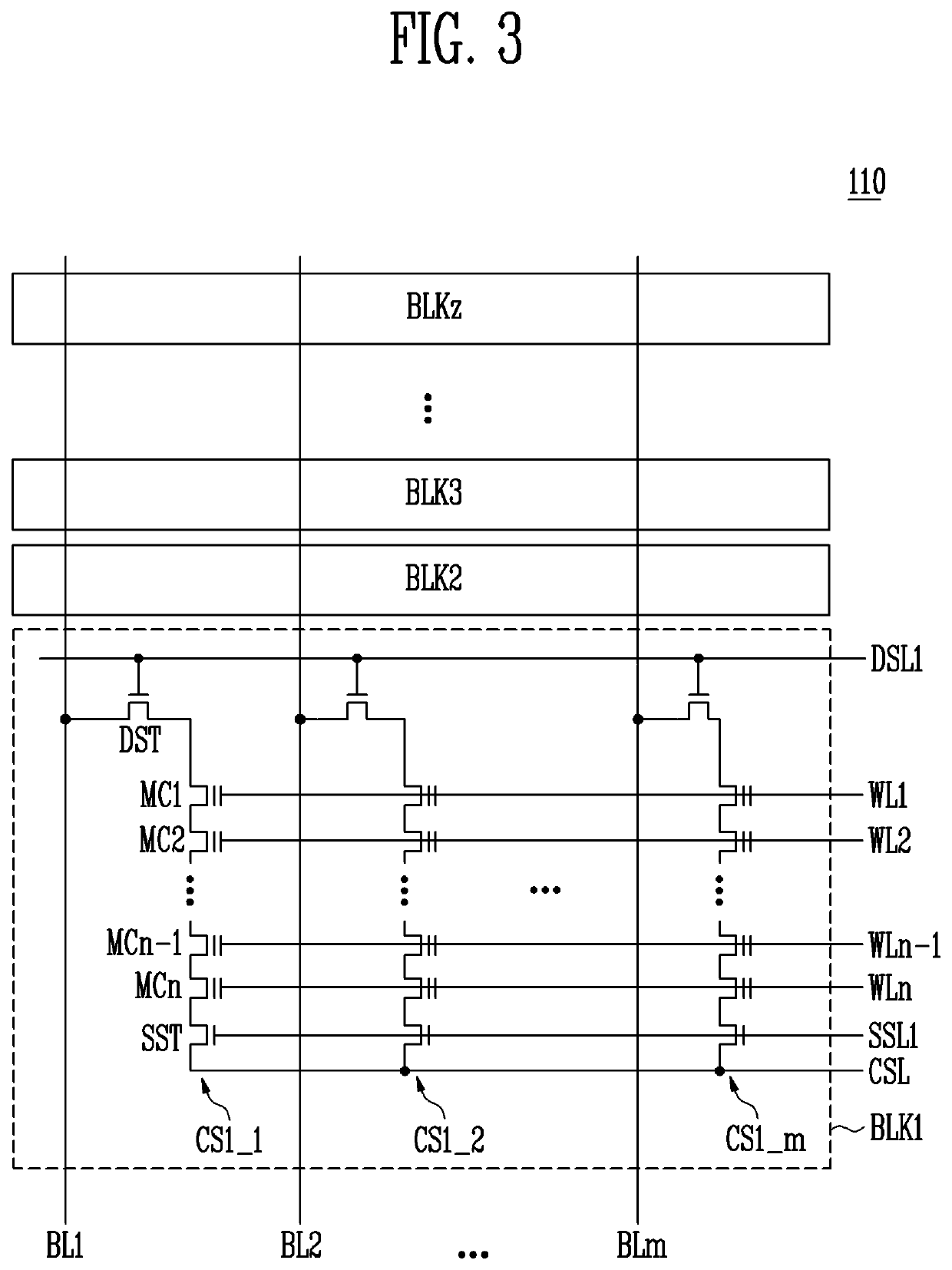

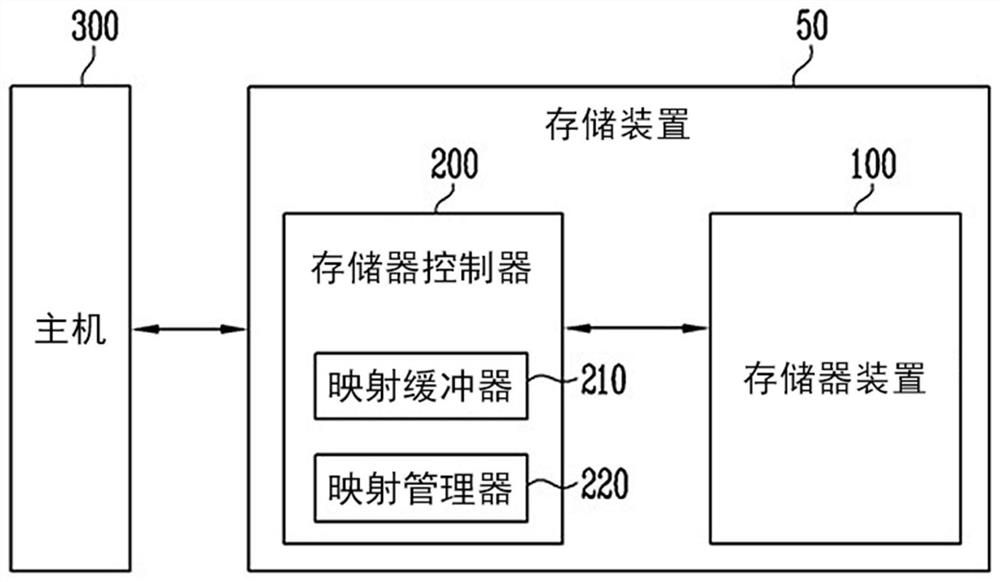

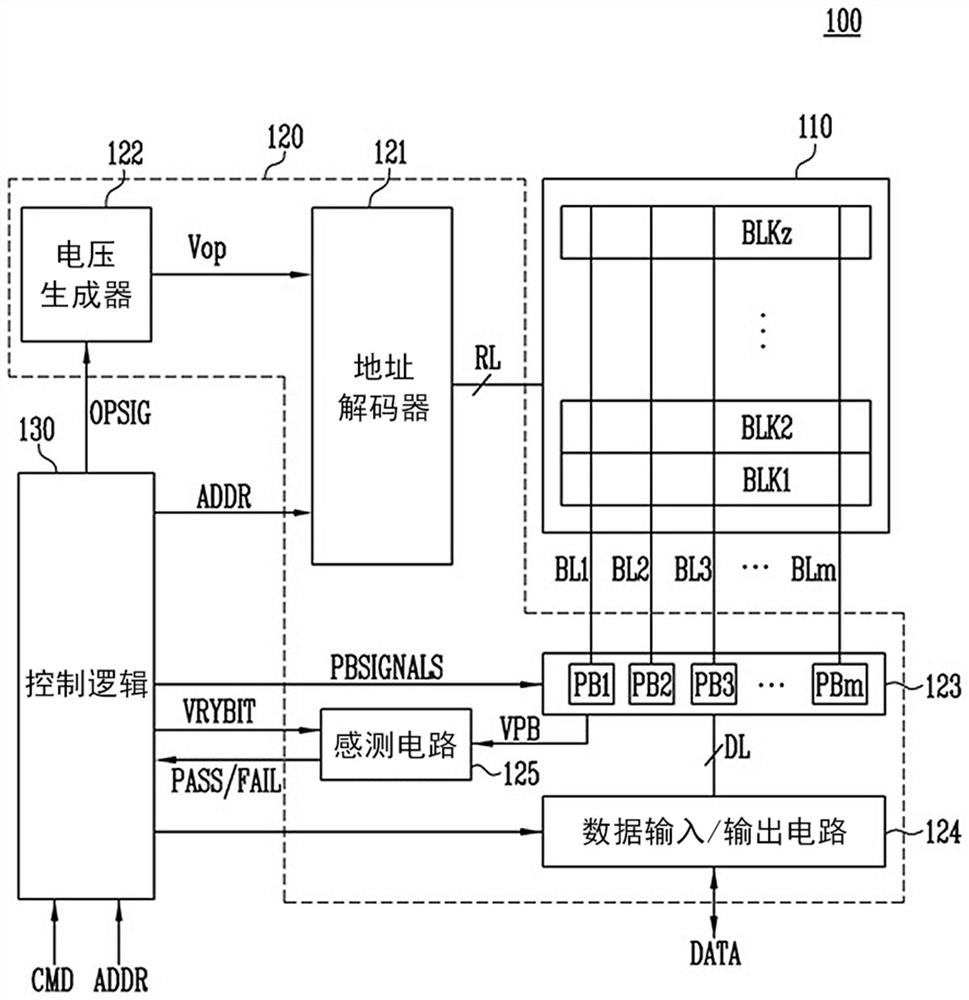

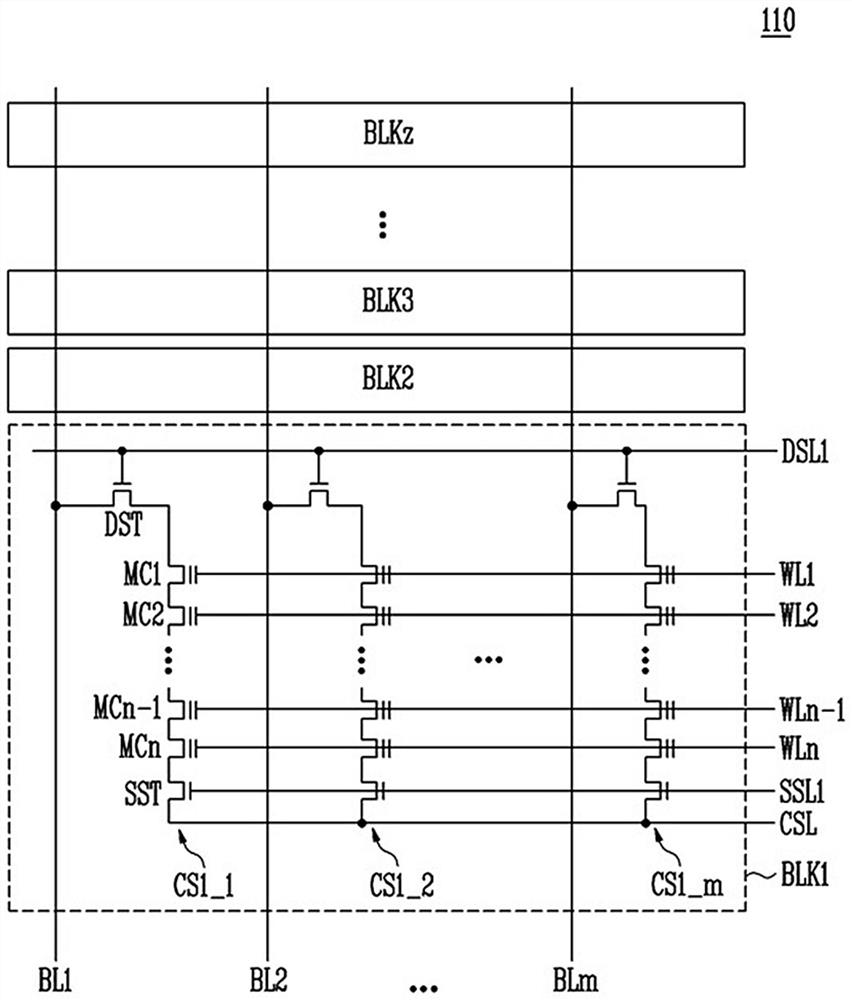

Memory system, memory controller and method of operating the same

ActiveUS20210303464A1Improved map search performanceMemory architecture accessing/allocationMemory adressing/allocation/relocationSegment descriptorControl store

Provided herein may be a memory controller configured to control a memory device. The memory controller may include a map buffer, a descriptor queue, and a descriptor controller. The map buffer may sequentially store map segments of a plurality of map segments stored in the memory device. The descriptor queue may store descriptors corresponding to the respective map segments, based on a plurality of addresses of the map buffer. The descriptor controller may search for a target descriptor among the stored descriptors based on a logical address received from a host, and reorder the stored descriptors while searching for the target descriptor.

Owner:SK HYNIX INC

Memory system, memory controller and method of operating same

InactiveCN113448501AMemory architecture accessing/allocationInput/output to record carriersSegment descriptorEngineering

The disclosure provides a memory controller configured to control a memory device. The memory controller may include a map buffer, a descriptor queue, and a descriptor controller. The map buffer may sequentially store map segments of a plurality of map segments stored in the memory device. The descriptor queue may store descriptors corresponding to the respective map segments, based on a plurality of addresses of the map buffer. The descriptor controller may search for a target descriptor among the stored descriptors based on a logical address received from a host, and reorder the stored descriptors while searching for the target descriptor.

Owner:SK HYNIX INC

Call gate expansion for 64 bit addressing

A processor supports a first processing mode in which the address size is greater than 32 bits. The address size may be nominally indicated as 64 bits, although various embodiments of the processor may implement any address size which exceeds 32 bits, up to and including 64 bits, in the first processing mode. The first processing mode may be established by placing an enable indication in a control register into an enabled state and by setting a first operating mode indication and a second operating mode indication in a segment descriptor to predefined states. Other combinations of the first operating mode indication and the second operating mode indication may be used to provide compatibility modes for 32 bit and 16 bit processing compatible with the x86 processor architecture (with the enable indication remaining in the enabled state). To call code operating in the first processing mode from the 32 bit or 16 bit code, a call gate descriptor is defined which occupies two entries in a segment descriptor table. By occupying two entries, each of which may otherwise store a segment descriptor, the call gate descriptor may include enough space to store an address in excess of 32 bits. Thus, a calling code segment may reference a call gate descriptor, which may reference the target code semgent and may provide an address within the address space of the target code segment, even if the address exceeds the address size in the calling code segment.

Owner:ADVANCED MICRO DEVICES INC

System, device and method of authority inspection for memory access operation

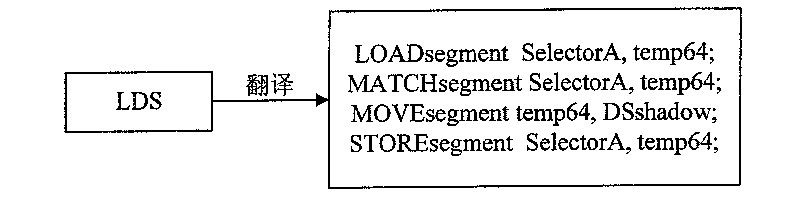

InactiveCN101079083BImplement permission checksRun fastDigital data authenticationSegment descriptorProtection mechanism

The invention discloses an authority limit check system, device and method for accessing and saving operation under the sectionalized protection mechanism in the complicate instruction set computer sectionalized protection mechanism technique field. The method comprises the following steps: A, judging accessing and saving instruction type of receiving self accessing and saving instruction launching device by the accessing and saving operation authority limit check device, proceeding the procedure B if the accessing and saving instruction is the special accessing and saving instruction, proceeding the procedure C if not; B, checking if the field selector type, the segment descriptor word type and the field franchise of the special accessing and saving instruction is legal by the accessing and saving operation authority limit check device, ending the check if all are legal, proceeding the procedure D if any one isn' t legal; D, transferring the exceptional signal to the exceptional dealing device by the accessing and saving operation limit check device. The invention achieves the authority limit check for accessing and saving operation.

Owner:INST OF COMPUTING TECH CHINESE ACAD OF SCI