A Synchronization Method for Multi-Core Processors Based on Delay Barrier Synchronization Operation Instructions

A multi-core processor, core processor technology, applied in concurrent instruction execution, electrical digital data processing, instruments, etc., can solve problems such as physical distance and cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0025] The present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments.

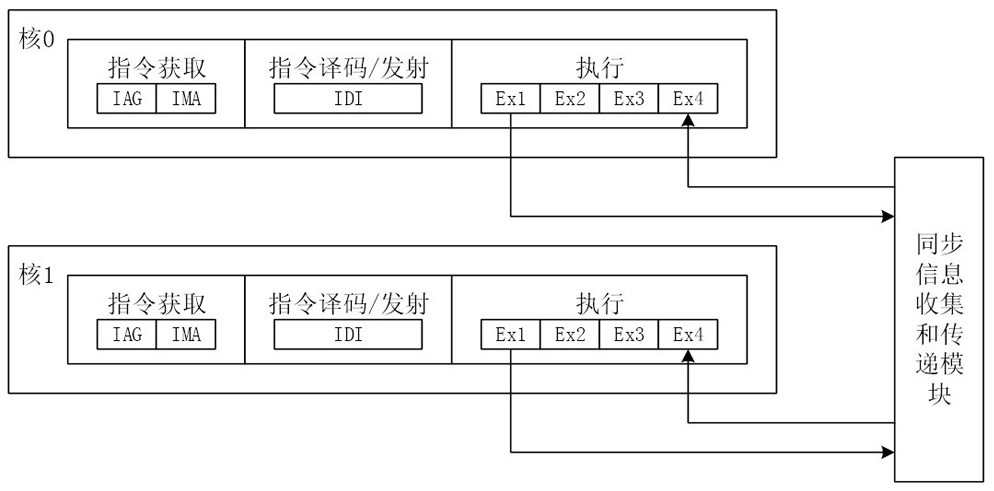

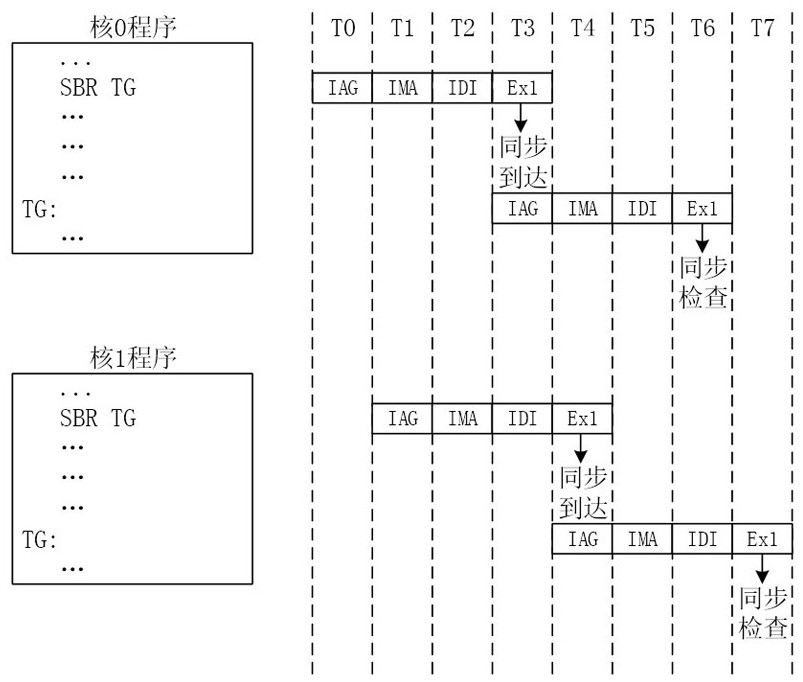

[0026] A kind of multi-core processor synchronization method based on delay barrier synchronous operation instruction of the present invention is: all participating core processors send the signal that this core processor has reached synchronization at the "synchronization arrival station", and confirm participation at the "synchronization checkpoint" Whether all the other core processors of the barrier synchronization arrive; if so, the core processor continues to execute, otherwise it enters the waiting state until the signal sent by the last arriving core processor is checked by the core processor.

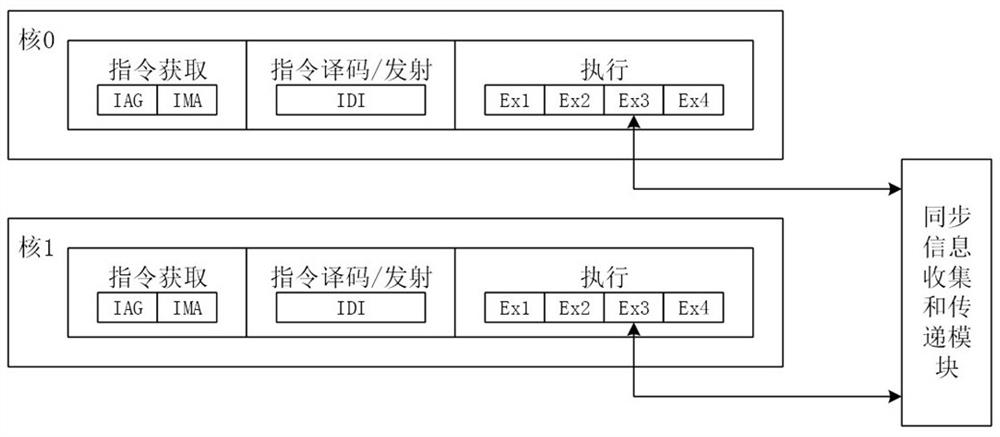

[0027] In a processor containing multiple cores, the cores participating in the synchronization are synchronized by executing a special synchronization operation instruction (including but not limited to synchronous branches, synchronou...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More