Patents

Literature

11151 results about "MicroBlaze" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

The MicroBlaze is a soft microprocessor core designed for Xilinx field-programmable gate arrays (FPGA). As a soft-core processor, MicroBlaze is implemented entirely in the general-purpose memory and logic fabric of Xilinx FPGAs.

System and method for securing sensitive data

ActiveUS20140344943A1Digital data processing detailsUser identity/authority verificationSoftware engineeringOperating system

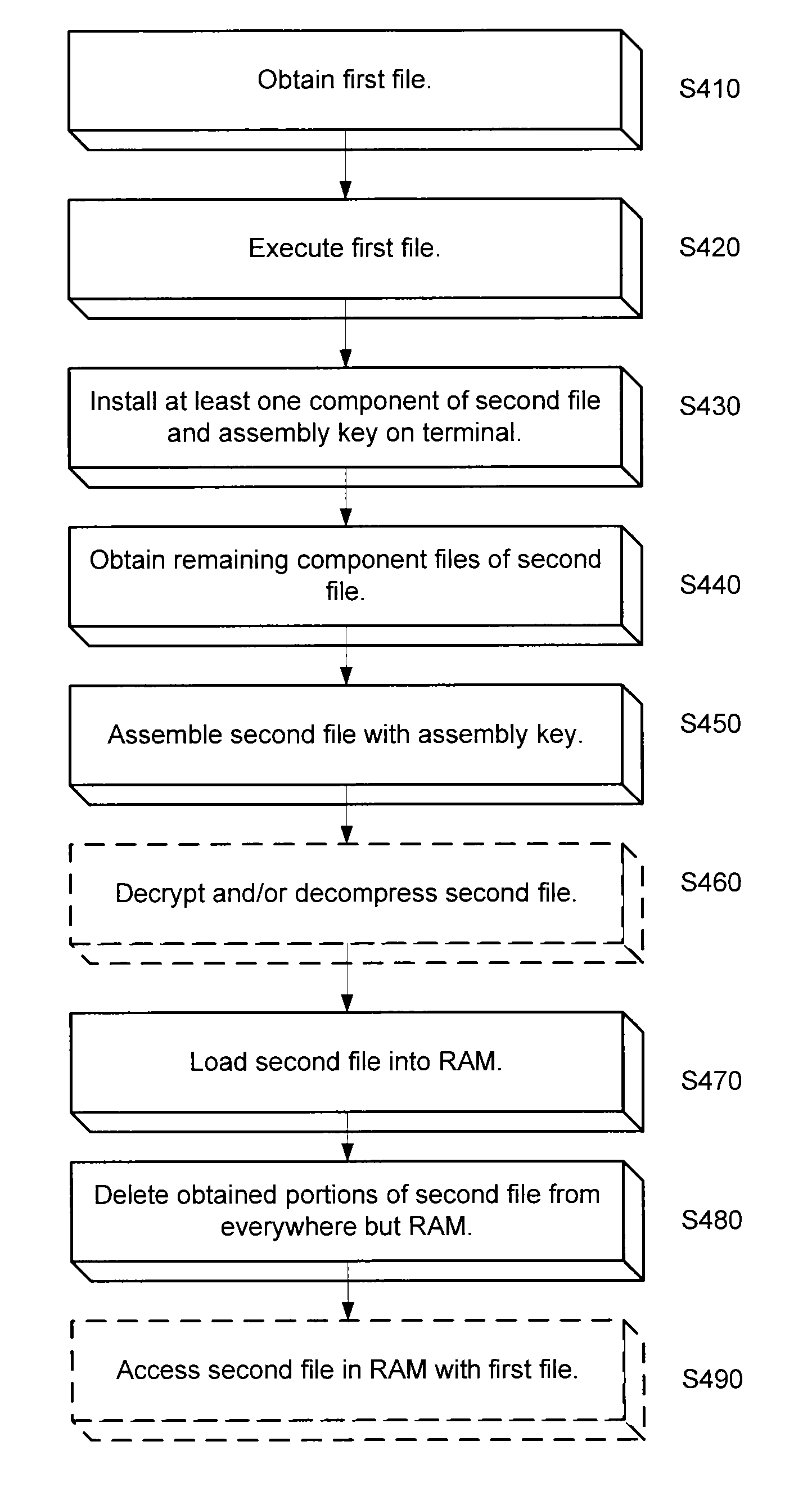

An approach is provided for securing data in a technical environment. In one embodiment, a processor obtains a first file, which when executed installs a first portion of a second file and an assembly key to assemble the second file. The processor executes this first file and then obtains the second portion of the second file. The processor assembles the second file using the first portion, the second portion, and the assembly key.

Owner:HAND HELD PRODS

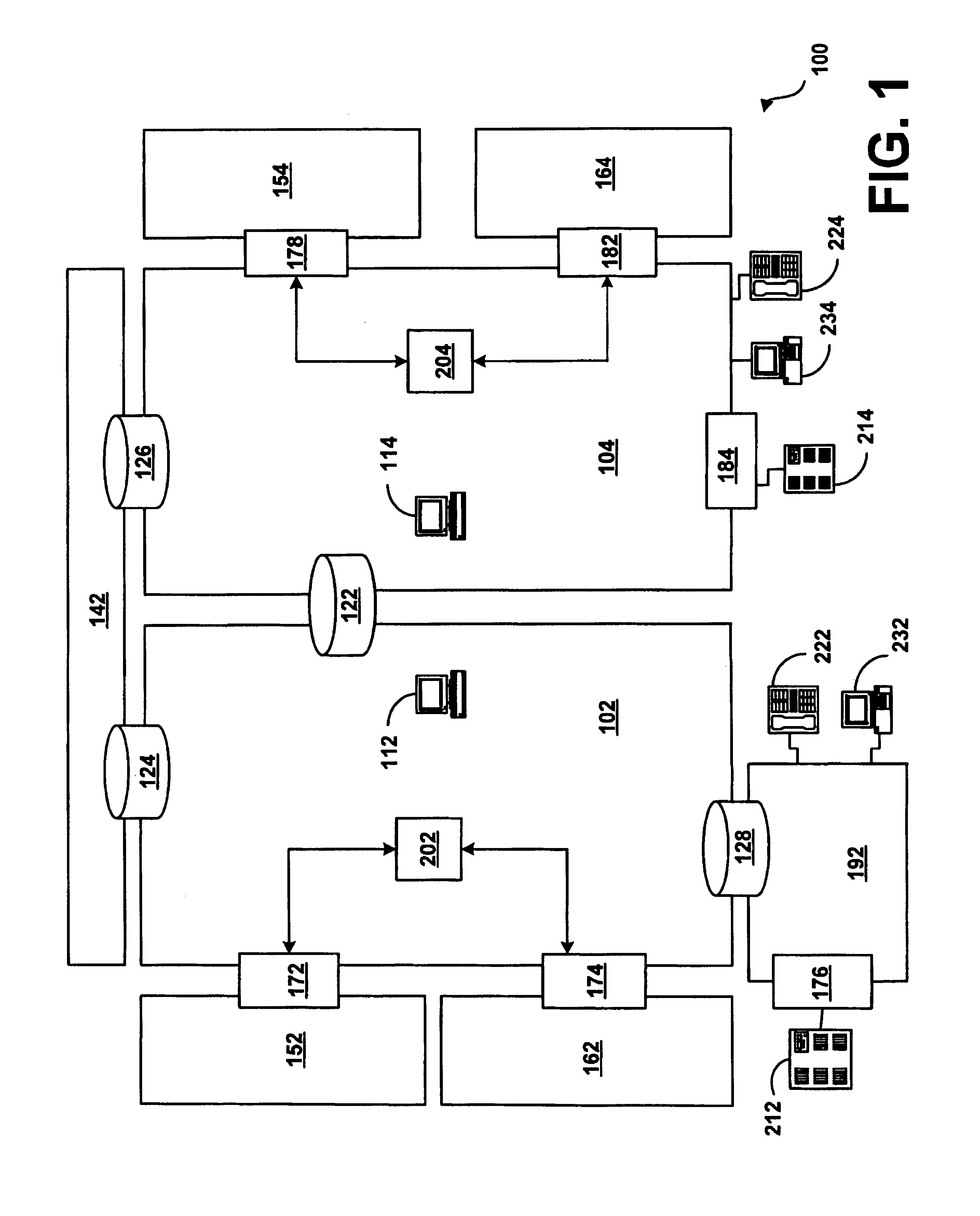

Method and apparatus for content protection in a personal digital network environment

InactiveUS20050144468A1Easy to disassembleReliable lockingTelevision system detailsUser identity/authority verificationGraphicsVideo processing

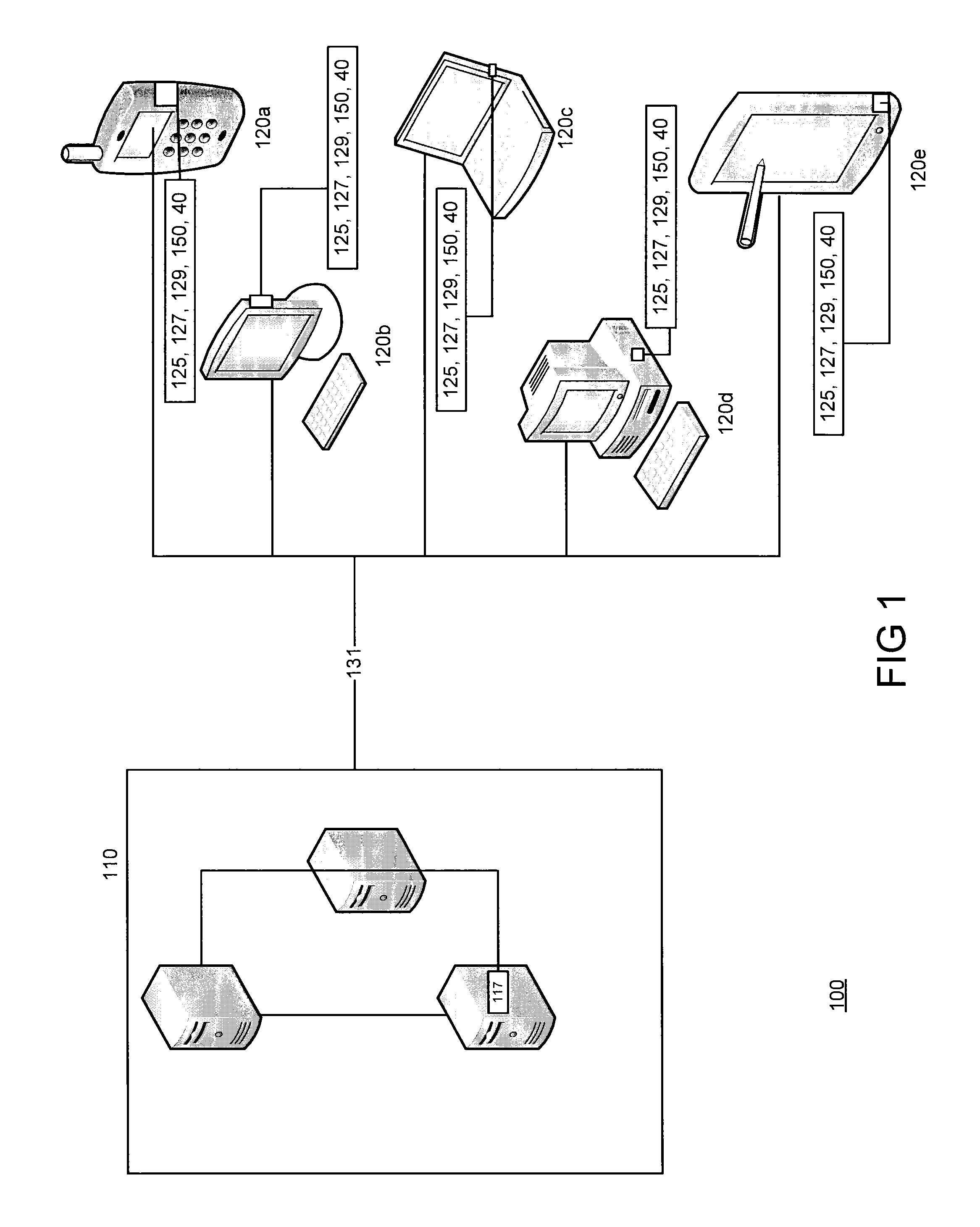

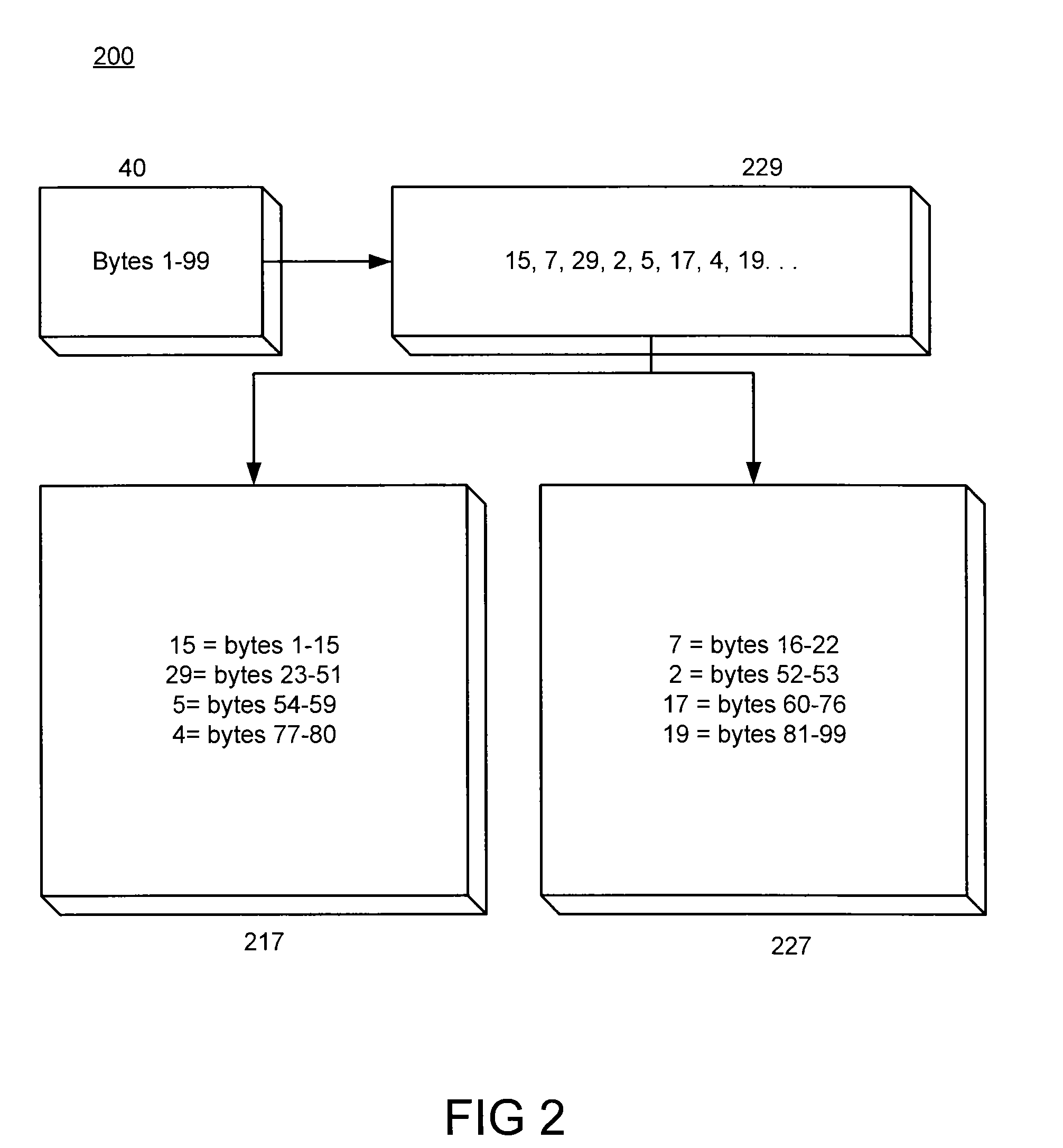

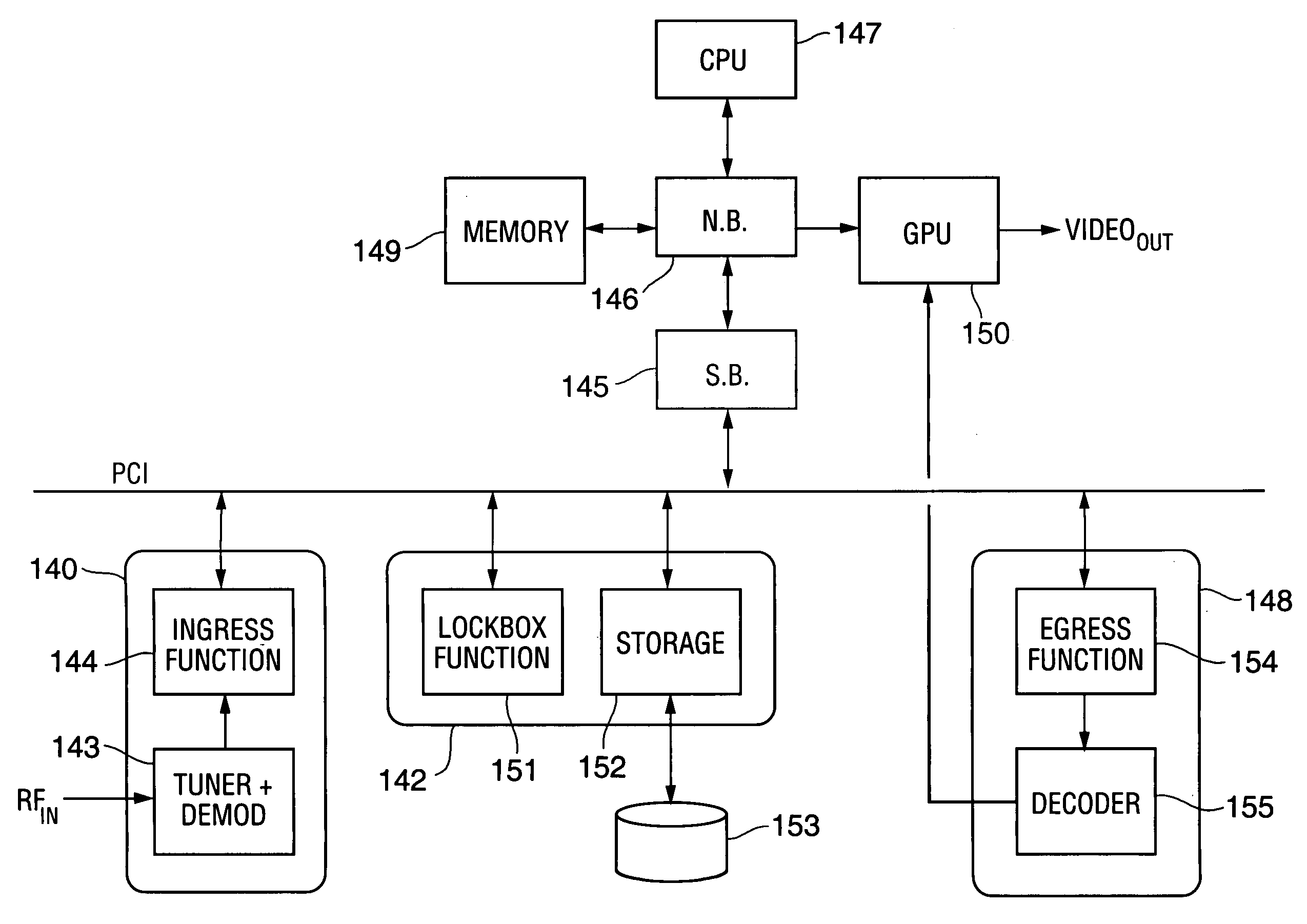

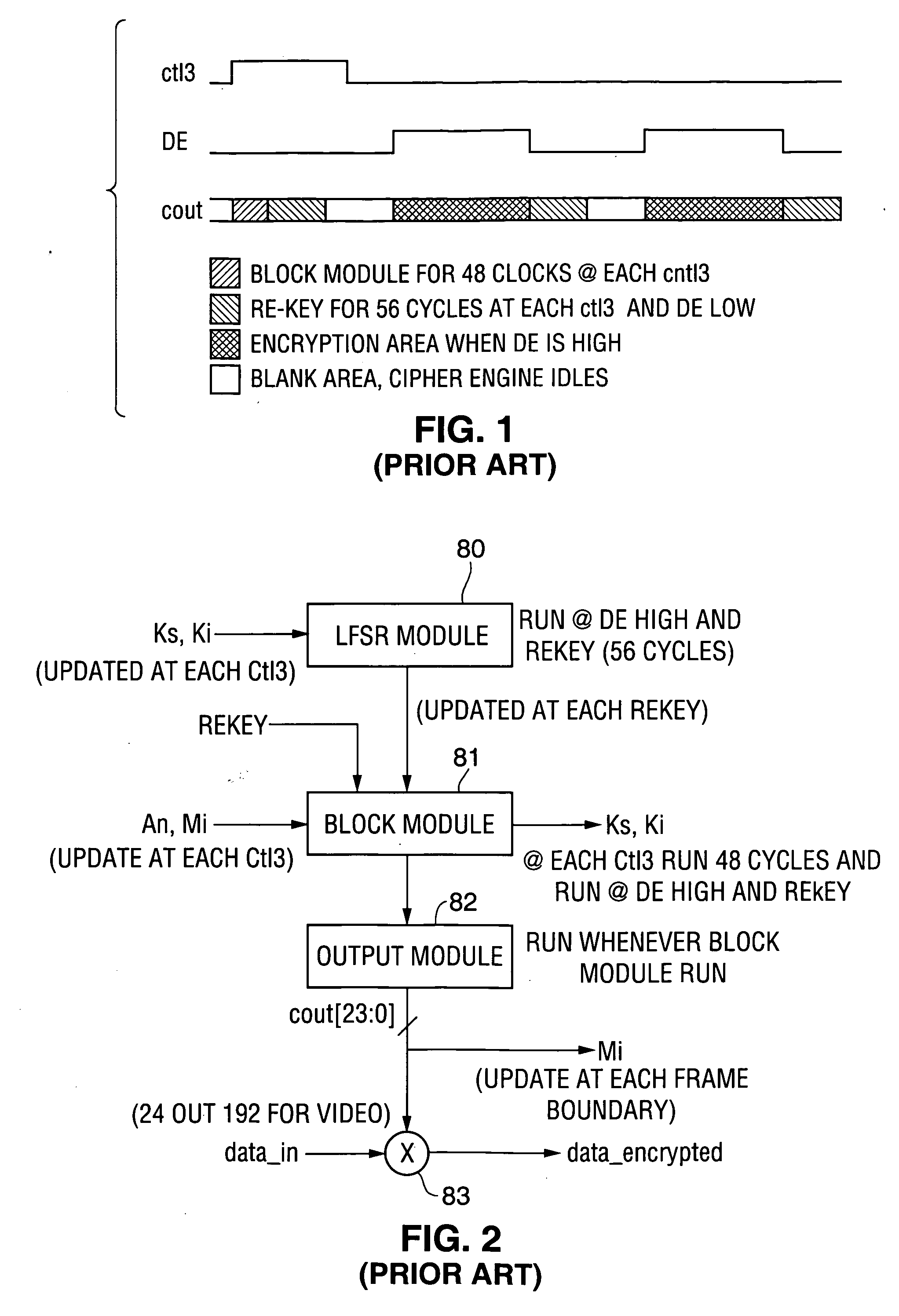

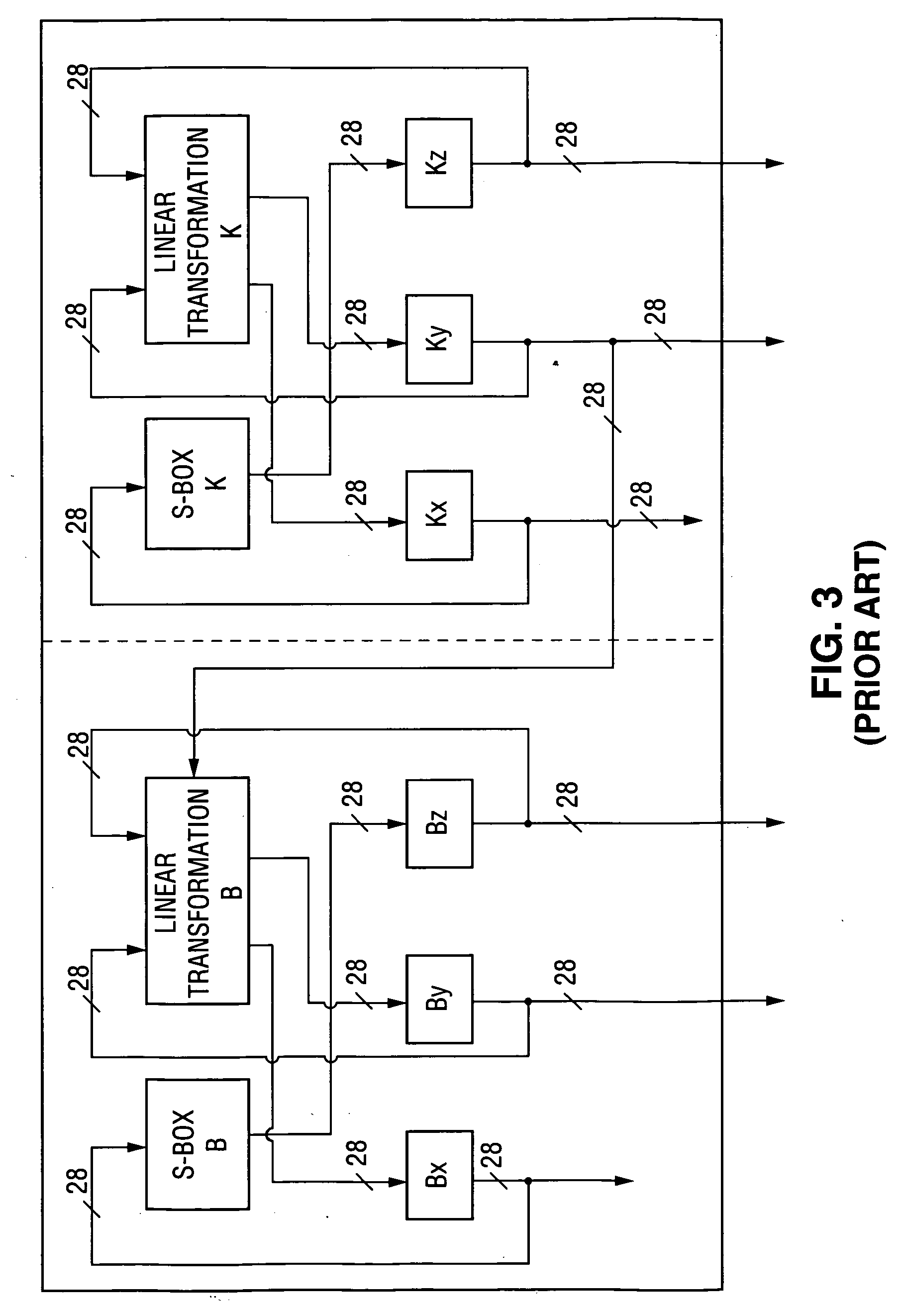

In some embodiments, the invention is a personal digital network (“PDN”) including hardware (sometimes referred to as Ingress circuitry) configured to transcrypt encrypted content that enters the PDN. Typically, the transcryption (decryption followed by re-encryption) is performed in hardware within the Ingress circuitry and the re-encryption occurs before the decrypted content is accessible by hardware or software external to the Ingress circuitry. Typically, transcrypted content that leaves the Ingress circuitry remains in re-encrypted form within the PDN whenever it is transferred between integrated circuits or is otherwise easily accessible by software, until it is decrypted within hardware (sometimes referred to as Egress circuitry) for display or playback or output from the PDN. Typically, the PDN is implemented so that no secret in Ingress or Egress circuitry (for use or transfer by the Ingress or Egress circuitry) is accessible in unencrypted form to software or firmware within the PDN or to any entity external to the PDN. Other aspects of the invention are methods for protecting content in a PDN (e.g., an open computing system) and devices (e.g., multimedia graphics cards, set top boxes, or video processors) for use in a PDN.

Owner:OPTIMUM CONTENT PROTECTION

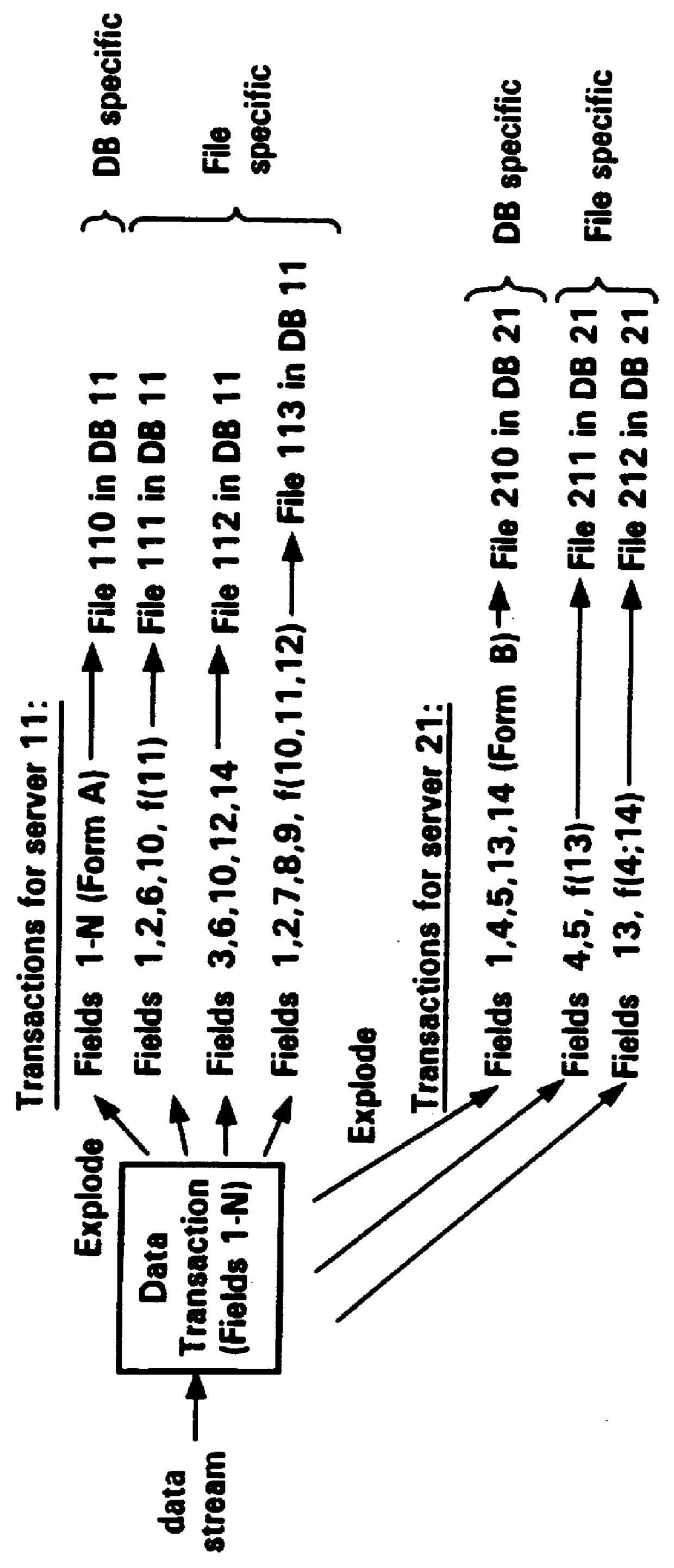

Data transaction assembly server

InactiveUS6044382ASpecial service for subscribersTwo-way working systemsData bufferApplication software

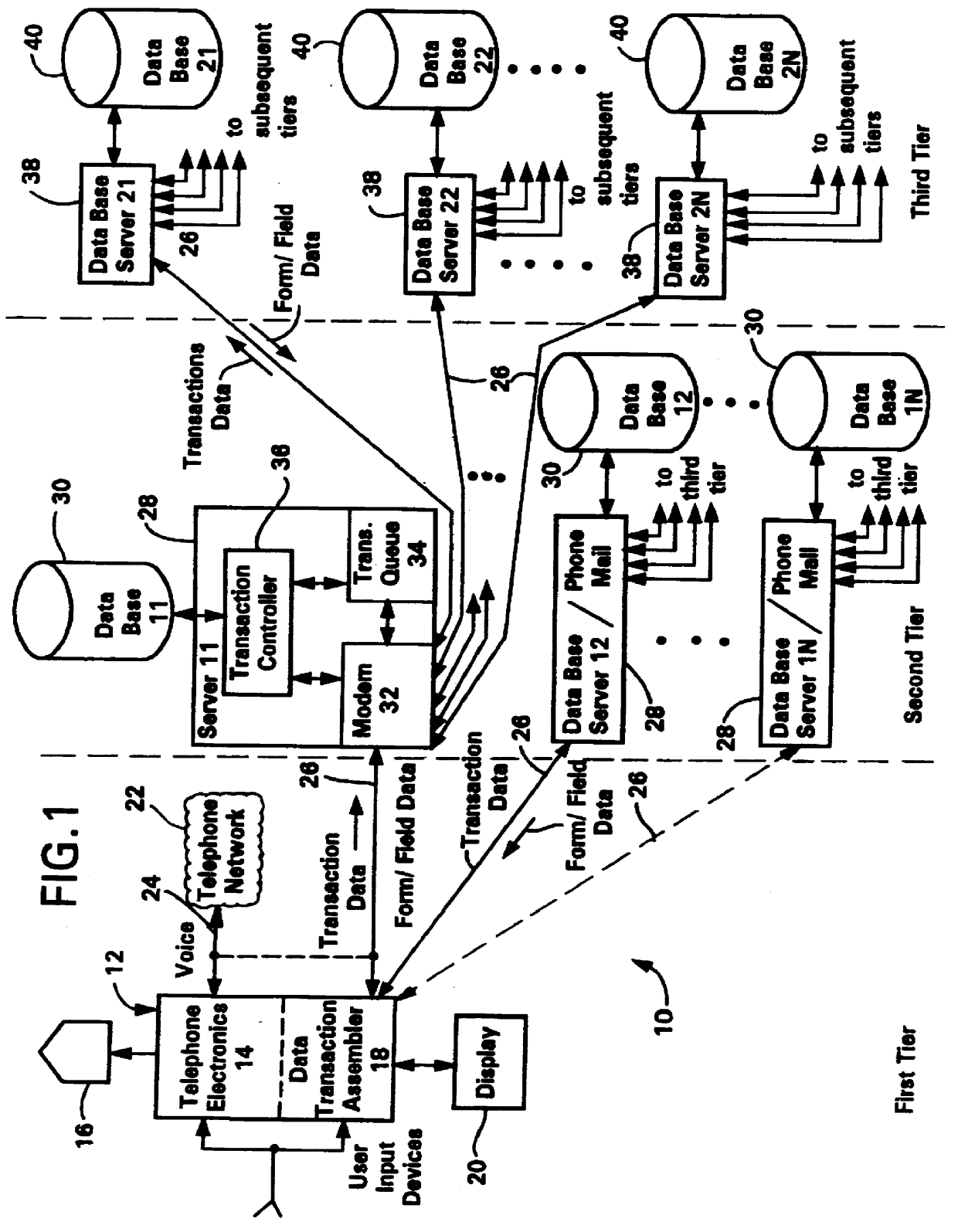

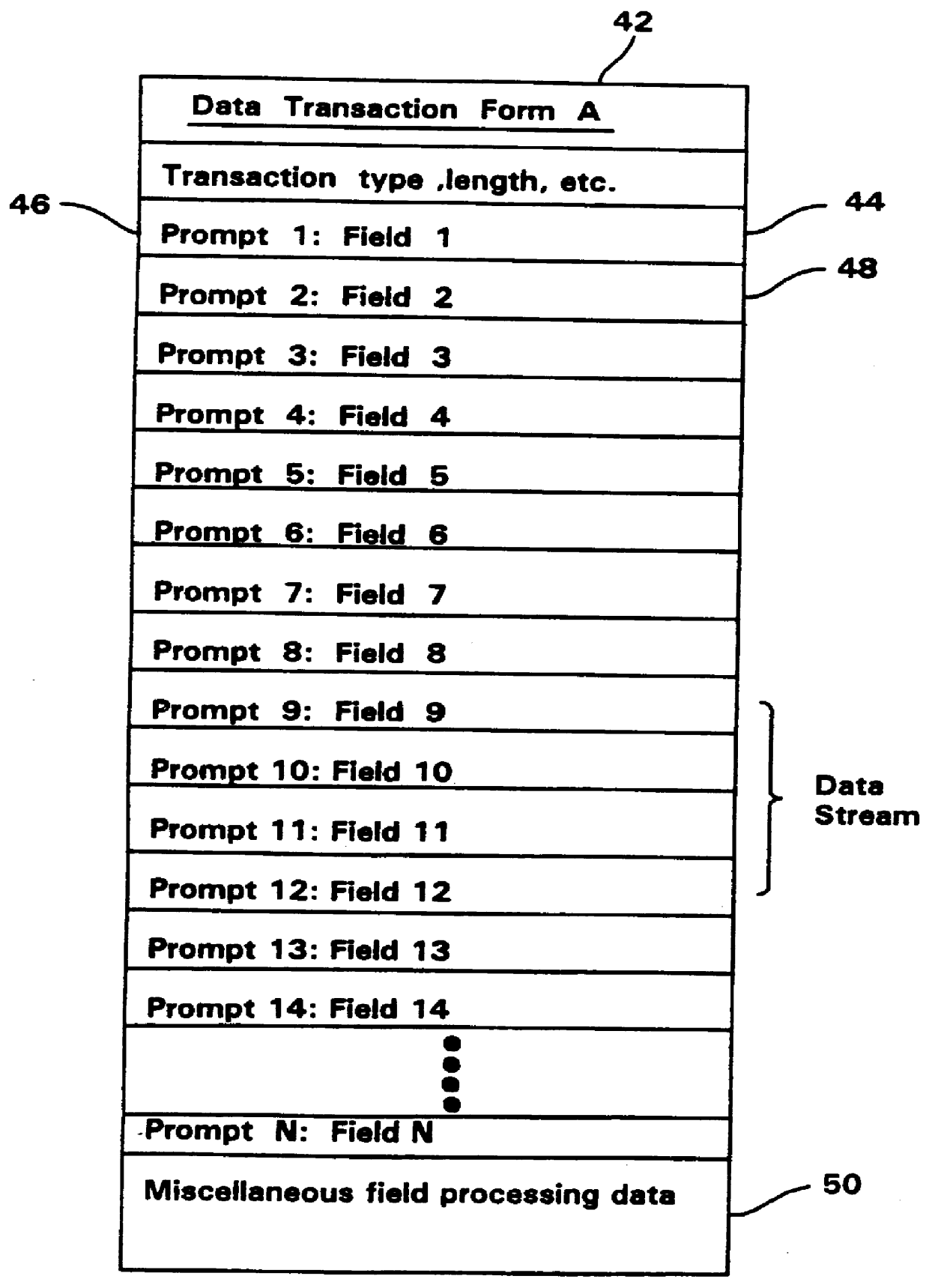

A form driven operating system which permits dynamic reconfiguration of any host processor into a virtual machine which supports any of a number of operating system independent applications. A data transaction assembly server (TAS) downloads menus and forms which are unique to each application requiring data to be input for local or remote processing. The data transactions and forms are exchanged between the TAS, which functions as a form driven operating system of the host computer, and a remote processor in a real-time fashion so that virtually any operating system independent software application may be implemented in which a form driven operating system may be used to facilitate input, and in which the data input into the form may be processed locally or remotely, returned as a data stream, and displayed to the user. The TAS merely requires a flash PROM for storing the TAS control firmware, a RAM for storing the data streams making up the forms and menus, and a small RAM which operates as an input / output transaction buffer for storing the data streams of the template and the user replies to the prompts during assembly of a data transaction.

Owner:CYBERFONE TECH

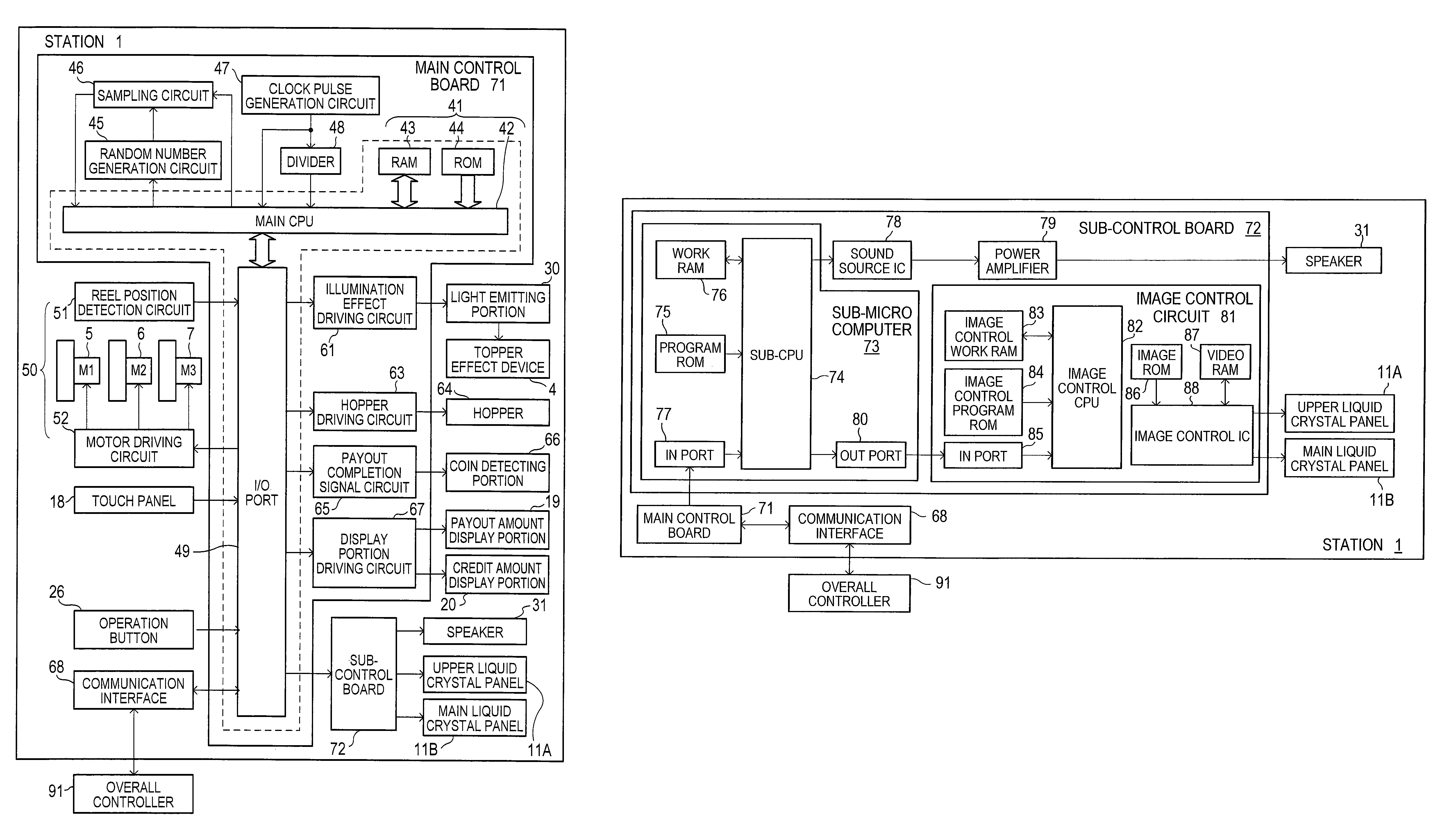

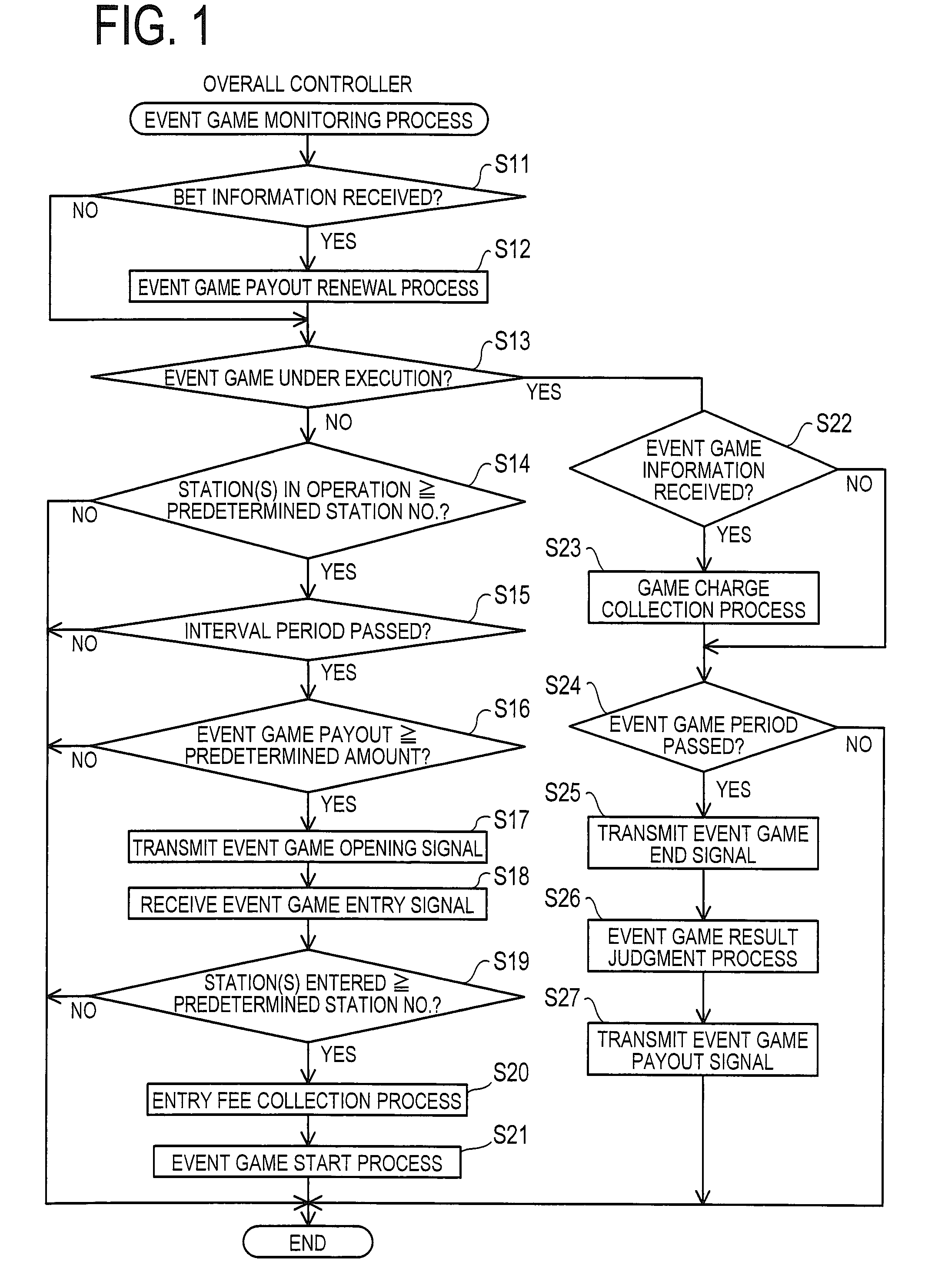

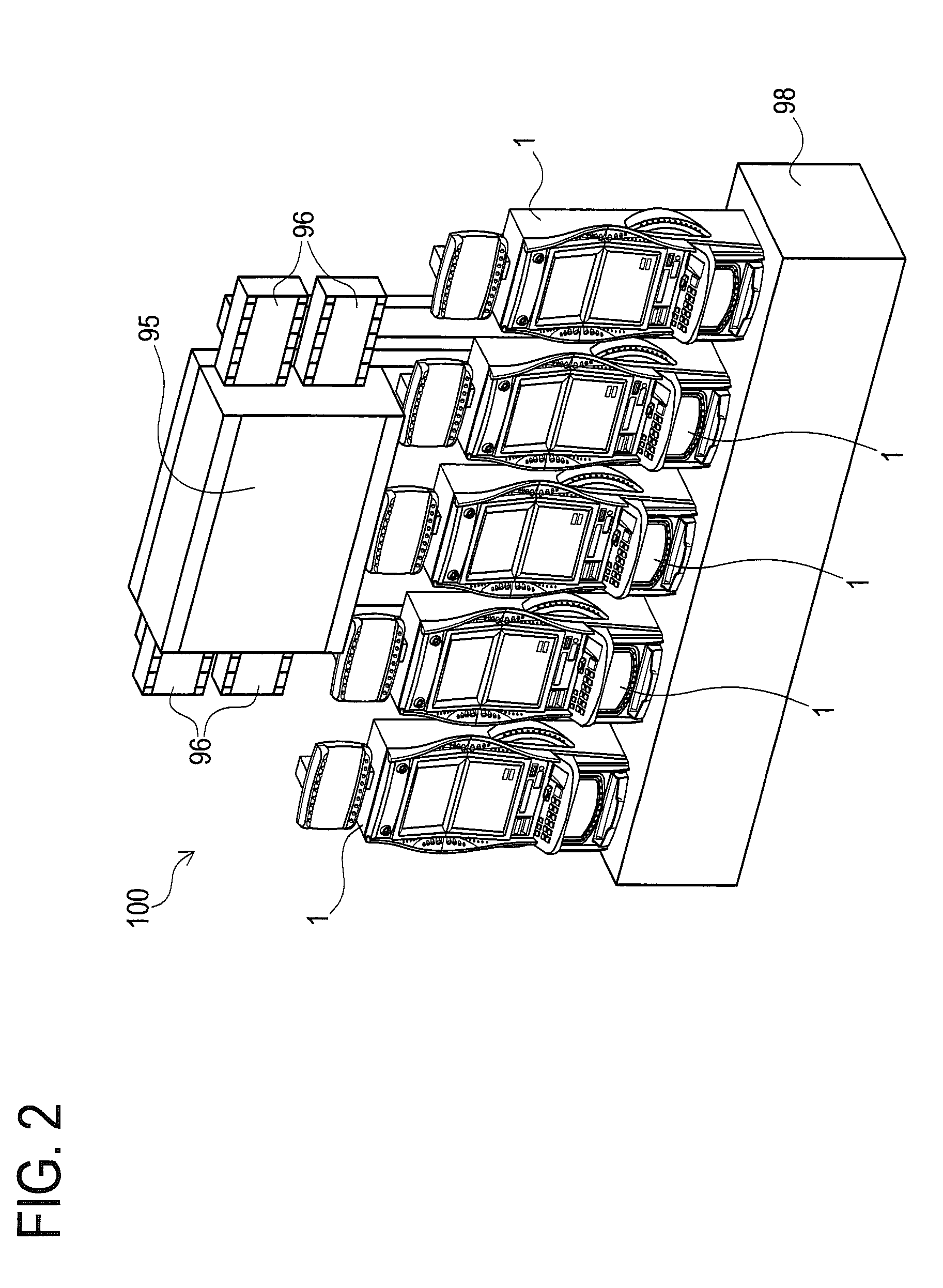

Gaming machine

InactiveUS8167699B2Apparatus for meter-controlled dispensingVideo gamesExecution unitHuman–computer interaction

A gaming machine includes plural stations and a processor. Each station can determine a game result and execute a game independently. The processor accepts each station's entry to an event game when a predetermined condition is satisfied. An event game consists of a plural number of unit event games. When executing unit event games, the processor collects a game charge from a station whose entry to the event game has been accepted.

Owner:UNIVERSAL ENTERTAINMENT CORP

System and method for implementing policy server based application interaction manager

ActiveUS20080046963A1Network connectionsSpecial data processing applicationsApplication IdentifierOperating system

In one example embodiment, an apparatus includes a policy repository for storing a policy for application interaction. The policy defines, for a subscriber, a priority associated with a set of specific application identifiers. The priority further defines establishment priority and retention priority for an application identified by a selected application identifier. Another example embodiment includes an apparatus including a processor operable to evaluate a policy for application interaction. The policy defines, for a subscriber, a priority associated with a set of specific application identifiers. The priority further defines establishment priority and retention priority for an application identified by a selected application identifier. The processor is further operable to execute a decision for the subscriber based on the evaluation of the policy.

Owner:CISCO TECH INC

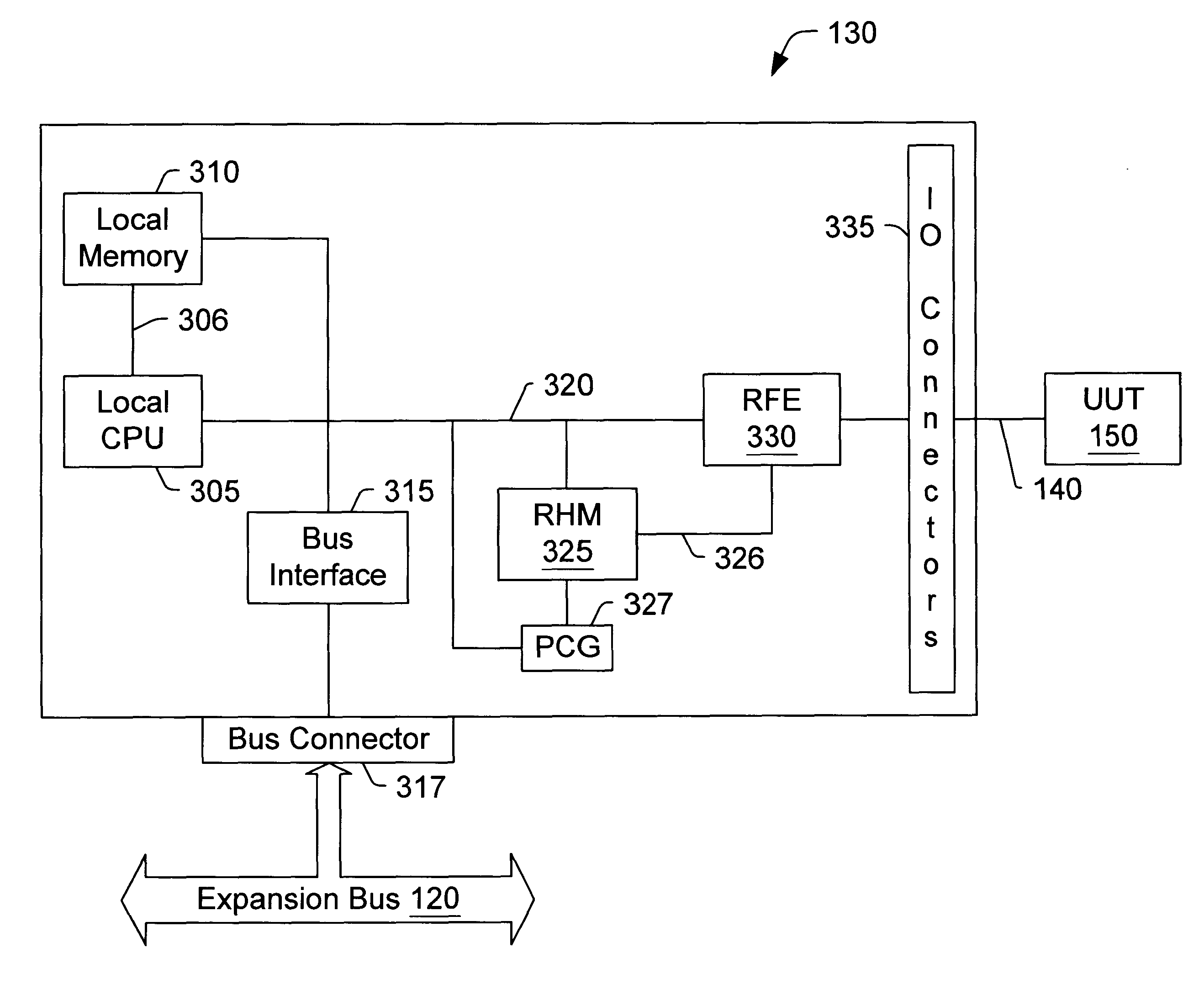

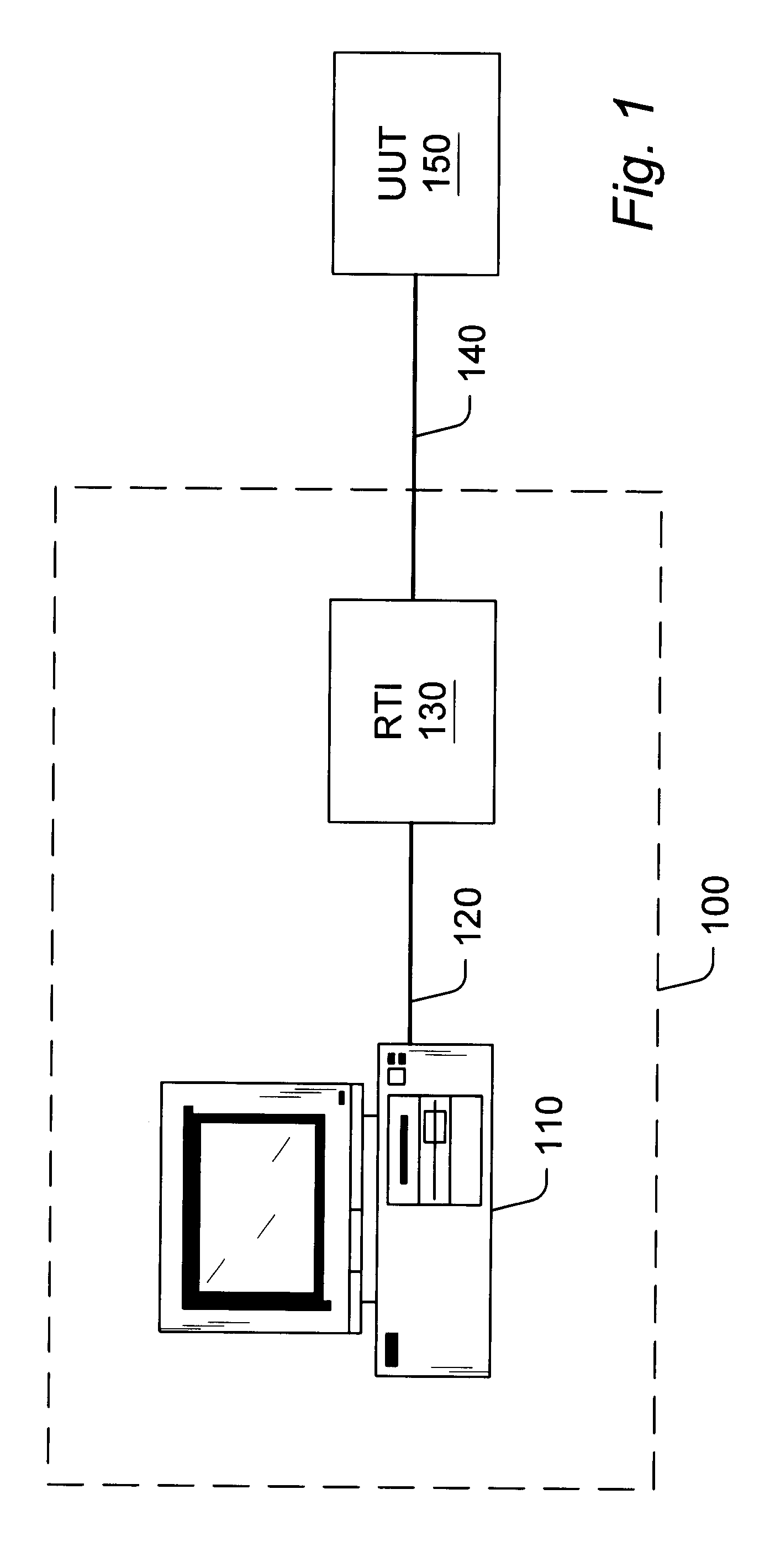

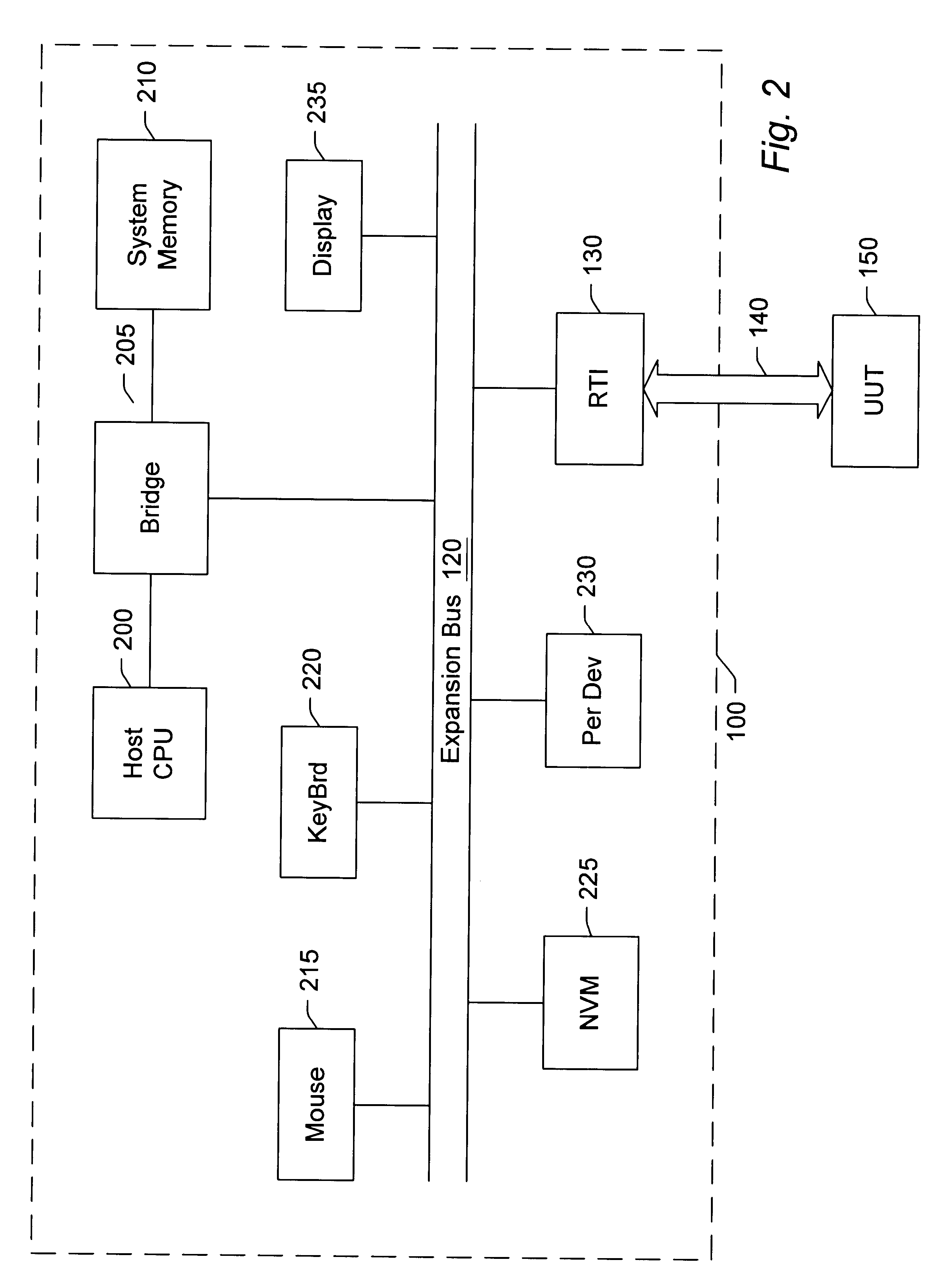

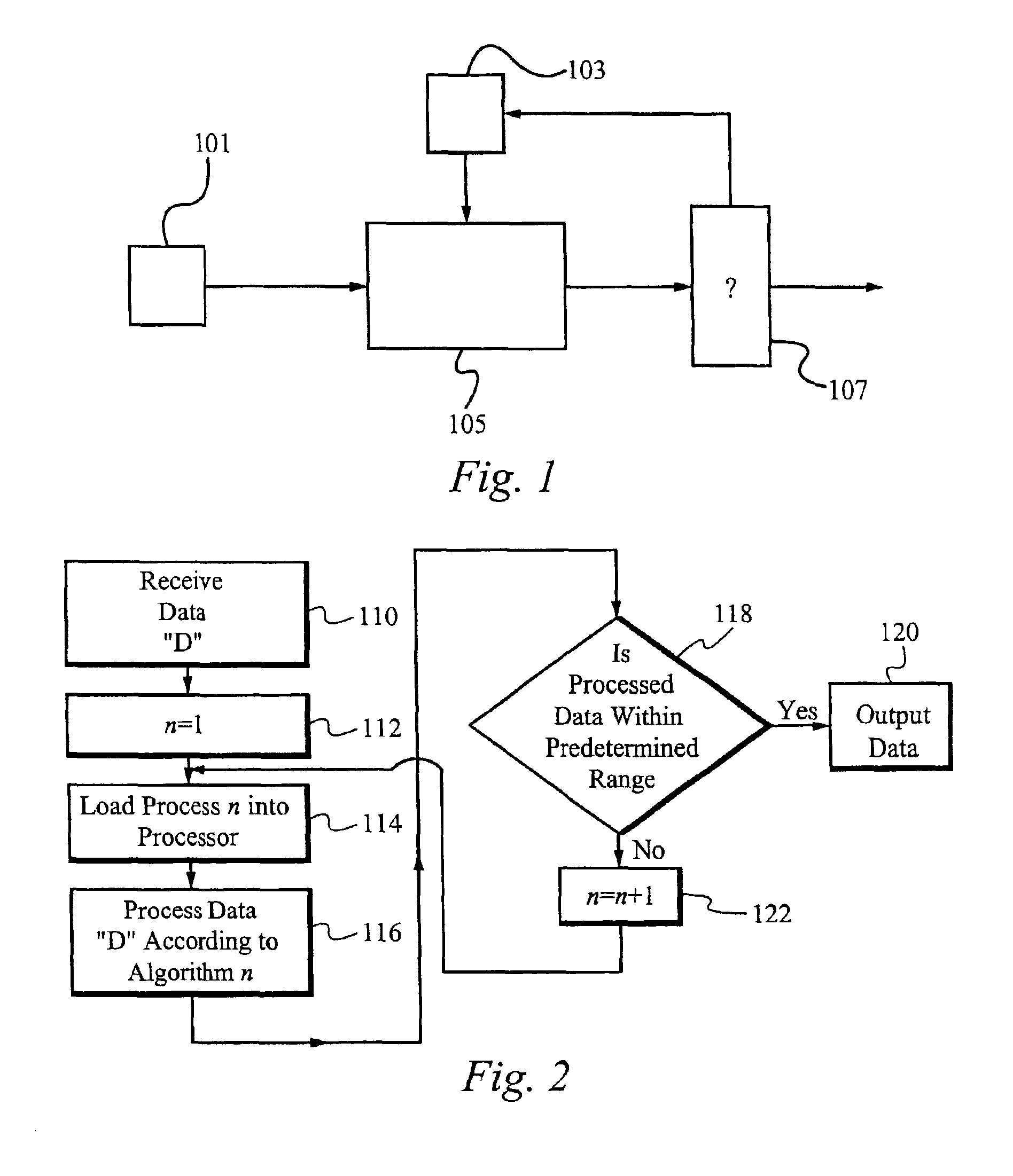

Reconfigurable test system

A reconfigurable test system including a host computer coupled to a reconfigurable test instrument. The reconfigurable test instrument includes reconfigurable hardware-i.e. a reconfigurable hardware module with one or more programmable elements such as Field Programmable Gate Arrays for realizing an arbitrary hardware architecture and a reconfigurable front end with programmable transceivers for interfacing with any desired physical medium-and optionally, an embedded processor. A user specifies system features with a software configuration utility which directs a component selector to select a set of software modules and hardware configuration files from a series of libraries. The modules are embedded in a host software driver or downloaded for execution on the embedded CPU. The configuration files are downloaded to the reconfigurable hardware. The entire selection process is performed in real-time and can be changed whenever the user deems necessary. Alternatively, the user may create a graphical program in a graphical programming environment and compile the program into various software modules and configuration files for host execution, embedded processor execution, or programming the reconfigurable hardware.

Owner:NATIONAL INSTRUMENTS

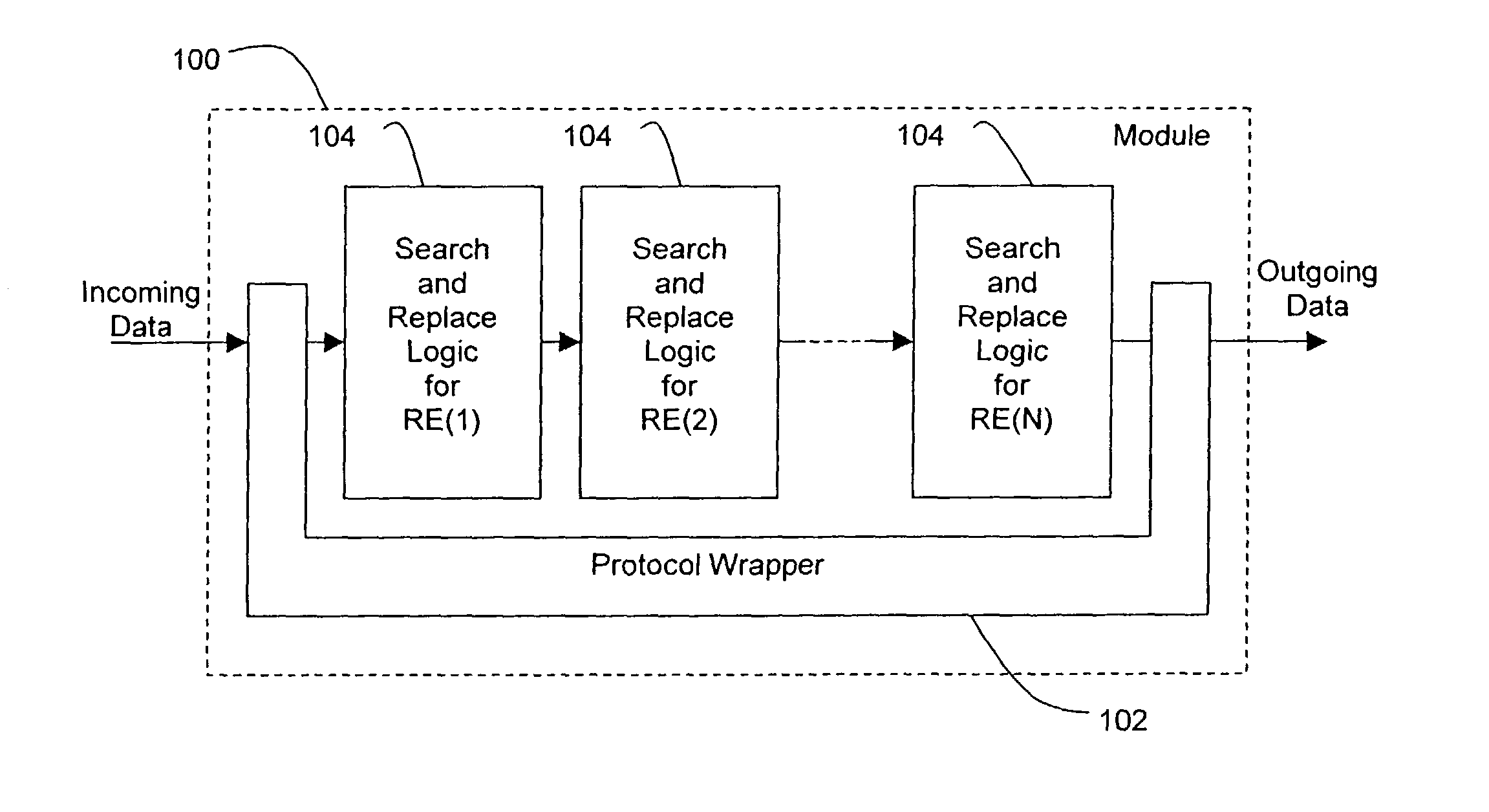

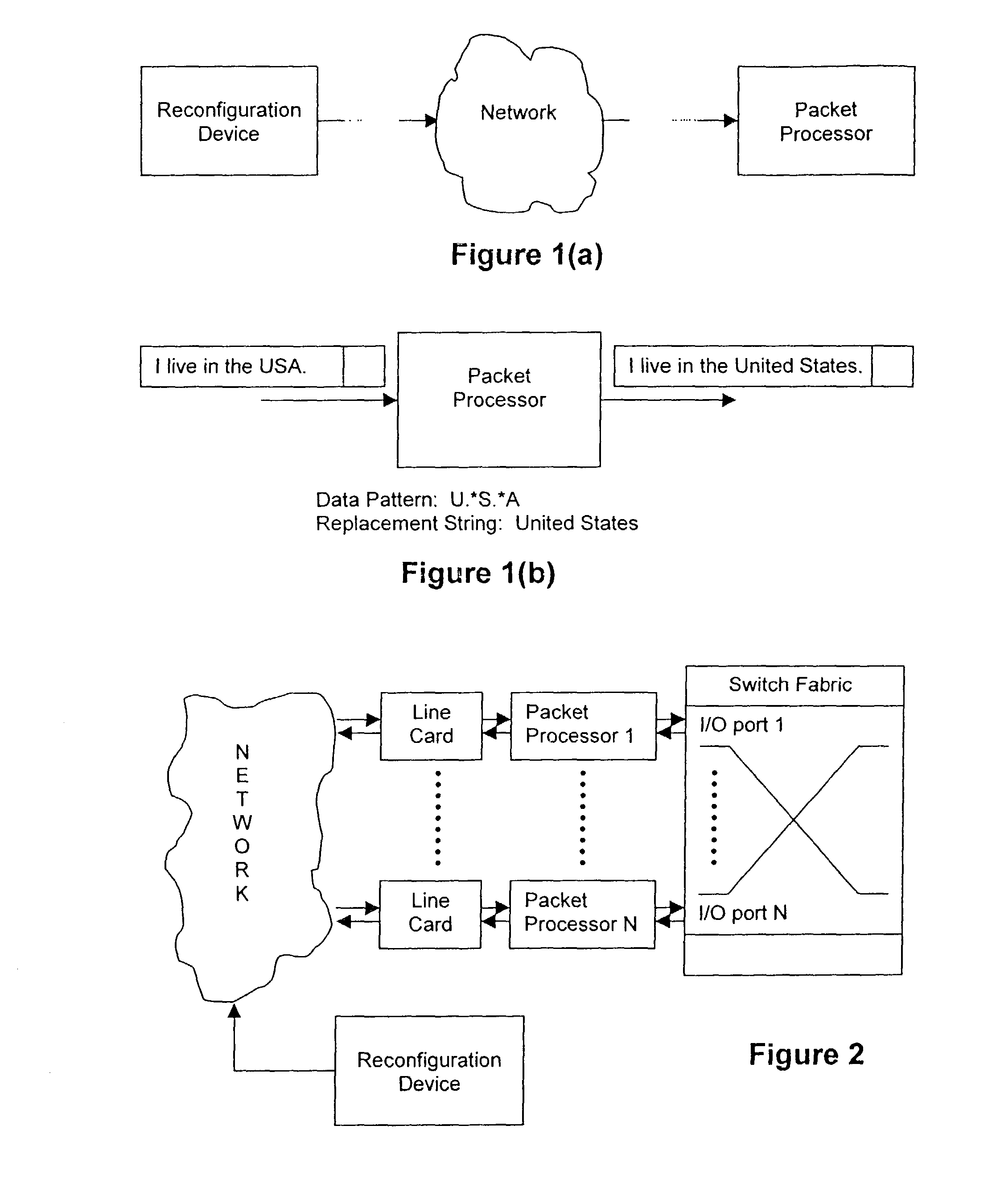

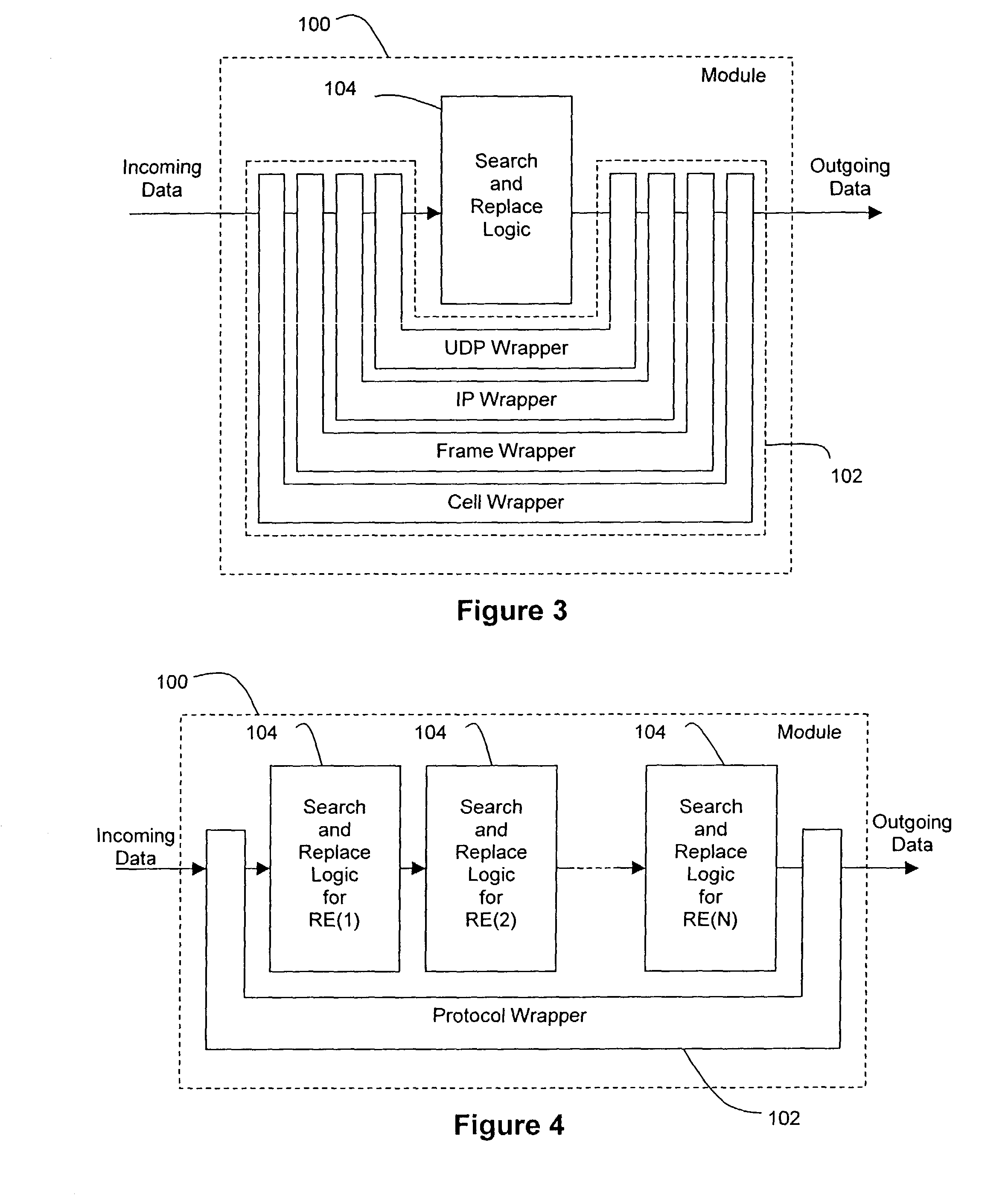

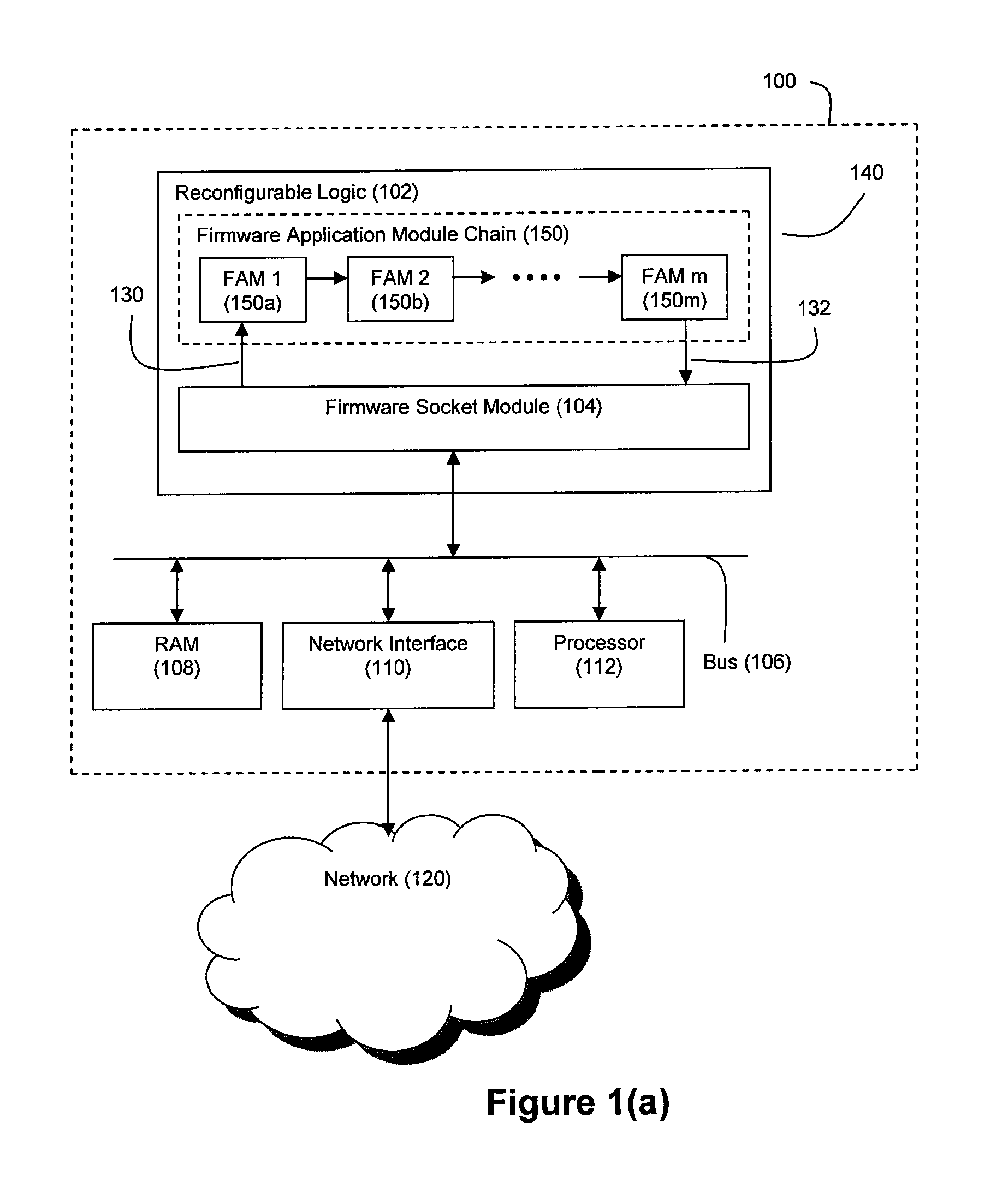

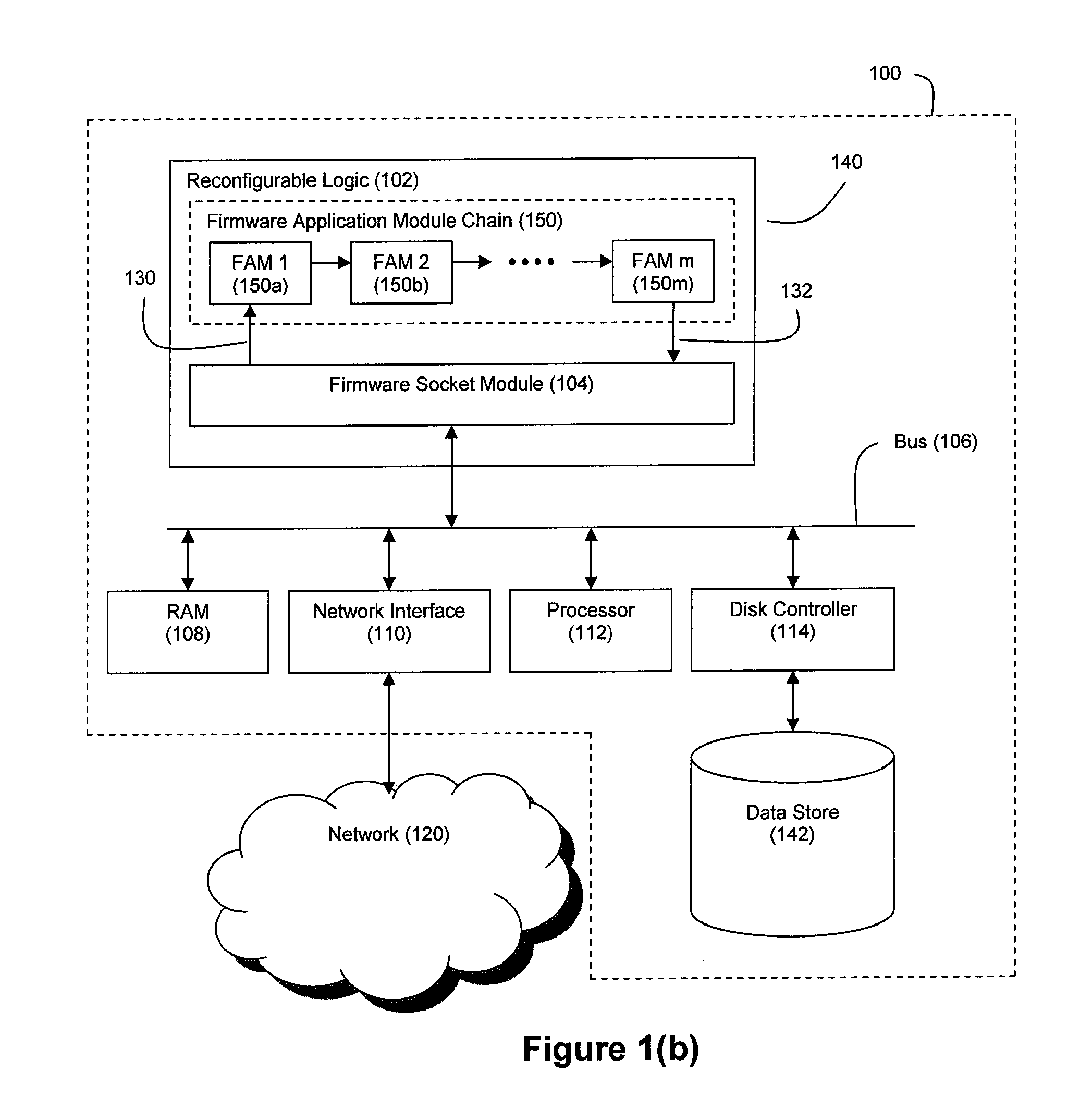

Methods, systems, and devices using reprogrammable hardware for high-speed processing of streaming data to find a redefinable pattern and respond thereto

InactiveUS7093023B2Prevent materialPrevented from reachingError detection/correctionMultiple digital computer combinationsProgrammable logic devicePacket processing

A reprogrammable packet processing system for processing a stream of data is disclosed herein. A reprogrammable data processor is implemented with a programmable logic device (PLD), such as a field programmable gate array (FPGA), that is programmed to determine whether a stream of data applied thereto includes a string that matches a redefinable data pattern. If a matching string is found, the data processor performs a specified action in response thereto. The data processor is reprogrammable to search packets for the presence of different data patterns and / or perform different actions when a matching string is detected. A reconfiguration device receives input from a user specifying the data pattern and action, processes the input to generate the configuration information necessary to reprogram the PLD, and transmits the configuration information to the packet processor for reprogramming thereof.

Owner:WASHINGTON UNIV IN SAINT LOUIS

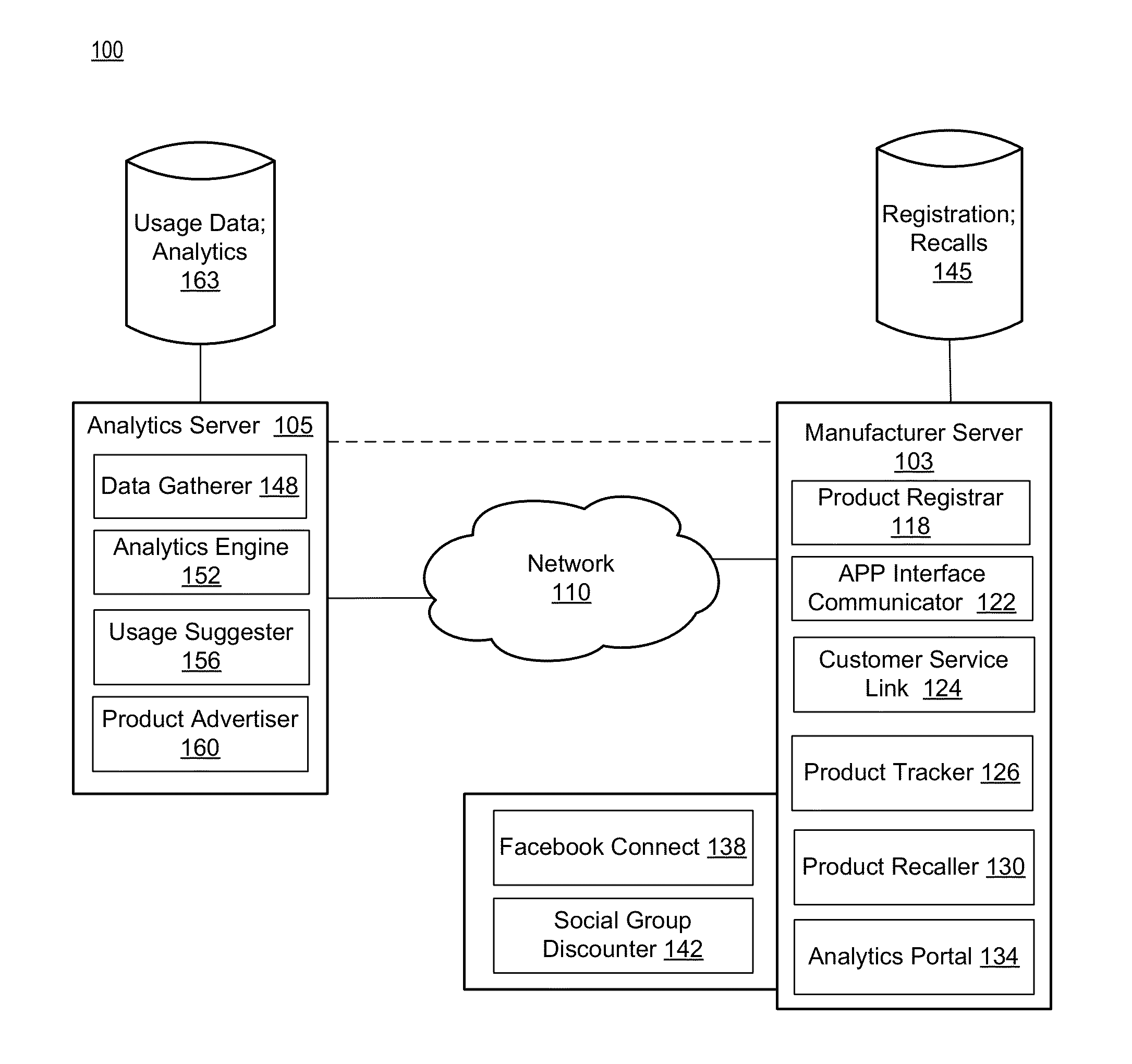

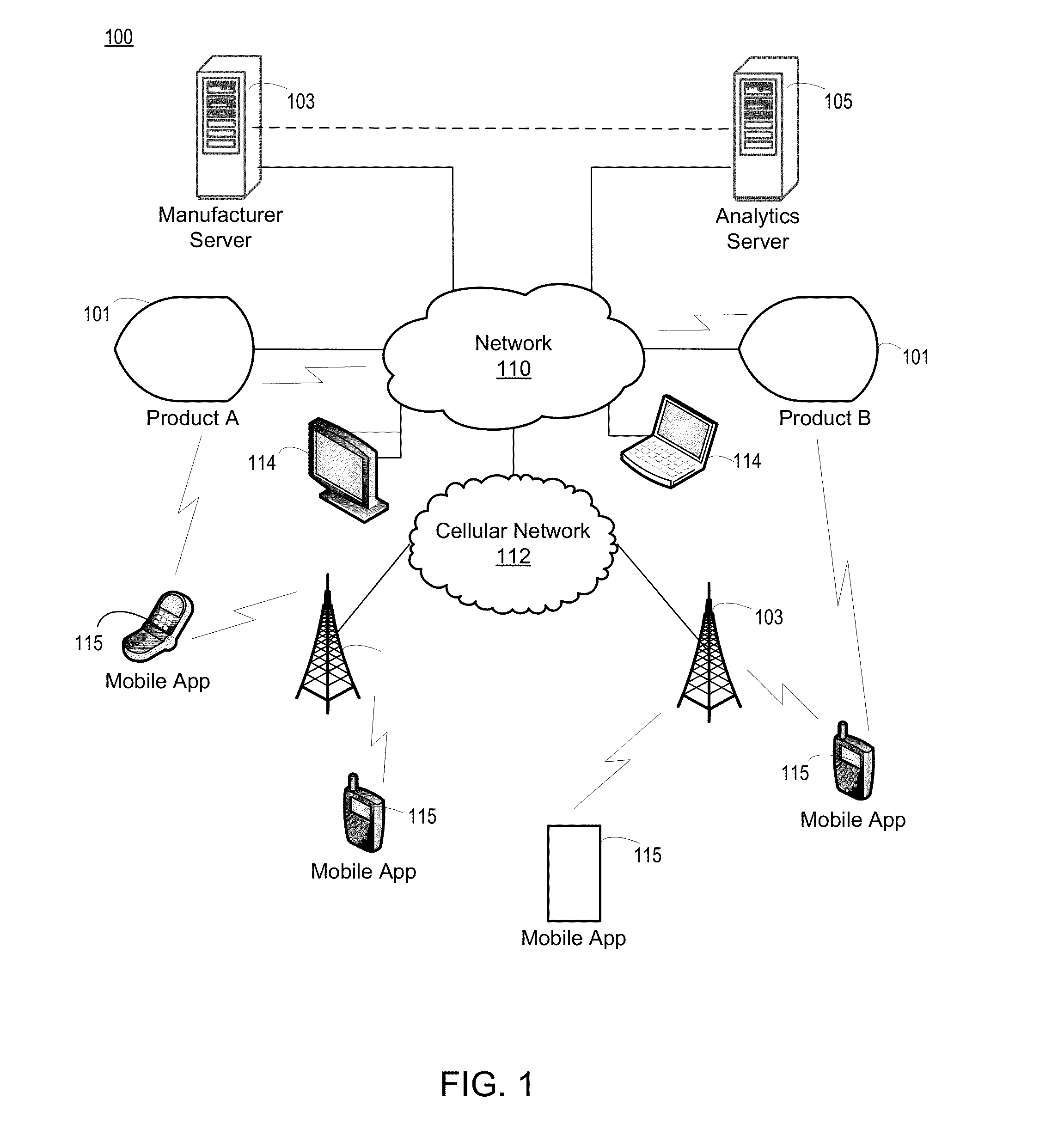

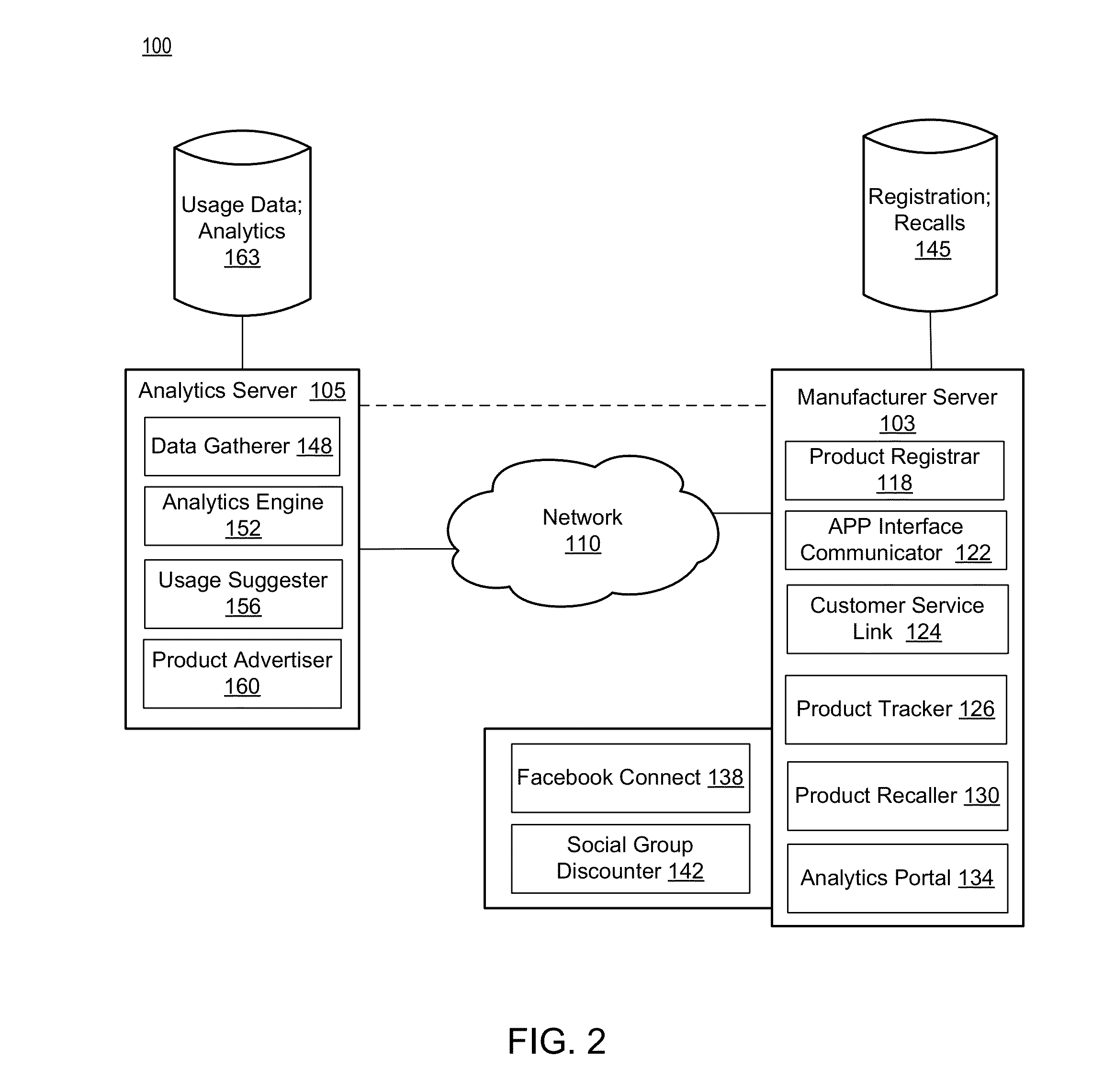

Product registration and tracking system

InactiveUS20130080251A1Convenient registrationCustomer relationshipMarketingApplication softwareComputer memory

A server for registration of products may include a processor and computer storage. The processor may be configured to receive, via a network, a communication from a product application executed on a computing device, the communication including a product identification (ID) associated with a product and an indication of registration of the product by a user of the product application. The processor may further be configured to register the product at least by storing, in the computer storage, the product ID and a relationship between the product and an identification of the user of the product application. The processor may further be configured to send a subsequent communication to the product application on the computing device based on the registration of the product.

Owner:ACCENTURE GLOBAL SERVICES LTD

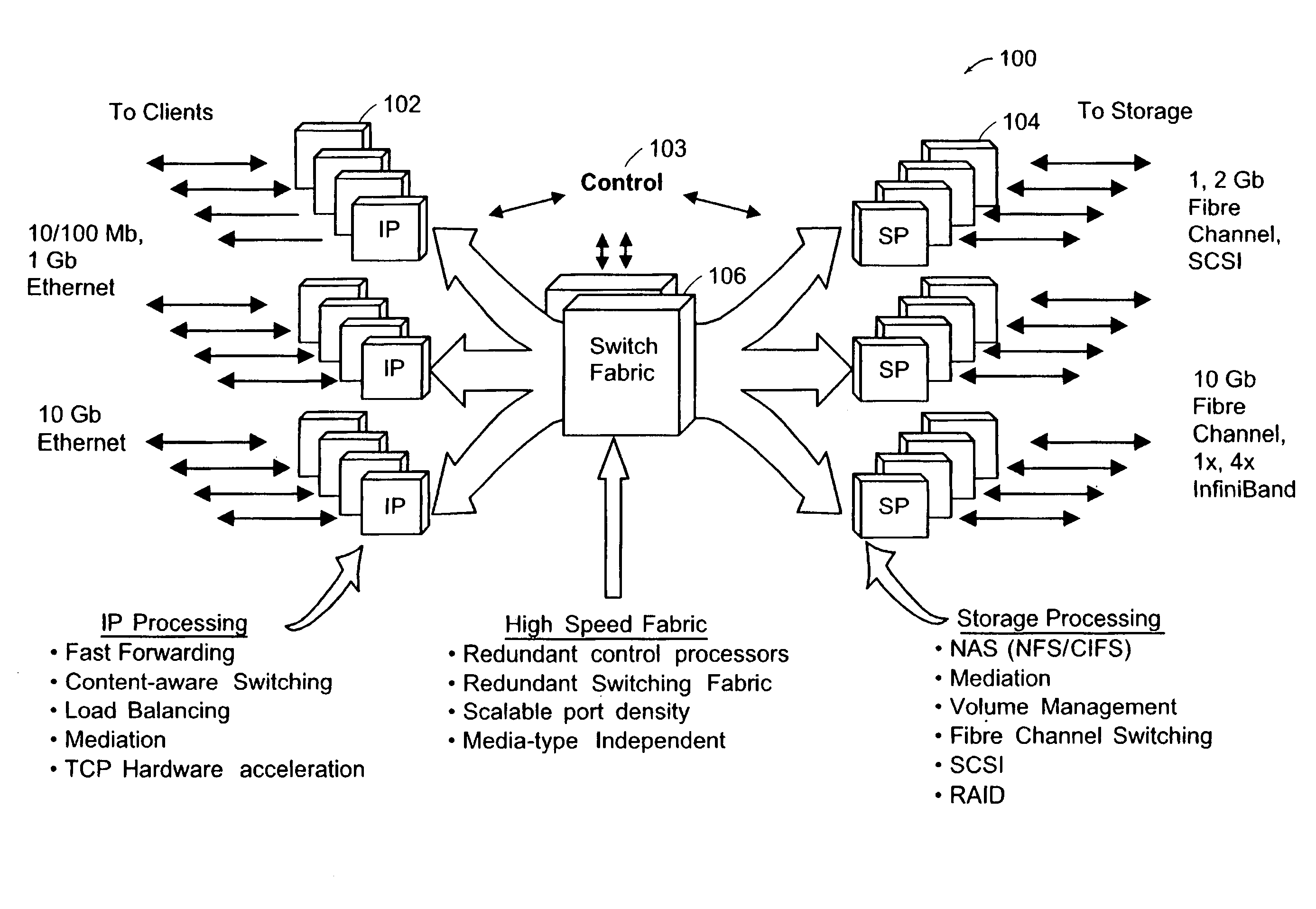

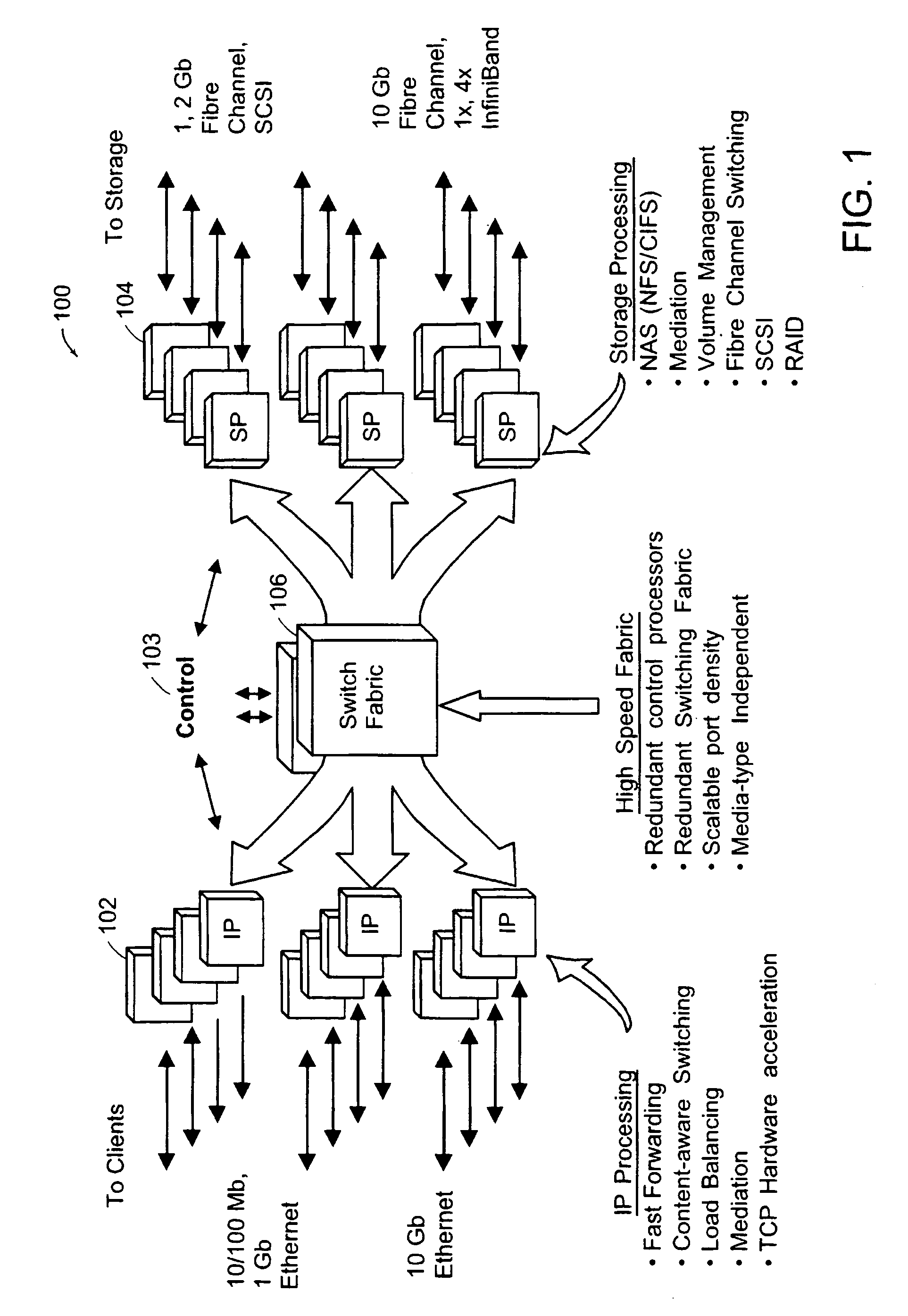

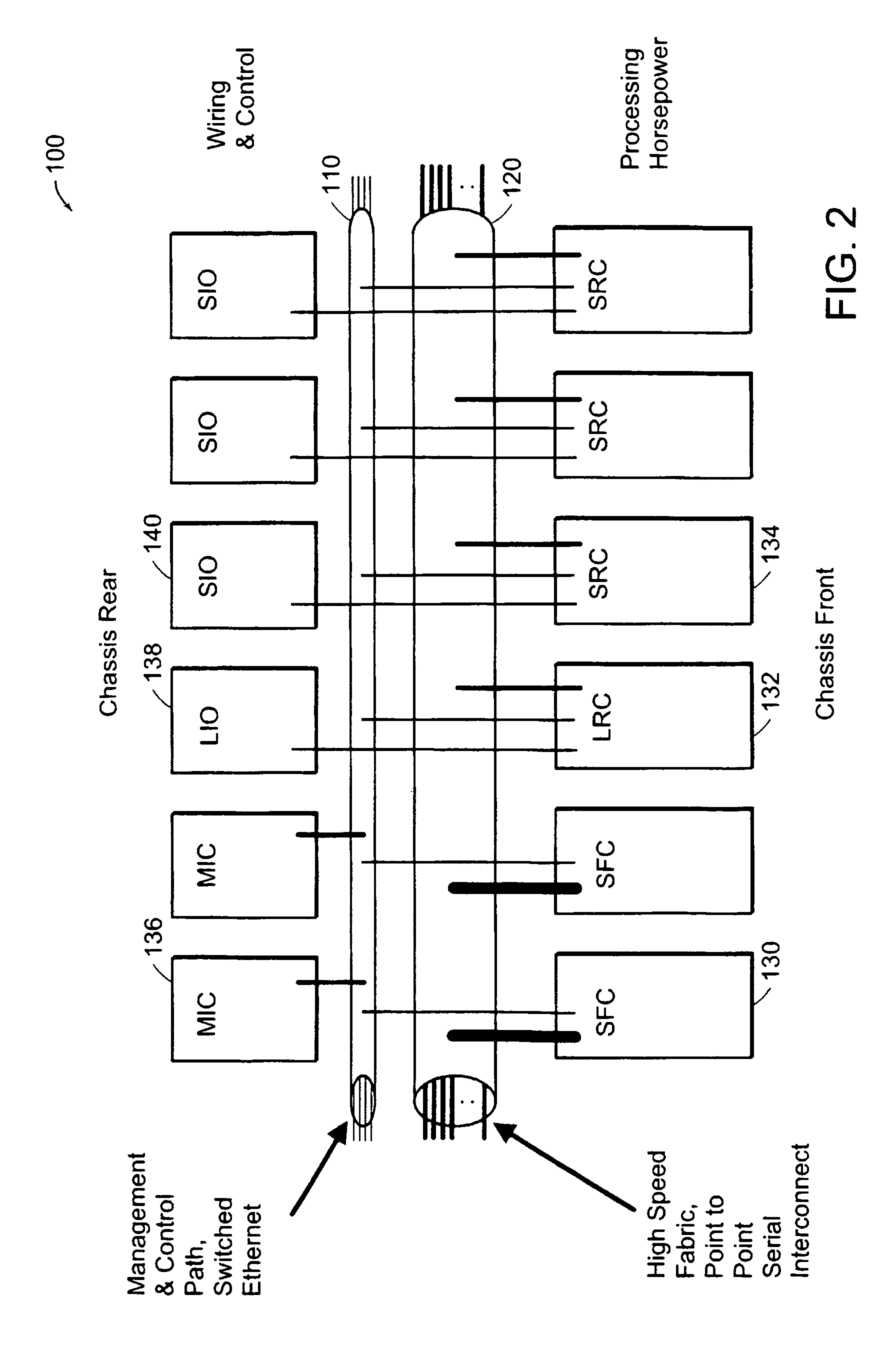

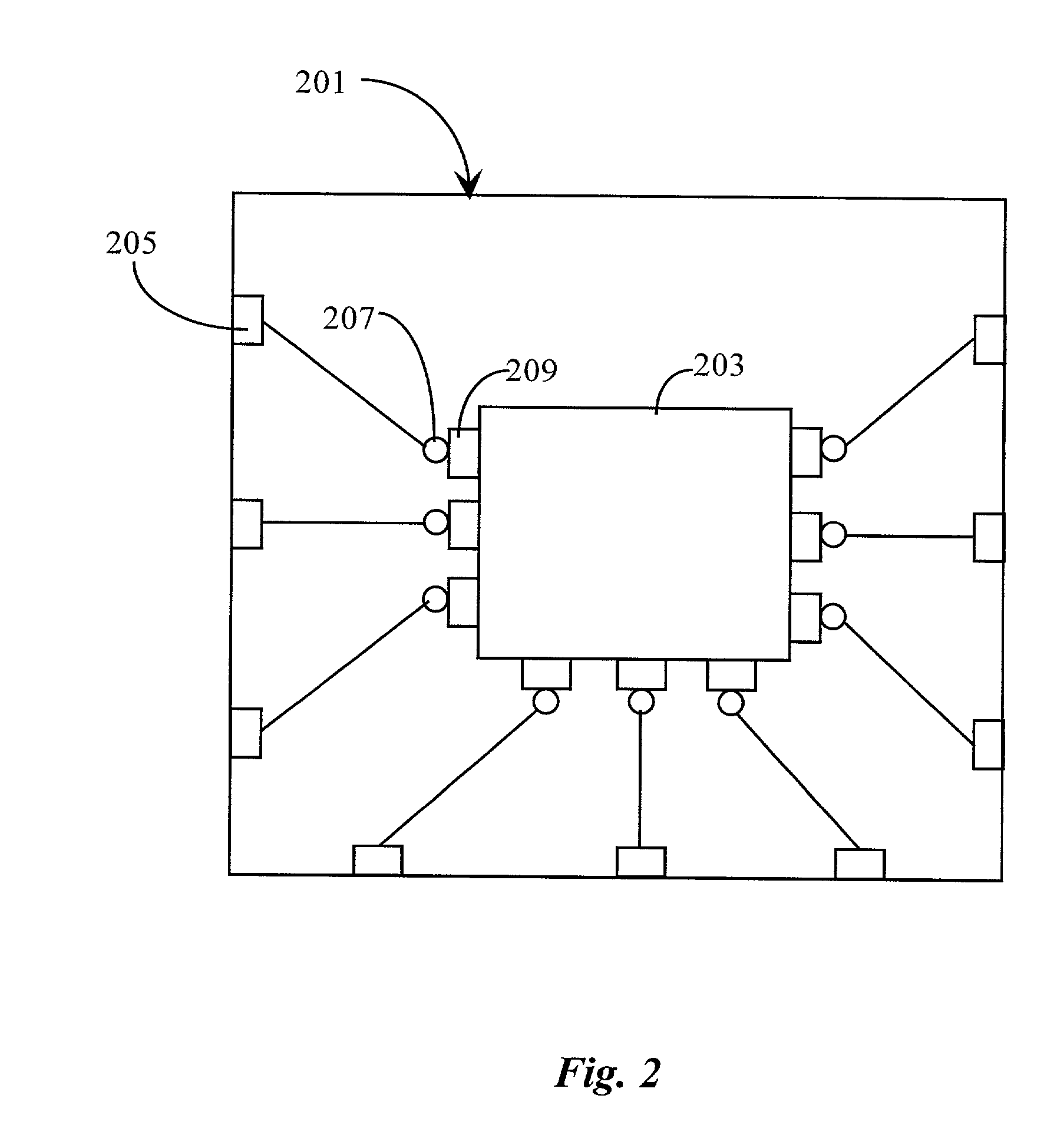

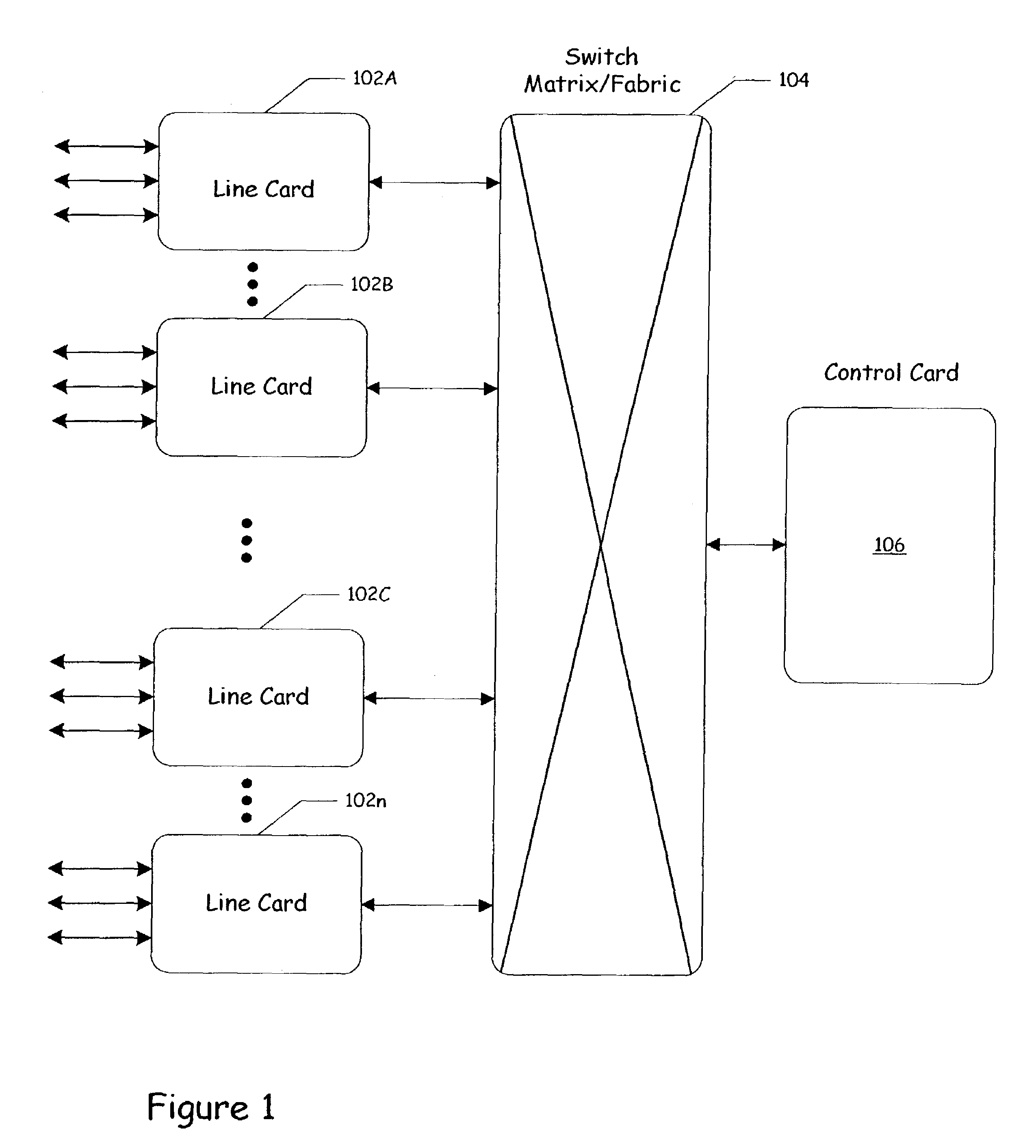

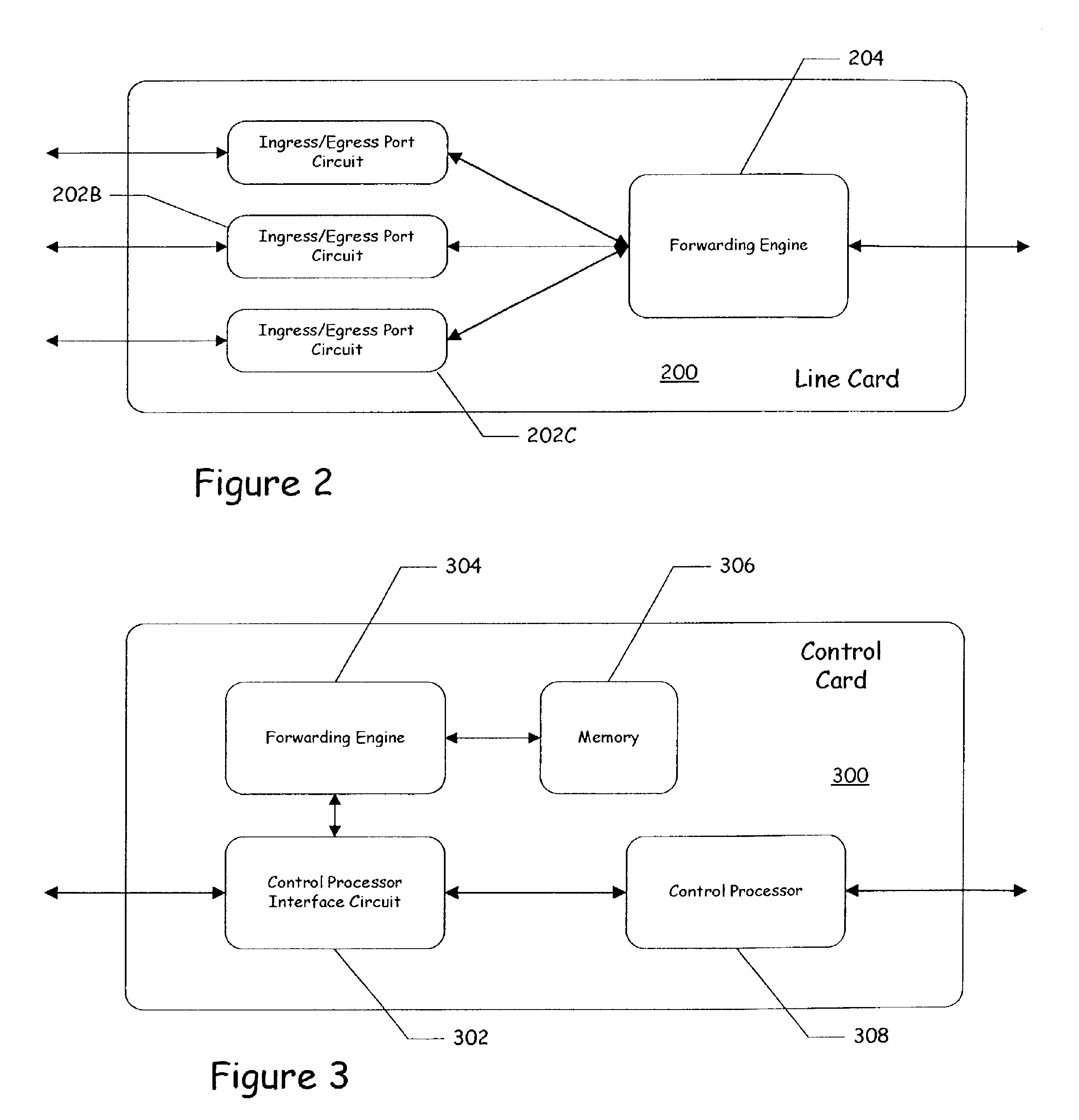

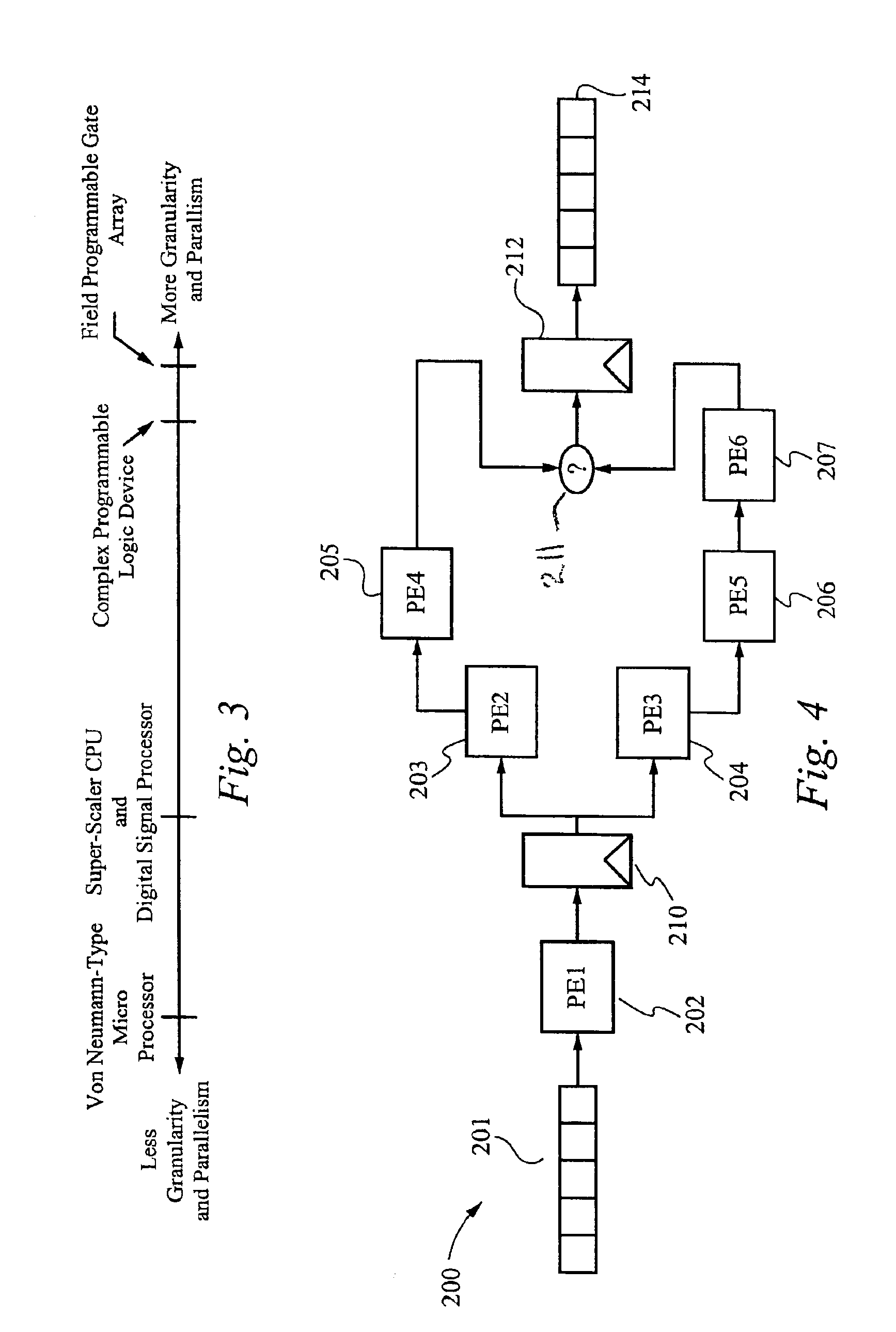

Switching system

ActiveUS7313614B2Accelerates TCP processingRobust systemInput/output to record carriersError detection/correctionProcessor elementComputer architecture

A system and method for provided a switch system (100) having a first configurable set of processor elements (102) to process storage resource connection requests (104), a second configurable set of processor elements capable of communications with the first configurable set of processor elements (102) to receive, from the first configurable set of processor elements, storage connection requests representative of client requests, and to route the requests to at least one of the storage elements (104), and a configurable switching fabric (106) interconnected between the first and second sets of processor elements (102), for receiving at least a first storage connection request (104) from one of the first set of processor elements (102), determining an appropriate one of the second set of processors for processing the storage connection request (104), automatically configuring the storage connection request in accordance with a protocol utilized by the selected one of the second set of processors, and forwarding the storage connection request to the selected one of the second set of processors for routing to at least one of the storage elements.

Owner:ORACLE INT CORP

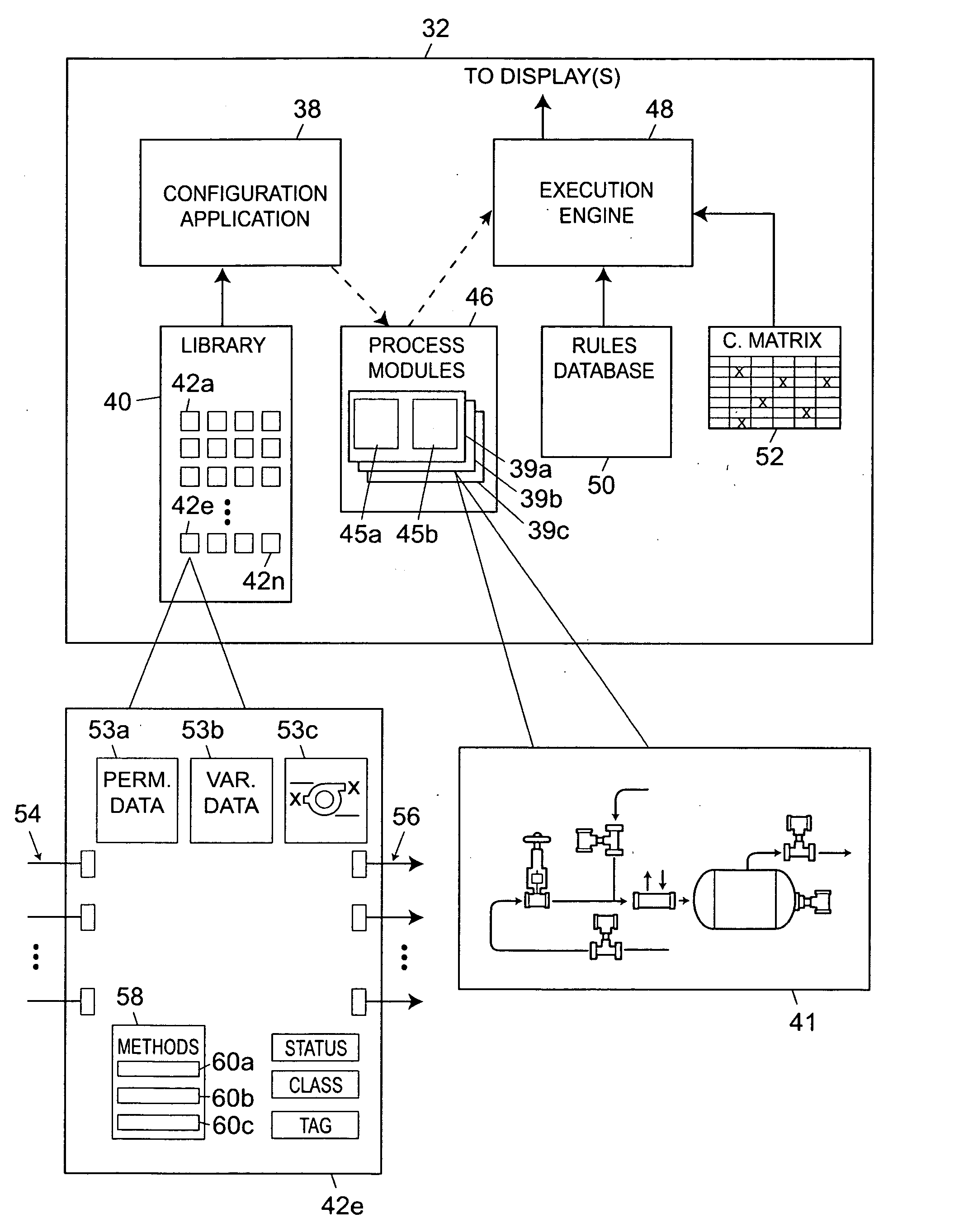

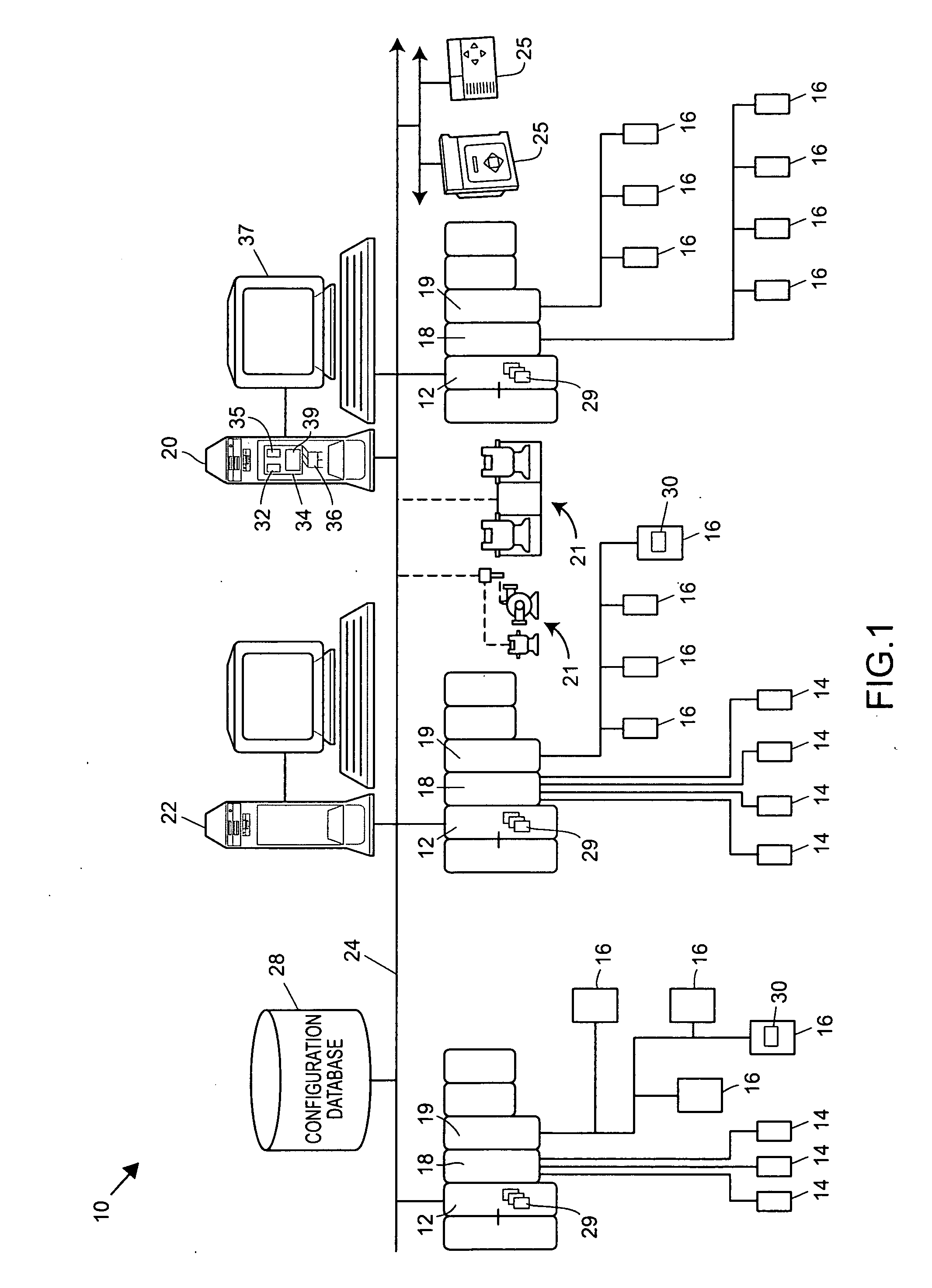

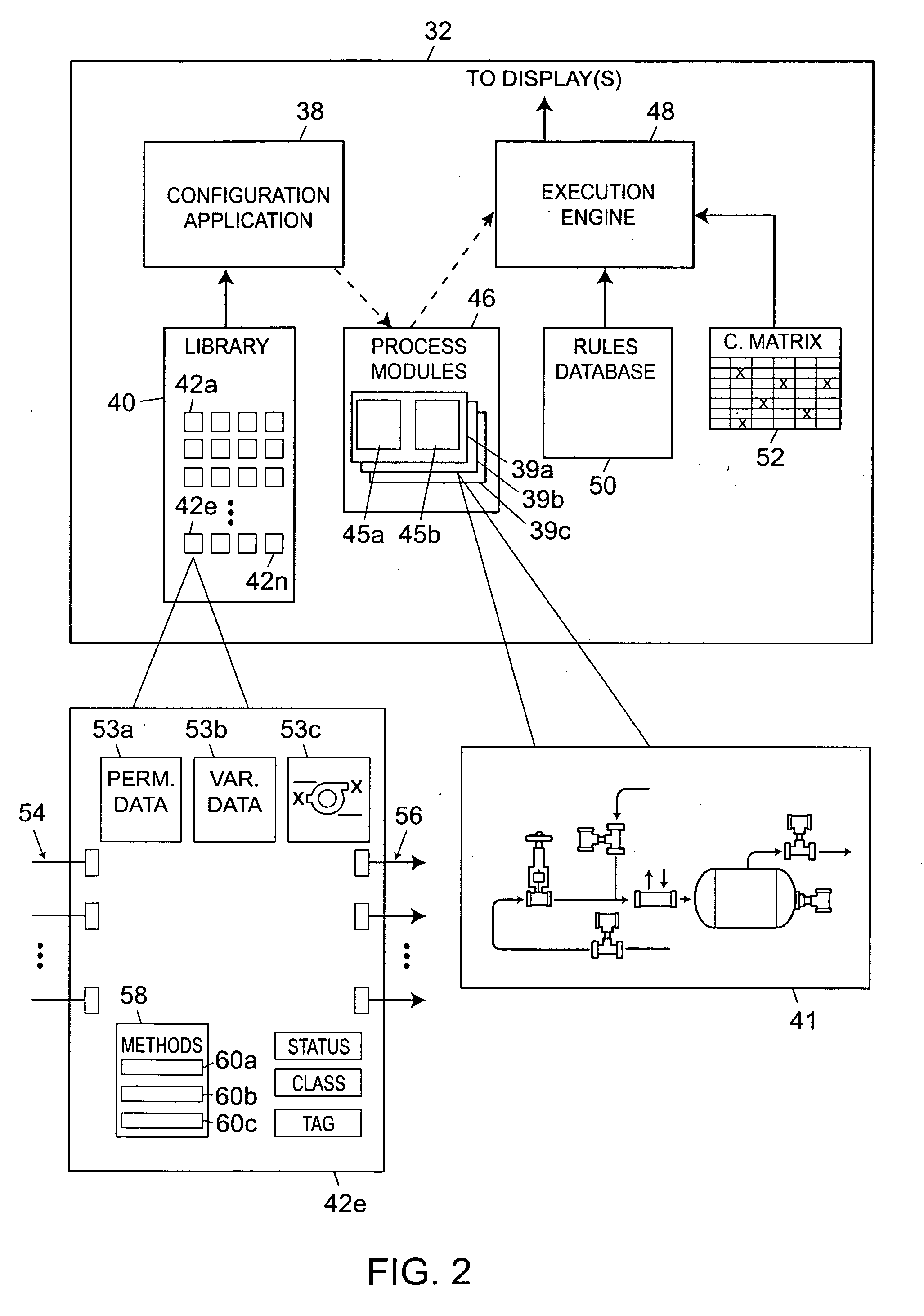

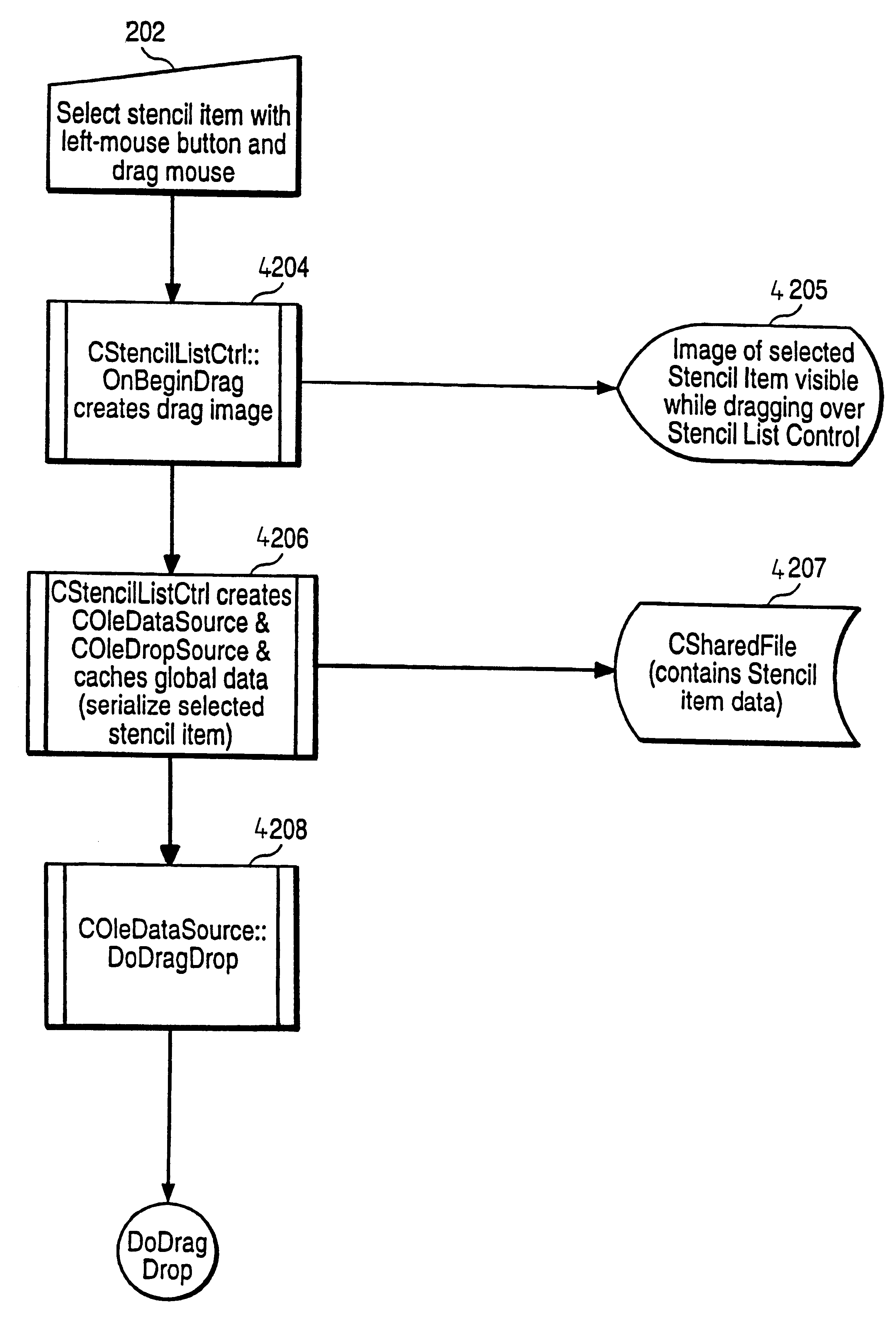

Integrated configuration system for use in a process plant

An integrated configuration viewing system for use in a process plant includes a computer readable memory and a plurality of template configuration objects stored on the computer readable memory. Each of the plurality of template configuration objects includes a graphical representation of a physical entity within the process plant, a parameter storage adapted to communicate with the process plant to obtain and store device parameter information associated with the physical entity within the process plant, and a configuration storage adapted to store configuration parameters associated with the physical entity within the process plant. A first routine is stored on the computer readable memory and adapted to be executed on the processor to present a library section on a user interface. The library section is adapted to present depictions of the plurality of template configuration objects to a user via the user interface. A second routine is stored on the computer readable memory and adapted to be executed on the processor to present a configuration area on the user interface. And a third routine is stored on the computer readable memory and adapted to be executed on the processor to enable a user to select one of the plurality of template configuration objects from the library section and to place the selected template configuration object within the configuration area to create a process configuration module within the configuration area.

Owner:FISHER-ROSEMOUNT SYST INC

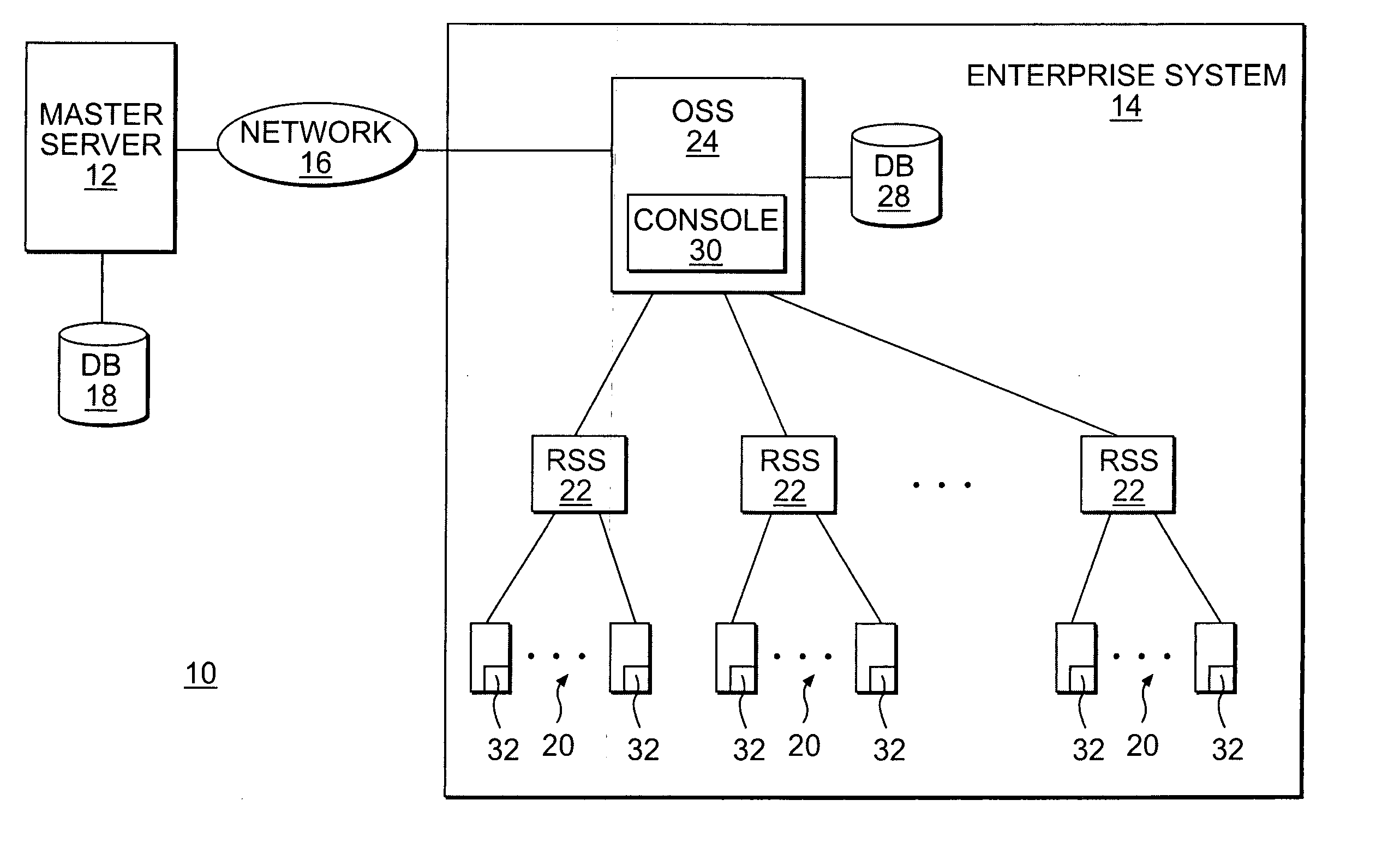

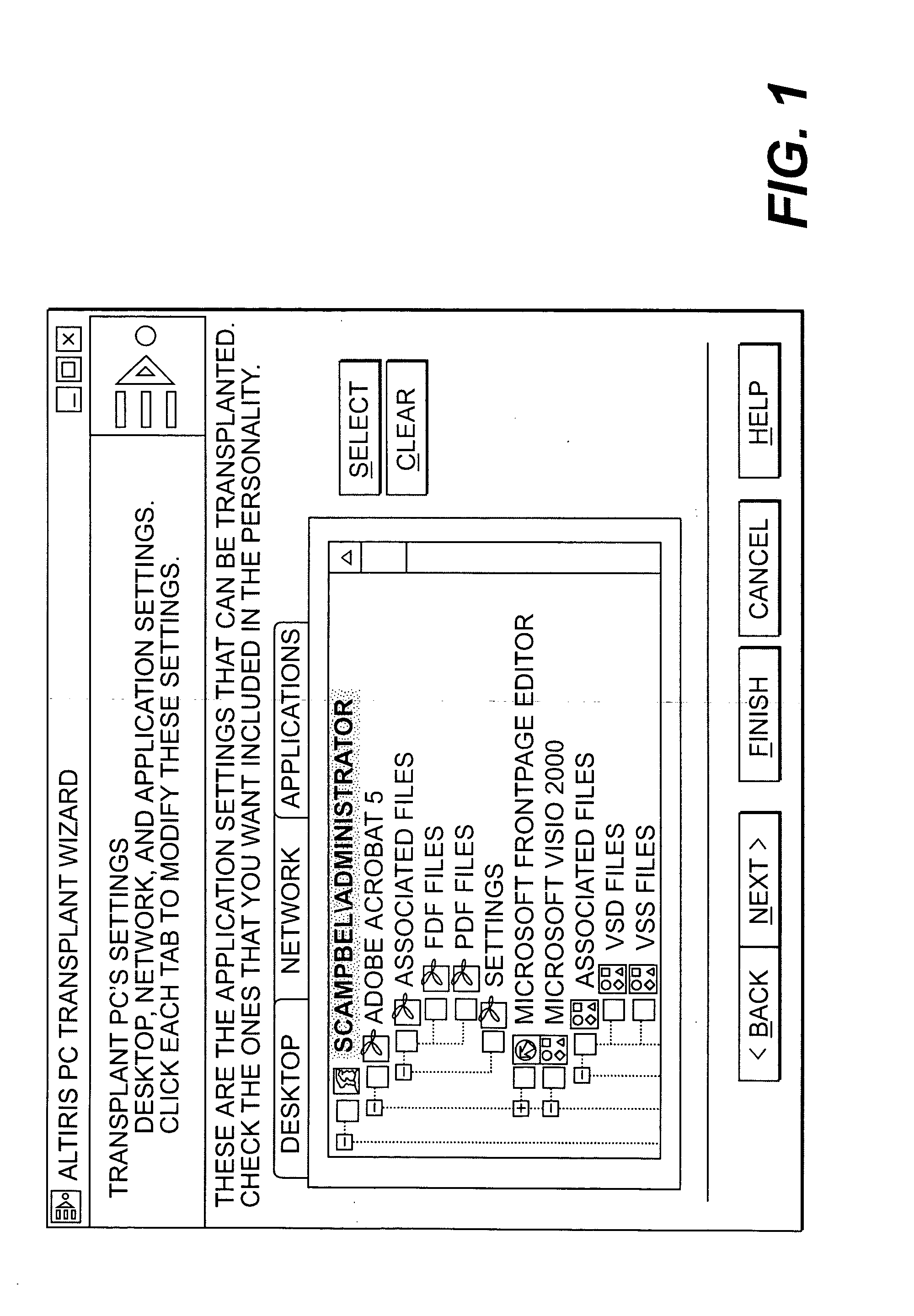

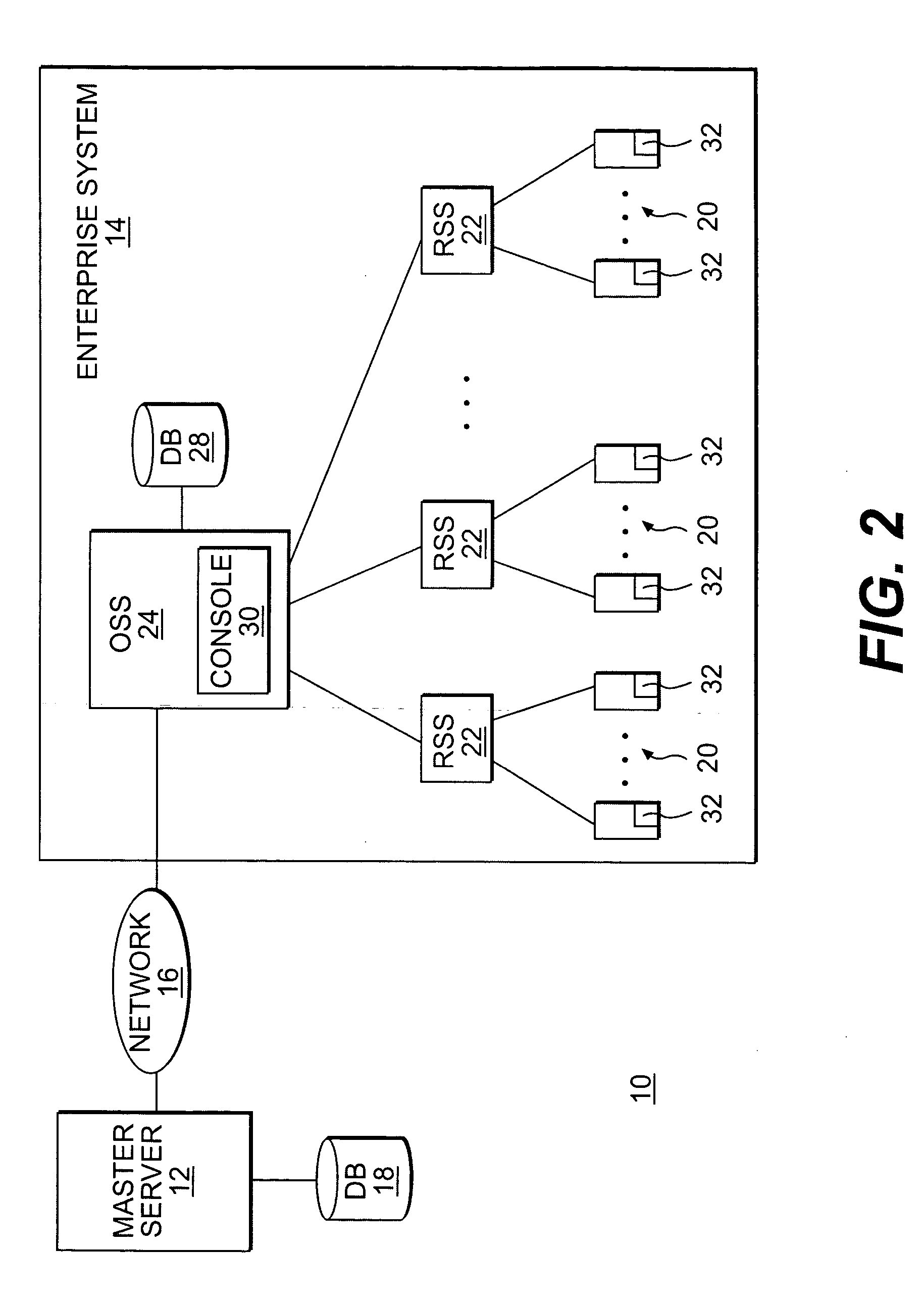

Method, system and article of manufacture for data preservation and automated electronic software distribution across an enterprise system

InactiveUS20050055357A1Digital data processing detailsMultiple digital computer combinationsSoftware distributionWorkstation

A method, system and article of manufacture for data preservation. A method for preserving data during system migration includes determining which files on a computer should not be preserved, preserving all files from the computer not identified by the determining step, performing a system migration on the computer, and downloading the preserved files to the computer. The determining step may determines which files should not be preserved by applying rules that specify which files should not be preserved. A system for preserving data during system migration includes a plurality of workstation computers and a remote site server connected to the plurality of workstation computers. Each workstation computer includes a plurality of files. The remote site server includes a processor that executes instructions on a memory, the memory including instructions for preserving data during system migration.

Owner:SECUREINFO CORP

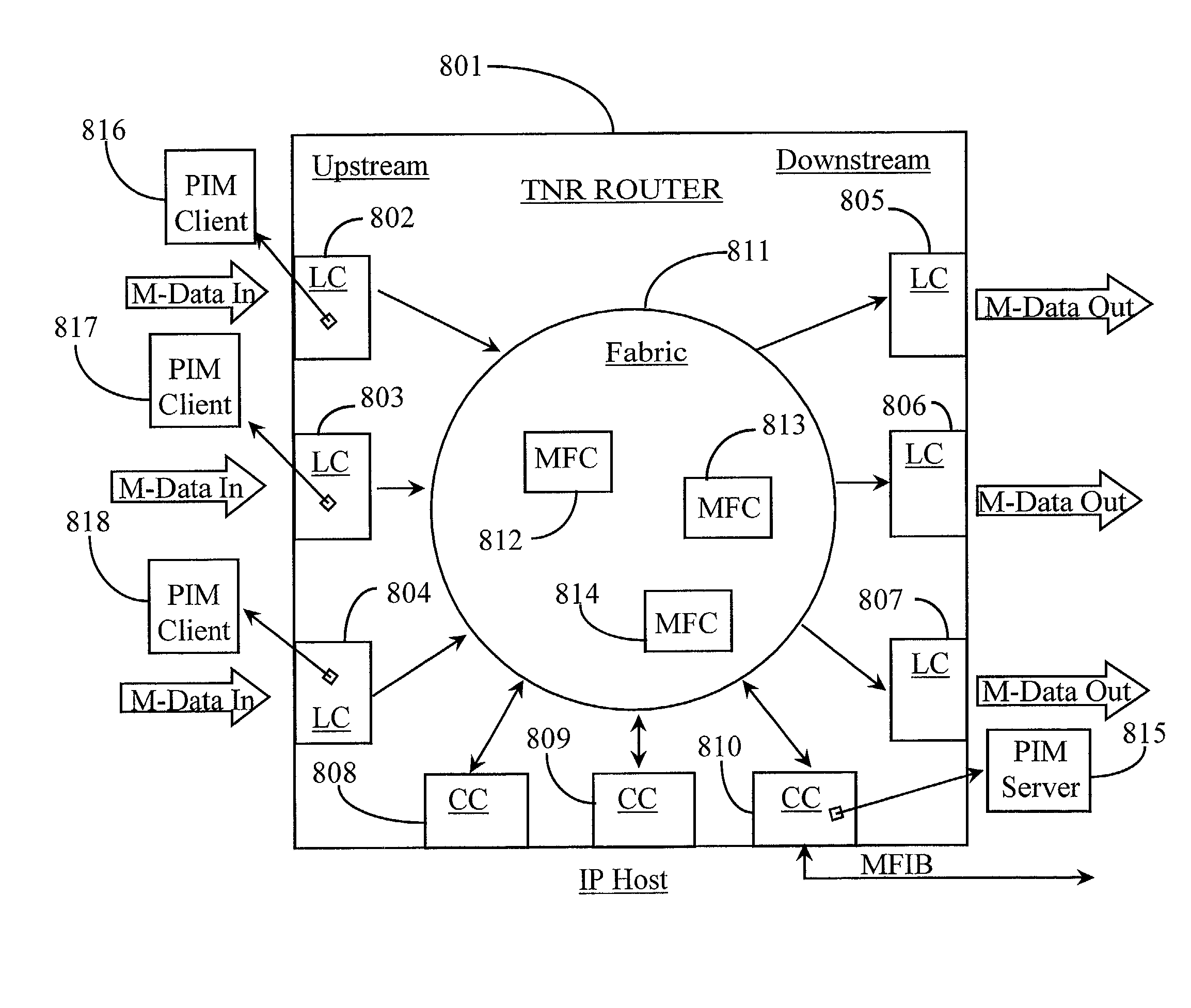

Method and apparatus for distributing routing instructions over multiple interfaces of a data router

InactiveUS20020126671A1Special service provision for substationError preventionCommunication interfaceInformation repository

A software application in a multi-processor data router in which a forwarding information base for the router is maintained is provided with a server module and one or more client modules, each client module associated with one or more communication interfaces of the data router. The application is characterized in that the server module sends to each client module only that portion of the forwarding information base specific to the communication interfaces associated with the client module.

Owner:PLURIS

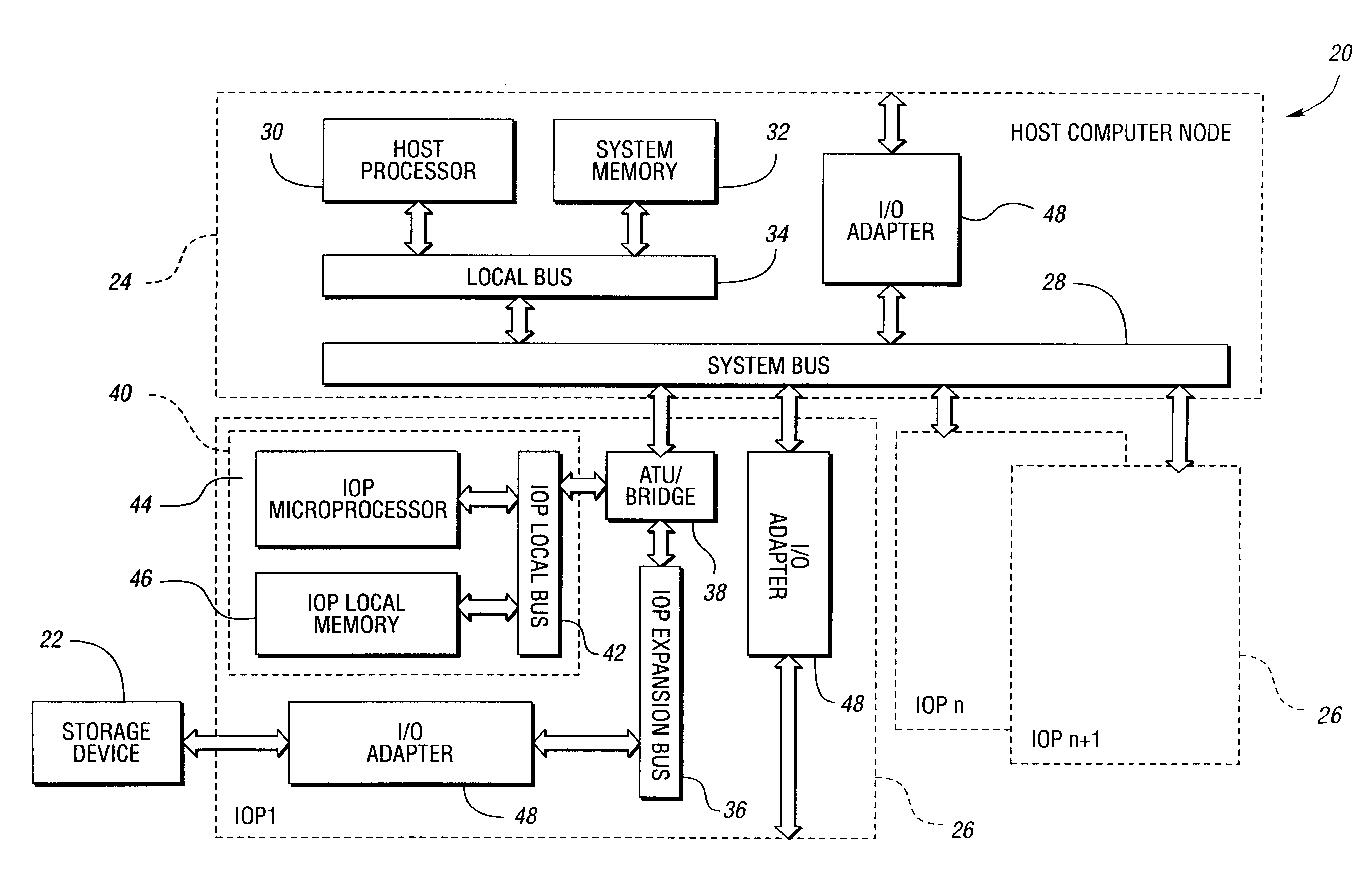

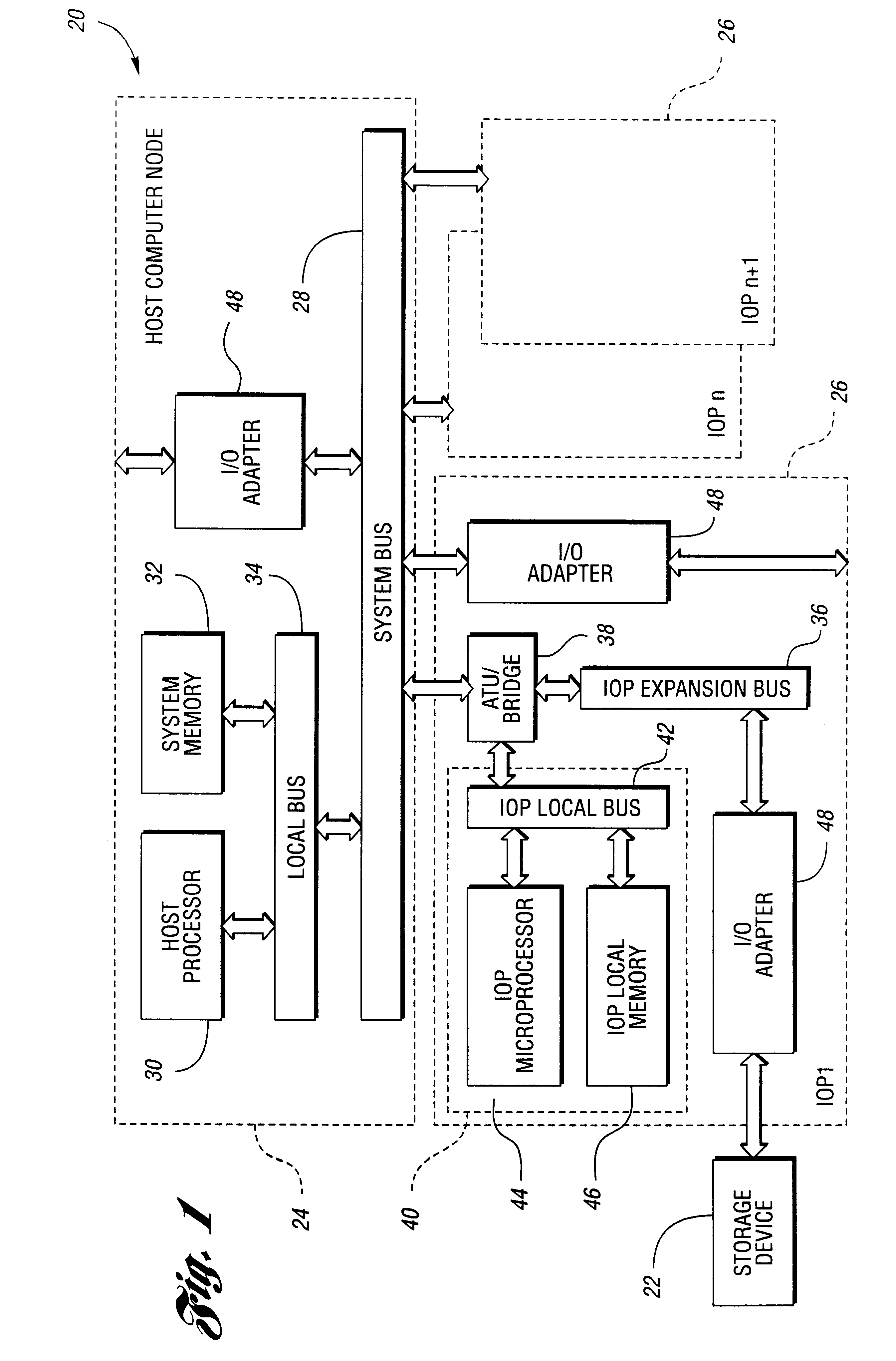

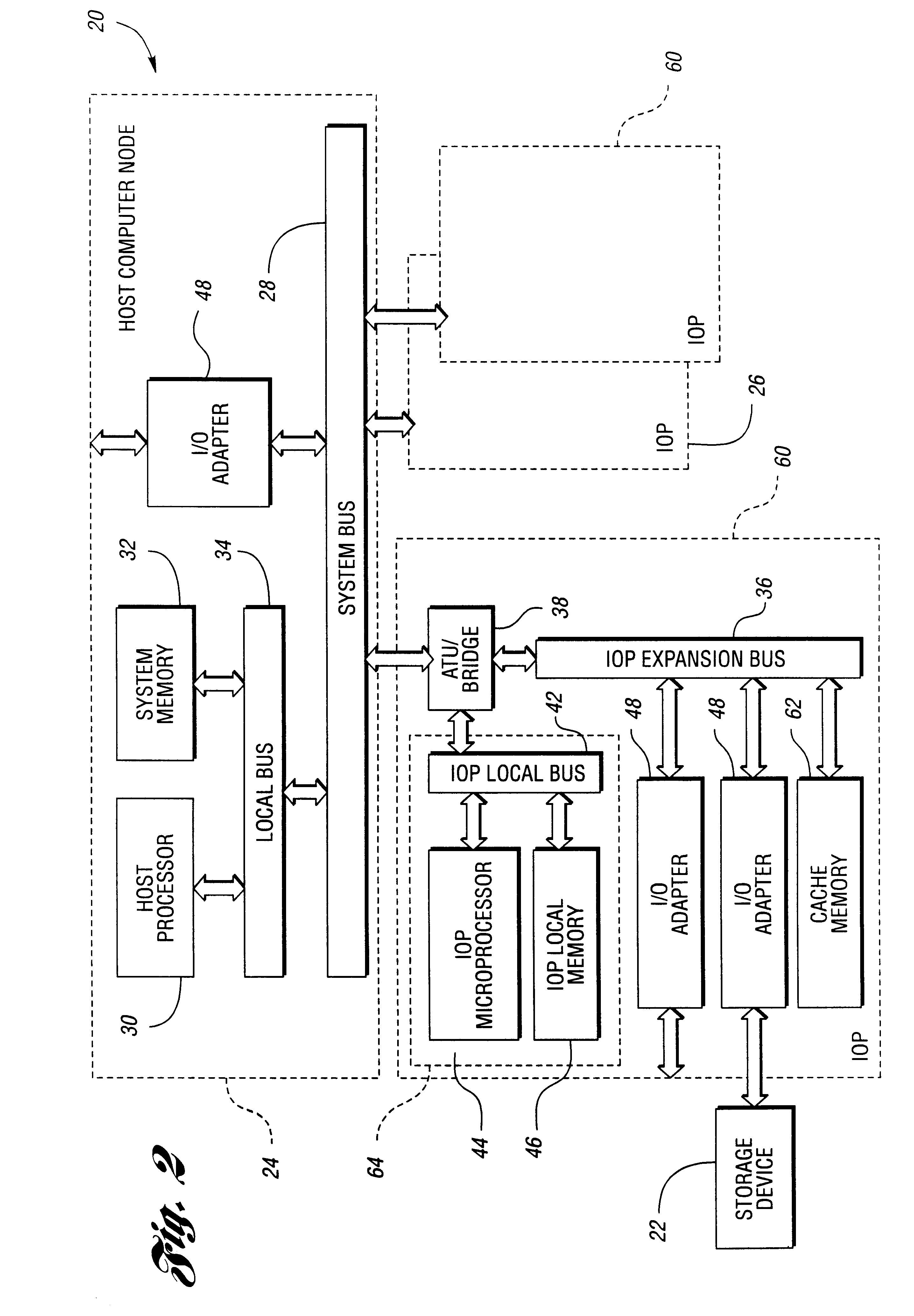

Computer system with storage device mapping input/output processor

InactiveUS6195730B1Memory adressing/allocation/relocationUnauthorized memory use protectionVirtualizationData transmission

An input / output processor provides device virtualization "on-board" through the use of a dedicated IO cache memory. A computer system includes at least one host processor and associated main memory each with access to a system bus. Each input / output processor is also connected to the system bus through an expansion bus. IO adapters within the input / output processor each connect at least one storage device to the expansion bus. Also connected to the expansion bus is the cache memory and a control logic. The control logic receives a data transfer request from a requesting host processor. The data transfer request is mapped to a cache device object. The cache device object has associated data maintained in the cache memory. If any storage device is required for the data transfer, the data transfer request is mapped to the storage device capable of servicing the request. A location in cache memory is determined based on the mapped cache device object. The data transfer is performed based on the location and, if needed, the determined storage devices. This provides the host computer with a virtual view of the storage devices.

Owner:ORACLE INT CORP

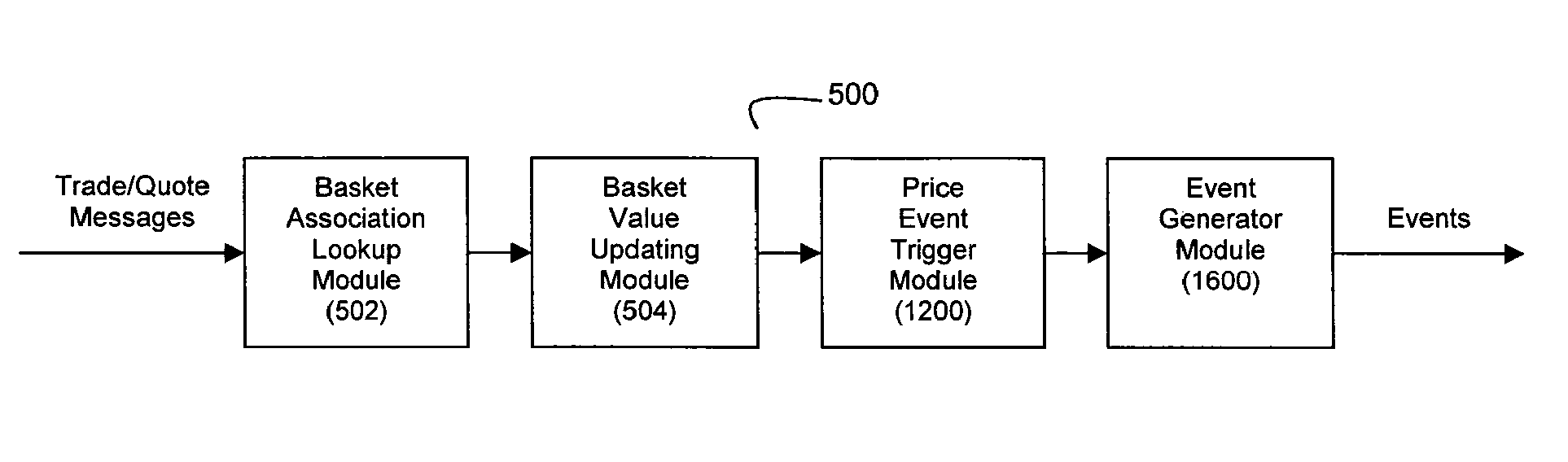

Method and System for Low Latency Basket Calculation

A basket calculation engine is deployed to receive a stream of data and accelerate the computation of basket values based on that data. In a preferred embodiment, the basket calculation engine is used to process financial market data to compute the net asset values (NAVs) of financial instrument baskets. The basket calculation engine can be deployed on a coprocessor and can also be realized via a pipeline, the pipeline preferably comprising a basket association lookup module and a basket value updating module. The coprocessor is preferably a reconfigurable logic device such as a field programmable gate array (FPGA).

Owner:EXEGY INC

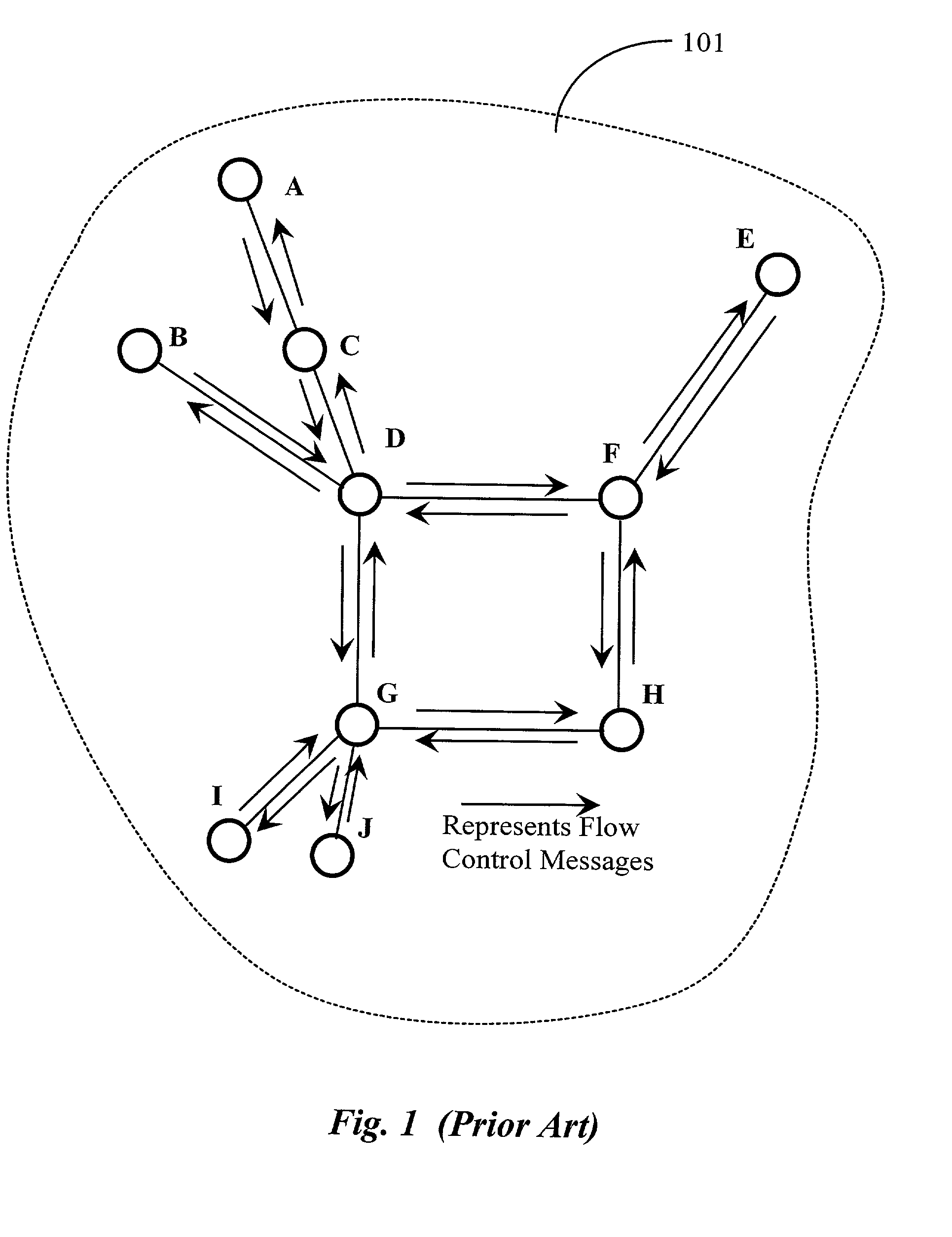

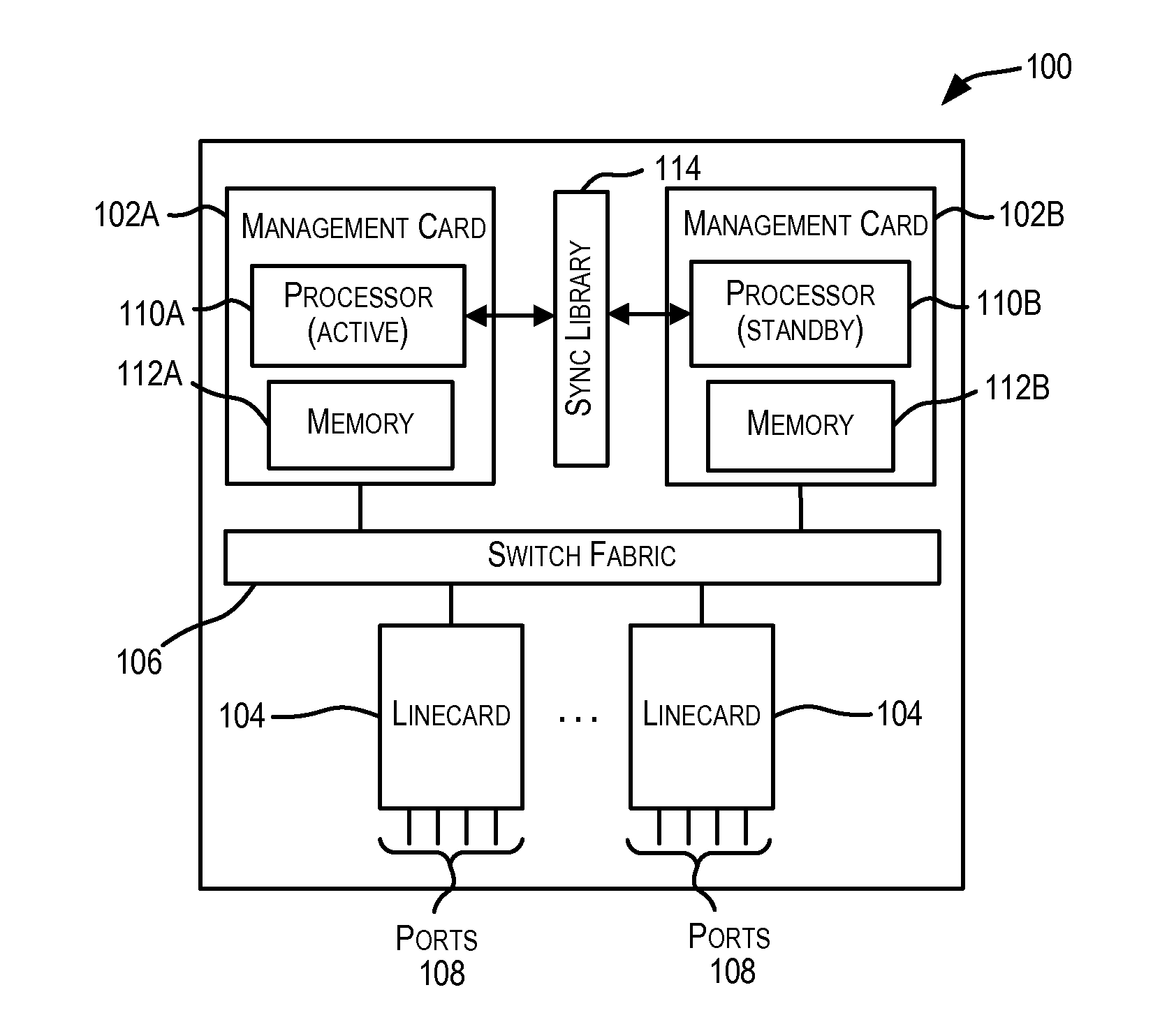

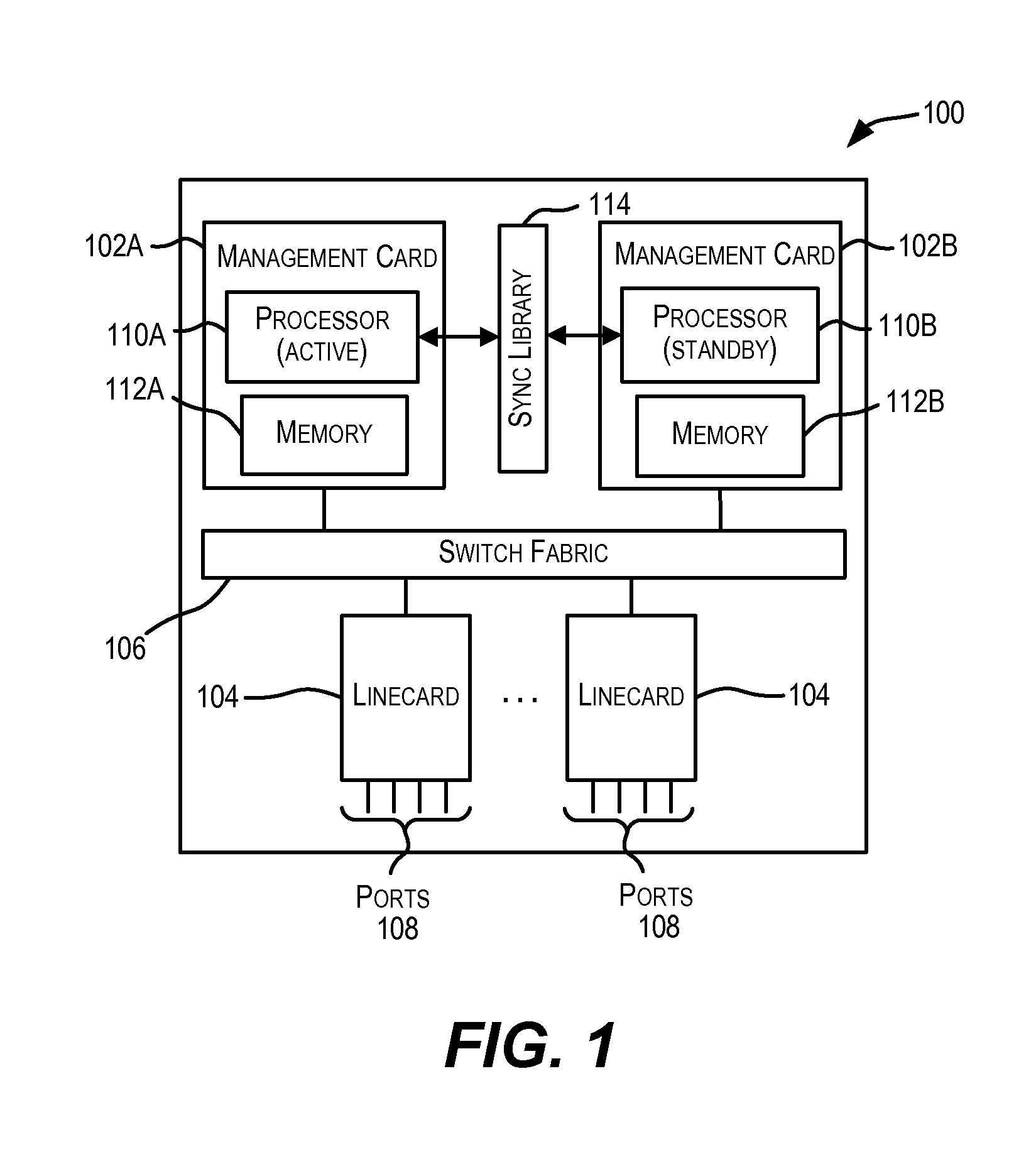

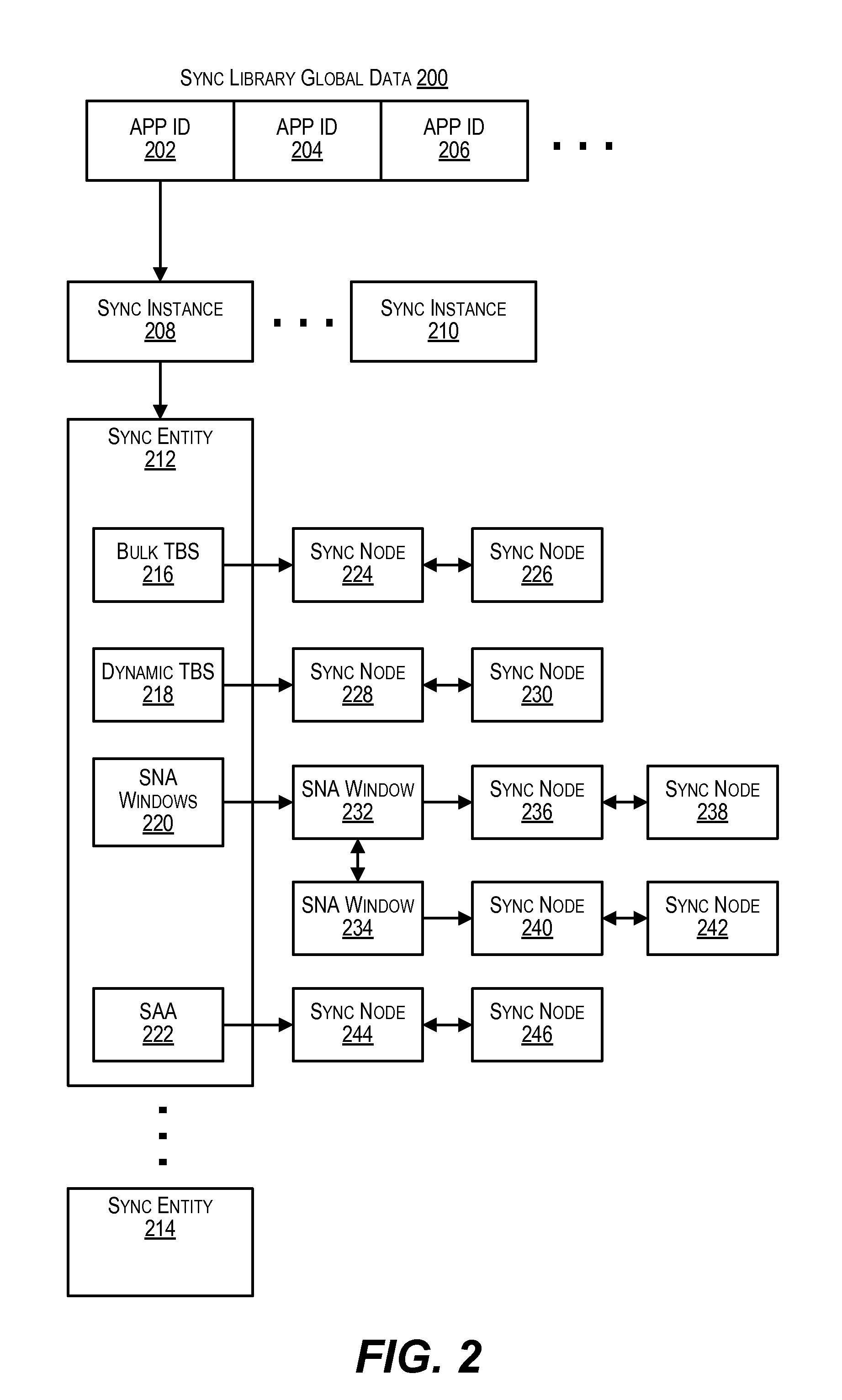

Techniques for synchronizing application object instances

InactiveUS20110231578A1Effective synchronizationDatabase distribution/replicationMultiple digital computer combinationsApplication objectData objects

Techniques for synchronizing data object instances between applications / processes in an efficient manner. In one set of embodiments, the techniques described herein can be implemented in one or more network routers to synchronize data between a process running on an active management processor and a process running on a standby management processor, thereby facilitating features such as non-stop routing (NSR).

Owner:AVAGO TECH INT SALES PTE LTD

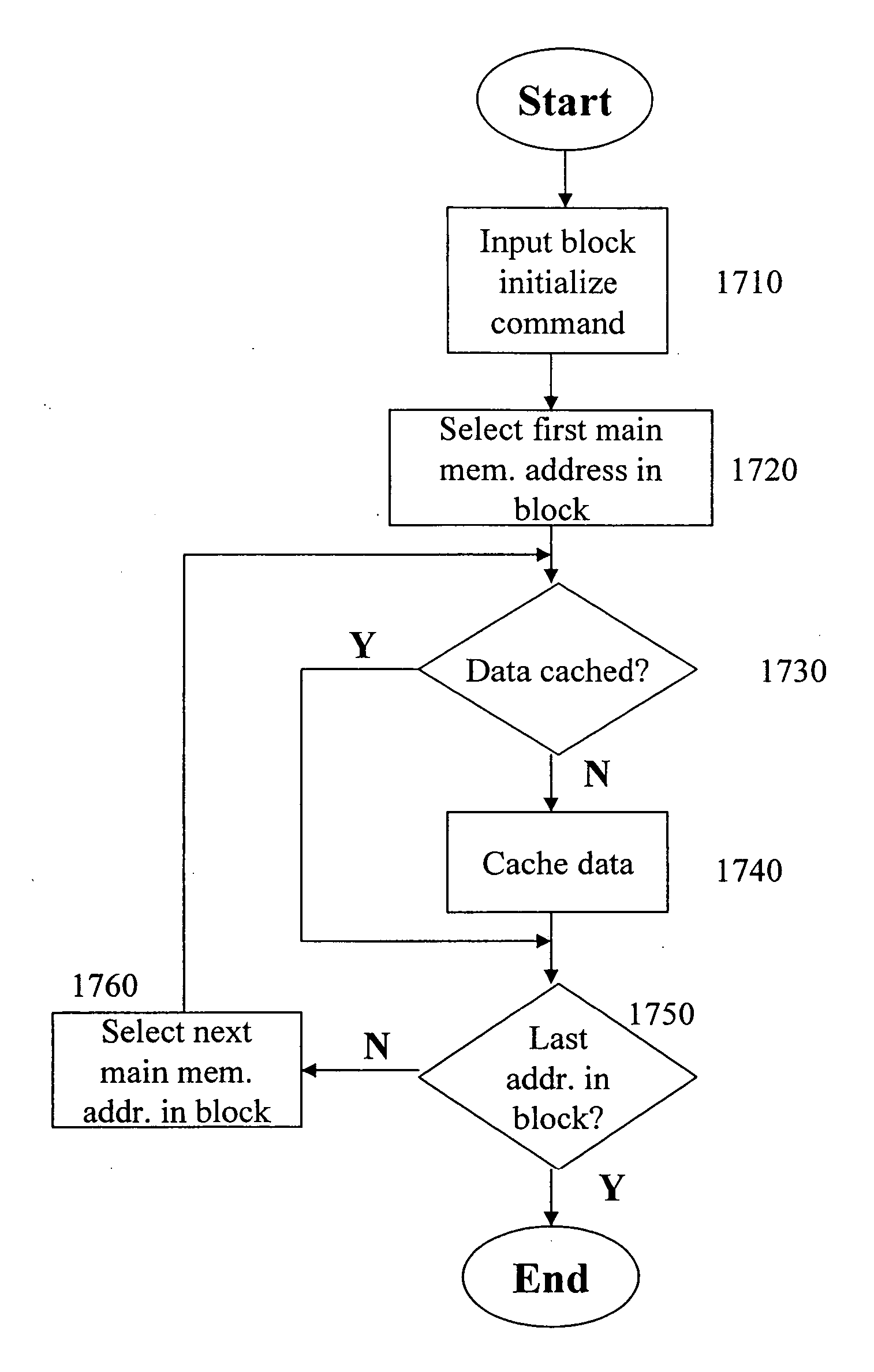

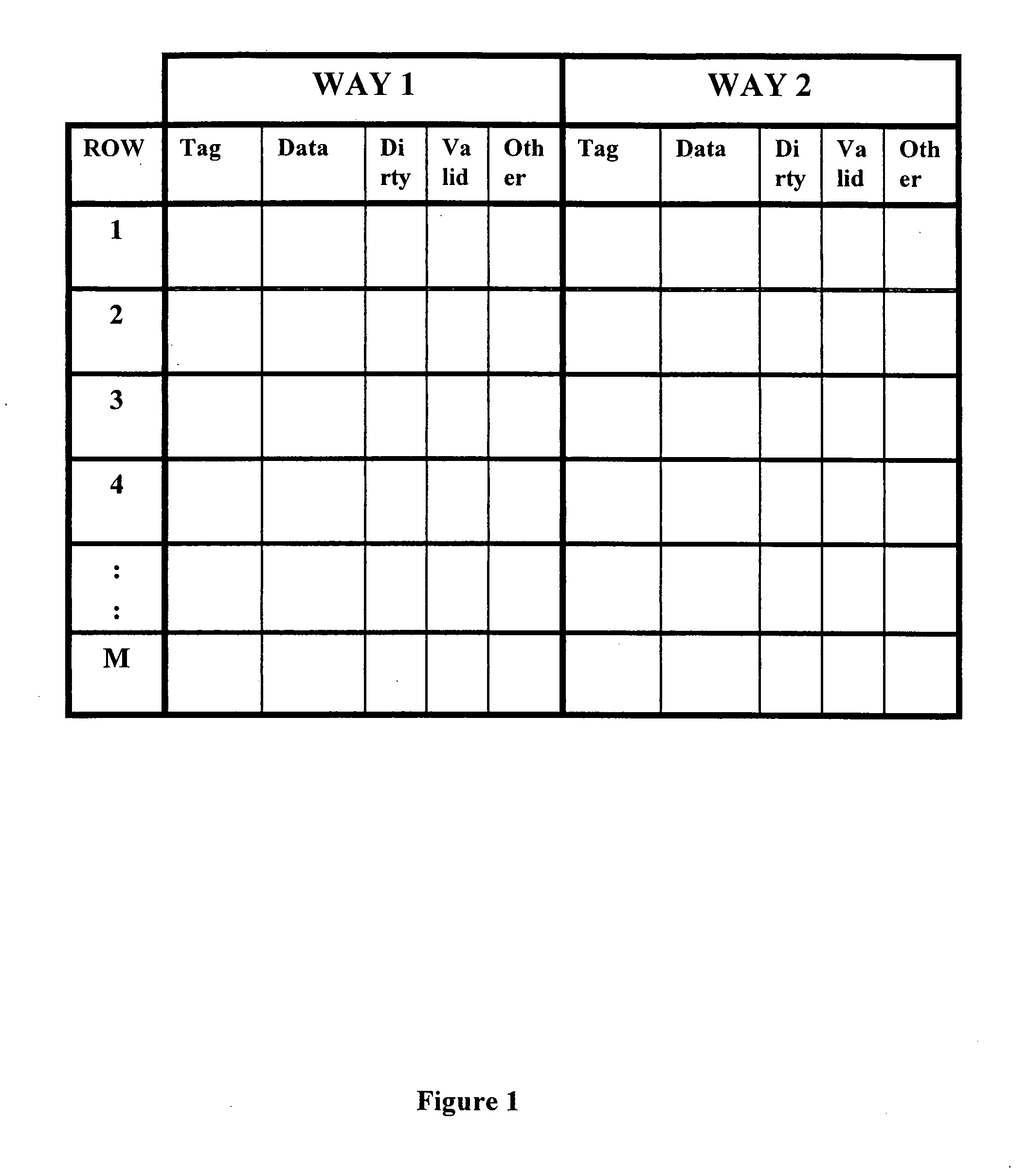

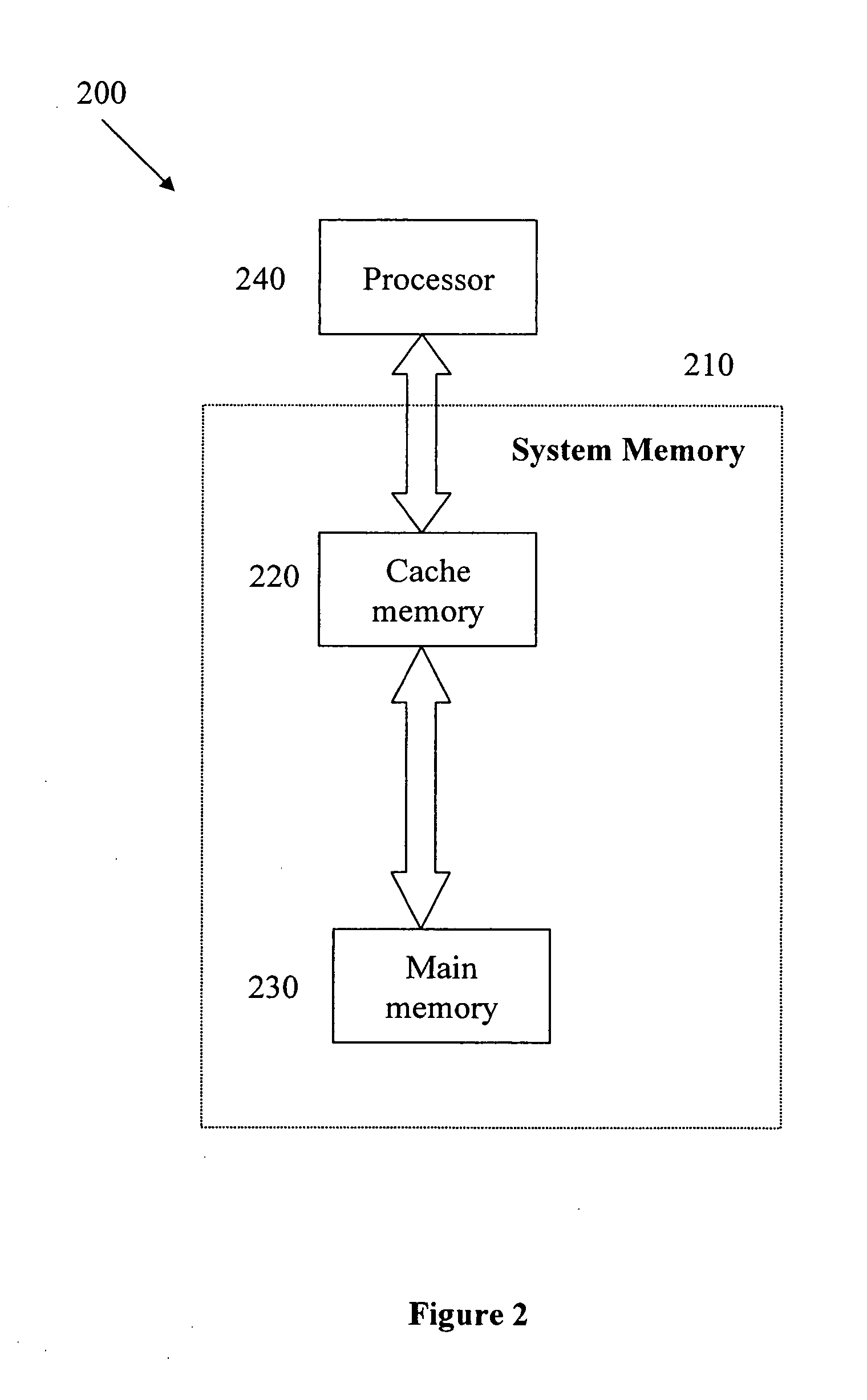

Cache memory background preprocessing

A cache memory preprocessor prepares a cache memory for use by a processor. The processor accesses a main memory via a cache memory, which serves a data cache for the main memory. The cache memory preprocessor consists of a command inputter, which receives a multiple-way cache memory processing command from the processor, and a command implementer. The command implementer performs background processing upon multiple ways of the cache memory in order to implement the cache memory processing command received by the command inputter.

Owner:ANALOG DEVICES INC

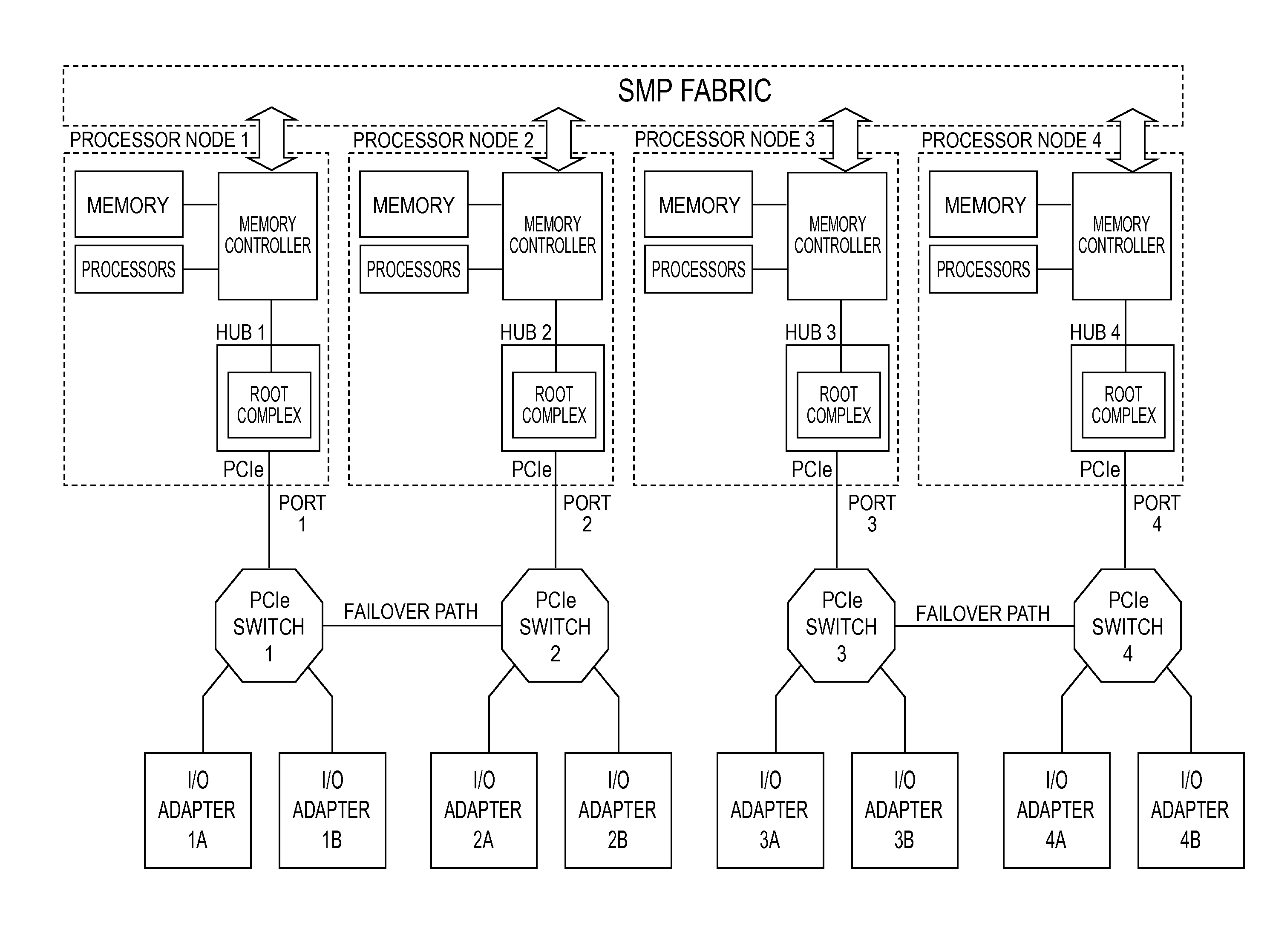

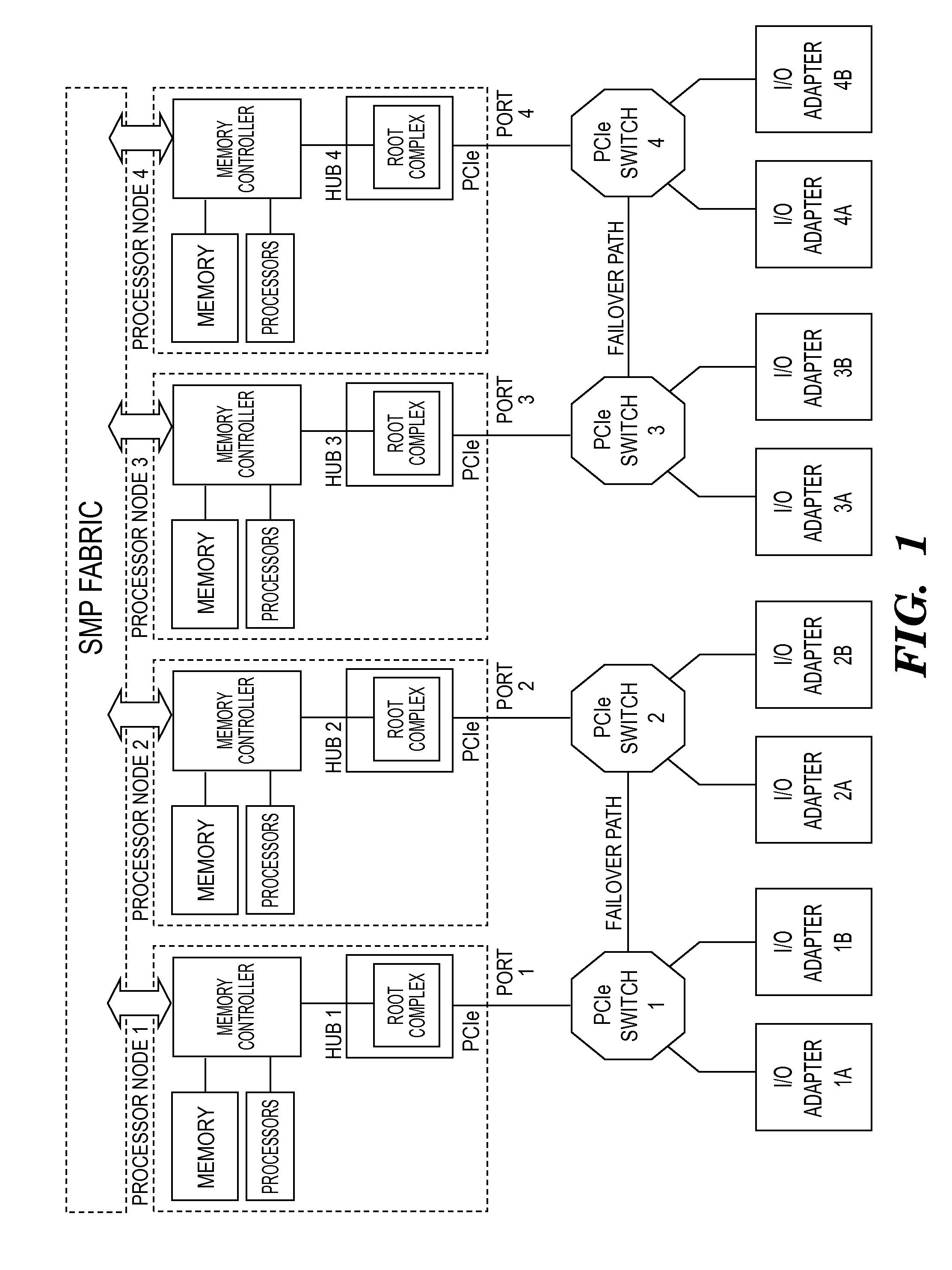

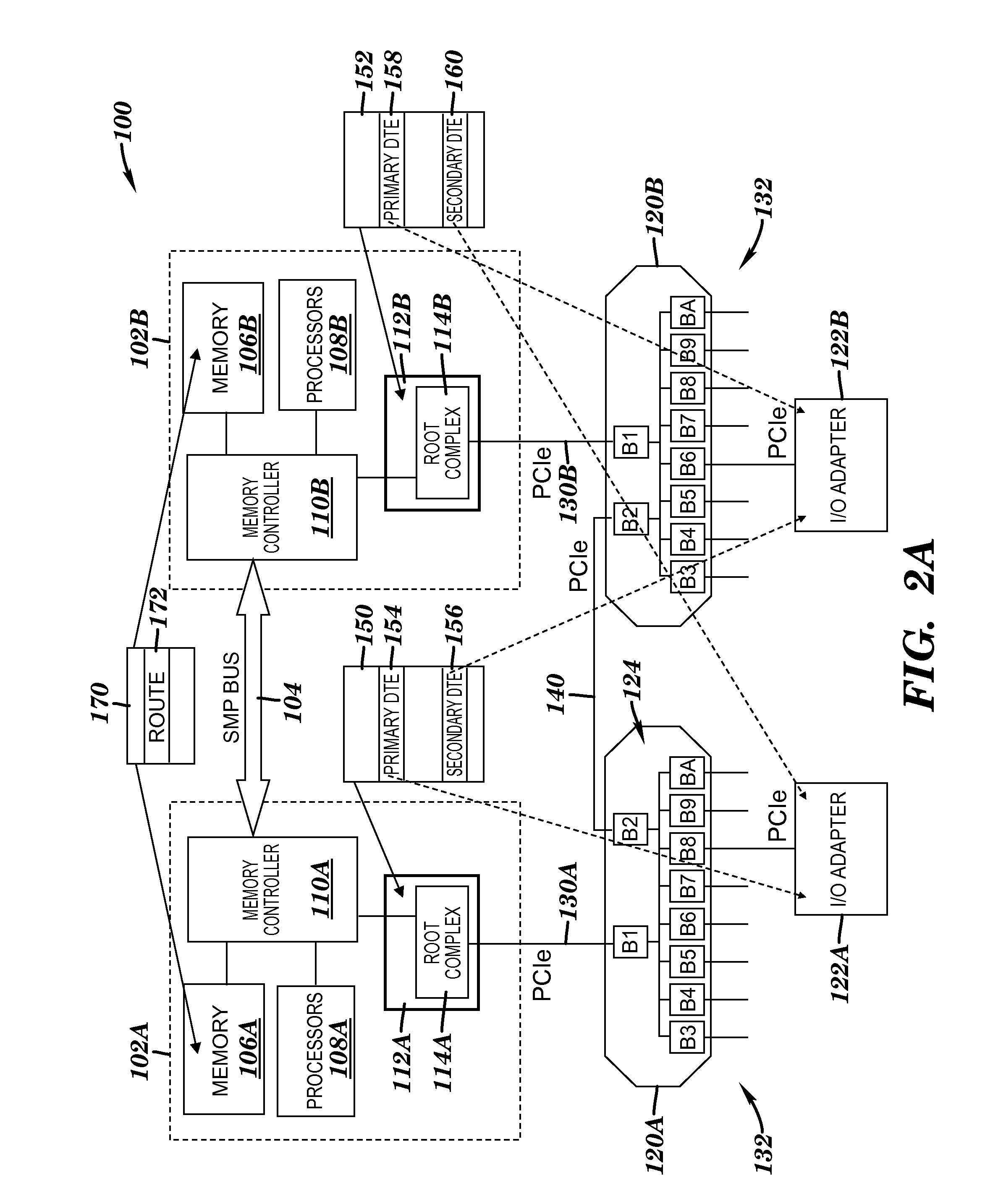

Switch failover control in a multiprocessor computer system

A system and a method for failover control comprising: maintaining a primary device table entry (DTE) in a first table activated for a first adapter in communication with a first processor node having a first root complex via a first switch assembly and maintaining a secondary DTE in standby for a second adapter in communication with a second processor node having a second root complex via a second switch assembly; maintaining a primary DTE in a second table activated for the second adapter and maintaining a secondary DTE in standby for the first adapter; and upon a failover, updating the secondary DTE in the first table as an active entry for the second adapter and forming a path to enable traffic to route from the second adapter through the second switch assembly over to the first switch assembly and up to the first root complex of the first processor node.

Owner:IBM CORP

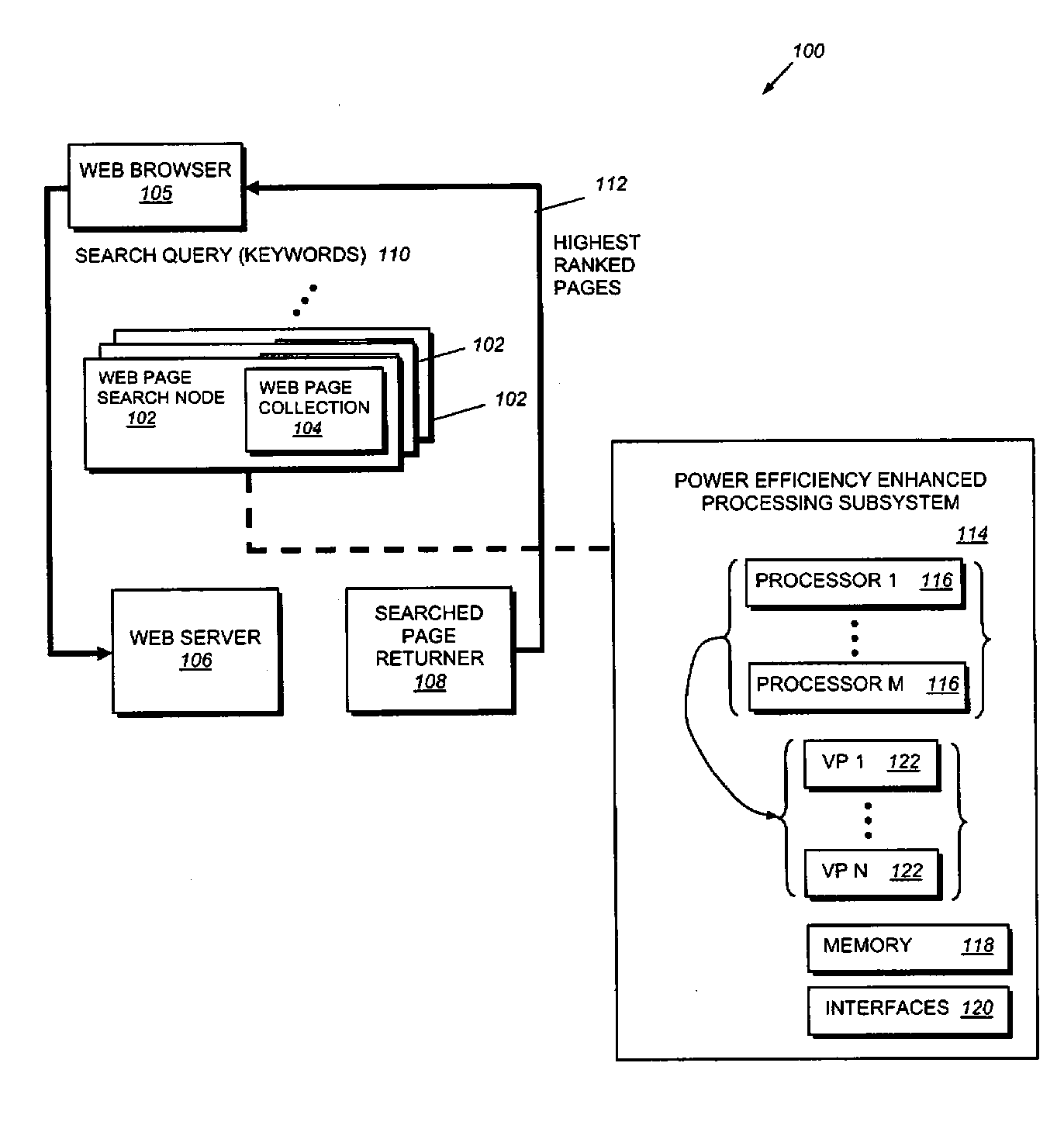

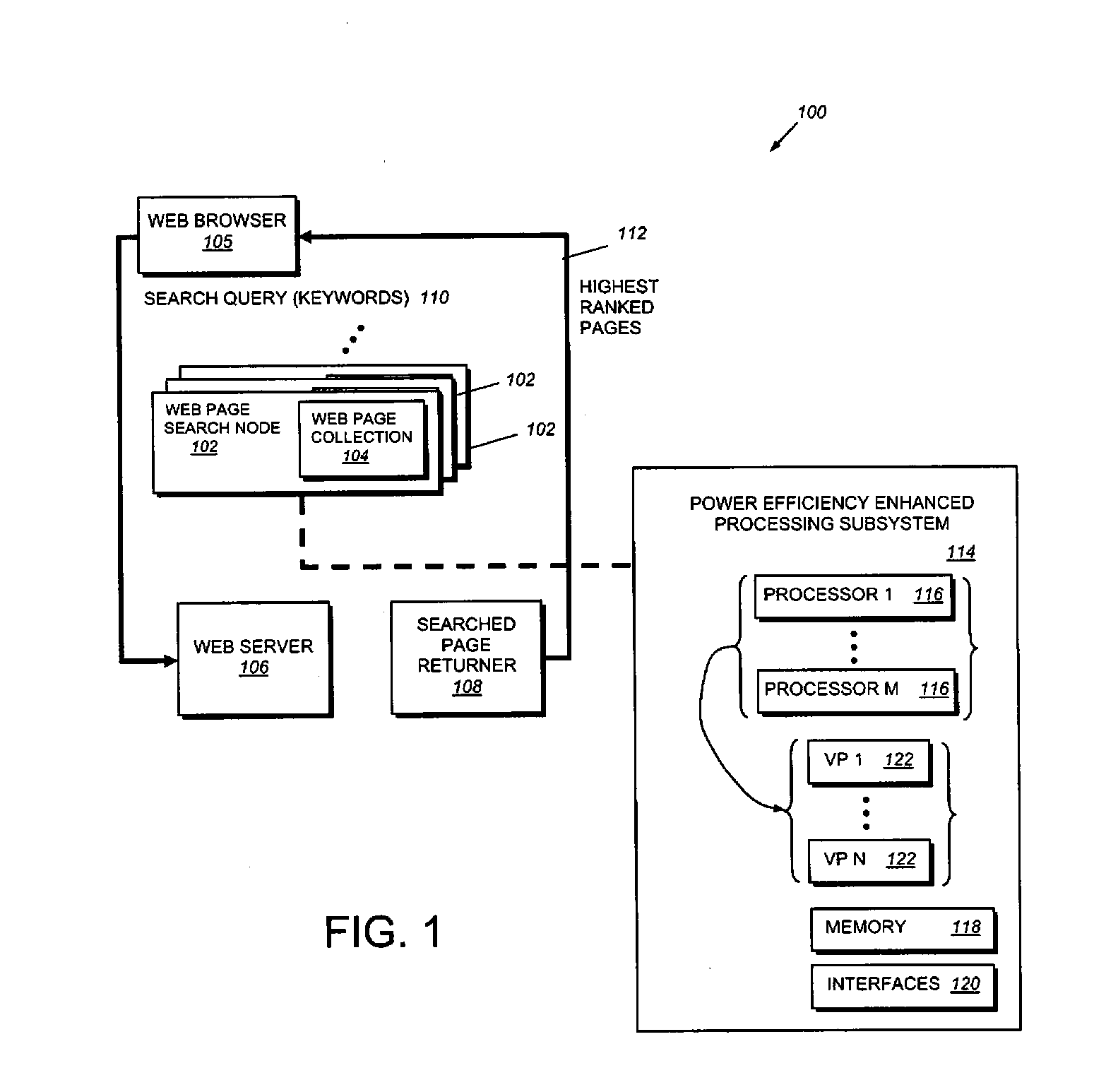

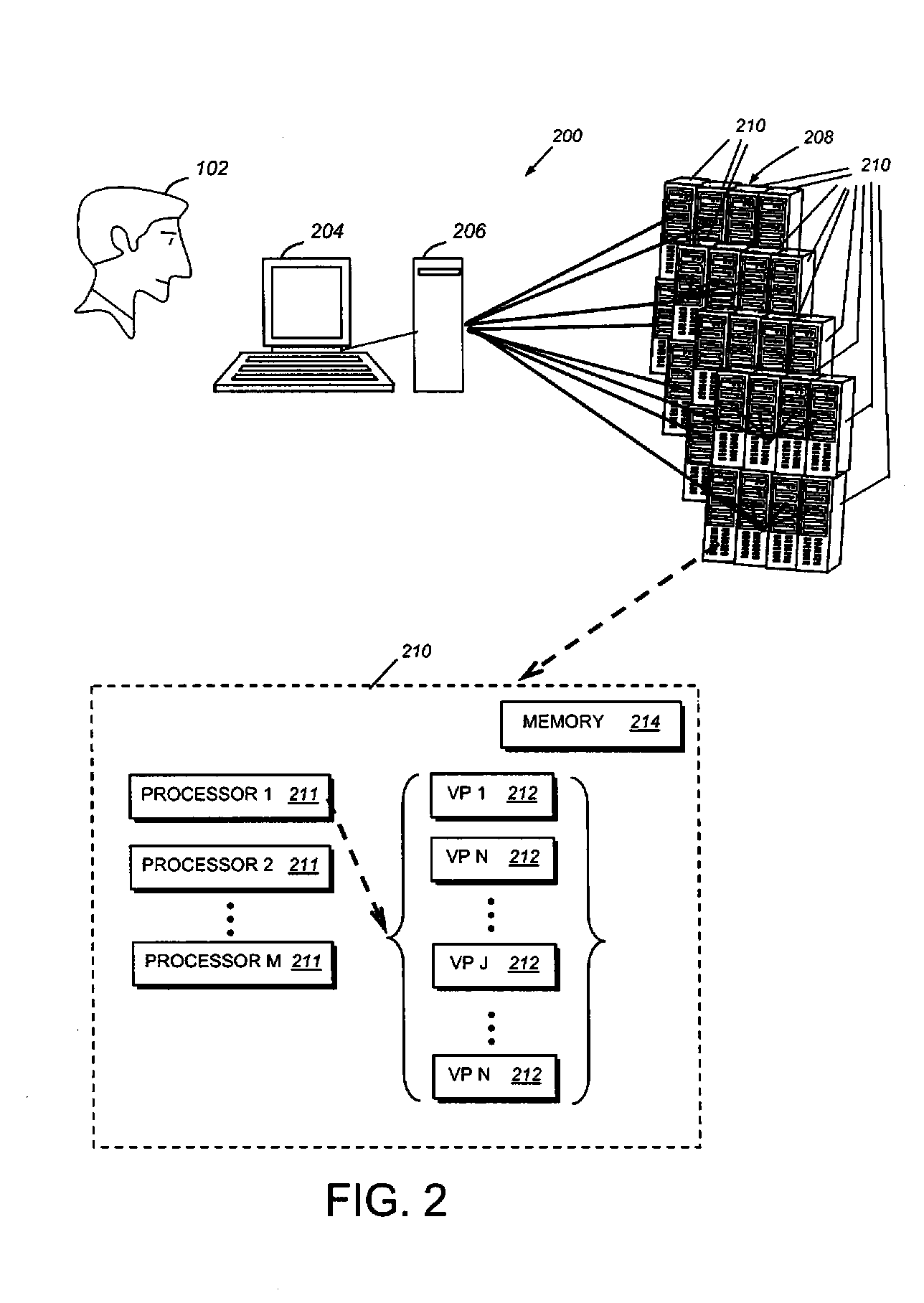

Parallel processing computer systems with reduced power consumption and methods for providing the same

ActiveUS20090083263A1Reduce power consumptionEnergy efficient ICTWeb data indexingWeb browserWeb service

This invention provides a computer system architecture and method for providing the same which can include a web page search node including a web page collection. The system and method can also include a web server configured to receive, from a given user via a web browser, a search query including keywords. The node is caused to search pages in its own collection that best match the search query. A search page returner may be provided which is configured to return, to the user, high ranked pages. The node may include a power-efficiency-enhanced processing subsystem, which includes M processors. The M processors are configured to emulate N virtual processors, and they are configured to limit a virtual processor memory access rate at which each of the N virtual processors accesses memory. The memory accessed by each of the N virtual processors may be RAM. In select embodiments, the memory accessed by each of the N virtual processors includes DRAM having a high capacity yet lower power consumption then SRAM.

Owner:GRANGER RICHARD

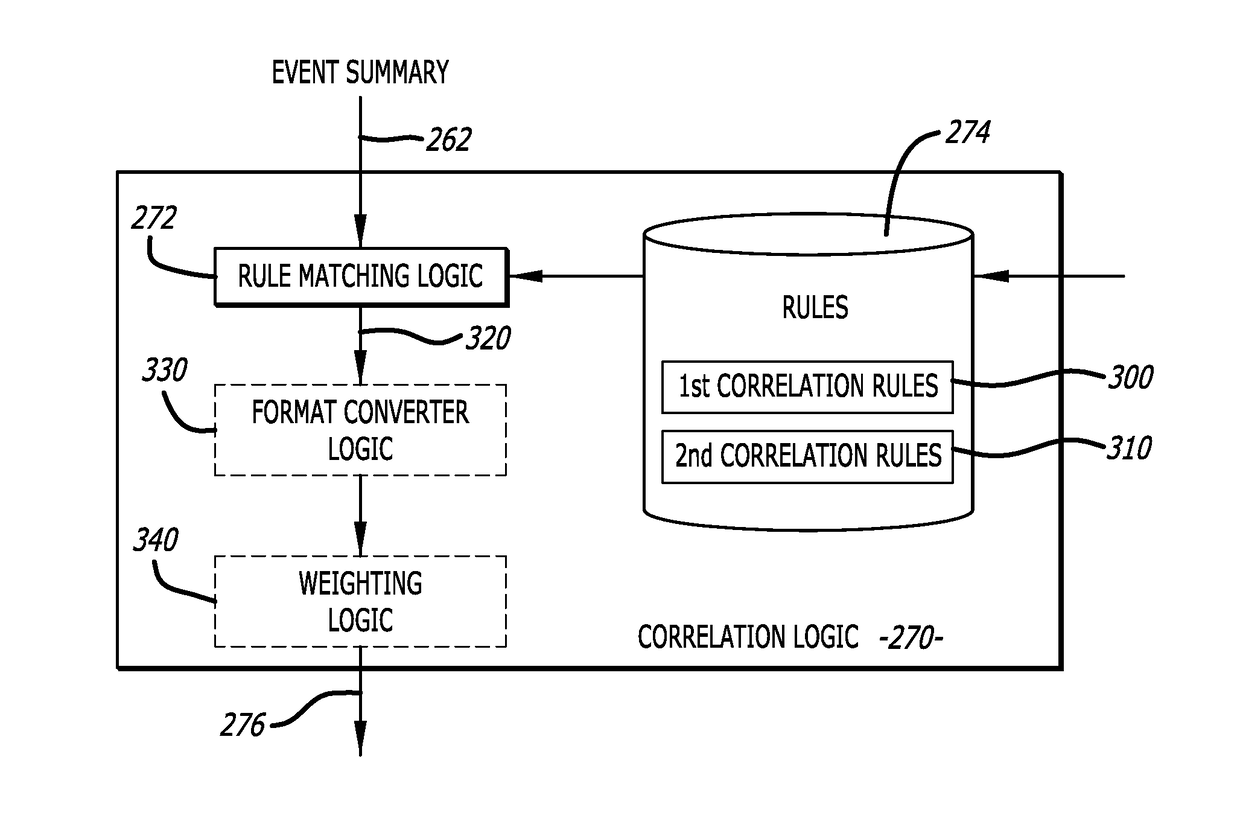

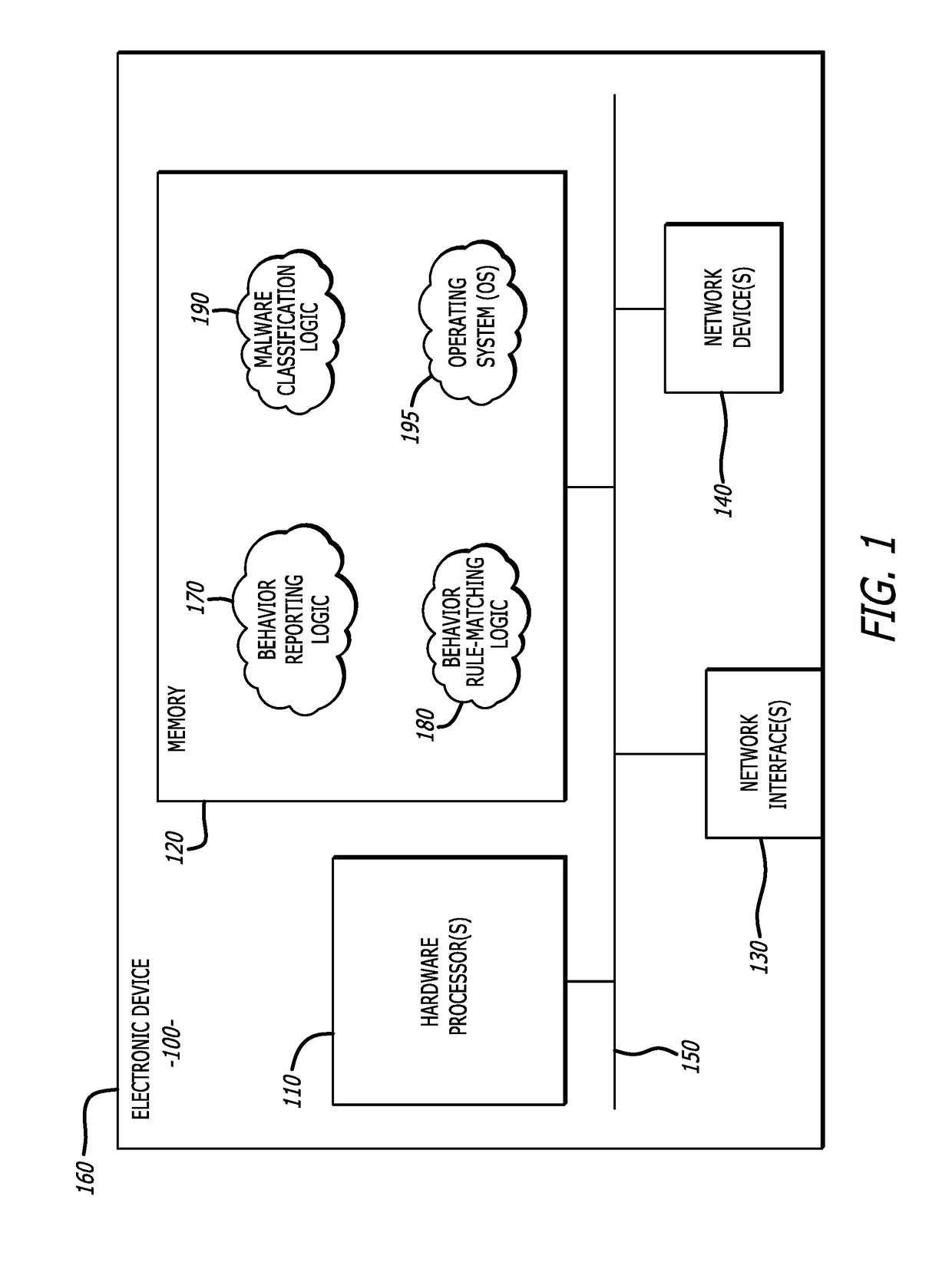

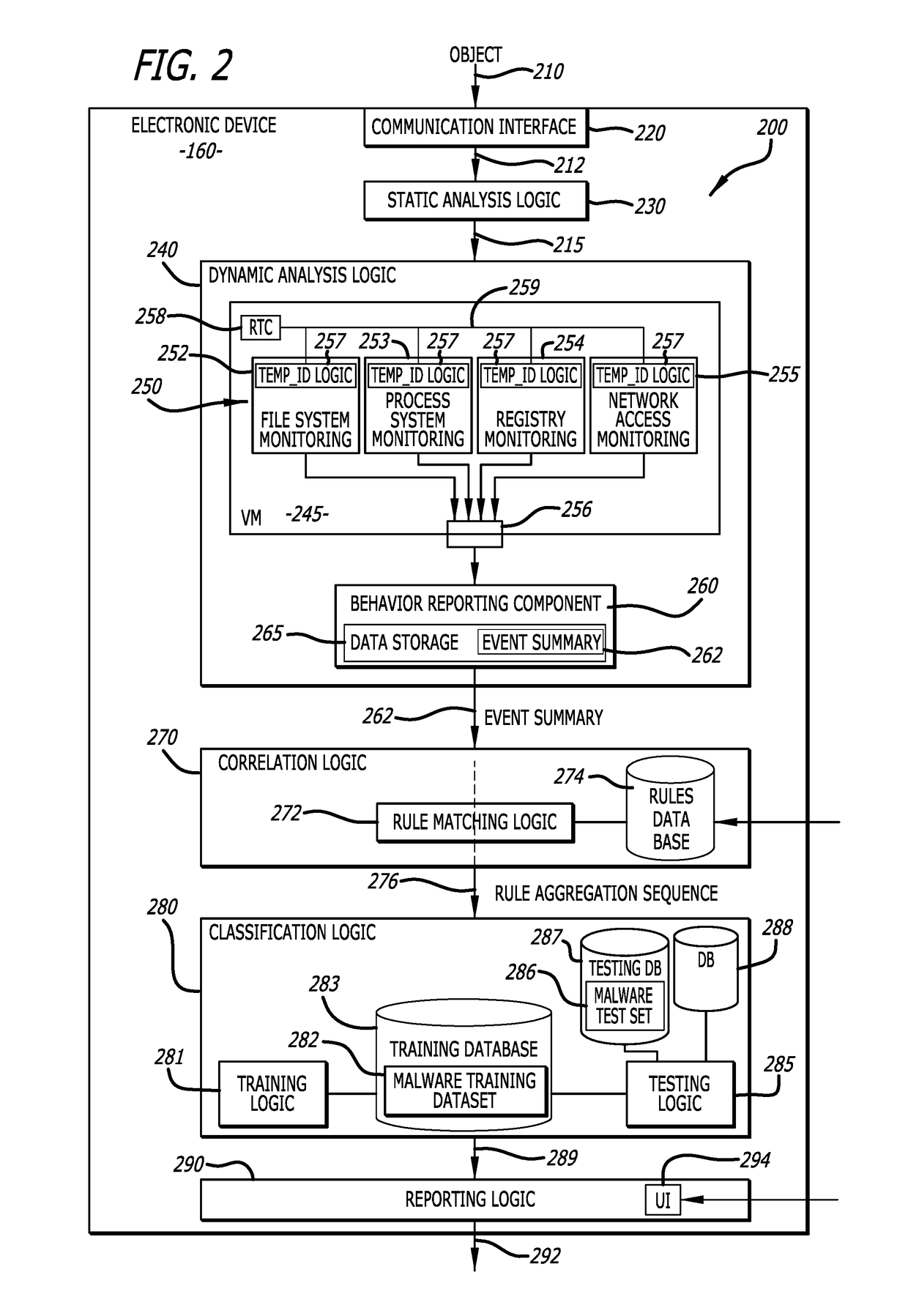

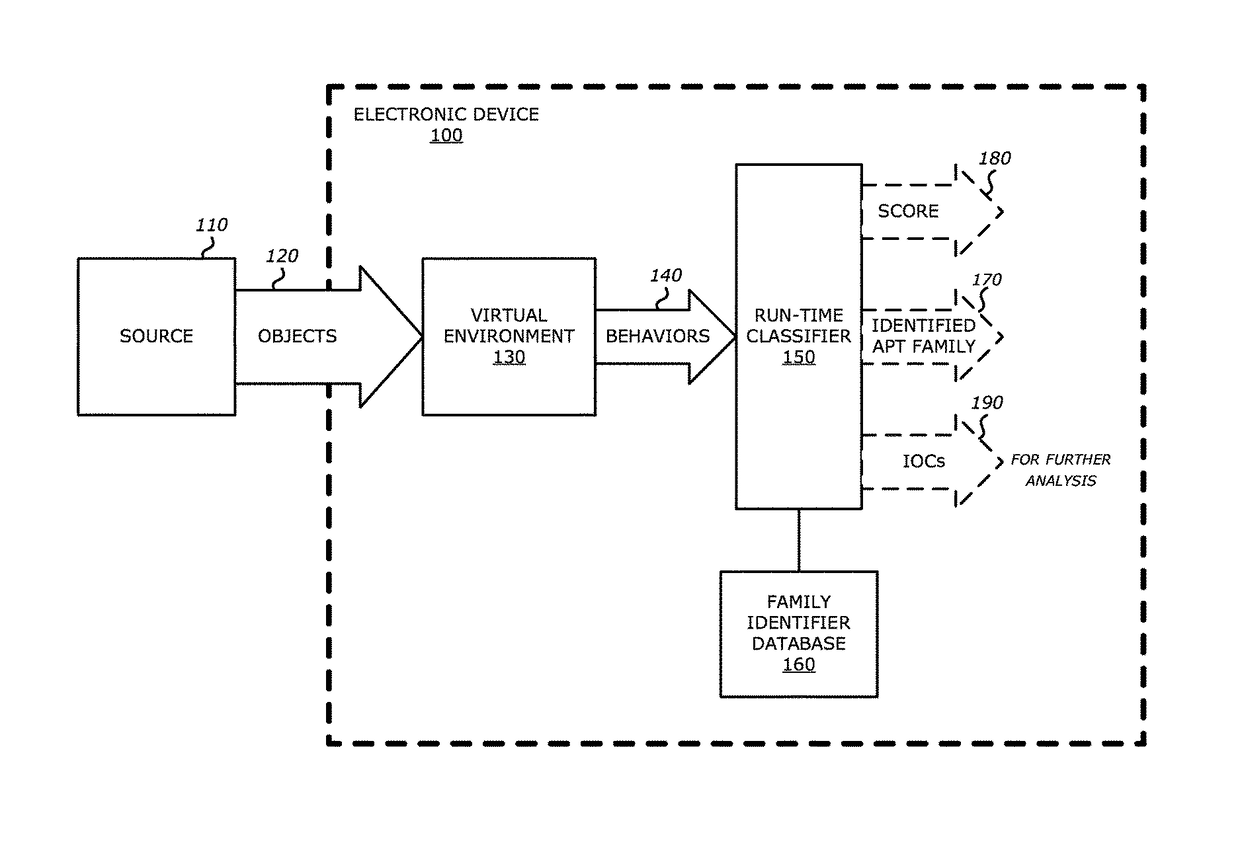

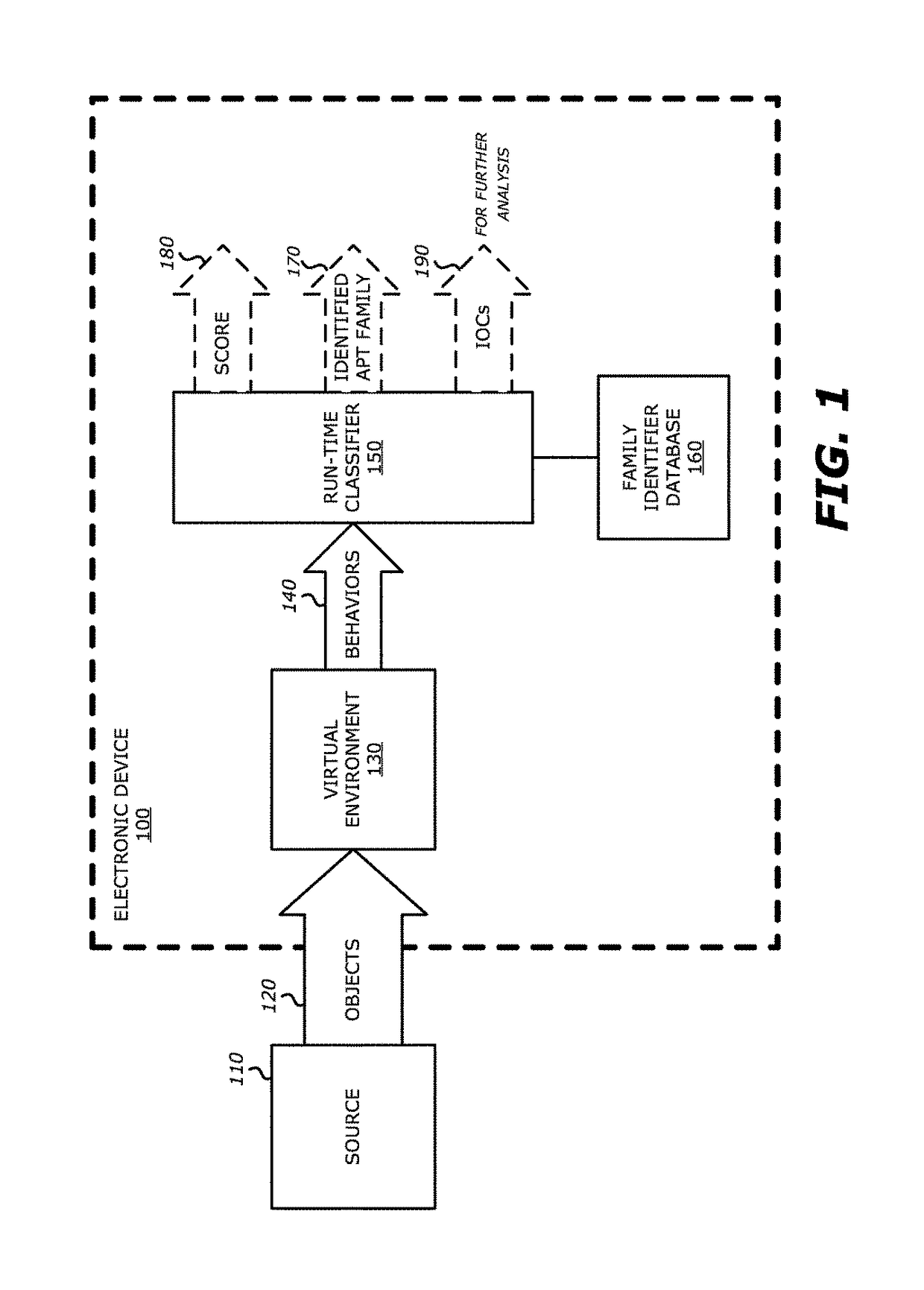

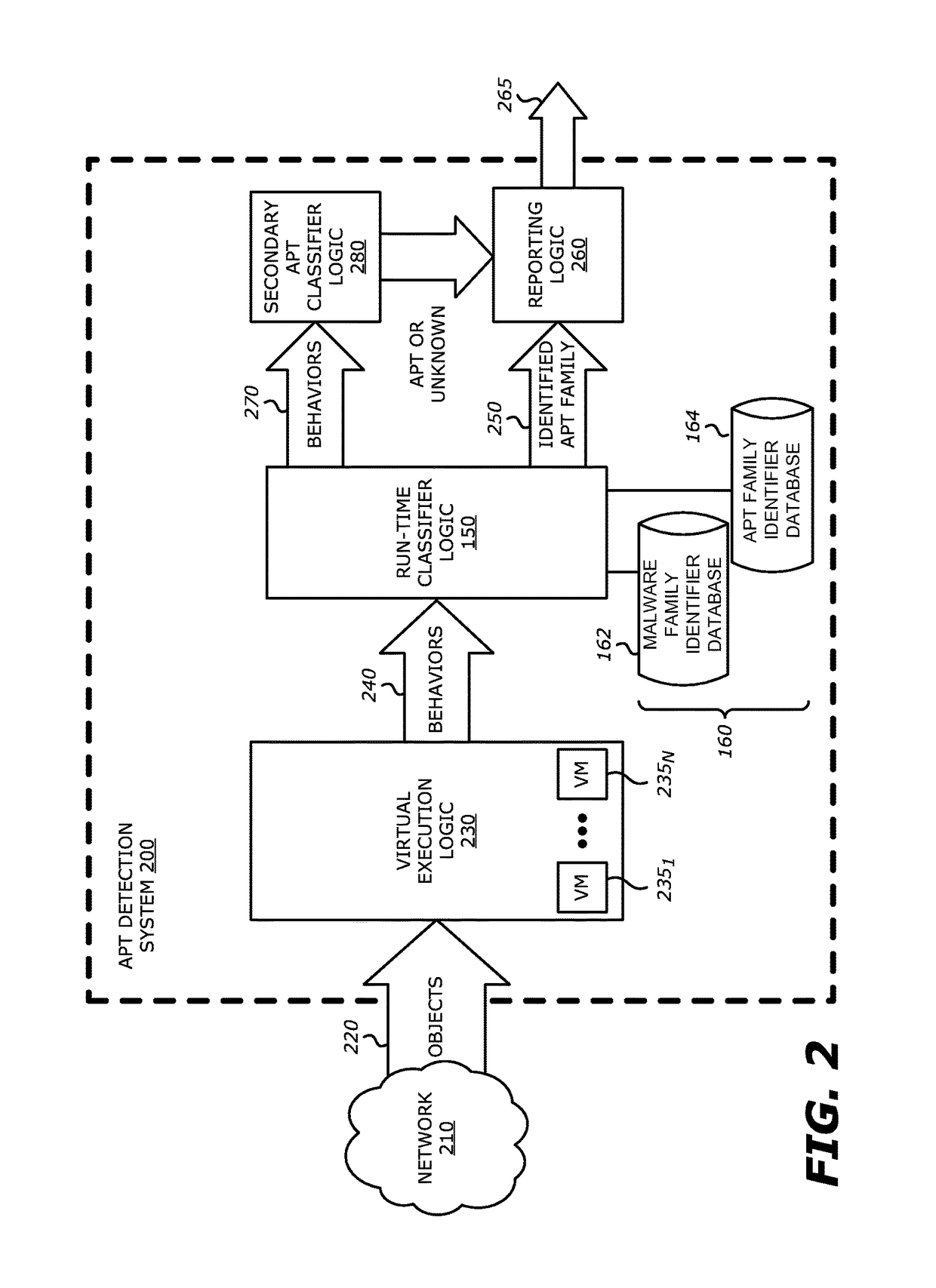

Leveraging behavior-based rules for malware family classification

According to one embodiment, a malware classification scheme operating with an electronic device, configured with one or more hardware processors and a memory that stores the software handling the malware classification scheme that is conducted through analysis of behavior-based rules, is described. This malware classification scheme (i) conducts a determination whether a sequence of rules correspond to potential malicious behaviors detected during analysis of a malware sample within one or more virtual machines, and in response to determining that the sequence of rules corresponds to potential malicious behaviors, (ii) conducts an attempt to classify the malware sample to at least one known malware family based on an analysis of the sequence of rules.

Owner:FIREEYE SECURITY HLDG US LLC

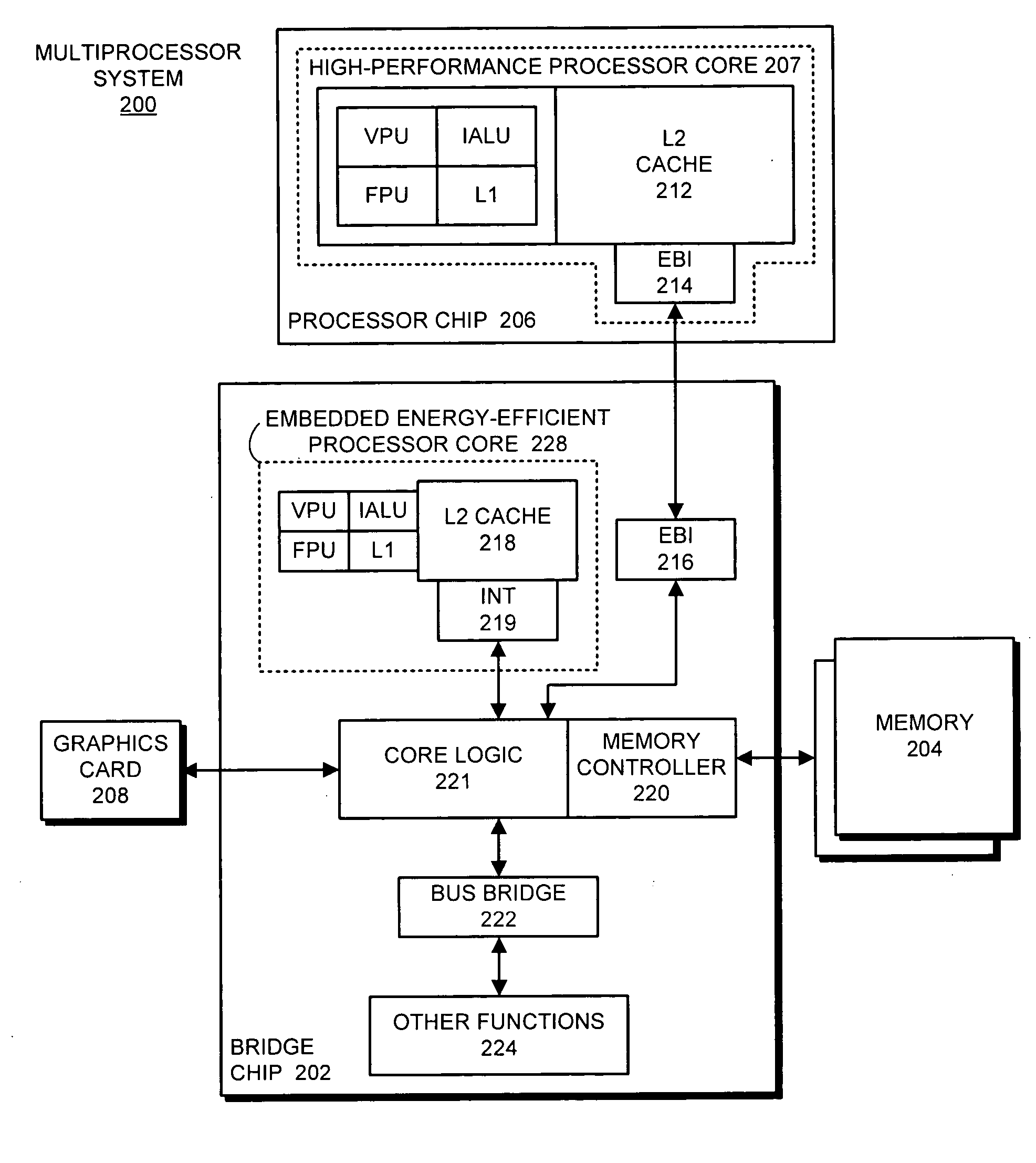

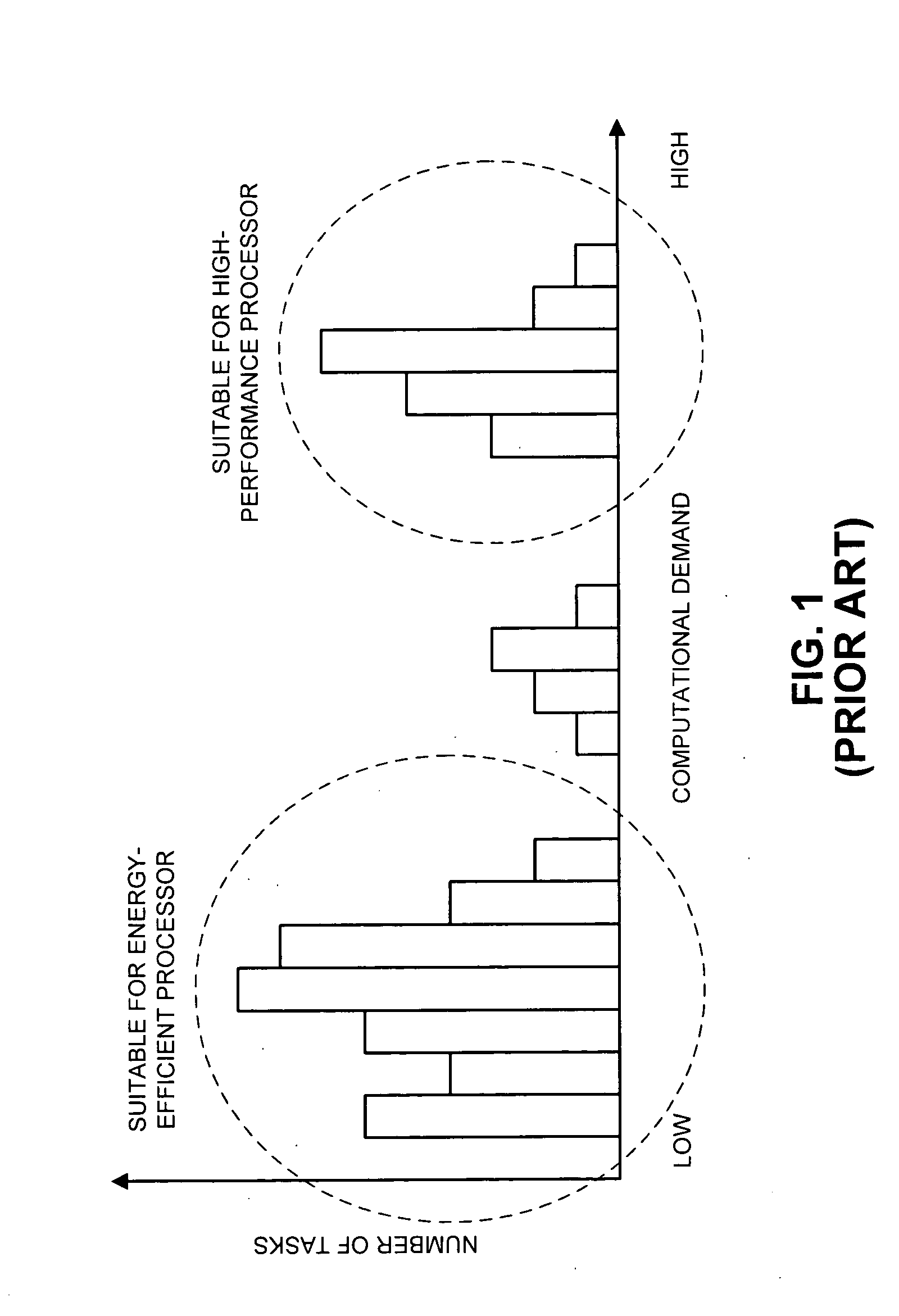

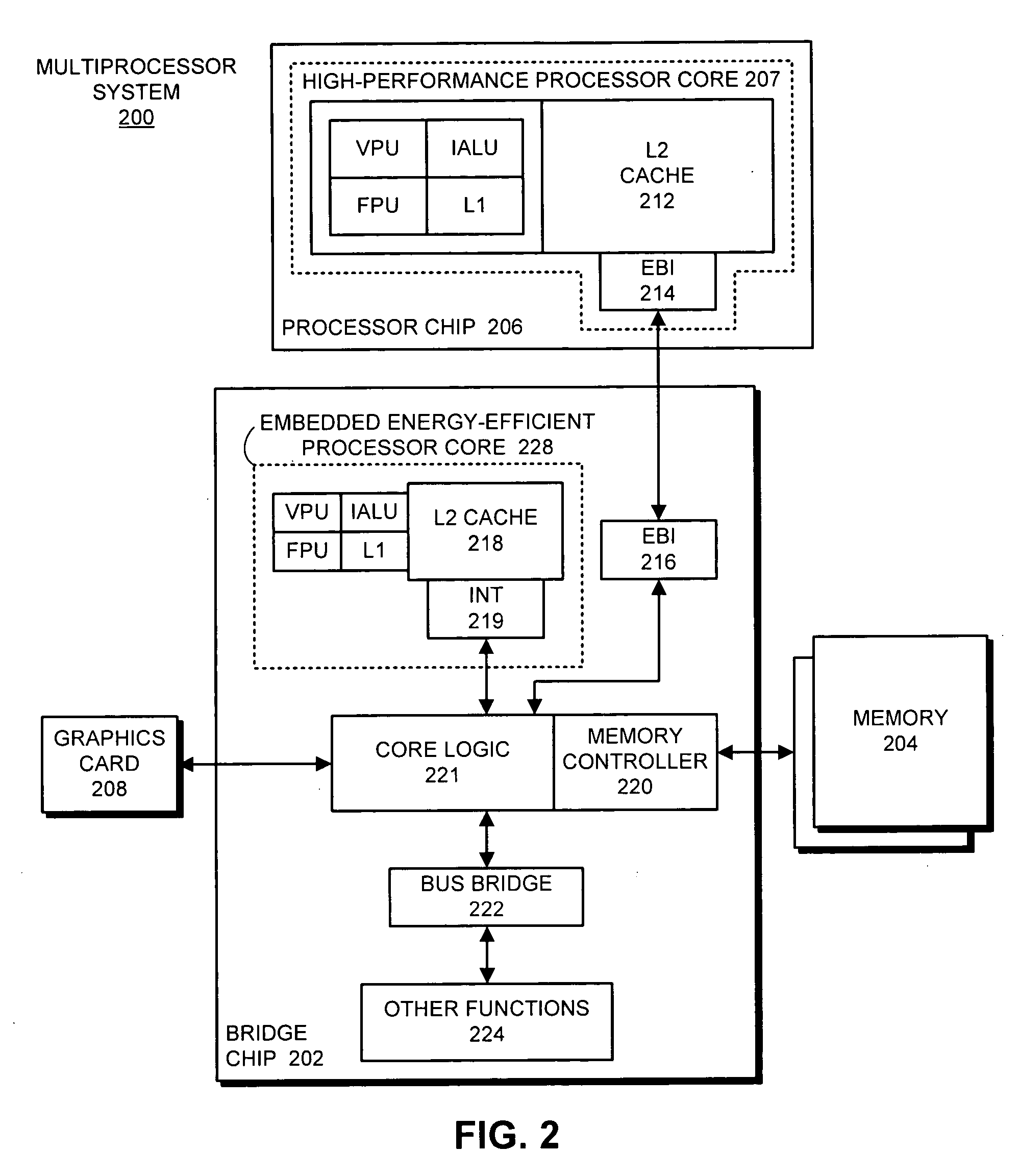

Almost-symmetric multiprocessor that supports high-performance and energy-efficient execution

InactiveUS20050132239A1Energy efficient ICTResource allocationMulti processorPerformance requirement

One embodiment of the present invention provides a system for controlling execution of tasks in a multiprocessor system, which contains both a high-performance processor and an energy-efficient processor. Upon receiving a task to be executed on the multiprocessor system, the system determines whether to execute the task on the high-performance processor or the energy-efficient processor based on performance requirements for the task and / or energy usage considerations for the multiprocessor system. Next, the system executes the task on either the high-performance processor or the energy-efficient processor based on the determination.

Owner:APPLE INC

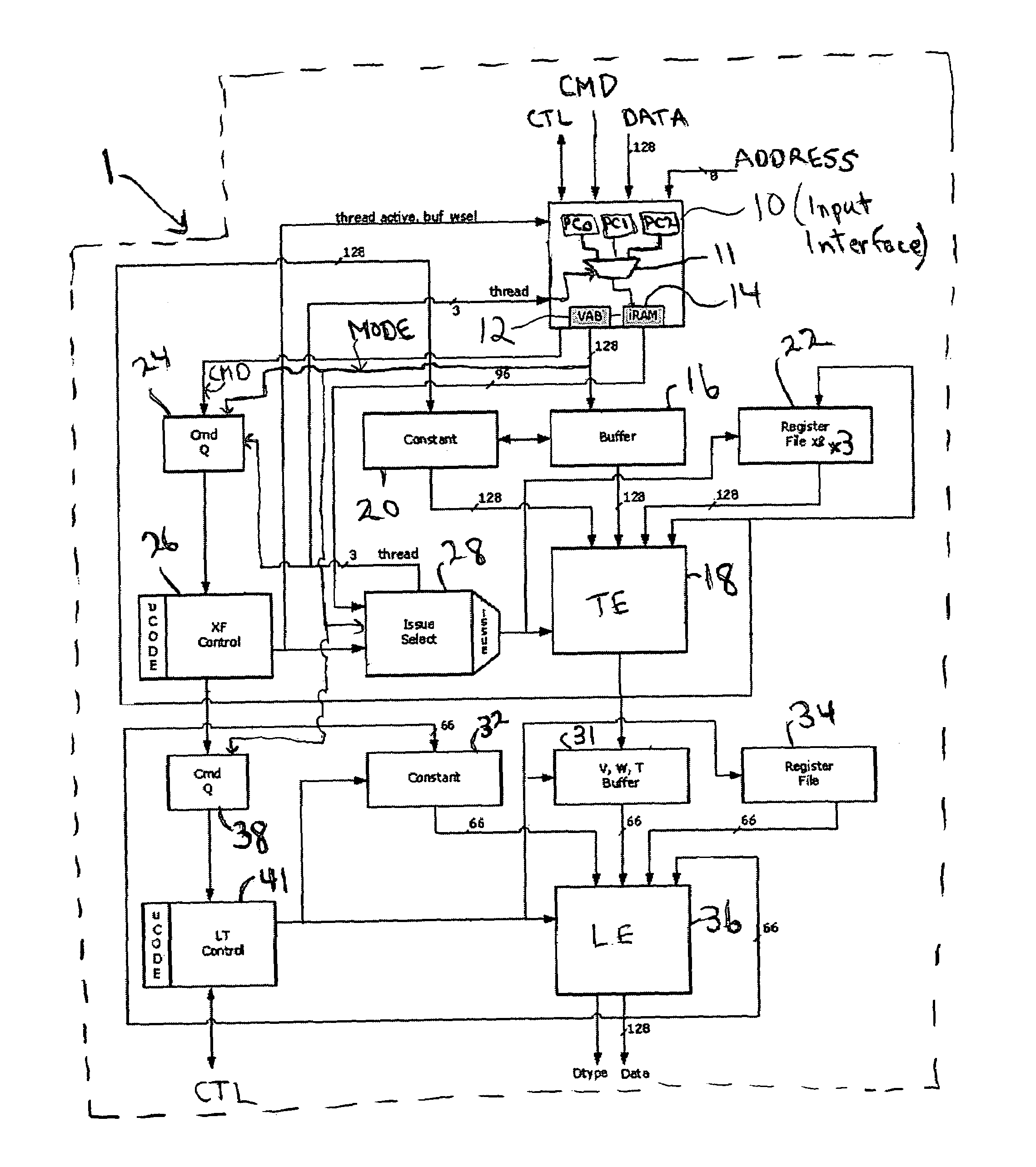

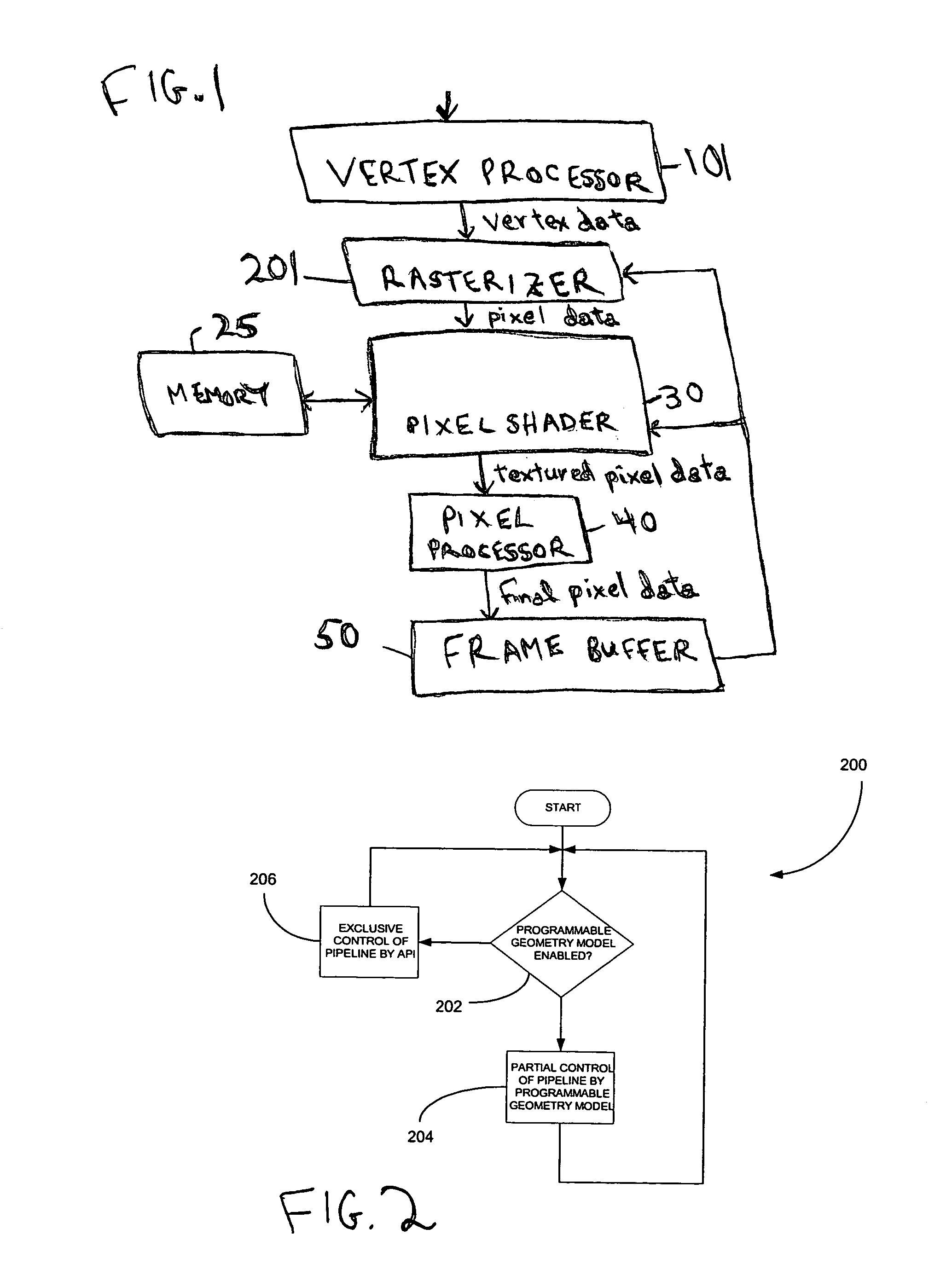

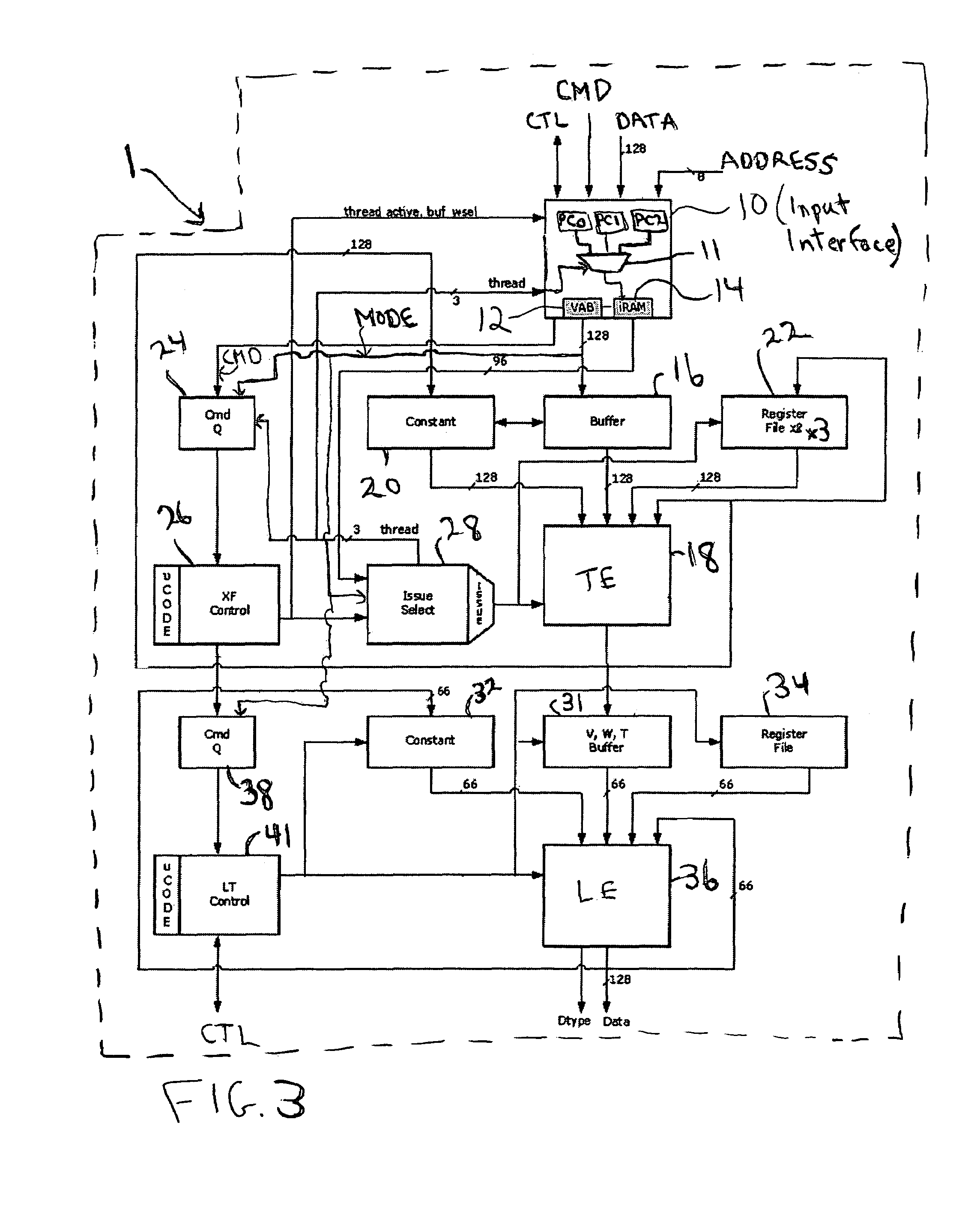

Method and system for programmable pipelined graphics processing with branching instructions

InactiveUS6947047B1Avoid confictMultiple digital computer combinationsProcessor architectures/configurationGraphicsMode control

A programmable, pipelined graphics processor (e.g., a vertex processor) having at least two processing pipelines, a graphics processing system including such a processor, and a pipelined graphics data processing method allowing parallel processing and also handling branching instructions and preventing conflicts among pipelines. Preferably, each pipeline processes data in accordance with a program including by executing branch instructions, and the processor is operable in any one of a parallel processing mode in which at least two data values to be processed in parallel in accordance with the same program are launched simultaneously into multiple pipelines, and a serialized mode in which only one pipeline at a time receives input data values to be processed in accordance with the program (and operation of each other pipeline is frozen). During parallel processing mode operation, mode control circuitry recognizes and resolves branch instructions to be executed (before processing of data in accordance with each branch instruction starts) and causes the processor to operate in the serialized mode when (and preferably only for as long as) necessary to prevent any conflict between the pipelines due to branching. In other embodiments, the processor is operable in any one of a parallel processing mode and a limited serialized mode in which operation of each of a sequence of pipelines (or pipeline sets) pauses for a limited number of clock cycles. The processor enters the limited serialized mode in response to detecting a conflict-causing instruction that could cause a conflict between resources shared by the pipelines during parallel processing mode operation.

Owner:NVIDIA CORP

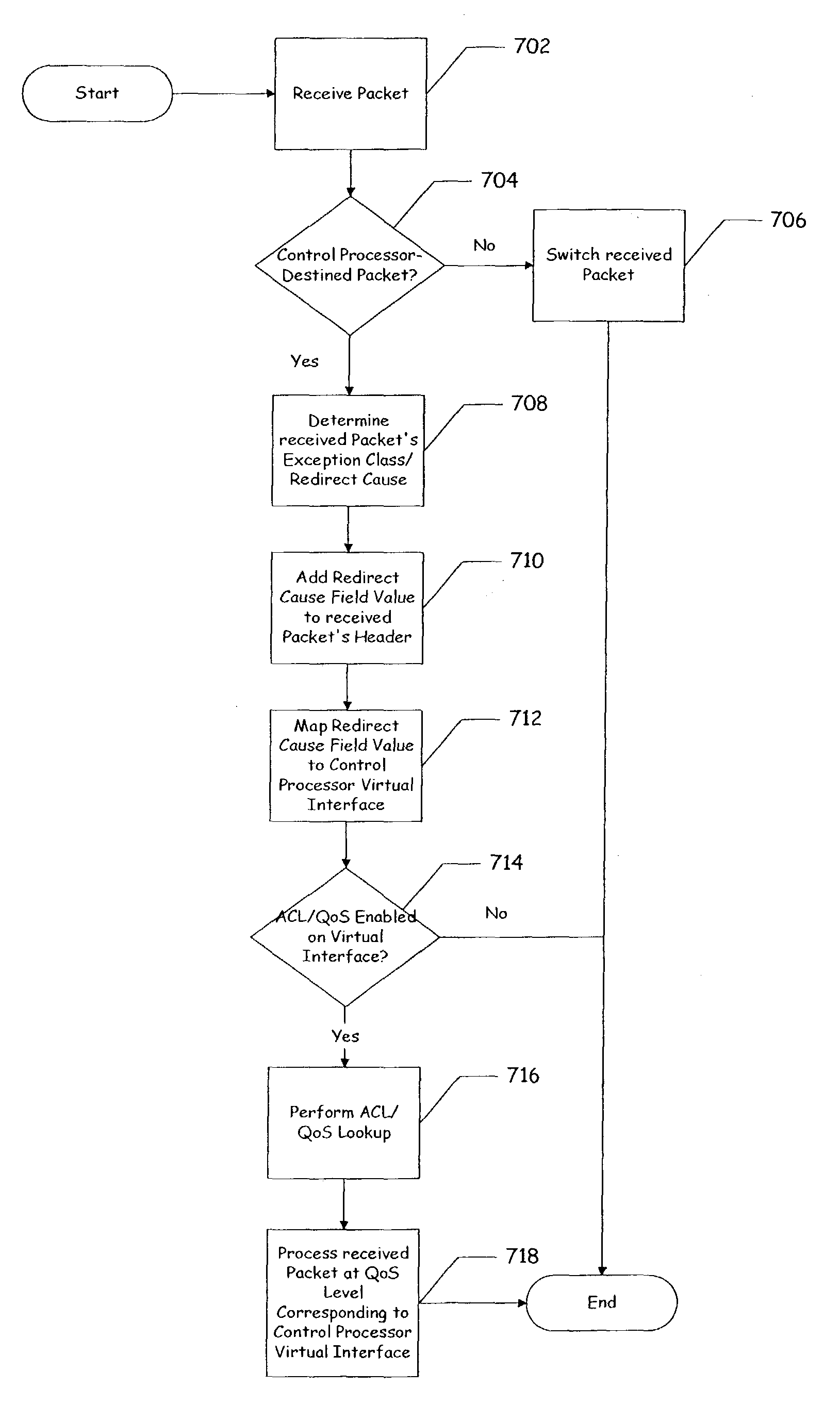

Method and apparatus to apply aggregate access control list/quality of service features using a redirect cause

ActiveUS7953885B1Fine granularityDigital computer detailsData switching by path configurationQuality of serviceDistributed computing

A method and apparatus to apply aggregate ACL / QoS features using a redirect cause is disclosed. According to one embodiment of the present invention, a control processor configured to support a plurality of virtual interfaces is provided, wherein each of the plurality of virtual interfaces is associated with a quality of service level. According to another embodiment, each quality of service level is associated with a processing bandwidth of the control processor. According to yet another embodiment, a control processor interface is provided coupled to the control processor which is configured to select a virtual interface of the plurality of virtual interfaces using data of a received data unit, and to transfer the received data unit to the selected virtual interface.

Owner:CISCO TECH INC

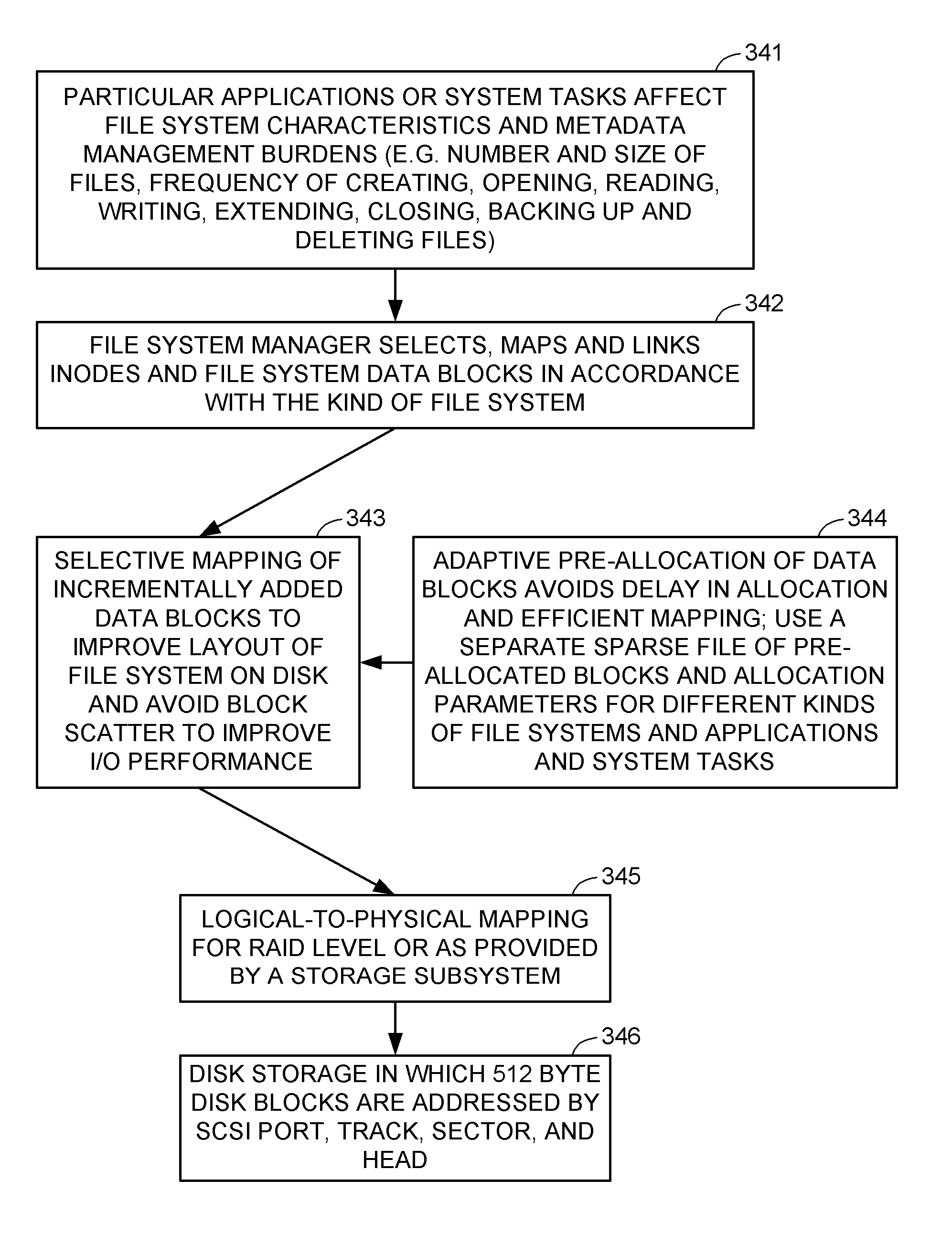

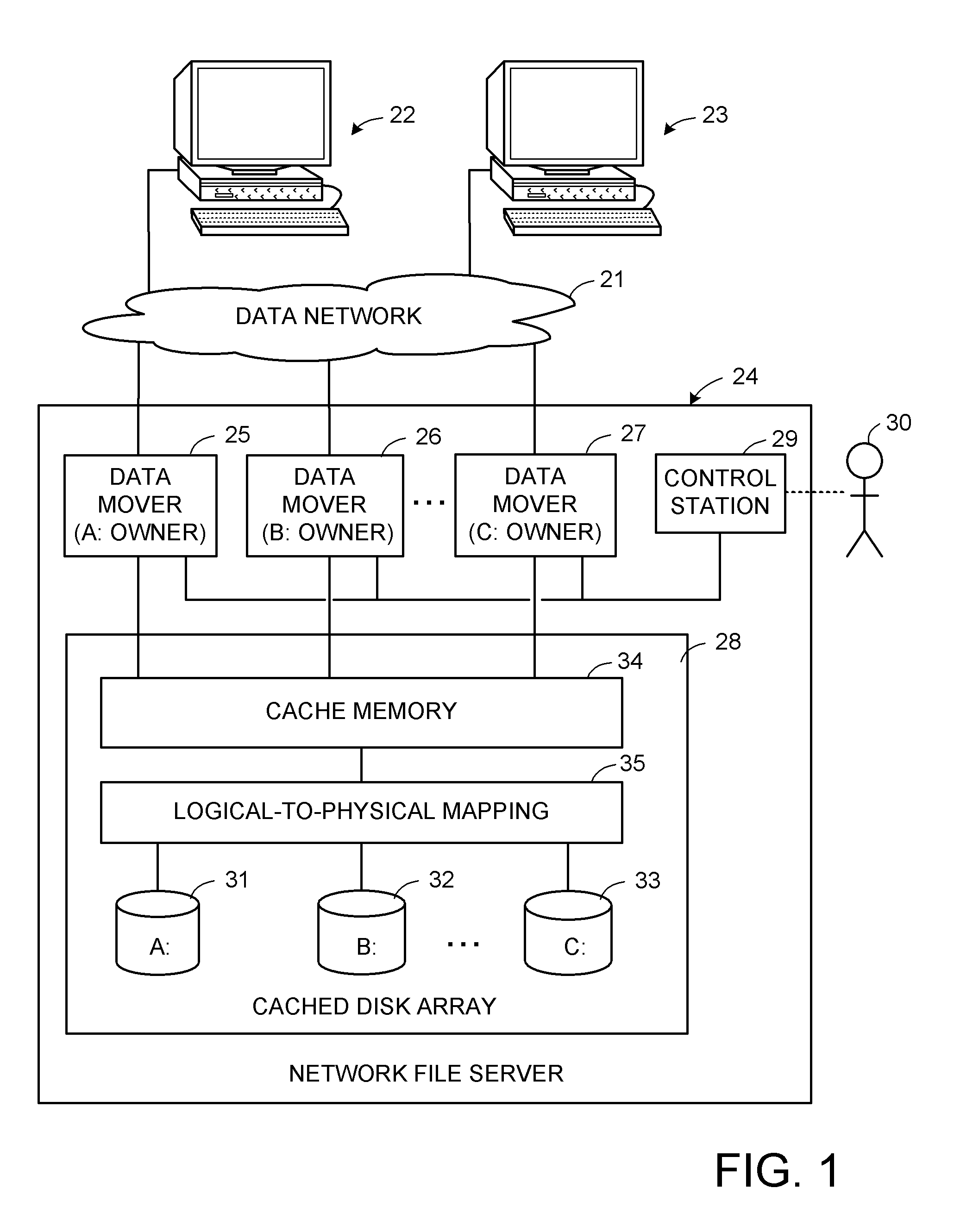

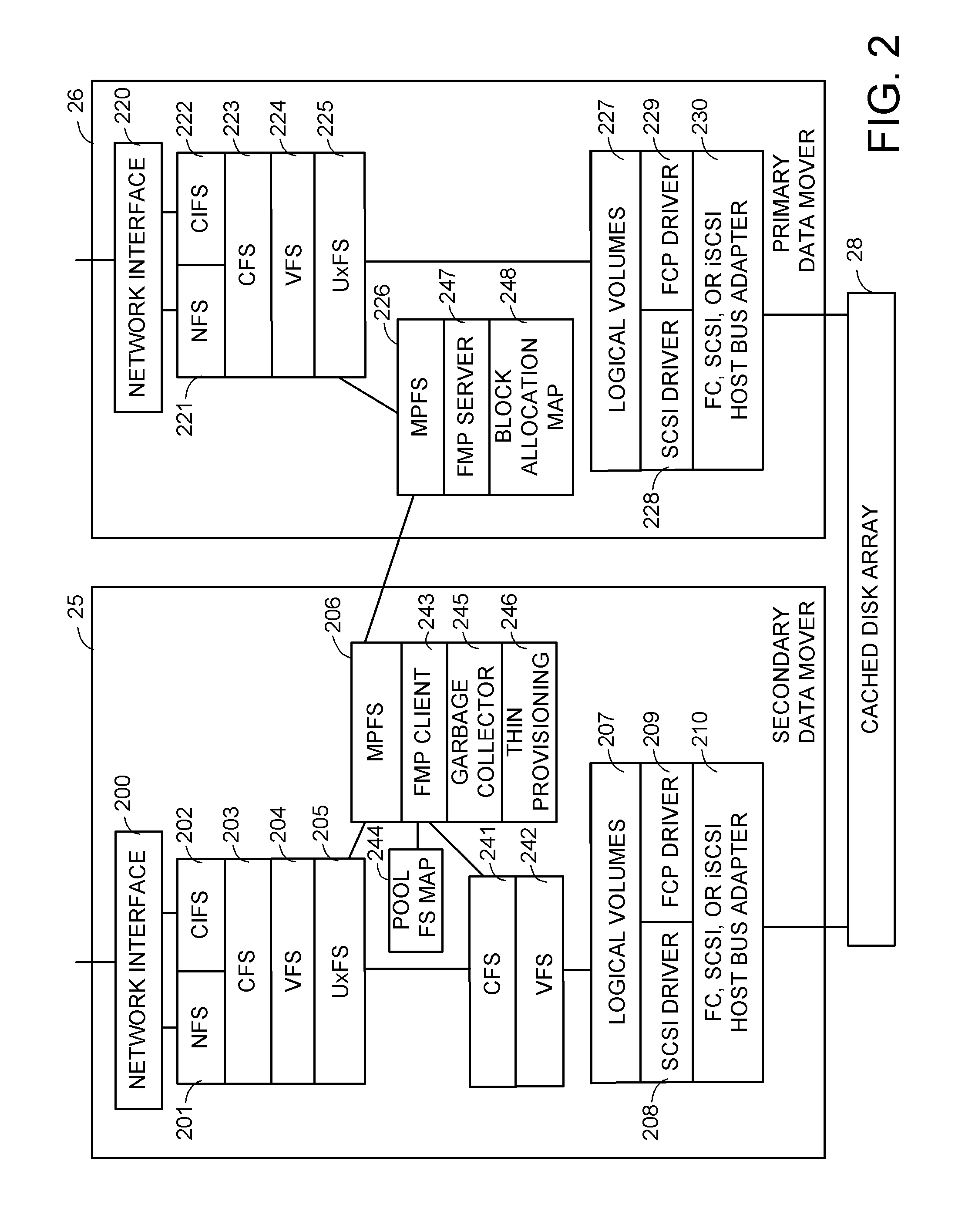

Pre-allocation and hierarchical mapping of data blocks distributed from a first processor to a second processor for use in a file system

ActiveUS20070260842A1Improve I/O performanceReduce block scatter on diskMemory systemsInput/output processes for data processingData processing systemFile system

In a data processing system, a first processor pre-allocates data blocks for use in a file system at a later time when a second processor needs data blocks for extending the file system. The second processor selectively maps the logical addresses of the pre-allocated blocks so that when the pre-allocated blocks are used in the file system, the layout of the file system on disk is improved to avoid block scatter and enhance I / O performance. The selected mapping can be done at a program layer between a conventional file system manager and a conventional logical volume layer so that there is no need to modify the data block mapping mechanism of the file system manager or the logical volume layer. The data blocks can be pre-allocated adaptively in accordance with the allocation history of the file system.

Owner:EMC IP HLDG CO LLC

Object-oriented programmable controller

InactiveUS6868538B1Good choiceProgramme controlComputer controlProgrammable logic controllerSoftware

An apparatus having a programmable processor and a memory for performing a plurality of user-selectable control functions includes a database for storing a plurality of items associated with each of the control functions. The items include, for each function, at least one procedure for performing an action associated with the control function and a specification of at least one state associated with the control function. The apparatus further includes software routines stored on the memory and adapted to be executed by the processor that facilitate selection of a procedure in the database, that access the database and cause performance of the selected procedure to achieve the state specified therein, and that monitor at least one resource associated with the action of the procedure and, based thereon, determine whether the specified state has been achieved.

Owner:FISHER-ROSEMOUNT SYST INC

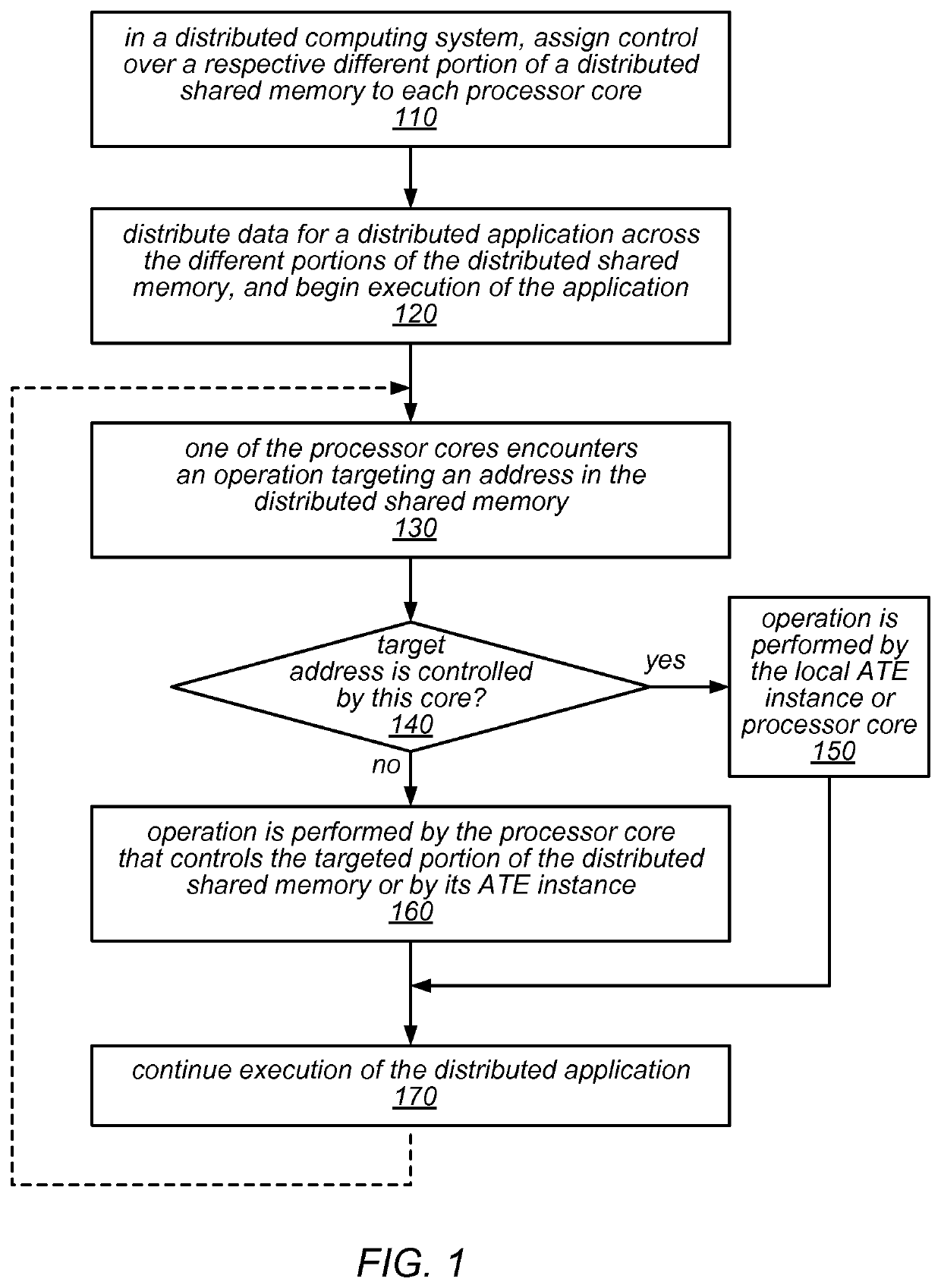

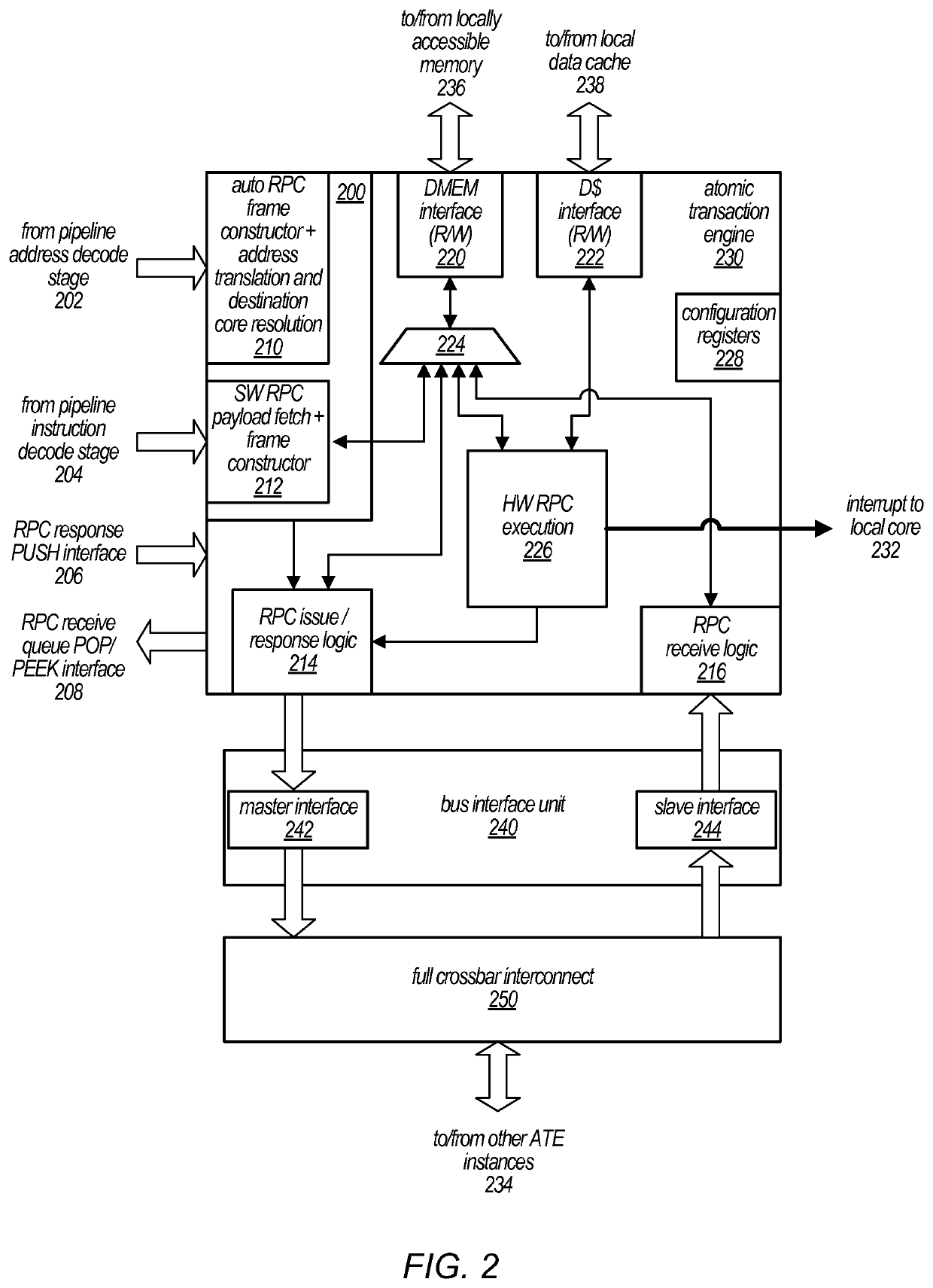

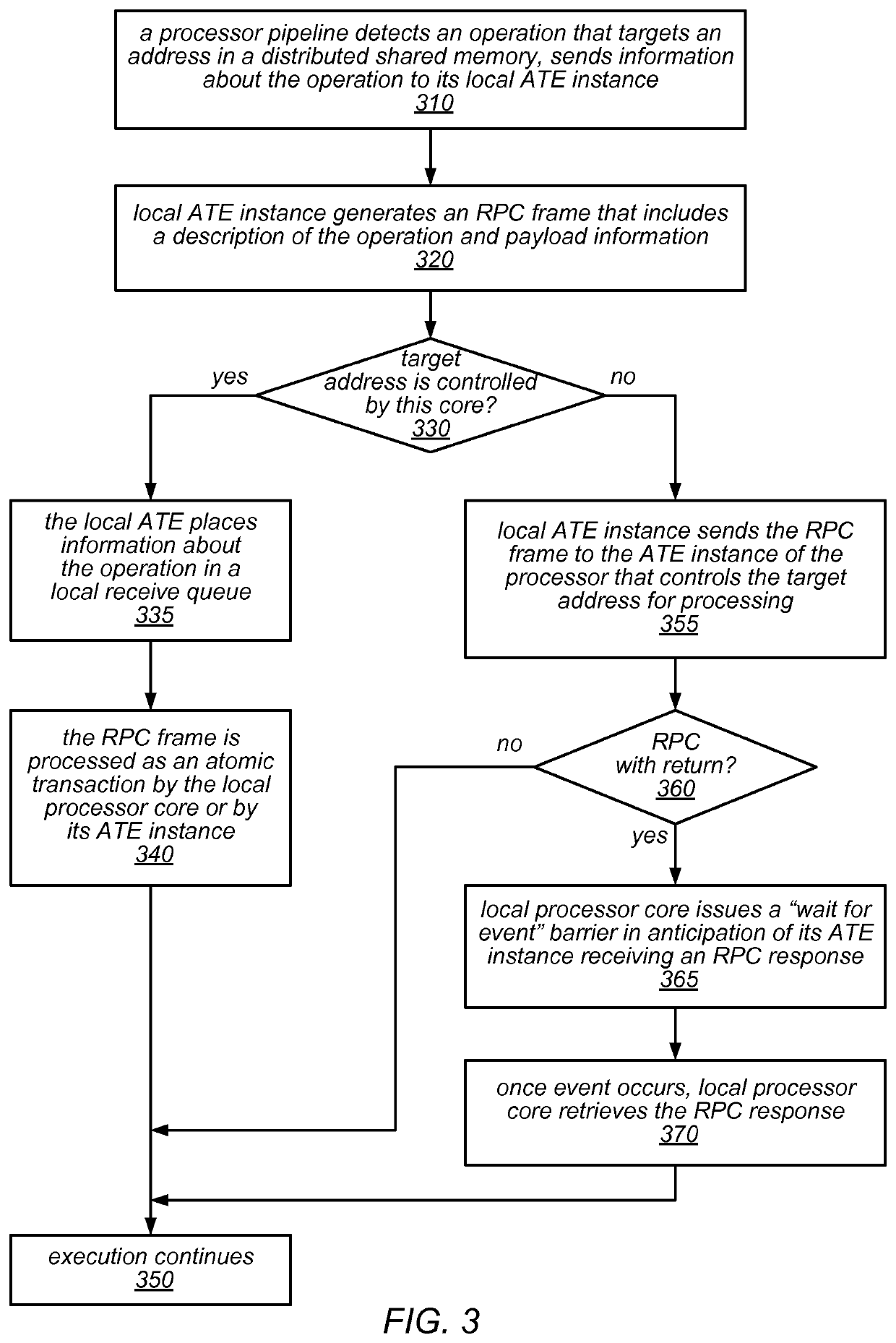

Distributed shared memory using interconnected atomic transaction engines at respective memory interfaces

ActiveUS10732865B2Light weightLess complexInput/output to record carriersProgram synchronisationComputer architectureMemory interface

A hardware-assisted Distributed Memory System may include software configurable shared memory regions in the local memory of each of multiple processor cores. Accesses to these shared memory regions may be made through a network of on-chip atomic transaction engine (ATE) instances, one per core, over a private interconnect matrix that connects them together. For example, each ATE instance may issue Remote Procedure Calls (RPCs), with or without responses, to an ATE instance associated with a remote processor core in order to perform operations that target memory locations controlled by the remote processor core. Each ATE instance may process RPCs (atomically) that are received from other ATE instances or that are generated locally. For some operation types, an ATE instance may execute the operations identified in the RPCs itself using dedicated hardware. For other operation types, the ATE instance may interrupt its local processor core to perform the operations.

Owner:ORACLE INT CORP

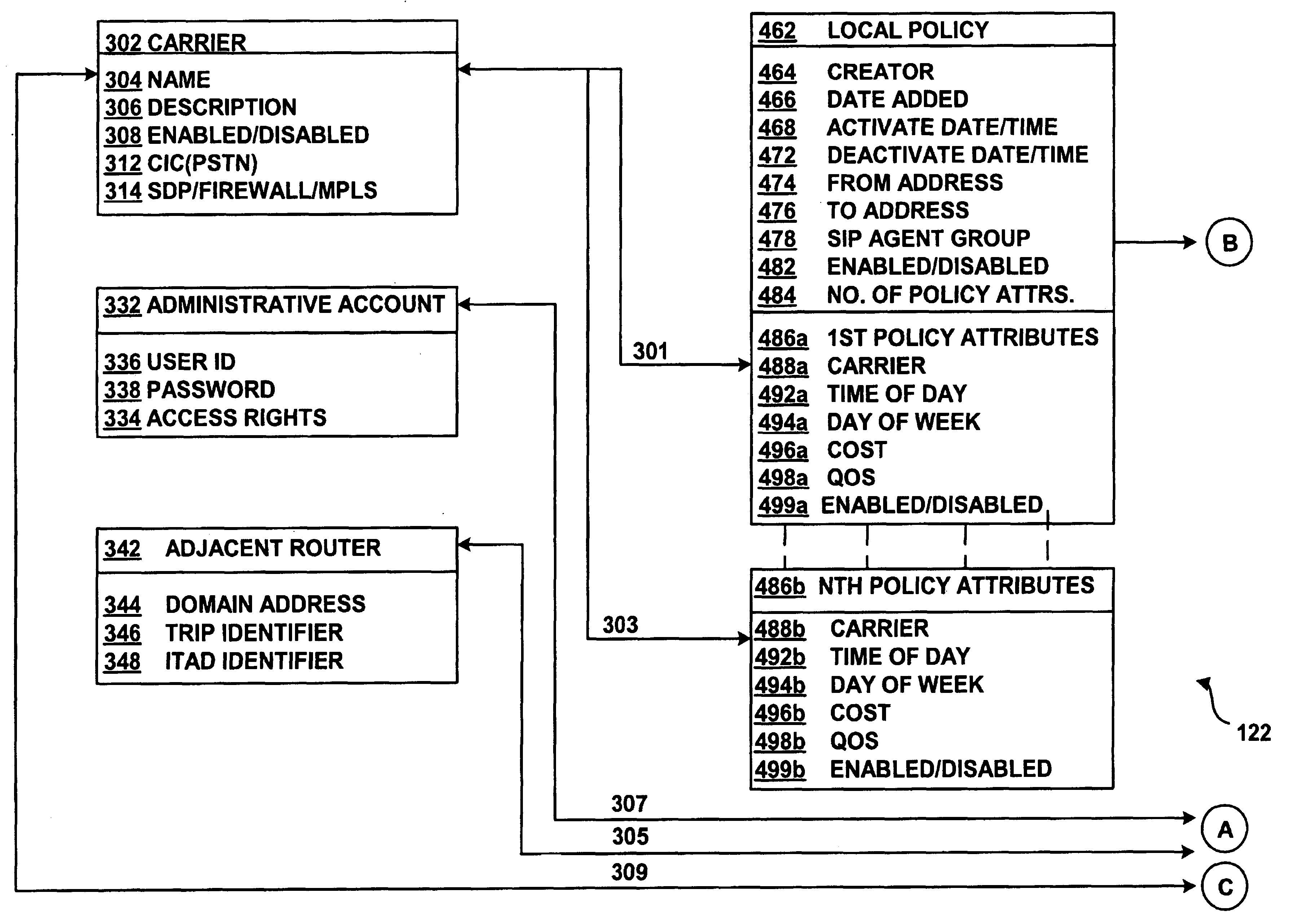

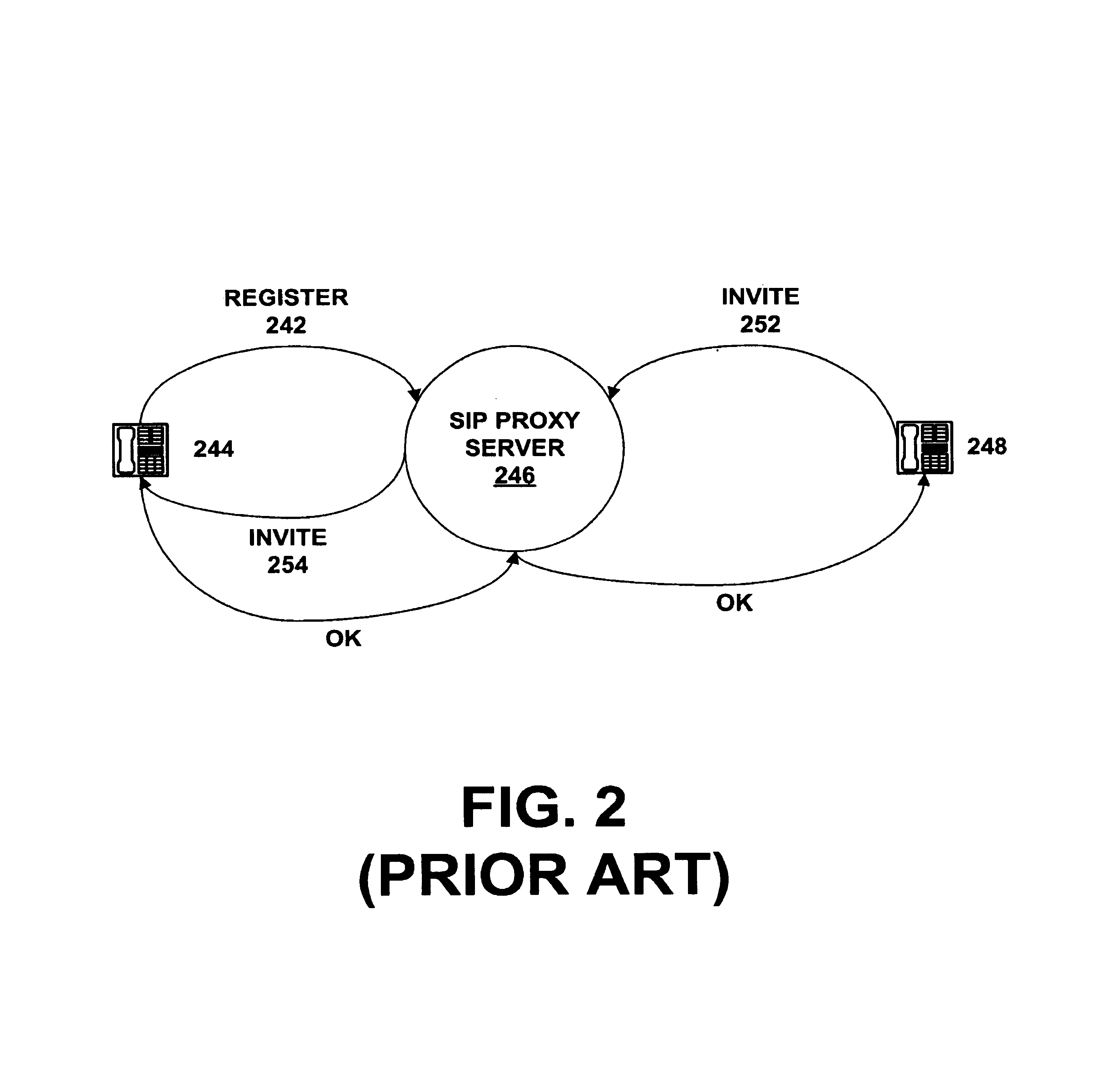

System and method for assisting in controlling real-time transport protocol flow through multiple networks via media flow routing

InactiveUS7028092B2Not easy to changeMultiplex system selection arrangementsInterconnection arrangementsTransceiverReal-time Transport Protocol

A system and method for assisting in controlling real-time transport protocol flow through multiple networks via media flow routing is disclosed. The system utilizes a first computer and a second computer connected to the first computer, via a group of associated computers, wherein each of the first computer, second computer, and group of associated computers comprise a transceiver, a memory, and a processor. The processor is configured by the memory to perform the functions of: performing an inbound screen on route information received from the first computer, to determine if the received route information should be discarded; if the route information is not discarded, comparing the received and screened route information to a local policy defined within the second computer; performing an outbound screen on the received and screened information prior to transmitting the received and screened route information to the first computer; and selecting a primary route from the received route information and local route information in accordance with the local policy, wherein the primary route is a path from the second computer to the first computer via the group of associated computers.

Owner:ACME PACKET +1

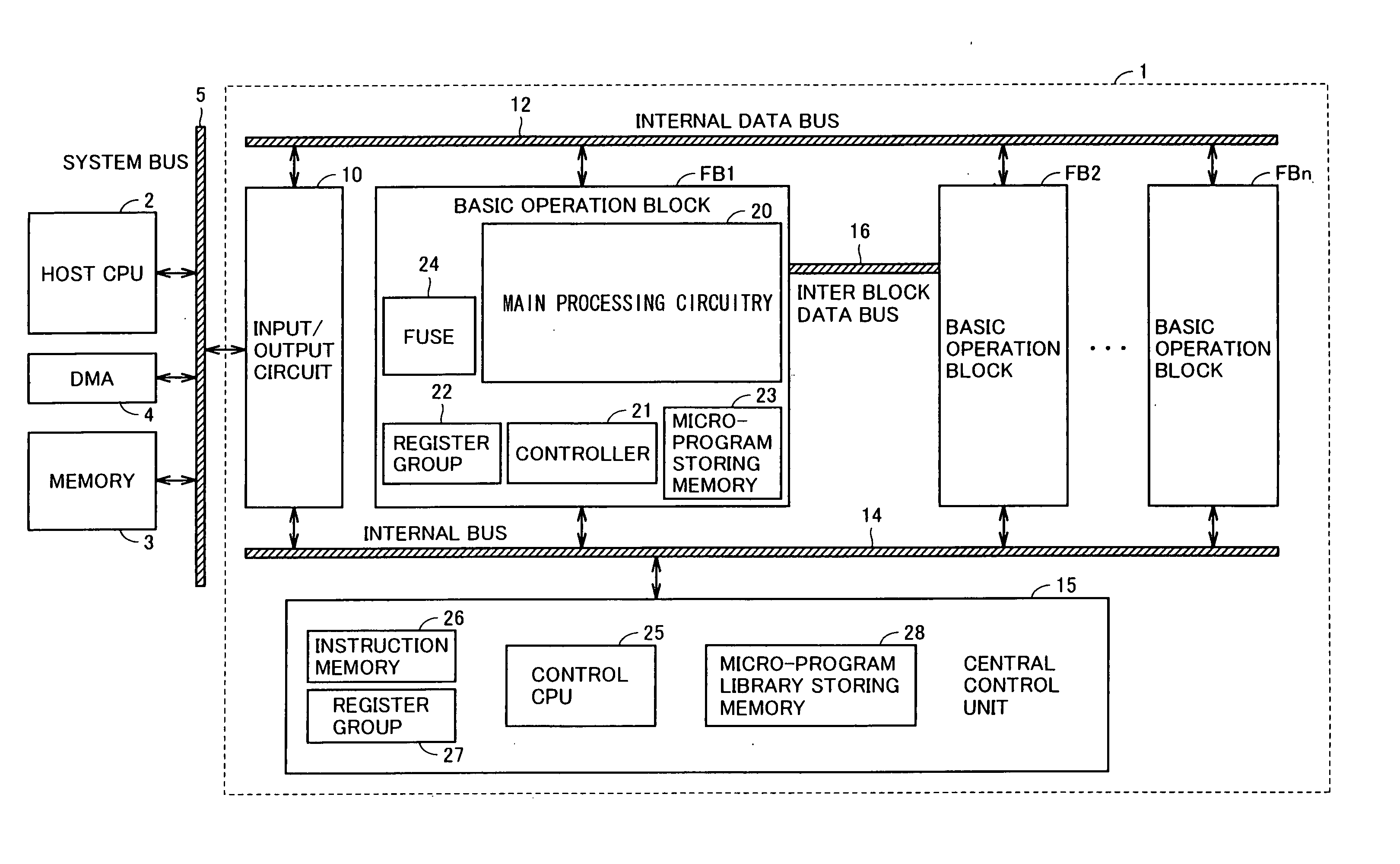

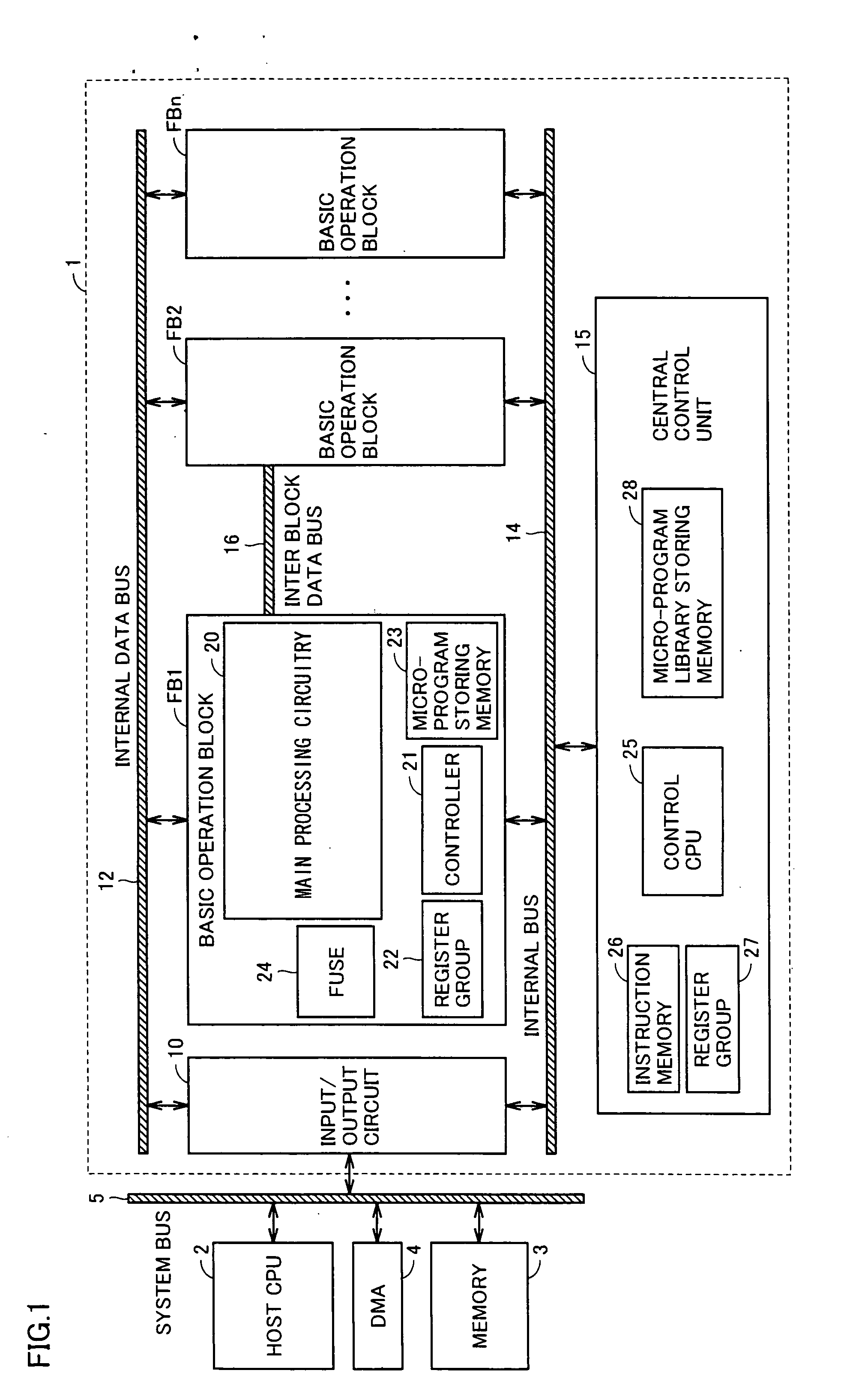

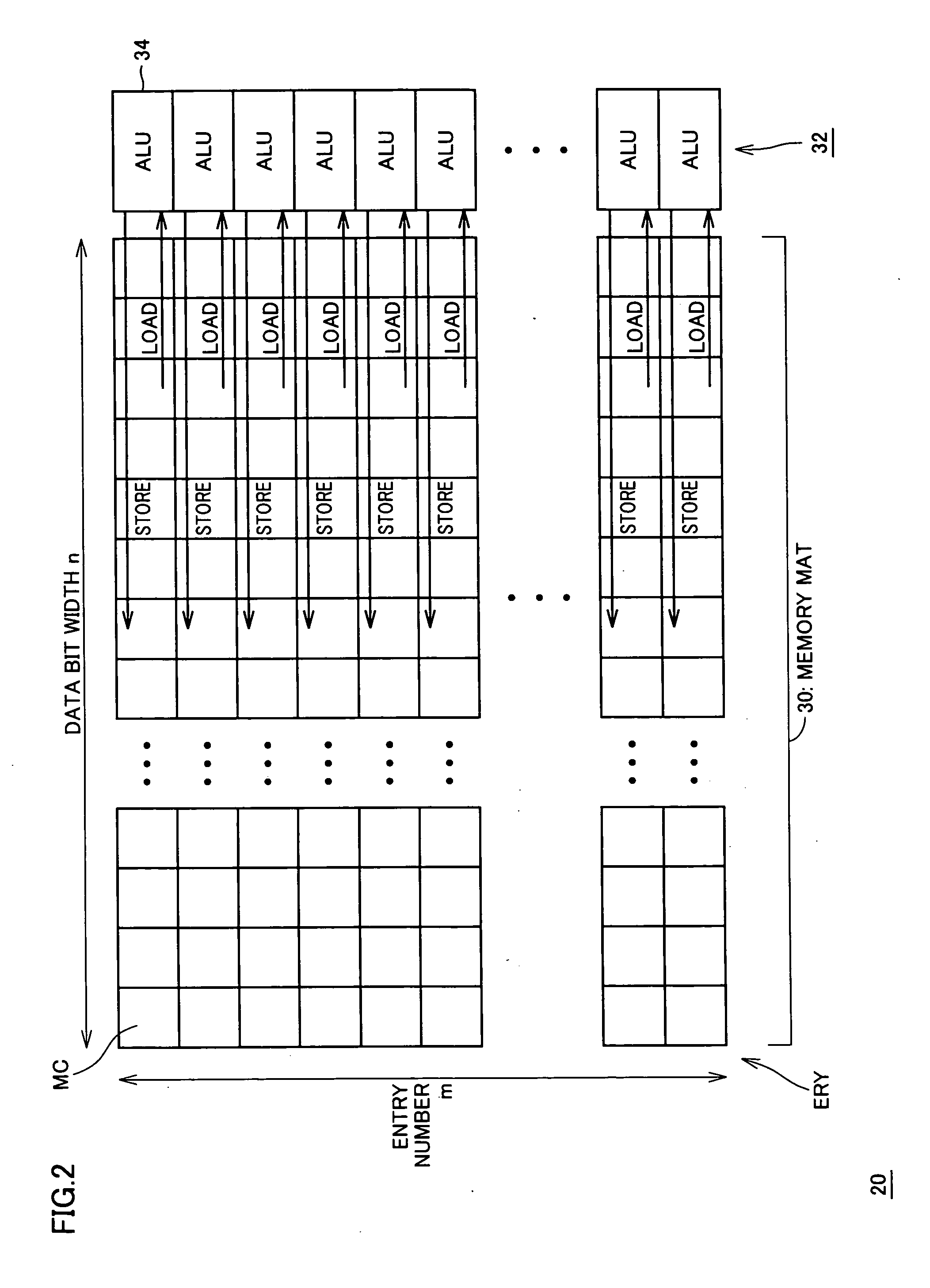

Semiconductor device and semiconductor signal processing apparatus

InactiveUS20050285862A1Operation control becomes easyEasy to processImage memory managementMultiple digital computer combinationsArithmetic logic unitDevice material

A memory cell mat is divided into a plurality of entries, and an arithmetic logic unit is arranged corresponding to each entry. Between the entries and the corresponding arithmetic logic units, arithmetic / logic operation is executed in bit-serial and entry-parallel manner. Where parallel operation is not very effective, data is transferred in entry-serial and bit-parallel manner to a group of processors provided at a lower portion of the memory mat. In this manner, a large amount of data can be processed at high speed regardless of the contents of operation or data bit width.

Owner:RENESAS ELECTRONICS CORP

System and method for run-time object classification

One embodiment of an electronic device comprises a processor and a memory accessible by the processor. The memory comprises virtual execution logic and run-time classifier logic. The virtual execution logic includes at least one virtual machine that is configured to virtually process content within an object under analysis and monitor for anomalous behaviors during the virtual processing that are indicative of malware. The run-time classifier logic performs, during run-time, a first analysis on the monitored anomalous behaviors and a pre-stored identifier to determine if the monitored anomalous behaviors indicate that the object is malware belonging to a classified malware family. The pre-stored identifier is a collection of data associated with anomalous behaviors that uniquely identify the malware family.

Owner:FIREEYE SECURITY HLDG US LLC +1

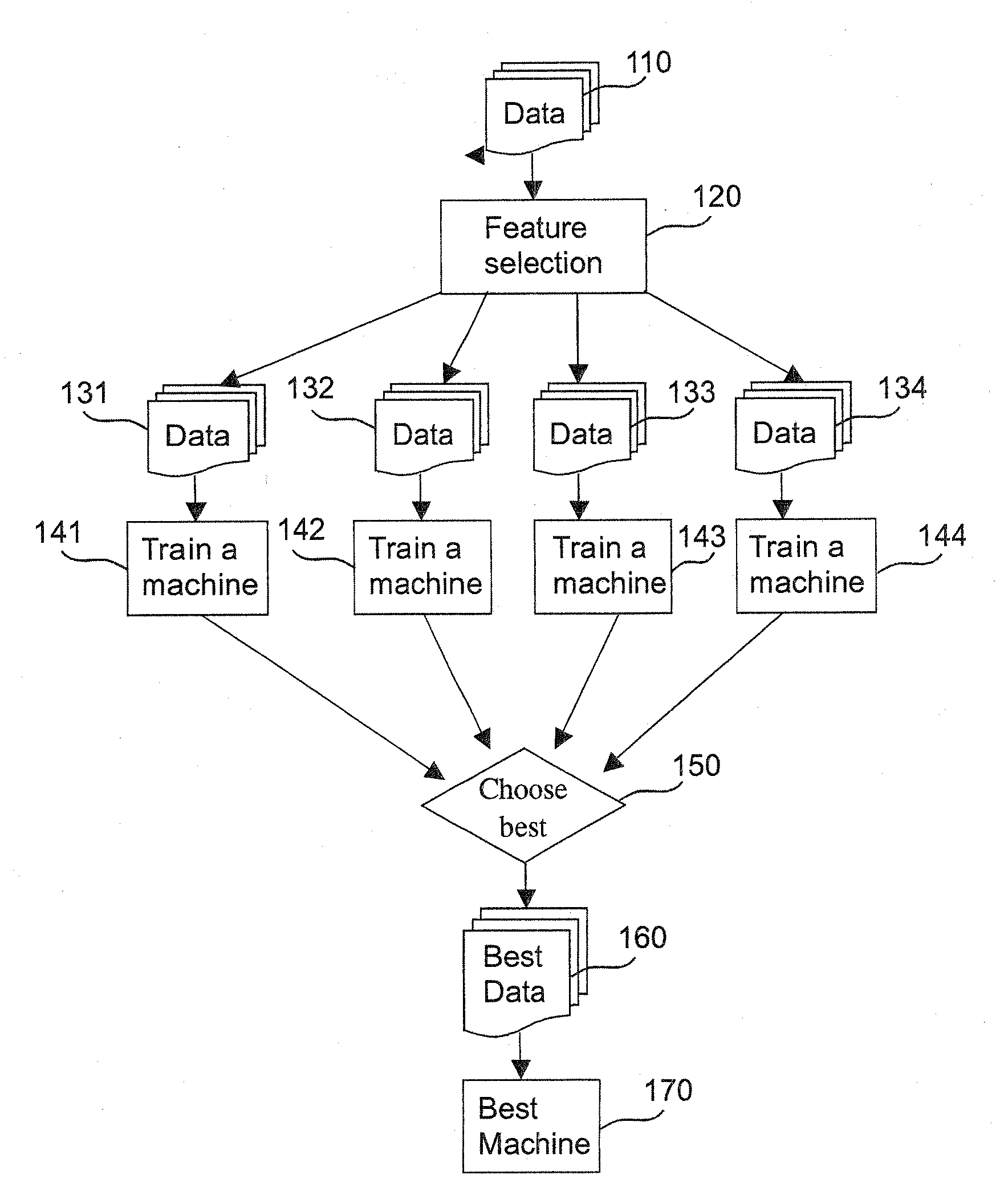

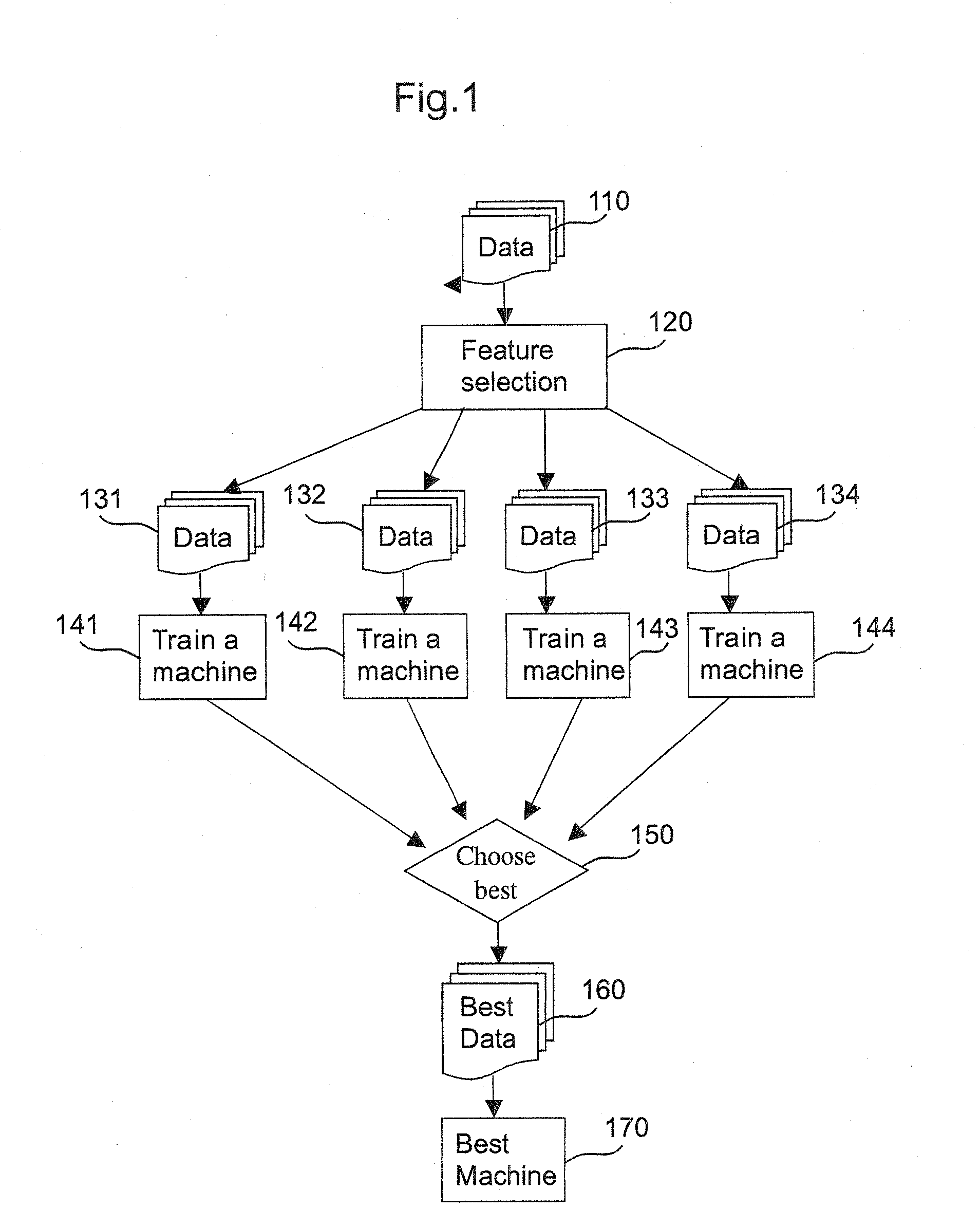

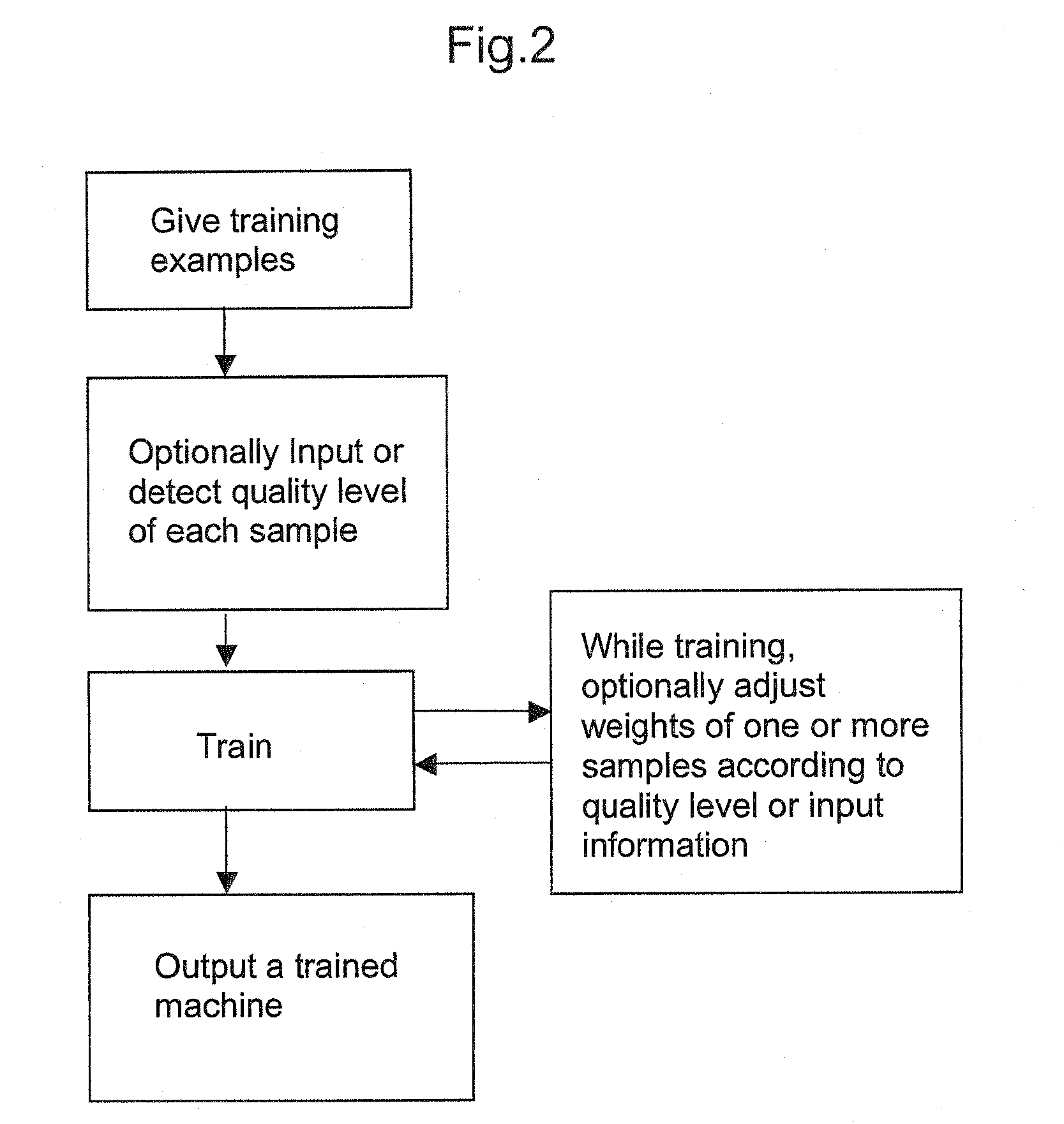

Machine learning methods and systems for identifying patterns in data

ActiveUS20100063948A1Reduce dimensionalityPromote resultsDigital data processing detailsKernel methodsData classSupport vector machine

Methods for training machines to categorize data, and / or recognize patterns in data, and machines and systems so trained. More specifically, variations of the invention relates to methods for training machines that include providing one or more training data samples encompassing one or more data classes, identifying patterns in the one or more training data samples, providing one or more data samples representing one or more unknown classes of data, identifying patterns in the one or more of the data samples of unknown class(es), and predicting one or more classes to which the data samples of unknown class(es) belong by comparing patterns identified in said one or more data samples of unknown class with patterns identified in said one or more training data samples. Also provided are tools, systems, and devices, such as support vector machines (SVMs) and other methods and features, software implementing the methods and features, and computers or other processing devices incorporating and / or running the software, where the methods and features, software, and processors utilize specialized methods to analyze data.

Owner:DIGITAL INFUZION

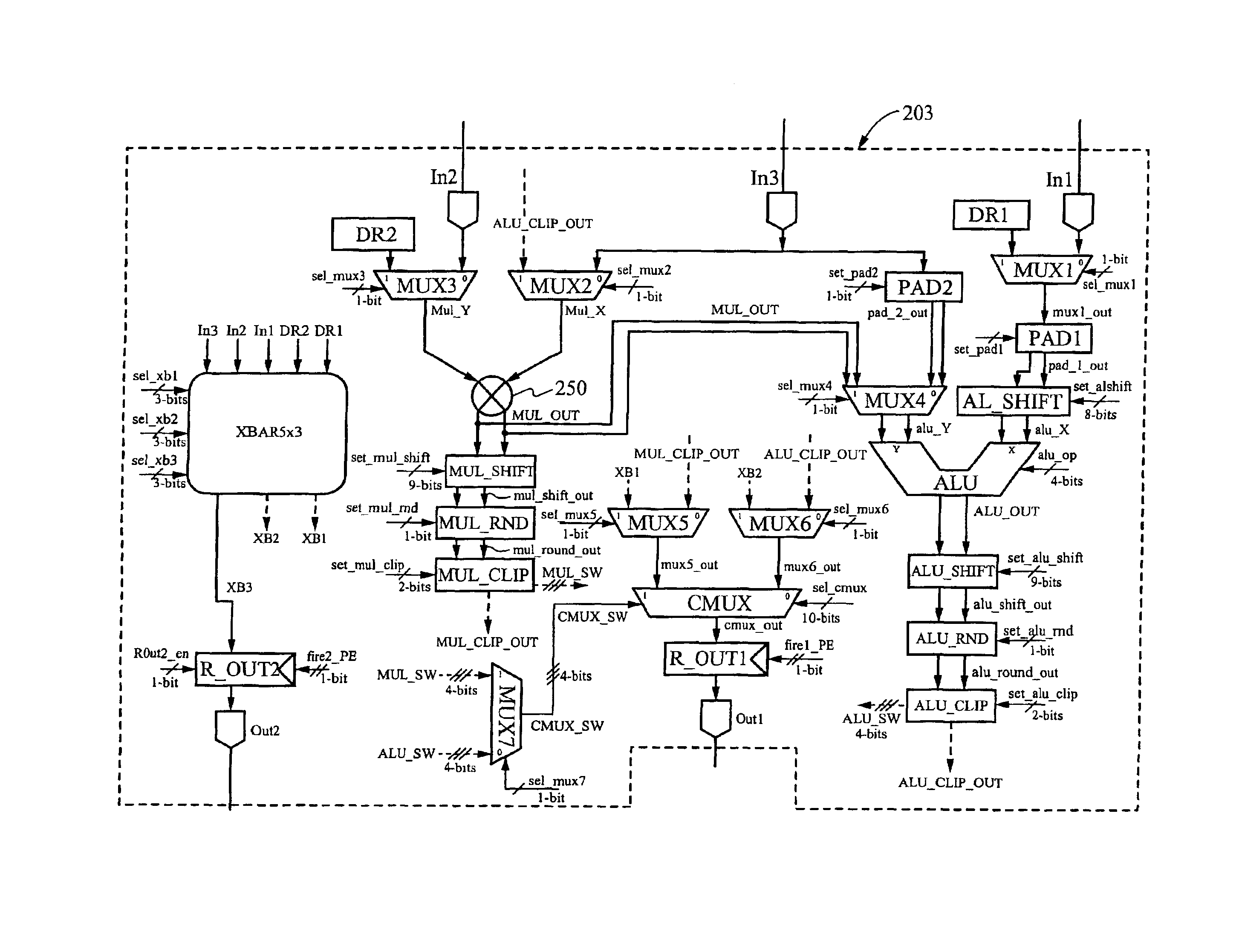

Reconfigurable data path processor

InactiveUS6883084B1Eliminates branchingCycle simpleEnergy efficient ICTConditional code generationMultiplexerProcessing element

A reconfigurable data path processor comprises a plurality of independent processing elements. Each of the processing elements advantageously comprising an identical architecture. Each processing element comprises a plurality of data processing means for generating a potential output. Each processor is also capable of through-putting an input as a potential output with little or no processing. Each processing element comprises a conditional multiplexer having a first conditional multiplexer input, a second conditional multiplexer input and a conditional multiplexer output. A first potential output value is transmitted to the first conditional multiplexer input, and a second potential output value is transmitted to the second conditional multiplexer output. The conditional multiplexer couples either the first conditional multiplexer input or the second conditional multiplexer input to the conditional multiplexer output, according to an output control command. The output control command is generated by processing a set of arithmetic status-bits through a logical mask. The conditional multiplexer output is coupled to a first processing element output. A first set of arithmetic bits are generated according to the processing of the first processable value. A second set of arithmetic bits may be generated from a second processing operation. The selection of the arithmetic status-bits is performed by an arithmetic-status bit multiplexer selects the desired set of arithmetic status bits from among the first and second set of arithmetic status bits. The conditional multiplexer evaluates the select arithmetic status bits according to logical mask defining an algorithm for evaluating the arithmetic status bits.

Owner:STC UNM +1