Patents

Literature

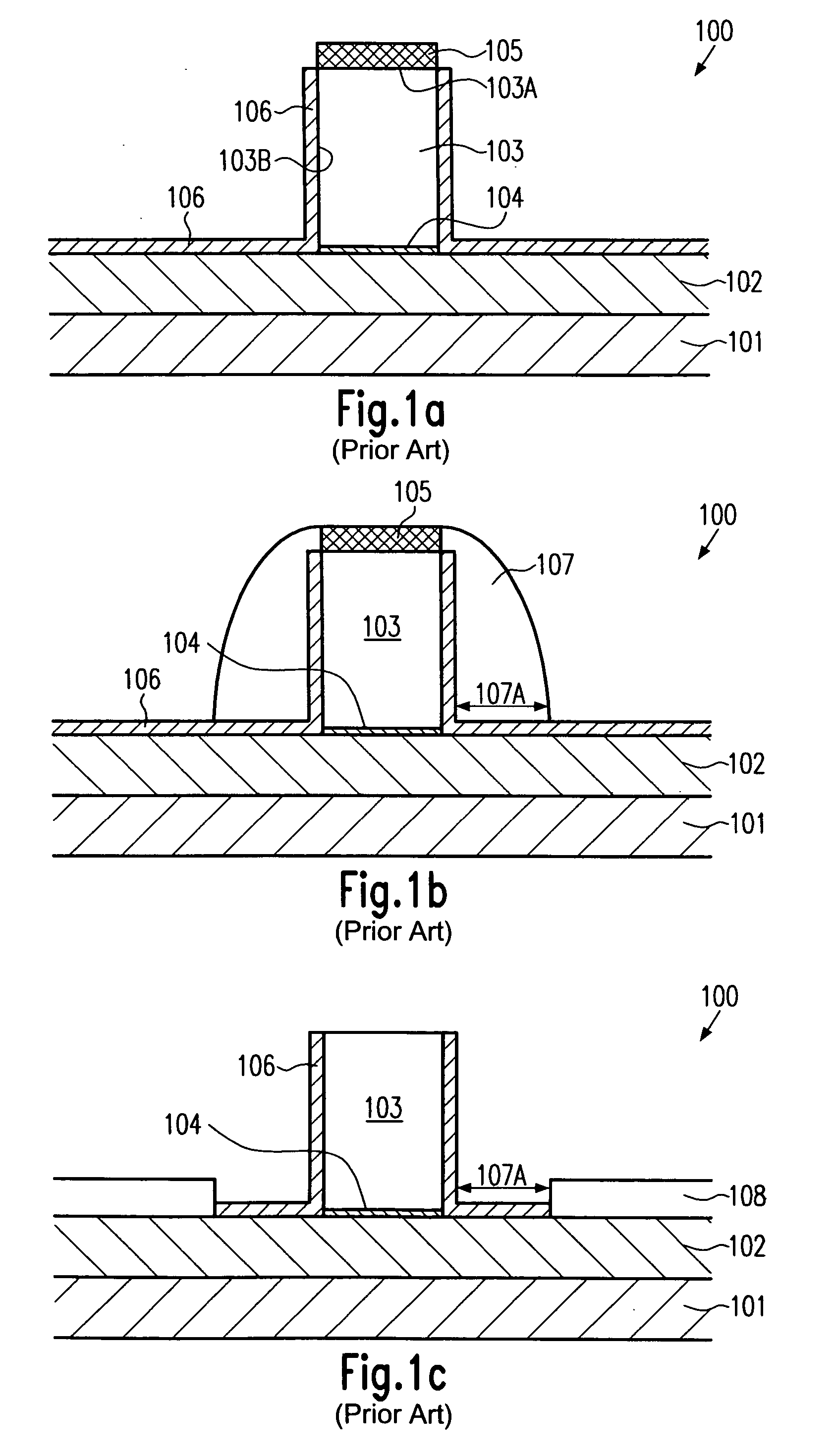

612 results about "Stress induced" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Definition of stress-induced in English: stress-induced. adjective. (especially of a medical problem) caused by stress or mental fatigue. ‘an increase of stress-induced diseases’. ‘he succumbed to a stress-induced ulcer and nervous breakdown’. ‘The princess has been suffering from a stress-induced disorder.’.

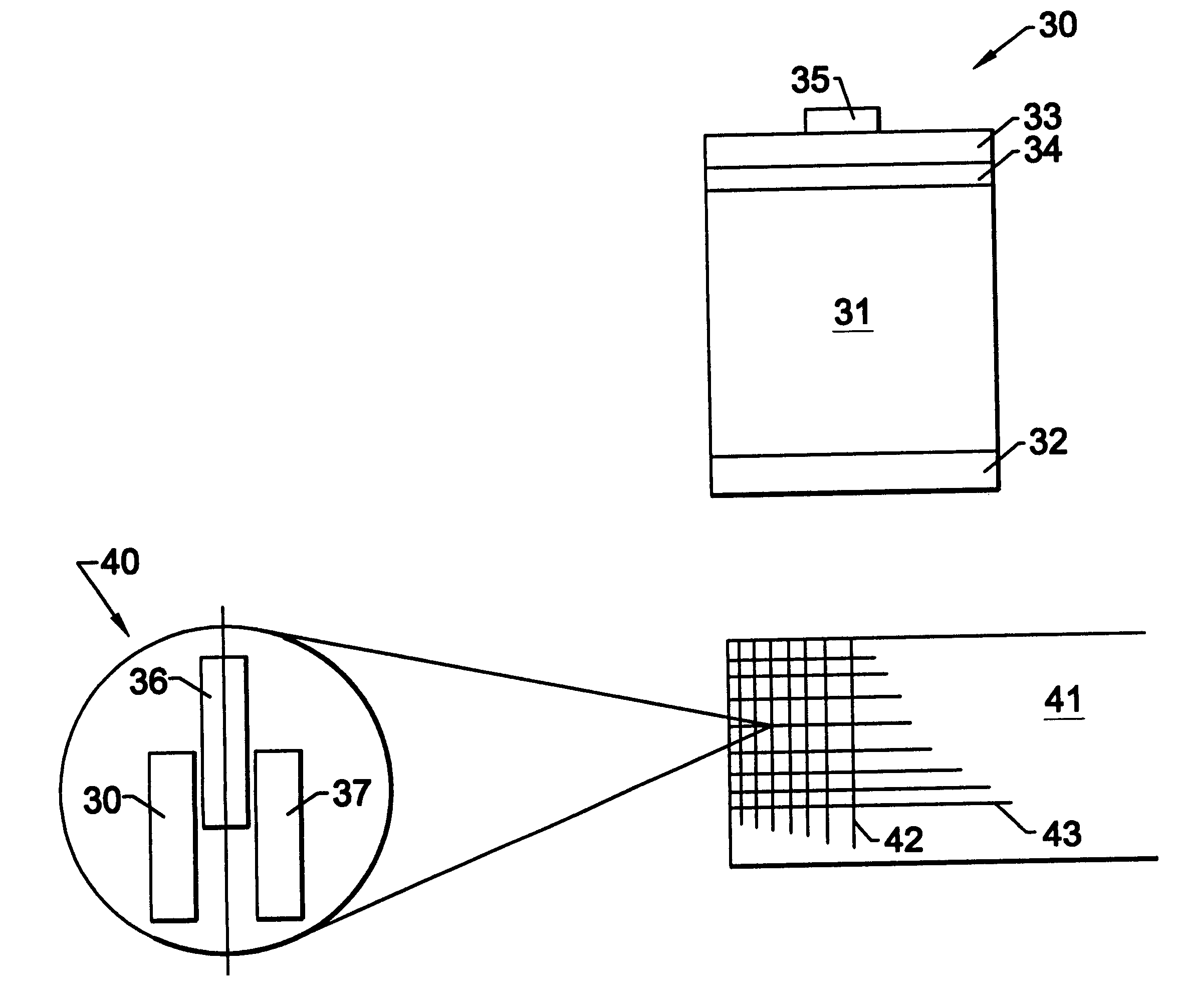

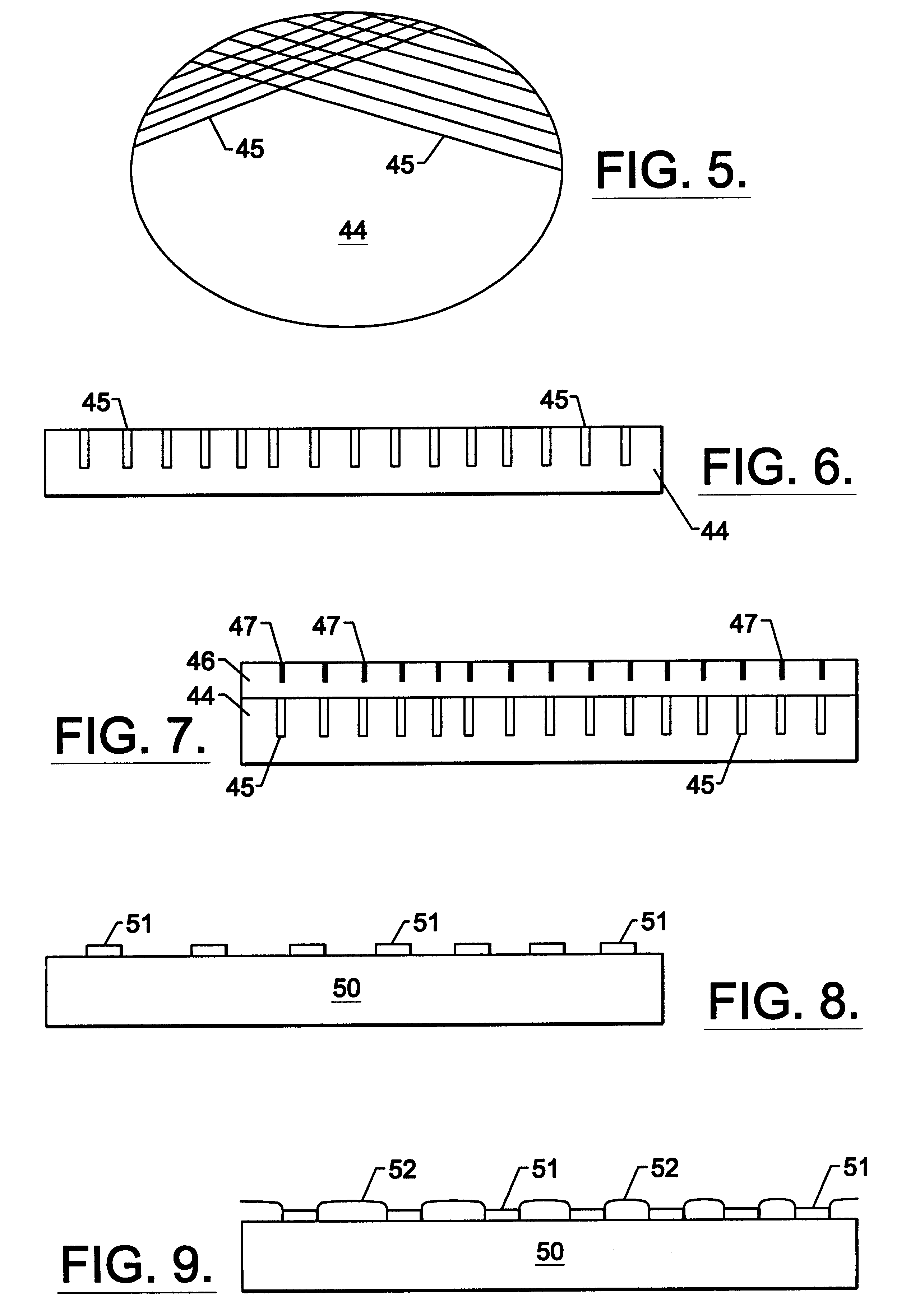

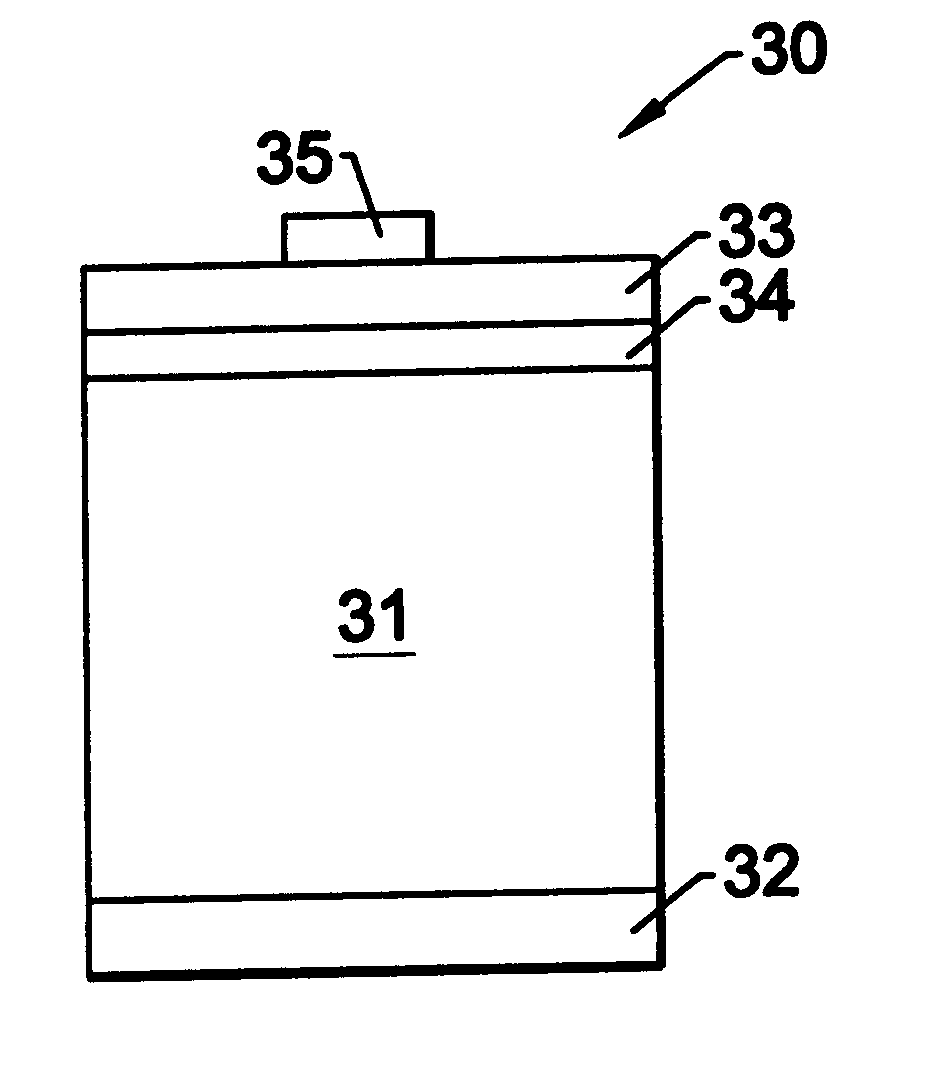

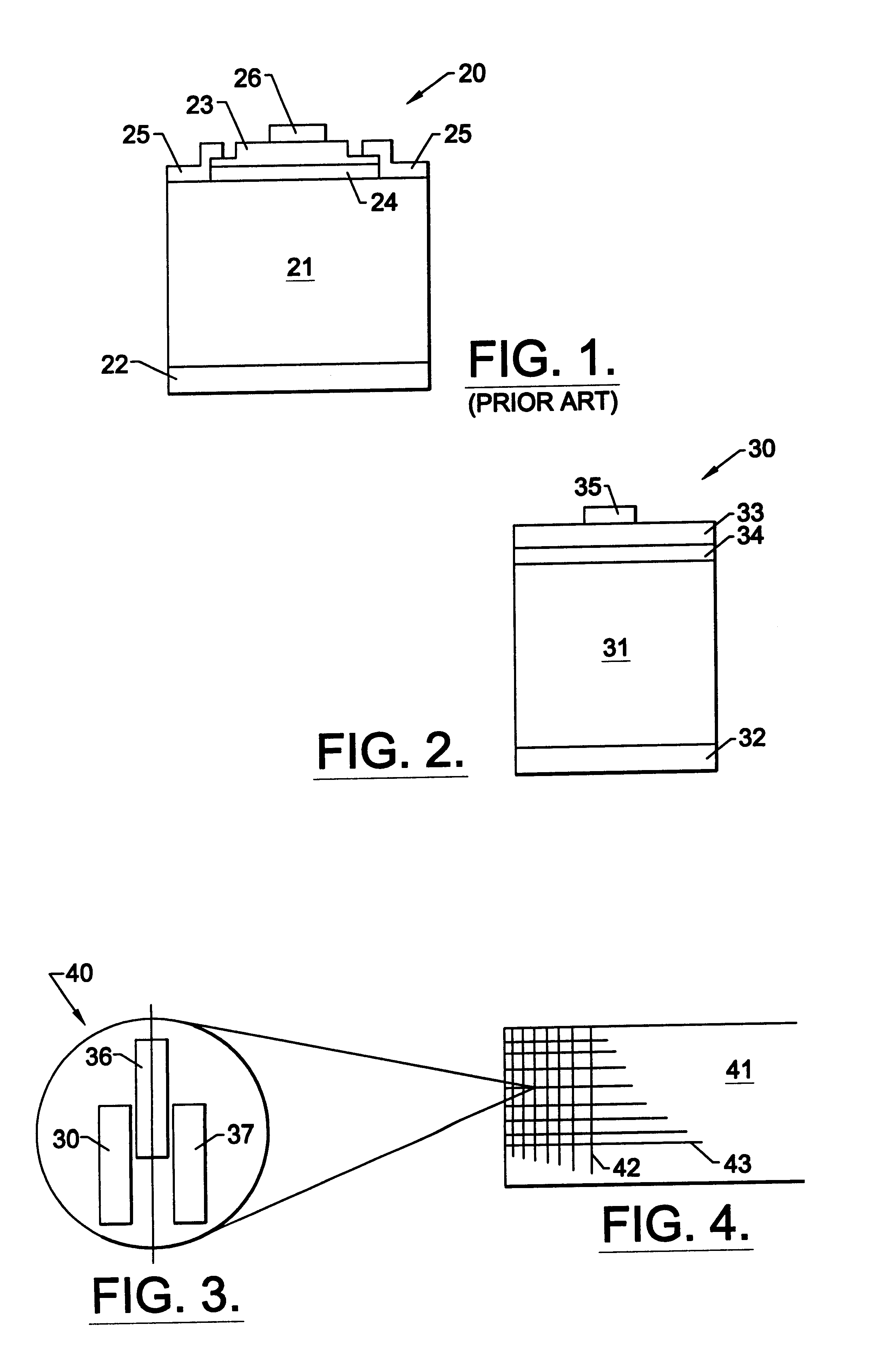

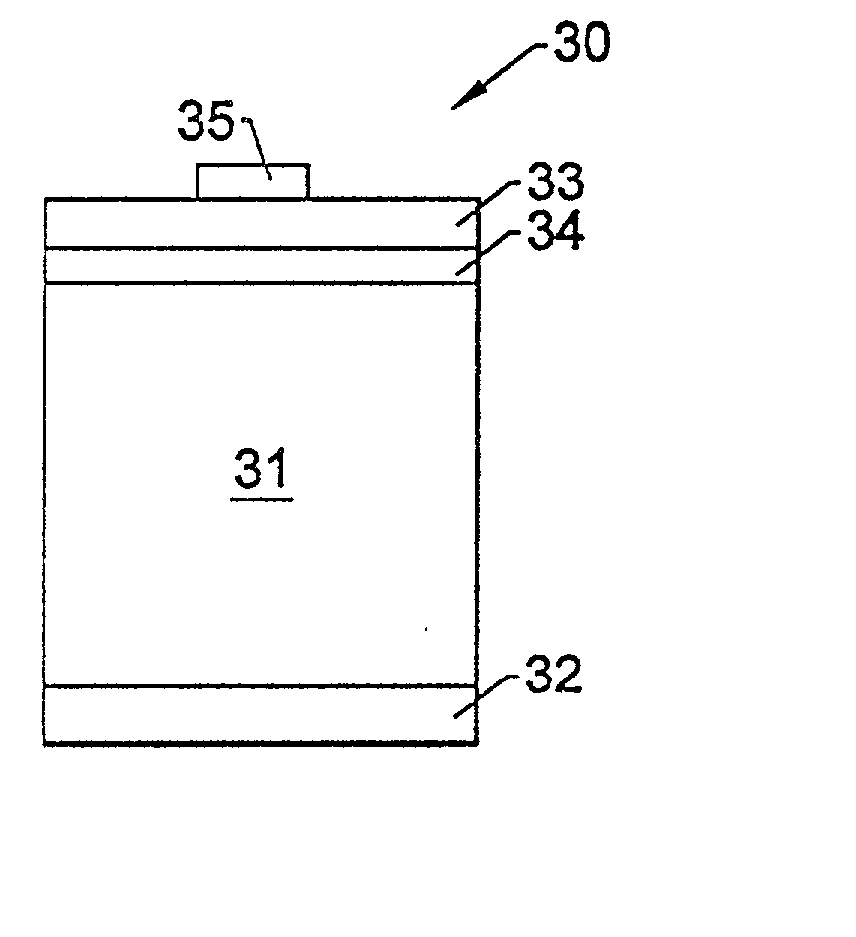

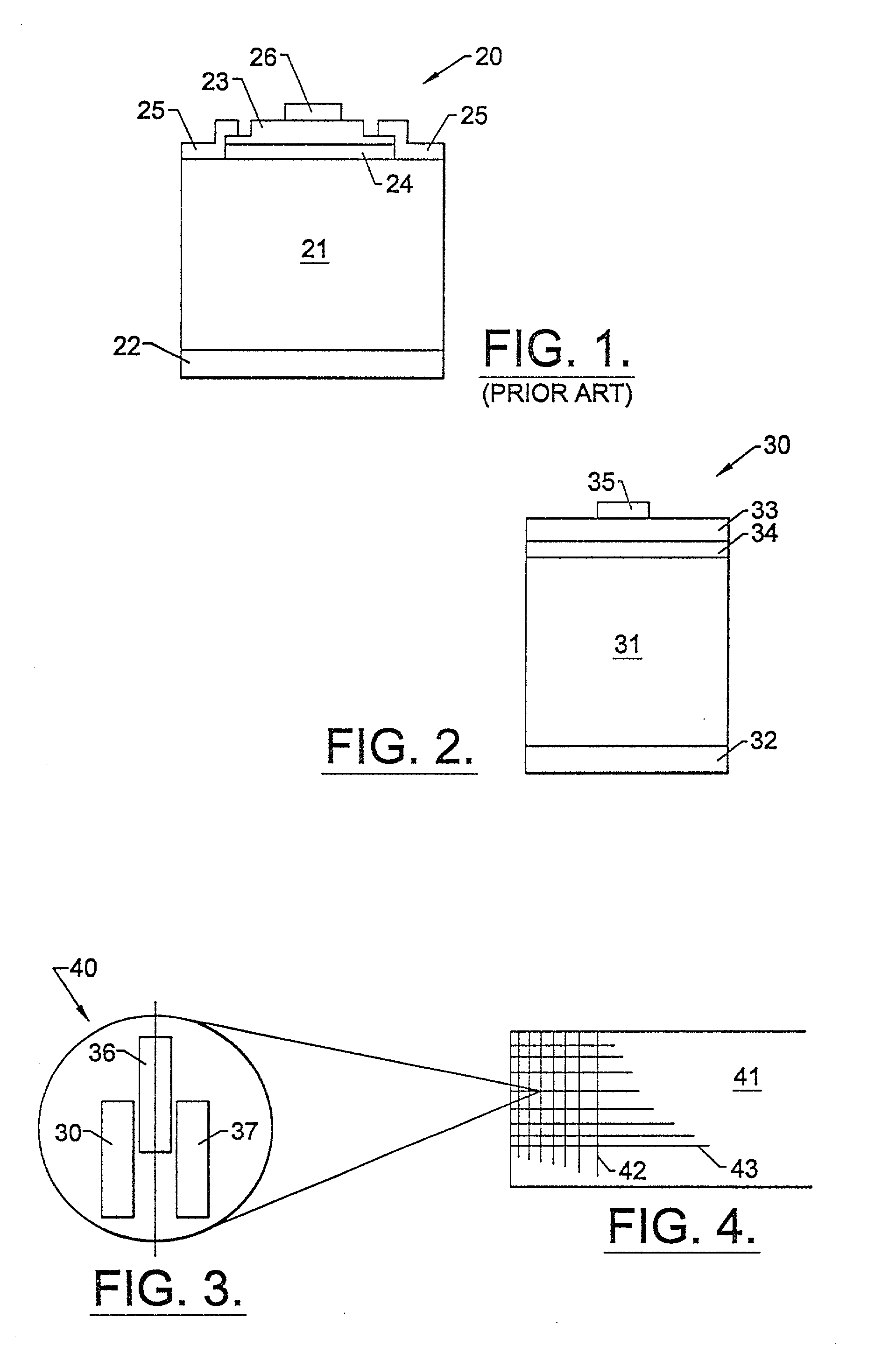

Group III nitride photonic devices on silicon carbide substrates with conductive buffer interlay structure

InactiveUS6201262B1Avoid crackingEasy to manufactureSemiconductor/solid-state device manufacturingSemiconductor devicesStress inducedStress relieving

An optoelectronic device with a Group III Nitride active layer is disclosed that comprises a silicon carbide substrate; an optoelectronic diode with a Group III nitride active layer; a buffer structure selected from the group consisting of gallium nitride and indium gallium nitride between the silicon carbide substrate and the optoelectronic diode; and a stress-absorbing structure comprising a plurality of predetermined stress-relieving areas within the crystal structure of the buffer structure, so that stress-induced cracking that occurs in the buffer structure occurs at predetermined areas rather than elsewhere in the buffer structure.

Owner:CREE INC

Group III nitride photonic devices on silicon carbide substrates with conductive buffer interlayer structure

InactiveUS6187606B1Avoid crackingMinimize and eliminate heterobarrierSemiconductor/solid-state device manufacturingSemiconductor devicesStress inducedStress relieving

An optoelectronic device with a Group III Nitride active layer is disclosed that comprises a silicon carbide substrate; an optoelectronic diode with a Group III nitride active layer; a buffer structure selected from the group consisting of gallium nitride and indium gallium nitride between the silicon carbide substrate and the optoelectronic diode; and a stress-absorbing structure comprising a plurality of predetermined stress-relieving areas within the crystal structure of the buffer structure, so that stress-induced cracking that occurs in the buffer structure occurs at predetermined areas rather than elsewhere in the buffer structure.

Owner:CREE INC

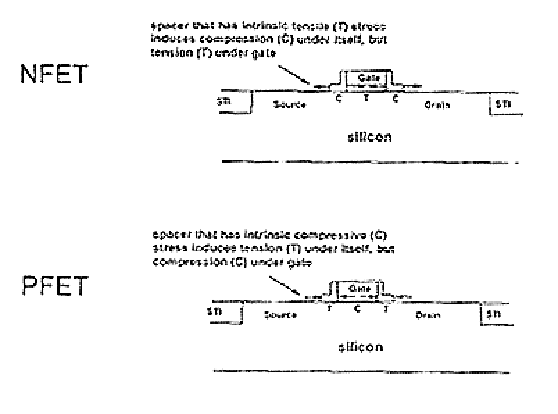

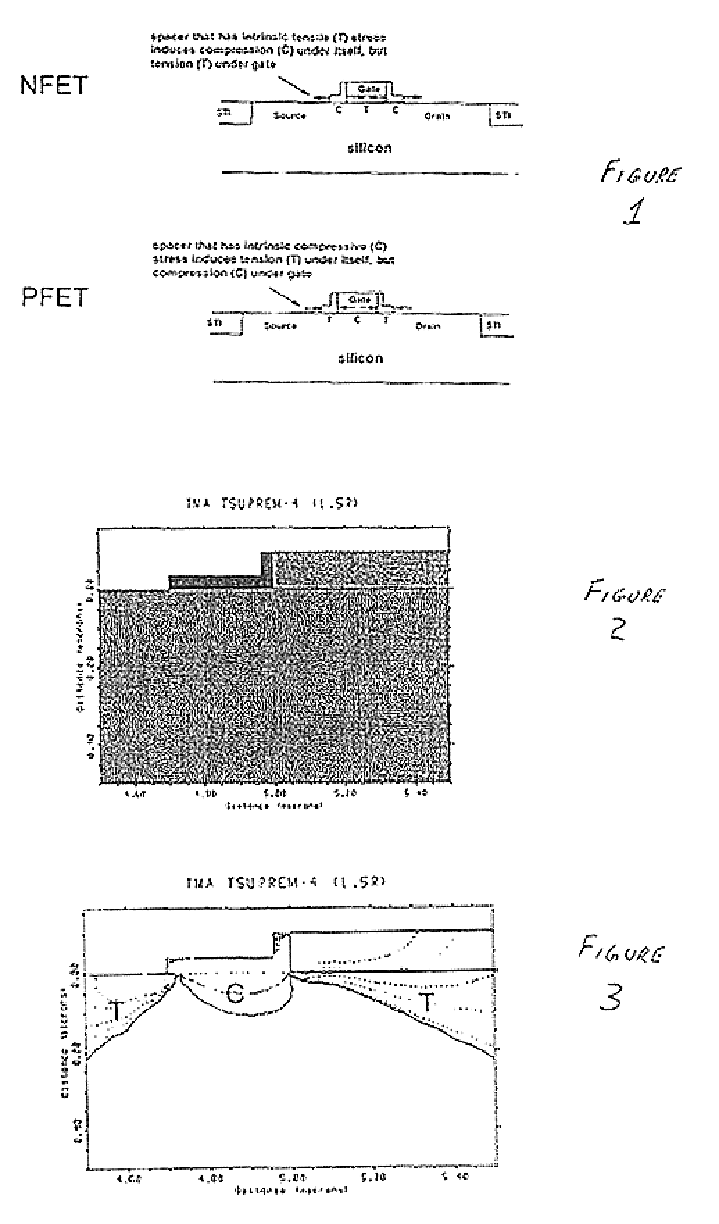

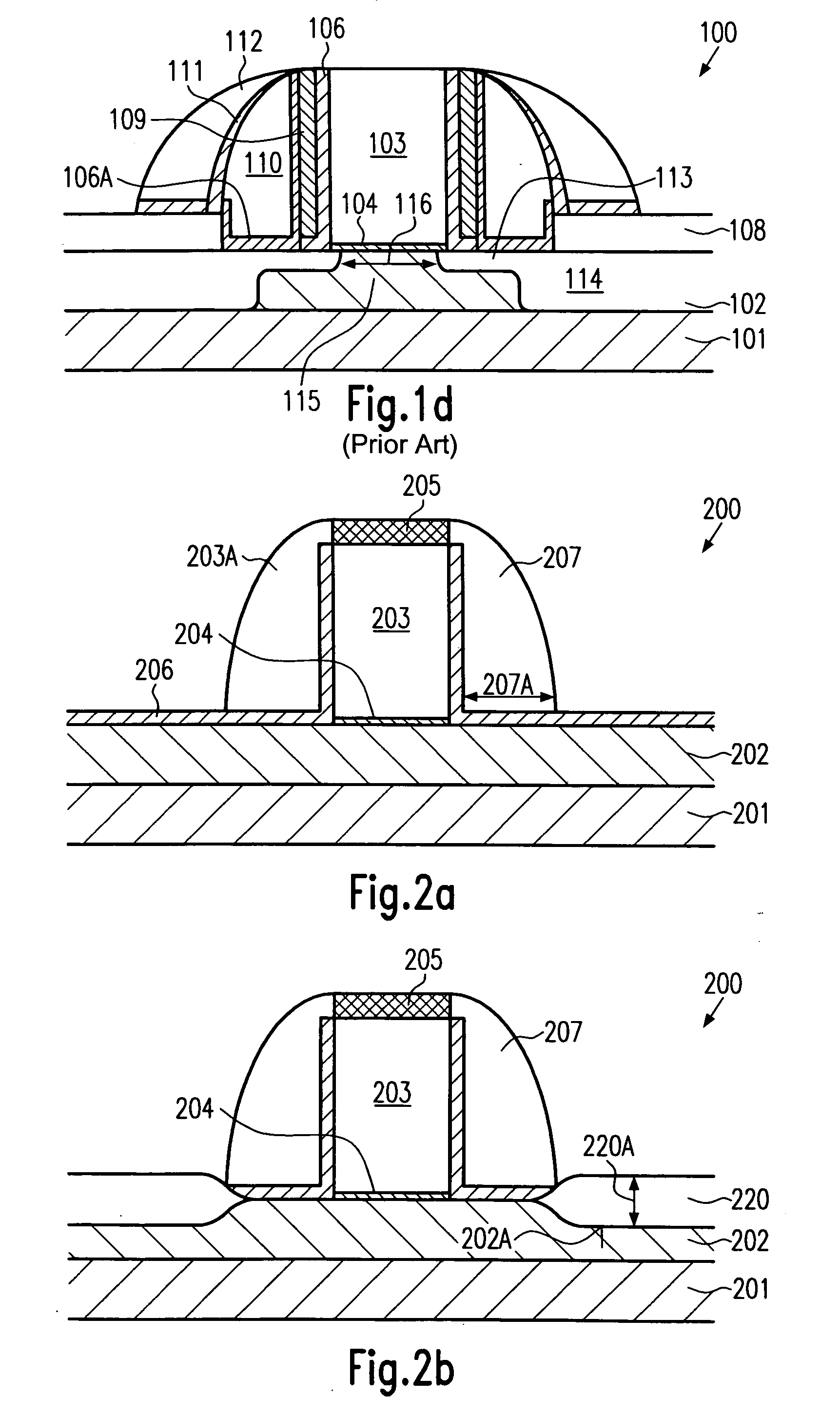

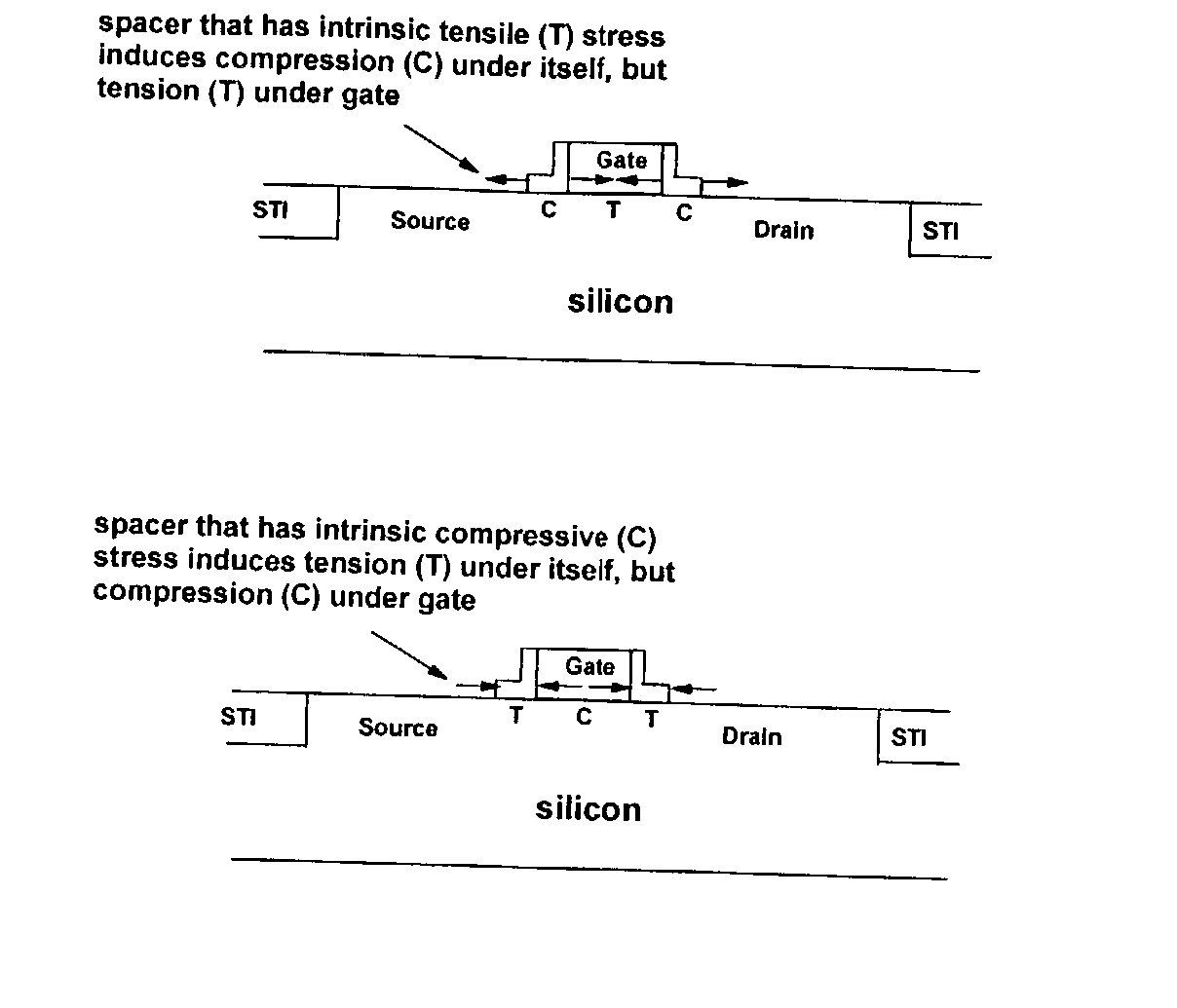

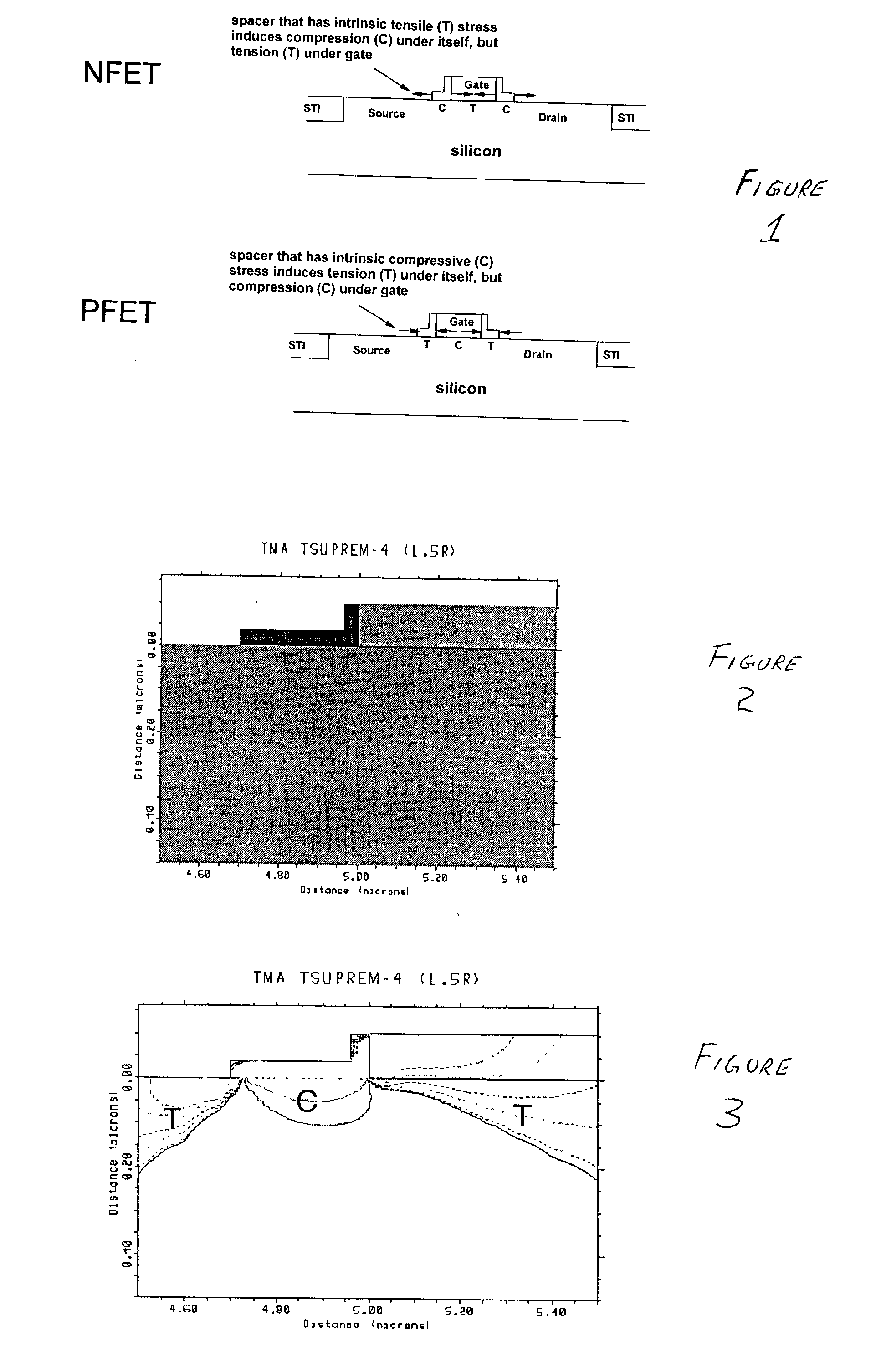

Stress inducing spacers

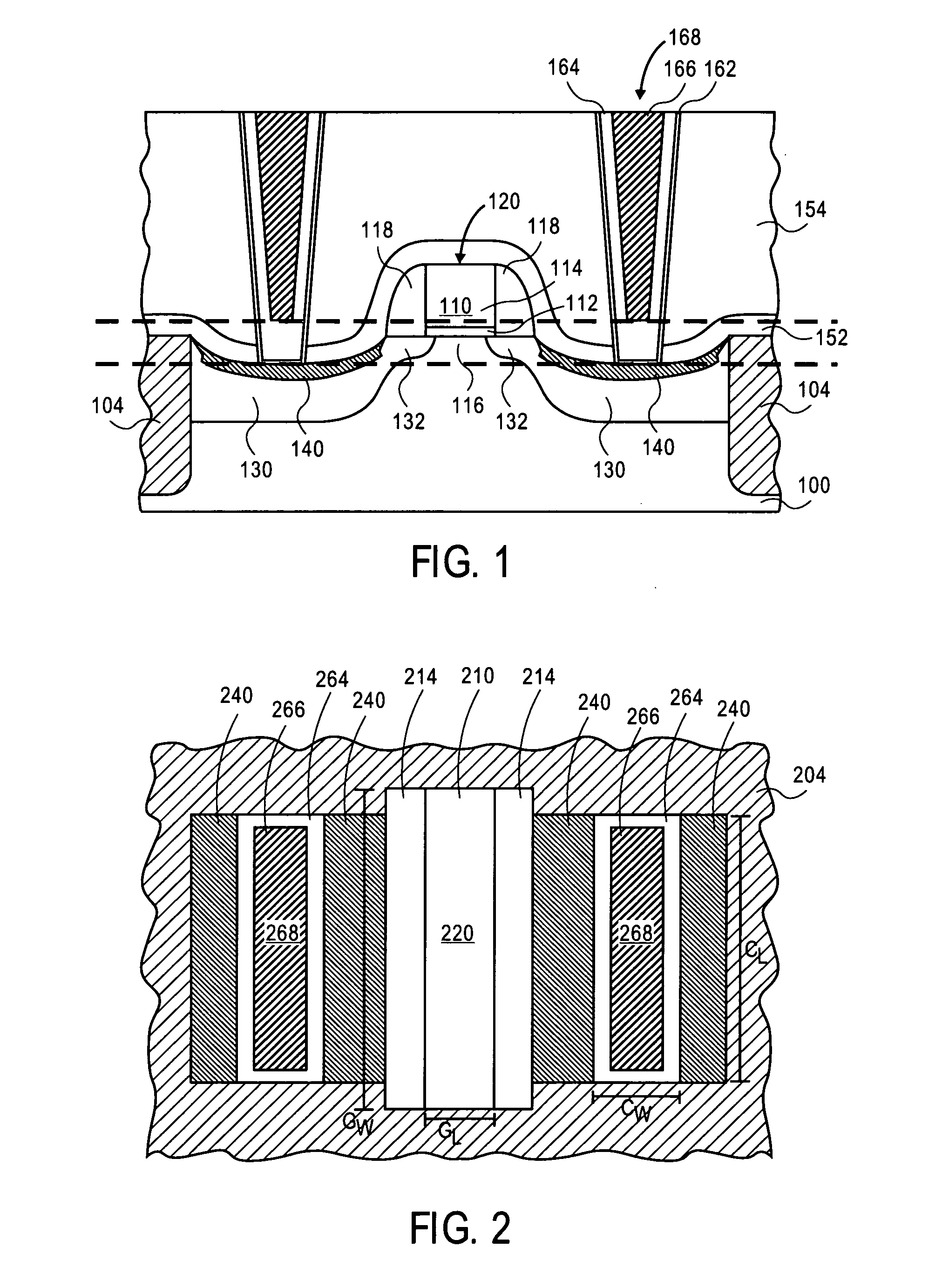

InactiveUS6825529B2Different stressImprove performanceTransducer detailsSolid-state devicesStress inducedDevice form

Owner:AURIGA INNOVATIONS INC

Method to control source/drain stressor profiles for stress engineering

ActiveUS20070235802A1Reduce duplicationSemiconductor/solid-state device manufacturingSemiconductor devicesStress inducedGate dielectric

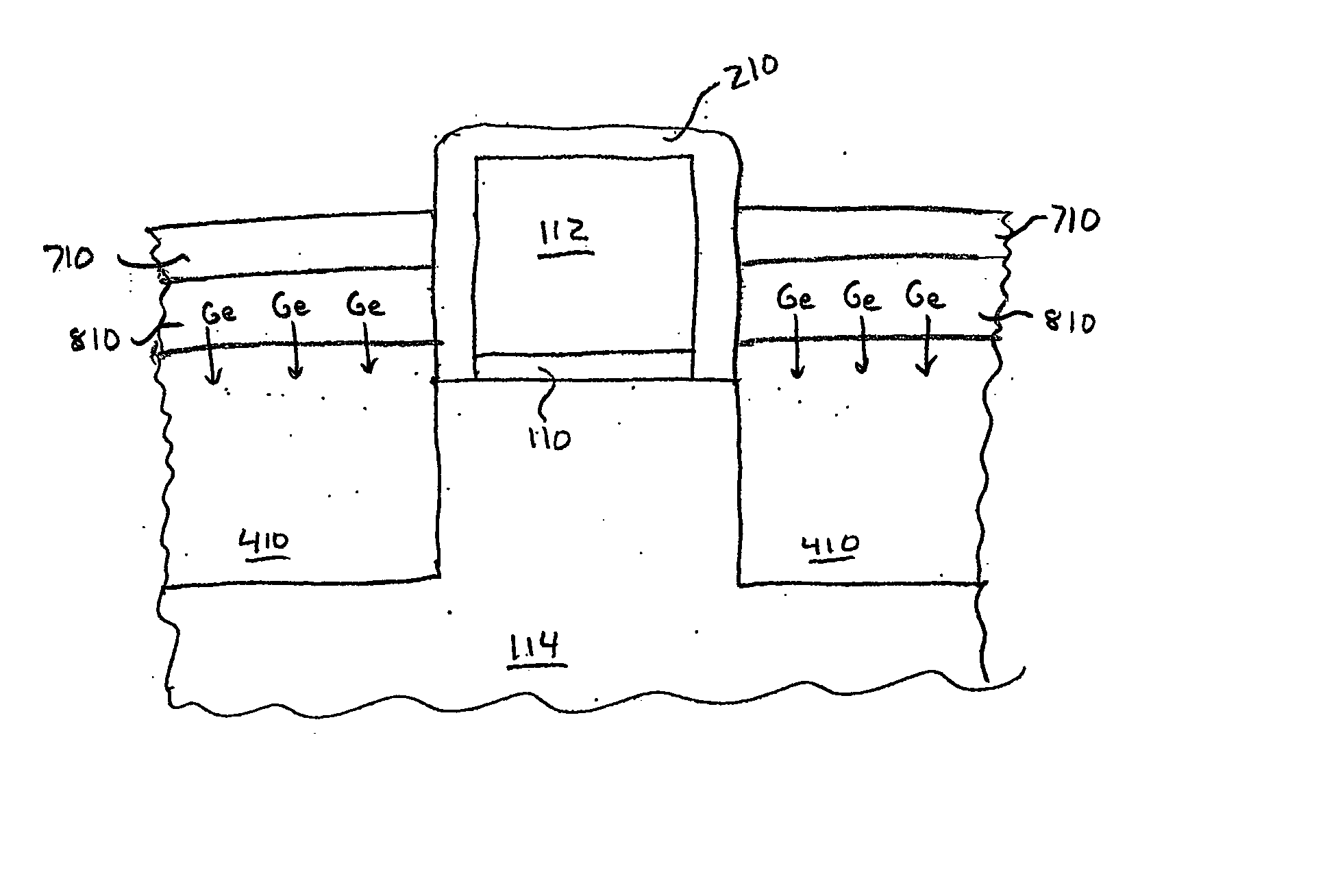

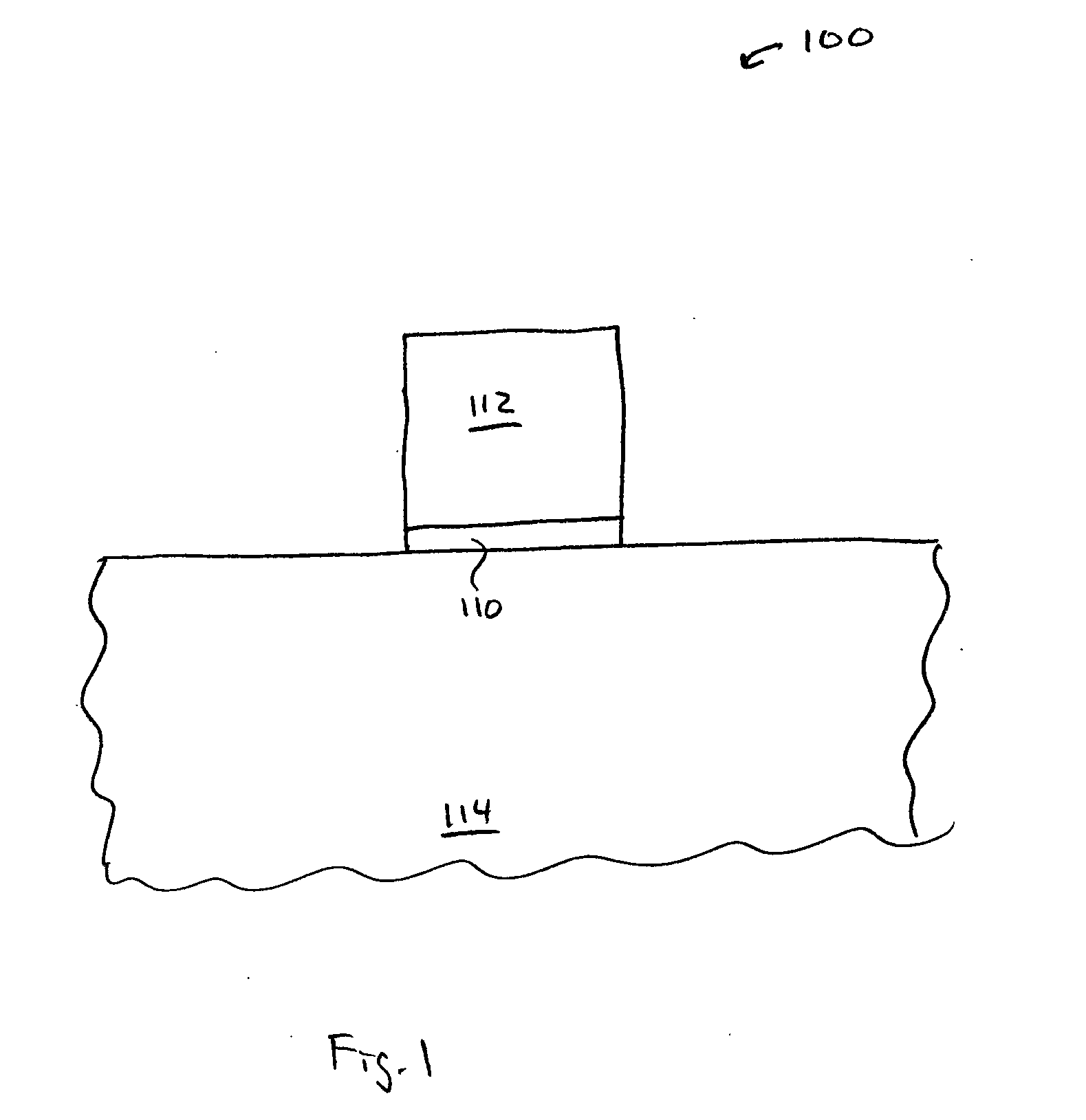

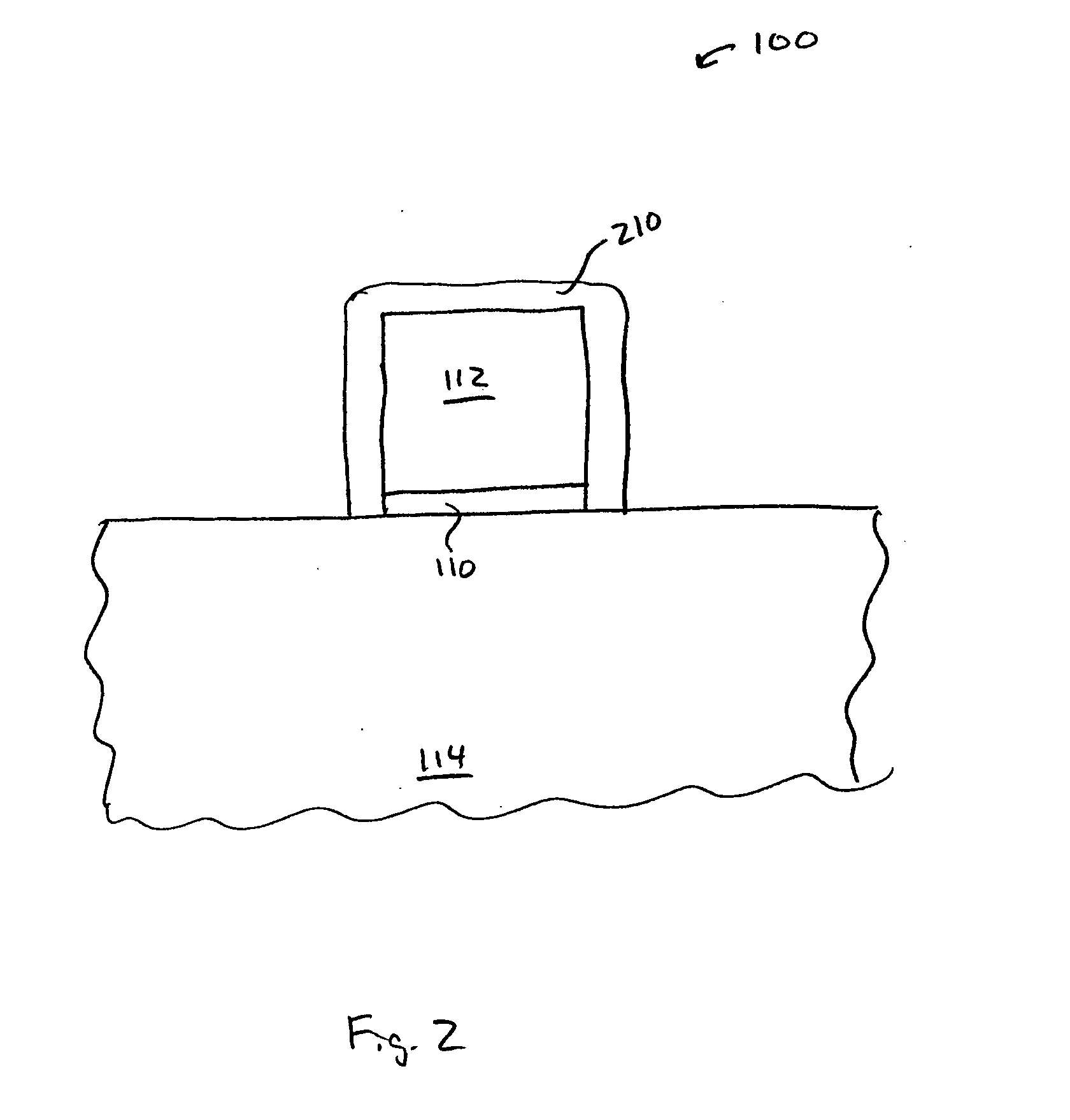

An example embodiment of a strained channel transistor structure comprises the following: a strained channel region comprising a first semiconductor material with a first natural lattice constant; a gate dielectric layer overlying the strained channel region; a gate electrode overlying the gate dielectric layer; and a source region and drain region oppositely adjacent to the strained channel region, one or both of the source region and drain region are comprised of a stressor region comprised of a second semiconductor material with a second natural lattice constant different from the first natural lattice constant; the stressor region has a graded concentration of a dopant impurity and / or of a stress inducing molecule. Another example embodiment is a process to form the graded impurity or stress inducing molecule stressor embedded S / D region, whereby the location / profile of the S / D stressor is not defined by the recess depth / profile.

Owner:IBM CORP +2

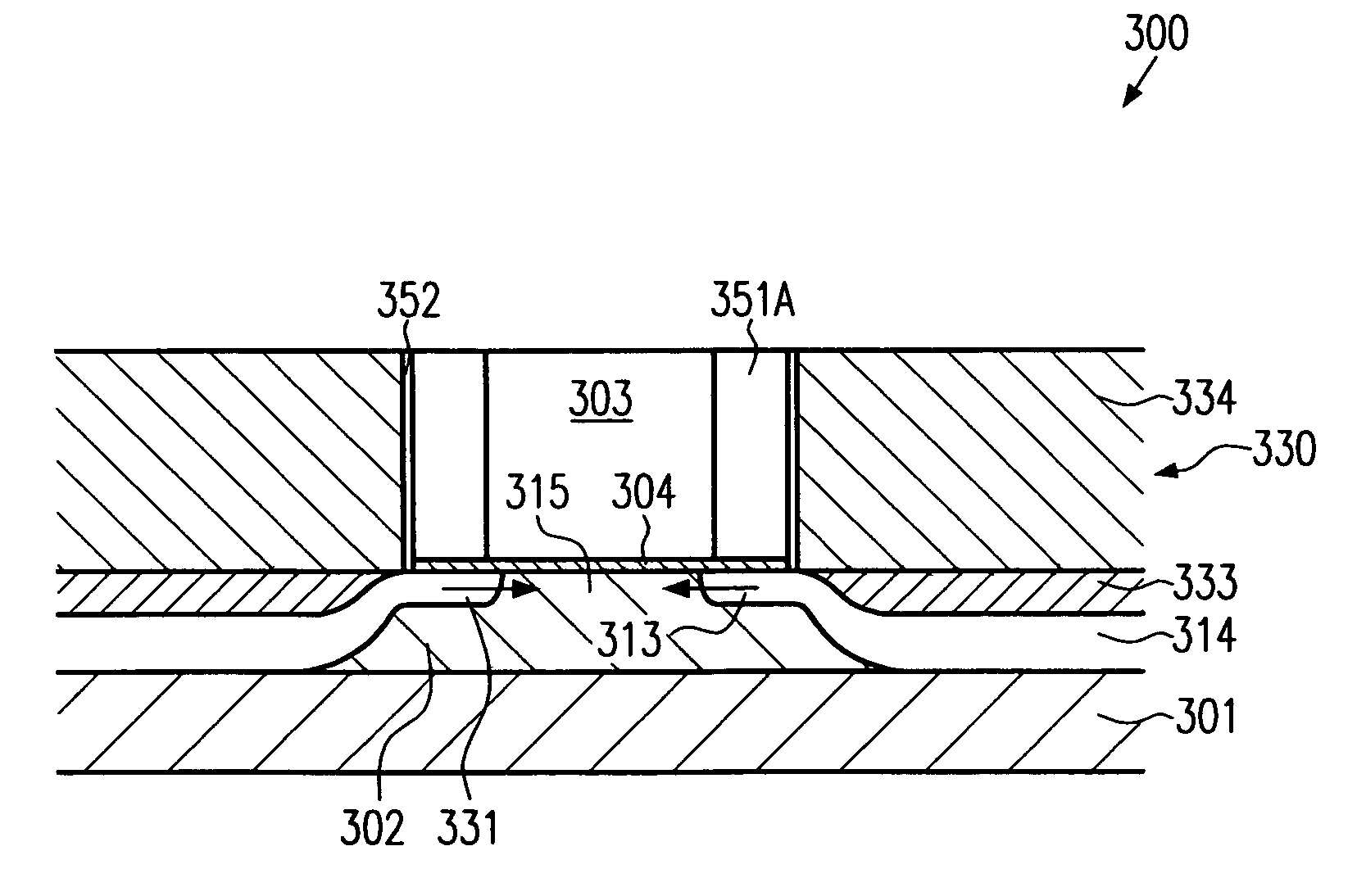

Stressed barrier plug slot contact structure for transistor performance enhancement

ActiveUS20080157208A1TransistorSemiconductor/solid-state device detailsStress inducedPerformance enhancement

A method for forming a slot contact structure for transistor performance enhancement. A contact opening is formed to expose a contact region, and a slot contact is disposed within the contact opening in order to induce a stress on an adjacent channel region. In an embodiment, a stress inducing barrier plug is disposed within a portion of the contact opening and the remainder of the contact opening is filled with a lower resistivity contact metal. By selecting the proper materials and deposition parameters, the slot contact can be tuned to induce a tensile or compressive stress on the adjacent channel region, thus being applicable for both p-type and n-type devices.

Owner:INTEL CORP

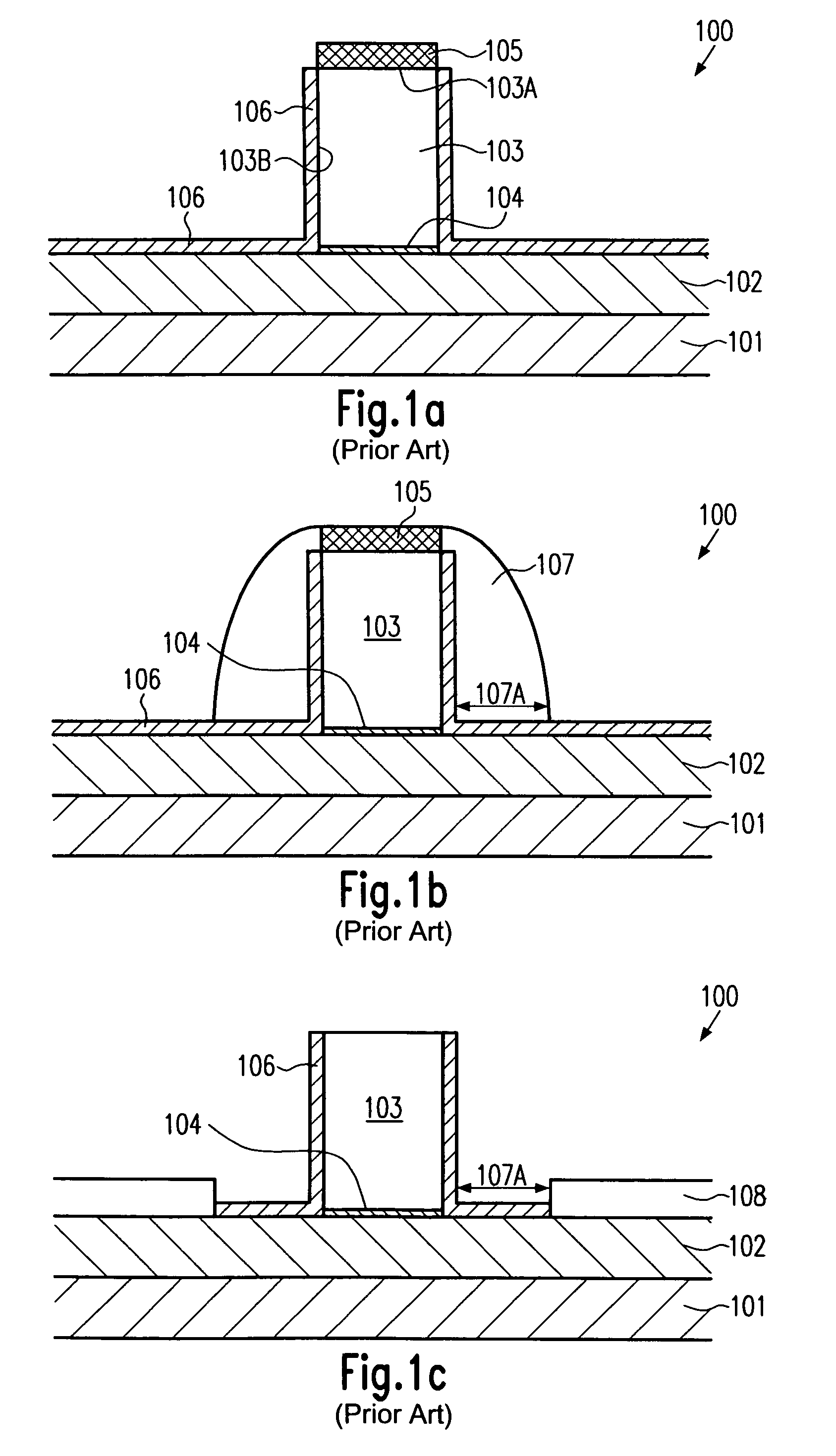

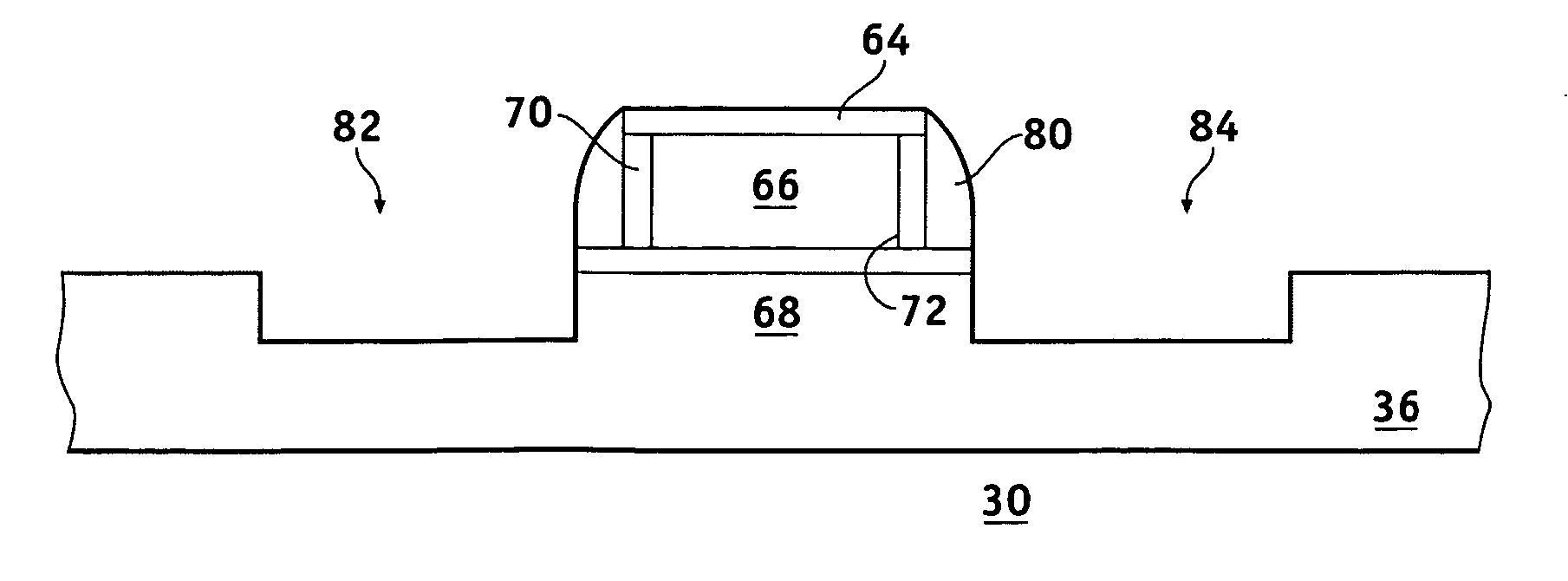

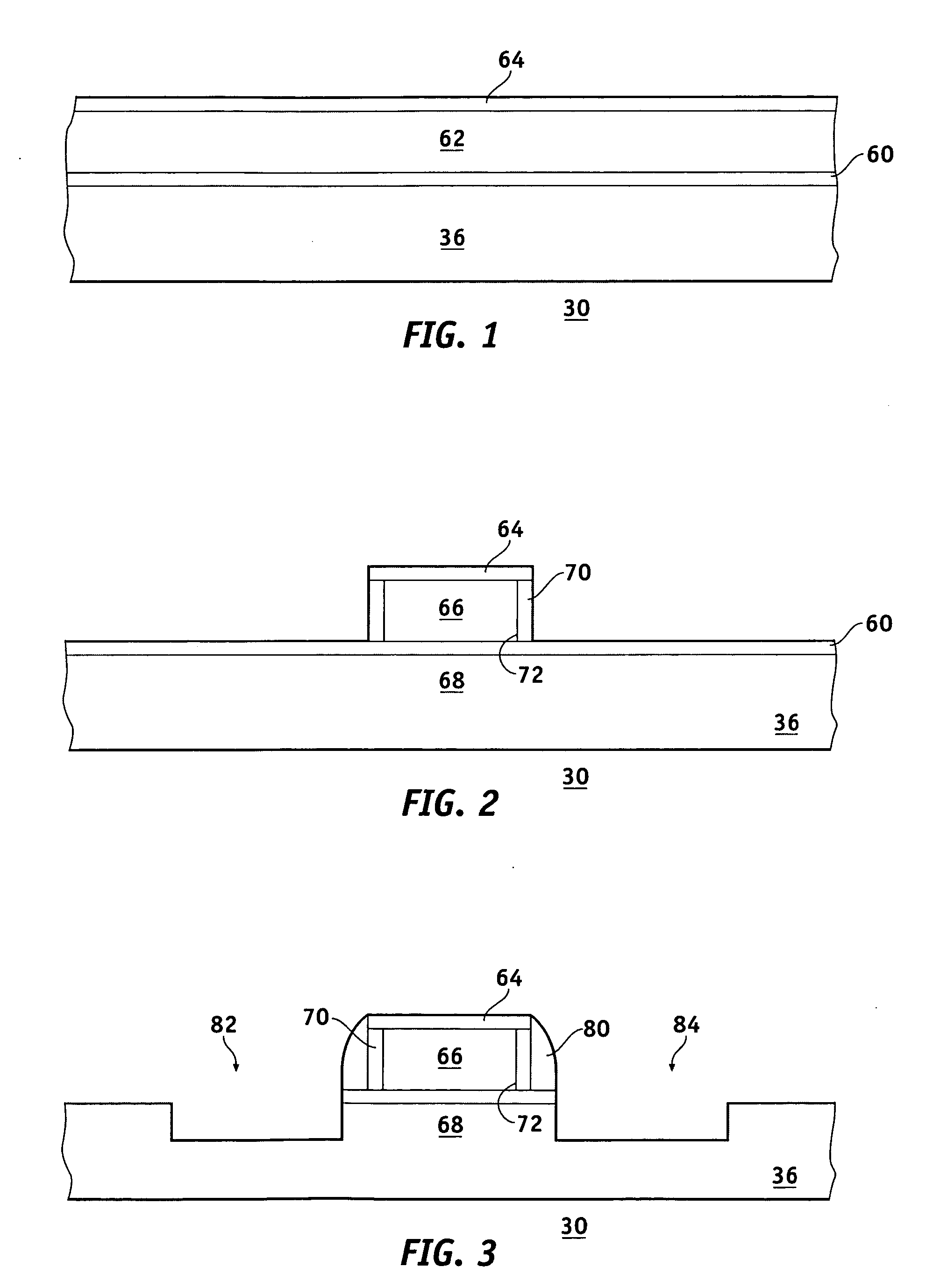

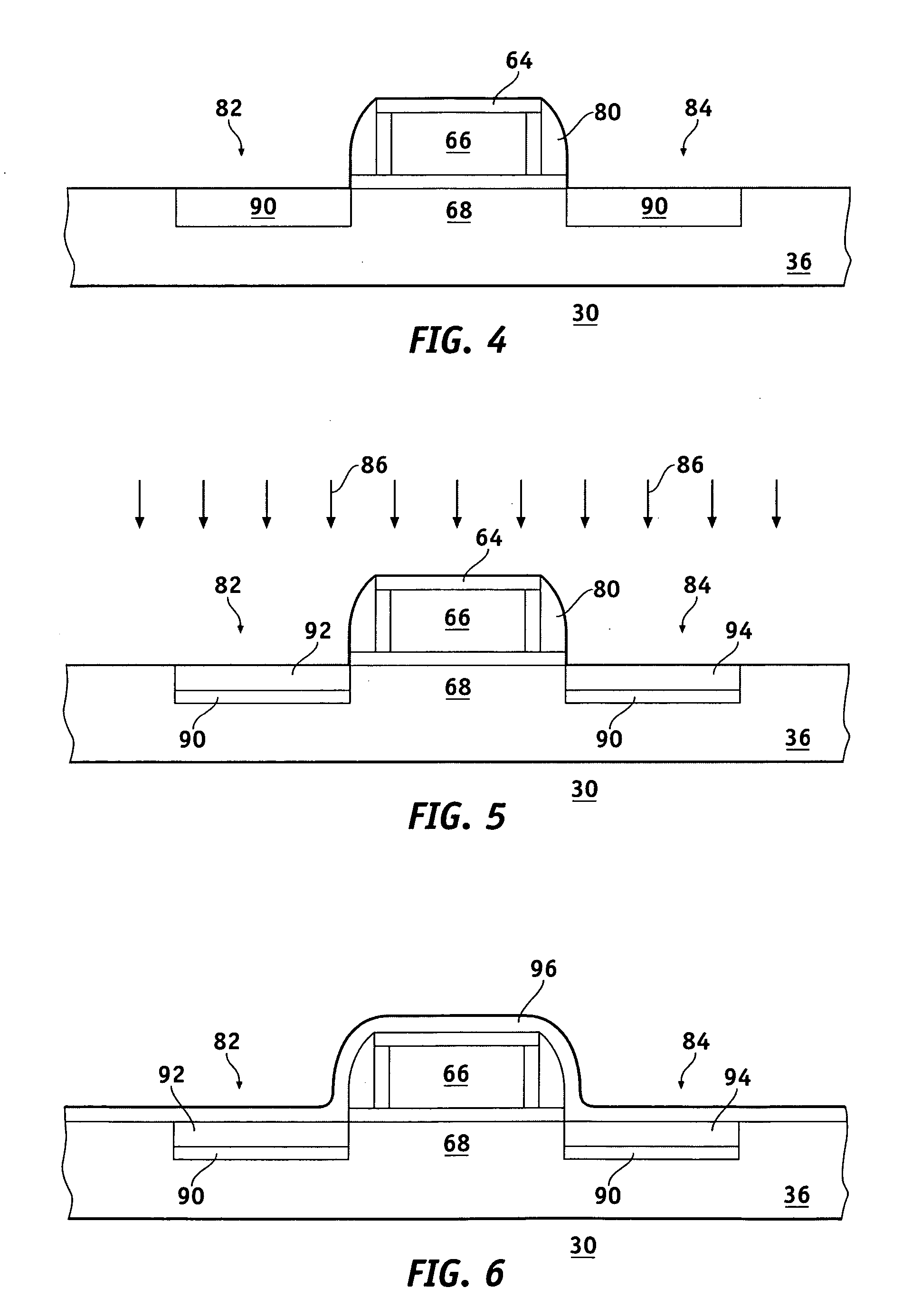

Advanced technique for forming a transistor having raised drain and source regions

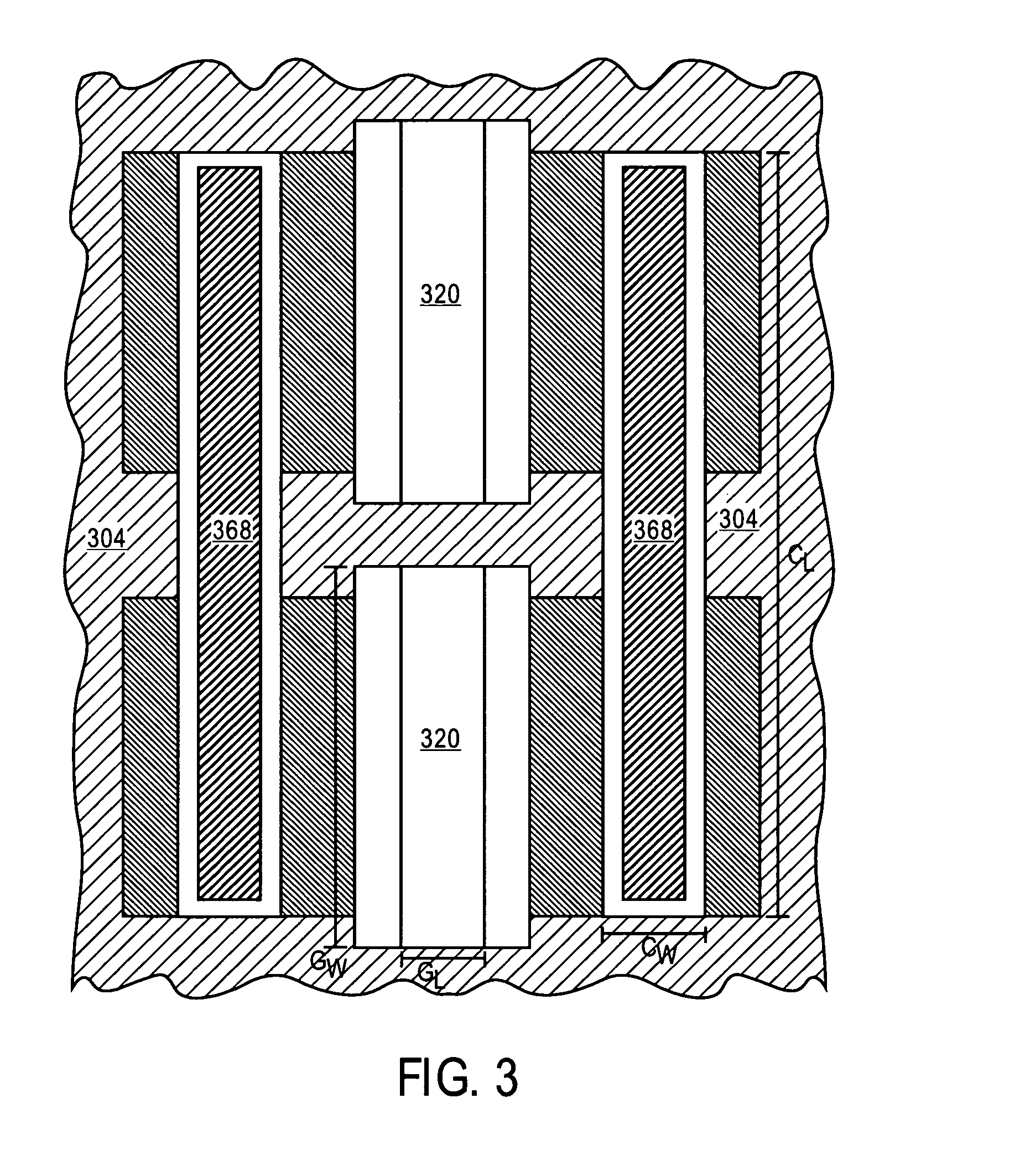

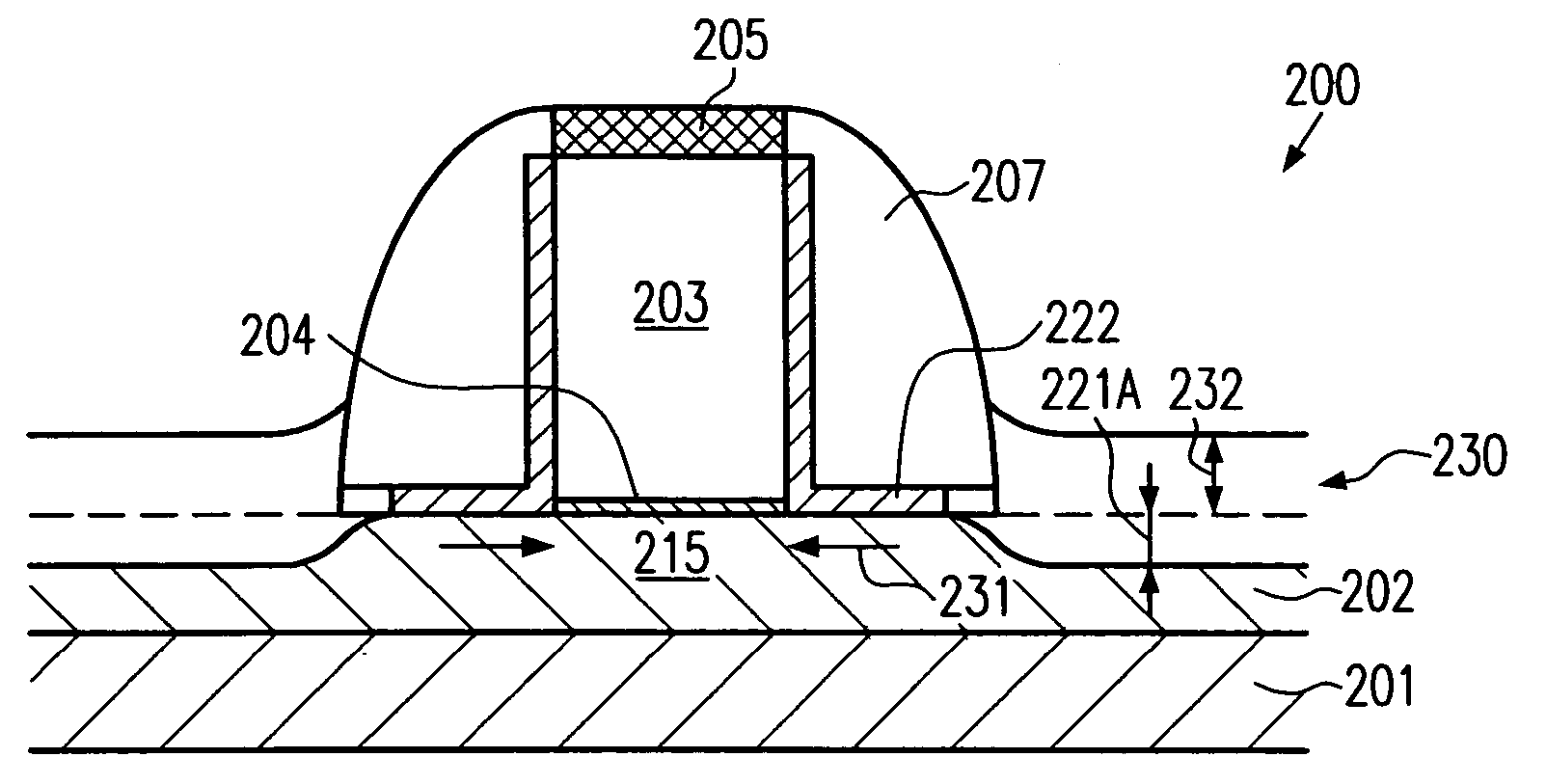

InactiveUS20050093075A1Create stressImprove featuresTransistorSemiconductor/solid-state device manufacturingDopantStress induced

By recessing a semiconductor layer, preferably by locally oxidizing the semiconductor layer, a stress-inducing material and / or a dopant species may be introduced into the thinned semiconductor layer in the vicinity of a gate electrode structure by means of a subsequent epitaxial growth process. In particular, the stress-inducing material formed adjacent to the gate electrode structure exerts compressive or tensile stress, depending on the type of material deposited, thereby also enhancing the mobility of the charge carriers in a channel region of the transistor element.

Owner:GLOBALFOUNDRIES INC

Stress inducing spacers

InactiveUS20040113217A1Different stressImprove performanceTransducer detailsSolid-state devicesStress inducedDevice form

Owner:AURIGA INNOVATIONS INC

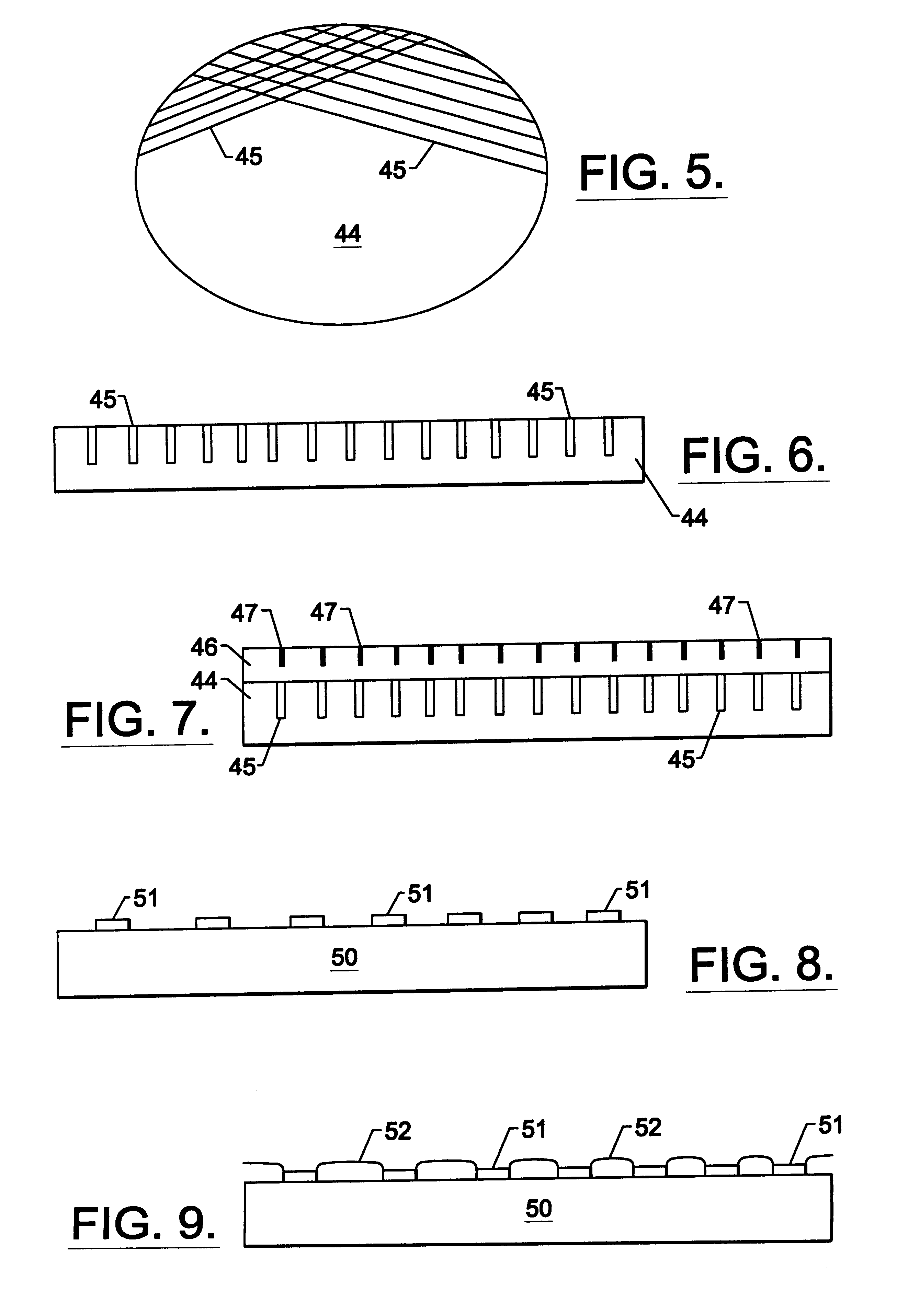

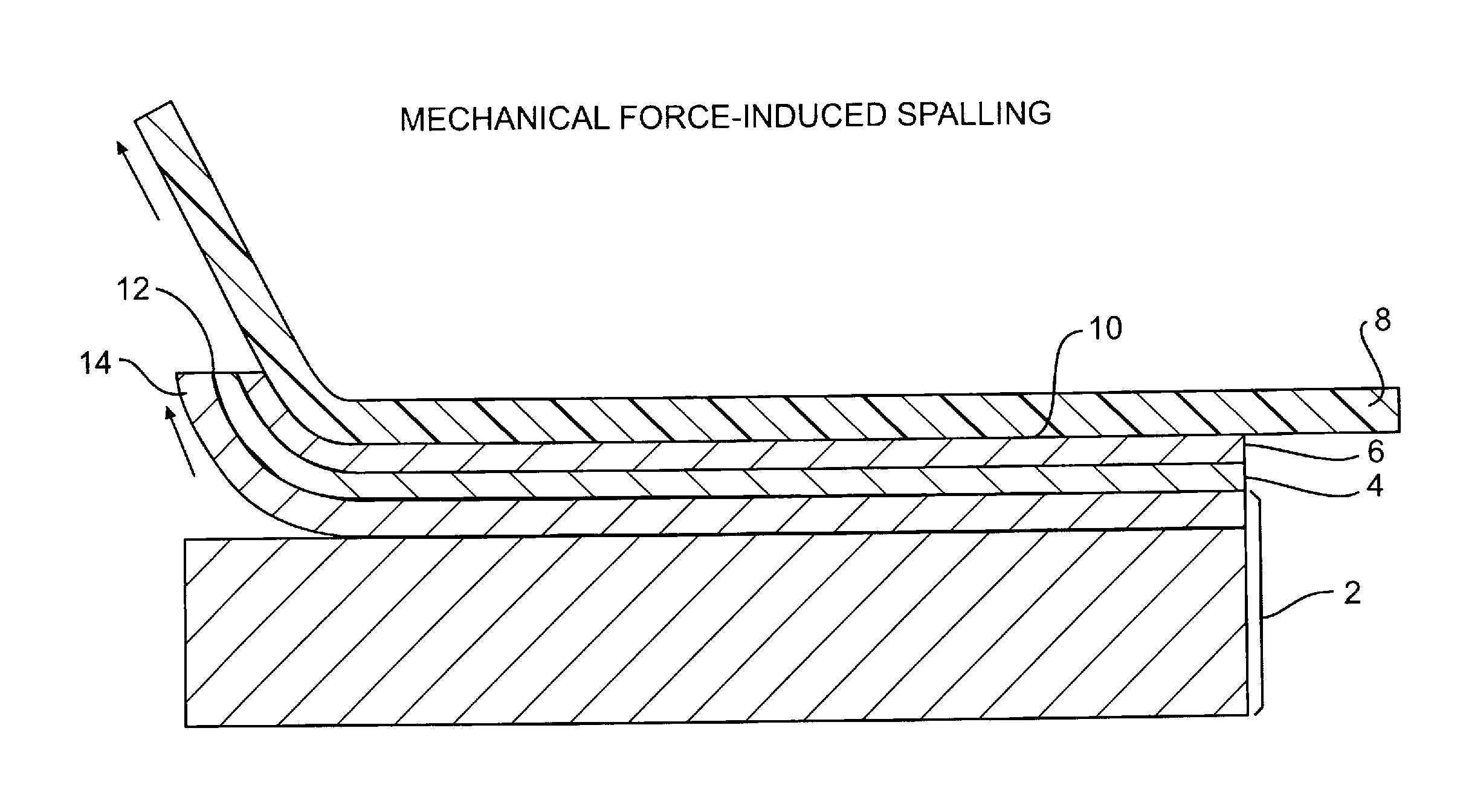

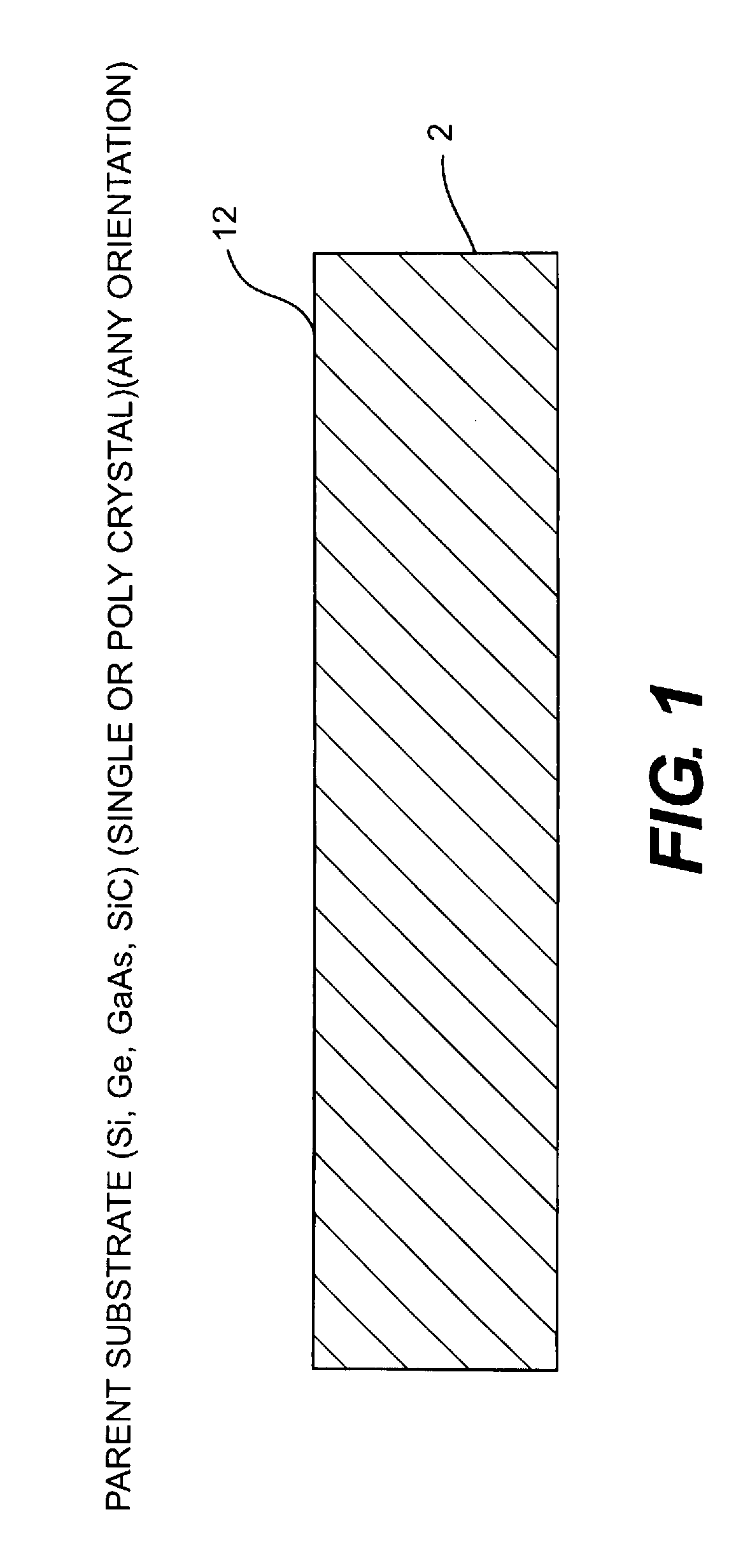

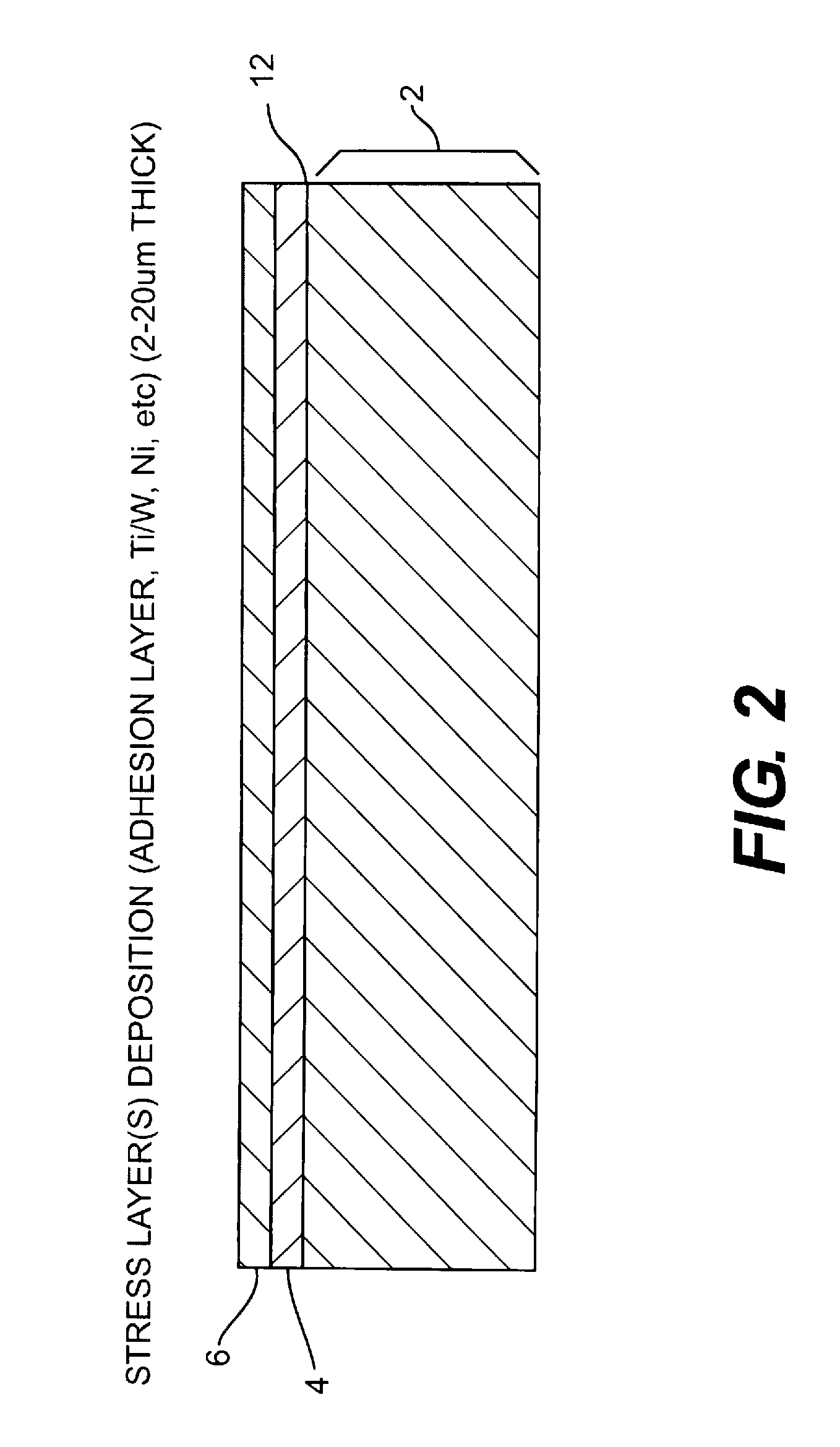

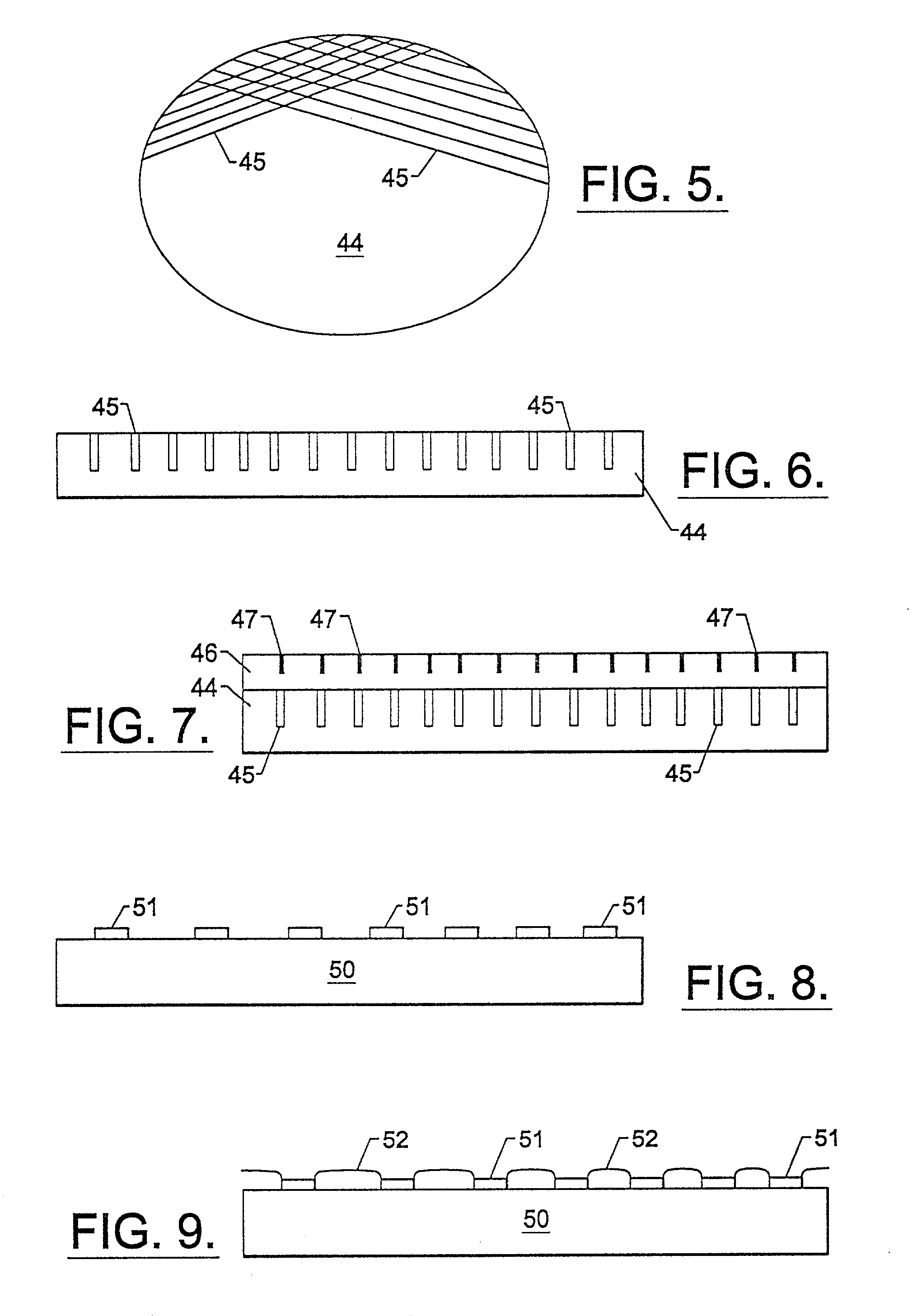

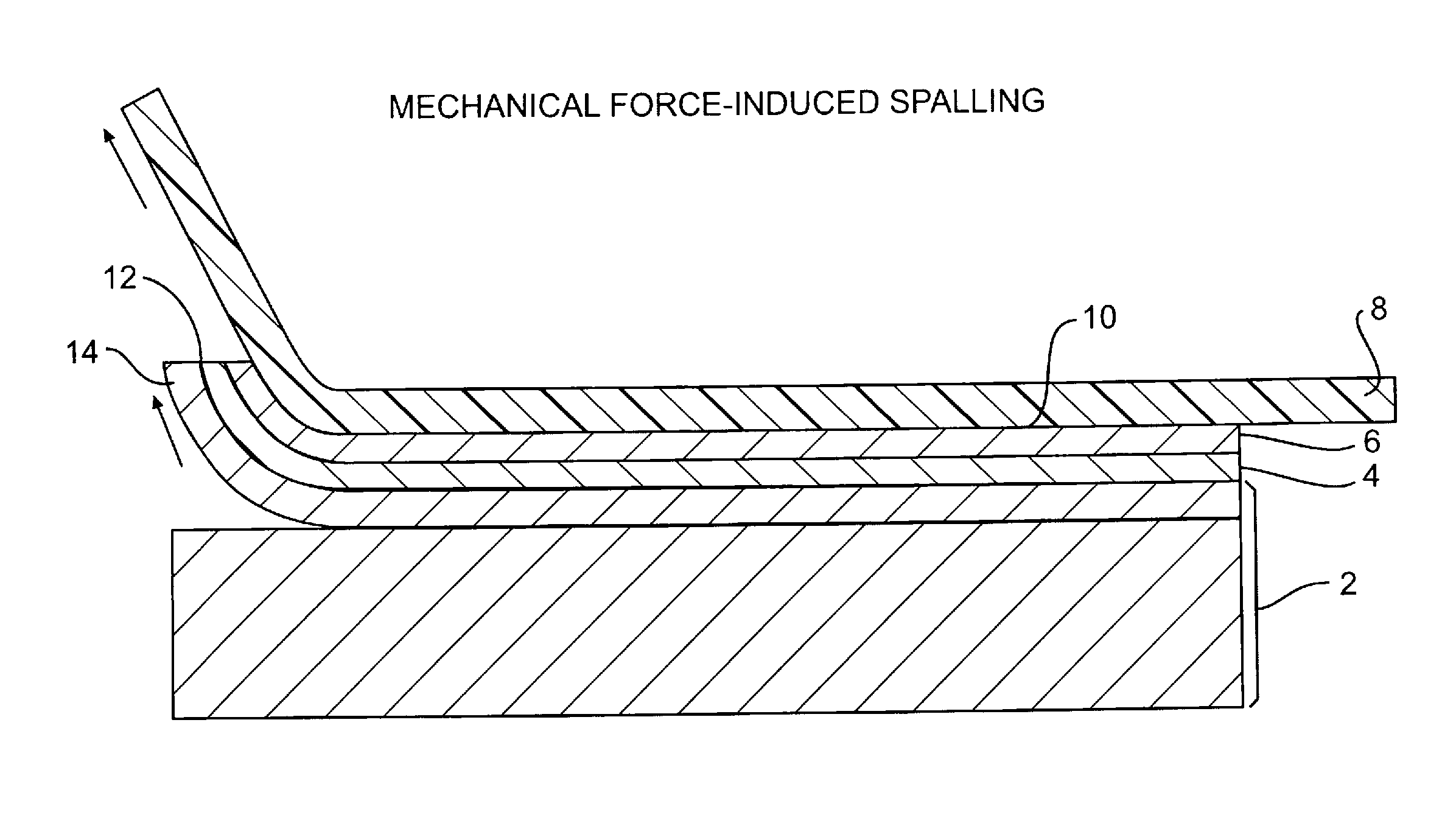

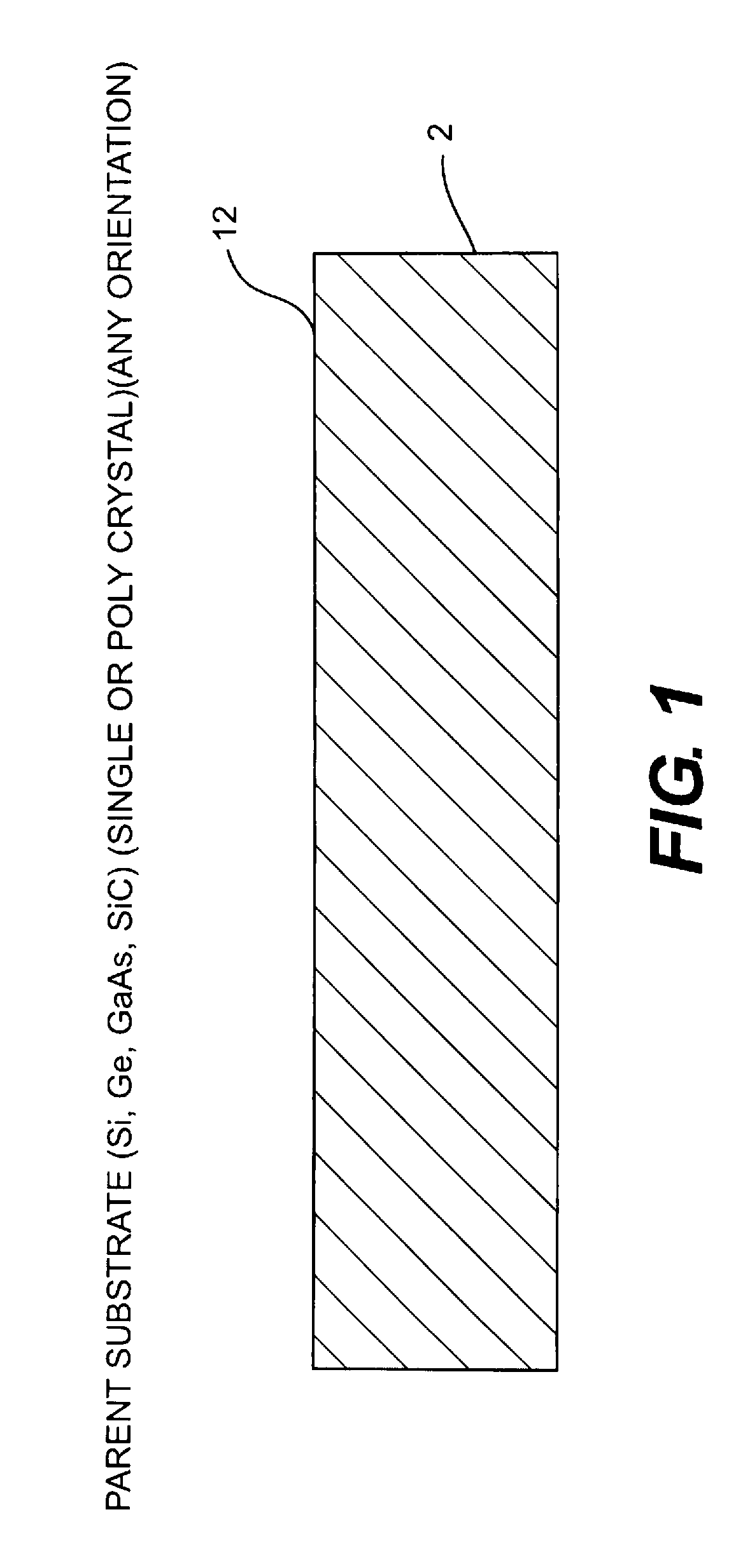

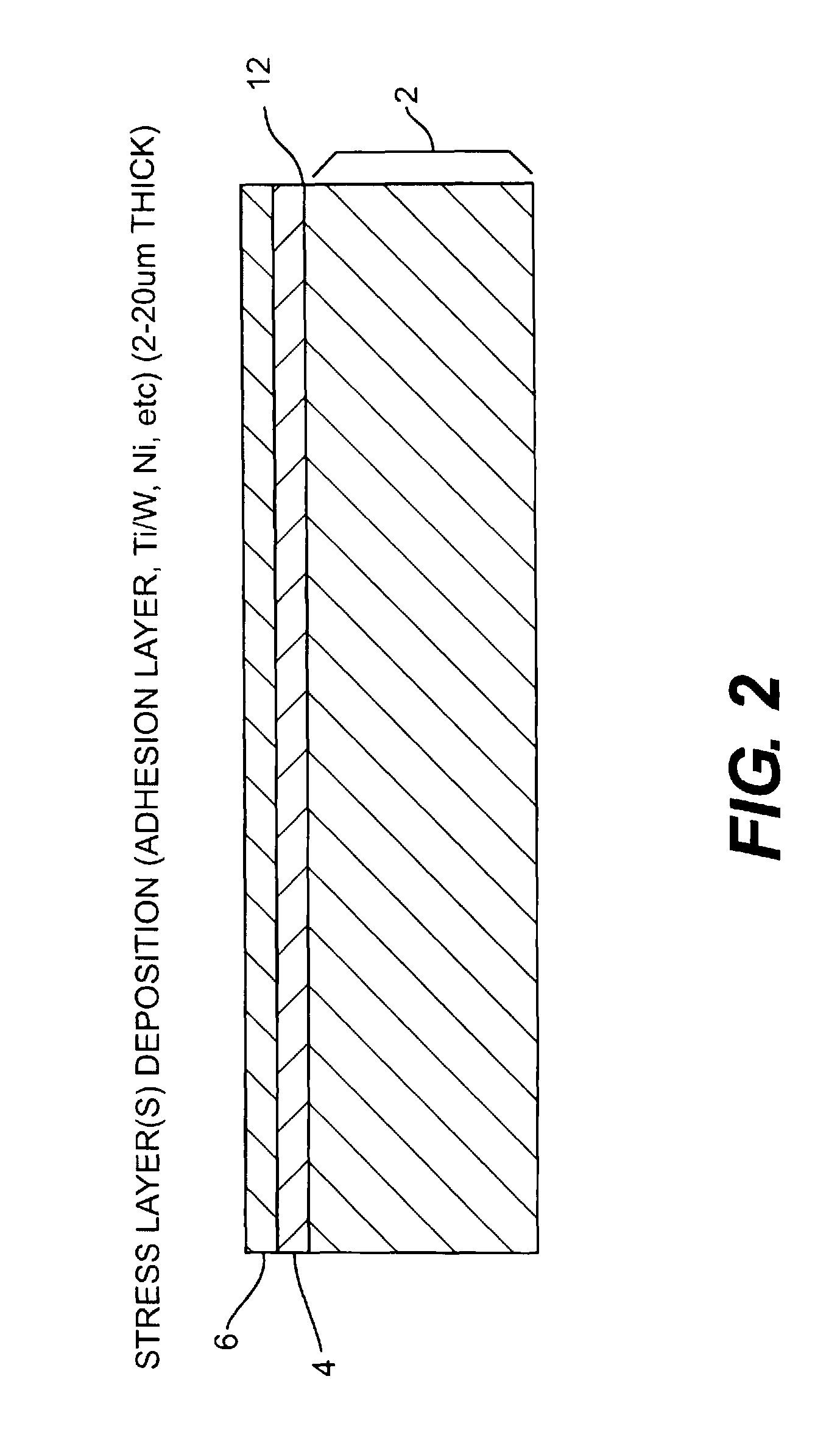

Thin substrate fabrication using stress-induced substrate spalling

ActiveUS20100311250A1Increase cost per Watt valueImprove efficiencyFinal product manufactureSemiconductor/solid-state device manufacturingStress inducedActive solar

A method for manufacturing a thin film direct bandgap semiconductor active solar cell device comprises providing a source substrate having a surface and disposing on the surface a stress layer having a stress layer surface area in contact with and bonded to the surface of the source substrate. Operatively associating a handle foil with the stress layer and applying force to the handle foil separates the stress layer from the source substrate, and leaves a portion of the source substrate on the stress layer surface substantially corresponding to the area in contact with the surface of the source substrate. The portion is less thick than the source layer. The stress layer thickness is below that which results in spontaneous spalling of the source substrate. The source substrate may comprise an inorganic single crystal or polycrystalline material such as Si, Ge, GaAs, SiC, sapphire, or GaN. In one embodiment the stress layer comprises a flexible material.

Owner:GLOBALFOUNDRIES US INC

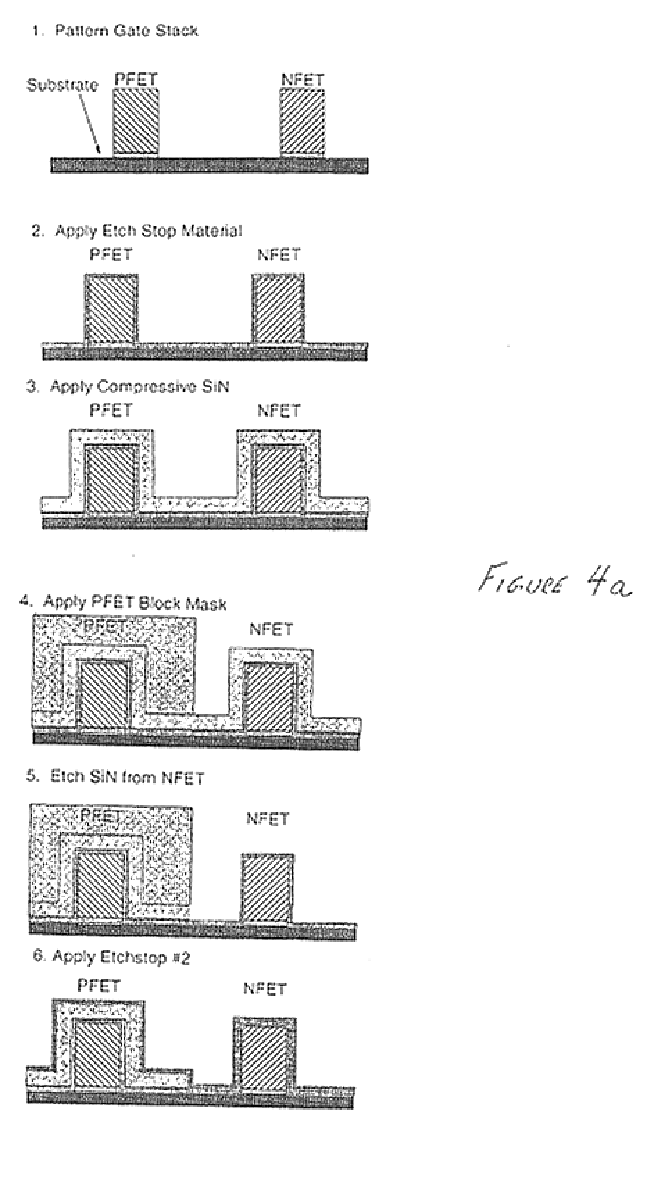

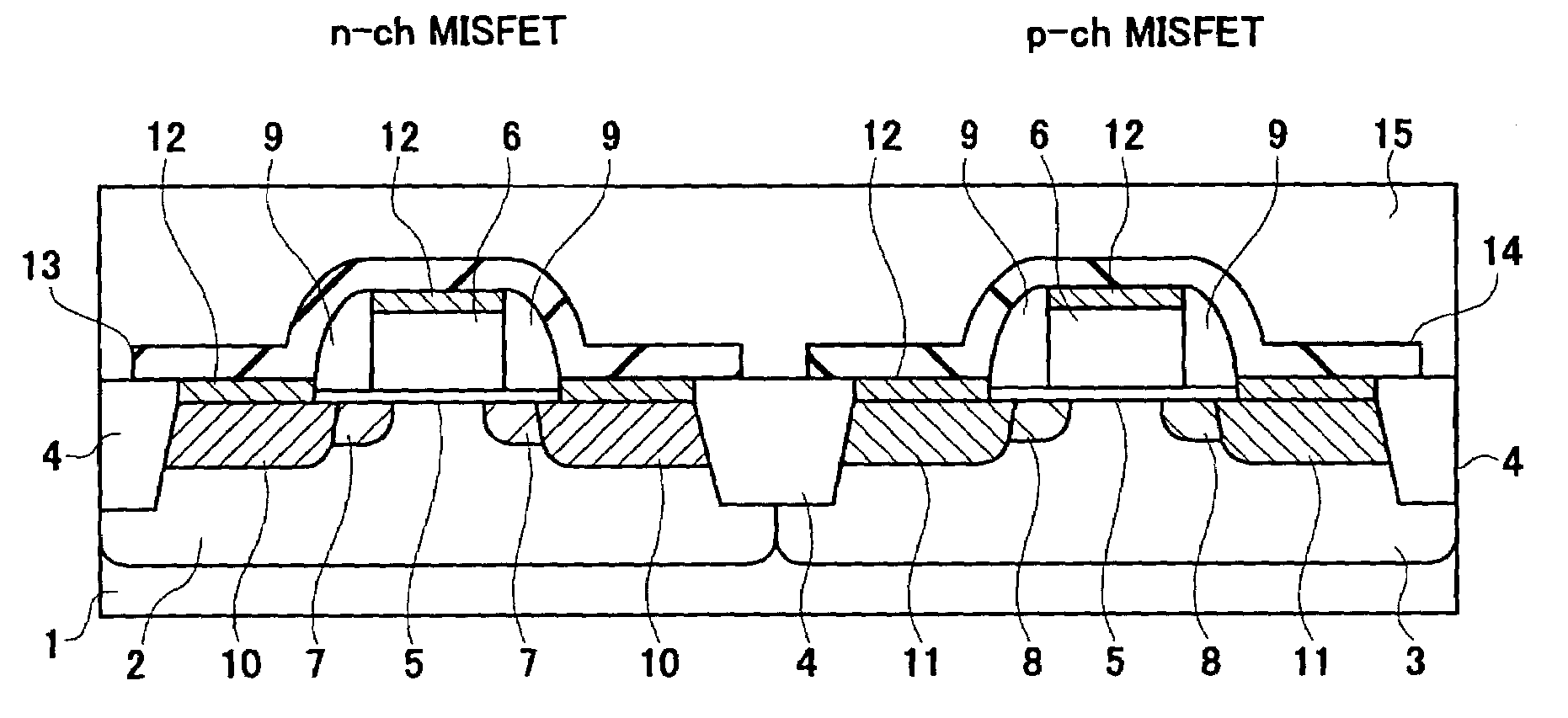

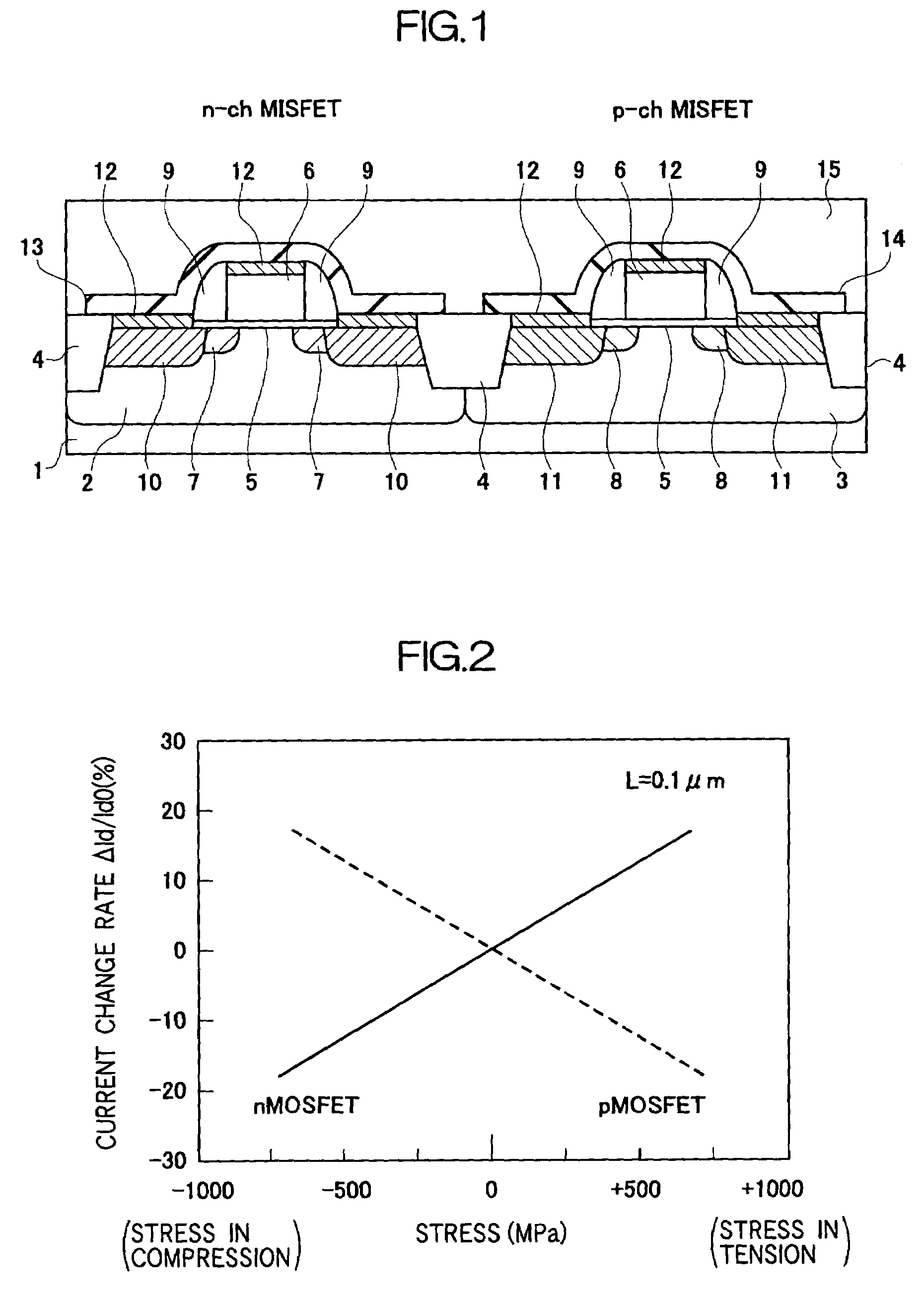

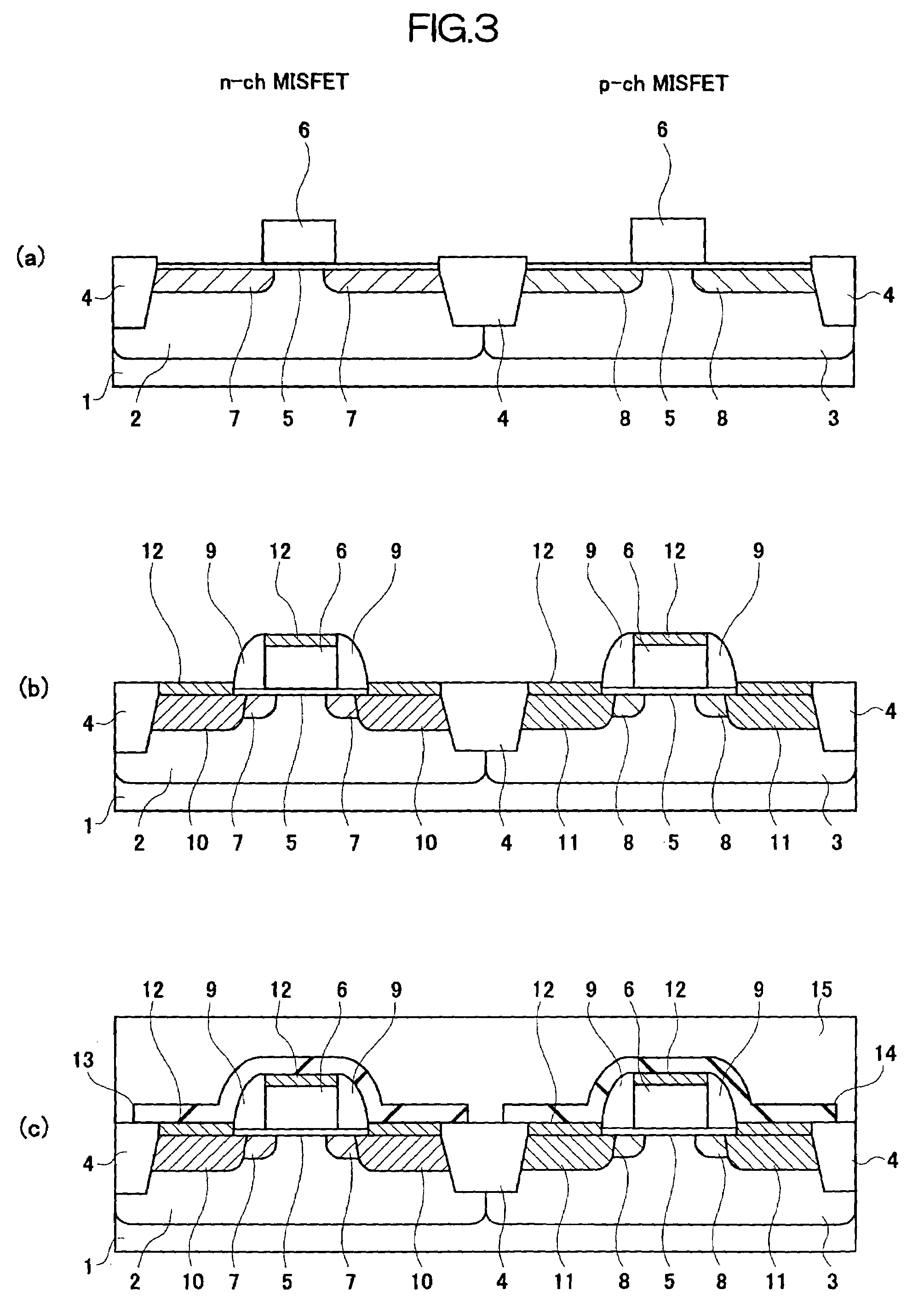

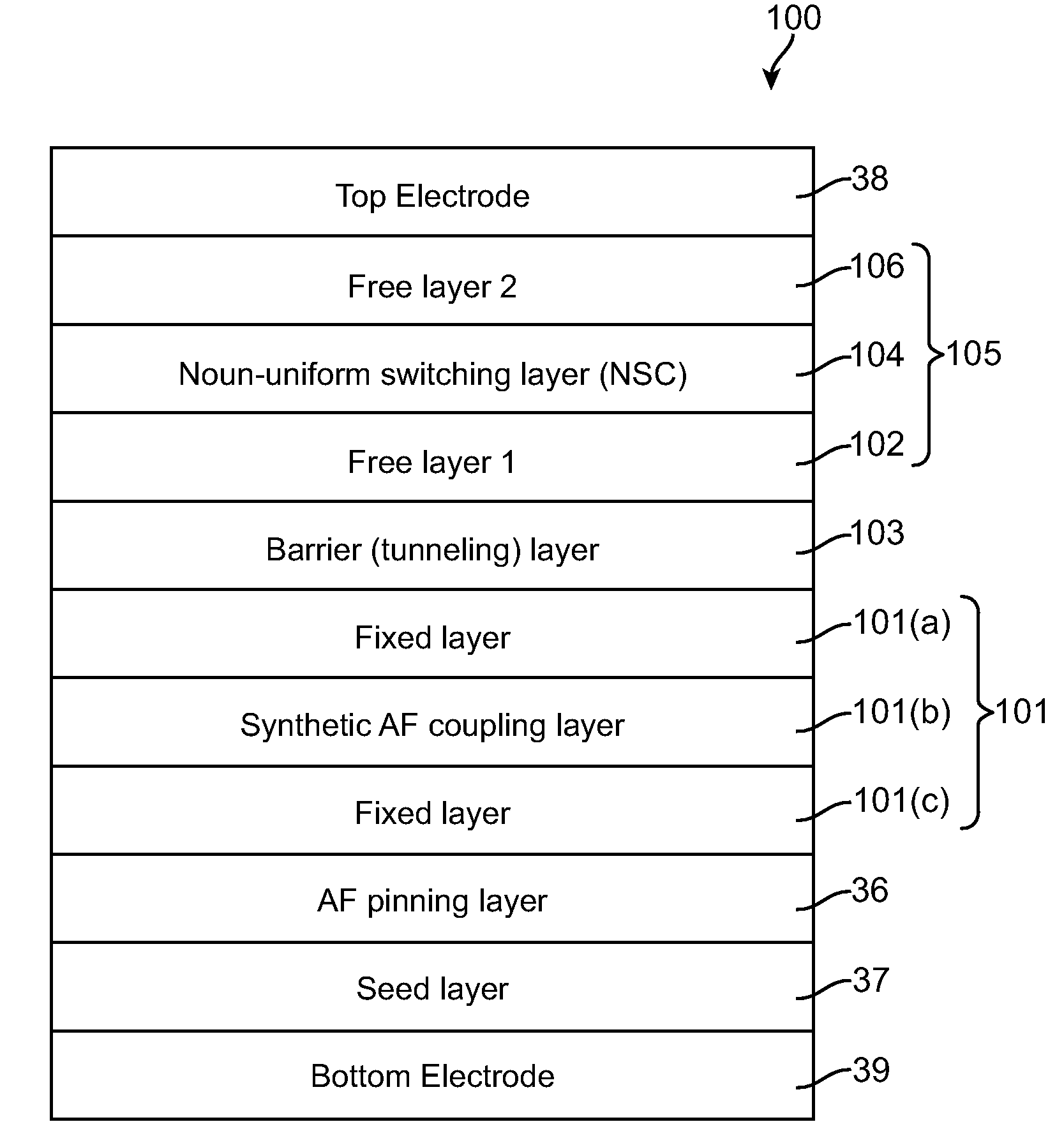

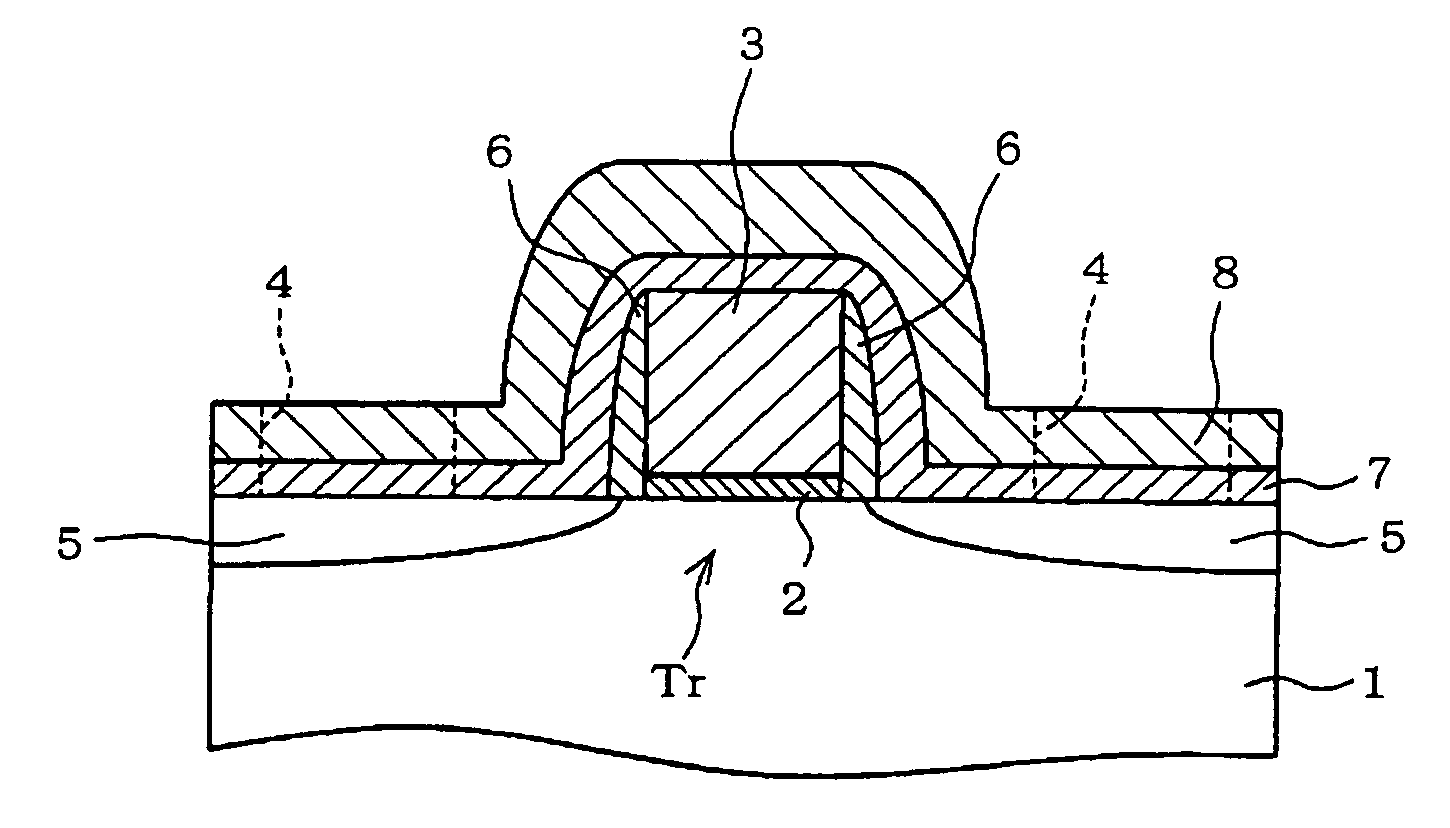

Semiconductor device including stress inducing films formed over n-channel and p-channel field effect transistors and a method of manufacturing the same

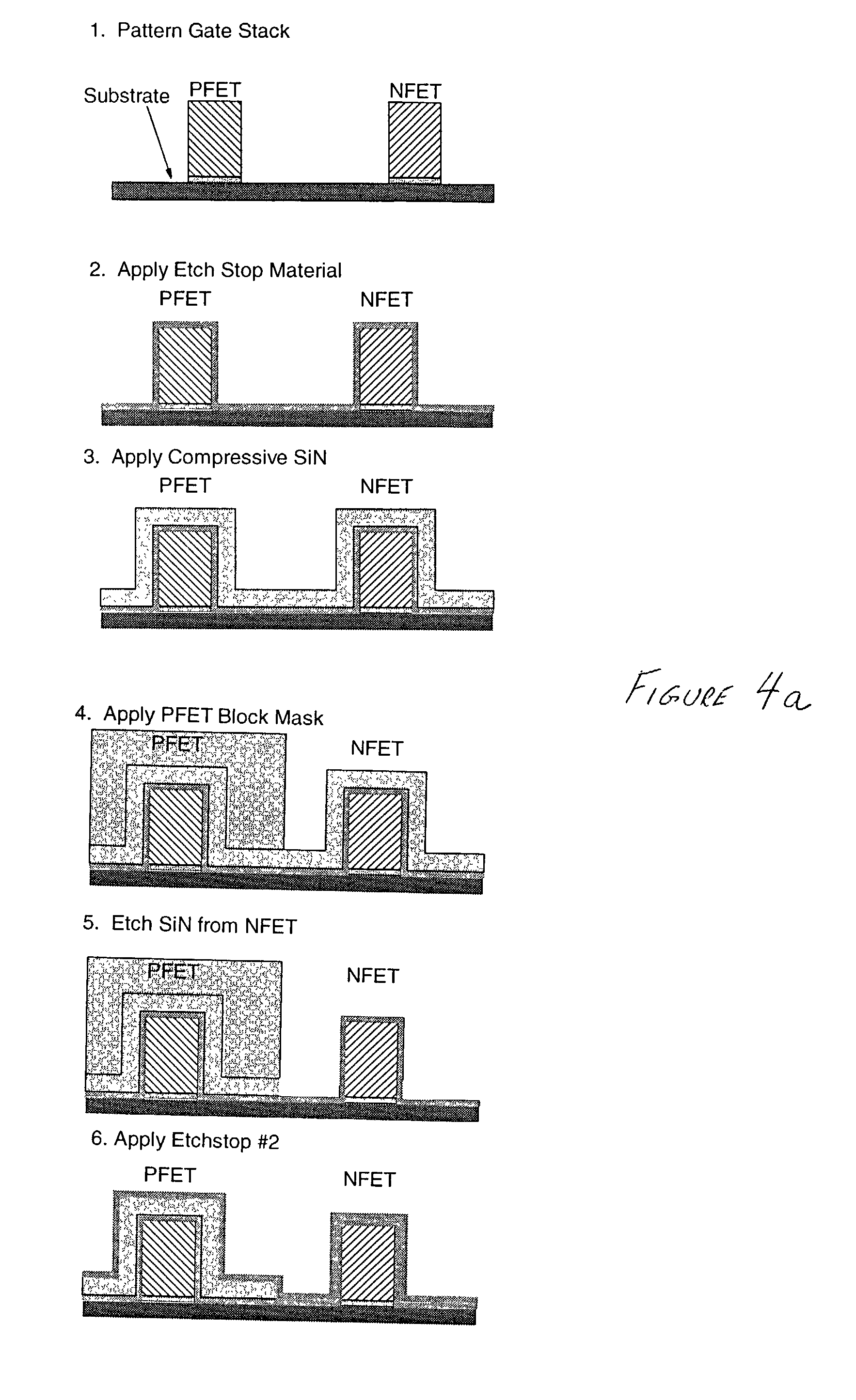

InactiveUS7115954B2Improve driving abilityImprove current drive capabilityTransistorSemiconductor/solid-state device detailsStress inducedField-effect transistor

A semiconductor device has an n channel conductivity type field effect transistor having a channel formation region formed in a first region on one main surface of a semiconductor substrate and a p channel conductivity type field effect transistor having a channel formation region formed in a second region on the main surface of the semiconductor substrate, which second region is different from the first region. An internal stress generated in the channel formation region of the n channel conductivity type field effect transistor is different from an internal stress generated in the channel formation region of the p channel conductivity type field effect transistor. The internal stress generated in the channel formation region of the n channel conductivity type field effect transistor is a tensile stress, while the internal stress generated in the channel formation region of the p channel conductivity type field effect transistor is a compressive stress.

Owner:RENESAS ELECTRONICS CORP

Repairing damage to low-k dielectric materials using silylating agents

ActiveUS20050095840A1Reduce hydrophobicityImprove hydrophobicitySemiconductor/solid-state device manufacturingStress inducedSilicate glass

A method for restoring hydrophobicity to the surfaces of organosilicate glass dielectric films which have been subjected to an etchant or ashing treatment. These films are used as insulating materials in the manufacture of integrated circuits to ensure low and stable dielectric properties in these films. The method deters the formation of stress-induced voids in these films. An organosilicate glass dielectric film is patterned to form vias and trenches by subjecting it to an etchant or ashing reagent in such a way as to remove at least a portion of previously existing carbon containing moieties and reduce hydrophobicity of said organosilicate glass dielectric film. The vias and trenches are thereafter filled with a metal and subjected to an annealing treatment. After the film is subjected to the etchant or ashing reagent, but before being subjected to an annealing treatment, the film is contacted with a toughening agent composition to restore some of the carbon containing moieties and increase the hydrophobicity of the organosilicate glass dielectric film.

Owner:HONEYWELL INT INC

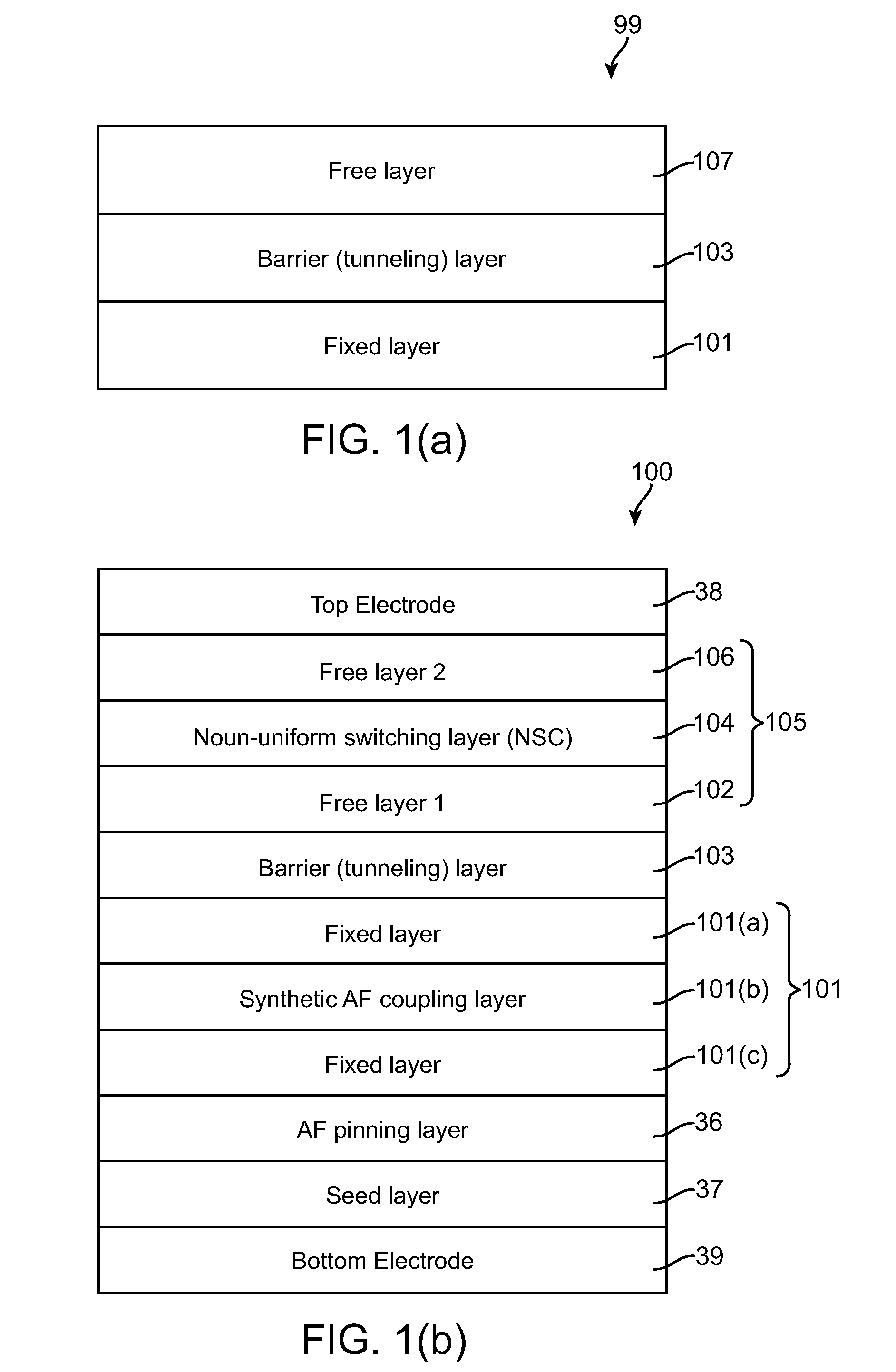

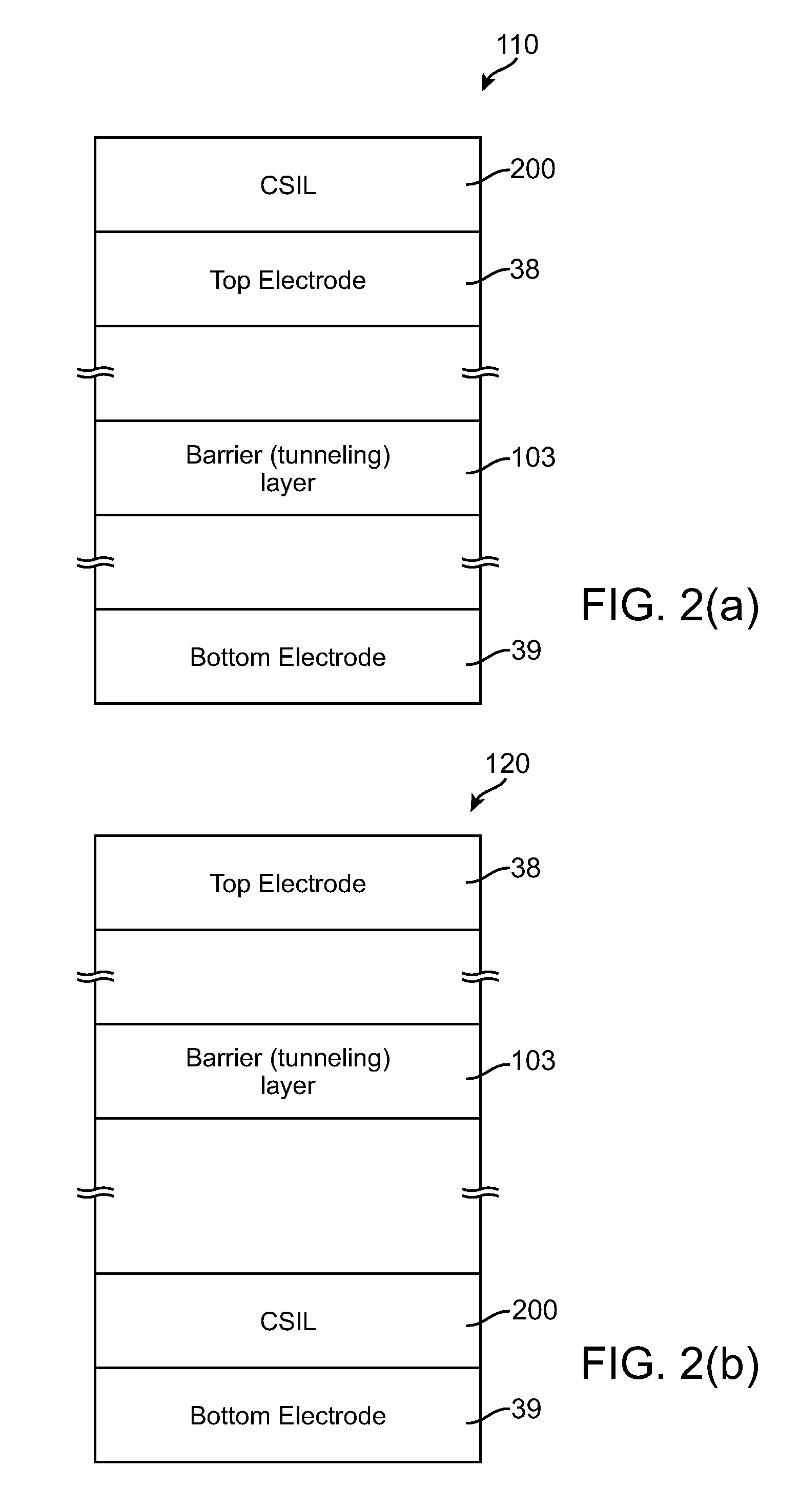

Low resistance high-tmr magnetic tunnel junction and process for fabrication thereof

ActiveUS20080164548A1Increase resistanceImprove scalabilityMagnetic-field-controlled resistorsSemiconductor/solid-state device manufacturingStress inducedMagnetic memory

One embodiment of the present invention includes a non-volatile magnetic memory element including a fixed layer, a barrier layer formed on top of the fixed layer, and a free layer formed on top of the barrier layer, wherein the electrical resistivity of the barrier layer is reduced by placing said barrier layer under compressive stress. Compressive stress is induced by either using a compressive stress inducing layer, or by using inert gases at low pressure during the sputtering process as the barrier layer is deposited, or by introducing compressive stress inducing molecules into the molecular lattice of the barrier layer.

Owner:AVALANCHE TECH

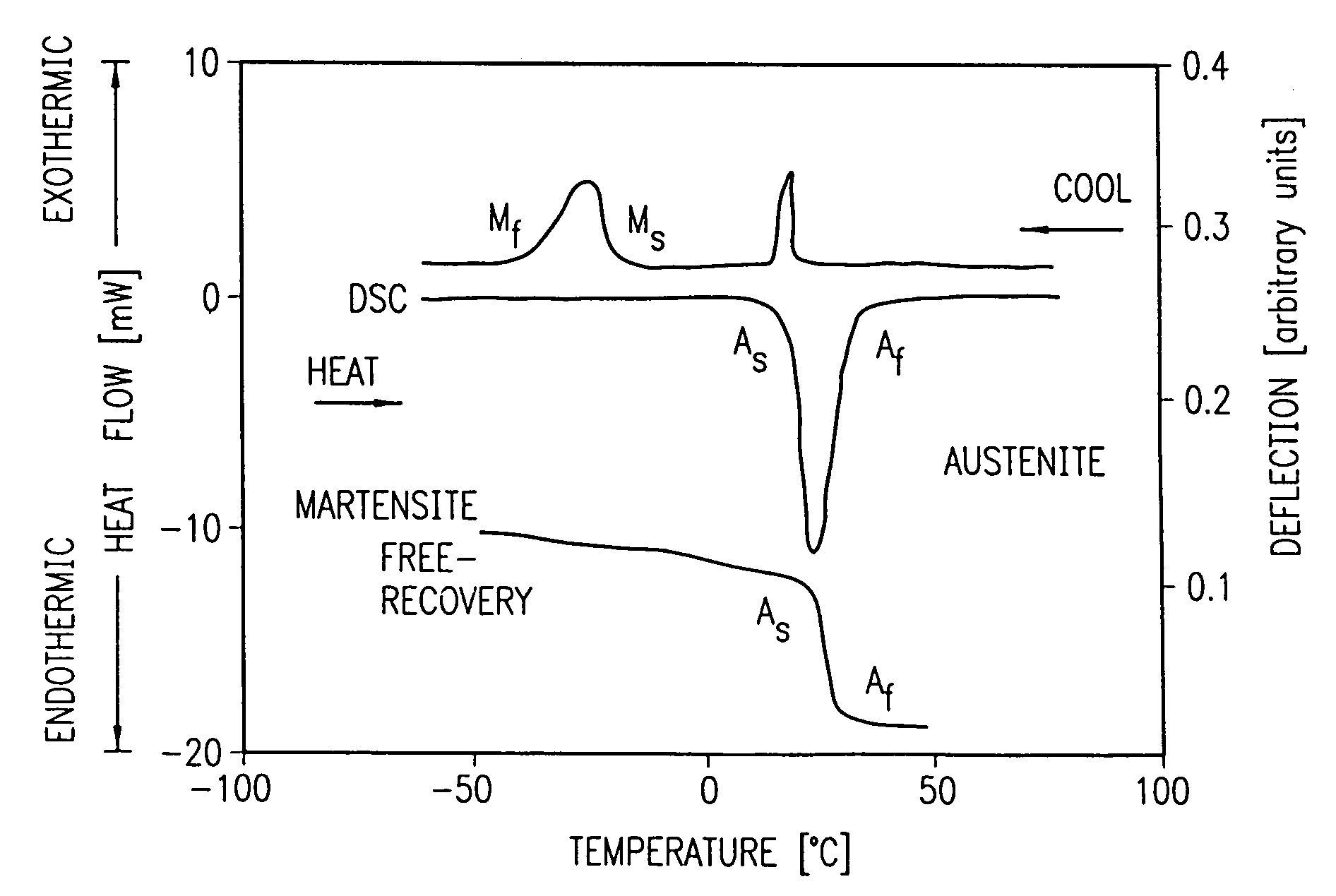

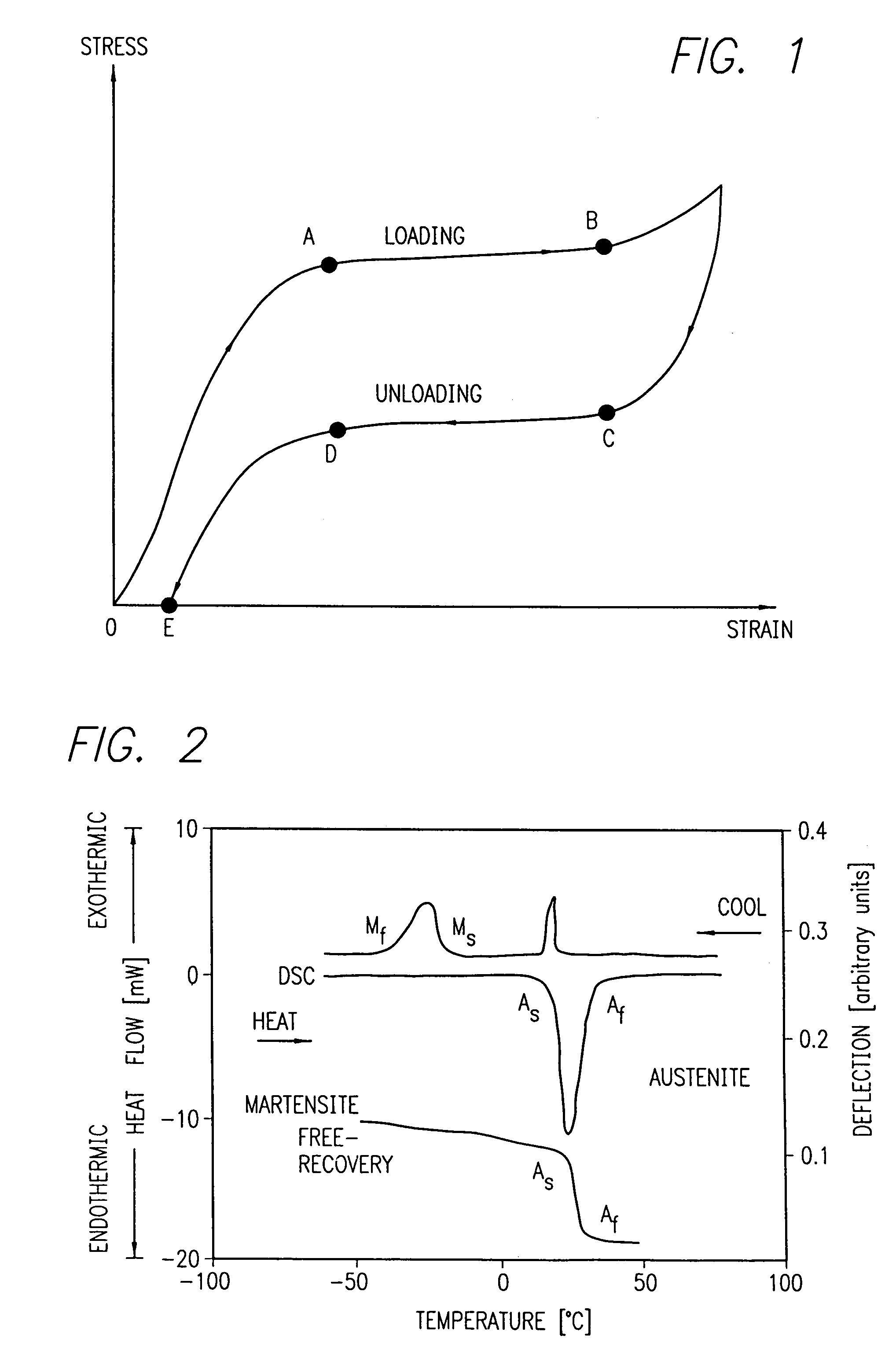

Avoiding stress-induced martensitic transformation in nickel titanium alloys used in medical devices

A process for assembling a medical device made from a nickel-titanium alloy for use in a mammalian body while avoiding the formation of stress-induced martensite and a medical device used in combination with a delivery system for deployment into the mammalian body are disclosed. By heating the nickel-titanium alloy of the medical device to a temperature above Md, and deforming and installing the device into a delivery system or holding capsule, it is possible to avoid the formation of stress-induced martensite in the stent, which stays in the austenitic phase throughout.

Owner:ABBOTT LAB INC

Group III nitride photonic devices on silicon carbide substrates with conductive buffer interlayer structure

InactiveUS20020008241A1Avoid crackingEasy to manufactureTransistorSolid-state devicesStress inducedStress relieving

An optoelectronic device with a Group III Nitride active layer is disclosed that comprises a silicon carbide substrate; an optoelectronic diode with a Group III nitride active layer; a buffer structure selected from the group consisting of gallium nitride and indium gallium nitride between the silicon carbide substrate and the optoelectronic diode; and a stress-absorbing structure comprising a plurality of predetermined stress-relieving areas within the crystal structure of the buffer structure, so that stress-induced cracking that occurs in the buffer structure occurs at predetermined areas rather than elsewhere in the buffer structure.

Owner:CREE INC

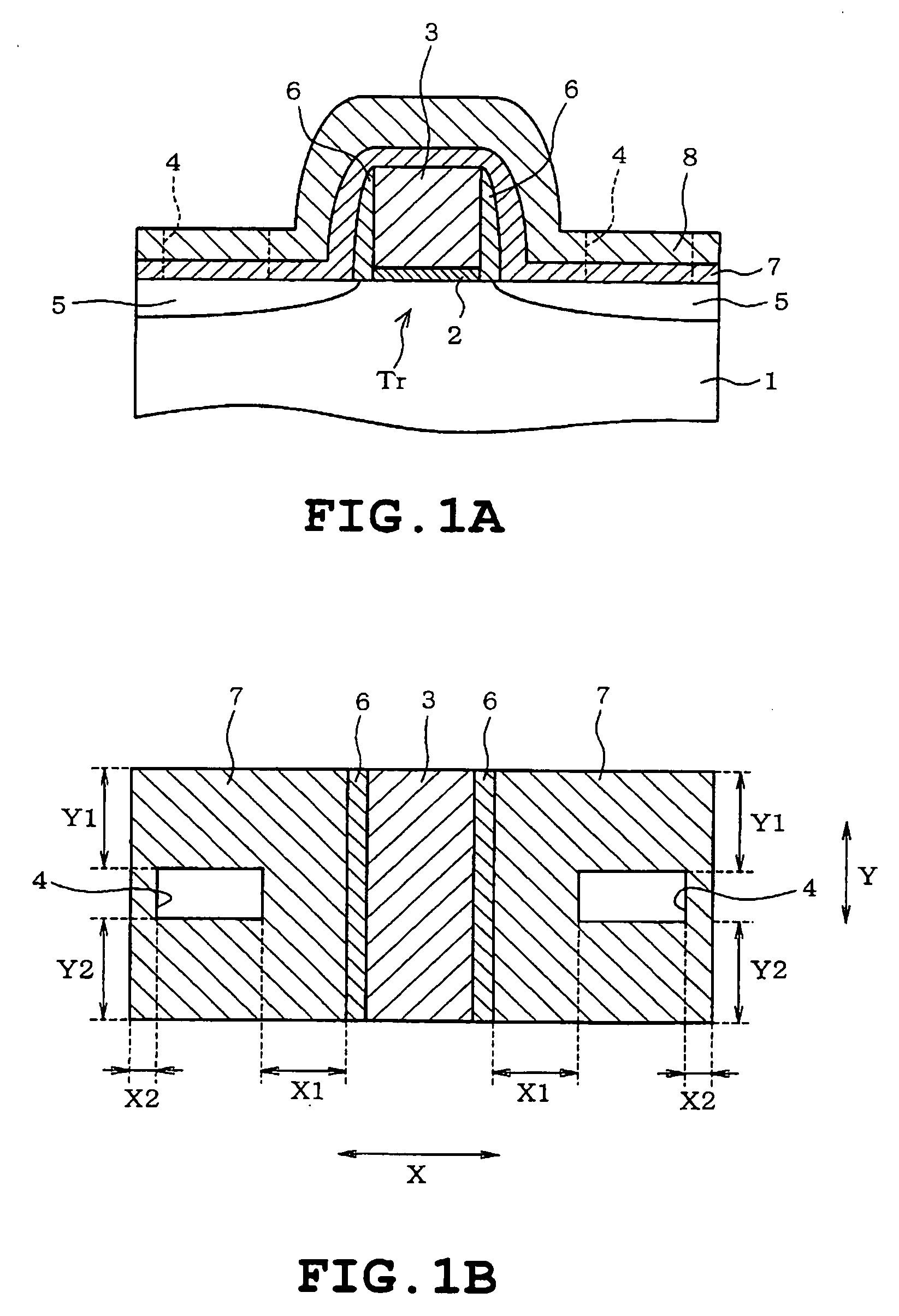

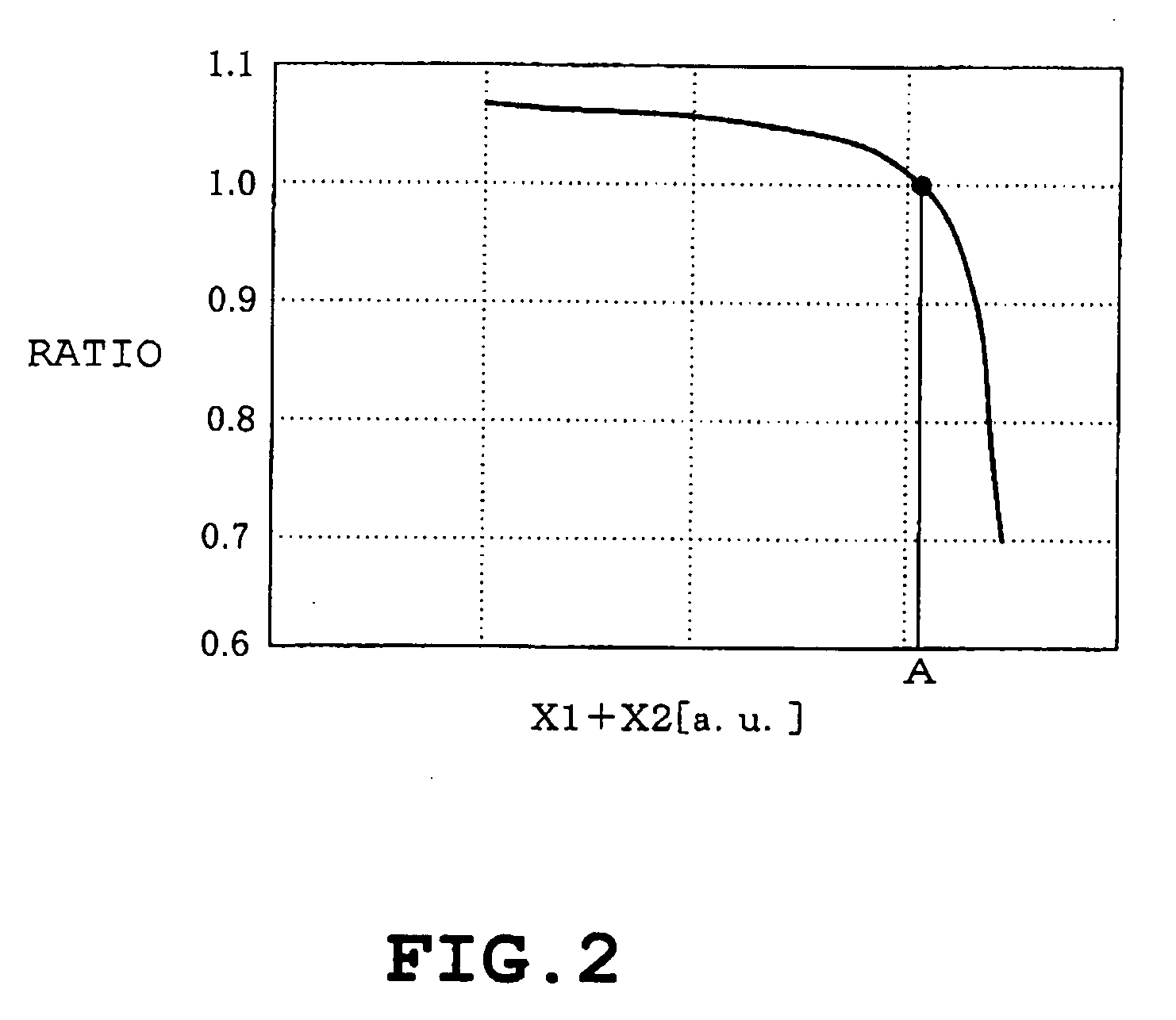

Semiconductor device and method of fabricating the same

InactiveUS20070023795A1Without deterioration in characteristicHigh speedSemiconductor/solid-state device manufacturingSemiconductor devicesStress inducedSurface layer

A semiconductor device includes a metal oxide semiconductor (MOS) transistor including two source / drain regions located at a surface layer side of the semiconductor substrate, a stress-inducing film formed so as to cover the source / drain region of the MOS transistor, the stress-inducing film applying stress to a channel region formed between the source / drain regions and having an opening corresponding to an electrical connection region of the source / drain regions, the opening having a first dimension with respect to a propagation direction of a charge carrier moving within the channel region of the MOS transistor and a second dimension with respect to a direction perpendicular to the propagation direction of the MOS transistor, the first dimension being larger than the second dimension.

Owner:KK TOSHIBA

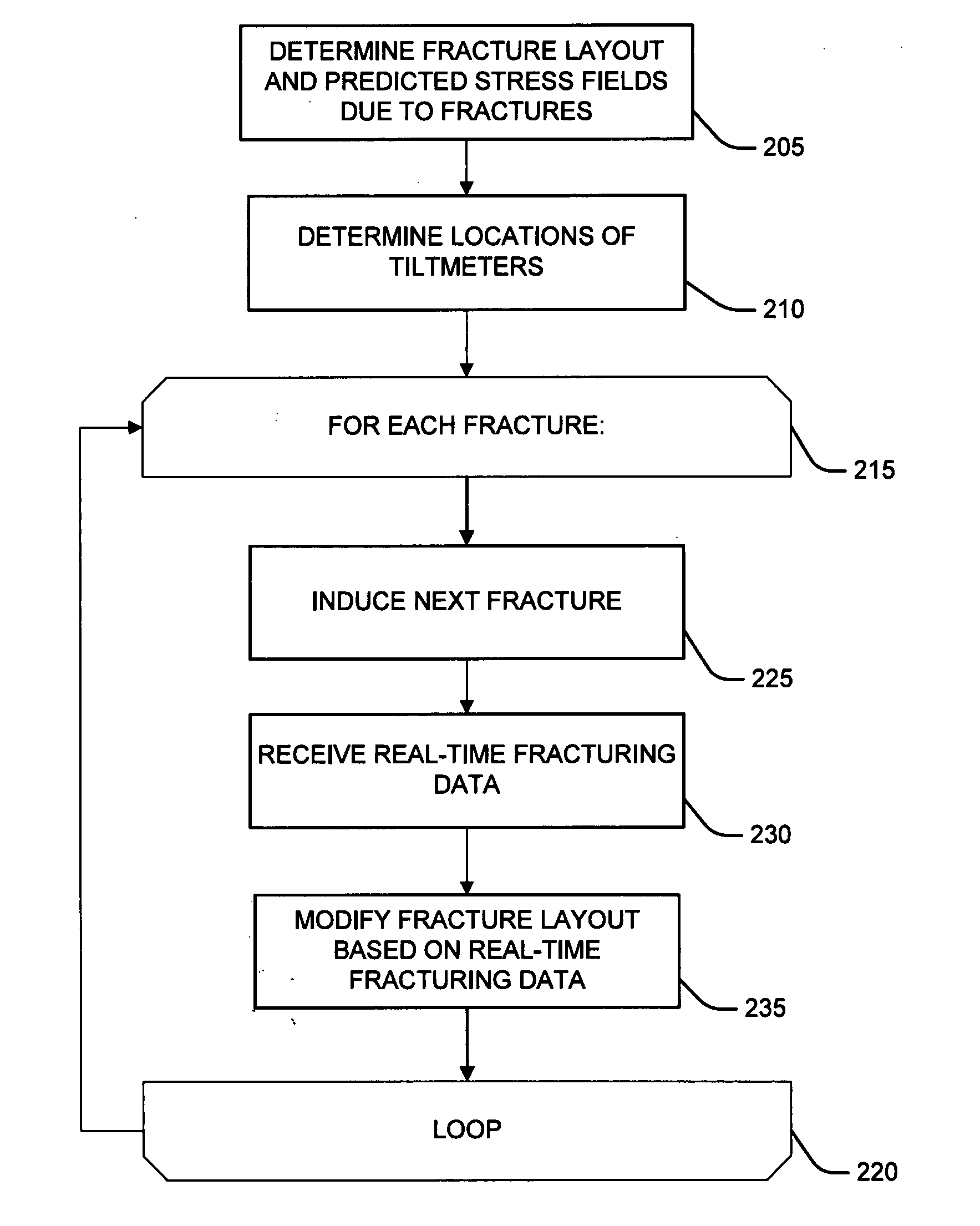

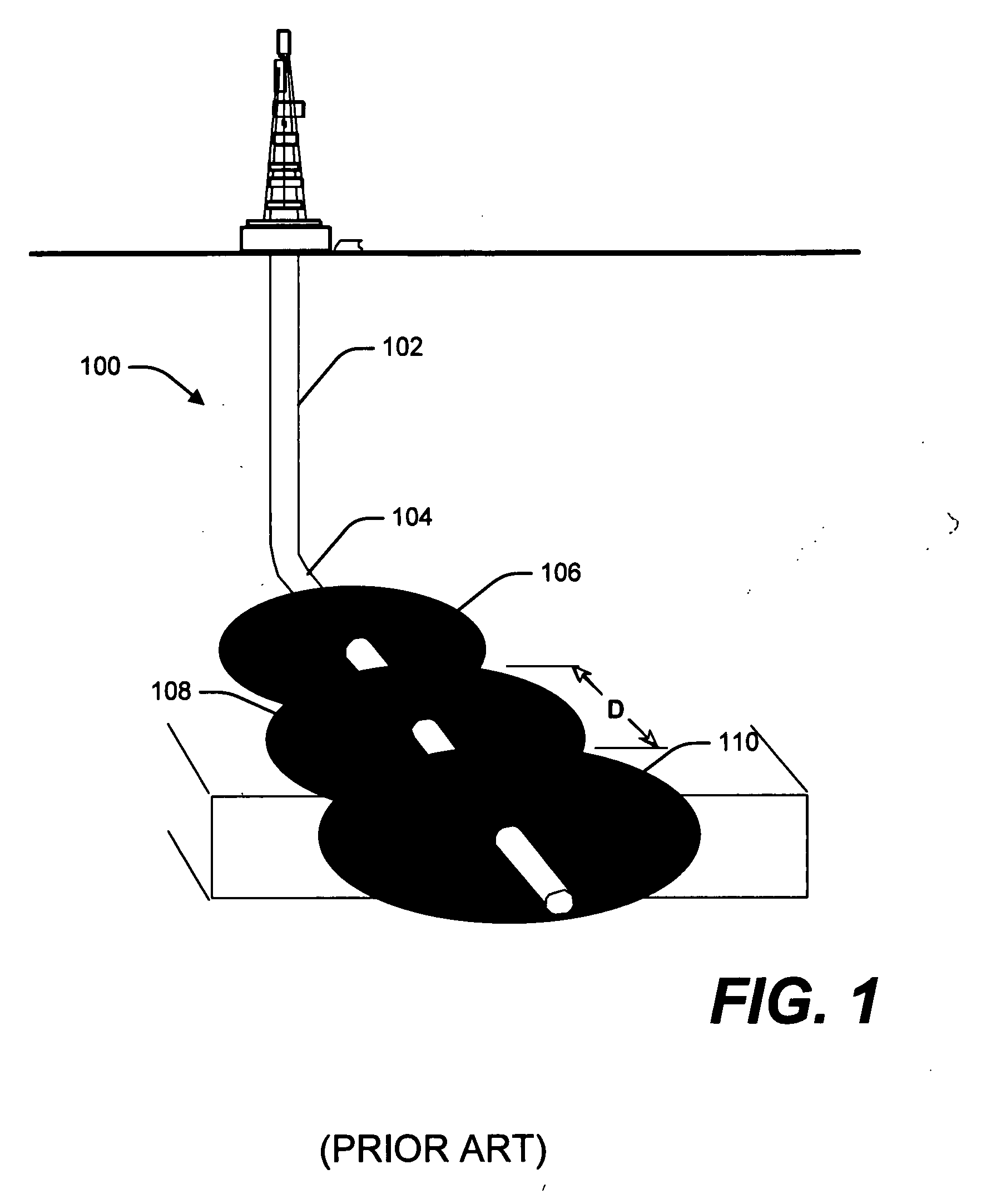

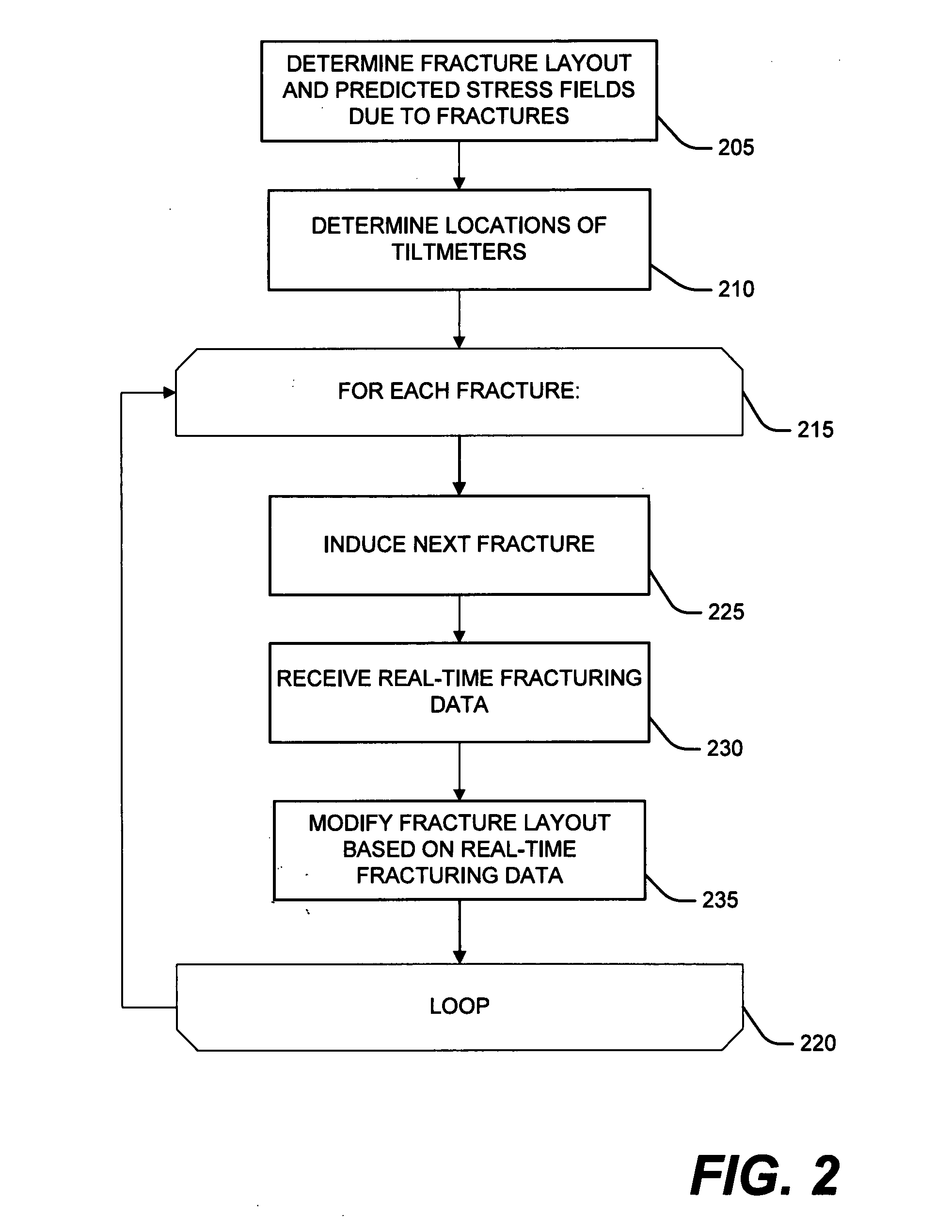

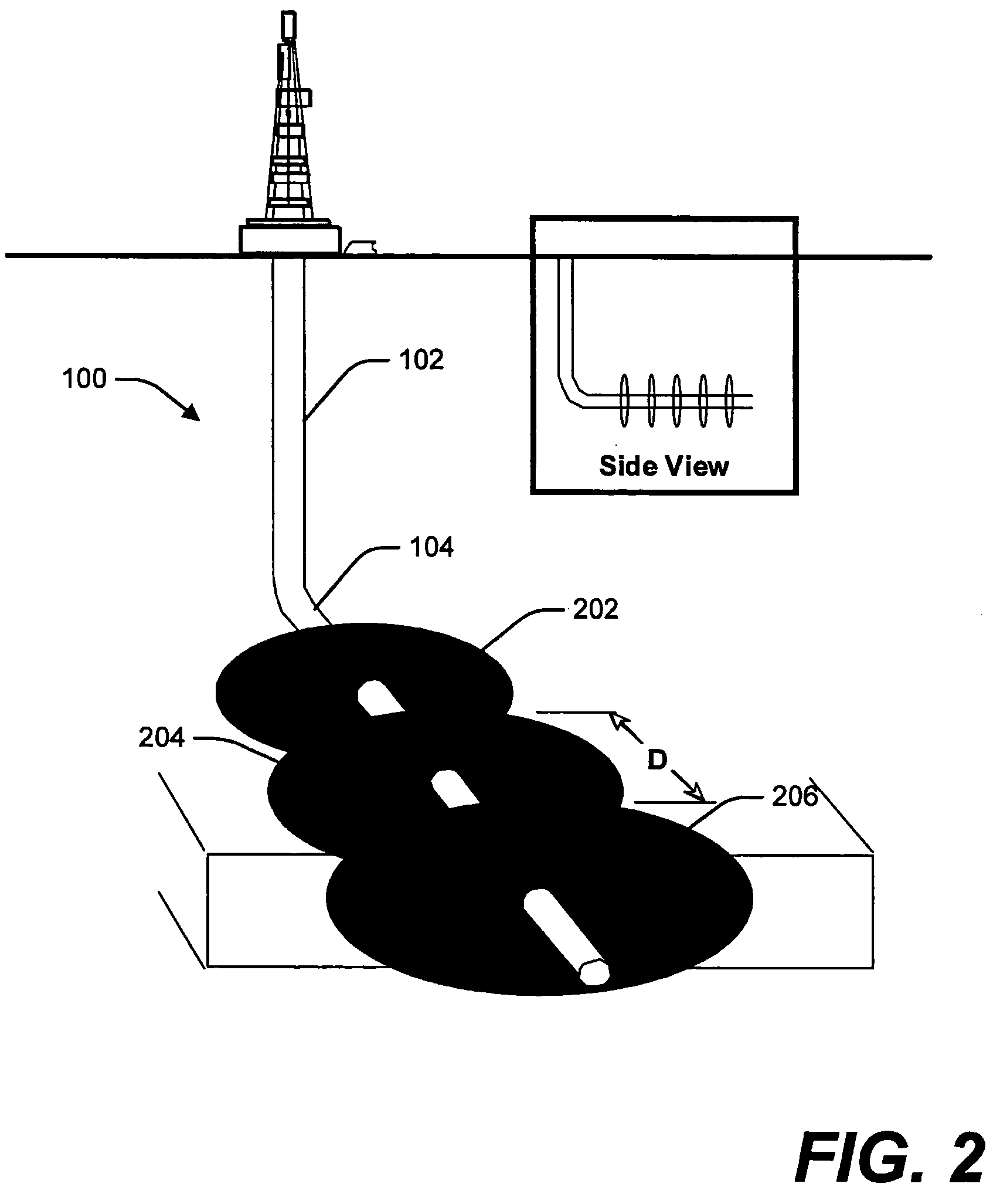

Methods for geomechanical fracture modeling

The present invention relates generally to methods for designing and optimizing the number, placement, and size of fractures in a subterranean formation and more particularly to methods that account for stress interference from other fractures when designing and optimizing the number, placement, and size of fractures in the subterranean formation. The present invention optimizes the number, placement and size of fractures in a subterranean formation. The present invention determines one or more geomechanical stresses induced by each fracture based on the dimensions and location of each fracture, including surface deformations caused by each fracture. The present invention determines a maximum number of fractures and a predicted stress field based on the geomechanical stresses induced by each of the fractures.

Owner:HALLIBURTON ENERGY SERVICES INC

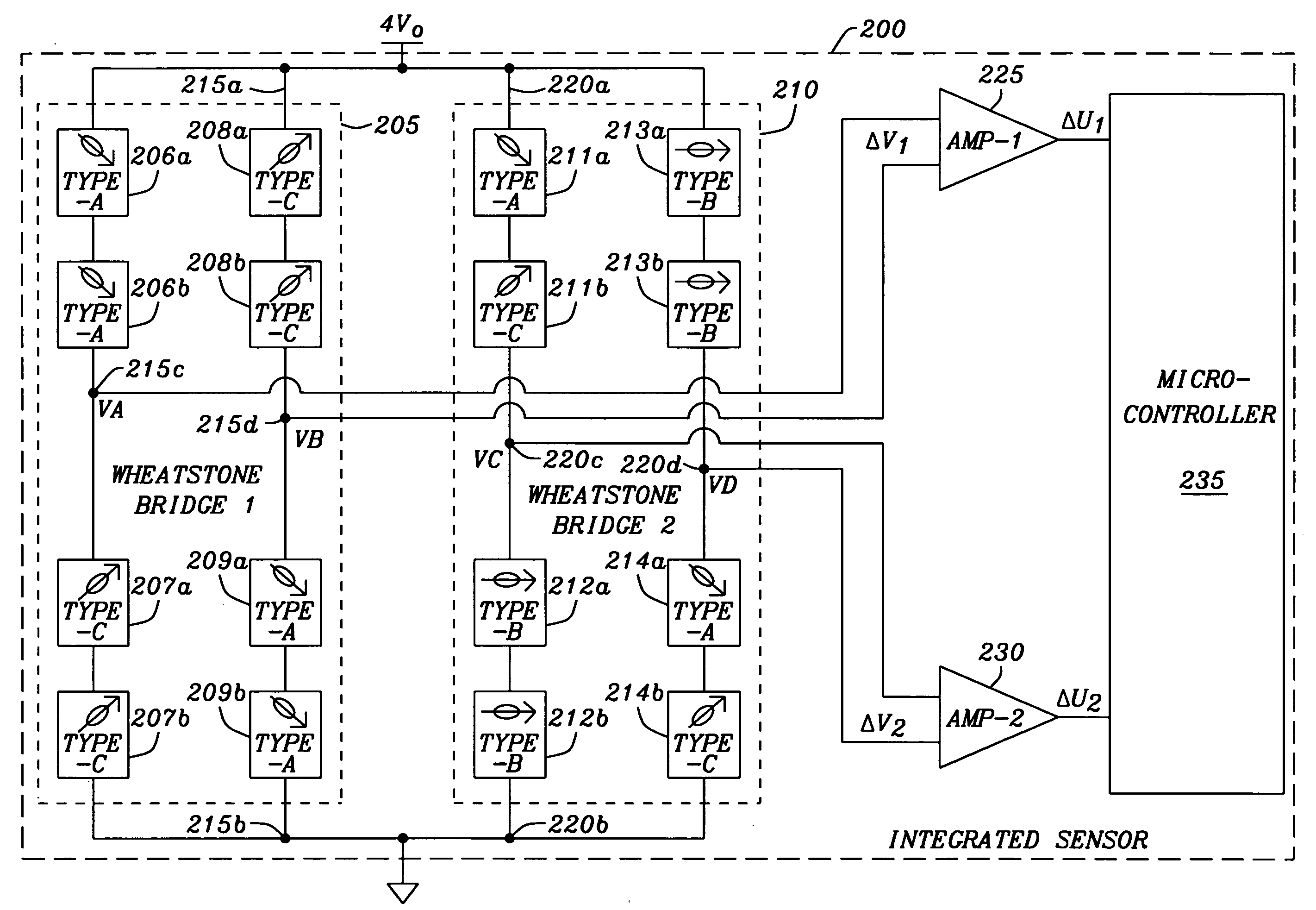

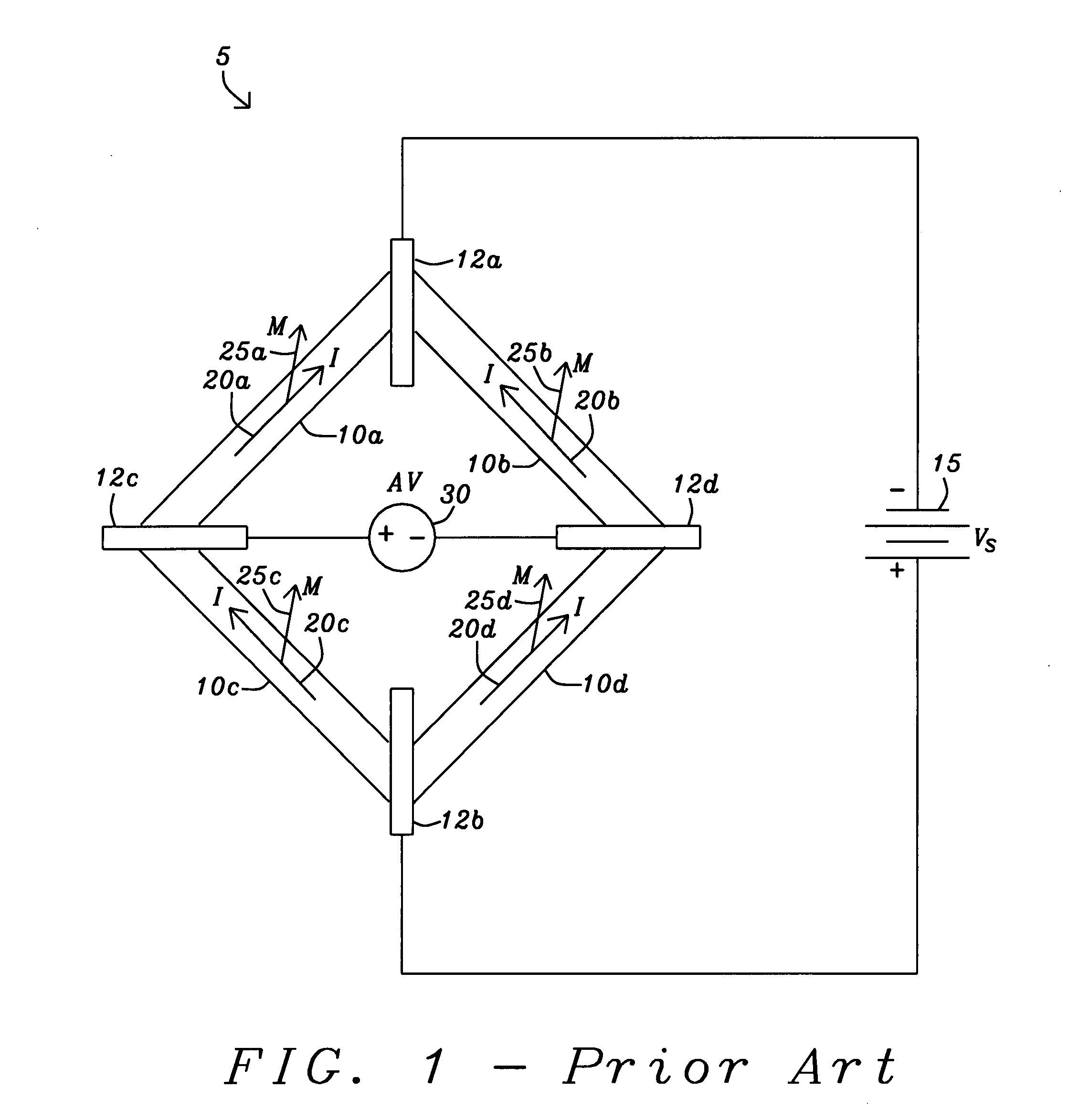

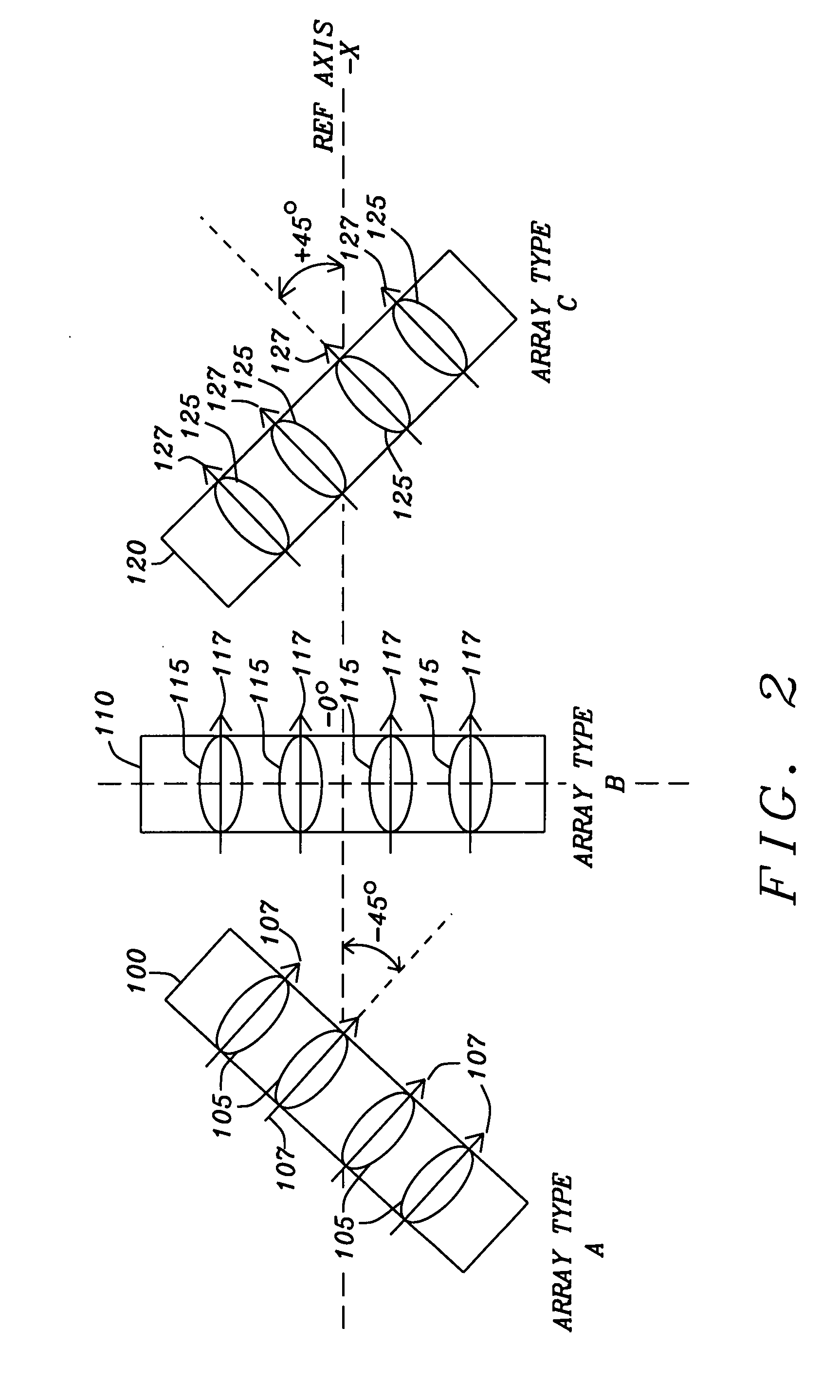

Magnetic tunnel junction (MTJ) based magnetic field angle sensor

A magnetic field angle sensor for measurement of a magnetic field angle over a 360° range has magnetic tunnel junction elements oriented at multiple angles. The magnetic field angle sensor includes multiple magnetic tunnel junction elements formed on a substrate that have an anti-ferromagnetic layer and pinned synthetic multiple layer. The magnetic tunnel junction elements are patterned to have a large dimensional aspect ratio and large anisotropies the pinned synthetic multiple layer of the magnetic tunnel junction elements. The magnetic tunnel junction elements are annealed in the presence of a strong magnetic field in a direction of the reference axis and the annealed for a second time with no external magnetic field so that exchange pinning is reduced and strong stress induced anisotropies of the pinned synthetic multiple layer align magnetization of the pinned synthetic multiple layer align a long axis of each of the magnetic tunnel junction elements.

Owner:HEADWAY TECH INC

Advanced technique for forming a transistor having raised drain and source regions

InactiveUS7138320B2Improve featuresTransistorSemiconductor/solid-state device manufacturingStress inducedCharge carrier

By recessing a semiconductor layer, preferably by locally oxidizing the semiconductor layer, a stress-inducing material and / or a dopant species may be introduced into the thinned semiconductor layer in the vicinity of a gate electrode structure by means of a subsequent epitaxial growth process. In particular, the stress-inducing material formed adjacent to the gate electrode structure exerts compressive or tensile stress, depending on the type of material deposited, thereby also enhancing the mobility of the charge carriers in a channel region of the transistor element.

Owner:GLOBALFOUNDRIES INC

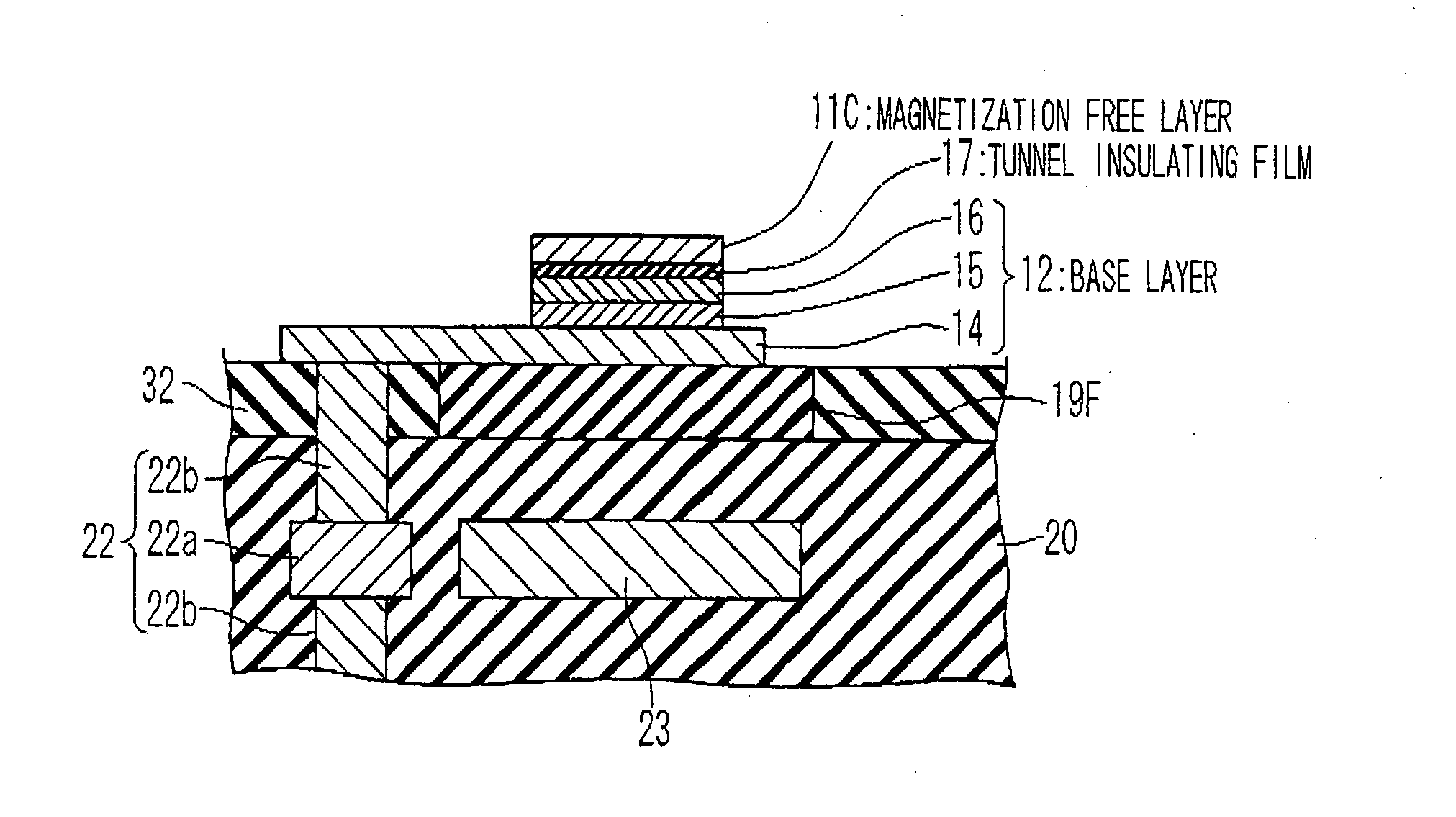

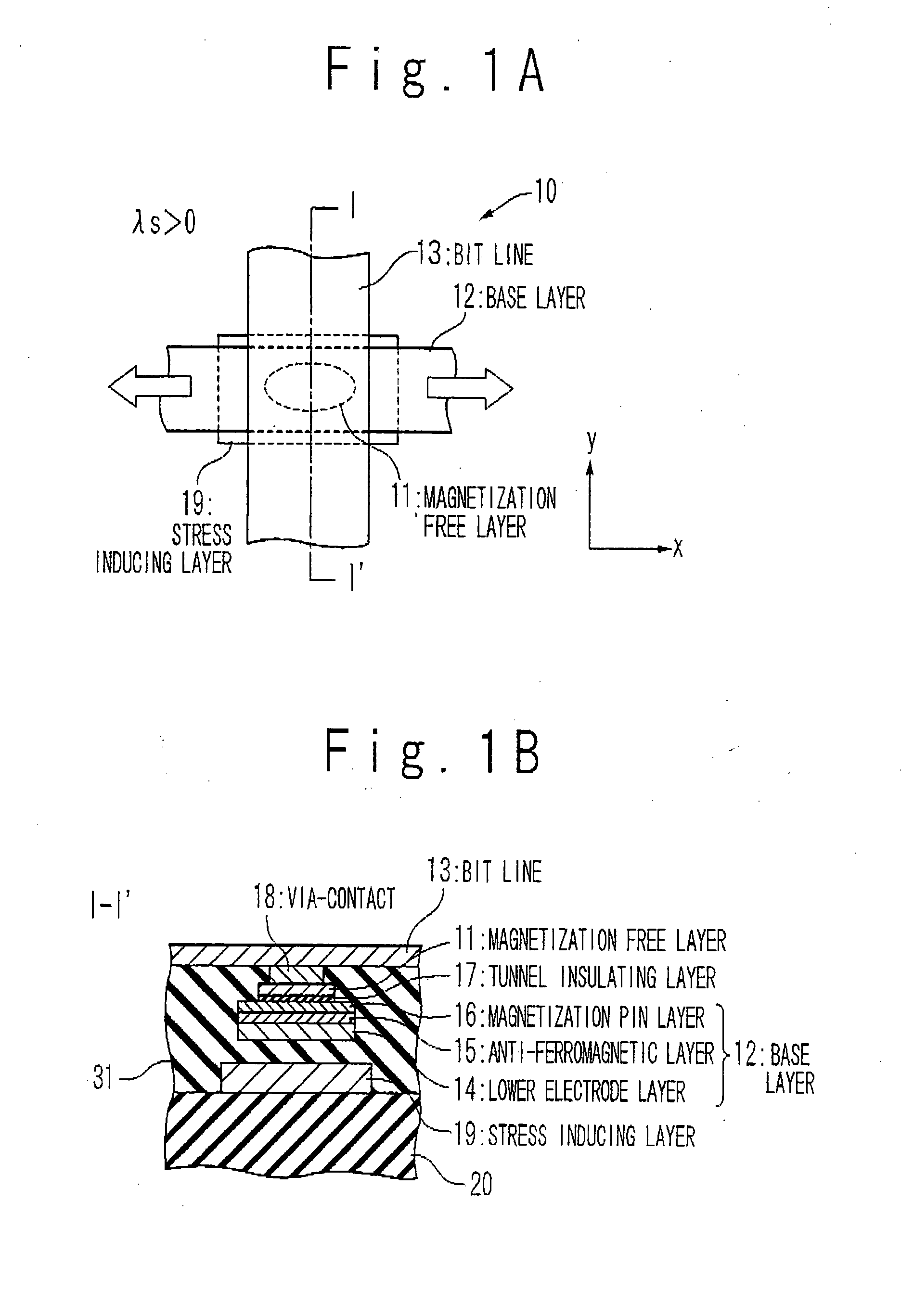

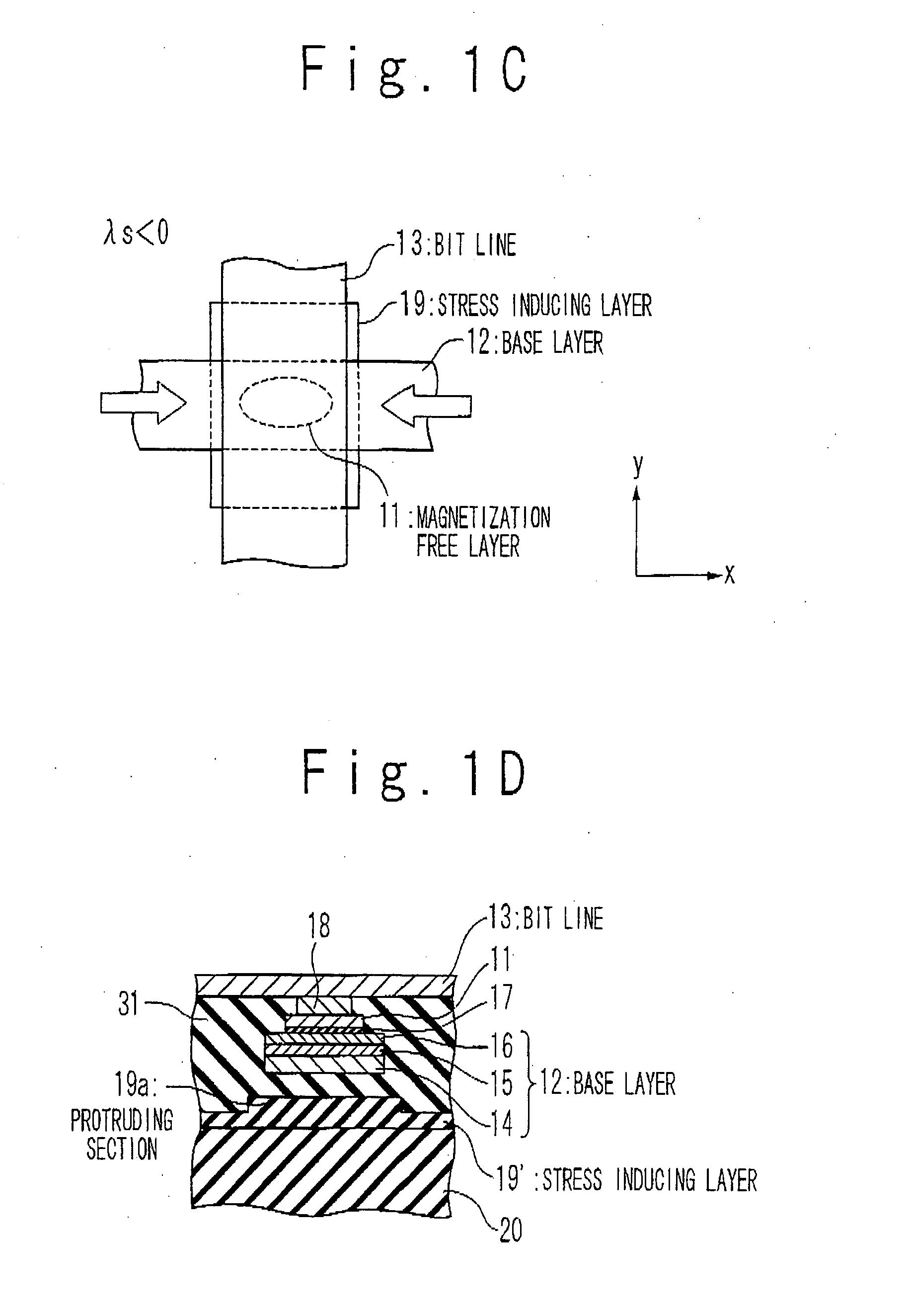

Magnetic Memory and Manufacturing Method For the Same

ActiveUS20080164502A1Suppress mutationReduce variationMagnetic-field-controlled resistorsSolid-state devicesStress inducedMagnetic anisotropy

The present invention to provide a new technique to reduce a variation in switching field of a magnetization free layer in a magnetic memory. The magnetic memory according to the present invention includes a magnetization free layer including a ferromagnetic layer having a shape magnetic anisotropy in a first direction and a magnetic strain constant is positive; and a stress inducing structure configured to apply a tensile stress to said magnetization free layer in a same direction as the first direction.

Owner:NEC CORP

Methods for geomechanical fracture modeling

The present invention relates generally to methods for designing and optimizing the number, placement, and size of fractures in a subterranean formation and more particularly to methods that account for stress interference from other fractures when designing and optimizing the number, placement, and size of fractures in the subterranean formation. The present invention optimizes the number, placement and size of fractures in a subterranean formation. The present invention determinines one or more geomechanical stresses induced by each fracture based on the dimensions and location of each fracture. The present invention determinines a maximum number of fractures and a predicted stress field based on the geomechanical stresses induced by each of the fractures

Owner:HALLIBURTON ENERGY SERVICES INC

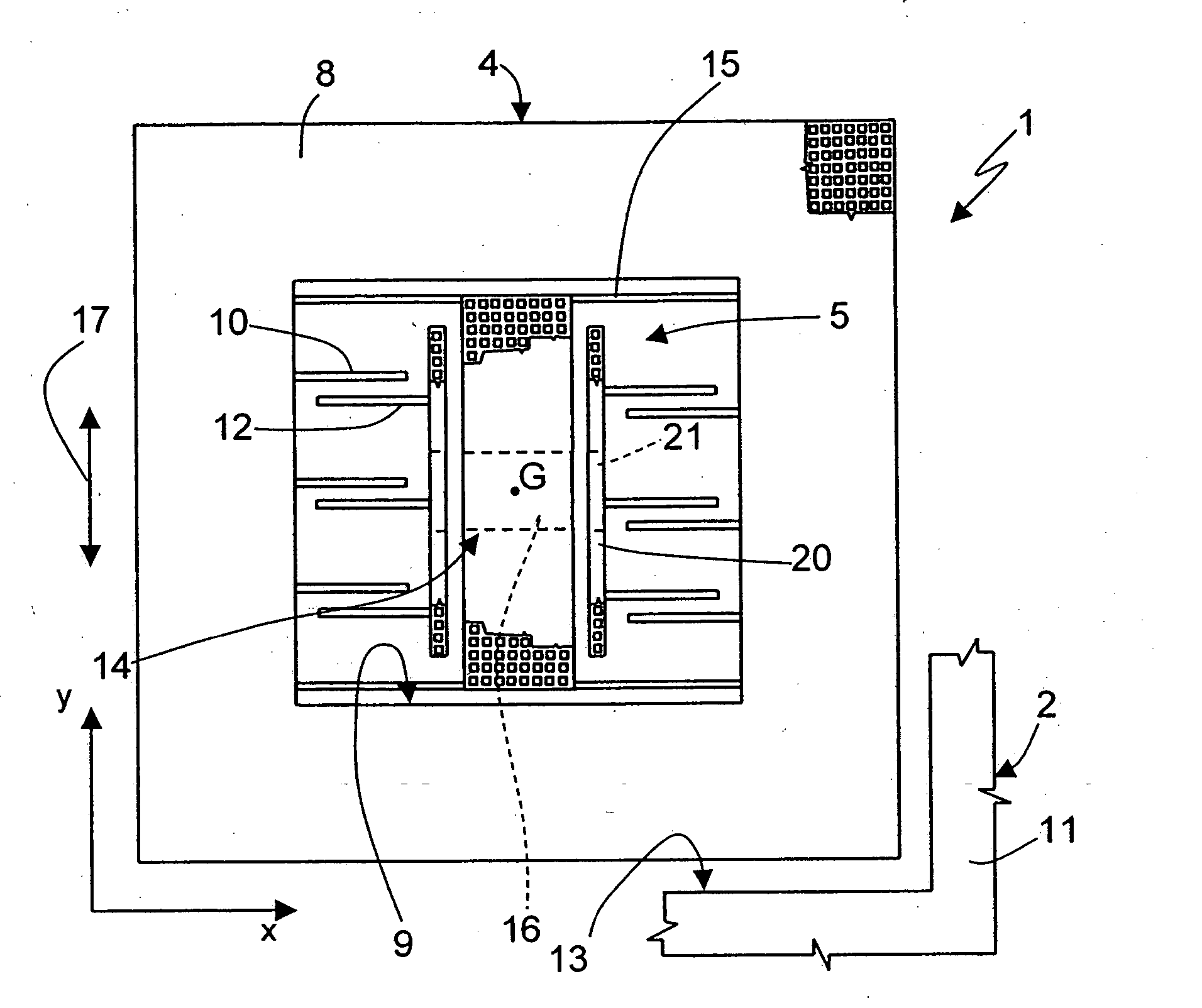

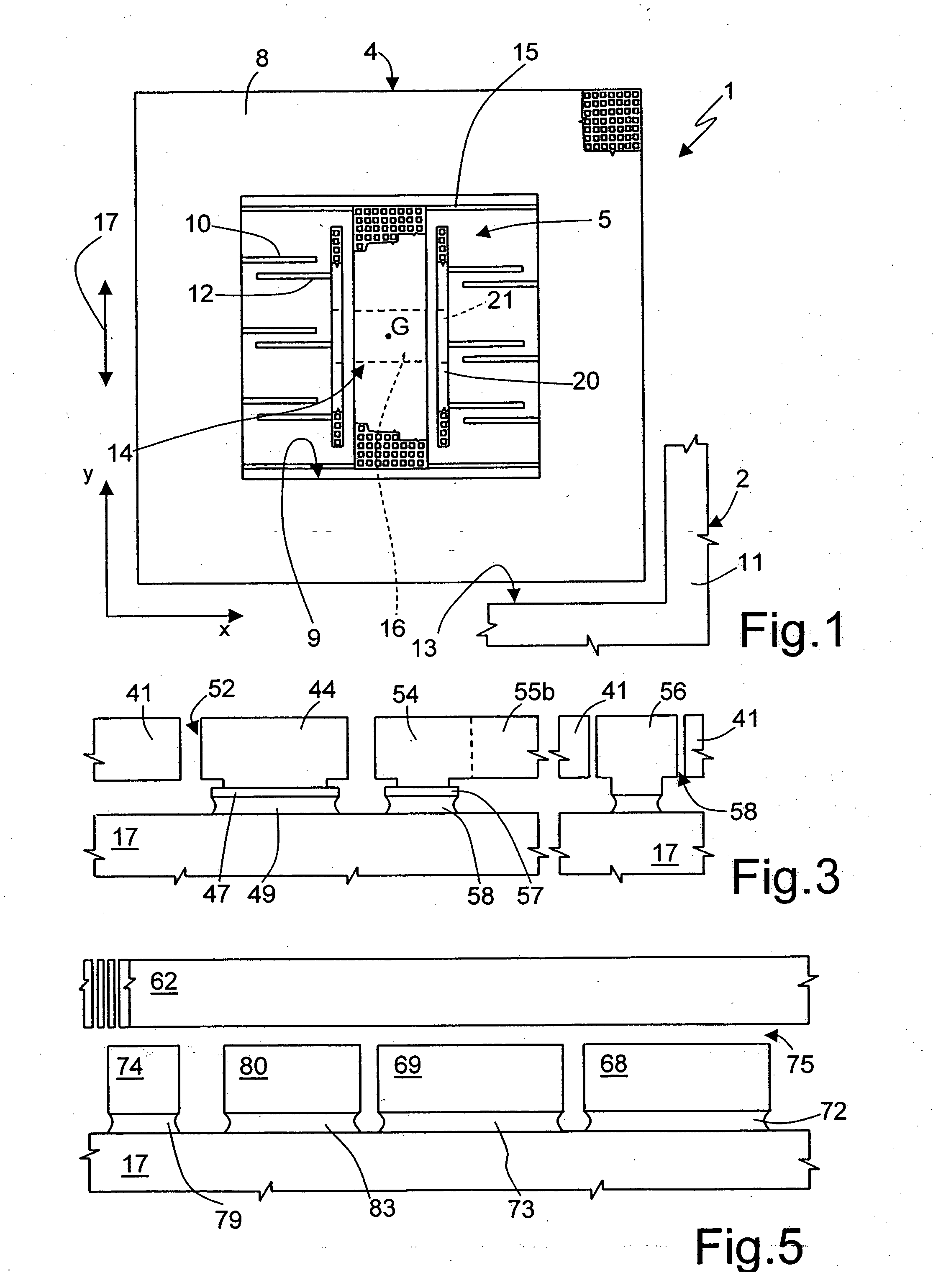

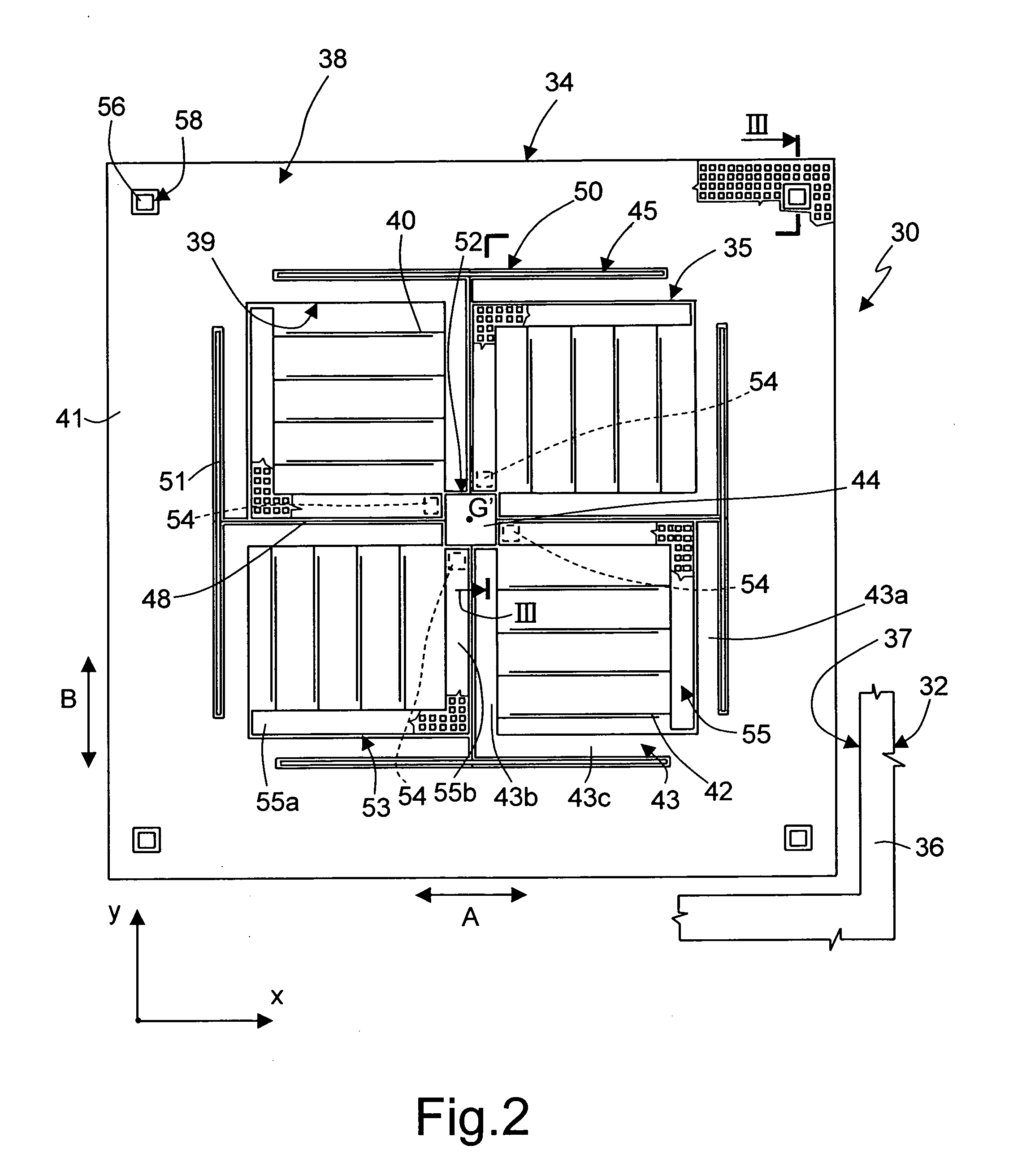

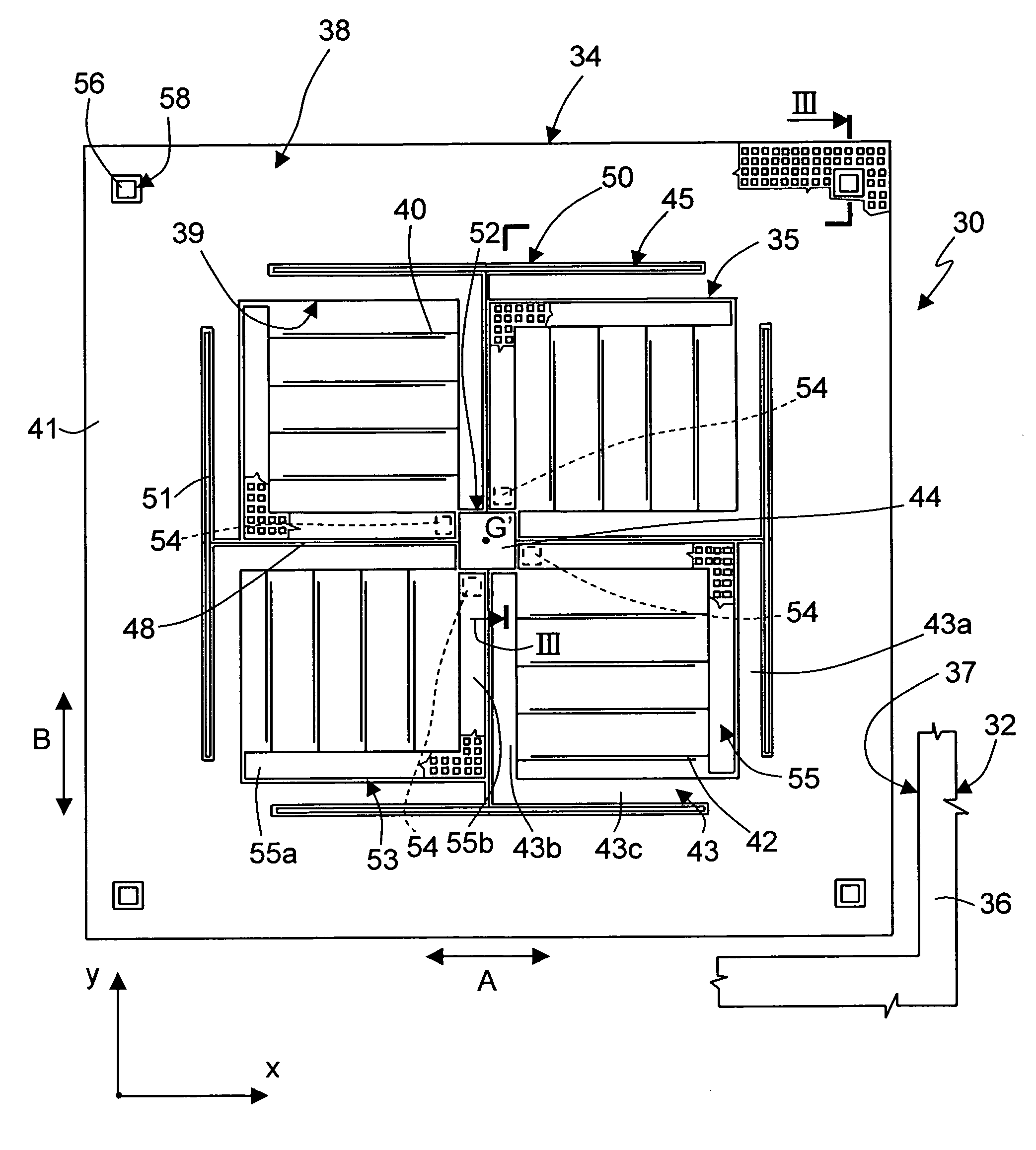

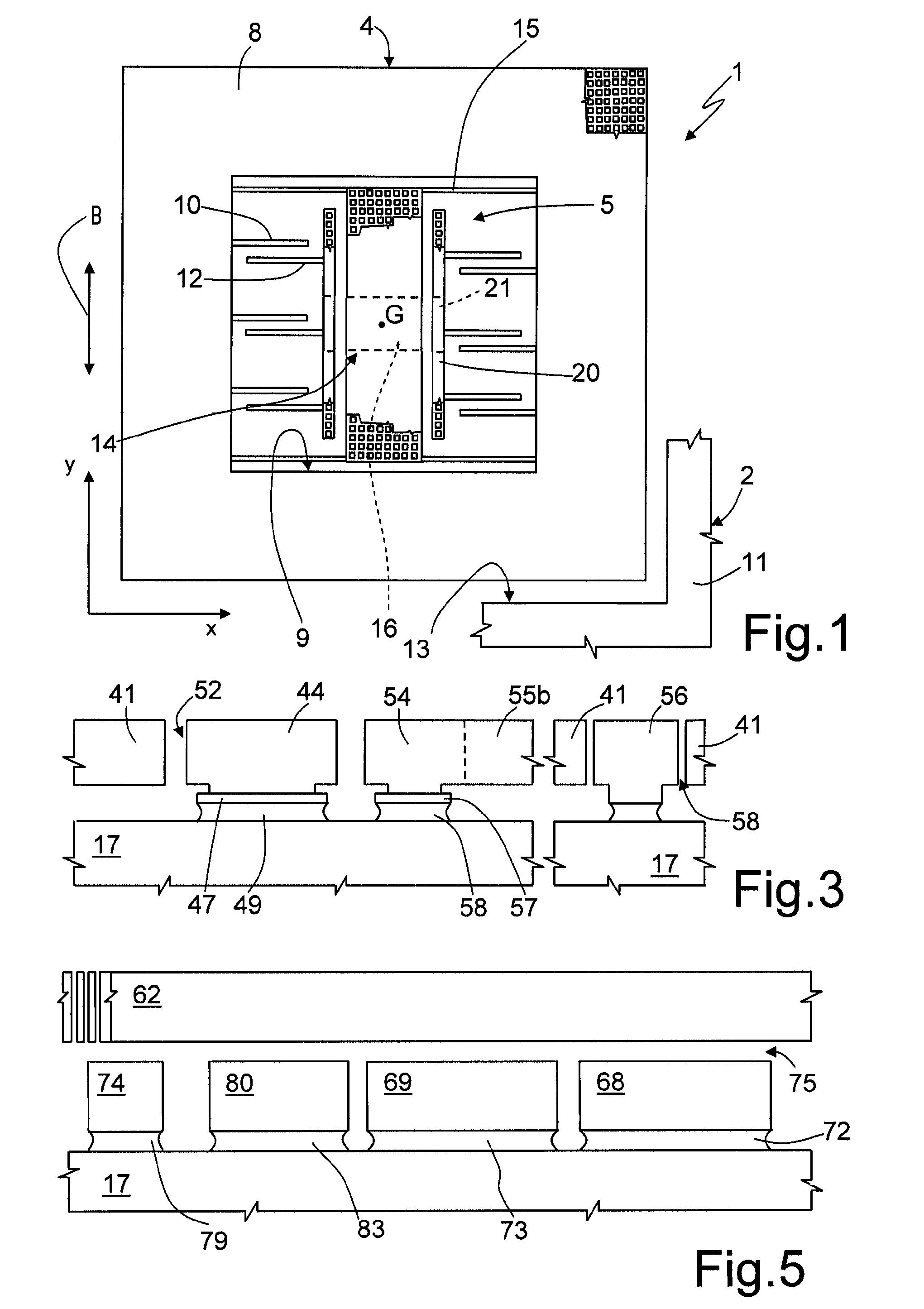

Micro-electromechanical structure with improved insensitivity to thermomechanical stresses induced by the package

ActiveUS20060032310A1Increase insensitivityAcceleration measurement using interia forcesSemiconductor/solid-state device detailsStress inducedEngineering

In a micro-electromechanical structure, a rotor has a centroidal axis and includes a suspended structure which carries mobile electrodes. A stator carries fixed electrodes facing the mobile electrodes. The suspended structure is connected to a rotor-anchoring region via elastic elements. The stator includes at least one stator element, which carries a plurality of fixed electrodes and is fixed to a stator-anchoring region. One of the rotor-anchoring regions and stator-anchoring regions extends along the centroidal axis and at least another of the rotor-anchoring regions and stator-anchoring regions extends in the proximity of the centroidal axis.

Owner:STMICROELECTRONICS SRL

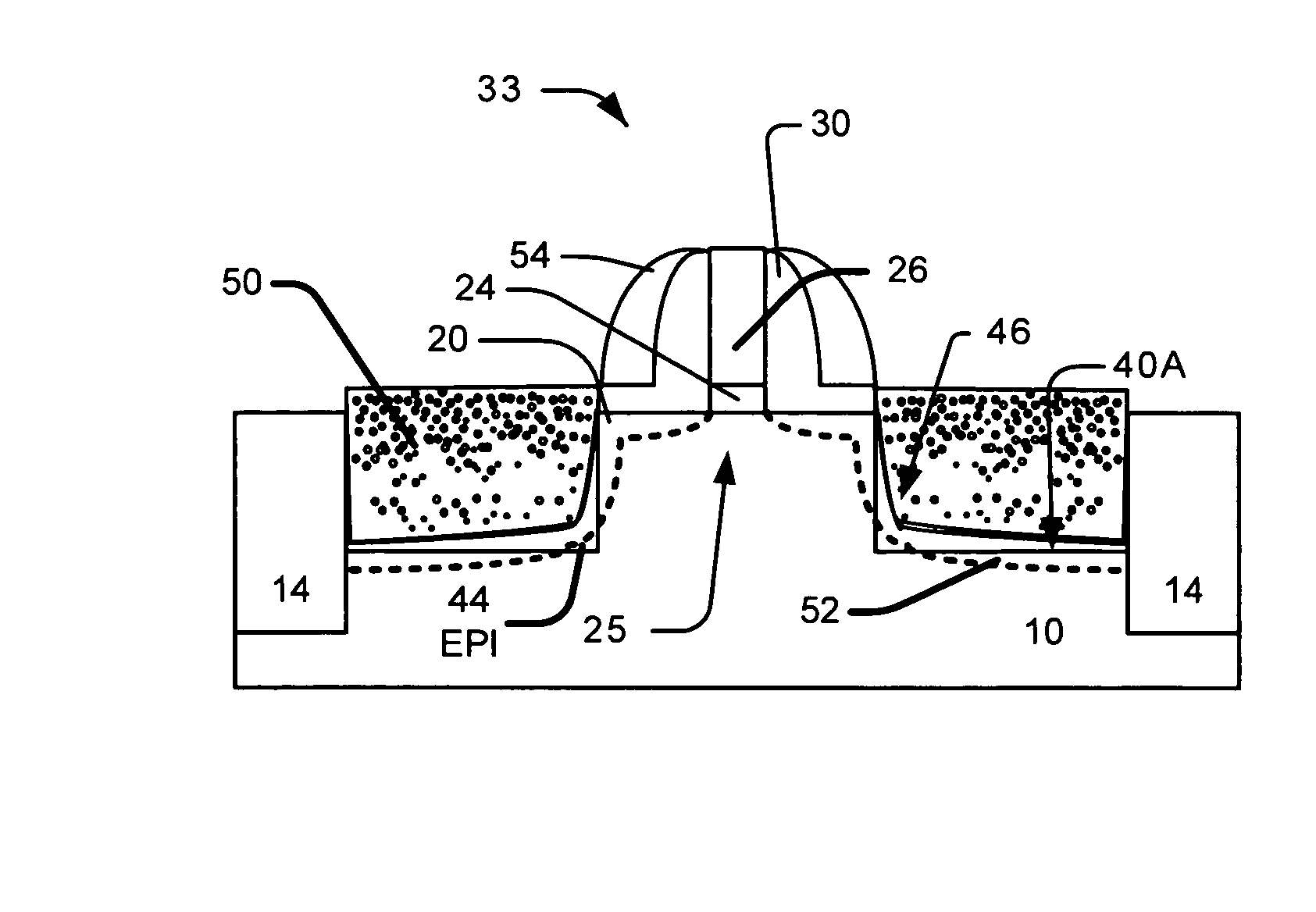

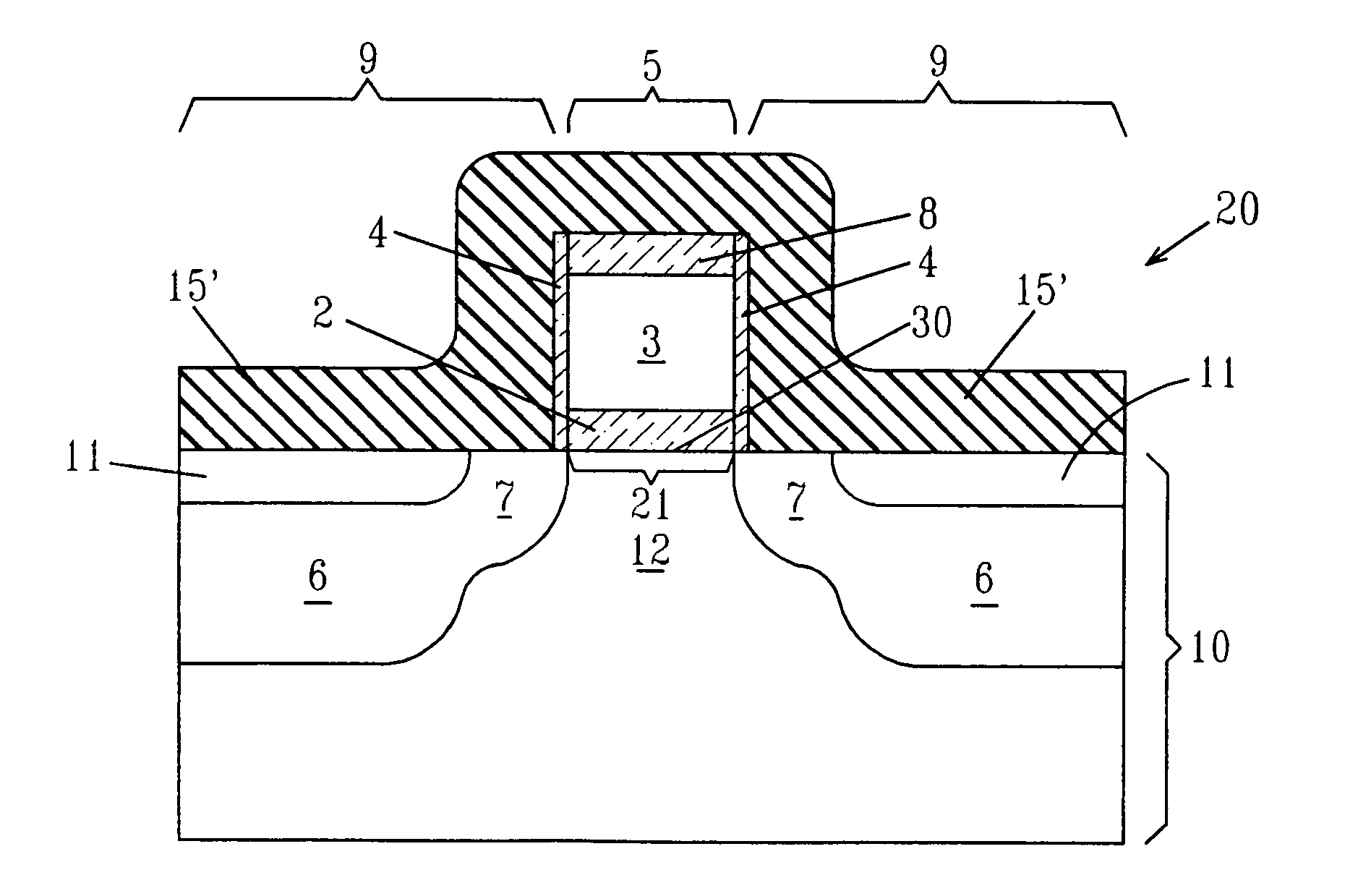

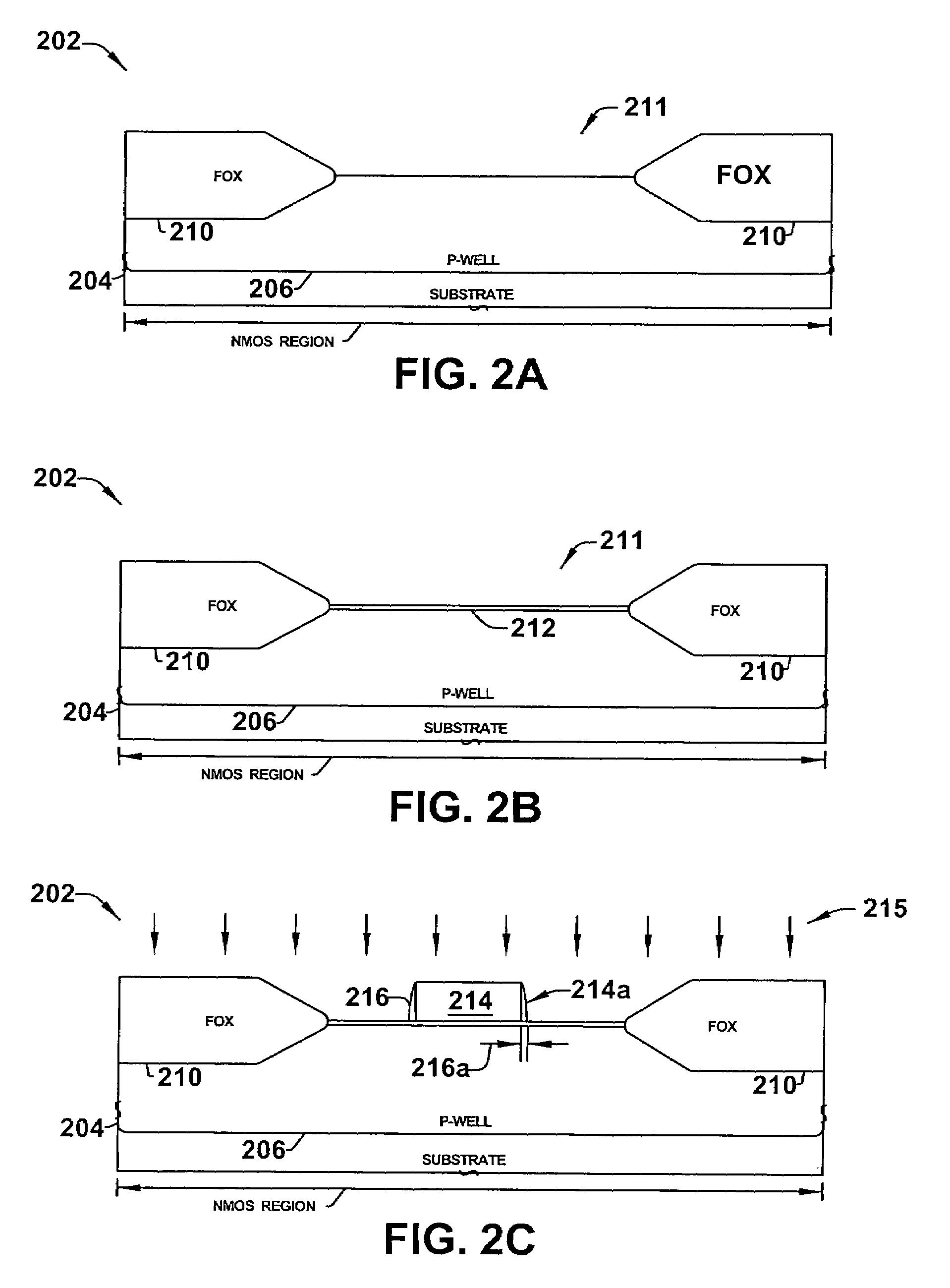

MOSFET device with localized stressor

InactiveUS20060151808A1Easy to operateSemiconductor/solid-state device manufacturingDigital video signal modificationMOSFETReaction layer

MOSFETs having localized stressors are provided. The MOSFET has a stress-inducing layer formed in the source / drain regions, wherein the stress-inducing layer comprises a first semiconductor material and a second semiconductor material. A treatment is performed on the stress-inducing layer such that a reaction is caused with the first semiconductor material and the second semiconductor material is forced lower into the stress-inducing layer. The stress-inducing layer may be either a recessed region or non-recessed region. A first method involves forming a stress-inducing layer, such as SiGe, in the source / drain regions and performing a nitridation or oxidation process. A nitride or oxide film is formed in the top portion of the stress-inducing layer, forcing the Ge lower into the stress-inducing layer. Another method embodiment involves forming a reaction layer over the stress-inducing layer and performing a treatment process to cause the reaction layer to react with the stress-inducing layer.

Owner:TAIWAN SEMICON MFG CO LTD

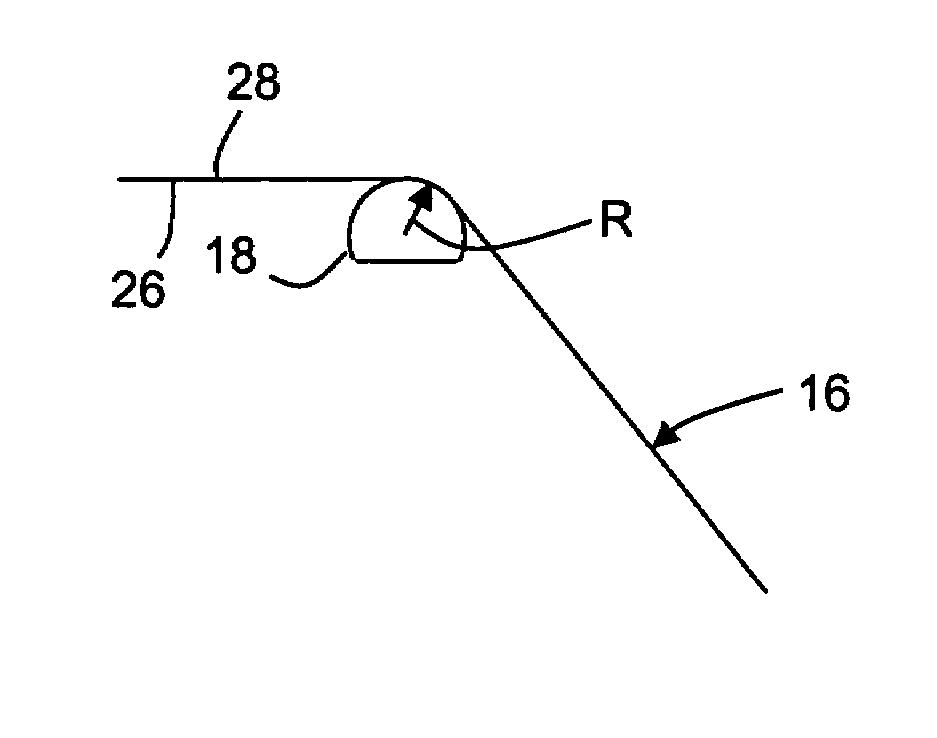

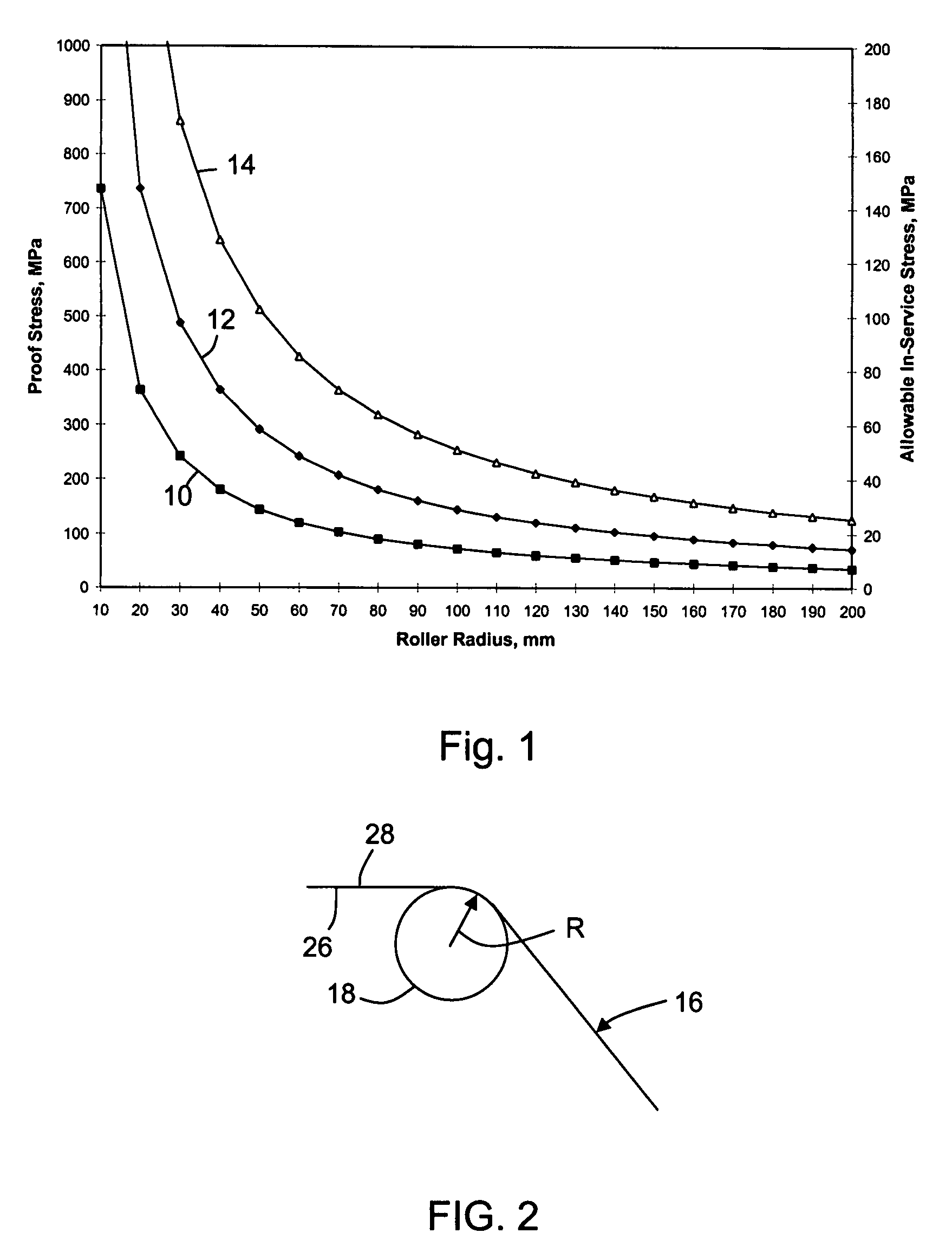

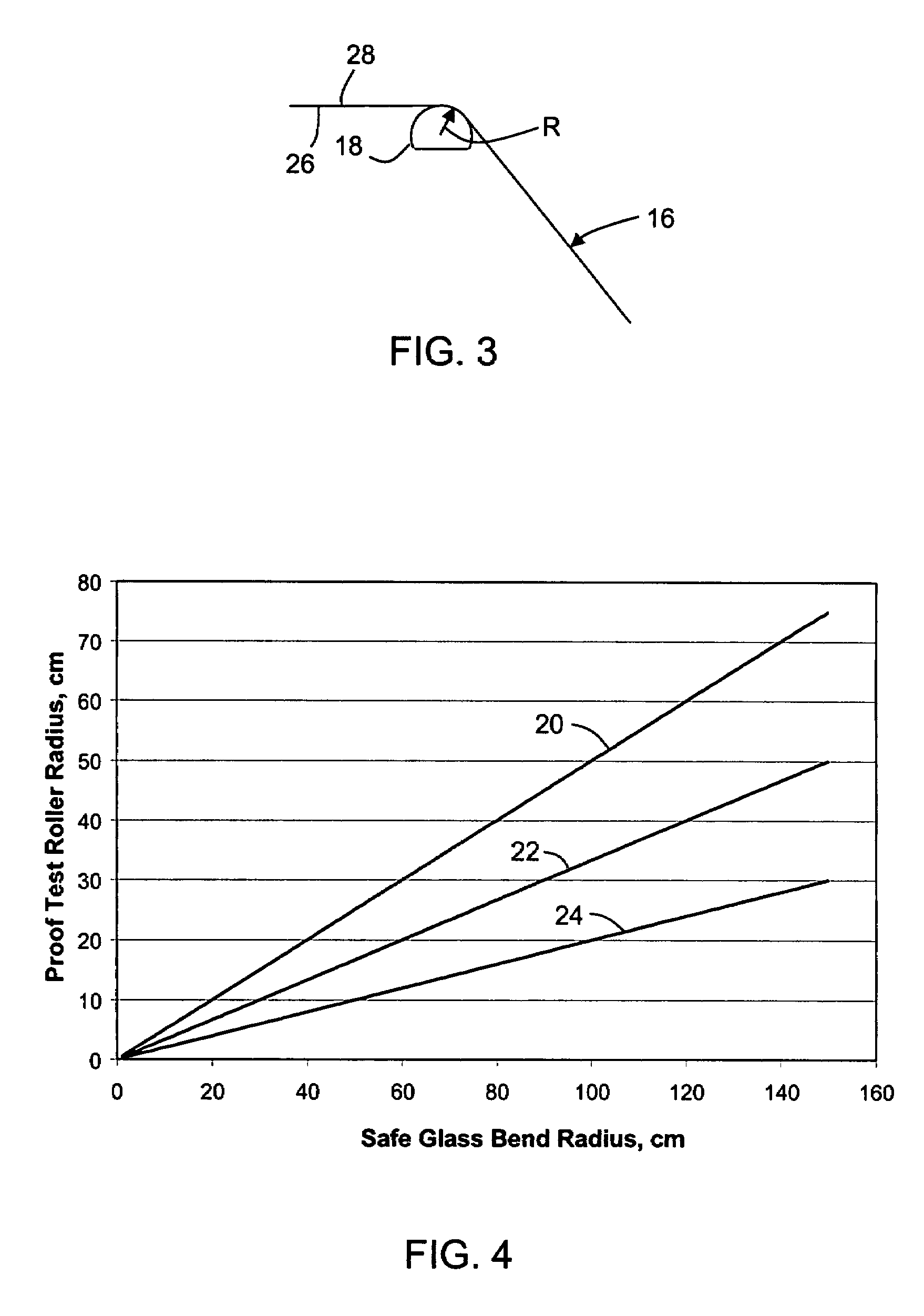

Method and apparatus for proof testing a sheet of brittle material

InactiveUS7461564B2Force measurementMaterial strength using tensile/compressive forcesStress inducedRelative motion

Disclosed is a method of proof testing a sheet of brittle material such as a glass or glass-ceramic based material. The method comprises bending the glass sheet over at least one arcuate member to detect sheets having a strength greater than a predetermined value. The method includes imparting a bend to the sheet and producing relative motion between the sheet and the bend such that the bend traverses the sheet, and wherein tensile stress induced in a surface of the sheet by the bend corresponds to the predetermined strength value. An apparatus for performing the proof testing is also disclosed.

Owner:CORNING INC

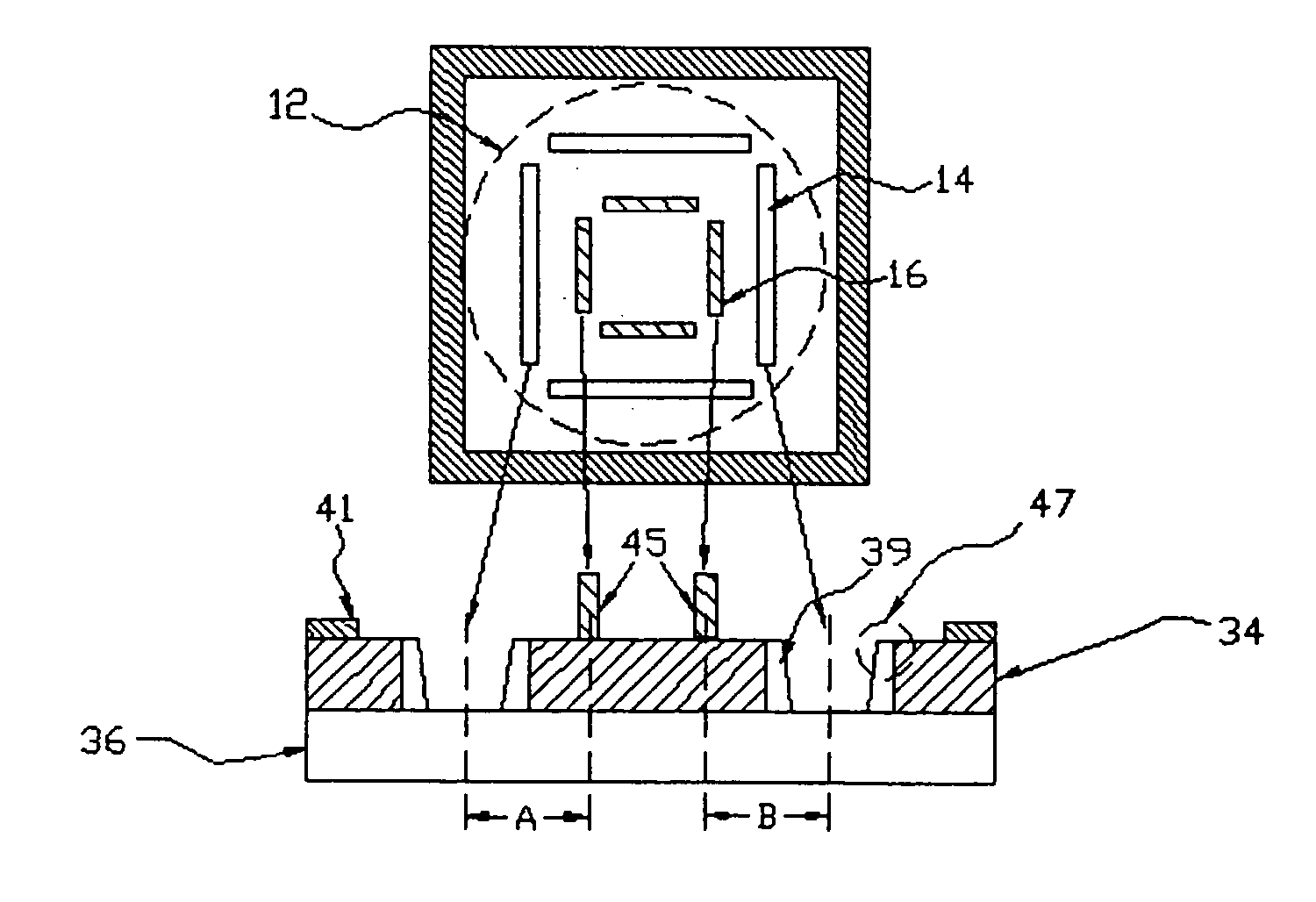

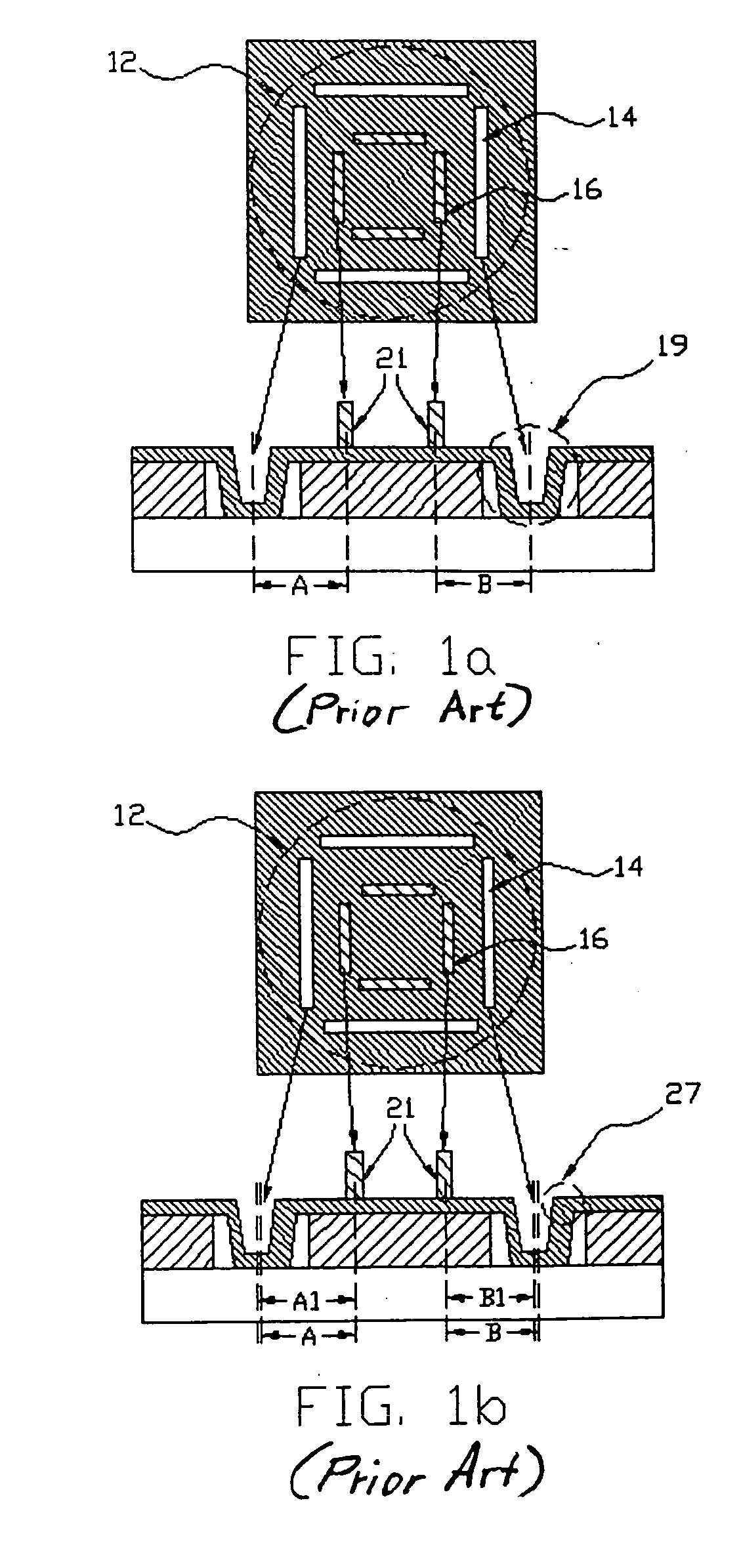

Method of reducing alignment measurement errors between device layers

ActiveUS20050272221A1Correct angular relationshipEasy alignmentSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsStress inducedIntegrated circuit

An integrated circuit in which measurement of the alignment between subsequent layers has less susceptibility to stress induced shift. A first layer of the structure has a first overlay mark. A second and / or a third layer are formed in the alignment structure and on the first layer. Portions of the second and / or third layer are selectively removed from regions in and around the first overlay mark. A second overlay mark is formed and aligned to the first overlay mark. The alignment between the second overlay mark and first overlay mark may be measured with an attenuated error due to reflection and refraction or due to an edge profile shift of the first overlay mark.

Owner:MACRONIX INT CO LTD

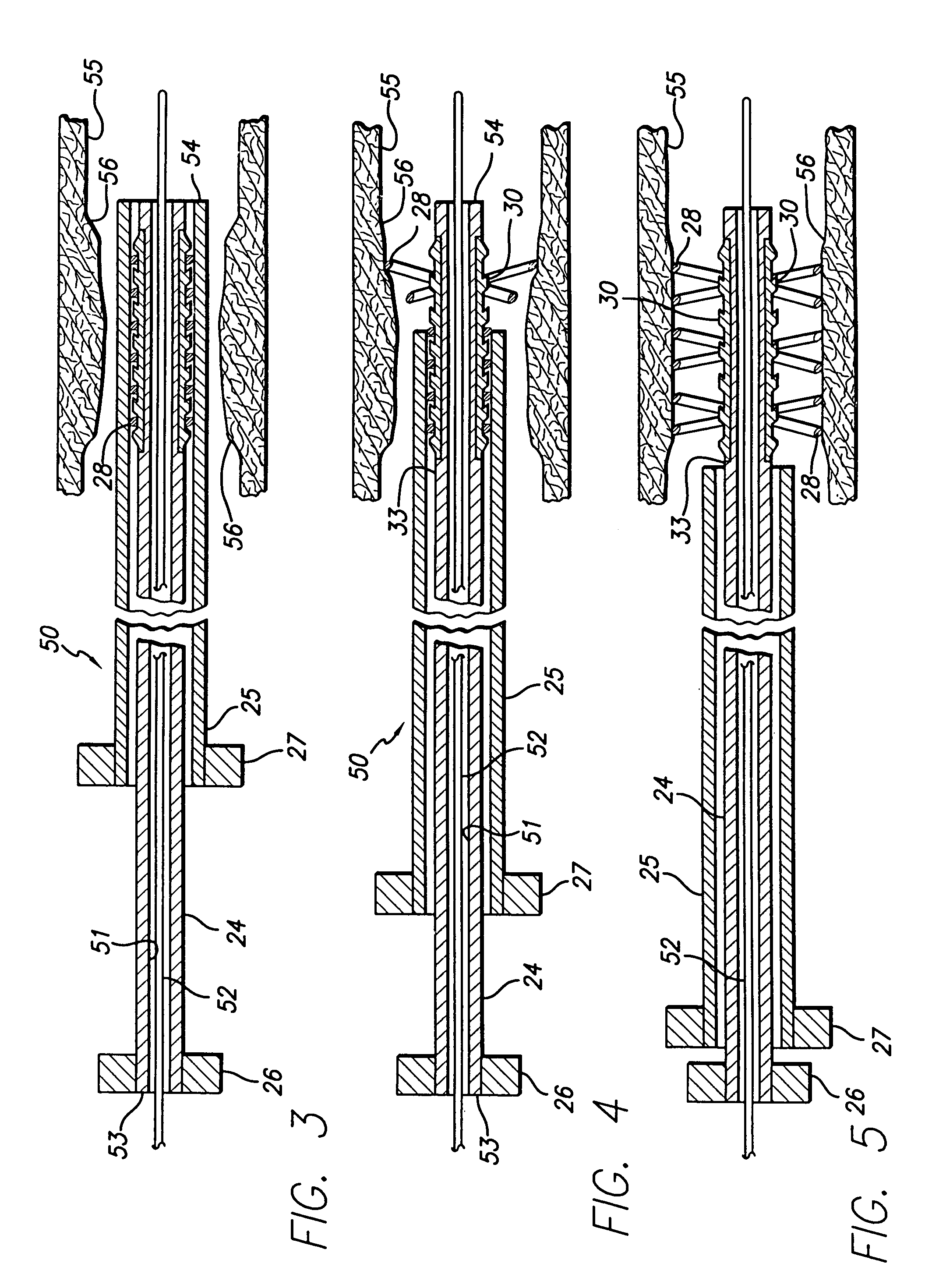

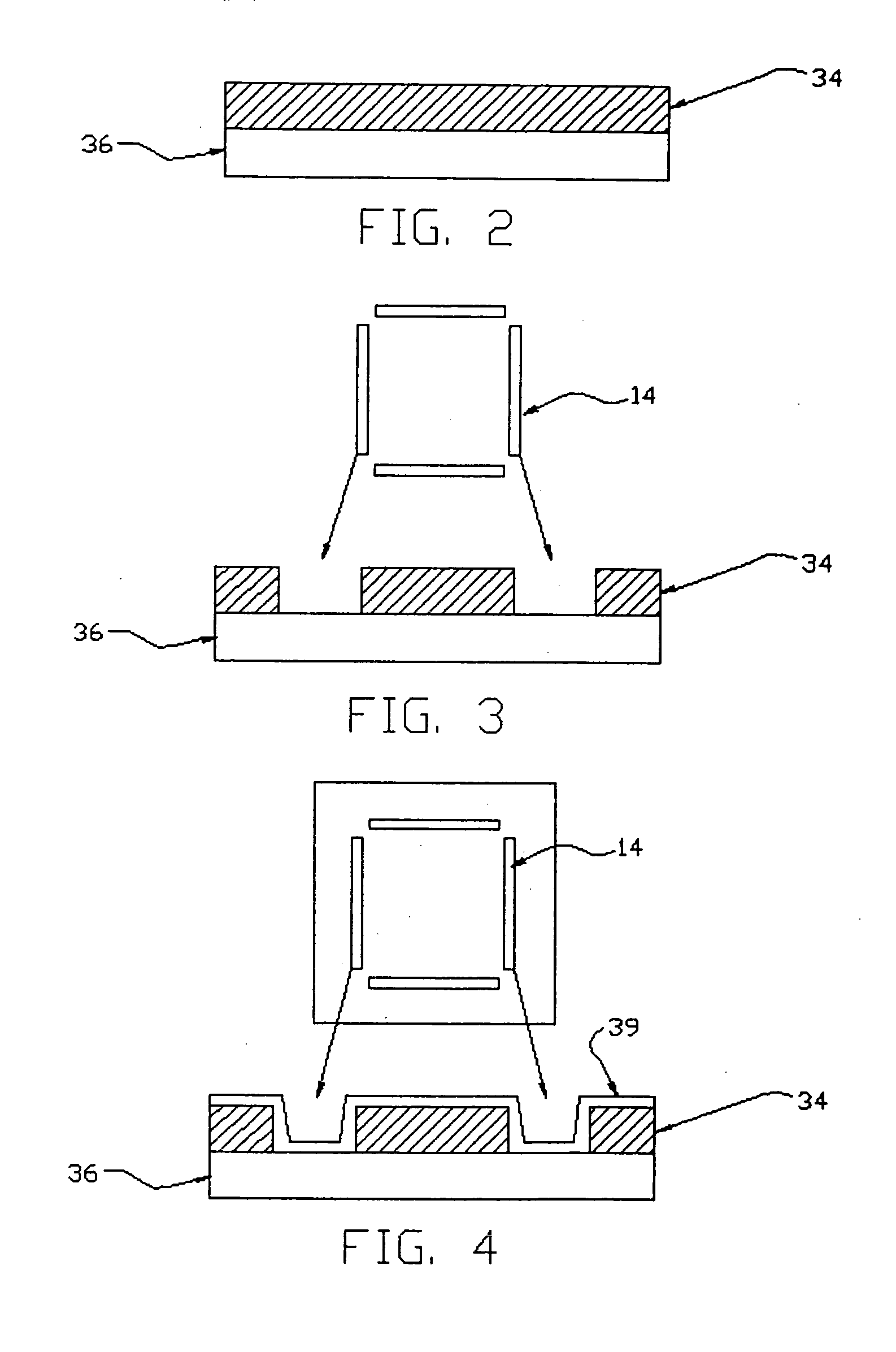

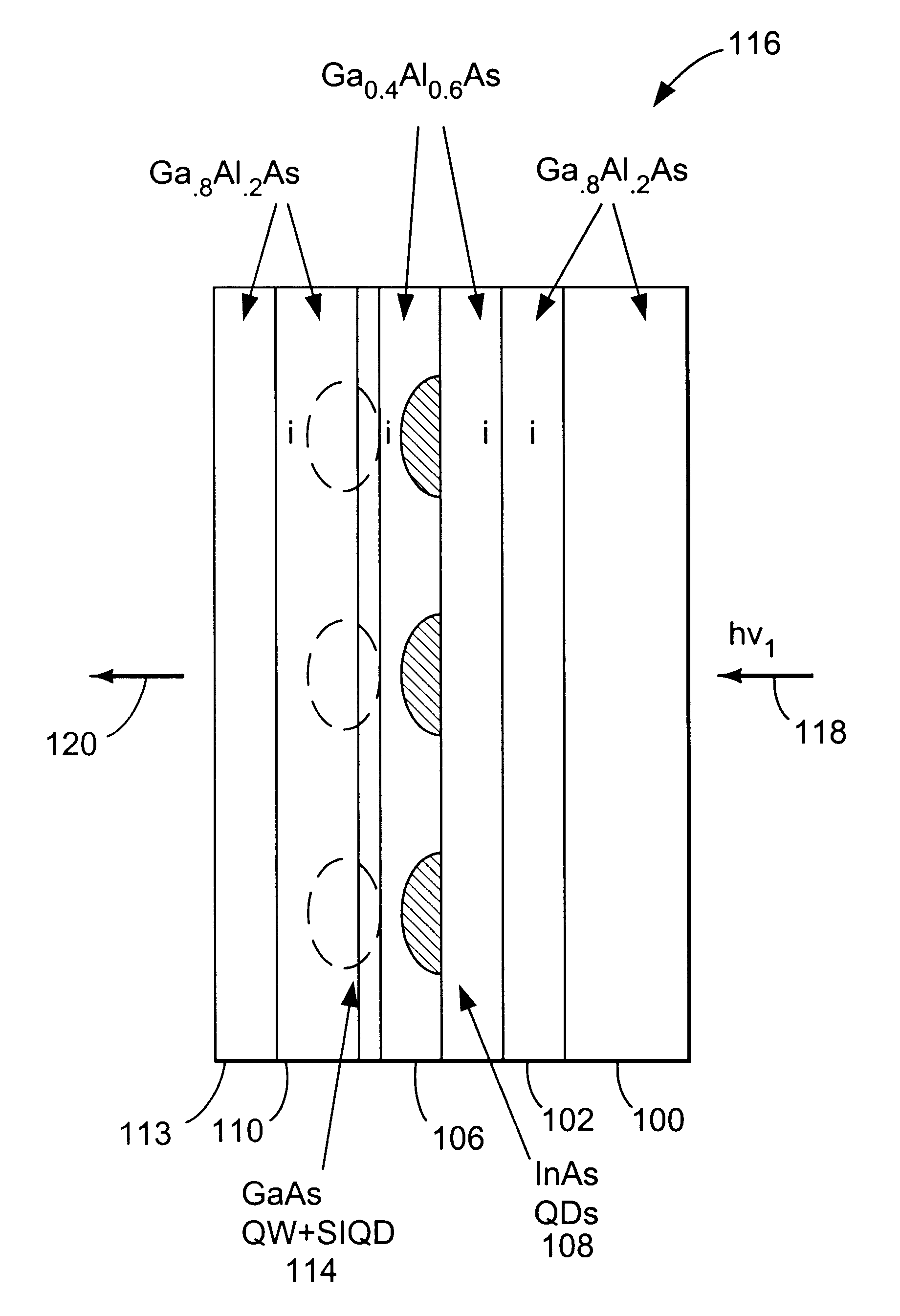

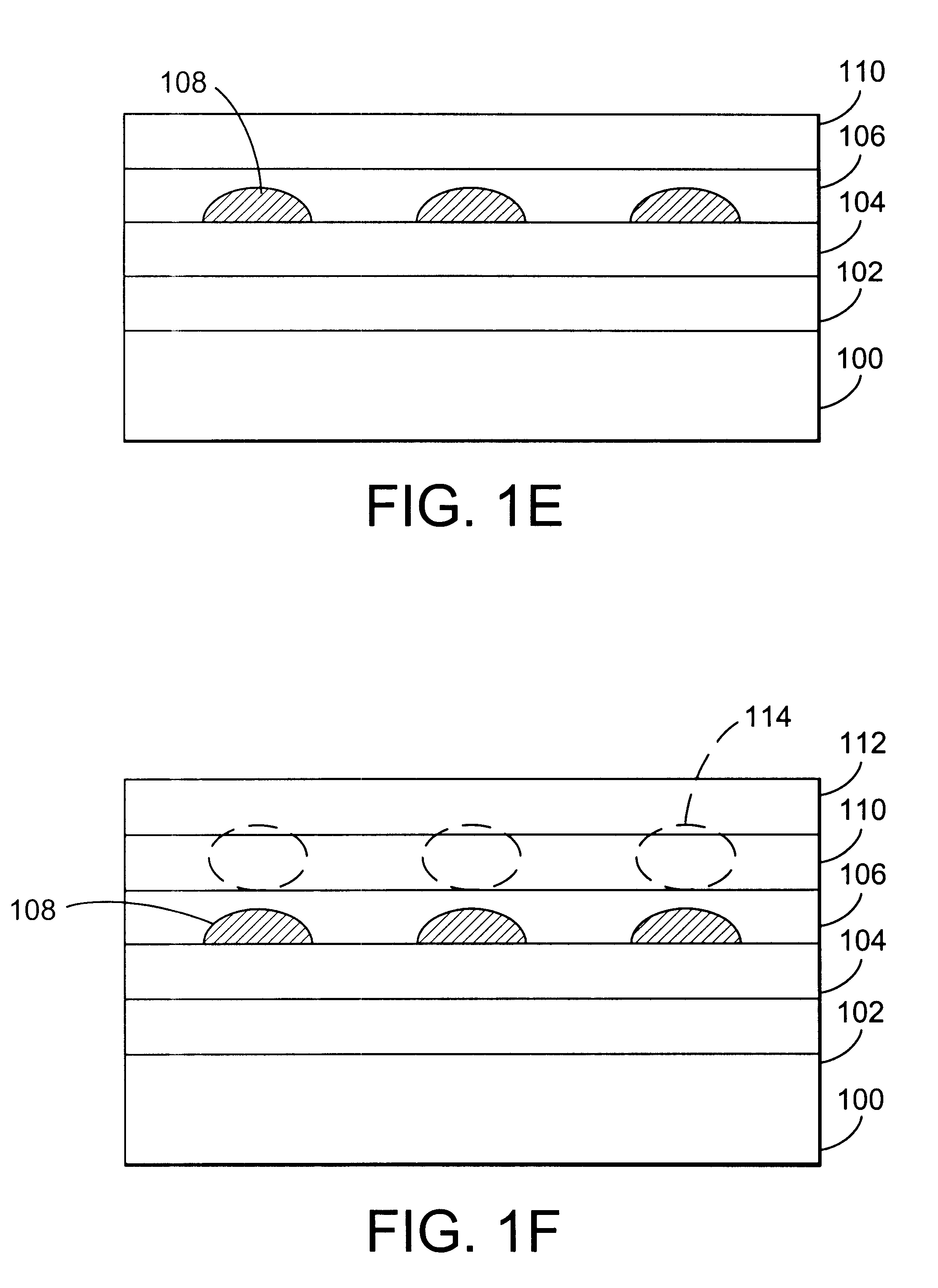

Mid infrared and near infrared light upconverter using self-assembled quantum dots

InactiveUS6541788B2NanoinformaticsSemiconductor/solid-state device manufacturingStress inducedPhoton

A method and device for converting light from a first wavelength to a second wavelength. The method comprises the steps of exciting an electron in a quantum dot with an incident infrared photon having the first wavelength, the excited electron having a first energy, tunneling the excited electron through a barrier into a stress induced quantum dot, and recombining the excited electron with a hole in the stress induced quantum dot, therein producing a photon having the second wavelength, typically in the visible range. The device comprises a substrate, a spacer layer, coupled to the substrate, a second layer, coupled to the spacer layer, wherein the second layer comprises a different material than the spacer layer, a third layer, coupled to the second layer, wherein the third layer comprises at least one quantum dot, a fourth layer, coupled to the third layer, comprising a quantum well corresponding to each quantum dot in the third layer, a fifth layer, coupled to the fourth layer, wherein the fourth layer and fifth layer comprise a strain induced quantum dot corresponding to each quantum dot in the third layer; and a sixth layer, coupled to the fifth layer, the substrate and the sixth layer for contacting the device.

Owner:RGT UNIV OF CALIFORNIA

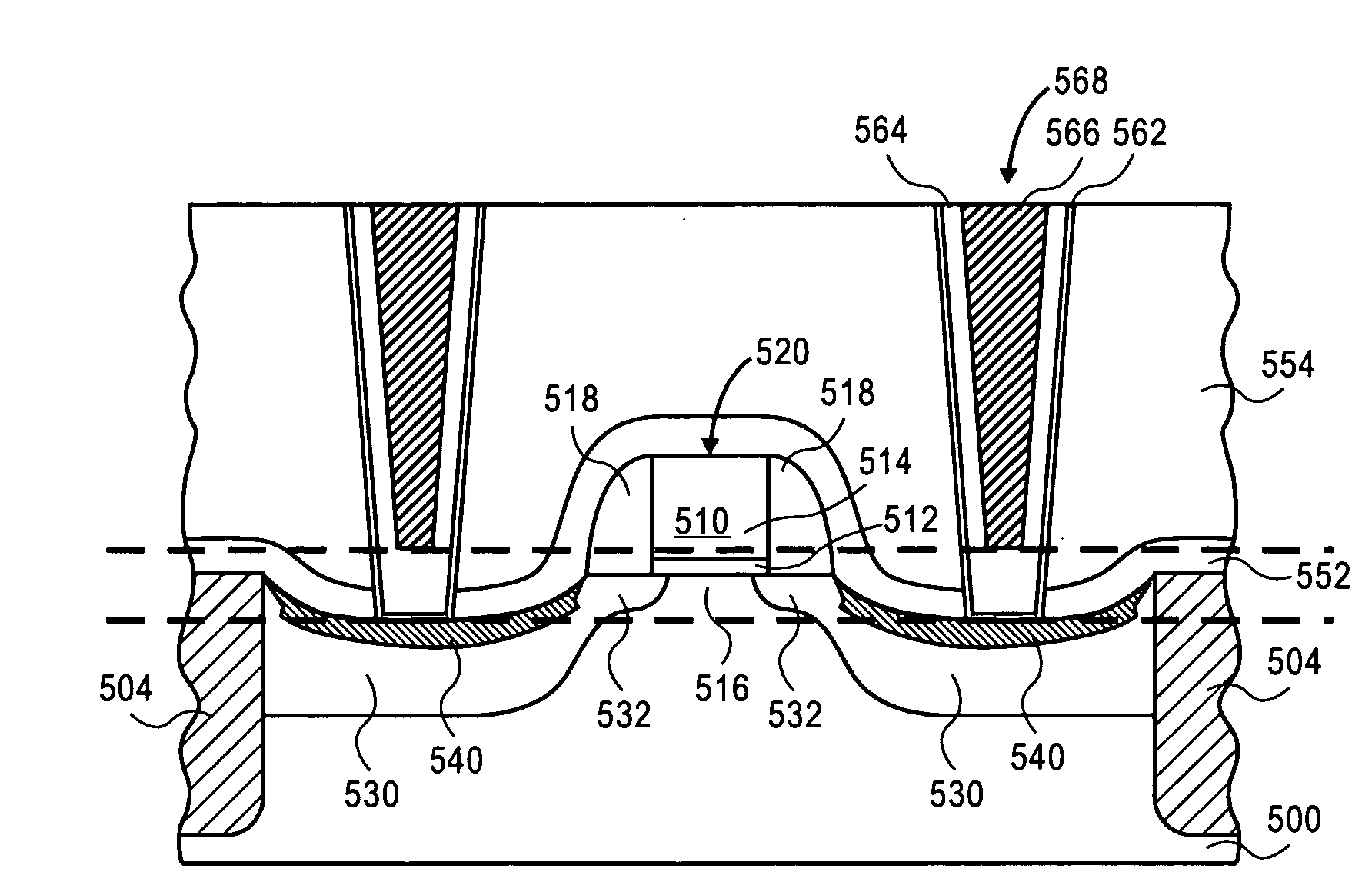

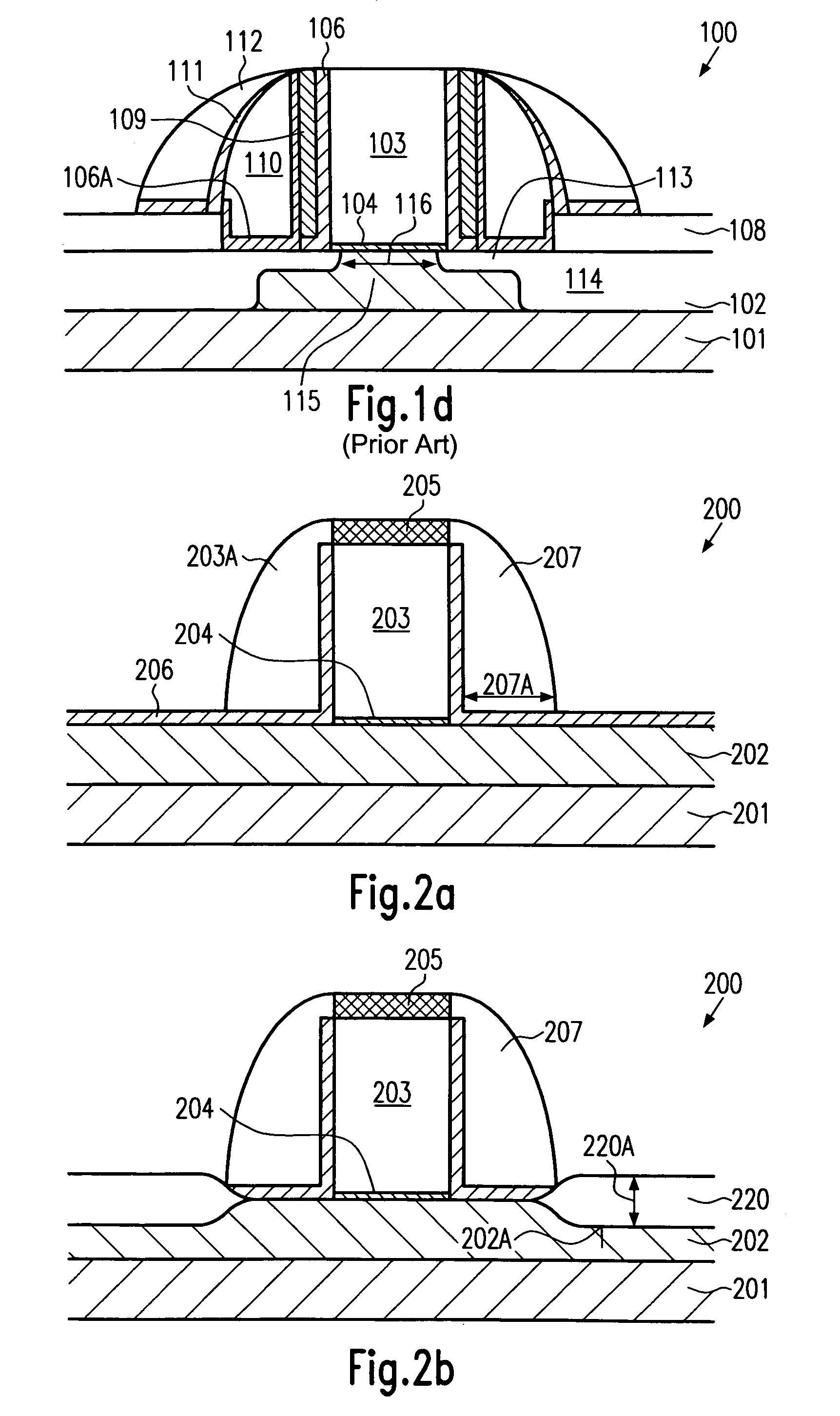

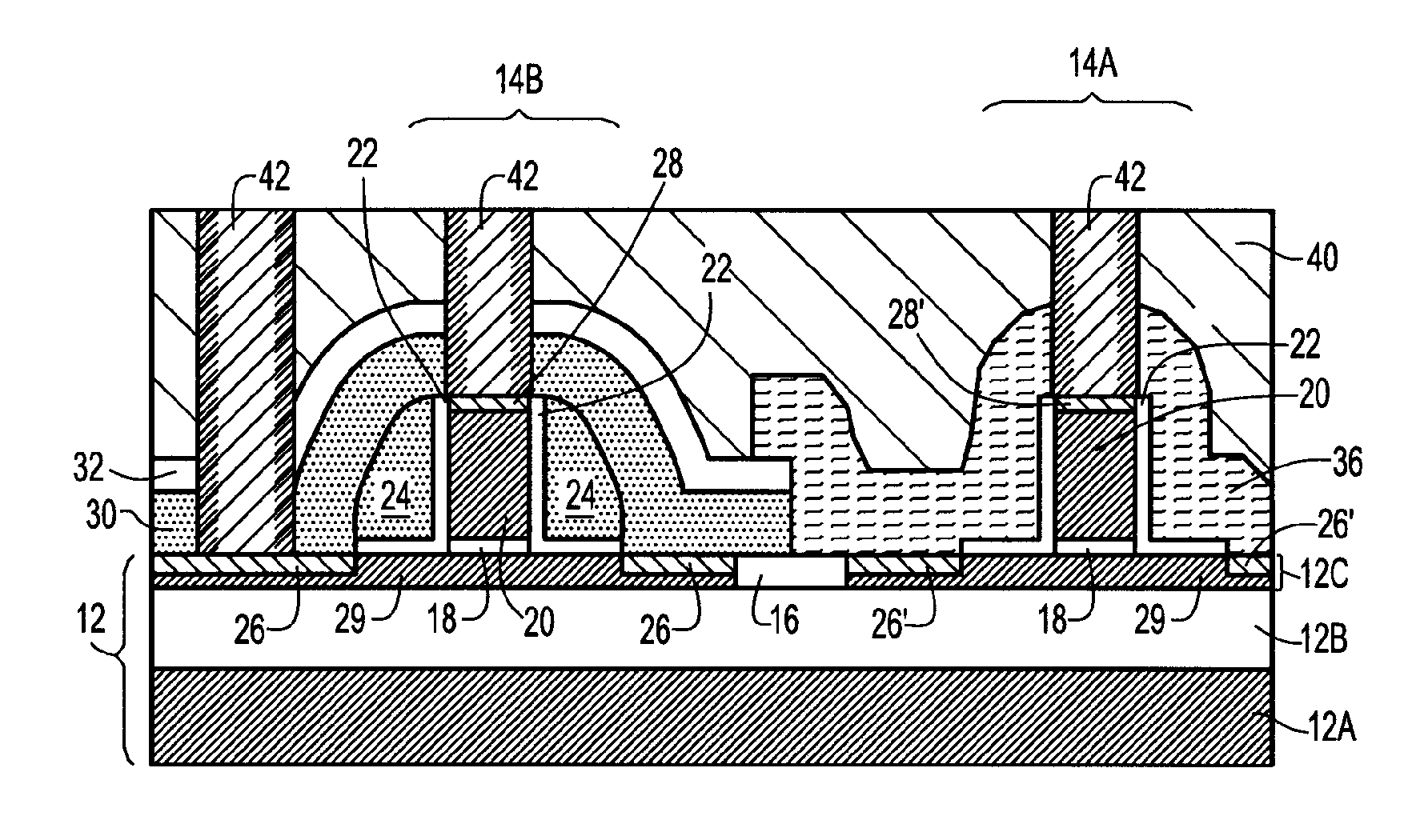

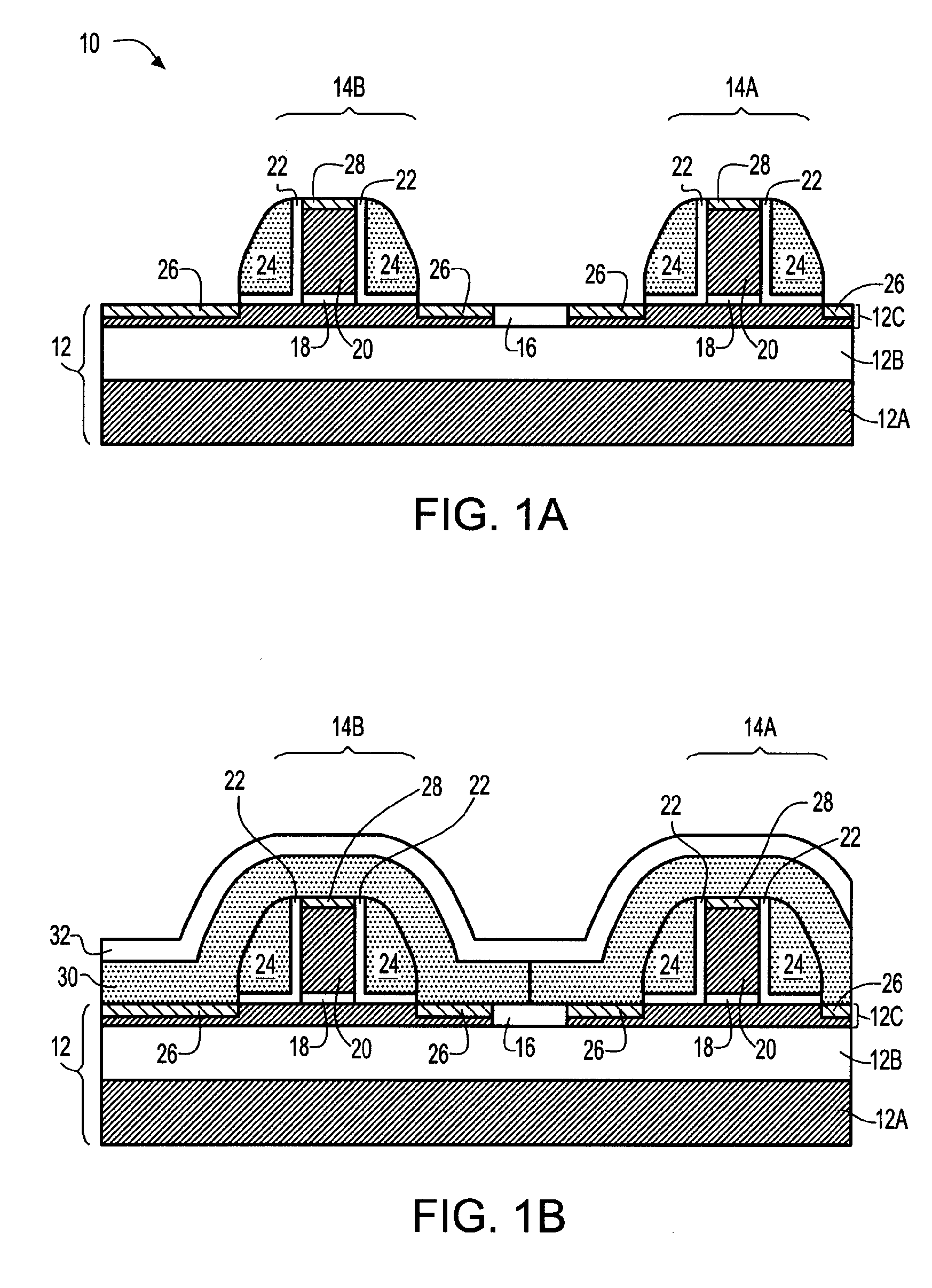

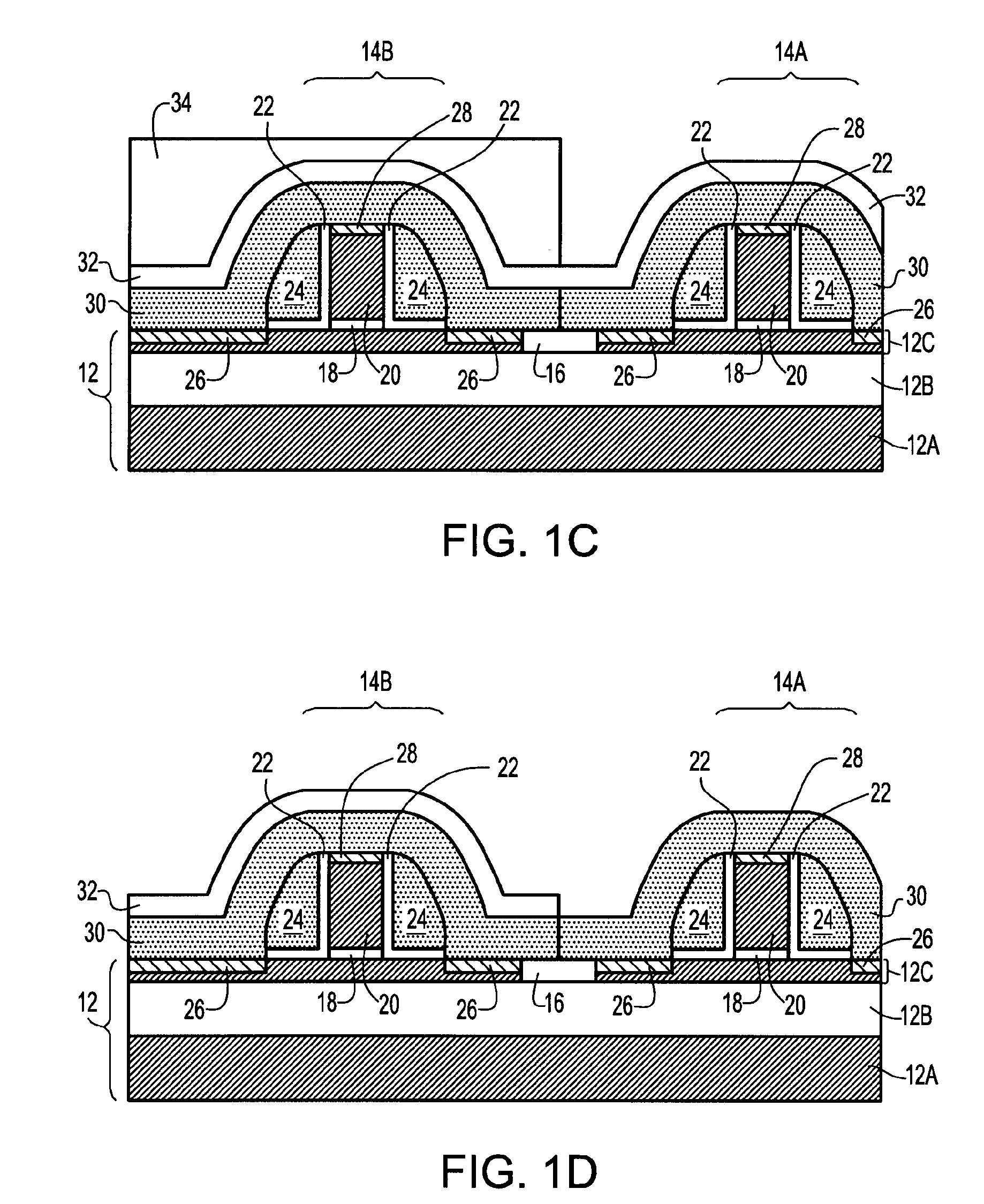

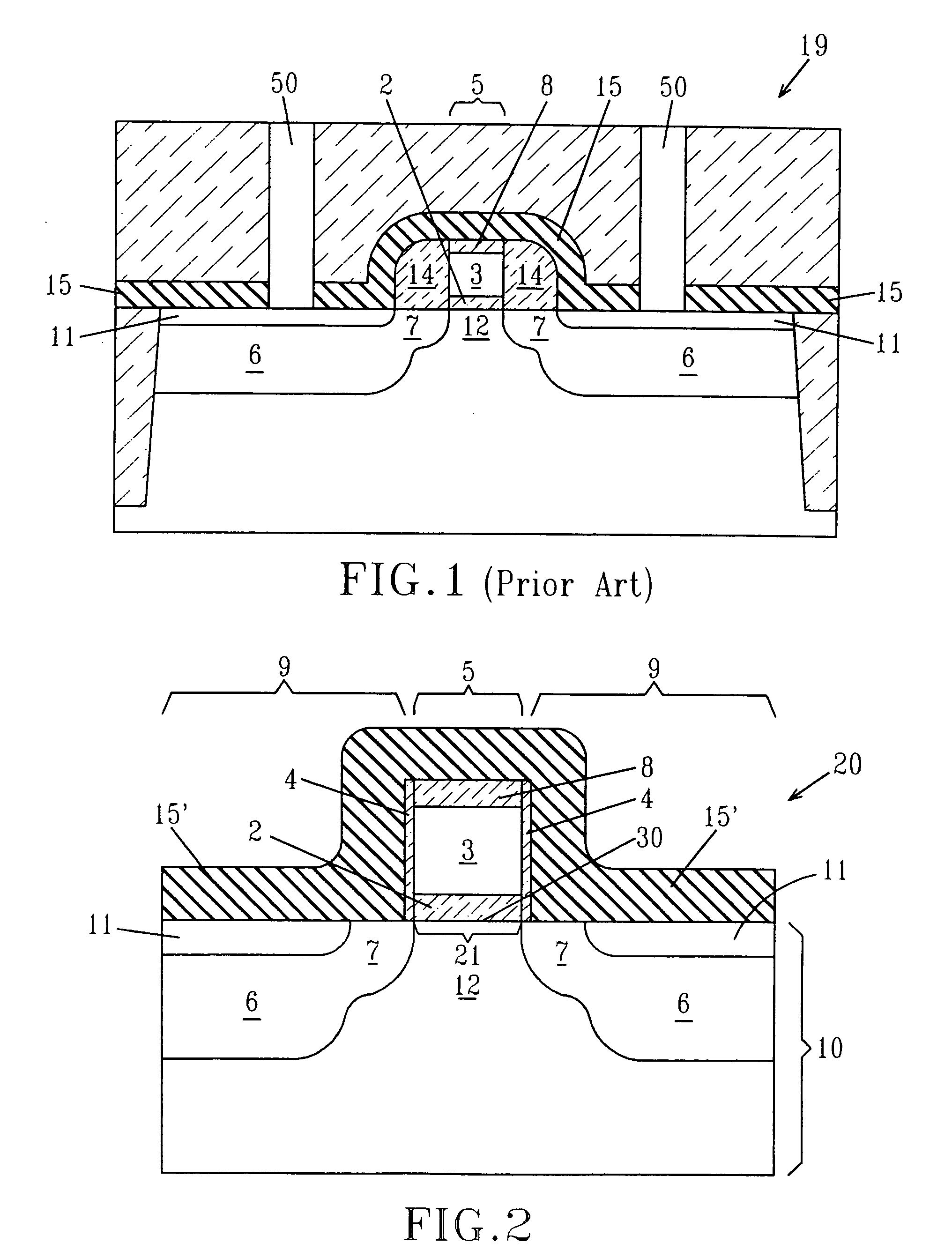

Structure and method to increase strain enhancement with spacerless fet and dual liner process

InactiveUS20070108525A1Strong strain enhancementImprove device speedSolid-state devicesSemiconductor/solid-state device manufacturingStress inducedSemiconductor structure

A semiconductor structure and a method of fabricating the same in which strain enhancement is achieved for both nFET and pFET devices is provided. In particular, the present invention provides at least one spacerless FET for stronger strain enhancement and defect reduction. The at least one spacerless FET can be a pFET, an nFET, or a combination thereof, with spacerless pFETs being particularly preferred since pFETs are generally fabricated to have a greater width than nFETs. The at least one spacerless FET allows to provide a stress inducing liner in closer proximity to the device channel than prior art structures including FETs having spacers. The spacerless FET is achieved without negatively affecting the resistance of the corresponding silicided source / drain diffusion contacts, which do not encroach underneath the spacerless FET.

Owner:GLOBALFOUNDRIES INC

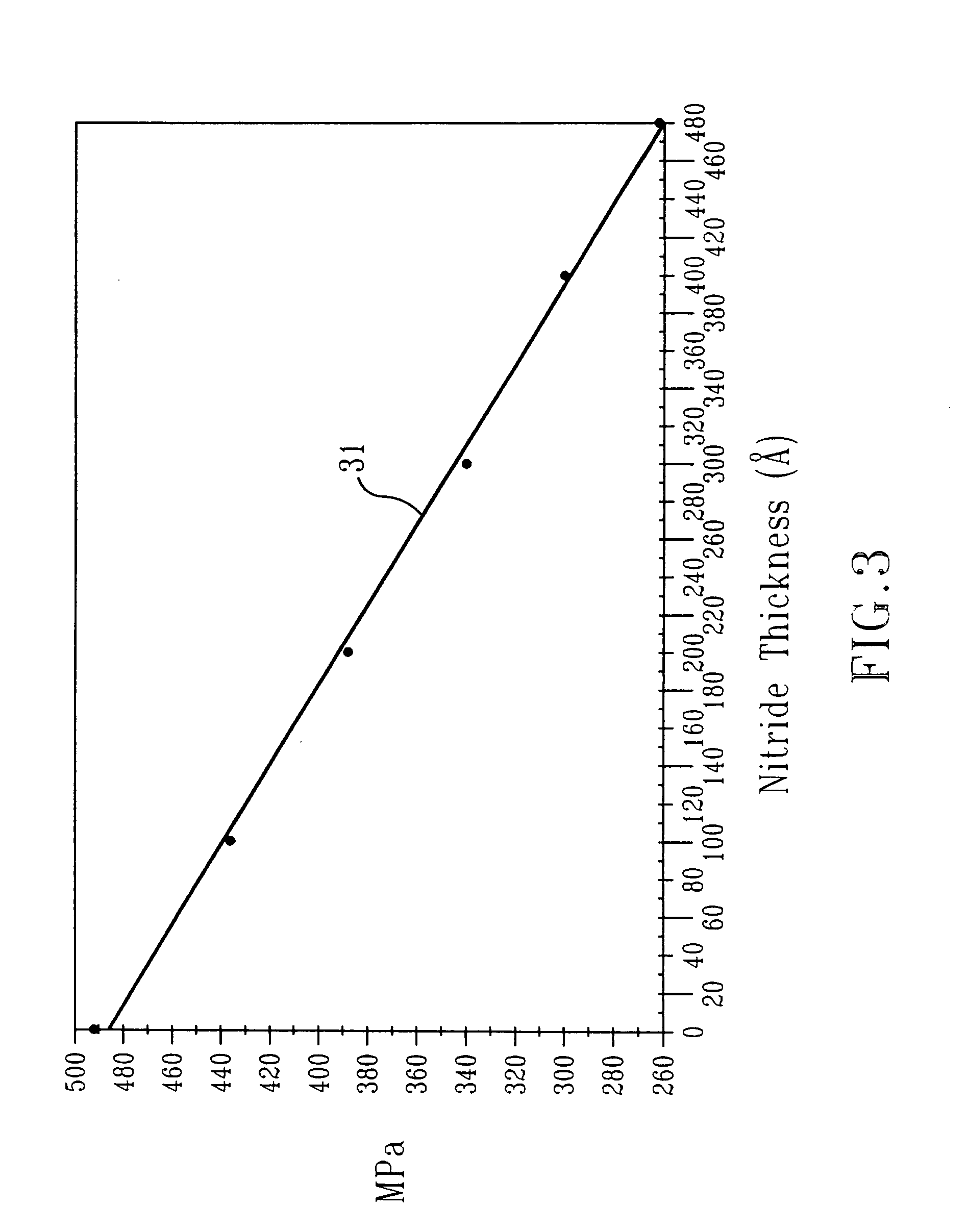

MOSFET structure with high mechanical stress in the channel

ActiveUS7002209B2Increase pressureImprove performanceTransistorSemiconductor/solid-state device manufacturingMOSFETStress induced

The present invention provides a semiconducting device including at least one gate region including a gate conductor located on a surface of a substrate, the substrate having an exposed surface adjacent the gate region; a silicide contact located adjacent the exposed surface; and a stress inducing liner located on the silicide contact, the exposed surface of the substrate adjacent to the gate region and the at least one gate region, wherein the stress inducing liner provides a stress to a device channel portion of the substrate underlying the gate region. The stress produced on the device channel is a longitudinal stress on the order of about 200 MPa to about 2000 MPa. The present invention also provides a method for forming the above-described semiconducting device.

Owner:AURIGA INNOVATIONS INC

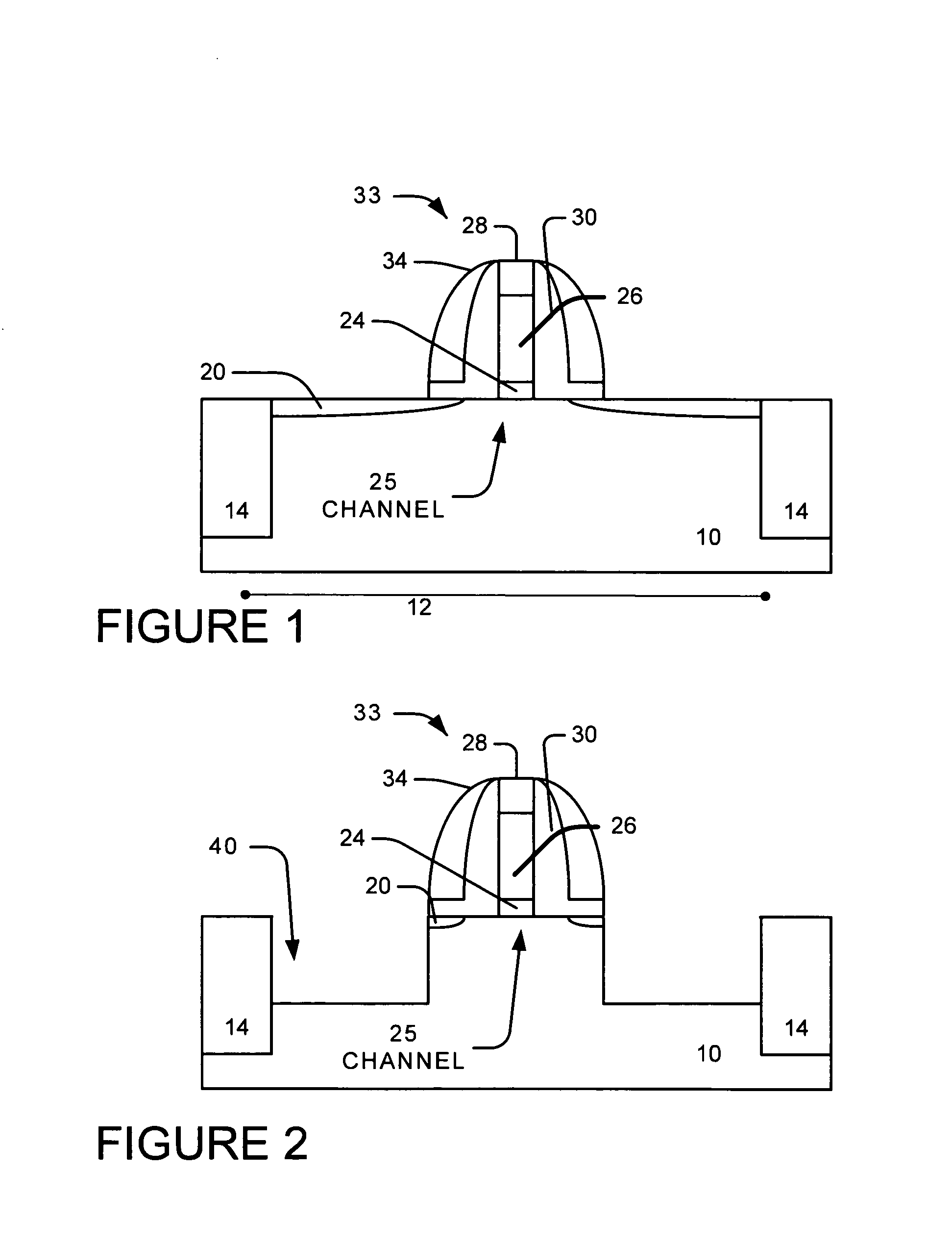

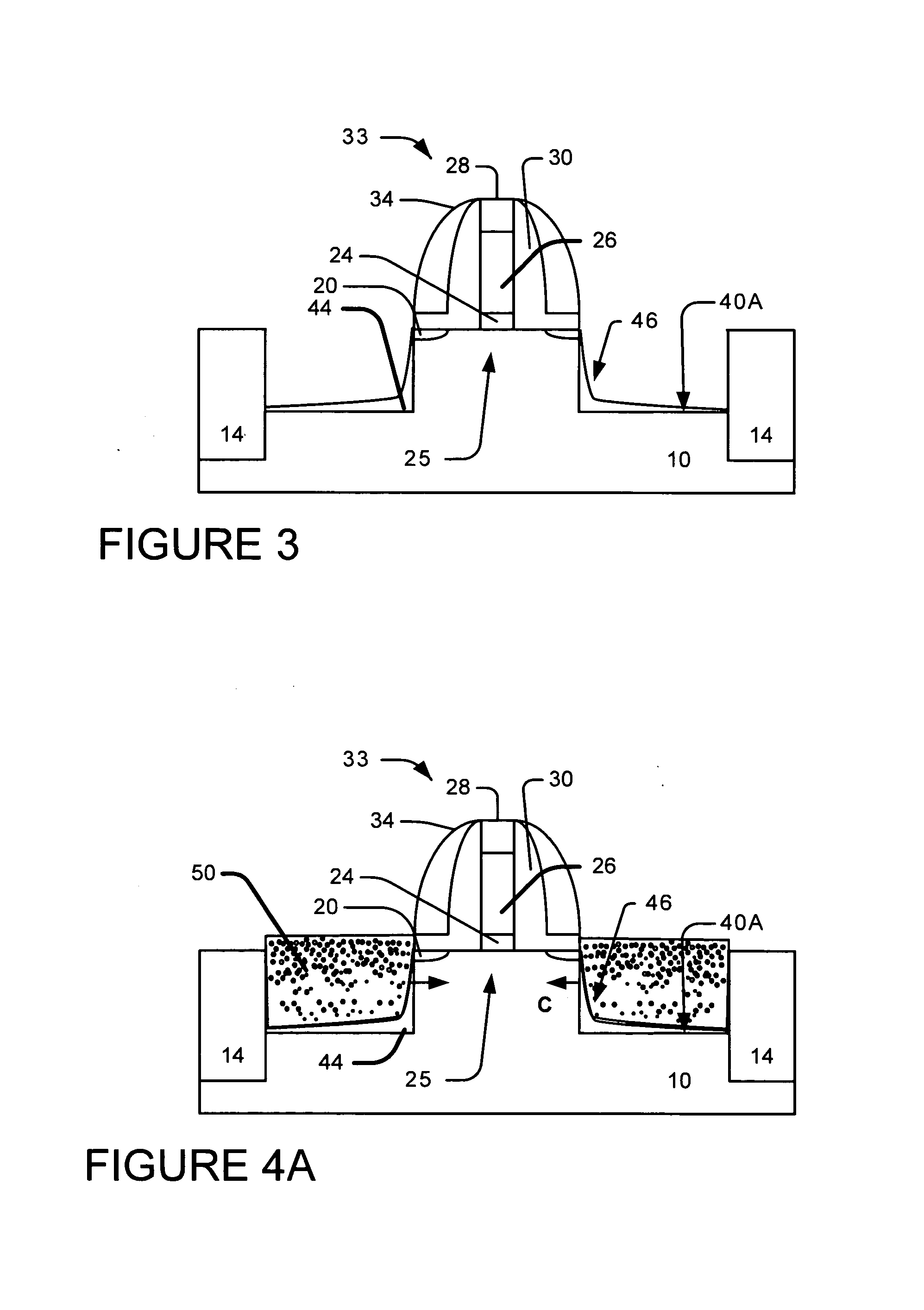

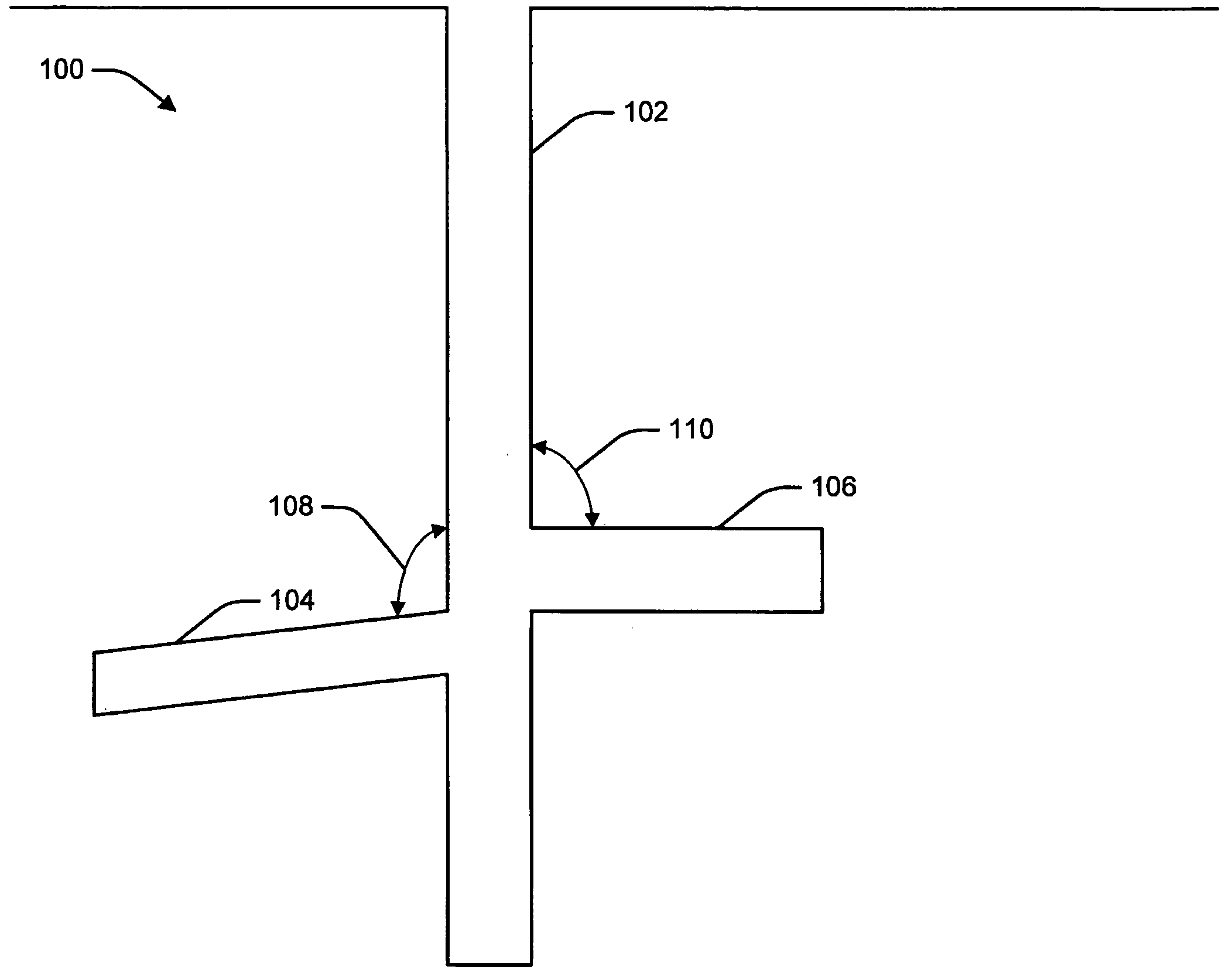

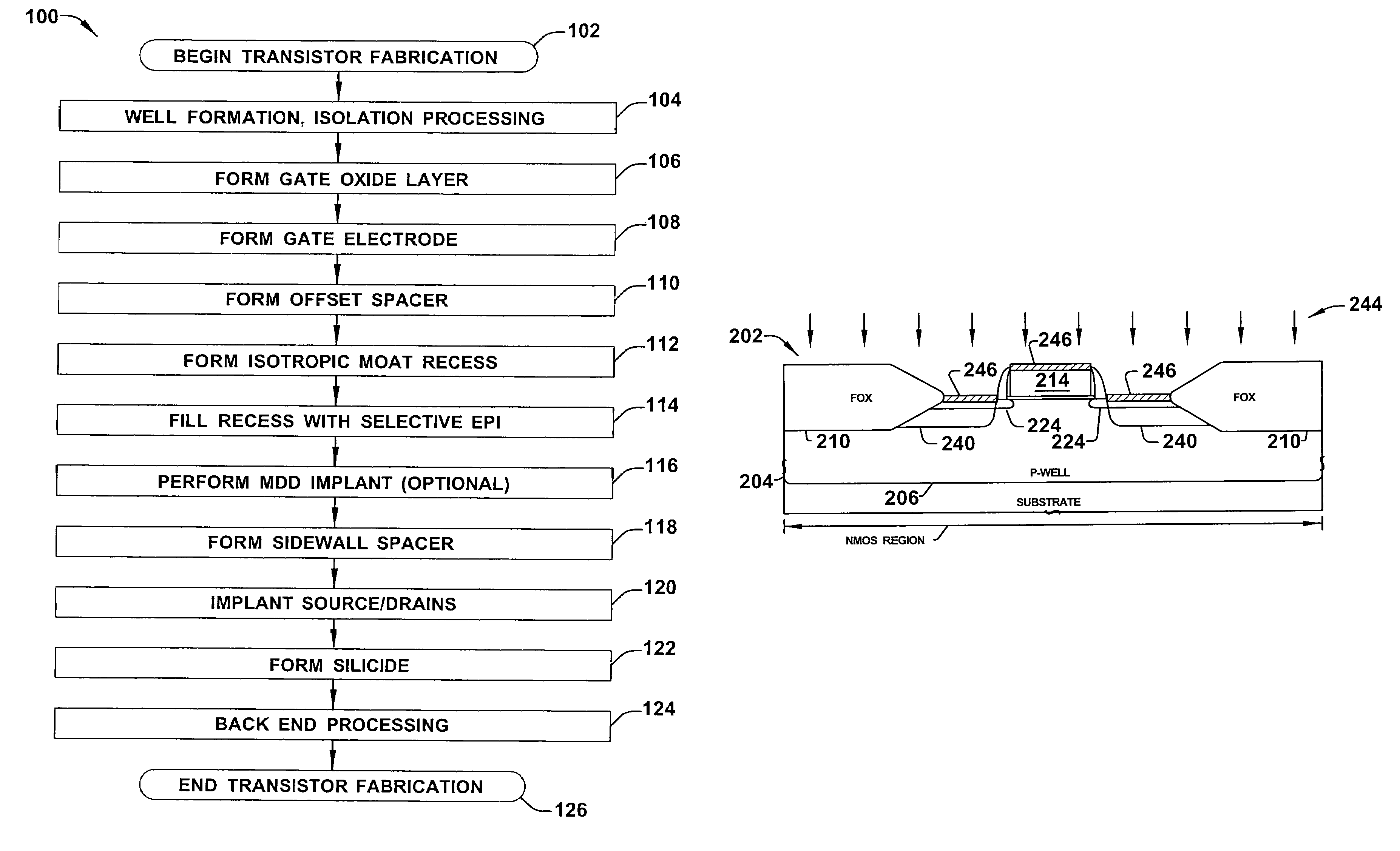

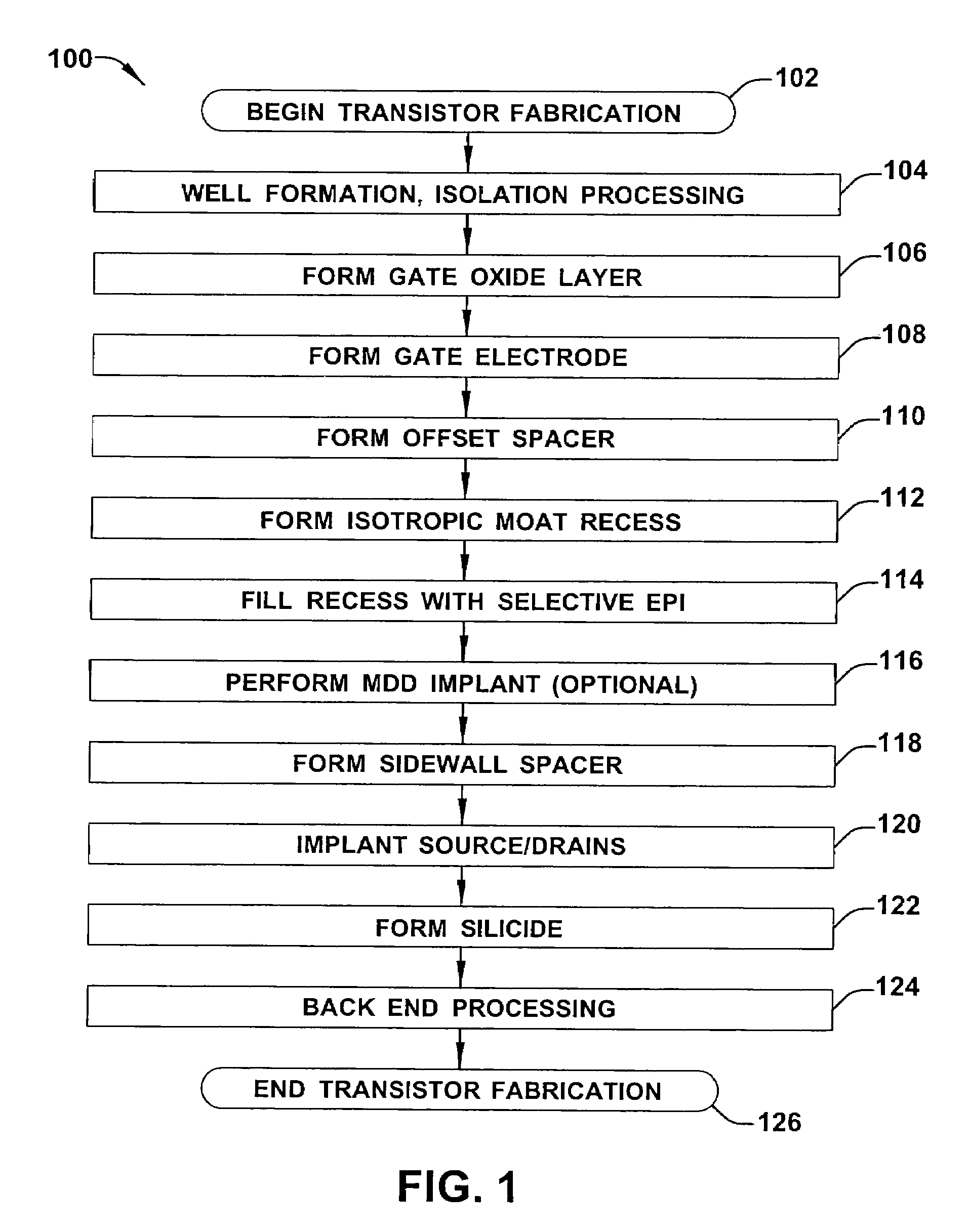

Increased drive current by isotropic recess etch

ActiveUS7060579B2Improve mobilityHigh carrier mobilityTransistorSemiconductor/solid-state device manufacturingStress inducedDriving current

A method (100) of forming a transistor includes forming a gate structure (108) over a semiconductor body and forming recesses (112) using an isotropic etch using the gate structure as an etch mask. The isotropic etch forms a recess in the semiconductor body that extends laterally in the semiconductor body toward a channel portion of the semiconductor body underlying the gate structure. The method further includes epitaxially growing silicon (114) comprising stress-inducing species in the recesses. The source and drain regions are then implanted (120) in the semiconductor body on opposing sides of the gate structure.

Owner:TEXAS INSTR INC

Thin substrate fabrication using stress-induced substrate spalling

ActiveUS8247261B2Increase valueImprove efficiencyFinal product manufactureSemiconductor/solid-state device manufacturingStress inducedSingle crystal

A method for manufacturing a thin film direct bandgap semiconductor active solar cell device comprises providing a source substrate having a surface and disposing on the surface a stress layer having a stress layer surface area in contact with and bonded to the surface of the source substrate. Operatively associating a handle foil with the stress layer and applying force to the handle foil separates the stress layer from the source substrate, and leaves a portion of the source substrate on the stress layer surface substantially corresponding to the area in contact with the surface of the source substrate. The portion is less thick than the source layer. The stress layer thickness is below that which results in spontaneous spalling of the source substrate. The source substrate may comprise an inorganic single crystal or polycrystalline material such as Si, Ge, GaAs, SiC, sapphire, or GaN. In one embodiment the stress layer comprises a flexible material.

Owner:GLOBALFOUNDRIES U S INC

Methods for fabricating a stressed MOS device

InactiveUS20070032024A1Semiconductor/solid-state device manufacturingSemiconductor devicesStress inducedImpurity ions

A method for fabricating a stressed MOS device in and on a semiconductor substrate is provided. The method comprises the steps of forming a gate electrode overlying the semiconductor substrate and etching a first trench and a second trench in the semiconductor substrate, the first trench and the second trench formed in alignment with the gate electrode. A stress inducing material is selectively grown in the first trench and in the second trench and conductivity determining impurity ions are implanted into the stress inducing material to form a source region in the first trench and a drain region in the second trench. To preserve the stress induced in the substrate, a layer of mechanically hard material is deposited on the stress inducing material after the step of ion implanting.

Owner:GLOBALFOUNDRIES INC

Micro-electromechanical structure with improved insensitivity to thermomechanical stresses induced by the package

ActiveUS7322242B2Increase insensitivityAcceleration measurement using interia forcesSemiconductor/solid-state device detailsStress inducedEngineering

In a micro-electromechanical structure, a rotor has a centroidal axis and includes a suspended structure which carries mobile electrodes. A stator carries fixed electrodes facing the mobile electrodes. The suspended structure is connected to a rotor-anchoring region via elastic elements. The stator includes at least one stator element, which carries a plurality of fixed electrodes and is fixed to a stator-anchoring region. One of the rotor-anchoring regions and stator-anchoring regions extends along the centroidal axis and at least another of the rotor-anchoring regions and stator-anchoring regions extends in the proximity of the centroidal axis.

Owner:STMICROELECTRONICS SRL