Patents

Literature

946 results about "Ashing" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Ashing is a test to deduce the amount of ash forming material present in a petroleum product so as to decide its use in certain applications. Ash-forming materials are considered to be undesirable impurities or contaminants.

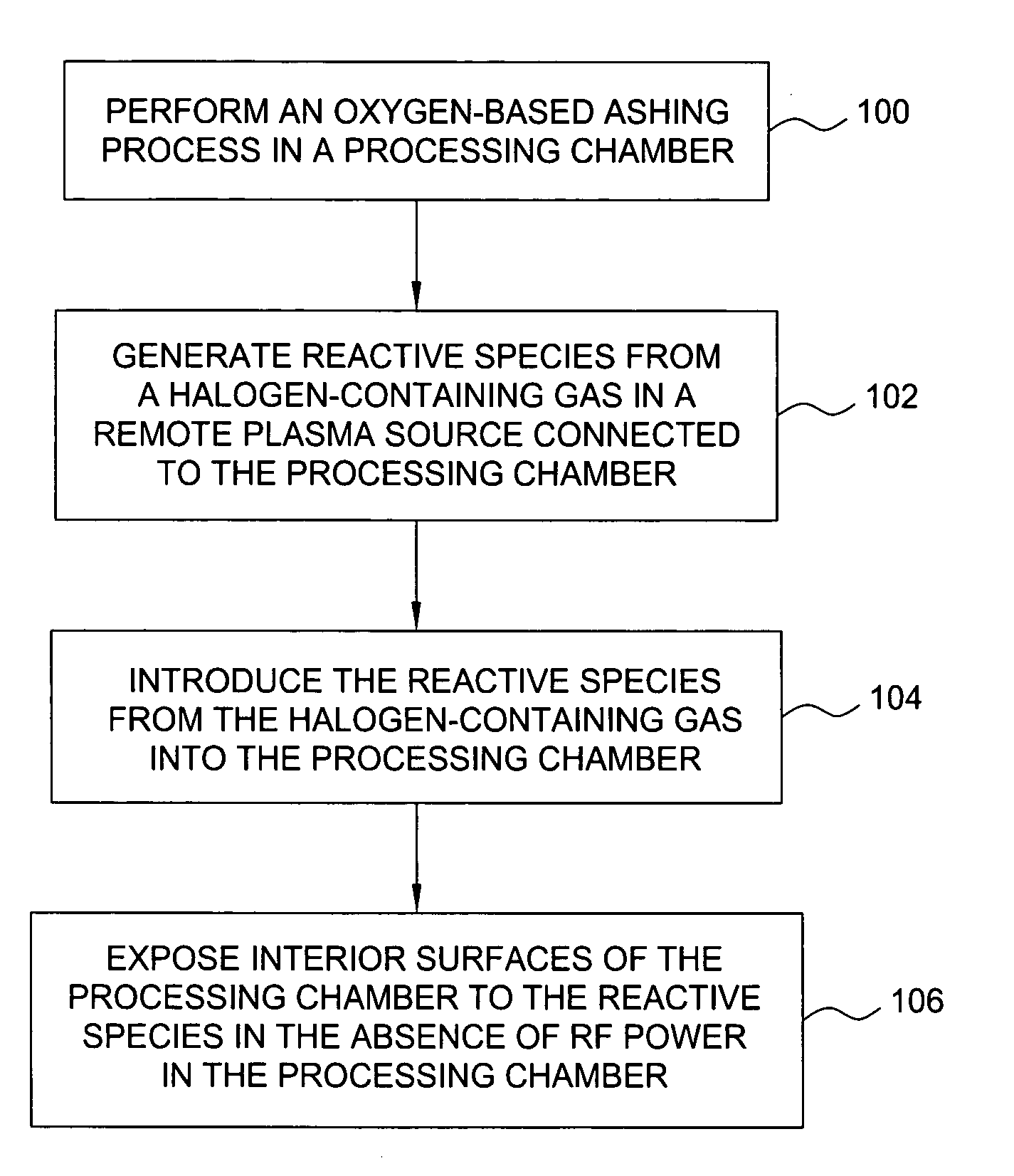

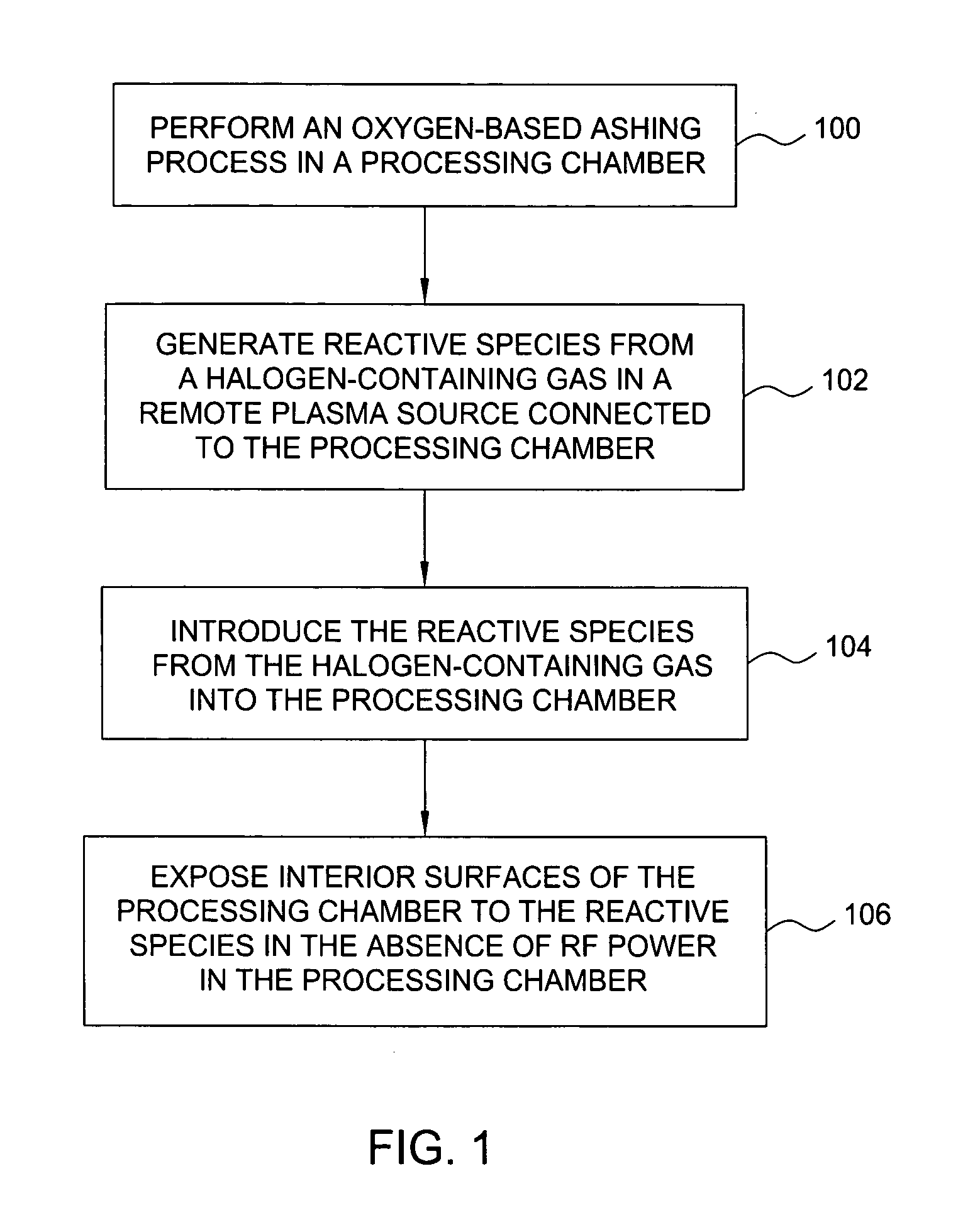

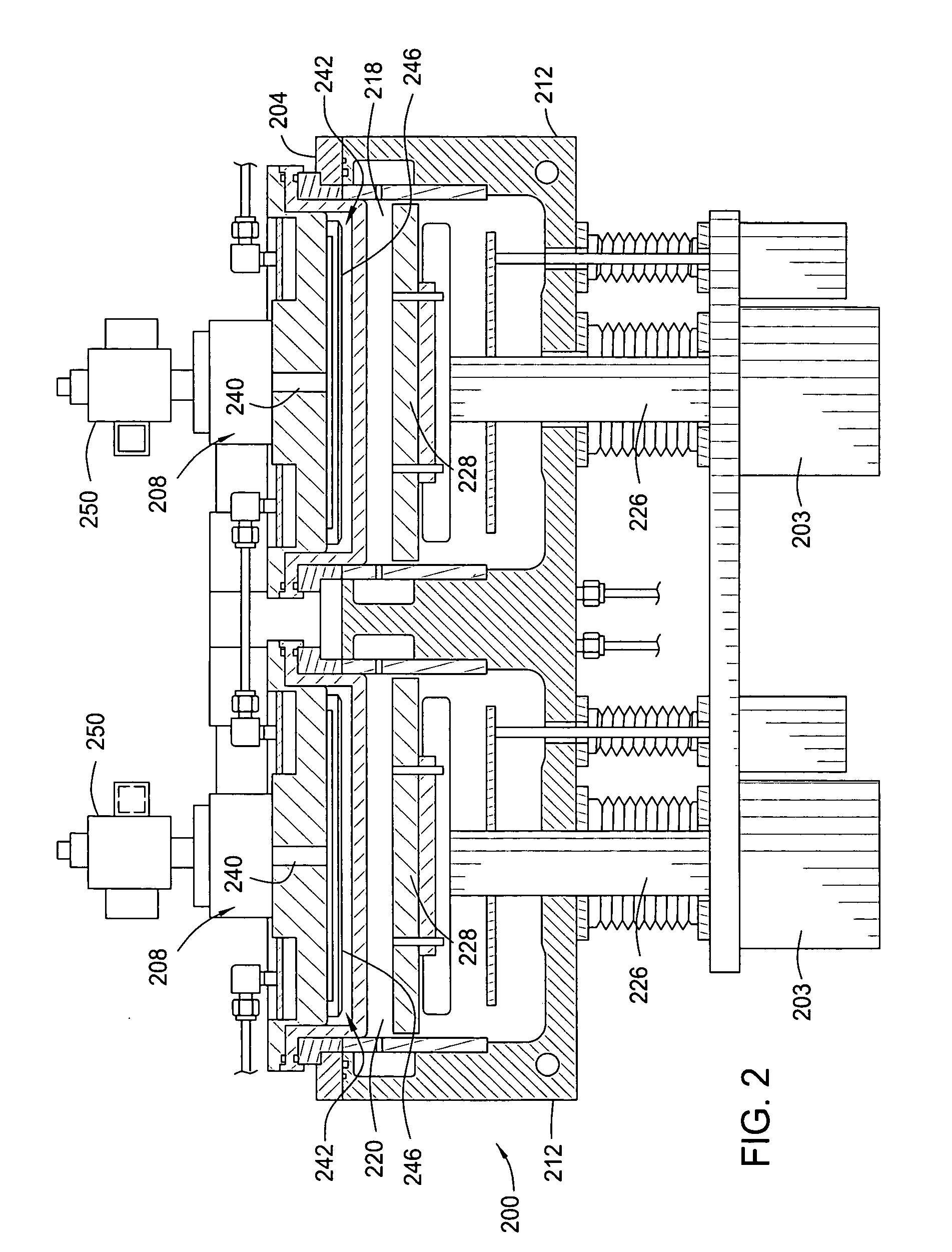

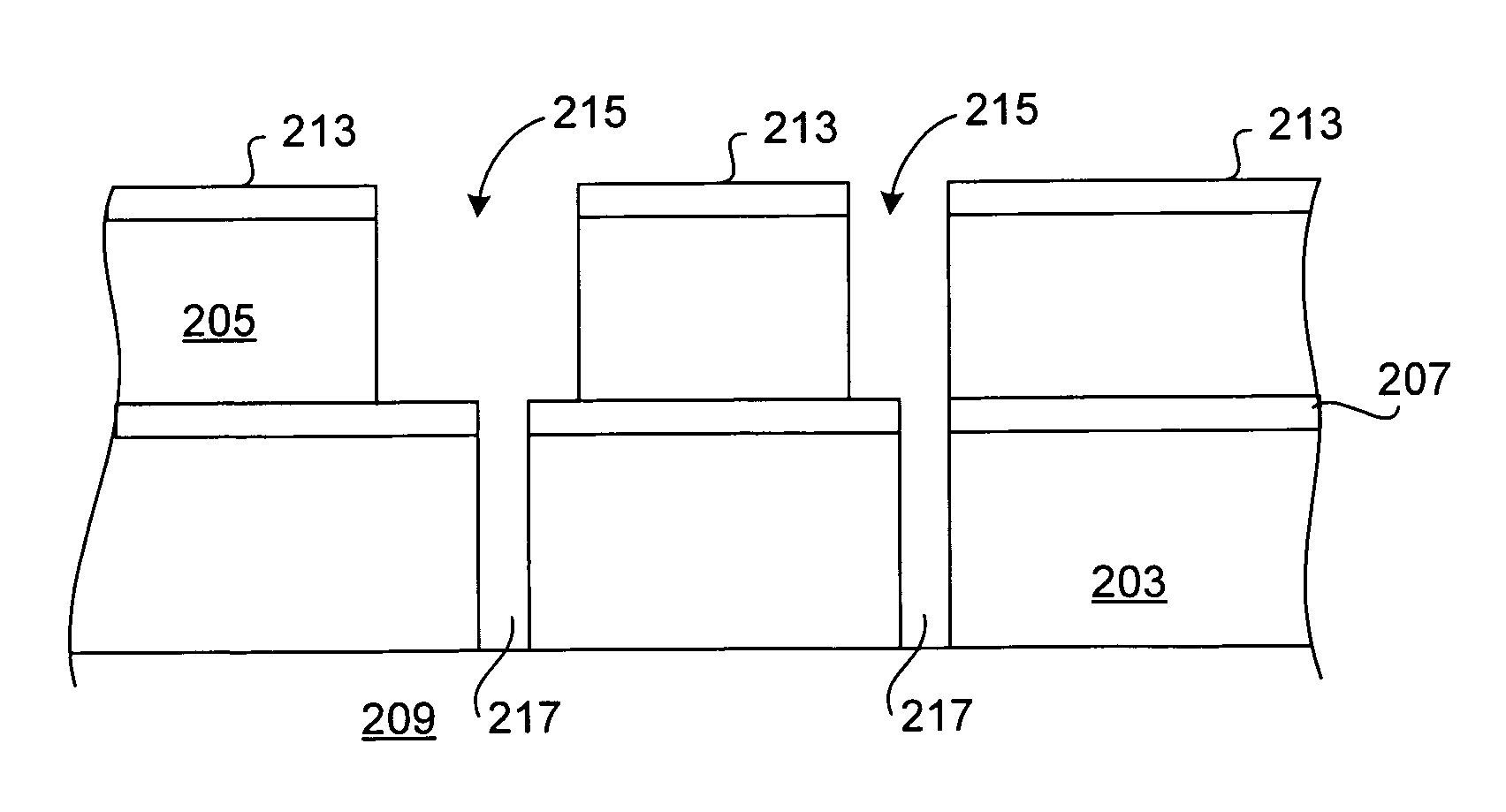

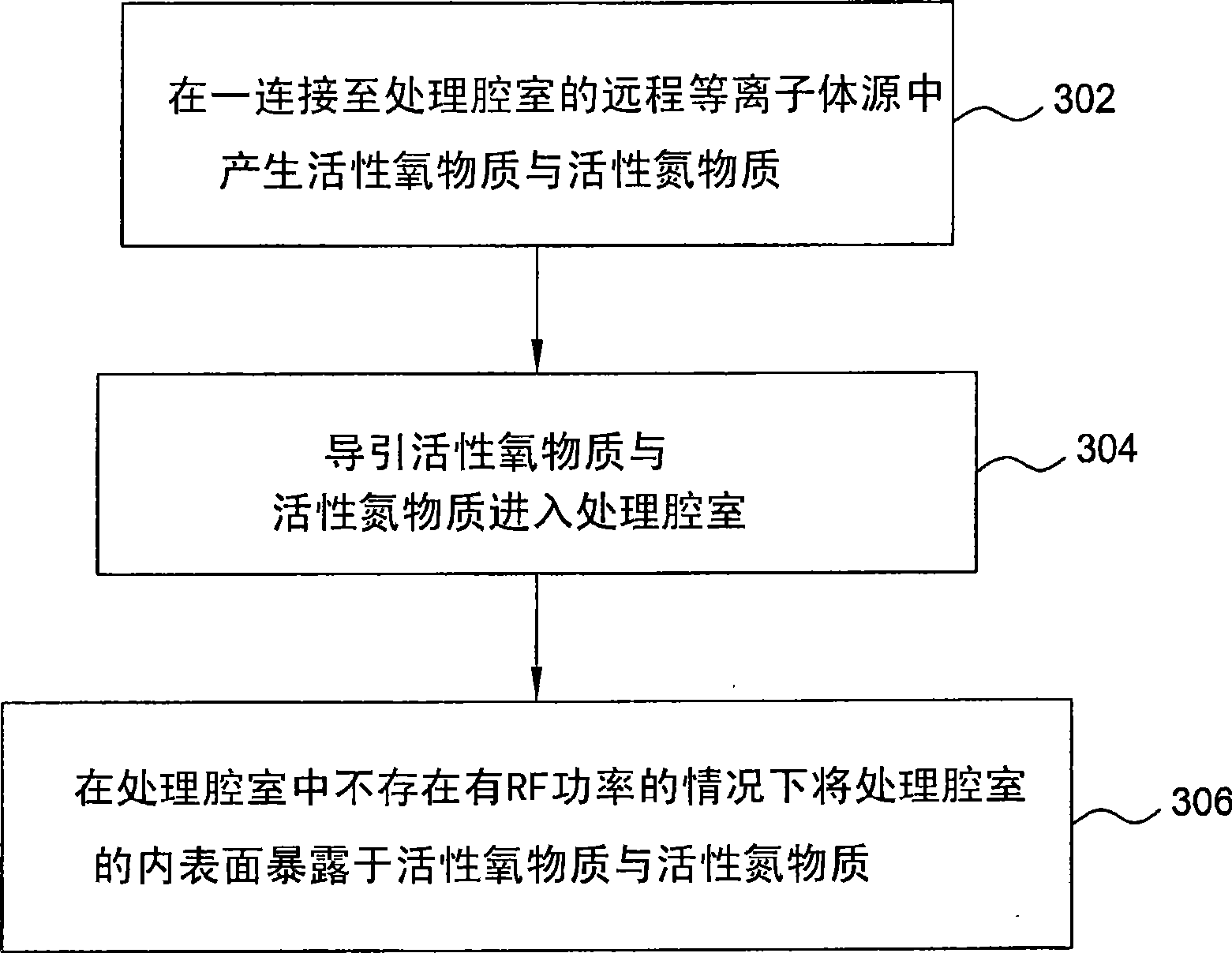

Enhancement of remote plasma source clean for dielectric films

Methods for cleaning semiconductor processing chambers used to process carbon-containing films, such as amorphous carbon films, barrier films comprising silicon and carbon, and low dielectric constant films including silicon, oxygen, and carbon are provided. The methods include using a remote plasma source to generate reactive species that clean interior surfaces of a processing chamber in the absence of RF power in the chamber. The reactive species are generated from an oxygen-containing gas, such as O2, and / or a halogen-containing gas, such as NF3. An oxygen-based ashing process may also be used to remove carbon deposits from the interior surfaces of the chamber before the chamber is exposed to the reactive species from the remote plasma source.

Owner:APPLIED MATERIALS INC

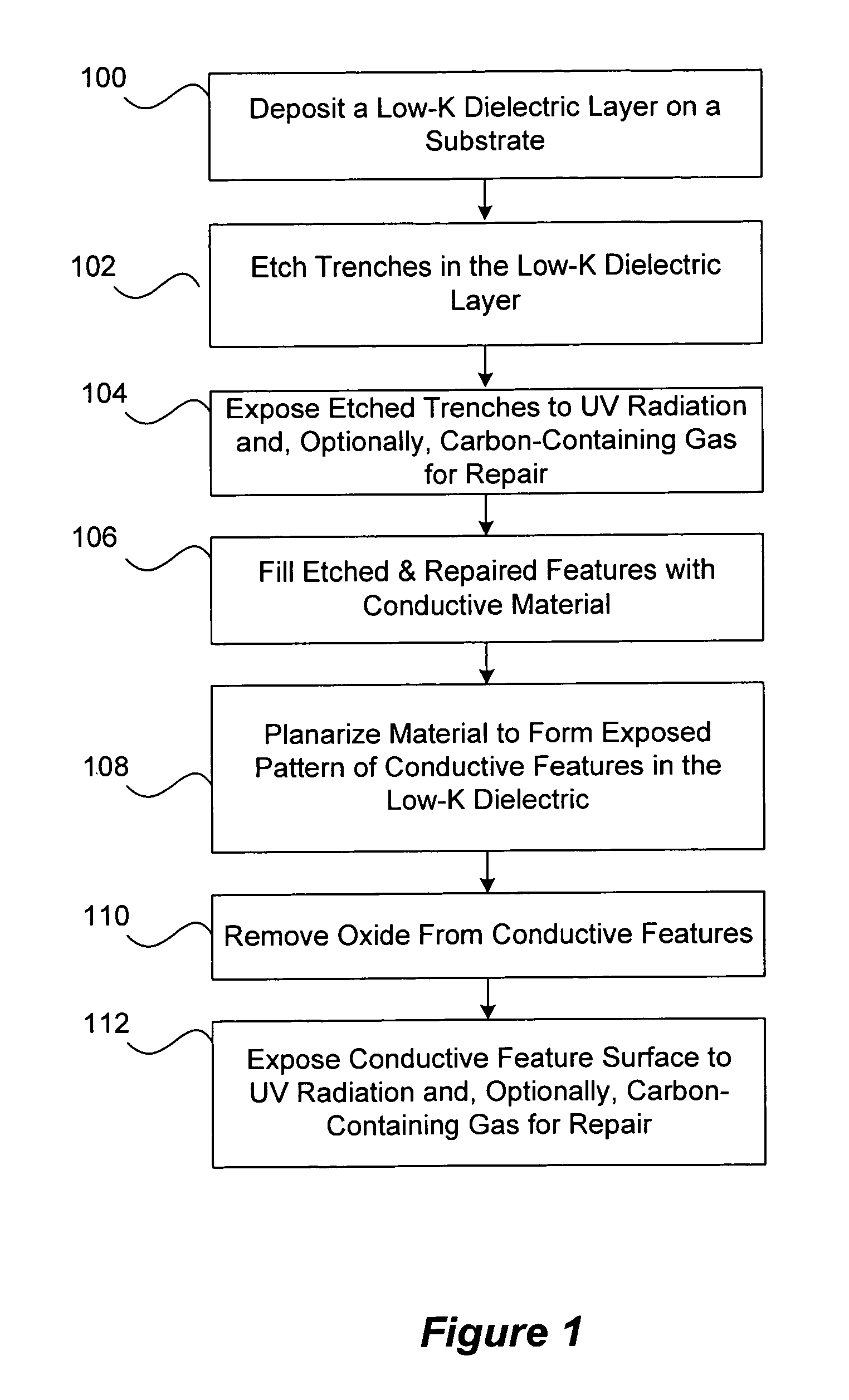

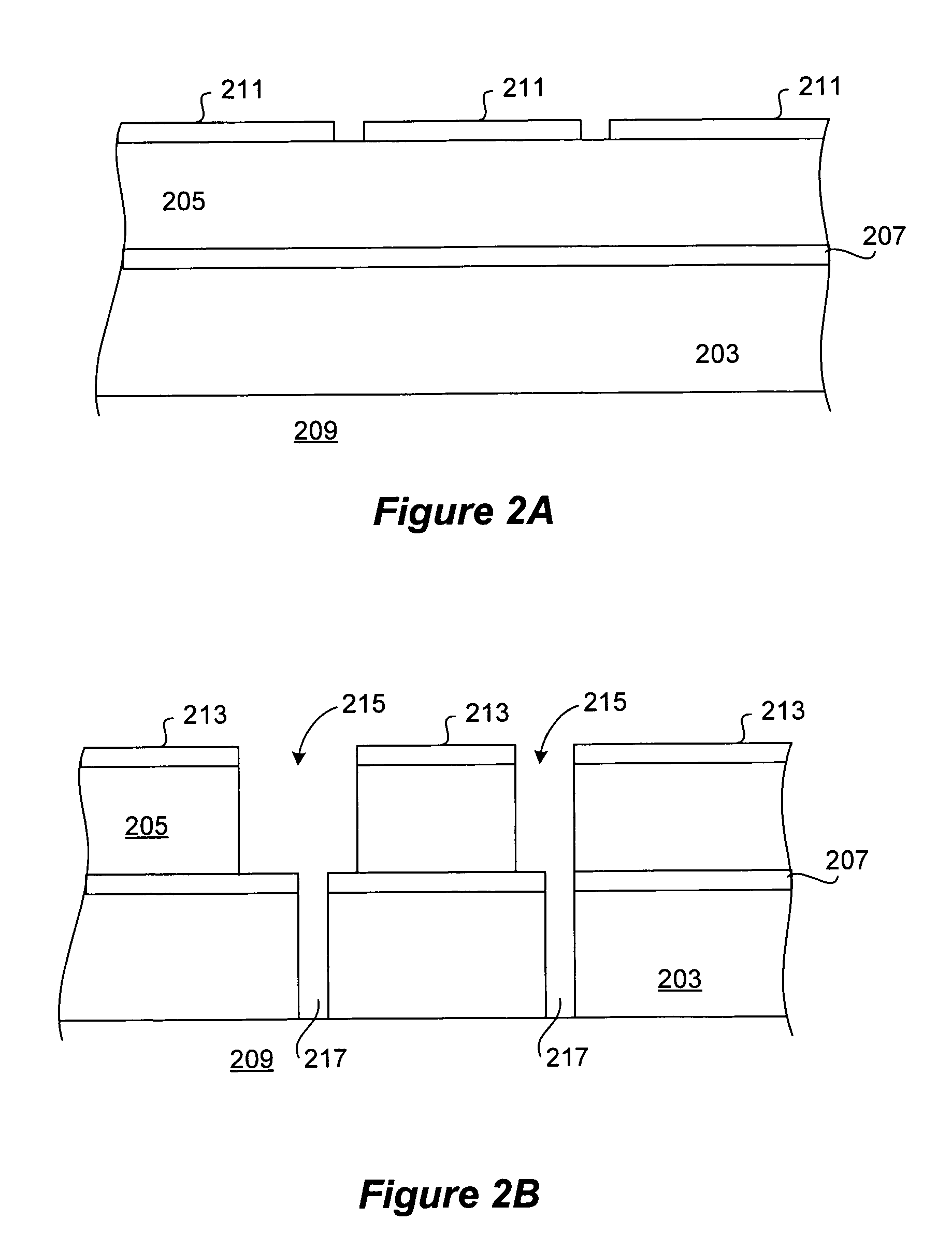

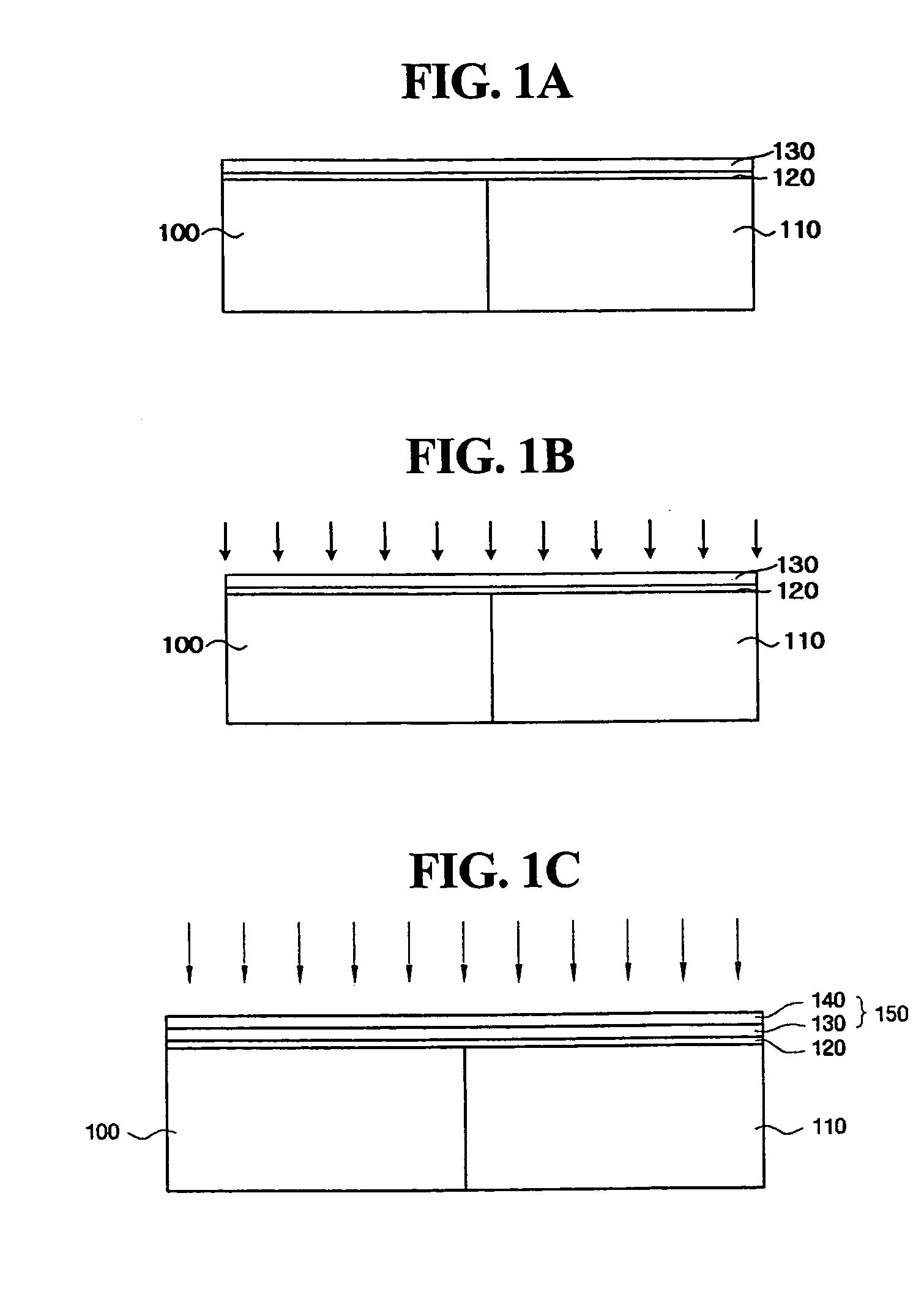

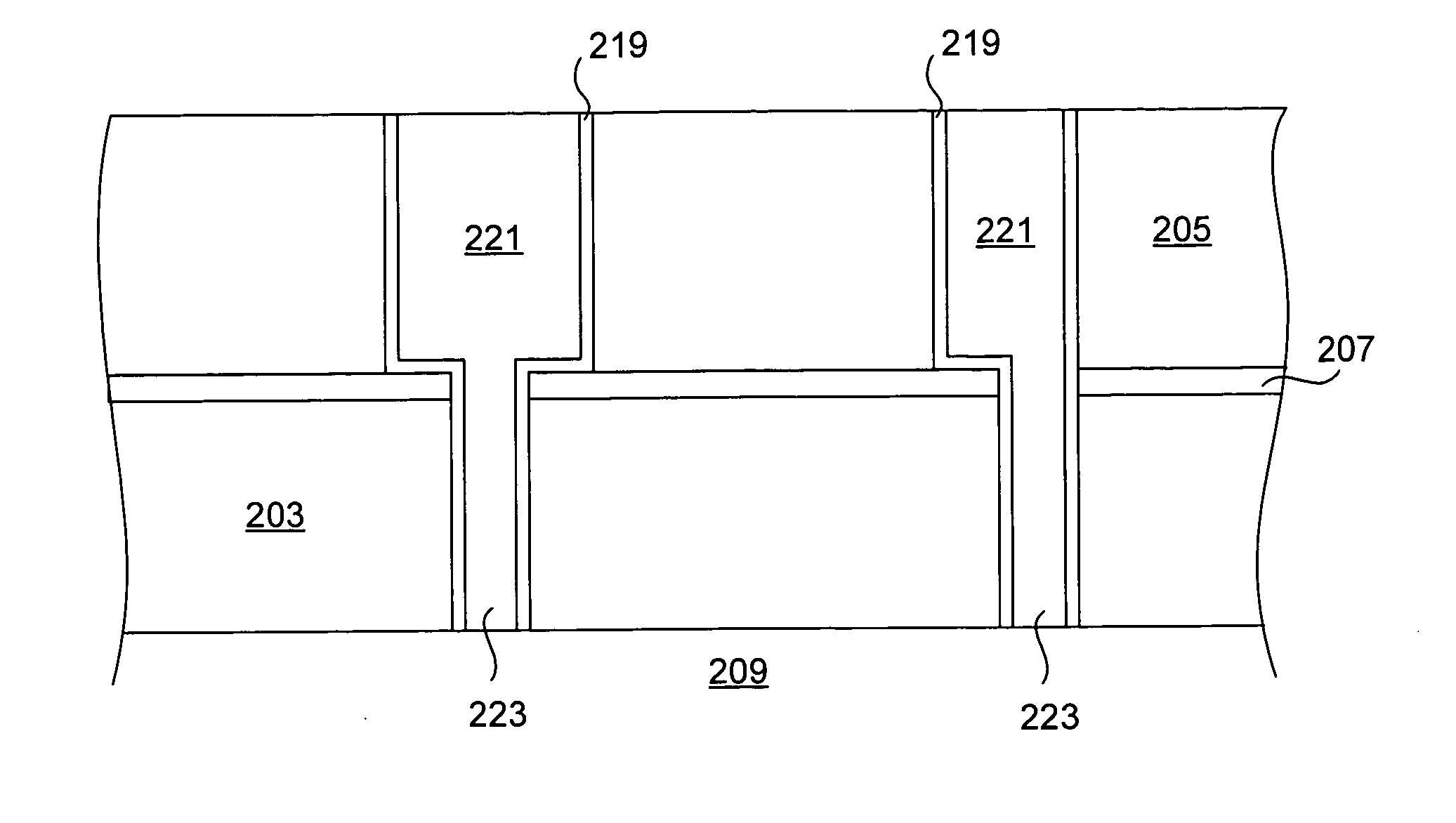

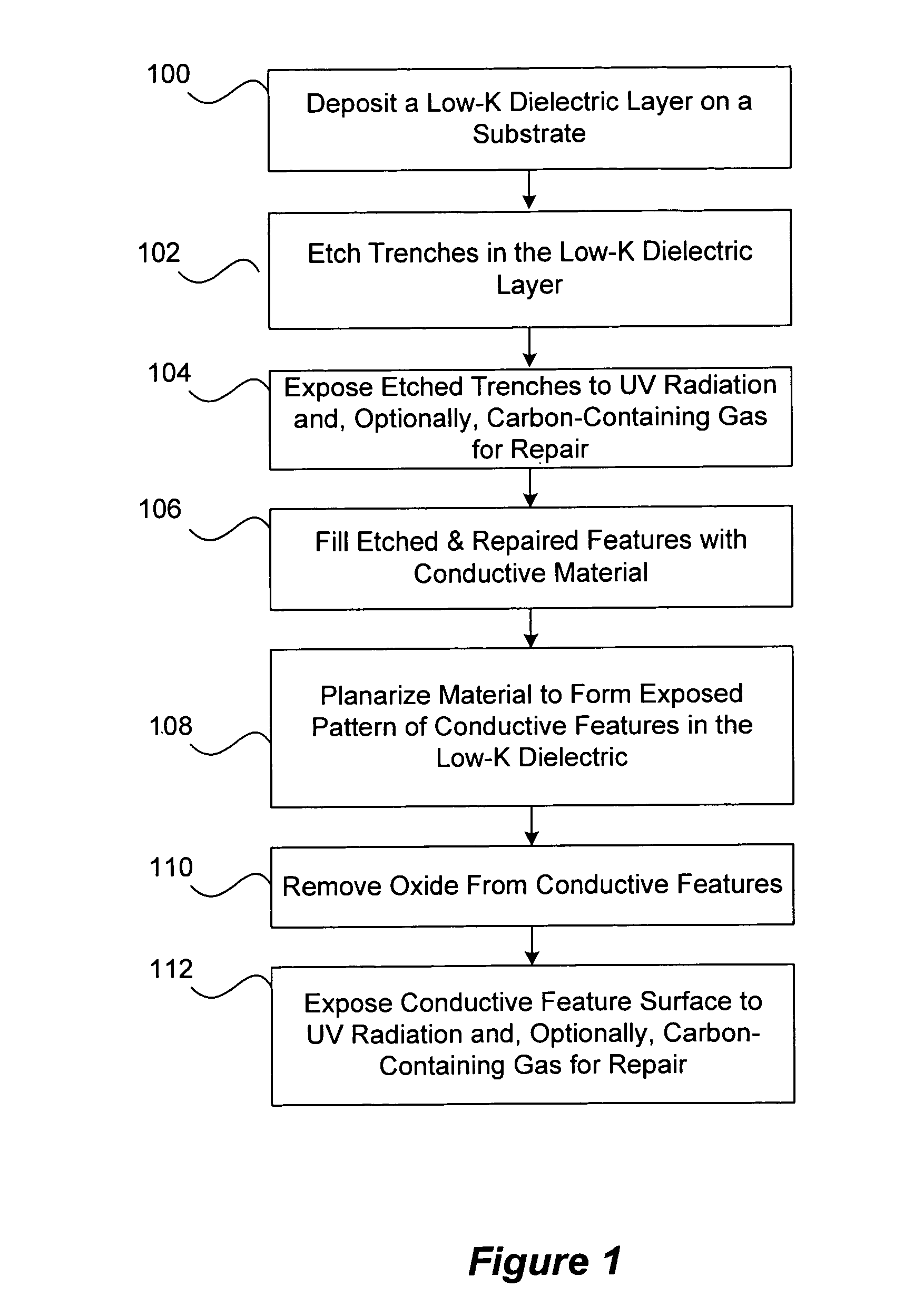

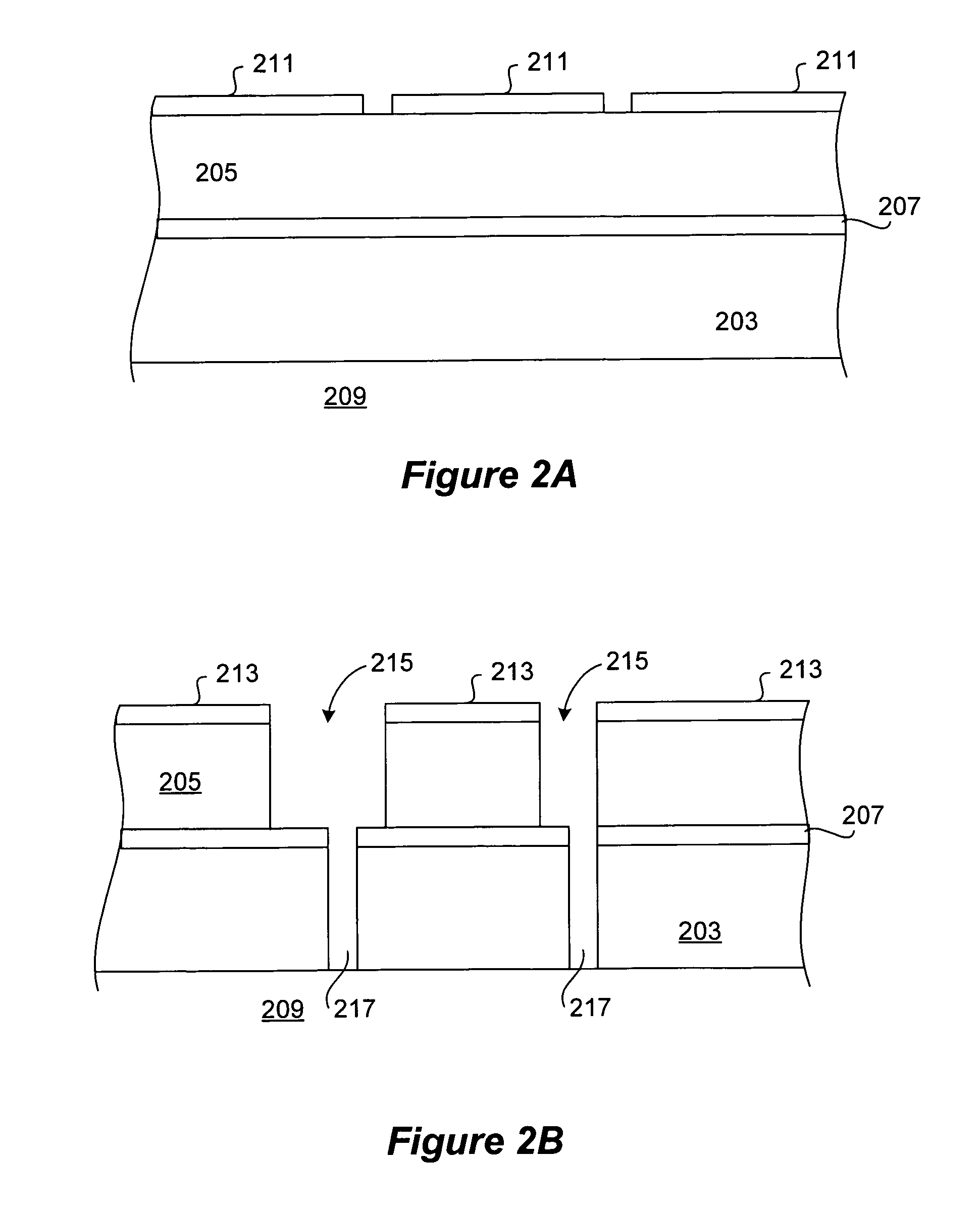

UV treatment for carbon-containing low-k dielectric repair in semiconductor processing

Owner:NOVELLUS SYSTEMS

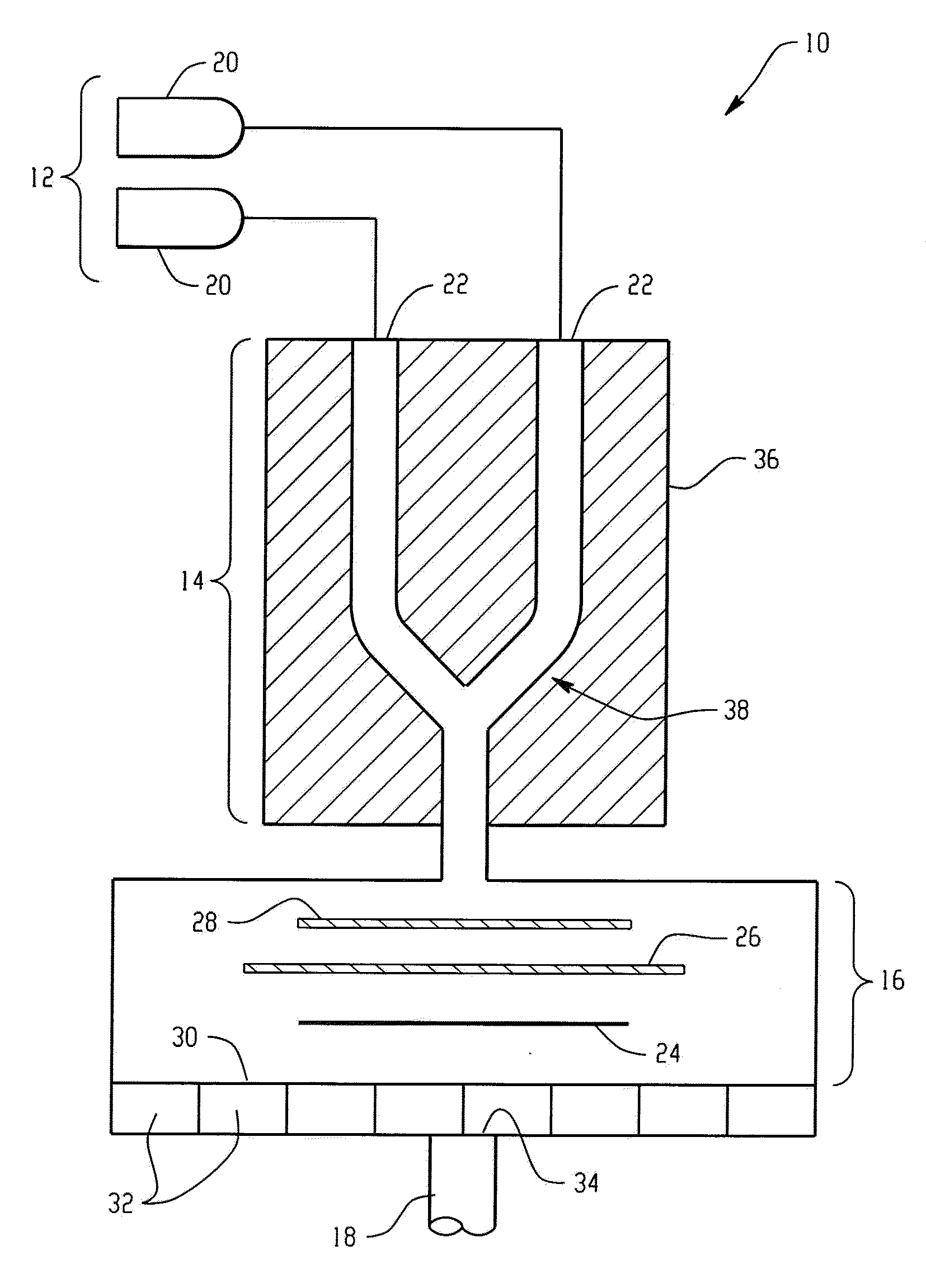

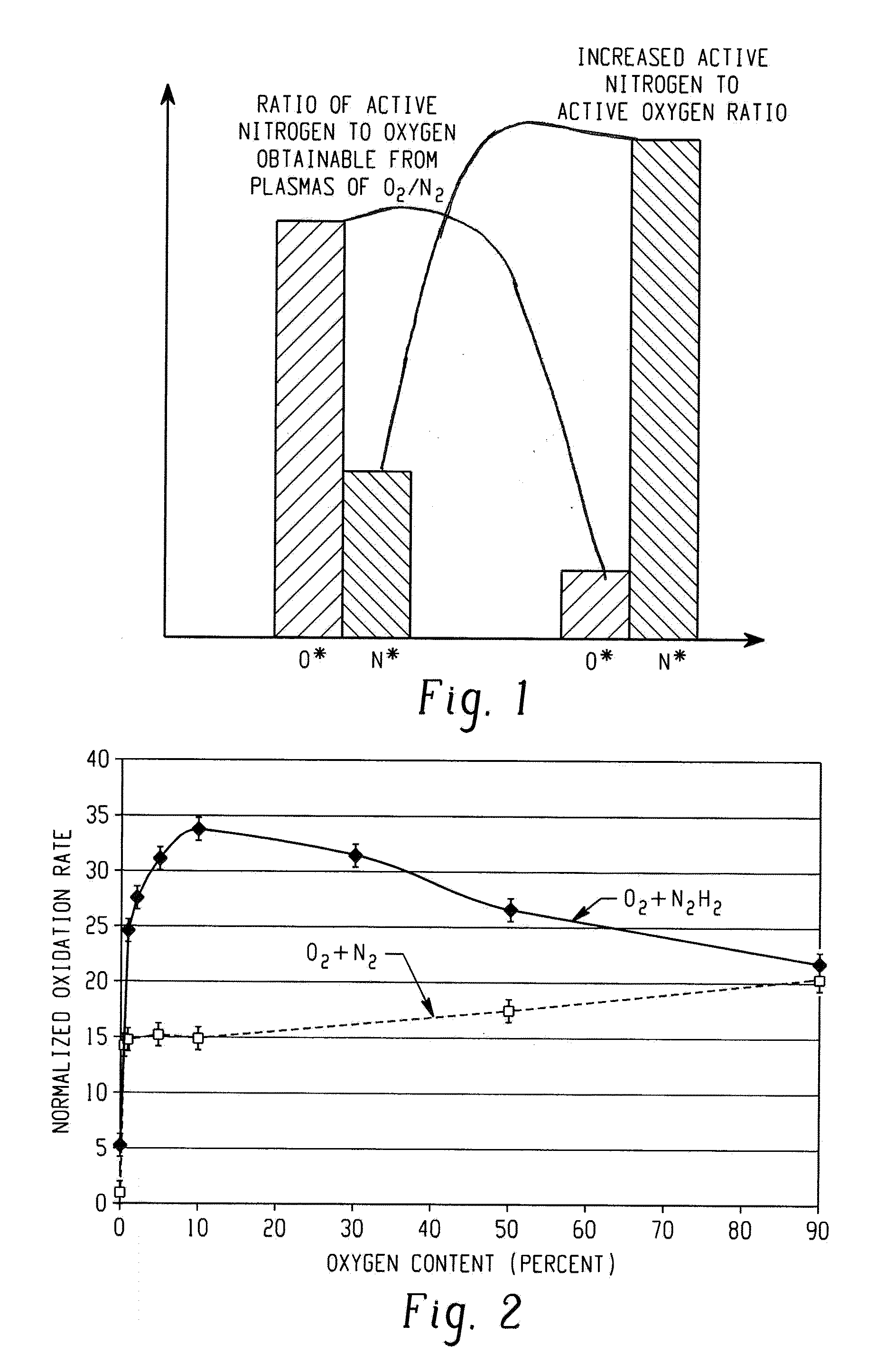

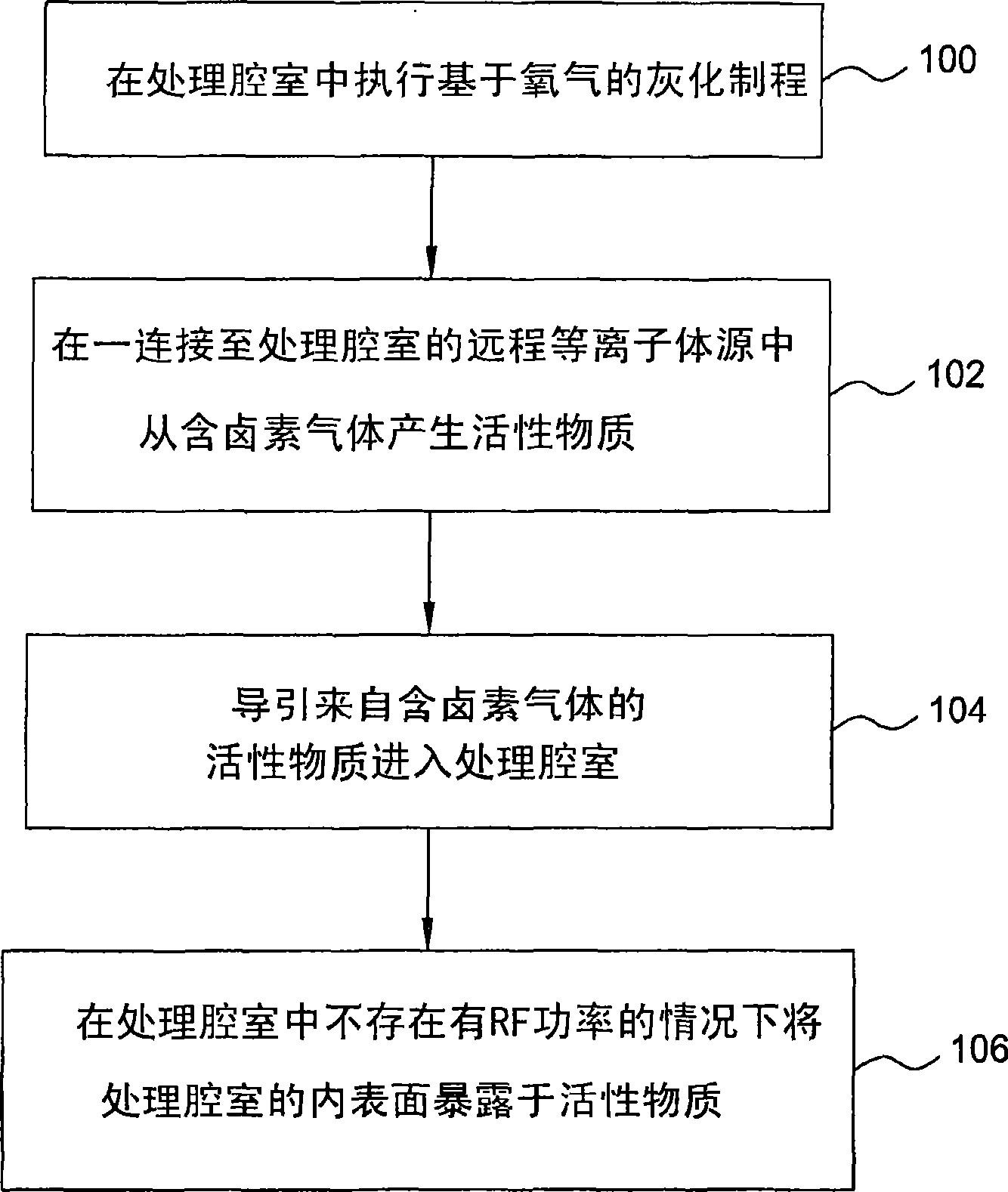

Front end of line plasma mediated ashing processes and apparatus

InactiveUS20100130017A1Increased formationElectric discharge tubesSemiconductor/solid-state device manufacturingResistFront end of line

Front end of line (FEOL) plasma mediated ashing processes for removing organic material from a substrate generally includes exposing the substrate to the plasma to selectively remove photoresist, implanted photoresist, polymers and / or residues from the substrate, wherein the plasma contains a ratio of active nitrogen and active oxygen that is larger than a ratio of active nitrogen and active oxygen obtainable from plasmas of gas mixtures comprising oxygen gas and nitrogen gas. The plasma exhibits high throughput while minimizing and / or preventing substrate oxidation and dopant bleaching. Plasma apparatuses are also described.

Owner:LAM RES CORP

UV assisted silylation for recovery and pore sealing of damaged low K films

Methods for the repair of damaged low k films are provided. Damage to the low k films occurs during processing of the film such as during etching, ashing, and planarization. The processing of the low k film causes water to store in the pores of the film and further causes hydrophilic compounds to form in the low k film structure. Repair processes incorporating ultraviolet (UV) radiation and silylation compounds remove the water from the pores and further remove the hydrophilic compounds from the low k film structure.

Owner:APPLIED MATERIALS INC

UV assisted silylation for recovery and pore sealing of damaged low k films

ActiveUS20120270339A1Dielectric constant be lowerSemiconductor/solid-state device manufacturingUltravioletSilylation

Methods for the repair of damaged low k films are provided. Damage to the low k films occurs during processing of the film such as during etching, ashing, and planarization. The processing of the low k film causes water to store in the pores of the film and further causes hydrophilic compounds to form in the low k film structure. Repair processes incorporating ultraviolet (UV) radiation and silylation compounds remove the water from the pores and further remove the hydrophilic compounds from the low k film structure.

Owner:APPLIED MATERIALS INC

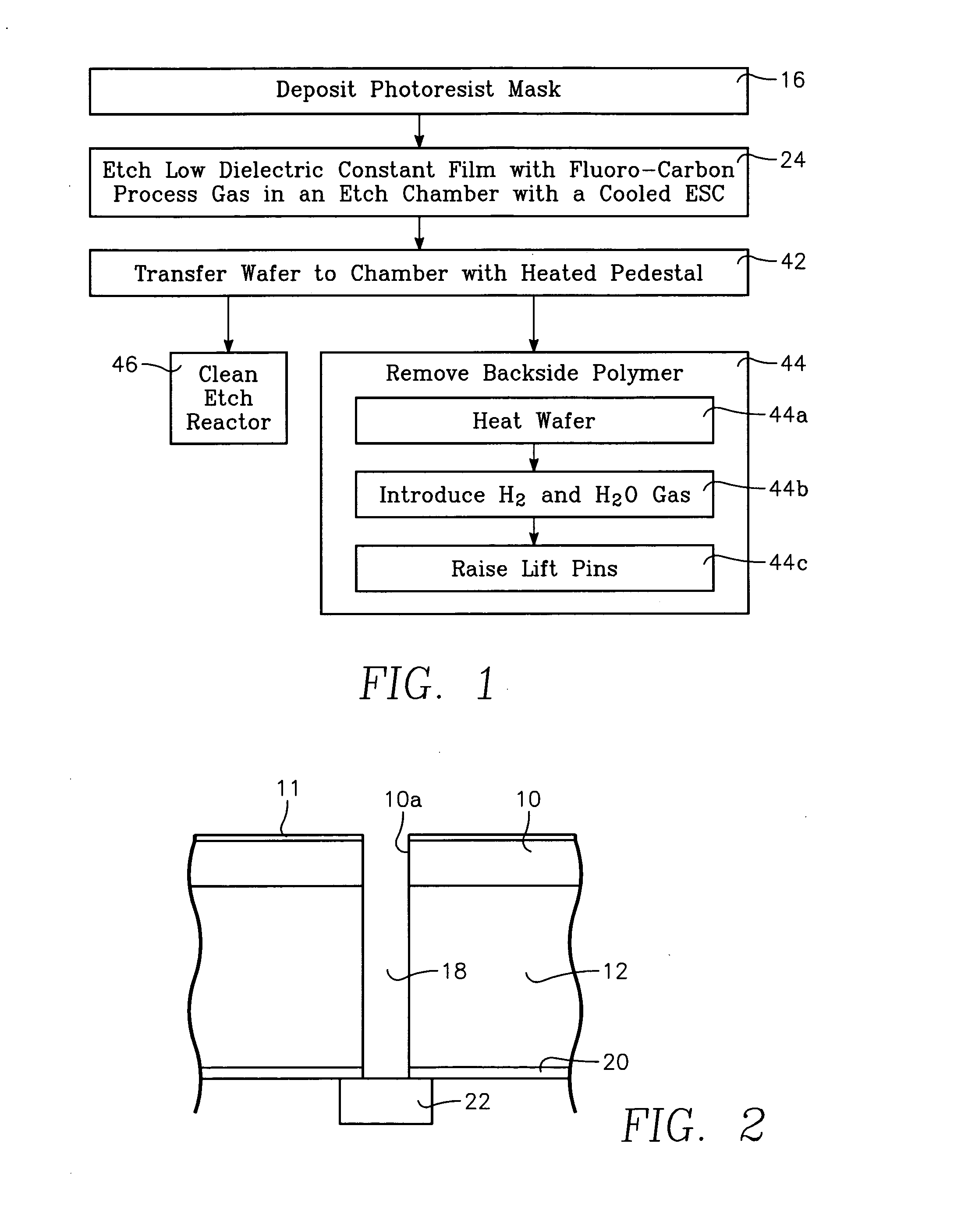

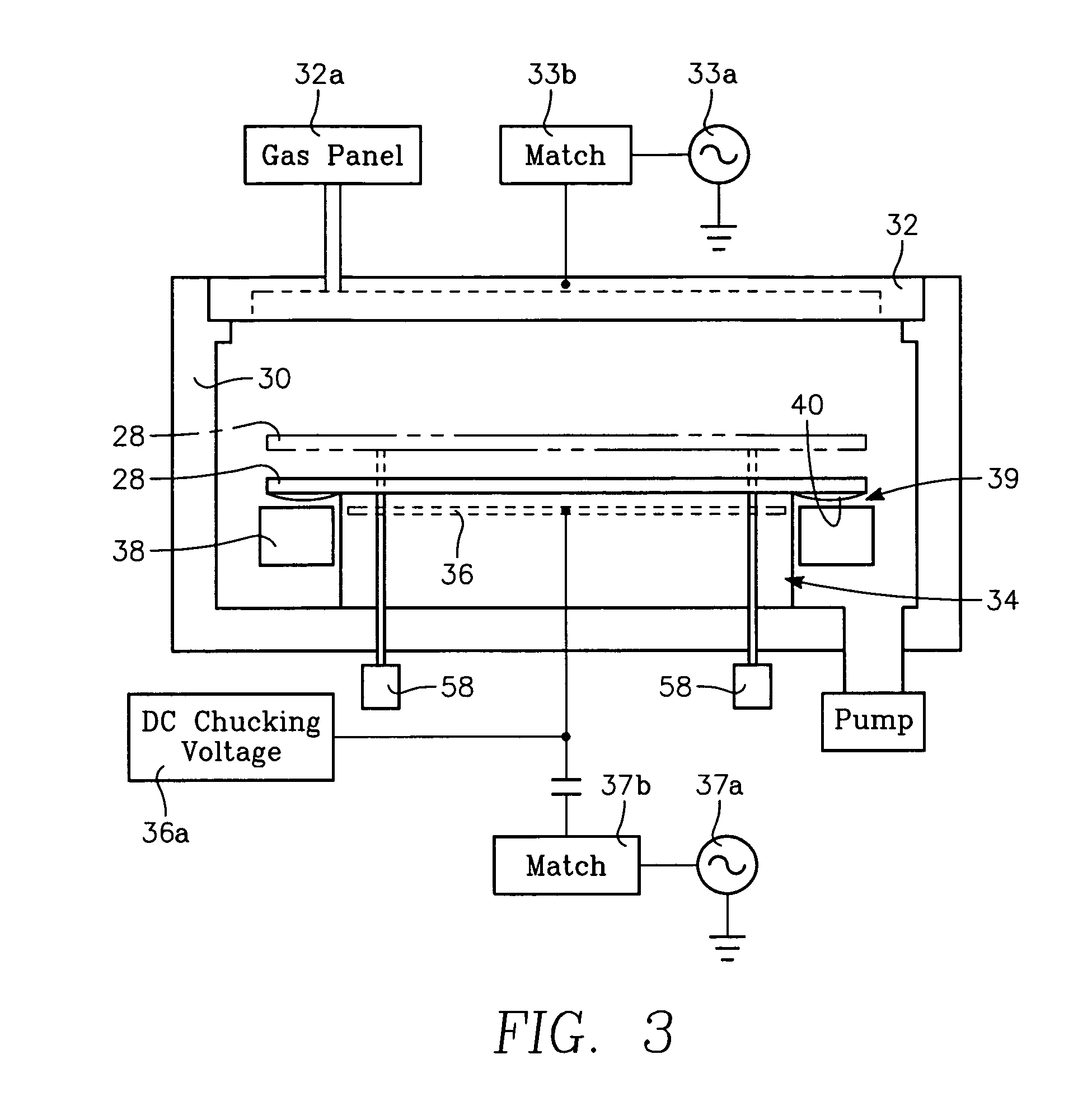

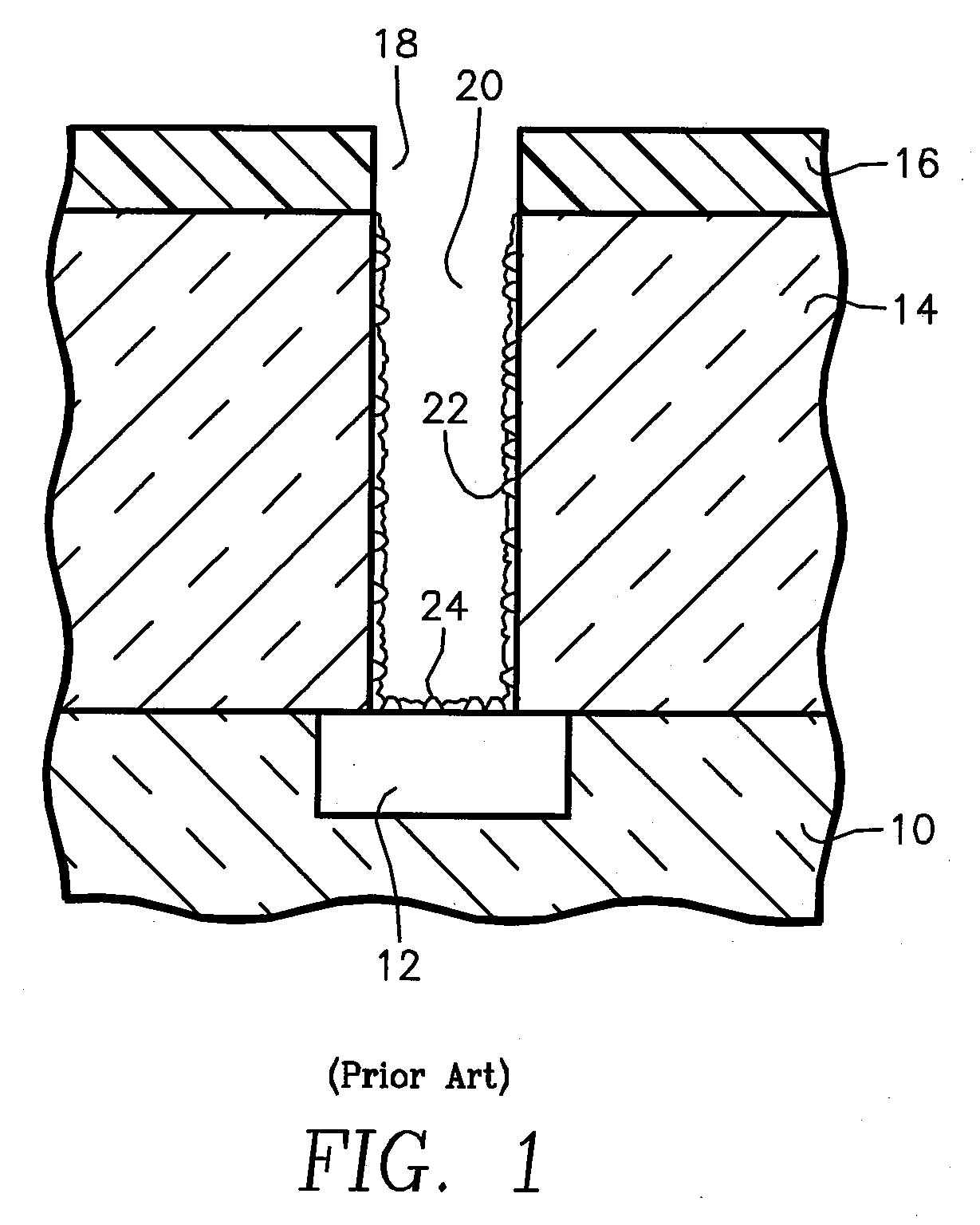

Plasma dielectric etch process including ex-situ backside polymer removal for low-dielectric constant material

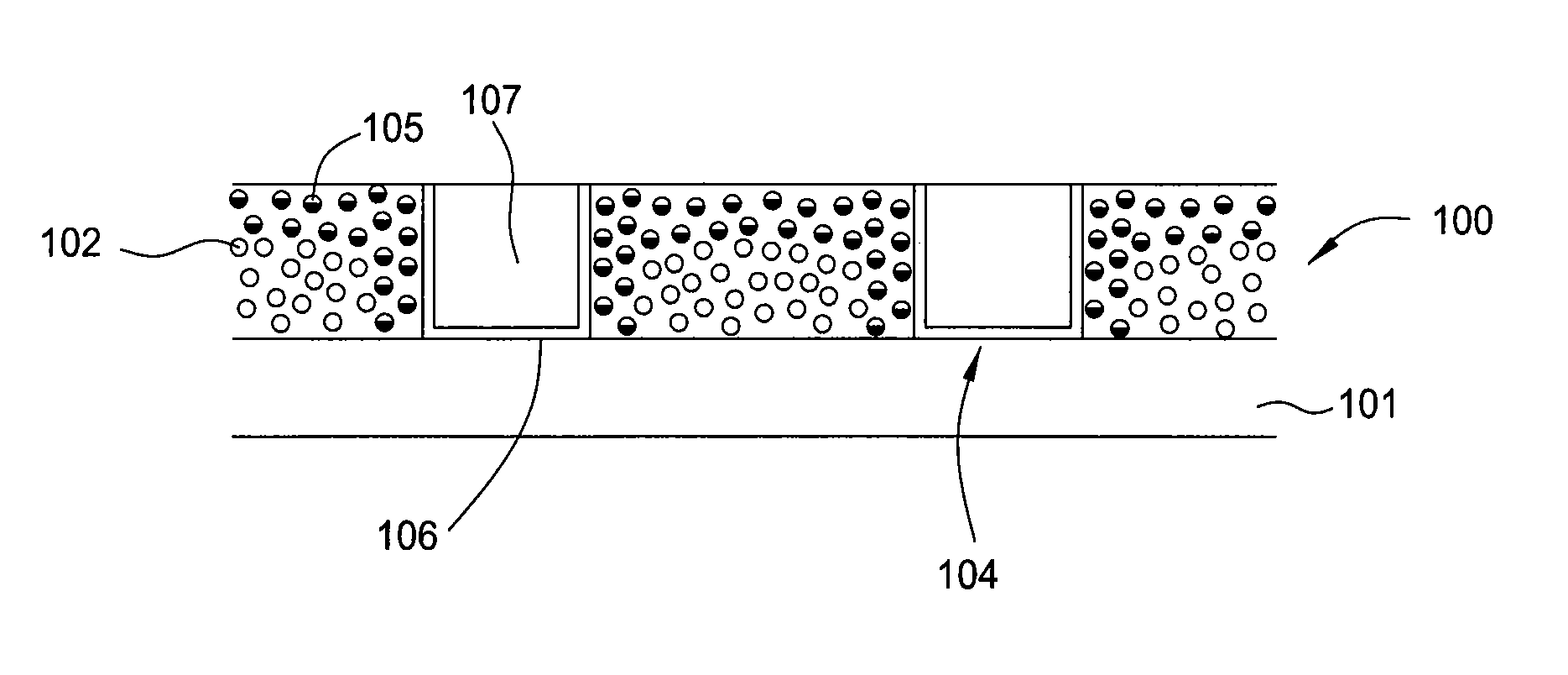

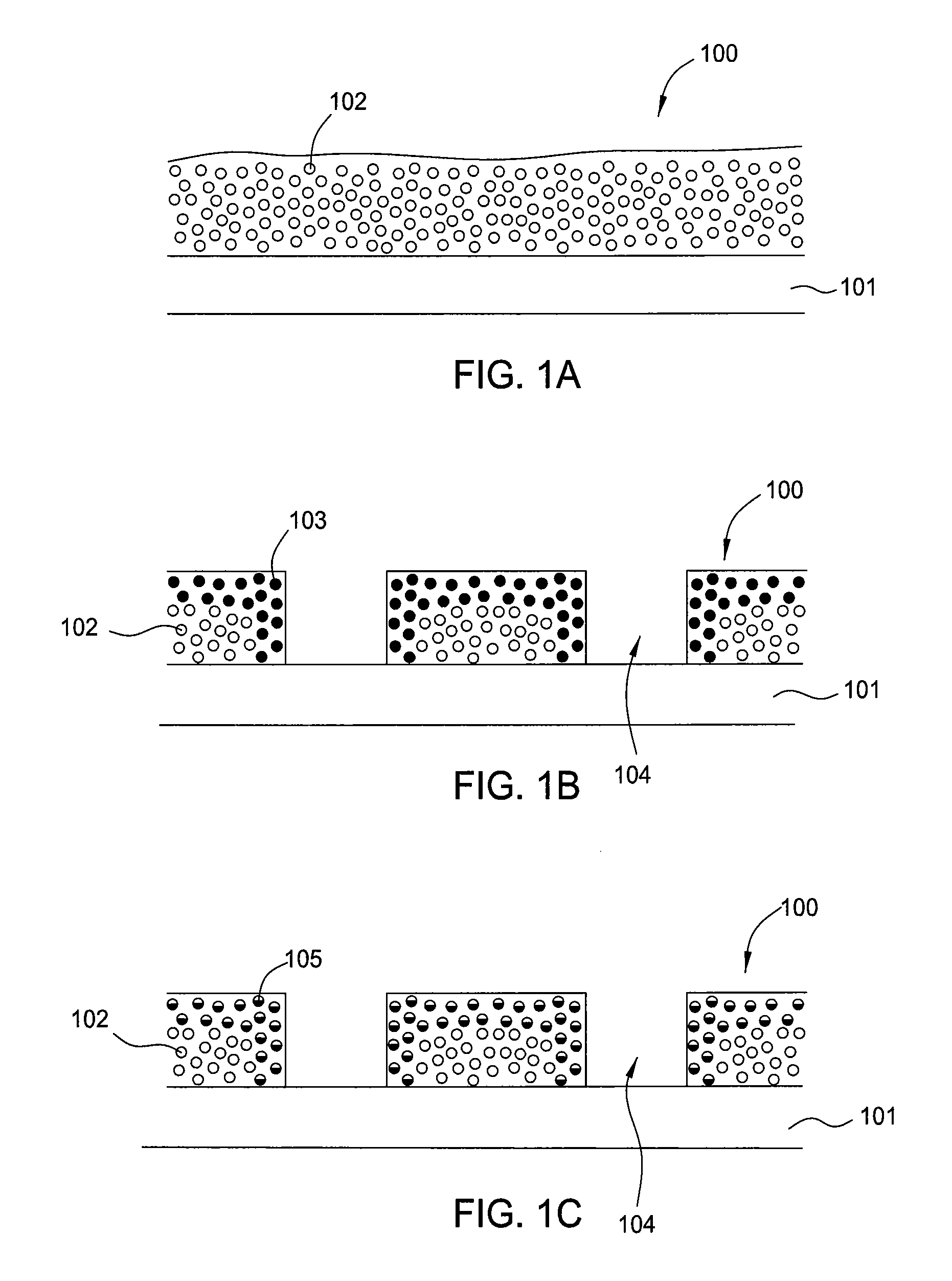

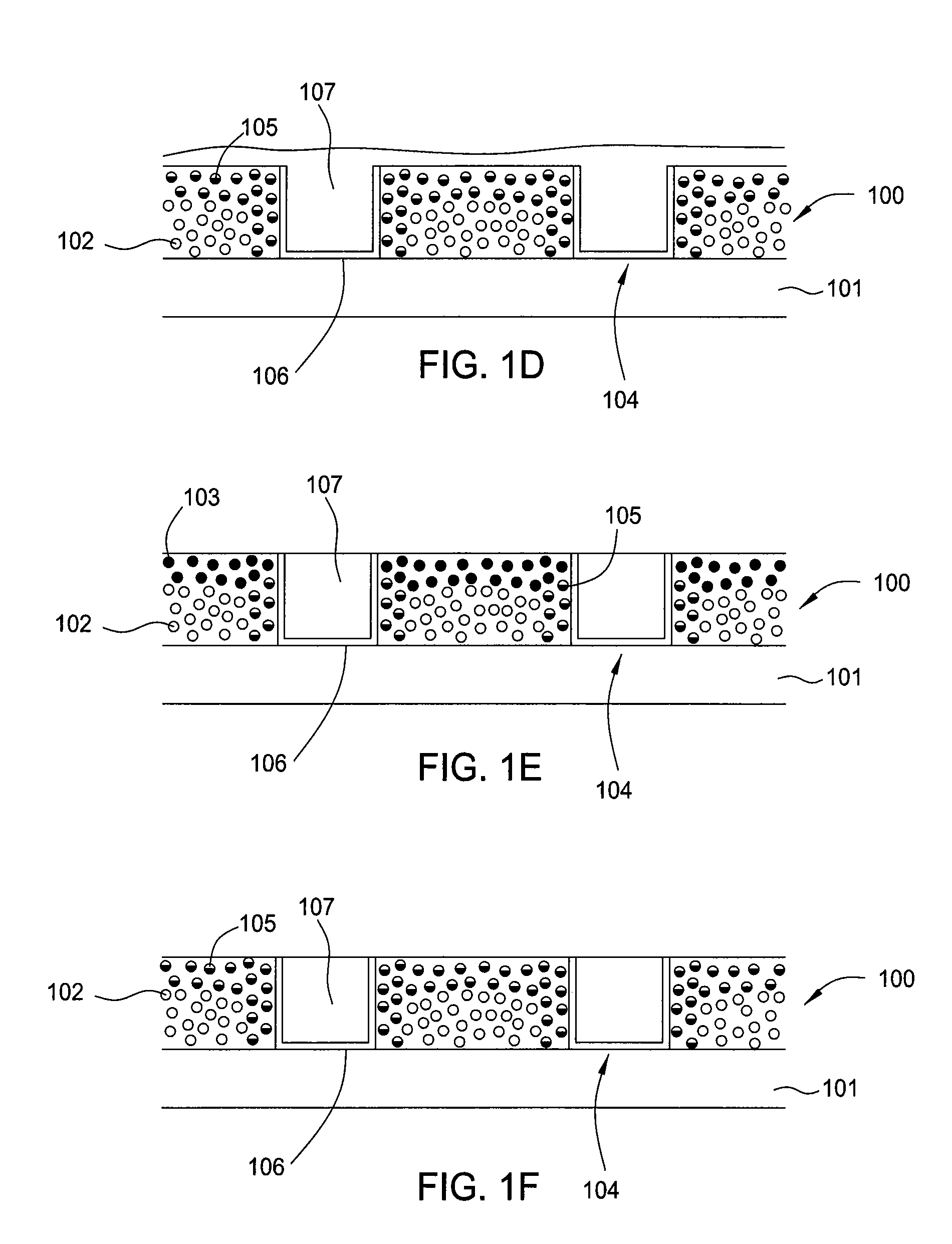

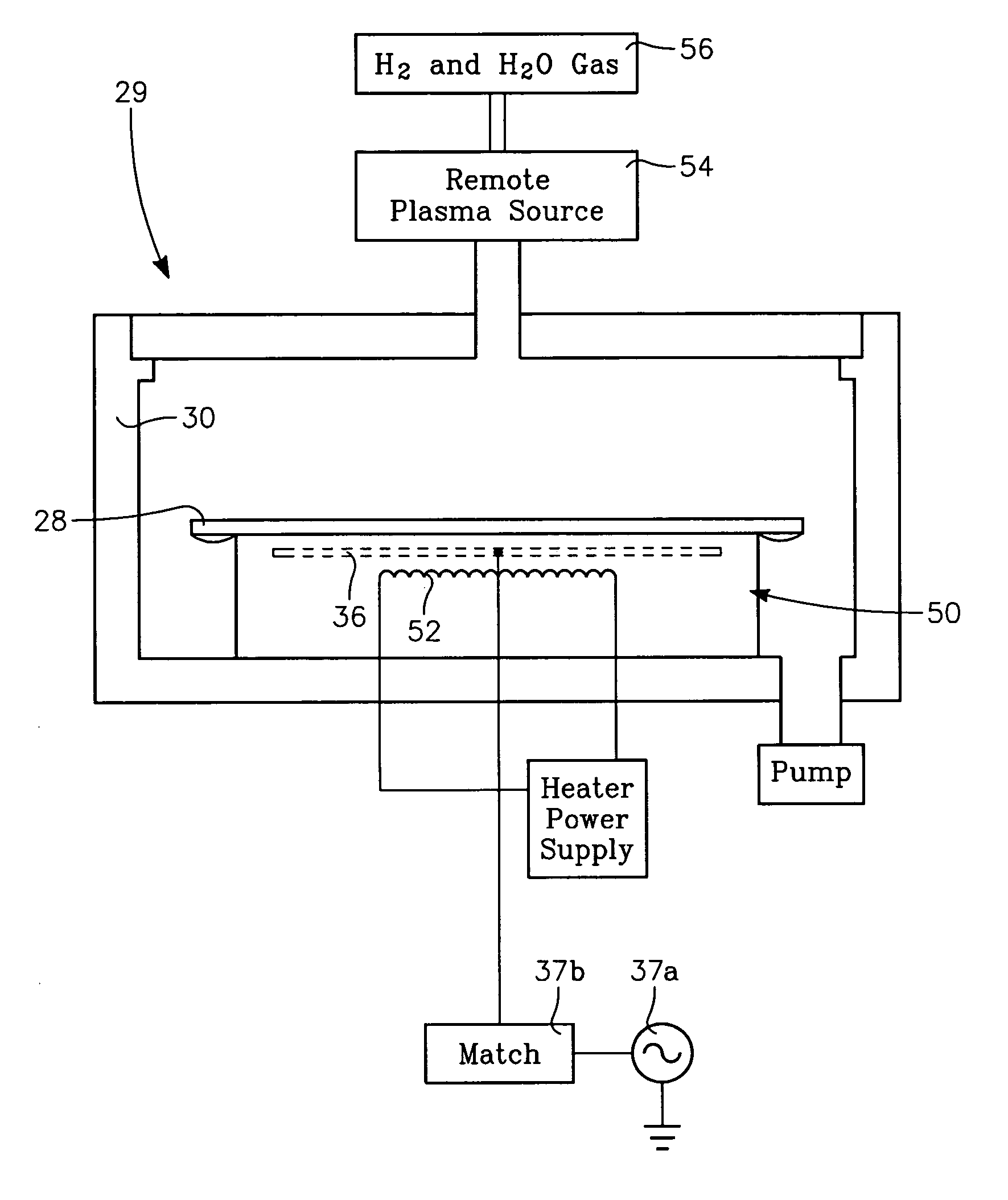

A plasma etch process for etching a porous carbon-doped silicon oxide dielectric layer using a photoresist mask is carried out first in an etch reactor by performing a fluorocarbon based etch process on the workpiece to etch exposed portions of the dielectric layer while depositing protective fluorocarbon polymer on the photoresist mask. Then, in an ashing reactor, polymer and photoresist are removed by heating the workpiece to over 100 degrees C., exposing a peripheral portion of the backside of said workpiece, and providing products from a plasma of a hydrogen process gas to reduce carbon contained in polymer and photoresist on said workpiece until the polymer has been removed from a backside of said workpiece. The process gas preferably contains both hydrogen gas and water vapor, although the primary constituent is hydrogen gas. The wafer (workpiece) backside may be exposed by extending the wafer lift pins.

Owner:APPLIED MATERIALS INC

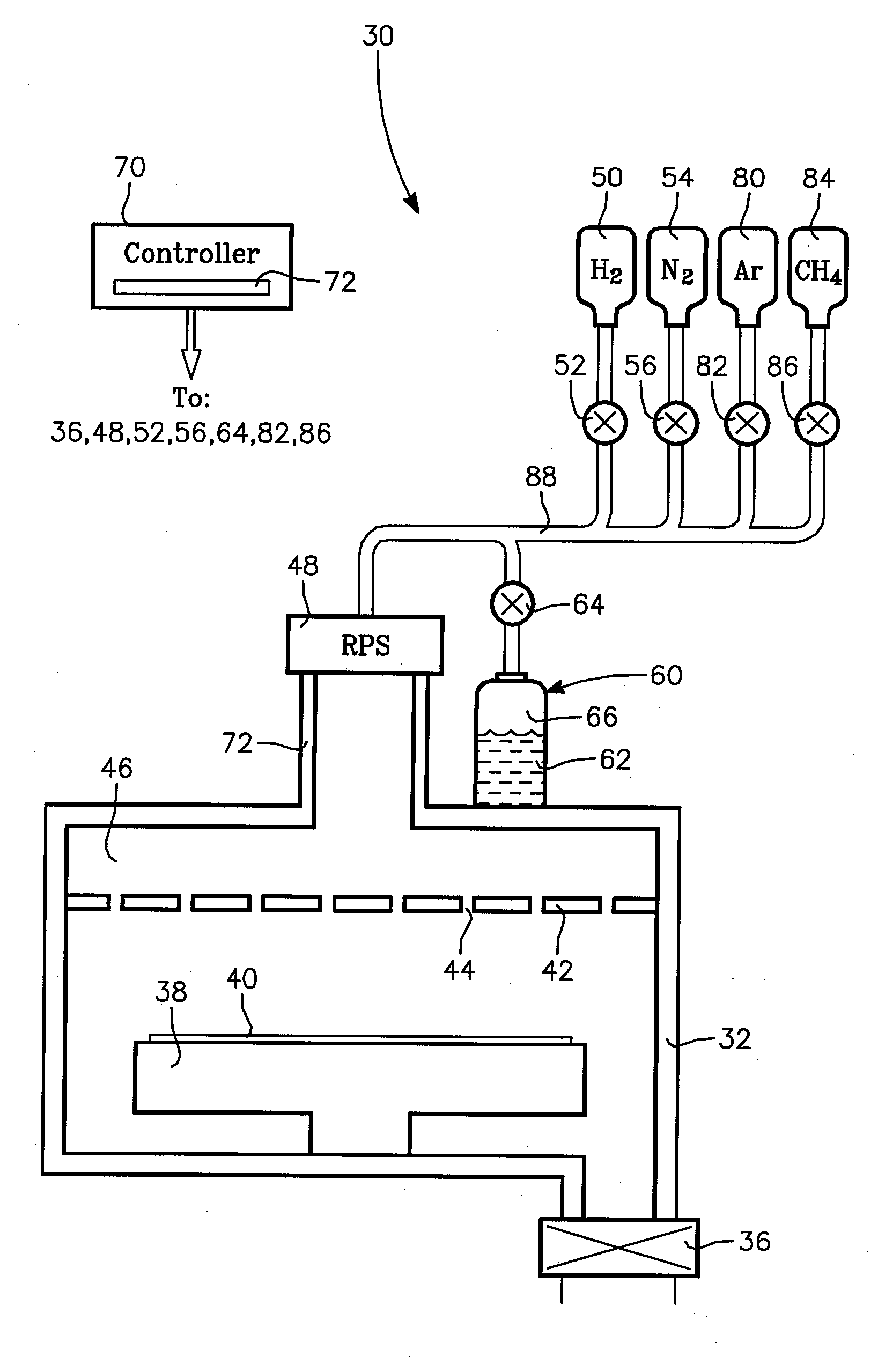

Hydrogen ashing enhanced with water vapor and diluent gas

ActiveUS20080261405A1Decorative surface effectsSemiconductor/solid-state device detailsWater vaporOxygen

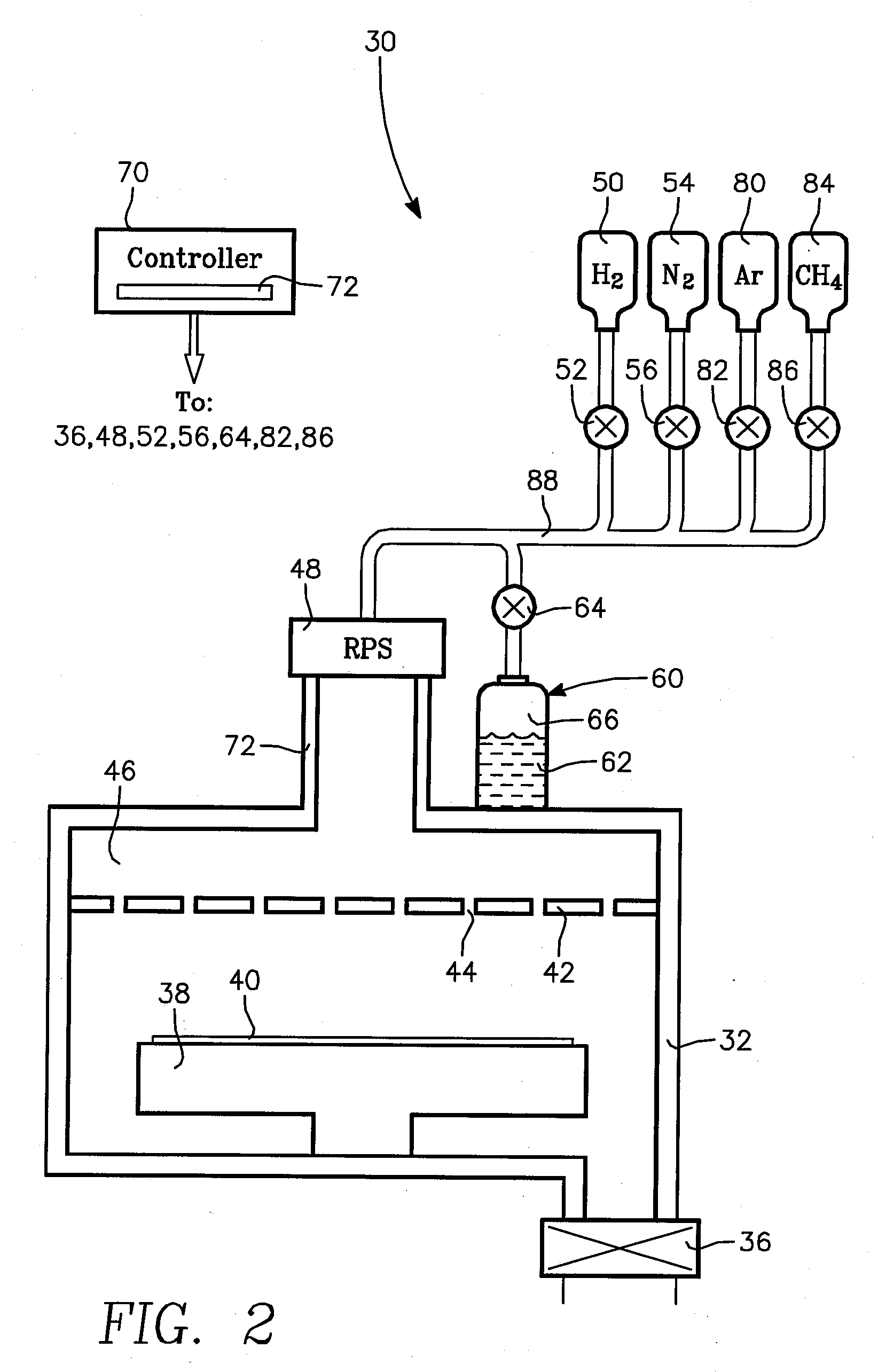

An oxygen-free hydrogen plasma ashing process particularly useful for low-k dielectric materials based on hydrogenated silicon oxycarbide materials. The main ashing step includes exposing a previously etched dielectric layer to a plasma of hydrogen and optional nitrogen, a larger amount of water vapor, and a yet larger amount of argon or helium. Especially for porous low-k dielectrics, the main ashing plasma additionally contains a hydrocarbon gas such as methane. The main ashing may be preceded by a short surface treatment by a plasma of a hydrogen-containing reducing gas such as hydrogen and optional nitrogen.

Owner:APPLIED MATERIALS INC

Method and apparatus for processing a wafer

InactiveUS20030045098A1Vacuum evaporation coatingPhotomechanical apparatusEngineeringMechanical engineering

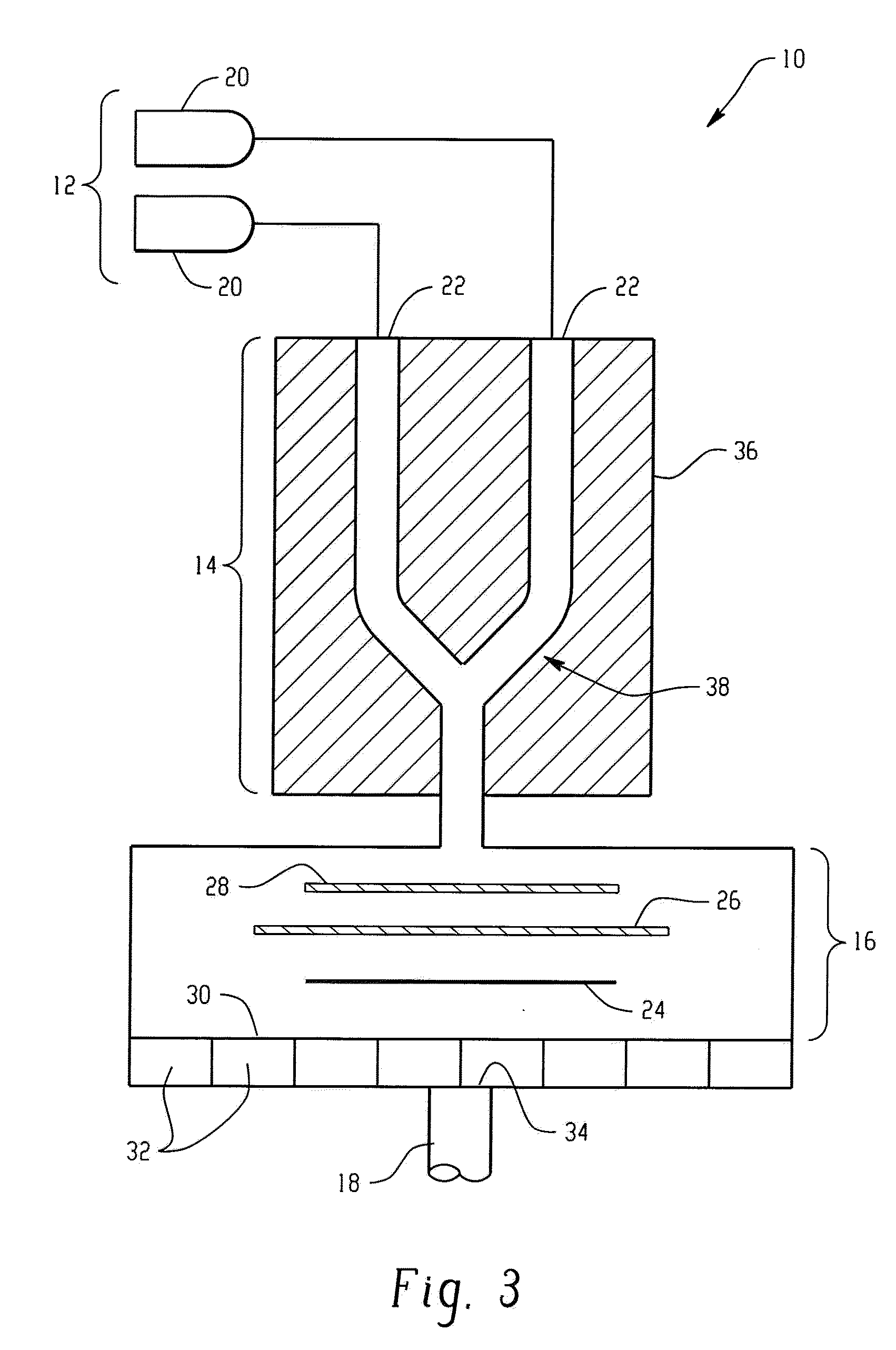

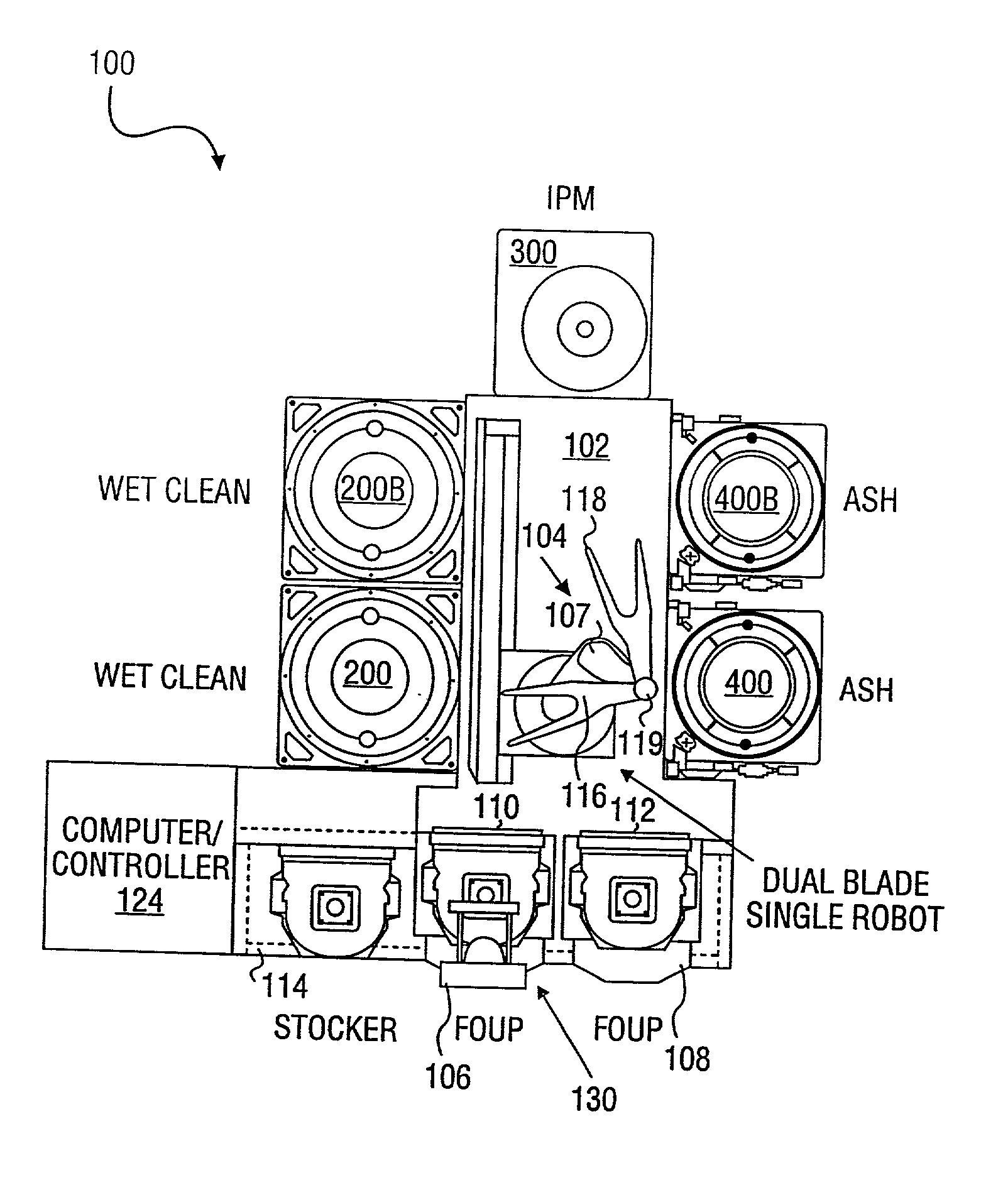

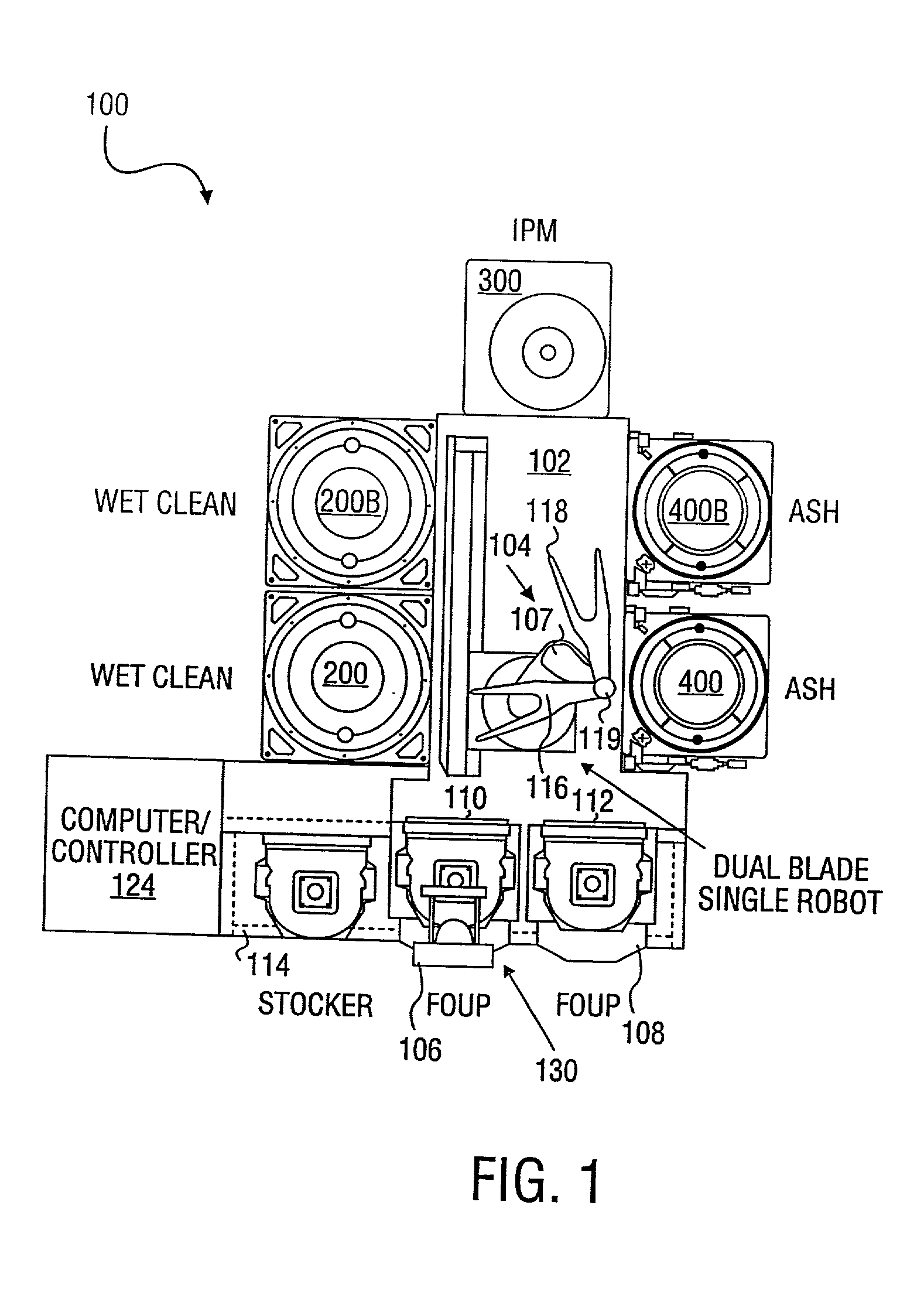

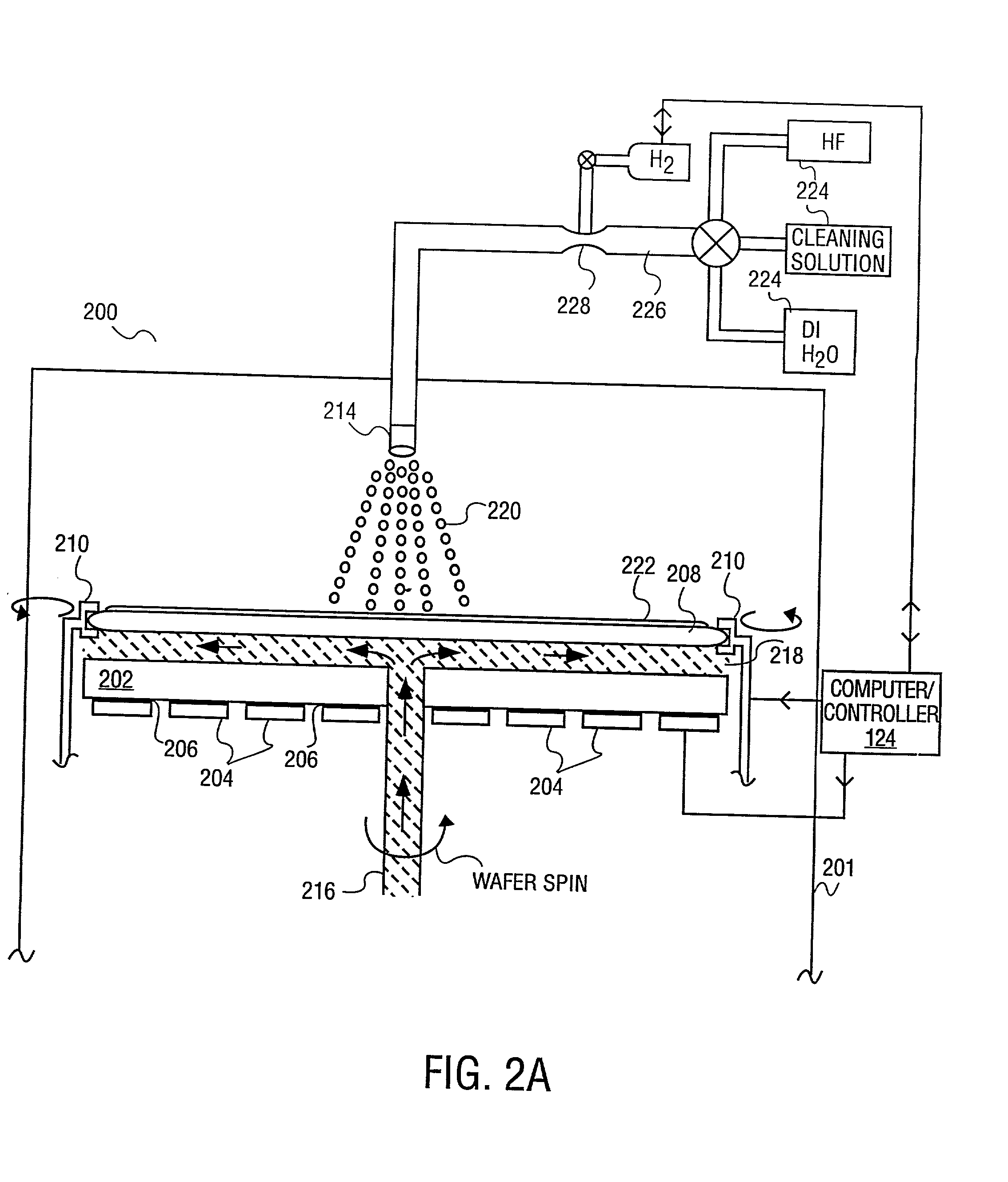

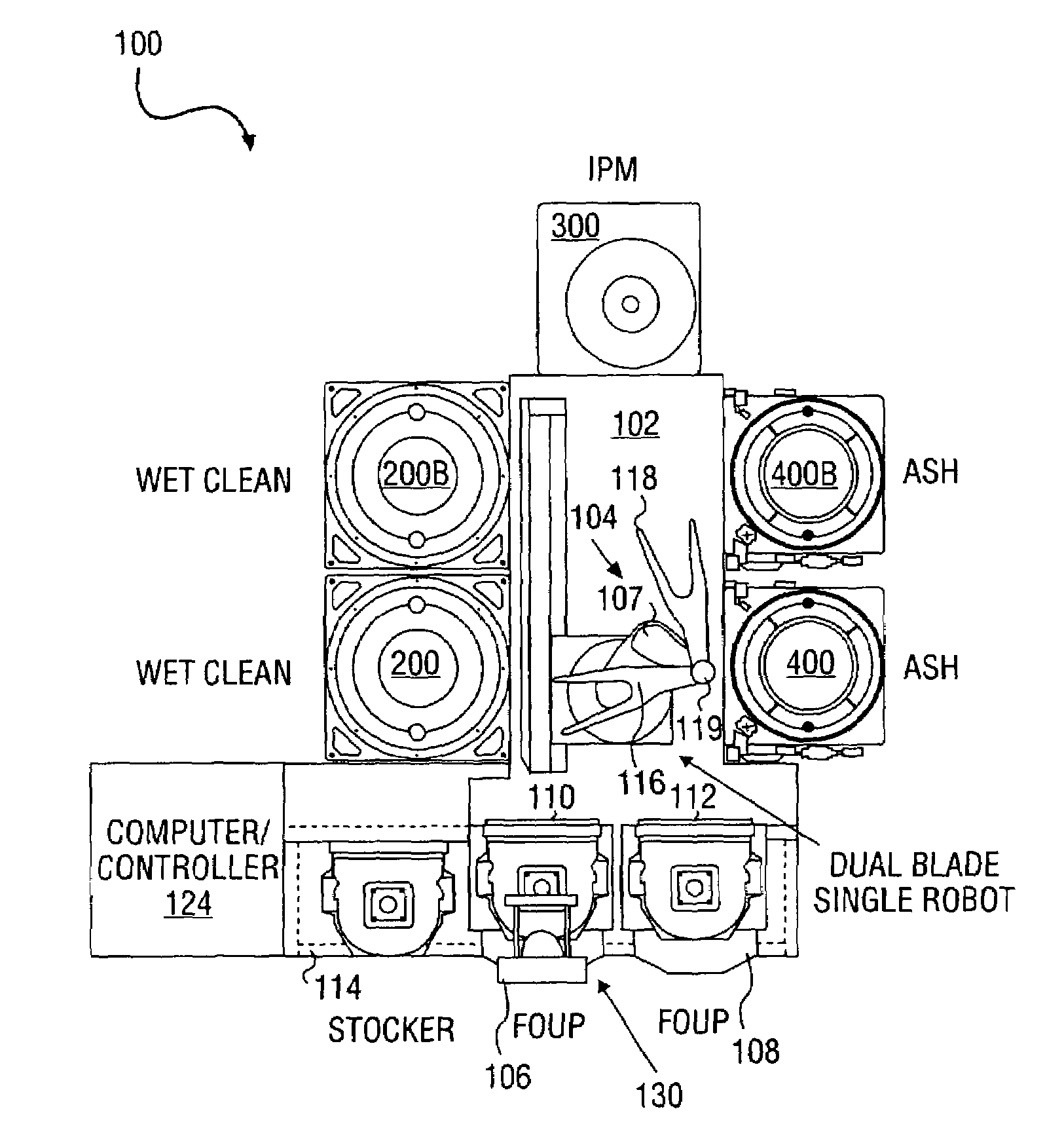

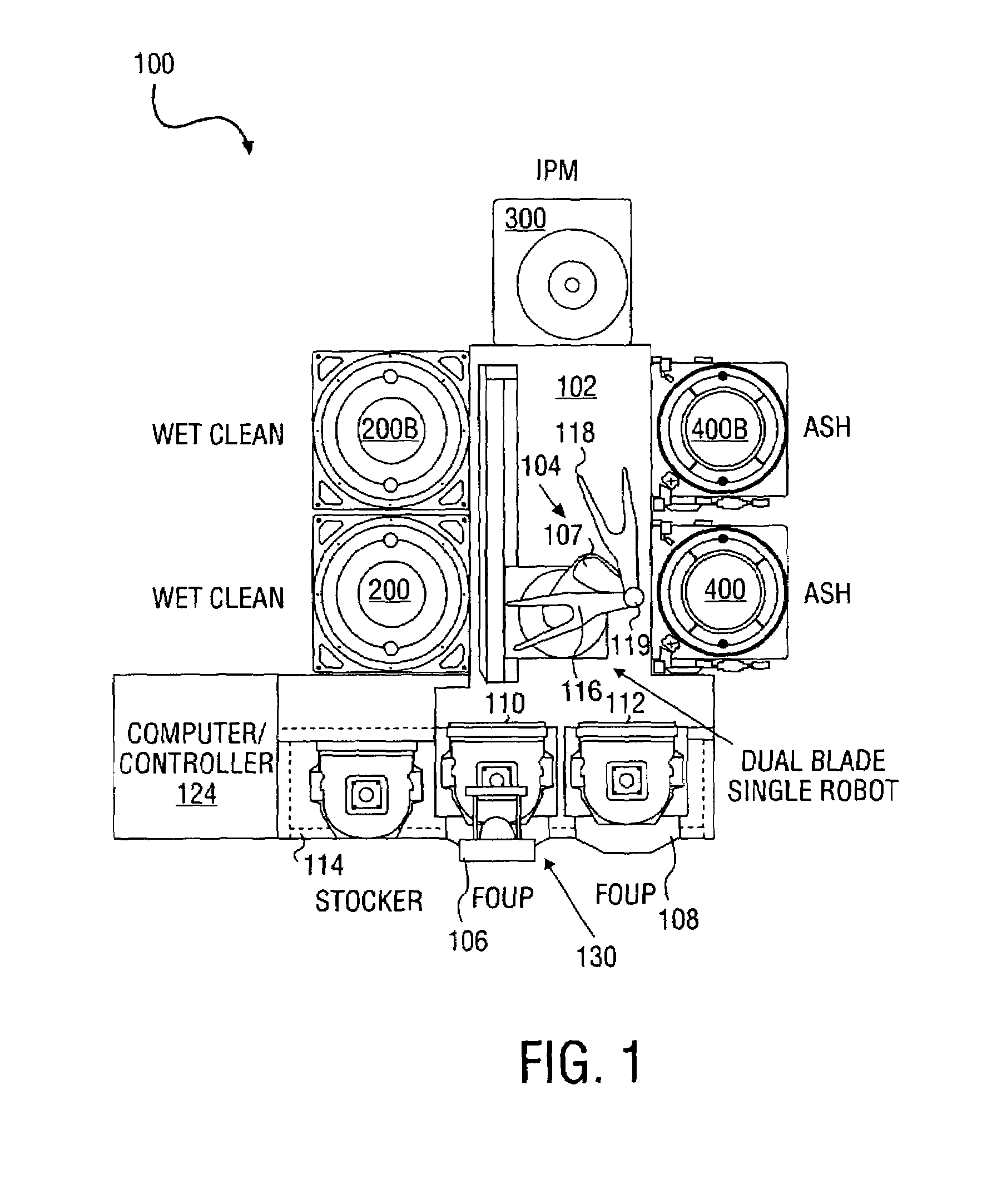

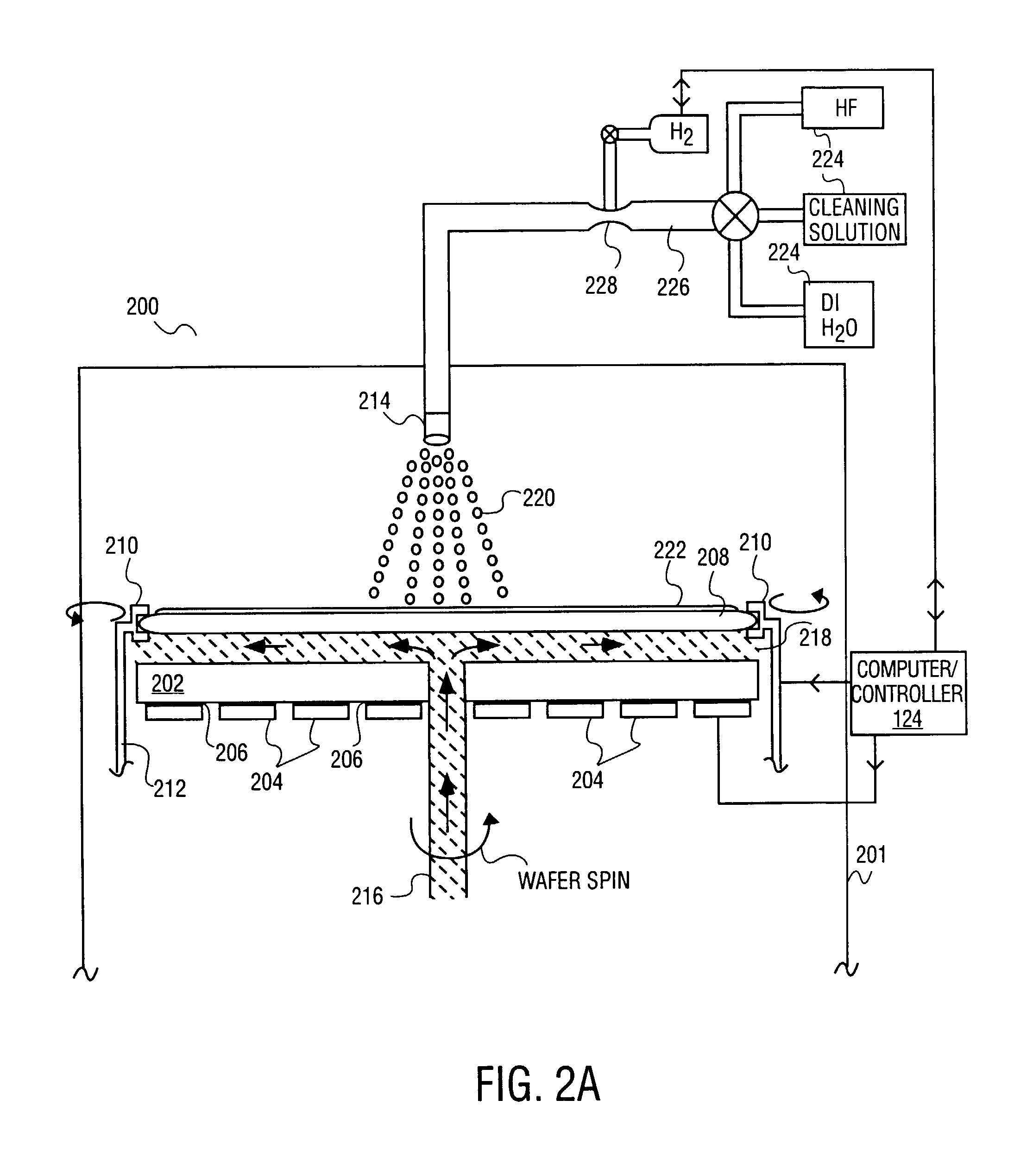

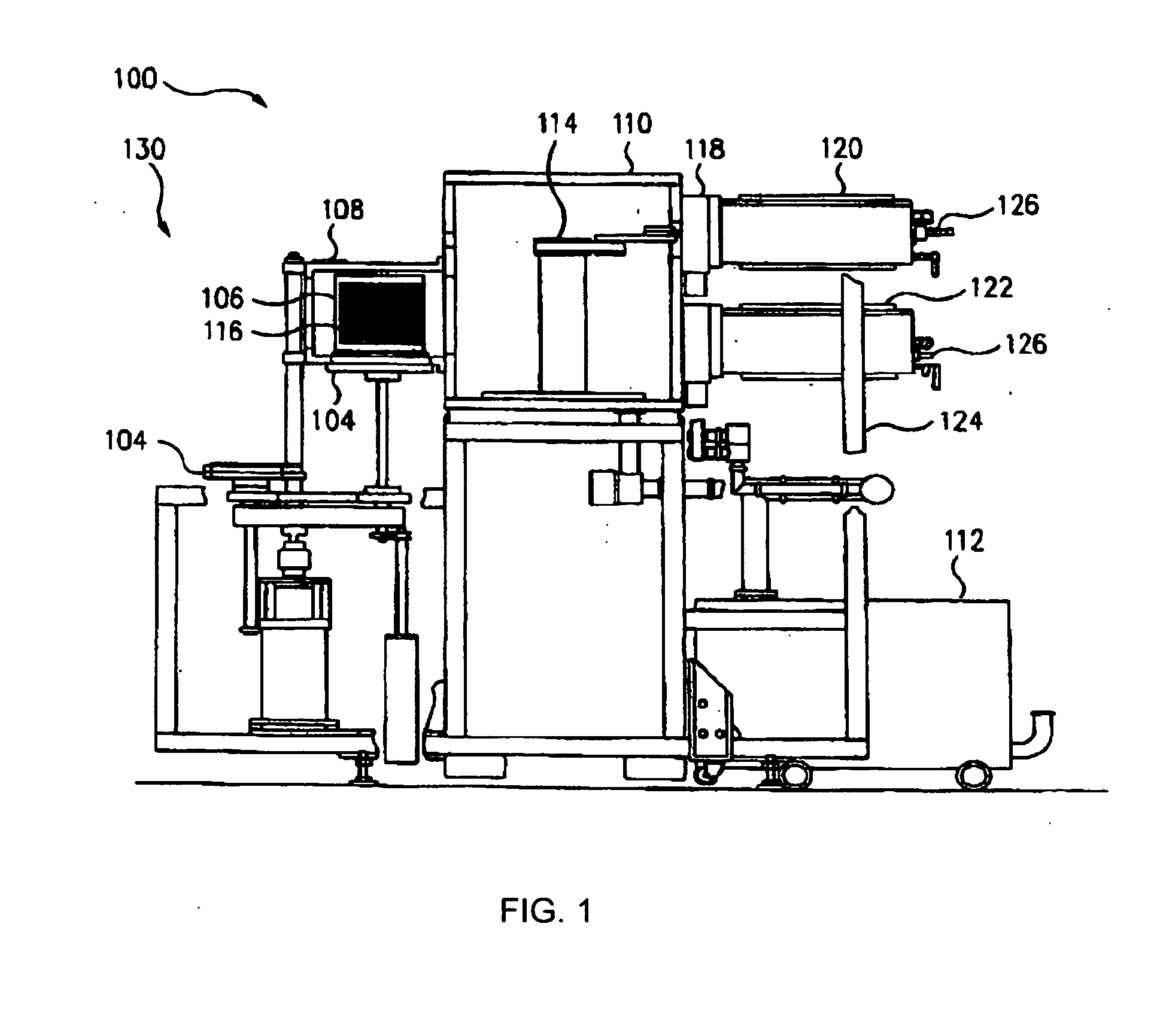

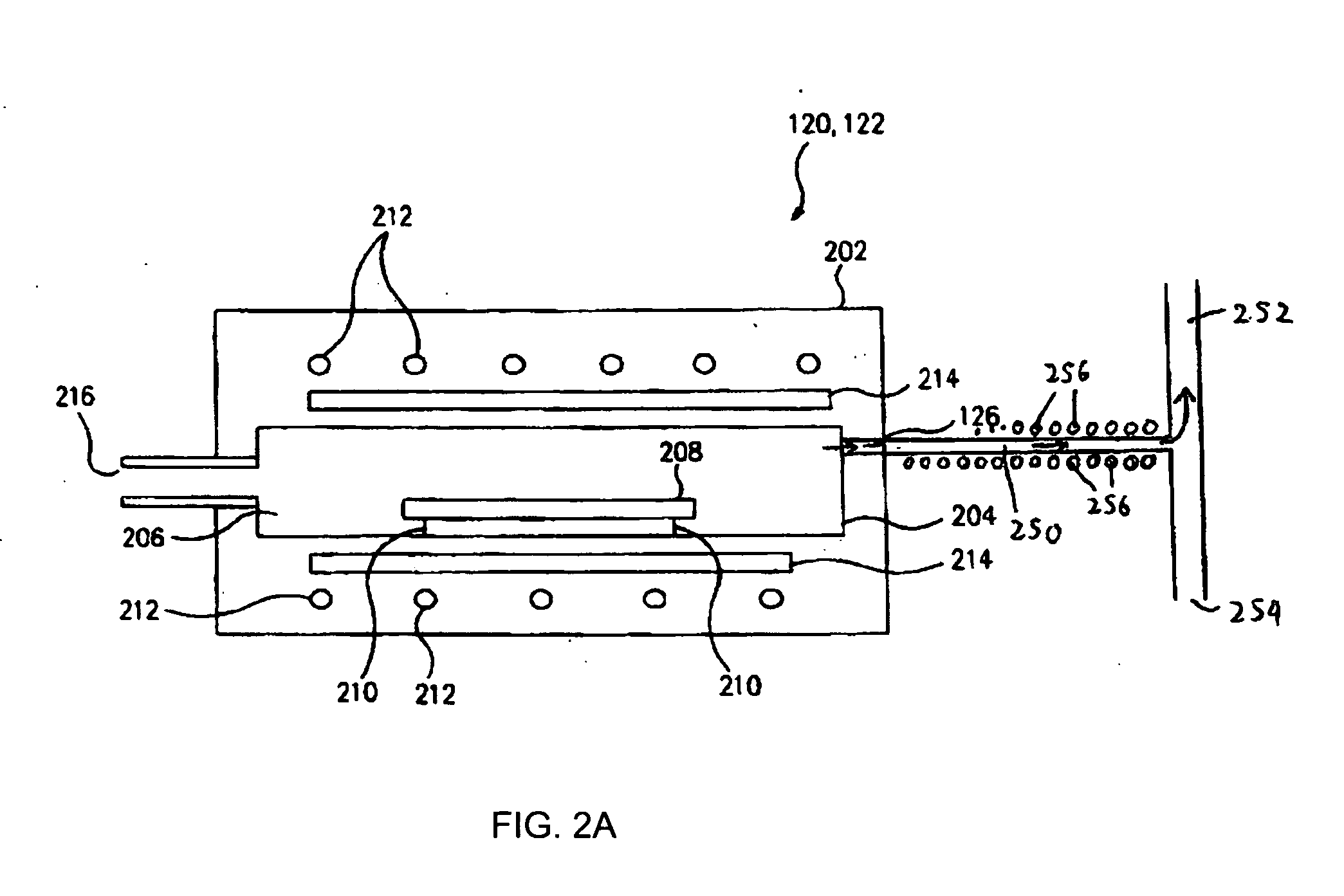

A method of a single wafer wet / dry cleaning apparatus comprising: a transfer chamber having a wafer handler contained therein; a first single wafer wet cleaning chamber directly coupled to the transfer chamber; and a first single wafer ashing chamber directly coupled to the transfer chamber.

Owner:APPLIED MATERIALS INC

Etch residue reduction by ash methodology

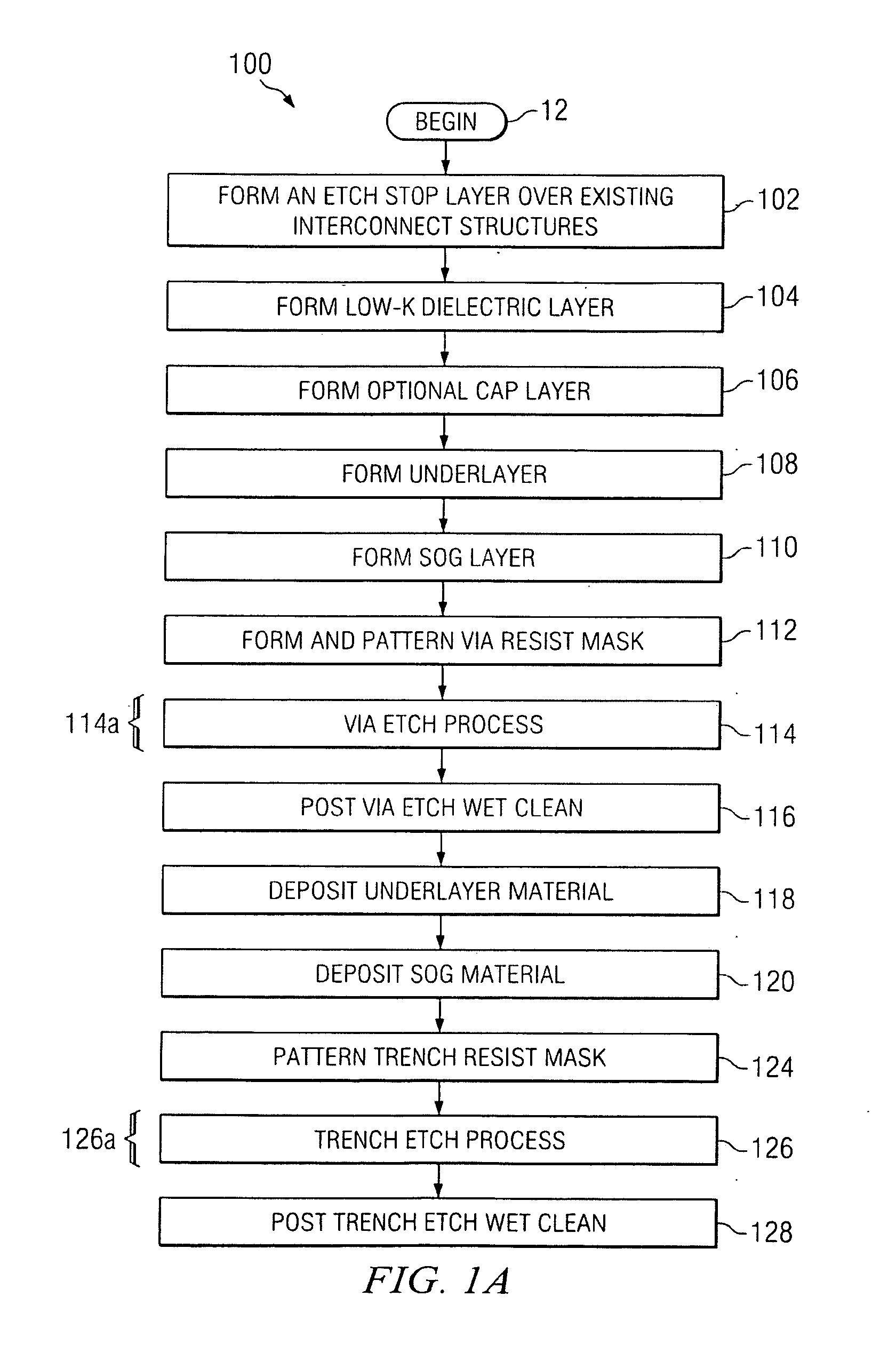

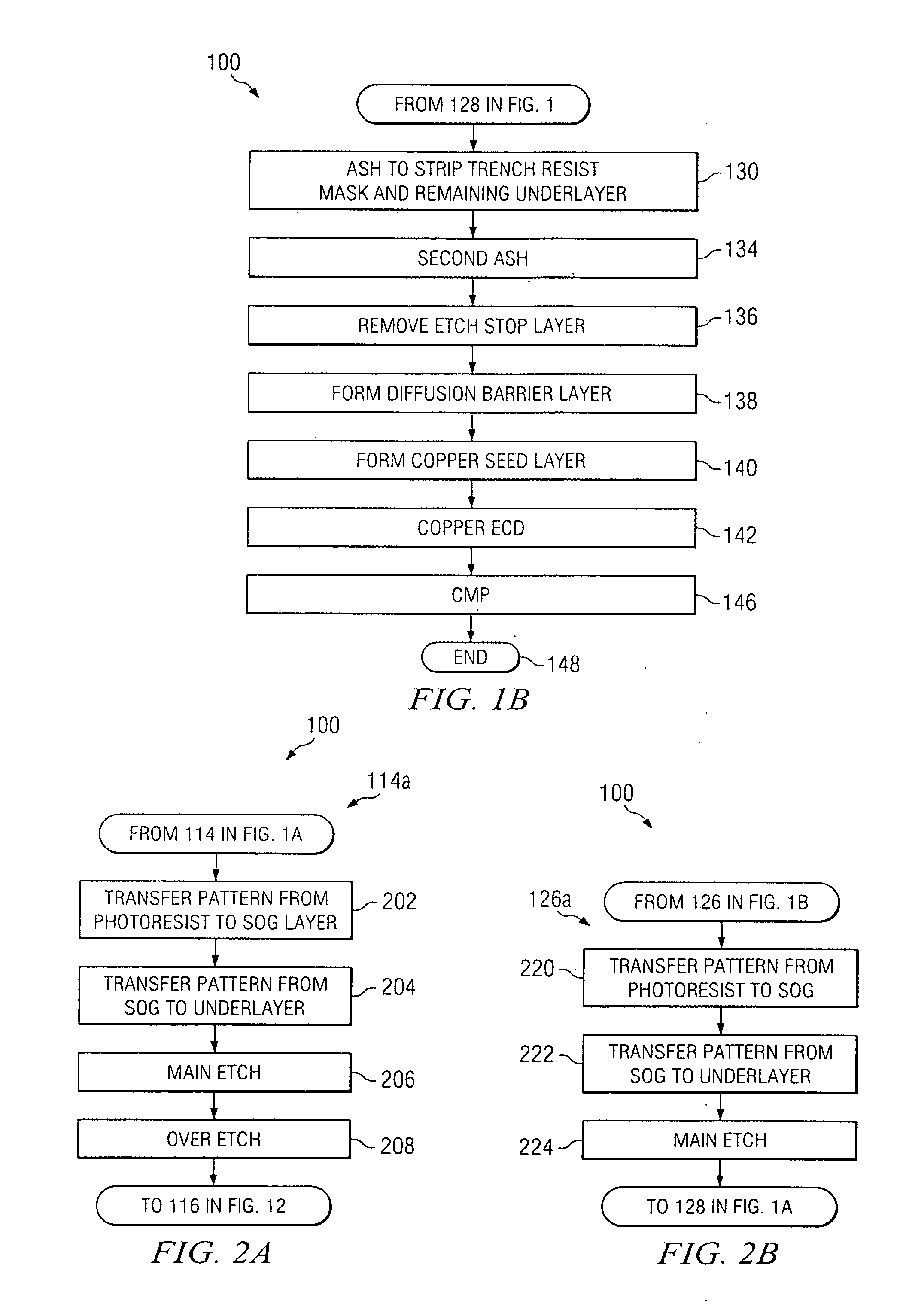

ActiveUS20090170221A1Semiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingEngineeringAshing

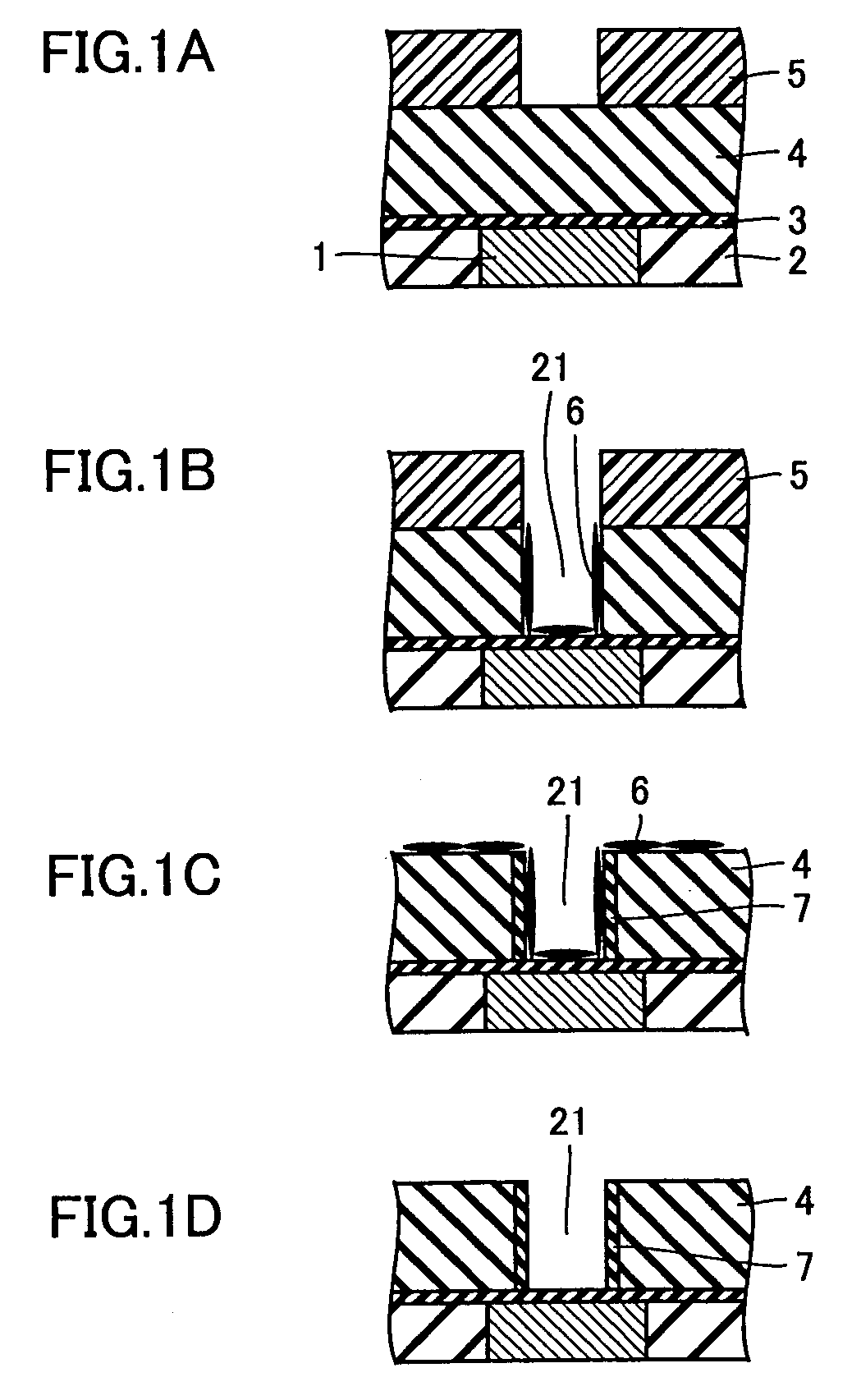

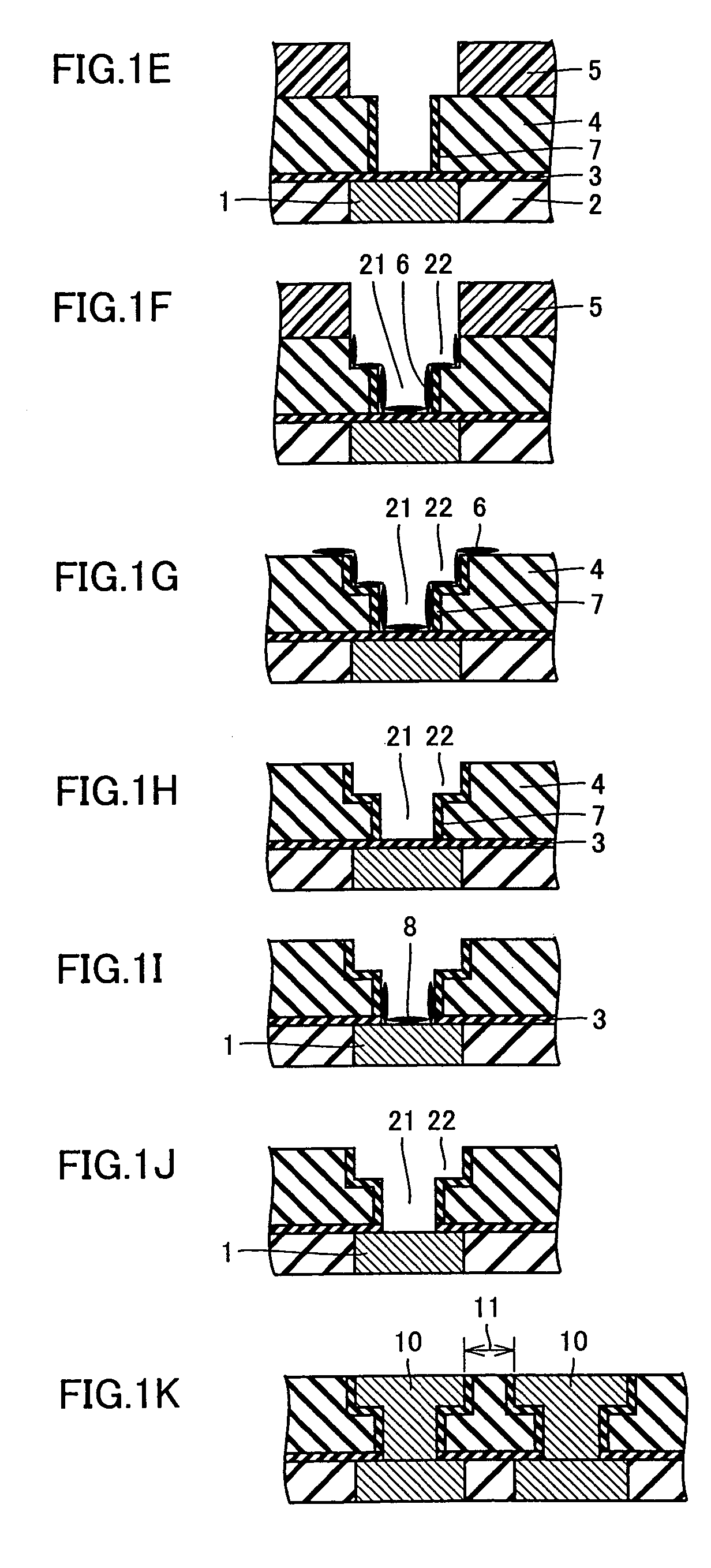

Methods for forming dual damascene interconnect structures are provided. The methods incorporate an ashing operation comprising a first ash operation and a second overash operation. The ashing operation is performed prior to etching of an etch stop layer. The operation removes residue from a cavity formed during formation of the interconnect structure and facilitates better CD control without altering the cavity profiles.

Owner:TEXAS INSTR INC

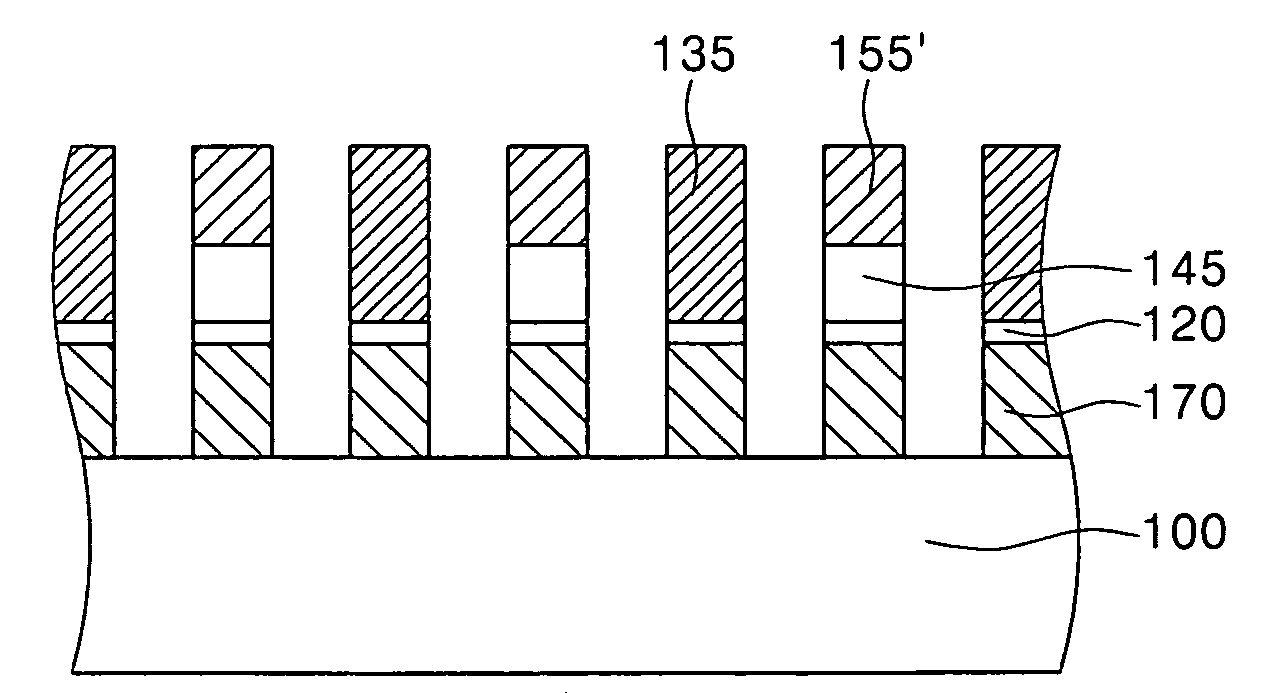

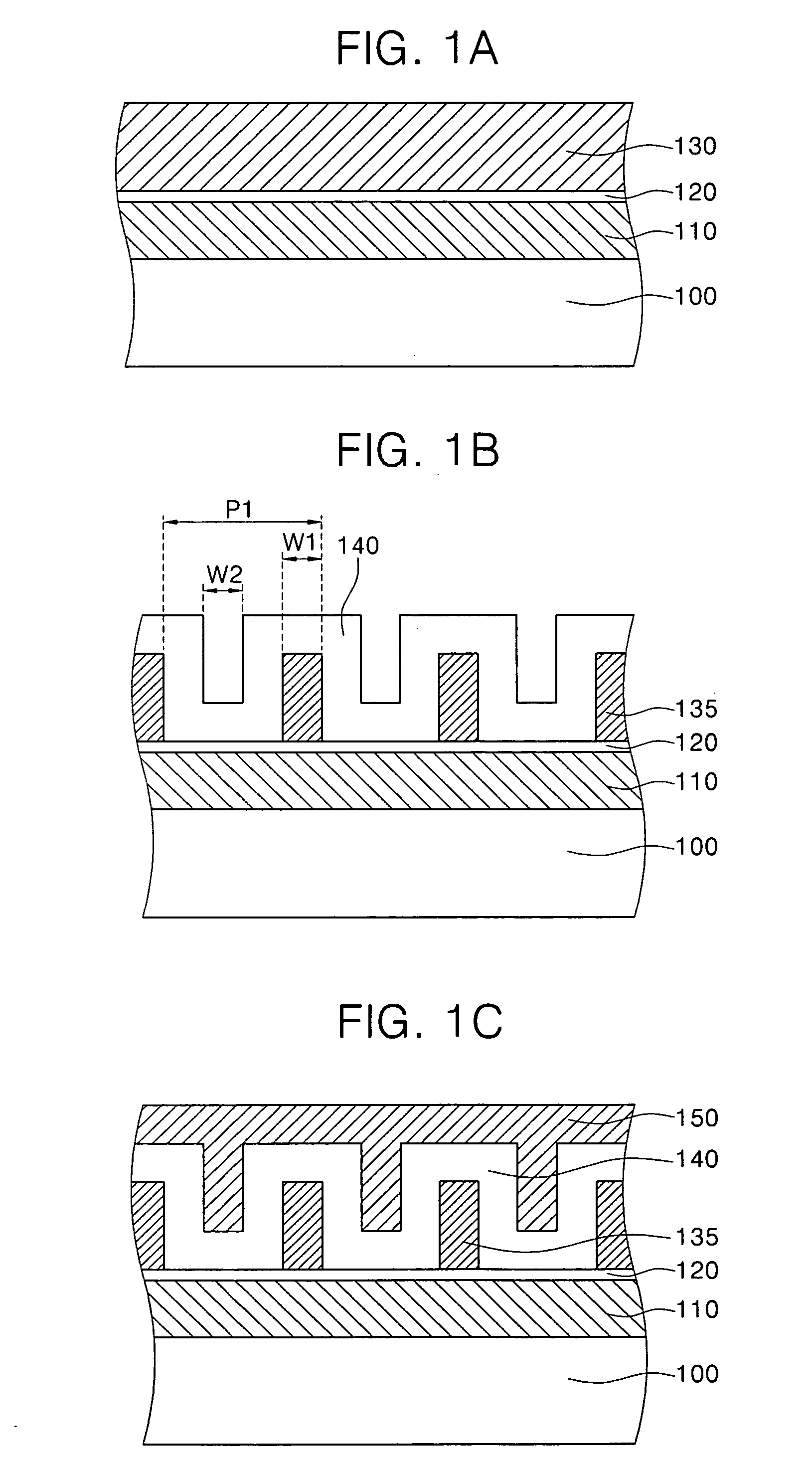

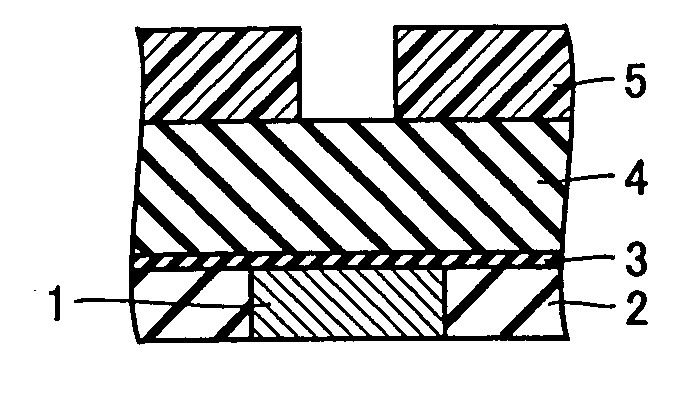

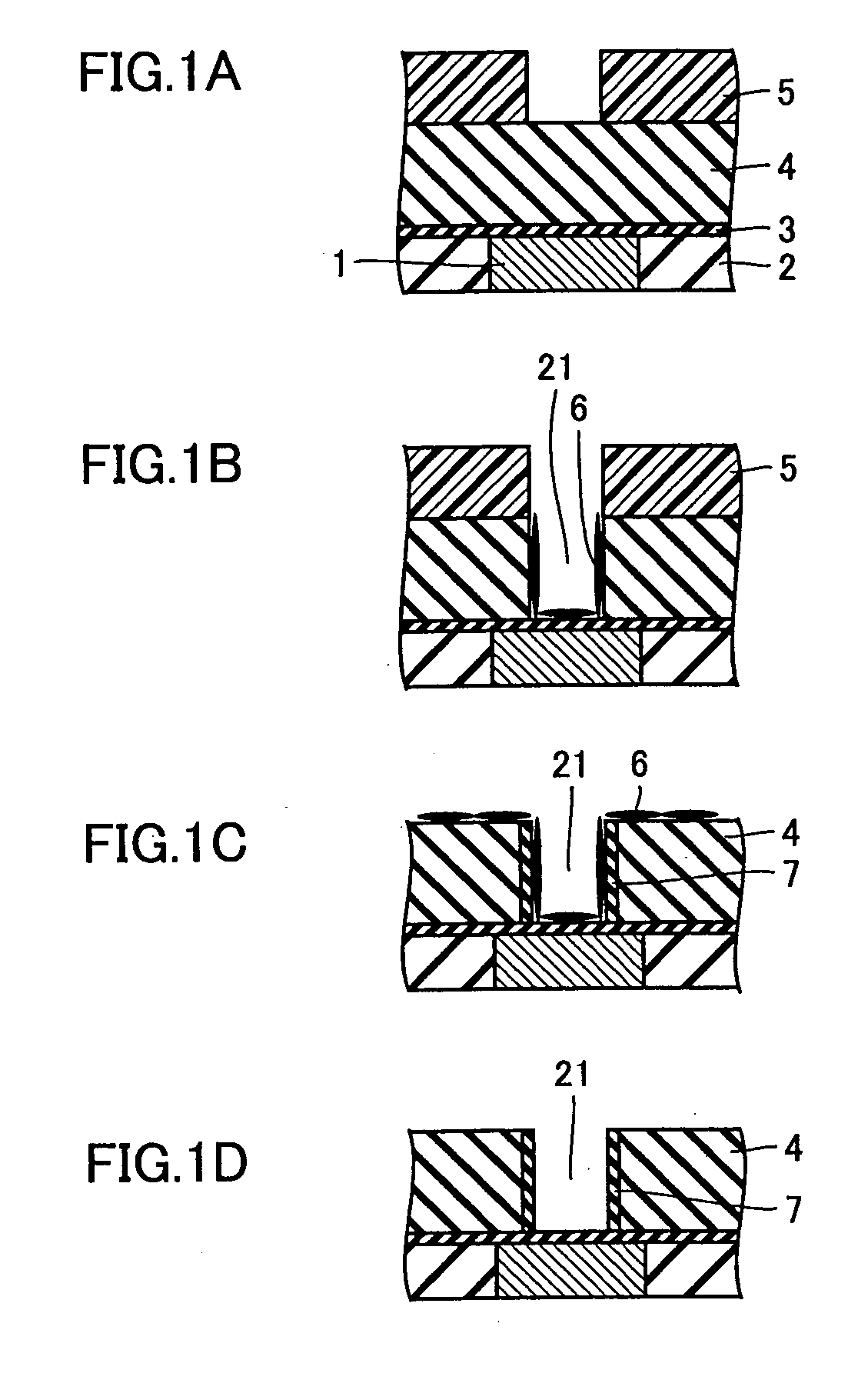

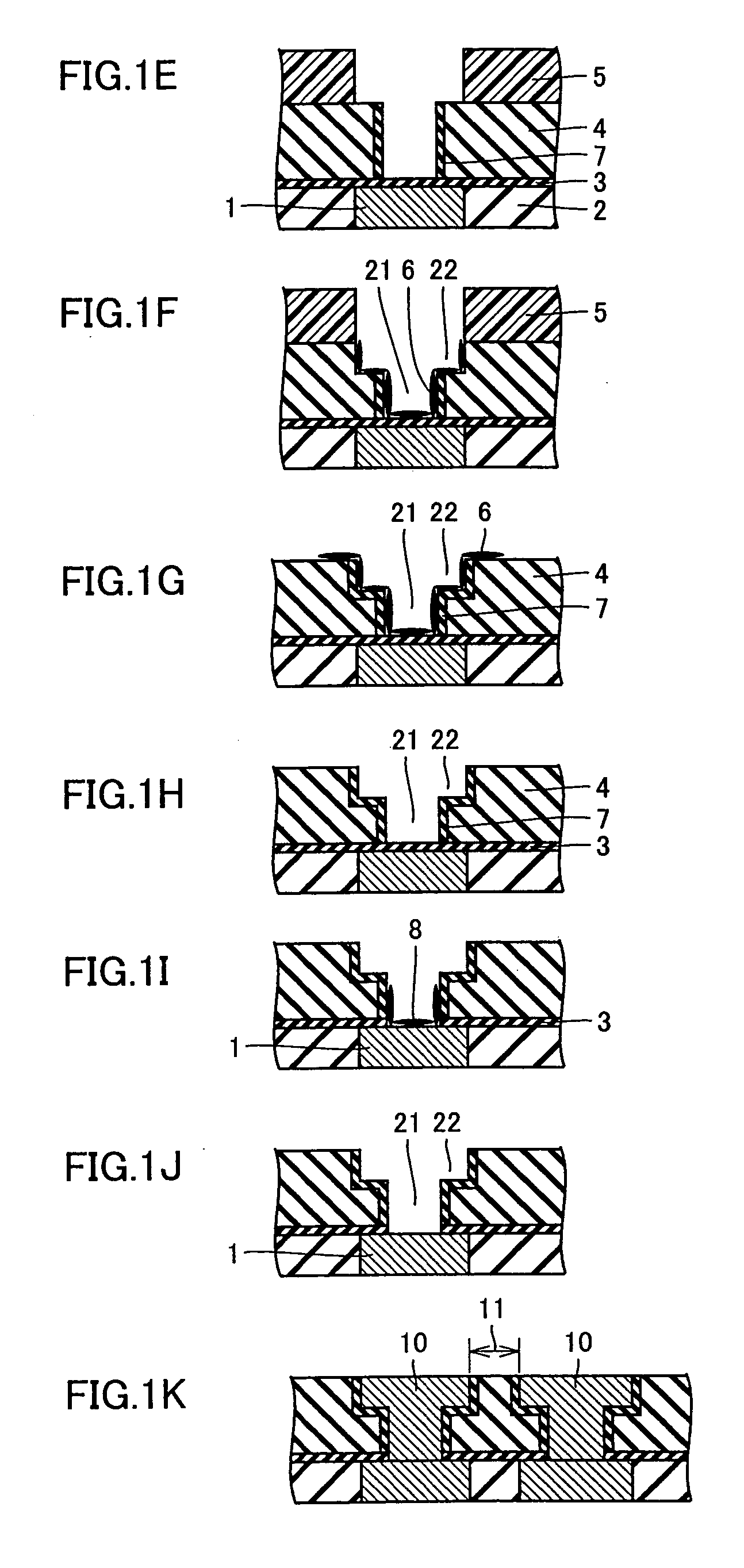

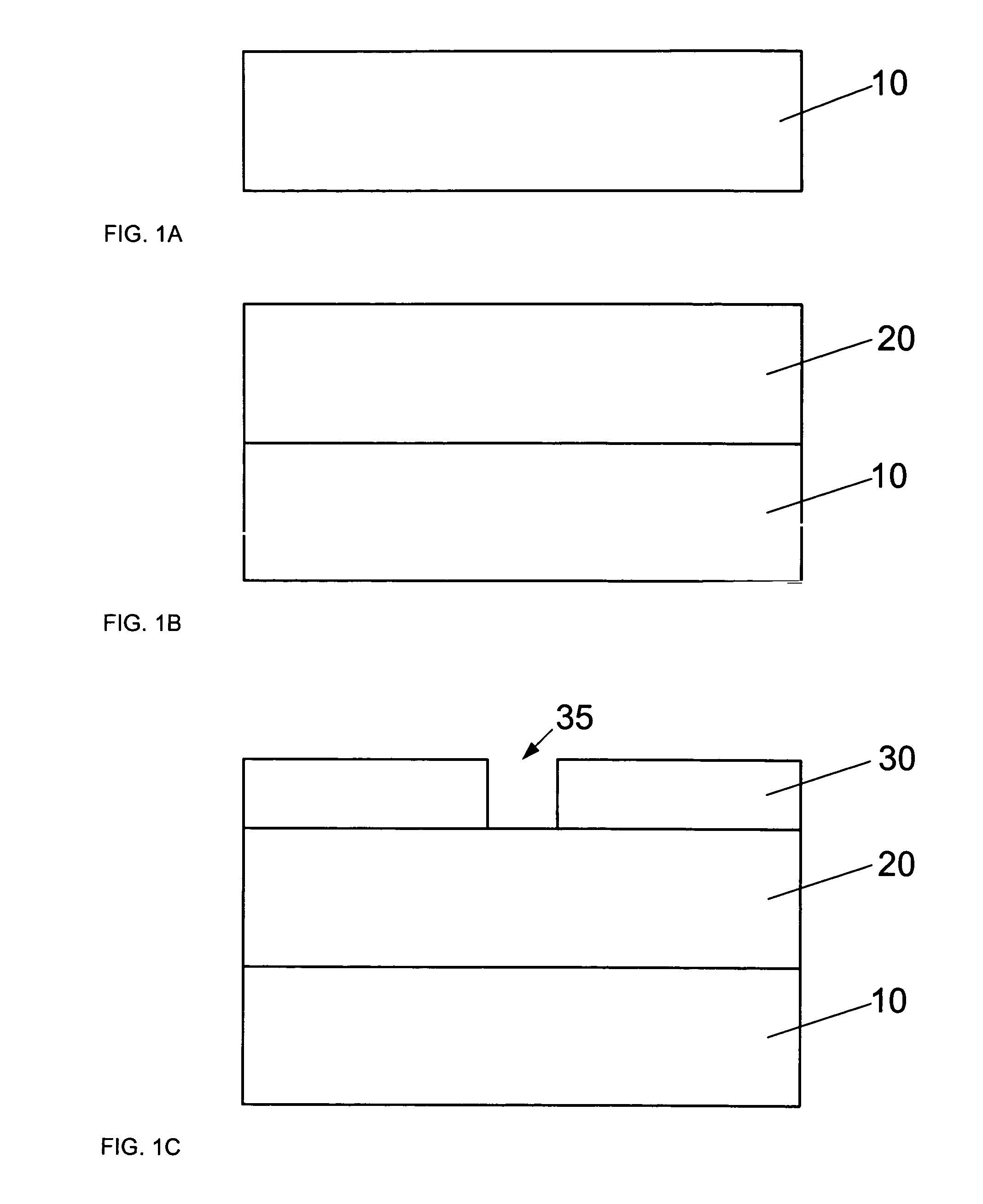

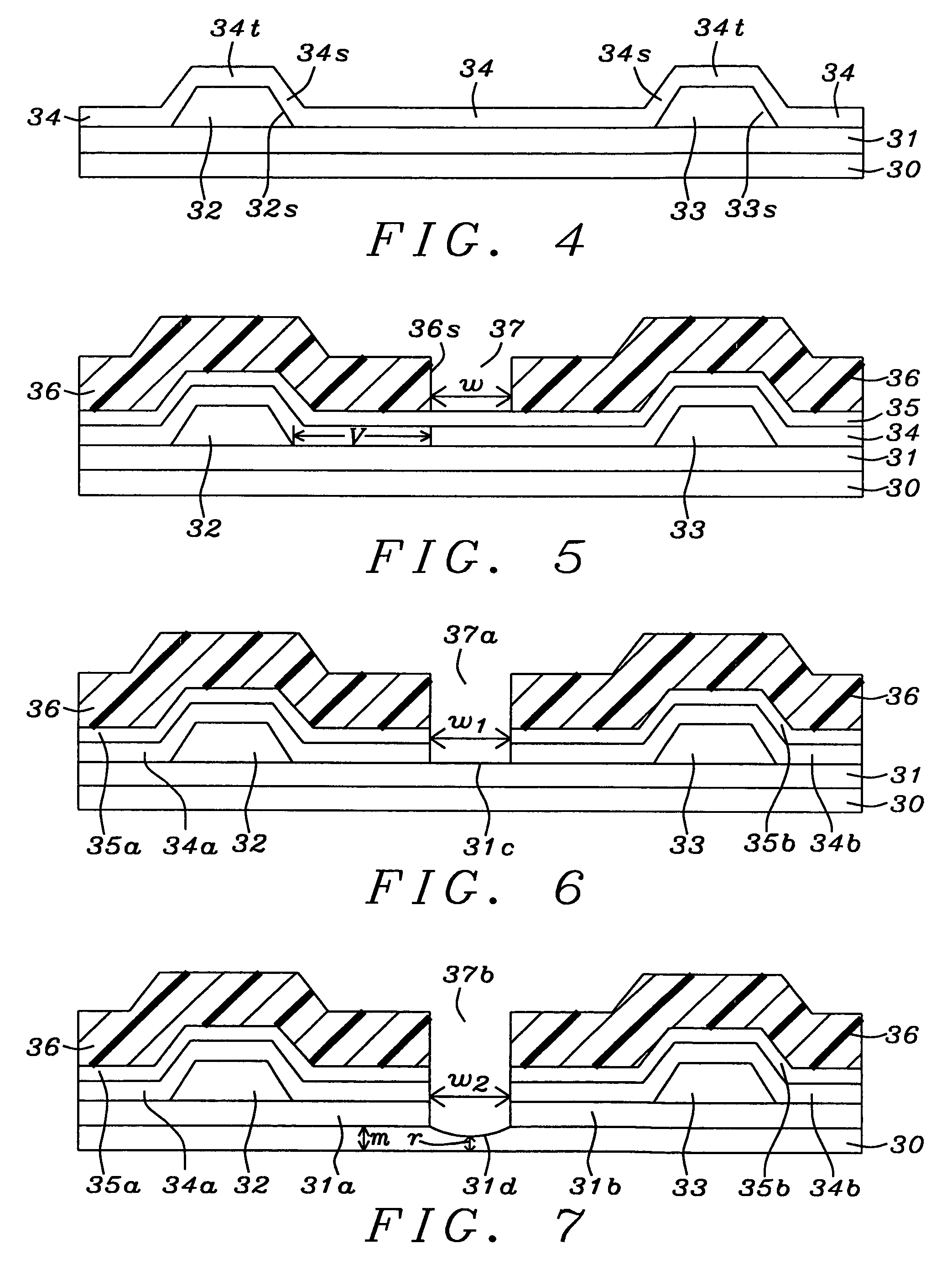

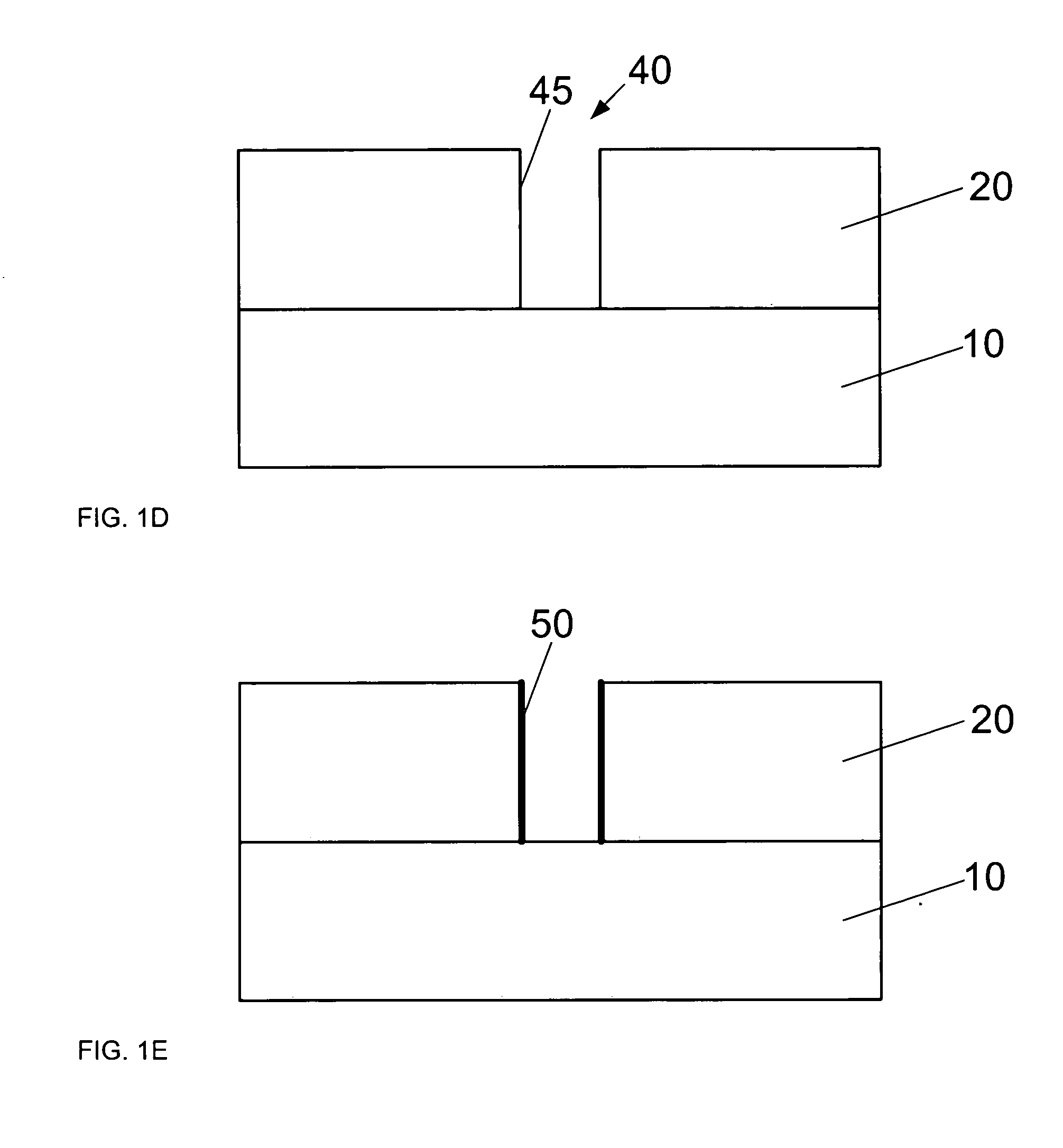

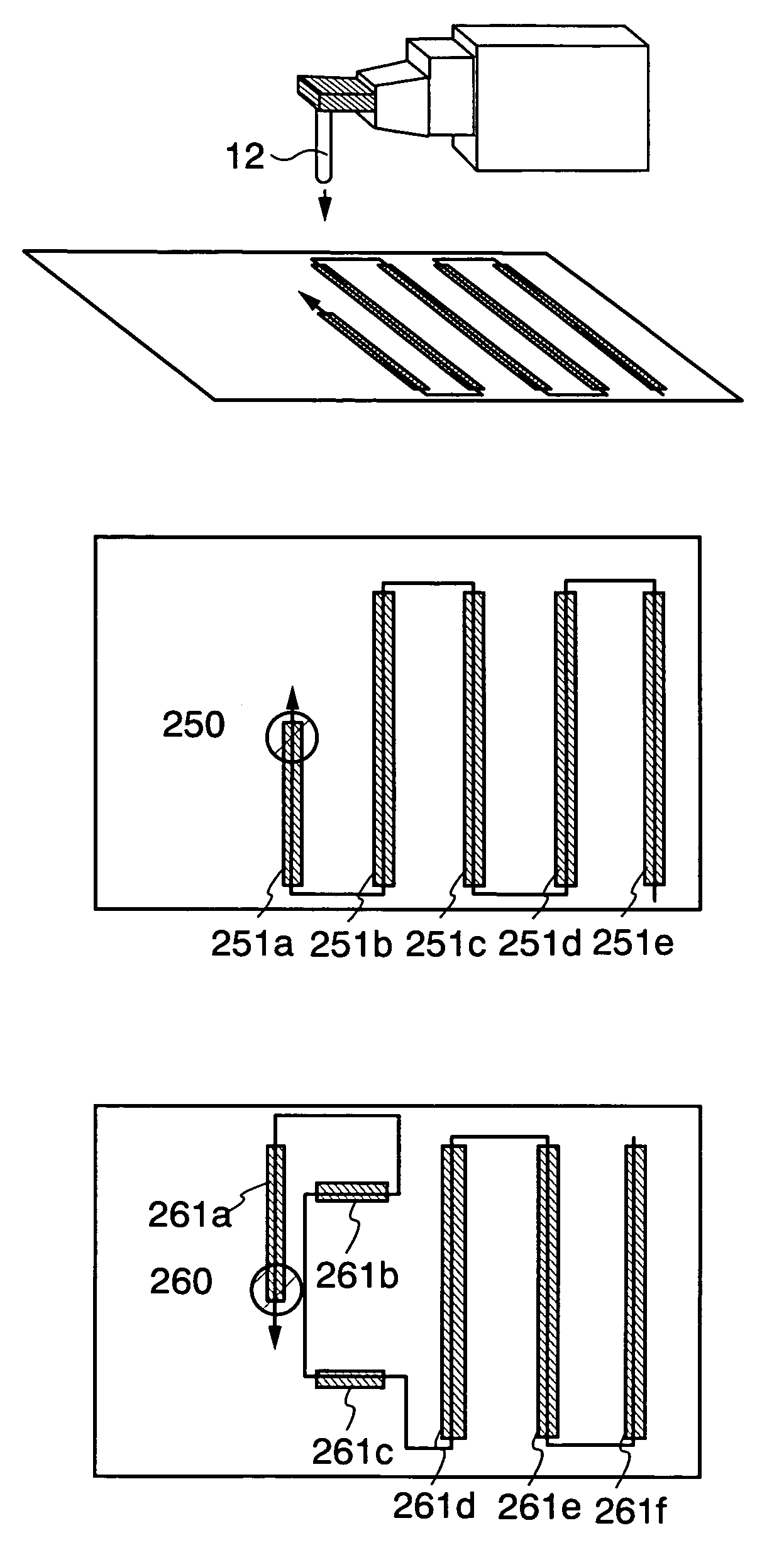

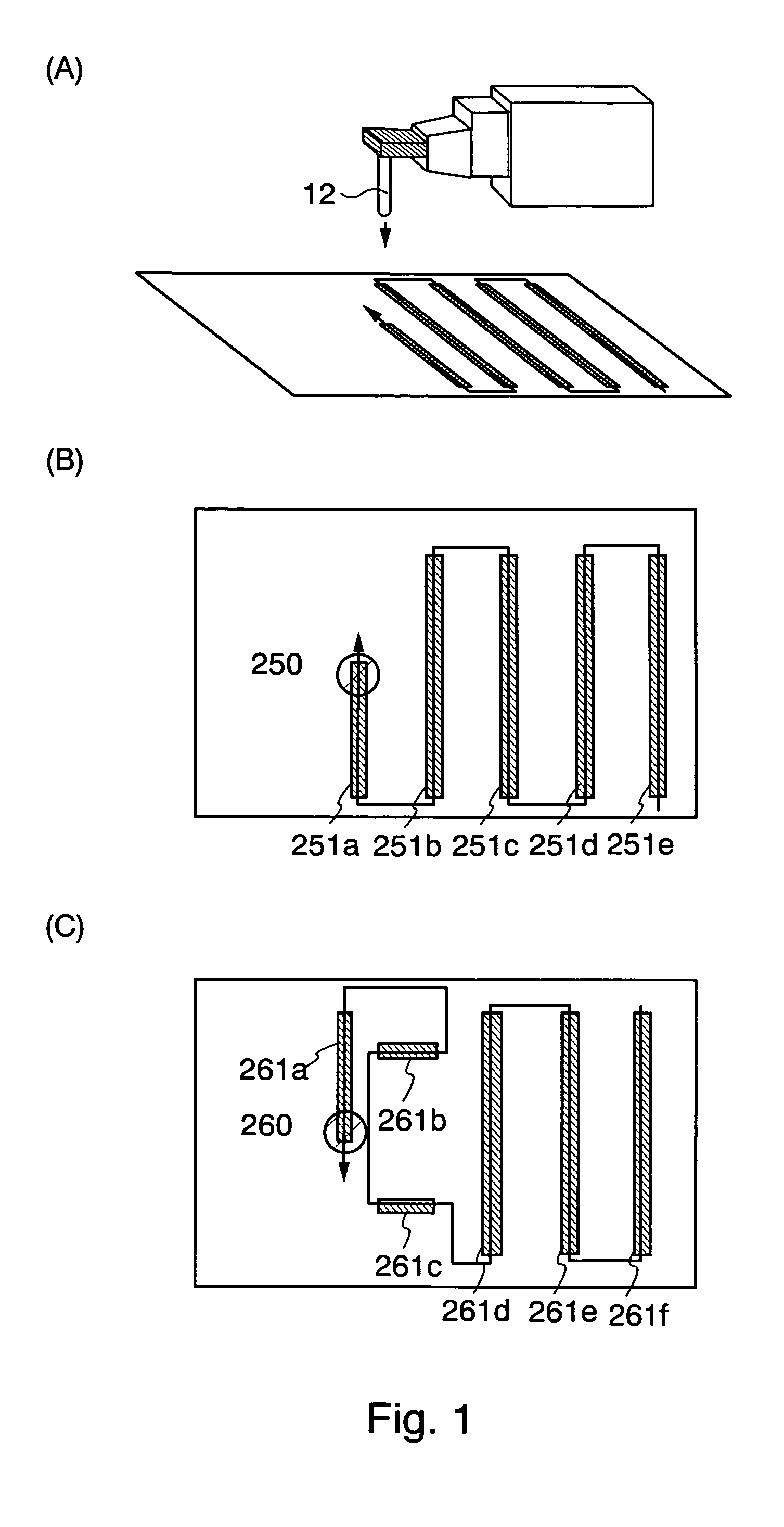

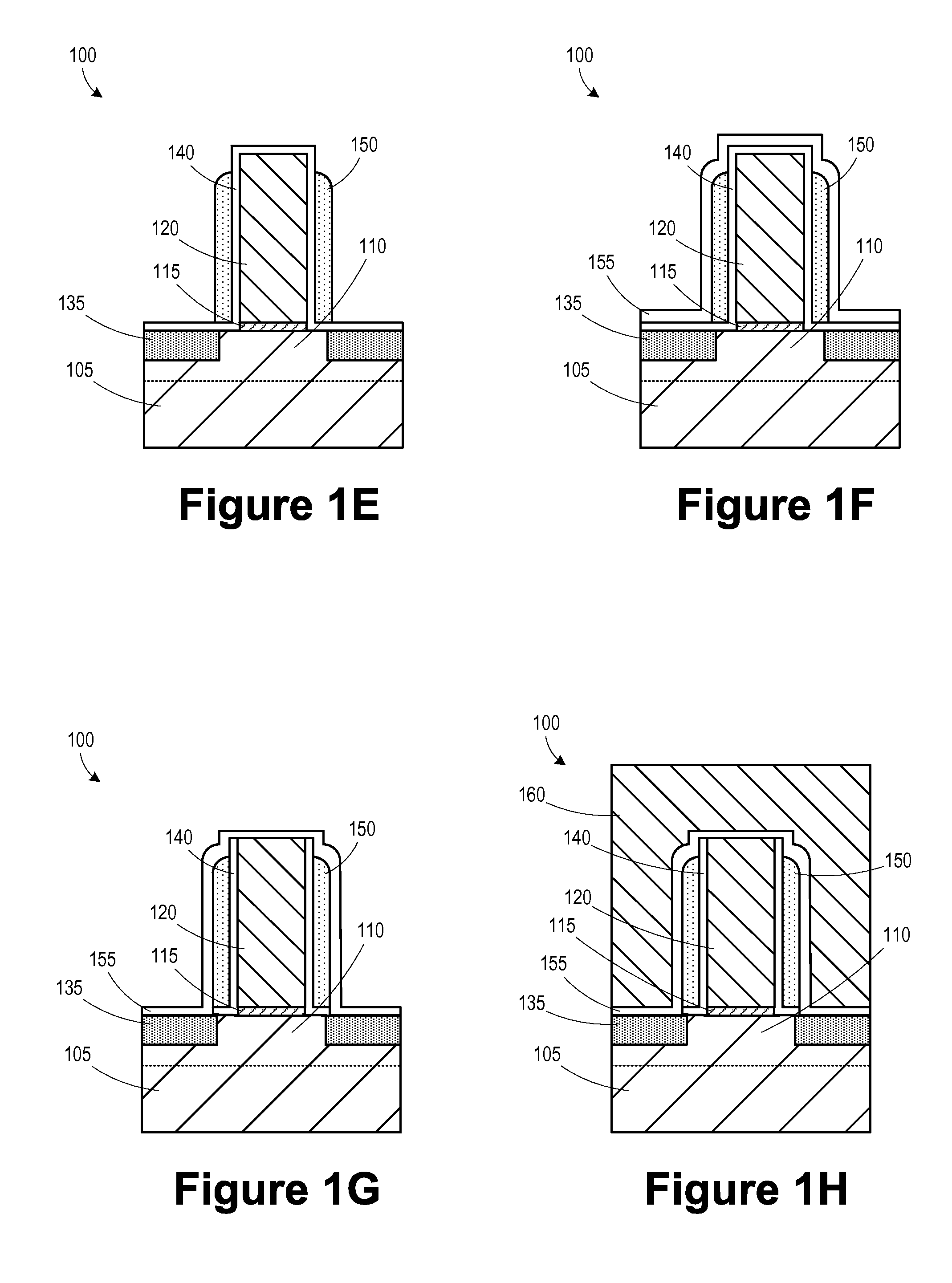

Method of forming self-aligned double pattern

ActiveUS20070148968A1Semiconductor/solid-state device manufacturingSemiconductor devicesEngineeringPhotolithography

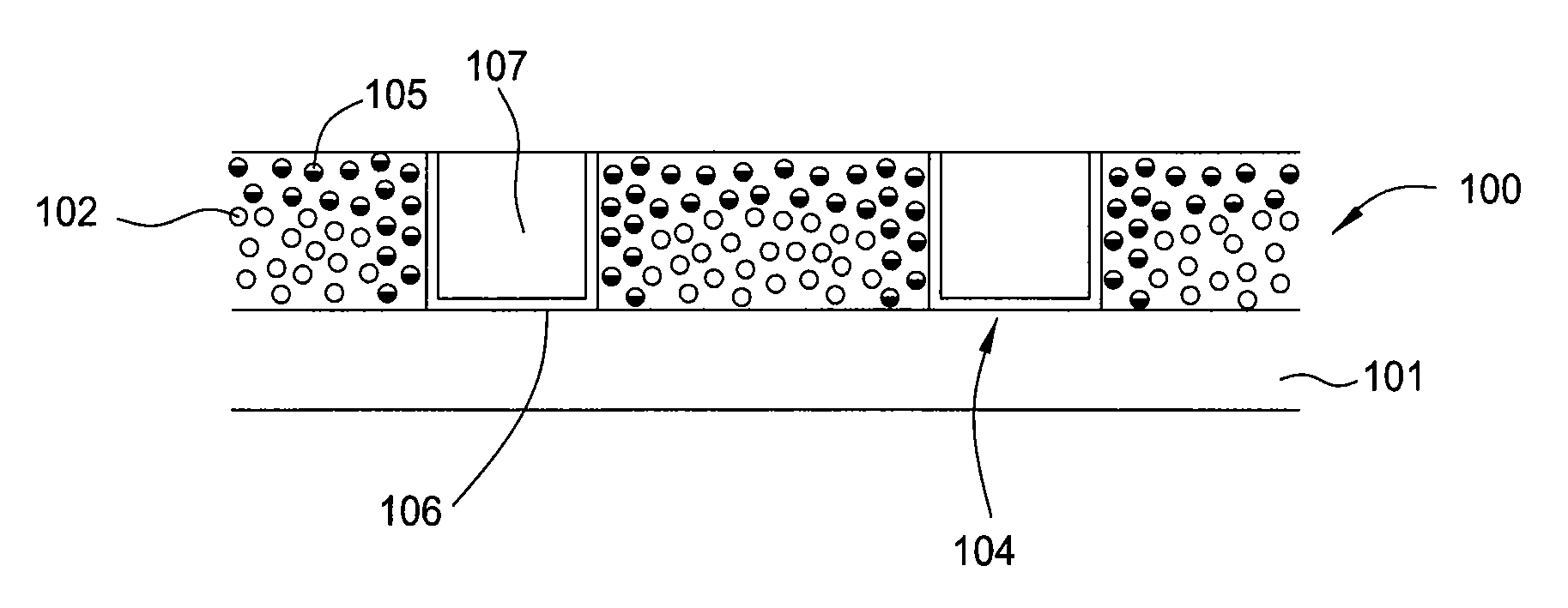

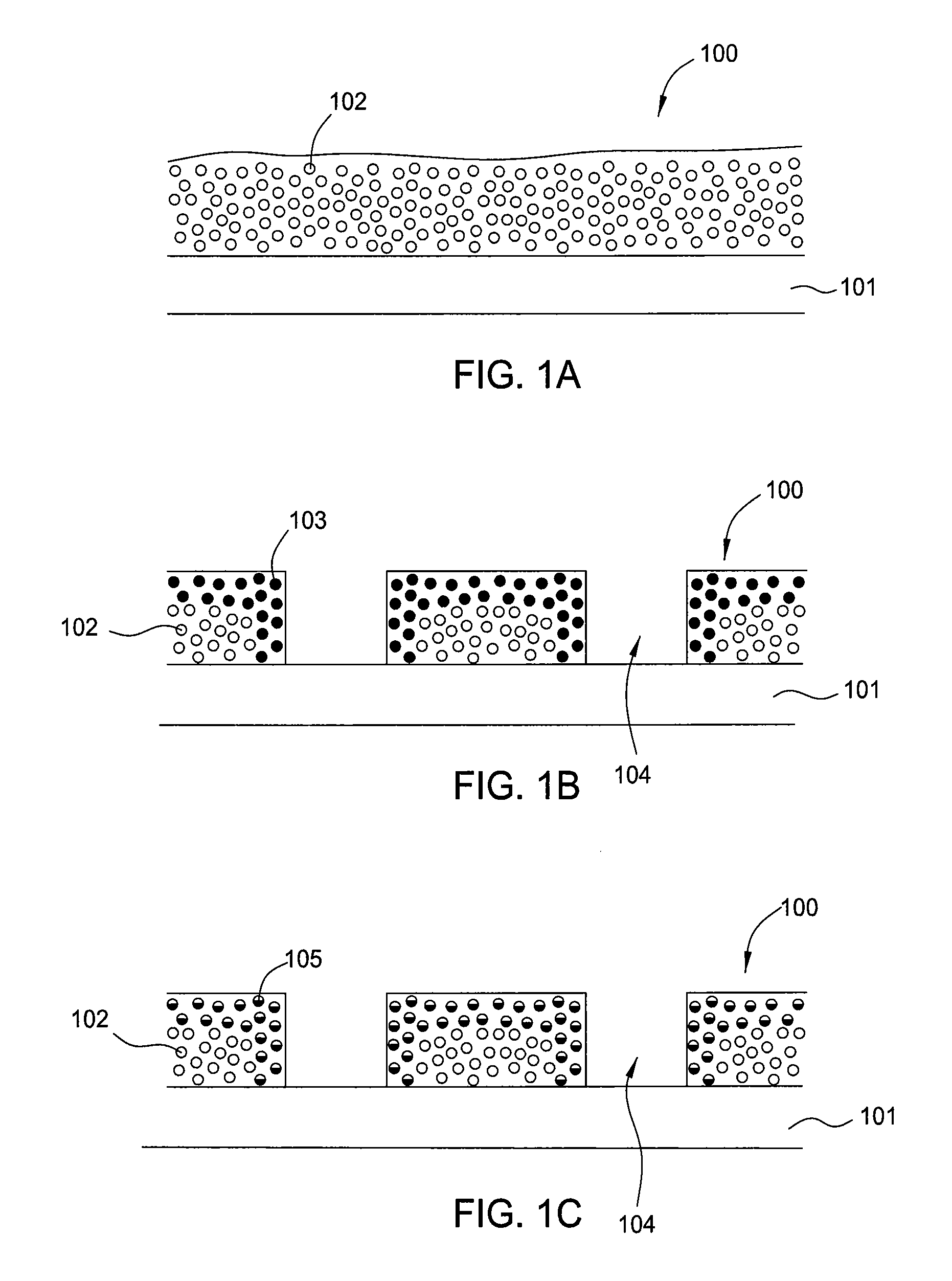

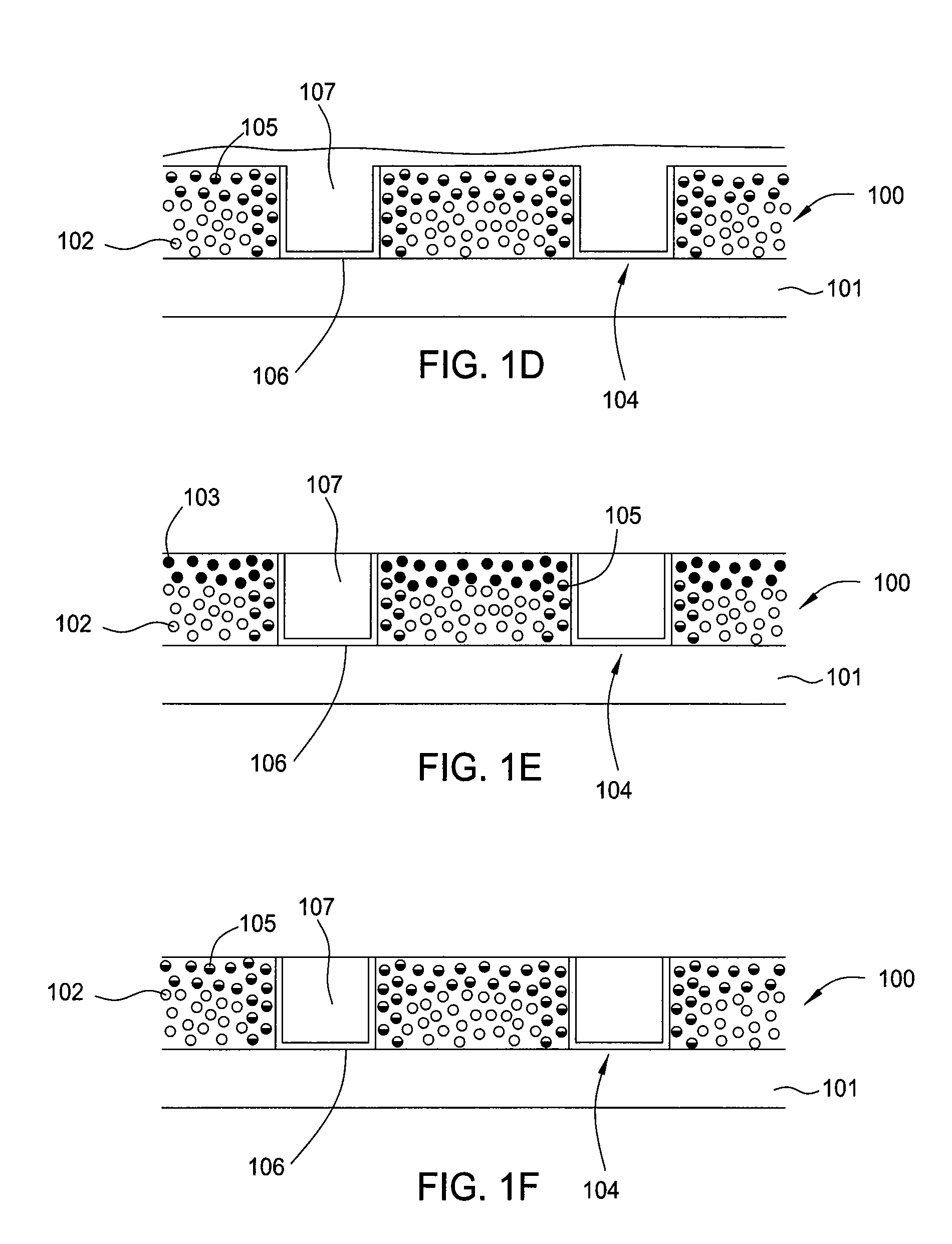

Mask patterns used for forming patterns or trenches may include first mask patterns, which may be formed by a typical photolithography process, and second mask patterns, which may be formed in a self-aligned manner between adjacent first mask patterns. A sacrificial layer may be deposited and planarized such that the tops of the first mask patterns and the second mask patterns have planar surfaces. After the planarization of the sacrificial layer, the remaining the sacrificial layer may be removed by an ashing process.

Owner:SAMSUNG ELECTRONICS CO LTD

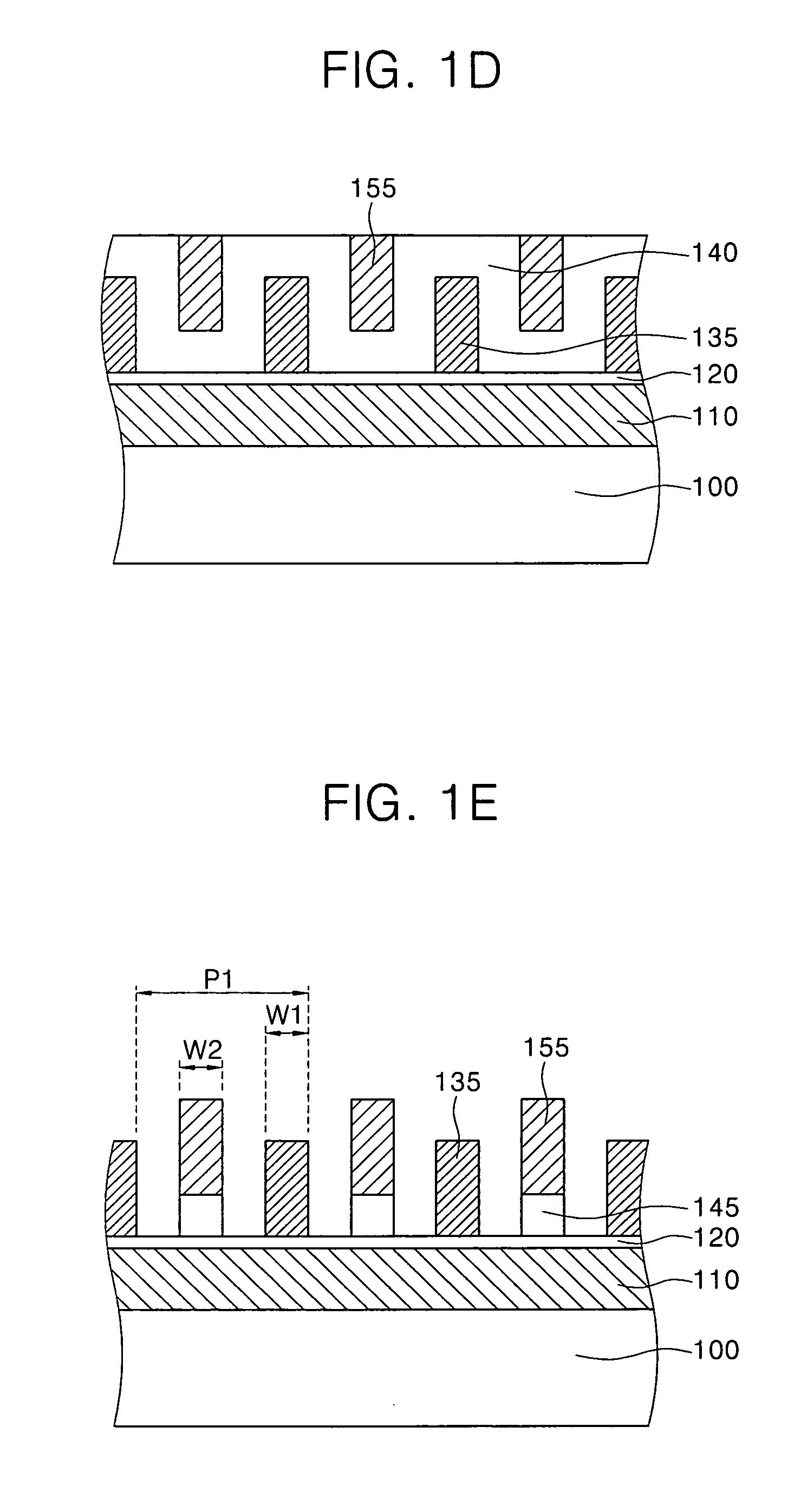

Enhancement of remote plasma source clean for dielectric films

Methods for cleaning semiconductor processing chambers used to process carbon-containing films, such as amorphous carbon films, barrier films comprising silicon and carbon, and low dielectric constant films including silicon, oxygen, and carbon are provided. The methods include using a remote plasma source to generate reactive species that clean interior surfaces of a processing chamber in the absence of RF power in the chamber. The reactive species are generated from an oxygen-containing gas, such as O2, and / or a halogen-containing gas, such as NF3. An oxygen-based ashing process may also be used to remove carbon deposits from the interior surfaces of the chamber before the chamber is exposed to the reactive species from the remote plasma source.

Owner:APPLIED MATERIALS INC

Cleaning composition for removing resists and method of manufacturing semiconductor device

InactiveUS20040106531A1Surface-active detergent compositionsNon-surface-active detergent compositionsResistCopper interconnect

The cleaning composition for removing resists includes a salt of hydrofluoric acid and a base not containing a metal (A component), a water-soluble organic solvent (B1 component), at least one acid selected from a group consisting of organic acid and inorganic acid (C component), water (D component), and optionally an ammonium salt (E1 component), and its hydrogen ion concentration (pH) is 4-8. Thus, in the manufacturing process of a semiconductor device such as a copper interconnecting process, removing efficiency of resist residue and other etching residue after etching or ashing improves, and corrosion resistance of copper and insulating film also improves.

Owner:PANASONIC CORP +2

Bottom electrode etching process in MRAM cell

ActiveUS8334213B2Not to damageImprove device yieldDecorative surface effectsSolid-state devicesBit lineWater based

A BE patterning scheme in a MRAM is disclosed that avoids damage to the MTJ array and underlying ILD layer while reducing BE-BE shorts and BE-bit line shorts. A protective dielectric layer is coated over a MTJ array before a photoresist layer is coated and patterned on the dielectric layer. The photoresist pattern is transferred through the dielectric layer with a dielectric etch process and then through the BE layer with a metal etch that includes a certain amount of overetch to remove metal residues. The photoresist is stripped with a sequence involving immersion or spraying with an organic solution followed by oxygen ashing to remove any other organic materials. Finally, a second wet strip is performed with a water based solution to provide a residue free substrate. In another embodiment, a bottom anti-reflective coating (BARC) is inserted between the photoresist and dielectric layer for improved critical dimension control.

Owner:TAIWAN SEMICON MFG CO LTD

Repairing damage to low-k dielectric materials using silylating agents

ActiveUS20050095840A1Reduce hydrophobicityImprove hydrophobicitySemiconductor/solid-state device manufacturingStress inducedSilicate glass

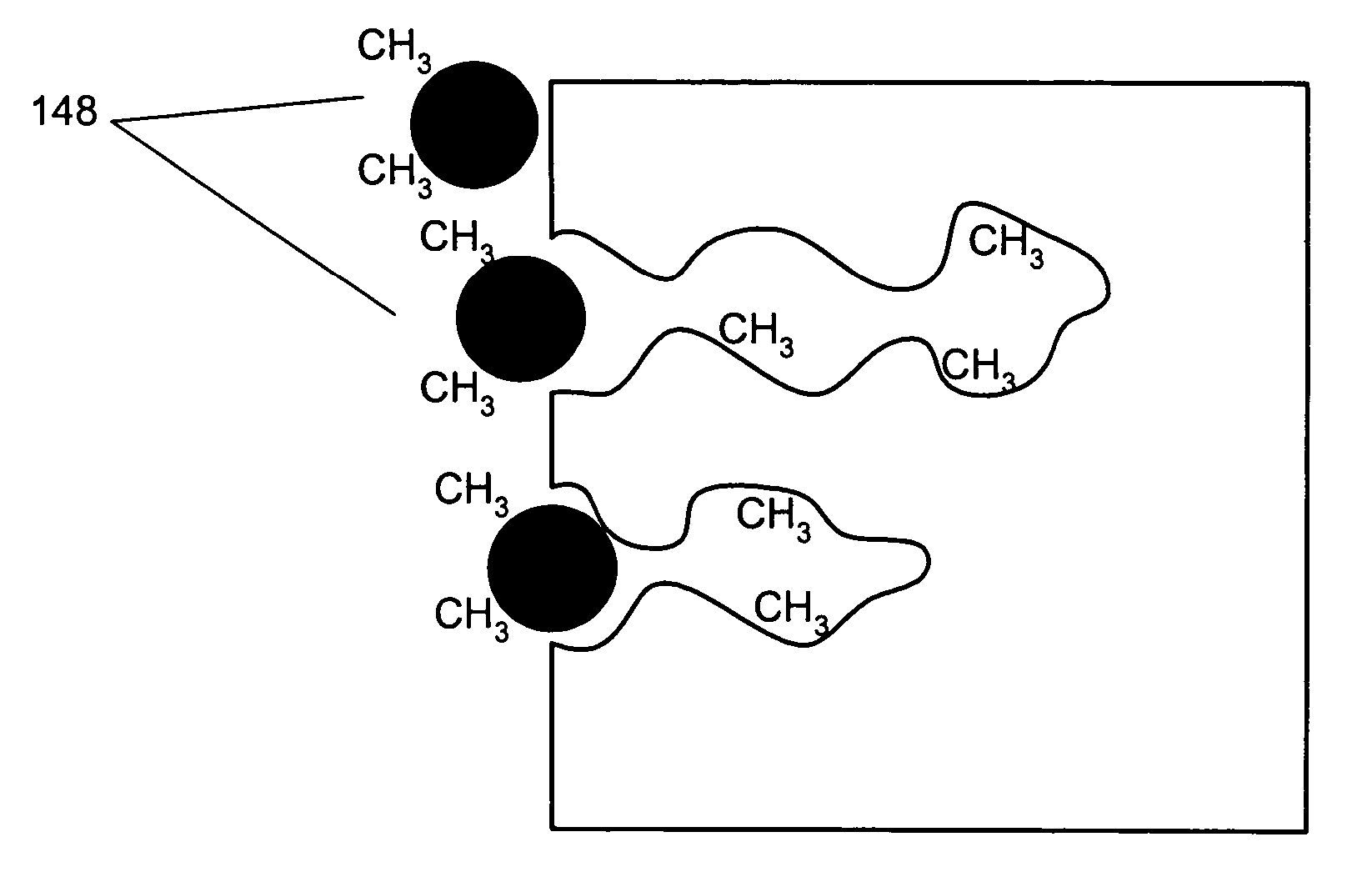

A method for restoring hydrophobicity to the surfaces of organosilicate glass dielectric films which have been subjected to an etchant or ashing treatment. These films are used as insulating materials in the manufacture of integrated circuits to ensure low and stable dielectric properties in these films. The method deters the formation of stress-induced voids in these films. An organosilicate glass dielectric film is patterned to form vias and trenches by subjecting it to an etchant or ashing reagent in such a way as to remove at least a portion of previously existing carbon containing moieties and reduce hydrophobicity of said organosilicate glass dielectric film. The vias and trenches are thereafter filled with a metal and subjected to an annealing treatment. After the film is subjected to the etchant or ashing reagent, but before being subjected to an annealing treatment, the film is contacted with a toughening agent composition to restore some of the carbon containing moieties and increase the hydrophobicity of the organosilicate glass dielectric film.

Owner:HONEYWELL INT INC

Cleaning composition for removing resists and method of manufacturing semiconductor device

InactiveUS7250391B2Good removal effectInhibitionSemiconductor/solid-state device manufacturingNon-surface-active detergent solventsResistCopper interconnect

The cleaning composition for removing resists includes a salt of hydrofluoric acid and a base not containing a metal (A component), a water-soluble organic solvent (B1 component), at least one organic acid or inorganic acid (C component), water (D component), and, optionally, an ammonium salt (E1 component), and having a pH 4-8. Thus, in manufacturing a semiconductor device, such as a copper interconnecting process, efficiency of removing resist residue and other etching residue after etching or ashing is improved, and corrosion resistance of a copper and an insulating film is also improved.

Owner:PANASONIC CORP +2

Method and apparatus for processing a wafer

InactiveUS7159599B2Semiconductor/solid-state device manufacturingCleaning using liquidsDirect couplingEngineering

A method of a single wafer wet / dry cleaning apparatus comprising:a transfer chamber having a wafer handler contained therein;a first single wafer wet cleaning chamber directly coupled to the transfer chamber; anda first single wafer ashing chamber directly coupled to the transfer chamber.

Owner:APPLIED MATERIALS INC

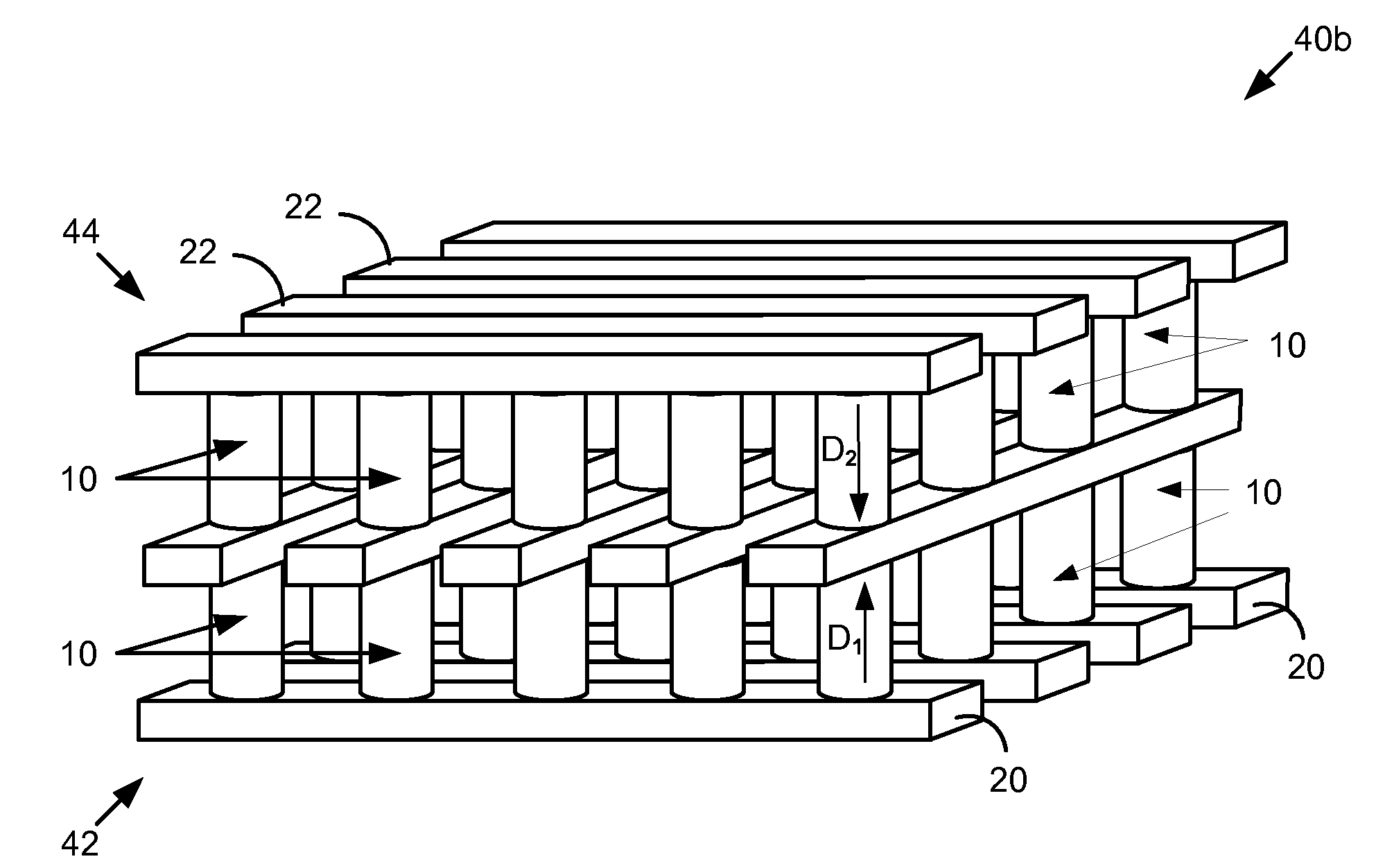

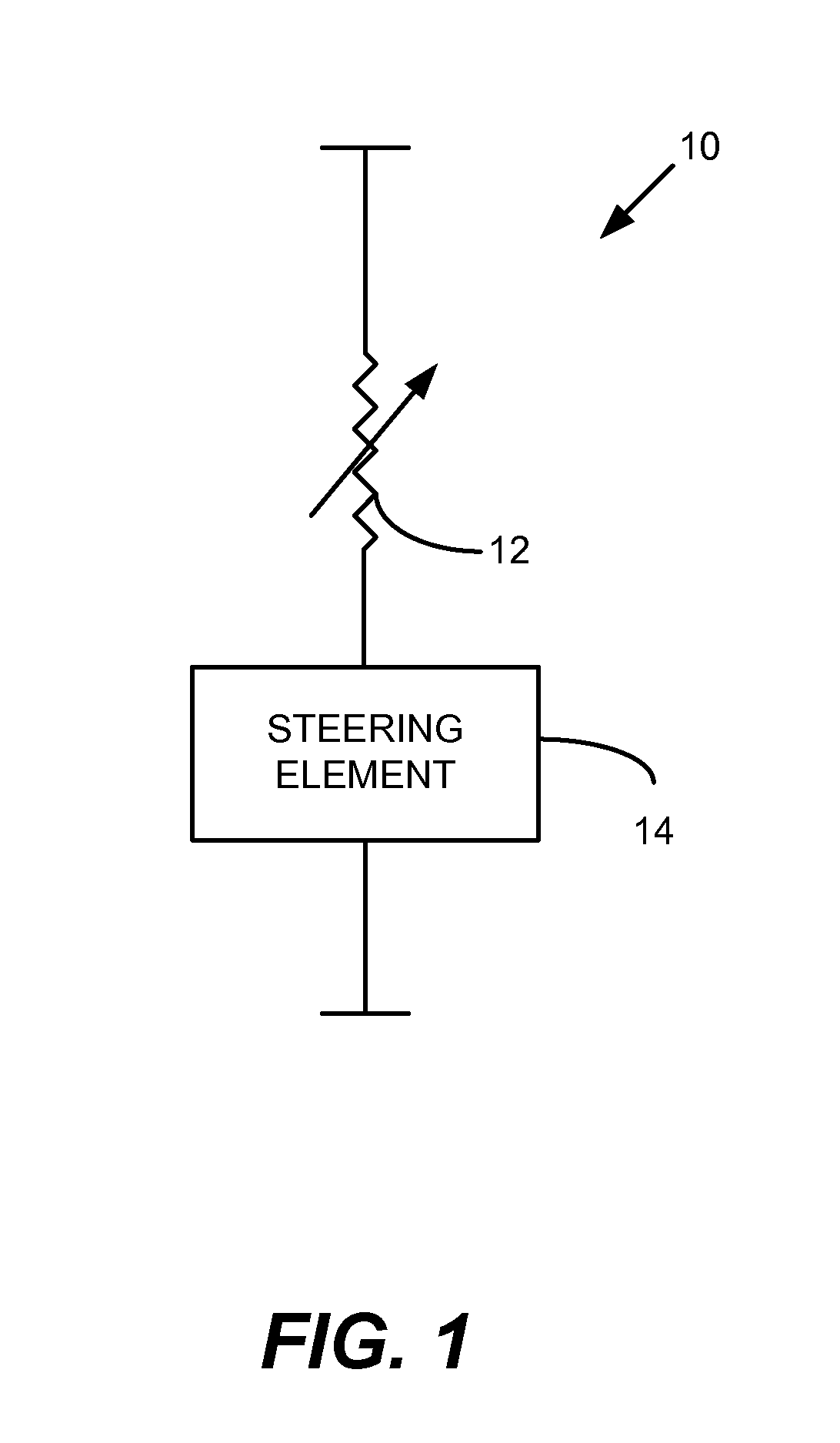

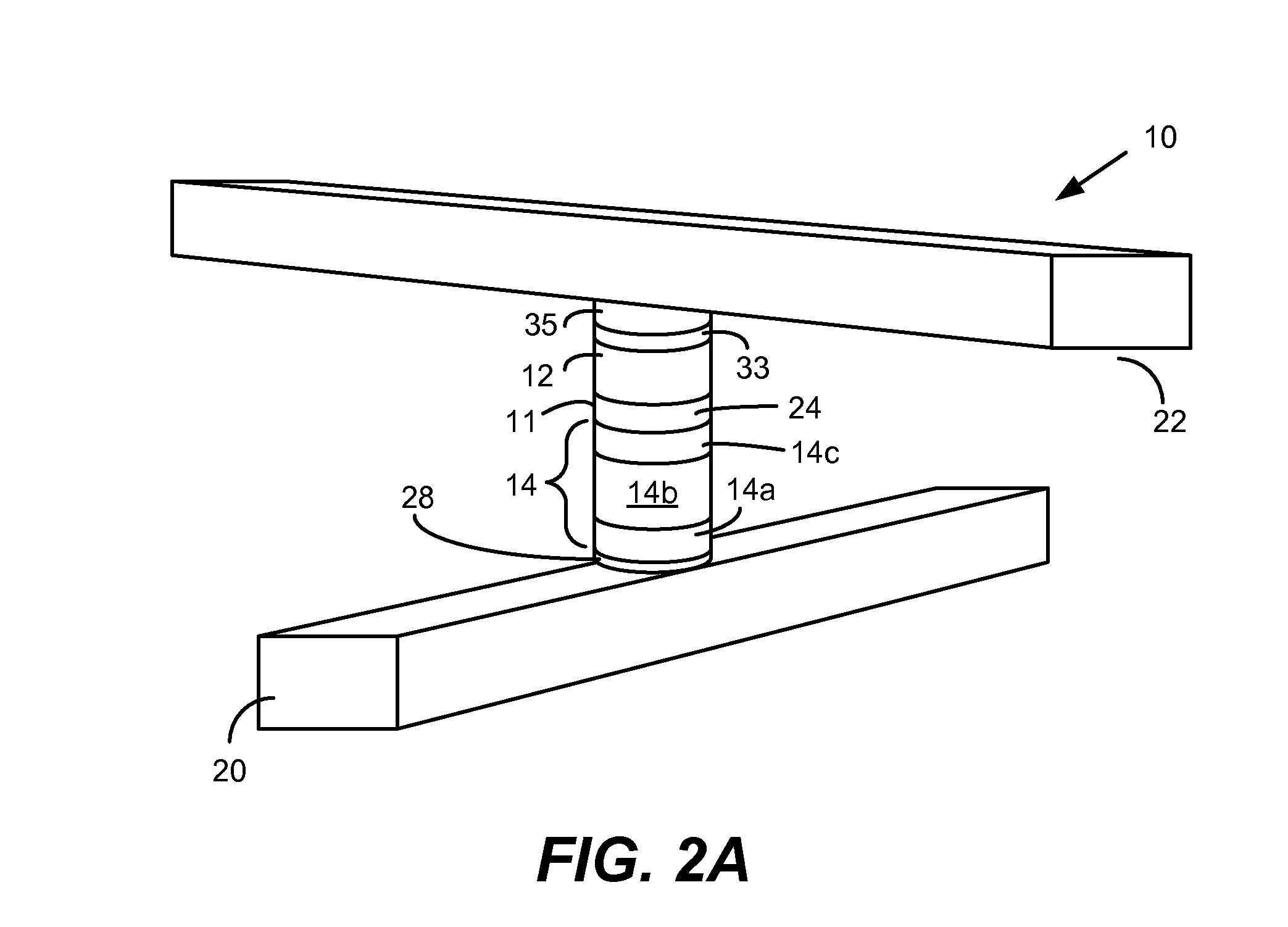

Memory cell that includes a carbon-based memory element and methods of forming the same

InactiveUS20100032640A1Solid-state devicesSemiconductor/solid-state device manufacturingResistCarbon layer

Memory cells, and methods of forming such memory cells, are provided that include a carbon-based reversible resistivity switching material. In particular embodiments, methods in accordance with this invention form a memory cell by forming a layer of carbon material above a substrate, forming a barrier layer above the carbon layer, forming a hardmask layer above the barrier layer, forming a photoresist layer above the hardmask layer, patterning and developing the photoresist layer to form a photoresist region, patterning and etching the hardmask layer to form a hardmask region, and using an ashing process to remove the photoresist region while the barrier layer remains above the carbon layer. Other aspects are also provided.

Owner:SANDISK TECH LLC

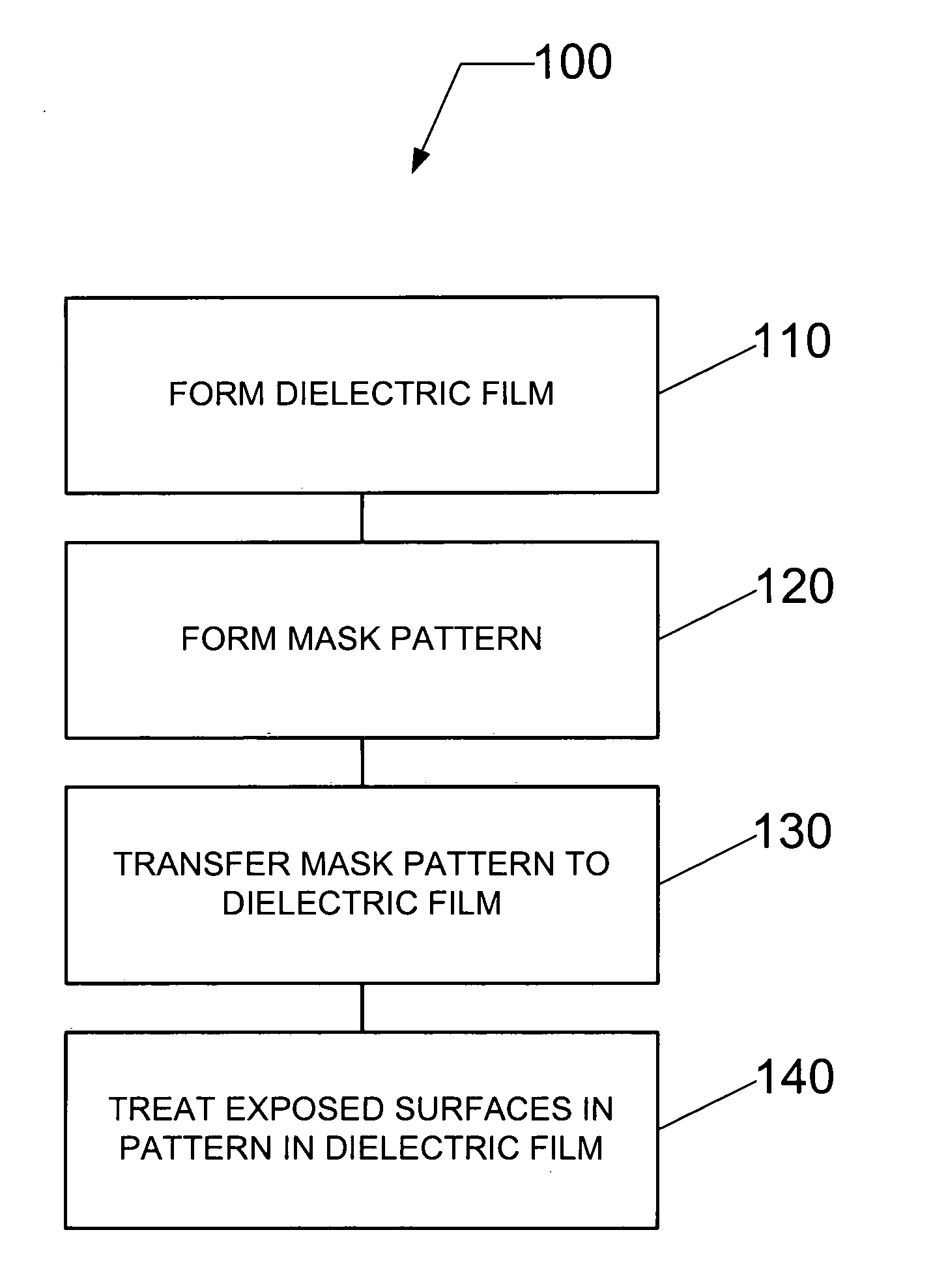

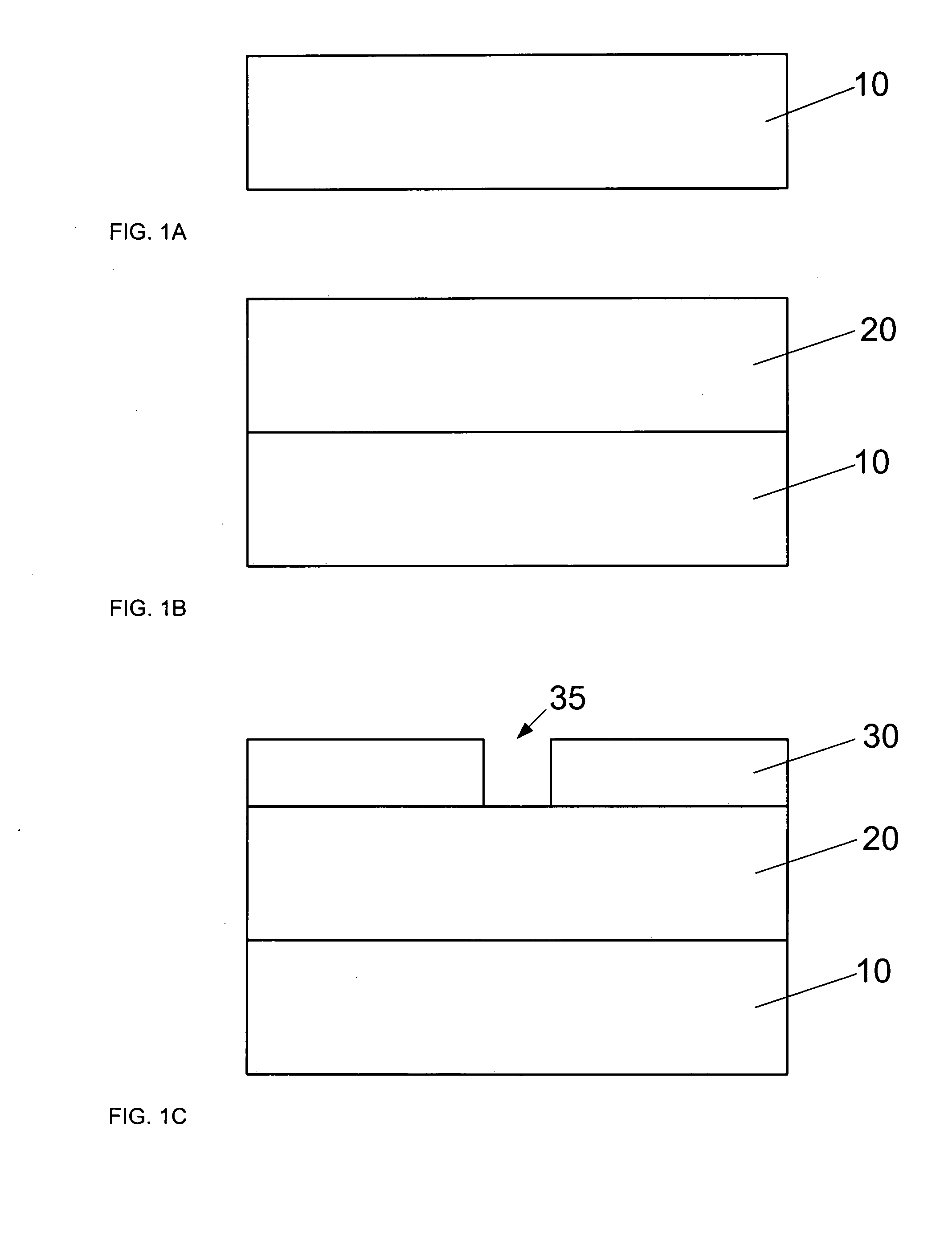

Method and system for treating a dielectric film

InactiveUS20050077597A1Reduce diffuseImprove adhesionSemiconductor/solid-state device detailsSolid-state devicesEngineeringDielectric permittivity

A method and system for treating a dielectric film includes exposing at least one surface of the dielectric film to a CxHy containing material, wherein x and y are each integers greater than or equal to a value of unity. The dielectric film can include a low dielectric constant film with or without pores having an etch feature formed therein following dry etch processing. As a result of the etch processing or ashing, exposed surfaces in the feature formed in the dielectric film can become damaged, or activated, leading to retention of contaminants, absorption of moisture, increase in dielectric constant, etc. Damaged surfaces, such as these, are treated by performing at least one of healing these surfaces to, for example, restore the dielectric constant (i.e., decrease the dielectric constant) and cleaning these surfaces to remove contaminants, moisture, or residue. Moreover, preparation for barrier layer and metallization of features in the film may include treating by performing sealing of sidewall surfaces of the feature to close exposed pores and provide a surface for barrier film deposition.

Owner:TOKYO ELECTRON LTD

Method of fabricating gate of semiconductor device using oxygen-free ashing process

A method of fabricating a gate of a semiconductor device using an oxygen-free ashing process is disclosed. The method includes forming a high-k dielectric film, having a dielectric constant higher than a silicon oxide film, on a semiconductor substrate including an NMOS region and a PMOS region, forming an etching target film on the high-k dielectric film, forming a photoresist pattern to expose any one region of the two regions, on the etching target film, etching the etching target film using the photoresist pattern as an etching mask, and removing the photoresist pattern using plasma formed in the presence of an oxygen-free reactive gas.

Owner:SAMSUNG ELECTRONICS CO LTD

Bottom electrode etching process in MRAM cell

ActiveUS20100311243A1Not to damageImprove device yieldSolid-state devicesSemiconductor/solid-state device manufacturingWater basedResist

A BE patterning scheme in a MRAM is disclosed that avoids damage to the MTJ array and underlying ILD layer while reducing BE-BE shorts and BE-bit line shorts. A protective dielectric layer is coated over a MTJ array before a photoresist layer is coated and patterned on the dielectric layer. The photoresist pattern is transferred through the dielectric layer with a dielectric etch process and then through the BE layer with a metal etch that includes a certain amount of overetch to remove metal residues. The photoresist is stripped with a sequence involving immersion or spraying with an organic solution followed by oxygen ashing to remove any other organic materials. Finally, a second wet strip is performed with a water based solution to provide a residue free substrate. In another embodiment, a bottom anti-reflective coating (BARC) is inserted between the photoresist and dielectric layer for improved critical dimension control.

Owner:TAIWAN SEMICON MFG CO LTD

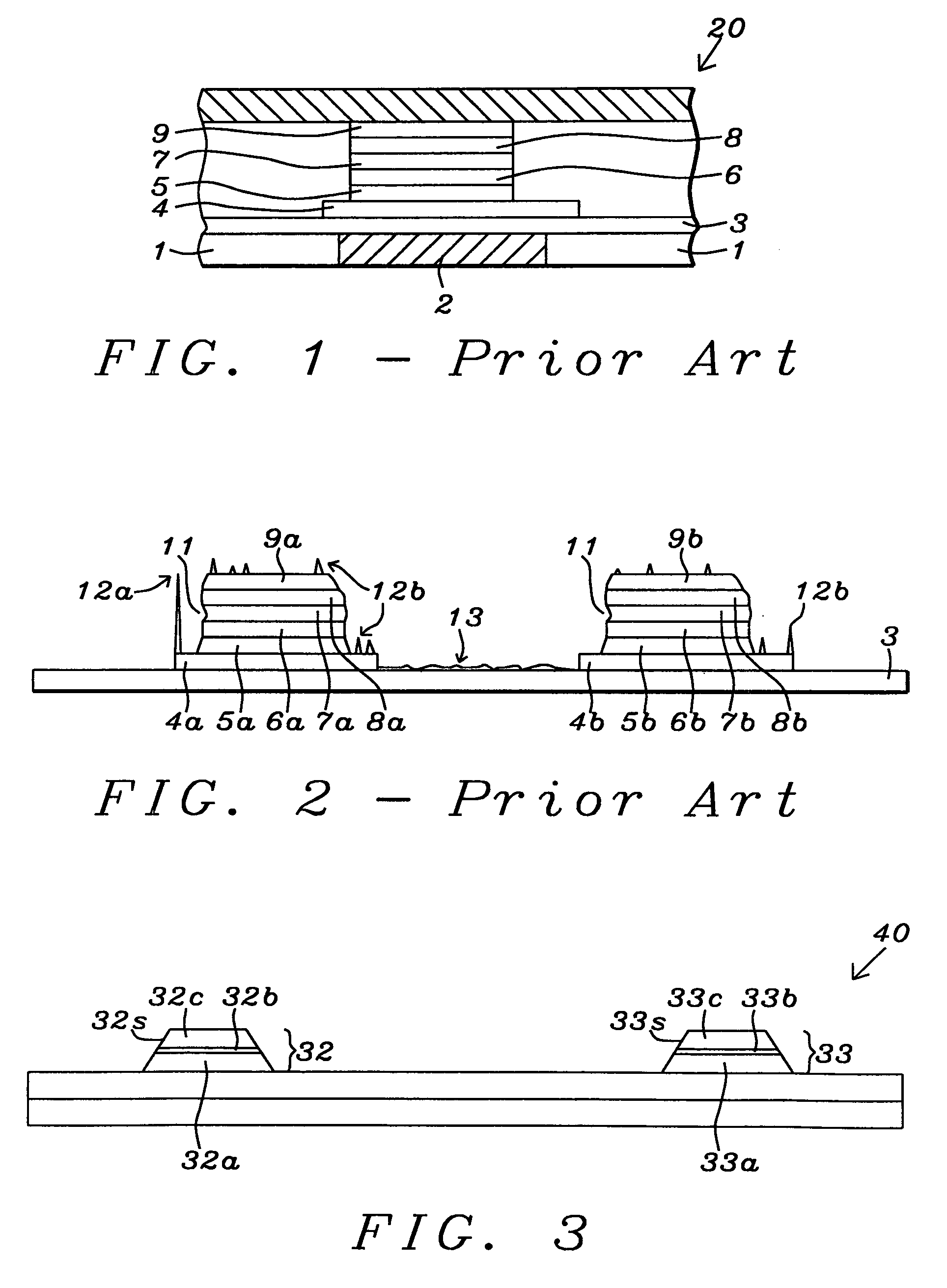

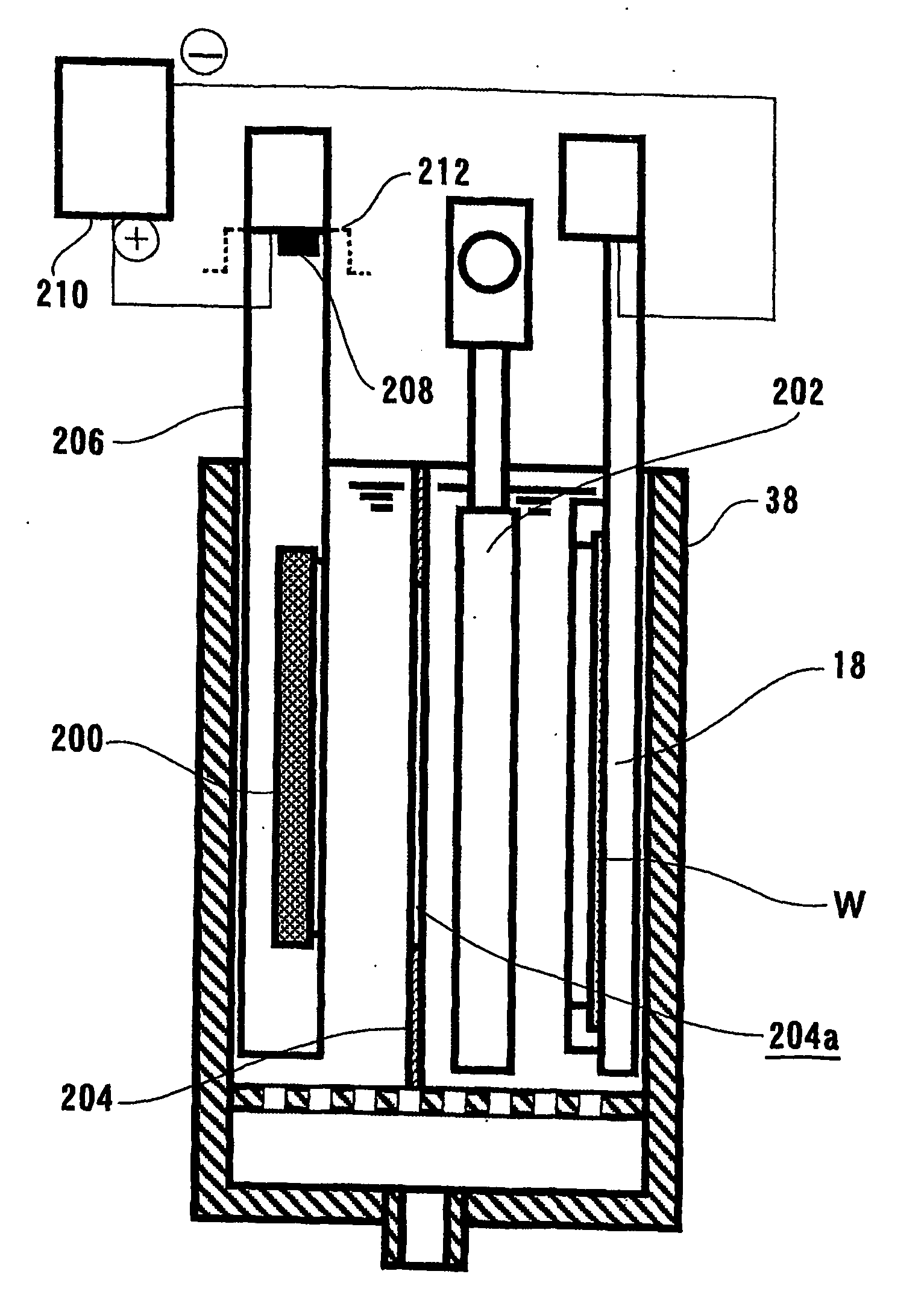

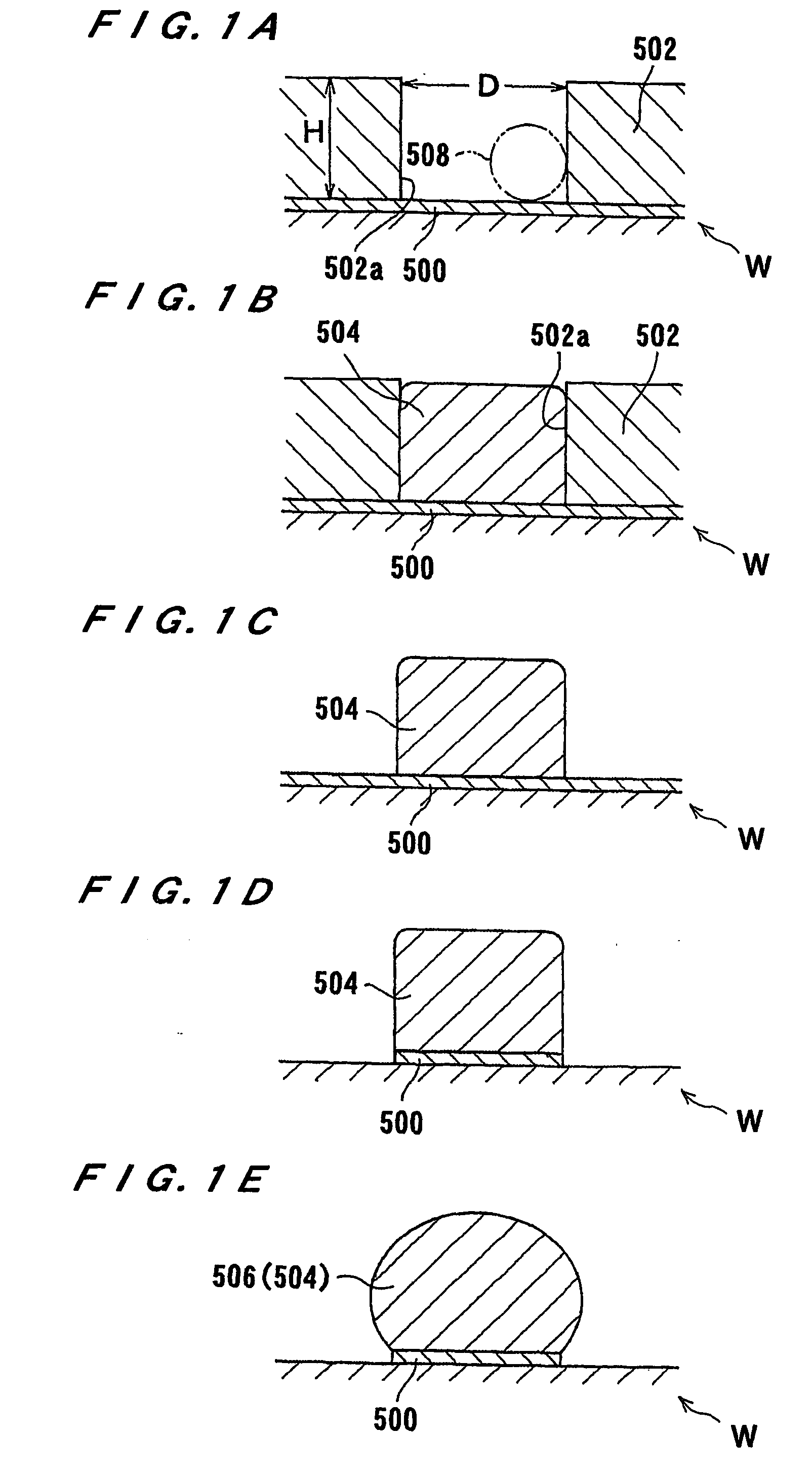

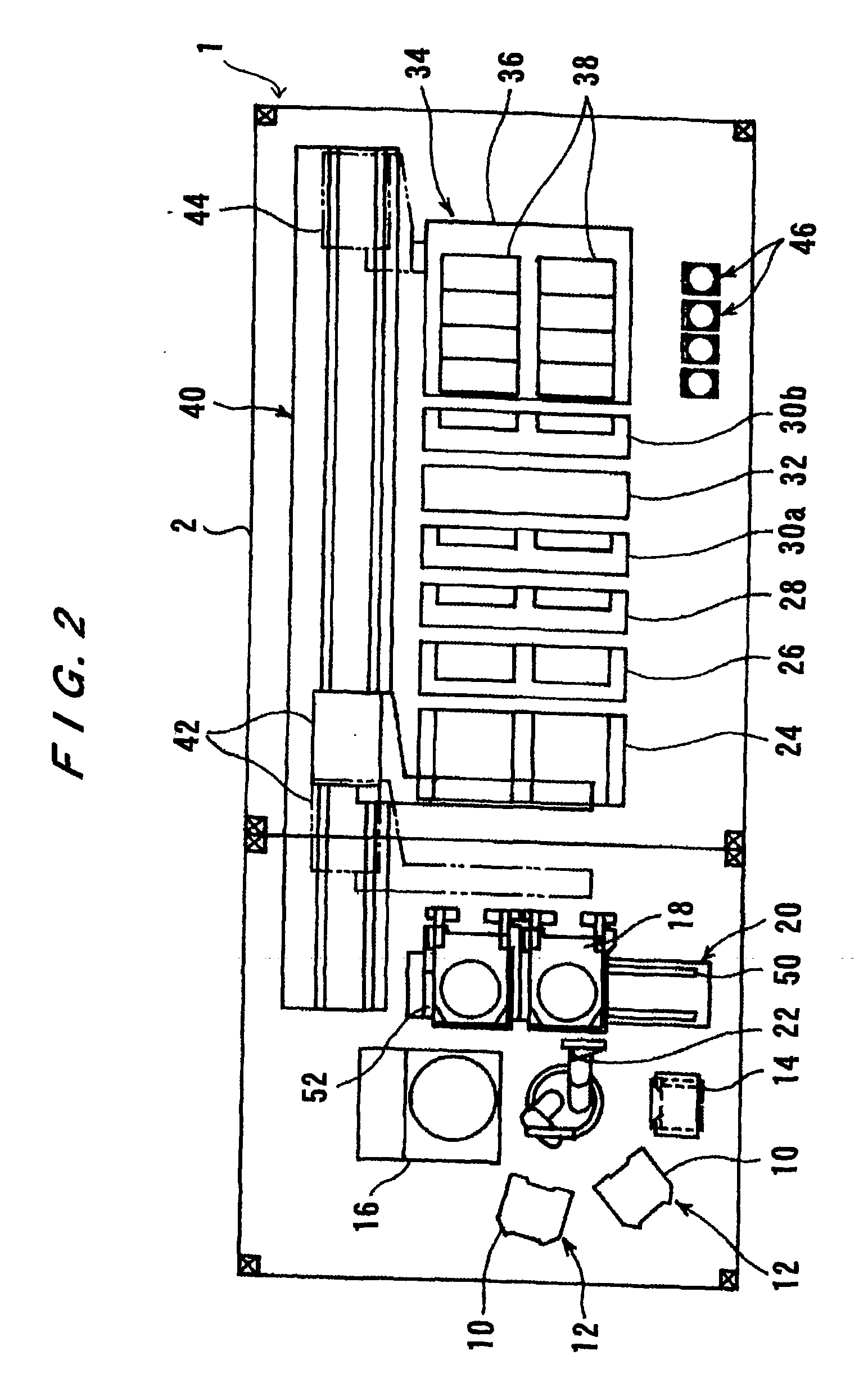

Plating apparatus and plating method

InactiveUS20060141157A1Facilitated releaseReduce spacingElectrolysis componentsSolid-state devicesResistEngineering

A plating apparatus has an ashing unit (300) configured to perform an ashing process on a resist (502) applied on a surface of a seed layer (500) formed on a substrate (W), and a pre-wetting section (26) configured to provide hydrophilicity to a surface of the substrate after the ashing process. The plating apparatus includes a pre-soaking section (28) configured to bring the surface of the substrate into contact with a treatment solution to clean or activate a surface of the seed layer formed on the substrate. The plating apparatus also includes a plating unit (34) configured to bring the surface of the substrate into a plating solution in a plating tank while the resist is used as a mask so as to form a plated film (504) on the surface of the seed layer formed on the substrate.

Owner:EBARA CORP

Method and system for treating a dielectric film

InactiveUS20050215072A1Reduce diffuseImprove adhesionSemiconductor/solid-state device detailsSolid-state devicesArylSilanes

A method and system for treating a dielectric film includes exposing at least one surface of the dielectric film to an alkyl silane, an alkoxysilane, an alkyl siloxane, an alkoxysiloxane, an aryl silane, an acyl silane, a cyclo siloxane, a polysilsesquioxane (PSS), an aryl siloxane, an acyl siloxane, or a halo siloxane, or any combination thereof. The dielectric film can include a low dielectric constant film with or without pores having an etch feature formed therein following dry etch processing. As a result of the etch processing or ashing, exposed surfaces in the feature formed in the dielectric film can become damaged, or activated, leading to retention of contaminants, absorption of moisture, increase in dielectric constant, etc. Damaged surfaces, such as these, are treated by performing at least one of healing these surfaces to, for example, restore the dielectric constant (i.e., decrease the dielectric constant) and cleaning these surfaces to remove contaminants, moisture, or residue. Moreover, preparation for barrier layer and metallization of features in the film may include treating by performing sealing of sidewall surfaces of the feature to close exposed pores and provide a surface for barrier film deposition.

Owner:TOKYO ELECTRON LTD

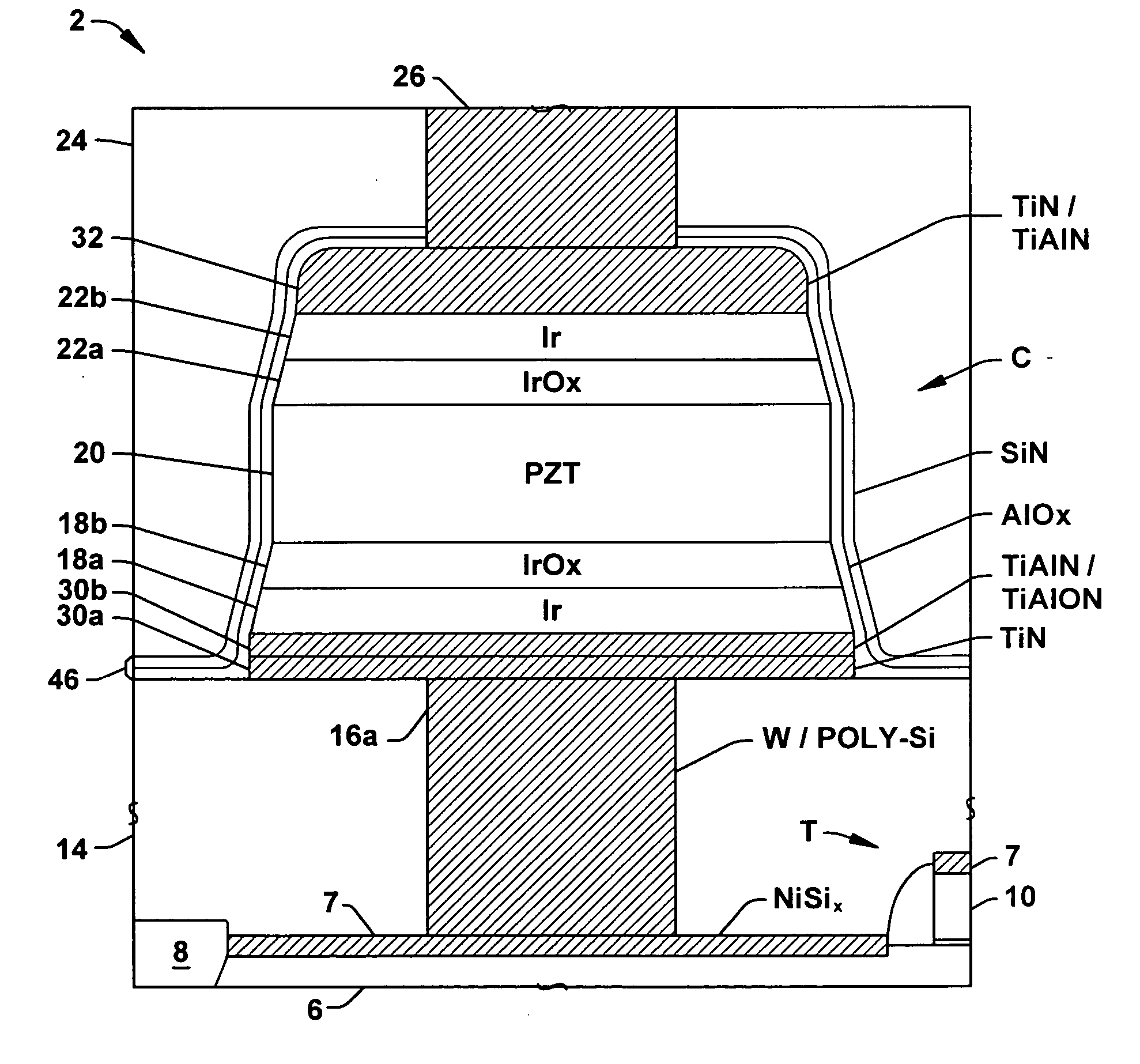

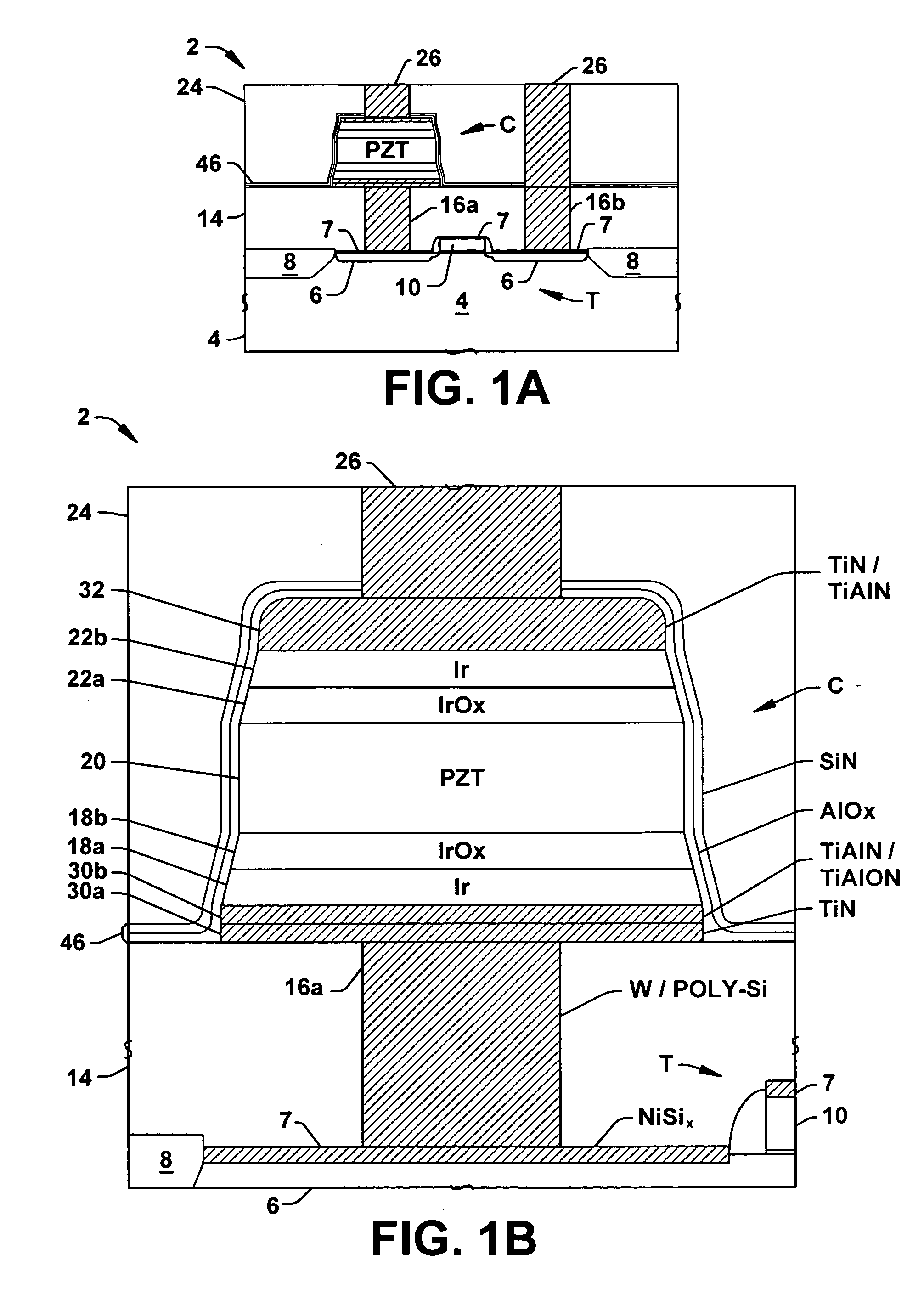

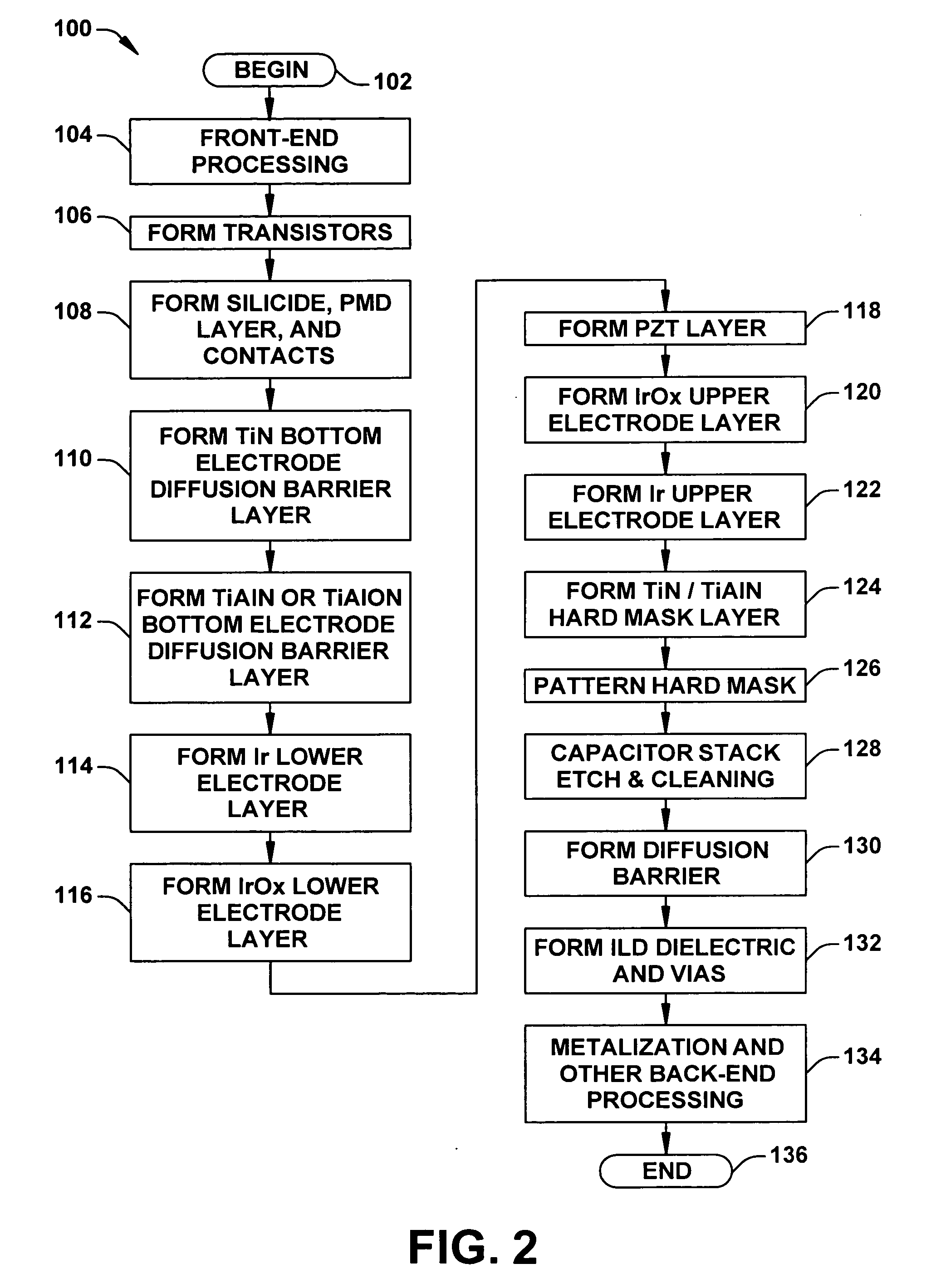

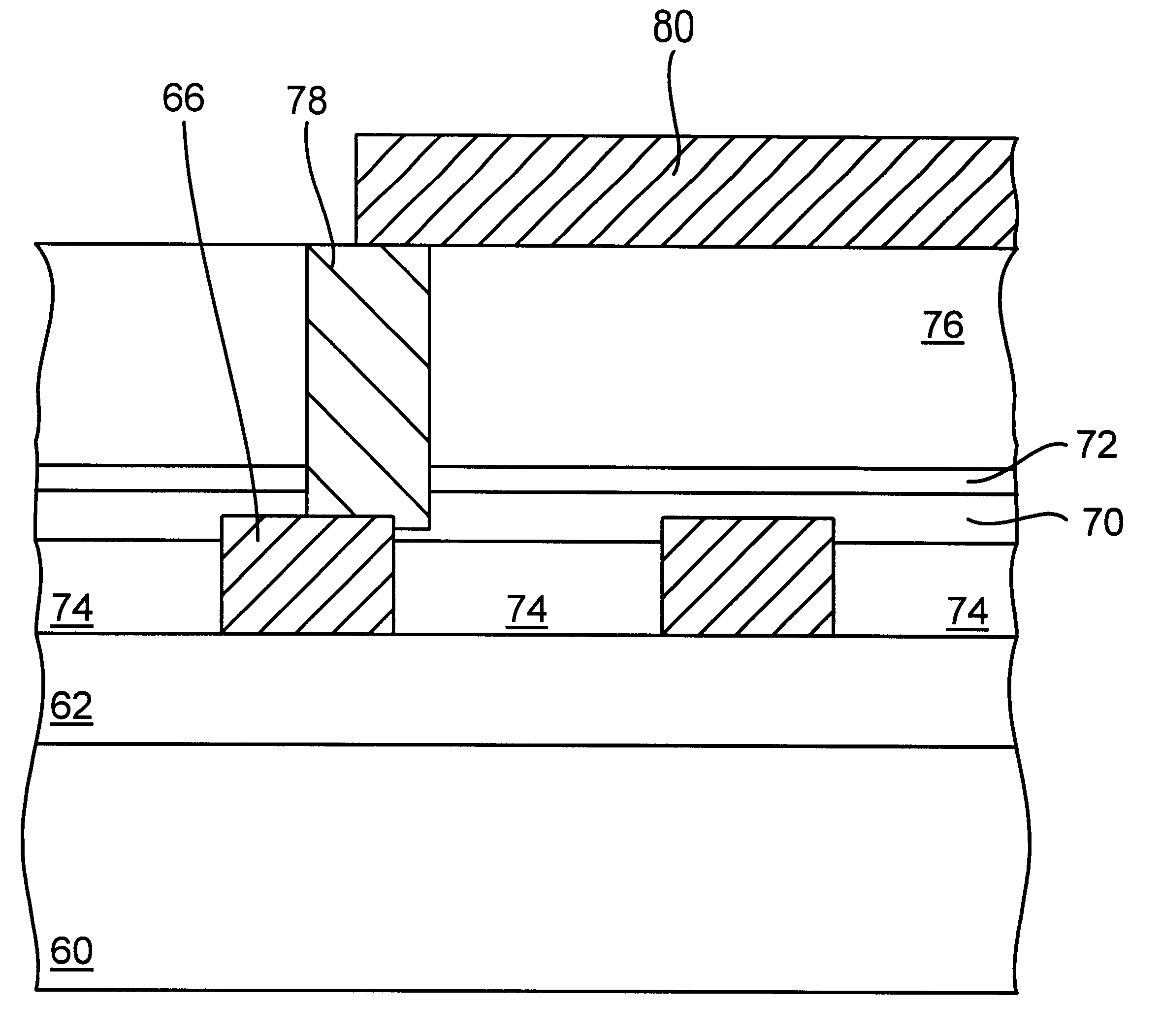

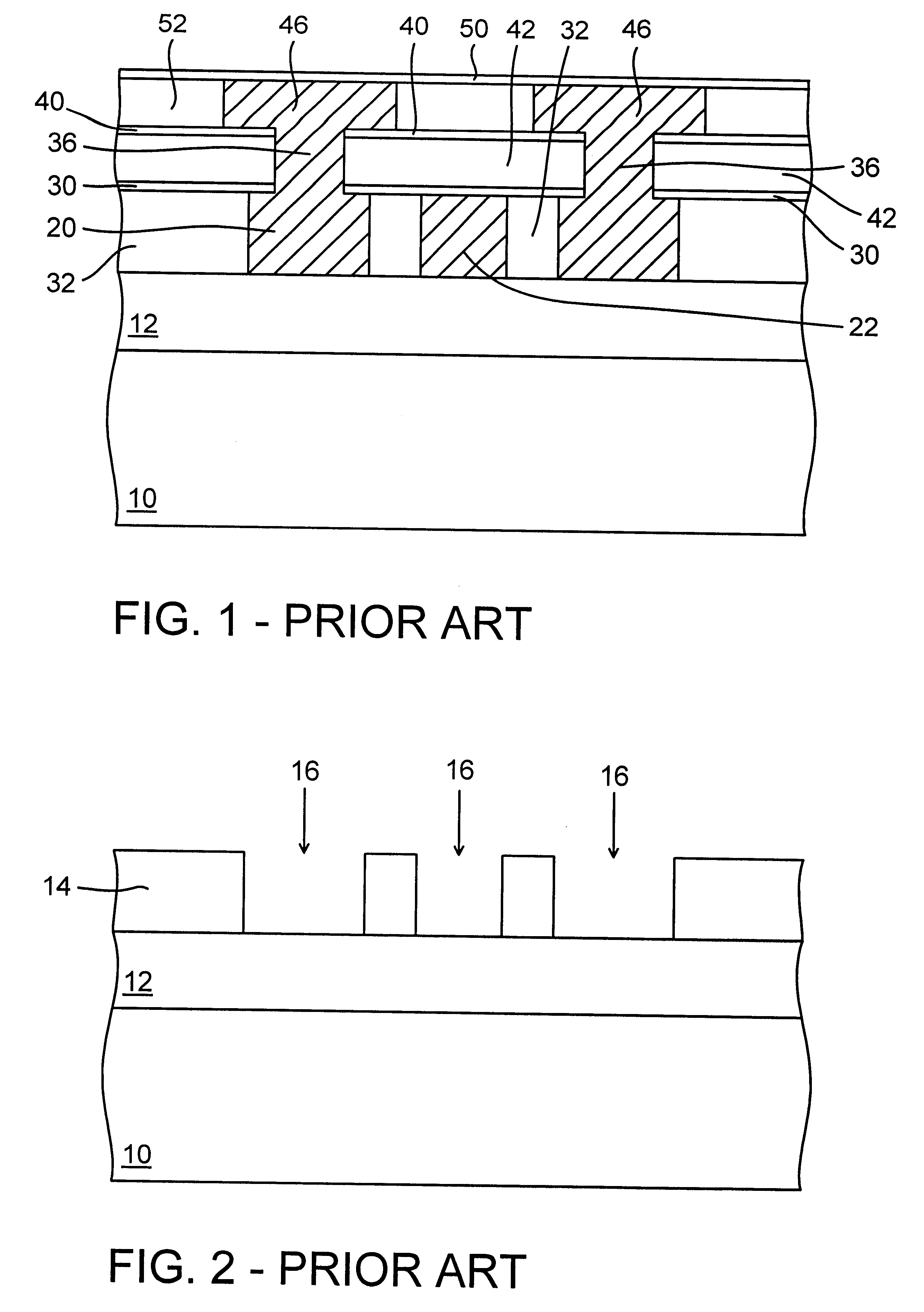

Ferroelectric capacitor stack etch cleaning methods

ActiveUS20060134808A1Mitigate ferroelectric material damageMitigate capacitor leakageSemiconductor/solid-state device manufacturingCapacitorsEtchingDevice material

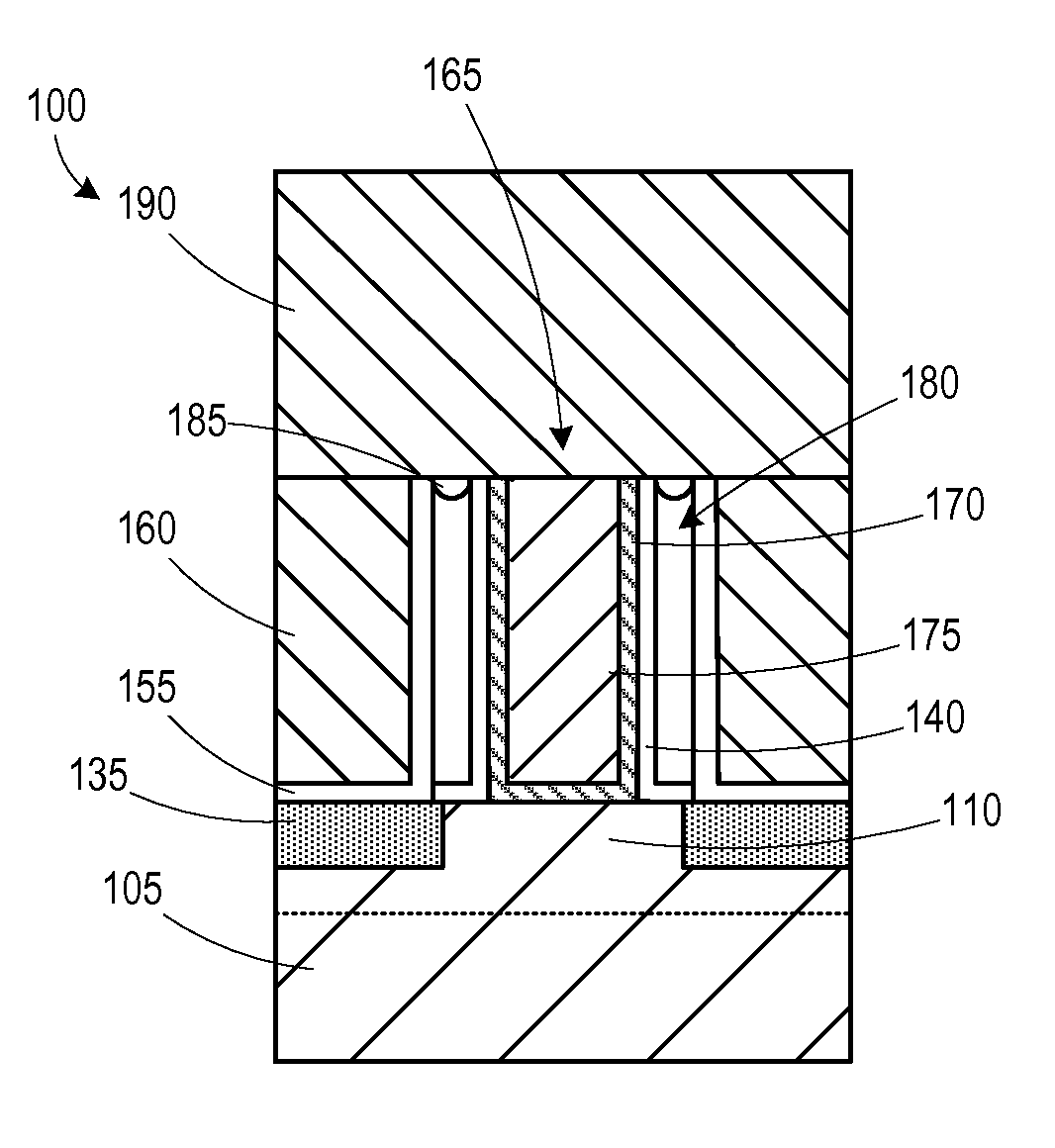

Methods (100) are provided for fabricating a ferroelectric capacitor structure including methods (128) for etching and cleaning patterned ferroelectric capacitor structures in a semiconductor device. The methods comprise etching (140, 200) portions of an upper electrode, etching (141, 201) ferroelectric material, and etching (142, 202) a lower electrode to define a patterned ferroelectric capacitor structure, and etching (143, 206) a portion of a lower electrode diffusion barrier structure. The methods further comprise ashing (144, 203) the patterned ferroelectric capacitor structure using a first ashing process, performing (145, 204) a wet clean process after the first ashing process, and ashing (146, 205) the patterned ferroelectric capacitor structure using a second ashing process directly after the wet clean process at a high temperature in an oxidizing ambient.

Owner:TEXAS INSTR INC

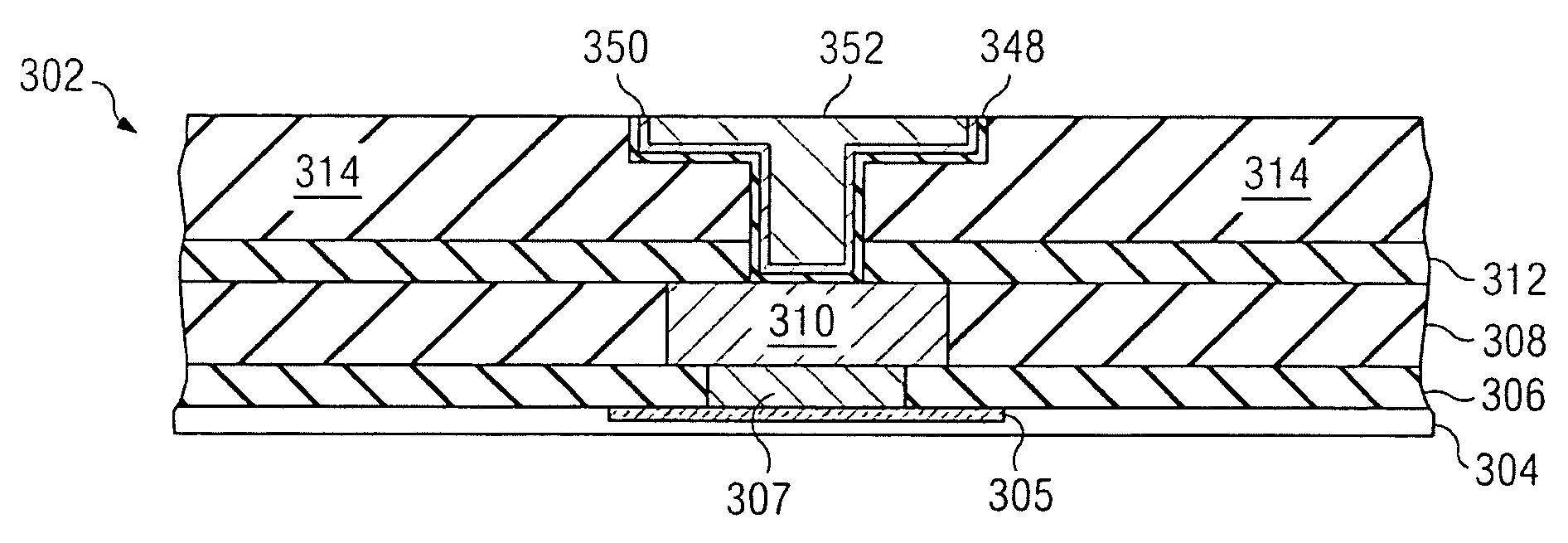

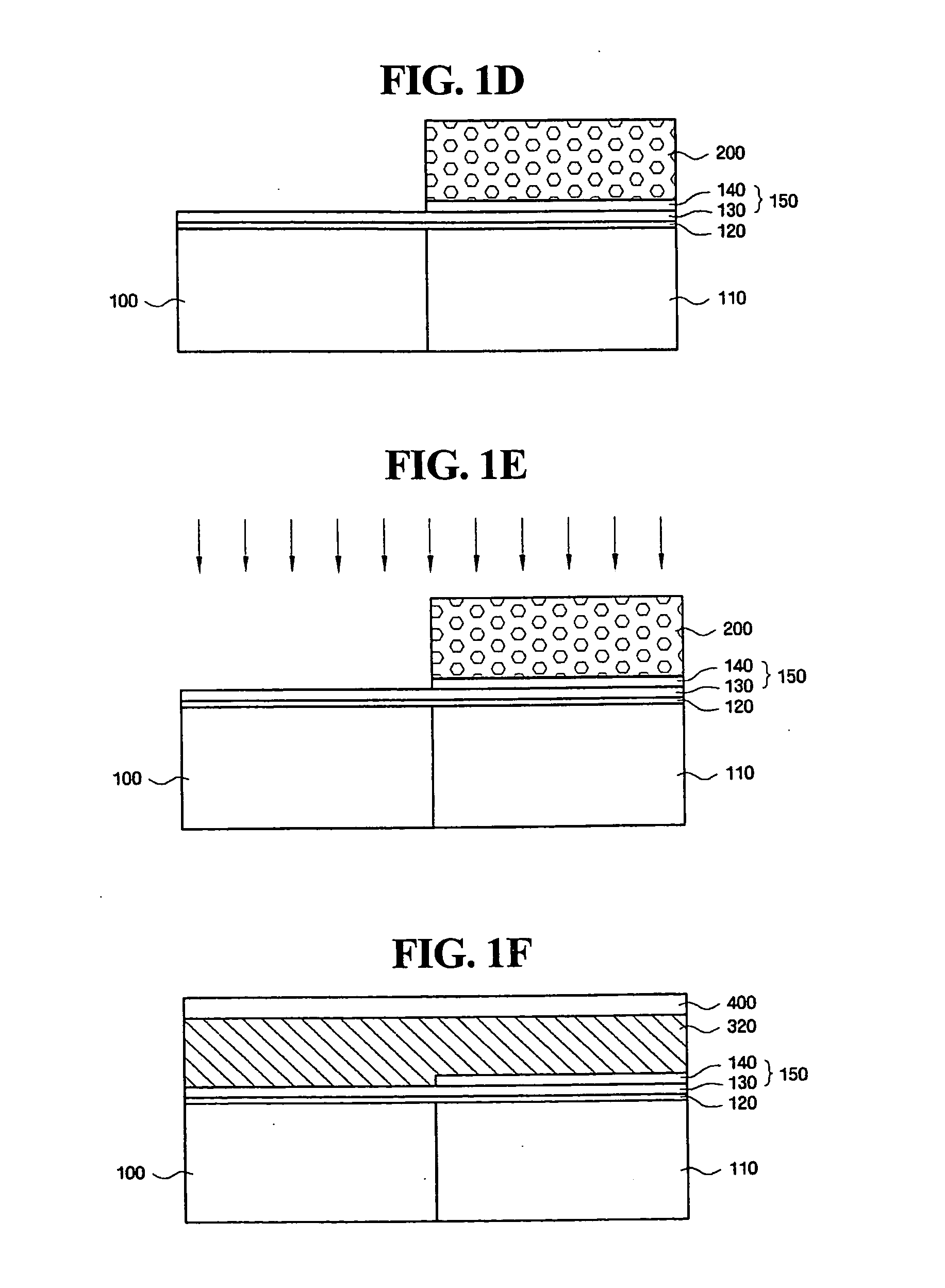

Interconnect structure with gas dielectric compatible with unlanded vias

A multilevel interconnect structure is formed which uses air as a dielectric between wiring lines and which is compatible with the presence of unlanded vias in the interconnect structure. A layer of carbon is deposited over an insulating surface and then a pattern for trenches is formed in the surface of the layer of carbon. Metal is deposited in the trenches and over the layer of carbon and then a chemical mechanical polishing process is used to define wiring lines. An ashing or etch back process is performed on the carbon layer to recess its surface below the surfaces of the wiring lines. An oxide capping layer is provided over the recessed surface of the carbon and the wiring lines, for example using HSQ and curing, and then the carbon layer is consumed through the capping layer using an oxidation process. Air replaces the sacrificial carbon layer during the consumption reaction. Next, a silicon nitride etch stop layer is provided over the surface of the capping layer and then an intermetal dielectric layer is provided. A via is formed by etching through the intermetal dielectric, stopping on the etch stop layer, and then etching through the etch stop layer and the capping layer in distinct processes. The via is filled with a metal plug and then second level wiring lines are formed.

Owner:UNITED MICROELECTRONICS CORP

Method of in-situ damage removal - post O2 dry process

InactiveUS20050106888A1Not to damageSemiconductor/solid-state device manufacturingPhotosensitive material processingHalogenFluorocarbon

An integrated process flow including a plasma step for removing oxide residues following oxygen ashing of a photoresist layer is disclosed. The oxide removal step is effective in preventing micro mask defects and is preferably performed in the same process chamber used for the oxygen ashing step and for a subsequent plasma etch used for pattern transfer. The oxide removal step takes less than 60 seconds and involves a halogen containing plasma that is generated from one or more of NF3, Cl2, CF4, CH2F2, and SF6. Optionally, HBr or a fluorocarbon CXFYHZ where x and y are integers and z is an integer or is equal to 0 may be used alone or with one of the aforementioned halogen containing gases. The oxide removal step may be incorporated in a variety of applications including a damascene scheme, shallow trench (STI) fabrication, or formation of a gate electrode in a transistor.

Owner:TAIWAN SEMICON MFG CO LTD

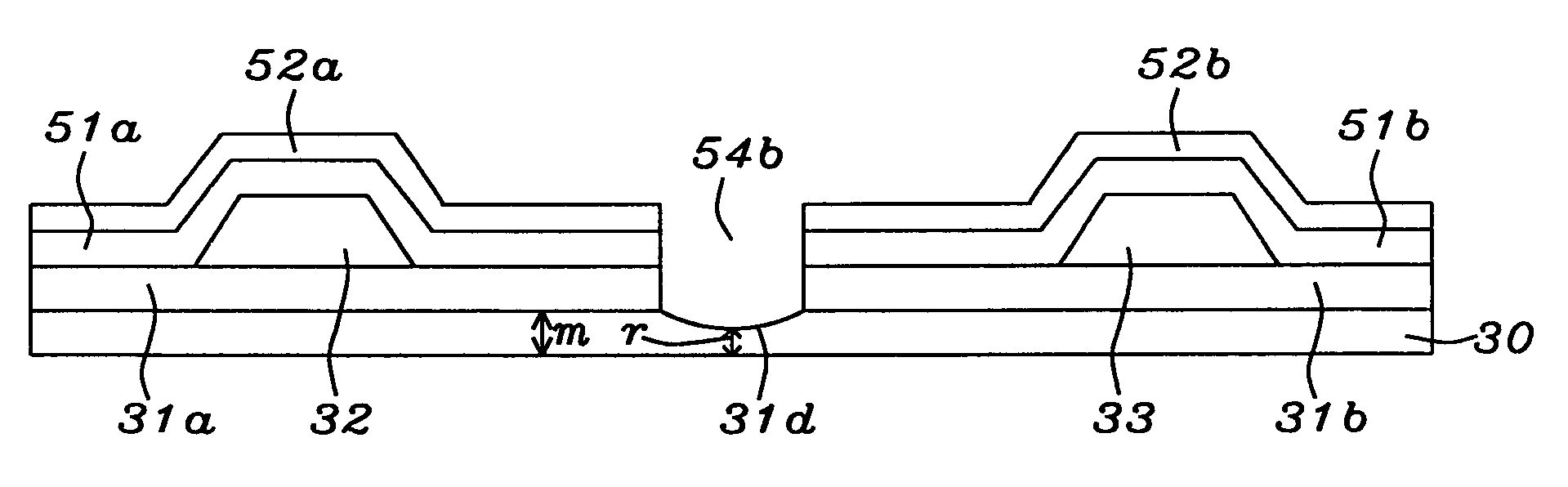

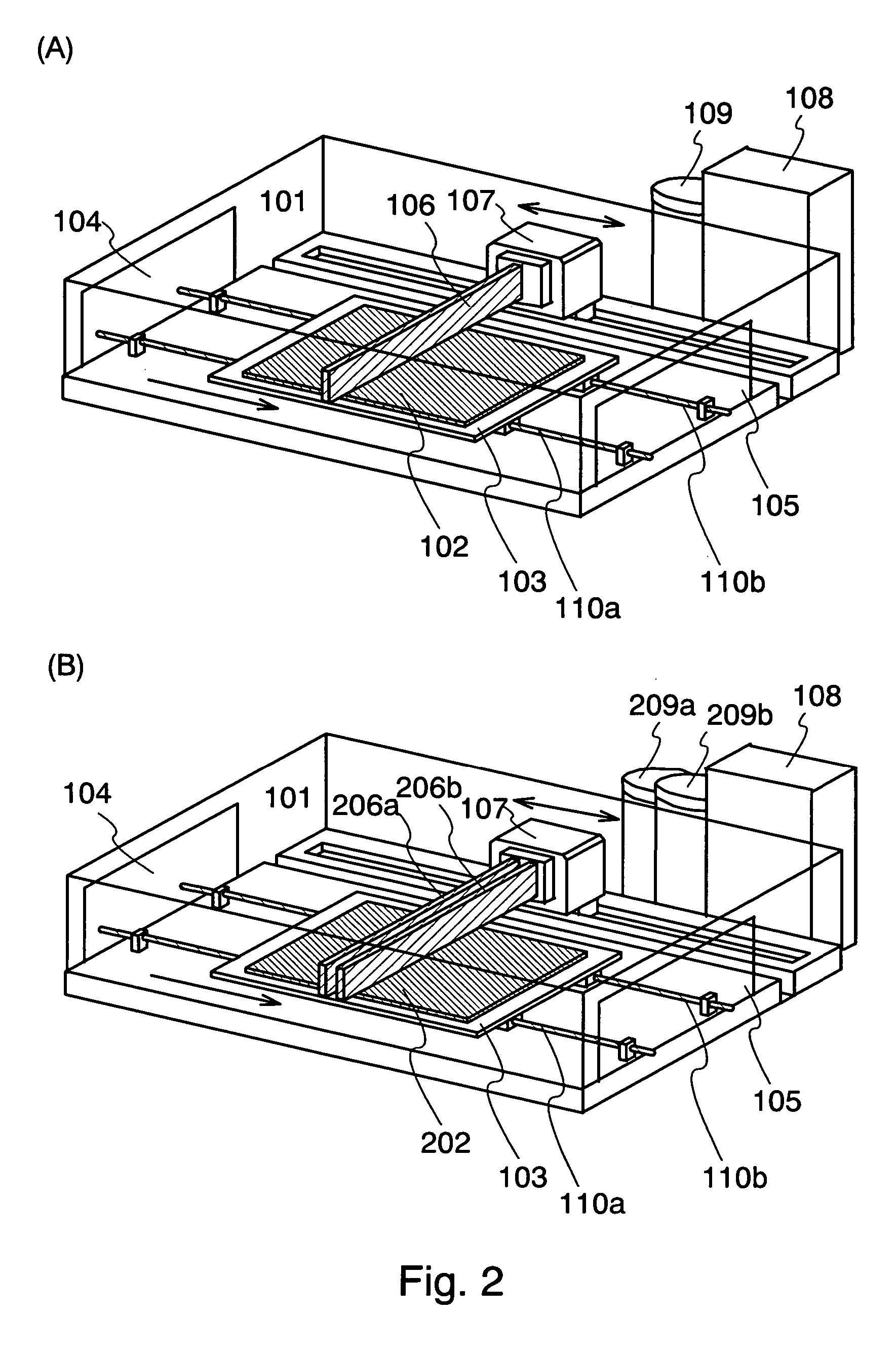

Method of manufacturing display device

InactiveUS20040253896A1Reduce usageSimple equipmentTransistorSolid-state devicesResistElectrical conductor

The present invention proposes a manufacturing method of a display device that accomplishes a lower production cost of a display device by using means for partially forming a resist film and means for partially forming a film and etching or ashing by plasma treatment at or near the atmospheric pressure. The manufacturing method of the display device according to the invention is characterized by including a step of partially forming a conductor film at or near the atmospheric pressure and forming wirings. Here, the wirings include all kinds of wirings such as connection wirings for sending signals from external input terminals to a pixel portion, wirings for connecting thin film transistors (TFT) to pixel electrodes, and so forth, besides wirings operating as gate wirings and source wirings at the pixel portion of an active matrix type display device.

Owner:SEMICON ENERGY LAB CO LTD

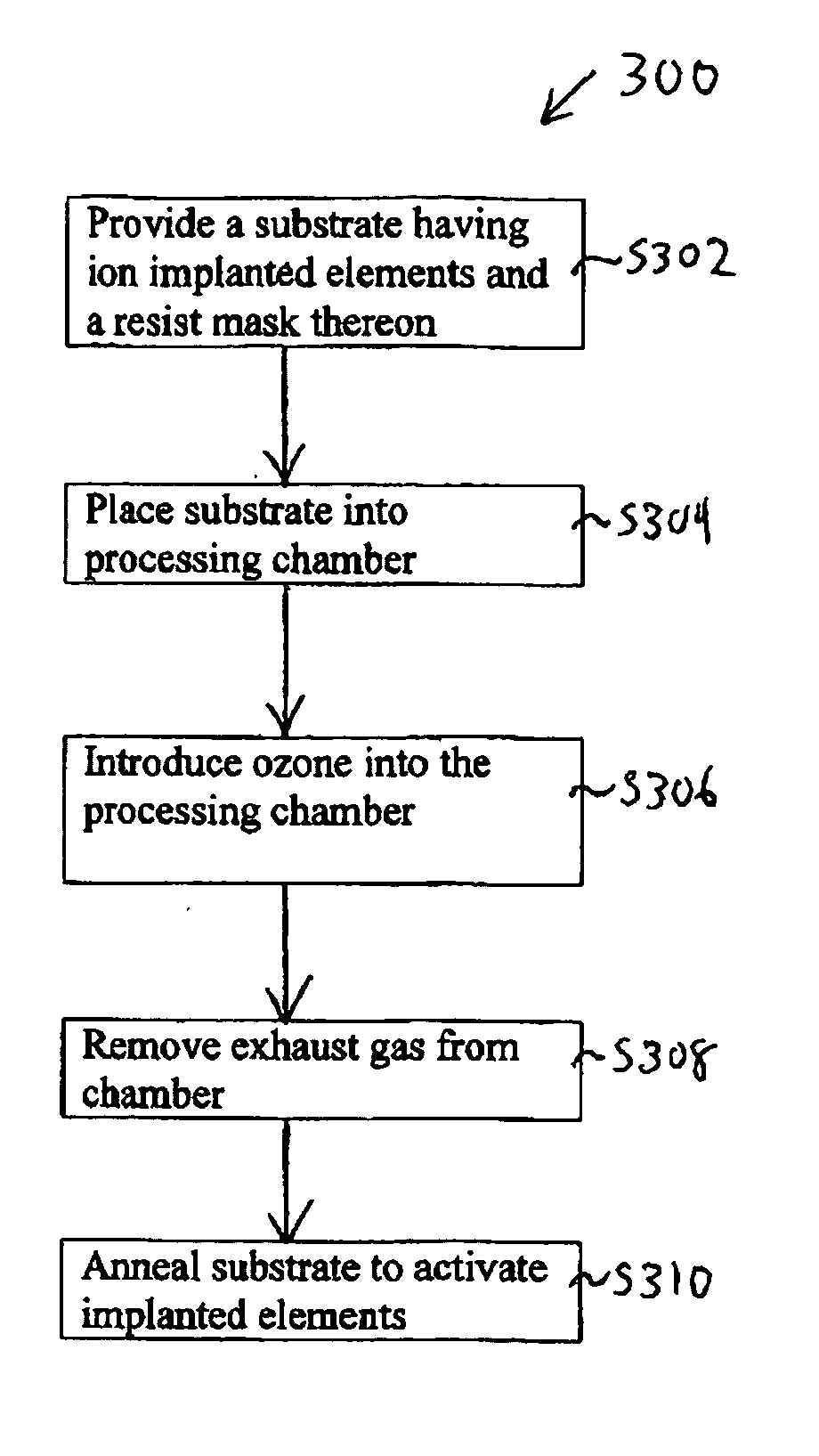

Integrated ashing and implant annealing method using ozone

InactiveUS20050085094A1Sufficient vacuum forceAvoid accumulationSemiconductor/solid-state device manufacturingPhotosensitive material processingResistIon implantation

After ion implantation, thermal ashing is performed using ozone at a pressure of between about 0.01 to about 1000 Torr at below 1000° C. to remove the resist. Since the process includes a substantial amount of ozone, the resist can be completely oxidized, thus leaving no residue or other contaminates to remain on the substrate. Using ozone allows fast resist removal with minimal residue at low temperatures.

Owner:WAFERMASTERS

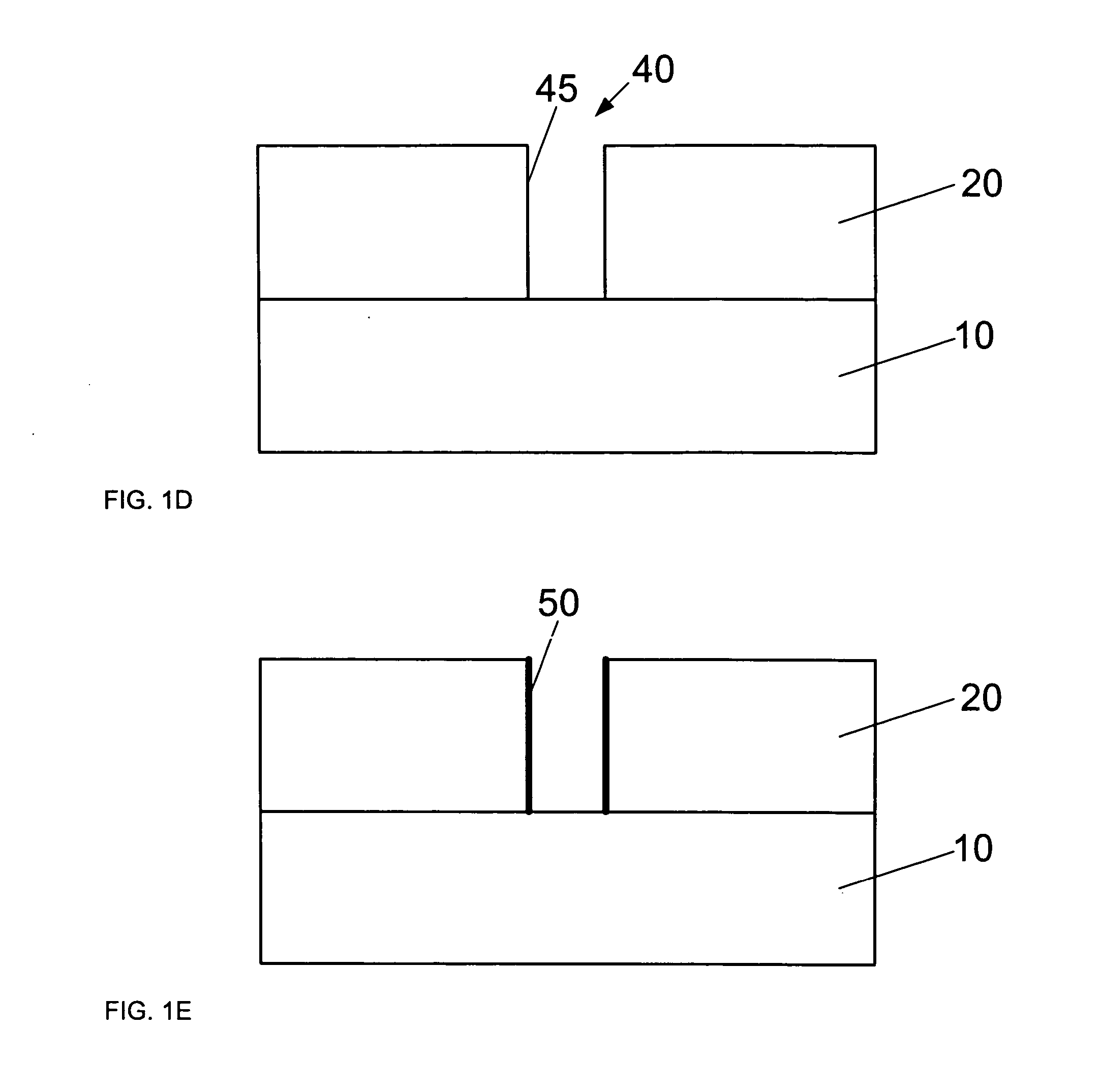

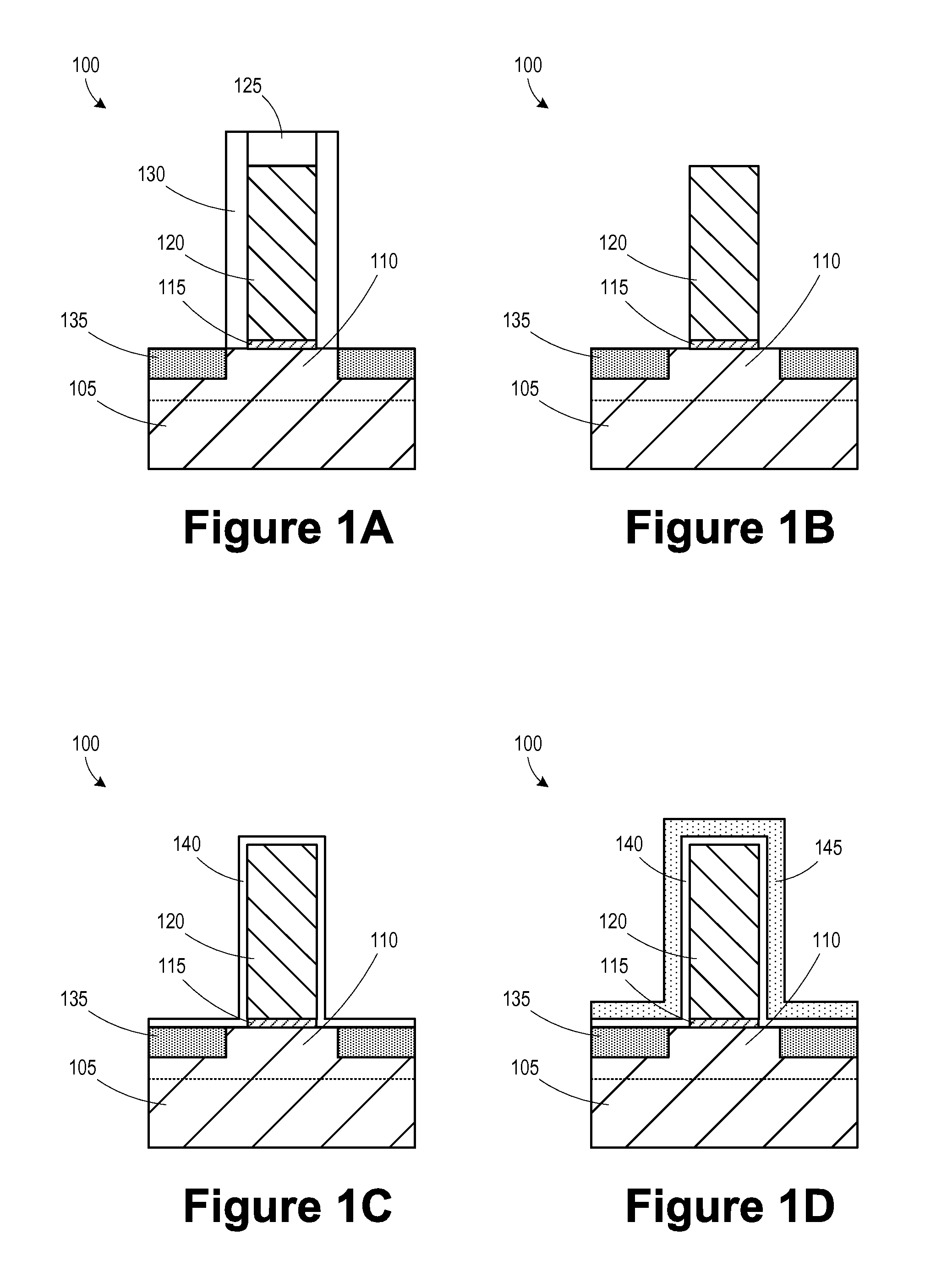

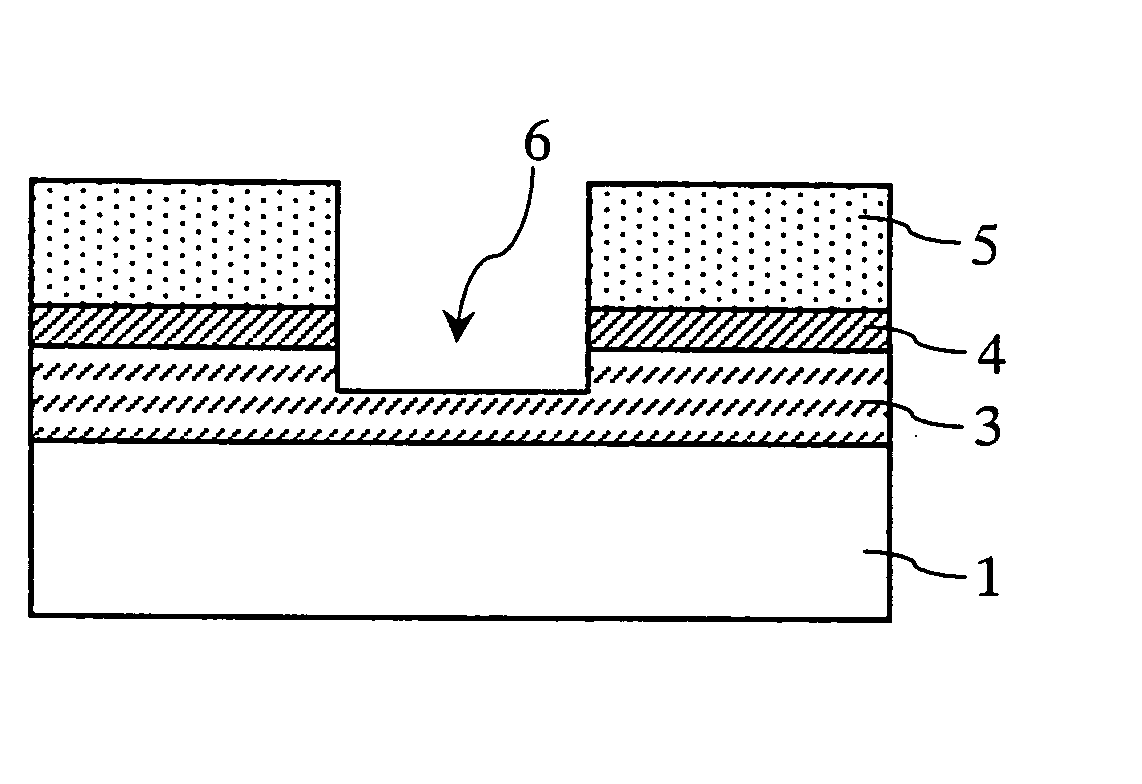

Method for forming air gap structure using carbon-containing spacer

ActiveUS20160163816A1Well formedSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringDielectric layer

A method includes forming a line feature above a substrate. Carbon-containing spacers are formed on sidewalls of the line feature. A first dielectric layer is formed above the carbon spacers and the line feature. The first dielectric layer is planarized to expose upper ends of the carbon-containing spacers. An ashing process is performed to remove the carbon-containing spacers and define air gaps adjacent the line feature. A cap layer is formed to seal the upper ends of the air gaps.

Owner:GLOBALFOUNDRIES US INC

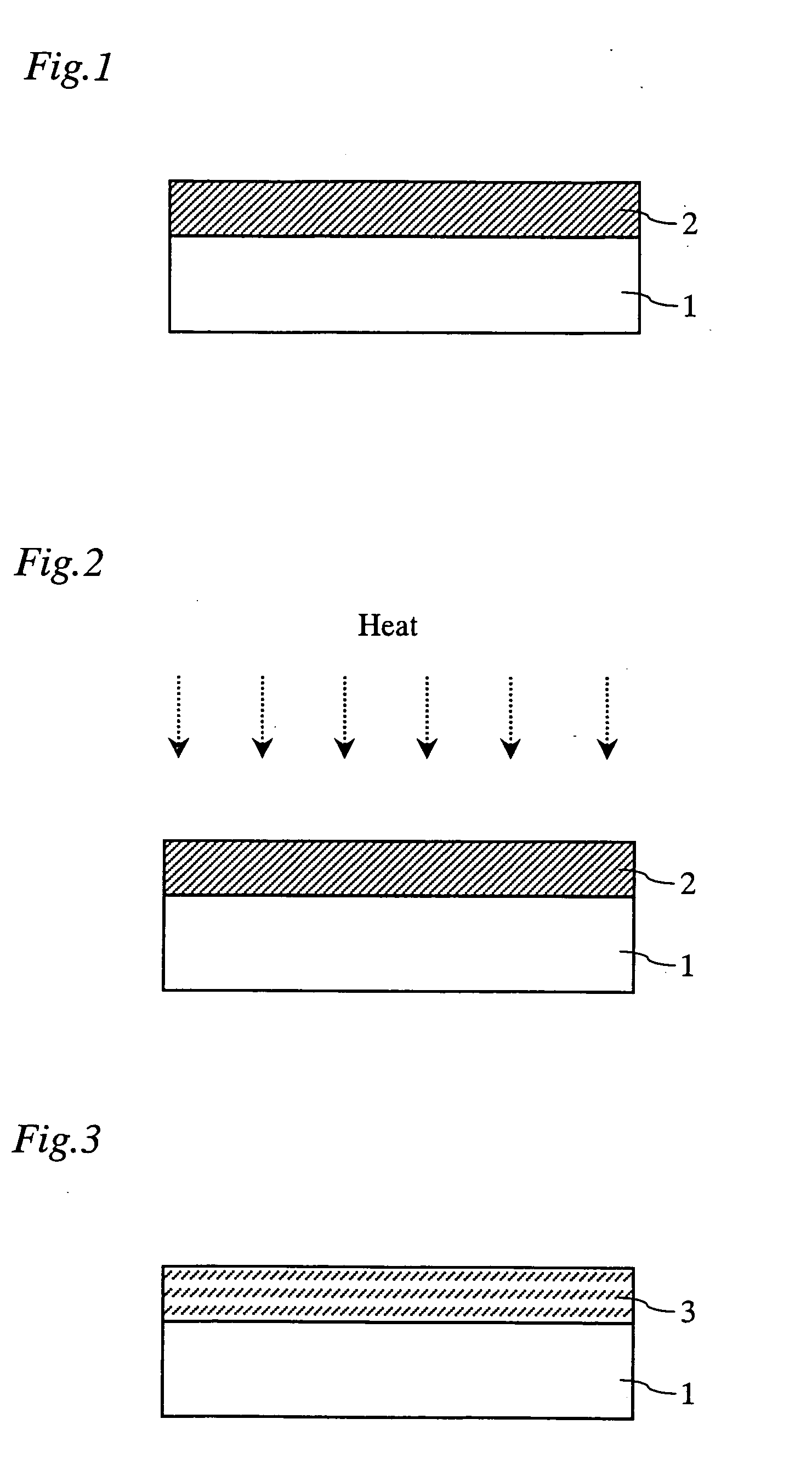

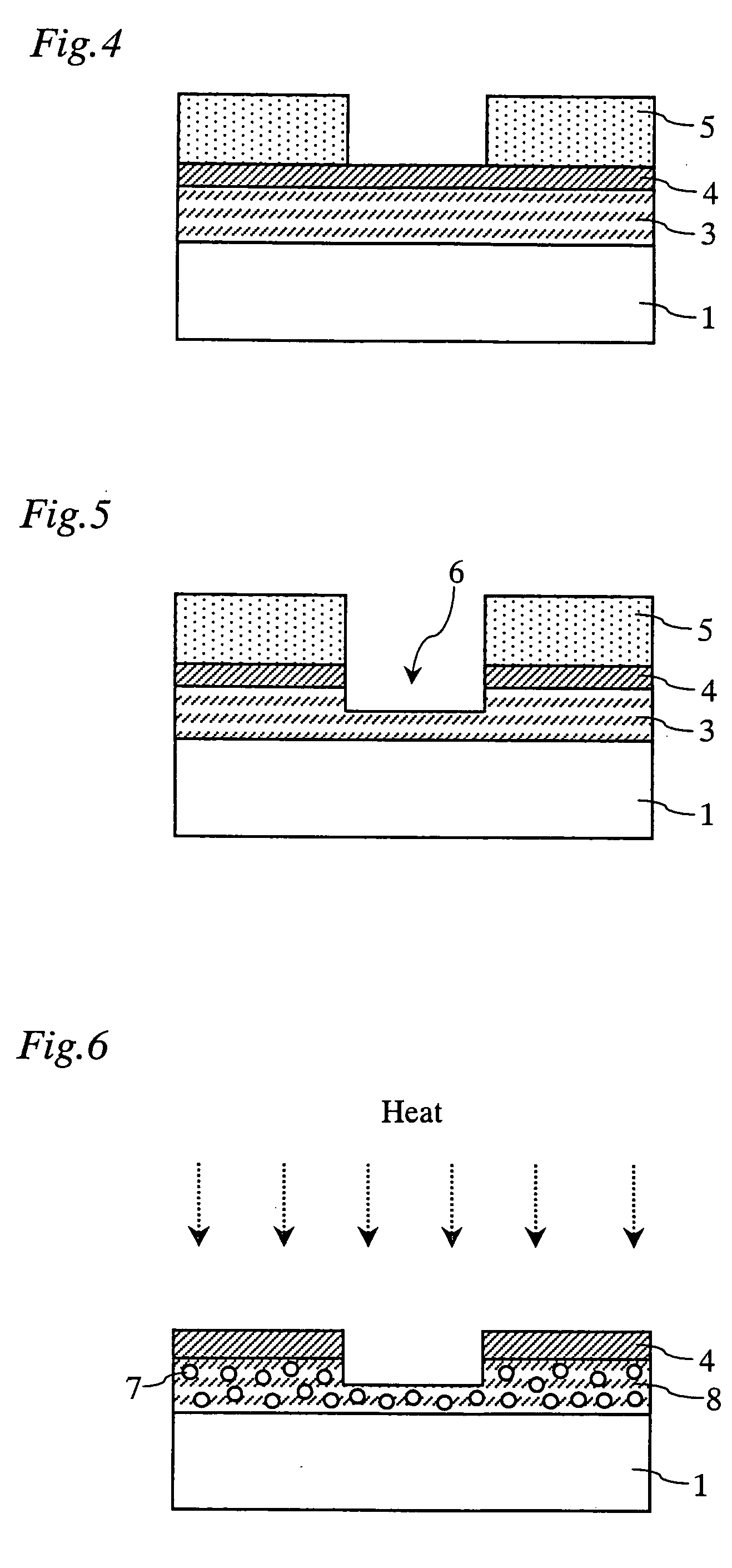

Method for manufacturing semiconductor device

InactiveUS20050191847A1Good electrical propertiesImprove reliabilitySemiconductor/solid-state device detailsSolid-state devicesResistDevice material

A heat treatment is performed to an insulating film composition, formed on a semiconductor substrates at a temperature of 350° C. in an inert gas ambient to form a non-porous insulating film. Next, dry etching is performed using a resist pattern as a mask to form a trench in the non-porous insulating film, ashing is performed to remove the resist pattern, and the surface of the semiconductor substrate is cleaned. Thereafter, a second heat treatment is performed for the non-porous insulating film to form a porous insulating film. Since the second heat treatment is performed in an oxidizing-gas atmosphere, the pore-generating material can be removed at a temperature lower than the temperature of conventional methods to form an insulating film having a low dielectric constant.

Owner:SANYO ELECTRIC CO LTD

UV treatment for carbon-containing low-k dielectric repair in semiconductor processing

ActiveUS20100261349A1Weaken energySemiconductor/solid-state device manufacturingGas phaseDevice material

Owner:NOVELLUS SYSTEMS