Patents

Literature

179 results about "Front end of line" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

The front-end-of-line (FEOL) is the first portion of IC fabrication where the individual devices (transistors, capacitors, resistors, etc.) are patterned in the semiconductor. FEOL generally covers everything up to (but not including) the deposition of metal interconnect layers.

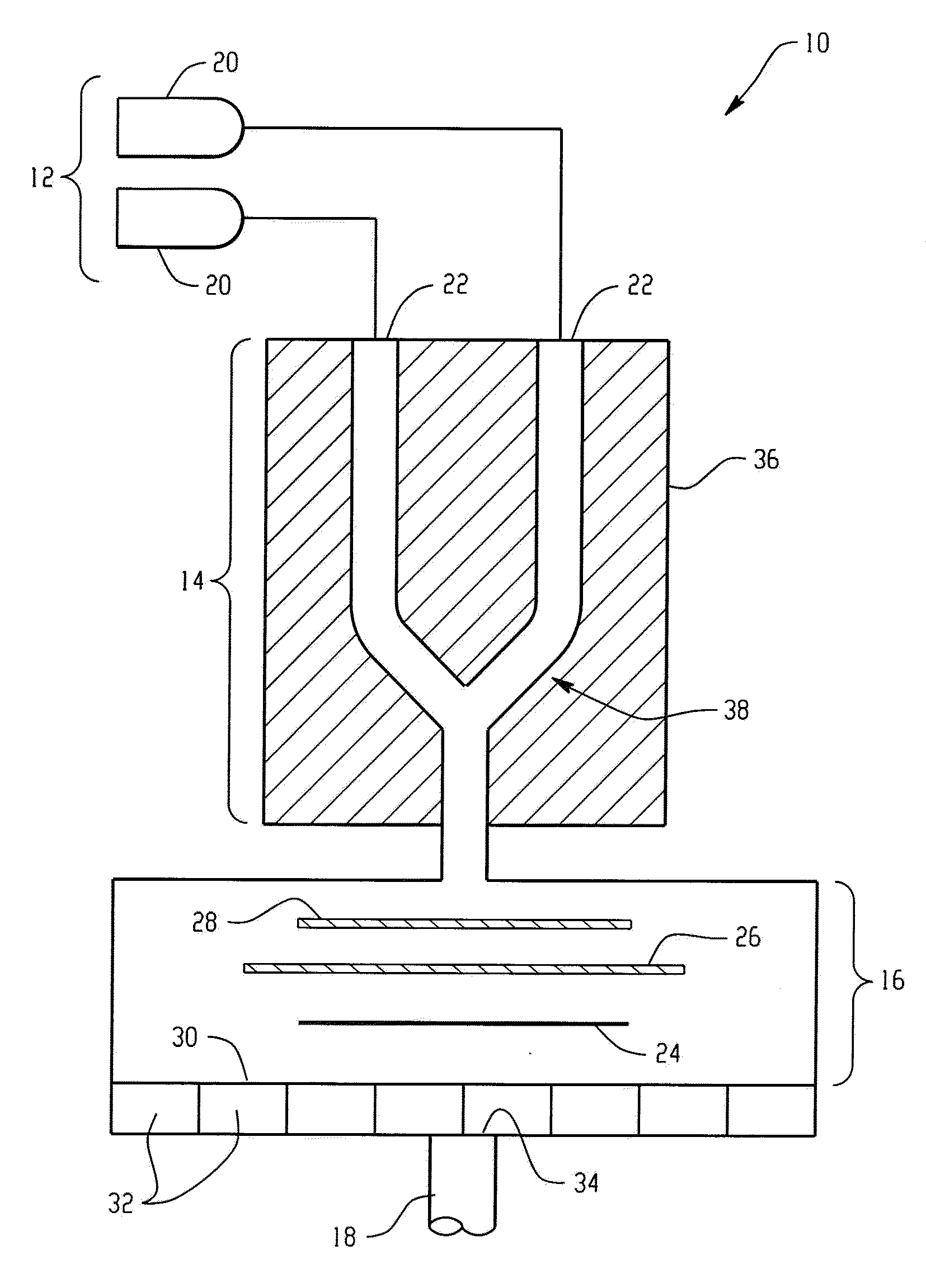

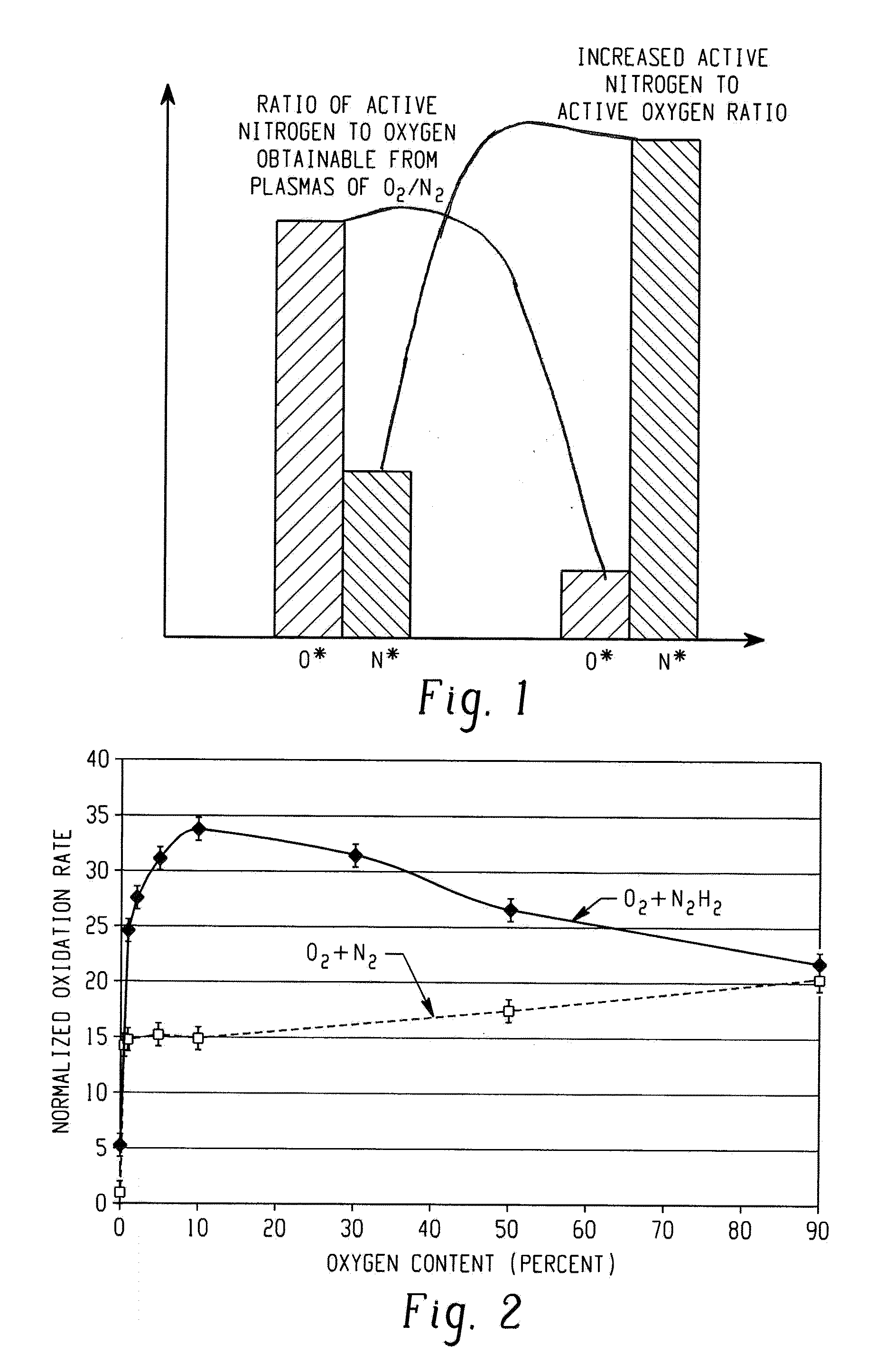

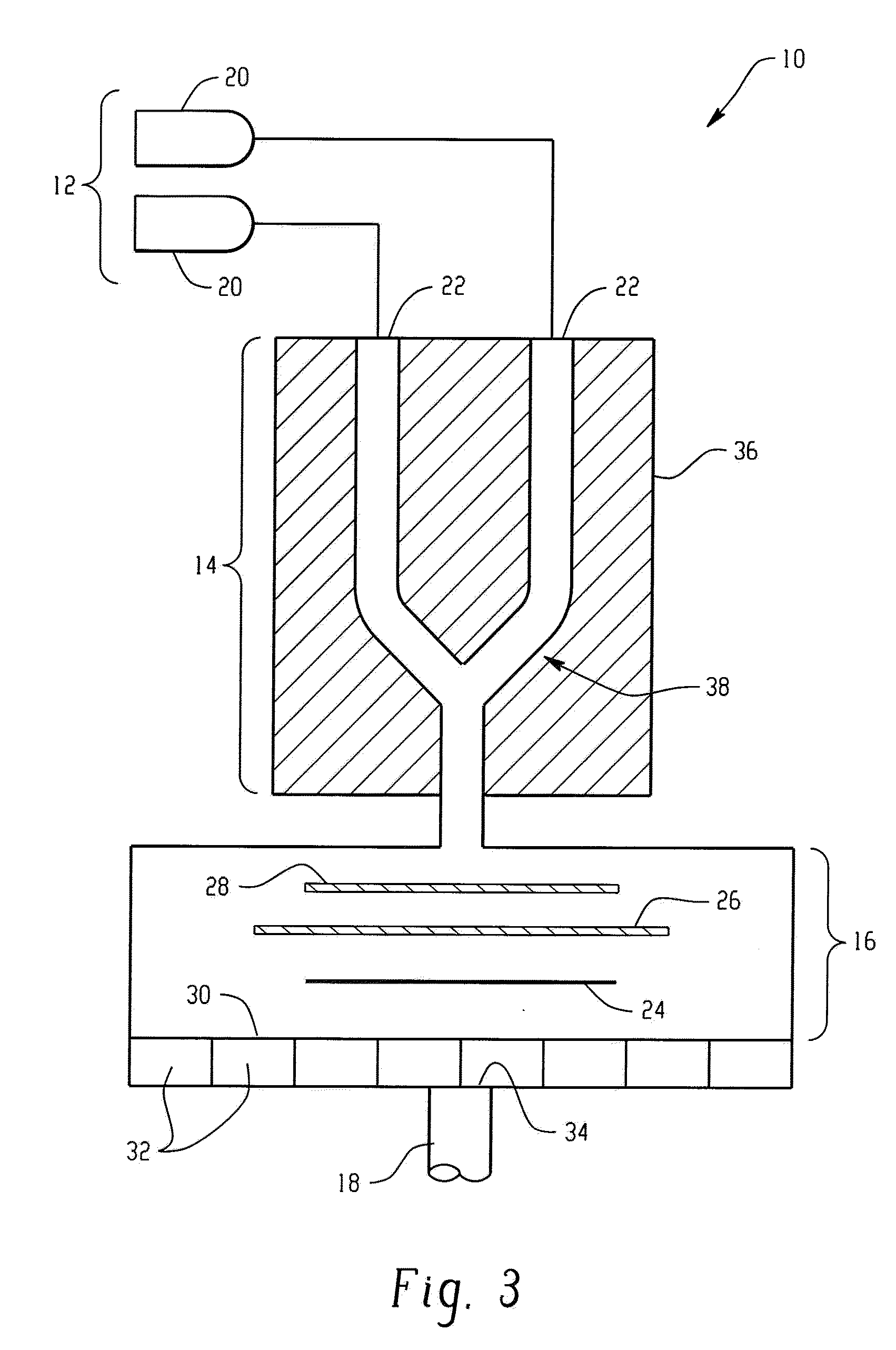

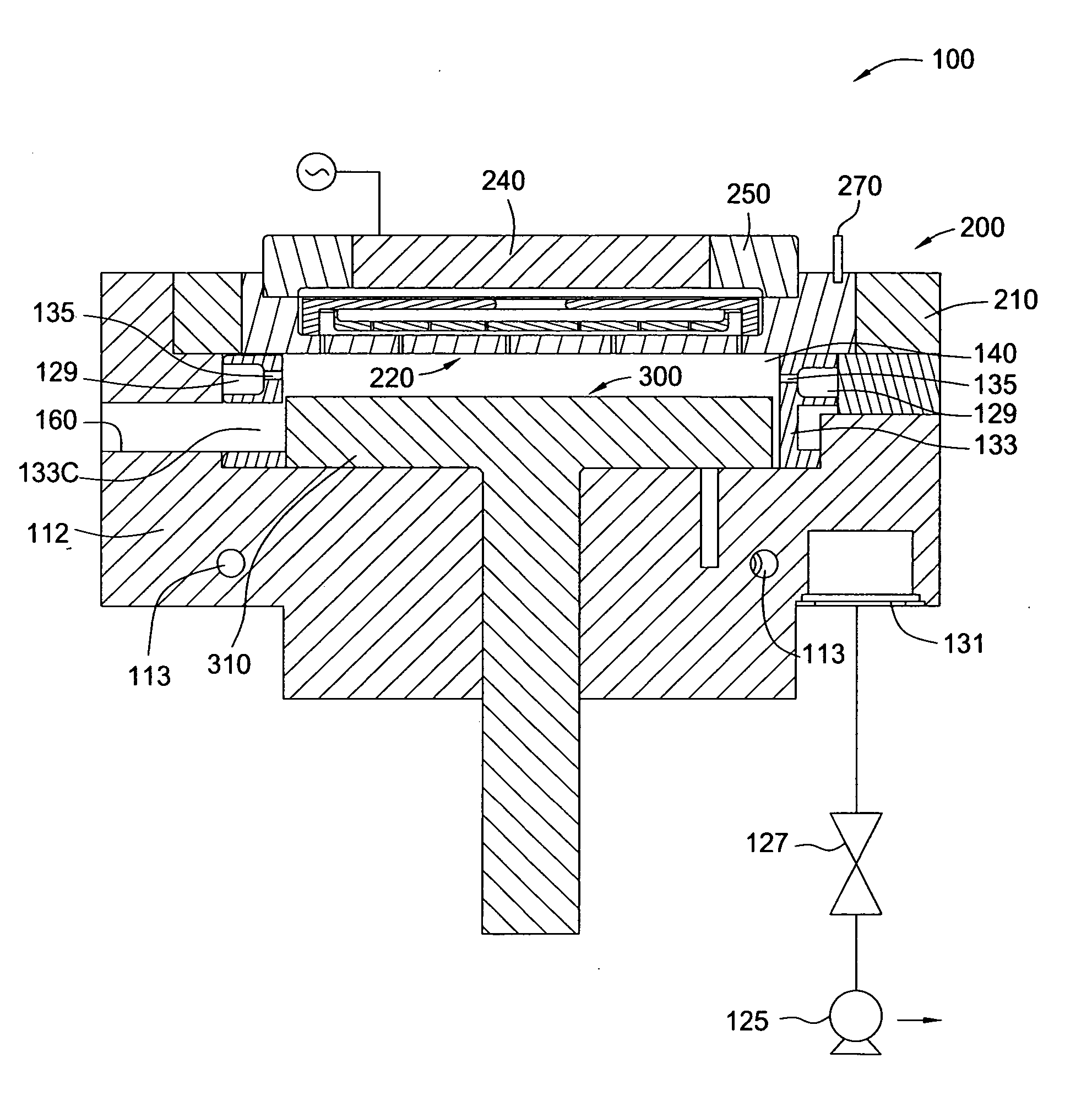

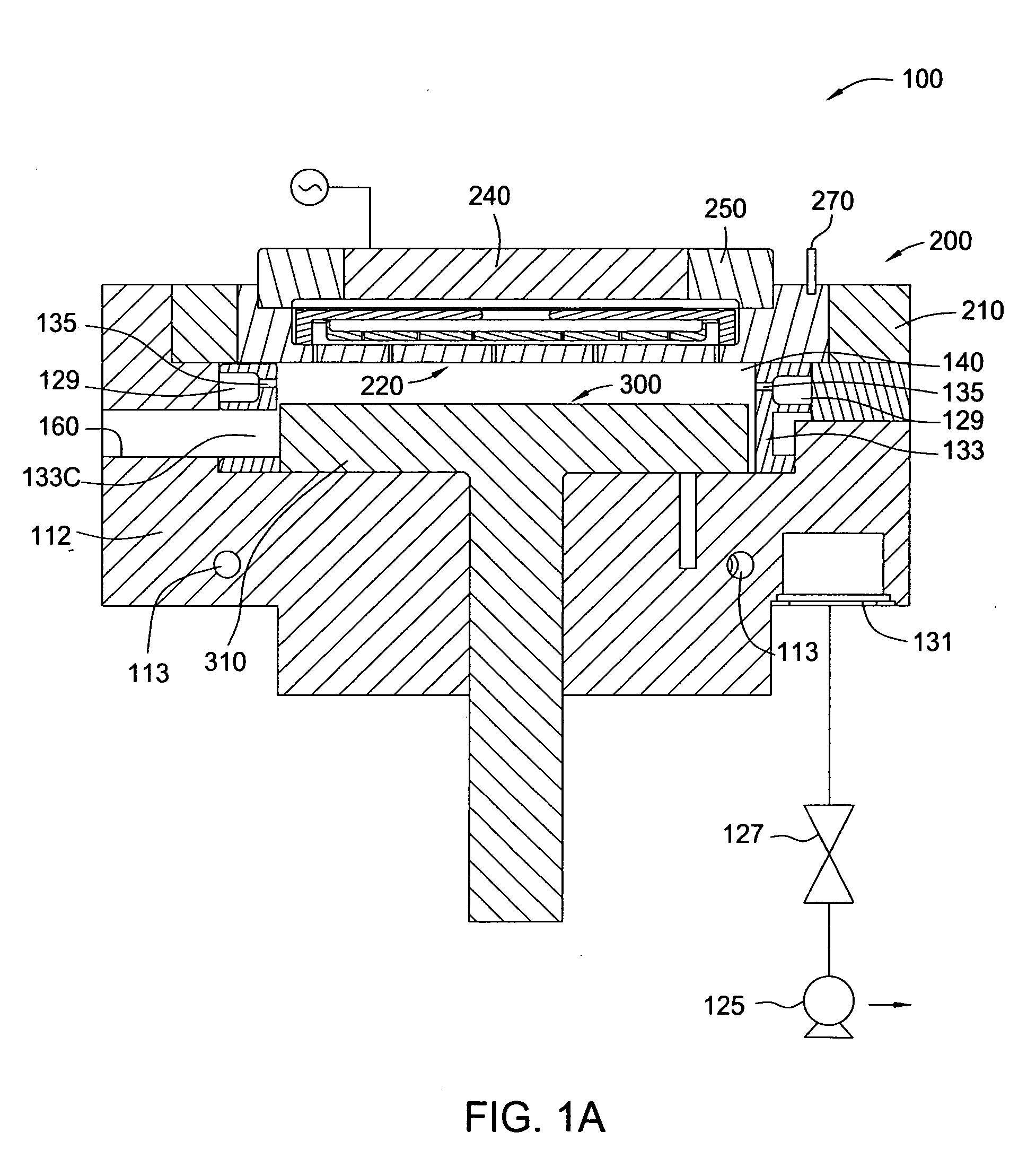

Front end of line plasma mediated ashing processes and apparatus

InactiveUS20100130017A1Increased formationElectric discharge tubesSemiconductor/solid-state device manufacturingResistFront end of line

Front end of line (FEOL) plasma mediated ashing processes for removing organic material from a substrate generally includes exposing the substrate to the plasma to selectively remove photoresist, implanted photoresist, polymers and / or residues from the substrate, wherein the plasma contains a ratio of active nitrogen and active oxygen that is larger than a ratio of active nitrogen and active oxygen obtainable from plasmas of gas mixtures comprising oxygen gas and nitrogen gas. The plasma exhibits high throughput while minimizing and / or preventing substrate oxidation and dopant bleaching. Plasma apparatuses are also described.

Owner:LAM RES CORP

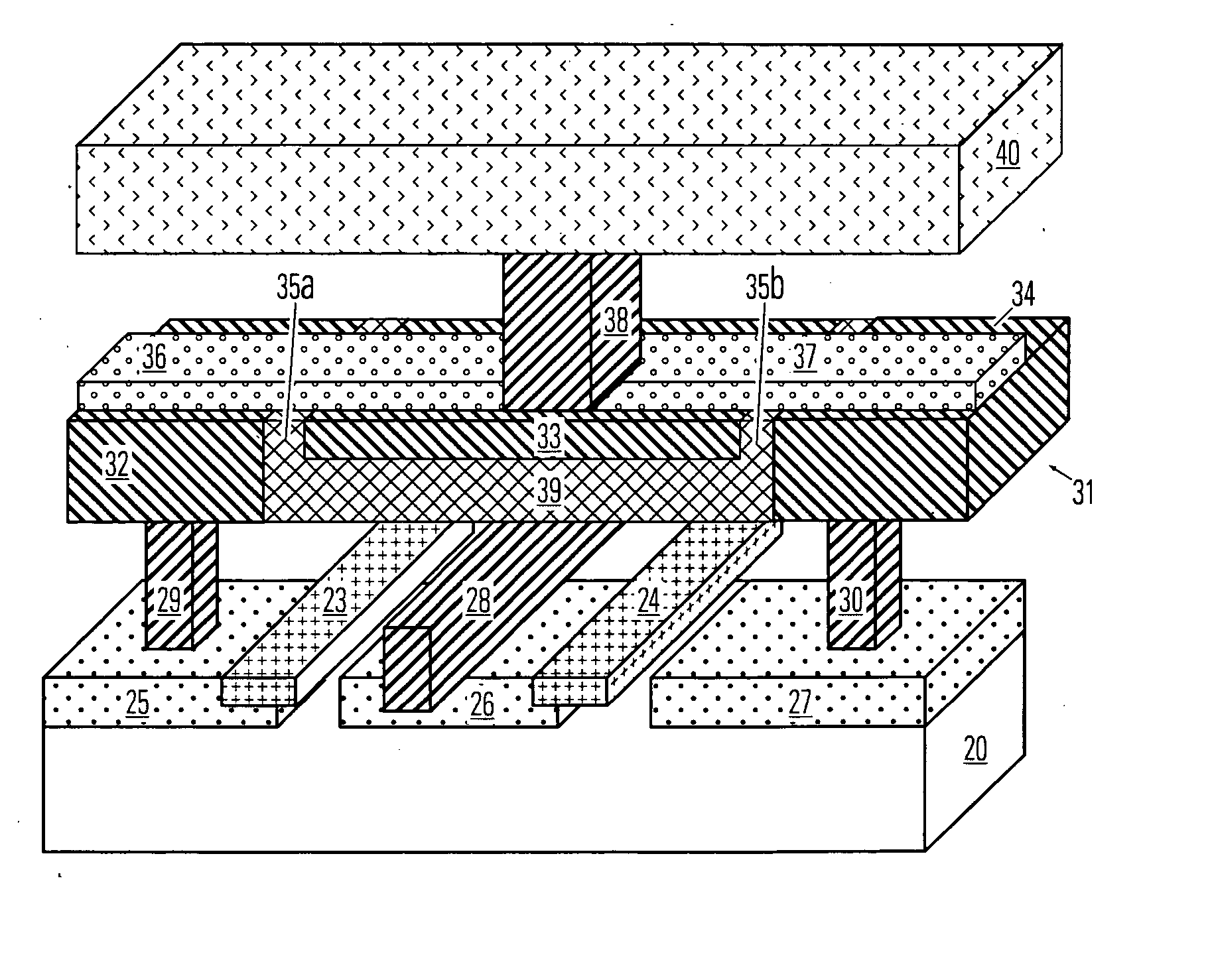

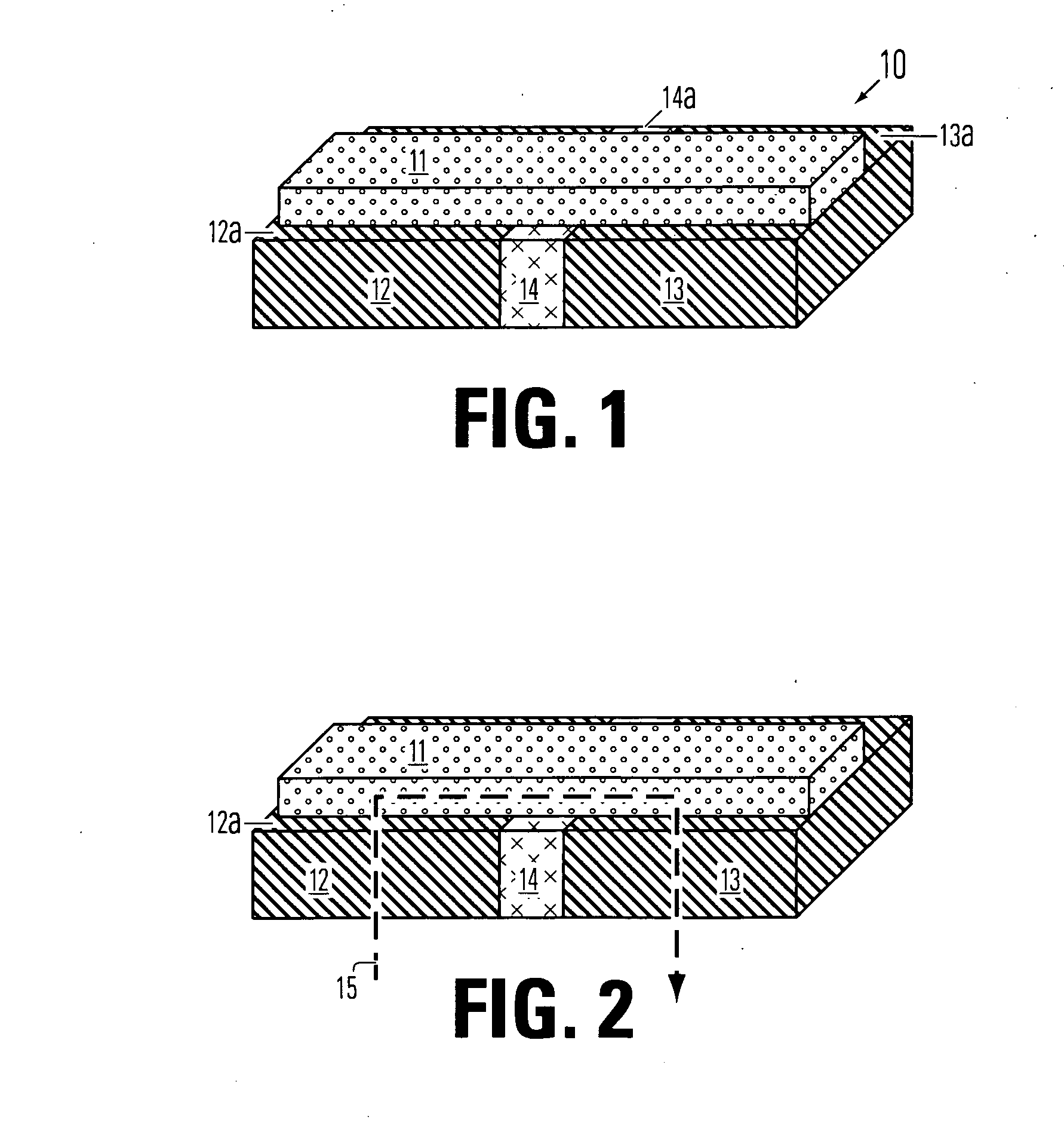

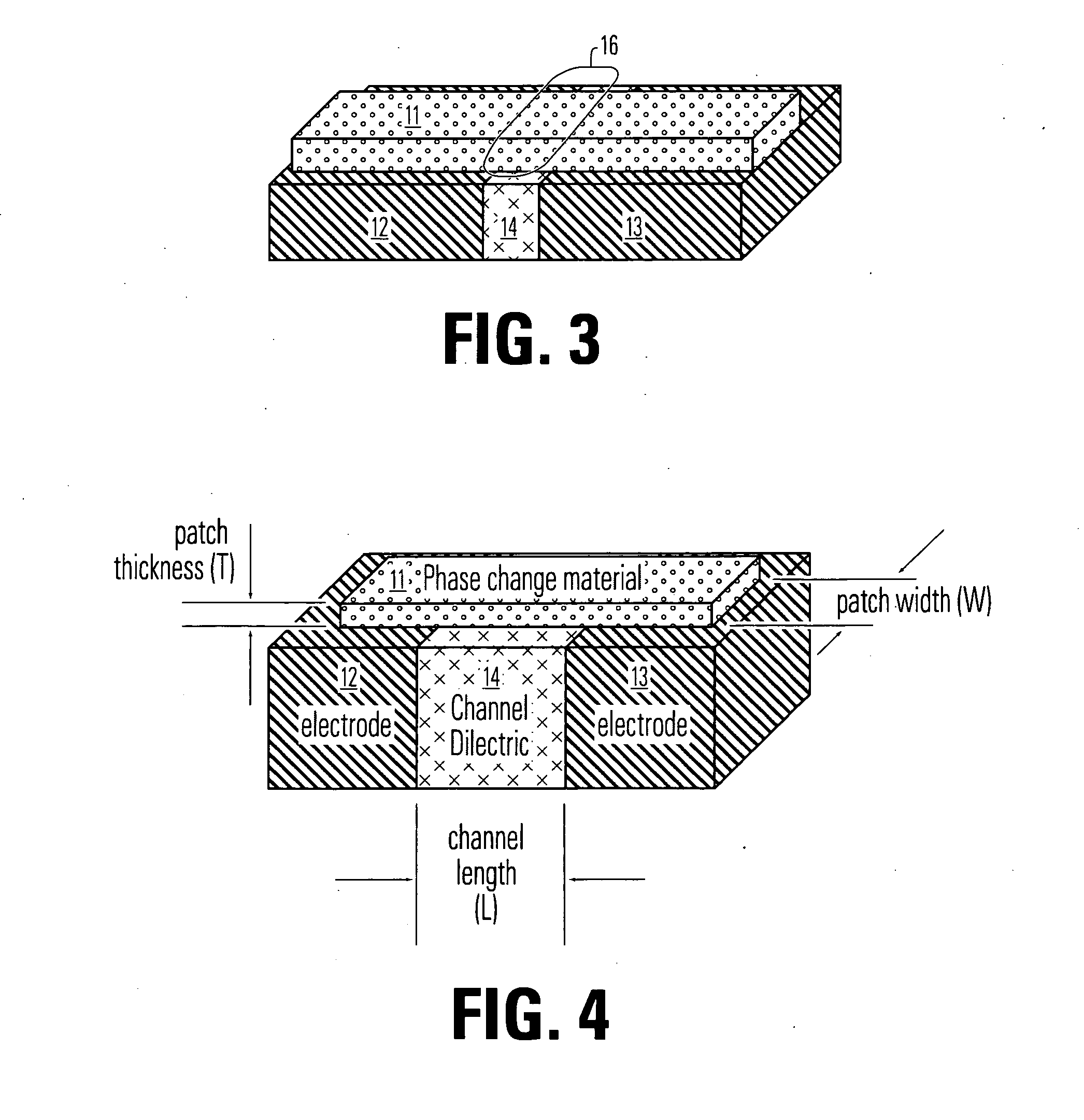

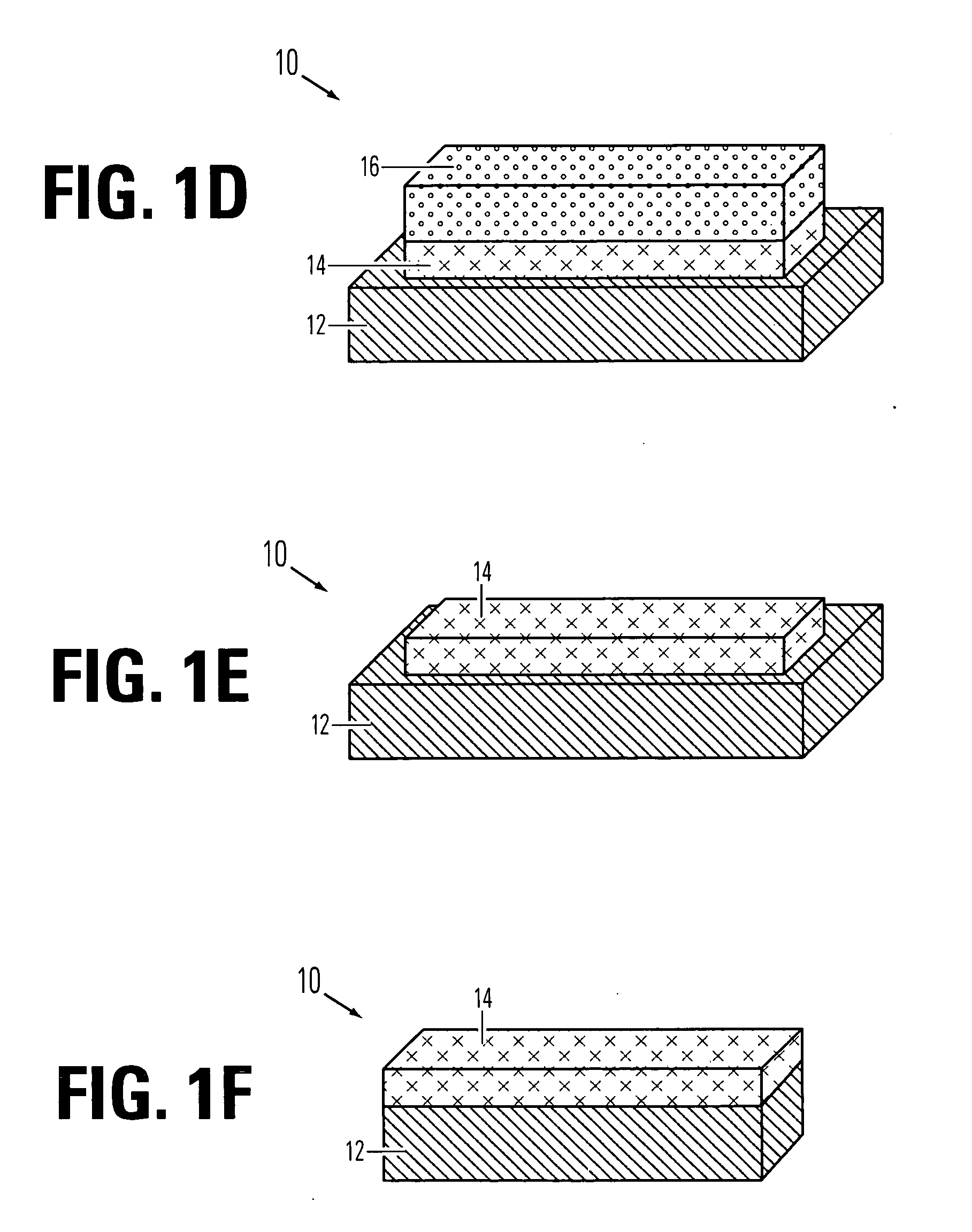

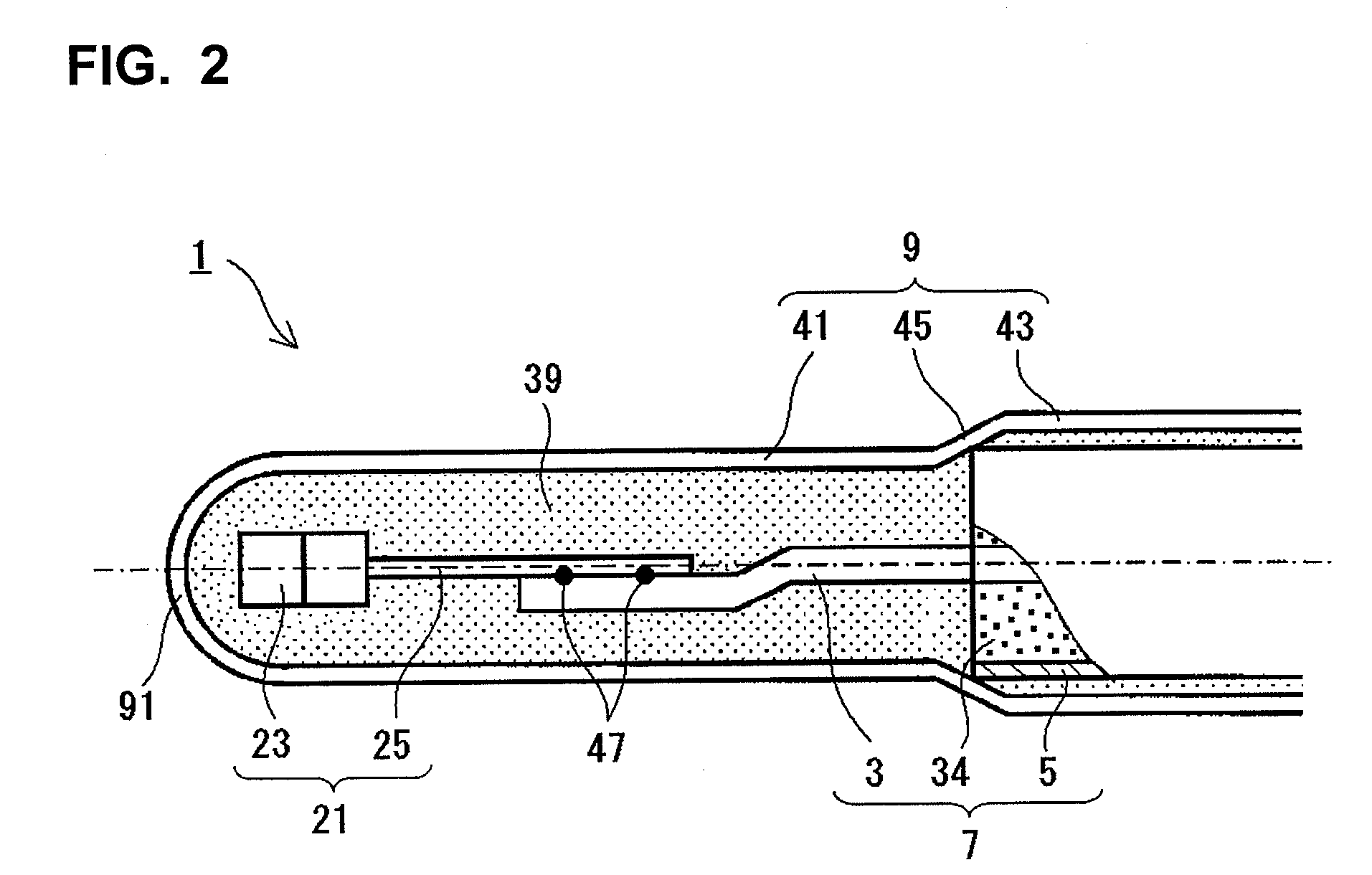

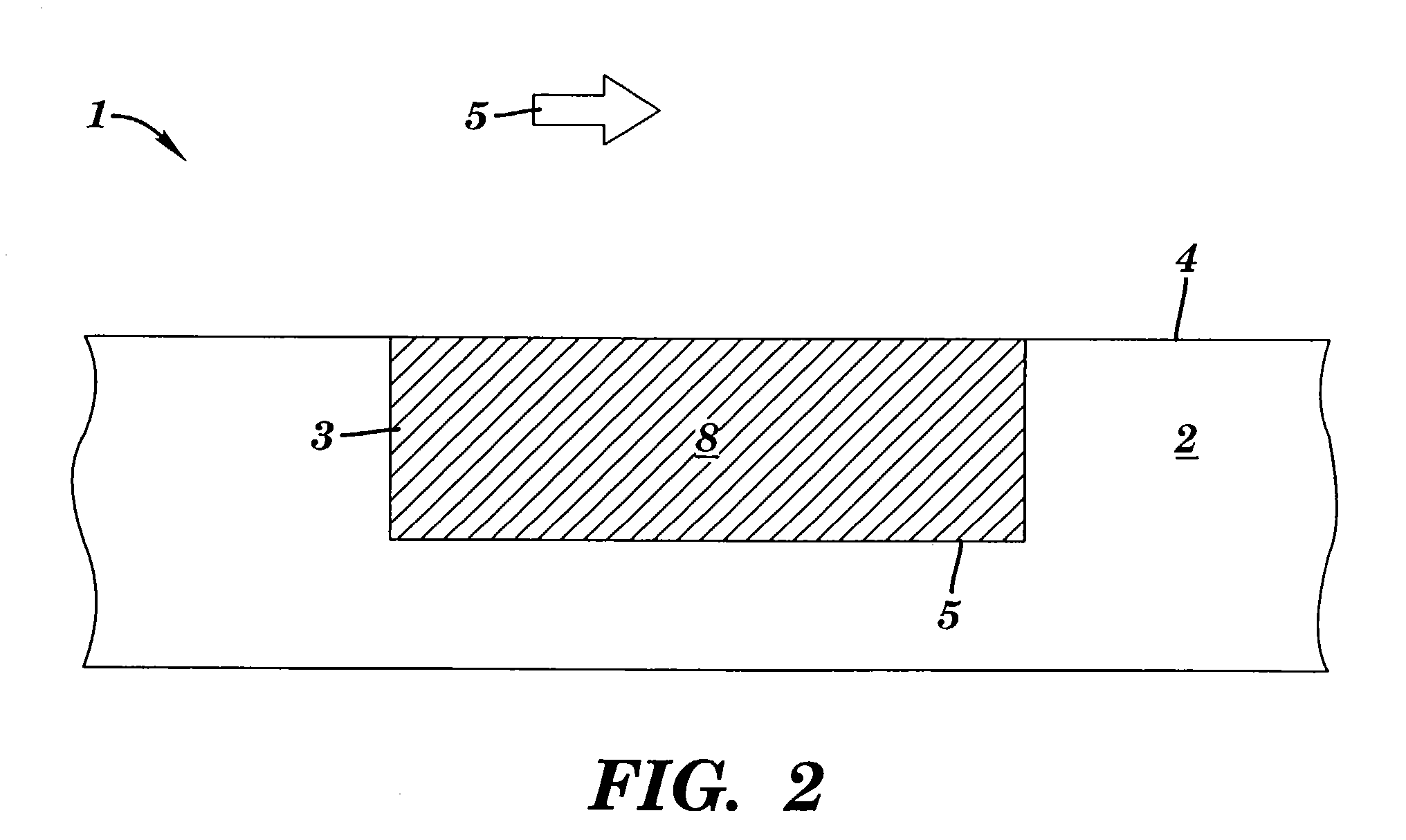

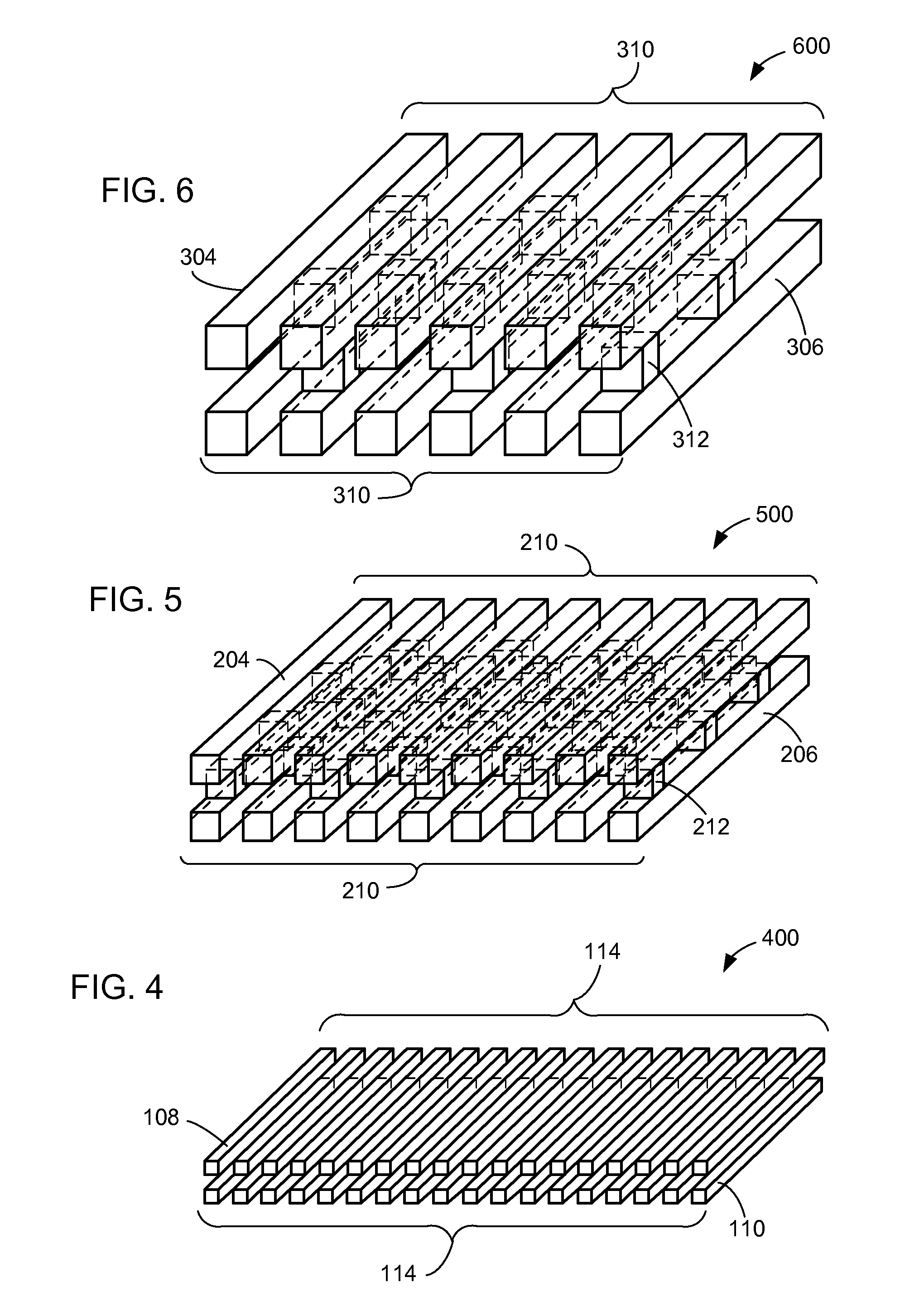

Manufacturing methods for thin film fuse phase change ram

InactiveUS20060286709A1Simple structureReduce power consumptionSolid-state devicesSemiconductor/solid-state device manufacturingPhase-change memoryOptoelectronics

A method for manufacturing a memory device comprises forming an electrode layer on a substrate which comprises circuitry made using front-end-of-line procedures. The electrode layer includes a first electrode and a second electrode, and an insulating member between the first and second electrodes for each phase change memory cell to be formed. A bridge of memory material is formed on the top surface of the electrode layer across the insulating member for each memory cell to be formed. An access structure over the electrode layer is made by forming a patterned conductive layer over said bridge, and forming a contact between said first electrode and said patterned conductive layer.

Owner:MACRONIX INT CO LTD

Substrate support for in-situ dry clean chamber for front end of line fabrication

InactiveUS20050221552A1Electric discharge tubesSemiconductor/solid-state device detailsFront end of lineBiomedical engineering

Owner:APPLIED MATERIALS INC

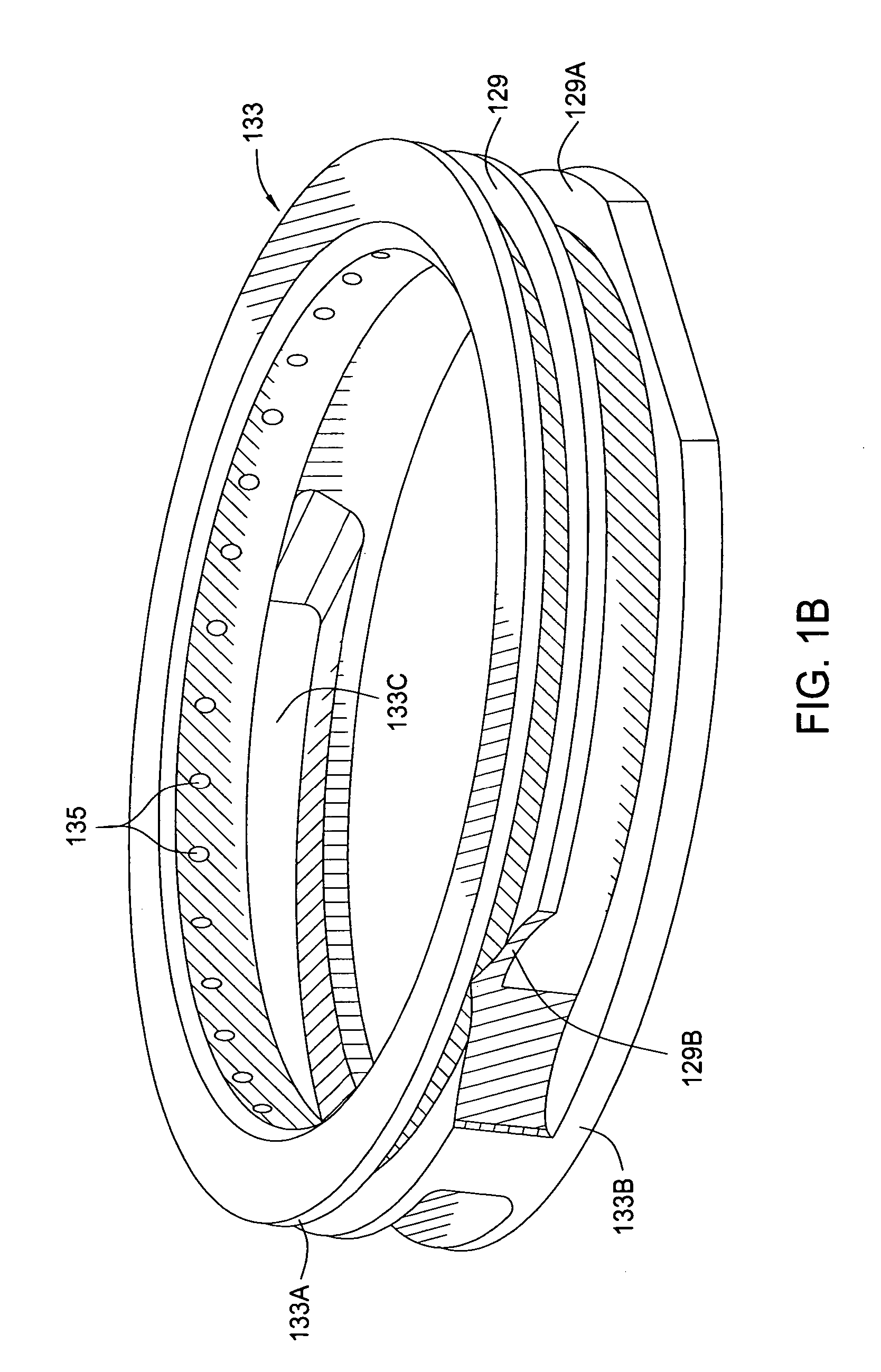

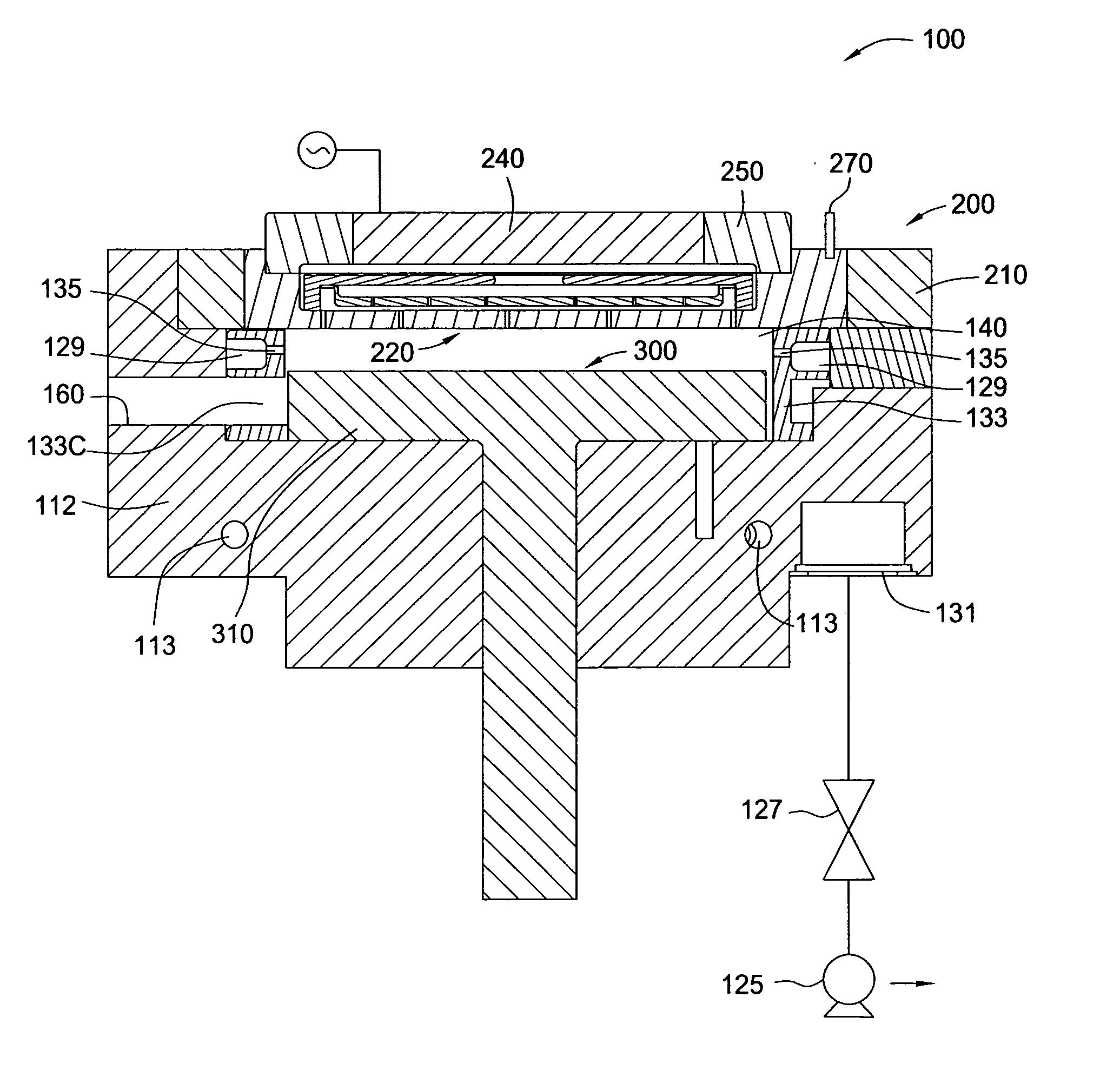

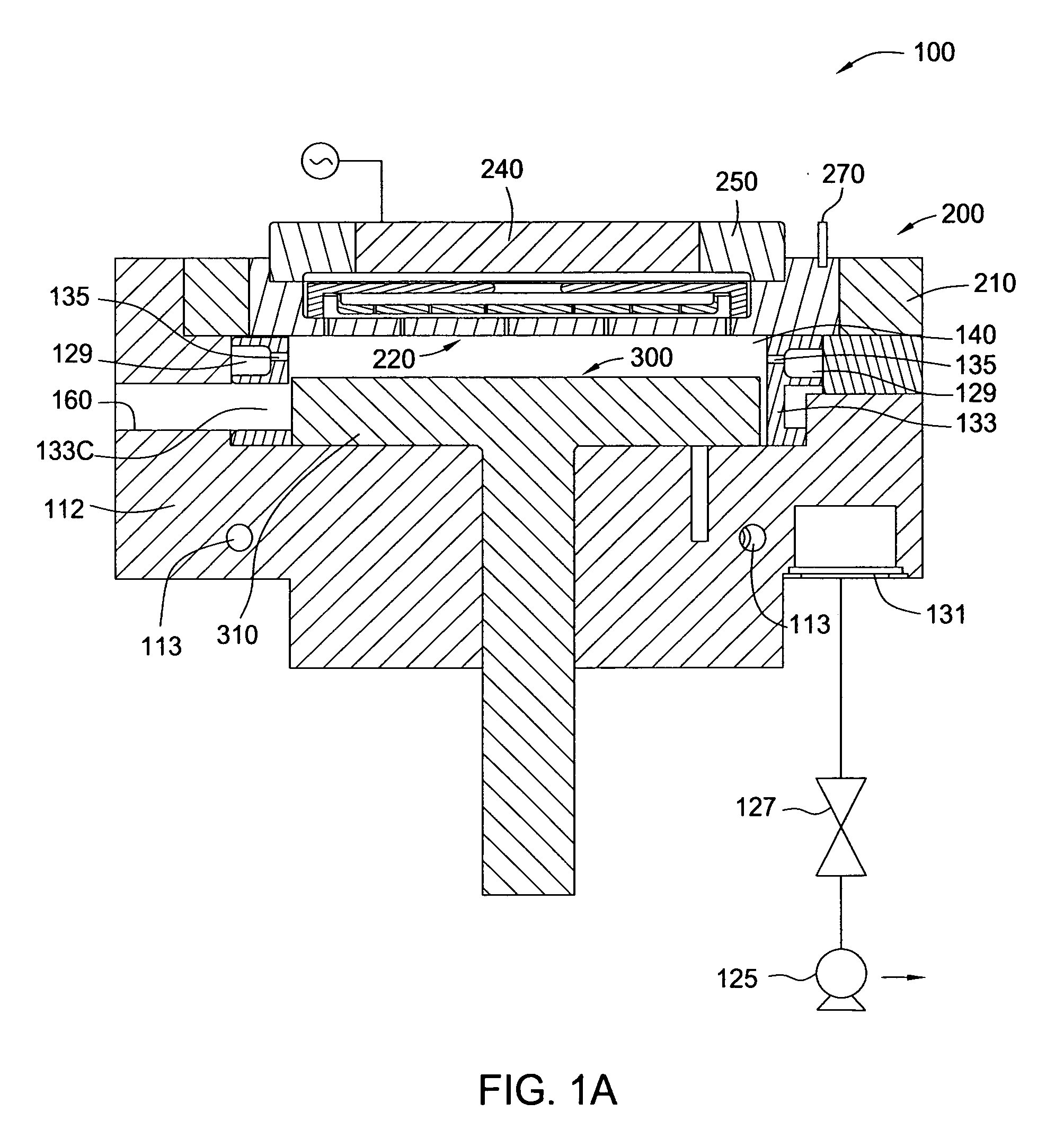

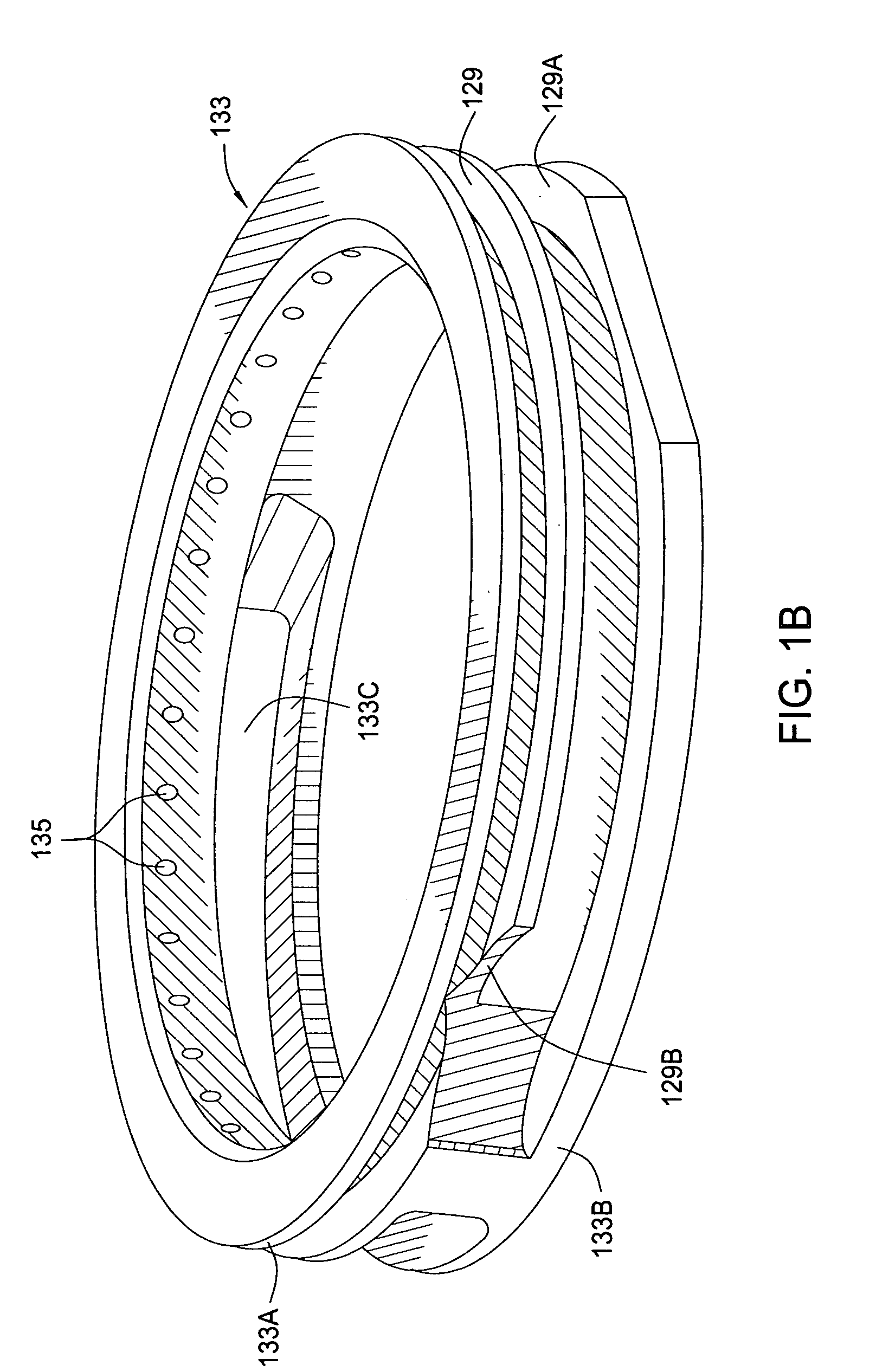

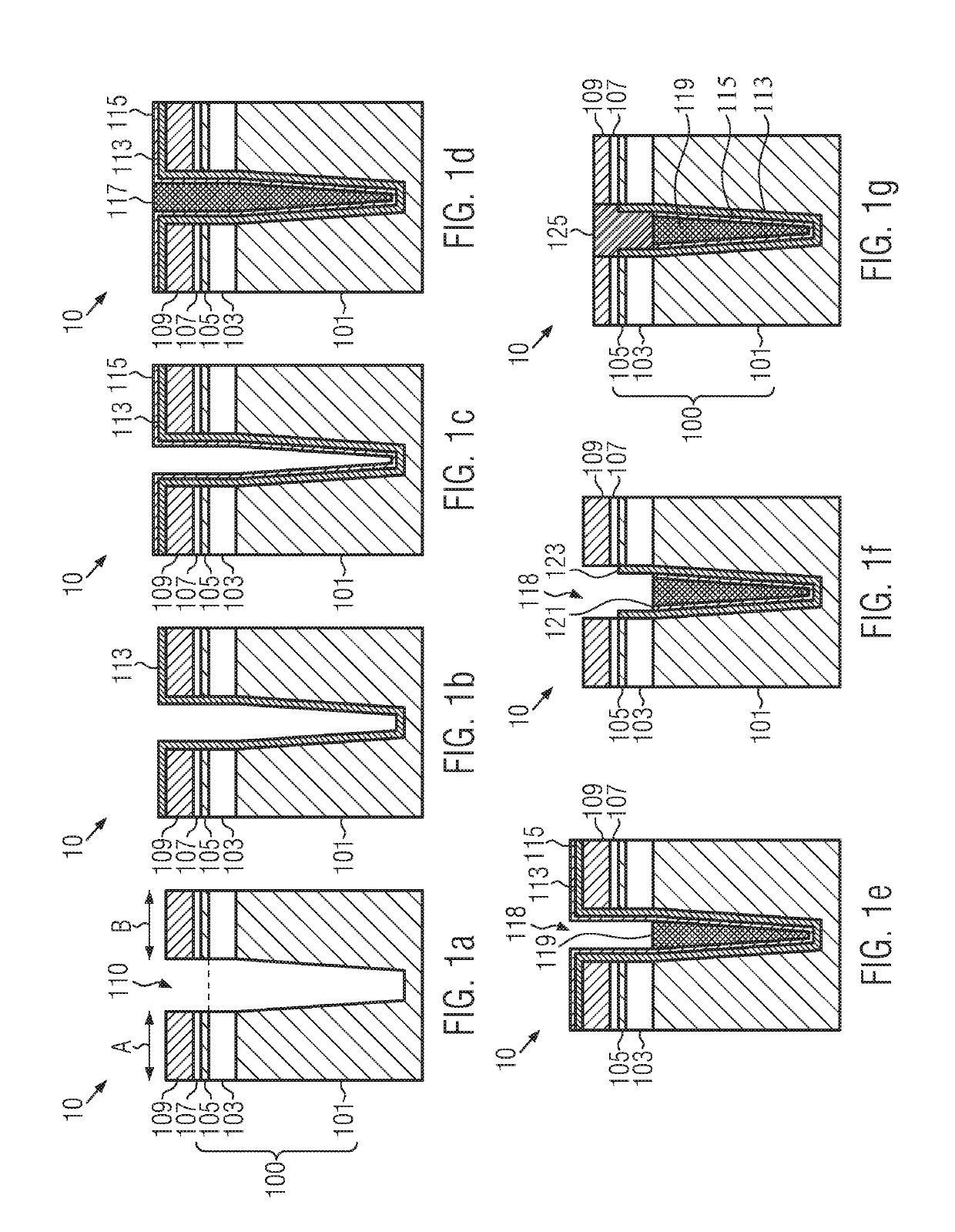

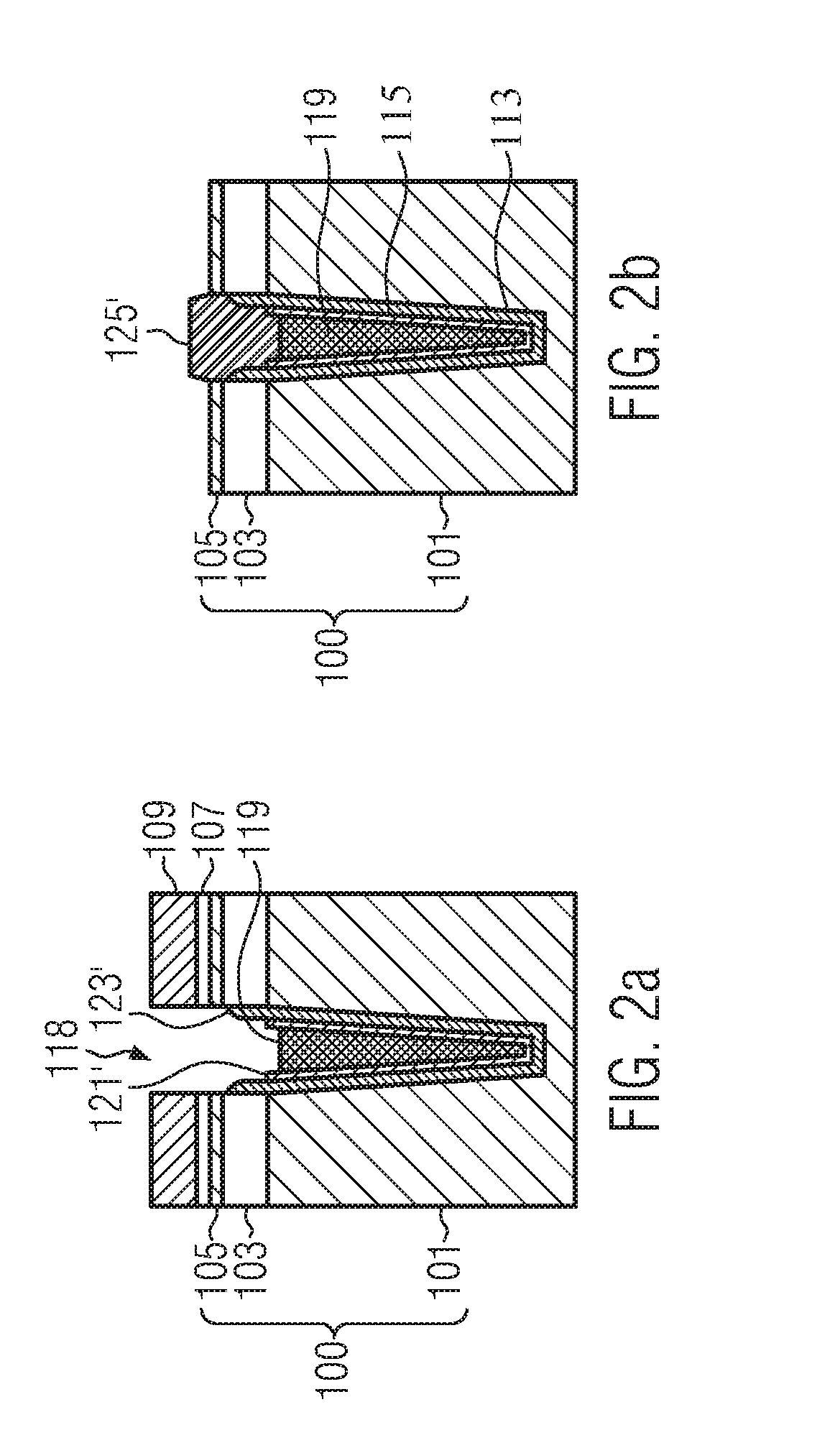

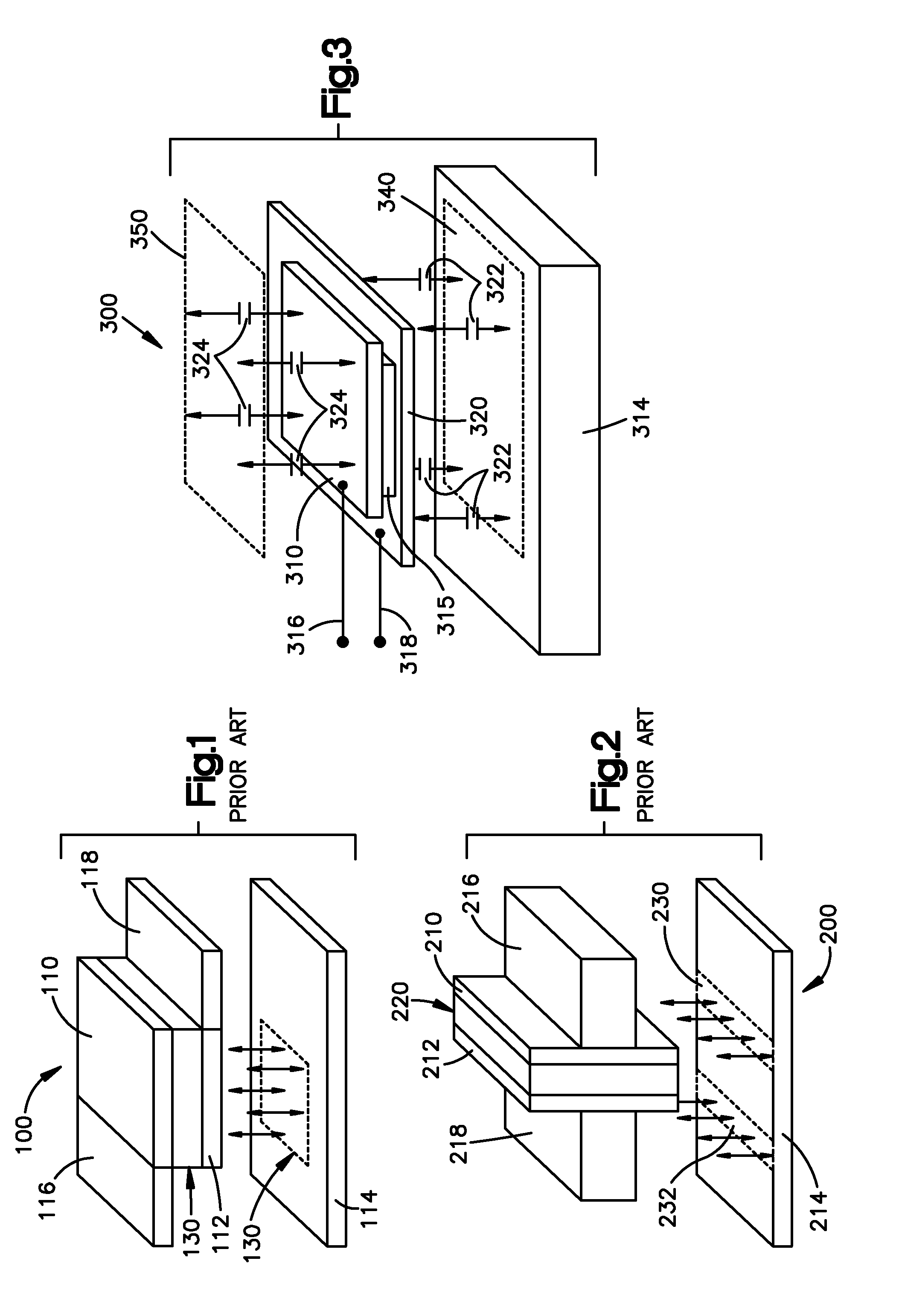

Lid assembly for front end of line fabrication

ActiveUS20050218507A1Electric discharge tubesSemiconductor/solid-state device detailsProduction lineFront end of line

A lid assembly for semiconductor processing is provided. In at least one embodiment, the lid assembly includes a first electrode comprising an expanding section that has a gradually increasing inner diameter. The lid assembly also includes a second electrode disposed opposite the first electrode. A plasma cavity is defined between the inner diameter of the expanding section of the first electrode and a first surface of the second electrode.

Owner:APPLIED MATERIALS INC

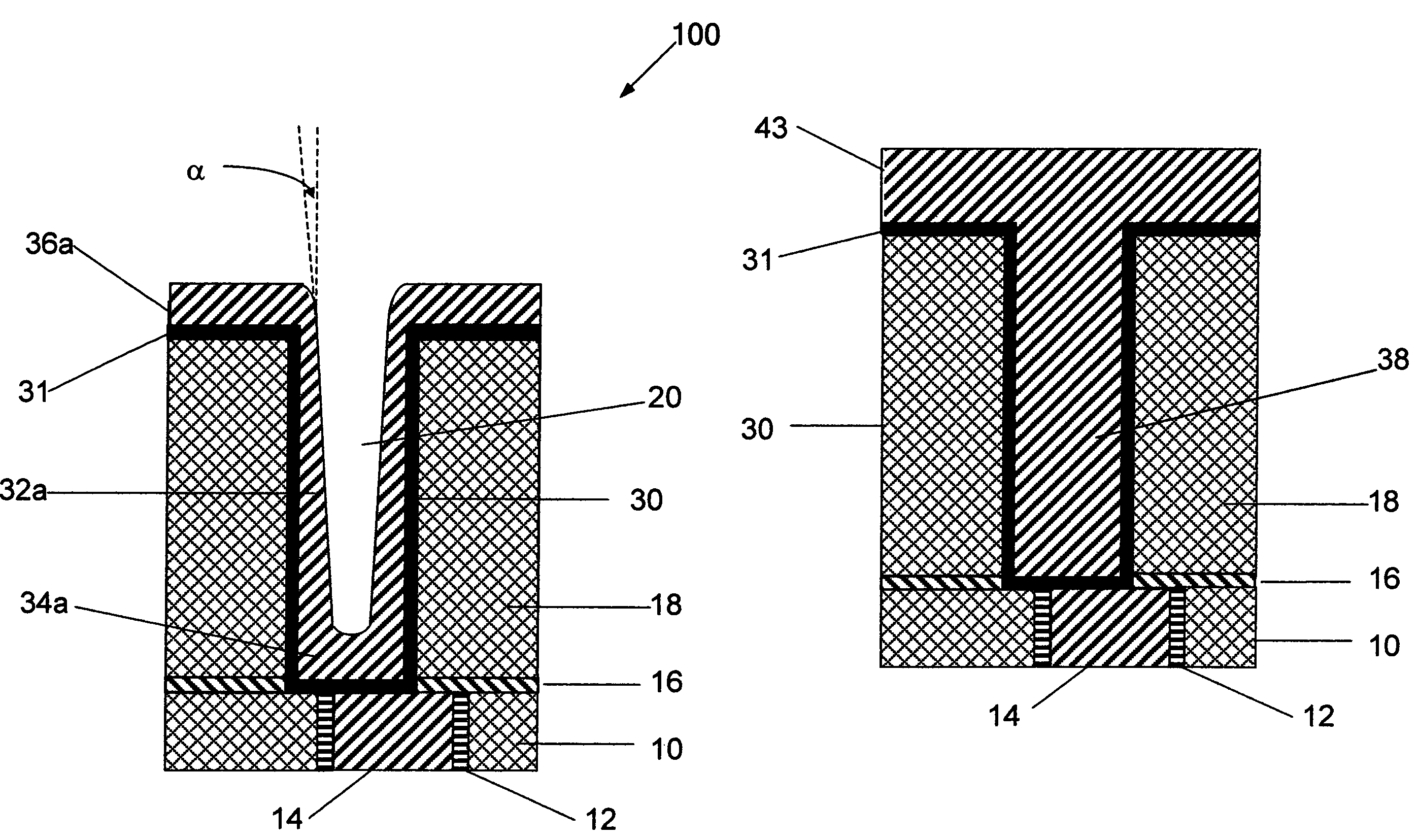

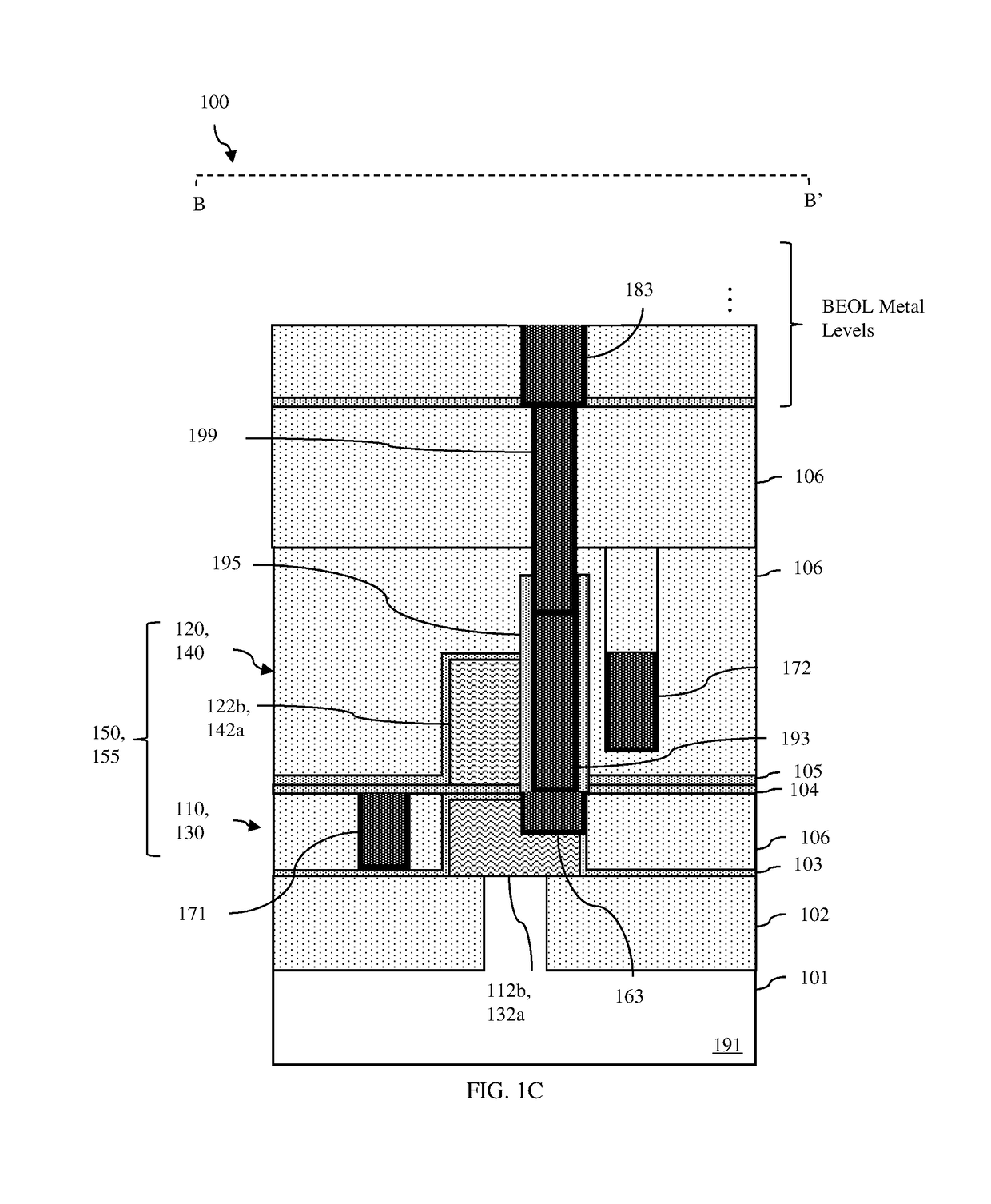

Front-end-of-line device structure and method of forming such a front-end-of-line device structure

ActiveUS10483154B1Well formedSemiconductor/solid-state device manufacturingSemiconductor devicesFilling materialsFront end of line

In various aspects, the present disclosure relates to device structures and a method of forming such a device structure. In some illustrative embodiments herein, a device is provided, including a semiconductor substrate having a first trench formed therein, and a first trench isolation structure formed in the first trench. The first trench isolation structure includes first and second insulating liners formed adjacent inner surfaces of the first trench, wherein the first insulating liner is in direct contact with inner surfaces of the first trench and the second insulating liner is formed directly on the first insulating liner, and a first insulating filling material which at least partially fills the first trench. In some aspects, a thickness of the first insulating liner is greater than a thickness of the second insulating liner.

Owner:GLOBALFOUNDRIES US INC

Self-aligned manufacturing method, and manufacturing method for thin film fuse phase change ram

ActiveUS20070173063A1Semiconductor/solid-state device manufacturingDigital storagePhase-change memoryEngineering

A method for manufacturing a self aligned narrow structure over a wider structure based on mask trimming. A method for manufacturing a memory device comprises forming an electrode layer on a substrate which comprises circuitry made using front-end-of-line procedures. The electrode layer includes a first electrode and a second electrode, and an insulating member between the first and second electrodes for each phase change memory cell to be formed. A patch of memory material is formed on the top surface of the electrode layer across the insulating member for each memory cell to be formed. The patch and the first and second electrodes are formed using a self-aligned process based on mask trimming.

Owner:MACRONIX INT CO LTD

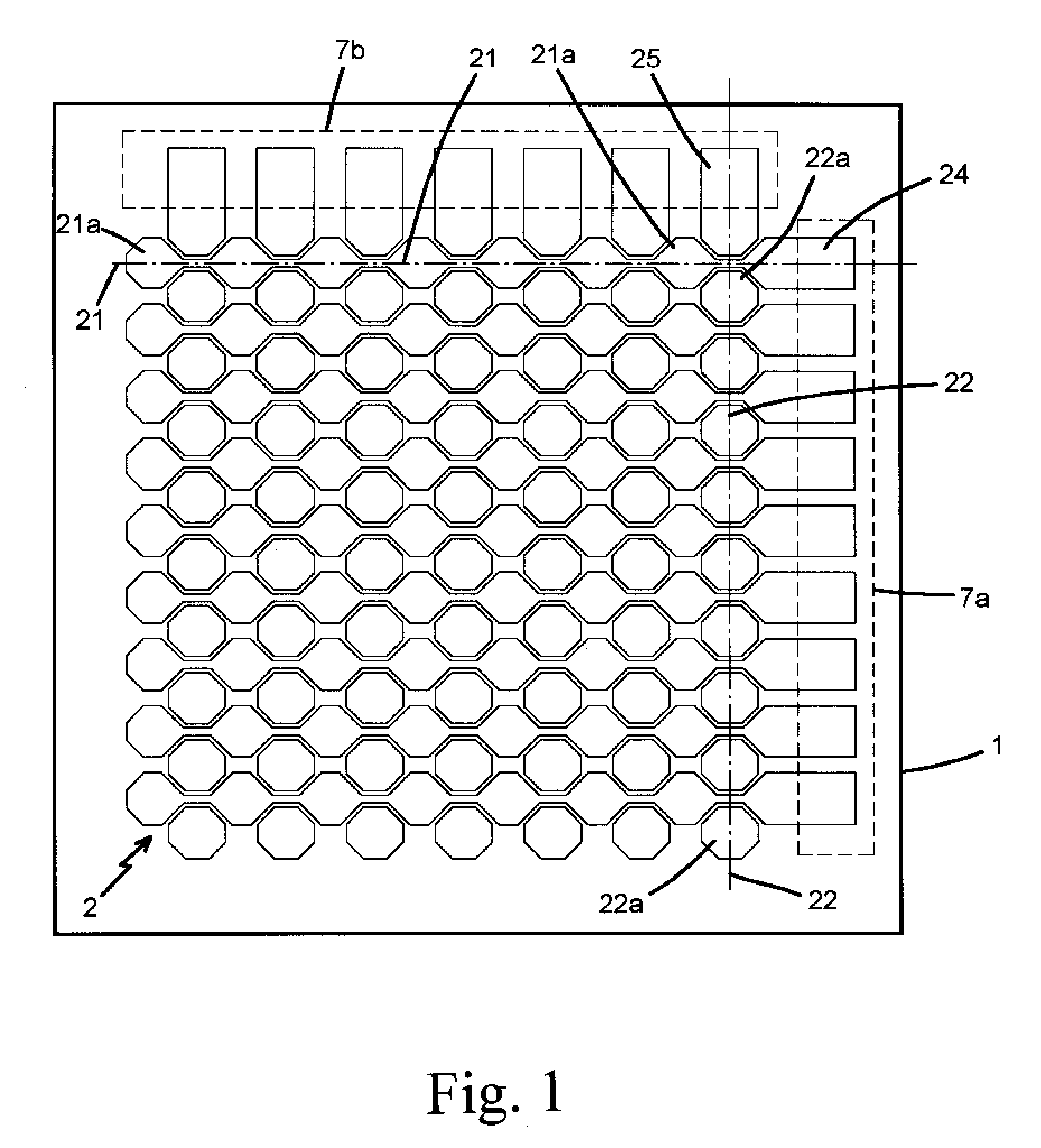

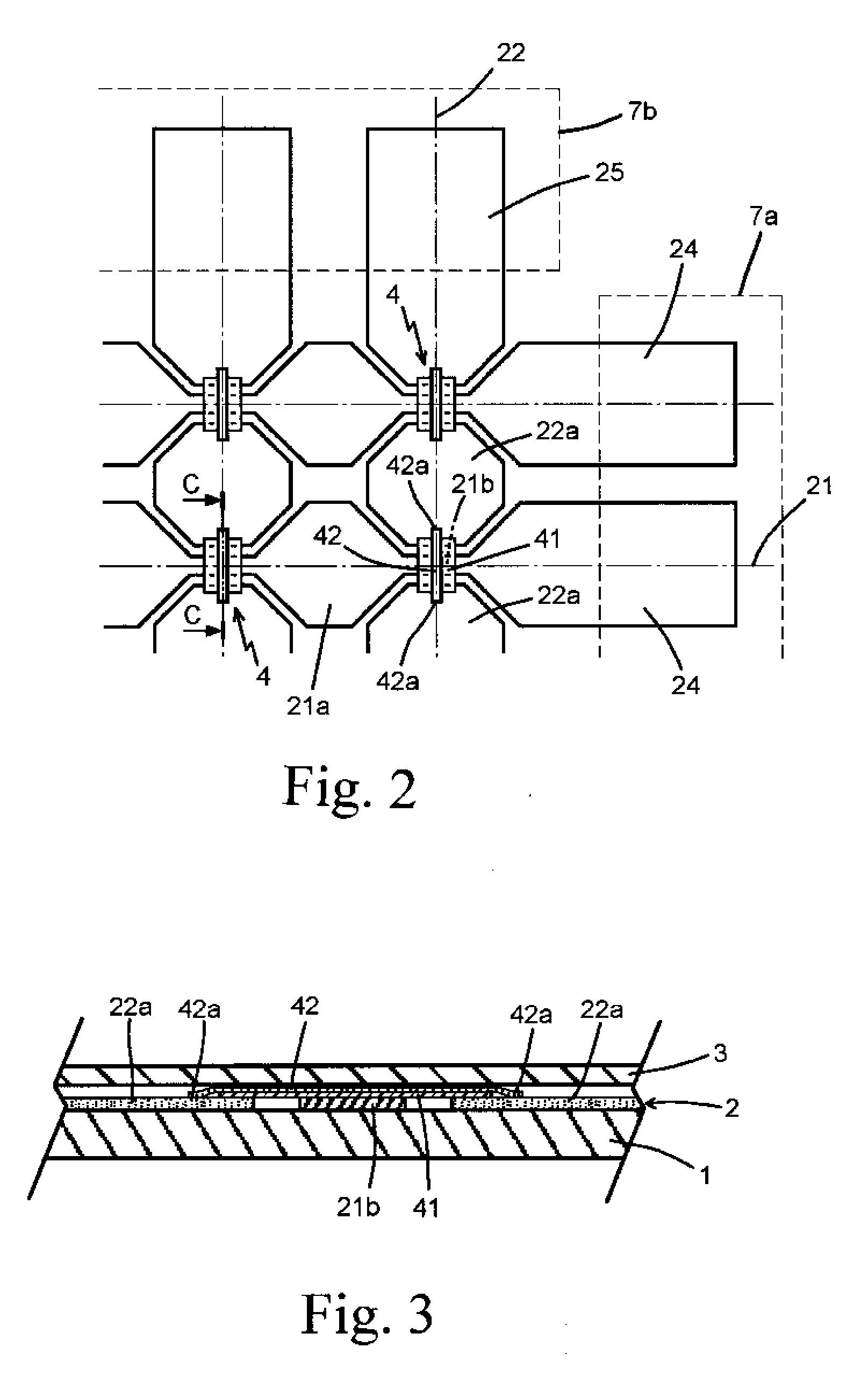

Capacitive touch panel

InactiveUS20090309850A1Improve sensitivity and precisionInput/output processes for data processingSurface layerFront end of line

A capacitive touch panel is assembled by a substrate layer, sensing layer, and surface layer. A plurality of transparent X and Y axis traces are arranged on the sensing layer and intersect each other as a matrix. A front end of each X trace and each Y trace has a joint. The plurality of X axis traces and Y axis traces are arranged at the same plane. Each X axis trace includes a plurality of induction-spots and each Y axis trace includes a plurality of induction-spots. The induction-spots of one X axis trace are connected one by one, while the induction-spots of one Y axis trace are formed separately with gaps. The adjacent induction-spots of Y axis trace are connected by a bridge structure and the induction-spots of the Y axis trace are insulated to the respective one of the plurality of X axis trace.

Owner:YOUNG FAST OPTOELECTRONICS

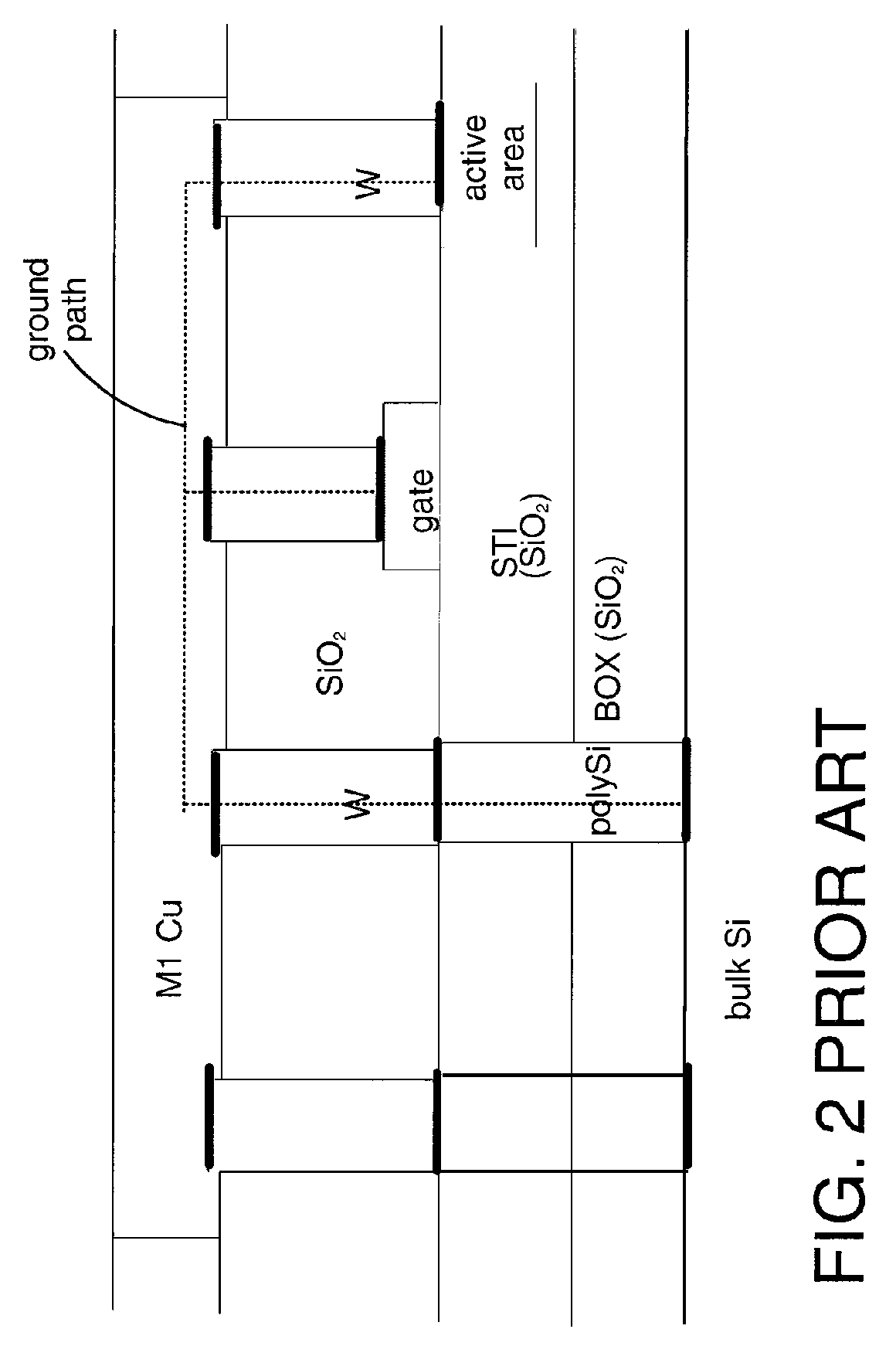

Grounding front-end-of-line structures on a SOI substrate

ActiveUS7518190B2Semiconductor/solid-state device detailsSolid-state devicesGround contactGate stack

Owner:TAIWAN SEMICON MFG CO LTD

Premetal dielectric integration process

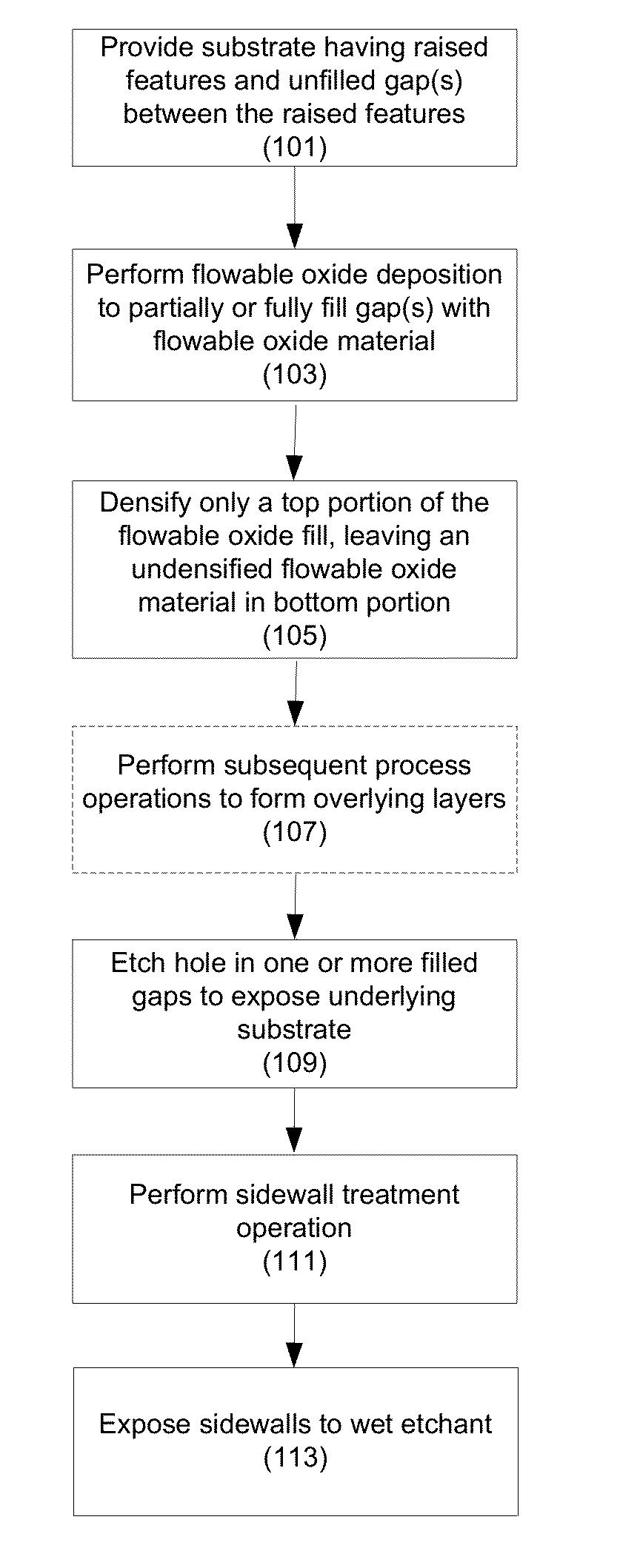

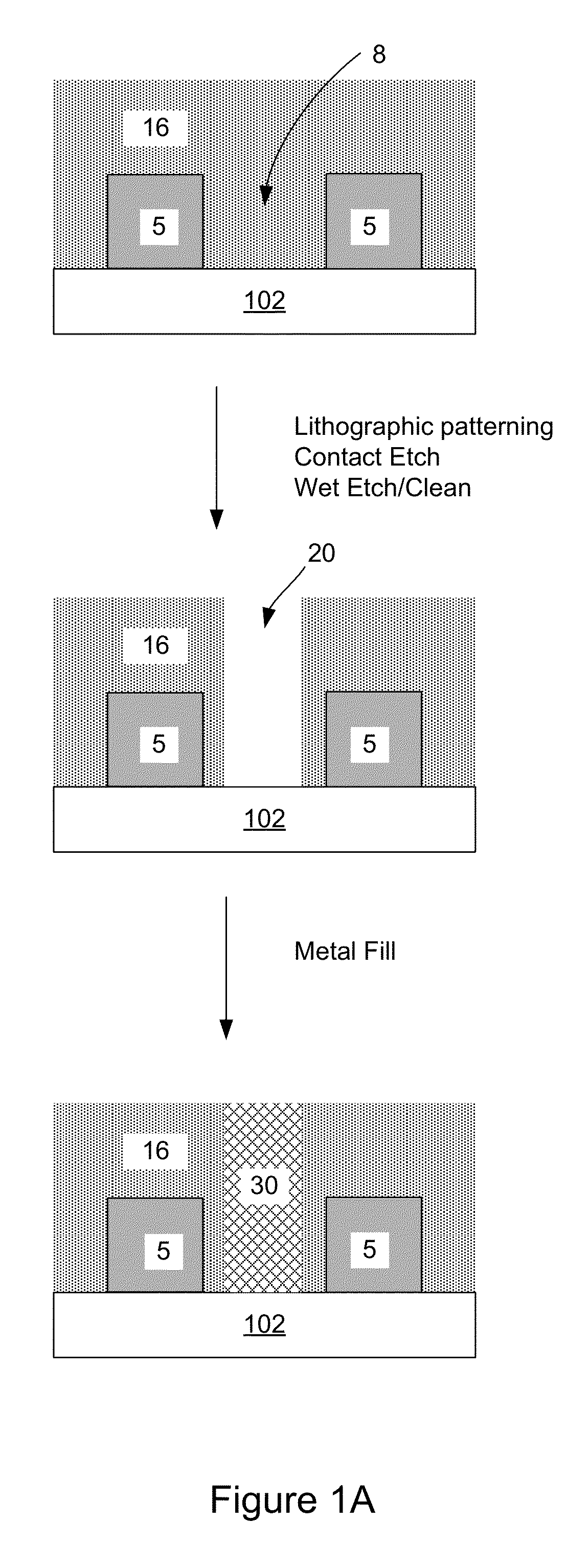

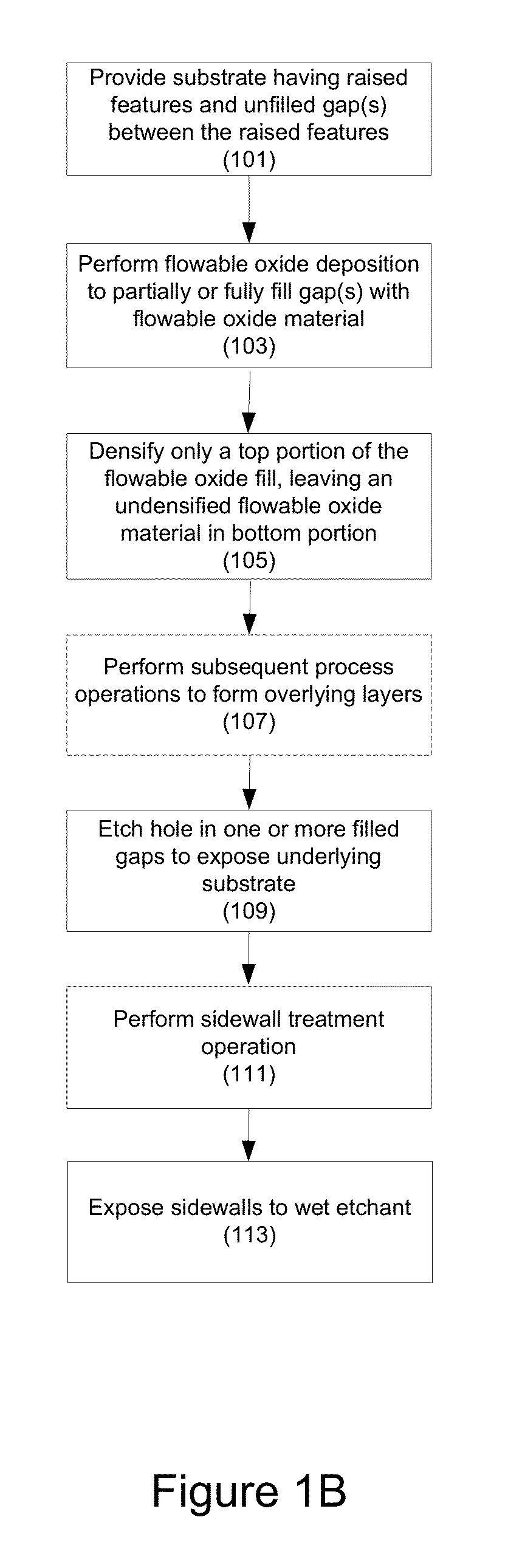

Provided herein are novel pre-metal dielectric (PMD) integration schemes. According to various embodiments, the methods involve depositing flowable dielectric material to fill trenches or other gaps between gate structures in a front end of line (FEOL) fabrication process. The flowable dielectric material may be partially densified to form dual density filled gaps having a low density region capped by a high density region. In certain embodiments, the methods include further treating at least a portion of the gap fill material after subsequent process operations such as chemical mechanical planarization (CMP) or contact etching.

Owner:NOVELLUS SYSTEMS

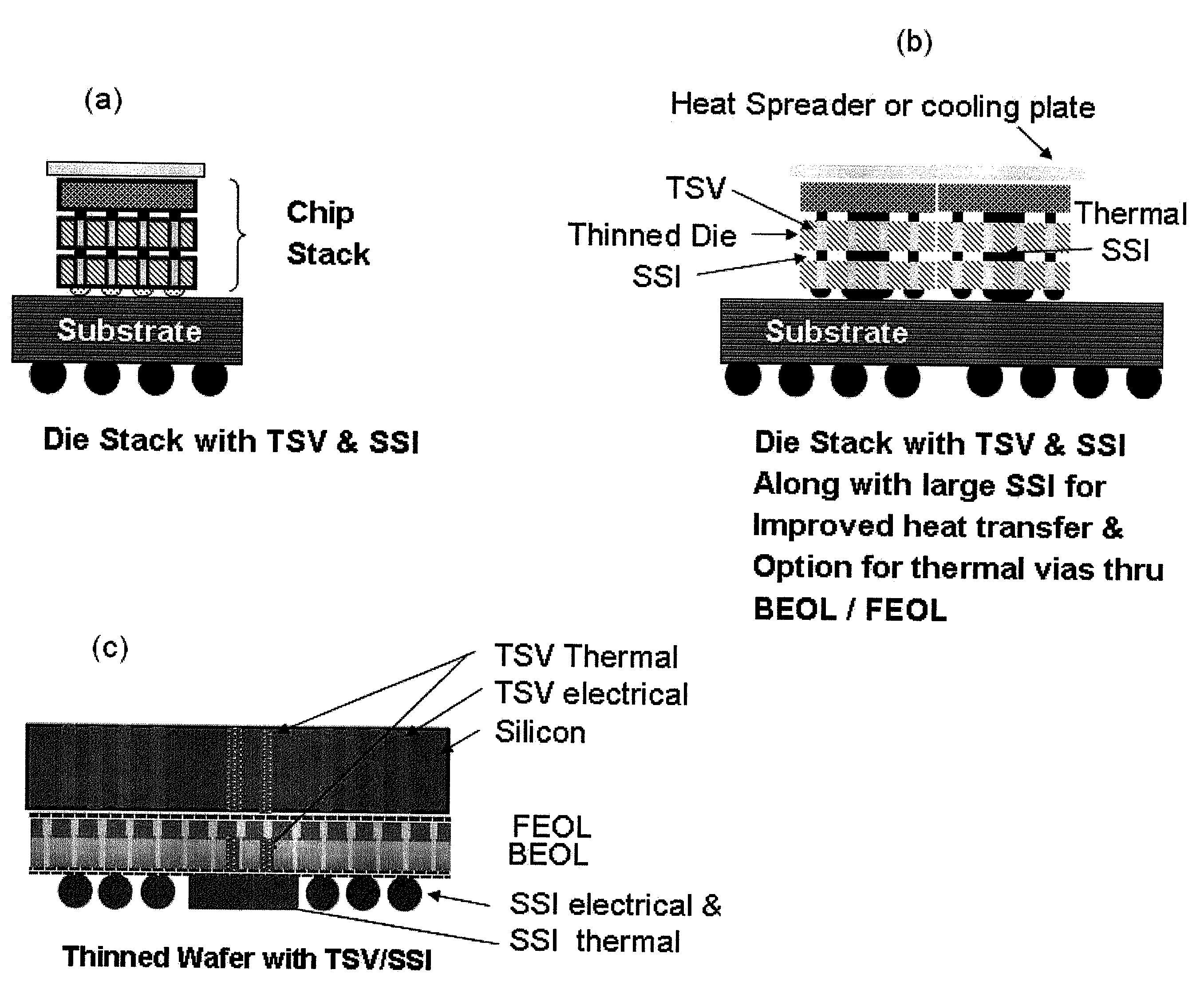

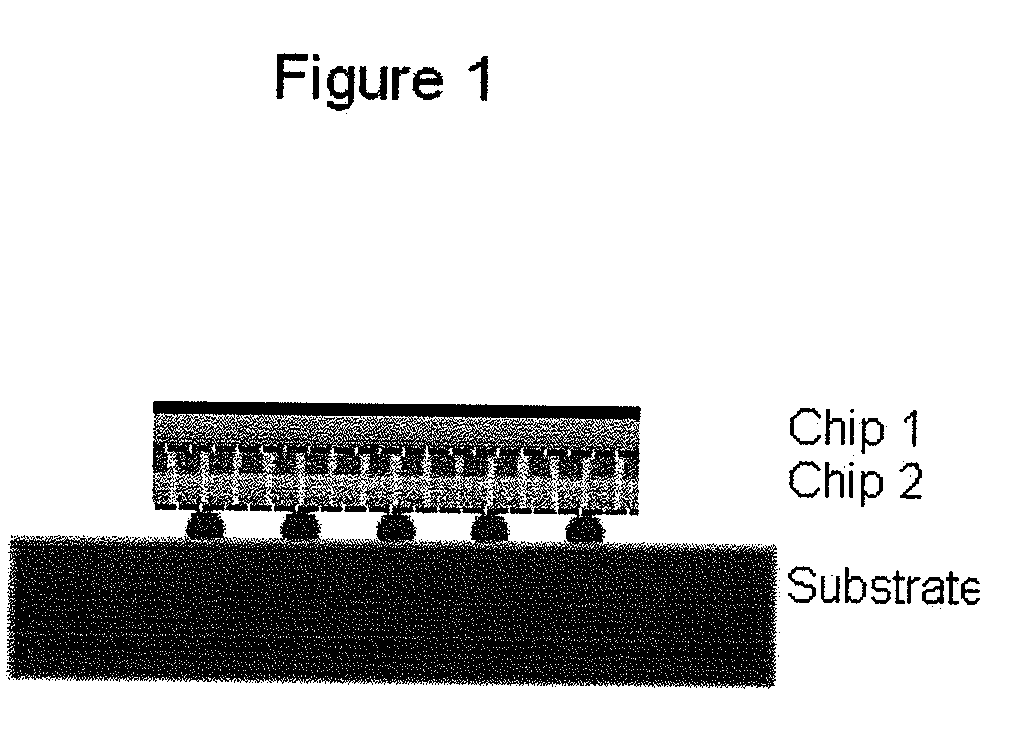

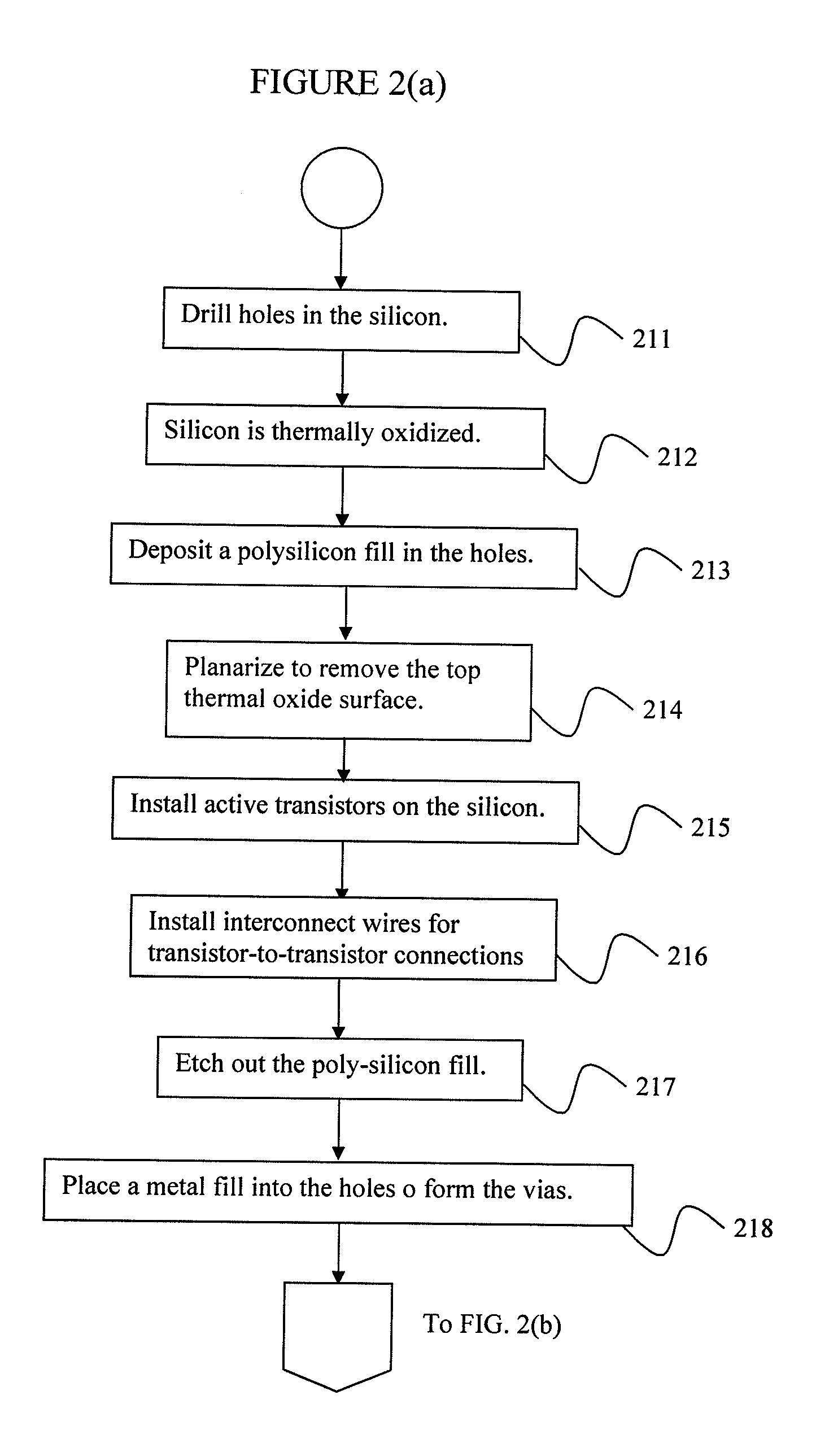

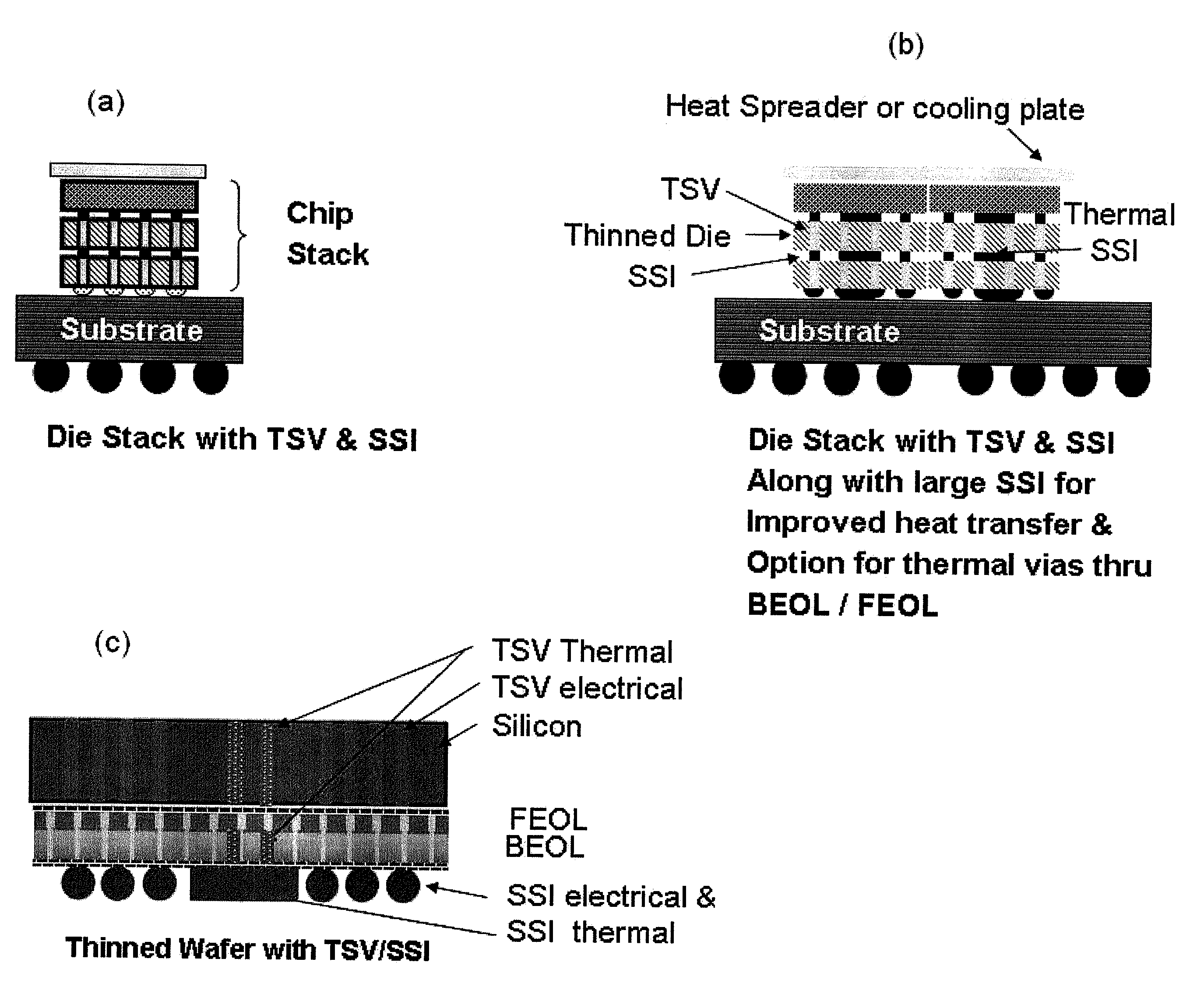

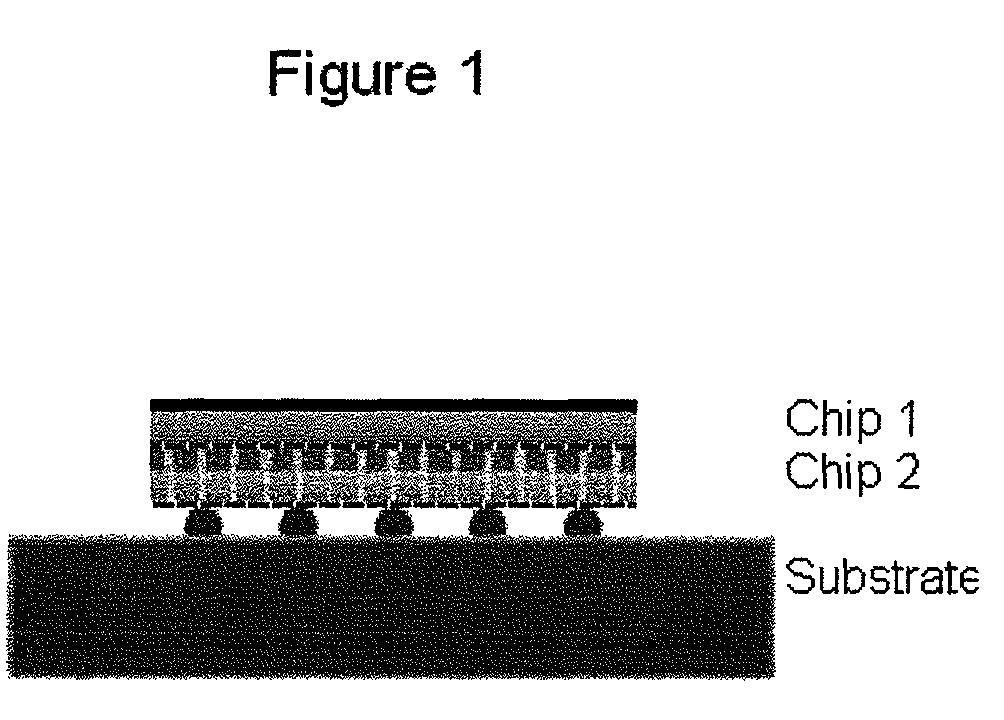

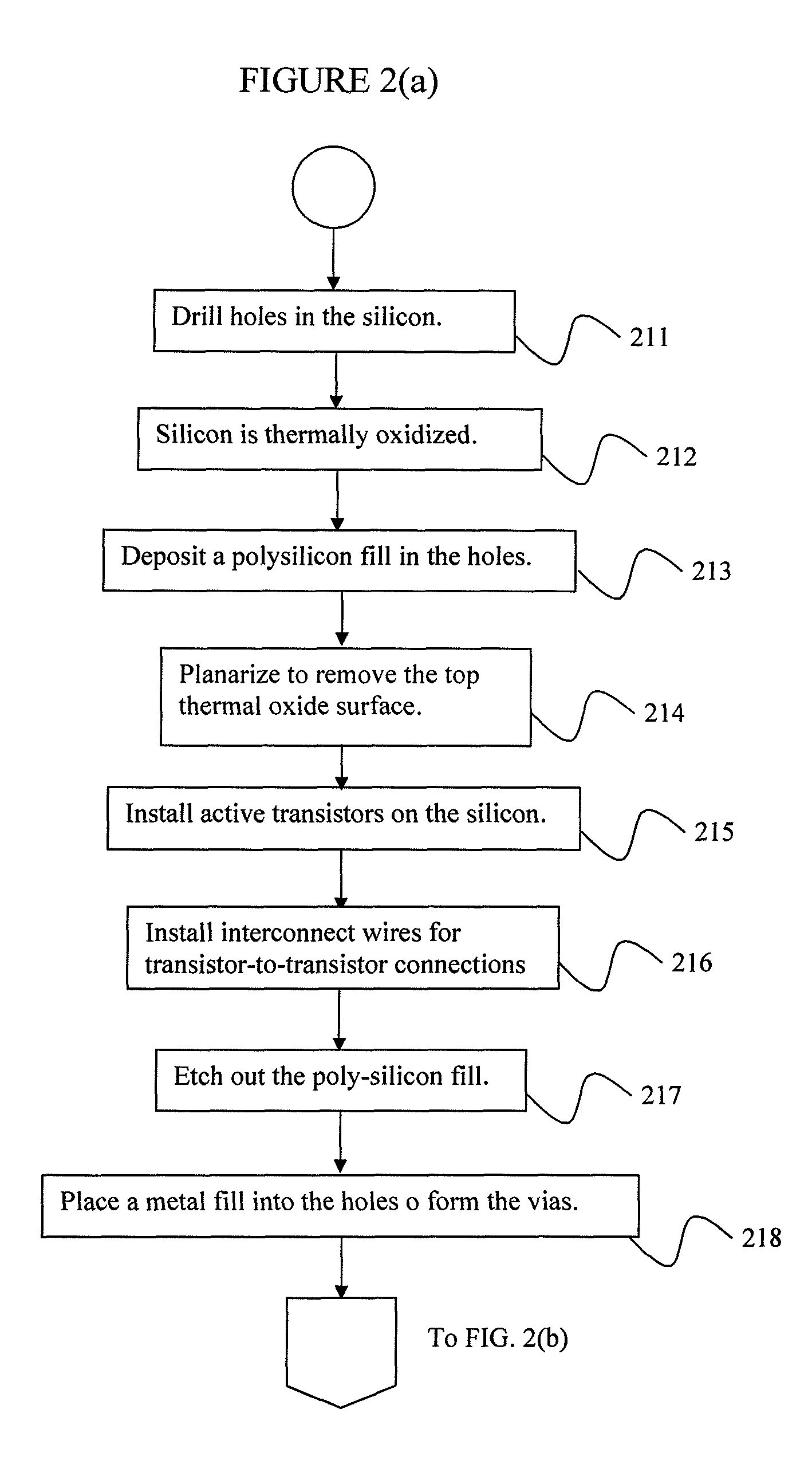

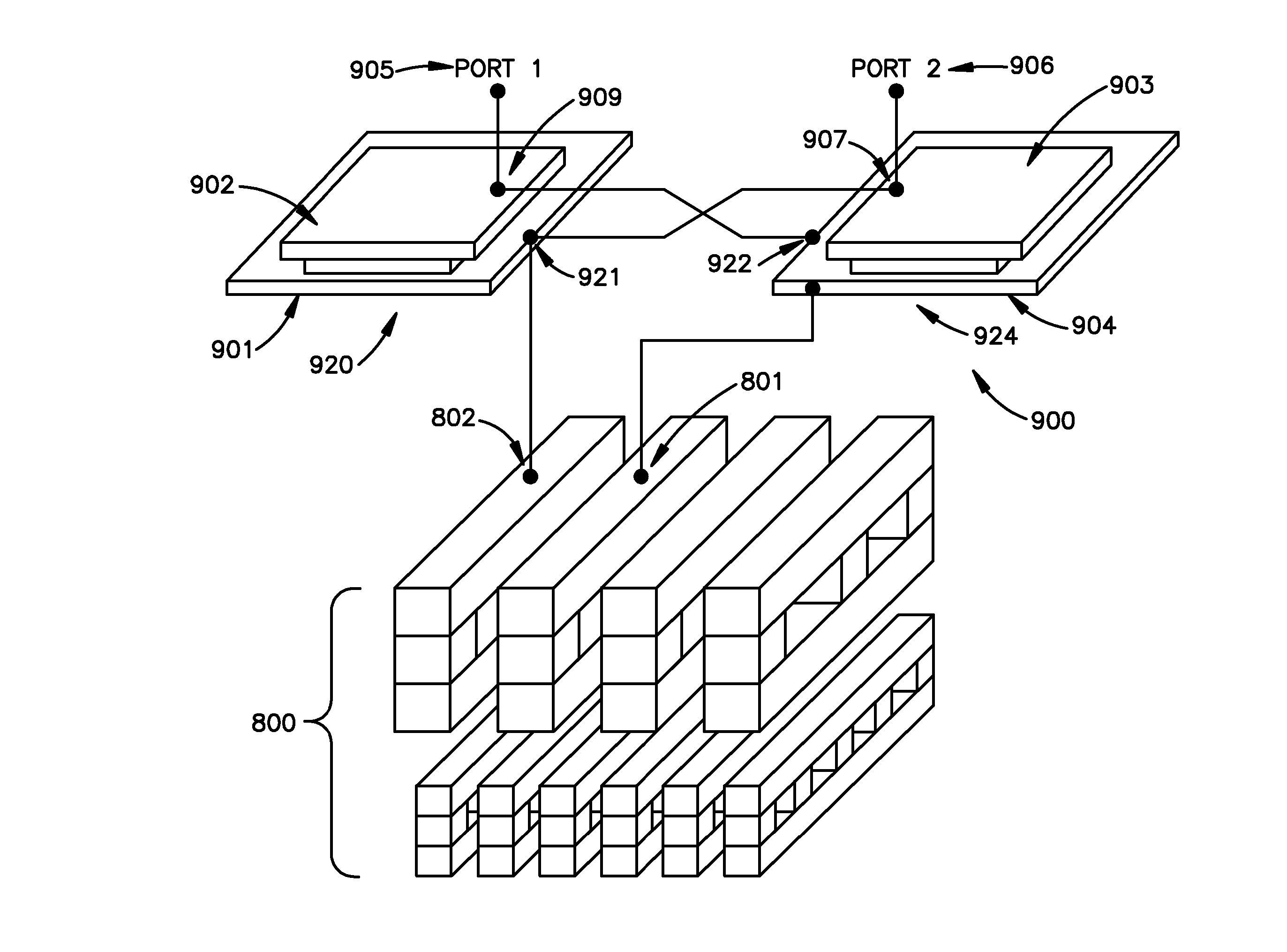

3D silicon-silicon die stack structure and method for fine pitch interconnection and vertical heat transport

InactiveUS20110042820A1Soft errorSuitable designSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsDielectricElectrical conductor

A method of fabricating a thin wafer die includes creating circuits and front-end-of-line wiring on a silicon wafer, drilling holes in a topside of the wafer, depositing an insulator on the drilled holes surface to provide a dielectric insulator, removing any excess surface deposition from the surface, putting a metal fill into the holes to form through-silicon-vias (TSV), creating back-end-of-line wiring and pads on the top surface for interconnection, thinning down the wafer to expose the insulator in from the TSVs to adapt the TSVs to be contacted from a backside of the wafer, depositing an insulating layer which contacts the TSV dielectric, thinning down the backside of the wafer, opening through the dielectric to expose the conductor of the TSV to provide a dielectric insulation about exposed backside silicon, and depositing ball limiting metallurgy pads and solder bumps on the backside of the wafer to form an integrated circuit.

Owner:GLOBALFOUNDRIES INC

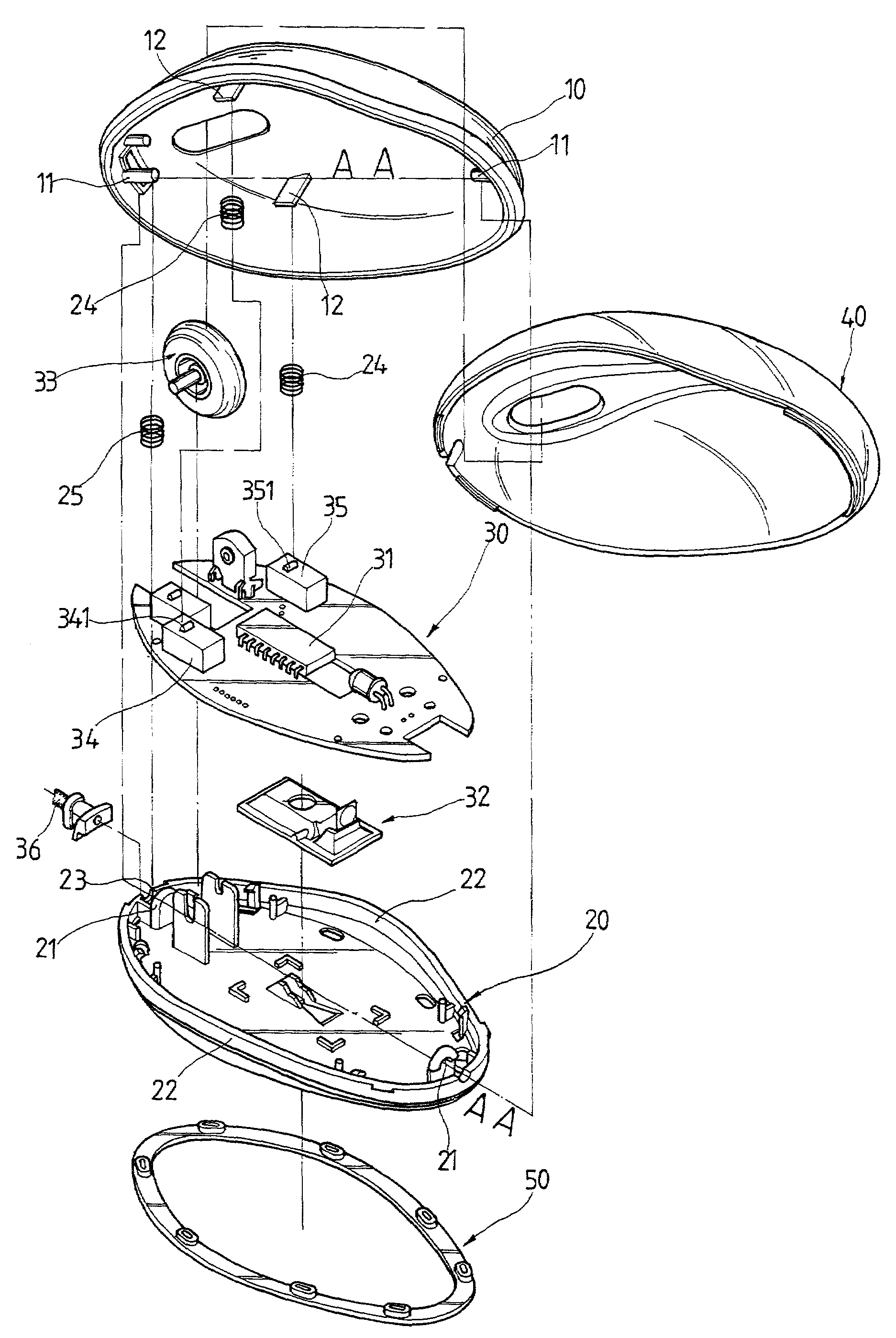

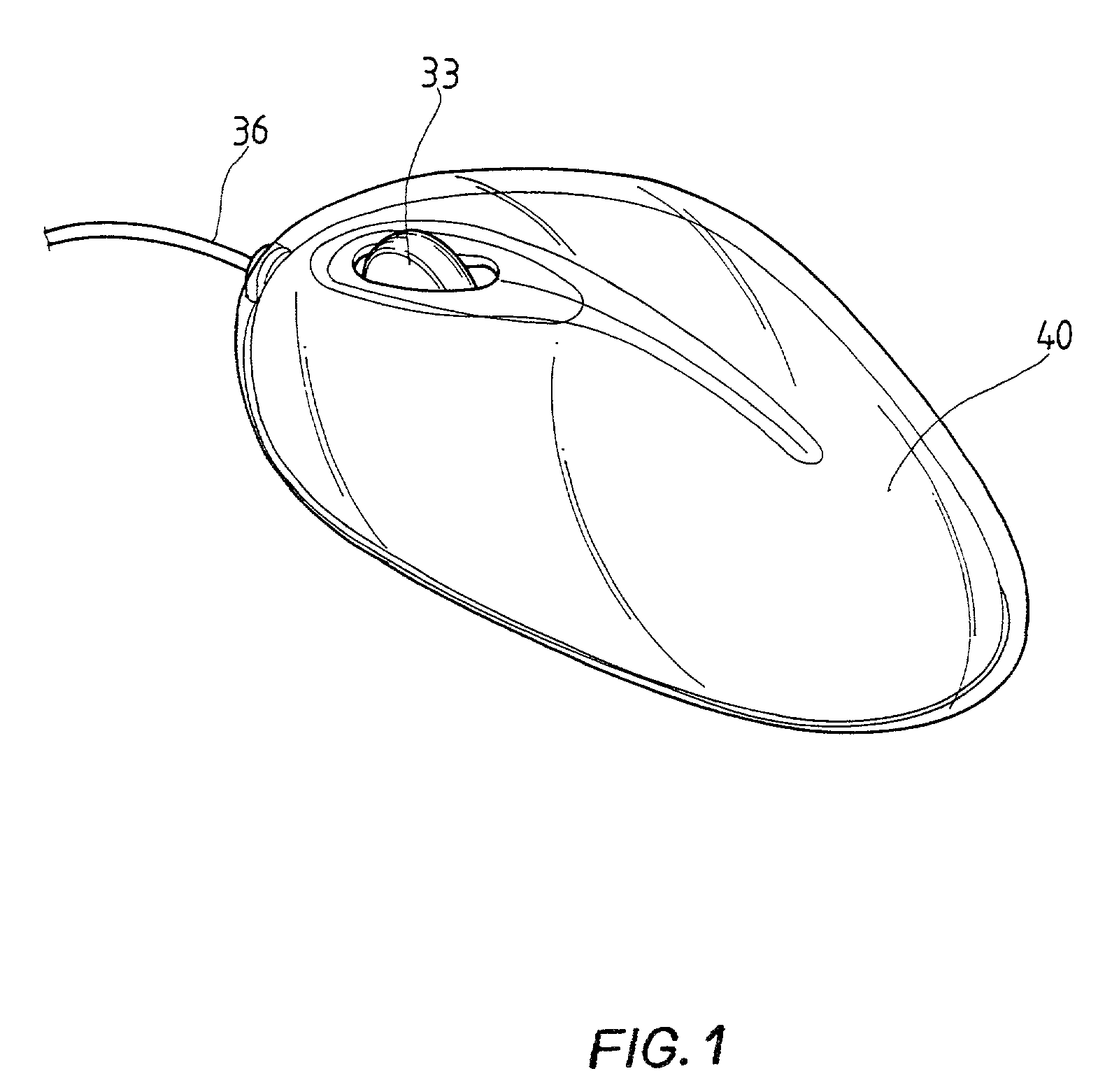

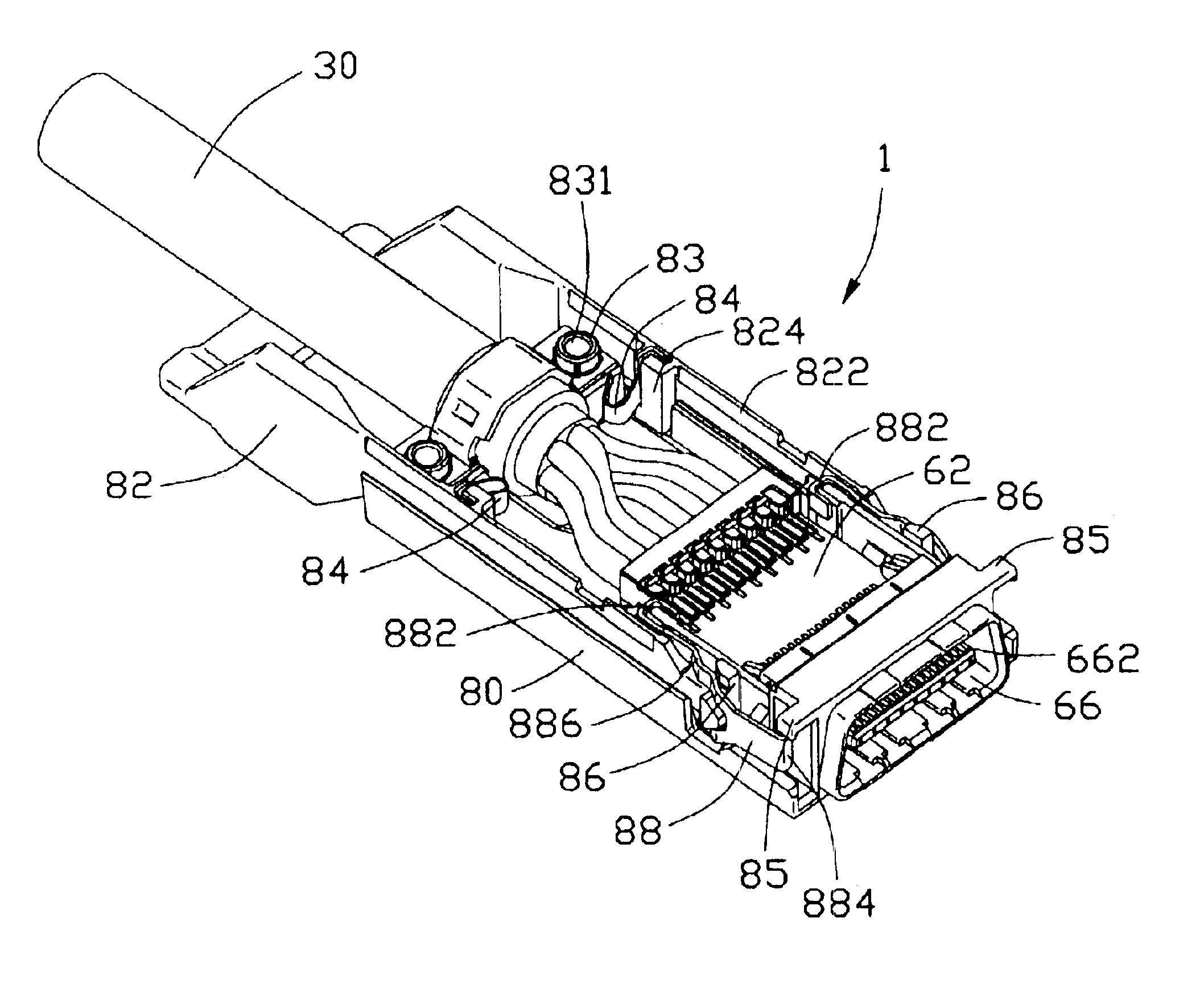

Key free mouse

InactiveUS7164412B2Input/output for user-computer interactionCathode-ray tube indicatorsFront end of lineEngineering

Owner:ADO MAX TECH

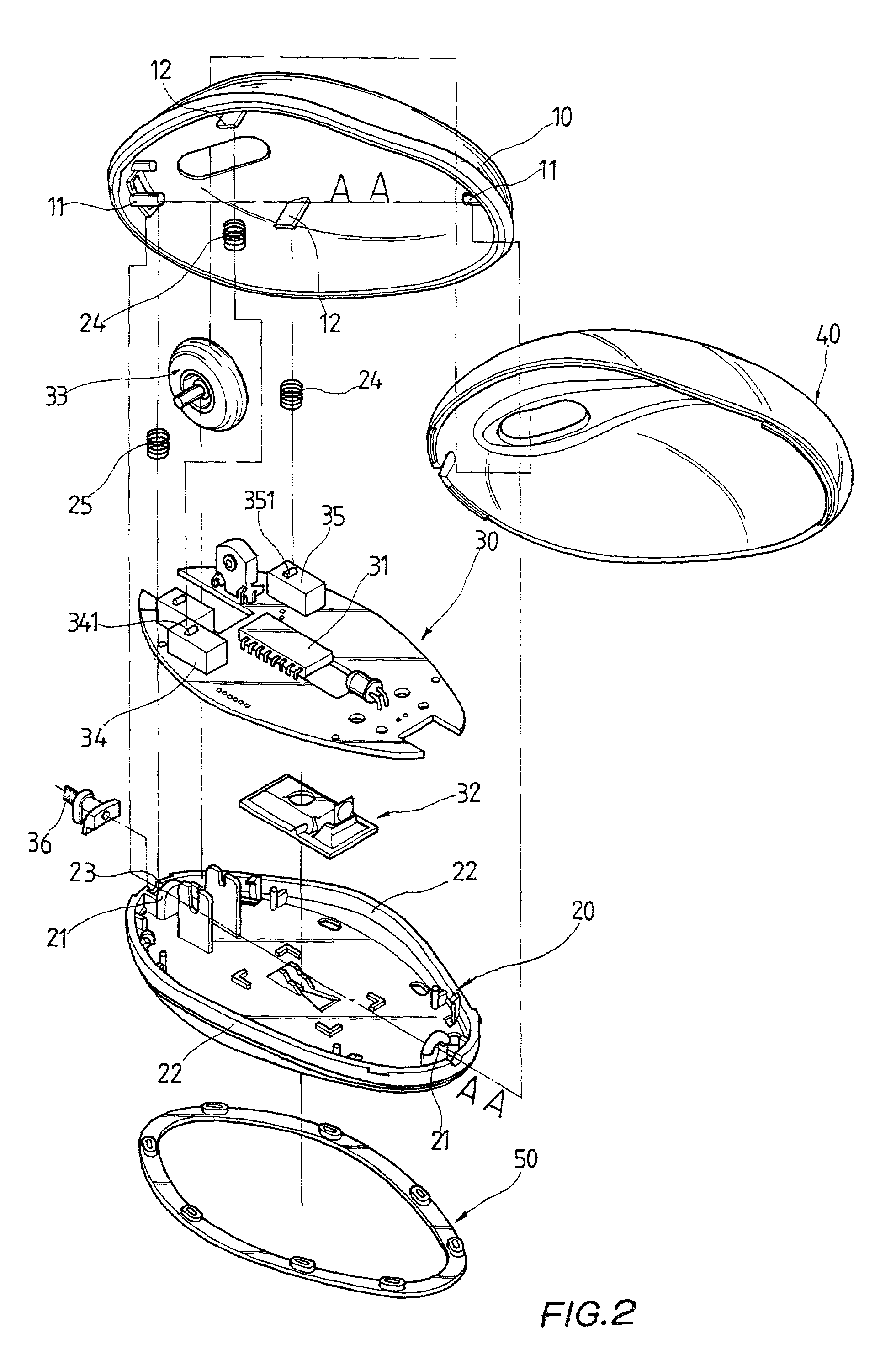

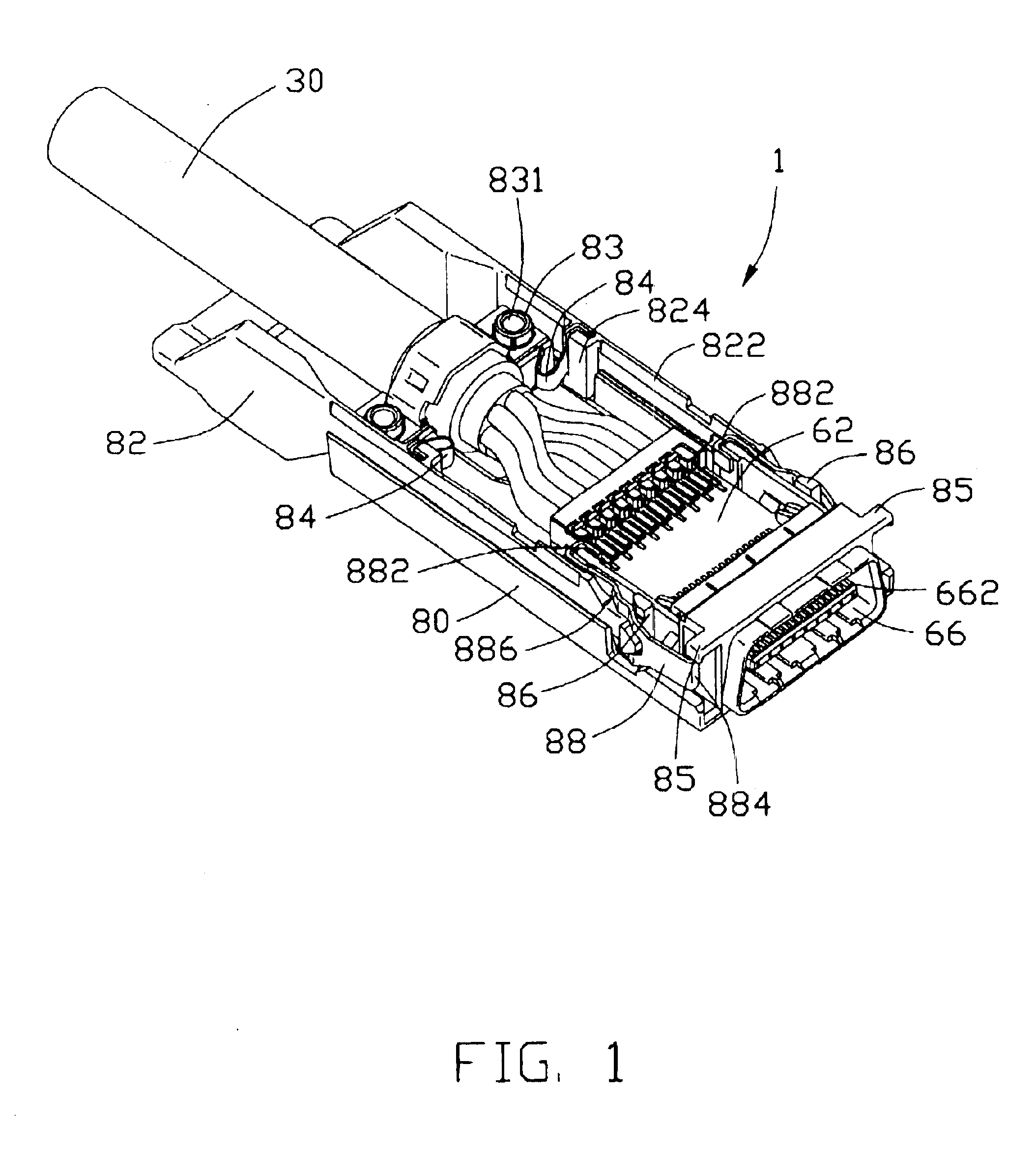

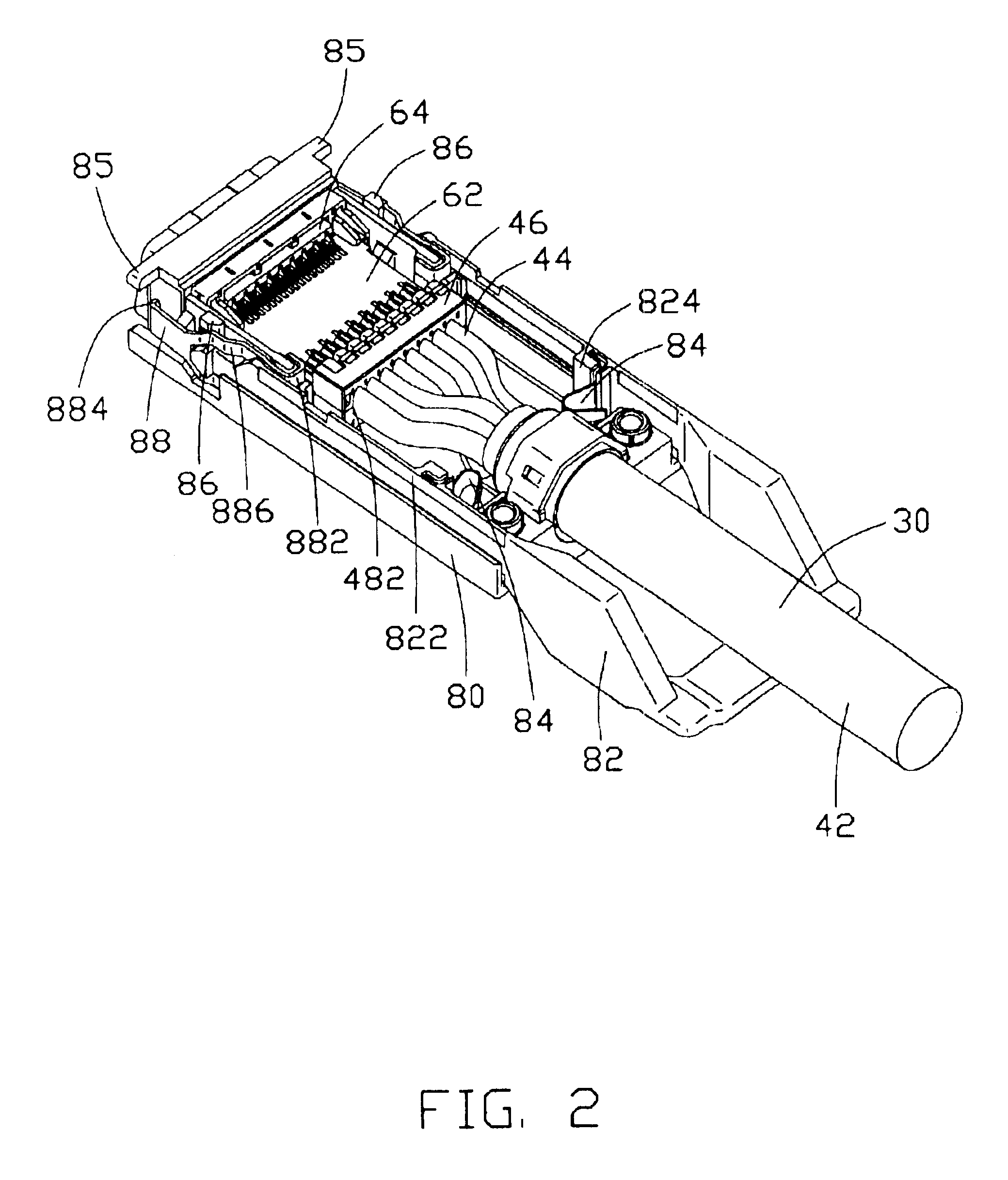

Cable connector having cross-talk suppressing feature and method for making the connector

InactiveUS6869308B2Increase speedEfficient reductionFixed connectionsCoupling protective earth/shielding arrangementsEngineeringFront end of line

A high speed cable connector (1) includes a cover (3), a base (80) and a cable assembly (30) mounted between the cover and the base. The cable assembly includes a cable (42) consisting of a plurality of lines (44). Each line has a pair of upper and lower signal wires (442, 444) and a grounding wire (446). Front ends of the lines are sandwiched between upper half (462) and lower half (464) of a spacer (46) to which upper and lower shielding plates (50, 52) are respectively mounted. The upper and lower shielding plates are electrically connected with each other. The upper and lower signal wires are soldered to signal circuitry on top and bottom faces of a printed circuit board (62), respectively. The upper and lower shielding plates have engaging arms (508) soldered to ground circuitry of on the top and bottom faces of the printed circuit board, respectively. Each grounding wire is soldered to a corresponding upper shielding plate. Each pair of upper and lower signal wires is located between two pairs of upper and lower shielding plates, whereby cross-talk between the signal wires of two neighboring lines can be effectively suppressed.

Owner:HON HAI PRECISION IND CO LTD

3D silicon-silicon die stack structure and method for fine pitch interconnection and vertical heat transport

InactiveUS8048794B2Improve integrityRaise transfer toSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsDielectricElectrical conductor

A method of fabricating a thin wafer die includes creating circuits and front-end-of-line wiring on a silicon wafer, drilling holes in a topside of the wafer, depositing an insulator on the drilled holes surface to provide a dielectric insulator, removing any excess surface deposition from the surface, putting a metal fill into the holes to form through-silicon-vias (TSV), creating back-end-of-line wiring and pads on the top surface for interconnection, thinning down the wafer to expose the insulator in from the TSVs to adapt the TSVs to be contacted from a backside of the wafer, depositing an insulating layer which contacts the TSV dielectric, thinning down the backside of the wafer, opening through the dielectric to expose the conductor of the TSV to provide a dielectric insulation about exposed backside silicon, and depositing ball limiting metallurgy pads and solder bumps on the backside of the wafer to form an integrated circuit.

Owner:GLOBALFOUNDRIES INC

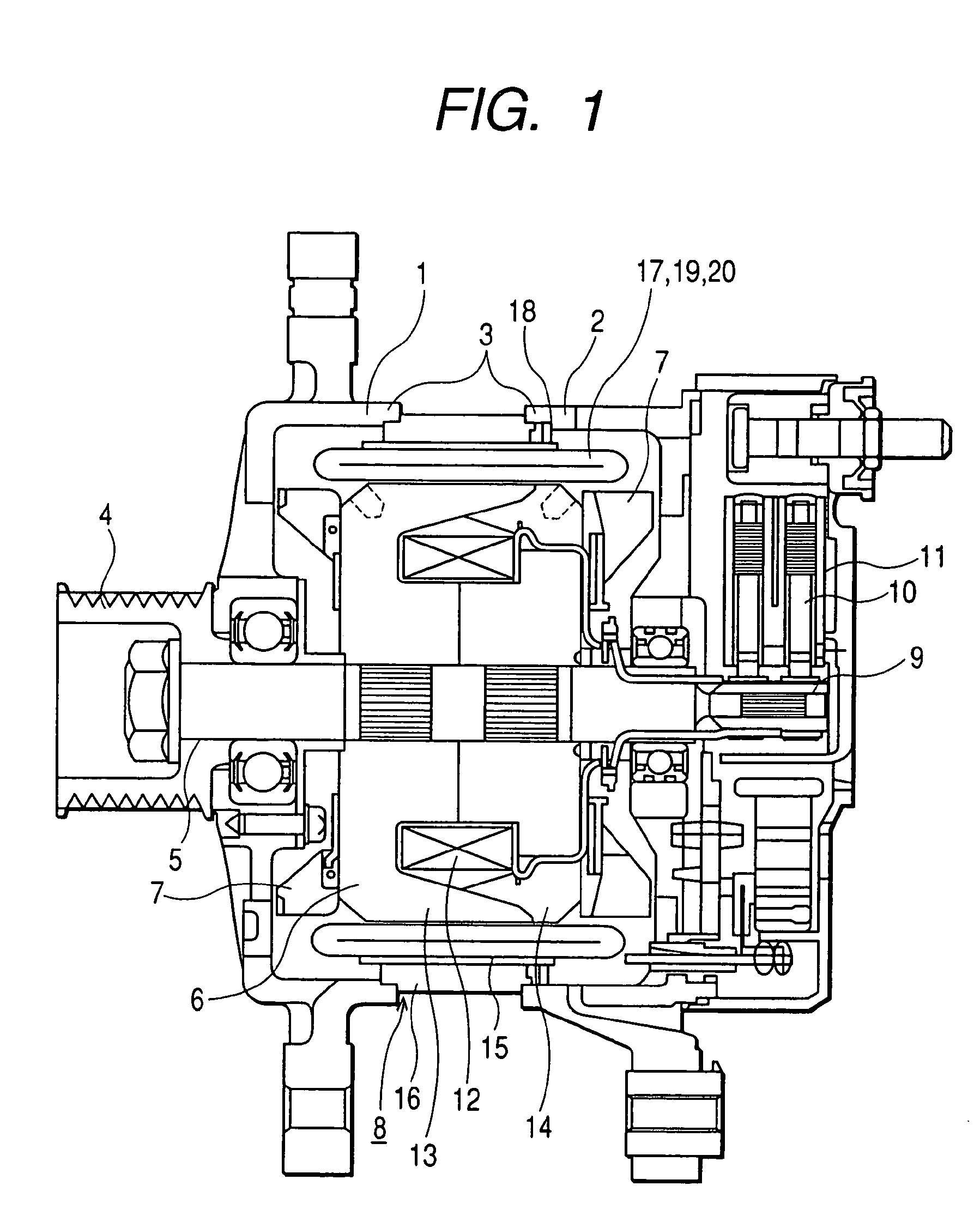

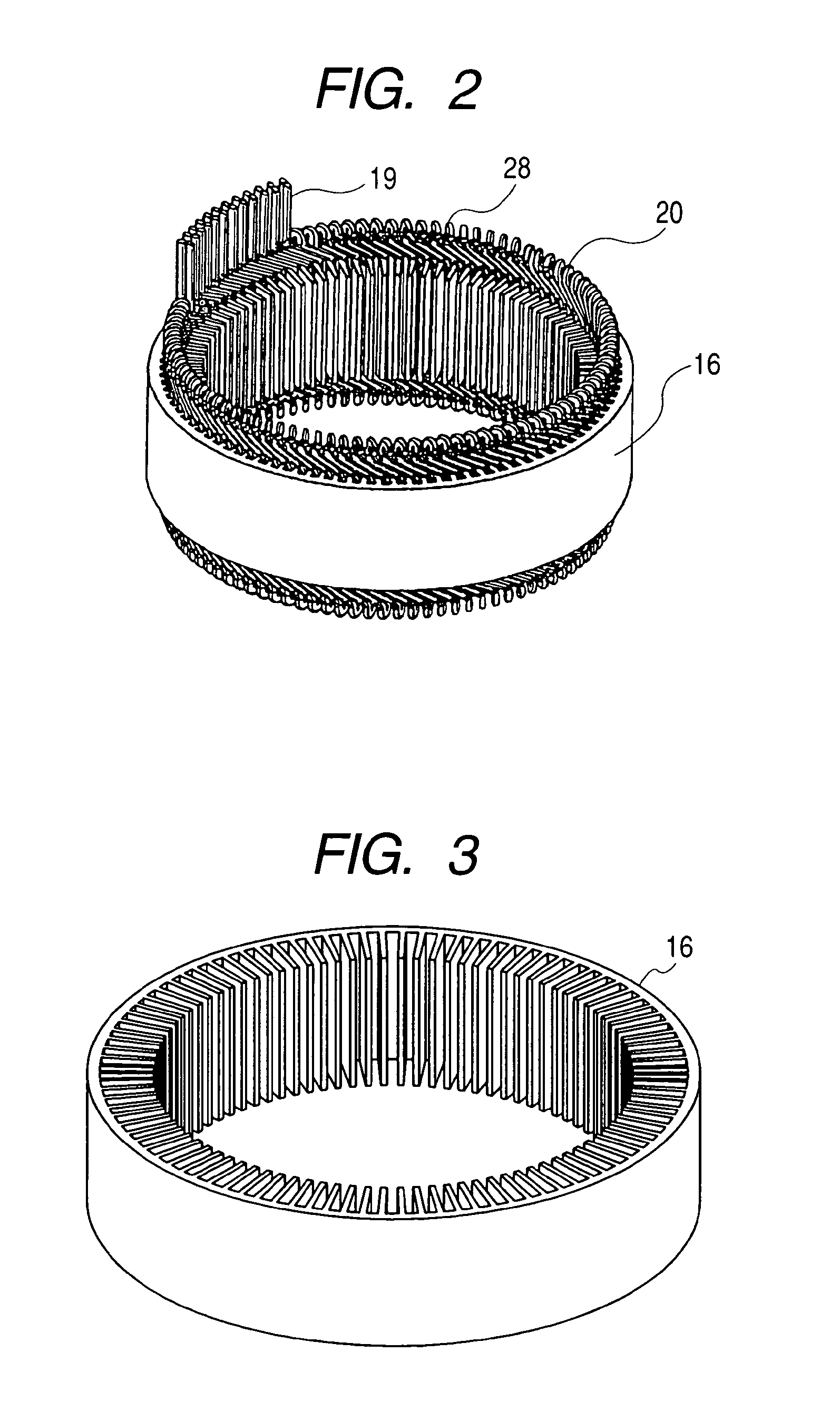

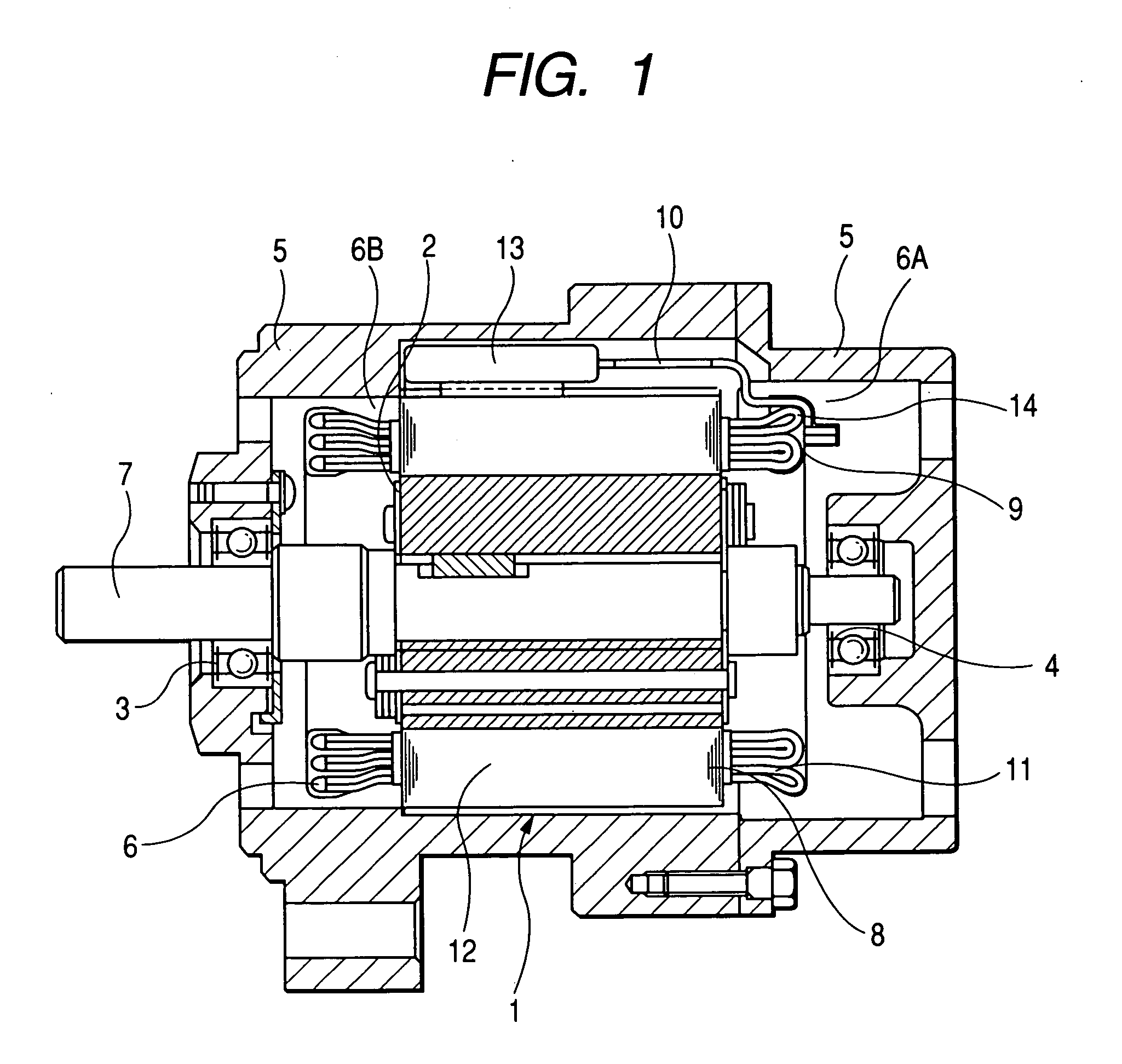

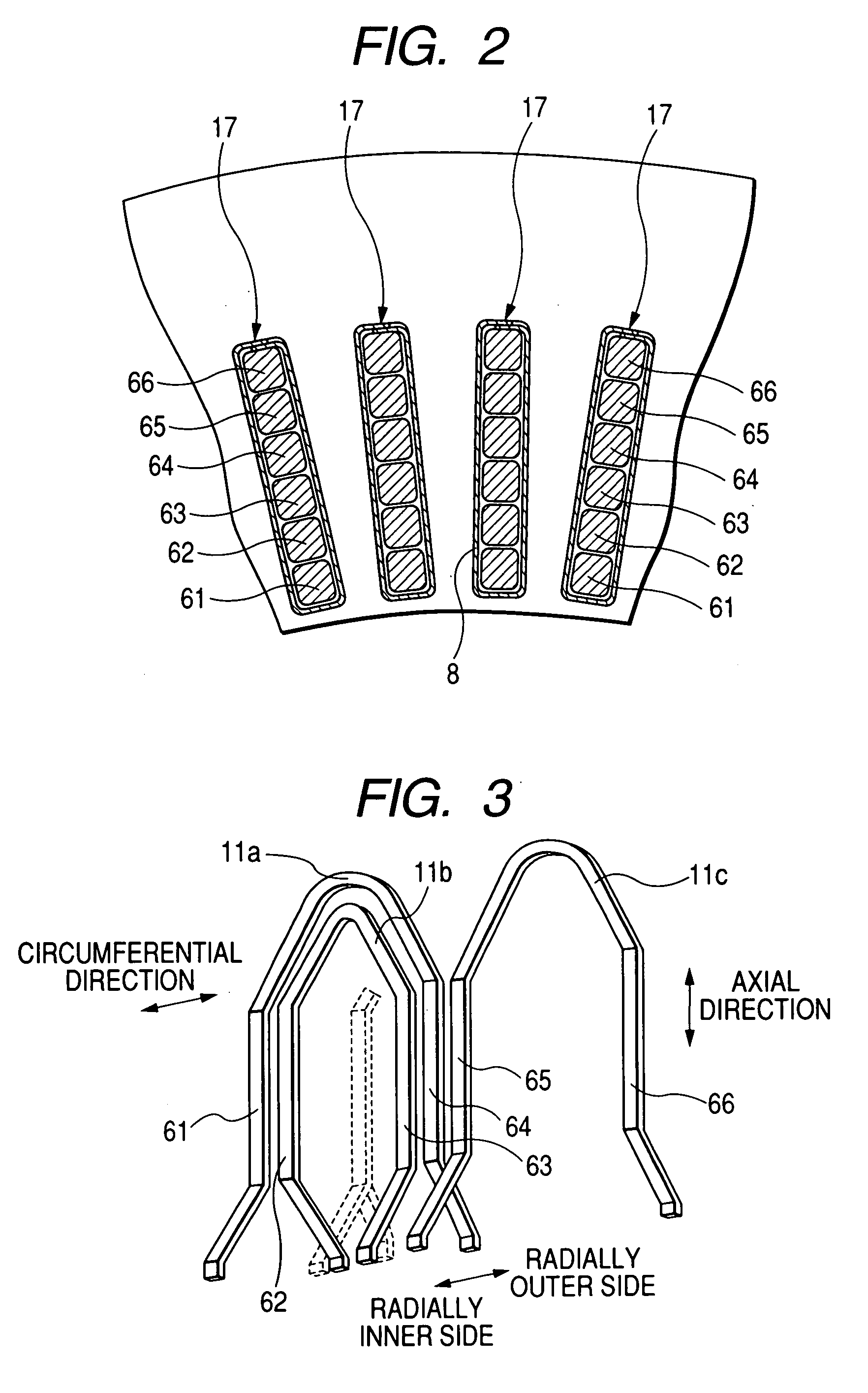

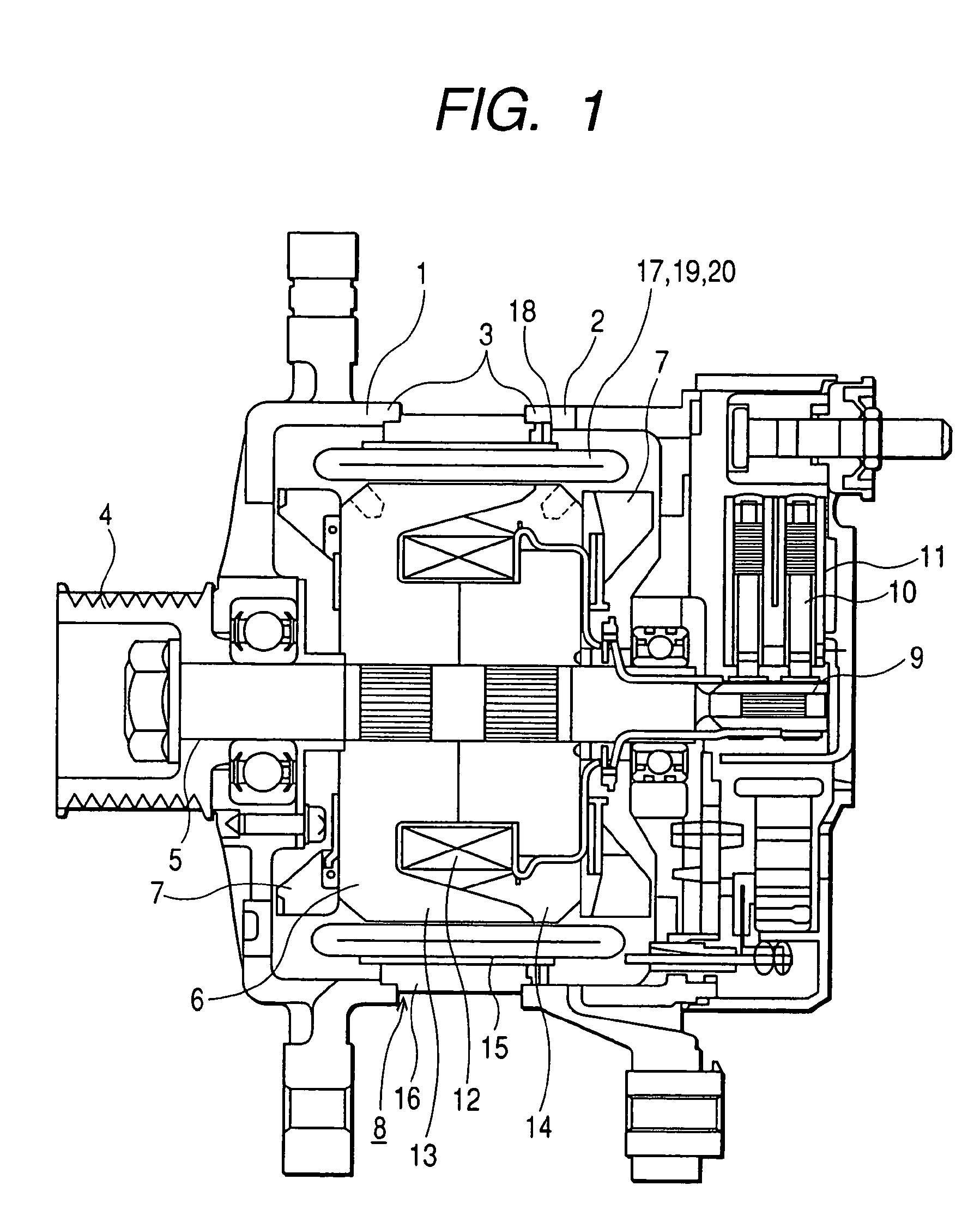

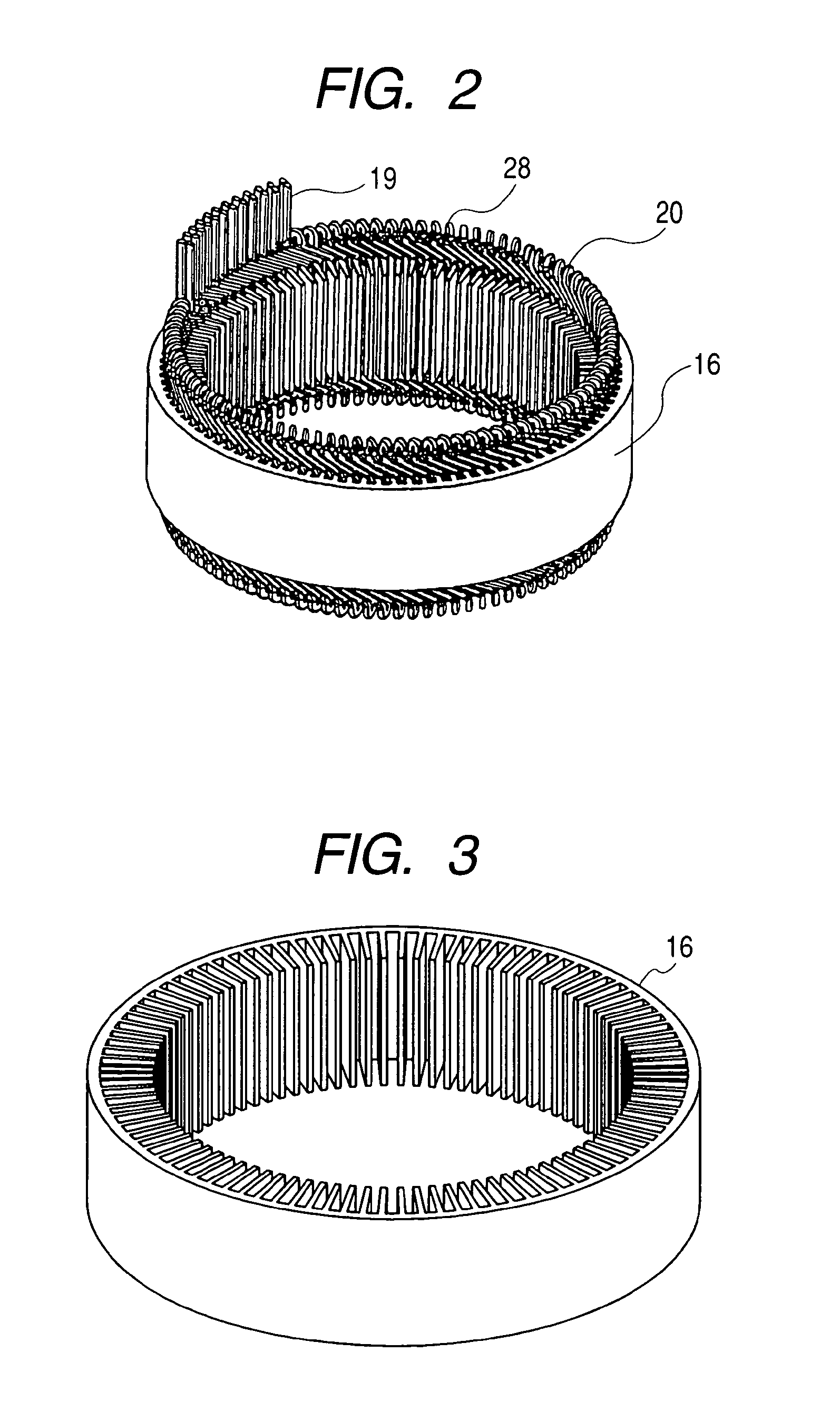

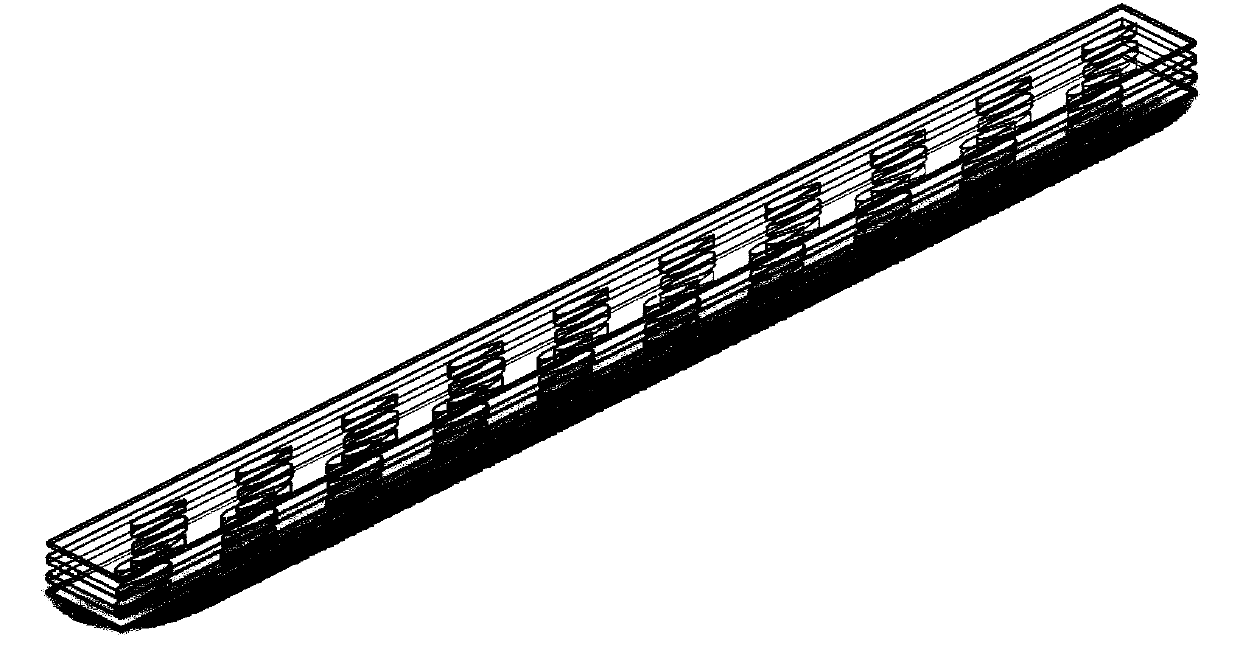

Electric Rotating Machine and Stator for the Same

InactiveUS20070180682A1Efficient assemblyMagnetic circuit stationary partsEmbedding prefabricated windingsEngineeringFront end of line

An electric rotating machine has a rotor having N and S poles and includes a stator with an annular stator core and slots. Multiple-phase stator windings are embedded in the slots, and are formed by winding continuous wires such that straight parts of the stator windings pressed in a flat shape are wound in rings around a grooved cylindrical member. The cylindrical member is inserted into a bore defined by the annular stator core so that the grooves of the cylindrical member are arranged opposite to the slots. The sets of the windings are folded back alternately outside the slots of the stator core and are wound so the sets of the windings are embedded alternately in the direction of the depth of the slots. Leading and trailing ends of the continuous wires are superposed after being wound at least one turn around the circumferentially arranged slots of the stator.

Owner:HITACHI LTD

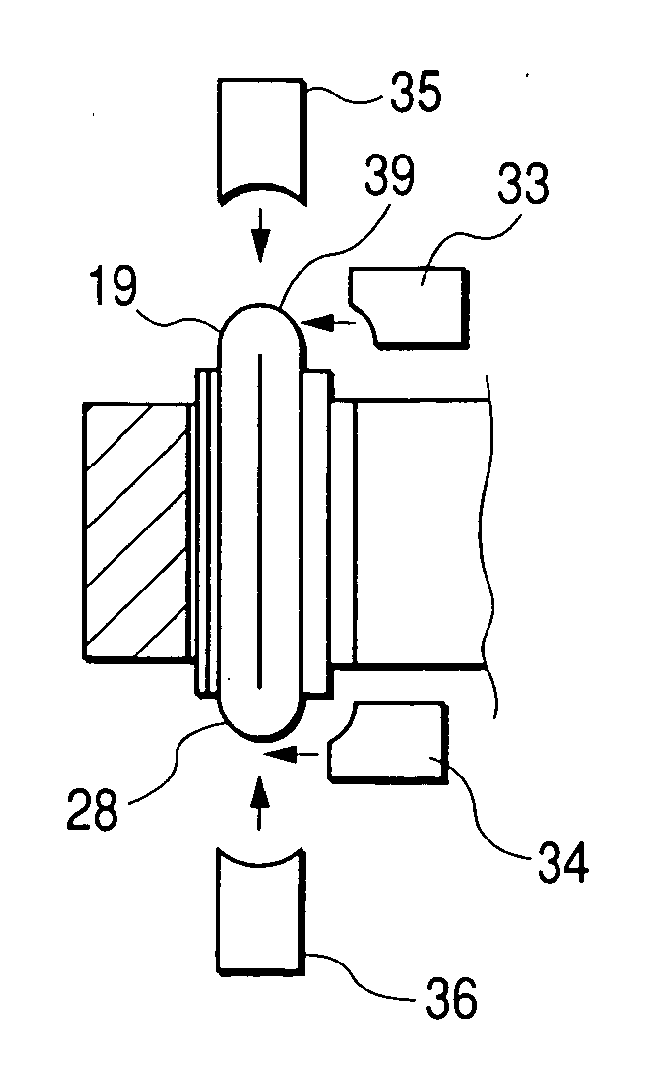

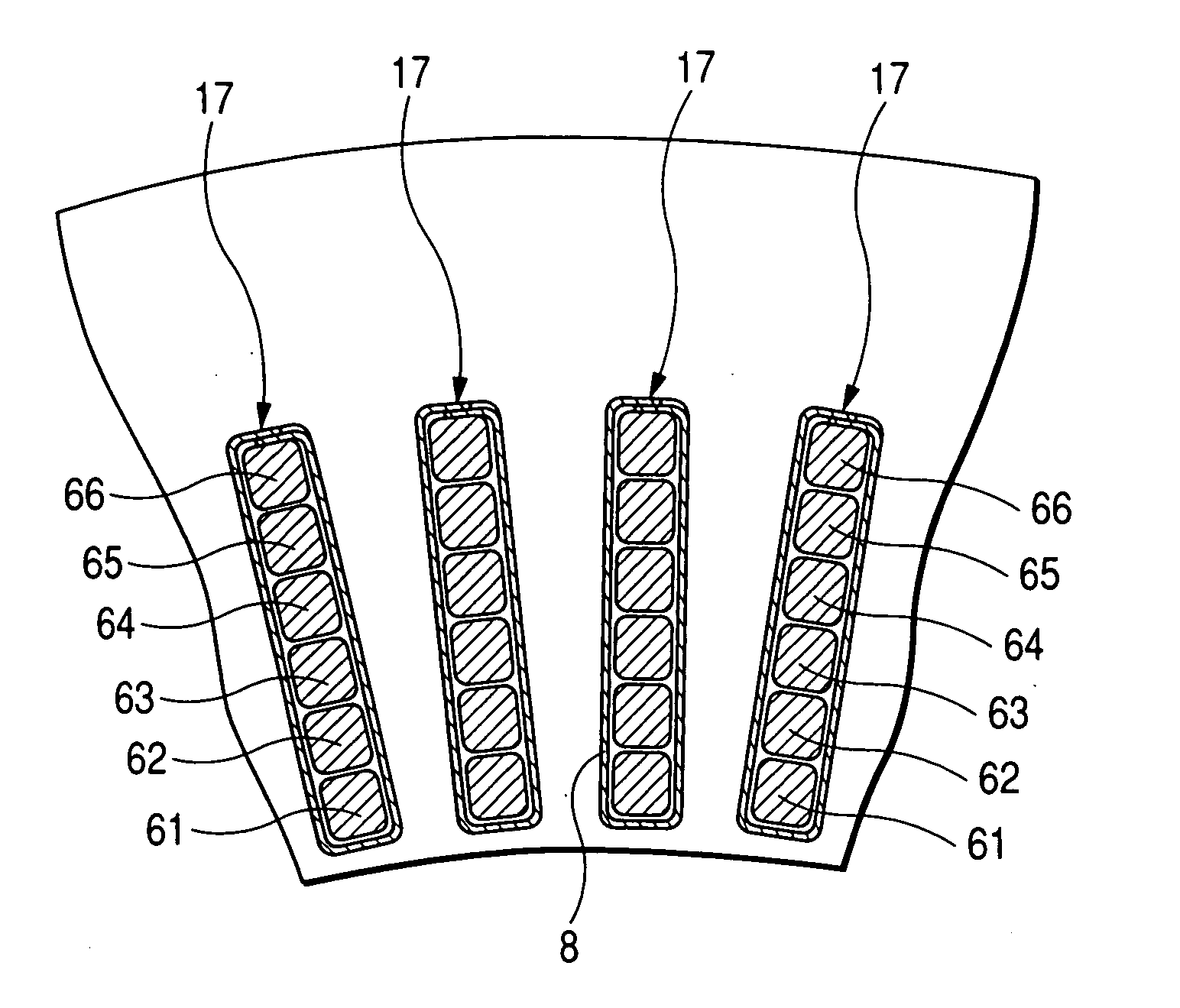

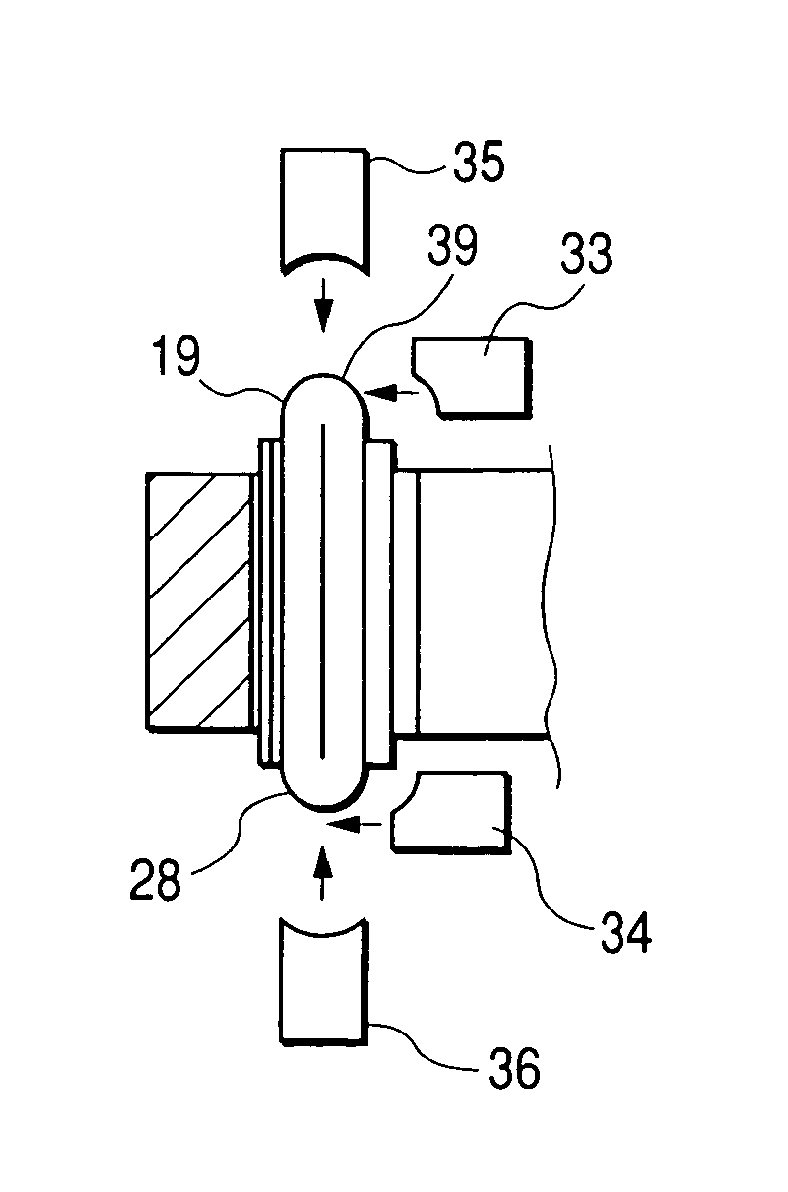

Segment connection type electric rotating machine

InactiveUS20060163959A1Easy to bendReduced external dimensionsWindings insulation shape/form/constructionMagnetic circuitConnection typeElectric machine

The segment connection type electric rotating machine includes a stator coil constituted by phase coils each of which includes a U-shaped segment continuum formed by U-shaped conductor segments inserted into slots of a stator core, an I-shaped leading conductor segment inserted into one of the slots and connected to a lead end of the U-shaped segment continuum, and an I-shaped terminating conductor segment inserted into one of the slots and connected to a terminal end of the U-shaped segment continuum. A connector box fixed to the outer periphery of the stator core. A power supply lead is laid between the connector box and the I-shaped leading conductor segment. The power supply lead is welded at a tip portion thereof to an end portion of the I-shaped leading conductor segment in the vicinity of head-side coil ends of the stator coil.

Owner:DENSO CORP

Electric rotating machine and stator for the same

InactiveUS7337525B2Efficient assemblyMagnetic circuit stationary partsEmbedding prefabricated windingsFront end of lineConductor Coil

An electric rotating machine has a rotor having N and S poles and includes a stator with an annular stator core and slots. Multiple-phase stator windings are embedded in the slots, and are formed by winding continuous wires such that straight parts of the stator windings pressed in a flat shape are wound in rings around a grooved cylindrical member. The cylindrical member is inserted into a bore defined by the annular stator core so that the grooves of the cylindrical member are arranged opposite to the slots. The sets of the windings are folded back alternately outside the slots of the stator core and are wound so the sets of the windings are embedded alternately in the direction of the depth of the slots. Leading and trailing ends of the continuous wires are superposed after being wound at least one turn around the circumferentially arranged slots of the stator.

Owner:HITACHI LTD

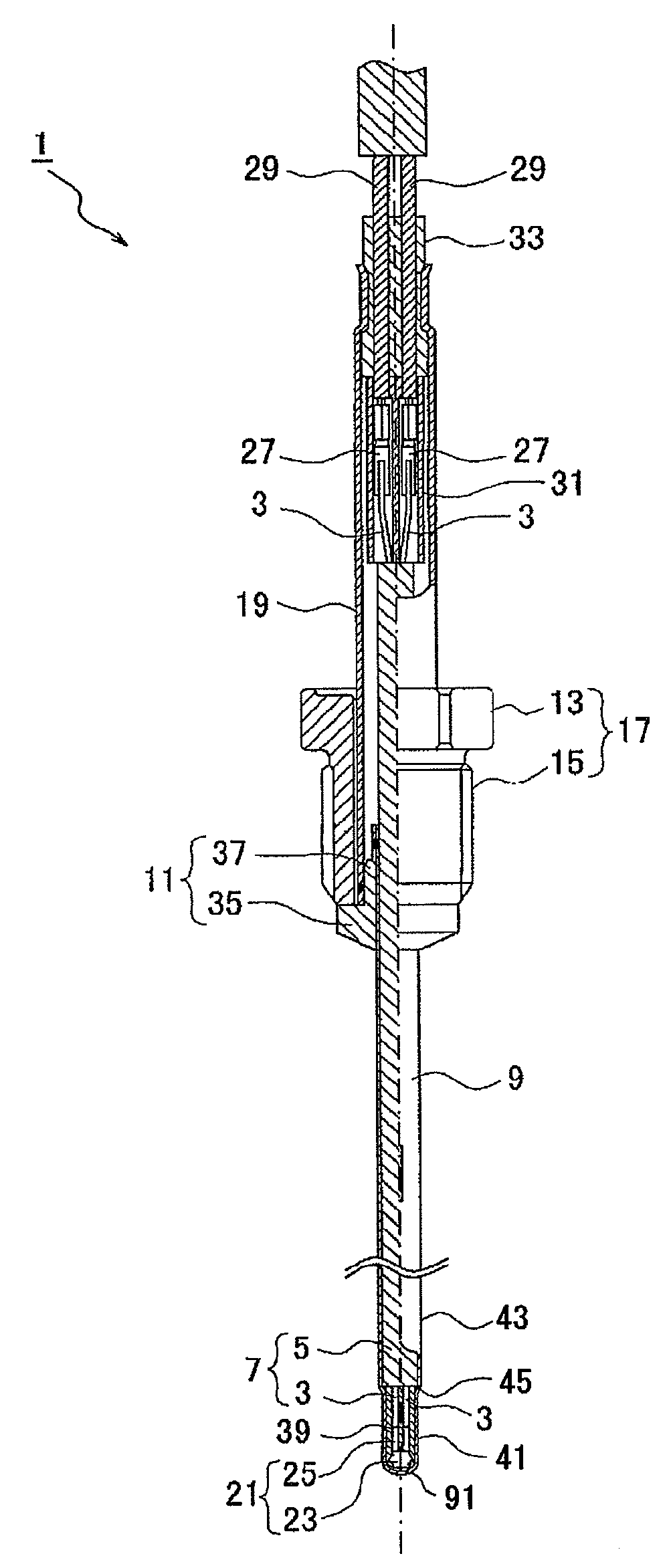

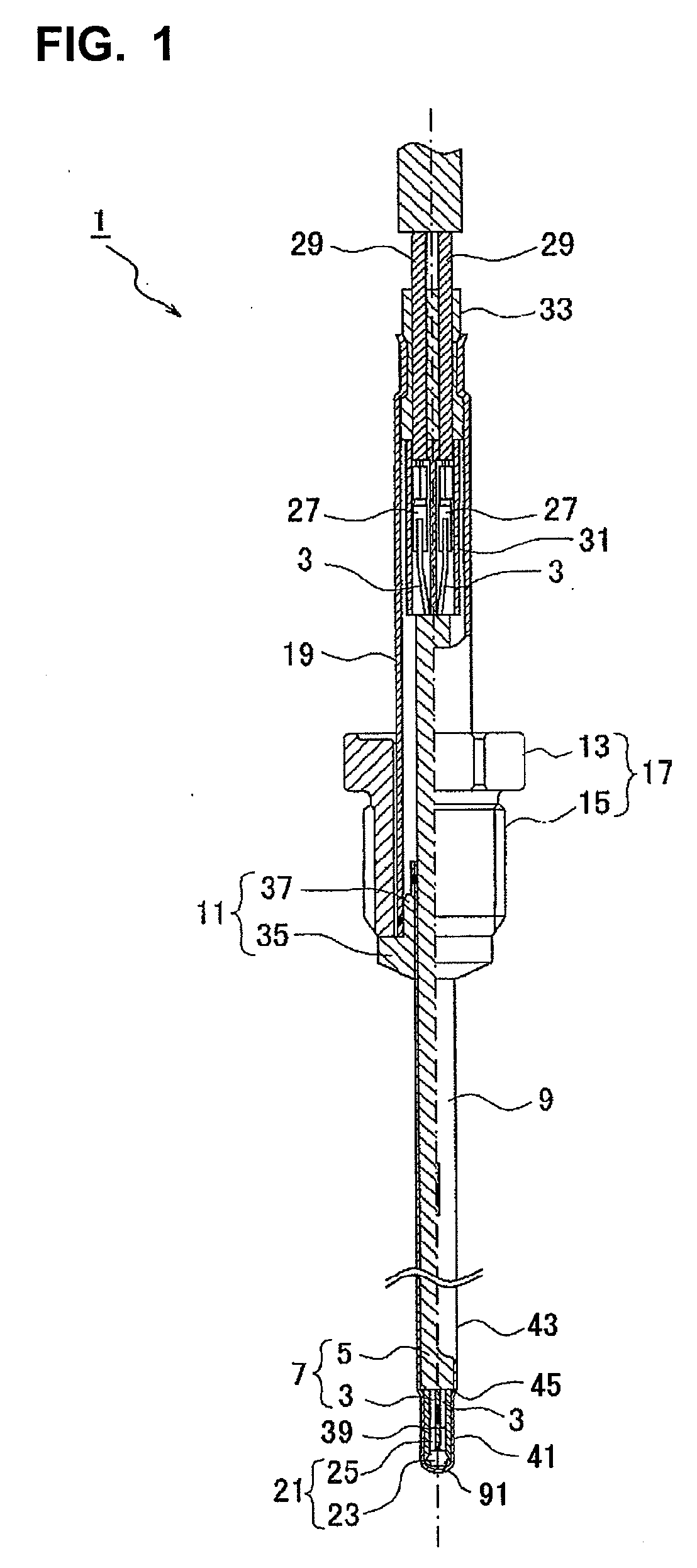

Temperature sensor

ActiveUS20090323765A1Improve solderabilityImprove welding strengthThermometer detailsThermometers using electric/magnetic elementsPlatinumStrontium

In a temperature sensor (1), a pair of electrode wires (25) of a thermistor element (21) are formed of a material prepared by adding strontium to platinum or a platinum alloy and without addition of zirconia or a like oxide. Rear end portions of the electrode wires (25) formed of the above-mentioned material and front end portions of sheath core wires (3) are laser-welded to one another in an overlapping condition.

Owner:NGK SPARK PLUG CO LTD

Air gap under on-chip passive device

InactiveUS7662722B2Semiconductor/solid-state device detailsSolid-state devicesDielectricFront end of line

Owner:GLOBALFOUNDRIES US INC

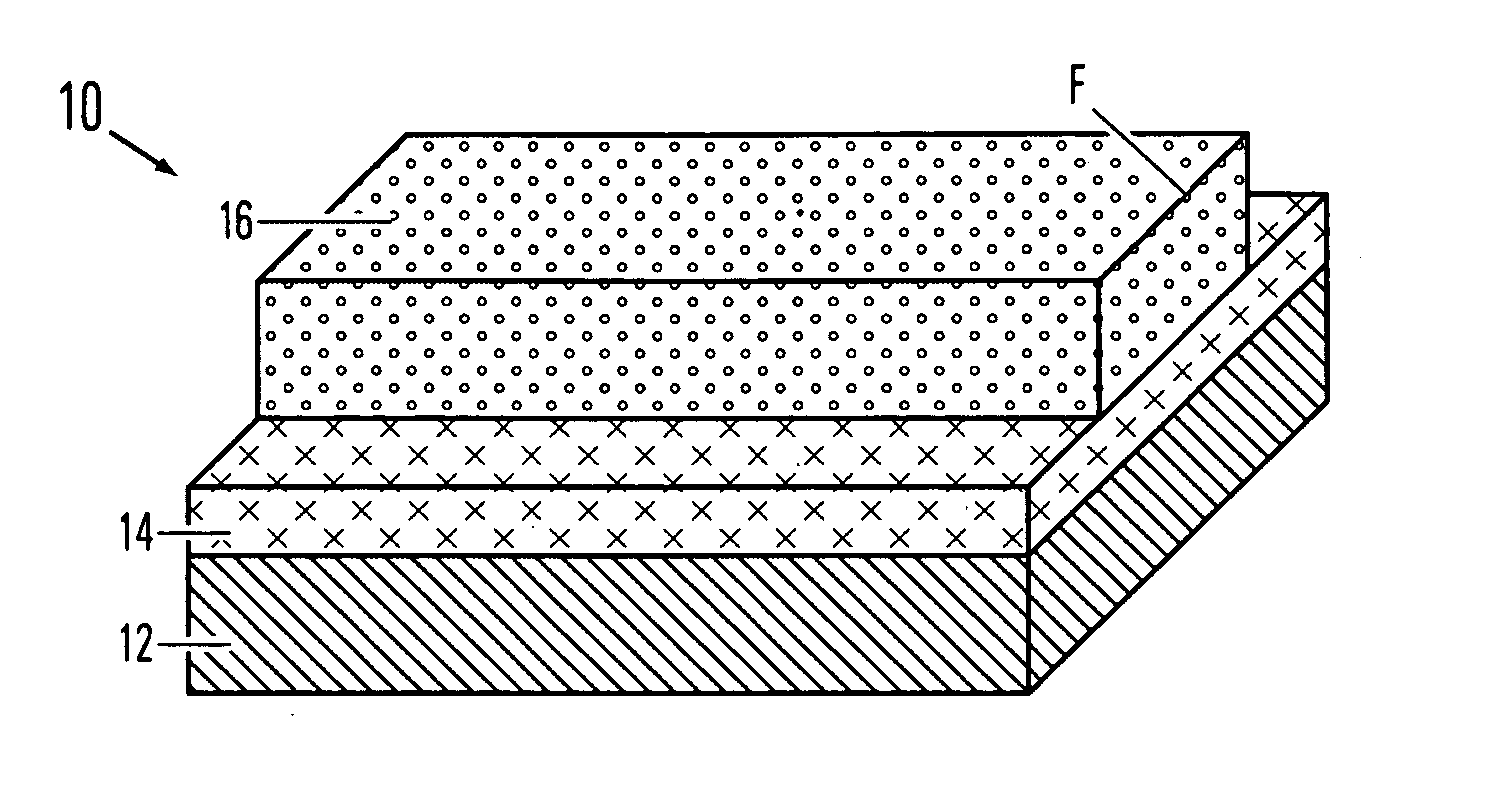

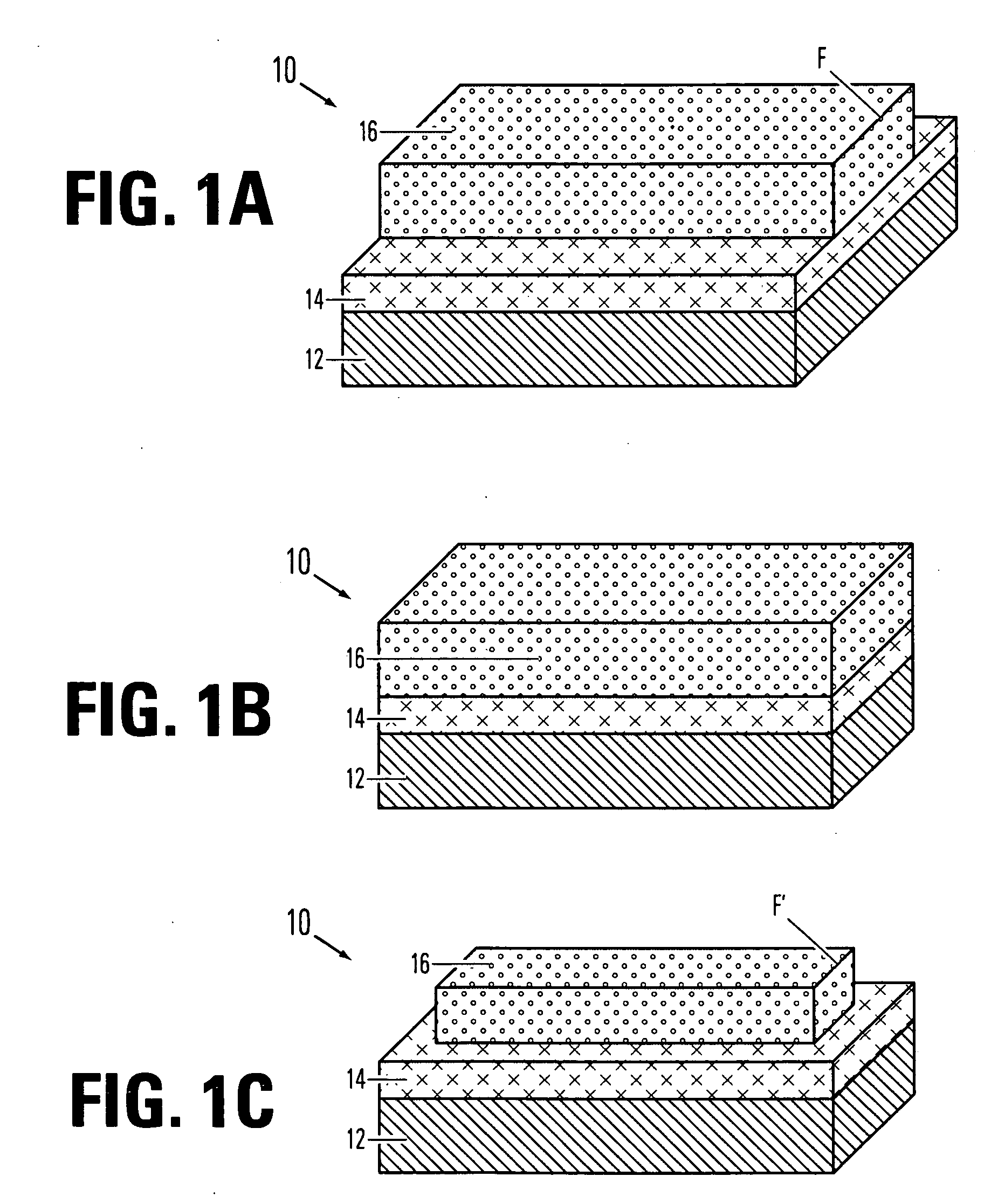

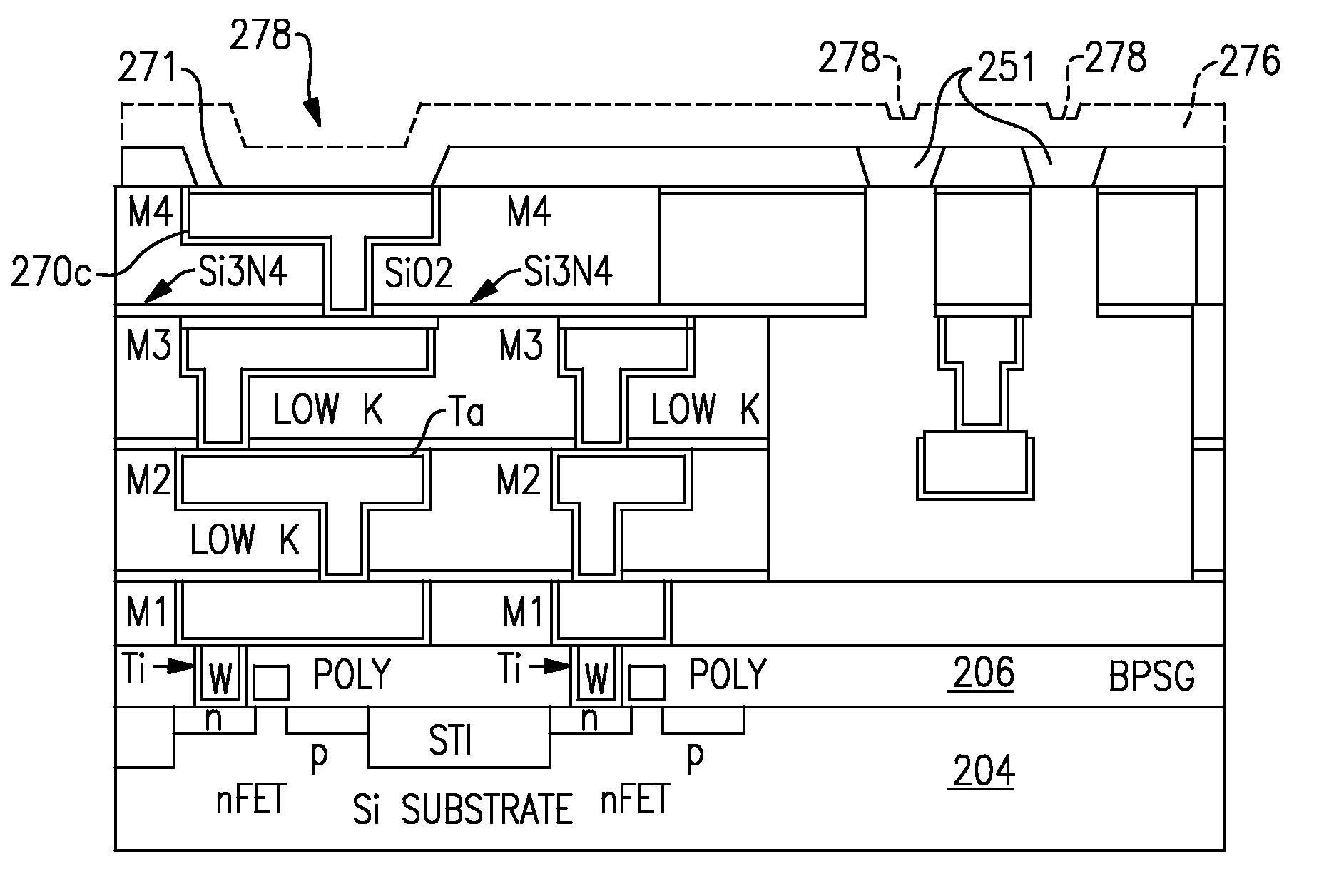

Apparatus and method for forming a battery in an integrated circuit

InactiveUS7045372B2More wiring levelSmall sizePrimary cell to battery groupingCell electrodesFront end of lineEngineering

A method and structure that provides a battery within an integrated circuit for providing voltage to low-current electronic devices that exist within the integrated circuit. The method includes Front-End-Of-Line (FEOL) processing for generating a layer of electronic devices on a semiconductor wafer, followed by Back-End-Of-Line (BEOL) integration for wires connecting the electronic devices together to form completed electrical circuits of the integrated circuit. The BEOL integration includes forming a multilayered structure of wiring levels on the layer of electronic devices. Each wiring level includes conductive metallization (e.g., metal-plated vias, conductive wiring lines, etc.) embedded in insulative material. The battery is formed during BEOL integration within one or more wiring levels, and the conductive metallization conductively couples positive and negative terminals of the battery to the electronic devices. The battery may have several different topologies relative to the structural and geometrical relationships among the battery electrodes and electrolyte. Multiple batteries may be formed within one or more wiring levels, and may be conductively coupled to the electronic devices. The multiple batteries may be connected in series or in parallel.

Owner:GLOBALFOUNDRIES US INC

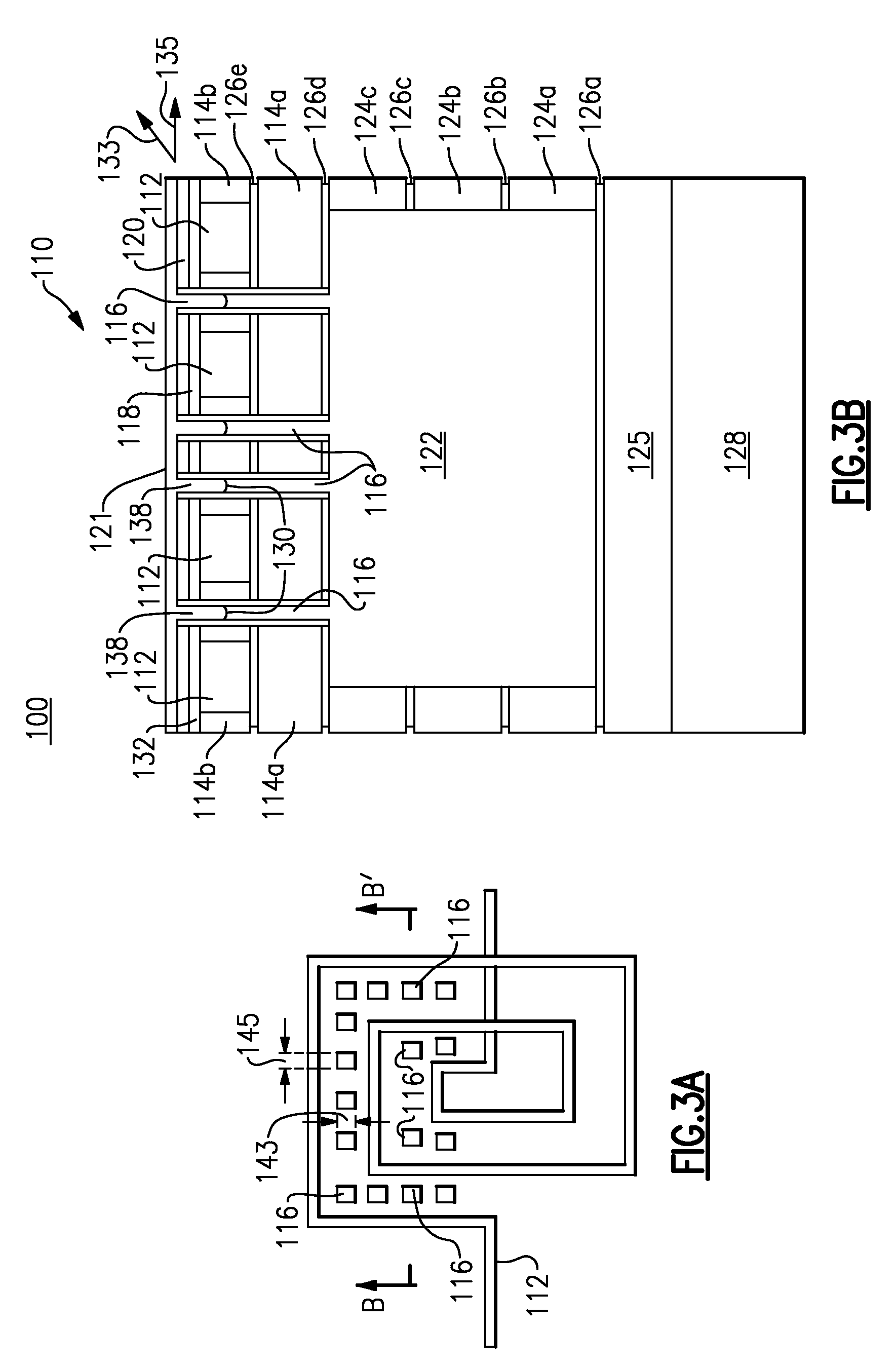

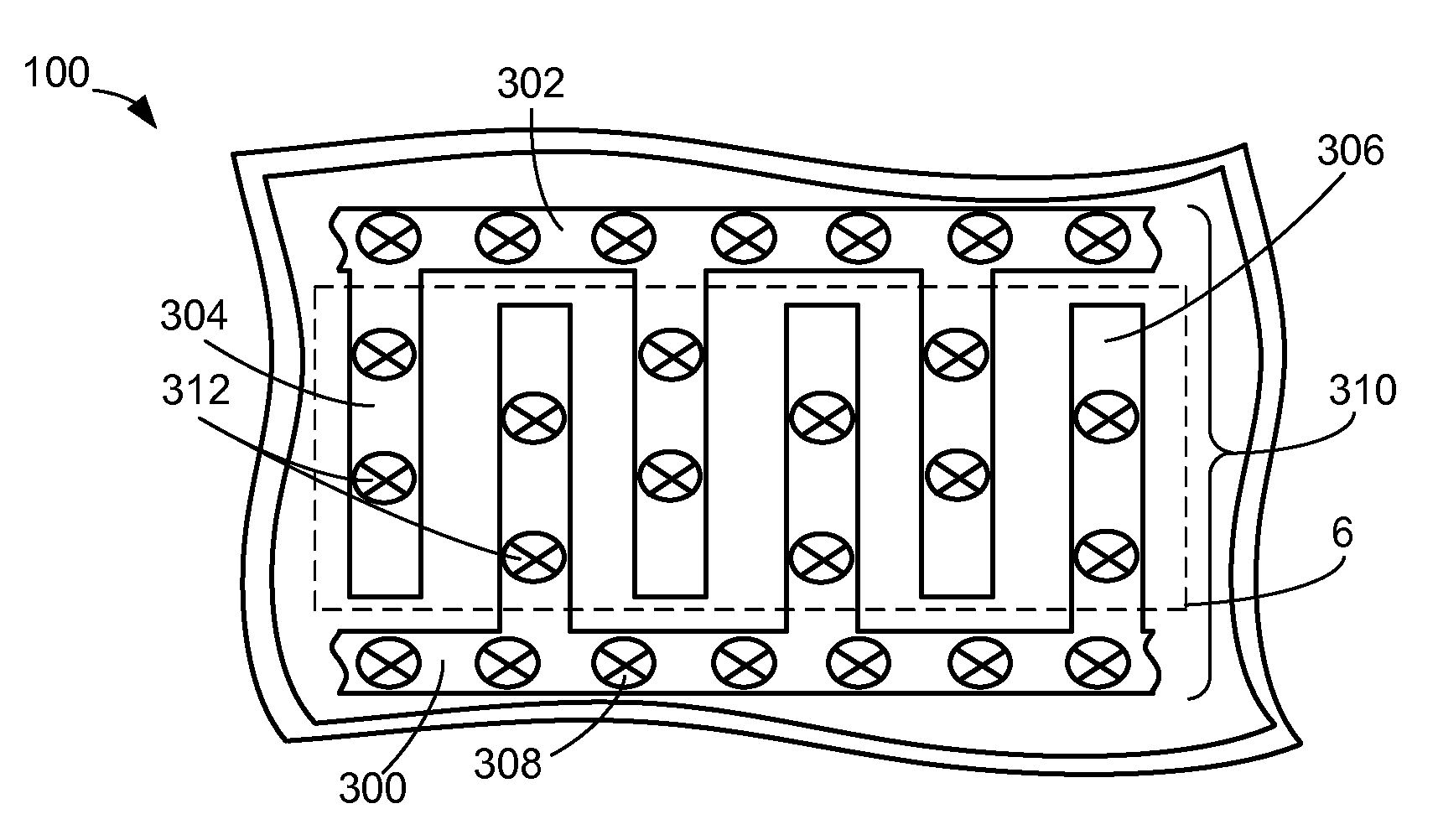

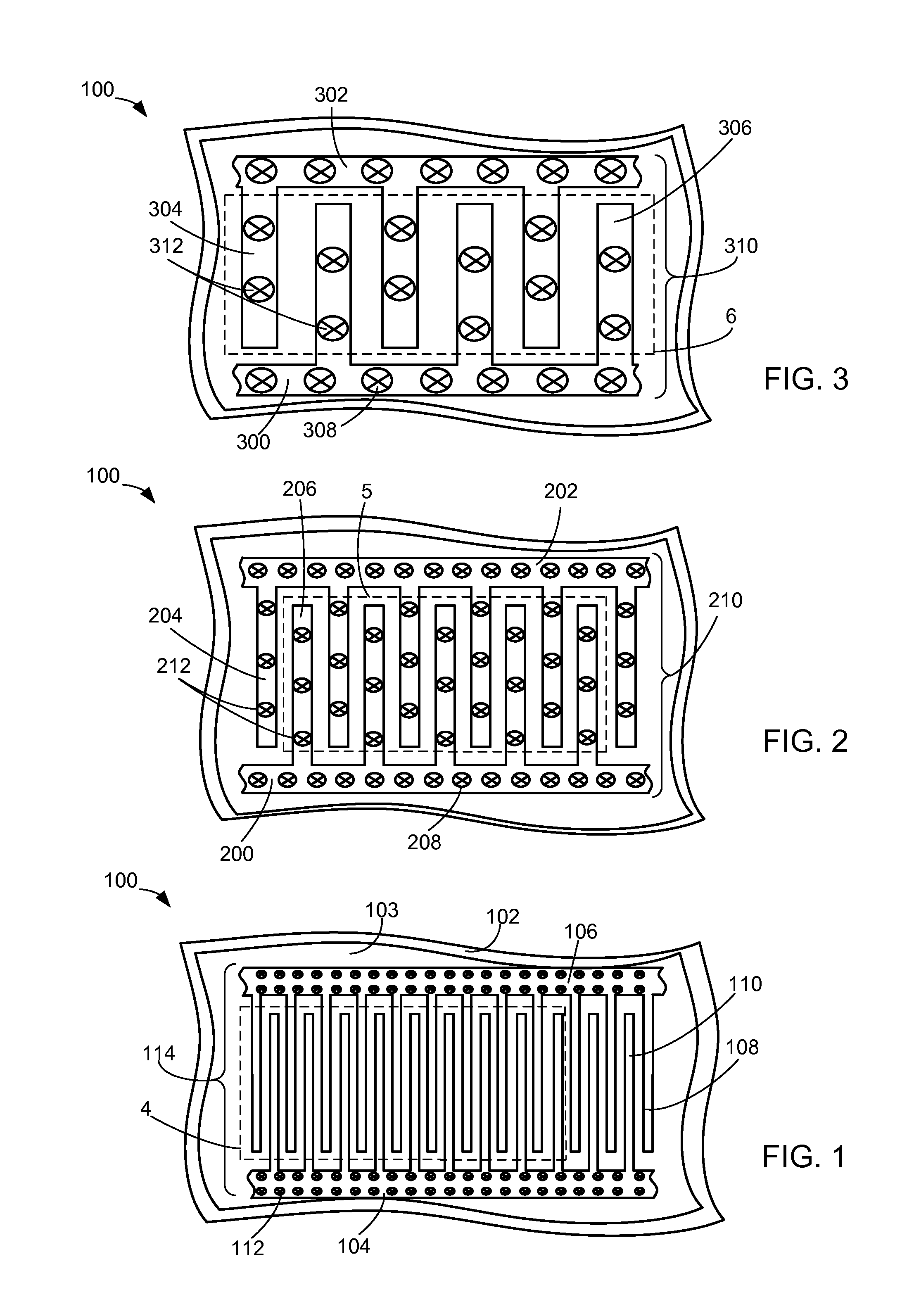

Integrated circuit system with hierarchical capacitor and method of manufacture thereof

ActiveUS20120007214A1Semiconductor/solid-state device detailsSolid-state devicesFront end of lineCapacitor

A method of manufacture of an integrated circuit system includes: providing a substrate including front-end-of-line circuitry; forming a first group of metal layers including a first finger and a second finger over the substrate utilizing a first design rule, the first group of metal layers being formed without a finger via; forming a second group of metal layers including a first finger, a second finger, and a finger via over the first group of metal layers utilizing a second design rule that is larger than the first design rule; and interconnecting the first group of metal layers, including interconnecting a first cluster adjacent to a second cluster, to form a capacitor.

Owner:GLOBALFOUNDRIES SINGAPORE PTE LTD

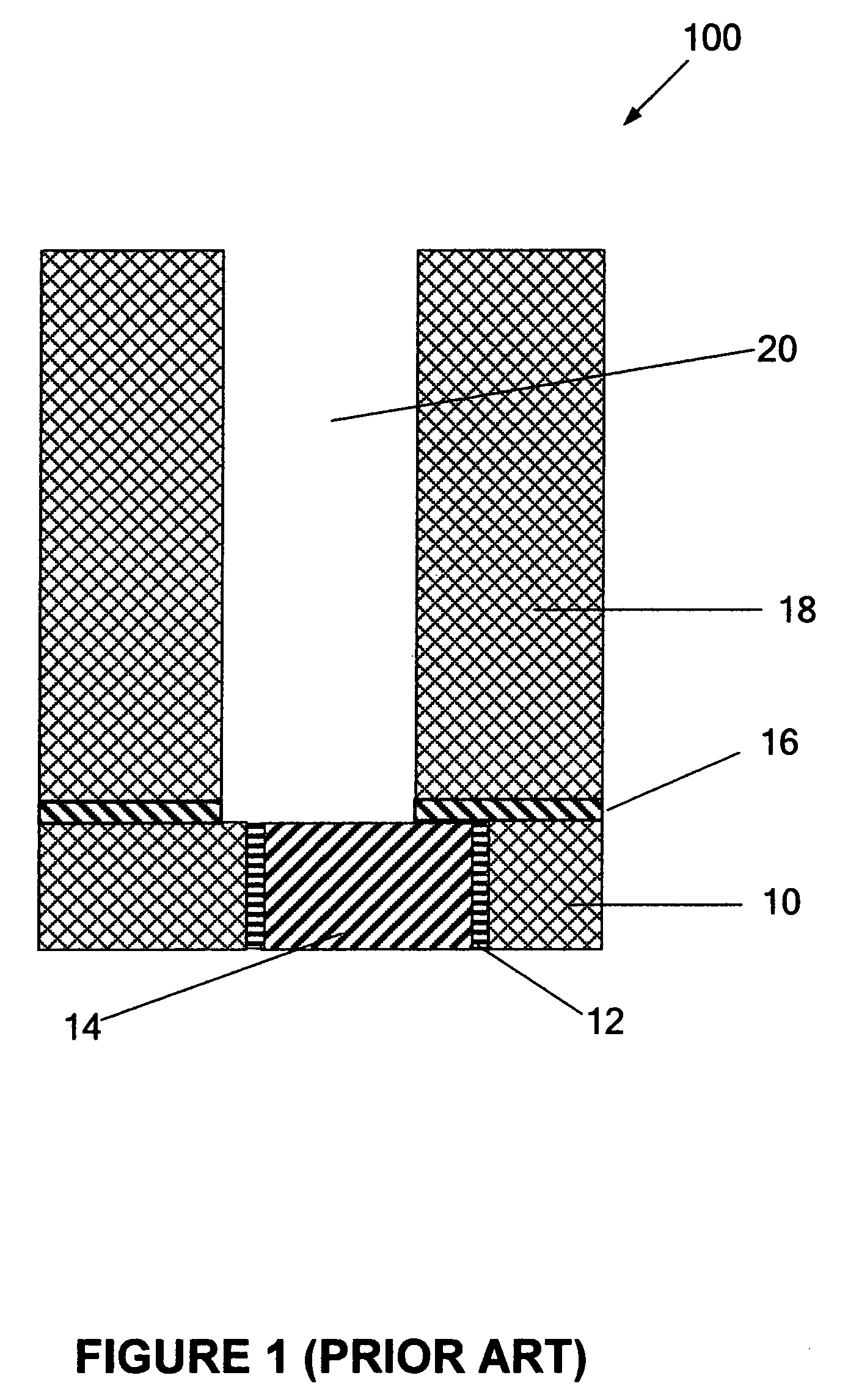

Method for filling of a recessed structure of a semiconductor device

InactiveUS7365005B1Quality improvementEasy to runSemiconductor/solid-state device manufacturingChemical vapor deposition coatingDevice materialGas phase

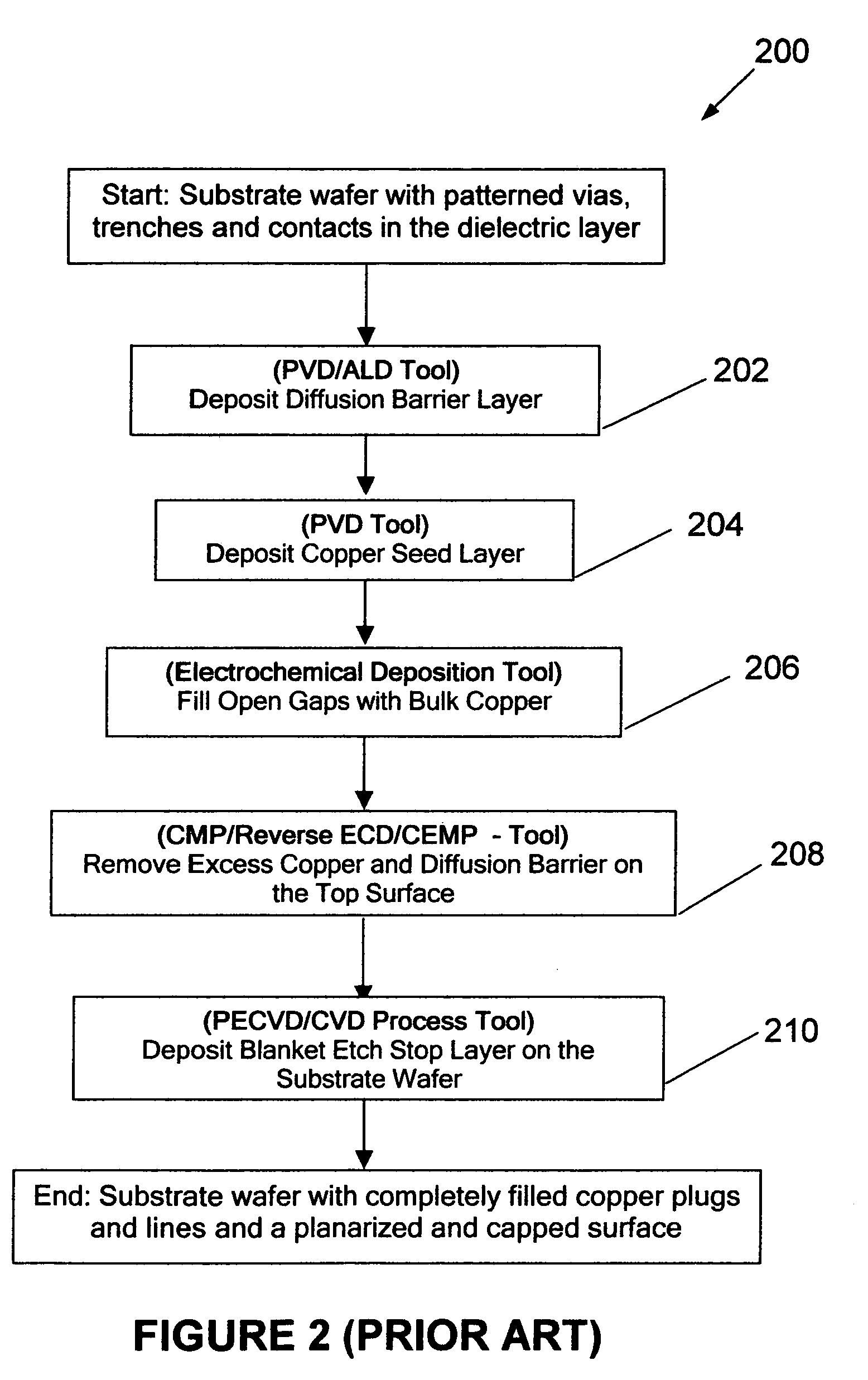

This invention relates to process sequence by high-speed atomic layer chemical vapor processing that includes deposition for diffusion barriers in the etched features on substrate followed by gap fill and subsequent in-situ removal of the blanket films on the top by plasma enhanced vapor phase processes. The apparatus and process sequences employed in these processing scheme allows the practitioner to complete all vapor phase process sequences of diffusion barrier deposition, gap fill and planarization of copper and diffusion barrier planarization. In case of copper metallization scheme, vapor phase gap fill can be employed to replace electrochemical deposition of copper and removal of copper and the diffusion barrier by vapor phase reactions can replace chemical-mechanical-polishing. Furthermore, such a processing scheme can be employed to deposit gate level dielectric layer, shallow trench isolation and also to form first metal contact plugs with a suitable barrier at the front end of line processing.

Owner:GADGIL PRASAD N

Cable end connector assembly and the method of making the same

InactiveUS6887104B2Protect electrical connectionsLine/current collector detailsRelieving strain on wire connectionElectrical connectionFront end of line

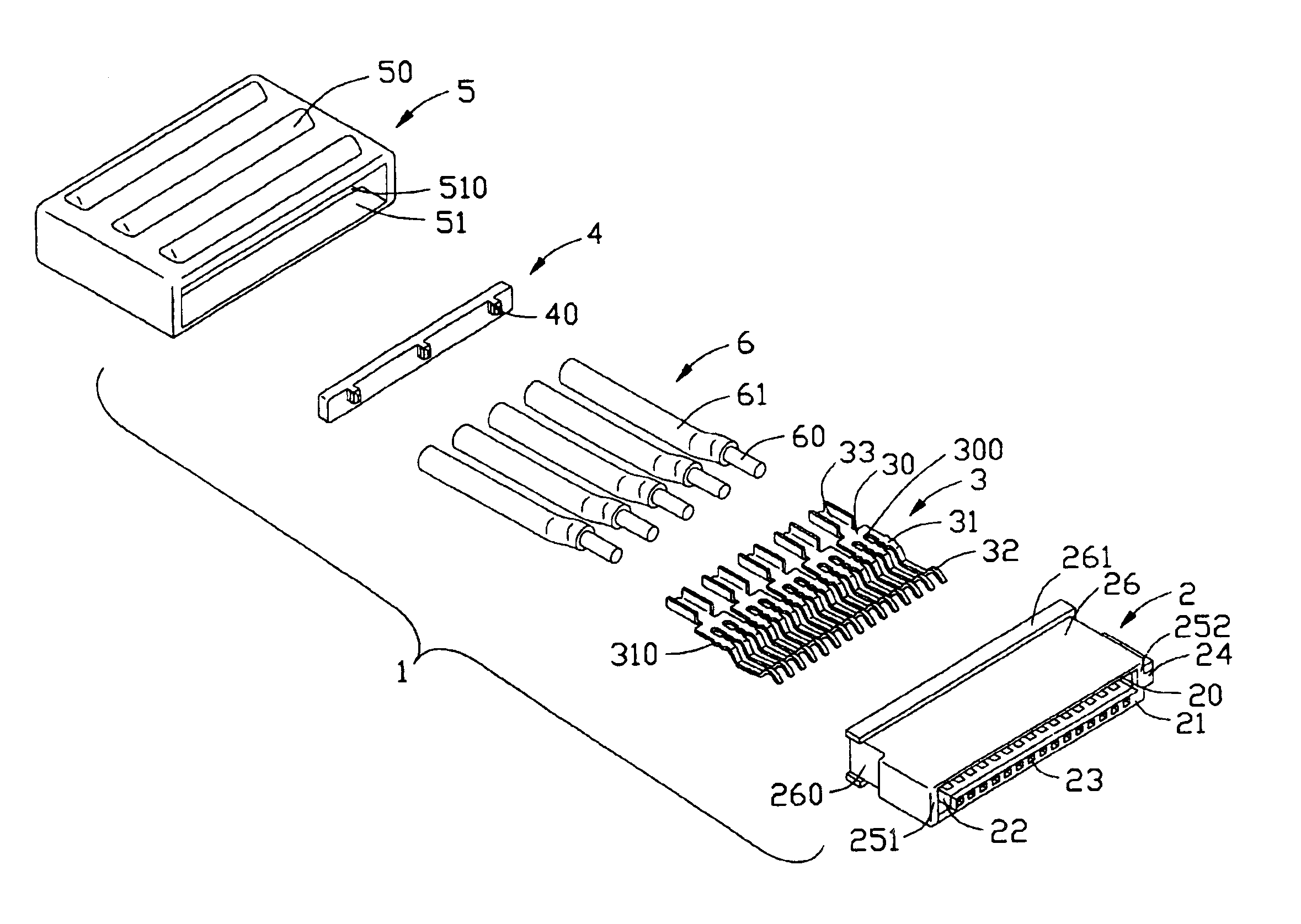

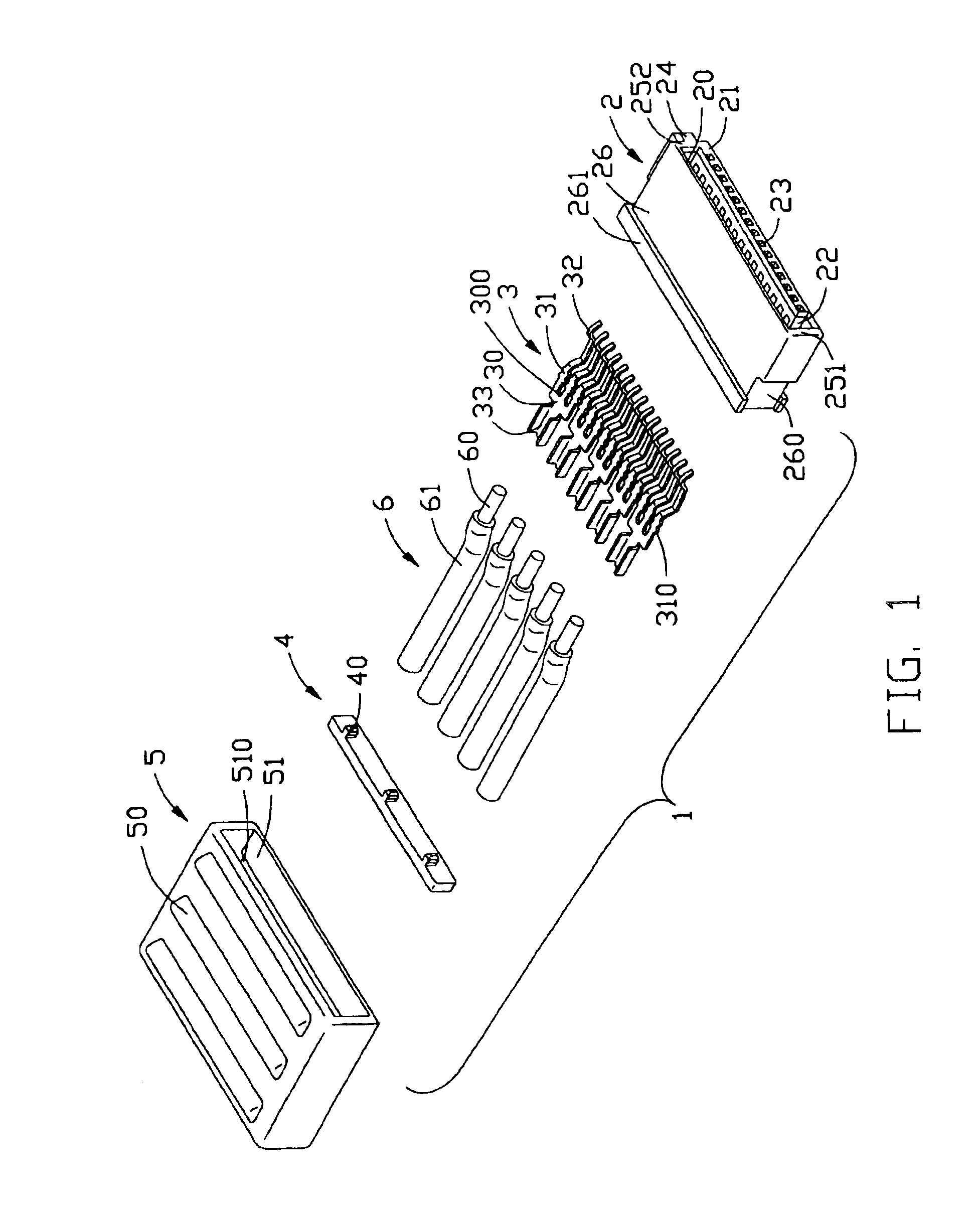

A cable end connector assembly (1) includes a dielectric housing (2), a plurality of contact units (3), a plurality of wires (6), and a cover (5). The housing includes an upper wall (20), a lower wall (21), and a pair of sidewalls (251, 252) connecting the upper and lower walls. Each contact unit comprises at least one mating portion (32) and a tail portion (33) opposite to the mating portion and extending beyond a rear face of the housing. The tail portion has a U-shaped configuration. Each wire comprises a conductive core (60) received in corresponding U-shaped tail portion and soldered with the tail portion to form electrical connection therebetween. The cover is over-molded with a rear end (26) of the housing and covers front ends of the wires and the tail portions of the contact units to protect the electrical connection between the wires and the contact units.

Owner:HON HAI PRECISION IND CO LTD

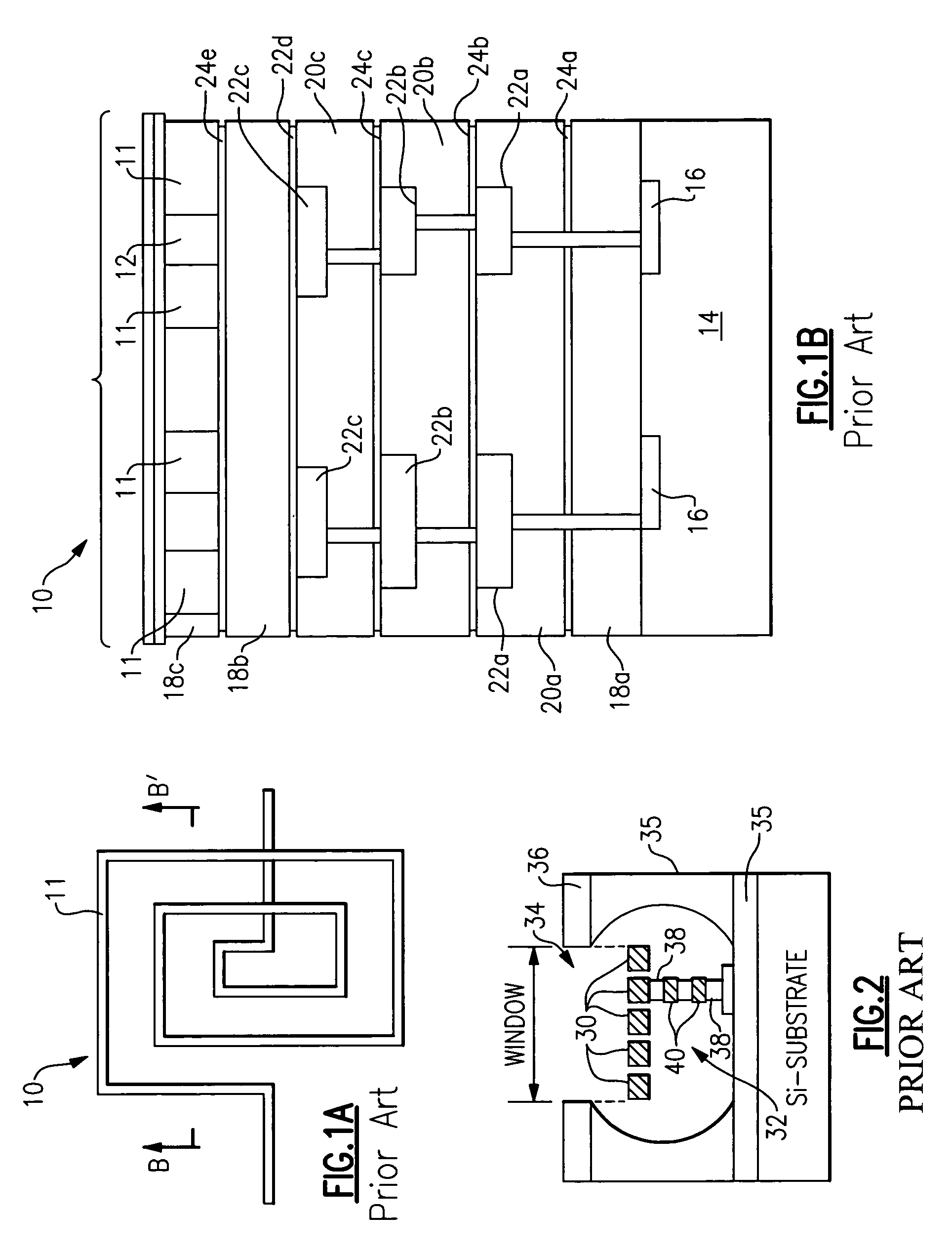

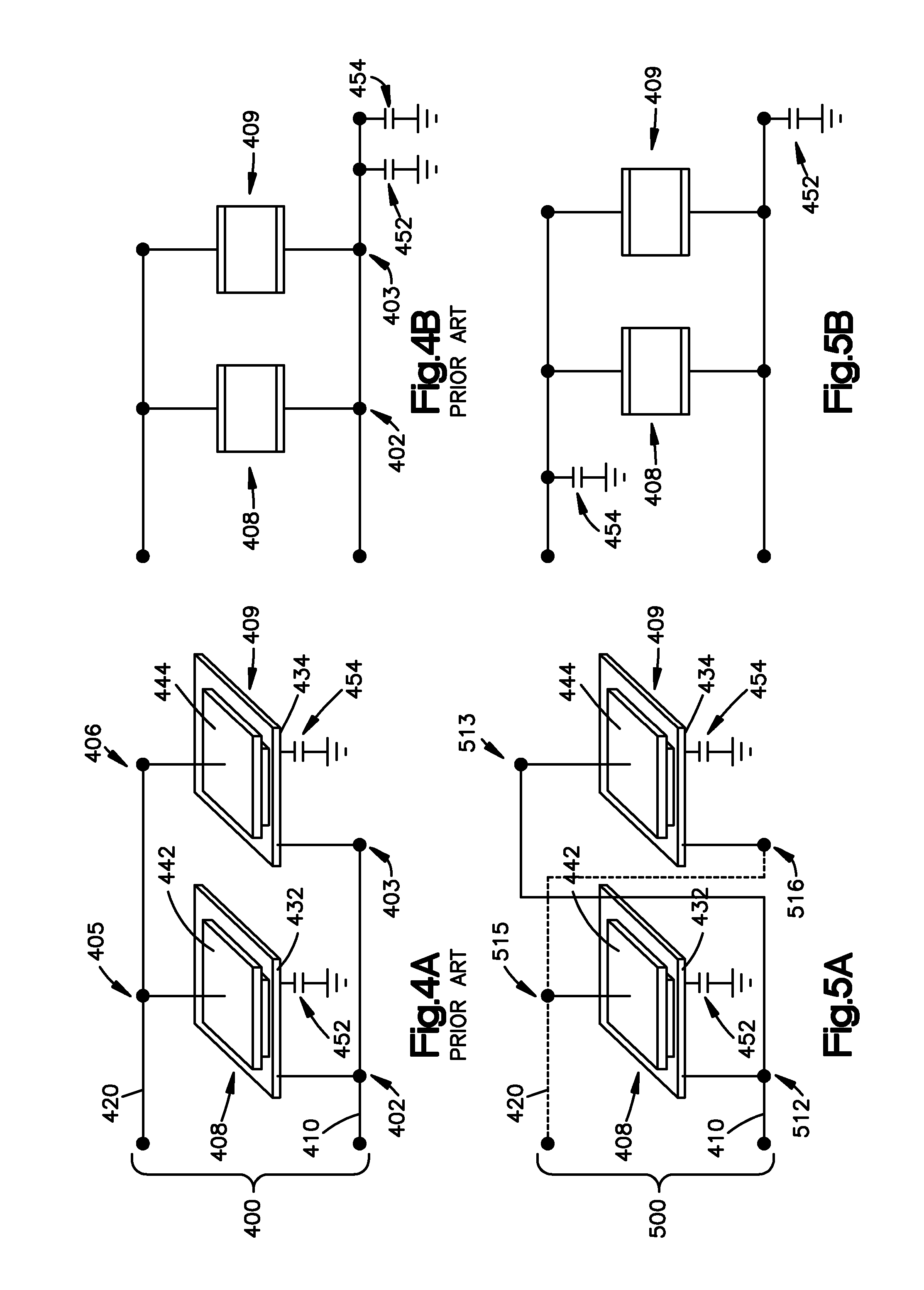

Method, system and design structure for symmetrical capacitor

InactiveUS20080099880A1Semiconductor/solid-state device detailsSolid-state devicesCapacitanceMetal-insulator-metal

Methods, articles and design structures for capacitance circuits are provided disposing a lower vertical-native capacitor metal layer above a planar front-end-of-line semiconductor base substrate, planar metal bottom plates spaced a bottom plate distance from the base and top plates above the bottom plates spaced a top plate distance from the base defining metal-insulator-metal capacitors, top plate footprints disposed above the base substrate smaller than bottom plate footprints and exposing bottom plate remainder upper lateral connector surfaces; disposing parallel positive port and negative port upper vertical-native capacitor metal layers over and each connected to top plate and bottom plate upper remainder lateral connector surface. Moreover, electrical connecting of the first top plate and the second bottom plate to the positive port metal layer and of the second top plate and the first bottom to the negative port metal layer impart equal total negative port and positive port metal-insulator-metal capacitor extrinsic capacitance.

Owner:TAIWAN SEMICON MFG CO LTD

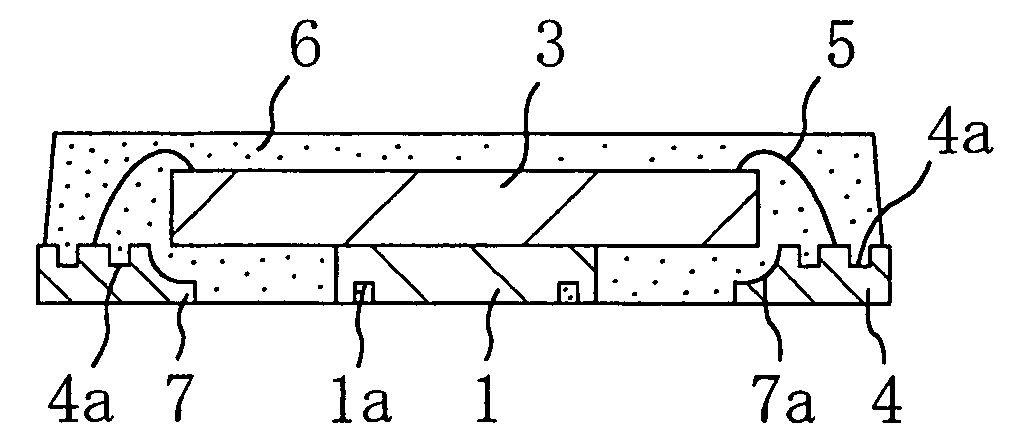

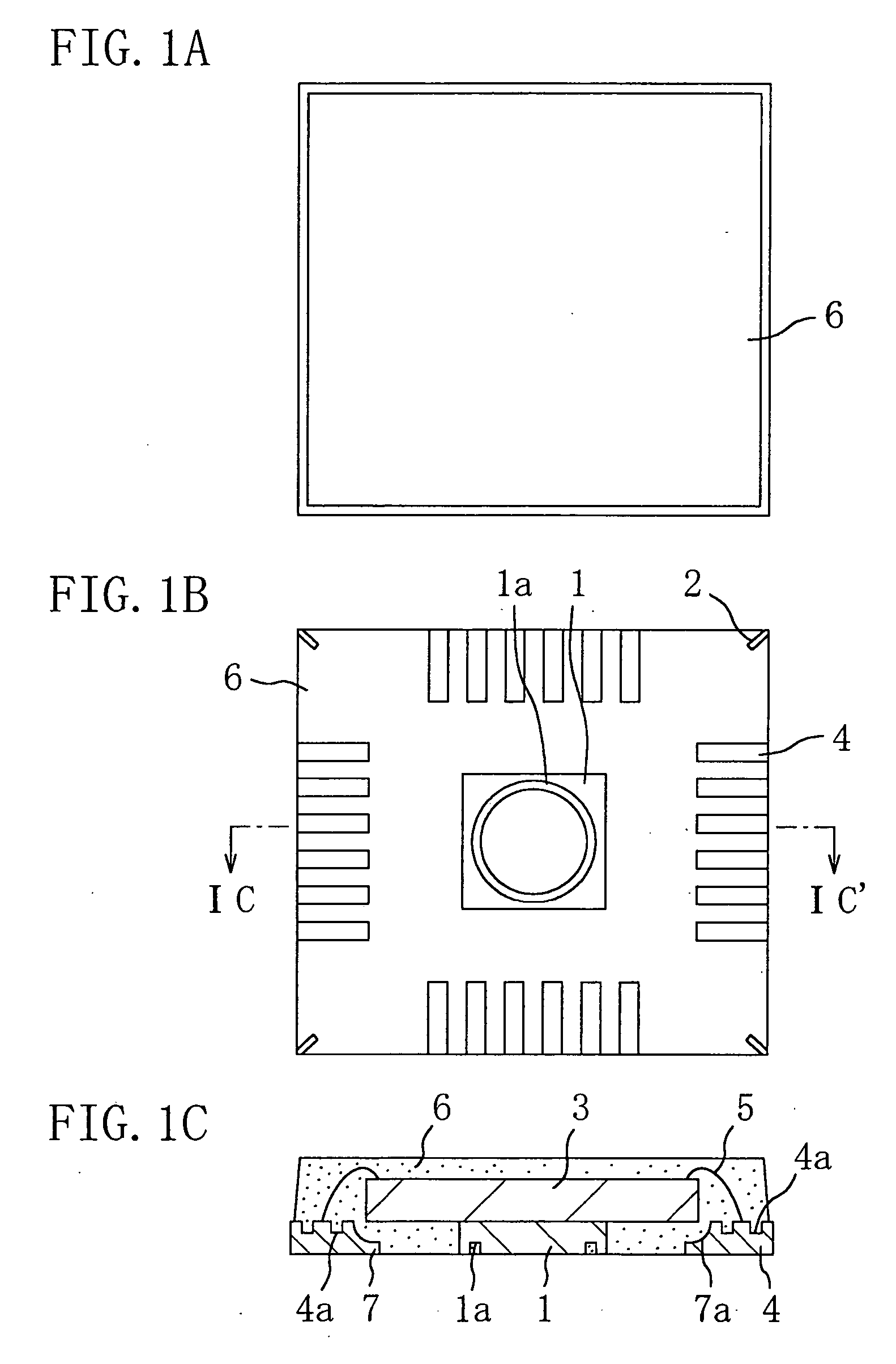

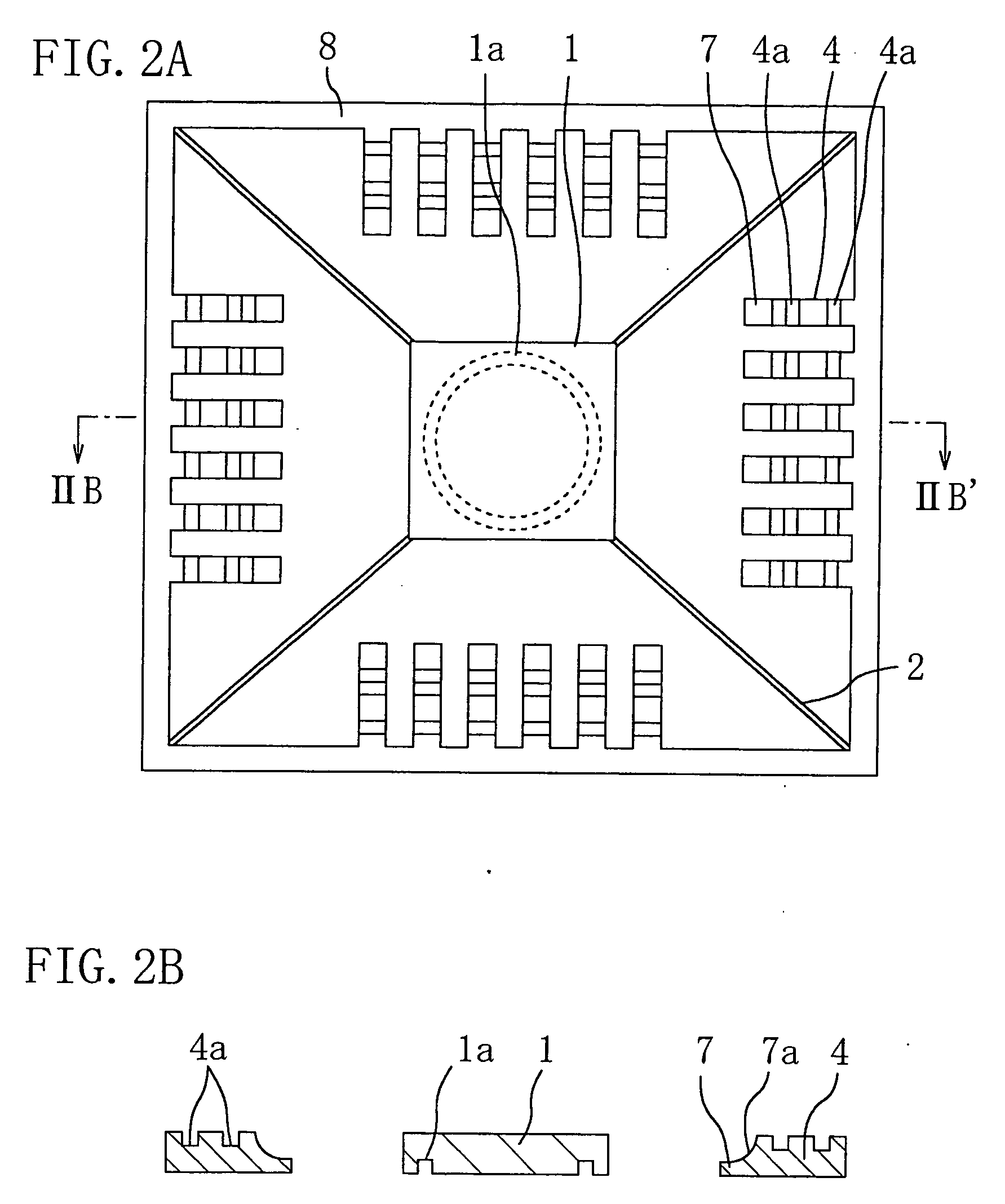

Resin-encapsulation semiconductor device and method for fabricating the same

InactiveUS20050167855A1Reduce thicknessSmall thicknessSemiconductor/solid-state device detailsSolid-state devicesDevice materialFront end of line

A resin-encapsulation semiconductor device of this invention includes a die pad for mounting a semiconductor element; a plurality of supporting leads; a semiconductor element; a plurality of leads disposed to have tips thereof opposing the die pad; metal wires; and an encapsulation resin for encapsulating the die pad excluding a bottom thereof, the leads excluding bottoms and outside edges thereof, connecting regions with the metal wires, the supporting leads and the semiconductor element. The outside edges of the leads are disposed on substantially the same plane as the side face of the encapsulation resin, and the tip of each lead has a thin portion where the thickness is reduced in an upper face thereof.

Owner:TESSERA ADVANCED TECH

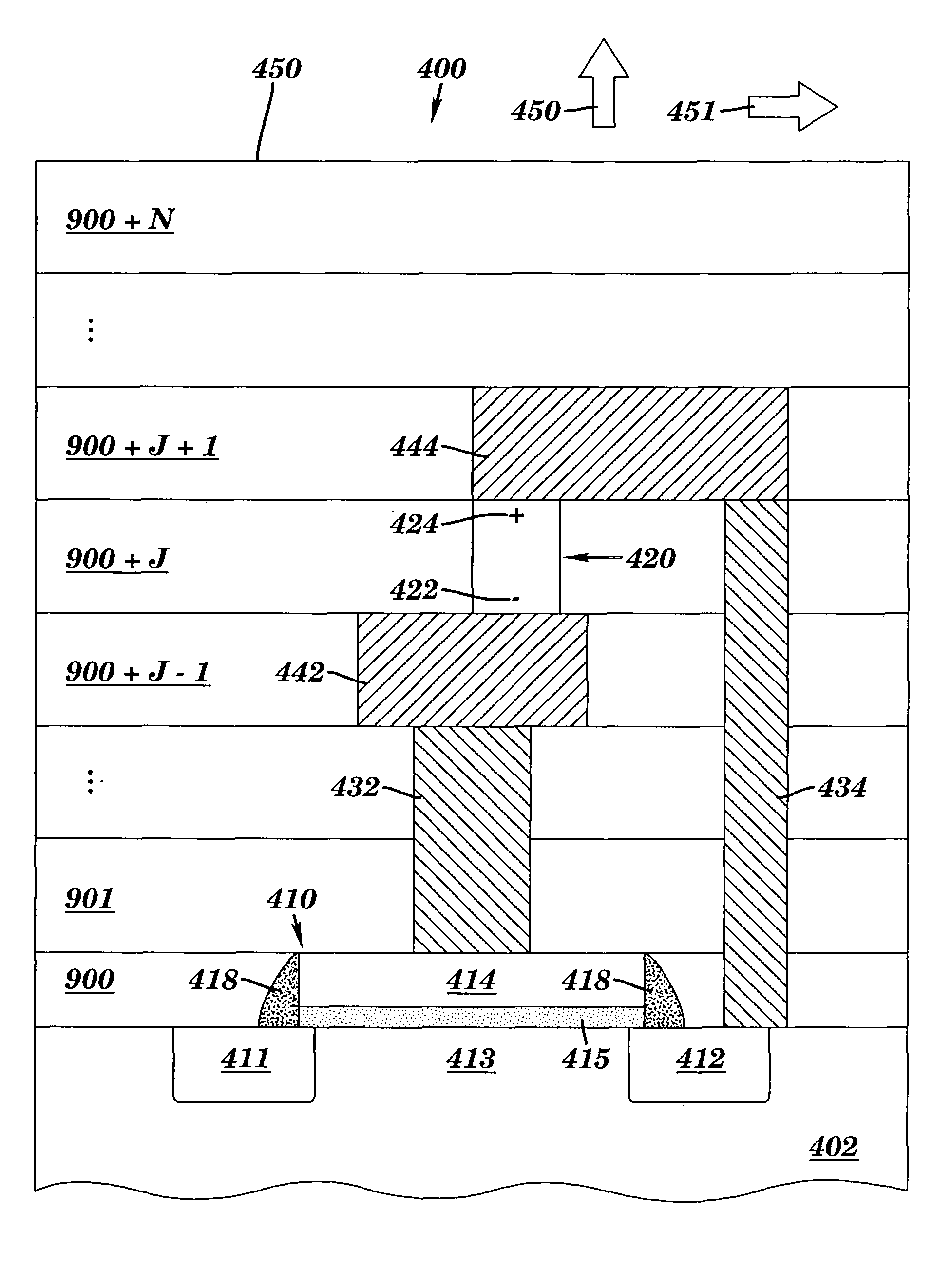

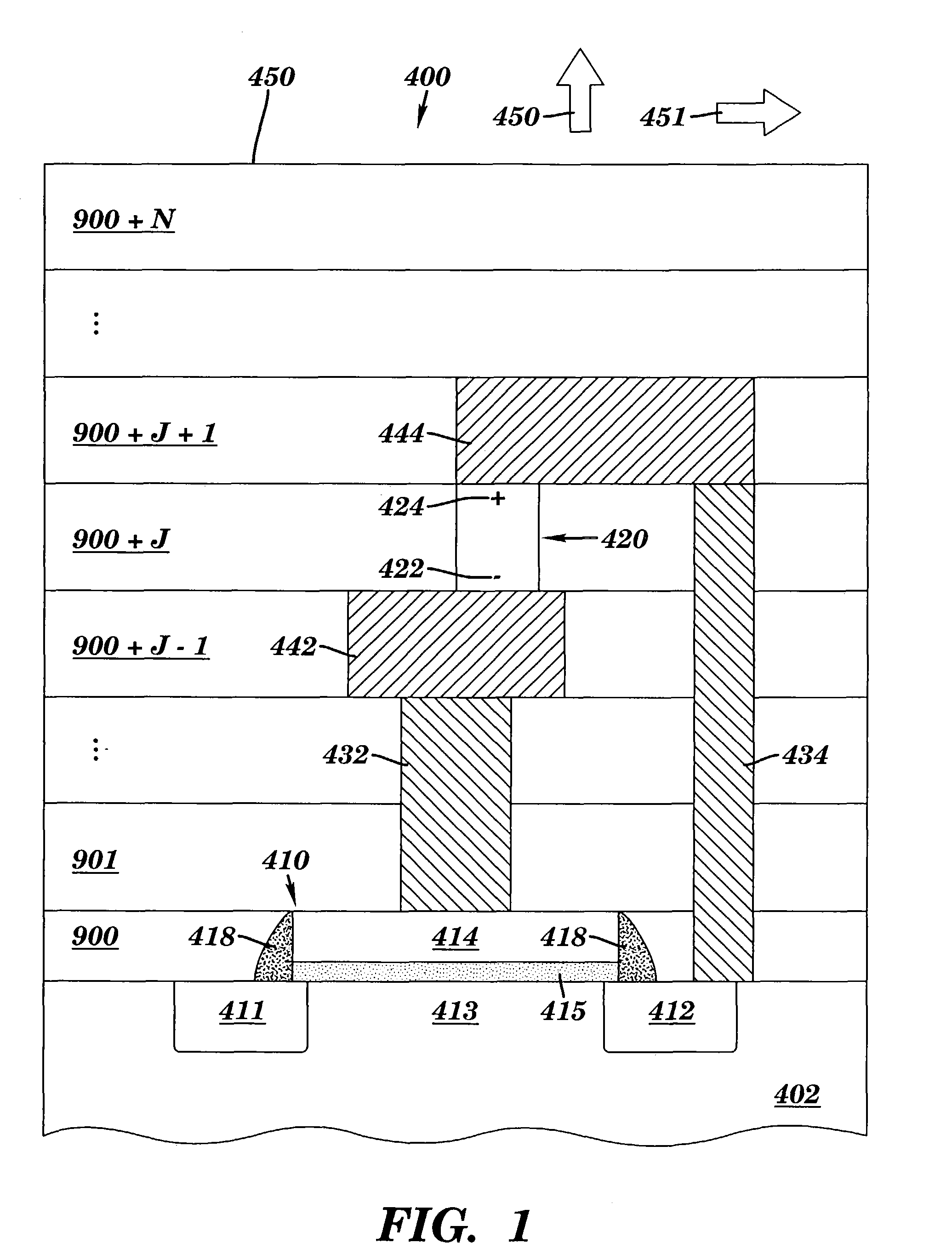

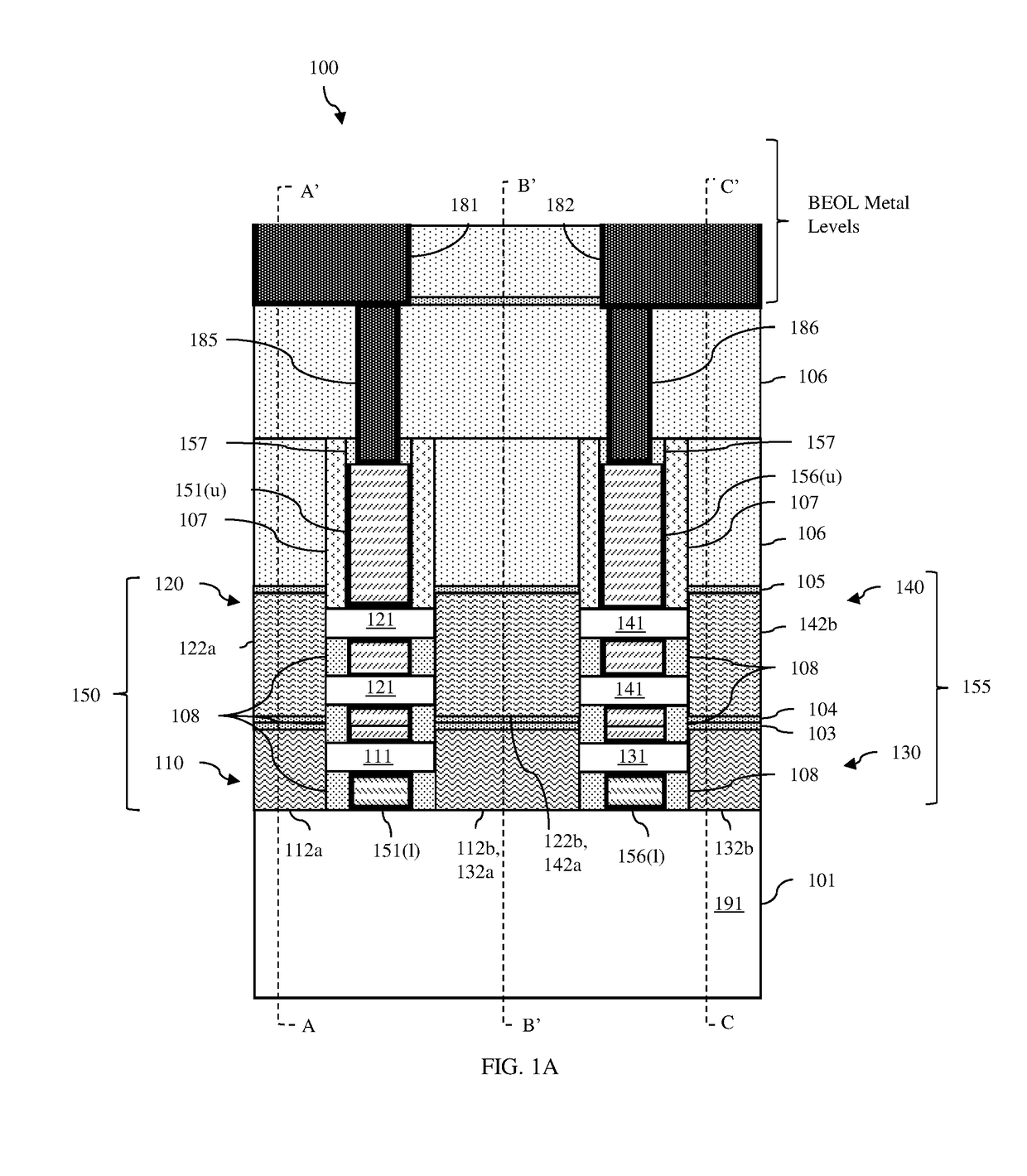

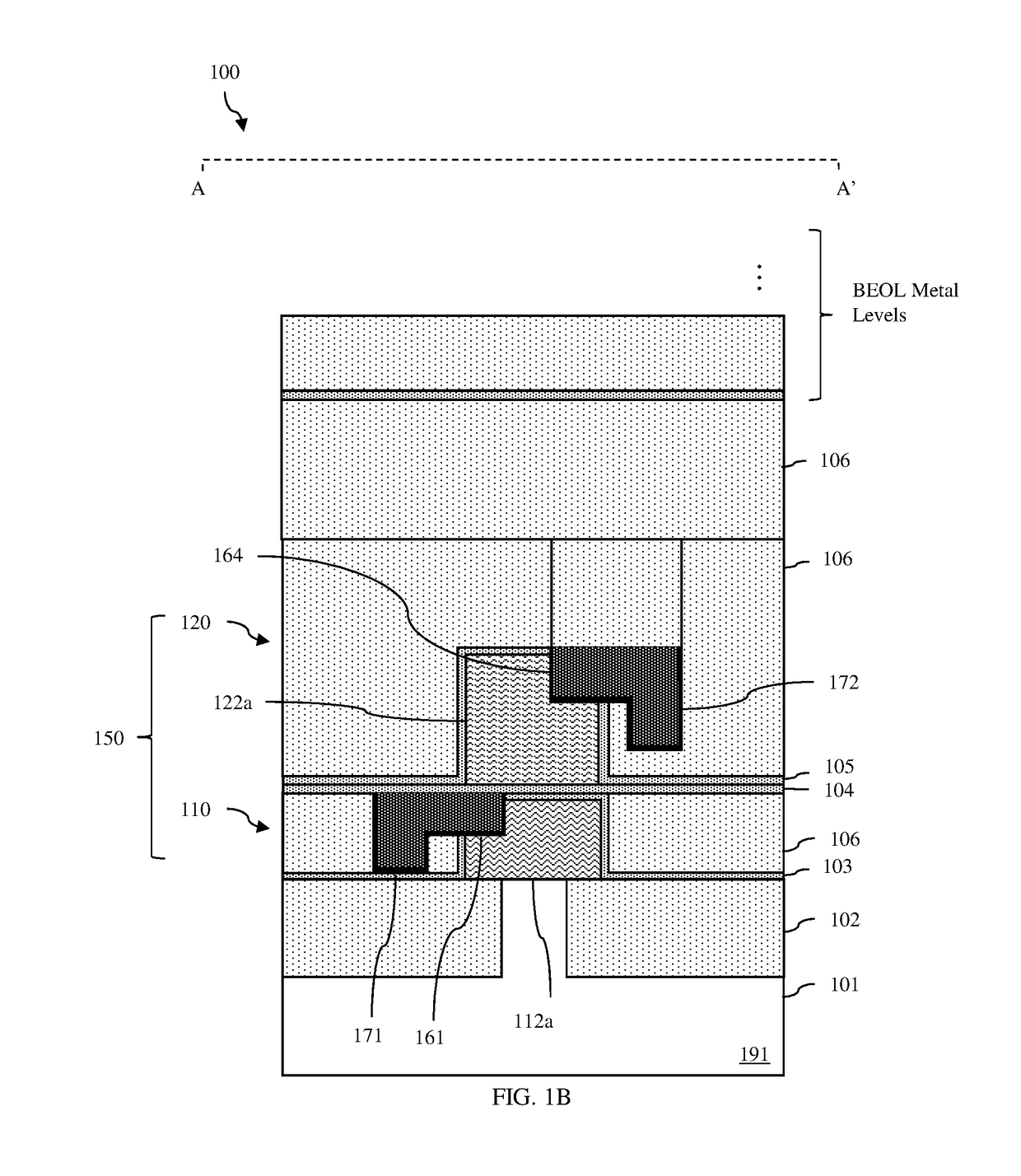

Integrated circuit structure incorporating stacked field effect transistors

Disclosed are integrated circuit (IC) structure embodiments that incorporate a stacked pair of field effect transistors (FETs) (e.g., gate-all-around FETs) and metal components that enable power and / or signal connections to source / drain regions of those FETs. Specifically, the IC includes a first FET and a second FET stacked on and sharing a gate with the first FET. The metal components include an embedded contact in a source / drain region of the first FET and connected to a wire (e.g., a power or signal wire). The wire can be a front end of the line (FEOL) wire positioned laterally adjacent to the source / drain region and the embedded contact can extend laterally from the source / drain region to the FEOL wire. Alternatively, the wire can be a back end of the line (BEOL) wire and an insulated contact can extend vertically from the embedded contact through the second FET to the BEOL wire.

Owner:GLOBALFOUNDRIES US INC

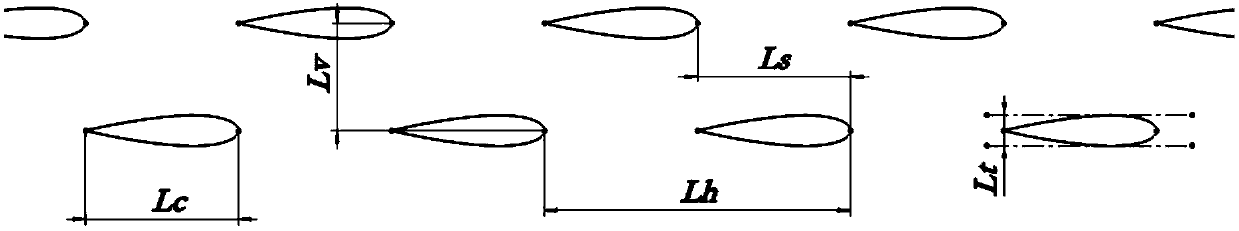

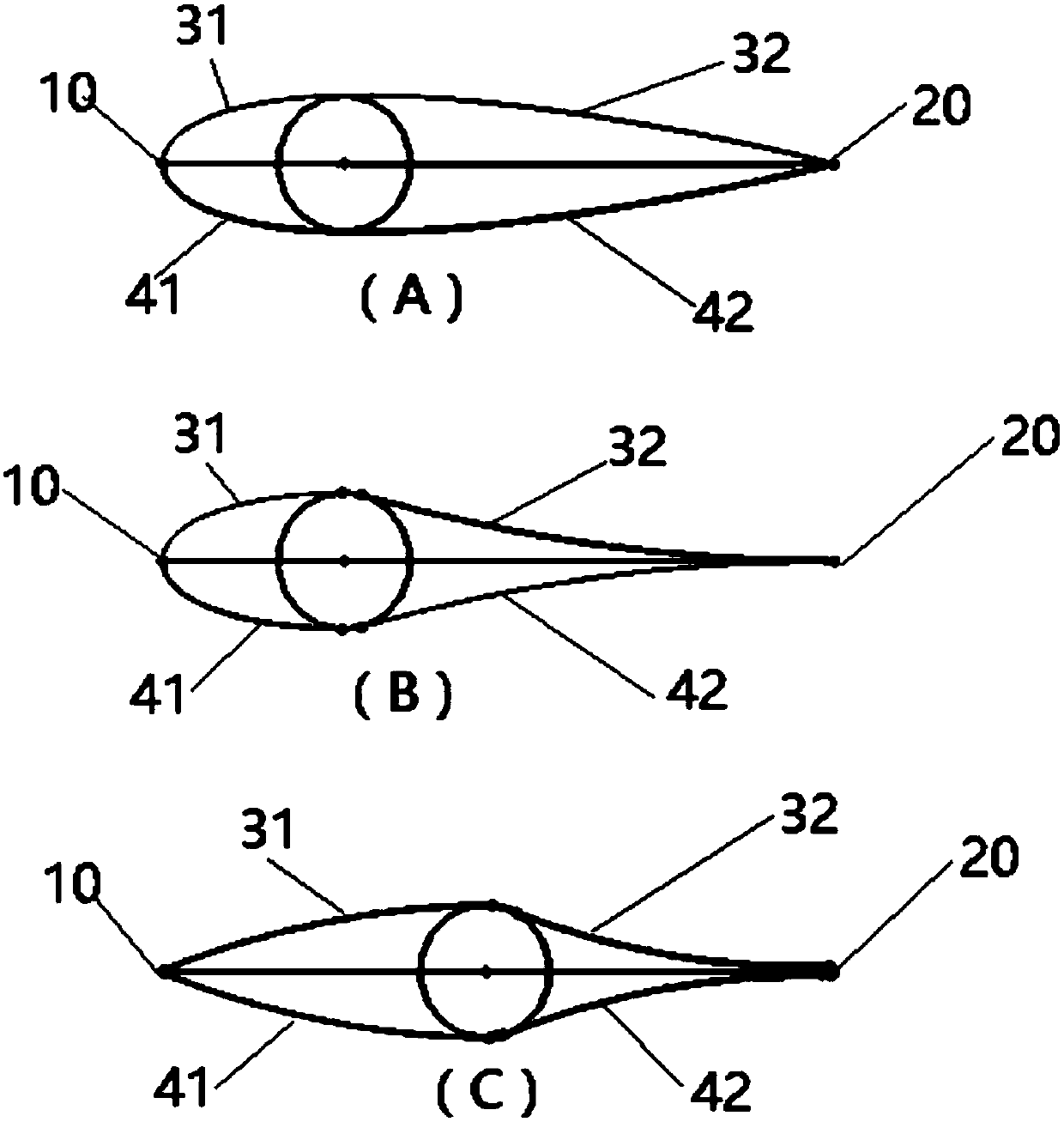

Heat exchange plate with streamline structure, and printed circuit board heat exchanger with same

ActiveCN107687780ATo achieve the purpose of heat exchangeDramatic changeLaminated elementsStationary plate conduit assembliesEngineeringFront end of line

The invention provides a heat exchange plate with a streamline structure, and a printed circuit board heat exchanger with same. The first segment of the upper arc and the first segment of the lower arc of a streamline rib extend to the position of a maximum incircle from the front edge of a wing form, each first segment is a convex smooth curve, the rear end of each convex smooth curve is in tangency with the maximum incircle, second segments extend to the rear edge of the wing form from the maximum incircle, each second segment is a concave smooth curve, the front end of each concave smooth curve is in tangency with the maximum incircle, and a smooth continuous curve is formed by each first segment and the corresponding second segment at the position of the maximum incircle. According tothe heat exchange plate with a streamline structure, and the printed circuit board heat exchanger with same, because the original structure of a wing-shaped rib is redesigned and optimized, when heatexchange fluid flows through wing-shaped ribs, changes between the front part and the rear part of the maximum width of a wing-shaped rib happen more violently, and the heat exchange performance of awing-shaped channel is improved; and because structural design is carried out on the front edge and the rear edge of a wing form, the heat exchange fluid can be guided to flow better, and therefore, the pressure drop loss of the wing-shaped channels is reduced.

Owner:INST OF ENGINEERING THERMOPHYSICS - CHINESE ACAD OF SCI

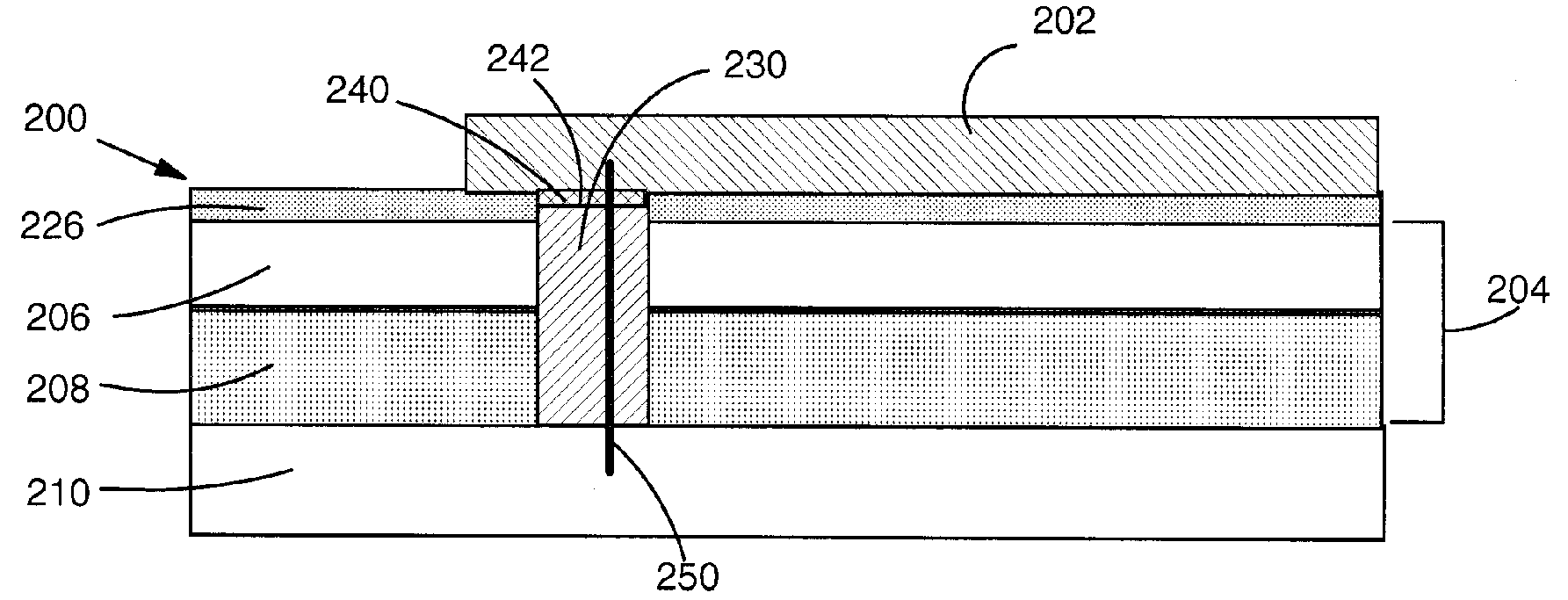

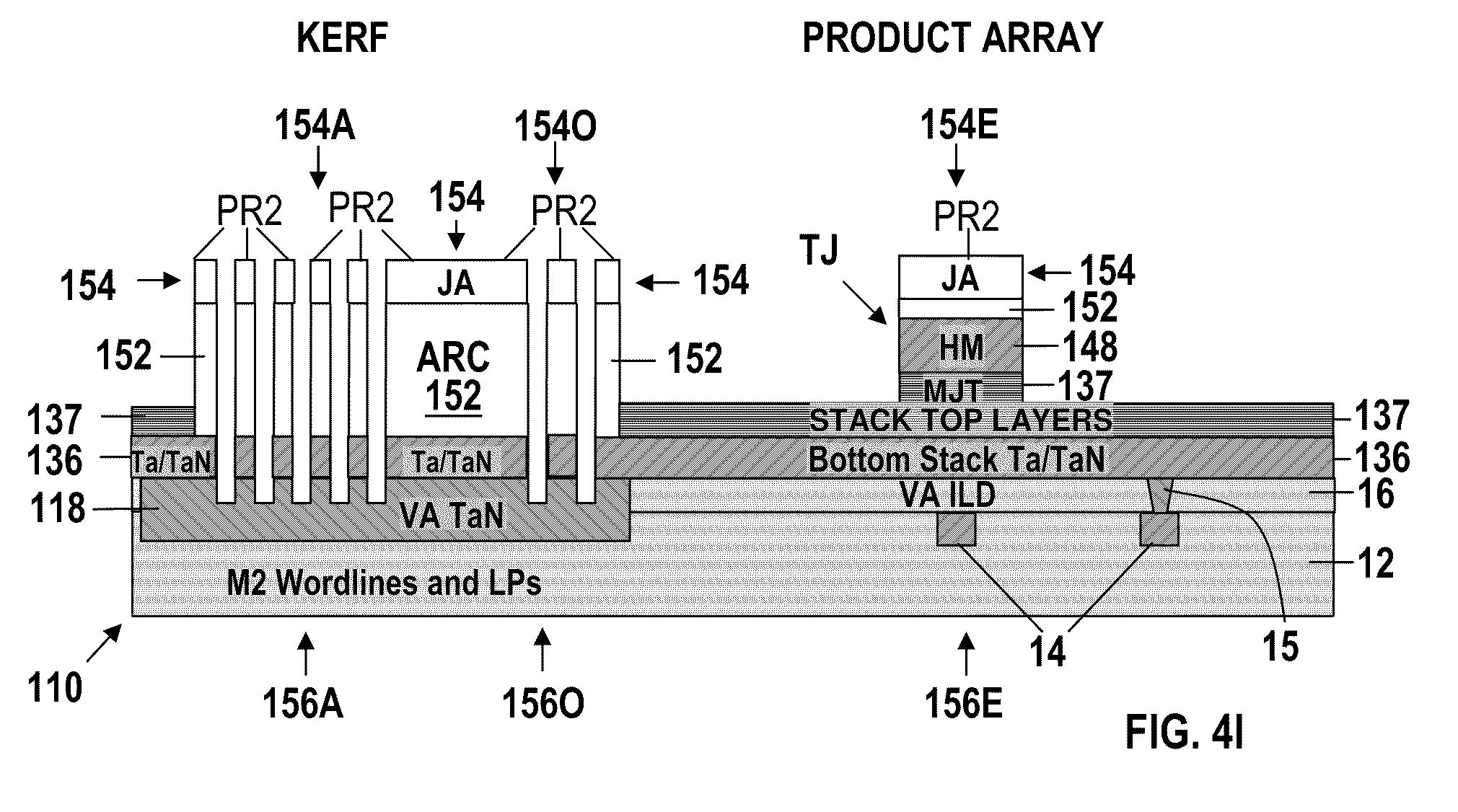

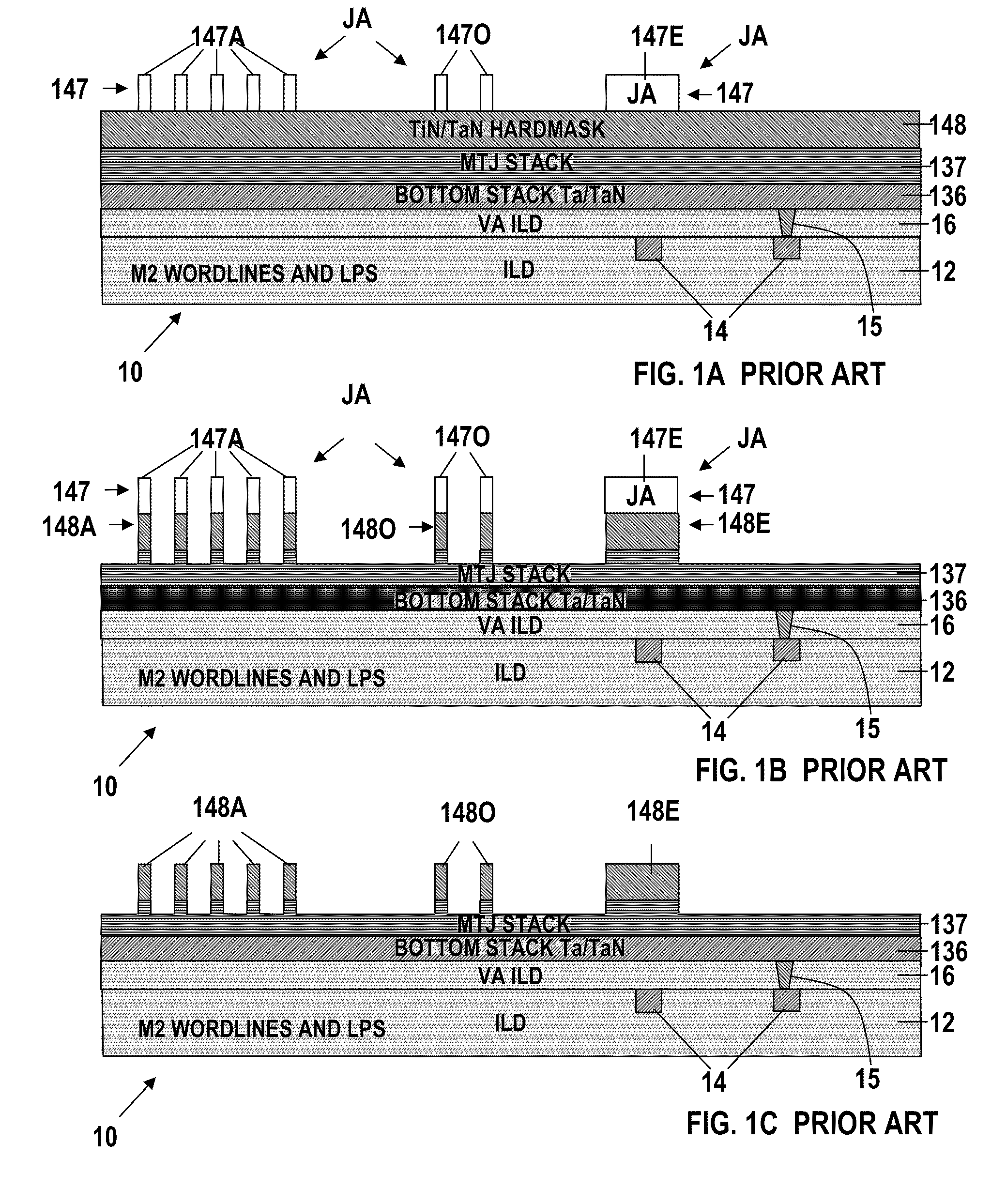

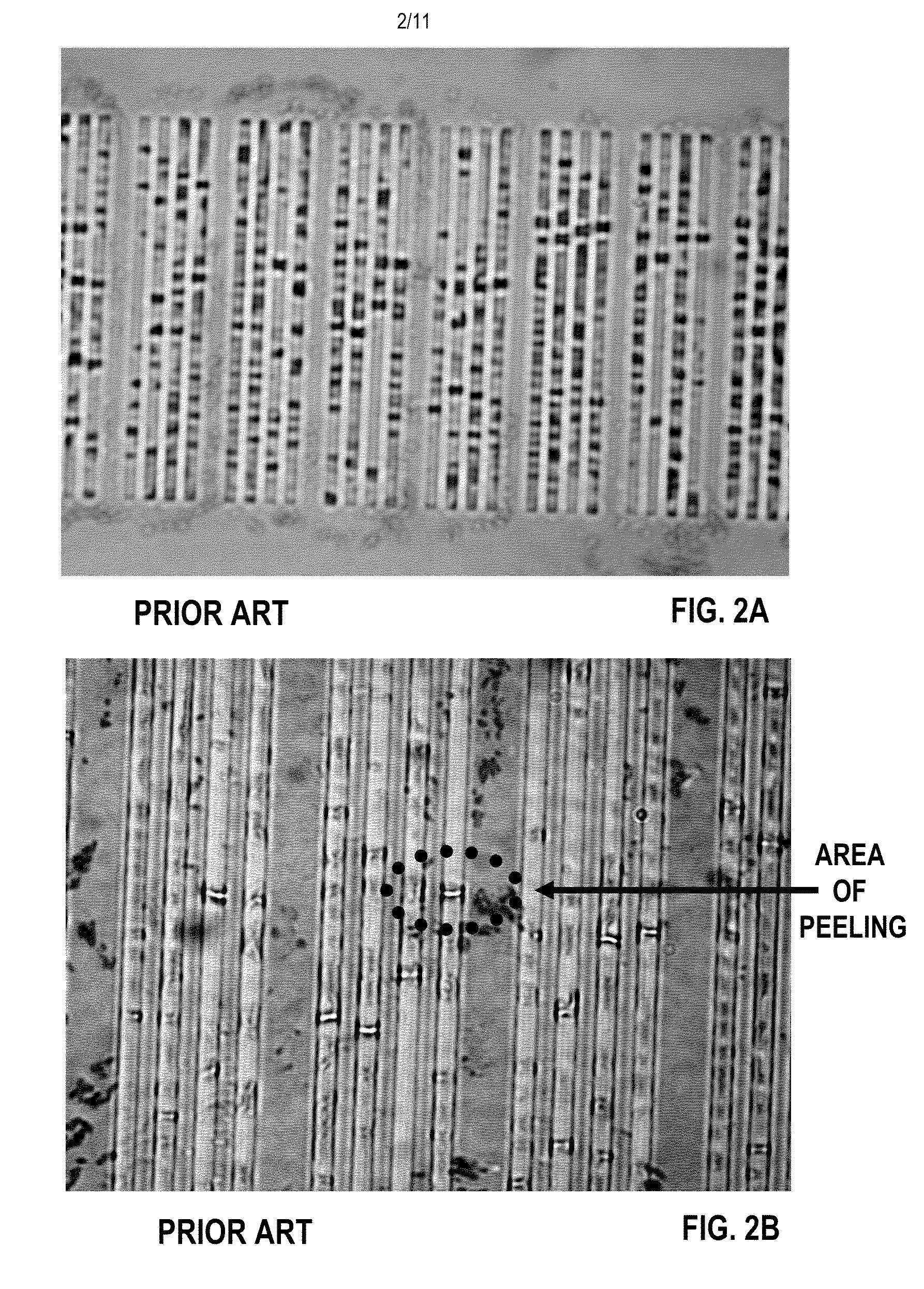

Method for integration of magnetic random access memories with improved lithographic alignment to magnetic tunnel junctions

InactiveUS7825000B2Easy alignmentSatisfactory reliabilitySemiconductor/solid-state device detailsSolid-state devicesDielectricStatic random-access memory

A magnetic memory device including a Magnetic Tunnel Junction (MTJ) device comprises a substrate and Front End of Line (FEOL) circuitry. A Via level (VA) InterLayer Dielectric (ILD) layer, a bottom conductor layer, and an MTJ device formed over the top surface of the VA ILD layer are formed over a portion of the substrate. An alignment region including alignment marks extends through the bottom conductor layer and extends down into the device below the top surface of the VA ILD layers is juxtaposed with the MJT device.

Owner:GLOBALFOUNDRIES US INC

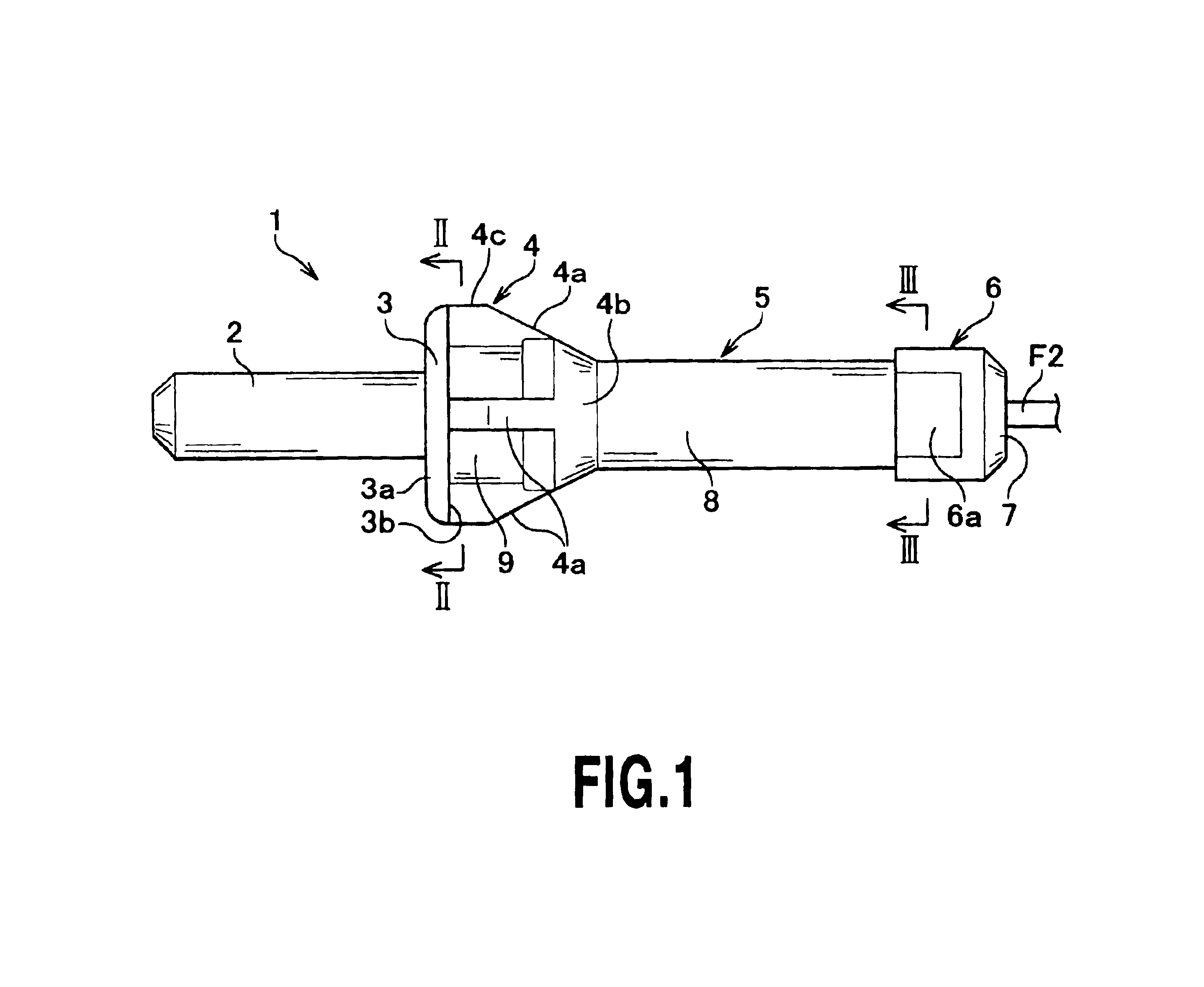

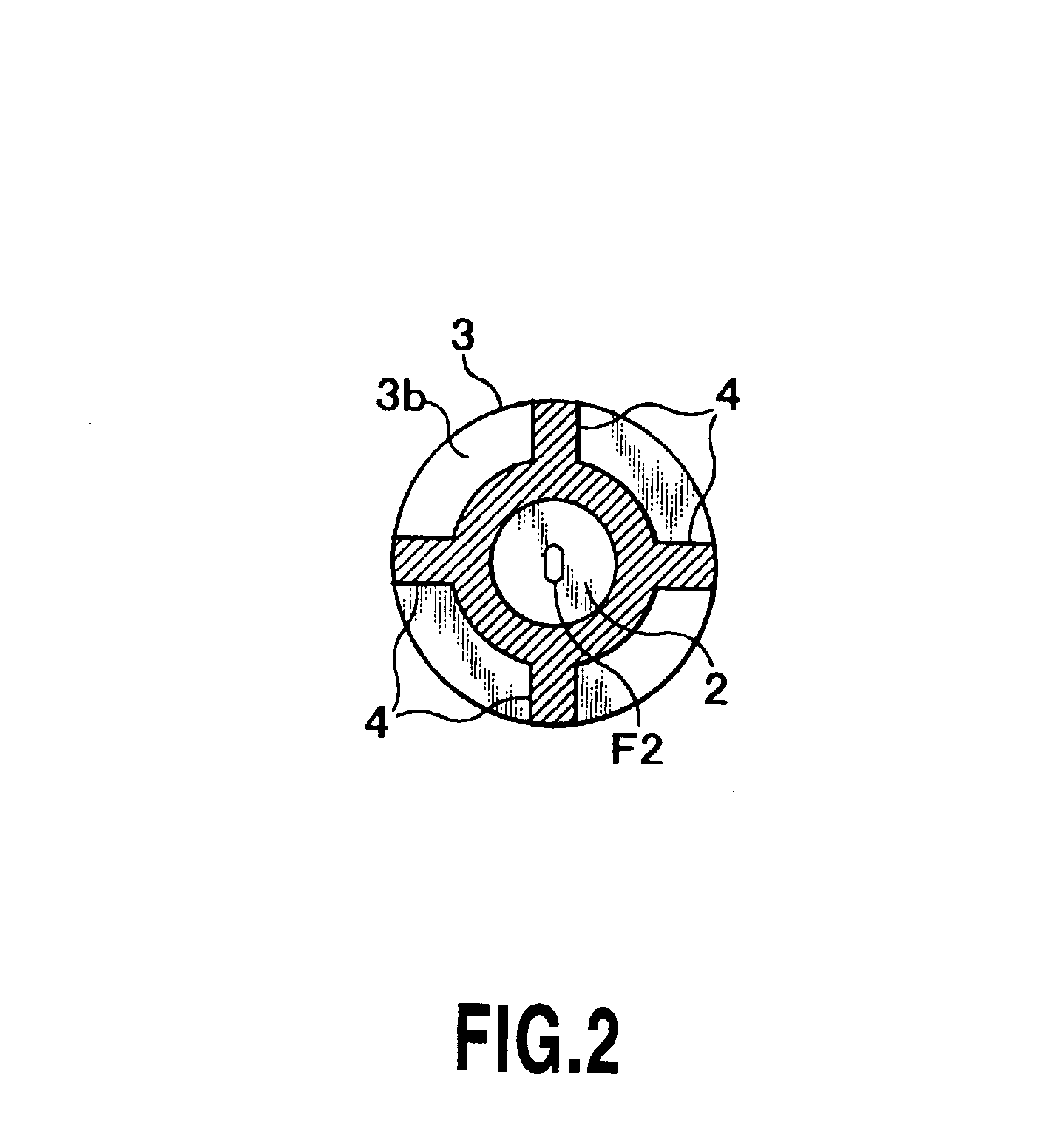

Optical fiber cross-connect with a connection block, an alignment block and a handling device

InactiveUS6877906B2Secure high reliabilityEliminate entanglementCoupling light guidesEngineeringFront end of line

An optical connector plug according to the present invention which is joined to a front end of an optical fiber cord covering an optical fiber and which is removably inserted to one end of an optical adapter having a locking member for locking the optical connector plug in an engaged state, includes an inserted portion removably inserted to one end of the optical adapter, a plug body joined to a front end of the optical fiber cord, a locking portion formed between the plug body and the inserted portion and locked by the locking member of the optical adapter, and a rotational phase reference surface formed on the plug body away from the locking portion. The optical connector plug according to the present invention can be applied to APC optical connector plug, secure high reliability for optical cross-connecting, and also reduce cost.

Owner:NIPPON TELEGRAPH & TELEPHONE CORP

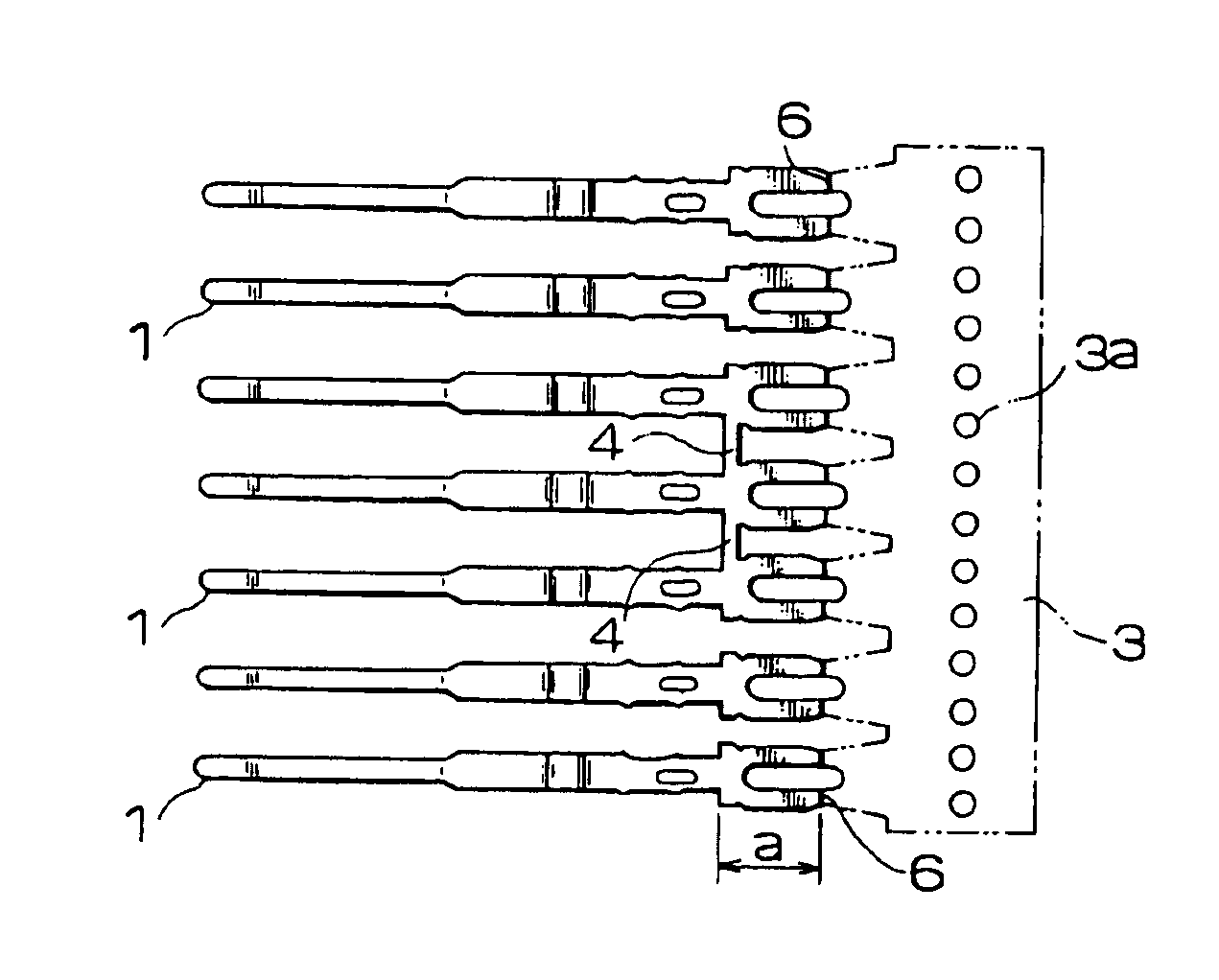

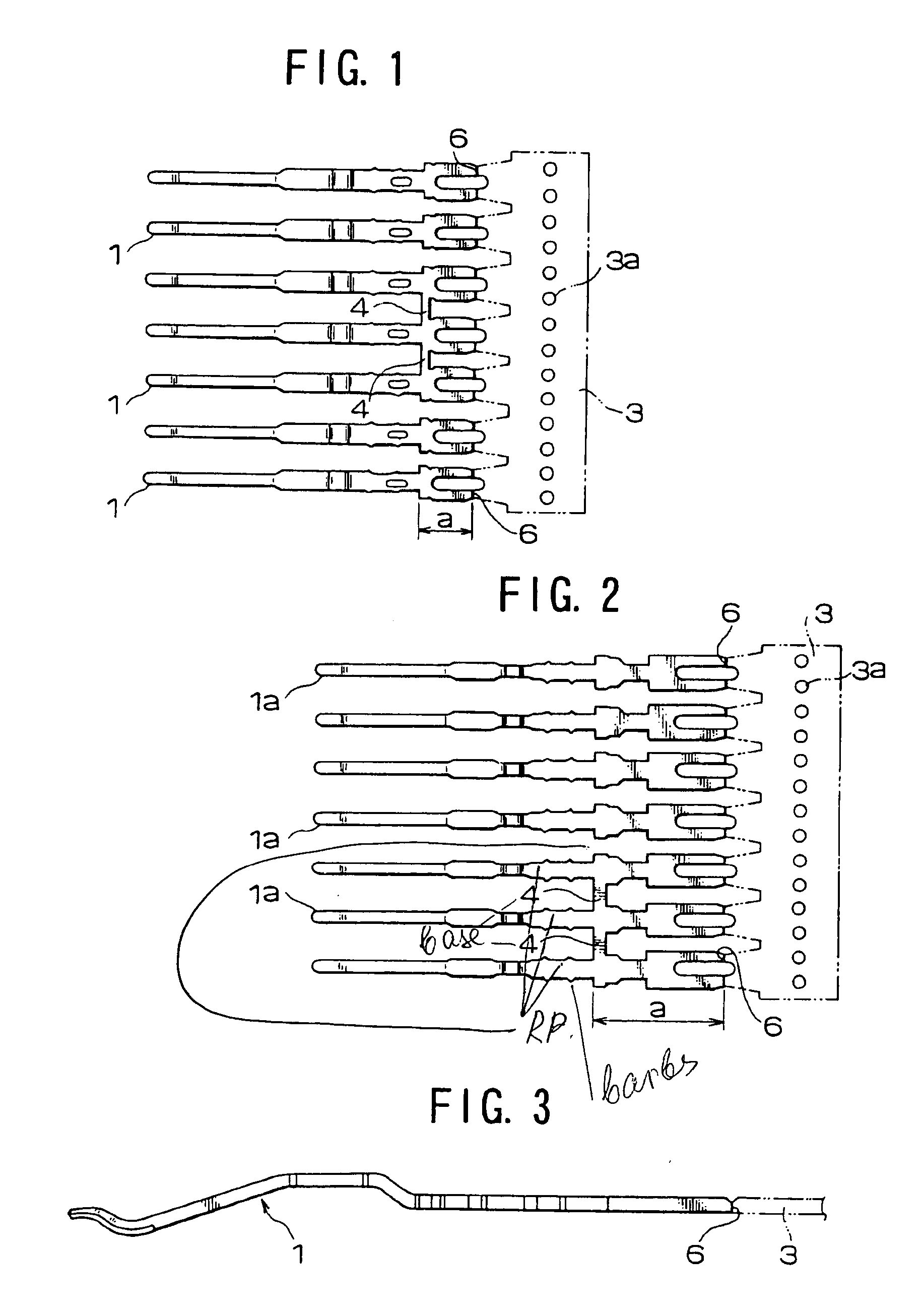

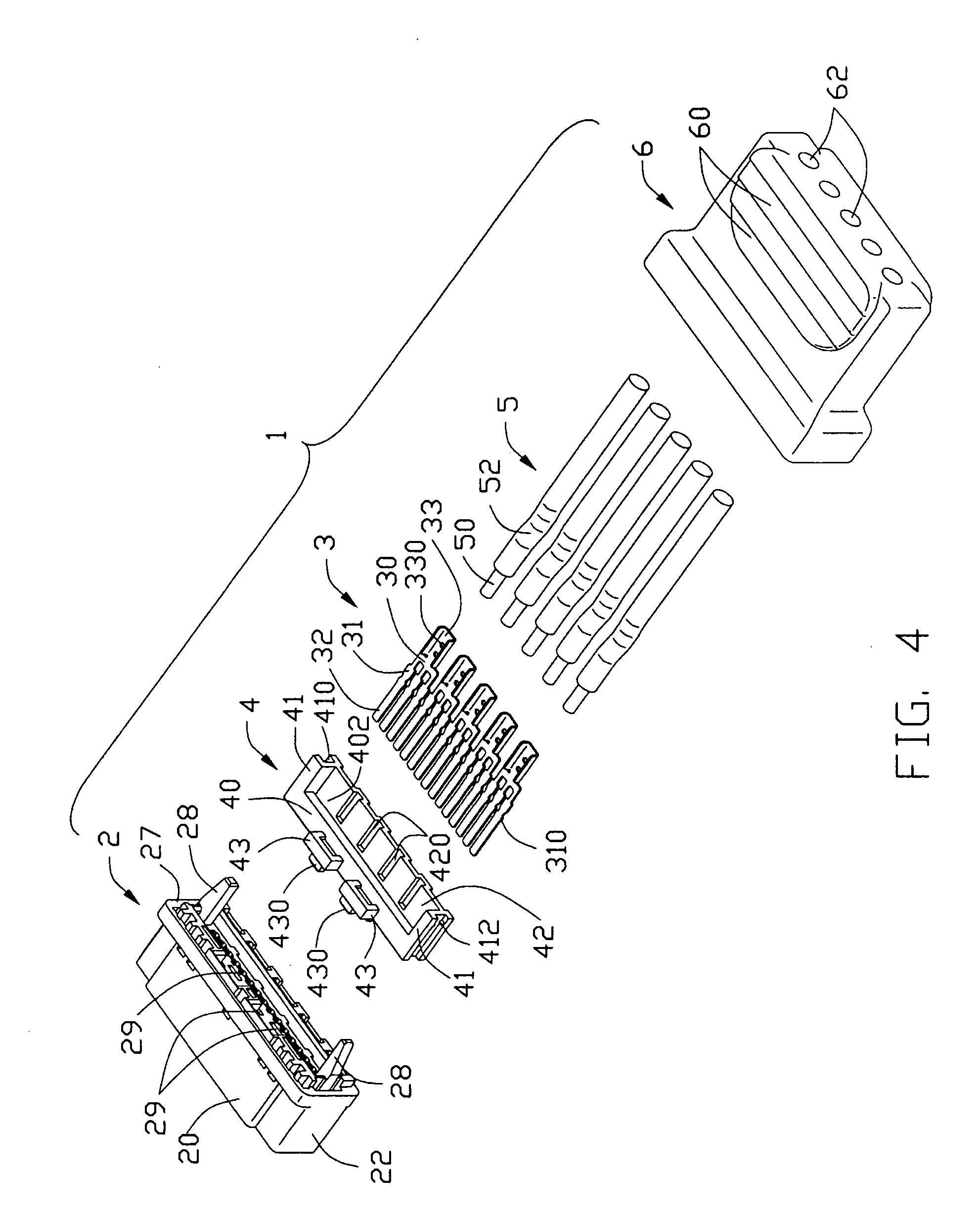

Cable end connector assembly with improved spacer

InactiveUS20050176305A1Firmly connectedElectrically conductive connectionsRelieving strain on wire connectionEngineeringFront end of line

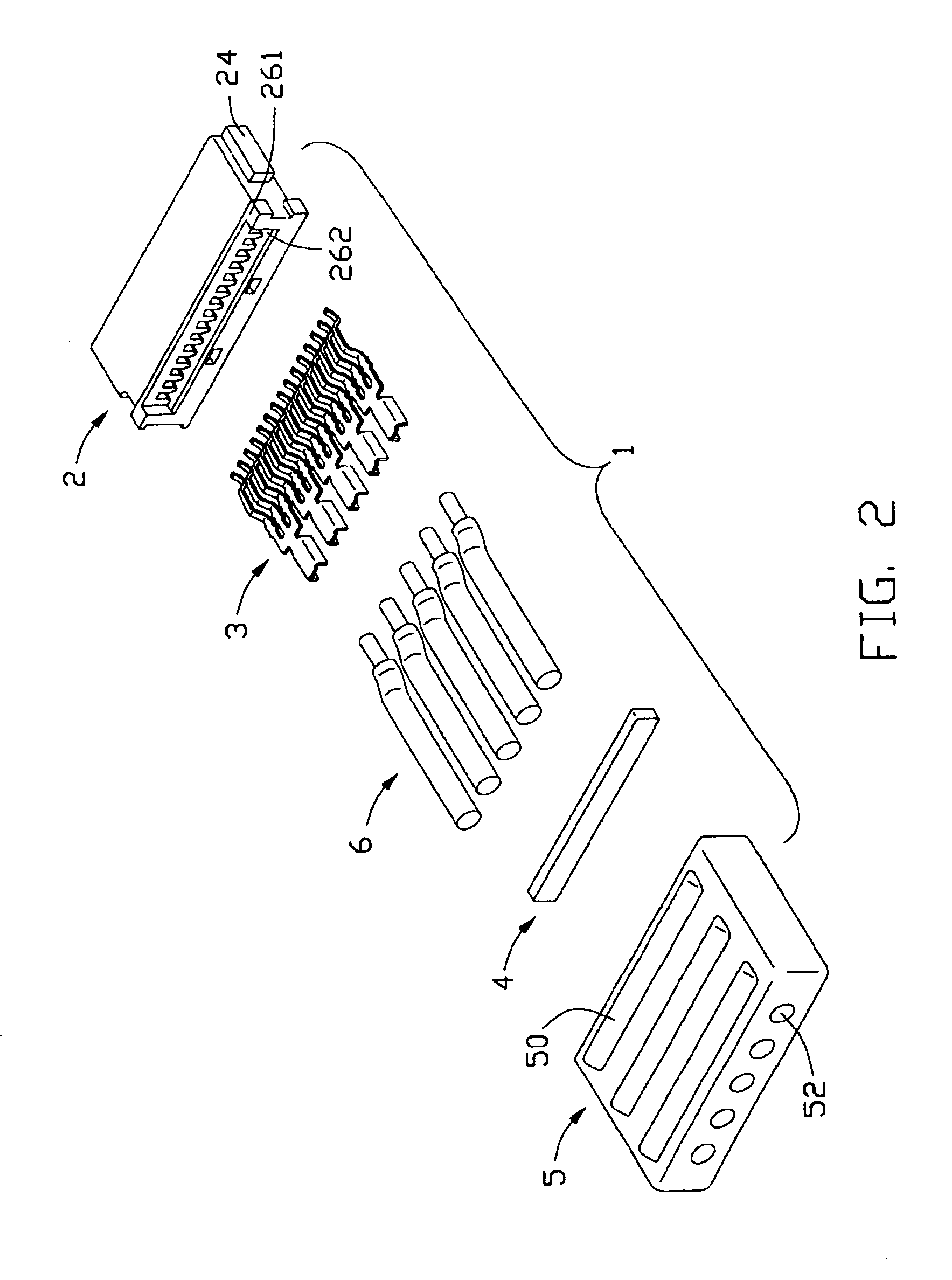

A cable end connector assembly (1) includes a housing (2), a number of contact units (3), a spacer (4), a number of wires (5), and a cover (6). The housing includes a pair of keys (28) in a rear wall thereof. Each contact unit comprises three mating portions (32) and a U-shaped tail portion (33) opposite to the mating portion. The spacer comprises a number of through holes (400) extending therethrough, a supporting portion (42) supporting the U-shaped tail portions, and a pair of keyways (410). The supporting portion defines a number of grooves (420) in a top surface thereof. Each wire comprises a conductive core (60) received in and soldered with the tail portion. The cover is over-molded with a rear end of the housing and front ends of the wires.

Owner:HON HAI PRECISION IND CO LTD

Copper bonding wire for semiconductor and bonding structure thereof

ActiveUS20120299182A1Reduce material costsImprove long-term reliabilitySemiconductor/solid-state device detailsSolid-state devicesFront end of lineCopper

It is an object of the present invention to provide a bonding structure and a copper bonding wire for semiconductor that are realizable at an inexpensive material cost, superior in a long-term reliability of a bonded portion bonded to an Al electrode, and suitable for use in a vehicle-mounted LSI. A ball-bonded portion is formed by bonding to the aluminum electrode a ball formed on a front end of the copper bonding wire. After being heated at any temperature between 130° C. and 200° C., the aforementioned ball-bonded portion exhibits a relative compound ratio R1 of 40-100%, the relative compound ratio R1 being a ratio of a thickness of a Cu—Al intermetallic compound to thicknesses of intermetallic compounds that are composed of Cu and Al and formed on a cross-sectional surface of the ball-bonded portion.

Owner:NIPPON STEEL CHEMICAL CO LTD +1

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com