Patents

Literature

670 results about "Aluminum electrode" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

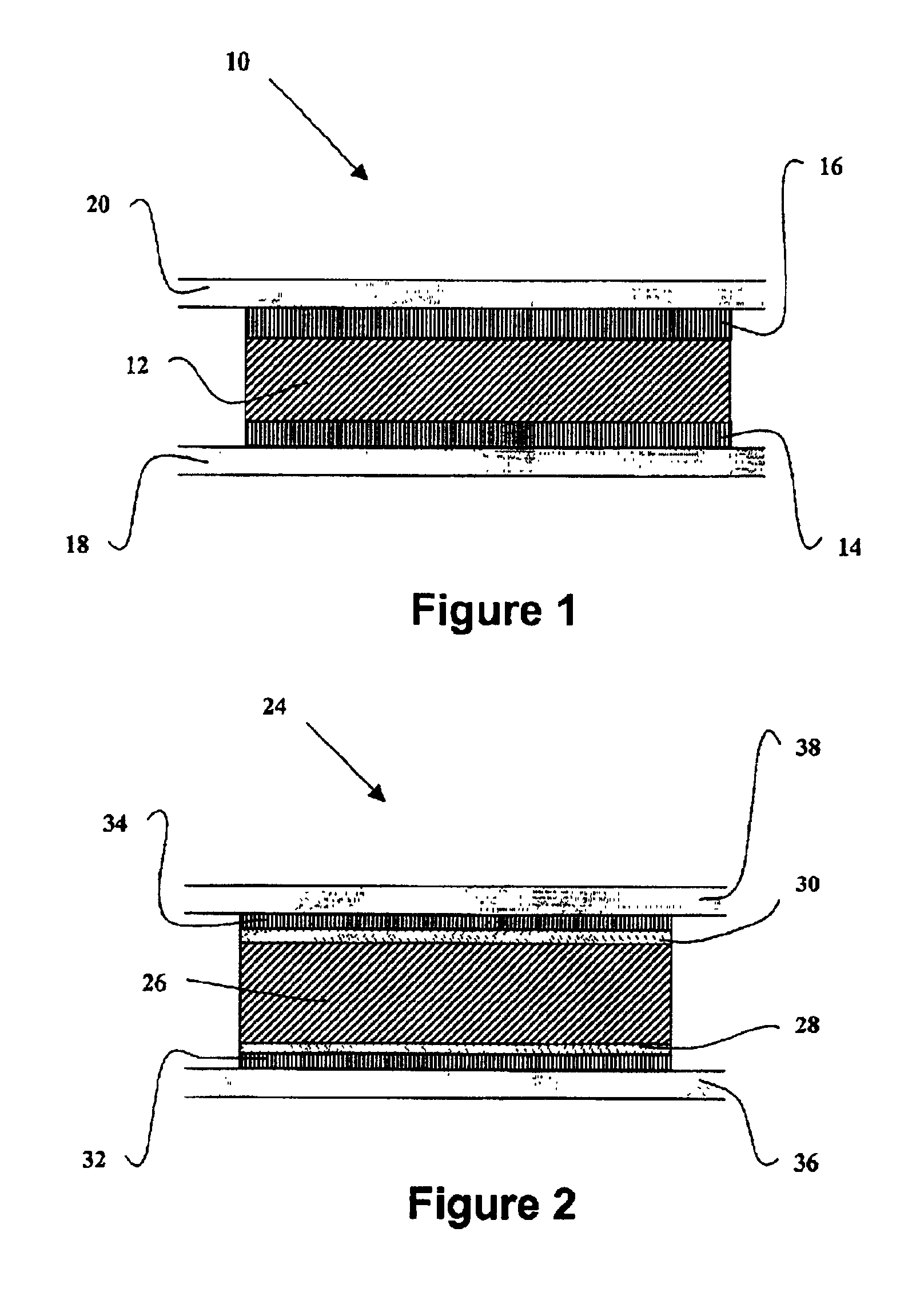

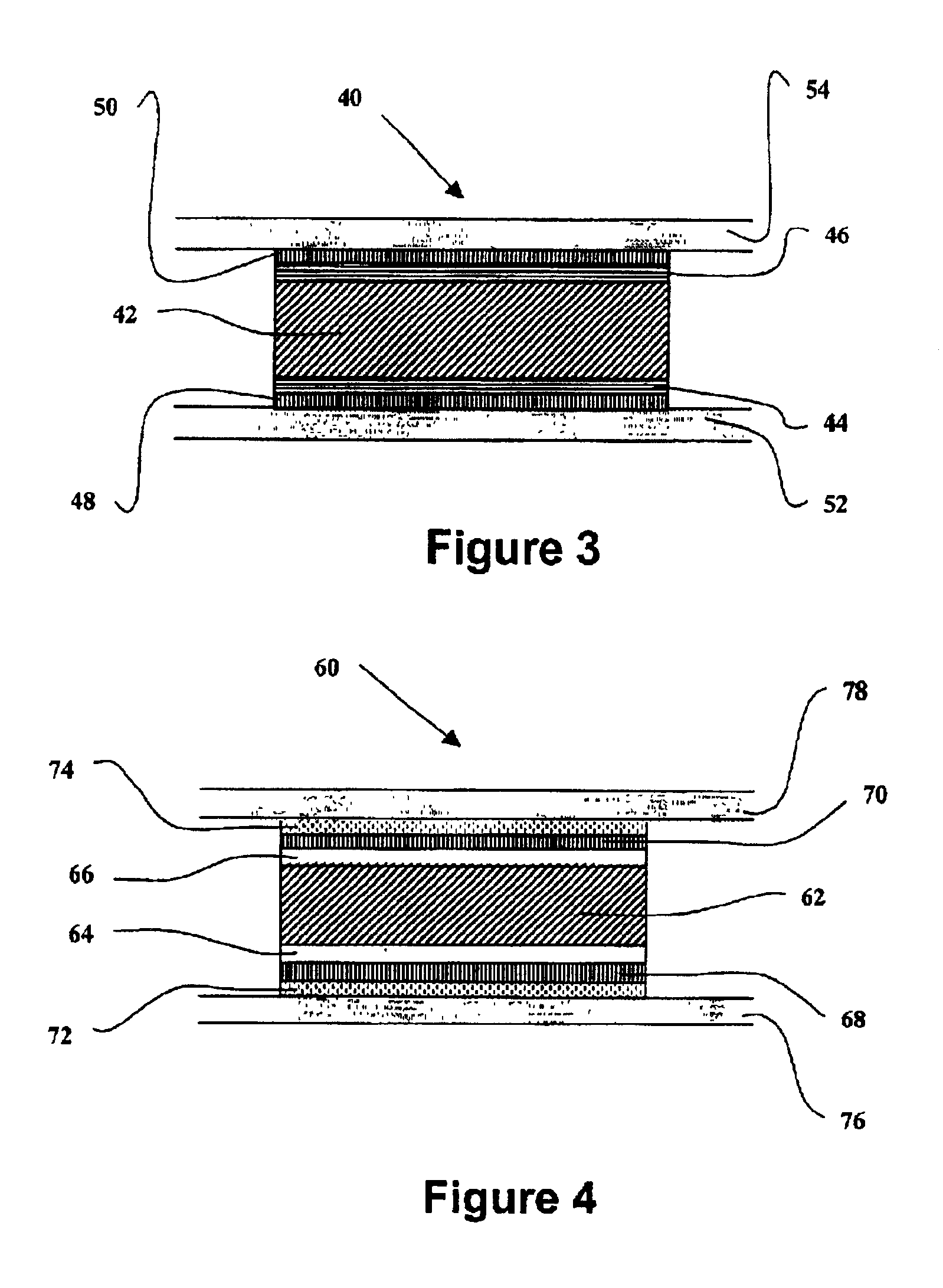

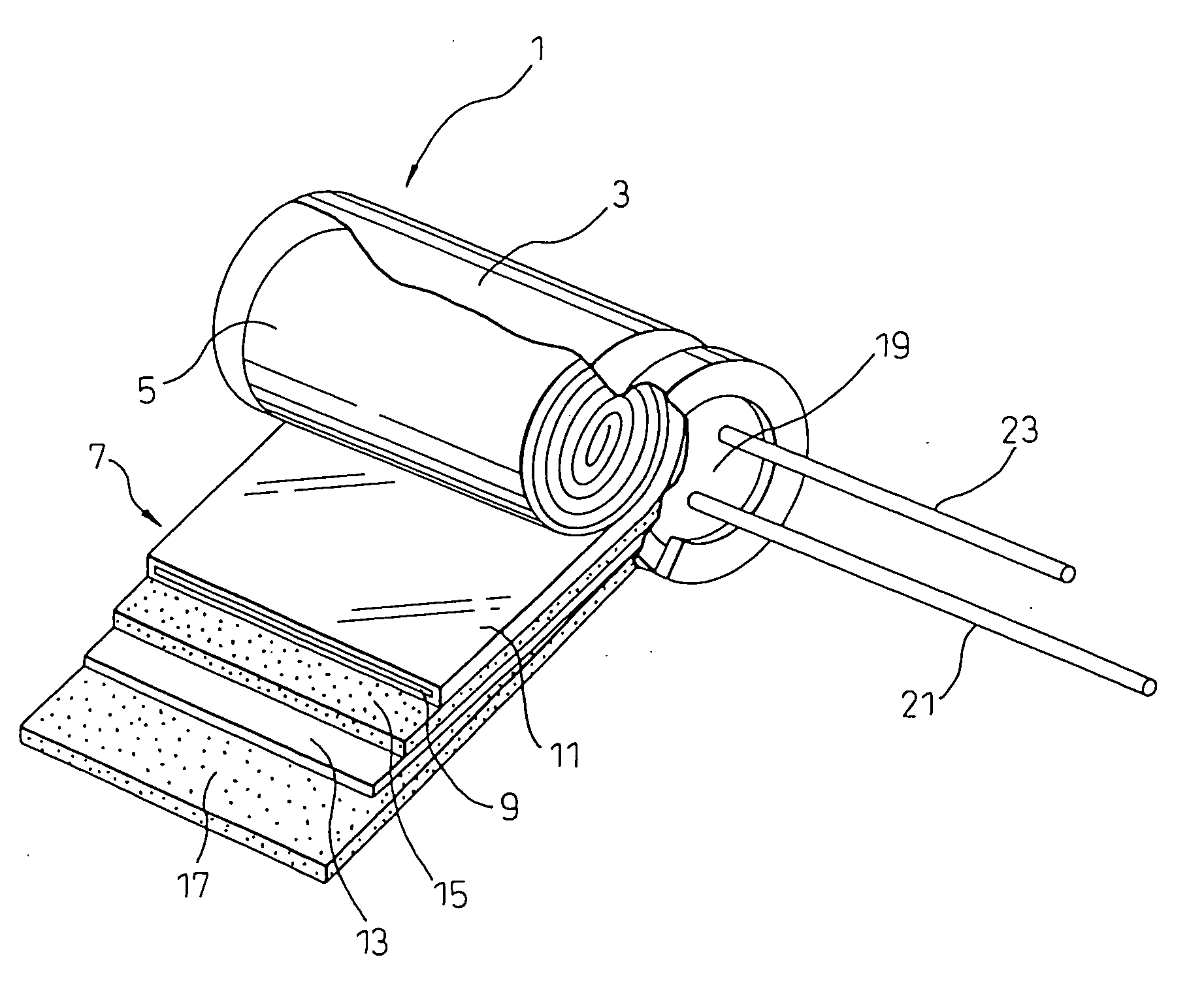

Utilization of poly(ethylene terephthalate) plastic and composition-modified barium titanate powders in a matrix that allows polarization and the use of integrated-circuit technologies for the production of lightweight ultrahigh electrical energy storage units (EESU)

InactiveUS7466536B1Low costLower sintering temperatureCell electrodesFixed capacitor dielectricManufacturing technologyBarium titanate

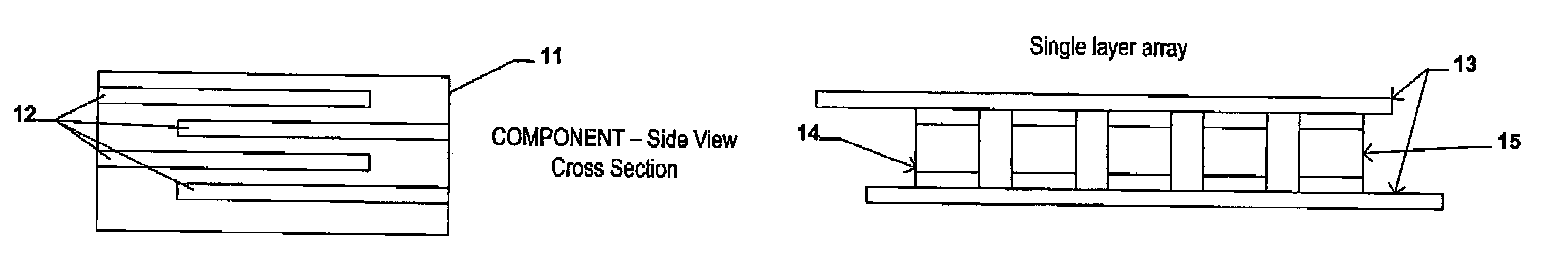

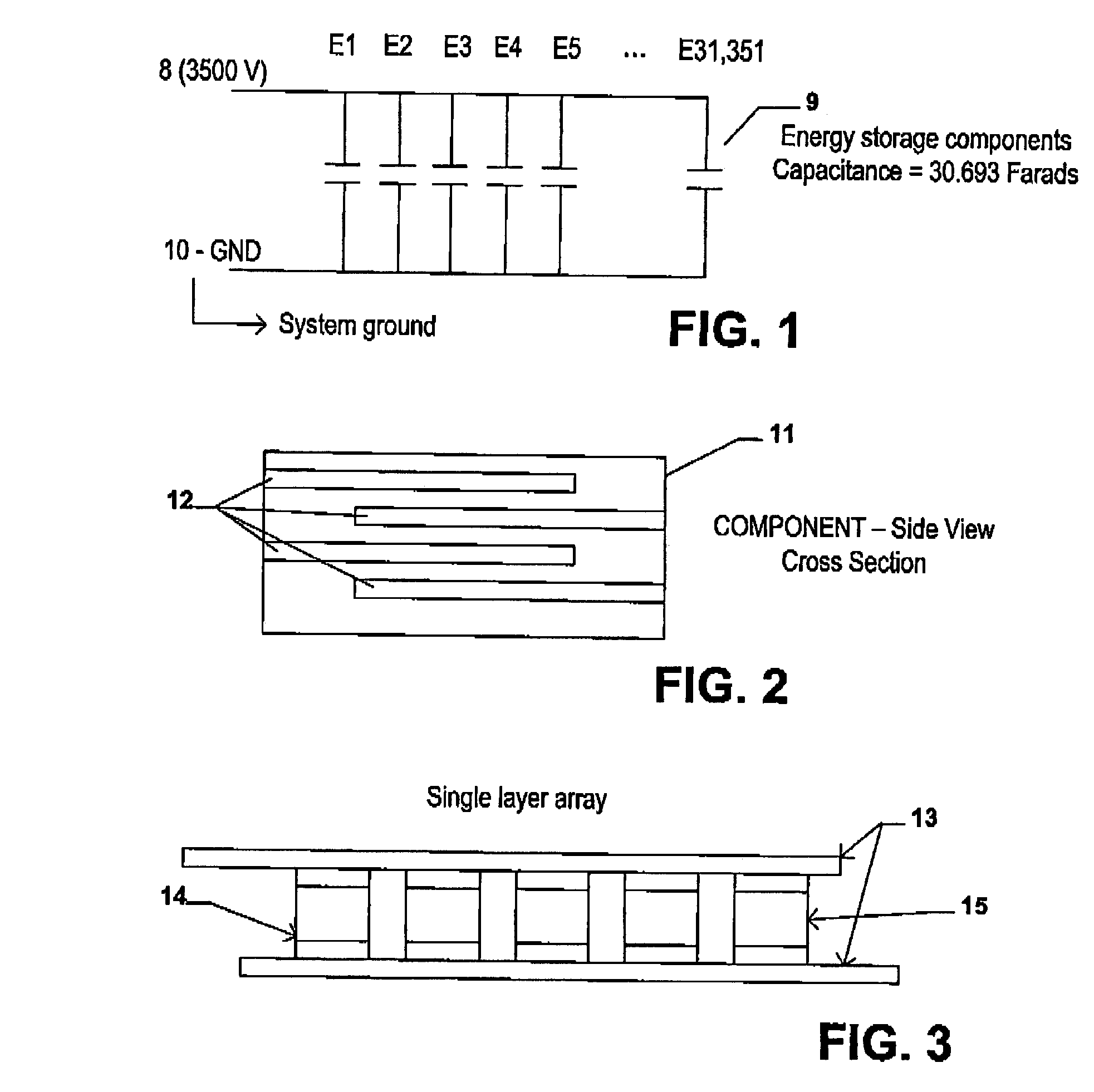

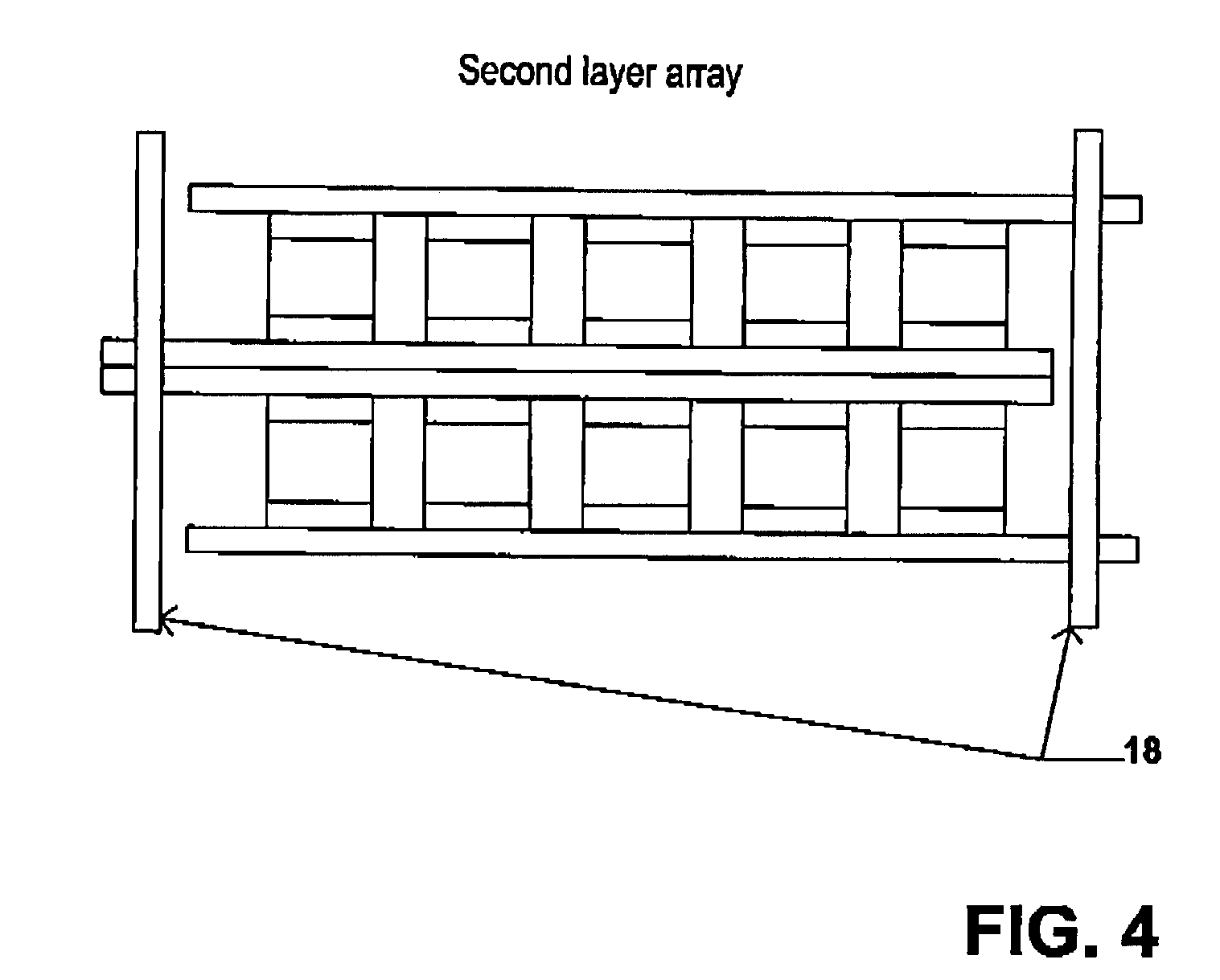

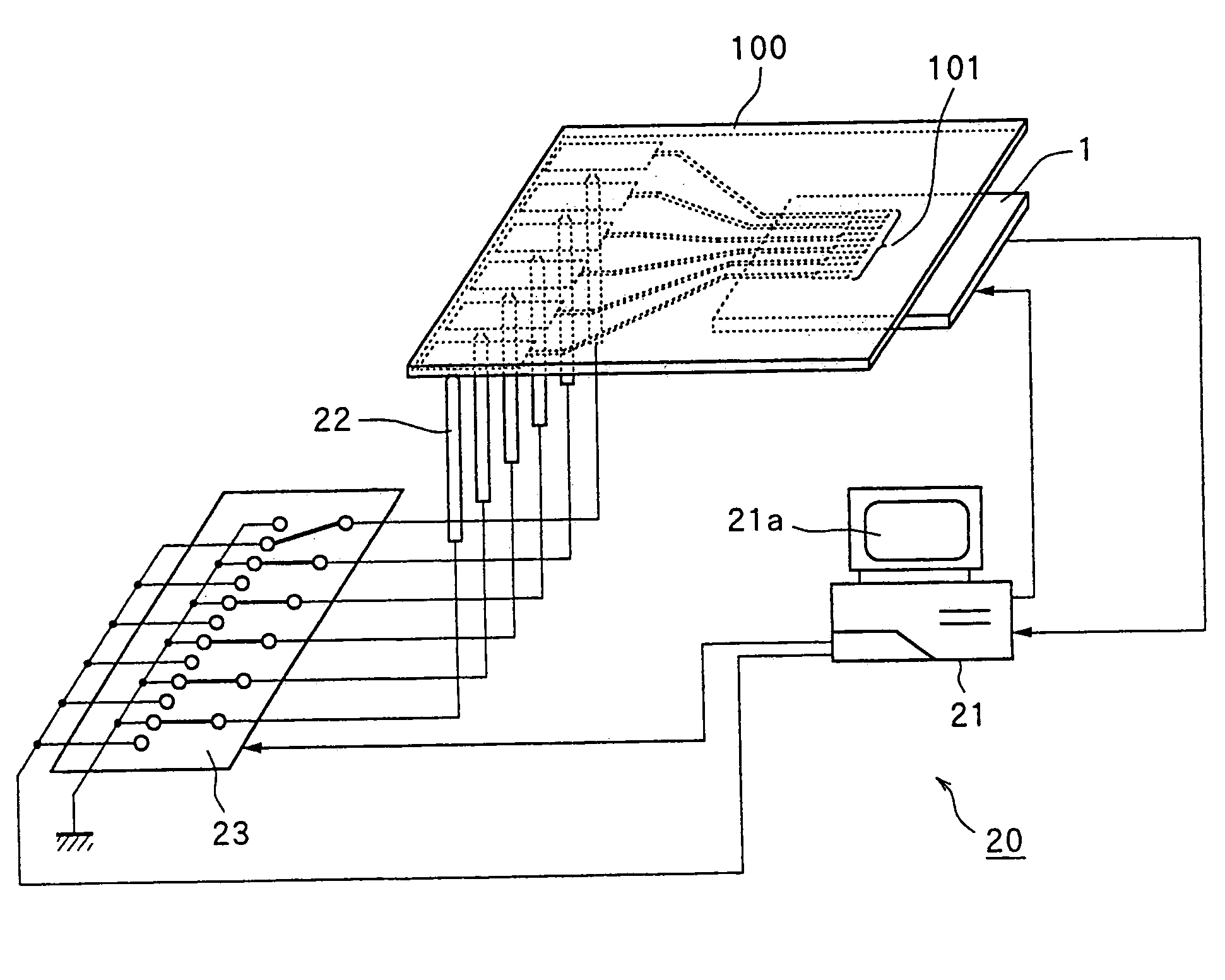

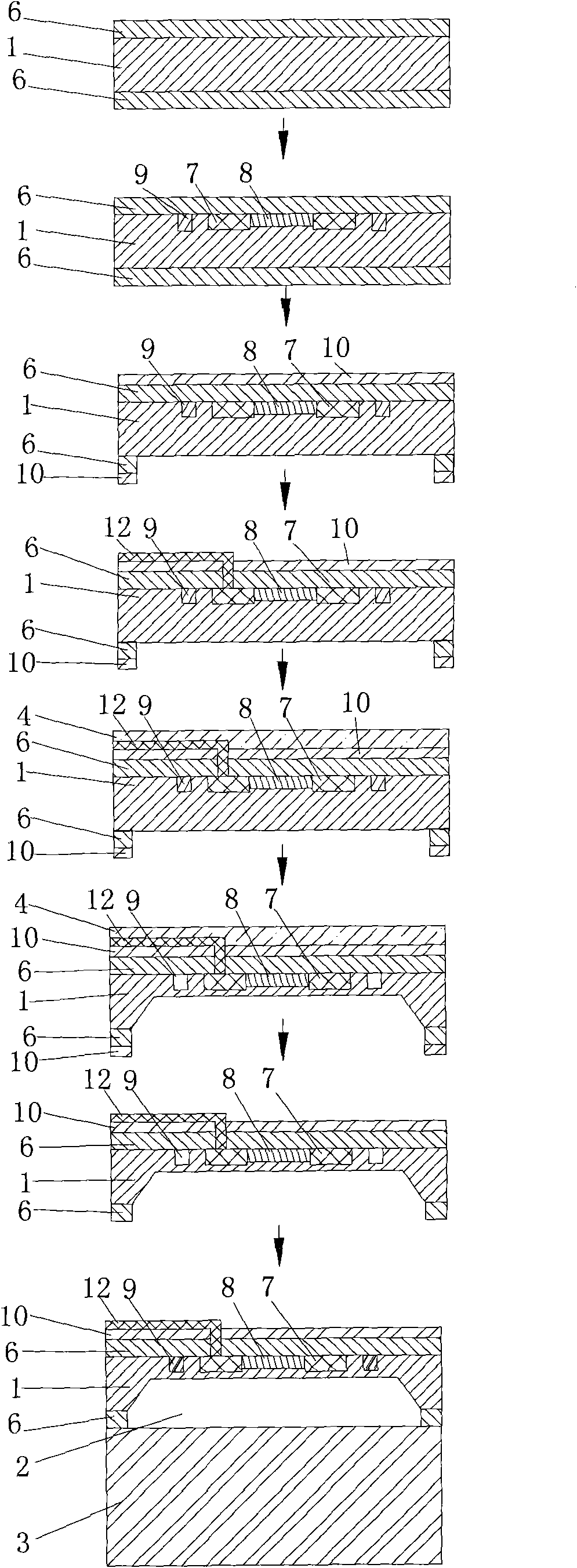

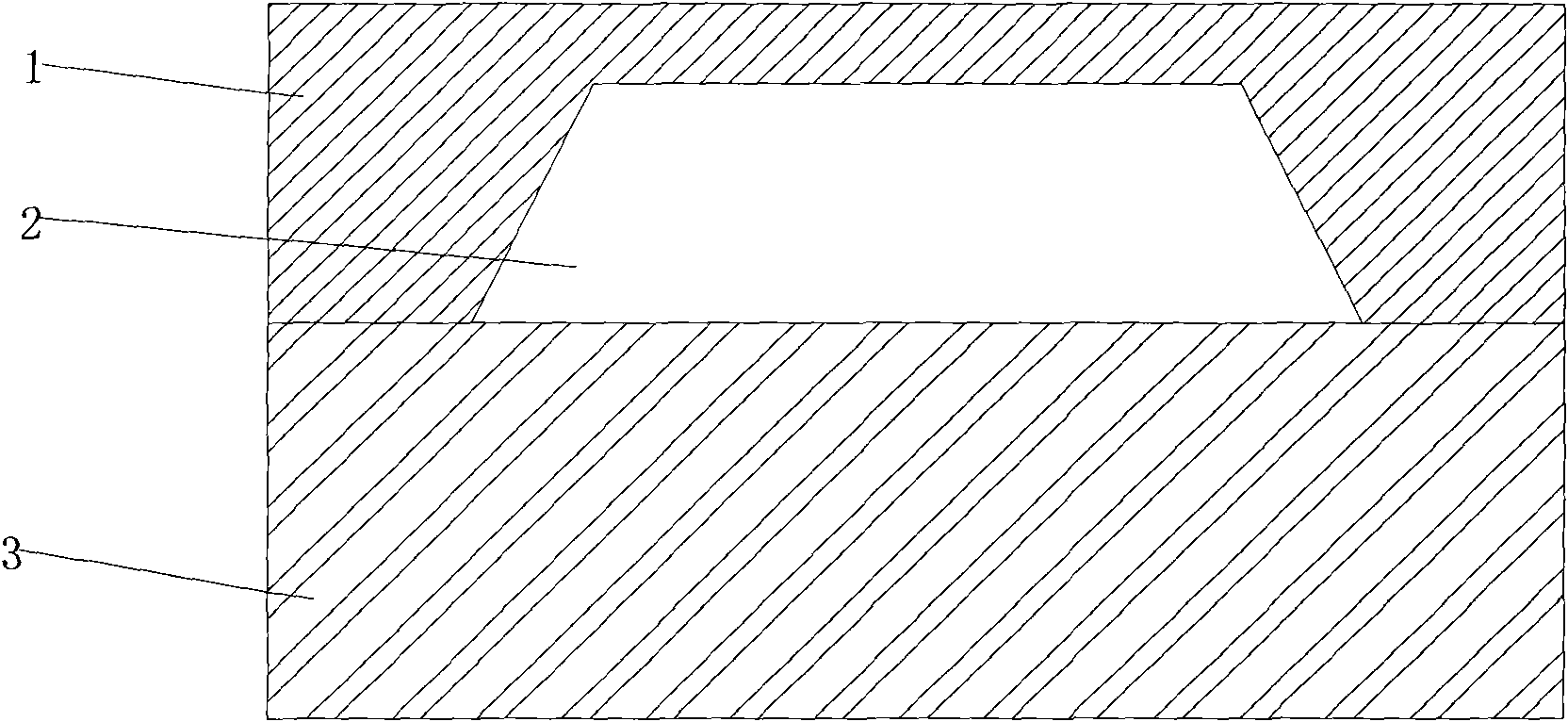

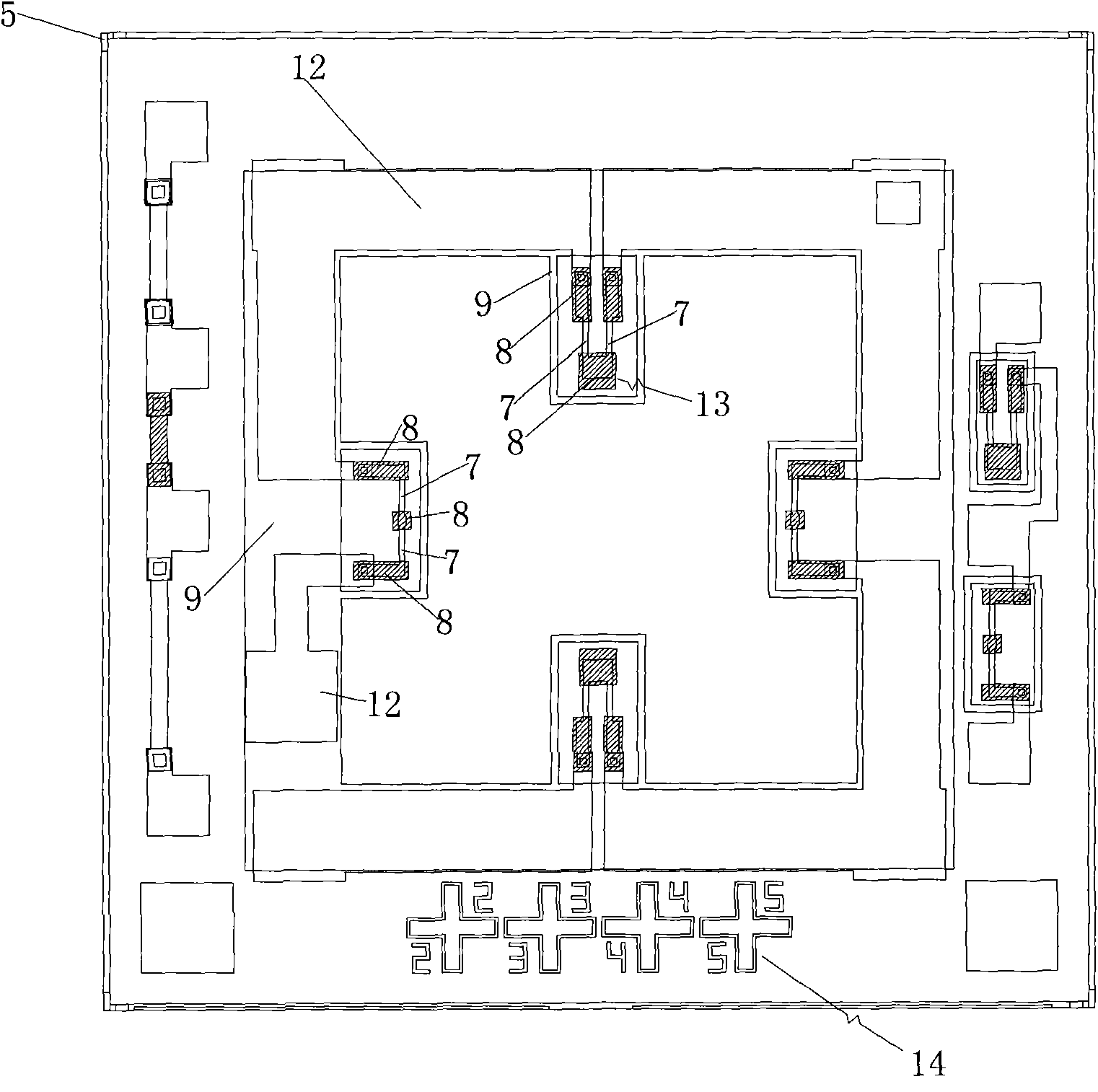

An electrical-energy-storage unit (EESU) has as a basis material a high-permittivity composition-modified barium titanate ceramic powder. This powder is single coated with aluminum oxide and then immersed in a matrix of poly(ethylene terephthalate) (PET) plastic for use in screen-printing systems. The ink that is used to process the powders via screen-printing is based on a nitrocellulose resin that provide a binder burnout, sintering, and hot isostatic pressing temperatures that are allowed by the PET plastic. These lower temperatures that are in the range of 40° C. to 150° C. also allows aluminum powder to be used for the electrode material. The components of the EESU are manufactured with the use of conventional ceramic and plastic fabrication techniques which include screen printing alternating multilayers of aluminum electrodes and high-permittivity composition-modified barium titanate powder, sintering to a closed-pore porous body, followed by hot-isostatic pressing to a void-free body. The 31,351 components are configured into a multilayer array with the use of a solder-bump technique as the enabling technology so as to provide a parallel configuration of components that has the capability to store at least 52.22 kW·h of electrical energy. The total weight of an EESU with this amount of electrical energy storage is 281.56 pounds including the box, connectors, and associated hardware.

Owner:EESTOR

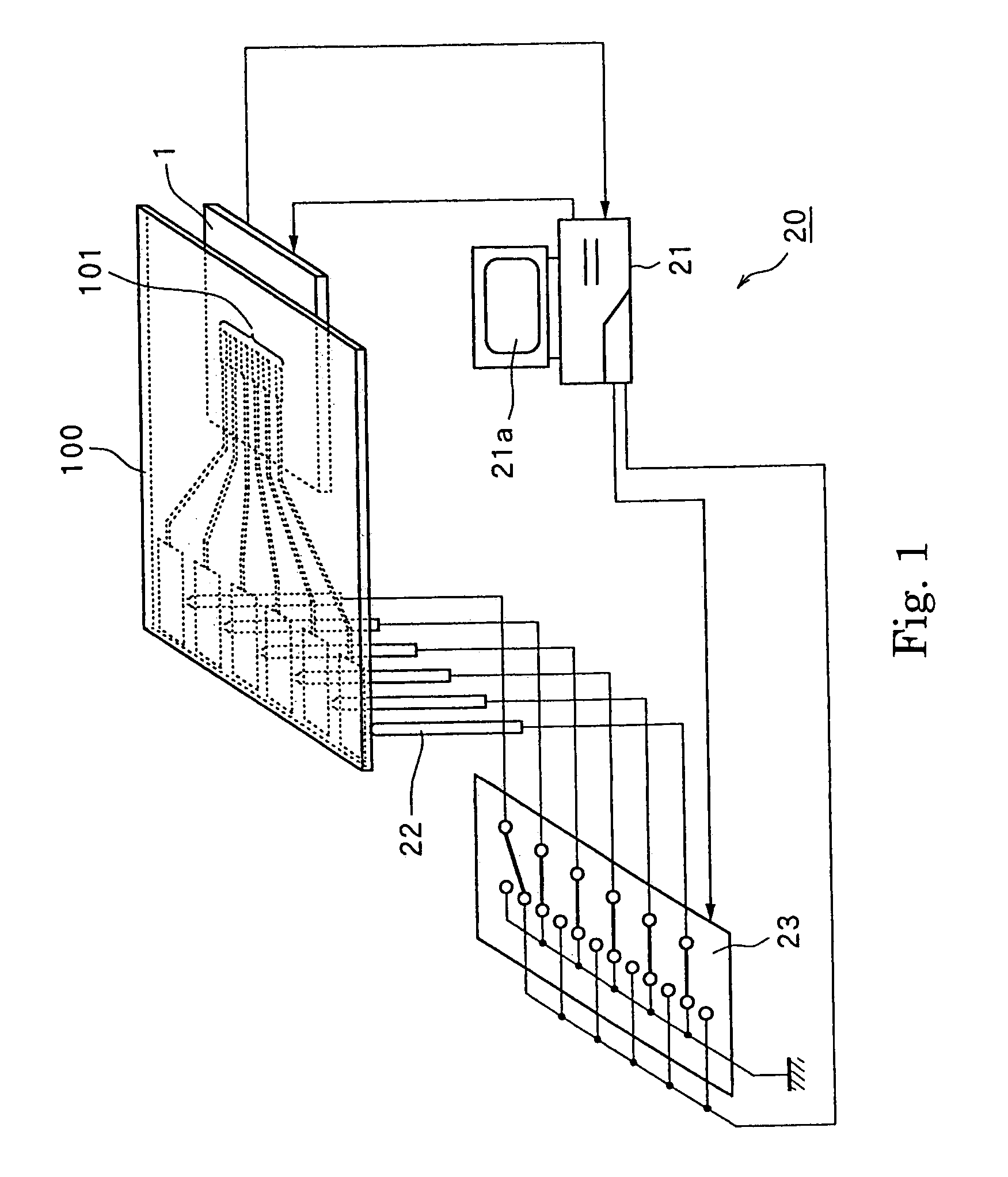

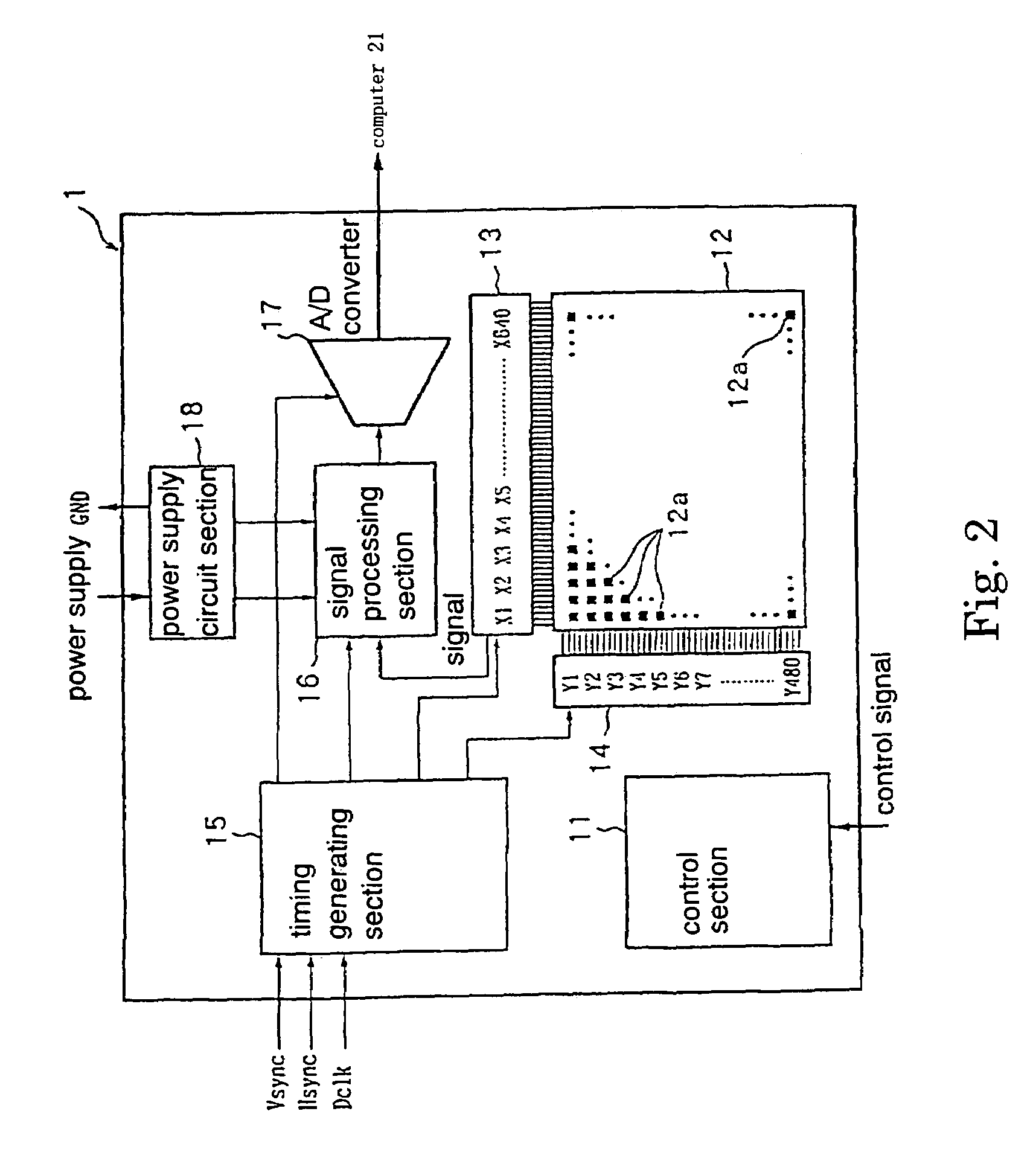

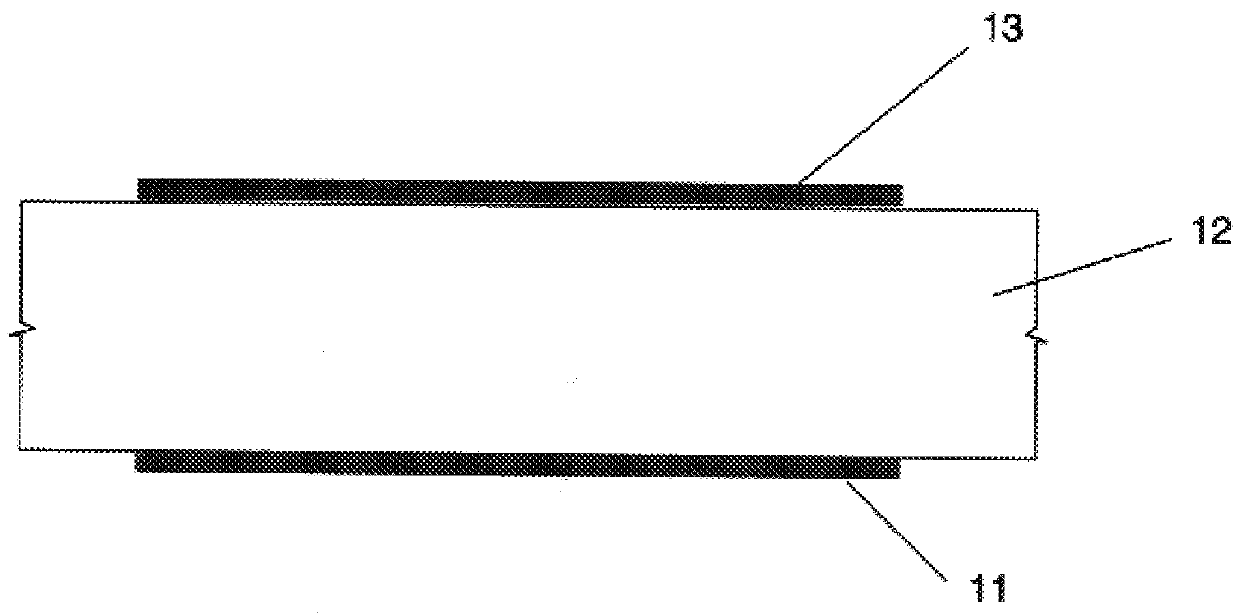

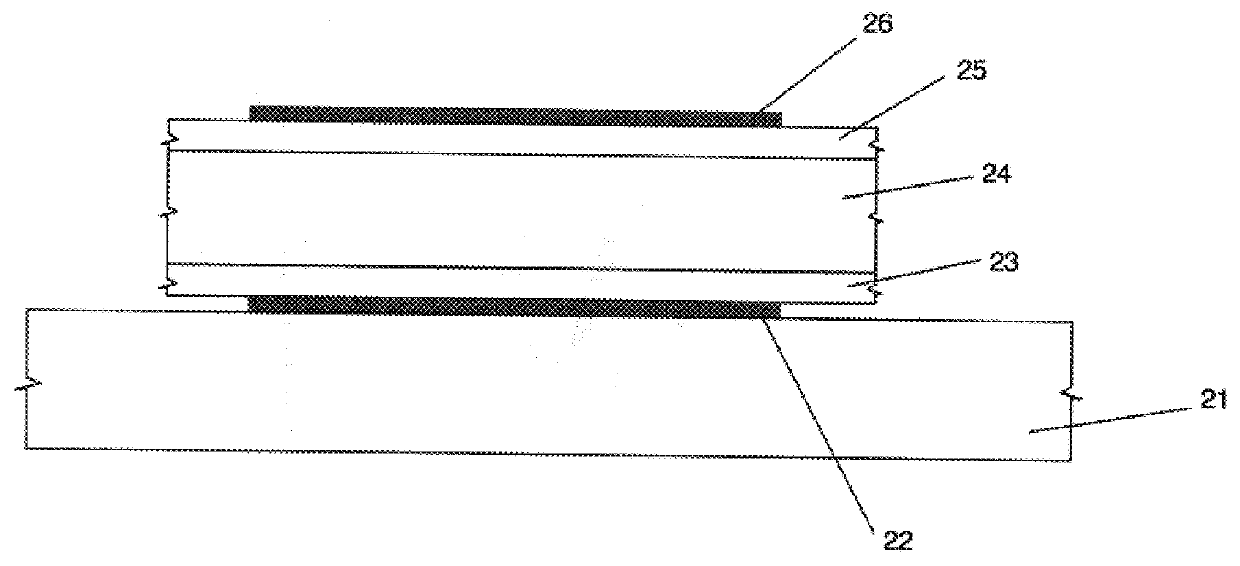

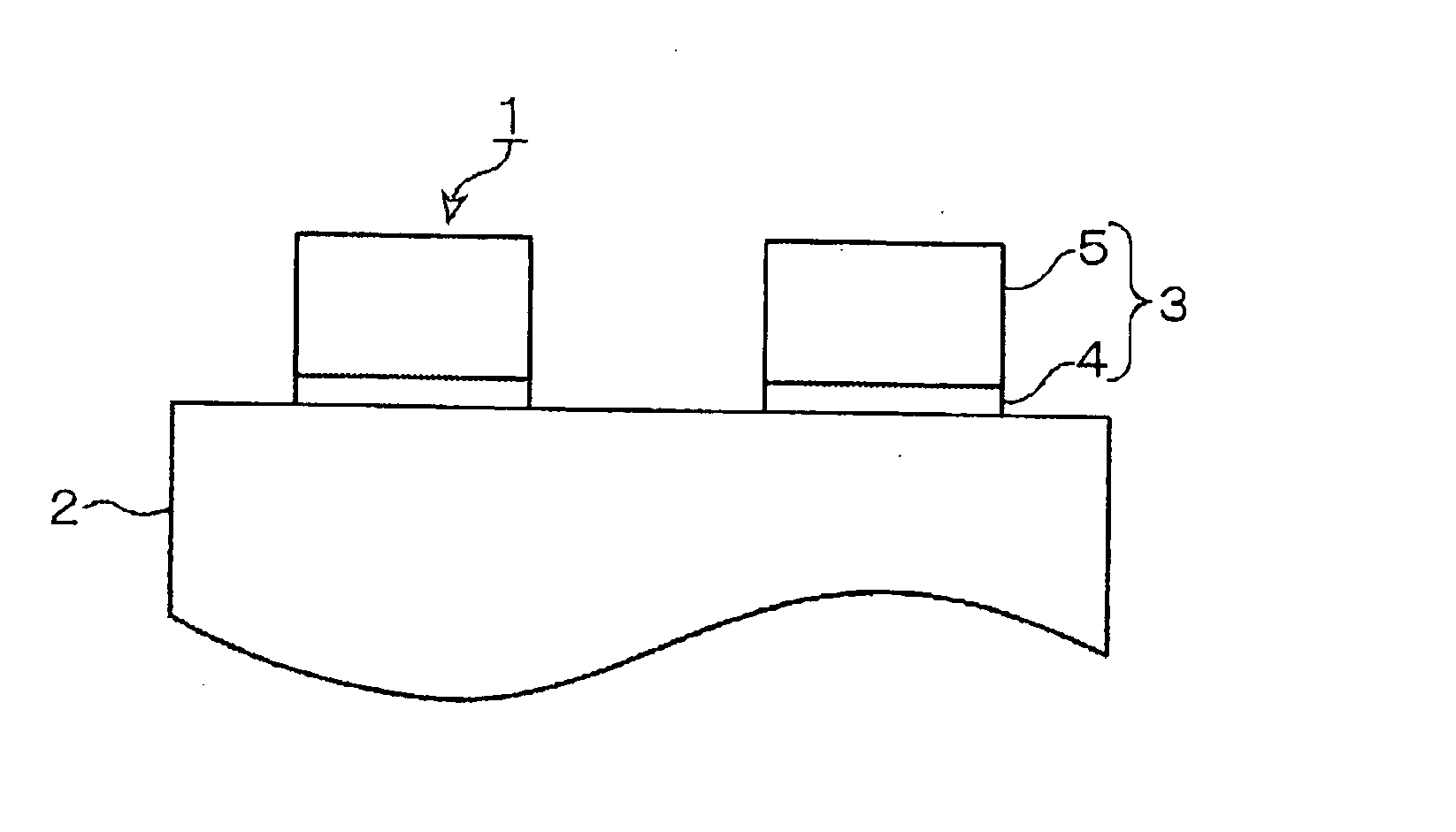

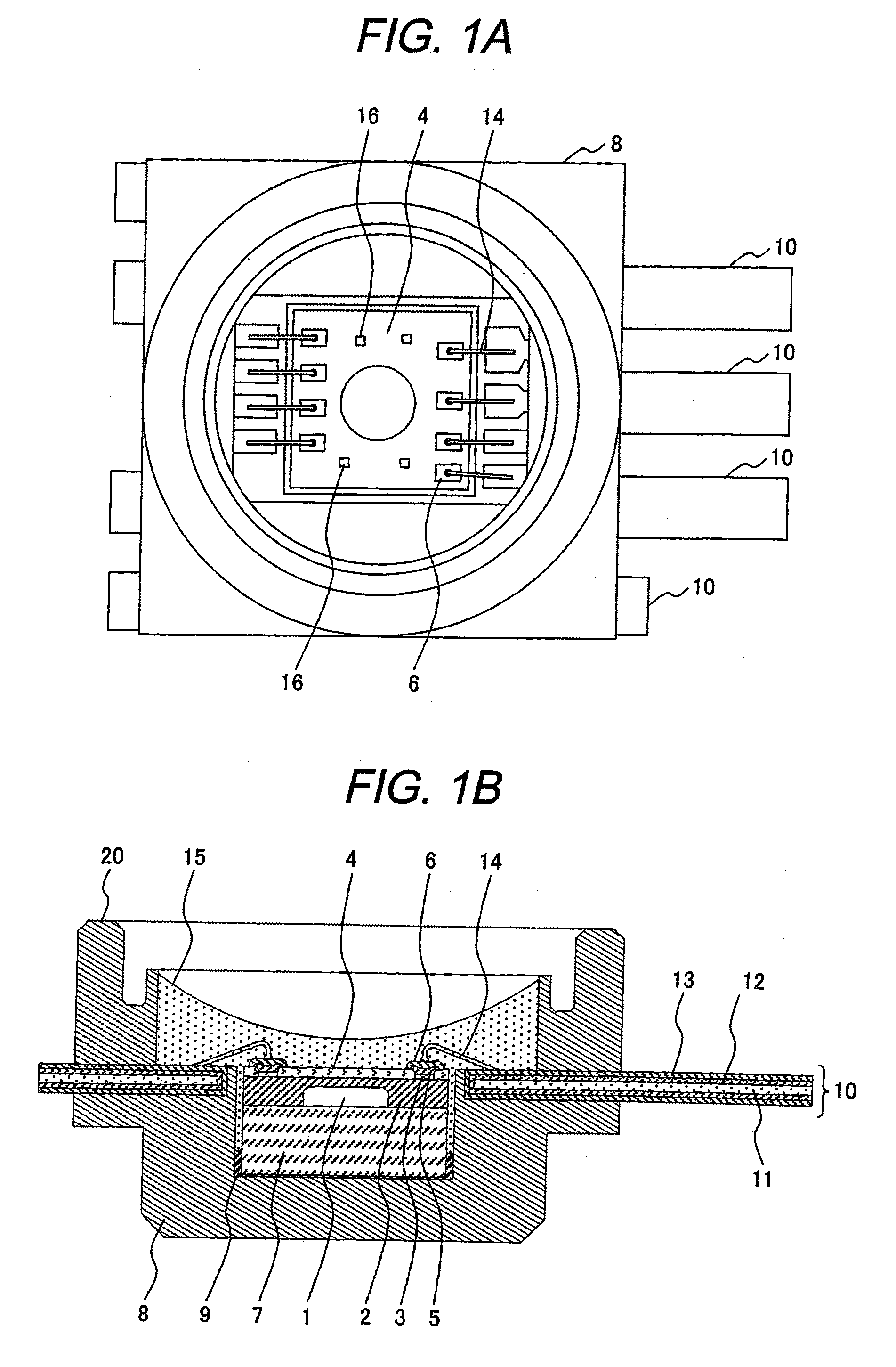

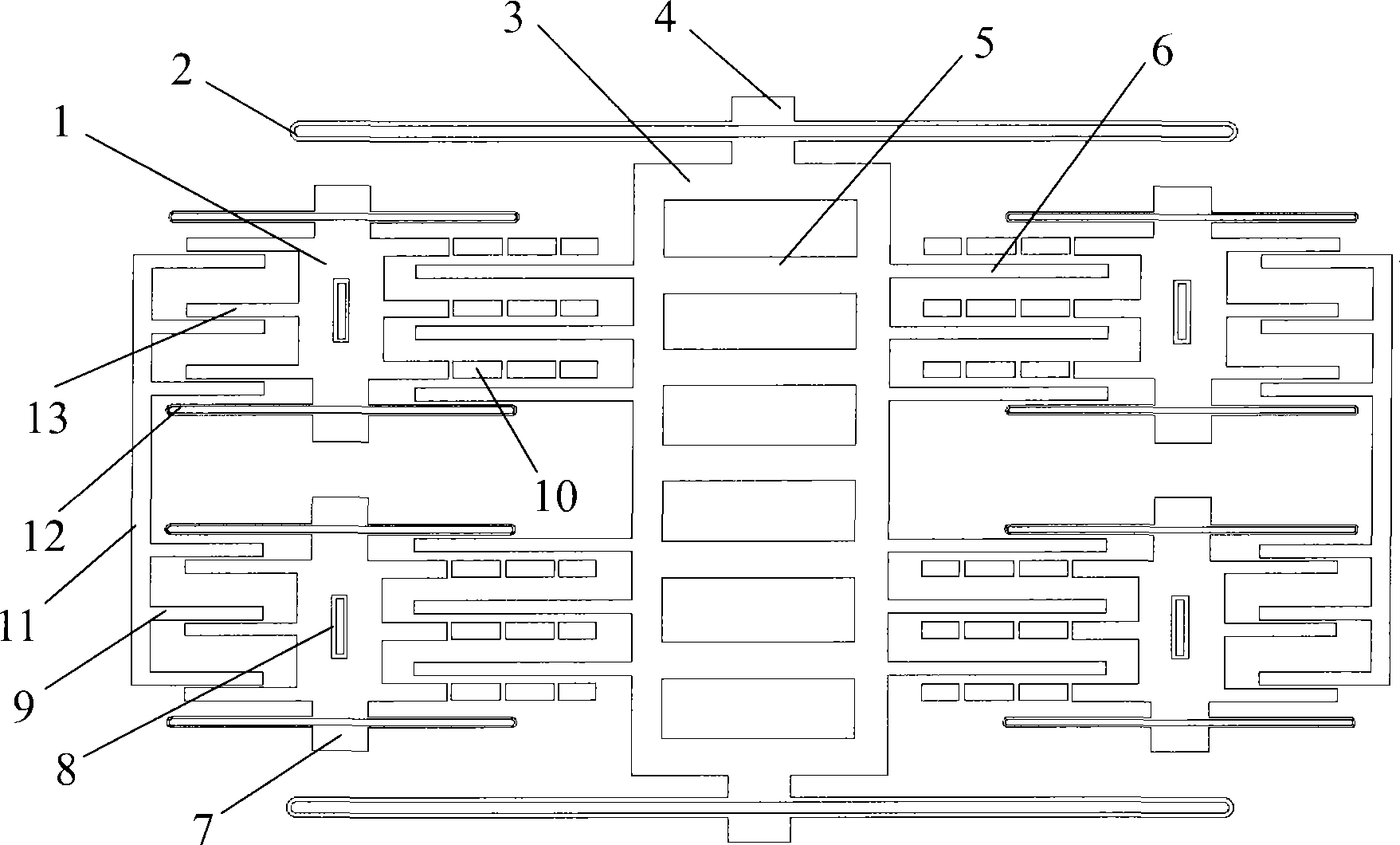

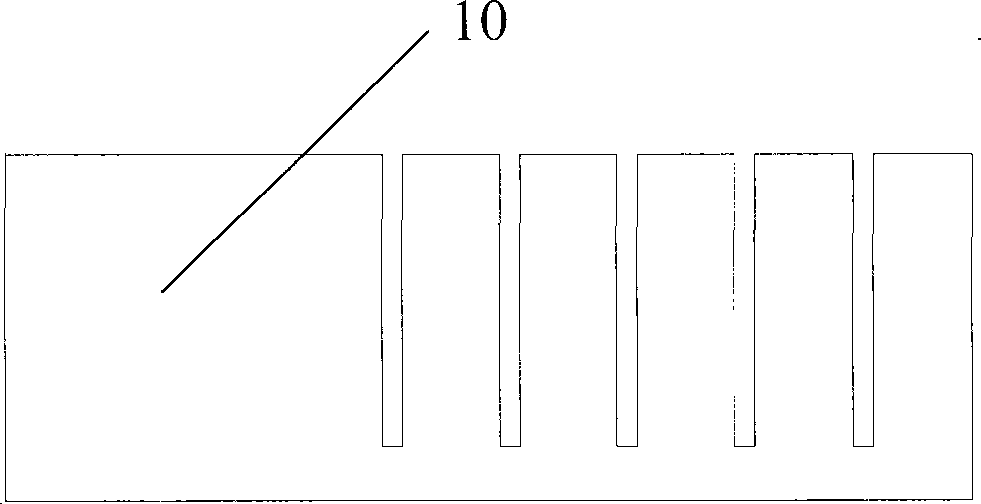

Sensor for inspection instrument and inspection instrument

InactiveUS7173445B2Inspection is accurateSemiconductor/solid-state device testing/measurementSolid-state devicesMOSFETEngineering

Disclosed is an inspection sensor and inspection apparatus capable of accurately inspecting the shape of a conductive pattern. A sensor element 12a includes an MOSFET, and an aluminum electrode (AL) serving as a passive element 80. The passive element or aluminum electrode 80 is connected to the gate of a MOSFET 81 and the source of a MOSFET 82. A voltage VDD is supplied from a power supply circuit 18 to the drain of the MOSFET 81, and the source of the MOSFET 81 is connected to the drain of a MOSFET 83. A reset signal is entered from a vertical selection section 14 into the gate of the MOSFET 82, and the voltage VDD is supplied from the power supply circuit 18 to the drain of the MOSFET 82. A selection signal is entered from the vertical selection section 14 into the gate of the MOSFET 83, and an output from the source of the MOSFET 83 is entered into a lateral selection section 13.

Owner:OHT

Encapsulated thin-film resonator and fabrication method

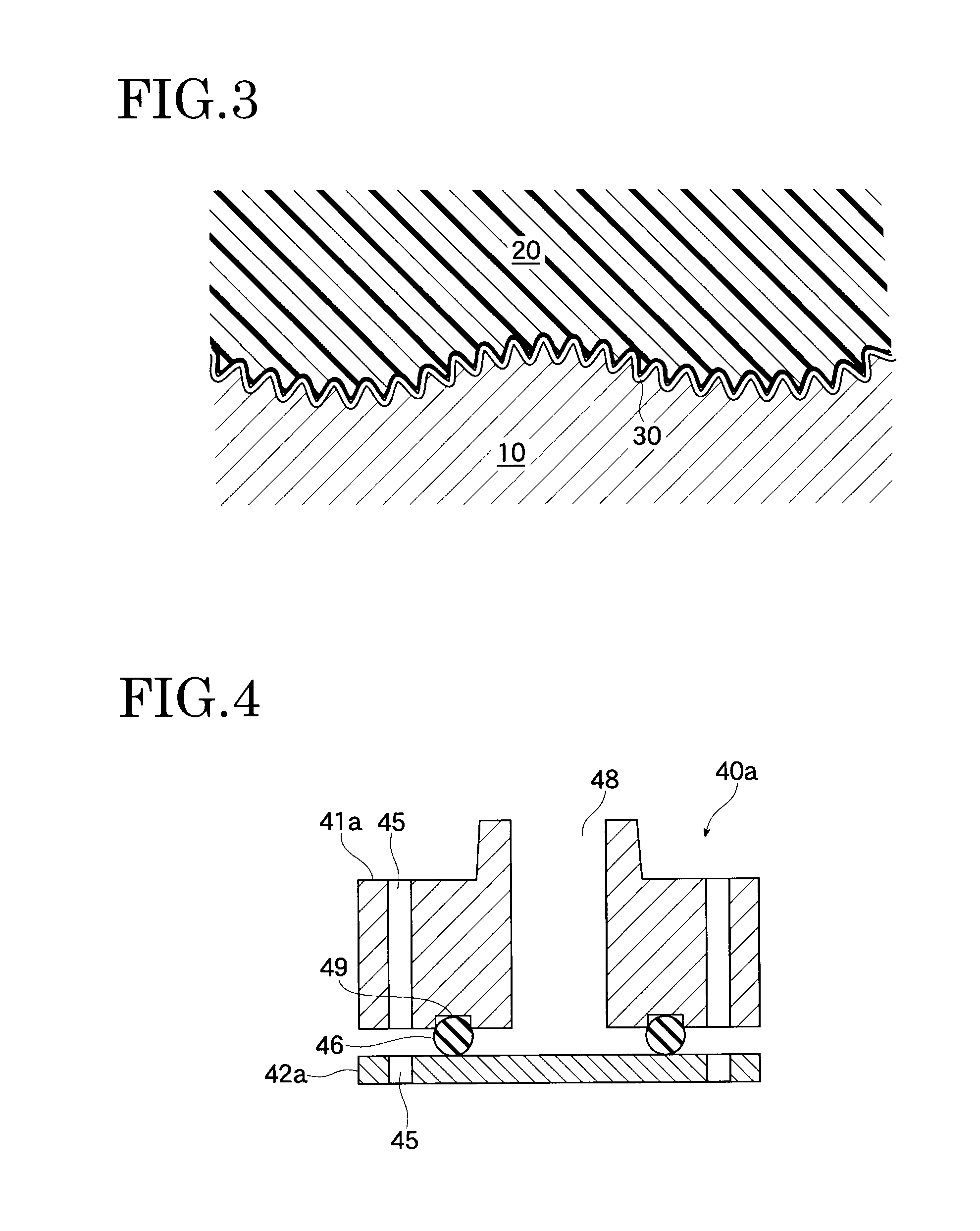

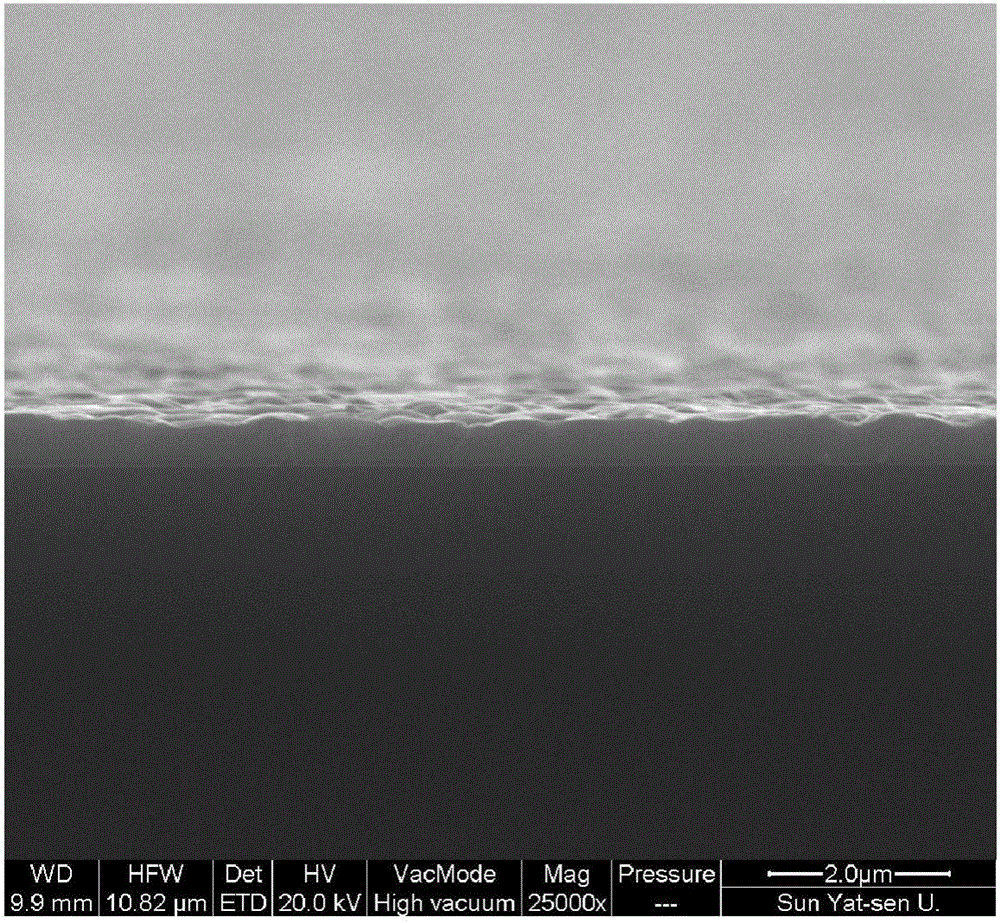

InactiveUS6239536B1Improve evenlyImprove performanceImpedence networksPiezoelectric/electrostriction/magnetostriction machinesStructural deformationCrystal orientation

A thin-film piezoelectric resonator and method of fabrication that includes a barrier layer of material between the underlying electrode and a layer of piezoelectric material. For example, in a resonator that uses zinc oxide for the layer of piezoelectric material, a barrier layer of aluminum nitride is deposited upon an underlying aluminum electrode to protect the aluminum electrode from oxidation or structural deformation during the subsequent deposition of the piezoelectric layer of zinc oxide. The barrier layer of aluminum nitride is deposited in a manner so as to provide a substrate having a substantial degree of uniformity of crystal orientation upon which the layer of piezoelectric material may then be deposited in a manner such that the piezoelectric layer will, itself, also have a substantial degree of uniformity in the orientations of its crystals. The resonator includes a second electrode deposited upon the upper surface of the piezoelectric material or upon the upper surface of a second barrier layer of aluminum nitride that is deposited upon the upper surface of the piezoelectric layer.

Owner:QORVO US INC

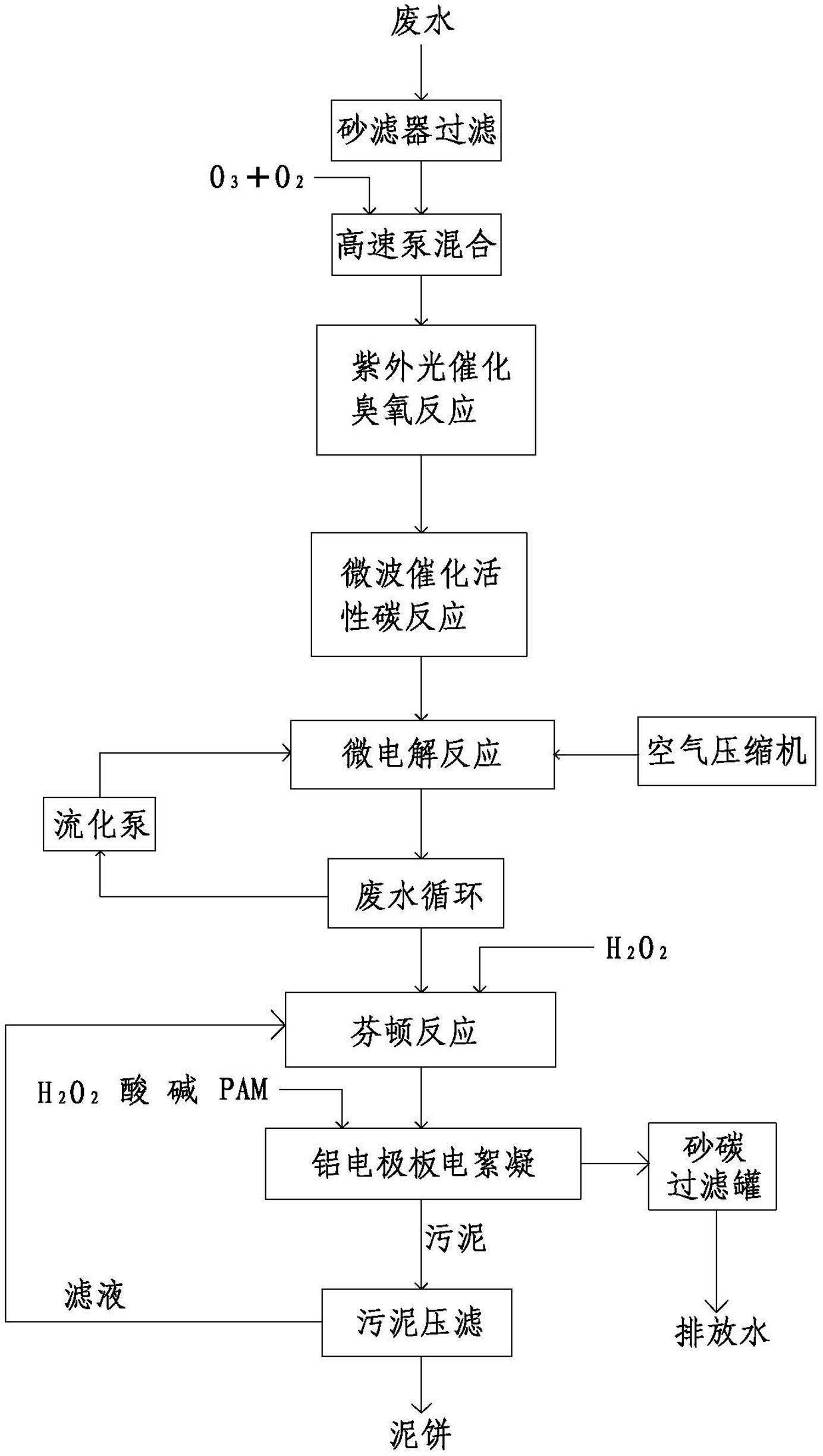

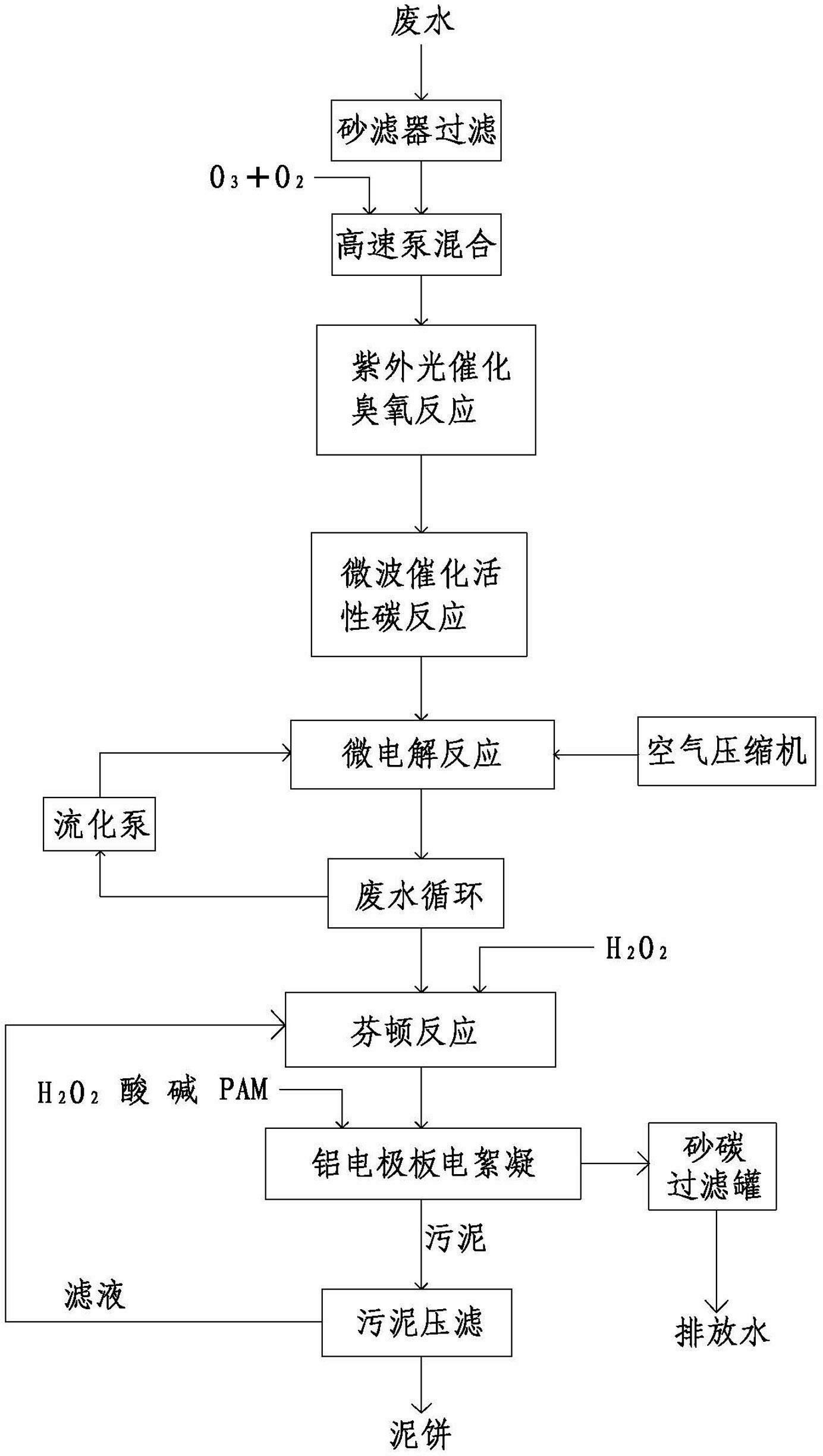

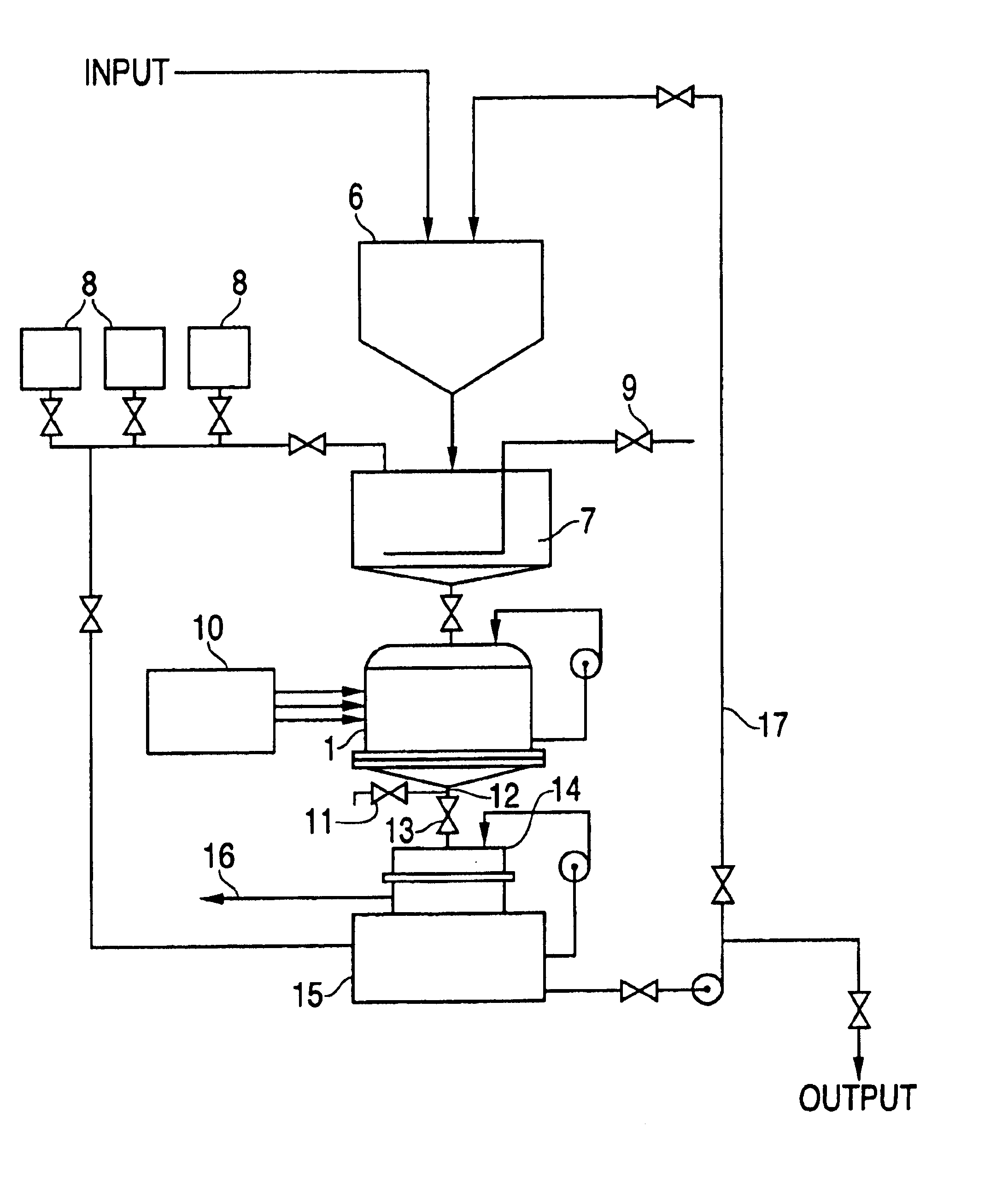

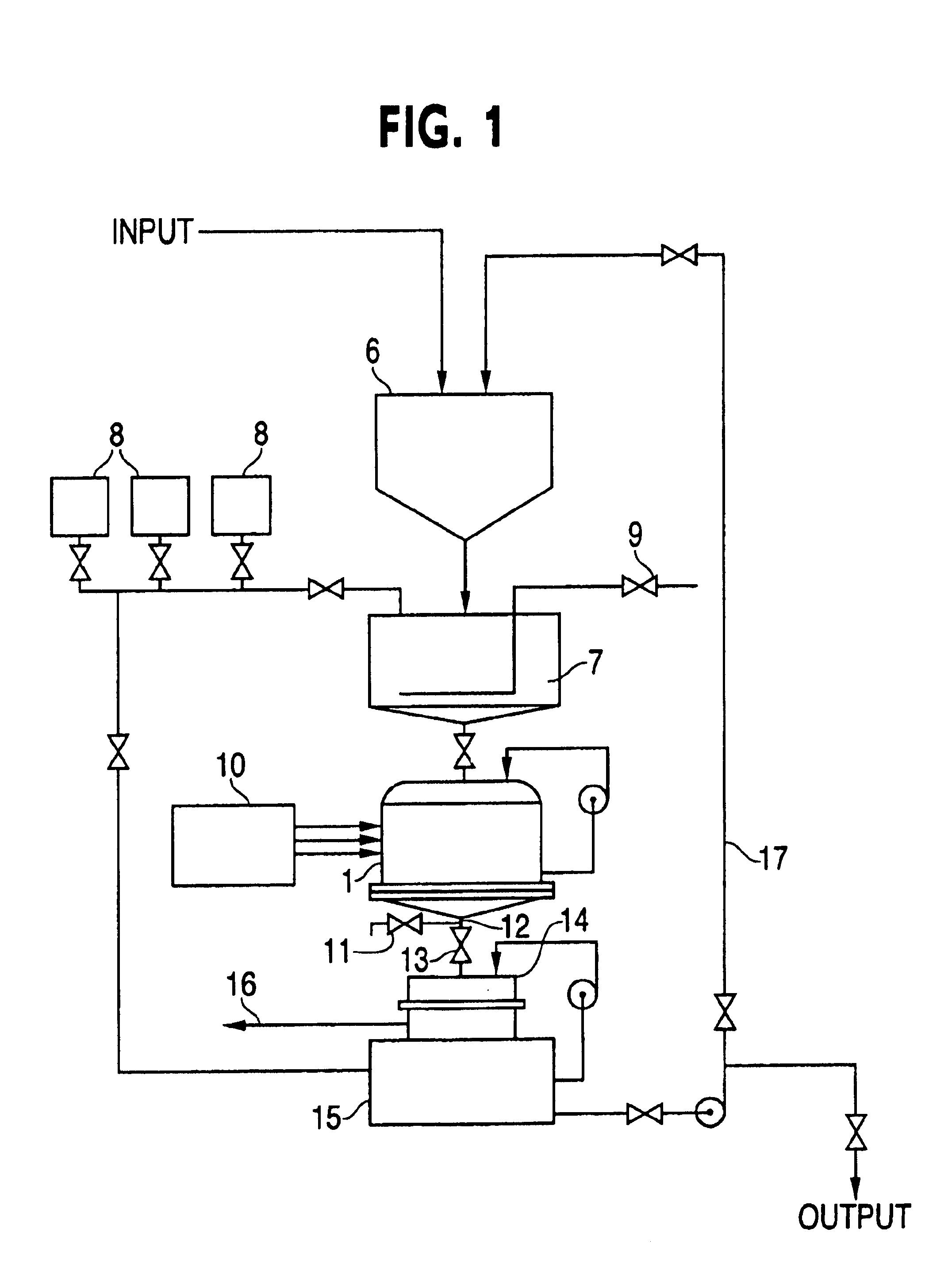

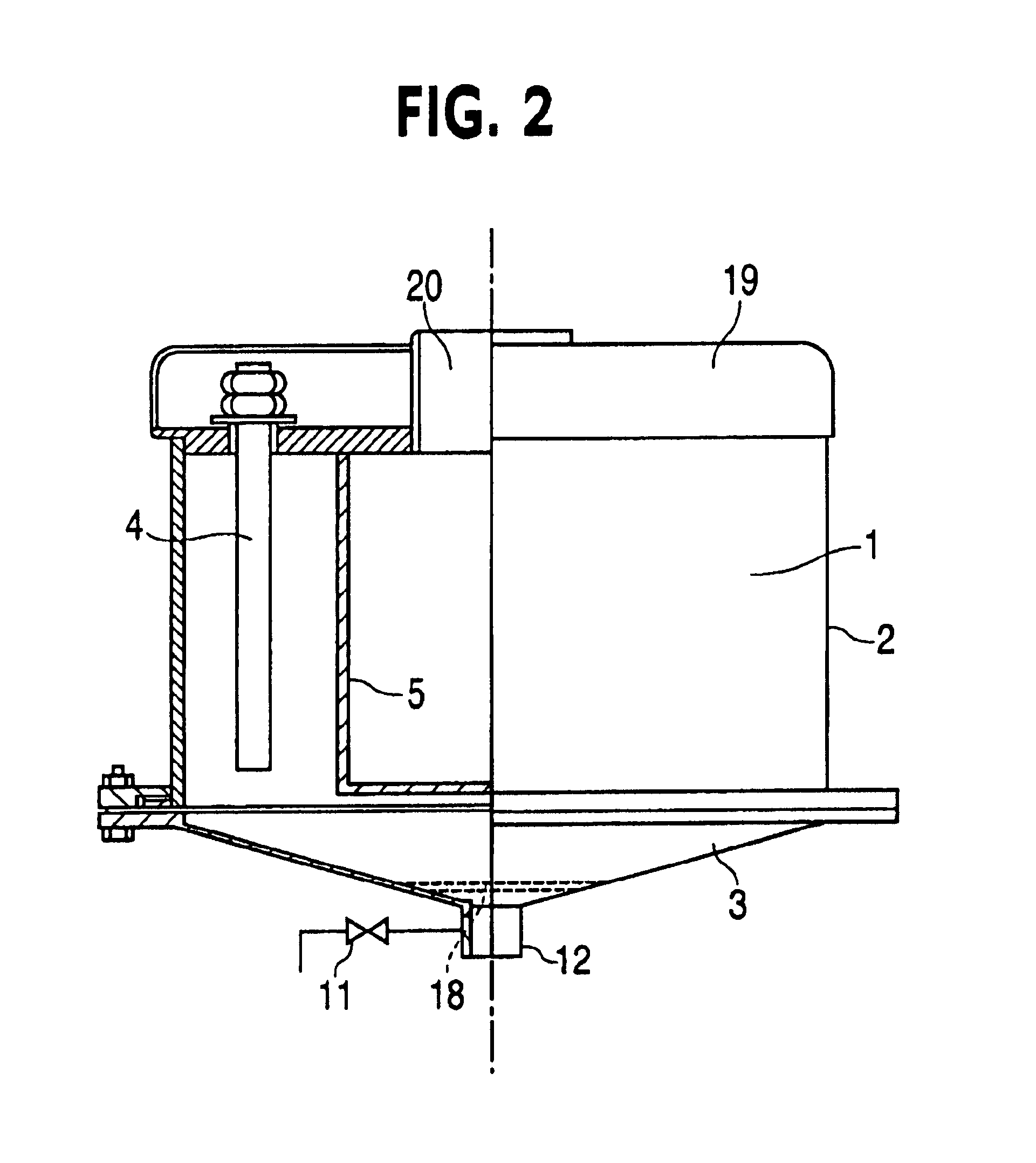

Complex heavy-metal waste water emergency quick treatment method

ActiveCN102603103AIncrease contact areaQuick responseMultistage water/sewage treatmentChemical oxygen demandSludge

The invention relates to a complex heavy-metal waste water emergency quick treatment method, comprising the following steps of: filtering by a sand filter; mixing by a high-speed pump; carrying out an ultraviolet catalyzing ozone reaction; carrying a microwave catalyzing active carbon reaction; carrying micro-electrolytic reaction; circulating waste water; carrying out a Fenton reaction; carryingout electric flocculation on an aluminum electrode plate; and pressing and filtering sludge. Waster water in a circulating slot is pumped into an iron carbon fluidized bed by a fluidizing pump to be circularly treated; an air compressor is connected with the iron carbon fluidized bed and prevents a filler in the iron carbon fluidized bed from blocking; and the microwave active carbon reactor is an active carbon filling tower, and a microwave emitter is arranged outside the body of the active carbon filling tower. The complex heavy-metal waste water emergency quick treatment method disclosed by the invention is used for treating the complex heavy-metal waste water, associated devices are simple, easy, quick, can meet an emergency, and can update and convert, no various chemical raw materials are fed, and various complex heavy-metal waste water with unknown elements can be quickly treated as long as the current magnitude is regulated, and thus the heavy metal in the waste water and chemical oxygen demand can immediately reach the standard and are discharged.

Owner:东莞市珠江海咸水淡化研究所有限公司

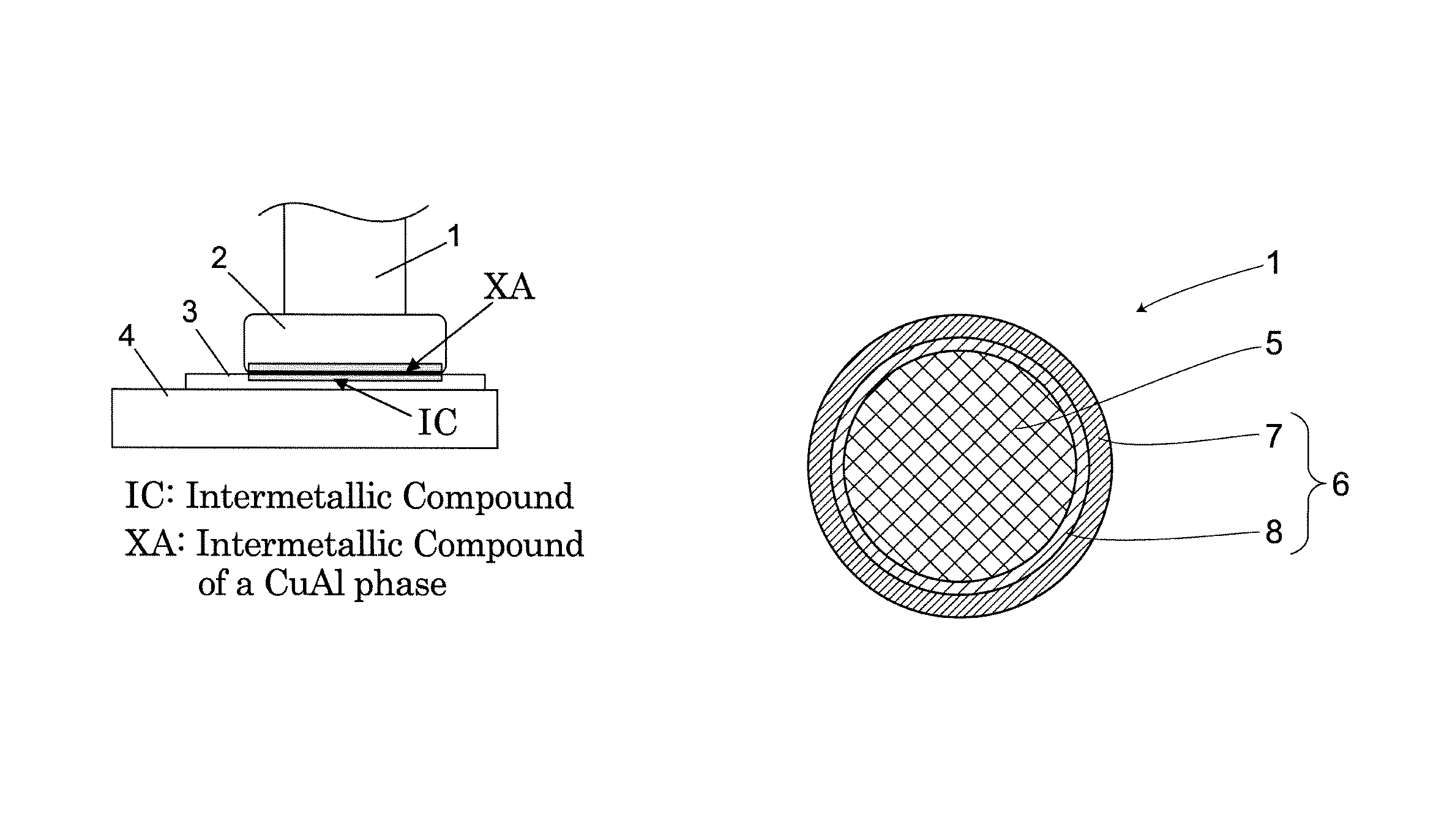

Copper bonding wire for semiconductor device and bonding structure thereof

ActiveUS8653668B2Reduce material costsImprove long-term reliabilitySemiconductor/solid-state device detailsSolid-state devicesCopperIntermetallic

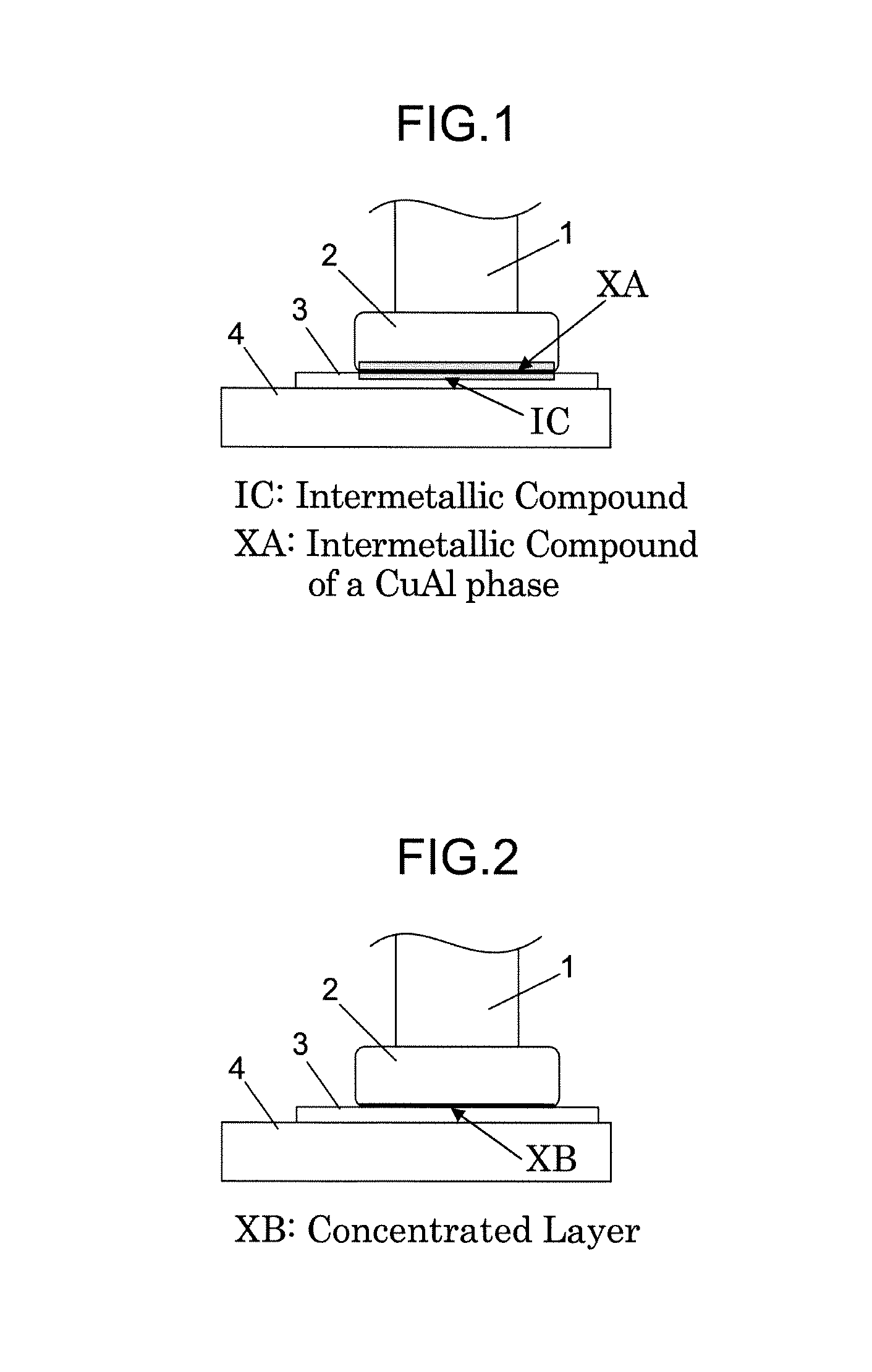

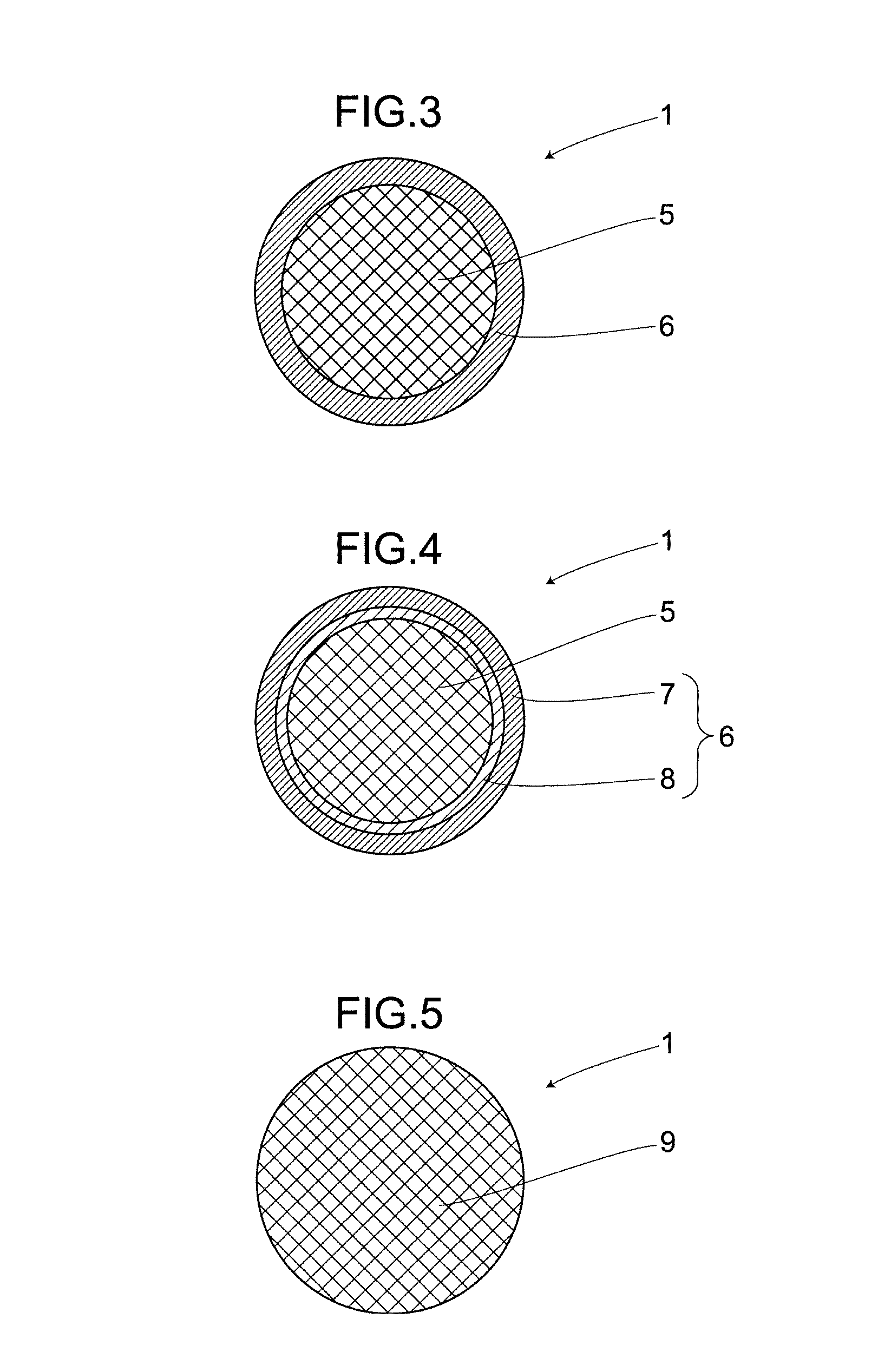

A bonding structure and a copper bonding wire for semiconductor device include a ball-bonded portion formed by bonding to the aluminum electrode a ball formed on a front end of the copper bonding wire. After being heated at any temperature between 130° C. and 200° C., the ball-bonded portion exhibits a relative compound ratio R1 of 40-100%, the relative compound ratio R1 being a ratio of a thickness of a Cu—Al intermetallic compound to thicknesses of intermetallic compounds that are composed of Cu and Al and formed on a cross-sectional surface of the ball-bonded portion.

Owner:NIPPON STEEL CHEMICAL CO LTD +1

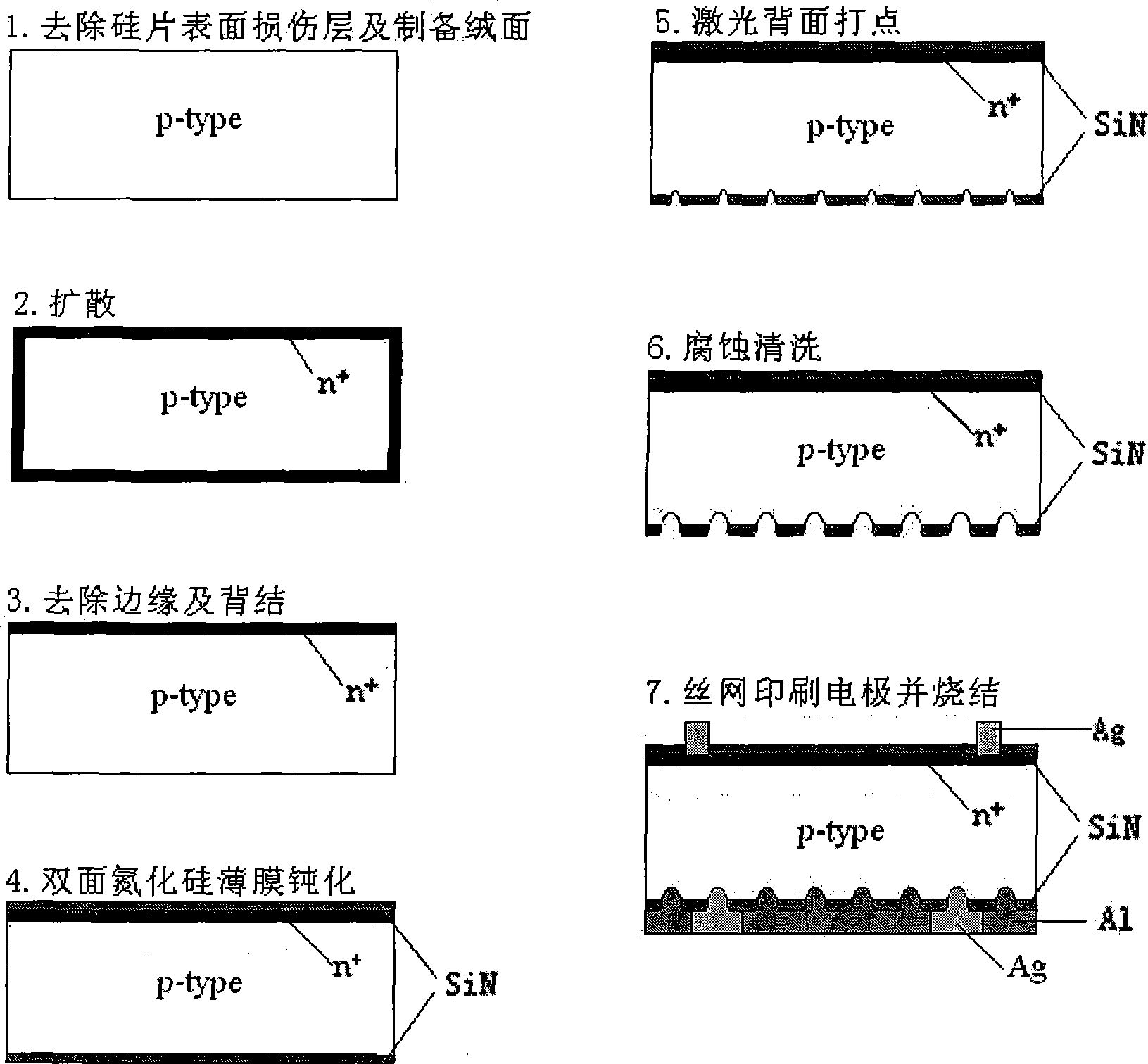

Method for preparing antapex contact crystalline silicon solar cell by utilizing passivation on double surfaces and laser dotting

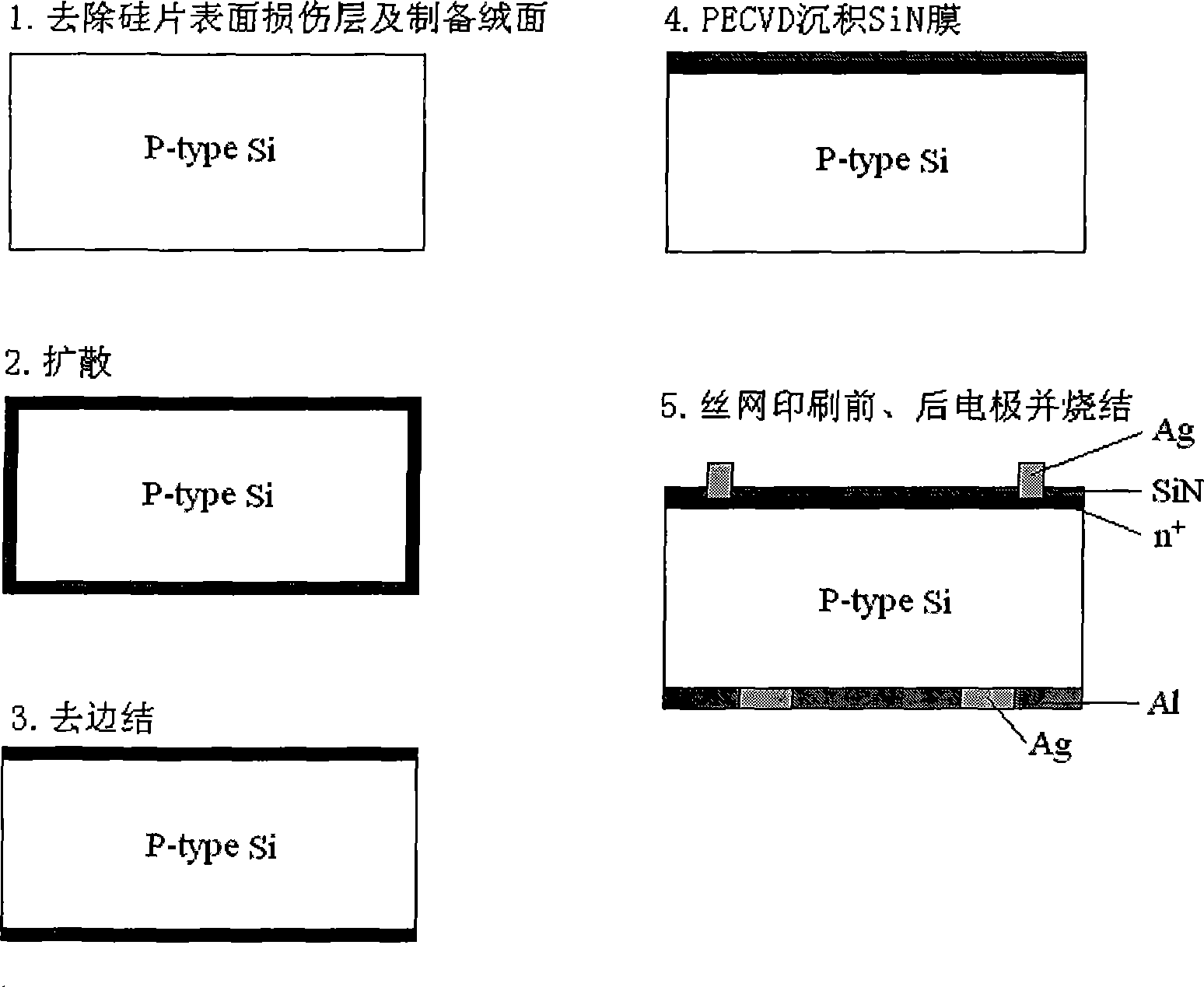

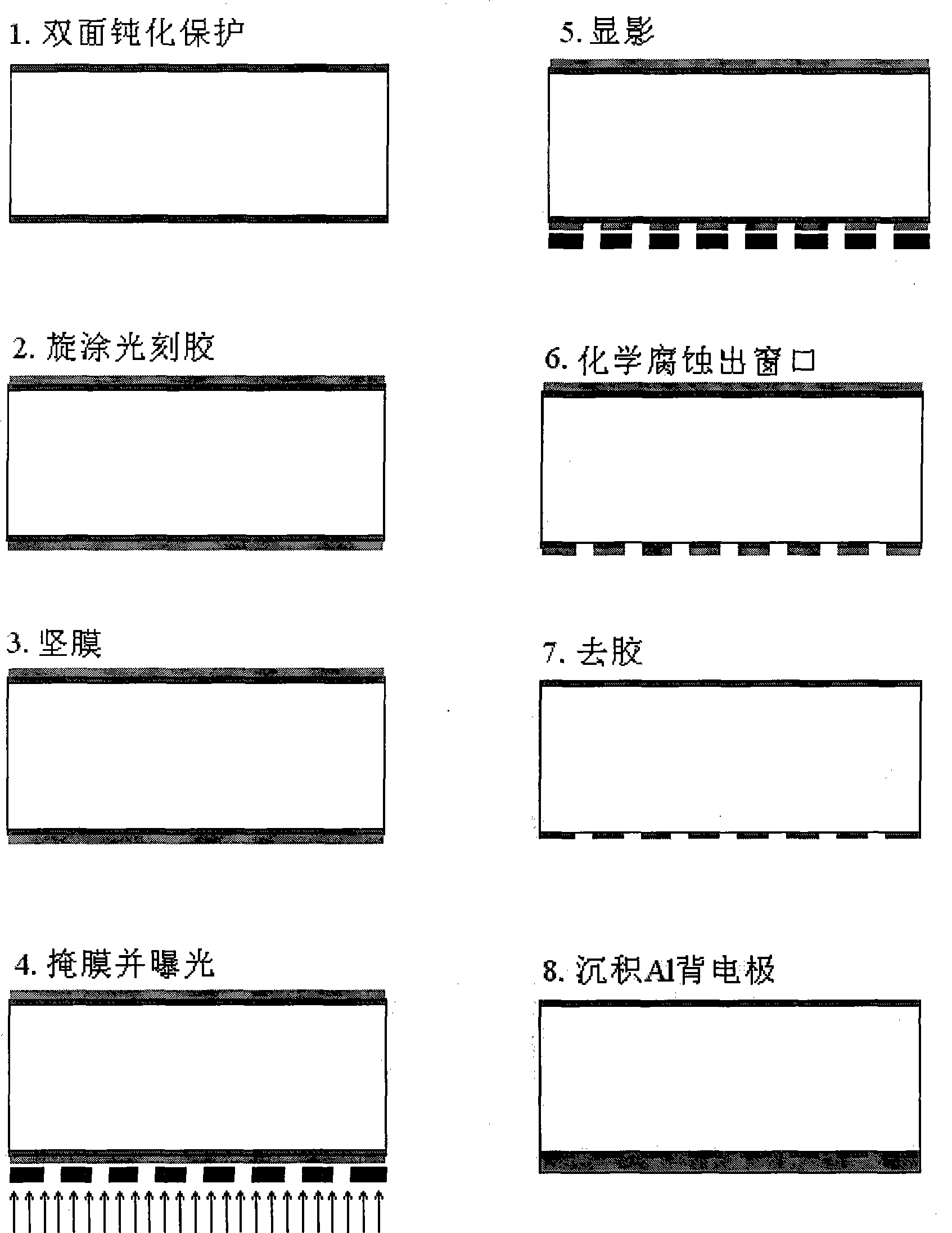

InactiveCN101447528AImprove conversion efficiencyReduce compound rateFinal product manufactureSemiconductor devicesLaser burnProduction line

The invention discloses a method for preparing an antapex contact crystalline silicon solar cell by utilizing passivation on double surfaces and laser dotting. In the method, on the basis of a conventional crystalline silicon solar cell preparation process, both the front and the back surfaces of the solar cell are passivated; then a passivation layer on the back surface of the solar sell is quickly dotted by lasers, and then a back electrode local contact window is formed; and after screen printing or electrode magnetron sputtering, the antapex contact crystalline silicon solar cell with relative high efficiency is prepared. The method utilizes the technology of directly opening a passivation layer window by lasers, so that whether compared with traditional photolithography or a laser burning thawing aluminum electrode method, process steps, process time and preparation costs of the method are greatly reduced; screen printing and the mode of using magnetron sputtering to prepare back electrode adopted by the method are highly beneficial to mass production; and especially, screen printing has a low cost and a high output, and is consistent with the current production line, thereby profitably pushing the industrialization of screen printing.

Owner:上海晶澳太阳能光伏科技有限公司

Barrier structures for integration of high K oxides with Cu and Al electrodes

InactiveUS6900498B2Improve the immunityImprove adhesionTransistorSemiconductor/solid-state device detailsInfraredMaterials science

An integrated circuit barrier structure disposed between high dielectric constant metal oxide and Cu or Al electrodes, for preventing diffusion of species such as oxygen, bismuth, or lead from the high dielectric constant metal oxide into the Cu or Al electrodes. Such barrier structure also protects the Cu or Al electrodes against oxidization during deposition of the high dielectric constant metal oxide. The barrier structure can be formed as (1) a single layer of Pt, Ir, IrO2, Ir2O3, Ru, RuO2, CuO, Cu2O, Al2O3, or a binary or ternary metal nitride, e.g., TaN, NbN, HfN, ZrN, WN, W2N, TiN, TiSiN, TiAlN, TaSiN, or NbAlN, or (2) double or triple layers of such materials, e.g., Pt / TiAlN, Pt / IrO2, Pt / Ir, Ir / TiAlN, Ir / IrO2, IrO2 / TiAlN, IrO2 / Ir, or IrO2 / Ir2O3 / Ir. Such barrier structures enable Cu or Al electrodes to be used in combination with high dielectric constant metal oxides in microelectronic structures such as ferroelectric stack and trench capacitors, non-volatile ferroelectric memory cells, and dynamic random access memory (DRAM) cells.

Owner:ENTEGRIS INC

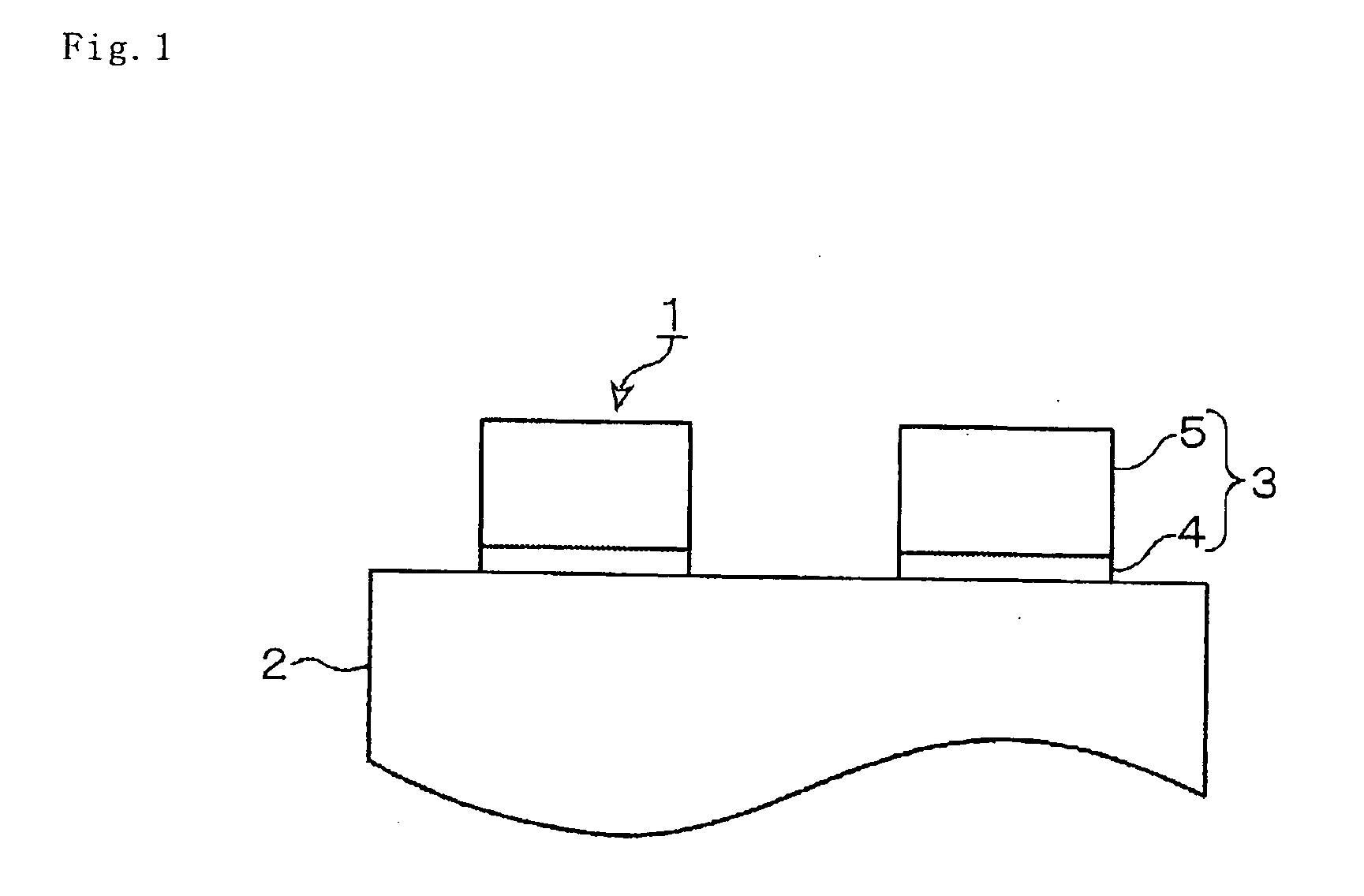

Surface acoustic wave device and method of manufacturing the same

ActiveUS20070103038A1Excellent power durabilityGood reproducibilityPiezoelectric/electrostrictive device manufacture/assemblyImpedence networksOptoelectronicsSingle crystal

In order to provide a surface acoustic wave device provided with a pseudo-single crystal aluminum electrode film, having excellent power durability, easy to manufacture, and possible to grow with good reproducibility, a titanium buffer film 4 and an electrode film composed of an aluminum film or an aluminum alloy film are formed on a piezoelectric substrate 2 composed of lithium tantalate or lithium niobate. The electrode film 5 comprises a pseudo-single crystal film composed of two (111) domains. Each of the <111> directions of two (111) domains tilts in the range of 0 to 10 degrees to the substrate surface, and the <11-2> directions in the respective (111) domain planes are 1 to 15 degrees apart.

Owner:NDK SAW DEVICES CO LTD

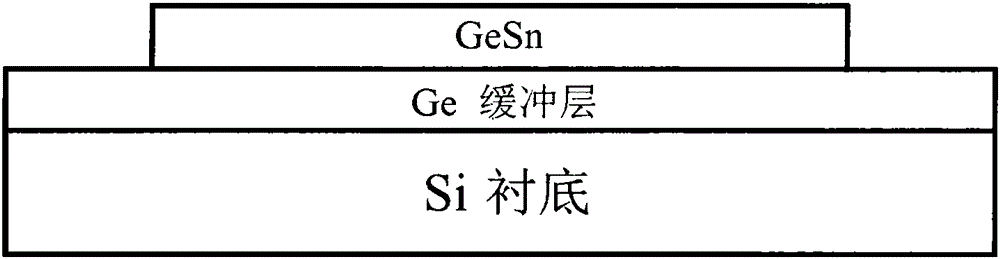

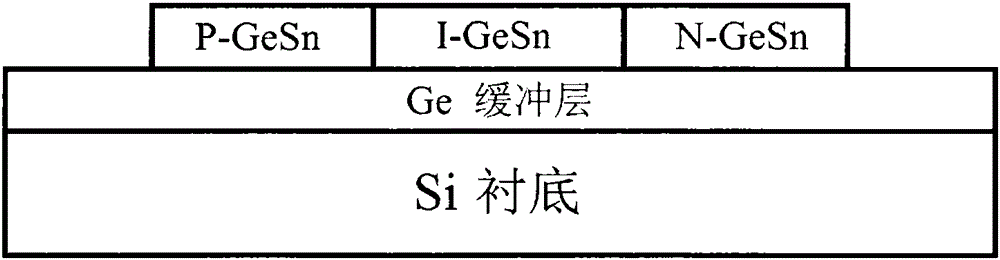

Silicon nitride membrane strained GeSn infrared LED device and preparation method thereof

ActiveCN104993025AOvercoming growing problemsImprove photoelectric conversion efficiencySemiconductor devicesAlloyLength wave

The invention discloses a silicon nitride membrane strained GeSn infrared LED device and a preparation method thereof. The infrared LED device comprises an Si substrate and a Ge buffer layer arranged on the silicon substrate, wherein the Ge buffer layer is successively provided with an aluminum electrode, a transverse P-I-N GeSn layer, a silicon nitride layer and an aluminum electrode from the left to the right, and a silicon nitride film is deposited above a GeSn P-I-N structure. According to the invention, the device and the method are compatible with a CMOS process, the problem of difficulty in growing a GeSn alloy with a high stannum ingredient content in the prior art is overcome, the stress size can be changed through adjusting the structure of a silicon nitride membrane so as to realize the demand of a GeSn material light source for different-wavelength light, the photoelectric conversion efficiency is quite high, the light stability is high, the processing is simple and convenient, and a concrete structure and a concrete implementation scheme are provided for realization of a light source on chip.

Owner:XIDIAN UNIV

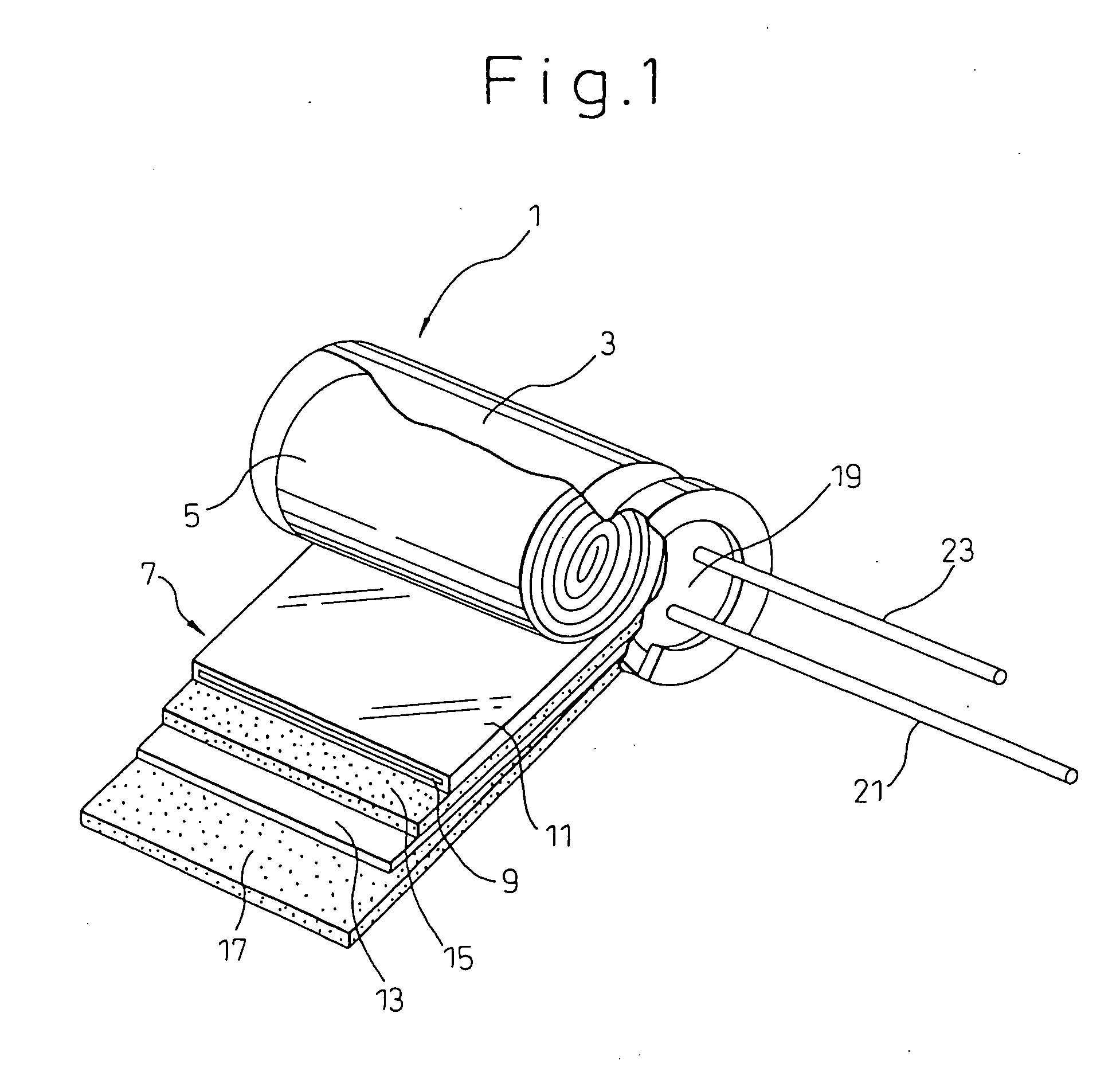

Secondary aluminum battery and preparation method thereof

InactiveCN101764253AReduce manufacturing costSimple processFinal product manufactureCell electrodesElectrolysisSlurry

The invention discloses a secondary aluminum battery and a preparation method thereof. The material of the positive electrode of the battery is organic polysulfide, the material of the negative electrode is aluminum or aluminum alloy, and the electrolyte is halogen aluminic acid ionic liquid; and the organic polysulfide is polysulfide carbine, thereby solving the problems that the elementary active substance is bad in conductivity and the frame is collapsed due to the dissolving of the reducing product. The electrolyte used is non-aqueous ionic liquid so that no oxide film, corrosive product or colloidal secondary product can be produced on the surface of the aluminum negative electrode so as to reduce the capacity loss of the negative electrode; the oxidation reduction reaction of the aluminum electrode in the electrolyte is reversible; and the battery is rechargeable. The preparation method for the secondary aluminum battery comprises the following steps: (1) preparing positive active material paste; (2) coating the positive active material paste on a foam nickel base, baking the paste and rolling the base into a positive plate; (3) rolling the positive plate, glass fiber non-woven membrane and the negative electrode made by taking any one of aluminum powder, aluminum foil and aluminum alloy as the negative active material into a battery core and arranging the battery core in a nickel-plated steel shell; then adding organic electrolyte in the steel shell; and sealing the steel shell to make the AA-type cylindrical secondary aluminum battery. The invention further discloses a preparation method for the positive material polysulfide carbyne of the battery.

Owner:无锡欧力达新能源电力科技有限公司

Method and device for electroextraction of heavy metals from technological solutions and wastewater

InactiveUS6887368B2Reduced heavy metal levelLess energy consumptionFrom normal temperature solutionsLiquid separation by electricityConductive materialsMaterials science

The basic principles of the method for heavy metals electroextraction from technological solutions and wastewater includes pretreating to remove Chromium-6 and high concentrations of heavy metals and periodically treating in a six-electrode bipolar cylindrical electroreactor made of non-conducting material to achieve lower accepted levels of impurities. Six cylindrical steel electrodes form two triode stacks and are fed with three-phase alternating current of commercial frequency (50-60 Hz), which can be pulsed. Each phase of the three-phase current is connected to three electrodes of one triode stack or in parallel to two triode stacks. The parallel connection of three-phase current to two triode stacks is performed so that the same phase of the three phase current is connected in parallel with each two opposite electrodes of six electrodes located along the periphery, or with two adjacent electrodes. A bipolar stationary aluminum electrode is situated in the inter-electrode space. In one of the embodiments, the bipolar electrode is made of a perforated heat-resistant plastic container filled with secondary aluminum and duralumin scrap. In another embodiment, the bipolar electrode of aluminum or duralumin scrap may be made without a perforated container and is placed in the inter-electrode space as a bulk scrap. In this case, to prevent shorts, each of six steel electrodes is placed in isolated perforated plastic shell with holes of 5 mm in diameter. Non-ferrous metals are extracted in a form of ferrite-chromites, and aluminates as well as hydroxyl salts deposited in the inter-electrode space without electrolysis deposits on electrodes. Deposits are separated from solution by known methods of filtration.

Owner:URAL PROCESS ENG +2

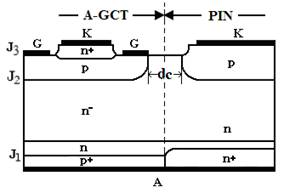

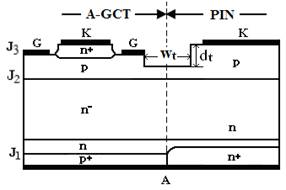

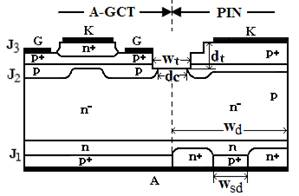

Combined PNP-trench isolation RC-GCT component and preparation method thereof

ActiveCN101853878ATaking into account featuresCompatible with switching characteristicsSemiconductor/solid-state device manufacturingSemiconductor devicesAluminum electrodeWave crest

The invention discloses a combined PNP-trench isolation RC-GCT (reverse conducting-gate commutated thyristor) component. The entire component is divided into an A-GCT (asymmetric gate commutated thyristor) and a PIN diode. The A-GCT is structurally characterized in that a wavelike P base region and a P+ base region are sequentially arranged in the upward direction of an N- region; an N+ cathode region is arranged on the upper surface of the middle section of the P+ base region, which corresponds to the wave crest of the wavelike P base region; a cathode aluminum electrode constitutes the upper surface of the N+ cathode region; gate aluminum electrodes are respectively arranged on the upper surfaces of the P+ base regions on two sides of the N+ cathode region; and an N buffer layer and a transparent P+ anode region are arranged in the downward direction of the N- region. The PIN diode is structurally characterized in that a P base region and a P+ base region are sequentially arranged in the upward direction of an N- region; a cathode aluminum electrode is arranged on the surface of the P+ base region; an N buffer layer is arranged in the downward direction of the N- region; and an N+ cathode region I of the PIN diode, a P+ short-circuit region and an N+ cathode region II of the PIN diode are arranged side by side below the N buffer layer. The invention further discloses a method for preparing the combined PNP-trench isolation RC-GCT component. The invention can effectively improve the characteristics of the PIN diode in reverse recovery, thus dispensing with the control on the minority carrier lifetime.

Owner:XIAN UNIV OF TECH

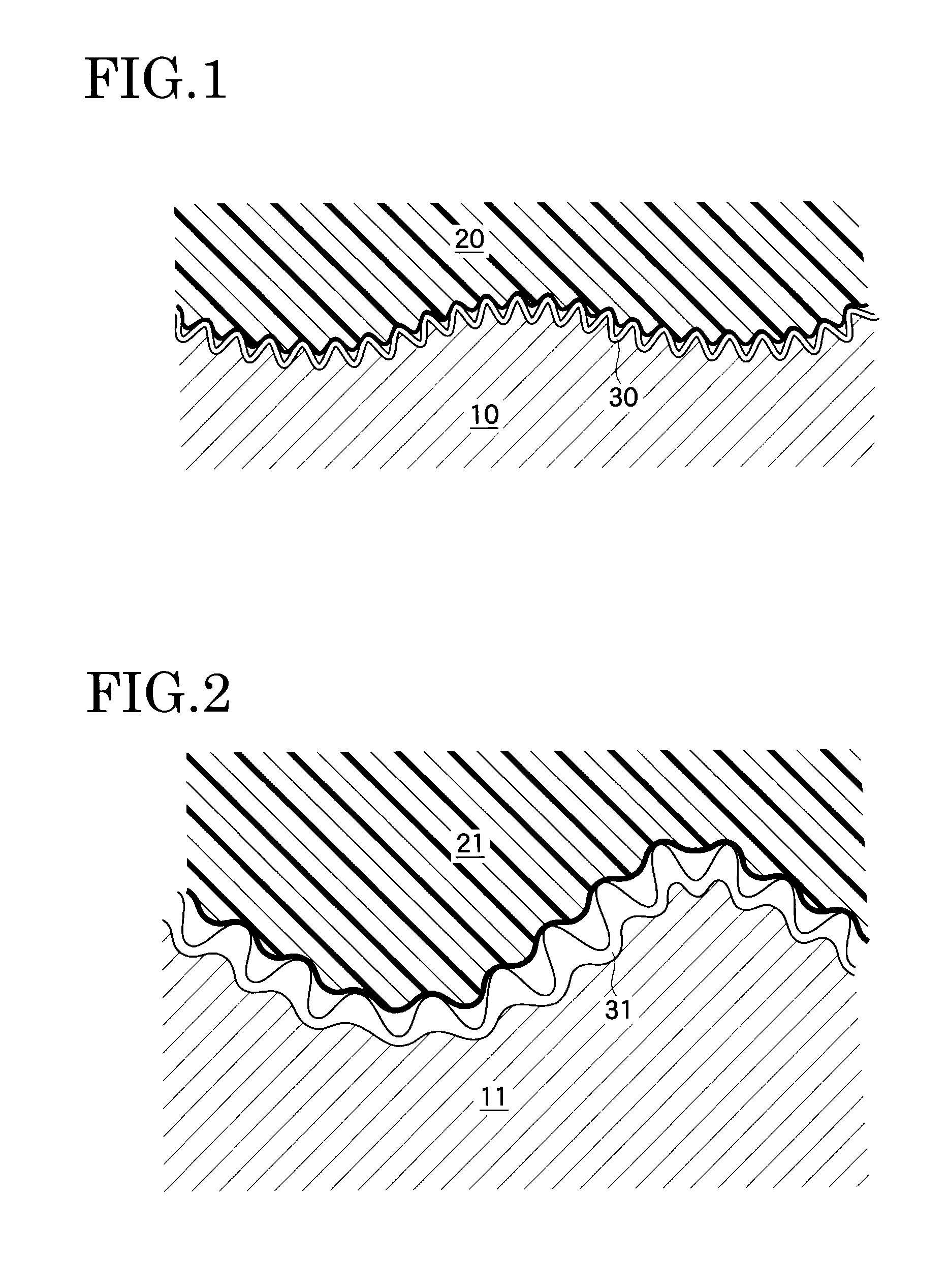

Electrolytic capacitor and electrolitic solution for driving electrolytic capacitor

InactiveUS20050094352A1Easy to controlIncrease surface areaCapacitor electrolytes/absorbentsAqueous electrolyte cellsElectrolysisOrganic solvent

The electrical properties and high-temperature characteristics of an electrolytic capacitor are rendered satisfactory by addition of a compound with an unsaturated bond-containing chain which serves to absorb hydrogen gas generated by reaction between the aluminum electrode foil and the electrolyte solution. The electrolytic capacitor contains the unsaturated compound which allows hydrogen addition, or the electrolytic solution, which comprises a solvent composed of 10-80 wt % of an organic solvent and 90-20 wt % water and at least one electrolyte selected from the group consisting of carboxylic acids or their salts and inorganic acids or their salts, also comprises one or more unsaturated compounds which are water-soluble or soluble in polar and protic polar solvents.

Owner:RUBYCON CORPORATION

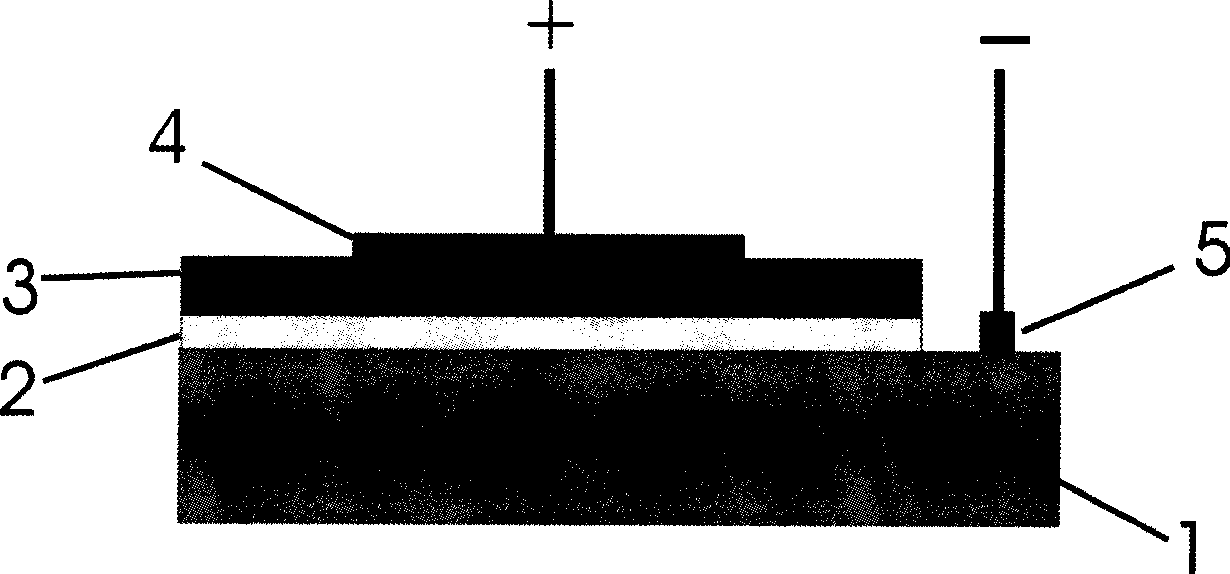

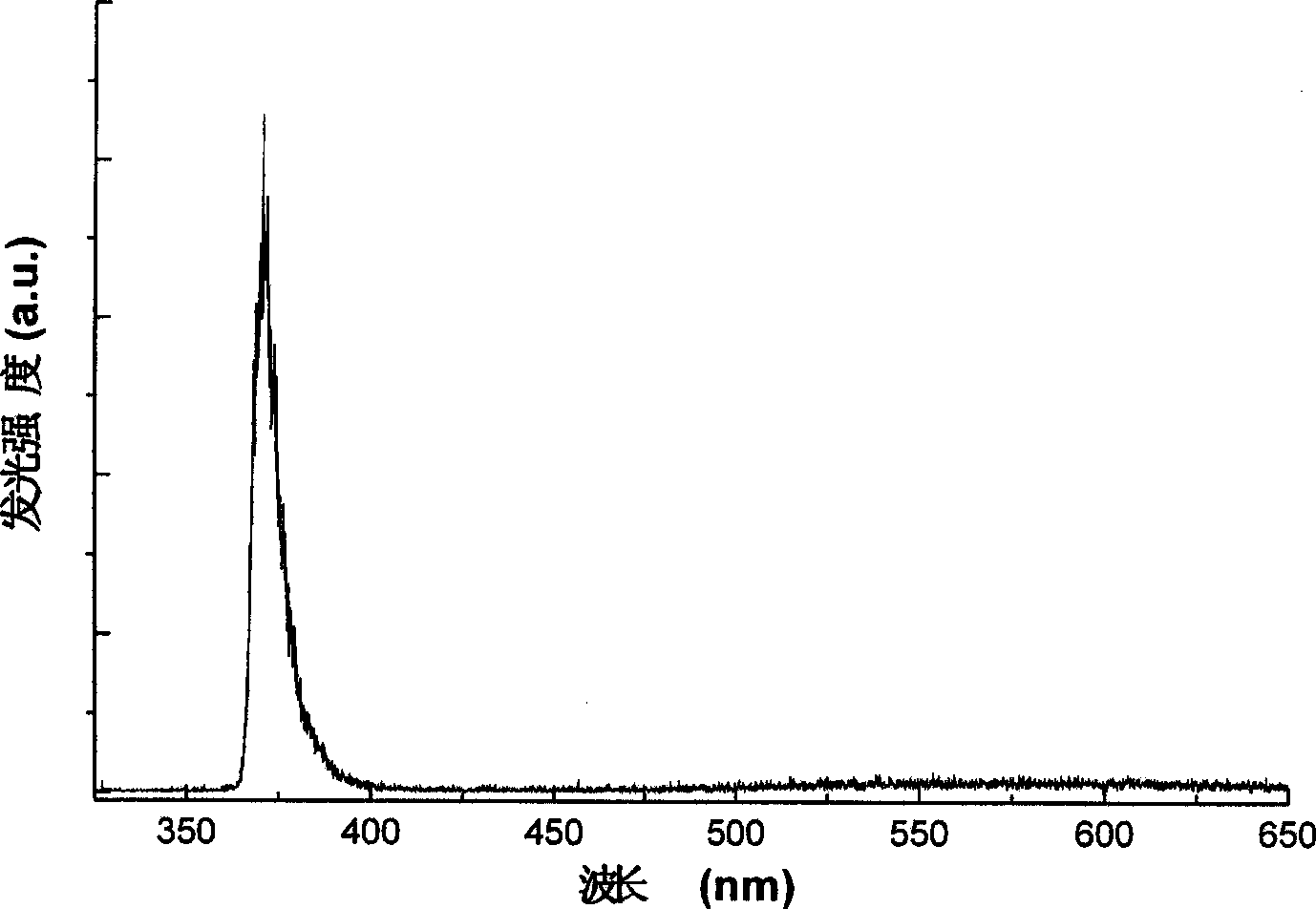

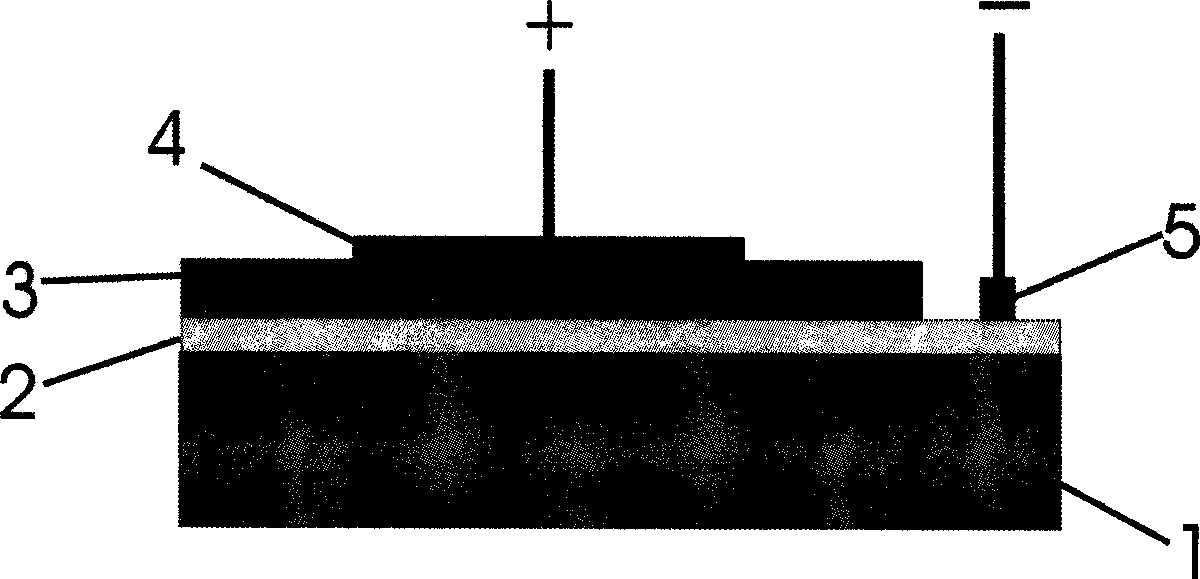

P-zinc oxide/N- nickel oxide heterogeneous PN junction ultraviolet laser diode and method for production

ActiveCN101505035AGood electro-ultraviolet lasing luminescence propertiesImprove performanceLaser detailsLaser active region structureIndiumRadio frequency magnetron sputtering

The invention discloses an n -zinc oxide / p- nickel oxide heterogeneous pn junction ultraviolet laser diode and a preparation method thereof. The heterogeneous pn junction diode at least comprises a pn junction, a substrate and an ohm contacting electrode, wherein the pn junction is the heterogeneous pn junction by plating a p-type nickel oxide film on an n-type zinc oxide film; and the substrate is a sapphire plated with n-type GaN. The preparation method comprises the following steps: firstly preparing the n-type ZnO film layer on the substrate by the radio frequency magnetron sputtering technology; then sputtering a p-type NiO film layer on the n-type ZnO film layer to form the heterogeneity pn junction; finally manufacturing a pn junction electrode by a sputtering method or a thermal evaporation method; sputtering gold electrodes or platinum electrodes or nickel platinum electrodes or ITO electrodes on the NiO surface; plating indium electrodes or aluminum electrodes or gold electrodes on the GaN or the edge of ZnO; and making the electrodes form ohm contact after annealing alloying. The heterogeneous pn junction diode has the advantages of better electro-ultraviolet lasing luminescence characteristic, peak luminous wavelength of about 375 nm, simple preparation process and low cost.

Owner:常熟紫金知识产权服务有限公司

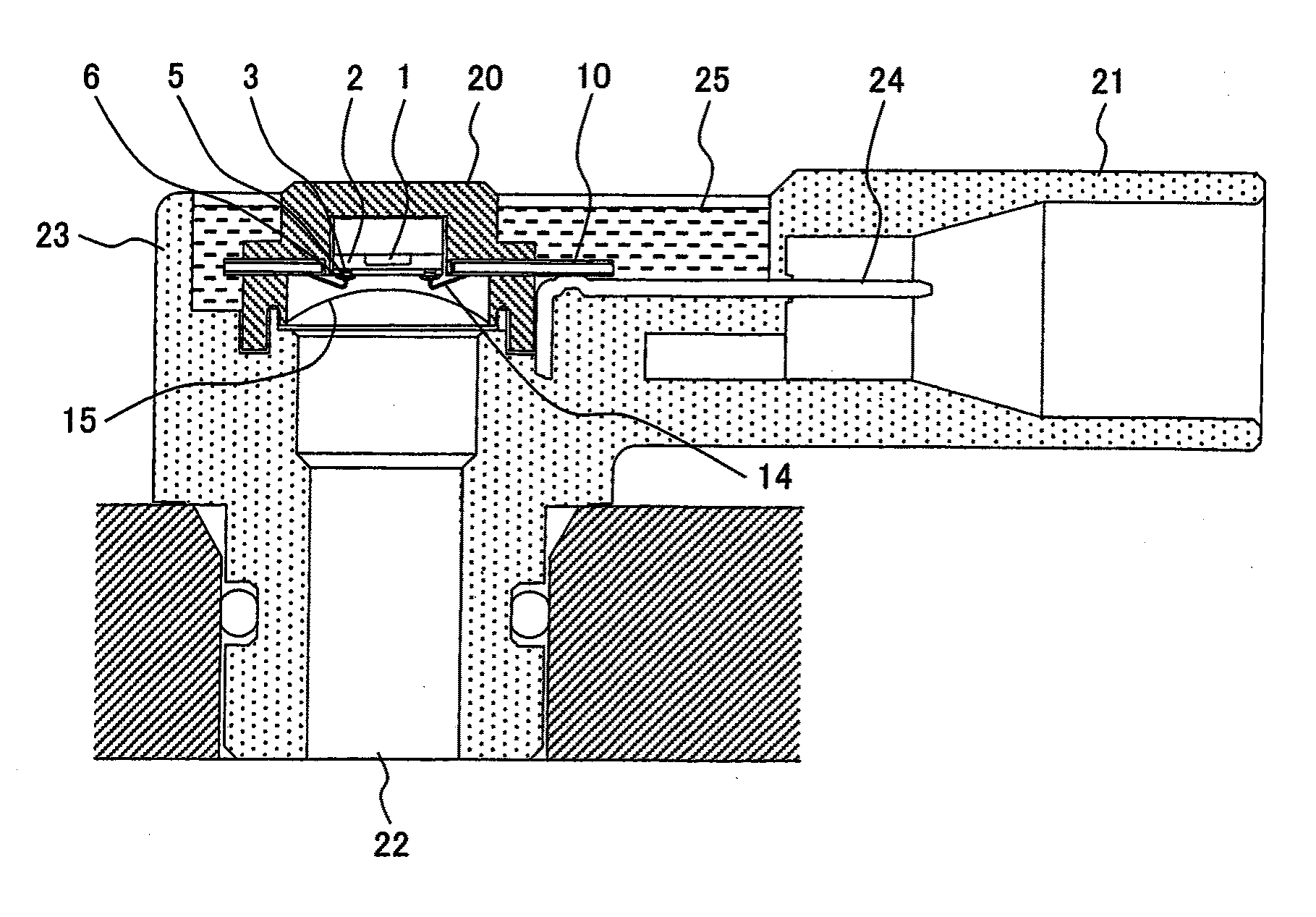

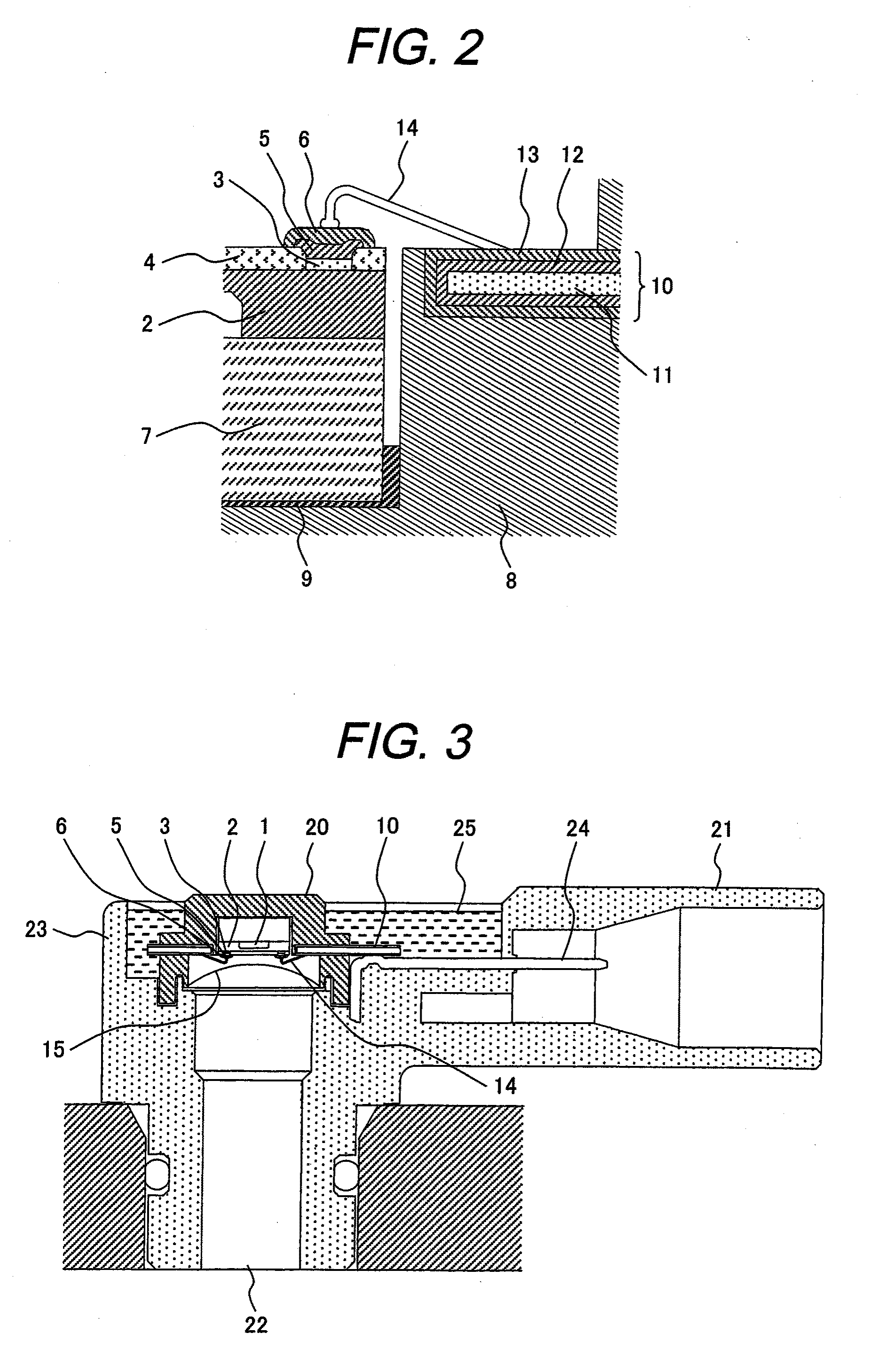

Semiconductor Pressure Sensor

ActiveUS20090218643A1Small ionization tendencyAvoid corrosionAcceleration measurement using interia forcesFluid pressure measurement by electric/magnetic elementsGold layerTitanium

An object of the present invention is to solve problems in that aluminum electrodes, aluminum wires, and I / O terminals are corroded by corrosive gasses when a pressure of a pressure medium containing corrosive matters such as exhaust gas is measured with a semiconductor sensor; and improve not only the corrosion resistance of the sensor chip but also the corrosion resistance of the portion particularly functioning as the pressure receiver.Each of the aluminum electrodes that is likely to be corroded portions is prevented from being corroded by forming a titanium-tungsten layer and gold layer on the aluminum electrode. The connecting wires are prevented from being corroded by corrosive matters by using gold wires. The I / O terminals are also prevented from being corroded by applying gold plating.

Owner:FUJI ELECTRIC CO LTD

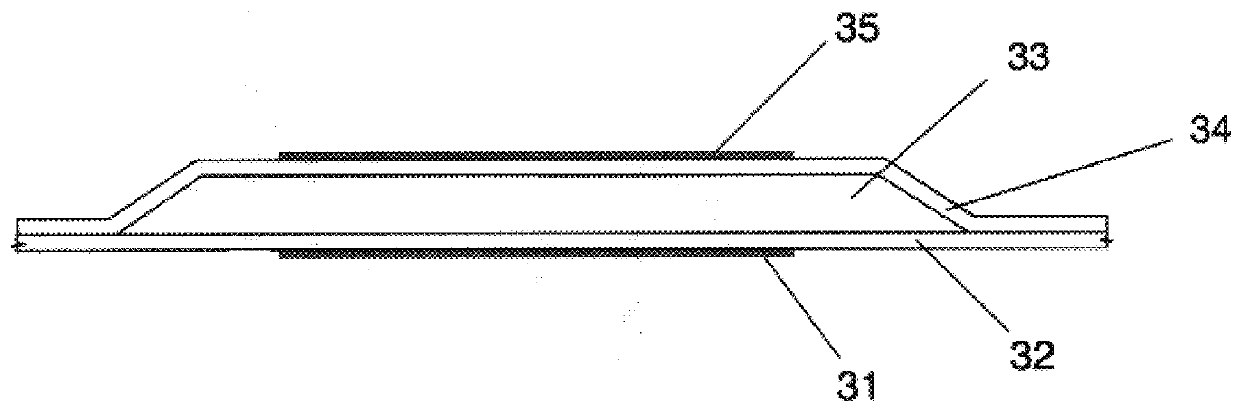

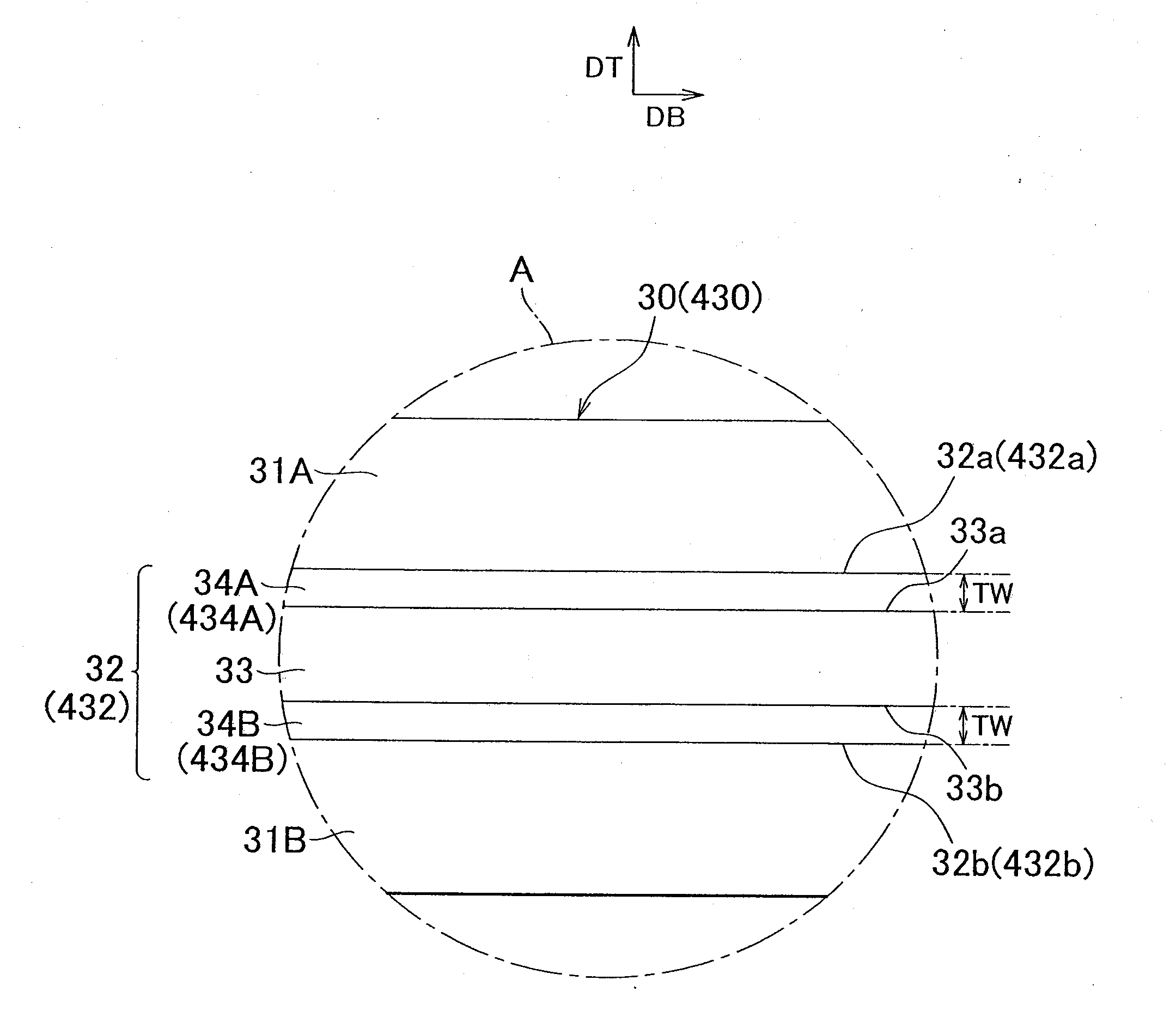

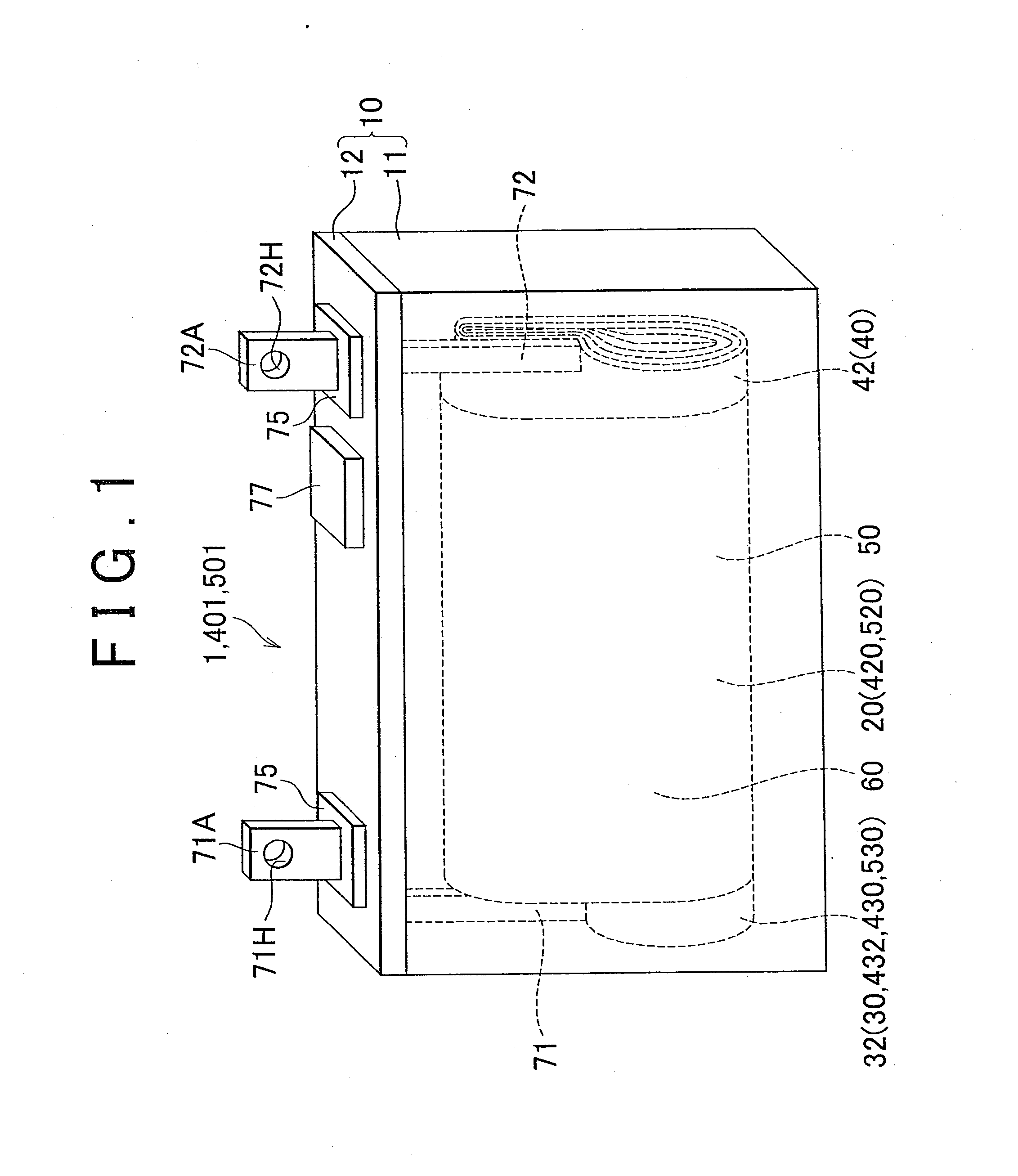

Battery-dedicated electrode foil, positive electrode plate, battery, vehicle, and battery-equipped appliance, and manufacture method for the battery-dedicated electrode foil, and manufacture method of the positive electrode plate

ActiveUS20110111290A1Inhibition formationSmall valueAlkaline accumulatorsFinal product manufactureTungstenMetal

A battery-dedicated electrode foil (32) includes an aluminum electrode foil (33) in which metal aluminum is exposed, and corrosion-resistant layers (34A, 34B) that are formed on surfaces (33a, 33b) of the aluminum electrode foil, and that are in direct contact with the metal aluminum that forms the aluminum electrode foil, and that is made of tungsten carbide.

Owner:TOYOTA JIDOSHA KK

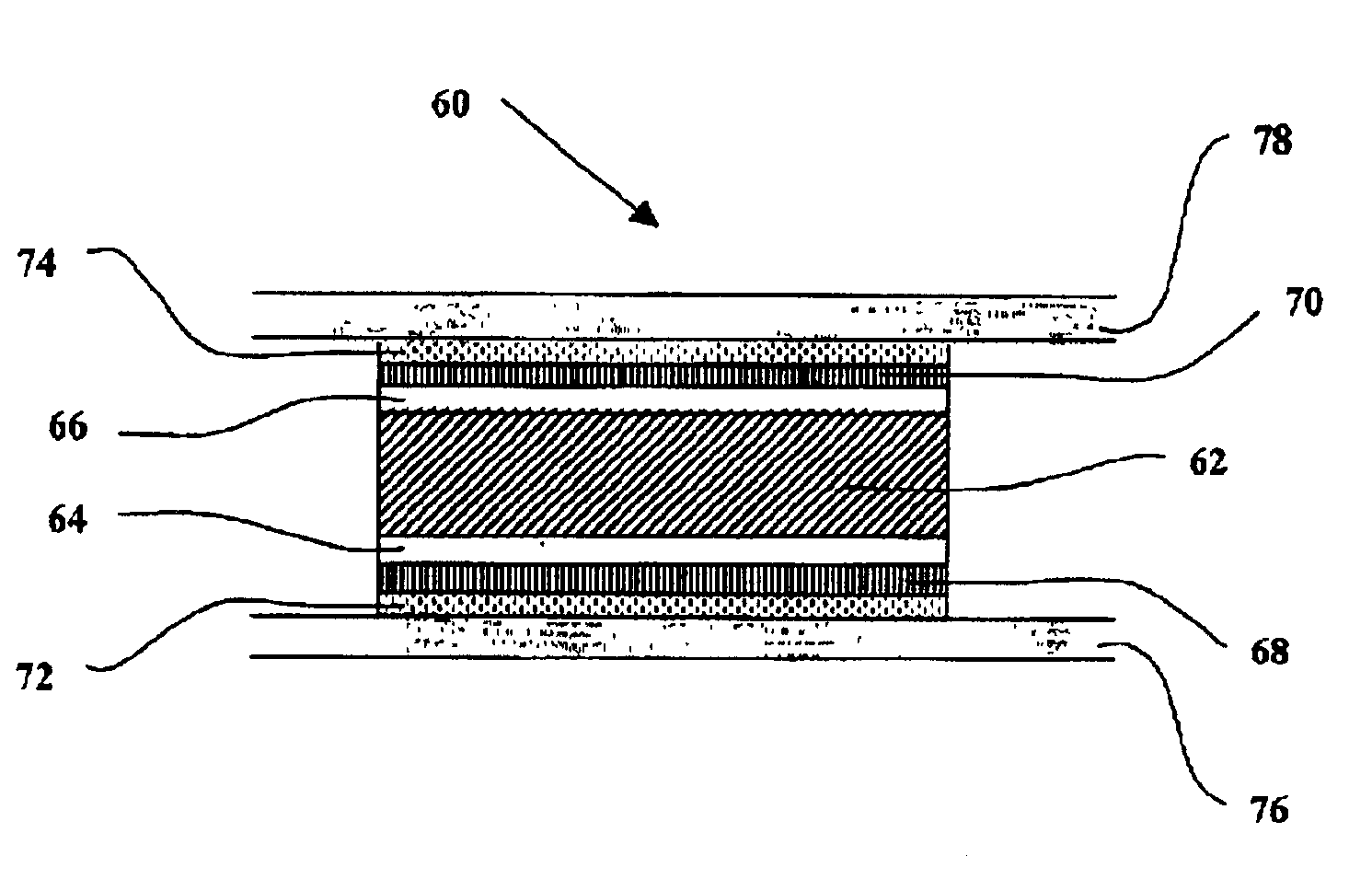

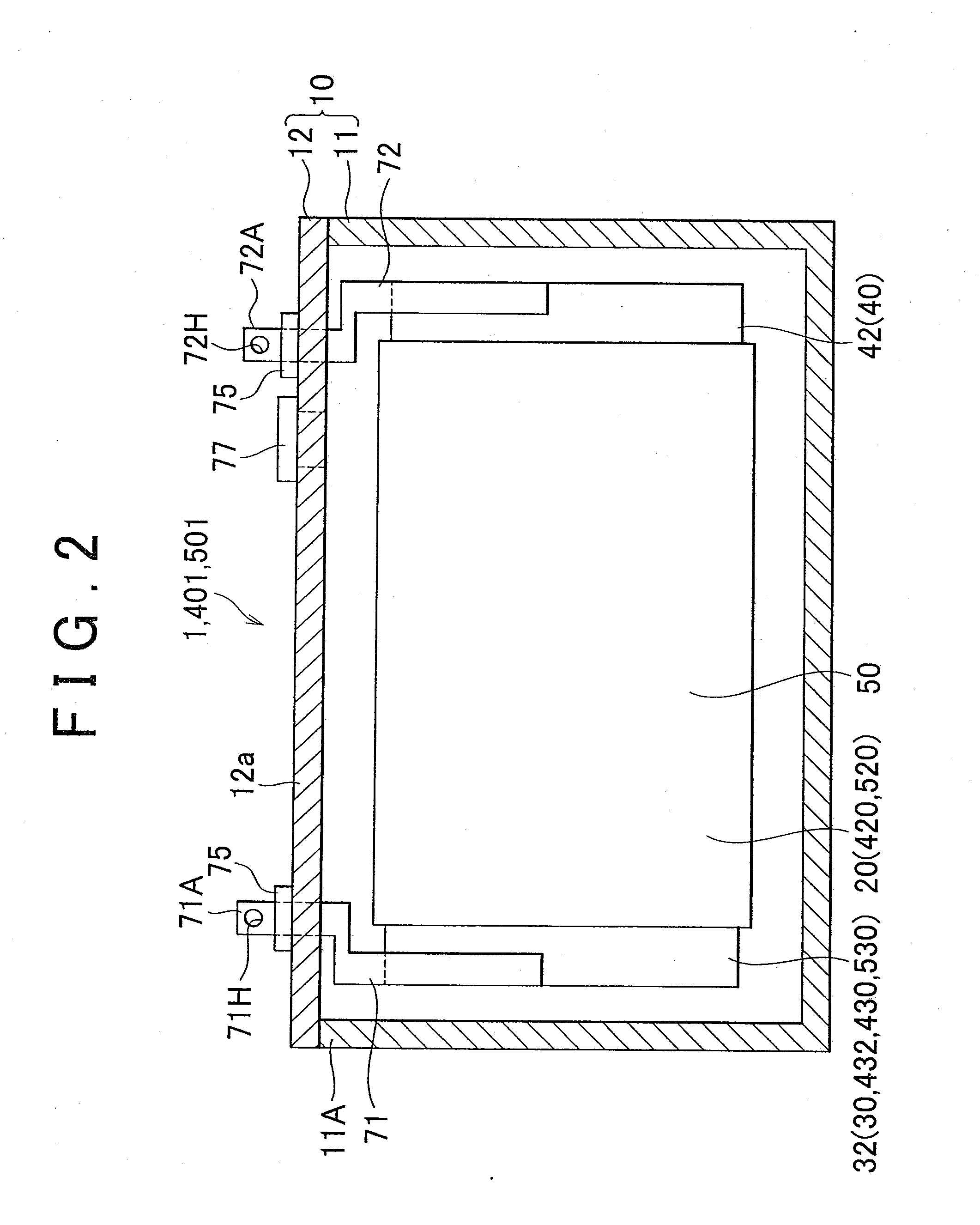

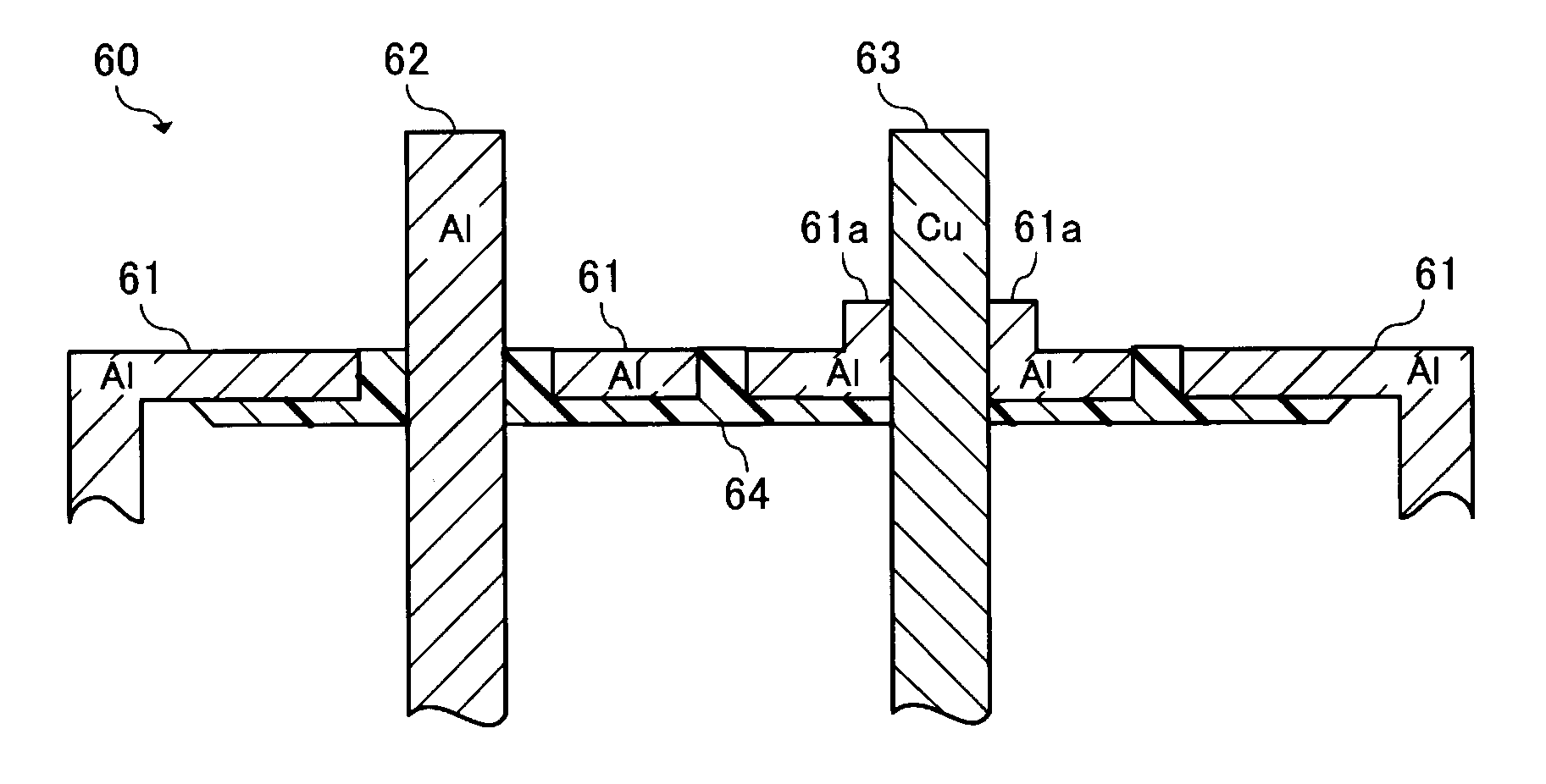

Metal-resin complex and process for production thereof

ActiveUS20140065472A1Improve air tightnessImprove sealingCell electrodesFinal product manufactureCopper electrodeLithium-ion battery

A metal-resin composite having high gas sealing properties is provided. An aluminum alloy structure having a shape surrounding the copper 63 is firstly formed, and the attached aluminum alloy is made closely contact with the copper electrode 63 and further made engaged into the copper electrode 63 by pressing or forging. It is then machined into a predetermined shape so as to prepare the copper alloy 63 attached with an aluminum alloy part 61a. Subsequently, the surface treatment of the NMT or NMT 2 is given to three members of an aluminum electrode 62, the copper electrode 63 attached with the aluminum alloy part 61a and an aluminum alloy lid 61. These three members are inserted into an injection mold, and a thermoplastic resin composition 64 of PPS resin is injected. The lithium-ion battery lid 60 having a structure as shown in FIG. 11 is thus obtained.

Owner:TAISEI PLAS CO LTD

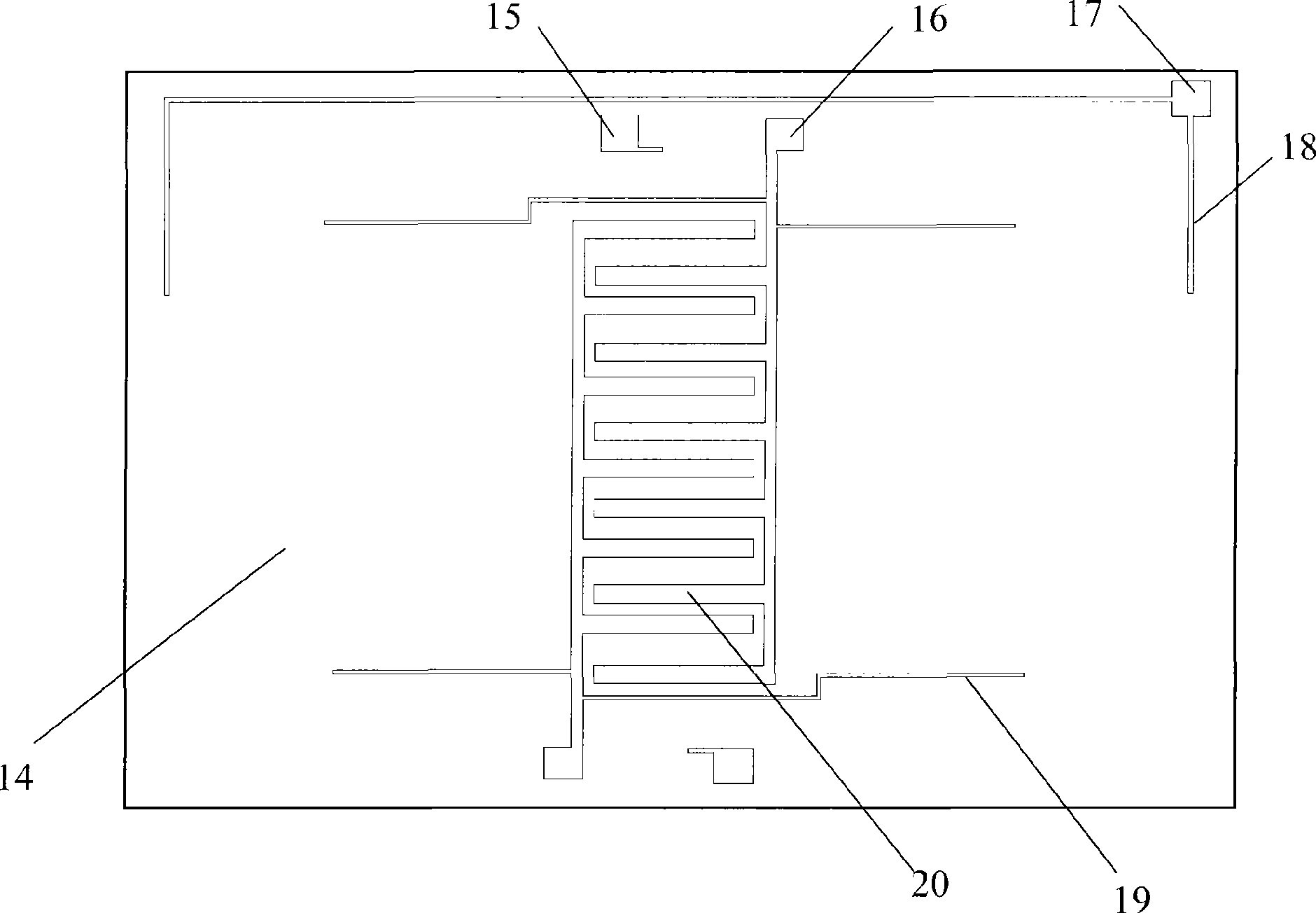

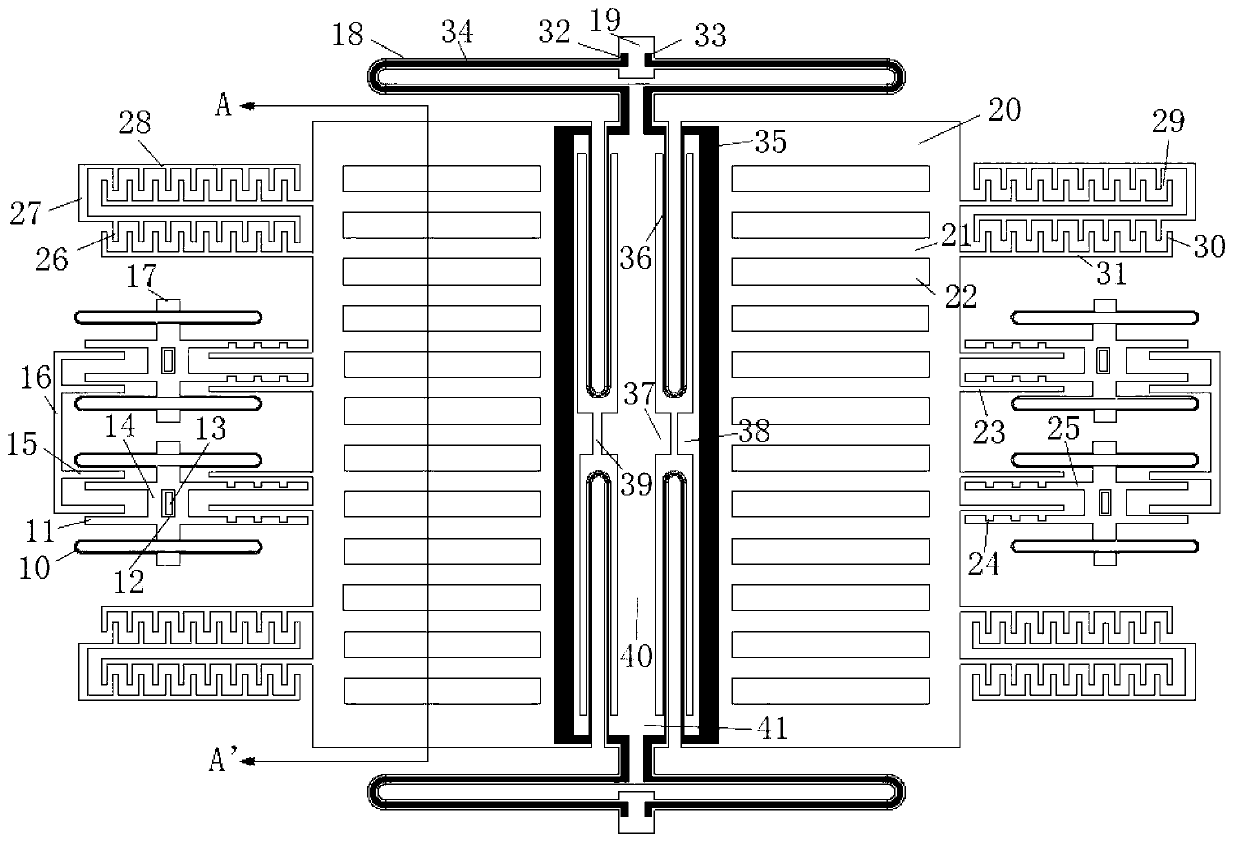

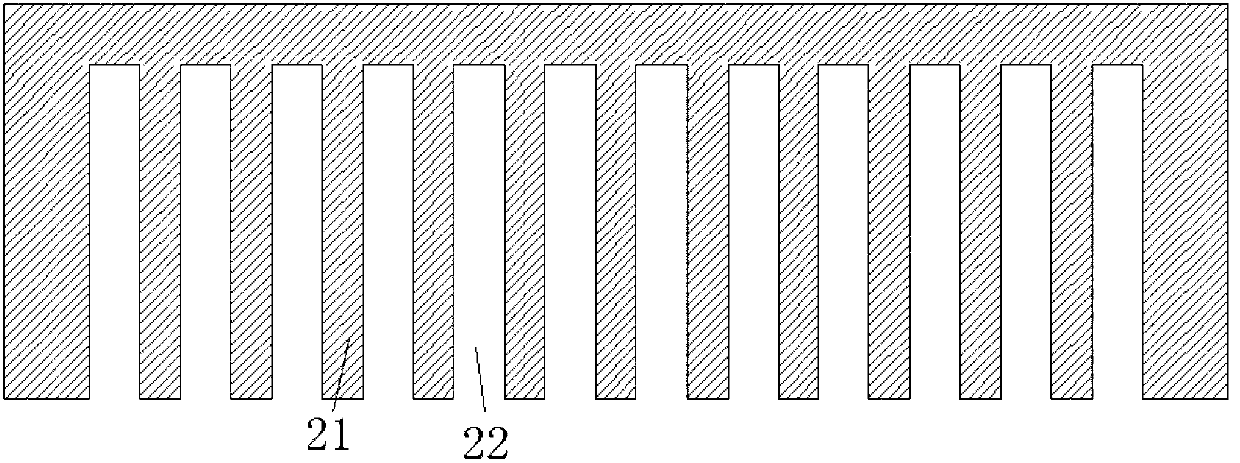

Micro-inertial sensor with variable pitch capacitor and method for producing the same

InactiveCN101481084AIncrease the quality of the vibratorNovel structureTelevision system detailsSemi-permeable membranesCapacitanceEngineering

The invention relates to a microinertia sensor of a variable pitch capacitor and a preparation method thereof. The prior product limits the increase in the mass of the sensor vibration generator and the decrease in the polar plate pitch. A sensor mass block is a rectangular silicon chip etched with fence-shaped strips, the two corresponding ends are connected with anchor points by a silicon supporting beam, and the other two corresponding ends are respectively provided with silicon strips with the same quantity and corresponding positions. Driver mass blocks are arranged at the two sides of the sensor mass block, an annular groove is etched in the middle, the two sides are provided with movable driving silicon strips and comb detection silicon strips, and the silicon strips connected with the sensor mass block and the corresponding detection silicon strips form a detection capacitor. The comb strips of the fixed driving silicon strips and the movable driving silicon strips from a driving capacitor. The sensor mass block corresponding to the bottom surface of the glass underlay is provided with interdigital aluminum electrodes, and each fence-shaped strip of the sensor mass block corresponds to each pair of interdigitals in the interdigital aluminum electrodes. The invention has simple technique, and contributes to lowering cost and improving rate of finished products.

Owner:HAIAN COUNTY SHENLING ELECTRICAL APPLIANCE MFG

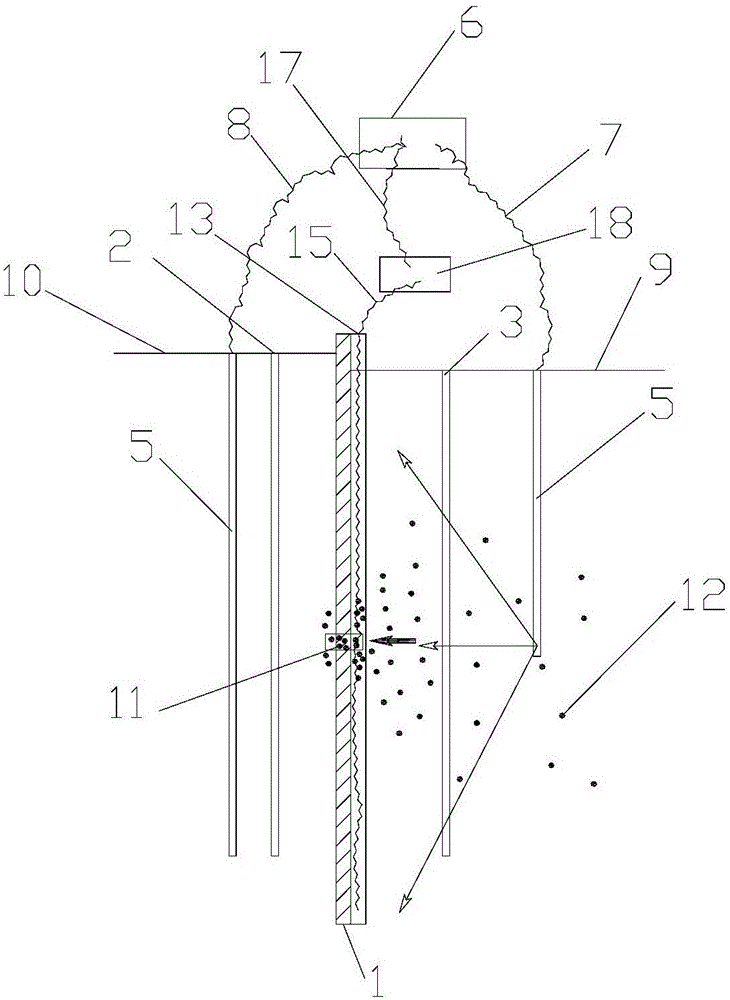

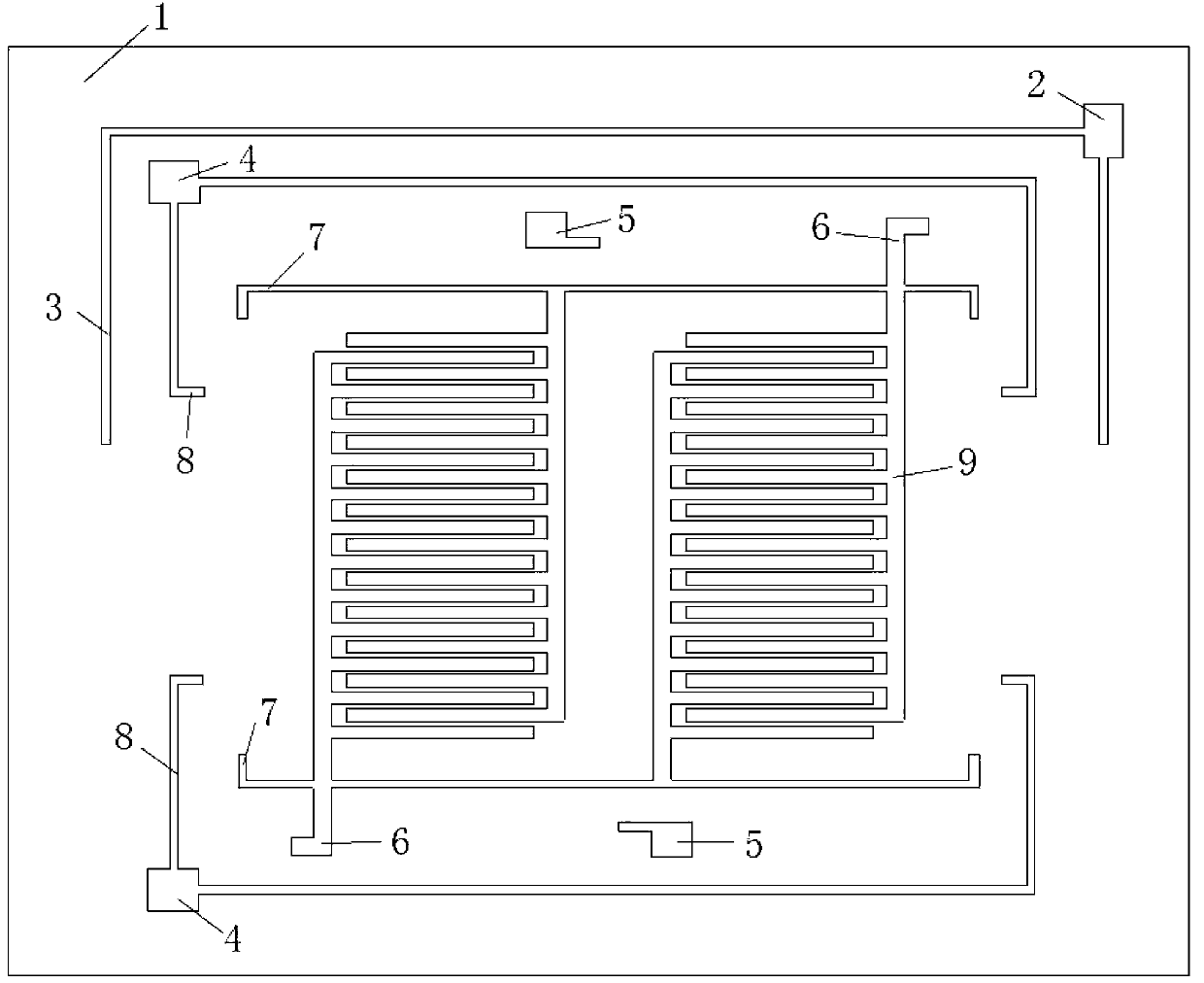

Soft soil area underground continuous wall leakage detecting system

The invention discloses a soft soil area underground continuous wall leakage detecting system, solves such defects as complex construction, difficult measurement and lower accuracy of measured results, and measures specific positions of leakage points more accurately. The transport process of underground ions and the gathering process of the underground ions are observed in real time, so that the specific positions of the leakage points can be obtained more quickly and accurately. The soft soil area underground continuous wall leakage detecting system relates to a underground continuous wall, an observation well, a precipitation well, a soft soil layer, an aluminum electrode, an electrifying device, an electrifying device positive pole, an electrifying device negative pole, an in-pit ground, an out-pit ground, the leakage points, aluminum ions, a sampling device, a slide cover, a bracket, an opening cylinder, a gauze, a separation plate, a round hole, a sensor, a circuit, a circuit fixator, a circuit negative pole and an acquiring system. The underground continuous wall is not limited by thickness and depth. The observation well is used for observing change of an underground water level on the outer side of a foundation pit; the gap and the depth of the observation well are determined according to actual engineering; and the observation well also can serve as a foundation pit outer side precipitation well. The precipitation well is a foundation pit inner side precipitation well, and can be used for observing a underground water level on the inner side of the foundation pit. The soft soil layer is a soil layer suitable for an electroosmosis method.

Owner:ZHEJIANG UNIVERSITY OF SCIENCE AND TECHNOLOGY

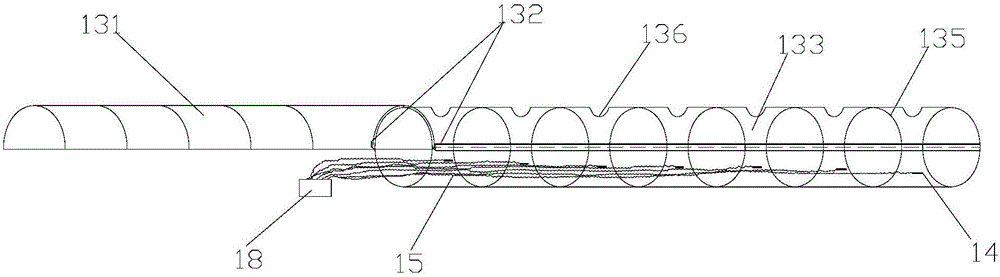

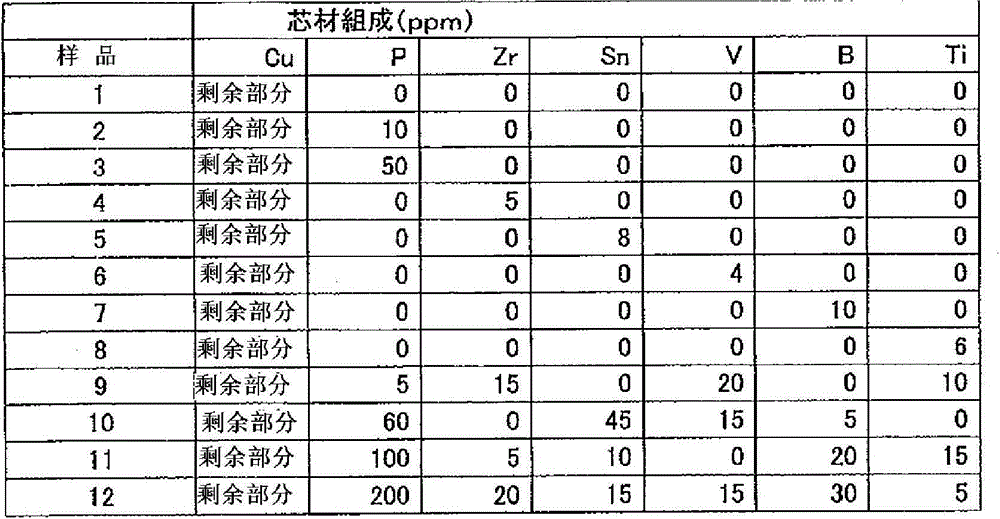

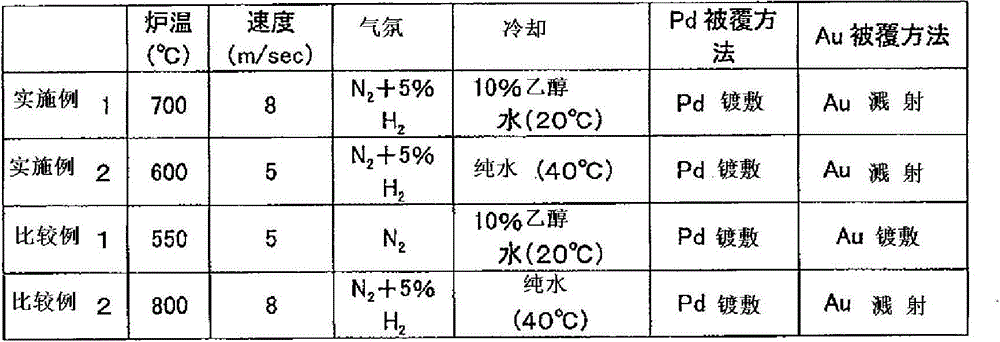

Pd-coated copper ball bonding wire

ActiveCN103339719AUniform and fine dispersionReliable stabilizationConductive materialSolid-state devicesBond interfaceCopper wire

To increase the reliability of joins to an aluminum electrode in a palladium-coated copper wire for ball bonding, a gold (Au) layer comprising an ultra-thin layer having a thickness of no greater than 5 nm is formed at the surface of a palladium (Pd) intermediate layer and heat processing is performed in an inert atmosphere containing hydrogen, causing the palladium of the intermediate layer to infiltrate the ultra-thin gold layer, forming a gold-palladium intermingled layer by means of Stranski-Krastanov growth such that a minute gold phase and palladium phase grow in 3D. In the heat processing process, the palladium absorbs hydrogen, and by means of rapid cooling after heat processing, the palladium in the intermingled layer is stabilized, and along with the gold that melts early during molten ball formation and covers a wire end surface, the palladium that has reached the end surface melts and is dispersed uniformly and minutely at the molten ball surface layer, suppressing the oxidation of aluminum at the bond interface with the aluminum.

Owner:TANAKA DENSHI KOGYO KK

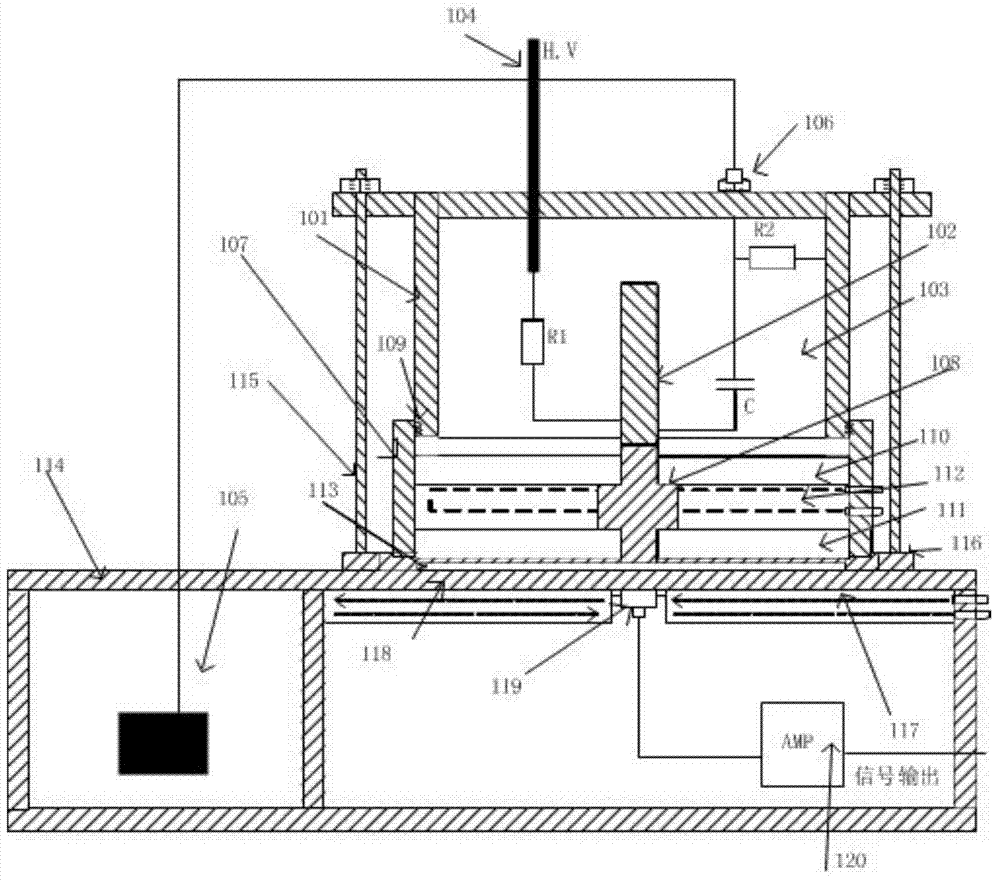

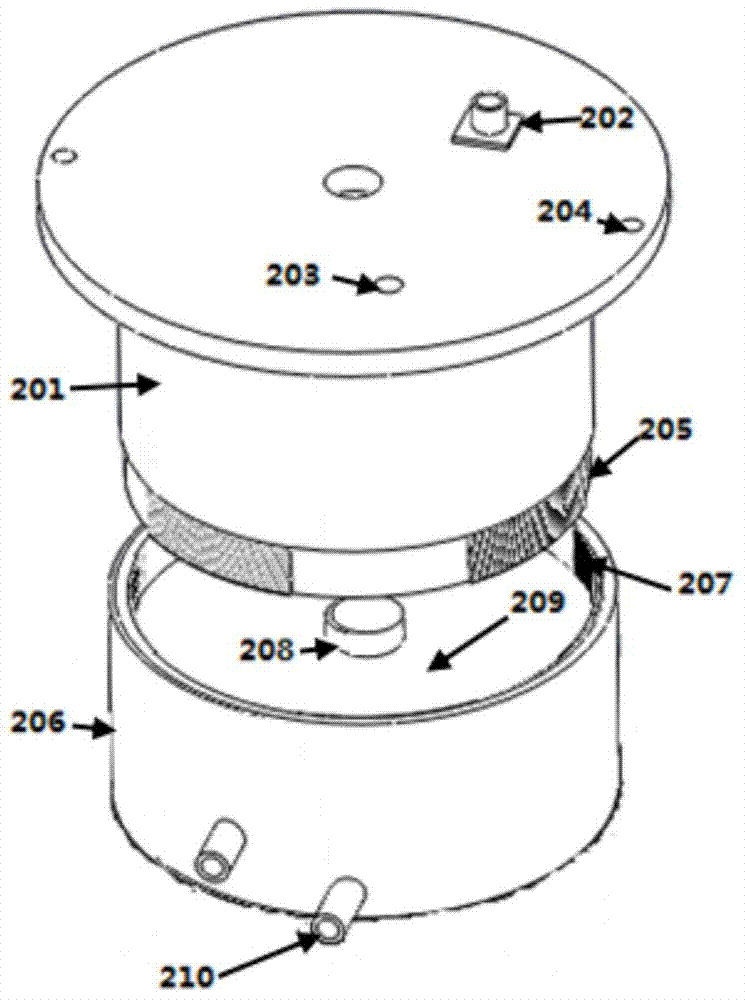

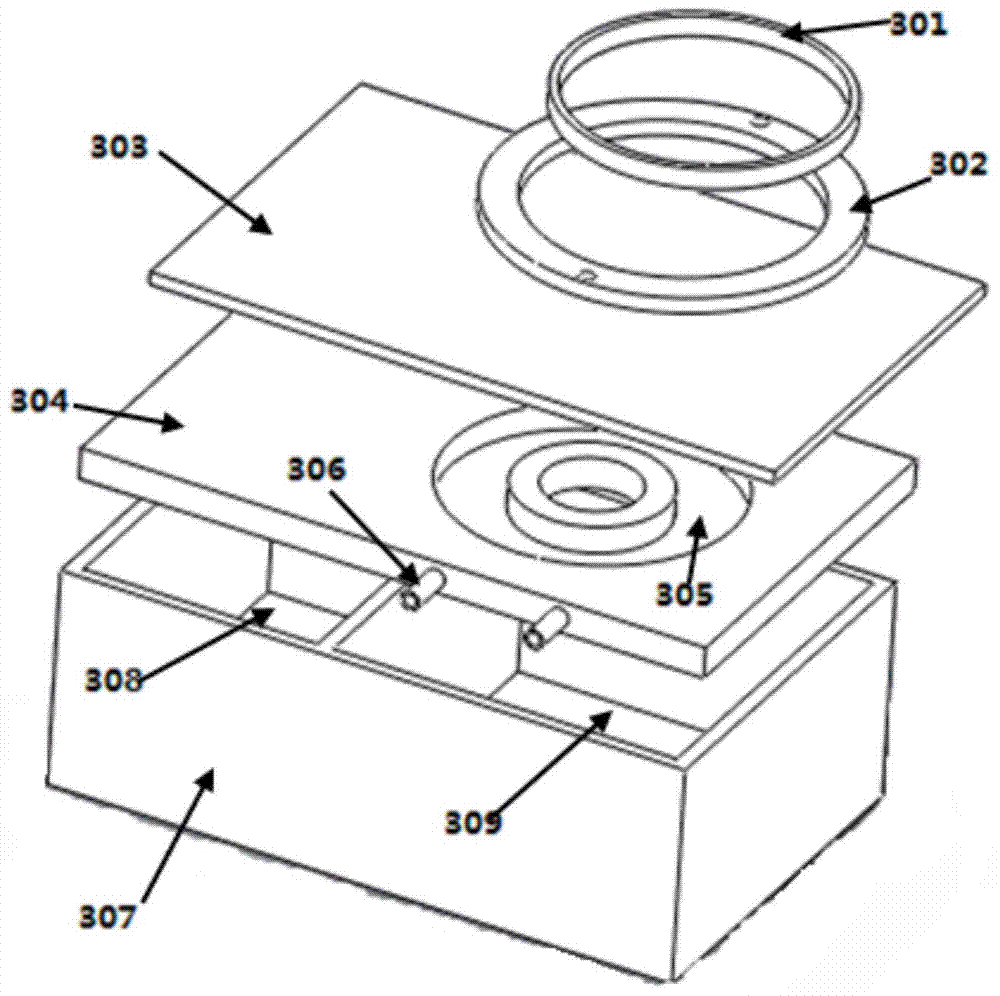

Detachable electroacoustic pulse space charge measurement device

ActiveCN104730354AIncrease volumeHeating up fastElectrical measurementsElectricityMeasurement device

The invention discloses a detachable electroacoustic pulse space charge measurement device. The detachable electroacoustic pulse space charge measurement device comprises an upper electrode unit and a lower electrode unit; a detachable temperature ladder electrode unit is further arranged between the upper electrode unit and the lower electrode unit. The upper electrode unit comprises an upper electrode shell and an upper electrode cavity, and an aluminum electrode is arranged in the upper electrode cavity; the lower electrode unit comprises a lower electrode shell and a lower electrode cavity, and a pulse generator and a signal collecting unit are arranged in the lower electrode cavity. The temperature ladder electrode unit comprises a temperature ladder electrode shell and a temperature ladder electrode cavity, and a cross-shaped aluminum electrode is arranged in the temperature ladder electrode cavity. The temperature ladder electrode unit further comprises a first constant temperature source used for transmitting the temperature to the temperature ladder electrode unit, a second constant temperature source used for transmitting the temperature to the lower electrode unit and a high-voltage direct-current power source used for transmitting the high-voltage direct-current electricity to an upper electrode. By means of the detachable electroacoustic pulse space charge measurement device, the space charge characteristics of materials under the constant temperature, the high temperature and the temperature ladder can be measured, the measurement operation is convenient and safe, and the measurement result is accurate.

Owner:XI AN JIAOTONG UNIV +1

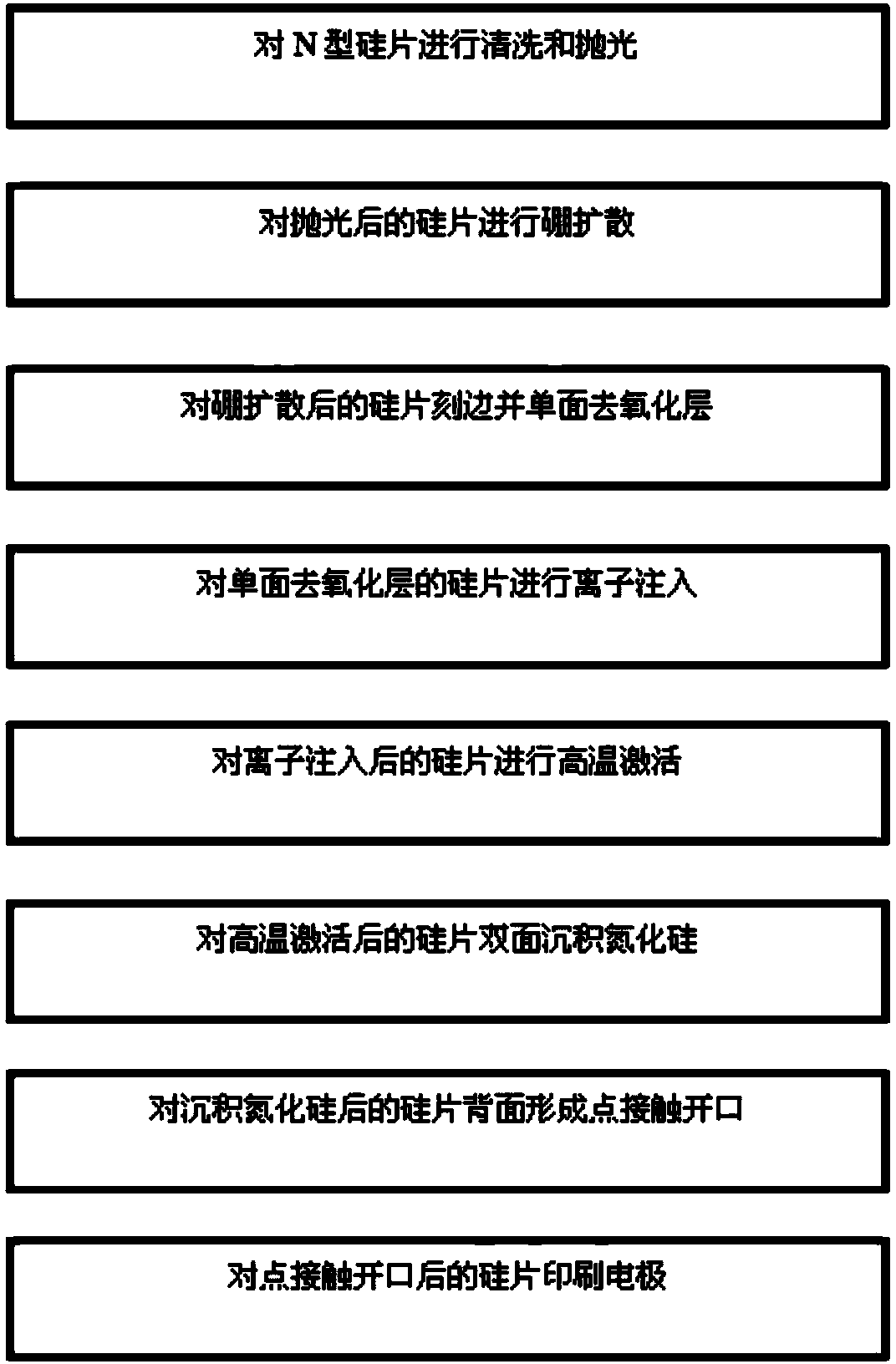

Preparation method for N-shaped back-junction solar cell

ActiveCN103904164ADoes not affect the passivation effectDoes not affect lifespanFinal product manufacturePhotovoltaic energy generationTetramethylammonium hydroxideSilver electrode

The invention discloses a preparation method for an N-shaped back-junction solar cell. The preparation method comprises the following steps: (1) cleaning and polishing; (2) diffusing boron and growing an oxidation layers on the front surface and the back surface of a silicon wafer; (3) etching the edge and the front surface of the silicon wafer to obtain a silicon wafer with the oxidation layer on the front surface removed; (4) conducting texturization on the front surface of the silicon wafer through tetramethyl ammonium hydroxide solution; (5) injecting ions; (6) activating at high temperature; (7) depositing silicon nitride on the two surfaces; (8) forming a point contact opening in the back surface of the silicon wafer; (9) printing an aluminum electrode and a silver electrode, and jointly sintering the aluminum electrode and the silver electrode to form metallization contact. According to the preparation method for the N-shaped back-junction solar cell, the oxidation layer retained on the back surface serves as a blocking layer to conduct texturization on the front surface, texturization on the front surface is achieved while the passivation effect of the oxidation layer on the back face is not influenced. In addition, the oxidation layer retained on the back surface serves as a passivation layer, and the oxidation layer or deposited aluminium oxide do not need to be formed at high temperature again, so that the processing steps are greatly simplified.

Owner:CSI CELLS CO LTD

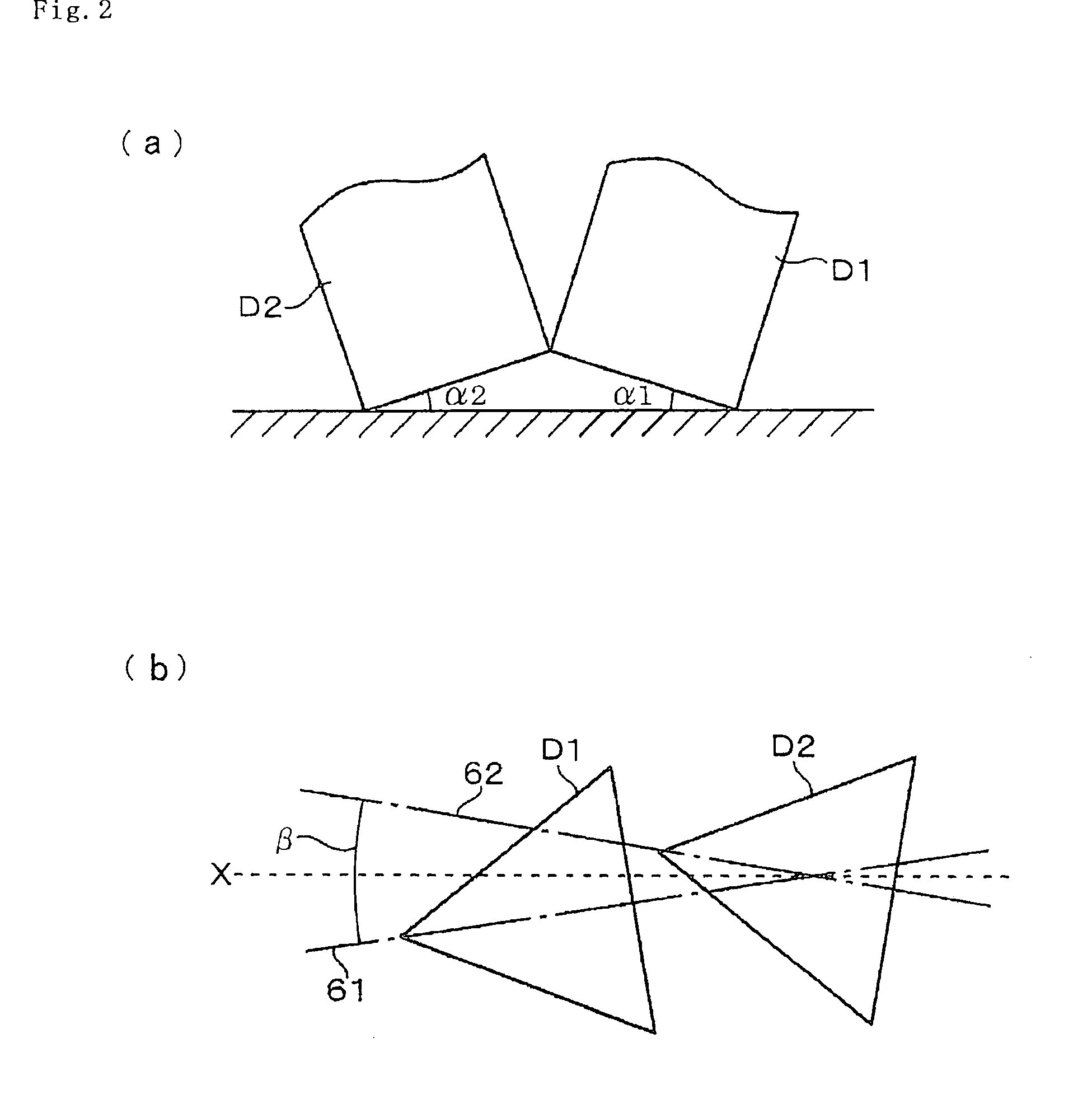

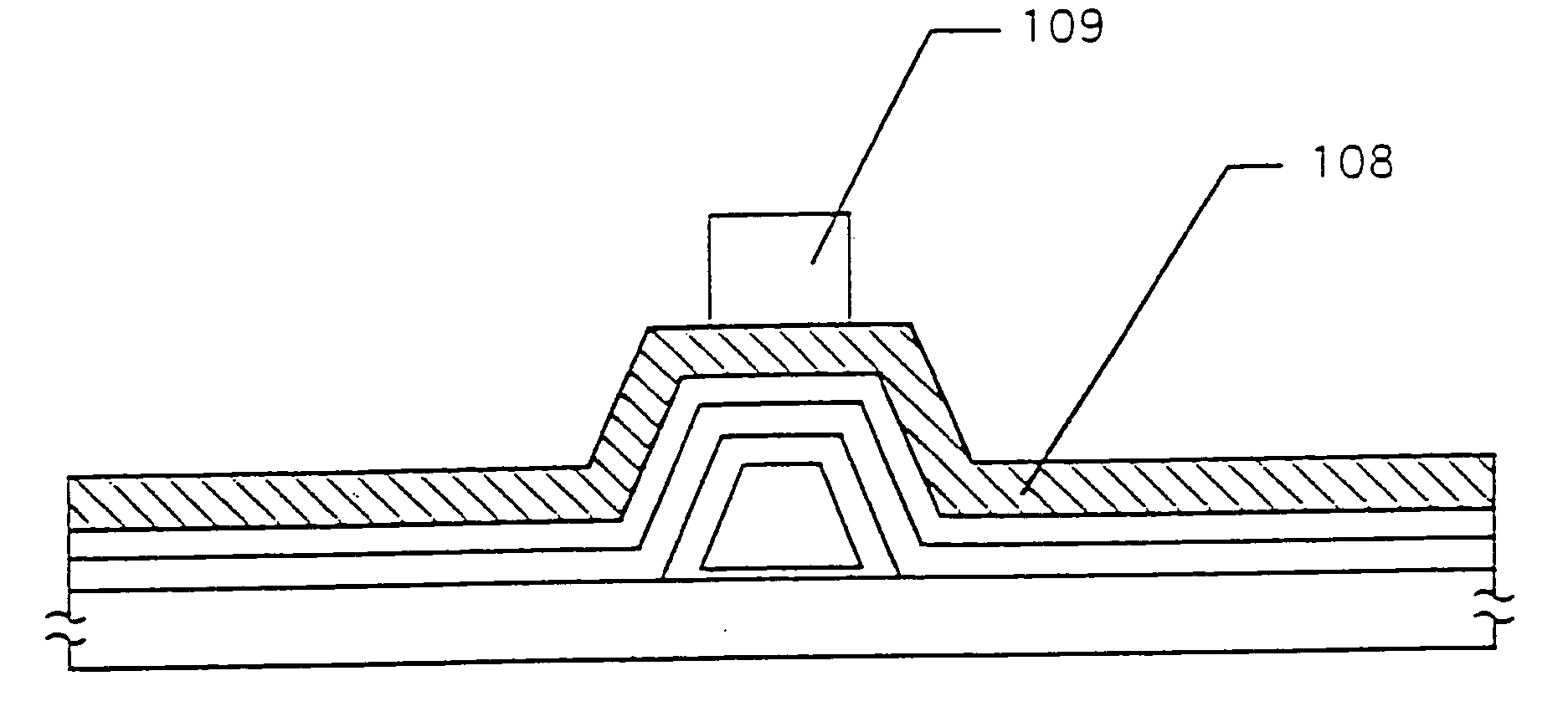

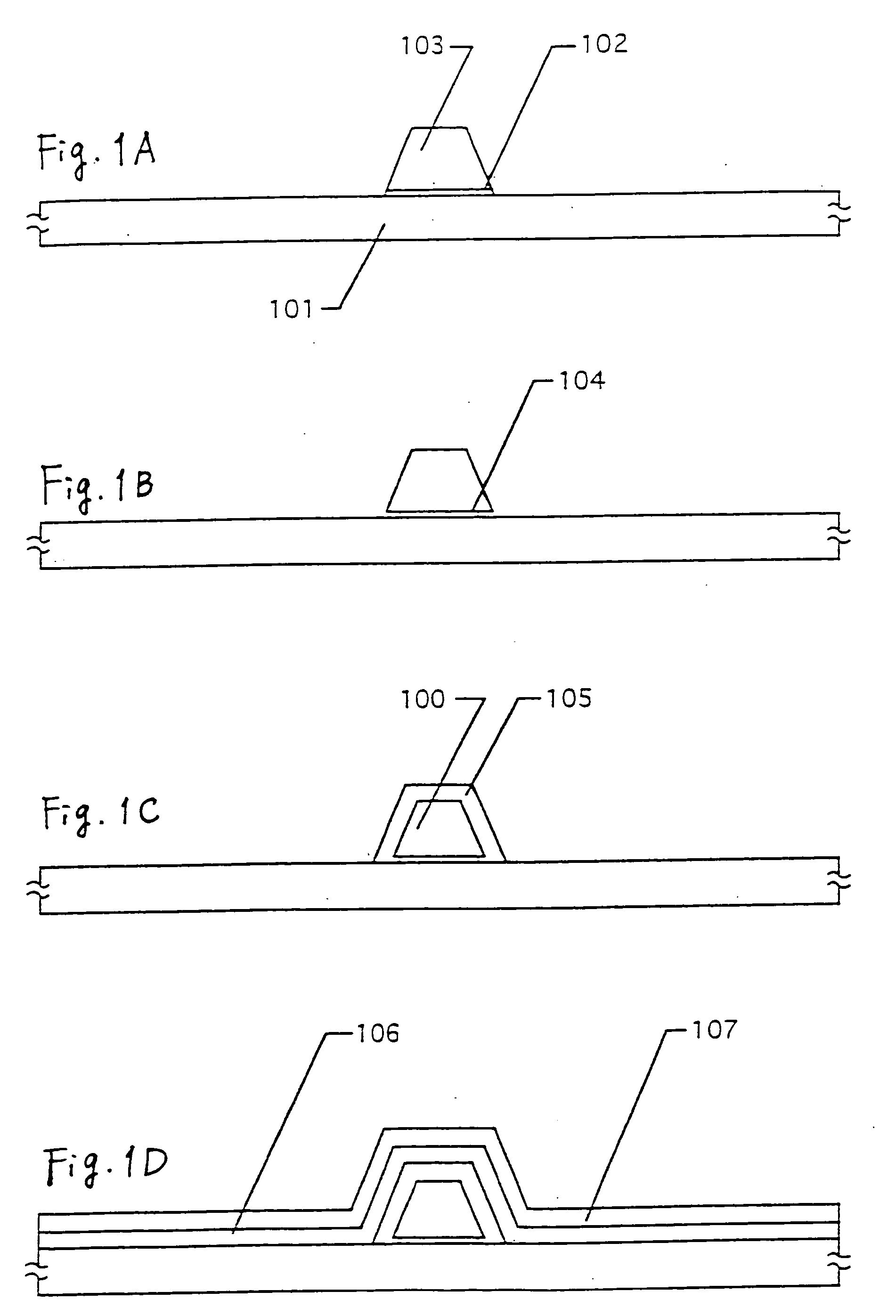

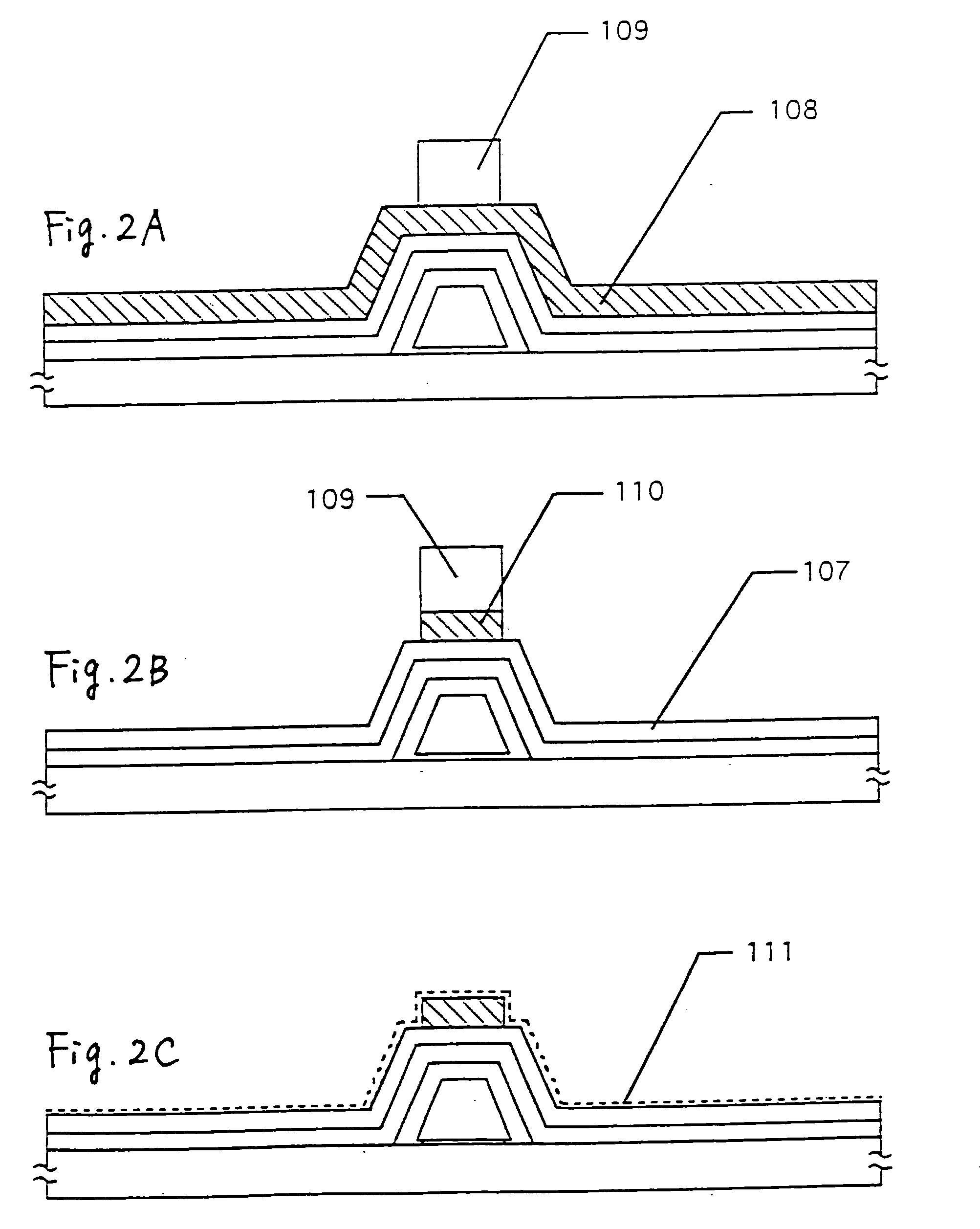

Semiconductor device and method for producing it

InactiveUS20050012096A1Promote formationSolid-state devicesSemiconductor/solid-state device manufacturingBottom gateLayered structure

Disclosed is a technique of improving the heat resistance of the aluminum gate electrode in bottom-gate-type TFT of which the active layer is made of a crystalline silicon film. A pattern of a laminate of a titanium film 102 and an aluminum film 103 is formed on a glass substrate 101. The pattern is to give a gate electrode 100. Then, the titanium film 102 is side-etched. Next, the layered substrate is heated to thereby intentionally form hillocks and whiskers-on the surface of the aluminum pattern 103. Next, the aluminum pattern 103 acting as an anode is subjected to anodic oxidation to form an oxide film 105 thereon. The anodic oxidation extends to the lower edge of the aluminum pattern 103, at which the titanium layer was side-etched. Next, a gate-insulating film 106 and an amorphous silicon film are formed. A mask is formed over the pattern, which is to give -the gate electrode, and then a nickel acetate solution is applied to the layered structure. Thus, nickel is kept in contact with the surface of the structure. Next, this is heated to induce crystal growth in the silicon film from the region contacted with nickel to the masked region. In the bottom-gate-type TFT thus produced, the active layer is made of a crystalline silicon film. In this process, since the anodic oxide film is formed as in FIG. 1(C), aluminum does neither melt to flow away nor diffuse away. Thus, the heat resistance of the aluminum electrode formed is improved.

Owner:SEMICON ENERGY LAB CO LTD

Copper bonding wire for semiconductor and bonding structure thereof

ActiveUS20120299182A1Reduce material costsImprove long-term reliabilitySemiconductor/solid-state device detailsSolid-state devicesFront end of lineCopper

It is an object of the present invention to provide a bonding structure and a copper bonding wire for semiconductor that are realizable at an inexpensive material cost, superior in a long-term reliability of a bonded portion bonded to an Al electrode, and suitable for use in a vehicle-mounted LSI. A ball-bonded portion is formed by bonding to the aluminum electrode a ball formed on a front end of the copper bonding wire. After being heated at any temperature between 130° C. and 200° C., the aforementioned ball-bonded portion exhibits a relative compound ratio R1 of 40-100%, the relative compound ratio R1 being a ratio of a thickness of a Cu—Al intermetallic compound to thicknesses of intermetallic compounds that are composed of Cu and Al and formed on a cross-sectional surface of the ball-bonded portion.

Owner:NIPPON STEEL CHEMICAL CO LTD +1

MEMS presser sensor chip and manufacturing method thereof

InactiveCN101776501AReduce Fragmentation RateImprove yieldTelevision system detailsPiezoelectric/electrostriction/magnetostriction machinesElectrical resistance and conductanceLinear region

The invention relates to an MEMS presser sensor chip, which can effectively improve sensitivity of a chip and enhance yield of the chip. The presser sensor chip comprises a silicon slice, a vacuum cavity, a glass substrate, a sensitive resistor configuration region, an outer electric connecting piece of the sensitive resistor configuration region and an alignment mark component and is characterized in that: the four corners of the positive face and the negative face of the silicon slice are respectively provided with an alignment mark structure; the maximum stress linear region of the positive face of the silicon slice is the sensitive resistor configuration region which is rectangular and comprises a piezoresistor, p+connection, an N+ isolation groove and an aluminum electrode; and the piezoresistor consists of two pairs of bridging resistors concretely, each bridging resistor comprises one pair of sensitive resistors which are linear resistors, each bridging resistor in each pair of the bridging resistors is arranged at two opposite sides of the four sides of the sensitive resistor configuration region respectively in a symmetric manner, and each bridging resistor is encircled by the N+ isolation groove.

Owner:淮安纳微传感器有限公司

Low-resistance high-efficiency lead-free back silver pulp for amorphous silicon solar battery

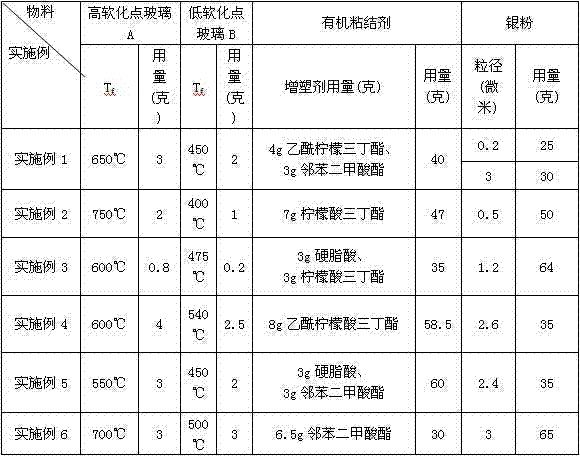

ActiveCN104505139APromote meltingAvoid crackingNon-conductive material with dispersed conductive materialSemiconductor devicesSilver electrodeMicrometer

The invention relates to low-resistance high-efficiency lead-free back silver pulp for an amorphous silicon solar battery. The lead-free back silver pulp comprises the following ingredients in percentage by mass: 35 to 65 percent of silver powder, 1 to 6.5 percent of inorganic bonding agents and 30 to 60 percent of organic bonding agents, wherein the silver powder is microcrystal silver powder with the average grain diameter being 0.2 to 3 micrometers, the lead-free glass powder is formed by combining A glass powder with the softening point being 550 to 750 DEG C and B glass powder with the softening point being 400 to 540 DEG C, the A glass powder is preferably the glass powder with the softening point being 600 to 700 DEG C, and the B glass powder is preferably the glass powder with the softening point being 425 to 500 DEG C. A battery cell manufactured by the back sliver pulp provided by the invention has the advantages that a back silver electrode and an aluminum electrode metal fusion layer have no crack gap, the contact resistance of a silver aluminum electrode is small, and the conversion efficiency of the battery cell is high.

Owner:乐凯胶片股份有限公司

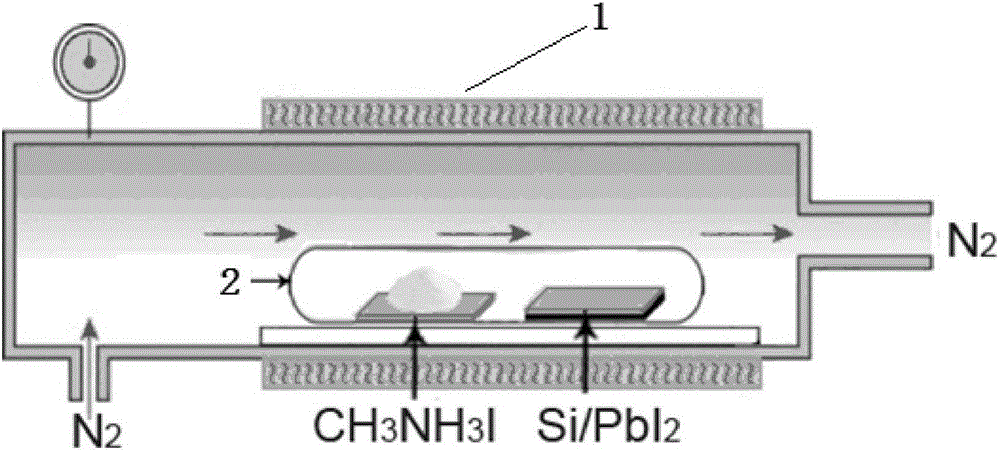

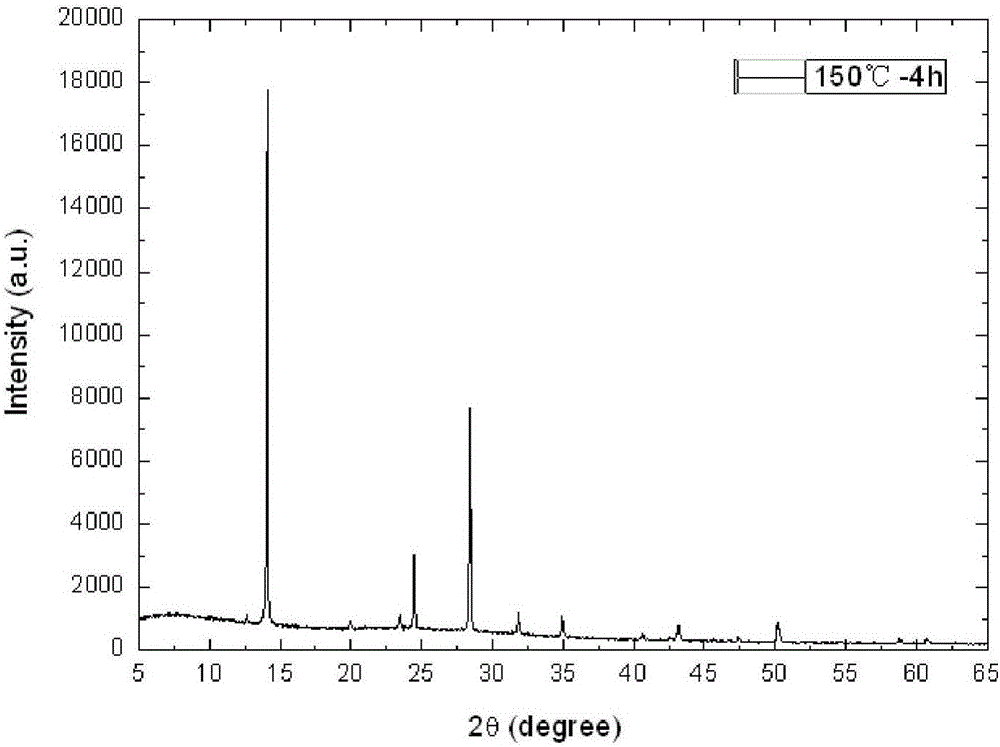

Silica-based perovskite heterojunction solar cell and preparation method thereof

ActiveCN104993059AFully absorbedPromote absorptionFinal product manufactureSolid-state devicesHeterojunctionSilver electrode

The invention discloses a silica-based perovskite heterojunction solar cell and a preparation method thereof. The silica-based perovskite heterojunction solar cell includes an aluminum electrode, a gold conducting film, perovskite, aluminum oxide, an N-type silicon wafer and a silver electrode arranged from top down, wherein the perovskite is CH3NH3PbI3. Compared with a traditional silica-based heterojunction solar cell material, silica-based perovskite heterojunction solar cell provided by the invention has better electric and optical performance. According to the invention, as to a transmitting electrode of the silica-based perovskite heterojunction solar cell, perovskite can absorb visible light while silicon can absorb infrared light, so that segmented light absorption can be realized and utilization of sunlight becomes more adequate. The invention also discloses a preparation method of the silica-based perovskite heterojunction solar cell.

Owner:江苏润阳悦达光伏科技有限公司

Capacitive micro inertial sensor with self calibration function

InactiveCN103344785AIncrease drive capacitanceReduce the driving voltageAcceleration measurementTesting/calibration of speed/acceleration/shock measurement devicesCapacitanceAnchor point

The invention relates to a capacitive micro inertial sensor with a self calibration function. An existing sensor with the self calibration function is small in calibration range. According to the capacitive micro inertial sensor with the self calibration function, one sensor mass block is a rectangular silicon slice etched with grid-shaped wells, two corresponding ends of the sensor mass block are connected with anchor points through silicon supporting beams, and rectangular silicon strips are respectively arranged the other two corresponding ends of the sensor mass block. Two driver mass blocks are arranged at two sides of the sensor mass block, an annular groove is formed in the middle of each driver mass block in an engraved mode, movable mass block driving silicon strips and driver driving silicon strips are arranged at two sides of each driver mass block, and the silicon strips connected with the sensor mass block form a mass block driving capacitor along with the corresponding mass block driving silicon strips. Comb tooth strips fixing the driving silicon strips and the movable driver driving silicon strips form a driver driving capacitor. Comb-shaped silicon strips and fixed detection silicon strips connected with the sensor mass block, a grid electrode and an interdigital aluminum electrode on the surface of a substrate form a detecting capacitor. The capacitive micro inertial sensor with the self calibration function increases the mass block driving capacitance, further reduces driving voltage, increases the mass of an oscillator, and reduces Brown noise.

Owner:HANGZHOU DIANZI UNIV

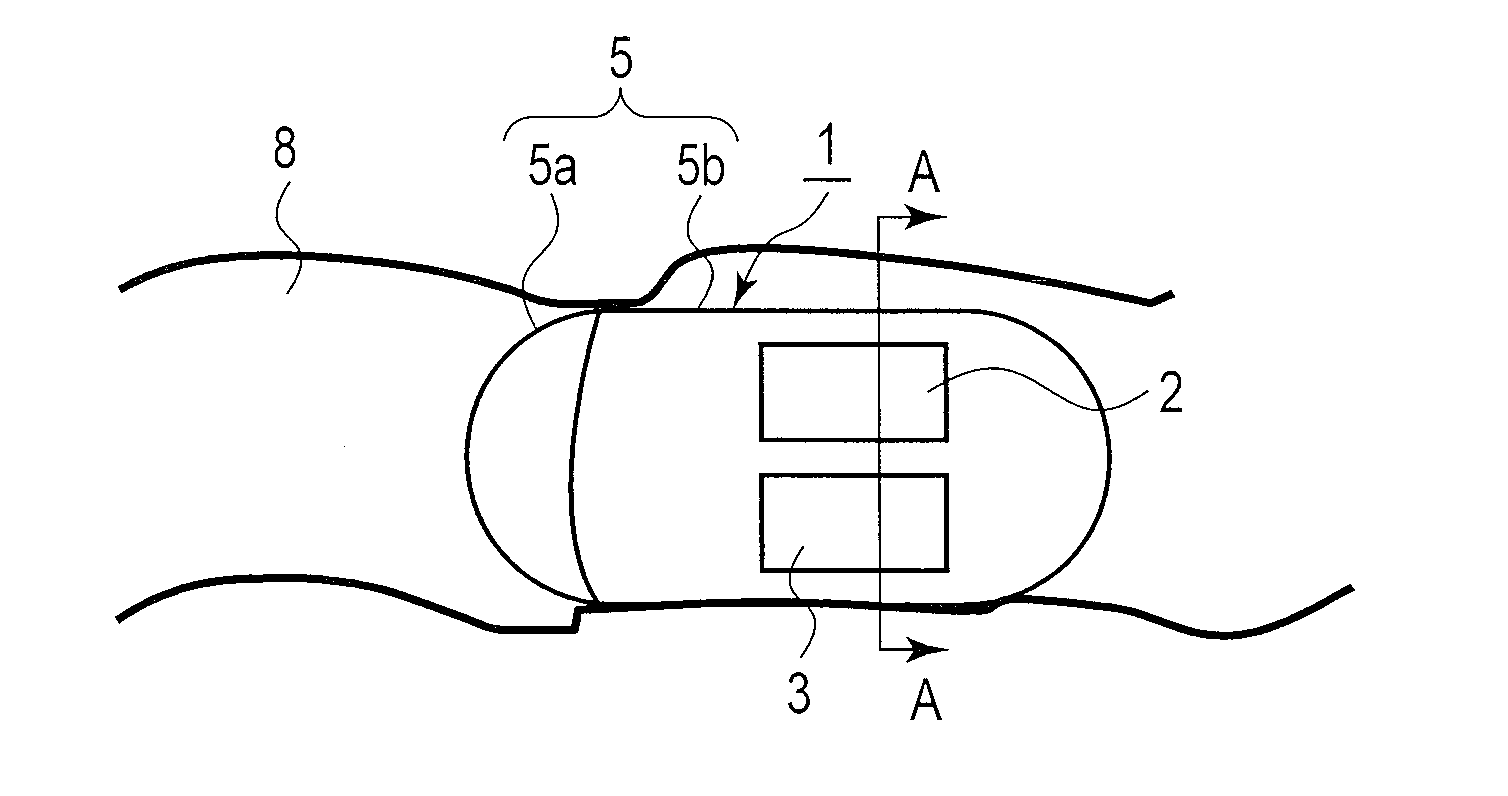

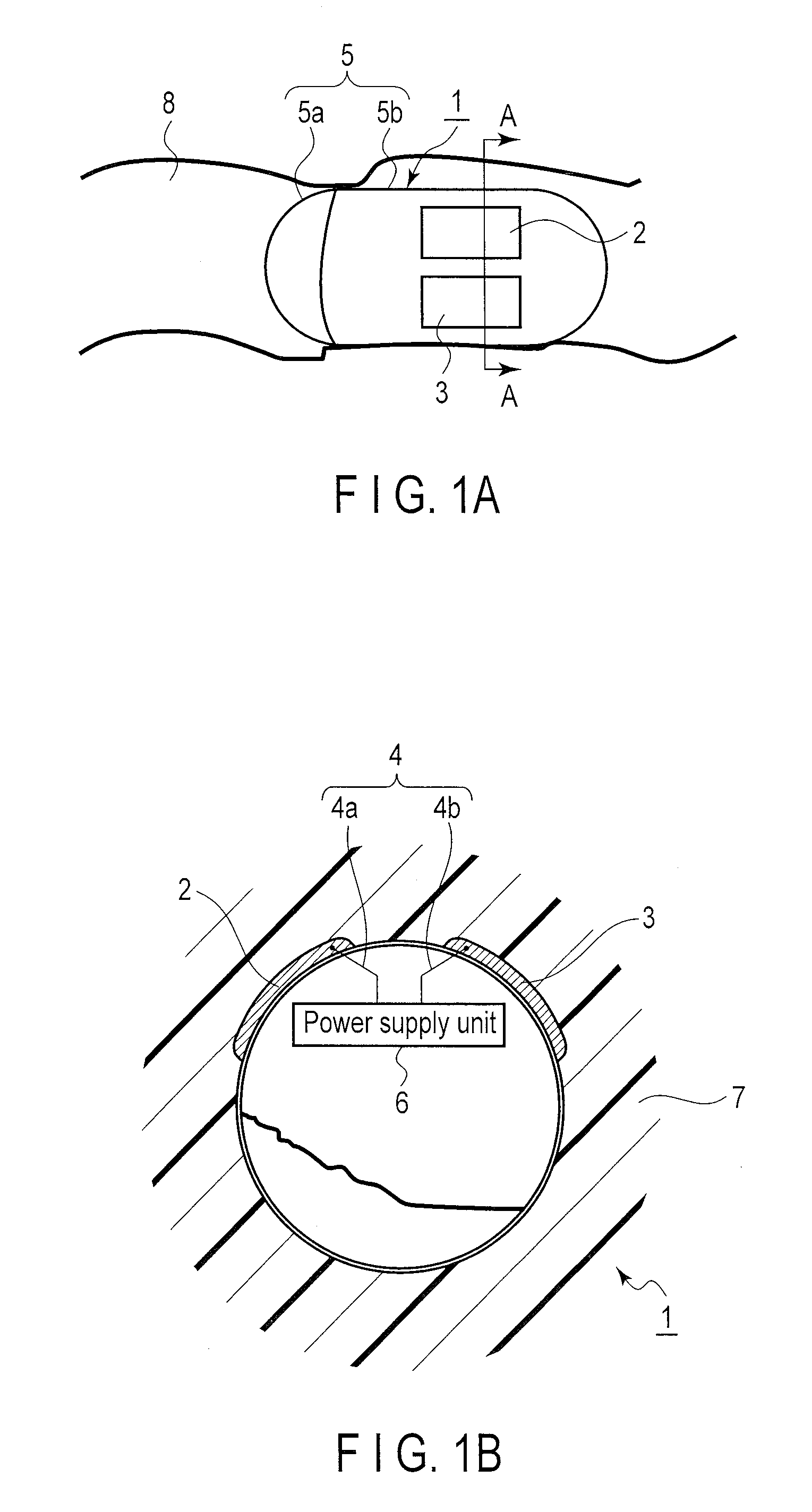

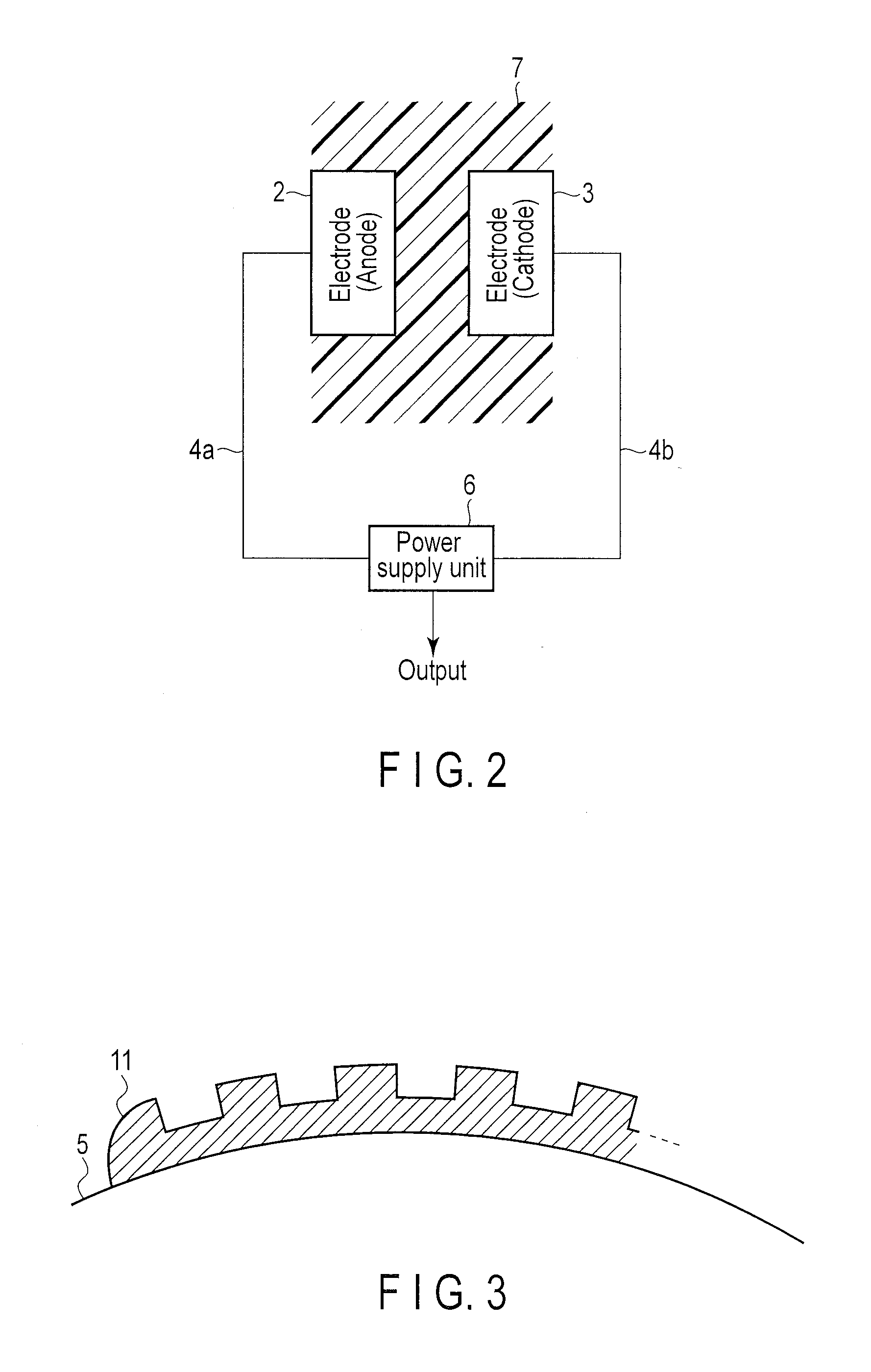

Power supply system and medical capsule device mounted with this power supply system

Provided are a power generation system which does not limit a patient's range of motion, is harmless to a living body, and can obtain a sufficient electricity generating capacity in the stomach or the intestines and a disposable medical capsule device which does not have to be collected after use. A power supply system is mounted in the capsule device, comprises an electrode pair including at least two electrodes provide on an outer wall surface of a capsule main body, for example, an aluminum electrode and a catalyst-supporting carbon electrode, generates power when immersed in an electrolytic solution consisting of gastric juice or intestinal juice, and supplies the power to constituent portions in the capsule device.

Owner:OLYMPUS CORP

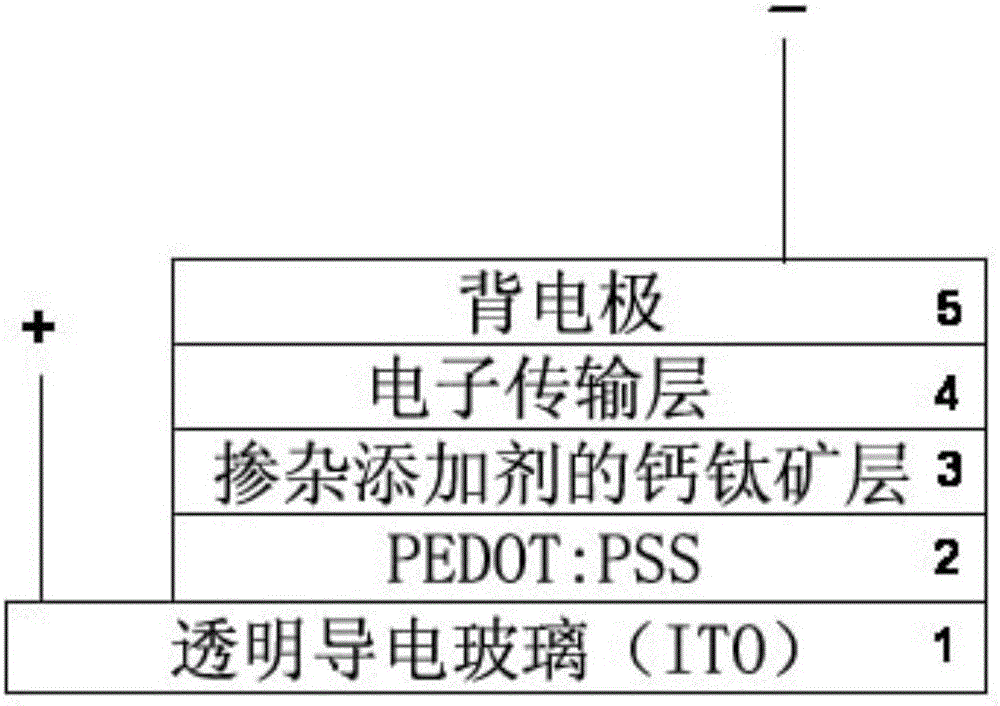

Method of improving perovskite solar cell efficiency by using ionic liquid additive

ActiveCN106816535AIncrease coverageGood lookingFinal product manufactureSolid-state devicesElectronic transmissionN dimethylformamide

The invention relates to a method of improving perovskite solar cell efficiency by using ionic liquid additive, and belongs to the organic optoelectronic technology field. The method comprises steps that (1) preparation of precursor mixed solution: lead acetate and methylammonium iodide are dissolved in an N,N-dimethylformamide solution to form the mixed solution; and 1-Ethylpyridinium chloride ionic liquid is adopted as the additive to prepare the precursor mixed solution; (2) preparation of a perovskite thin film: the precursor mixed solution is used to form a film by adopting a spin-coating technology, and is disposed on a conductive glass substrate provided with PEDOT:PSS, and annealing is carried out on a heating stage to acquire the perovskite thin film; (3) deposition of an electronic transmission layer: by adopting a thermal evaporation deposition way or a solution spin-coating way, the electronic transmission is deposited on the perovskite thin film; (4) evaporation deposition of a counter electrode: evaporation deposition of a metal aluminum electrode is carried out by adopting a vacuum evaporation film. The method has advantages of mild and controllable condition, simple preparation, low costs, and applicability in large-scale commercialized production.

Owner:CHINA ELECTRONIC TECH GRP CORP NO 18 RES INST