Patents

Literature

817 results about "Bond interface" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

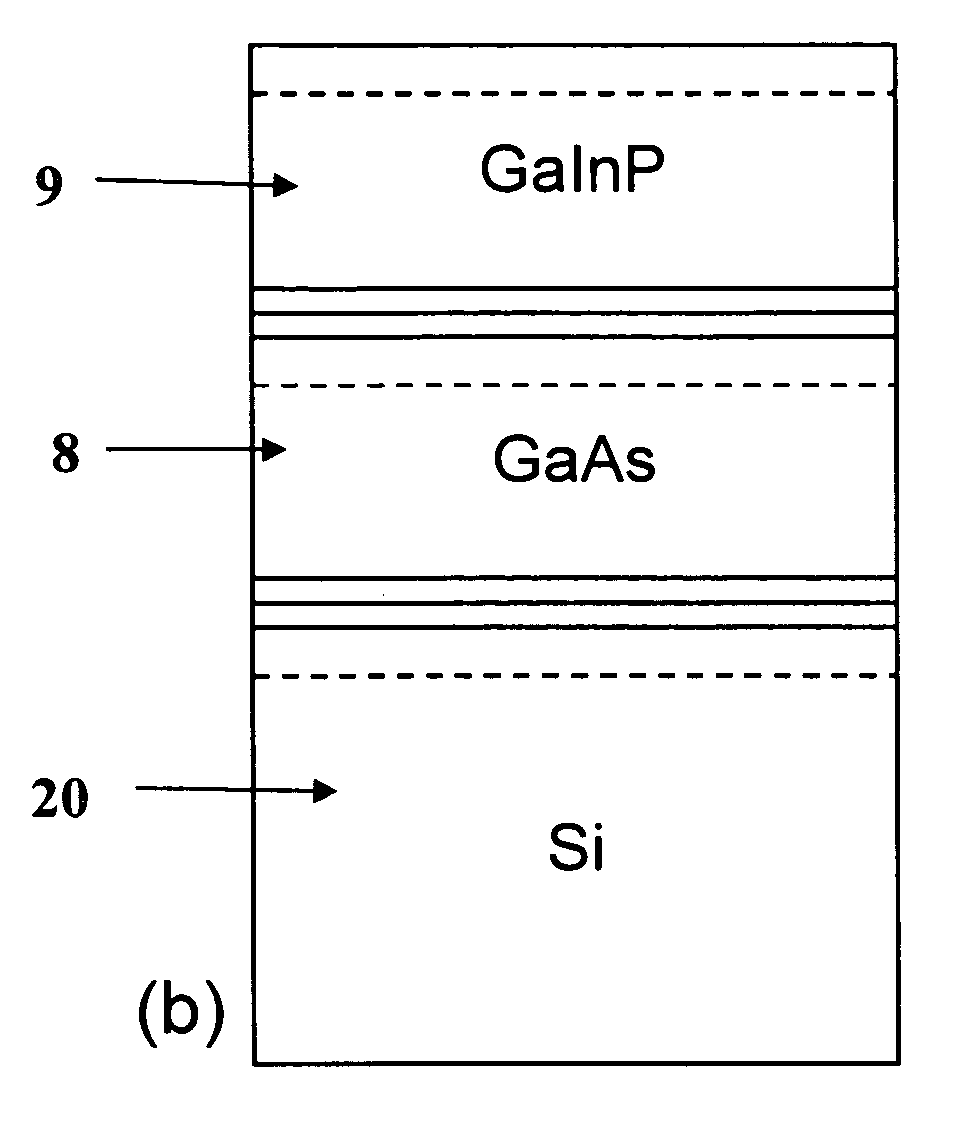

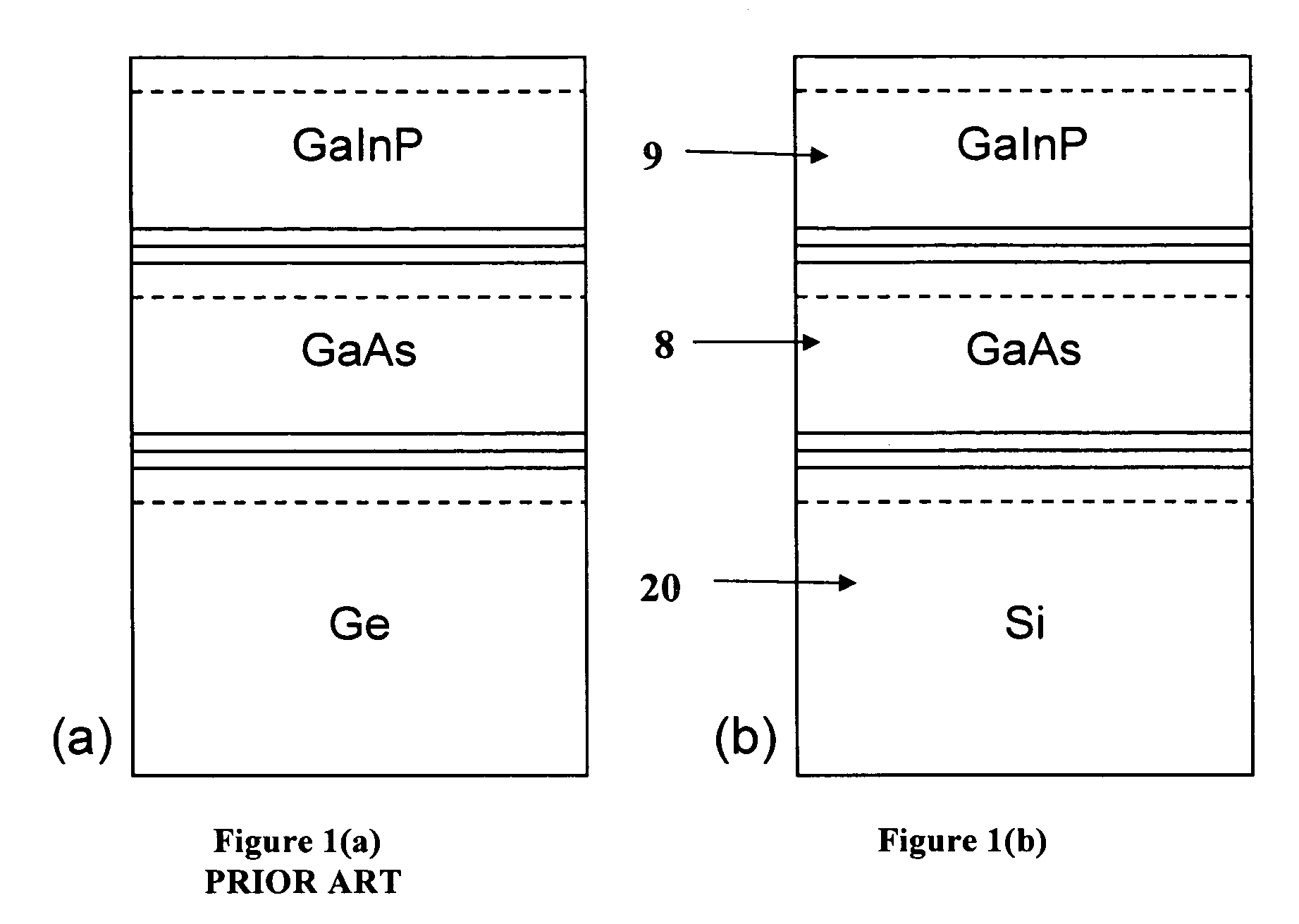

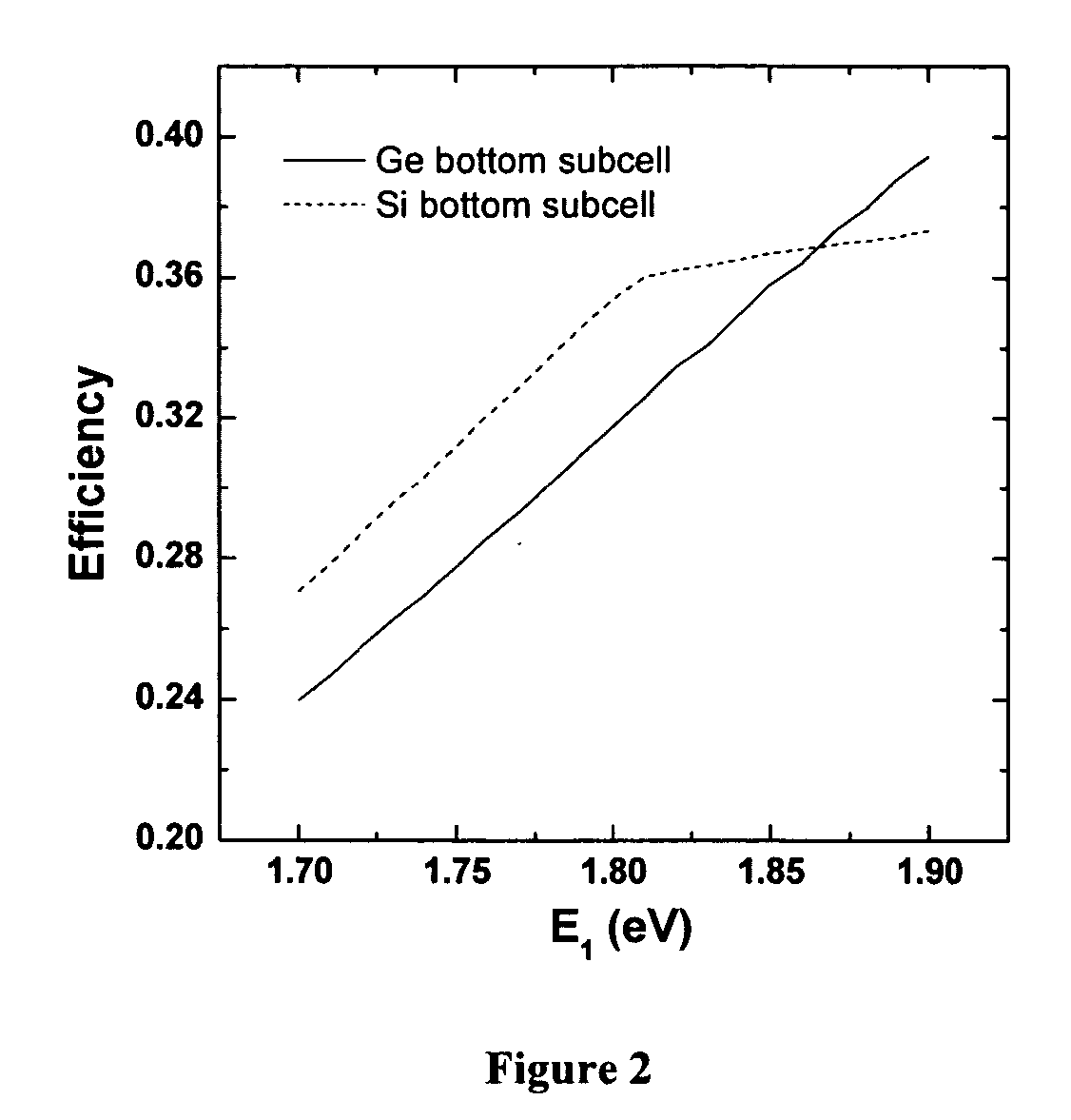

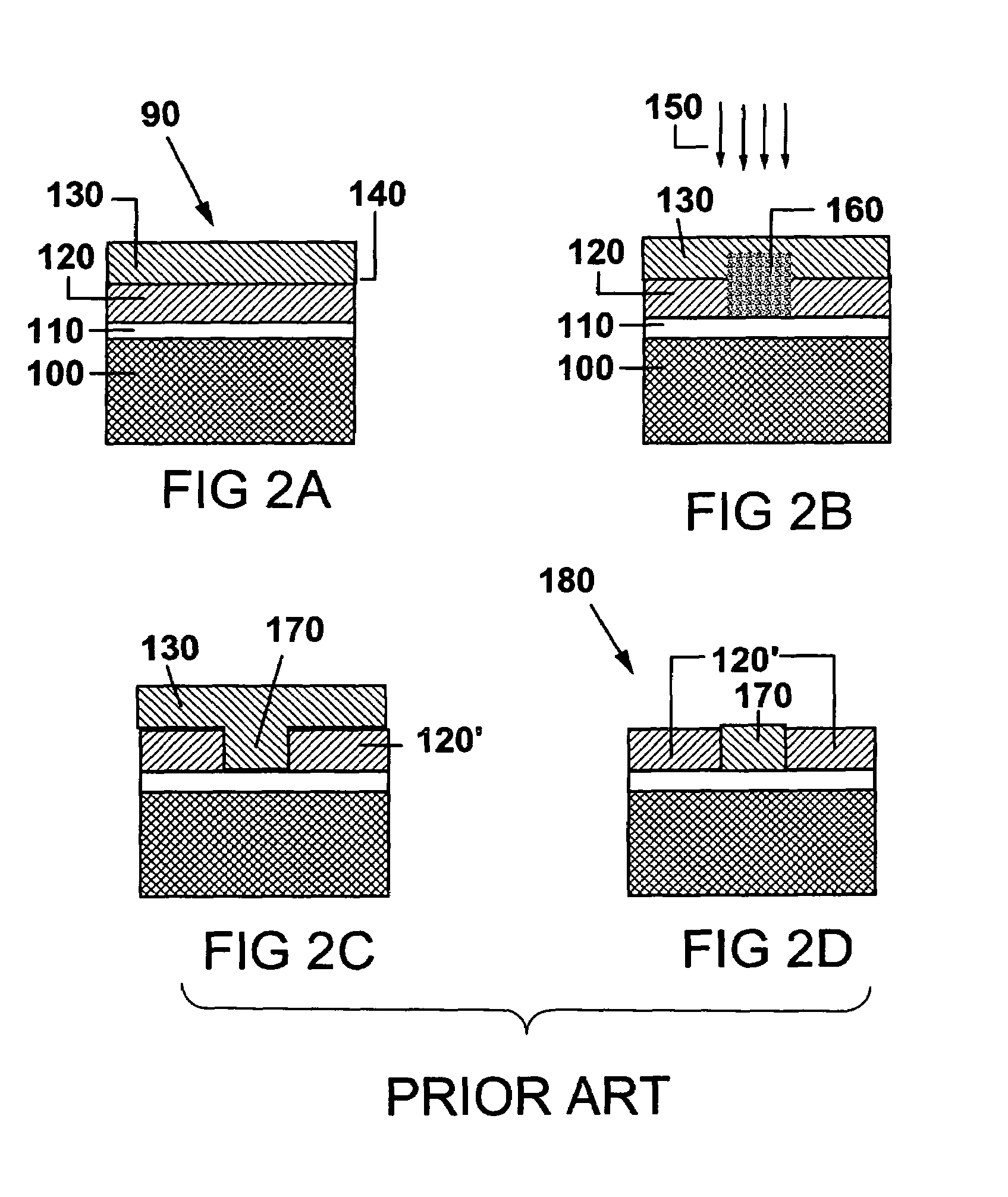

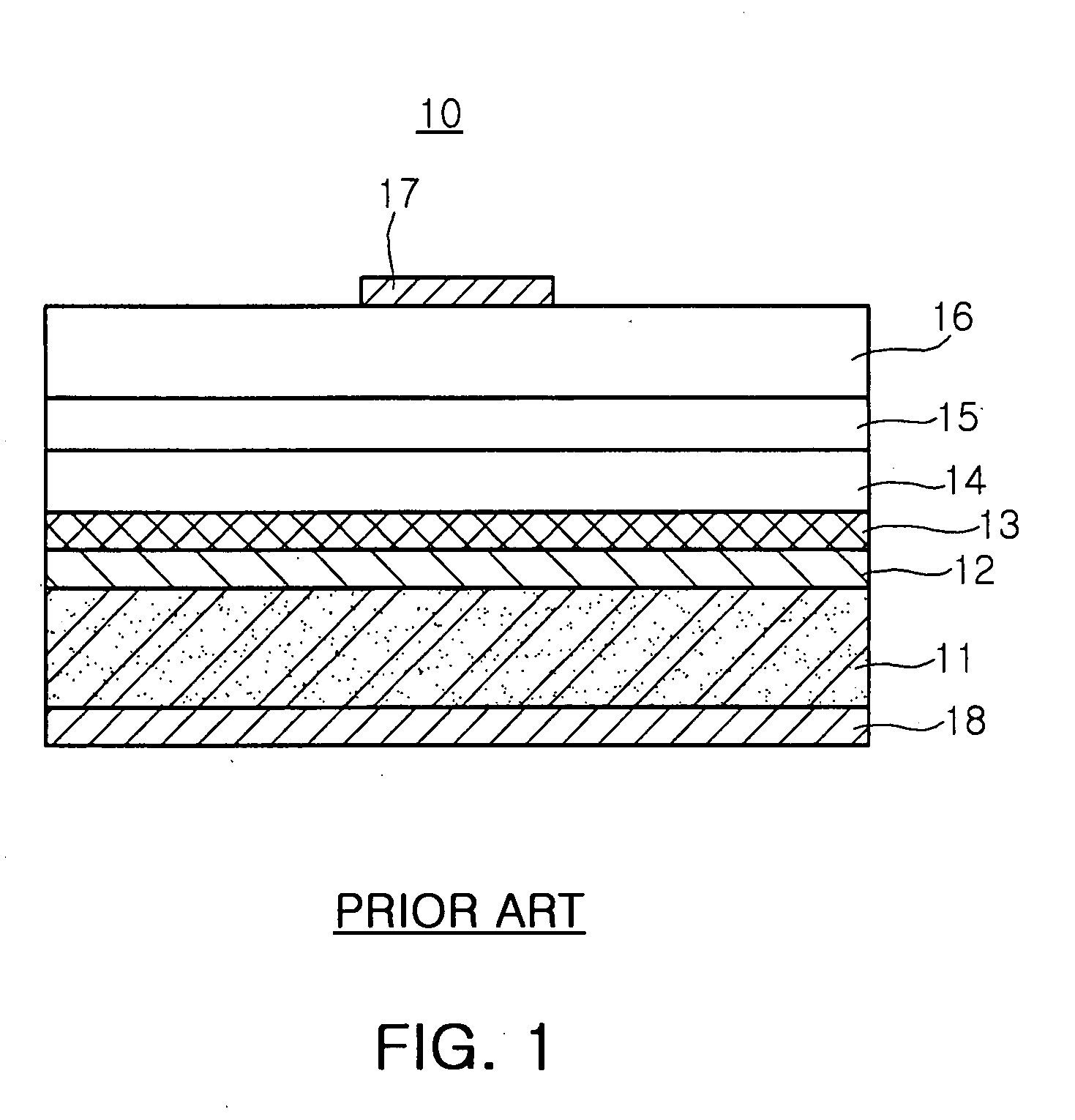

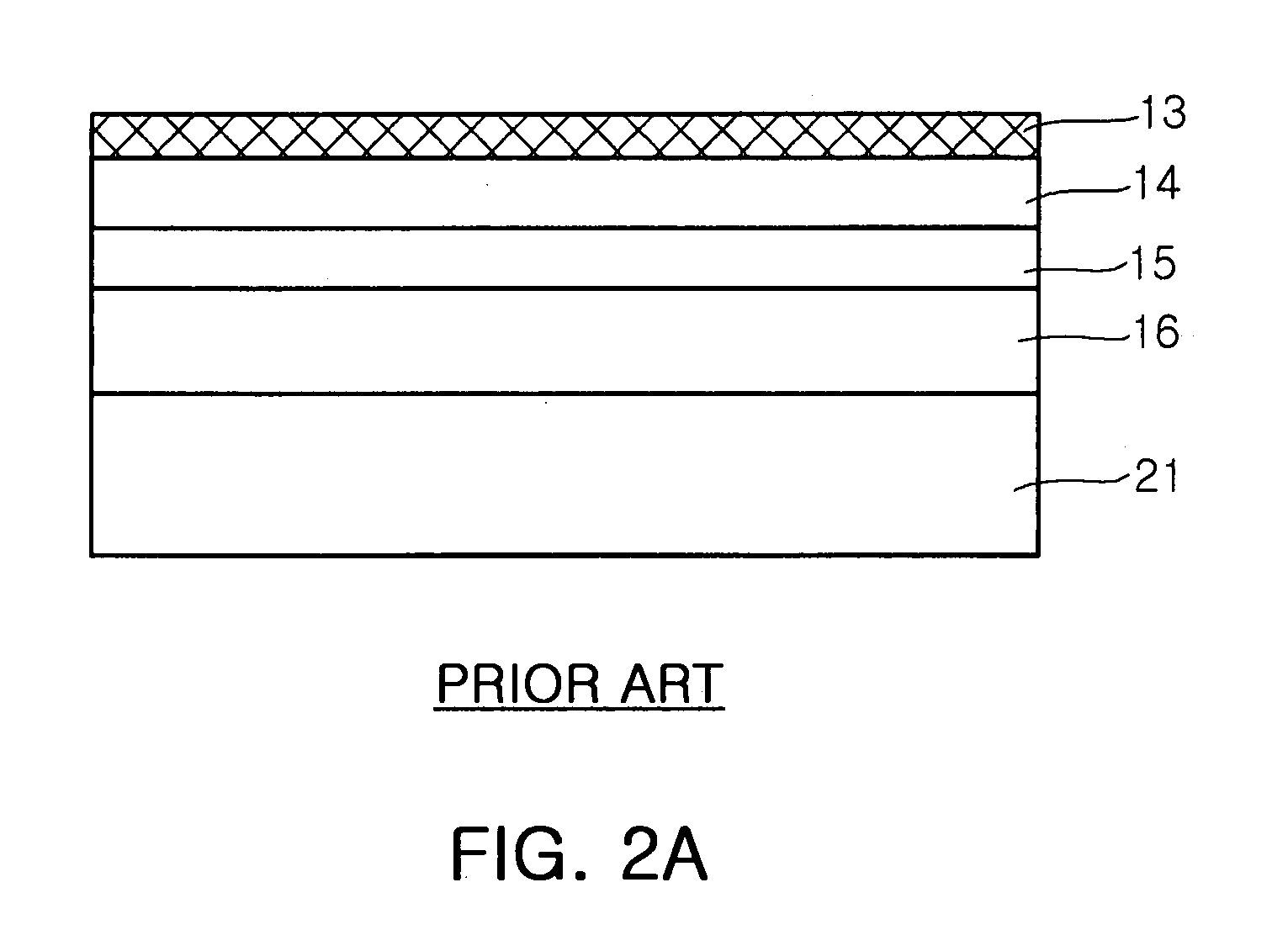

GaInP / GaAs / Si triple junction solar cell enabled by wafer bonding and layer transfer

InactiveUS20060021565A1Polycrystalline material growthFinal product manufactureBond interfaceWafer bonding

A multi-junction solar cell includes a silicon solar subcell, a GaInP solar subcell, and a GaAs solar subcell located between the silicon solar subcell and the GaInP solar subcell. The GaAs solar subcell is bonded to the silicon solar subcell such that a bonded interface exists between these subcells.

Owner:AONEX TECH

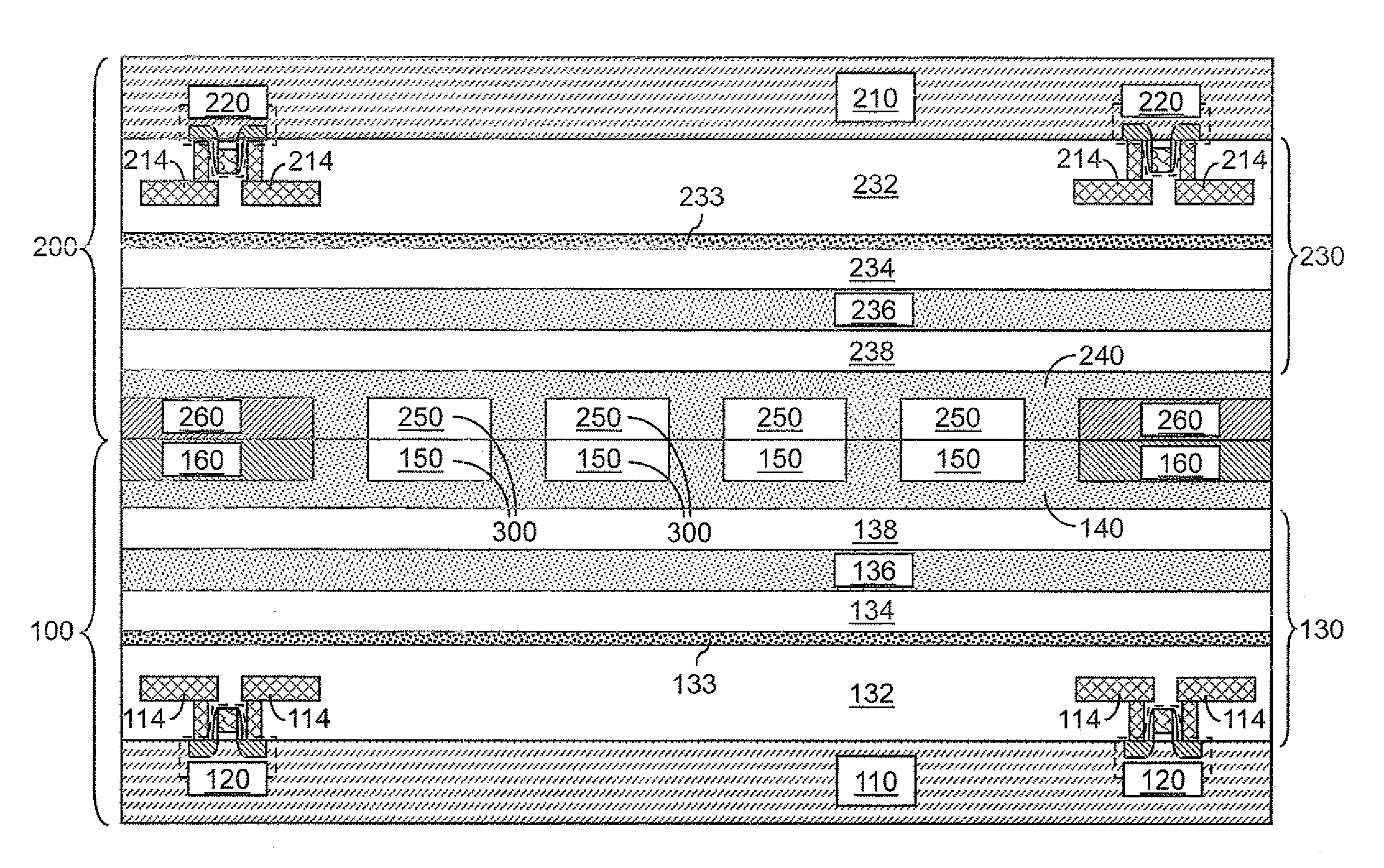

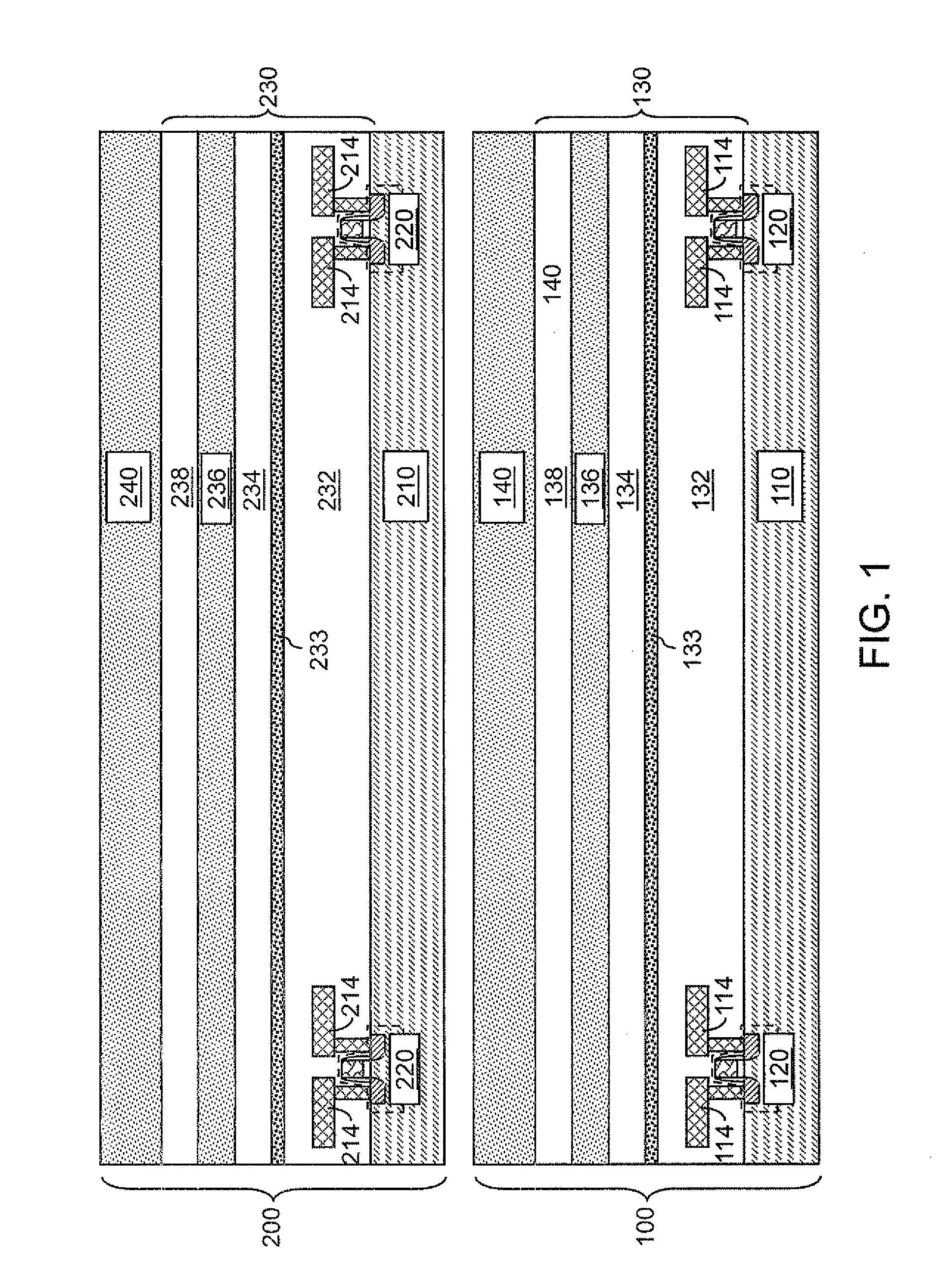

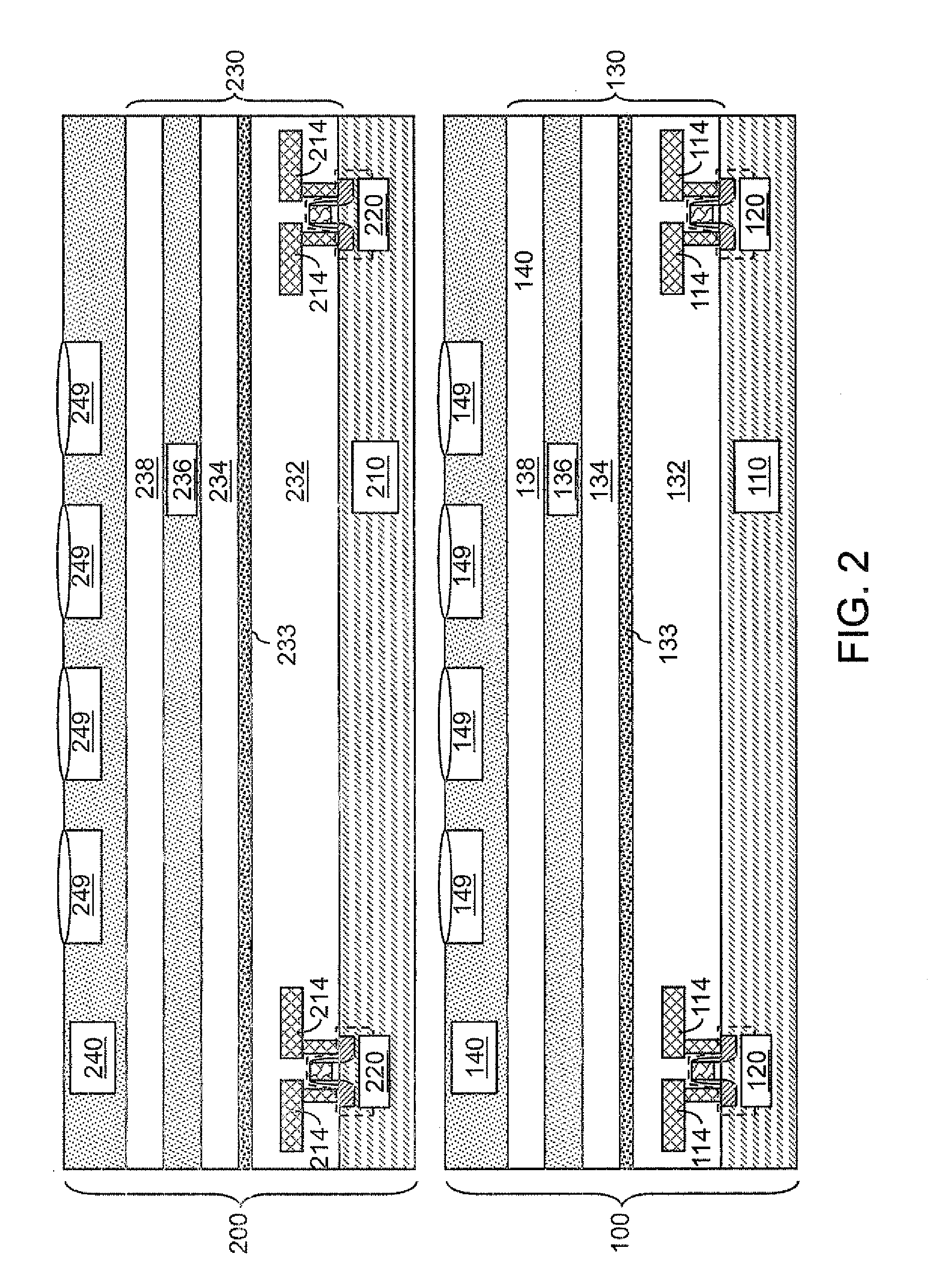

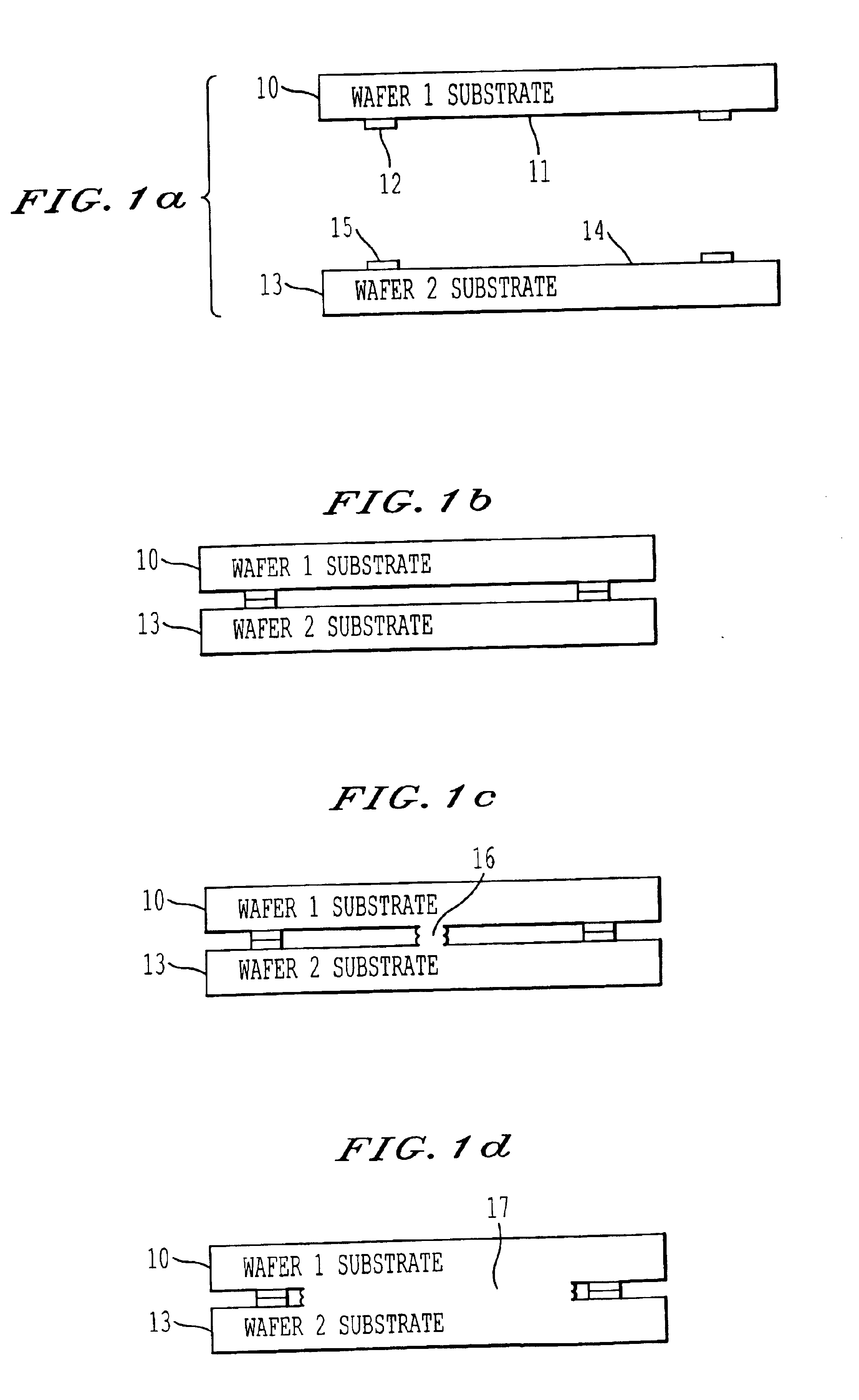

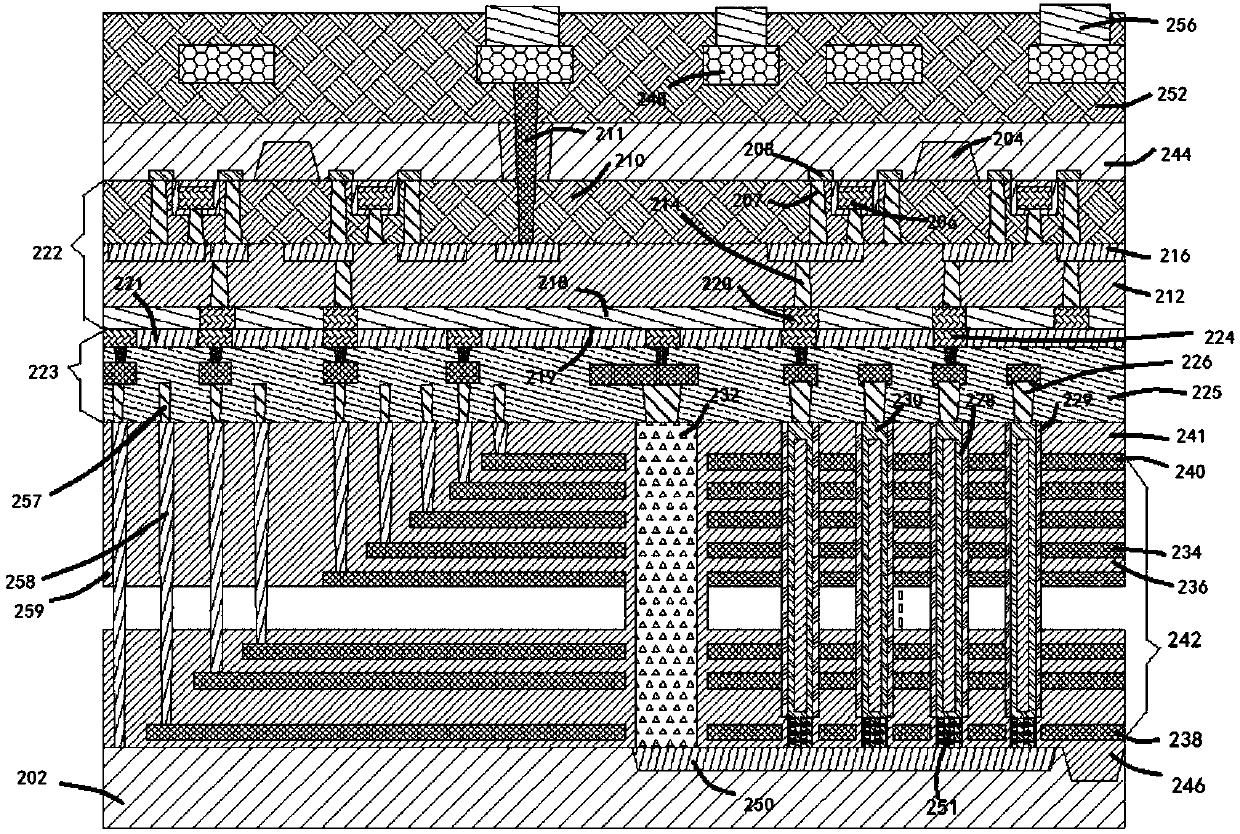

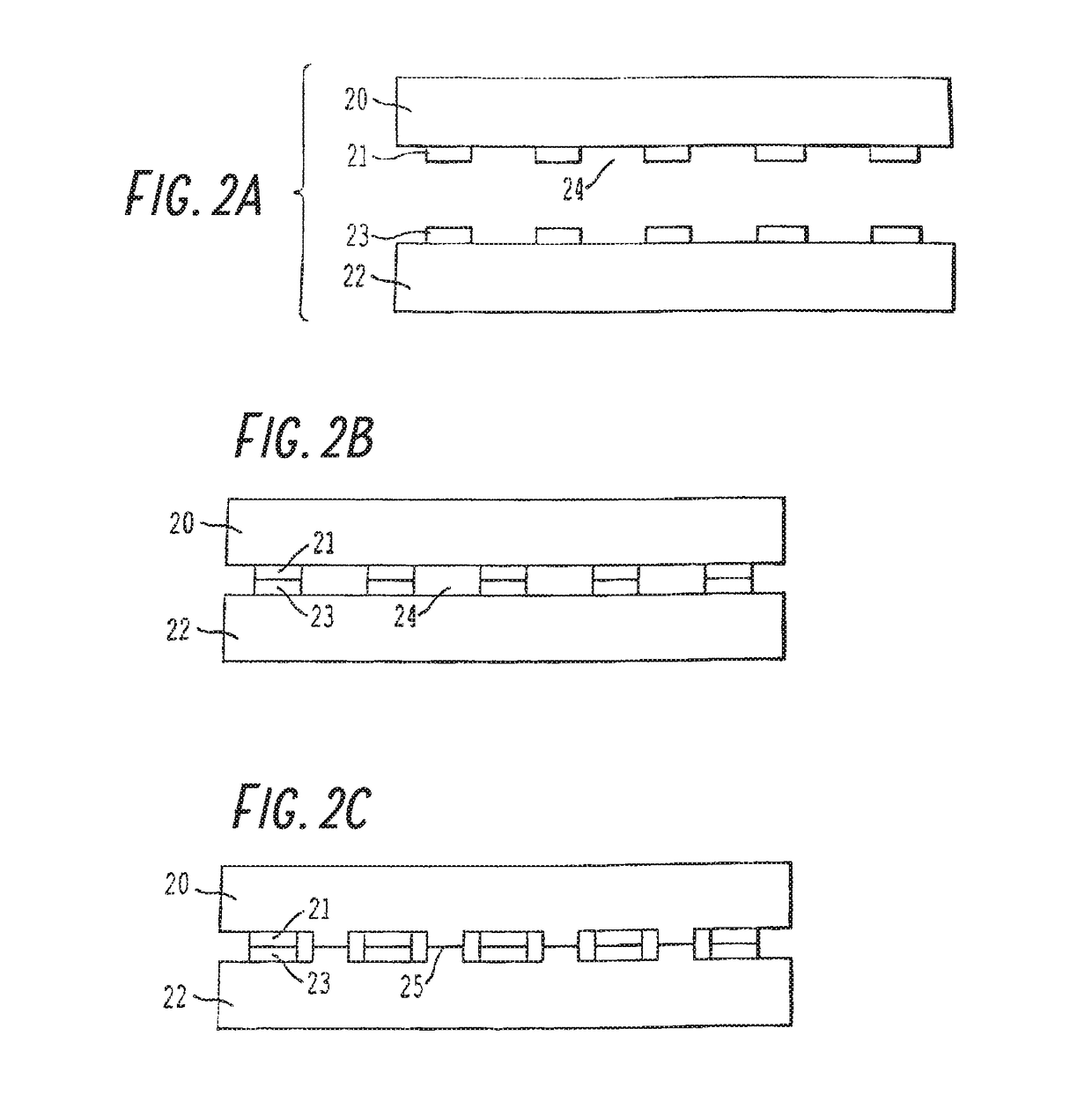

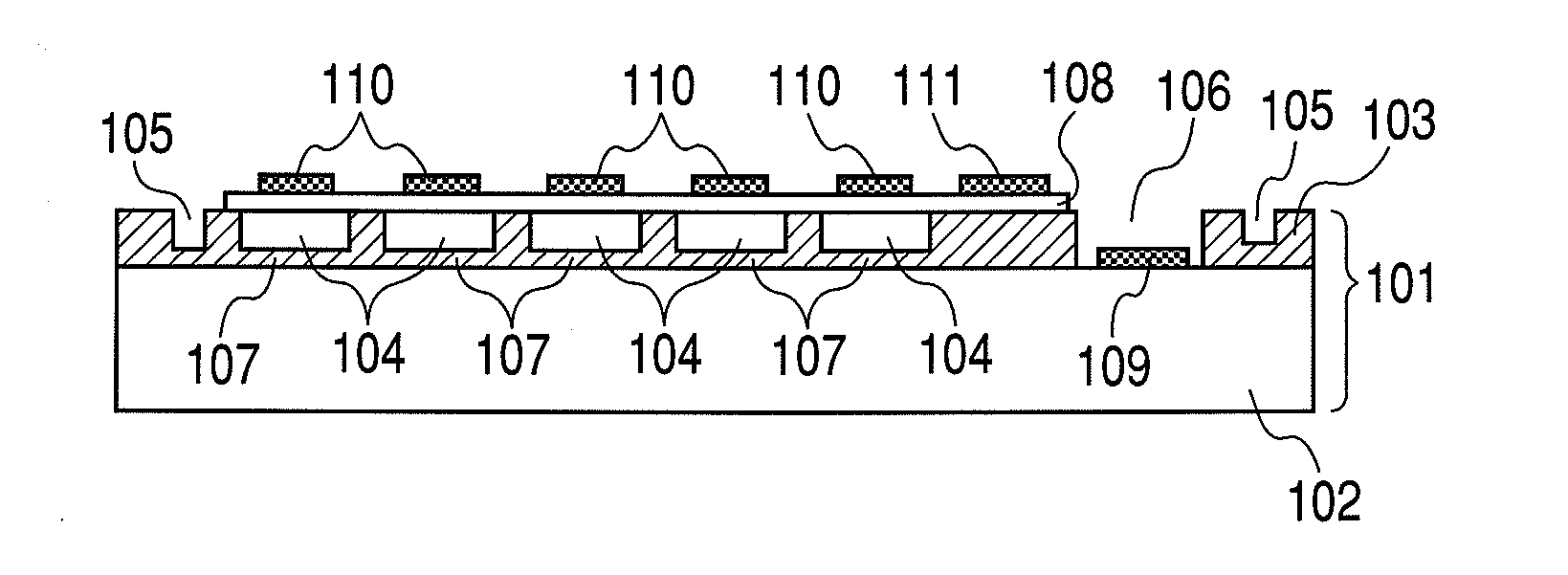

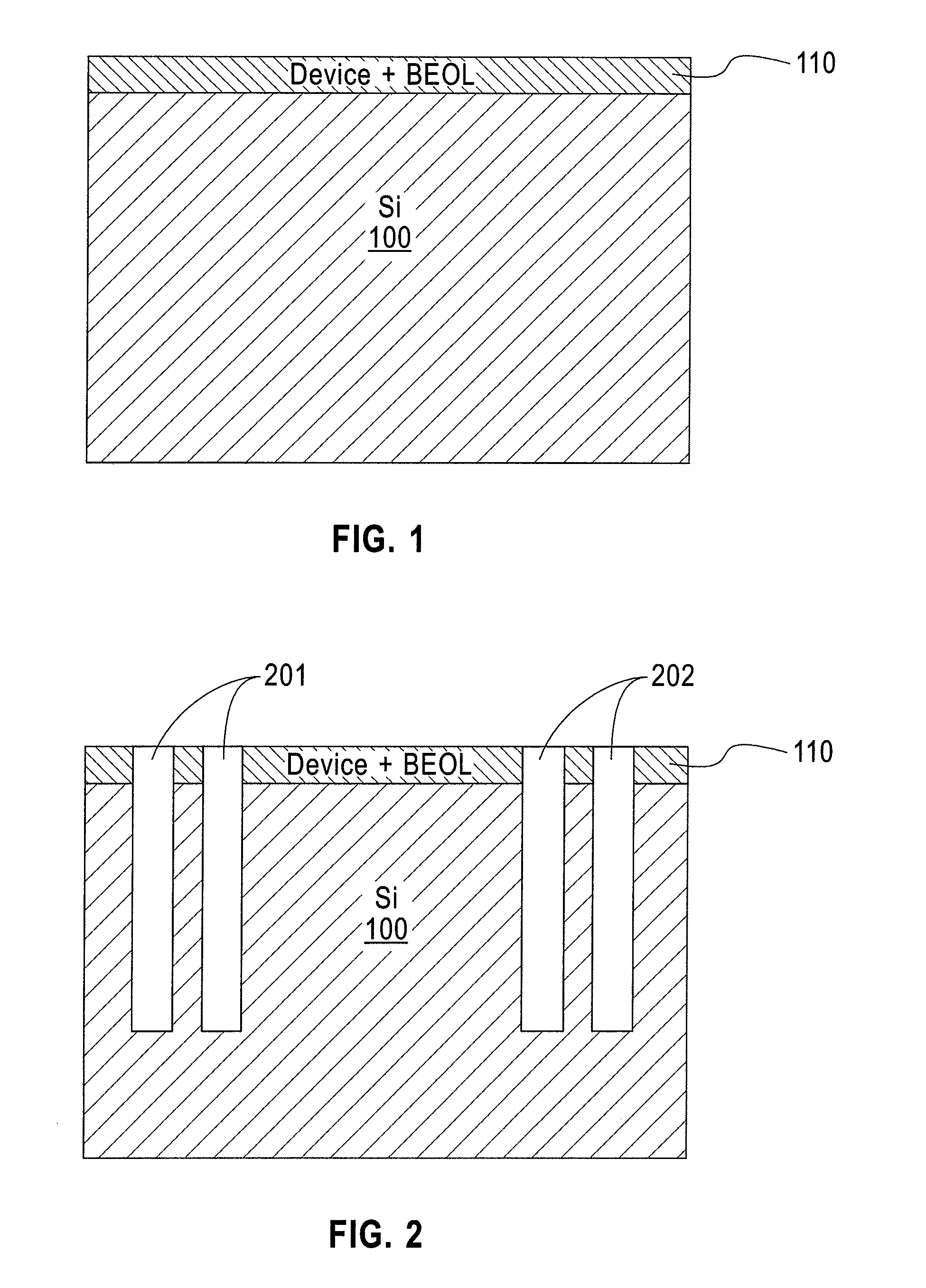

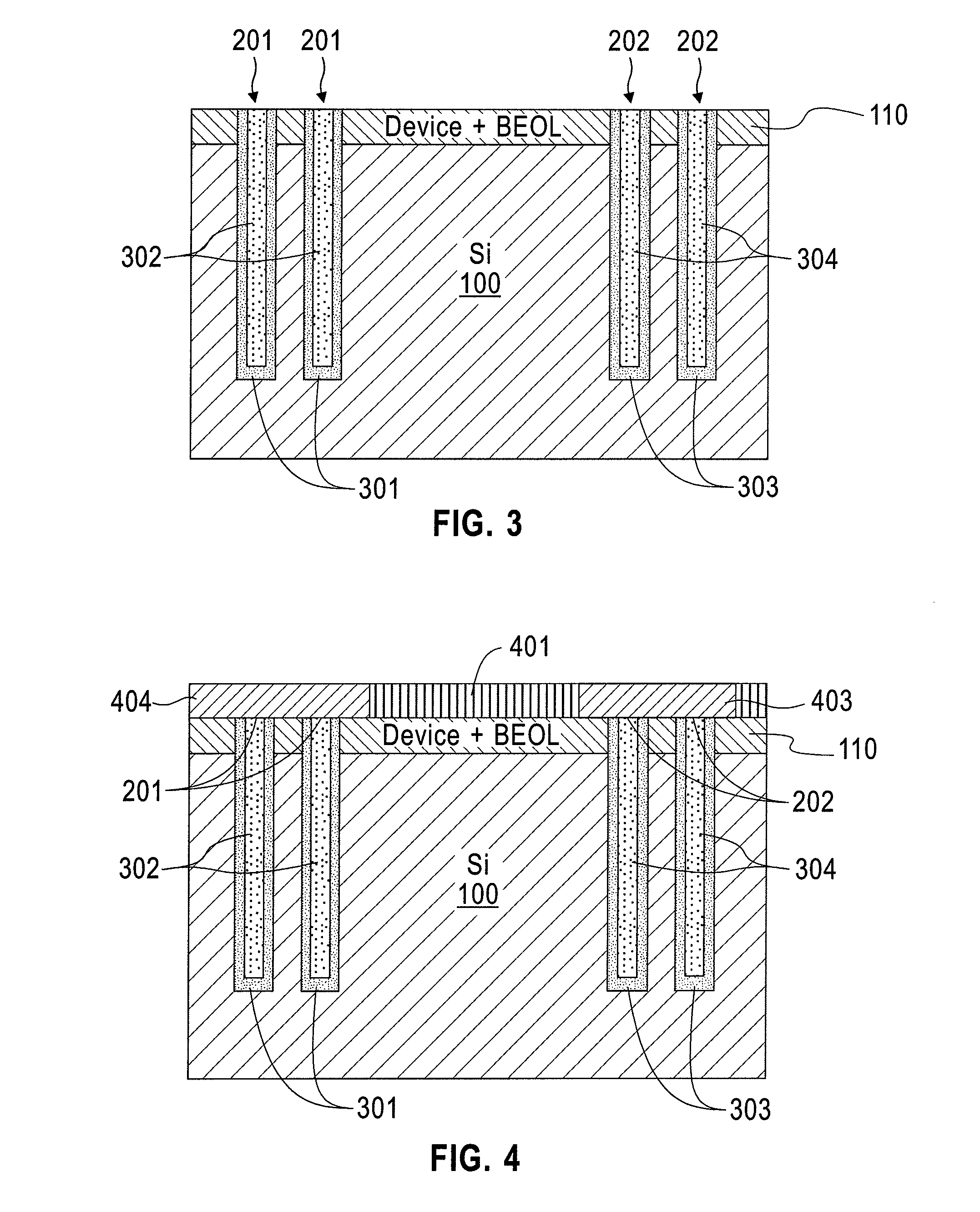

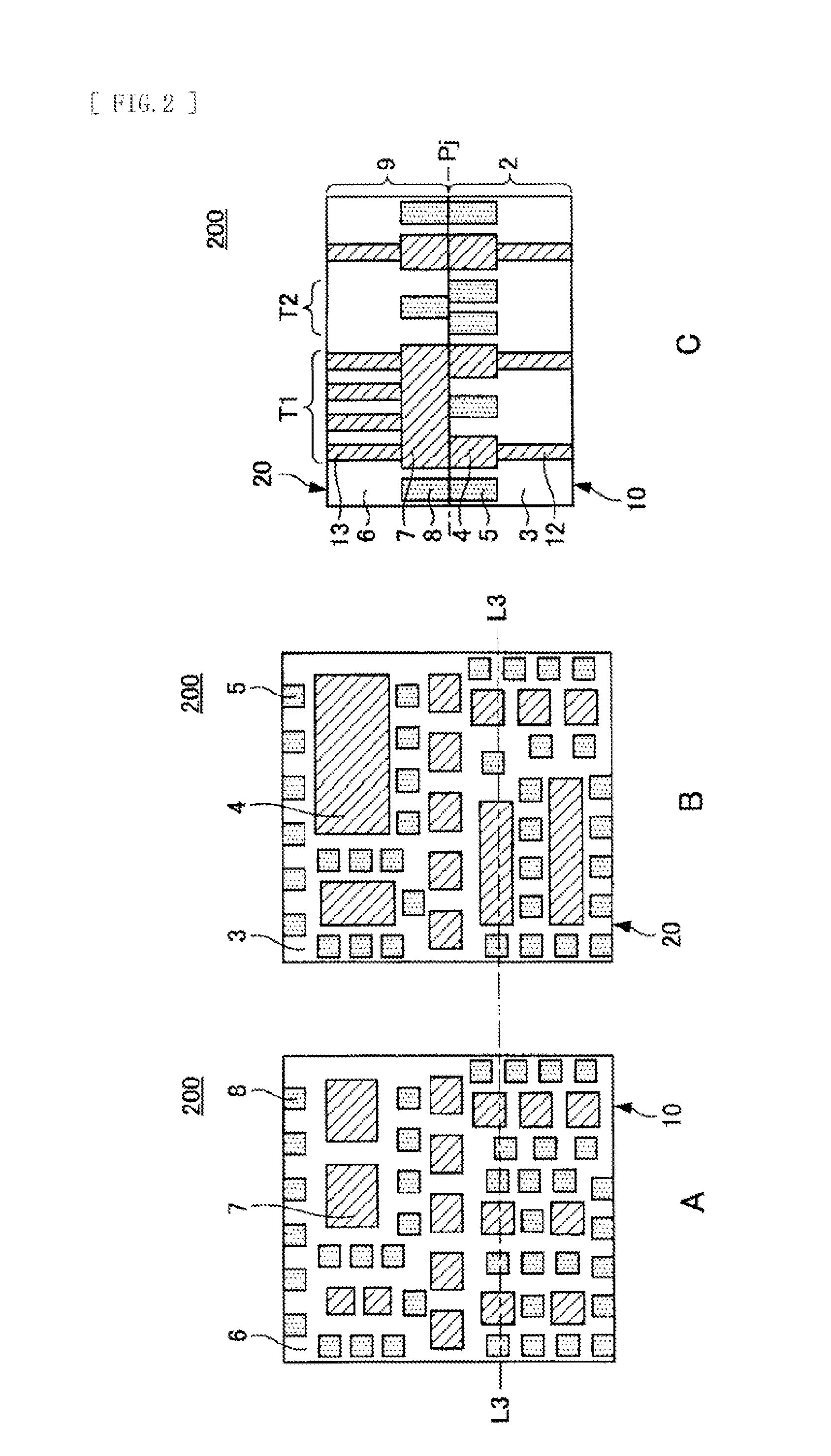

Hybrid bonding interface for 3-dimensional chip integration

ActiveUS20110101537A1Semiconductor/solid-state device detailsSolid-state devicesDielectricBond interface

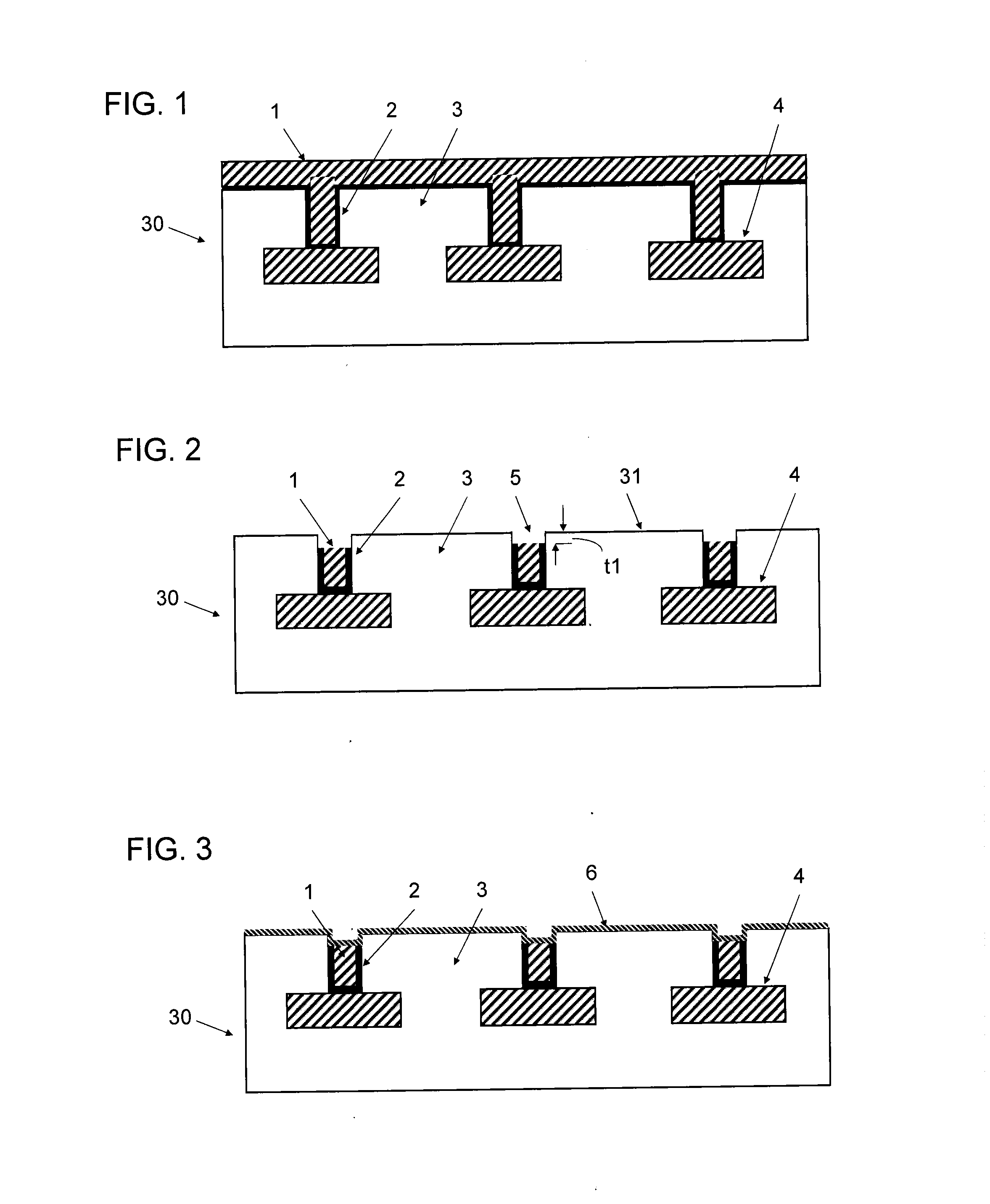

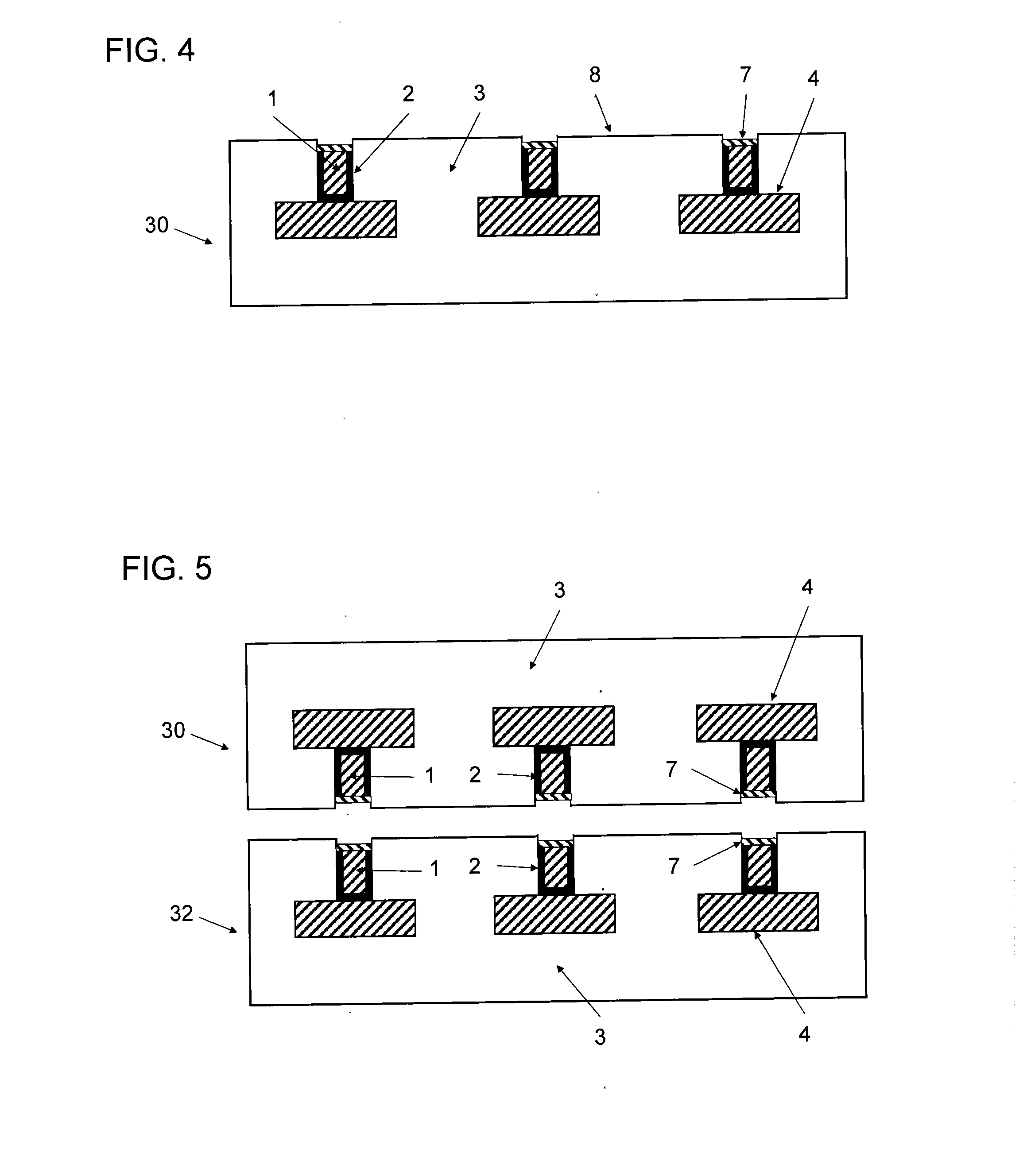

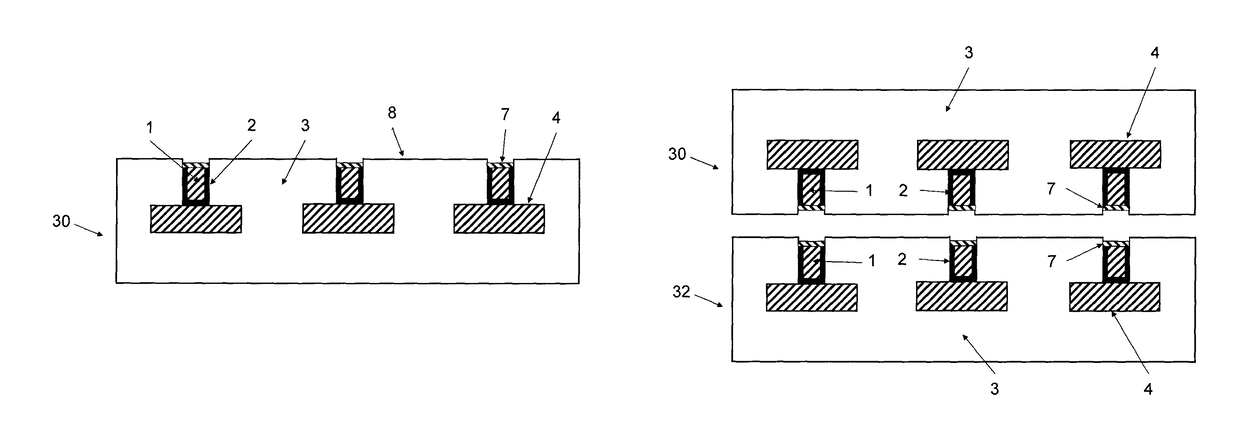

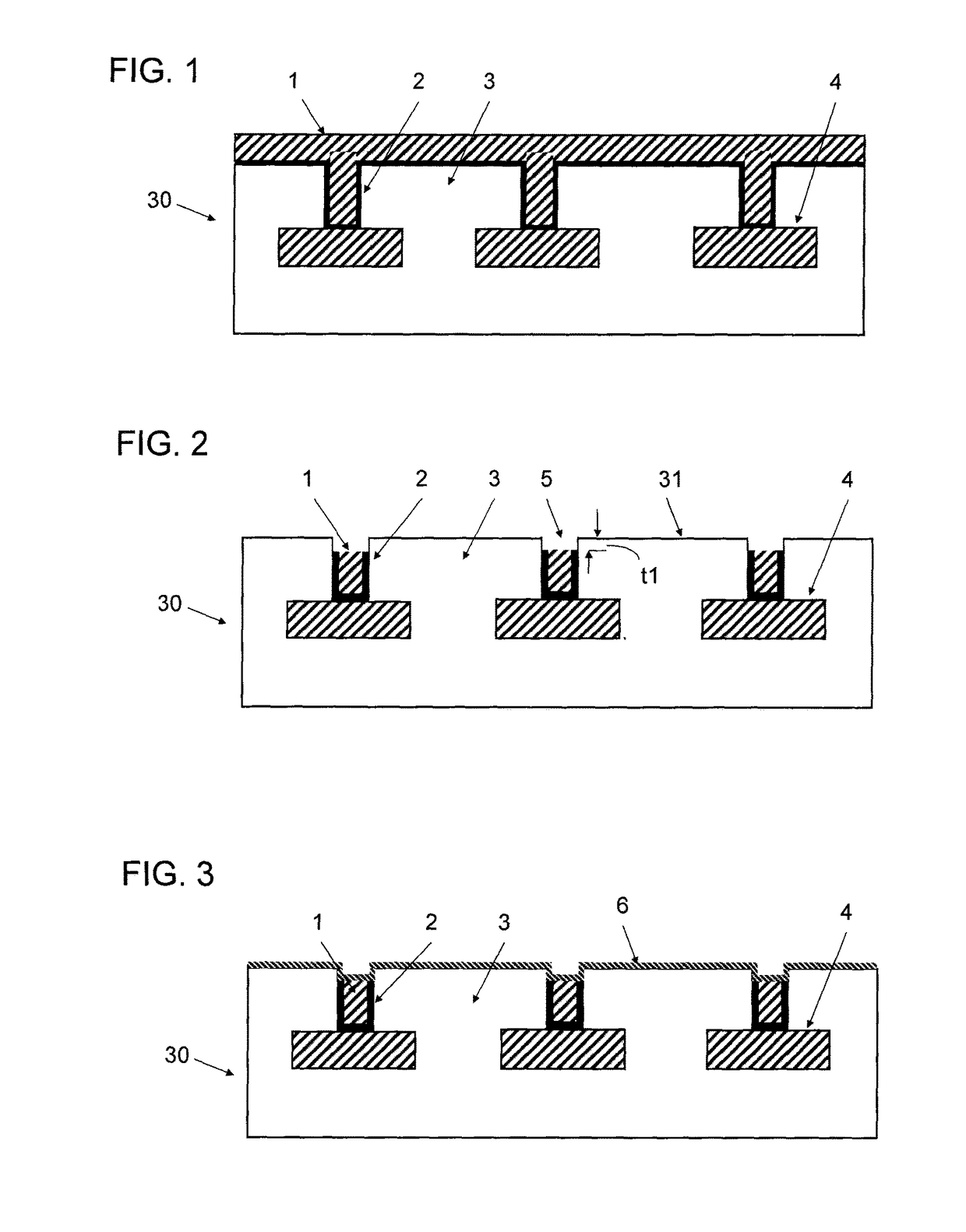

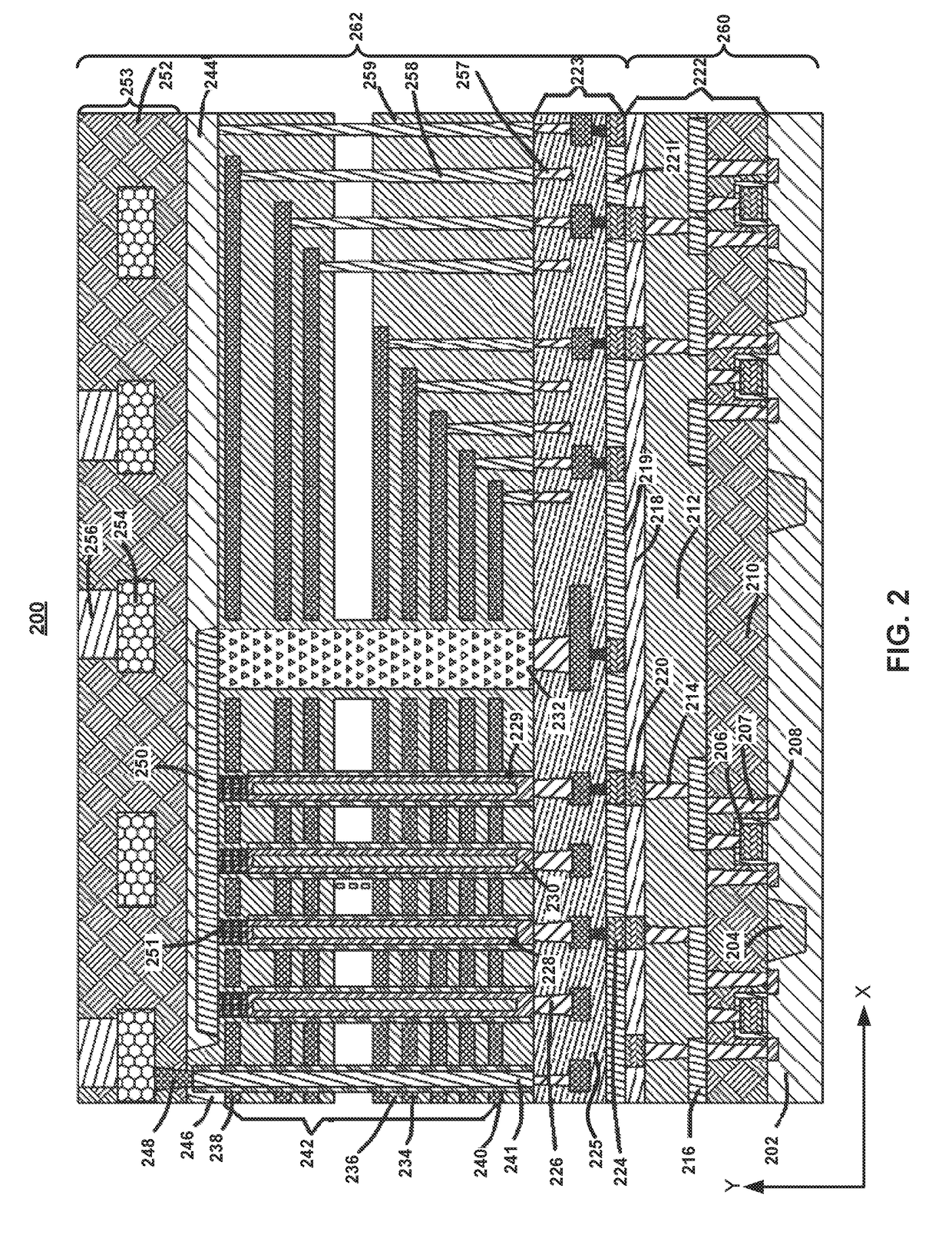

Each of a first substrate and a second substrate includes a surface having a diffusion resistant dielectric material such as silicon nitride. Recessed regions are formed in the diffusion resistant dielectric material and filled with a bondable dielectric material. The patterns of the metal pads and bondable dielectric material portions in the first and second substrates can have a mirror symmetry. The first and second substrates are brought into physical contact and bonded employing contacts between metal pads and contacts between the bondable dielectric material portions. Through-substrate-via (TSV) structures are formed through bonded dielectric material portions. The interface between each pair of bonded dielectric material portions located around a TSV structure is encapsulated by two diffusion resistant dielectric material layers so that diffusion of metal at a bonding interface is contained within each pair of bonded dielectric material portions.

Owner:GLOBALFOUNDRIES US INC

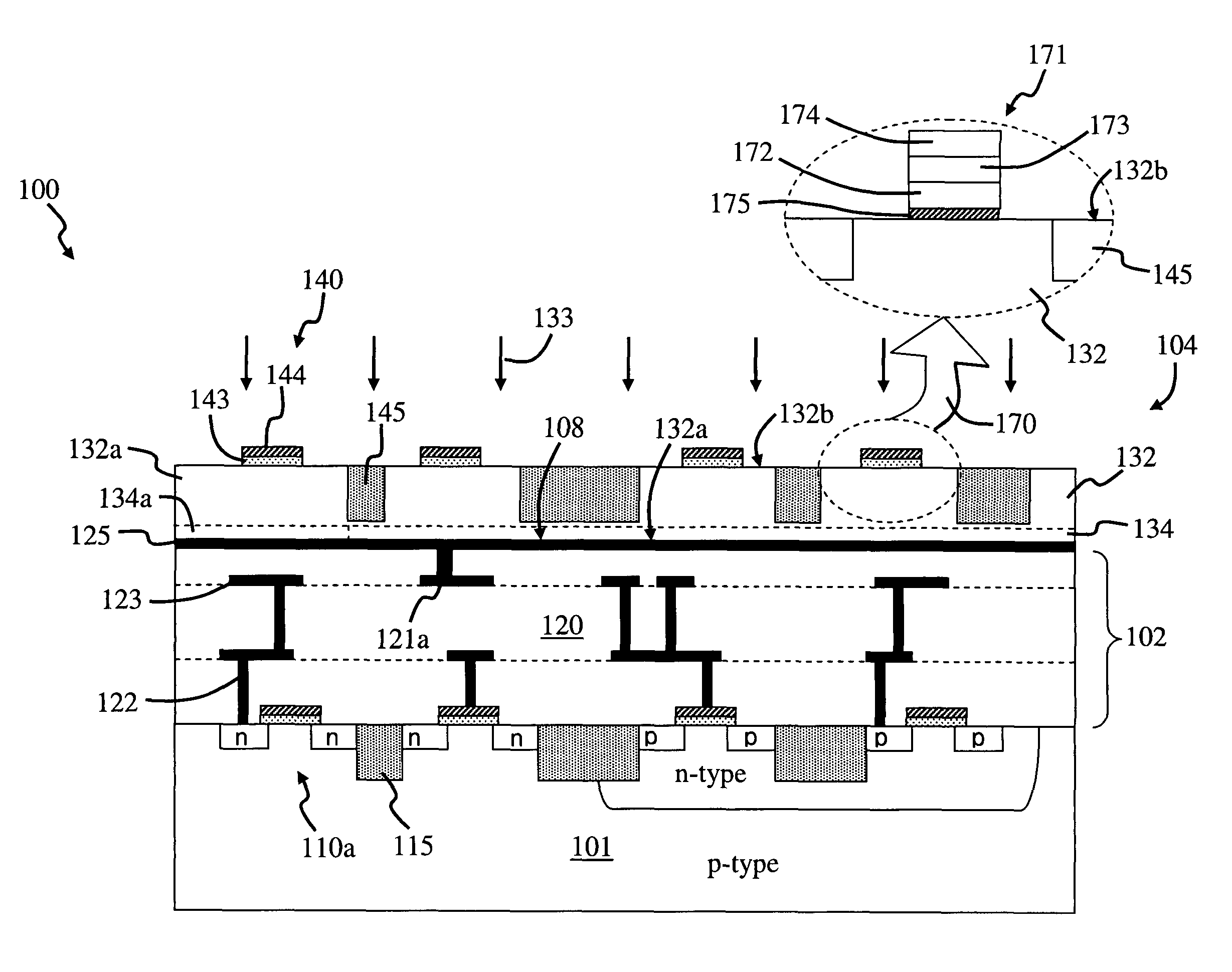

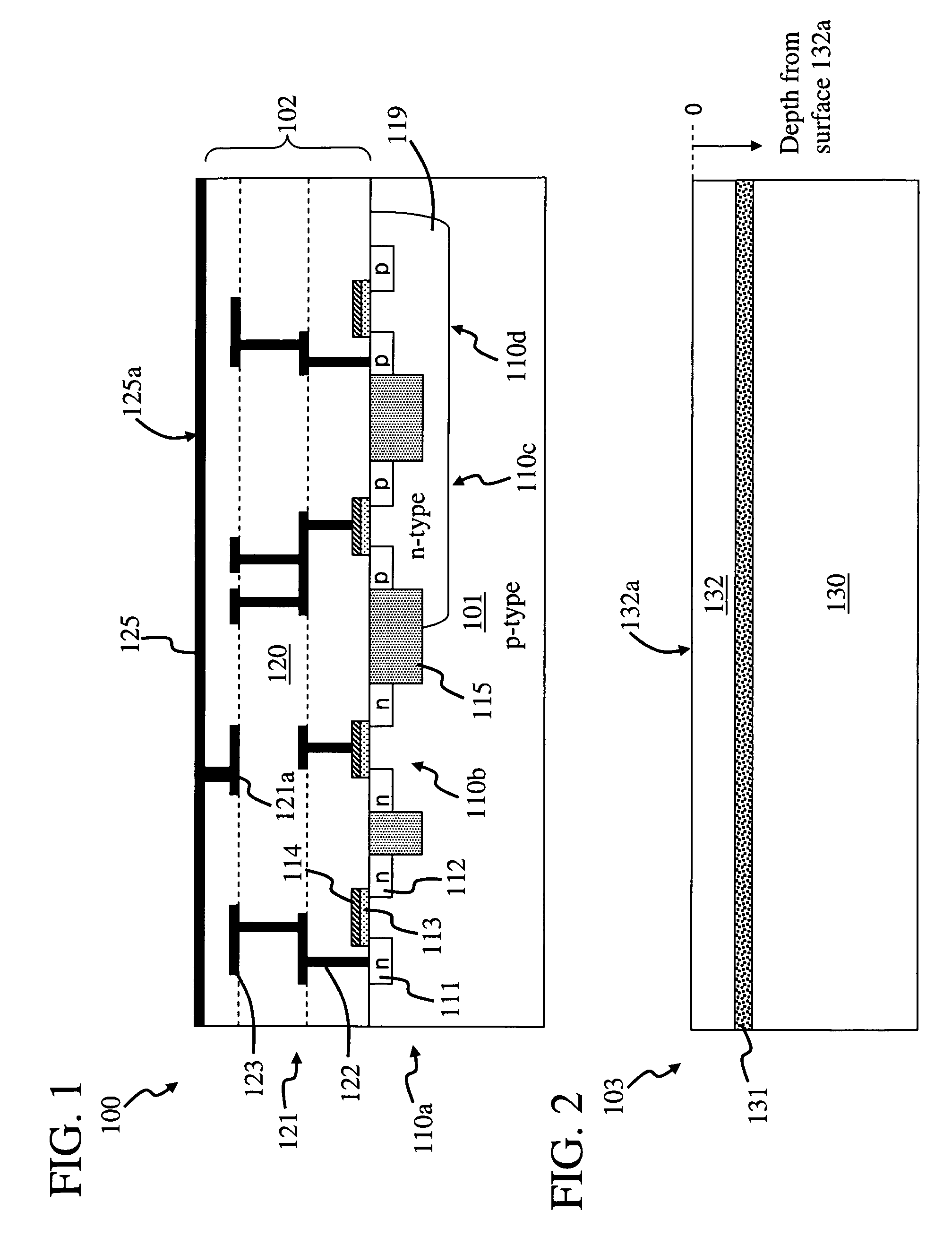

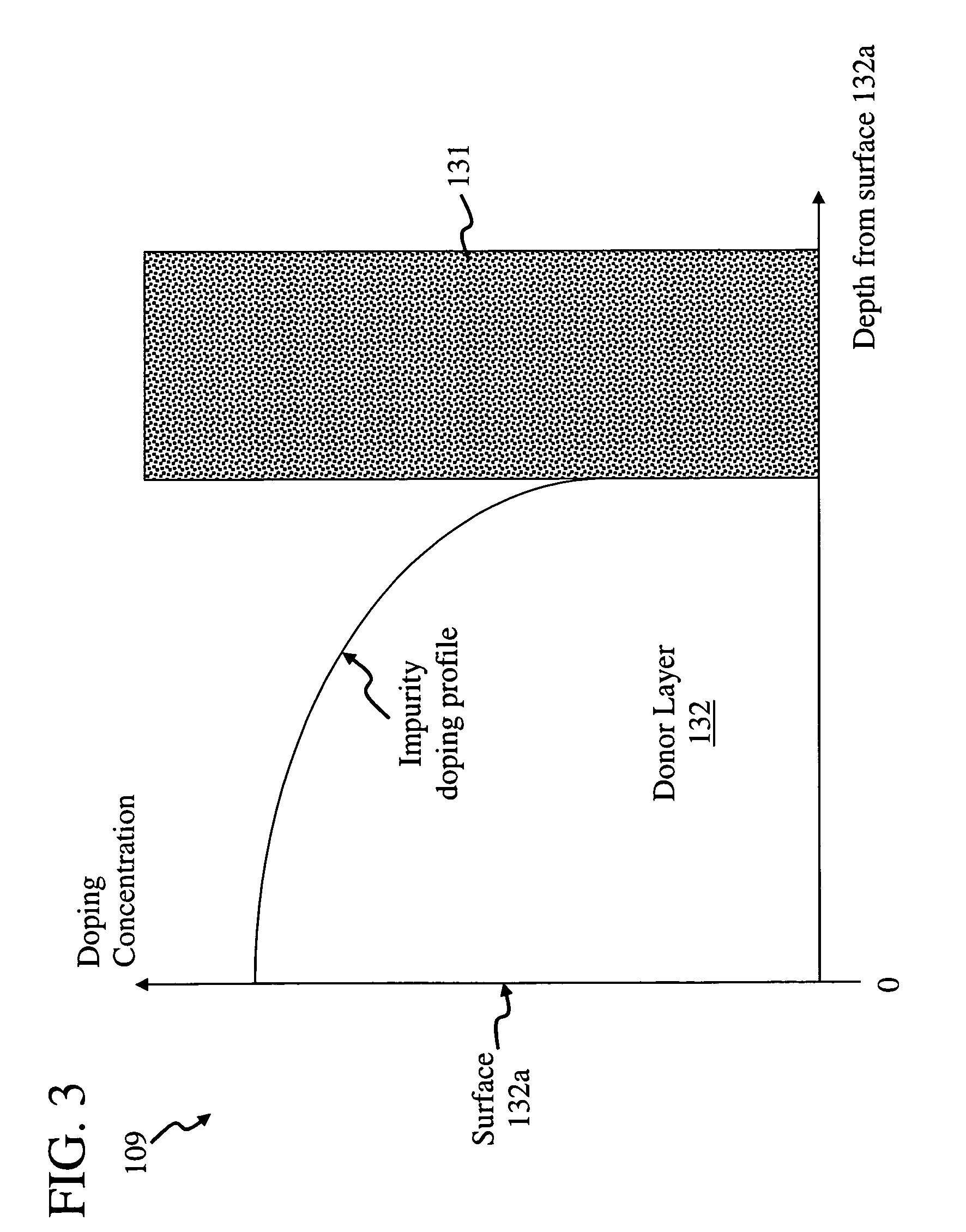

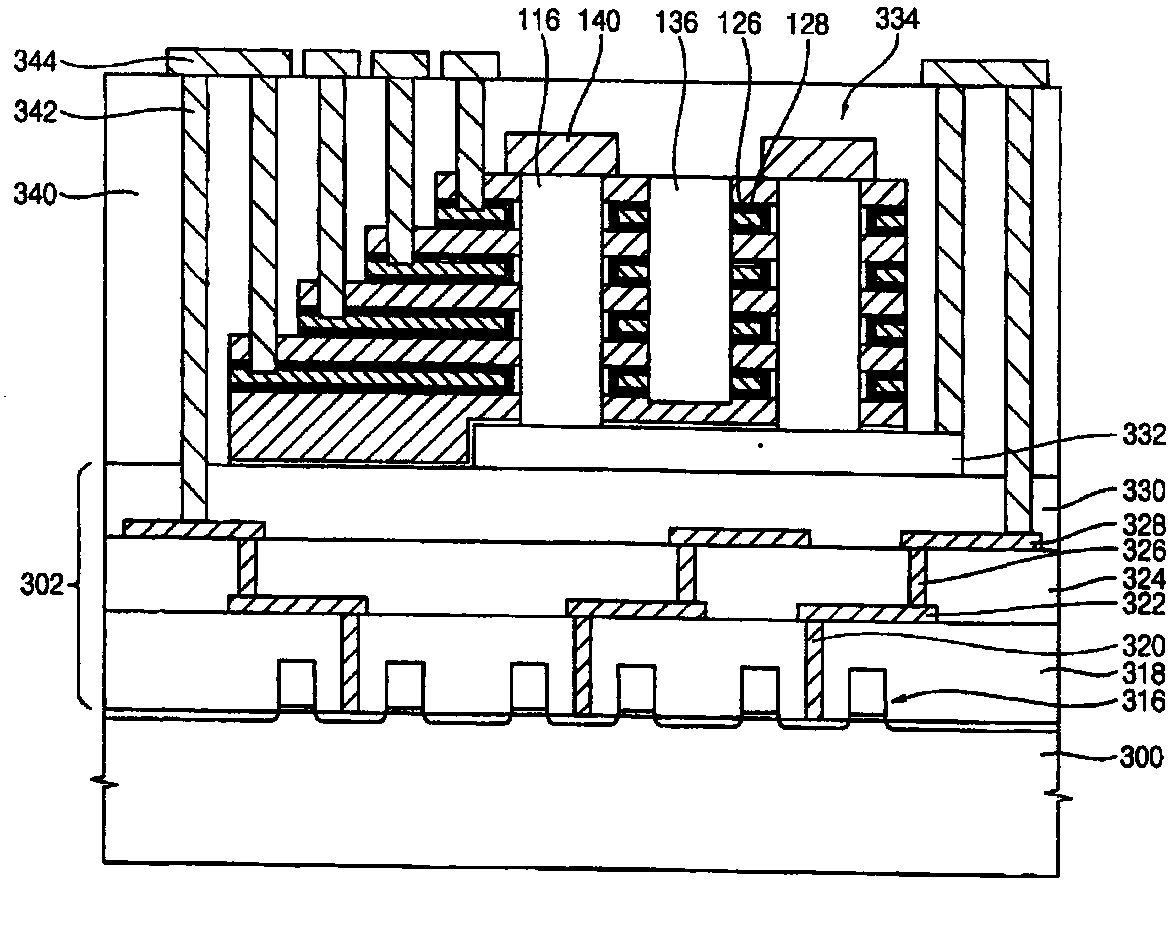

Semiconductor circuit

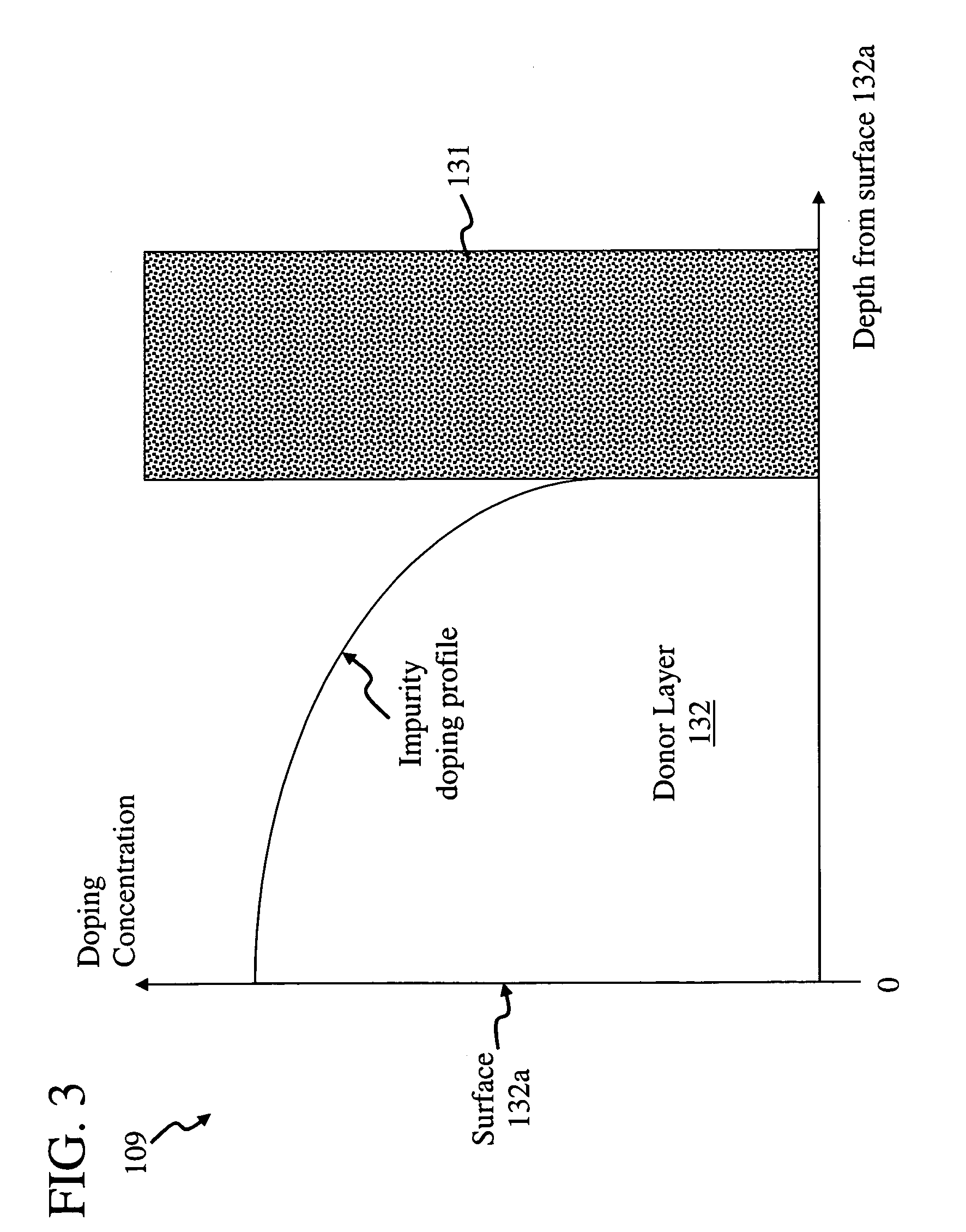

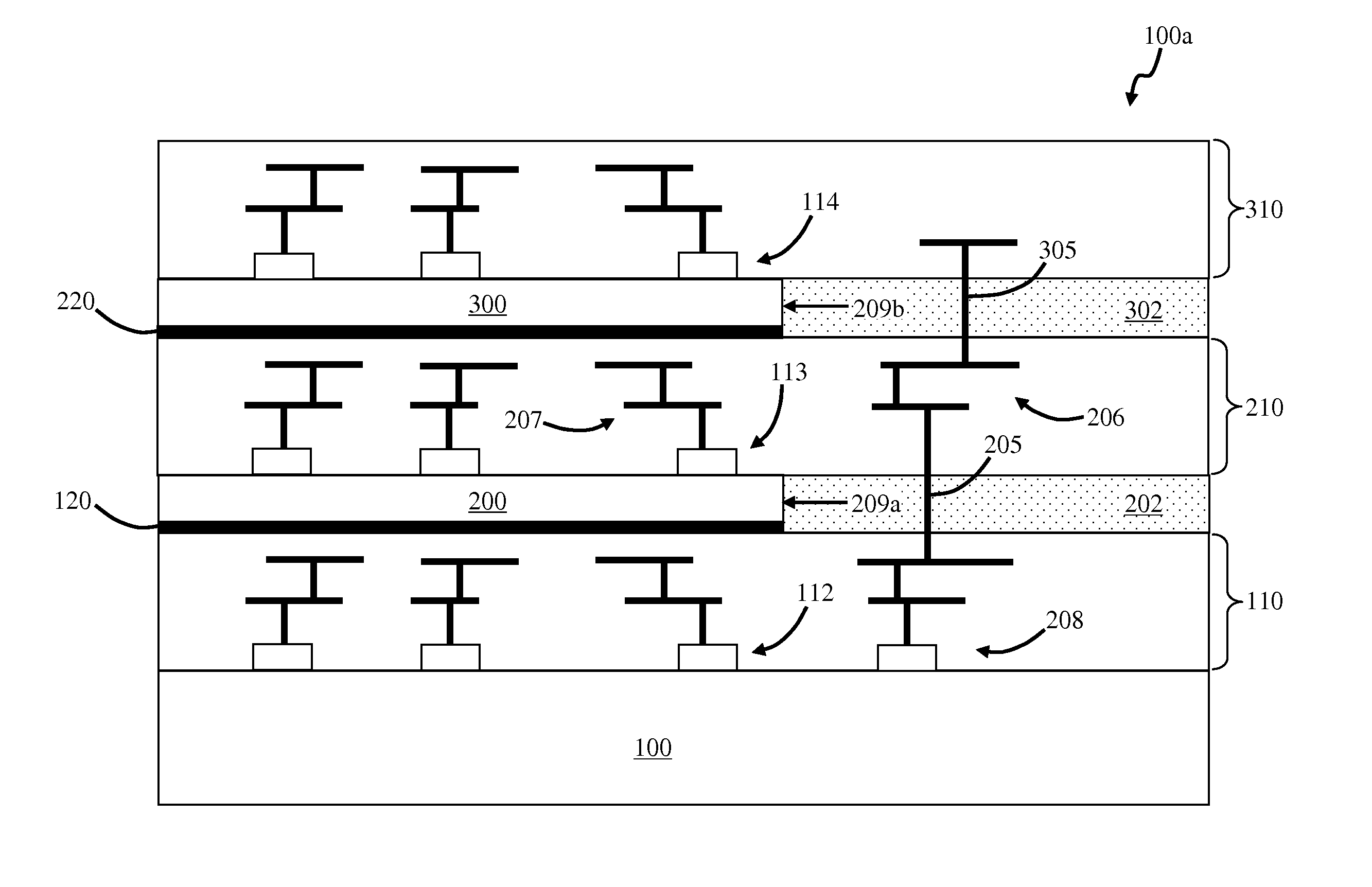

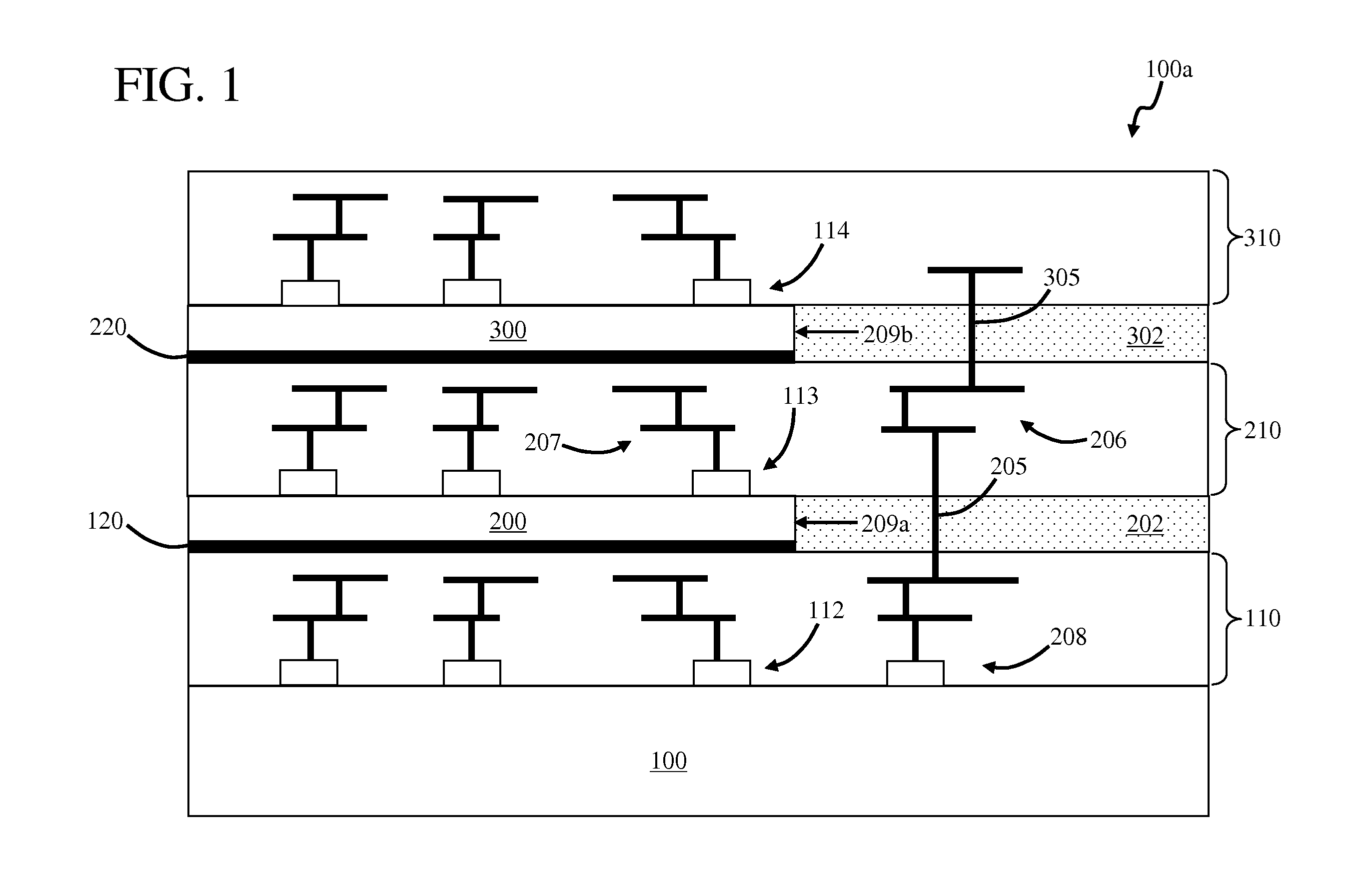

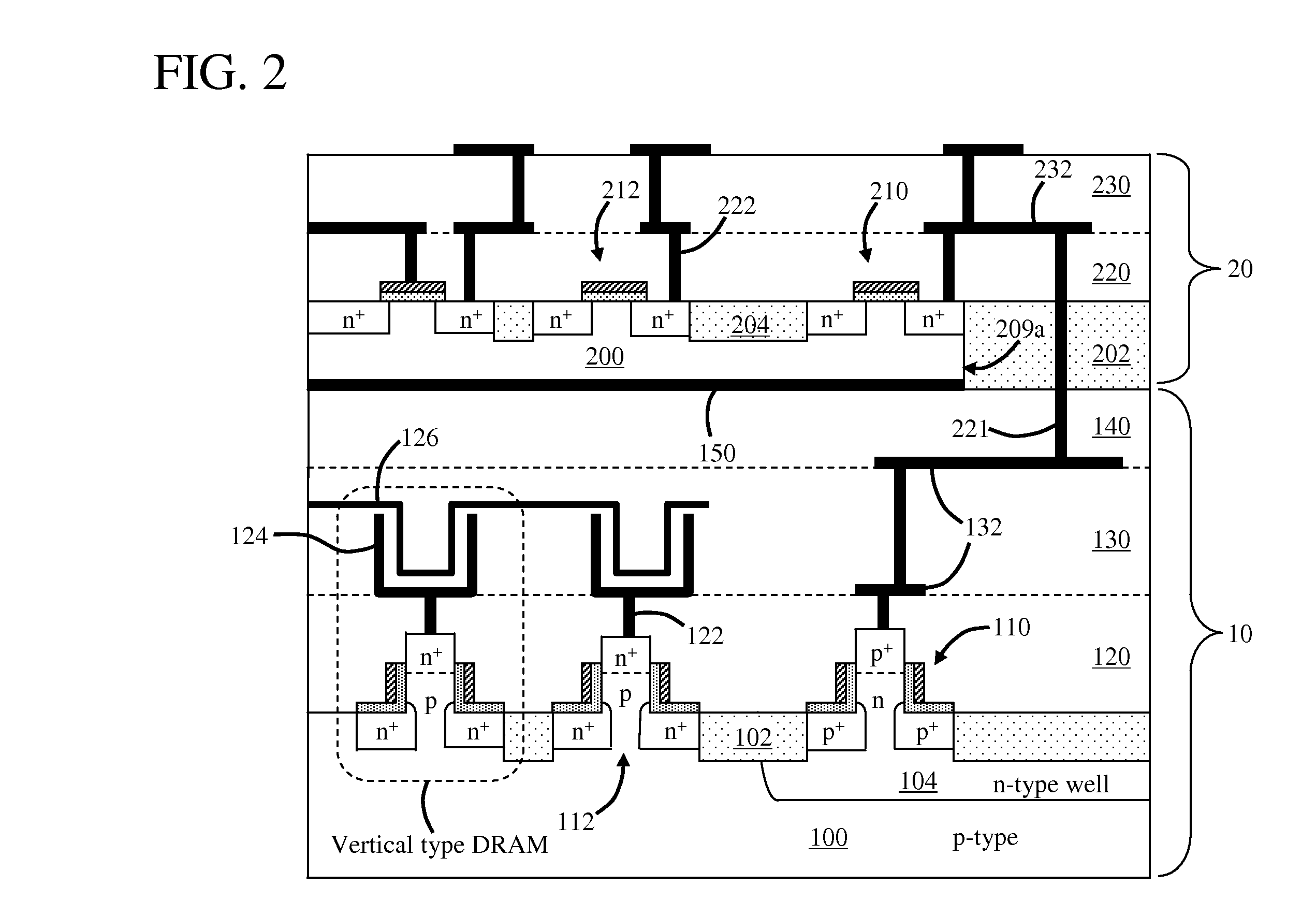

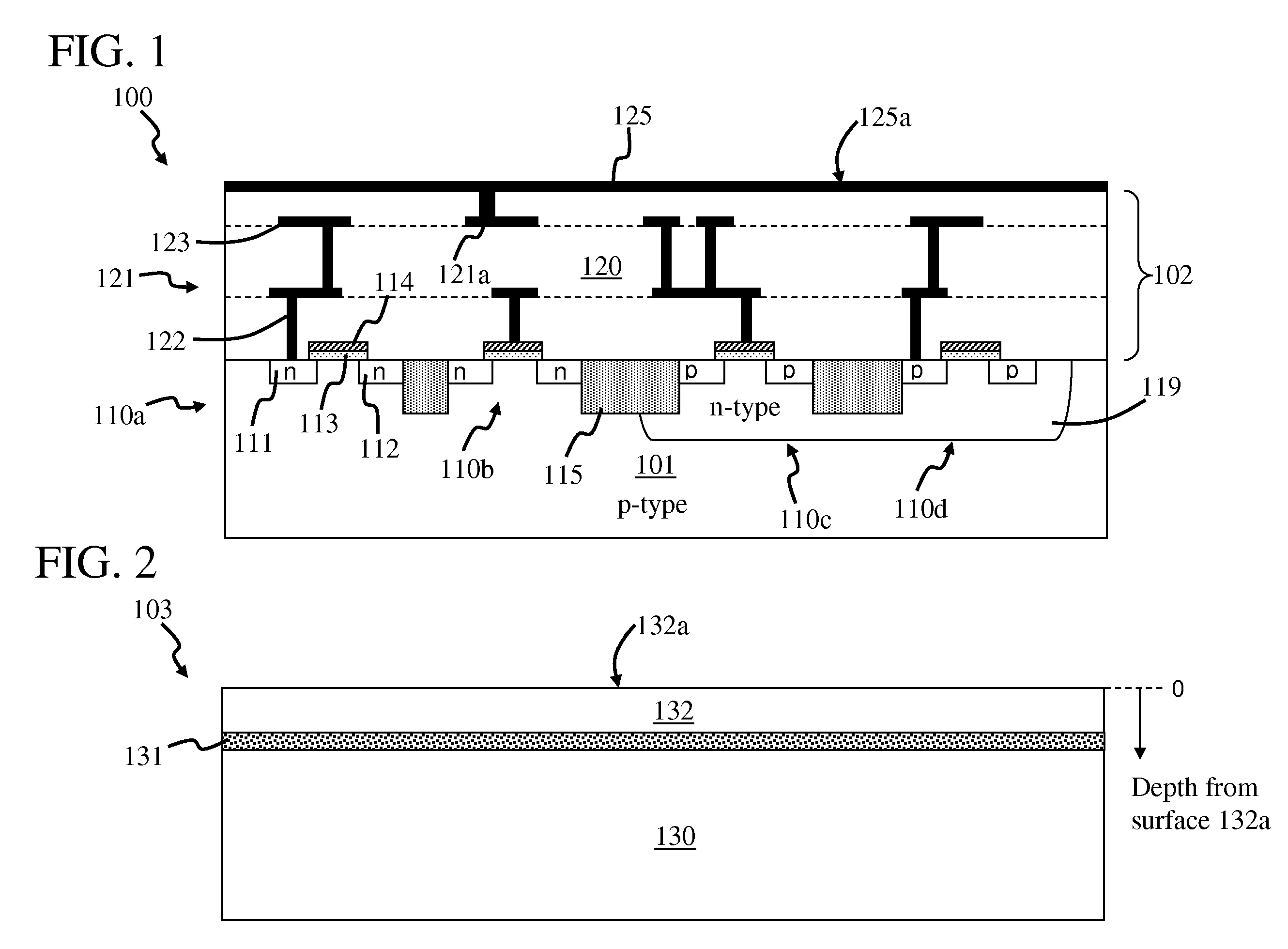

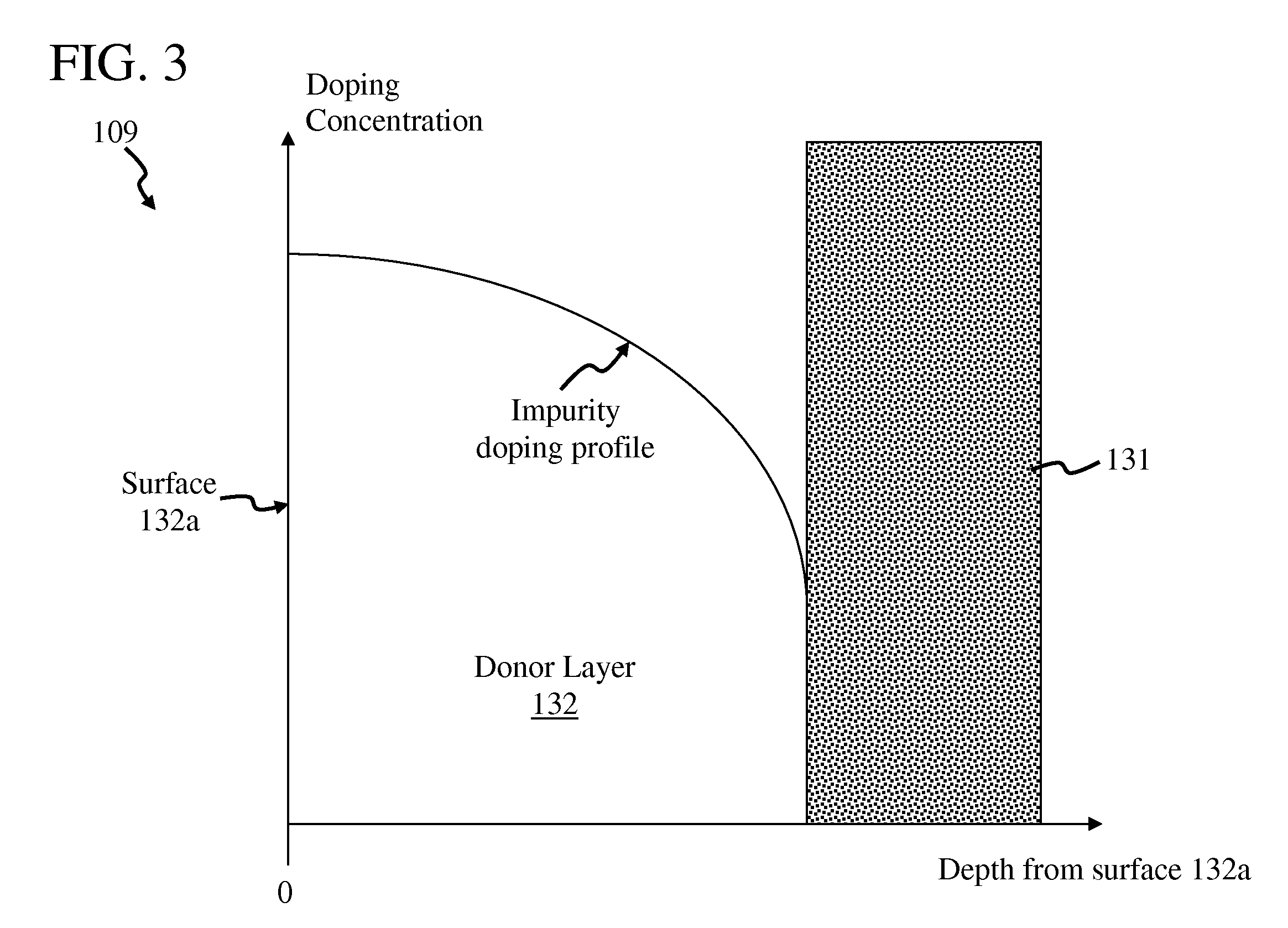

InactiveUS20080191312A1Solid-state devicesSemiconductor/solid-state device manufacturingBond interfaceEngineering

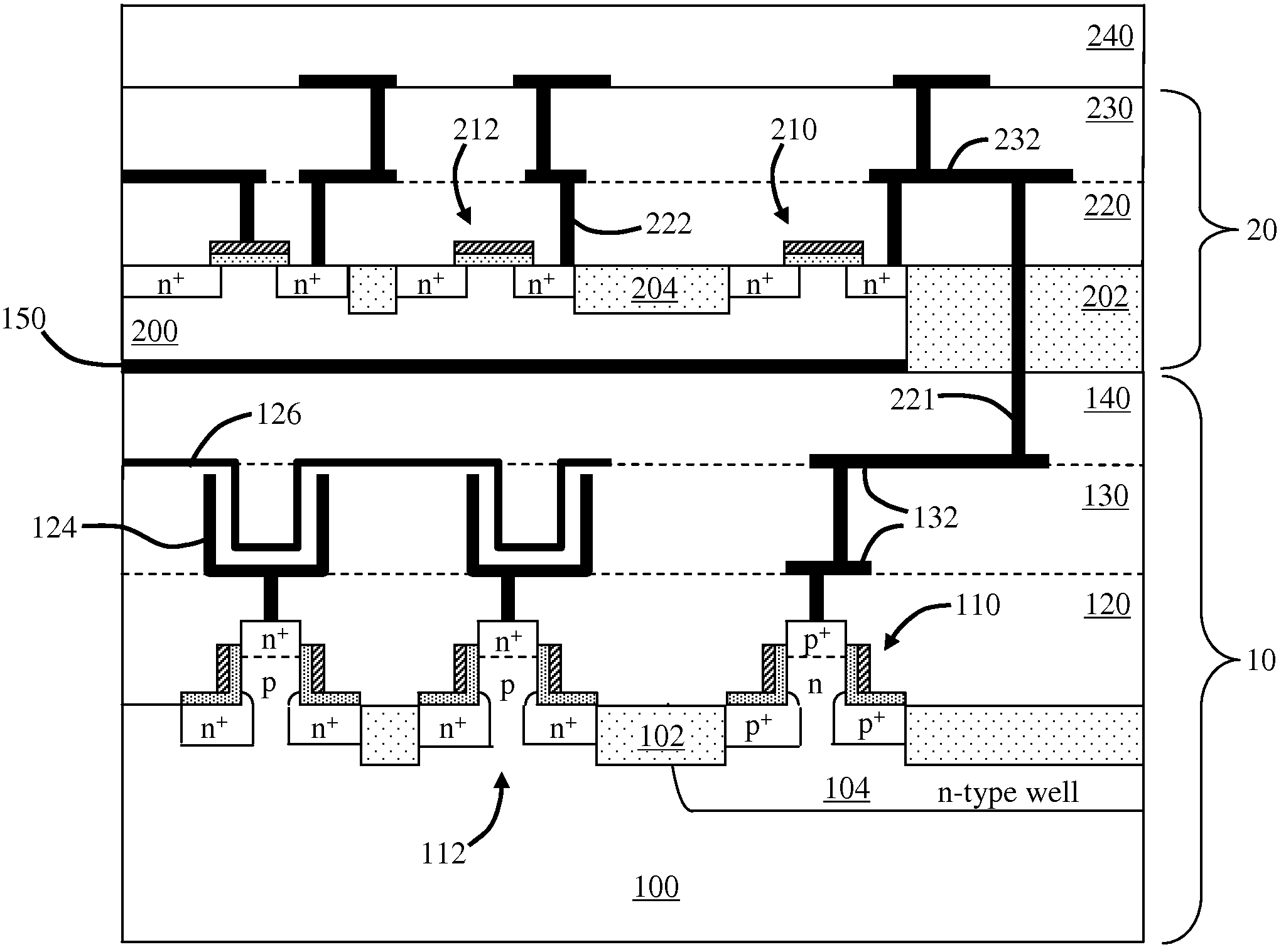

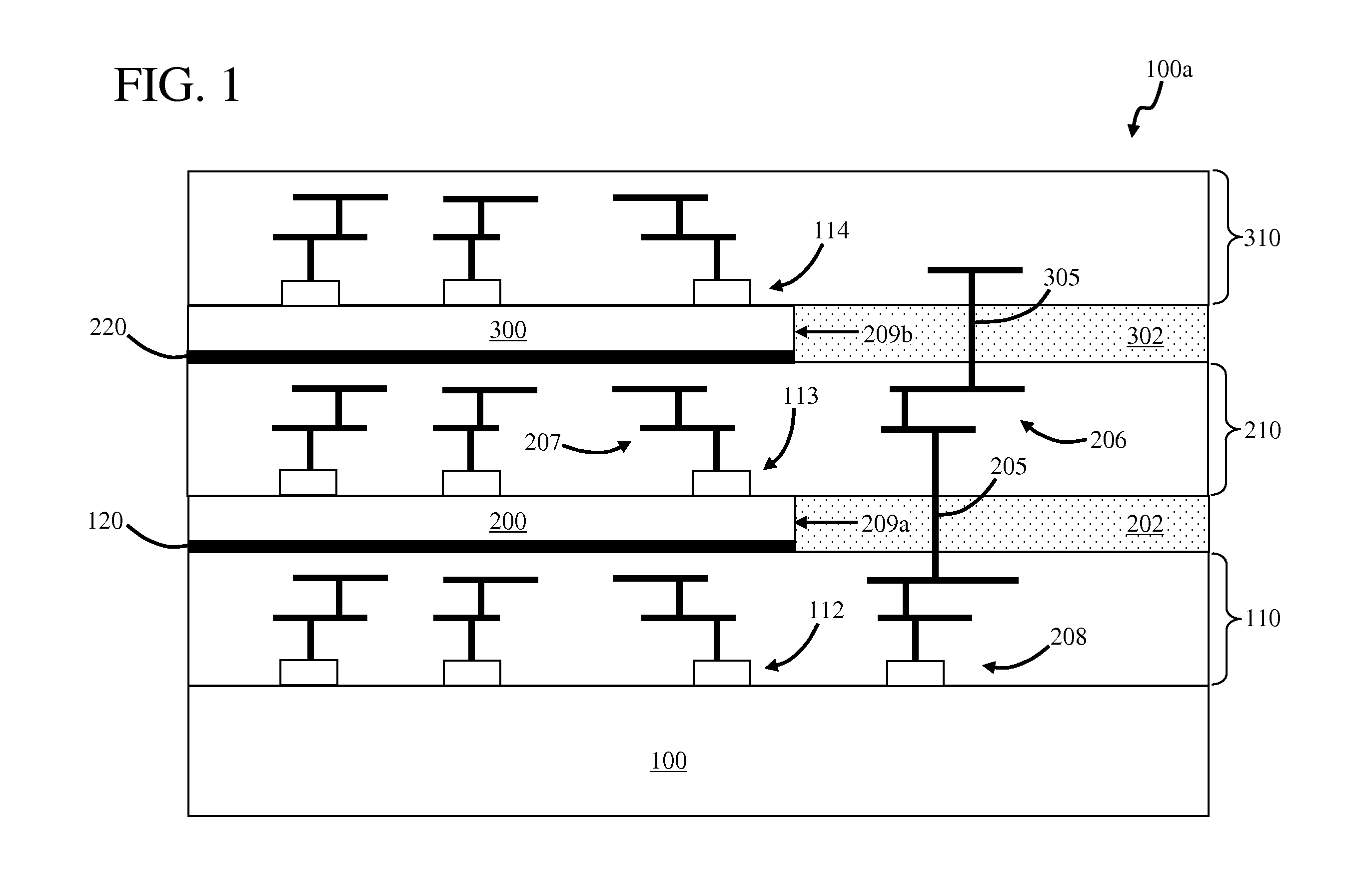

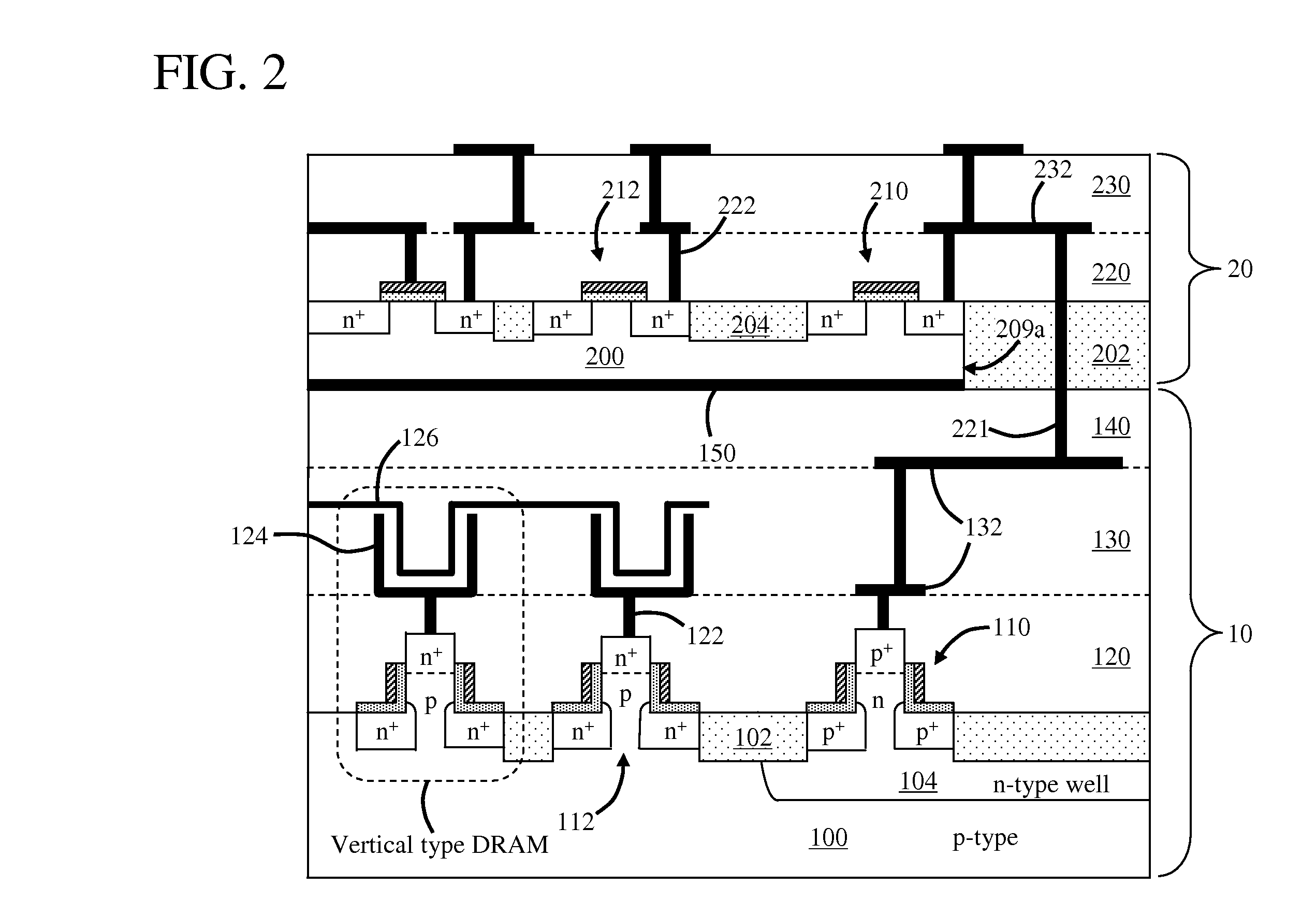

A semiconductor memory device includes a substrate and an interconnect region carried by the substrate. A donor layer is coupled to the interconnect region through a bonding interface. An electronic device is formed with the donor layer, wherein the electronic device is formed after the bonding interface is formed. A capacitor is connected to the electronic device so that the electronic device and capacitor operate as a dynamic random access memory device.

Owner:BESANG

Bonded semiconductor structure and method of fabricating the same

InactiveUS20090325343A1Solid-state devicesSemiconductor/solid-state device manufacturingBond interfaceSemiconductor structure

A method of forming a bonded semiconductor structure circuit includes providing a support substrate which carries a first semiconductor circuit and providing a first interconnect region carried by the support substrate. The method includes providing a bonded semiconductor substrate which is bonded to the first interconnect region through a bonding interface and forming a second semiconductor circuit which is carried by the first bonded semiconductor substrate.

Owner:BESANG

Bonded semiconductor structure and method of fabricating the same

InactiveUS7799675B2Solid-state devicesSemiconductor/solid-state device manufacturingBond interfaceSemiconductor structure

A method of forming a bonded semiconductor structure circuit includes providing a support substrate which carries a first semiconductor circuit and providing a first interconnect region carried by the support substrate. The method includes providing a bonded semiconductor substrate which is bonded to the first interconnect region through a bonding interface and forming a second semiconductor circuit which is carried by the first bonded semiconductor substrate.

Owner:BESANG

Semiconductor circuit

InactiveUS20110053332A1Solid-state devicesSemiconductor/solid-state device manufacturingBond interfaceEngineering

A semiconductor memory device includes a substrate and an interconnect region carried by the substrate. A donor layer is coupled to the interconnect region through a bonding interface. An electronic device is formed with the donor layer, wherein the electronic device is formed after the bonding interface is formed. A capacitor is connected to the electronic device so that the electronic device and capacitor operate as a dynamic random access memory device.

Owner:BESANG

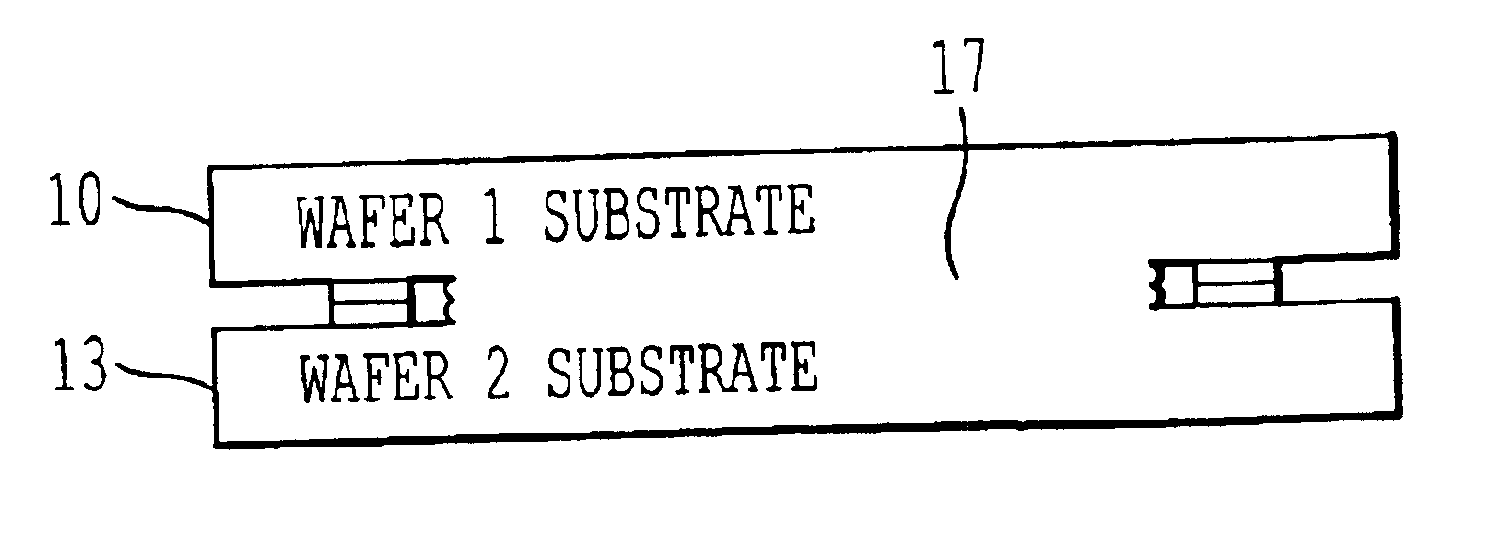

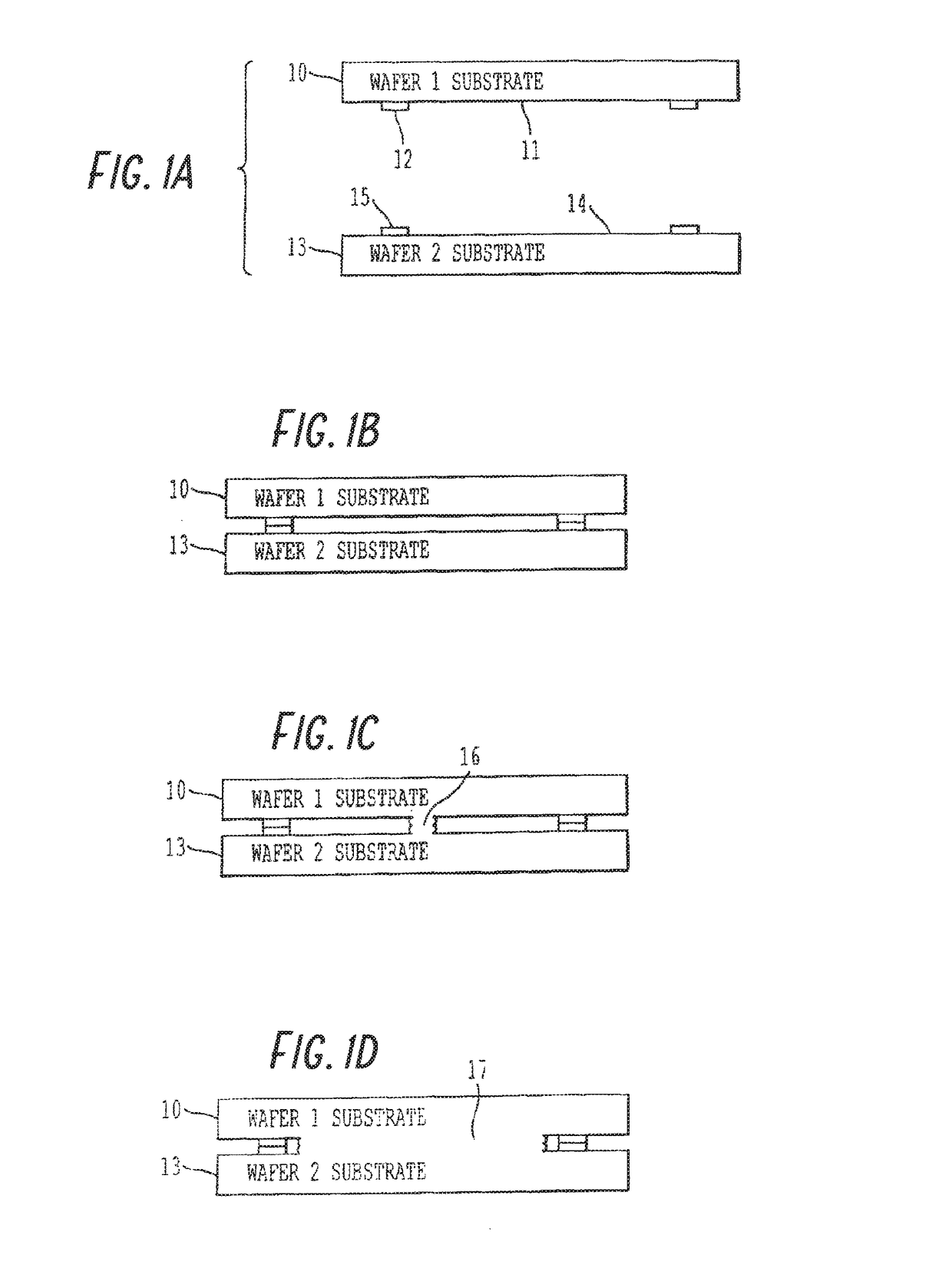

Wafer bonding method

InactiveUS7632738B2Reduce in quantitySolid-state devicesSemiconductor/solid-state device manufacturingBond interfaceEngineering

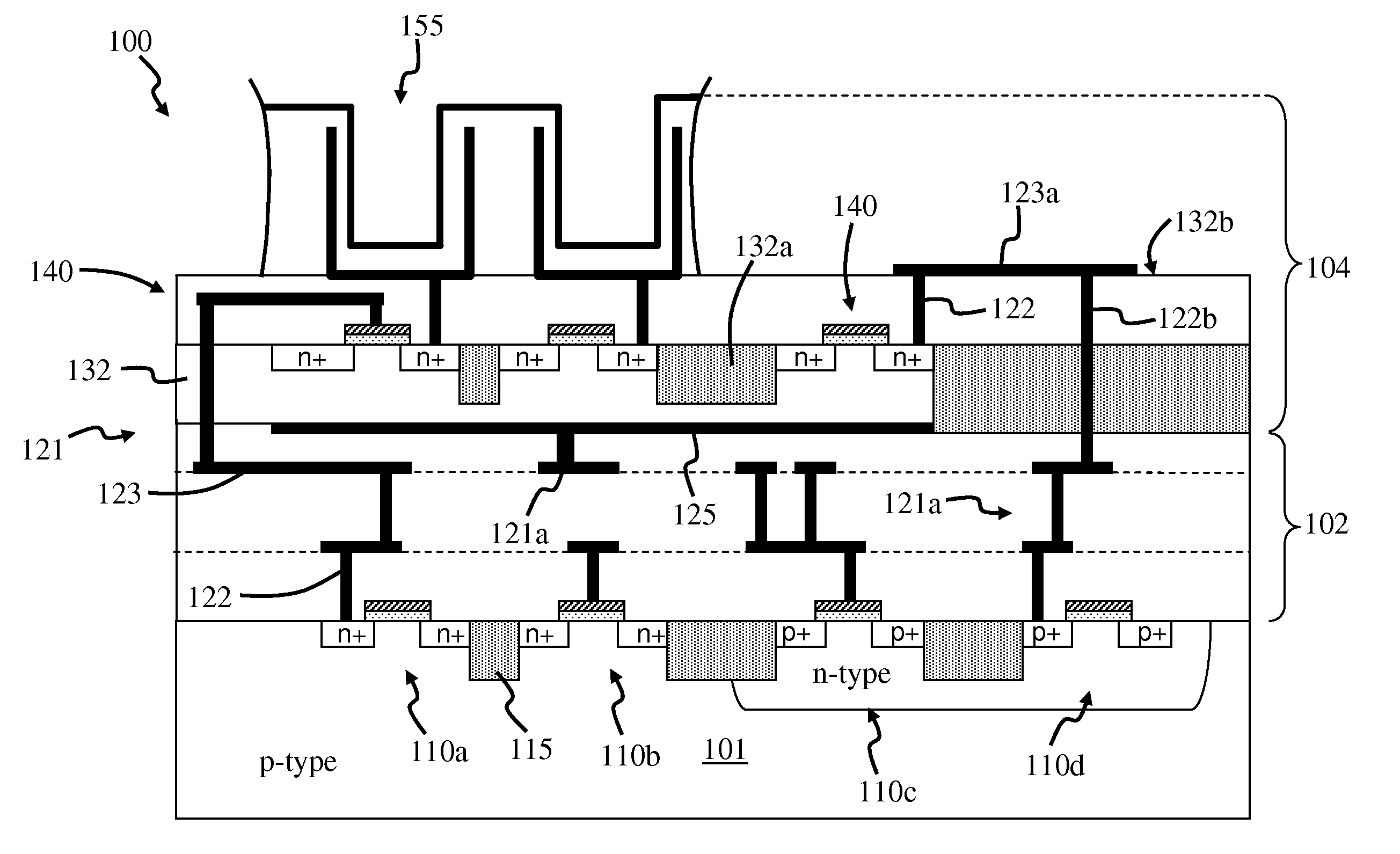

A method includes steps of providing first and second substrates, and forming a bonding interface between them using a conductive bonding region. A portion of the second substrate is removed to form a mesa structure. A vertically oriented semiconductor device is formed with the mesa structure. A portion of the conductive bonding region is removed to form a contact. The vertically oriented semiconductor device is carried by the contact.

Owner:BESANG

Semiconductor circuit

InactiveUS7800199B2Solid-state devicesSemiconductor/solid-state device manufacturingBond interfaceCapacitor

A semiconductor memory device includes a substrate and an interconnect region carried by the substrate. A donor layer is coupled to the interconnect region through a bonding interface. An electronic device is formed with the donor layer, wherein the electronic device is formed after the bonding interface is formed. A capacitor is connected to the electronic device so that the electronic device and capacitor operate as a dynamic random access memory device.

Owner:BESANG

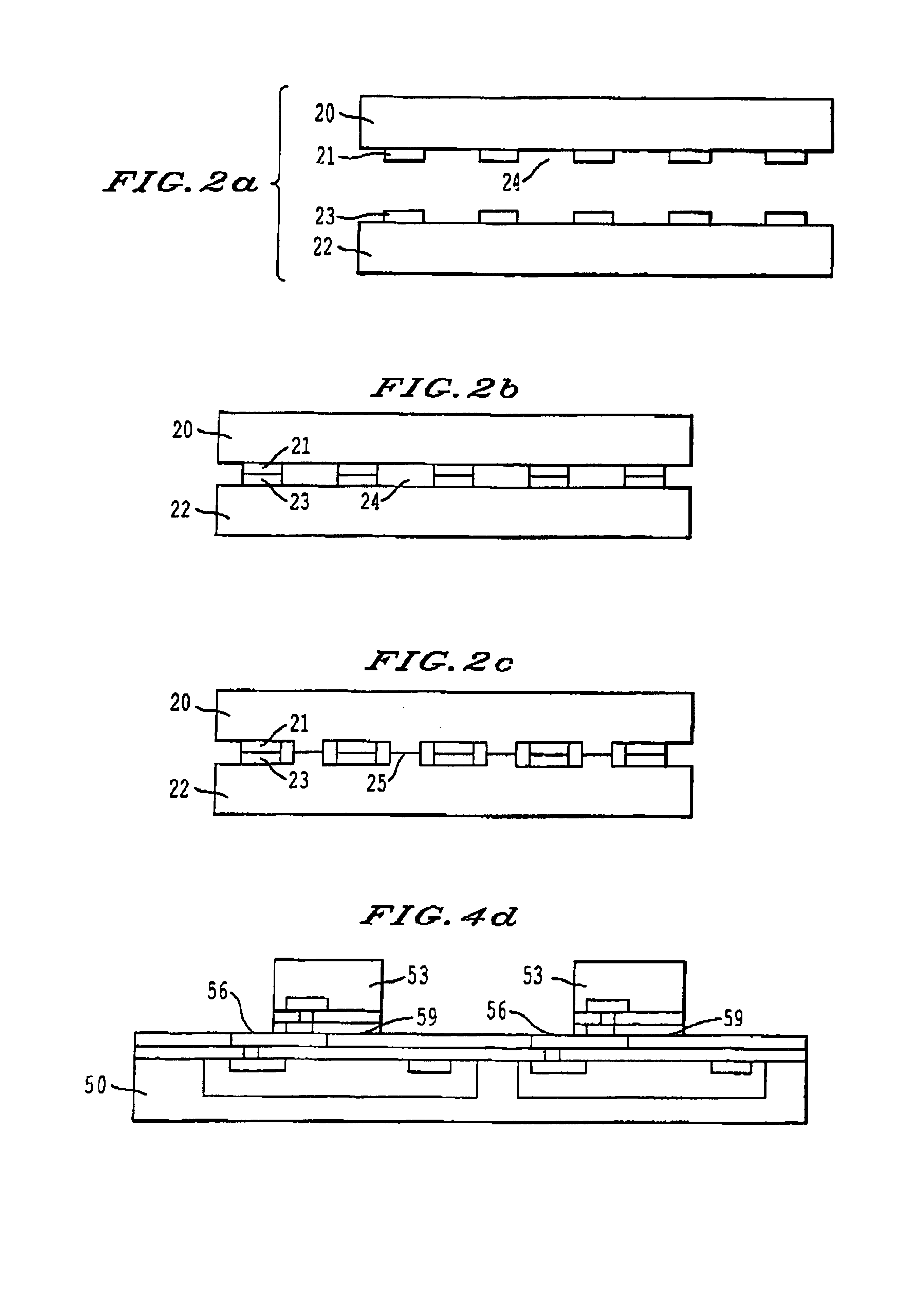

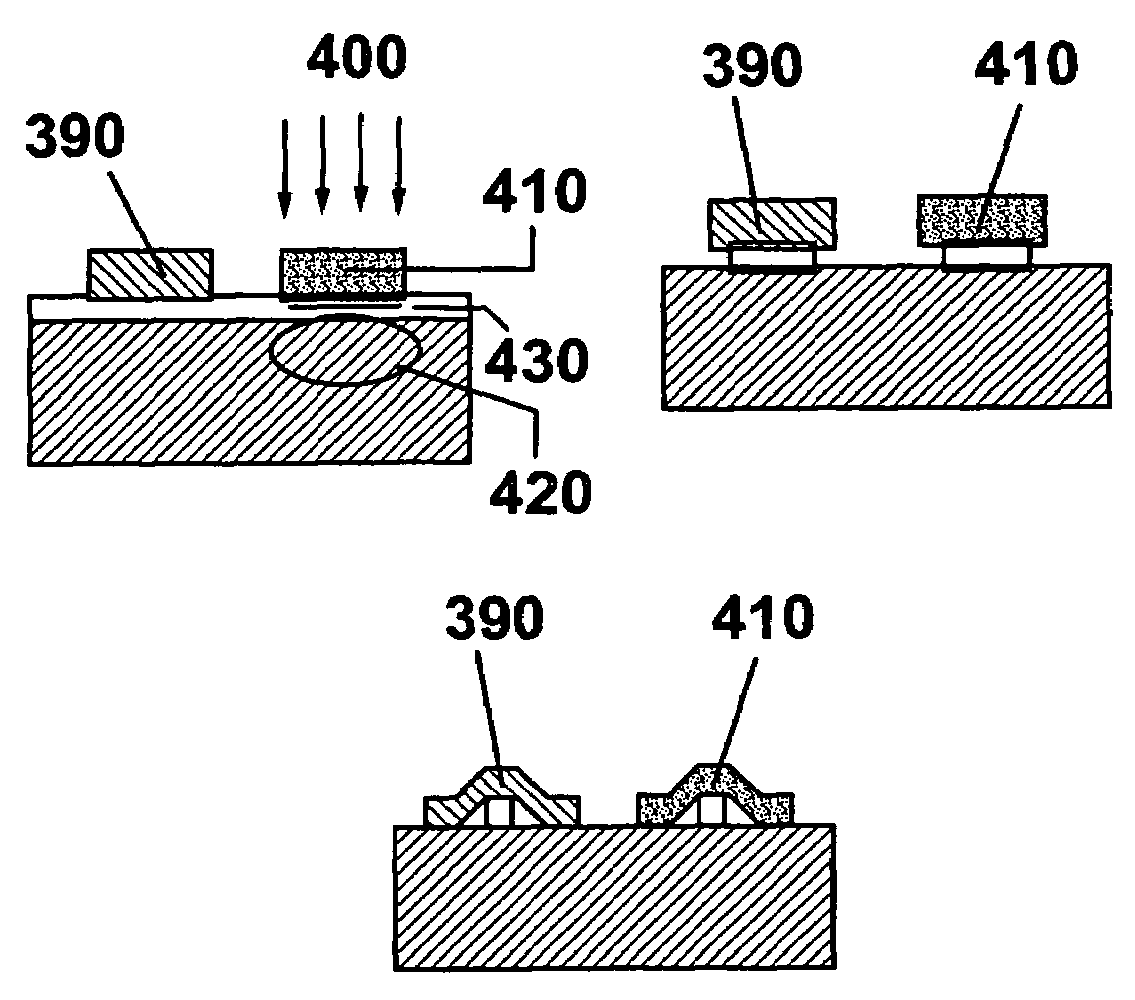

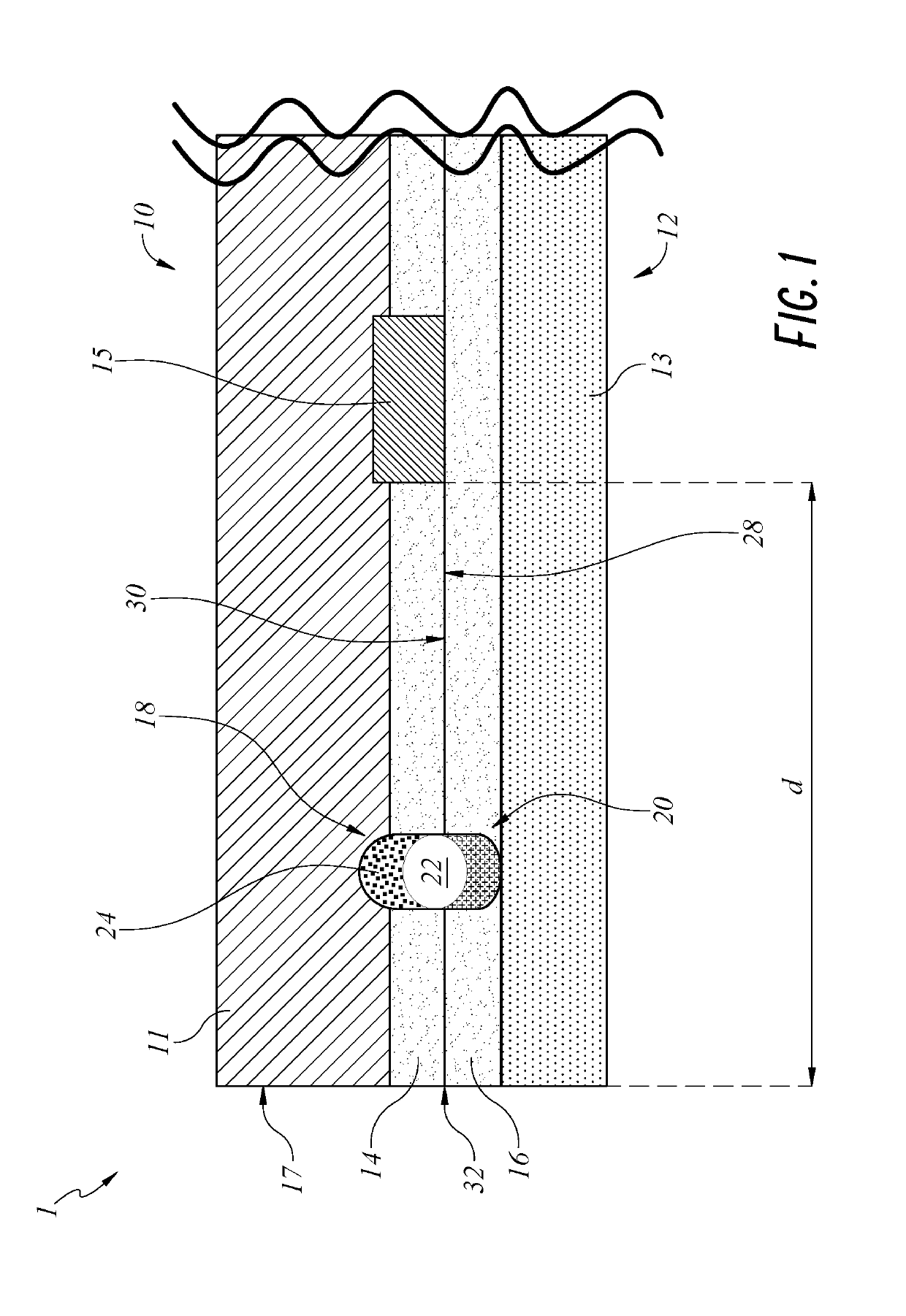

Method for room temperature metal direct bonding

InactiveUS6962835B2Solid-state devicesSemiconductor/solid-state device manufacturingBond interfaceRoom temperature

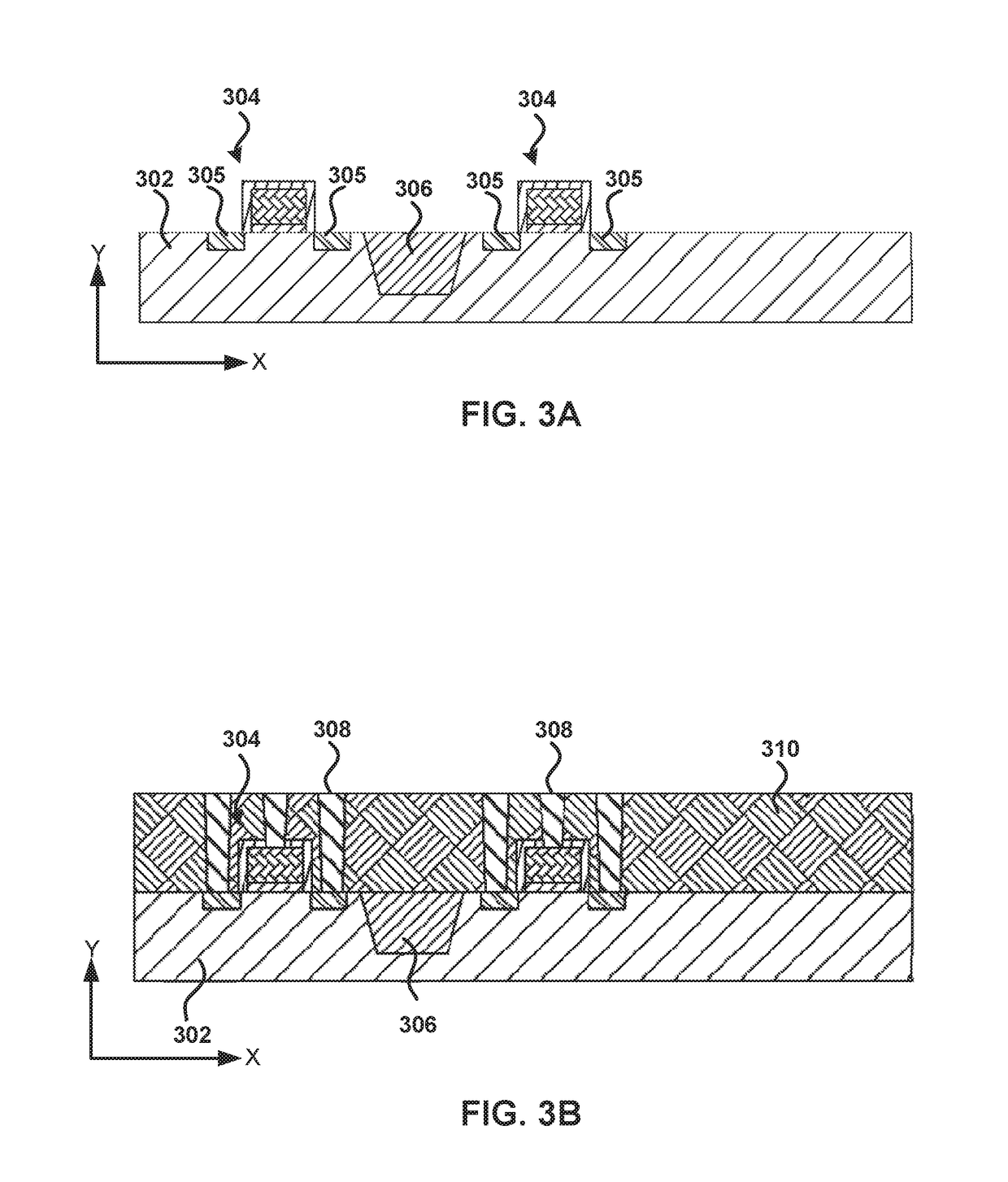

A bonded device structure including a first substrate having a first set of metallic bonding pads, preferably connected to a device or circuit, and having a first non-metallic region adjacent to the metallic bonding pads on the first substrate, a second substrate having a second set of metallic bonding pads aligned with the first set of metallic bonding pads, preferably connected to a device or circuit, and having a second non-metallic region adjacent to the metallic bonding pads on the second substrate, and a contact-bonded interface between the first and second set of metallic bonding pads formed by contact bonding of the first non-metallic region to the second non-metallic region. At least one of the first and second substrates may be elastically deformed.

Owner:INVENSAS BONDING TECH INC

Conductive barrier direct hybrid bonding

ActiveUS20170062366A1Semiconductor/solid-state device detailsSolid-state devicesBond interfaceMetallic bonding

A method for forming a direct hybrid bond and a device resulting from a direct hybrid bond including a first substrate having a first set of metallic bonding pads, preferably connected to a device or circuit, capped by a conductive barrier, and having a first non-metallic region adjacent to the metallic bonding pads on the first substrate, a second substrate having a second set of metallic bonding pads capped by a second conductive barrier, aligned with the first set of metallic bonding pads, preferably connected to a device or circuit, and having a second non-metallic region adjacent to the metallic bonding pads on the second substrate, and a contact-bonded interface between the first and second set of metallic bonding pads capped by conductive barriers formed by contact bonding of the first non-metallic region to the second non-metallic region.

Owner:INVENSAS BONDING TECH INC

Conductive barrier direct hybrid bonding

ActiveUS9953941B2Semiconductor/solid-state device detailsSolid-state devicesBond interfaceMetallic bonding

Owner:INVENSAS BONDING TECH INC

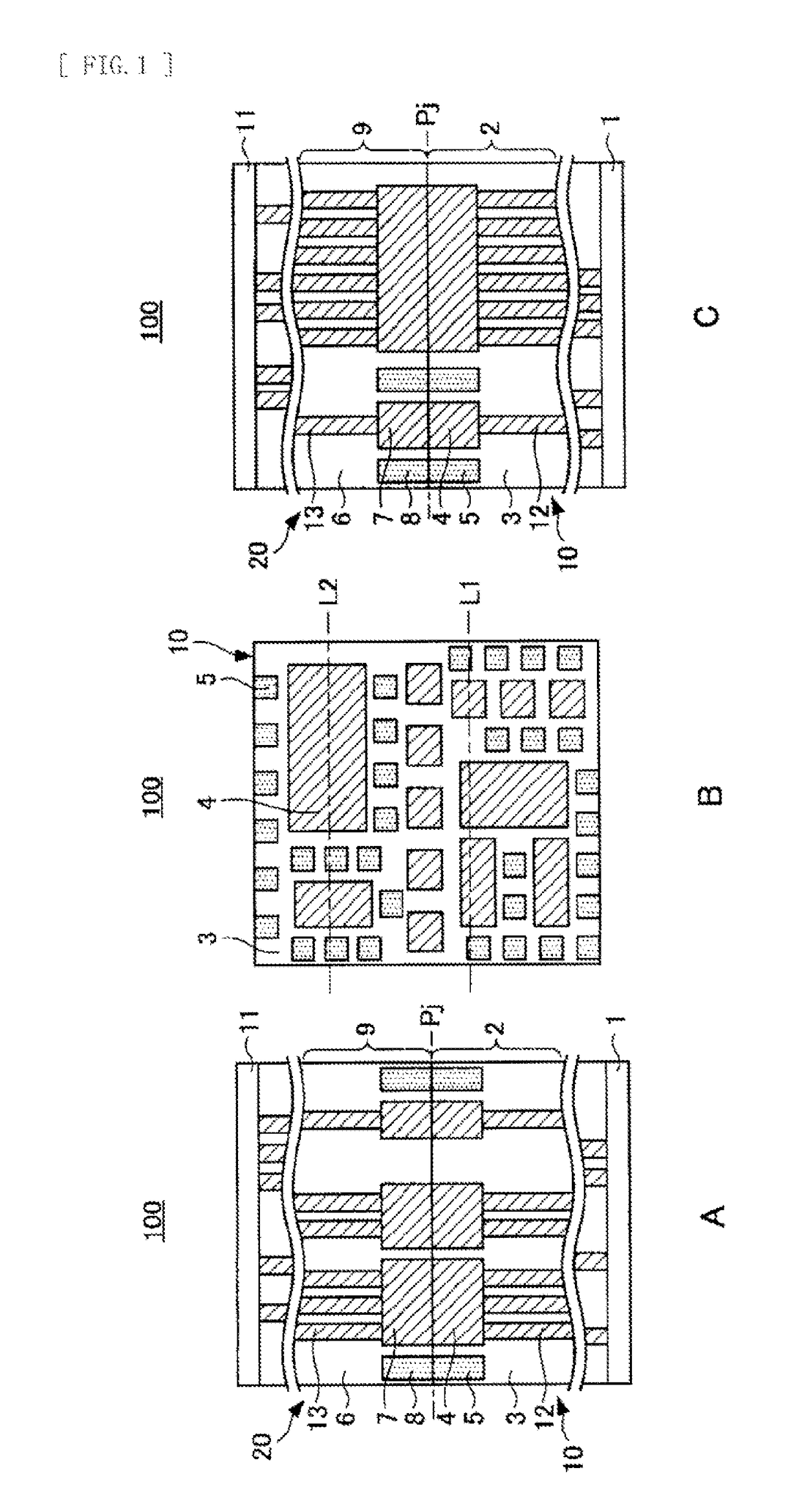

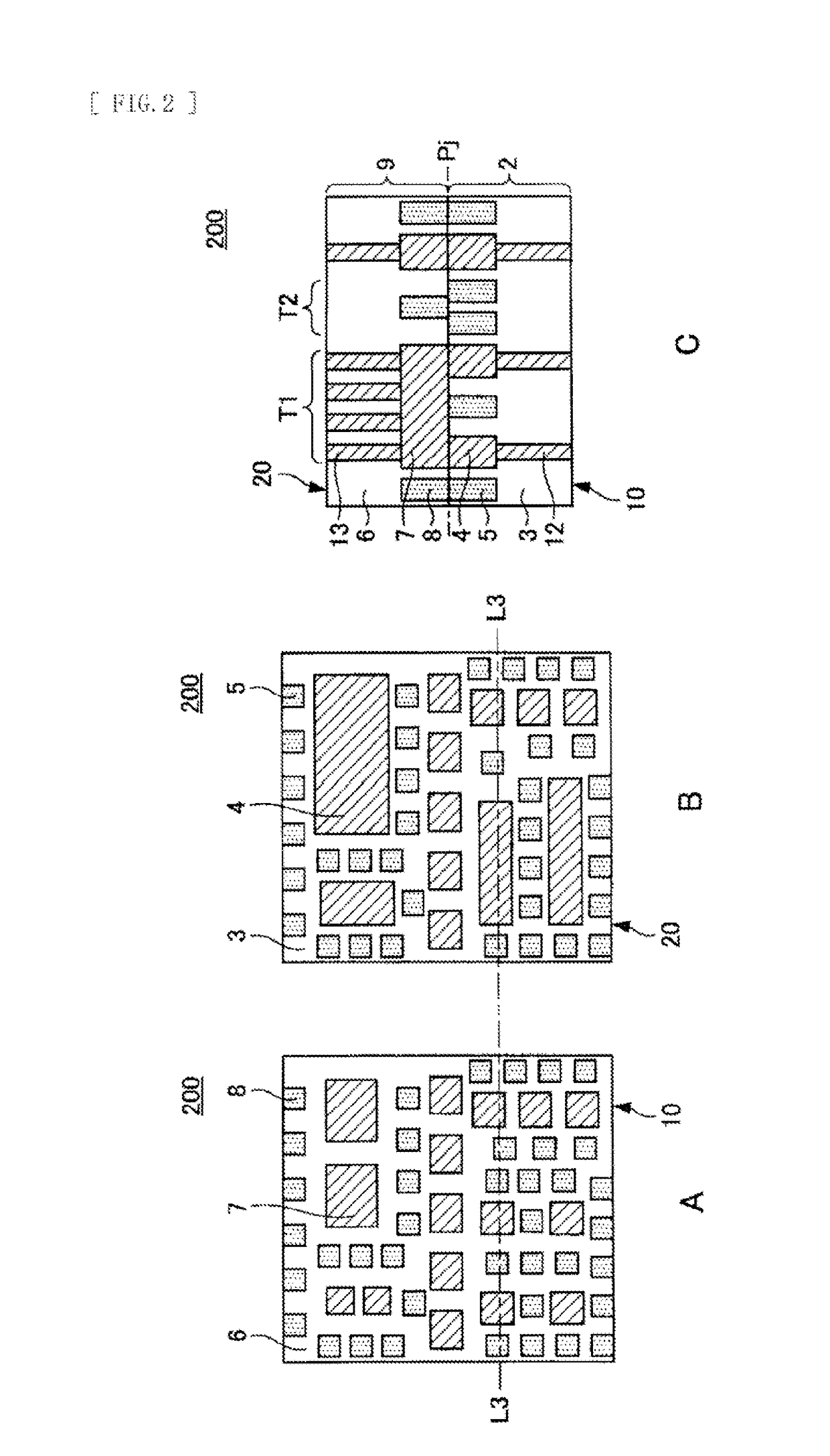

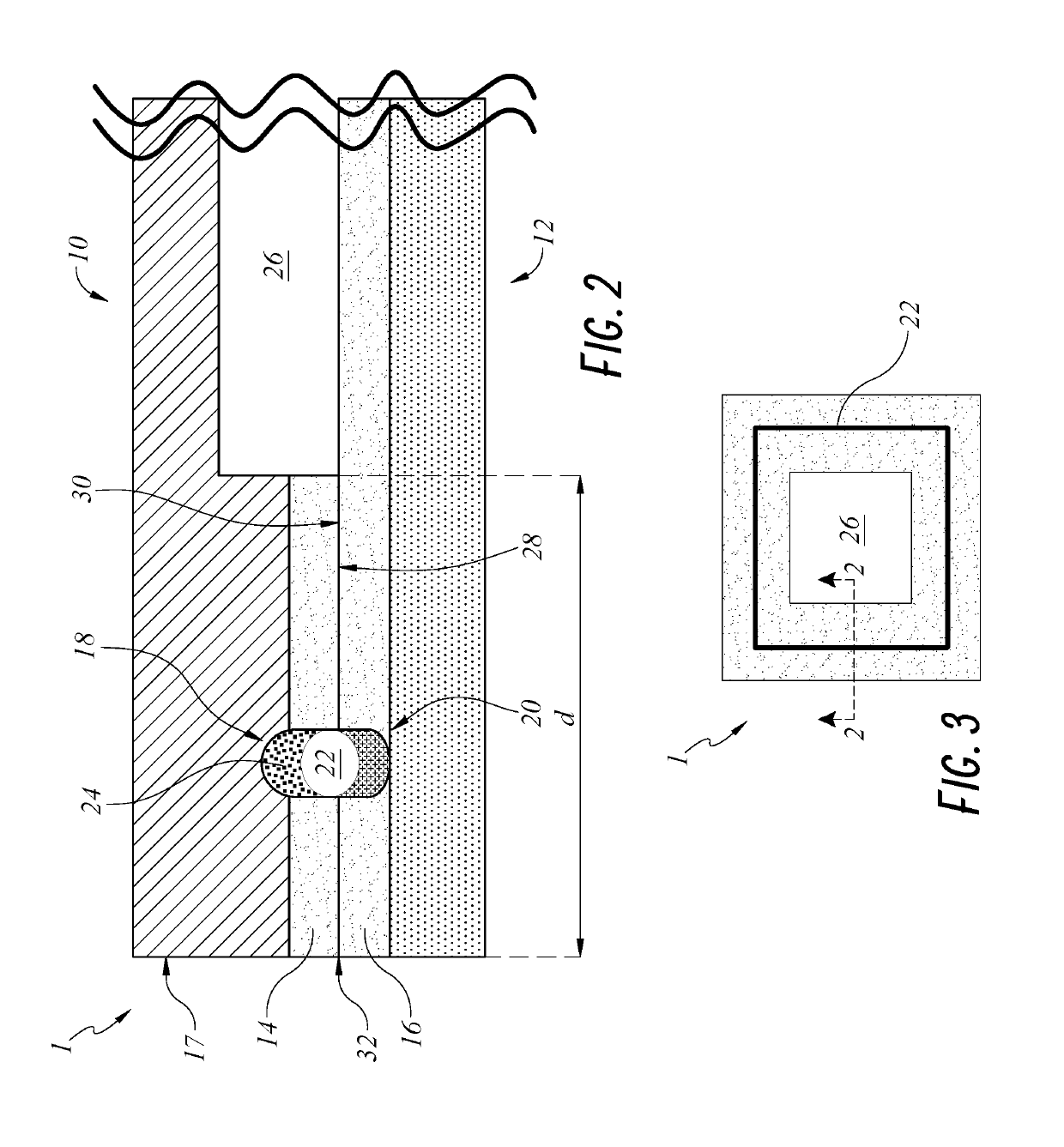

Semiconductor device

ActiveUS9799587B2Improve performanceReliable bonding surfaceSemiconductor/solid-state device detailsSolid-state devicesBond interfaceSemiconductor

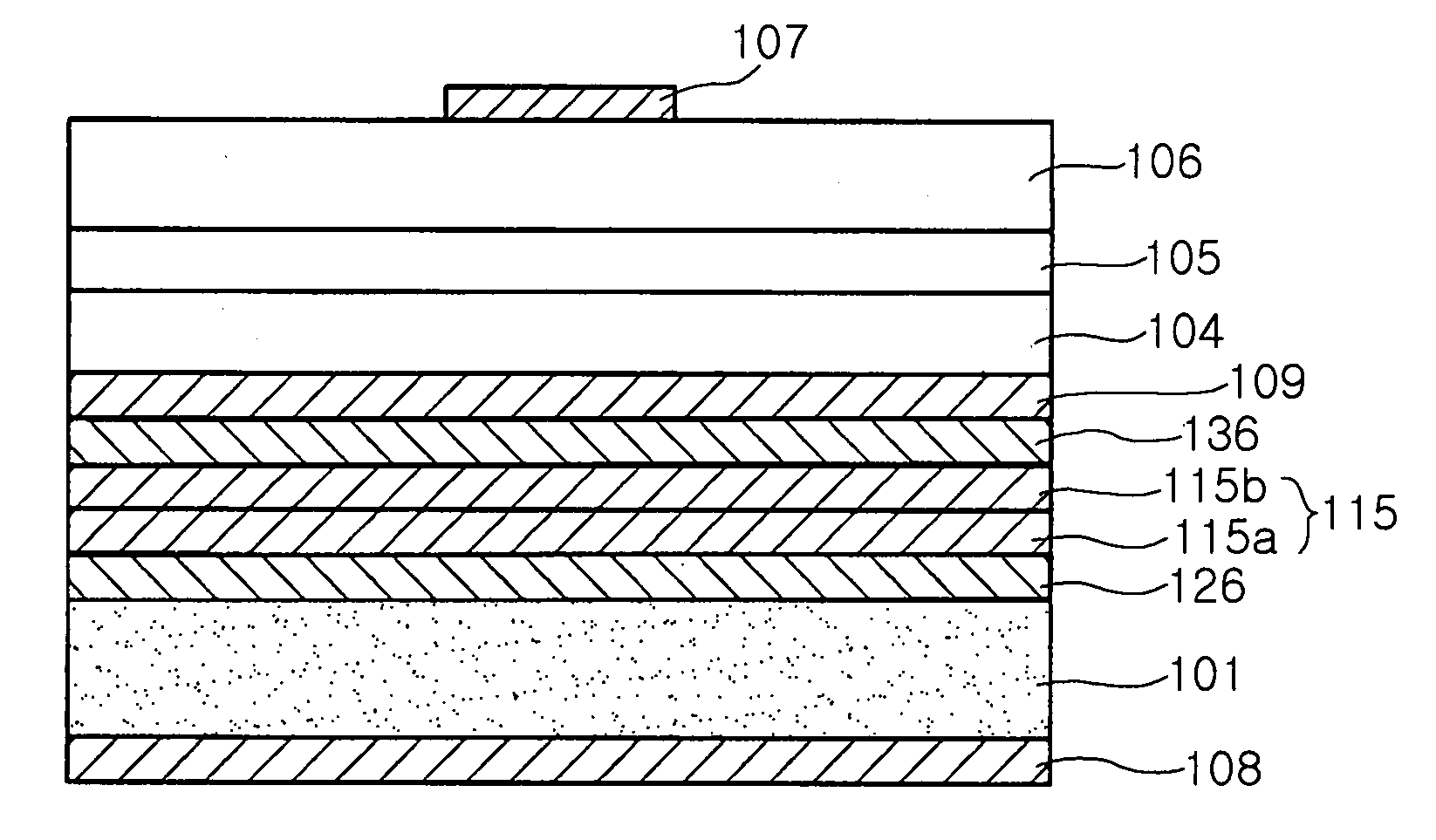

A first semiconductor device includes: a first wiring layer including a first interlayer insulating film, a first electrode pad, and a first dummy electrode, the first electrode pad being embedded in the first interlayer insulating film and having one surface located on same plane as one surface of the first interlayer insulating film, and the first dummy electrode being embedded in the first interlayer insulating film, having one surface located on same plane as the one surface of the first interlayer insulating film, and being disposed around the first electrode pad; and a second wiring layer including a second interlayer insulating film, a second electrode pad, and a second dummy electrode, the second electrode pad being embedded in the second interlayer insulating film, having one surface located on same surface as one surface of the second interlayer insulating film, and being bonded to the first electrode pad, and the second dummy electrode having one surface located on same plane as the surface located closer to the first interlayer insulating film of the second interlayer insulating film, being disposed around the second electrode pad, and being bonded to the first dummy electrode. A second semiconductor device includes: a first semiconductor section including a first electrode, the first electrode being formed on a surface located closer to a bonding interface and extending in a first direction; and a second semiconductor section including a second electrode and disposed to be bonded to the first semiconductor section at the bonding interface, the second electrode being bonded to the first electrode and extending in a second direction that intersects with the first direction.

Owner:SONY CORP

Semiconductor device and preparation method thereof

ActiveCN107658317ASolve the problem of temperature limitAvoid mutual influenceSolid-state devicesSemiconductor devicesPower semiconductor deviceBond interface

The invention discloses a semiconductor device and a preparation method thereof. The semiconductor device sequentially comprises a silicon substrate, one or more NAND strings formed at the upper partof the silicon substrate, one or more peripheral devices formed at the upper parts of the NAND strings, a monocrystal silicon layer formed at the upper parts of the one or more peripheral devices, andone or more first interconnection layers formed between the one or more peripheral devices and between the one or more NAND strings from bottom to top, wherein the peripheral devices are bonded withan array device through a bonding interface. The preparation process that two devices are affected by each other when prepared can be avoided through separating preparation of the array device and theperipheral devices, so that the problem of temperature limitation of preparation of the front layer to preparation of the back layer in the prior art is solved, thereby obtaining good performance ofthe peripheral devices. In addition, the peripheral devices are superposed on the array device, thereby achieving high device density.

Owner:YANGTZE MEMORY TECH CO LTD

Increased contact alignment tolerance for direct bonding

ActiveUS9852988B2Easy temperatureSemiconductor/solid-state device detailsSolid-state devicesBond interfaceParasitic capacitance

Owner:INVENSAS BONDING TECH INC

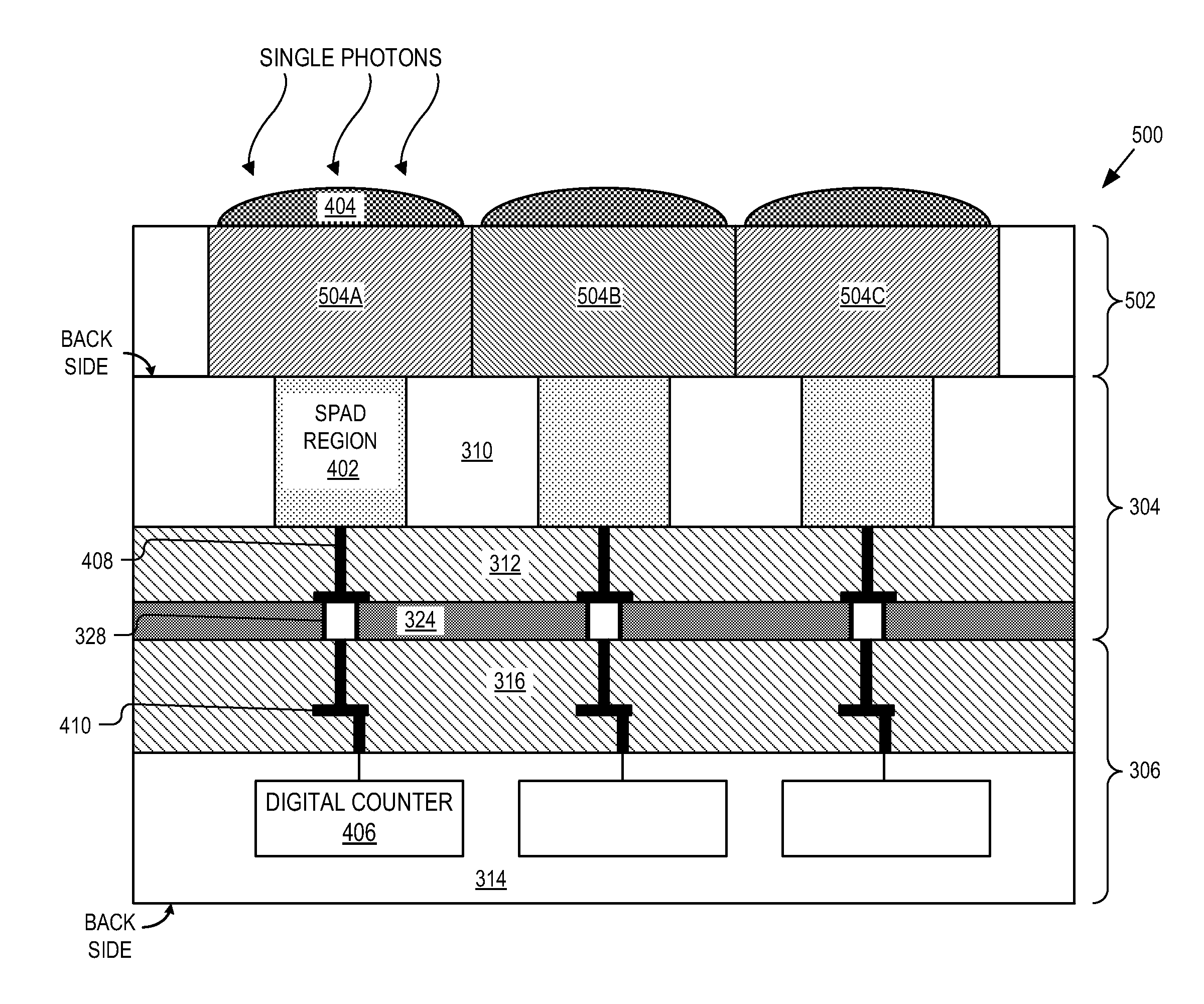

Stacked chip spad image sensor

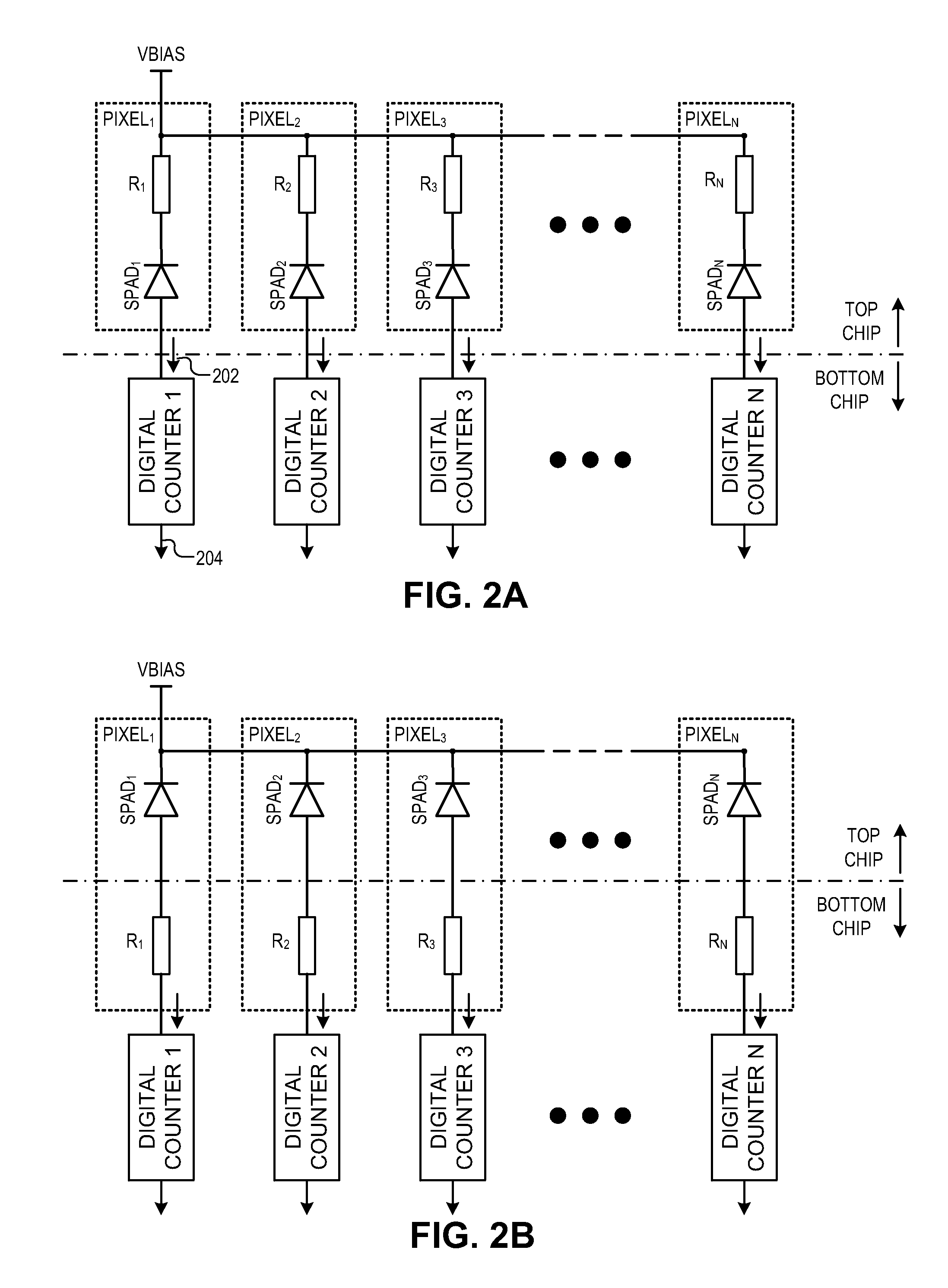

ActiveUS20150115131A1Solid-state devicesMaterial analysis by optical meansSingle-photon avalanche diodeElectrical conductor

An example imaging sensor system includes a Single-Photon Avalanche Diode (SPAD) imaging array formed in a first semiconductor layer of a first wafer. The SPAD imaging array includes an N number of pixels, each including a SPAD region formed in a front side of the first semiconductor layer. The first wafer is bonded to a second wafer at a bonding interface between a first interconnect layer of the first wafer and the second interconnect layer of the second wafer. An N number of digital counters are formed in a second semiconductor layer of the second wafer. Each of the digital counters are configured to count output pulses generated by a respective SPAD region.

Owner:OMNIVISION TECH INC

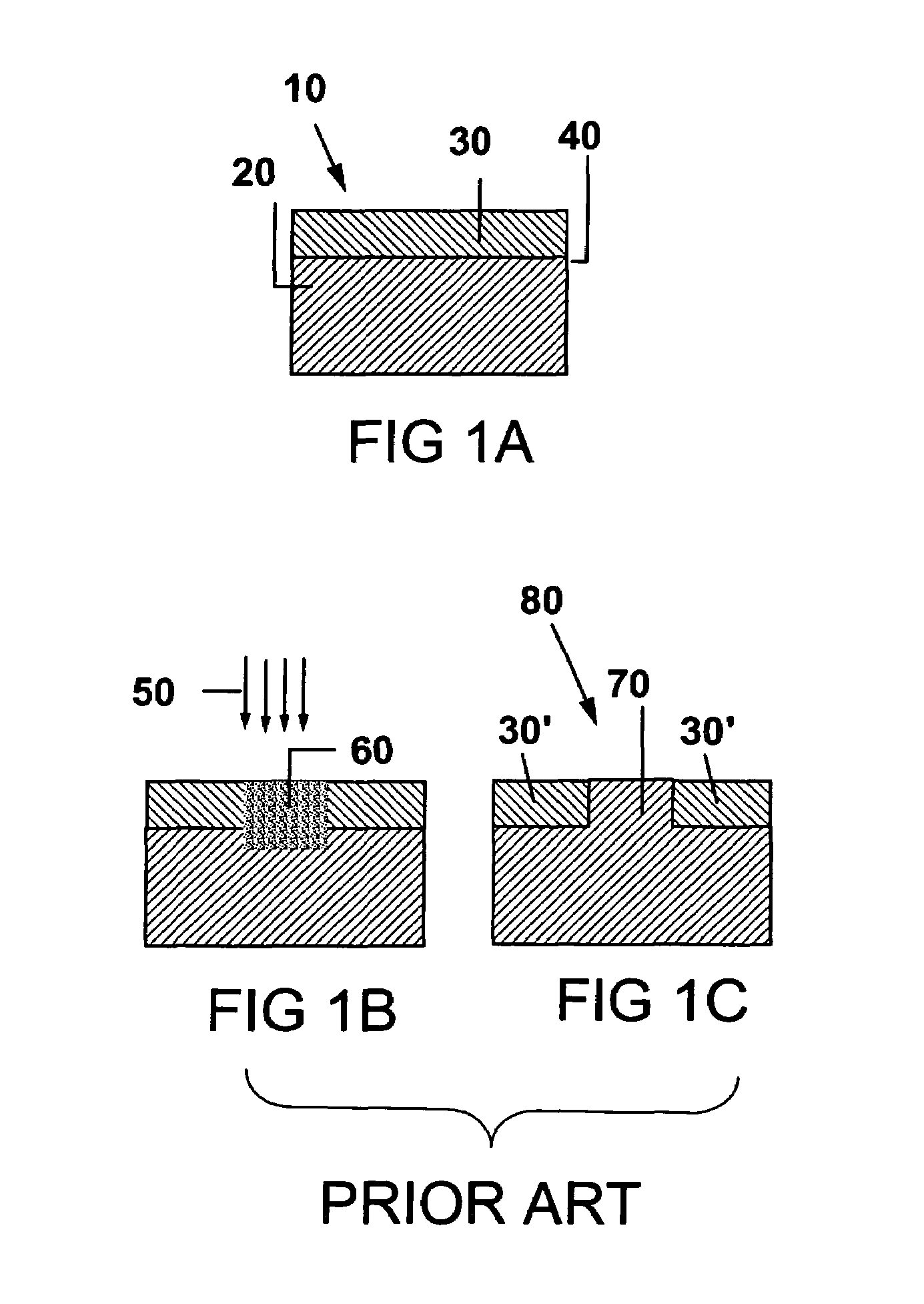

Hybrid orientation substrates by in-place bonding and amorphization/templated recrystallization

InactiveUS7060585B1Free from damageClear interfaceSemiconductor/solid-state device manufacturingBond interfaceElectrical conductor

A method utilizing in-place bonding and amorphization / templated recrystallization (ATR) is provided for making bulk and semiconductor-on-insulator substrates having coplanar semiconductor layers of different crystallographic orientations. First and second semiconductor layers having different orientations are bonded to opposite sides of a sacrificial spacer layer. Selected areas in one of the semiconductor layers are amorphized; in-place bonding is then performed in a wet etch solution to remove the sacrificial layer and leave the semiconductor layers bonded to each other. The amorphized regions are recrystallized across the bonded interface, using the semiconductor on the non-amorphized side of the bonded interface as a template.

Owner:IBM CORP

Three-dimensional memory devices and methods for forming the same

ActiveUS20190081069A1High bonding strengthPromote interdiffusionSemiconductor/solid-state device detailsSolid-state devicesBond interfaceCrystalline silicon

Embodiments of three-dimensional (3D) memory devices and methods for forming the 3D memory devices are disclosed. In an example, a NAND memory device includes a substrate, one or more peripheral devices on the substrate, a plurality of NAND strings above the peripheral devices, a single crystalline silicon layer above and in contact with the NAND strings, and interconnect layers formed between the peripheral devices and the NAND strings. In some embodiments, the NAND memory device includes a bonding interface at which an array interconnect layer contacts a peripheral interconnect layer.

Owner:YANGTZE MEMORY TECH CO LTD

Vertical structure led device and method of manufacturing the same

ActiveUS20080135859A1Preventing crystal defectInhibit the occurrence of cracksSemiconductor/solid-state device manufacturingSemiconductor devicesBond interfaceCompound (substance)

A method of manufacturing a vertical structure light emitting diode device, the method including: sequentially forming a first conductivity type III-V group compound semiconductor layer, an active layer, and a second conductivity type III-V group compound semiconductor layer on a substrate for growth; bonding a conductive substrate to the second conductivity type III-V group compound semiconductor layer; removing the substrate for growth from the first conductivity type III-V group compound semiconductor layer; and forming an electrode on an exposed portion of the first conductive III-V group compound semiconductor layer due to the removing the substrate for growth, wherein the bonding a conductive substrate comprises partially heating a metal bonding layer by applying microwaves to a bonding interface while bringing the metal bonding layer into contact with the bonding interface.

Owner:SAMSUNG ELECTRONICS CO LTD

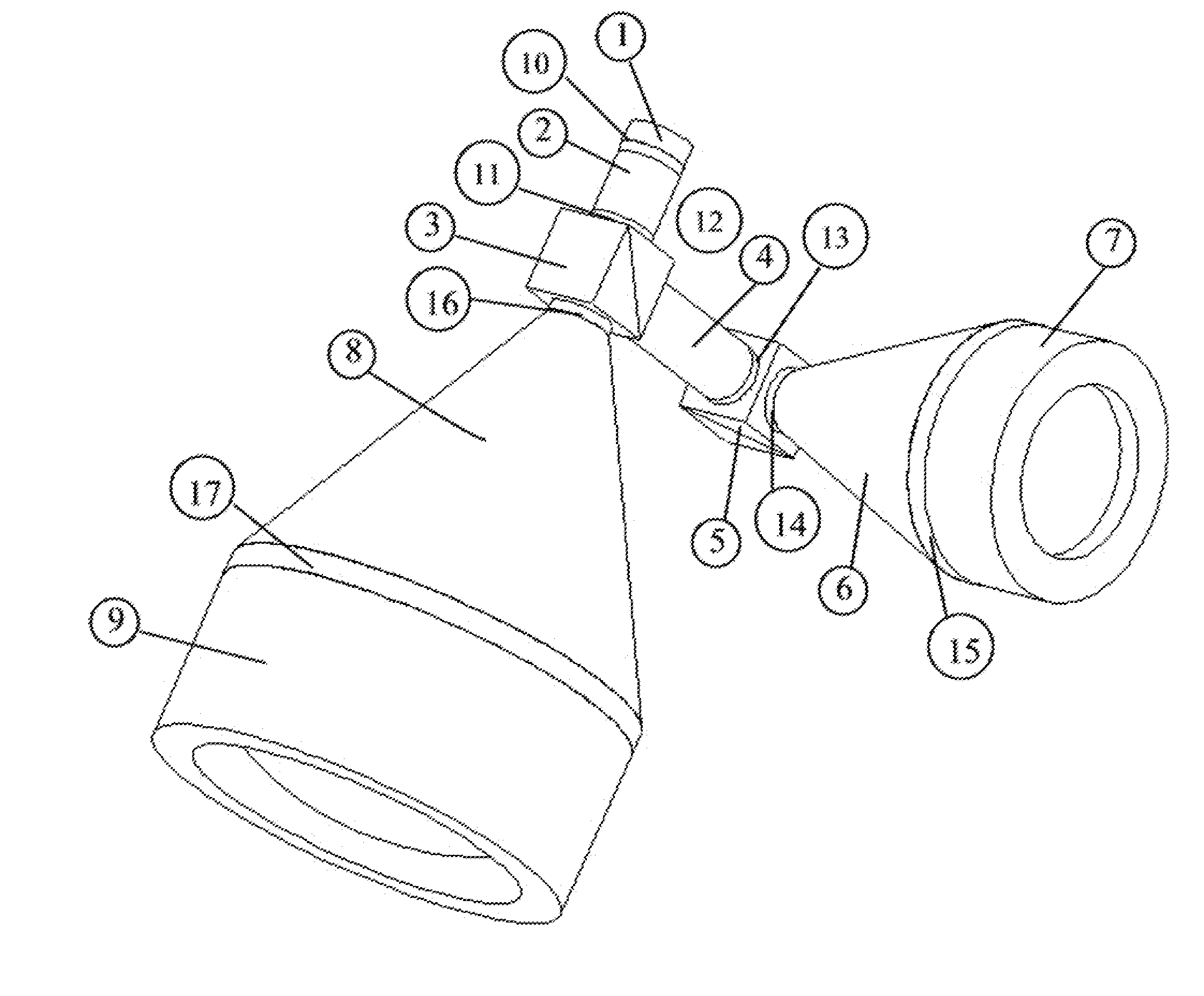

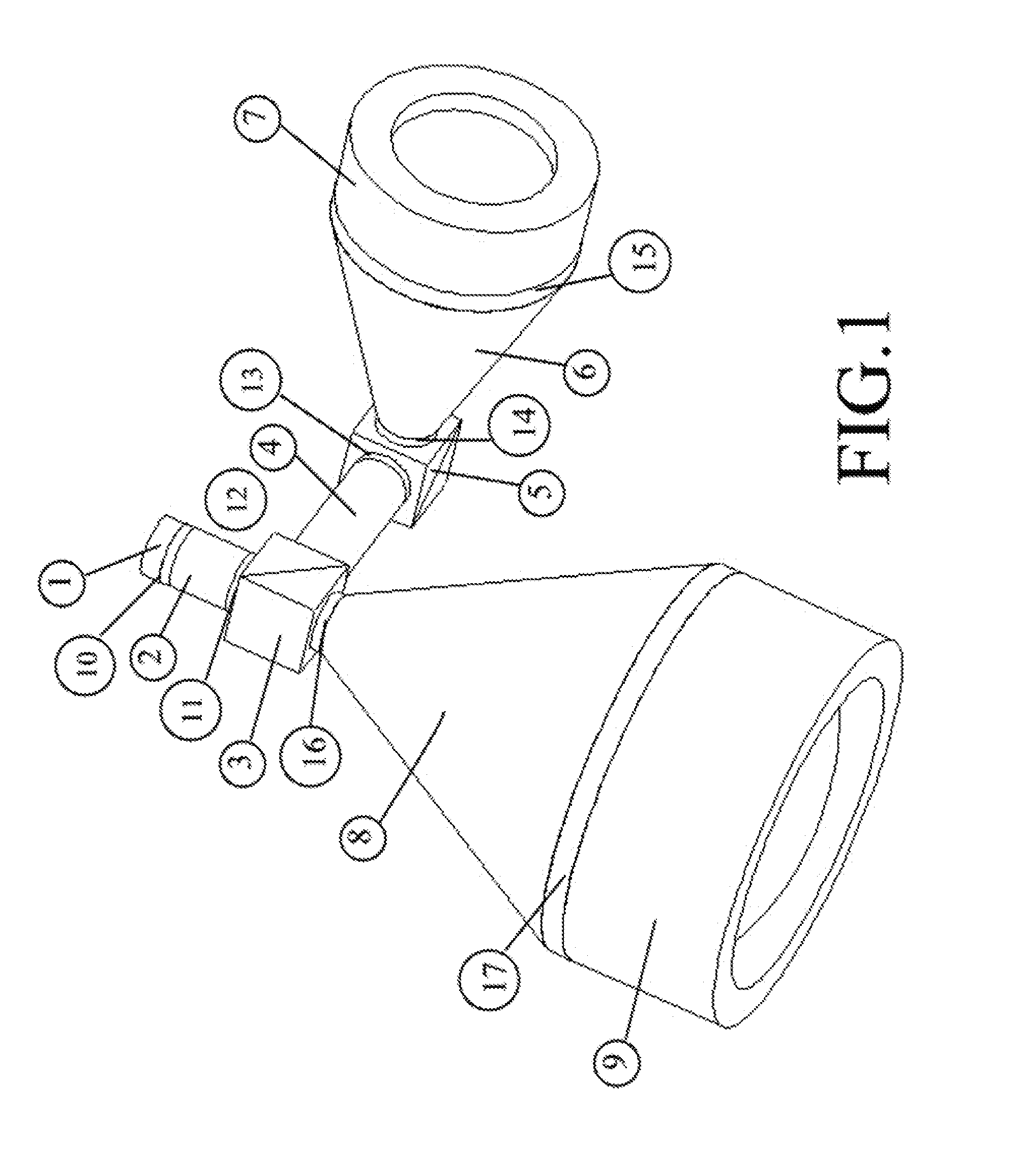

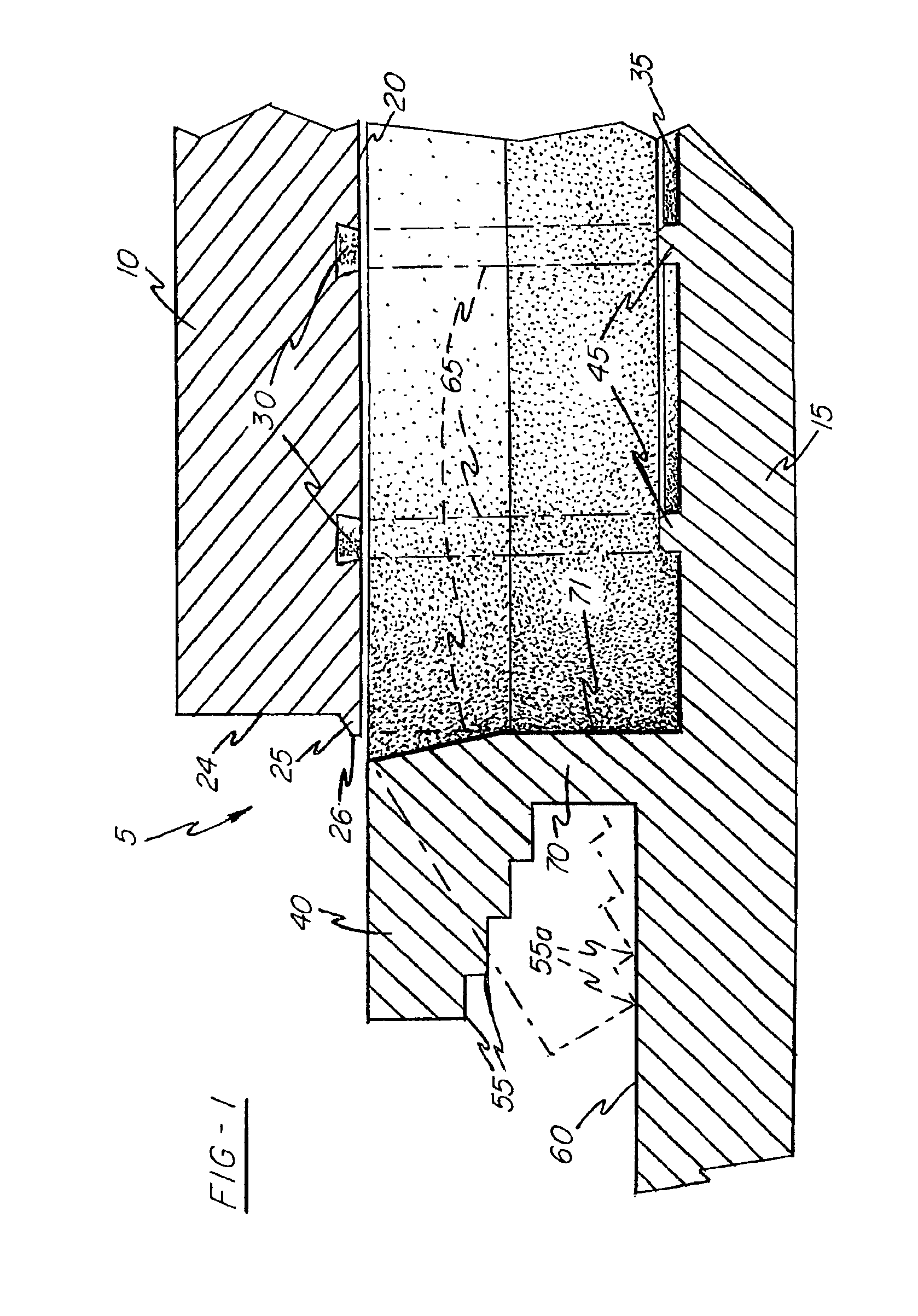

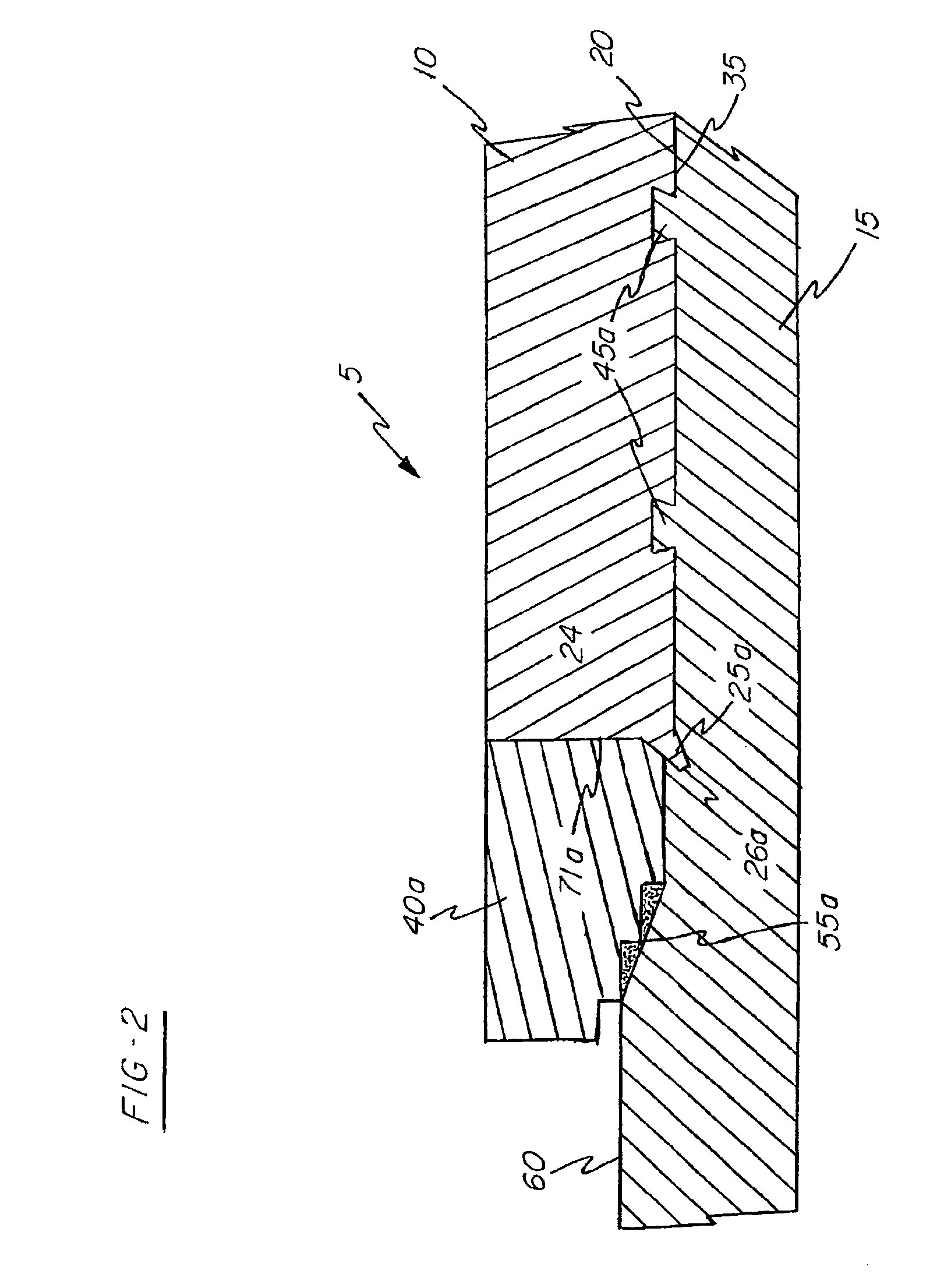

Coefficient of thermal expansion adaptor

InactiveUS20080160274A1Improve accuracyAfter-treatment detailsLamination ancillary operationsBond interfaceThermal expansion

In designing a precision monolithic structure having all discrete components with different Coefficient of Thermal Expansion (CTE) permanently bonded together, to avoid internal stress caused by changing of temperature: The Coefficient of Thermal Expansion (CTE) Adaptor must be bonded between two components having different Coefficient of Thermal Expansion (CTE); the Bonding Interfaces must be parallel; the Coefficient of Thermal Expansion (CTE) Adaptor is made of material having varied CTE, the variation must be gradual and in only one direction, which is perpendicular to the said Bonding Interfaces; at each Bonding Interface, the CTE of the CTE Adaptor must match the CTE of bonding component in certain degree.

Owner:DANG CHI HUNG

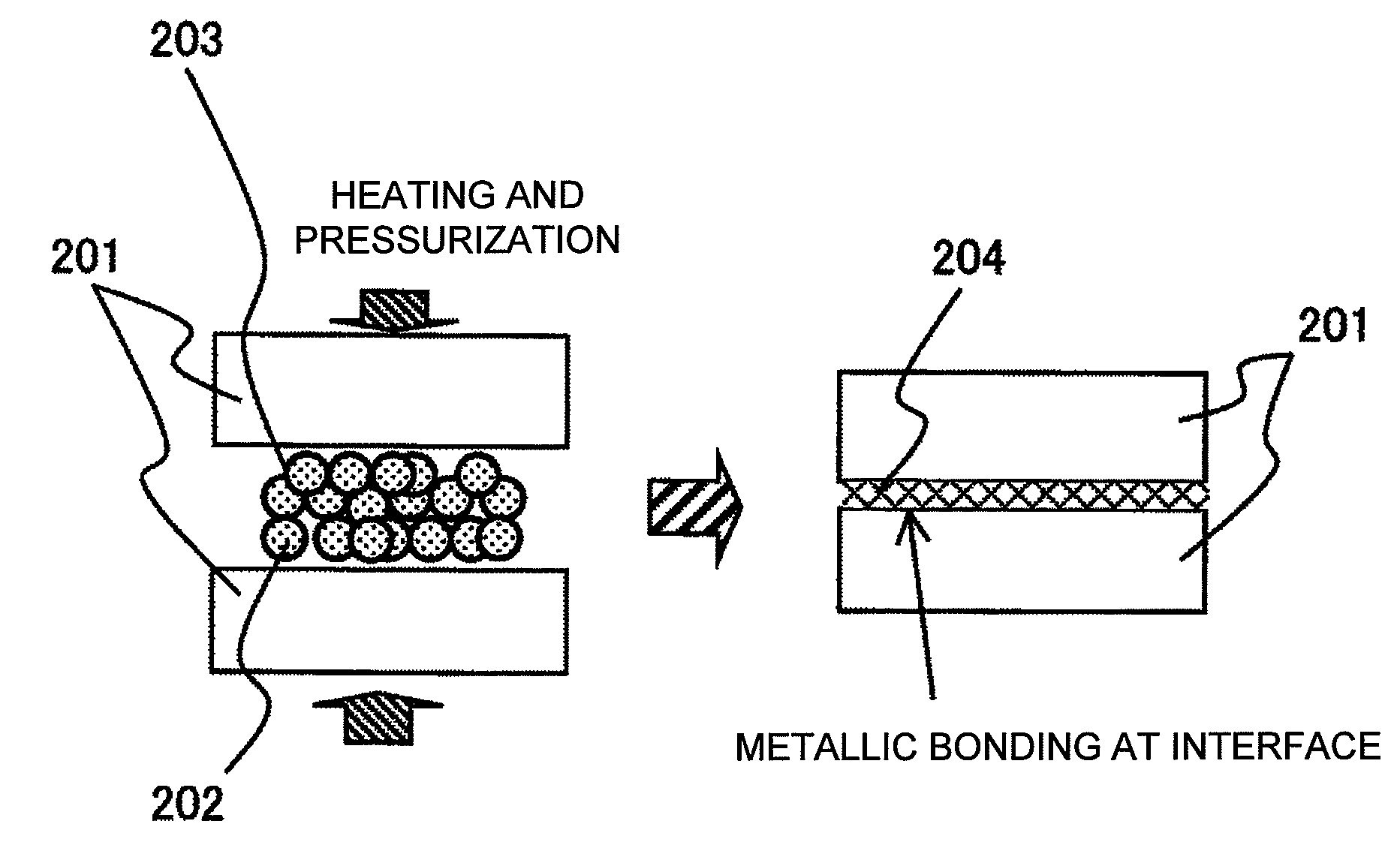

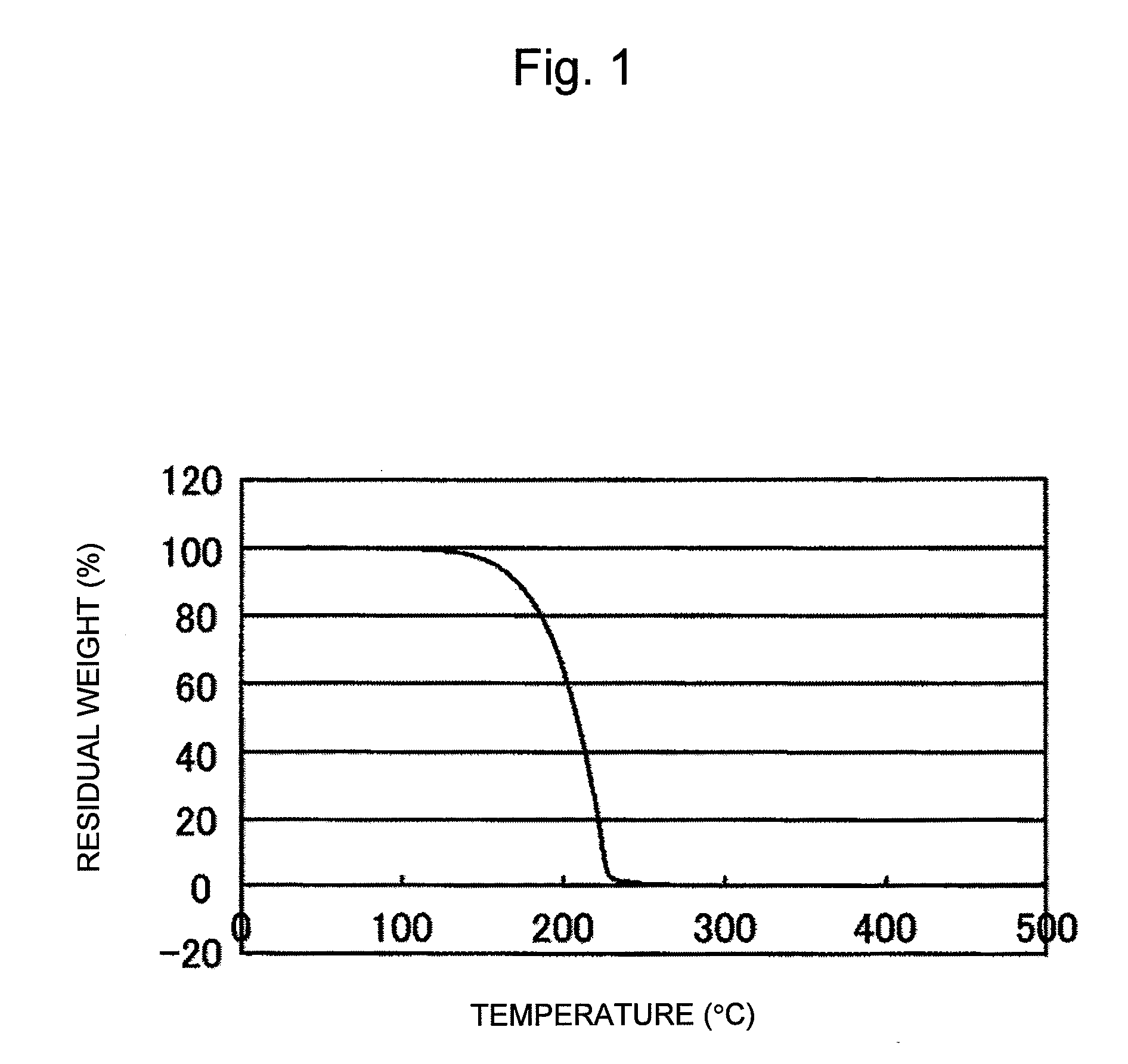

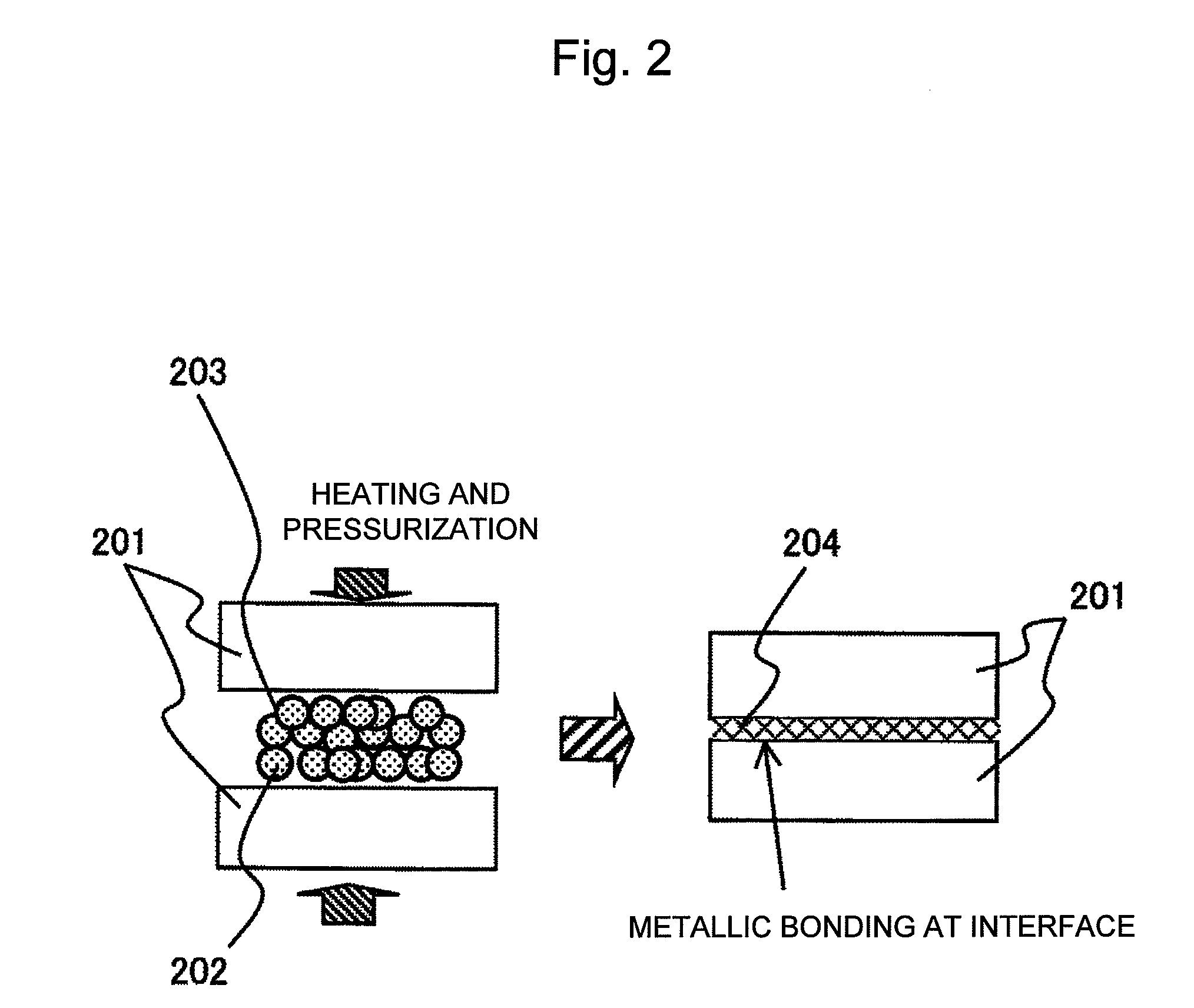

Bonding method and bonding material using metal particle

InactiveUS20080156398A1Semiconductor/solid-state device detailsSolid-state devicesBond interfaceCarboxylic salt

It is an object of this invention to provide a bonding material capable of realizing bonding by metallic bonding at a bonding interface at a lower temperature compared to a bonding material using a metal particle having an average particle diameter of not more than 100 nm and a bonding method. There is provided a bonding material including a metal particle precursor being at least one selected from the group consisting of a particle of a metal oxide, a particle of a metal carbonate, and a particle of a metal carboxylate and having an average particle diameter of 1 nm to 50 μm and a reducing agent composed of an organic substance, wherein the content of the metal particle precursor is more than 50 parts by mass and not more than 99 parts by mass per 100 parts by mass of the bonding material.

Owner:HITACHI LTD

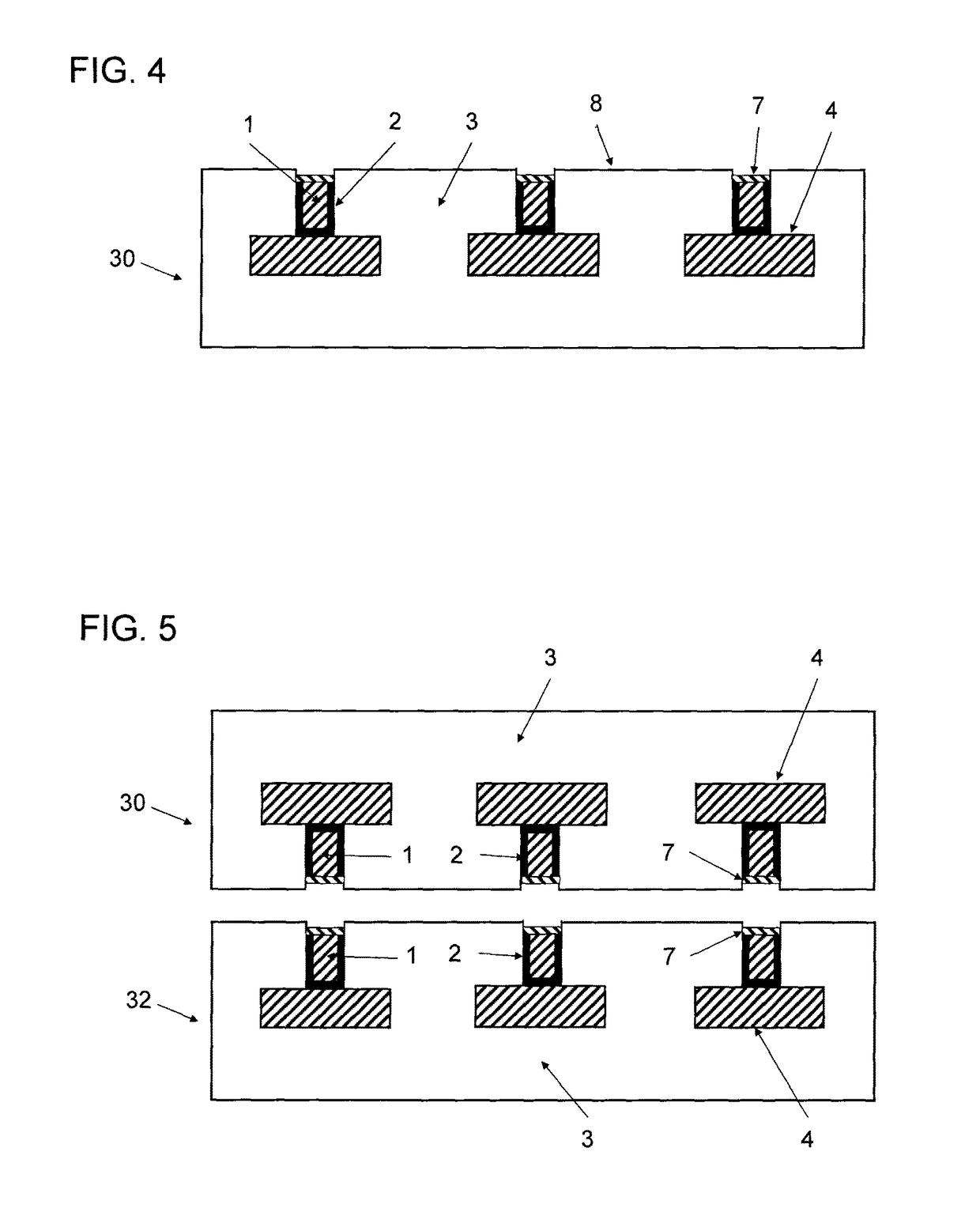

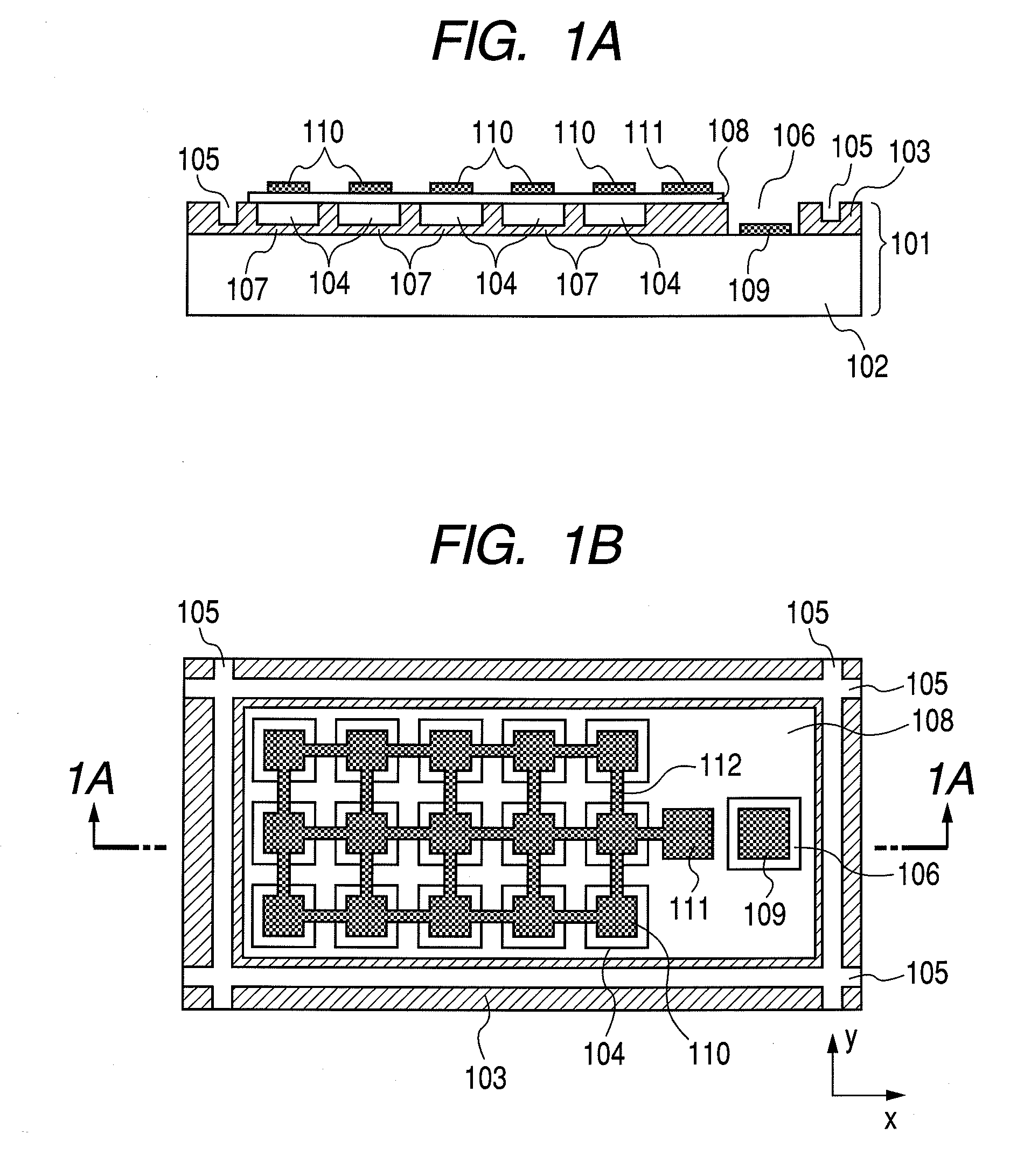

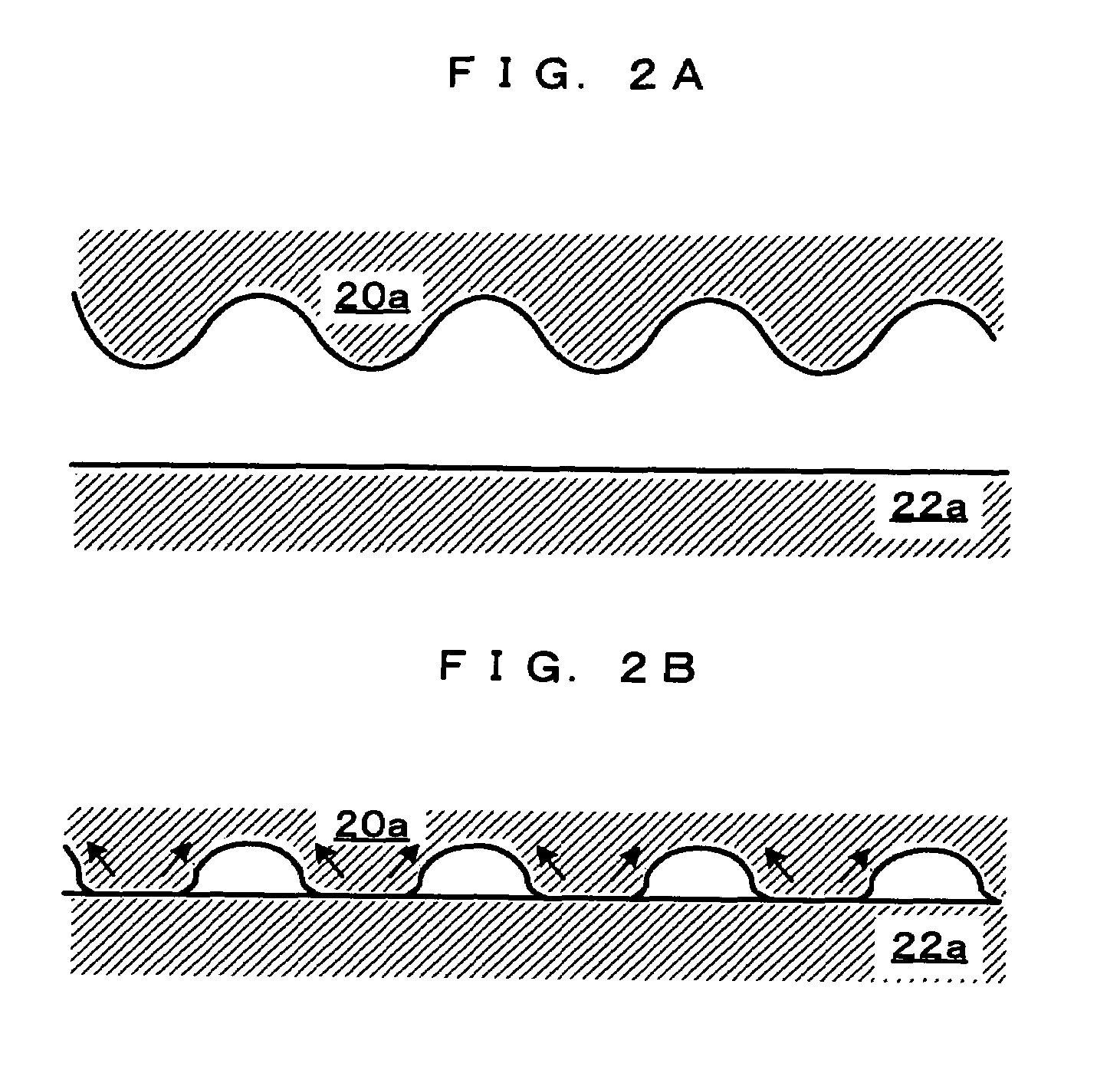

Process for producing capacitive electromechanical conversion device, and capacitive electromechanical conversion device

InactiveUS20110084570A1Poor bondingBeacon systems using ultrasonic/sonic/infrasonic wavesWave amplification devicesBond interfaceEngineering

A process for producing a capacitive electromechanical conversion device by bonding together a substrate and a membrane member to form a cavity sealed between the substrate and the membrane member, the process for producing a capacitive electromechanical conversion device comprises the steps of: providing a gas release path penetrating from a bonded interface between the substrate and the membrane member to the outside, and forming the cavity by bonding the membrane member with the substrate with the gas release path provided; the gas release path being provided at a location where the path does not communicate with the cavity.

Owner:CANON KK

Low temperature sputter target/backing plate method and assembly

InactiveUS7146703B2Firmly connectedSolve the lack of resistanceCellsElectric discharge tubesBond interfaceBond strength

A sputtering target and a backing plate are diffusion-bonded with or without an insert or inserts interposed there-between so as to have a solid phase diffusion-bonded interface. The sputtering target substantially maintains its metallurgical characteristic and properties even though it has been diffusion-bonded to the backing plate. The solid-diffusion bonding of the target and backing plate, is achieved at a low temperature and pressure and results in interdiffusion of constituent atoms to attain high adhesion and bond strength without attendant deterioration or large deformation of the target material, while inhibiting the crystal growth in the target material. The bond undergoes no abrupt decrease in bond strength upon elevation of the service temperature. One hundred percent bonding is achieved with non-bonded portions such as pores left along the interface.

Owner:TOSOH SMD

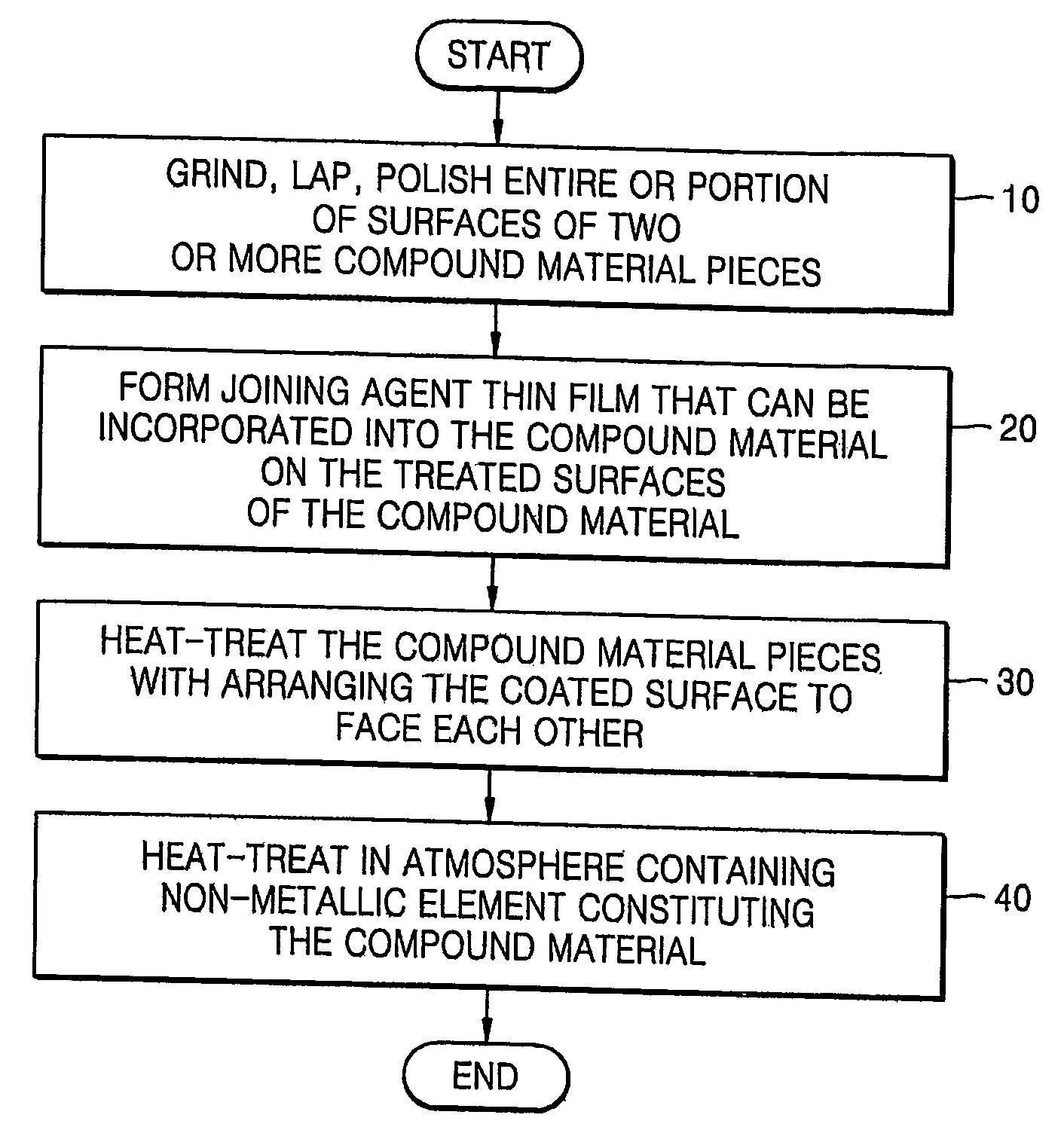

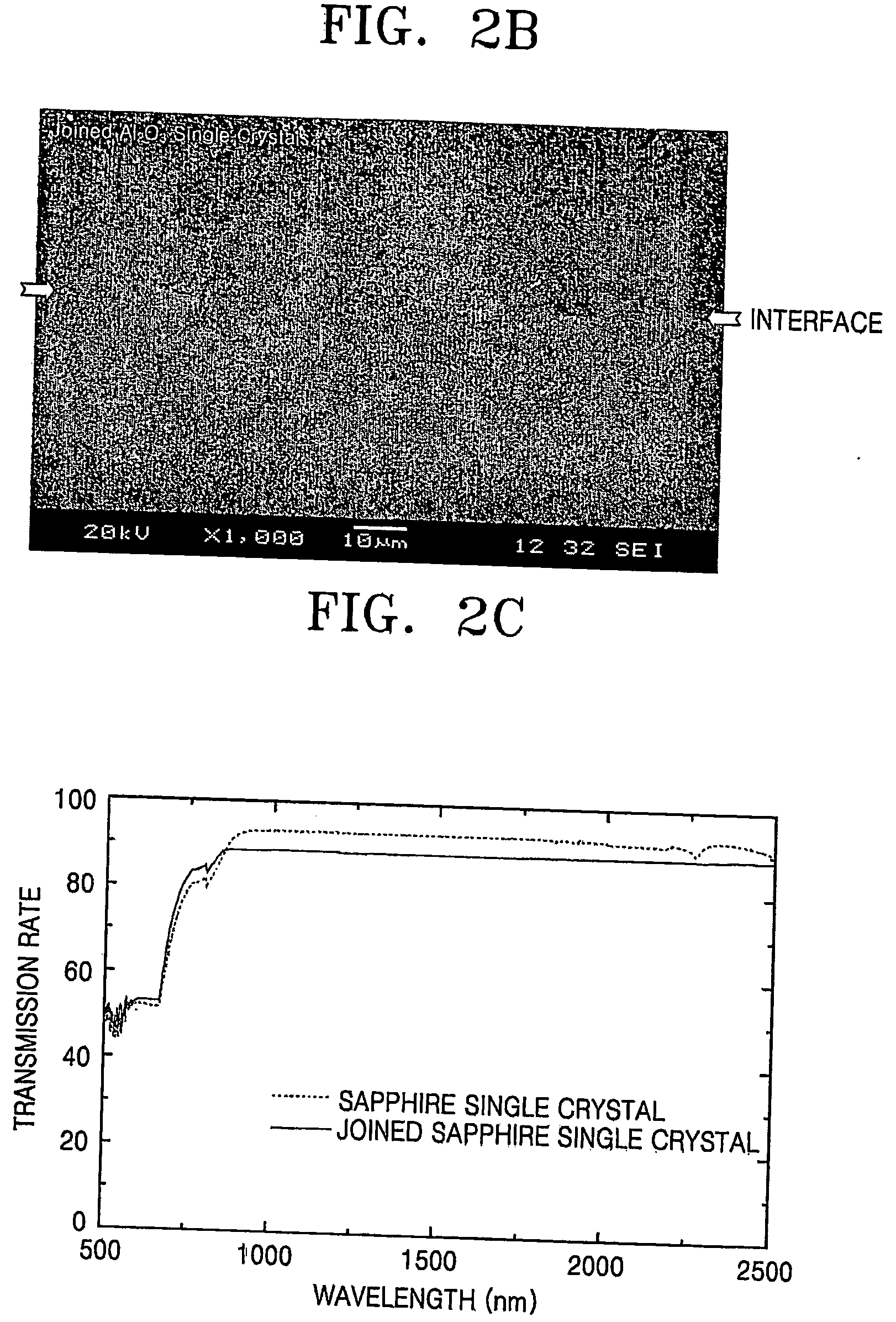

Method of joining ceramics: reaction diffusion-bonding

InactiveUS20060162849A1Suitable characteristicMaintain structural integrityAfter-treatment detailsLamination ancillary operationsBond interfaceSolid solution

Provided is a method of joining compound materials such as ceramics. The method is a combination of diffusion bonding and reaction bonding, which is called reaction diffusion bonding (RDB). The method includes: grinding, lapping, or polishing entire or portions of surfaces to be joined of two or more pieces of a compound material; forming a thin film of a joining agent on one or more of the ground, lapped, or polished surfaces by one of inserting, spreading, depositing, plating, and coating, the joining agent being able to transform into the compound material by being incorporated into the compound material or by forming a solid solution with the compound material upon heat treating; and forming a directly bonded interface without a second phase by heat treating the pieces of the compound material with the to-be-joined surfaces on which the joining agent film is formed arranged to face each other, wherein the joining agent thin film is composed of a material selected from the group consisting of metals, metal organics, and metal compounds.

Owner:CERAWEL

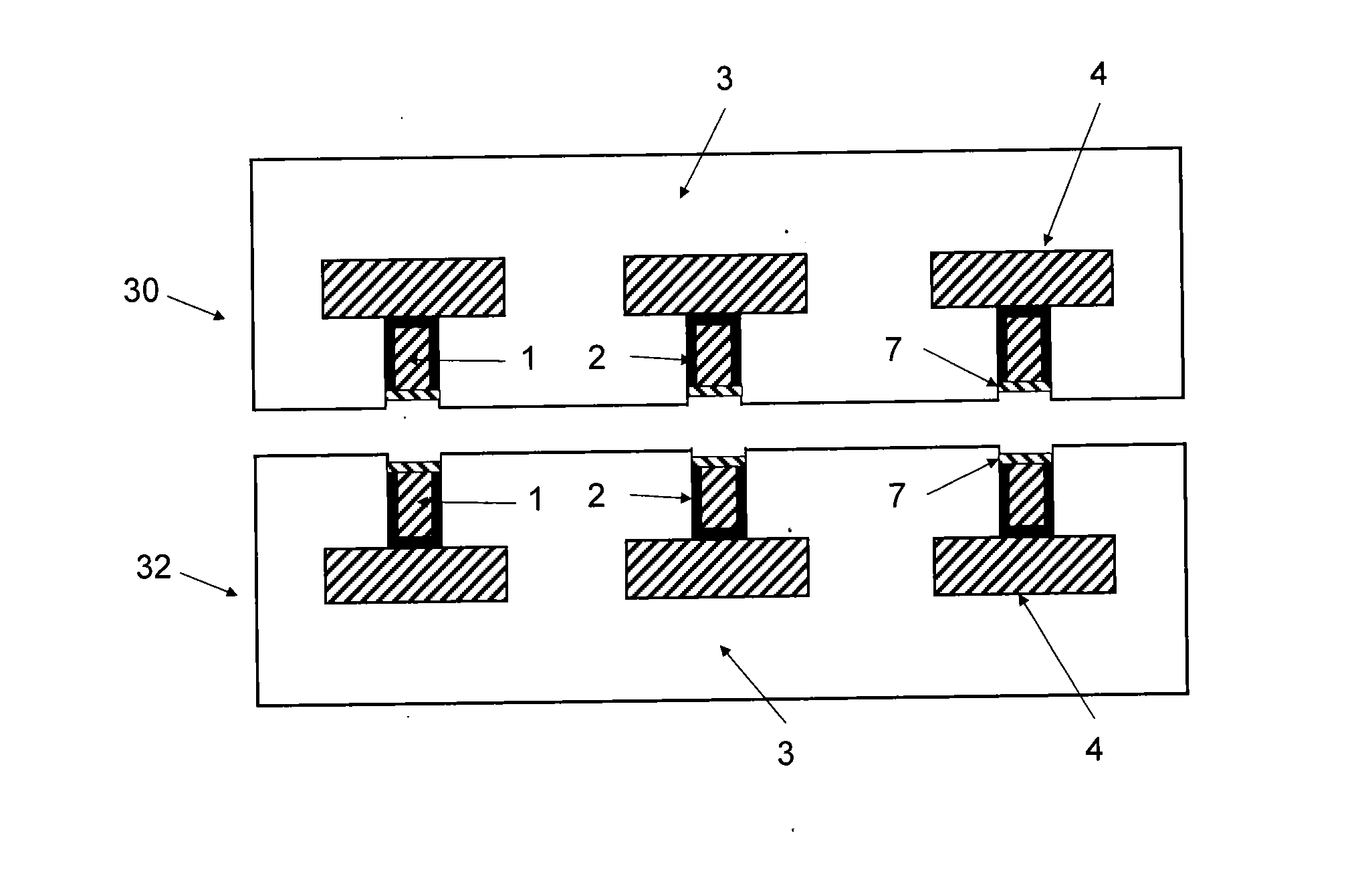

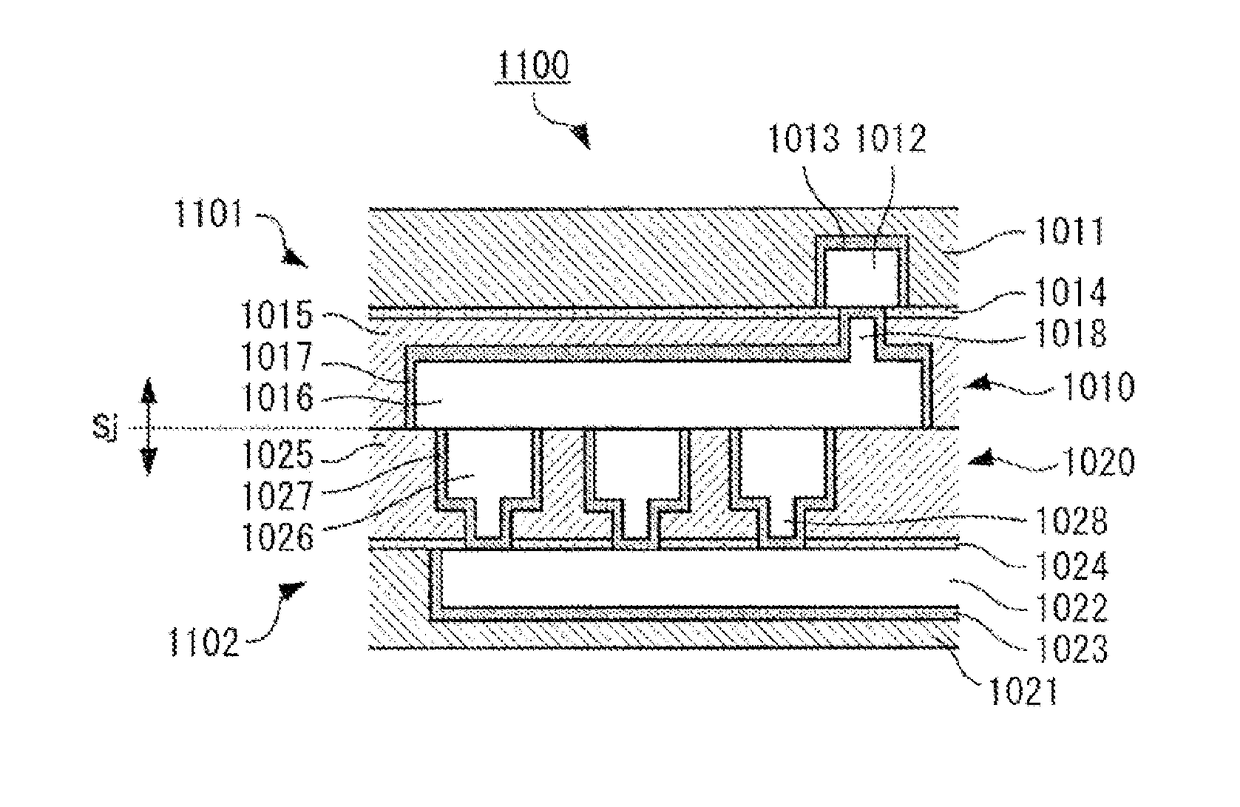

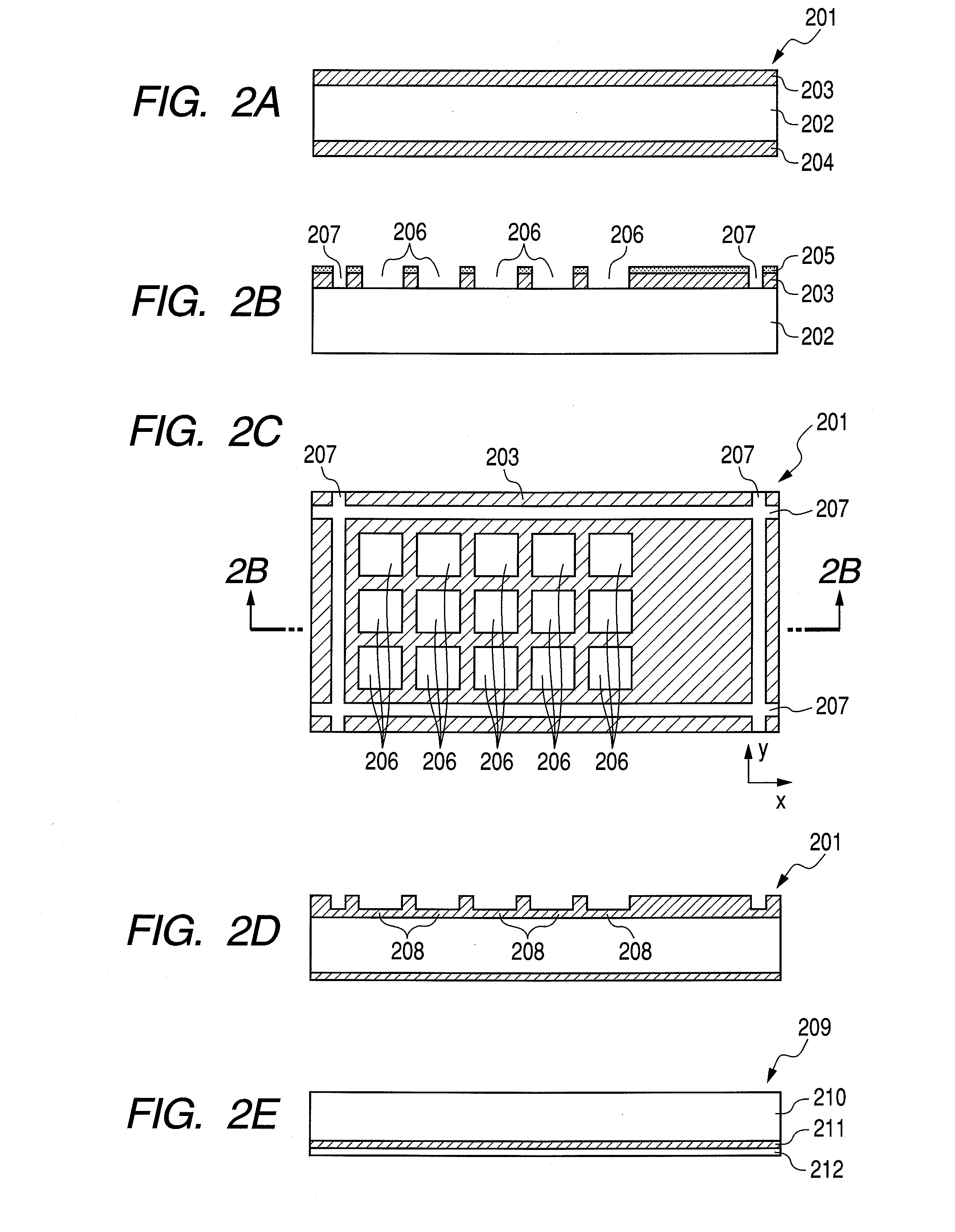

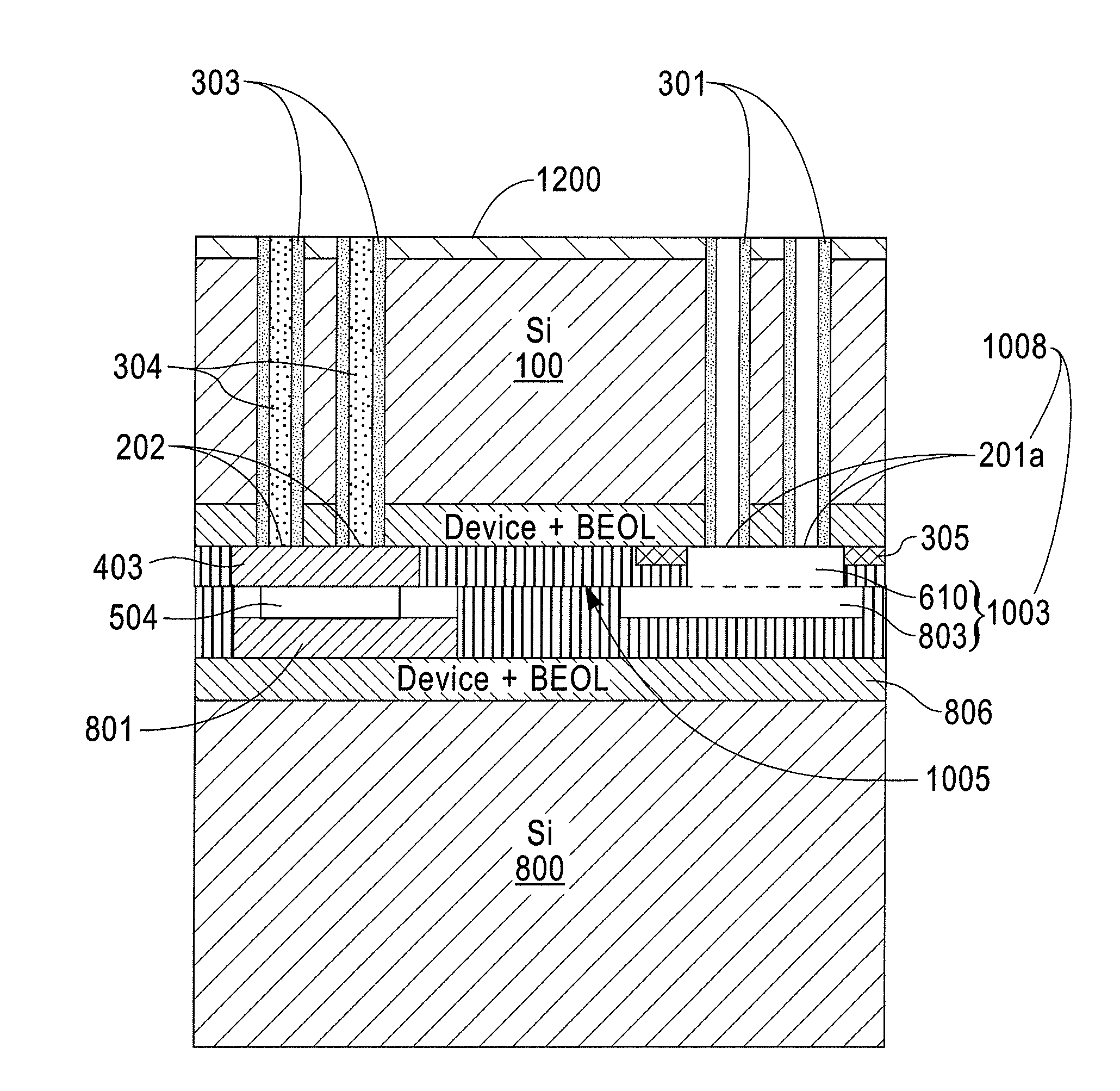

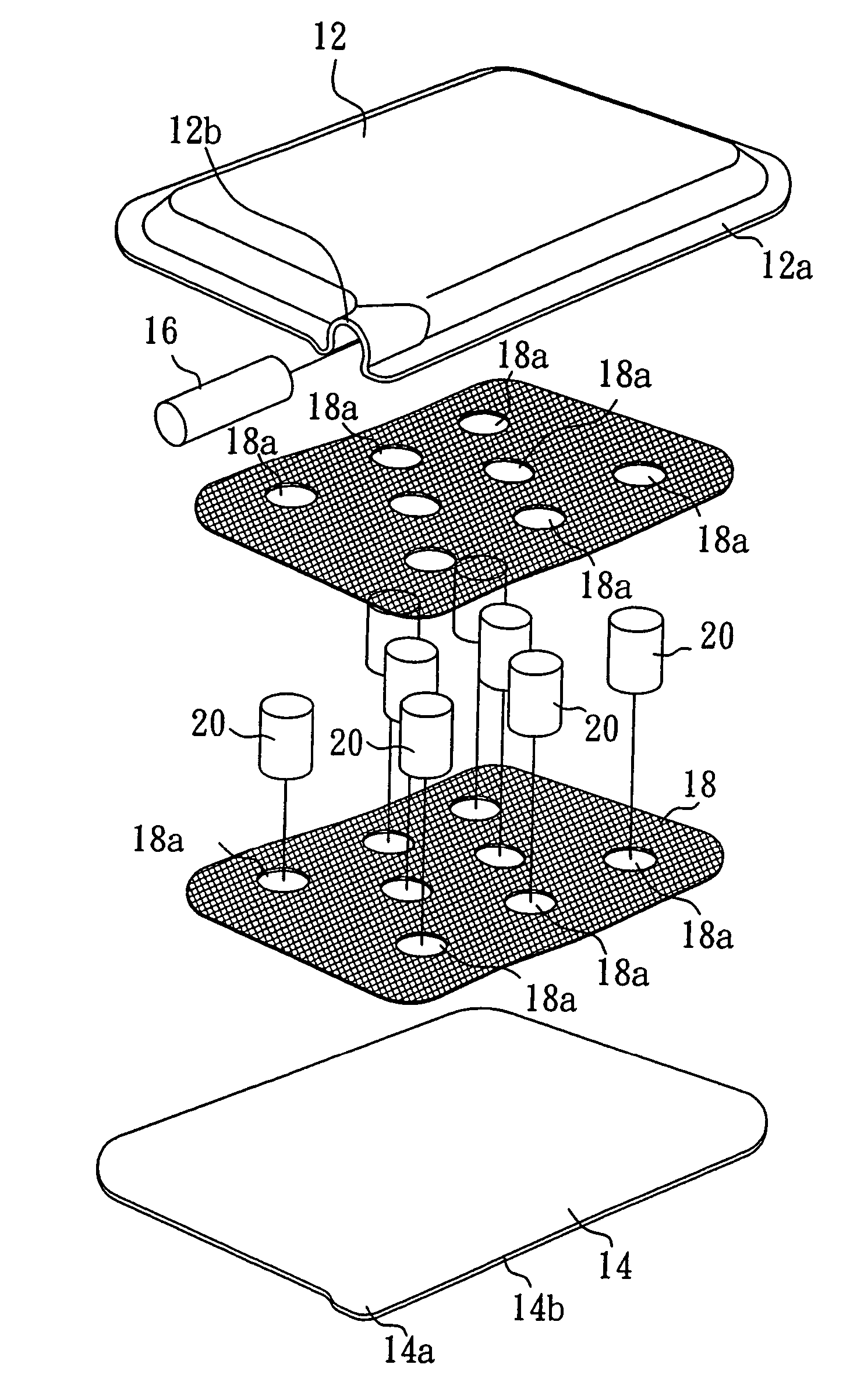

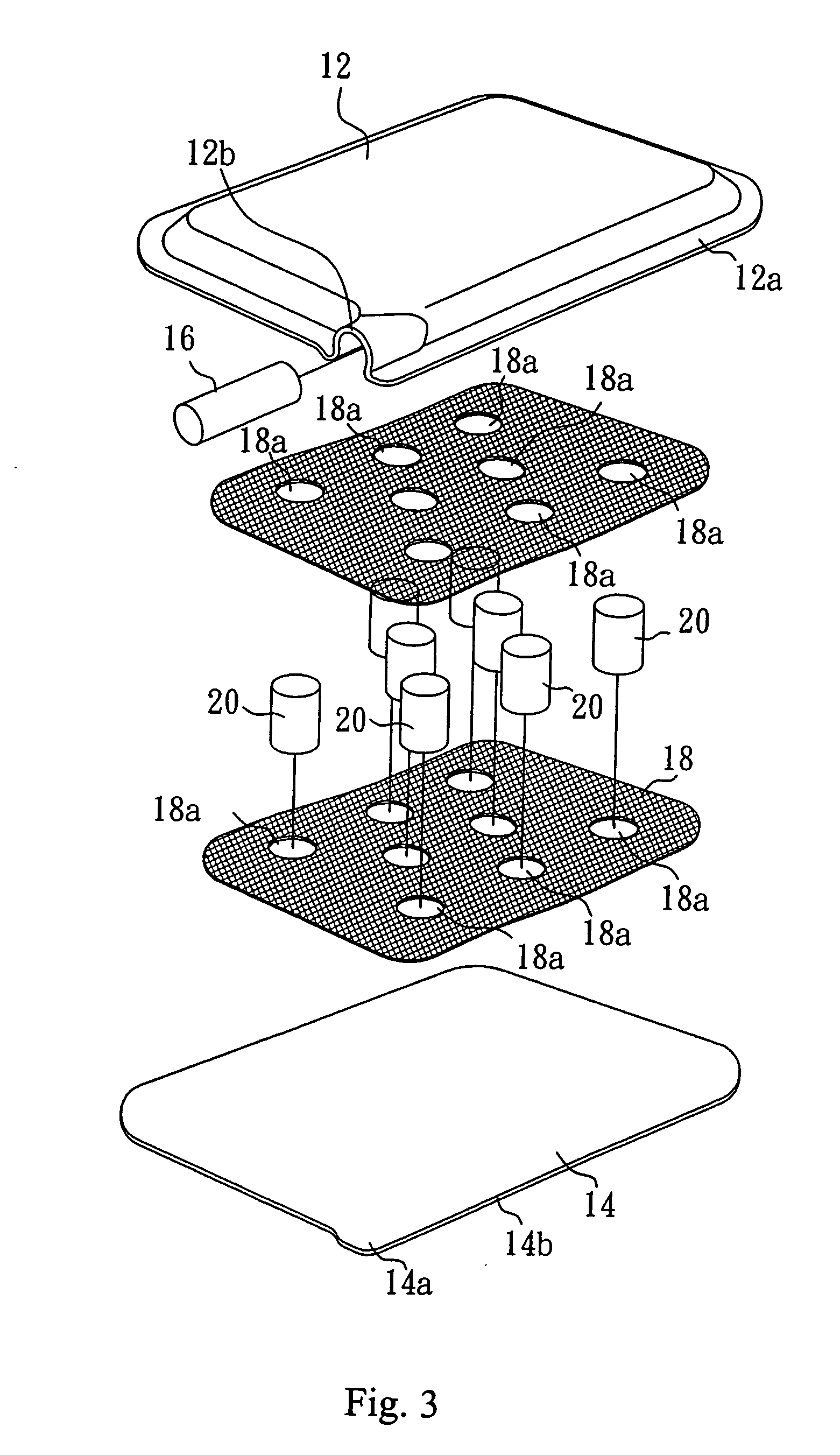

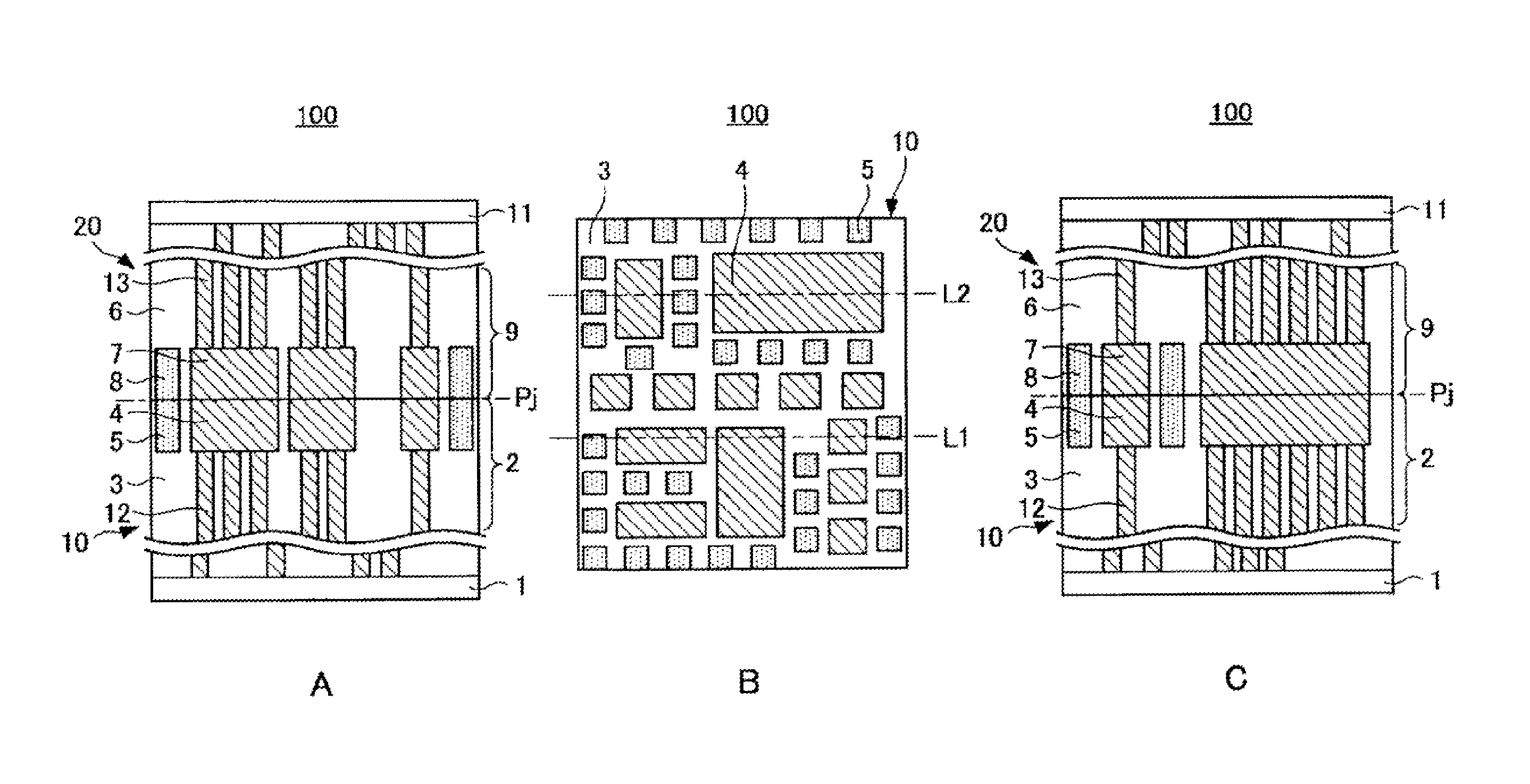

Air channel interconnects for 3-d integration

ActiveUS20110031633A1Remove heatSemiconductor/solid-state device detailsSolid-state devicesBond interfaceWafer bonding

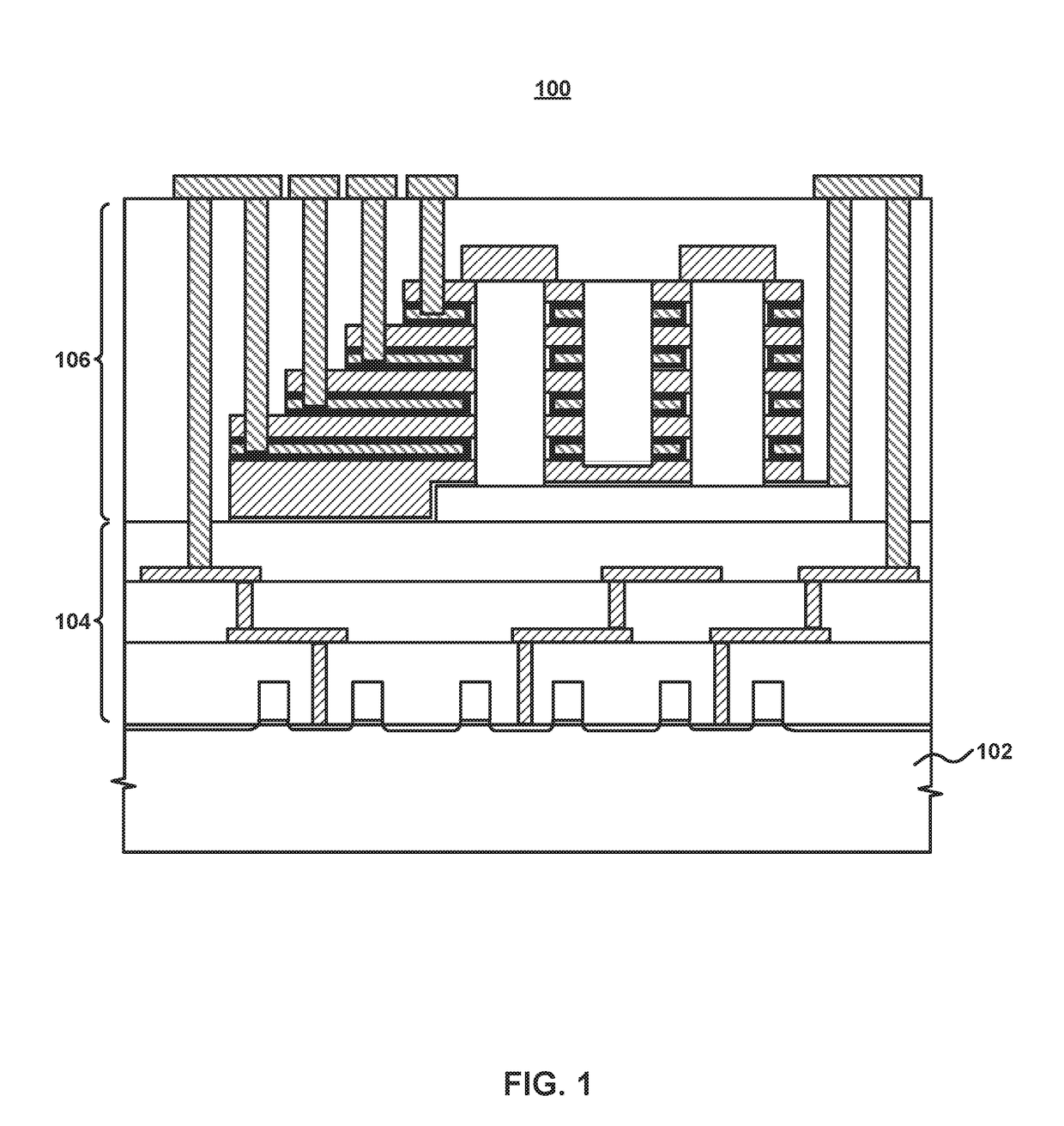

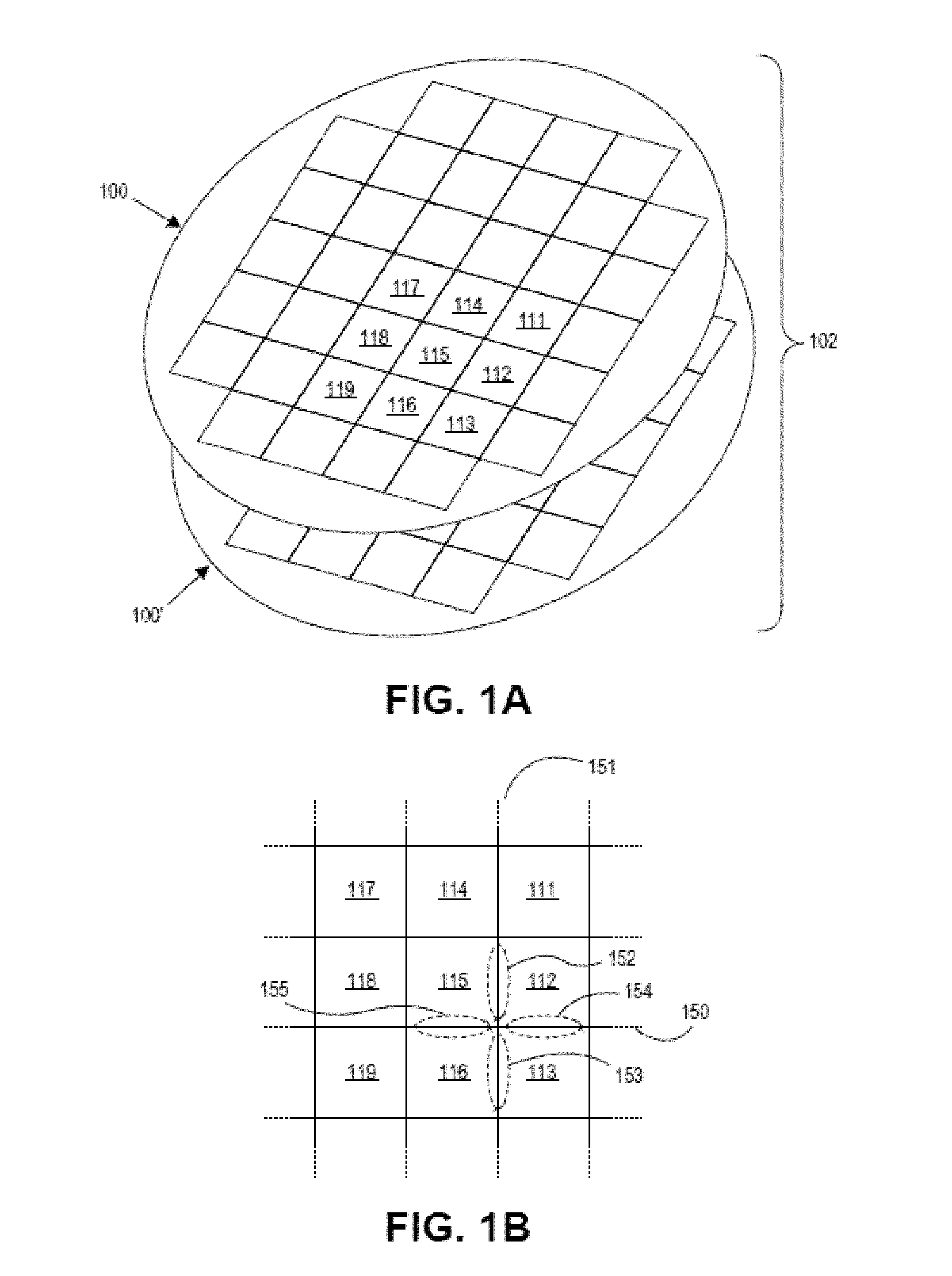

A three-dimensional (3D) chip stack structure and method of fabricating the structure thereof are provided. The 3D chip stack structure includes a plurality of vertically stacked chips which are interconnected and bonded together, wherein each of the vertically stacked chips include one or more IC device strata. The 3D chip stack structure further includes an air channel interconnect network embedded within the chip stack structure, and wherein the air channel interconnect network is formed in between at least two wafers bonded to each other of the vertically stacked wafers and in between at least two bonded wafers of the vertically stacked wafers at a bonding interface thereof. In addition, the 3D chip stack structure further includes one or more openings in a peripheral region of the chip stack structure that lead into and out of the air channel interconnect network, so that air can flow into and out of the air channel interconnect network through the one or more openings to remove heat from the chip stack structure.

Owner:GLOBALFOUNDRIES US INC

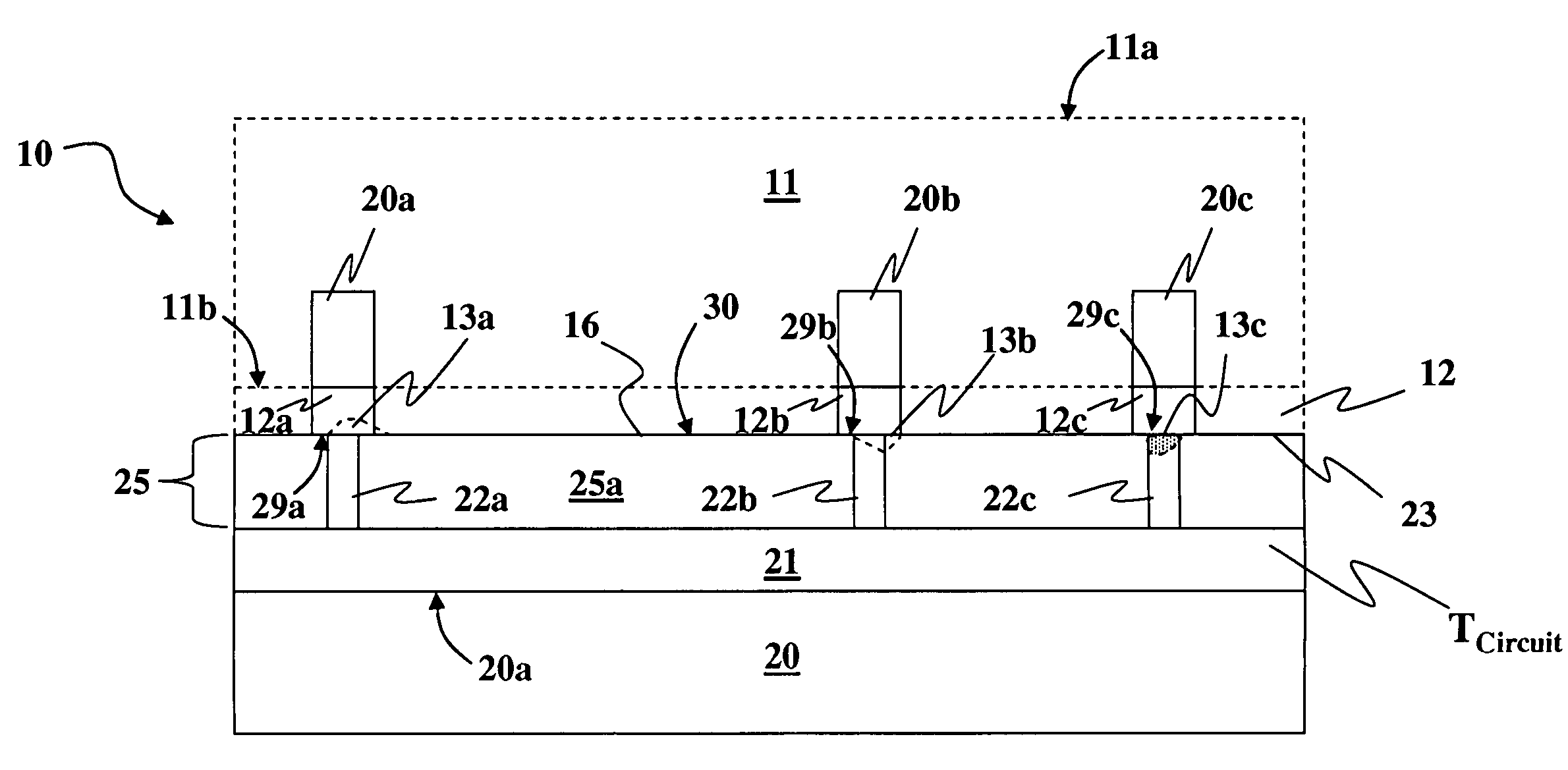

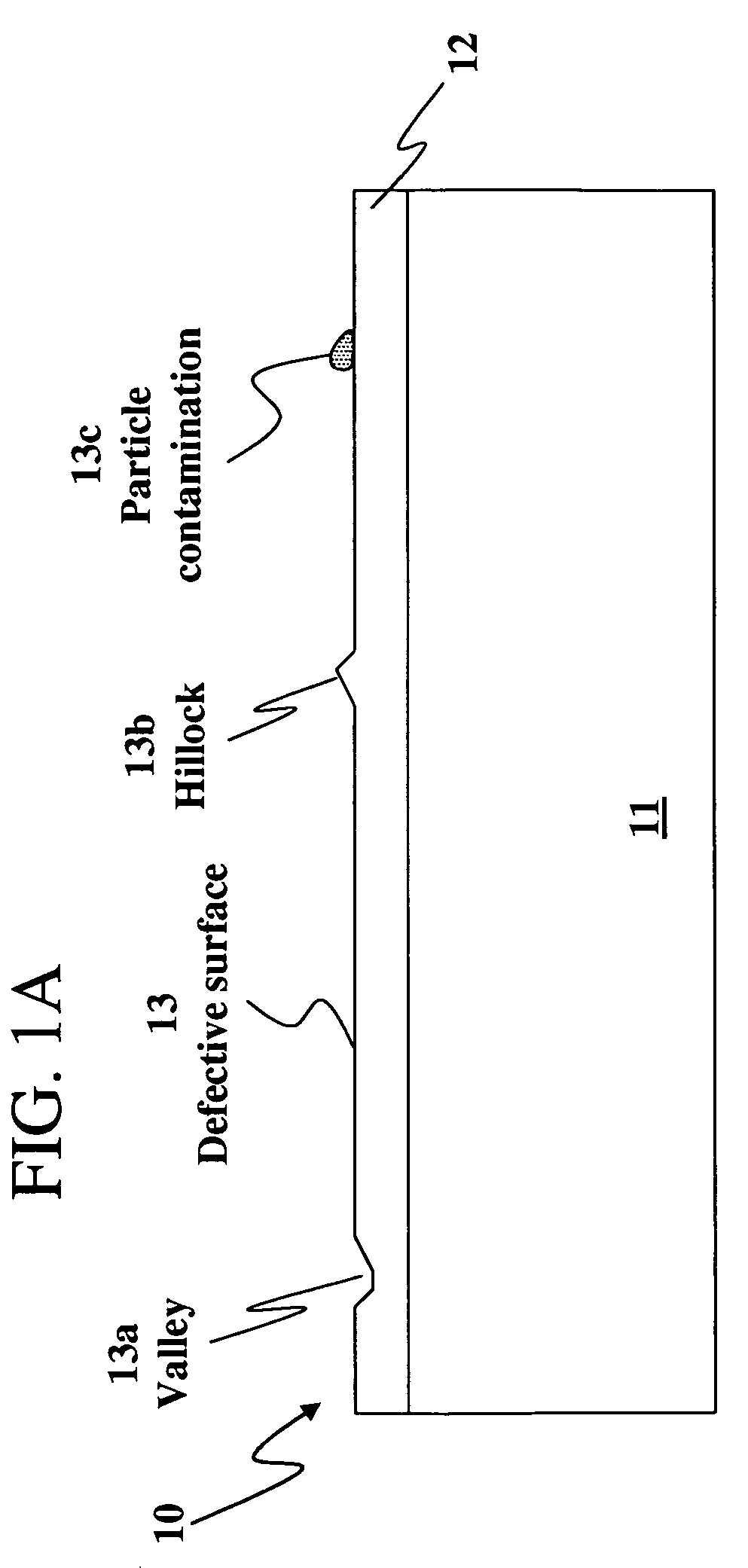

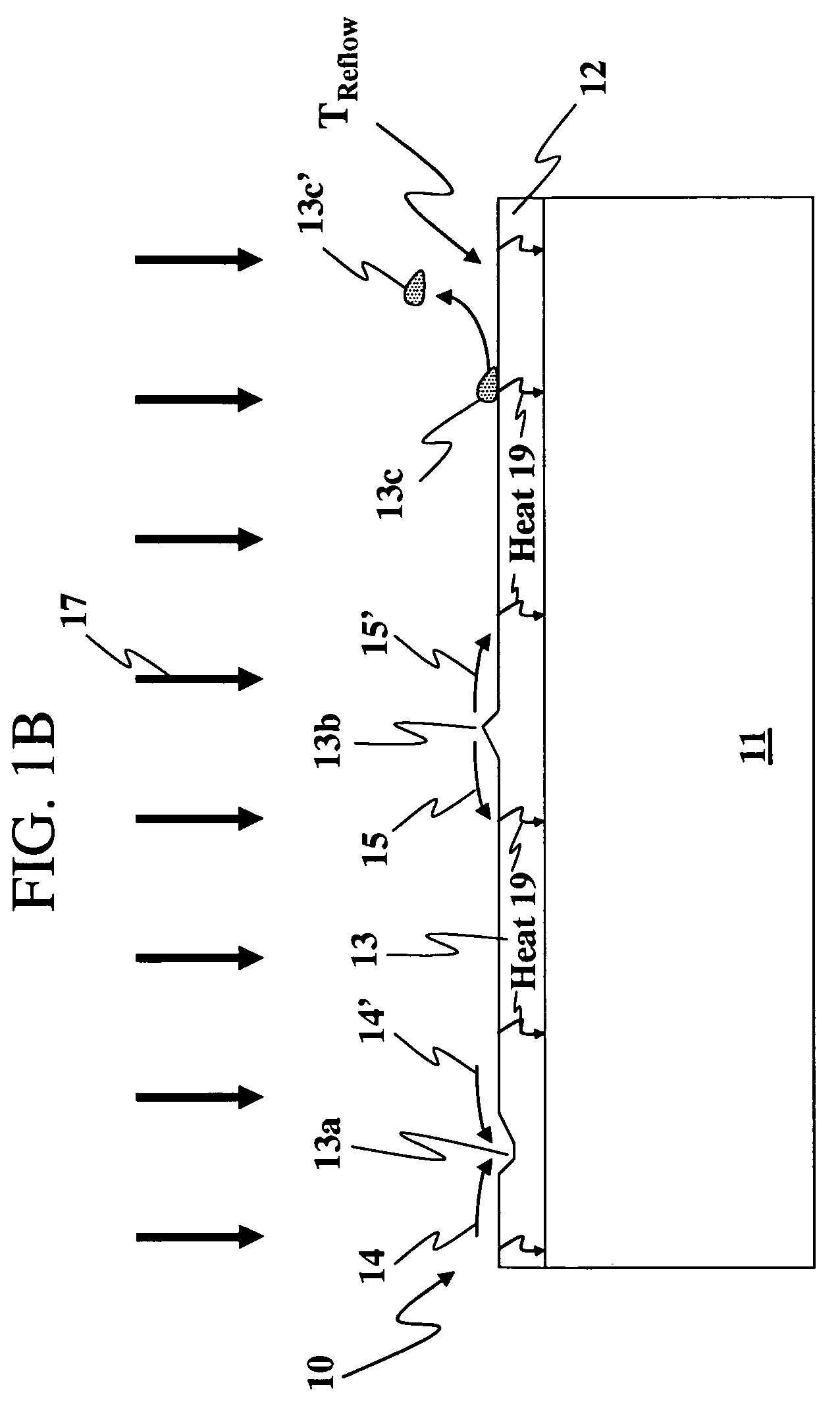

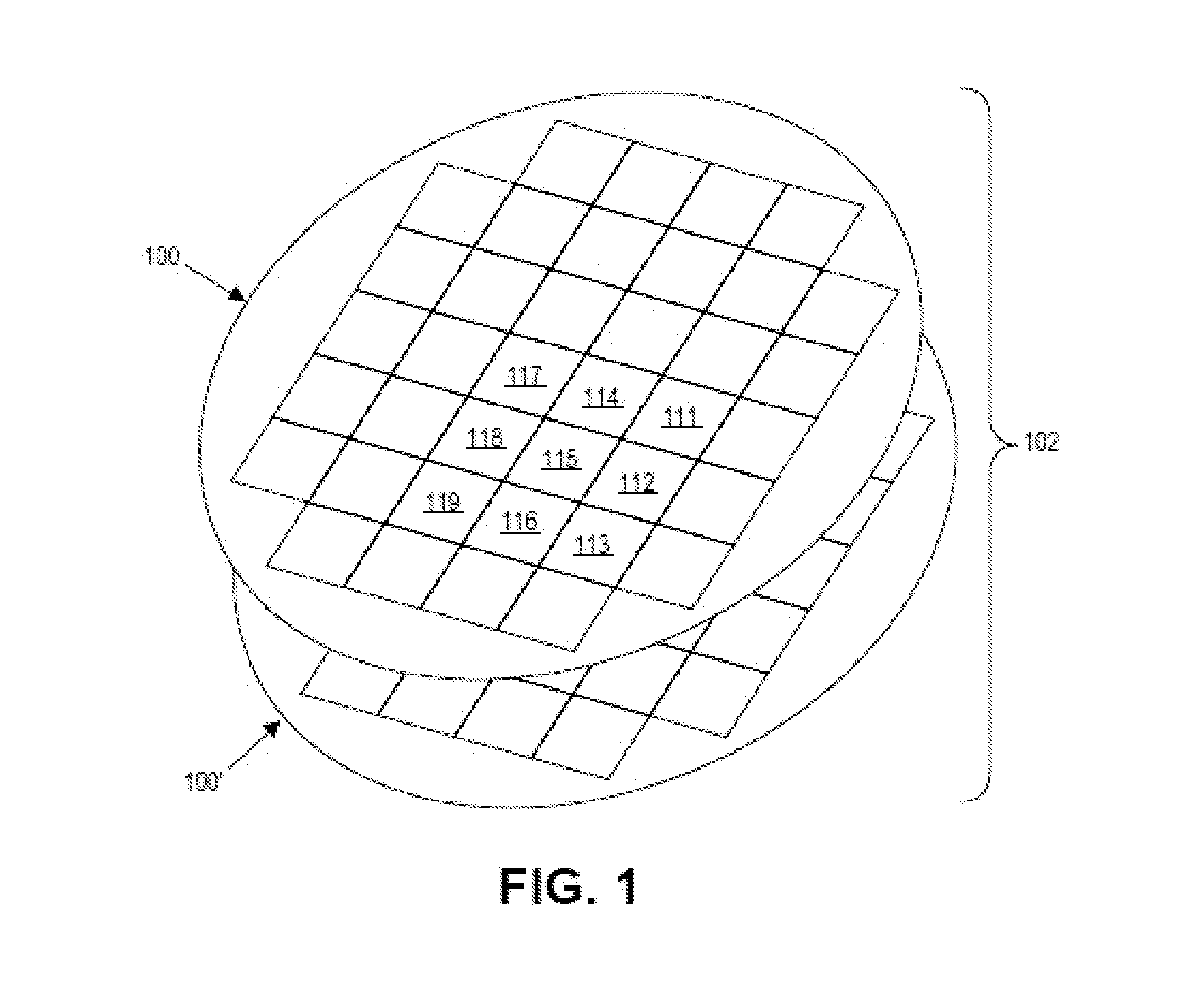

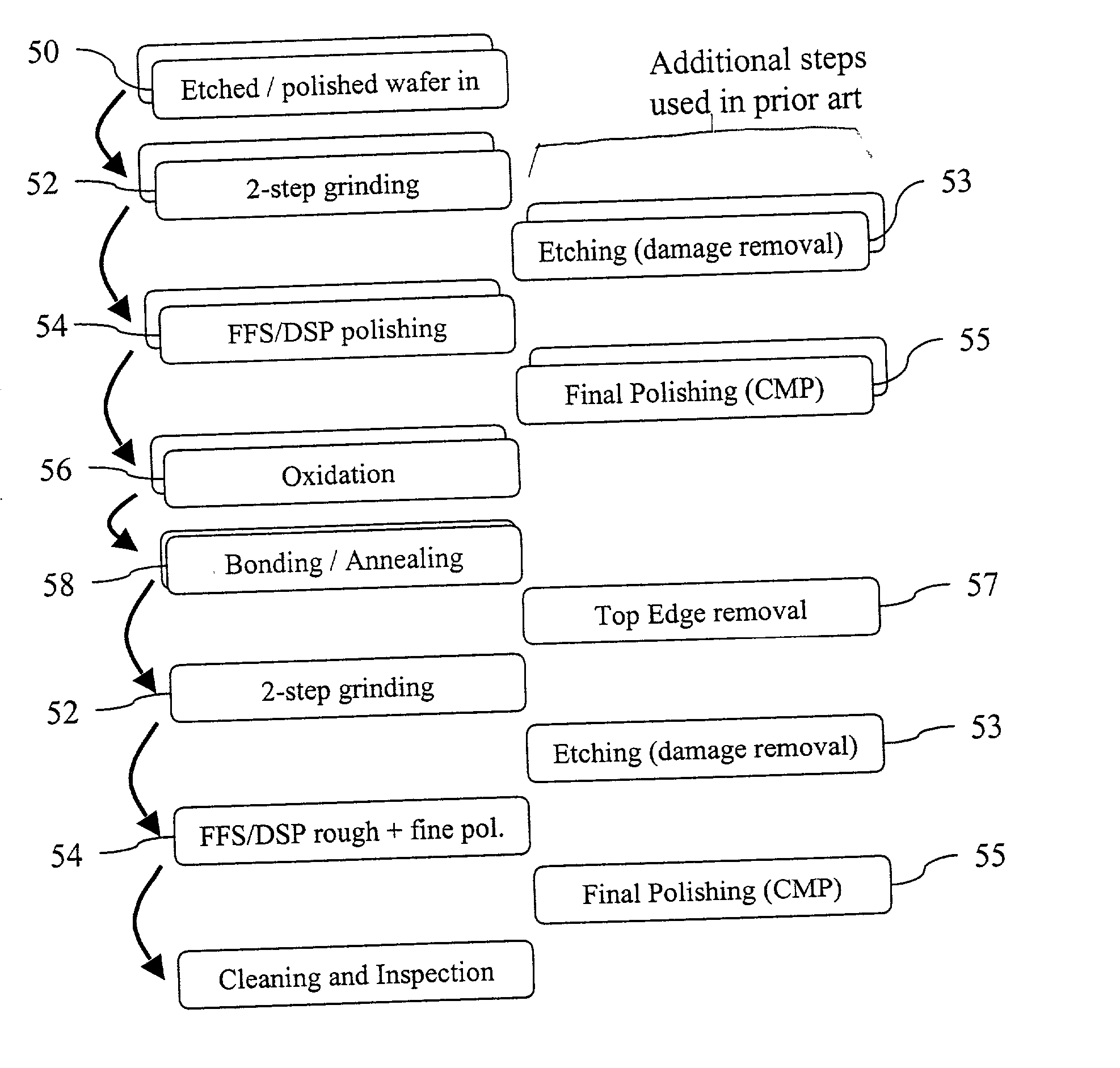

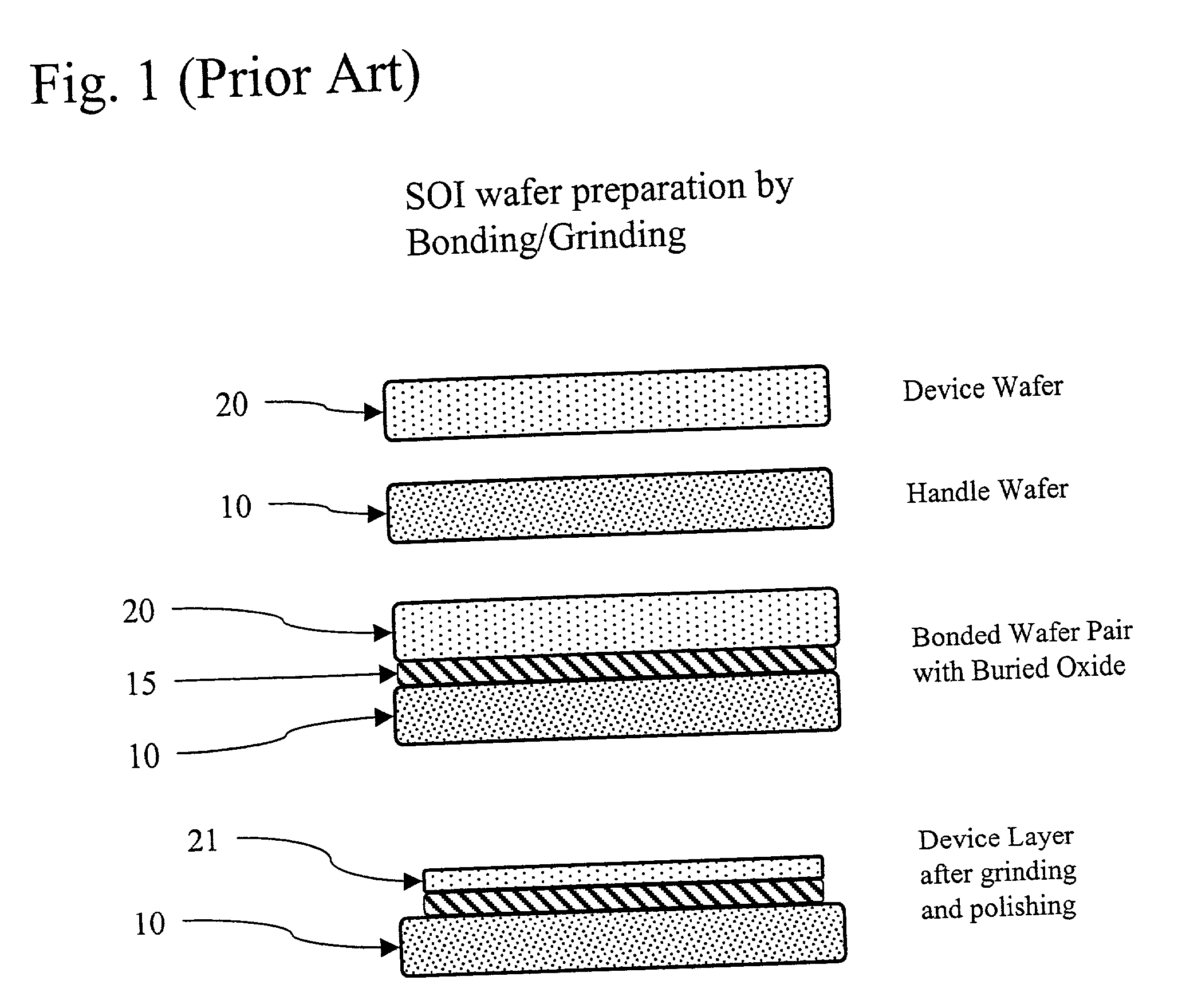

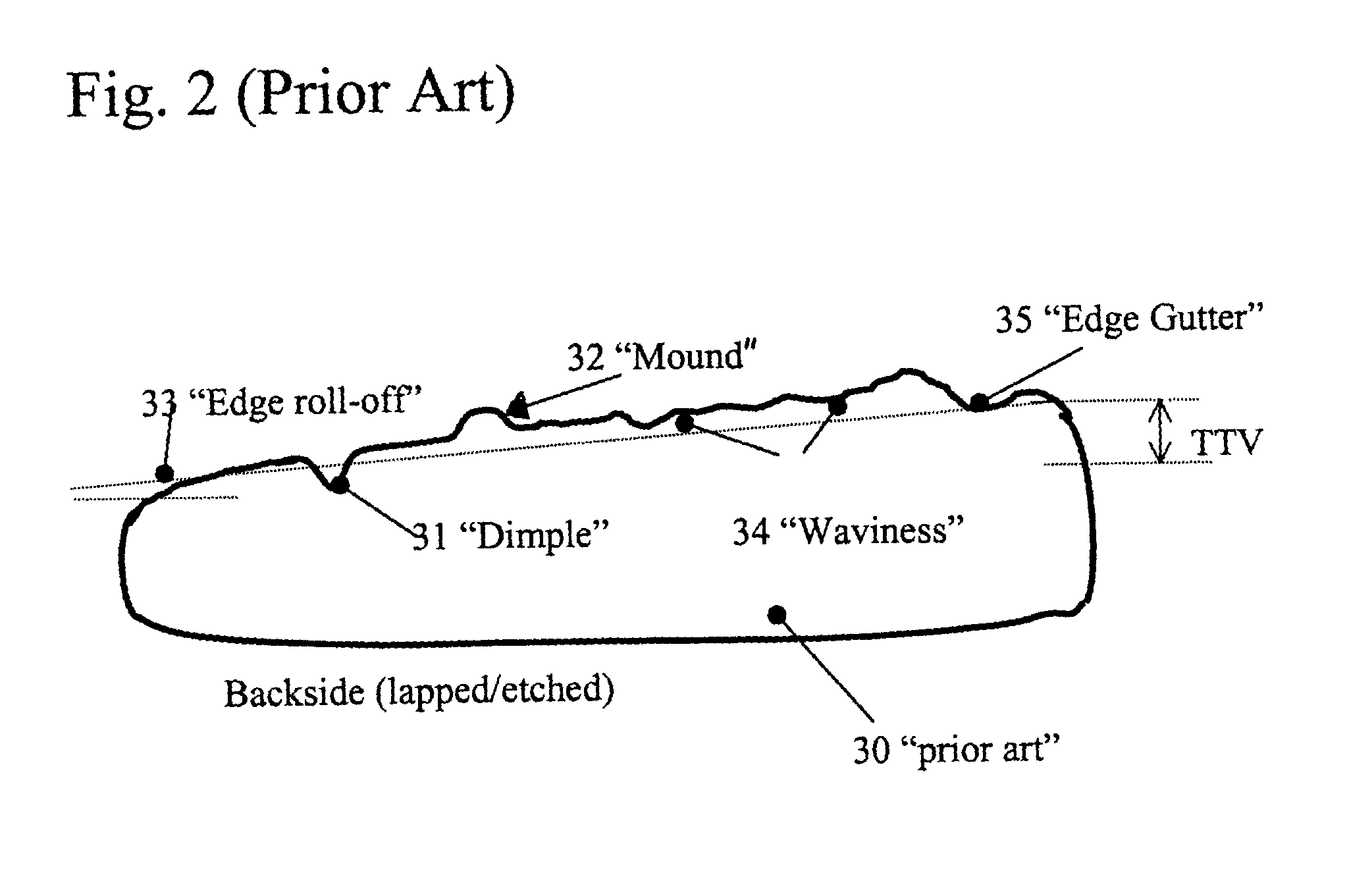

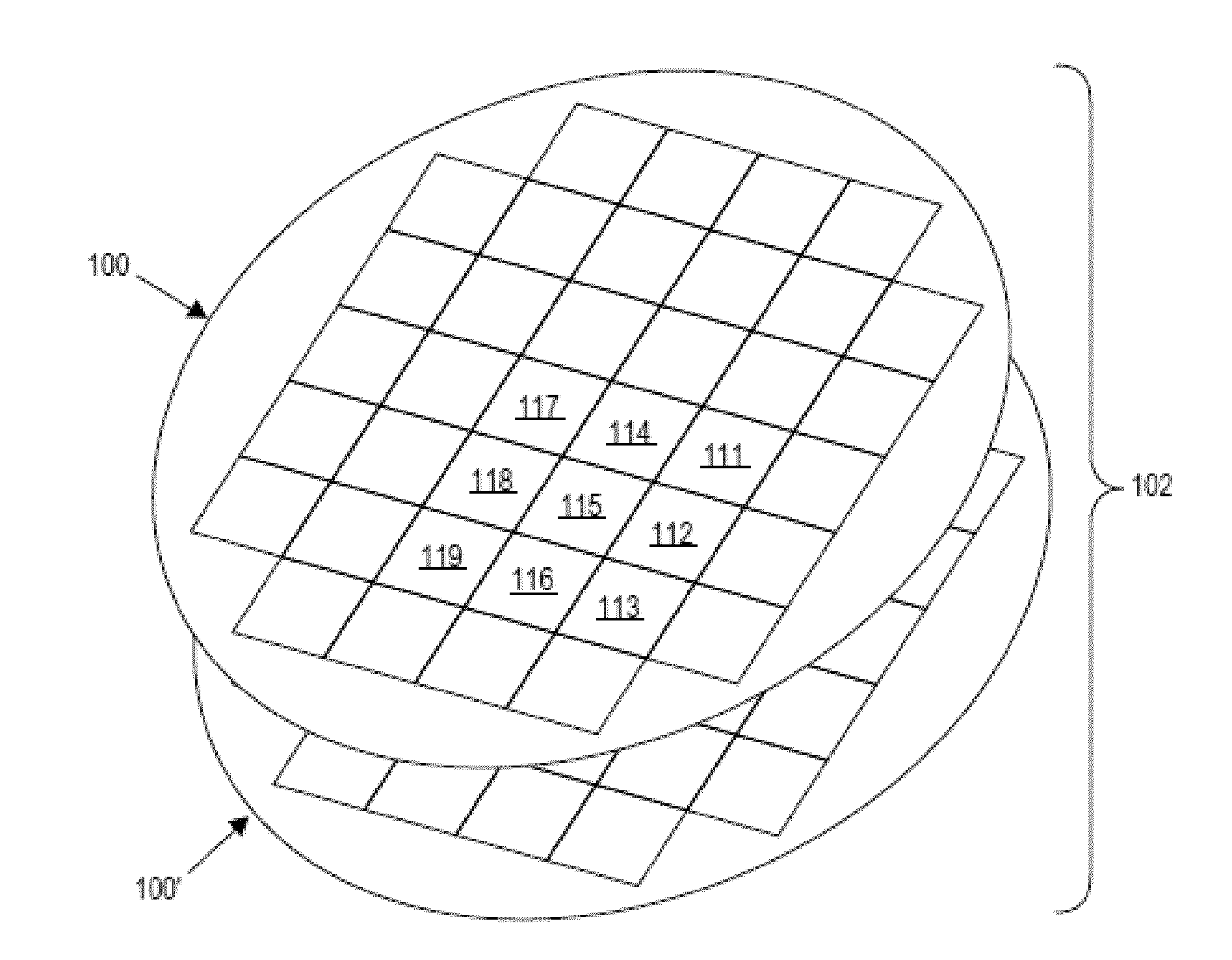

Methods for silicon-on-insulator (SOI) manufacturing with improved control and site thickness variations and improved bonding interface quality

A method for the production of silicon-on-insulator (SOI) wafers for controlling the device layer thickness variations and improvement of bonding quality at the interface of the wafers is disclosed. Using standard etched wafers, a unique sequence of process steps consisting of 2-step front side grinding, free-floating simultaneous double side polishing prepares wafers with low TTV and reduced edge roll off zones. The much smaller unbonded edge zone eliminates the requirements for edge grinding or etching in most cases. When the same s-step grinding / FFS-DSP sequence is applied after bonding and annealing of a Silicon-on-Insulator package, the resulting thickness variation in the device layer is usually smaller than what would be obtained from prior art processes.

Owner:SILICON EVOLUTION

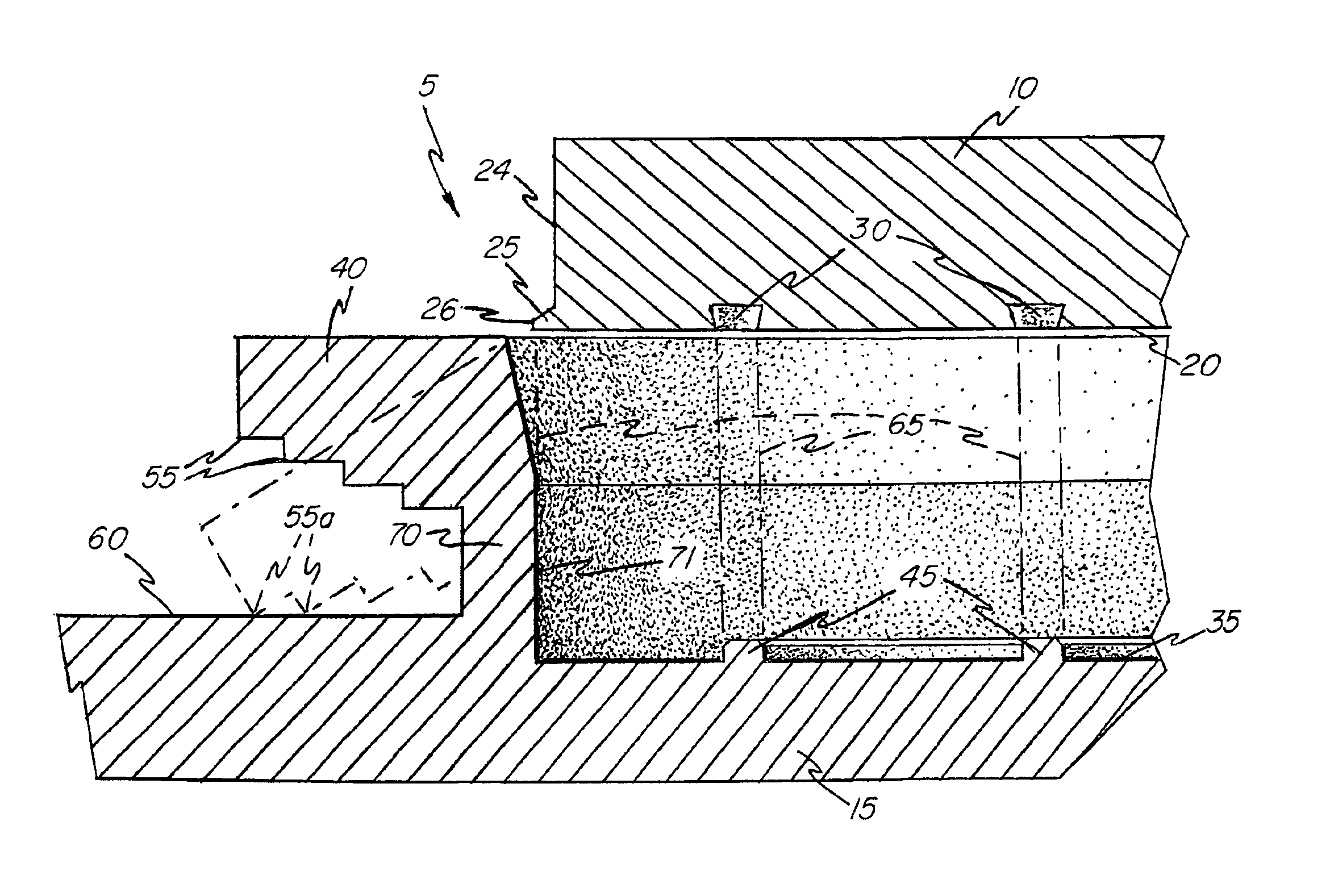

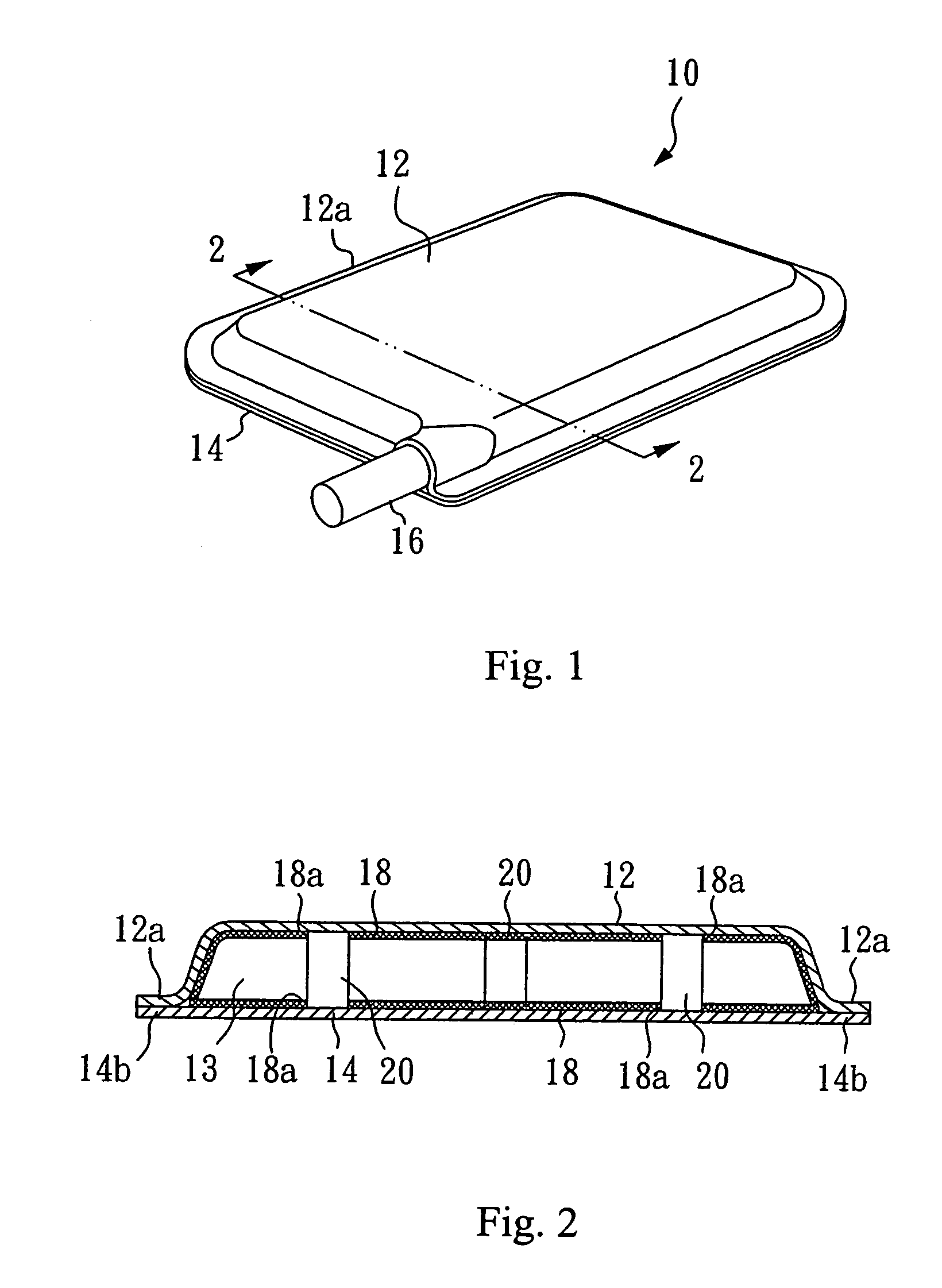

Bendable heat spreader with metallic wire mesh-based microstructure and method for fabricating same

InactiveUS20060098411A1Semiconductor/solid-state device detailsMetal-working apparatusBond interfaceWorking fluid

The present invention discloses a heat spreader and method for making the heat spreader. The heat spreader comprises: a hollow metallic housing including an upper cover having an inner surface and a lower cover having an inner surface, the upper and lower covers being bonded together along their perimeters defining a cavity; a capillary structure in a form of metallic meshes bonded to the inner surfaces of the upper and lower covers of the metallic housing; a plurality of reinforcing members disposed in the cavity and bonded between the inner surfaces of the upper and lower covers of the metallic housing; and a working fluid receive in the cavity; wherein bonded surfaces between the metallic meshes and the inner surfaces of the metallic housing, the upper cover and the lower cover, and the reinforcing members and the inner surfaces of the metallic housing all are diffusion-bonded interfaces.

Owner:TAIWAN MICROLOOPS CORP

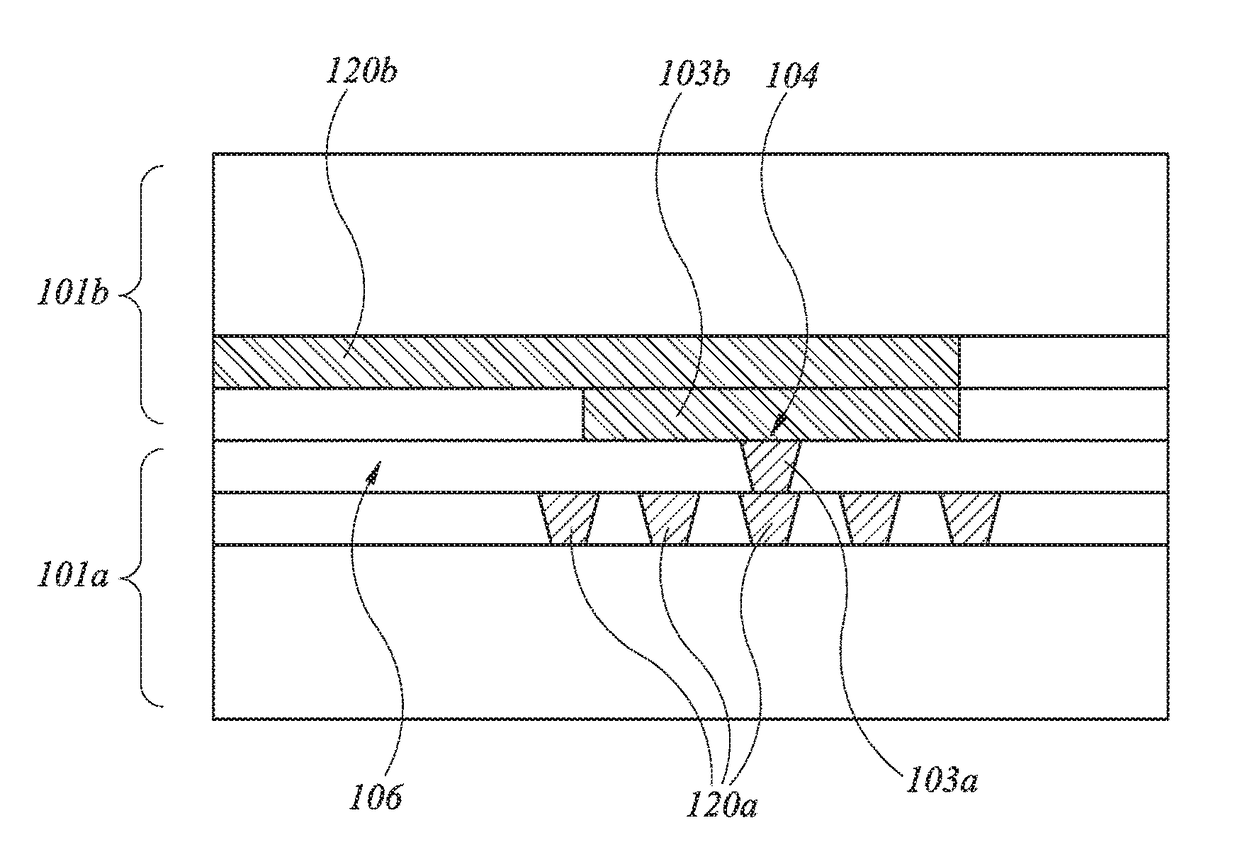

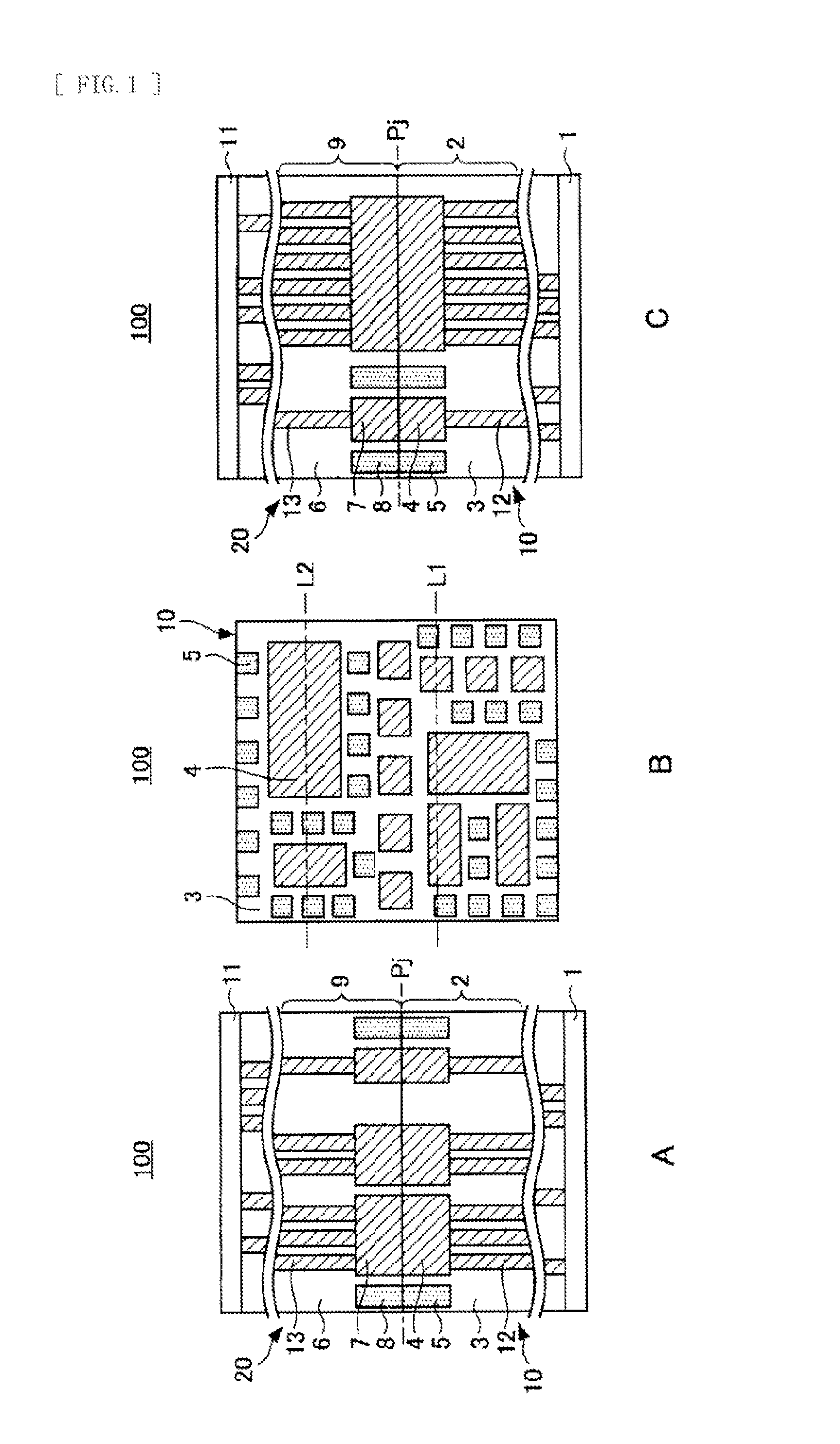

Semiconductor device

ActiveUS20140145338A1Reliable bonding surfaceBonding strengthSemiconductor/solid-state device detailsSolid-state devicesBond interfaceSemiconductor

A first semiconductor device includes: a first wiring layer including a first interlayer insulating film, a first electrode pad, and a first dummy electrode, the first electrode pad being embedded in the first interlayer insulating film and having one surface located on same plane as one surface of the first interlayer insulating film, and the first dummy electrode being embedded in the first interlayer insulating film, having one surface located on same plane as the one surface of the first interlayer insulating film, and being disposed around the first electrode pad; and a second wiring layer including a second interlayer insulating film, a second electrode pad, and a second dummy electrode, the second electrode pad being embedded in the second interlayer insulating film, having one surface located on same surface as one surface of the second interlayer insulating film, and being bonded to the first electrode pad, and the second dummy electrode having one surface located on same plane as the surface located closer to the first interlayer insulating film of the second interlayer insulating film, being disposed around the second electrode pad, and being bonded to the first dummy electrode. A second semiconductor device includes: a first semiconductor section including a first electrode, the first electrode being formed on a surface located closer to a bonding interface and extending in a first direction; and a second semiconductor section including a second electrode and disposed to be bonded to the first semiconductor section at the bonding interface, the second electrode being bonded to the first electrode and extending in a second direction that intersects with the first direction.

Owner:SONY CORP

Bonded structures

ActiveUS20190198409A1Precision positioning equipmentSemiconductor/solid-state device detailsBond interfaceEngineering

A bonded structure is disclosed. The bonded structure can include a first element that has a first bonding surface. The bonded structure can further include a second element that has a second bonding surface. The first and second bonding surfaces are bonded to one another along a bonding interface. The bonded structure can also include an integrated device that is coupled to or formed with the first element or the second element. The bonded structure can further include a channel that is disposed along the bonding interface around the integrated device to define an effectively closed profile The bonded structure can also include a getter material that is disposed in the channel. The getter material is configured to reduce the diffusion of gas into an interior region of the bonded structure.

Owner:INVENSAS BONDING TECH INC

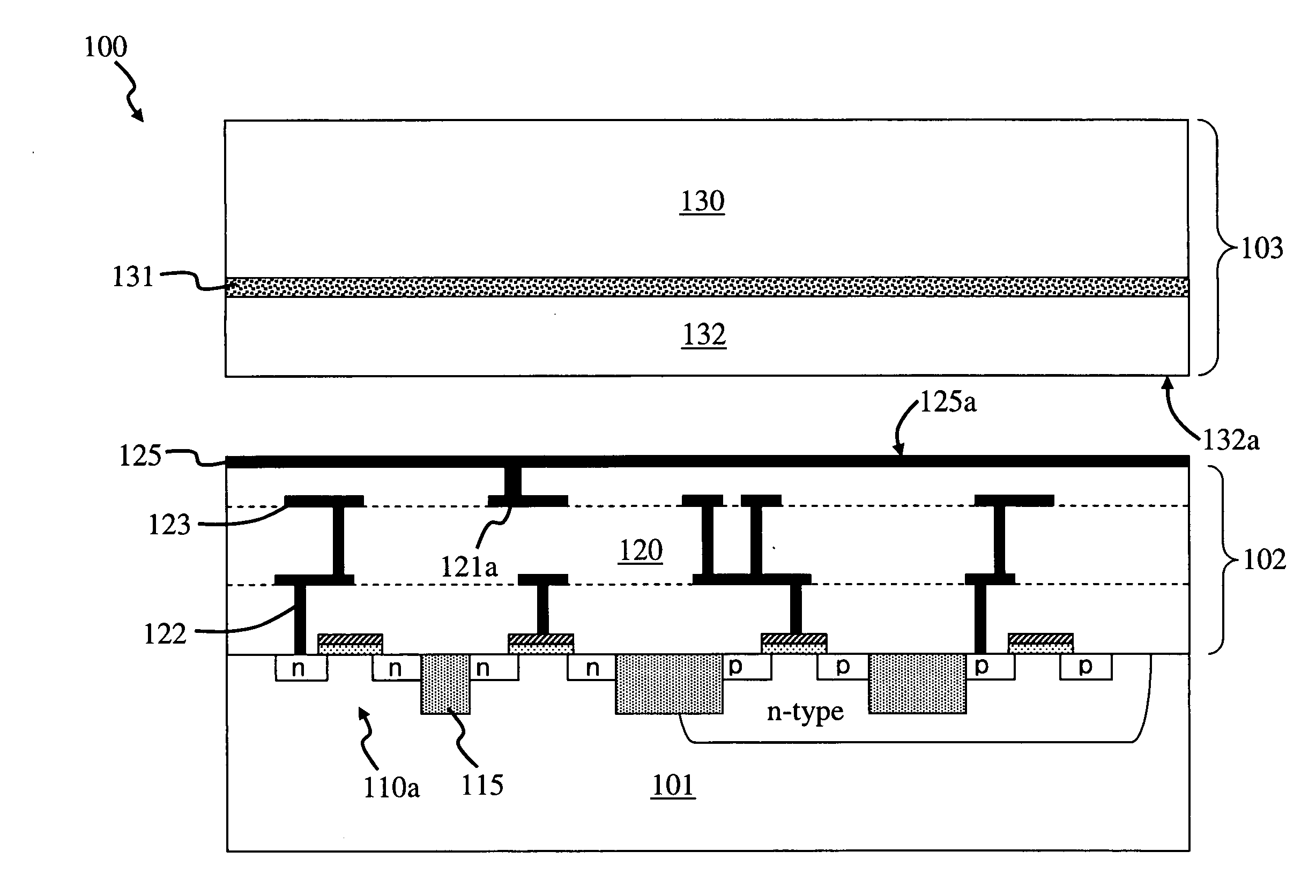

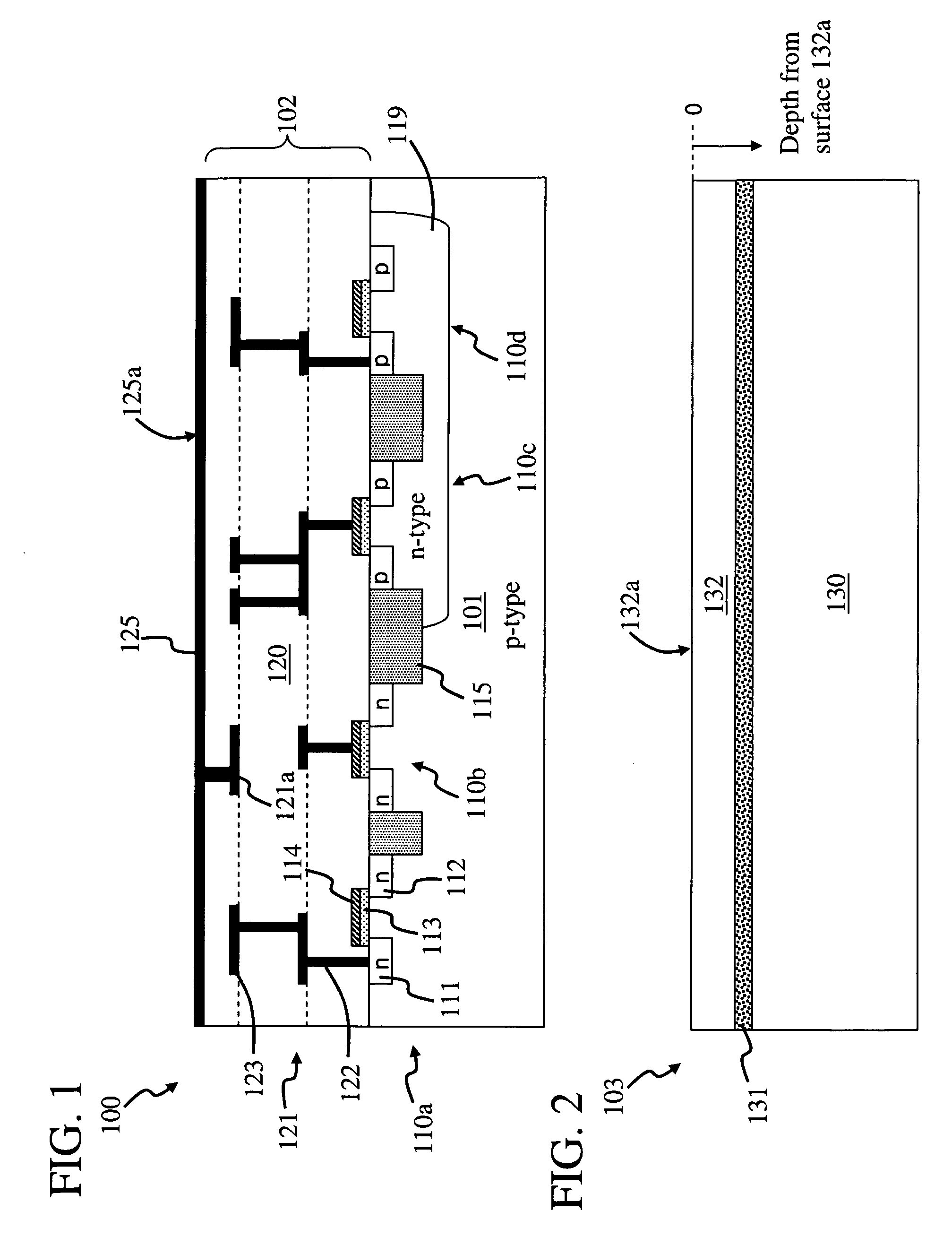

Die seal ring for integrated circuit system with stacked device wafers

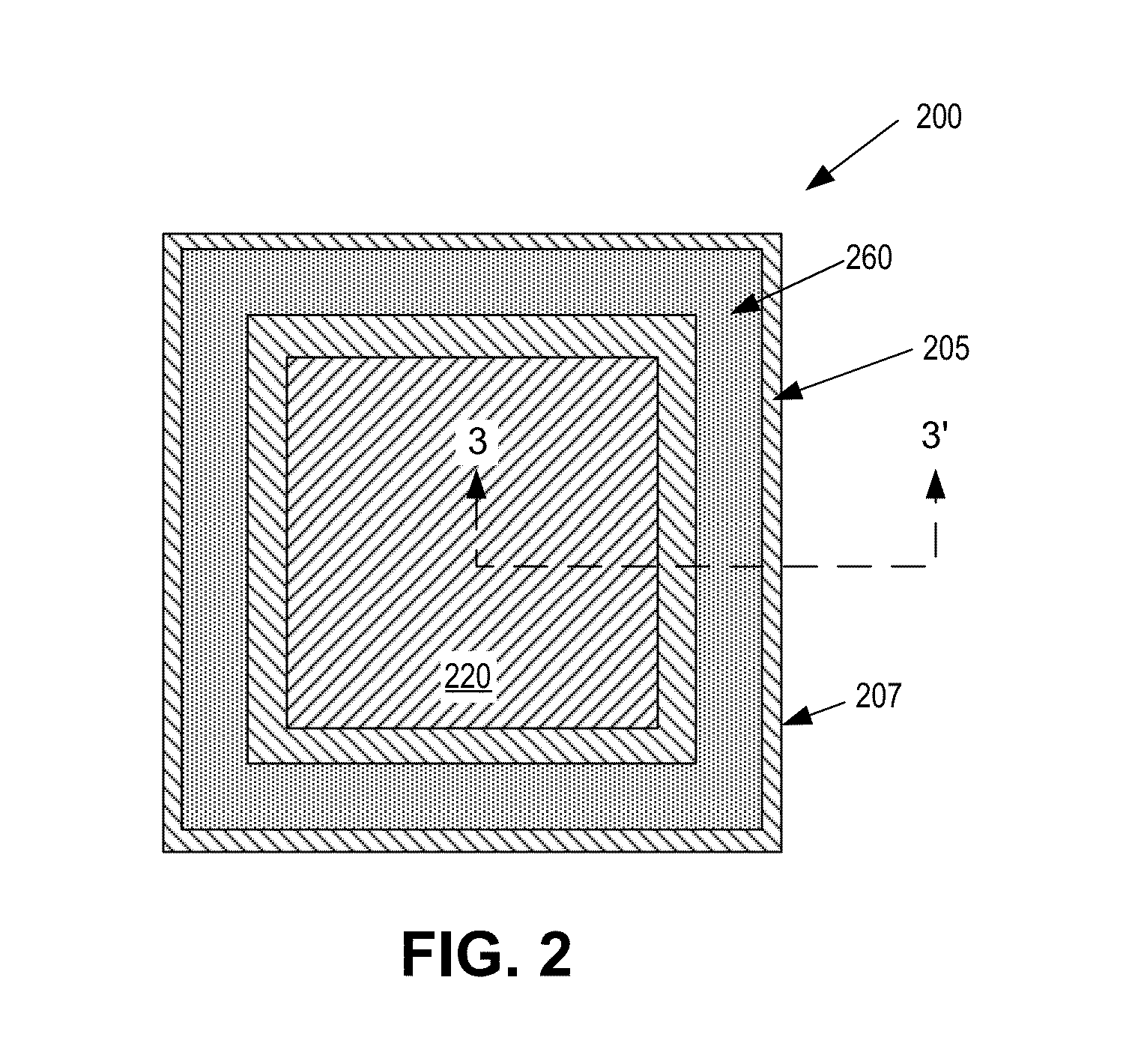

ActiveUS20140124889A1Semiconductor/solid-state device detailsSolid-state devicesDielectricBond interface

An integrated circuit system includes a first device wafer bonded to a second device wafer at a bonding interface of dielectrics. Each wafer includes a plurality of dies, where each die includes a device, a metal stack, and a seal ring that is formed at an edge region of the die. Seal rings included in dies of the second device wafer each include a first conductive path provided with metal formed in a first opening that extends from a backside of the second device wafer, through the second device wafer, and through the bonding interface to the seal ring of a corresponding die in the first device wafer.

Owner:OMNIVISION TECH INC

Joining Method and Device Produced by this Method and Joining Unit

ActiveUS20080245843A1High profile irregularityPrevent charging damageLaser detailsSolid-state devicesBond interfaceRoom temperature

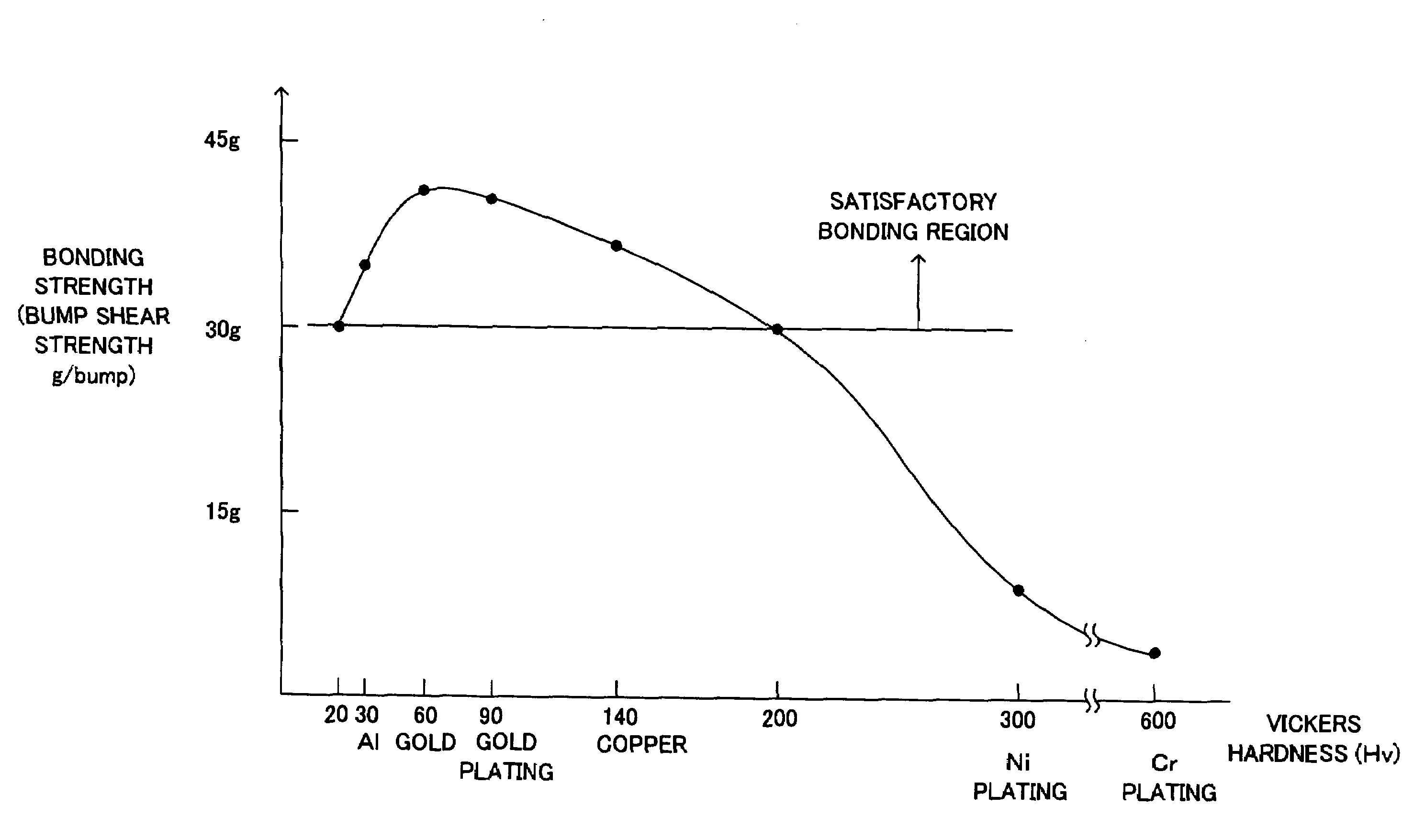

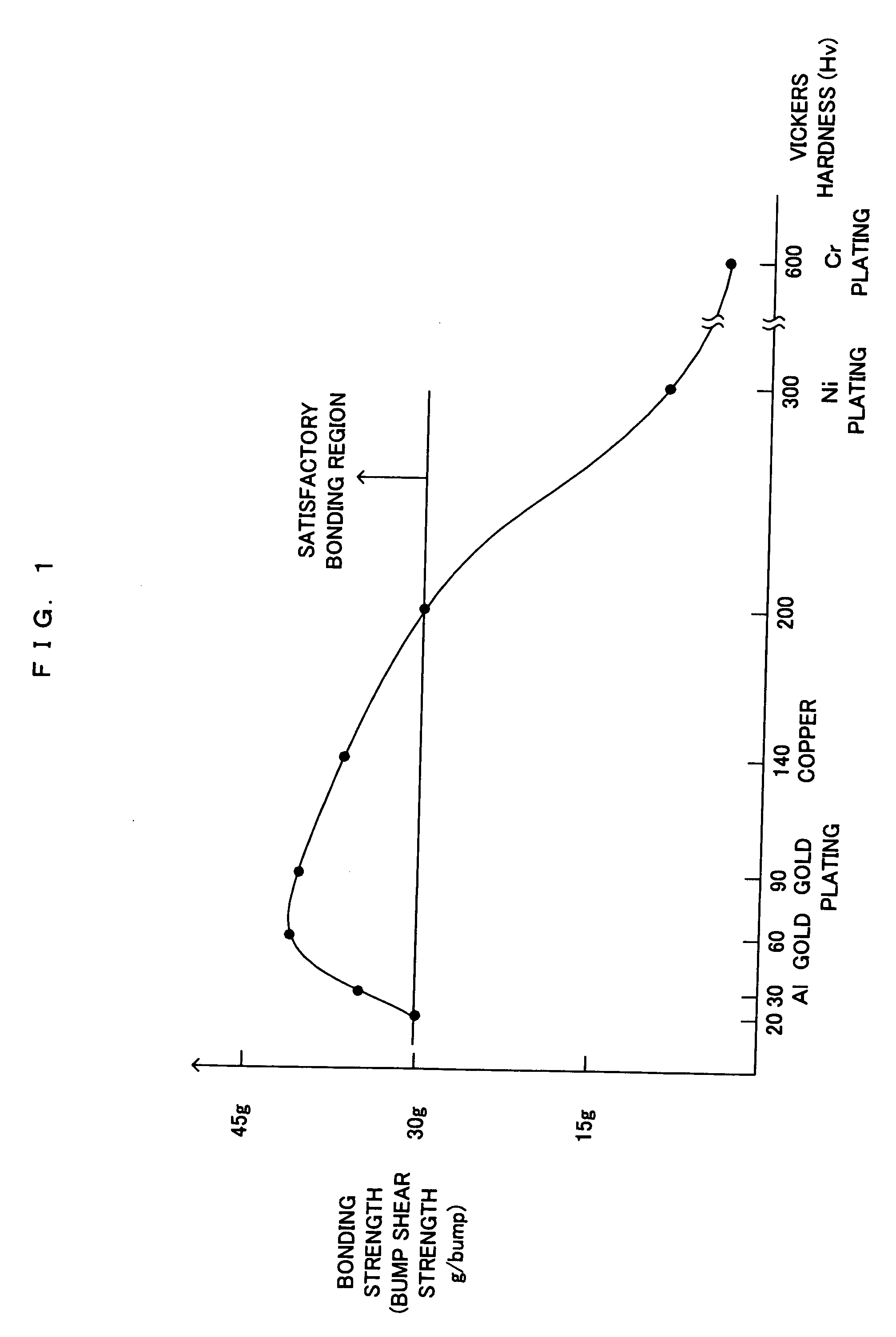

A practical bonding technique is provided for solid-phase room-temperature bonding which does not require a profile irregularity of the order of several nanometers, in which a high-vacuum energy wave treatment and continuous high-vacuum bonding are not required.Since an adhering substance layer is thin immediately after a surface activating treatment using an energy wave, a bonding interface is spread by crushing the adhering substance layer to perform bonding, so that a new surface appears on a bonding surface, and objects to be bonded are bonded together. In order to crush the adhering substance layer more easily, a bonding metal of a bonding portion of the object to be bonded needs to have a low hardness. According to the results of various experiments conducted by the present inventors, it was found that the hardness of the bonding portion which is a Vickers hardness of 200 Hv or less is particularly effective for room-temperature bonding.

Owner:SUGA