Patents

Literature

435 results about "Three-dimensional integrated circuit" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A three-dimensional integrated circuit (3D IC) is a MOS (metal-oxide semiconductor) integrated circuit (IC) manufactured by stacking silicon wafers or dies and interconnecting them vertically using, for instance, through-silicon vias (TSVs) or Cu-Cu connections, so that they behave as a single device to achieve performance improvements at reduced power and smaller footprint than conventional two dimensional processes. The 3D IC is one of several 3D integration schemes that exploit the z-direction to achieve electrical performance benefits, in microelectronics and nanoelectronics.

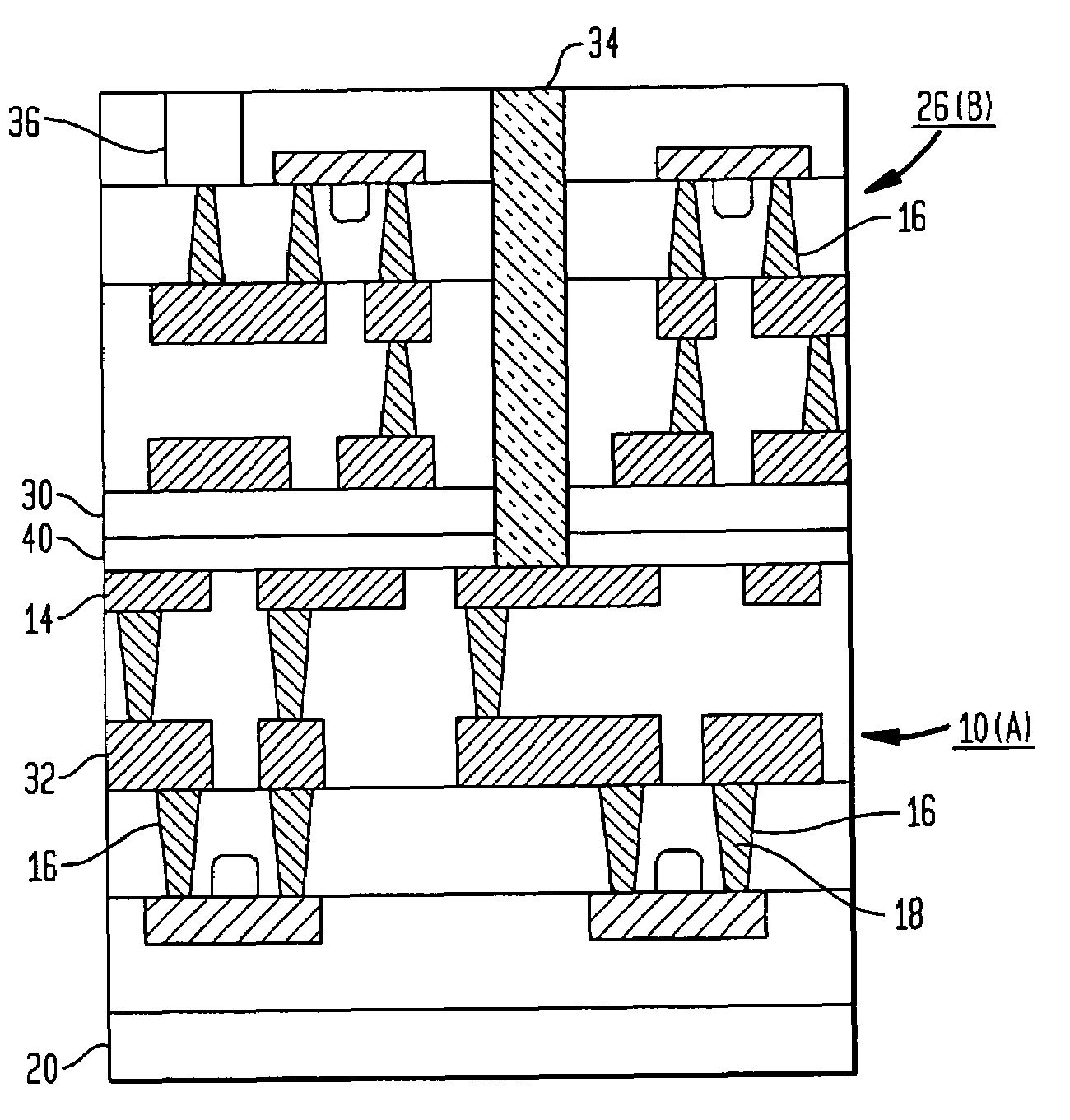

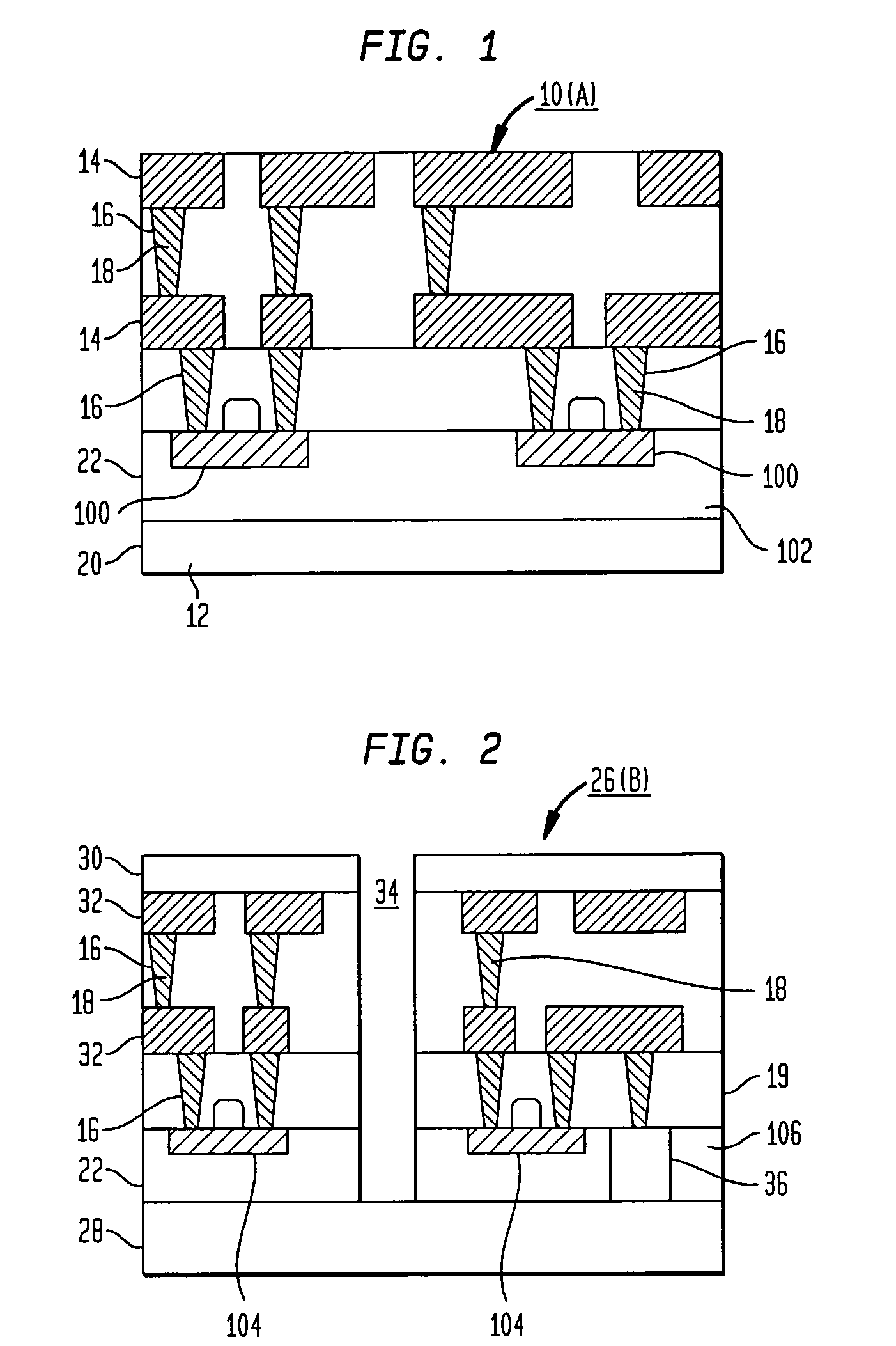

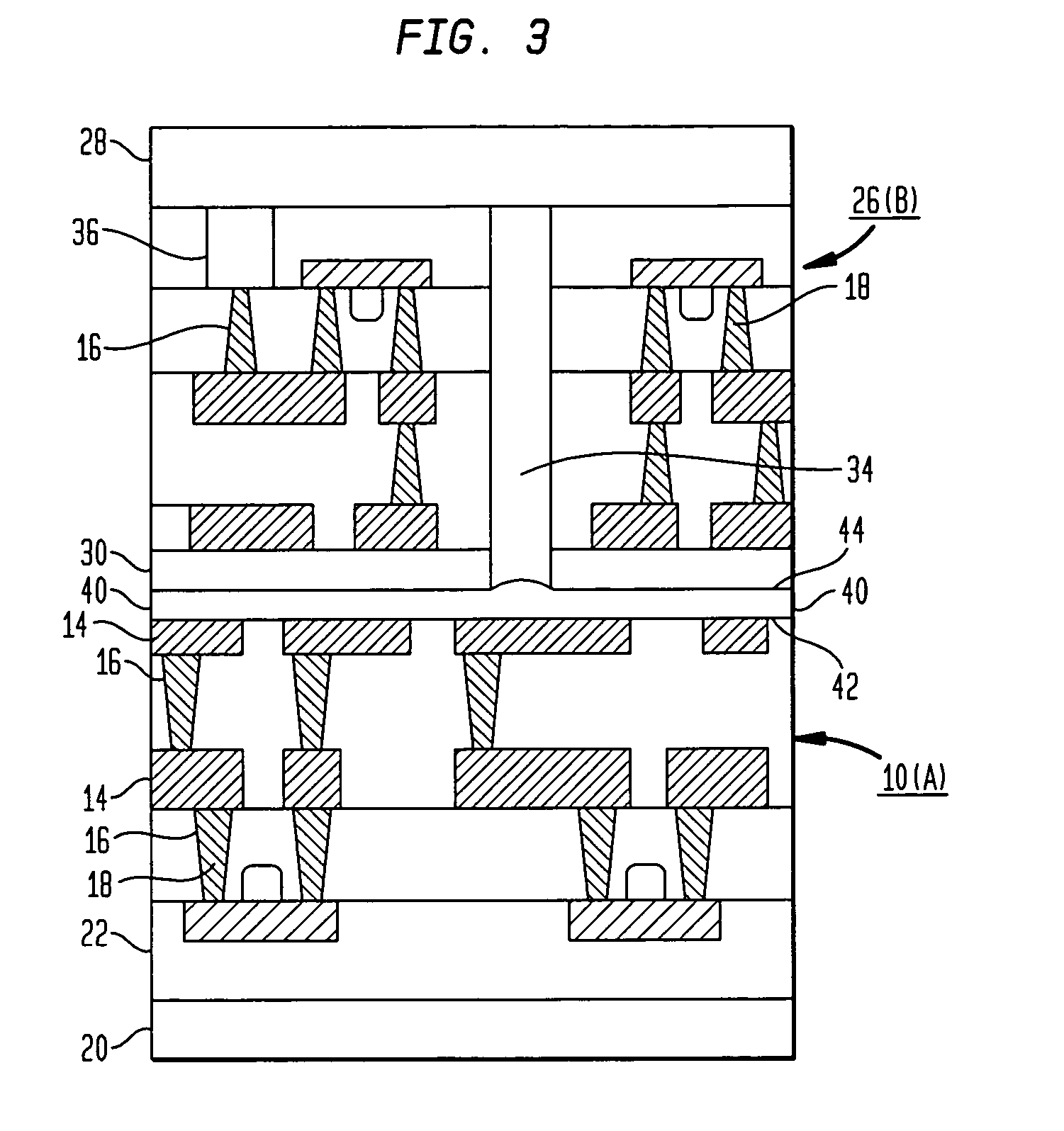

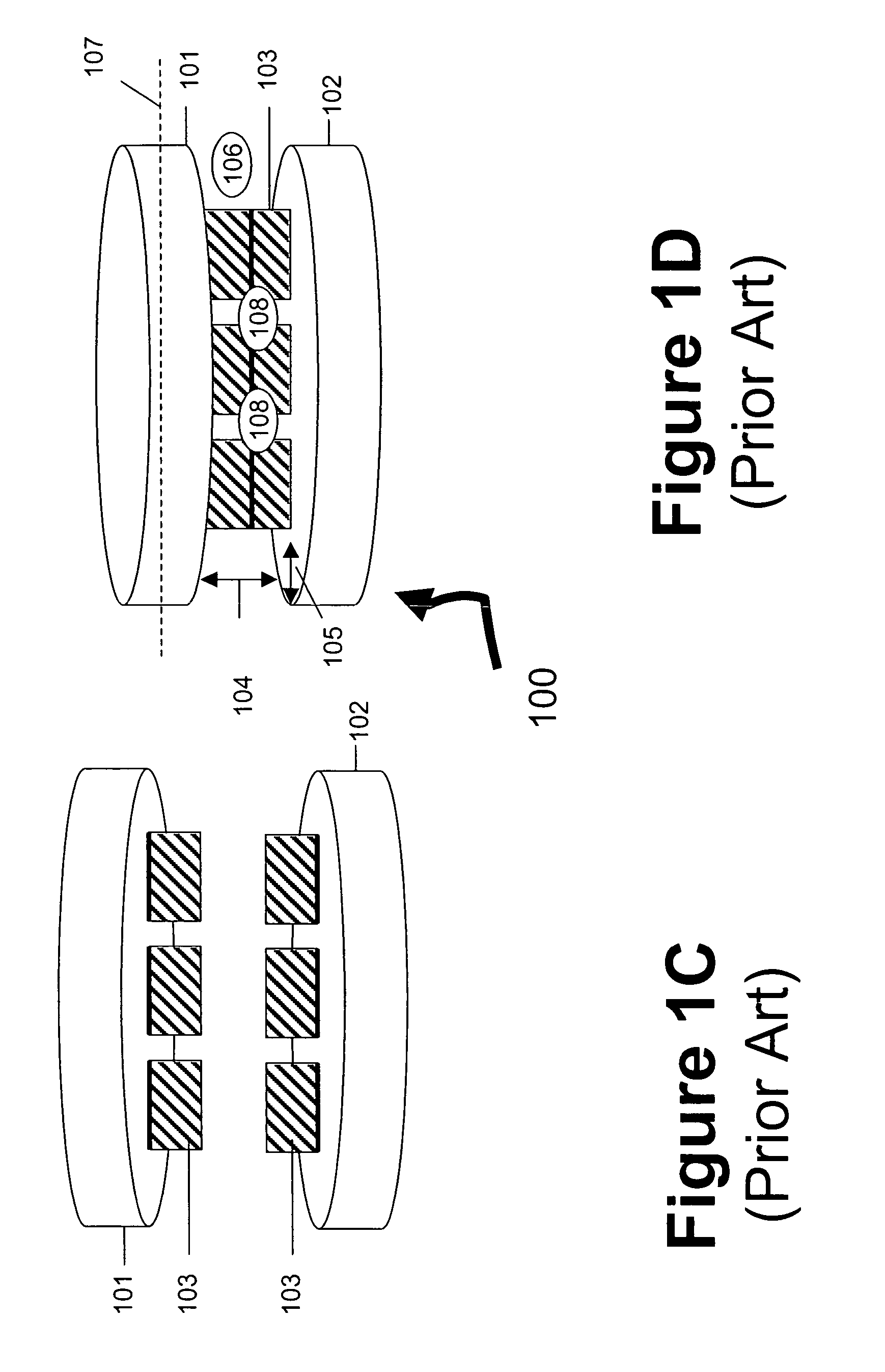

Three-dimensional chip stacking assembly

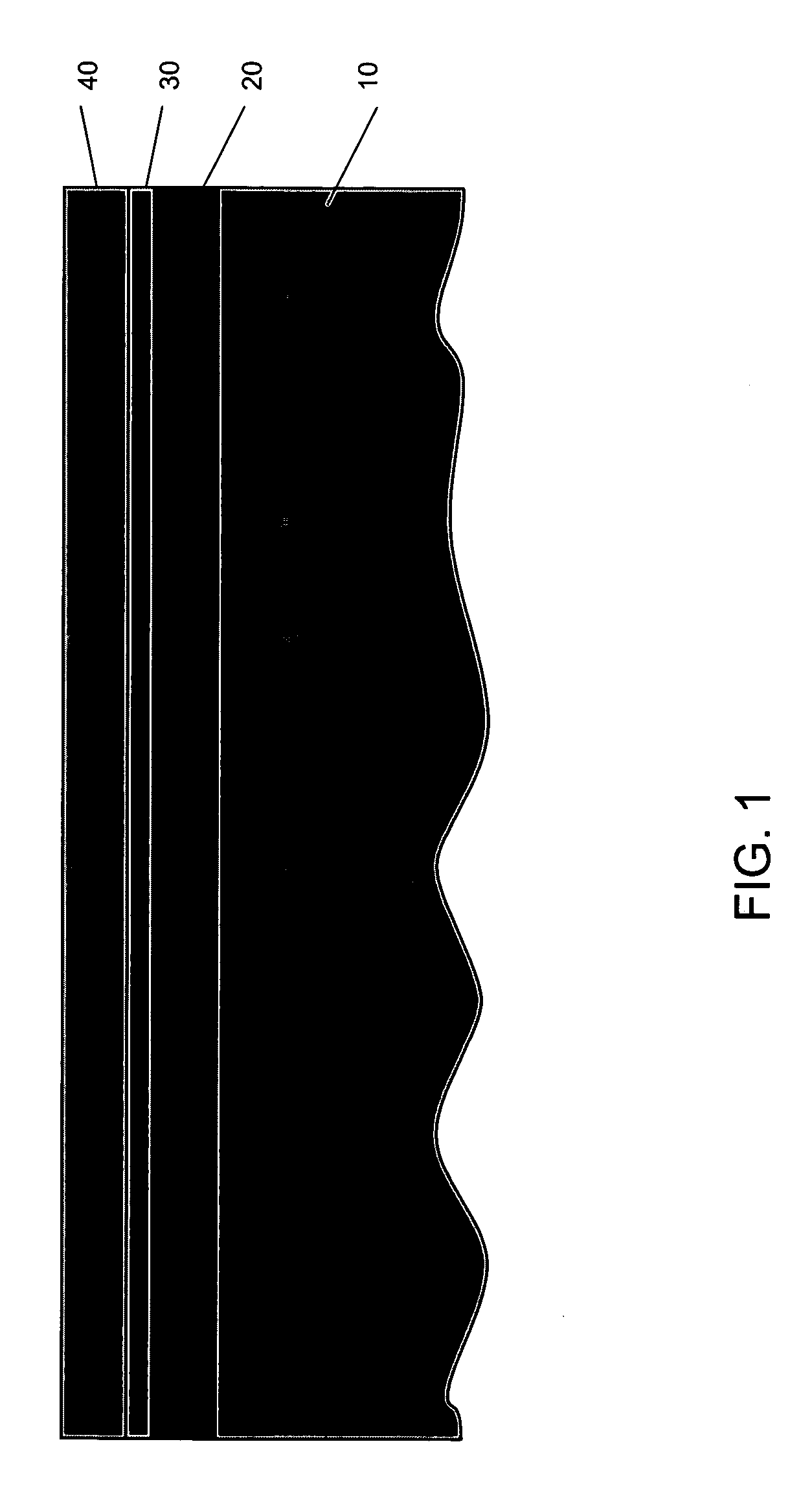

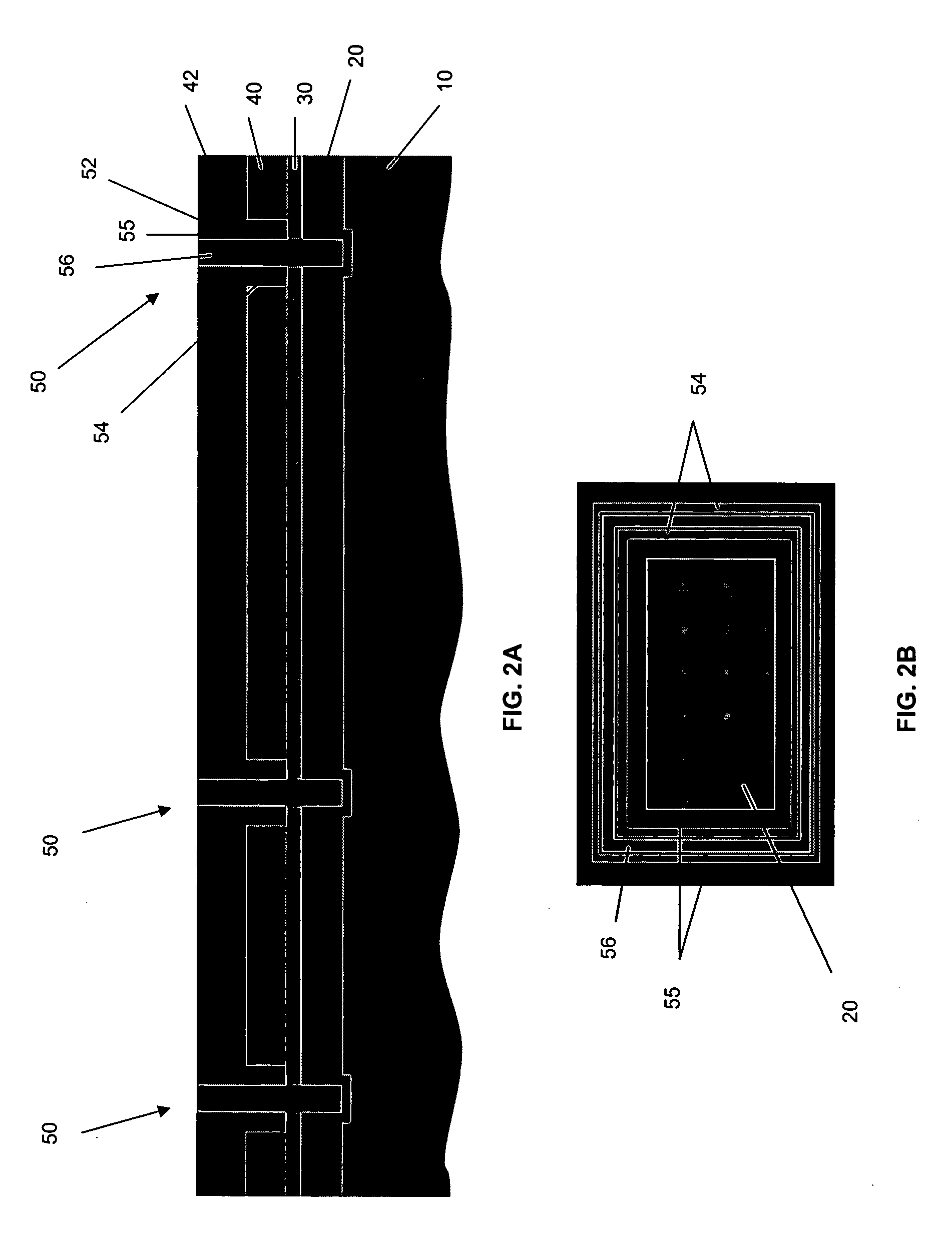

InactiveUS6355501B1Precise alignmentGood mechanical integritySolid-state devicesSemiconductor/solid-state device manufacturingEngineeringThree-dimensional integrated circuit

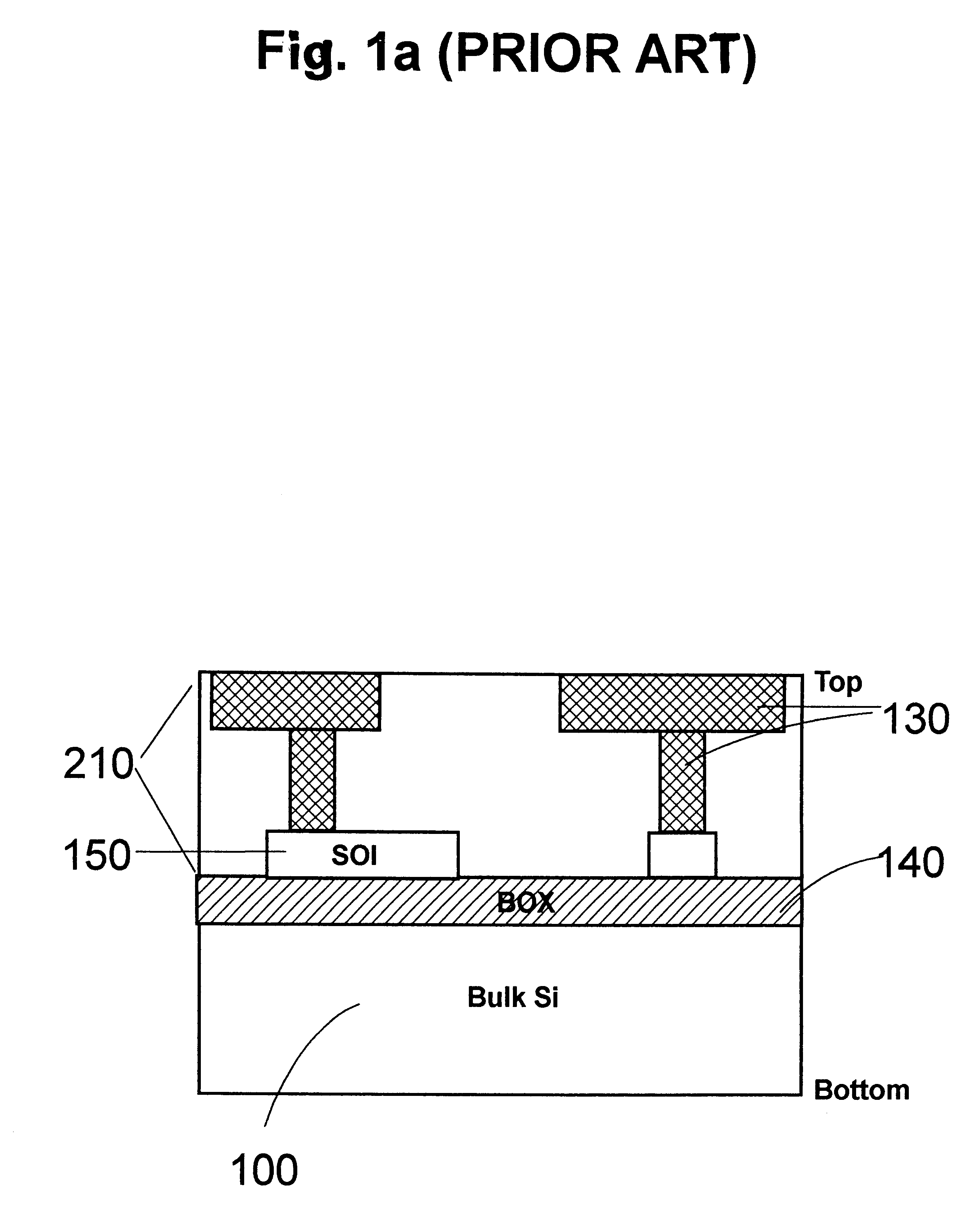

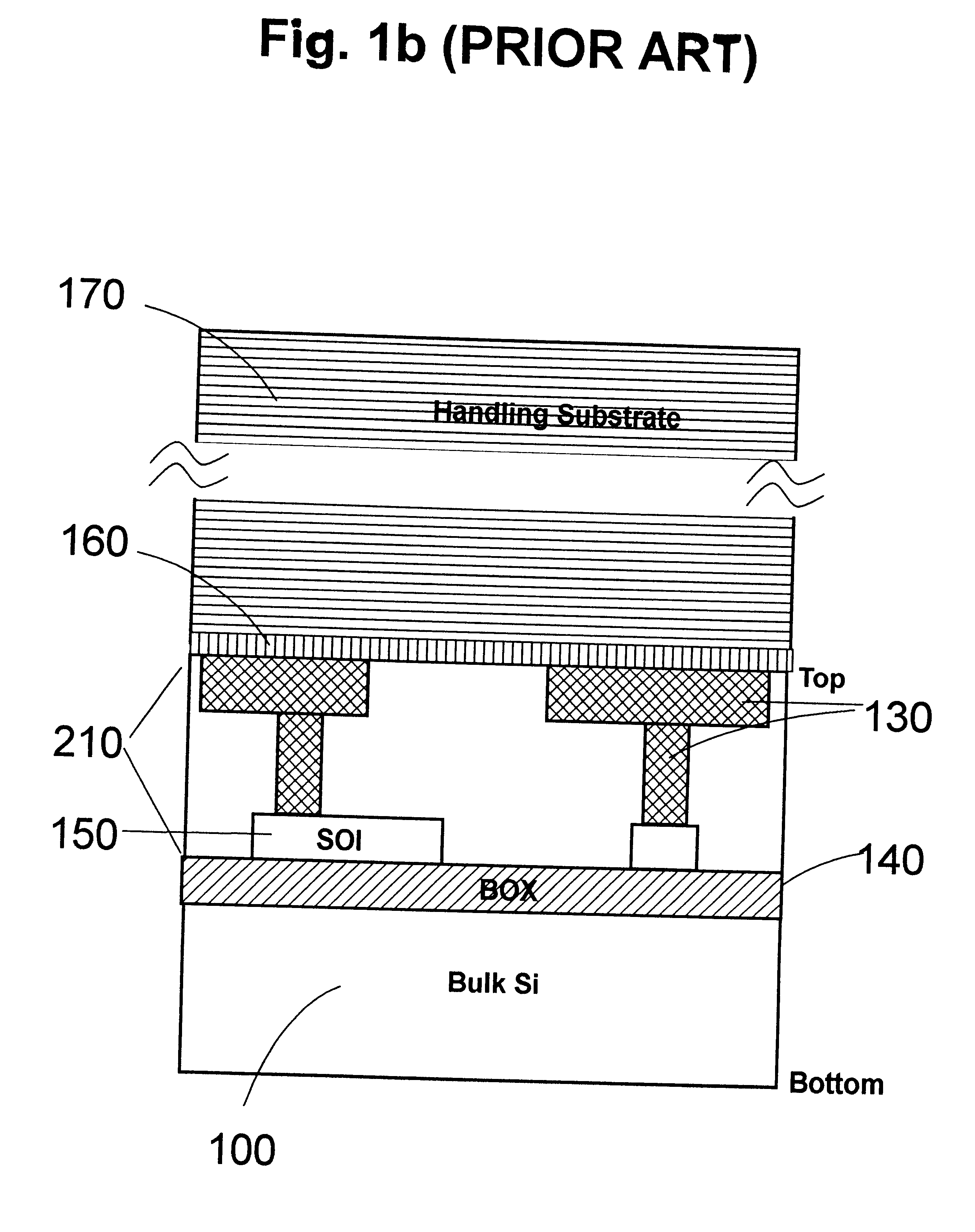

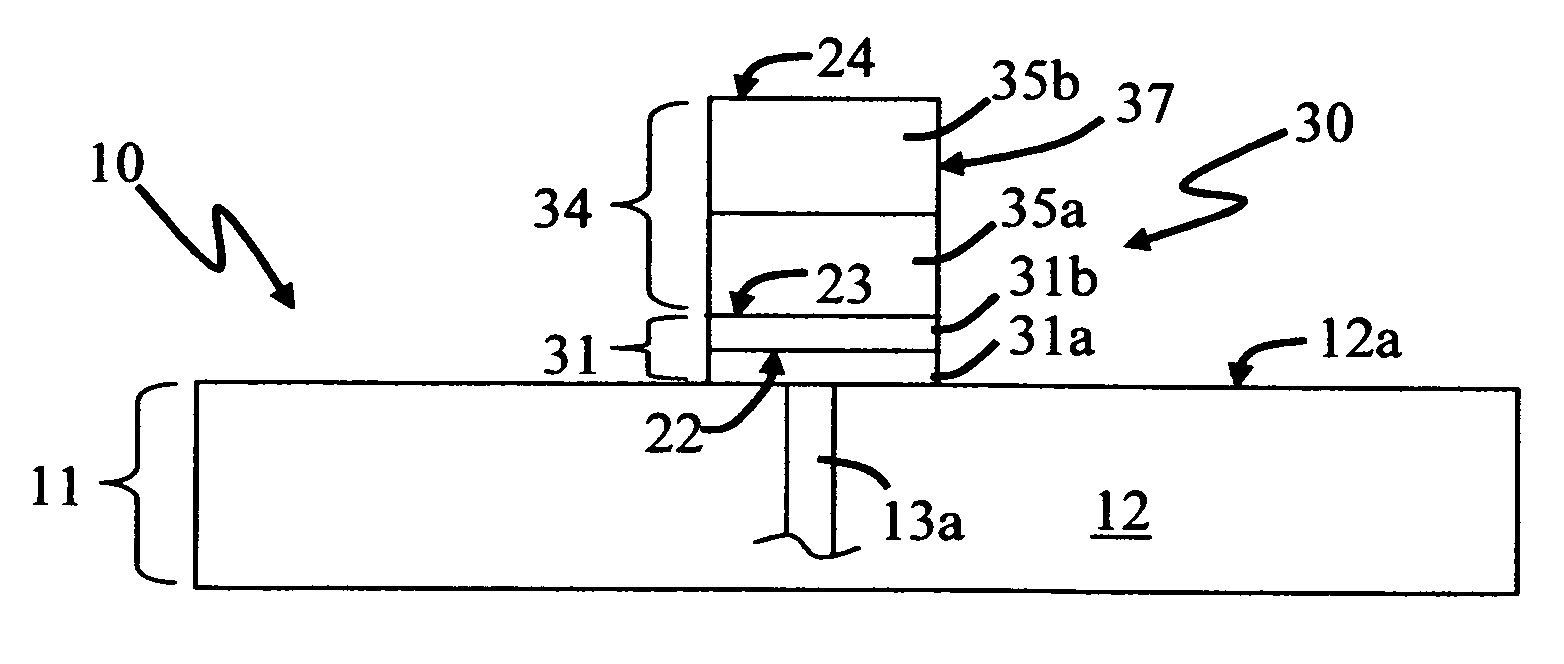

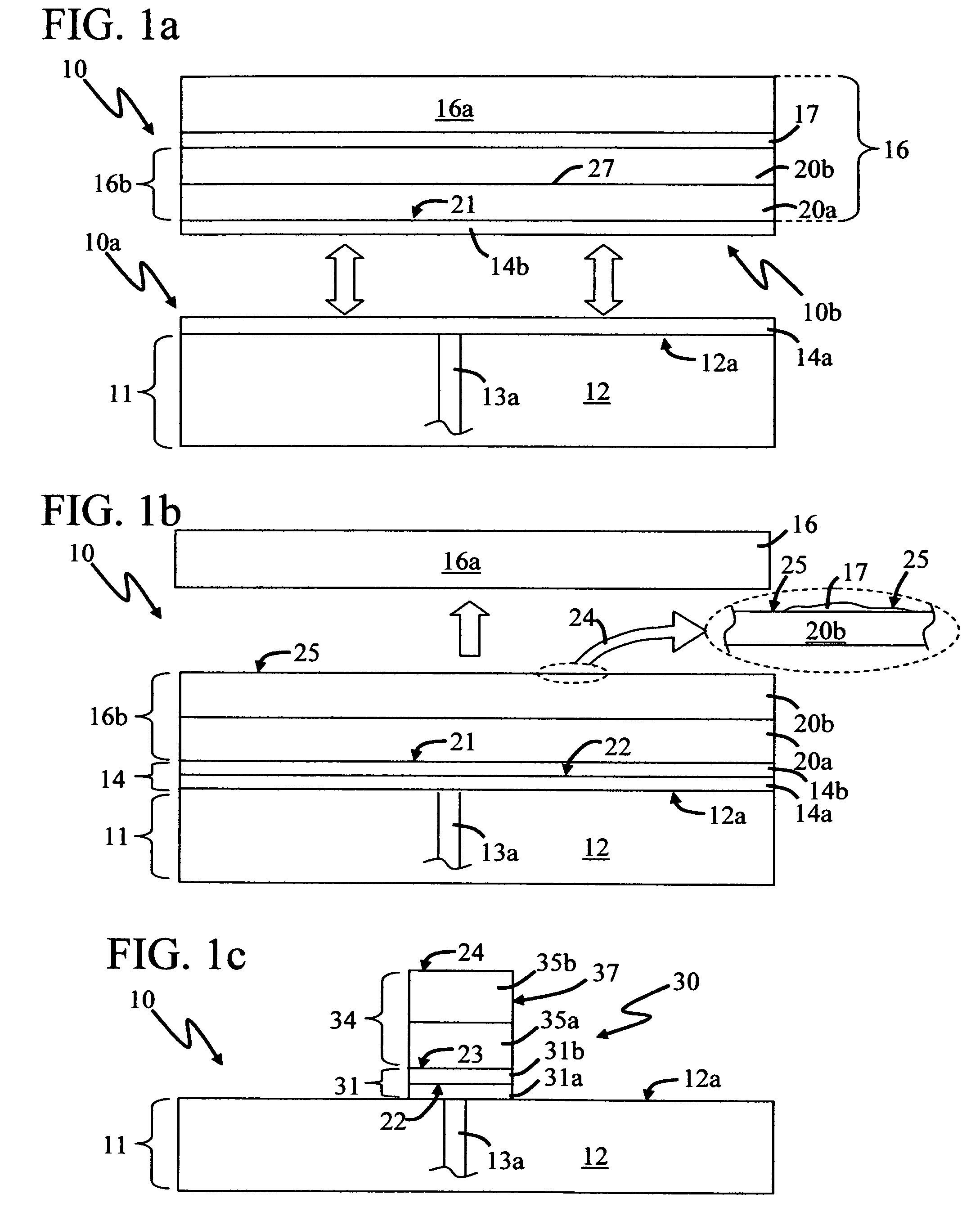

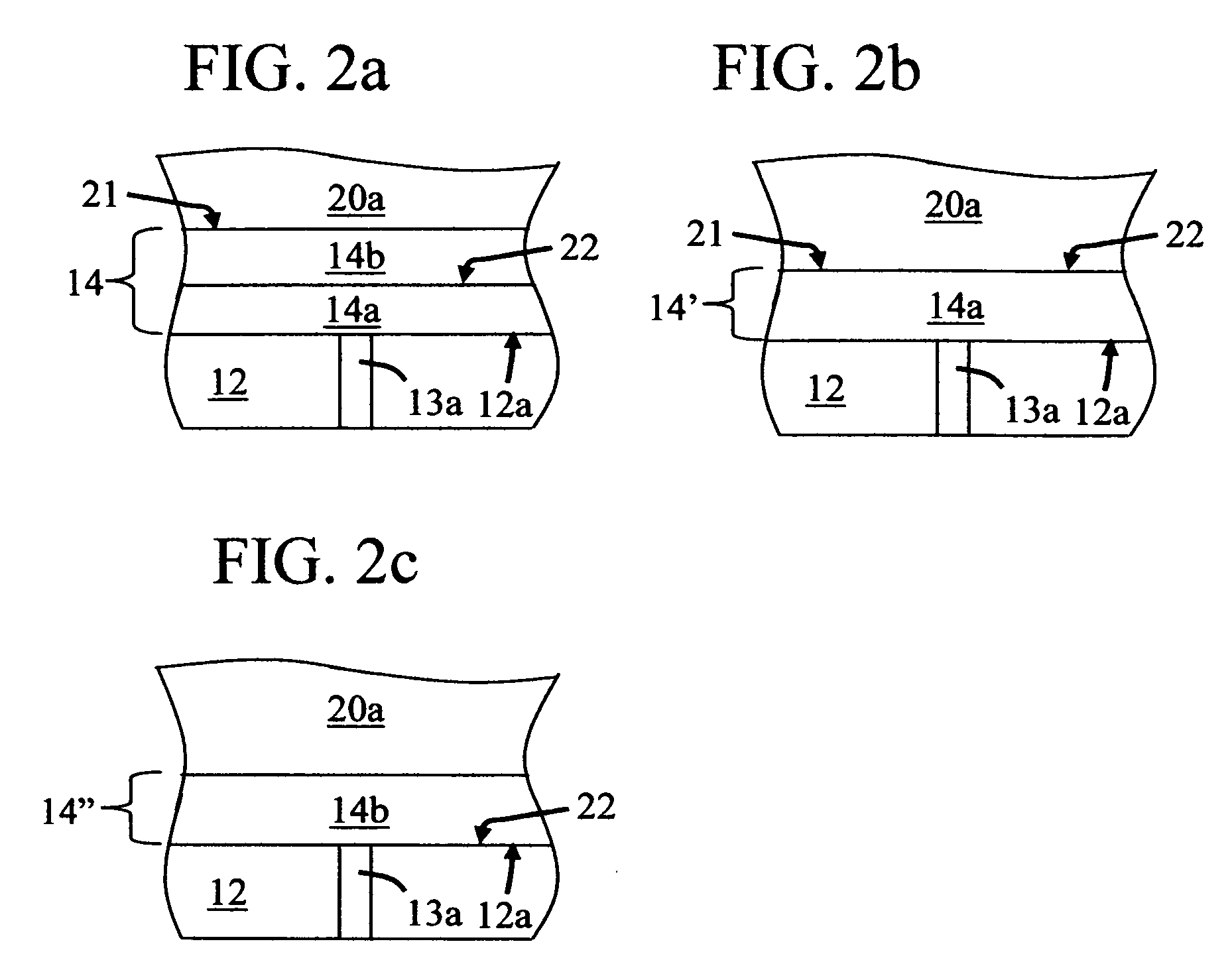

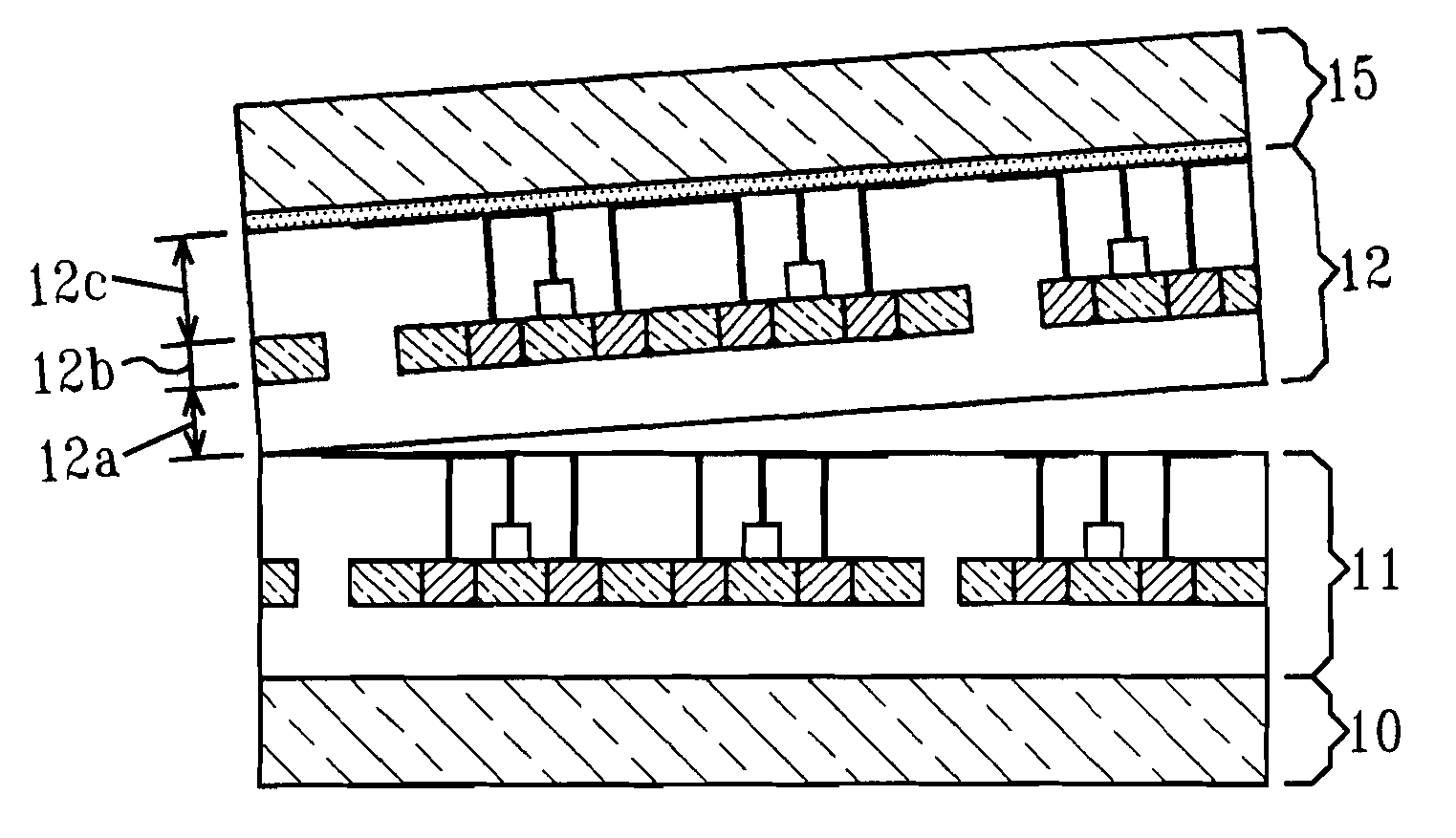

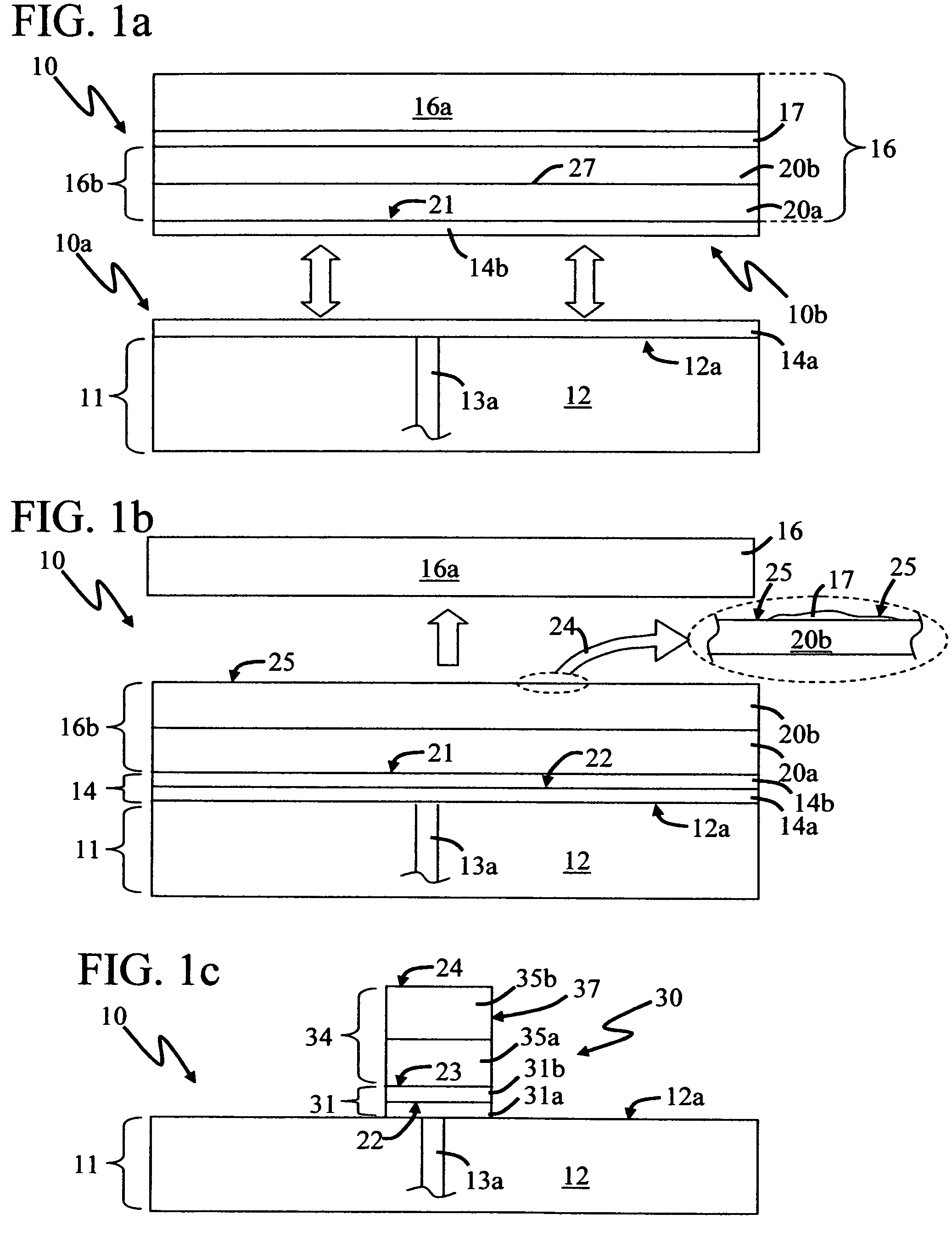

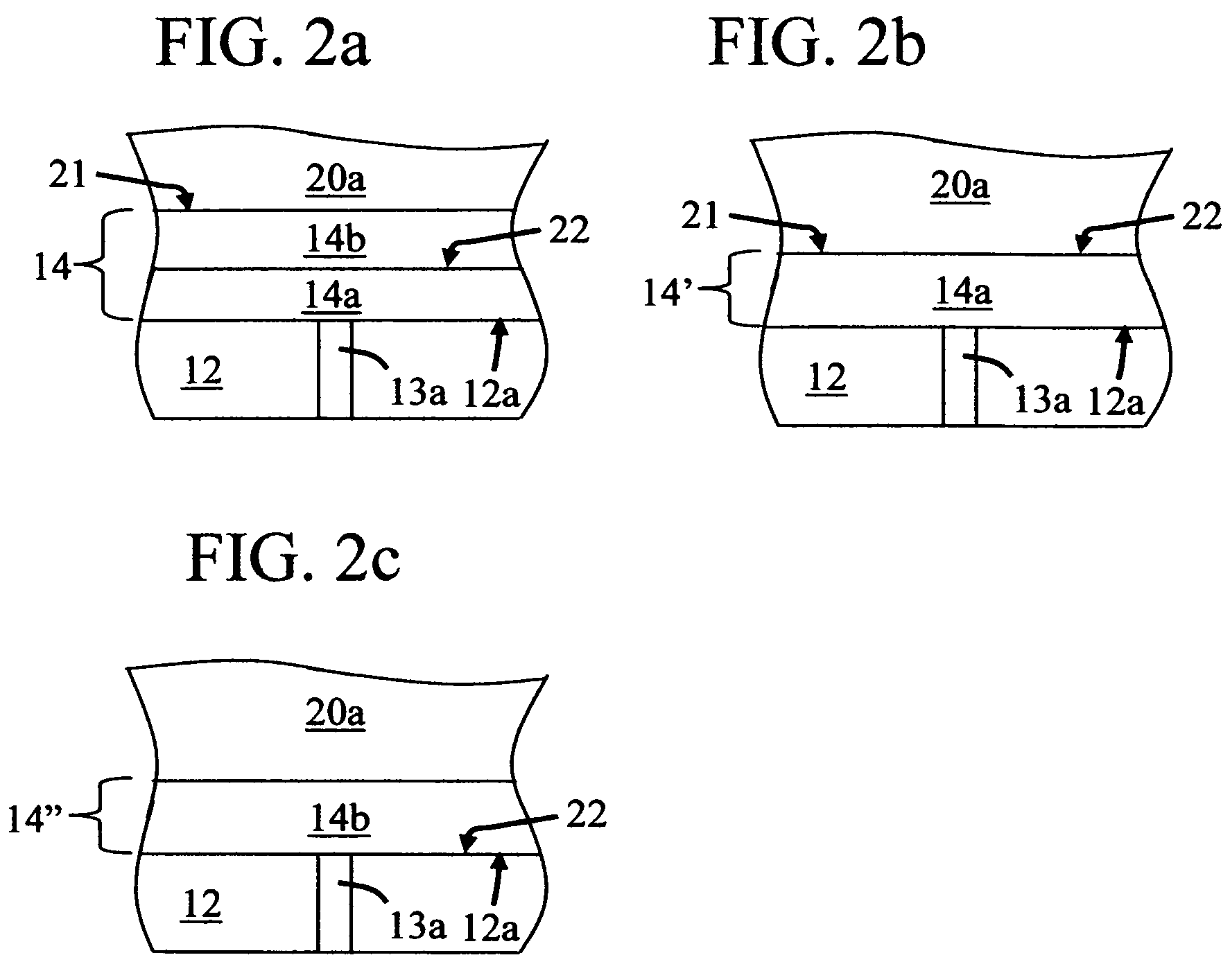

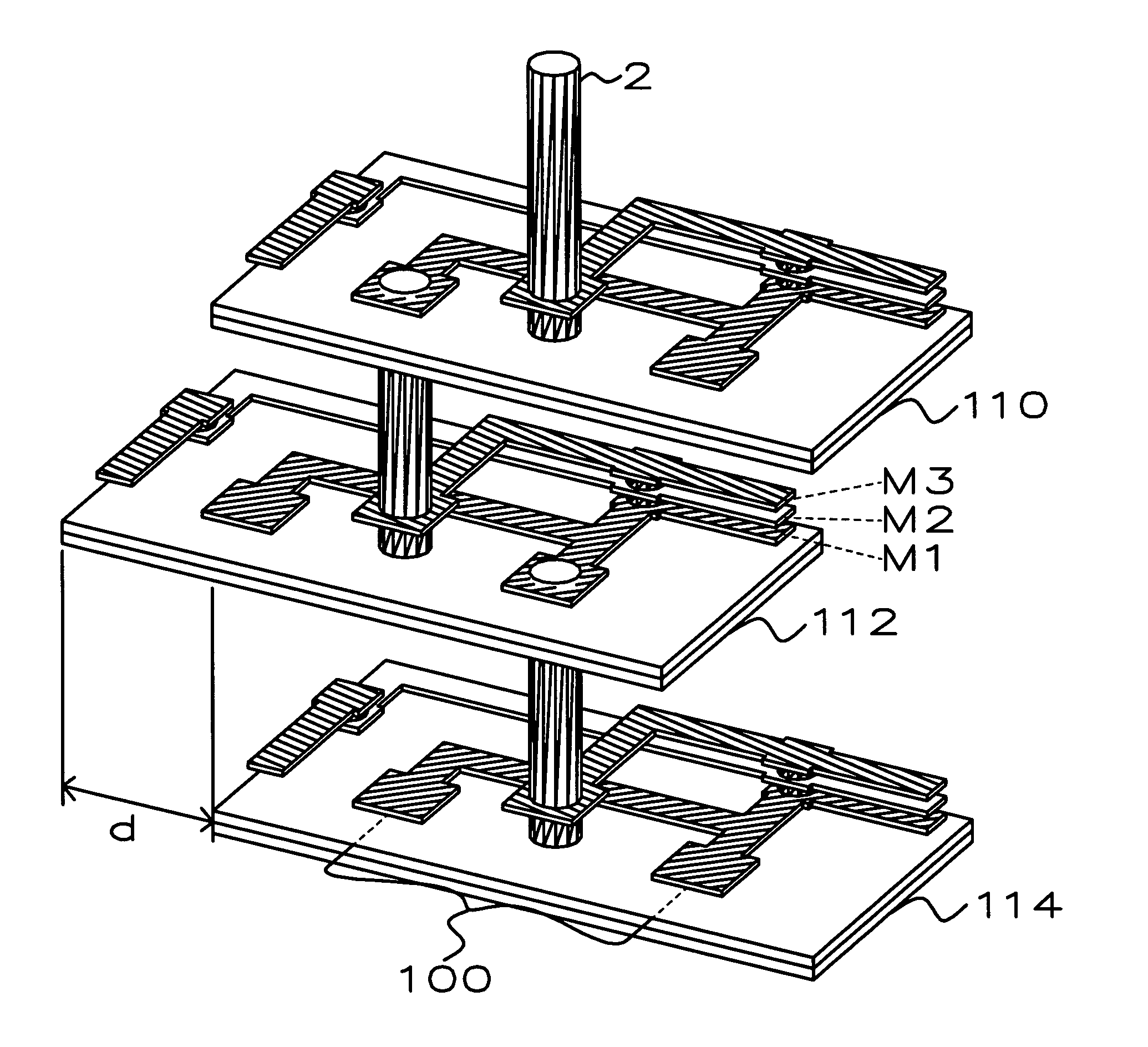

An assembly consisting of three dimensional stacked SOI chips, and a method of forming such integrated circuit assembly, each of the SOI chips including a handler making mechanical contact to a first metallization pattern making electrical contact to a semiconductor device. The metalized pattern, in turn, contacts a second metallization pattern positioned on an opposite surface of the semiconductor device. The method of fabricating the three-dimensional IC assembly includes the steps of: a) providing a substrate having a third metalized pattern on a first surface of the substrate; b) aligning one of the SOI chips on the first surface of the substrate, by having the second metallization pattern of the SOI chip make electrical contact with the third metalized pattern of the substrate; c) removing the handler from the SOI chip, exposing the first metallization pattern of the SOI chip; d) aligning a second one of the SOI chips with the first SOI chip, having the second metallization pattern of the second SOI chip make electrical contact to the exposed first metallization pattern of the first SOI chip; and e) repeating steps c) and d) for mounting subsequent SOI chips one on top of the other.

Owner:IBM CORP

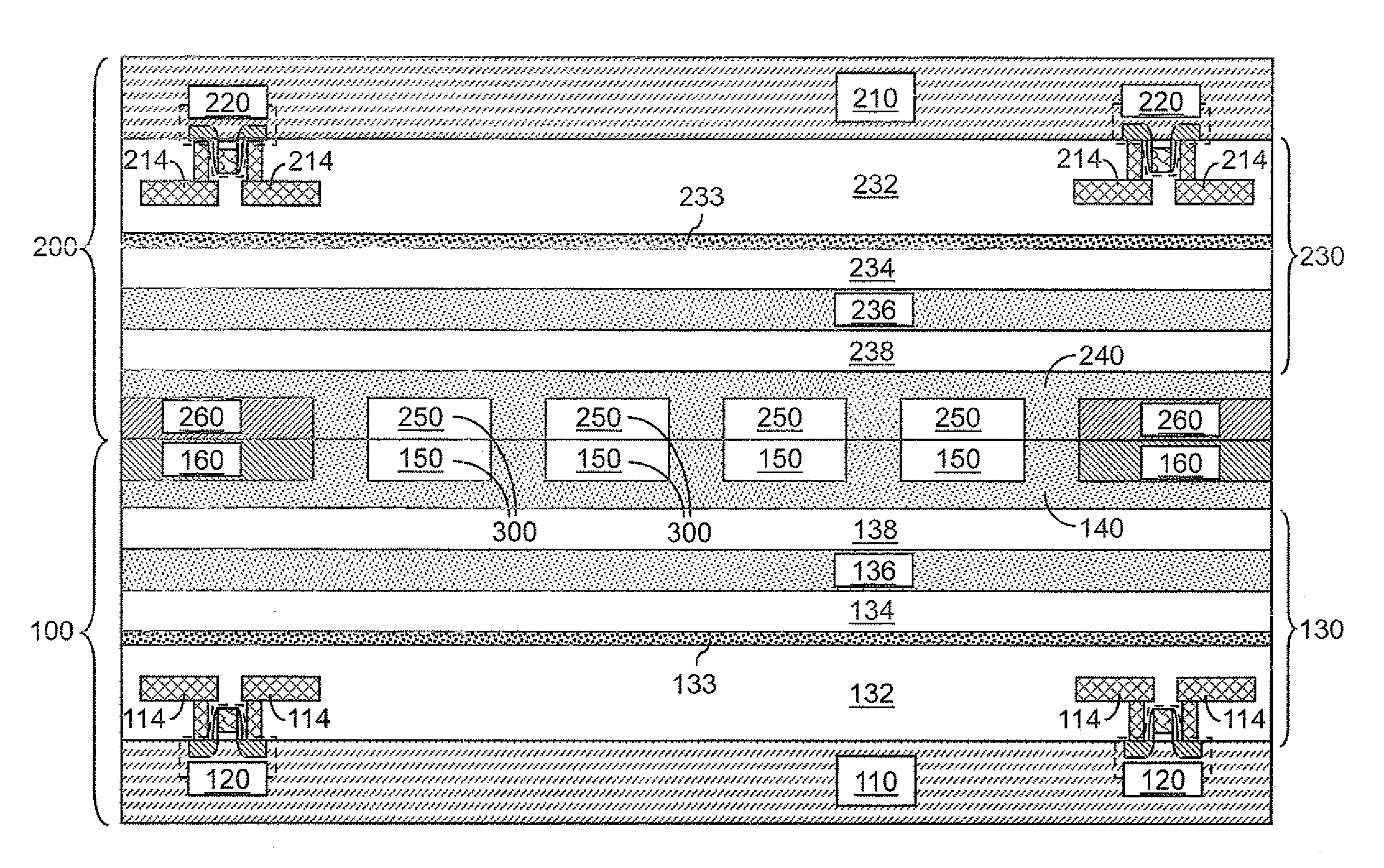

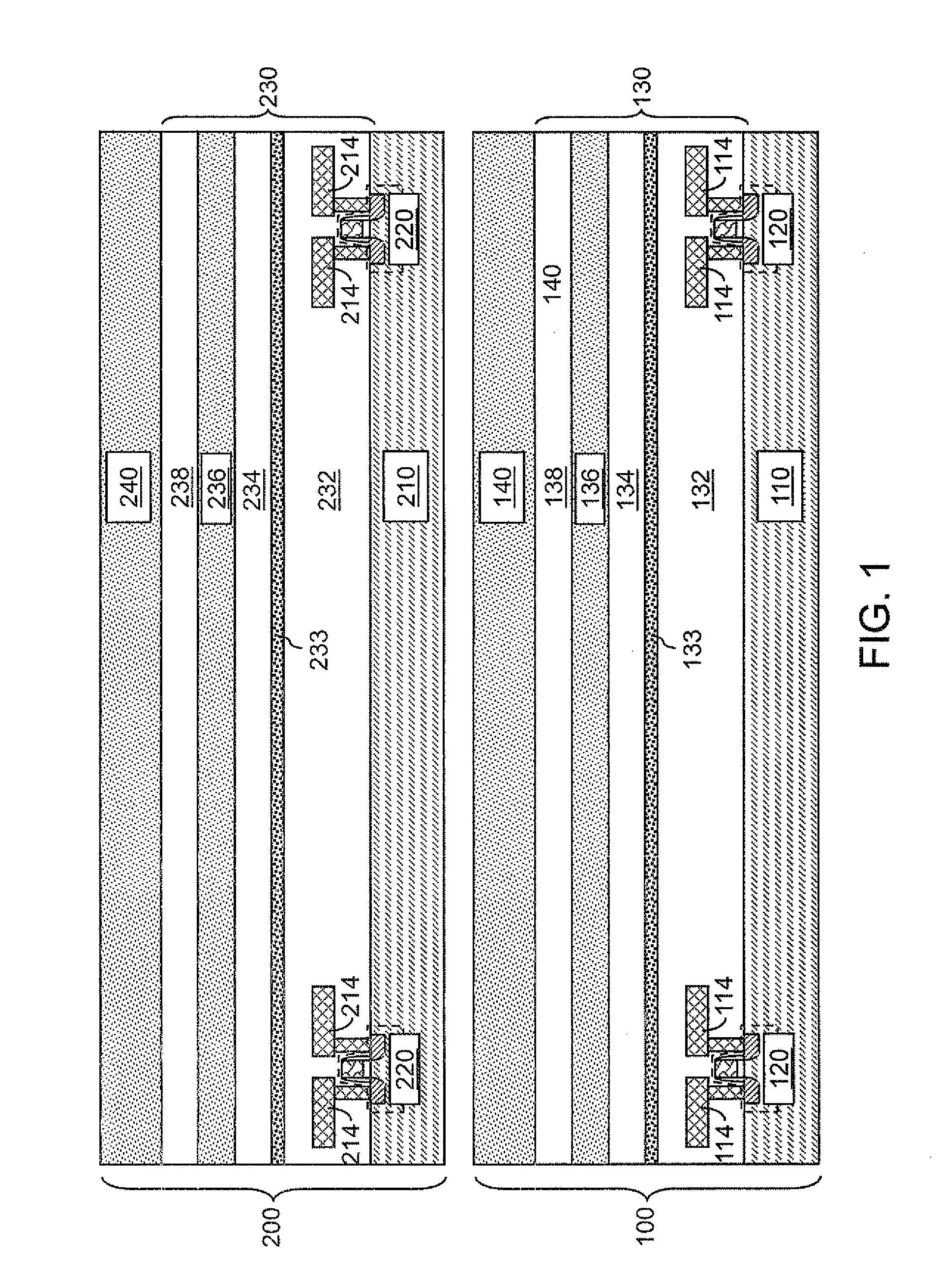

Hybrid bonding interface for 3-dimensional chip integration

ActiveUS20110101537A1Semiconductor/solid-state device detailsSolid-state devicesDielectricBond interface

Each of a first substrate and a second substrate includes a surface having a diffusion resistant dielectric material such as silicon nitride. Recessed regions are formed in the diffusion resistant dielectric material and filled with a bondable dielectric material. The patterns of the metal pads and bondable dielectric material portions in the first and second substrates can have a mirror symmetry. The first and second substrates are brought into physical contact and bonded employing contacts between metal pads and contacts between the bondable dielectric material portions. Through-substrate-via (TSV) structures are formed through bonded dielectric material portions. The interface between each pair of bonded dielectric material portions located around a TSV structure is encapsulated by two diffusion resistant dielectric material layers so that diffusion of metal at a bonding interface is contained within each pair of bonded dielectric material portions.

Owner:GLOBALFOUNDRIES US INC

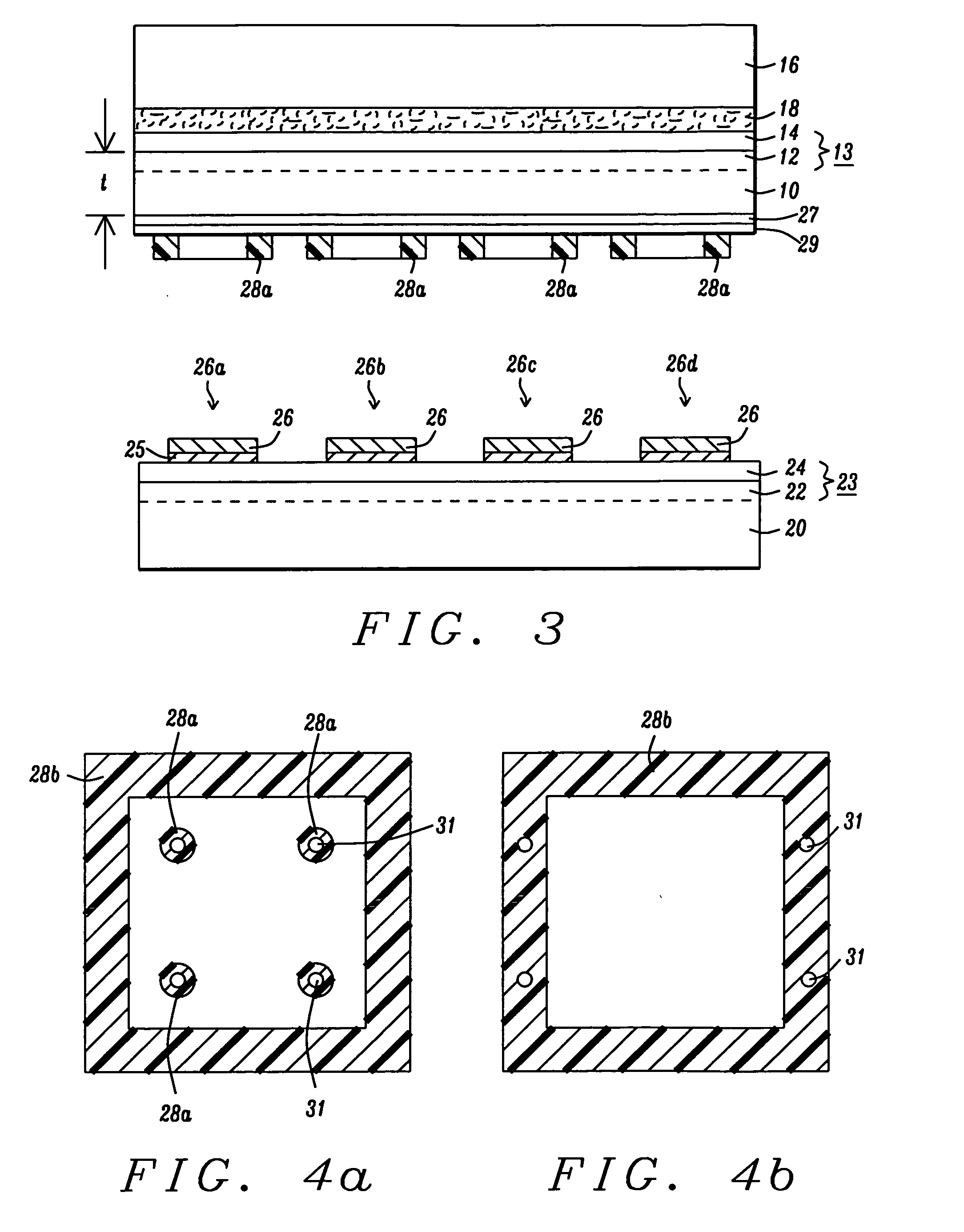

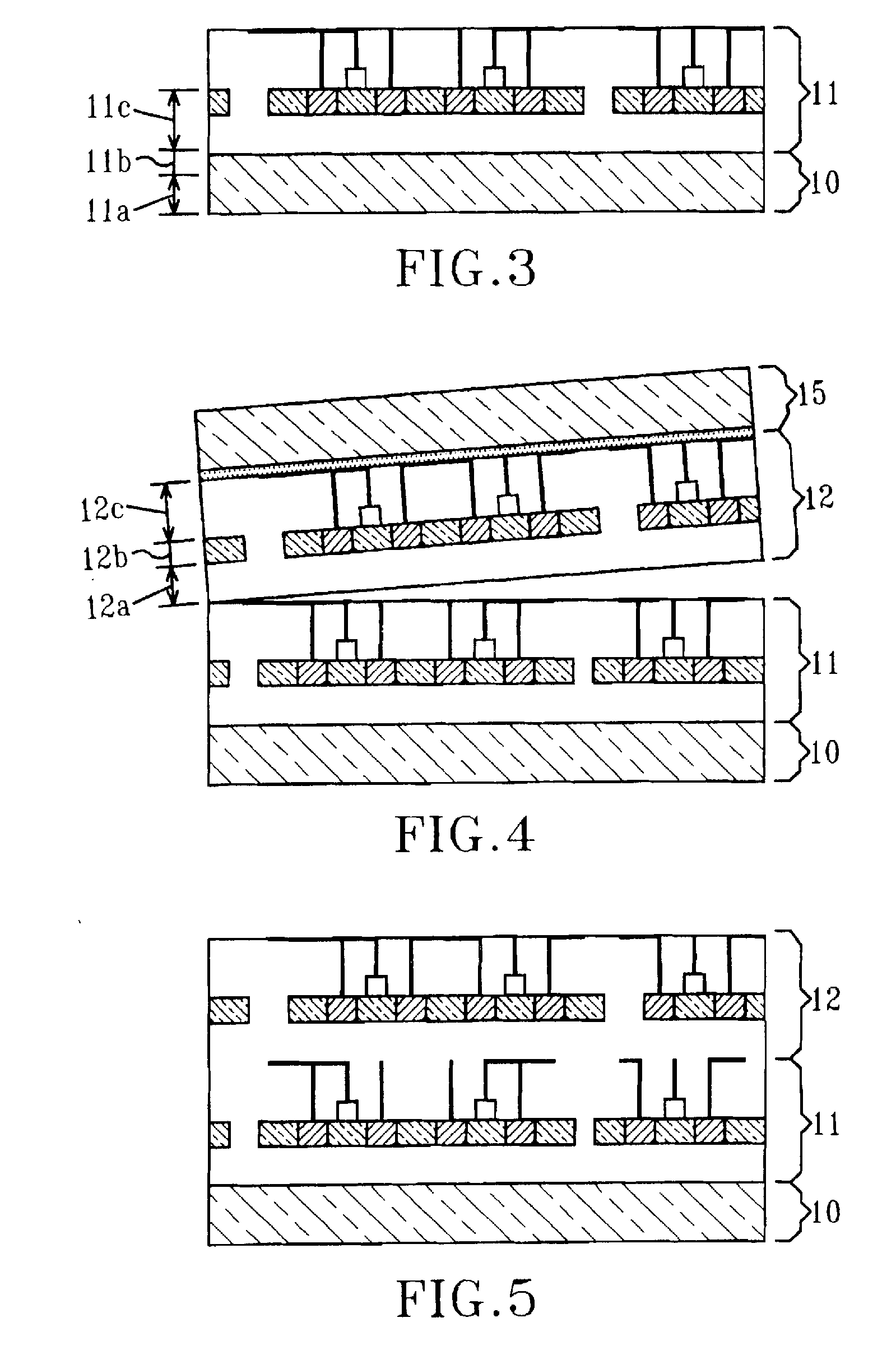

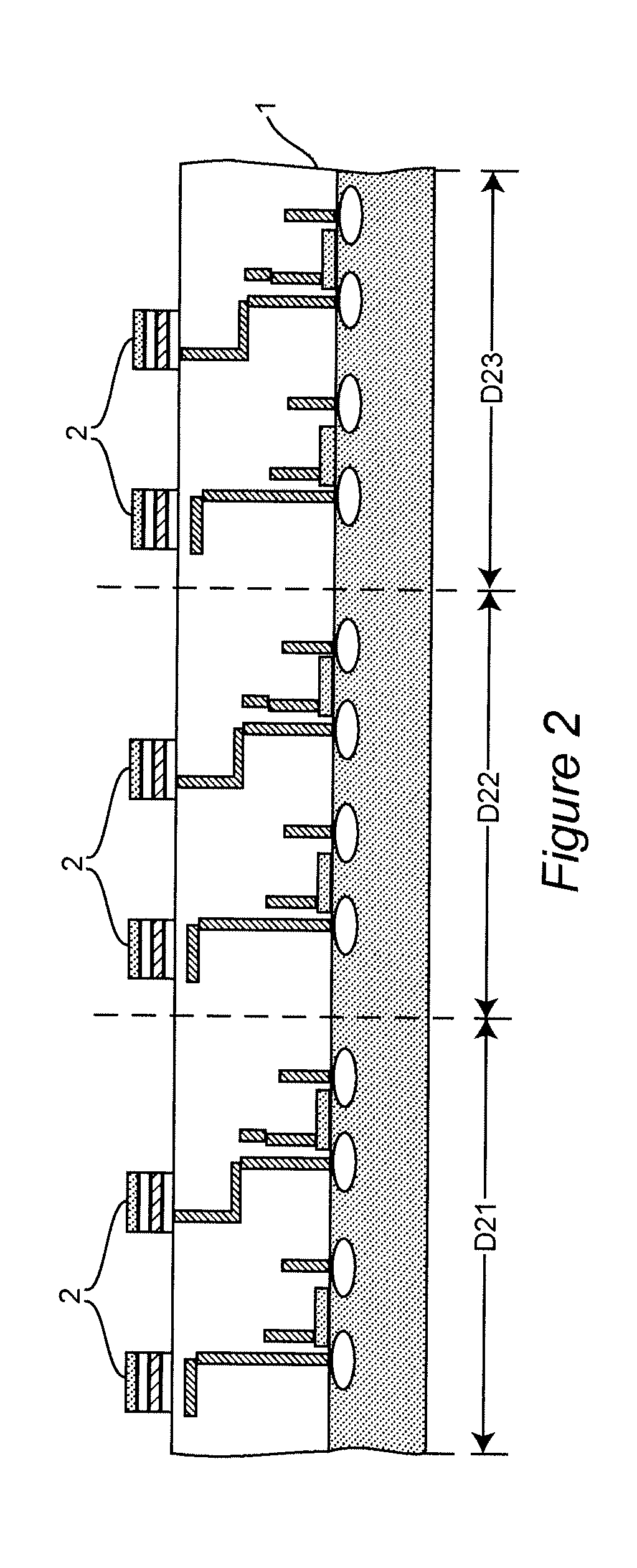

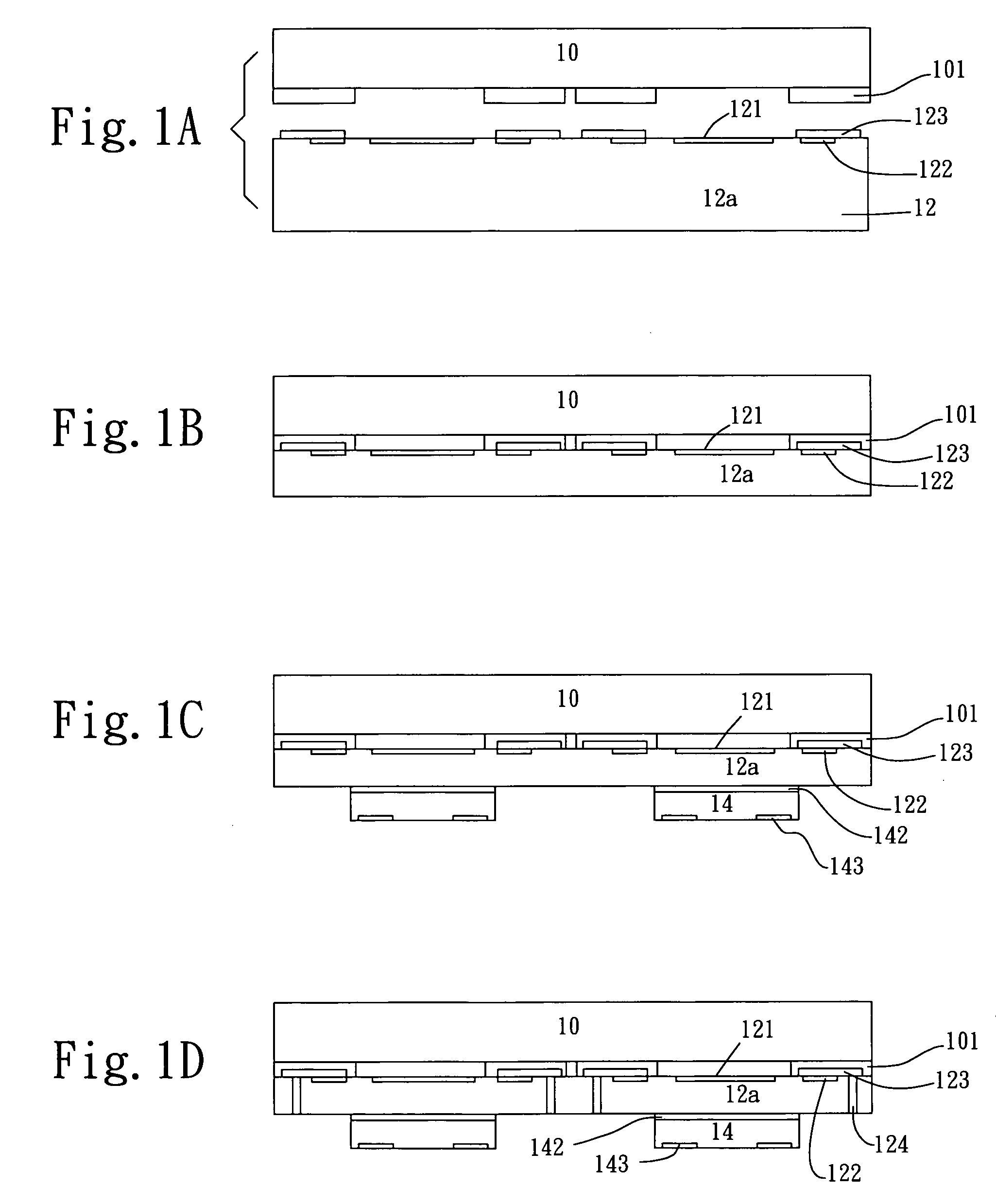

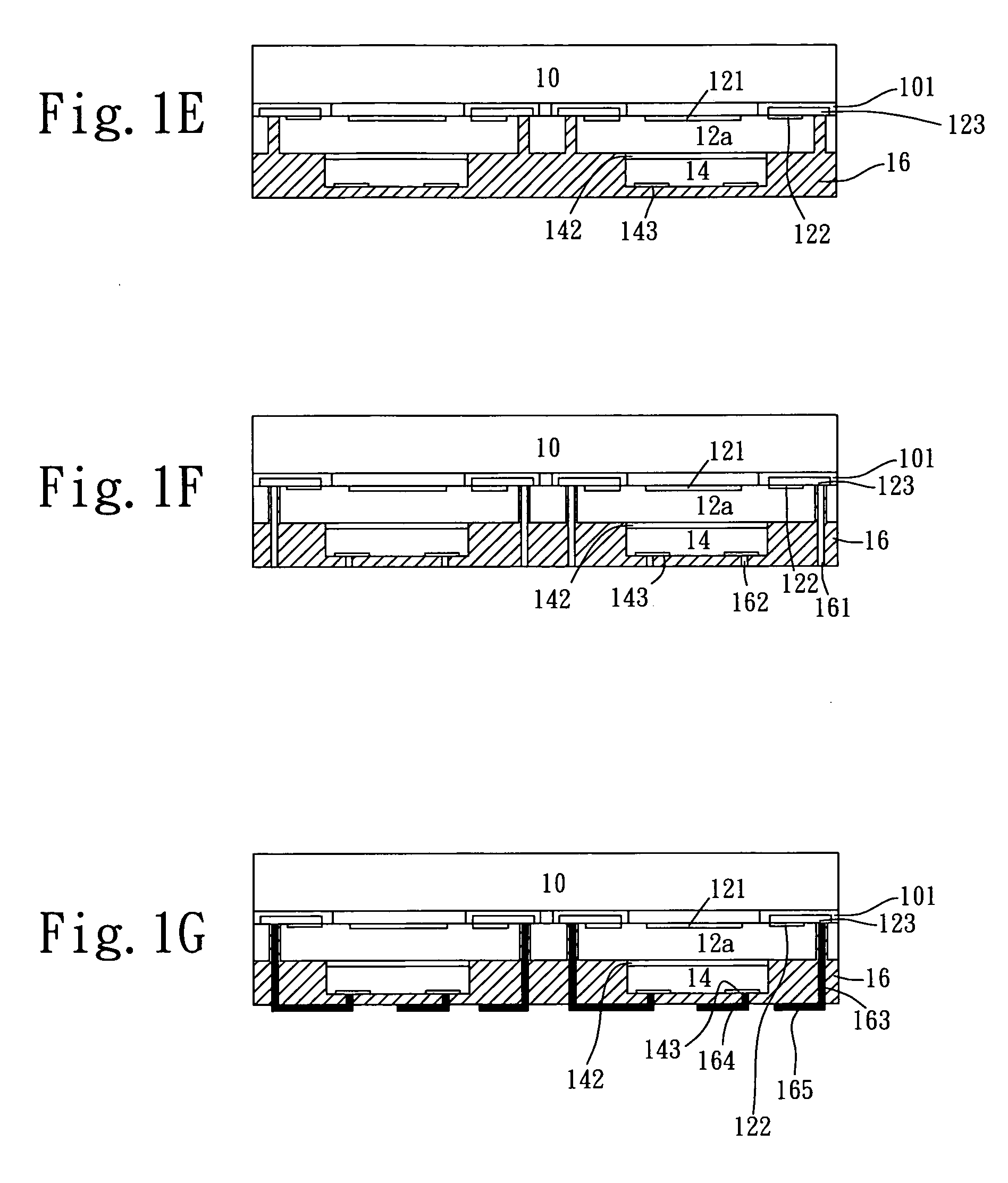

Accessible chip stack and process of manufacturing thereof

InactiveUS7528494B2Readily capable being thinnedYield maximizationSemiconductor/solid-state device detailsSolid-state devicesEngineeringThree-dimensional integrated circuit

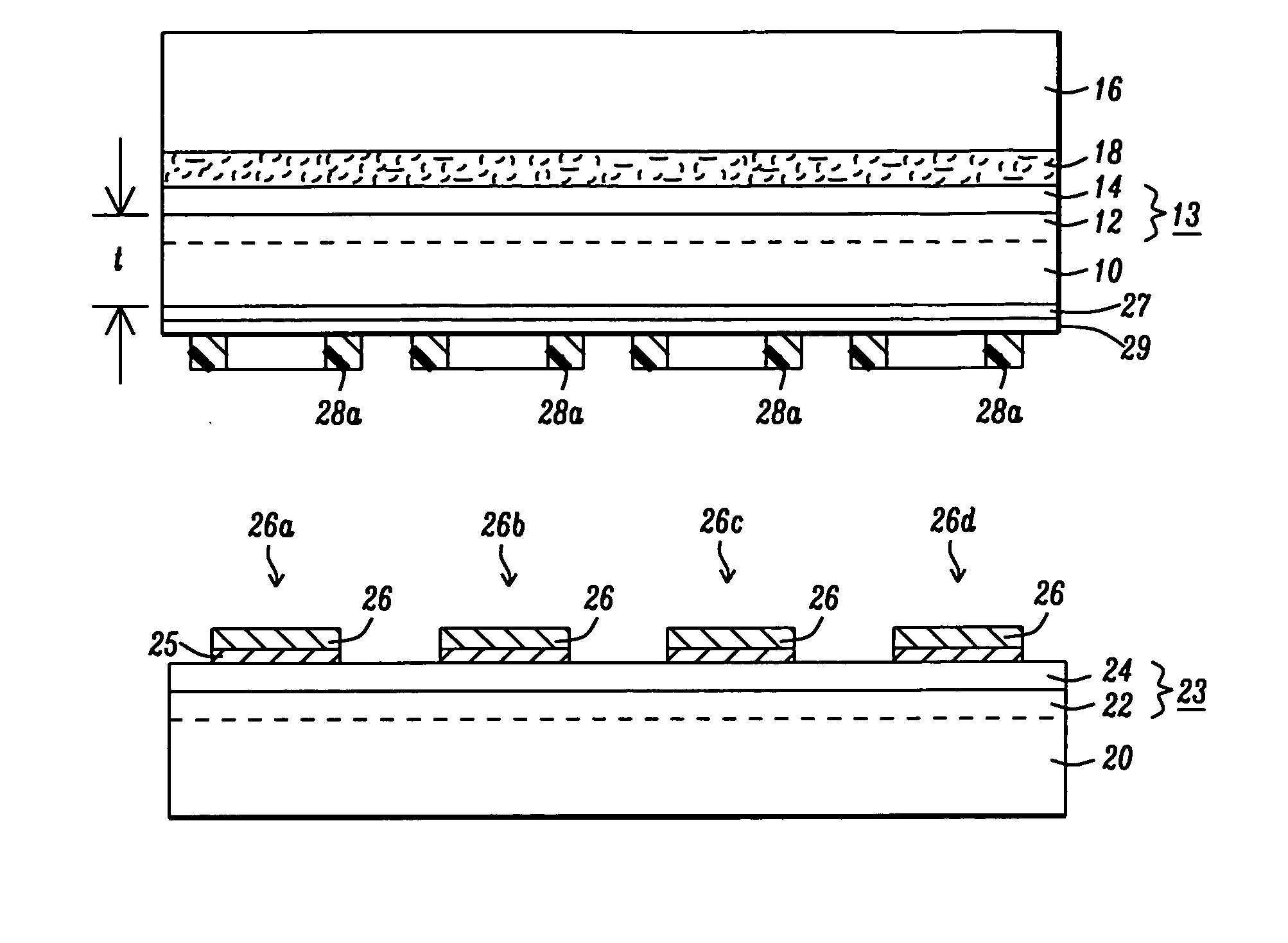

A process of manufacturing a three-dimensional integrated circuit chip or wafer assembly and, more particularly, a processing of chips while arranged on a wafer prior to orienting the chips into stacks. Also disclosed is the manufacture of the three-dimensional integrated circuit wherein the chip density can be very high and processed while the wafers are still intact and generally of planar constructions.

Owner:ALSEPHINA INNOVATIONS INC

Three-dimensional integrated circuit structure

InactiveUS20070077694A1Solid-state devicesSemiconductor/solid-state device manufacturingSemiconductor structureDevice material

A semiconductor structure includes an interconnect region and a semiconductor stack bonded to the interconnect region through a bonding region. The stack includes at least two semiconductor layers having different electrical properties. The stack also includes single crystalline semiconductor material. The stack can be processed to form a mesa structure and the mesa structure can be processed to from a vertically oriented semiconductor device.

Owner:BESANG

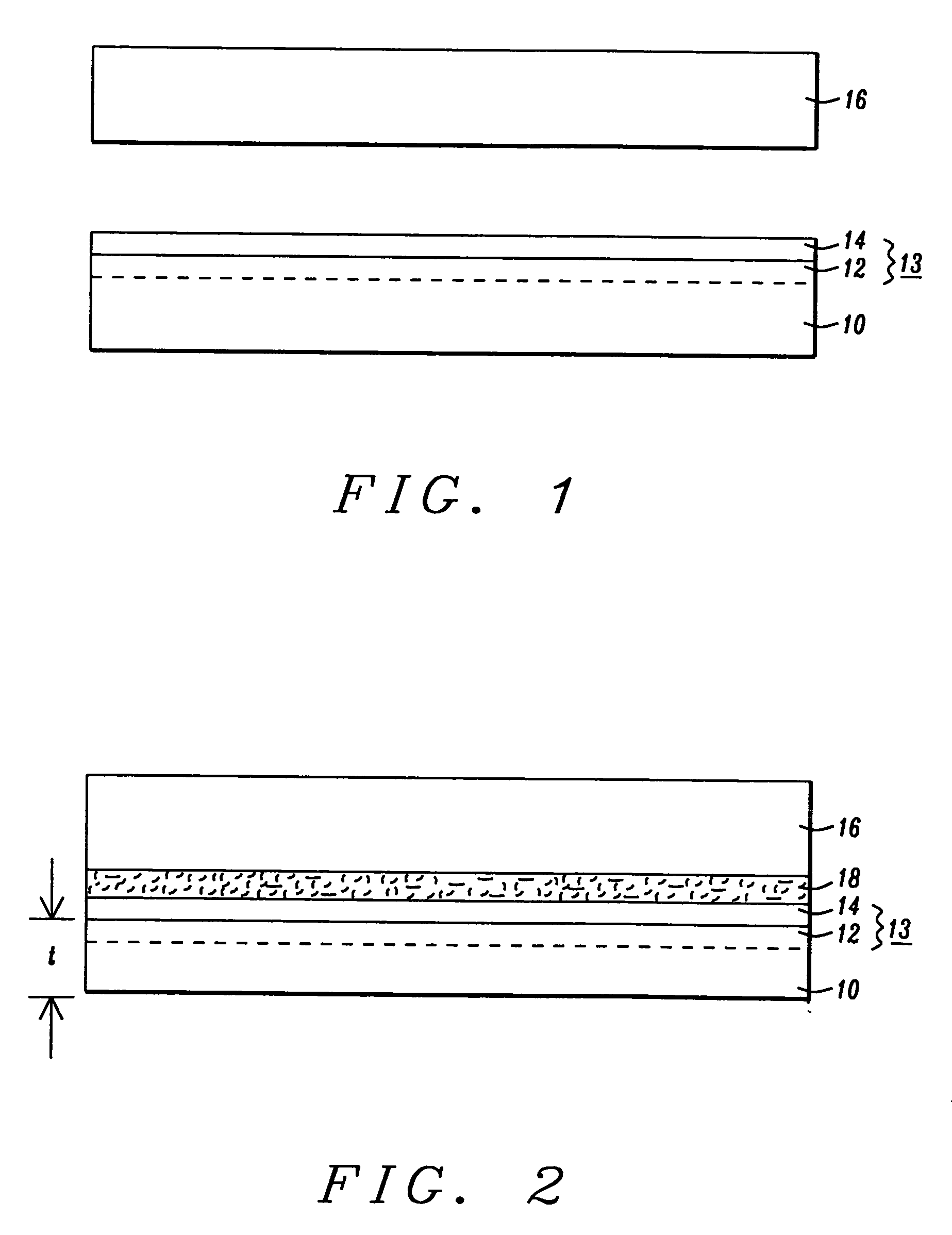

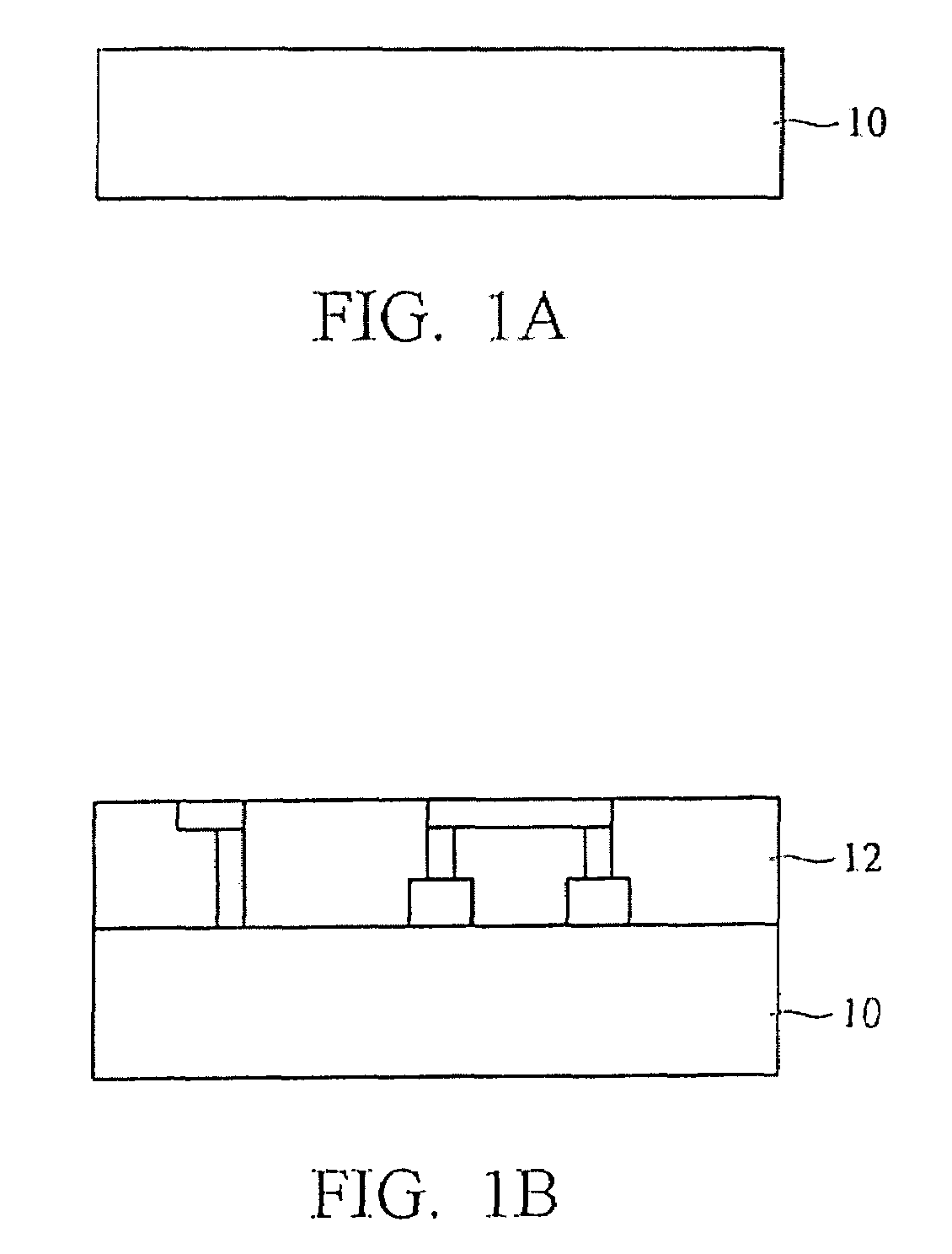

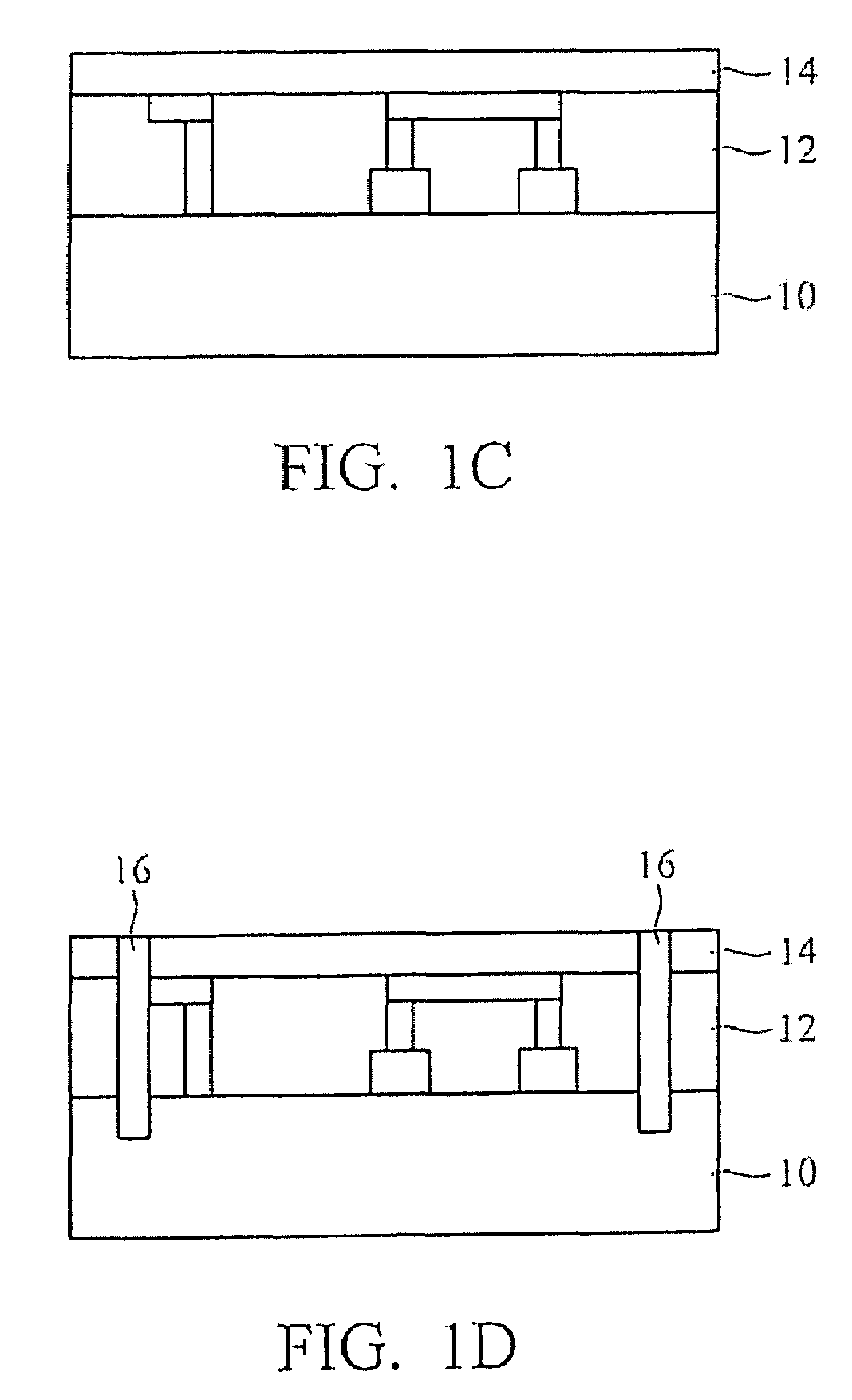

Method of stacking thin substrates by transfer bonding

InactiveUS20060057836A1Semiconductor/solid-state device detailsSolid-state devicesCost effectivenessAdhesive

This invention describes a method of stacking, bonding, and electrically interconnecting a plurality of thin integrated circuit wafers to form an interconnected stack of integrated circuit layers. The first integrated circuit layer is formed by conventional processing on a silicon wafer to the stage where bond pads are patterned on a wiring layer interconnecting the subjacent semiconductive devices. The remaining integrated circuit layers are formed by first processing a standard wafer to form integrated circuit devices and wiring levels up to but not including bond pads. Each of these wafers is mounted onto a handler wafer by its upper face with a sacrificial bonding agent. The wafer is thinned, permanently fastened to the top surface of the first base wafer by a non-conductive adhesive applied to the thinned under face, and dismounted from the handler. Vertical openings are etched through the thinned layer to the bond pads on the subjacent wafer. Robust conductive pass-through plugs with integrated upper bond pads are formed in the openings. Additional thinned integrated circuit layers may be prepared, thinned, cemented onto the stack. Wiring interconnections can be made between any two or more layers. The process is unique in that it can be used to further stack and interconnect any number of thinned wafer layers to form a three dimensional integrated circuits, including MEMS devices. This approach provides a low temperature wafer bonding method using an adhesive which results in process simplicity and cost effectiveness by eliminating an additional masking and patterning process for under bump metal thereby enabling standard wafers to be integrated into a 3D stack with existing wire bonded wafers.

Owner:AGENCY FOR SCI TECH & RES

Method to fill the gap between coupled wafers

ActiveUS7087538B2Protection gapSemiconductor/solid-state device detailsSolid-state devicesEngineeringThree-dimensional integrated circuit

A three-dimensional integrated circuit formed by applying a material to fill a gap between coupled wafers and slicing the coupled wafers into dice. A method for filling a gap between coupled wafers. Various embodiments include at least one of spinning a coupled wafer pair, drilling a hole into one of the coupled wafers, and using a vacuum to aid in the dispersion of the material.

Owner:TAHOE RES LTD

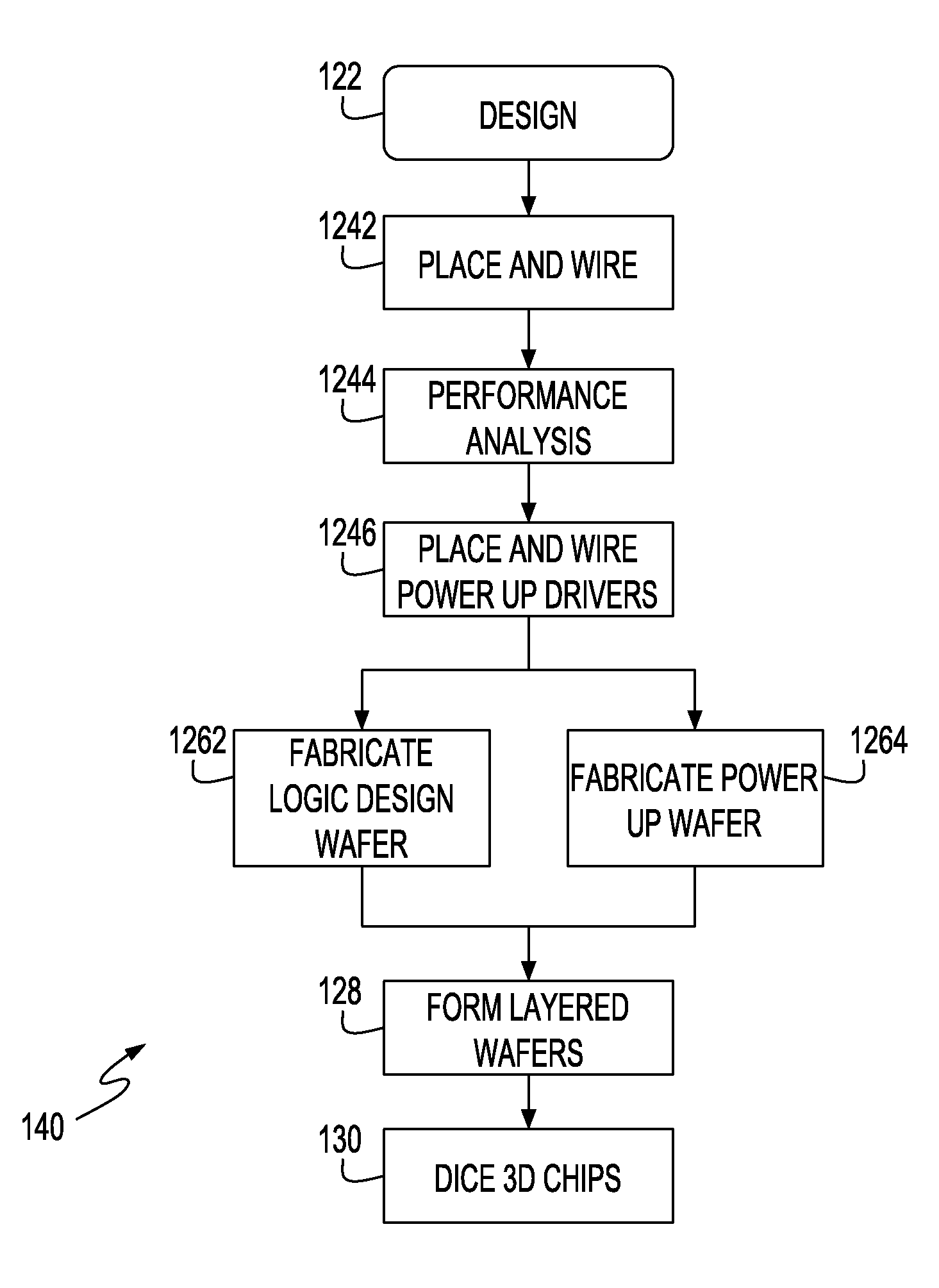

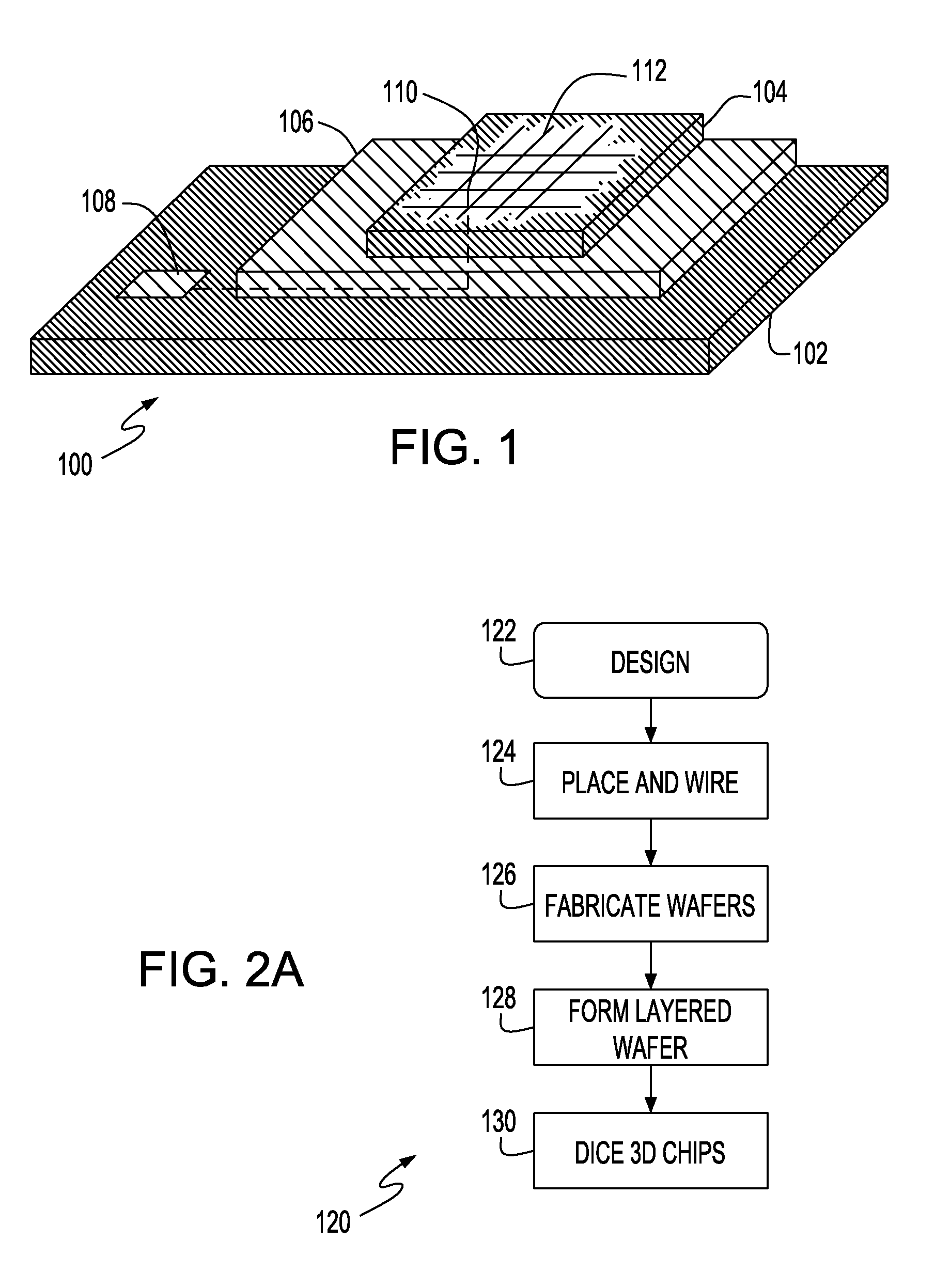

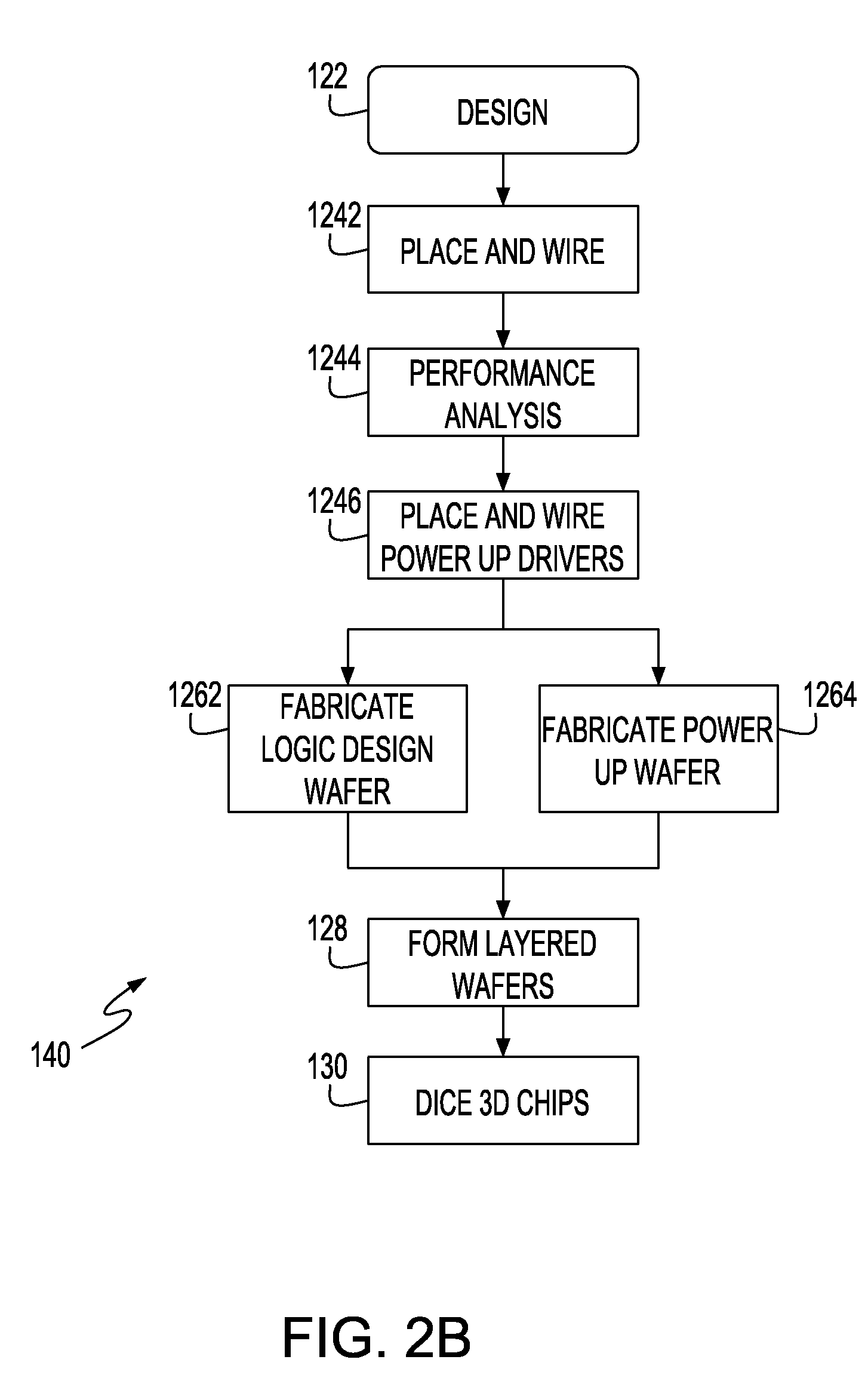

Three dimensional integrated circuit and method of design

InactiveUS20070287224A1Function increaseSimple designFluid pressure measurement by electric/magnetic elementsSolid-state devicesCMOSEngineering

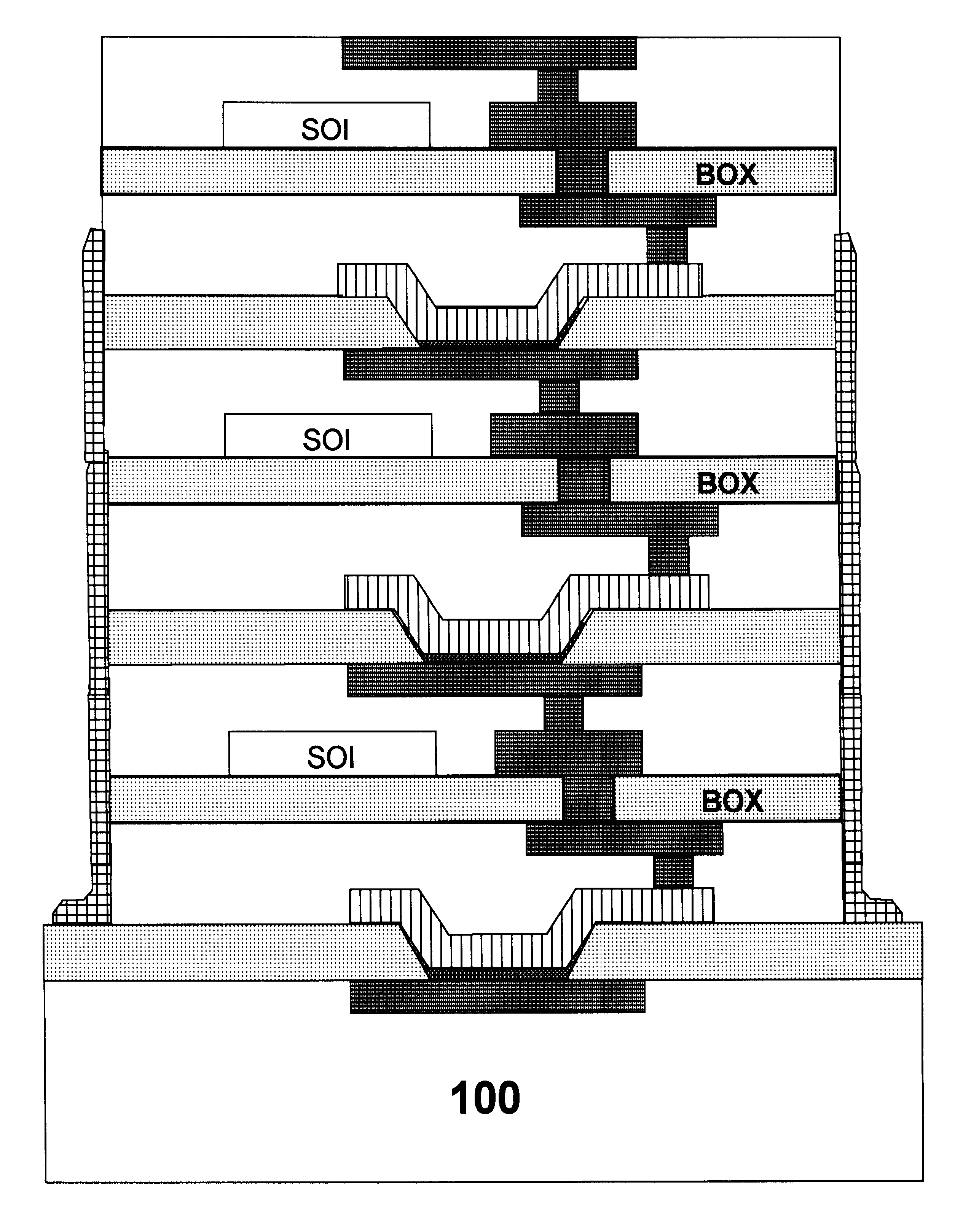

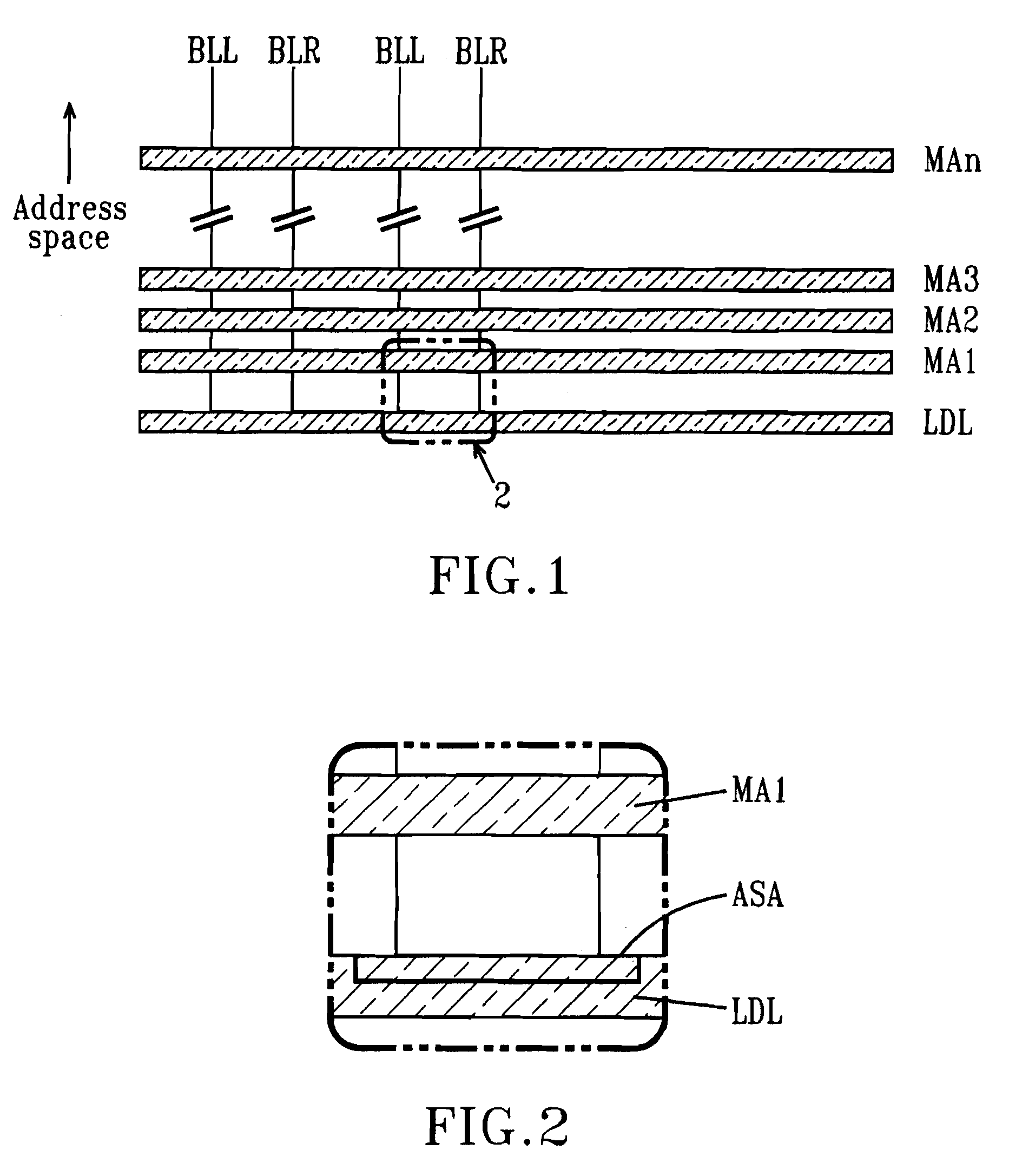

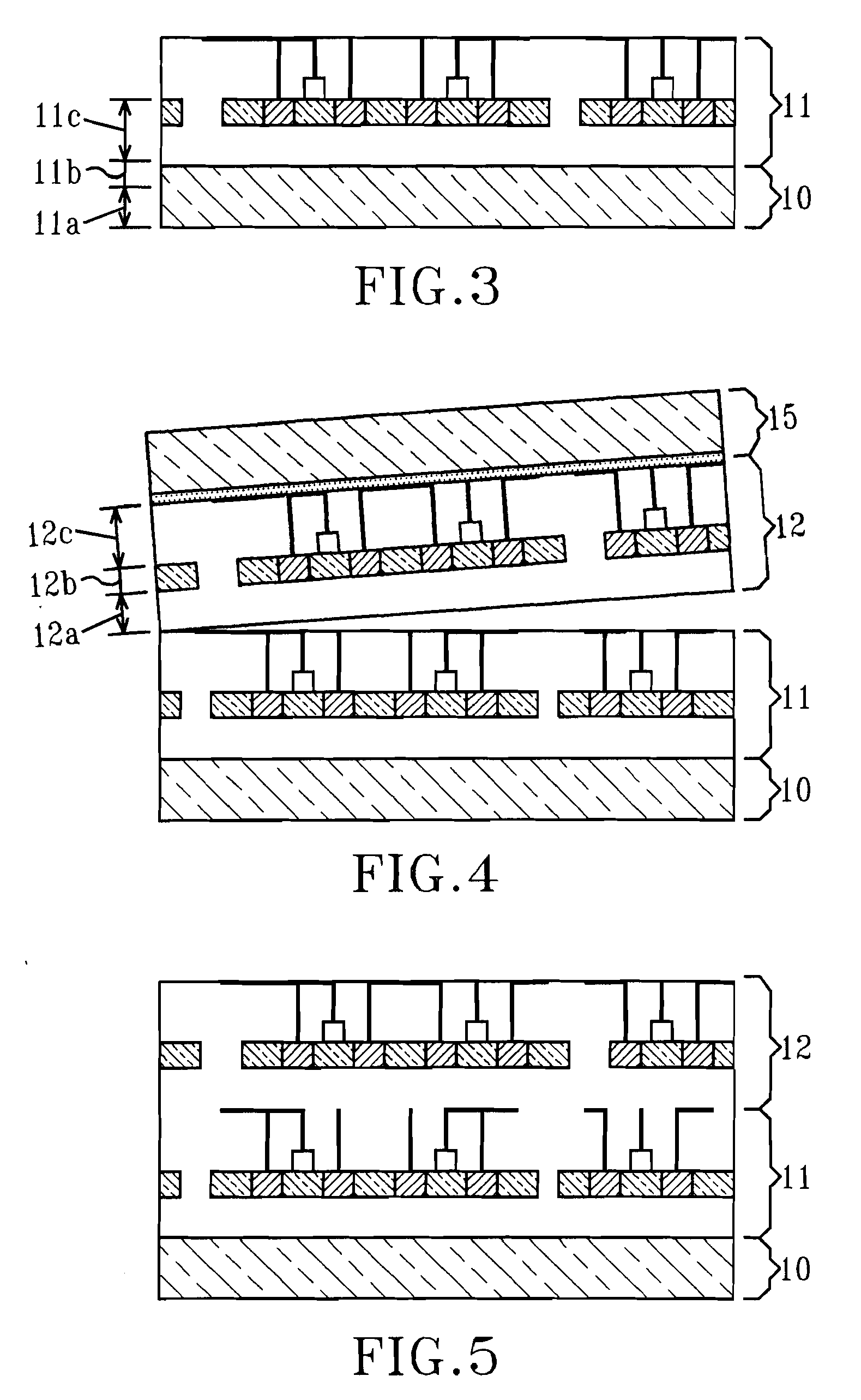

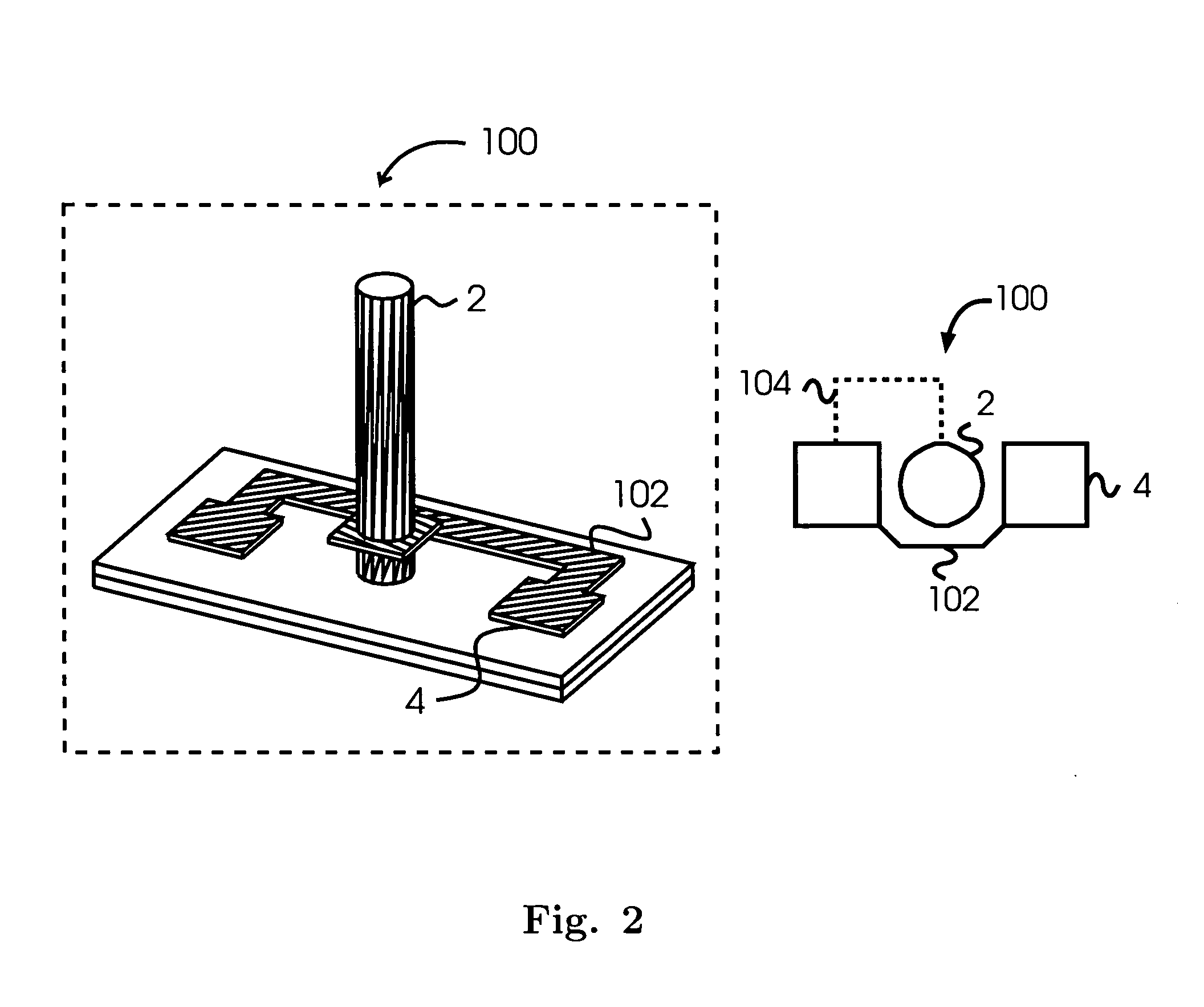

A three dimensional (3D) integrated circuit (IC), 3D IC chip and method of fabricating a 3D IC chip. The chip includes multiple layers of circuits, e.g., silicon insulator (SOI) CMOS IC layers, each including circuit elements. The layers may be formed in parallel and one layer attached to another to form a laminated 3D chip.

Owner:GLOBALFOUNDRIES INC

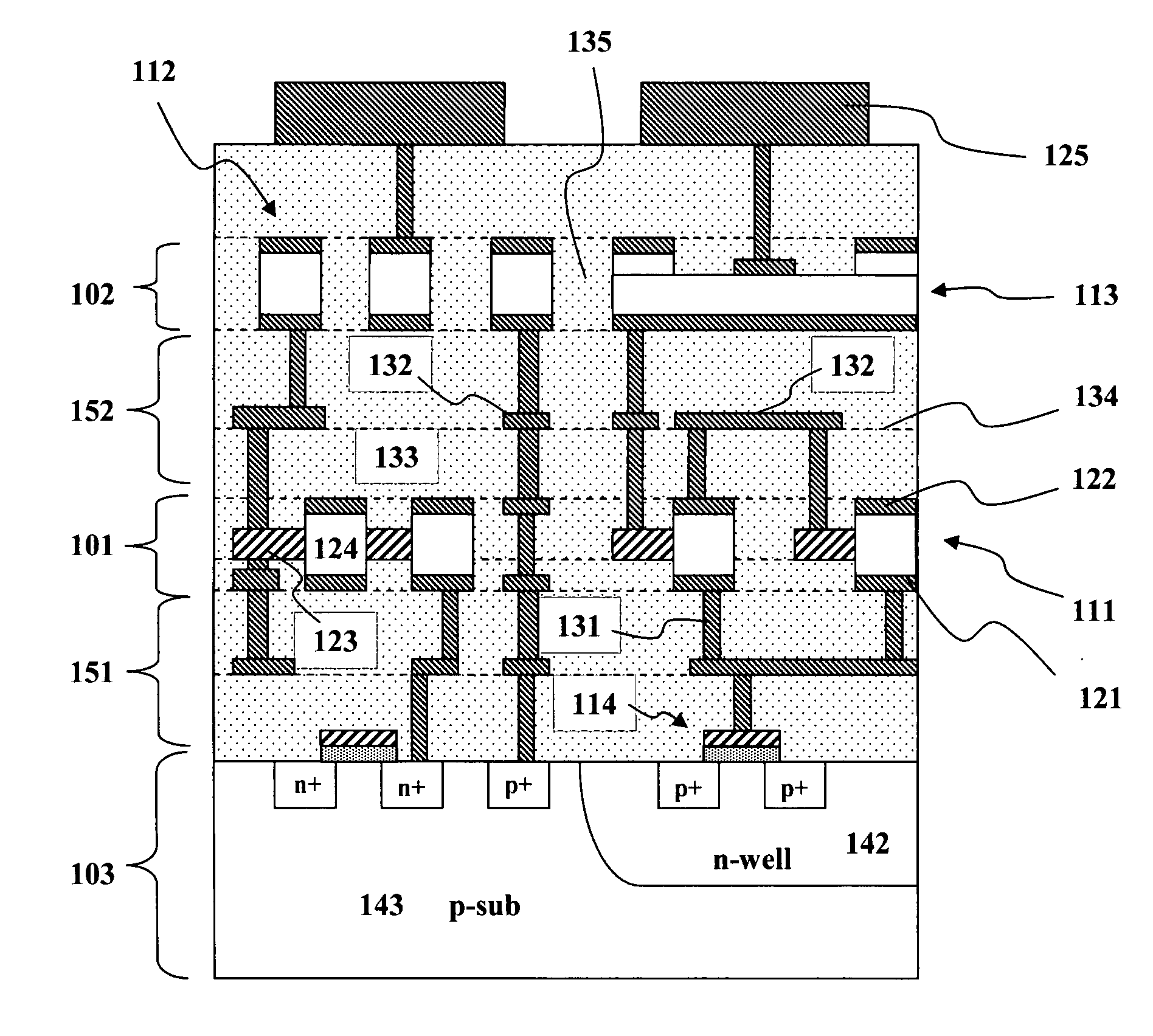

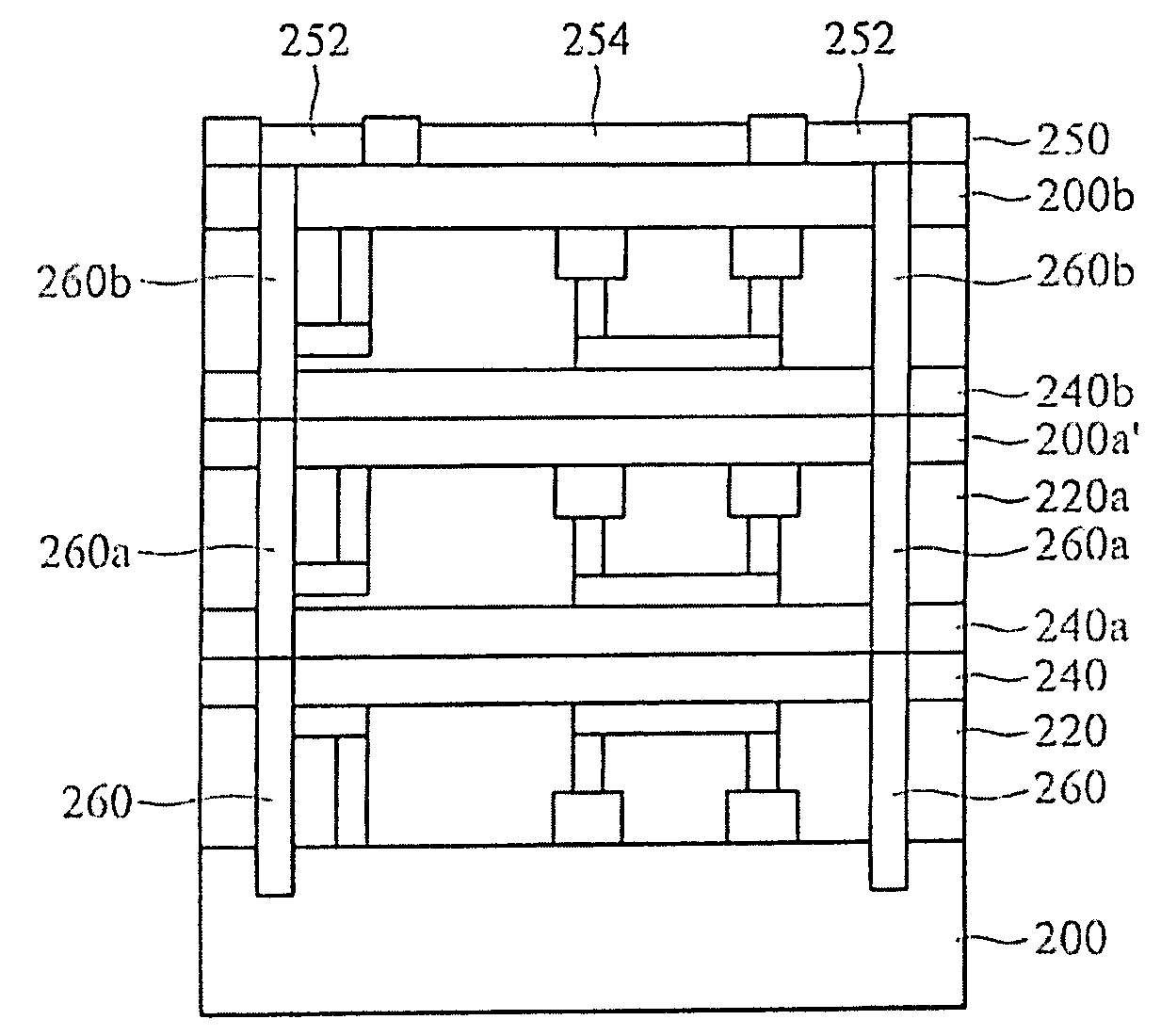

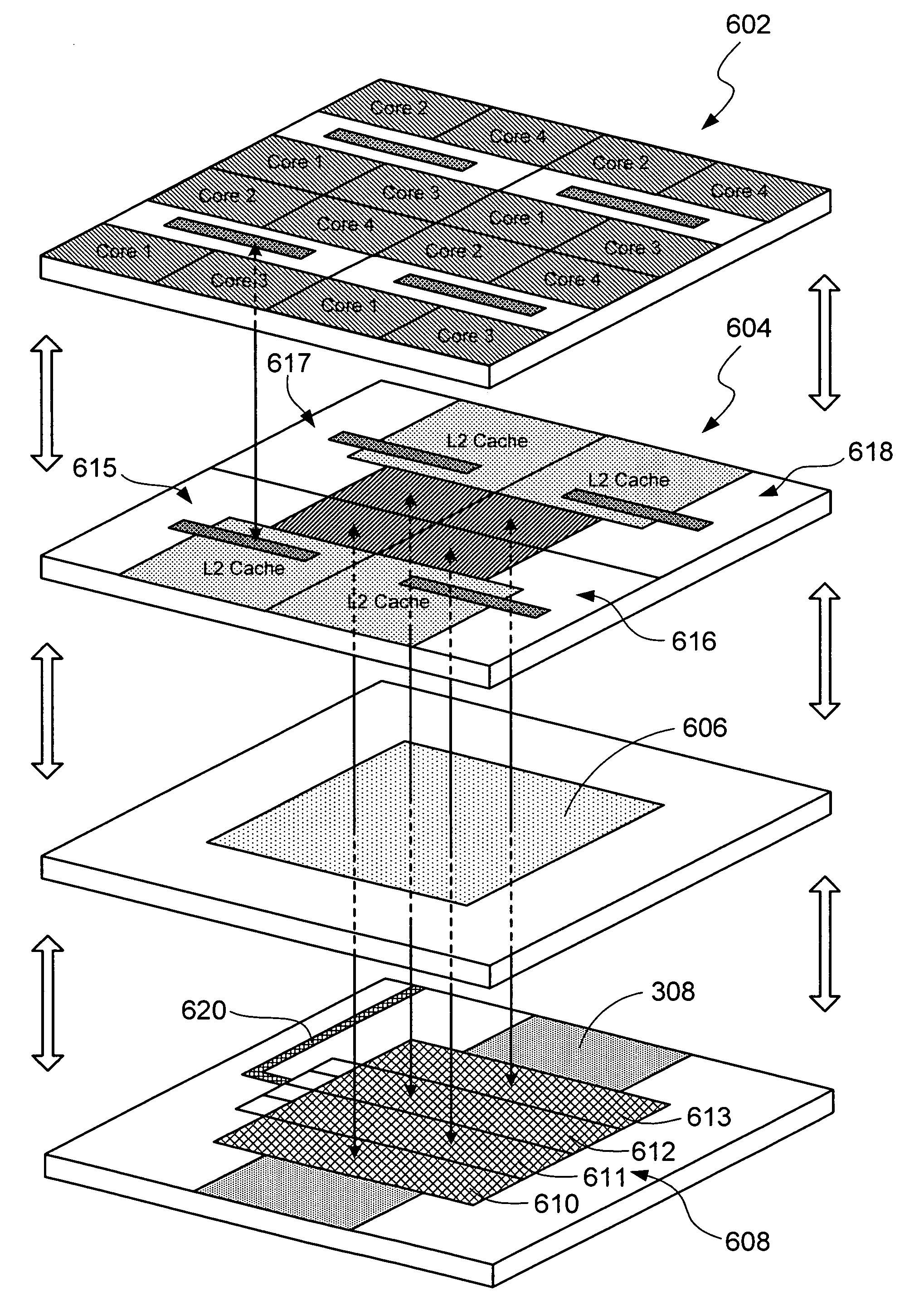

3-dimensional integrated circuit architecture, structure and method for fabrication thereof

ActiveUS20070228383A1Solid-state devicesSemiconductor/solid-state device manufacturingPerformance enhancementAudio power amplifier

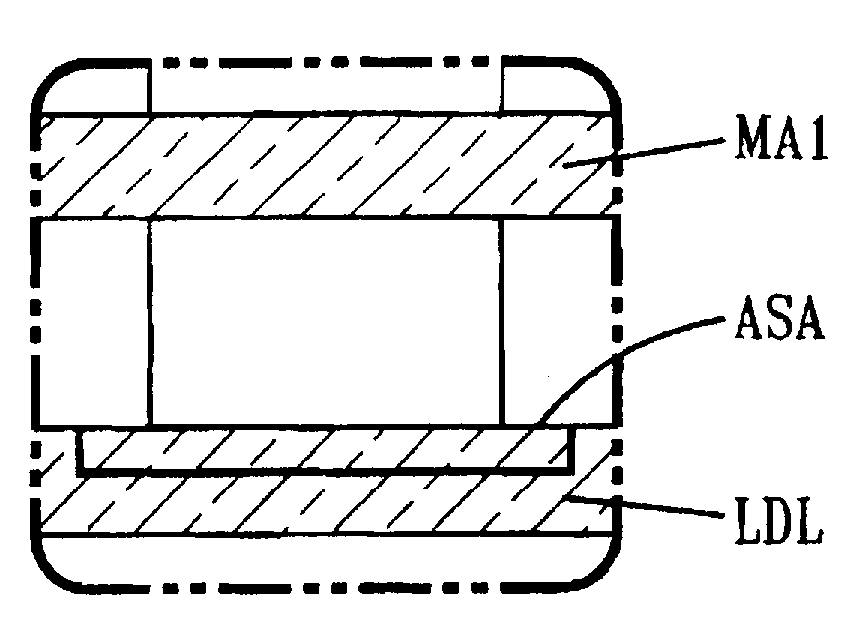

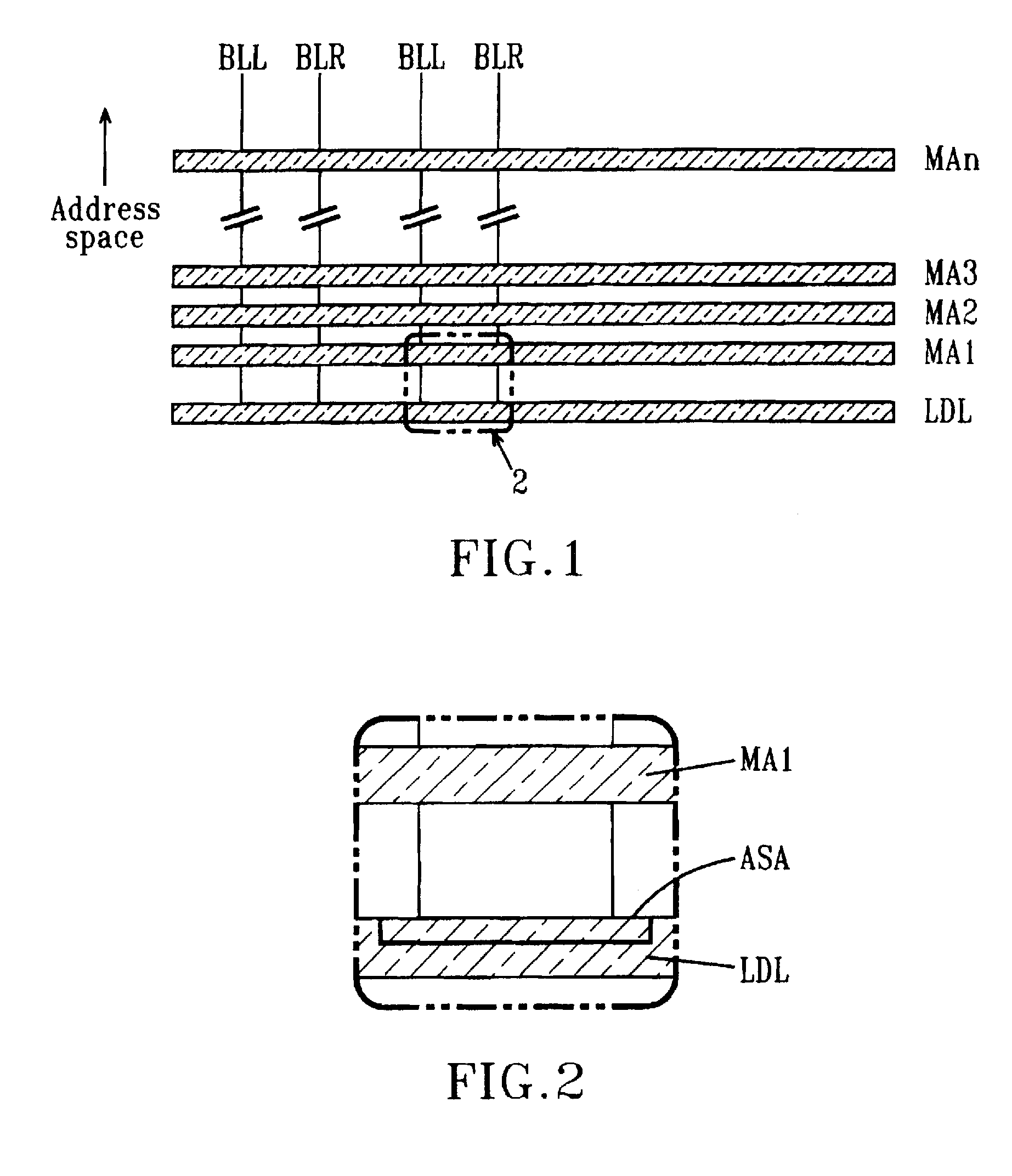

An integrated circuit design, structure and method for fabrication thereof includes at least one logic device layer and at least two additional separate memory array layers. Each of the logic device layer and the at least two memory array layers is independently optimized for a particular type of logic device or memory device disposed therein. Preferably also disposed within the logic device layer are array sense amplifiers, memory array output drivers and like higher performance circuitry otherwise generally disposed within memory array layer substrates. All layers may be independently powered to provide additional performance enhancement.

Owner:IBM CORP

Three-dimensional integrated circuit structure

InactiveUS7888764B2Solid-state devicesSemiconductor/solid-state device manufacturingSemiconductor structureSemiconductor package

Owner:BESANG

Structure comprising 3-dimensional integrated circuit architecture, circuit structure, and instructions for fabrication thereof

ActiveUS20070283298A1Allow optimizationSolid-state devicesSemiconductor/solid-state device manufacturingAudio power amplifierPerformance enhancement

A design structure comprising an integrated circuit architecture, circuit structure, and / or instructions for fabrication thereof. The circuit structure includes at least one logic device layer and at least two additional separate memory array layers. Each of the logic device layer and the at least two memory array layers is independently optimized for a particular type of logic device or memory device disposed therein. Preferably also disposed within the logic device layer are array sense amplifiers, memory array output drivers and like higher performance circuitry otherwise generally disposed within memory array layer substrates. All layers may be independently powered to provide additional performance enhancement.

Owner:IBM CORP

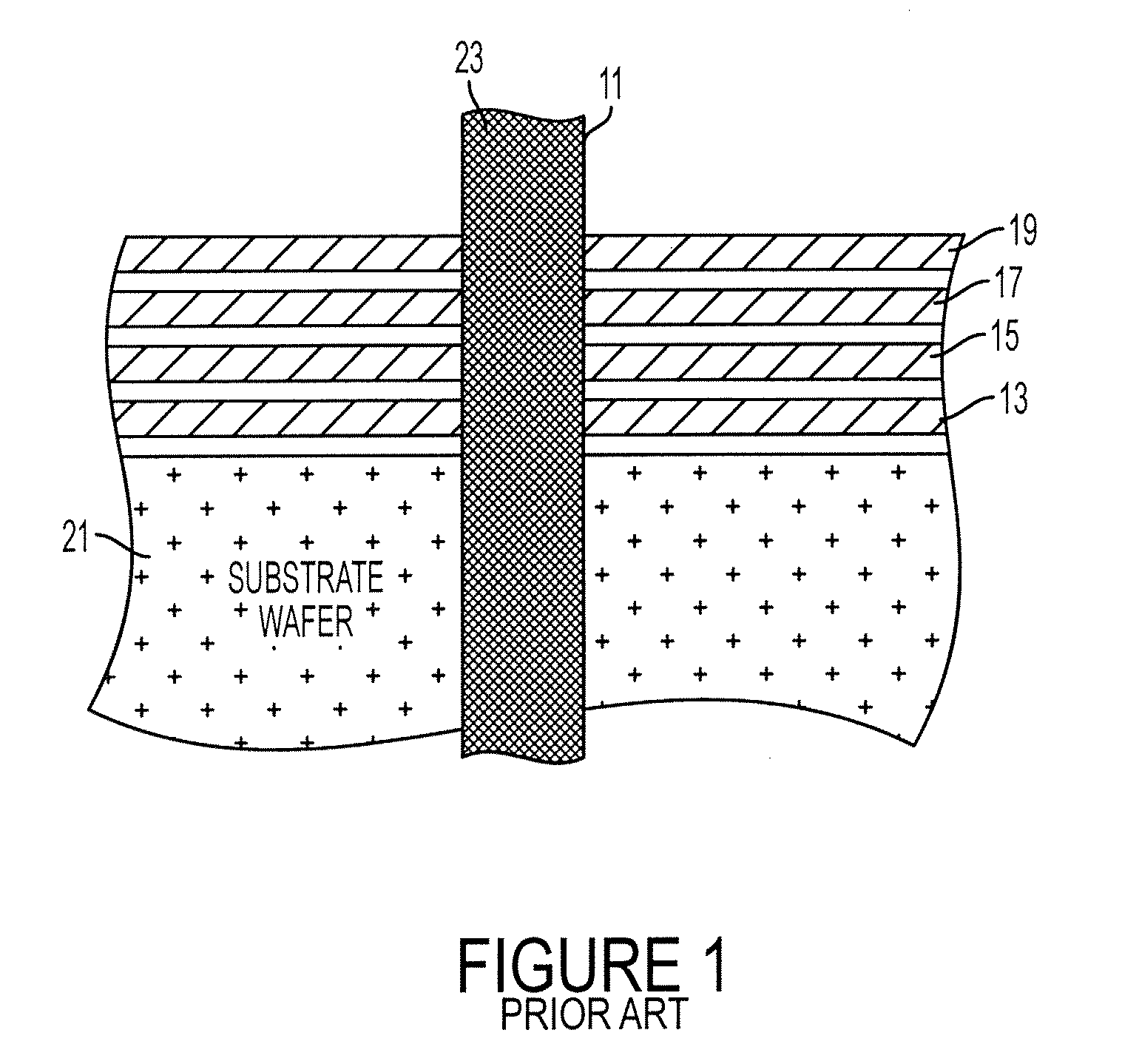

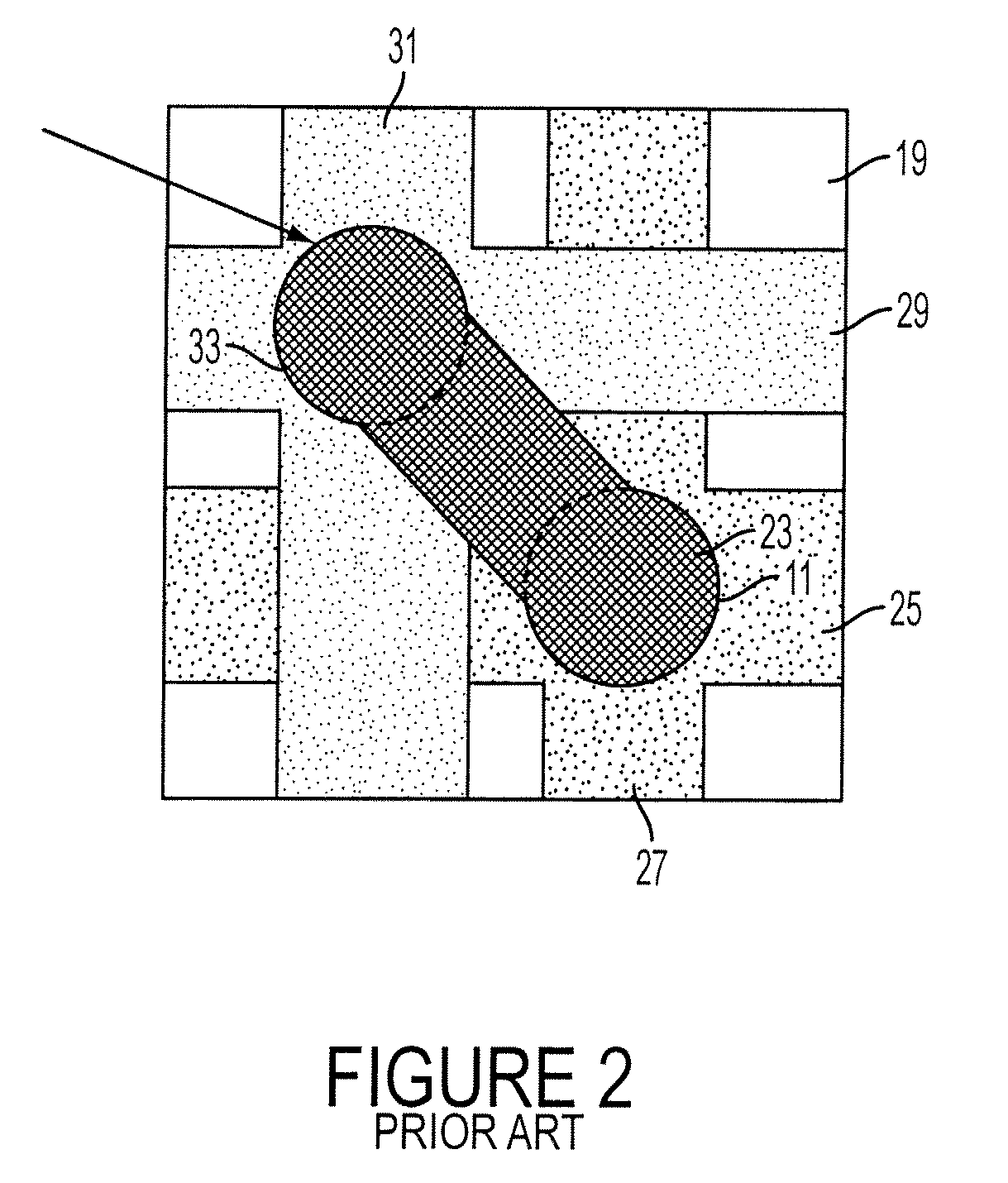

Buried via technology for three dimensional integrated circuits

InactiveUS7671460B2Semiconductor/solid-state device detailsSolid-state devicesThree-dimensional integrated circuitMetal

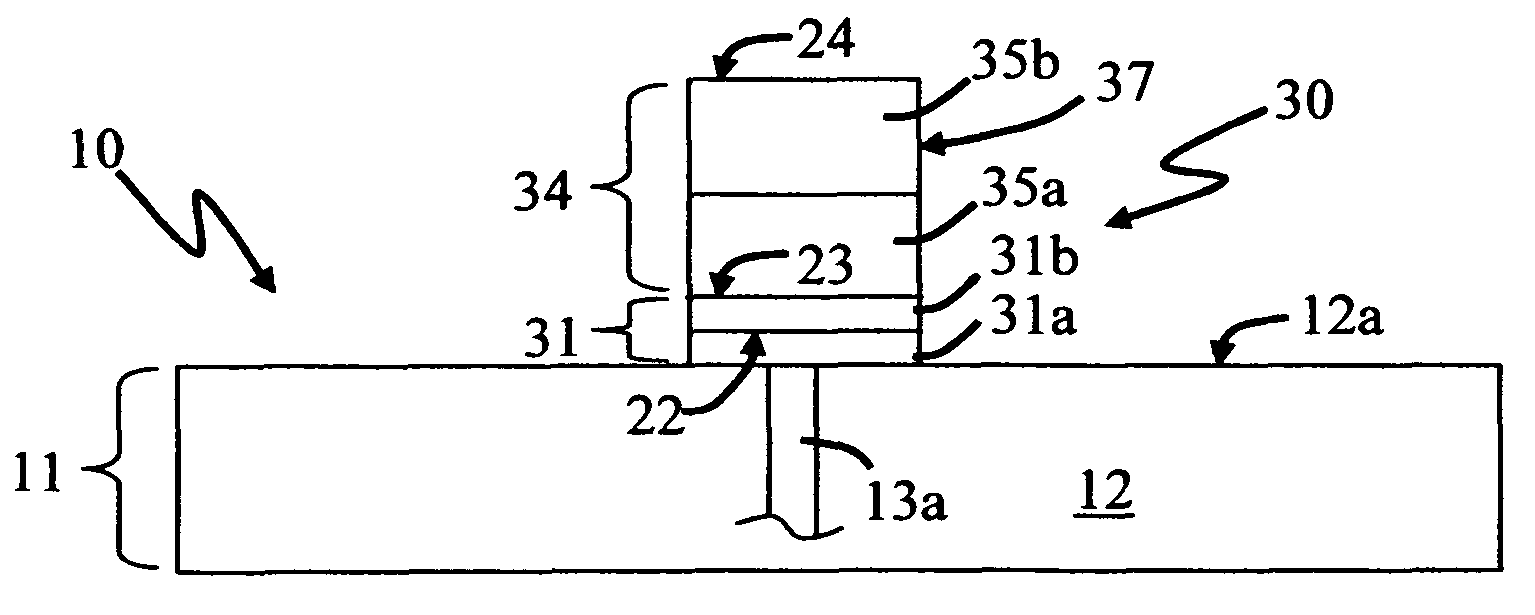

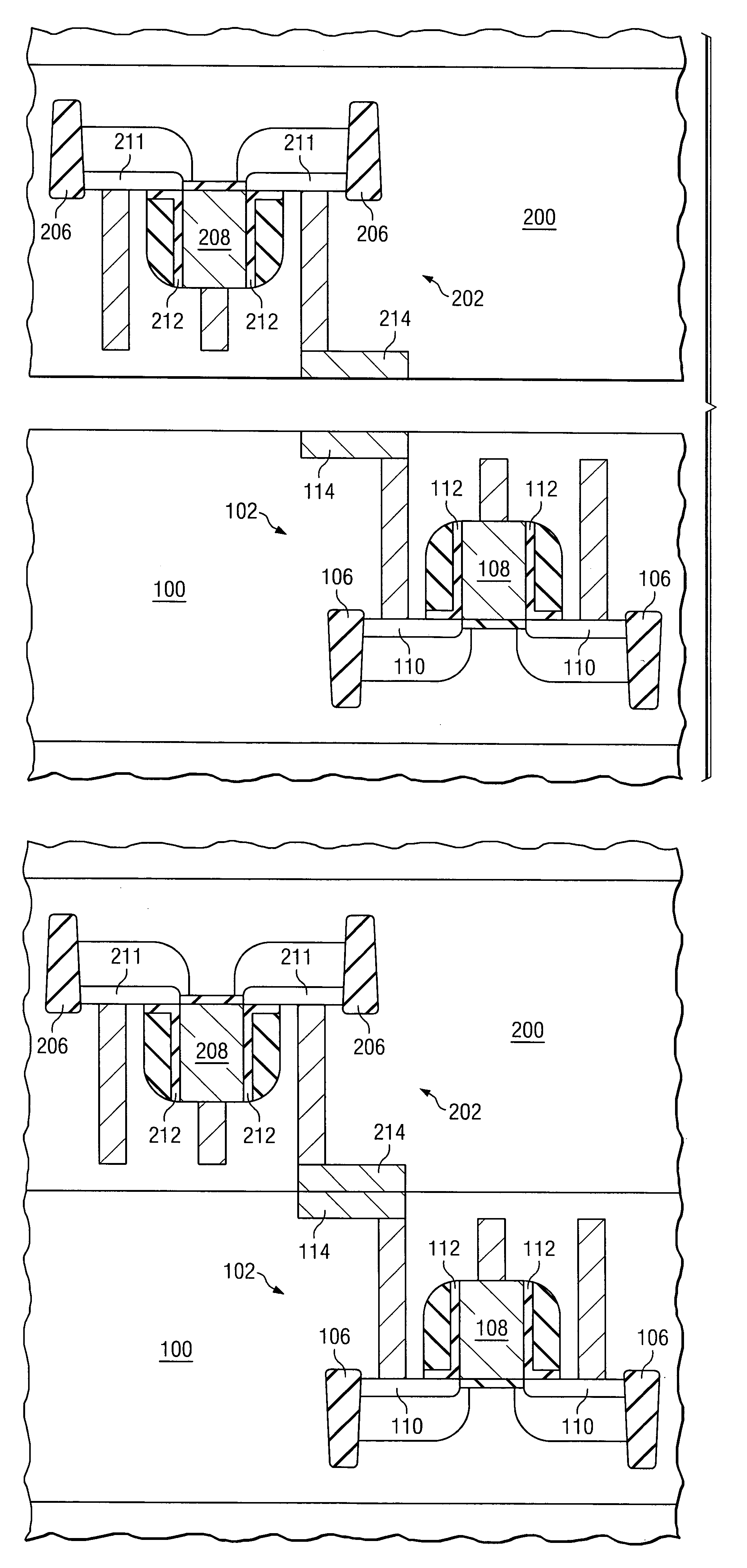

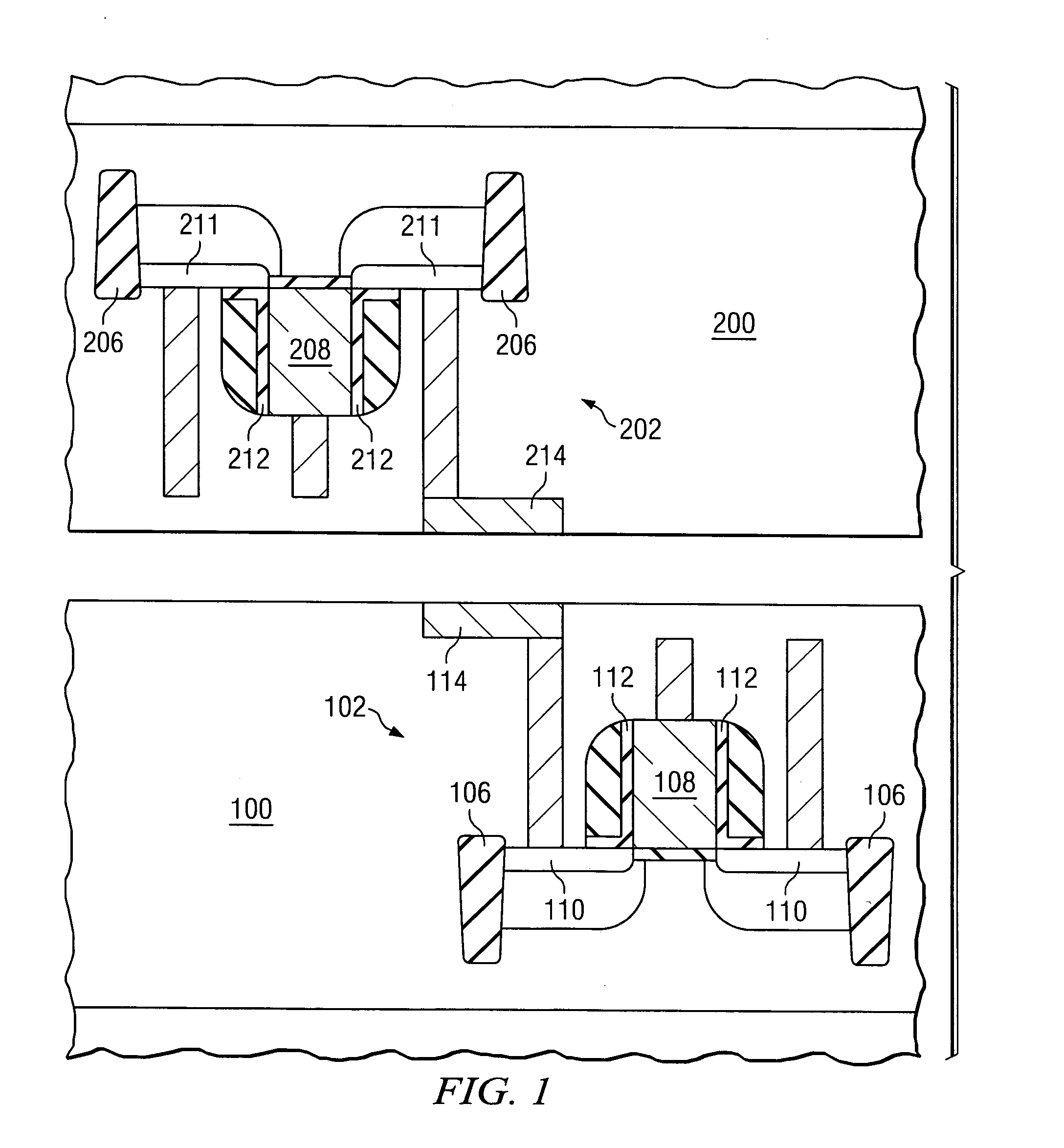

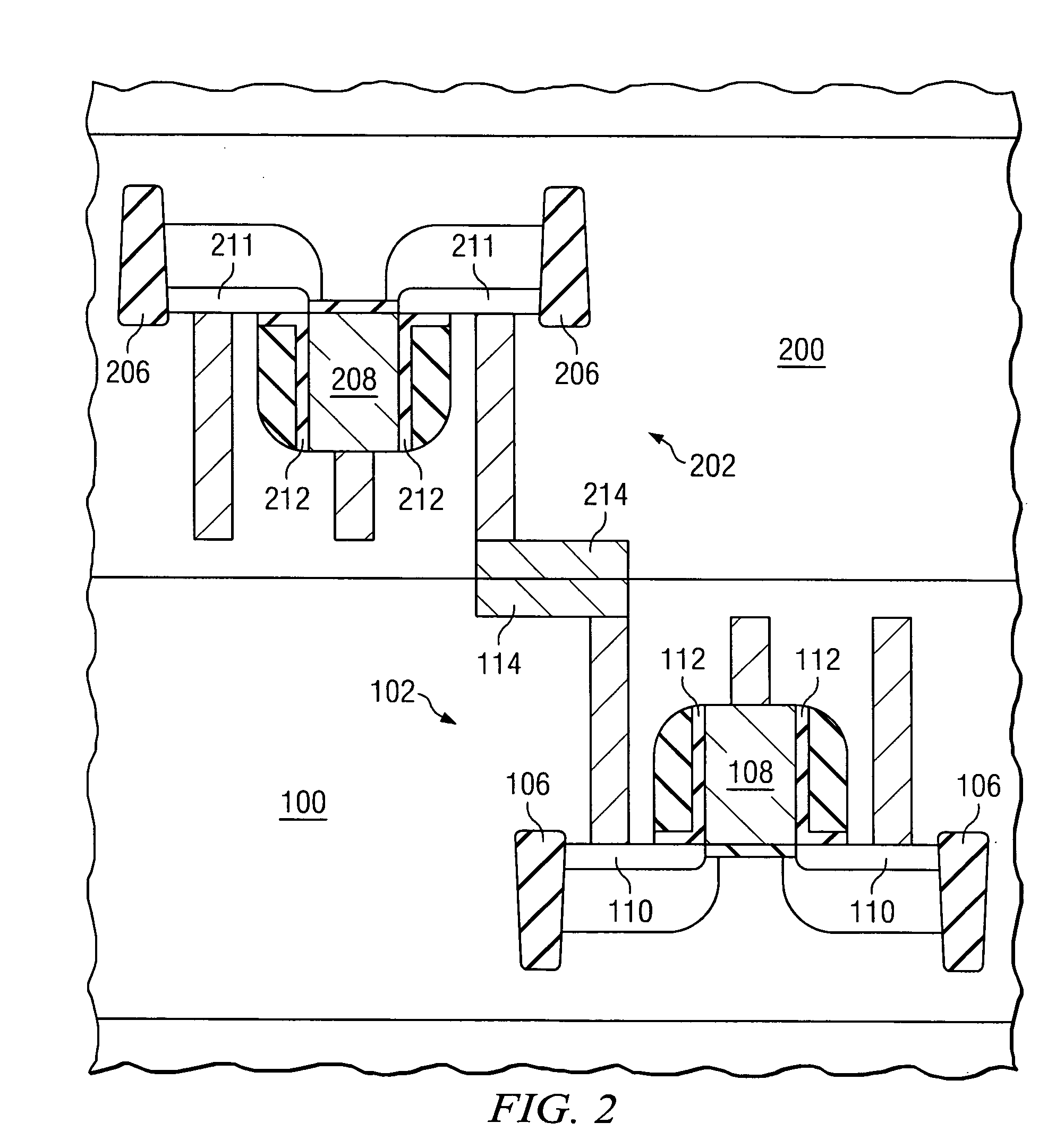

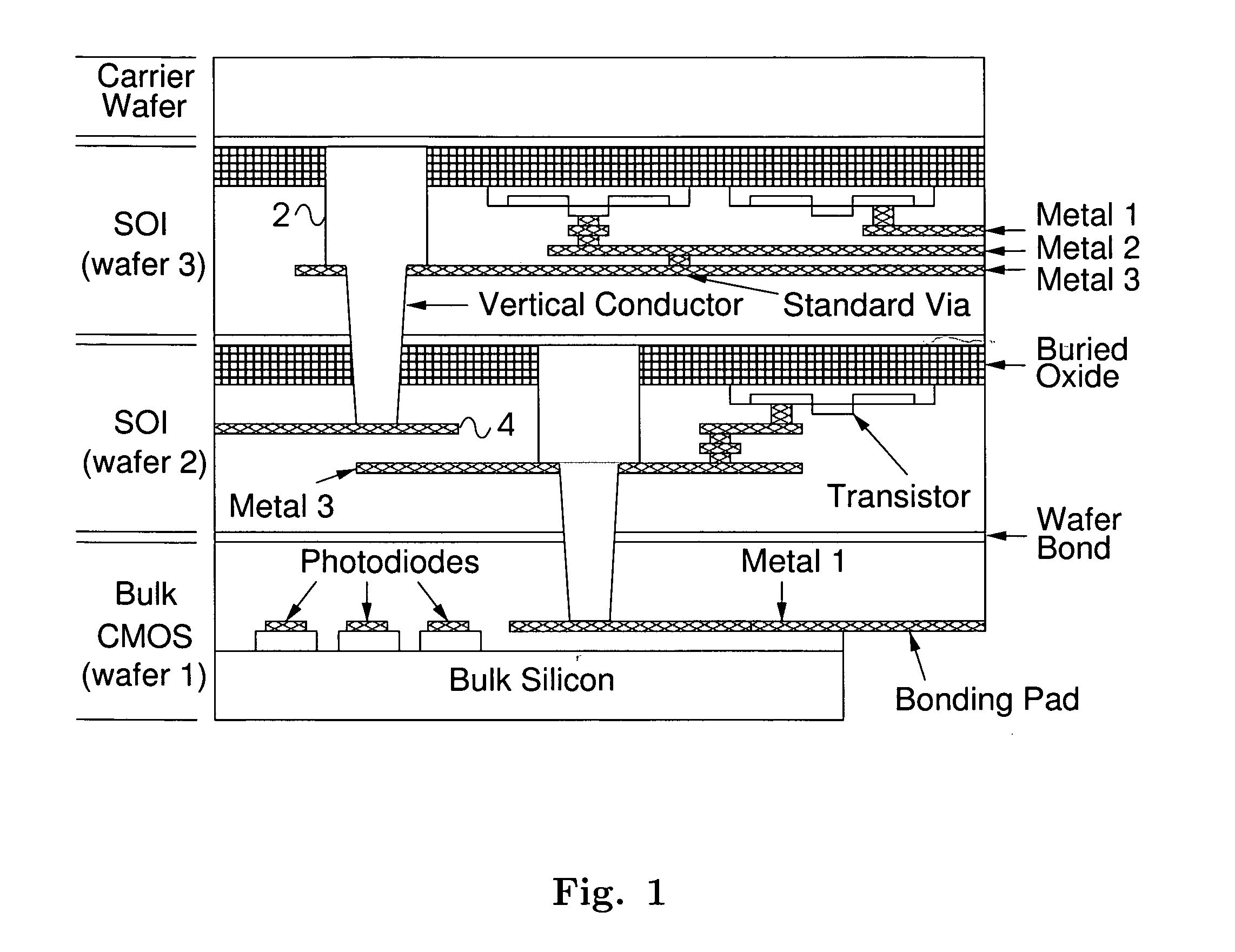

A three dimensional integrated circuit and method for making the same. The three dimensional integrated circuit has a first and a second active circuit layers with a first metal layer and a second metal layer, respectively. The metal layers are connected by metal inside a buried via. The fabrication method includes etching a via in the first active circuit layer to expose the first metal layer without penetrating the first metal layer, depositing metal inside the via, the metal inside the via being in contact with the first metal layer, and bonding the second active circuit layer to the first active circuit layer using a metal bond that connects the metal inside the via to the second metal layer of the second active circuit layer.

Owner:TELEDYNE SCI & IMAGING

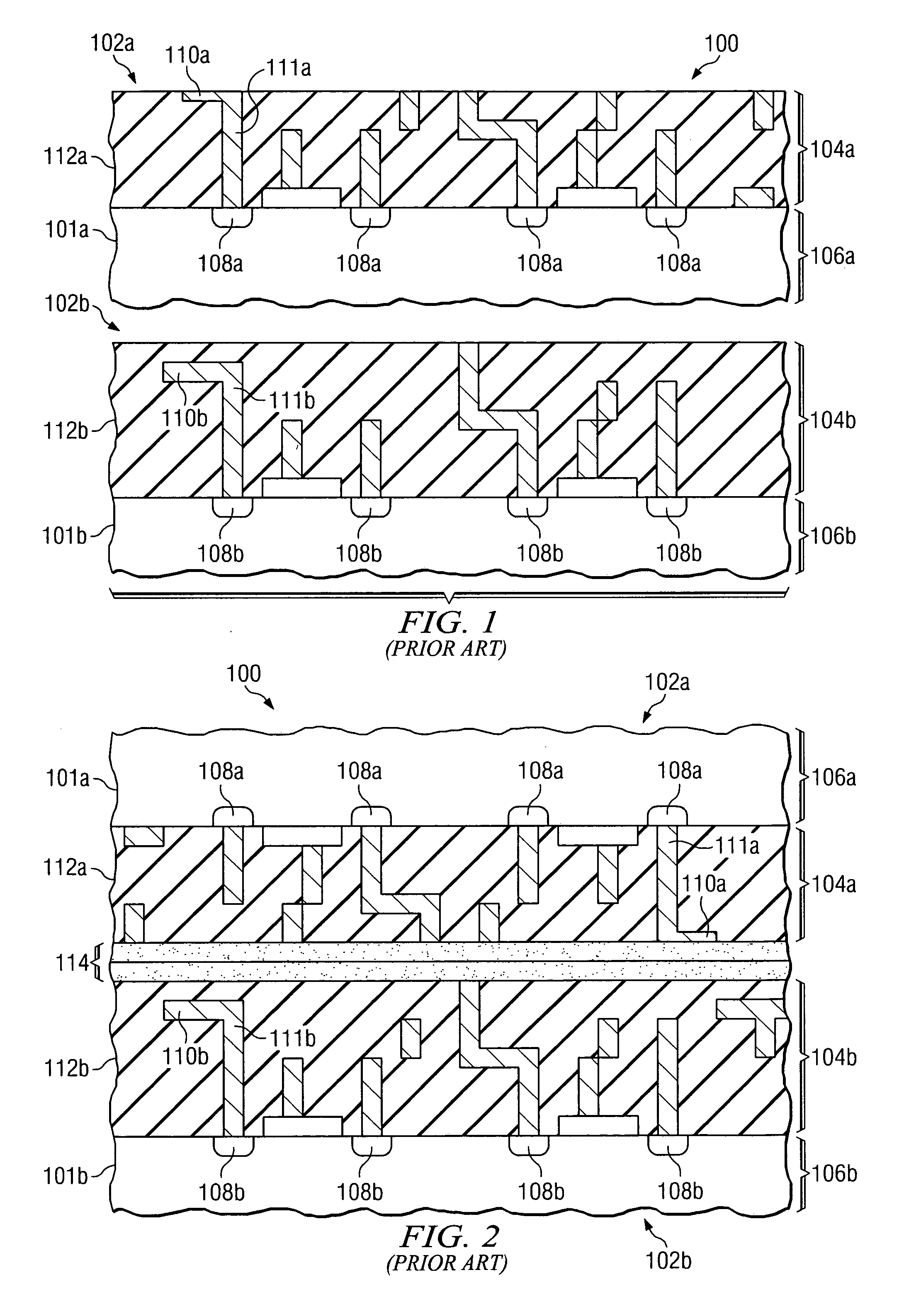

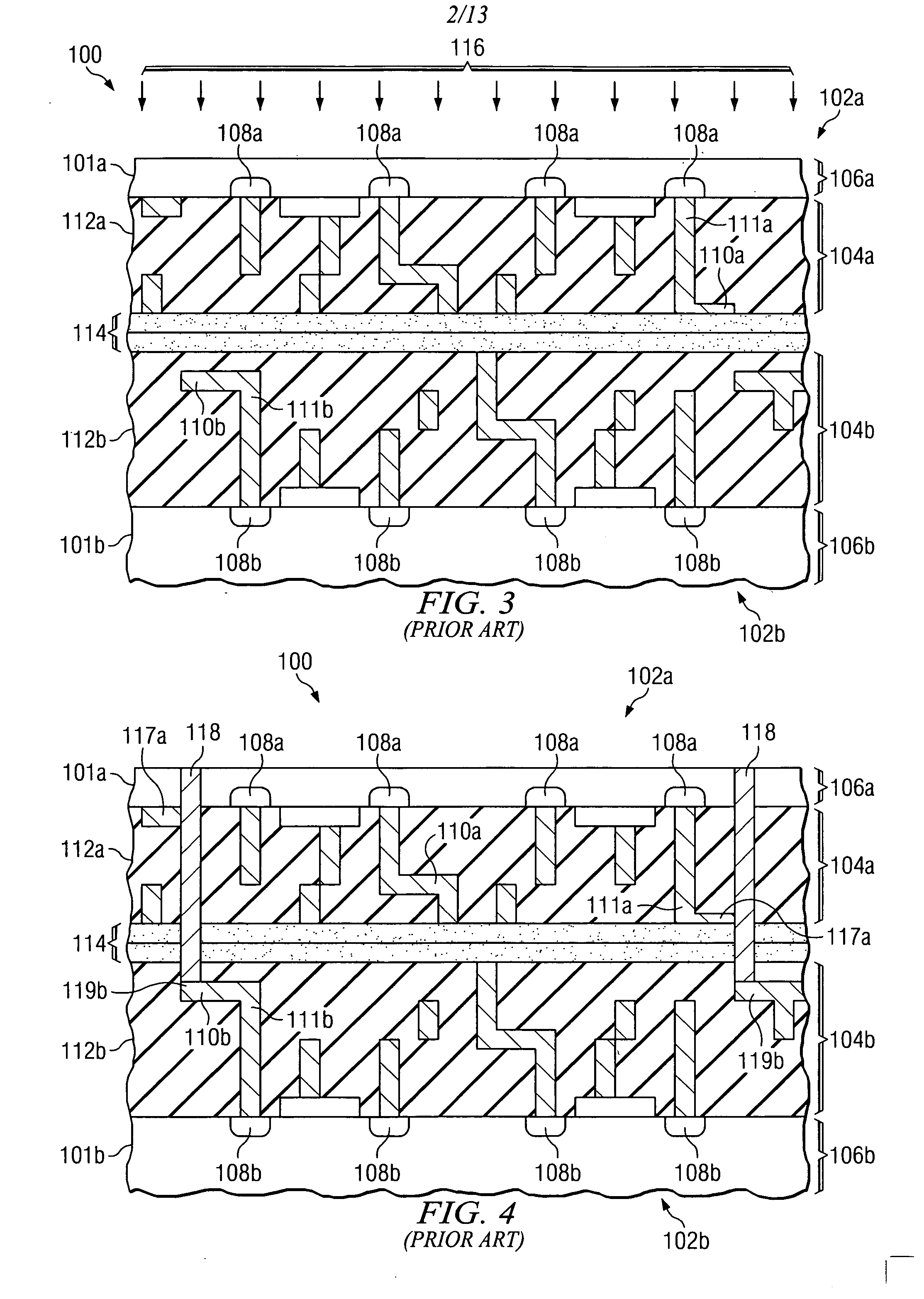

Three dimensional integrated circuit and method of making the same

ActiveUS7385283B2Semiconductor/solid-state device detailsSolid-state devicesEngineeringThree-dimensional integrated circuit

A three dimensional integrated circuit structure includes at least first and second devices, each device comprising a substrate and a device layer formed over the substrate, the first and second devices being bonded together in a stack, wherein the bond between the first and second devices comprises a metal-to-metal bond and a non-metal-to-non-metal bond.

Owner:TAIWAN SEMICON MFG CO LTD

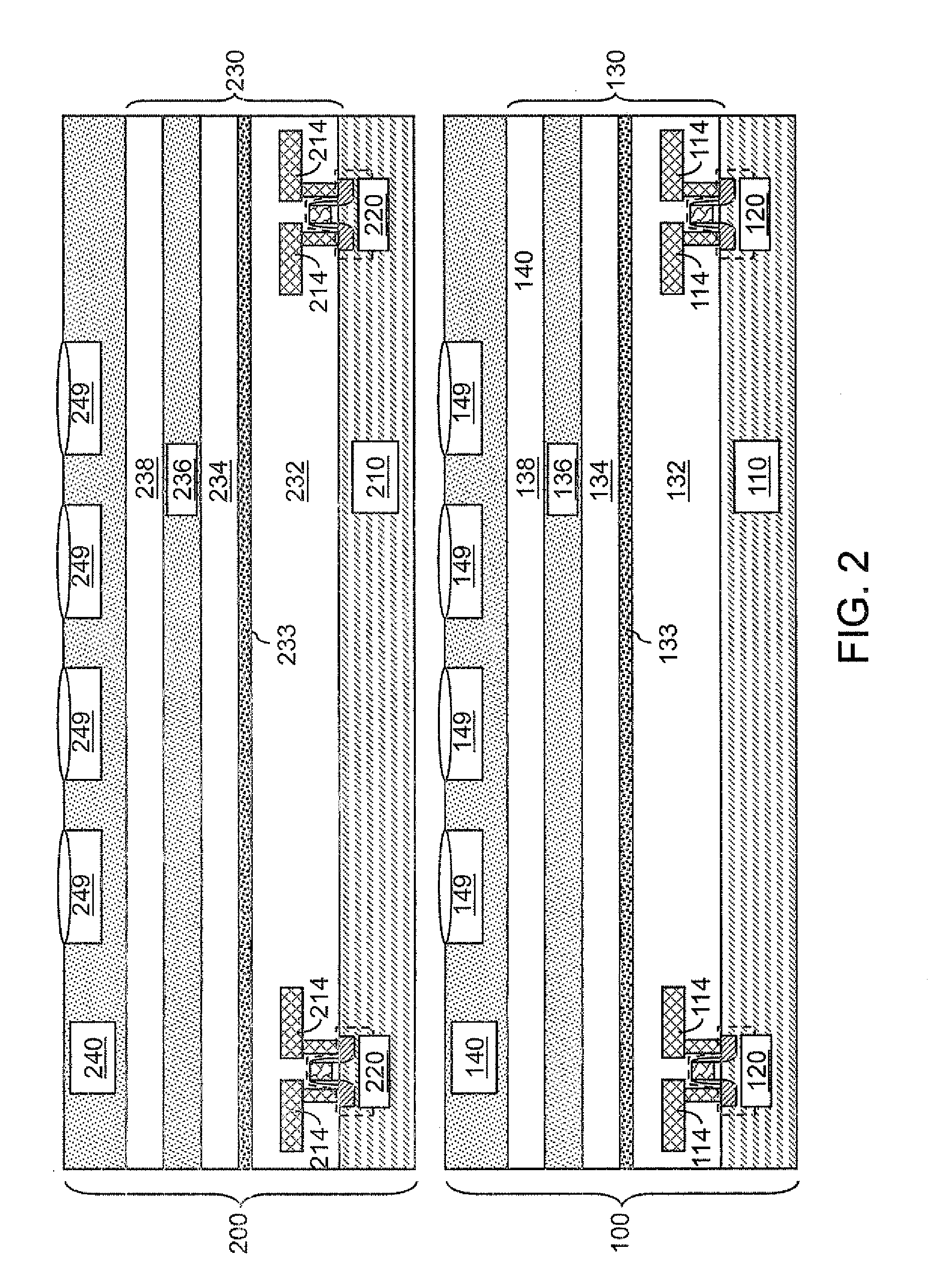

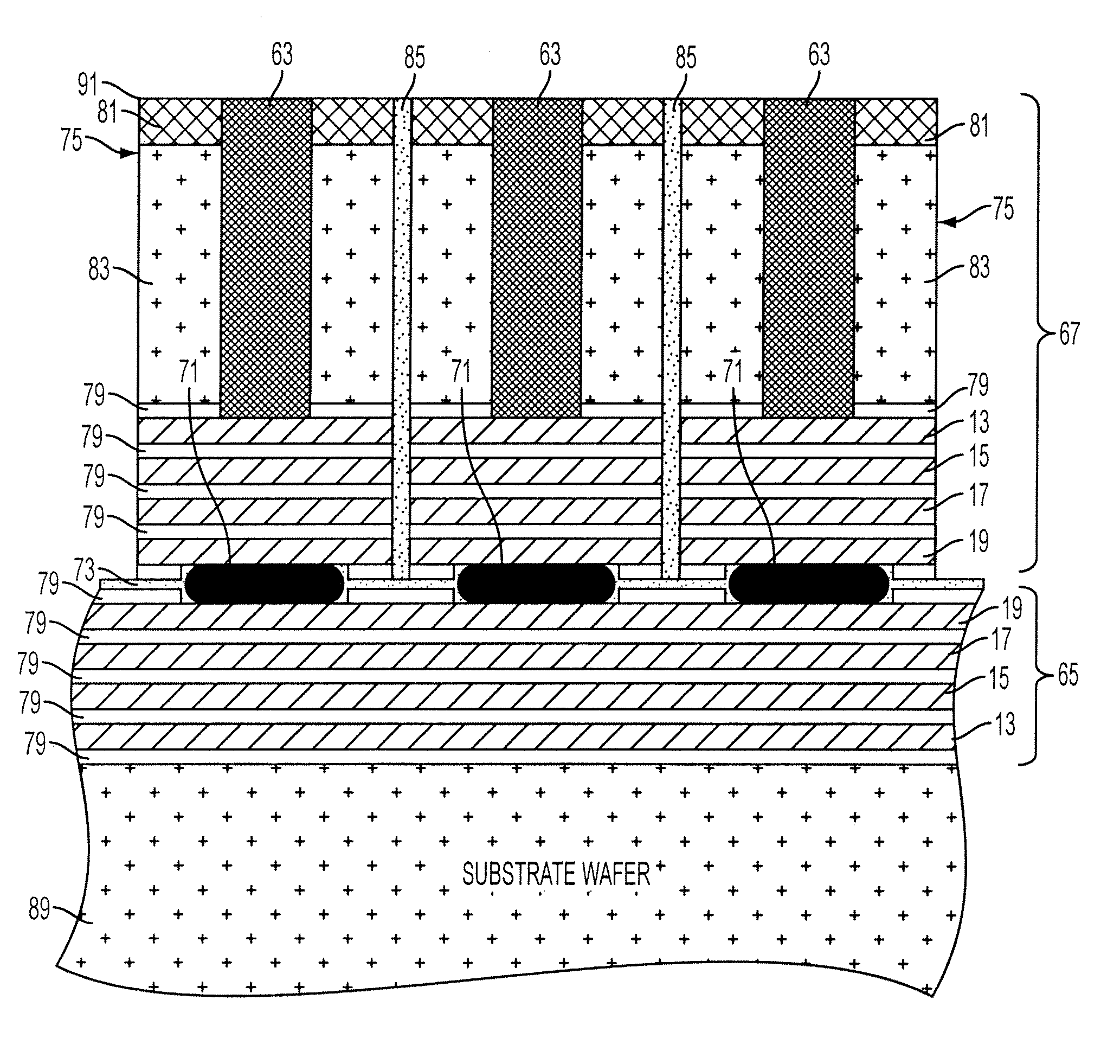

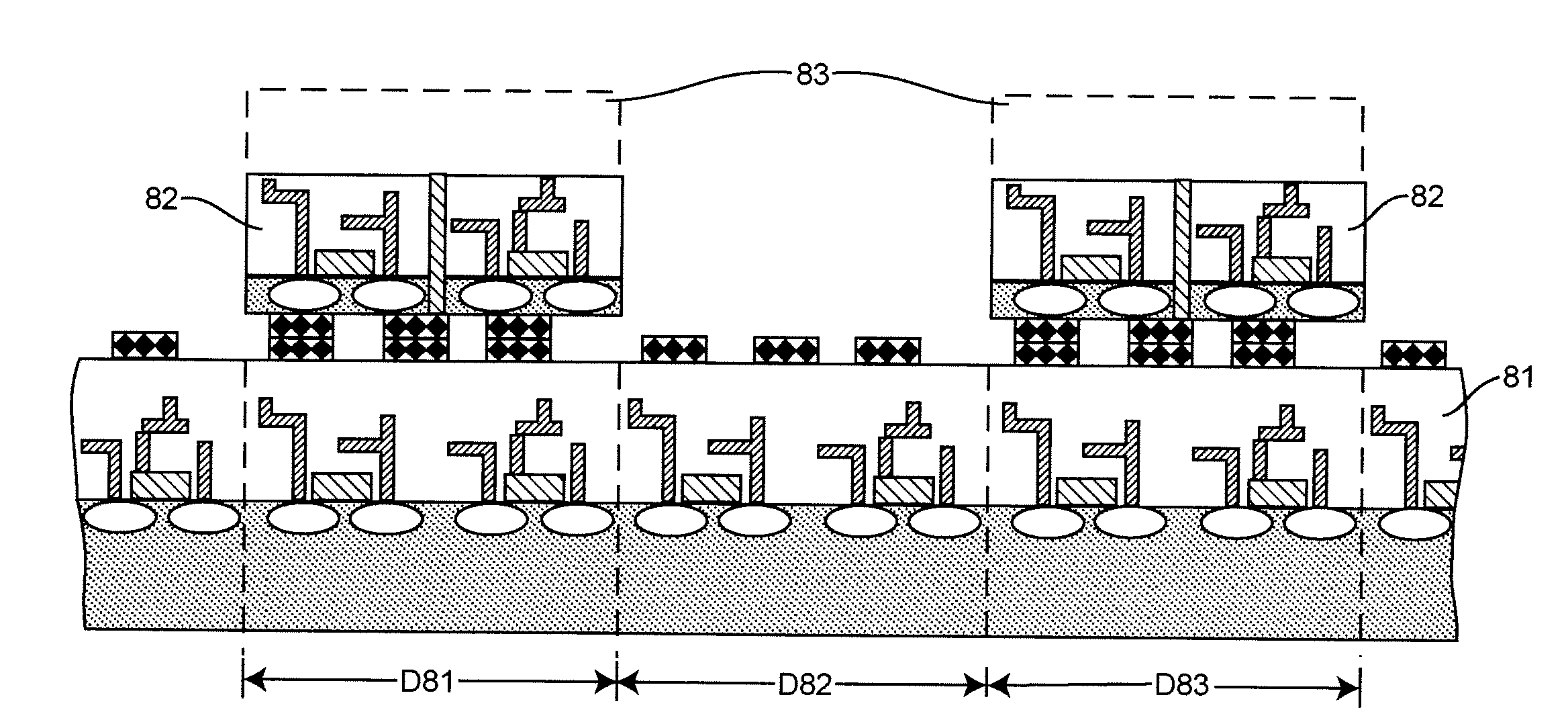

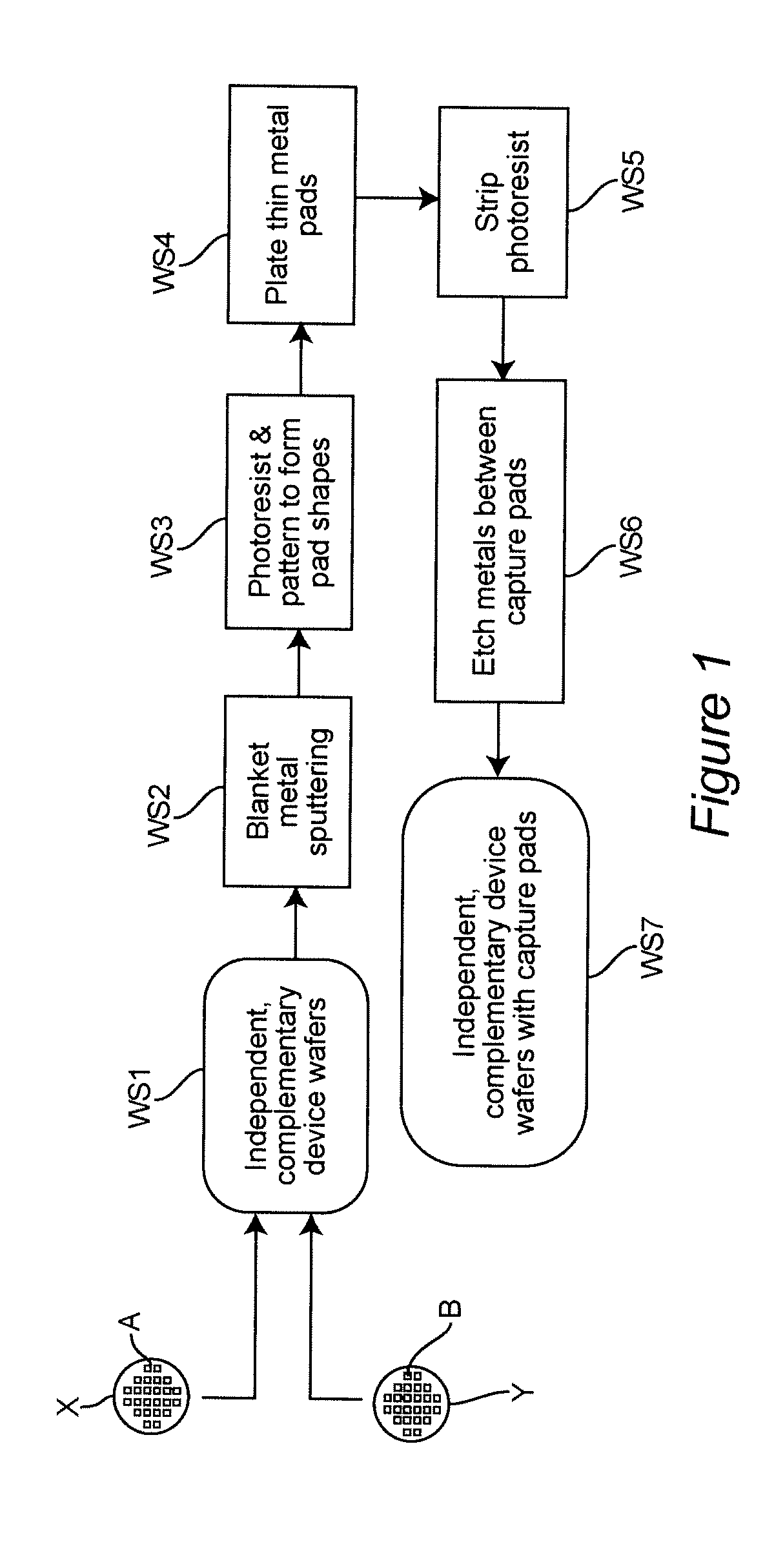

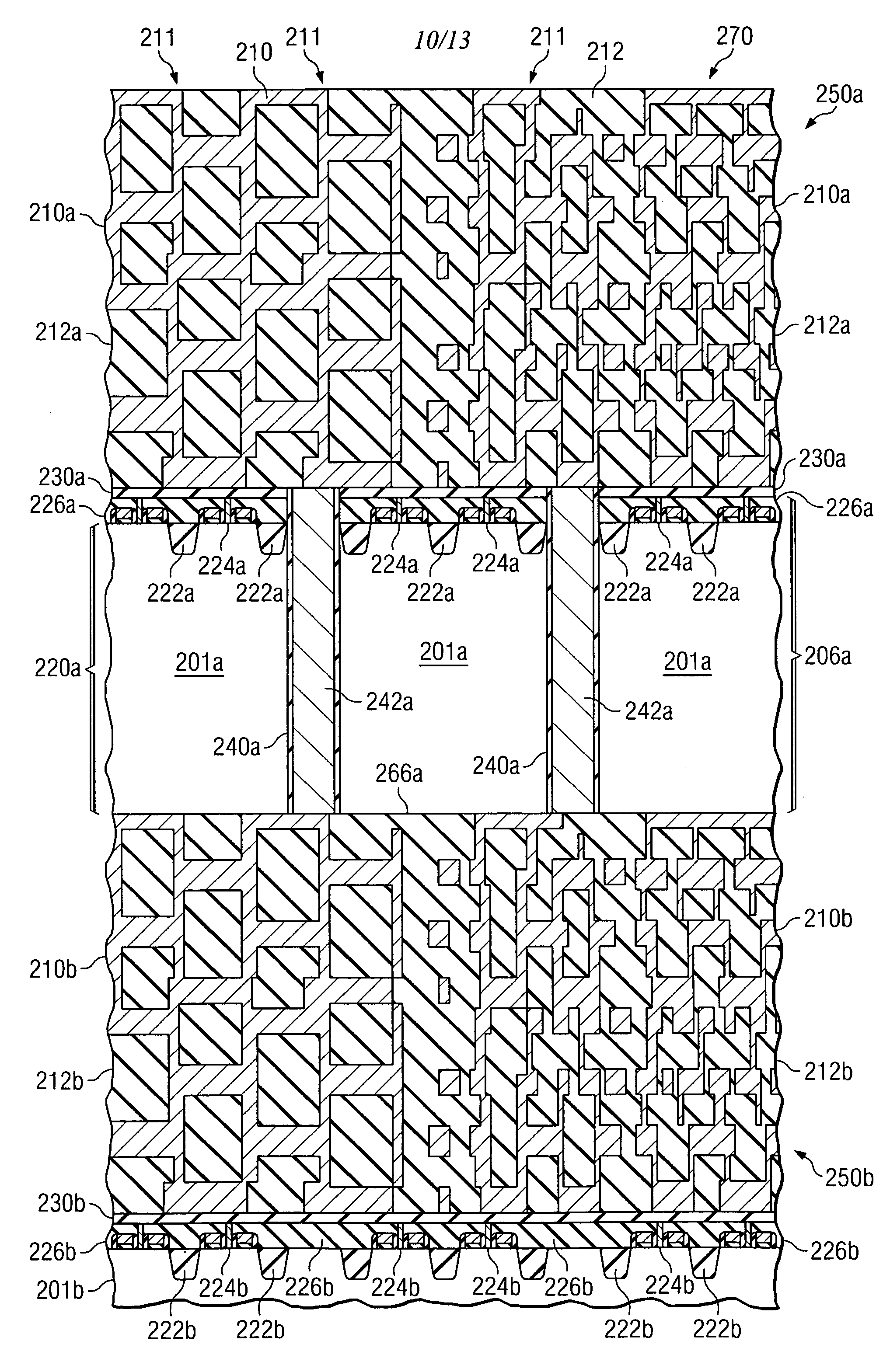

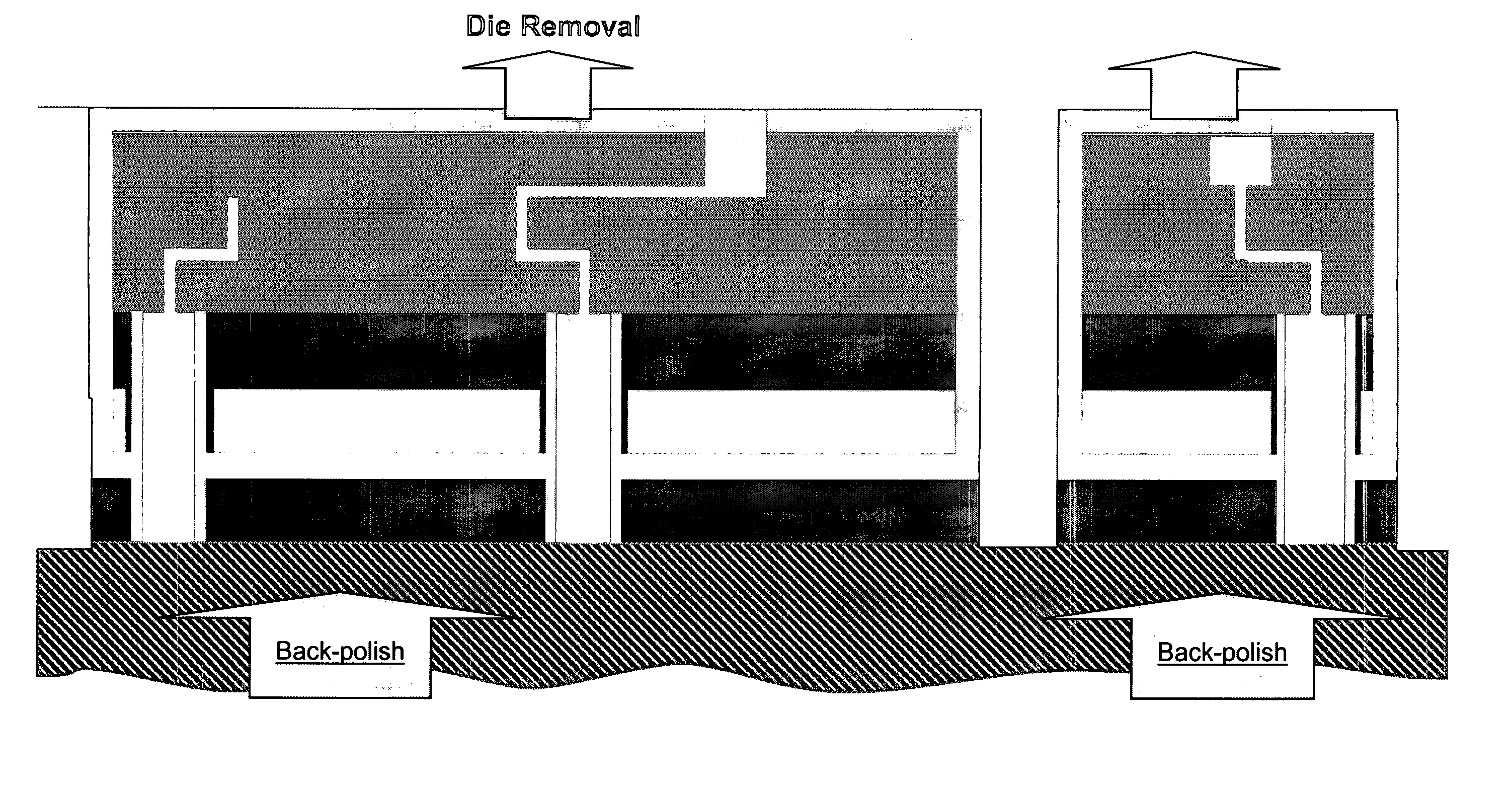

Method and Structure for Optimizing Yield of 3-D Chip Manufacture

ActiveUS20080142959A1Maximize frequencyLow costSemiconductor/solid-state device detailsSolid-state devicesThin metalEtching

The process begins with separate device wafers having complimentary chips. Thin metal capture pads, having a preferred thickness of about 10 microns so that substantial pressure may be applied during processing without damaging capture pads, are deposited on both device wafers, which are then tested and mapped for good chip sites. A handle wafer is attached to one device wafer, which can then be thinned to improve via etching and filling. Capture pads are removed and replaced after thinning. The device wafer with handle wafer is diced, and good chips with attached portions of the diced handle wafer are positioned and bonded to the good chip sites of the other device wafer, and the handle wafer portions are removed. The device wafer having known good 3-D chips then undergoes final processing.

Owner:INT BUSINESS MASCH CORP

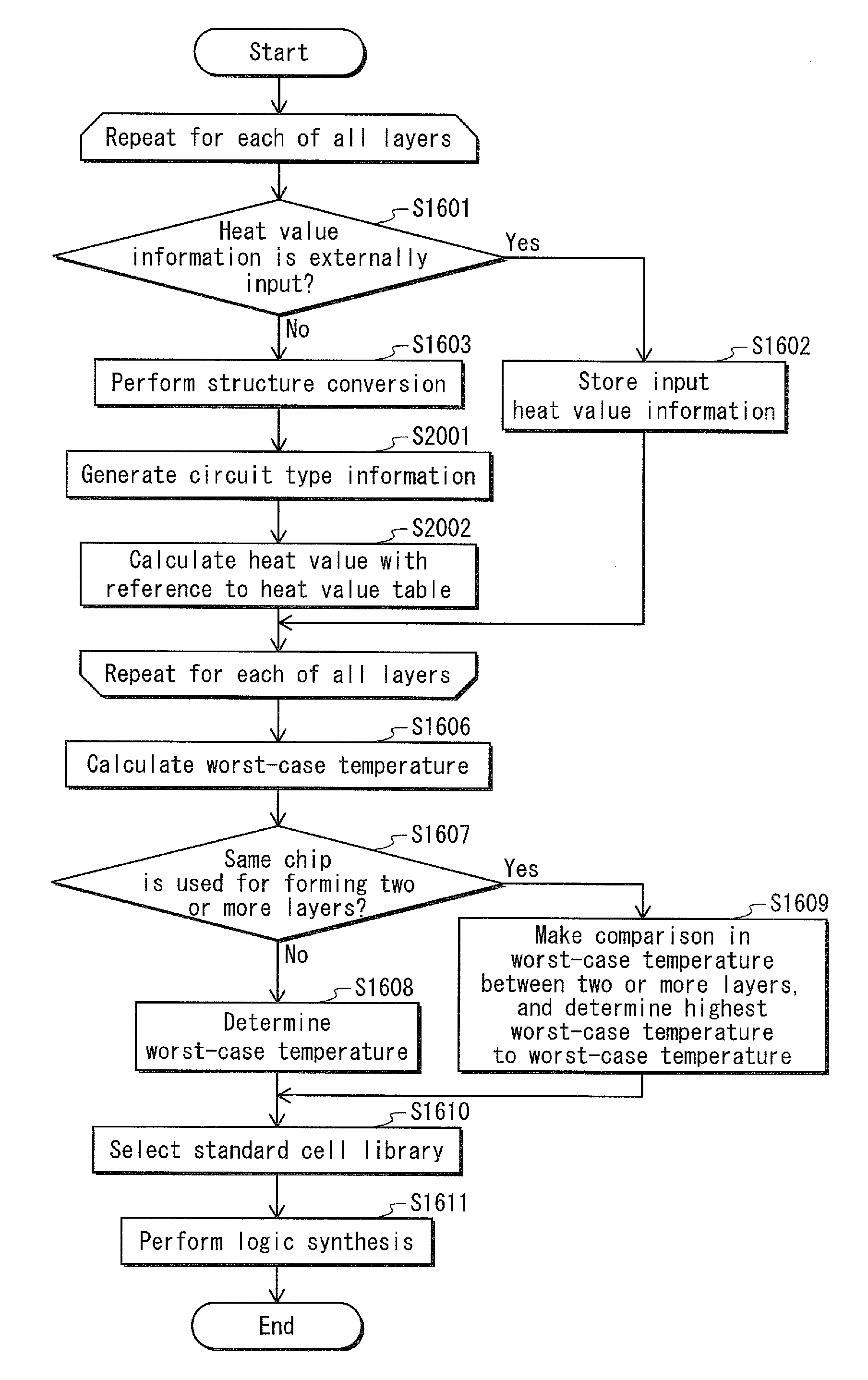

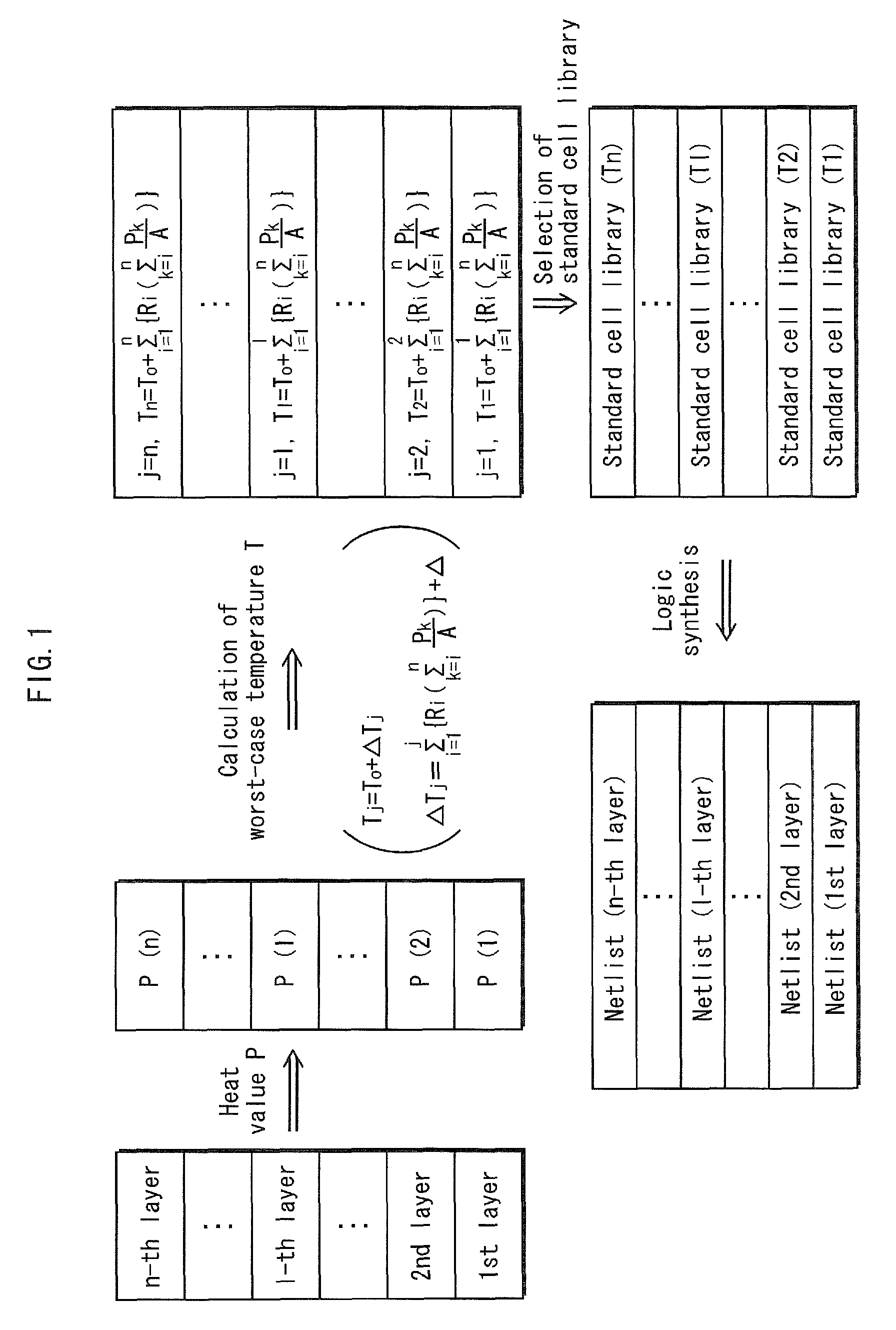

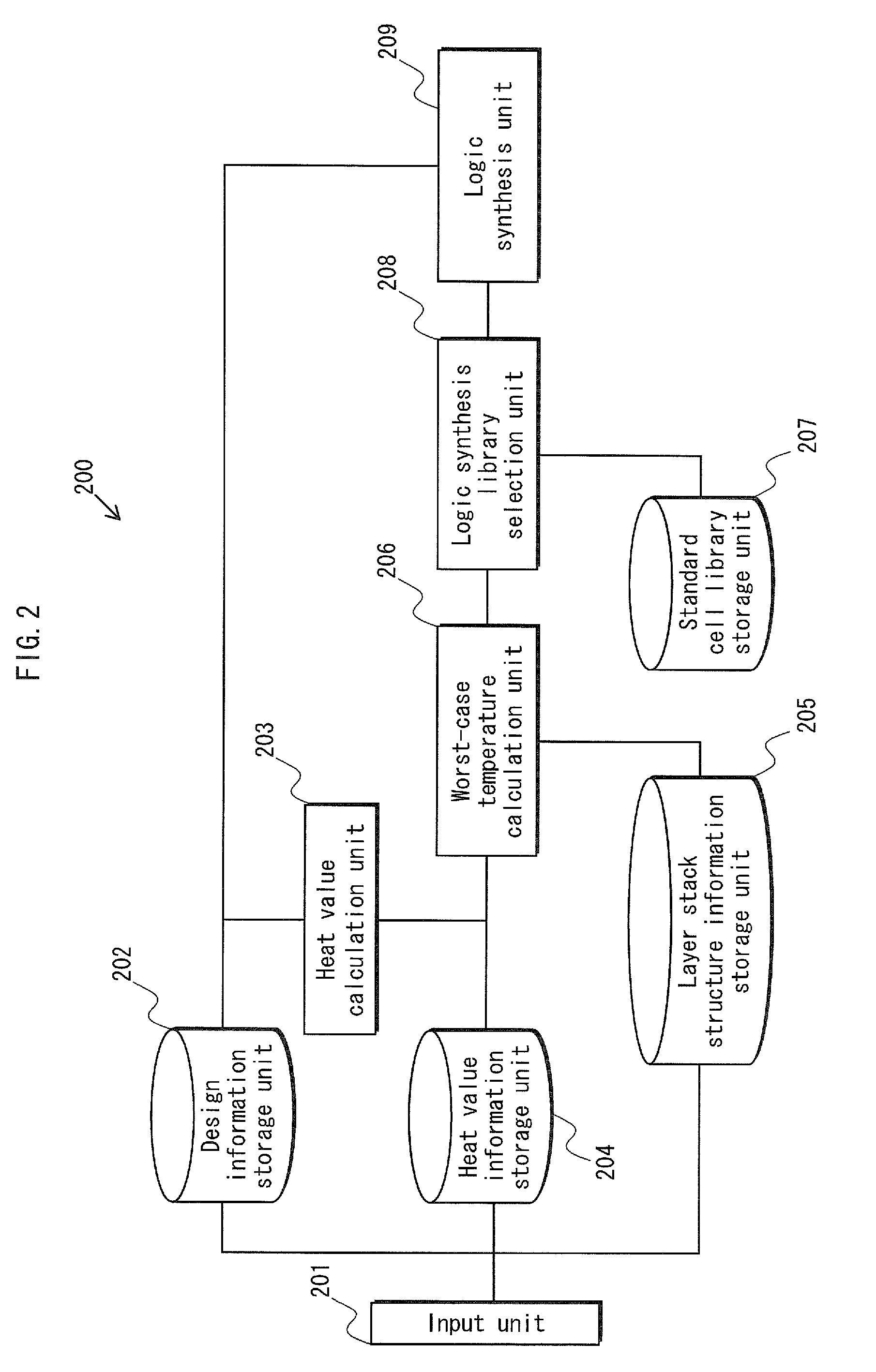

Three-dimensional integrated circuit design device, three-dimensional integrated circuit design, method, and program

InactiveUS8566762B2Increase the areaReduce power consumptionSolid-state devicesComputer aided designEngineeringThree-dimensional integrated circuit

A worst-case temperature calculation unit calculates, based on heat value information of each layer of a three-dimensional integrated circuit to be designed and stack structure information of the three-dimensional integrated circuit, a worst-case temperature of a layer during operation that is targeted for logic synthesis. A logic synthesis library selection unit selects a library appropriate for the calculated worst-case temperature. A logic synthesis unit performs logic synthesis on the targeted layer with use of the selected library.

Owner:PANASONIC CORP

Semiconductor devices and methods of manufacture thereof

InactiveUS20070166997A1Semiconductor/solid-state device detailsSolid-state devicesDevice materialElectrical connection

Vertically stacked integrated circuits and methods of fabrication thereof are disclosed. Deep vias that provide vertical electrical connection for vertically stacked integrated circuits are formed early in the manufacturing process, before integrated circuits are bonded together to form a three dimensional integrated circuit (3D-IC).

Owner:INFINEON TECH AG

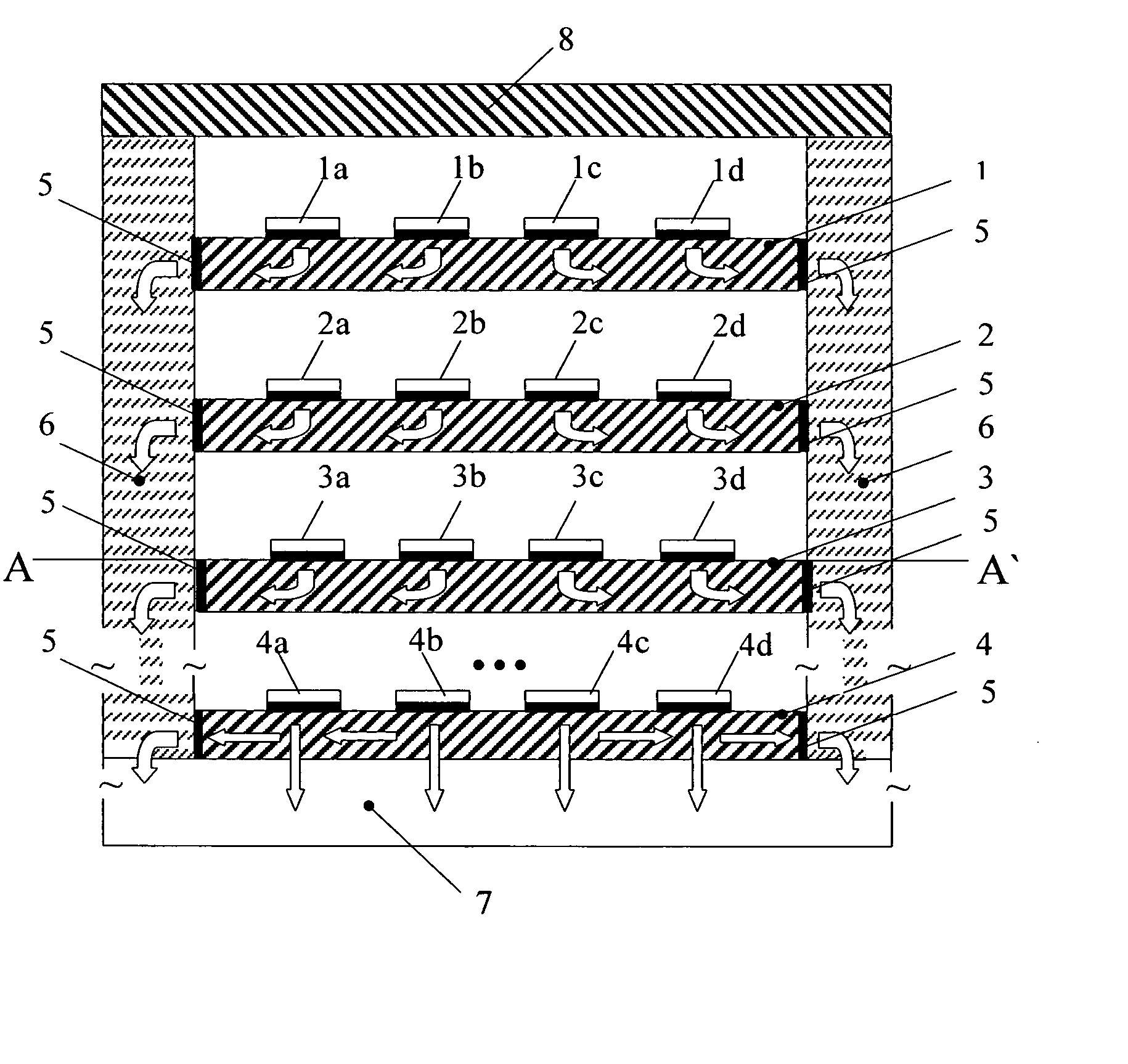

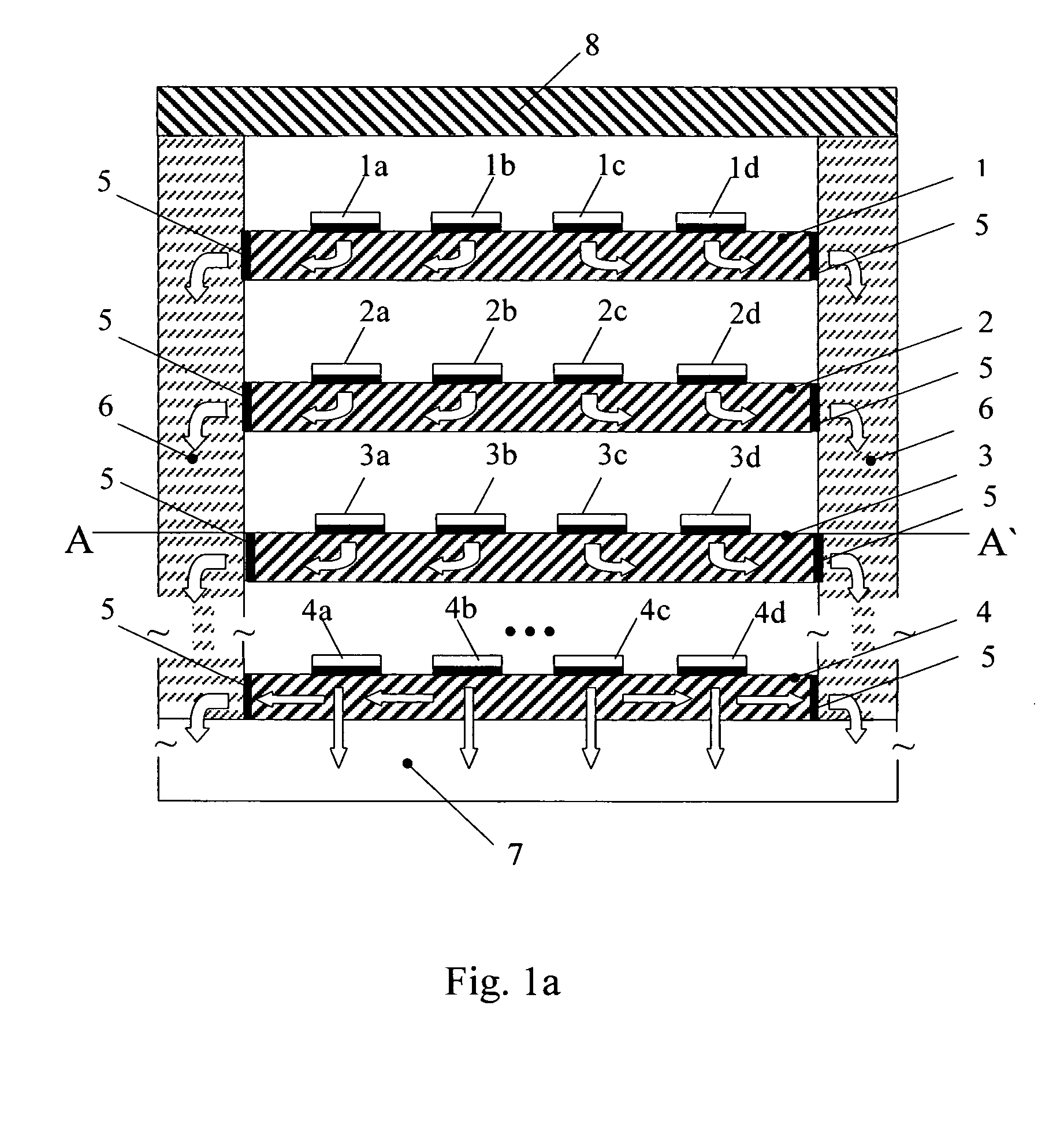

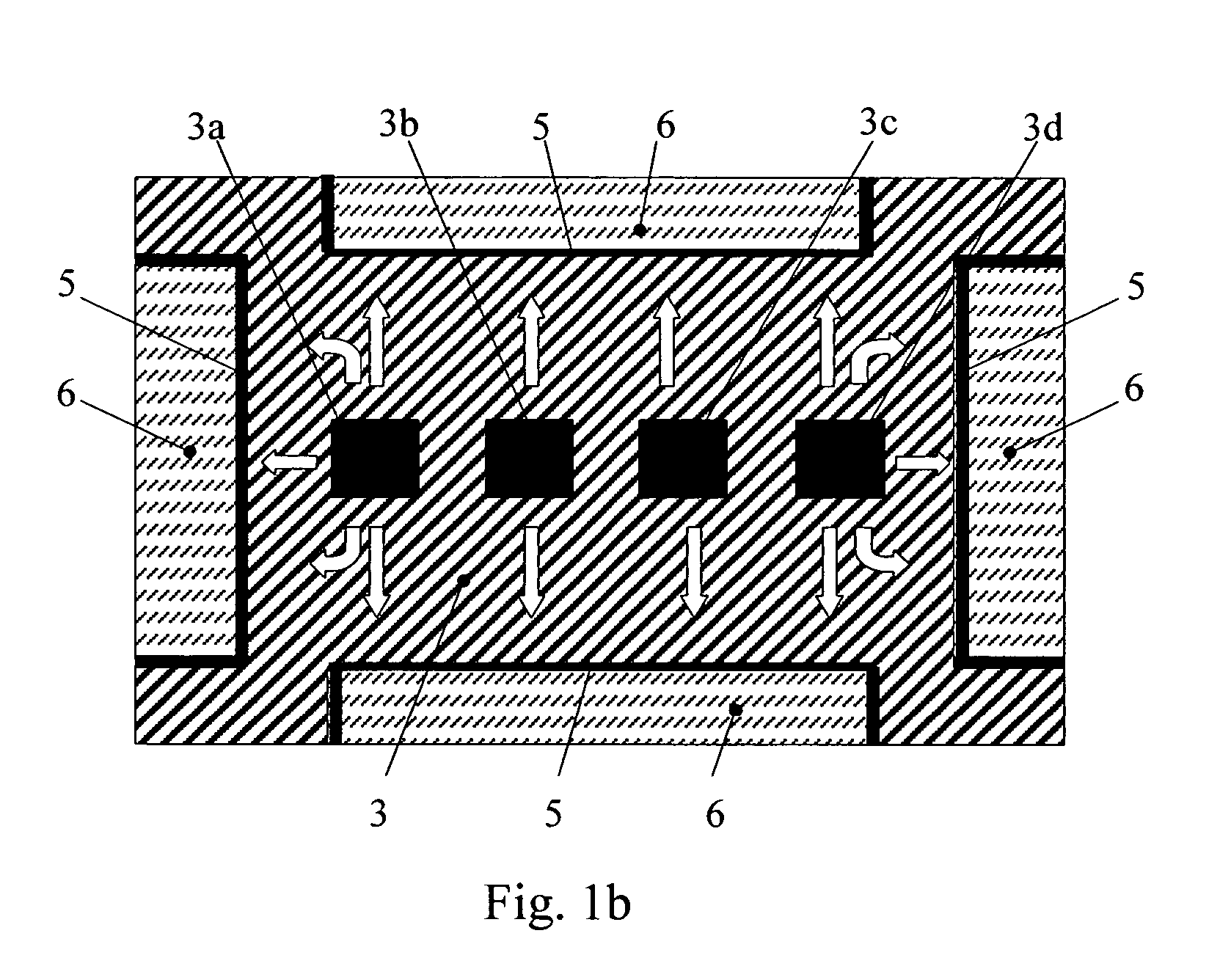

Three-dimensional integrated circuit with integrated heat sinks

InactiveUS20050104027A1Improve cooling effectSolid-state devicesBuilding constructionsEngineeringThree-dimensional integrated circuit

The present invention is directed to a three-dimensional semiconducting integrated circuit incorporating an integrated heat-sink dissipating heat produced by the semiconductor device mounted thereon.

Owner:NITTO DENKO CORP

Image sensor module with a three-dimensional die-stacking structure

ActiveUS20080308928A1Image degradationShorten connection lengthSemiconductor/solid-state device detailsSolid-state devicesElectrical connectionConductive materials

This invention provides an image sensor module with a three-dimensional die-stacking structure. By filling a conductive material into through silicon vias within at least one image sensor die, and into via holes within an insulating layer, vertical electrical connections are formed between the image sensor die and an image processor buried in the insulating layer. A plurality of solder bumps is formed on a backside of the image sensor module so that the module can be directly assembled onto a circuit board. The image sensor module of this invention is characterized by a wafer-level packaging architecture and a three-dimensional die-stacking structure, which reduces electrical connection lengths within the module and thus reduces an area and height of the whole packaged module.

Owner:IND TECH RES INST

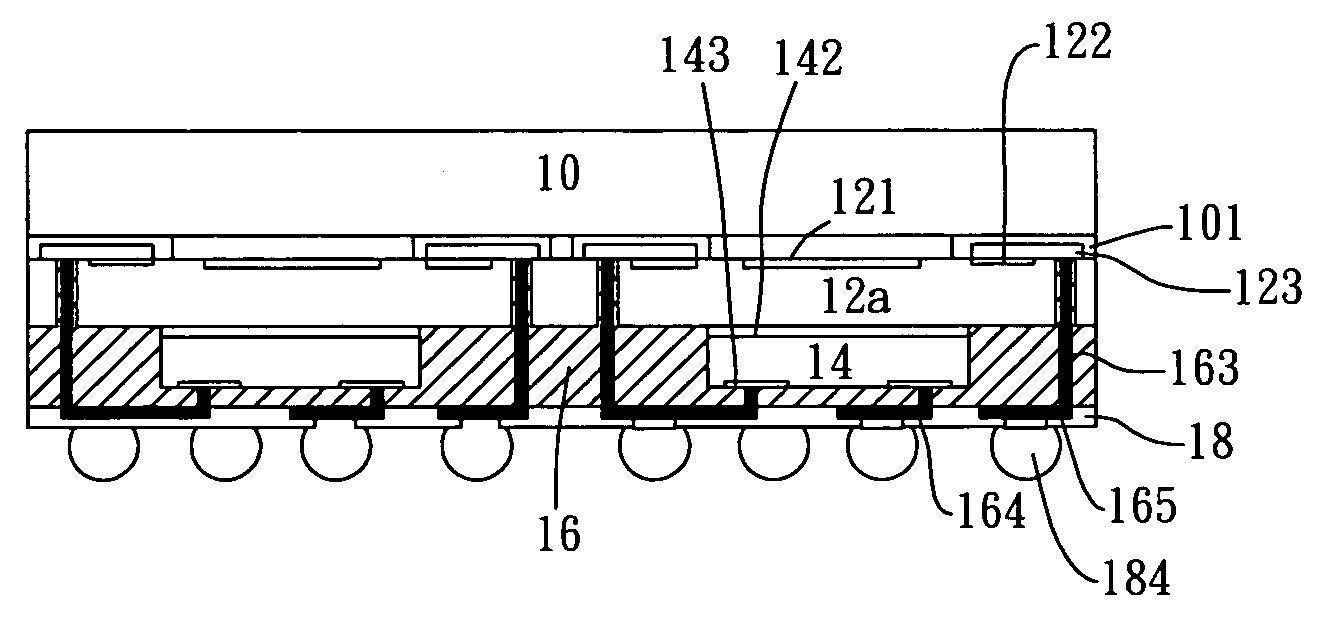

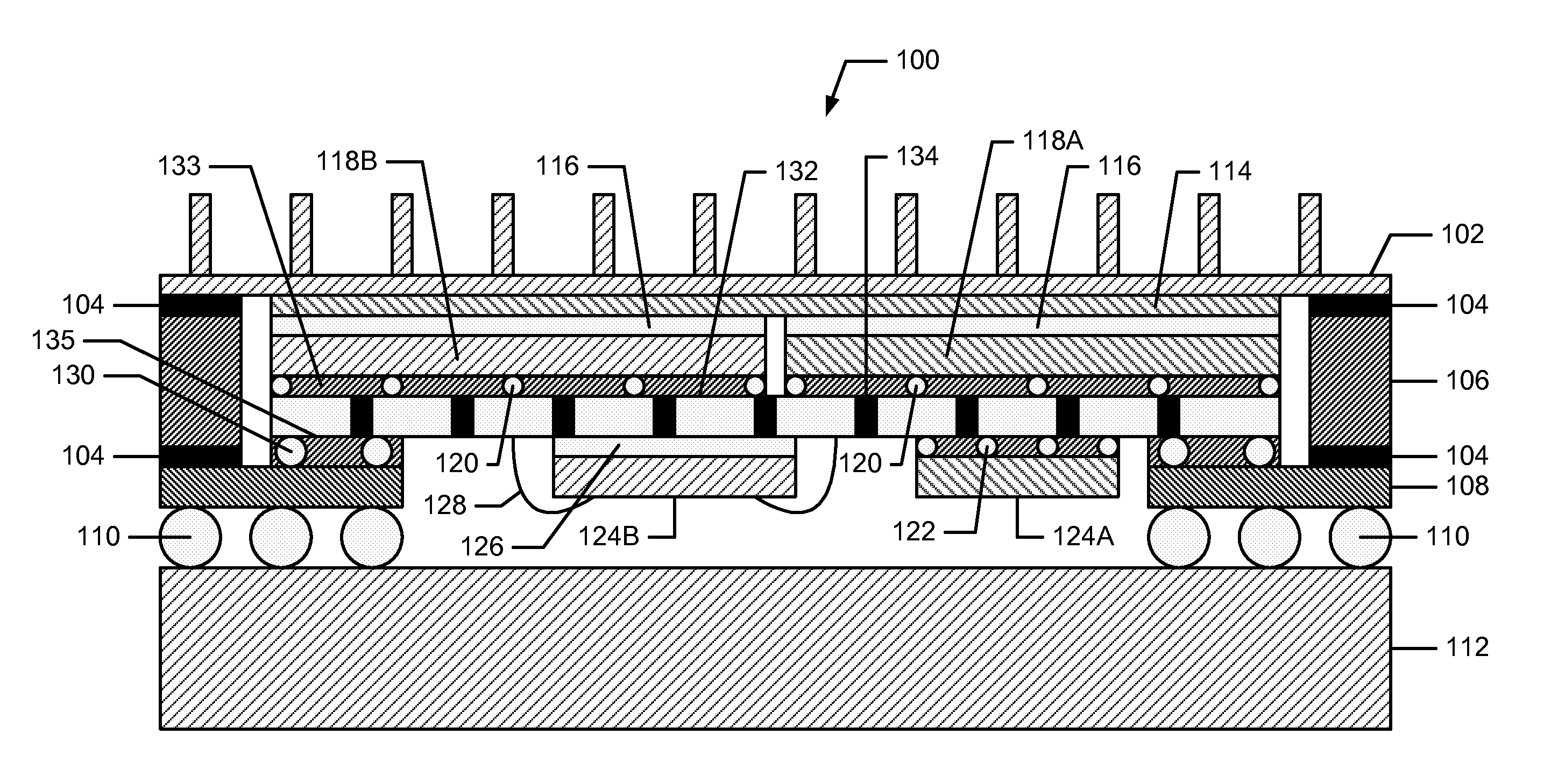

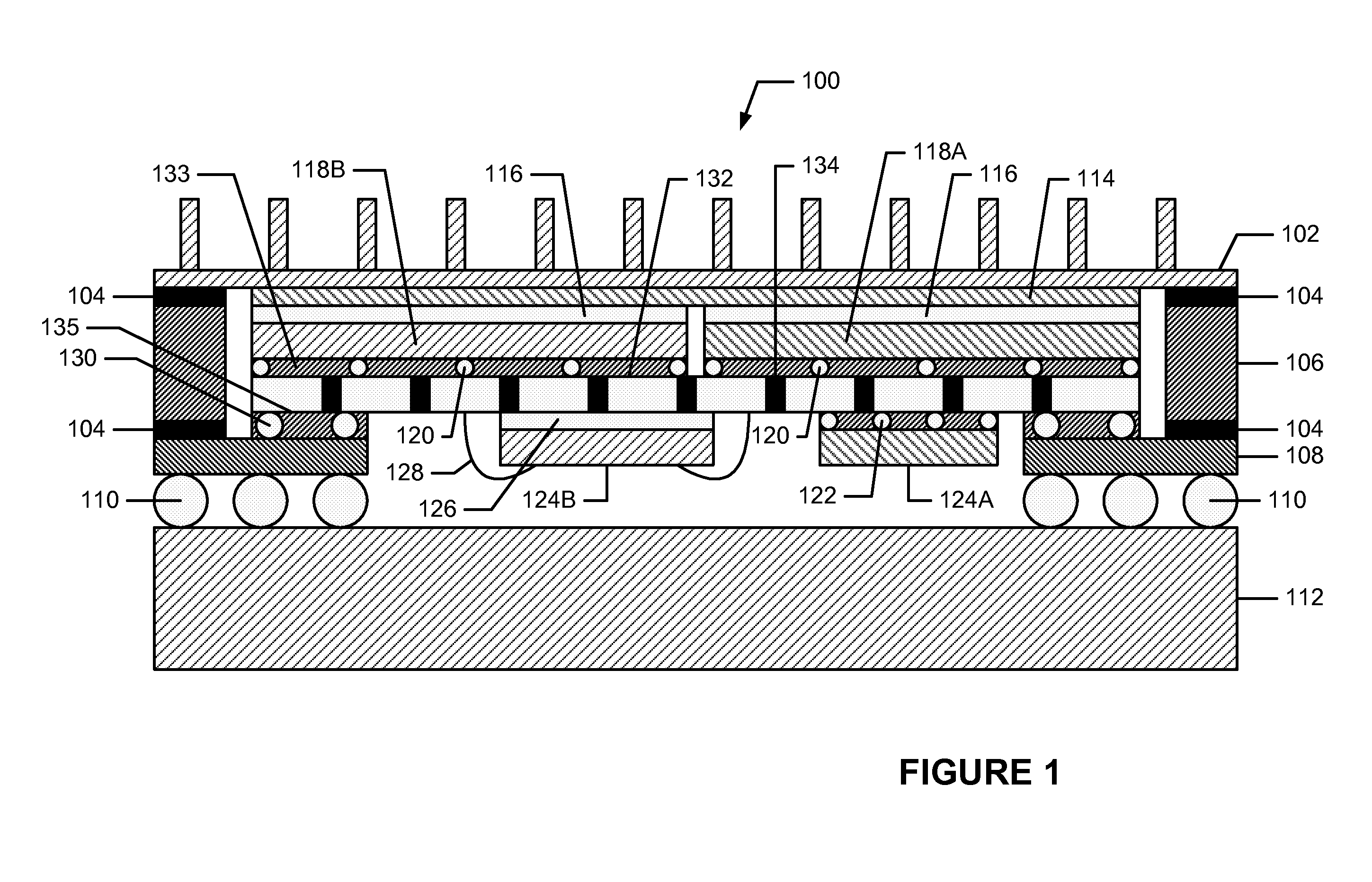

Apparatus having thermal-enhanced and cost-effective 3D IC integration structure with through silicon via interposers

ActiveUS20100213600A1Improved thermal managementImprove thermal performanceSemiconductor/solid-state device detailsSolid-state devicesRedistribution layerInterposer

An apparatus having a three-dimensional integrated circuit structure is described herein. The apparatus include an interposer for carrying a plurality of high and low-power chips. The high-power chips are attached and connected to one side of the interposer, while the low-power chips are attached and connected to the other side of the interposer. In generally, the high-power chips produce more heat than does the low-power chip during their operations. The interposer further include through silicon vias and redistribution layers for connecting the chips on both surfaces. In addition, the interposer assembly is attached and connected to a substrate layer, which is in turn attached and connected to a printed circuit board. In order to provide improve thermal management, the interposer surface carrying the high-power chips are oriented away from the circuit board. A heat spreader is attached to the back sides of the high-power chips for dissipating the heat.

Owner:THE HONG KONG UNIV OF SCI & TECH

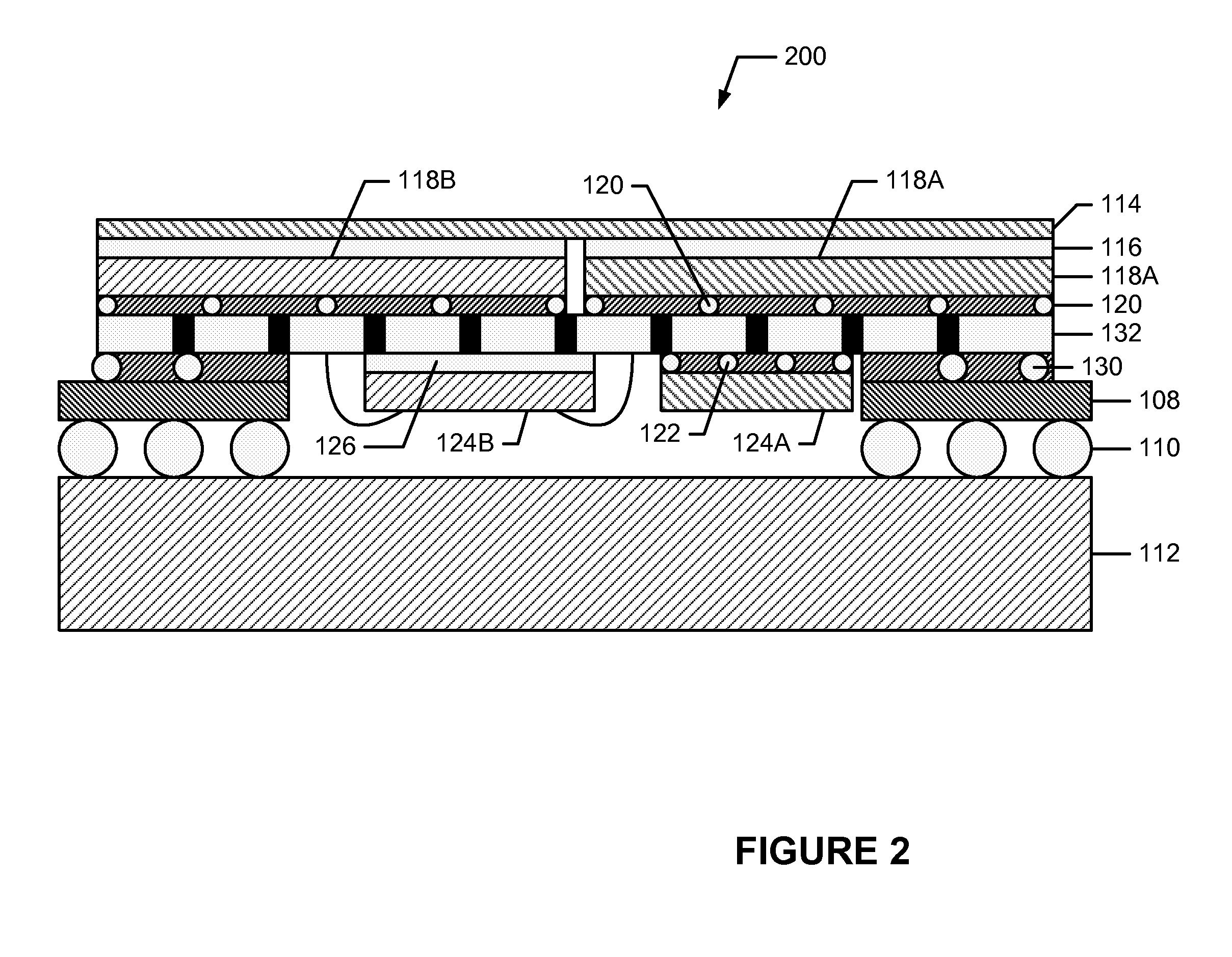

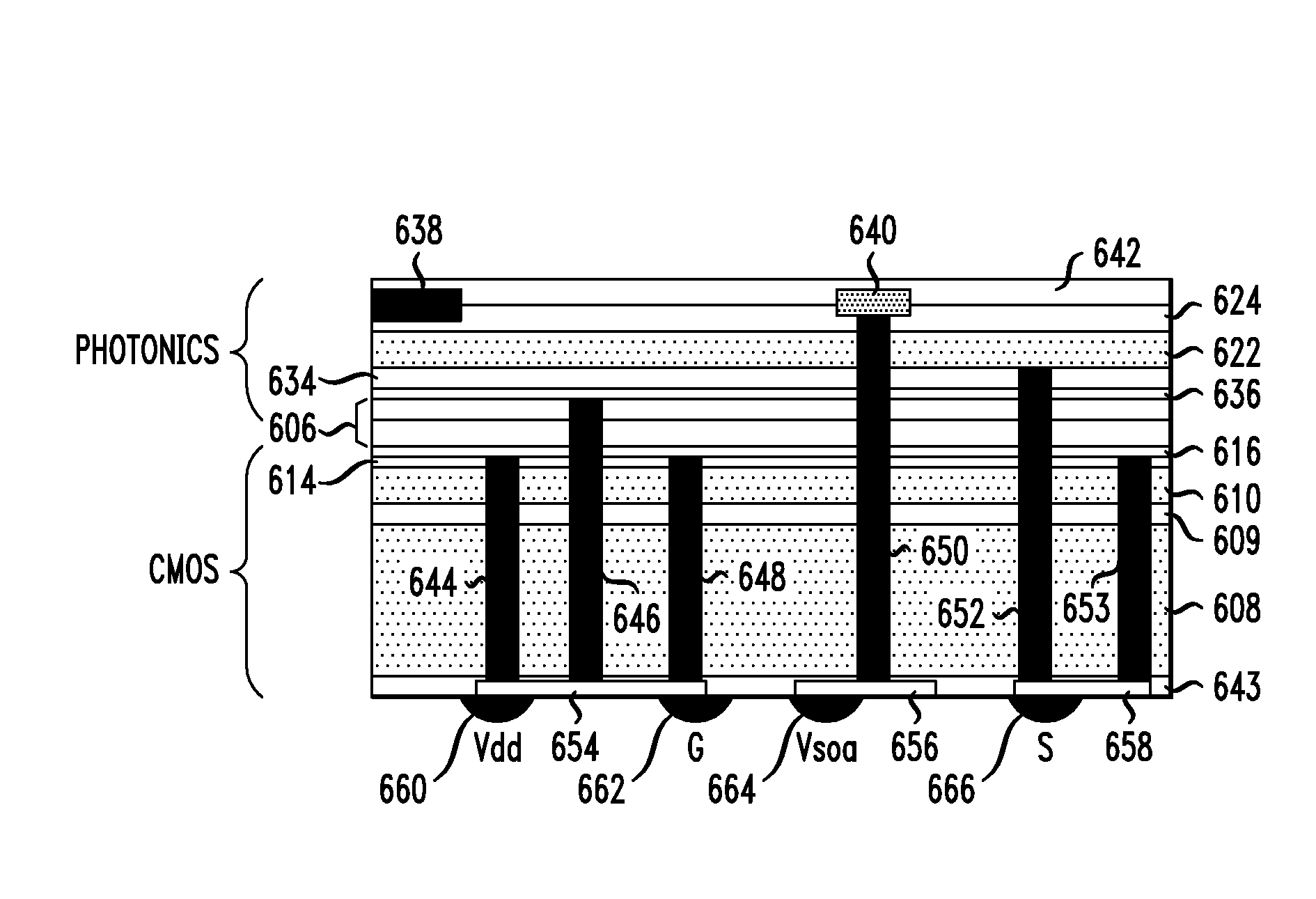

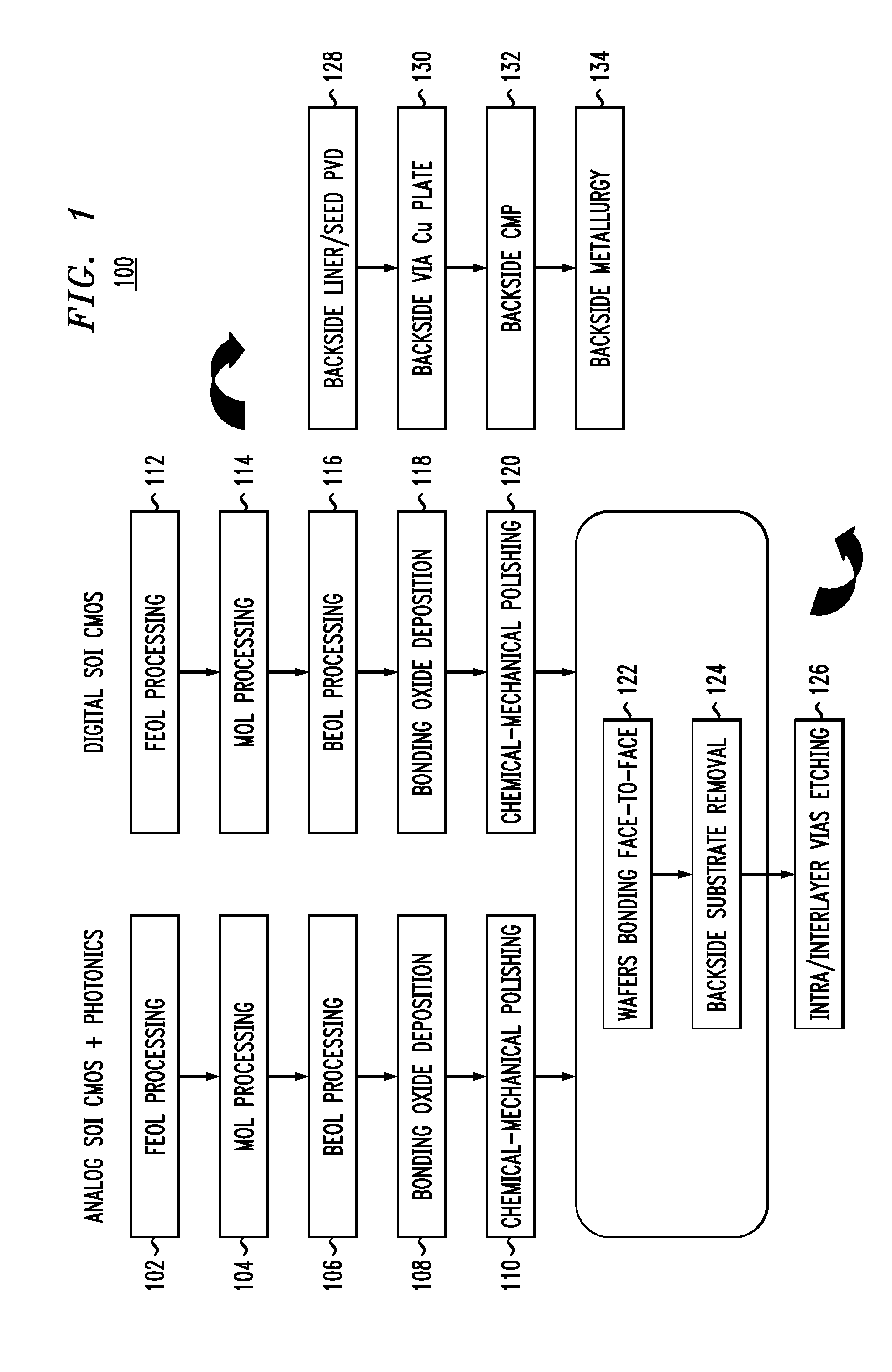

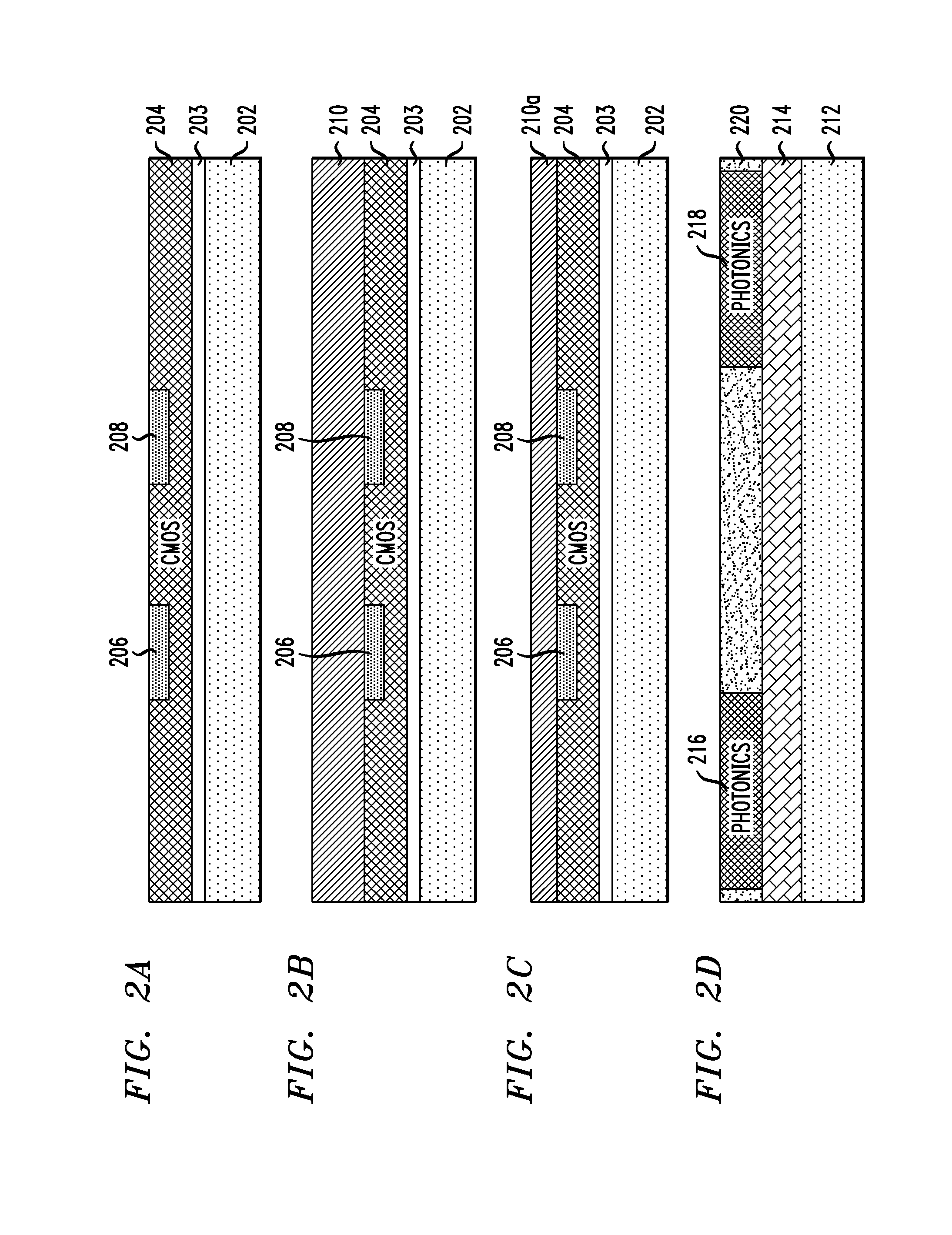

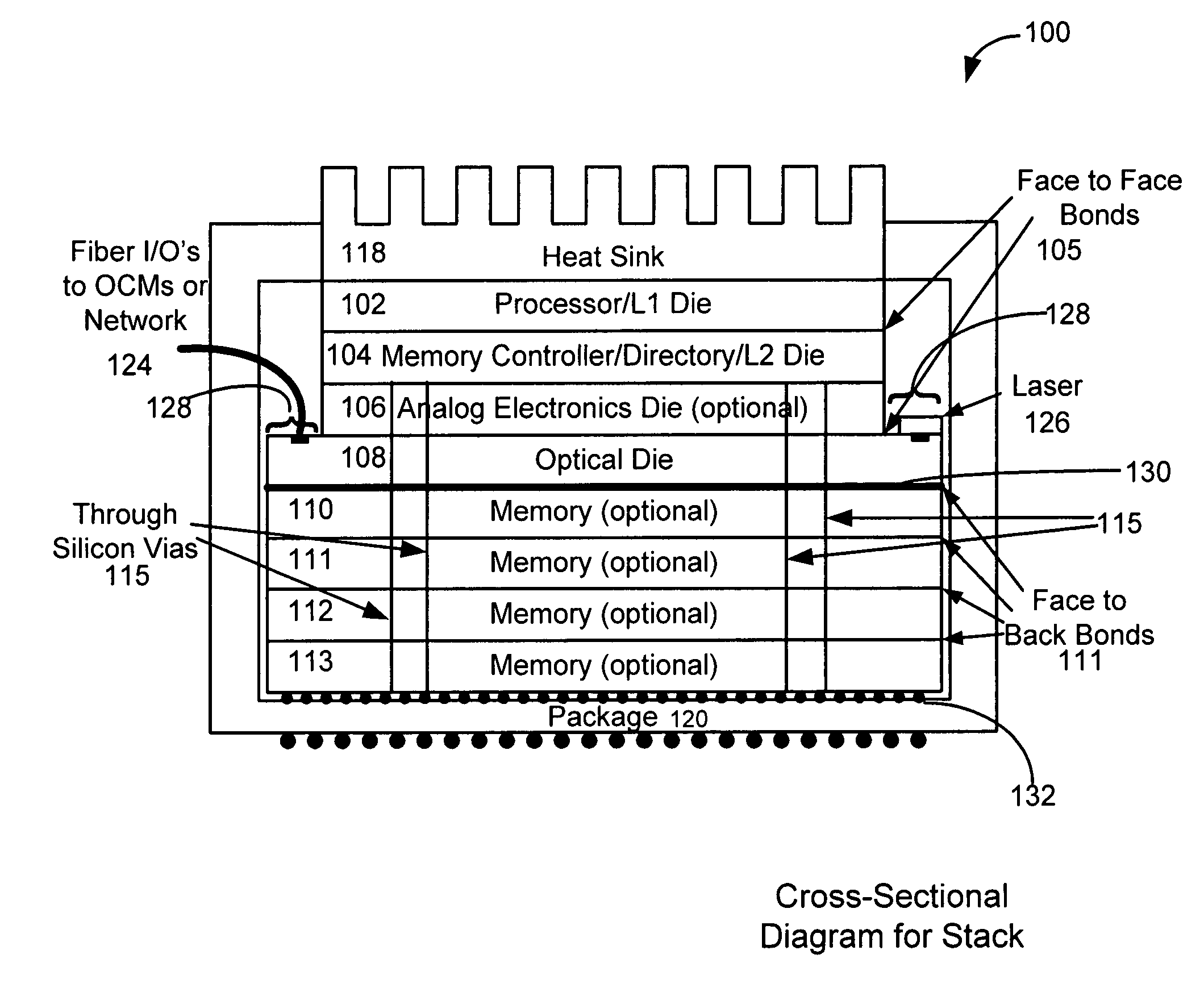

Three-Dimensional Integrated Circuits and Techniques for Fabrication Thereof

ActiveUS20090294814A1Solid-state devicesSemiconductor/solid-state device manufacturingManufacturing technologyPhotonics

Integrated circuits having complementary metal-oxide semiconductor (CMOS) and photonics circuitry and techniques for three-dimensional integration thereof are provided. In one aspect, a three-dimensional integrated circuit comprises a bottom device layer and a top device layer. The bottom device layer comprises a substrate; a digital CMOS circuitry layer adjacent to the substrate; and a first bonding oxide layer adjacent to a side of the digital CMOS circuitry layer opposite the substrate. The top device layer comprises an analog CMOS and photonics circuitry layer formed in a silicon-on-insulator (SOI) layer having a buried oxide (BOX) with a thickness of greater than or equal to about 0.5 micrometers; and a second bonding oxide layer adjacent to the analog CMOS and photonics circuitry layer. The bottom device layer is bonded to the top device layer by an oxide-to-oxide bond between the first bonding oxide layer and the second bonding oxide layer.

Owner:GLOBALFOUNDRIES US INC

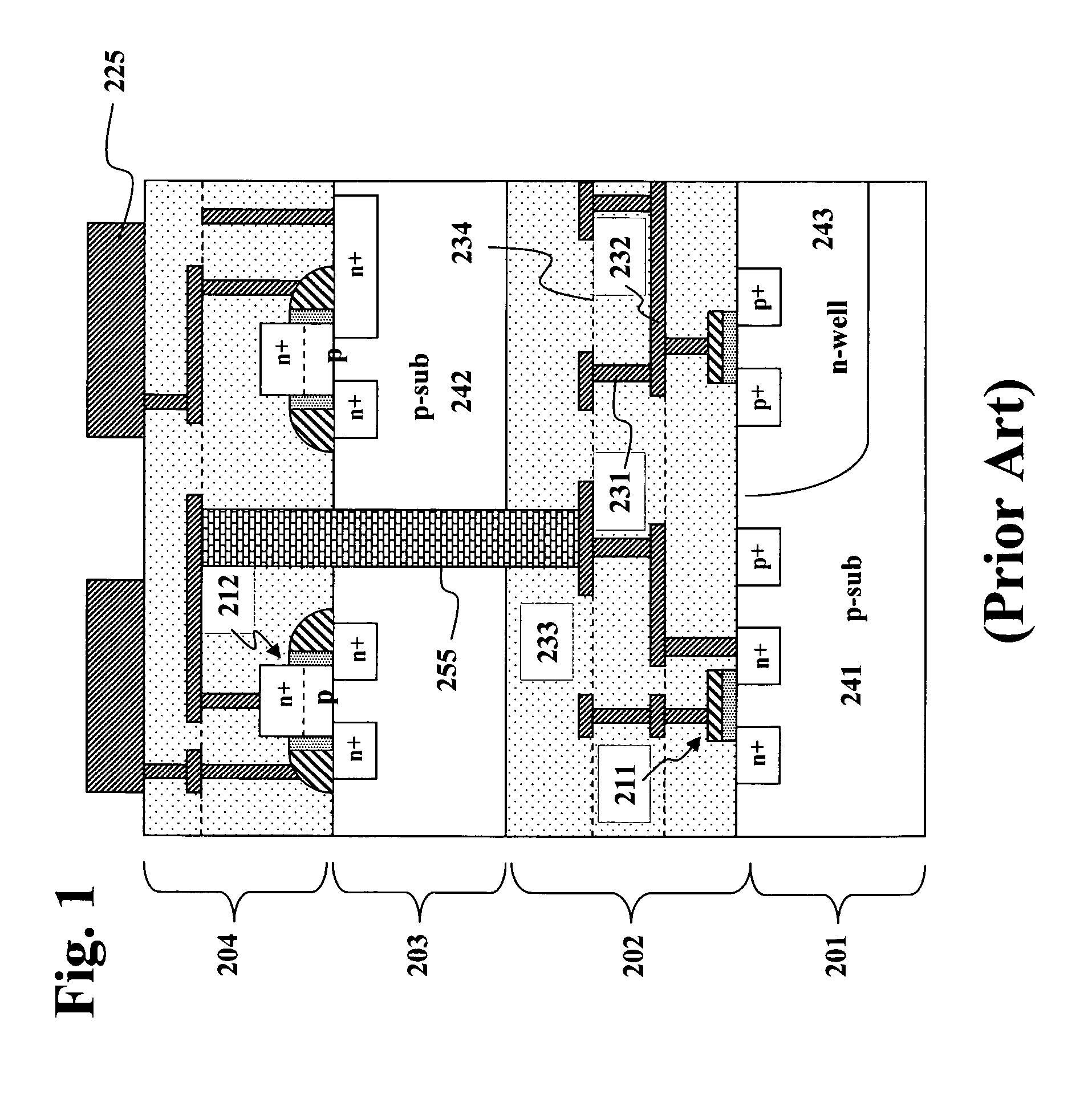

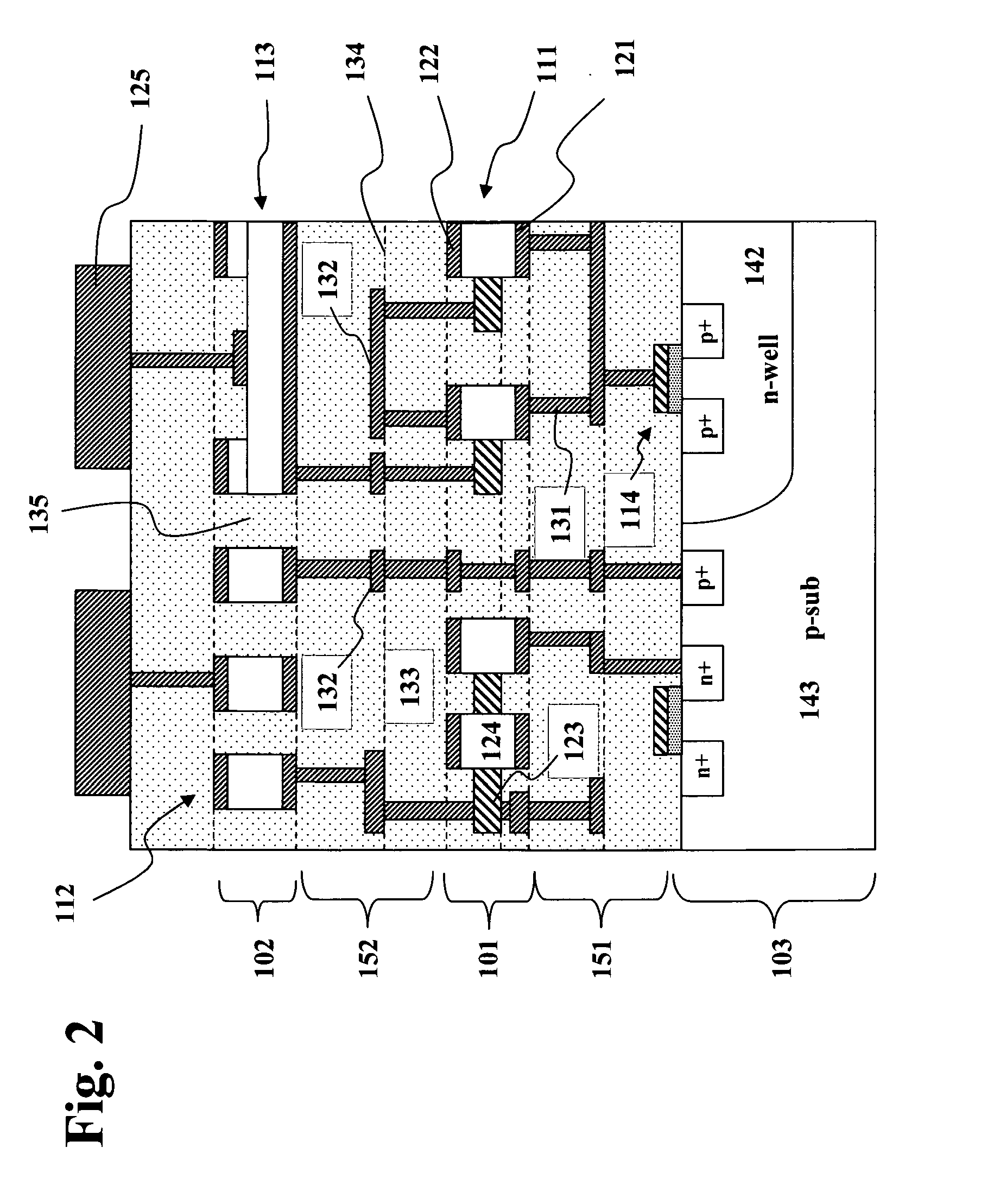

Three-dimensional integrated circuit structure

InactiveUS20070145367A1Simplify the manufacturing processImprove performanceSolid-state devicesSemiconductor/solid-state device manufacturingSemiconductor structureEngineering

The preferred embodiments of the present invention provide a three-dimensional (3D) semiconductor structure and a method of forming the same. The 3D semiconductor structure includes a first substrate bonded to a second substrate. The first substrate includes substantially all NMOS devices. The second substrate includes substantially all PMOS devices. The substrates can be bonded face-to-face, face-to-back, or back-to-back. The method includes providing a first substrate and a second substrate, forming a first circuit comprising at least one NMOS device on the first substrate, wherein the first substrate includes substantially no PMOS devices, forming a second circuit comprising at least one PMOS device on the second substrate, wherein the second substrate includes substantially no NMOS devices, and bonding the first and second substrates after forming the first and second circuits.

Owner:TAIWAN SEMICON MFG CO LTD

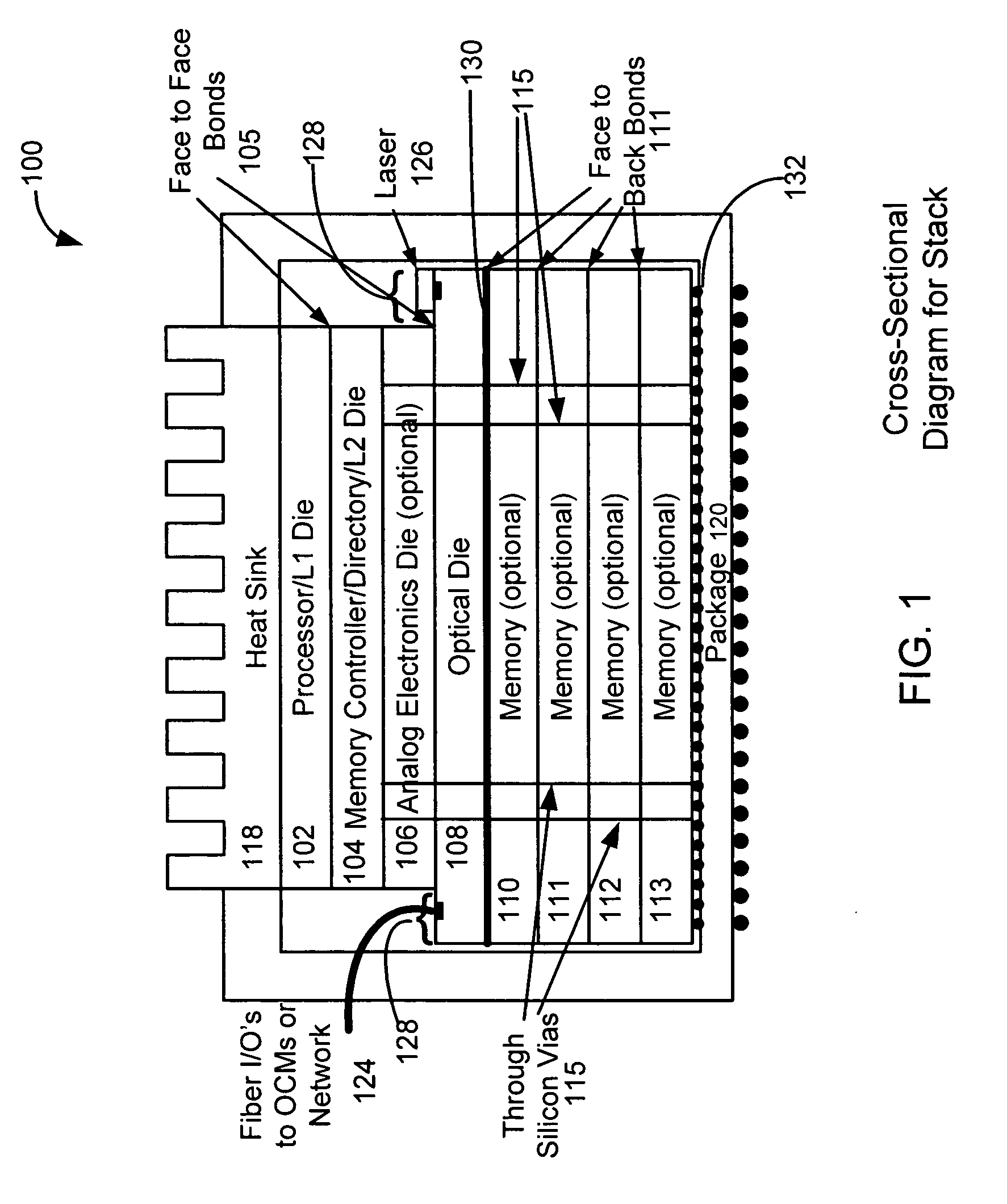

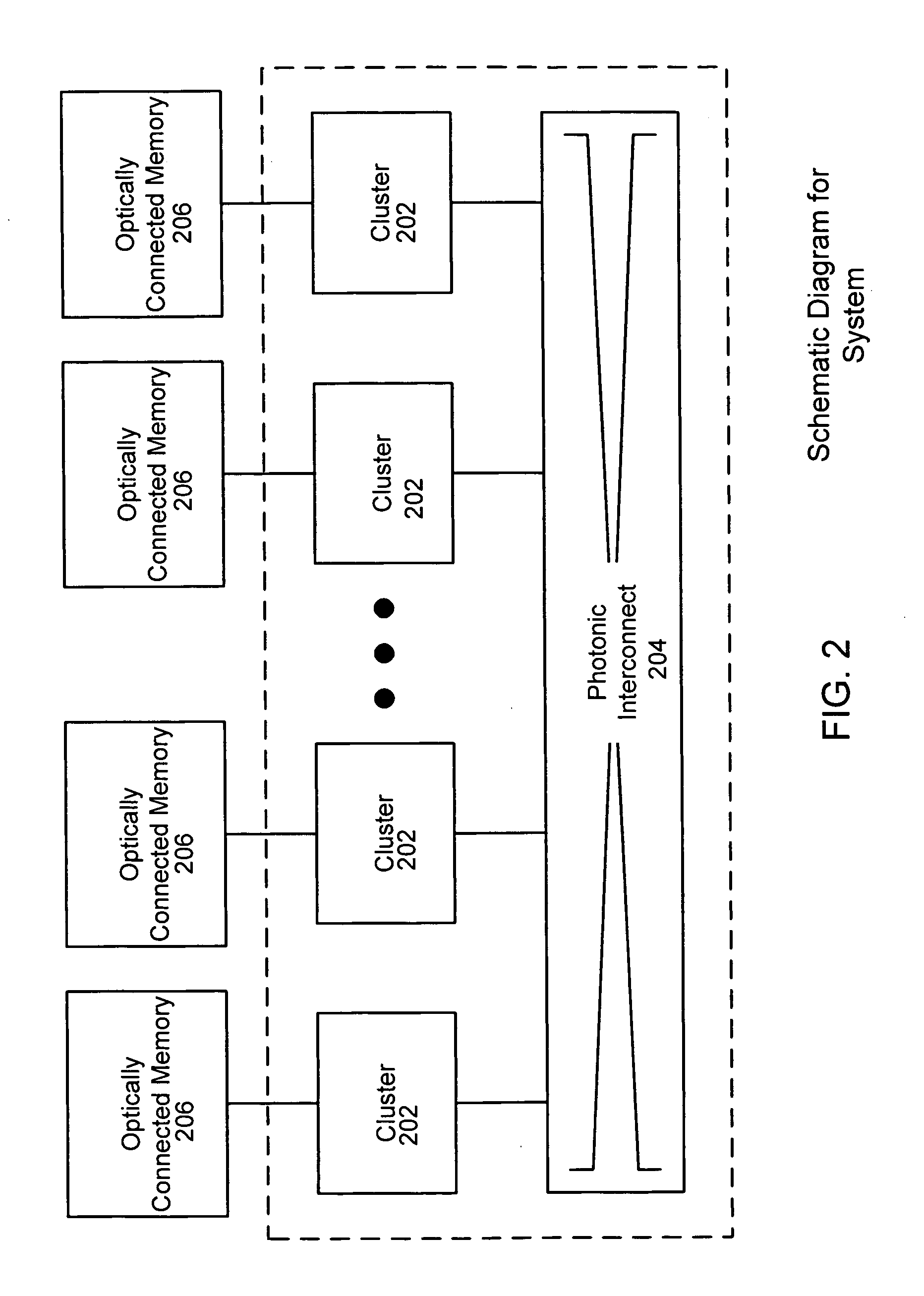

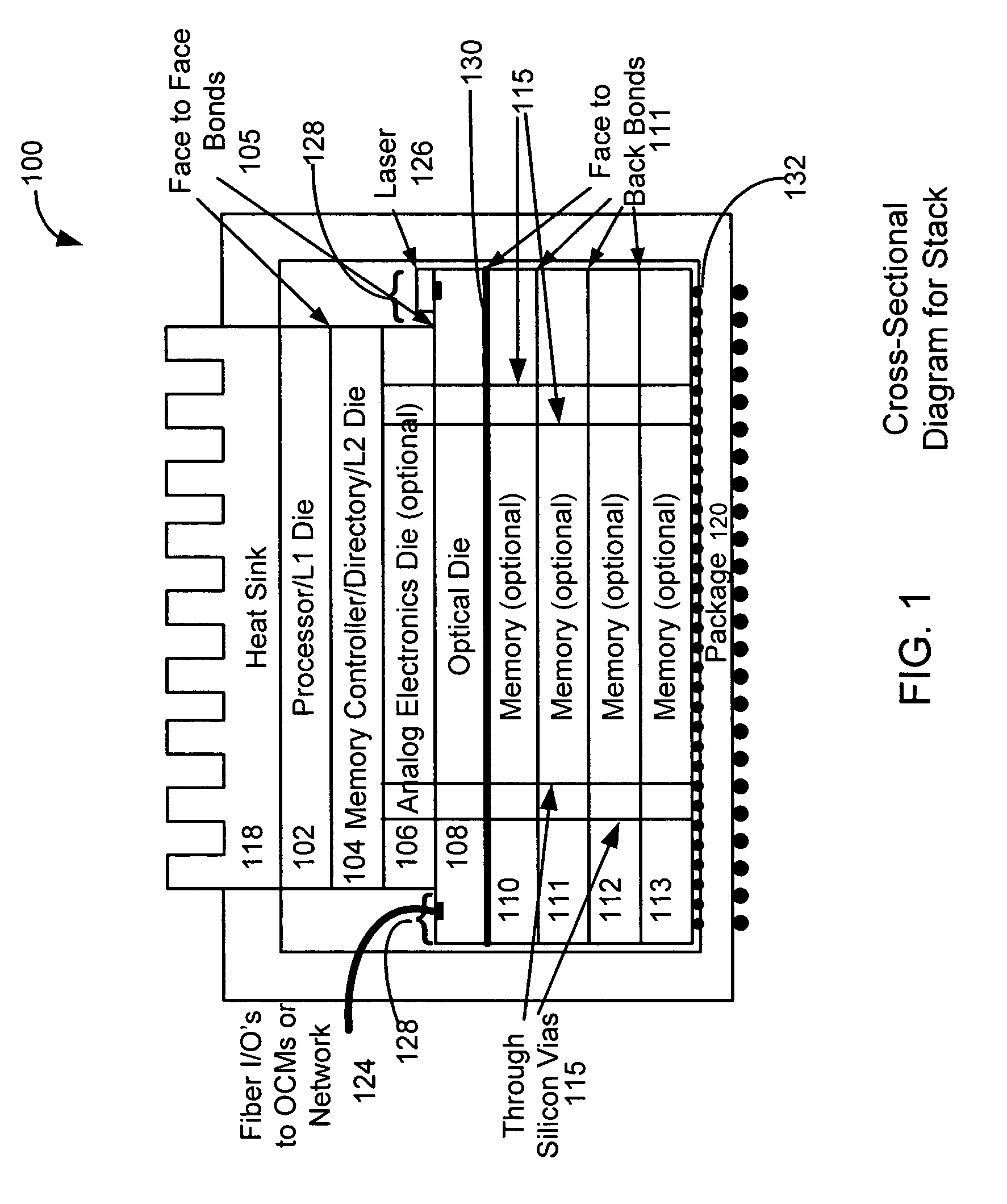

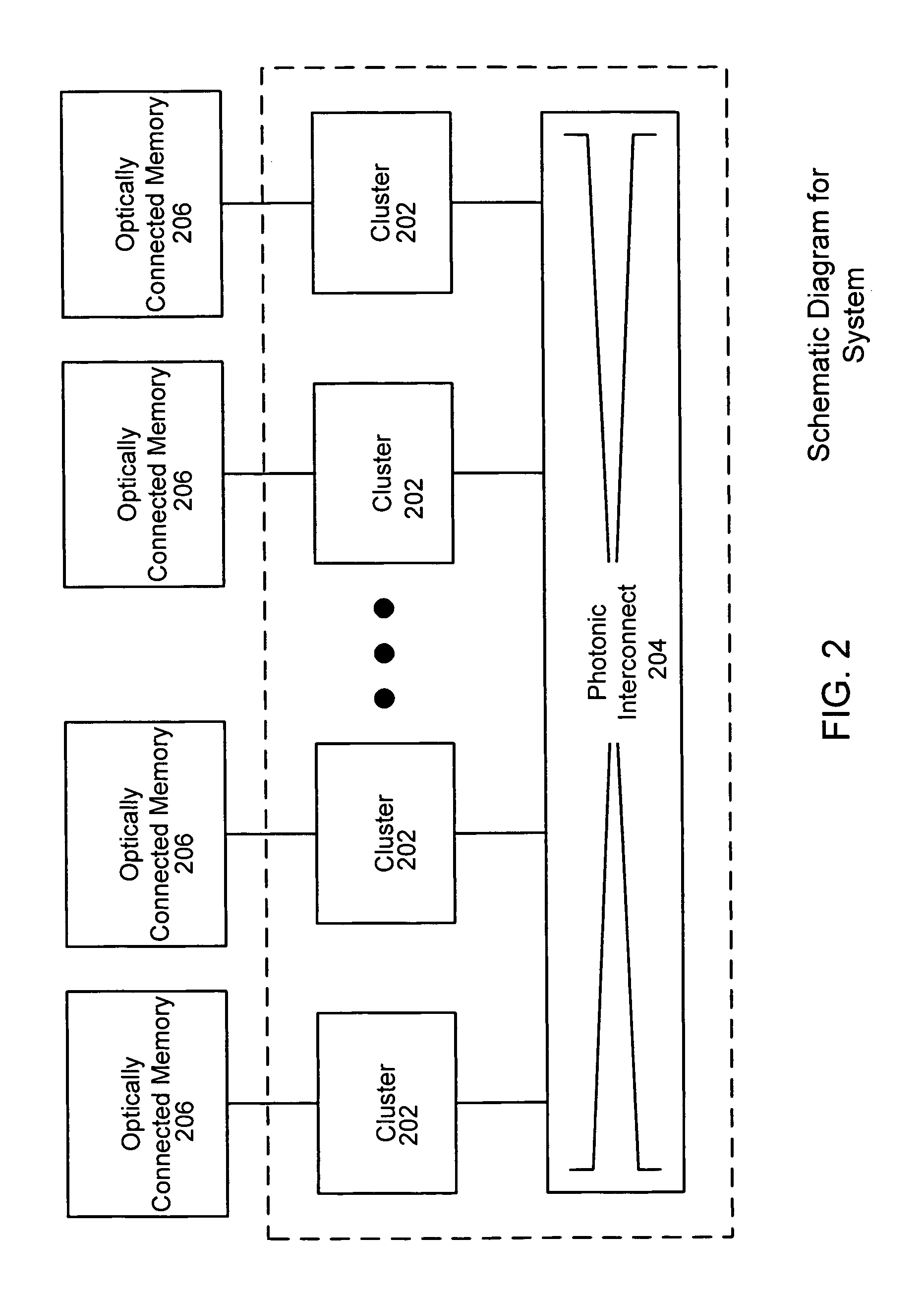

Three-dimensional die stacks with inter-device and intra-device optical interconnect

ActiveUS20090103855A1Reduce areaSolid-state devicesSemiconductor/solid-state device manufacturingComputerized systemEngineering

Examples of a computer system packaged in a three-dimensional stack of dies are described. The package includes an electrical die and an optical die coupled to and stacked with the electrical die. The electrical die includes circuitry to process and communicate electrical signals, and the optical die includes structures to transport optical signals. The electrical die has a smaller area than the optical die so that the optical die includes an exposed mezzanine which is configured with optical input / output ports. Additionally, the packaging can be configured to provide structural support against insertion forces for external optical connections.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP

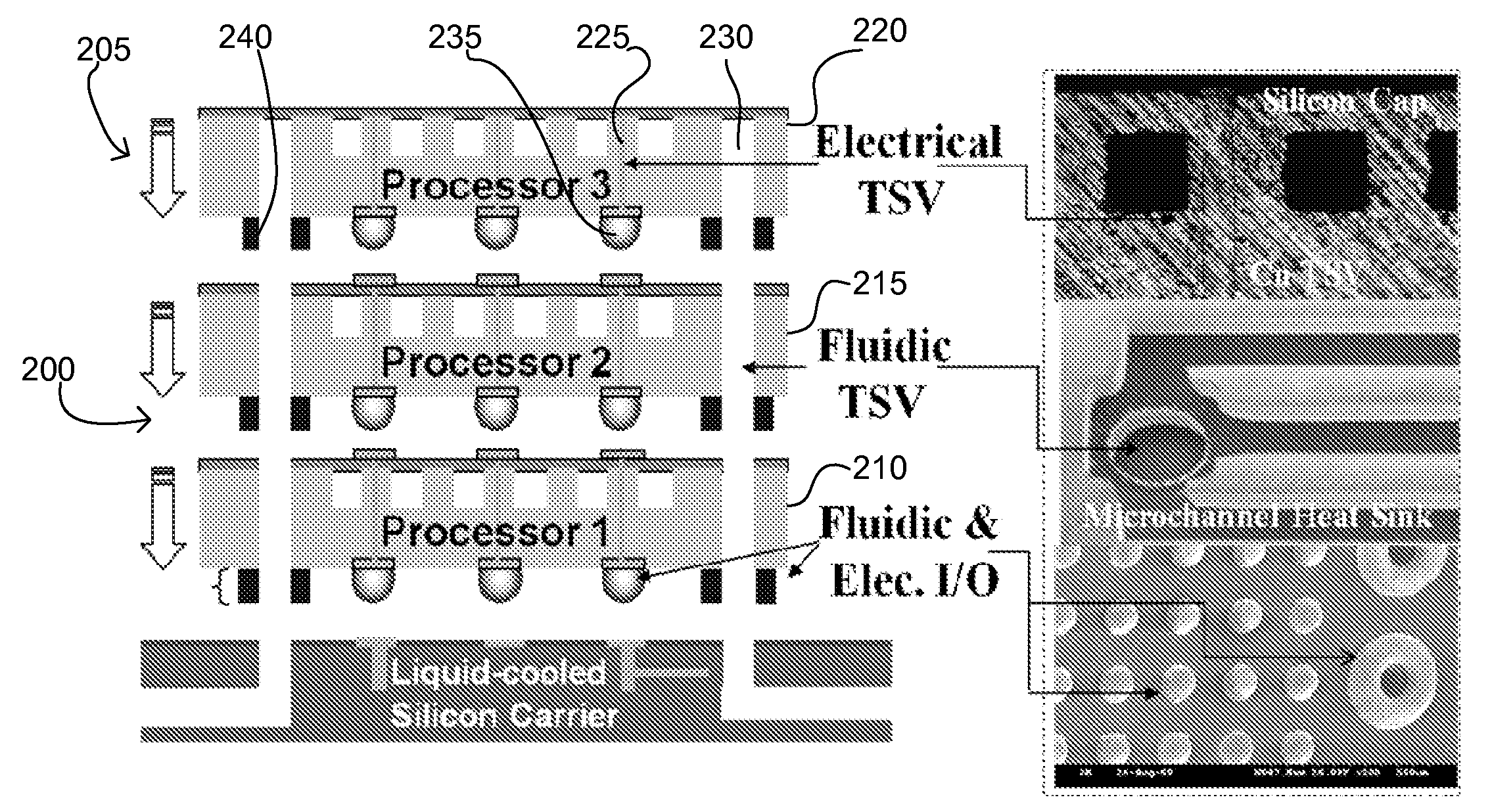

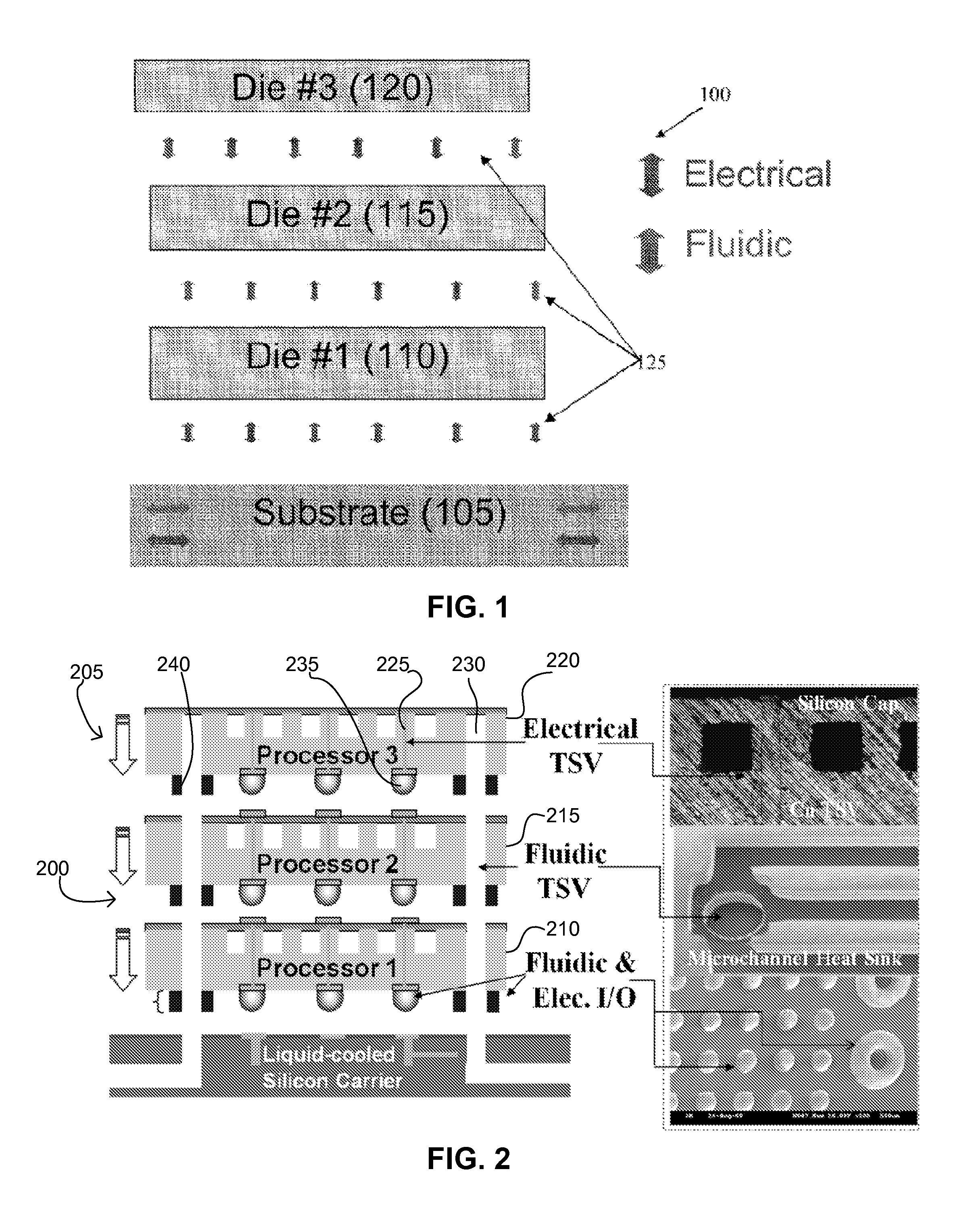

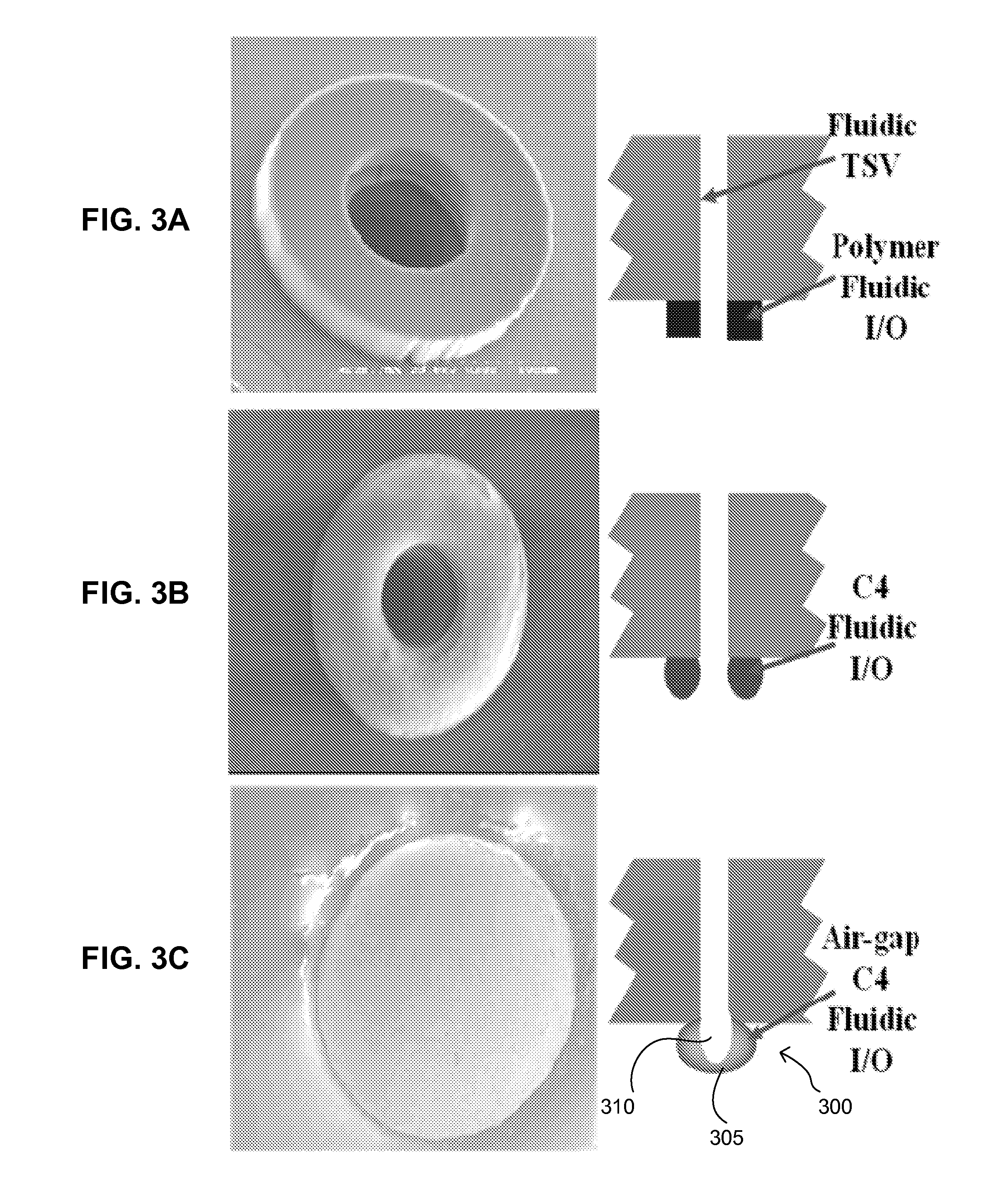

Air-gap c4 fluidic I/O interconnects and methods of fabricating same

An exemplary embodiment of the present invention provides a chip for use in fabricating a three-dimensional integrated circuit, the chip comprising a wafer, one or more metallic-filled, electrical vias, and one or more hollow, fluidic vias. The wafer can comprise a first surface and a second surface. The one or more metallic-filled, electrical vias can extend through the wafer. Each electrical via can be in electrical communication with an electrical interconnect proximate the first surface, providing electrical communication between chips in the integrated circuit. The one or more hollow, fluidic vias can extend through the wafer. Each fluidic via can be in fluid communication with a fluidic interconnect, providing fluid communication between adjacent chips in the integrated circuit. Each fluidic interconnect can comprise a first end proximate the first surface, a second end, and a cap proximate the second end, defining an air-filled space within the fluidic interconnect.

Owner:GEORGIA TECH RES CORP

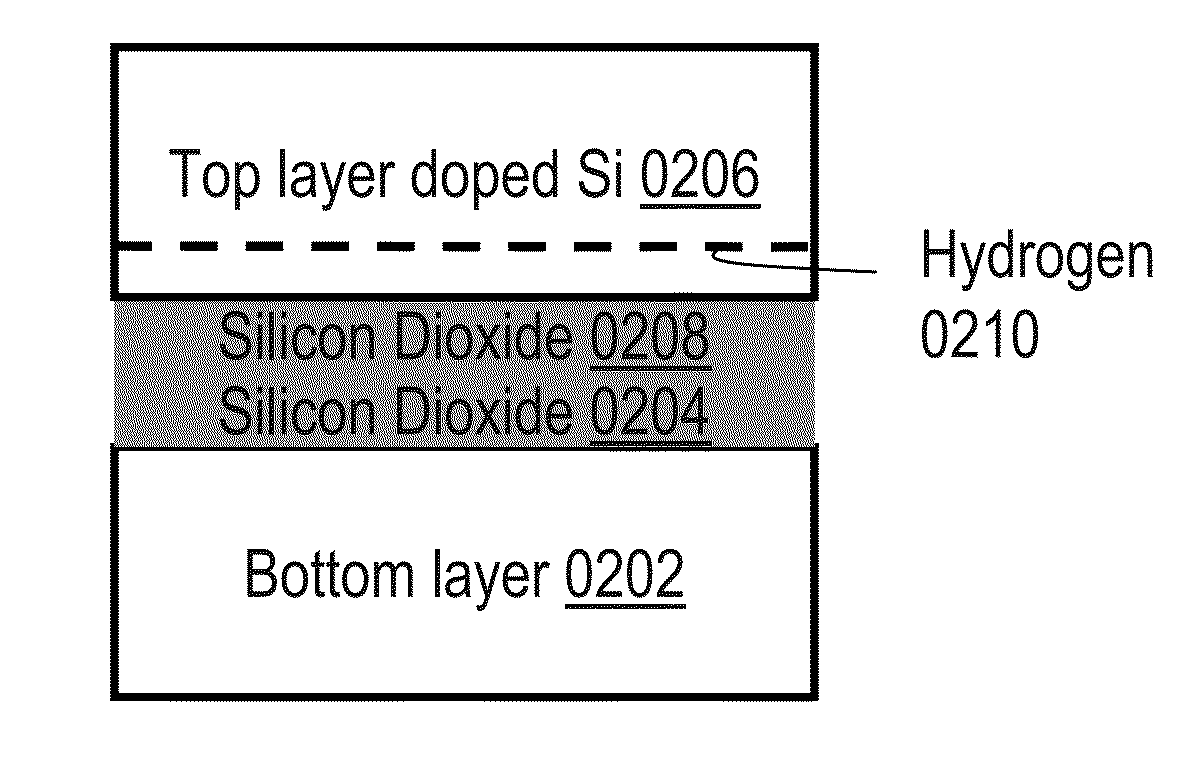

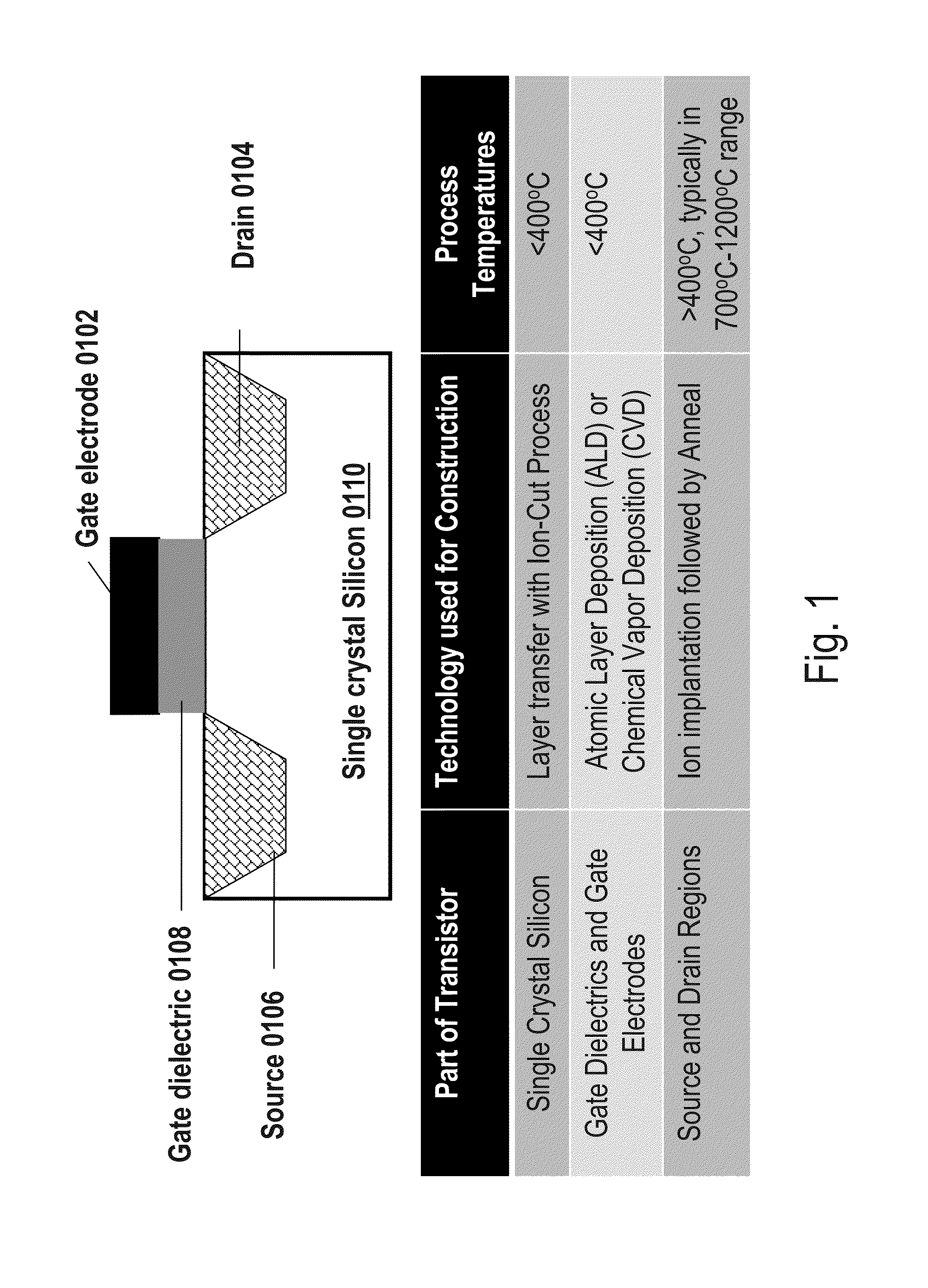

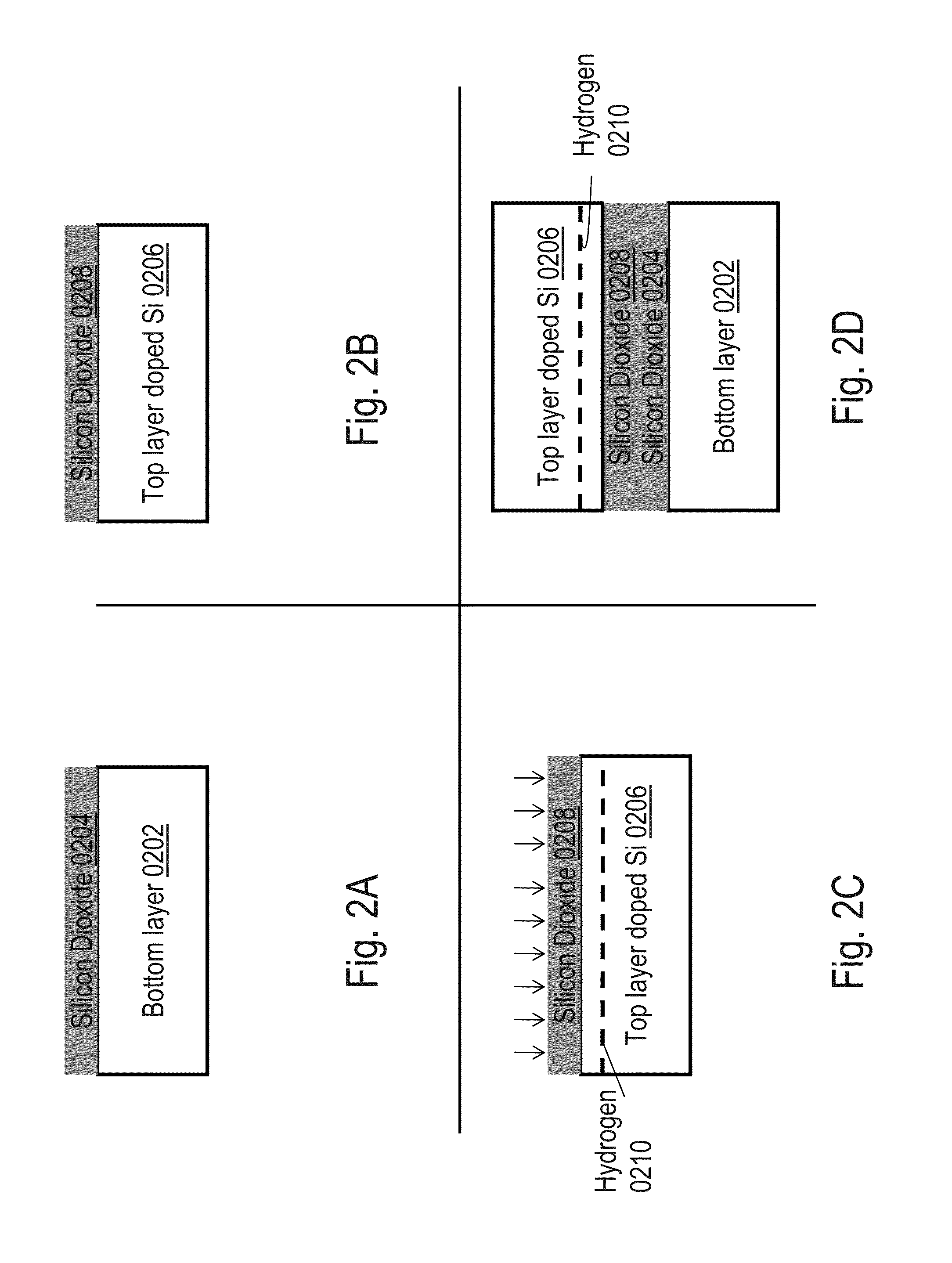

Method of forming three dimensional integrated circuit devices using layer transfer technique

A method for formation of a semiconductor device including a first wafer including a first single crystal layer comprising first transistors and first alignment mark, the method including: implanting to form a doped layer within a second wafer; forming a second mono-crystalline layer on top of the first wafer by transferring at least a portion of the doped layer using layer transfer step, and completing the formation of second transistors on the second mono-crystalline layer including a step of forming a gate dielectric followed by second transistors gate formation step, wherein the second transistors are horizontally oriented.

Owner:MONOLITHIC 3D

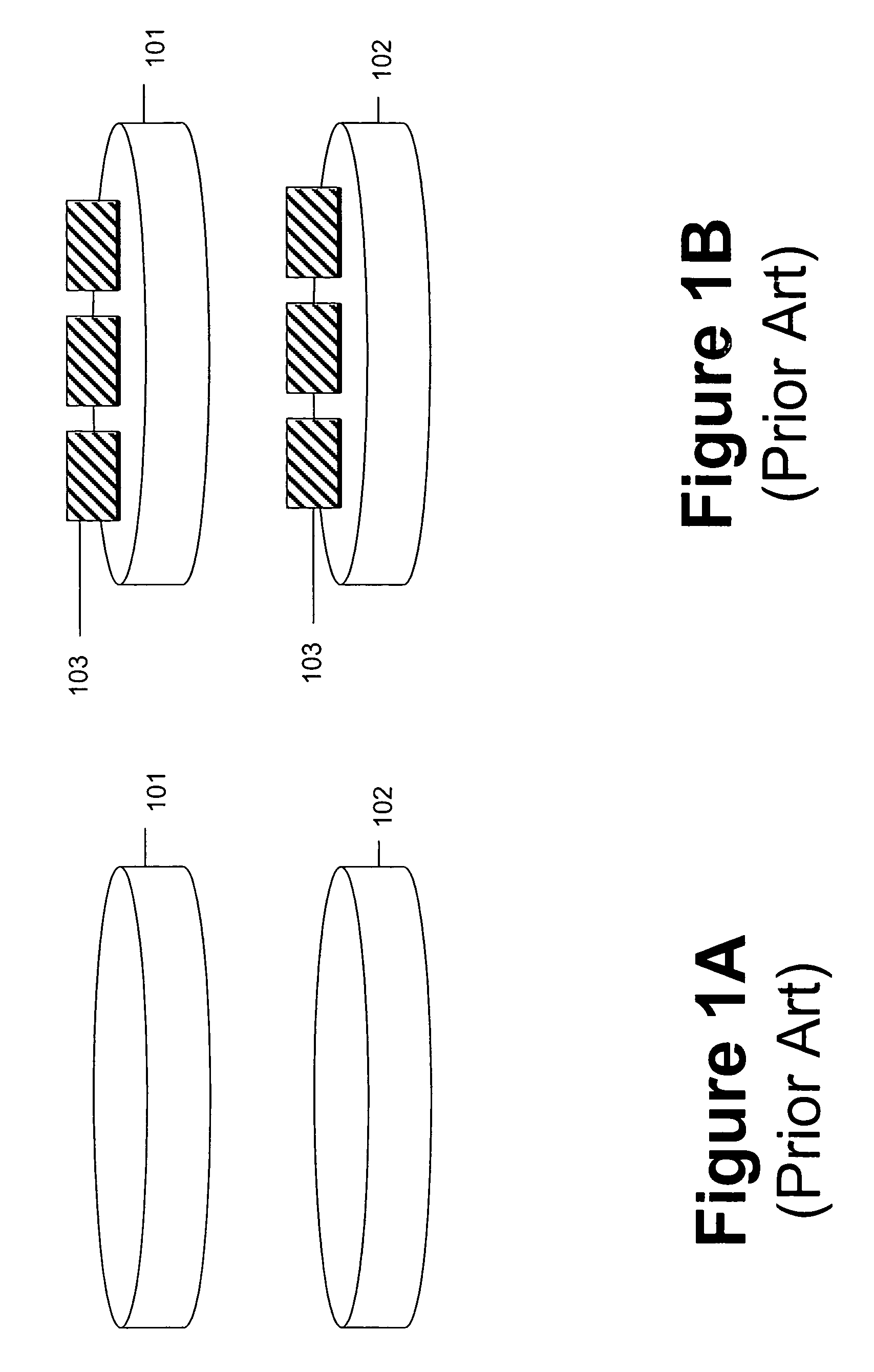

Method for scalable architectures in stackable three-dimensional integrated circuits and electronics

InactiveUS7046522B2Improve the level ofSemiconductor/solid-state device detailsPrinted circuit aspectsEngineeringThree-dimensional integrated circuit

The design methods described enable three-dimensional integrated circuit systems in which all of the dies, in a vertically bonded stack of dies, are identical. Only one mask set and wafer type is required since a single circuit design is produced for one die in the stack and reused for all the dies with little or no modification. The system scales directly as the level of stacking is increased while incurring no extra design effort, beyond that required for the initial design.

Owner:SUNG RAYMOND JIT HUNG +4

Three-dimensional die stacks with inter-device and intra-device optical interconnect

ActiveUS8064739B2Solid-state devicesSemiconductor/solid-state device manufacturingComputerized systemThree-dimensional integrated circuit

Examples of a computer system packaged in a three-dimensional stack of dies are described. The package includes an electrical die and an optical die coupled to and stacked with the electrical die. The electrical die includes circuitry to process and communicate electrical signals, and the optical die includes structures to transport optical signals. The electrical die has a smaller area than the optical die so that the optical die includes an exposed mezzanine which is configured with optical input / output ports. Additionally, the packaging can be configured to provide structural support against insertion forces for external optical connections.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP

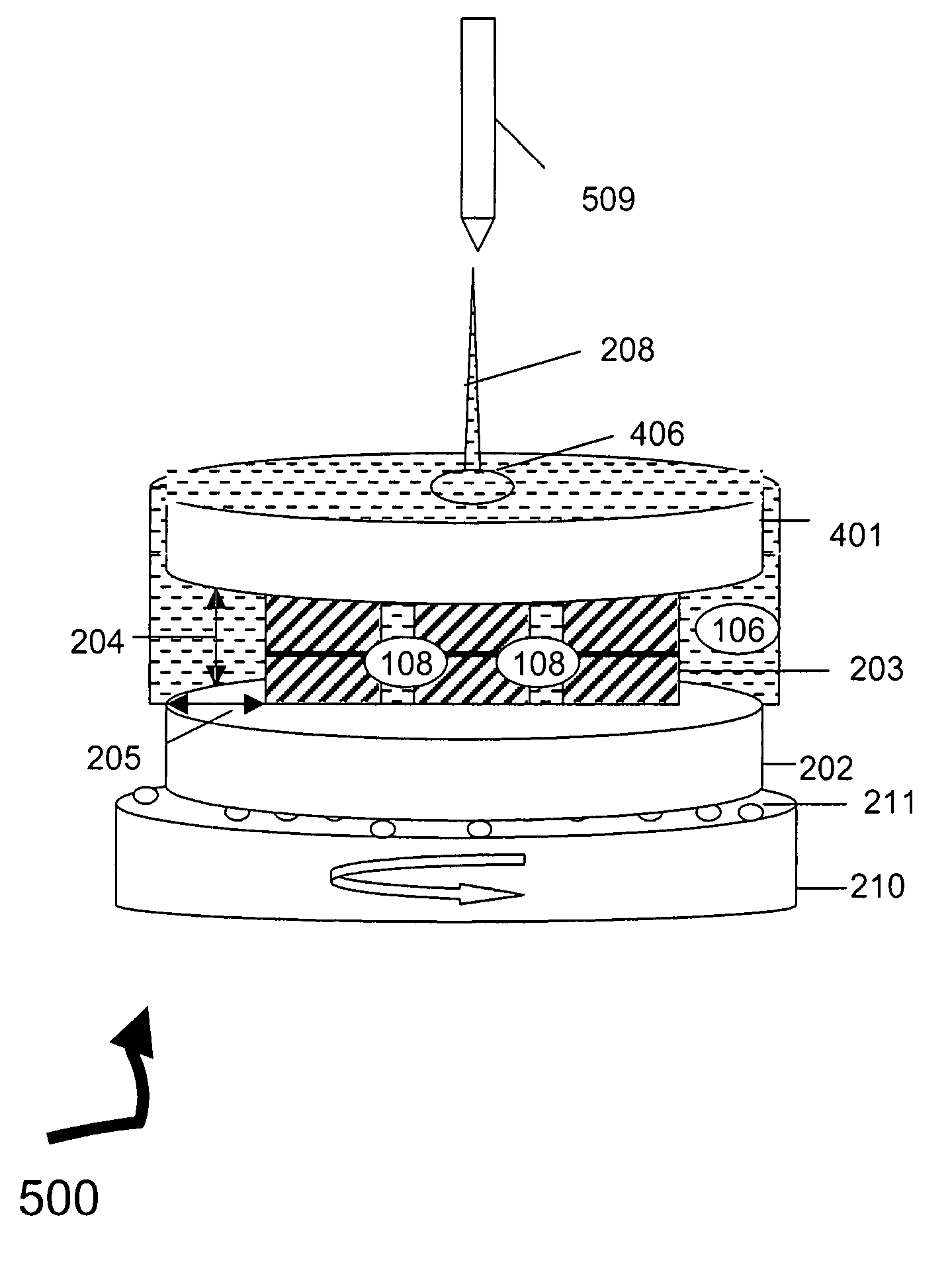

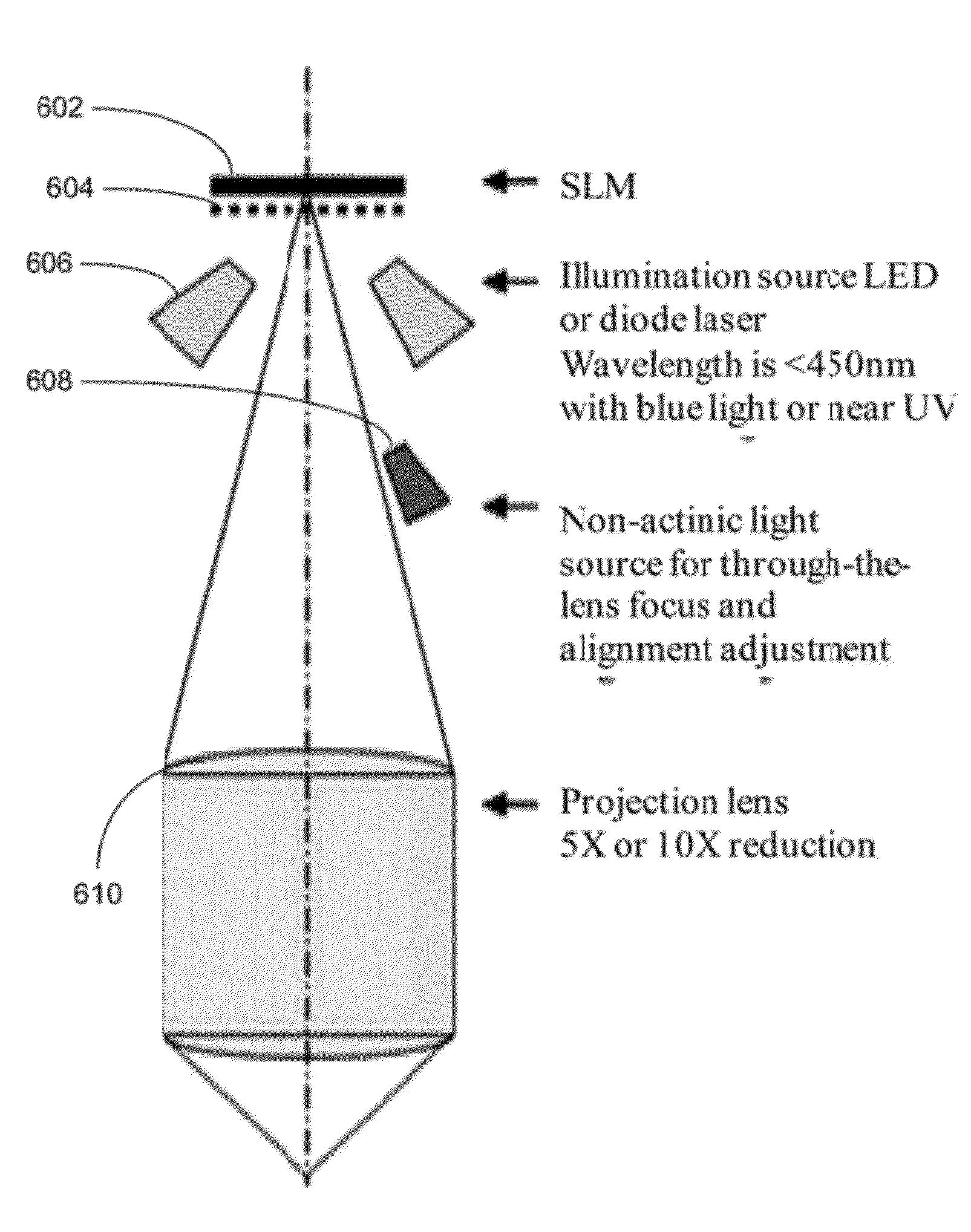

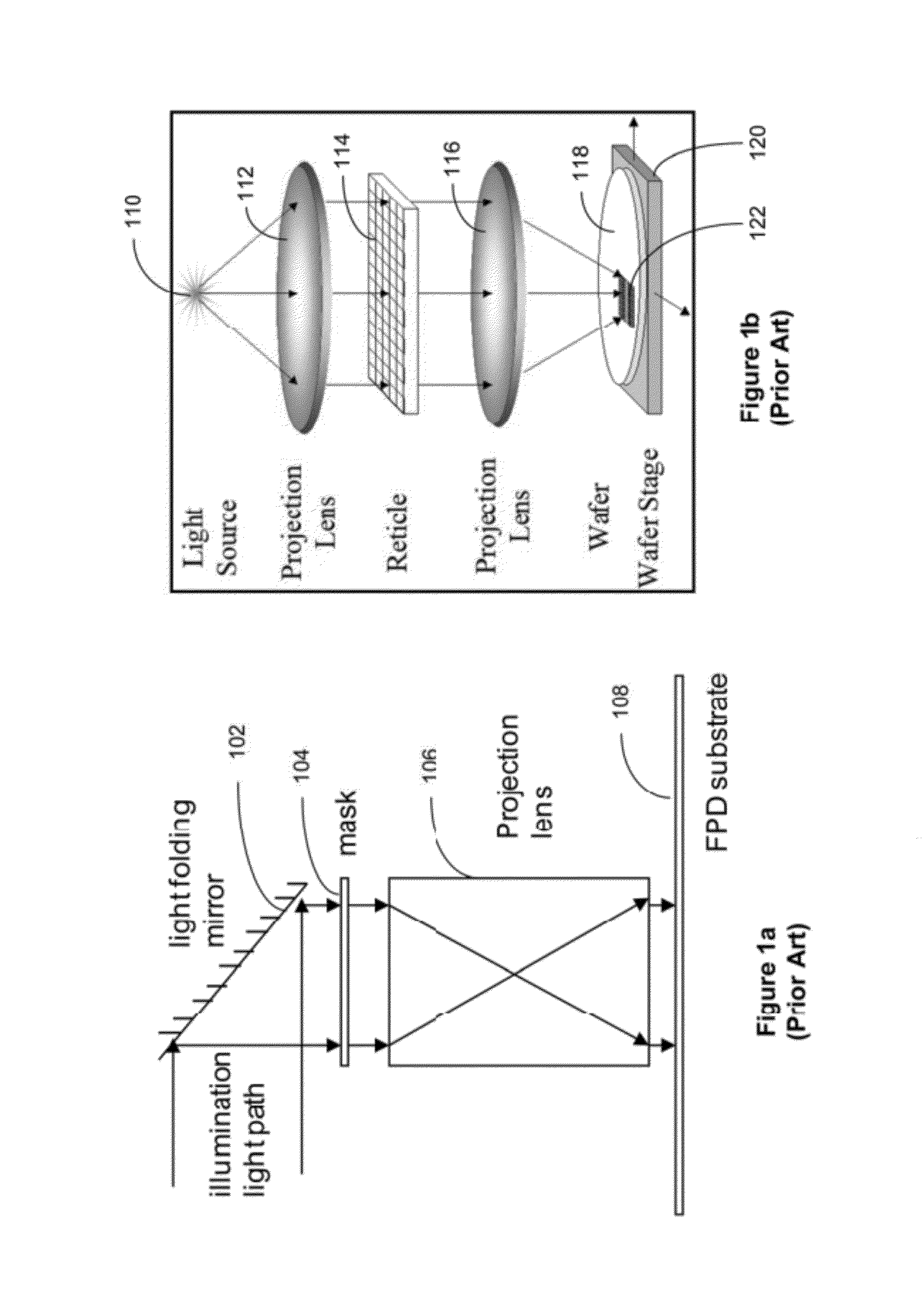

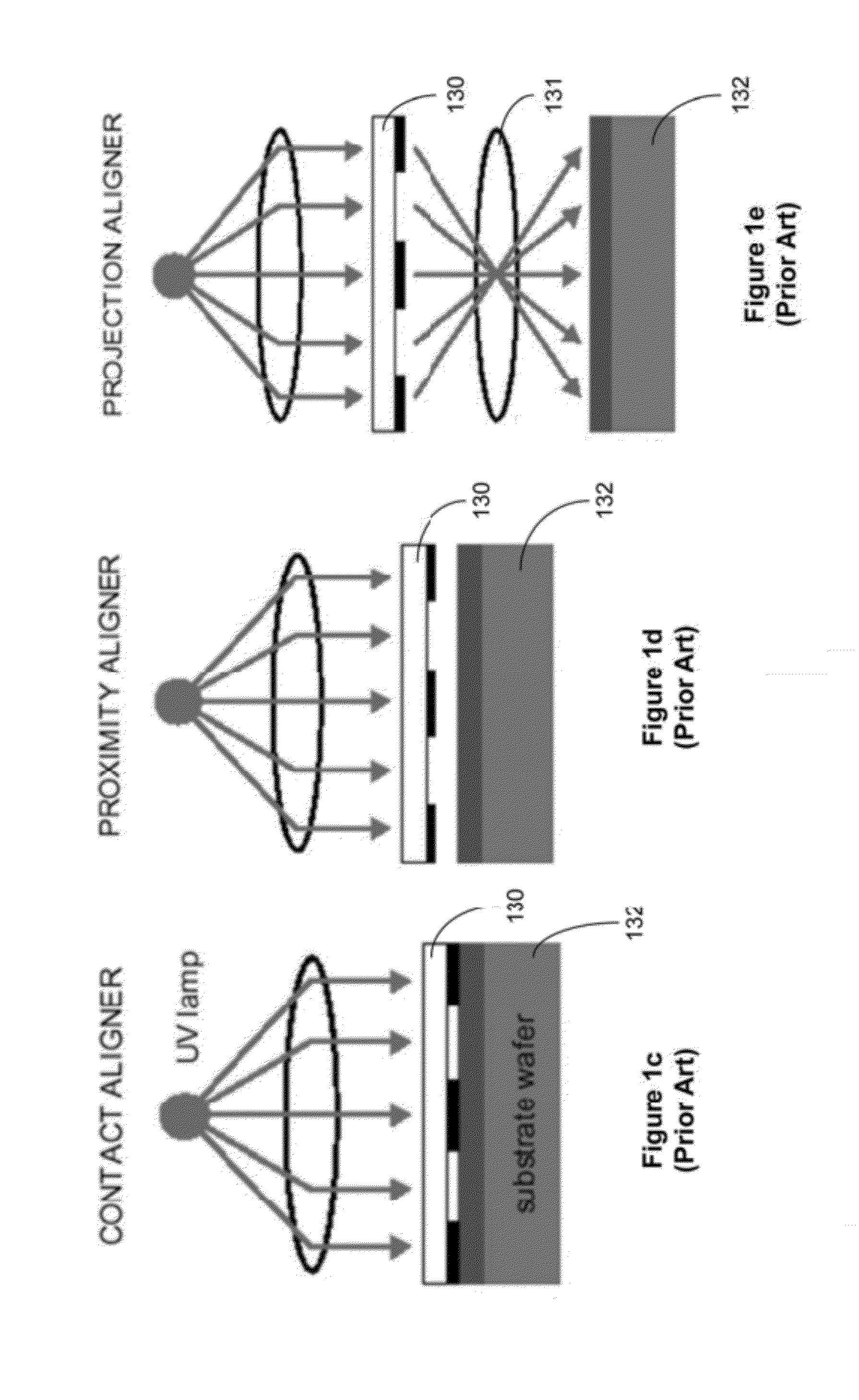

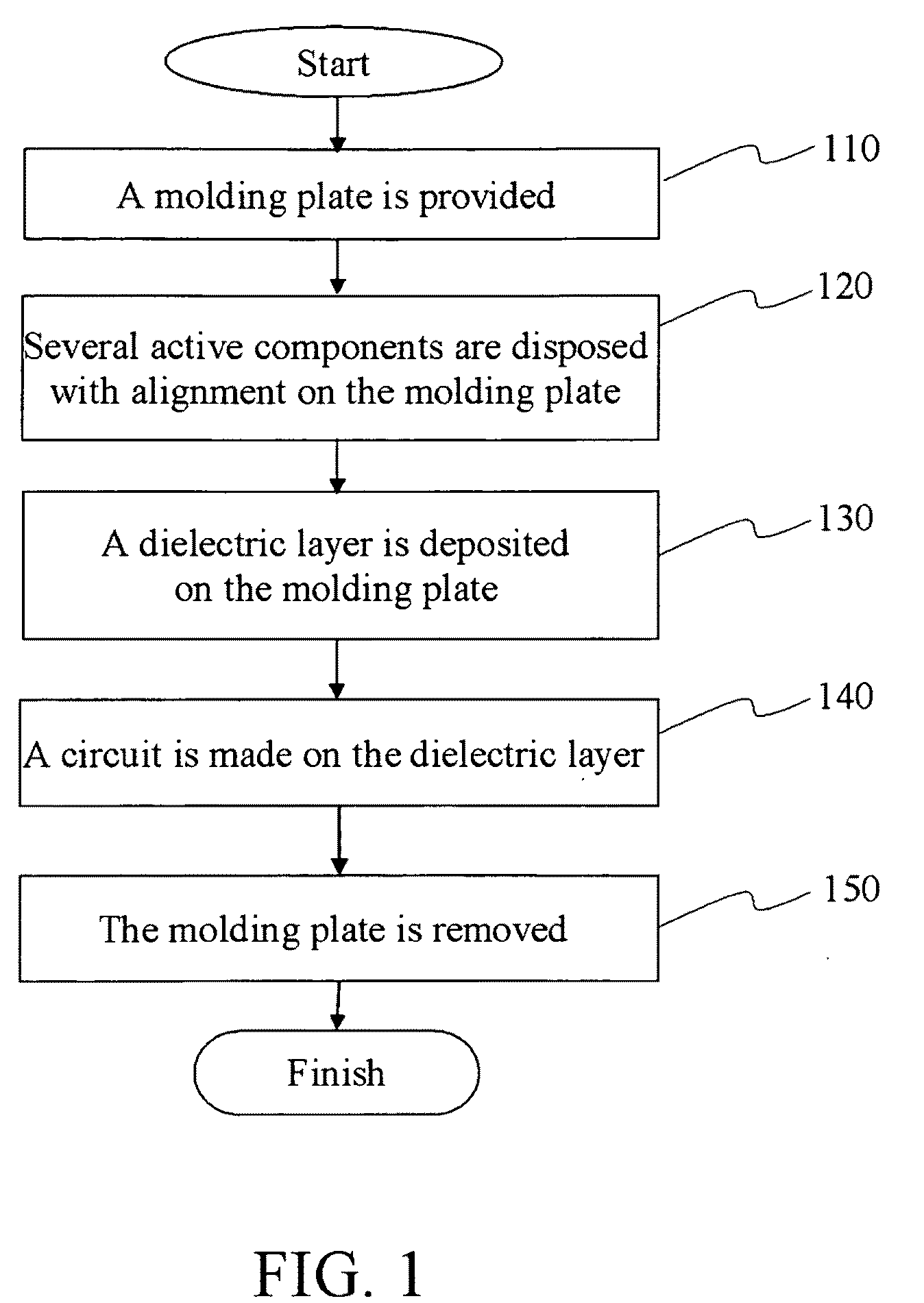

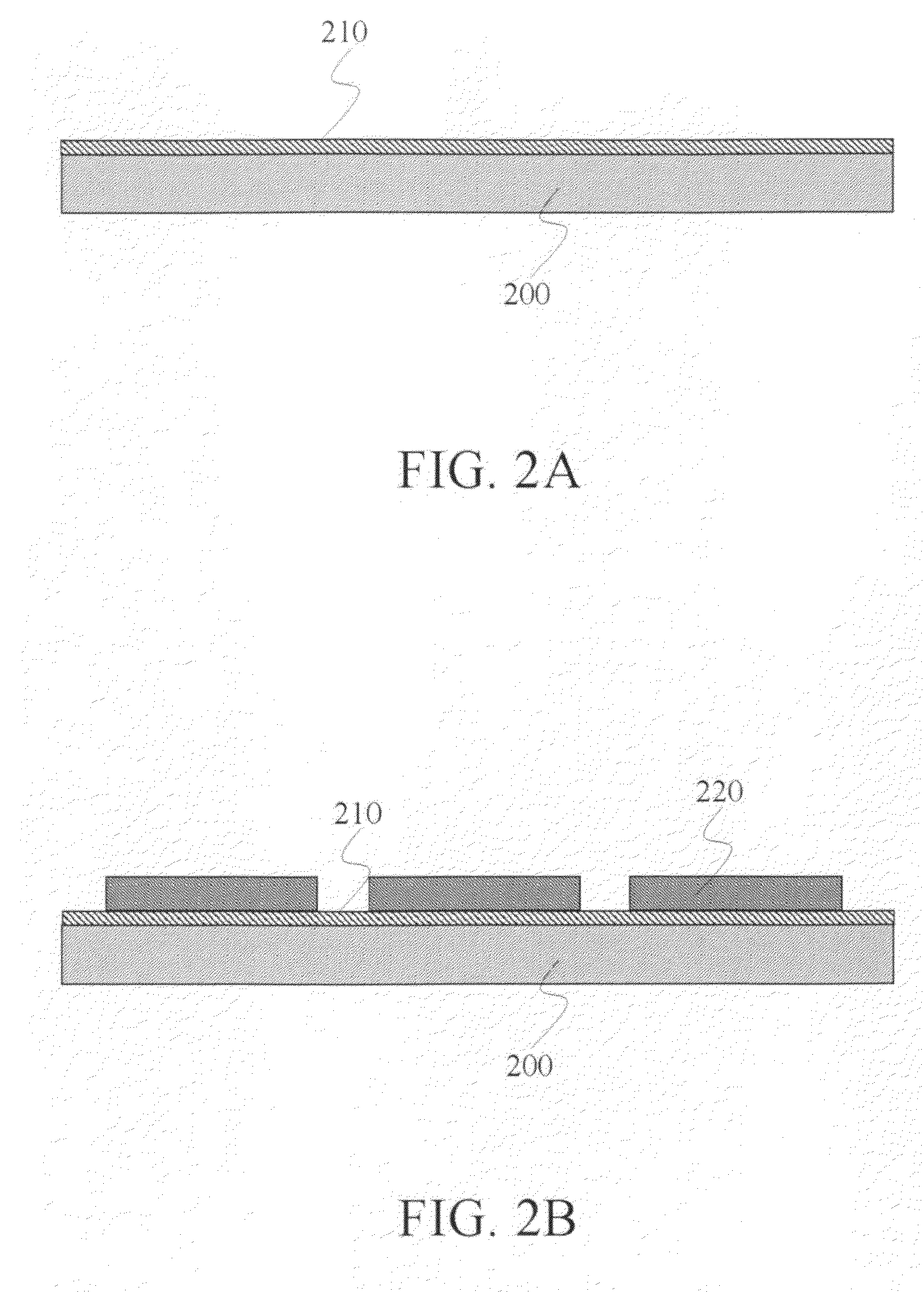

System and Method for Manufacturing Three Dimensional Integrated Circuits

ActiveUS20120026478A1Photomechanical apparatusPhotographic printingSpatial light modulatorEngineering

System and method for manufacturing three-dimensional integrated circuits are disclosed. In one embodiment, the method includes providing an imaging writer system that includes a plurality of spatial light modulator (SLM) imaging units arranged in one or more parallel arrays, receiving mask data to be written to one or more layers of the three-dimensional integrated circuit, processing the mask data to form a plurality of partitioned mask data patterns corresponding to the one or more layers of the three-dimensional integrated circuit, assigning one or more SLM imaging units to handle each of the partitioned mask data pattern, and controlling the plurality of SLM imaging units to write the plurality of partitioned mask data patterns to the one or more layers of the three-dimensional integrated circuits in parallel. The method of assigning performs at least one of scaling, alignment, inter-ocular displacement, rotational factor, or substrate deformation correction.

Owner:APPLIED MATERIALS INC

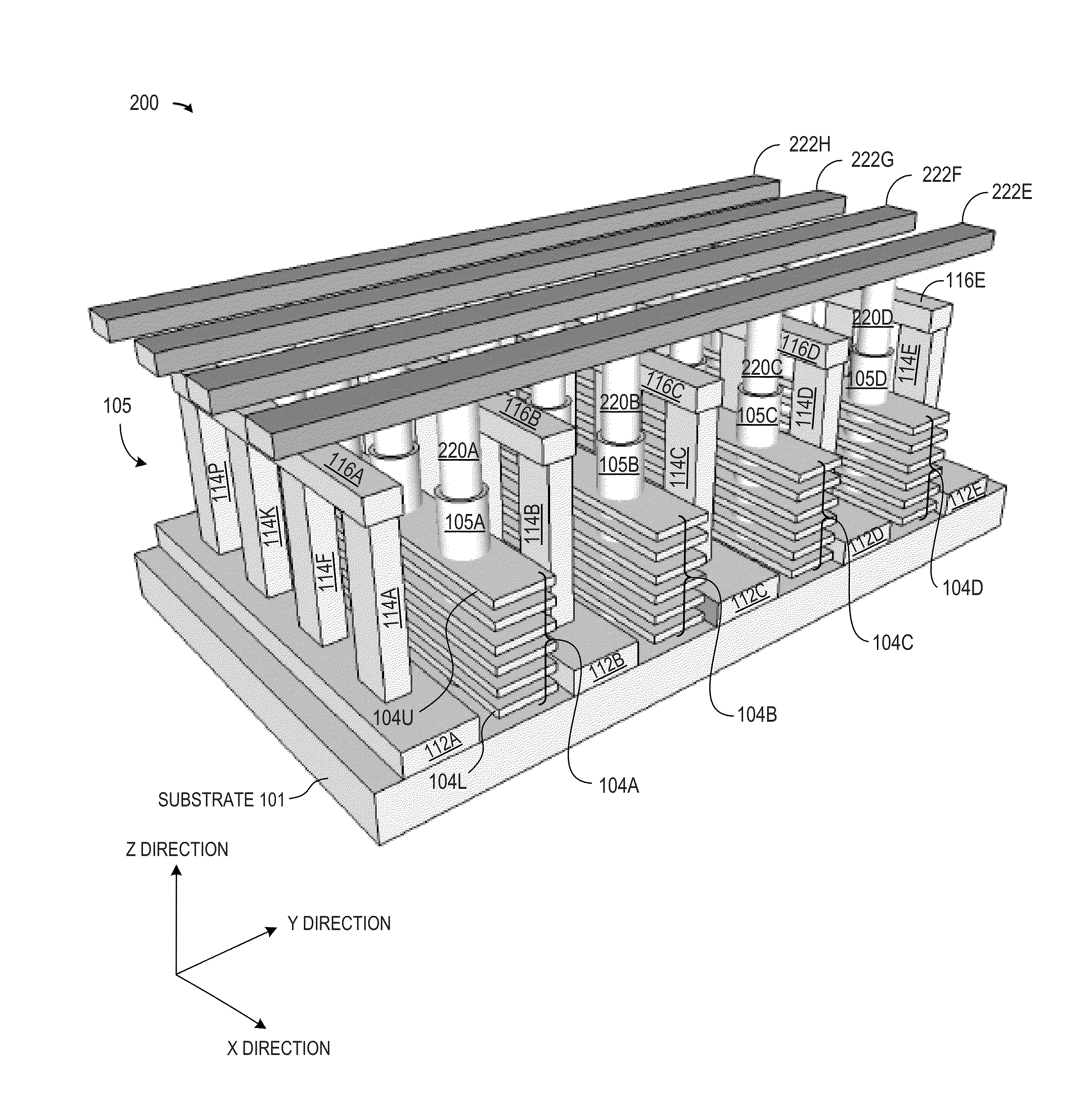

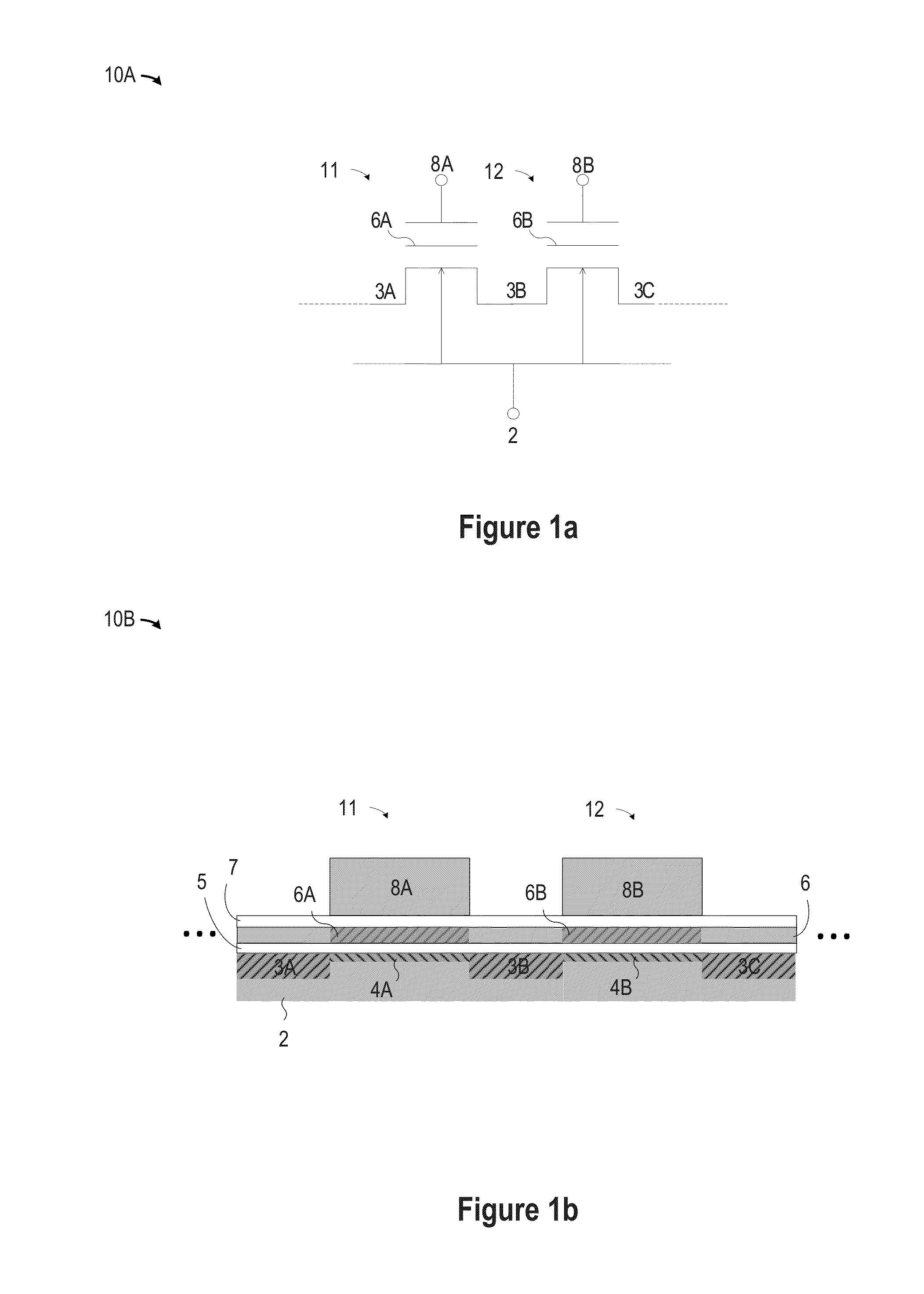

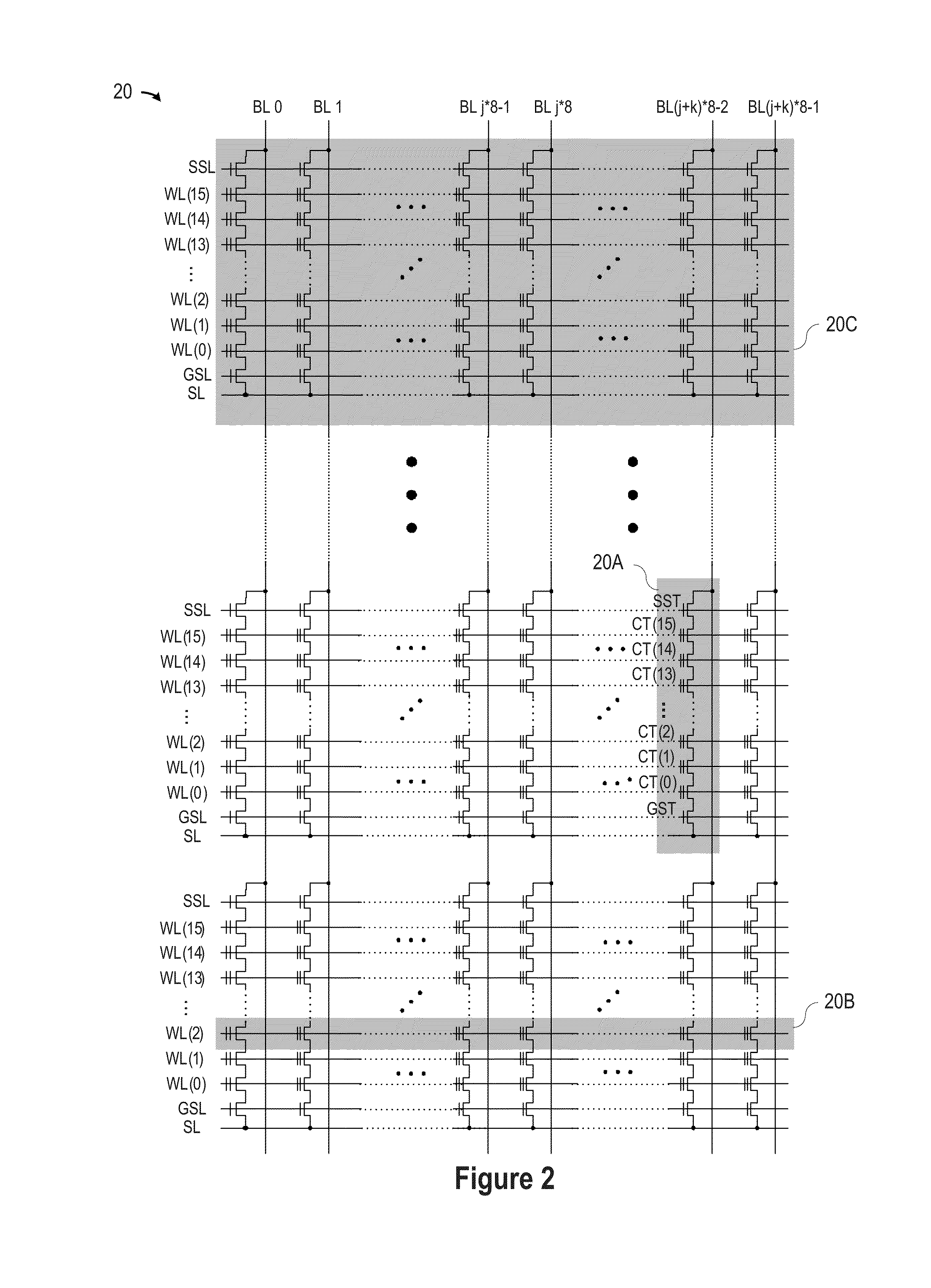

Access Transistor of a Nonvolatile Memory Device and Method for Fabricating Same

ActiveUS20160233224A1Solid-state devicesSemiconductor devicesVertical channelThree-dimensional integrated circuit

A three-dimensional integrated circuit nonvolatile memory array includes a memory array of vertical channel NAND flash strings connected between an upper layer connection bit line and a substrate which includes one or more elevated source regions disposed on at least one side of each row of NAND flash strings so that each NAND flash string includes a lower select transistor with a first channel portion that runs perpendicular to the surface of the substrate through a vertical channel string body, a second channel portion that runs parallel to the surface of the substrate, and a third channel portion that runs perpendicular to the surface of the substrate through the elevated source region.

Owner:MOSAID TECH

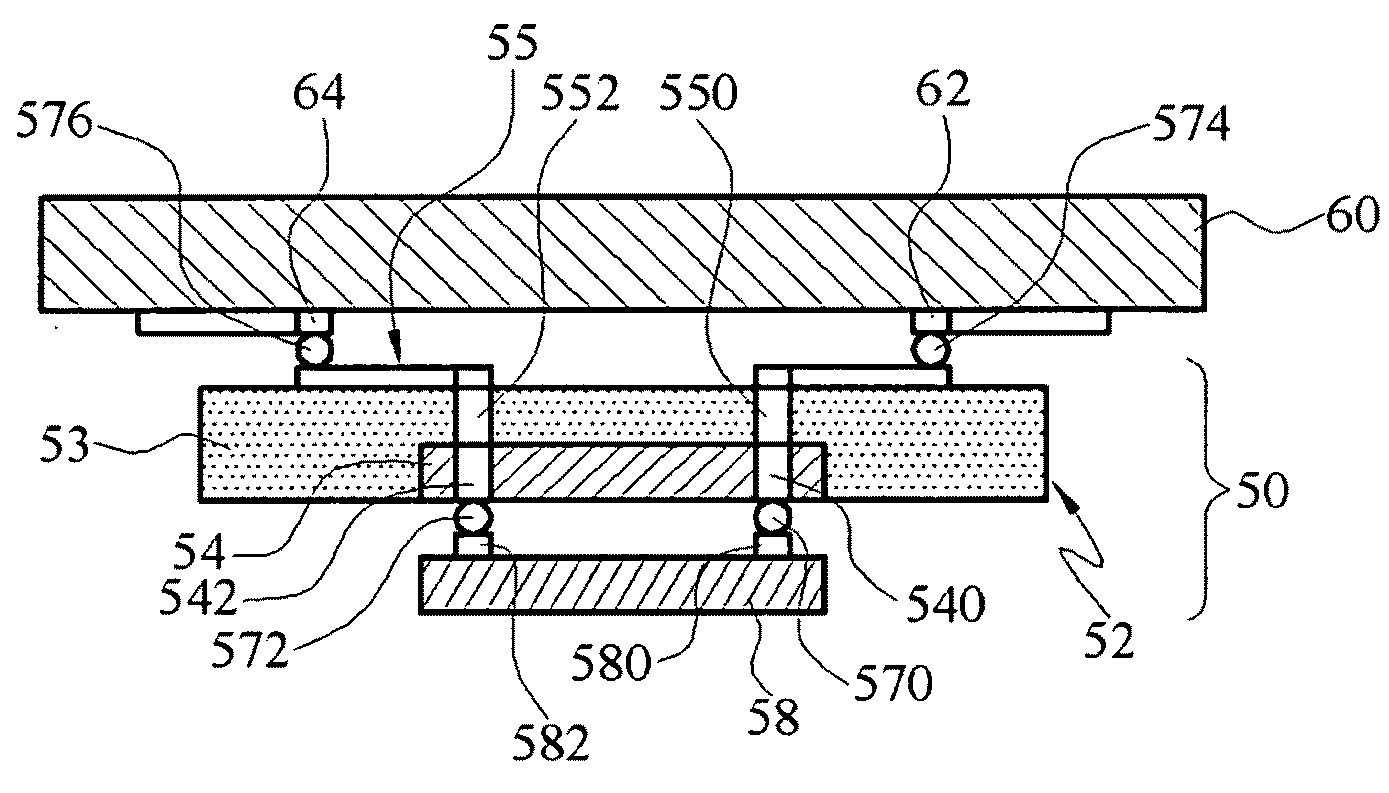

Three-dimensional chip-stack package and active component on a substrate

InactiveUS20090008792A1Less thermo stressLess stressSemiconductor/solid-state device detailsSolid-state devicesActive componentElectrical connection

The 3D chip-stack package comprises a component-embedded plate and a side IC. The PCB has a plurality of conductive contacts. The component-embedded plate comprises a dielectric layer; an active component embedded in the dielectric layer, one surface of each active component exposed outside the dielectric layer, the active components having a plurality of TSVs (Through Silicon Via), one ends of the TSVs exposed outside the exposed surface, the other ends of the TSVs corresponding to the conductive contacts of the PCB; and an electrical circuit on the dielectric layer and in electrical connection between the other ends of the TSVs of the active component and the corresponding conductive contacts of the PCB, respectively. The side IC has a plurality of pads. The pads are electrically connected with the exposed ends of the TSVs of the active component.

Owner:IND TECH RES INST

Three dimensional integrated circuits

InactiveUS20050269665A1TransistorSemiconductor/solid-state device detailsEngineeringThree-dimensional integrated circuit

A three-dimensional integrated circuit that provides reduced interconnect signal delay over known 2-dimensional systems. The three-dimensional integrated circuit also allows improved circuit cooling. The three-dimensional integrated circuit comprises two or more electrically connected integrated circuits, separated by a cooling channel.

Owner:CABOT MICROELECTRONICS CORP