Patents

Literature

160results about How to "Shorten connection length" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

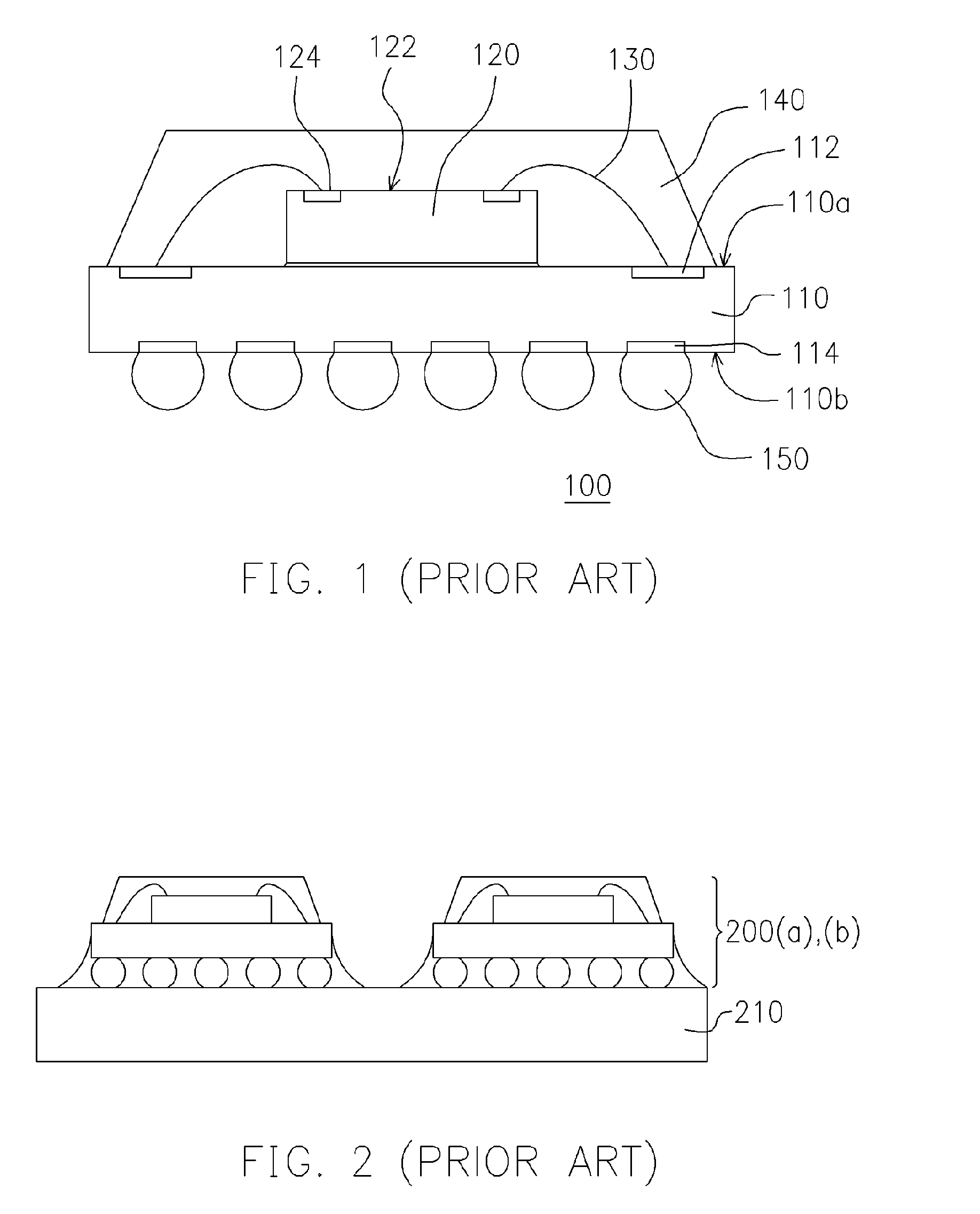

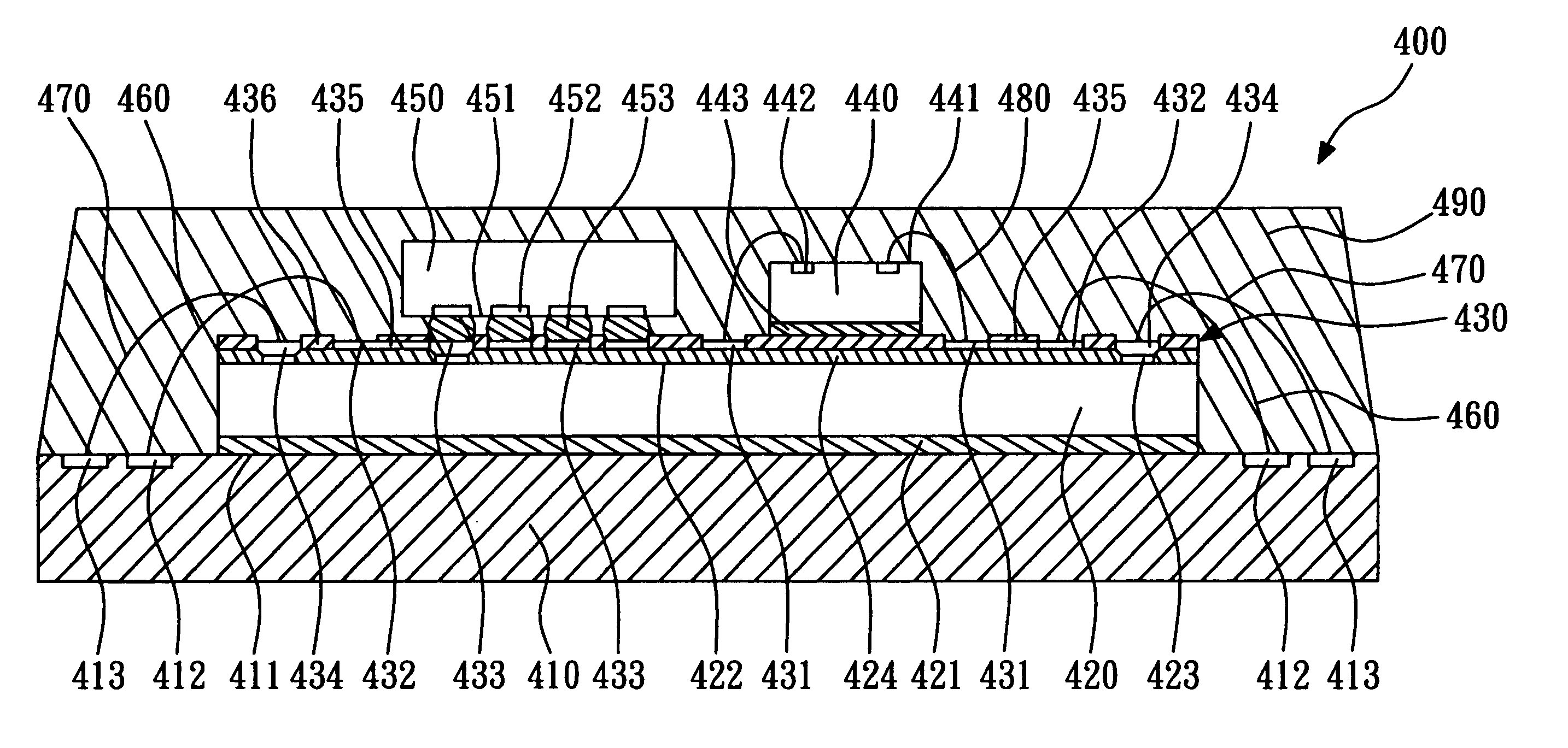

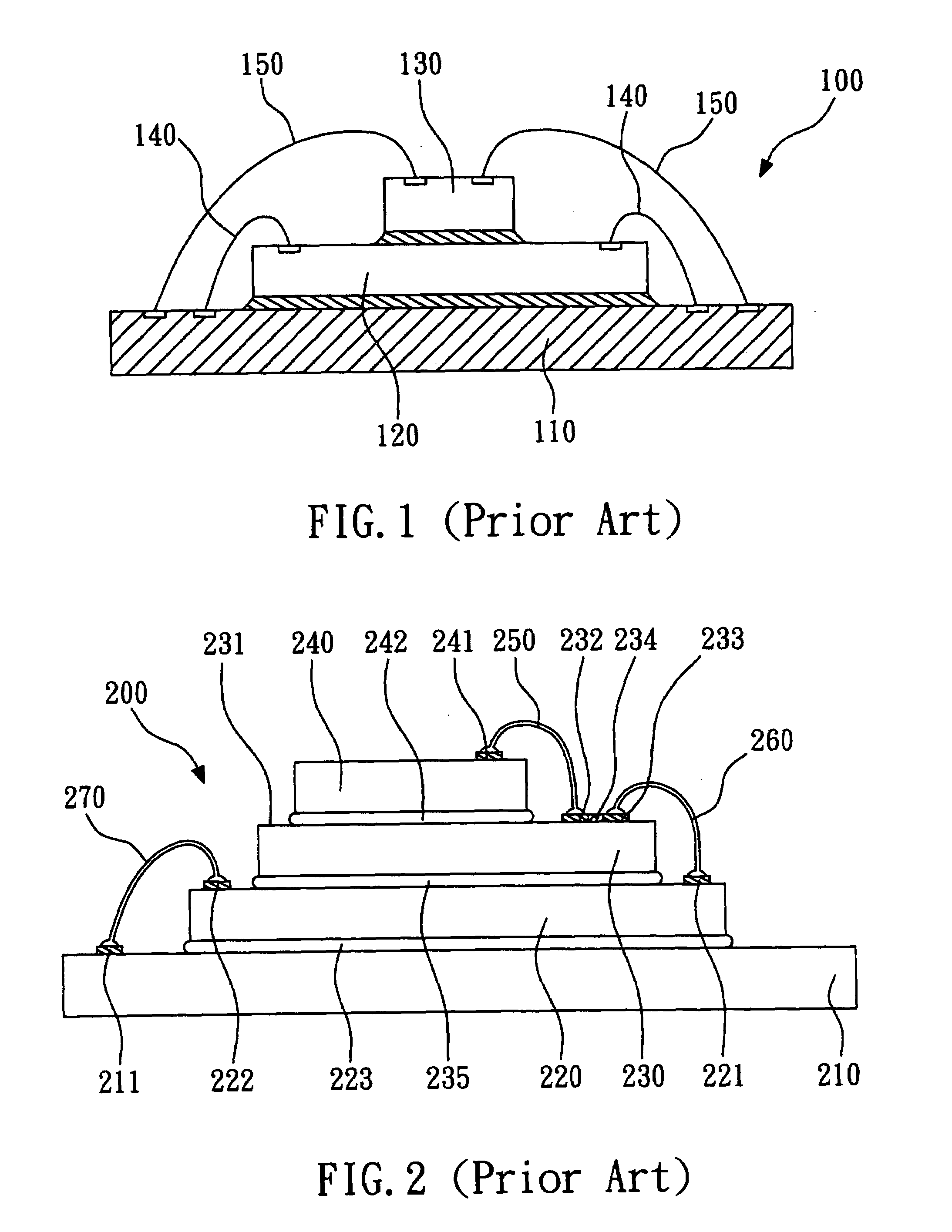

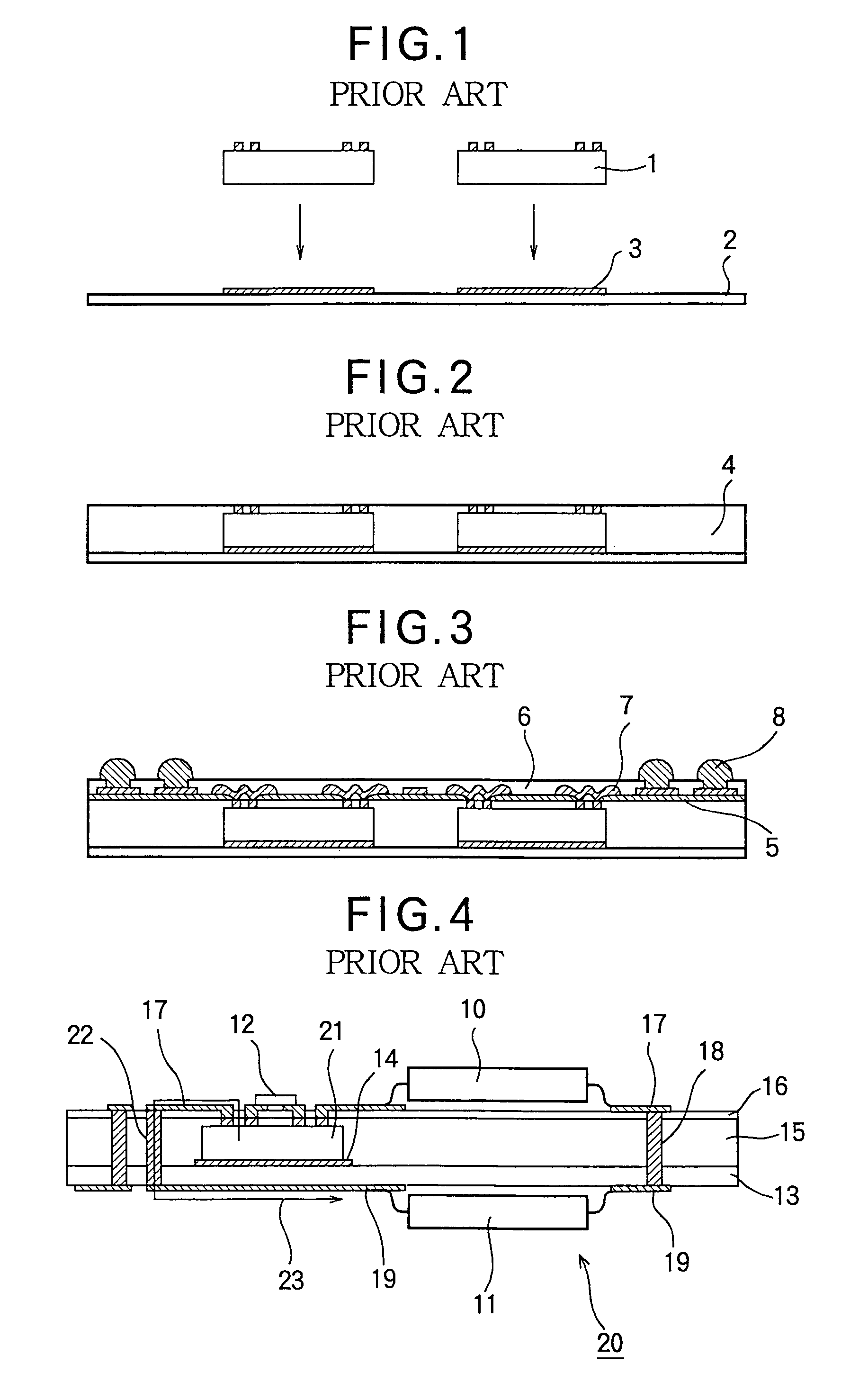

Stacked chip-packaging structure

ActiveUS7026709B2Shorten connection lengthReduce spacingSemiconductor/solid-state device detailsSolid-state devicesSolder ballMiniaturization

A stacked chip-packaging structure consisting of a plurality of chip-packaging units is provided. Each of the chip-packaging units includes a substrate, a chip, a plurality of wires, a molding compound, and a plurality of solder balls. The chip-packaging units are, for example, of a BGA structure with high pin count, and are stacked up one over another and electrically connected through solder balls. With such structural features, the space that the stacked chip-packaging structure occupies is reduced and consequently the entire structure can be miniaturized.

Owner:ADVANCED SEMICON ENG INC

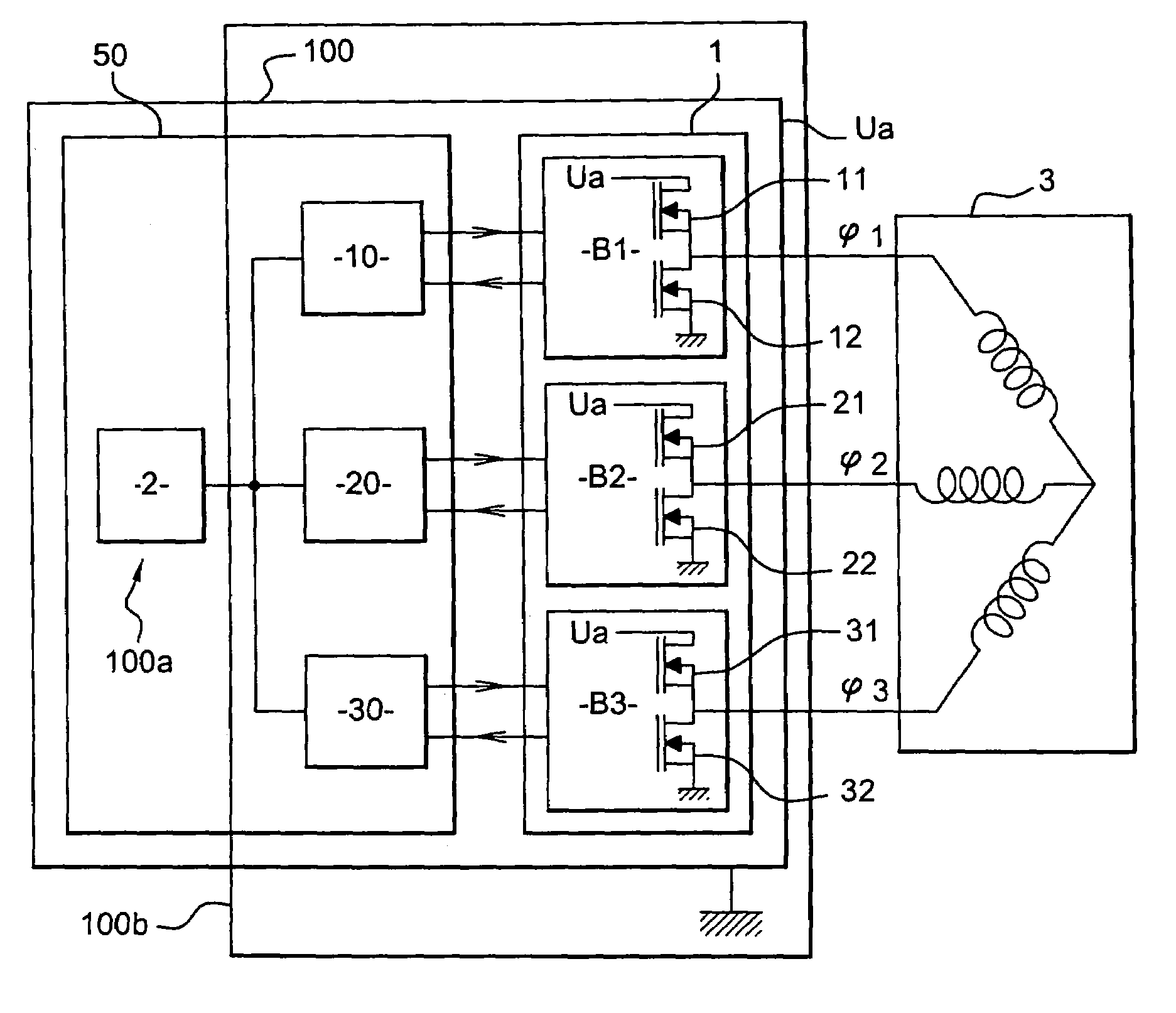

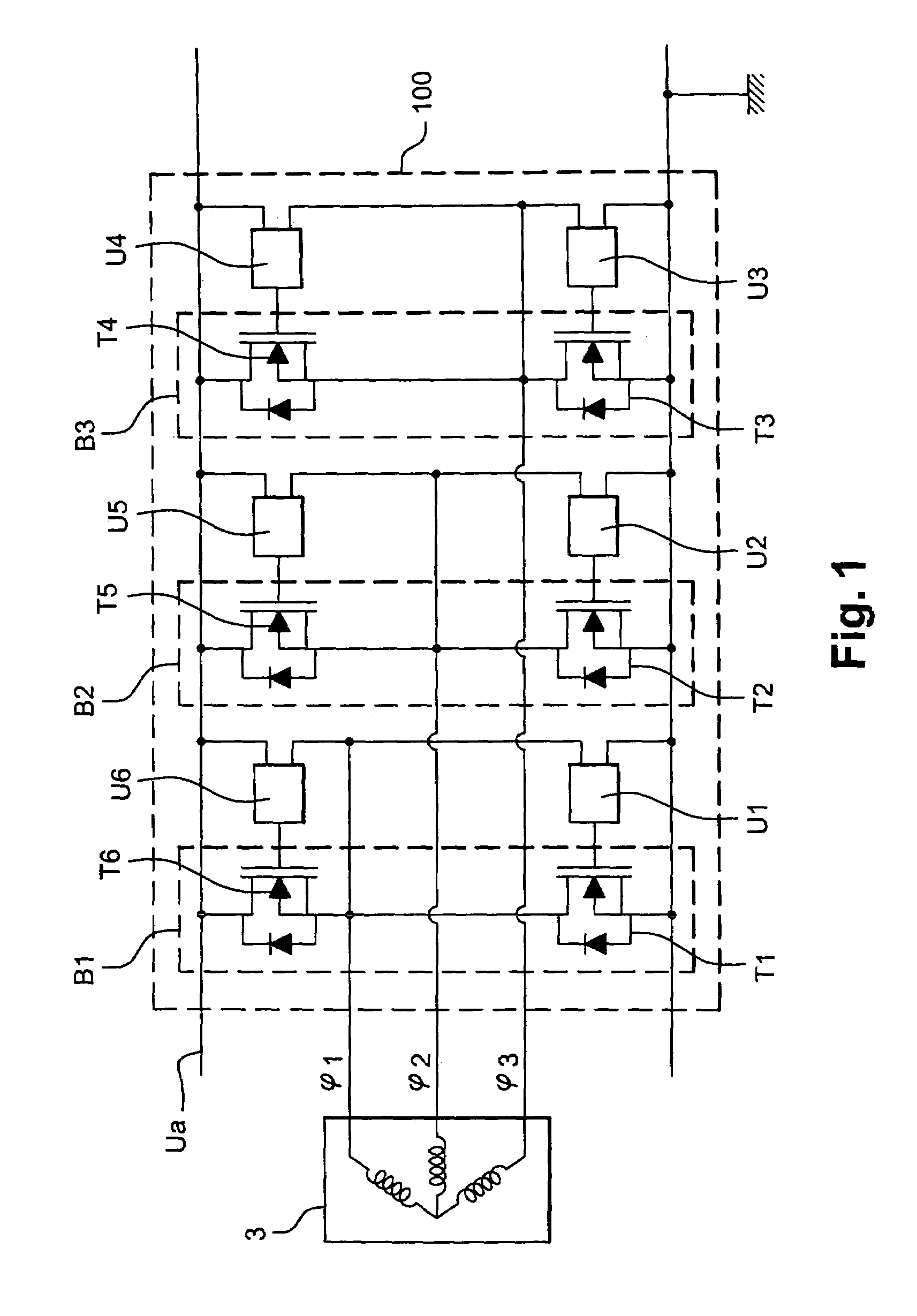

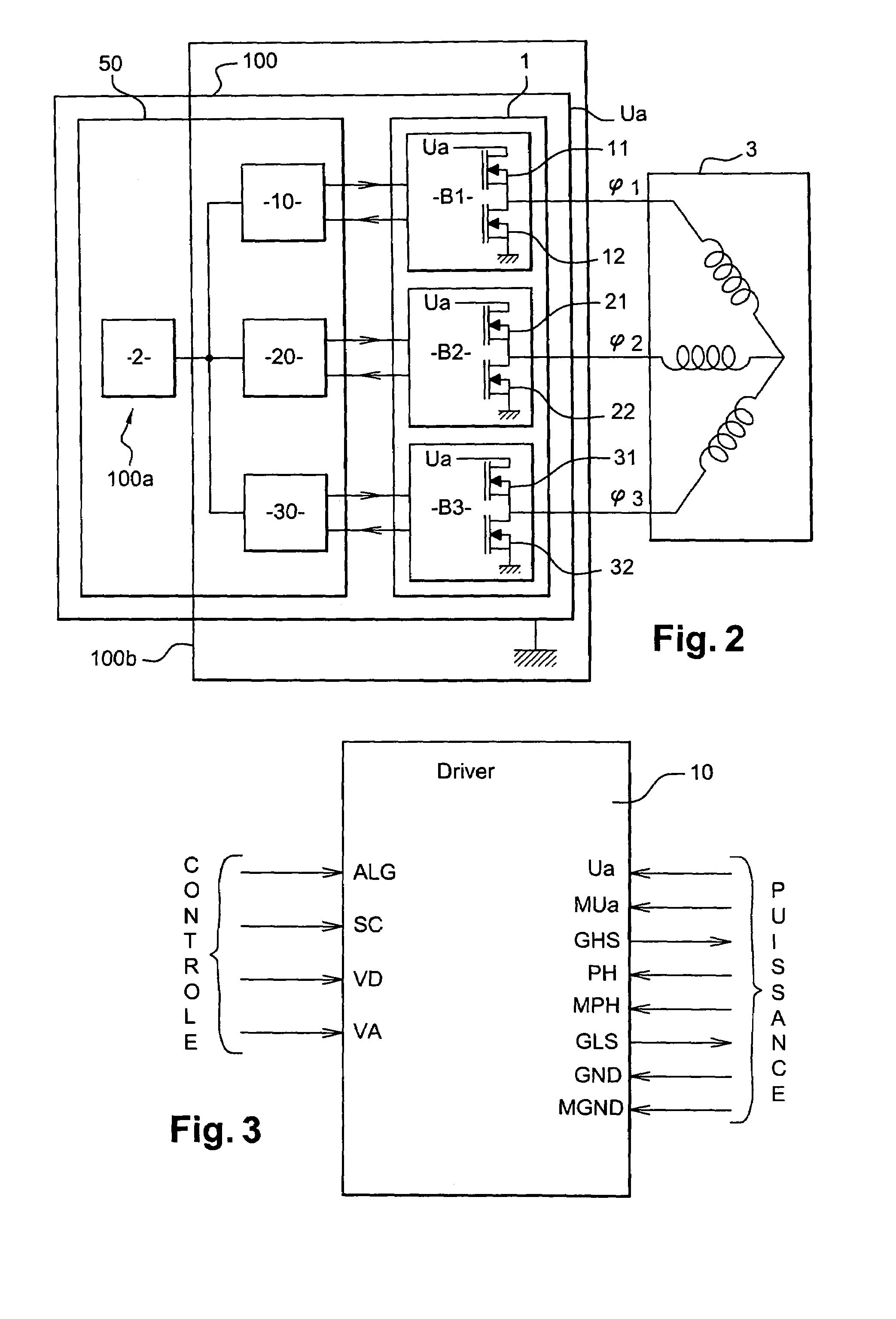

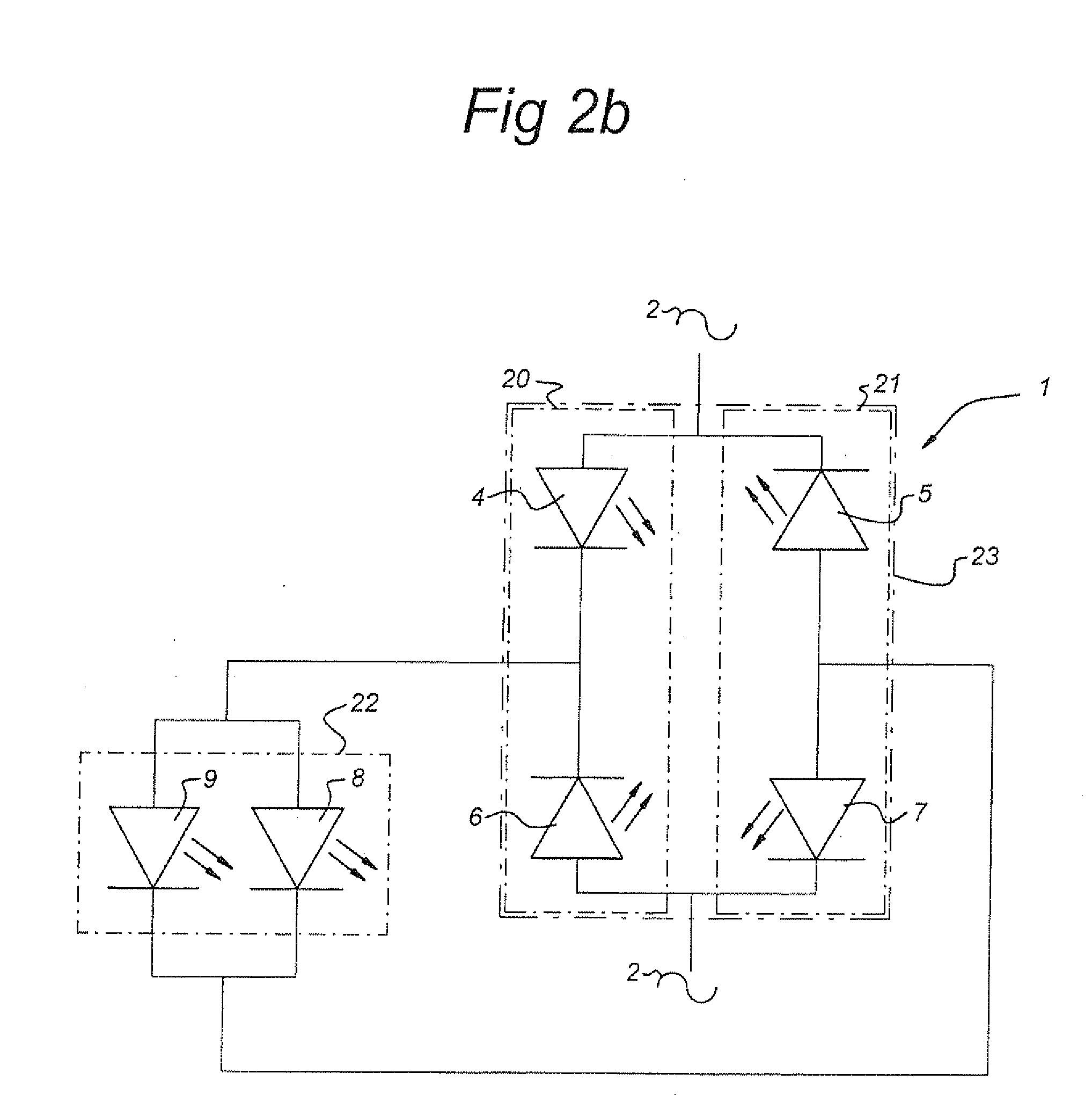

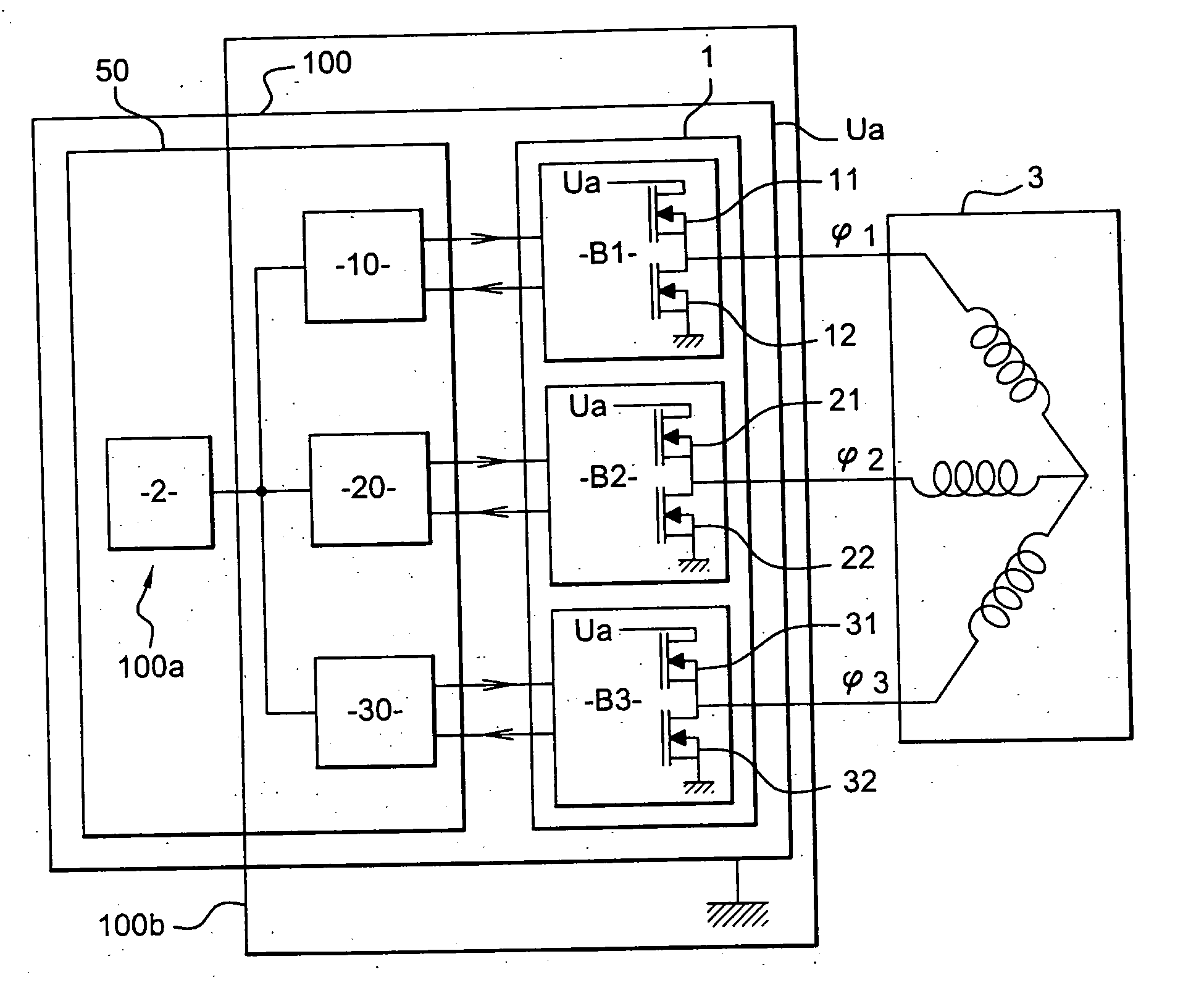

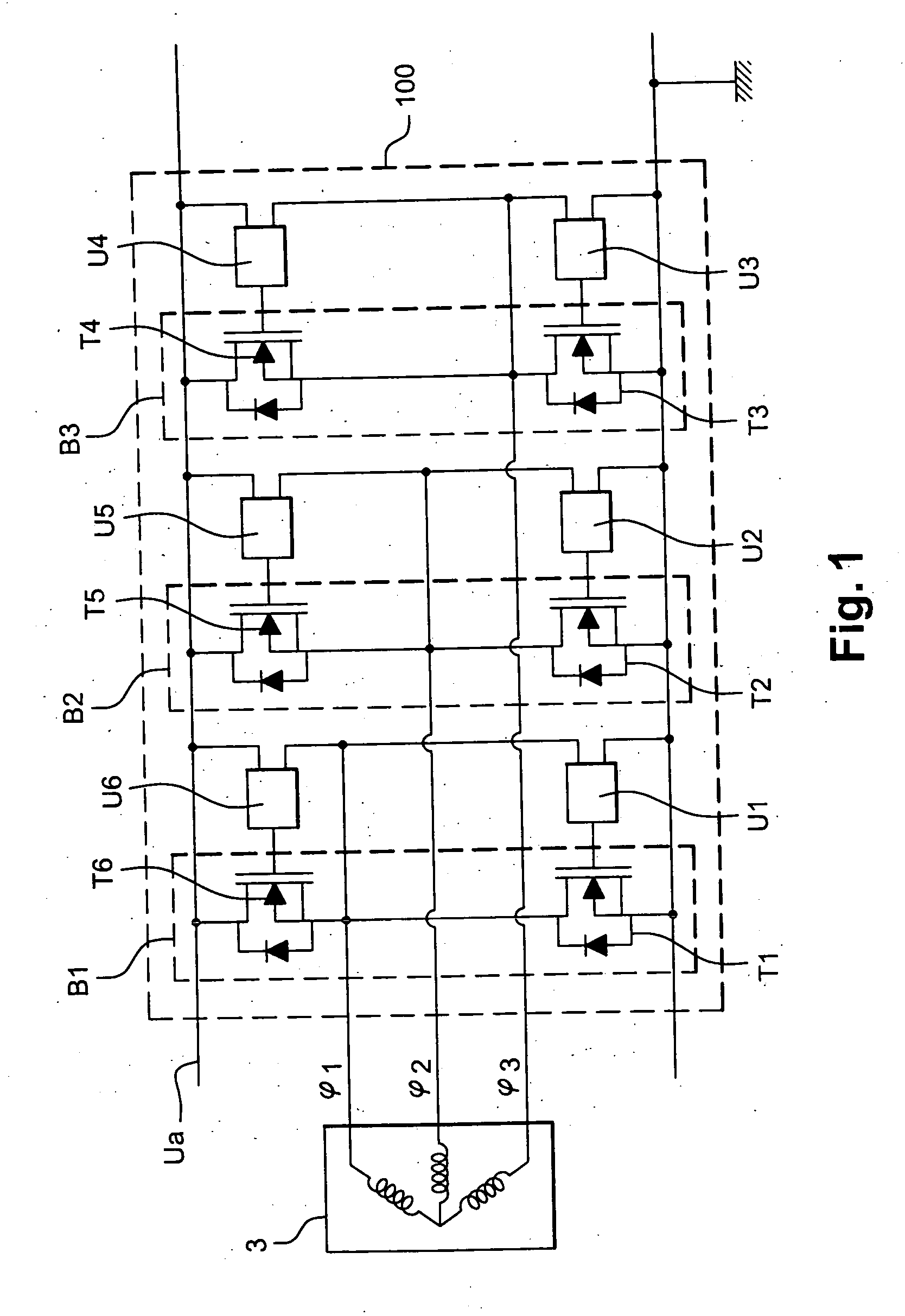

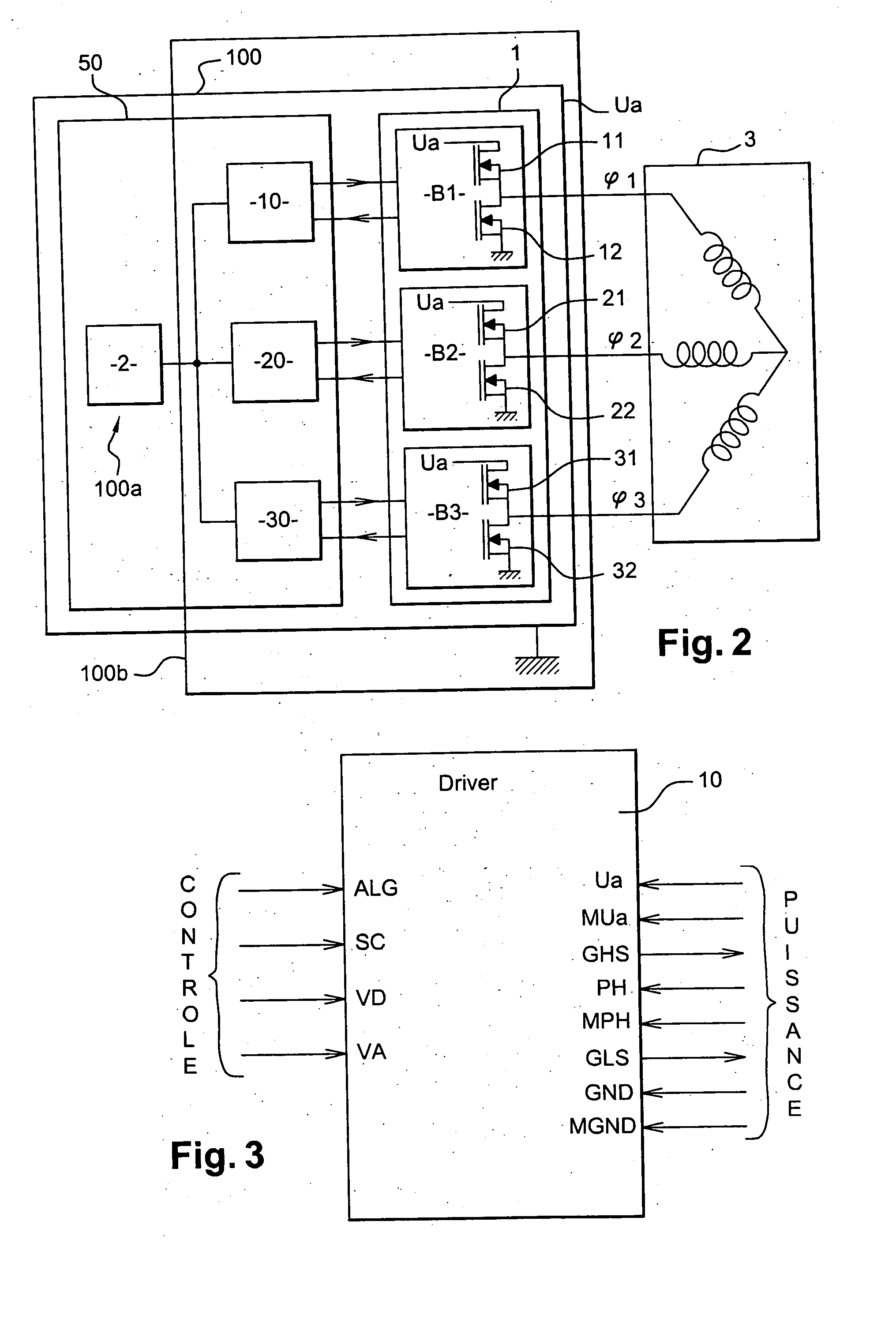

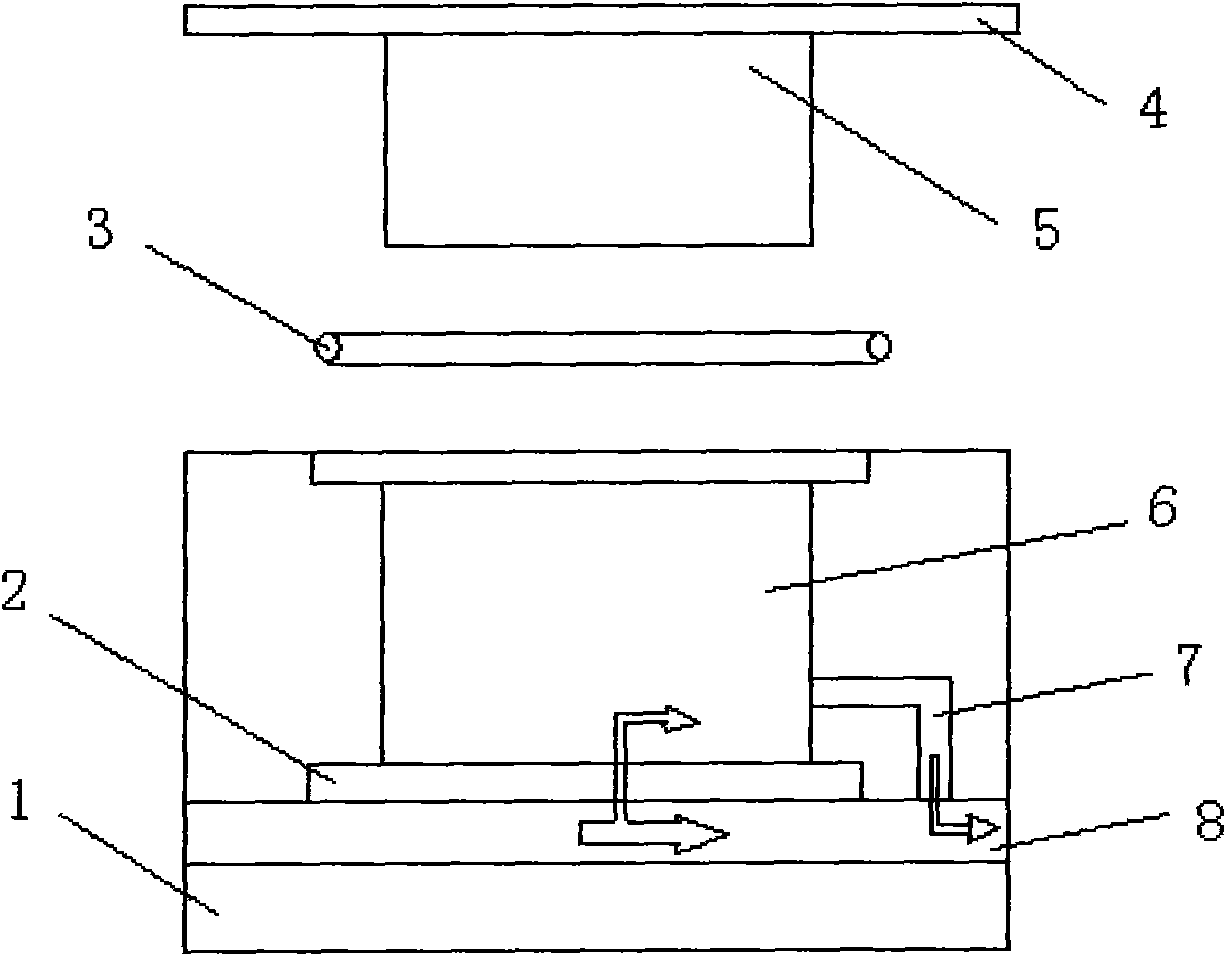

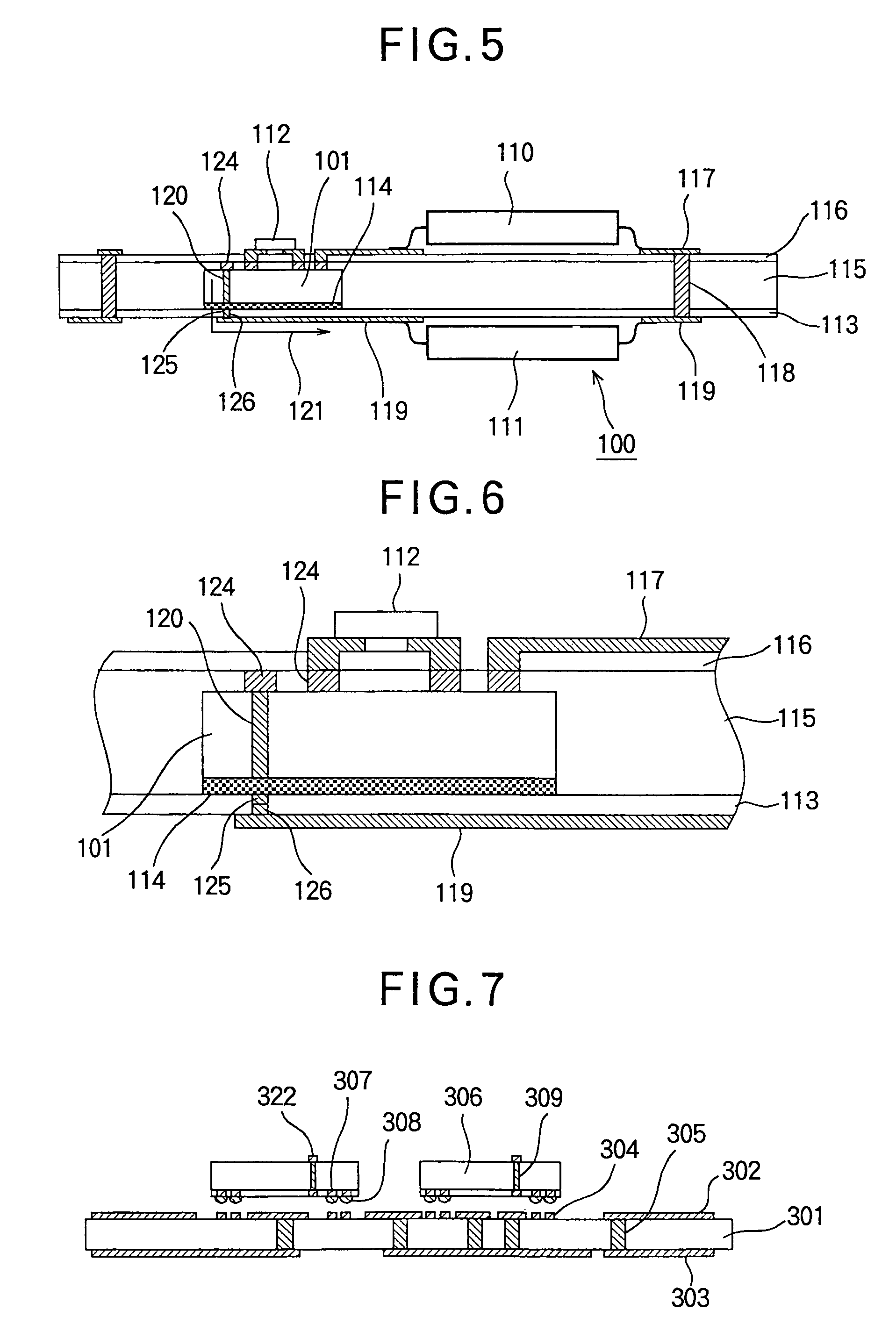

Control and power module for integrated alternator-starter

ActiveUS7224145B2Shorten connection lengthEasy to measureEmergency protective circuit arrangementsSolid-state devicesAlternatorOn board

The invention relates to a control and power module for an alternator-starter for a motor vehicle, connected between the alternator-starter (3), an on-board wiring network (Ua) and a ground line (GND) of the vehicle, and comprising:a transistor bridge with several branches (B1–B3), anda control unit for comparing a phase voltage (ψ) of the machine with a reference voltage (Ua, GND) and for controlling the transistors as a function of the result of the comparison,the control unit comprising:a driver (10, 20, 30) for each branch of the transistor bridge, the driver being connected close to the transistors of the branch, anda control circuit for controlling the drivers.

Owner:VALEO EQUIP ELECTRIC MOTEUR

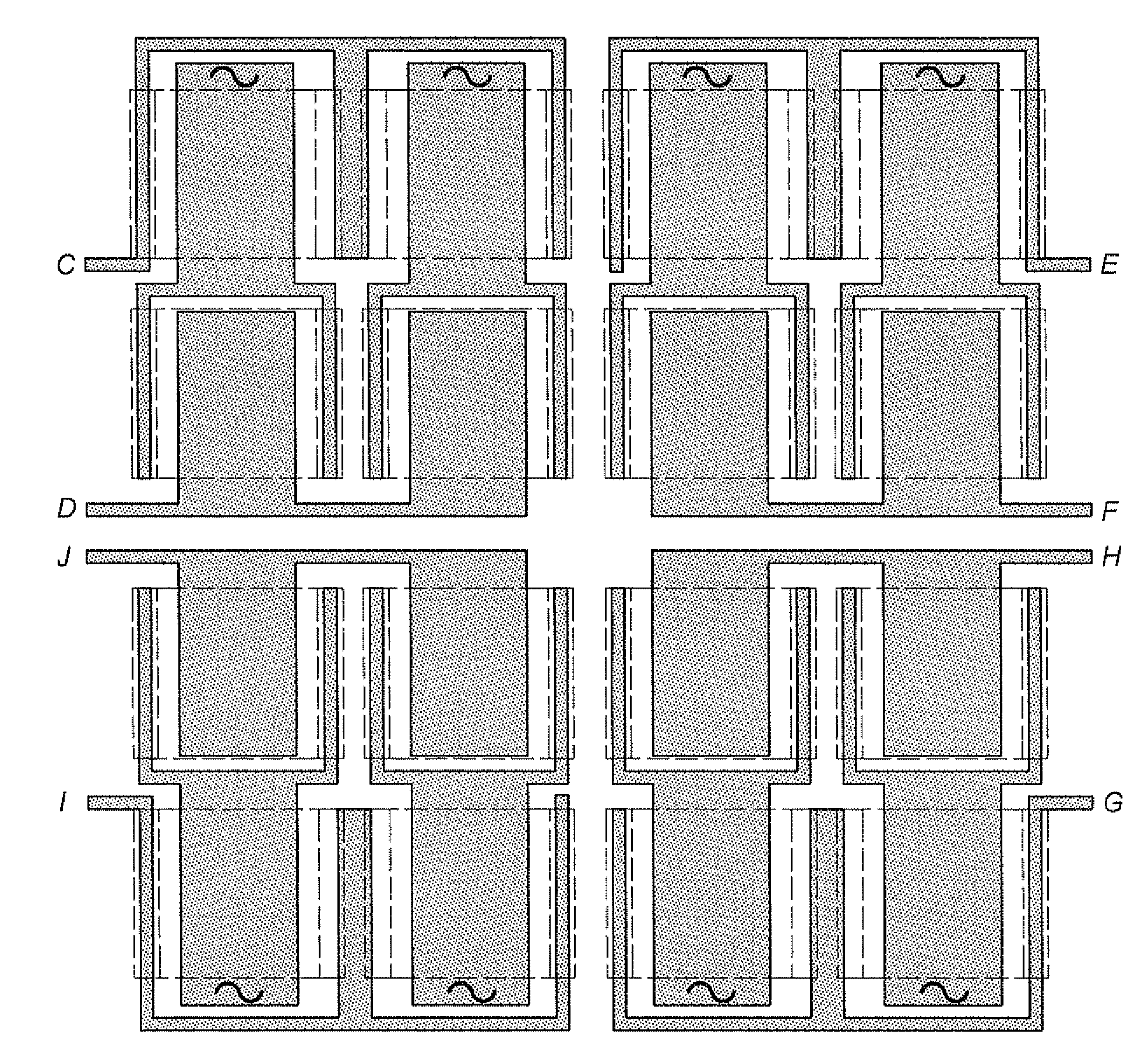

Method for Preparing an Electric Circuit Comprising Multiple Leds

InactiveUS20080203405A1Shorten connection lengthComponents is relatively effectiveElectroluminescent light sourcesSolid-state devicesElectrical conductorSemiconductor materials

The invention relates to a method for preparing an electric circuit comprising a plurality of Light-Emitting Diodes (LEDs). First, a continuous layer of a first semiconductor material is provided. On this a first pattern of a material of a second semiconductor type is applied. Next, a substrate comprising a second pattern of at least one conducting layer (34) is attached to the first pattern. After this, the continuous layer is cut according to a third pattern. Thus the plurality of LEDs is formed.

Owner:LEMNIS LIGHTING PATENT HLDG

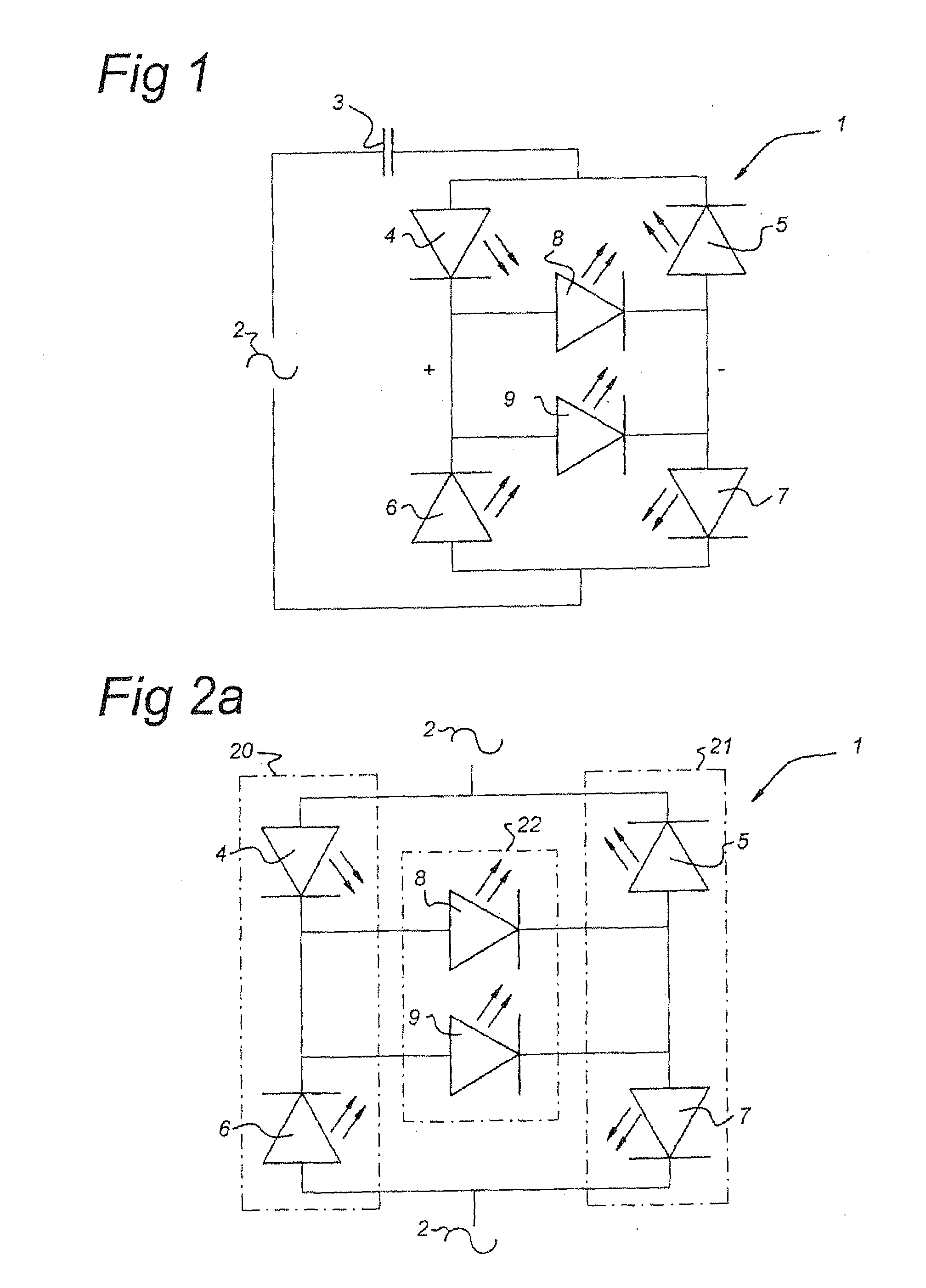

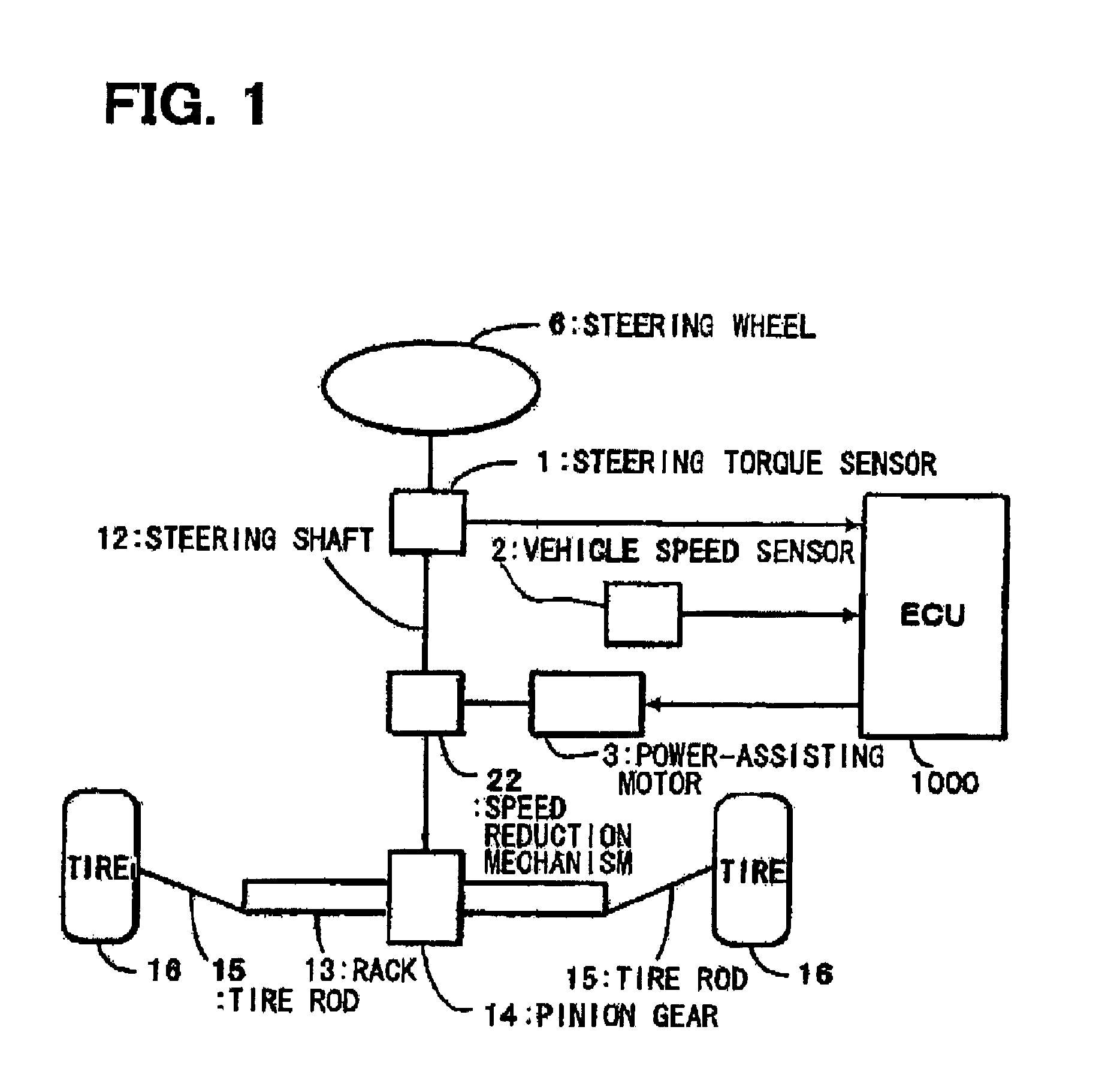

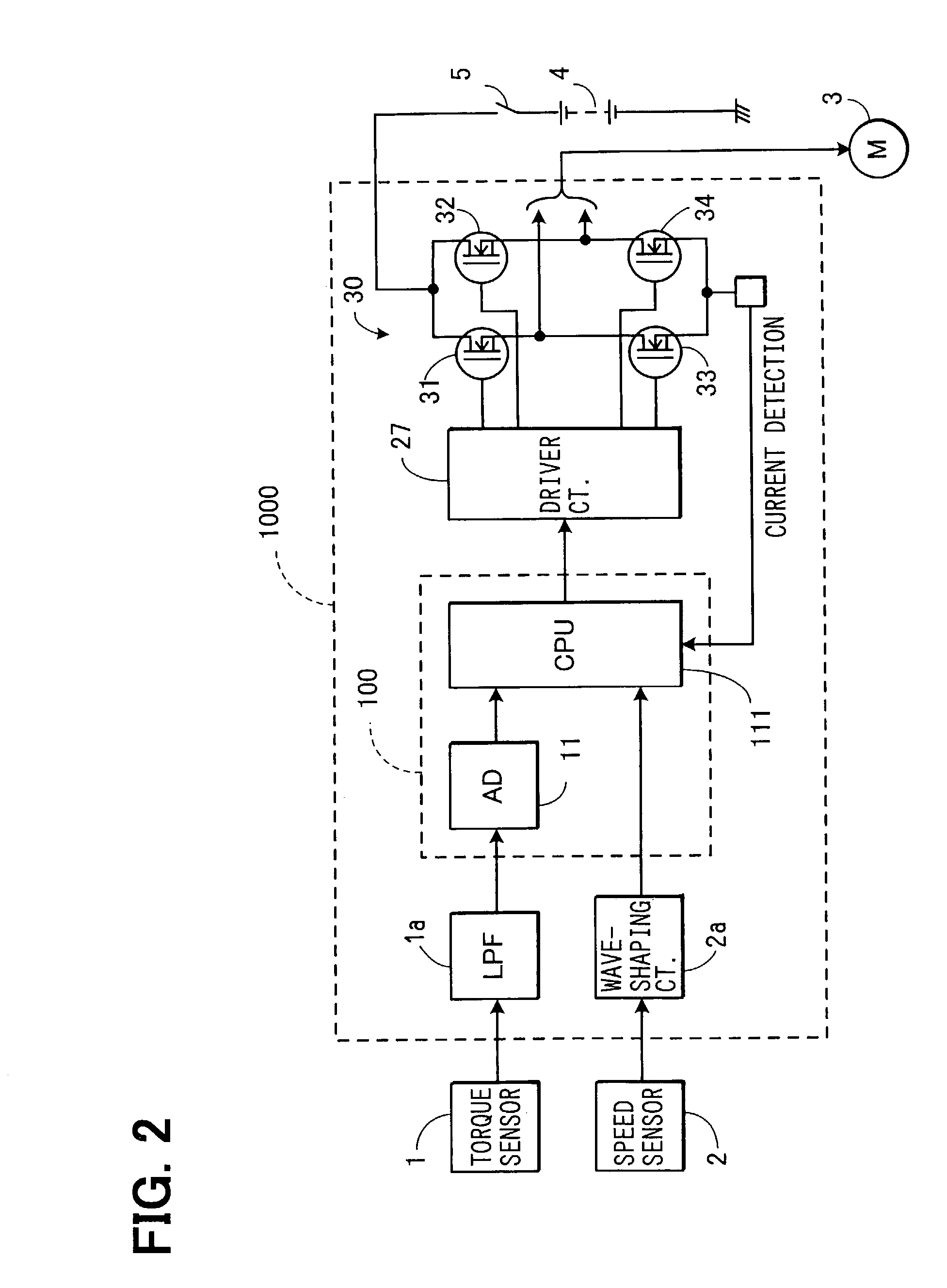

Switching device for controlling large amount of current

InactiveUS7081691B2Precise positioningLow heat generationElectric devicesPrinted circuit aspectsElectricityPower switching

Owner:DENSO CORP

Control and power module for integreated alternator-starter

ActiveUS20050253457A1Reduce lengthReduced length of connectionElectric devicesEmergency protective circuit arrangementsGround lineVoltage reference

The invention relates to a control and power module for an alternator-starter for a motor vehicle, connected between the alternator-starter (3), an on-board wiring network (Ua) and a ground line (GND) of the vehicle, and comprising: a transistor bridge with several branches (B1-B3), and a control unit for comparing a phase voltage (ψ) of the machine with a reference voltage (Ua, GND) and for controlling the transistors as a function of the result of the comparison, the control unit comprising: a driver (10, 20, 30) for each branch of the transistor bridge, the driver being connected close to the transistors of the branch, and a control circuit for controlling the drivers.

Owner:VALEO EQUIP ELECTRIC MOTEUR

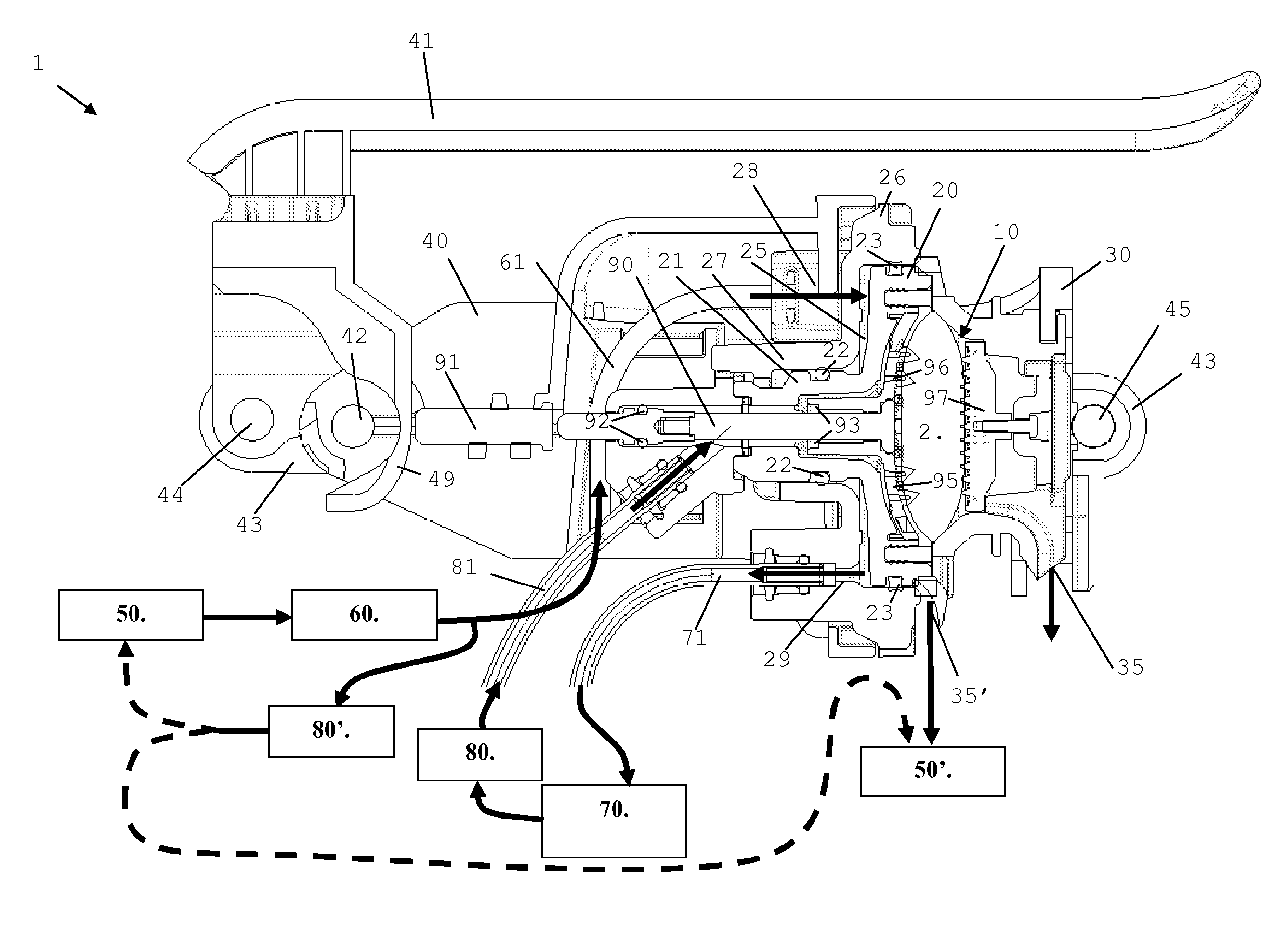

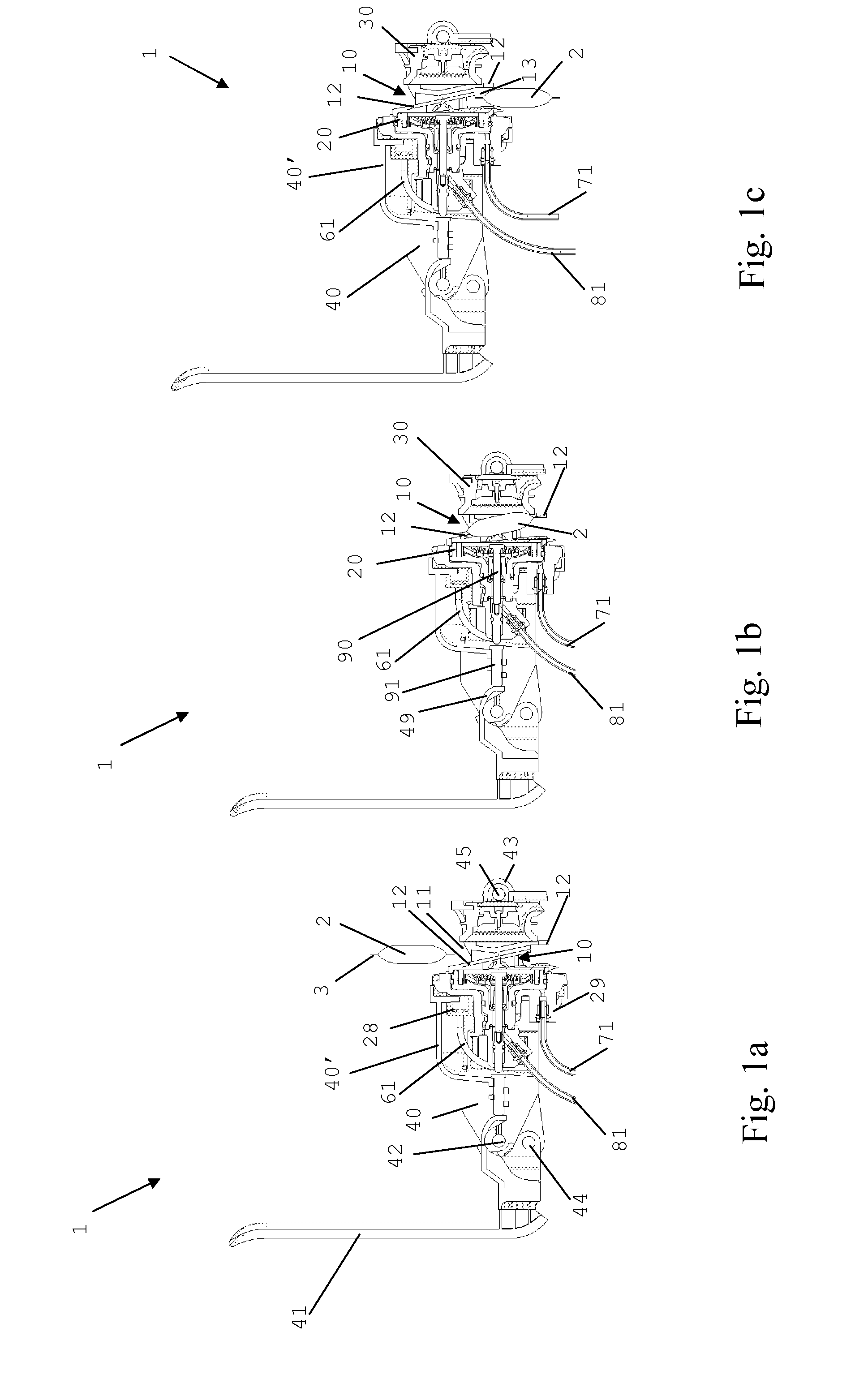

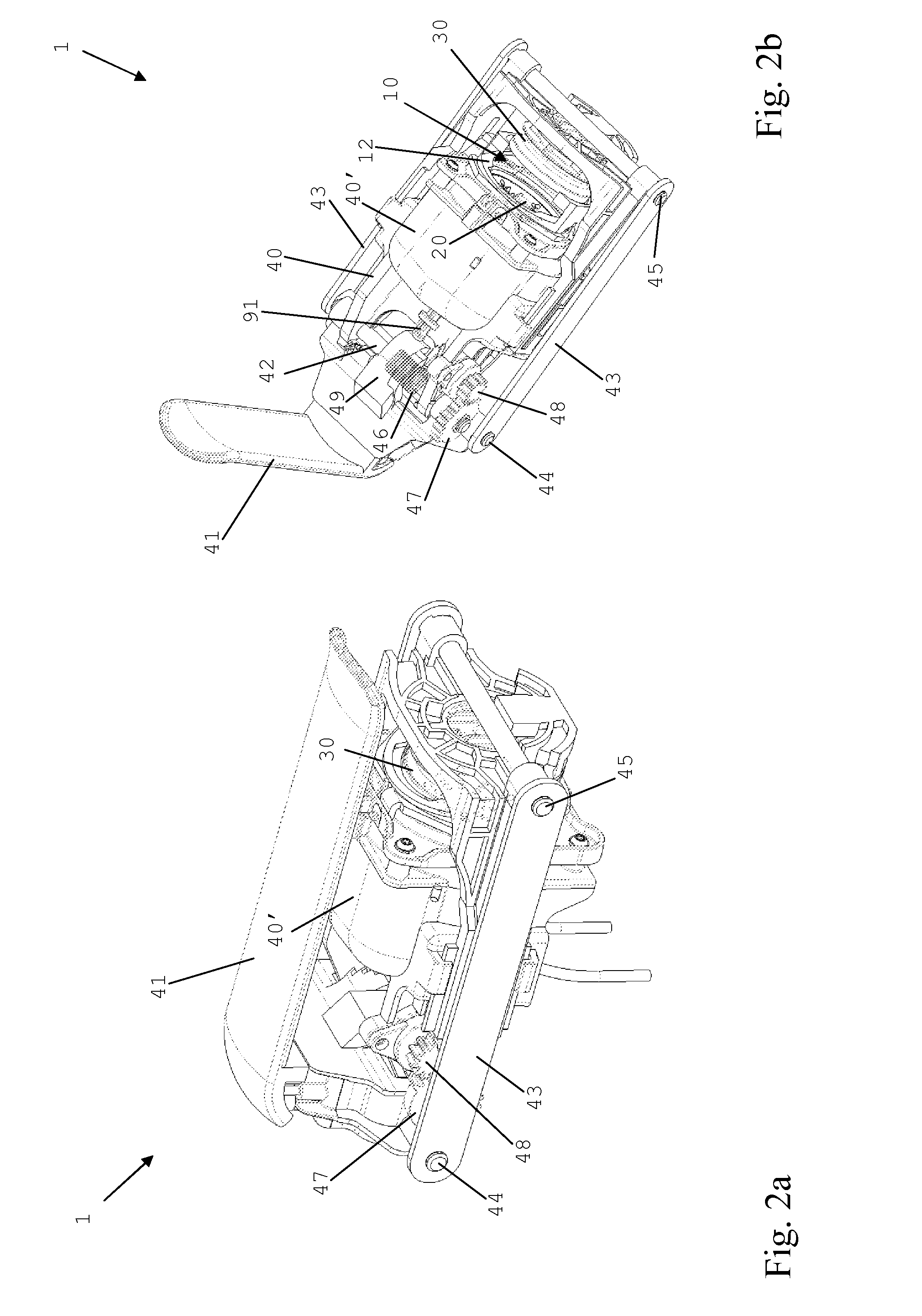

Cartridge extraction device

ActiveUS20120266755A1Prevent scalingShorten connection lengthBeverage vesselsFood scienceEngineeringLiquid injection

A device (1) has: a cartridge seat (10) arranged to receive an ingredient cartridge (2) for extraction; a beverage outlet (35) connected to this cartridge seat for dispensing beverage during extraction; and a liquid injection arrangement (50, 60, 61, 70, 80, 81) comprising a pump (60) for pressurising and circulating liquid from a source (50) via the cartridge seat into the beverage outlet. The liquid injection arrangement further comprises a valve (80′) between the pump and the cartridge seat. The liquid injection arrangement is configured to release via the valve (80′) pressure from this pressurised liquid in the injection arrangement and maintain liquid in the injection arrangement from the pump (60) to the cartridge seat (10) after the pump is stopped, so as to inhibit dripping from the beverage outlet (35).

Owner:SOC DES PROD NESTLE SA

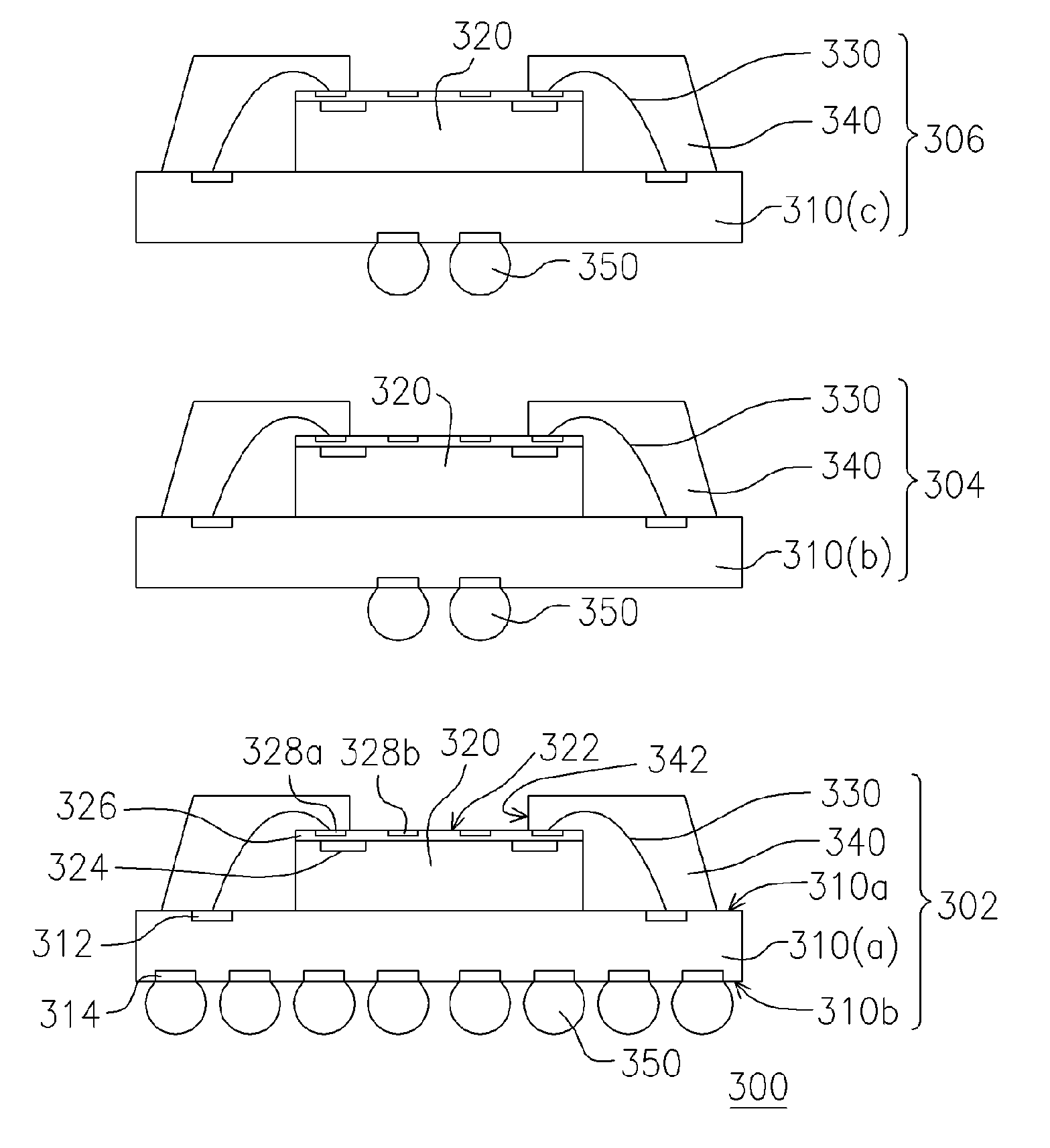

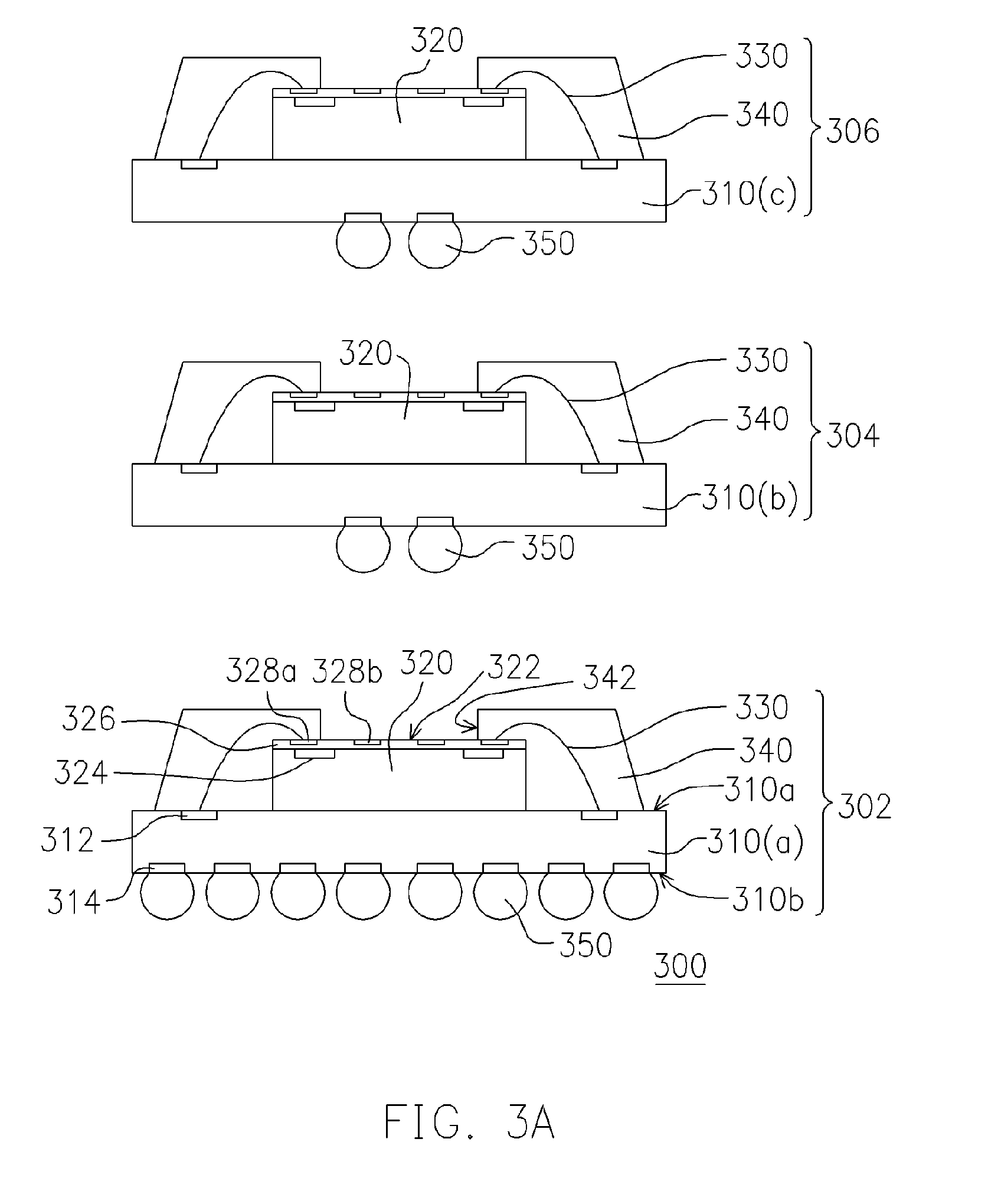

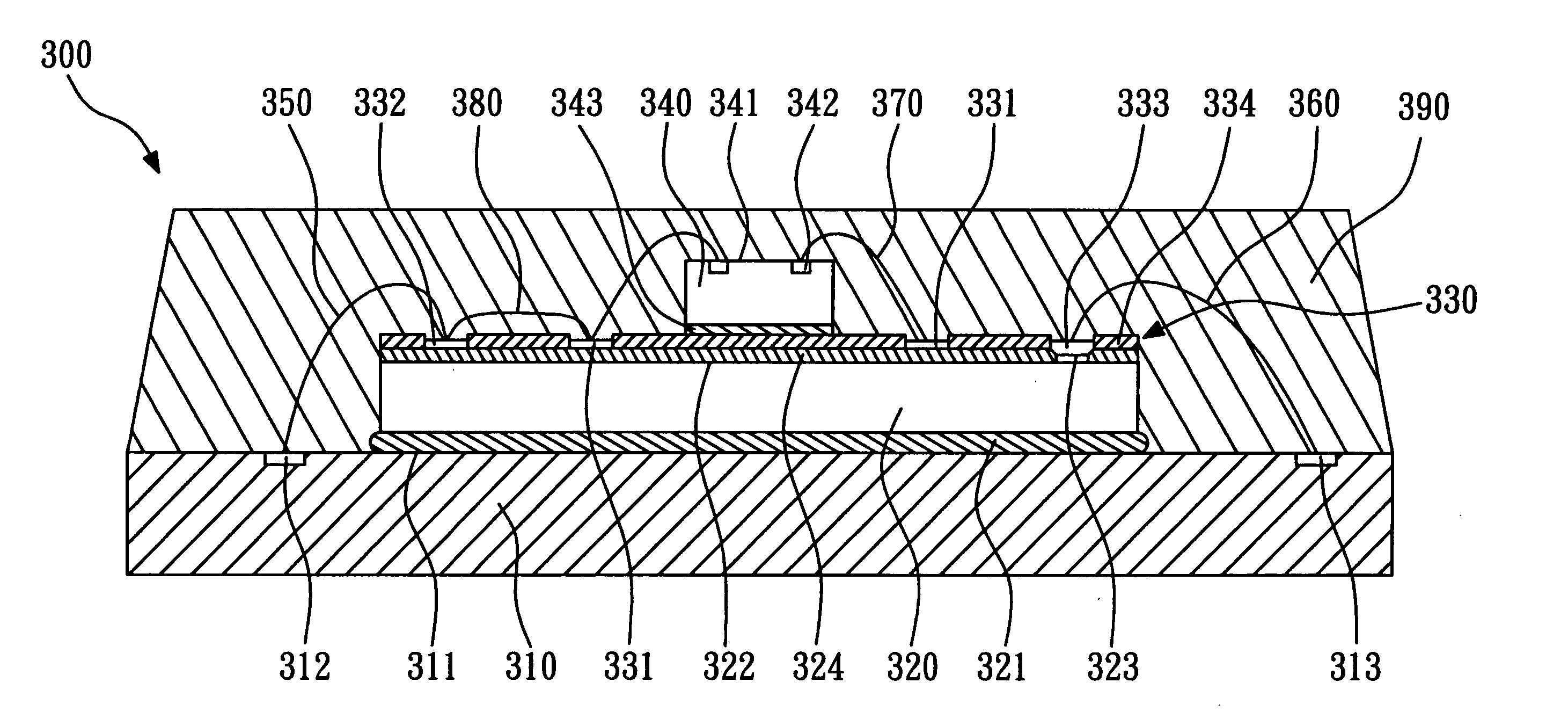

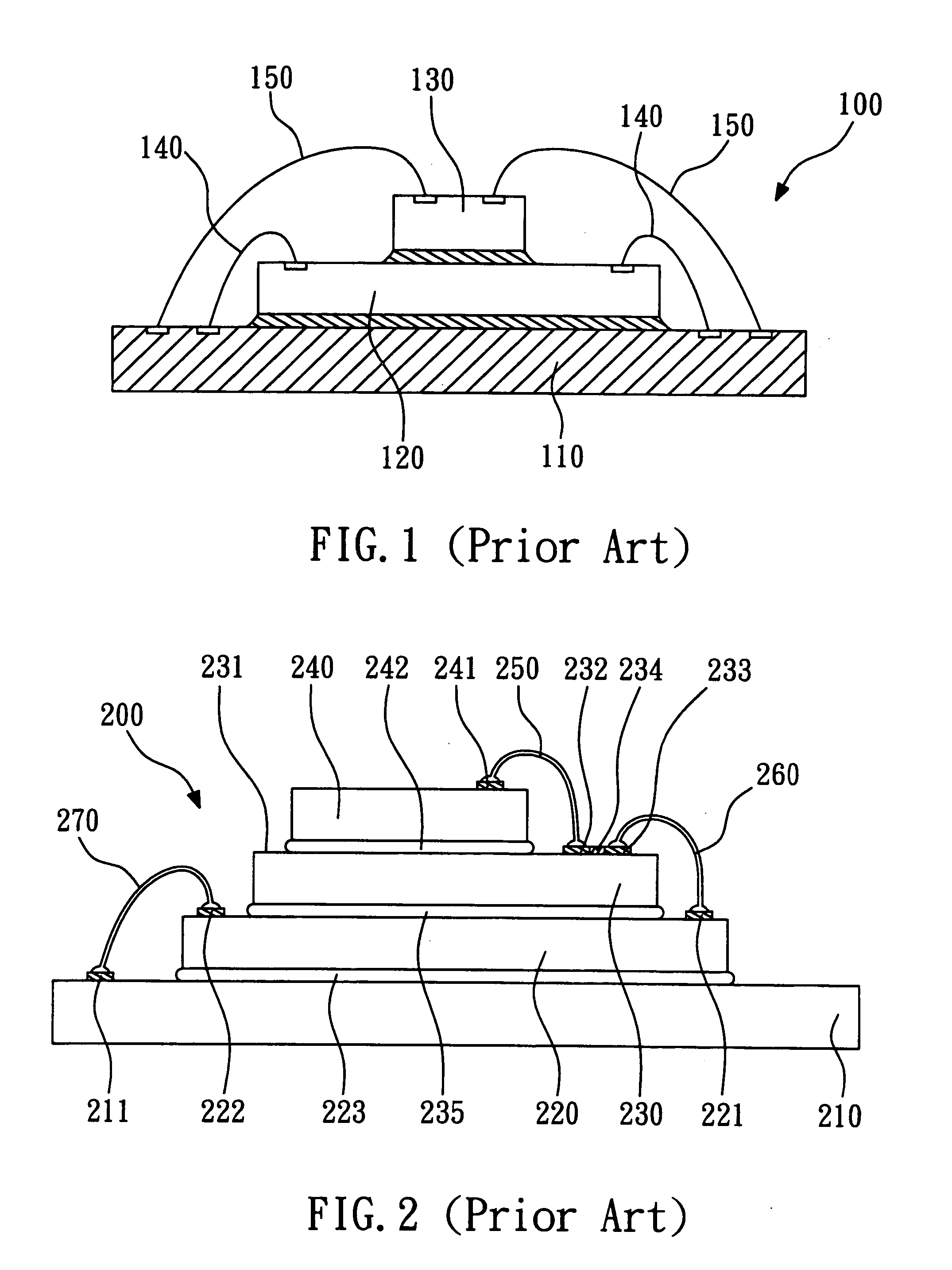

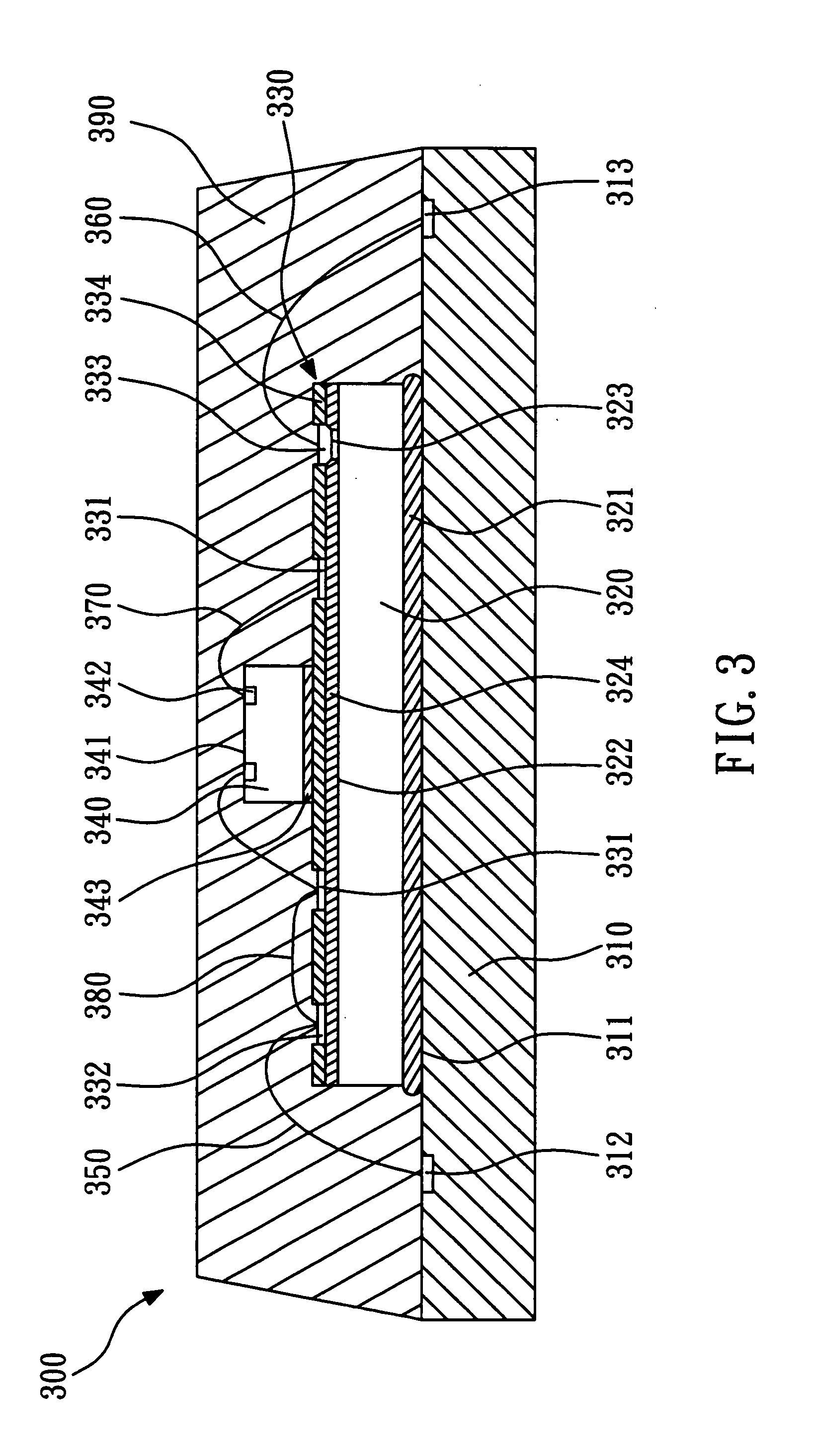

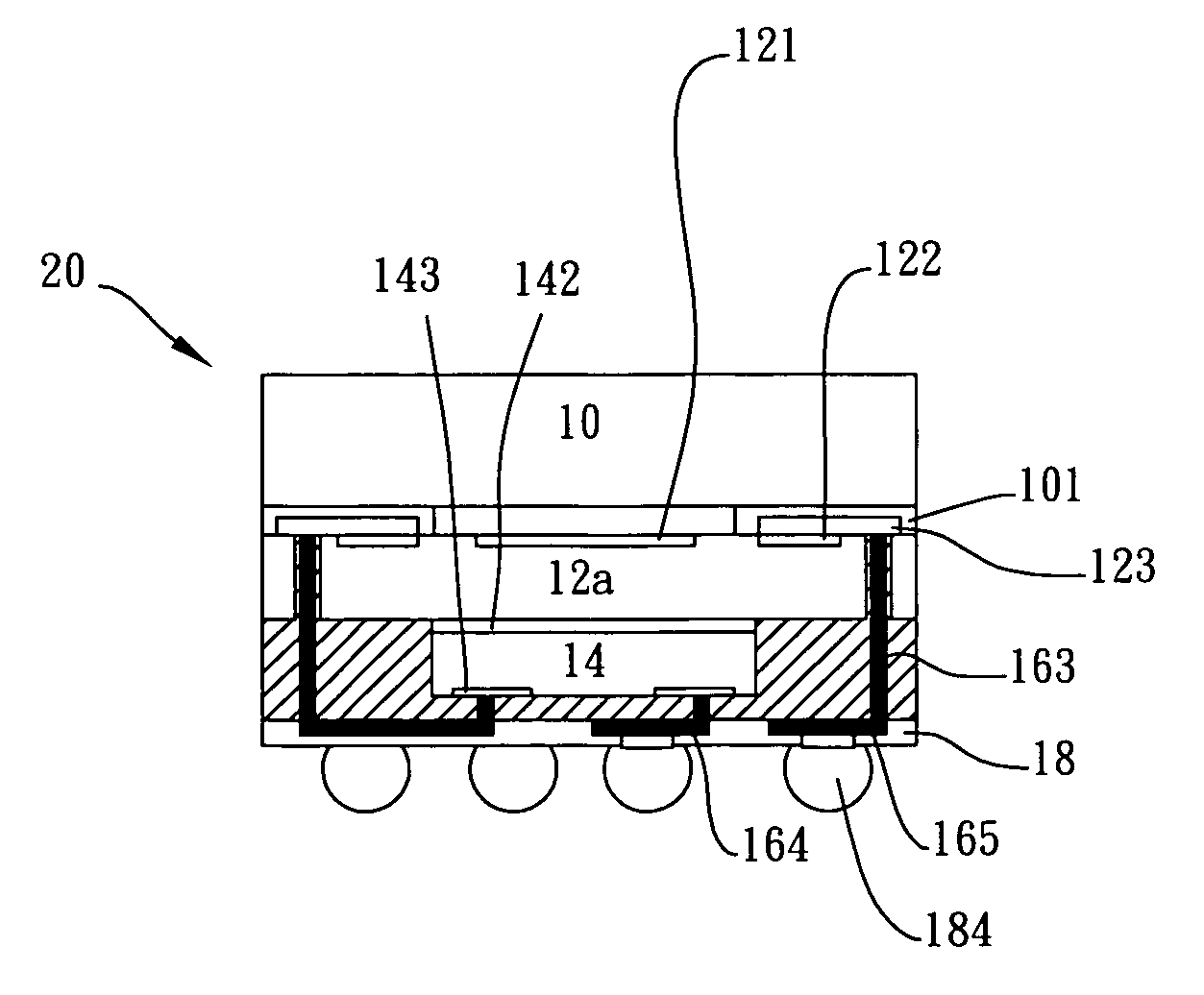

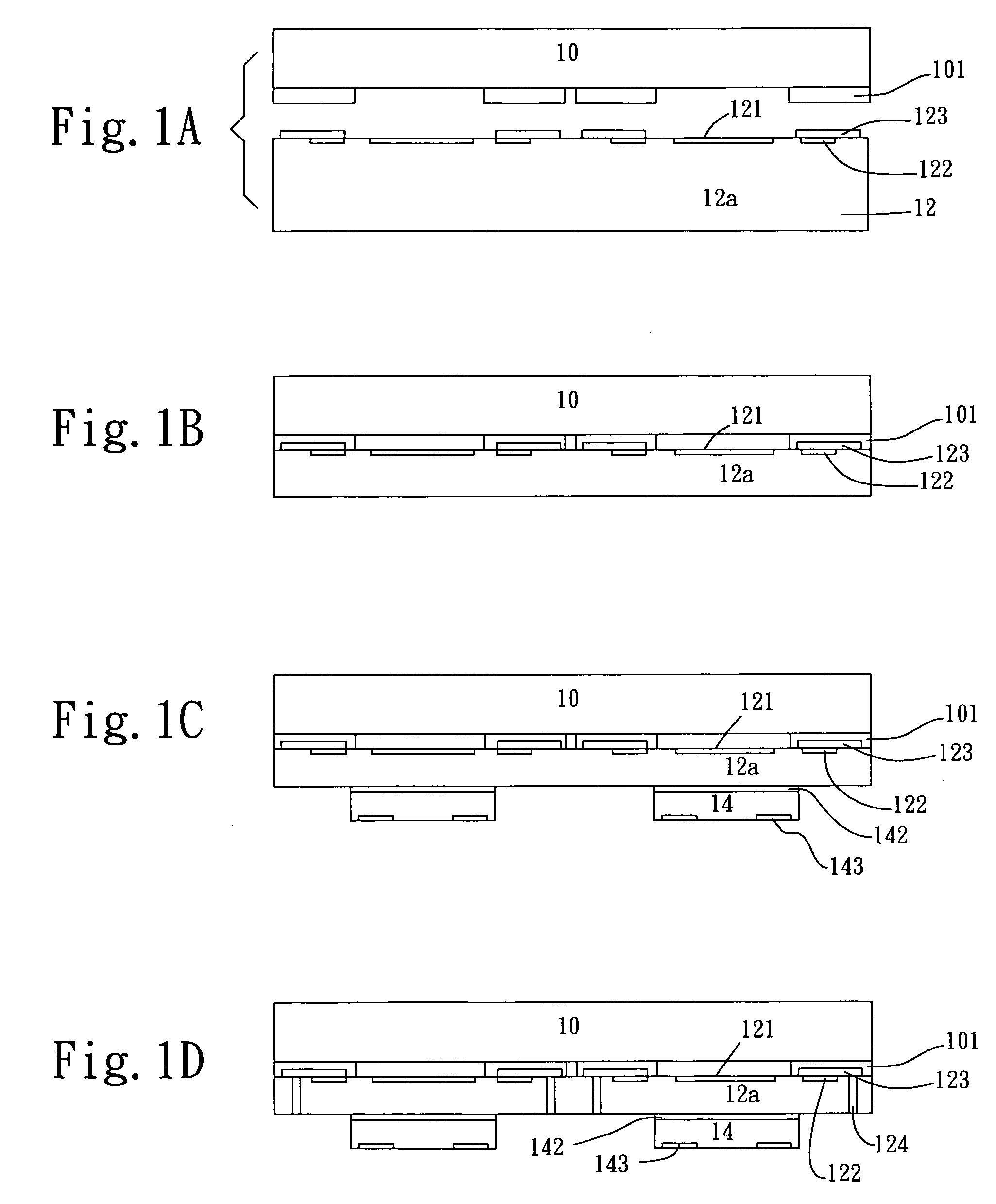

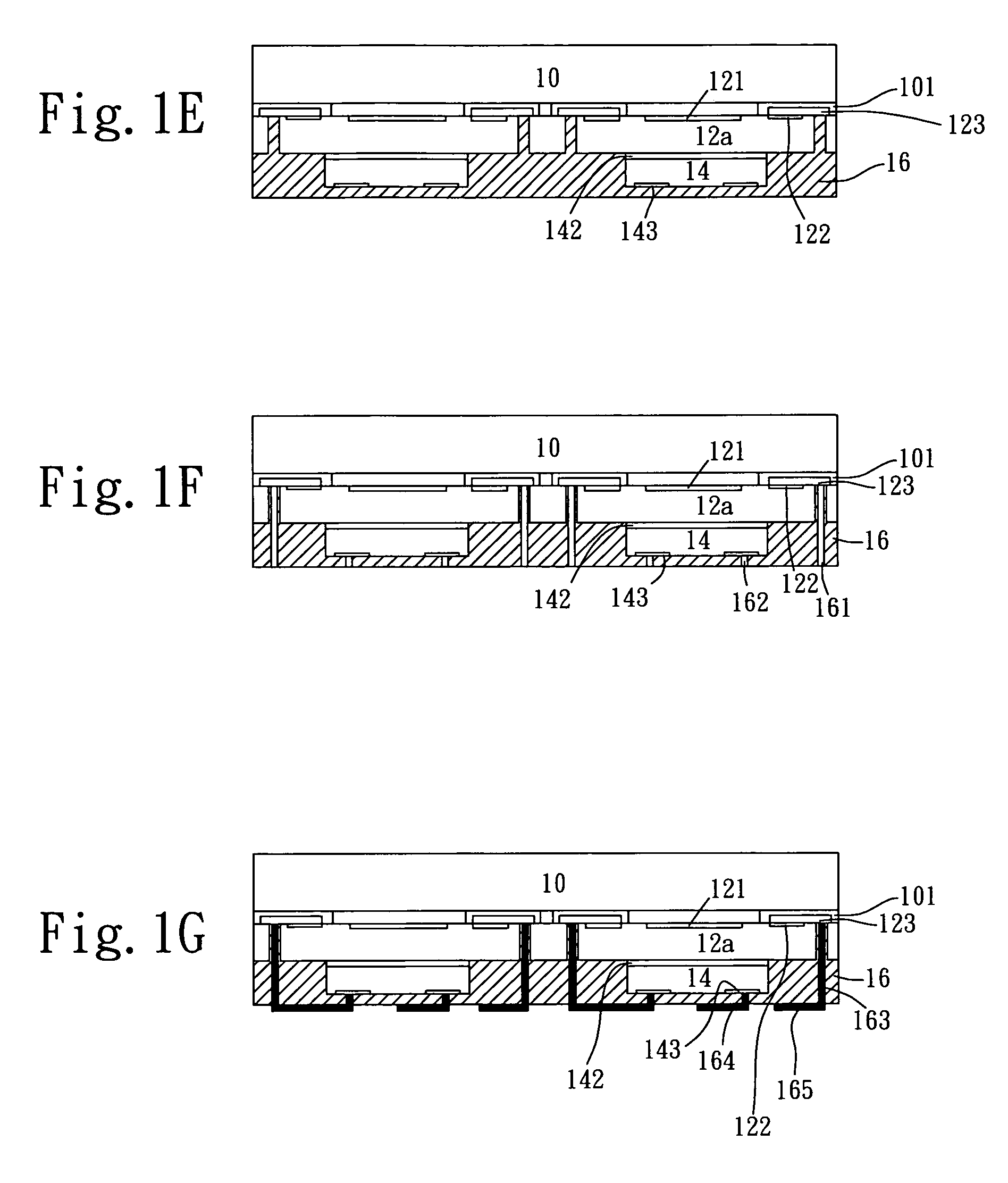

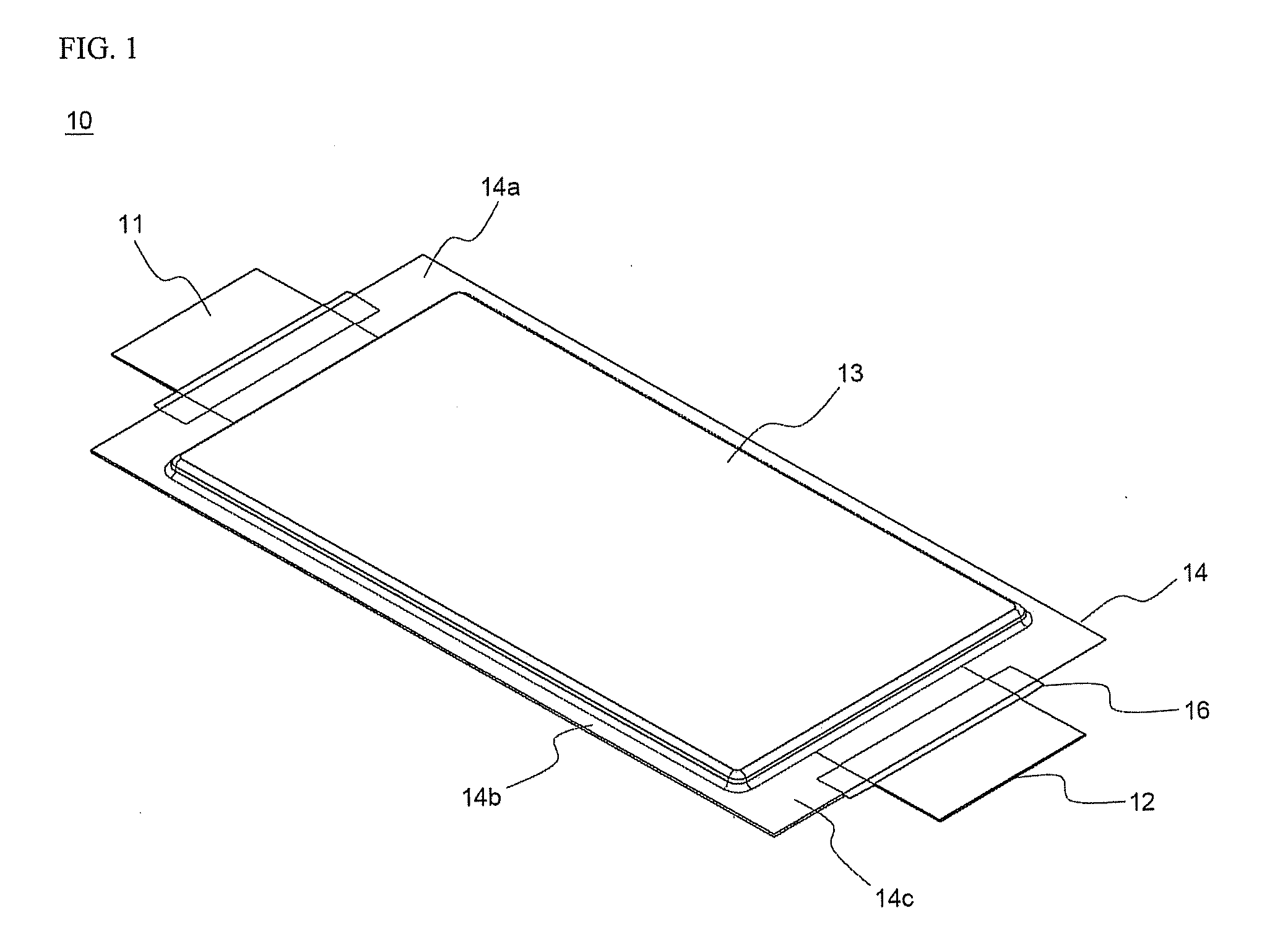

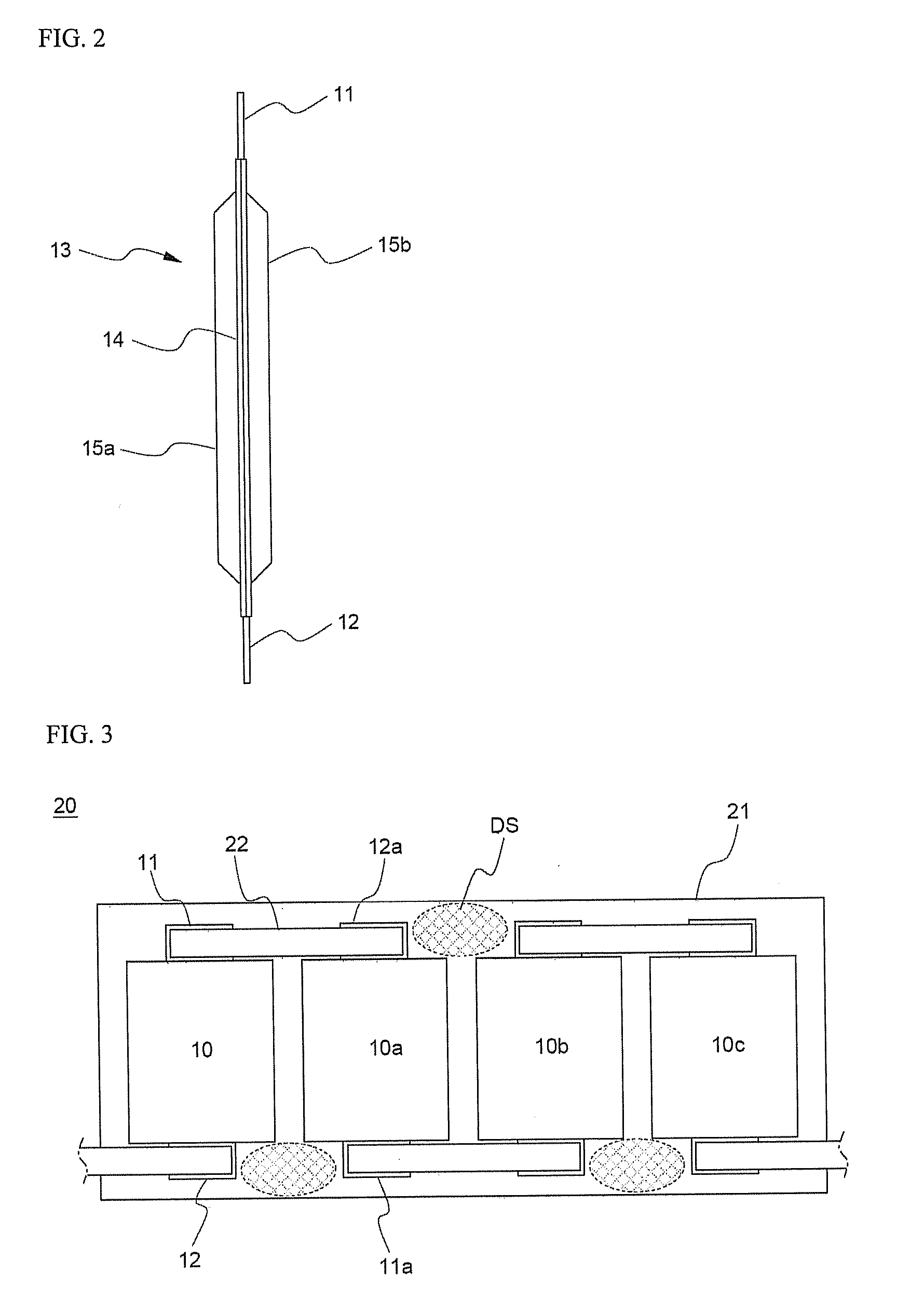

Multi-chip stack package

ActiveUS20060091560A1Shorten connection lengthShort circuitSemiconductor/solid-state device detailsSolid-state devicesEngineeringChip stacking

A multi-chip stack package mainly comprises a substrate, a first chip, a redistribution structure and at least one second chip. The first chip is disposed on the substrate by an active surface facing upwards. The redistribution structure comprises a plurality of first intermediate pads, a plurality of second intermediate pads and a plurality of external pads. The first intermediate pads, the second intermediate pads, and the external pads are formed on the first active surface of the first chip, wherein the first intermediate pads and the second intermediate pads are electrically connected with each other. The second chip is disposed on the redistribution structure, and electrically connected to the first intermediate pads. The second intermediate pads are electrically connected to the substrate through a plurality of bonding wires, so that the second chip and the substrate are electrically conducted, and the connection length of the bonding wires is reduced.

Owner:ADVANCED SEMICON ENG INC

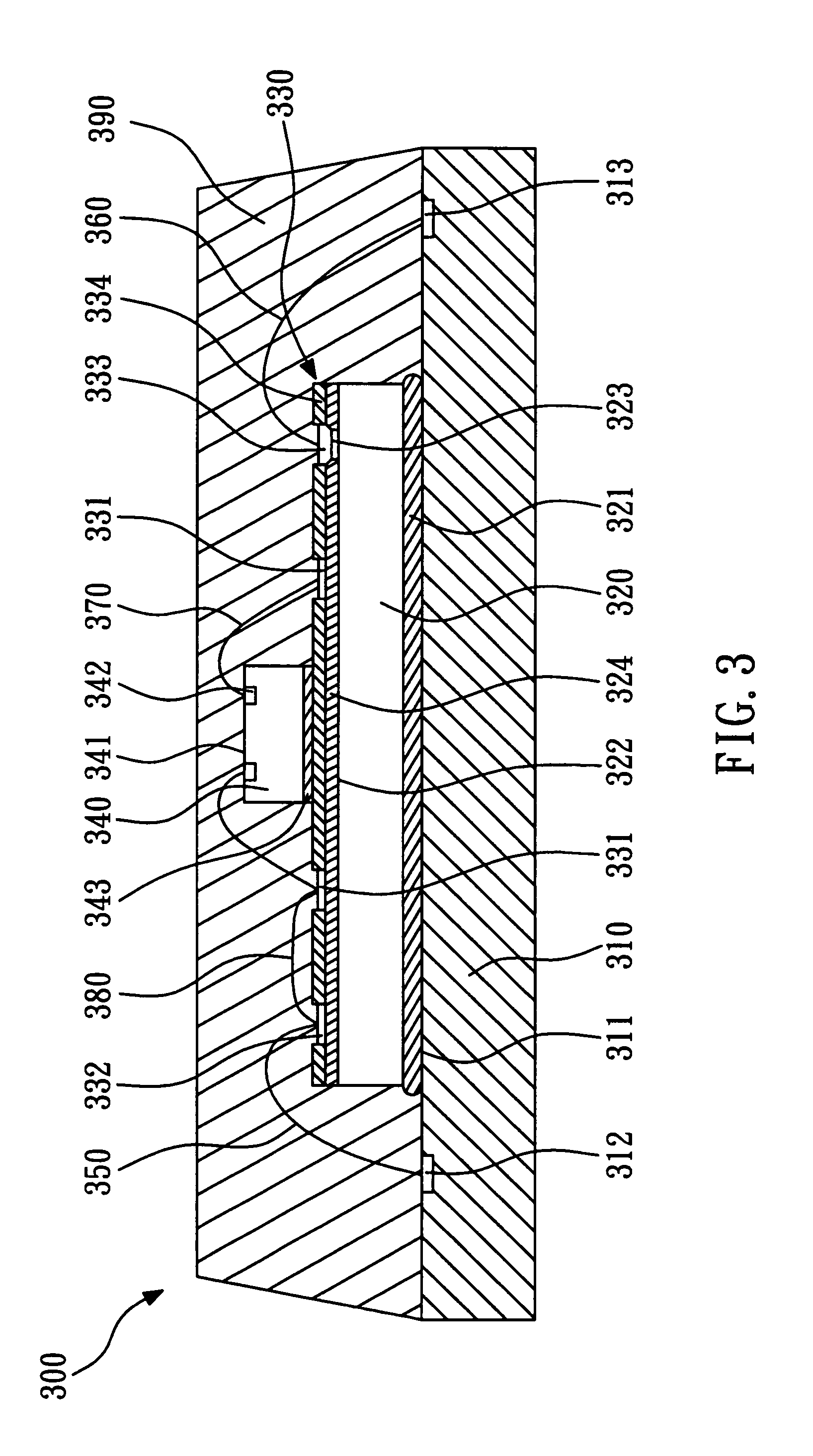

Image sensor module with a three-dimensional die-stacking structure

ActiveUS7663231B2Image degradationShorten connection lengthSemiconductor/solid-state device detailsSolid-state devicesElectrical connectionConductive materials

This invention provides an image sensor module with a three-dimensional die-stacking structure. By filling a conductive material into through silicon vias within at least one image sensor die, and into via holes within an insulating layer, vertical electrical connections are formed between the image sensor die and an image processor buried in the insulating layer. A plurality of solder bumps is formed on a backside of the image sensor module so that the module can be directly assembled onto a circuit board. The image sensor module of this invention is characterized by a wafer-level packaging architecture and a three-dimensional die-stacking structure, which reduces electrical connection lengths within the module and thus reduces an area and height of the whole packaged module.

Owner:IND TECH RES INST

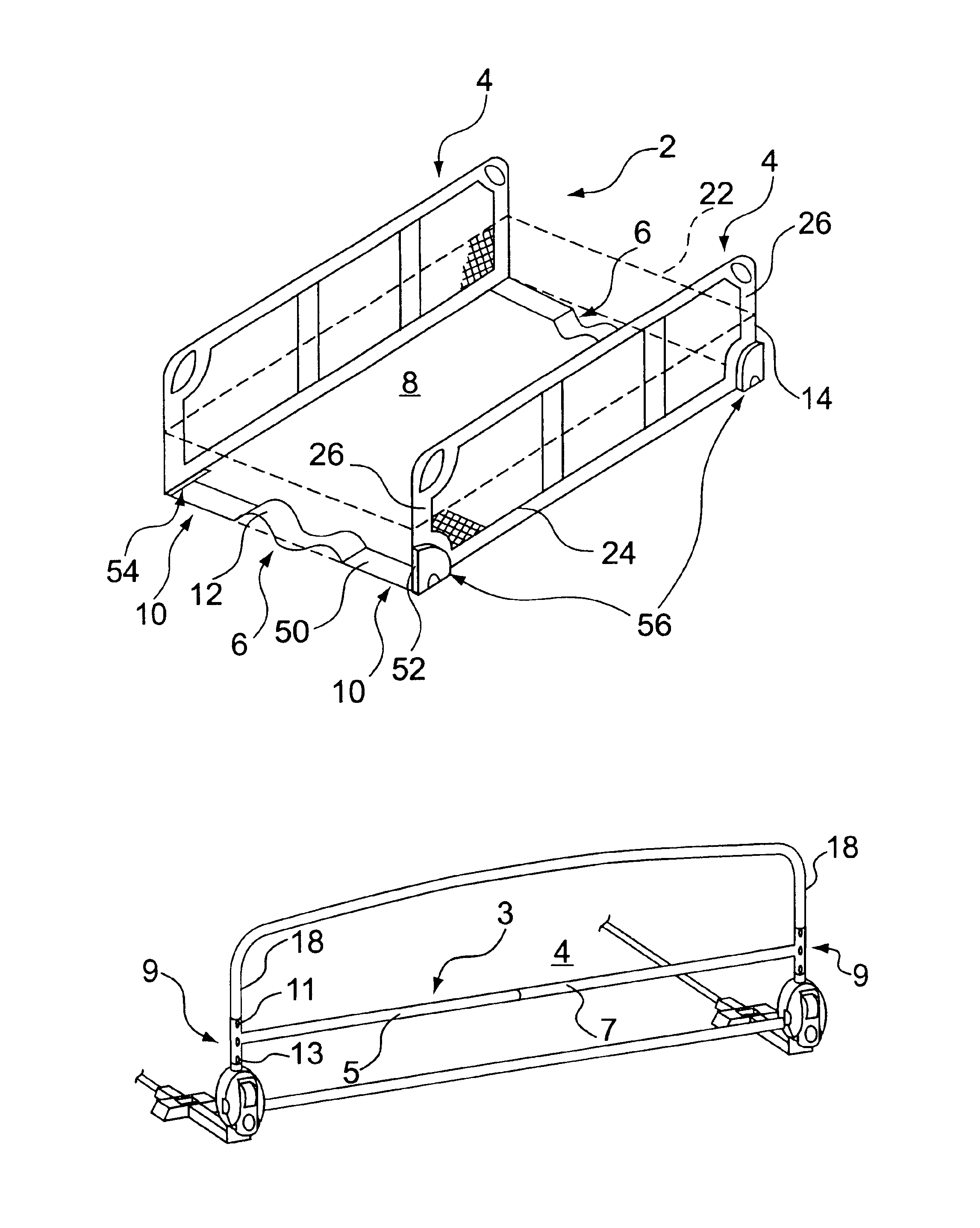

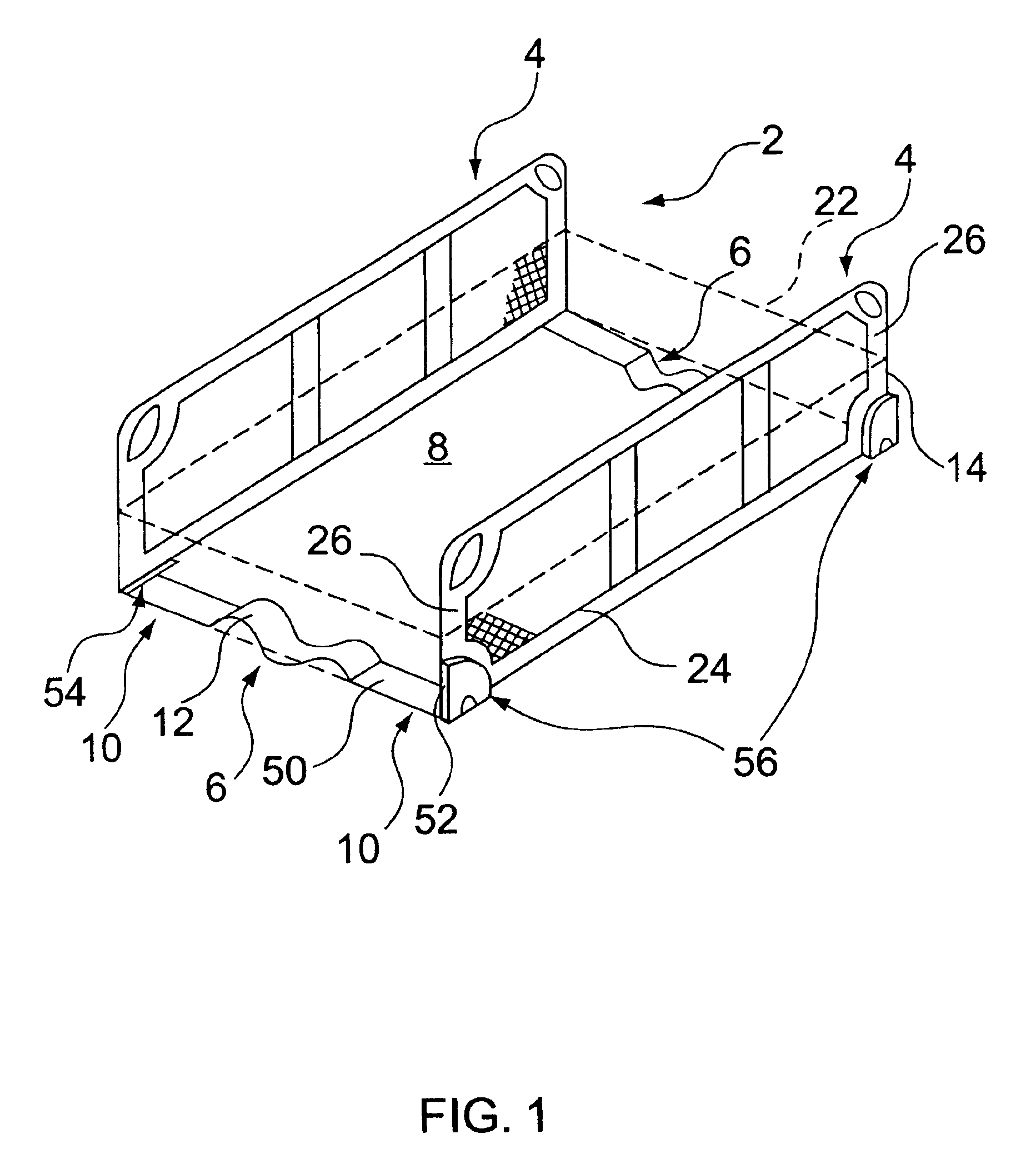

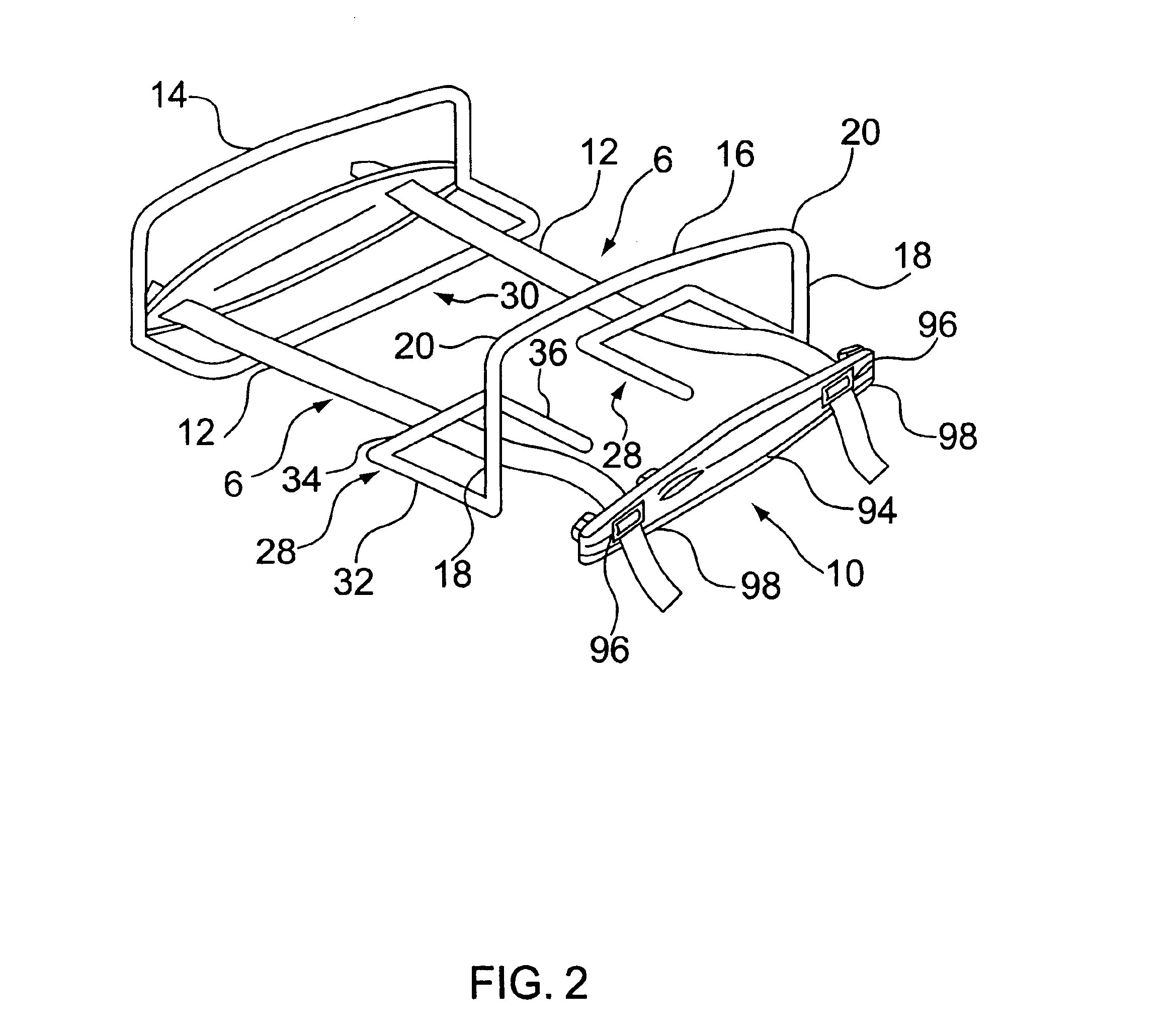

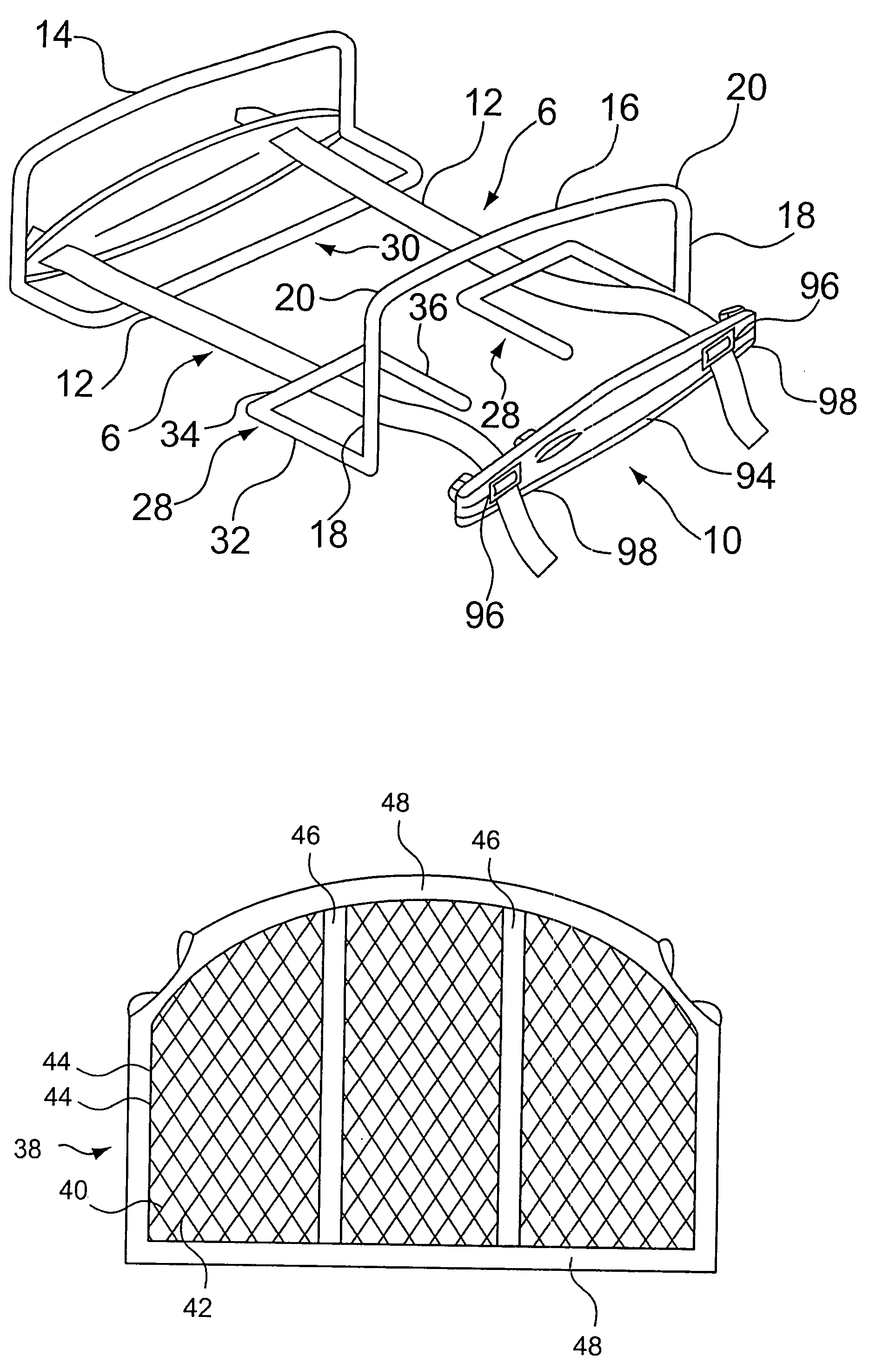

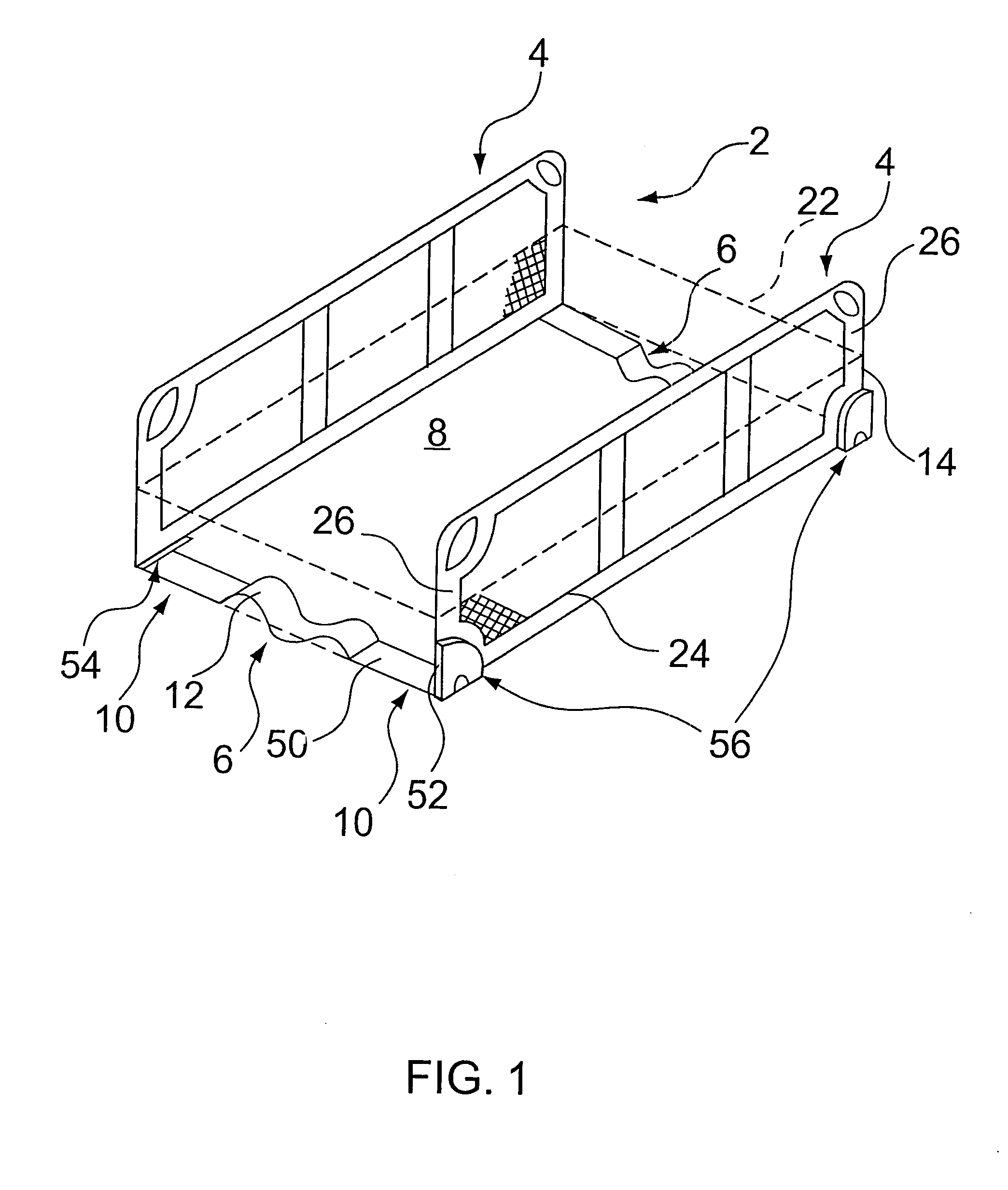

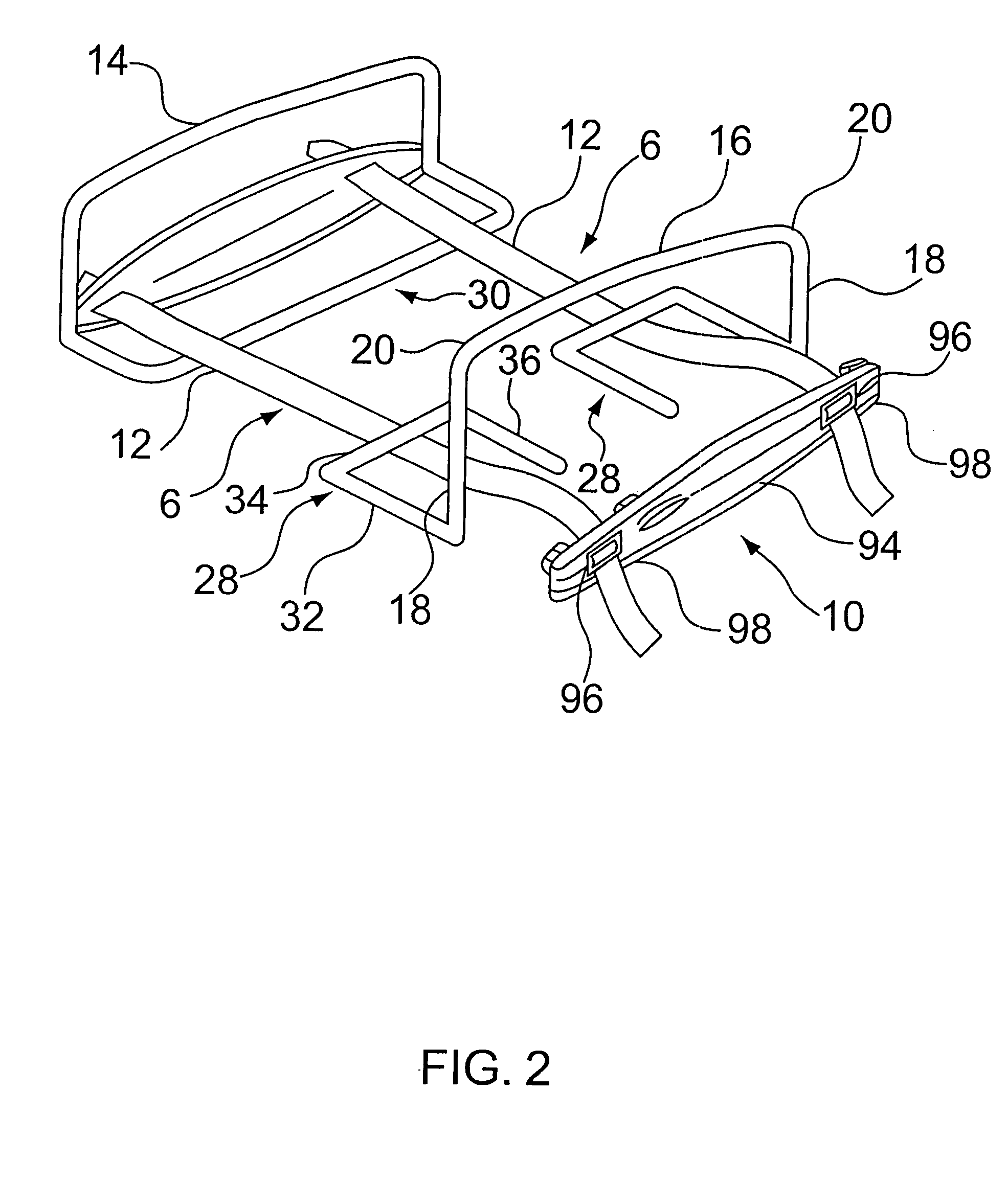

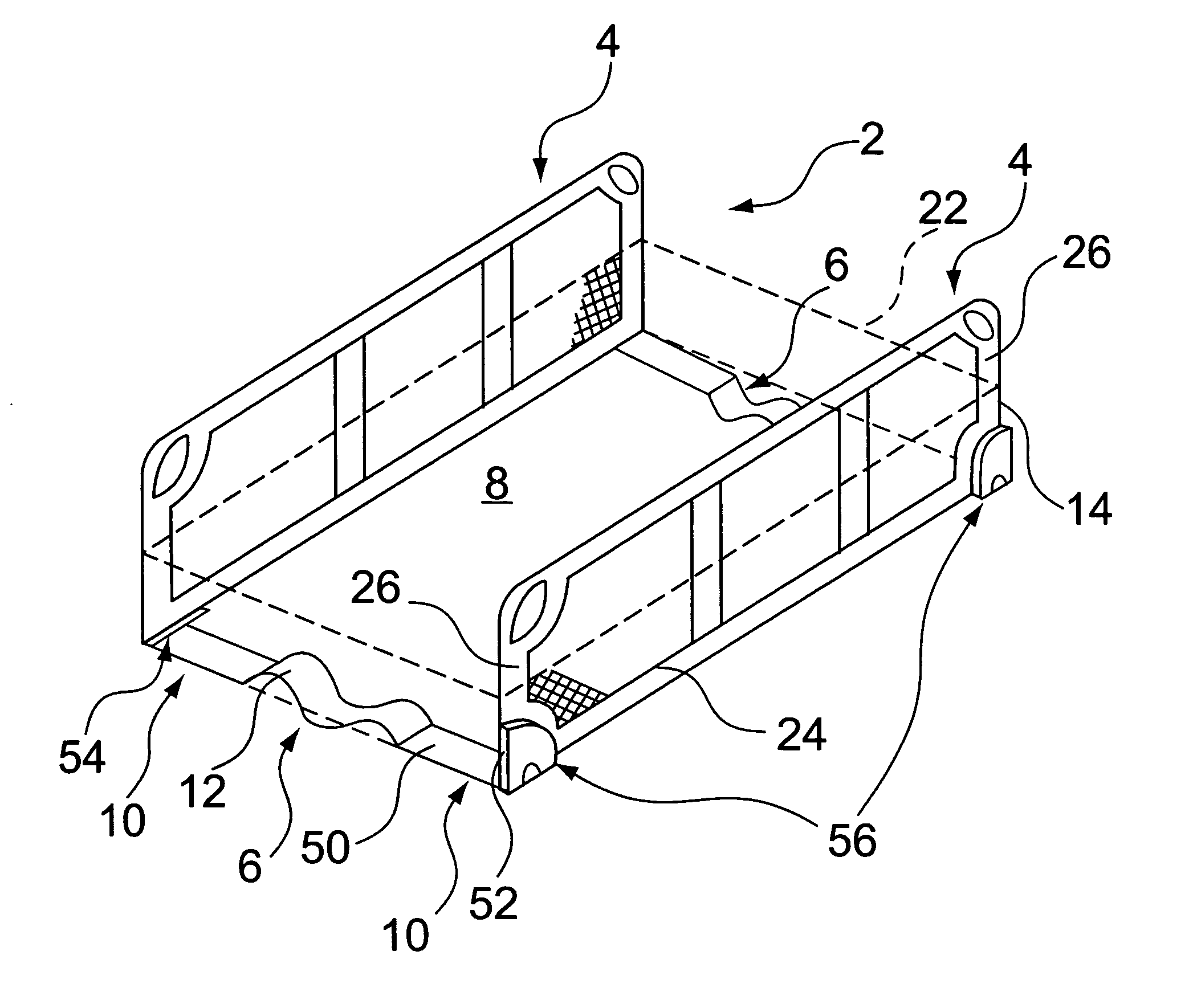

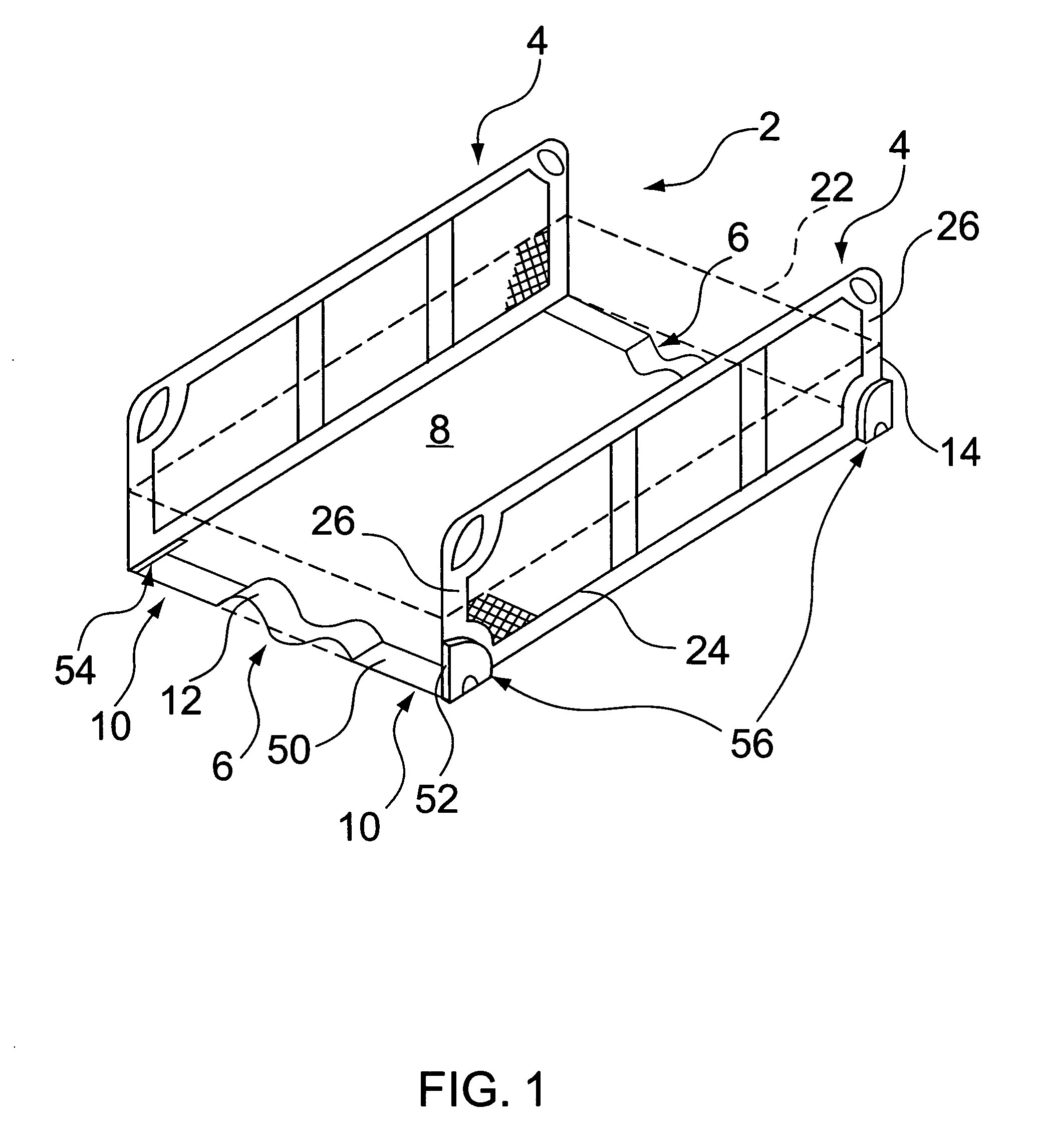

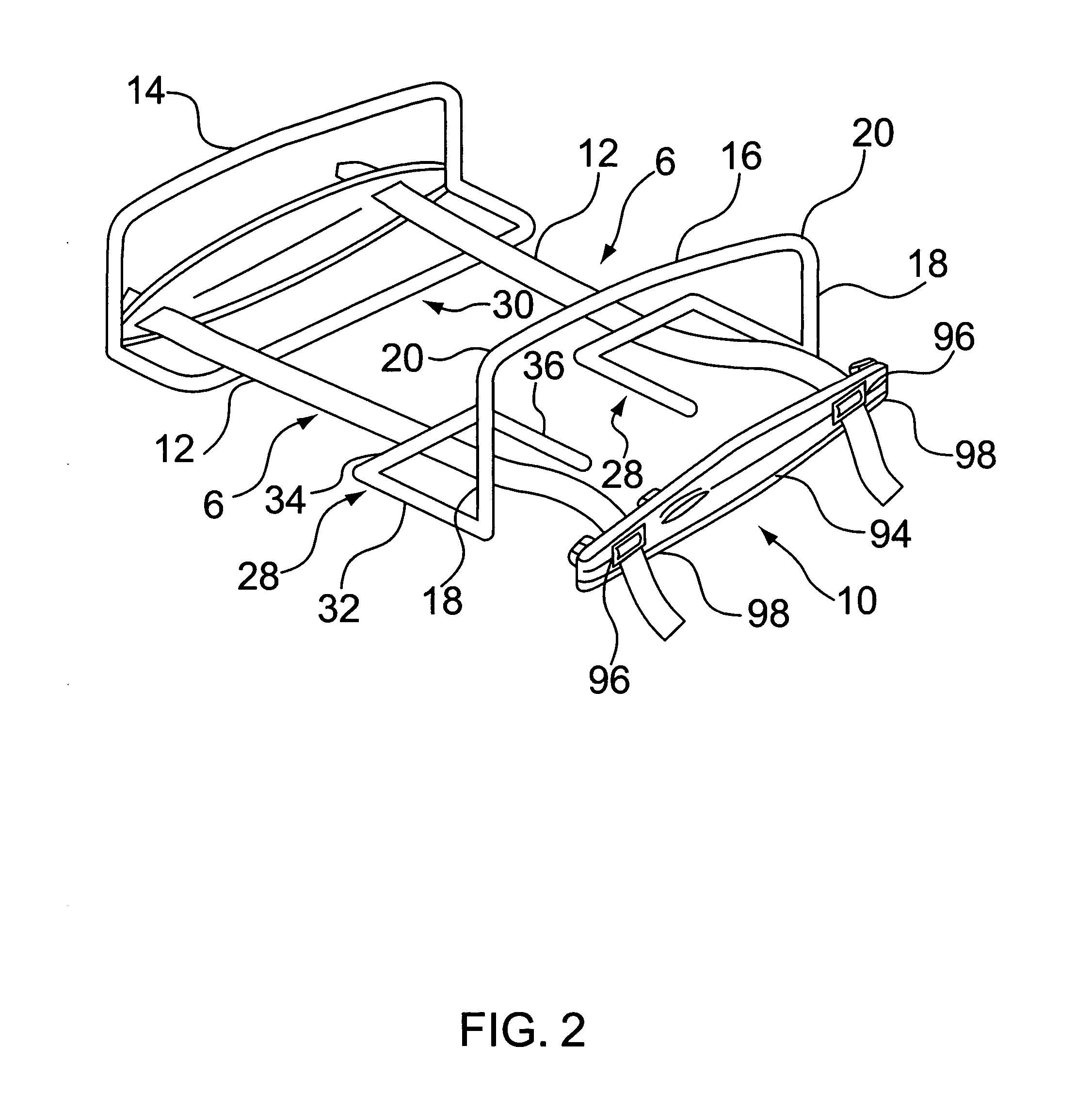

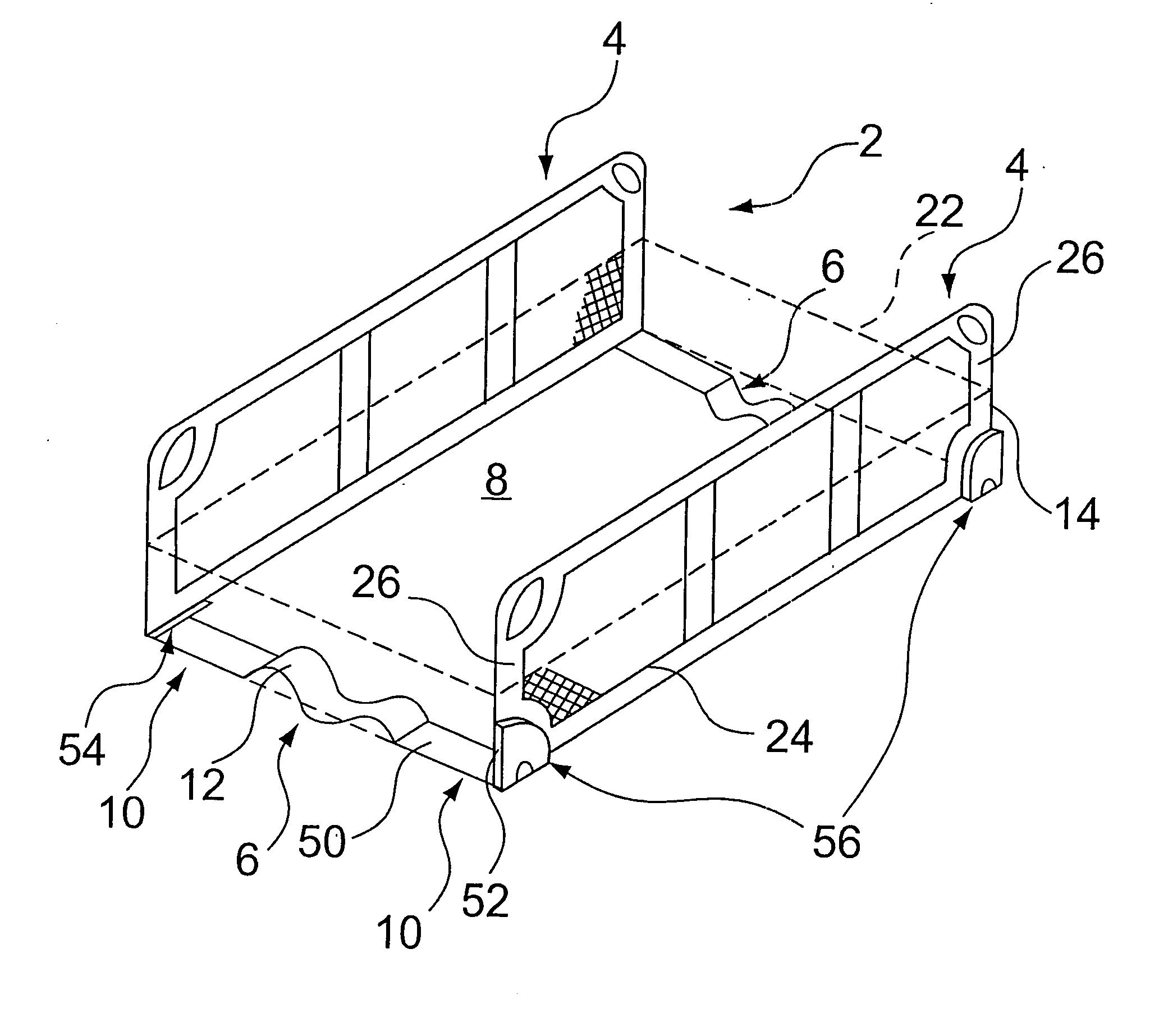

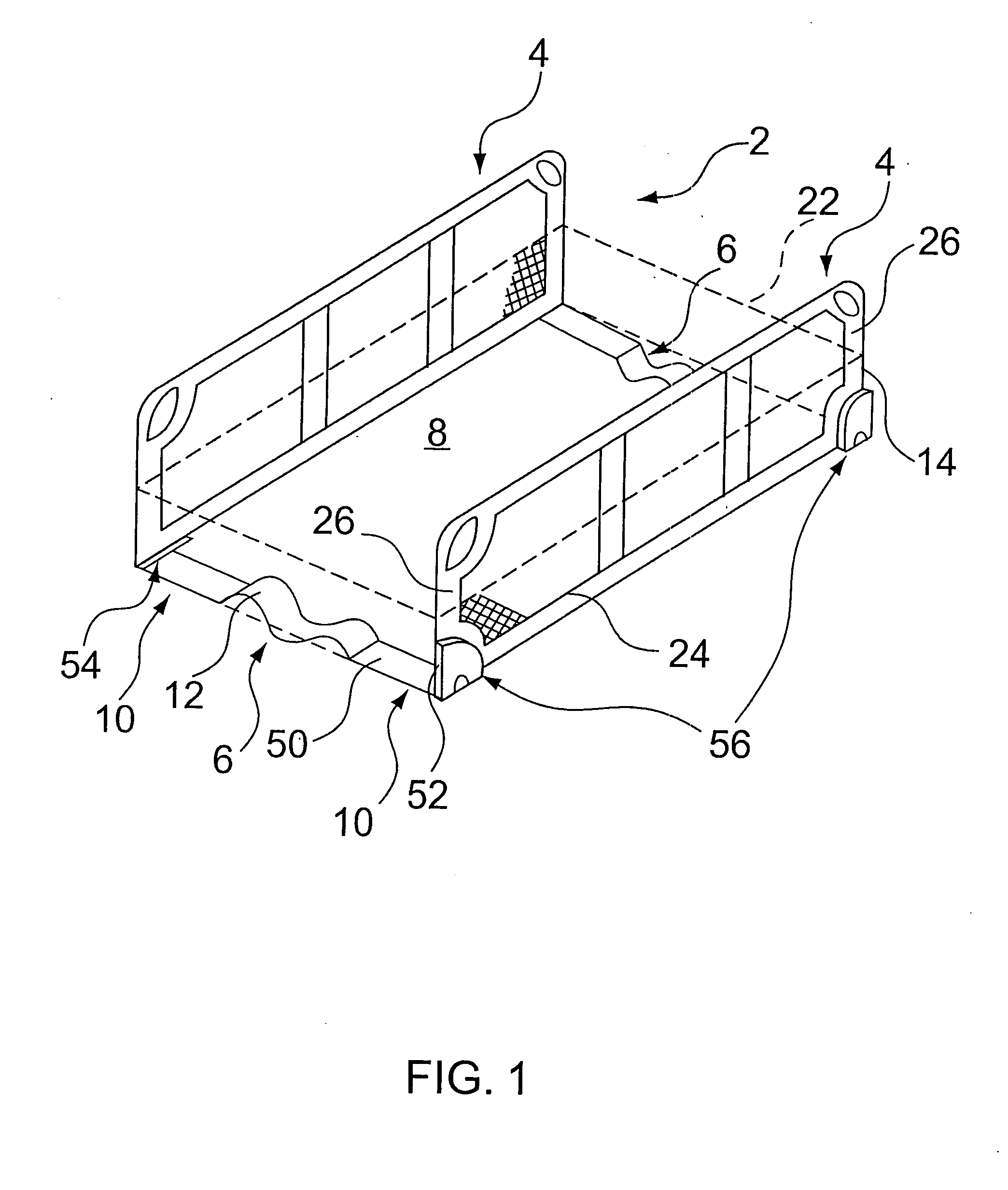

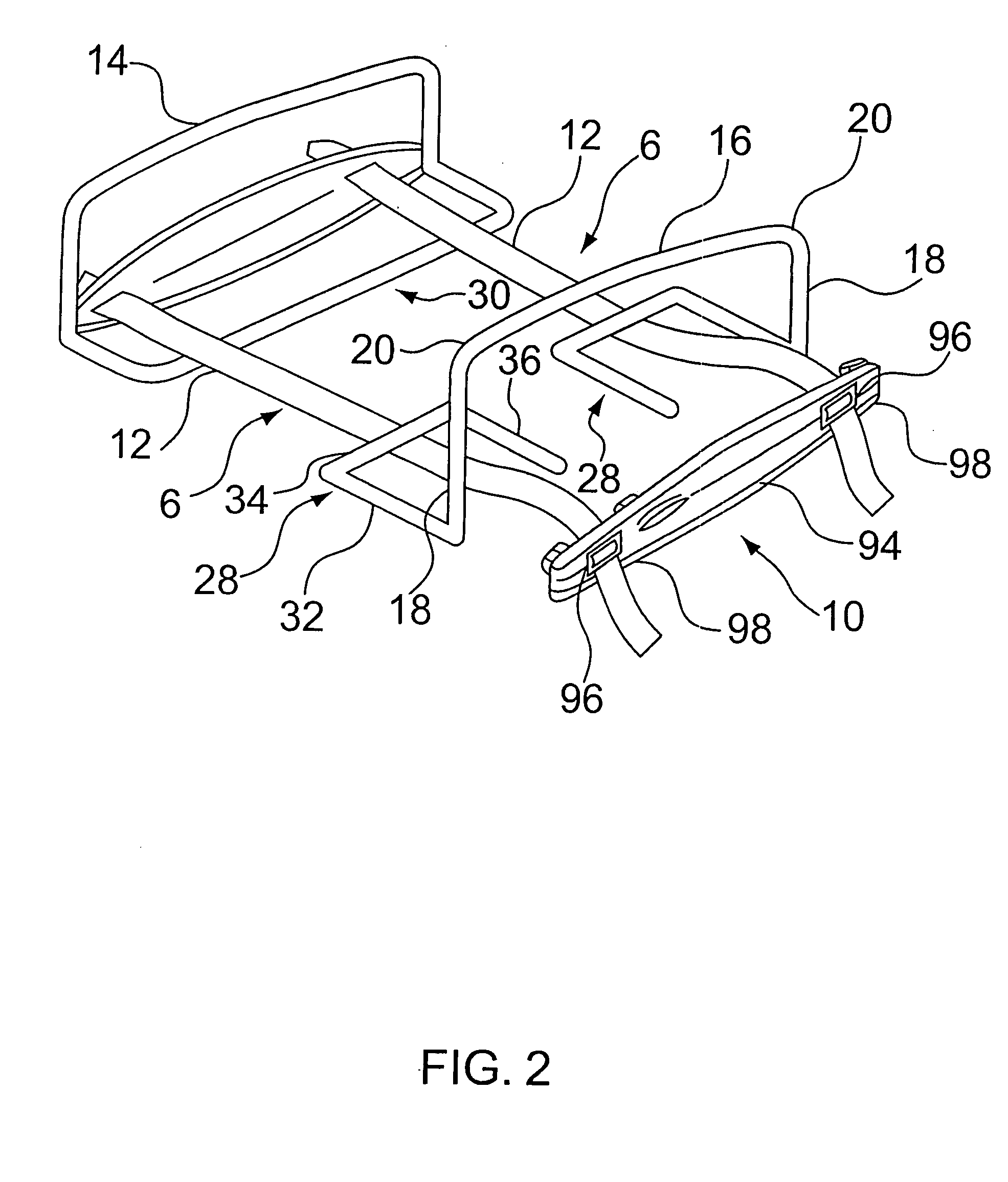

Bed guard assembly

InactiveUS6959463B2Easy to storeQuick and easy implementationKids bedsSofasMechanical engineeringRigid frame

A bed guard assembly includes a number of end panels, flexible connecting material for placement beneath a mattress, and connection pieces. The connection pieces connect the flexible connecting material to the end panels such that at least one end panel opposes another end panel when the flexible connecting material is disposed beneath a mattress. The end panel includes a rigid frame, a substantially horizontal rigid segment spanning an interior of the outer frame, and a fabric cover. The connection pieces are adjustable, and include a mechanism for pulling taut the connecting material.

Owner:SUMMER INFANT USA

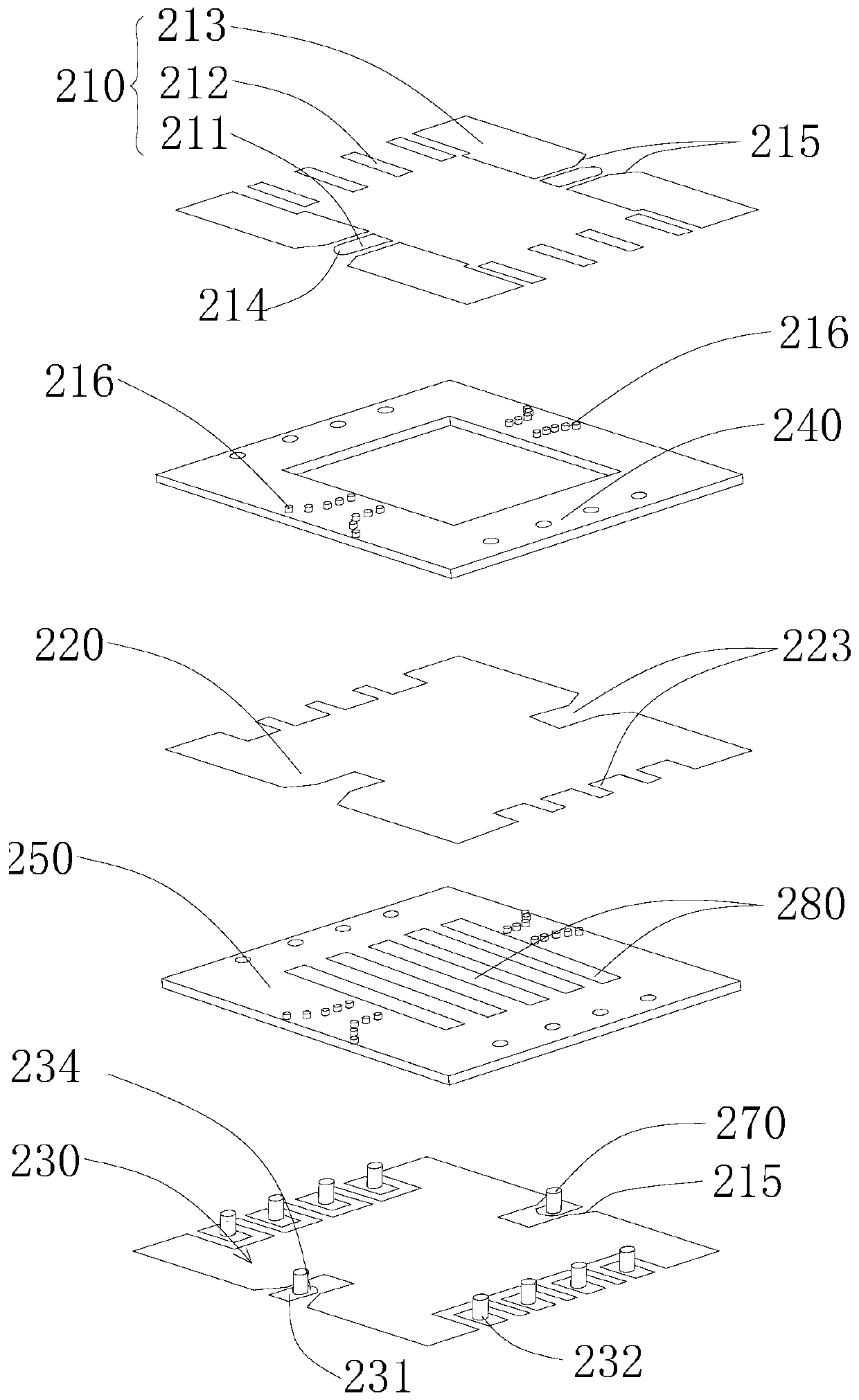

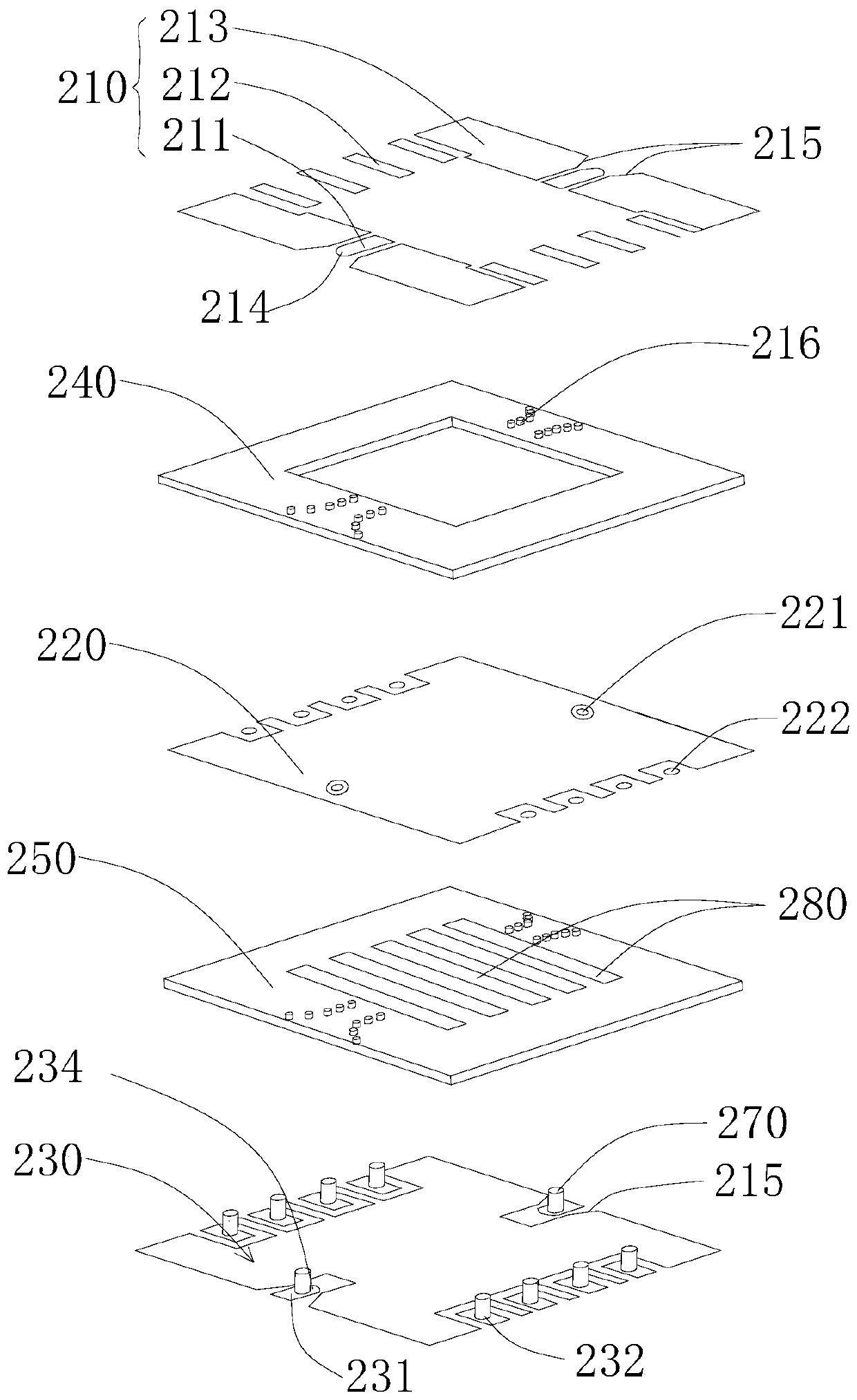

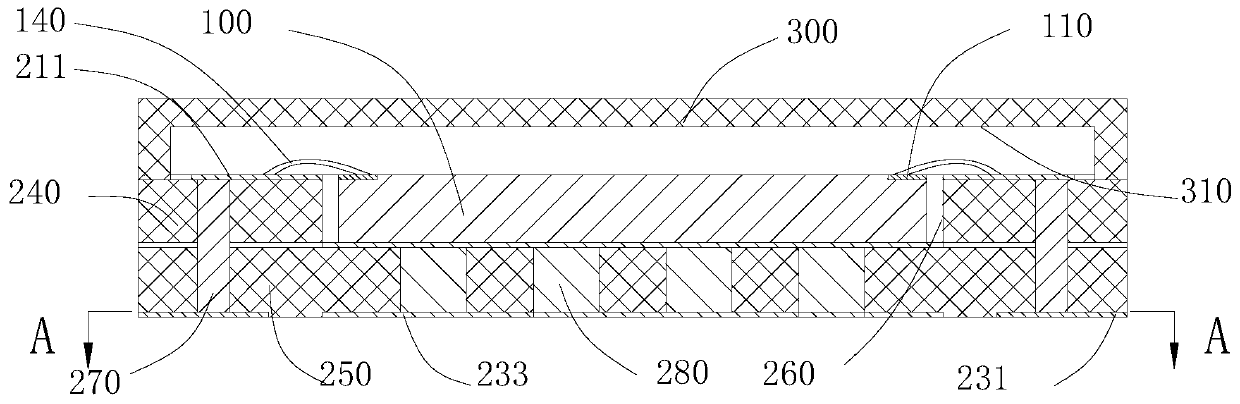

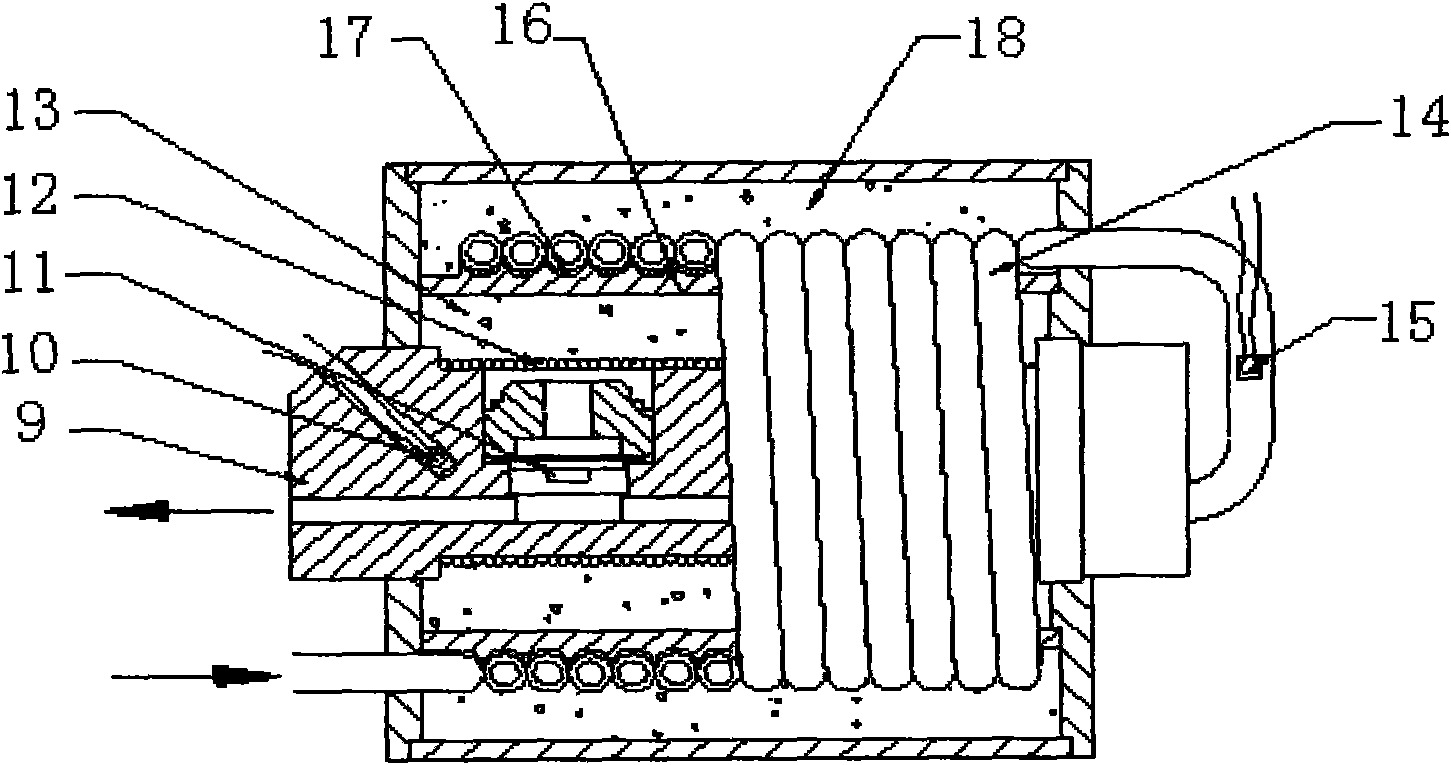

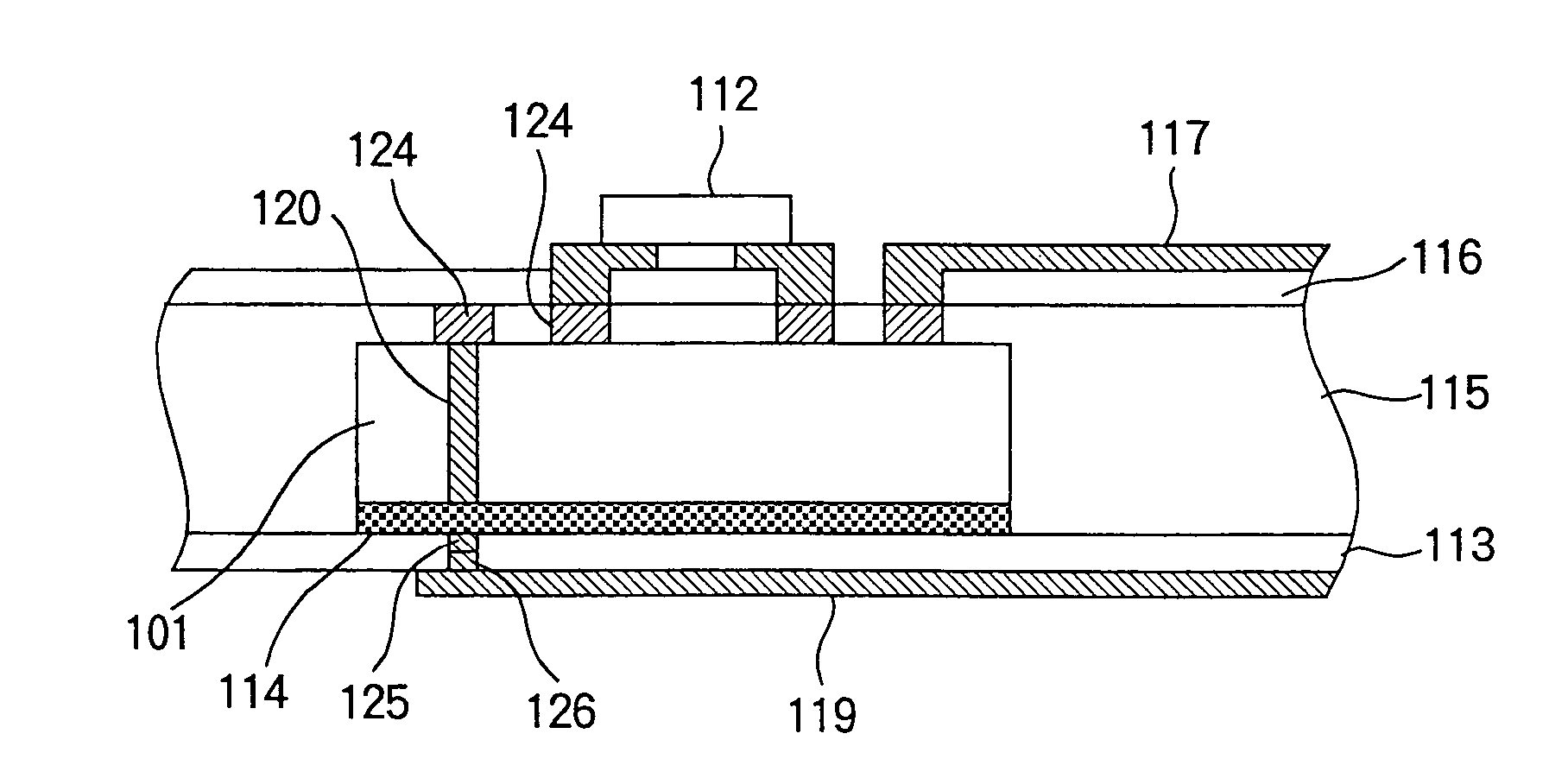

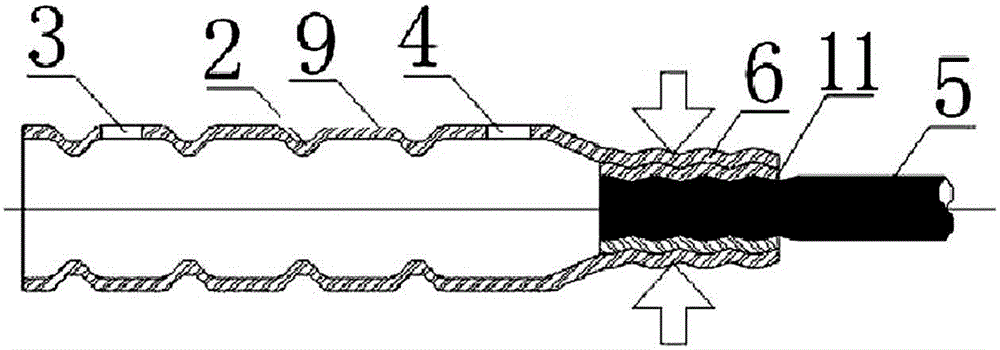

Millimeter wave frequency band amplifier chip packaging structure and manufacturing method thereof

PendingCN110739288AImprove transmission performanceImprove your own RF performanceSemiconductor/solid-state device detailsSolid-state devicesMillimetre waveRadio frequency

The invention provides a millimeter wave frequency band amplifier chip packaging structure and a manufacturing method thereof and relates to the technical field of chip packaging. The structure comprises a chip, a packaging substrate and a sealing cover, wherein the packaging substrate is provided with a first metal layer, a first dielectric layer, a second metal layer, a second dielectric layer and a third metal layer which are sequentially stacked from top to bottom, the sealing cover is arranged on the packaging substrate and used for sealing the packaging substrate, and the sealing cover is provided with an inner cavity with a downward opening. The millimeter wave frequency band amplifier chip packaging structure is advantaged in that the packaging substrate and the sealing cover are combined, an accommodating groove is formed in the packaging substrate so that the chip is accommodated, the connection length between the chip and the packaging substrate is effectively shortened, theparasitic inductance is conveniently reduced, and the transmission capability of the chip is improved; the sealing cover with the inner cavity enables connection between a chip direct-current port ofthe chip and the packaging substrate to be in direct contact with air, so loss of a high-frequency band is reduced, and radio frequency performance of the chip is improved.

Owner:NORTH-CHINA INTEGRATED CIRCUIT CO LTD

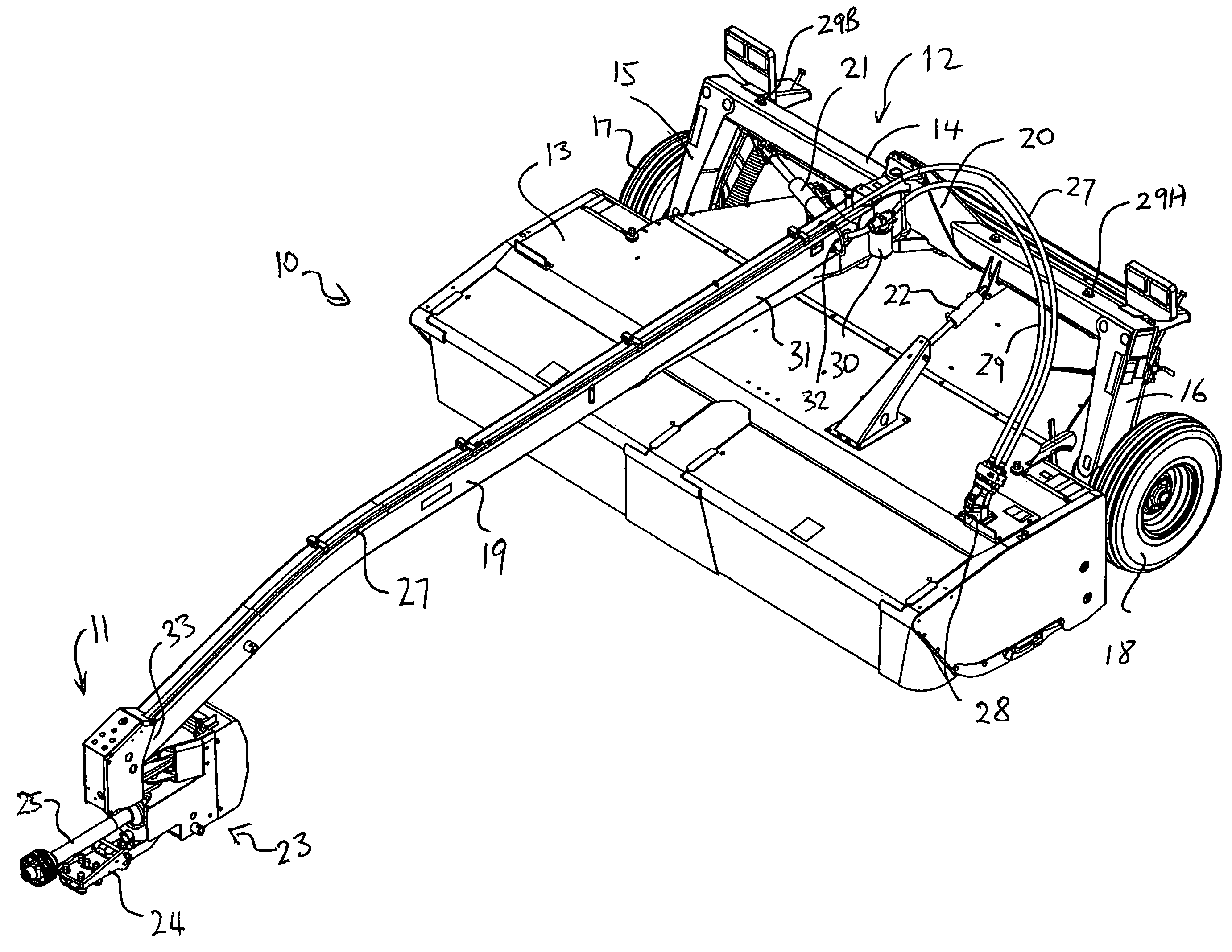

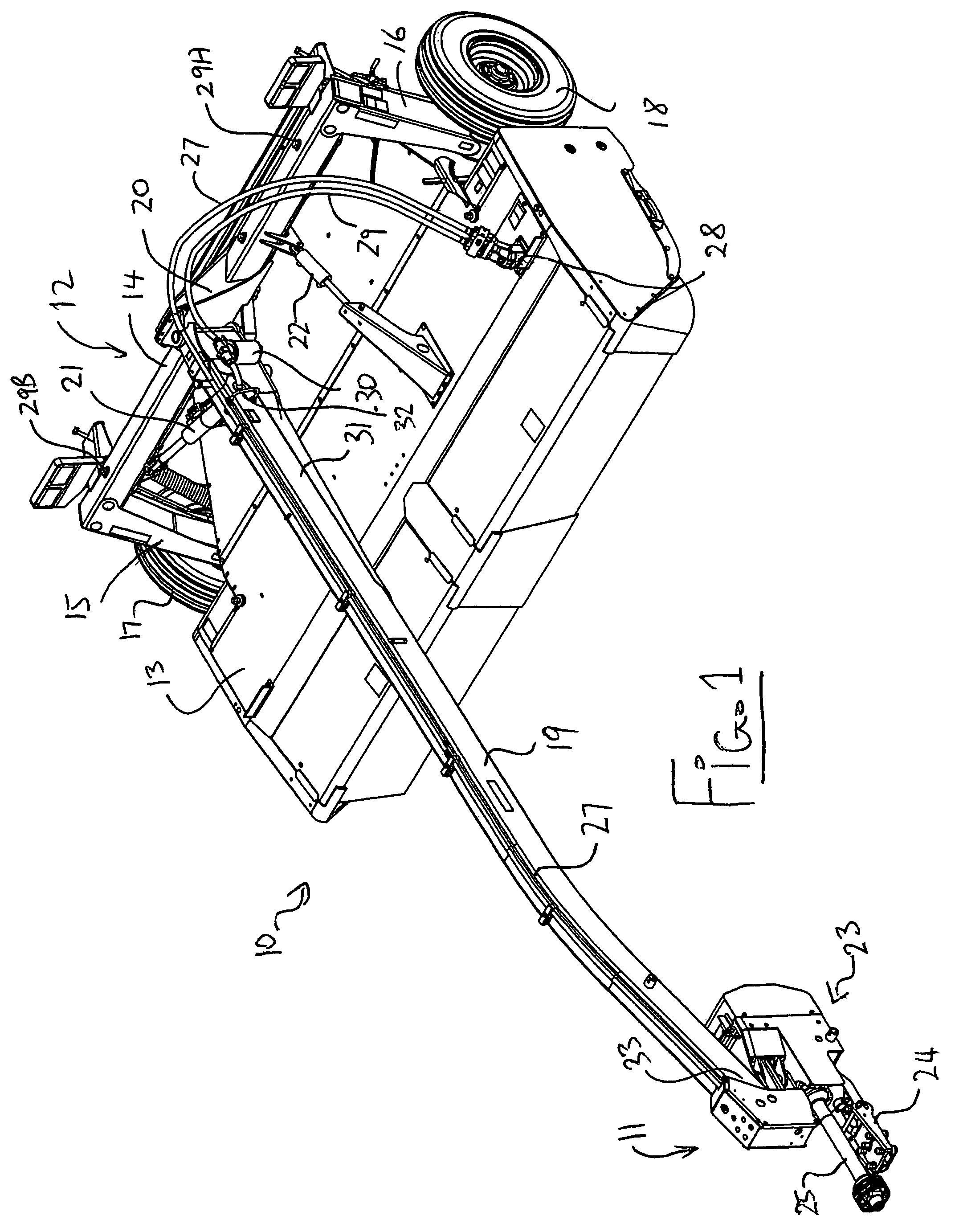

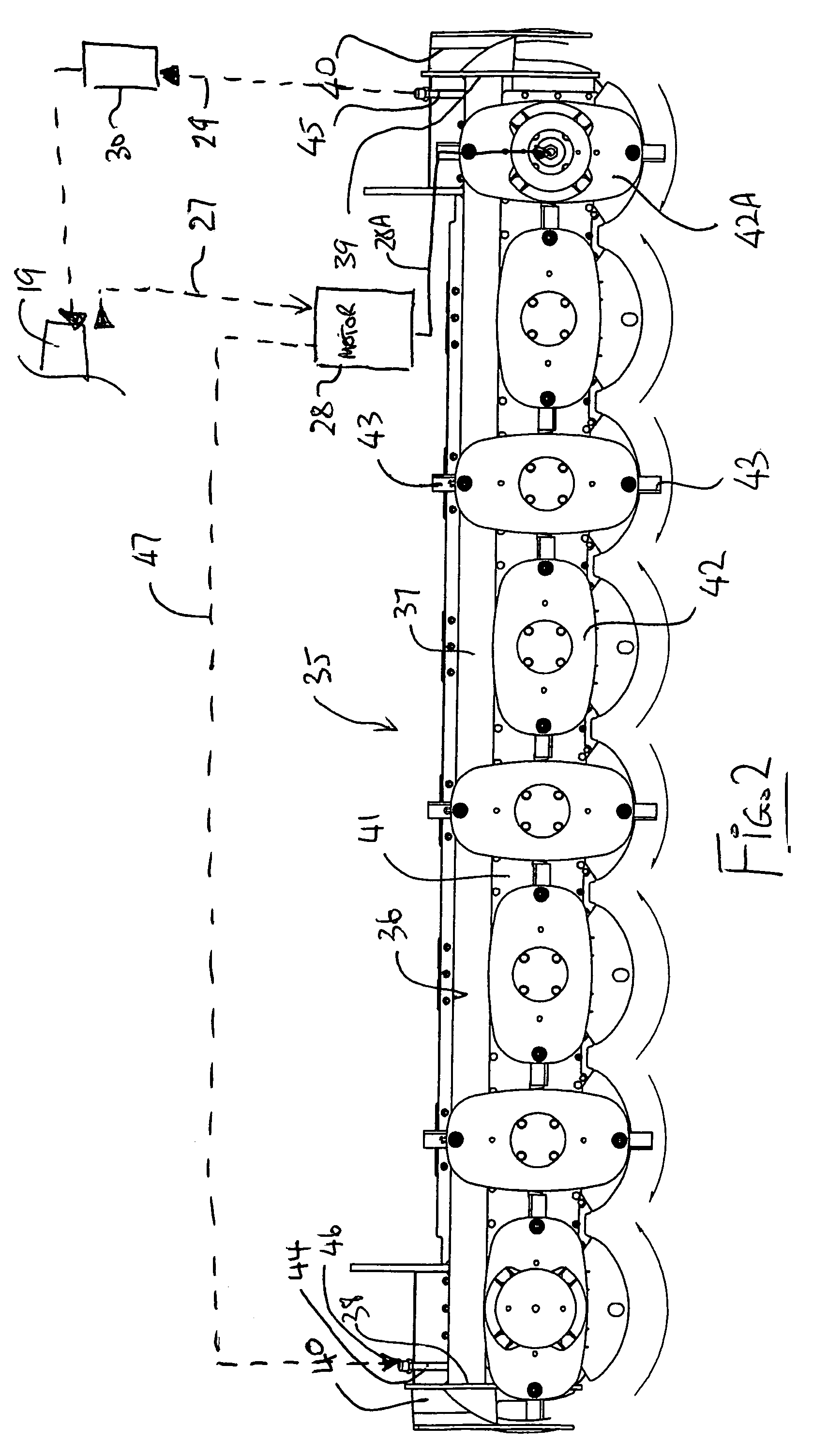

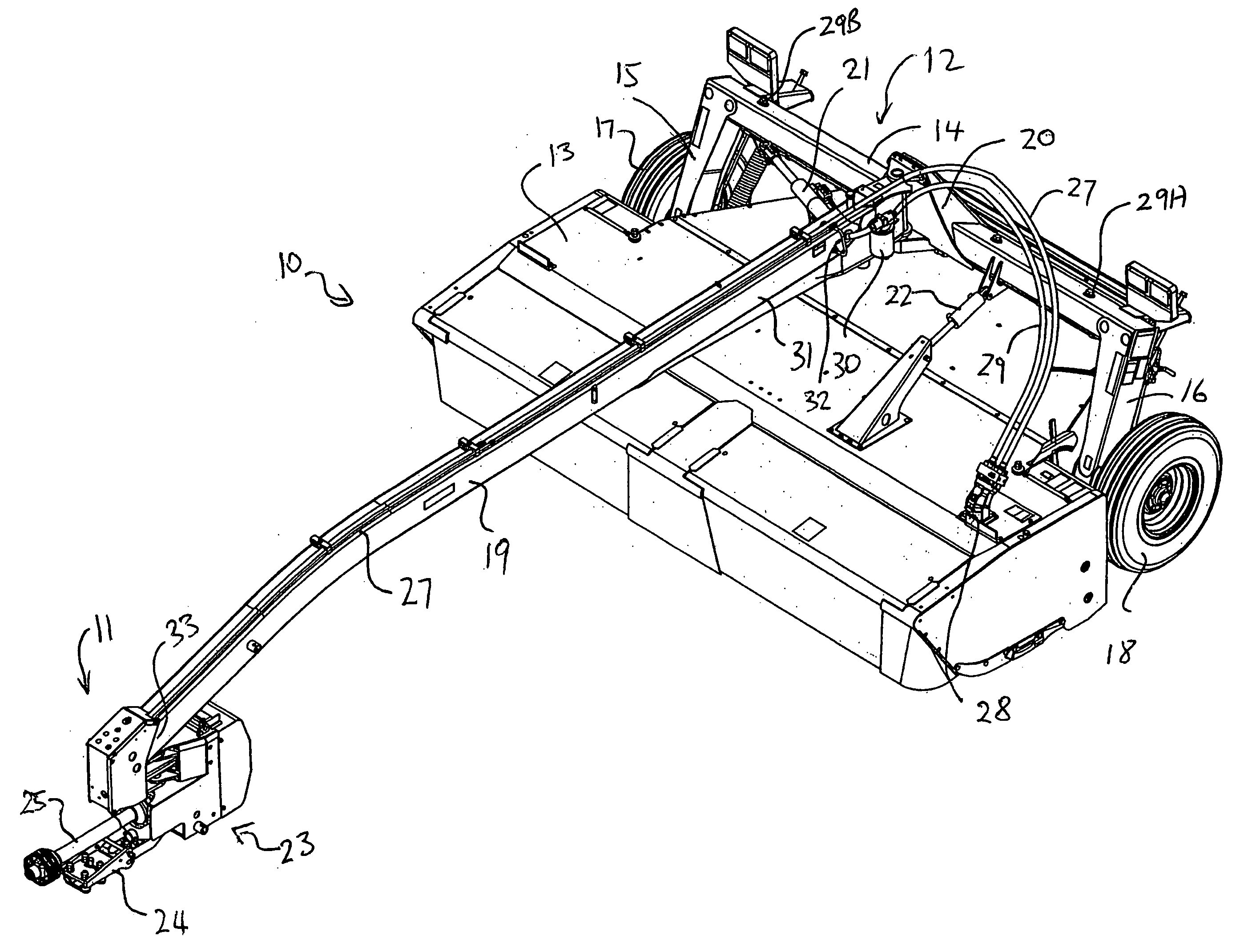

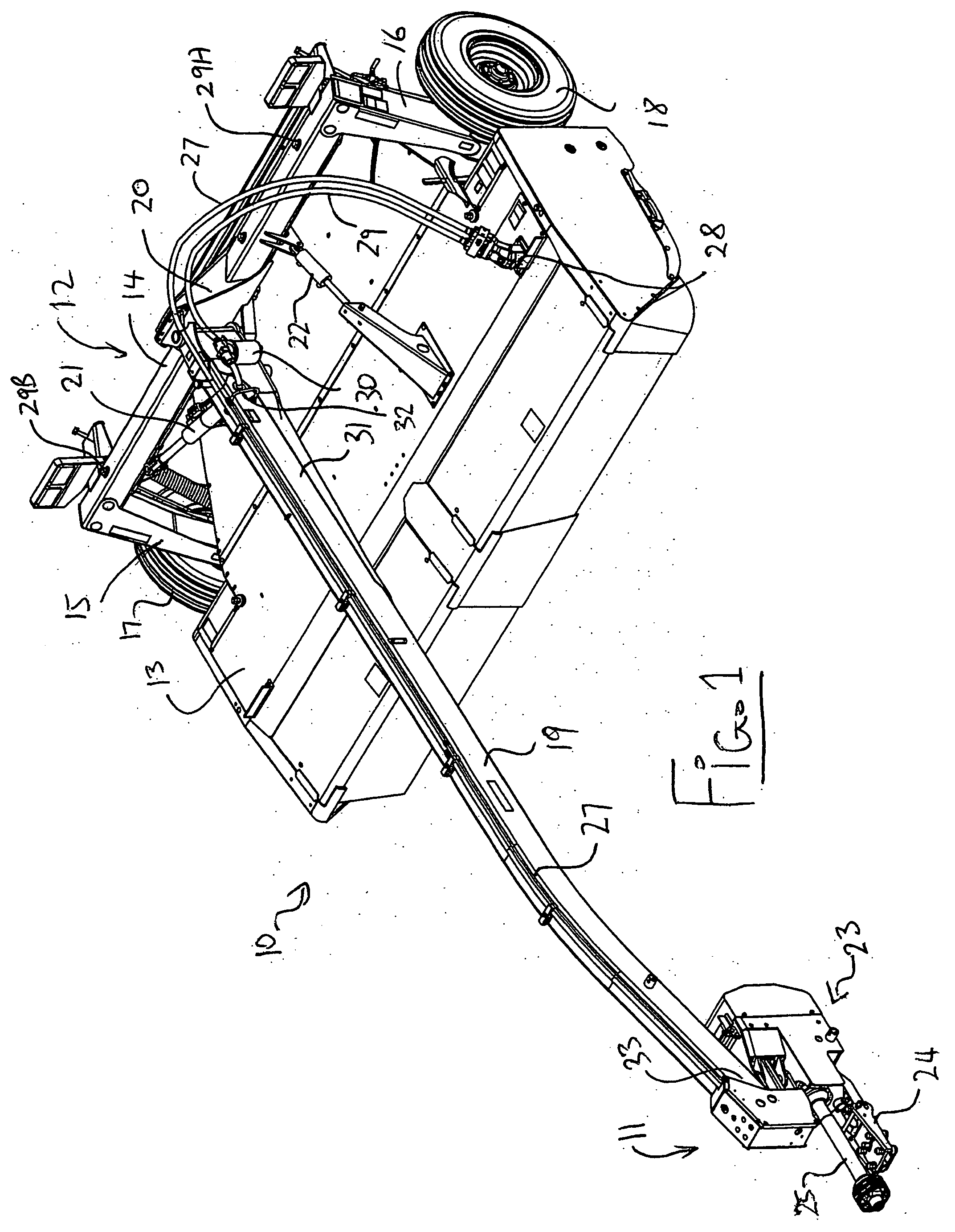

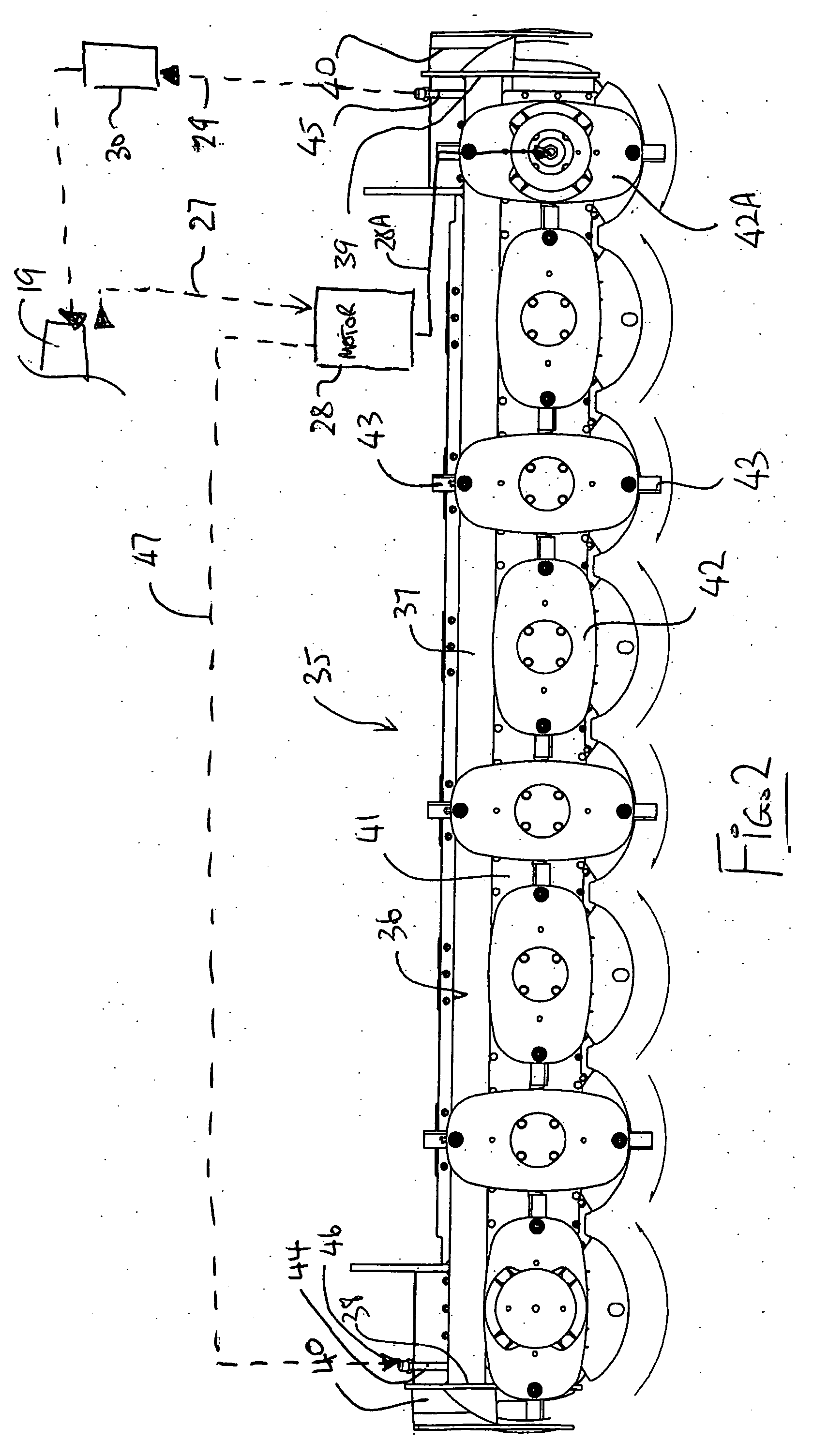

Hydraulic drive arrangement for the cutter of a pull-type crop harvesting machine

InactiveUS7306252B2Simple mechanical connectionReduce weightAgricultural machinesMowersCircular discHydraulic circuit

A pull-type crop harvesting machine has disk cutter carried on a frame mounted on ground wheels with a hitch arm extending from the frame over the header to a hitch connector of a tractor. The hitch arm is mounted for pivotal movement about a generally upright axis such that in a first position the tractor tows the frame in echelon to one side and in a second position the tractor tows the frame in echelon. The disks are hydraulically driven by a pump at the front end of the hitch arm and a motor at the frame with the hydraulic circuit including a sump tank defined by a hollow interior of the hitch arm and a cooling radiator defined by a tubular frame member which is preferably located at the disk drive as a support therefore as it is cooled by the air flow from the disks and contact with the crop and carries a low volume of fluid.

Owner:MACDON INDS

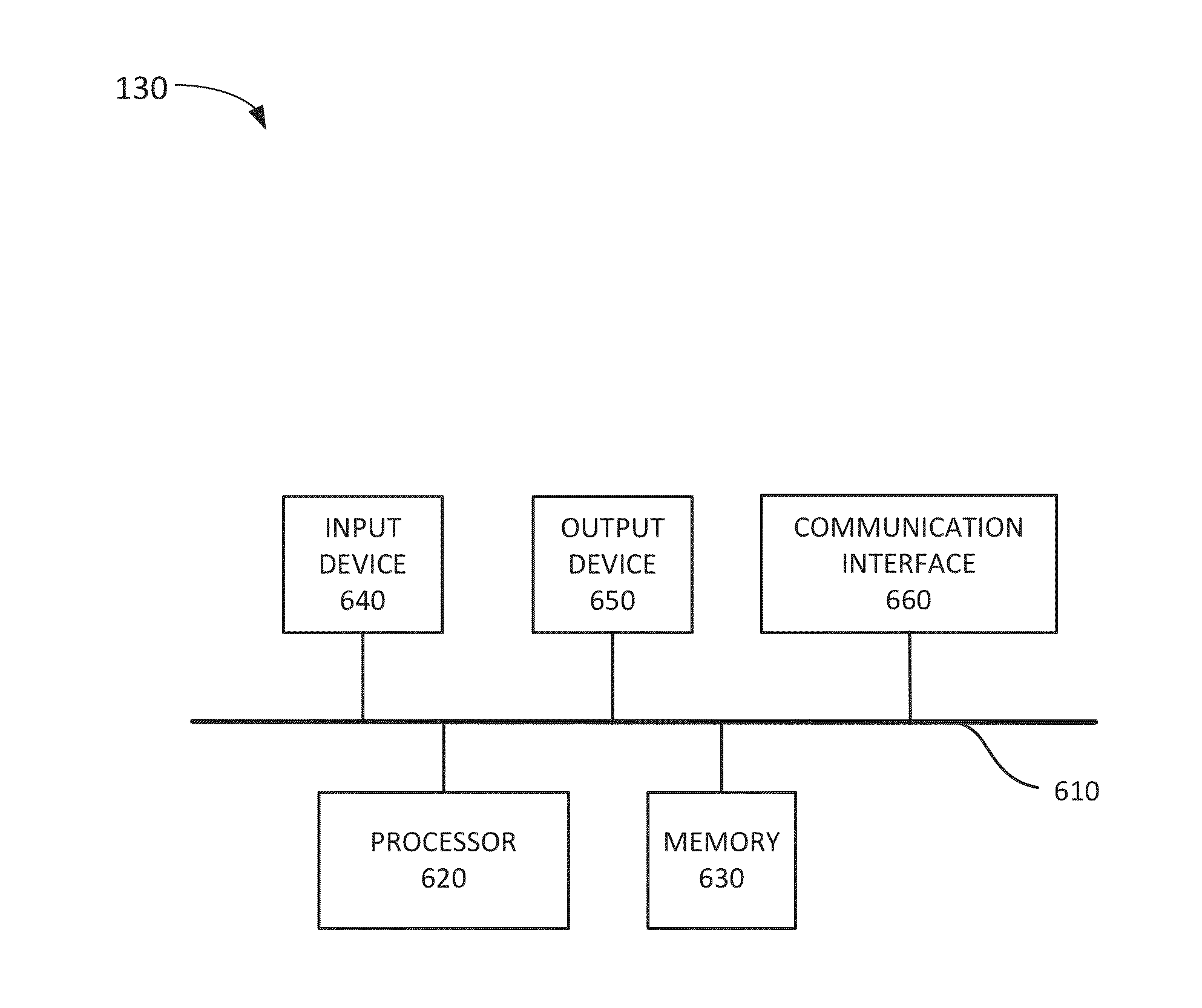

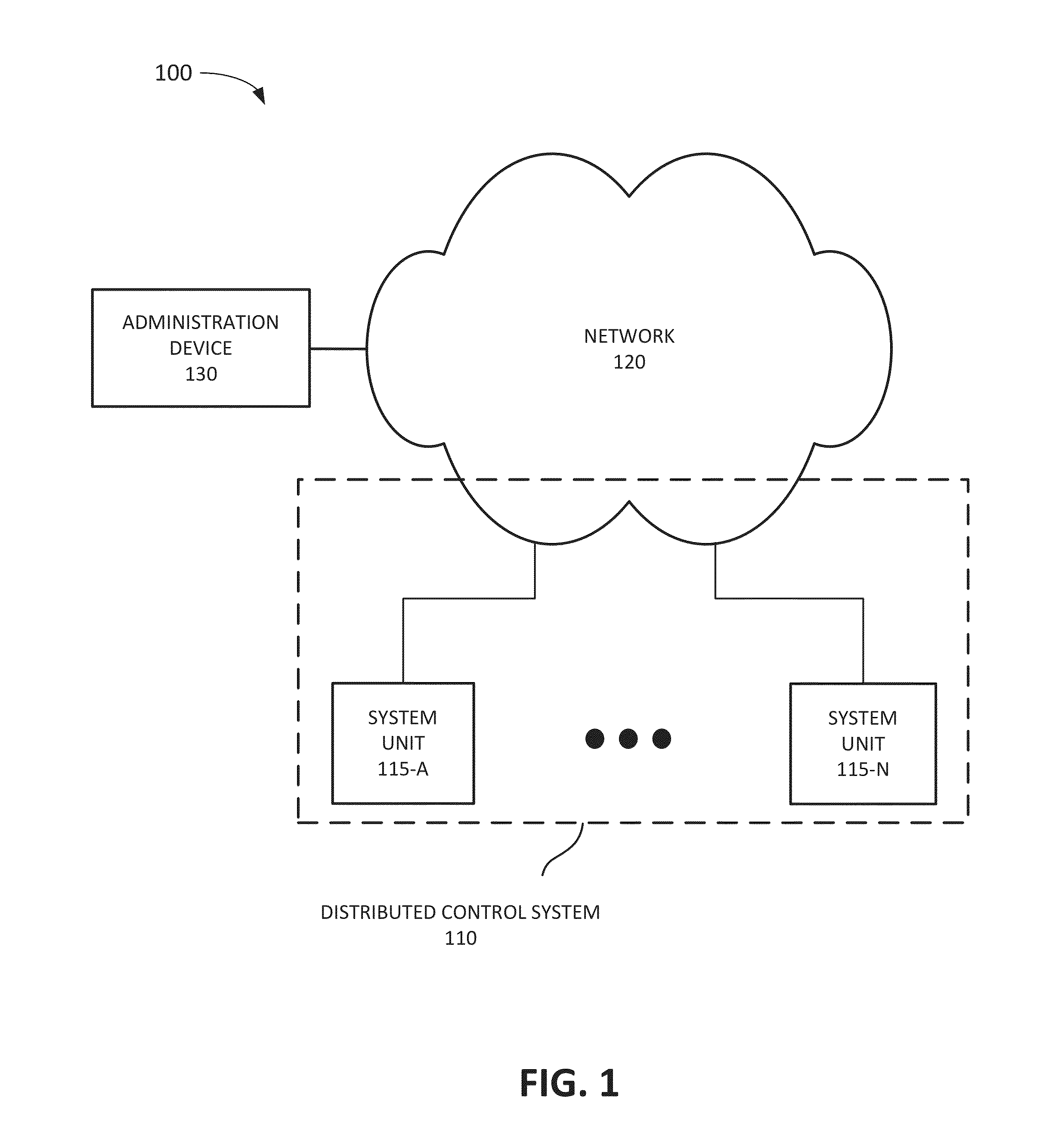

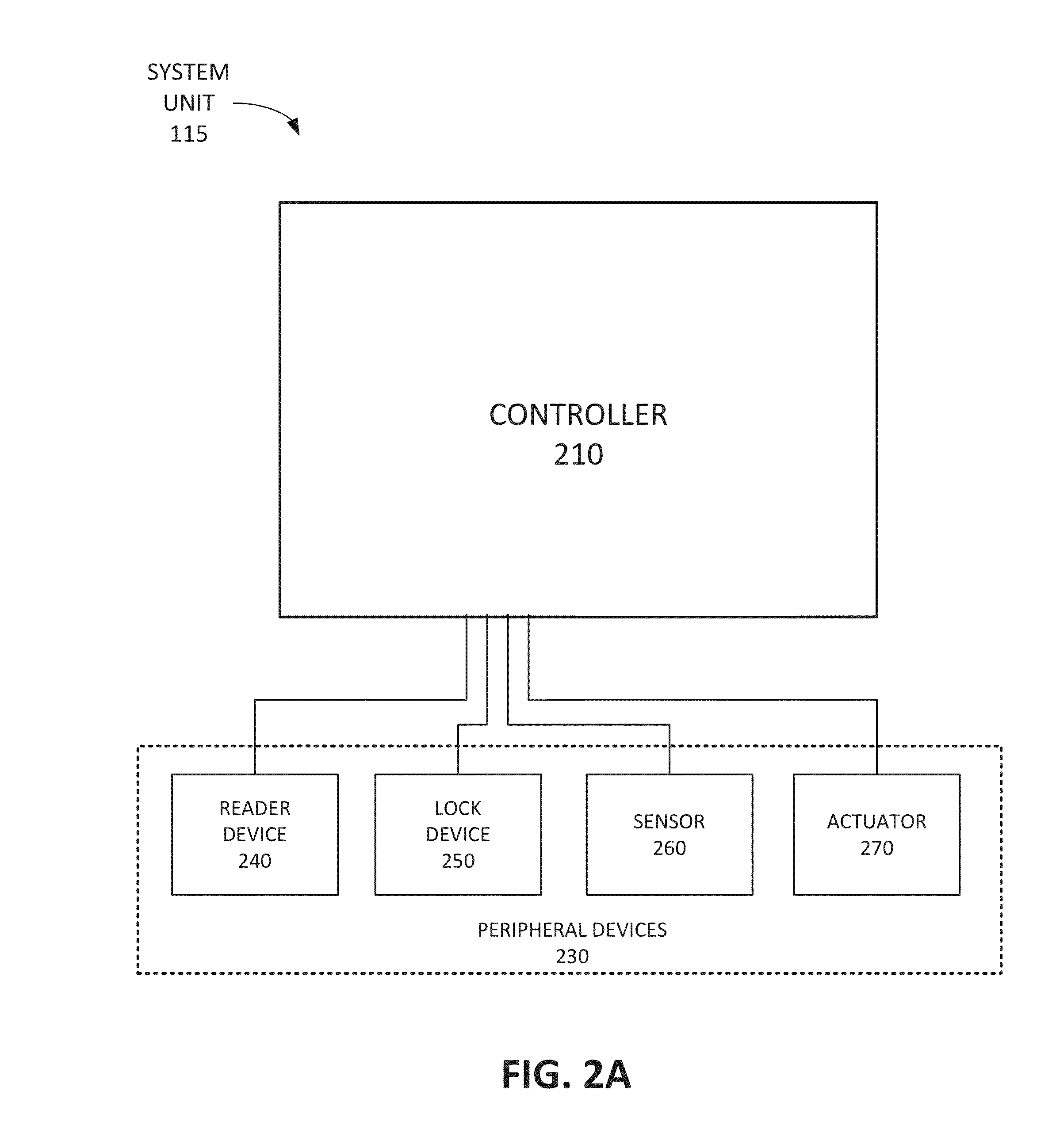

Control system configuration within an operational environment

ActiveUS20150081928A1Reduce complexityShorten connection lengthProgramme controlSpecific program execution arrangementsControl systemPhysical access

A method configures an installation of a control system within an operational environment, where the control system may include distributed physical access control system. The method may provide options for installing peripheral devices compatible with a controller, and receive selections based on the provided options. The selections may be associated with an operational environment of at least one selected peripheral device. The method may generate instructions to command the controller to specify individual pins from a plurality of pins for connecting the controller to at least one selected peripheral device. The method may subsequently create a report to describe connections between the specified individual pins associated with the controller and wires associated with at least one selected peripheral device. An apparatus can implement the method to configure the installation of the control system in its operational environment.

Owner:AXIS

Bed guard assembly

InactiveUS7080419B2Easy to storeQuick and easy implementationSofasBedsEngineeringMechanical engineering

Owner:SUMMER INFANT USA

Hydraulic drive arrangement for the cutter of a pull-type crop harvesting machine

InactiveUS20070199293A1Simple mechanical connectionReduce weightAgricultural machinesMowersHydraulic circuitEngineering

A pull-type crop harvesting machine has disk cutter carried on a frame mounted on ground wheels with a hitch arm extending from the frame over the header to a hitch connector of a tractor. The hitch arm is mounted for pivotal movement about a generally upright axis such that in a first position the tractor tows the frame in echelon to one side and in a second position the tractor tows the frame in echelon. The disks are hydraulically driven by a pump at the front end of the hitch arm and a motor at the frame with the hydraulic circuit including a sump tank defined by a hollow interior of the hitch arm and a cooling radiator defined by a tubular frame member which is preferably located at the disk drive as a support therefore as it is cooled by the air flow from the disks and contact with the crop and carries a low volume of fluid.

Owner:MACDON INDS

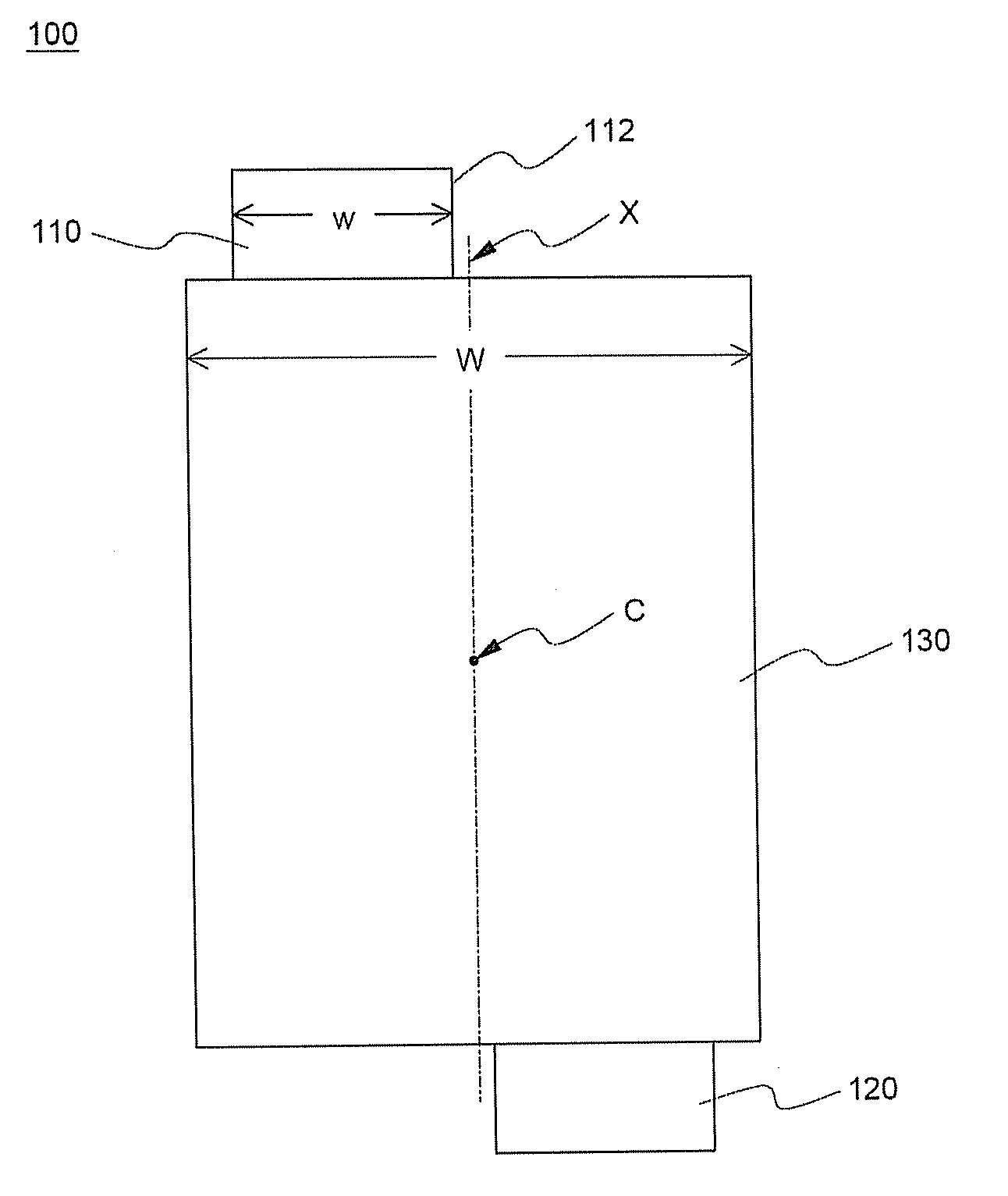

Battery suitable for preparation of battery module

ActiveUS20070059593A1Increase in sizeShorten connection lengthLarge-sized flat cells/batteriesFinal product manufactureEngineeringBattery cell

Disclosed herein are a battery having an electrode assembly which can be charged and discharged, mounted in a plate-shaped battery case, and cathode and anode terminals protruding from opposite ends of the battery case, wherein the electrode terminals are deviated from each other about the vertical central axis on the plane of the battery cell while the electrode terminals are arranged in a symmetrical fashion, the battery case includes an upper case and a lower case, only one of which is provided with a location part for receiving the electrode assembly, and the electrode terminals are deviated toward the upper or lower case which has no location part on the vertical section of the battery cell, and a battery module including the same.

Owner:LG ENERGY SOLUTION LTD

Bed guard assembly

InactiveUS20050235419A1Quick and easy implementationEasy to storeSofasBedsEngineeringMechanical engineering

A bed guard assembly includes a number of end panels, flexible connecting material for placement beneath a mattress, and connection pieces. The connection pieces connect the flexible connecting material to the end panels such that at least one end panel opposes another end panel when the flexible connecting material is disposed beneath a mattress. The end panel includes a rigid frame, a substantially horizontal rigid segment spanning an interior of the outer frame, and a fabric cover. The connection pieces are adjustable, and include a mechanism for pulling taut the connecting material.

Owner:SUMMER INFANT USA

Bed guard assembly

A bed guard assembly includes an end panel, flexible connecting material for placement beneath a mattress, a base element coupled to the flexible connecting material, and connection pieces that connect the flexible connecting material to the end panel such that the end panel opposes the base element when the flexible connecting material is disposed beneath a mattress. The end panel includes a rigid outer frame and a substantially horizontal rigid segment spanning an interior of the outer frame.

Owner:SUMMER INFANT USA

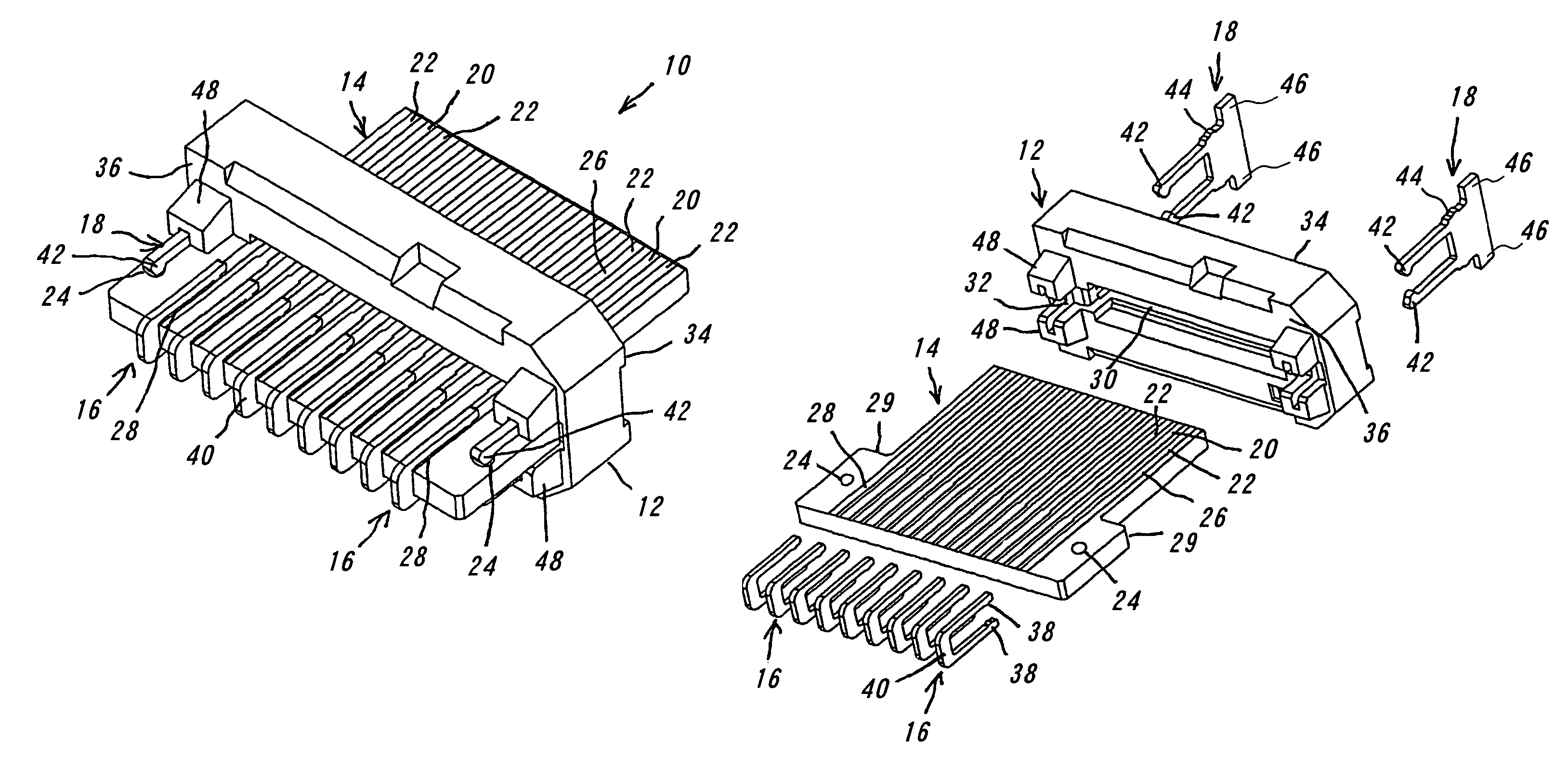

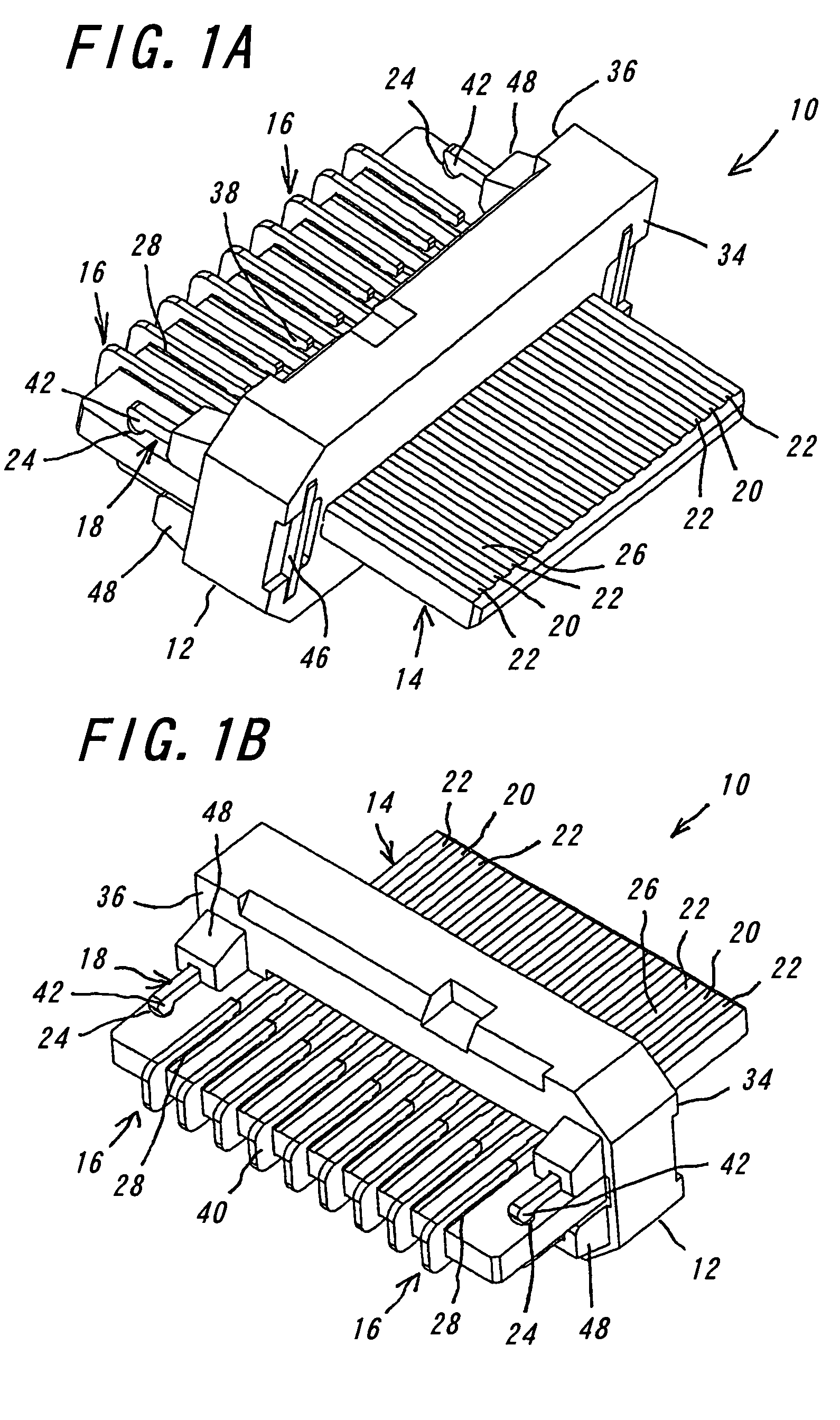

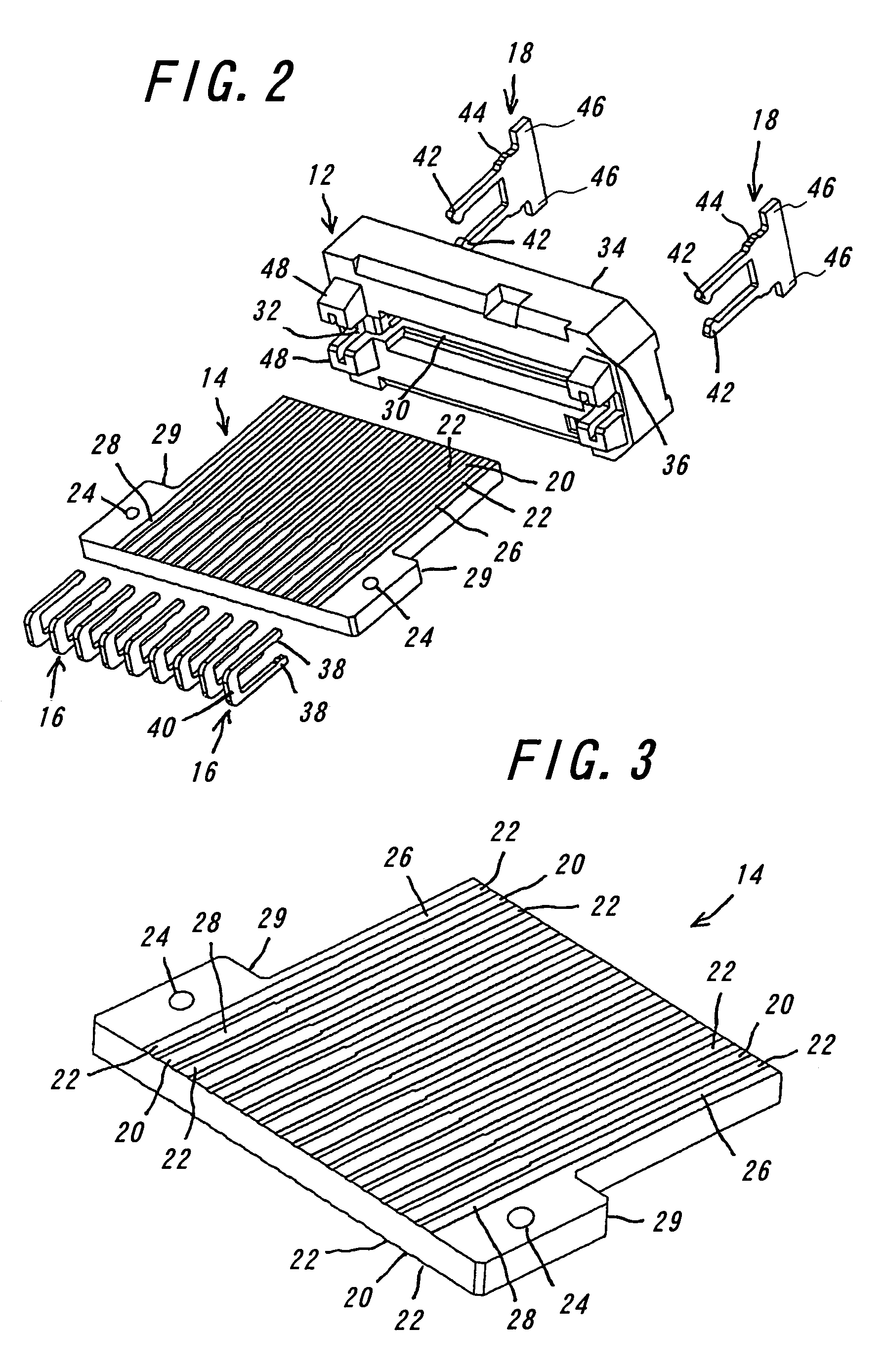

Electrical connector using a substrate as a contacting member

InactiveUS7232345B2Shorten connection lengthReduction in crosstalk regardlessElectric discharge tubesCoupling device detailsMiniaturizationEngineering

An electrical connector includes a housing, a substrate, and shielding plates. The housing has an inserting hole for the substrate, and the substrate has a plurality of signal patterns and a plurality of ground patterns alternately arranged on at least one surface of the substrate in a manner that one signal pattern is between two ground patterns. The signal patterns and the ground patterns each have a contact portion to contact a mating object and a connection portion to be connected to a cable. The shielding plates are each connected to the connection portion of the ground pattern for shielding. With this construction, the electrical connector achieves its miniaturization and reduction in crosstalk regardless of length of connected cables.

Owner:DDK LTD

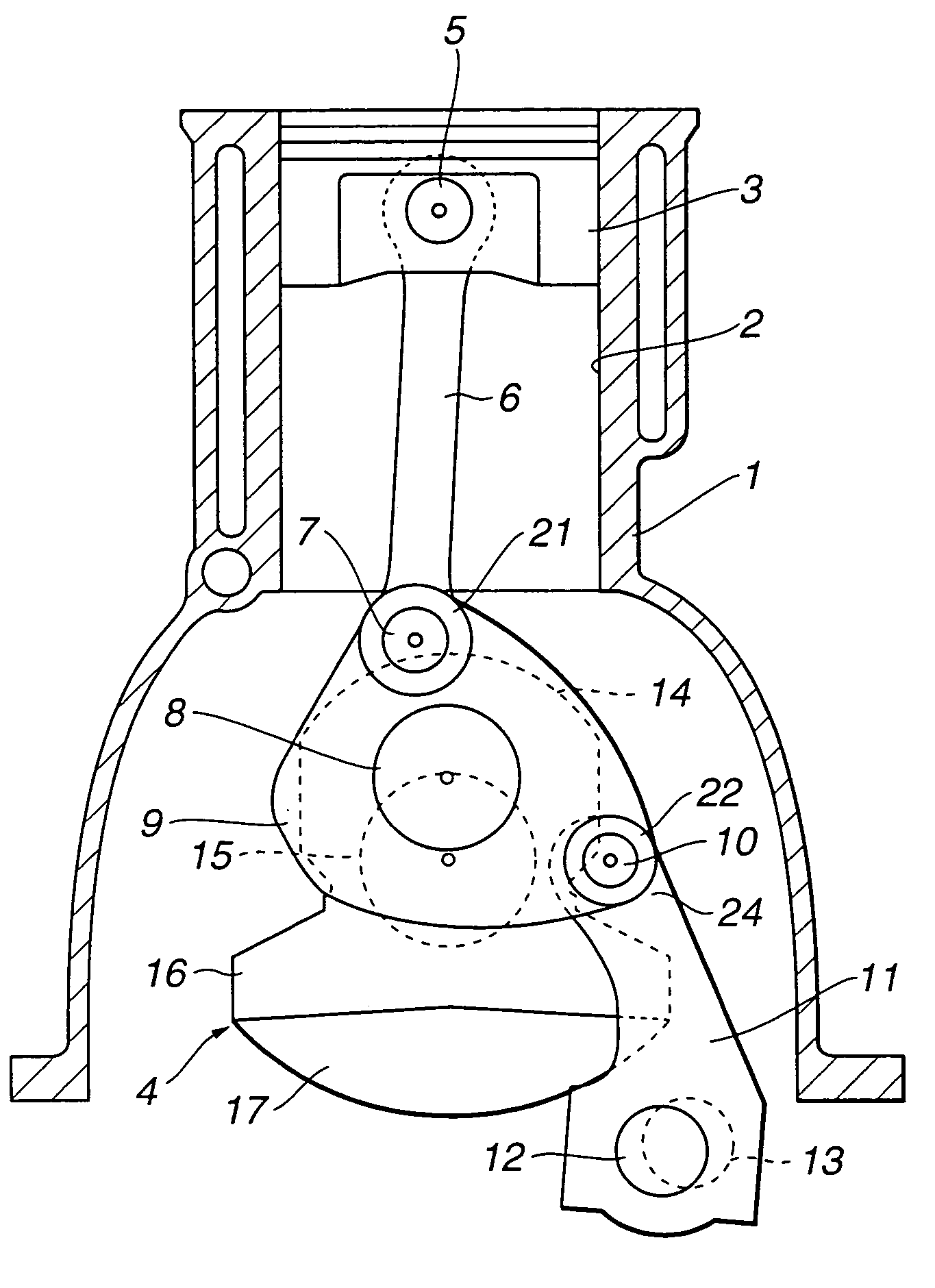

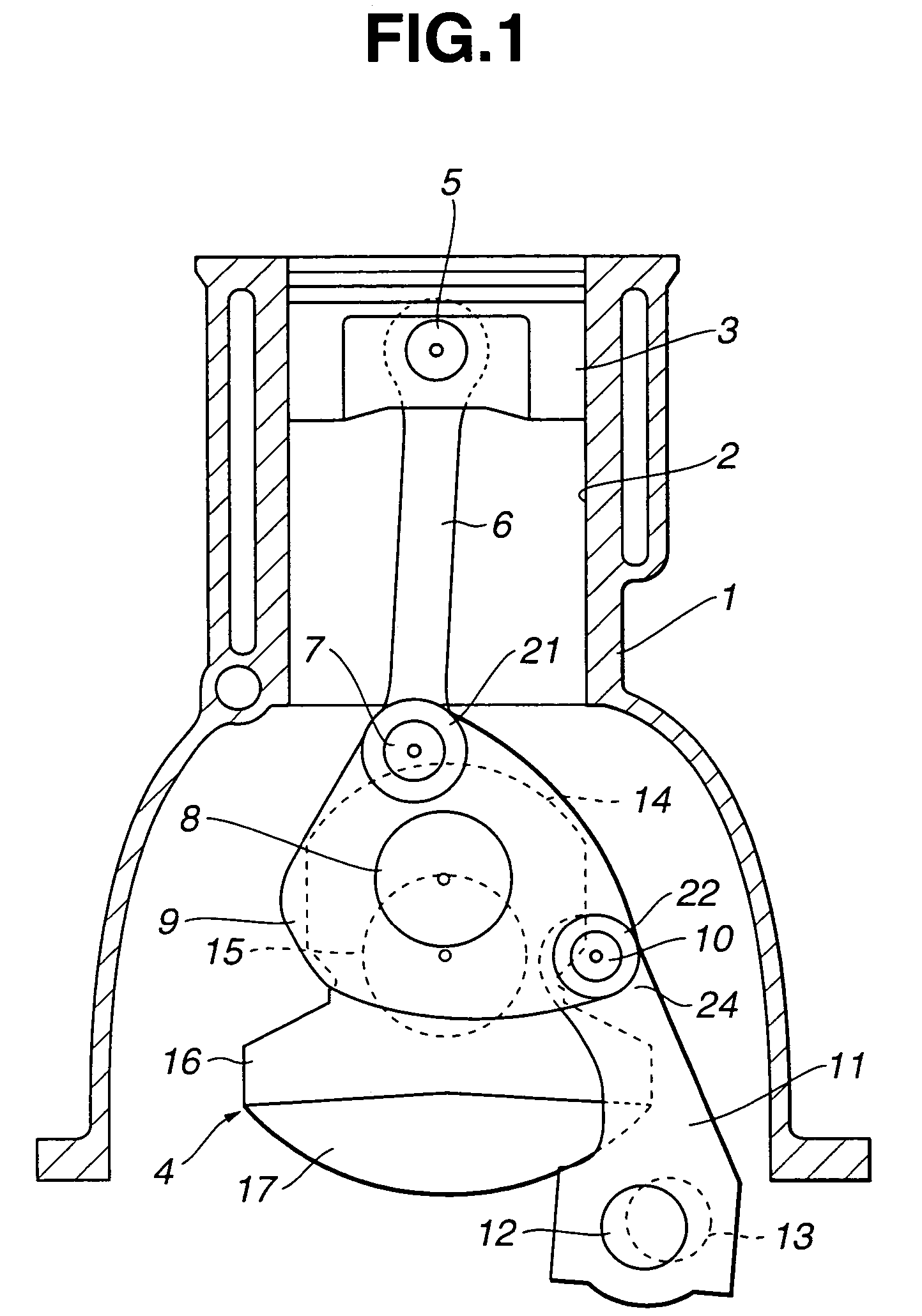

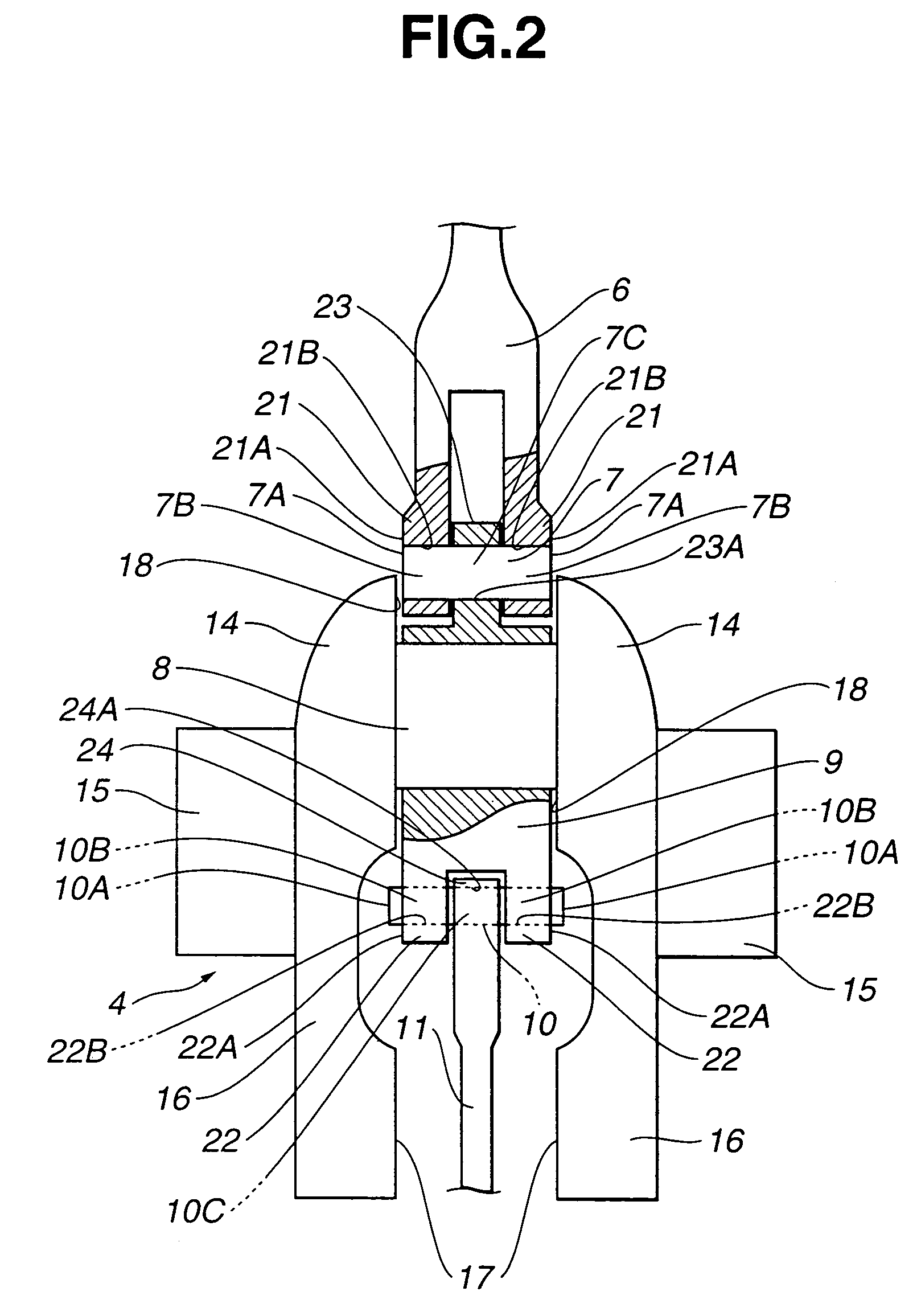

Multi-link piston crank mechanism for internal combustion engine

ActiveUS7121251B2Optimization mechanismAvoid interferenceConnecting rodsGearingMulti linkInternal combustion engine

A multi-link piston crank mechanism for an internal combustion engine, including a crankshaft having a crank pin, and crank webs connected with each other through the crank pin. A pair of thrust surfaces are formed on the crank webs so as to be opposed in a direction of a center axis of the crank pin. A first link pivotally supported on the crank pin is coupled to a second link through a connection pin located in a space between the thrust surfaces. The connection pin is moveable about the crank pin to form a circular trace along which the thrust surfaces extend. The end surfaces of the connection pin and the thrust surfaces come into mutual contact to prevent the connection pin from falling out of the space between the thrust surfaces.

Owner:NISSAN MOTOR CO LTD

Multi-chip stack package

ActiveUS7218006B2Shorten connection lengthAvoiding short circuitSemiconductor/solid-state device detailsSolid-state devicesChip stackingActive surface

A multi-chip stack package mainly includes a substrate, a first chip, a redistribution structure and at least one second chip. The first chip is disposed on the substrate with an active surface facing upwards. The redistribution structure includes a plurality of first intermediate pads, a plurality of second intermediate pads and a plurality of external pads. The first intermediate pads, the second intermediate pads, and the external pads are formed on the first active surface of the first chip, wherein the first intermediate pads and the second intermediate pads are electrically connected with each other. The second chip is disposed on the redistribution structure, and electrically connected to the first intermediate pads. The second intermediate pads are electrically connected to the substrate through a plurality of bonding wires, so that the second chip and the substrate are electrically conducted, and the connection length of the bonding wires is reduced.

Owner:ADVANCED SEMICON ENG INC

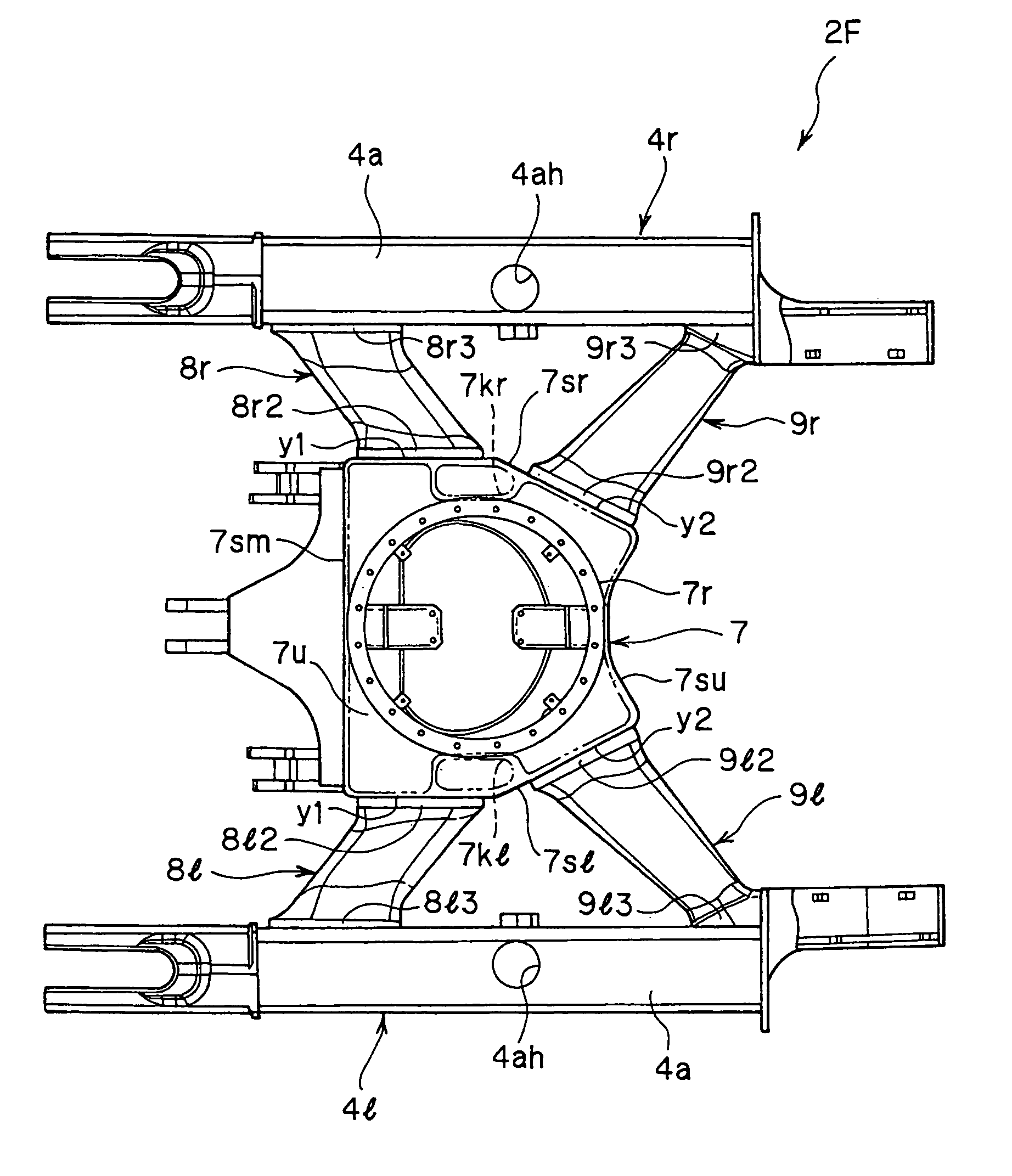

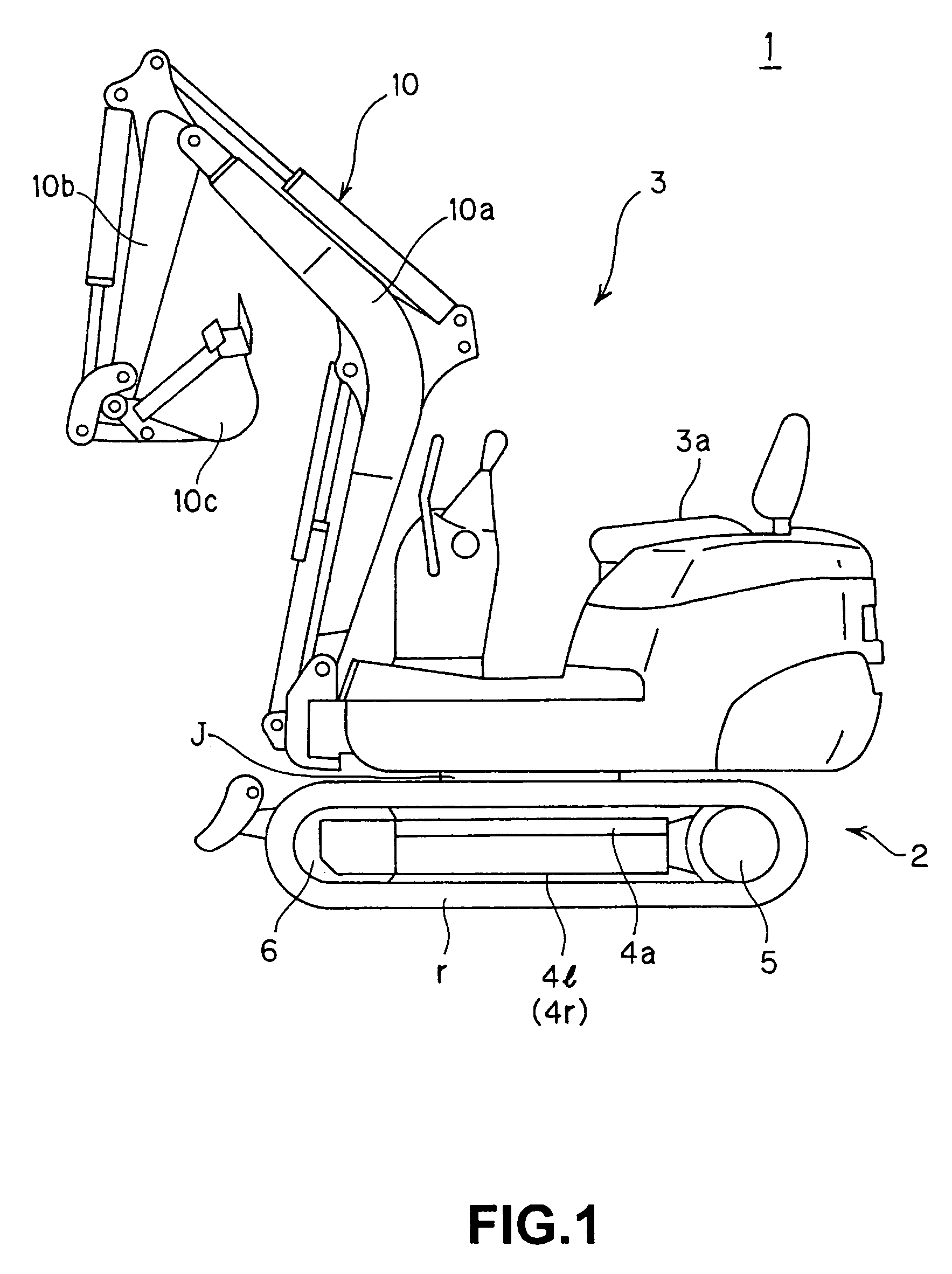

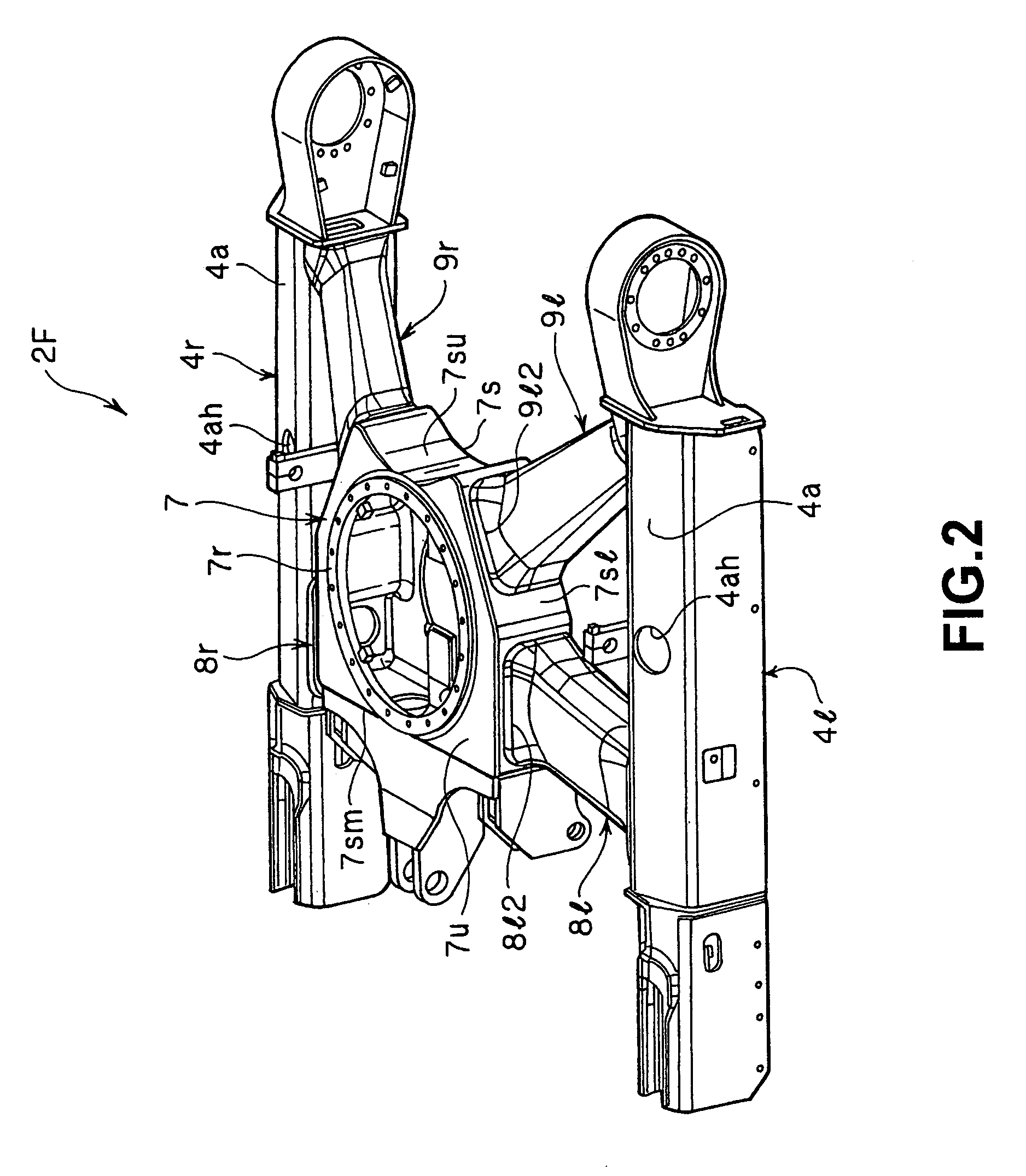

Construction machine

InactiveUS7204519B2Increase in moment of loadShorten connection lengthVehicle seatsVehicle body-frame connectionsEngineeringMechanical engineering

A construction machine where an operating load is transferred to a location having good rigidity, thereby ensuring the strength of a vehicle body and increasing the load-withstanding strength in relation to running loads. The frame of the lower traveling body of the construction machine comprising a hollow center frame having an upper plate with an attachment ring, a lower plate, and side plates that surrounding sides of the frame and that jut out from the attachment ring, and reinforcing ribs which connect the upper plate to the lower plate in the interior of the center frame beneath the attachment ring.

Owner:KOMATSU LTD +1

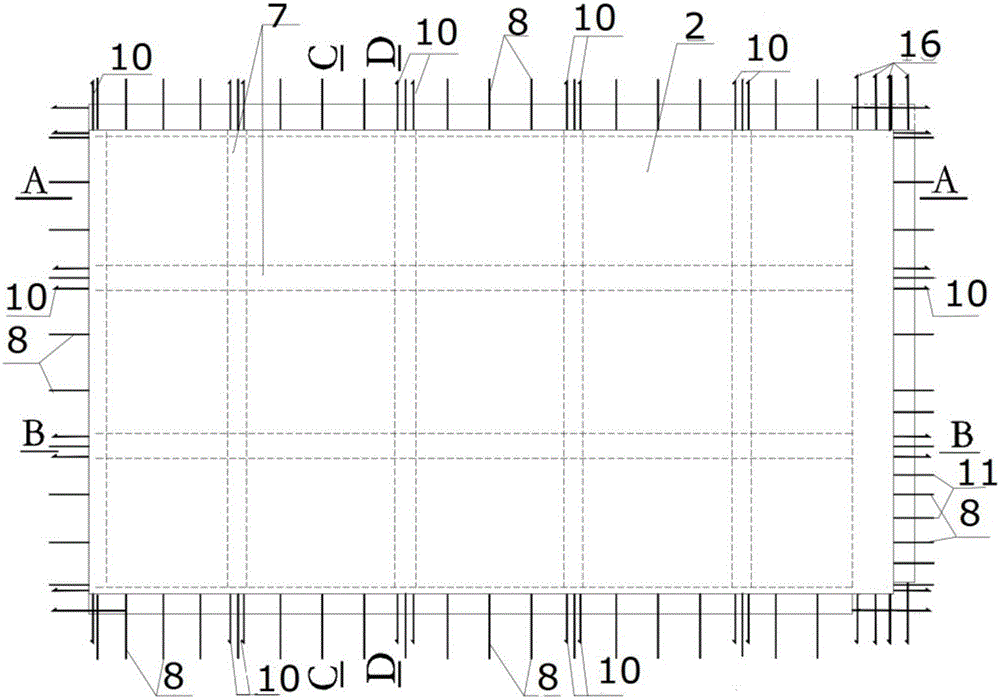

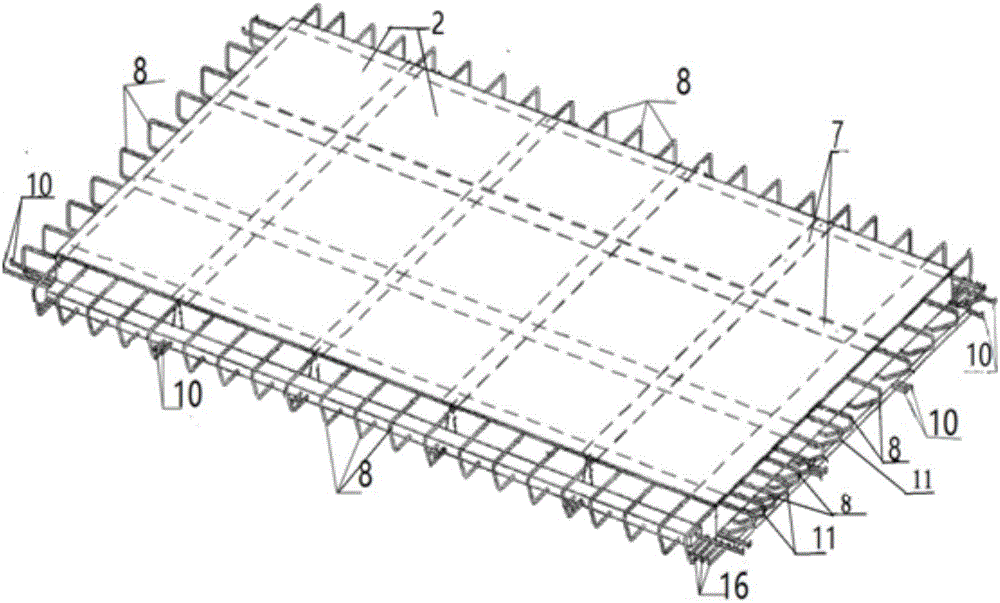

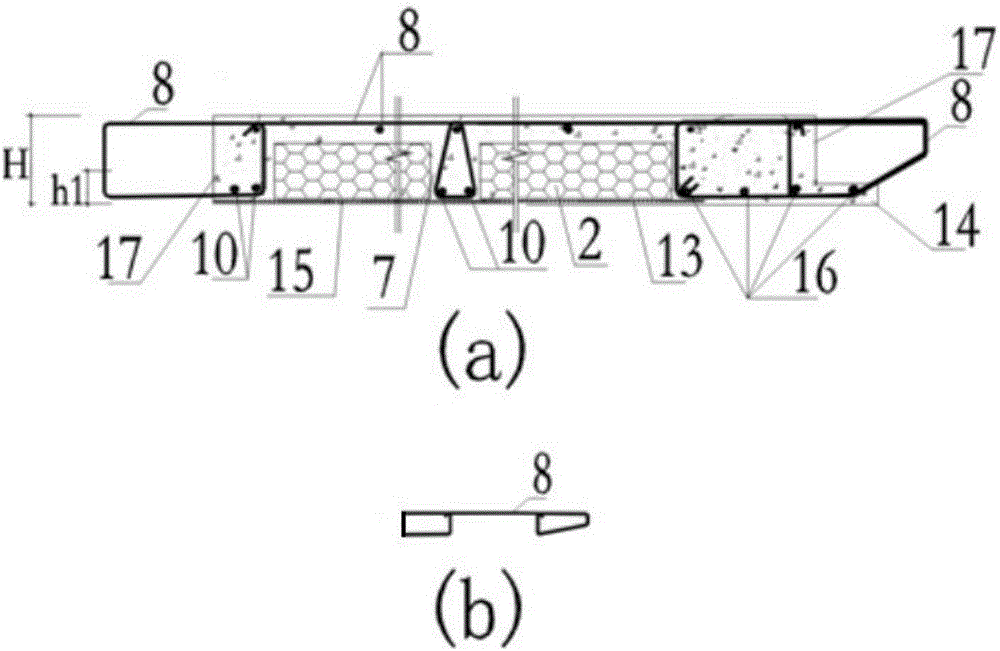

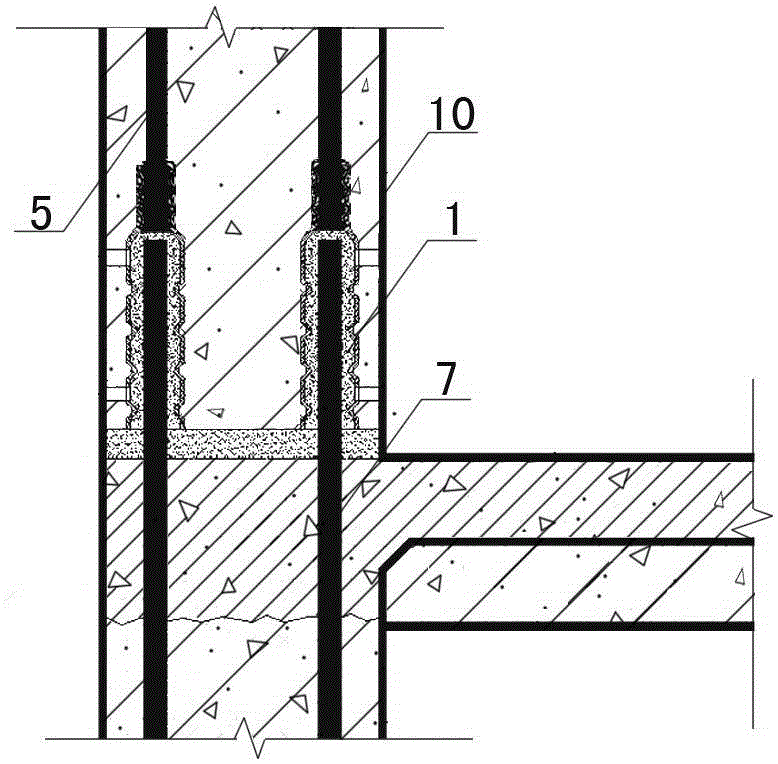

Connecting node of assembled whole thick prefabricated slab unit and slab unit thereof

The invention discloses a connecting node of an assembled whole thick prefabricated slab. Connecting steel bars are reserved on the connecting surface of a prefabricated slab unit in the mode, the exposed parts of the connecting steel bars are ' '-shaped, and the exposed parts and the connecting surface form a closed polygon. In the connecting mode for the prefabricated slab unit and a beam or a wall, the connecting steel bars of the prefabricated slab unit are inserted with steel bars configured for the beam or the wall together at the connecting positions in a penetrating mode. Viewing from the cross section of the whole connecting node, the connecting steel bars and the steel bars configured for the beam or the wall form a single closed stirrup or a composite stirrup, and longitudinal bolt steel bars penetrate into the inner corner position of the single closed stirrup or the composite stirrup. The connecting node of the whole thick prefabricated slab unit can achieve the equivalent performance as a prefabricated slab connecting nodes and a cast-in-place concrete structure while achieving higher prefabrication rate and assembly rate. The invention further provides the whole thick prefabricated slab unit for achieving the connecting mode.

Owner:刘祥锦

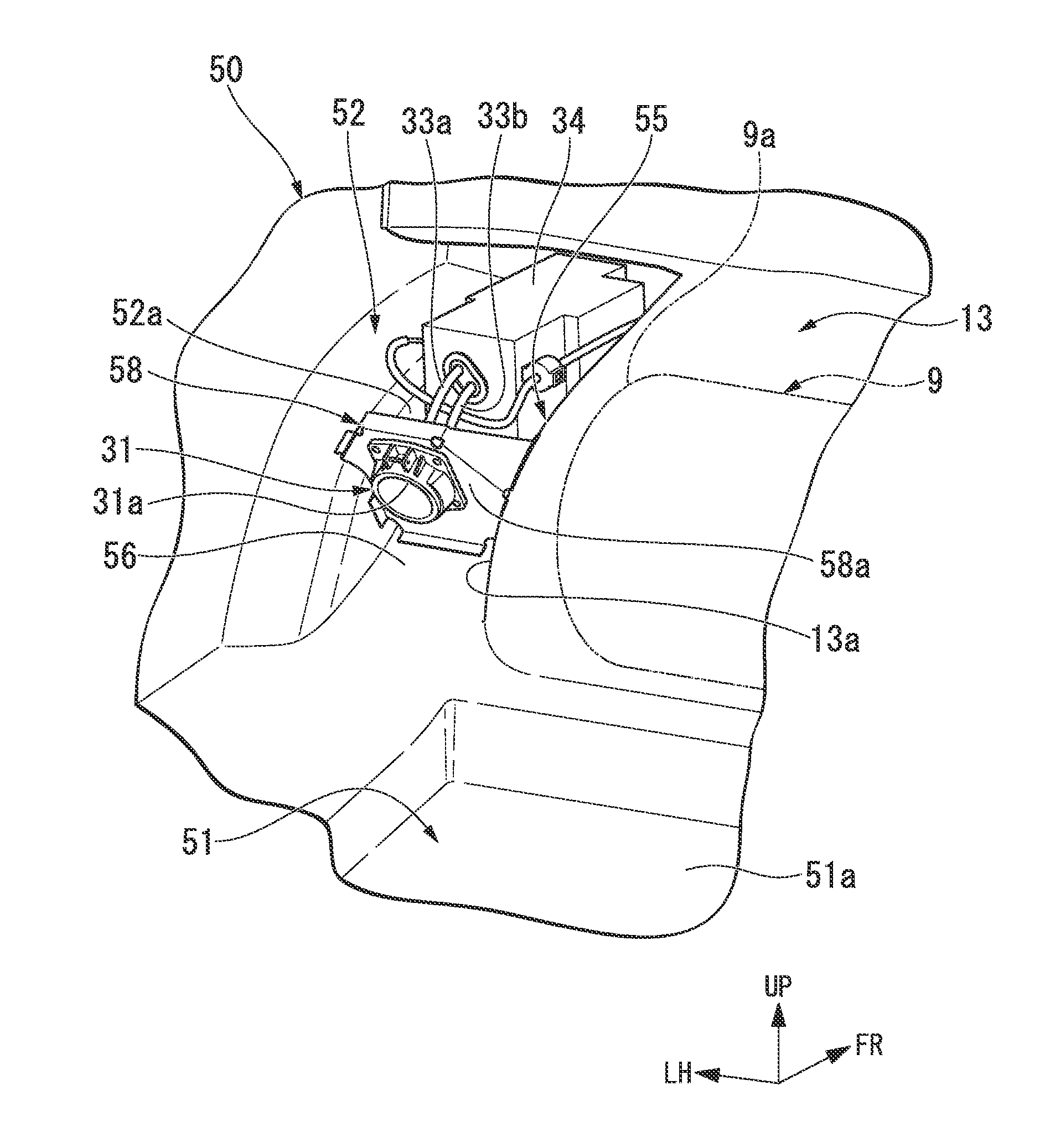

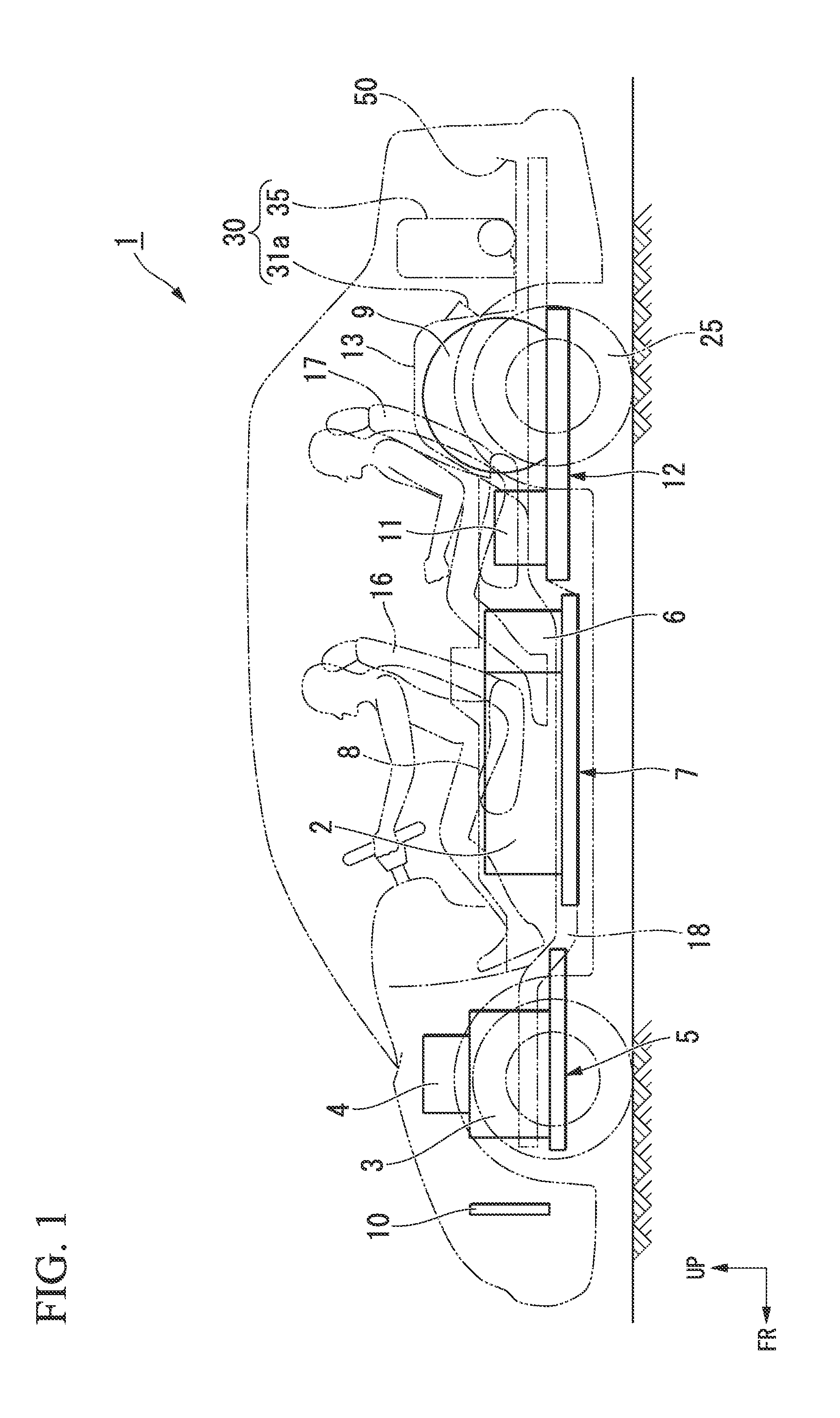

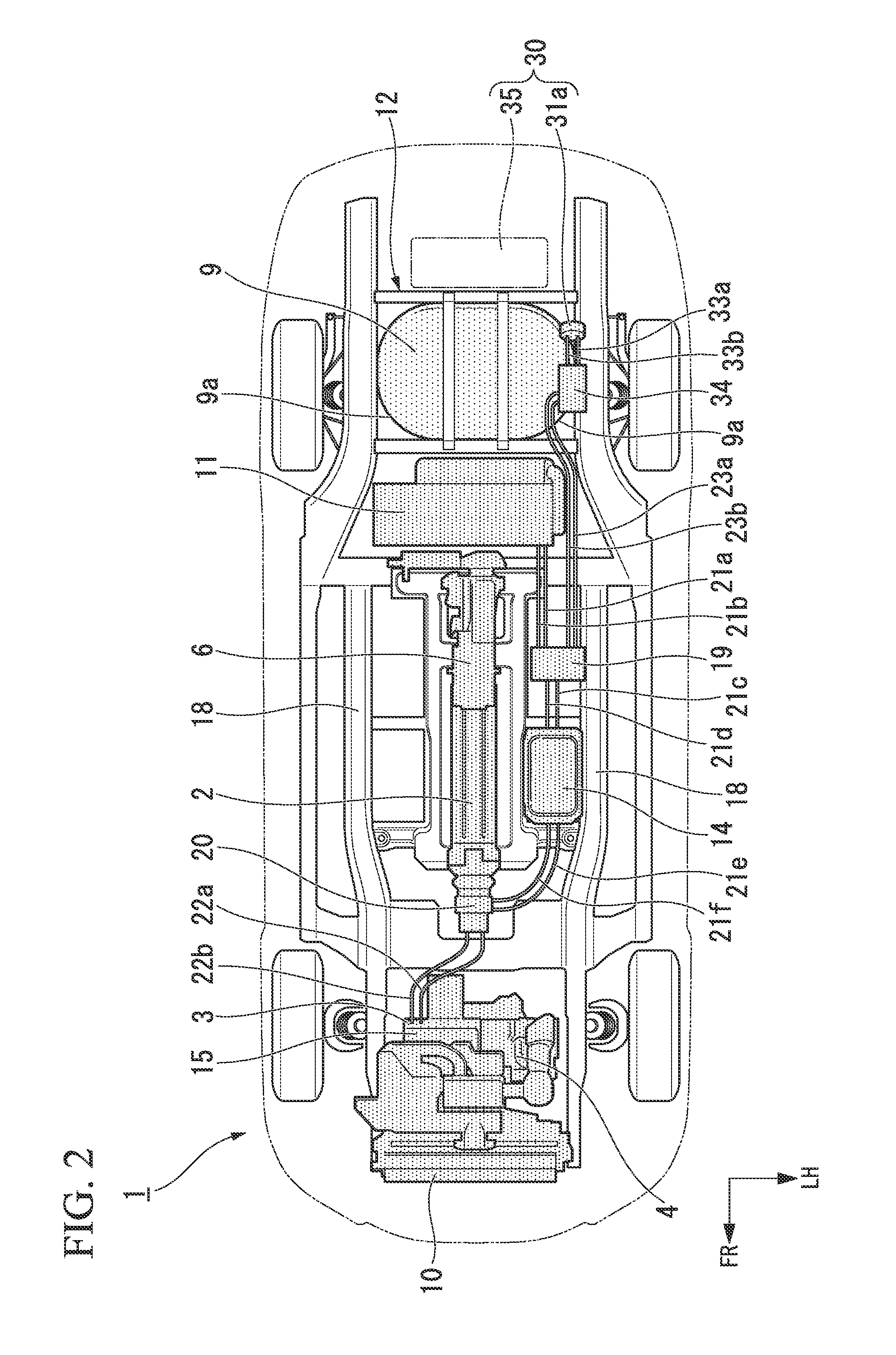

Vehicle power supply system

ActiveUS20130187449A1Increase stiffnessPrevent penetrationElectric devicesElectrical apparatusElectricityPower inverter

A vehicle power supply system includes a power supply connector having a power supply port which is provided within a trunk room and electrically connected to a DC power source, and an inverter device which is provided separately from a fuel cell automobile (an electrically driven vehicle) and is disposed within the trunk room, wherein the trunk room is provided therein with an inverter installation space where the inverter device may be installed at a position which does not overlap with the power supply port when viewed from a forward and rearward direction of the vehicle, and the invert device is provided with a connection cable which is drawn from a side surface thereof and of which a front end portion has a connector portion connected to the power supply port.

Owner:HONDA MOTOR CO LTD

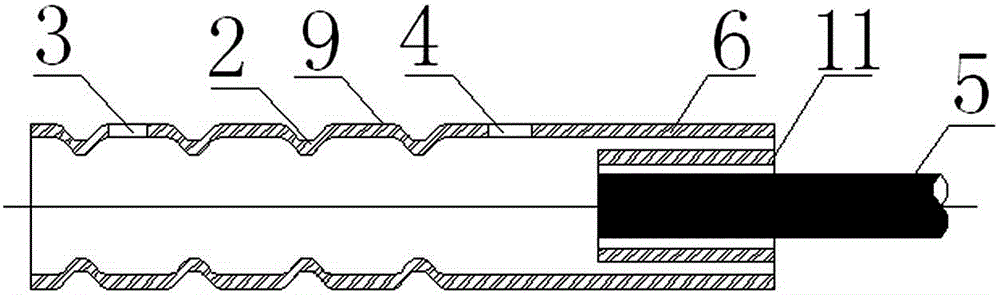

Circuit board with embedded component and method of manufacturing same

InactiveUS7989706B2Improve installation densityImprove productivityPrinted circuit assemblingSemiconductor/solid-state device detailsElectrical conductorChip size

A circuit board has an embedded electronic component such as an integrated circuit chip with a wafer level chip size package. A via hole extends through the electronic component. Another via hole extends through the substrate or prepreg on which the electronic component is mounted inside the circuit board. Conductors in the via holes enable a terminal on the surface of the electronic component to be electrically connected to a wiring pattern or another electronic component on the opposite side of the substrate or prepreg. Routing the connection through the electronic component itself saves space and reduces the length of the connection.

Owner:LAPIS SEMICON CO LTD

Extruded semi-grouting reinforced sleeve with built-in casing, connective structure, and construction method

InactiveCN105178516AReduce workloadImprove work efficiencyBuilding reinforcementsBuilding material handlingConcrete beamsEngineering

Disclosed are an extruded semi-grouting reinforced sleeve with a built-in casing, a connective structure, and a construction method. The sleeve is a hot-rolled seamless steel tube. The wall of the sleeve is provided with a grout inlet and a grout outlet. The sleeve is provided with circular inner projections. One end of the sleeve is an extruded end, and the rest is a grout-anchoring end. The built-in casing is arranged inside the extruded end. The inner diameter of the built-in casing is equal to the outer diameter of a rebar to be connected, and less than the inner diameter of the grout-anchoring end. All of the grout inlet, the grout outlet and the circular inner projections are located at the grout-anchoring end. By the use of the built-in casing, the deformation of the extruded end is lessened to avoid the extruded end being damaged during crimping; the sleeve is widely applicable to the rebar connection of prefabricated concrete columns in multi-storey and high-rise prefabricated assembled concrete frame structures, shear wall structures or frame shear wall structures, as well as the connection of horizontal rebars in prefabricated concrete beams, the connection of rebars in prefabricated concrete shear walls and the connection of rebars in existing reinforcement projects.

Owner:CHINA STATE CONSTRUCTION ENGINEERING CORPORATION +1

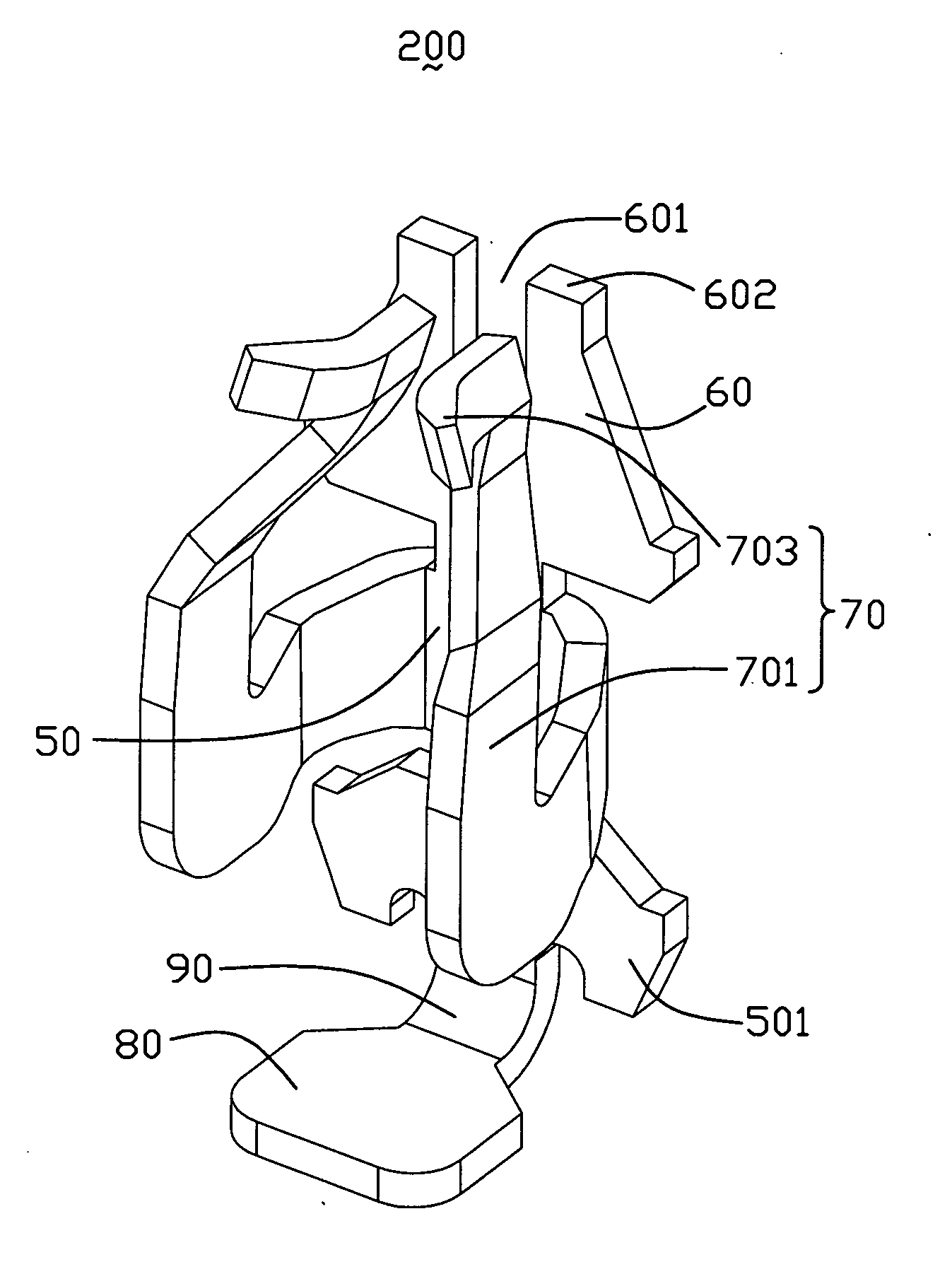

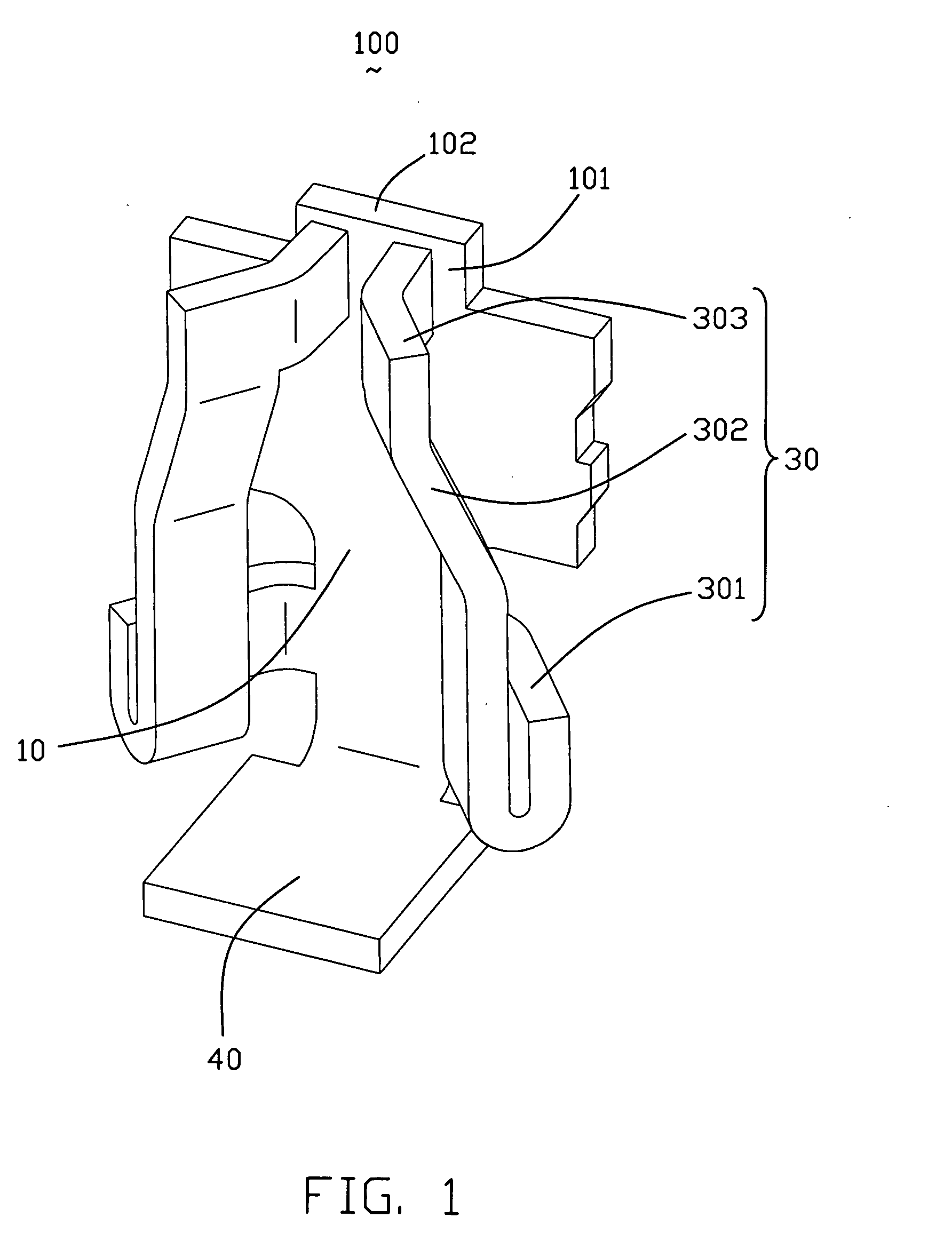

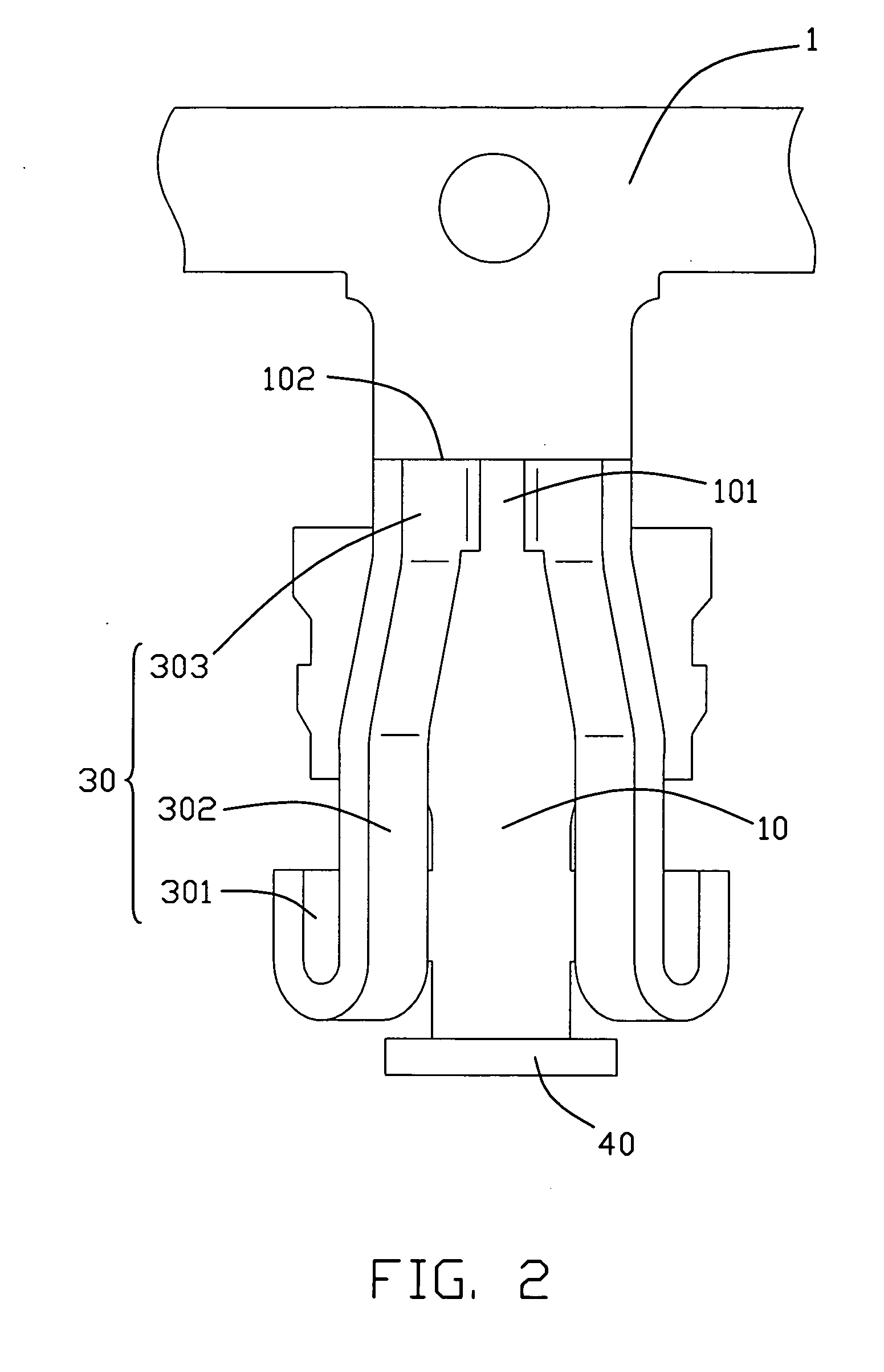

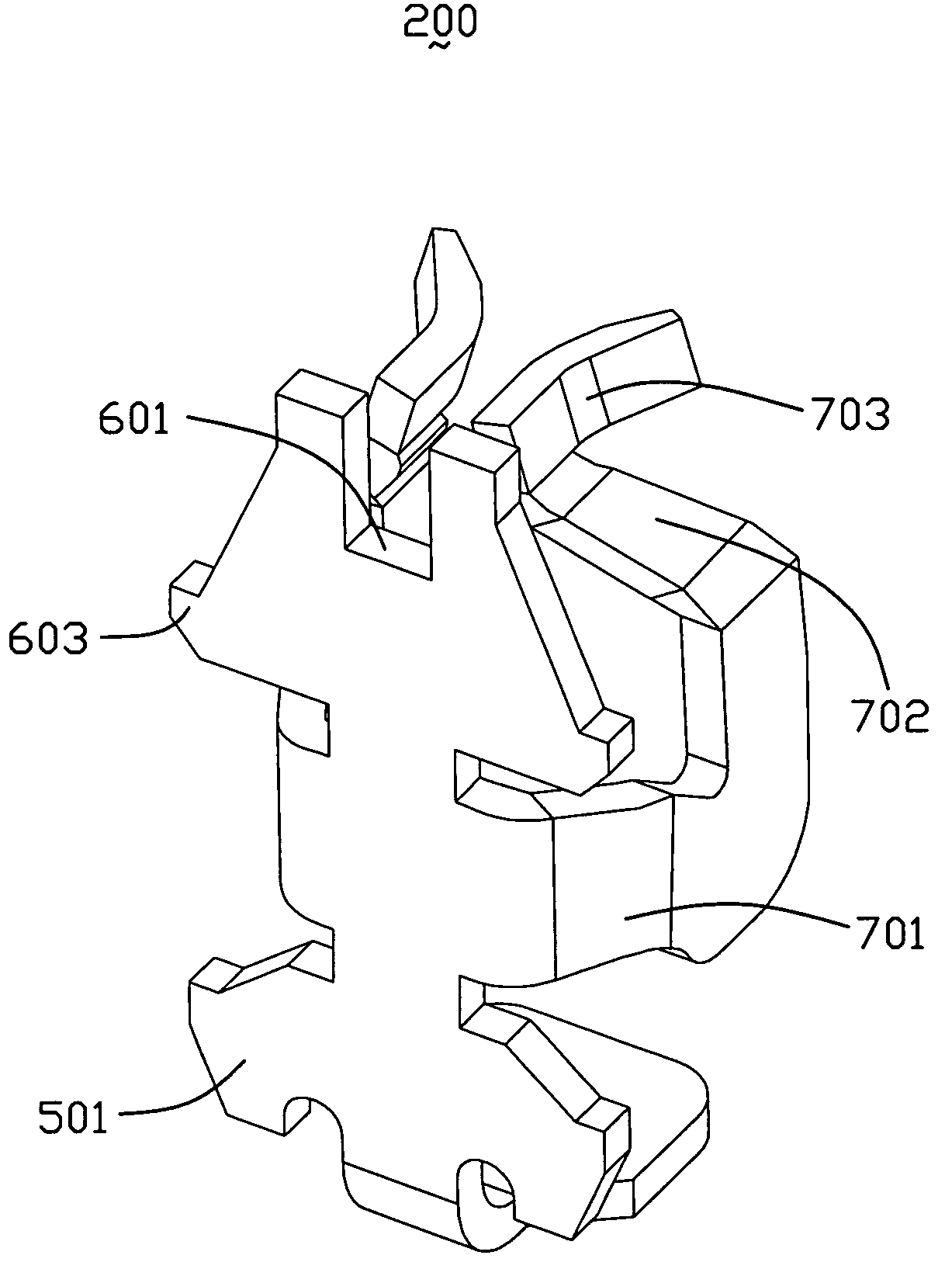

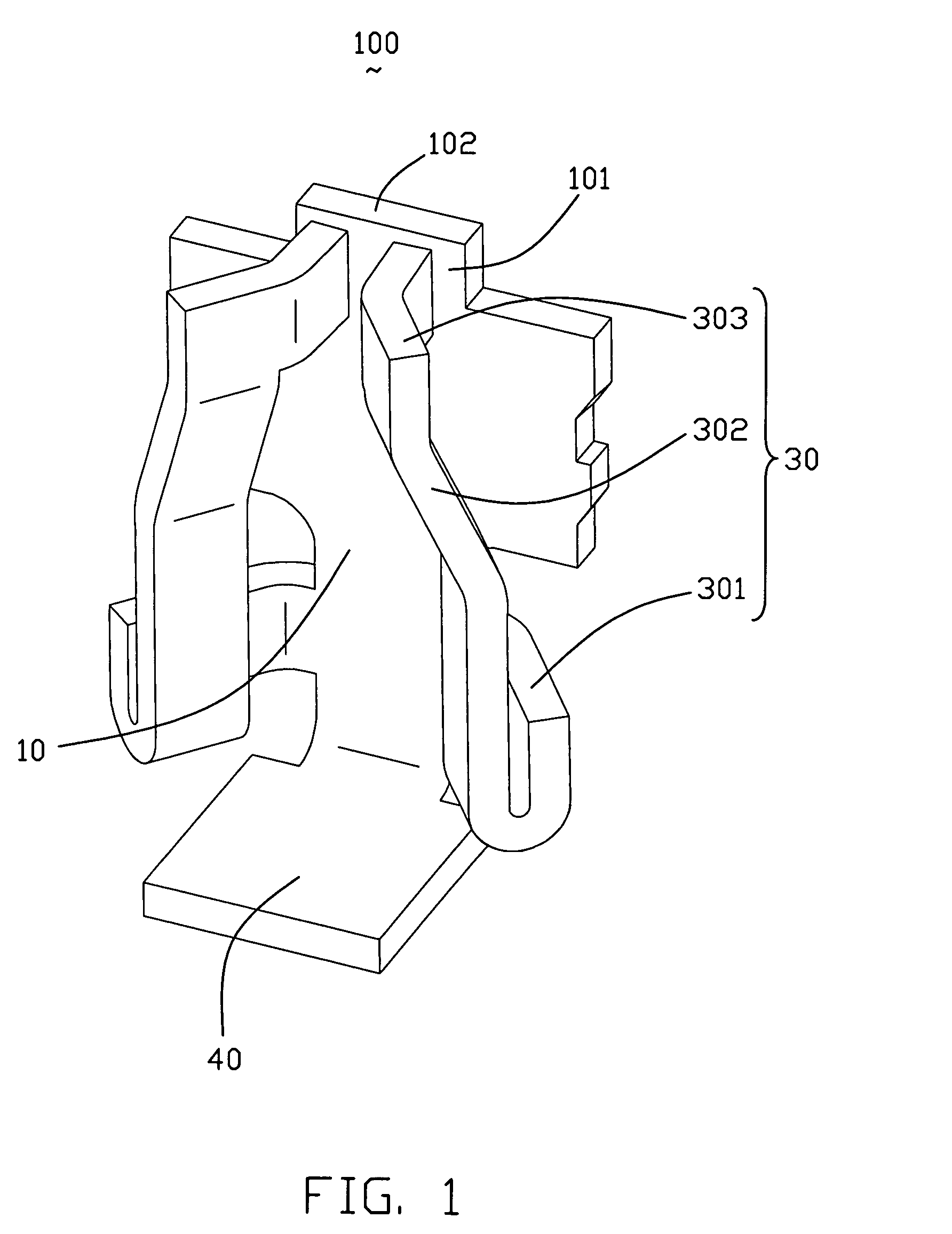

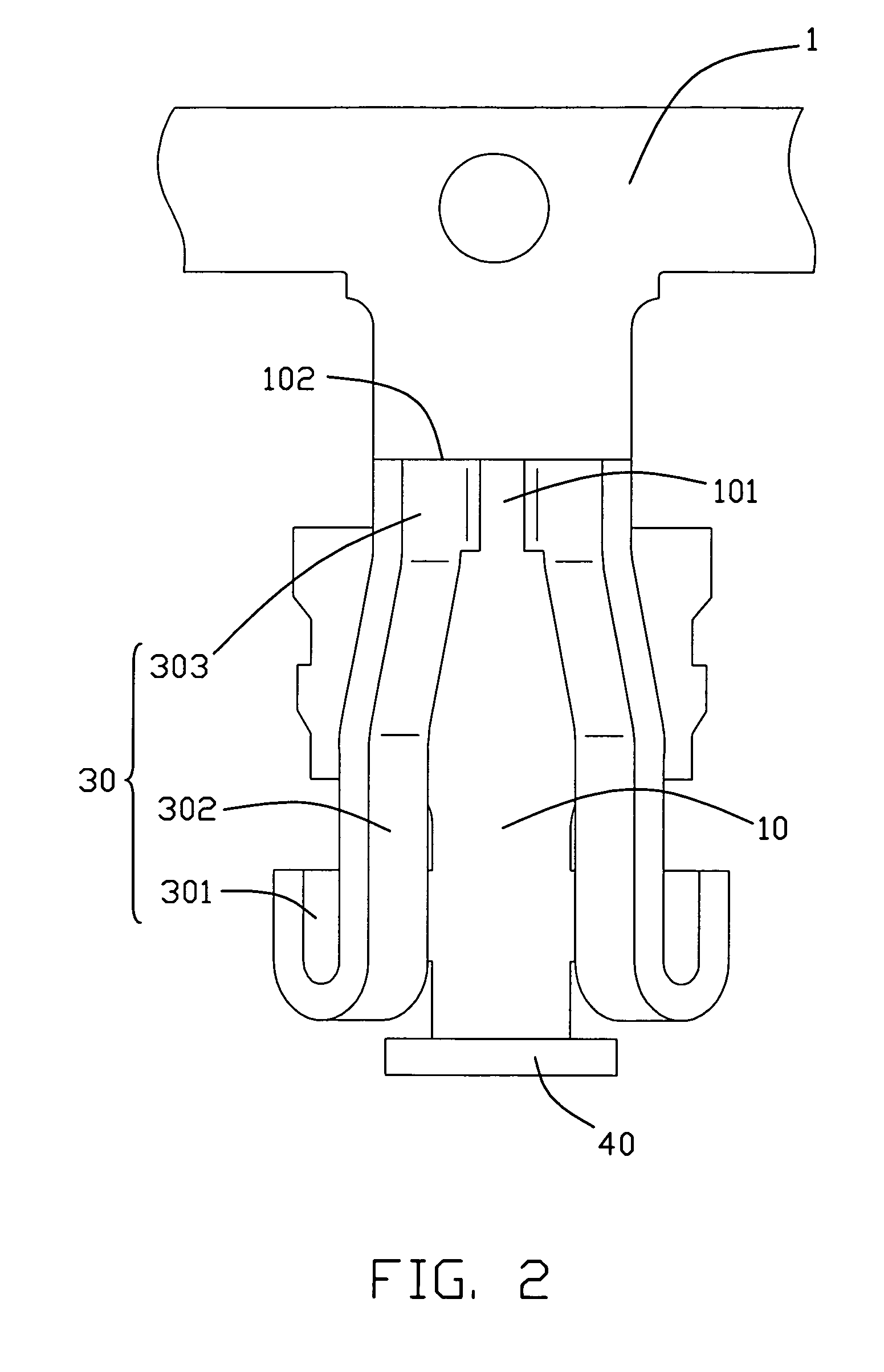

Conductive contact for CPU socket connector

InactiveUS20080227324A1Low costImprove efficiencyCoupling contact membersElectric connection basesCPU socketEngineering

A conductive contact (200) for electrically connecting with a chip module and a printed circuit board comprises a base portion (50), a top head portion (60) formed above the base portion adapted for connecting with a belt, at least one spring arm (70) extending sidewardly from the base portion and forming at least one contacting section (703) adapted for elastically contacting with the chip module, and a bottom soldering portion (80) extending form at least one of the base portion and the spring arm adapted for being soldered to the printed circuit board. The head portion defines a cutout (601) recessed downwardly from a top edge (602) thereof to reduce connecting length between the head portion and the belt and reduce siphonic effect when plating the spring arm.

Owner:HON HAI PRECISION IND CO LTD

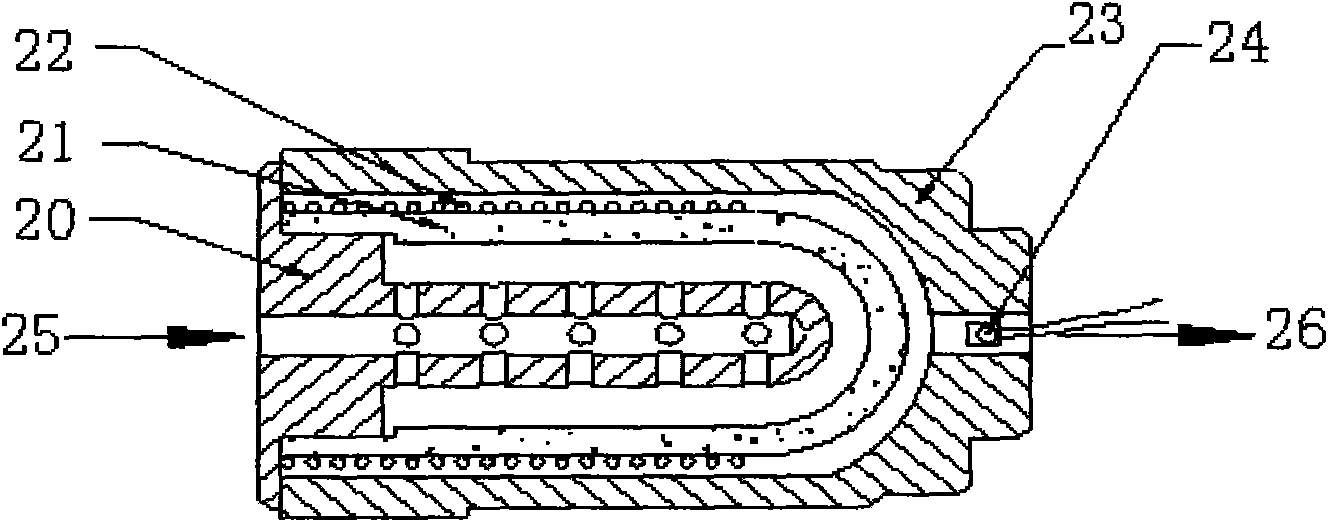

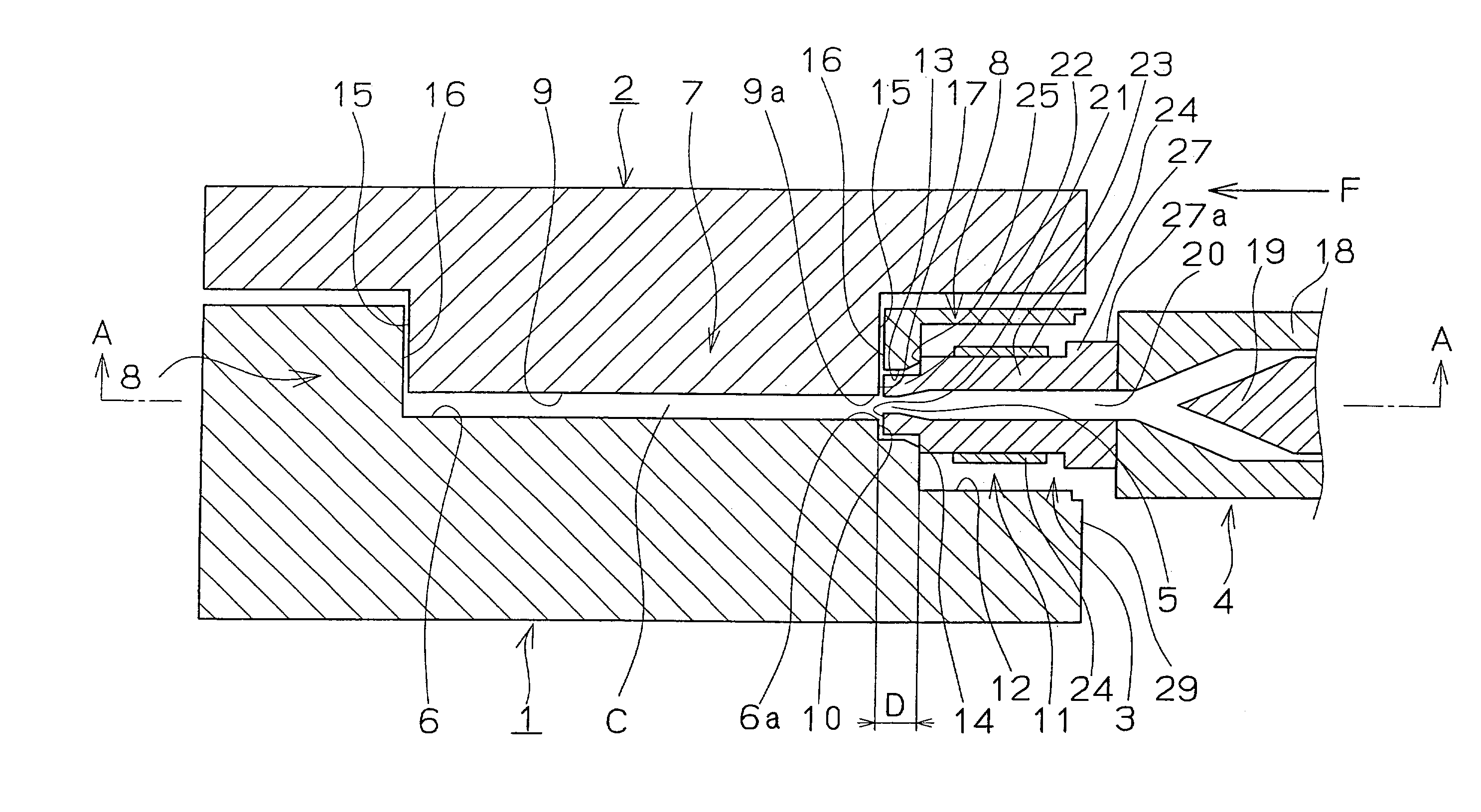

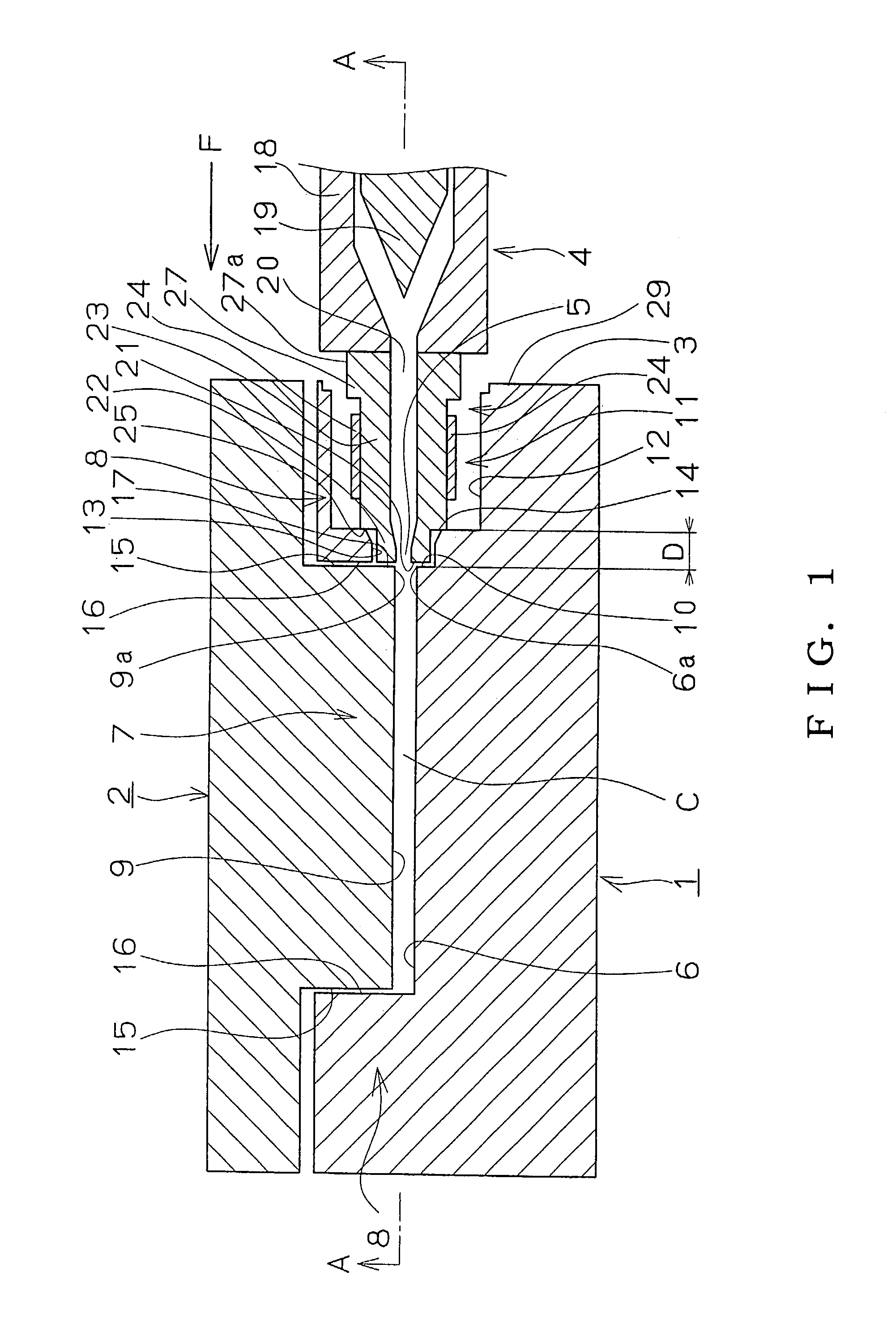

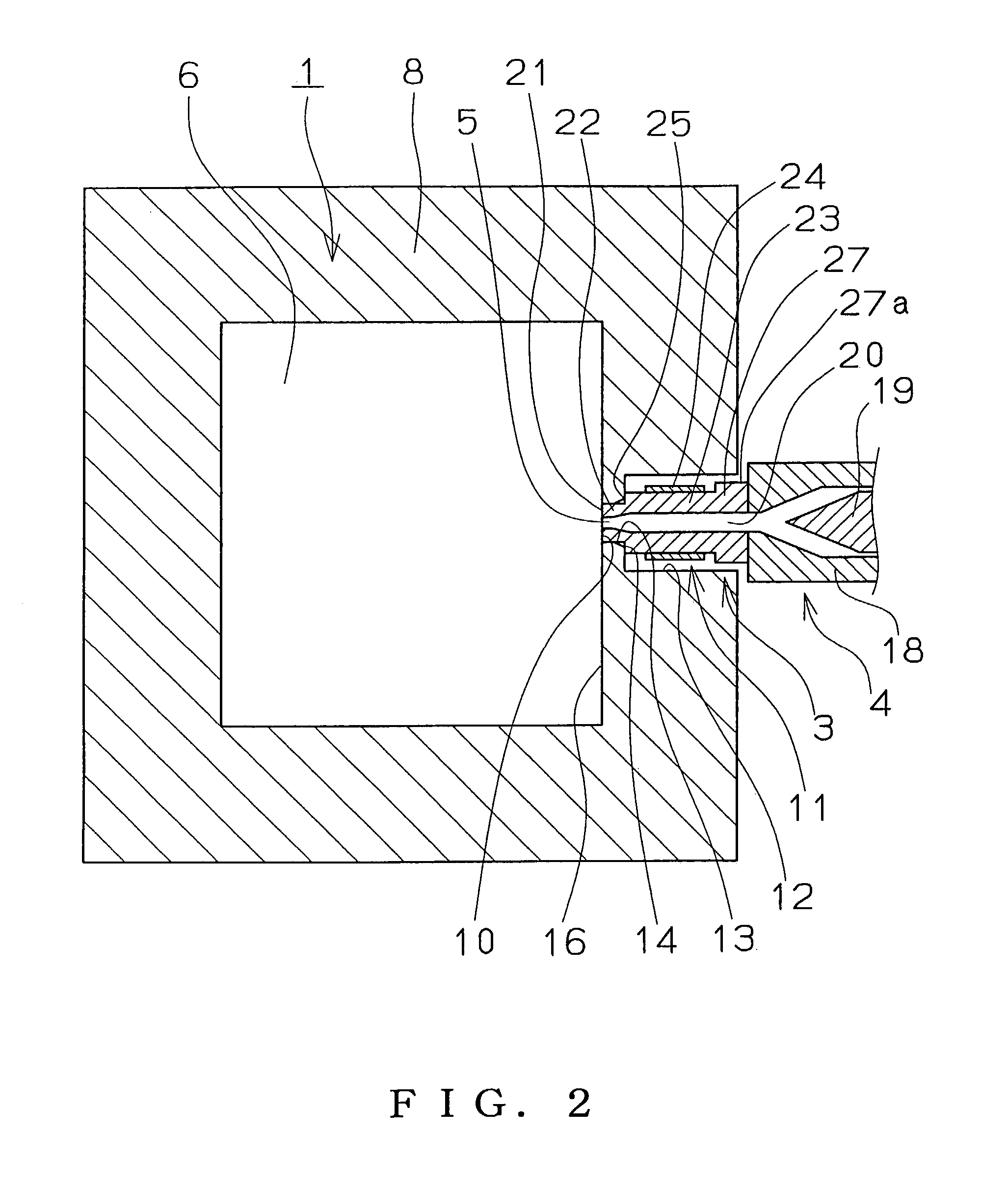

Injection compression molding apparatus and injection compression molding method

In an injection compression molding apparatus and an injection compression method according to the present invention, the structure of the dies can be simplified and a loss of resin as well as of heat due to solidification of the resin in the path at the time of molding can be eliminated. Further, injection pressure loss can be reduced when melted resin is injected into a cavity. A resin injection hole in a nozzle that is attached to an injection device is connected at a position between a stationary die and a movable die directly to the cavity that has a larger volume than a volume of a molded product by means of the movable die, melted resin is injected into said cavity directly from said resin injection hole by said injection device, then the movable die is moved, in the die closing direction, to reduce the distance of the connection between said resin injection hole and said cavity by means of a side wall of the movable die, and to reduce the volume of the cavity so as to compress said melted resin.

Owner:MEIKI

Conductive contact for CPU socket connector

InactiveUS7601036B2Low costImprove efficiencyCoupling contact membersElectric connection basesCPU socketEngineering

A conductive contact (200) for electrically connecting with a chip module and a printed circuit board comprises a base portion (50), a top head portion (60) formed above the base portion adapted for connecting with a belt, at least one spring arm (70) extending sidewardly from the base portion and forming at least one contacting section (703) adapted for elastically contacting with the chip module, and a bottom soldering portion (80) extending form at least one of the base portion and the spring arm adapted for being soldered to the printed circuit board. The head portion defines a cutout (601) recessed downwardly from a top edge (602) thereof to reduce connecting length between the head portion and the belt and reduce siphonic effect when plating the spring arm.

Owner:HON HAI PRECISION IND CO LTD

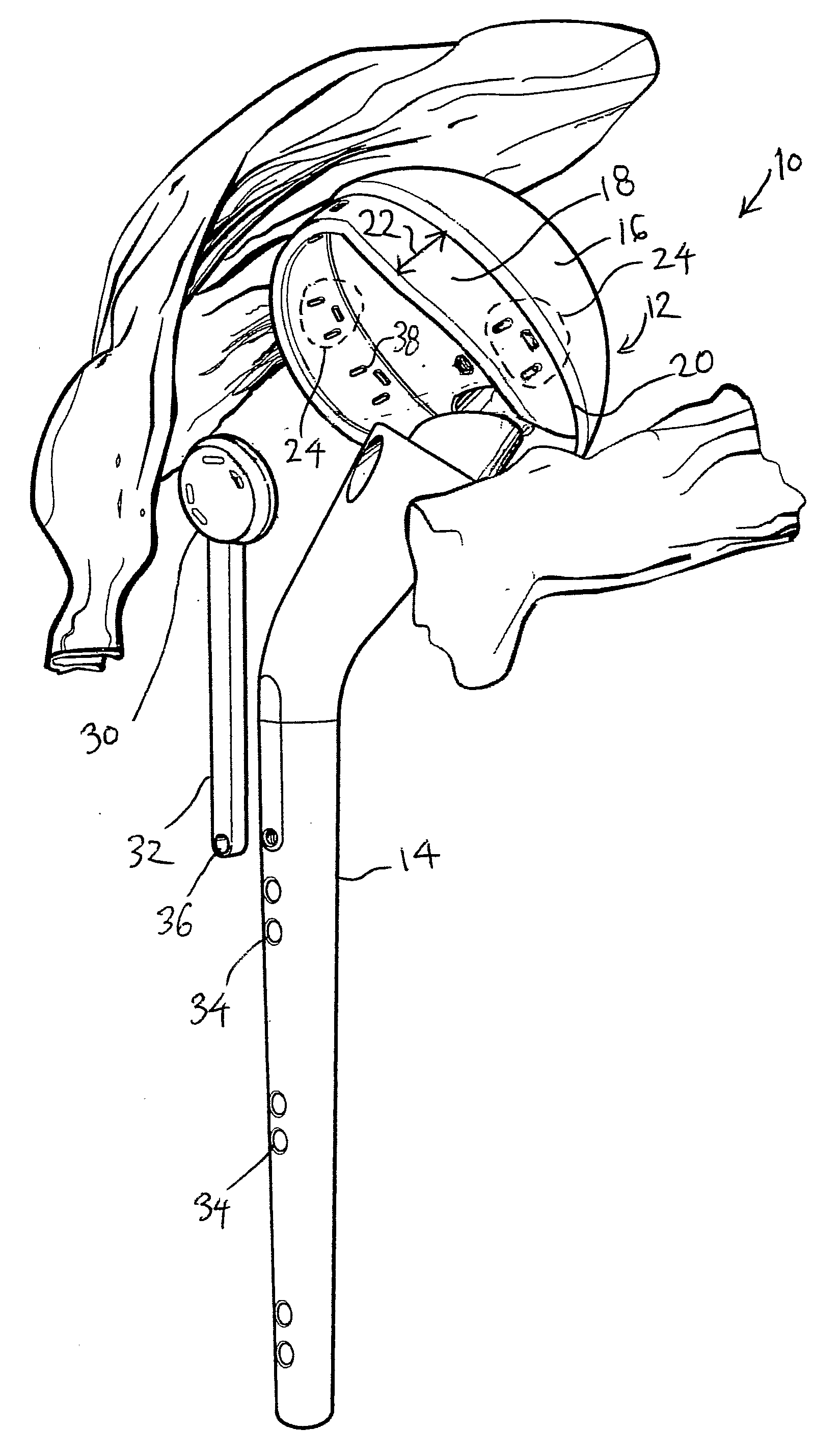

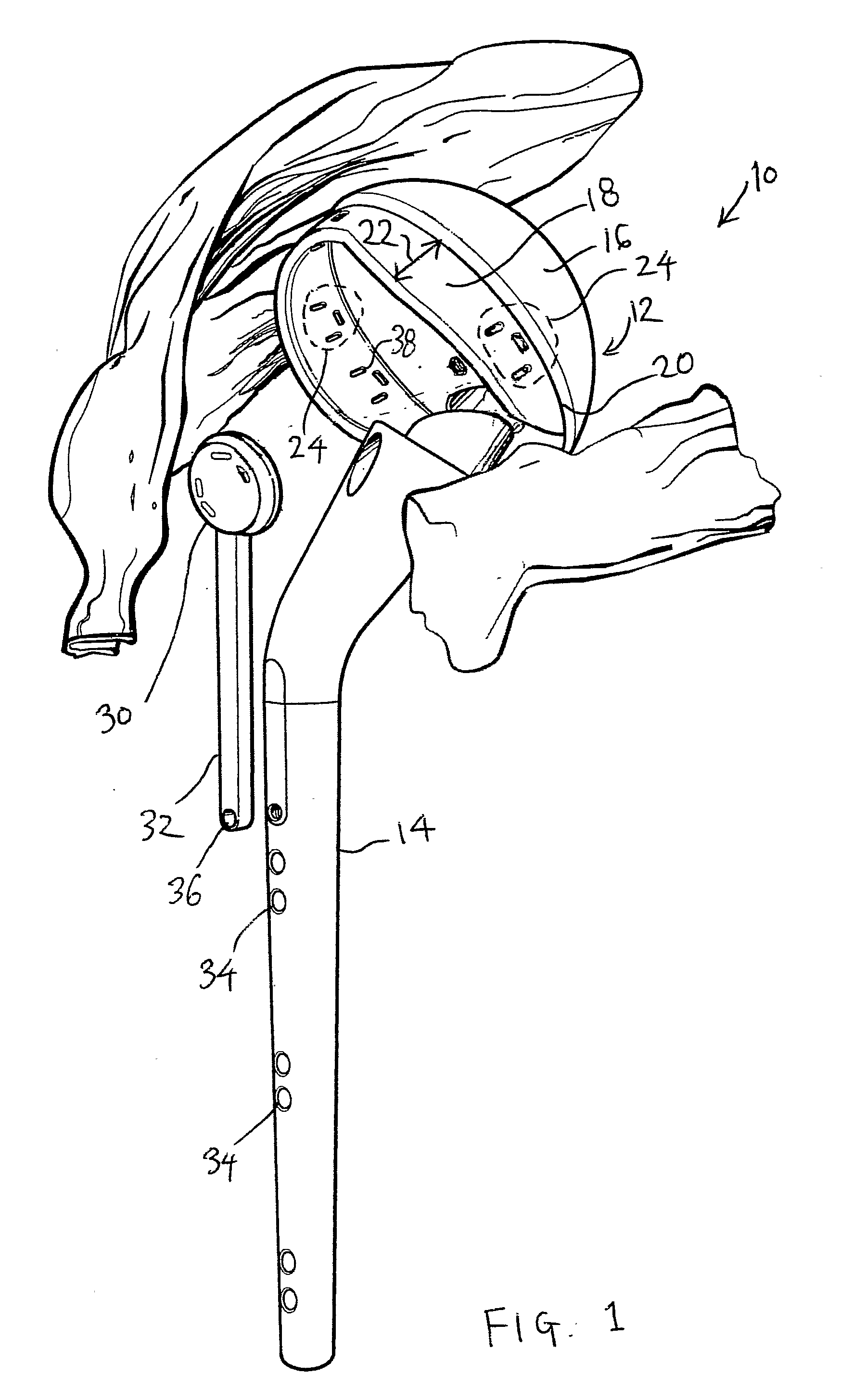

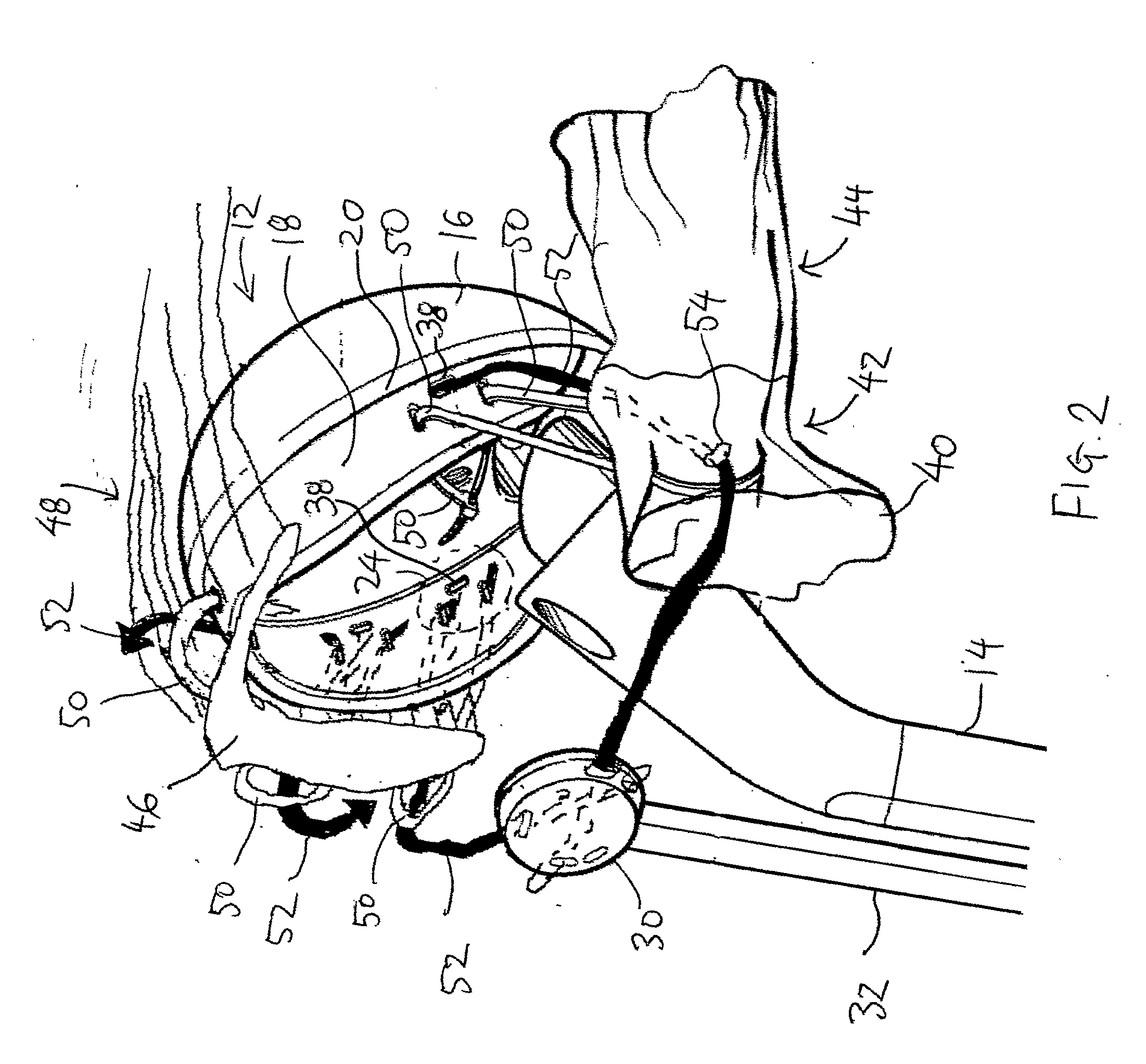

Shoulder replacement

InactiveUS20100292802A1Avoid vertical movementAvoid the needBone implantSurgeryLesser TuberosityShoulder joint prosthesis

A shoulder replacement prosthesis has a head (12) for replacing the humeral head and a connection shaft (14). The head has a domed portion (16) and a flange (18) positioned at an end region of the domed portion, and the flange (18) has a width (22) which varies around the domed portion, having a greater width at a part corresponding to a region of the greater tuberosity than at a part corresponding to a region of the lesser tuberosity. The flange is provided with a plurality of connection portions (24) for securing the tendons attached to the tuberosities. By dimensioning the flange appropriately, the anatomical positioning of the tendon to bone connections can be more accurately replicated. In particular, the flange acts to bridge the so-called bare area of the humeral head. The flange (18) provides a firm immovable surface area to which connections can be made, for example by partridge bands of greater surface area and rigidity than conventional sutures. Bands may also pass to a clamp so that a plastic cage surrounds the tuberosities.

Owner:BOROWSKY KEITH