Patents

Literature

295 results about "CPU socket" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In computer hardware, a CPU socket or CPU slot contains one or more mechanical components providing mechanical and electrical connections between a microprocessor and a printed circuit board (PCB). This allows for placing and replacing the central processing unit (CPU) without soldering.

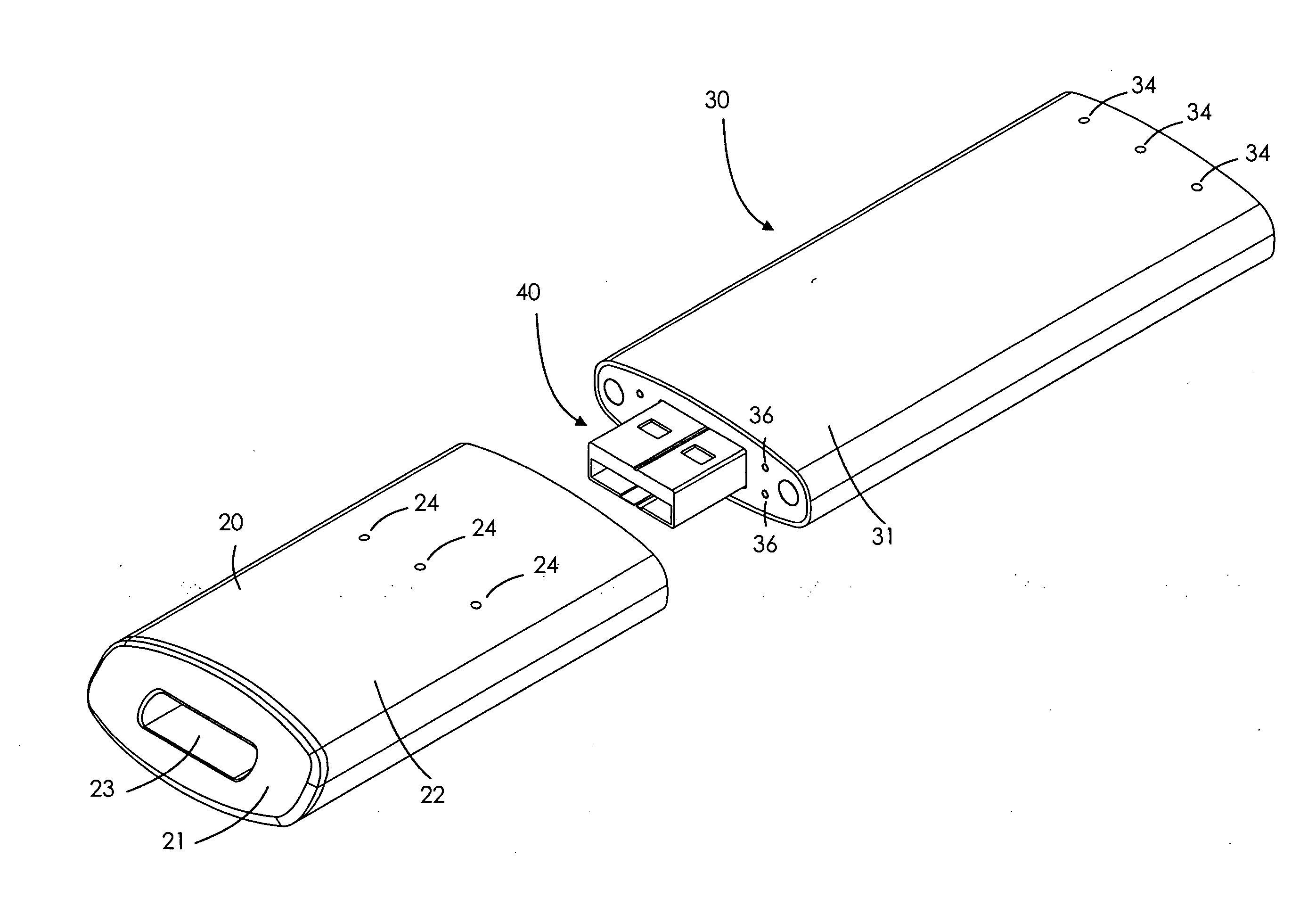

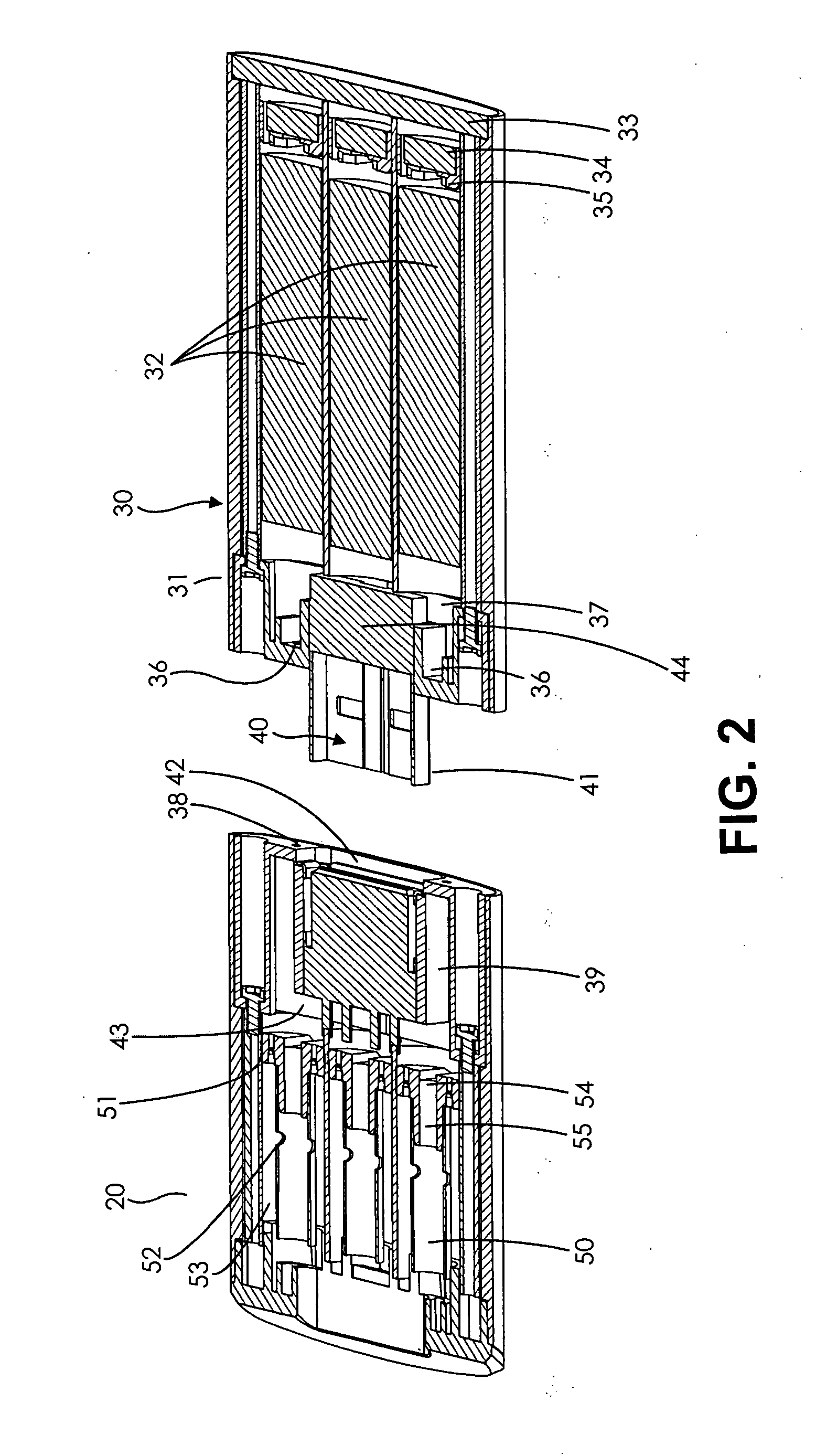

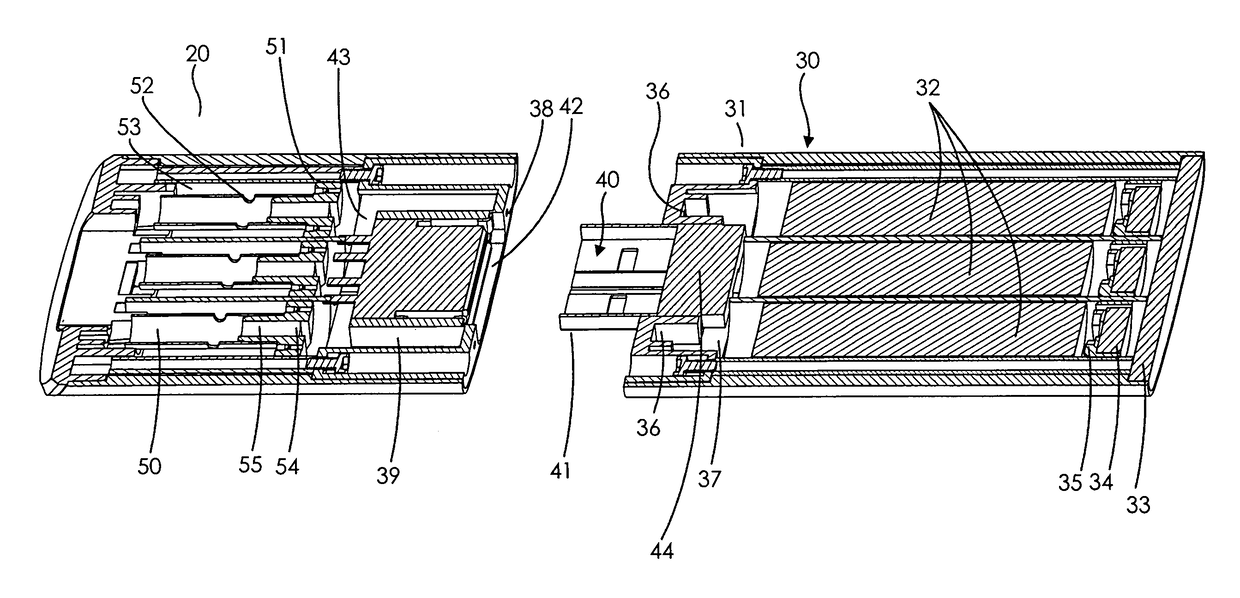

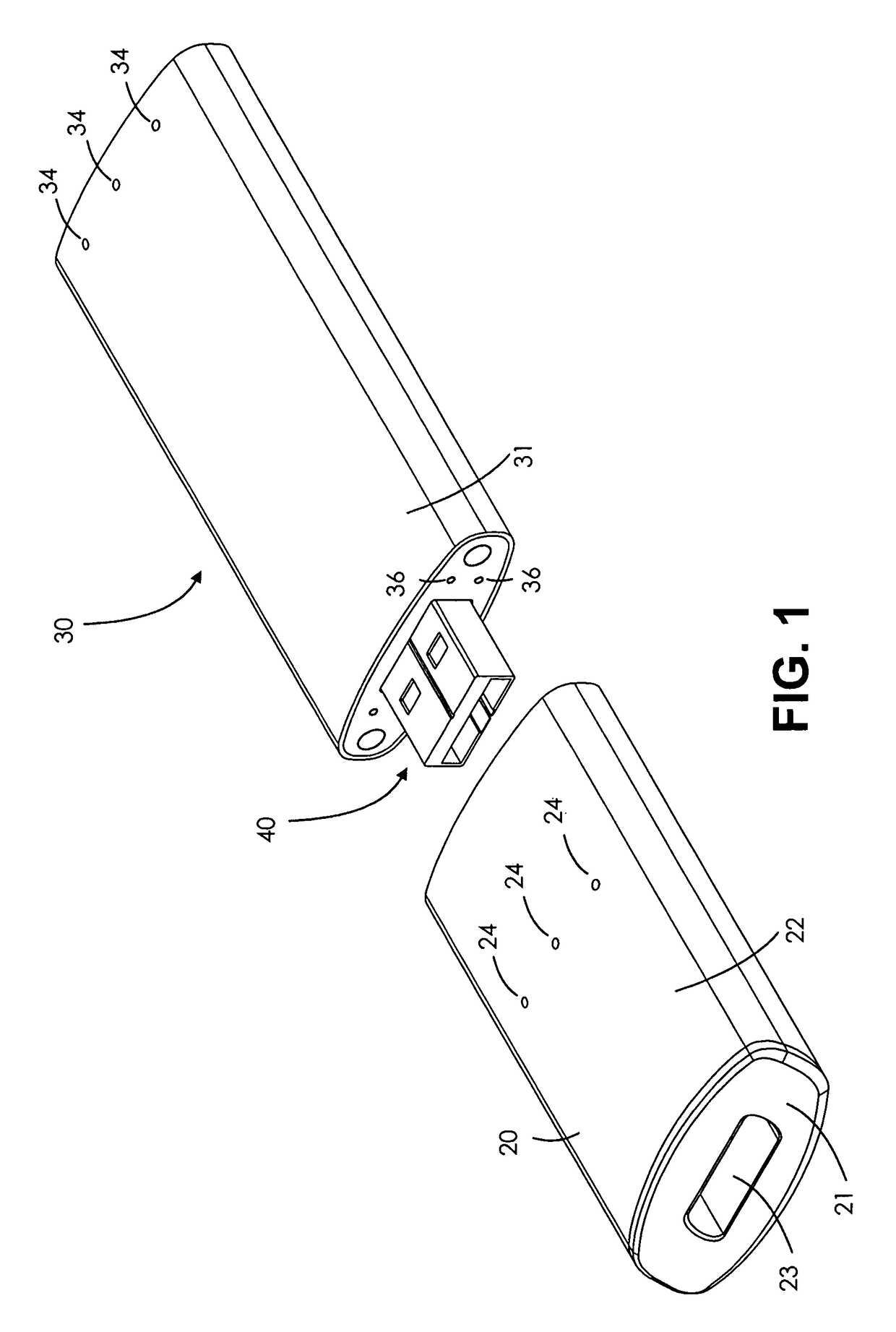

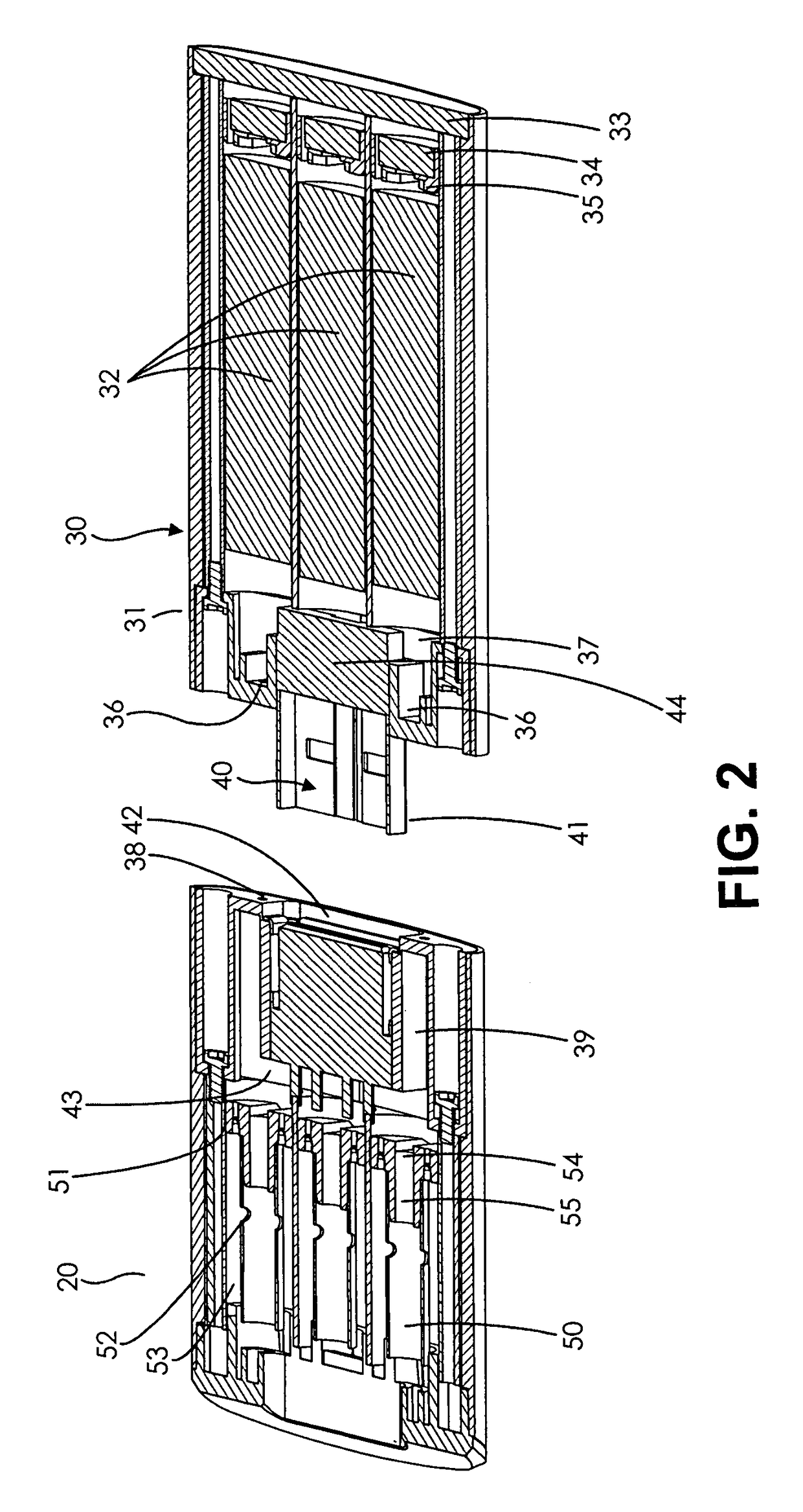

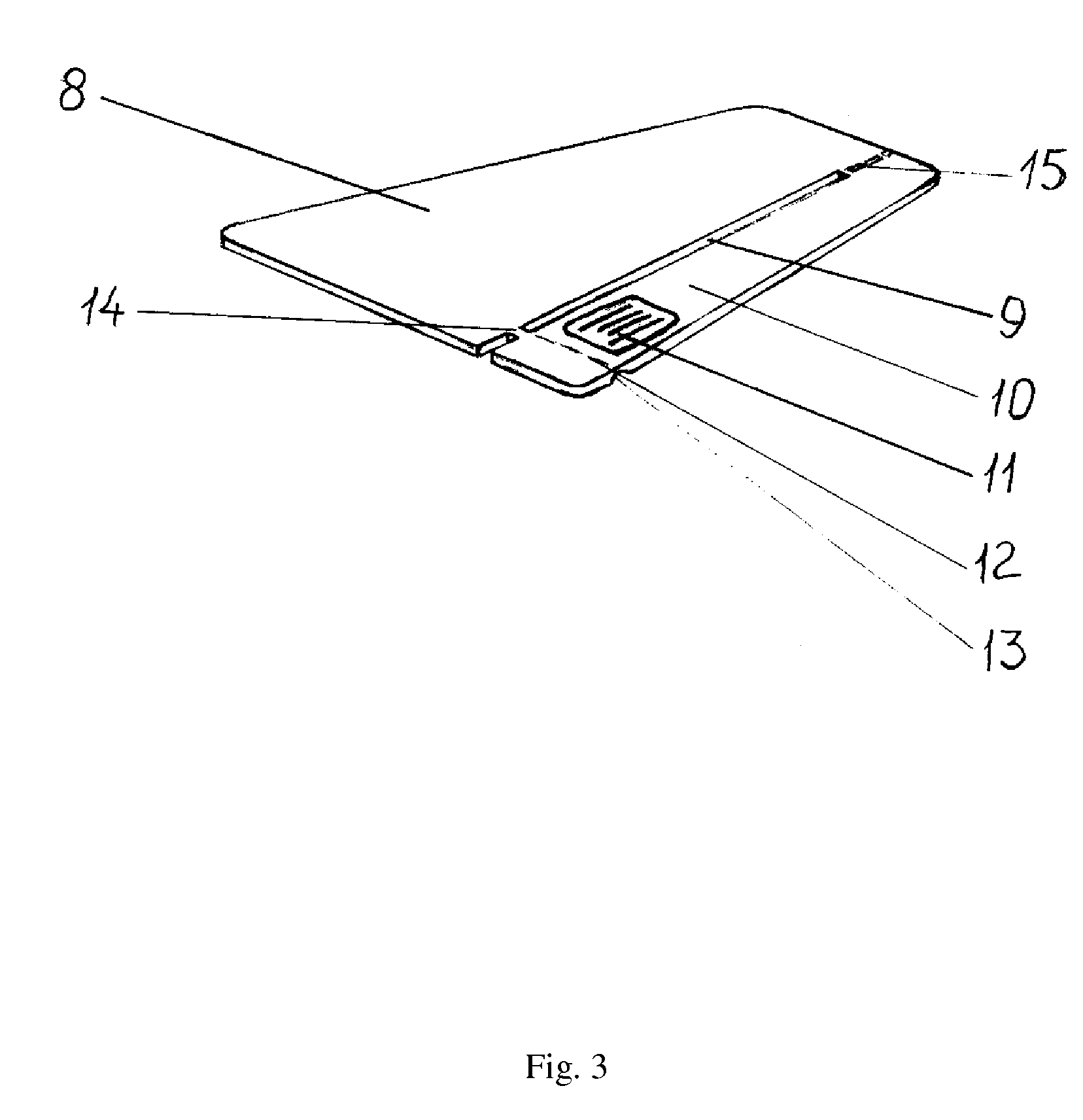

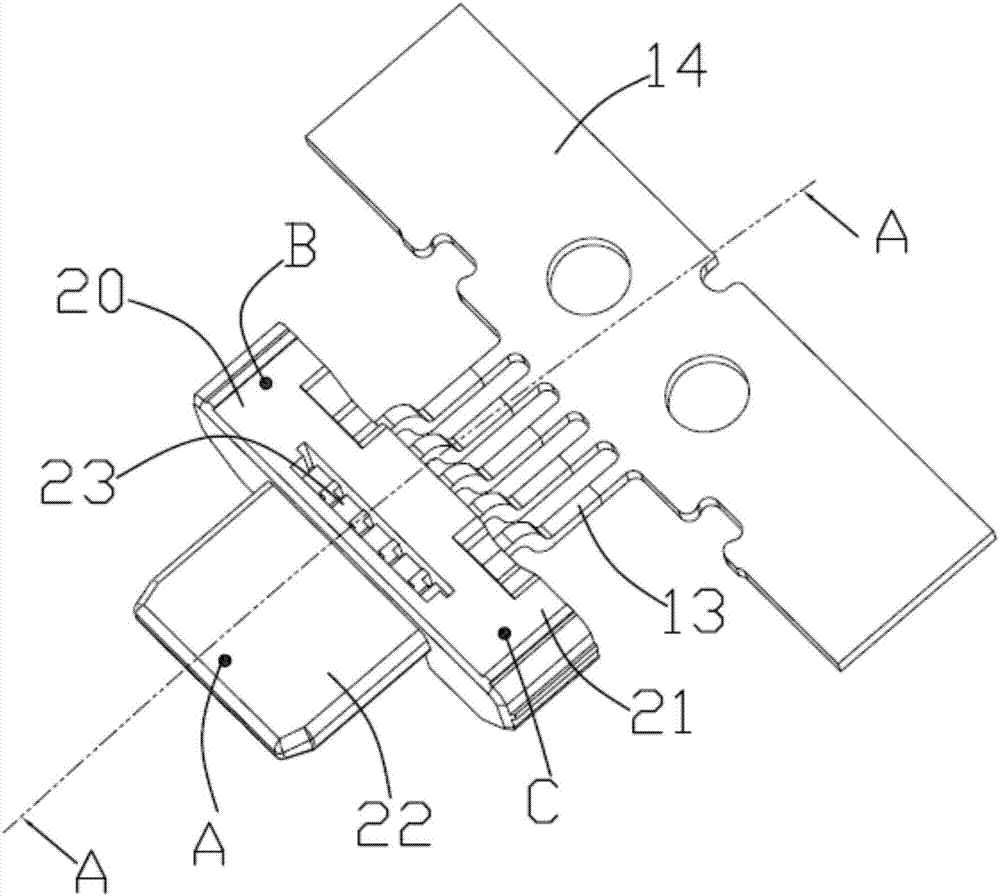

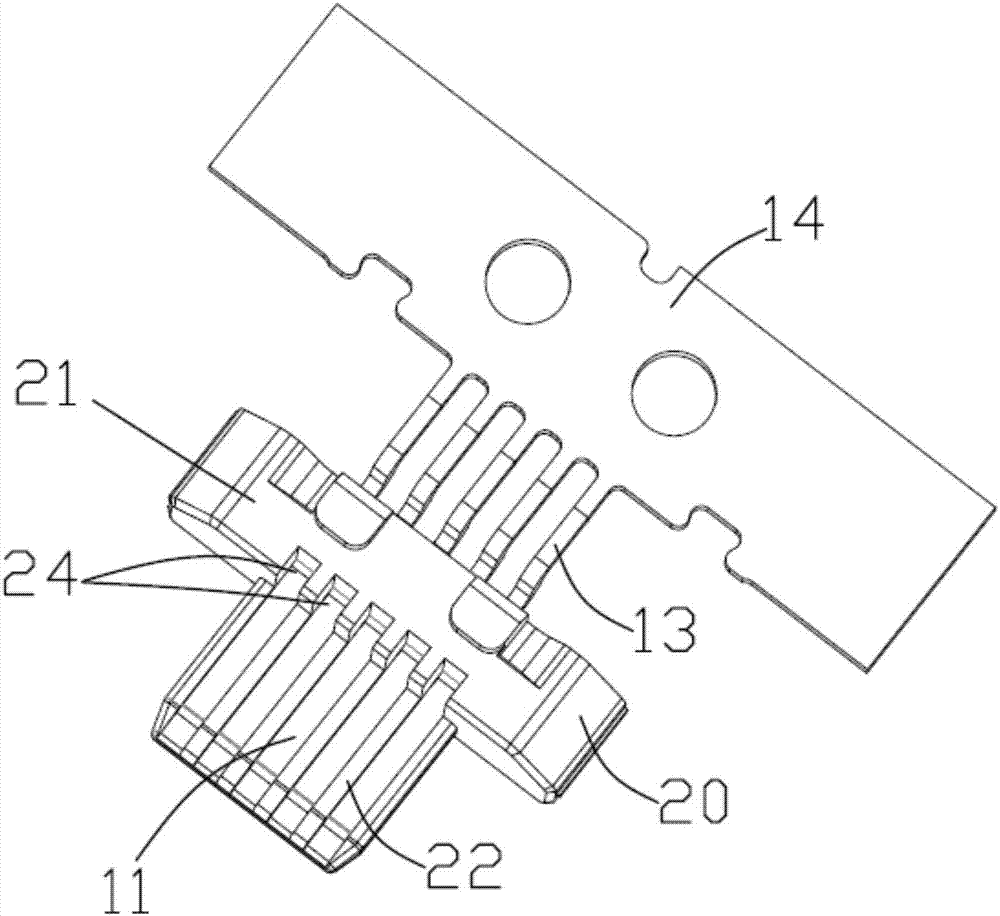

Electronic cigarette

A USB electronic cigarette has an atomizer section. The atomizer section has a heat chamber configured to receive liquid from a fluid reservoir. A USB connector is formed on the atomizer section. The USB connector includes a USB socket mounted to the atomizer section. A battery section is releasable and detachable from the atomizer section at the USB connector. The USB connector includes a USB protrusion configured to fit into the USB socket. The USB protrusion is mounted to the battery section. A rechargeable battery is housed within the battery section and configured to be recharged via the USB protrusion. A user is provided a smokable USB stick that is USB rechargeable.

Owner:SHANGHAI GREEN VAPER TECH CO LTD

Electronic cigarette

A USB electronic cigarette has an atomizer section. The atomizer section has a heat chamber configured to receive liquid from a fluid reservoir. A USB connector is formed on the atomizer section. The USB connector includes a USB socket mounted to the atomizer section. A battery section is releasable and detachable from the atomizer section at the USB connector. The USB connector includes a USB protrusion configured to fit into the USB socket. The USB protrusion is mounted to the battery section. A rechargeable battery is housed within the battery section and configured to be recharged via the USB protrusion. A user is provided a smokable USB stick that is USB rechargeable.

Owner:SHANGHAI GREEN VAPER TECH CO LTD

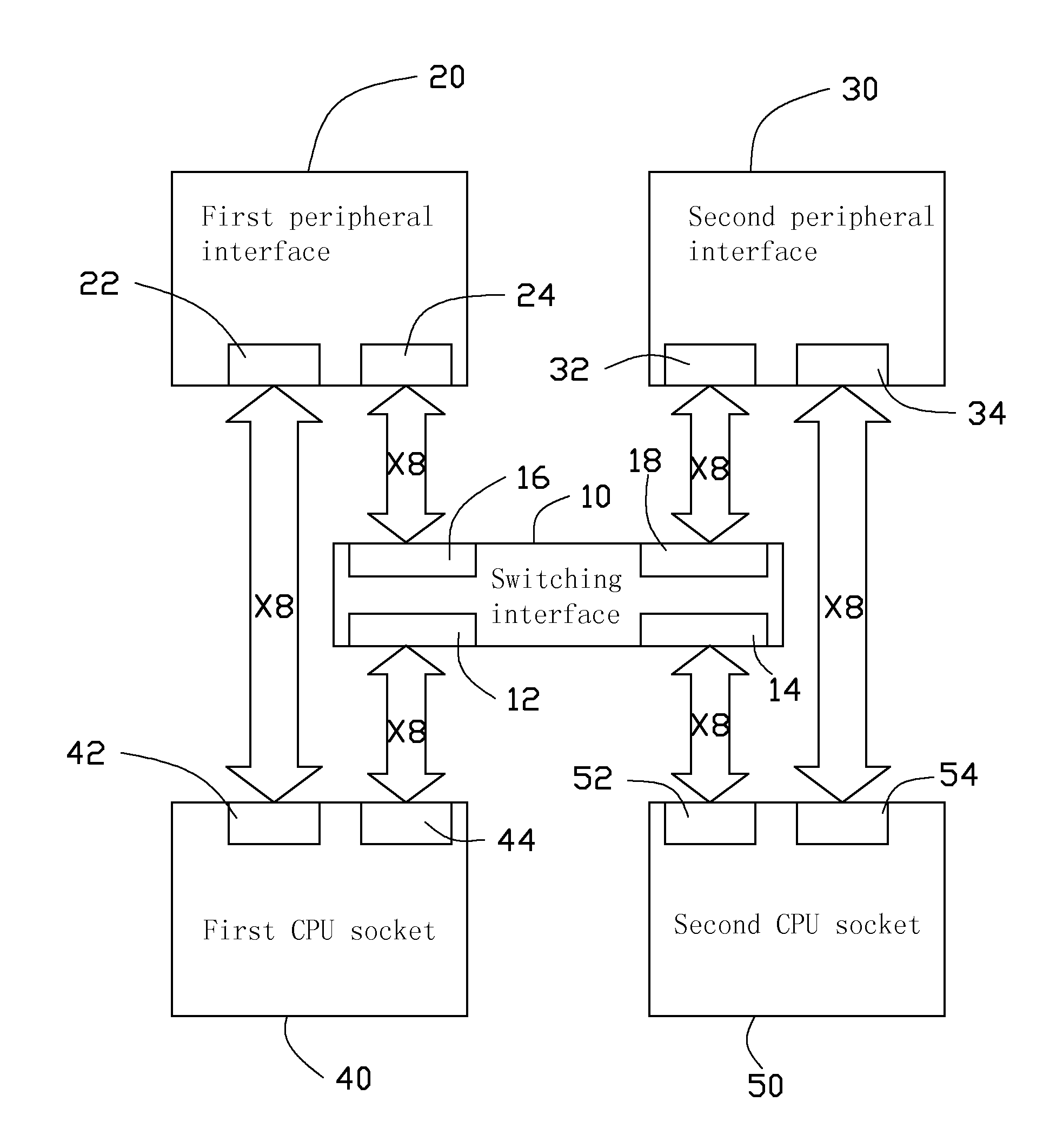

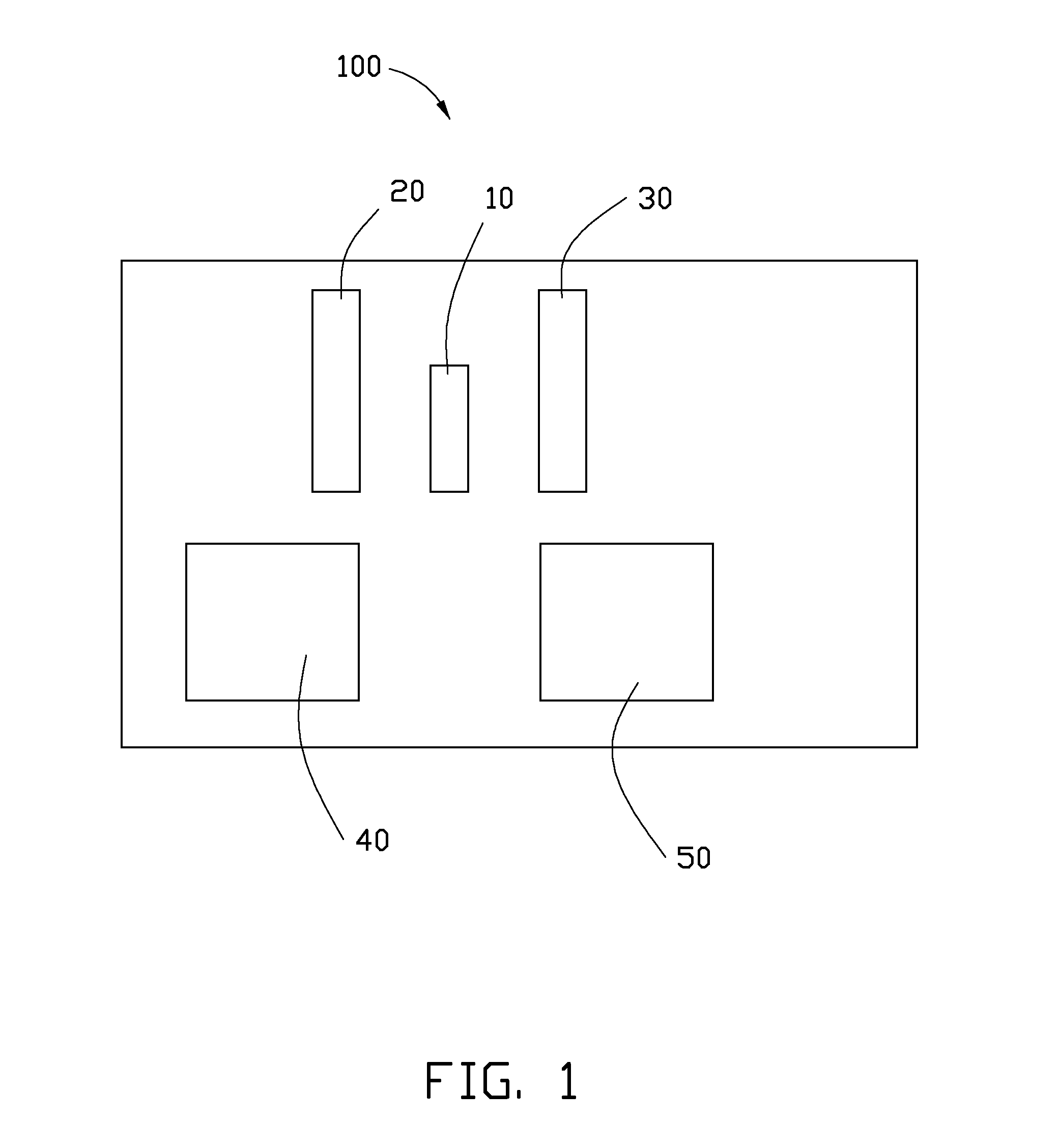

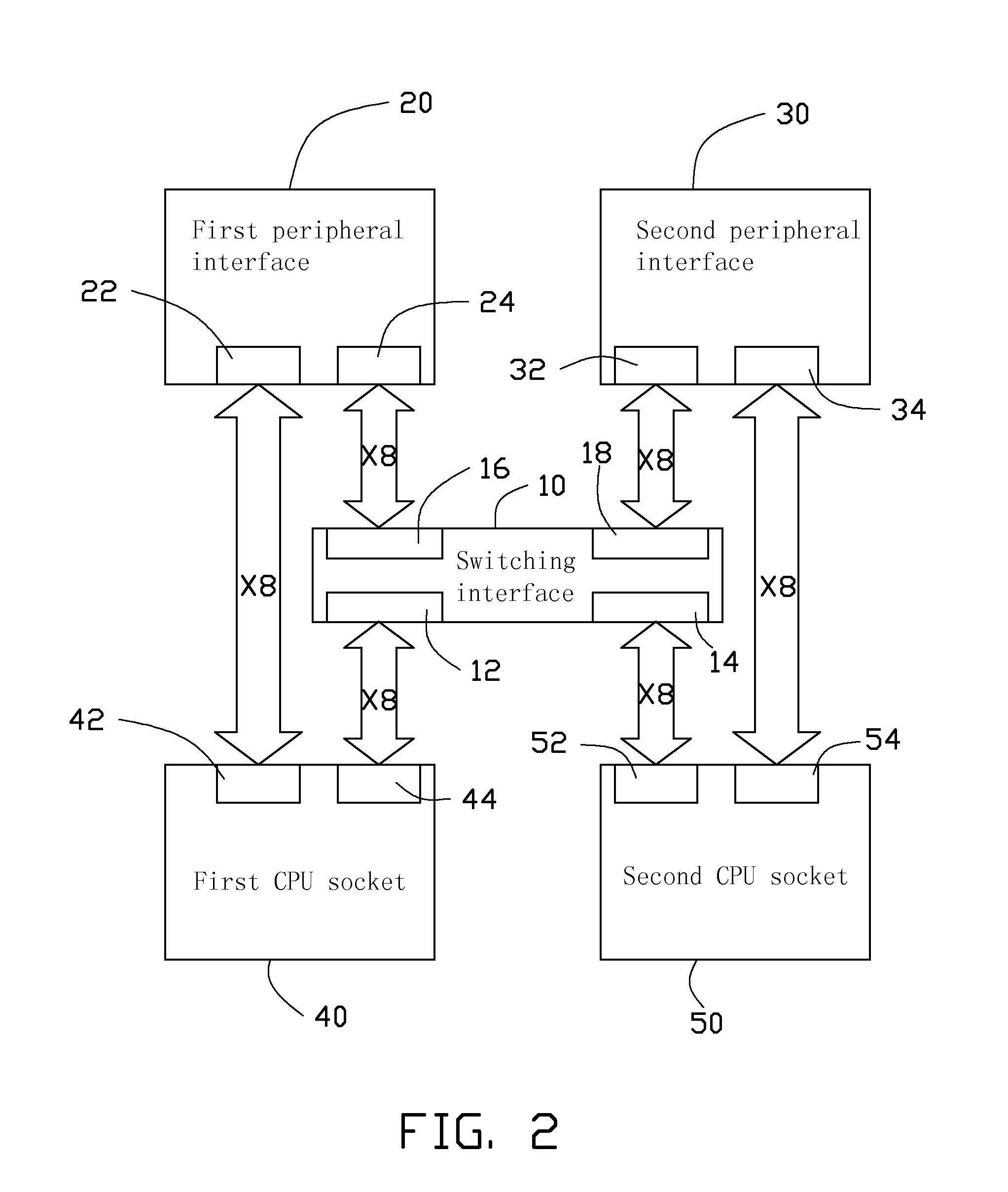

Computer motherboard

A computer motherboard includes first and second peripheral interfaces, a switching interface, a switching card inserted into the switching card, and first and second central processing unit (CPU) sockets. The switching interface is placed between the first and second peripheral interfaces. The switching card includes first and second interface. Pins of the first interface of the switching card are interconnected, and pins of the second interface of the switching card are interconnected. Connection between the first and second peripheral sockets and the first and second CPU sockets is adjustable by selectively connecting one of the first and second interfaces of the switching card to the switching interface.

Owner:HON HAI PRECISION IND CO LTD

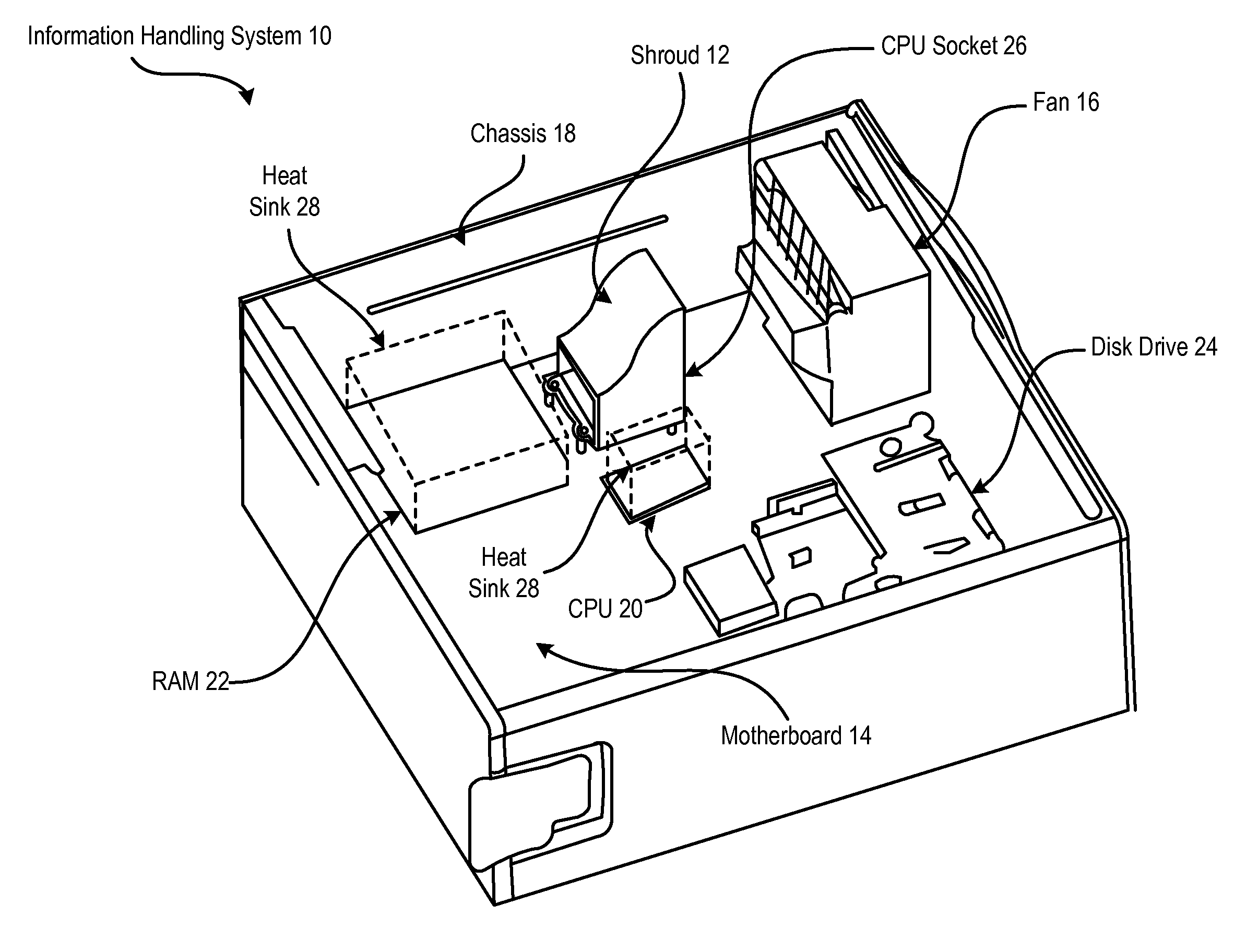

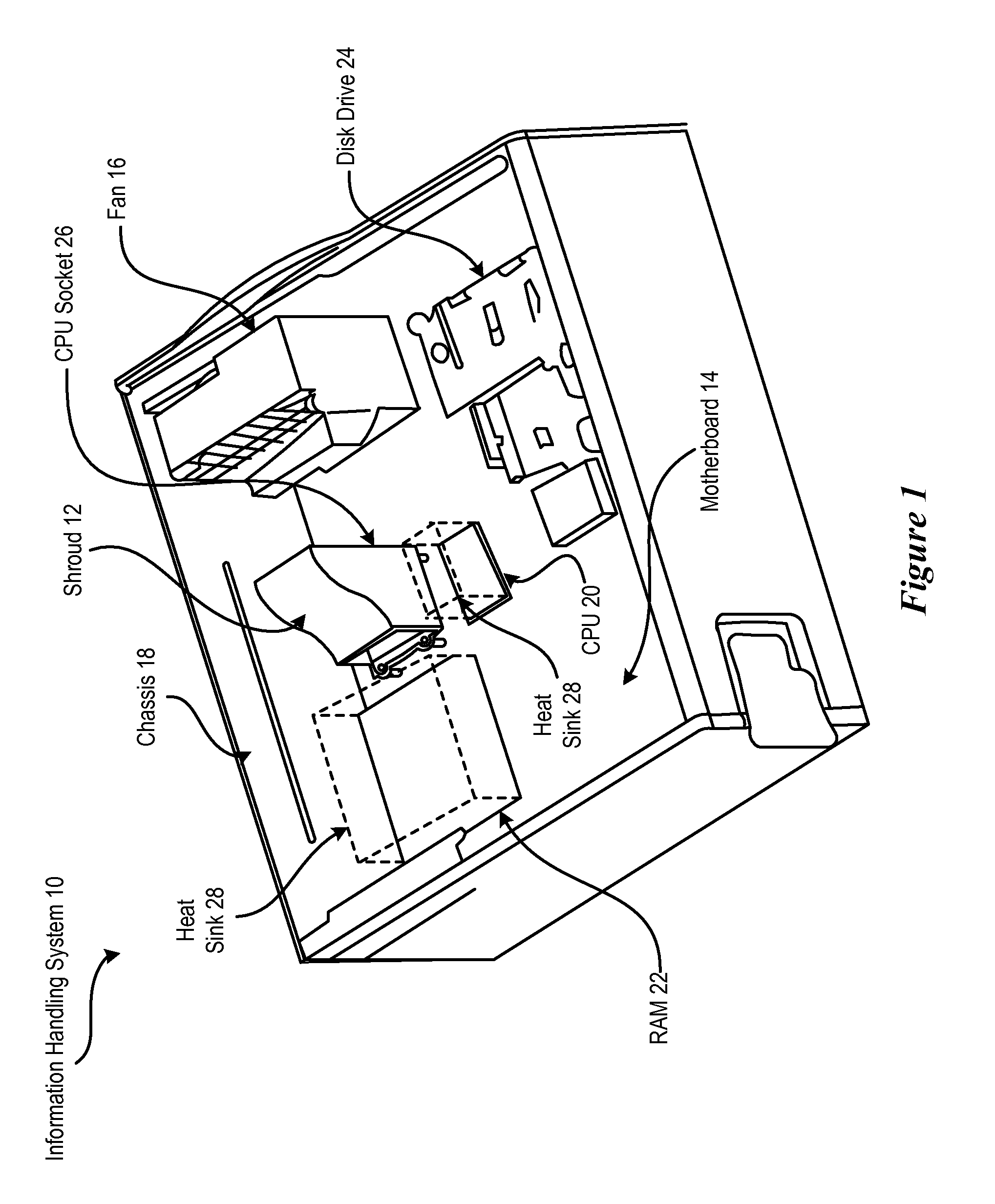

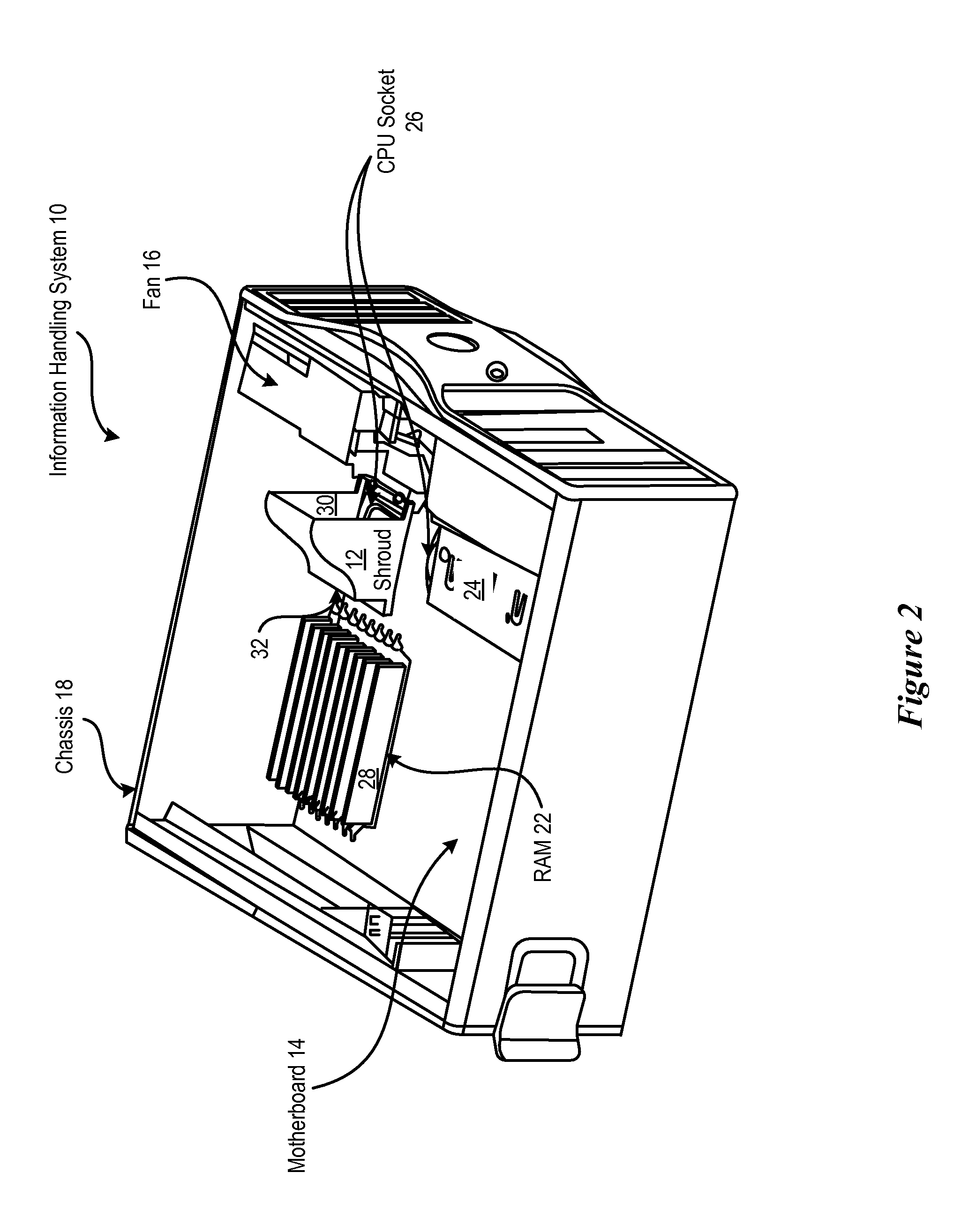

System and Method for Managing Cooling Airflow for a Multiprocessor Information Handling System

ActiveUS20080068796A1Reduce disadvantagesReduce problemsDigital data processing detailsCooling/ventilation/heating modificationsCPU socketHandling system

Cooling airflow through an information handling system is redirected at positions of a motherboard having an unpopulated processing component towards positions of the motherboard having processing component. For example, a shroud shaped as a nozzle couples to a heat sink connector of the motherboard to cover an unpopulated CPU socket. The shroud has a nozzle-shaped channel with an inlet accepting cooling airflow and an outlet exhausting the cooling airflow towards a processing component. For instance, the inlet is proximate a cooling fan and the outlet directs the airflow from the cooling fan towards a heat sink associated with RAM populated on the motherboard.

Owner:DELL PROD LP

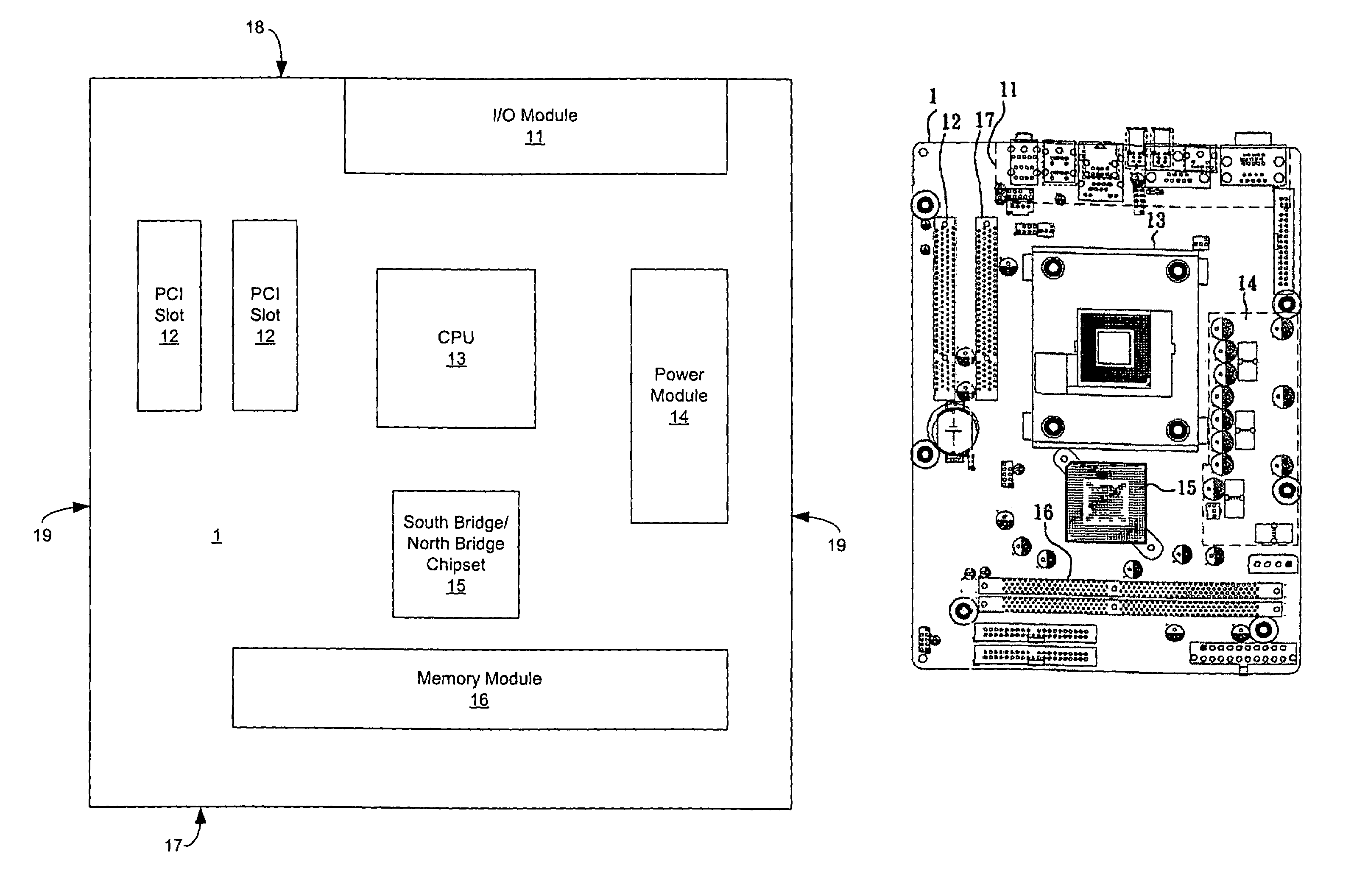

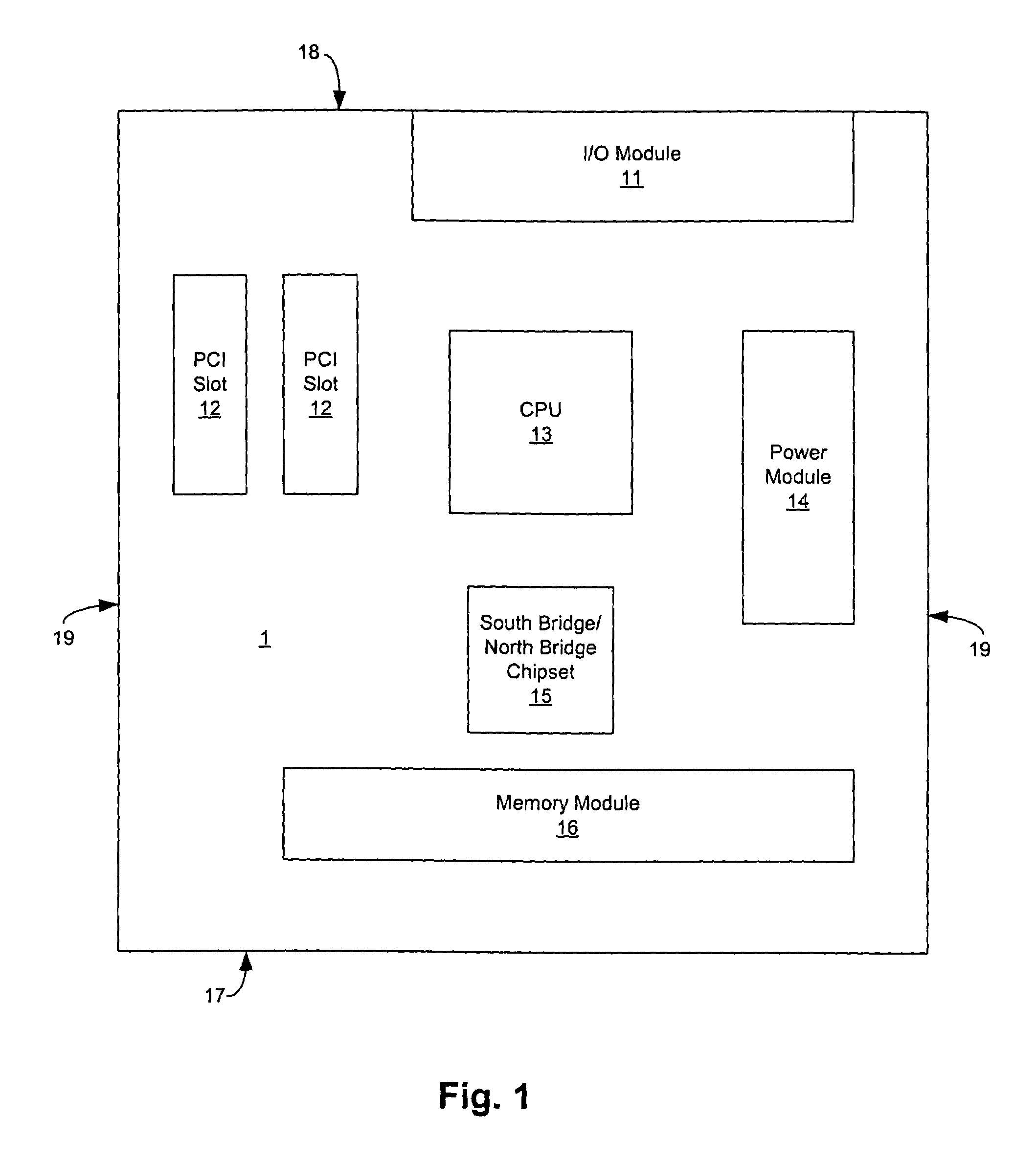

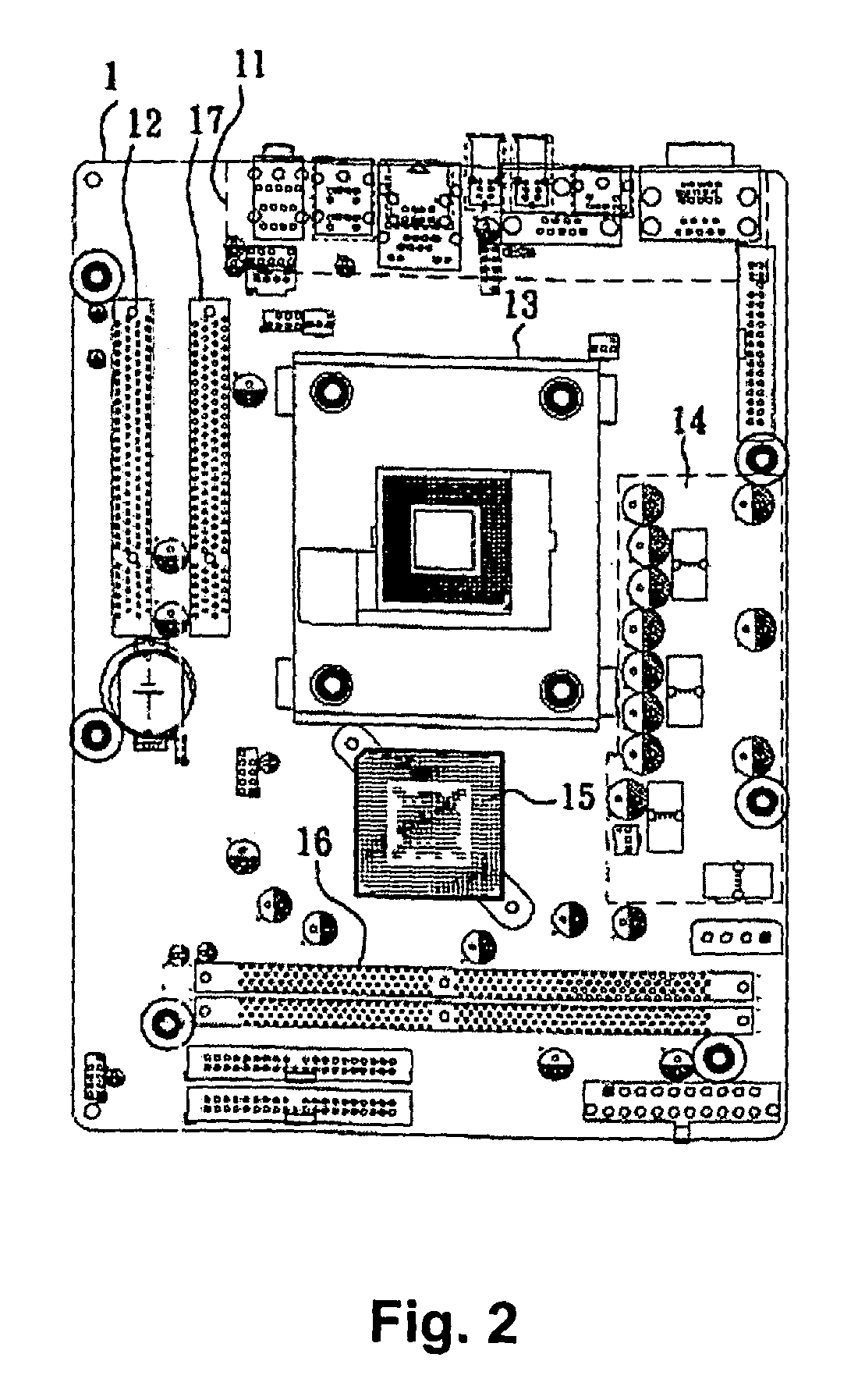

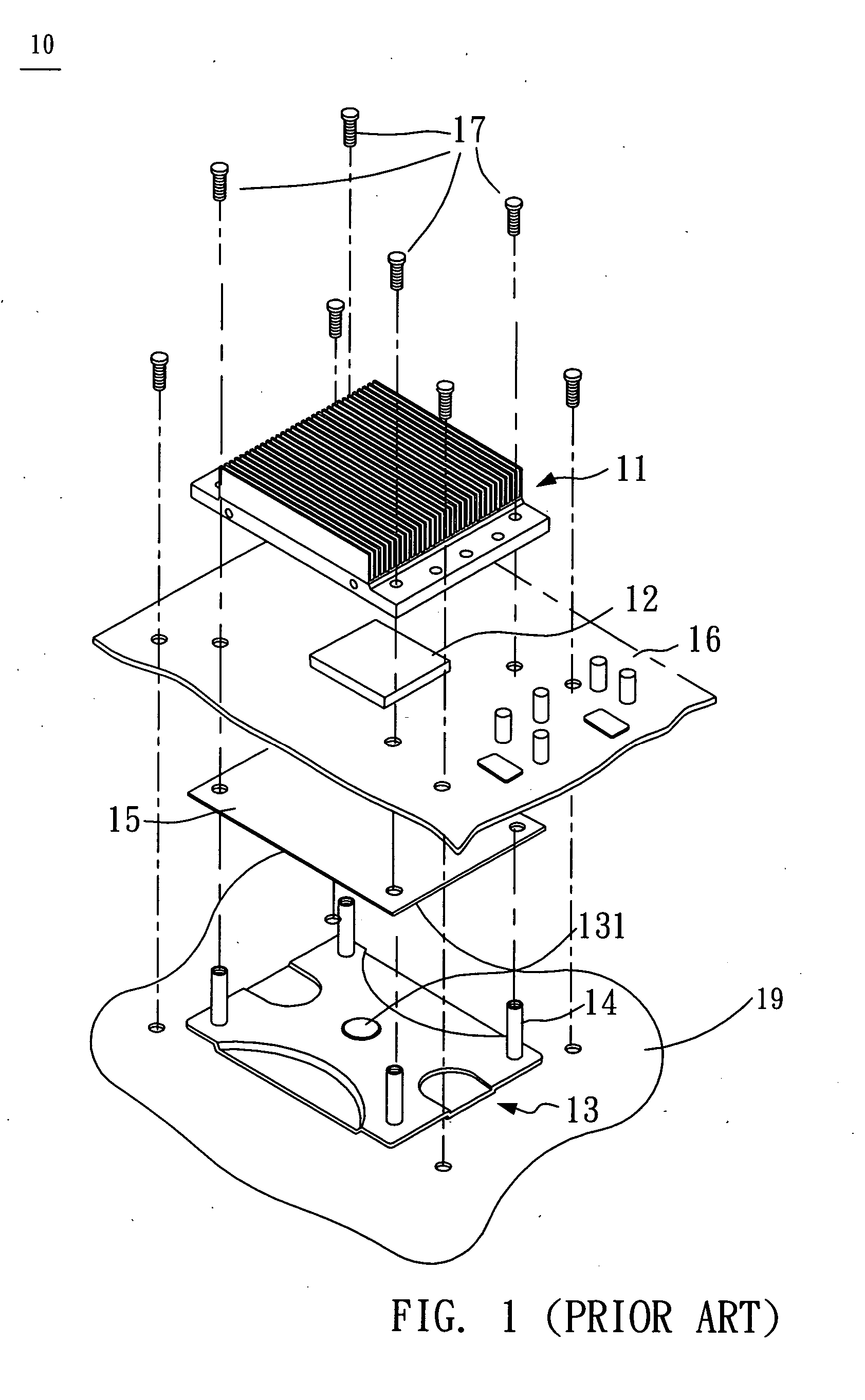

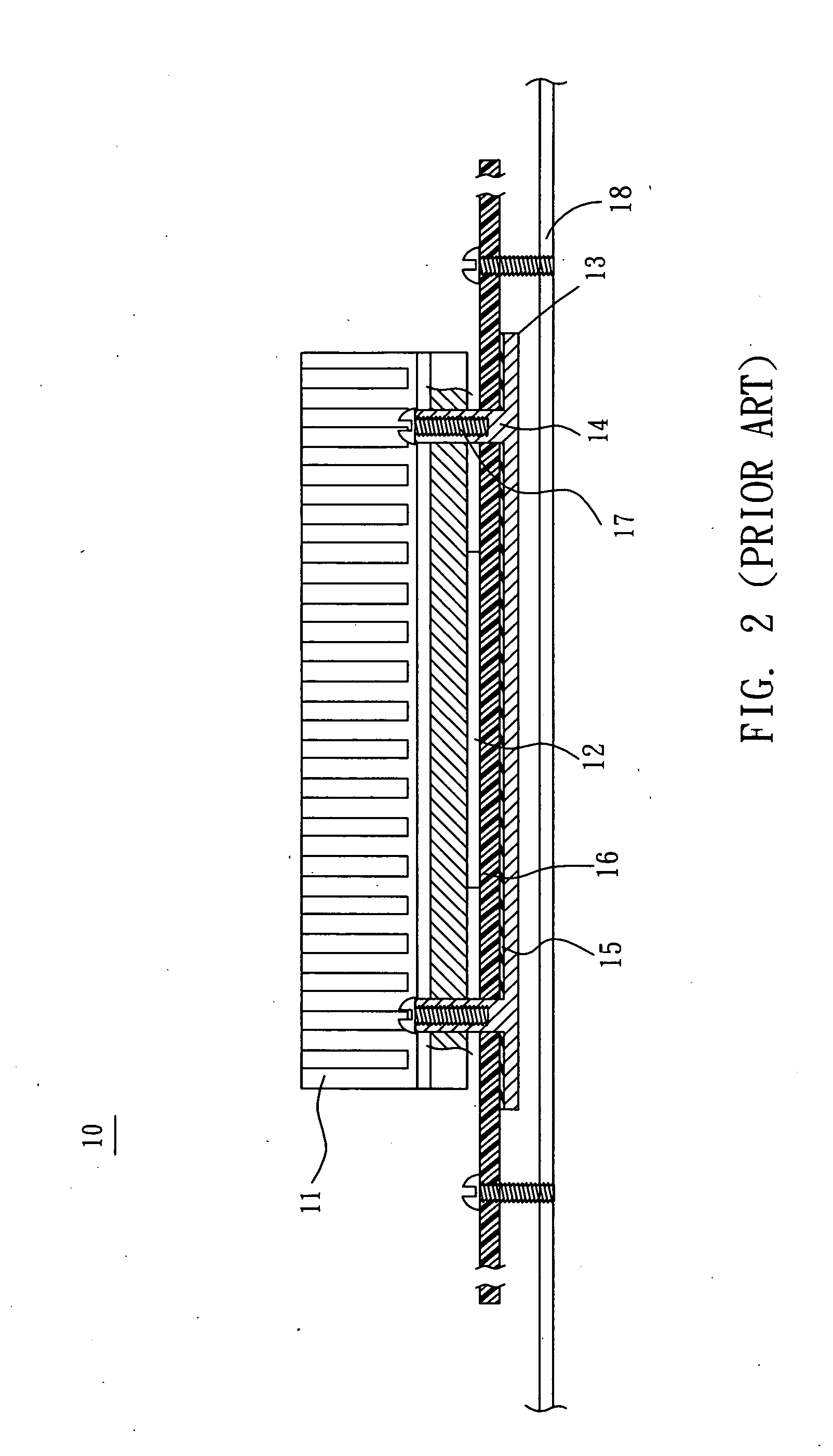

Placement structure of an integrated motherboard for small form factor computer

InactiveUS7054165B2Effective coolingSmall sizeDigital processing power distributionCircuit arrangements on conductive chasisCPU socketChipset

An integrated motherboard for a small form factor computer comprises a CPU socket located in a central region of the motherboard. A south bridge / north bridge chipset is located next to the CPU socket towards the front of the motherboard, and a memory module is located next to the south bridge / north bridge chipset towards the front of the motherboard. One or more PCI slots are located on one side of the CPU socket, and a power module is located on the other side of the CPU socket.

Owner:SHUTTLE

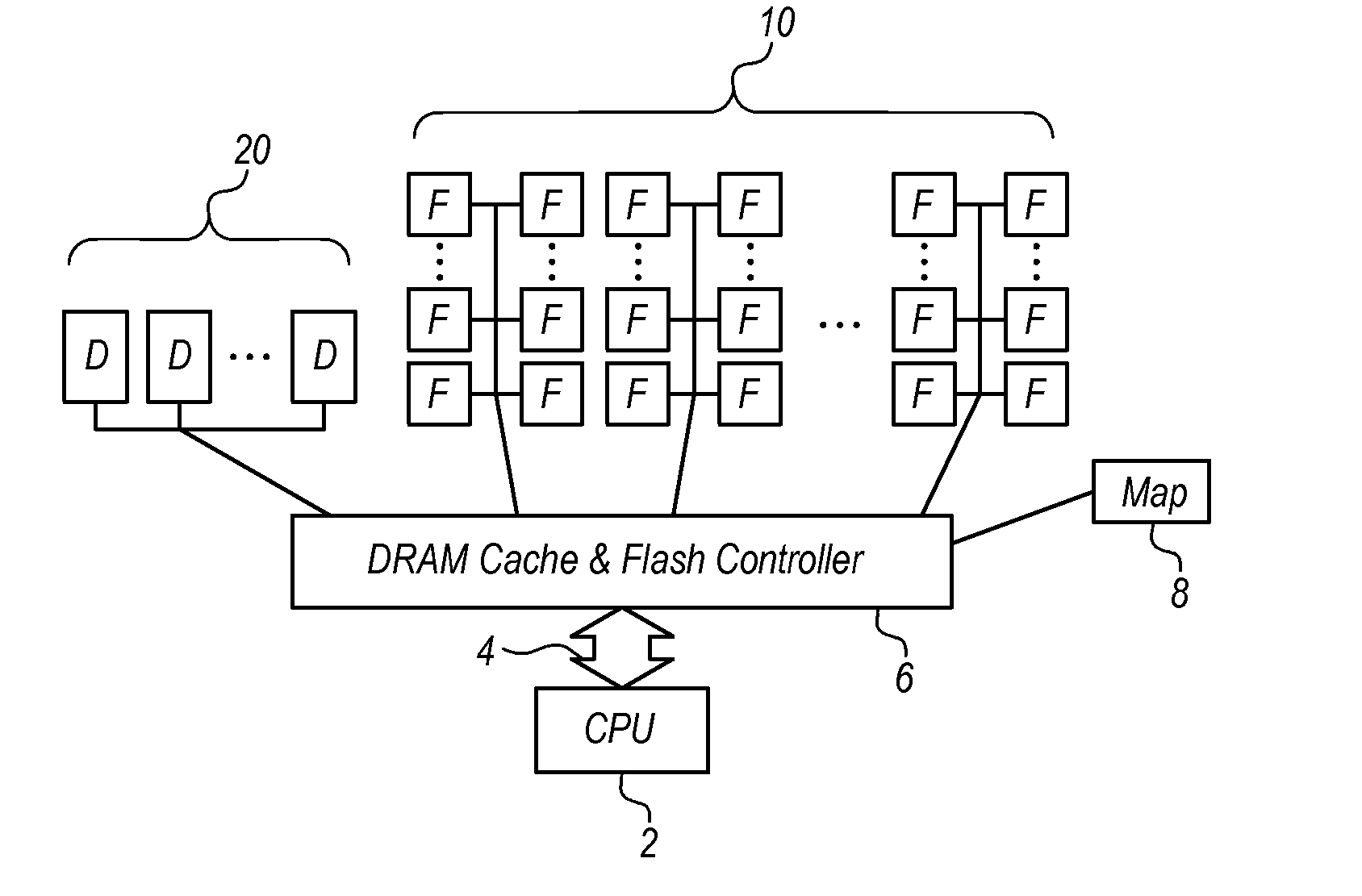

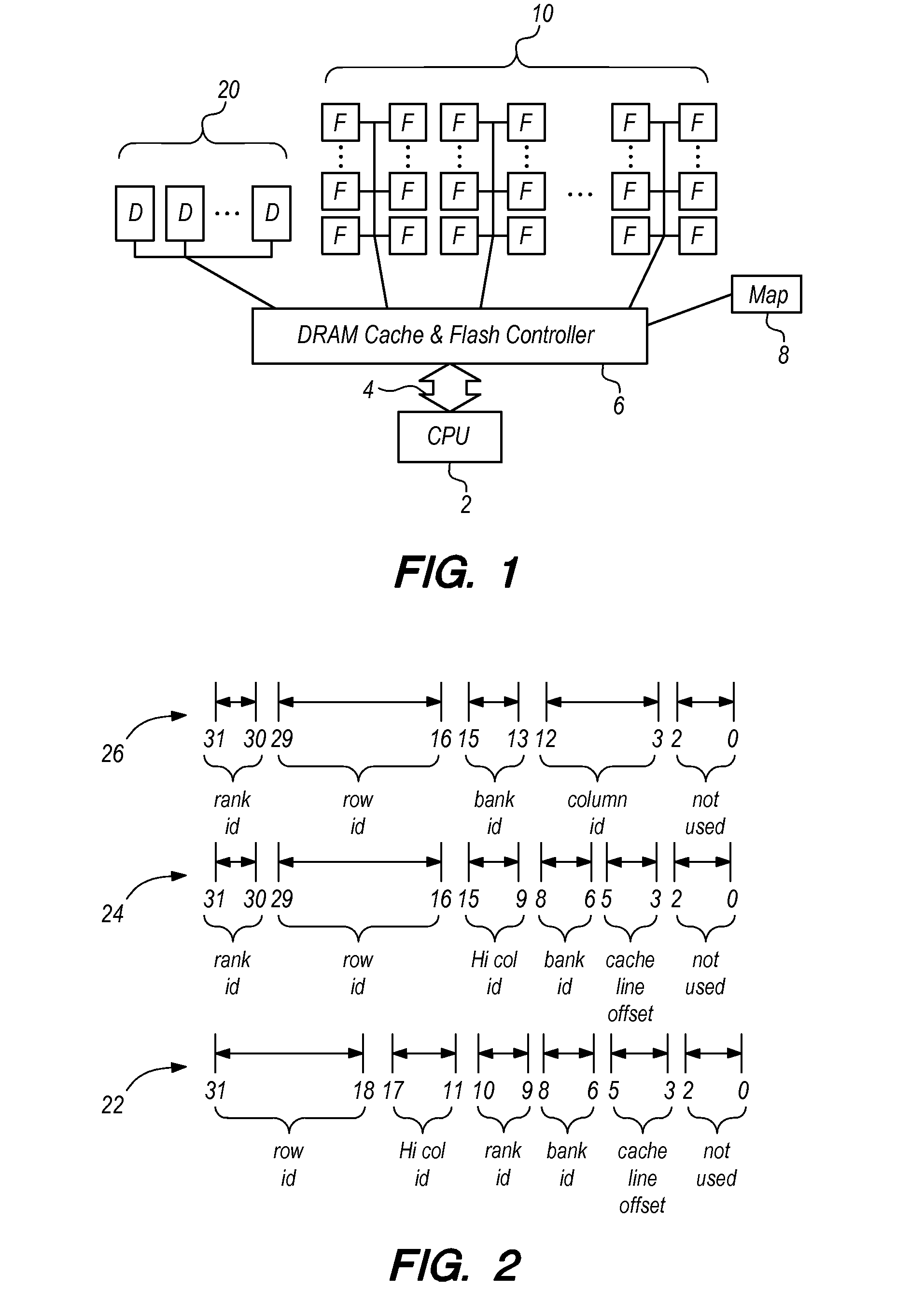

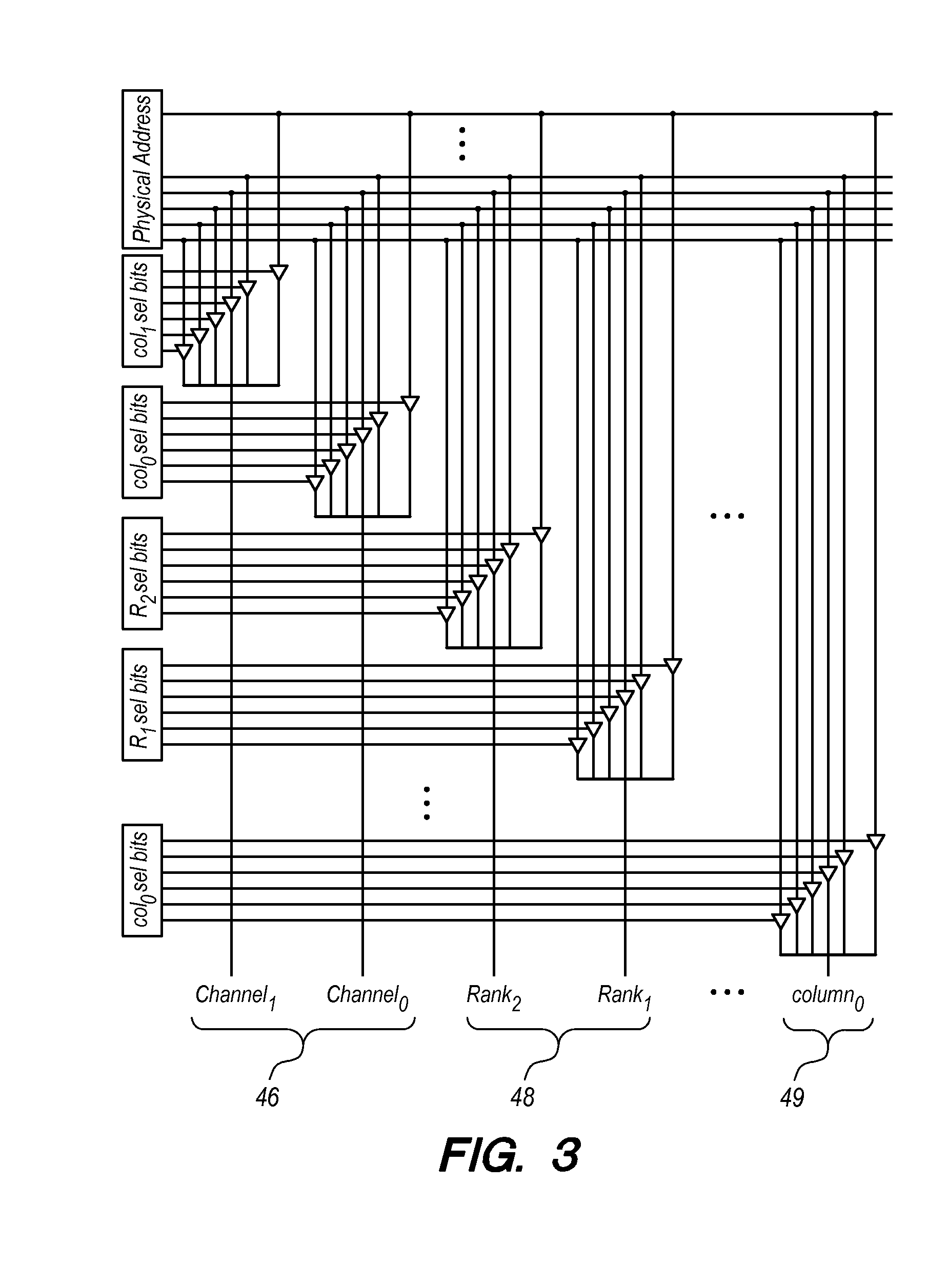

NVMM: An Extremely Large, Logically Unified, Sequentially Consistent Main-Memory System

InactiveUS20160253123A1Large capacityReduce power consumptionMemory architecture accessing/allocationInput/output to record carriersArea networkApplication software

Embodiments of both a non-volatile main memory (NVMM) single node and a multi-node computing system are disclosed. One embodiment of the NVMM single node system has a cache subsystem composed of all DRAM, a large main memory subsystem of all NAND flash, and provides different address-mapping policies for each software application. The NVMM memory controller provides high, sustained bandwidths for client processor requests, by managing the DRAM cache as a large, highly banked system with multiple ranks and multiple DRAM channels, and large cache blocks to accommodate large NAND flash pages. Multi-node systems organize the NVMM single nodes in a large inter-connected cache / flash main memory low-latency network. The entire interconnected flash system exports a single address space to the client processors and, like a unified cache, the flash system is shared in a way that can be divided unevenly among its client processors: client processors that need more memory resources receive it at the expense of processors that need less storage. Multi-node systems have numerous configurations, from board-area networks, to multi-board networks, and all nodes are connected in various Moore graph topologies. Overall, the disclosed memory architecture dissipates less power per GB than traditional DRAM architectures, uses an extremely large solid-state capacity of a terabyte or more of main memory per CPU socket, with a cost-per-bit approaching that of NAND flash memory, and performance approaching that of an all DRAM system.

Owner:JACOB BRUCE LEDLEY

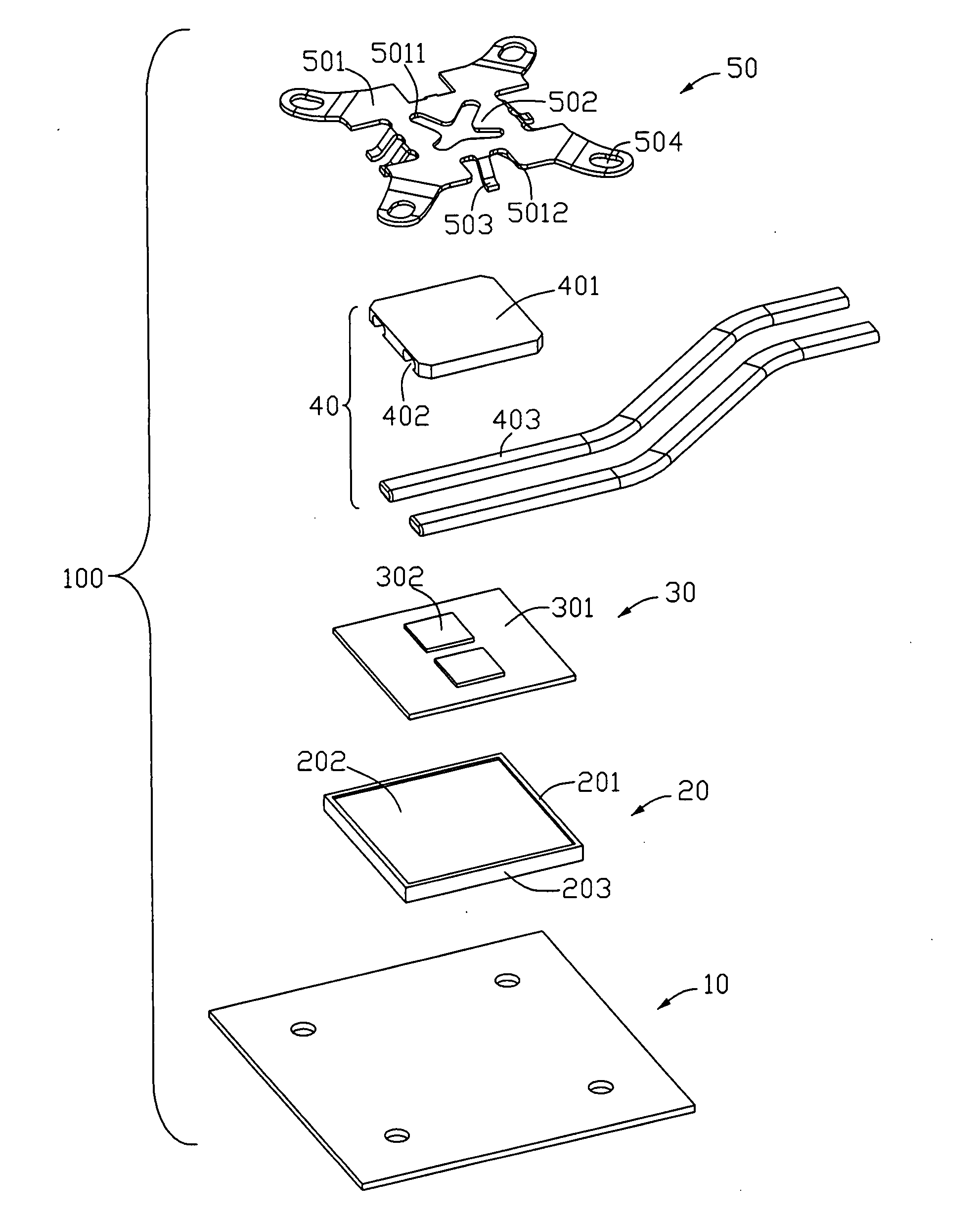

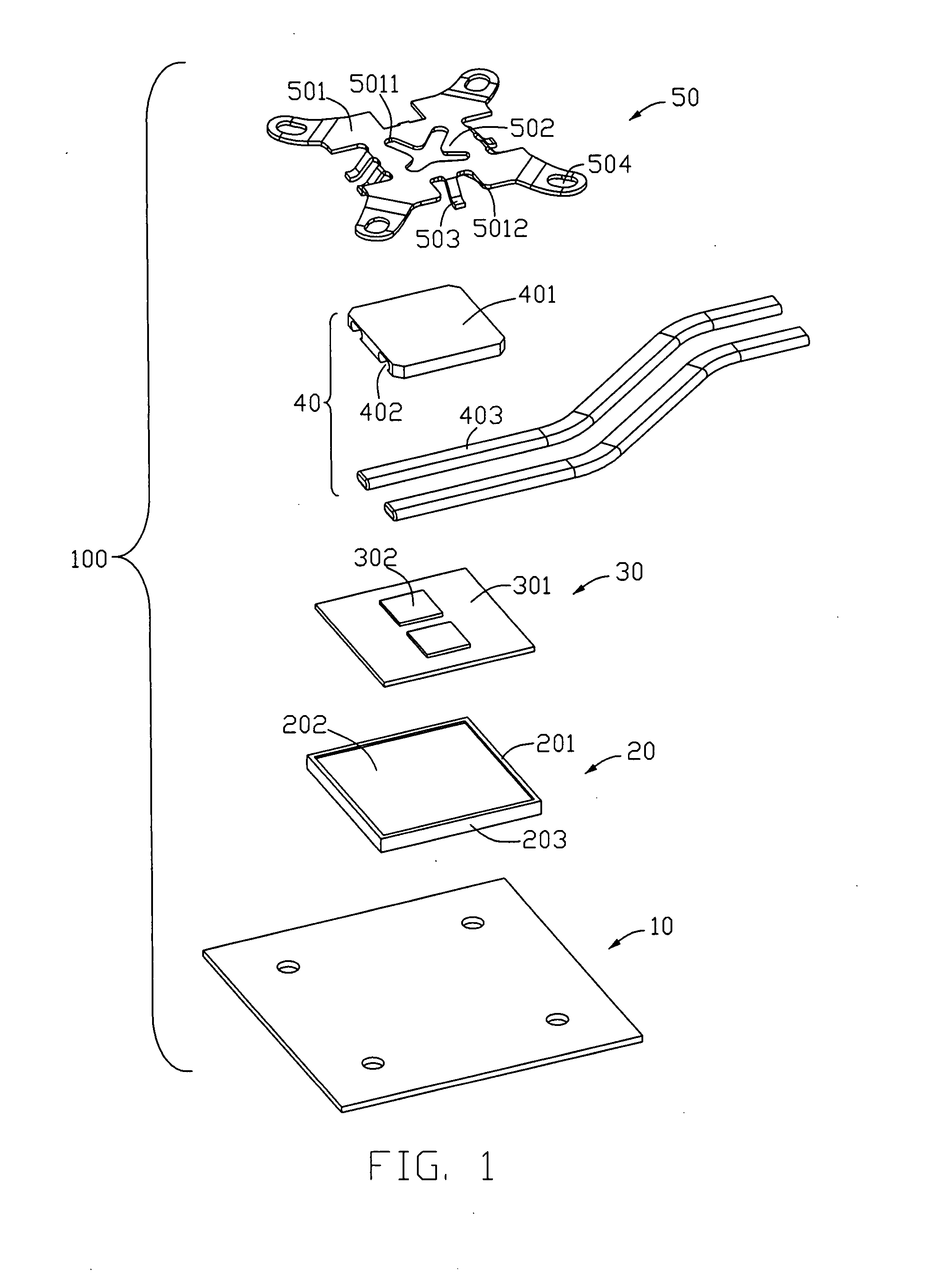

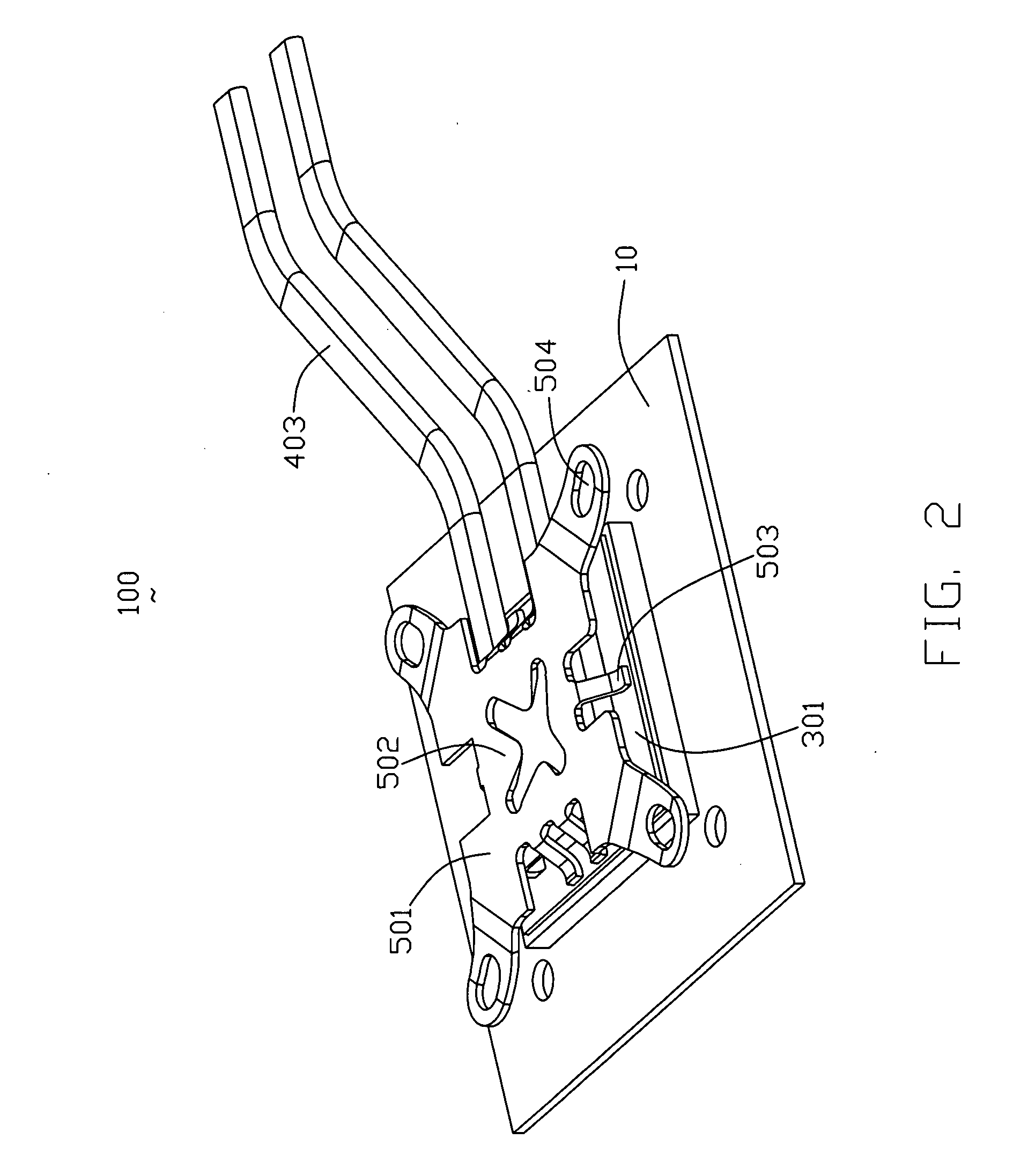

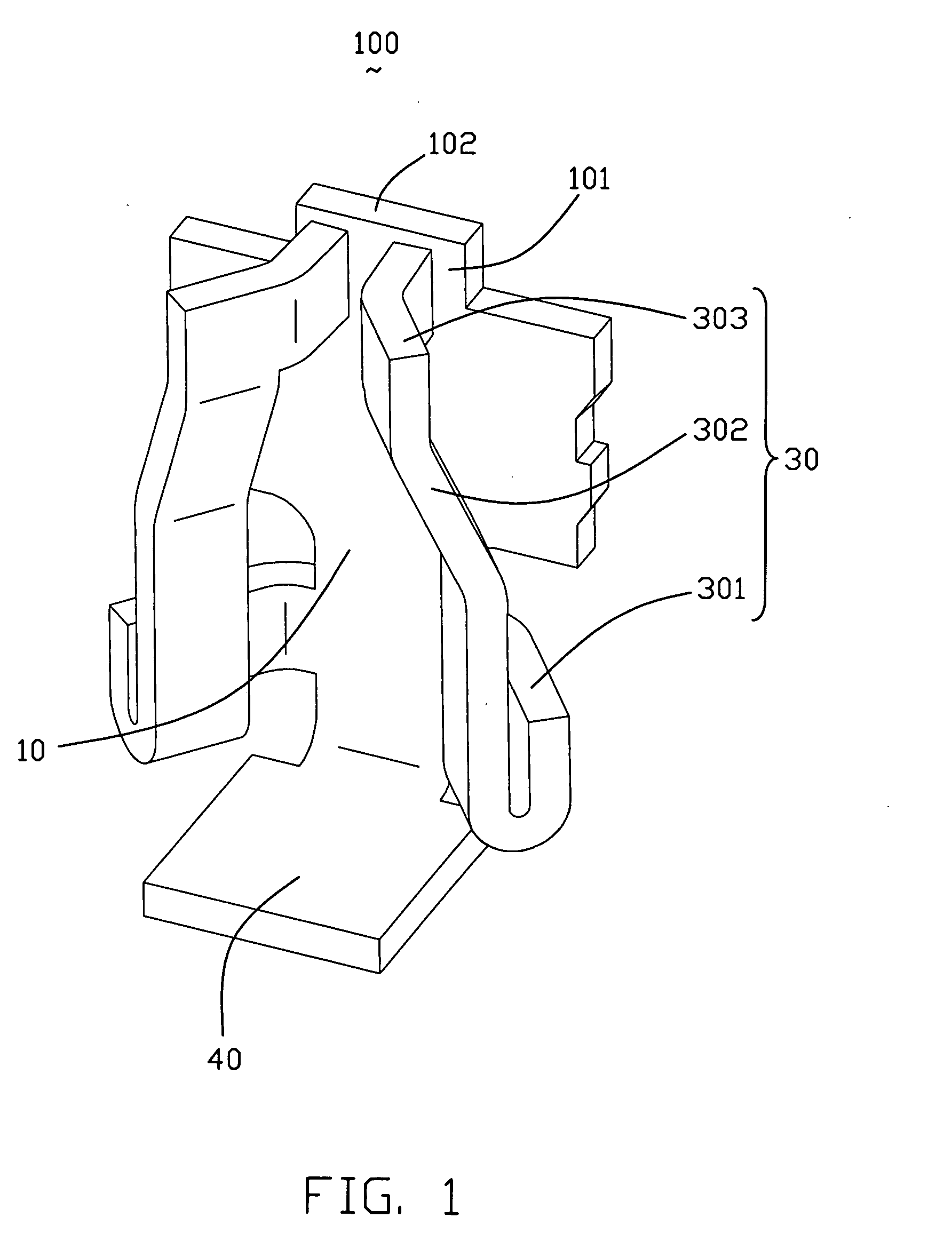

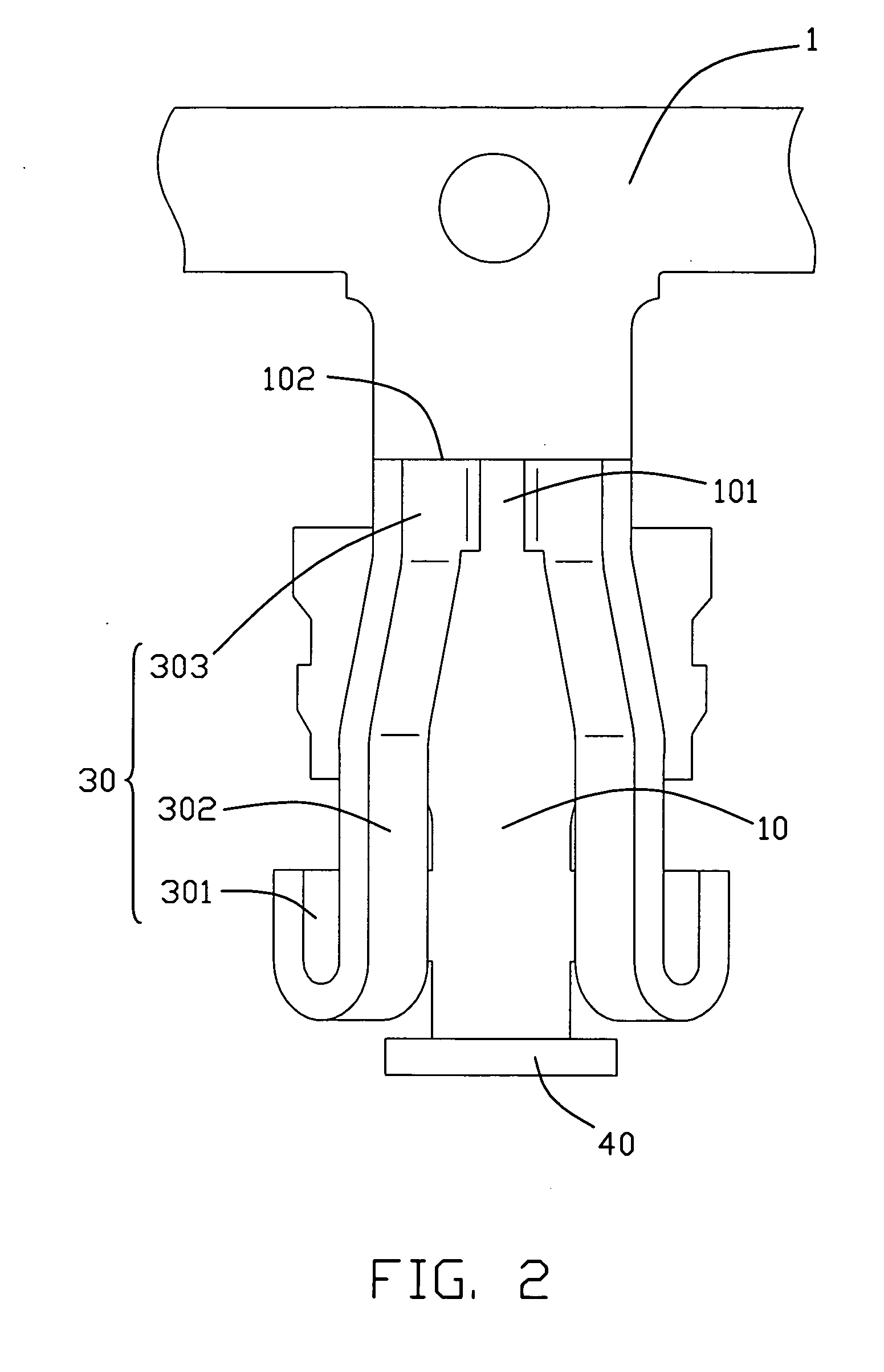

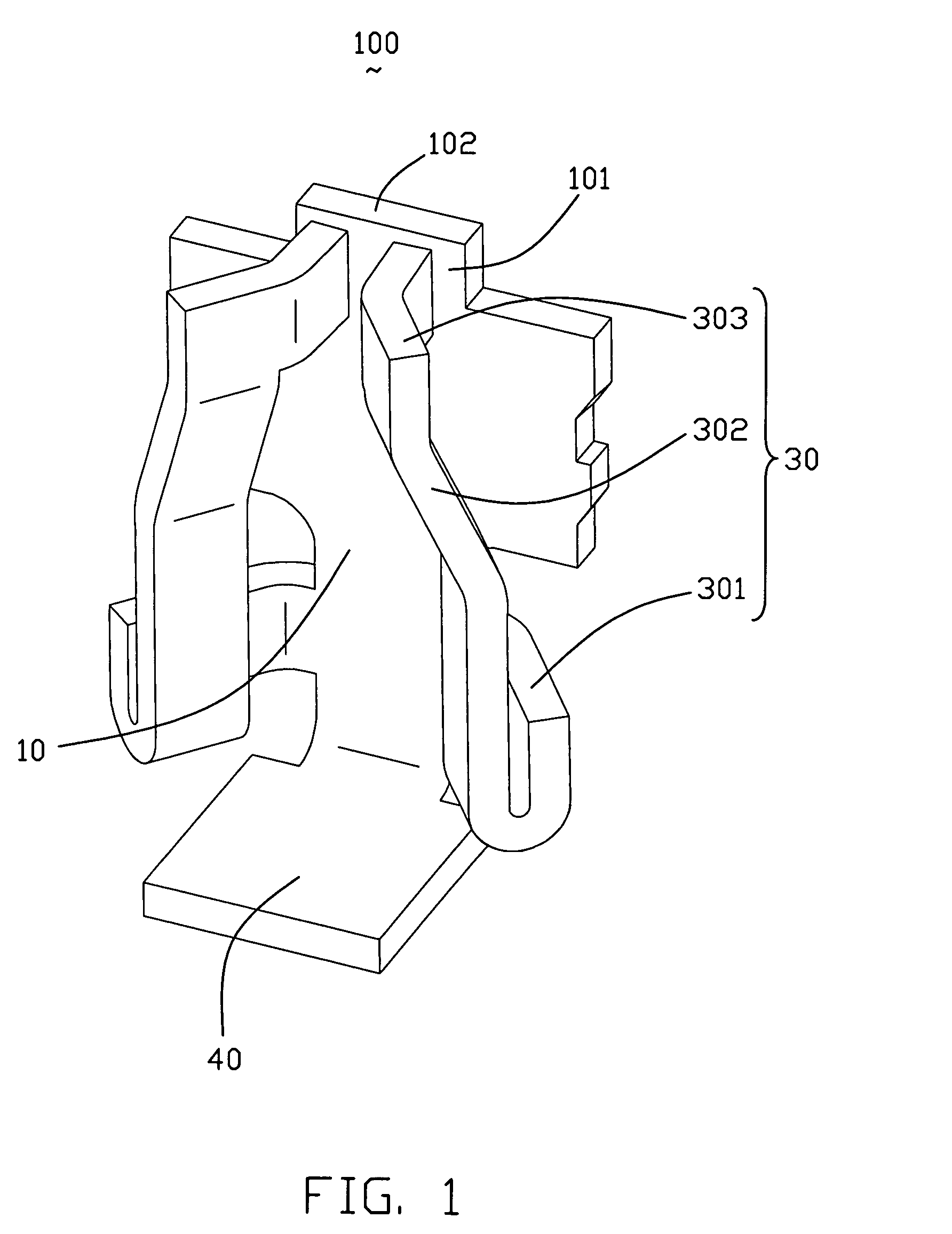

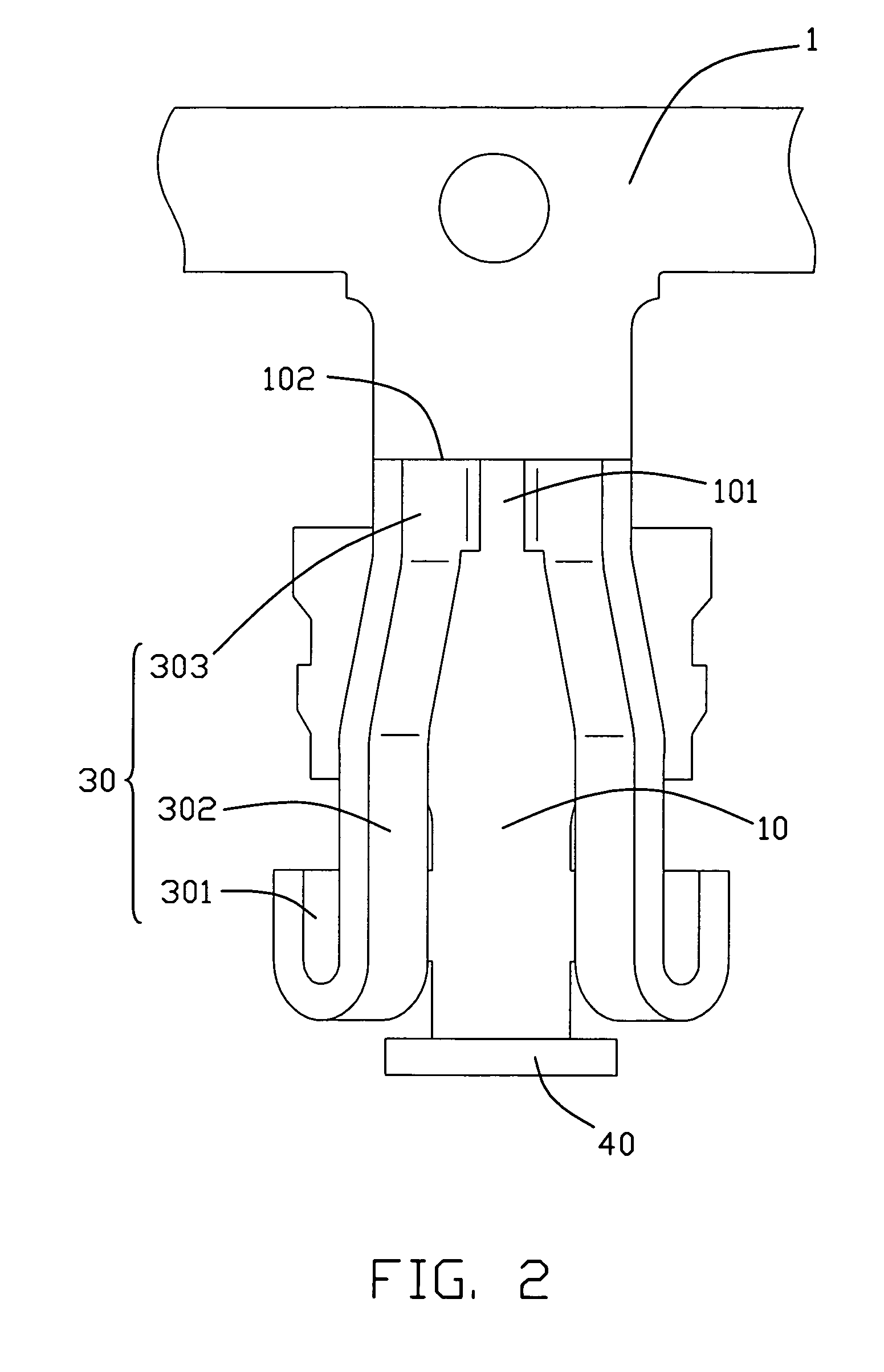

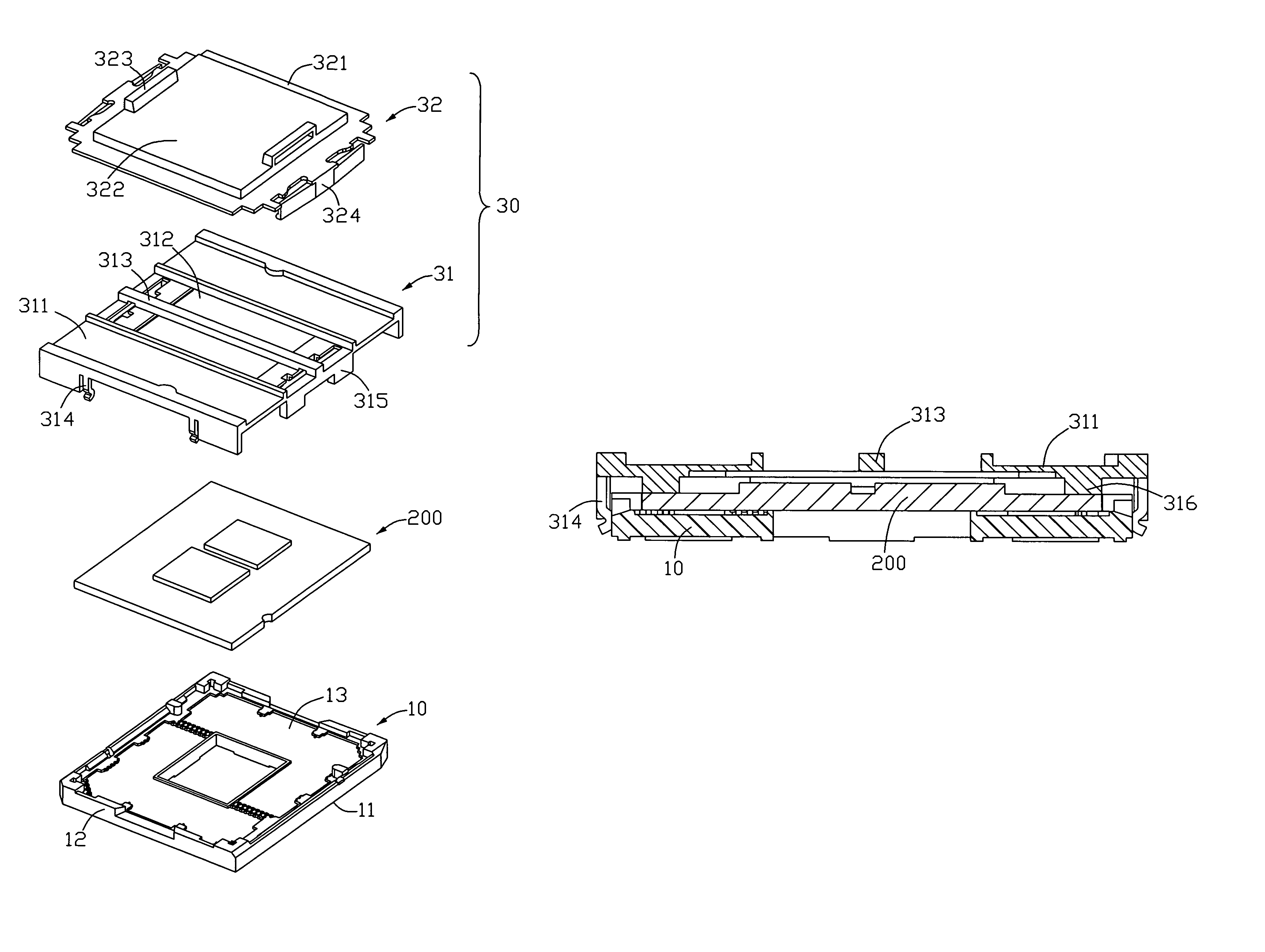

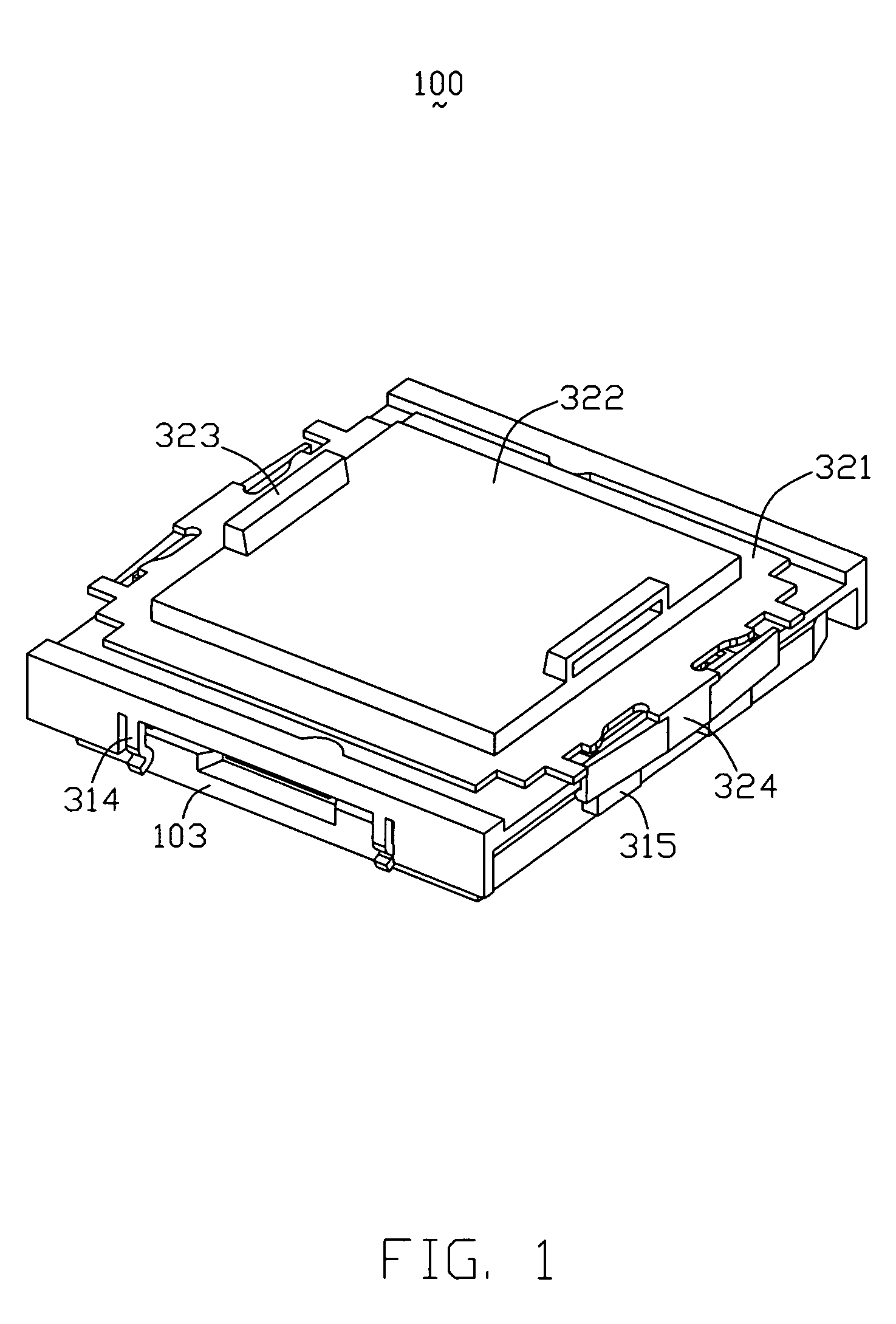

Electrical connector with clip mechanism

InactiveUS20080291638A1Equally distributedEfficiently prevent the CPU chip from warpageSemiconductor/solid-state device detailsCoupling device detailsCPU socketEngineering

Provided a clip set (50) for pressing a CPU toward LGA contacts of a CPU socket comprises, a rigid body having an elongate base (501) with upper and lower edges. A set of first pressing finger (502) extends from the upper edge traversally and away from the base. Each of the first pressing fingers includes a first pressing pad located at a first plane. A set of second pressing finger (503) extends from and away from the base, and includes a second pressing pad located at a second plane differential to the first plane. The set of first and second pressing fingers are dimensioned to be located in two different levels so as to assert downward pressure to a die (302) of the CPU and a substrate (301) of the CPU, respectively.

Owner:HON HAI PRECISION IND CO LTD

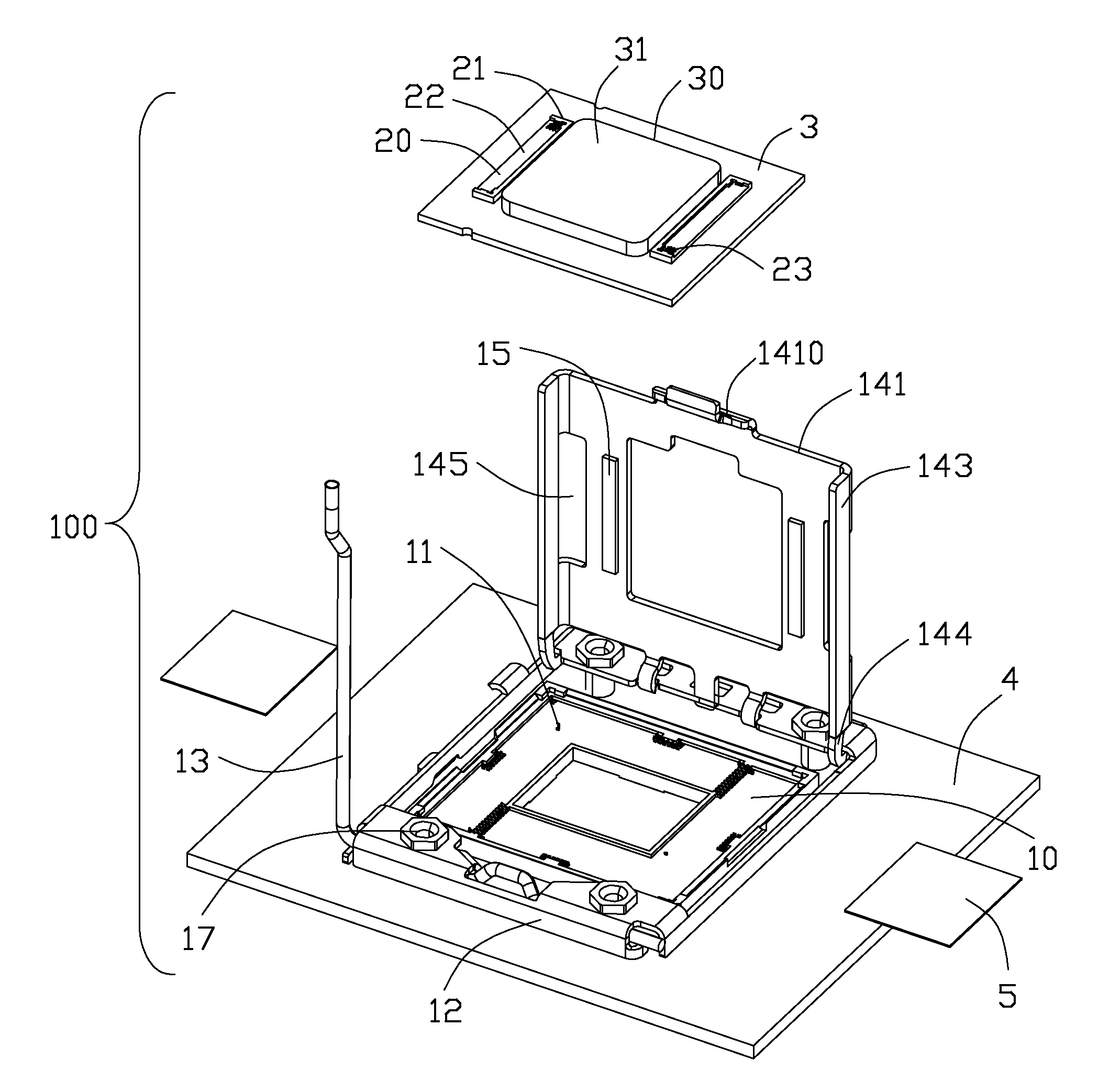

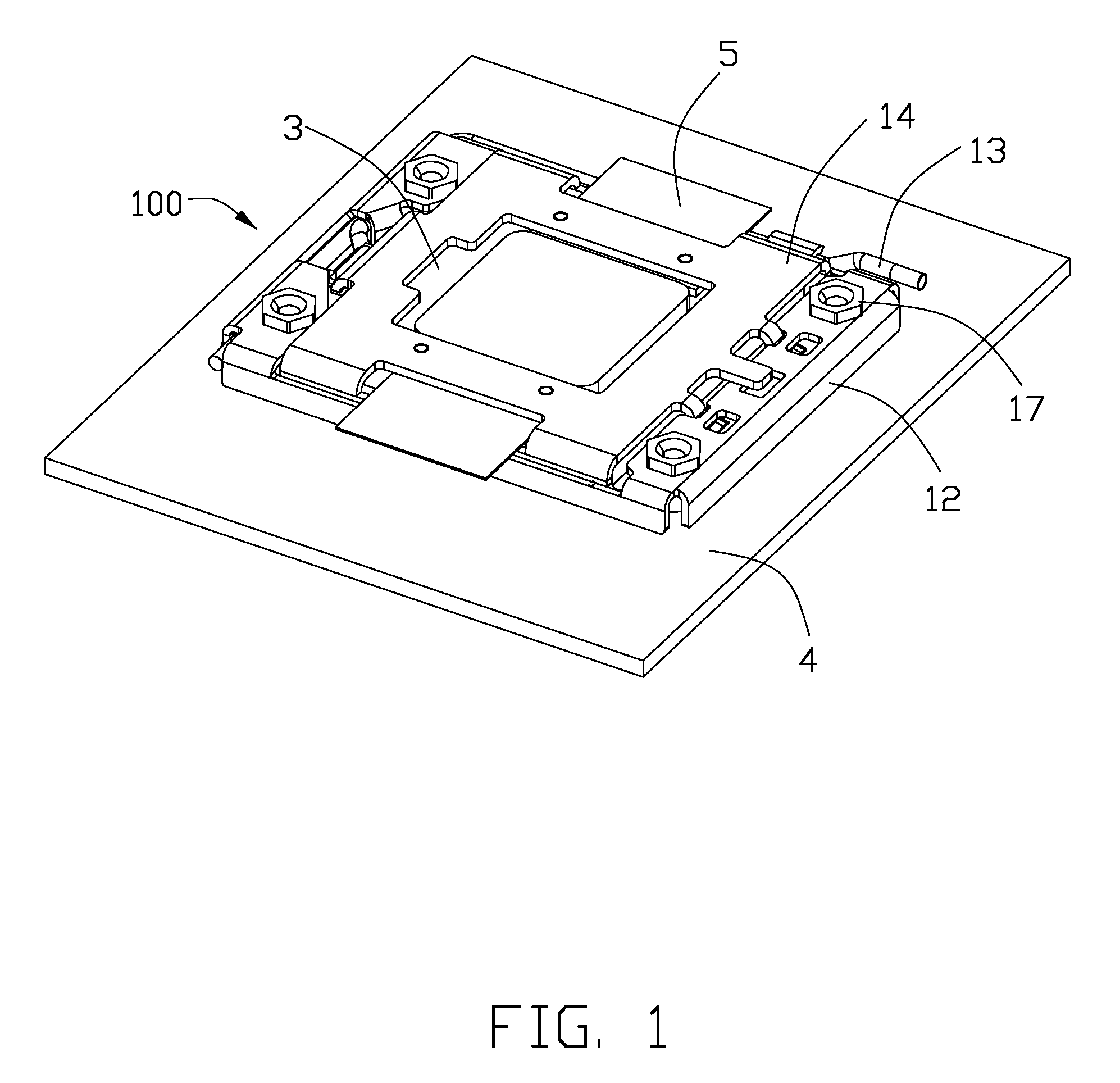

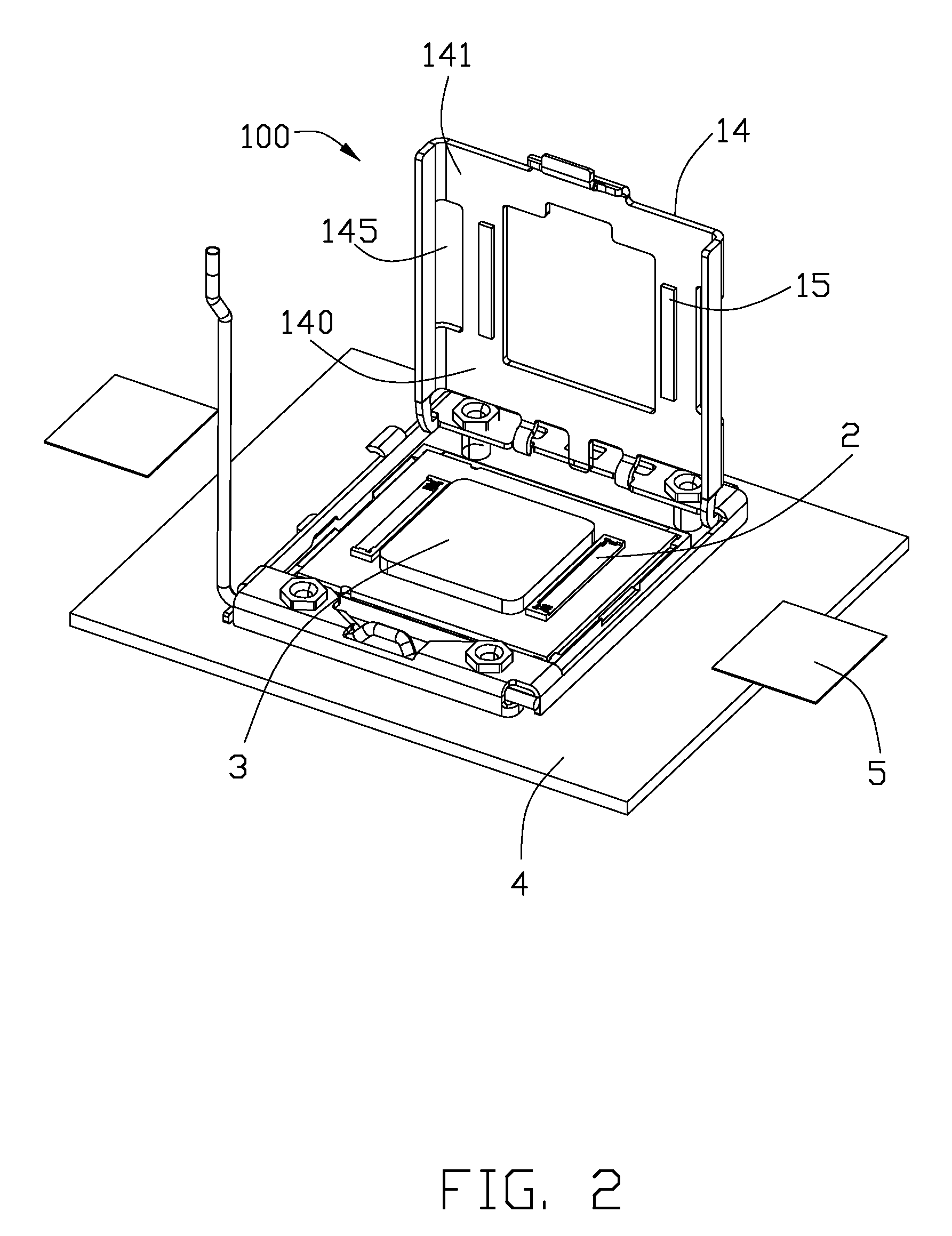

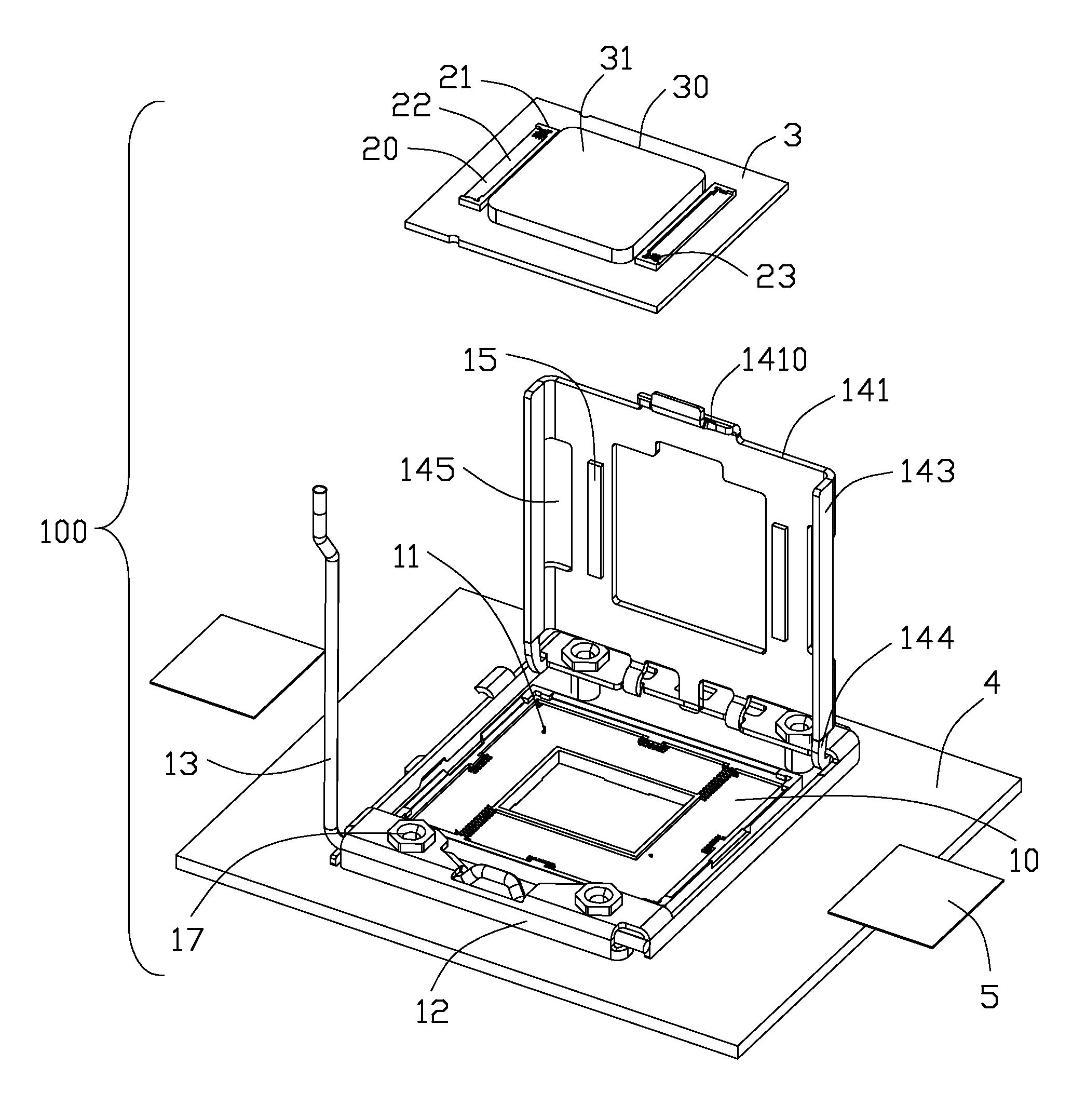

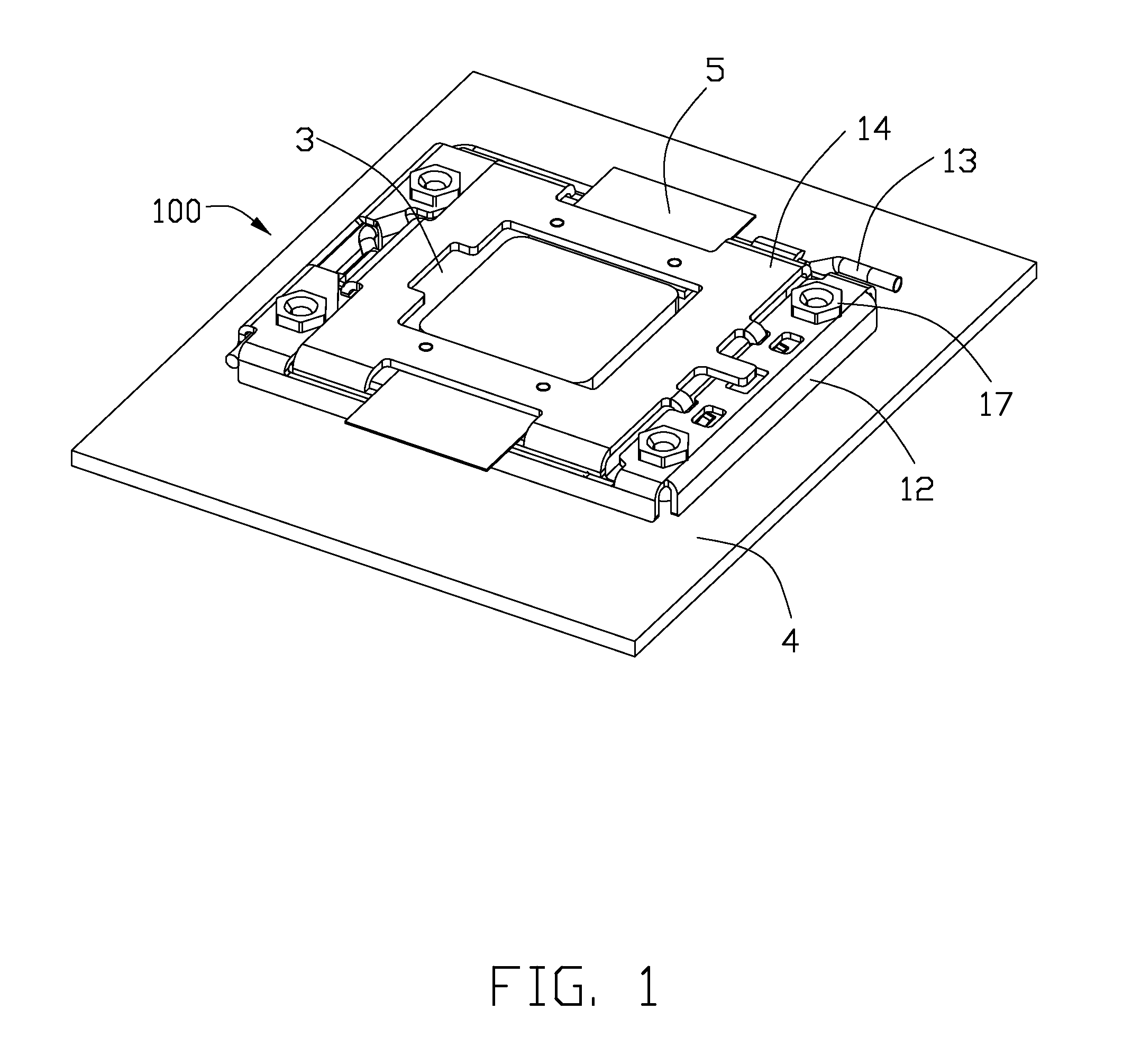

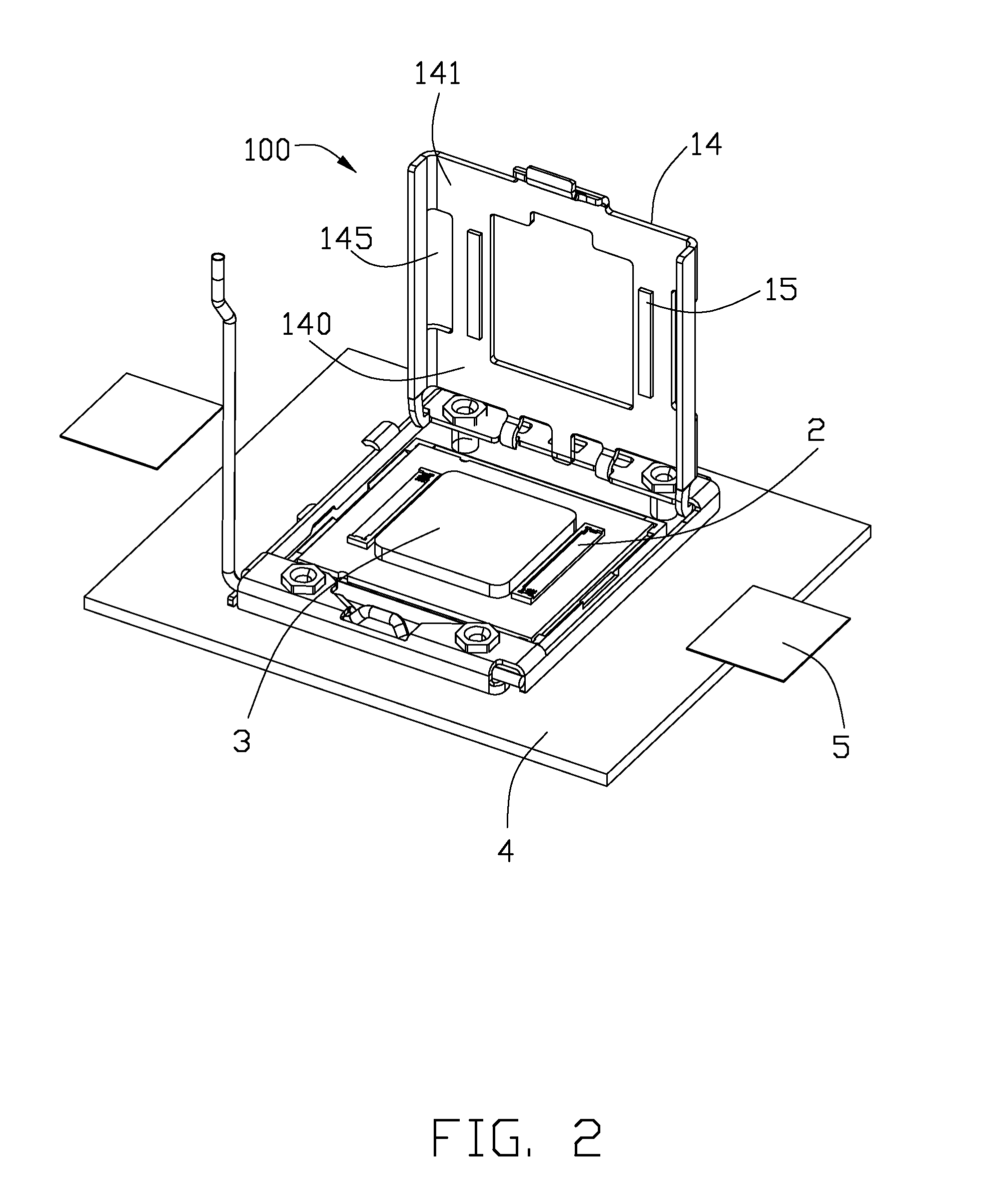

Independent loading mechanism facilitating interconnections for both CPU and flexible printed cable

Owner:HON HAI PRECISION IND CO LTD

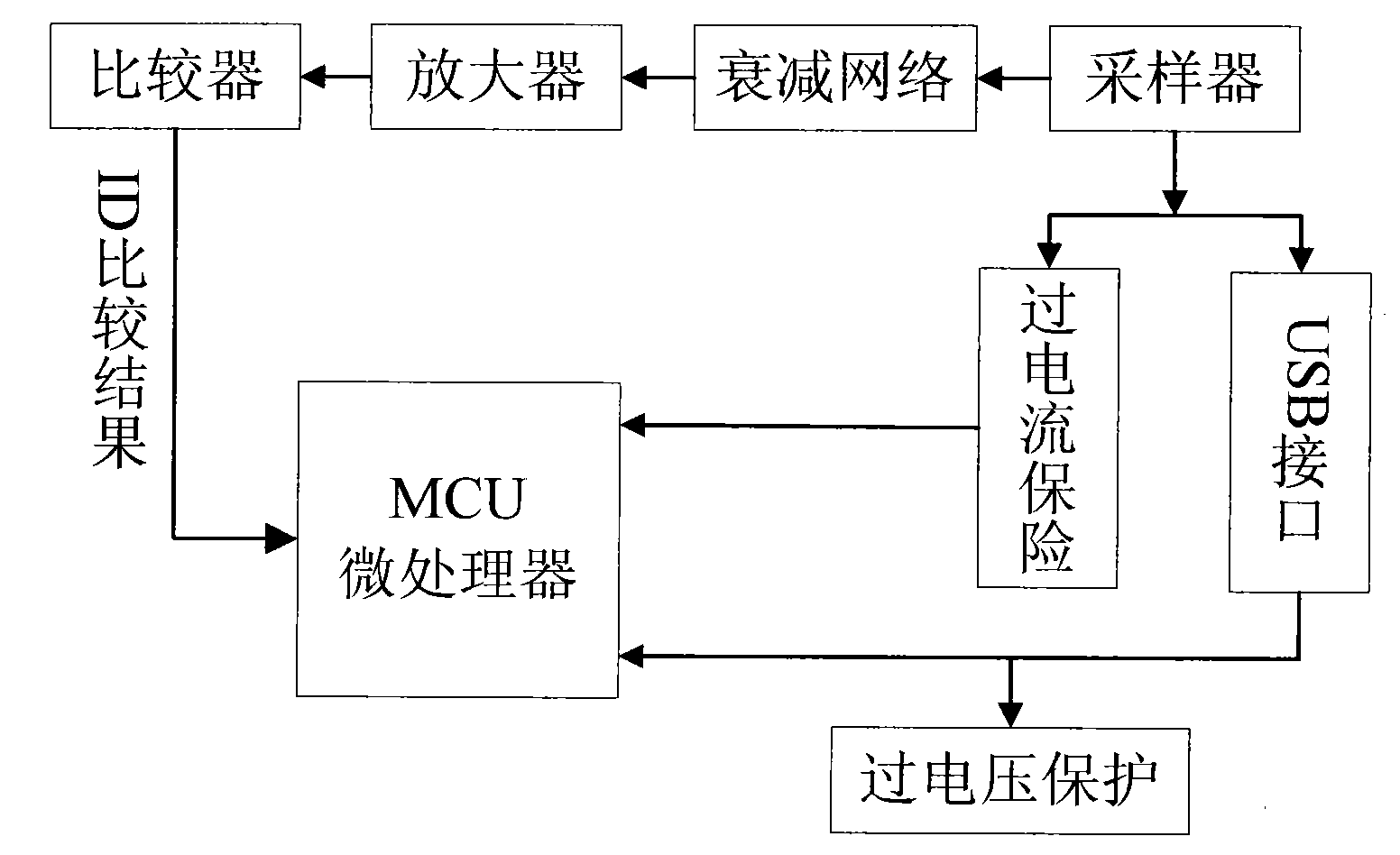

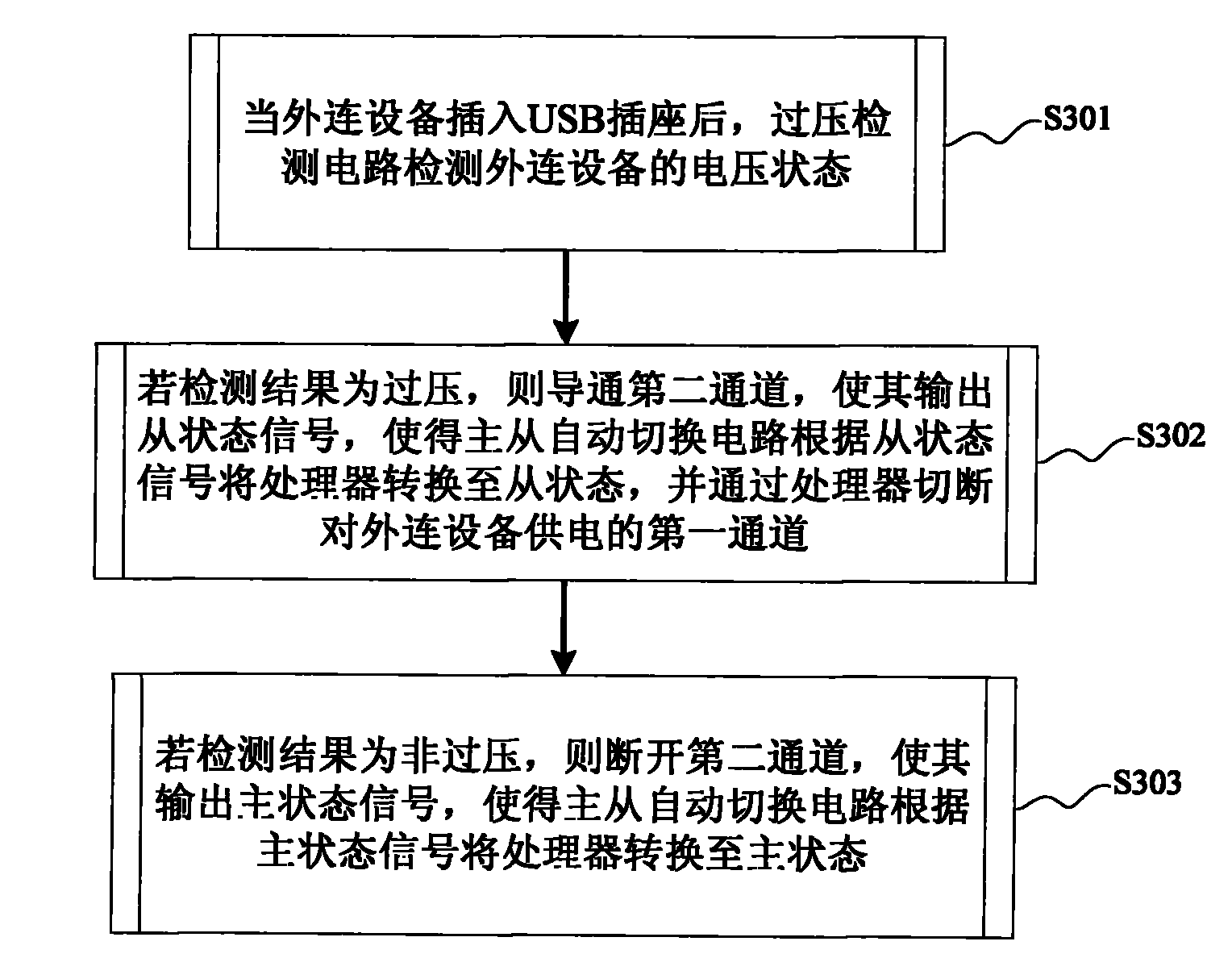

Method and device for realizing OTG based on USB socket

InactiveCN101944074ARealize automatic switchingAvoid conflict situationsElectric digital data processingElectricityOvervoltage

The invention discloses a method and a device for realizing OTG based on a UBS socket. The device comprises a first channel, an overvoltage detection circuit, a second channel, an automatic master-slave switching circuit and a slave state holding circuit, wherein the first channel is used for supplying electricity to external equipment; the overvoltage detection circuit is used for detecting the voltage state on the channel of the external equipment; the second channel is used for controlling state switching according to a received detection result sent by the overvoltage detection circuit and outputting corresponding signals to a processor; the automatic master-slave switching circuit controls the processor which is connected with the automatic master-slave switching circuit to switch to the slave state according to the slave state signal, and cuts off the first channel for supplying the electricity to the external equipment through the processor, or controls the processor which is connected with the automatic master-slave switching circuit to switch to the master state according to the master state signal; and the slave state holding circuit enables the second channel to keep on state according to the slave state signal of the processor. By successfully adopting effective combination of a passive device and a voltage standard, the method and the device realize the automatic switching of an ID state and effectively avoid the phenomenon that similar states collide.

Owner:ZTE CORP

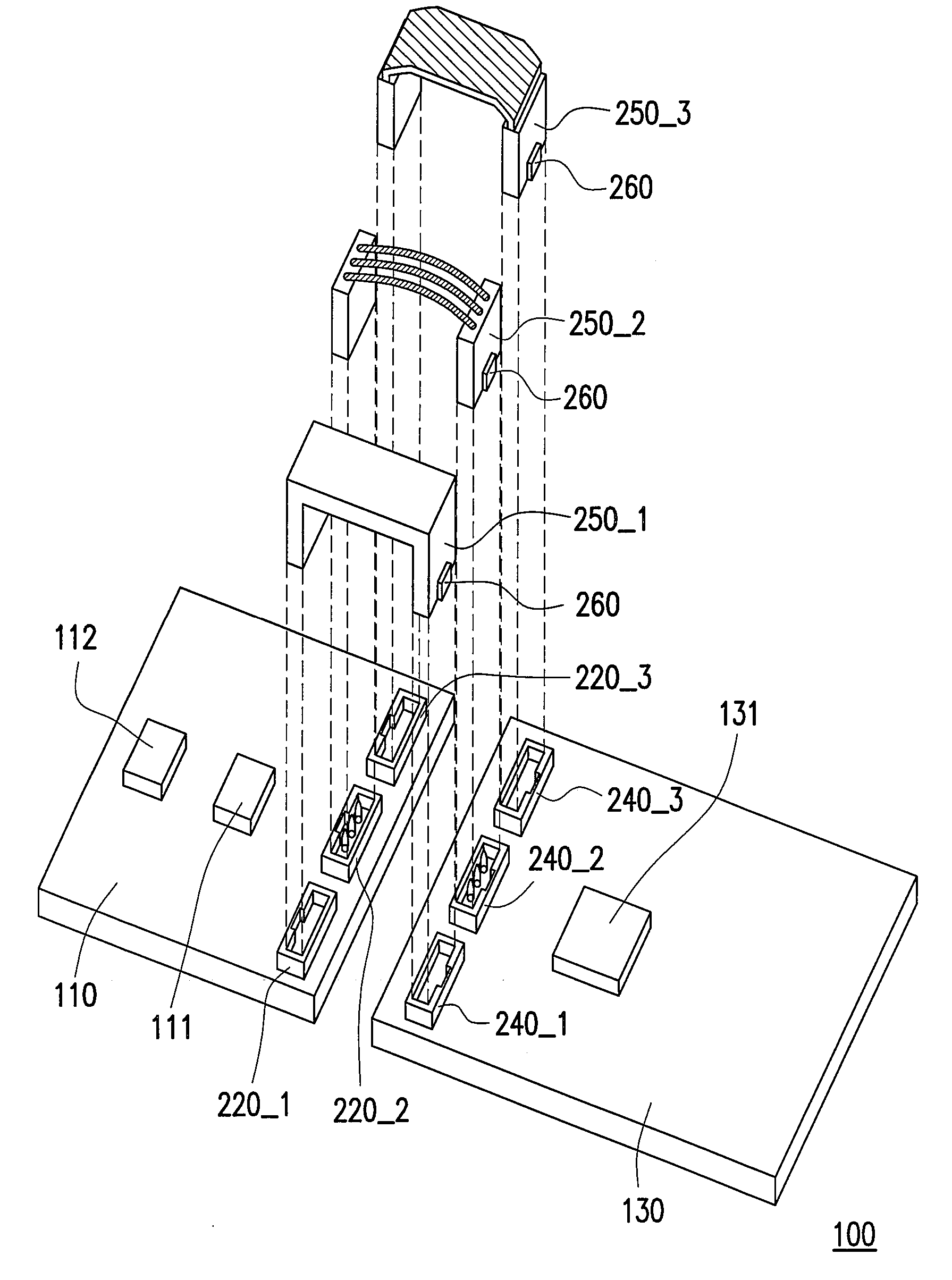

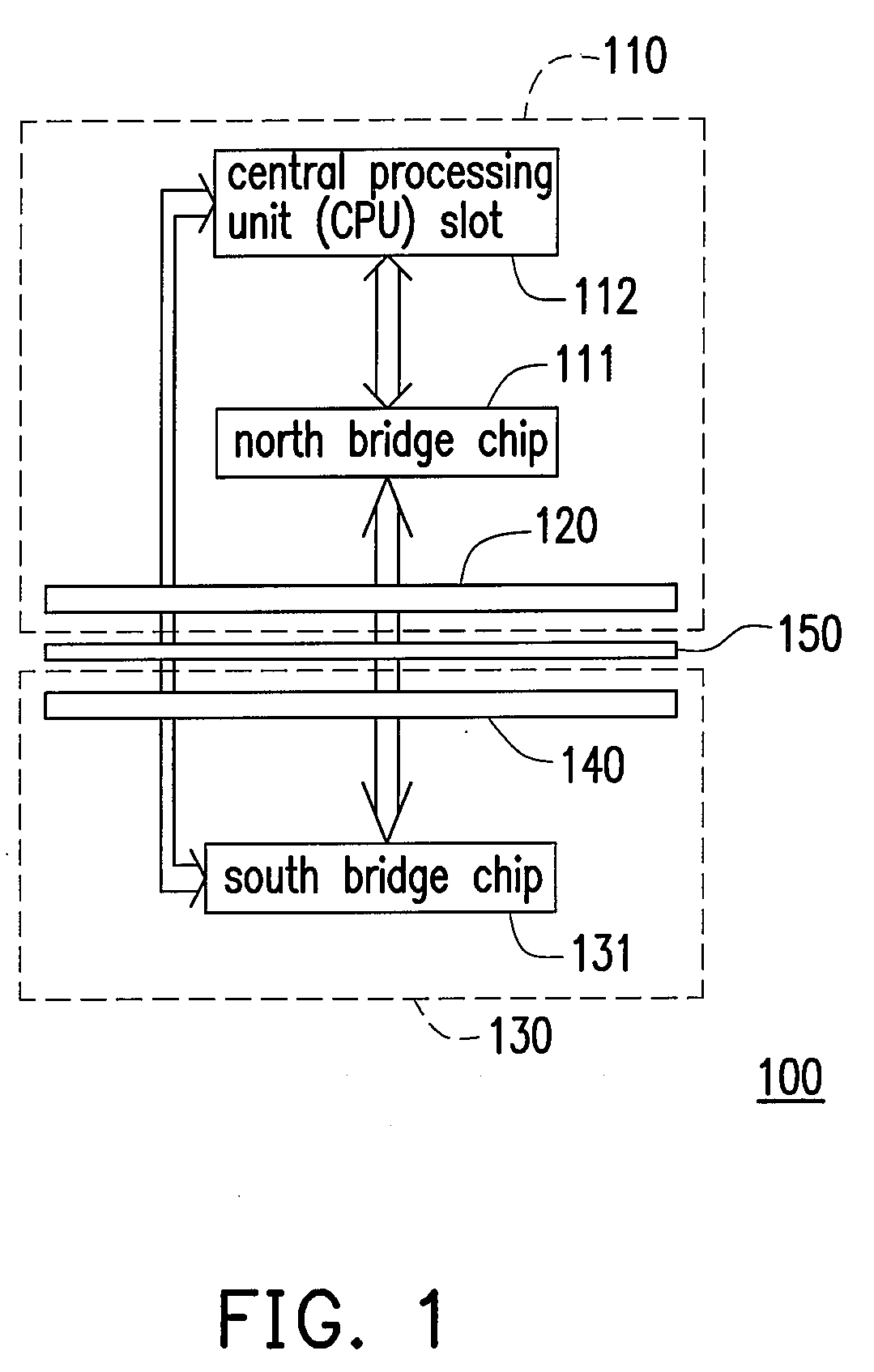

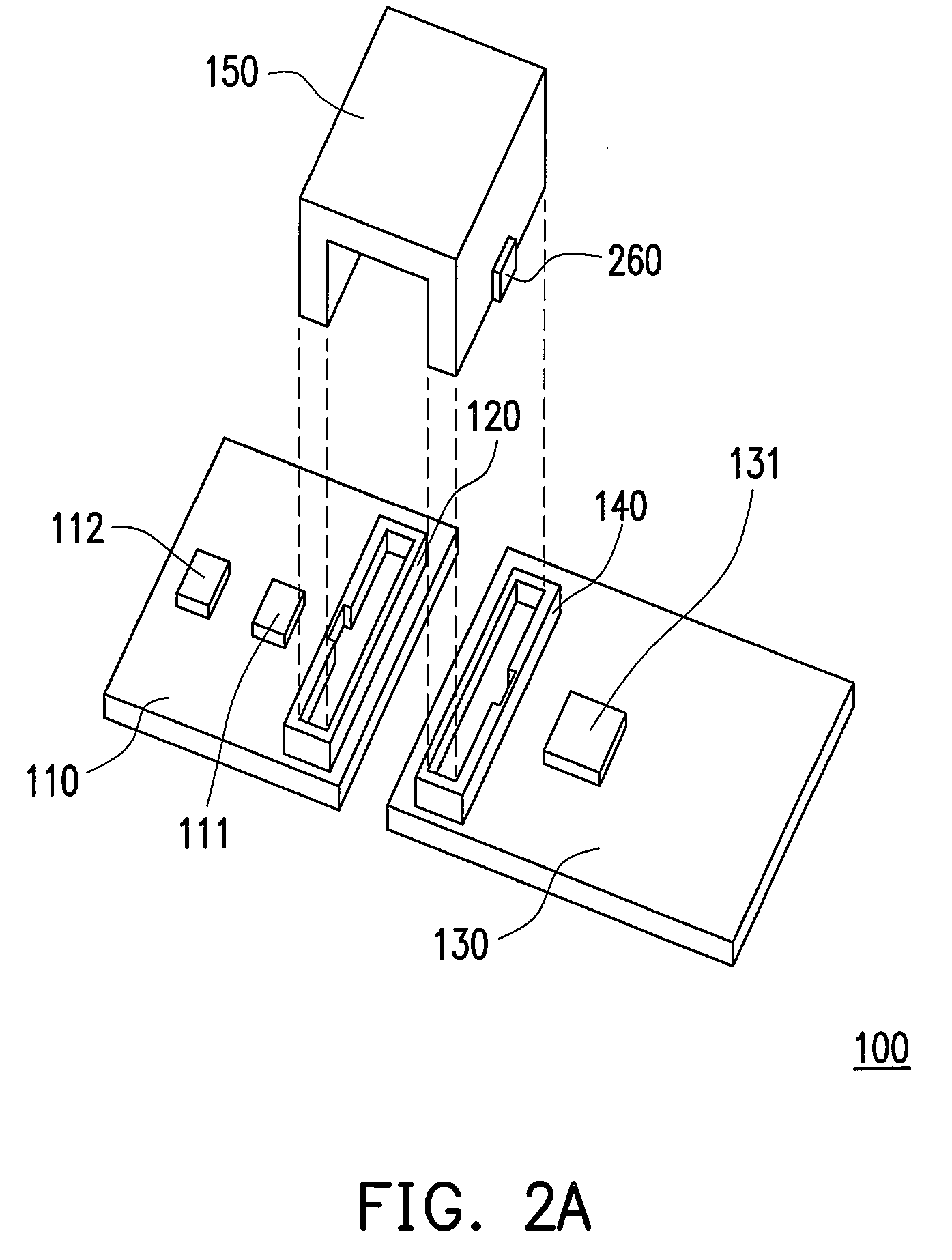

Modularized motherboard

InactiveUS20090031062A1Improve computing powerRecovery functionOrthogonal PCBs mountingElectric digital data processingModularityCPU socket

A modularized motherboard is provided. The modularized motherboard includes a first circuit board, a second circuit board and a connecting device. The first circuit board includes a north bridge chip, a central processing unit (CPU) slot and a first connecting port. The CPU slot is coupled to the north bridge chip and is used for installing a CPU. The second circuit board is independent of the first circuit board. The second circuit board includes a second connecting port and a south bridge chip. The south bridge chip is coupled to the north bridge chip via the second connecting port the first connecting port. The connecting device is coupled between the first connecting port and the second connecting port.

Owner:ASUSTEK COMPUTER INC

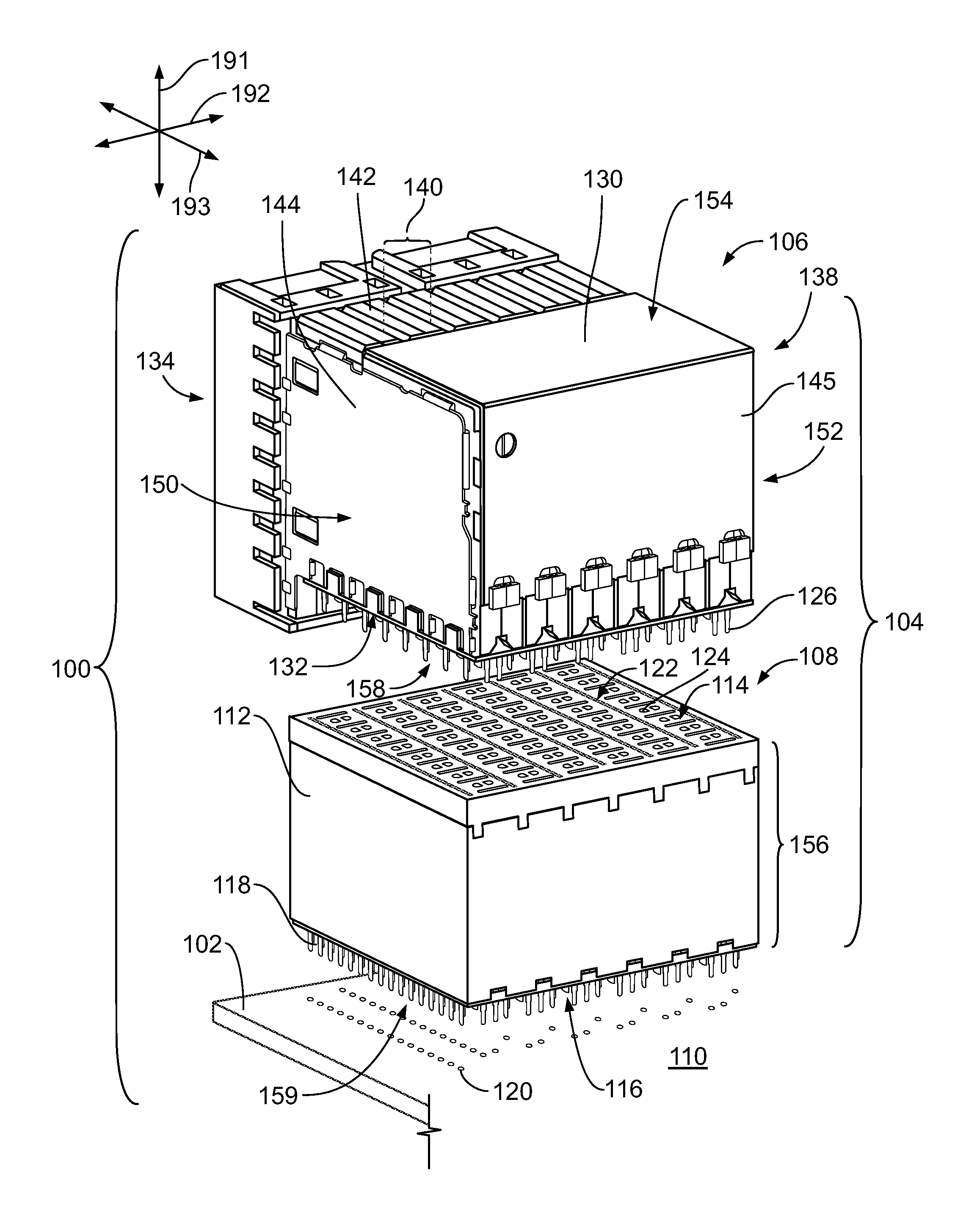

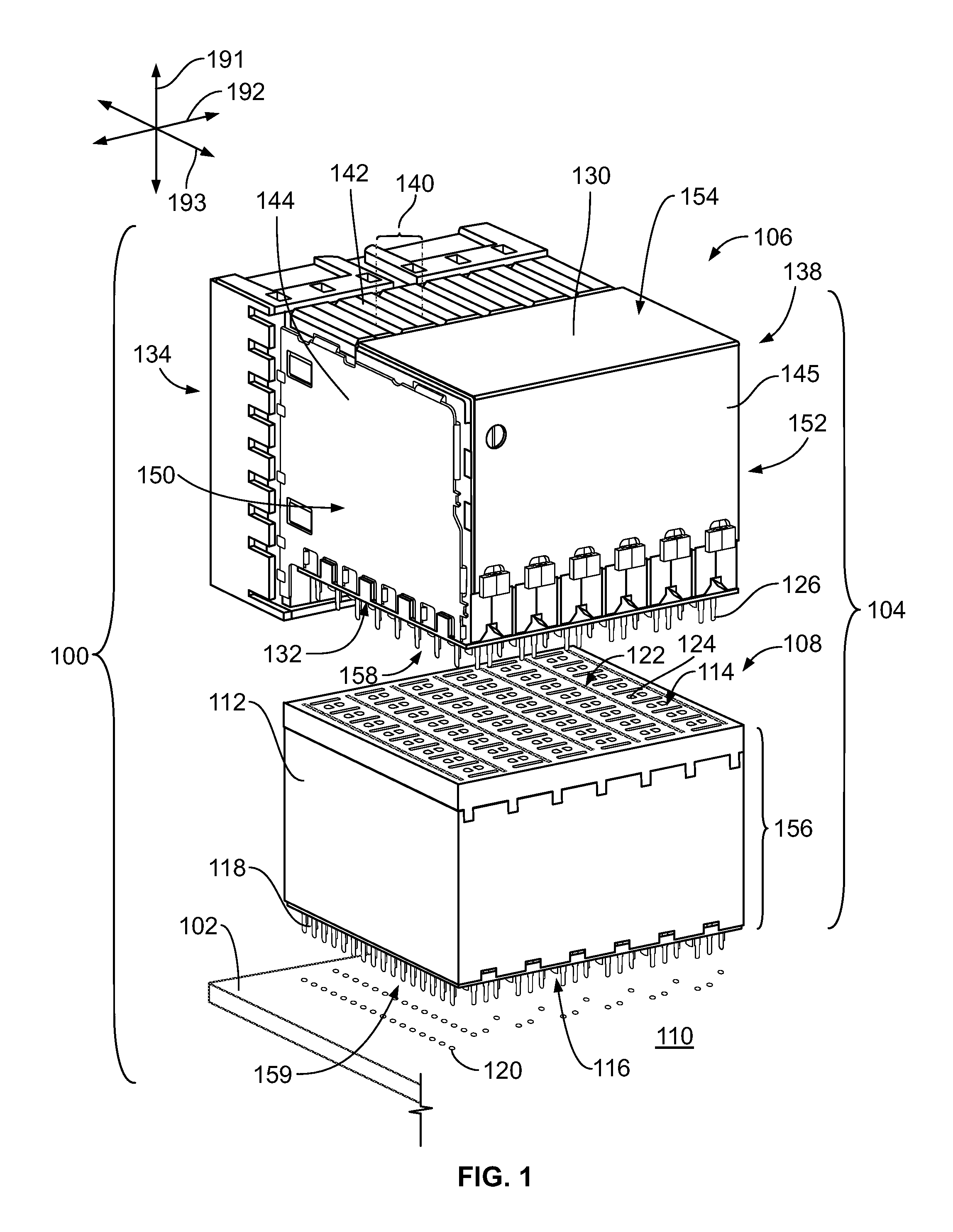

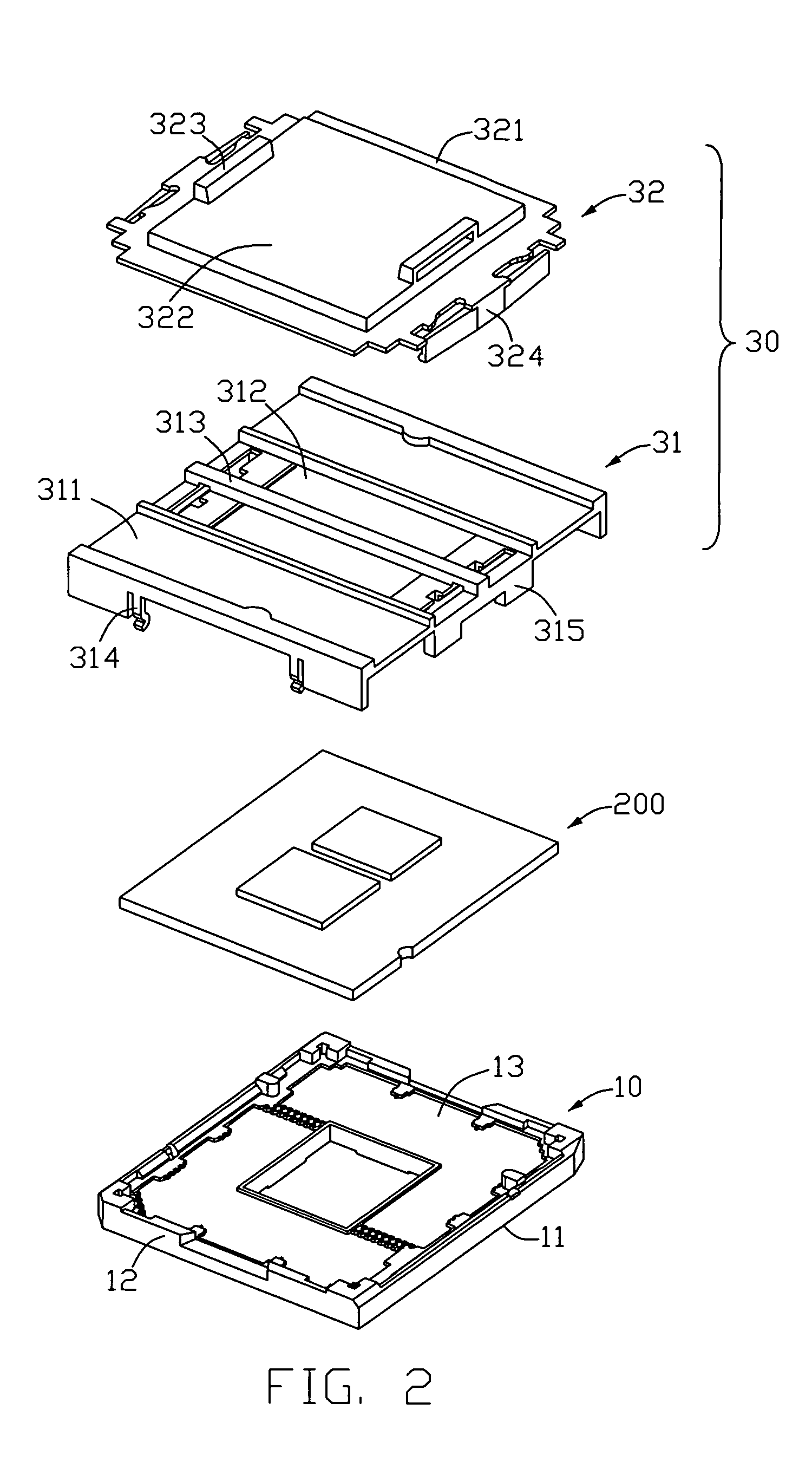

Independent loading mechanism facilitating interconnections for both CPU and flexible printed cable

InactiveUS20110287639A1Engagement/disengagement of coupling partsTwo-part coupling devicesElectricityCPU socket

An electrical connector assembly comprises a central processing unit (CPU), a plurality of cable connectors soldered on the CPU and a CPU socket for electrical connecting the CPU to a printed circuit board (PCB). Each cable connector includes a base having a plurality of first terminals received therein, for contacting with conductive points of the cable. The CPU socket includes an insulating housing having a plurality of second terminals received therein and a loading mechanism attached to the insulating housing. The loading mechanism can simultaneously pressing the cables against the cable connectors and the CPU toward the CPU socket for electrically connecting the CPU with the cables and the PCB.

Owner:HON HAI PRECISION IND CO LTD

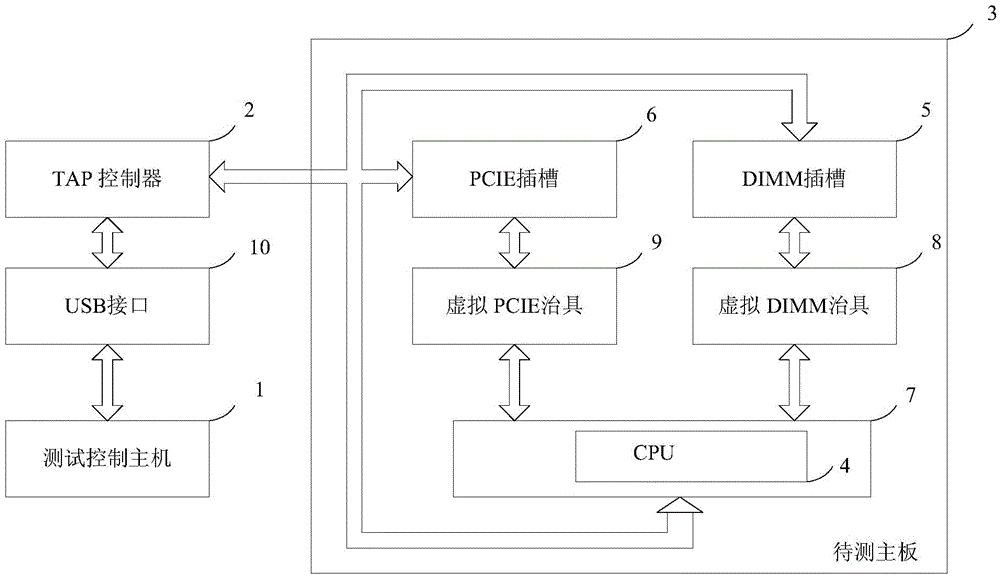

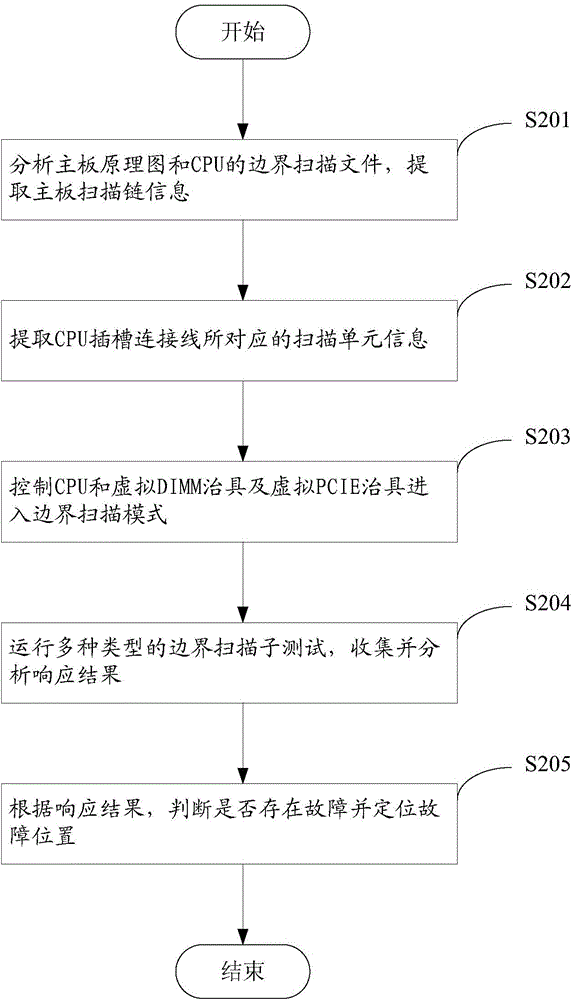

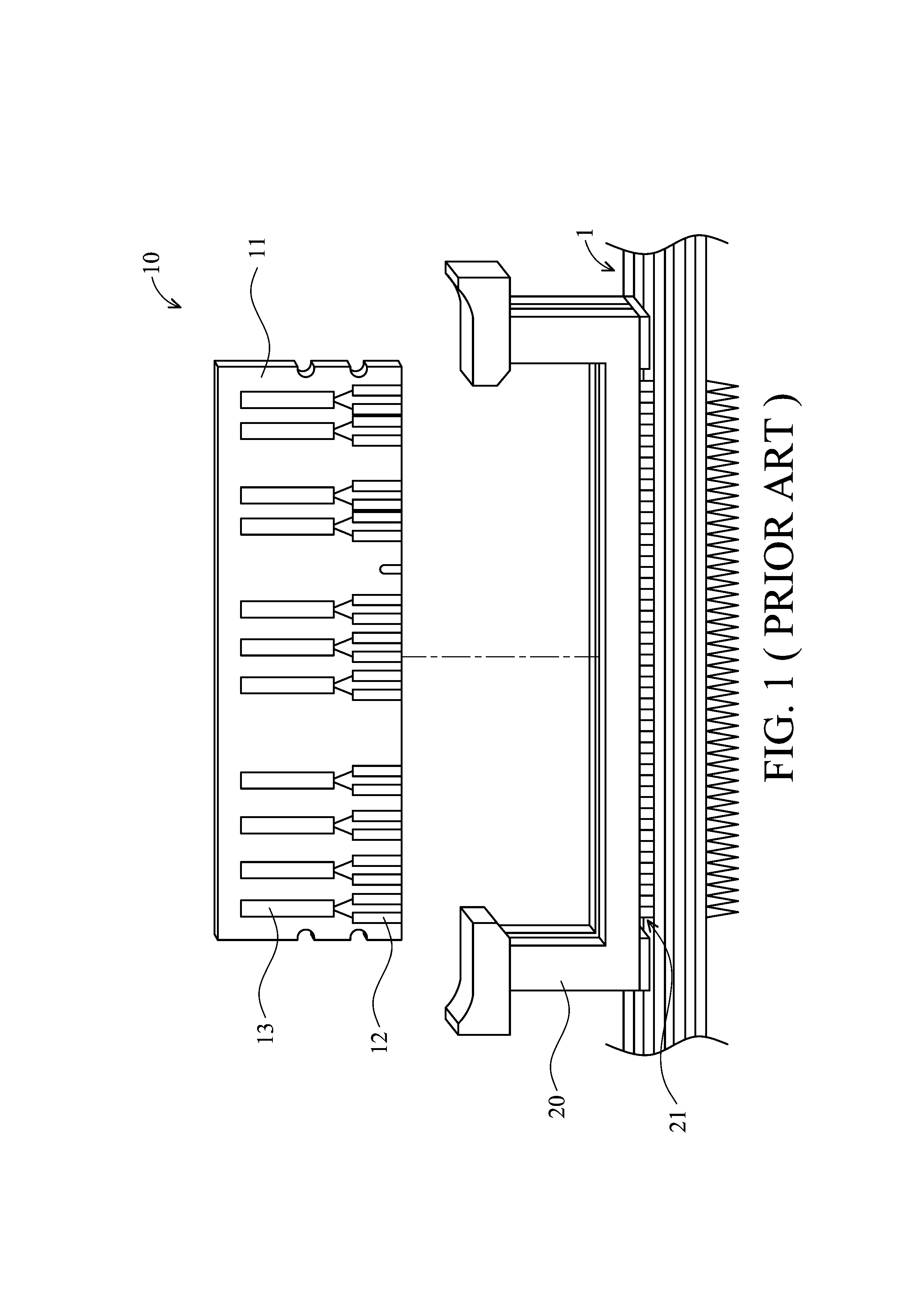

Connection test method and device of motherboard CPU (Central Processing Unit) slot based on boundary scan

The invention provides a connection test method of a motherboard CPU (Central Processing Unit) slot based on boundary scan, which comprises the following steps of analyzing a to-be-tested motherboard schematic diagram and a boundary scan description language file of a motherboard CPU, a virtual DIMM (dual In-line memory module) jig and a virtual PCIE jig, and extracting scan chain information of the to-be-tested motherboard; extracting scan unit information corresponding to a to-be-tested motherboard CPU slot connecting line; a to-be-tested motherboard CPU, the virtual DIMM jig and the virtual PCIE jig are controlled on a test control motherboard through a TAP controller to enter a boundary scan mode; running multiple types of boundary scan child tests, and collecting and analyzing a responding result; judging whether the to-be-tested motherboard is fault or not and locating the fault position according to the responding result. According to a connection test device and the method, a CPU signal transfer jig is no need to be designed and manufactured, although the virtual DIMM jig and the virtual PCIE jig are needed to be used, the design and the manufacturing process are both simple. Outage for switching hardware in the testing process is not needed. Once the inserting connection of the hardware is finished, all tests can be completed at one time.

Owner:INVENTEC PUDONG TECH CORPOARTION +2

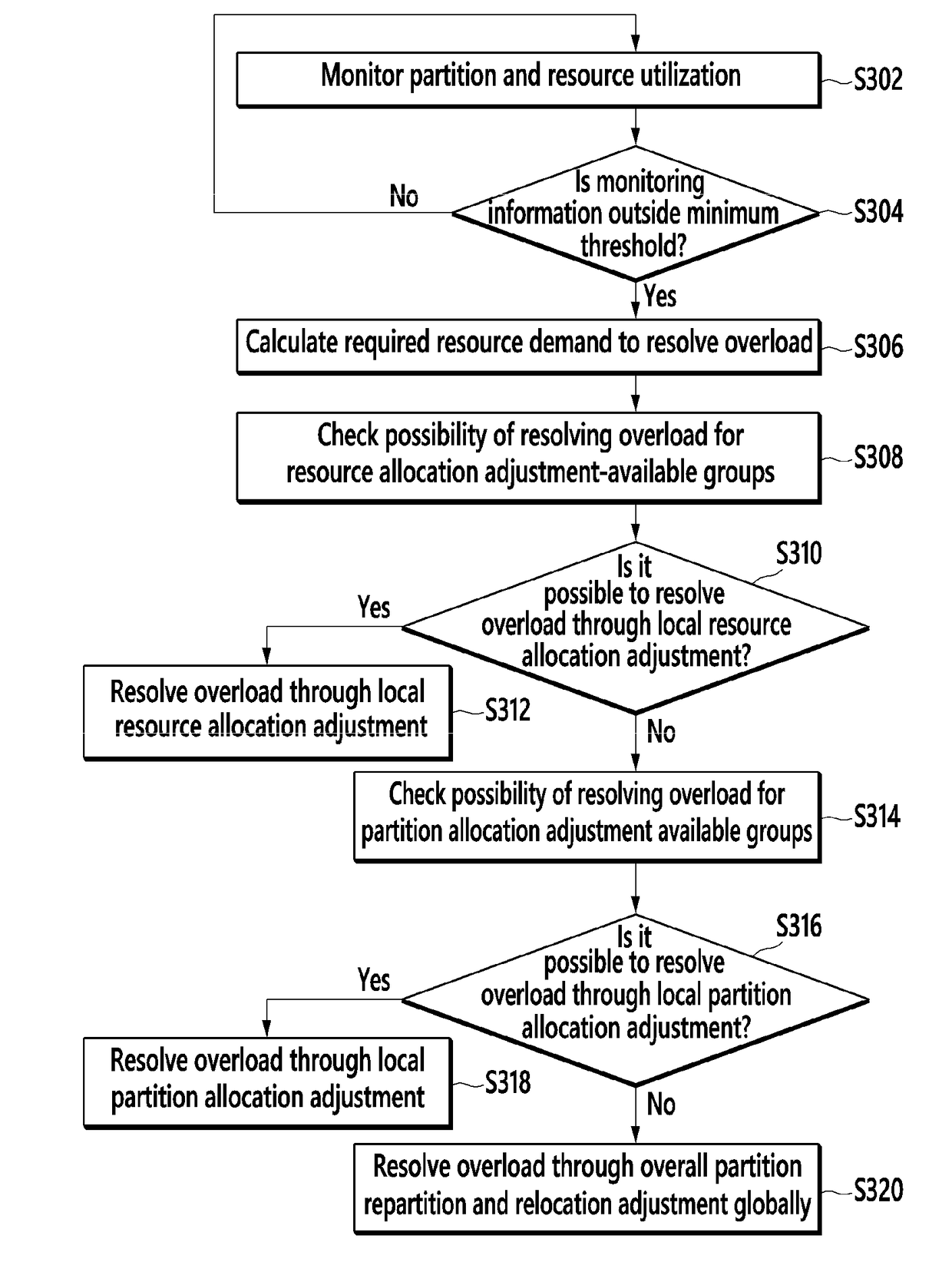

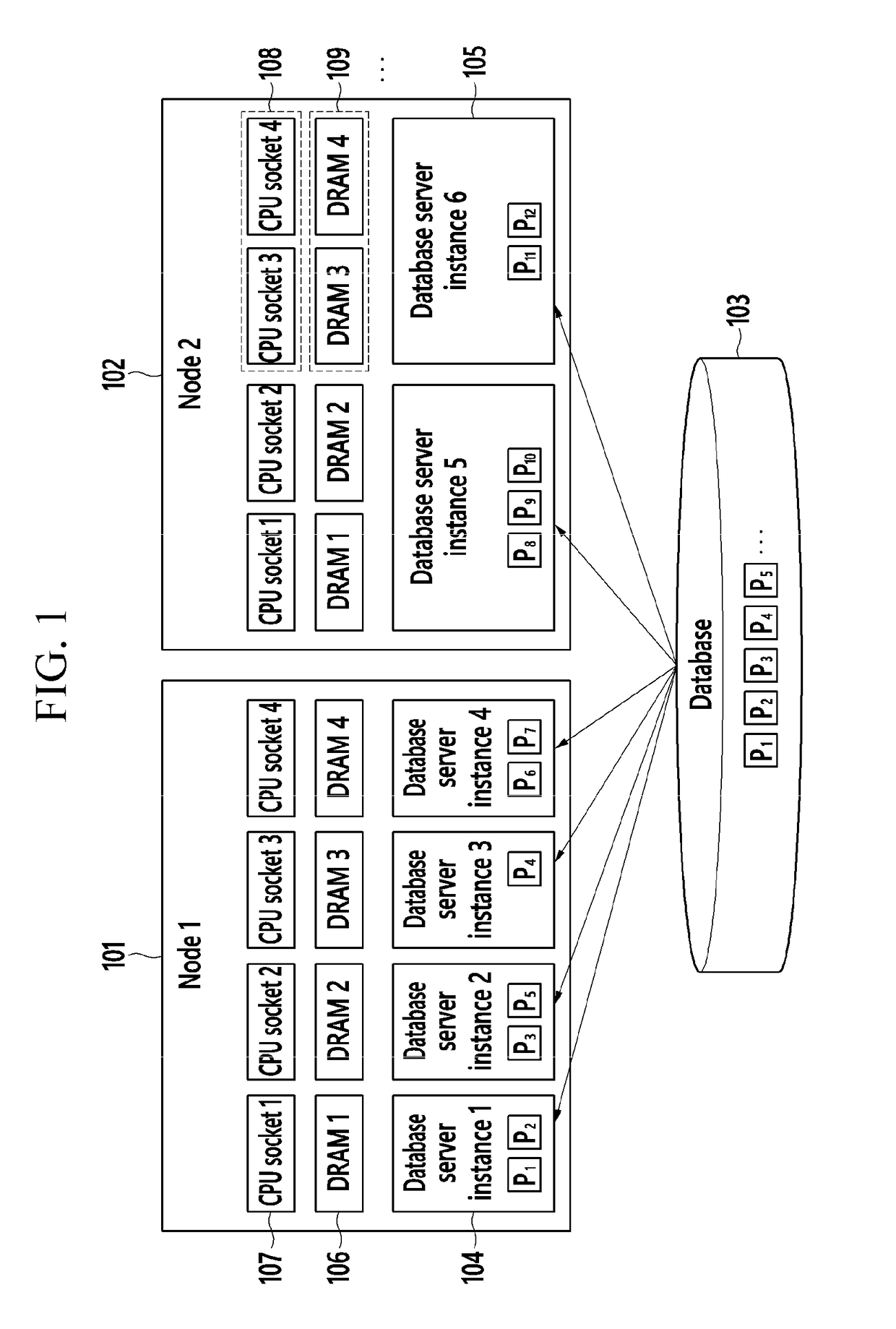

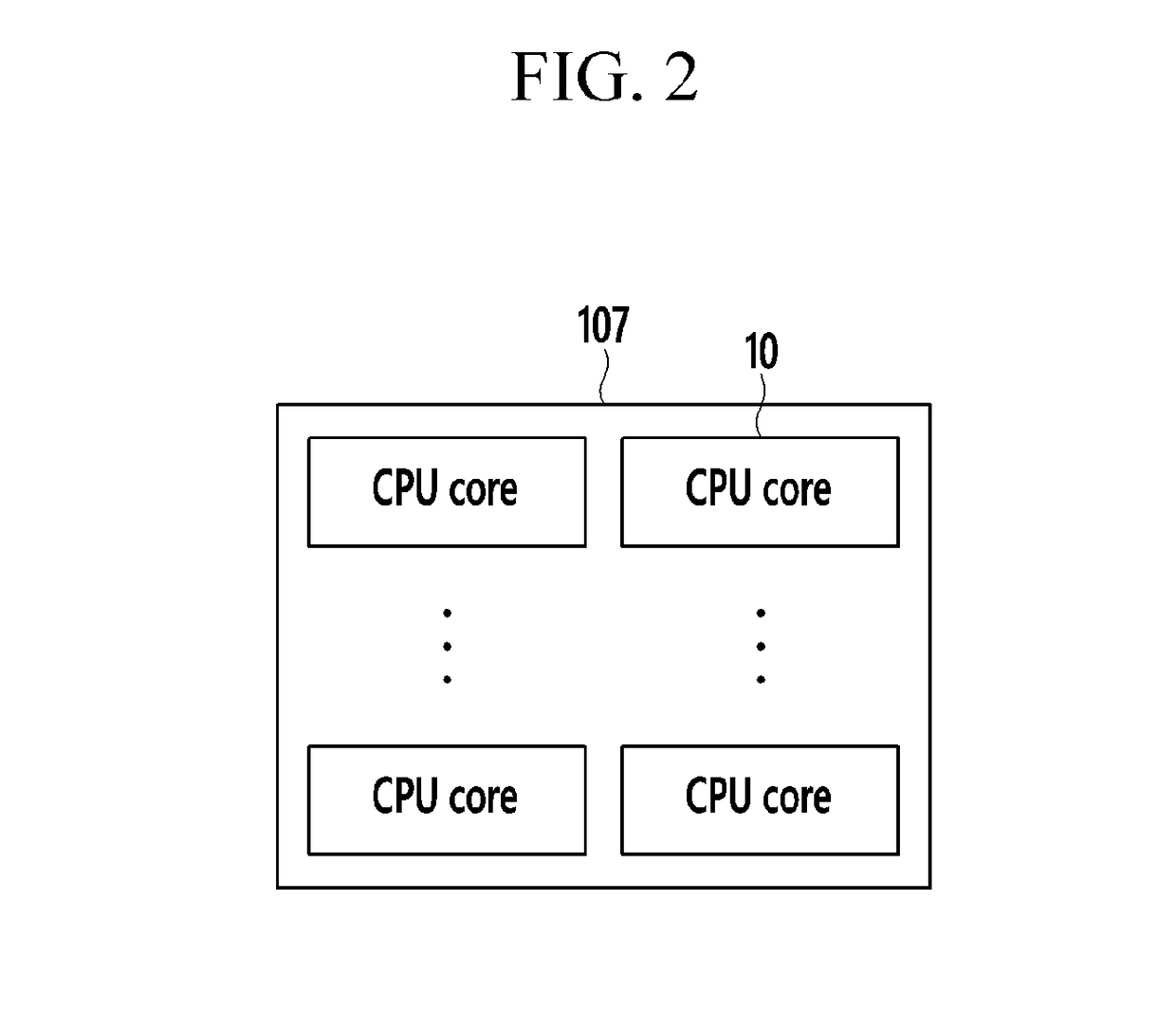

Distributed in-memory database system and method for managing database thereof

InactiveUS20180157729A1Low costImprove processing speedResource allocationDatabase distribution/replicationIn-memory databaseDistributed memory

Disclosed herein is a distributed in-memory database system for partitioning a database and allocating the partitioned database to a plurality of distributed nodes, wherein at least one of the plurality of nodes includes a plurality of central processing unit (CPU) sockets in which a plurality of CPU cores are installed, respectively; a plurality of memories respectively connected to the plurality of CPU sockets; and a plurality of database server instances managing allocated database partitions, wherein each database server instance is installed in units of CPU socket groups including a single CPU socket or at least two CPU sockets.

Owner:ELECTRONICS & TELECOMM RES INST

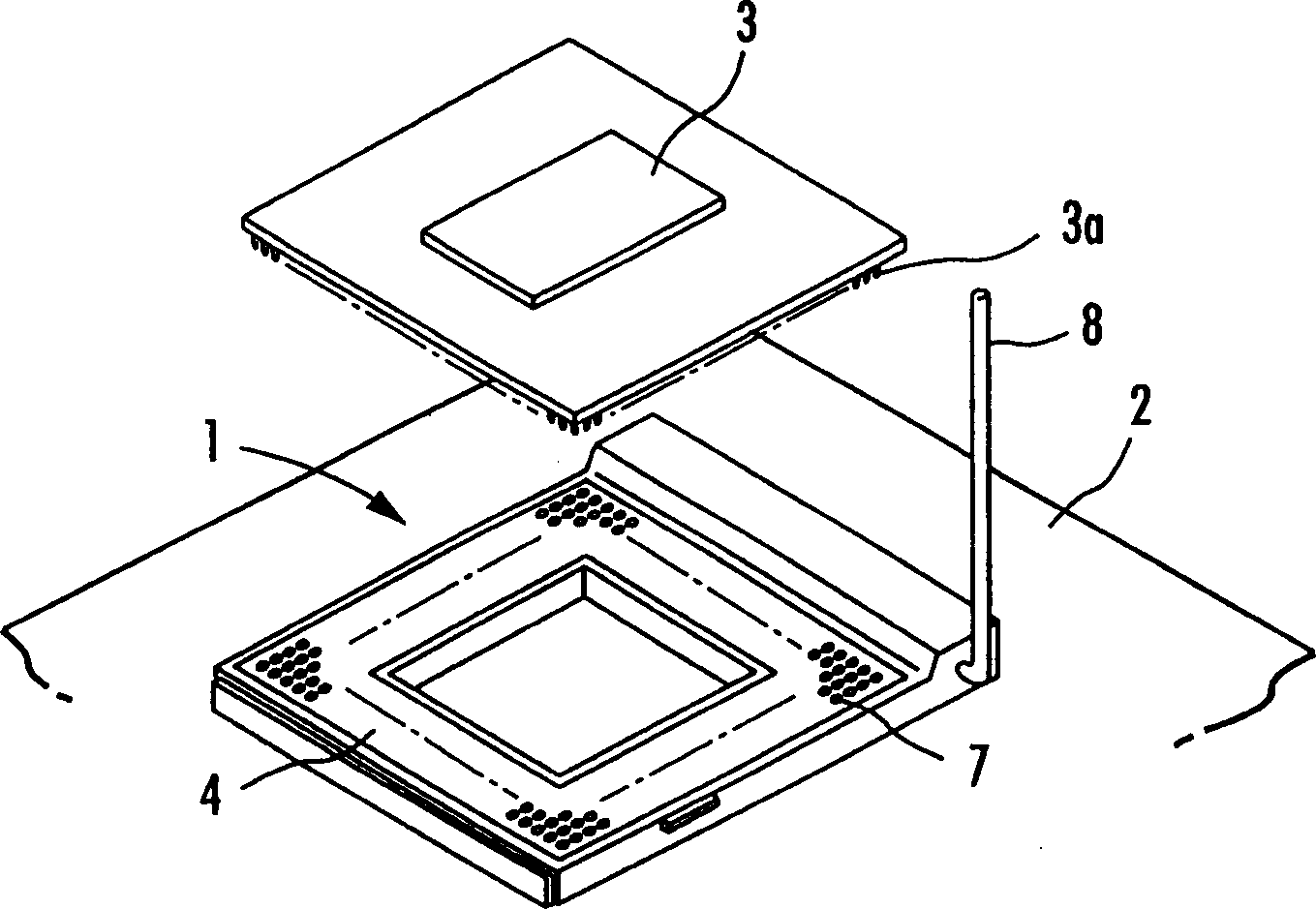

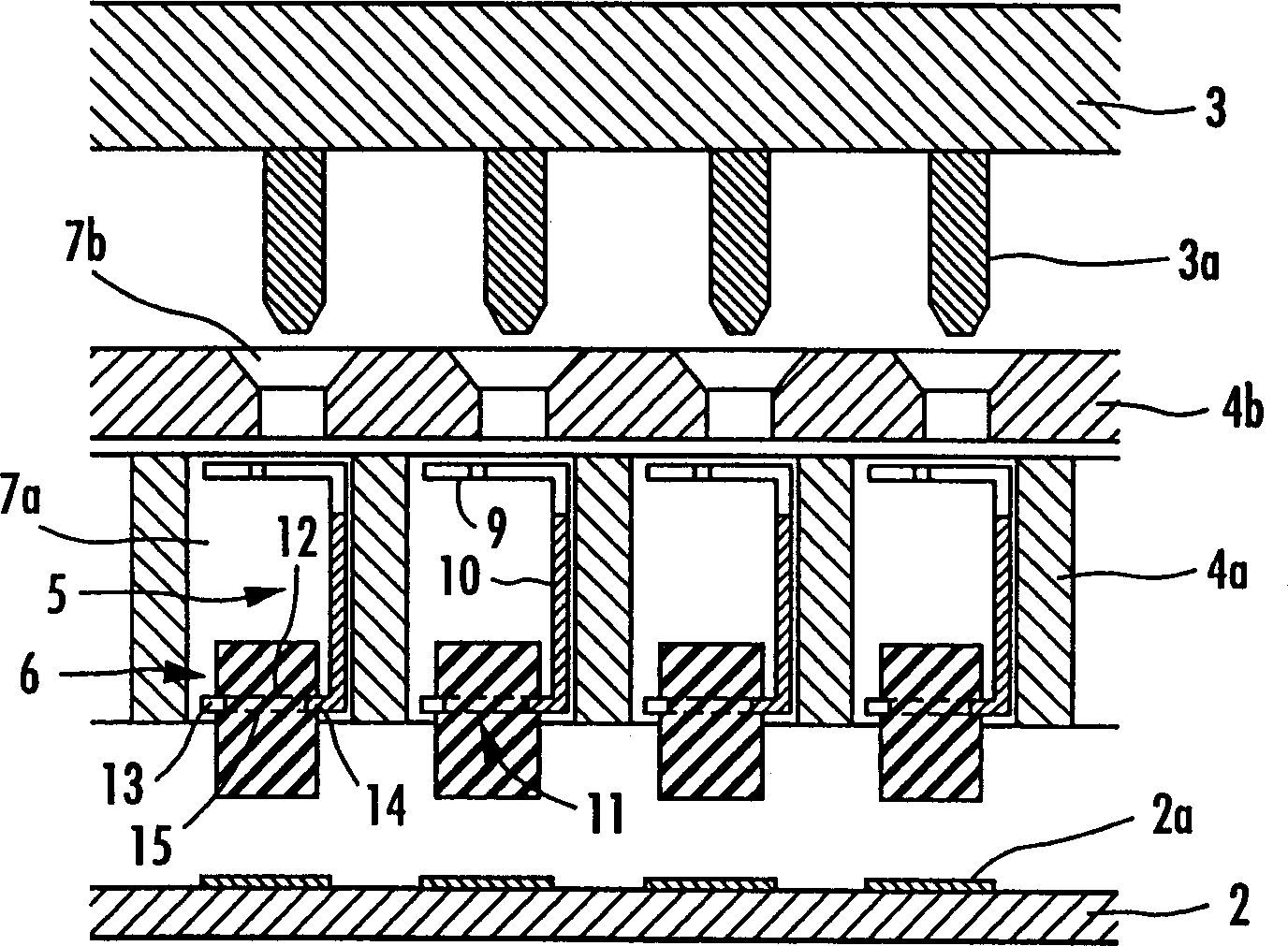

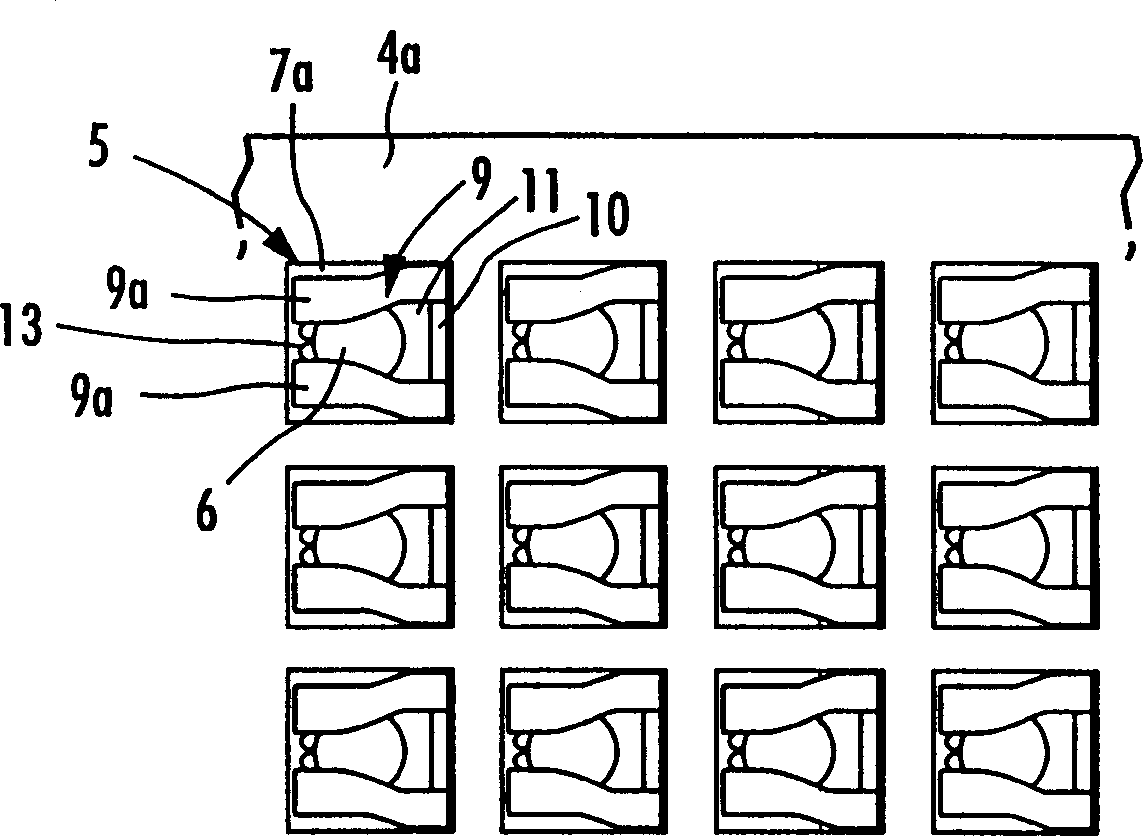

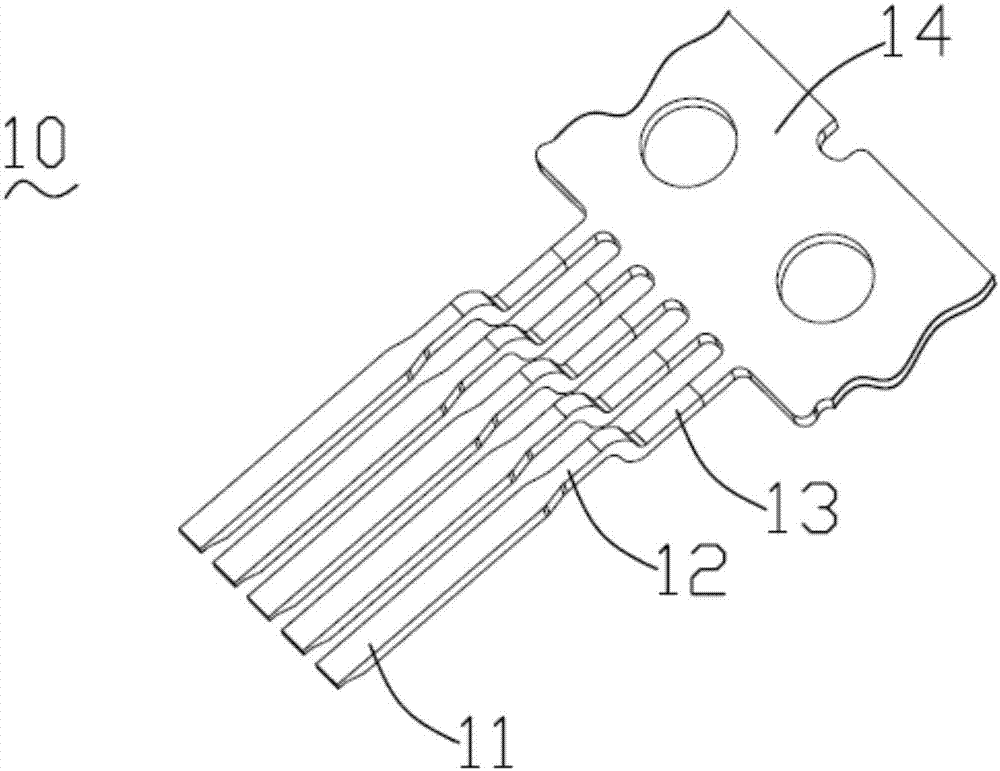

Connector and its mfg. method

InactiveCN1398018APrevent prolapsePrinted circuit assemblingContact member assembly/disassemblySurface mountingCPU socket

The invention provides a connector which is easily manufactured and connects a circuit board in good condition. The connector according to the invention is a CPU socket to be surface-mounted on a circuit board 2, comprising a terminal 5 attached inside an internal case 4a made of an insulating material and a solder 6 fixed to the terminal 5. A connecting section 11 of the terminal 5 is provided with a pair of bar-like pieces 12, and has first claw sections 13 and a second claw section 14. In order to fix the solder 6 to the connecting section 11, tip ends of the first claw sections 13 are caulked by bending so that the tip ends contact with each other. The connecting section 11 is provided with an internal passage 15 connecting the upper and lower sides thereof. The solder 6 does not come off the terminal 5 because the solder 6 is attached to the internal case 4a after fixed to the connecting section 11 of the terminal 5 by caulking. In addition, it is easy to improve coplanarity of the tip end of each solder 6 because a length of the solder 6 protruding from the connecting section 11 is adjustable by changing the caulking position of the solder 6.

Owner:MORUDETABUKU

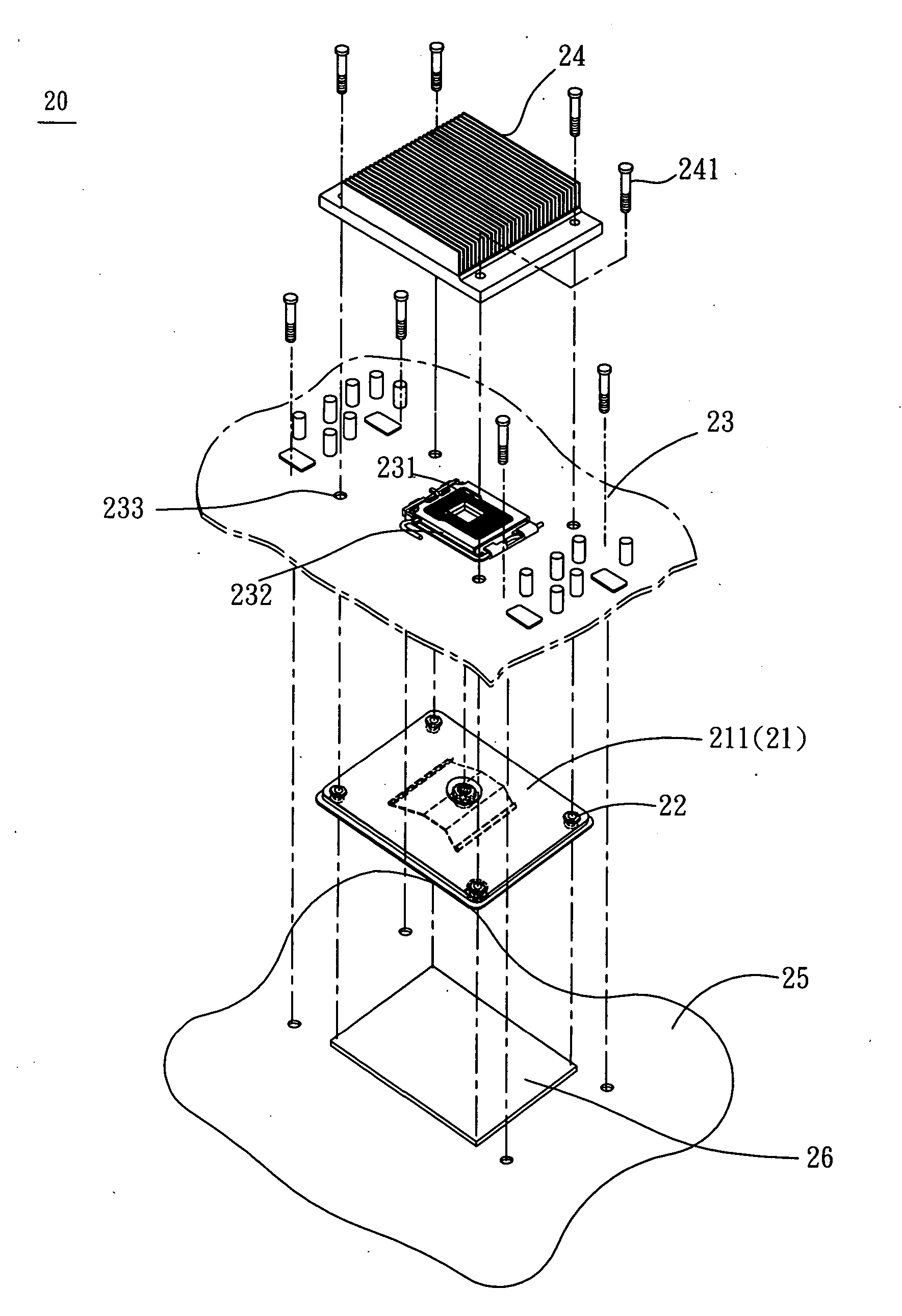

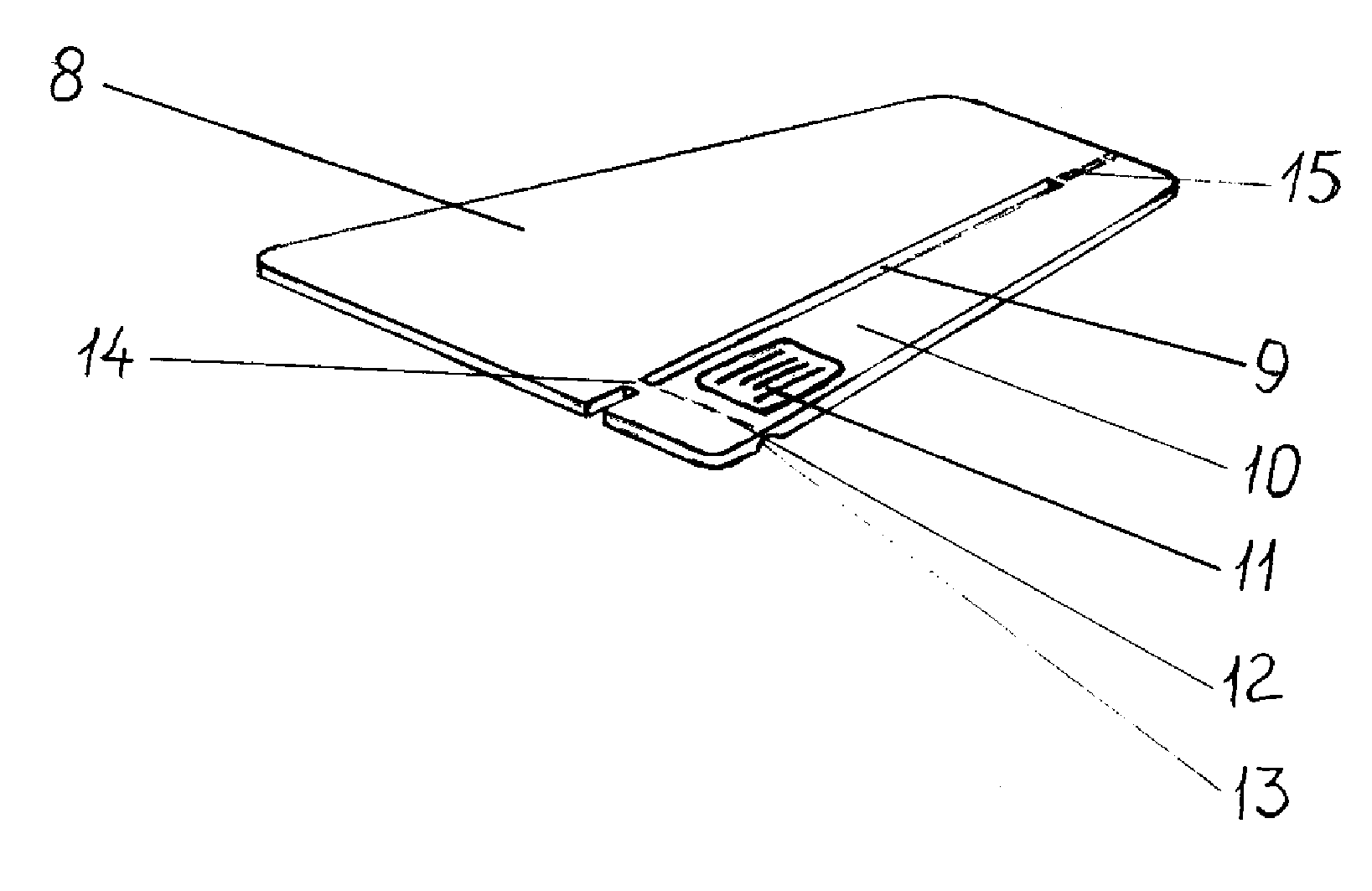

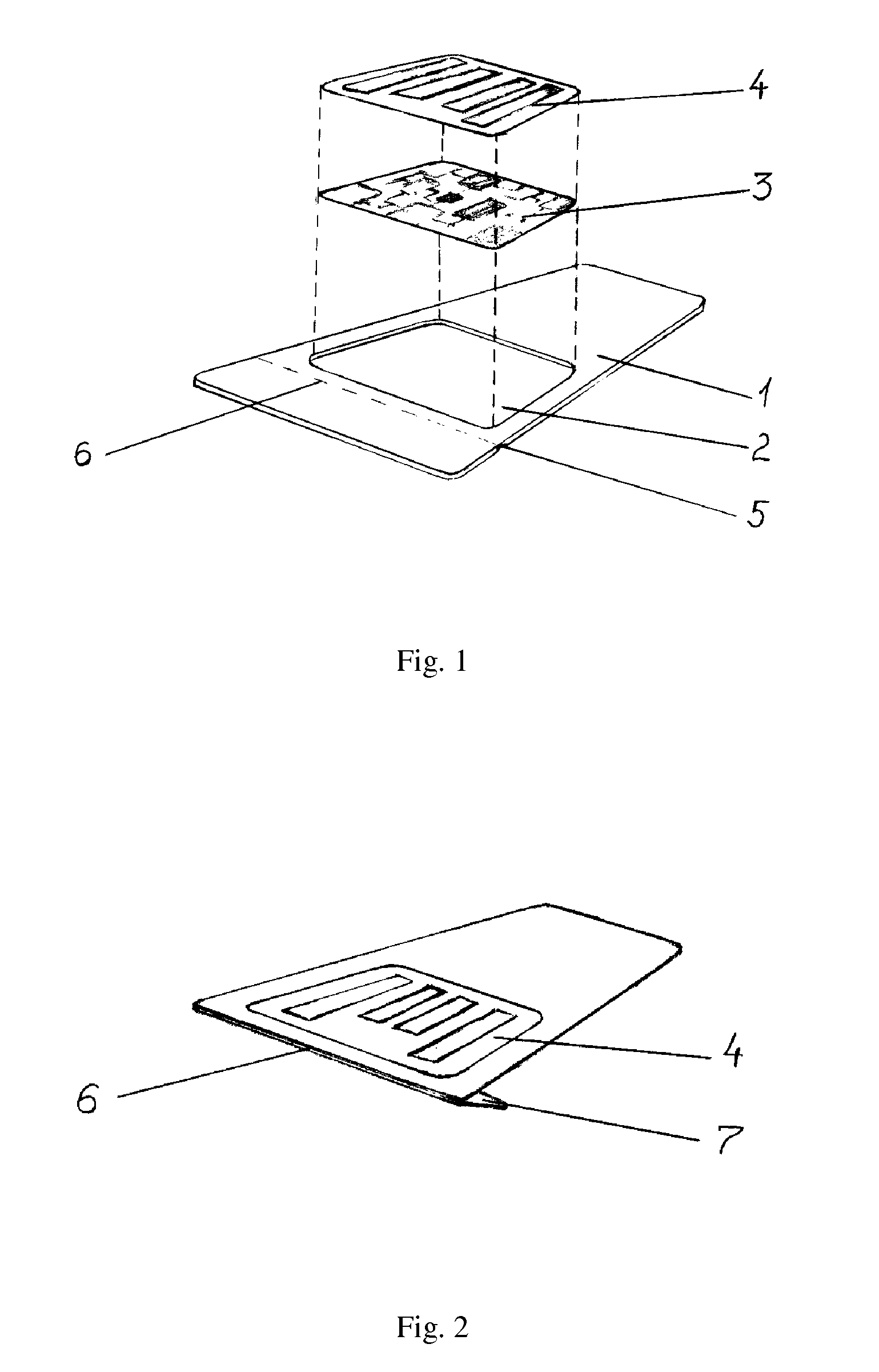

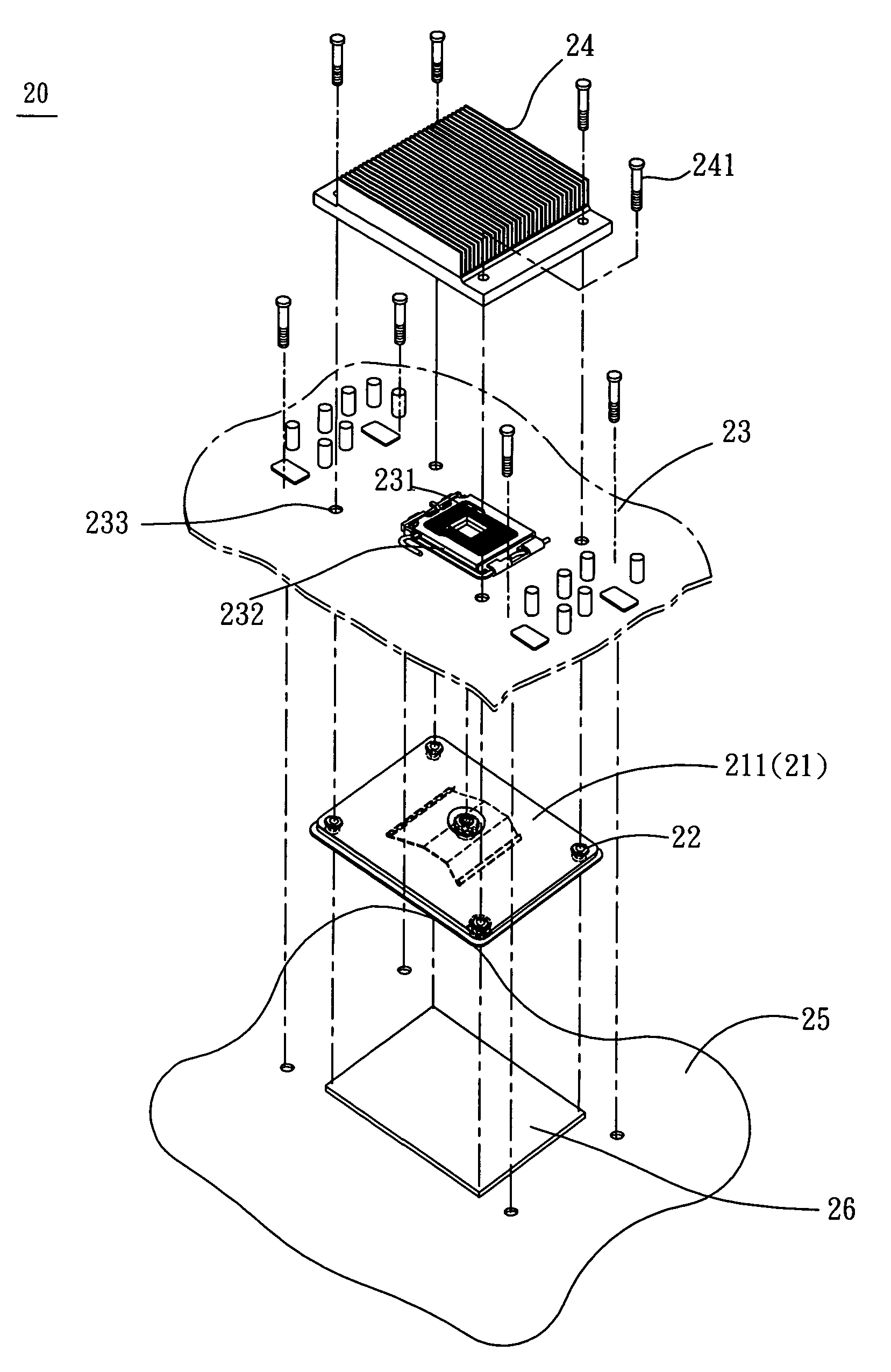

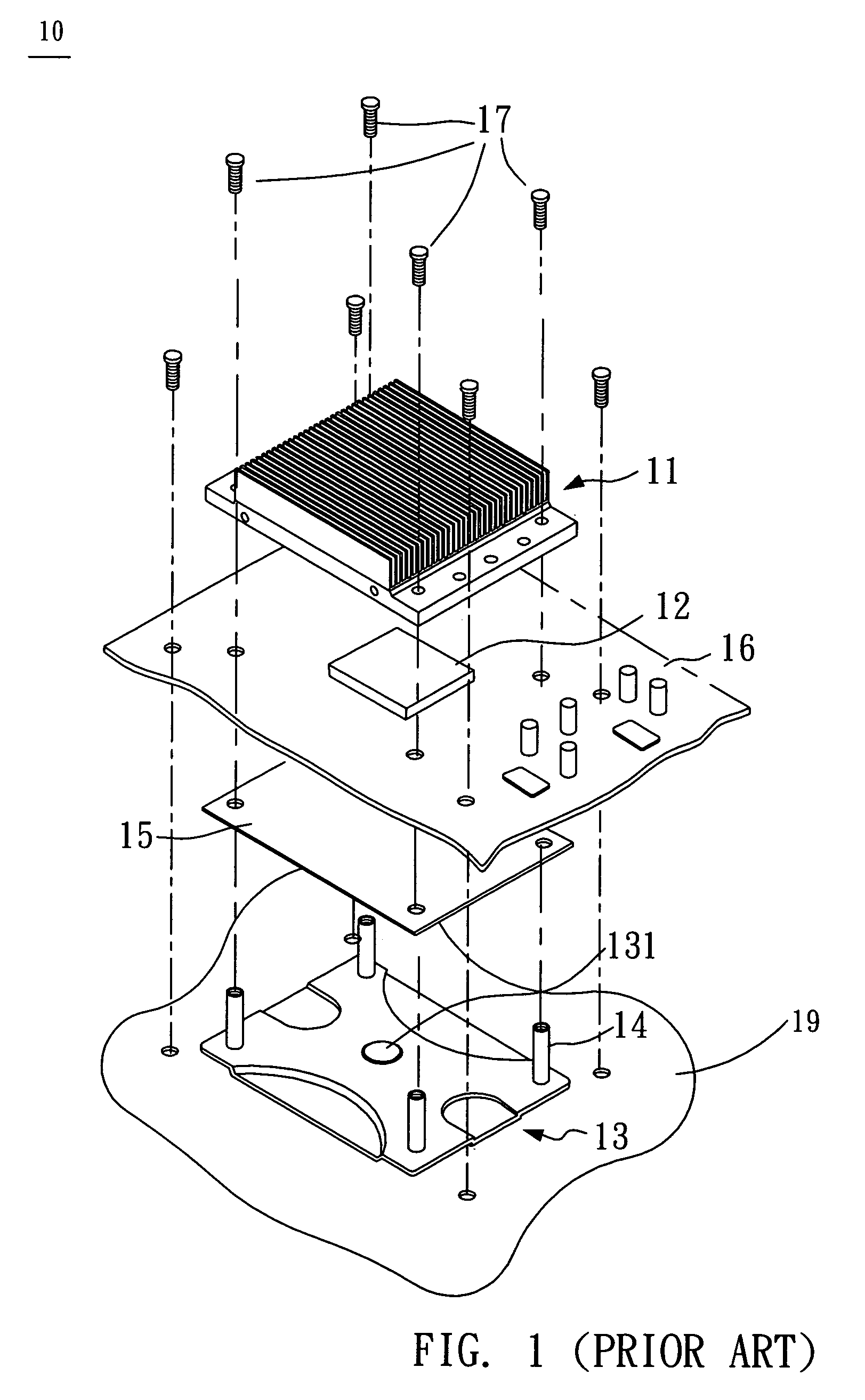

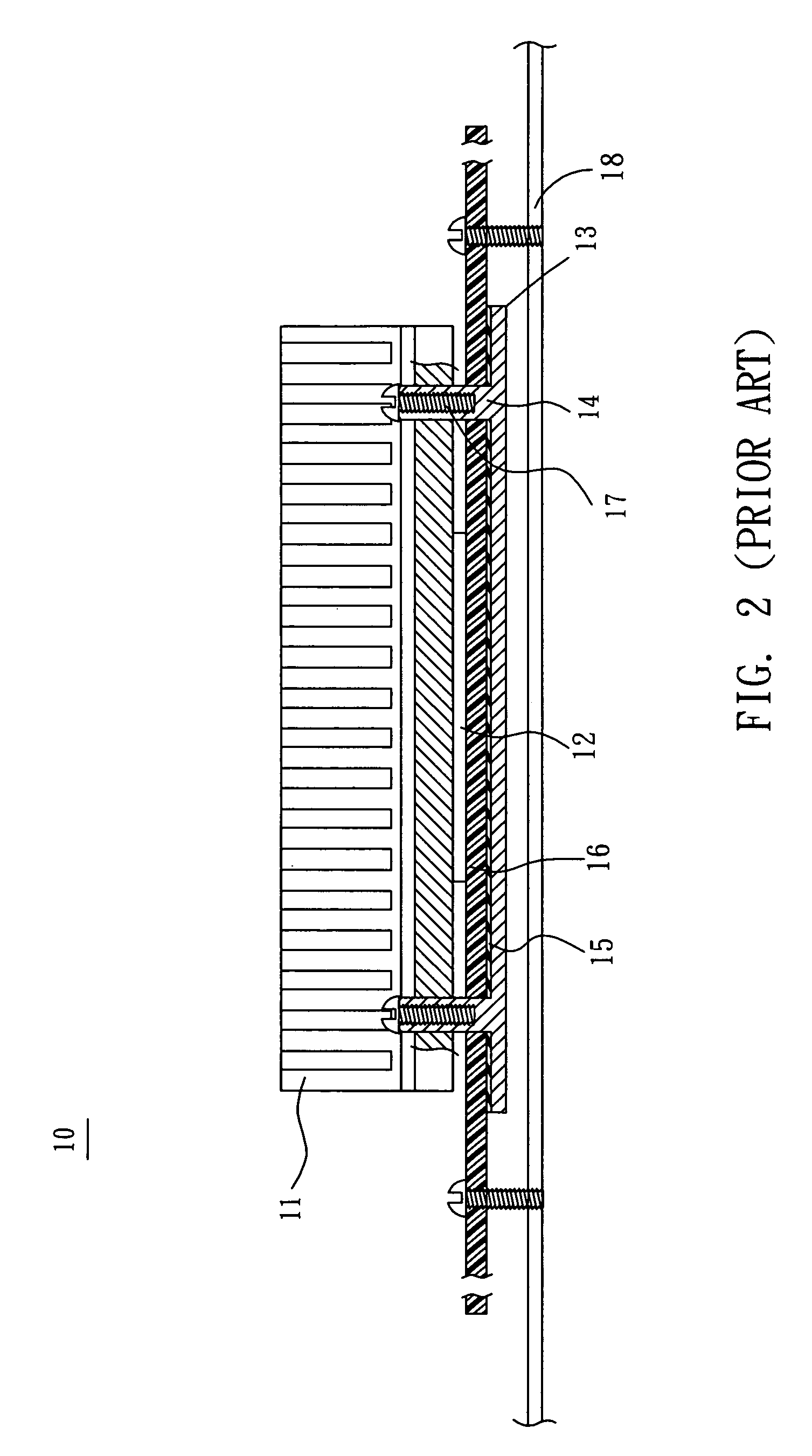

Auxiliary supporting structure of circuit board and assembling method for the same

ActiveUS20060044764A1Improve compatibilityImprove product qualityDigital data processing detailsSemiconductor/solid-state device detailsCPU socketEngineering

An auxiliary supporting structure of a circuit board is for supporting at least one part of the circuit board. The circuit board has a CPU socket for connected to a CPU, and a through hole through which a heat sink fixing element passes. The auxiliary supporting structure includes a buffer body and a supporting element. In this case, the buffer body is disposed on a housing and has a first surface facing the circuit board. The buffer body is positioned between the circuit board and the housing. The supporting element is disposed on the buffer body and faces the through hole. The heat sink fixing element passes through the through hole and is fixed to the supporting element. An assembling method for the auxiliary supporting structure of the circuit board is provided.

Owner:ASUSTEK COMPUTER INC

Plastic card provided with electrical contacts

InactiveUS8061623B2Increase elasticityIncrease the number ofPrinted circuitsRecord carriers used with machinesElectricityCPU socket

Owner:BALCHAITIS VADIM EVGENEVICH

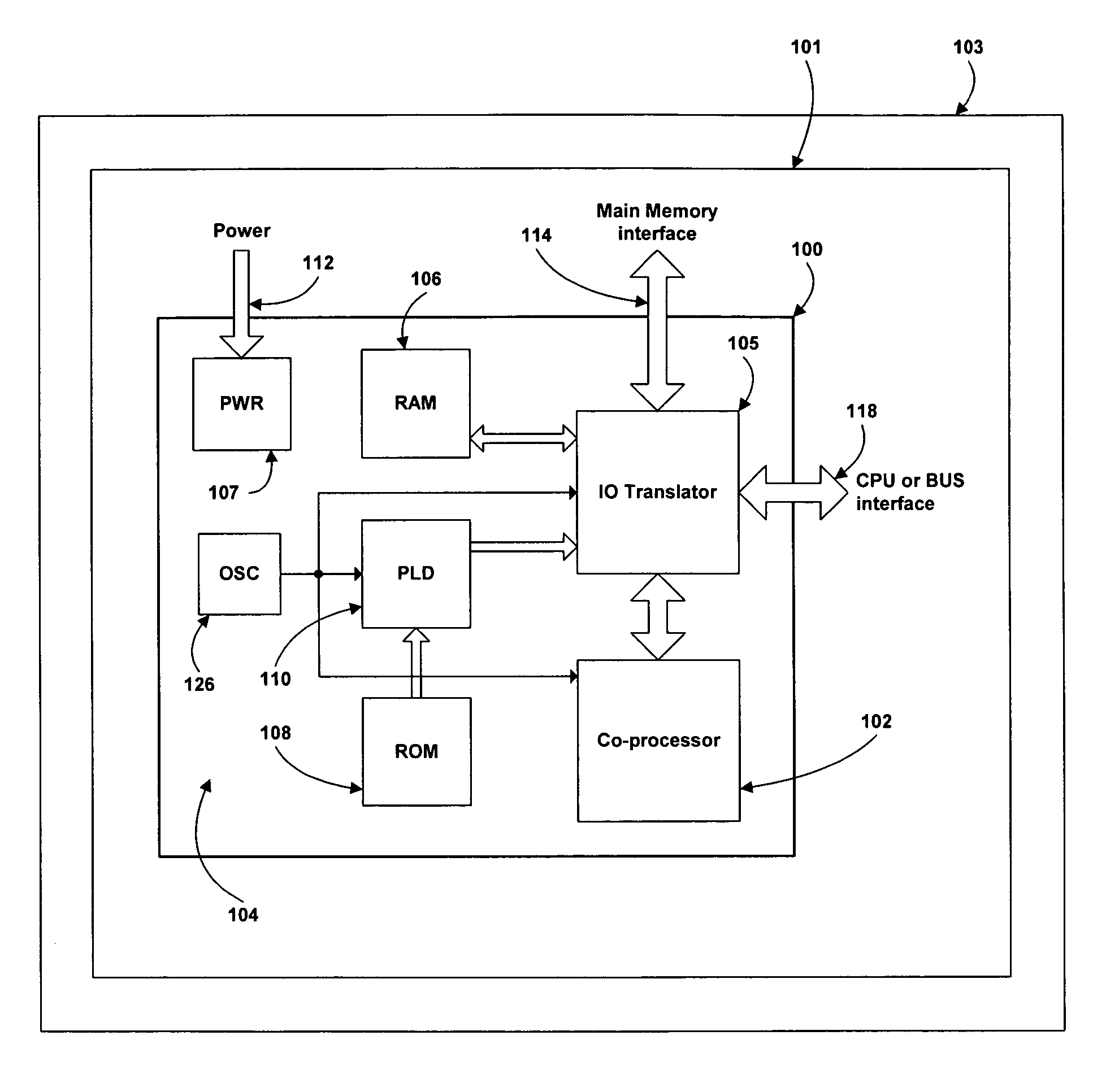

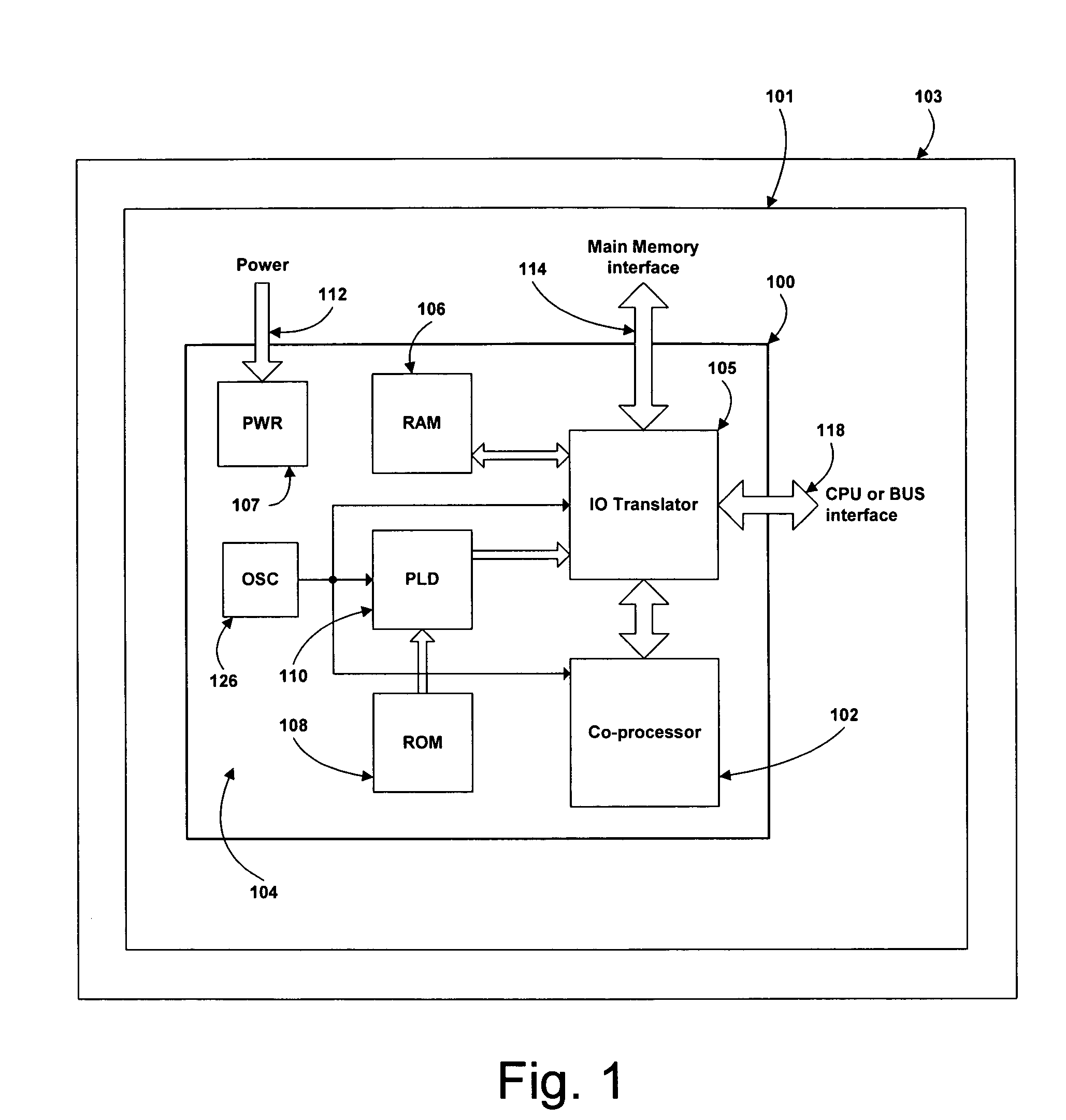

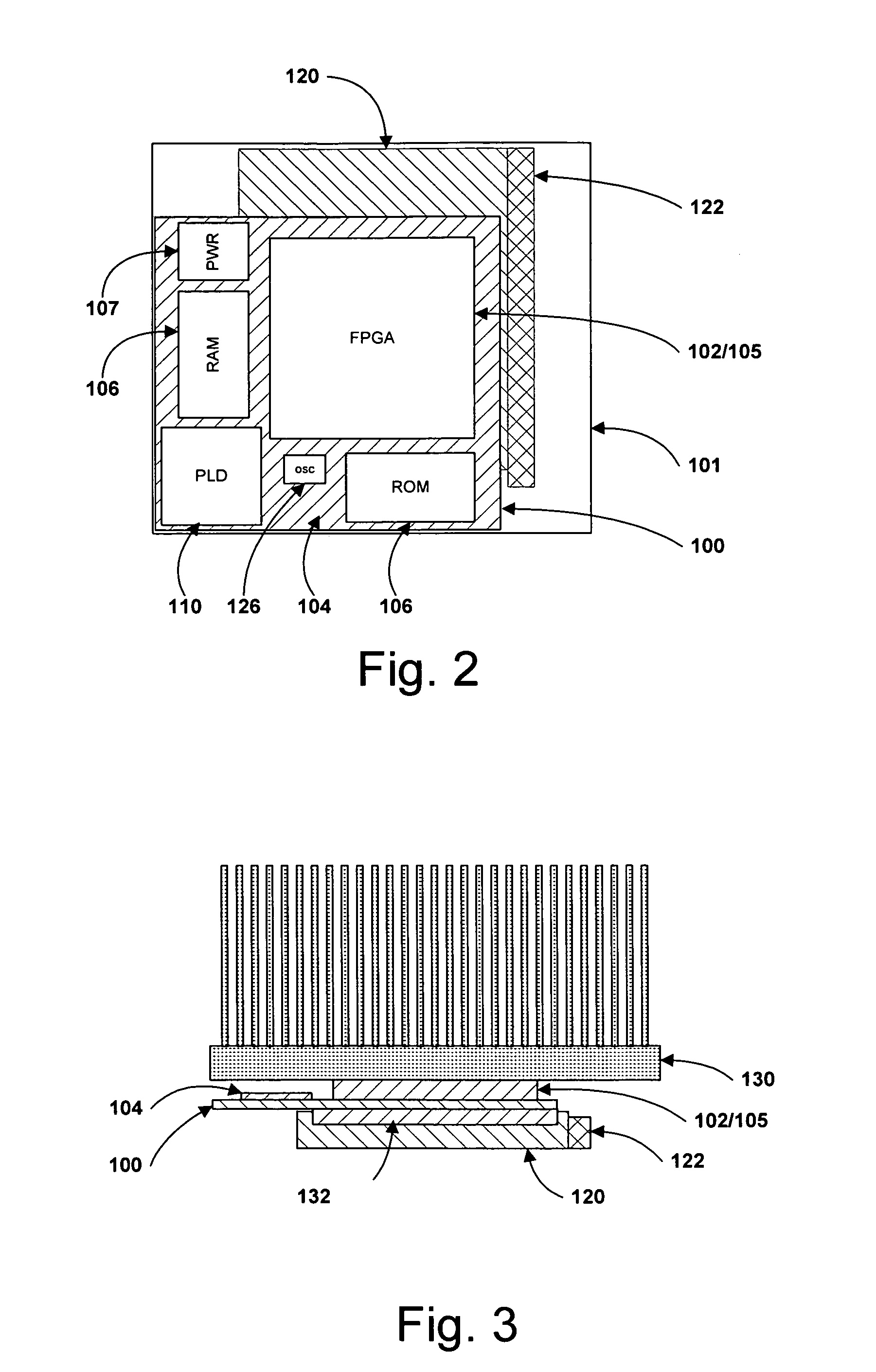

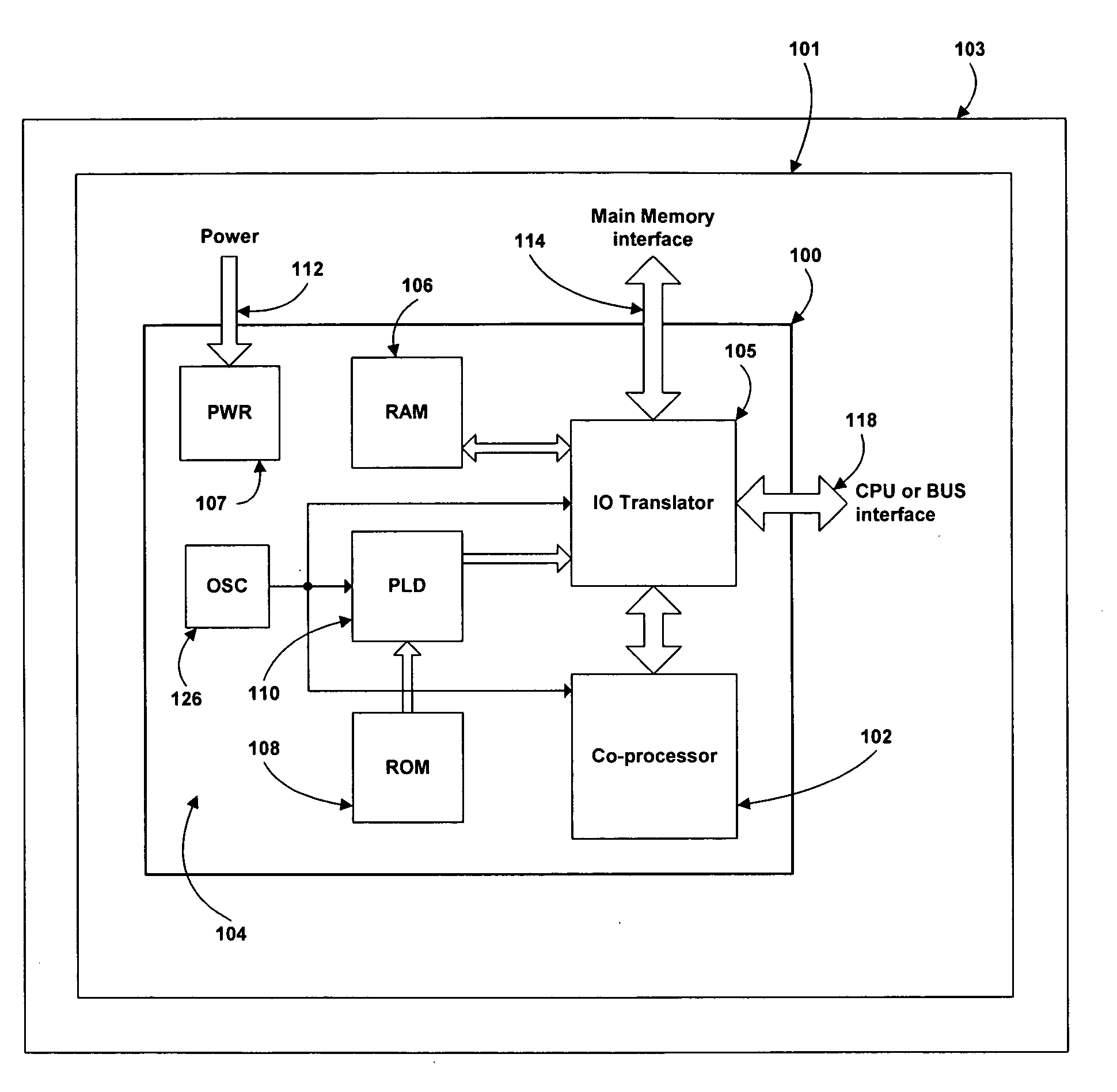

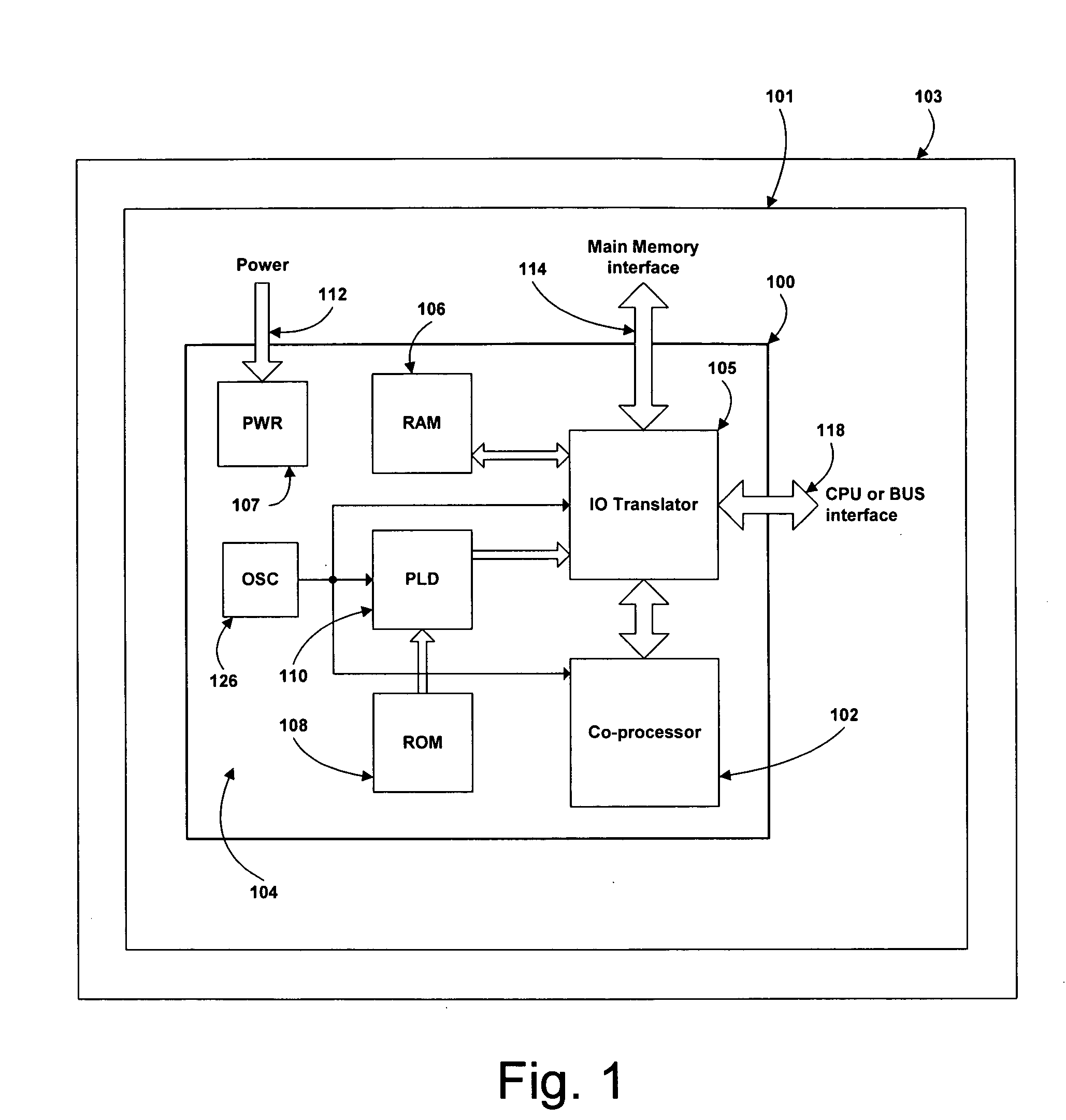

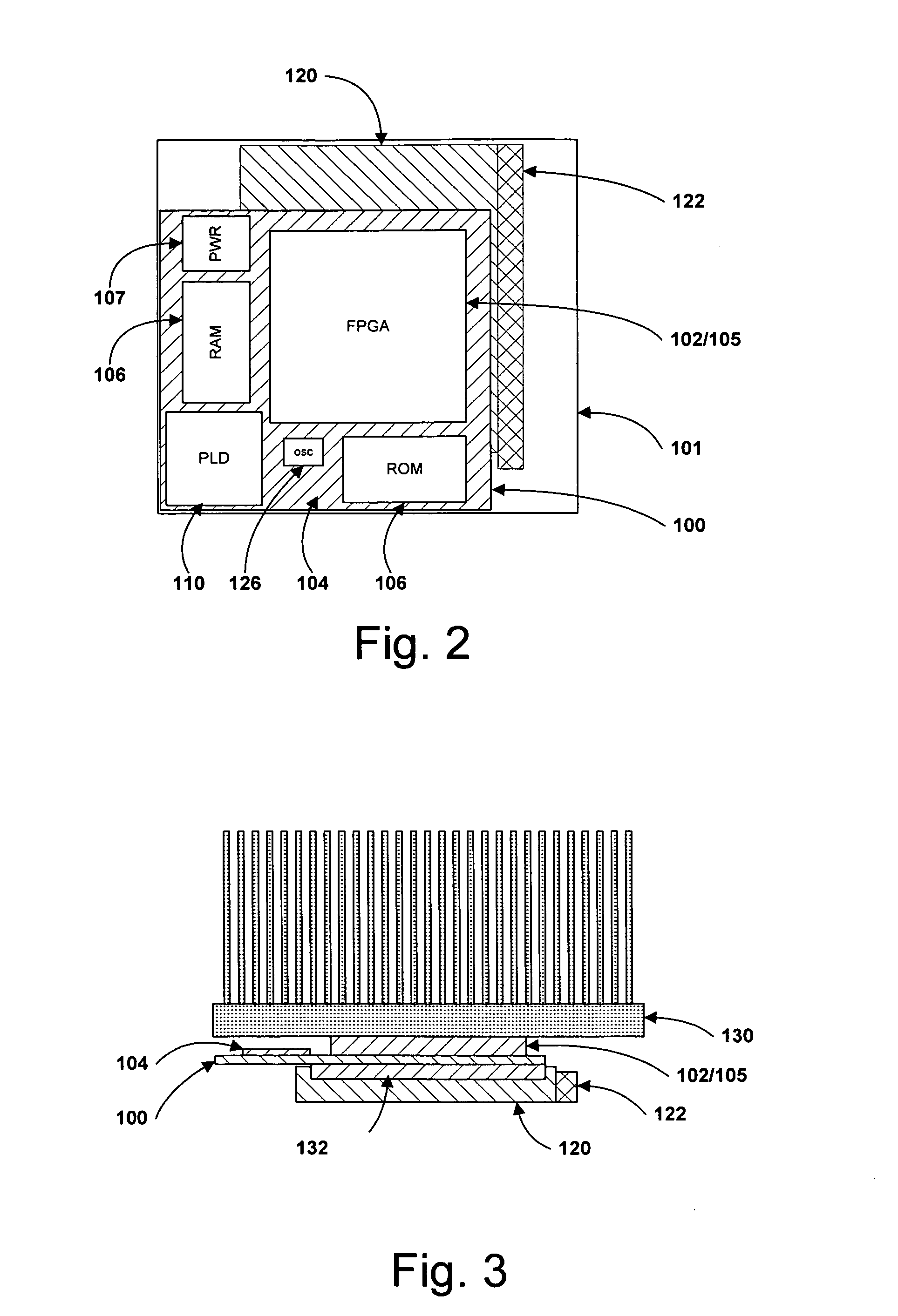

Systems and methods for providing co-processors to computing systems

ActiveUS7454550B2Simple designLow costDigital data processing detailsPrinted circuit aspectsComputer hardwareComputerized system

Computing systems with conventional CPUs coupled to co-processors or accelerators implemented in FPGAs (Field Programmable Gate Arrays). One embodiment of the systems and methods according to the invention includes a FPGA accelerator implemented in a computer system by providing an adapter board configured to be used in a standard CPU socket.

Owner:XTREMEDATA INC

Auxiliary supporting structure of circuit board and assembling method for the same

ActiveUS7352586B2Improve compatibilityImprove product qualityDigital data processing detailsSemiconductor/solid-state device detailsCPU socketHeat spreader

An auxiliary supporting structure of a circuit board is for supporting at least one part of the circuit board. The circuit board has a CPU socket for connected to a CPU, and a through hole through which a heat sink fixing element passes. The auxiliary supporting structure includes a buffer body and a supporting element. In this case, the buffer body is disposed on a housing and has a first surface facing the circuit board. The buffer body is positioned between the circuit board and the housing. The supporting element is disposed on the buffer body and faces the through hole. The heat sink fixing element passes through the through hole and is fixed to the supporting element. An assembling method for the auxiliary supporting structure of the circuit board is provided.

Owner:ASUSTEK COMPUTER INC

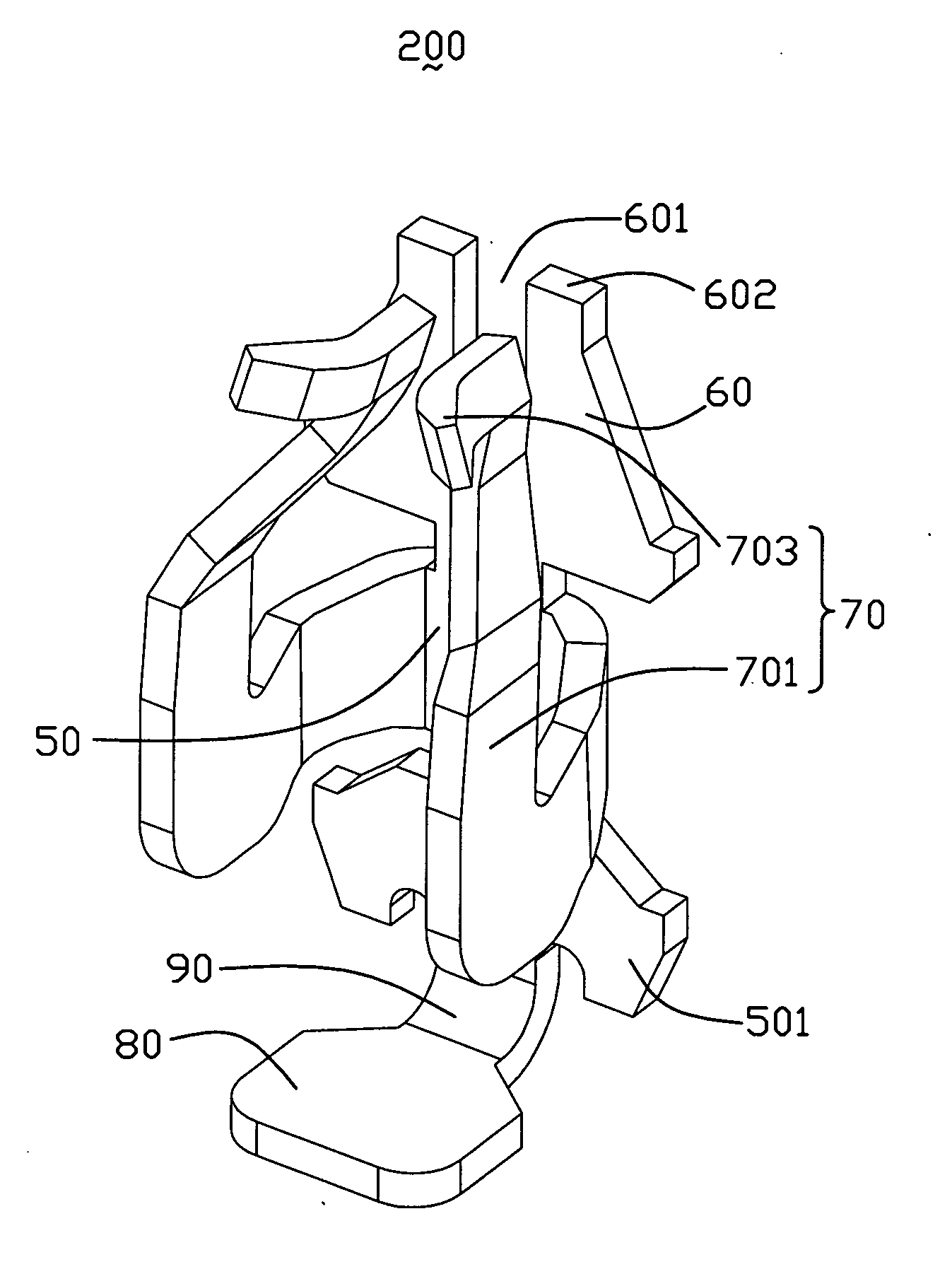

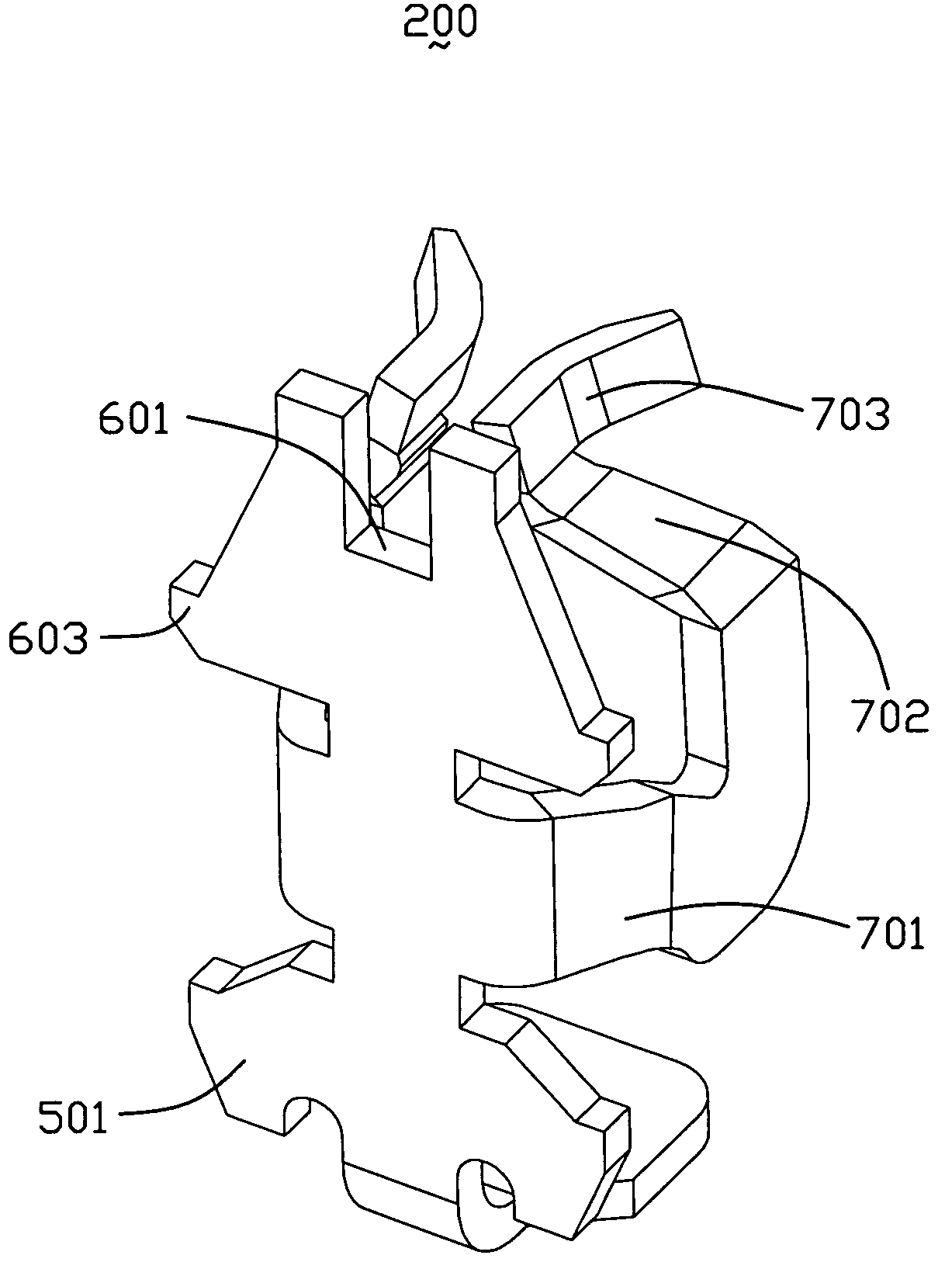

Conductive contact for CPU socket connector

InactiveUS20080227324A1Low costImprove efficiencyCoupling contact membersElectric connection basesCPU socketEngineering

A conductive contact (200) for electrically connecting with a chip module and a printed circuit board comprises a base portion (50), a top head portion (60) formed above the base portion adapted for connecting with a belt, at least one spring arm (70) extending sidewardly from the base portion and forming at least one contacting section (703) adapted for elastically contacting with the chip module, and a bottom soldering portion (80) extending form at least one of the base portion and the spring arm adapted for being soldered to the printed circuit board. The head portion defines a cutout (601) recessed downwardly from a top edge (602) thereof to reduce connecting length between the head portion and the belt and reduce siphonic effect when plating the spring arm.

Owner:HON HAI PRECISION IND CO LTD

Conductive contact for CPU socket connector

InactiveUS7601036B2Low costImprove efficiencyCoupling contact membersElectric connection basesCPU socketEngineering

A conductive contact (200) for electrically connecting with a chip module and a printed circuit board comprises a base portion (50), a top head portion (60) formed above the base portion adapted for connecting with a belt, at least one spring arm (70) extending sidewardly from the base portion and forming at least one contacting section (703) adapted for elastically contacting with the chip module, and a bottom soldering portion (80) extending form at least one of the base portion and the spring arm adapted for being soldered to the printed circuit board. The head portion defines a cutout (601) recessed downwardly from a top edge (602) thereof to reduce connecting length between the head portion and the belt and reduce siphonic effect when plating the spring arm.

Owner:HON HAI PRECISION IND CO LTD

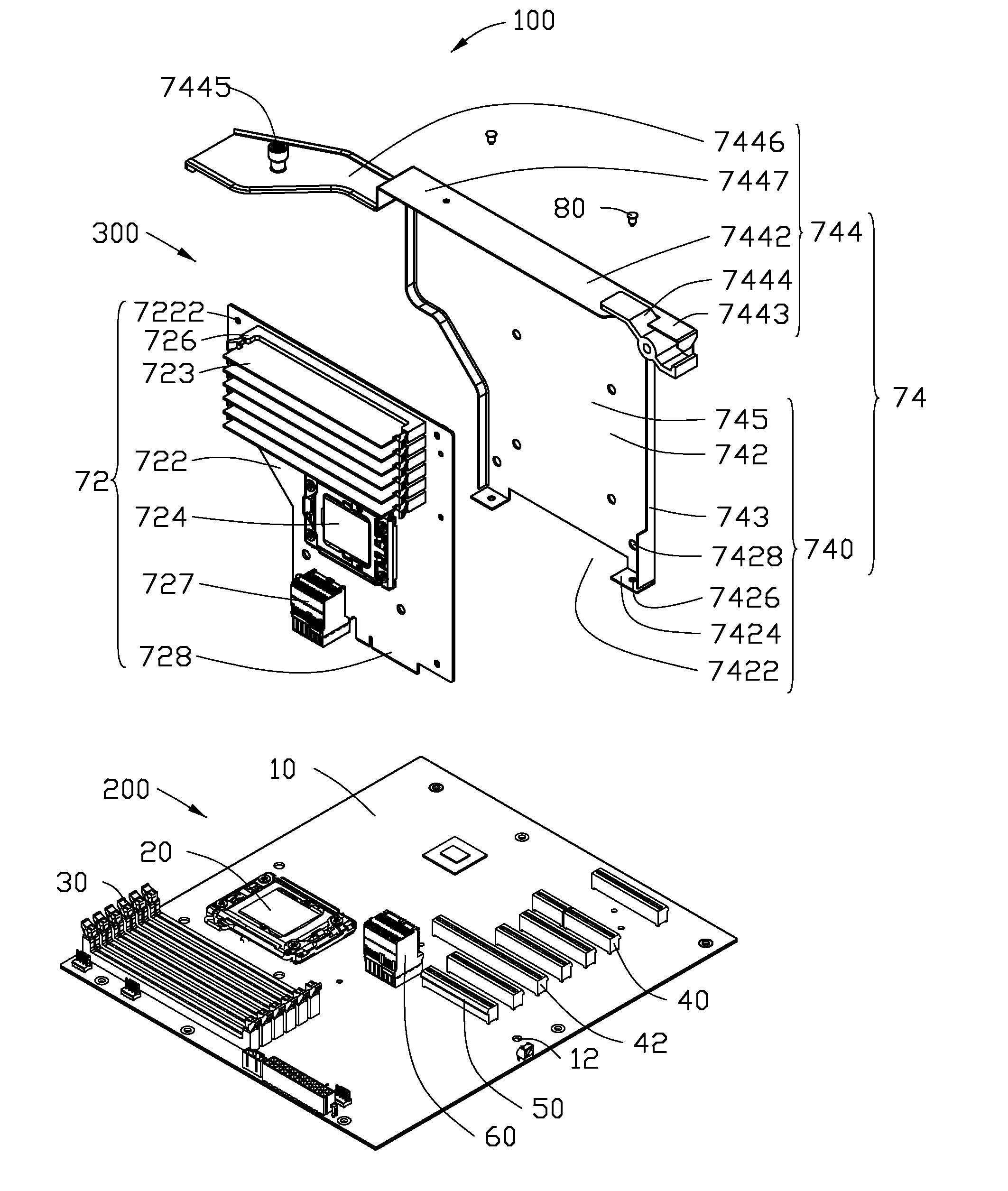

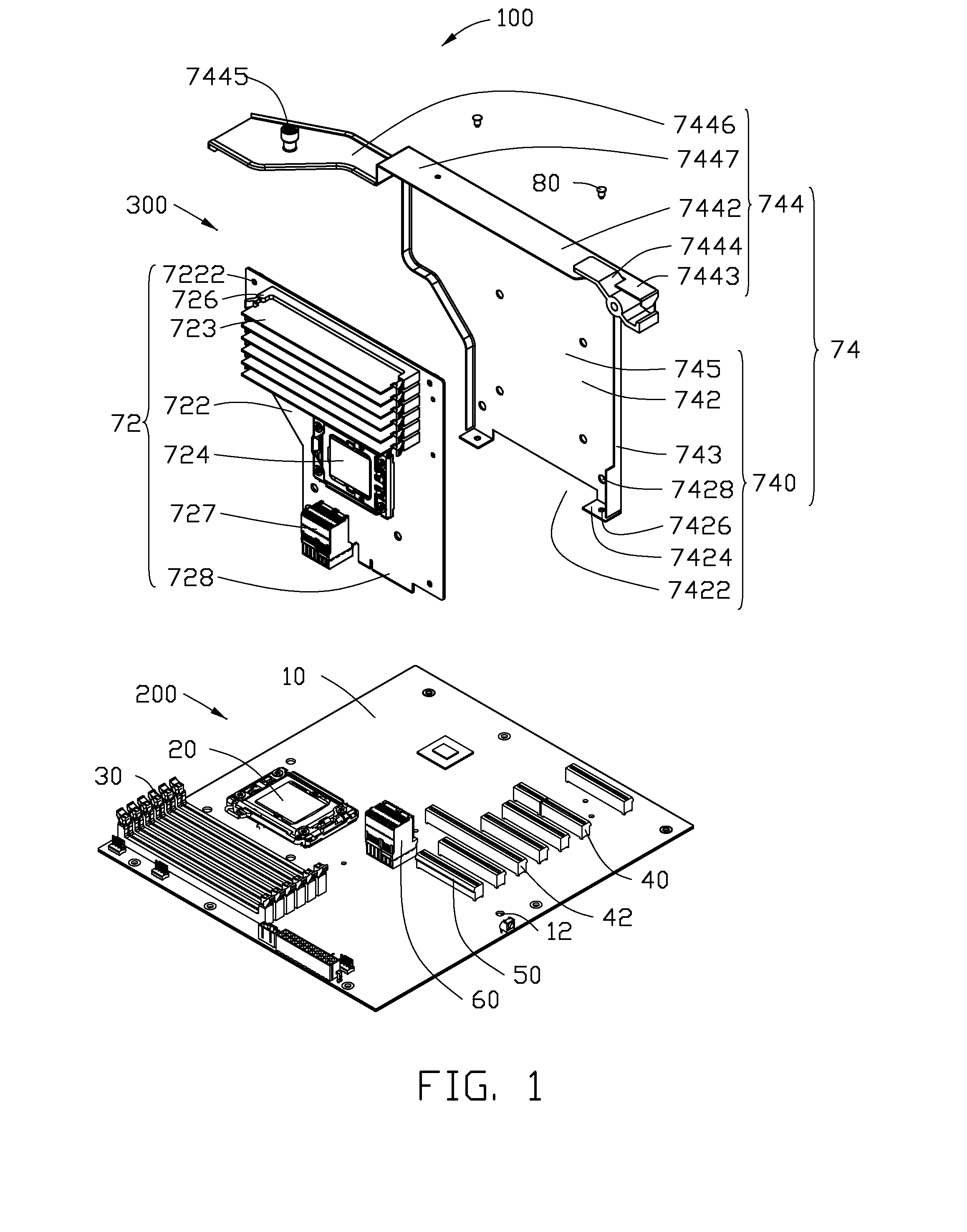

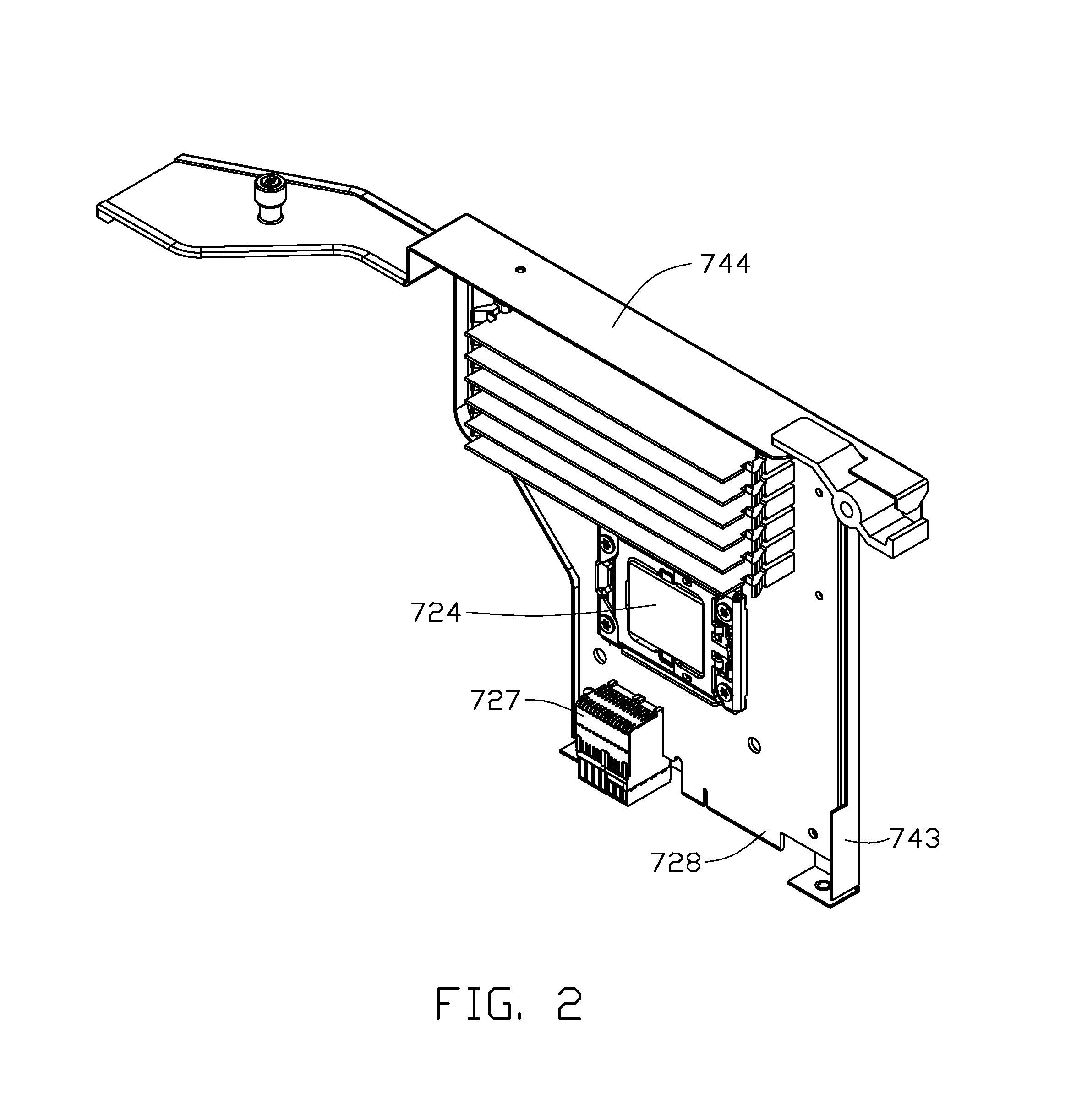

Motherboard assembly and central processing unit expansion card

InactiveUS20130021742A1Digital data processing detailsElectrical apparatus contructional detailsExpansion cardCPU socket

A central processing unit (CPU) expansion card may be inserted into a first connector of a motherboard. The CPU expansion card includes a board, a CPU socket mounted on the board, a number of memory slots mounted on the board and electrically connected to the CPU socket, and a second connector electrically connected to the CPU socket and mounted on the bottom side of the board to be inserted into the first connector of the motherboard.

Owner:HON HAI PRECISION IND CO LTD

Connector adapter and circuit board assembly including the same

Connector adapter includes an adapter body having a mating side and a mounting side. The mating side includes signal cavities that open to the mating side. The connector adapter also includes signal conductors extending through the adapter body. Each of the signal conductors has and extends between a pin socket positioned at the mating side and a signal tail positioned at the mounting side. The pin sockets are positioned within corresponding signal cavities. Each of the pin sockets includes first and second arms that oppose each other and define a thru-hole therebetween. The first and second arms engage a signal tail of an electrical connector when the signal tail of the electrical connector is inserted into the thru-hole.

Owner:TE CONNECTIVITY CORP

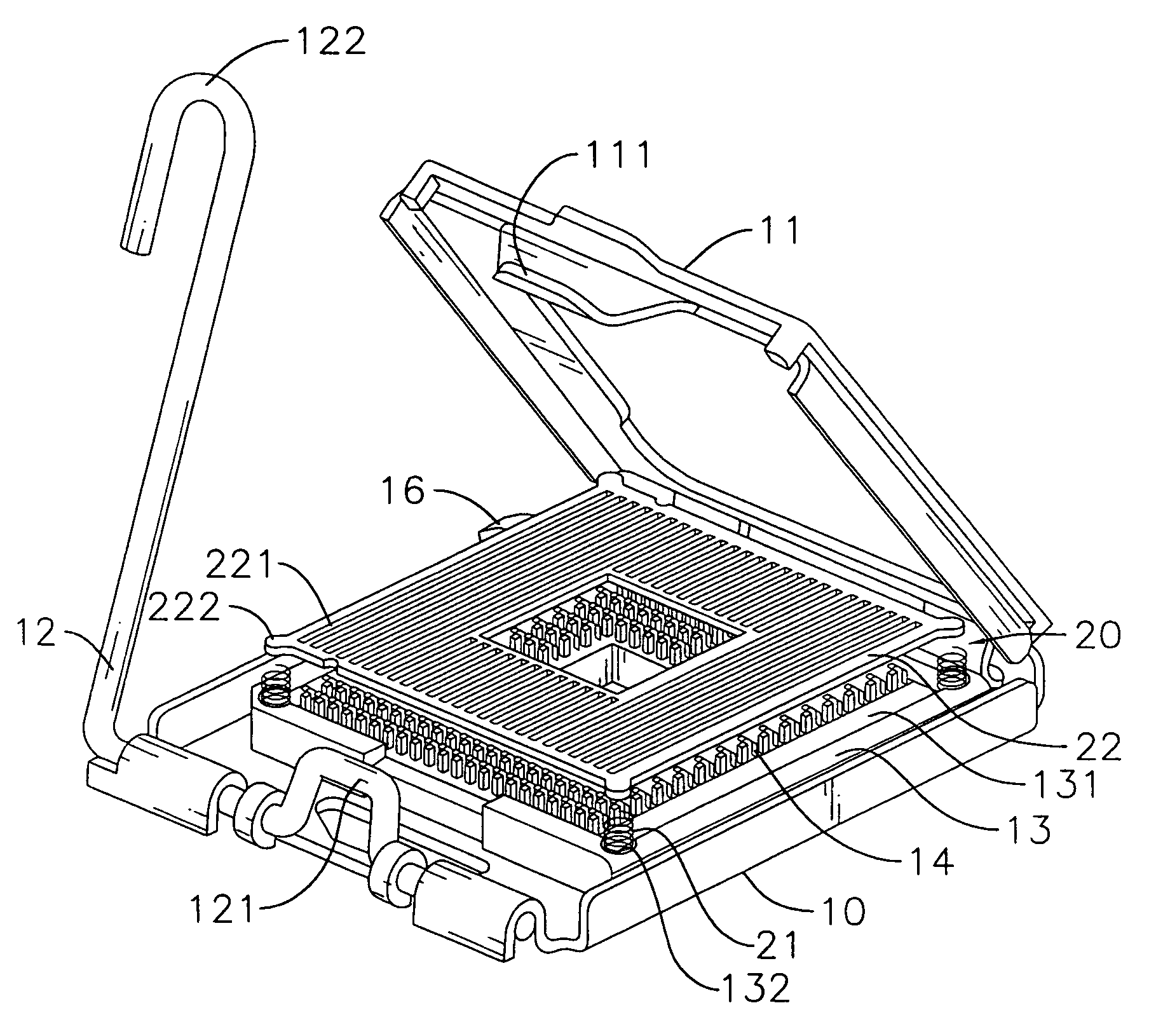

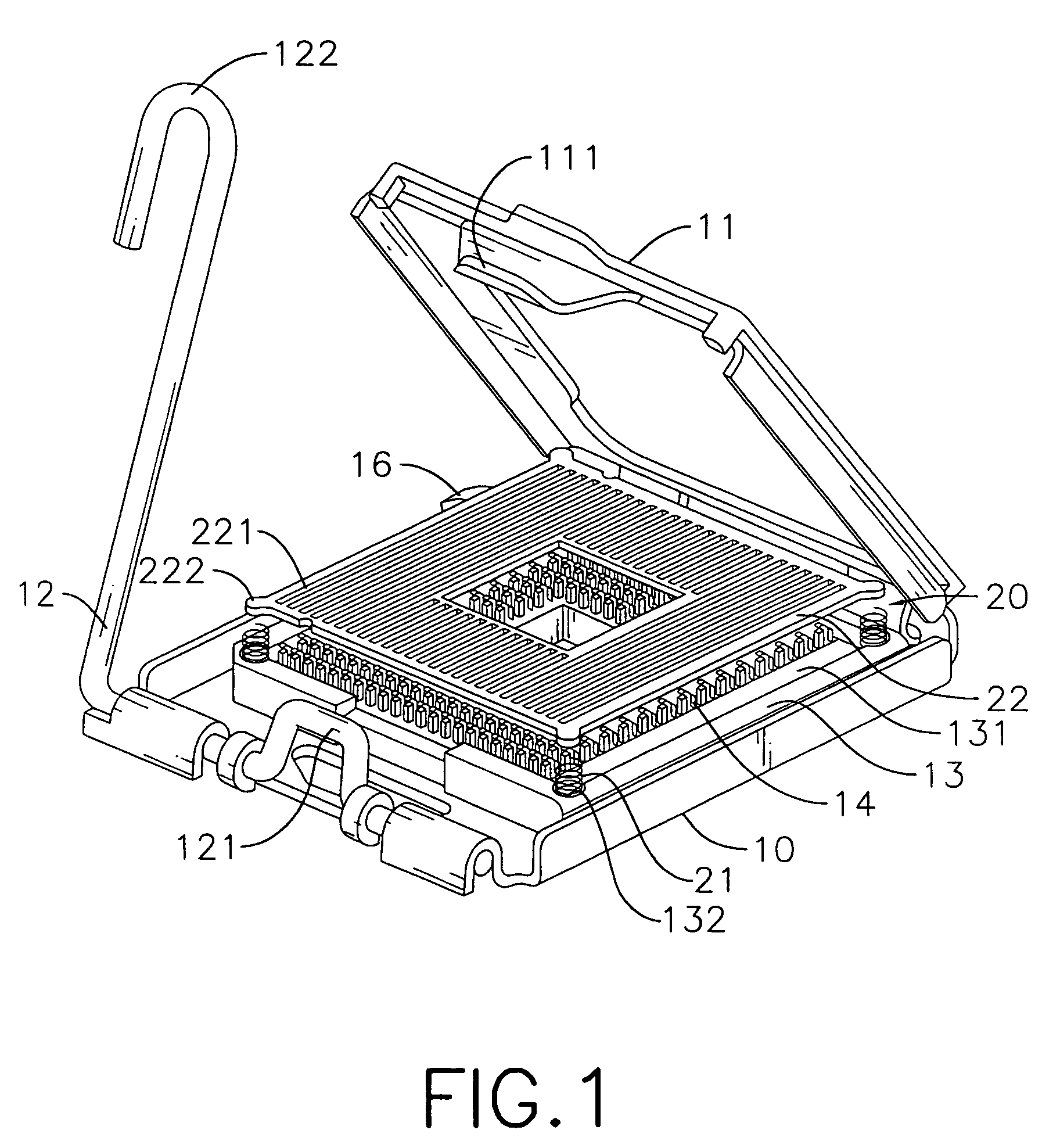

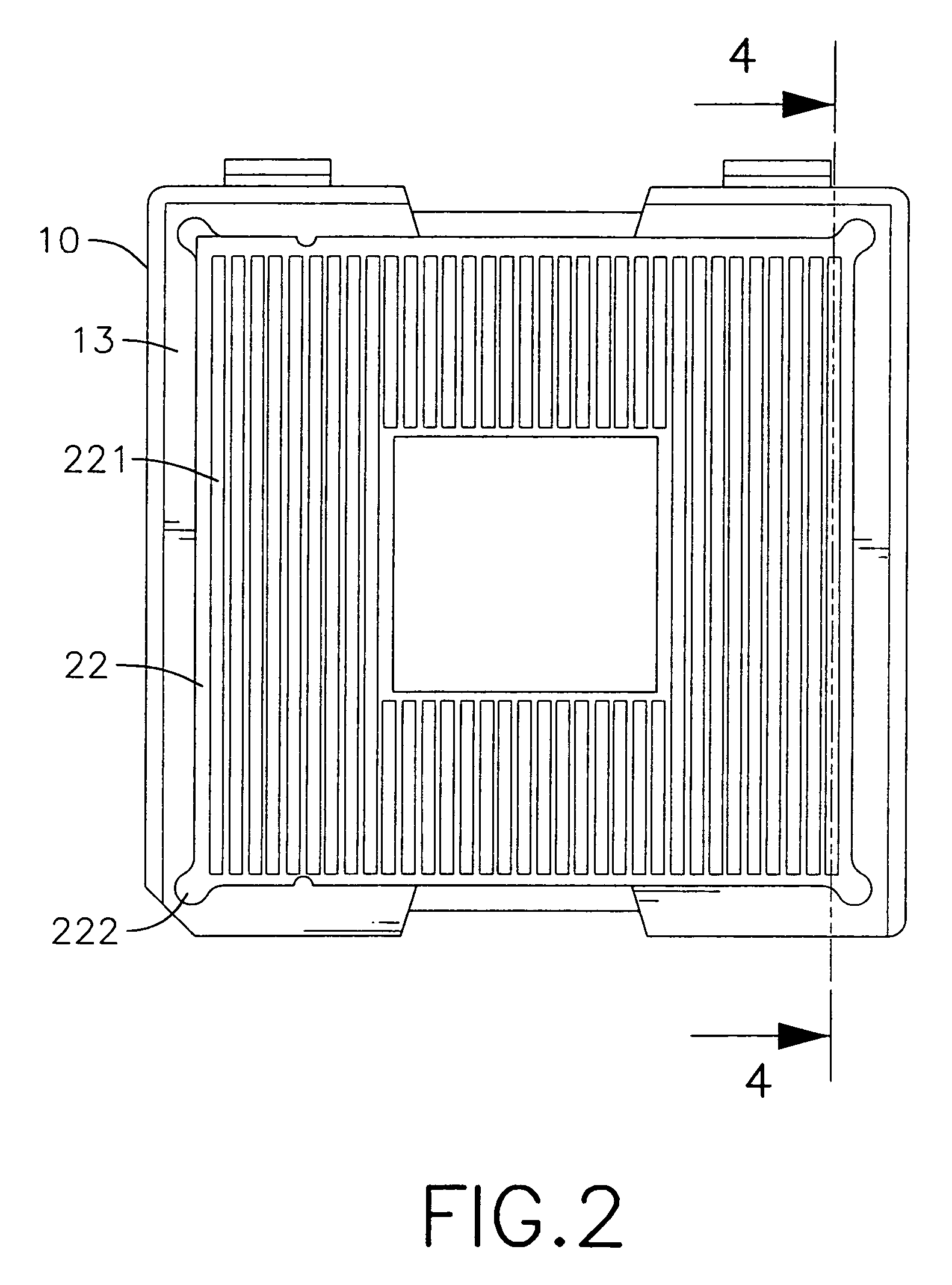

CPU socket assembly with package retention mechanism

InactiveUS7866985B2Live contact access preventionElectrical apparatus contructional detailsCPU socketElectrical contacts

A CPU socket assembly includes a CPU socket and a pick up cap mounted to the CPU socket. The CPU socket has an insulative housing with a receiving space, a number of electrical contacts secured to the insulative housing with contact portions disposed in the receiving space; and a retention piece attached to the insulative housing. The retention piece has a pressing section covering part of the receiving space to retaining a package in the CPU socket.

Owner:HON HAI PRECISION IND CO LTD

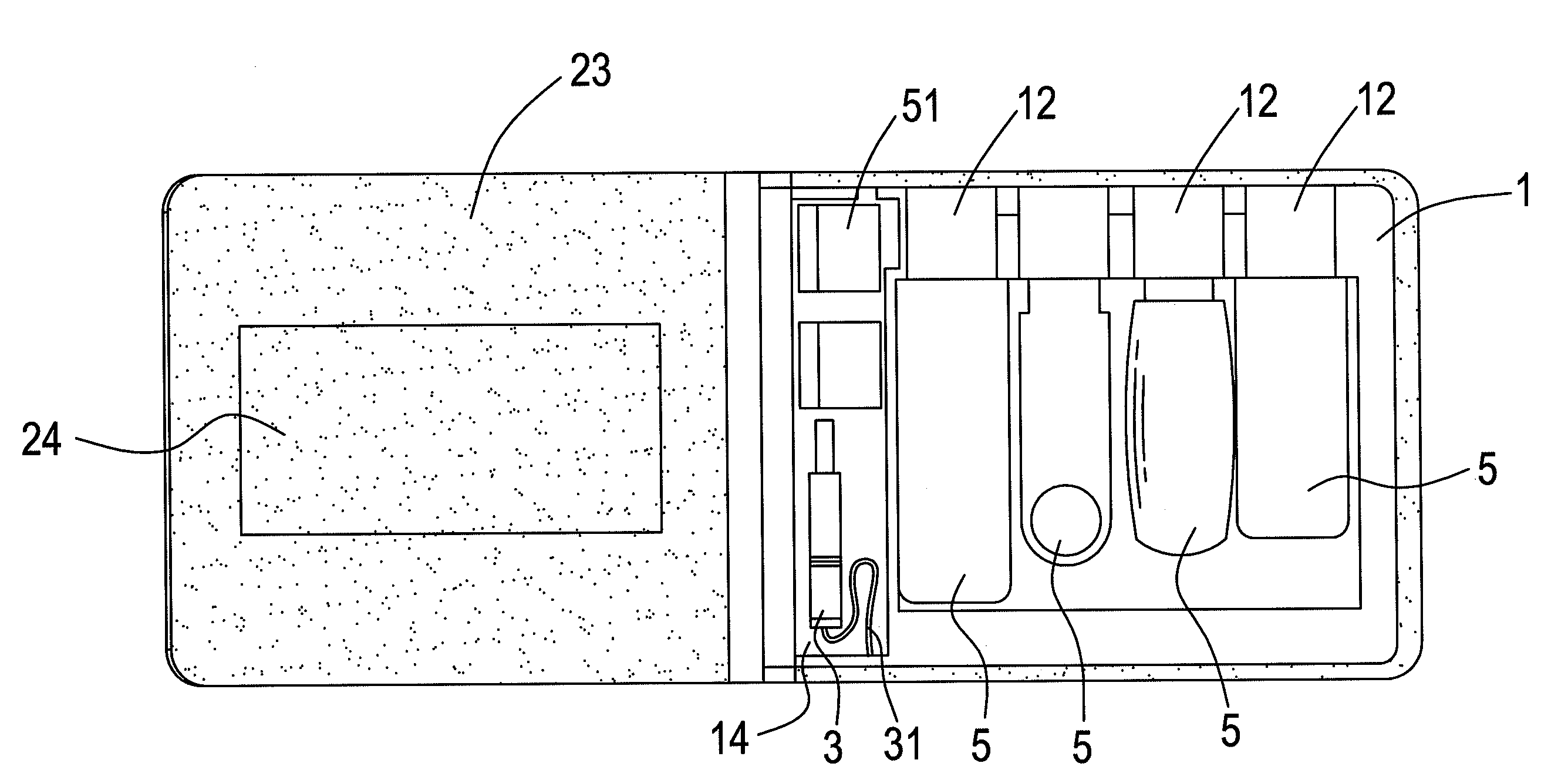

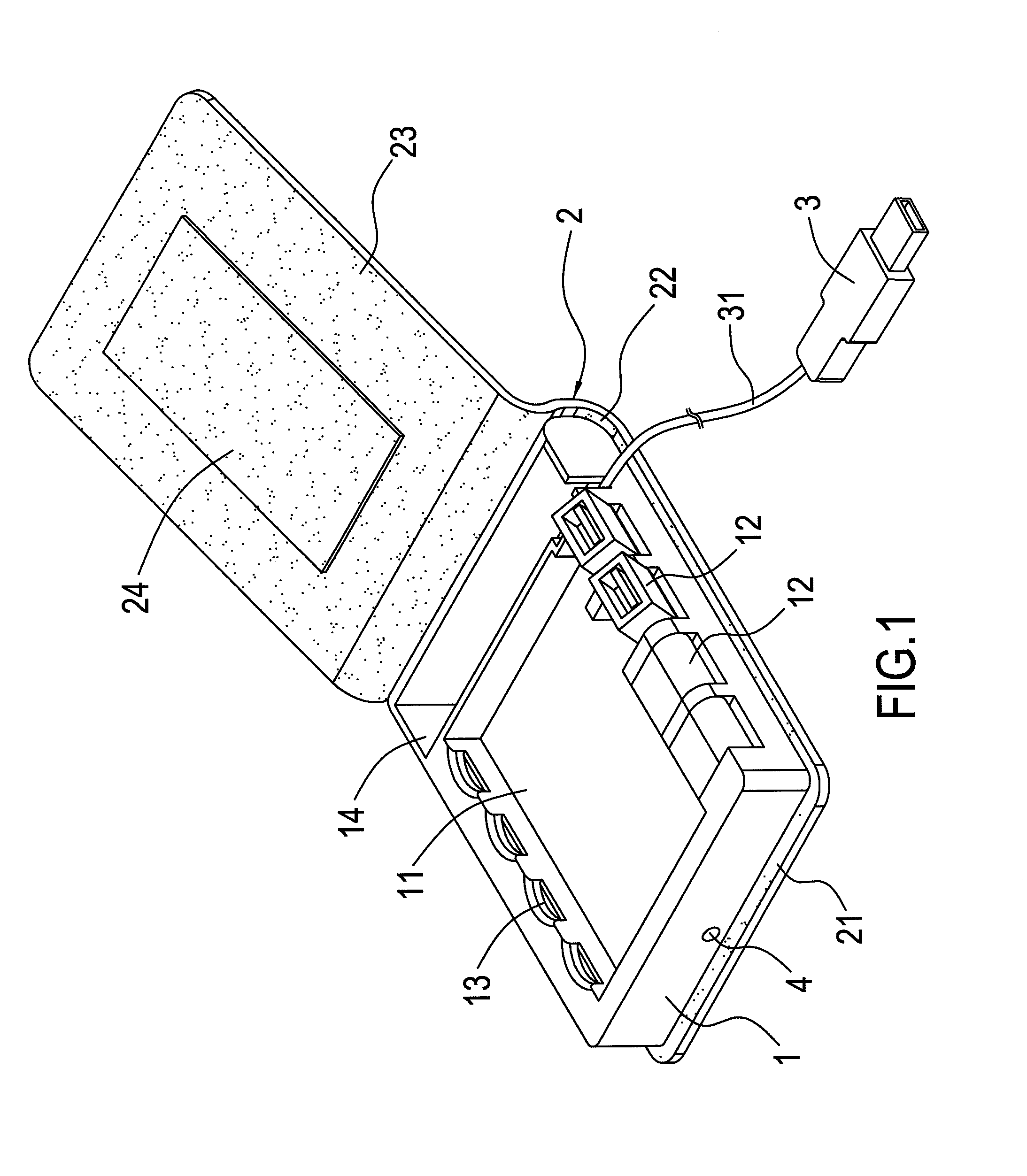

Multifunctional universal serial bus flash drive organizer

A multifunctional USB flash drive organizer includes a main unit, an interior of which is provided with a containing chamber to put USB flash drives. A side of the containing chamber is pivoted with USB sockets which can turn and a wire containing slot is provided beside the containing chamber. The main unit is provided with a wire collection device and a USB connector, with that a connection cable of the USB connector is electrically interconnected with the wire collection device. In addition, multiple USB flash drives can all operate at a same time. A wallet unit encloses the main unit as a box which is convenient in labeling for drive management and can be carried easily.

Owner:MICROLAN INTEGRATION

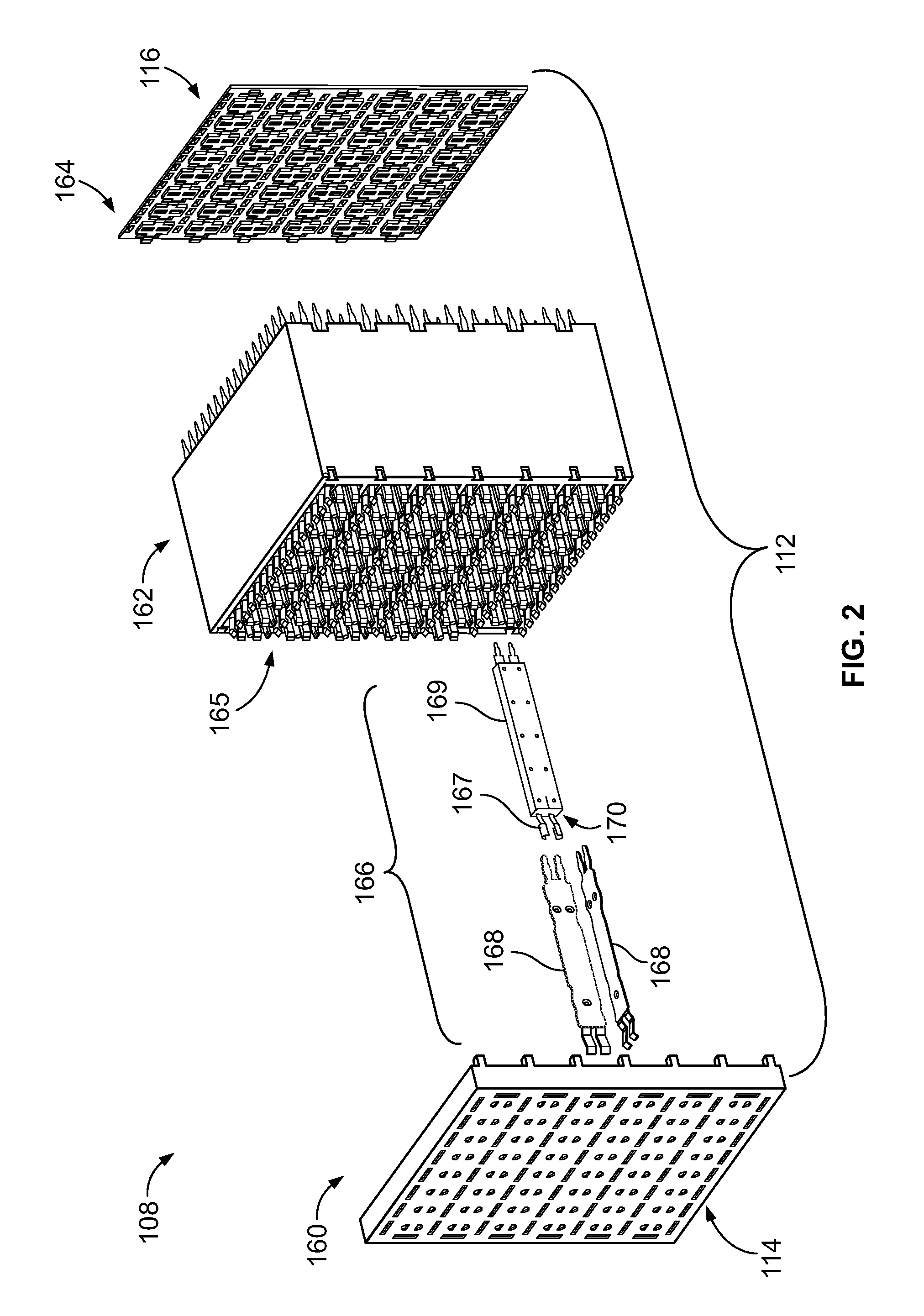

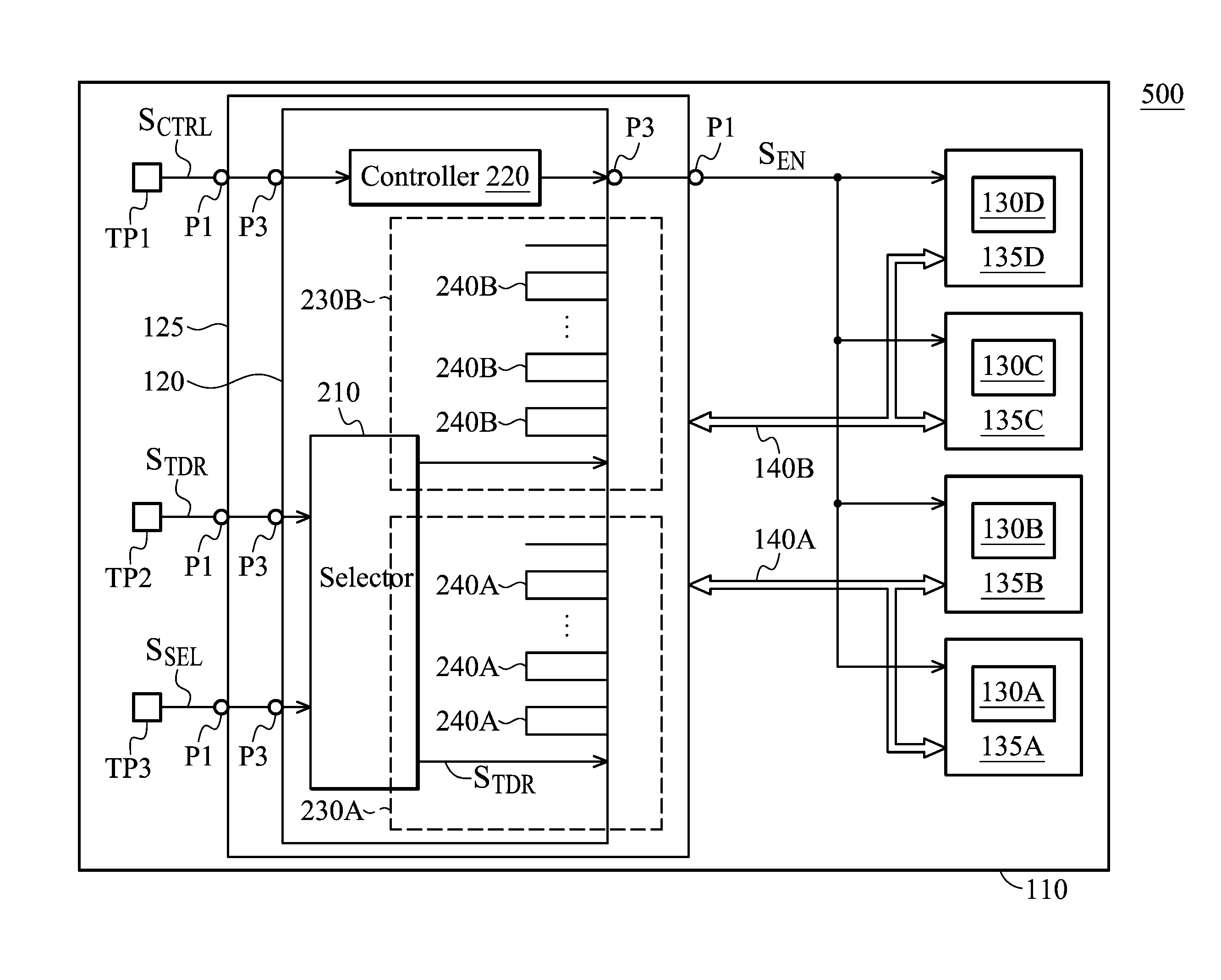

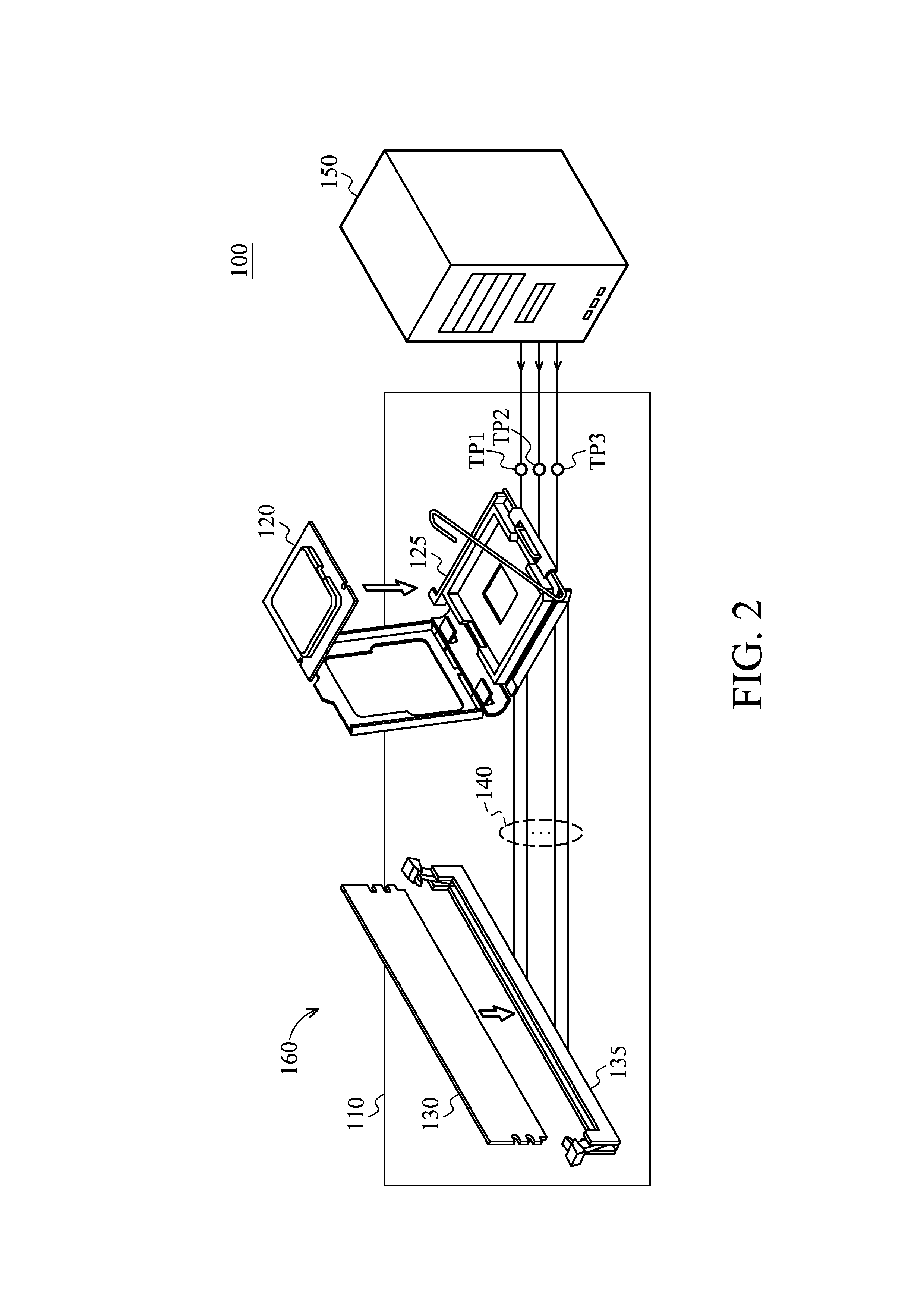

Test system and test method for pcba

InactiveUS20130181737A1Fault location by pulse reflection methodsContactless circuit testingAutomatic test equipmentCPU socket

A test system is provided. A printed circuit board (PCB) includes a plurality of traces and at least one test point. A central processing unit (CPU) socket including a plurality of first pins and a memory module slot including a plurality of second pins are disposed on the PCB. Each of the second pins is coupled to the corresponding first pin of the CPU socket via the corresponding trace. A CPU interposer board is inserted into the CPU socket, and a memory interposer board is inserted into the memory module slot. The traces form a test loop via the CPU interposer board and the memory interposer board. When an automatic test equipment (ATE) provides a test signal to the test loop via the test point, the ATE determines whether the test loop is normal according to a reflectometry result of the test signal.

Owner:WISTRON CORP

CPU socket with a cushion

A center processing unit (CPU) socket holds a CPU and has a base and a cushion. The base has a bottom, a contact seat, multiple contacts, a cover and a latch. The contact seat is mounted in the bottom and has a recess. The contacts are mounted in the recess in multiple lines. The cover is mounted pivotally on the base and has a latch tab. The latch has a locking tab selectively engaging the latch tab. The cushion is mounted in the recess and has multiple springs and a CPU backplate. The springs are mounted in the recess. The CPU backplate is mounted on the springs and has multiple slots corresponding to the contacts. The CPU backplate cooperates with the springs during installation of a CPU to oppose a force pushing the CPU down in the CPU socket so the contacts will not be damaged.

Owner:HUANG HUANG CHOU

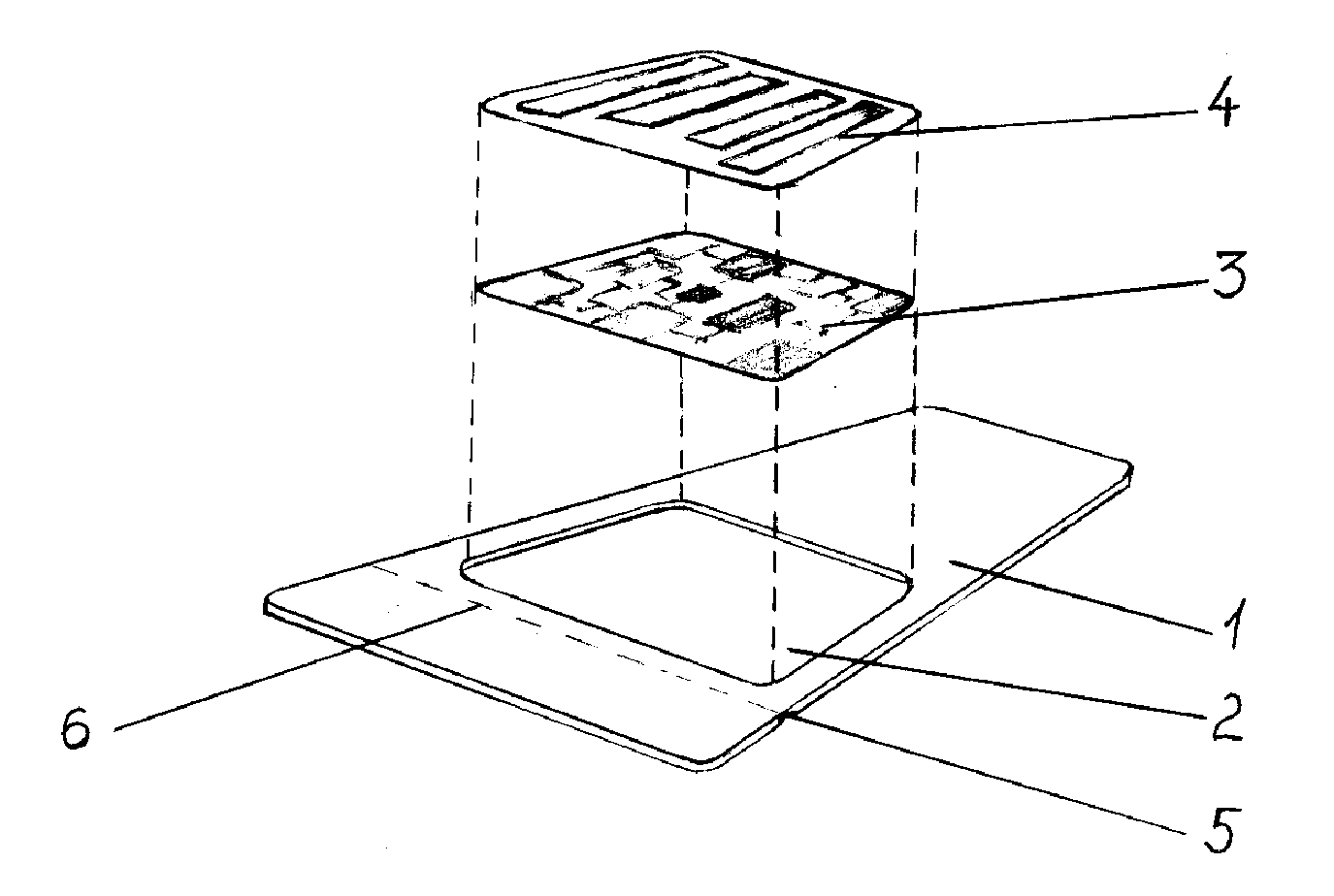

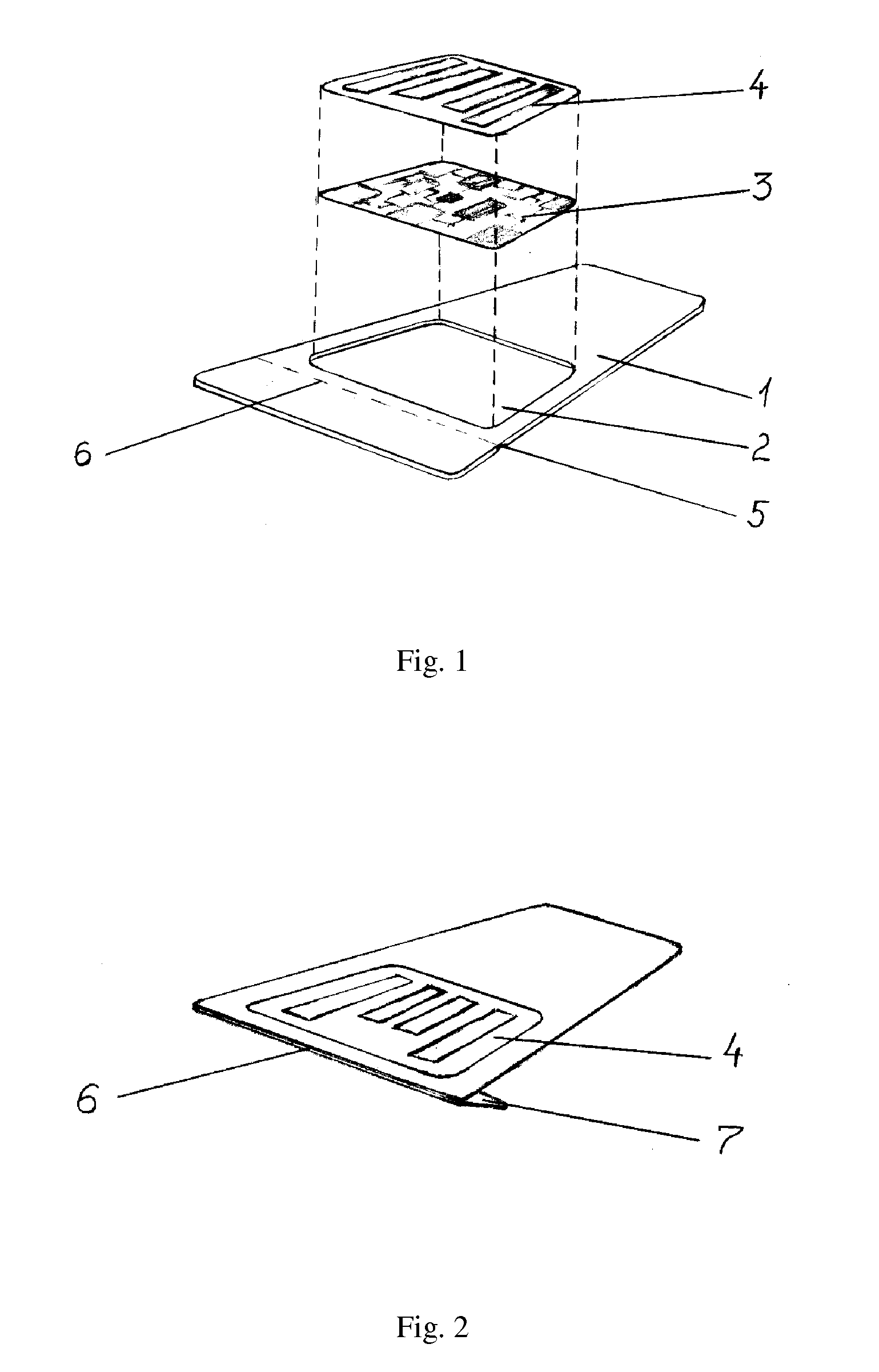

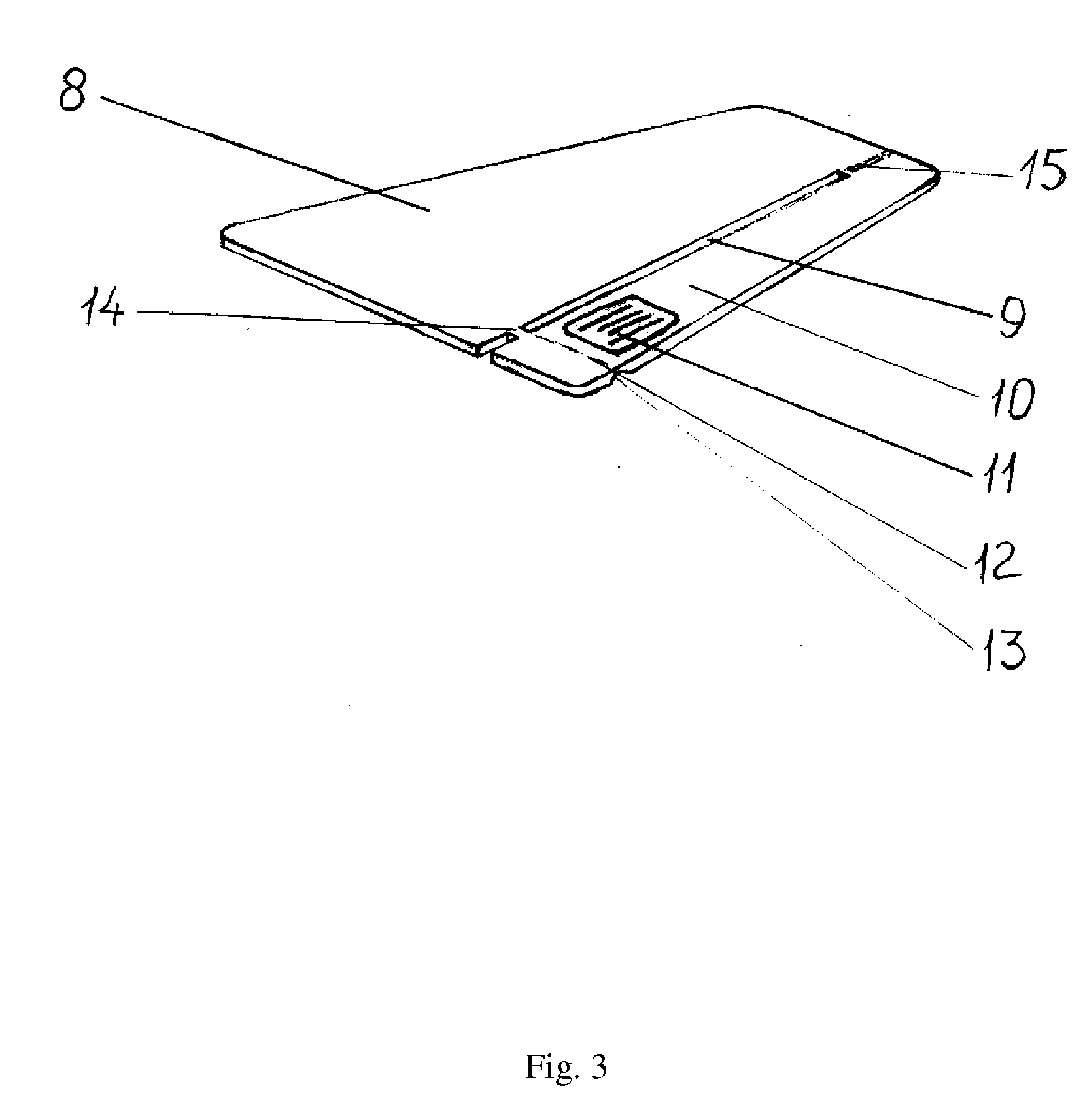

USB socket and injection molding method thereof

ActiveCN107394447AAvoid rising manufacturing costsContact member assembly/disassemblySecuring/insulating coupling contact membersCPU socketEngineering

The invention discloses a USB socket and an injection molding method thereof. The USB socket comprises a plurality of conductive terminals, and an insulating body which is integrally formed on the conductive terminals; the insulating body comprises a base part, and a butt tongue part extending from the forward direction of the base part; each of the conductive terminals comprises a contact part molded on the butt tongue part, a fixing part which extends backwards from the contact part and is molded inside the base part, and a welding part which extends backward from the fixing part; the first side of the contact part is embedded in the butt tongue part, and the second side of the contact part is exposed out of a first tongue part; the first side of the base part is provided with an open slot at the position corresponding to the fixing part of the conductive terminal; the second side of the base part is provided with a locating slot at the position corresponding to the fixing part of the conductive terminal; and the open slot and the locating slot are at least partially overlapped in the vertical direction. The USB socket provided by the invention can reduce the manufacturing cost of the USB socket.

Owner:SHENZHEN EVERWIN PRECISION TECH

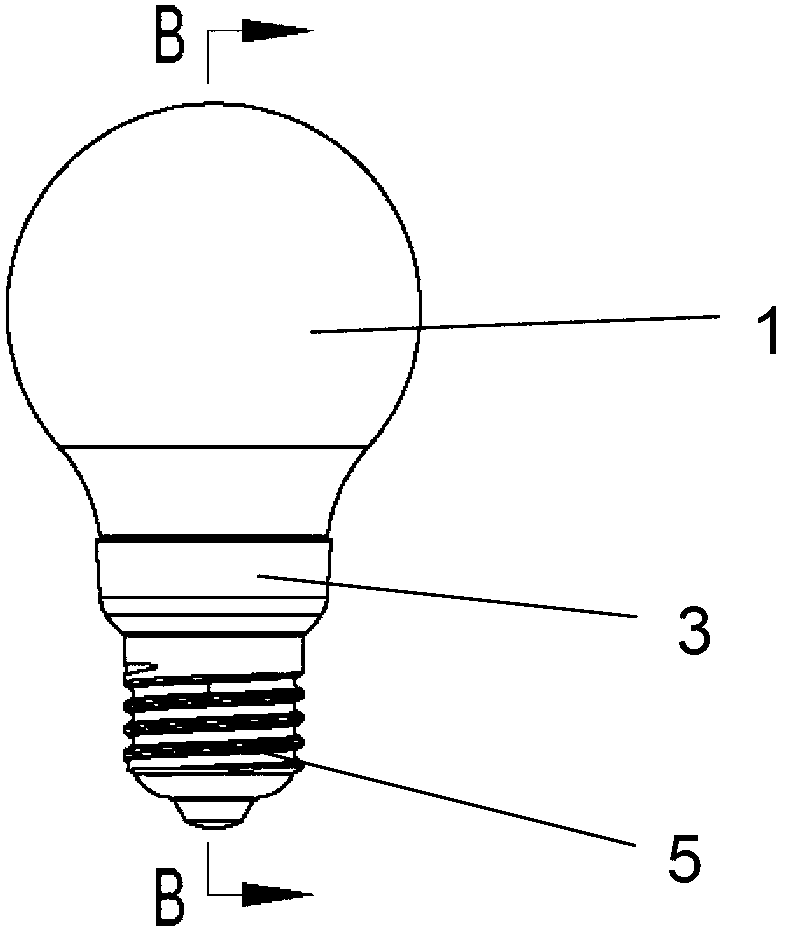

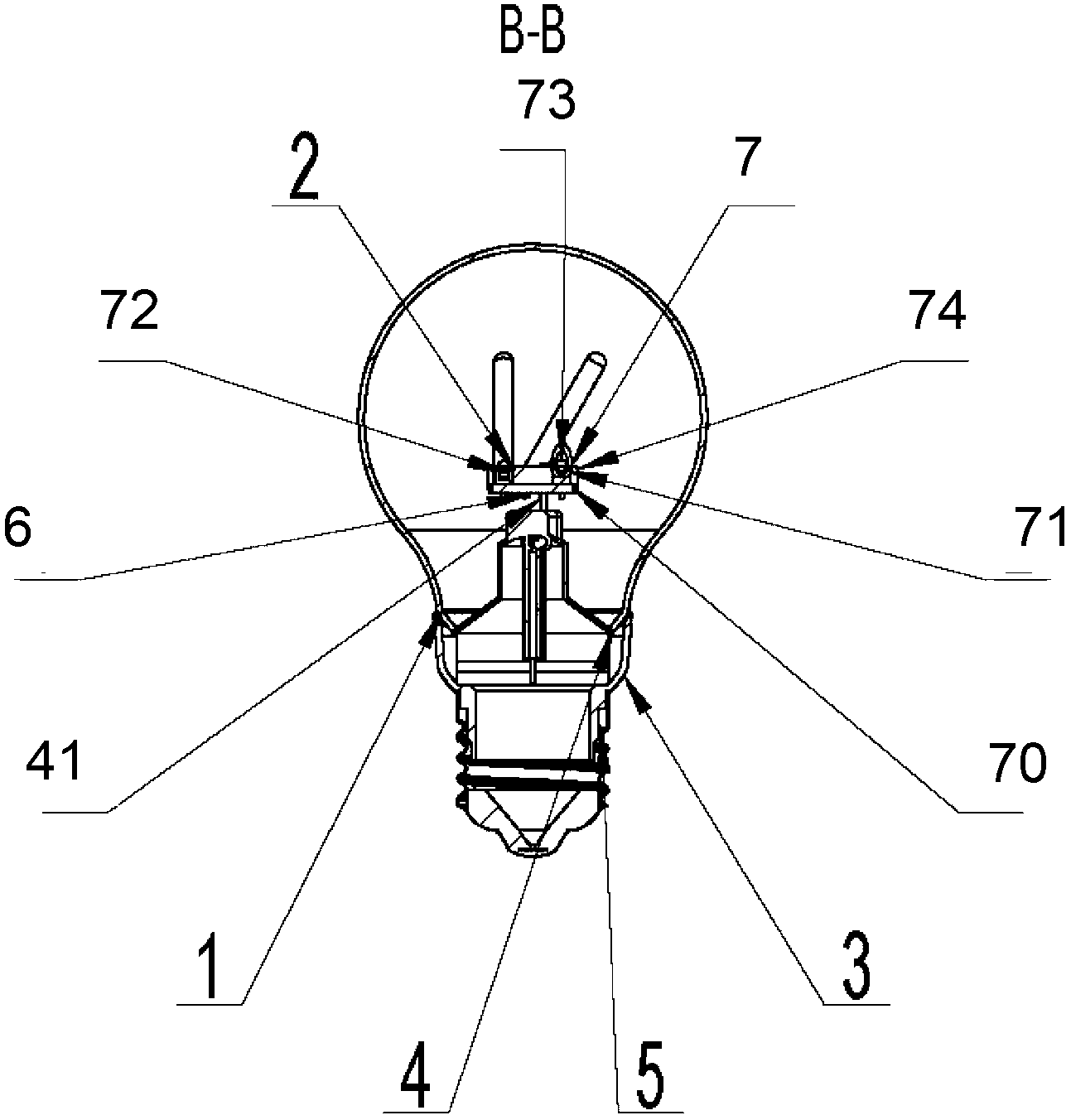

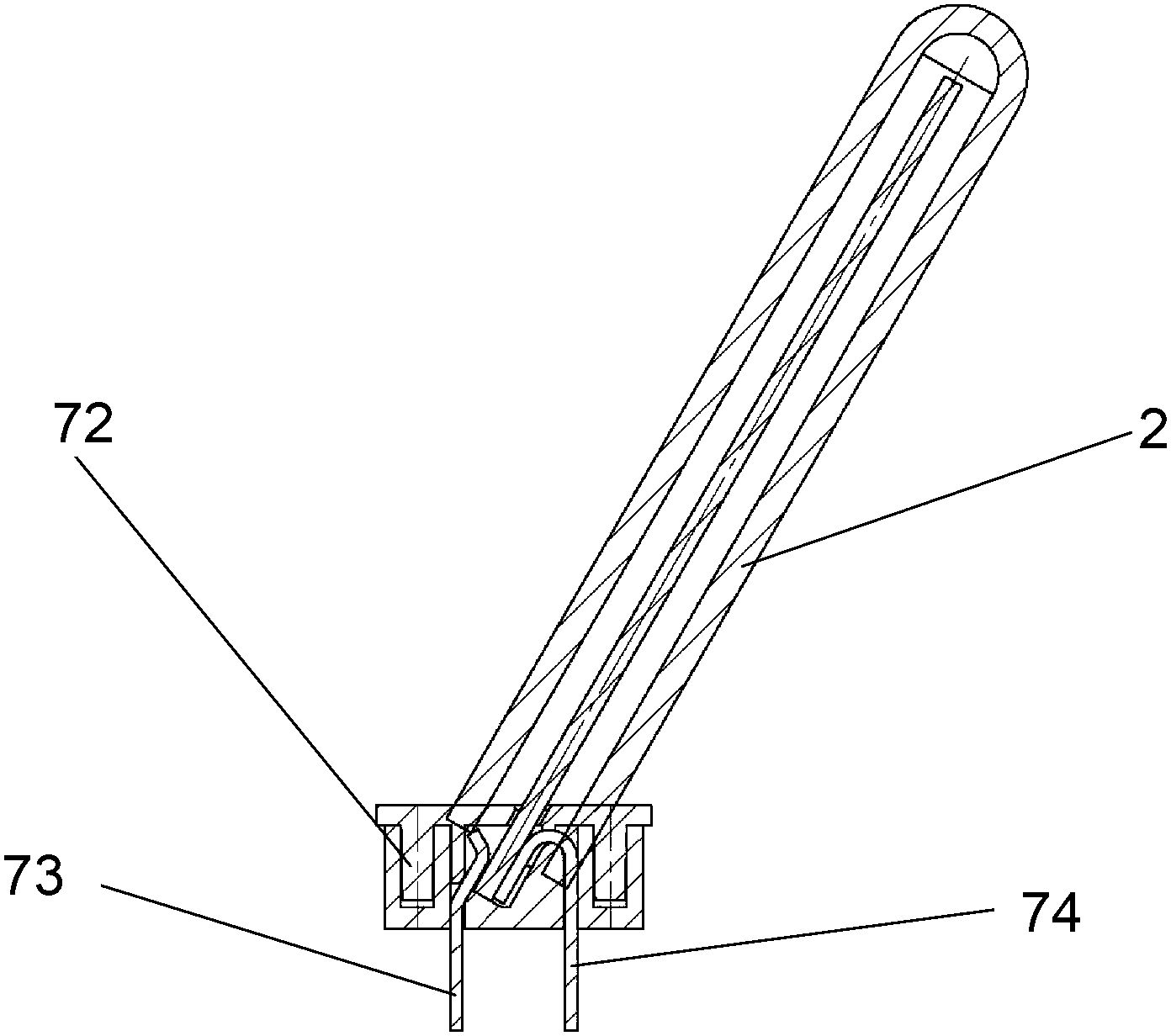

LED bulb

InactiveCN103322459ASolve the cooling problemGood light distributionPoint-like light sourceElectric circuit arrangementsCPU socketEngineering

The invention discloses an LED bulb which comprises a cap, a cap plastic part, a glass core, an envelope, a plurality of LED filaments and a socket. The cap plastic part is connected with the cap, the glass core is connected with the cap plastic part, the envelope is connected with the glass core tightly, the LED filaments are disposed in the envelope, the socket is connected with the upper end of the glass core, and the LED filaments are inserted to the socket. The socket comprises a socket base plate with a plurality of connection holes and also comprises a plurality of sub sockets matched with the connection holes, and the LED filaments are inserted to the sub sockets. The included angles between the LED filaments and the plane of the socket base plate are smaller than 90 degrees. Since the LED filaments are fixed in an inserted manner, various defects in welding process in the prior art are overcome, and quick and reliable assembling can be achieved. Since the included angles between the LED filaments and the plane of the socket base plate are smaller than 90 degrees, the light distribution effect of lamps is improved.

Owner:王铁俊

Plastic card provided with electrical contacts

InactiveUS20080299788A1Avoid crackingFit tightlyPrinted circuitsRecord carriers used with machinesElectricityCPU socket

Owner:BALCHAITIS VADIM EVGENEVICH

Systems and methods for providing co-processors to computing systems

ActiveUS20060149883A1Simple designLow costDigital data processing detailsPrinted circuit aspectsComputer hardwareComputerized system

Computing systems with conventional CPUs coupled to co-processors or accelerators implemented in FPGAs (Field Programmable Gate Arrays). One embodiment of the systems and methods according to the invention includes a FPGA accelerator implemented in a computer system by providing an adapter board configured to be used in a standard CPU socket.

Owner:XTREMEDATA INC