Patents

Literature

3305results about "Functional testing" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

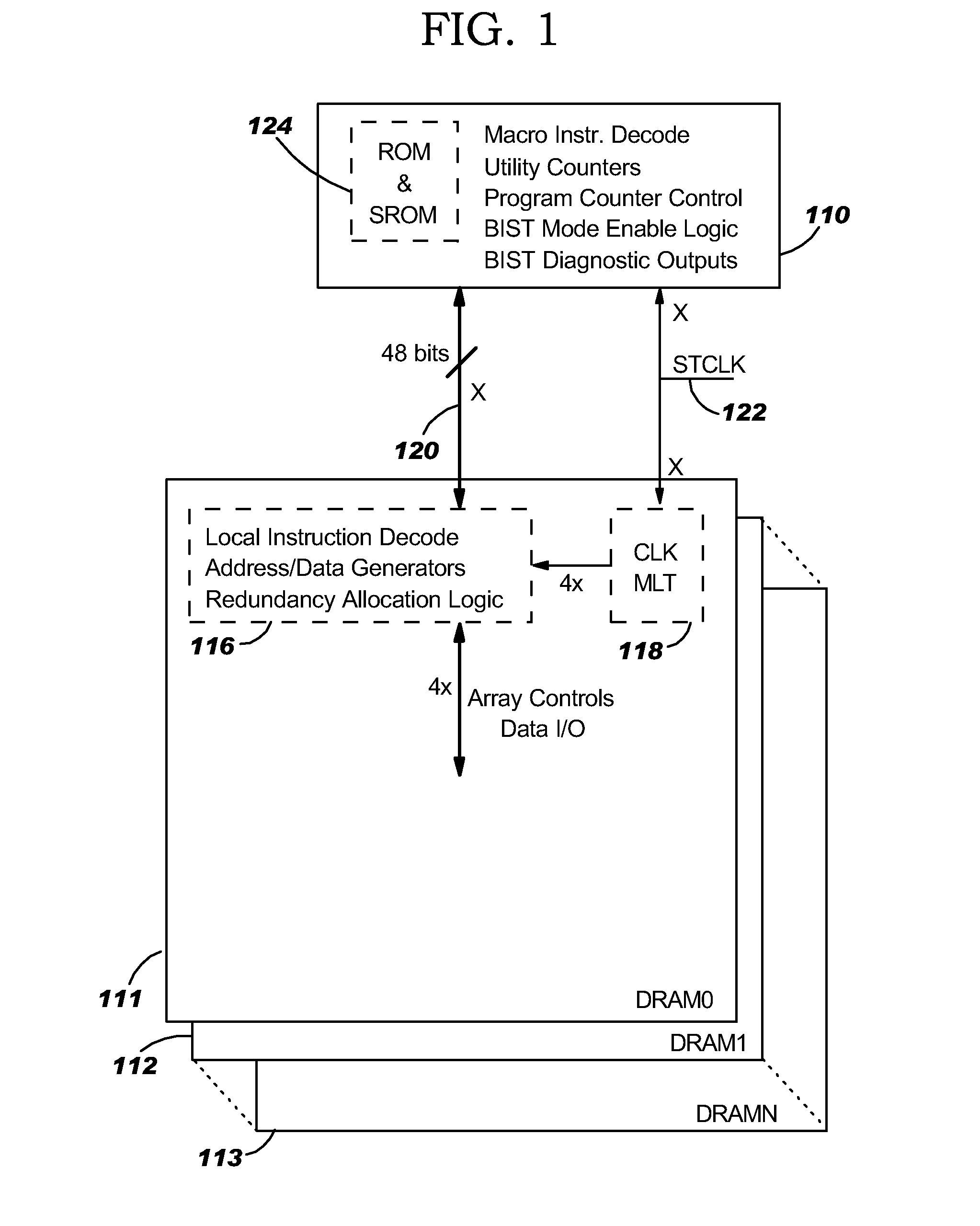

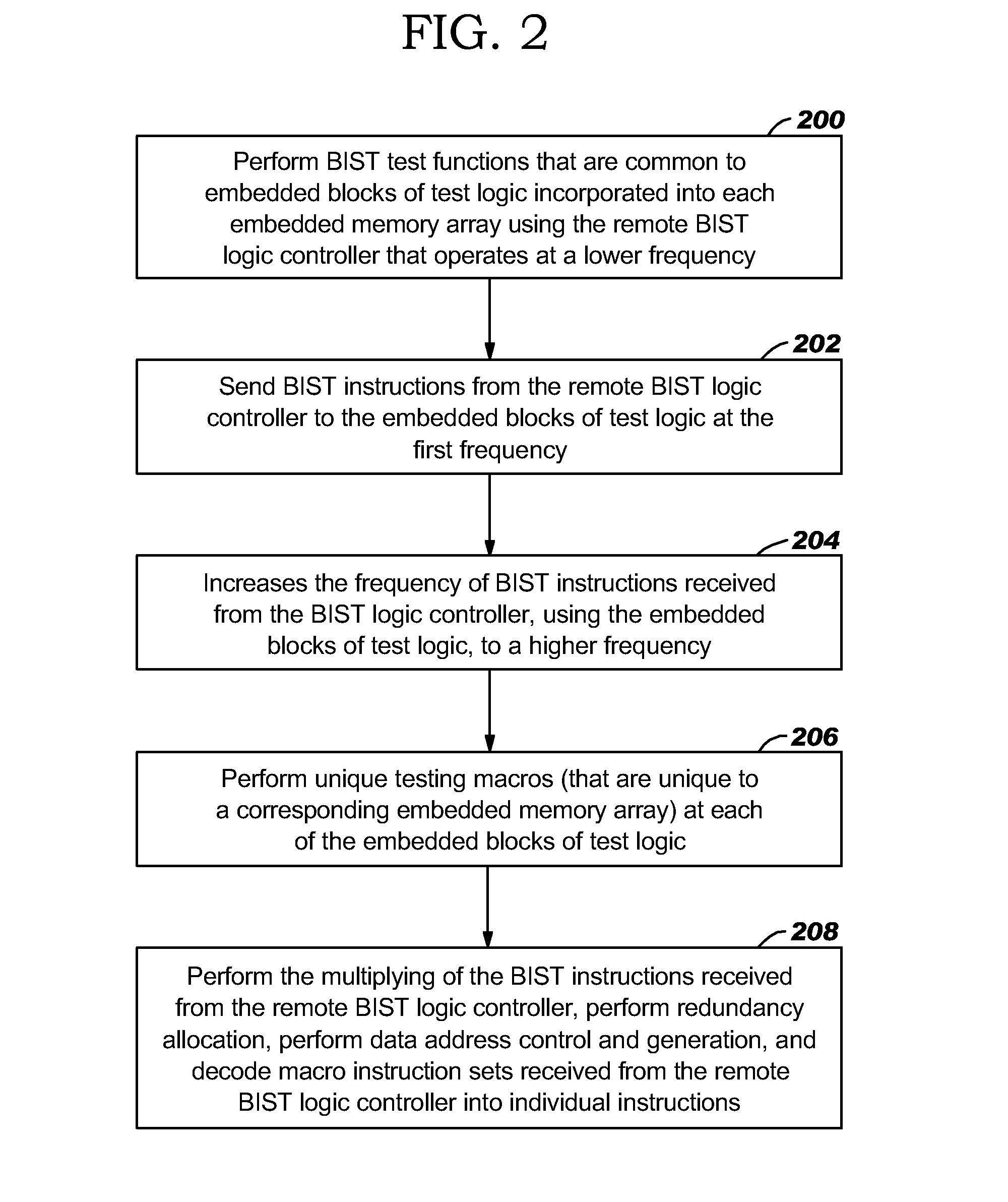

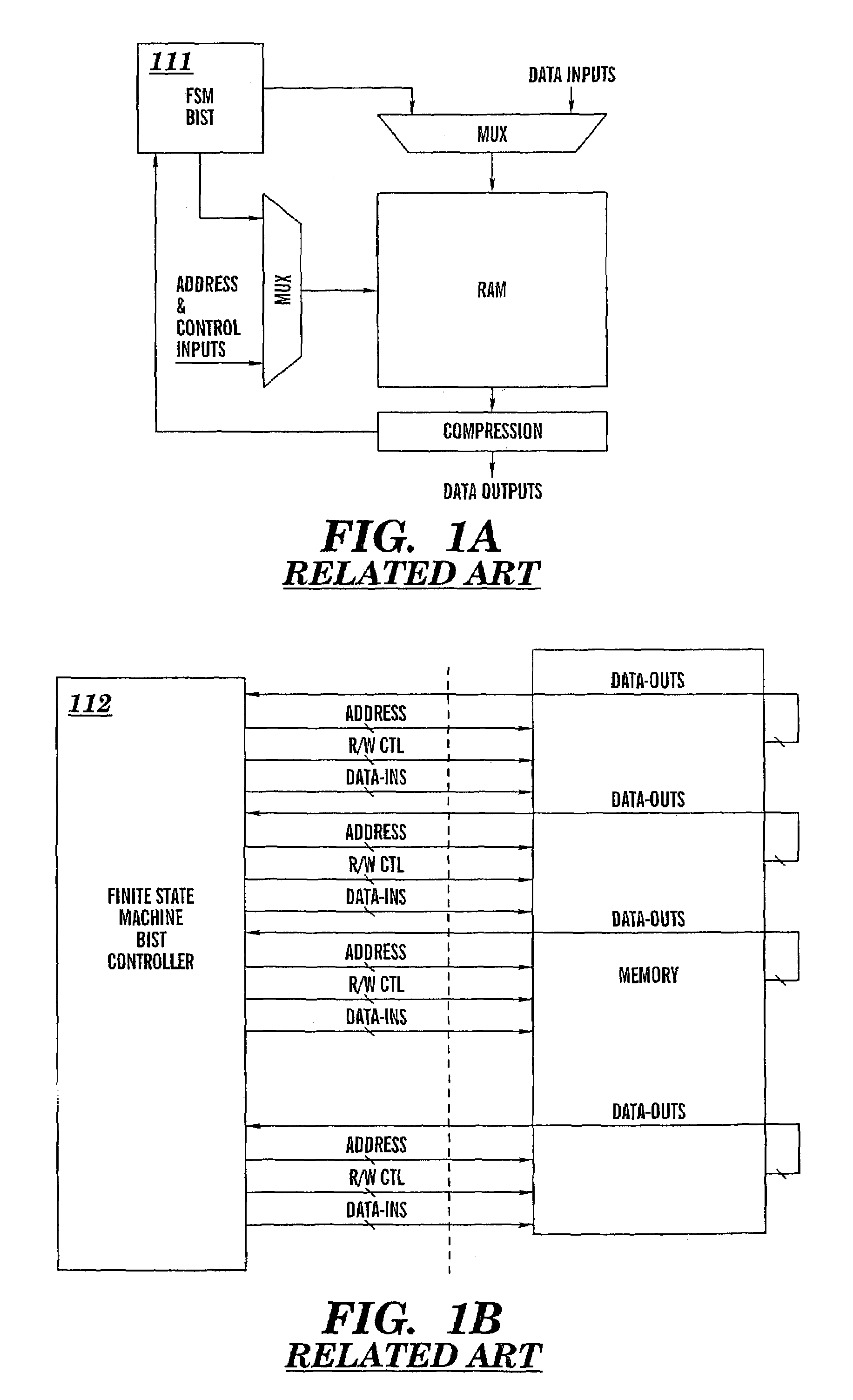

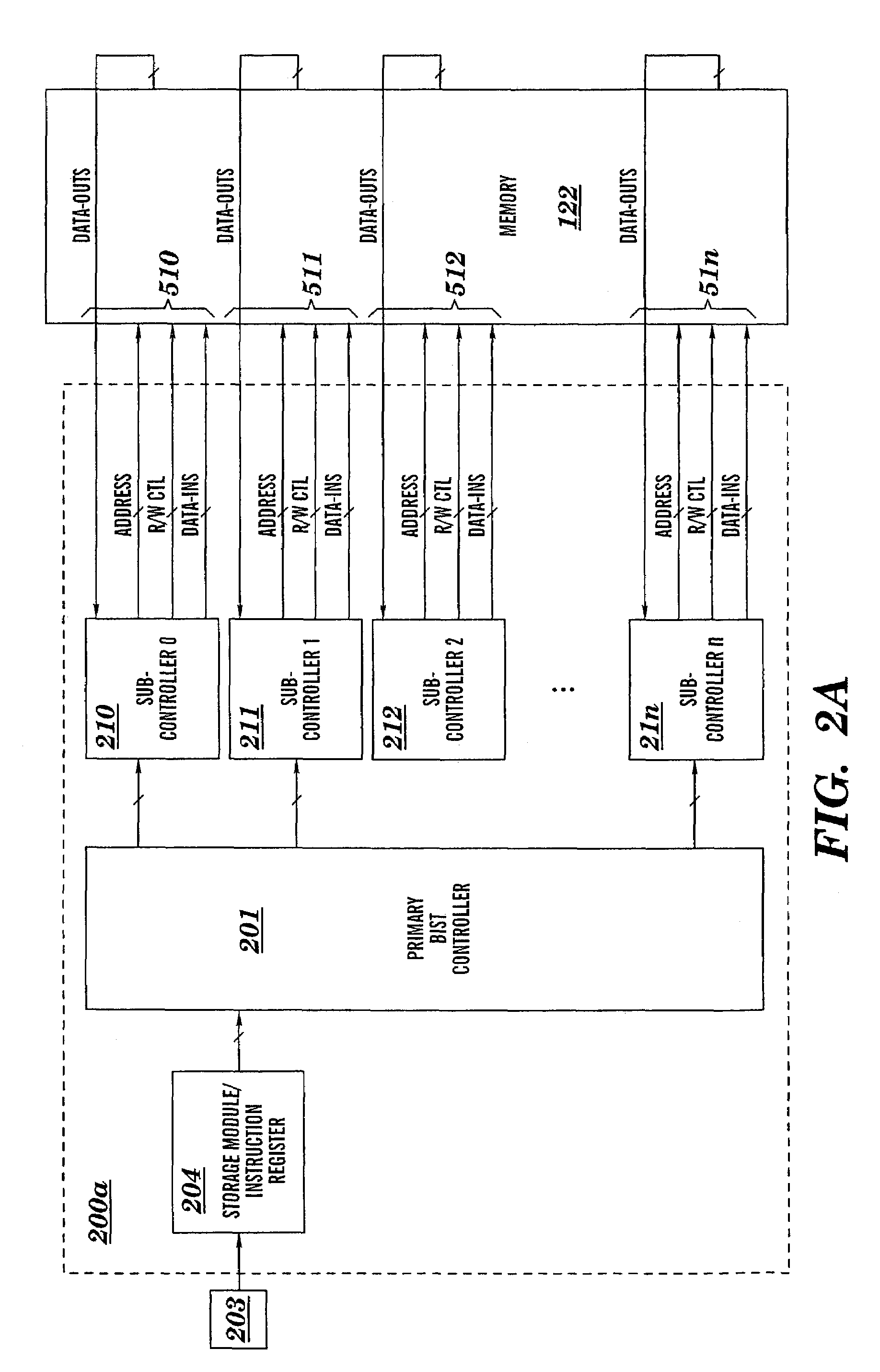

Hybrid built-in self test (BIST) architecture for embedded memory arrays and an associated method

ActiveUS20080178053A1Reduce frequencyMore test pattern flexibilityElectronic circuit testingFunctional testingSpecific testNormal mode

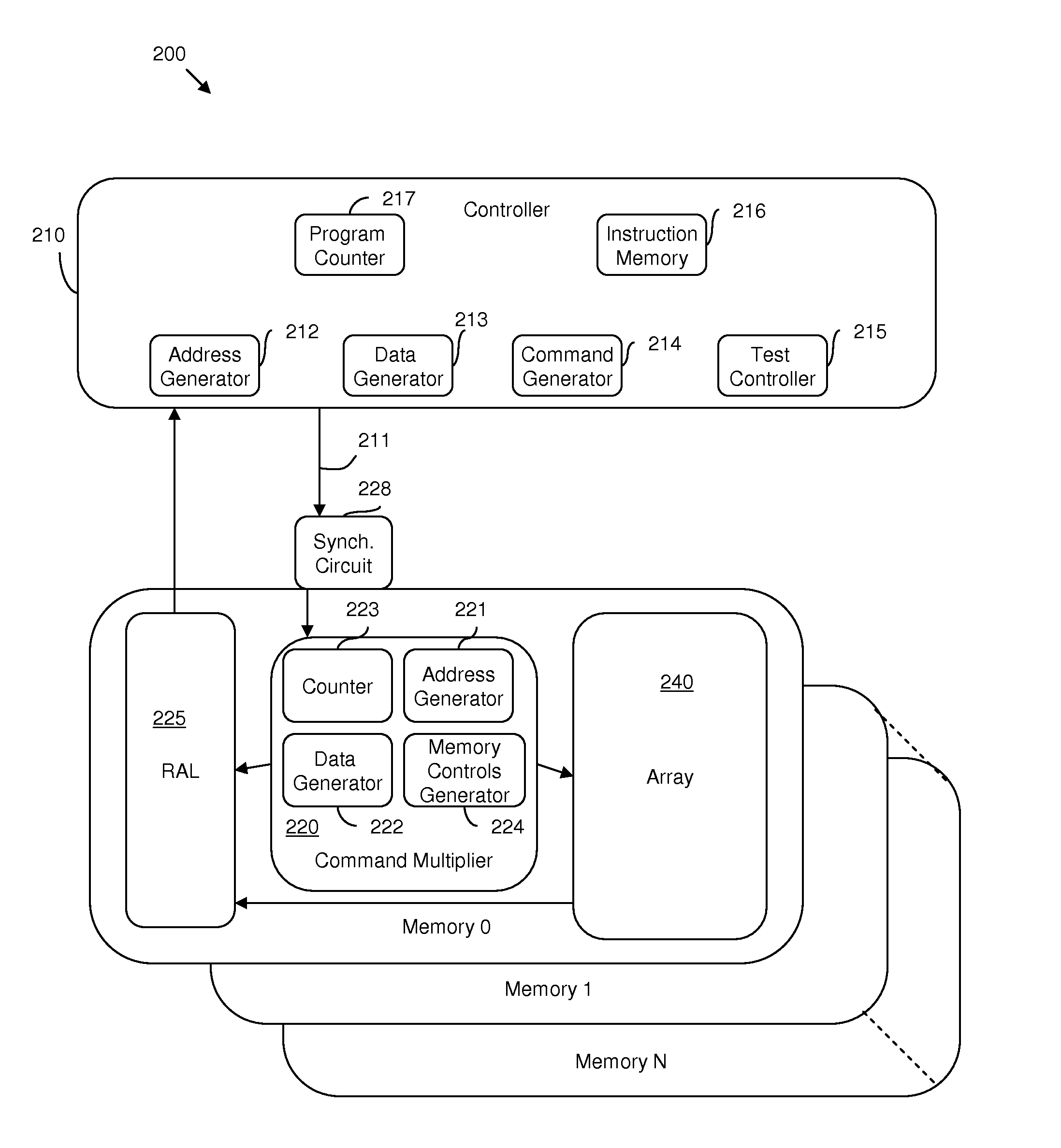

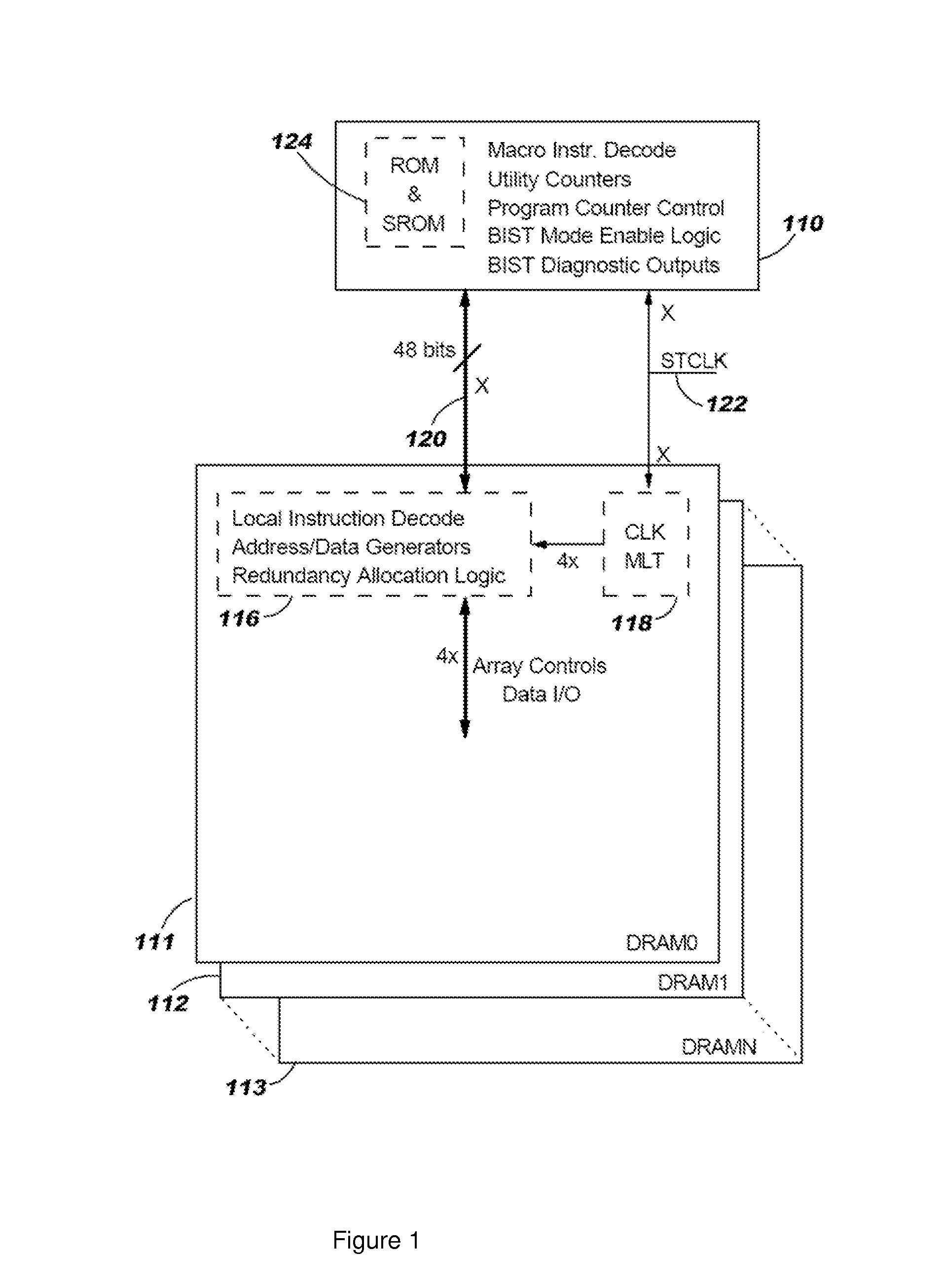

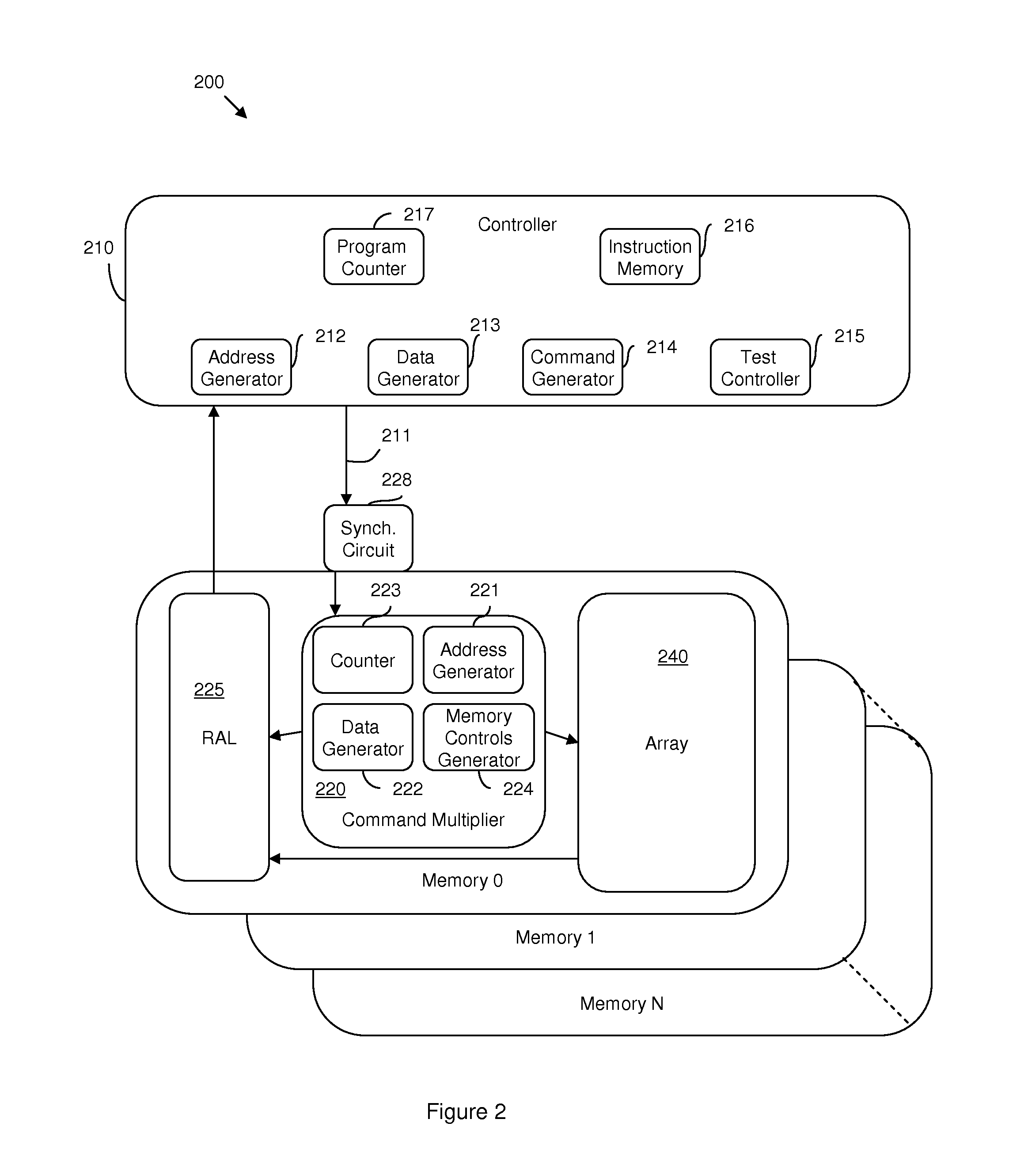

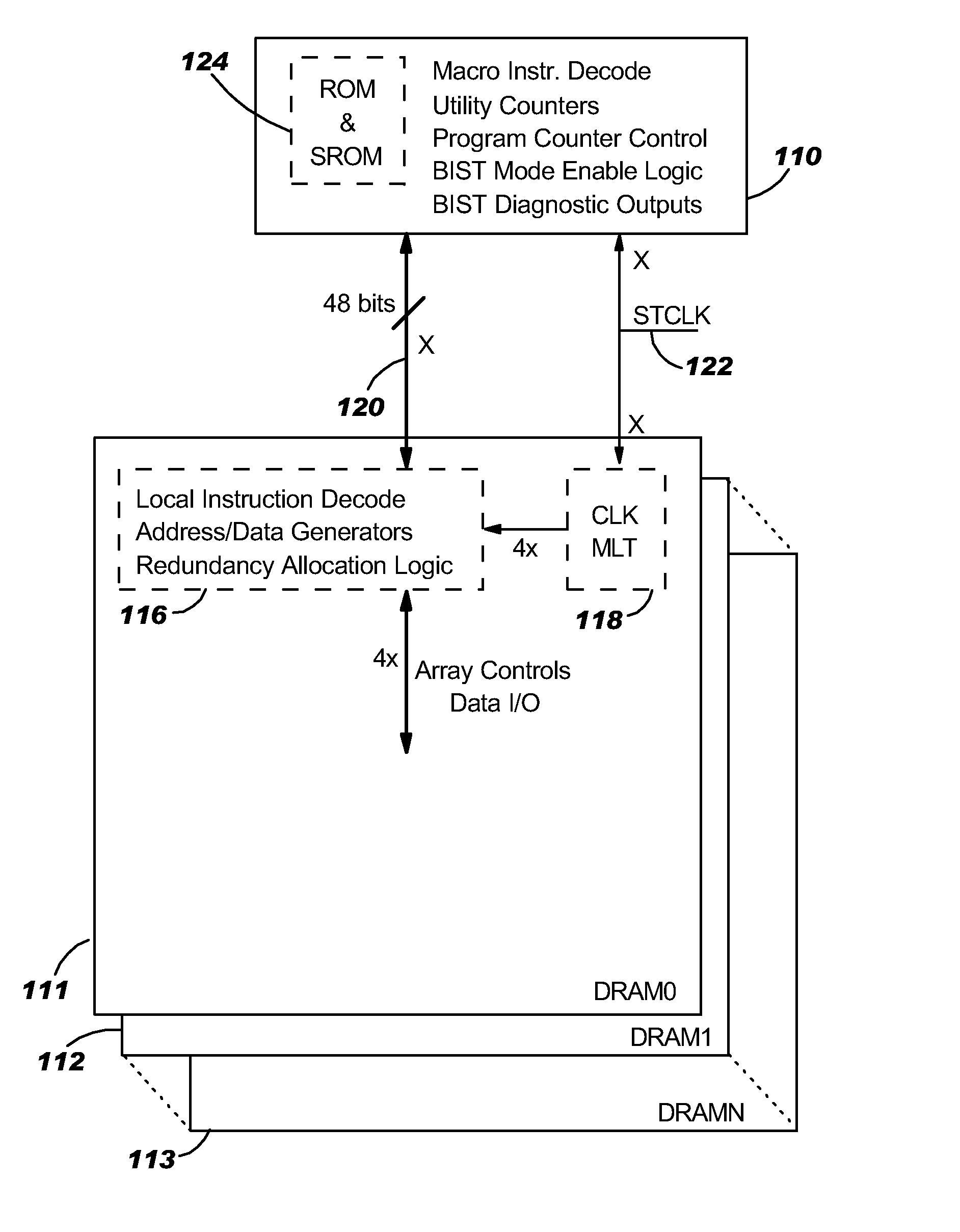

Disclosed are embodiments of a built-in self-test (BIST) architecture that incorporates a standalone controller that operates at a lower frequency to remotely perform test functions common to a plurality of embedded memory arrays. The architecture also incorporates command multipliers that are associated with the embedded memory arrays and that selectively operate in one of two different modes: a normal mode or a bypass mode. In the normal mode, instructions from the controller are multiplied so that memory array-specific test functions can be performed locally at the higher operating frequency of each specific memory array. Whereas, in the bypass mode, multiplication of the instructions is suspended so that memory array-specific test functions can be performed locally at the lower operating frequency of the controller. The ability to vary the frequency at which test functions are performed locally, allows for more test pattern flexibility.

Owner:META PLATFORMS INC

Remote bist for high speed test and redundancy calculation

InactiveUS20080215937A1Reduce frequencyIncrease processing frequencyDigital circuit testingFunctional testingLow speedSpeed test

Disclosed in a hybrid built-in self test (BIST) architecture for embedded memory arrays that segments BIST functionality into remote lower-speed executable instructions and local higher-speed executable instructions. A standalone BIST logic controller operates at a lower frequency and communicates with a plurality of embedded memory arrays using a BIST instruction set. A block of higher-speed test logic is incorporated into each embedded memory array under test and locally processes BIST instructions received from the standalone BIST logic controller at a higher frequency. The higher-speed test logic includes a multiplier for increasing the frequency of the BIST instructions from the lower frequency to the higher frequency. The standalone BIST logic controller enables a plurality of higher-speed test logic structures in a plurality of embedded memory arrays.

Owner:META PLATFORMS INC

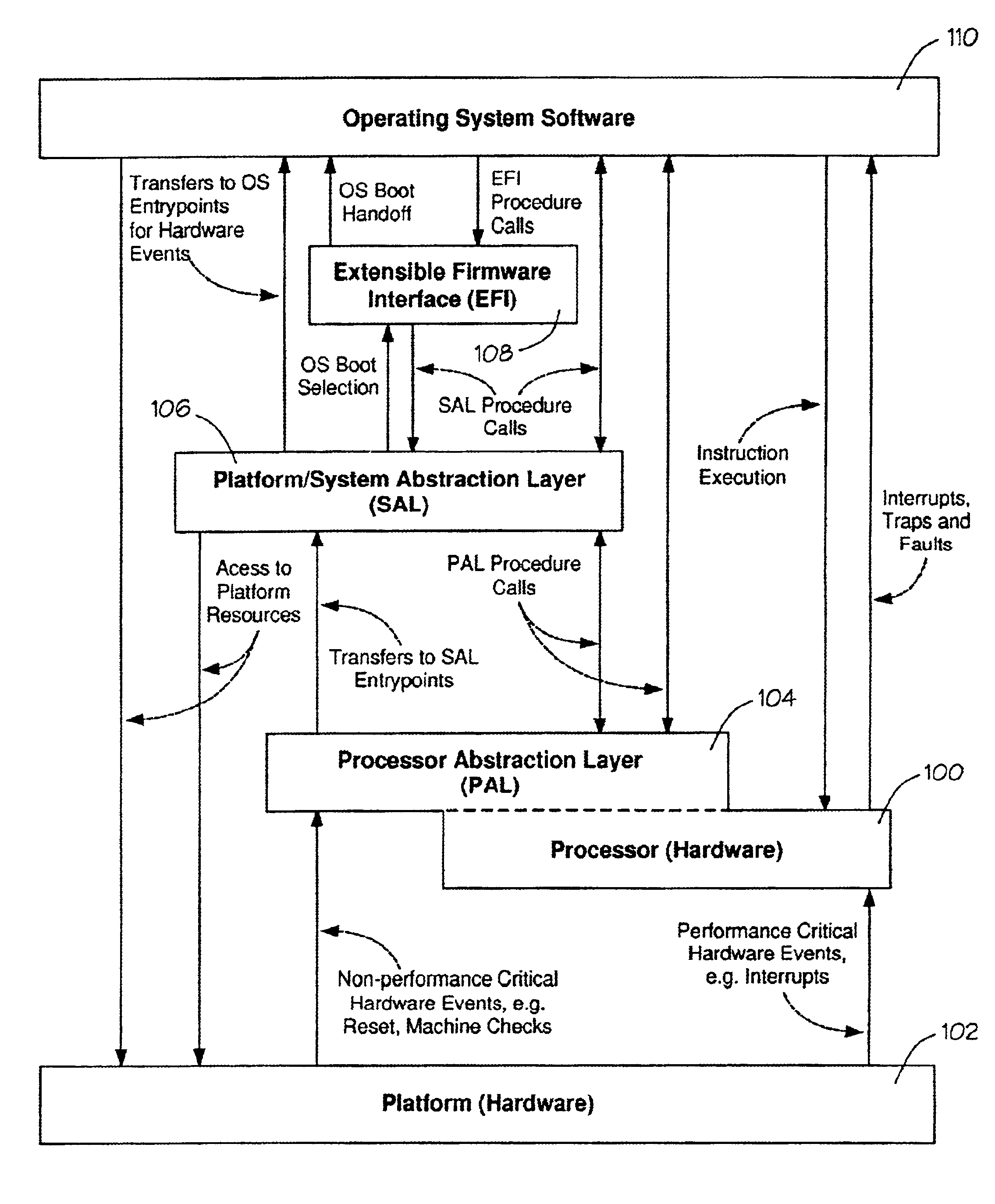

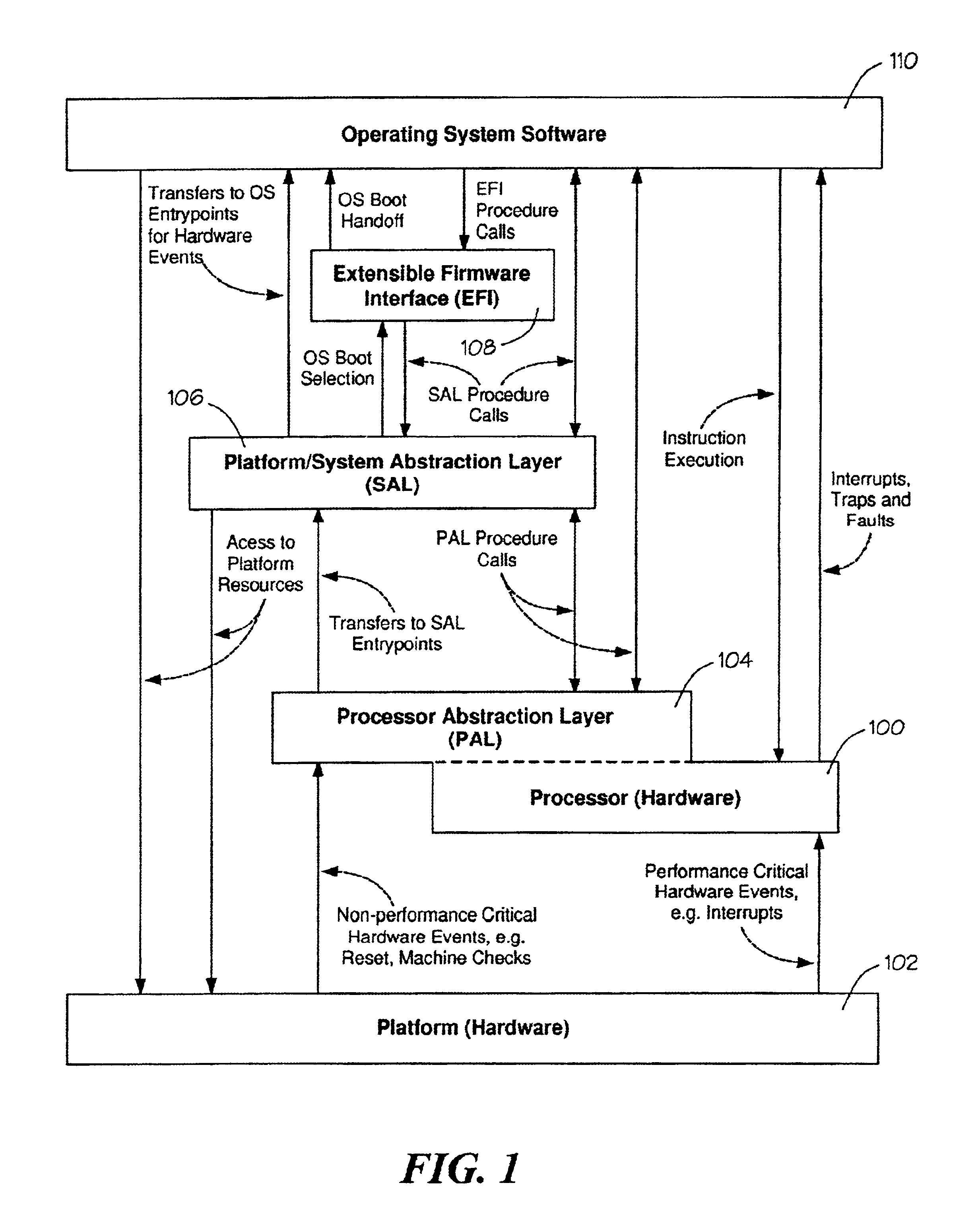

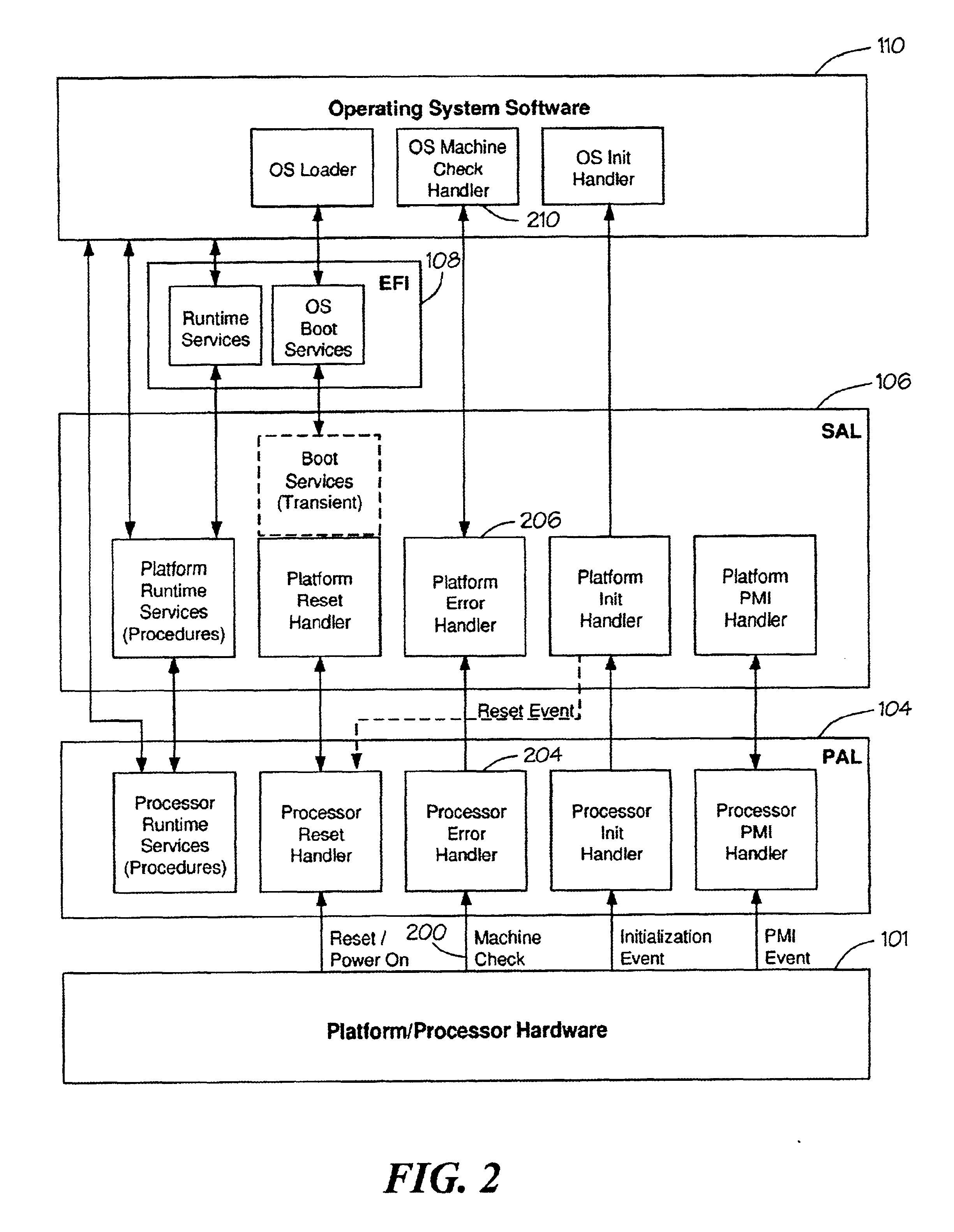

Method of correcting a machine check error

Processor implementation-specific instructions save a processor state in a system memory and attempt to correct the error. Control is then transferred to processor-independent instructions. Control is returned to the processor implementation-specific instructions which then return to an interrupted context of the processor by restoring the processor state.

Owner:INTEL CORP

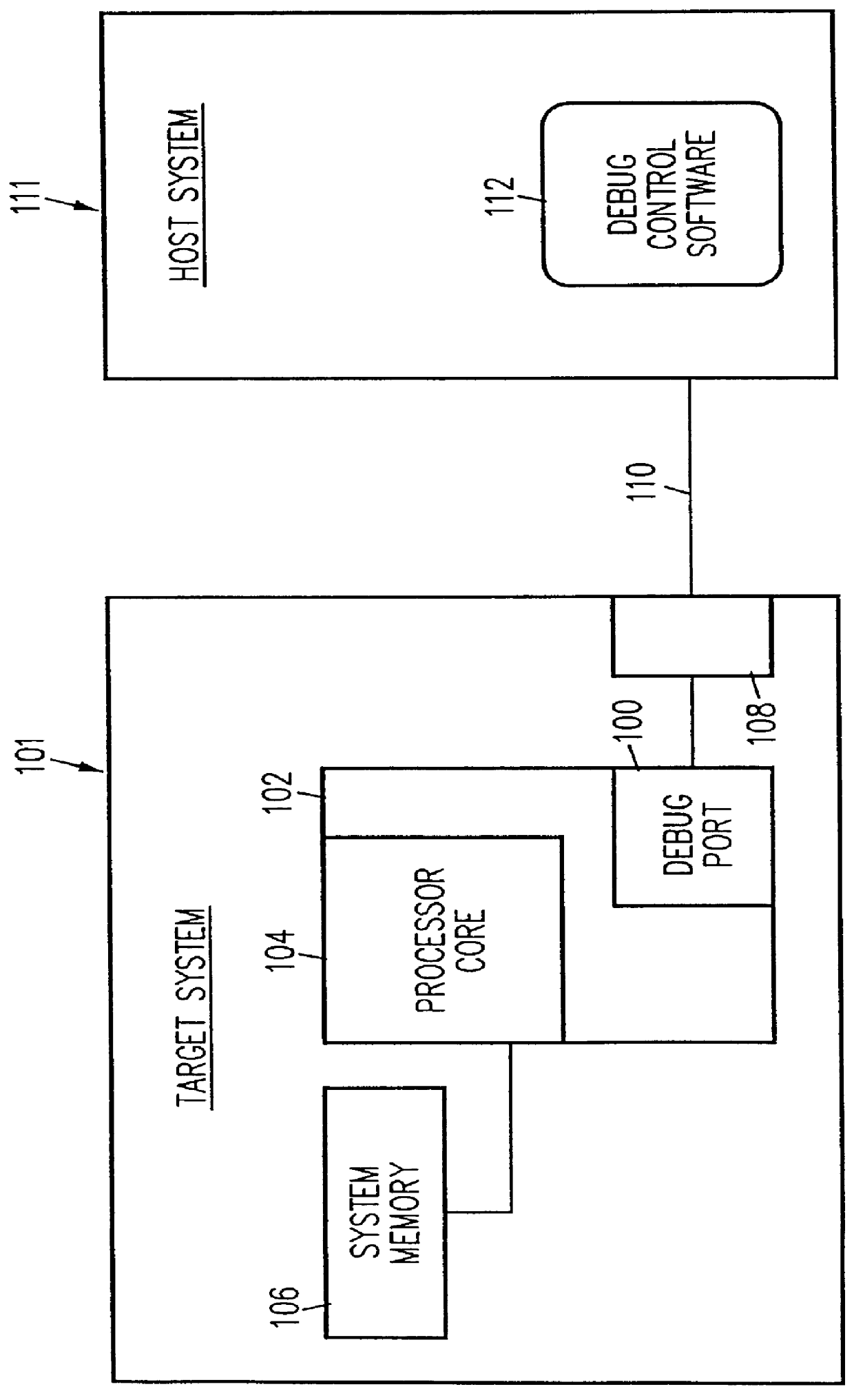

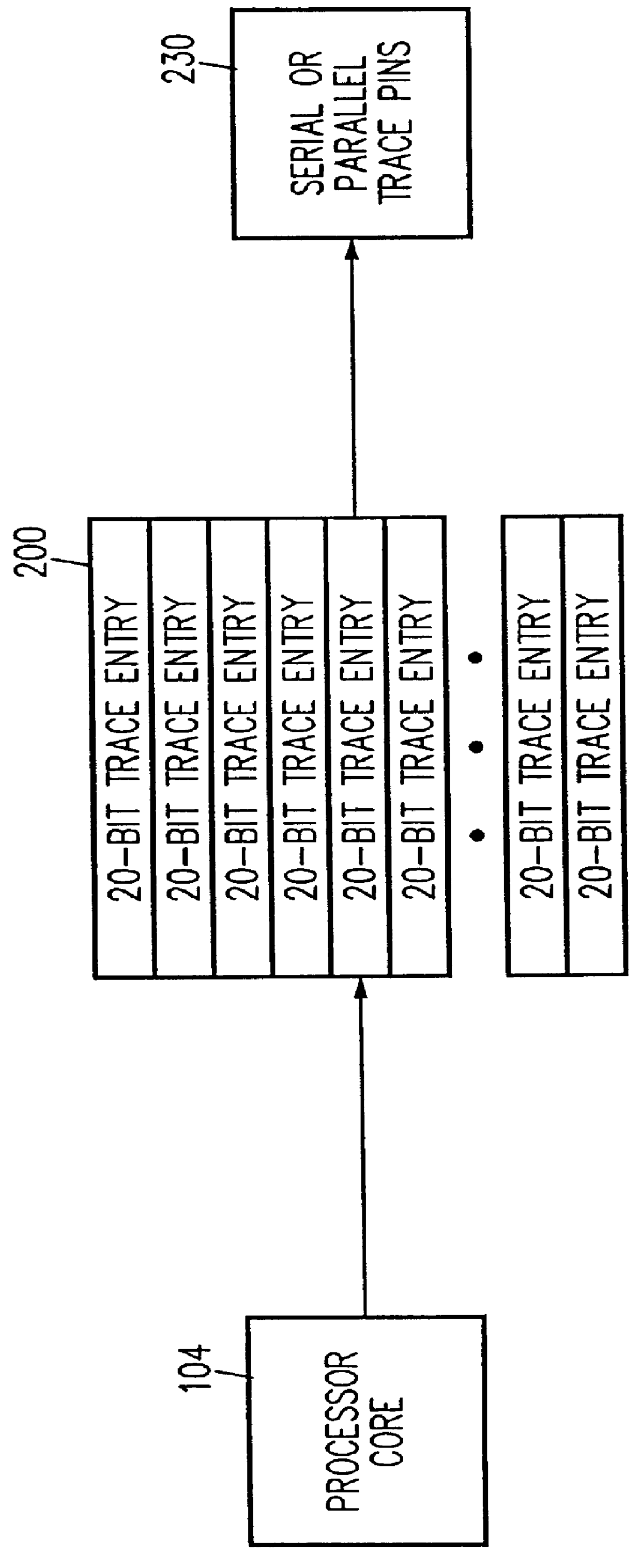

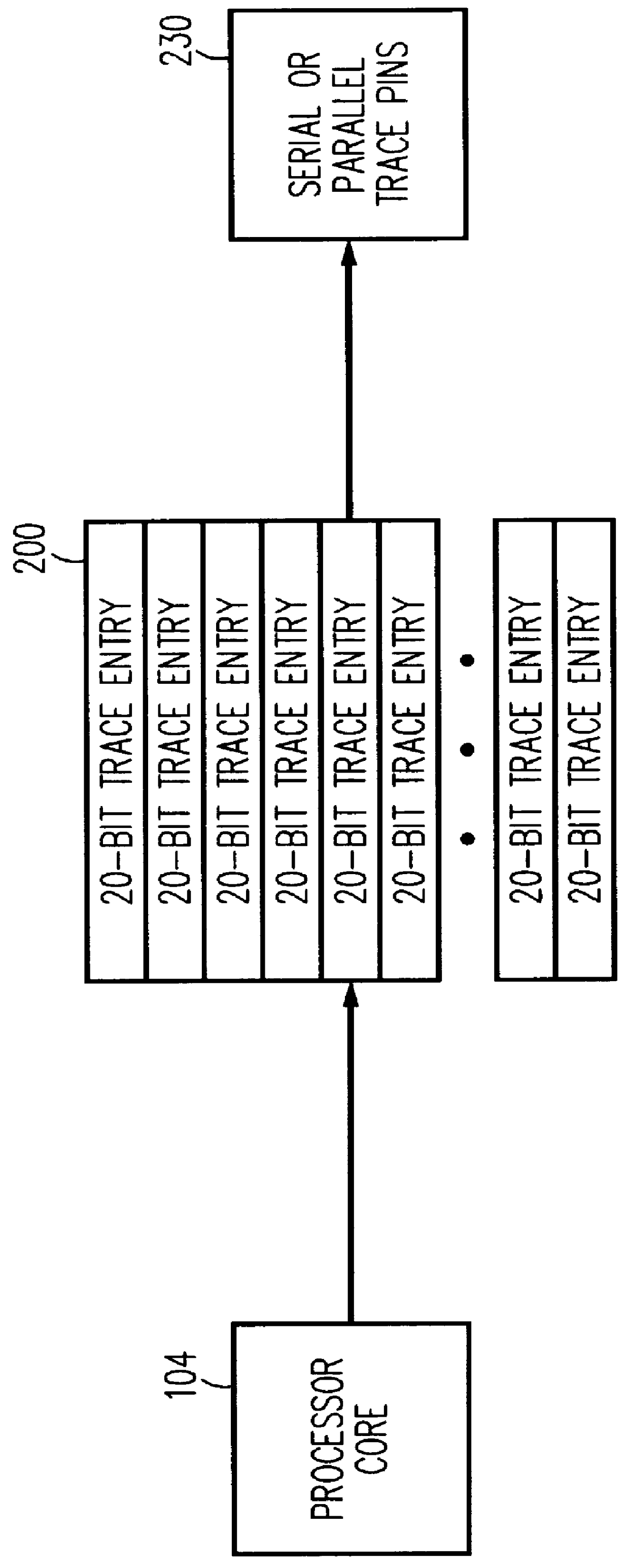

Debug interface including a compact trace record storage

InactiveUS6094729AReliability increasing modificationsHardware monitoringInformation typeParallel computing

In-circuit emulation (ICE) and software debug facilities are included in a processor via a debug interface that interfaces a target processor to a host system. The debug interface includes a trace controller that monitors signals produced by the target processor to detect specified conditions and produce a trace record of the specified conditions including a notification of the conditions are selected information relating to the conditions. The trace controller formats a trace information record and stores the trace information record in a trace buffer in a plurality of trace data storage elements. The trace data storage elements have a format that includes a trace code (TCODE) field indicative of a type of trace information and a trace data (TDATA) field indicative of a type of trace information data.

Owner:GLOBALFOUNDRIES INC

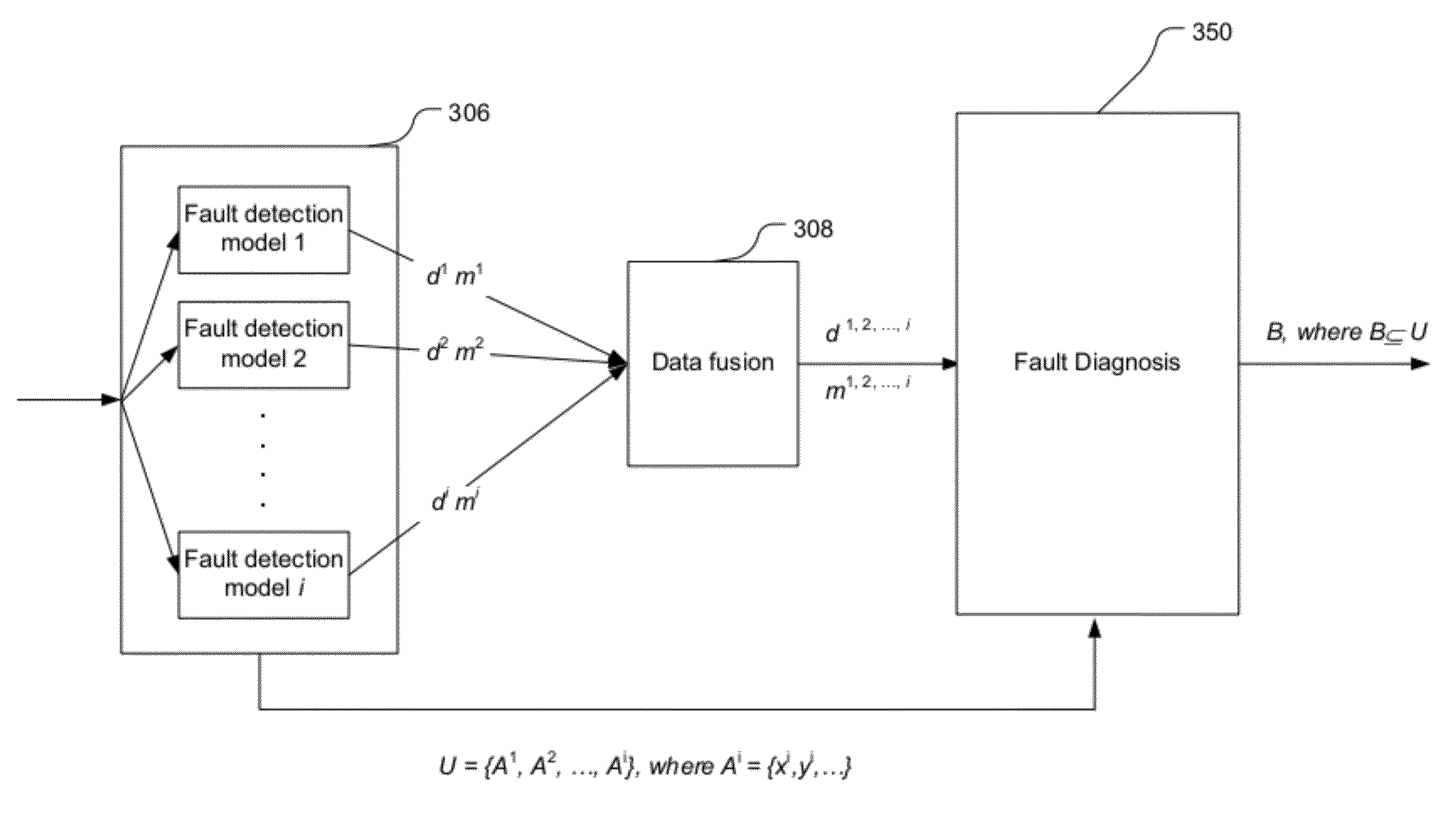

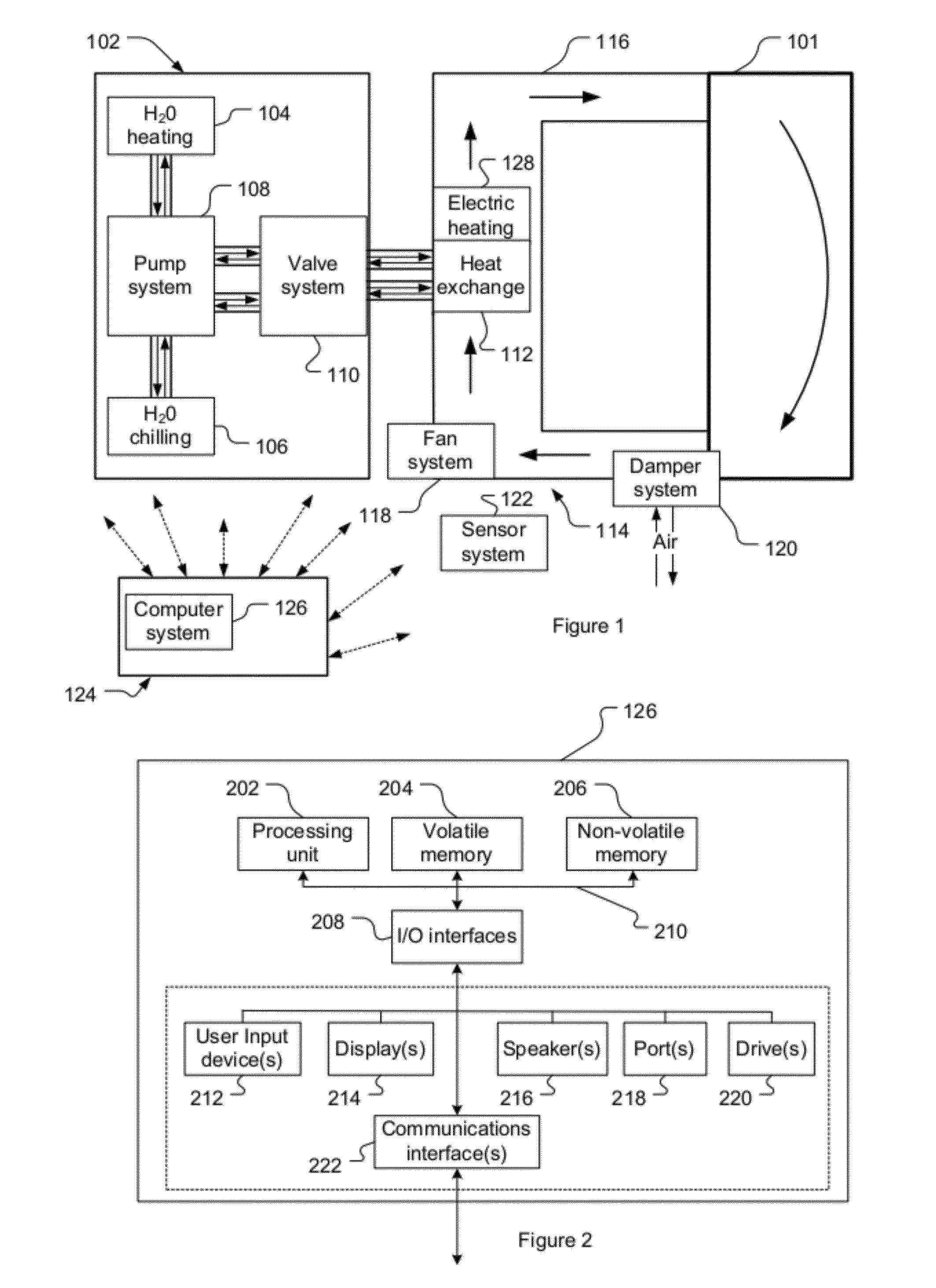

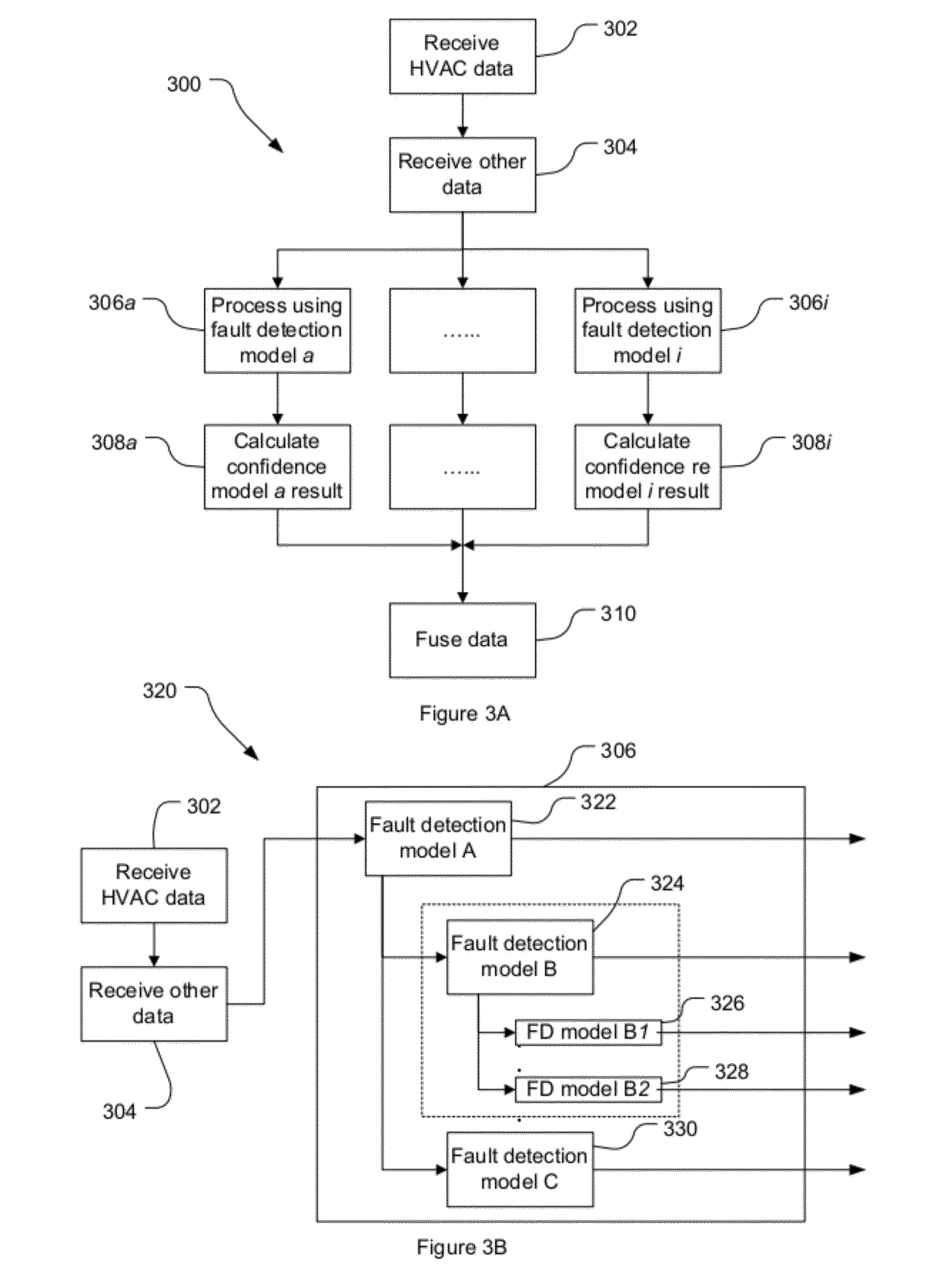

System and method for detecting and/or diagnosing faults in multi-variable systems

ActiveUS20120185728A1Improve reliabilityGood clusteringProgramme controlMechanical apparatusComputer scienceMulti variable

A method for detecting faulty operation of a multi-variable system is described. The method includes receiving operational data from a plurality of components of the multi-variable system and processing the operational data in accordance with a plurality of dynamic machine learning fault detection models to generate a plurality of fault detection results. Each fault detection model uses a plurality of variables to model one or more components of the multi-variable system and is adapted to detect normal or faulty operation of an associated component or set of components of the multi-variable system. The plurality of fault detection results are output.

Owner:COMMONWEALTH SCI & IND RES ORG

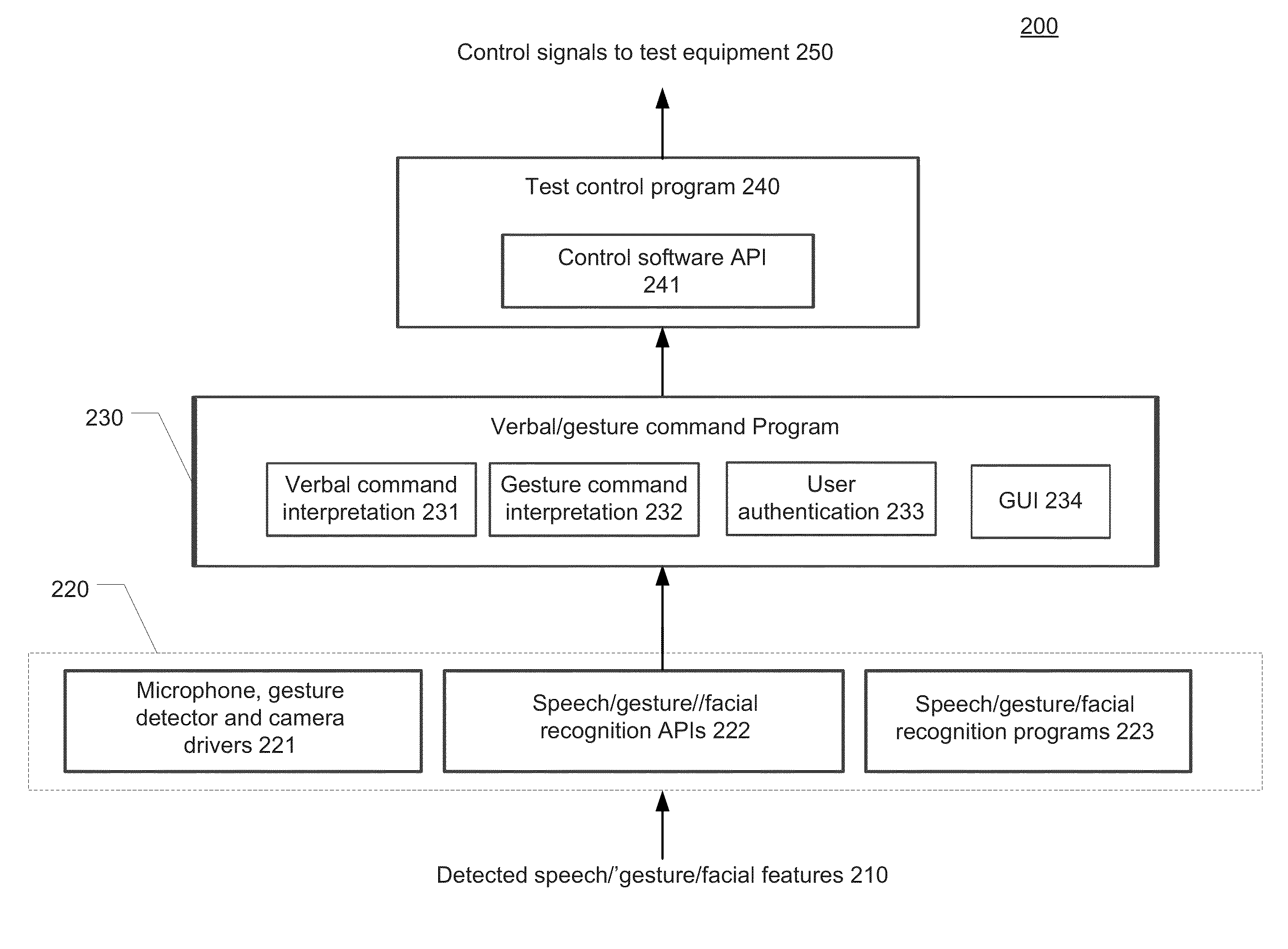

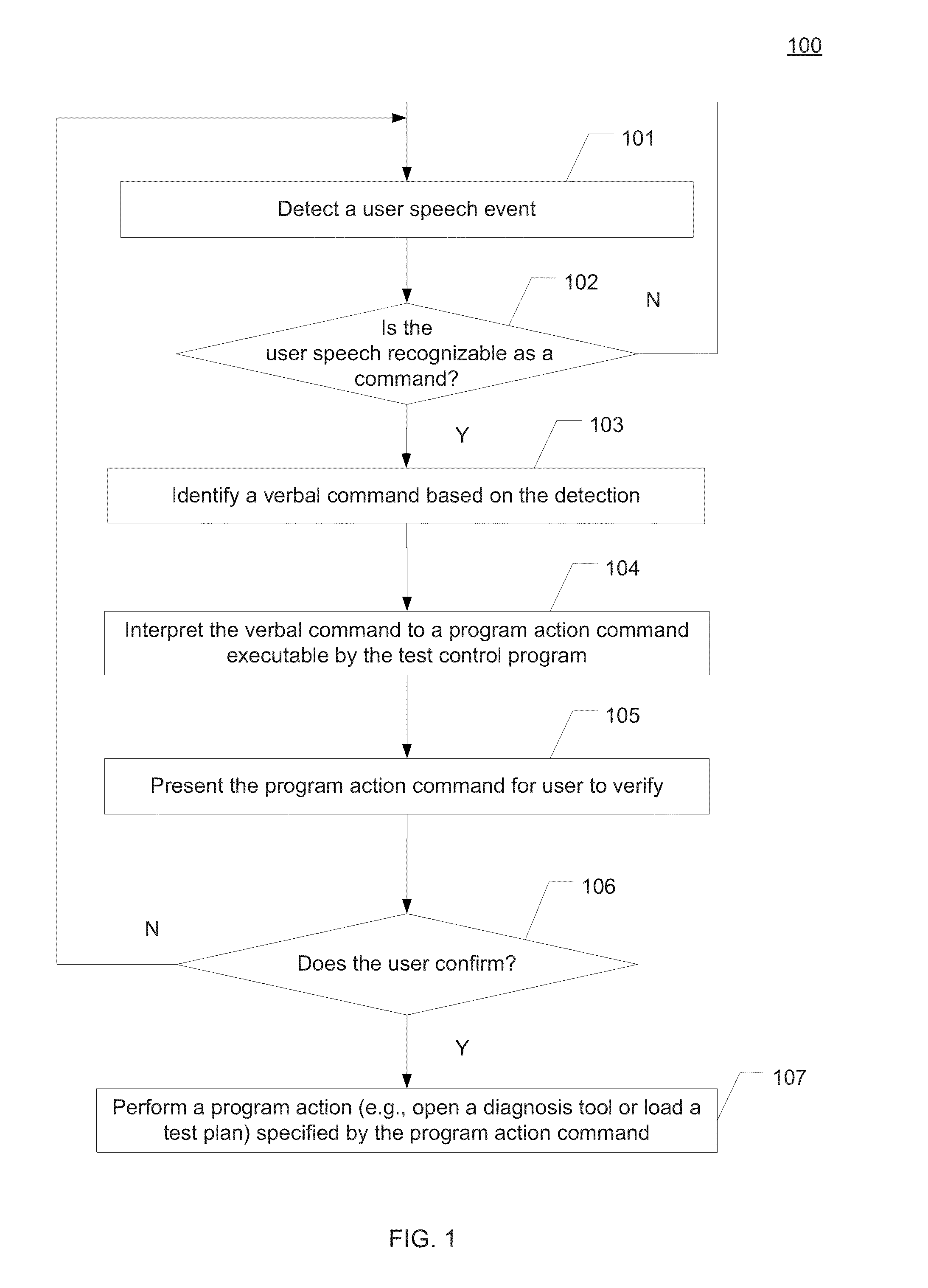

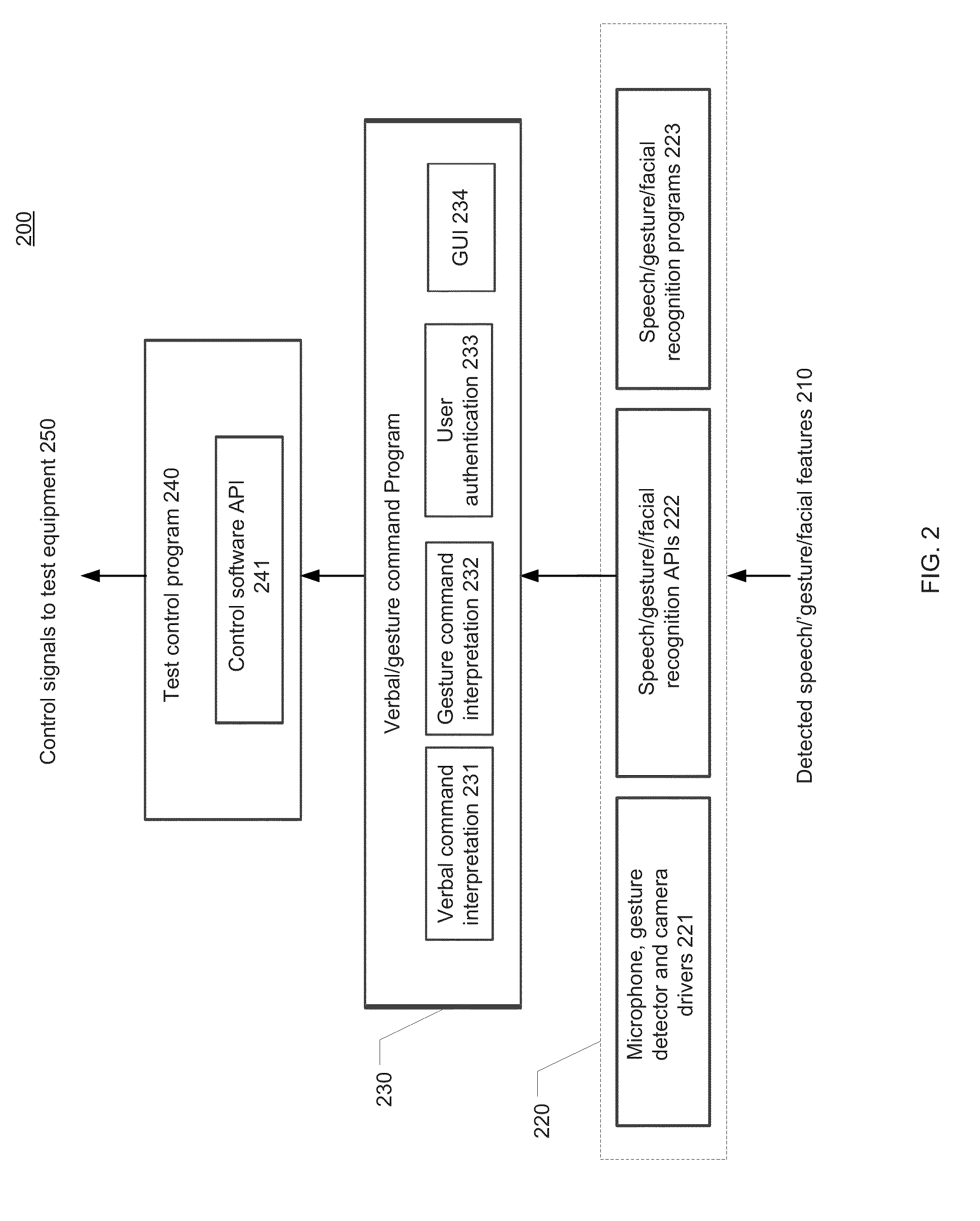

Voice recognition virtual test engineering assistant

ActiveUS20140344627A1Improve user interactionEliminating operator potential mischievous unwanted behaviorFunctional testingExecution for user interfacesComputer hardwareControl software

System and method of systems and methods of controlling an IC test equipment in response to verbal commands issued by test equipment users. A control apparatus according to the present disclosure includes a speech detection device operable to detect verbal commands and test control software configured to control operations of the test equipment. The control software is added with verbal command recognition capabilities. Program action commands defined in the test control software are associated with respective recognizable verbal commands. Upon a recognizable verbal command is detected, it is interpreted into the corresponding program action command which triggers the intended test program actions. The control apparatus may also have a gesture detection device, through which user gesture commands can be detected and interpreted into corresponding program actions commands.

Owner:ADVANTEST CORP

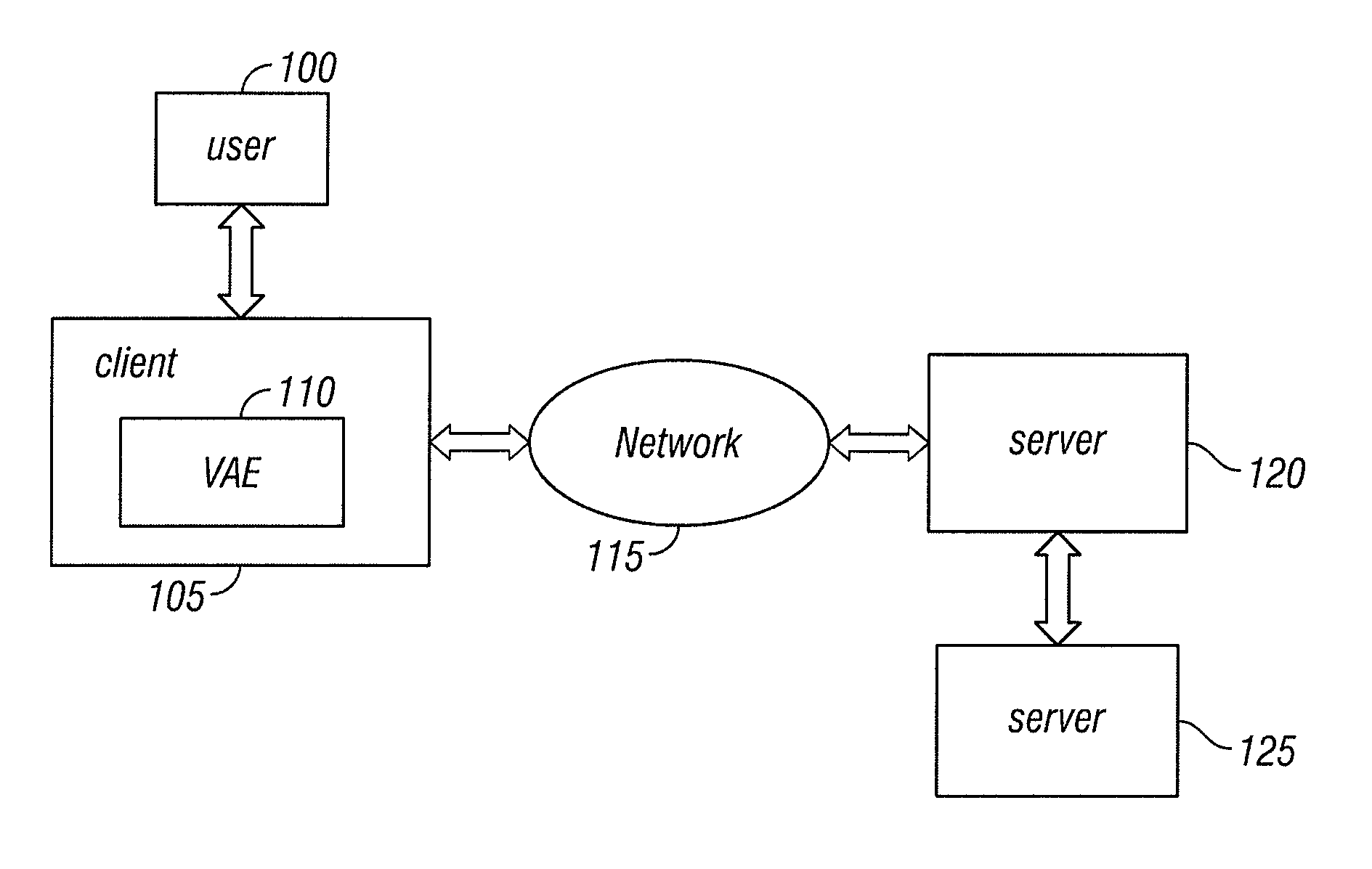

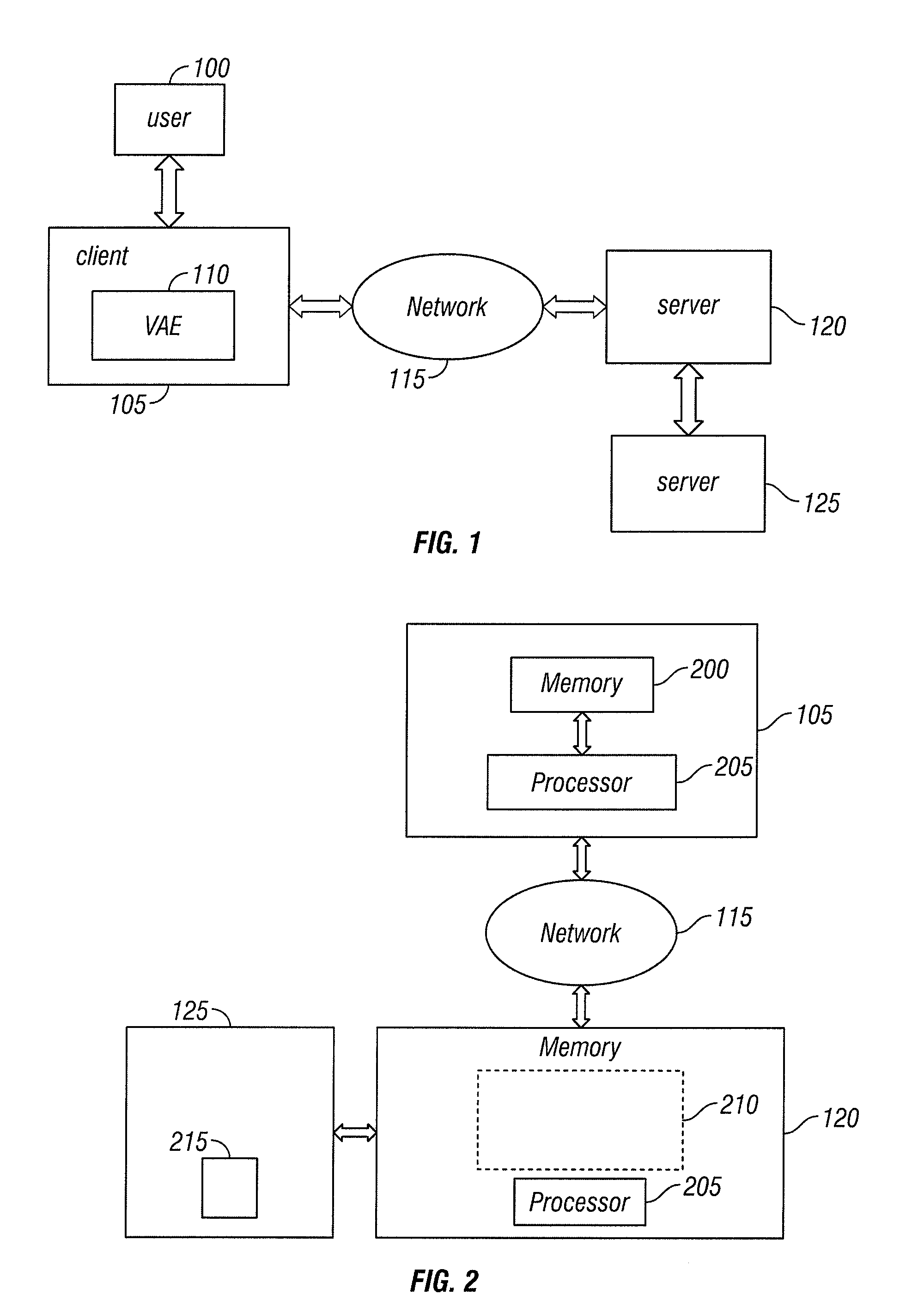

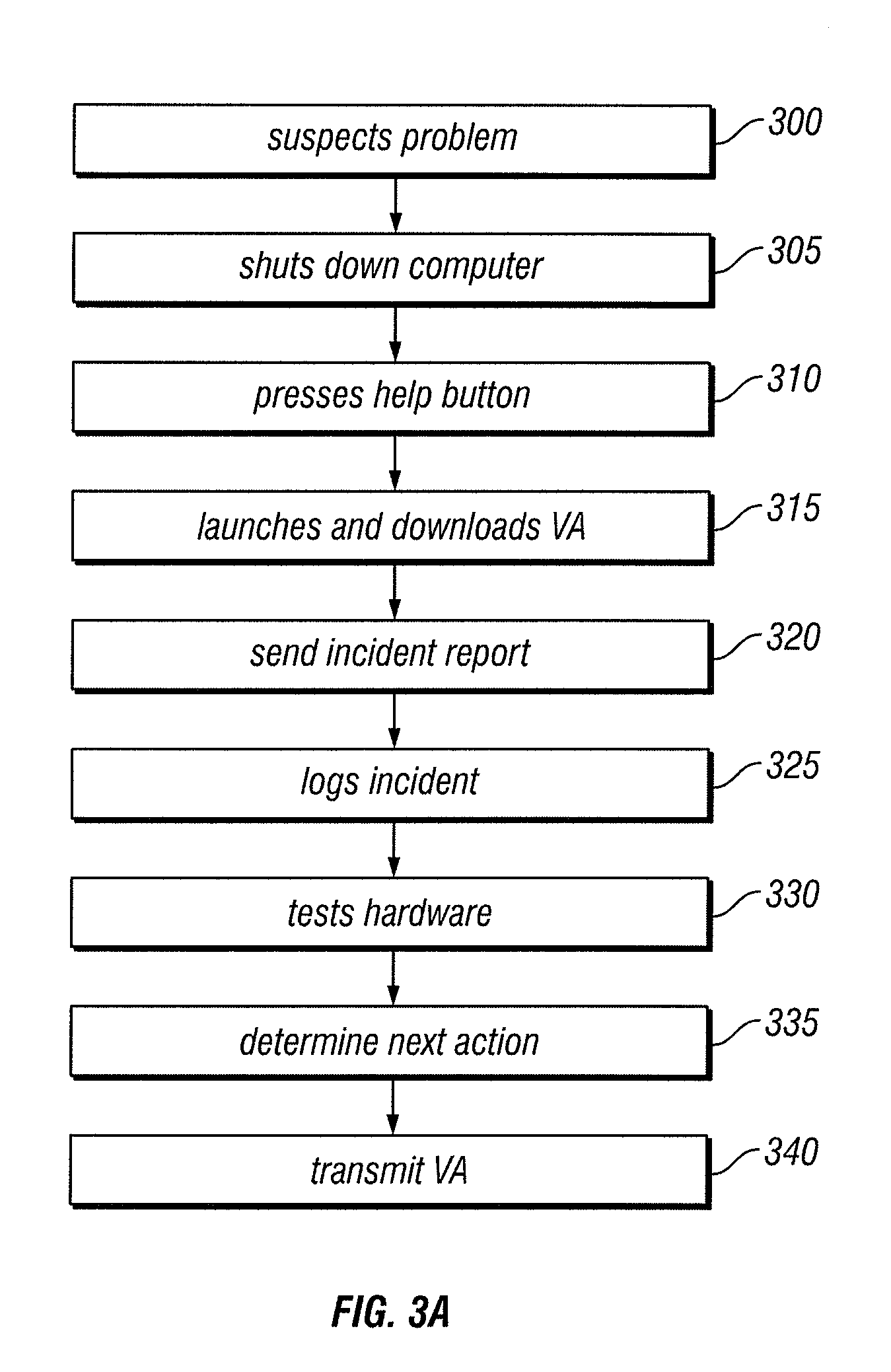

Diagnostic Virtual Appliance

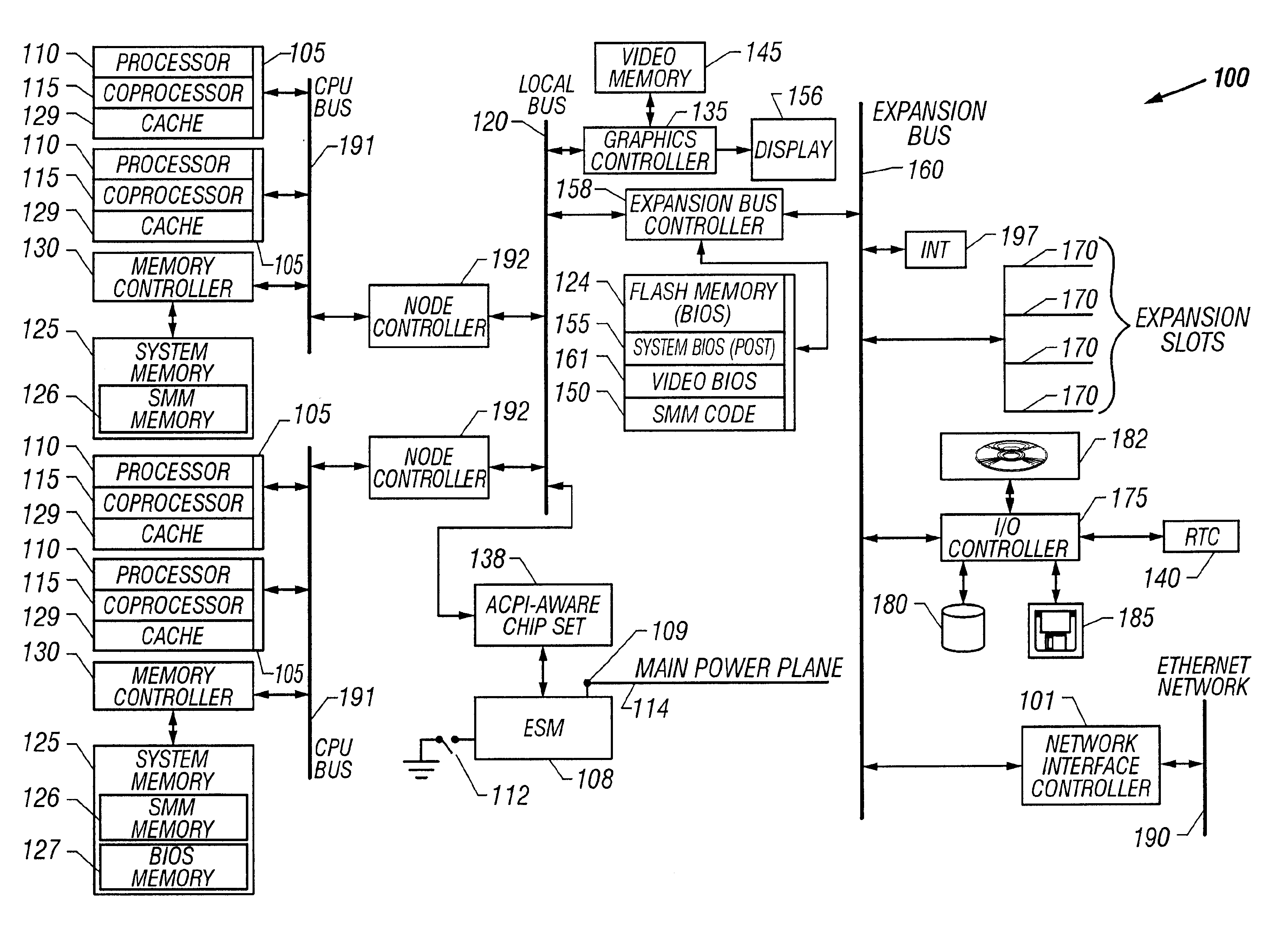

InactiveUS20090037496A1Memory loss protectionDetecting faulty hardware by remote testMass storageBIOS

A virtual appliance environment (VAE) consists of components residing on a computer BIOS ROM and also on a mass storage device. The VAE includes a virtual appliance (VA) for diagnosing malfunctioning hardware or software. The VA for diagnosing malfunctions tests the hardware and / or software resident in the computer and transmits the results of the test to a server, which diagnoses the problem and transmits instructions to the VAE for saving the data, determining whether the computer is under warranty, and providing shipping information to a user. The VAE can also download a VA for scanning viruses. The VAE transmits the results of the virus scan to the server, which determines the type of virus infecting the computer and transmits instructions to the virtual appliance for downloading the appropriate VA for removing the virus. The VAE can save the data to another source, remove the virus, and restore the data or simply remove the virus.

Owner:SPLASHTOP INC

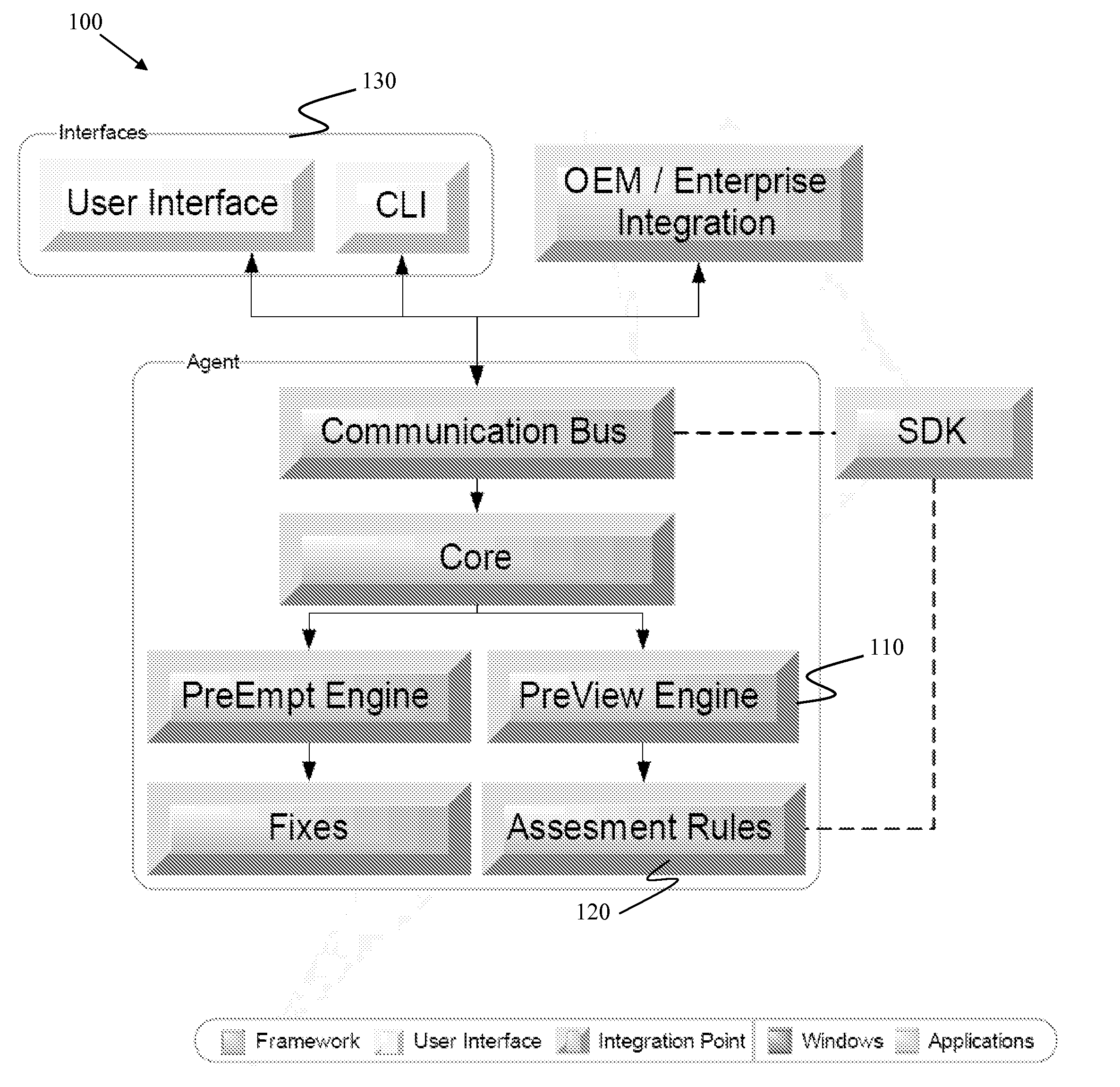

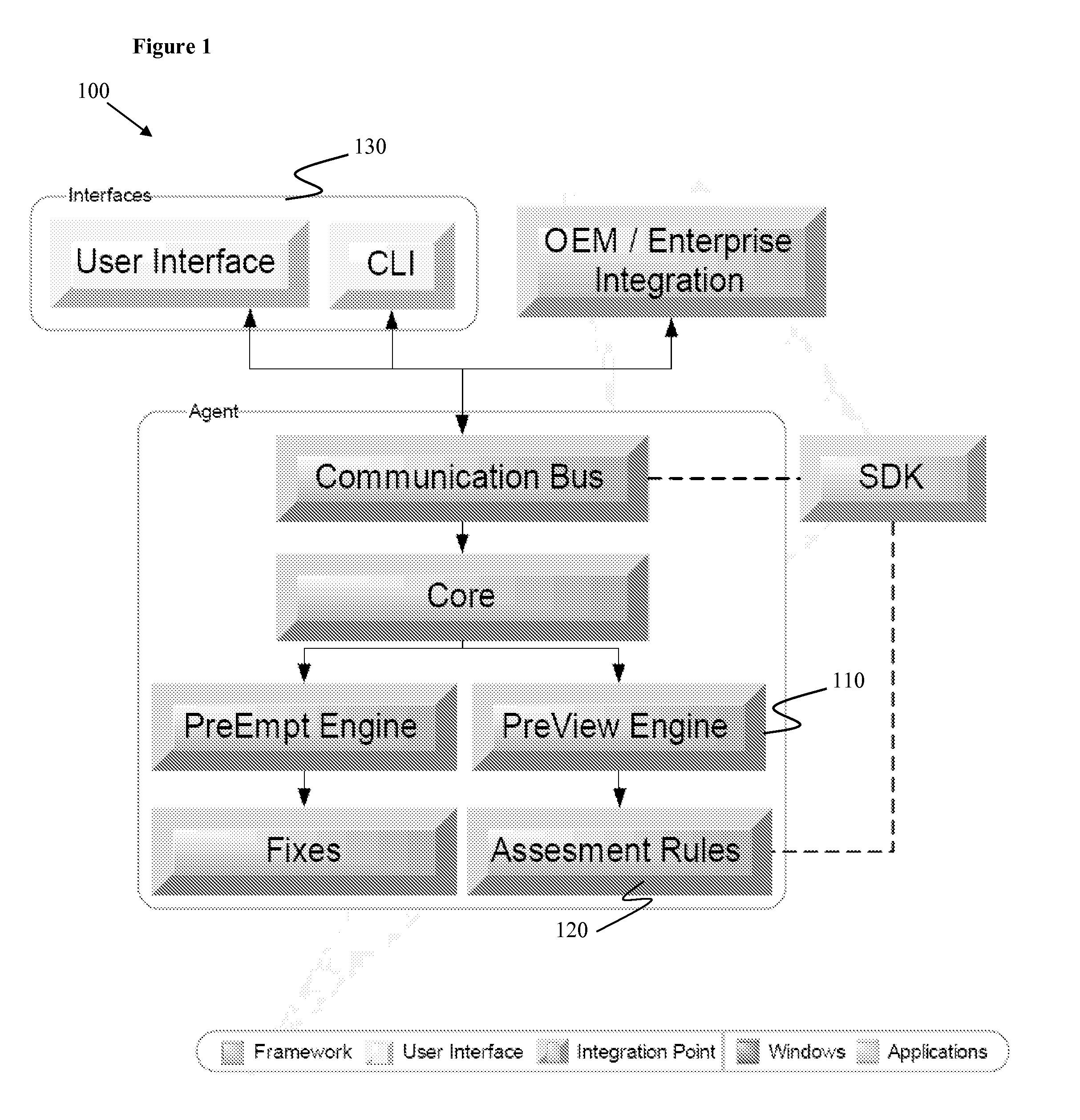

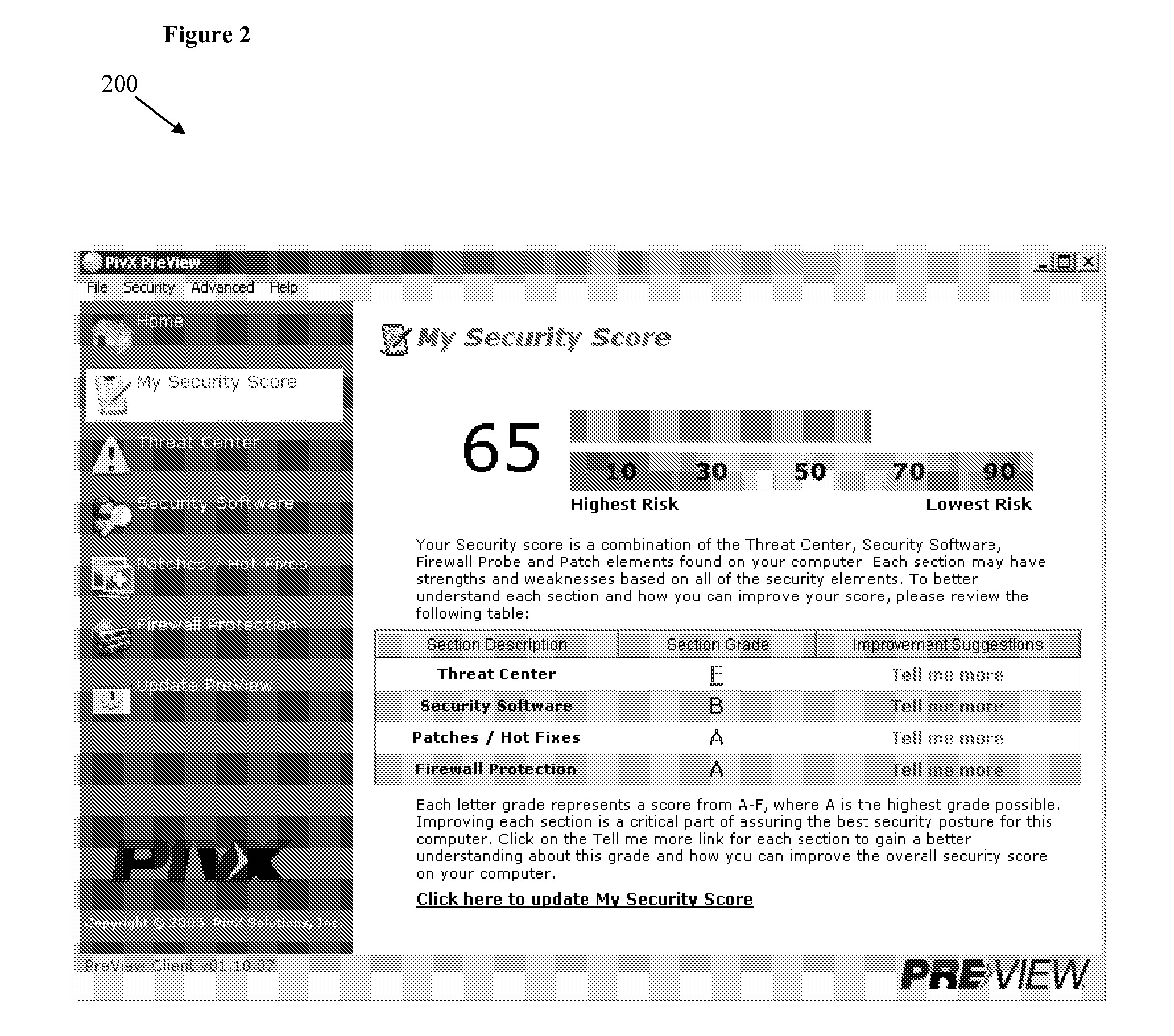

Systems and Methods for Vulnerability Detection and Scoring with Threat Assessment

InactiveUS20080028470A1Memory loss protectionUnauthorized memory use protectionSeverity levelComputer science

Certain embodiments of the present invention provide a system for vulnerability detection and scoring with threat assessment including an analysis engine adapted to perform at least one of automated and semi-automated analysis of a computing system of at least one of known threats, vulnerabilities, and risk factors. The analysis engine is further adapted to determine a security score for the computing system based on the analysis and a schedule indicating a severity level for each threat, vulnerability, and risk factor.

Owner:REMINGTON MARK +3

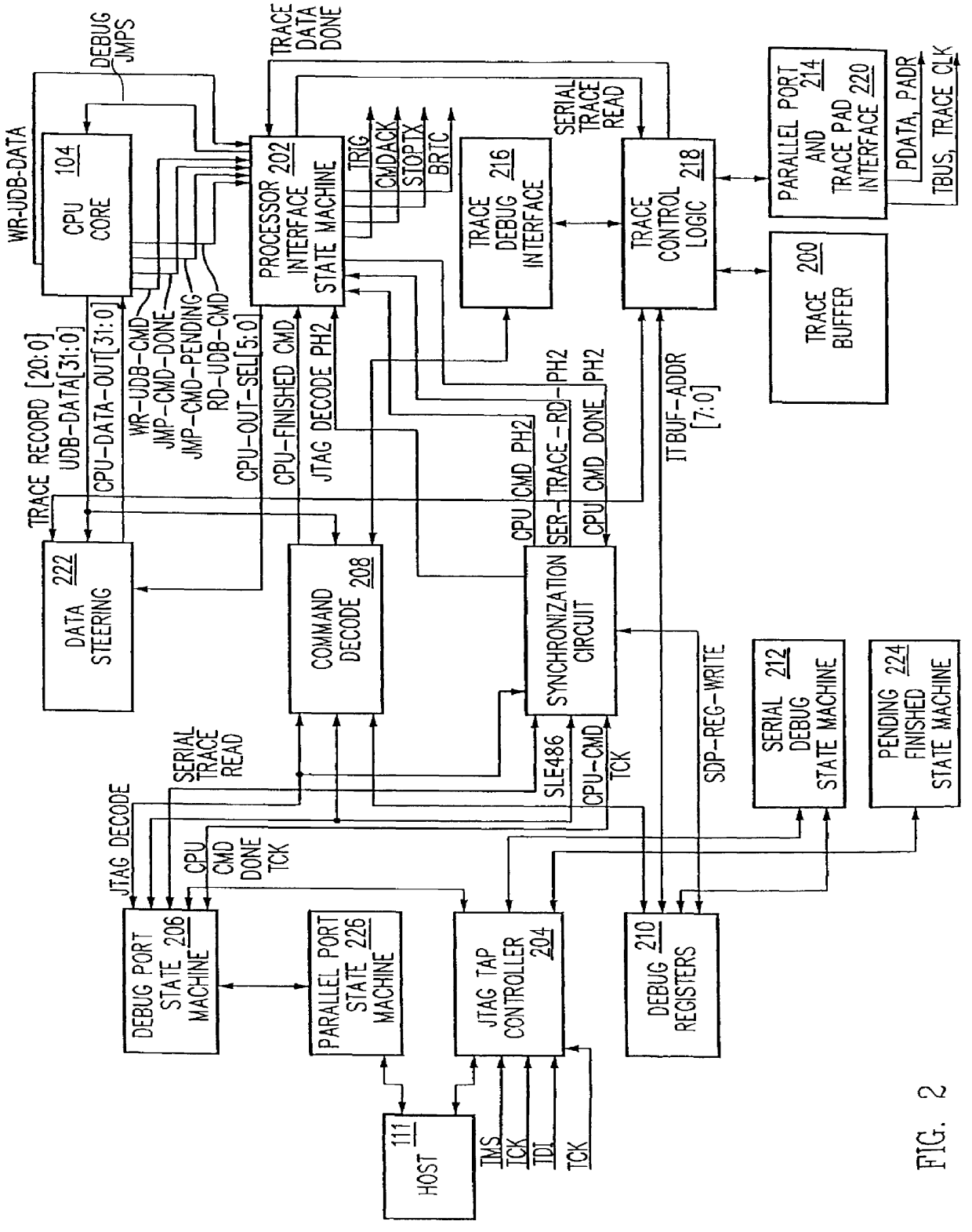

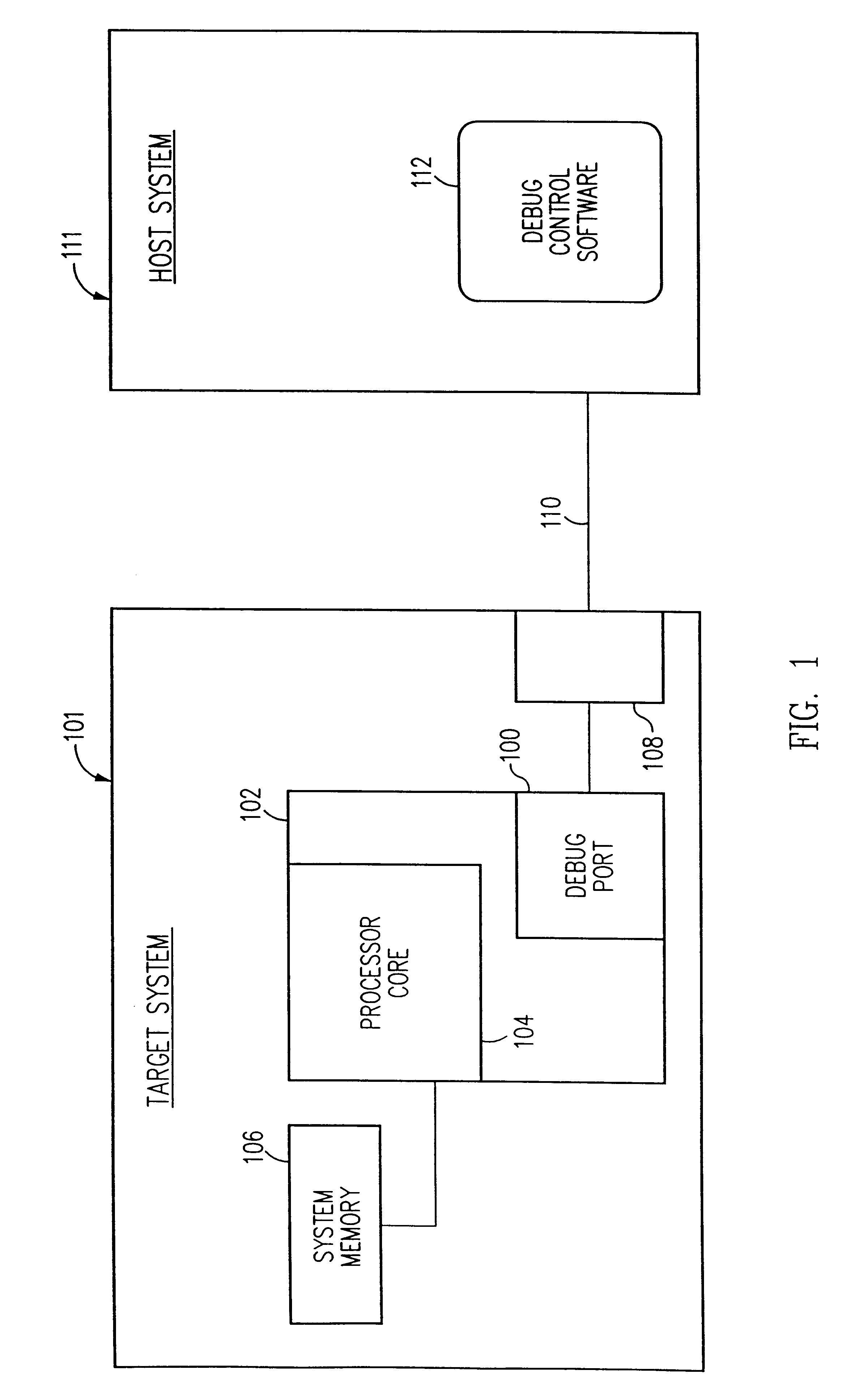

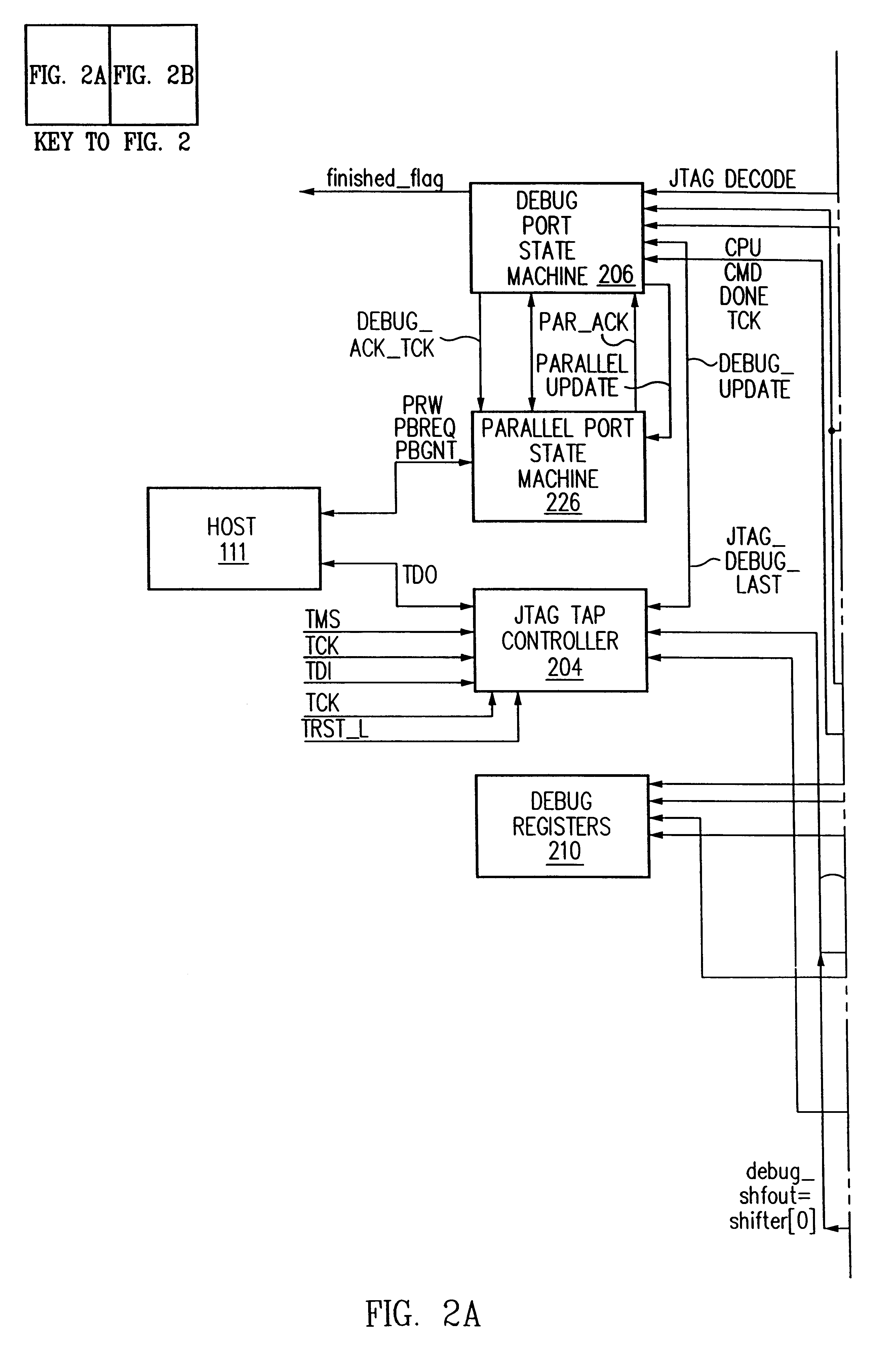

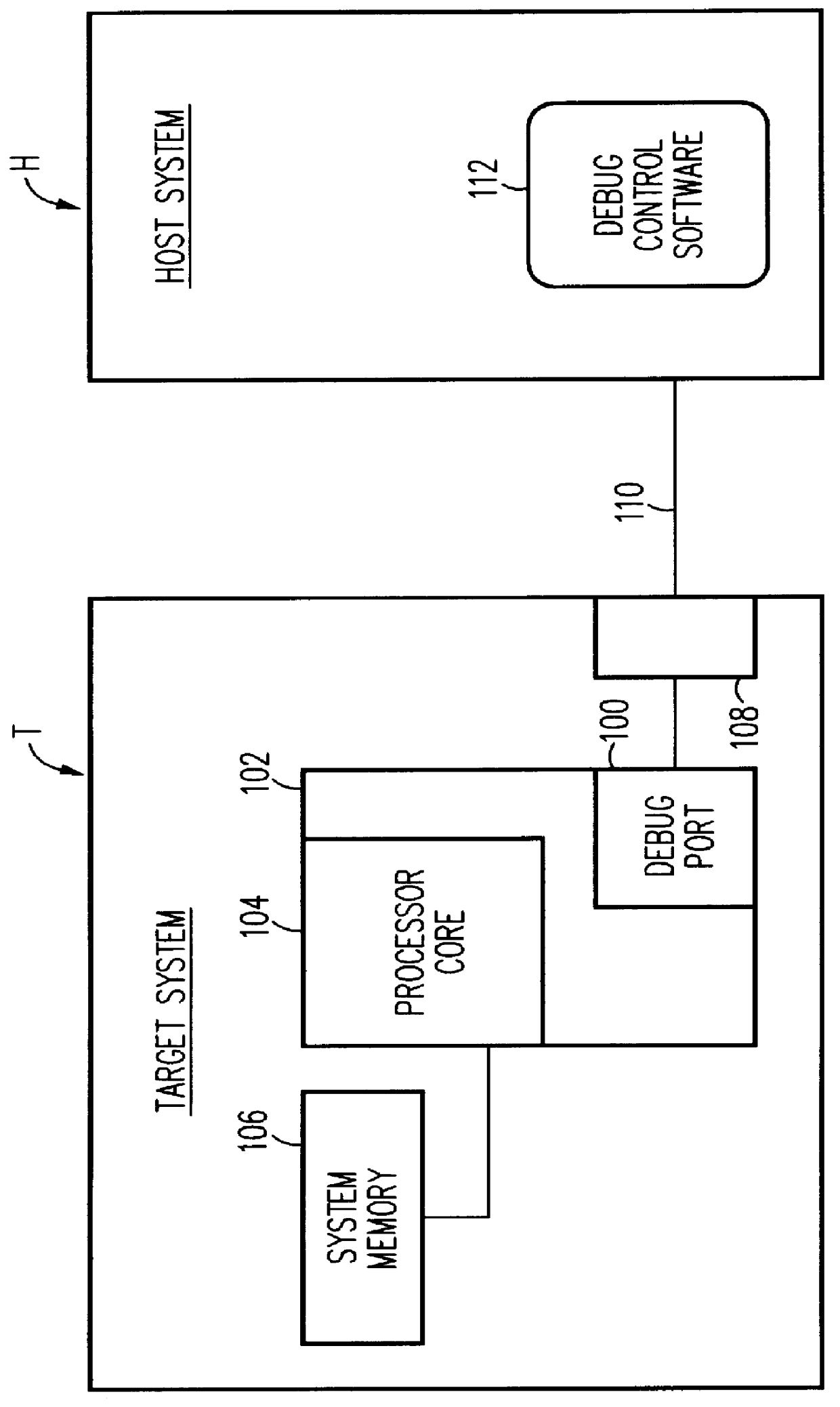

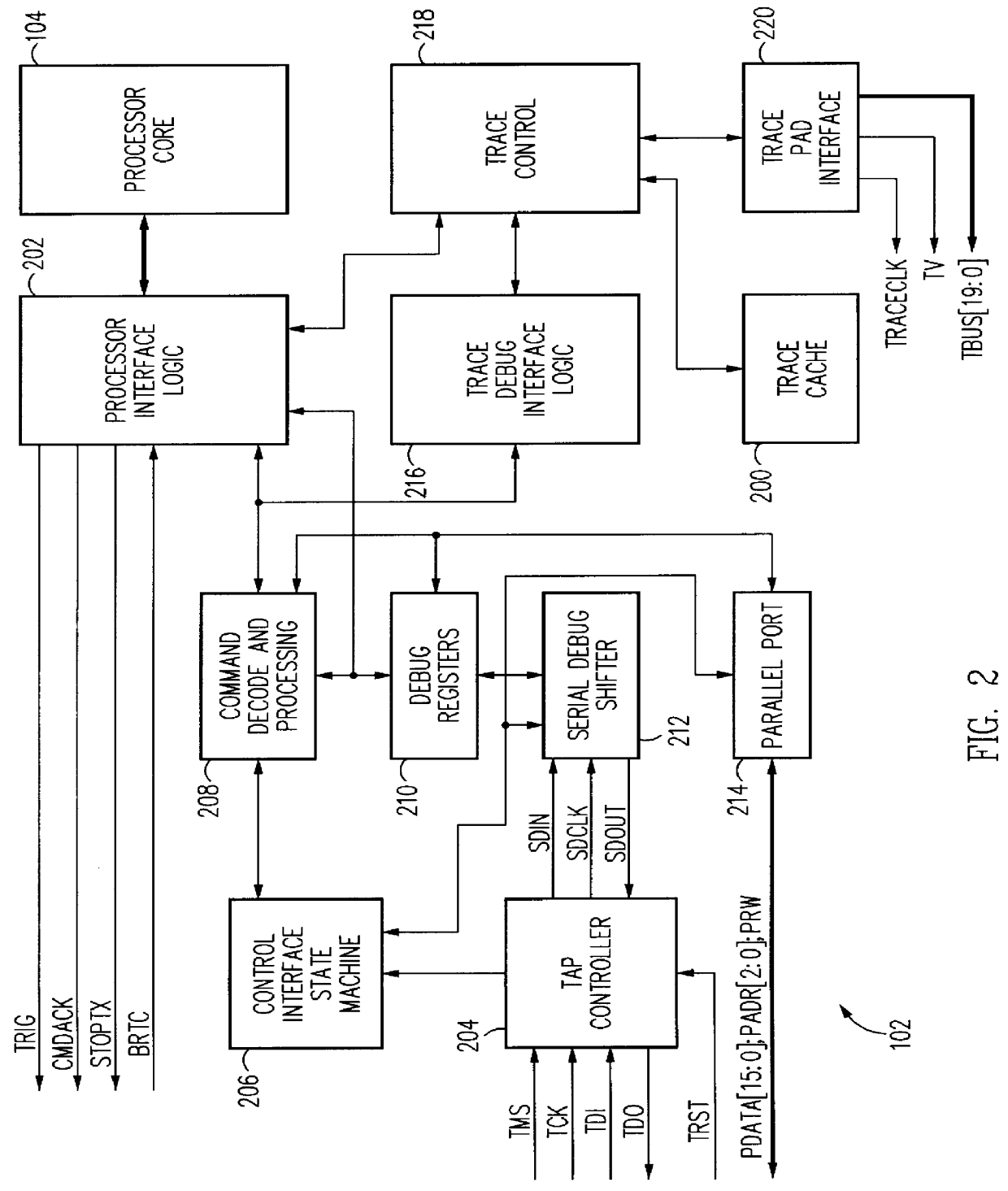

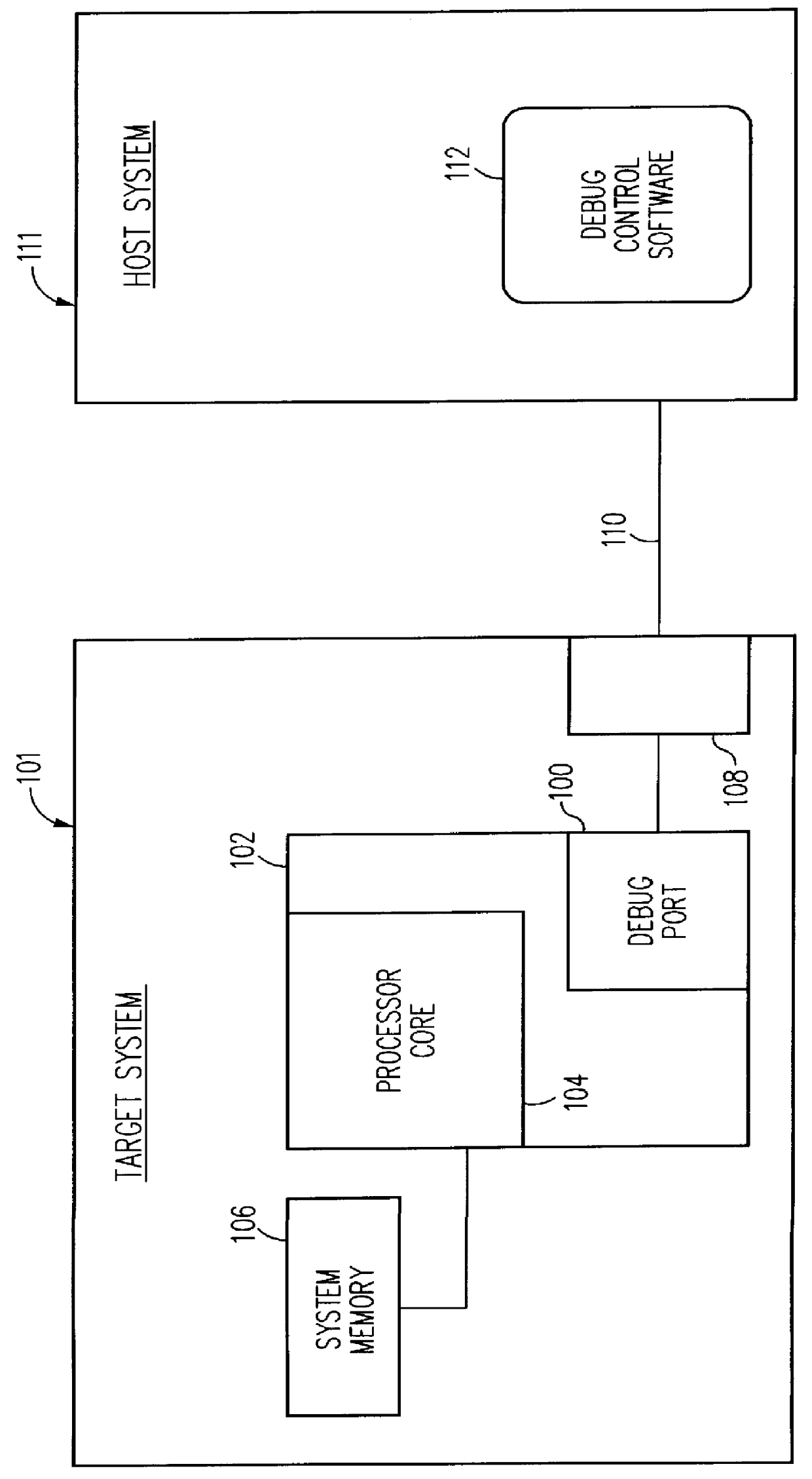

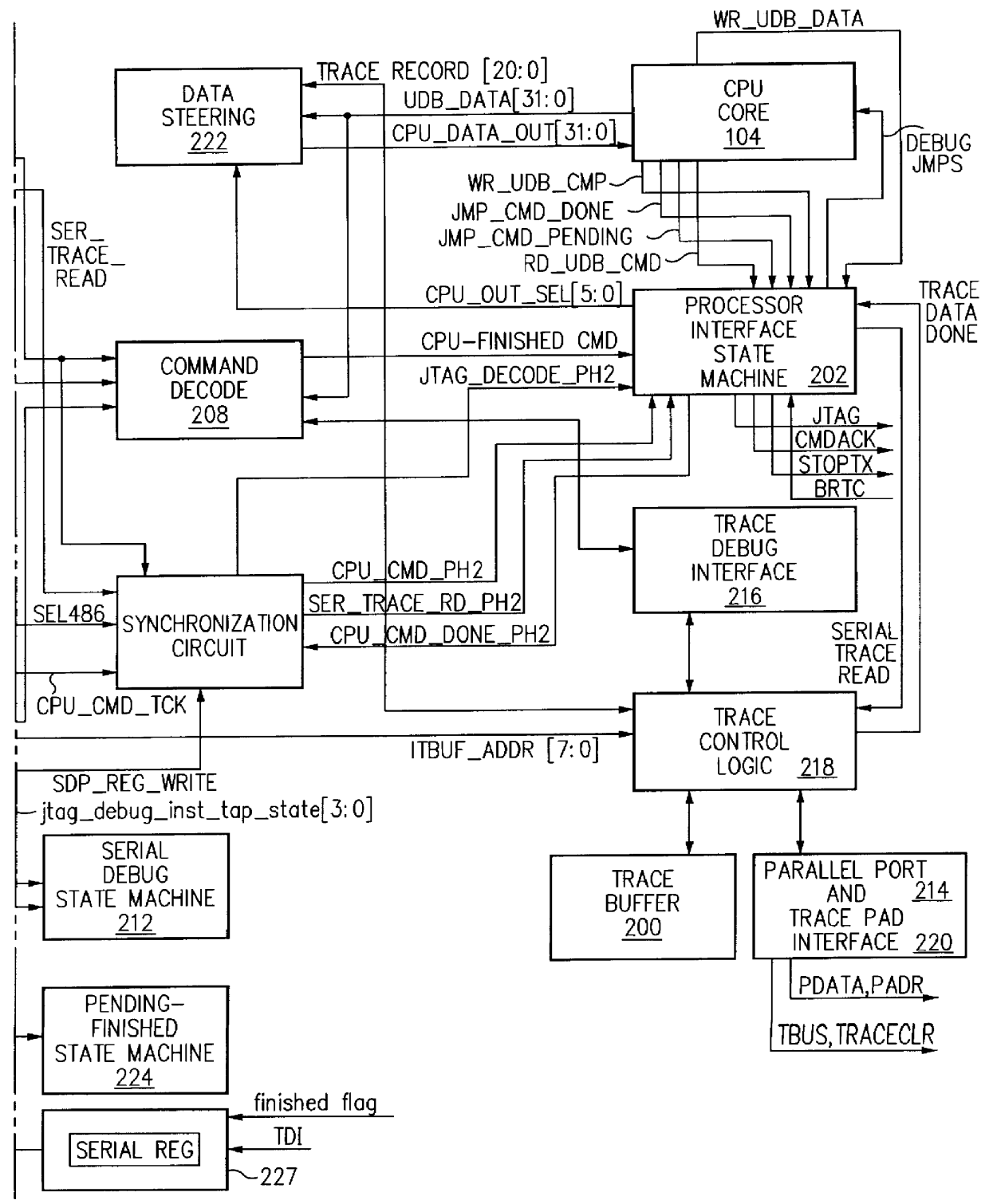

Debug interface including logic generating handshake signals between a processor, an input/output port, and a trace logic

A system for debugging a processor includes a debug interface including a handshake logic for communicating commands and data from a serial input / output port to a processor and to a trace control logic with a low delay. The handshake logic results in a low latency through the inclusion of a state machine that operates at the same speed as the processor. The state machine generates handshake signals to communicate among the serial input / output port, the processor, and the trace control logic.

Owner:ADVANCED MICRO DEVICES INC

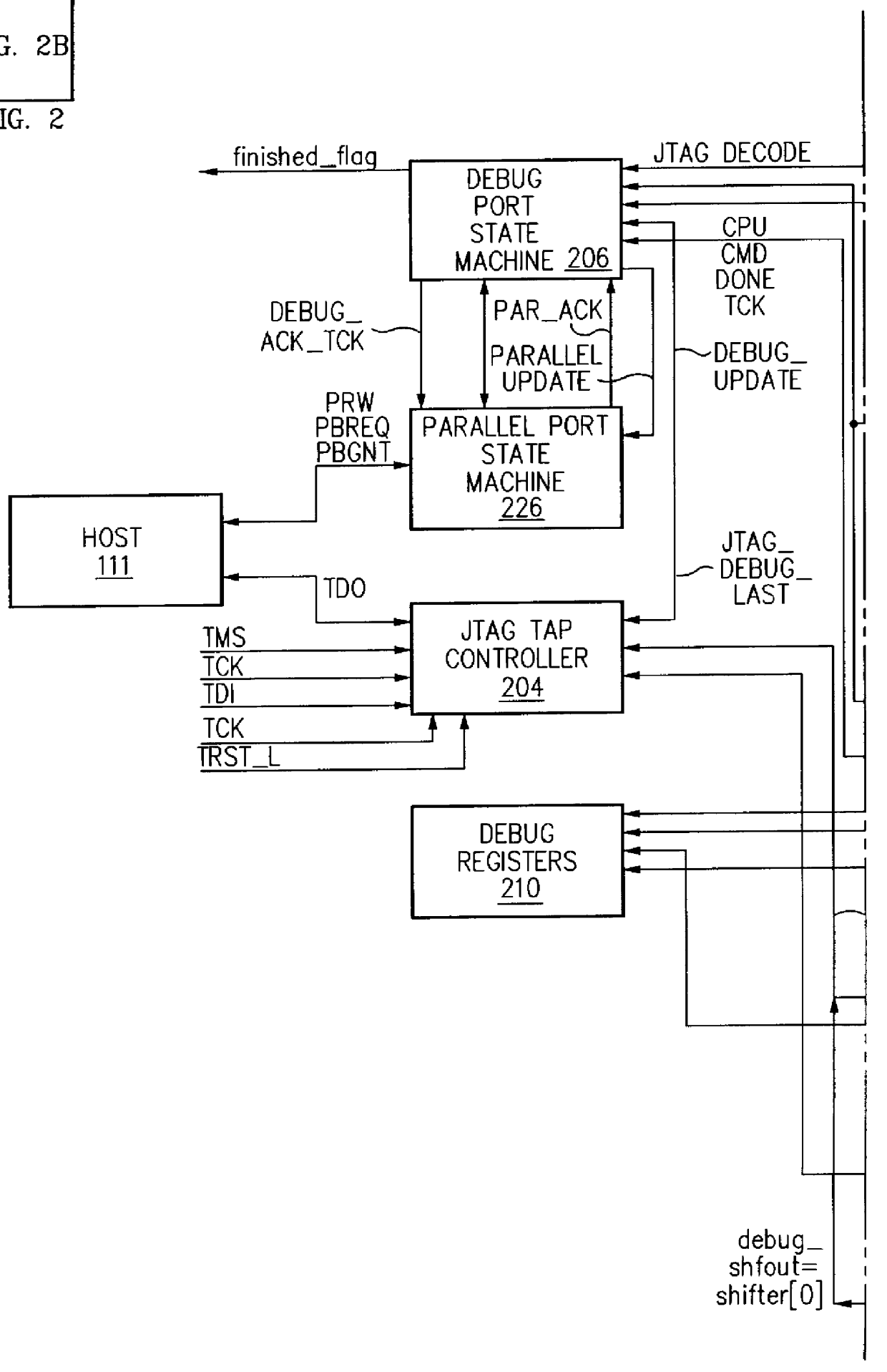

Parallel and serial debug port on a processor

A processor has both a serial debug port and a parallel debug port. The processor includes a processor core. The serial debug port is formed of a plurality of pins configured to send and receive signals to and from external software debug equipment. The parallel debug port is formed of a plurality of pins and configured to send and receive signals from external software debug equipment. A plurality of debug registers are accessible to the serial debug port and the parallel debug port. The debug registers are also coupled to the processor core for receiving and providing debug data and control signals. The processor core performs various software debug operations in response to signals from the external software debug equipment sent over one of the parallel and serial debug ports and communicates the results of the debug operation back over one of the serial and parallel debug ports.

Owner:ADVANCED MICRO DEVICES INC

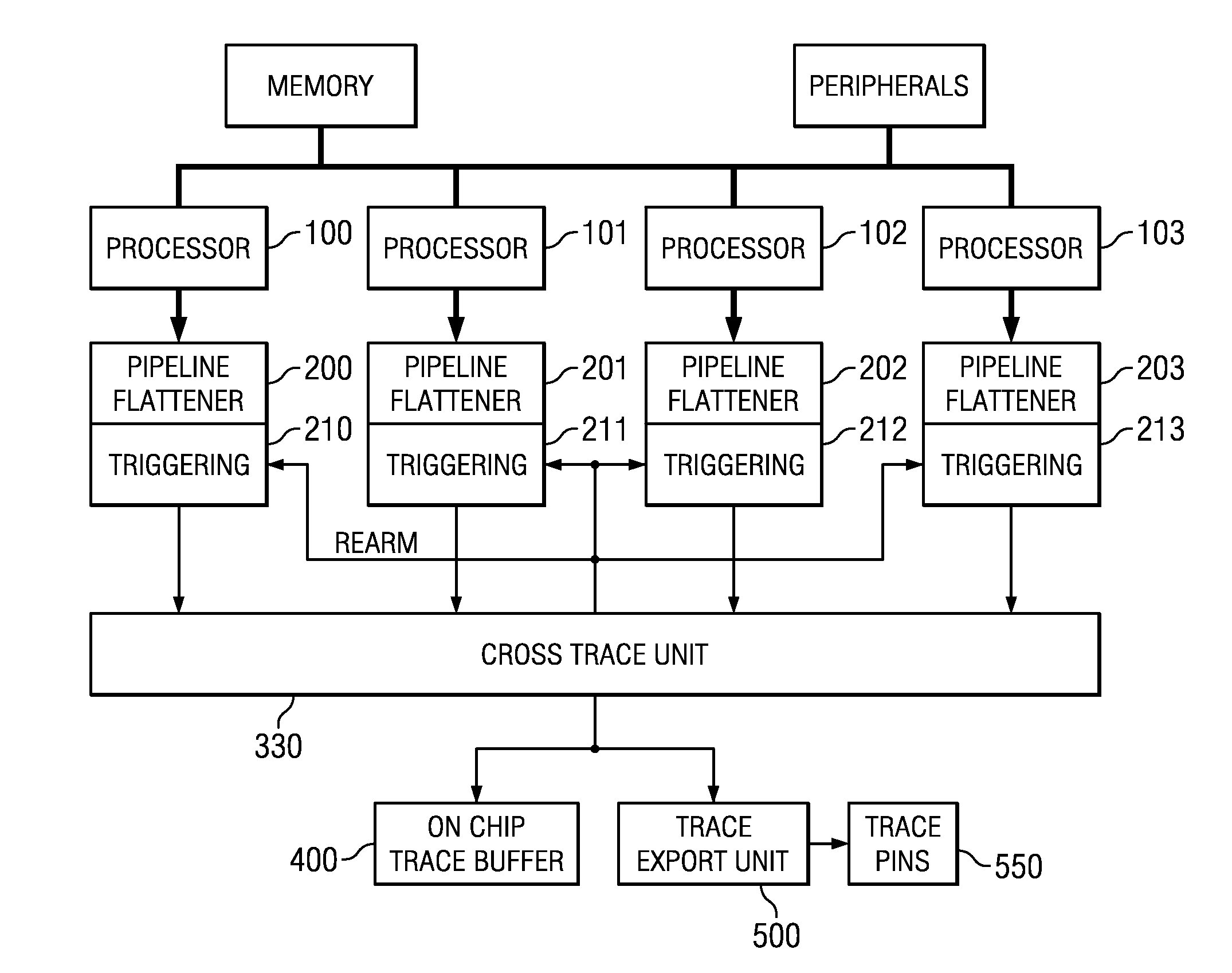

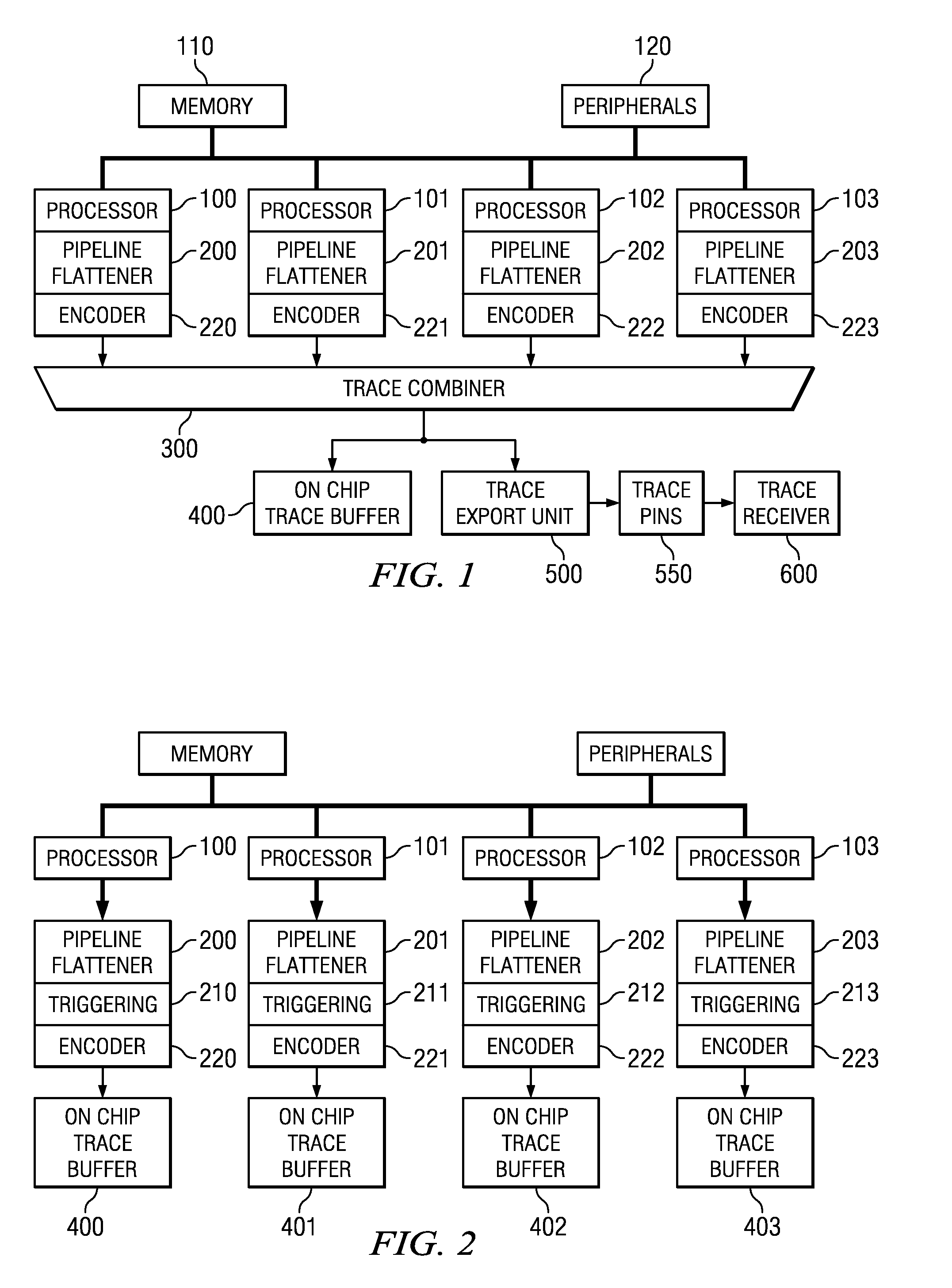

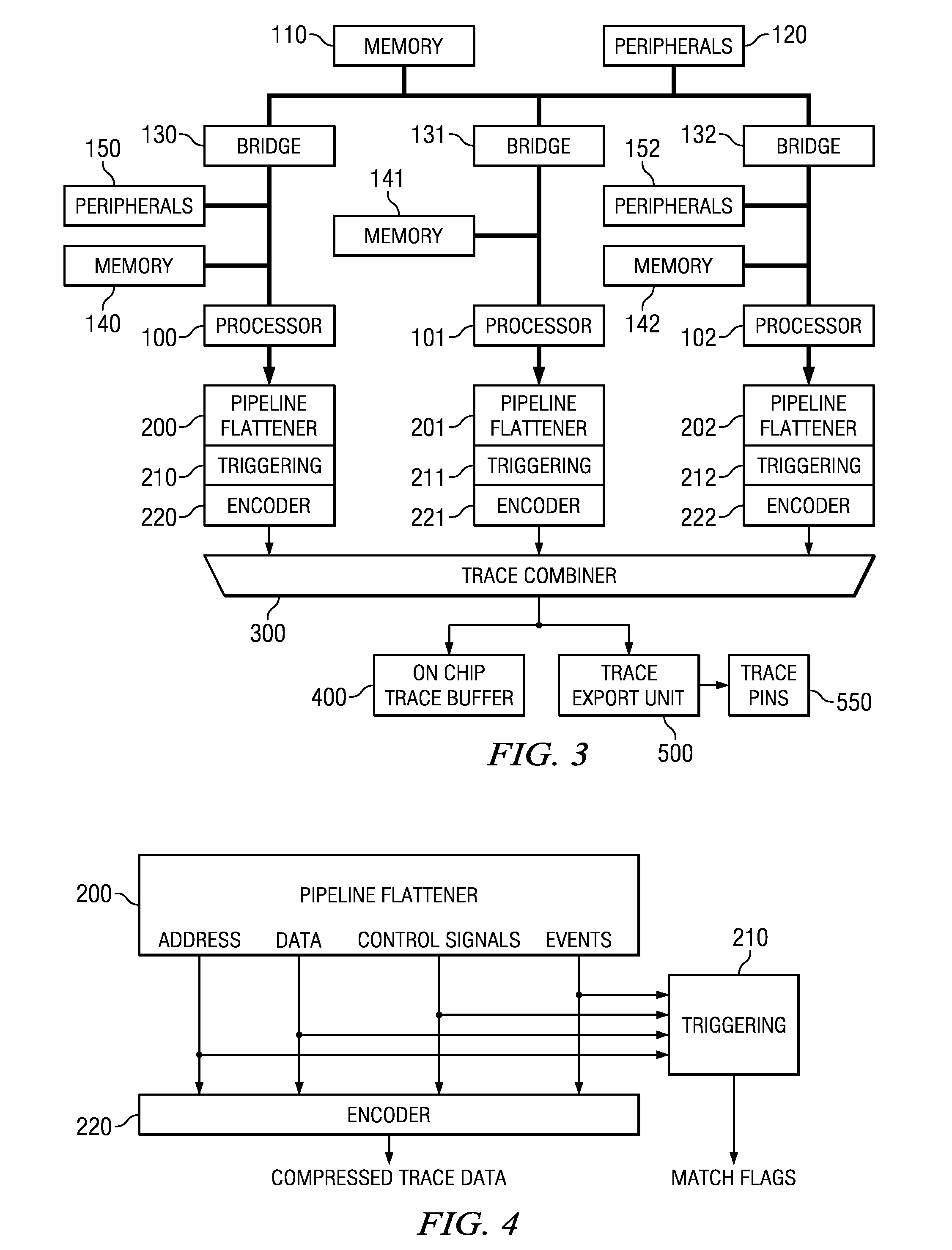

Circuits, systems, apparatus and processes for monitoring activity in multi-processing systems

ActiveUS20100332909A1Hardware monitoringFunctional testingWireless handheld devicesParallel computing

An electronic circuit includes a first processor (100) operable to perform processing operations, a first trace buffer (230) coupled to the first processor (100), a first triggering circuit (210) coupled to the first processor (100), the first triggering circuit (210) operable to detect a specified sequence of particular processing operations in the first processor (100); a second processor (101), a second trace buffer (231) coupled to the second processor (101), a second triggering circuit (211) coupled to the second processor (101), the second triggering circuit (211) operable to detect at least one other processing operation in the second processor (101); and a cross trace circuit (330) having a trace output and having inputs coupled to the first triggering circuit (210) and to the second triggering circuit (211), the cross trace circuit (330) configurably operable to respond to a sequence including both a detection of the sequence of particular processing operations of the first processor (100) by the first triggering circuit (210) and a detection of the at least one other processing operation of the second processor (101) by the second triggering circuit (211), to couple at least one of the first trace buffer (230) and the second trace buffer (231) to the trace output. Various circuits, devices, telecommunications products, wireless handsets, systems and processes of operation and manufacture are disclosed.

Owner:TEXAS INSTR INC

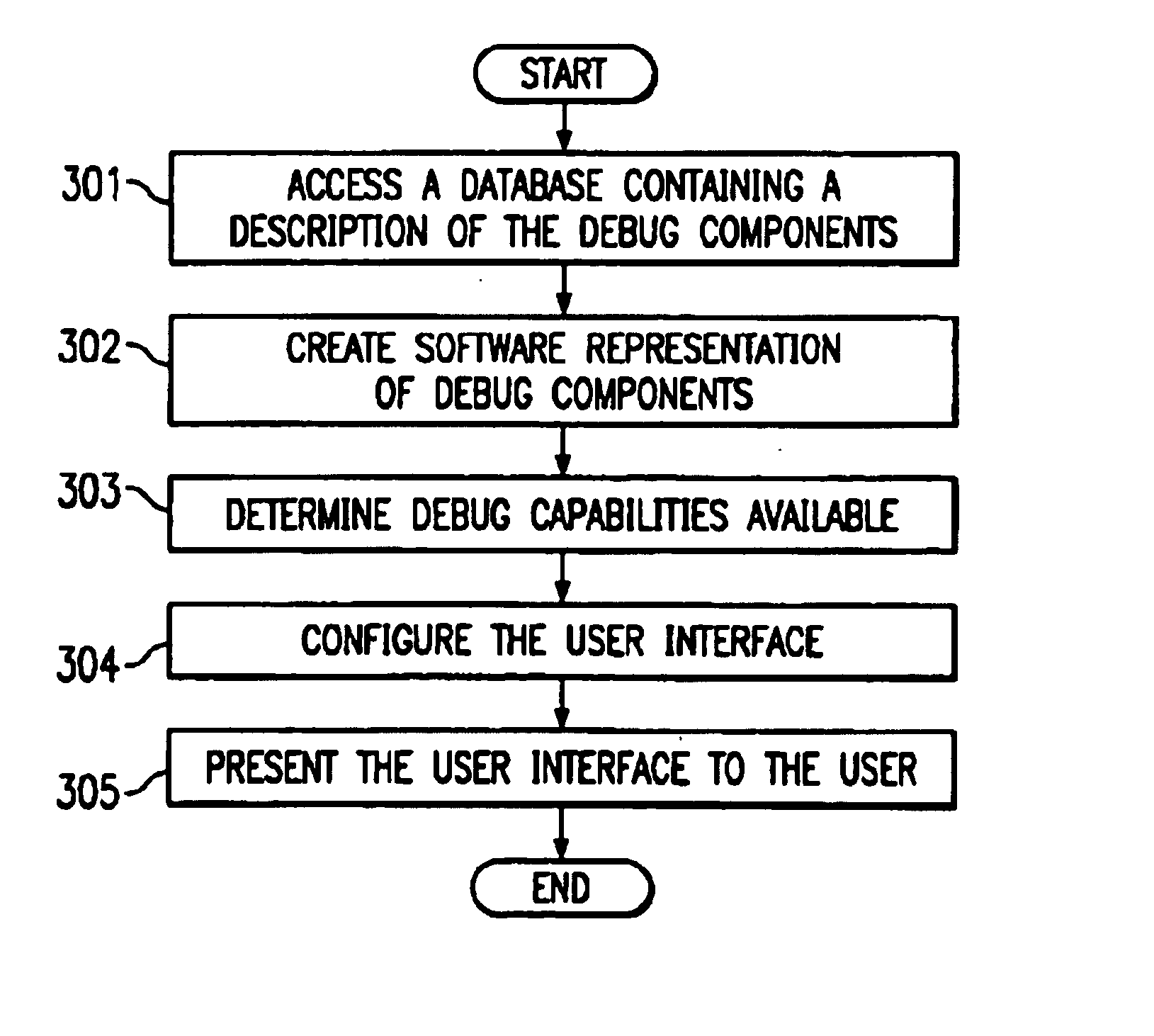

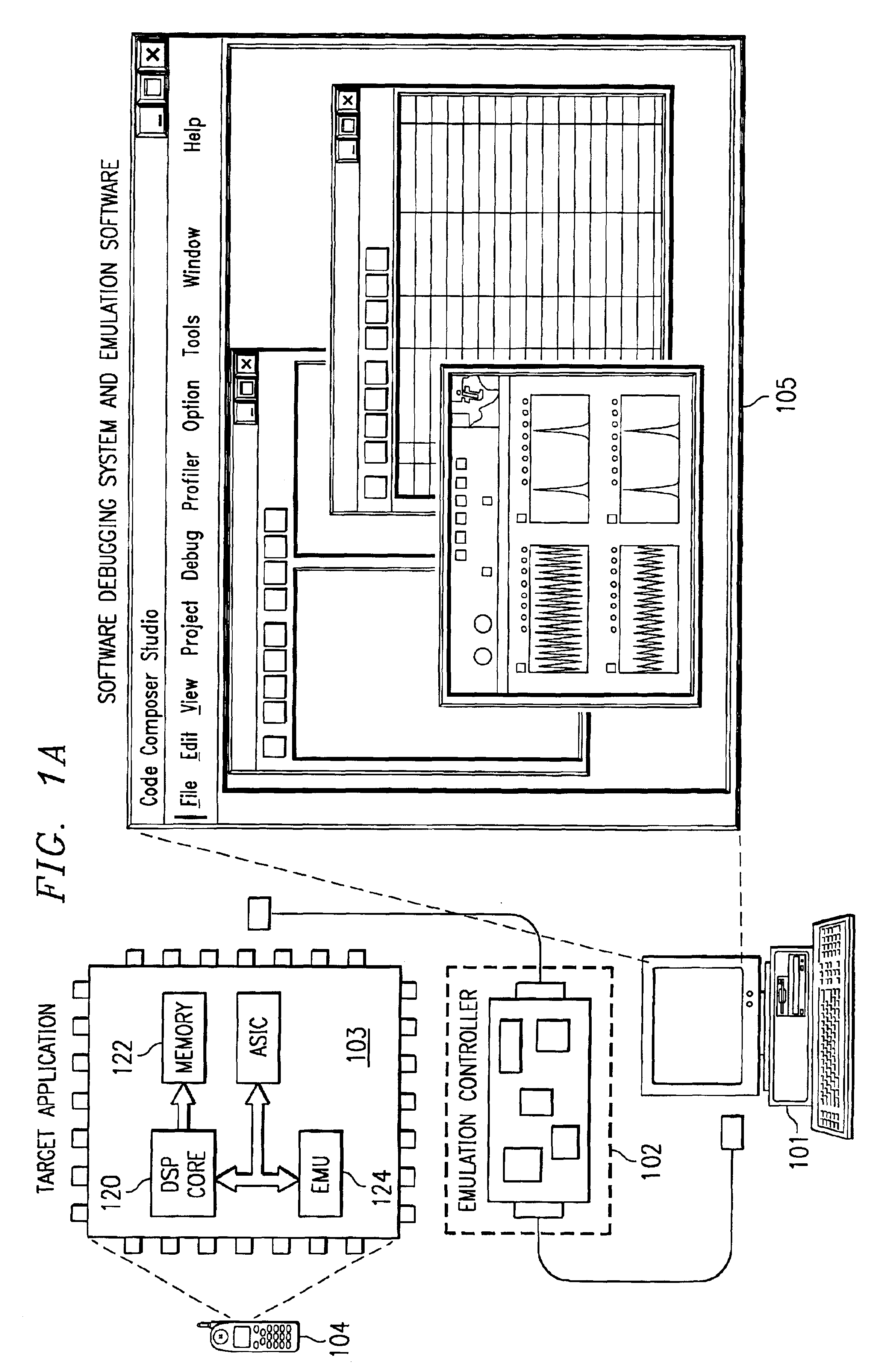

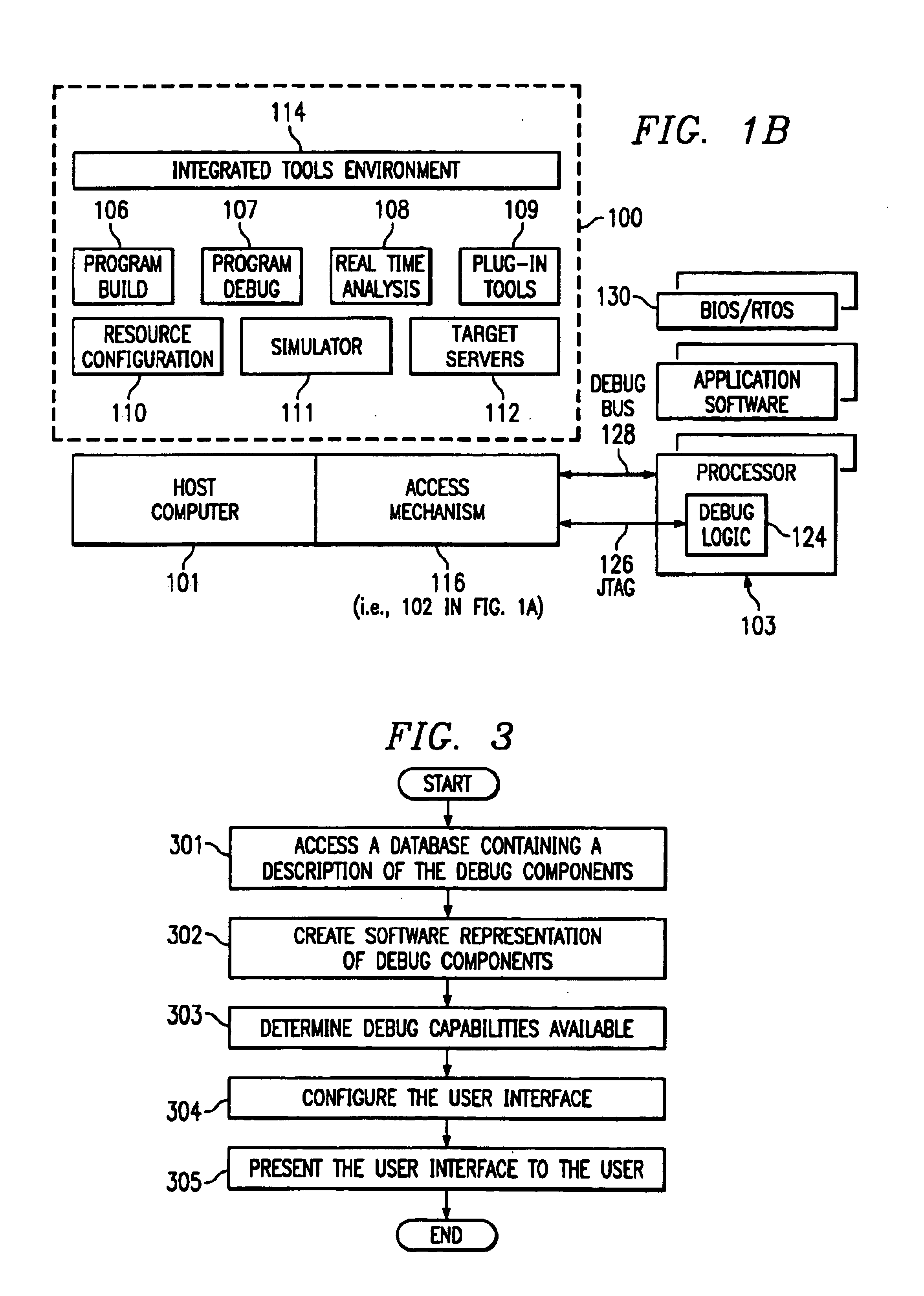

Configurable debug system with dynamic menus

InactiveUS7055136B2Easy to operateHardware monitoringFunctional testingGraphicsGraphical user interface

The invention relates to a software system and method for dynamically varying context sensitive menus of a software system. In this method, a menu item is added to a context sensitive menu of a graphical user interface (GUI) at the request of a subsystem module. Then, an activation event for the context sensitive menu is received from the GUI. The added menu item is displayed as either active or inactive based on a response to a query from the software system to a second subsystem module. The action associated with the menu item specified by the first subsystem module is executed when the menu item is selected only if it is active.

Owner:TEXAS INSTR INC

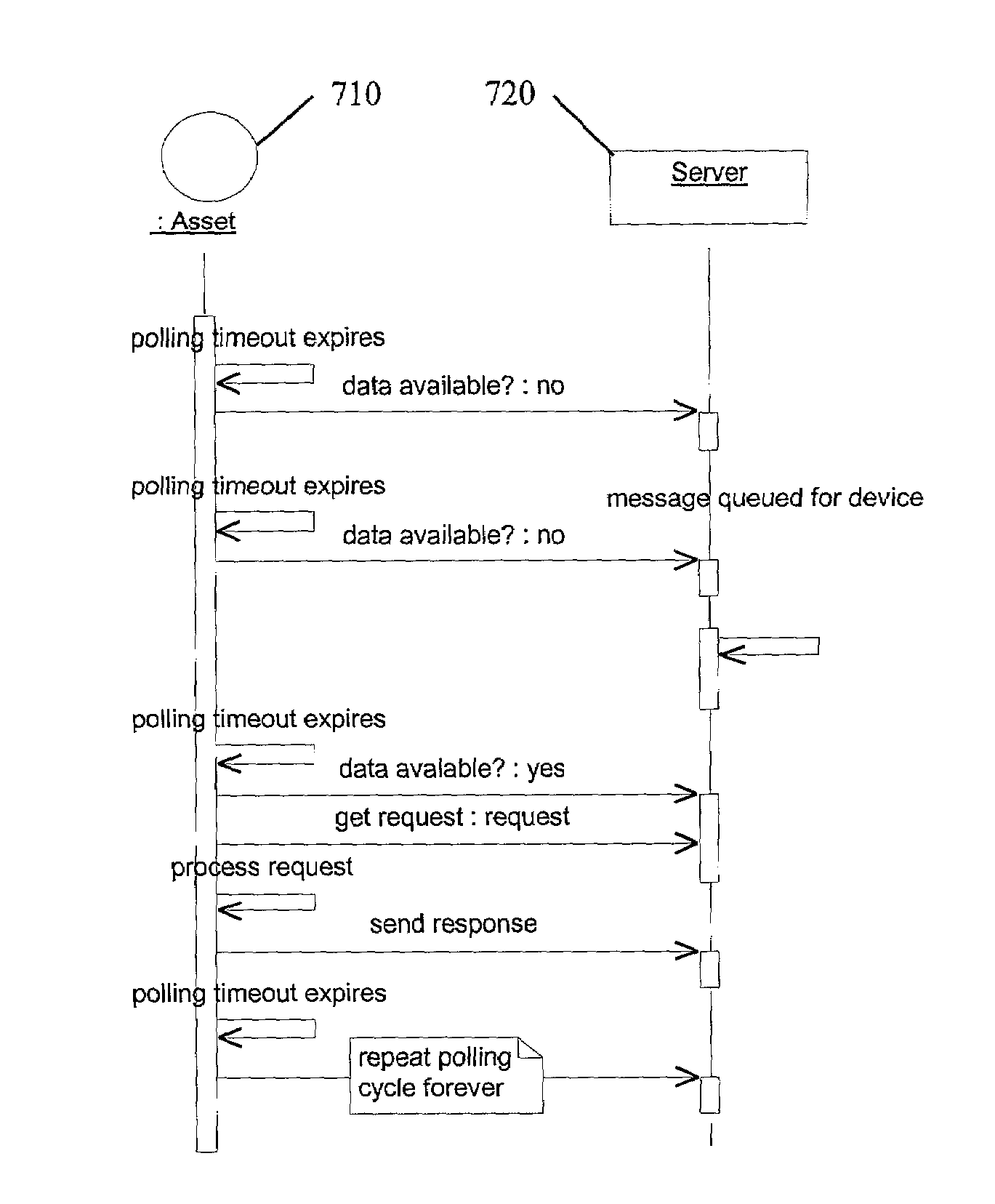

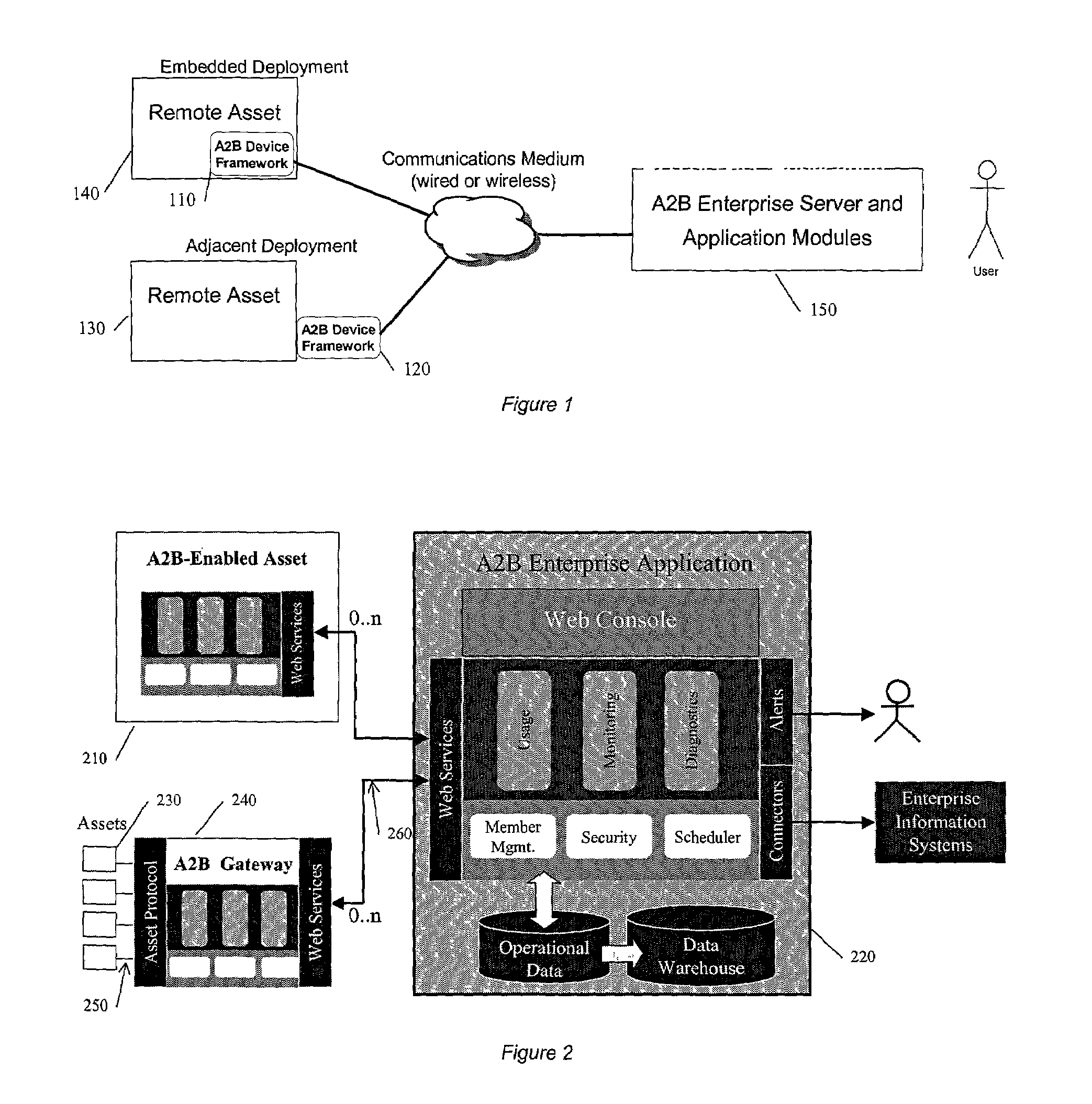

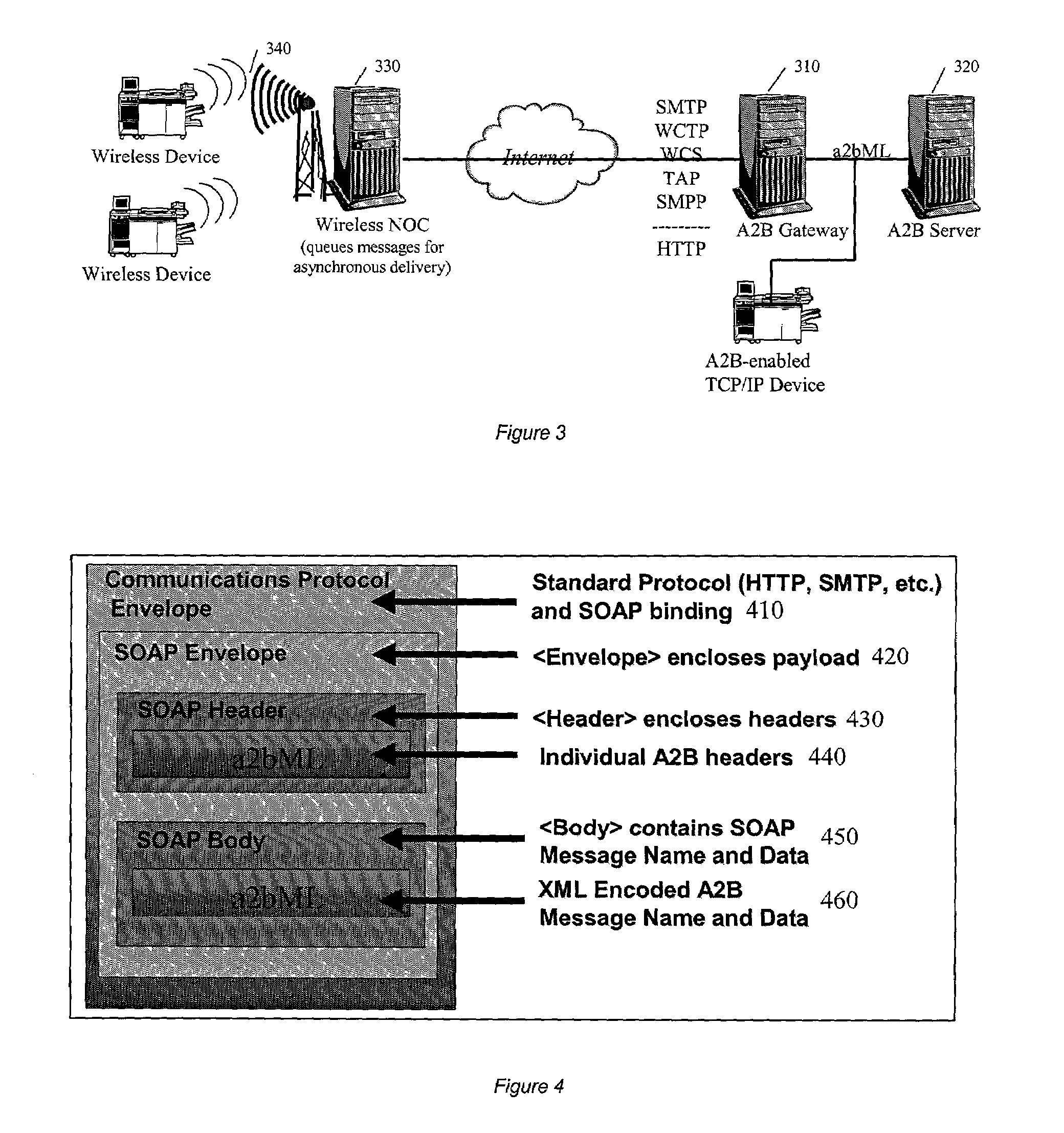

Method and apparatus for managing intelligent assets in a distributed environment

InactiveUS7254601B2Detecting faulty hardware by remote testFunctional testingIntelligent equipmentApplication module

A method is described which provides for managing intelligent equipment that is deployed remotely. The capabilities of managing such distributed assets include both infrastructural capabilities to establish and maintain connection through a variety of wired and wireless mechanisms and application modules that provide distributed asset management capabilities.

Owner:PARAMETRIC TECH CORP

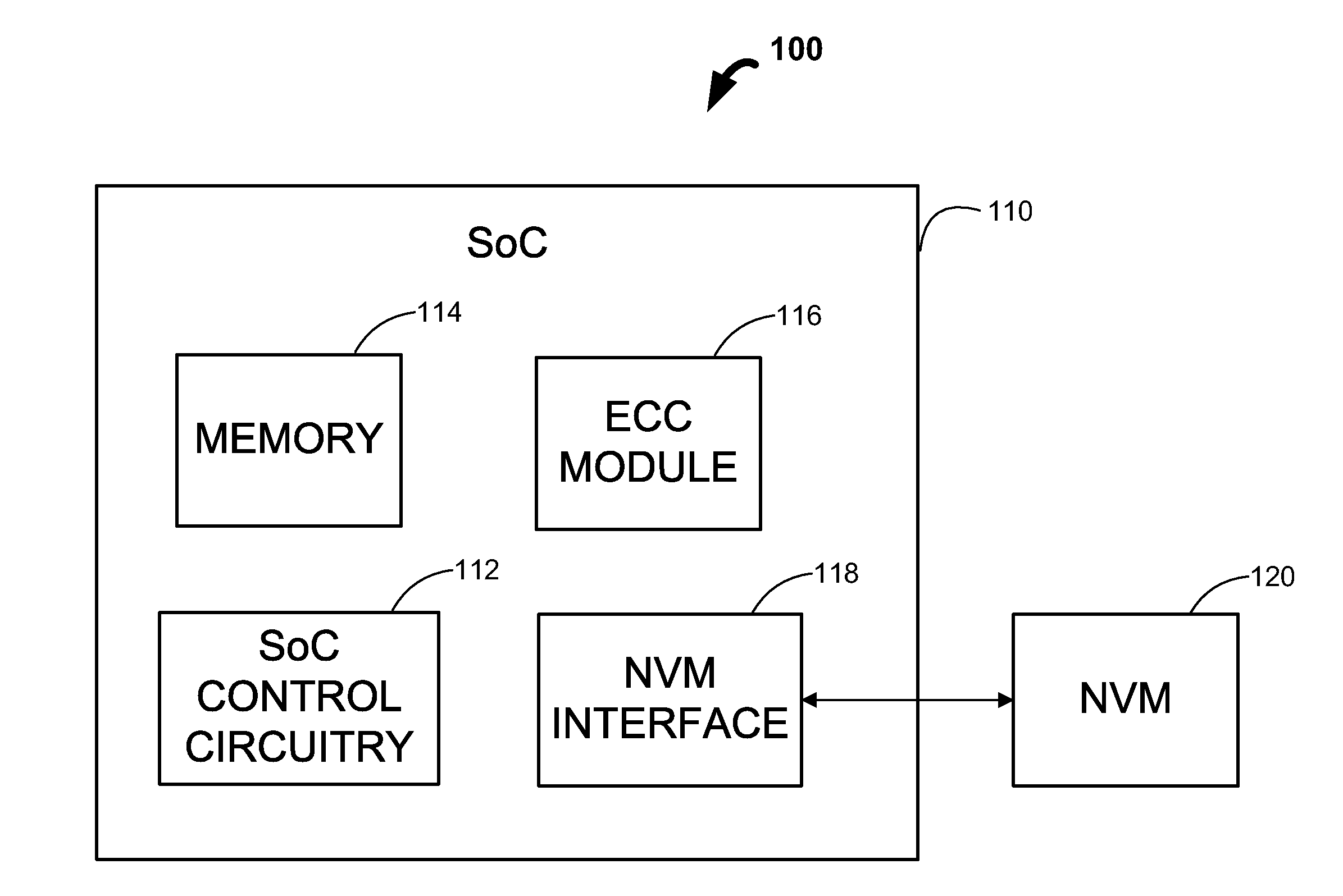

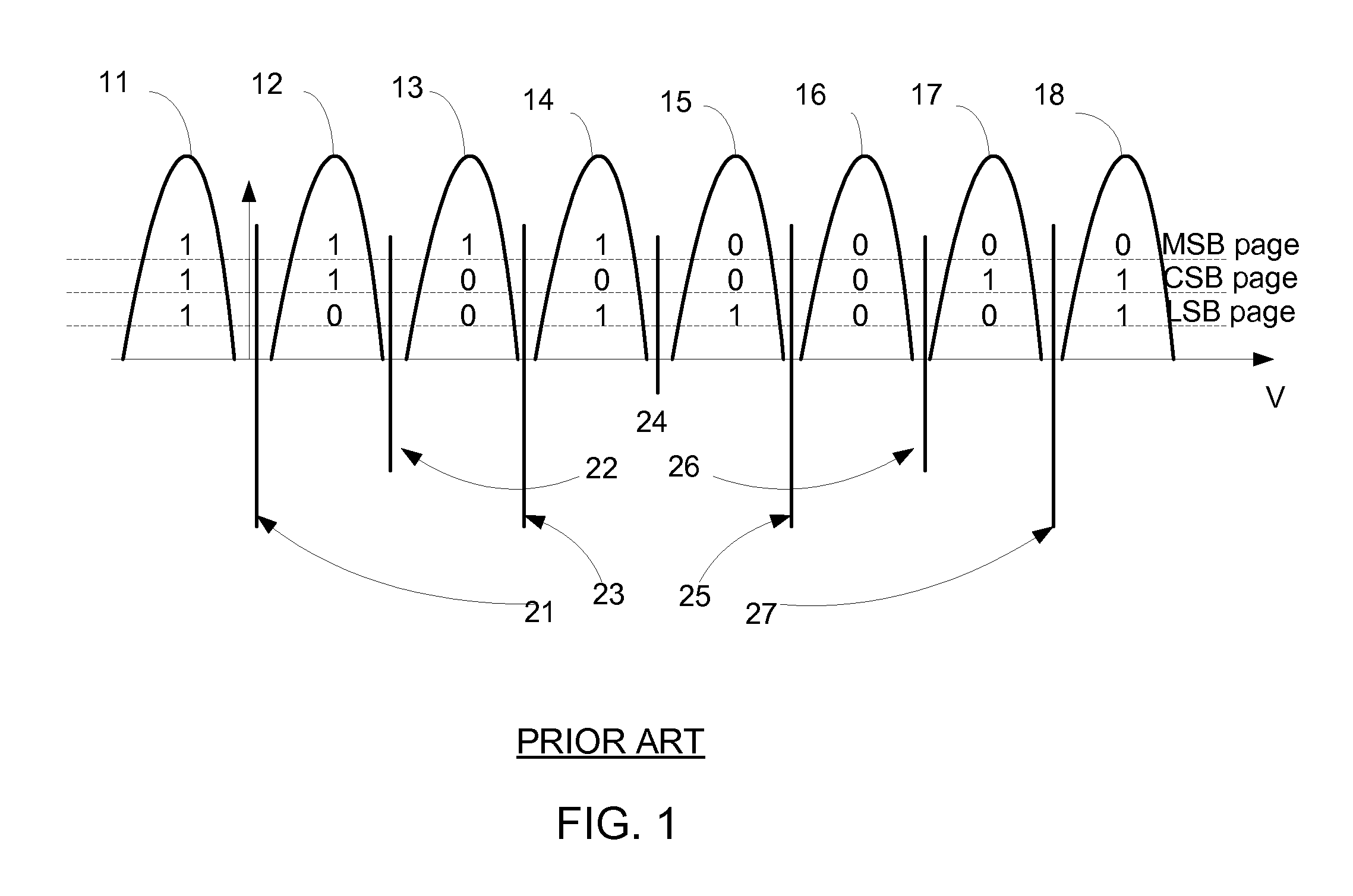

Systems and methods for generating dynamic super blocks

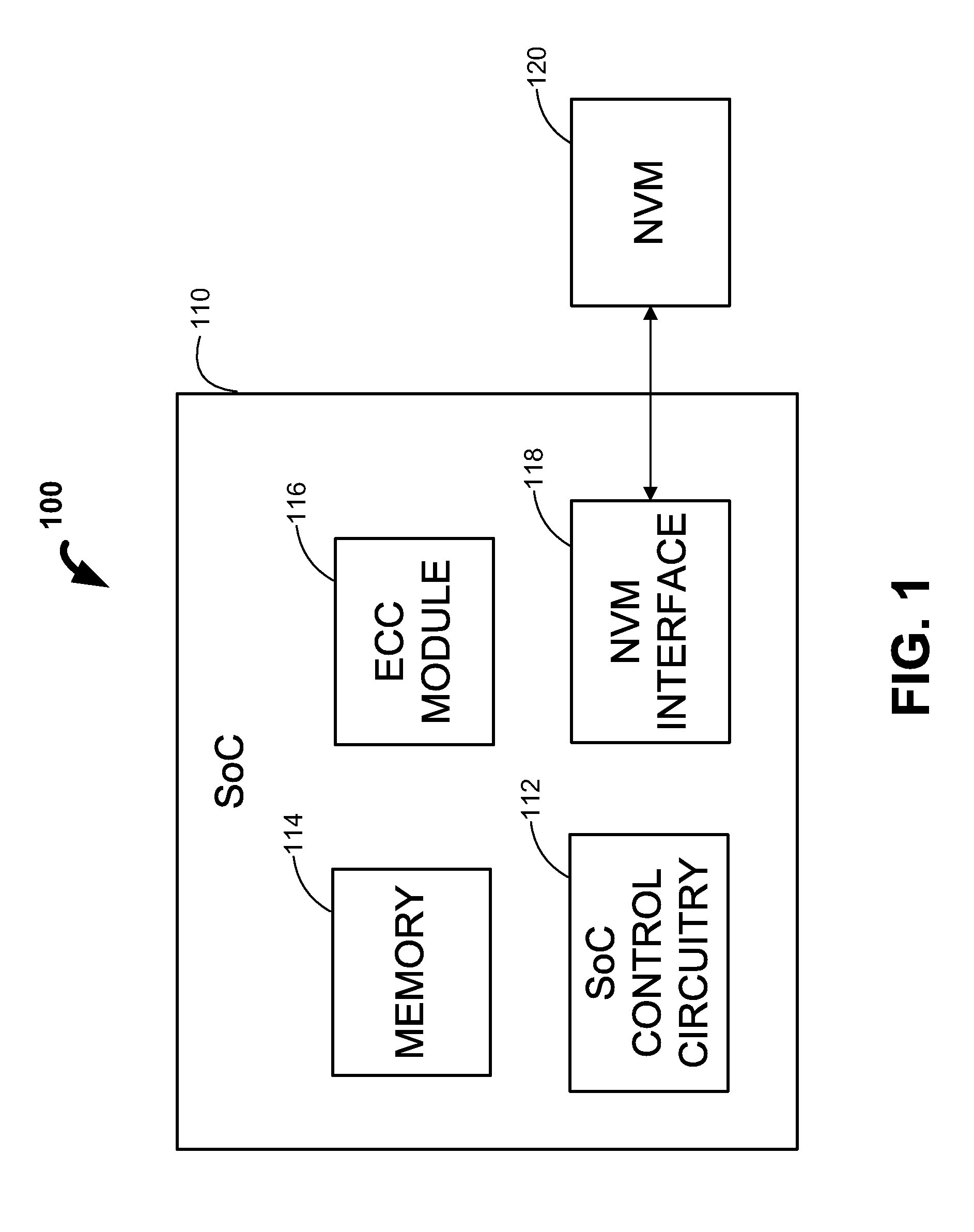

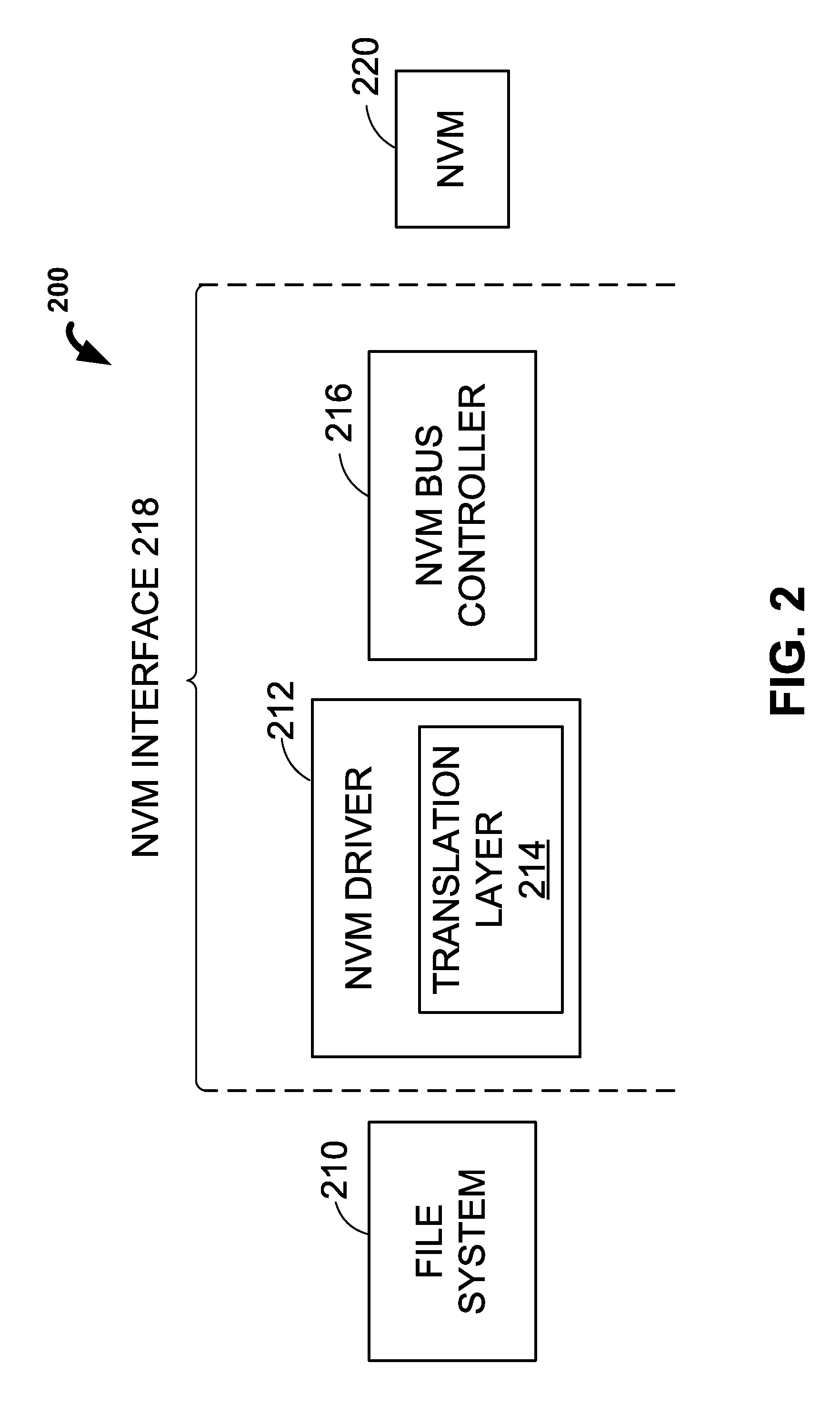

ActiveUS20120047409A1Reduce probabilityExtend your lifeMemory architecture accessing/allocationCode conversionParallel computingNon-volatile memory

Systems and methods are disclosed for generating dynamic super blocks from one or more grown bad blocks of a non-volatile memory (“NVM”). In some embodiments, a dynamic super block can be formed by striping together a subset of memory locations of grown bad blocks from one or more dies of a NVM. The subset of memory locations may be selected based on at least one reliability measurement of the subset of memory locations. In some embodiments, in response to detecting one or more access failures in a portion of the dynamic super block, the NVM interface can retire at least a portion of the dynamic super block. In some embodiments, the NVM interface can reconstruct a new dynamic super block from the dynamic super block by progressively increasing the size of the new dynamic super block.

Owner:APPLE INC

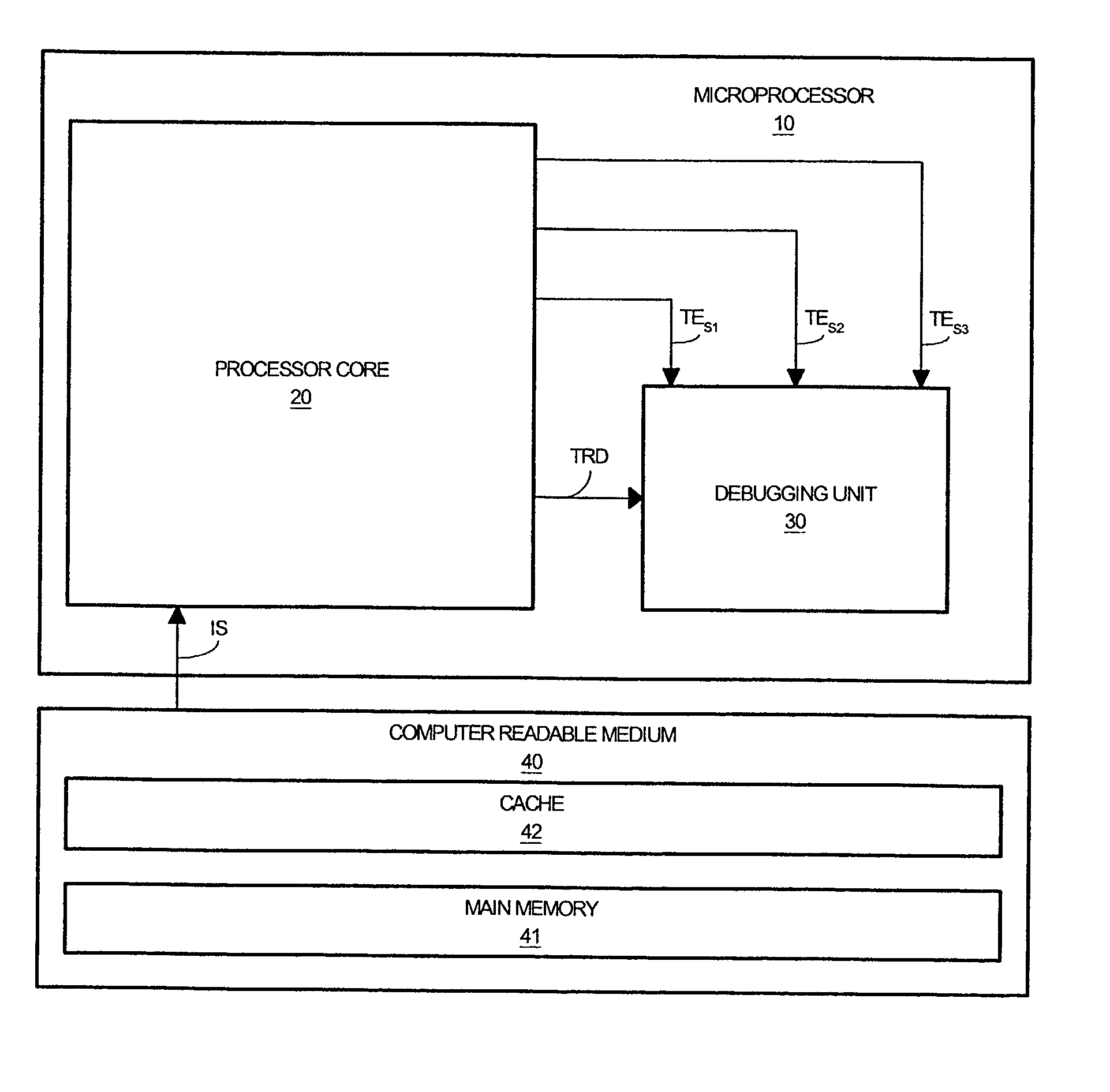

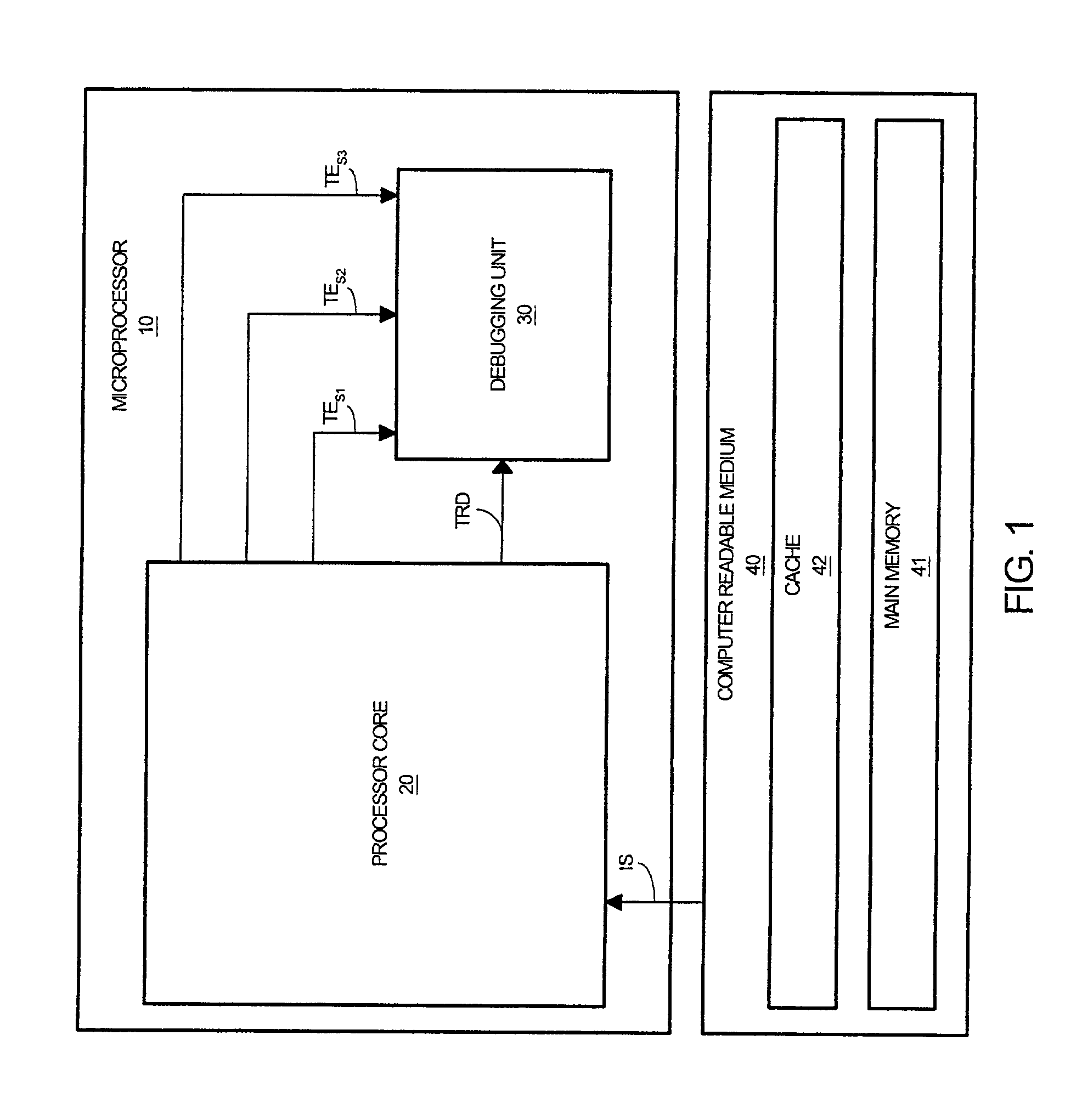

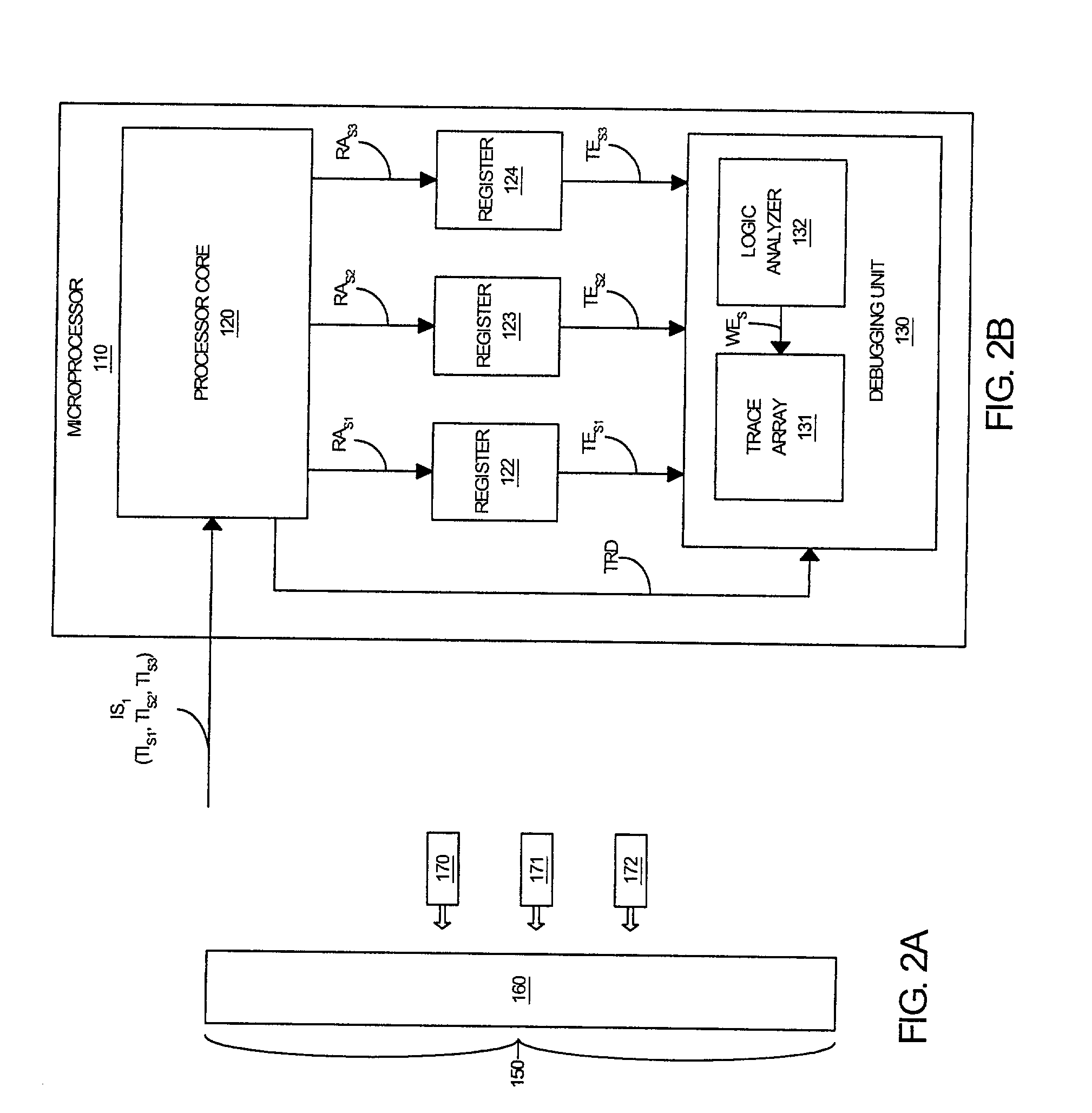

Method and system for triggering a debugging unit

InactiveUS20020129309A1Electronic circuit testingDigital computer detailsProcessing InstructionDynamic storage

A processor core for transitioning a debugging unit between a plurality of operating states in response to an instruction stream is disclosed. The processor core generates trace data as it processes operating signals of the instruction stream. The processor core provides a first trigger event signal to the debugging unit in response to a first trigger instruction signal within the instruction stream that is representative of a triggering instruction to transitions the debugging unit to a base operating state. The processor core provides a second trigger event signal to the debugging unit in response to a second trigger instruction signal within the instruction stream that is representative of a triggering instruction to dynamically store trace data within the memory component of the debugging unit. The processor core provides a third trigger event signal to the debugging unit in response to a third trigger instruction signal within the instruction stream that is representative of a triggering instruction to statically store trace data within the memory component of the debugging unit. Concurrently or alternatively, the processor core can provide one or more of the trigger event signals to the debugging unit as a function of a generated trigger data in response to additional operational instructions within the instruction stream.

Owner:IBM CORP

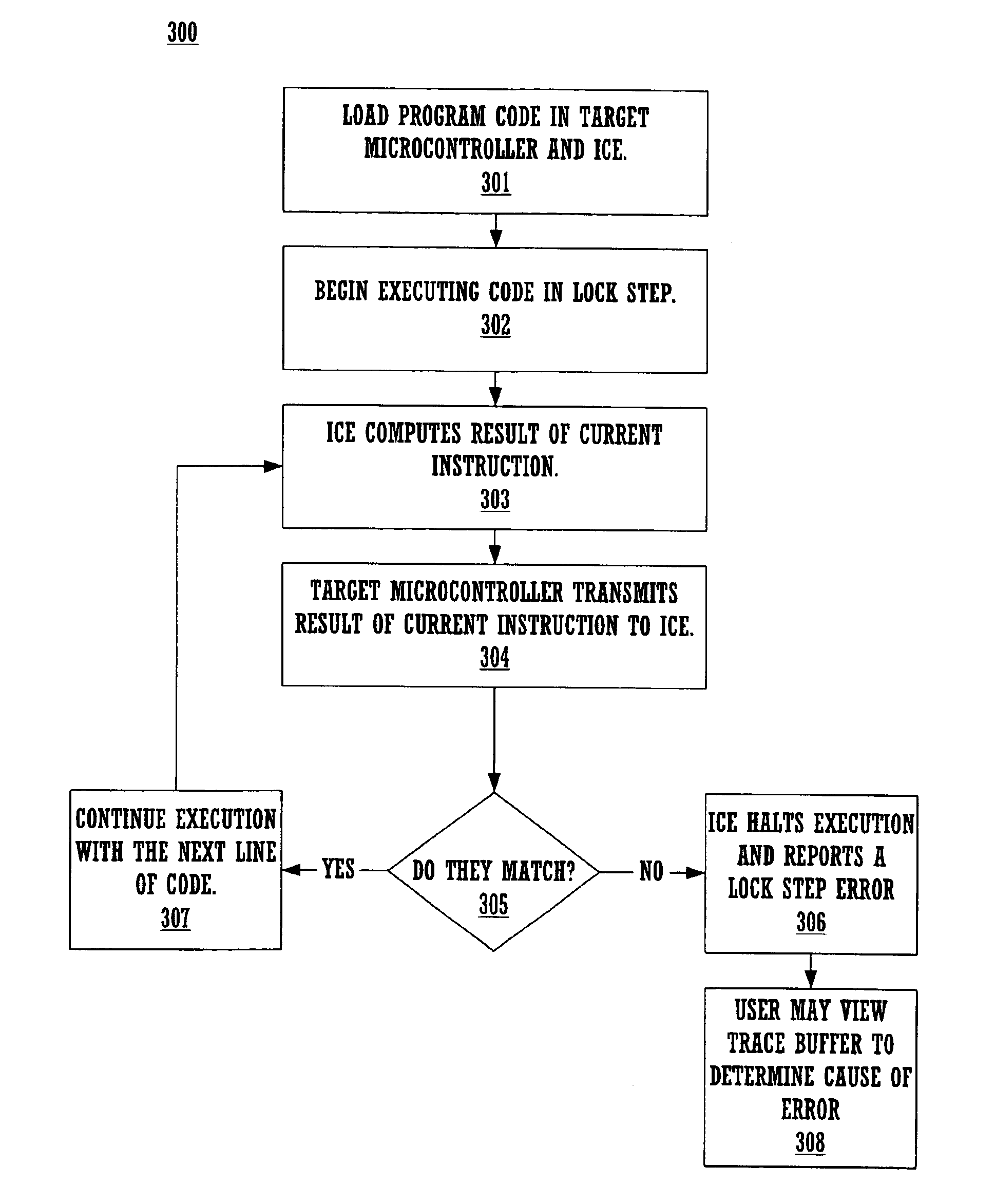

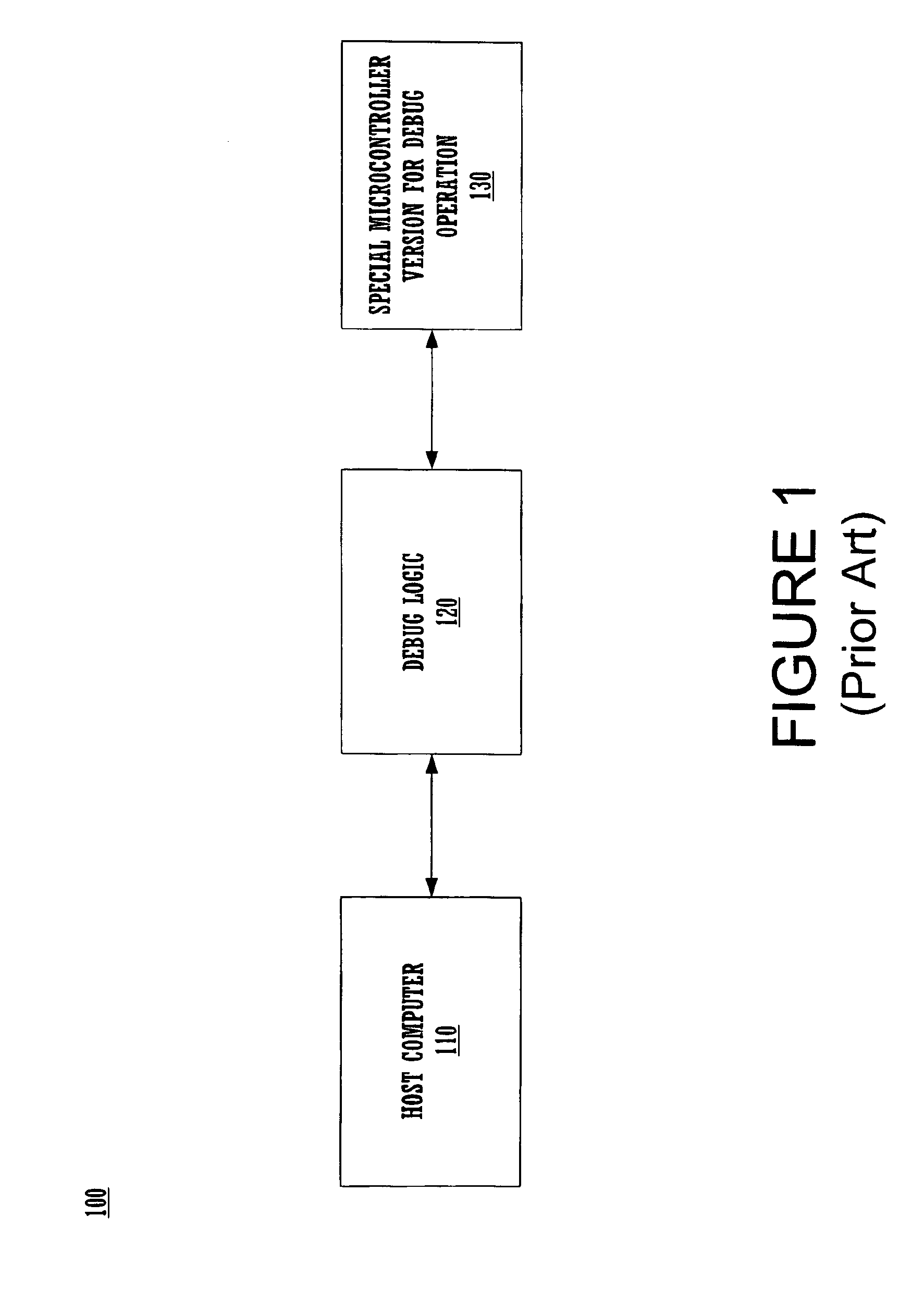

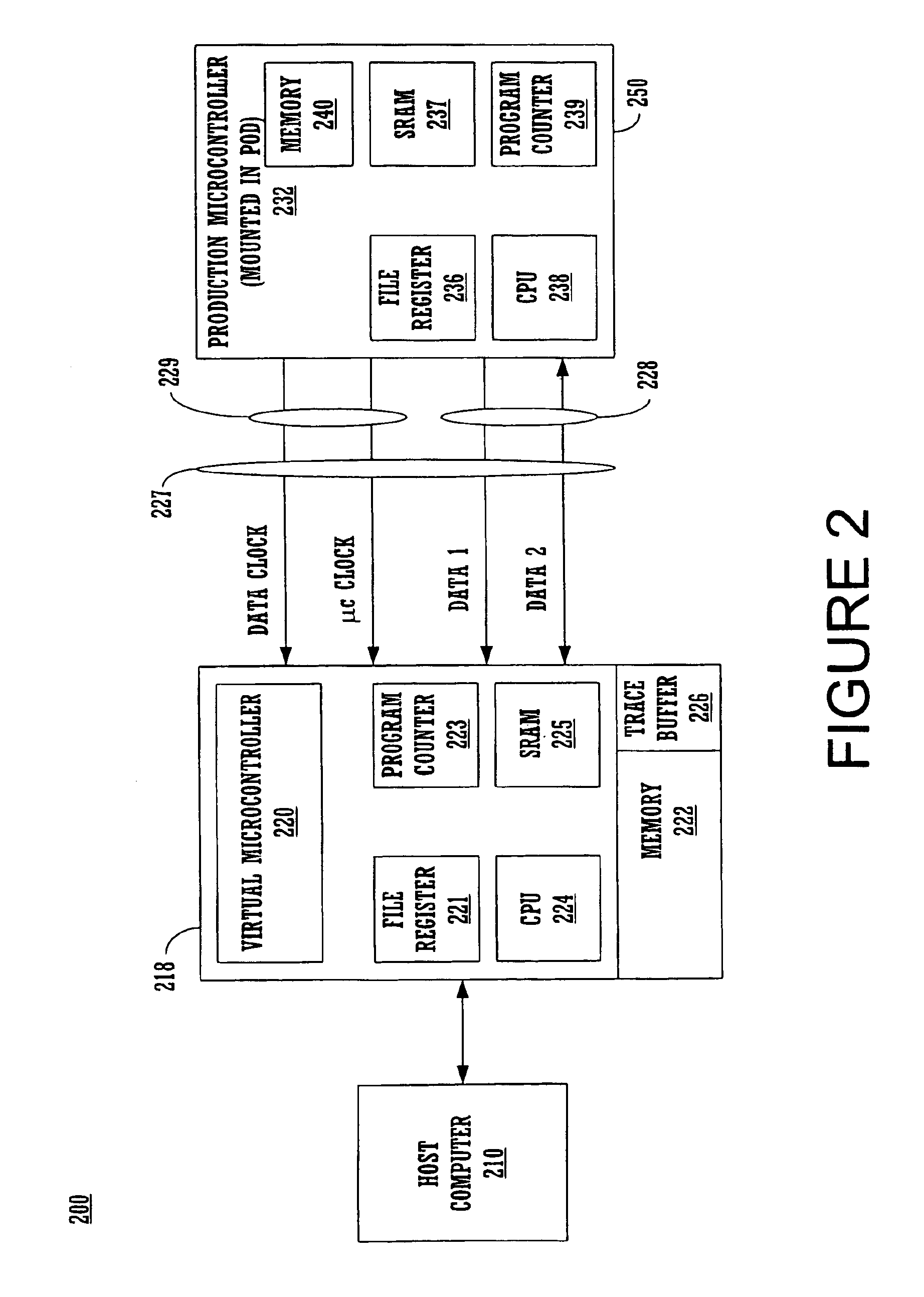

System and a method for checking lock step consistency between an in circuit emulation and a microcontroller while debugging process is in progress

InactiveUS6922821B1Analogue computers for electric apparatusFunctional testingMicrocontrollerParallel computing

Checking the consistency of a lock step process while debugging a microcontroller code is in progress. A method provides a production microcontroller to execute an instruction code and provides the result of the instruction code to an ICE. The ICE, independent from the production microcontroller and simultaneously, executes the same instruction code and produces a result. The ICE compares the result of its computation and the result received from the production microcontroller. The ICE issues a “lock step error” when the result of the comparison is a mismatch. A trace buffer residing in the host device provides the location of the line of code causing the mismatch. After identifying the line of code causing the mismatch the user debugs the erroneous line of code. The debugging process resumes on the next line of code in the microcontroller code under test.

Owner:MONTEREY RES LLC

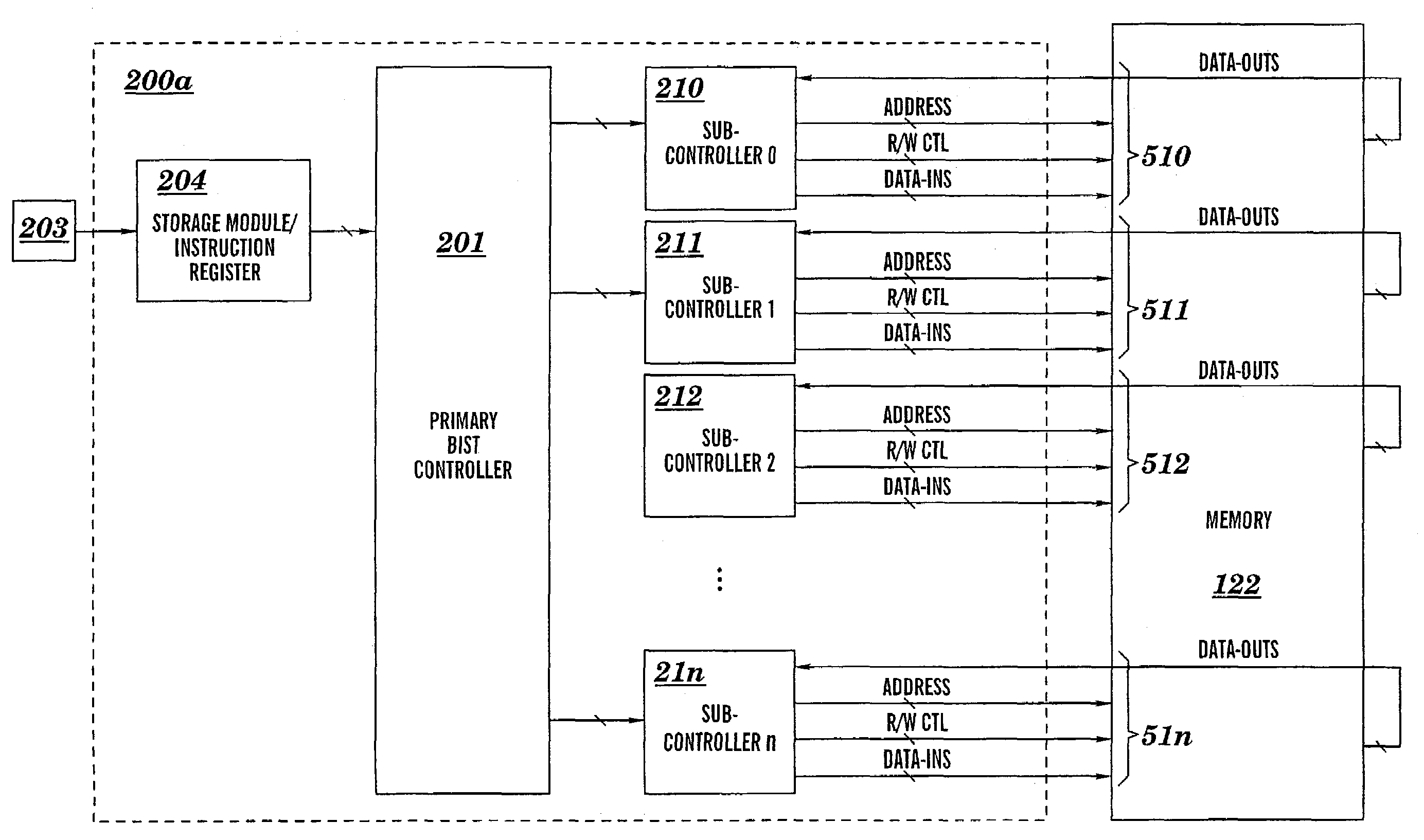

Programable multi-port memory BIST with compact microcode

InactiveUS7168005B2Easy to testIncrease flexibilityElectronic circuit testingFunctional testingAs DirectedMaster controller

A microcode programmable built-in-self-test (BIST) circuit and method for testing a multiported memory via multiple ports, either simultaneously or sequentially, as directed by a microcode instruction word. The microcode instruction word contains a plurality of executable subinstructions and one bit of information that controls whether the test operations prescribed in the plurality of subinstructions shall be executed in parallel or in series. The executable subinstructions are dispatched by a primary controller to subcontrollers which perform test operations at each port according to the subinstructions. The microcode programable BIST architecture flexibly facilitates the testing of multiple devices, multiported devices, including multiported memory structures and complex dependent multiported memory structures. The BIST supports in-situ testing of the functionality of the memory at wafer, module, and burn-in, as well as system-level testing.

Owner:CADENCE DESIGN SYST INC

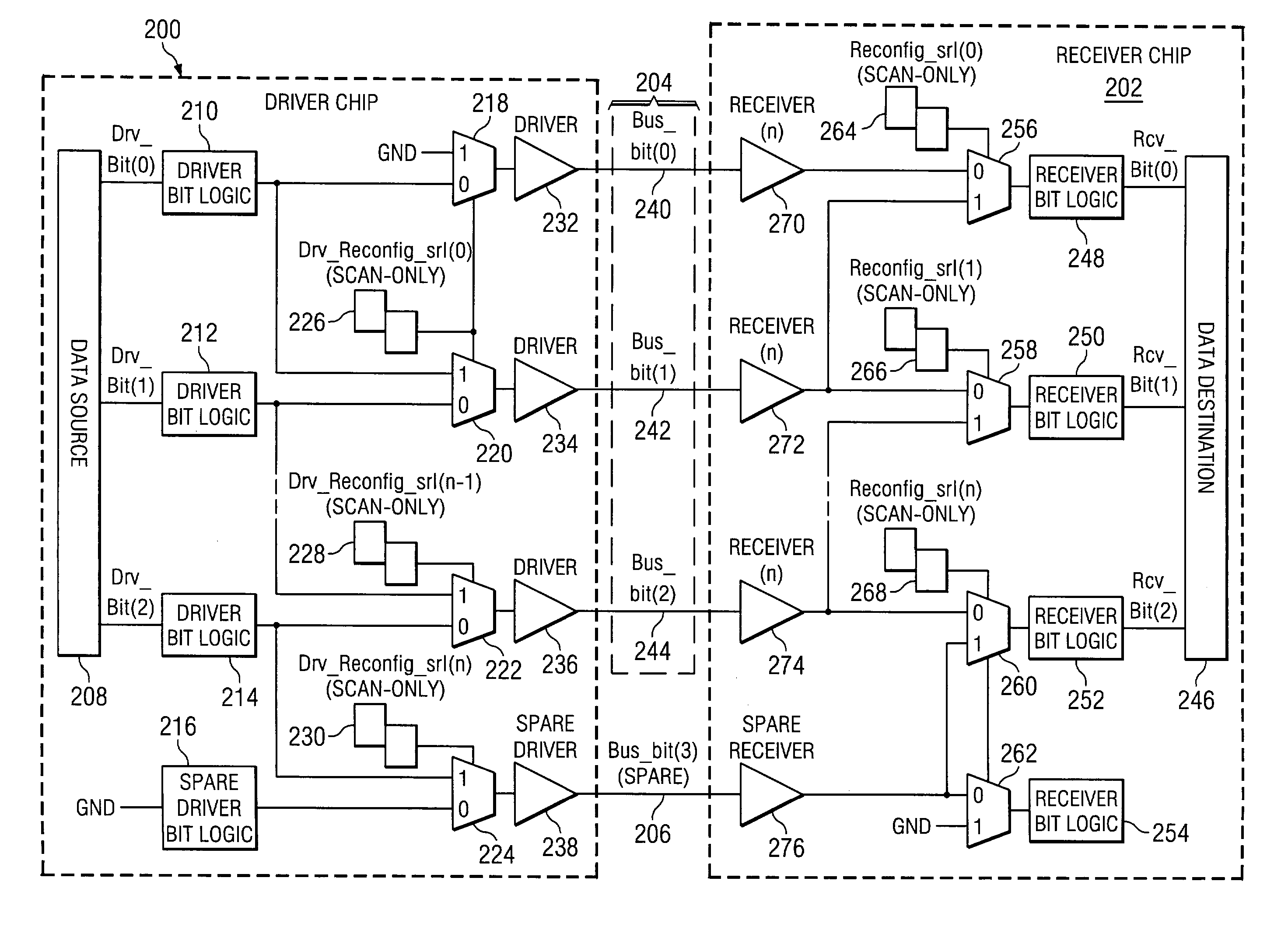

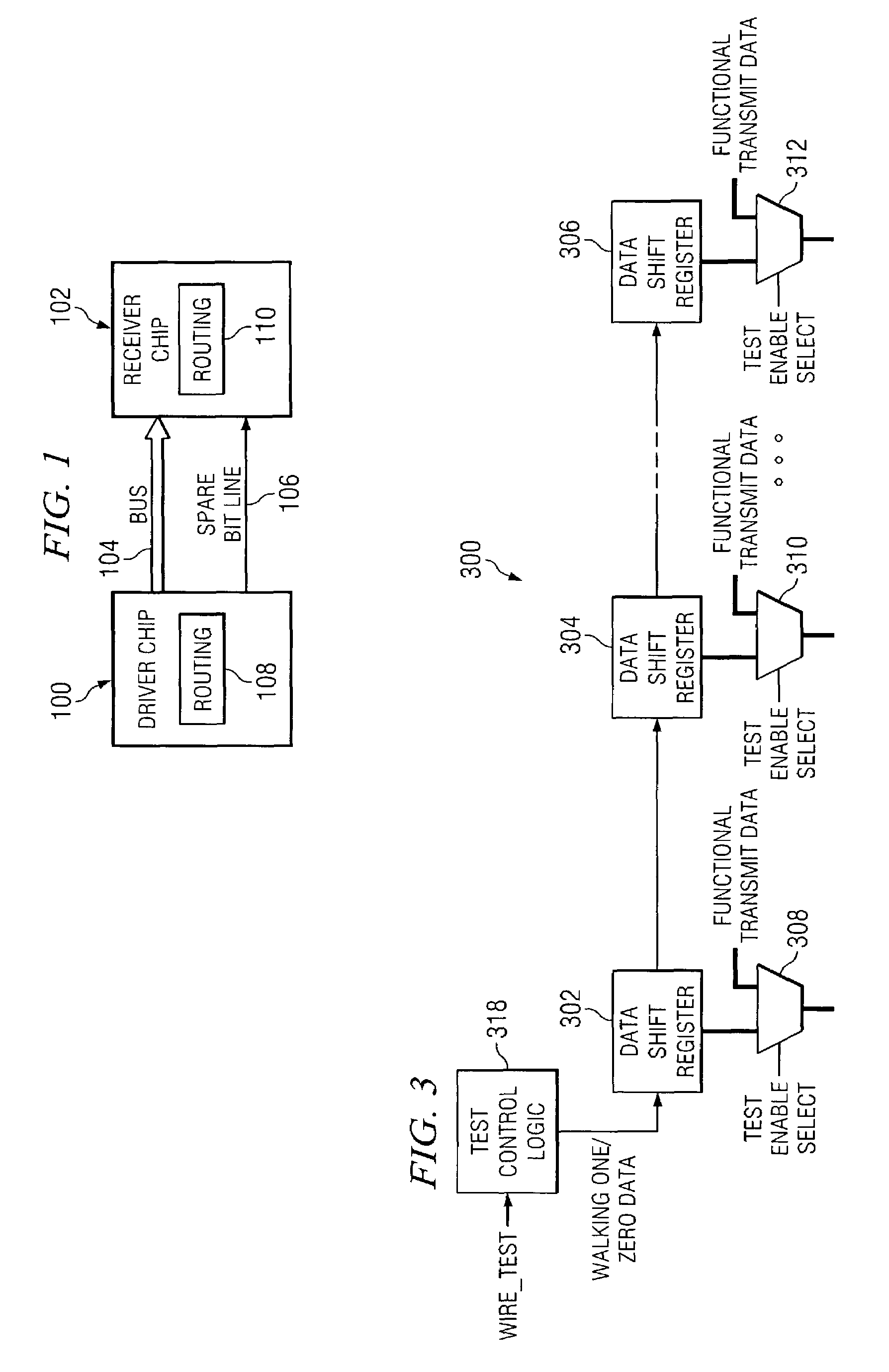

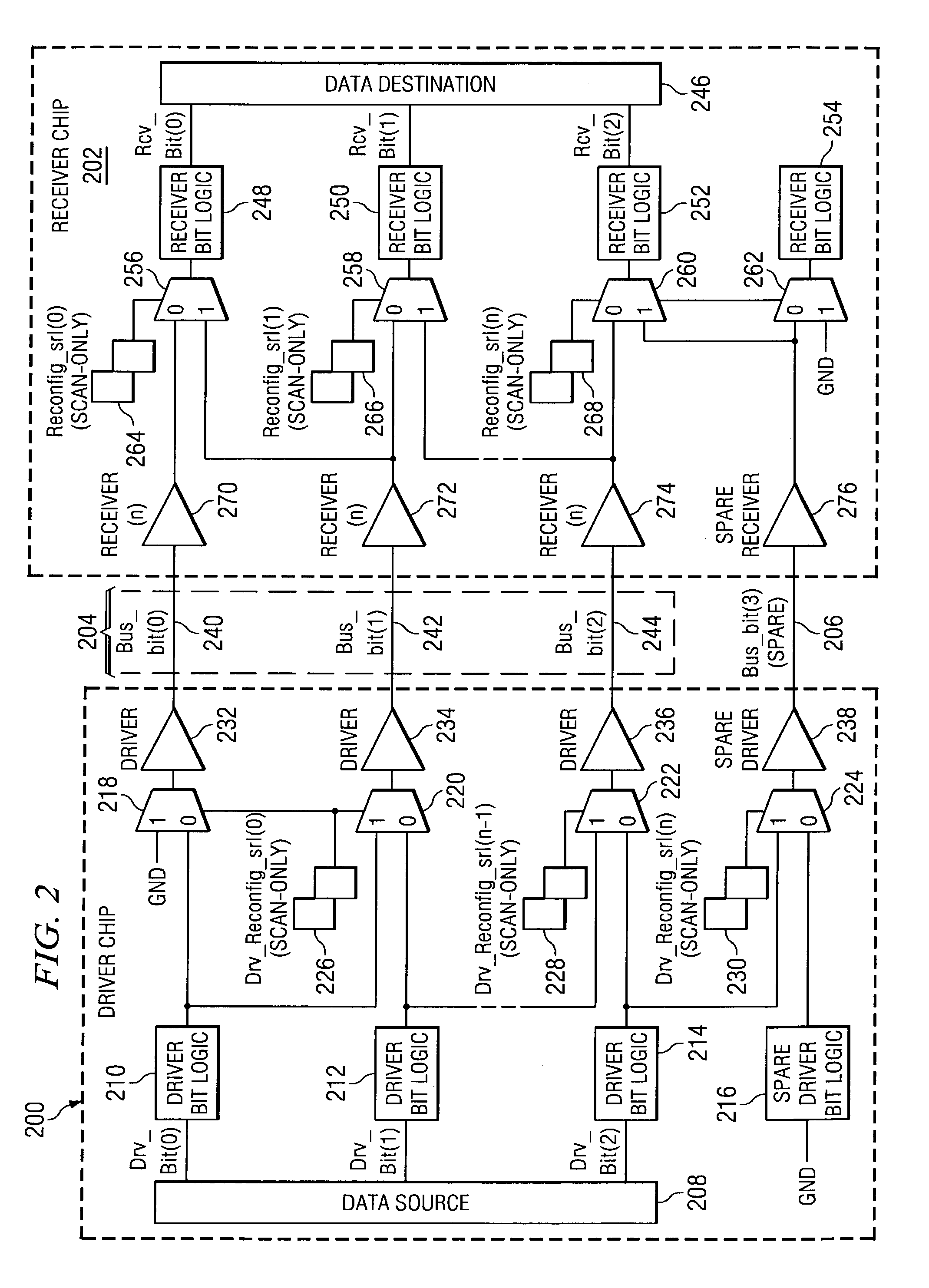

Self-healing chip-to-chip interface

InactiveUS7362697B2Error preventionSemiconductor/solid-state device testing/measurementSelf-healingData signal

A method, apparatus, and computer instructions for managing a set of signal paths for a chip. A defective signal path within the set of signal paths for the chip is detected. Signals are re-routed through the set of signal paths such that the defective signal path is removed from the set of signal paths and sending signals using remaining data signal paths in the set of signal paths and using an extra signal path in response to detecting the defective signal path.

Owner:INT BUSINESS MASCH CORP

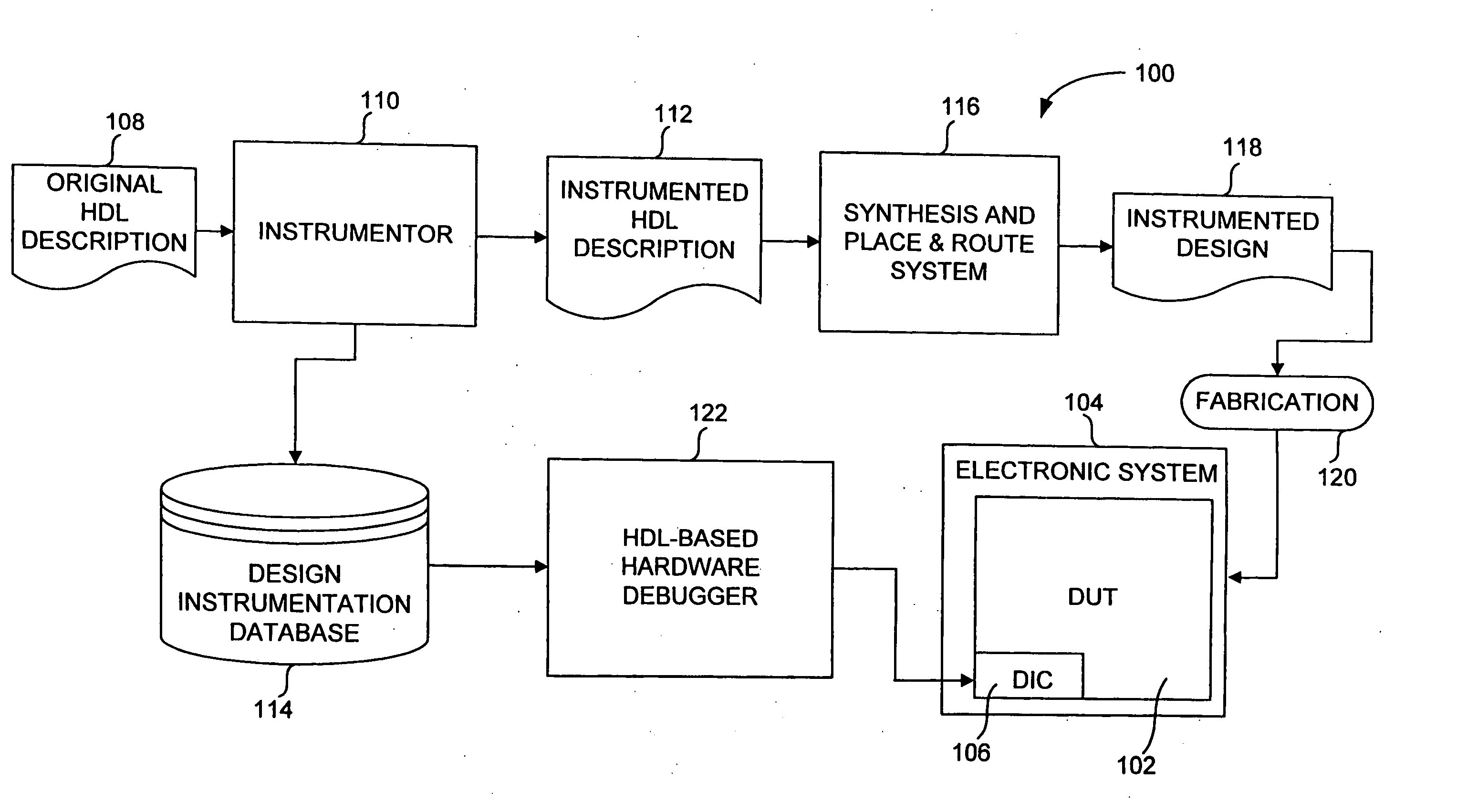

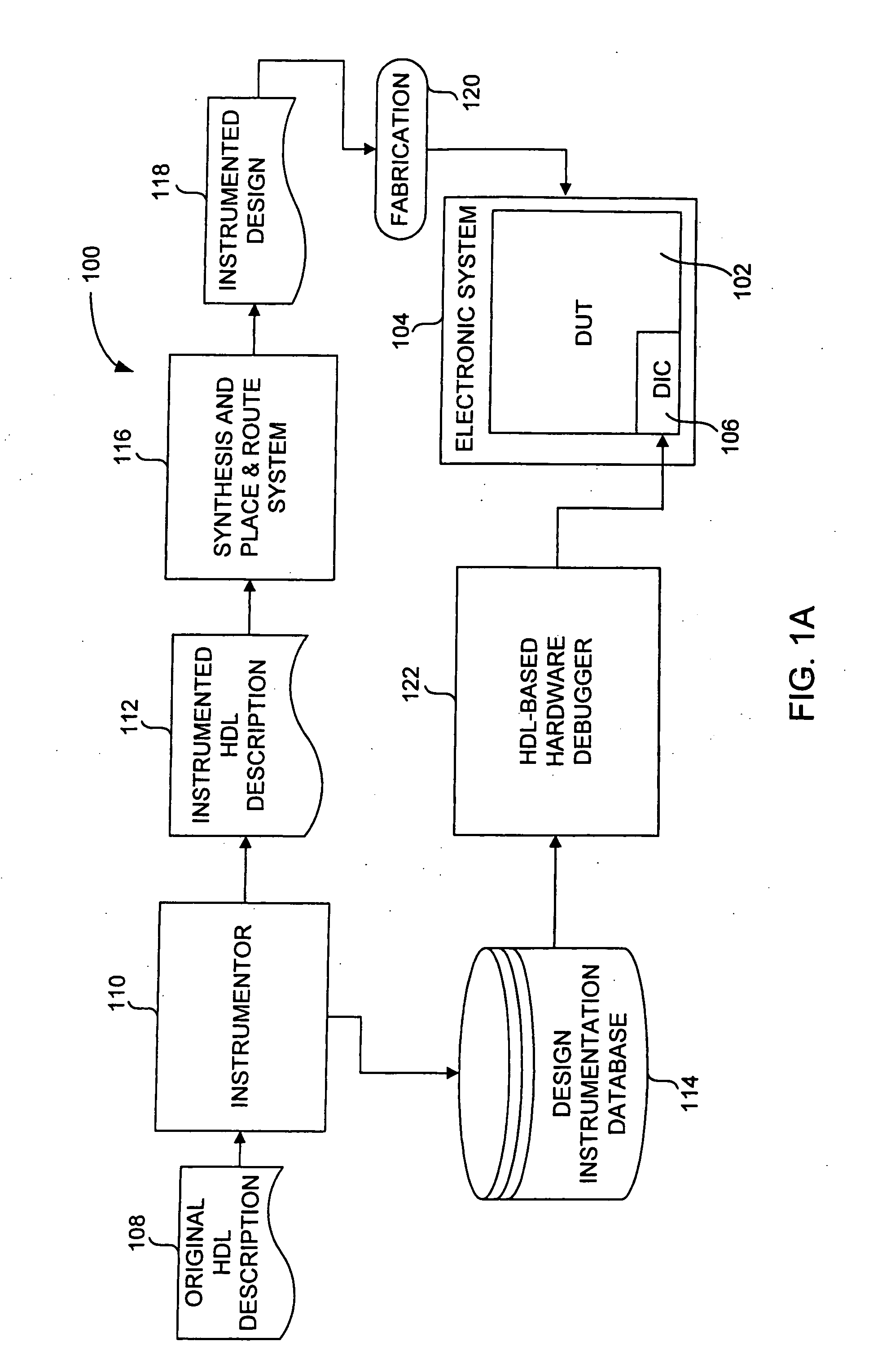

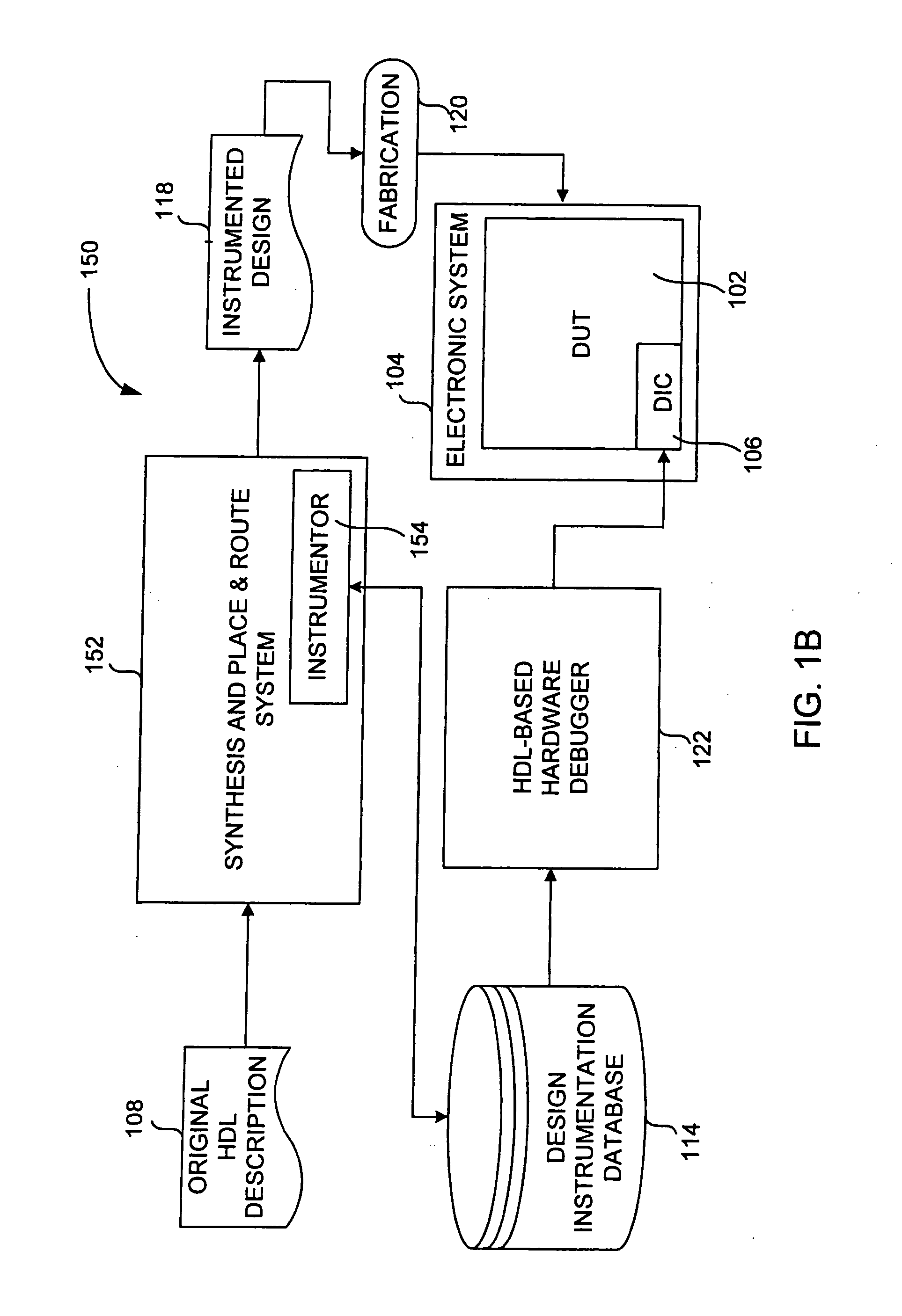

Hardware debugging in a hardware description language

InactiveUS20050125754A1Facilitates correction and adjustmentElectrical testingFunctional testingEmbedded systemIntegrated circuit

Owner:SYNOPSYS INC

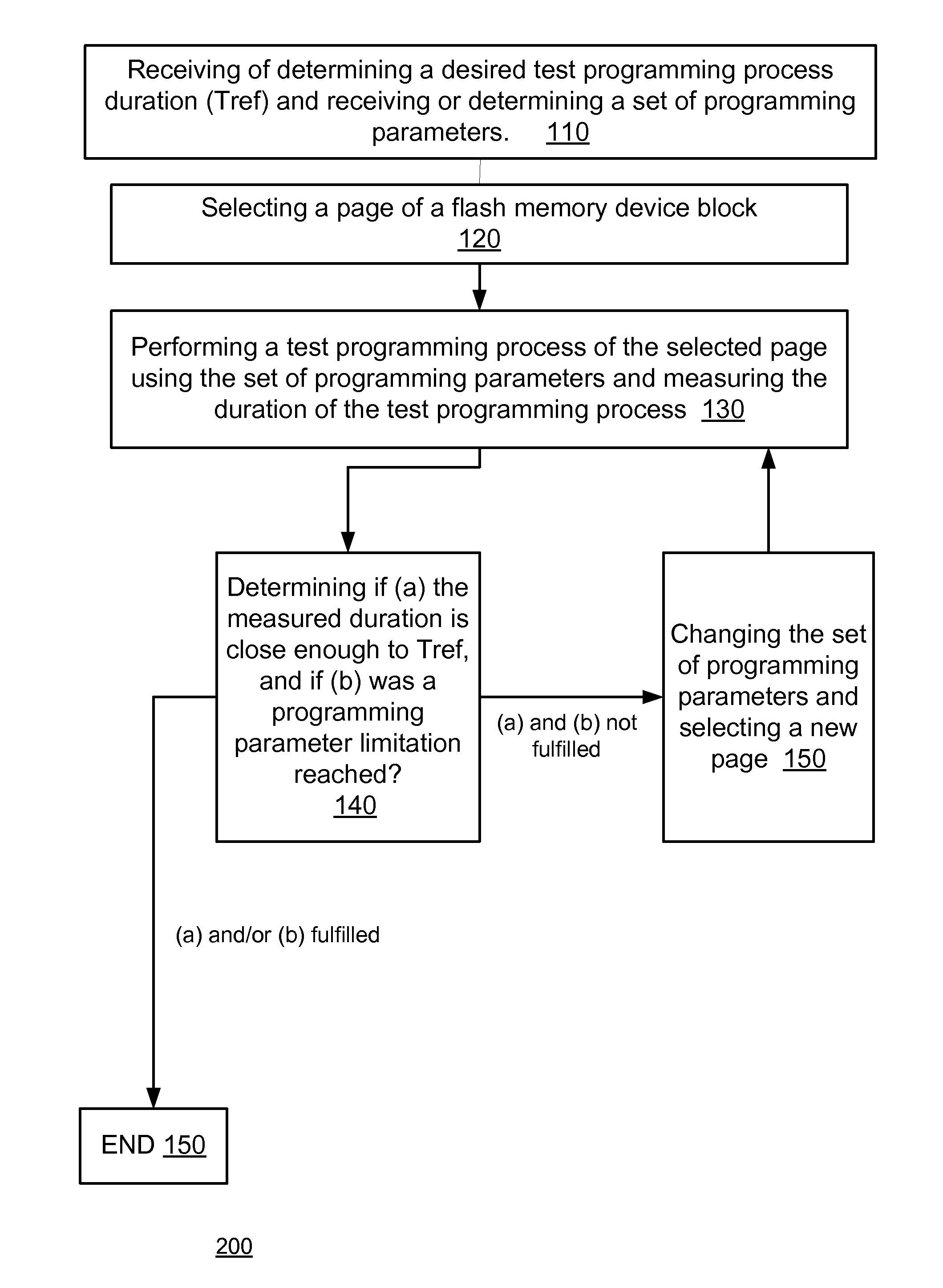

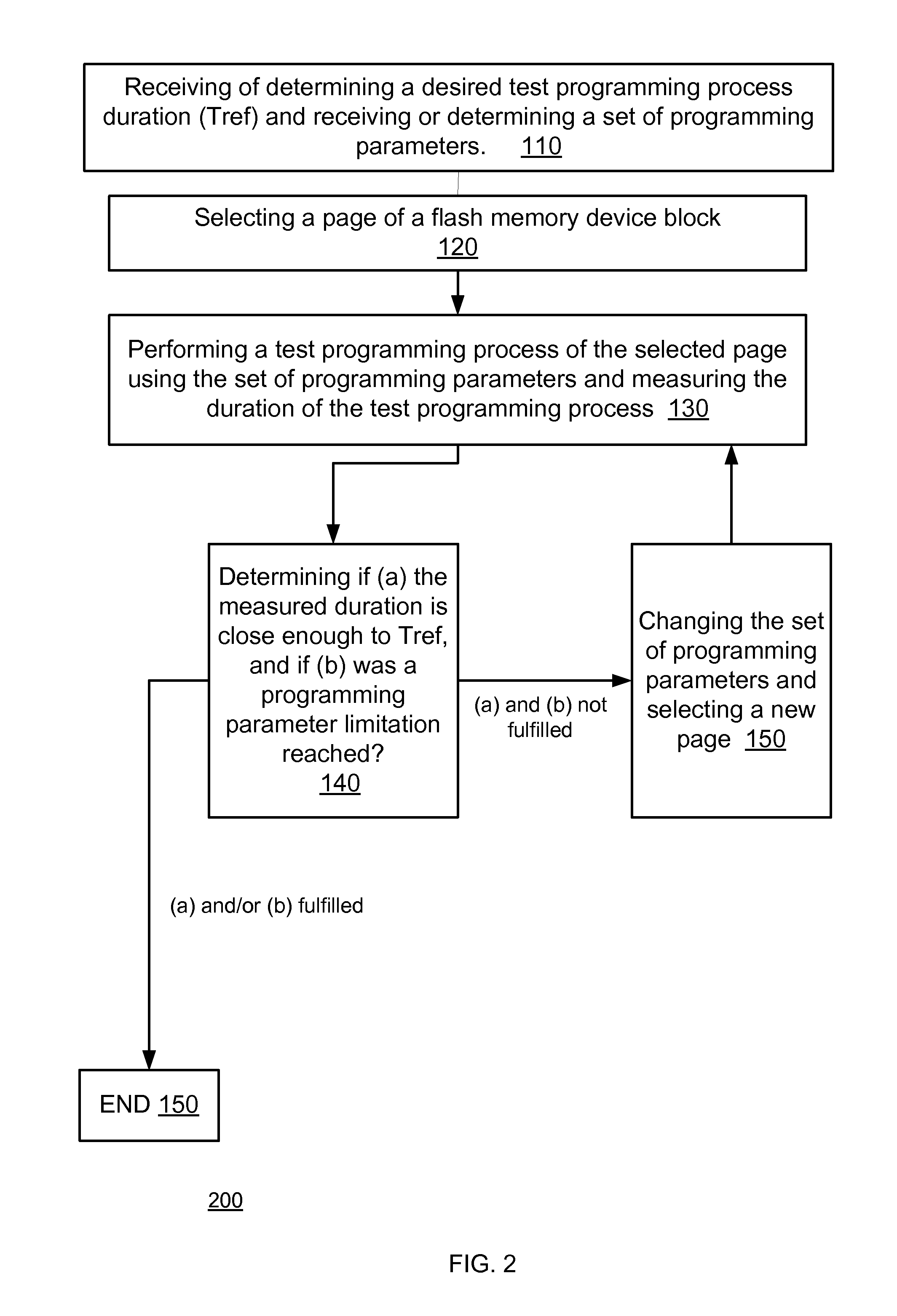

Devices and method for wear estimation based memory management

A system, a non-transitory computer readable medium and a method for wear estimation of a flash memory device, the method may include: programming information to a first portion of the flash memory device during a test programming process; measuring a duration of the test programming process; and estimating a wear characteristic of the first portion of the flash memory device thereby providing an estimated wear characteristic, wherein the estimating is responsive to the duration of the test programming process.

Owner:AVAGO TECH INT SALES PTE LTD

Automated verification of user interface tests on low-end emulators and devices

Testing of computing devices is automated by recording each of the tests once, capturing user interface operations as a record, and then rerunning the tests repetitively and automatically on the same or different instances of the target device, substantially without human intervention. A successful test is indicated by identity of corresponding screens captured from a reference device and the target device.

Owner:ORACLE INT CORP

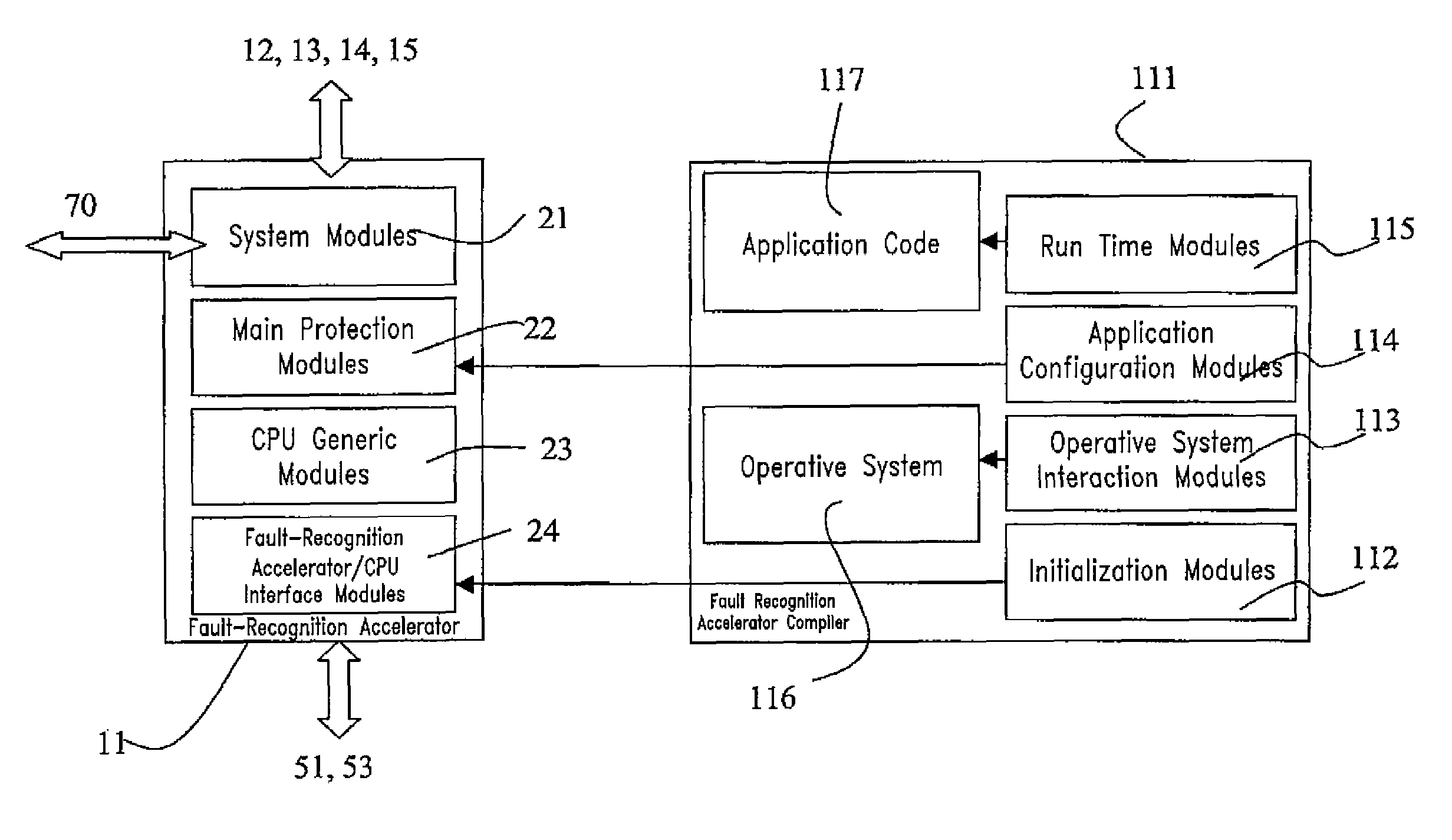

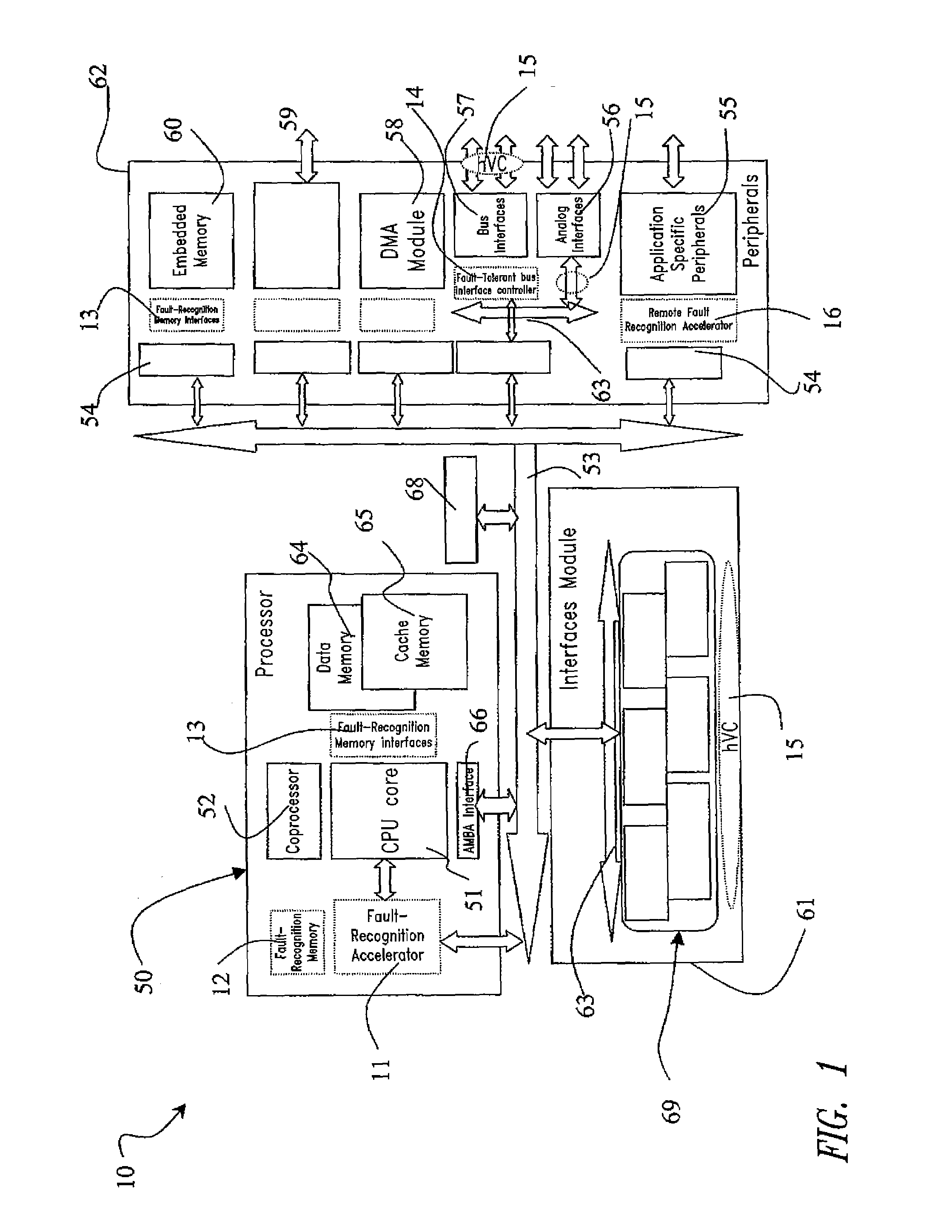

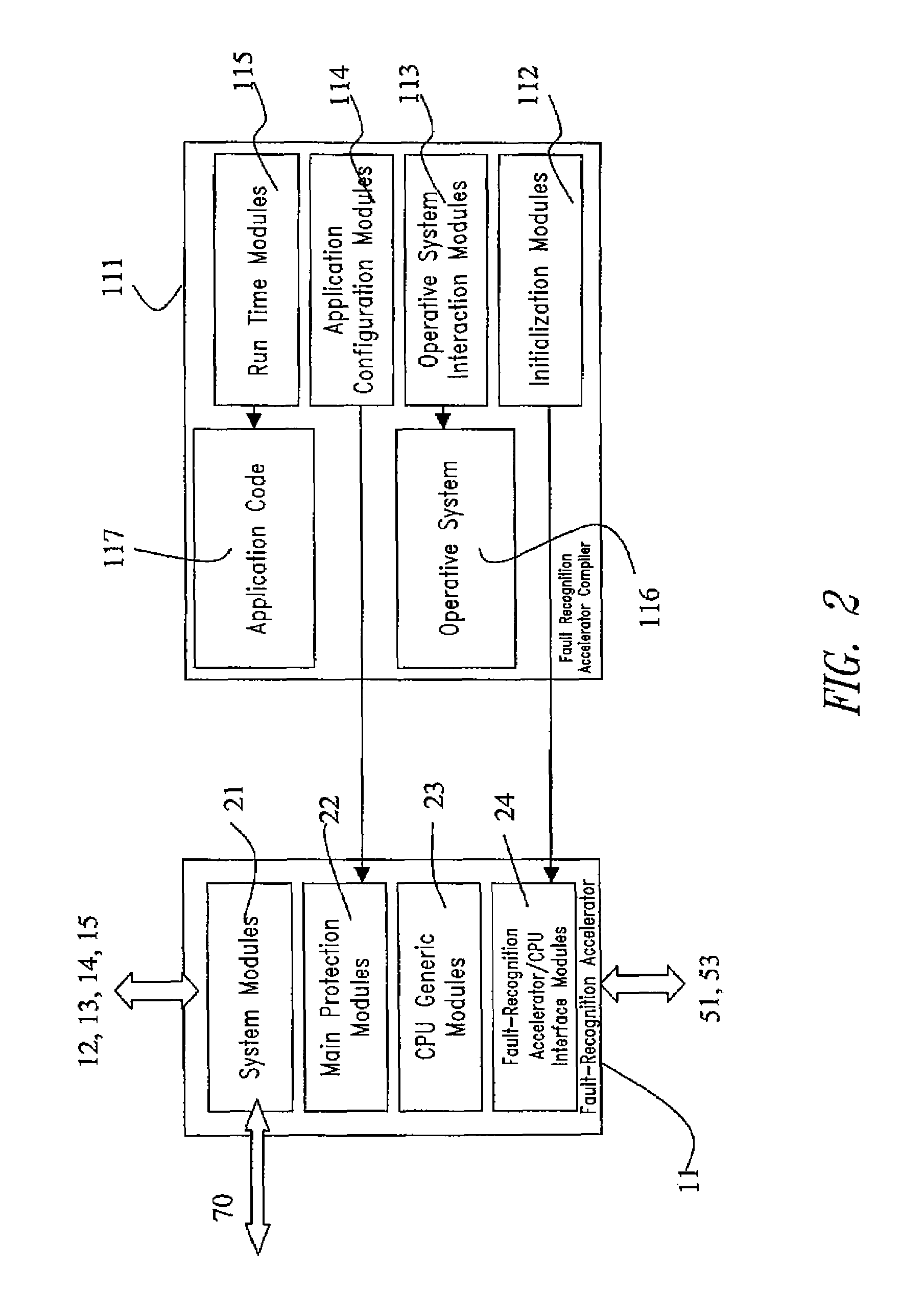

Dependable microcontroller, method for designing a dependable microcontroller and computer program product therefor

ActiveUS7472051B2Improve reliabilityEfficient use ofAnalogue computers for electric apparatusHardware monitoringMicrocontrollerFault tolerance

A microcontroller comprising a central processing unit and a further fault processing unit suitable for performing validation of operations of said central processing unit. The further fault processing unit is external and different with respect to said central processing unit and said further fault processing unit comprises at least a module for performing validation of operations of said central processing unit and one or more modules suitable for performing validation of operations of other functional parts of said microcontroller. Validation of operations of said central processing unit is performed by using one or more of the following fault tolerance techniques: data shadowing; code&flow signature; data processing legality check; addressing legality check; ALU concurrent integrity checking; concurrent mode / interrupt check. The proposed microcontroller is particularly suitable for application in System On Chip (SoC) and was developed by paying specific attention to the possible use in automotive System On Chip. The invention also includes a method for designing and verify such fault-robust system on chip, and a fault-injection technique based on e-language.

Owner:TAHOE RES LTD

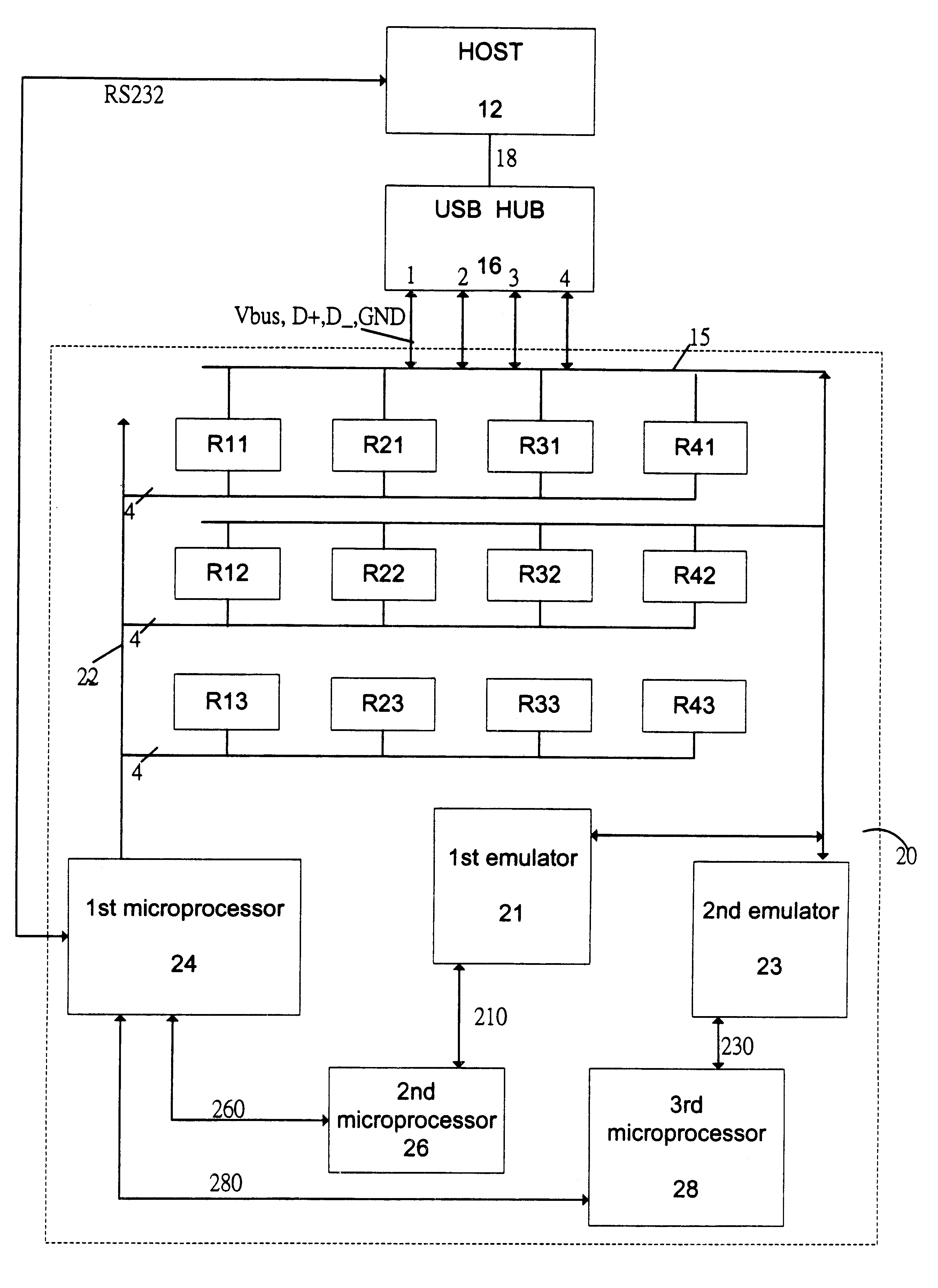

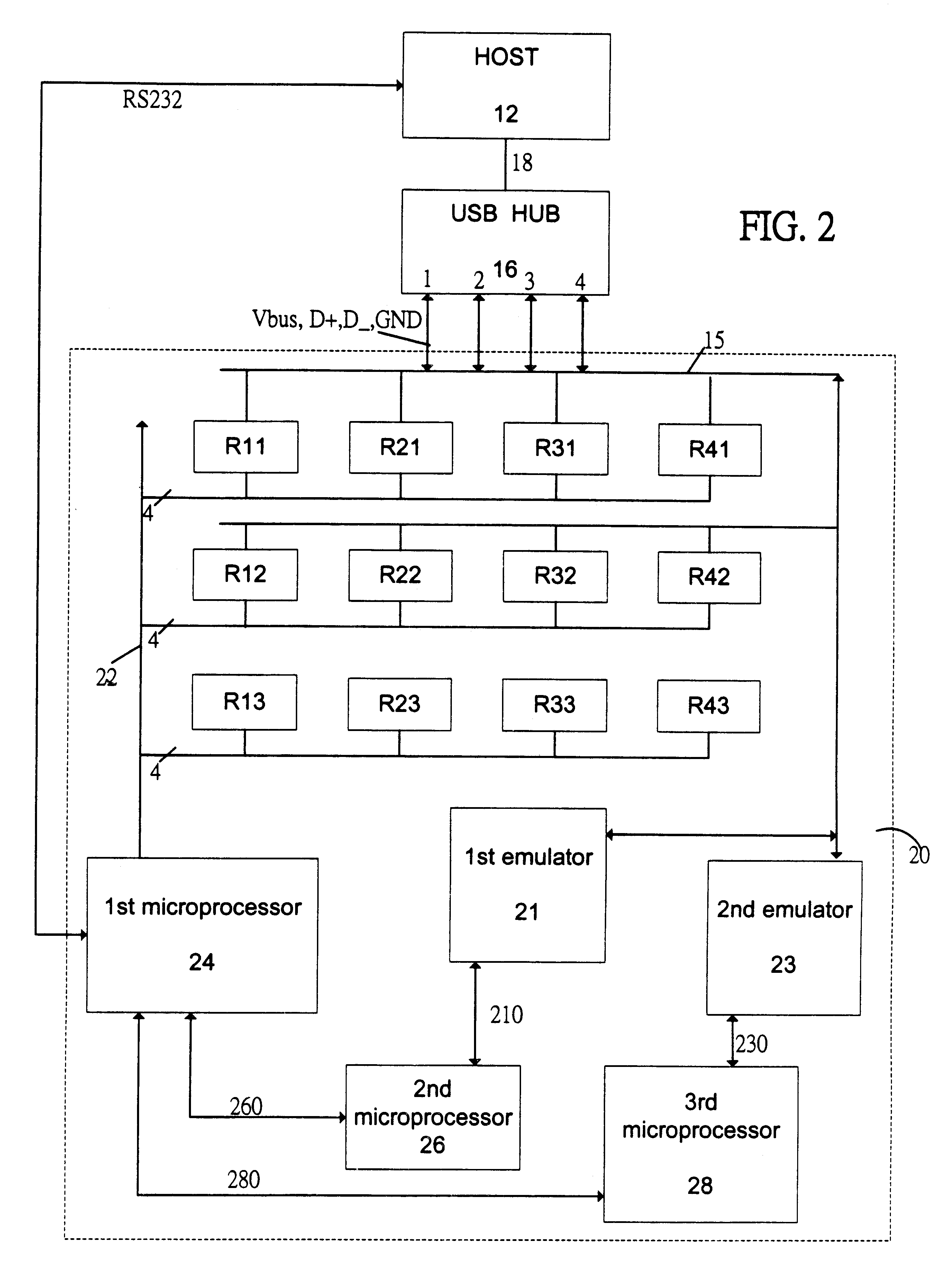

Testing of USB hub

A test apparatus for testing function of a USB hub under the control of a USB host computer is provided. The USB host computer issues a USB command during the test. The test apparatus includes a USB bus, an emulation device, a standard bus and a micro-controller device. The USB bus is coupled to the USB hub. The emulation device emulates an USB device connected to the USB bus. The standard bus is connected to the USB host computer. The micro-controller device is connected to the standard bus and the emulation device respectively to process a USB transaction corresponding to the USB command. The invention provides a testing environment which is fully compliant to the WINDOWS 98 environment.

Owner:WINBOND ELECTRONICS CORP

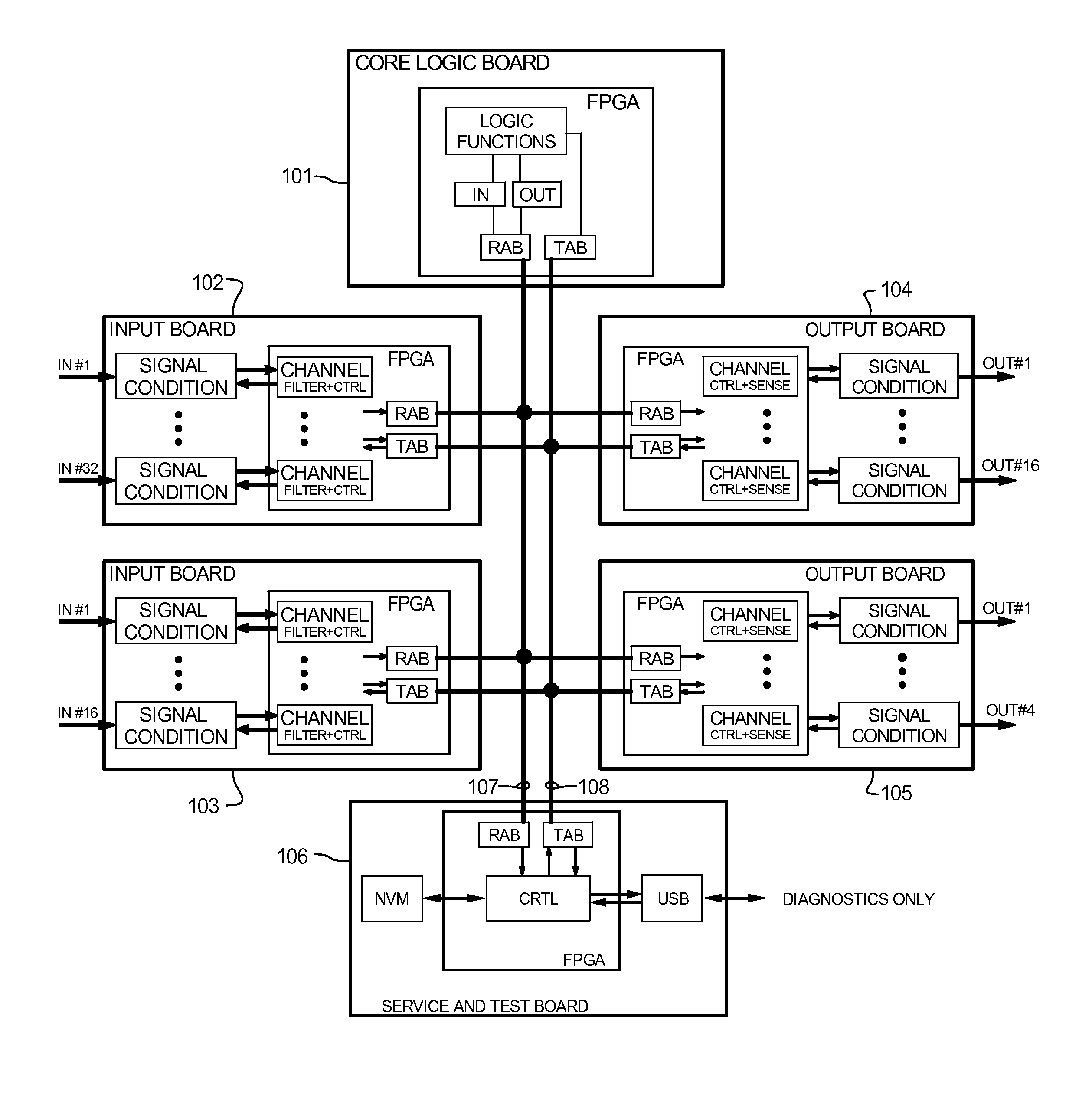

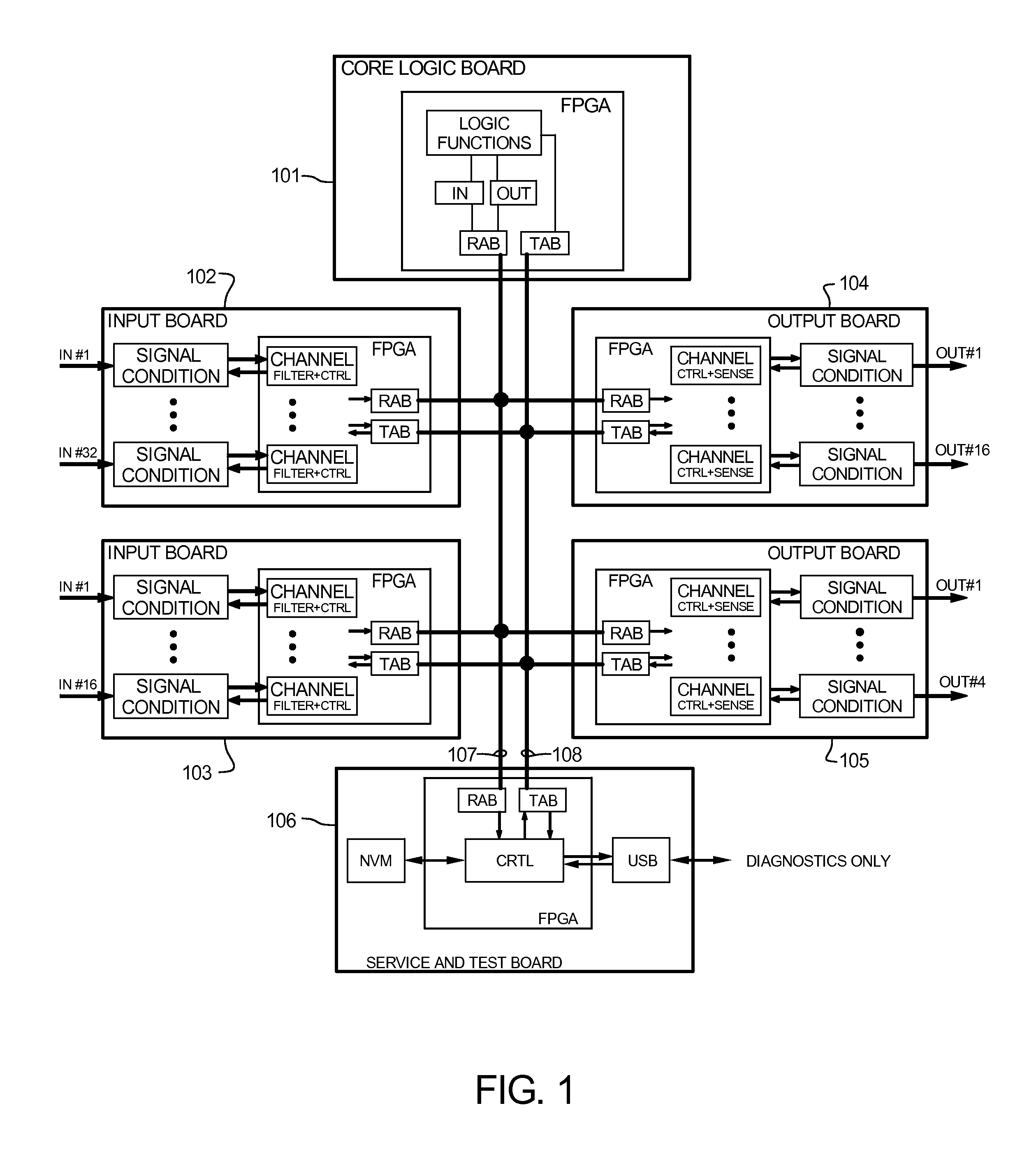

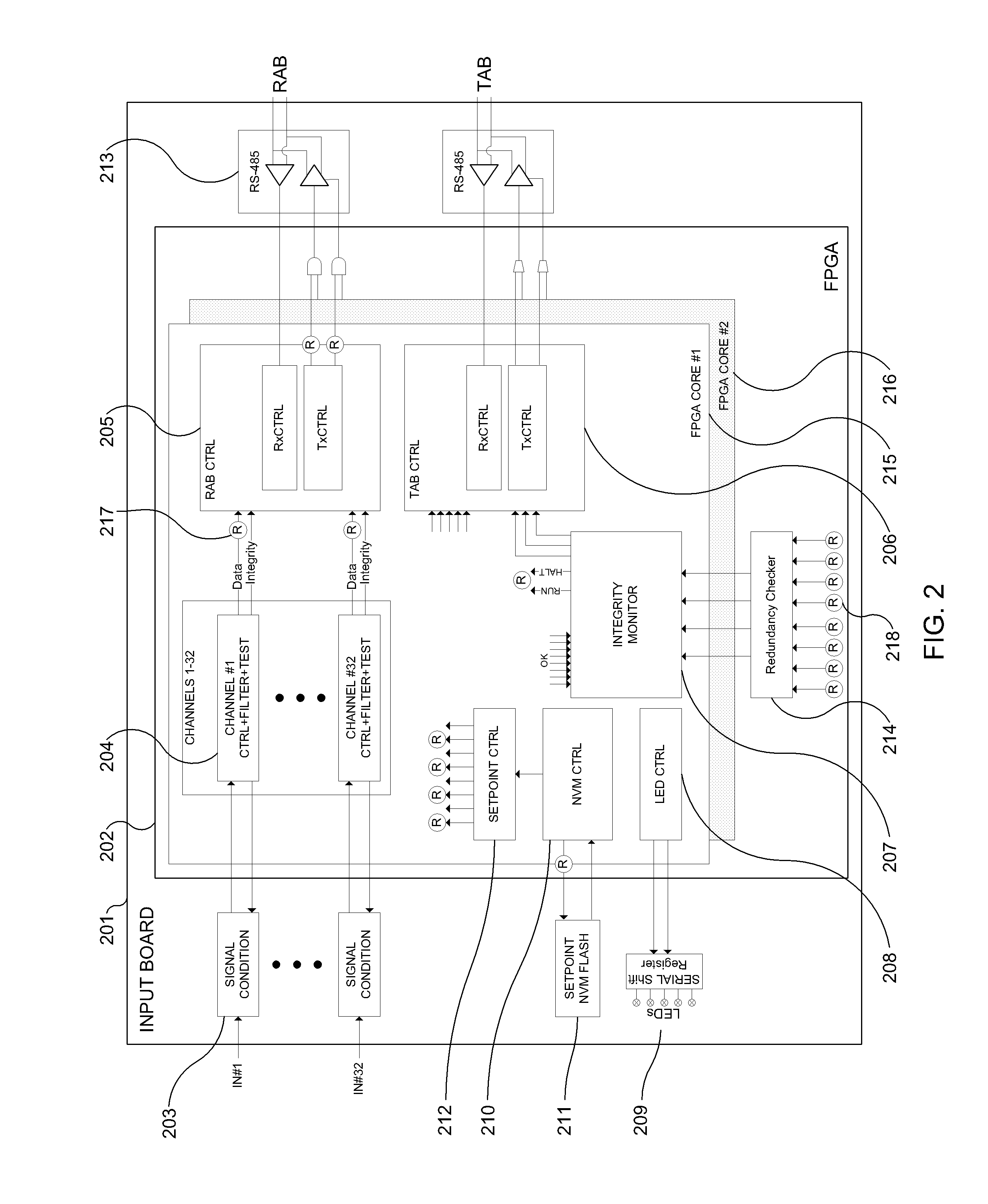

Advanced logic system

ActiveUS7870299B1Improve reliabilityImprove maintainabilityProgramme controlTesting/monitoring control systemsNuclear plantCommon mode failure

The Advanced Logic System (ALS) is a complete control system architecture, based on a hardware platform rather than a software-based microprocessor system. It is significantly different from other PLC-type control system architectures, by implementing a FPGA in the central control unit. Standard FPGA logic circuits are used rather than a software-based microprocessor which eliminate problems with software based microprocessor systems, such as software common-mode failures. It provides a highly reliable system suitable for safety critical control systems, including nuclear plant protection systems. The system samples process inputs, provides for digital bus communications, applies a control logic function, and provides for controlled outputs. The architecture incorporates advanced features such as diagnostics, testability, and redundancy on multiple levels. It additionally provides significant improvements in failure detection, isolation, and mitigation for the highest level of integrity and reliability.

Owner:WESTINGHOUSE ELECTRIC CORP

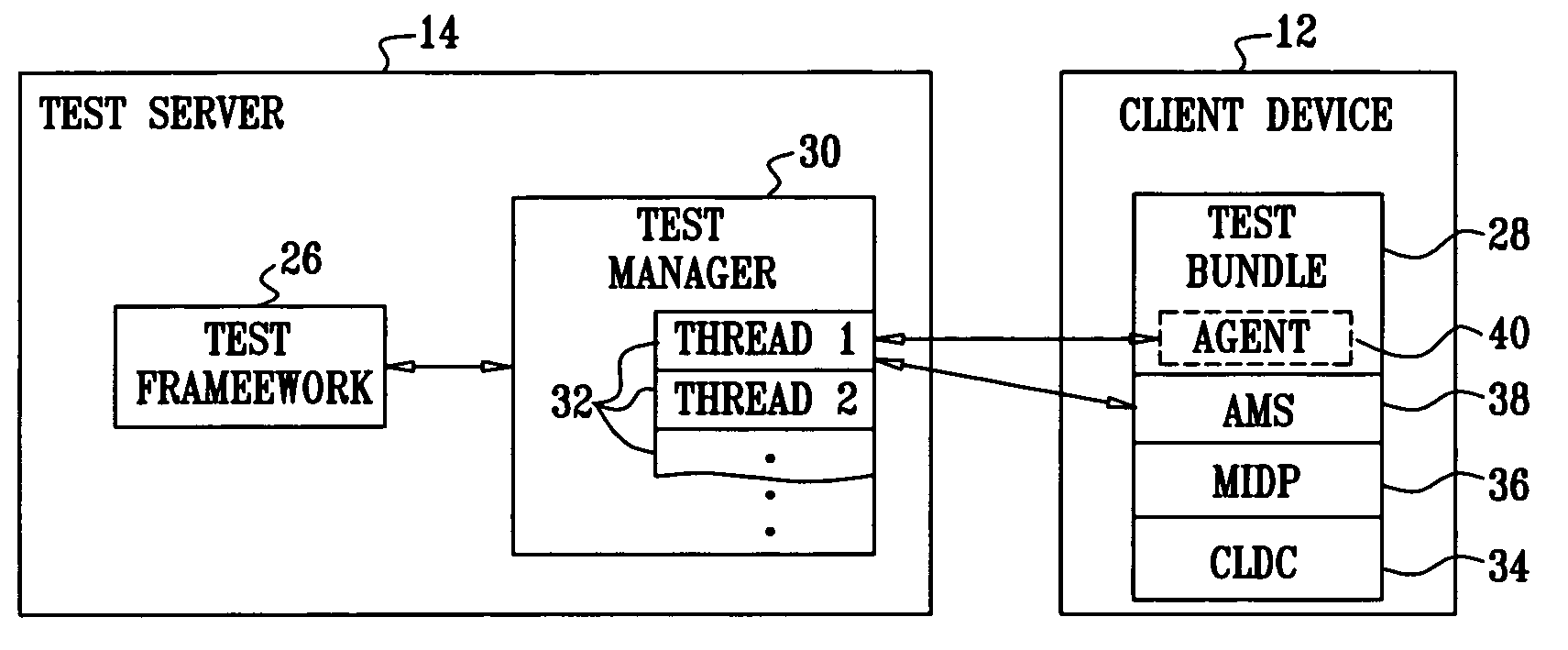

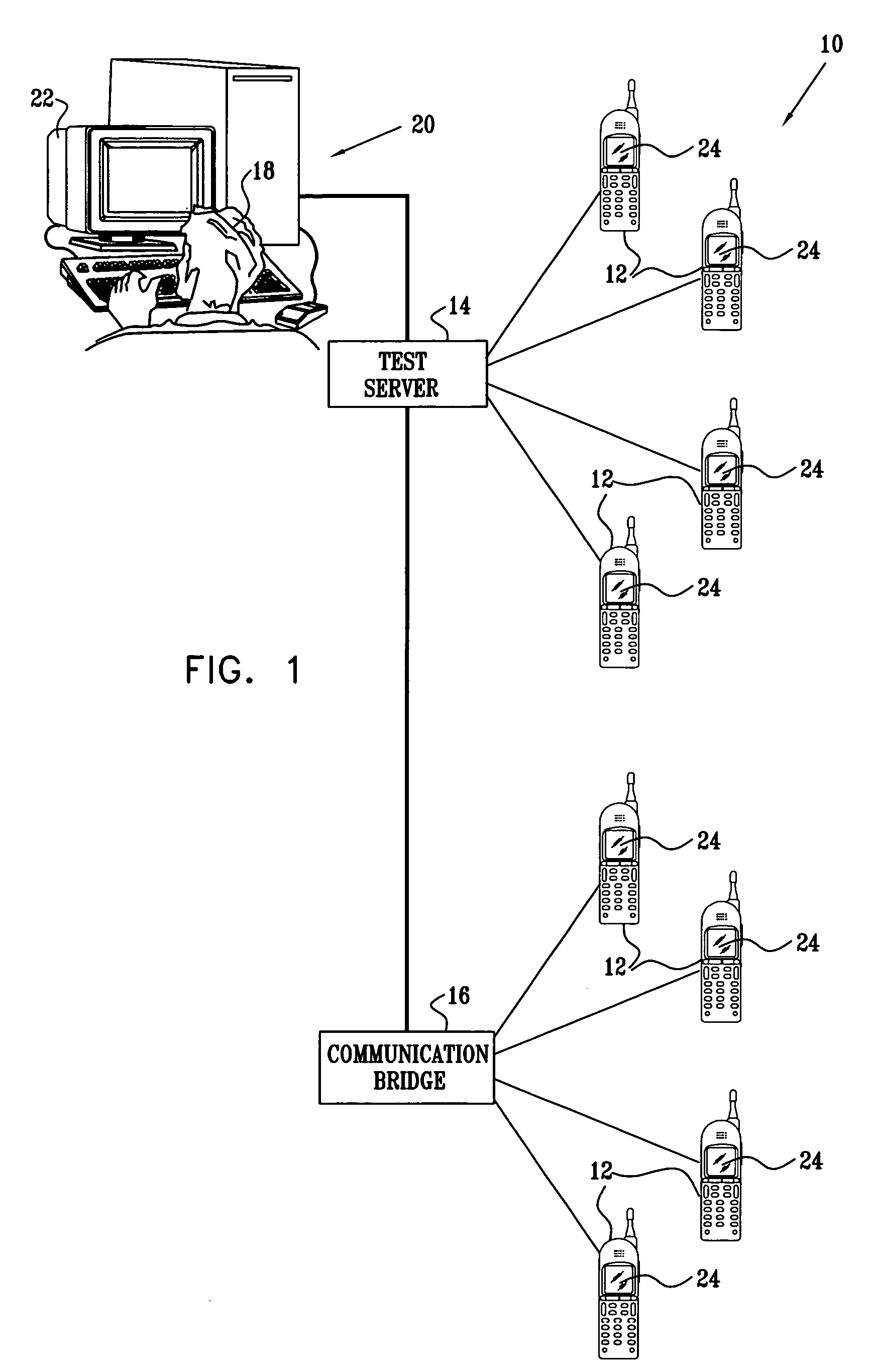

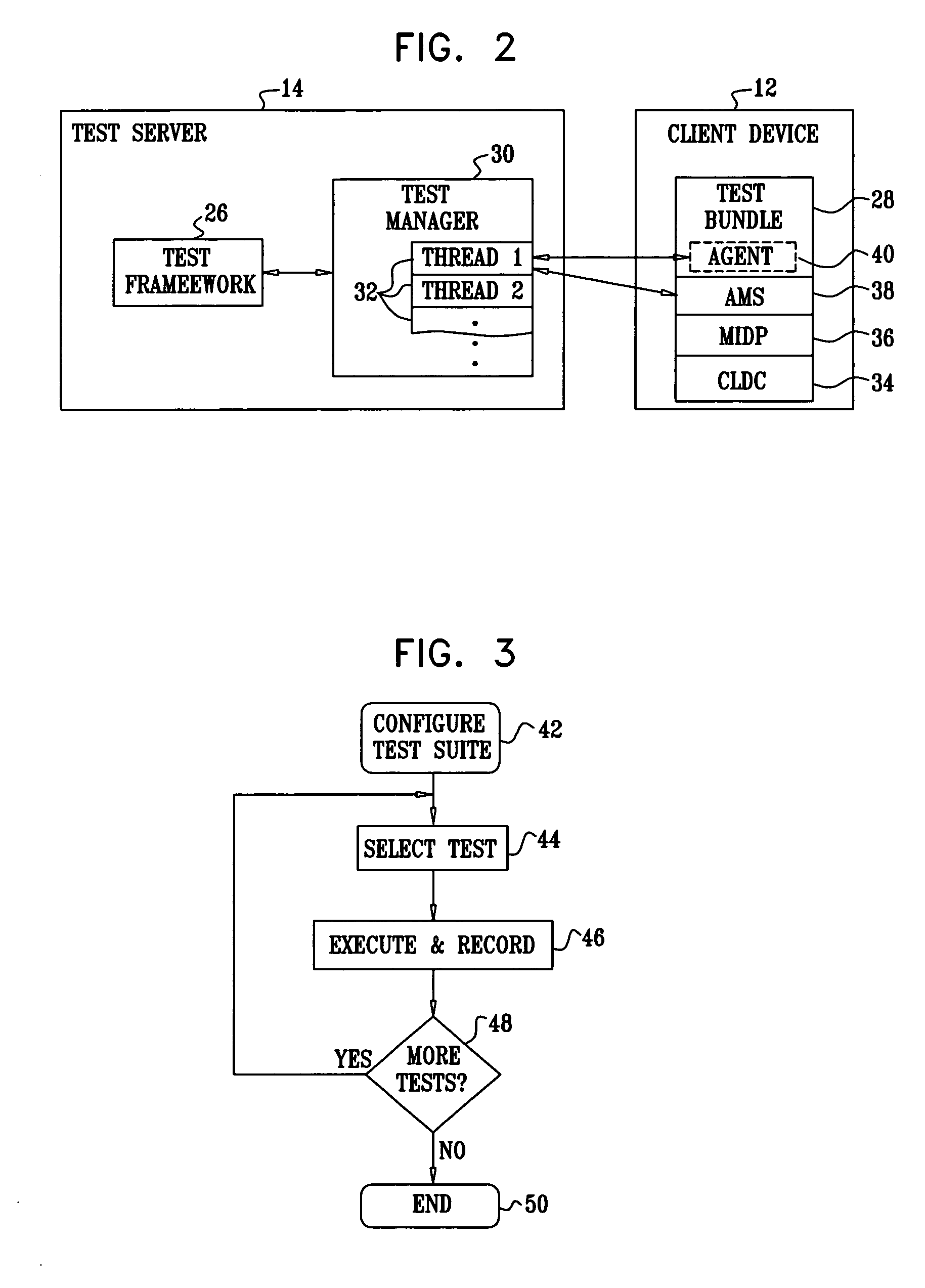

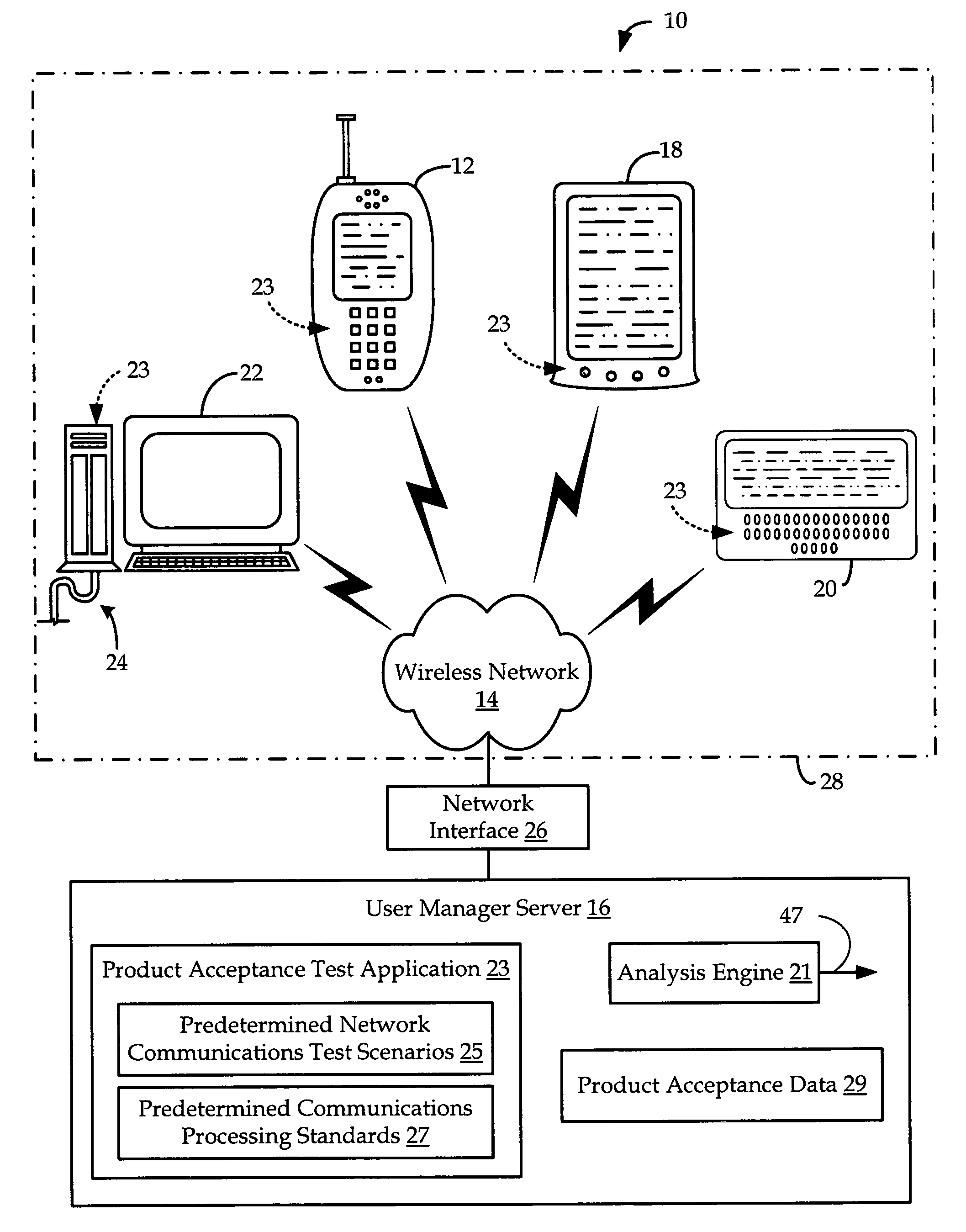

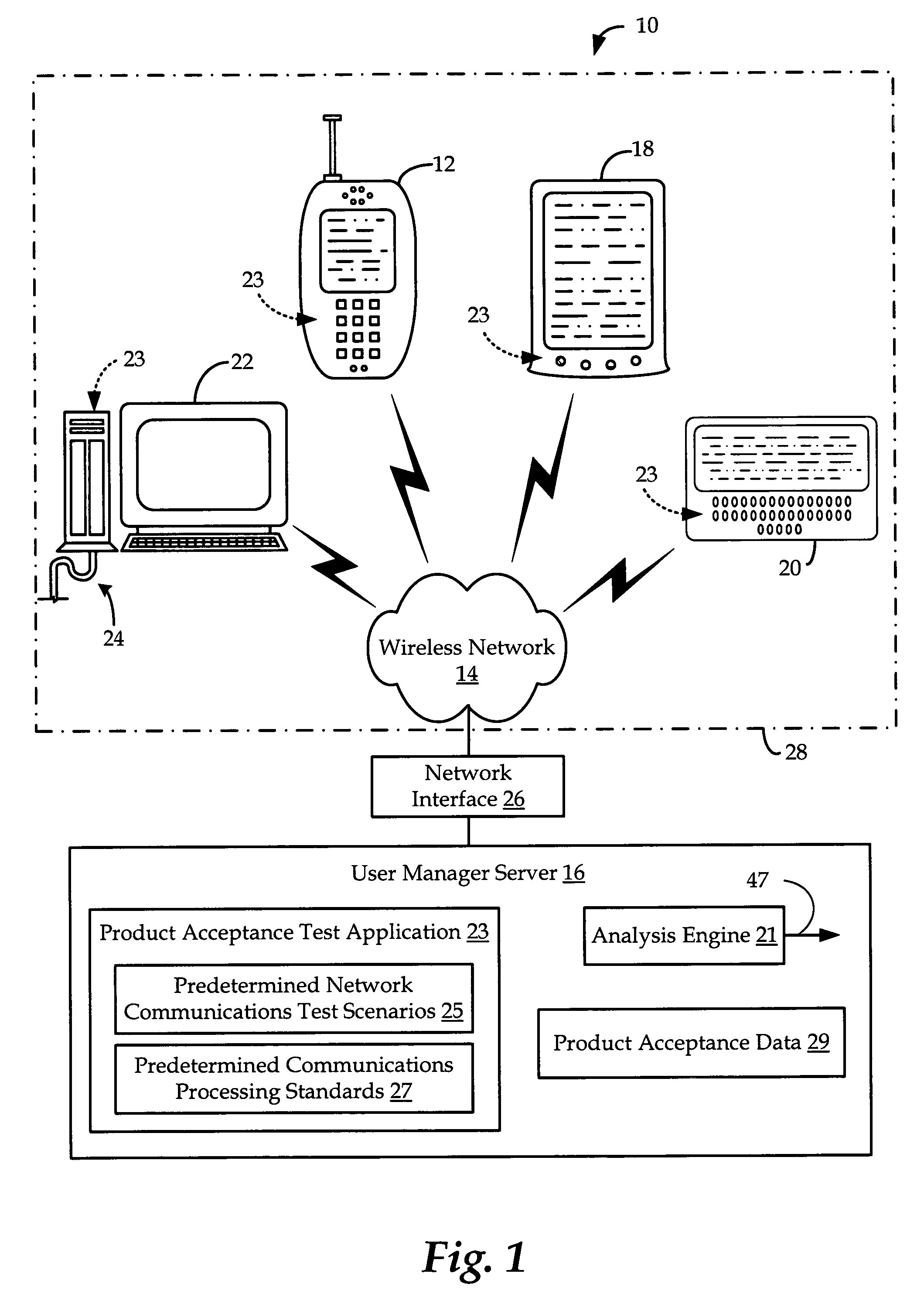

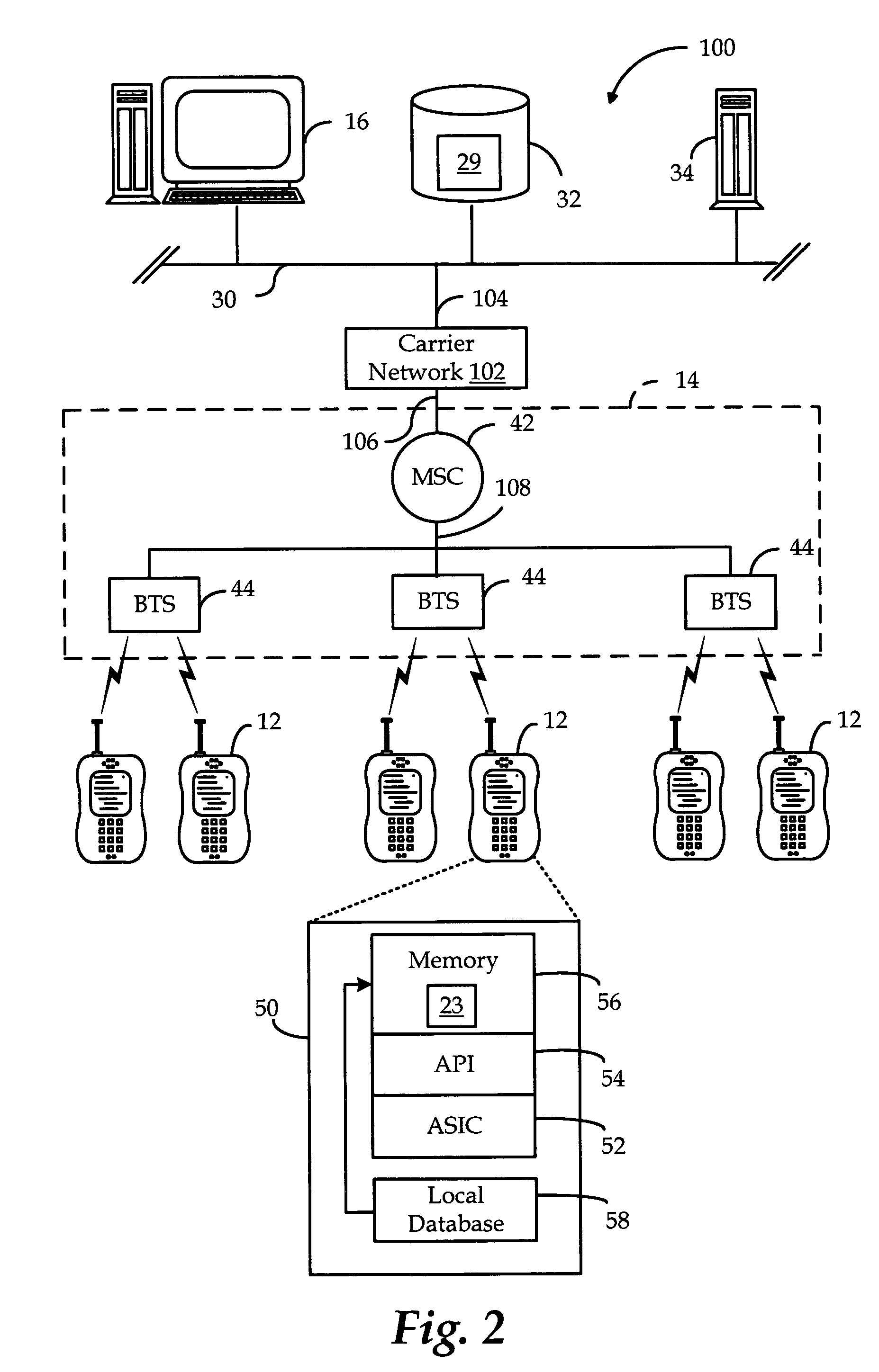

Apparatus and methods for product acceptance testing on a wireless device

InactiveUS20060205398A1Functional testingSoftware testing/debuggingAcceptance testingWireless network

Apparatus, methods, and programs for testing the communications processing ability, and determining product acceptance, of a wireless device. Embodiments include a product acceptance test application disposed on the wireless device and including simulated communications representative of actual communications with a wireless network. A communications processing engine disposed on the wireless device is operable to process the simulated communications, and thereby generates product acceptance data associated with a product acceptance decision.

Owner:QUALCOMM INC

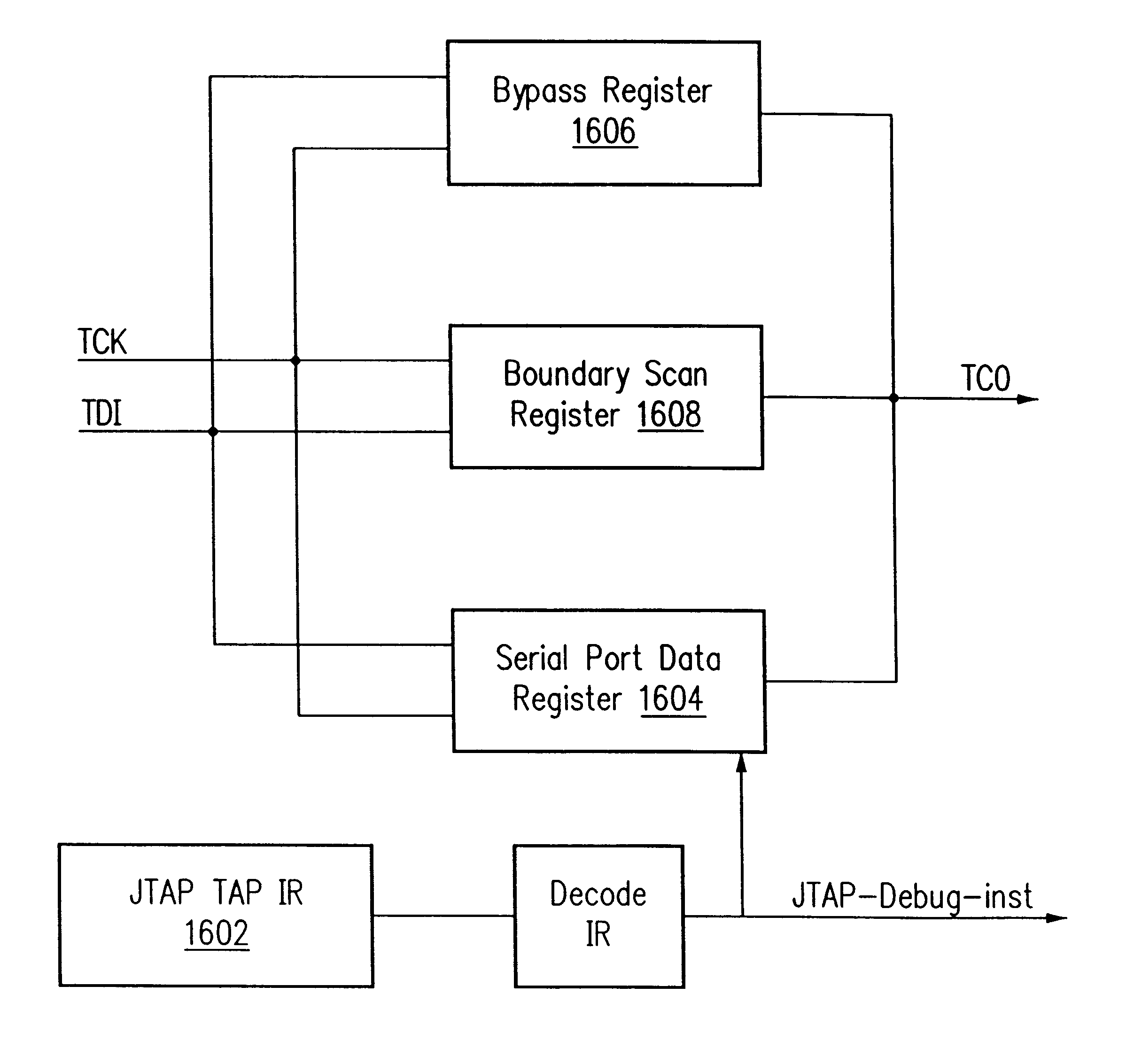

Debug interface including state machines for timing synchronization and communication

A system for debugging a processor includes logic circuits for communicating commands and data between a serial input / output port, a trace logic, and the processor. Some embodiments of the debugging system also include a parallel input / output port so that the logic circuits also communicate commands and data between the parallel input / output port, the trace logic, and the processor. The debug system includes a plurality of state machines that read the commands and data from the serial input / output ports. The commands are decoded by a decode logic. Some of the commands, such as commands for reading data from memory, utilize processor intervention and are transferred to the processor for execution. The state machines operate only on a single command at one time so that an active state machine does not accept additional commands until completion of the command that is currently executed. Once execution of the command is complete, the state machines generate an indication of the completion event or condition, typically by setting a flag in a debug register or by asserting a readable output pin. The completion event or condition is accessed by a debug tool such as a host processor, a monitoring tool, or the like.

Owner:ADVANCED MICRO DEVICES INC

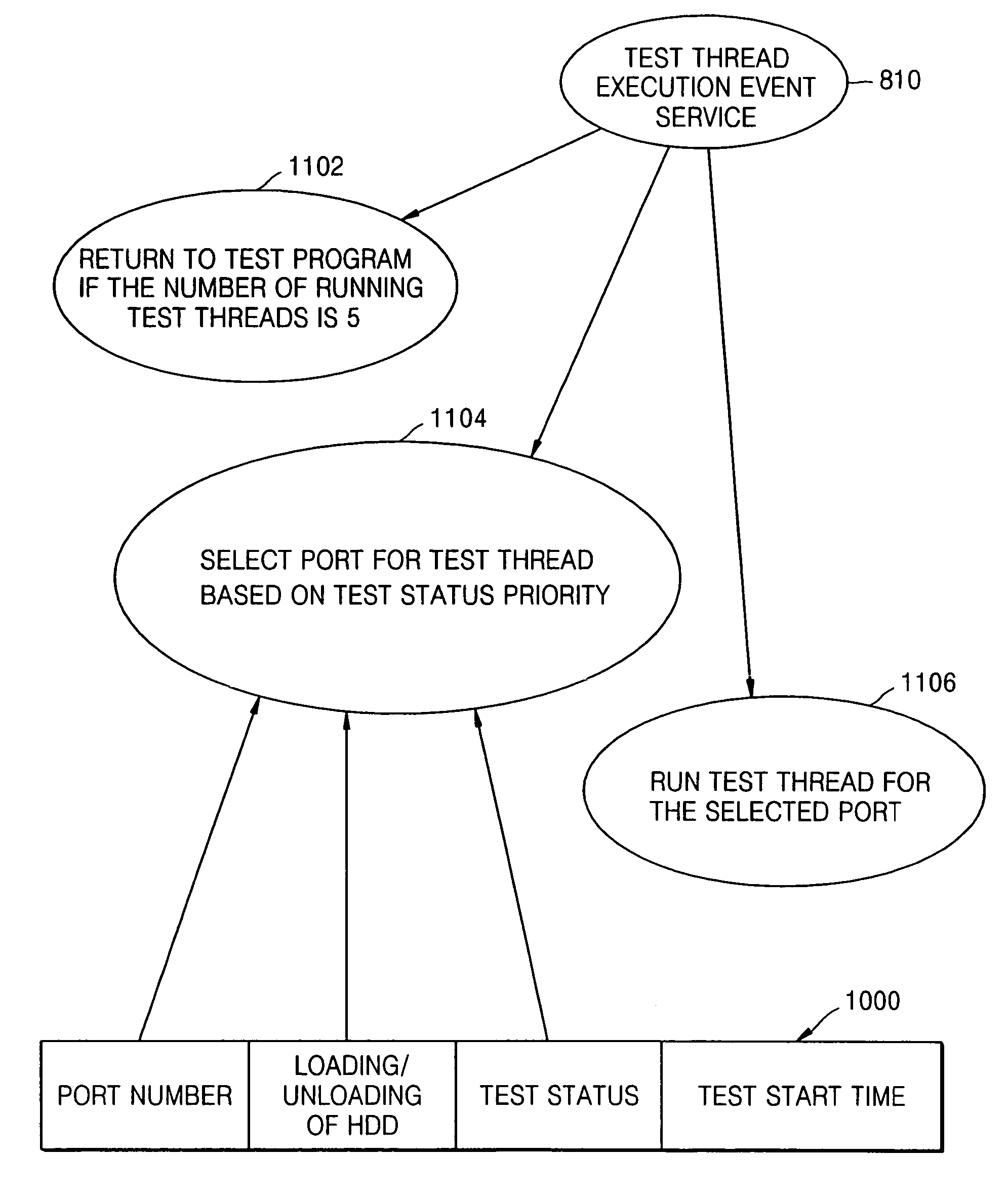

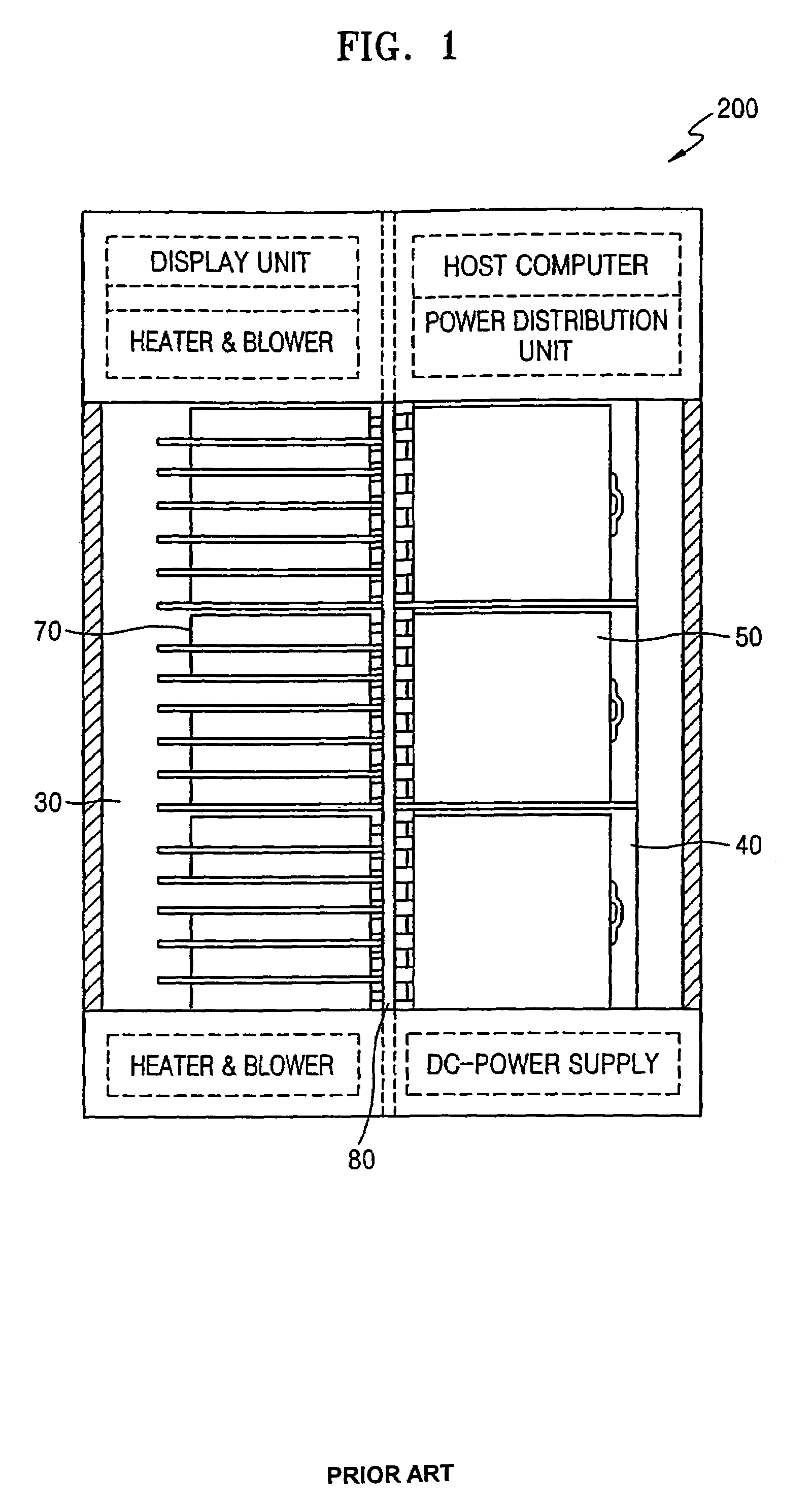

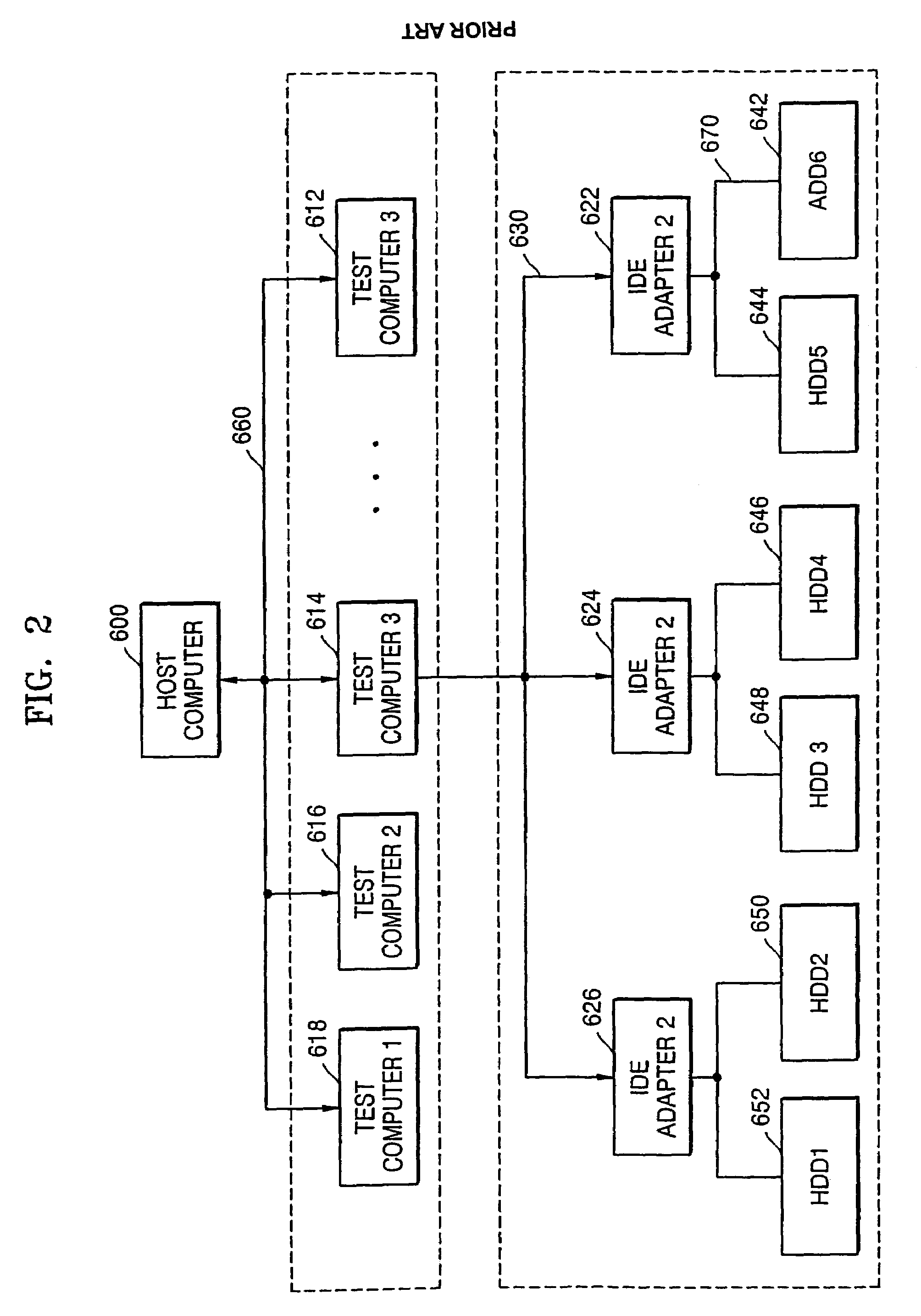

Method of testing hard disk drive and computer readable medium therefor

A method of testing a plurality of devices, such as hard disk drives, in response to a random request by checking whether hard disk drive have been loaded, and sequentially allocating one test thread for each loaded hard disk drive. Each allocated thread performs a series of test job operations one by one when called and required for testing the loaded hard disk drive, and records a test status of each hard disk drive whenever one job operation of the test by the test thread is terminated to allow a next test thread to refer to the recorded test status. Each hard disk drive is tested according to a time required to test that hard disk drive.

Owner:SAMSUNG ELECTRONICS CO LTD

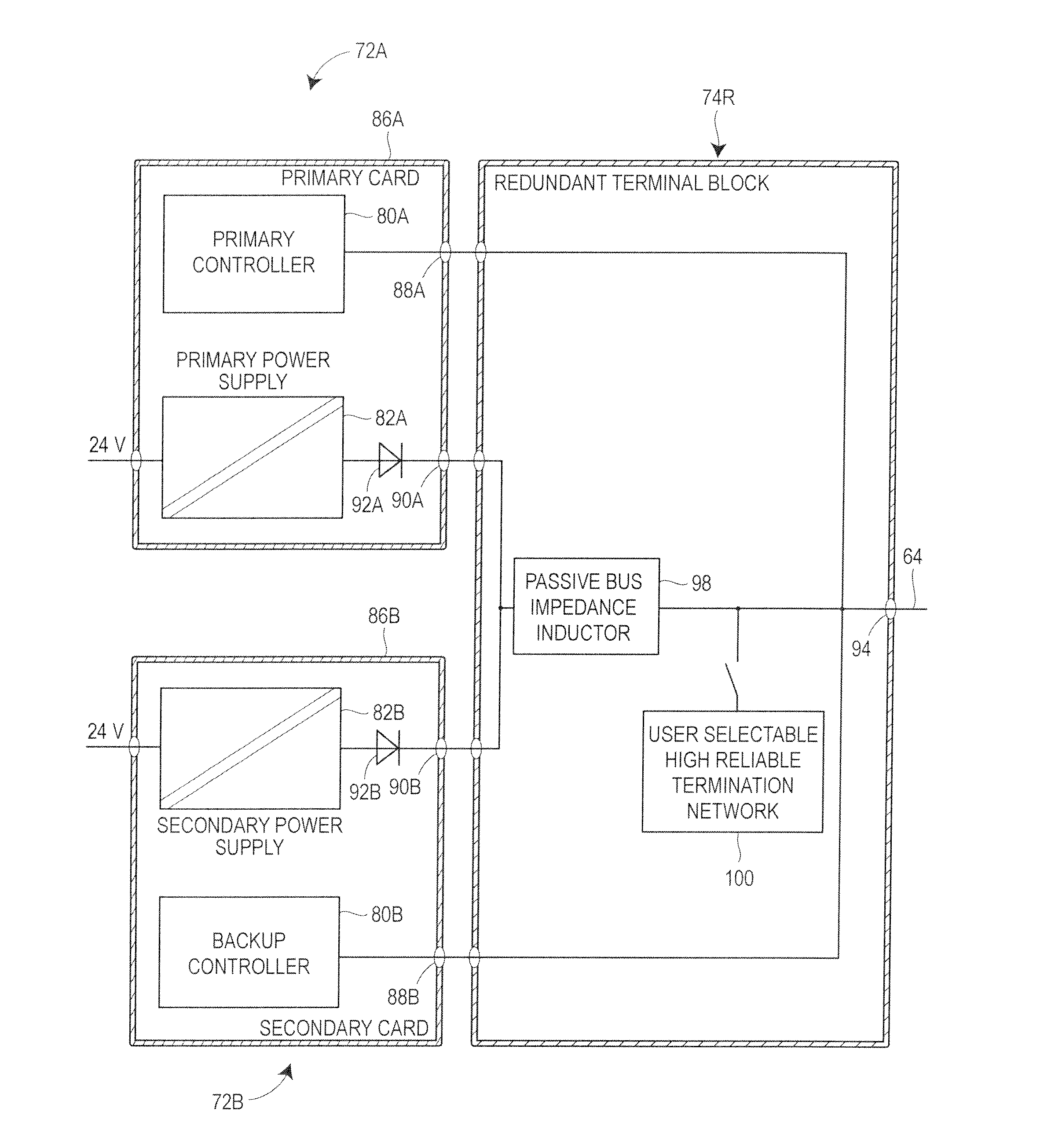

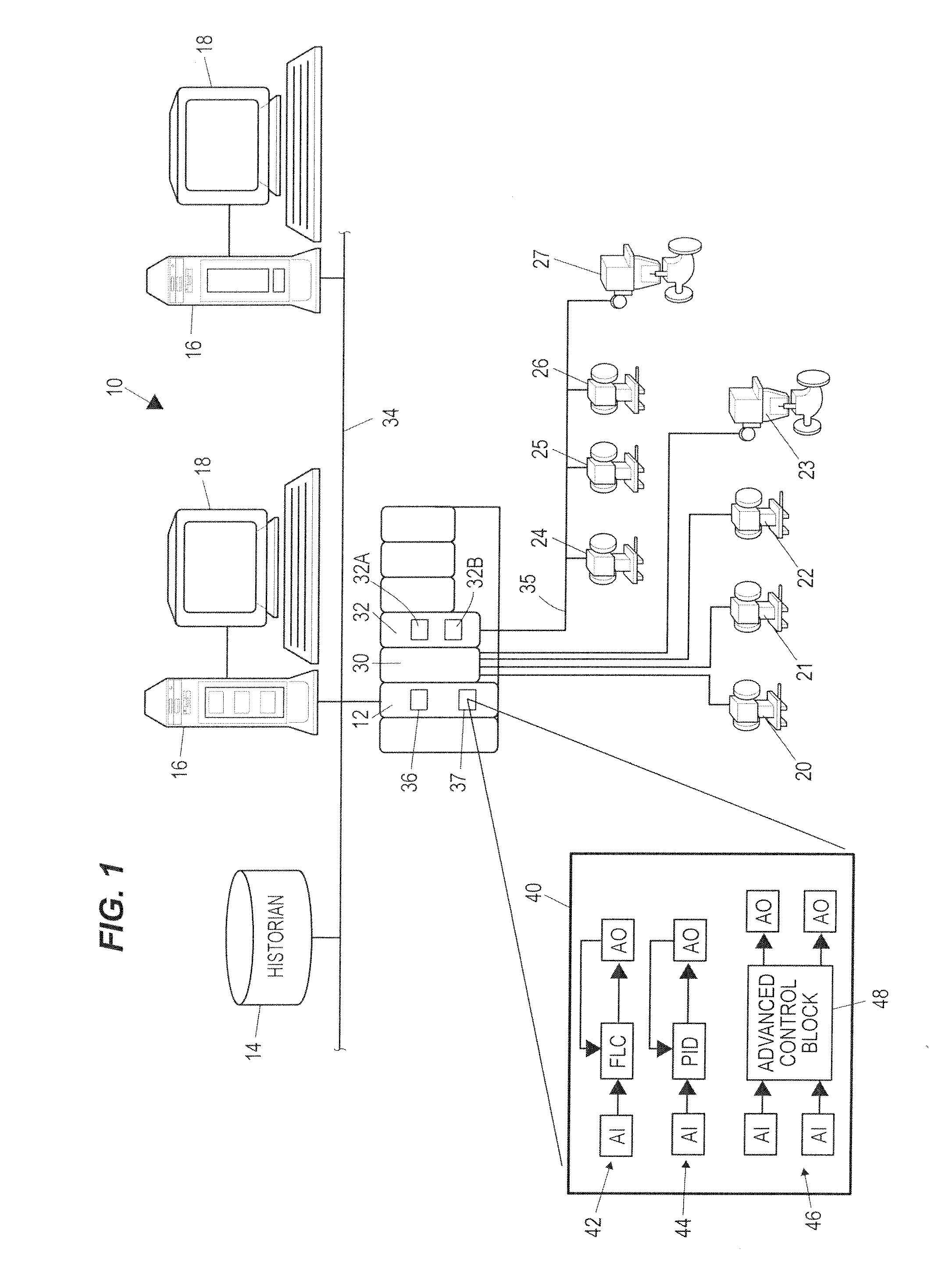

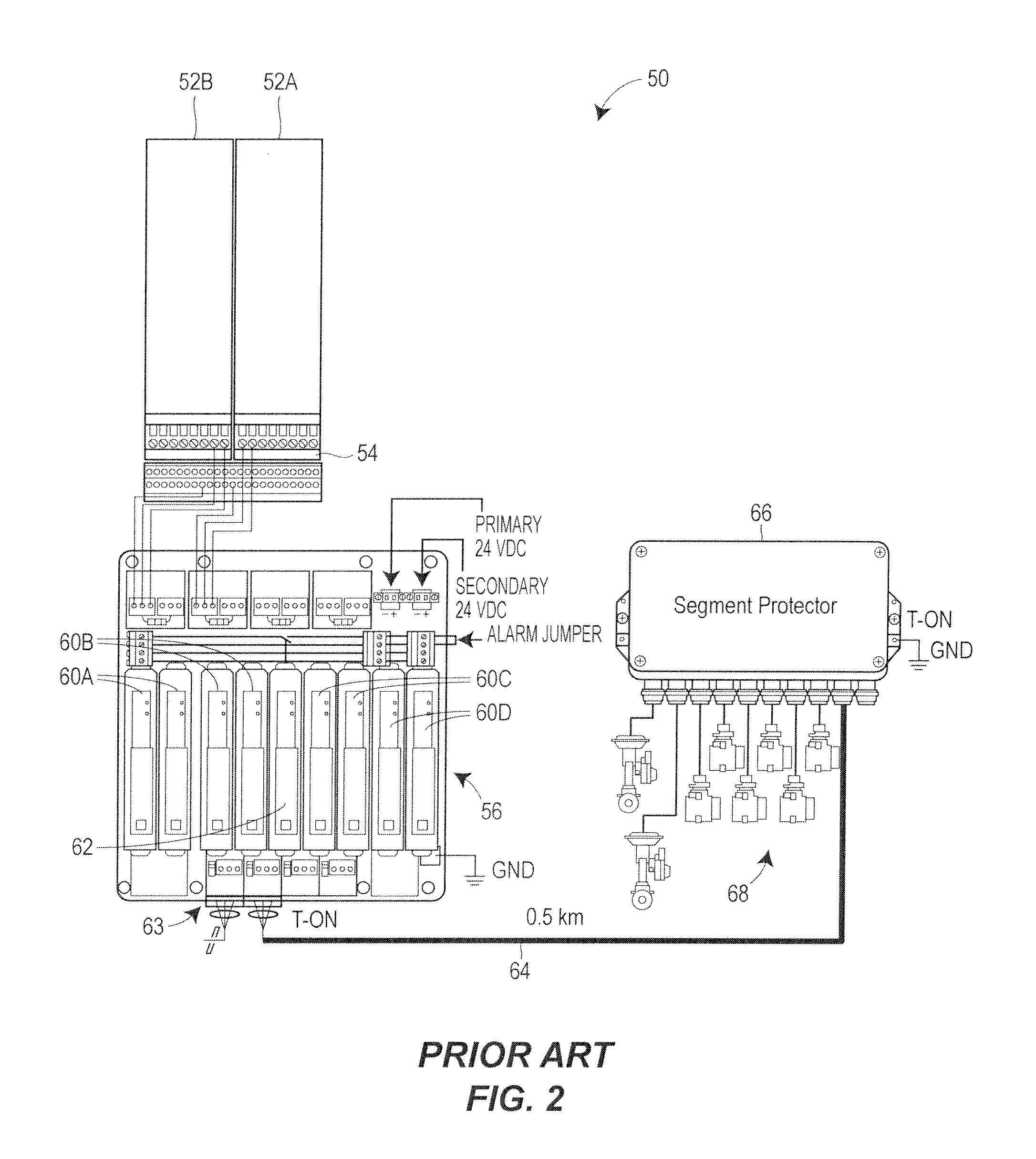

Integrated bus controller and power supply device for use in a process control system

ActiveUS20110131455A1Reducing wire neededReduce configurationProgramme controlVolume/mass flow measurementControl systemPower strip

An integrated bus controller and power supply device includes a typical or standard bus controller and a bus power supply disposed in a common housing, the size and external configuration of which may match a standard bus controller device associated with a typical I / O communication network. The bus controller may store and implement one or more control routines using one or more field devices connected to the I / O communication network while the bus power supply generates and provides the appropriate power signal to the bus of the I / O communication network, the power signal being used to power the field devices connected to the I / O communication network. The integrated bus controller and power supply device can be easily connected to the bus of the I / O communication network to provide both bus controller functionality and bus power supply functionality on the I / O communication network, without the need of configuring and attaching separate, dedicated bus controller and power supply devices to the bus and having to wire these devices together using multiple different terminal blocks.

Owner:FISHER-ROSEMOUNT SYST INC

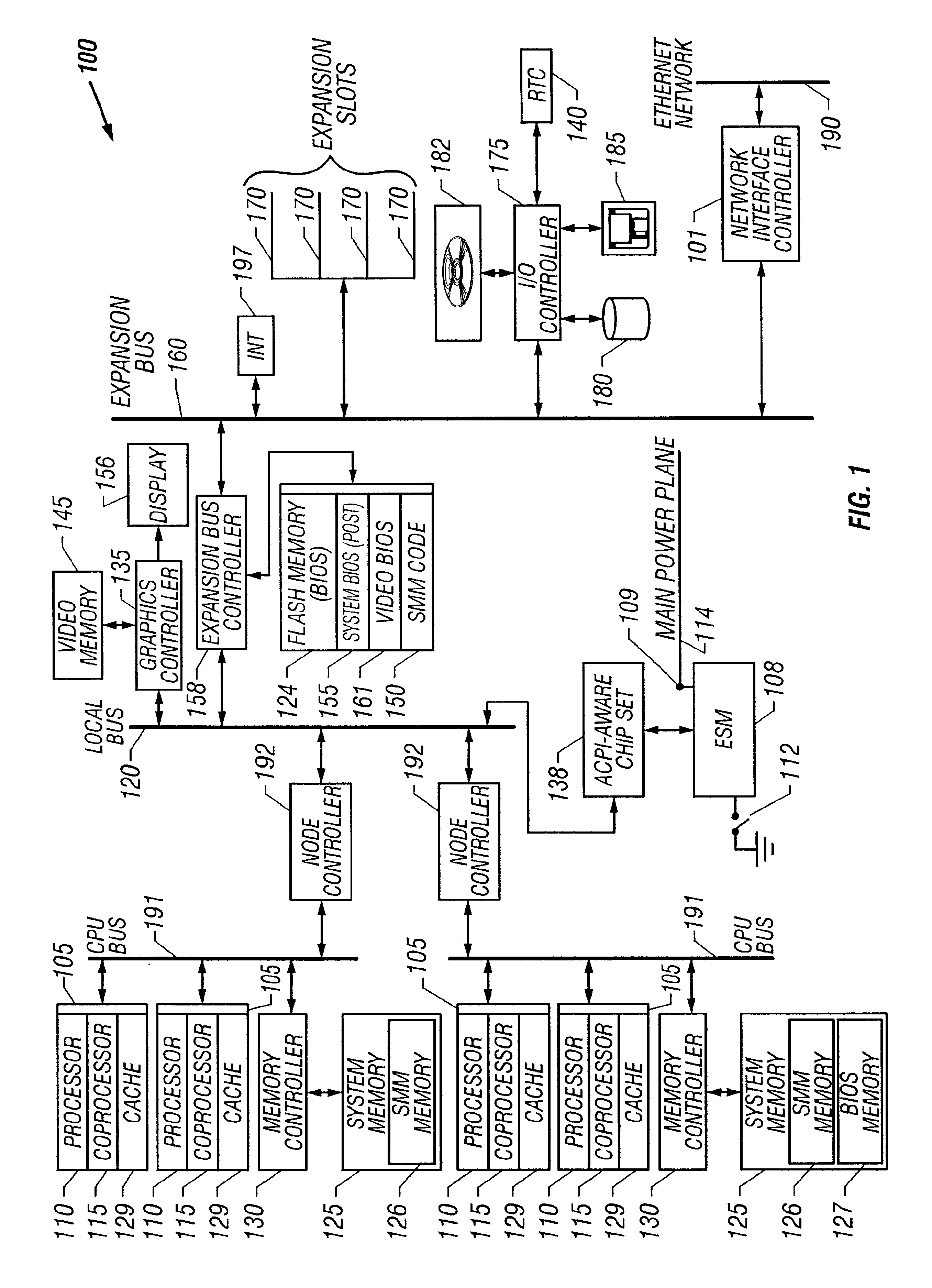

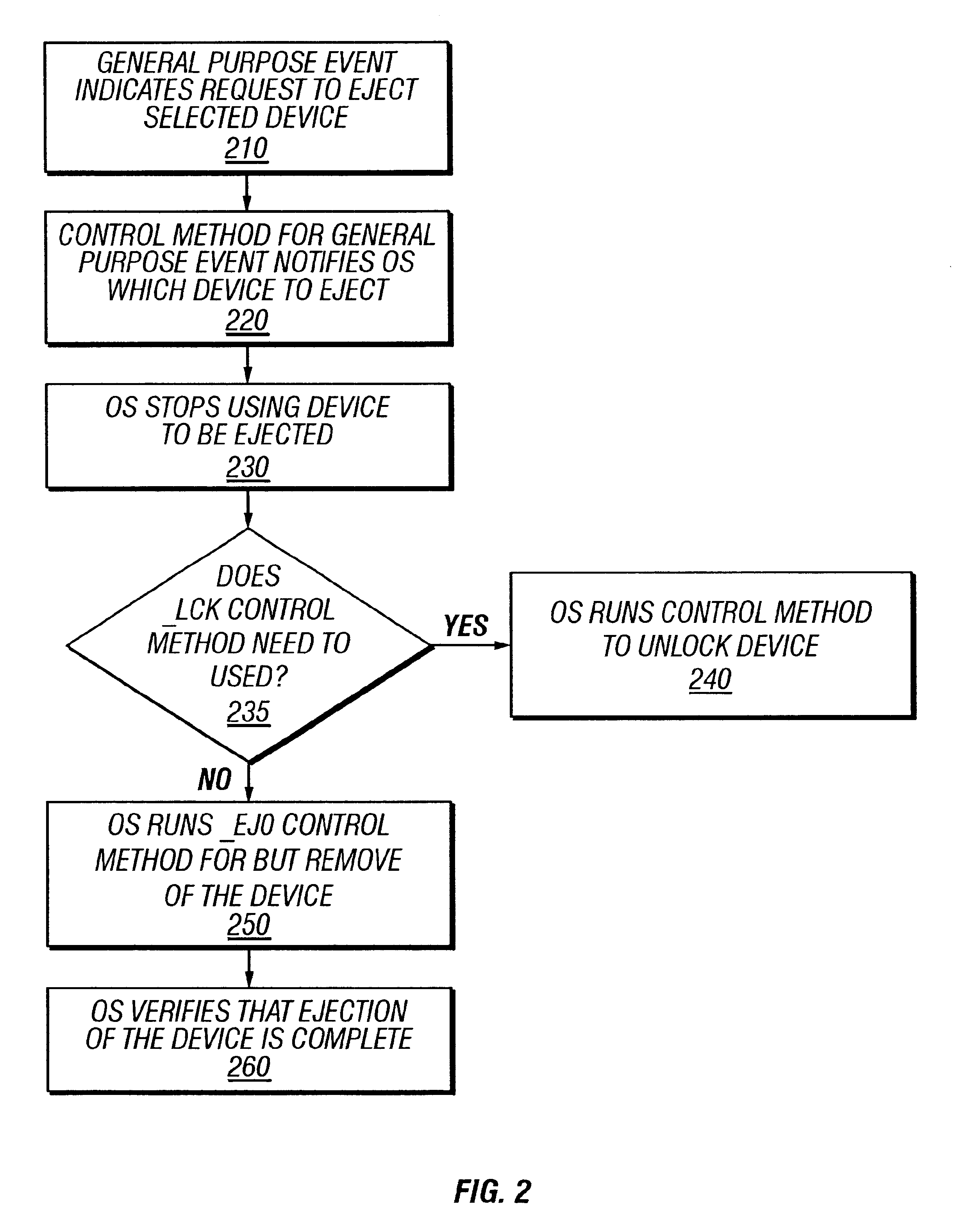

Performing diagnostic tests of computer devices while operating system is running

A system and method of performing diagnostic tests of computer devices, including but not limited to memory, while the operating system is running, is presented. One embodiment comprises making a device unavailable for use by a running operating system; making a processor unavailable for use by the running operating system; and running a diagnostic test of the device, the processor executing the diagnostic test to determine whether the device is functioning acceptably, while the processor and the device are unavailable for use by the running operating system.

Owner:DELL PROD LP

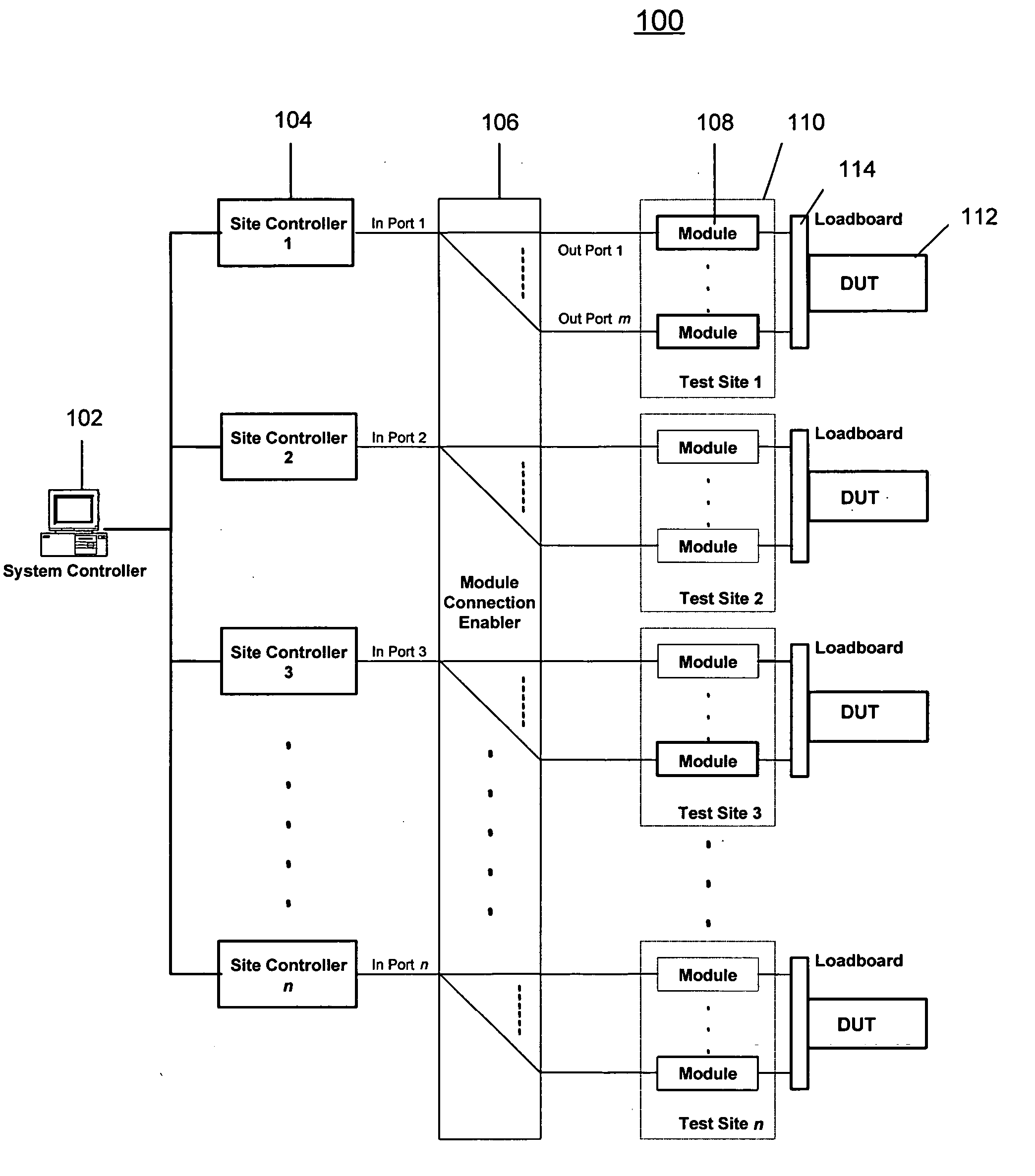

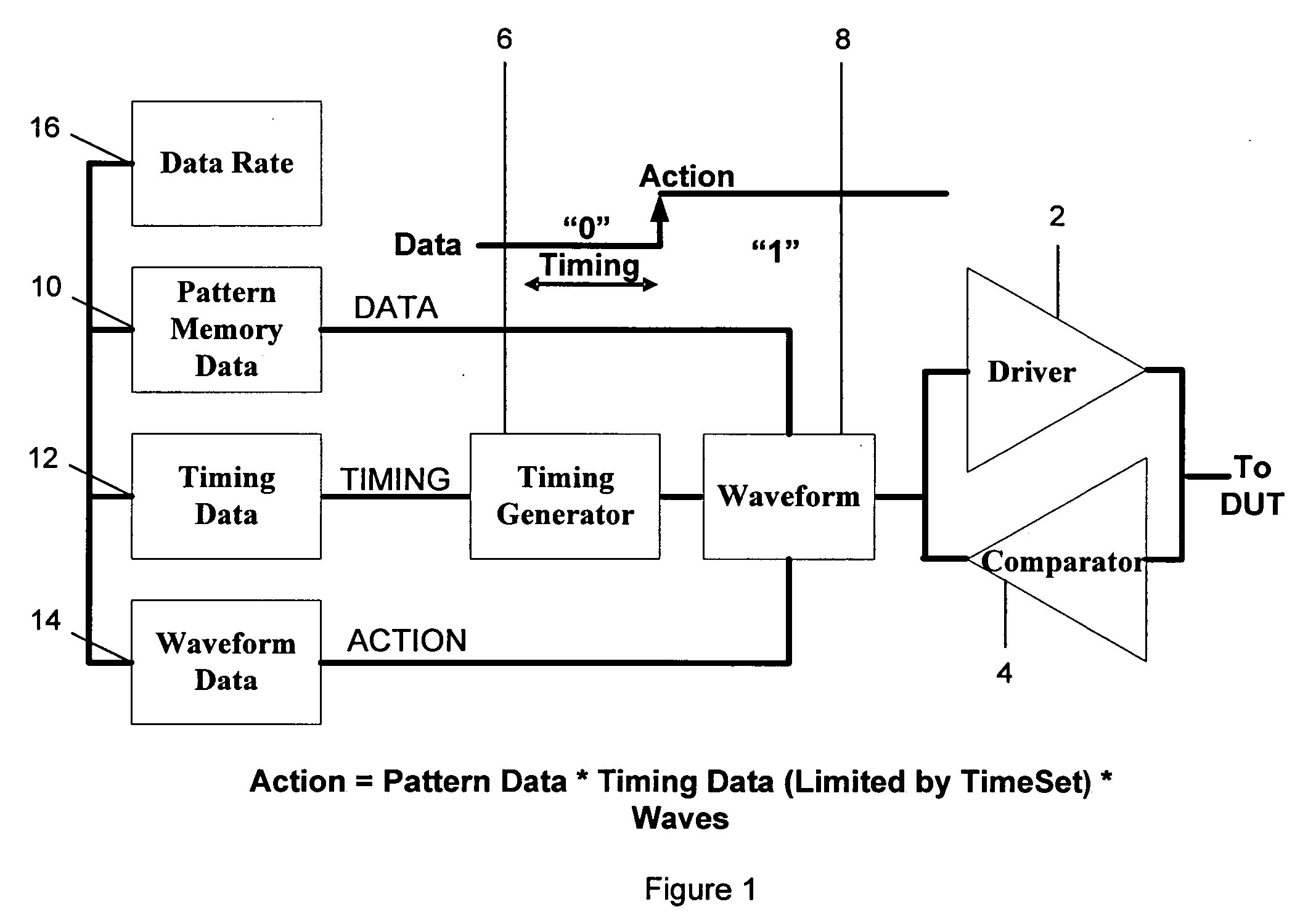

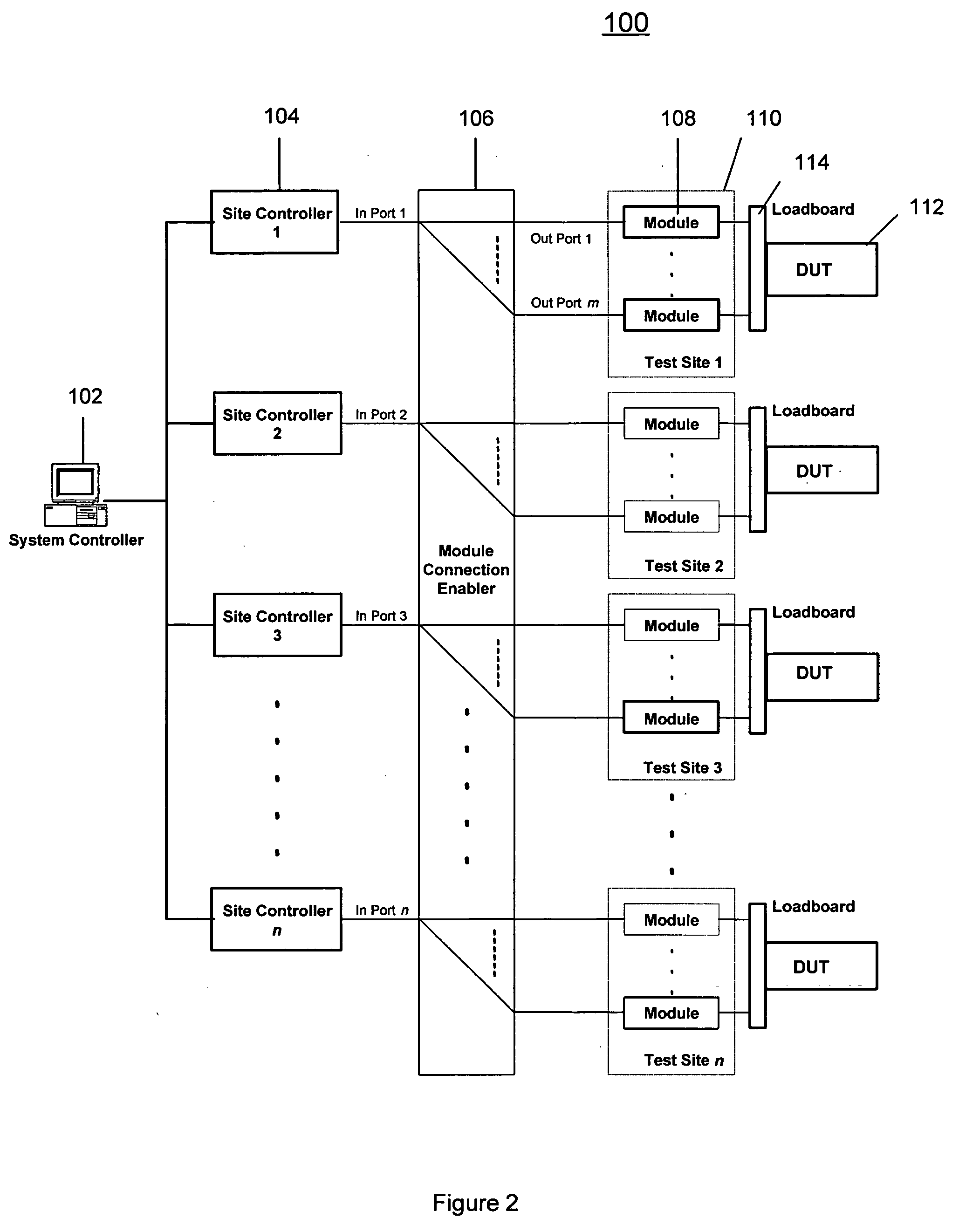

Method and structure to develop a test program for semiconductor integrated circuits

ActiveUS20050154550A1Digital circuit testingResistance/reactance/impedenceModularitySystem controller

A method for managing a pattern object file in a modular test system is disclosed. The method includes providing a modular test system, where the modular test system comprises a system controller for controlling at least one site controller, and where the at least one site controller controls at least one test module and its corresponding device under test (DUT). The method further includes creating an object file management framework for establishing a standard interface between vendor-supplied pattern compilers and the modular test system, receiving a pattern source file, creating a pattern object metafile based on the pattern source file using the object file management framework, and testing the device under test through the test module using the pattern object metafile.

Owner:ADVANTEST AMERICA R & D CENT