Patents

Literature

79 results about "Trace buffer" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Usage of the trace buffer. System trace records are stored in the trace buffer of each process when the TraceFlagBuffer is switched on. The trace buffer is a ring; trace records are written sequentially into the buffer, and when the end of the buffer is reached, storage continues at the beginning of the buffer, overwriting older records.

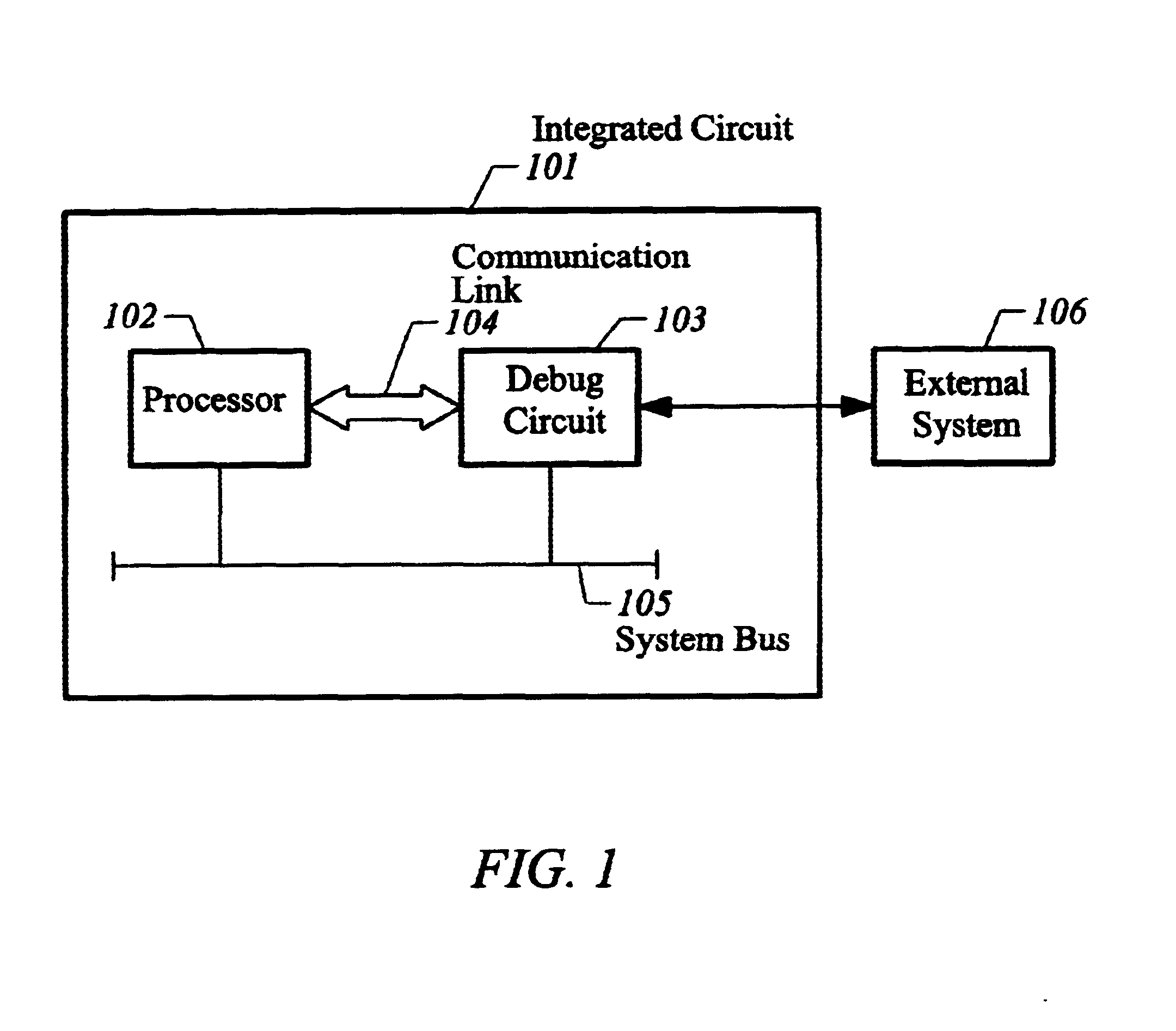

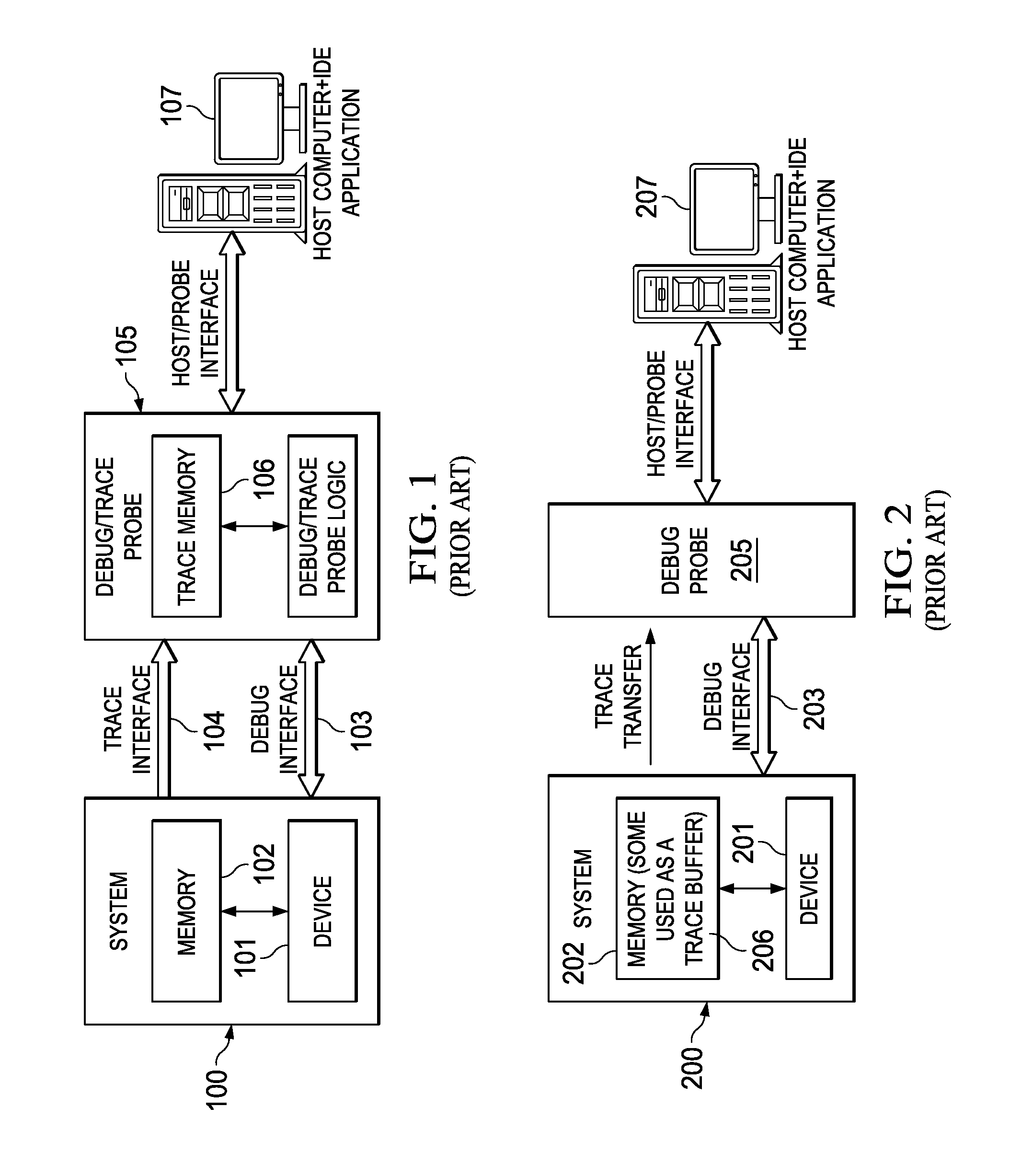

Debug interface including a compact trace record storage

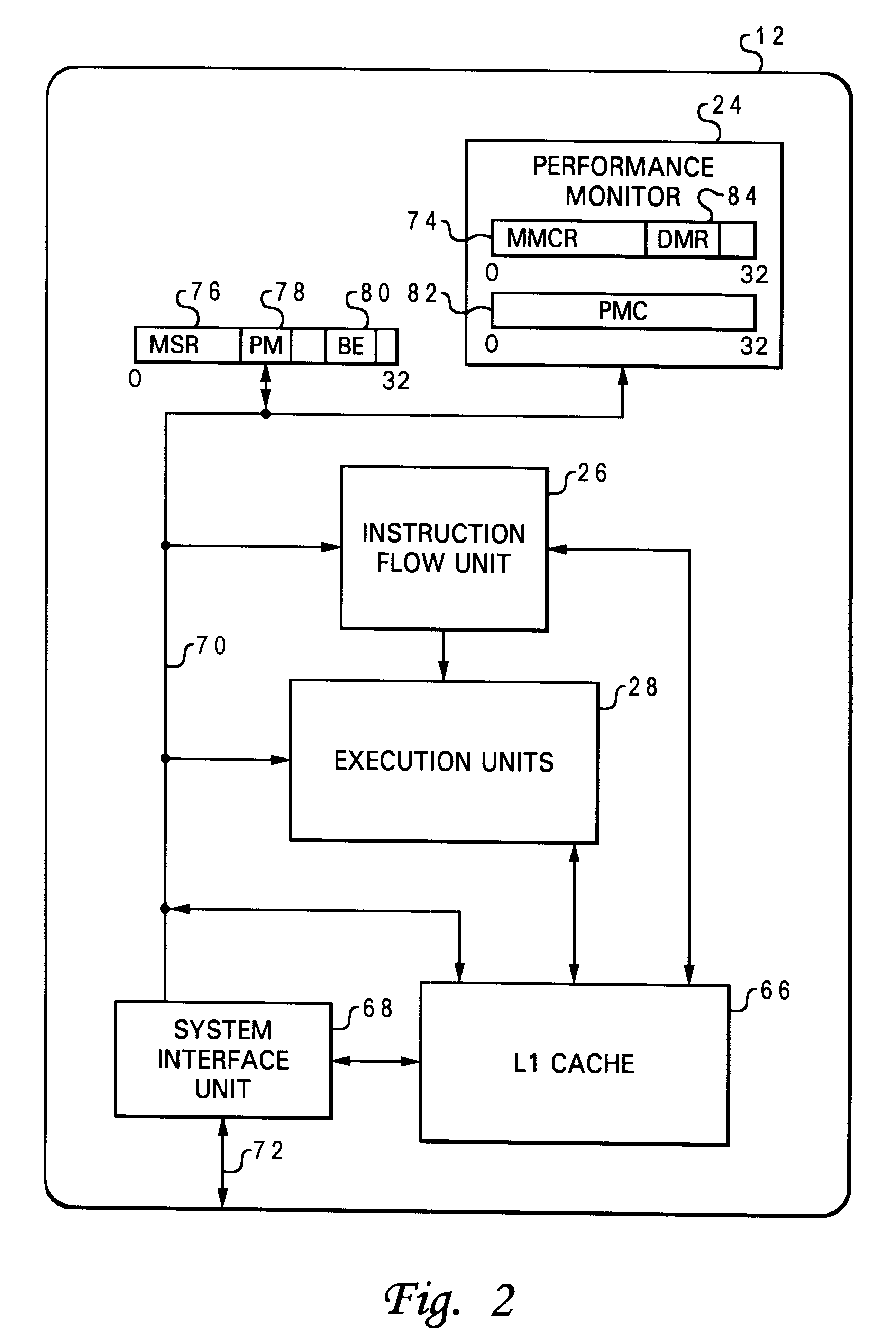

InactiveUS6094729AReliability increasing modificationsHardware monitoringInformation typeParallel computing

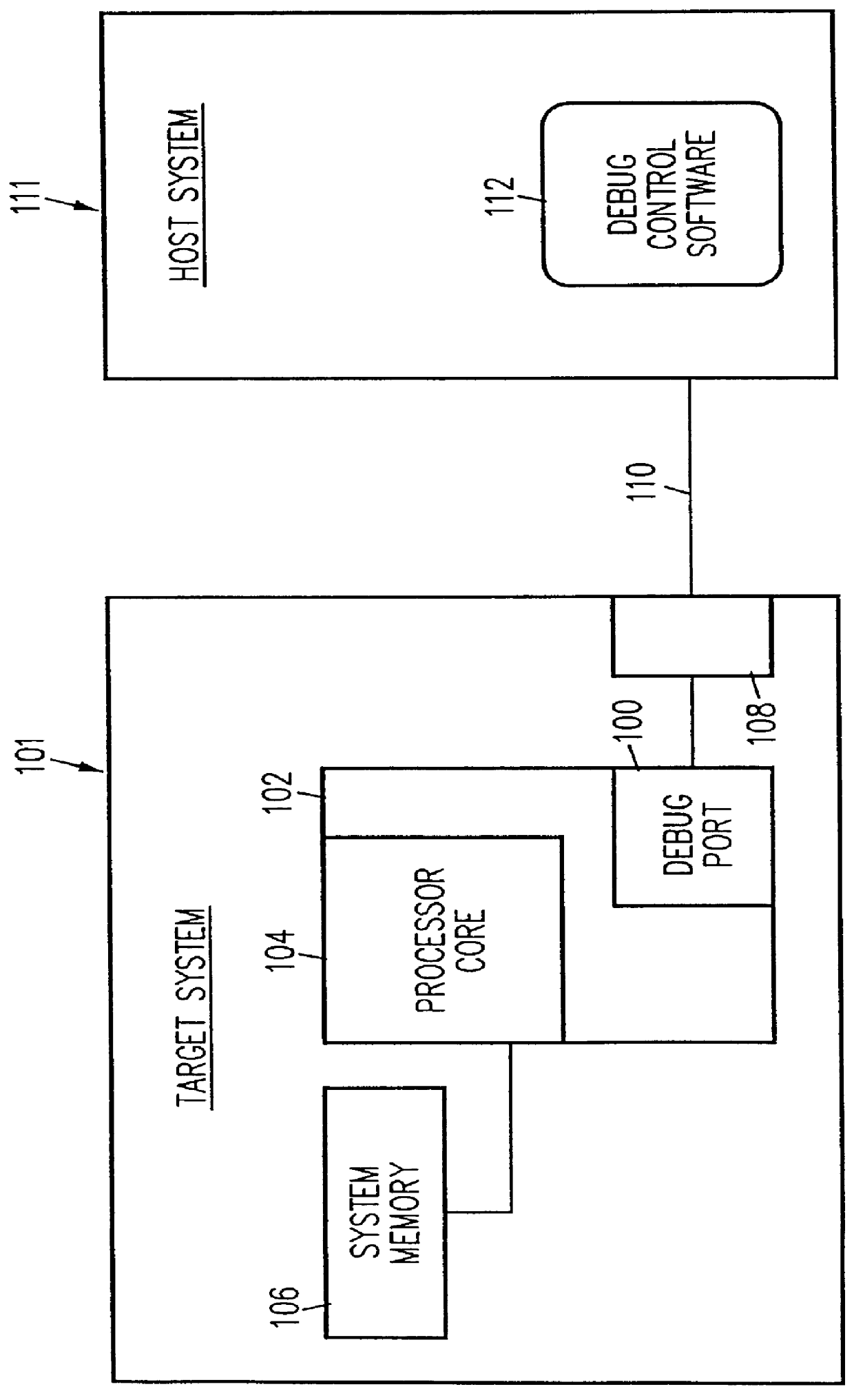

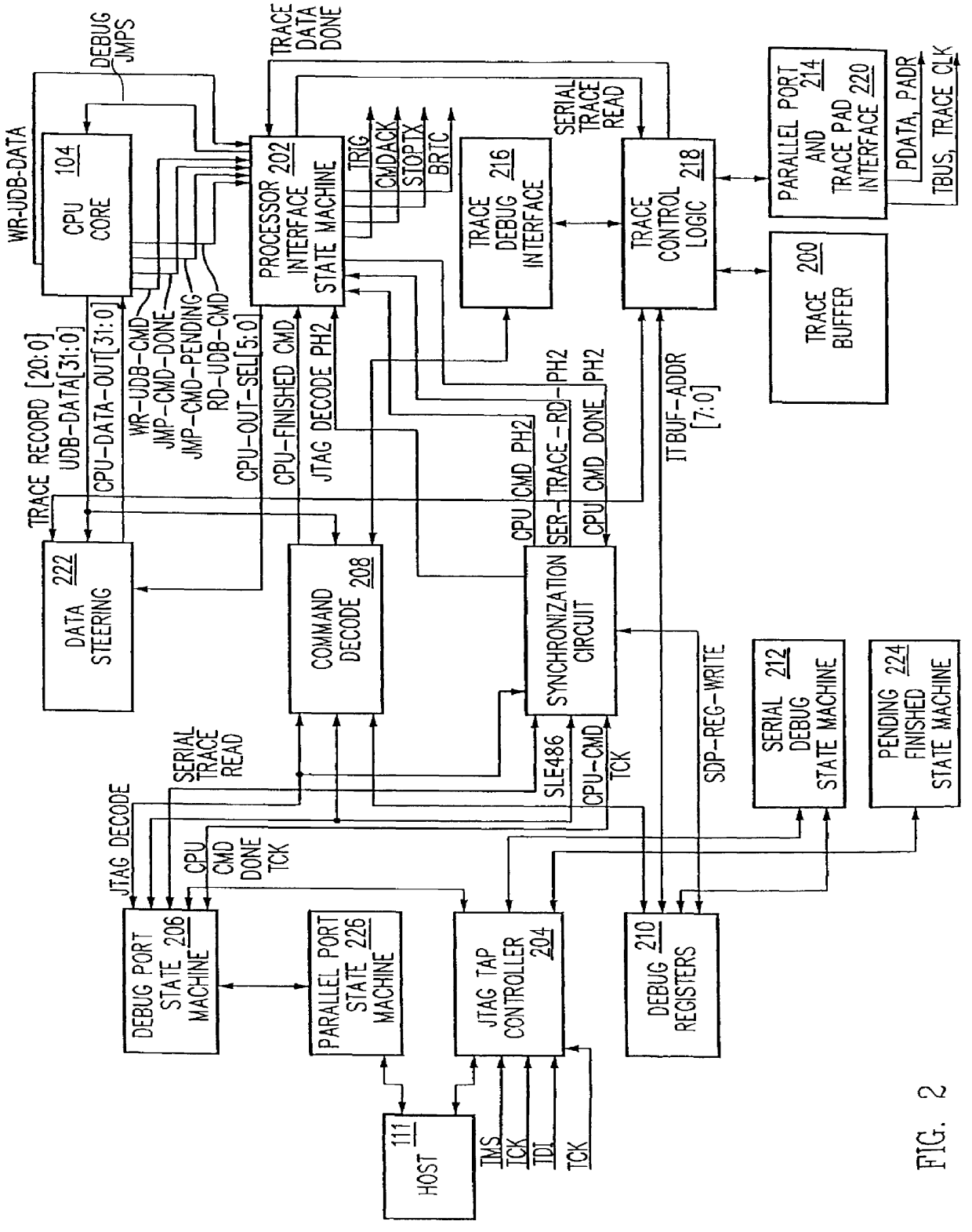

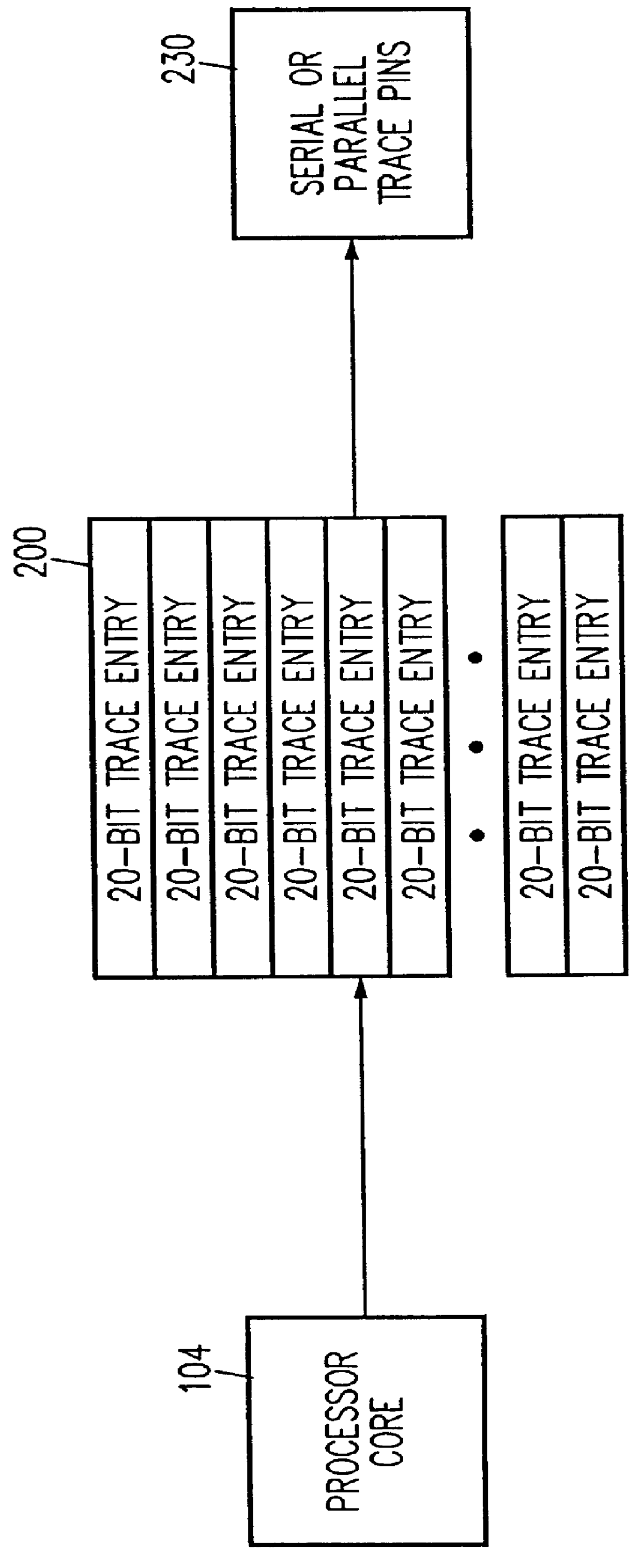

In-circuit emulation (ICE) and software debug facilities are included in a processor via a debug interface that interfaces a target processor to a host system. The debug interface includes a trace controller that monitors signals produced by the target processor to detect specified conditions and produce a trace record of the specified conditions including a notification of the conditions are selected information relating to the conditions. The trace controller formats a trace information record and stores the trace information record in a trace buffer in a plurality of trace data storage elements. The trace data storage elements have a format that includes a trace code (TCODE) field indicative of a type of trace information and a trace data (TDATA) field indicative of a type of trace information data.

Owner:GLOBALFOUNDRIES INC

Method for compressing and decompressing trace information

InactiveUS6918065B1Maximizes on-chip trace storageEliminating duplicate informationCode conversionHardware monitoringParallel computingMemory map

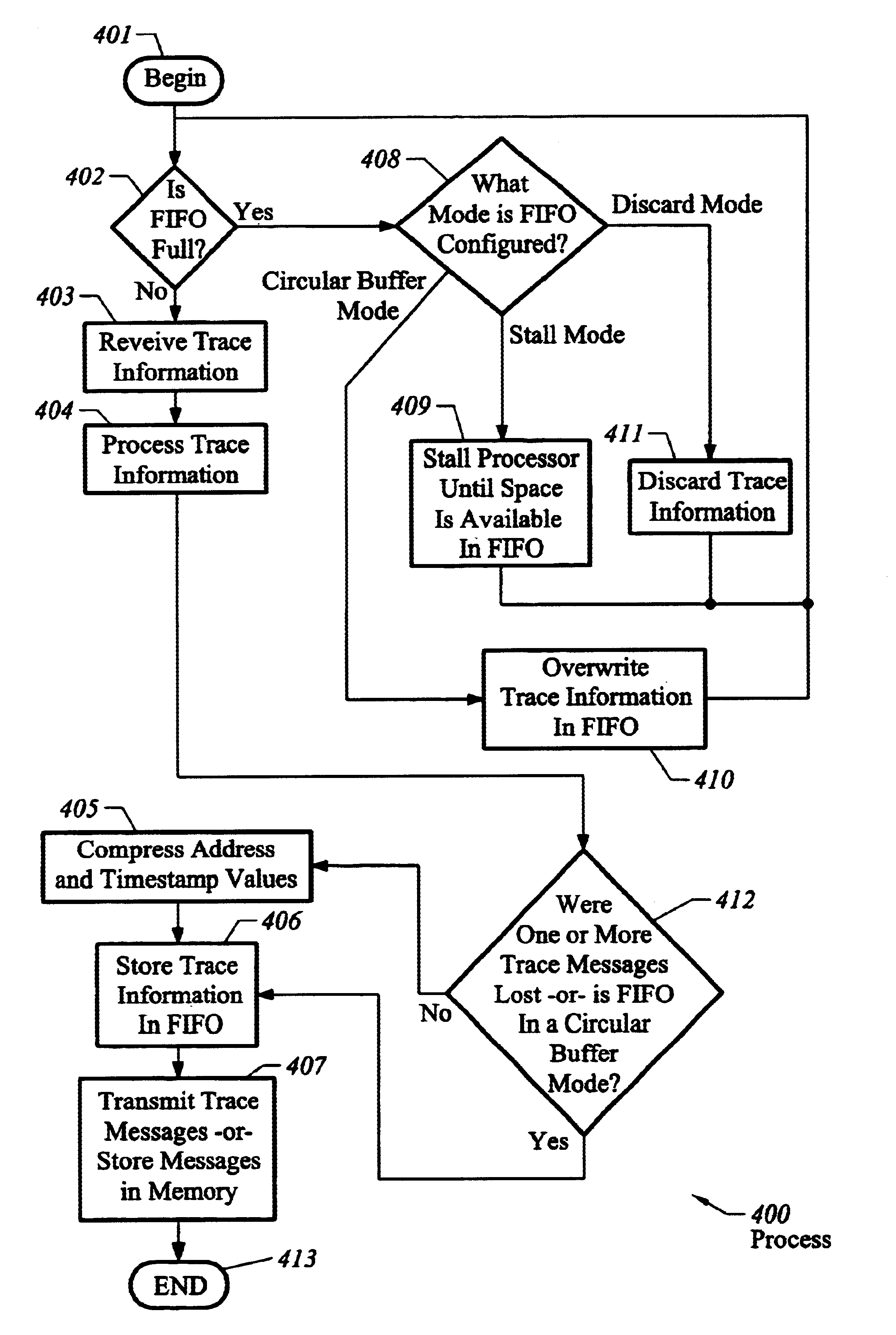

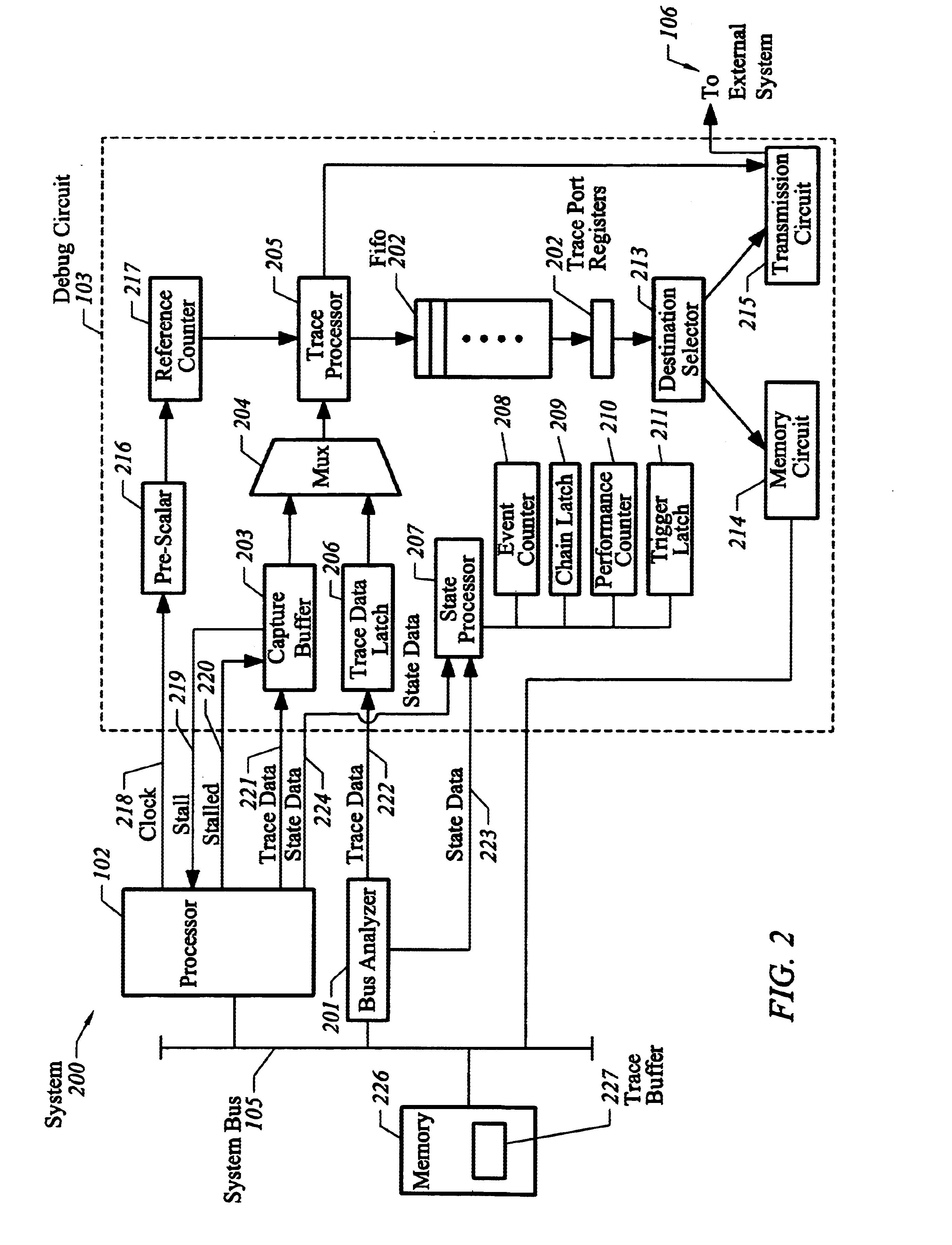

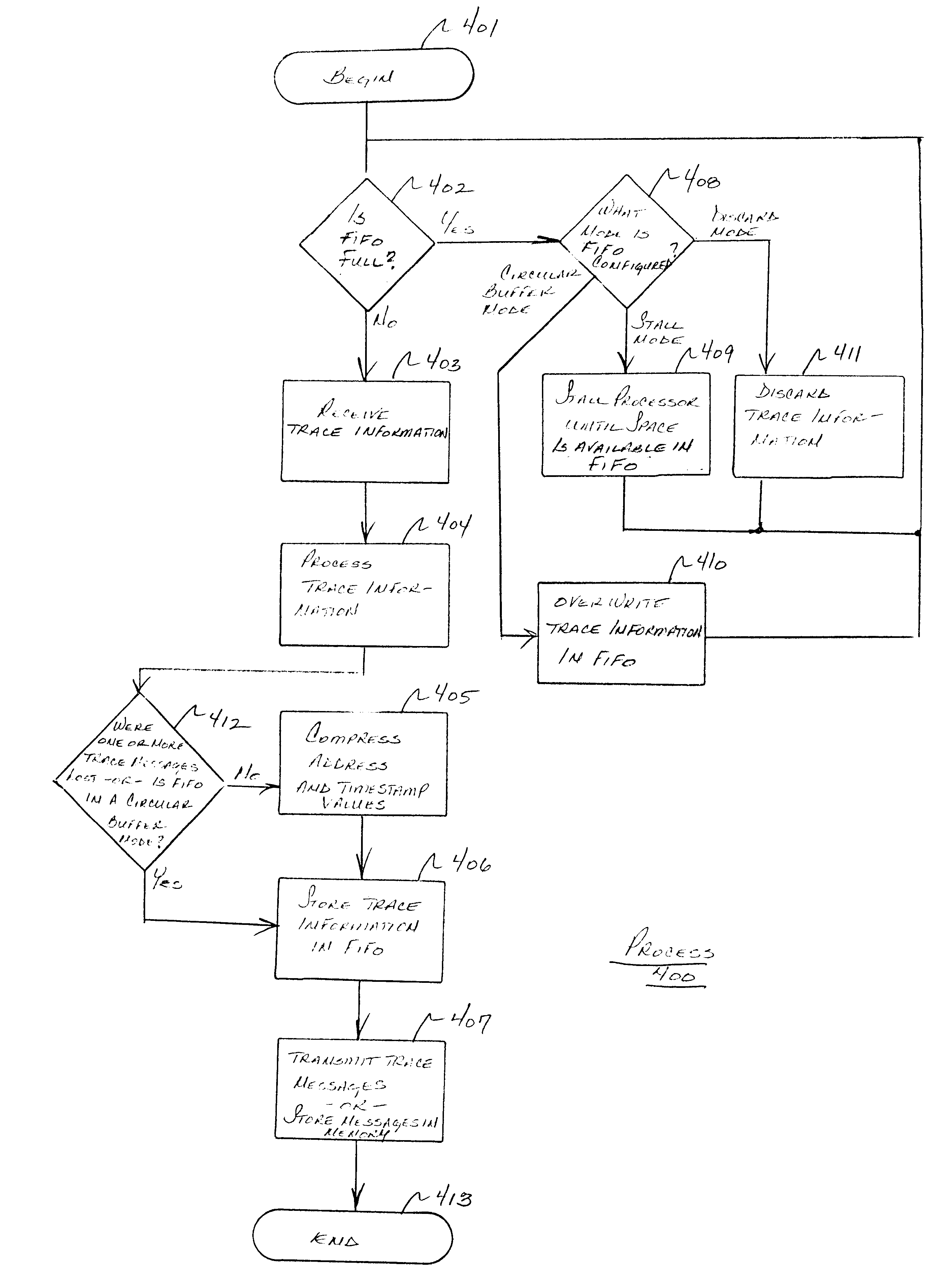

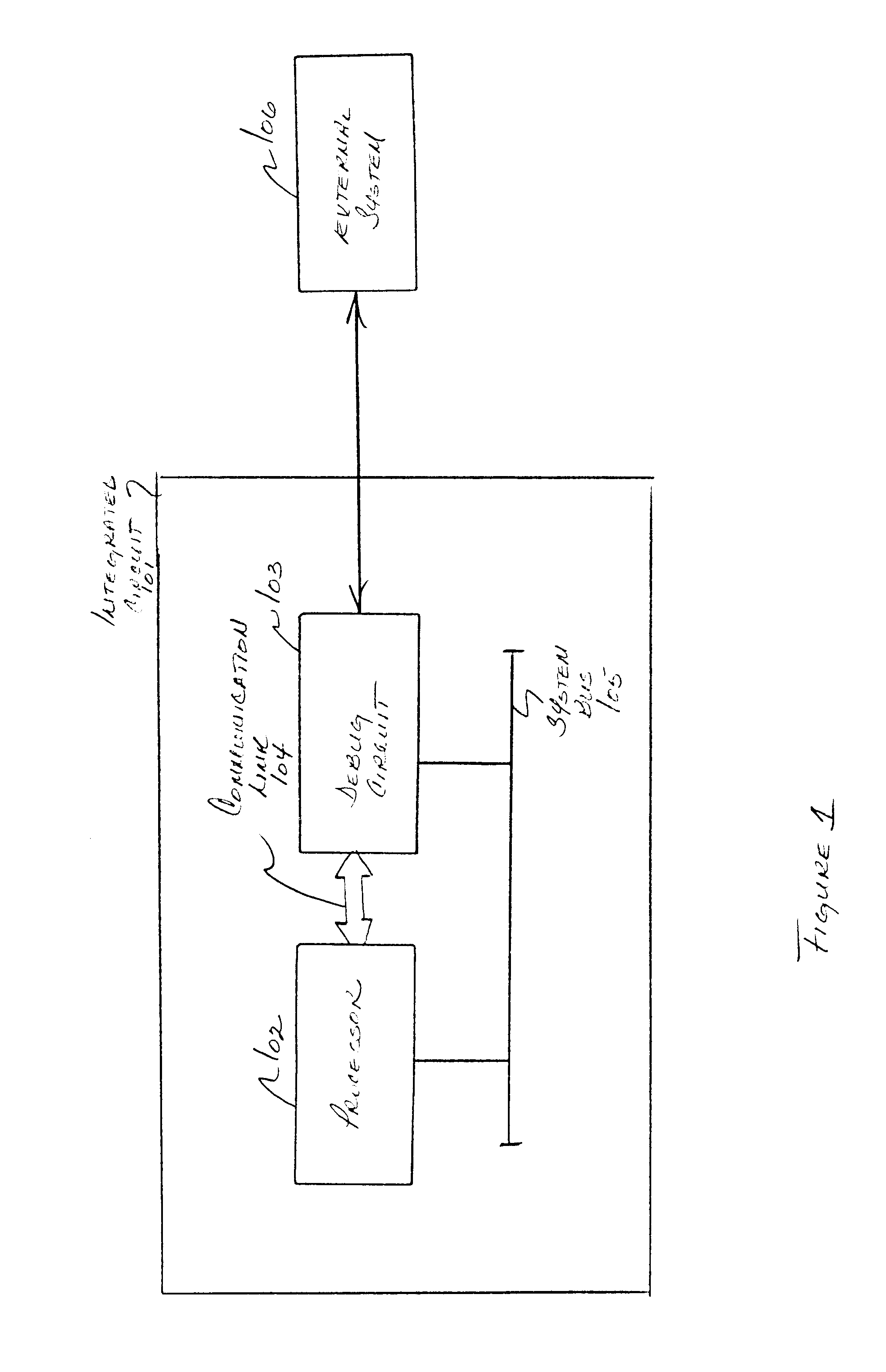

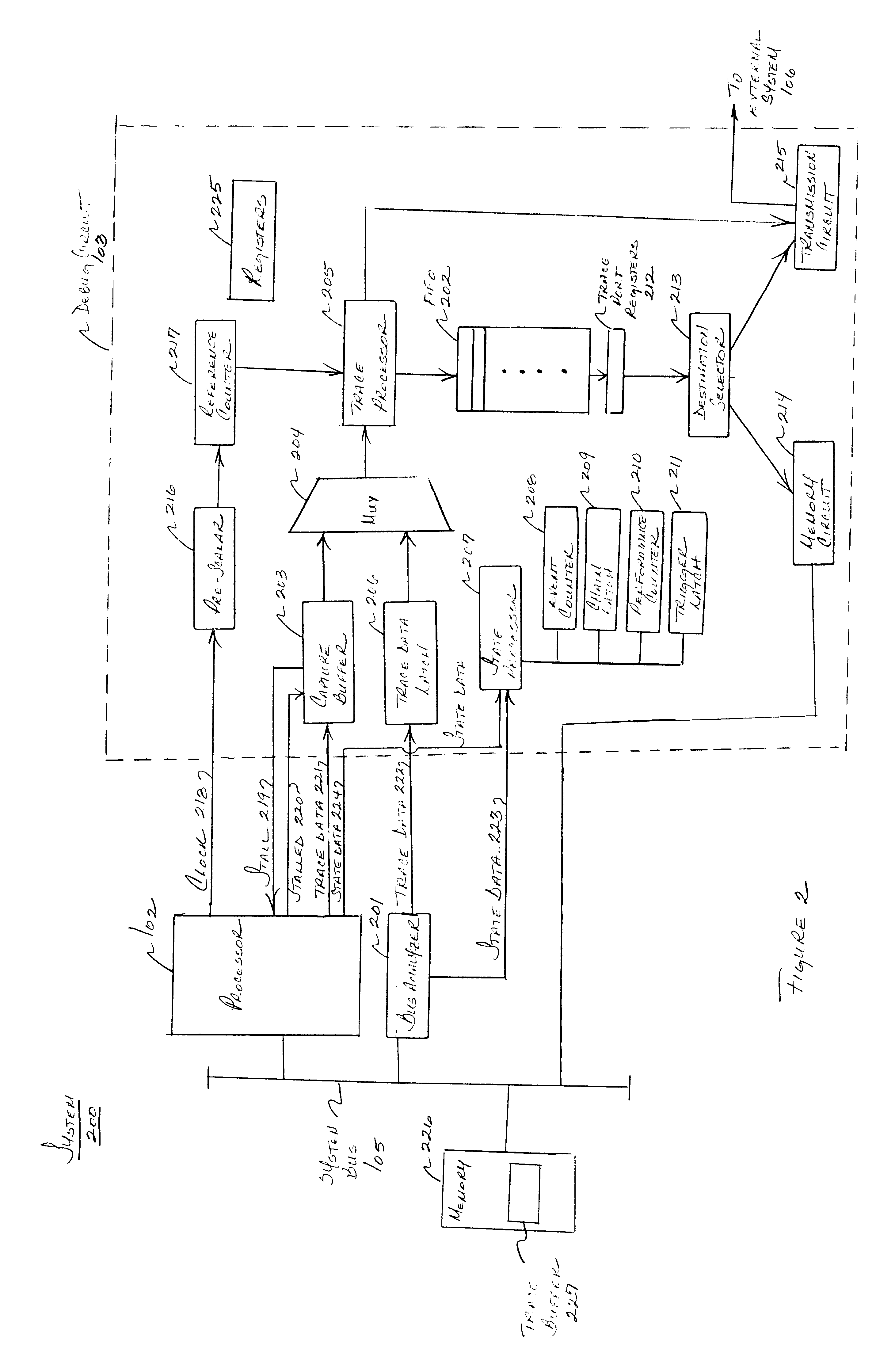

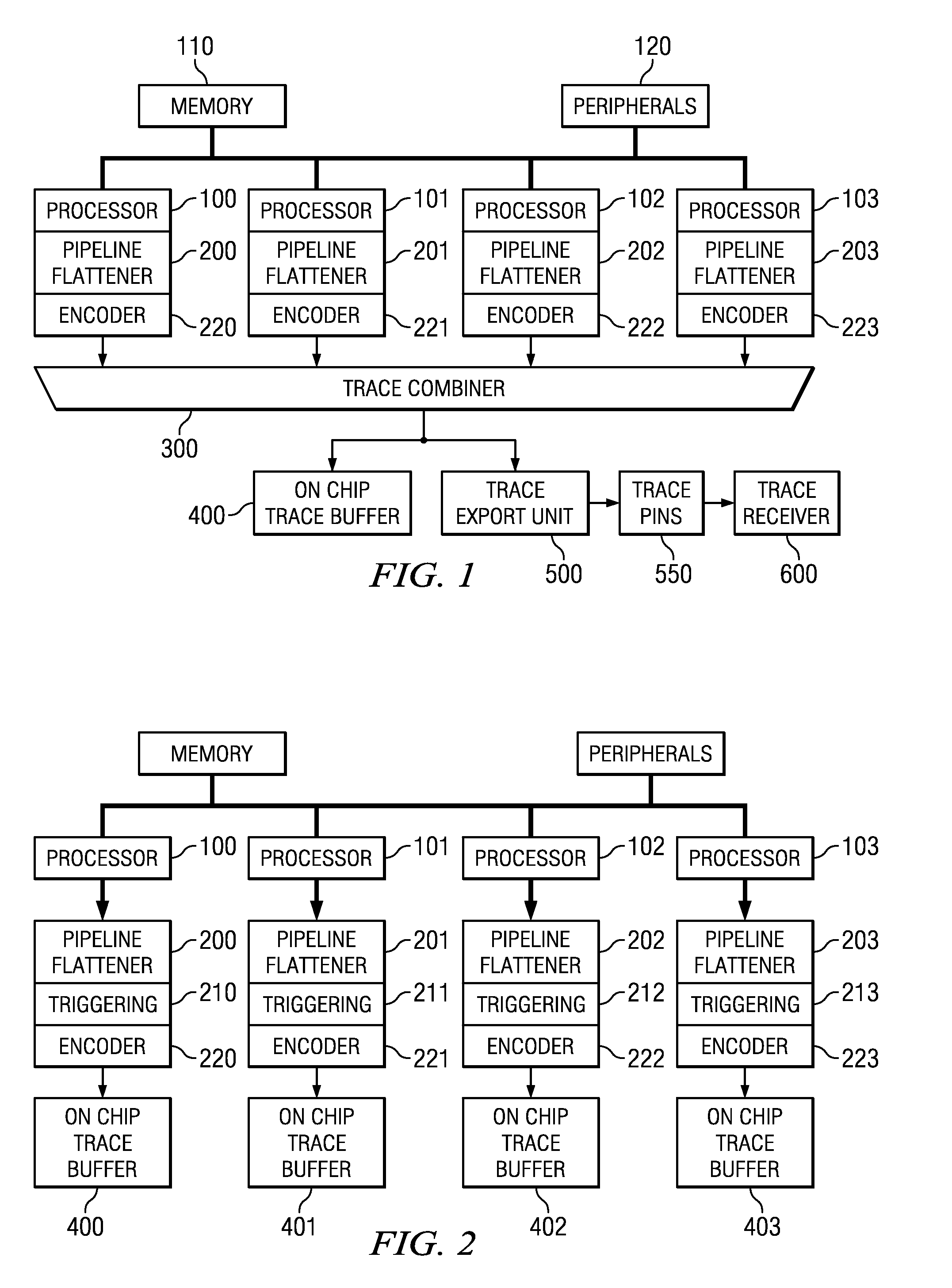

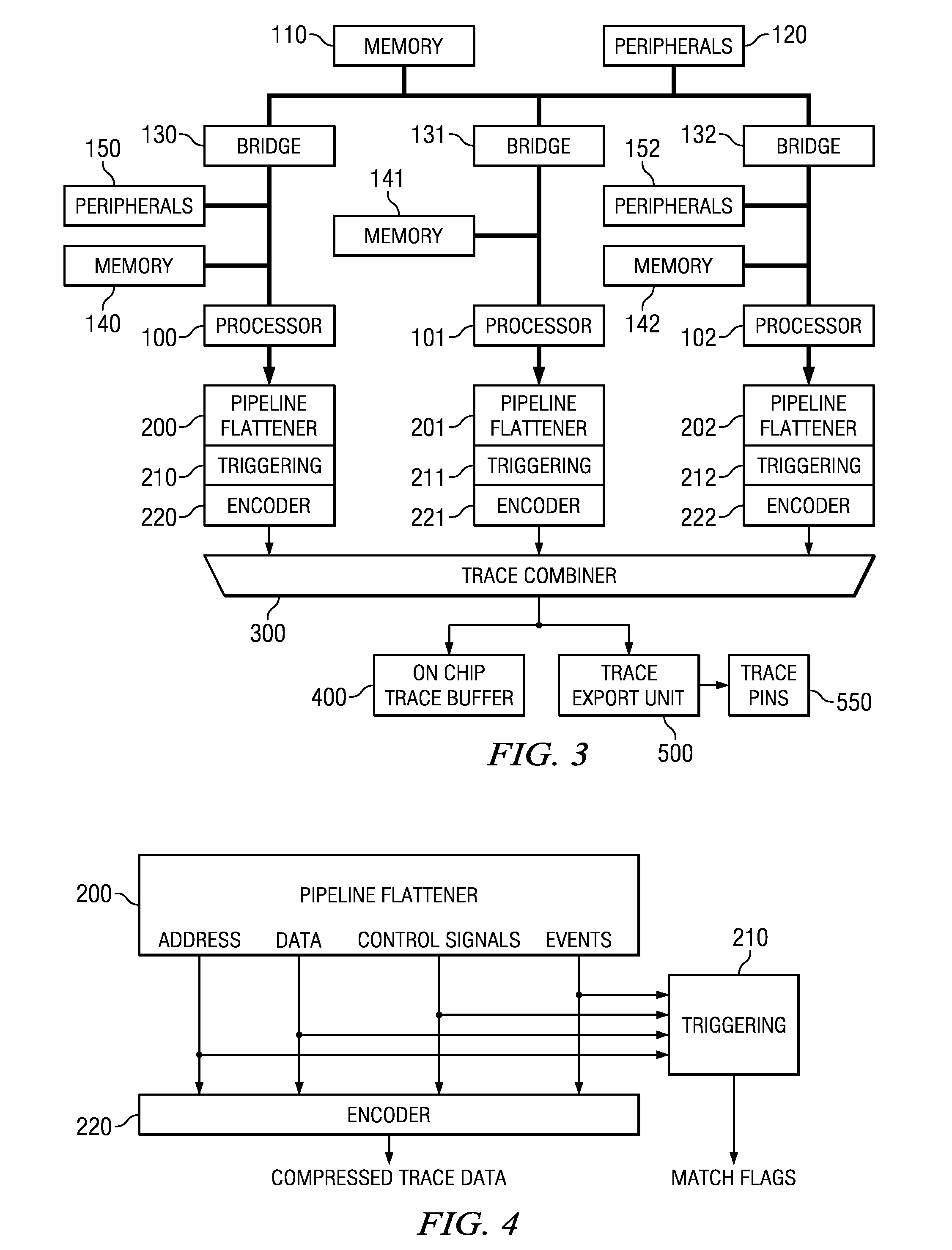

A system for performing non-intrusive trace is provided which receives trace information from one or more processors. The trace system may be configured by a user to operate in various modes for flexibly storing or transmitting the trace information. The trace system includes a FIFO which is memory-mapped and is capable of being accessed without affecting processor performance. In one aspect, the trace system includes a trace buffer which receives trace information at an internal clock speed of the processor. In another embodiment, a compression protocol is provided for compressing trace messages on-chip prior to transmitting the messages to an external system or storing the messages in memory.

Owner:RENESAS ELECTRONICS CORP

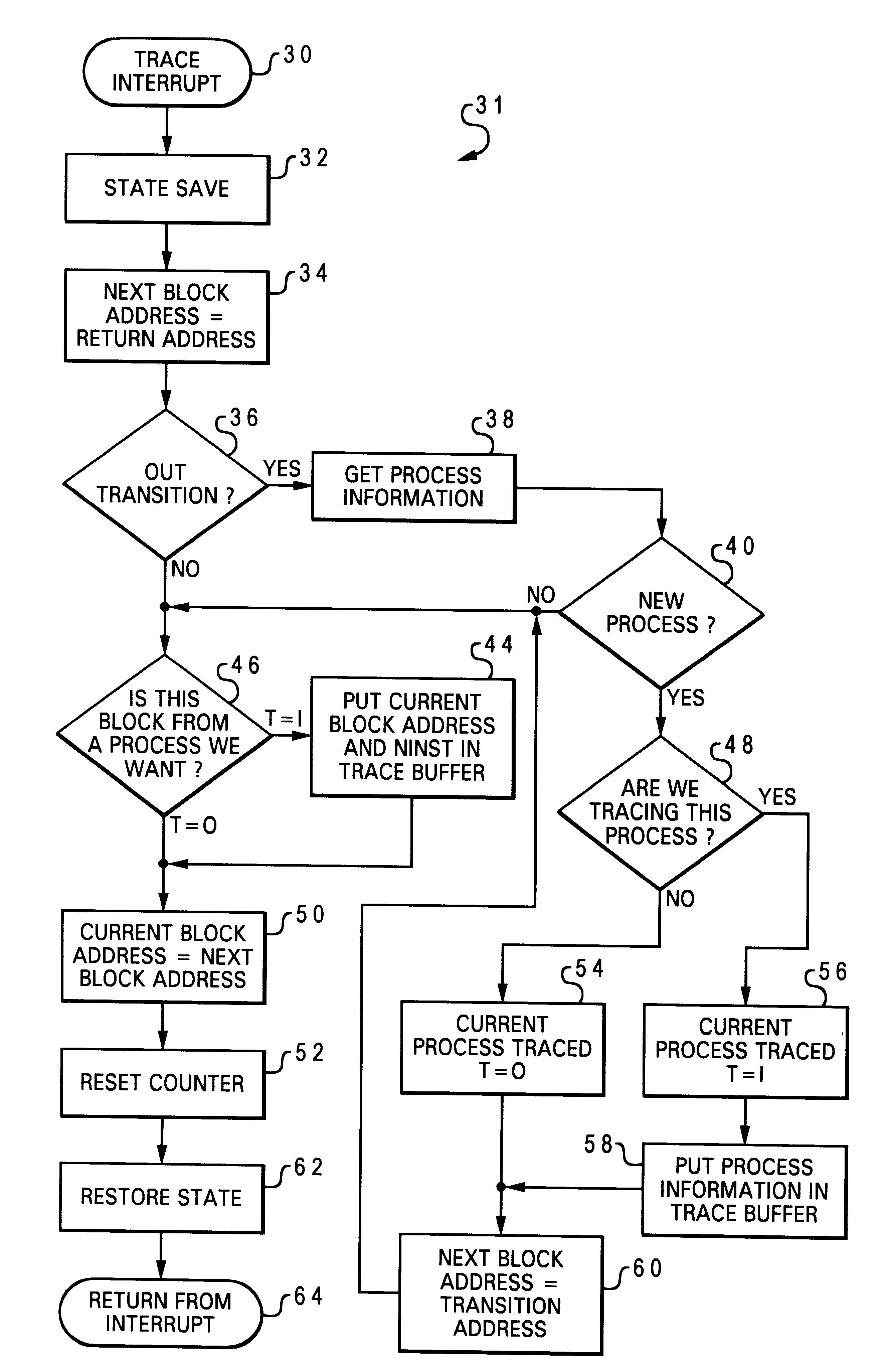

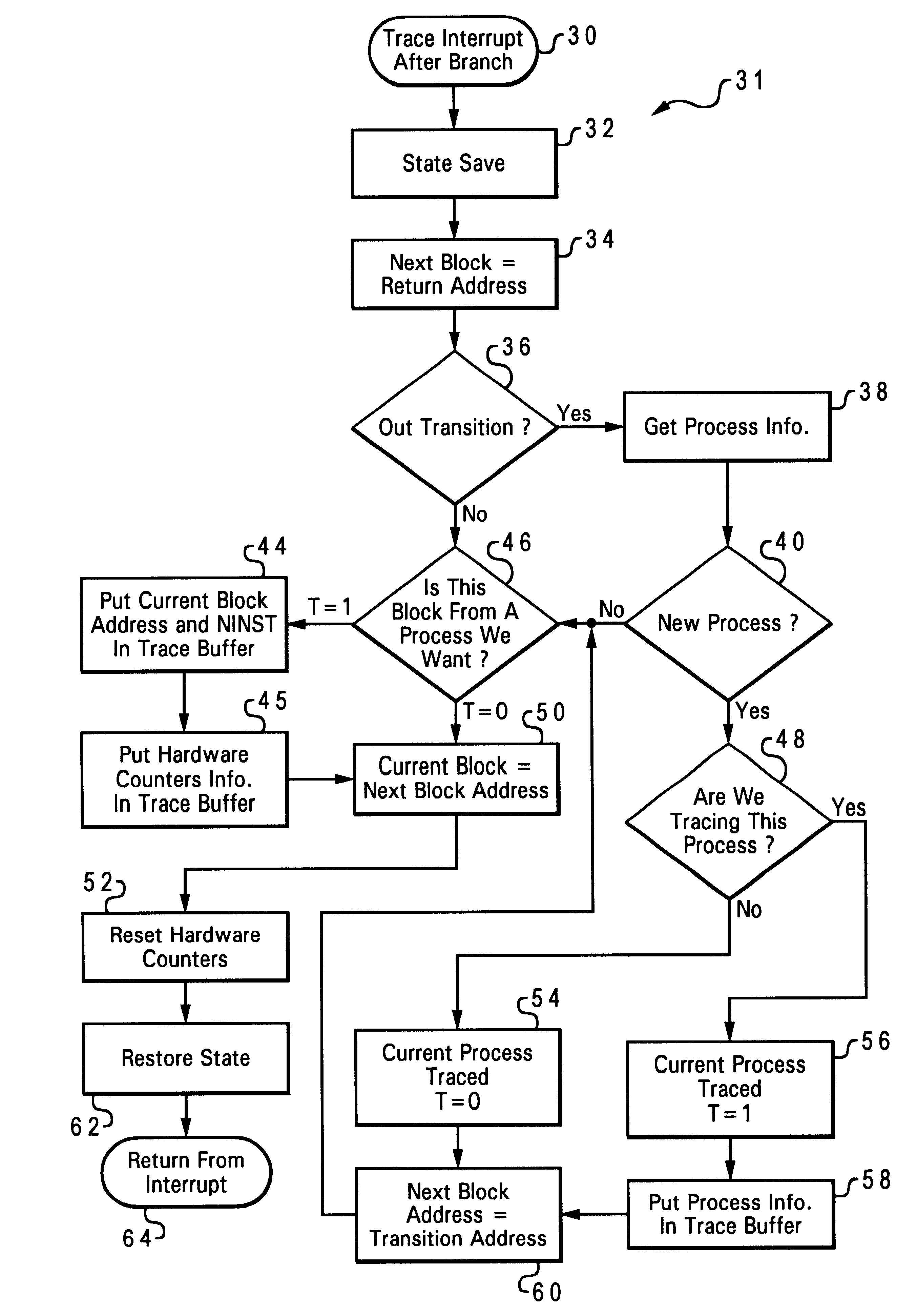

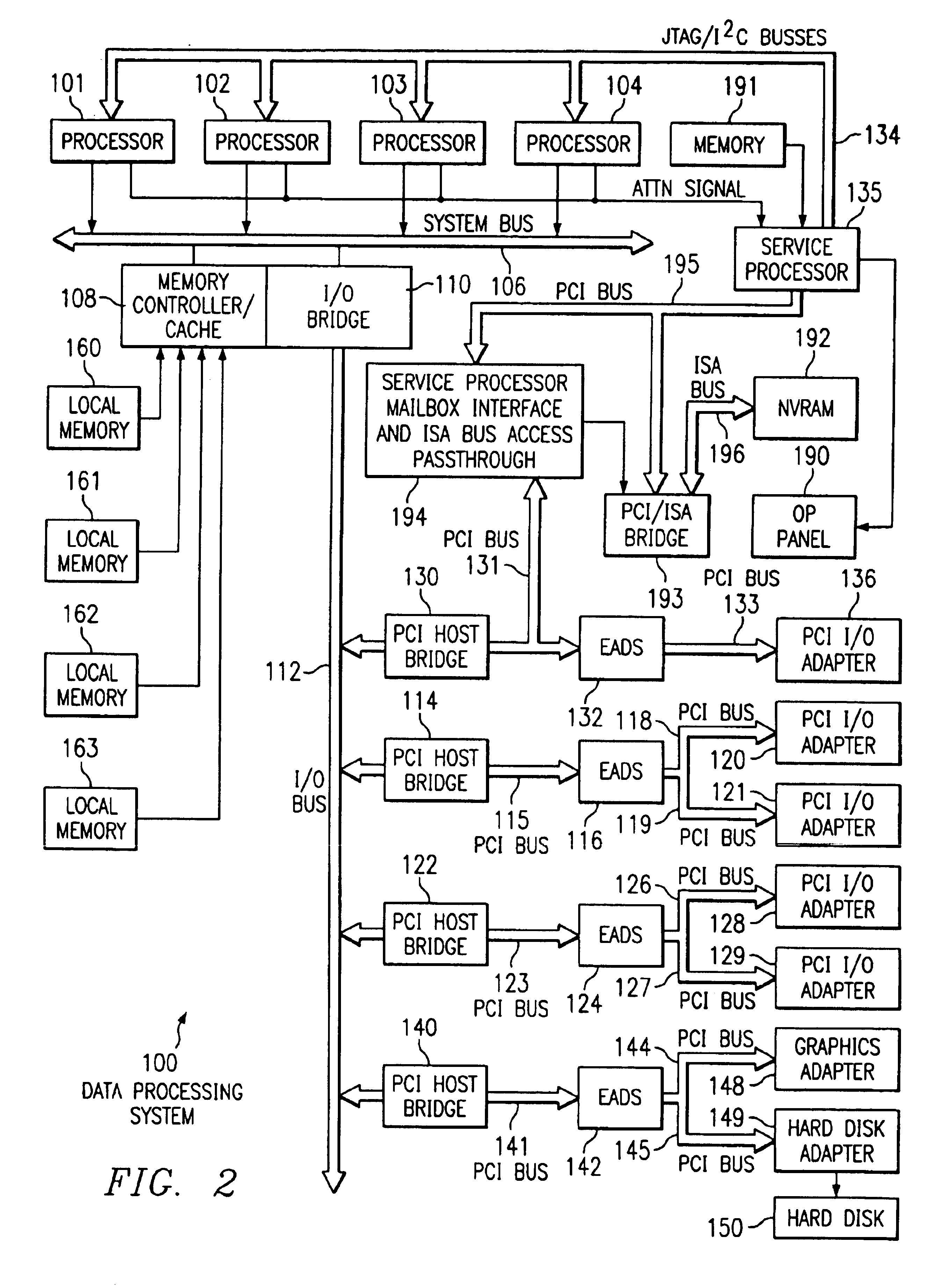

Method and system for software instruction level tracing in a data processing system

A method and system within a data processing system are disclosed for directly accessing code during a process by taking a trace by way of using an interruption. According to the present invention, the processor is programmed to generate a trace interrupt after each branch, or at the end of each basic block from the current process. This allows generation of exactly the same number of interruptions as would be produced by an instrumentation approach but without having to know where the basic blocks are in advance. By programming the performance monitor feature to count instructions, the exact size of each basic block is known. At each interrupt, the address of the beginning of the next basic block is saved which is the address where the interruption came from. Tracing information for the previous basic block including its address and its size (the current value of a counter) is created. If the current process is a process to be traced, the tracing information is stored in a trace buffer, the counter is reset to zero returning back to the process from the interrupt.

Owner:IBM CORP

Circuit for processing trace information

InactiveUS6684348B1Maximizes on-chip trace storageEliminating duplicate informationSoftware testing/debuggingArchitecture with single central processing unitMemory mapTrace buffer

A system for performing non-intrusive trace is provided which receives trace information from one or more processors. The trace system may be configured by a user to operate in various modes for flexibly storing or transmitting the trace information. The trace system includes a FIFO which is memory-mapped and is capable of being accessed without affecting processor performance. In one aspect, the trace system includes a trace buffer which receives trace information at an internal clock speed of the processor. In another embodiment, a compression protocol is provided for compressing trace messages on-chip prior to transmitting the messages to an external system or storing the messages in memory.

Owner:RENESAS ELECTRONICS CORP

Circuits, systems, apparatus and processes for monitoring activity in multi-processing systems

ActiveUS20100332909A1Hardware monitoringFunctional testingWireless handheld devicesParallel computing

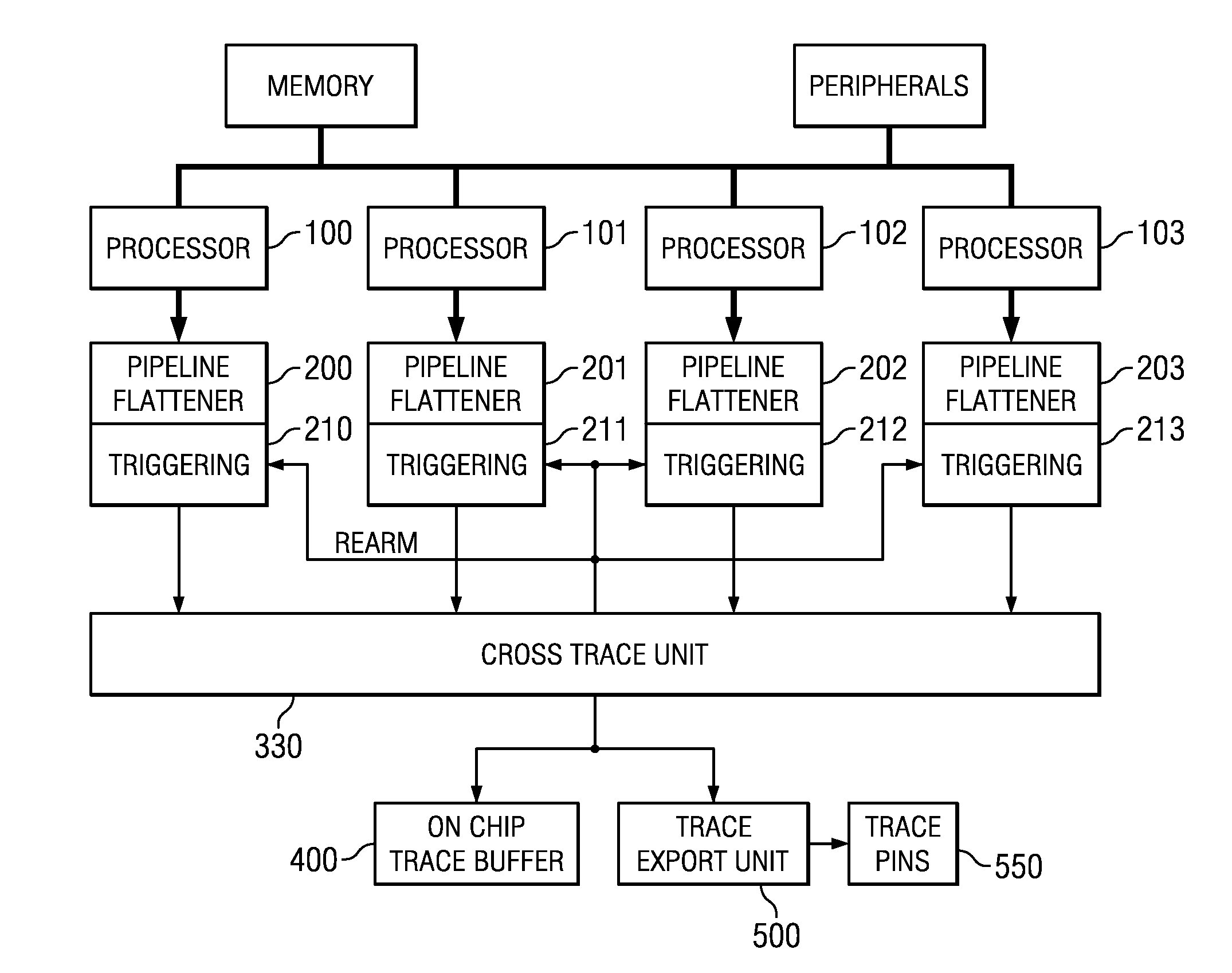

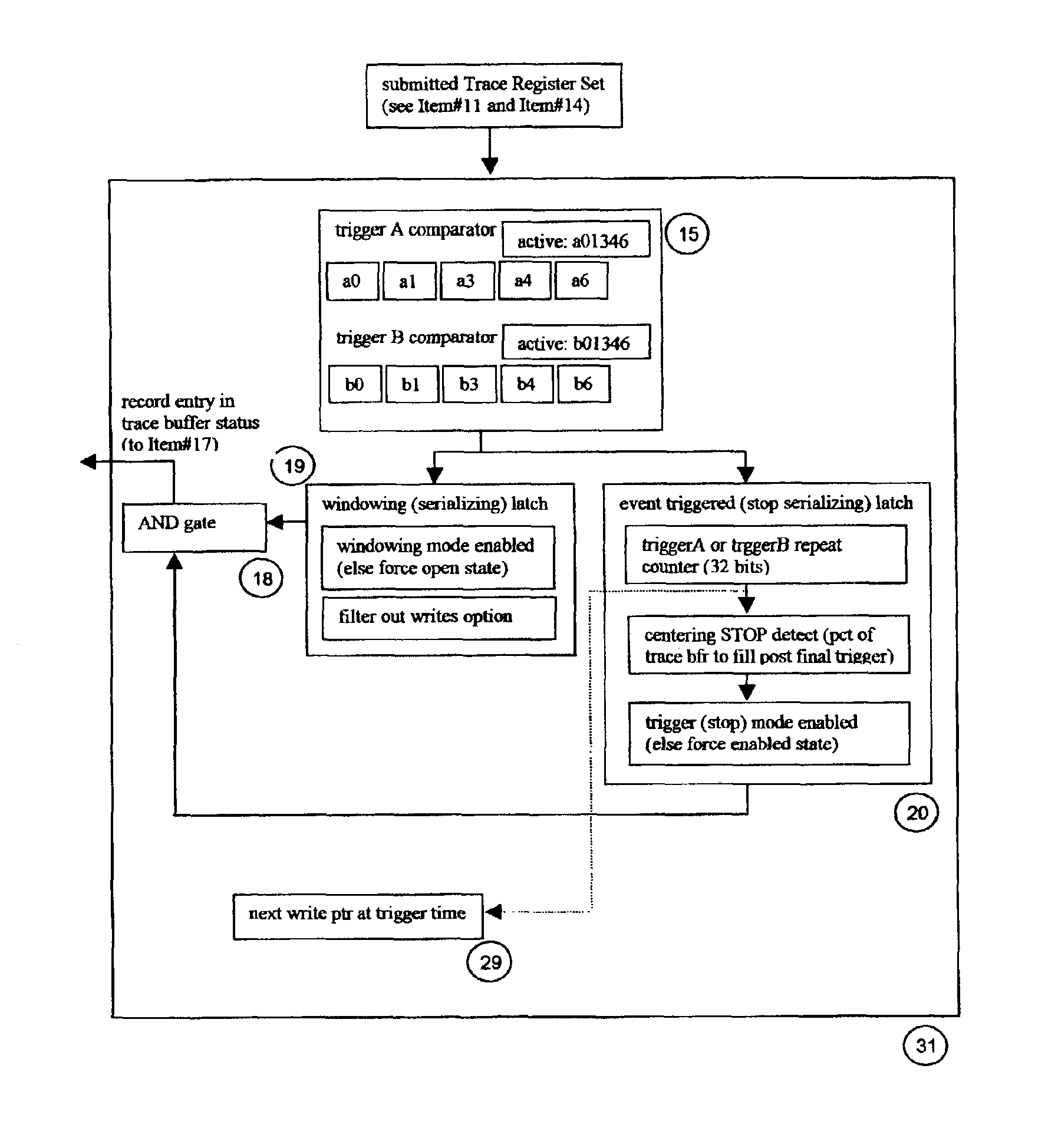

An electronic circuit includes a first processor (100) operable to perform processing operations, a first trace buffer (230) coupled to the first processor (100), a first triggering circuit (210) coupled to the first processor (100), the first triggering circuit (210) operable to detect a specified sequence of particular processing operations in the first processor (100); a second processor (101), a second trace buffer (231) coupled to the second processor (101), a second triggering circuit (211) coupled to the second processor (101), the second triggering circuit (211) operable to detect at least one other processing operation in the second processor (101); and a cross trace circuit (330) having a trace output and having inputs coupled to the first triggering circuit (210) and to the second triggering circuit (211), the cross trace circuit (330) configurably operable to respond to a sequence including both a detection of the sequence of particular processing operations of the first processor (100) by the first triggering circuit (210) and a detection of the at least one other processing operation of the second processor (101) by the second triggering circuit (211), to couple at least one of the first trace buffer (230) and the second trace buffer (231) to the trace output. Various circuits, devices, telecommunications products, wireless handsets, systems and processes of operation and manufacture are disclosed.

Owner:TEXAS INSTR INC

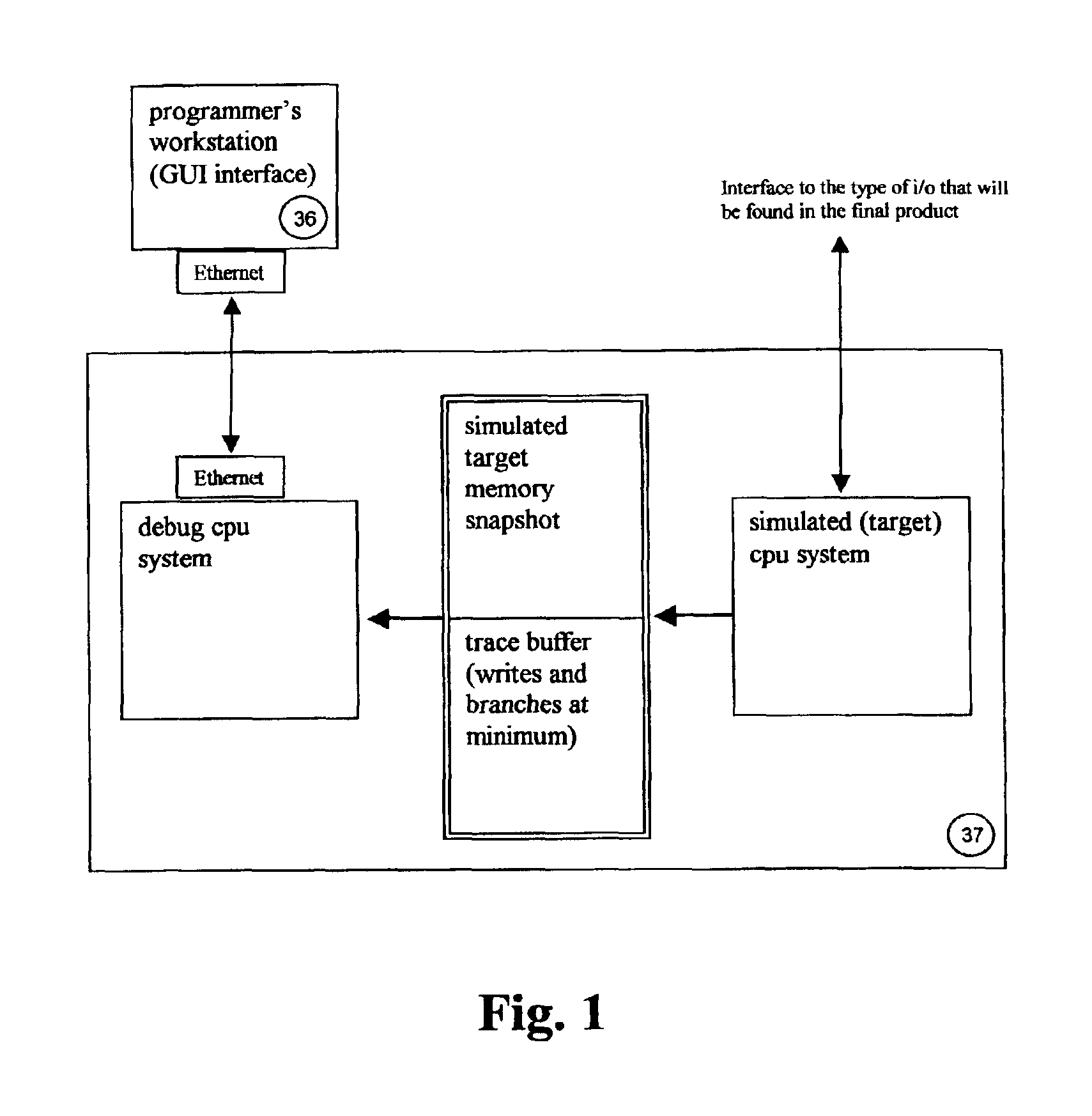

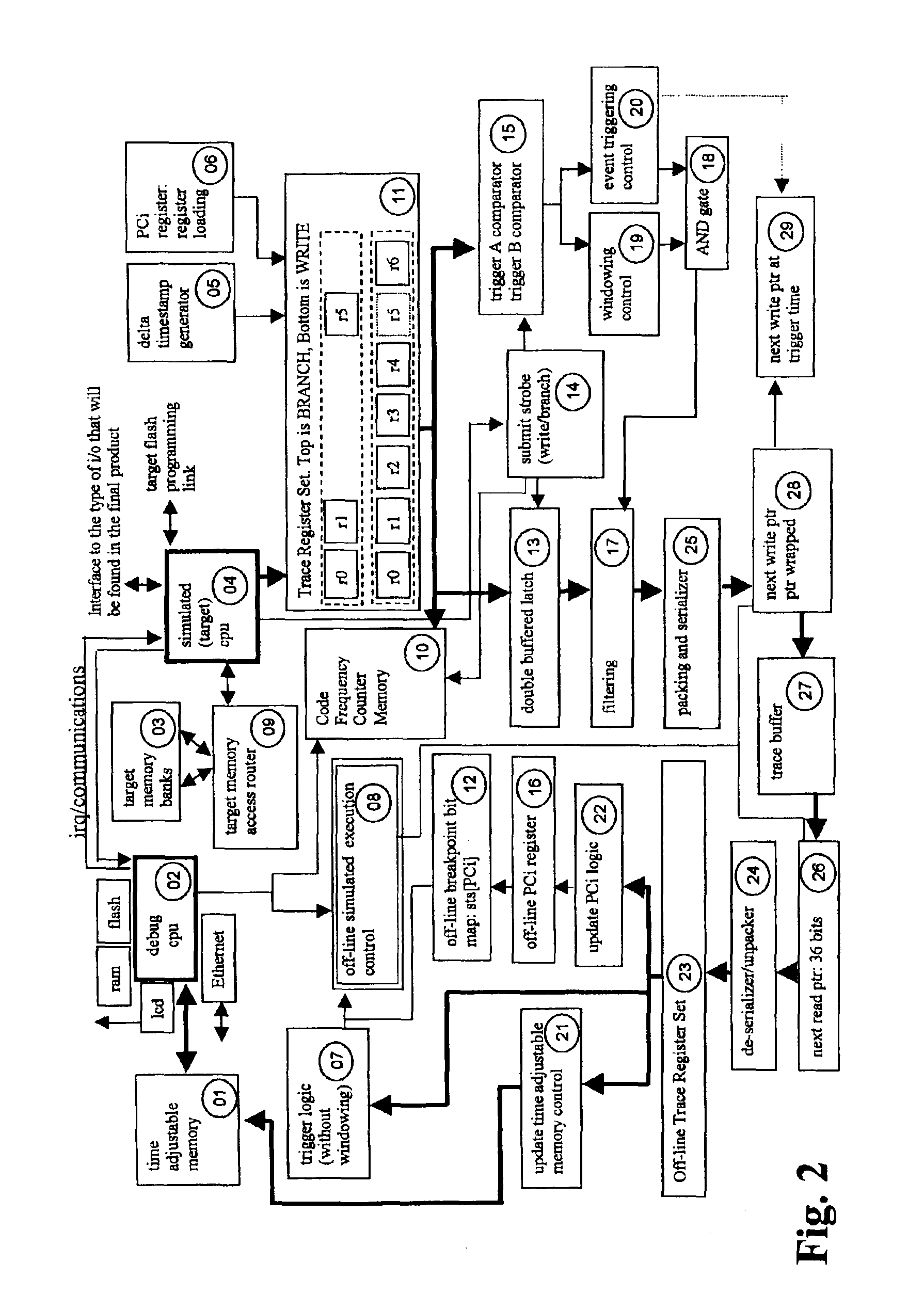

Method for software debugging via simulated re-execution of a computer program

InactiveUS6901581B1Software testing/debuggingSpecific program execution arrangementsTrace bufferSoftware debugging

An invention is provided for debugging a computer program. Program information is recorded in a trace buffer. The program information generally includes write accesses from the computer program and the execution path of the computer program. In addition, a memory image snapshot of at least a portion of memory being utilized by the computer program is captured. Simulated re-execution of the computer program then occurs by adjusting the state of the memory image snapshot based on the program information. Further, debugging logic can be inserted into a simulated re-execution at particular points in the computer program. In particular, the debugging logic does not change the trace buffer or the memory image snapshot, and as such, do not alter the captured sequence events being debugged.

Owner:ERIDON CORP

System for tracing hardware counters utilizing programmed performance monitor to generate trace interrupt after each branch instruction or at the end of each code basic block

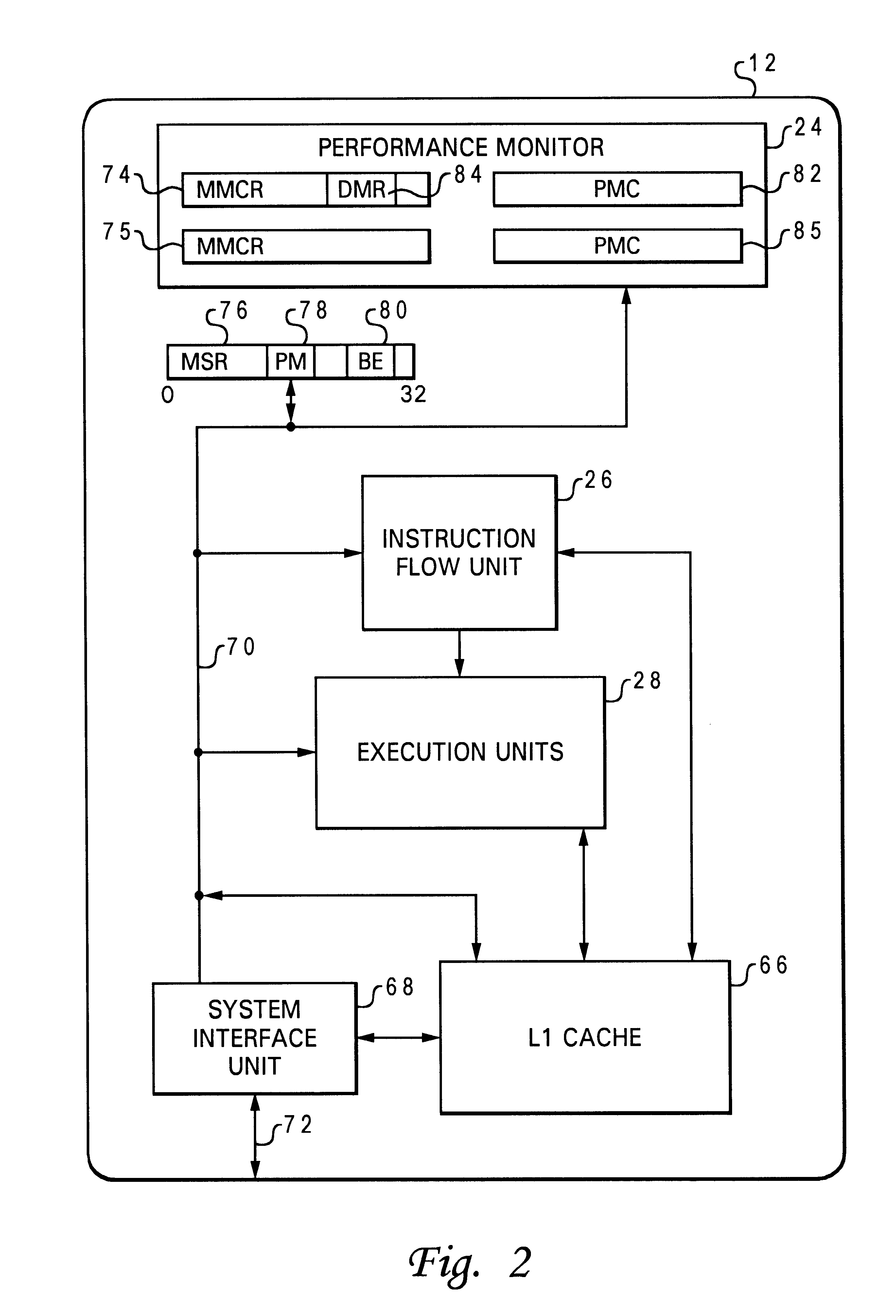

A method and system within a data processing system or information handling system are disclosed for counting various events from a running program (hereafter called a process) by taking a trace by way of using an interruption. According to the present invention, a performance monitor feature within a data processing system is programmed to generate a trace interrupt after each branch instruction, or at the end of each basic block of code from a currently running program or process. By programming monitor mode control registers within the performance monitor feature, one or more counters are programmed to count various events happening on the data processing system thereby creating tracing information. If the current process is a process to be traced, the tracing information is stored in a trace buffer for post-processing analysis, the counters are reset to zero returning back to the process from the interrupt.

Owner:IBM CORP

System and a method for checking lock step consistency between an in circuit emulation and a microcontroller while debugging process is in progress

InactiveUS6922821B1Analogue computers for electric apparatusFunctional testingMicrocontrollerParallel computing

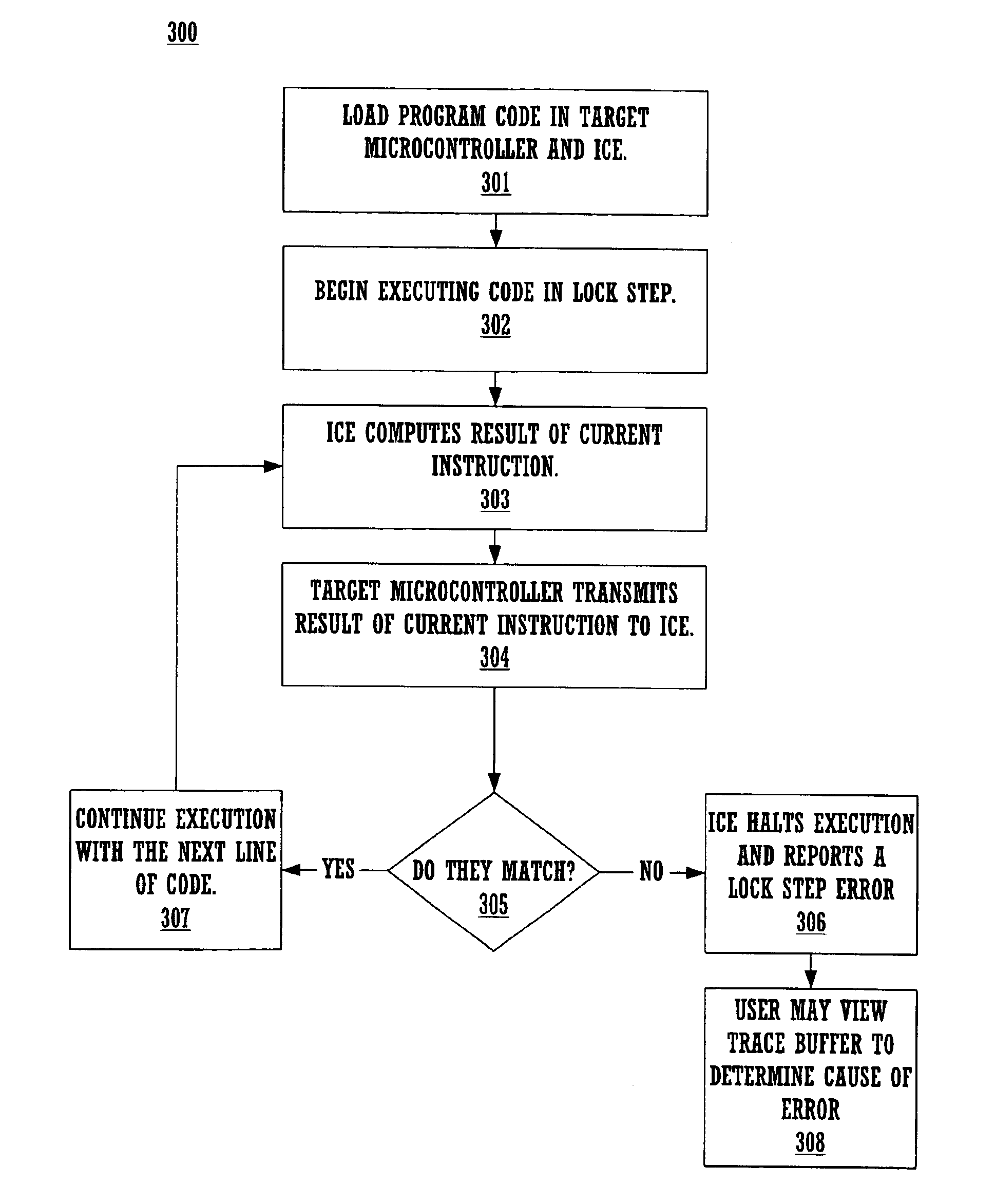

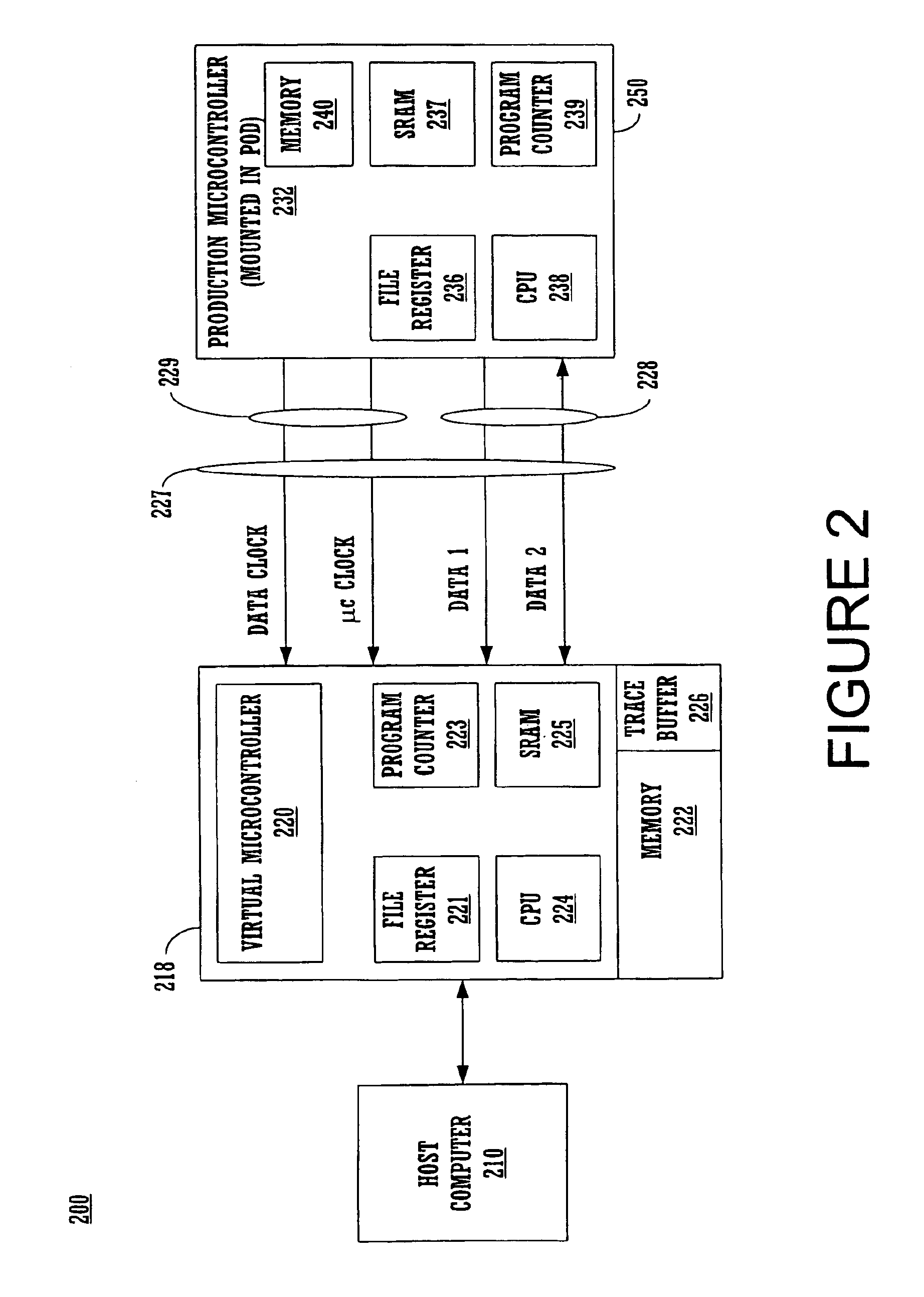

Checking the consistency of a lock step process while debugging a microcontroller code is in progress. A method provides a production microcontroller to execute an instruction code and provides the result of the instruction code to an ICE. The ICE, independent from the production microcontroller and simultaneously, executes the same instruction code and produces a result. The ICE compares the result of its computation and the result received from the production microcontroller. The ICE issues a “lock step error” when the result of the comparison is a mismatch. A trace buffer residing in the host device provides the location of the line of code causing the mismatch. After identifying the line of code causing the mismatch the user debugs the erroneous line of code. The debugging process resumes on the next line of code in the microcontroller code under test.

Owner:MONTEREY RES LLC

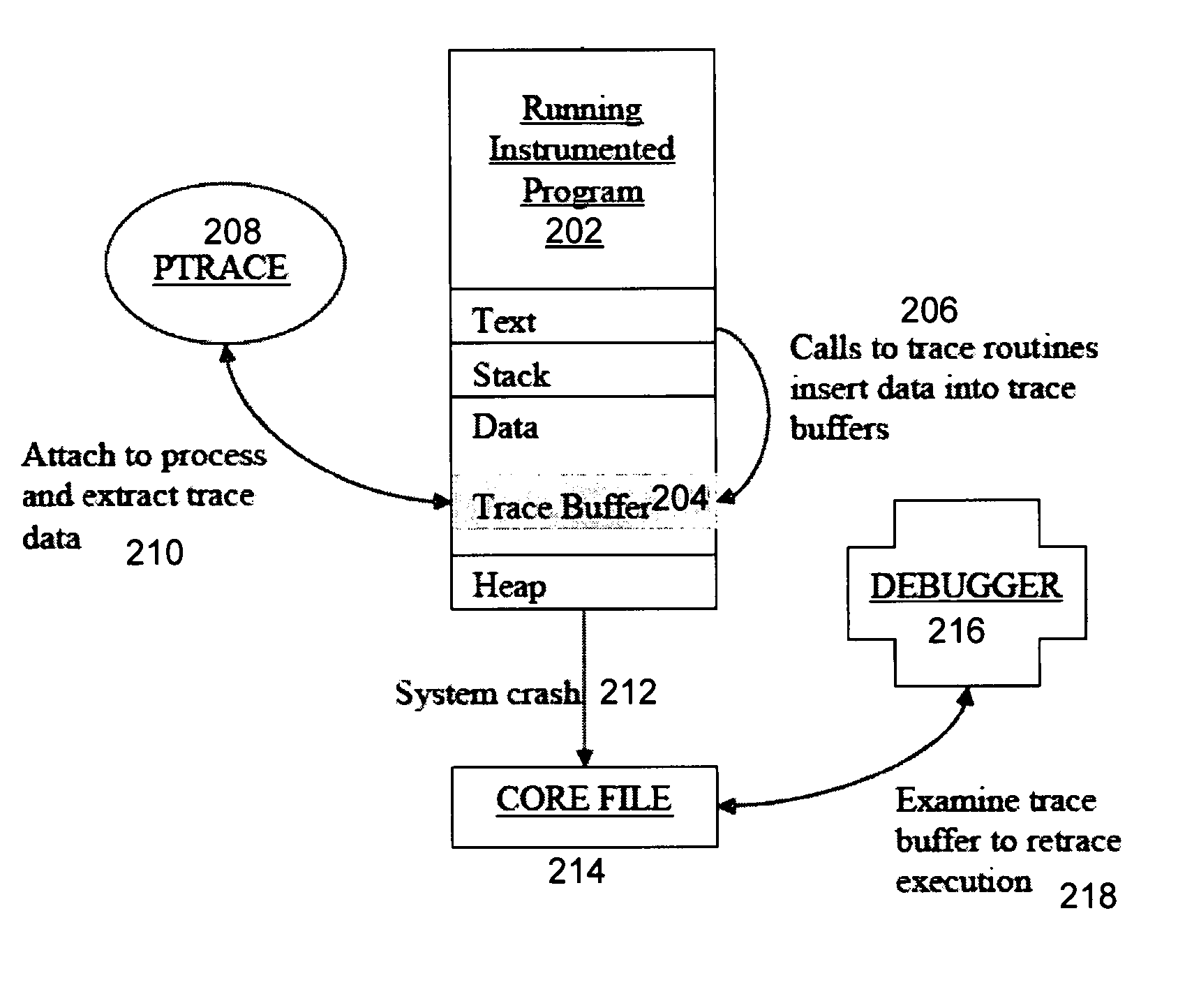

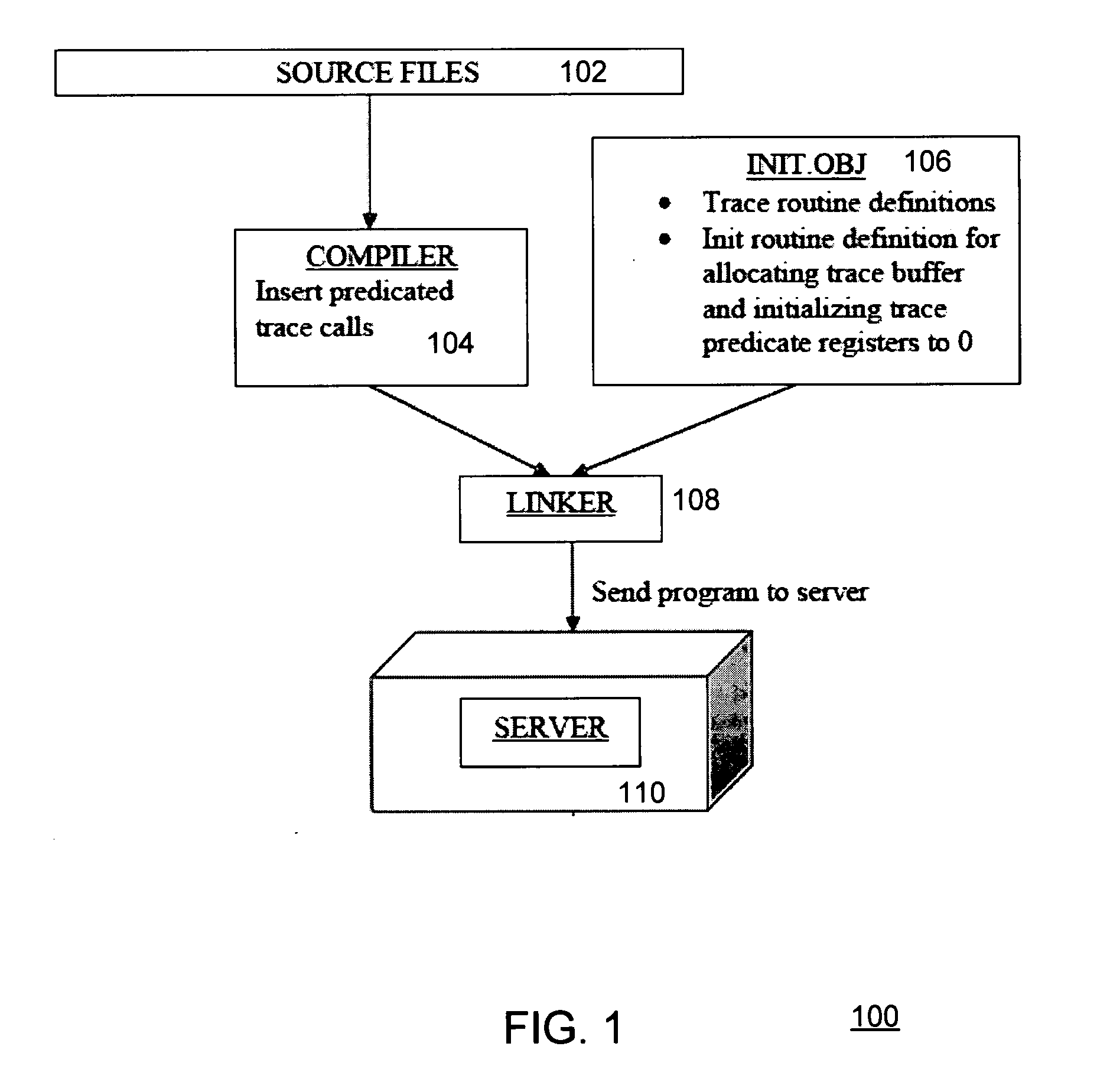

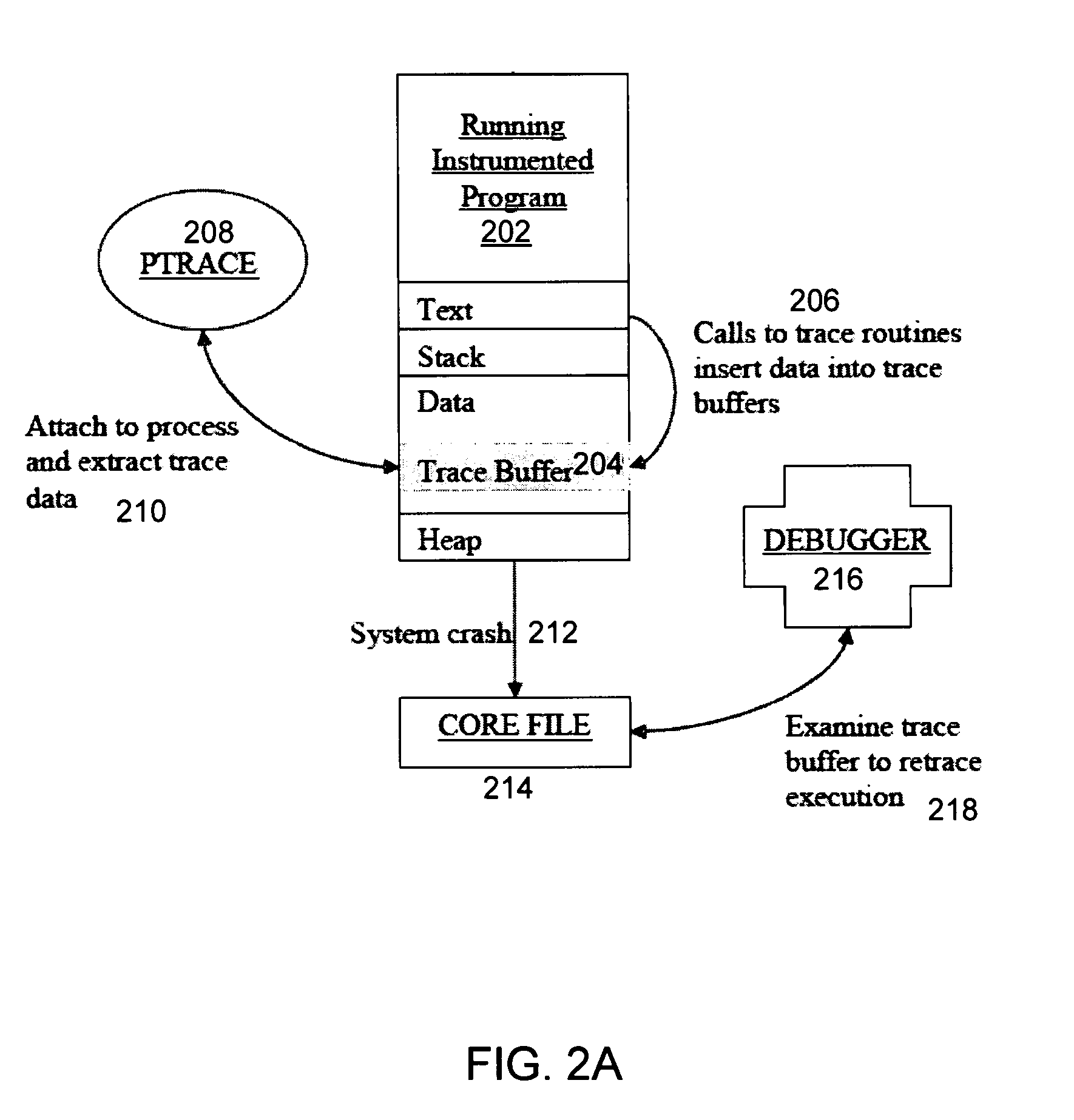

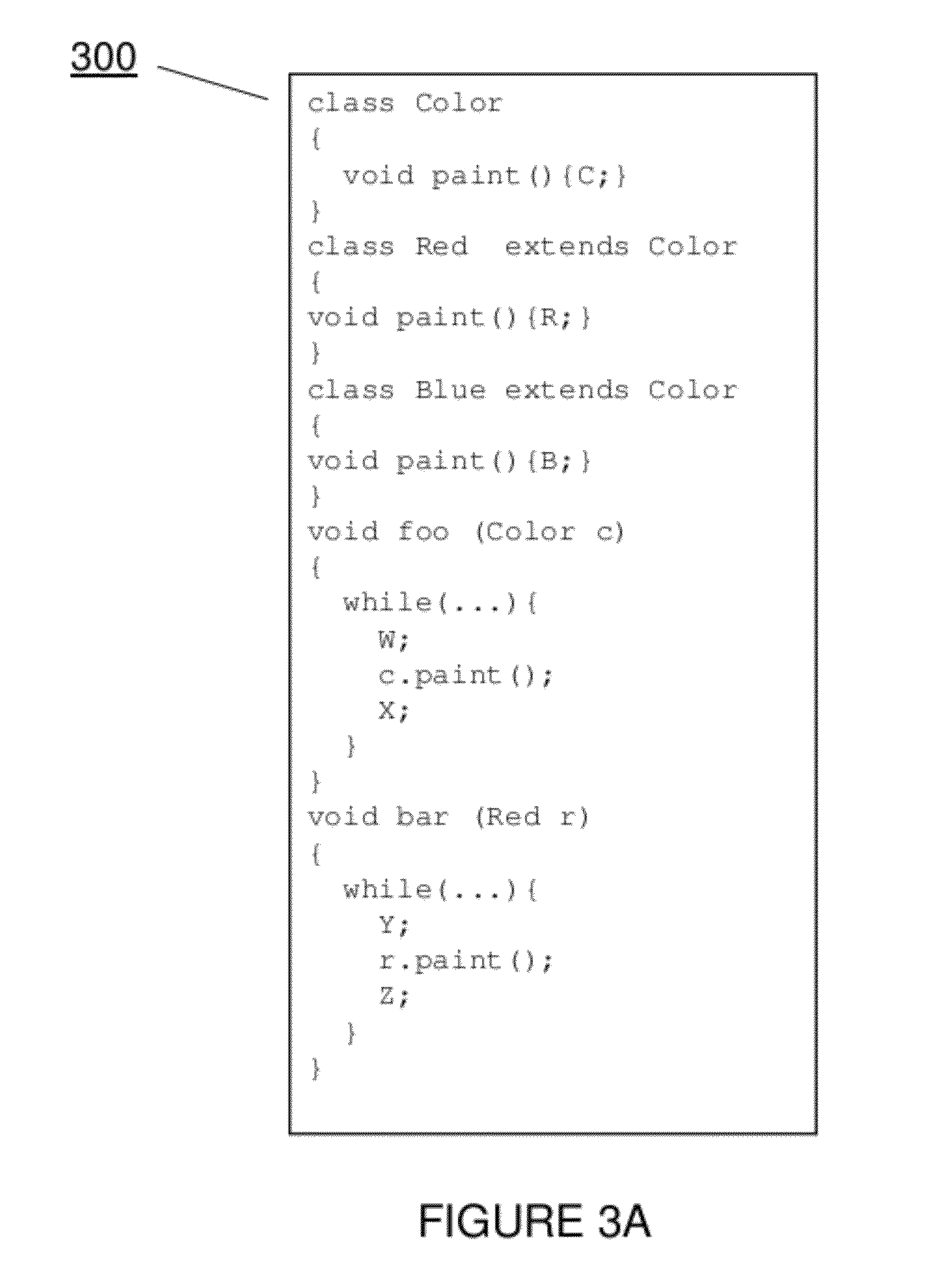

Compiler-inserted predicated tracing

InactiveUS20090037887A1Error detection/correctionSpecific program execution arrangementsObject codeParallel computing

One embodiment relates to a computer-implemented method of generating an executable program which includes inserting predicated calls to trace routines during compilation of the source code. Each predicated call comprises a function call that is conditional upon a value stored in a predicate register. The object code generated from compiling said source code is subsequently linked with object code which includes the trace routines. Another embodiment relates to a computer-implemented method of executing a deployed computer program with low-level tracing using compiler-inserted predicated tracing calls. A tracing mode is enabled by setting one or more predicate register bits in a microprocessor. Predicated calls to trace routines insert trace data into at least one trace buffer. Upon a system crash, a core file including said trace data is written out. Other embodiments, aspects and features are also disclosed.

Owner:HEWLETT PACKARD DEV CO LP

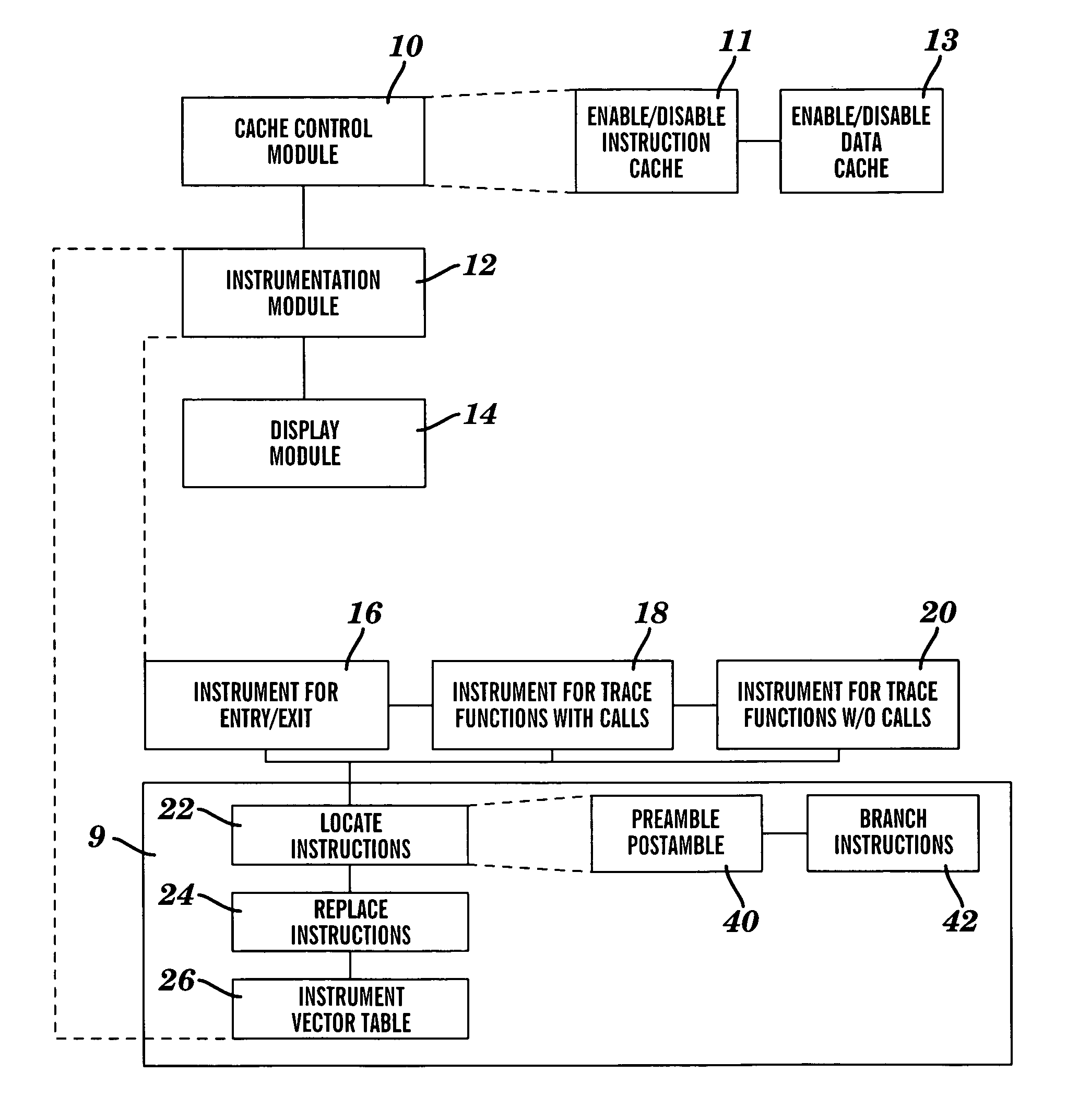

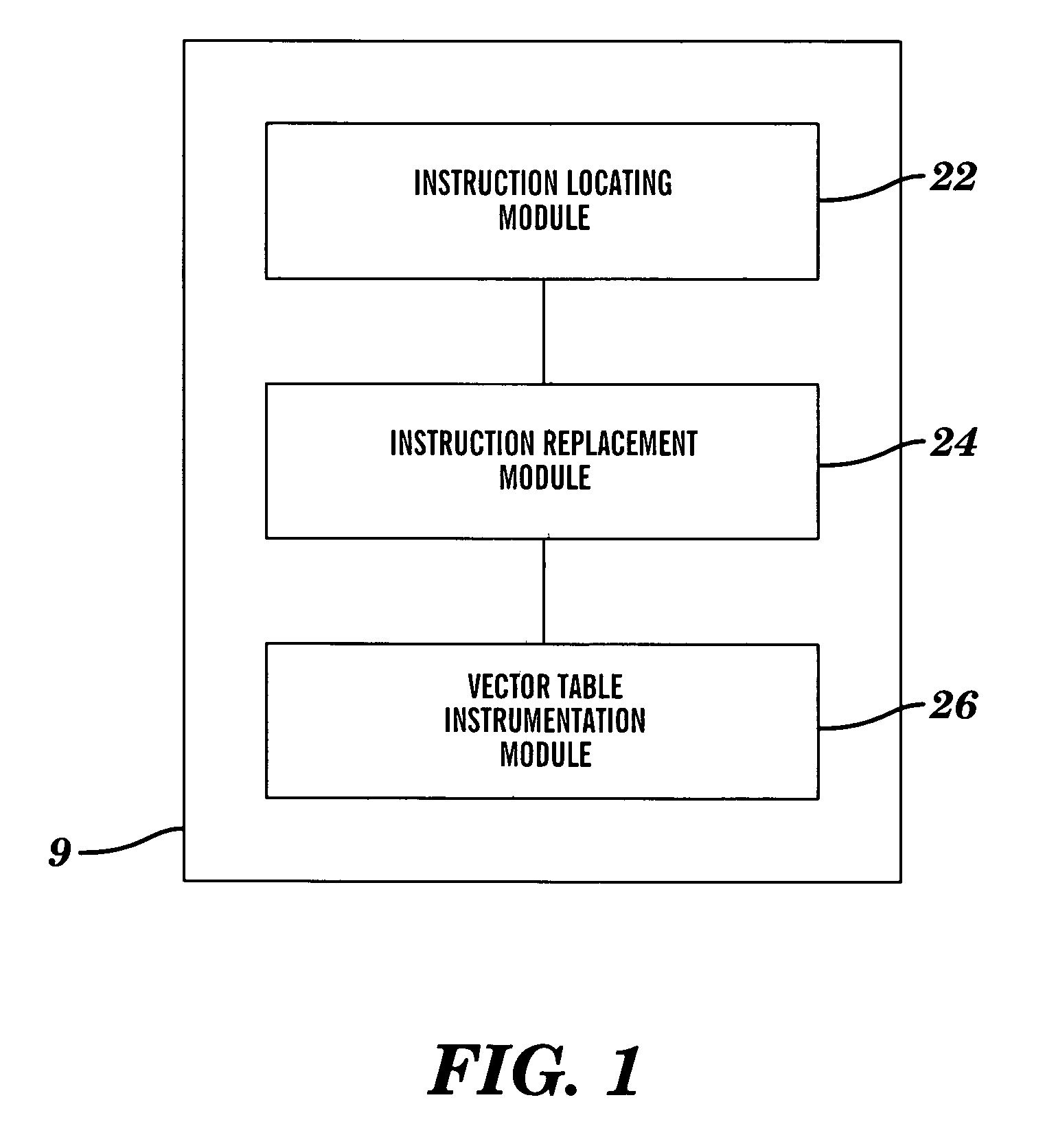

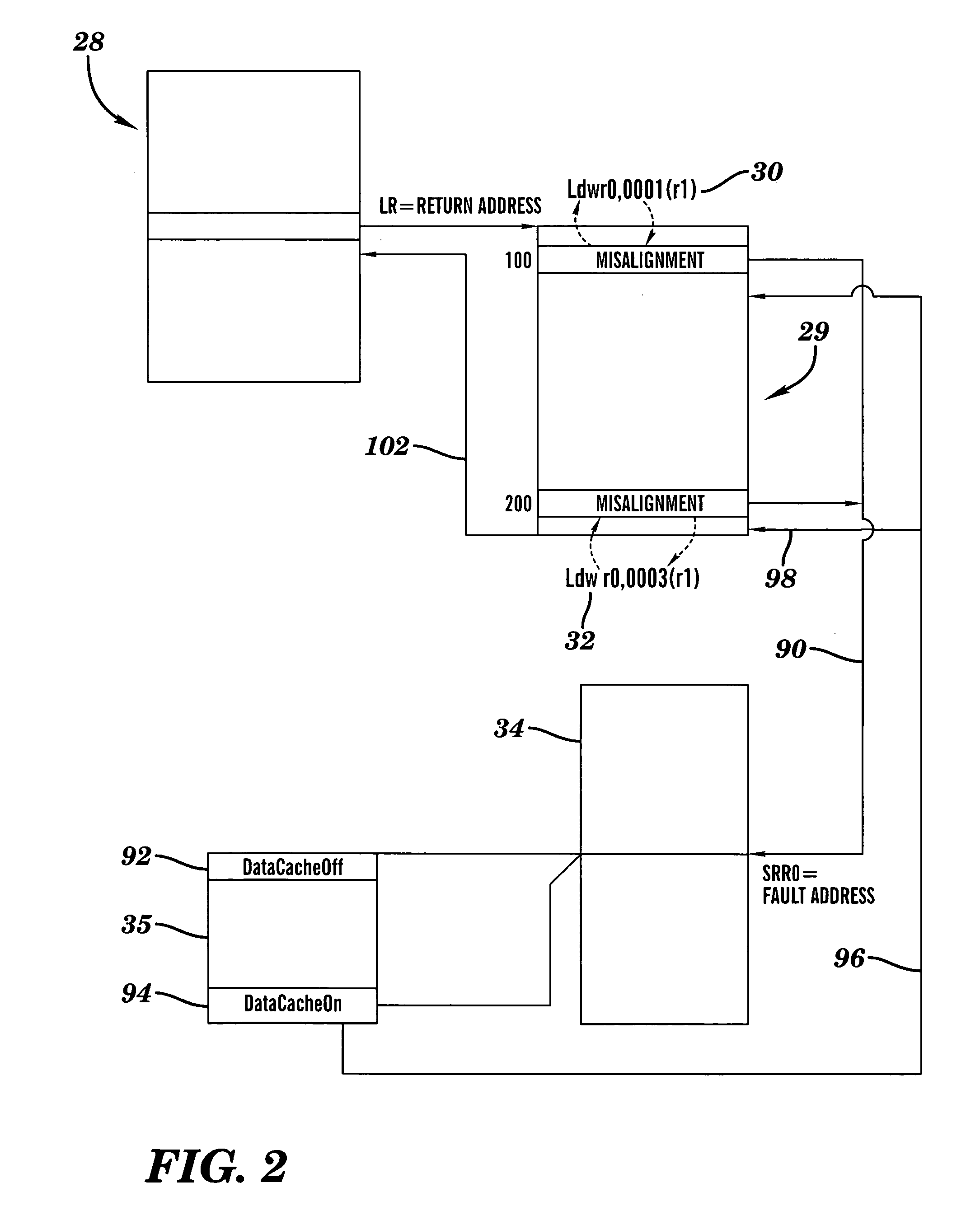

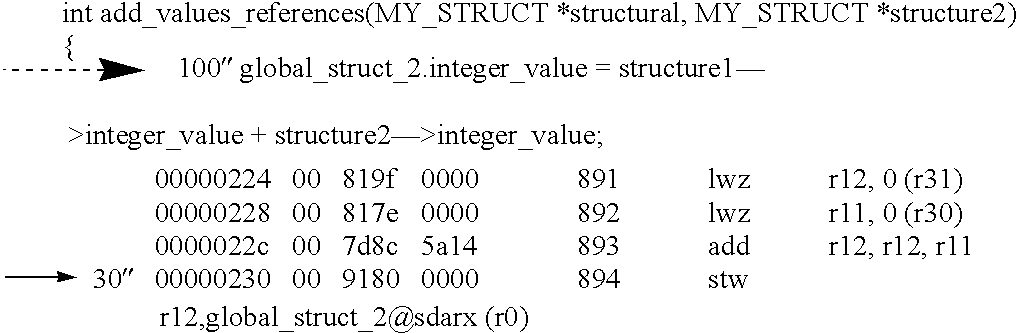

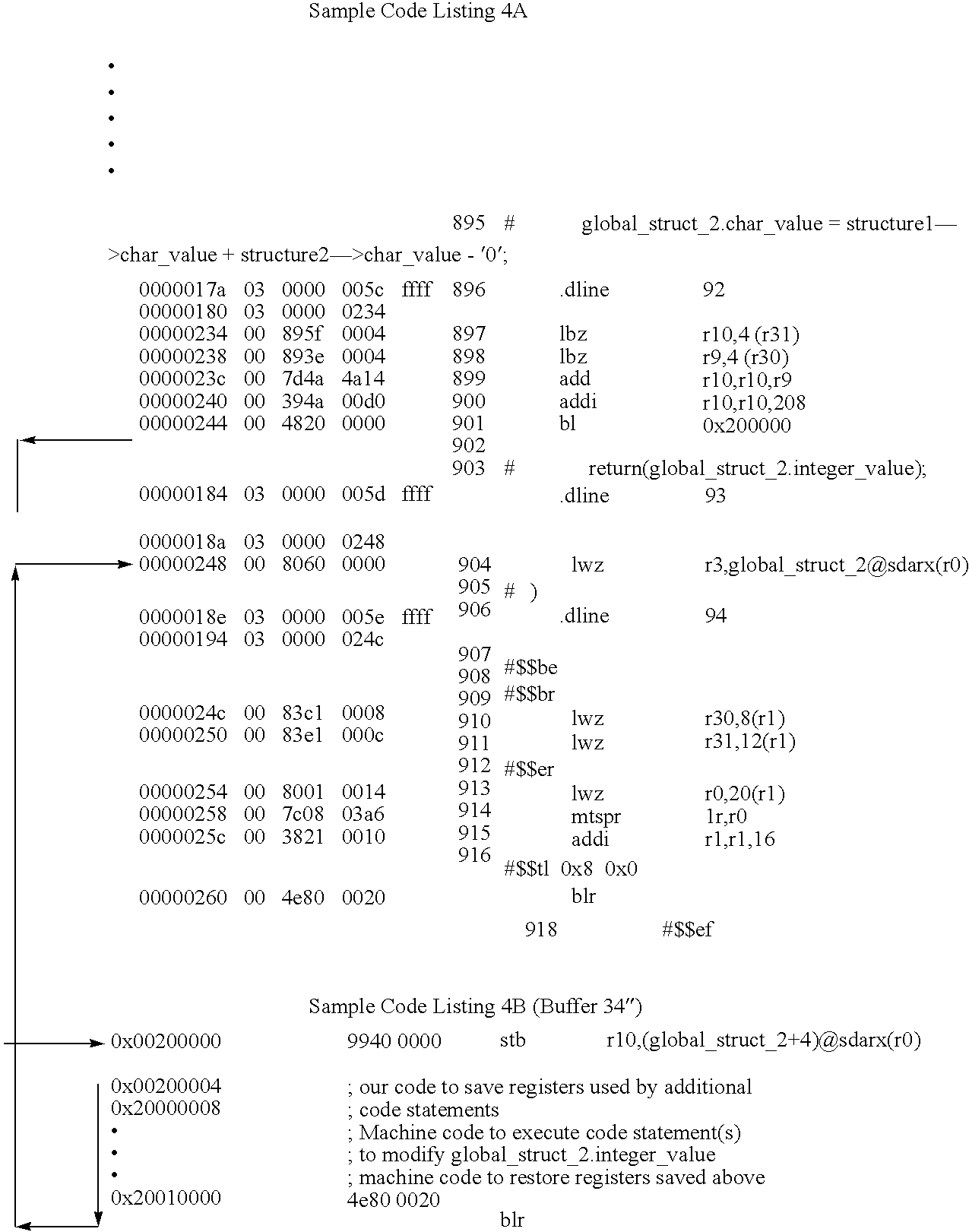

Dynamic software code instrumentation method and system

A method and system of monitoring code after being compiled or assembled is provided. Software code instructions, such as a function preamble and / or a data manipulation instruction, are identified using debug information and then dynamically replaced with an instruction that will branch execution to a scratchpad buffer. A routine is inserted into the scratchpad buffer, and includes instruction(s) to generate output to a trace buffer. Subsequent instructions in the scratchpad may execute the replaced instruction(s) and branch back to the address of the program code immediately following the original address of the replaced instruction.

Owner:WIND RIVER SYSTEMS

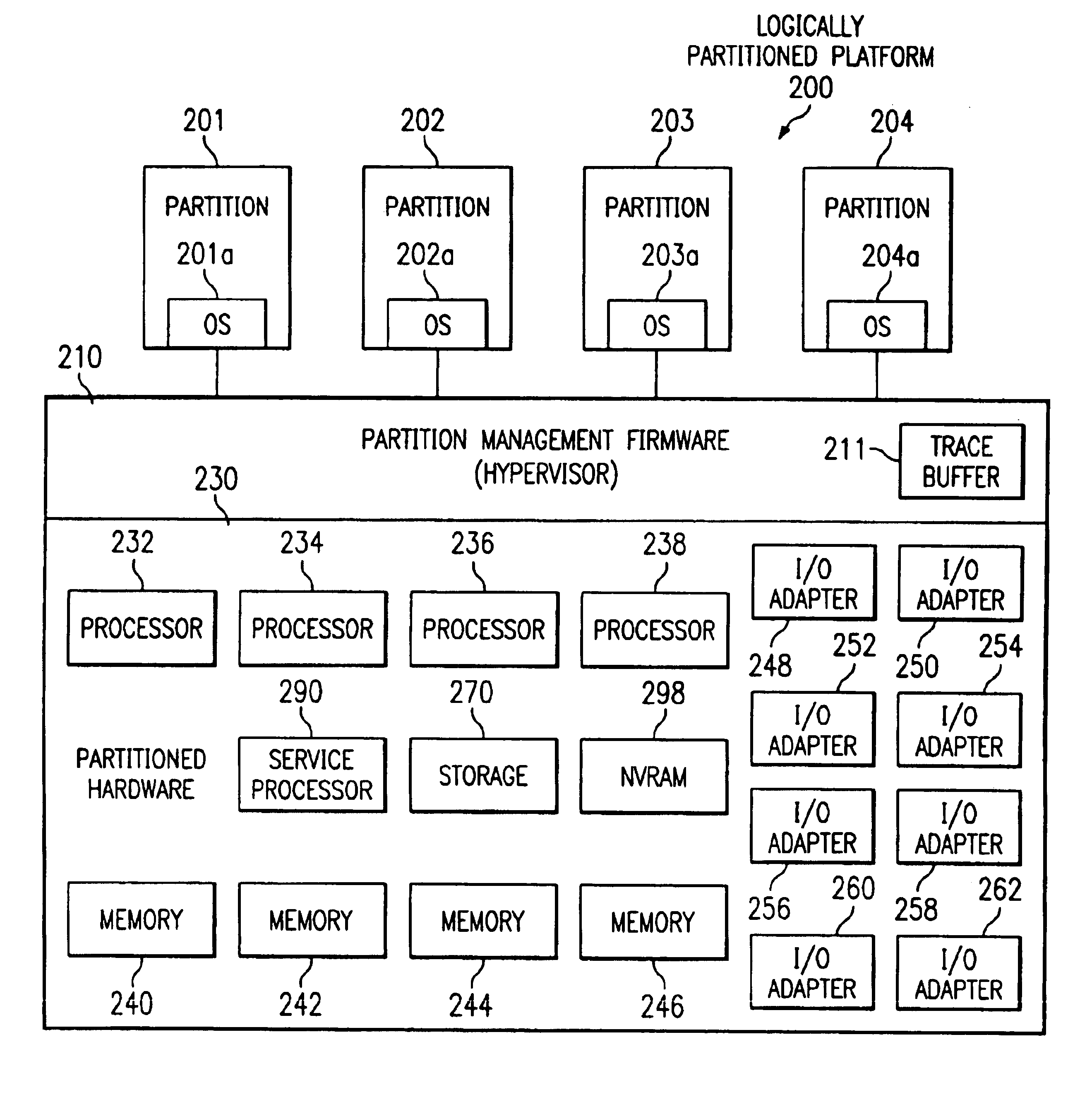

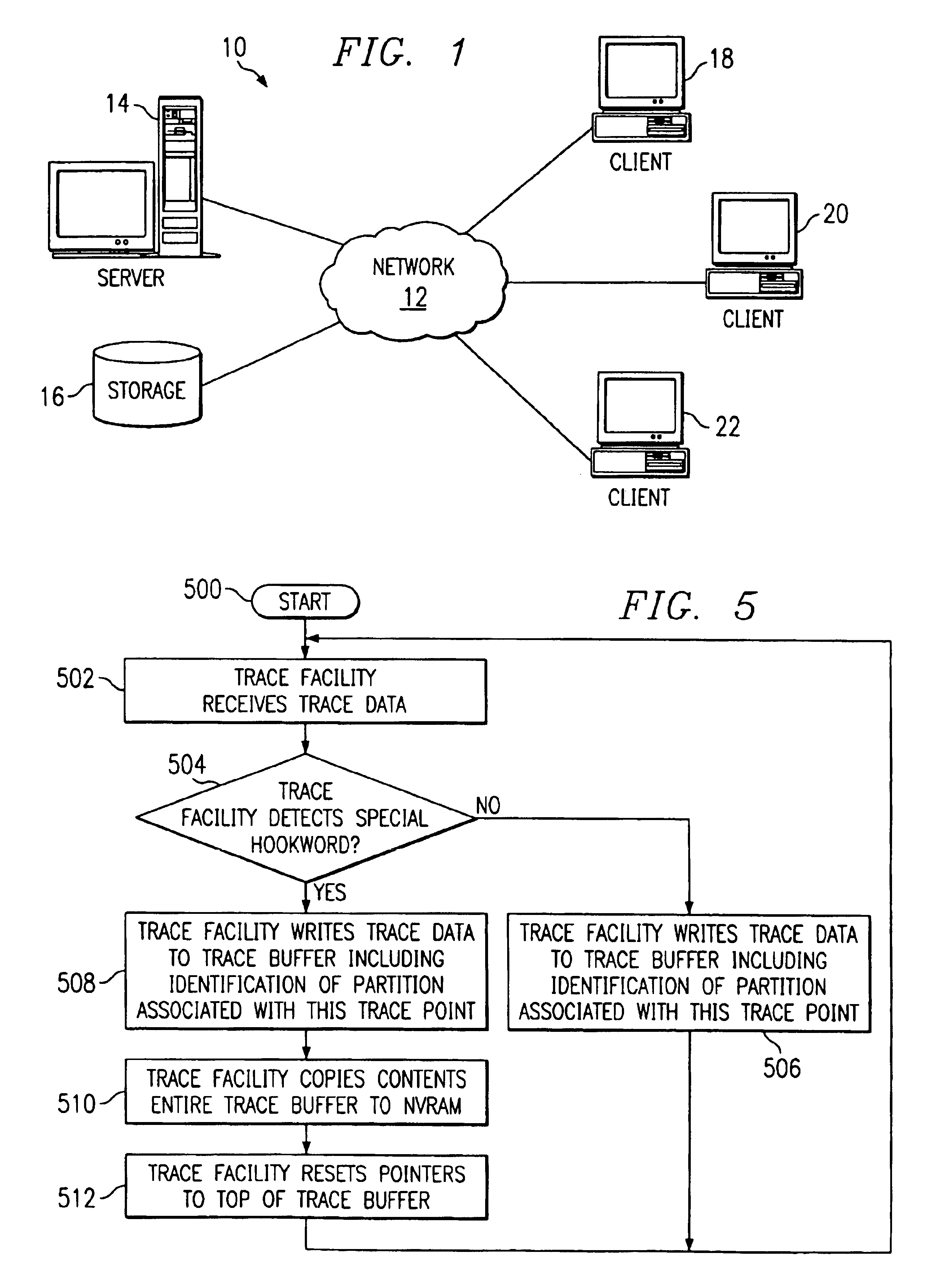

System, method, and computer program product for preserving trace data after partition crash in logically partitioned systems

InactiveUS6910160B2Reliability increasing modificationsInput/output to record carriersData processing systemTrace buffer

A system, method, and product in a logically partitioned data processing system are disclosed for preserving trace data after a partition crash. The logically partitioned data processing system includes multiple, different processors. An error is encountered in one of the processors. Data associated with the error is stored in a trace buffer. Contents of the trace buffer are stored prior to the data being overwritten.

Owner:IBM CORP

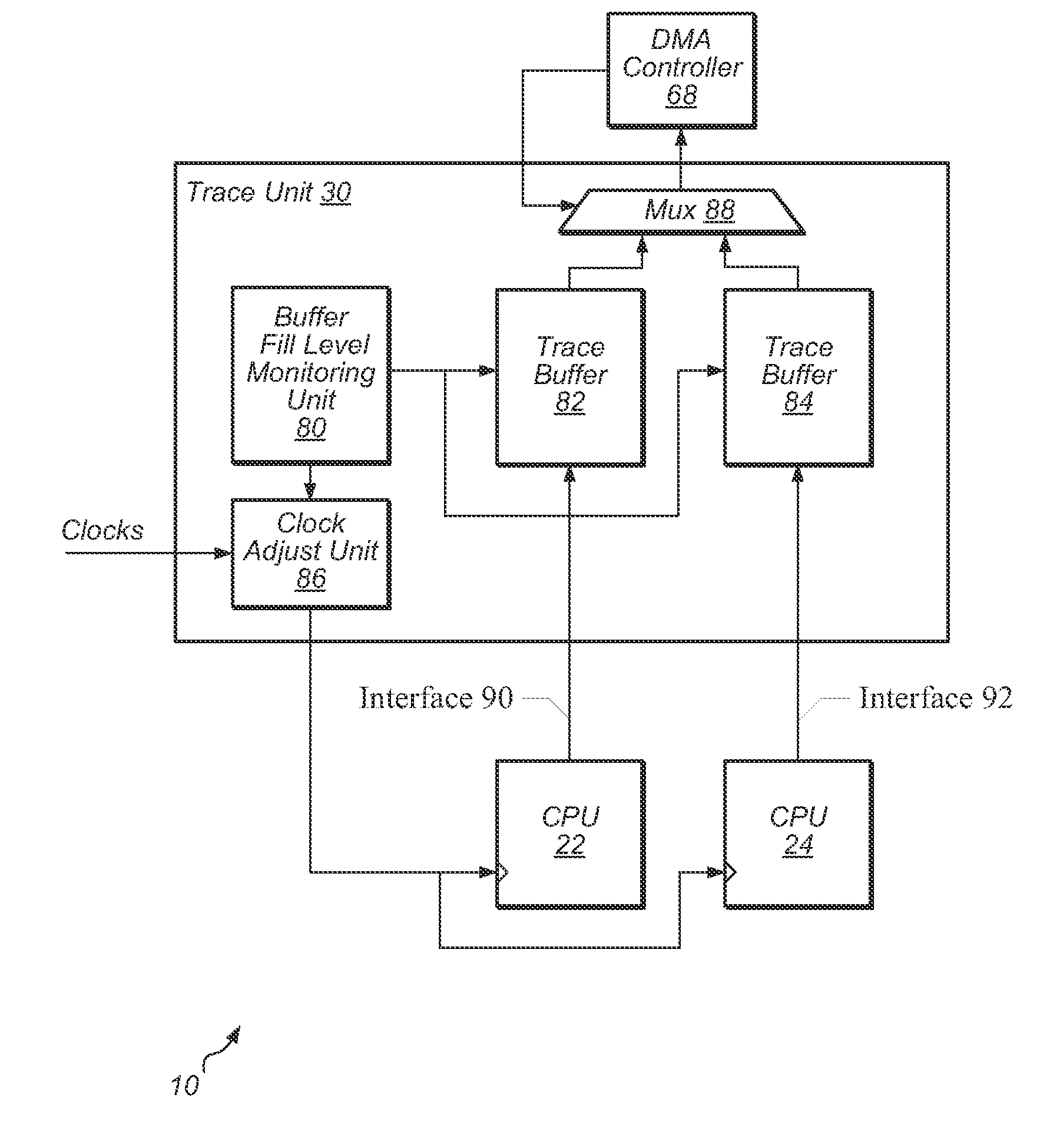

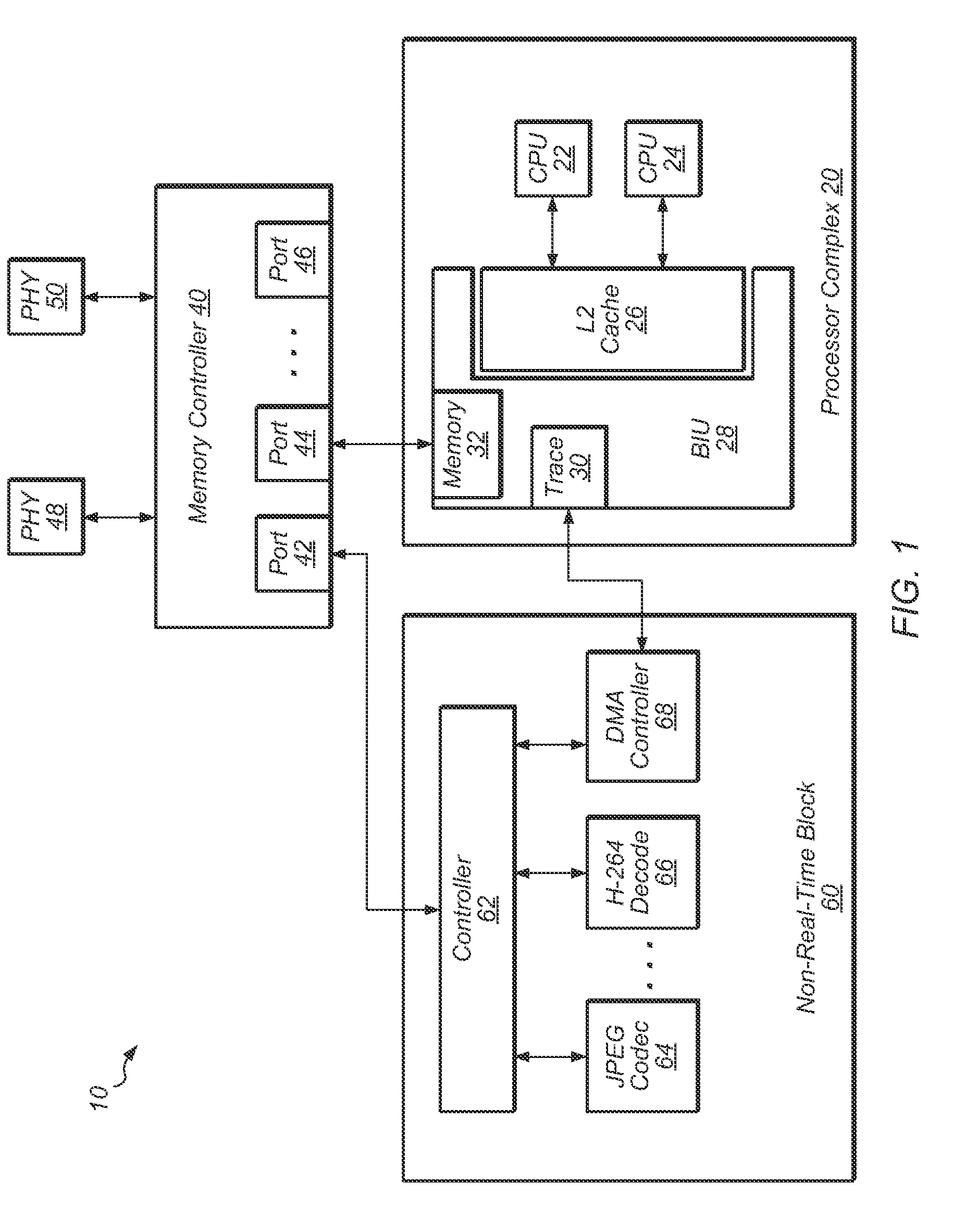

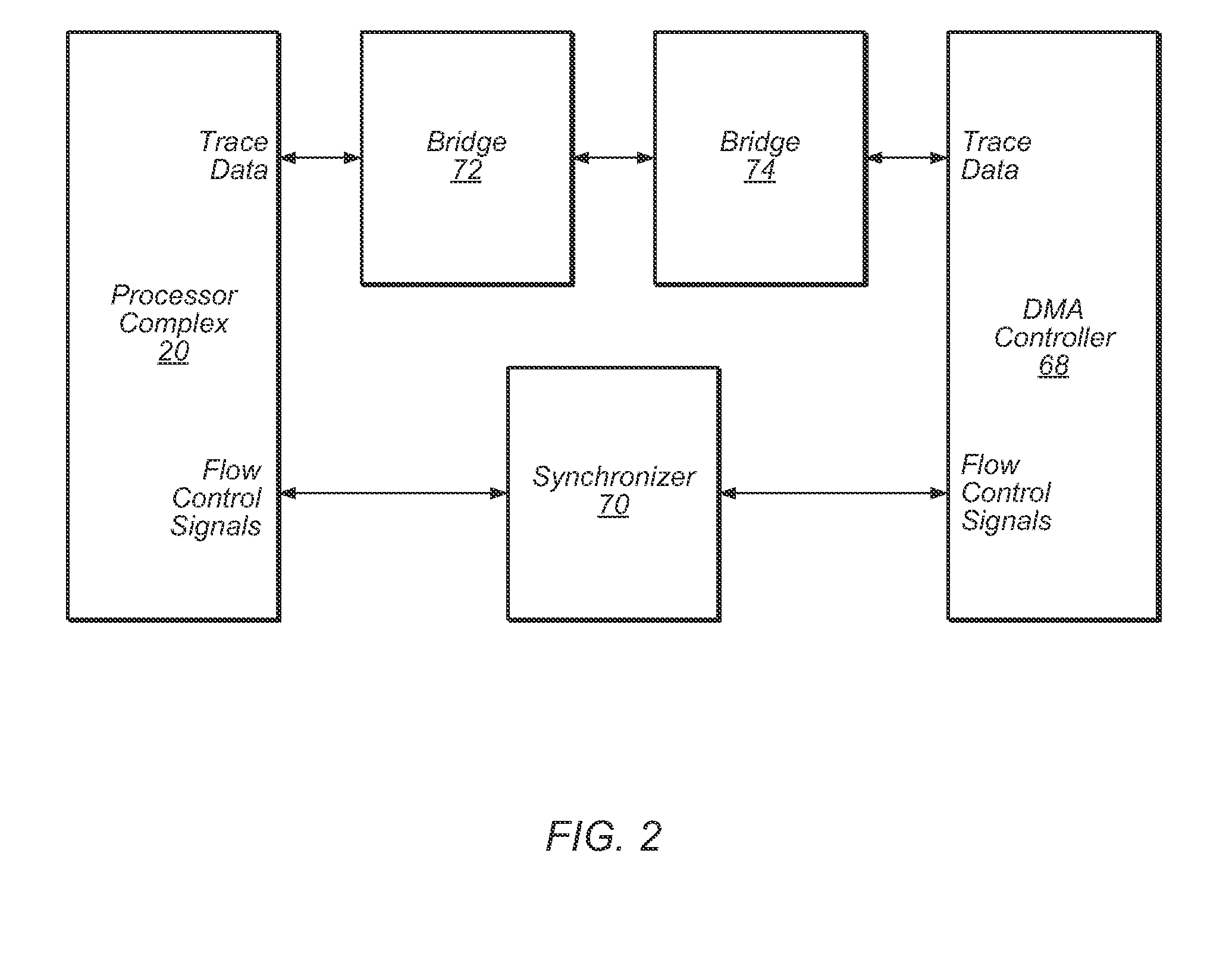

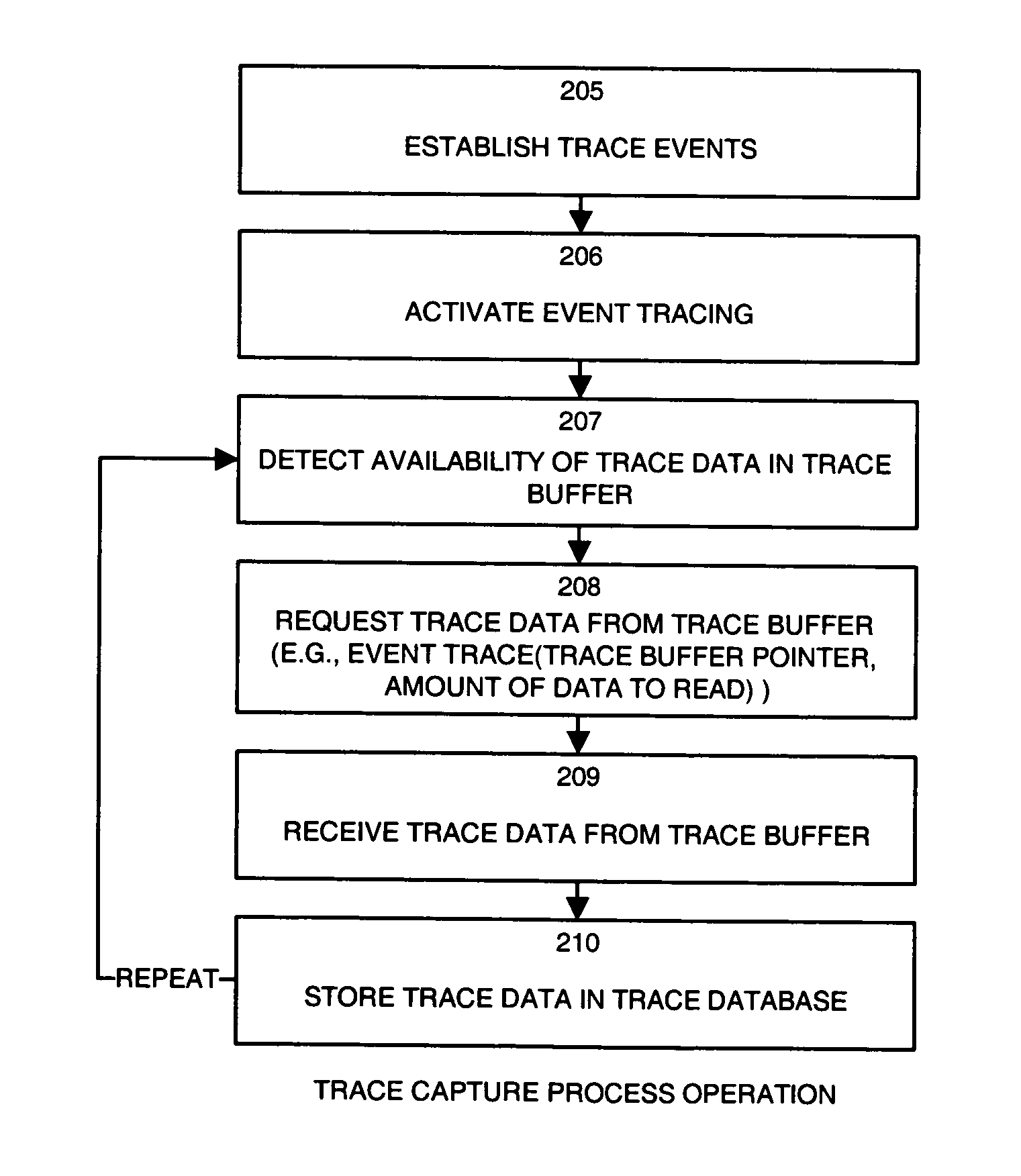

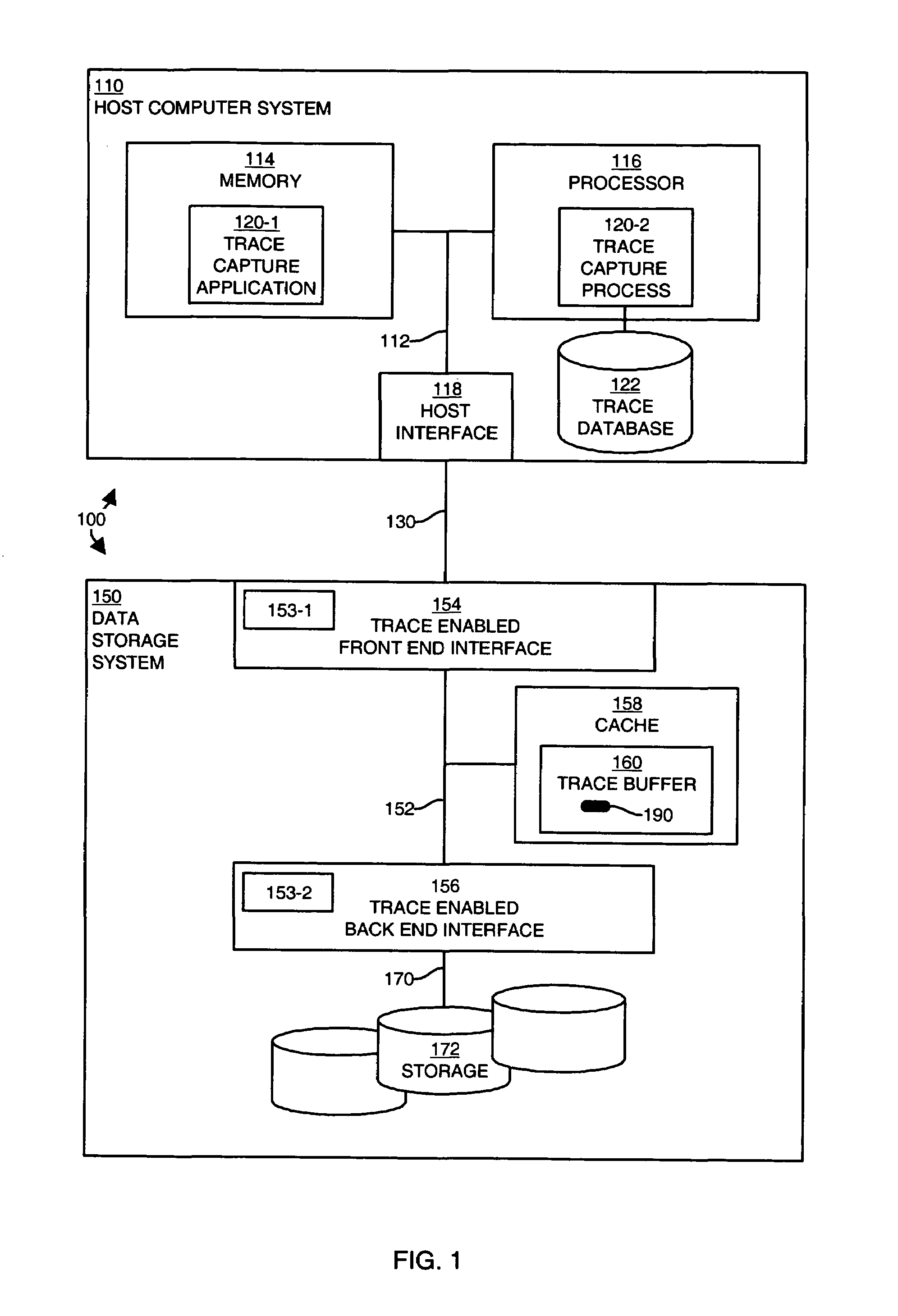

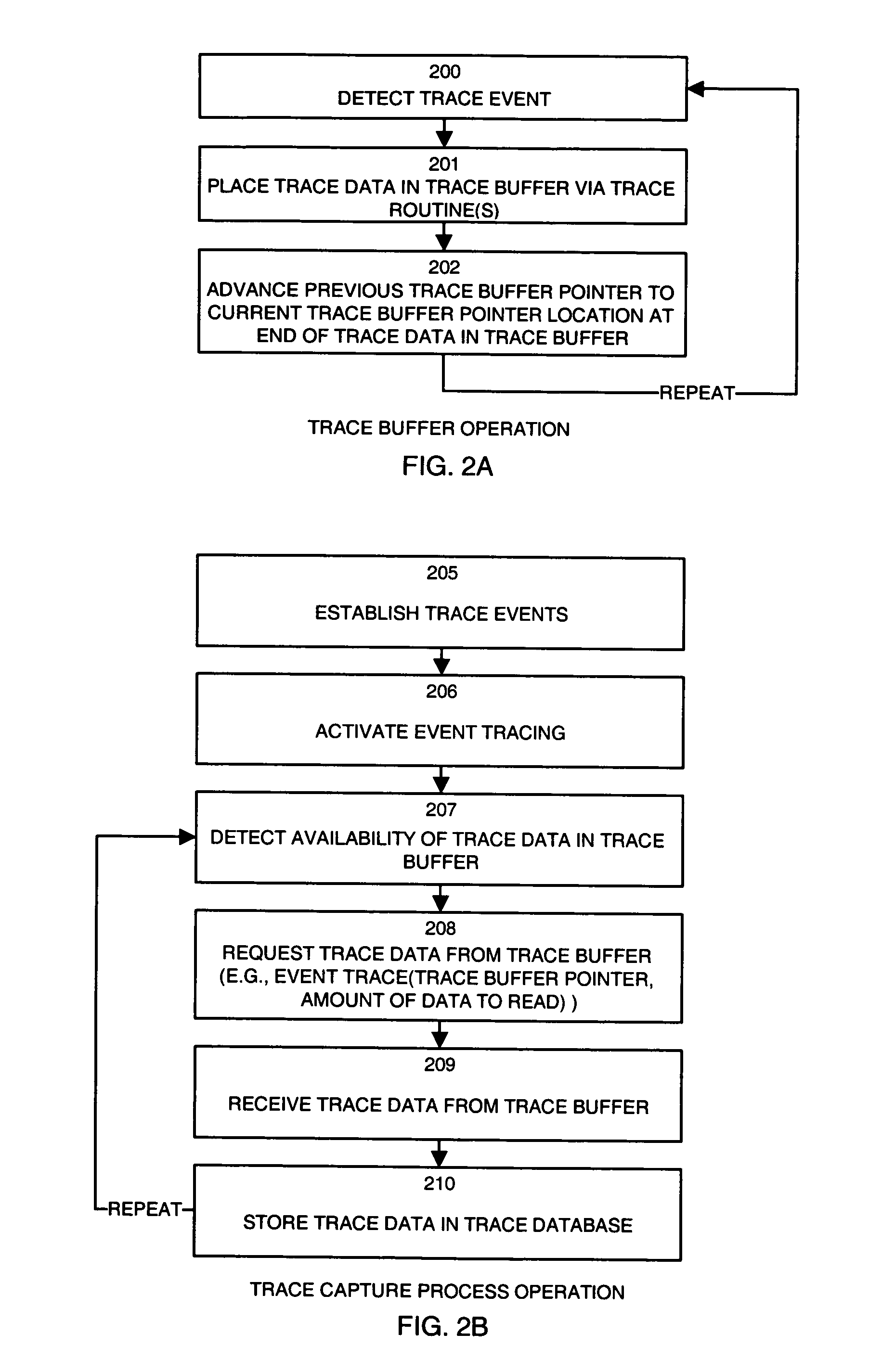

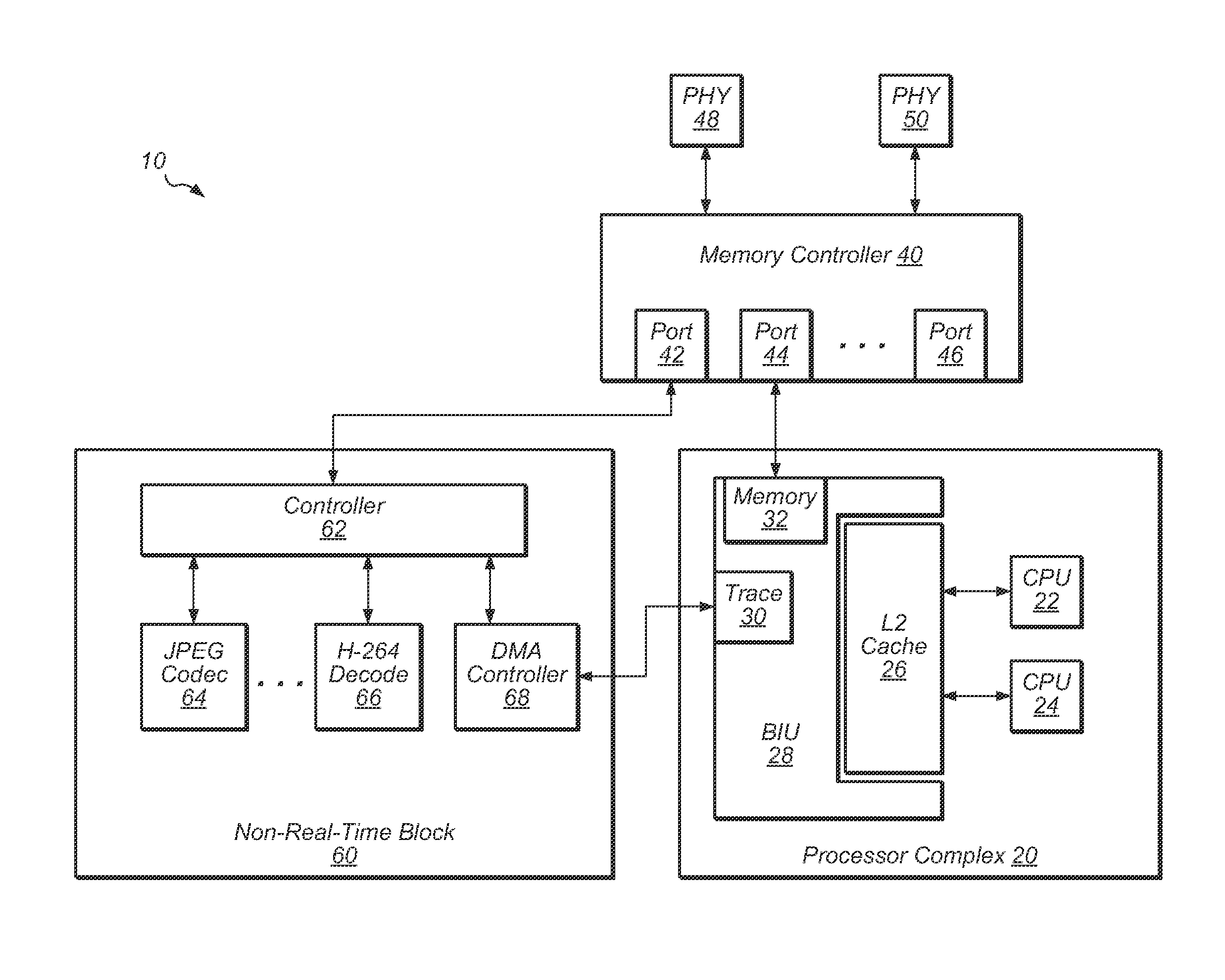

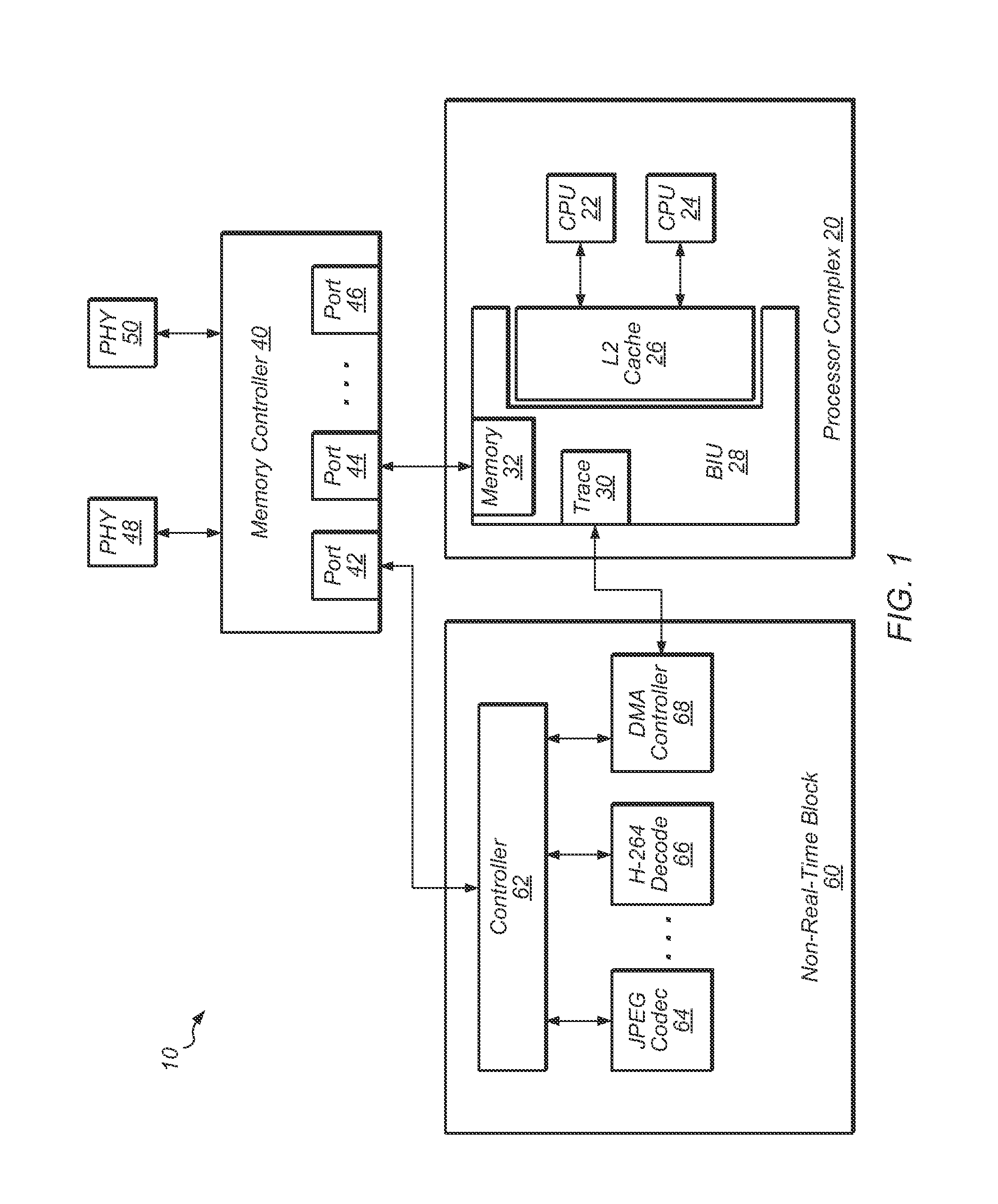

Non-intrusive processor tracing

A system, apparatus, and method for writing trace data to storage. Trace data is captured from one or more processors, and then the trace data is written to a trace buffer. The trace data includes program counters of instructions executed by the processors and other debug data. A direct memory access (DMA) controller in a non-real-time block of the system reads trace data from the trace buffer and then writes the trace data to memory via a non-real-time port of a memory controller.

Owner:APPLE INC

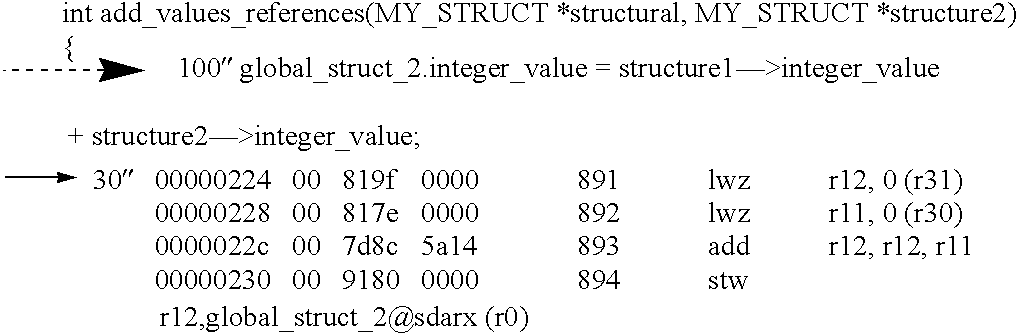

Methods and apparatus for accessing trace data

InactiveUS7260692B1Reduce in quantityOvercome deficienciesHardware monitoringSoftware testing/debuggingData accessSystem call

A system provides mechanisms and techniques to retrieve trace data from a trace buffer residing in a data storage system. The software program operating on a processor within the data storage system operates in trace mode to produce trace data in the trace buffer upon occurrence of trace events. An event trace routine operates in response to a system call to access the trace buffer and return either a current value of a trace buffer pointer or the current trace buffer pointer as well as trace data read from the trace buffer beginning at a location and in an amount as specified in the system call to the event trace routine. The trace capture process can operate either within the data storage system or preferably on a remote host computer system to access trace data in the trace buffer in the data storage system by using the event trace routine. The trace capture process can periodically query the event trace routine with a frequency determined by an adaptive timing algorithm in order to detect the addition of trace data to the trace buffer. Upon detecting such a condition, the trace capture process can use the event trace routine to retrieve the trace data from the trace buffer. The trace capture process can also detect if trace data is written beyond the end of the trace buffer and can perform the proper sequence of trace data access operations using the event trace routine in order to provide continuous remote access to all trace data produced in the trace buffer.

Owner:EMC IP HLDG CO LLC

Dynamic software code instrumentation method and system

A method and system of monitoring code after being compiled or assembled is provided. Software code instructions, such as a function preamble and / or a data manipulation instruction, are identified using debug information and then dynamically replaced with an instruction that will branch execution to a scratchpad buffer. A routine is inserted into the scratchpad buffer, and includes instruction(s) to generate output to a trace buffer. Subsequent instructions in the scratchpad may execute the replaced instruction(s) and branch back to the address of the program code immediately following the original address of the replaced instruction.

Owner:WIND RIVER SYSTEMS

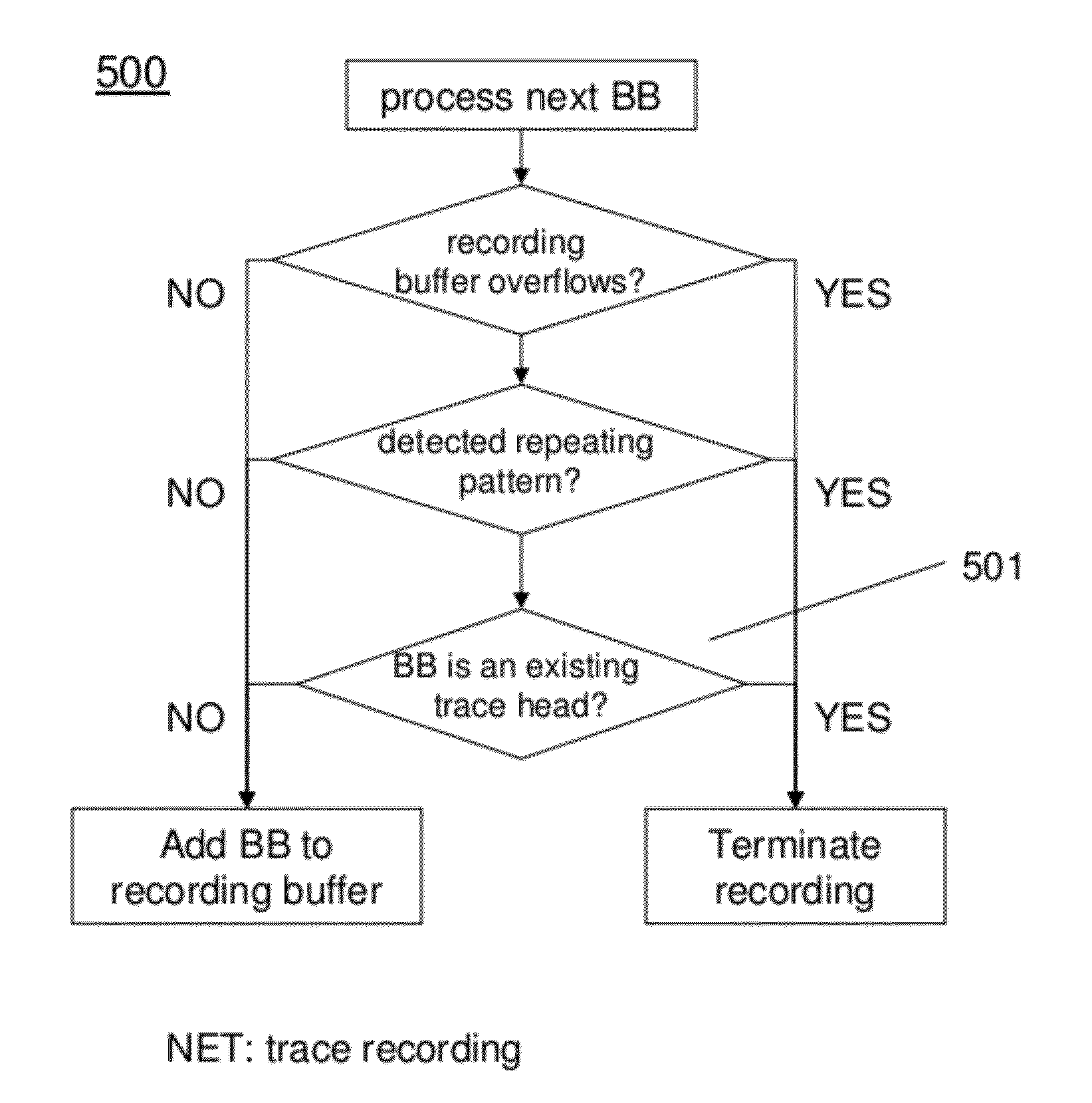

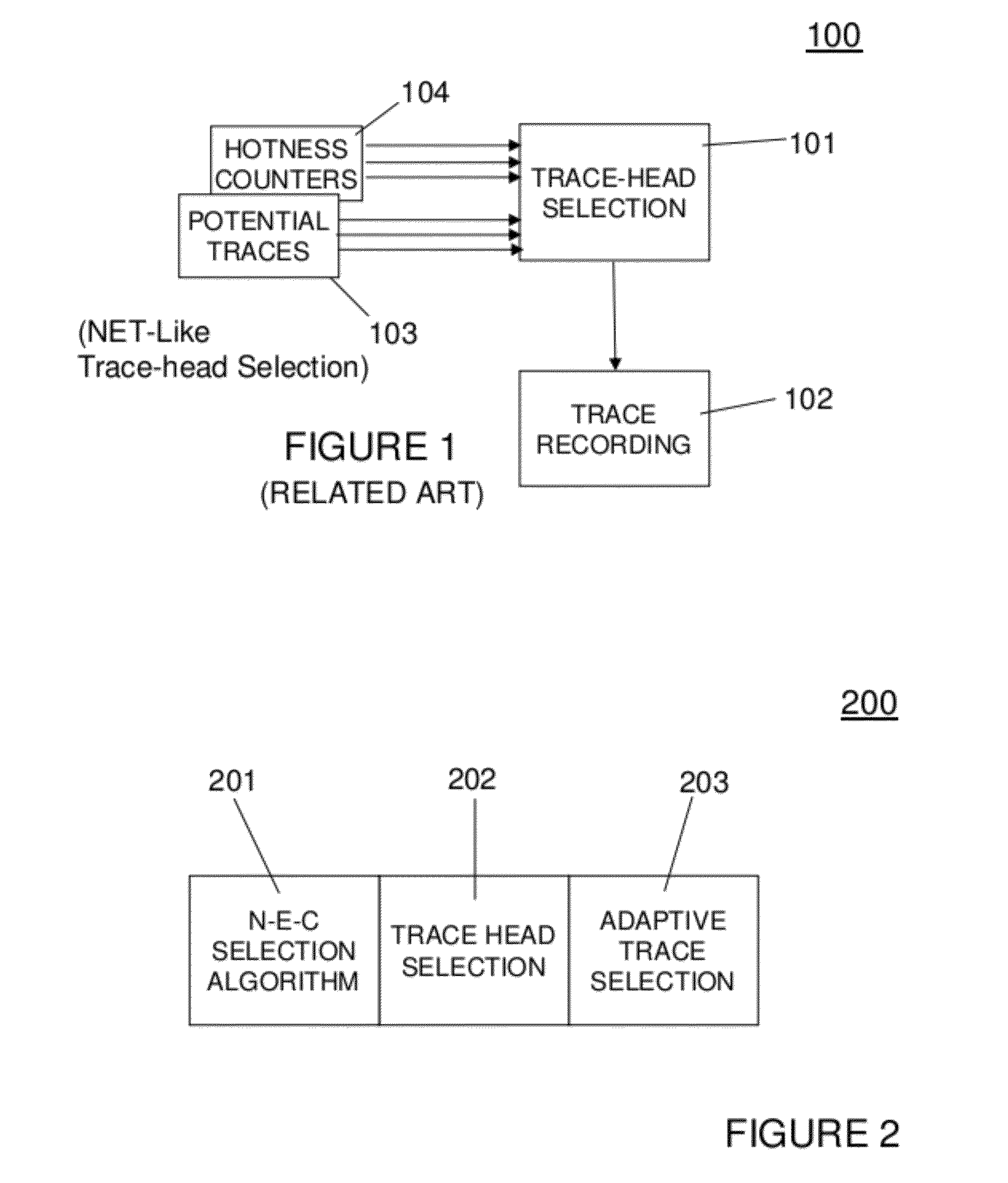

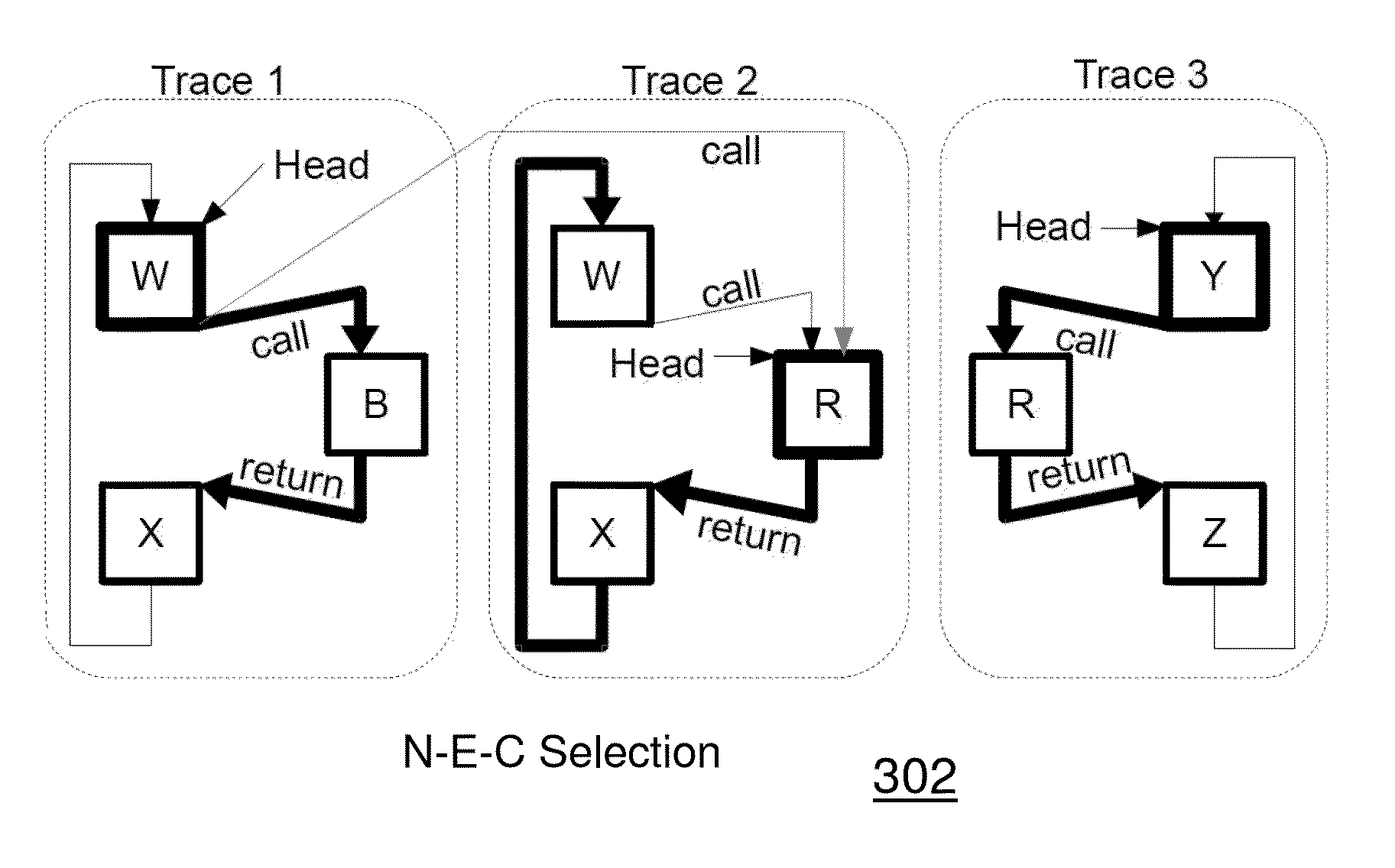

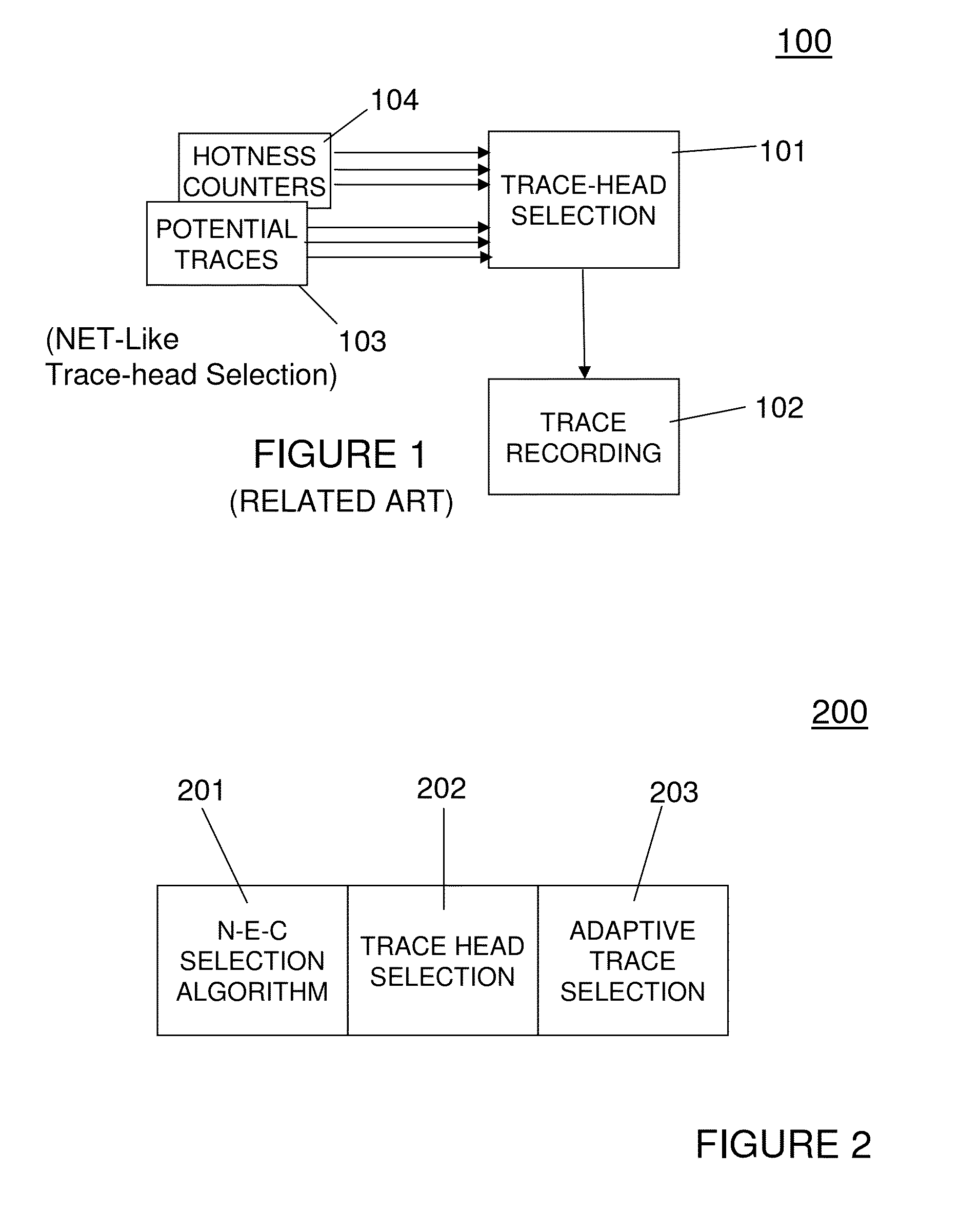

Adaptive next-executing-cycle trace selection for trace-driven code optimizers

ActiveUS20120204164A1Compilation is improvedReduce the amount of solutionSoftware engineeringProgram controlDynamic compilationParallel computing

An apparatus includes a processor for executing instructions at runtime and instructions for dynamically compiling the set of instructions executing at runtime. A memory device stores the instructions to be executed and the dynamic compiling instructions. A memory device serves as a trace buffer used to store traces during formation during the dynamic compiling. The dynamic compiling instructions includes a next-executing-cycle (N-E-C) trace selection process for forming traces for the instructions executing at runtime. The N-E-C trace selection process continues through an existing trace-head when forming traces without terminating a recording of a current trace if an existing trace-head is encountered.

Owner:GLOBALFOUNDRIES US INC

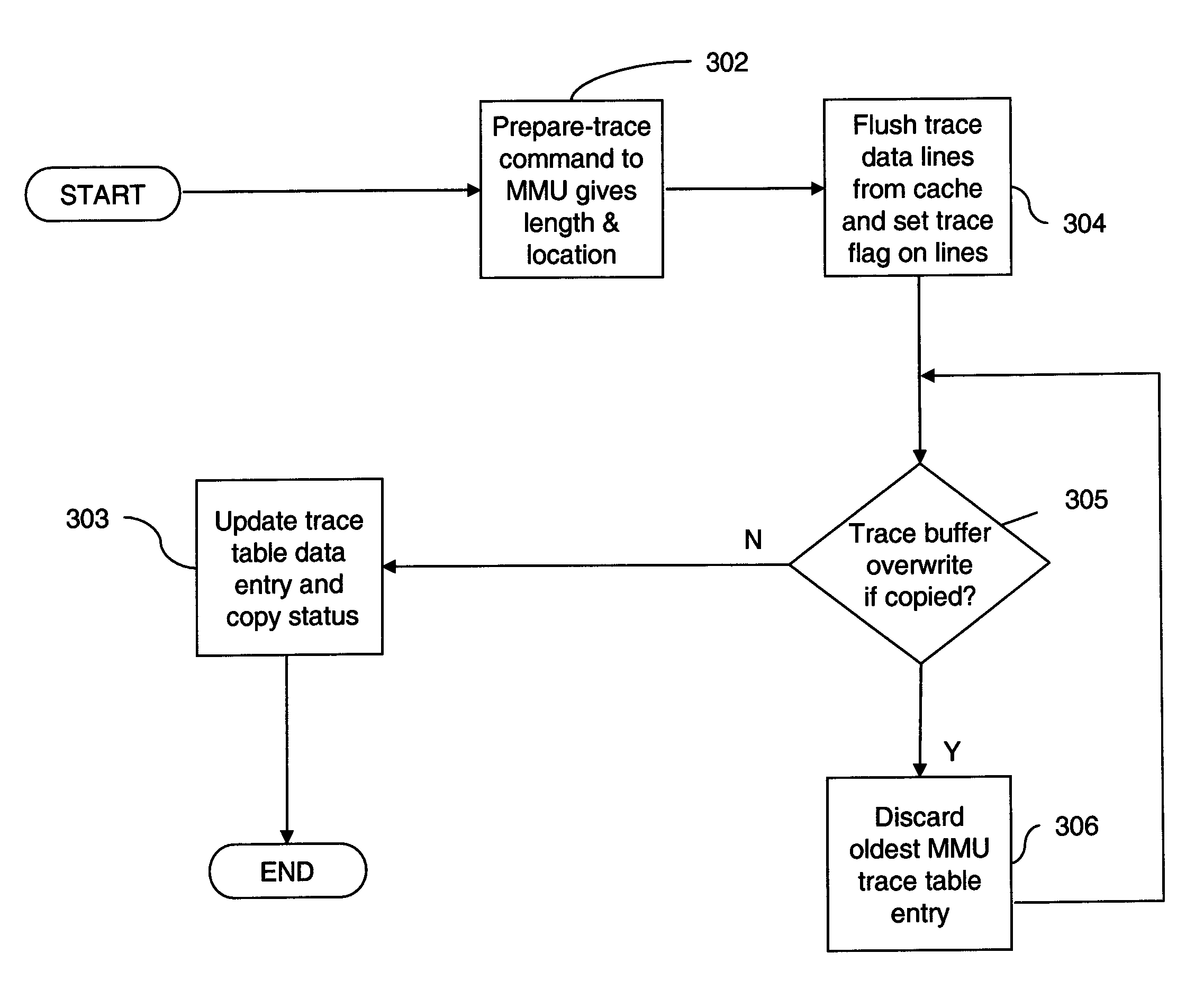

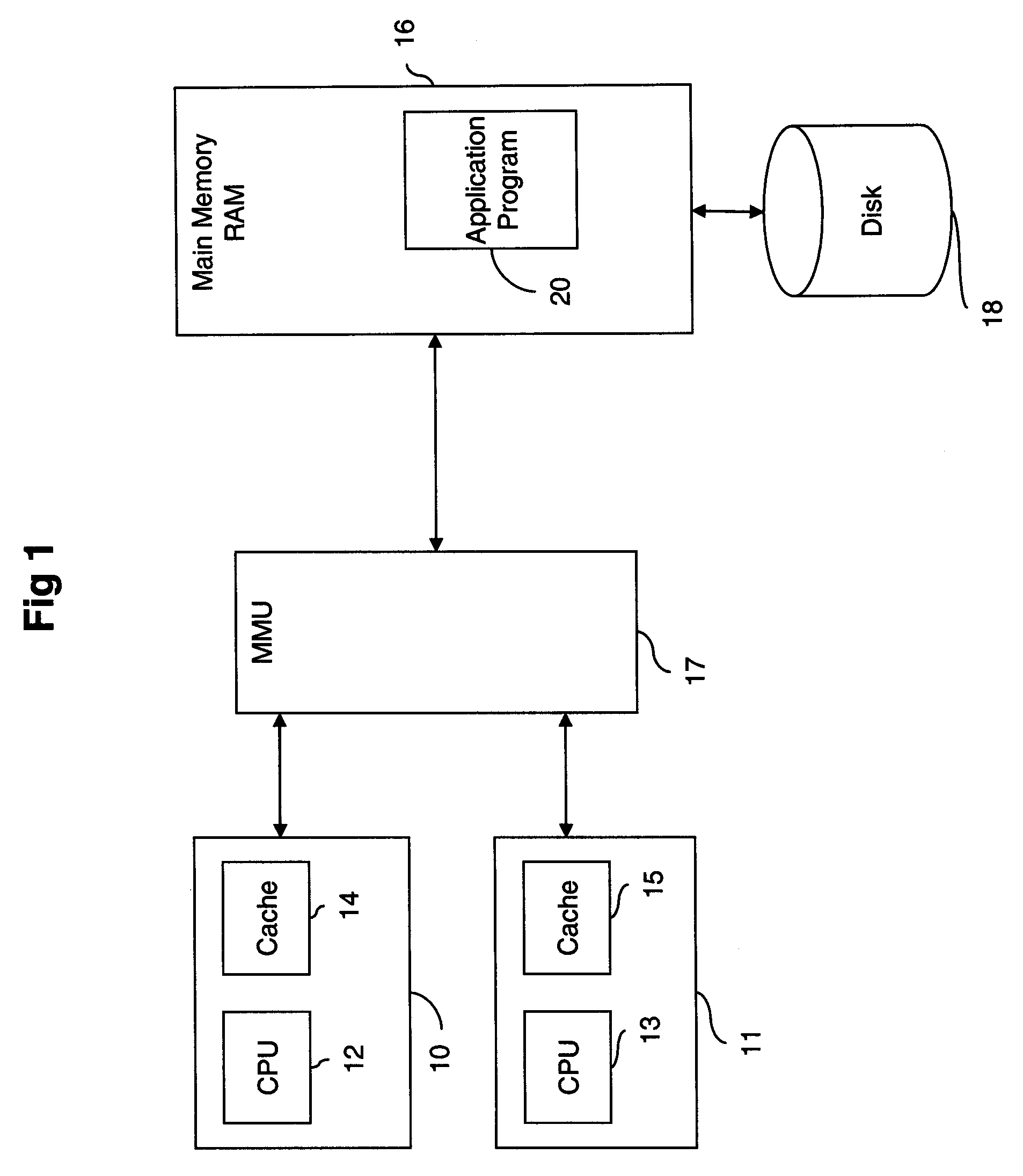

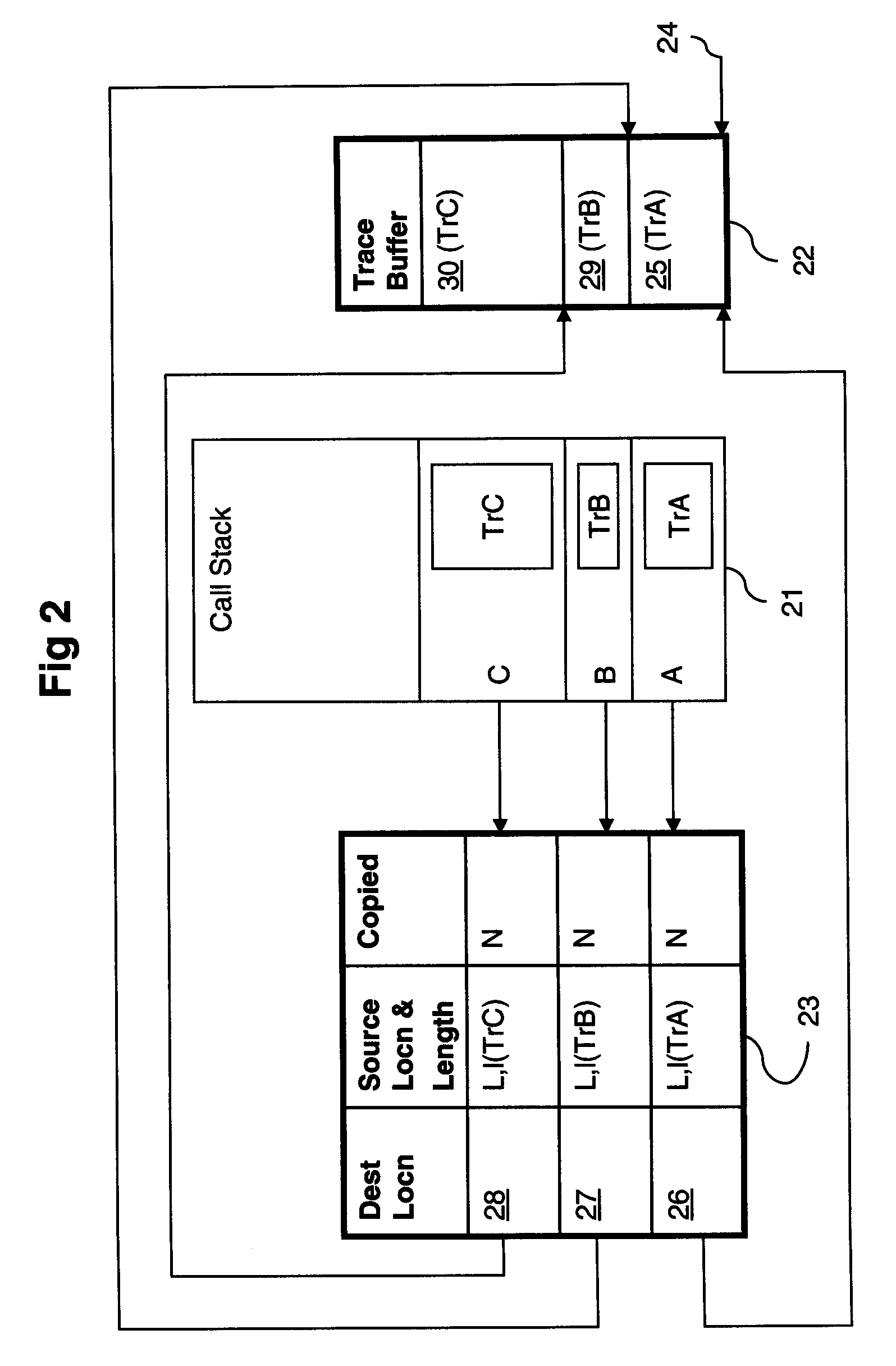

Managing the tracing of the execution of a computer program

InactiveUS20090113398A1Conserve costSaves processor cycles directlyError detection/correctionSpecific program execution arrangementsData processing systemParallel computing

A method and system for the management of tracing data of interest in a data processing system comprises identifying the location and length of one or more such units of interest as each unit is stored in main memory during execution of the program and recording a logical assignment of each unit of interest to a slot in a wrap around trace buffer. Copying of the units of interest to the trace buffer is deferred unless one or more predefined events occur. Such events may include an attempt to overwrite the data which has been logically assigned or a request for information stored in the trace buffer. The recorded assignments are discarded whenever it is calculated that the capacity of the trace buffer would be exceeded resulting in the corresponding units never needing to be copied to the trace buffer.

Owner:IBM CORP

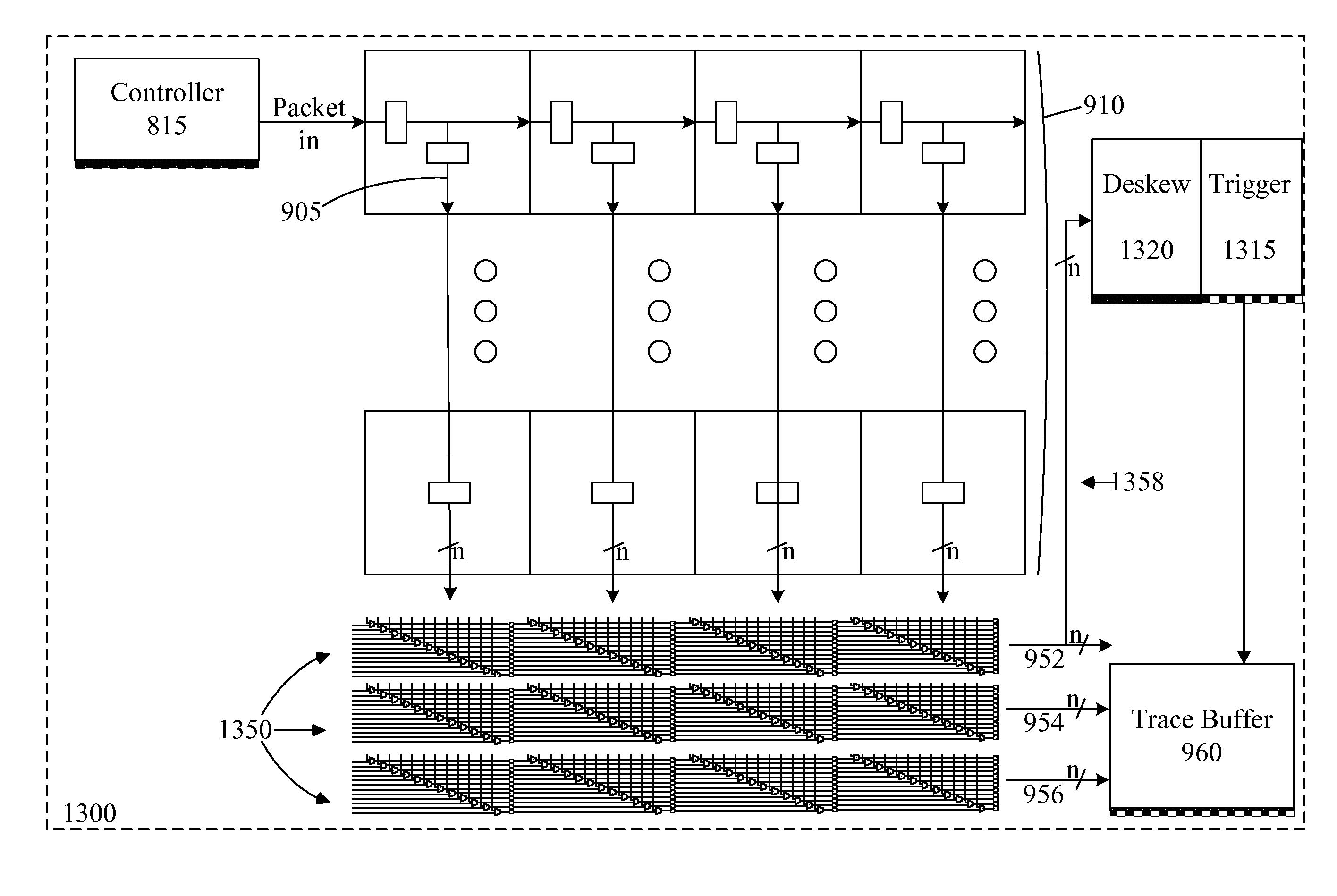

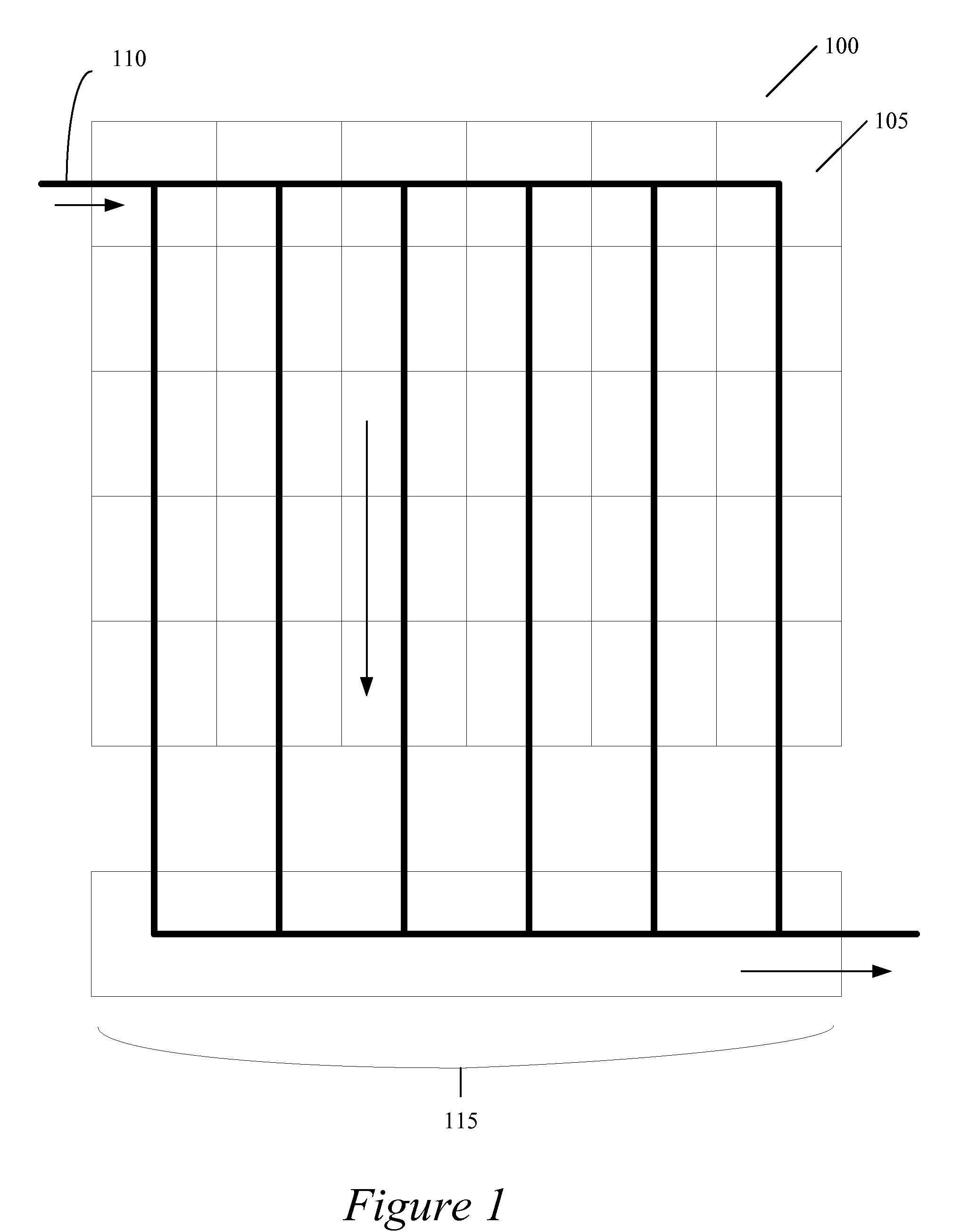

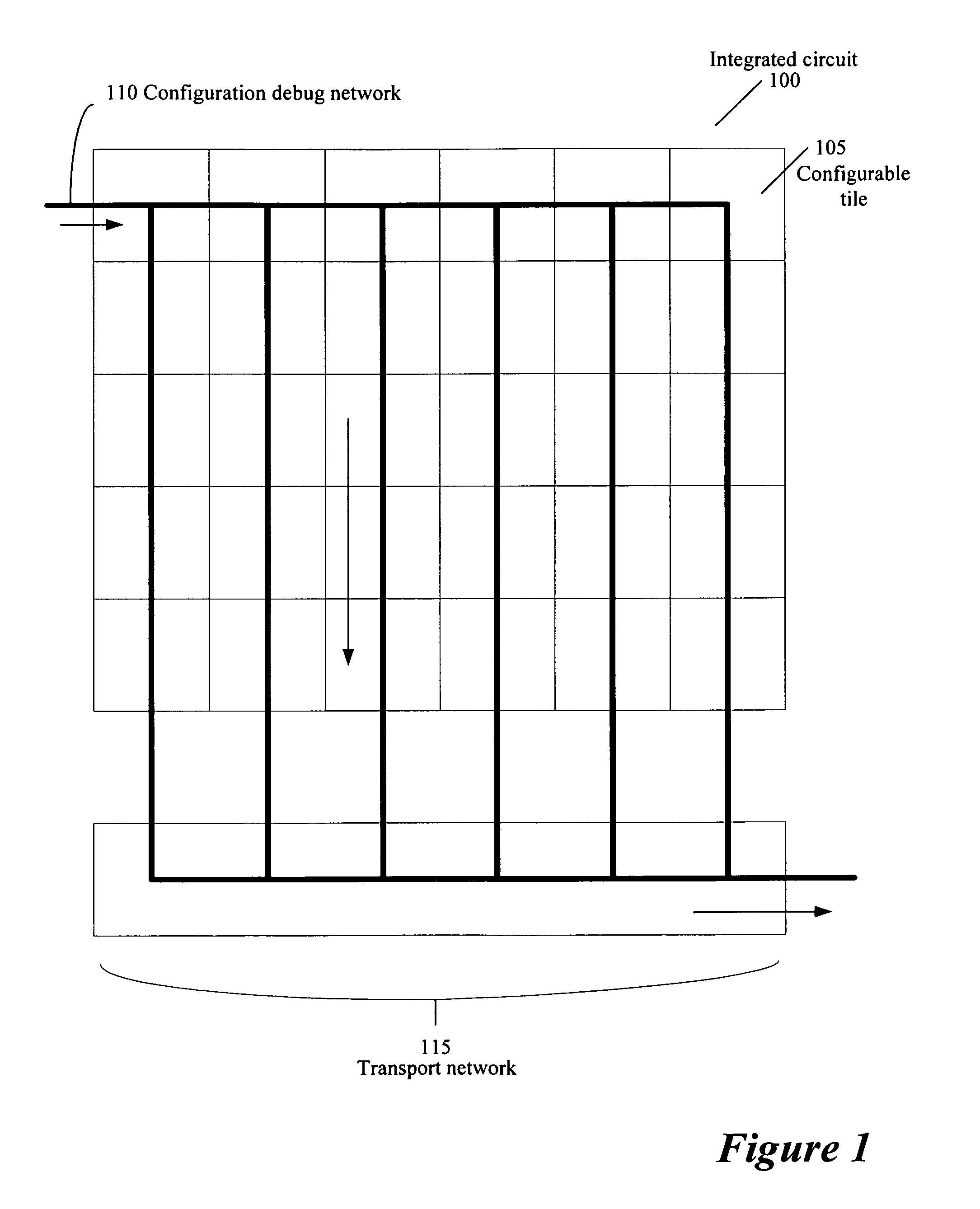

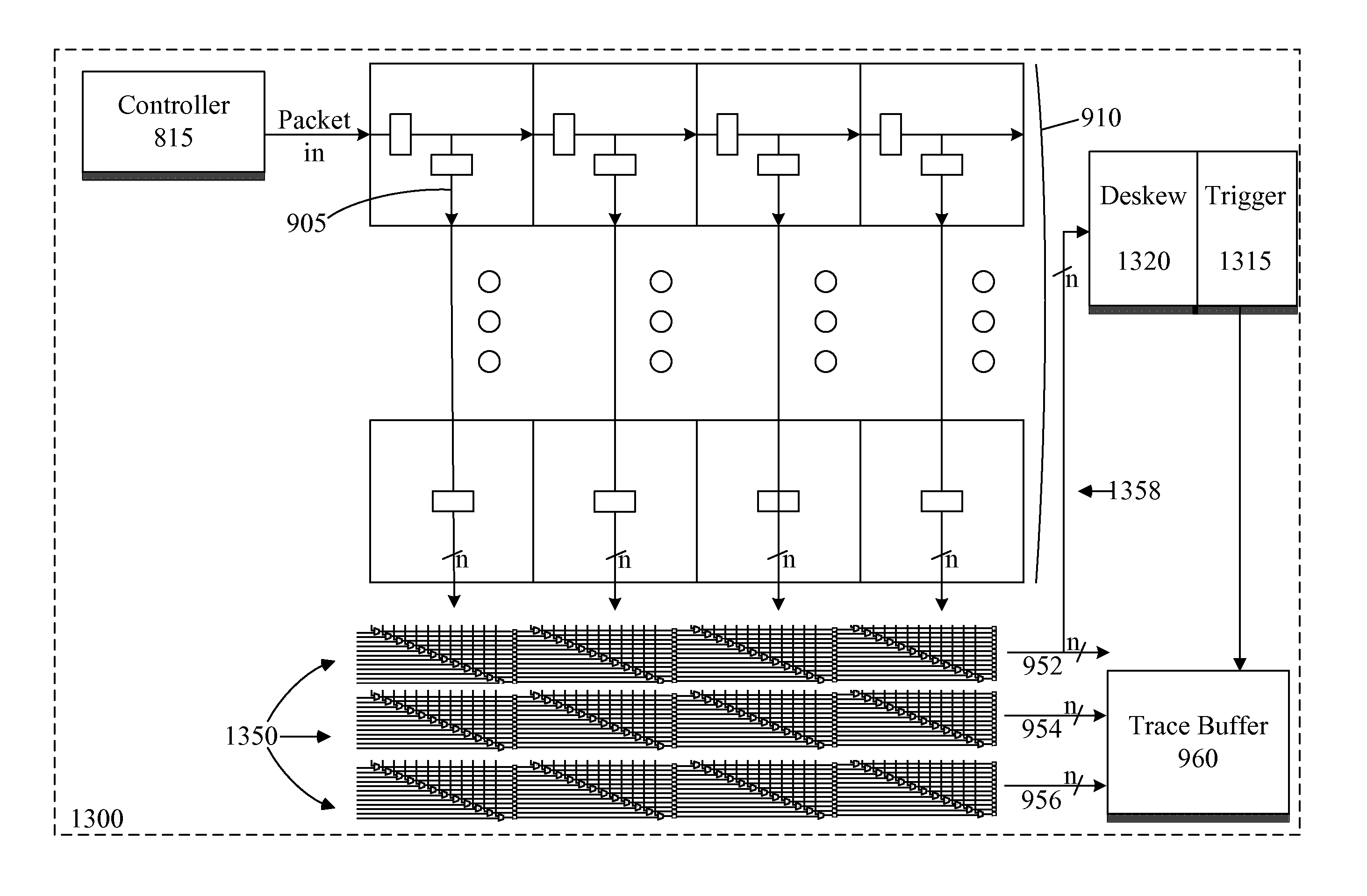

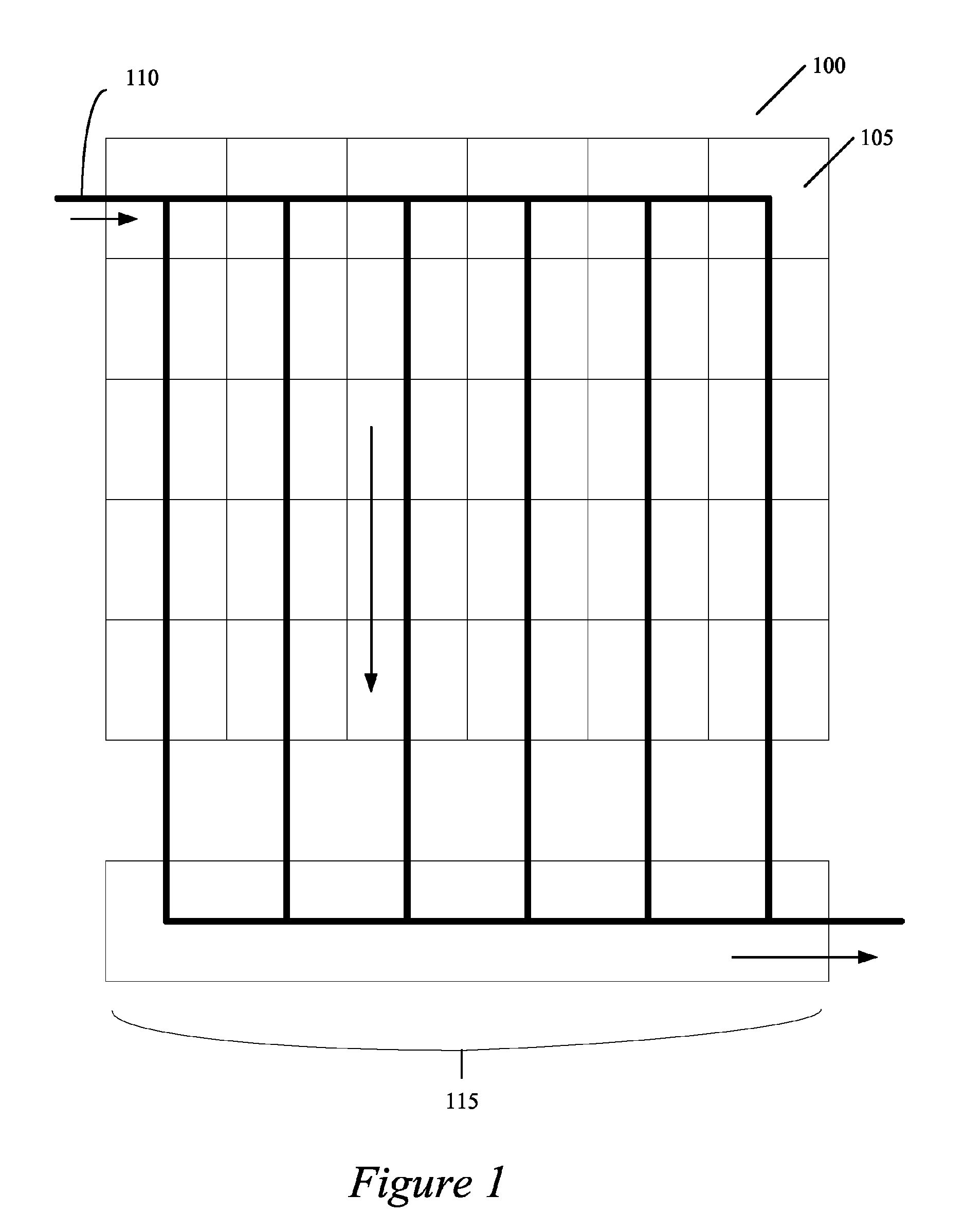

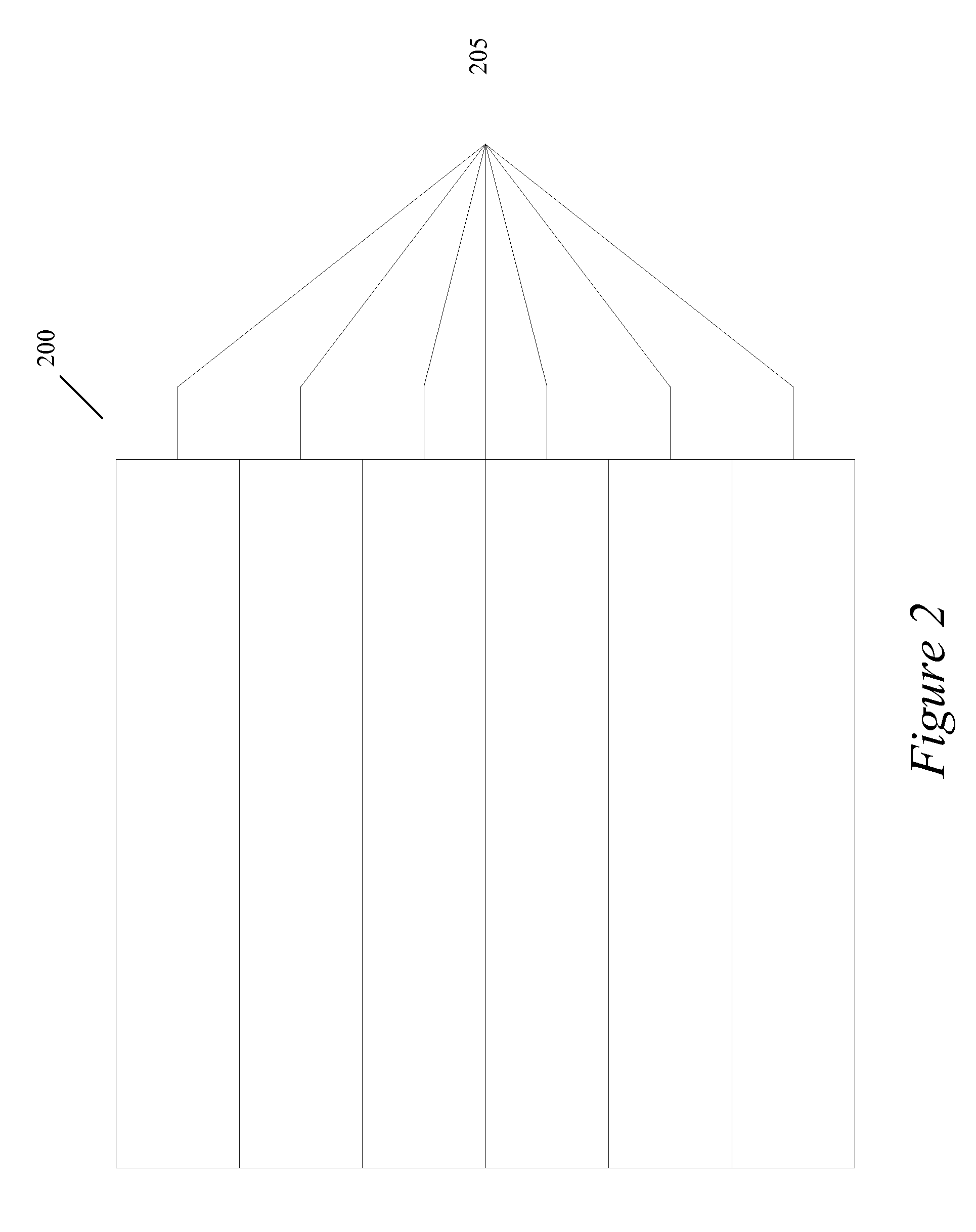

Transport network for a configurable IC

InactiveUS7501855B2Solid-state devicesLogic circuits using elementary logic circuit componentsTrace bufferTransport network

Some embodiments provide a configurable integrated circuit (IC) with an arrangement of circuit elements, a trace buffer, and a transport network separate from the arrangement of circuit elements. The transport network transports data from the arrangement of circuit elements to the trace buffer.In some embodiments the configurable IC is on a single chip. In some embodiments the configurable IC further includes trigger circuits for triggering the trace buffer to stop recording a set of data. In some such embodiments the configurable IC further includes deskew circuits for temporally aligning a subset of the data. In some embodiments the subset of the data passes through the transport network on its way to the deskew circuits.

Owner:ALTERA CORP

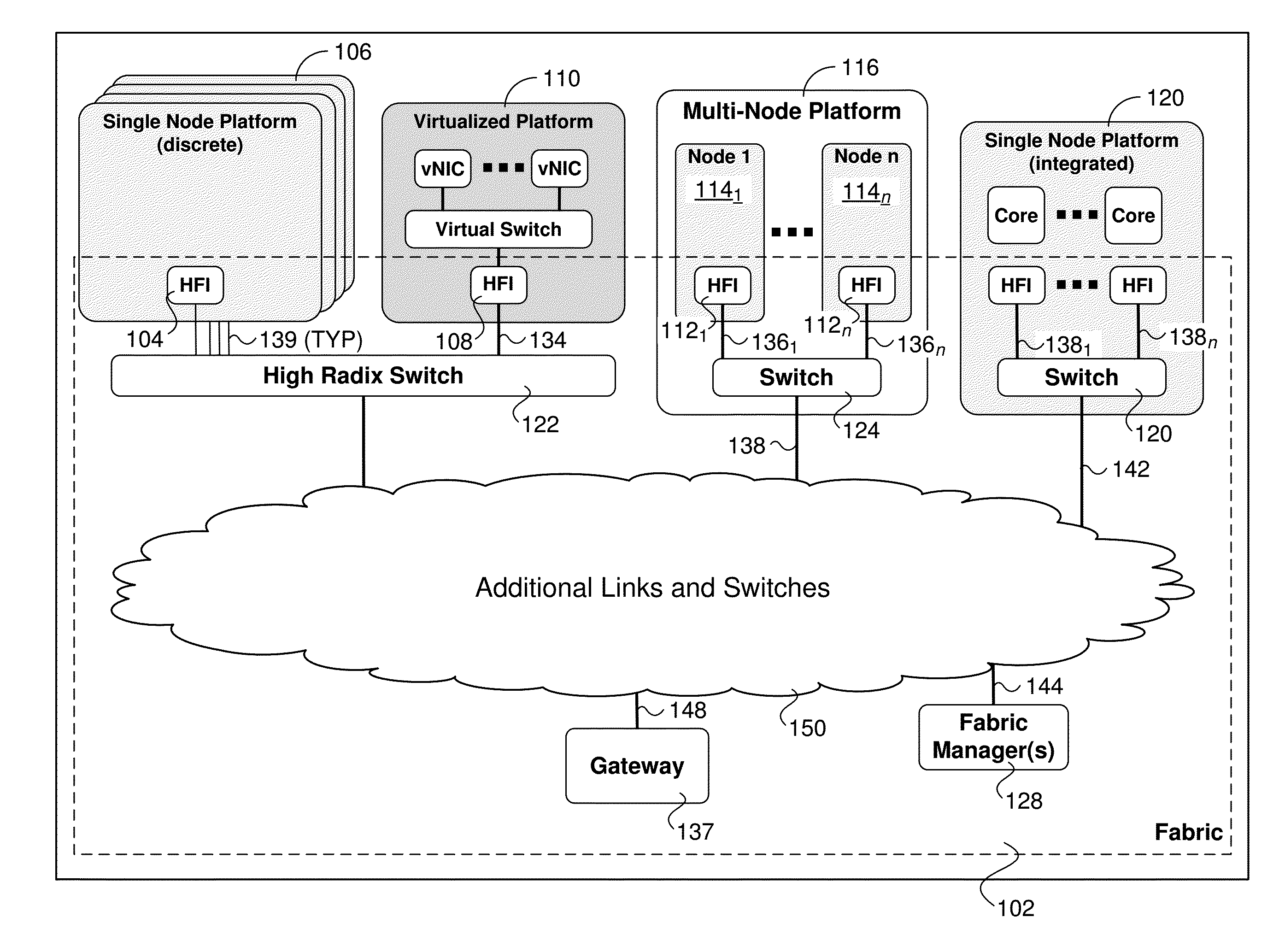

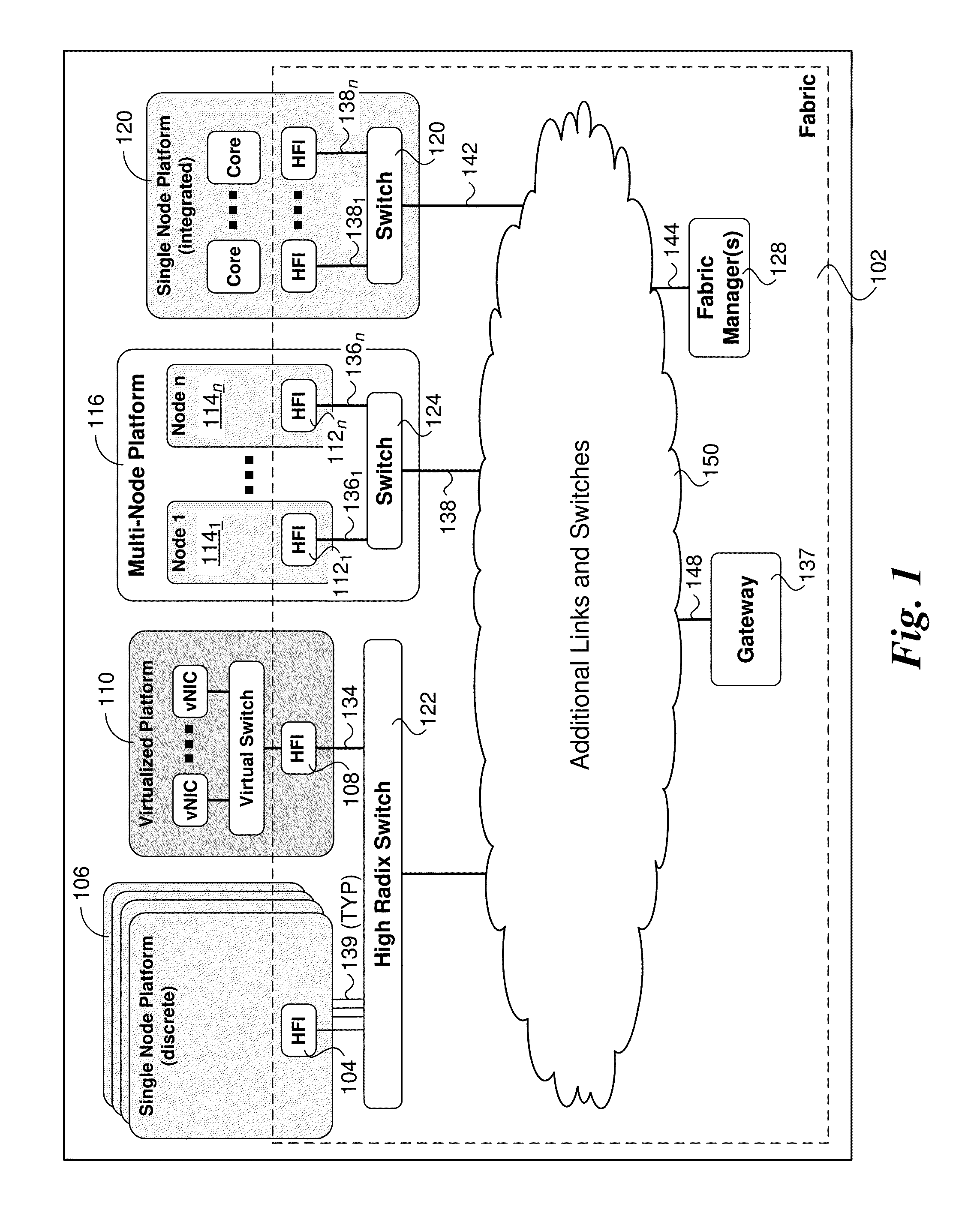

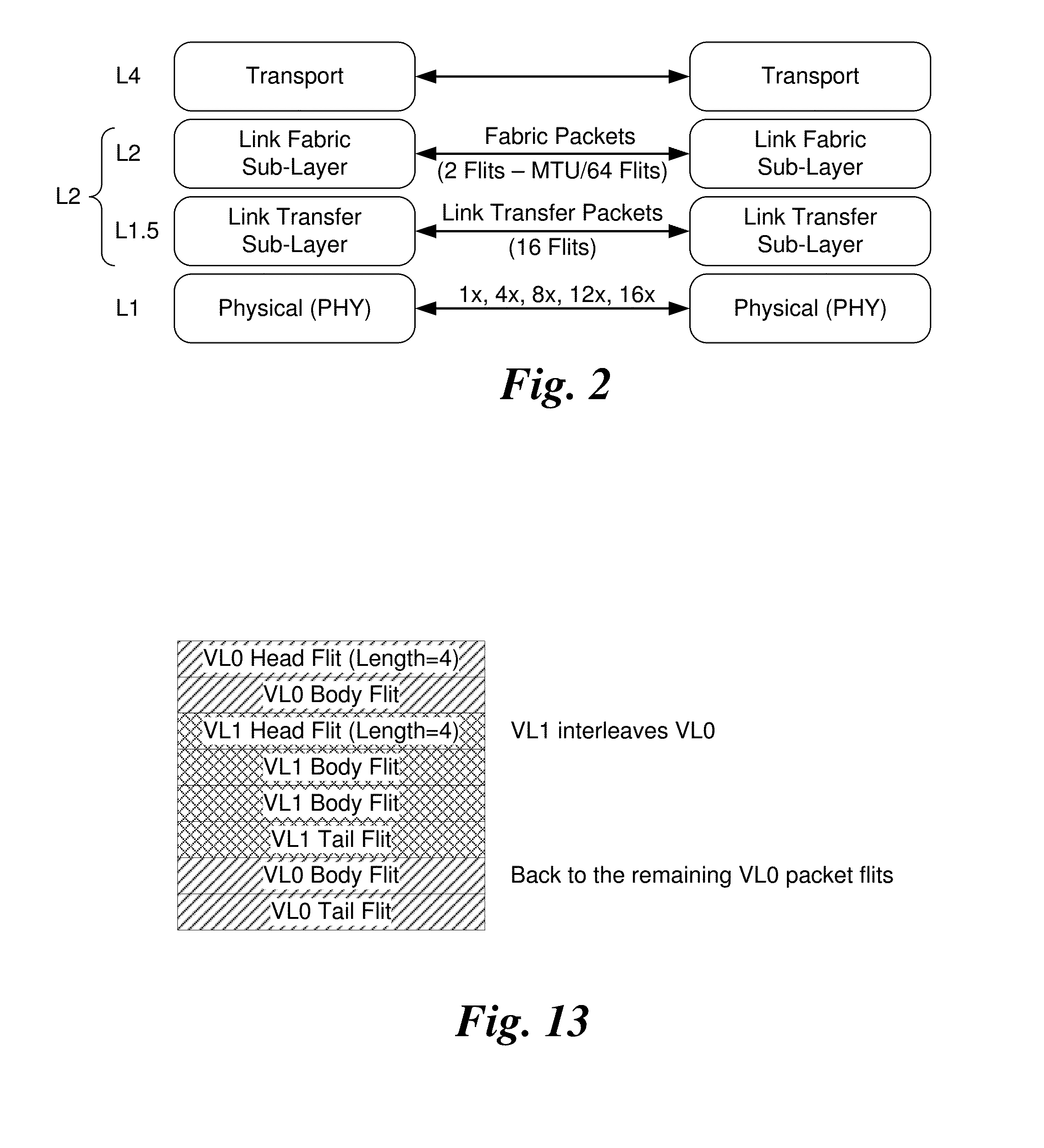

Method and system for flexible credit exchange within high performance fabrics

InactiveUS20150180790A1Multiplex system selection arrangementsCircuit switching systemsTrace bufferData transmission

Owner:INTEL CORP

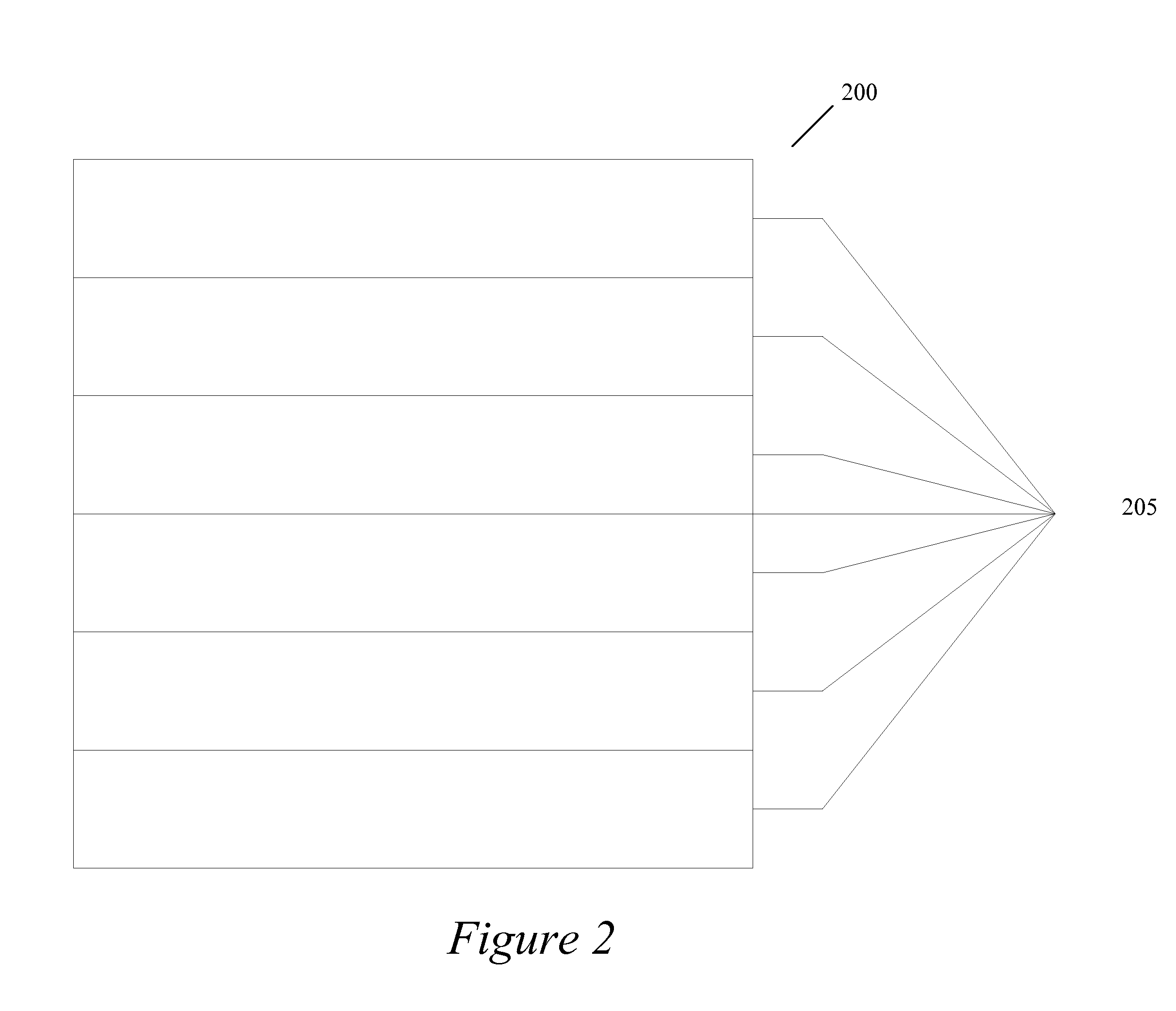

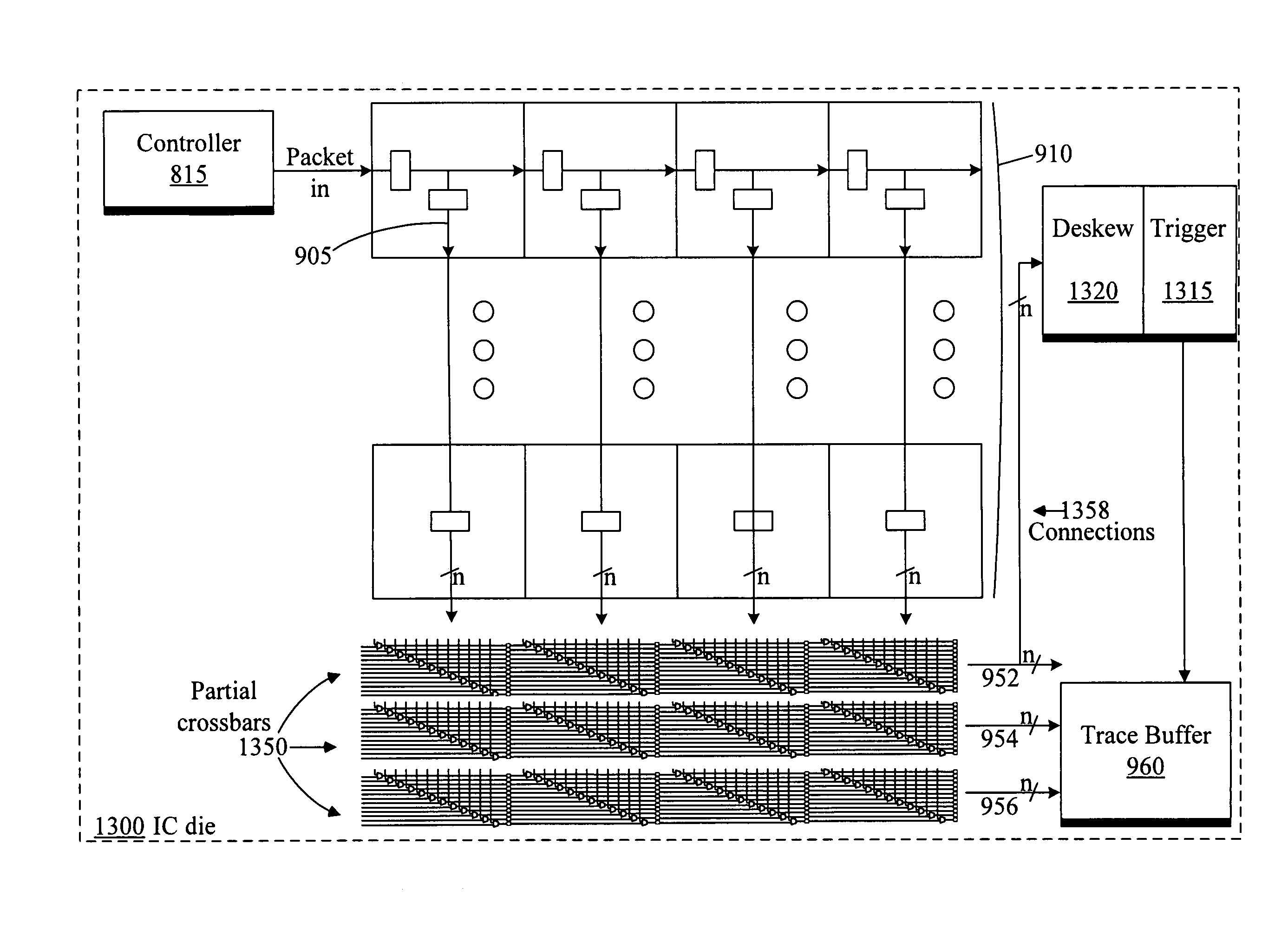

Restructuring data from a trace buffer of a configurable IC

InactiveUS7579867B2Reliability increasing modificationsSolid-state devicesTrace bufferComputer science

Some embodiments provide a method that outputs from a configurable IC a first set of data bits from a trace buffer. Each bit of the first set of data bits is simultaneously generated in the configurable circuits and, in some embodiments, multiple data bits of the first set of data bits do not reach the traced buffer simultaneously. The method also determines a set of relative delays for the first set of data bits and arranges the first set of data bits into a second set of data bits by compensating for the relative delays.

Owner:ALTERA CORP

Efficient trace capture buffer management

ActiveUS20140052930A1Efficiently storing traceDetecting faulty computer hardwareMemory adressing/allocation/relocationTrace bufferGlobal time

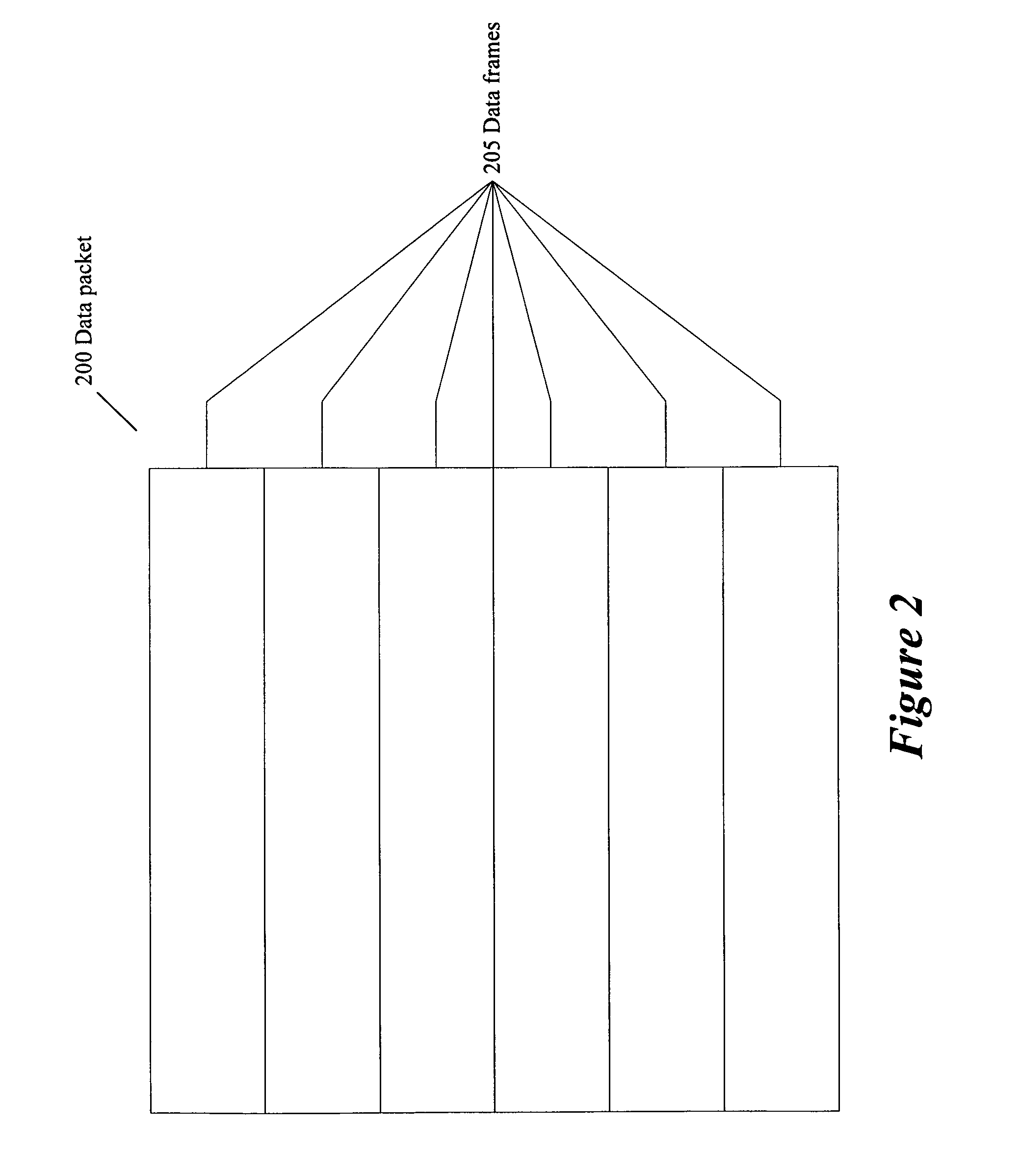

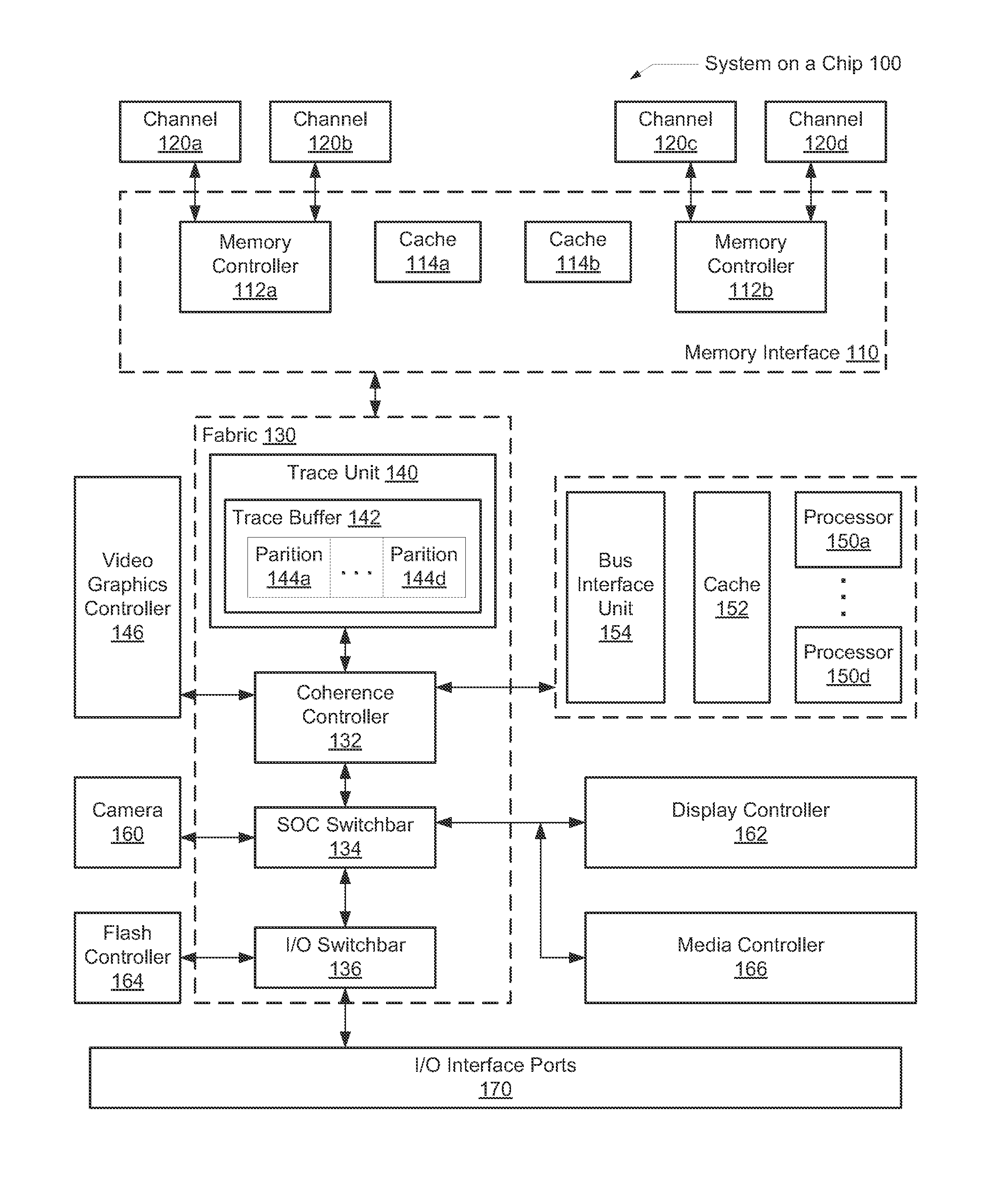

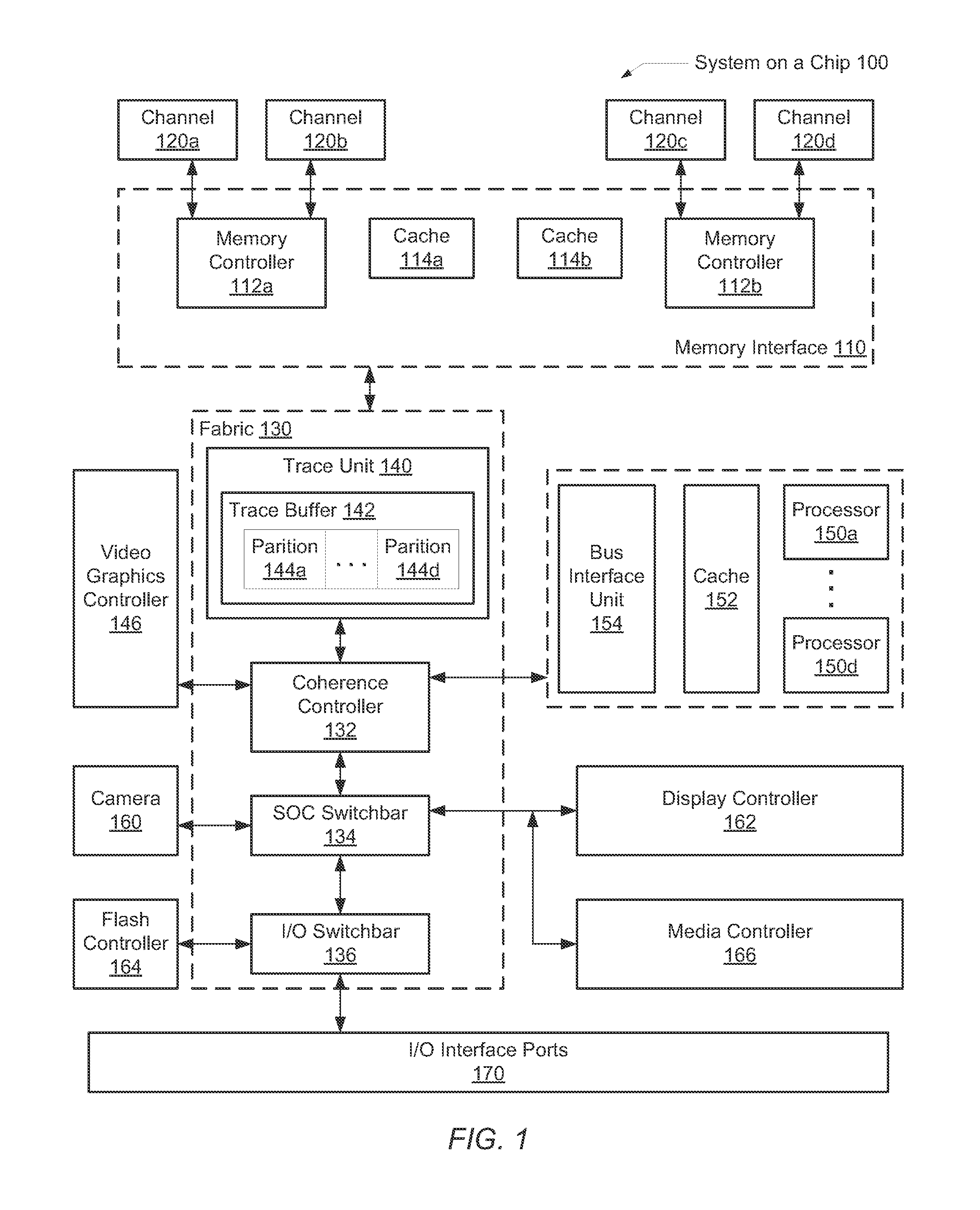

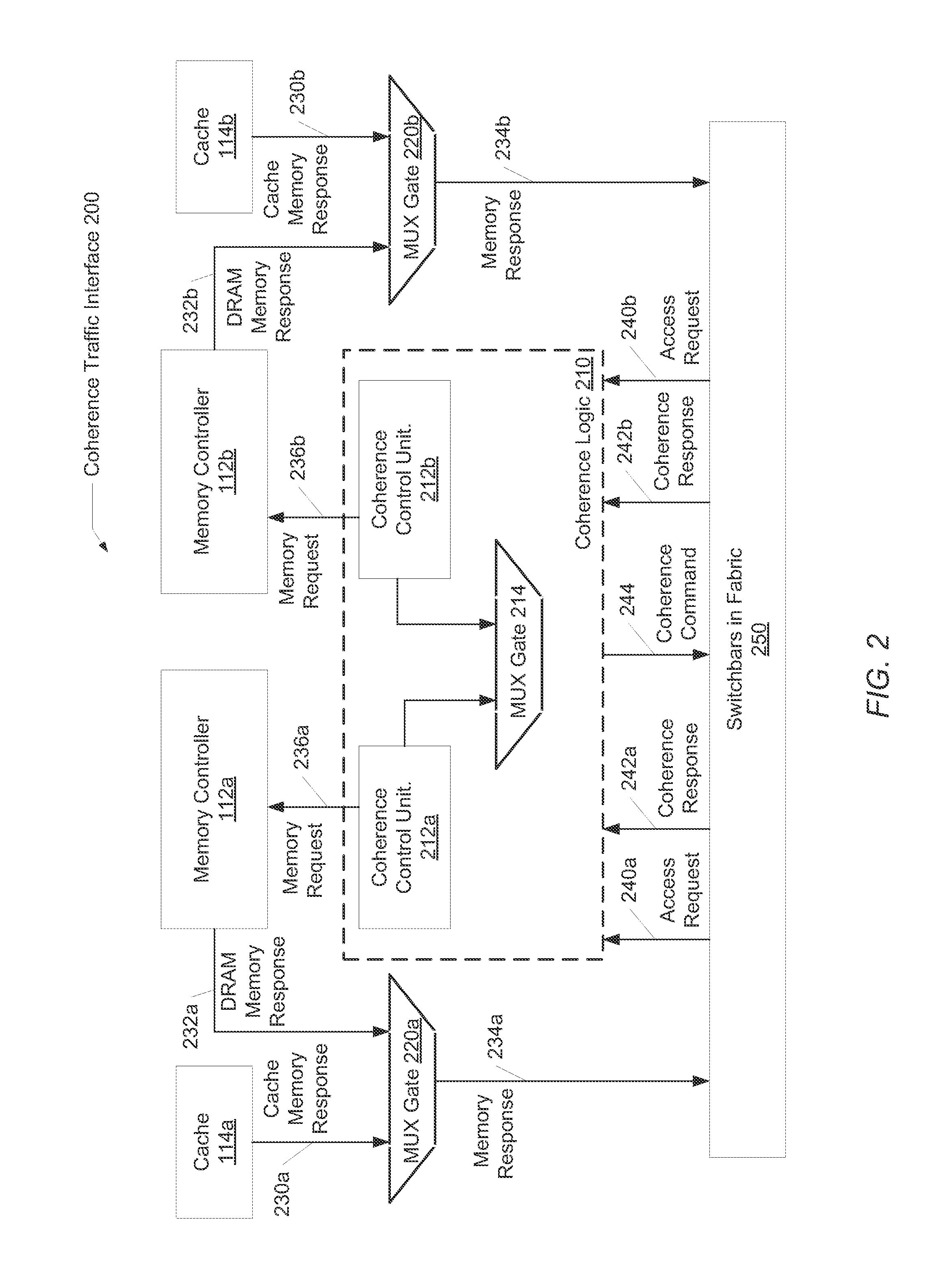

A system and method for efficiently storing traces of multiple components in an embedded system. A system-on-a-chip (SOC) includes a trace unit for collecting and storing trace history, bus event statistics, or both. The SOC may transfer cache coherent messages across multiple buses between a shared memory and a cache coherent controller. The trace unit includes a trace buffer with multiple physical partitions assigned to subsets of the multiple buses. The number of partitions is less than the number of multiple buses. One or more trace instructions may cause a trace history, trace bus event statistics, local time stamps and a global time-base value to be stored in a physical partition within the trace buffer.

Owner:APPLE INC

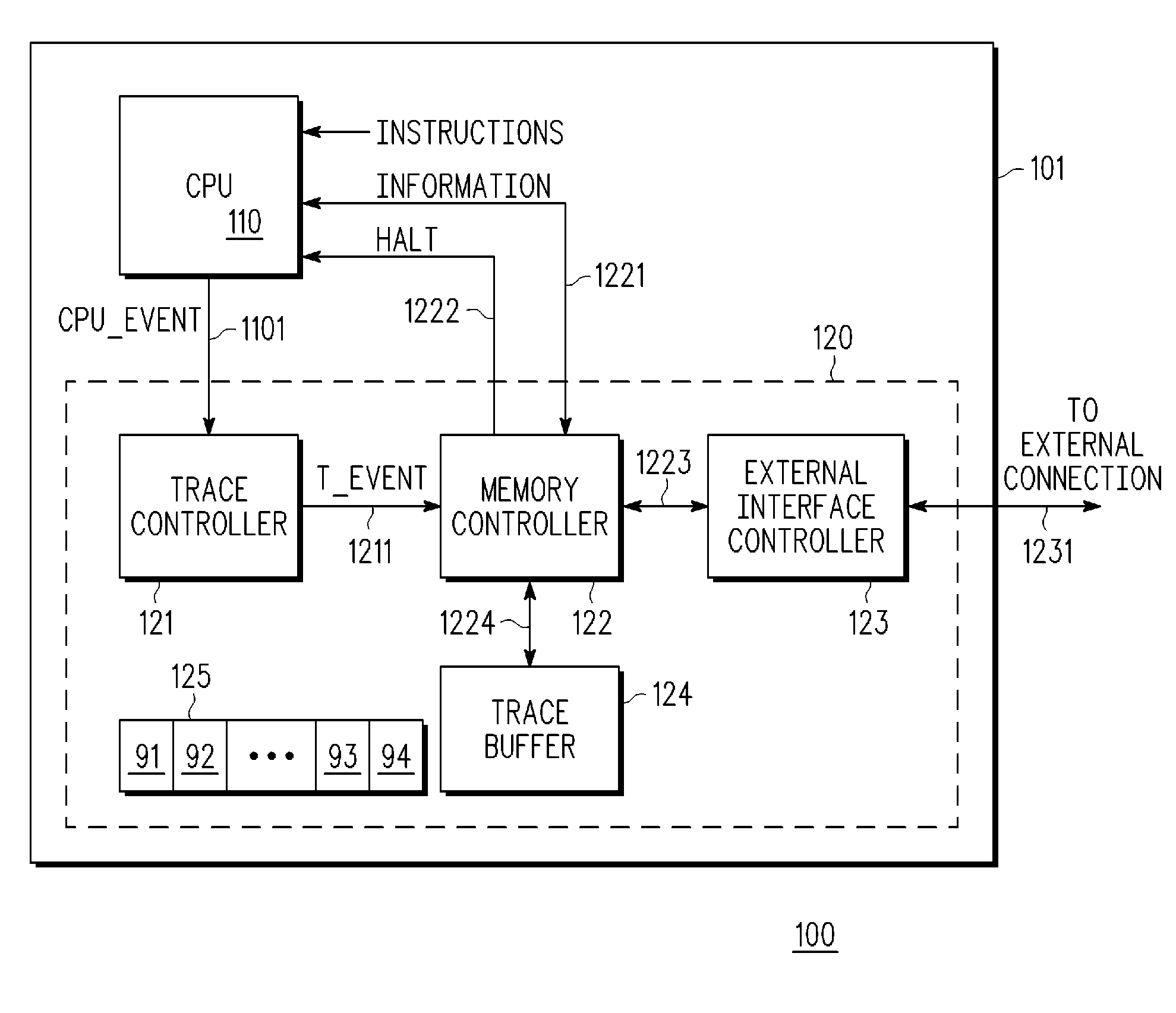

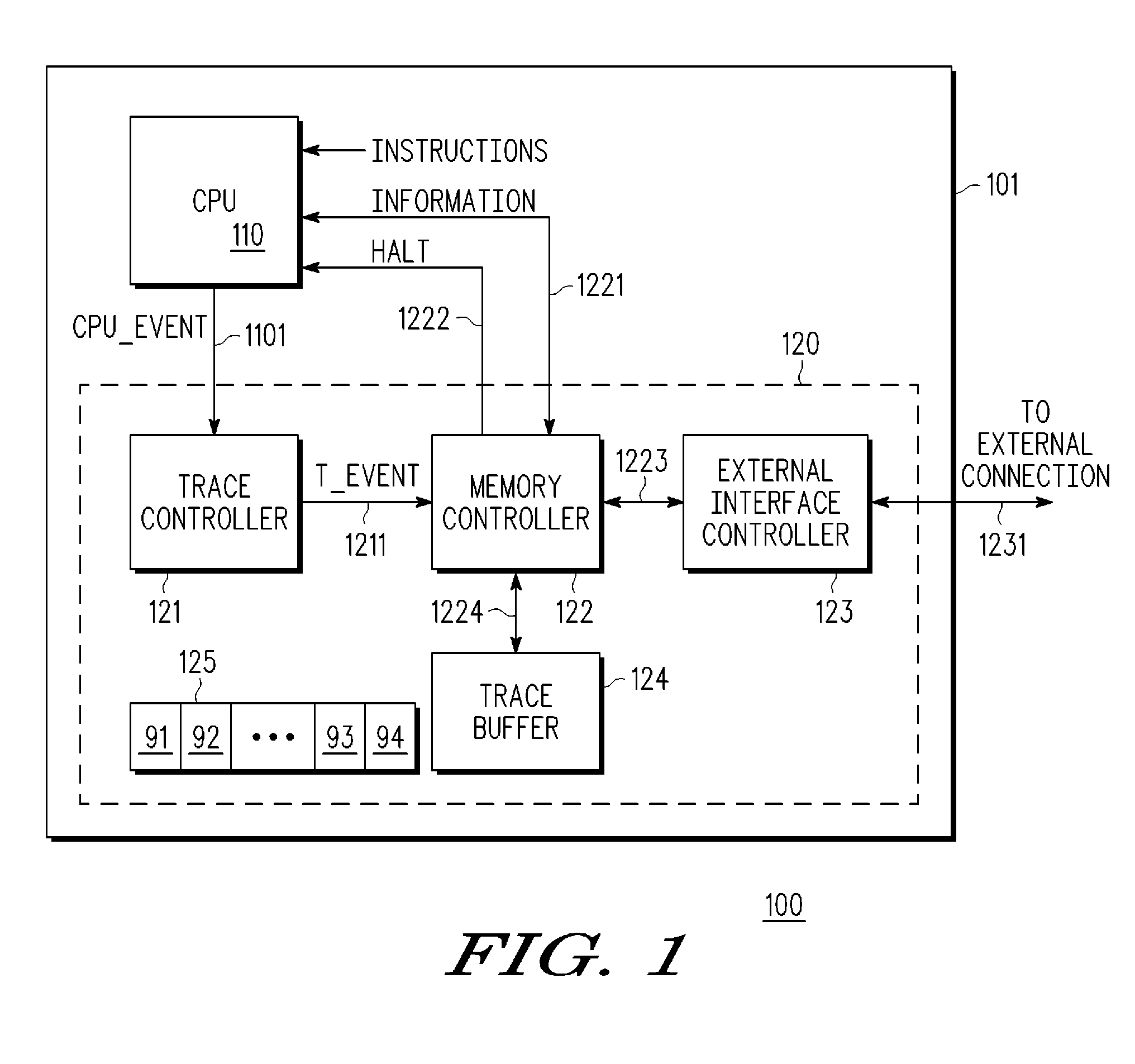

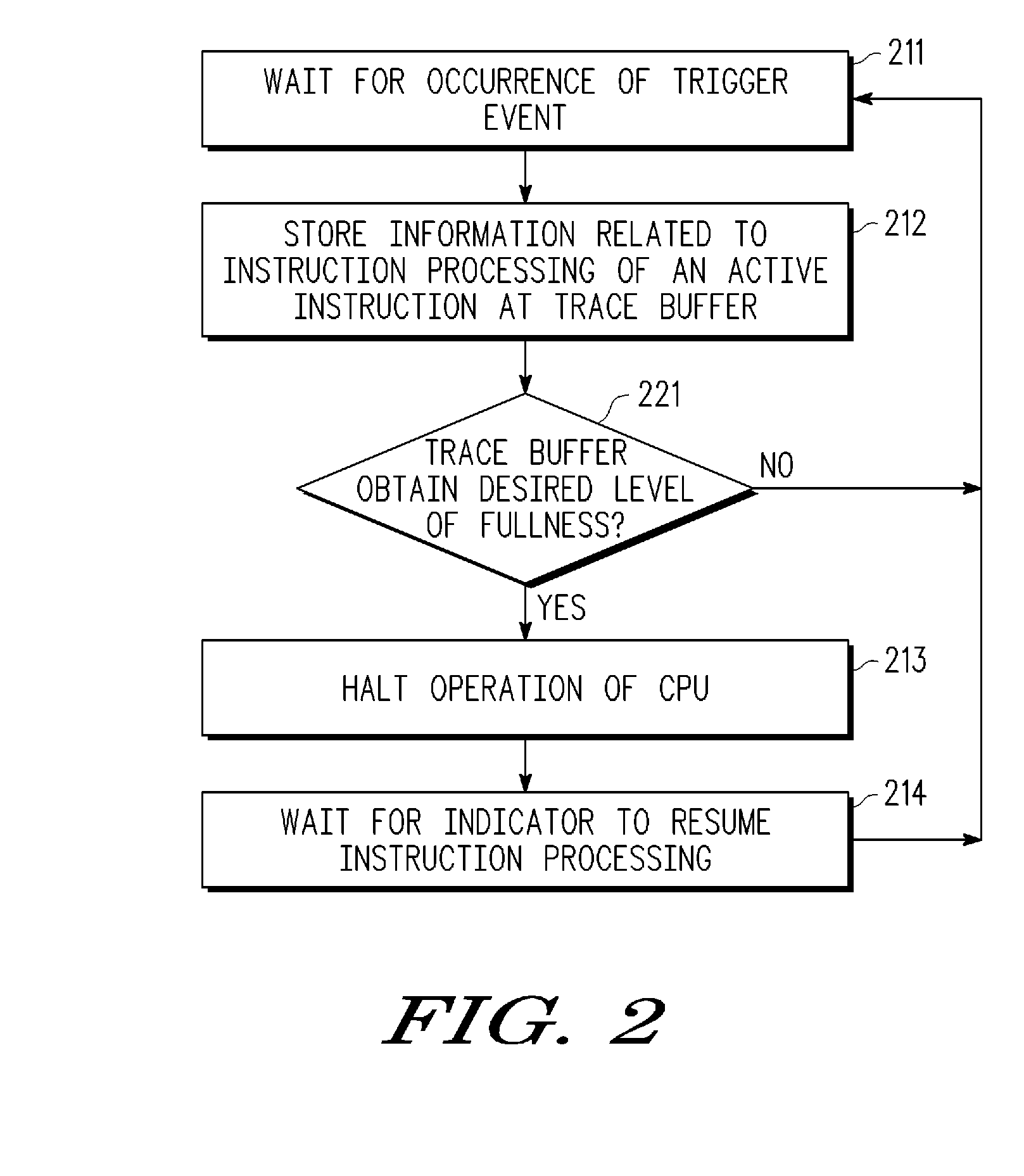

Data processor device having trace capabilities and method

Owner:VLSI TECH LLC

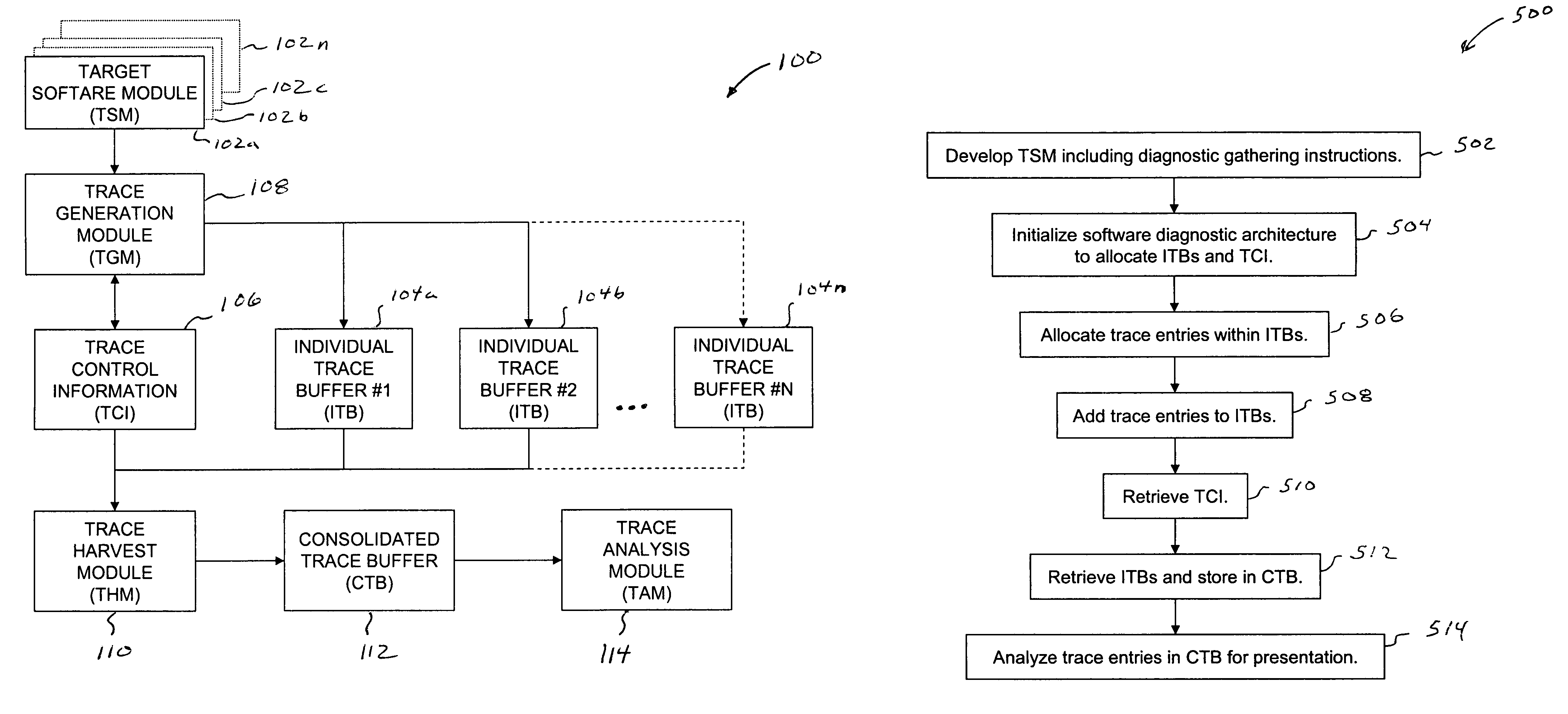

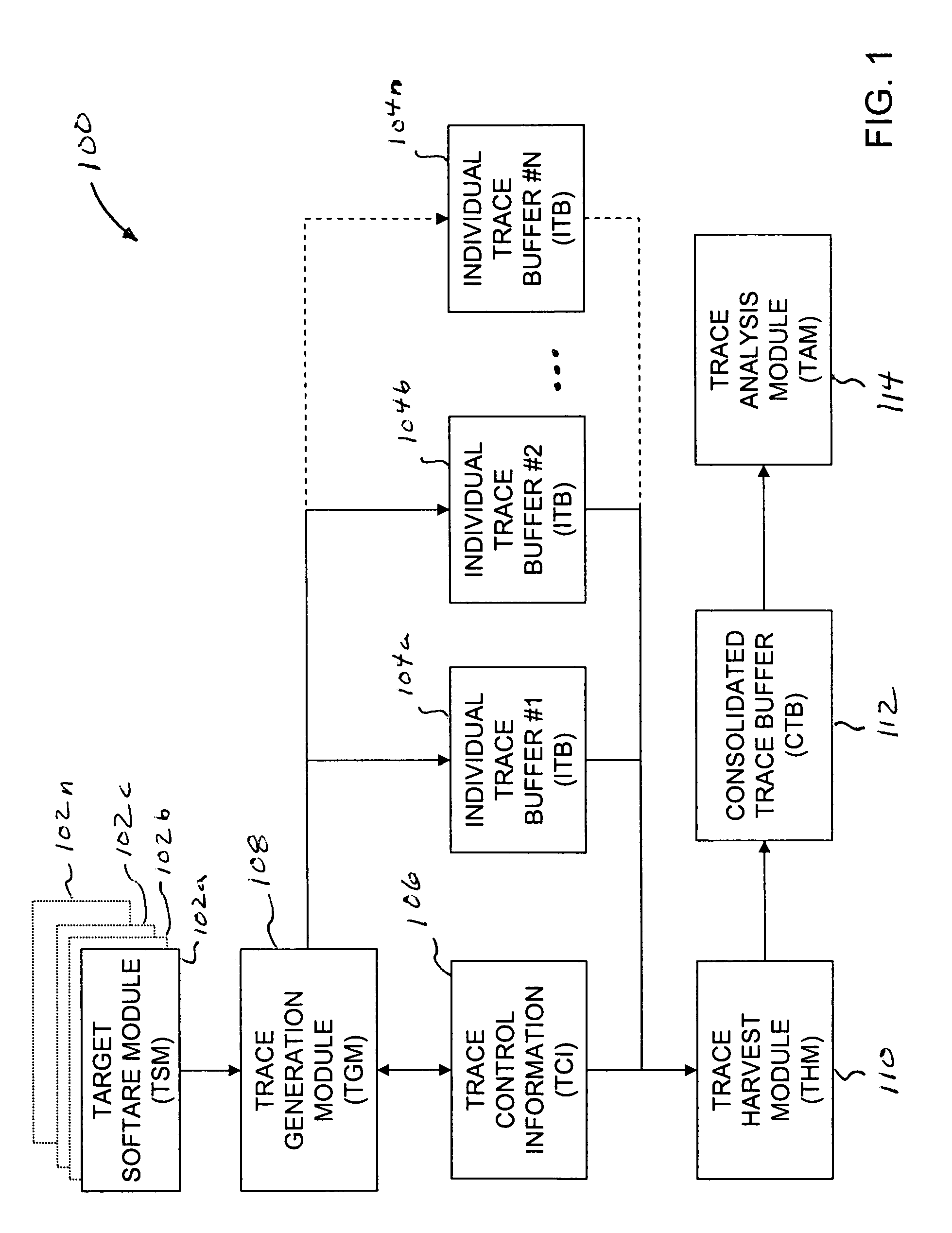

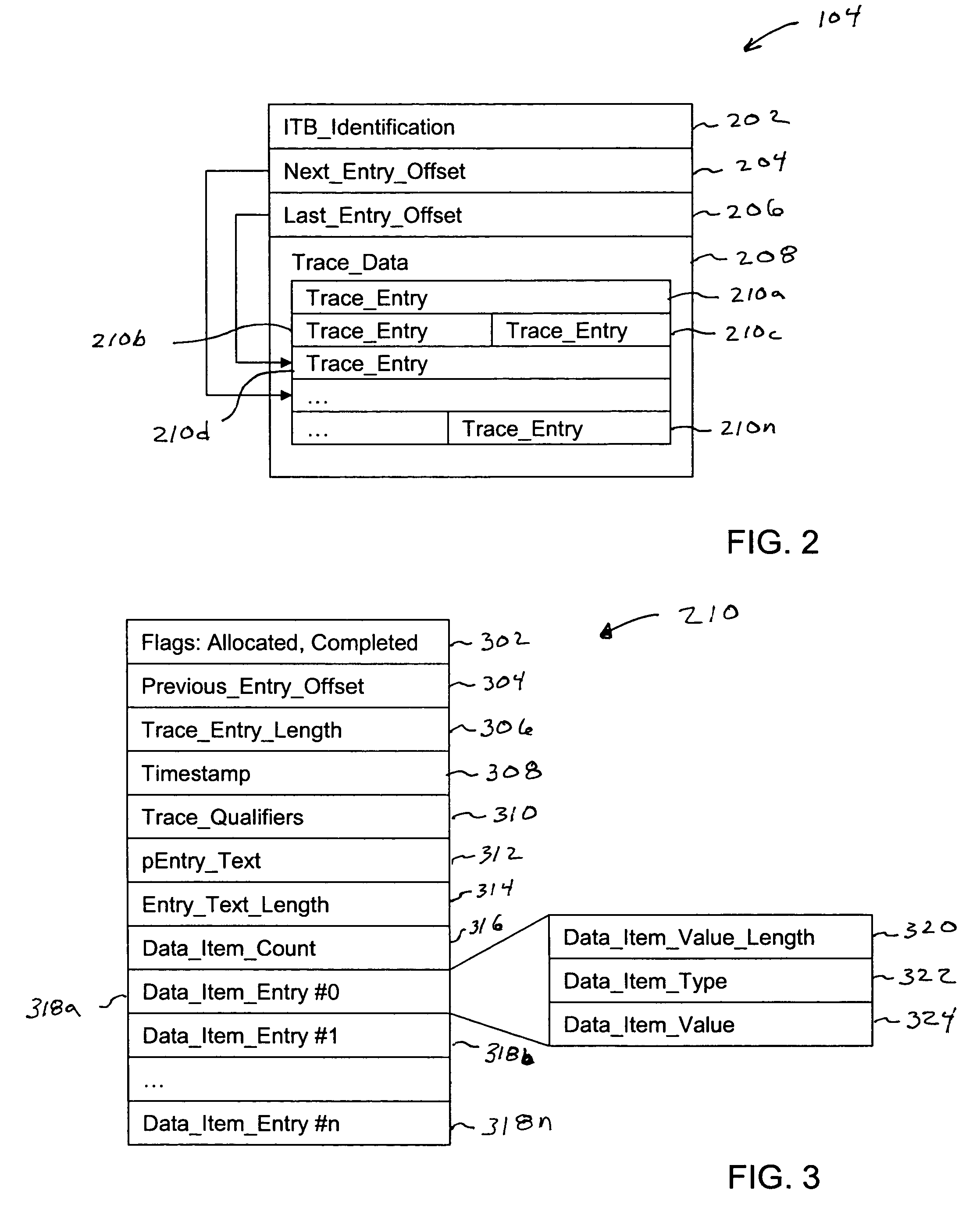

Methods and apparatus to diagnose software

Methods and apparatus to diagnose software including diagnostic gathering instructions are disclosed. The software is diagnosed by storing diagnostic information to a plurality of individual trace buffers responsive to the diagnostic gathering instructions, consolidating the diagnostic information from the plurality of individual trace buffers to a consolidated trace buffer, and presenting at least a portion of the consolidated diagnostic information.

Owner:UNISYS CORP

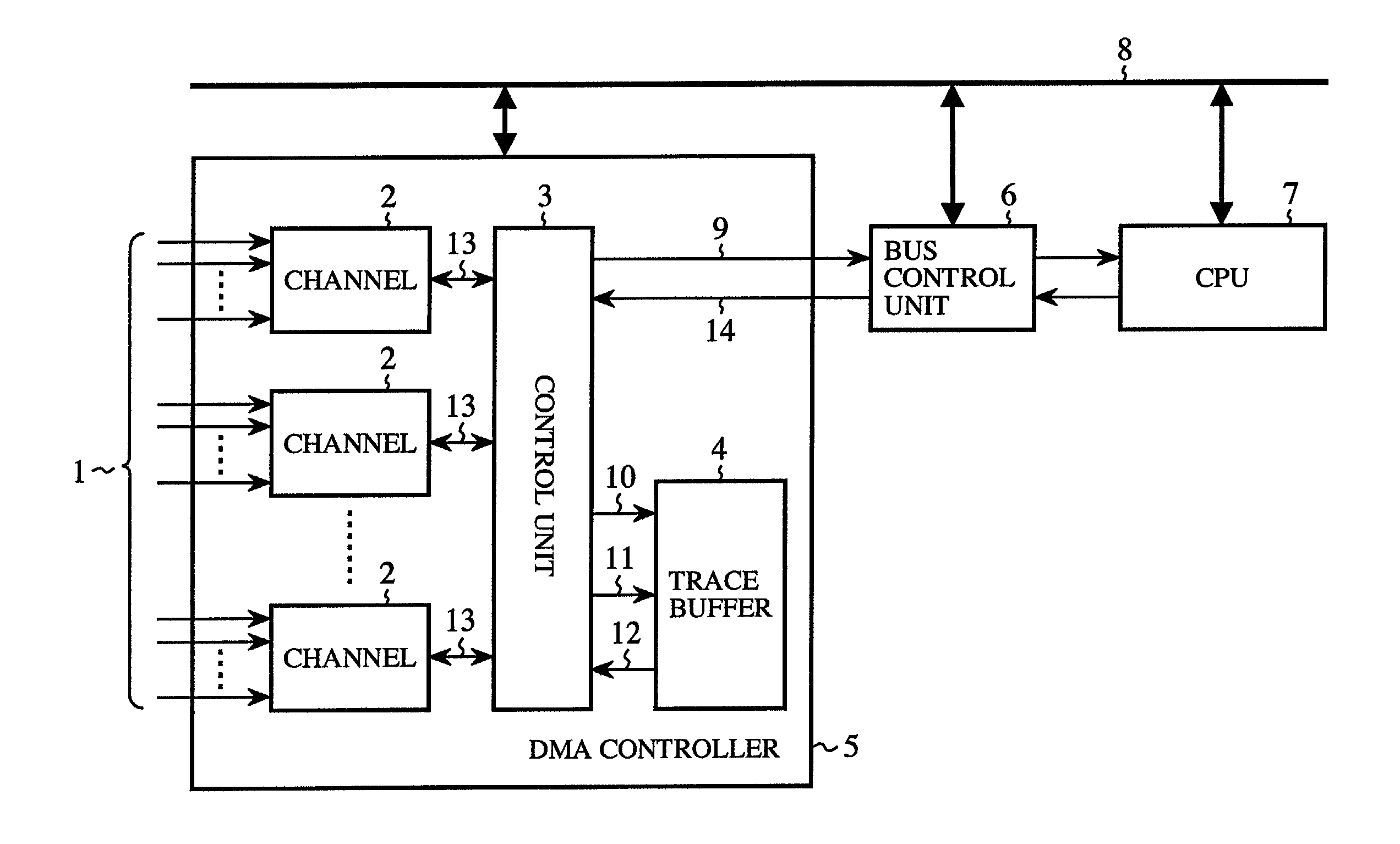

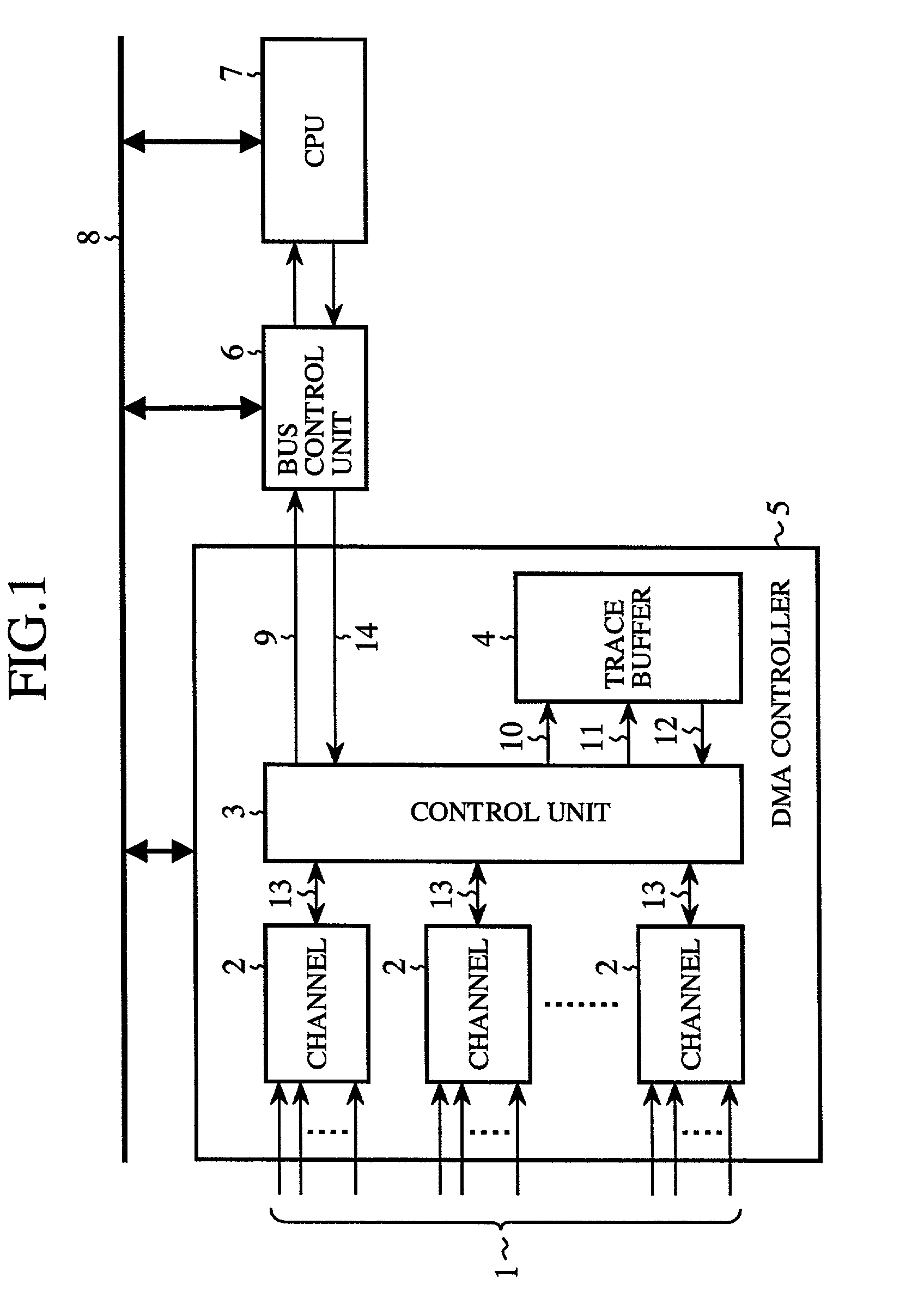

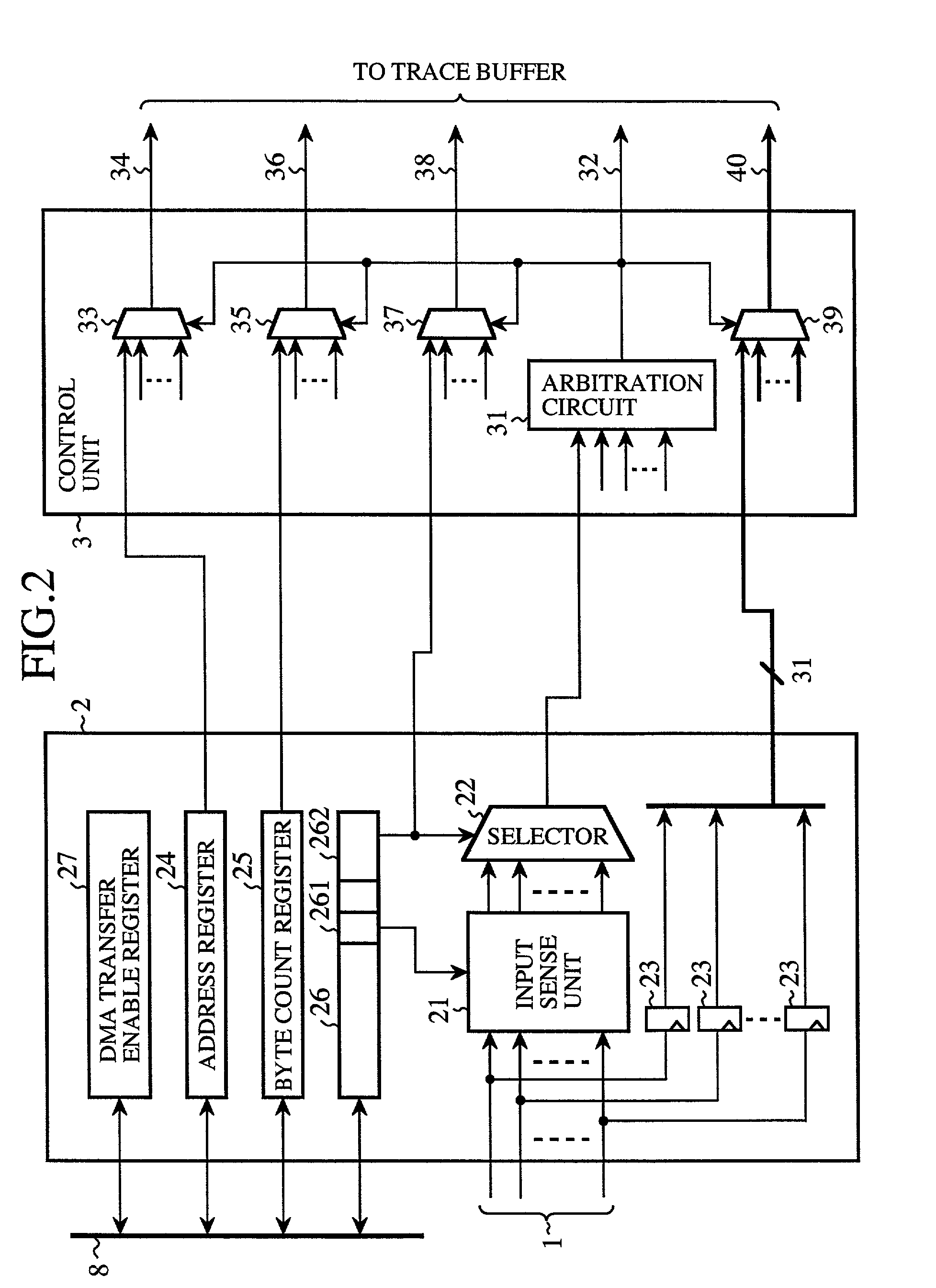

DMA controller having a trace buffer

InactiveUS7143205B2Stable supportEasy to debugEnergy efficient ICTHardware monitoringTrace bufferData buffer

A DMA controller comprises an arbitration unit for arbitrating among a plurality of channels so as to select a DMA request from among a plurality of DMA requests accepted by way of the plurality of channels according to priorities assigned to the plurality of channels in advance, and a trace buffer for storing trace data associated with the DMA request selected by the arbitration unit. The DMA controller can also include a write control unit for enabling or disabling writing of the trace data associated with the DMA request selected by the arbitration unit in the trace buffer.

Owner:RENESAS ELECTRONICS CORP

Configurable IC with deskewing circuits

Some embodiments provide a configurable integrated circuit (IC) comprising multiple deskew circuits for delaying data passage. Each of the deskew circuits comprises a stepwise delay circuit with multiple outputs and an input selection circuit with multiple inputs. Multiple outputs connect to multiple inputs. In some embodiments the configurable IC is a subcycle reconfigurable IC. In some such embodiments each of the deskew circuits further includes a space-time load control circuit for commanding the stepwise delay circuit to load during a selected subcycle. In some embodiments the multiple deskew circuits send data to trigger circuit. In some such embodiments the trigger circuit triggers a trace buffer to stop recording a data stream. In some such embodiments the trigger circuit triggers the trace buffer to stop after a programmable delay.

Owner:ALTERA CORP

System, method and program product for dynamically adjusting trace buffer capacity based on execution history

InactiveUS20090204949A1Error detection/correctionSpecific program execution arrangementsParallel computingTrace buffer

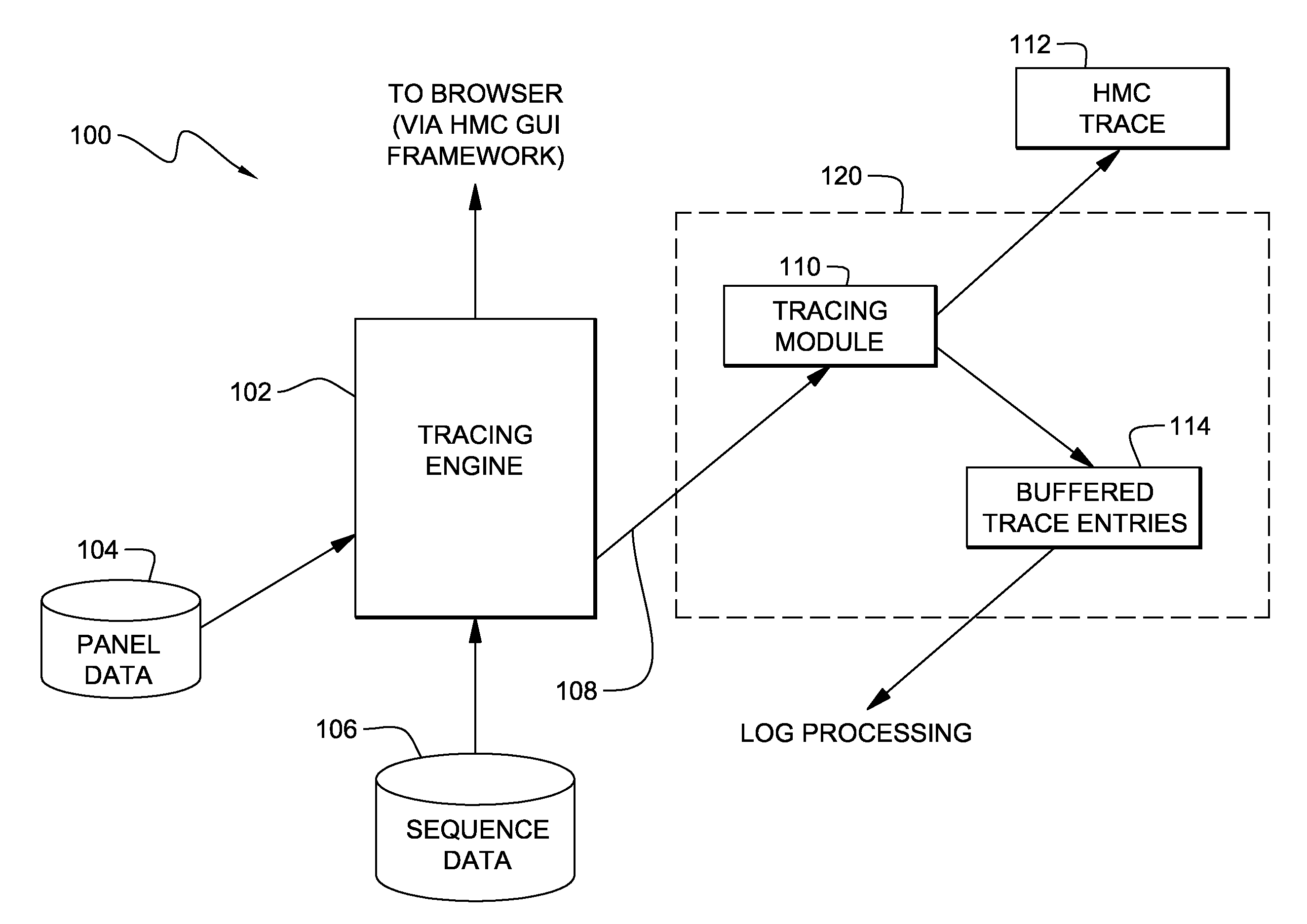

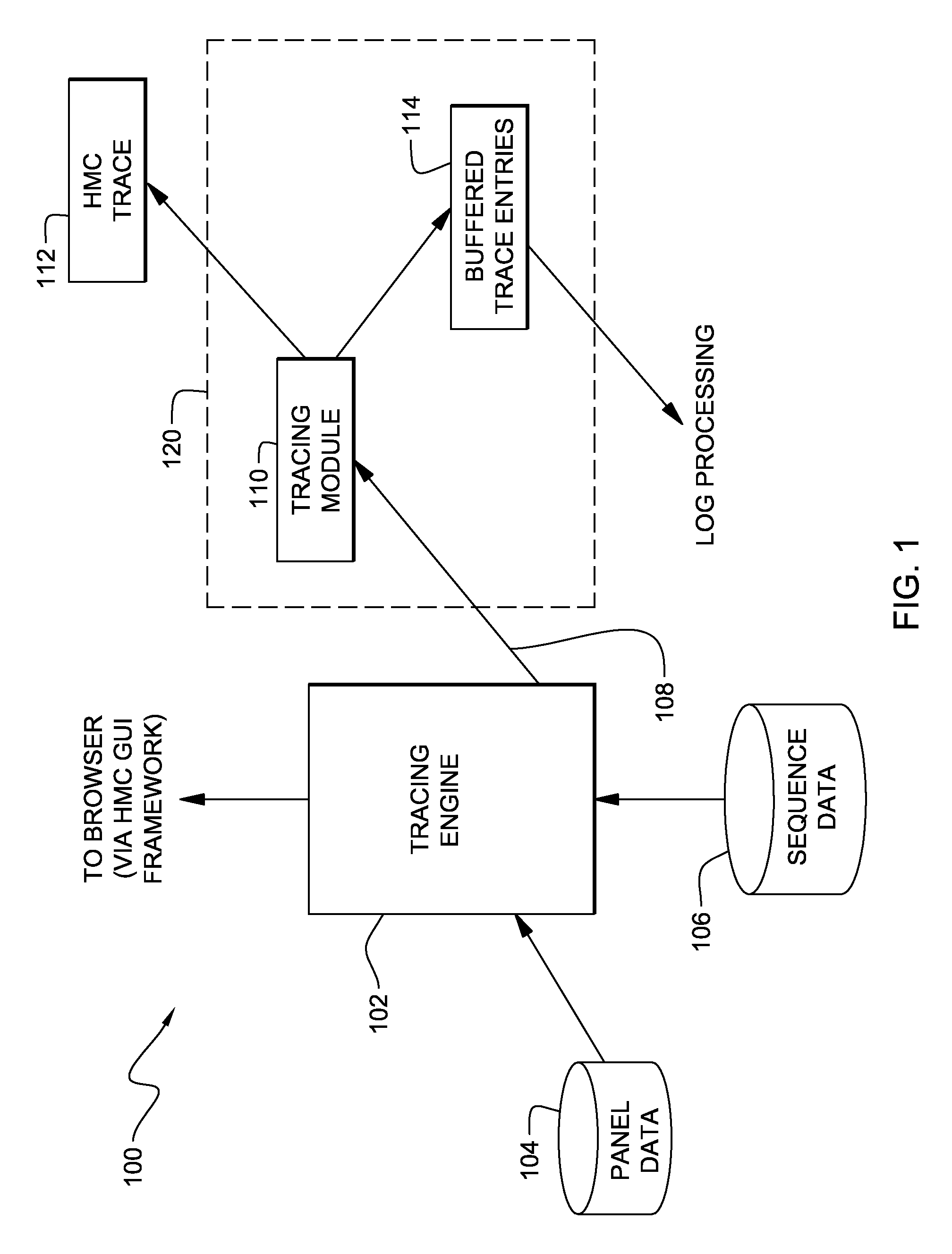

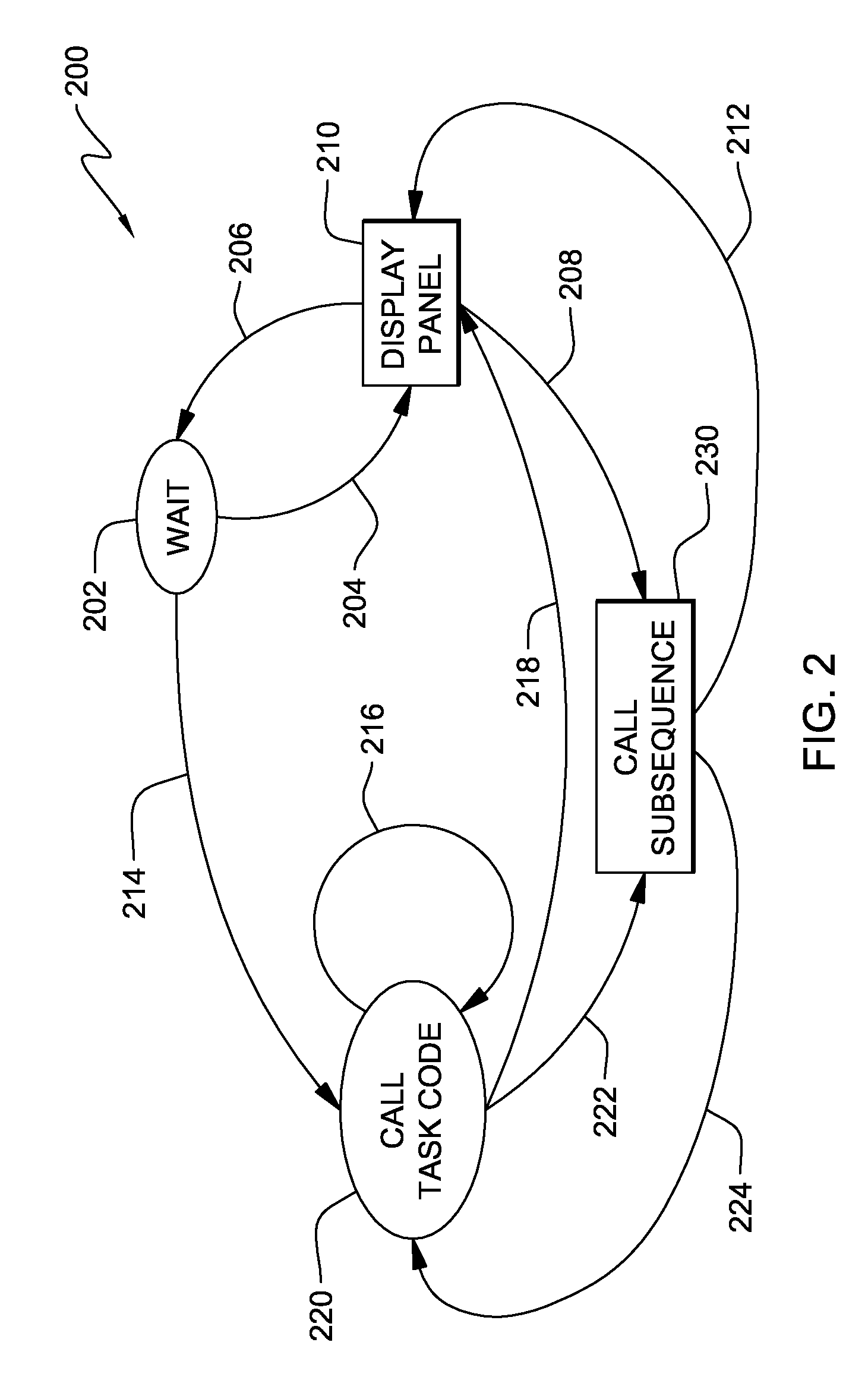

A method, system and program product for dynamically adjusting trace buffer capacity based on execution history. The method includes receiving, by a module configured to trace, a plurality of traces pertaining to one or more trace events generated during execution of a program being traced, the trace events generated including panel data and sequence data. The method further includes determining, using trace data captured from the plurality of traces received, whether or not a path for a trace event is a new path. If the path for the trace event is determined to be a new path, the method includes dynamically adjusting, by the module, an initial size of a trace buffer configured to store the trace data captured, such that, the module increases the initial size of the trace buffer upon making a determination that the trace event is a new trace event based on execution history.

Owner:IBM CORP

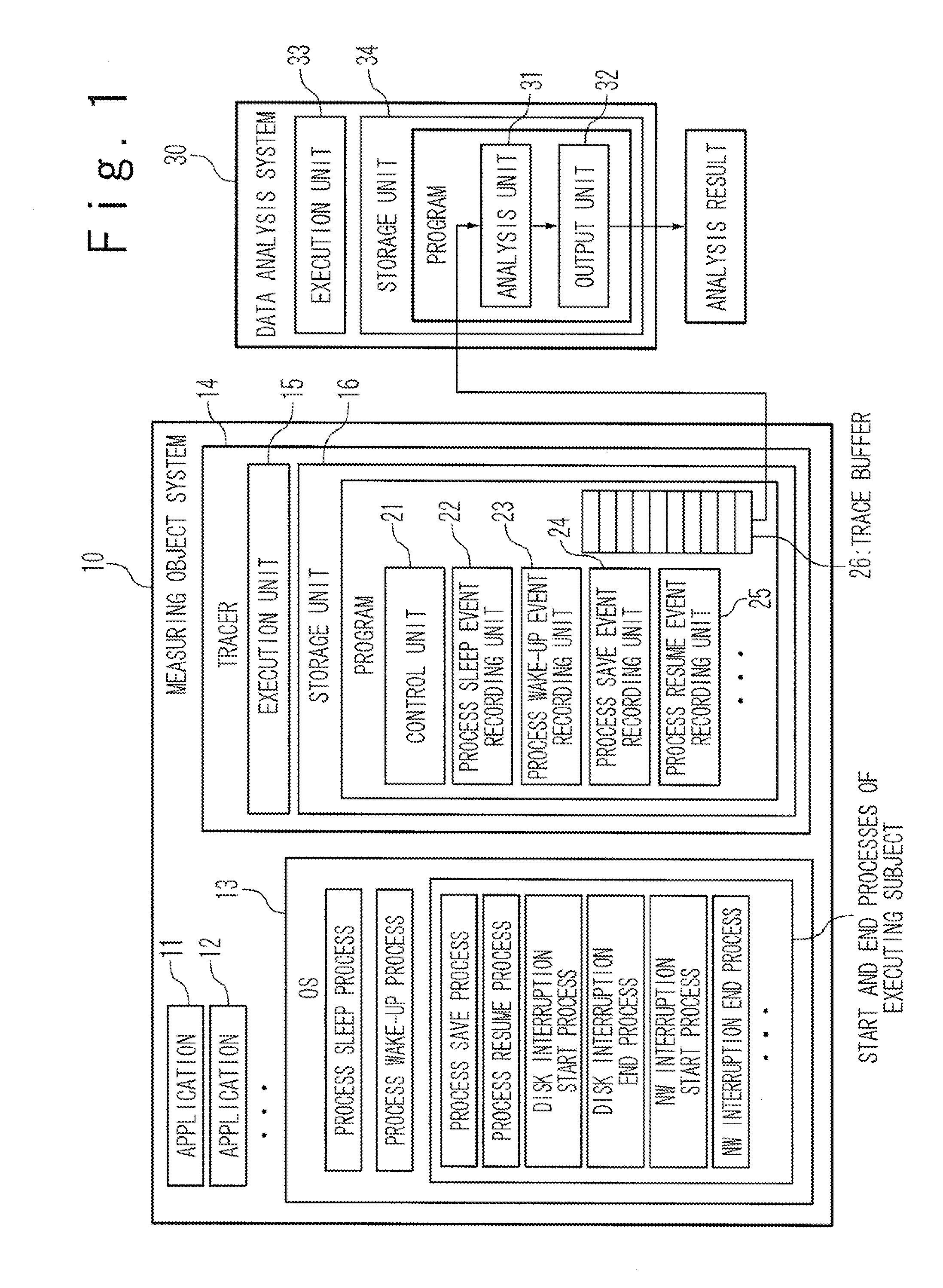

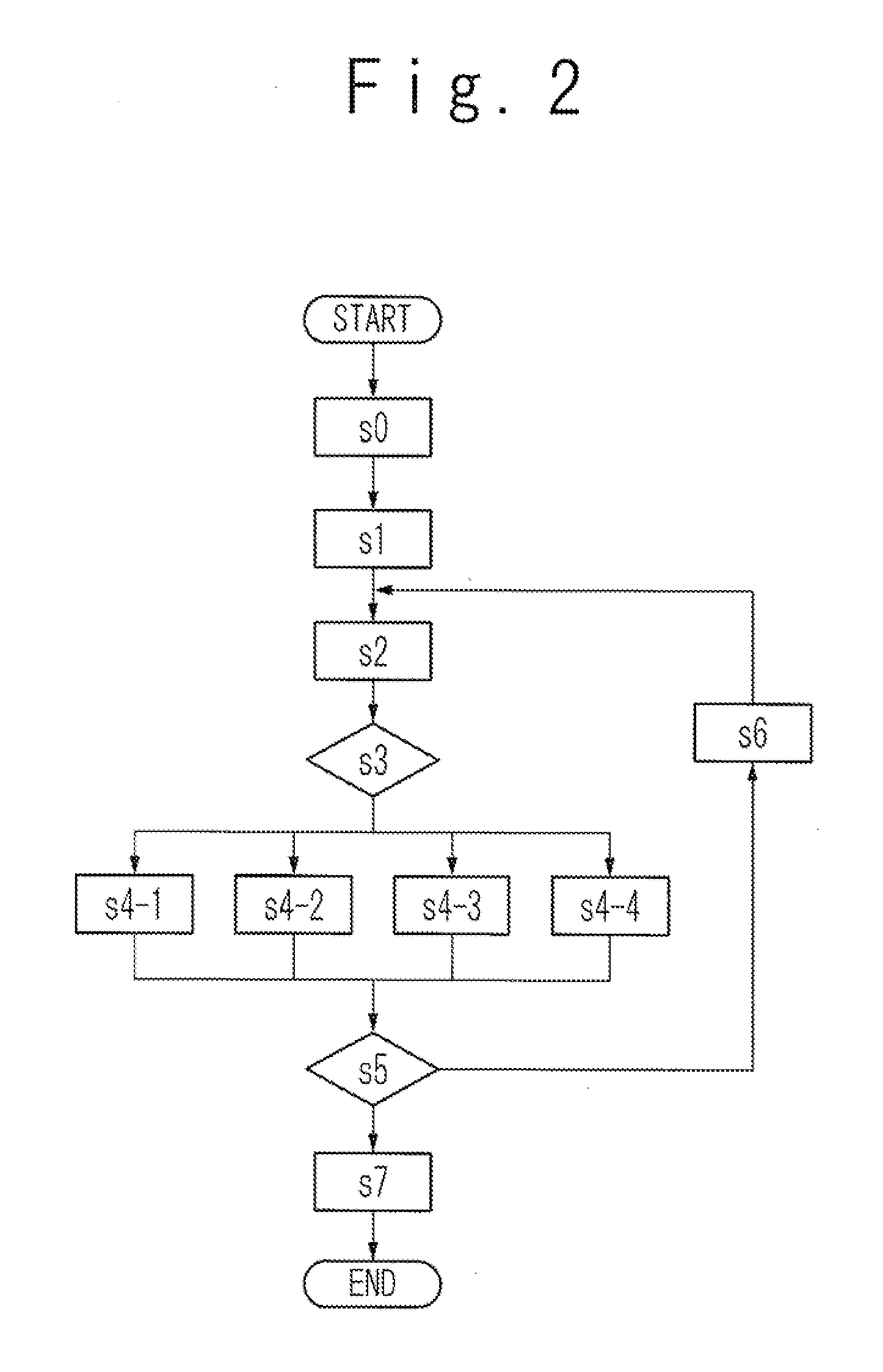

It system behavior measurement and analysis system and method thereof

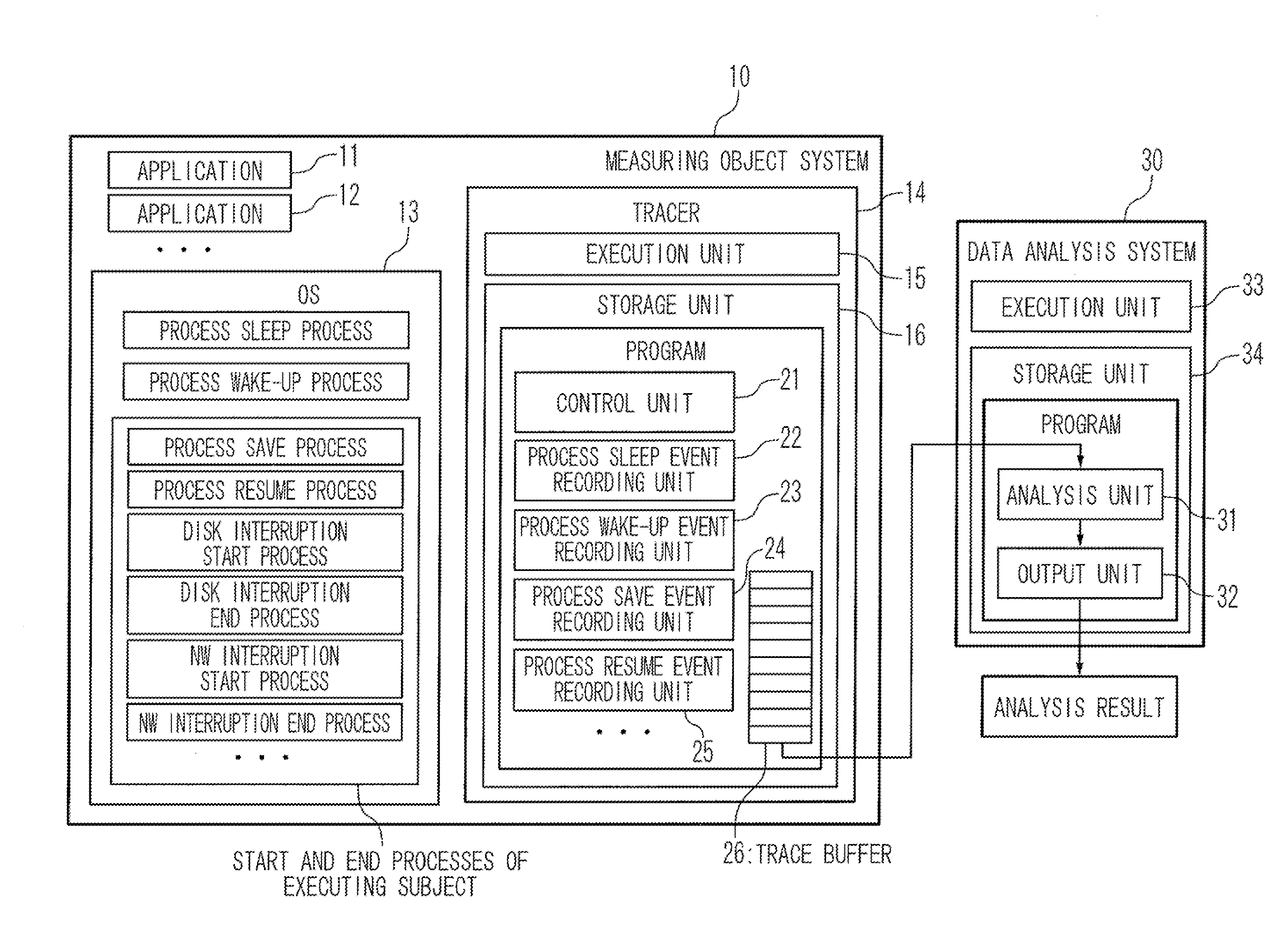

When a process sleep event, a process wake-up event, a process save event, and a process resume event occur in an IT system having a multiprocessor configuration, a tracer respectively generates sleep event data, wake-up event data, save event data, and resume event data and records them as trace data in a trace buffer. The analysis unit generates an analysis result by referring to the trace data to accumulate a number of times of execution of the process wake-up process and a first time as a time from the process save event to the process wake-up event or to the process resume event with respect to a plurality of processes to be executed. When a contention for a shared resource occurs, the process wake-up process is repeatedly executed among relevant processes. For this reason, based on the analysis result, a possibility can be presented that the shared resource contention occurs in the IT system.

Owner:NEC CORP

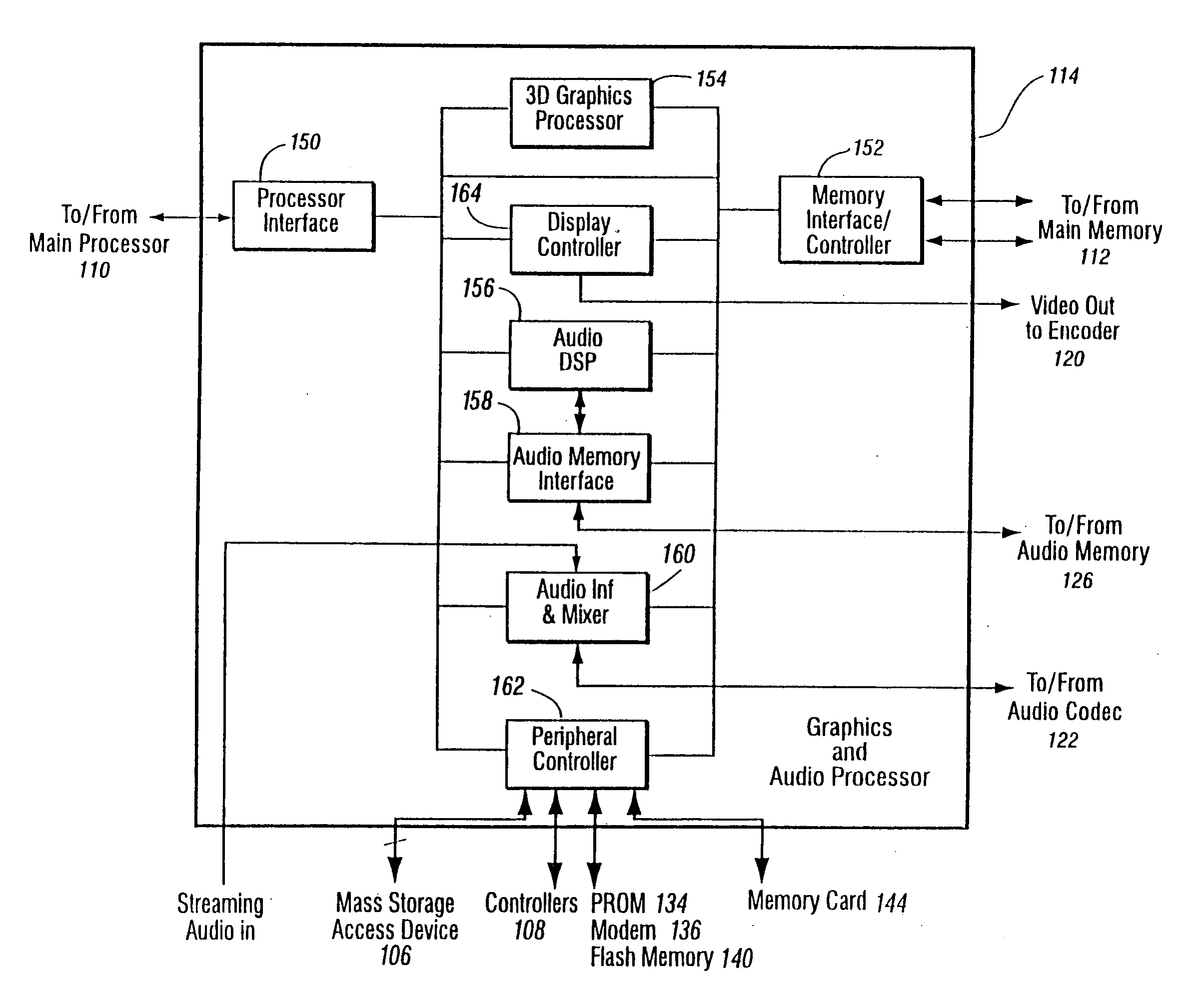

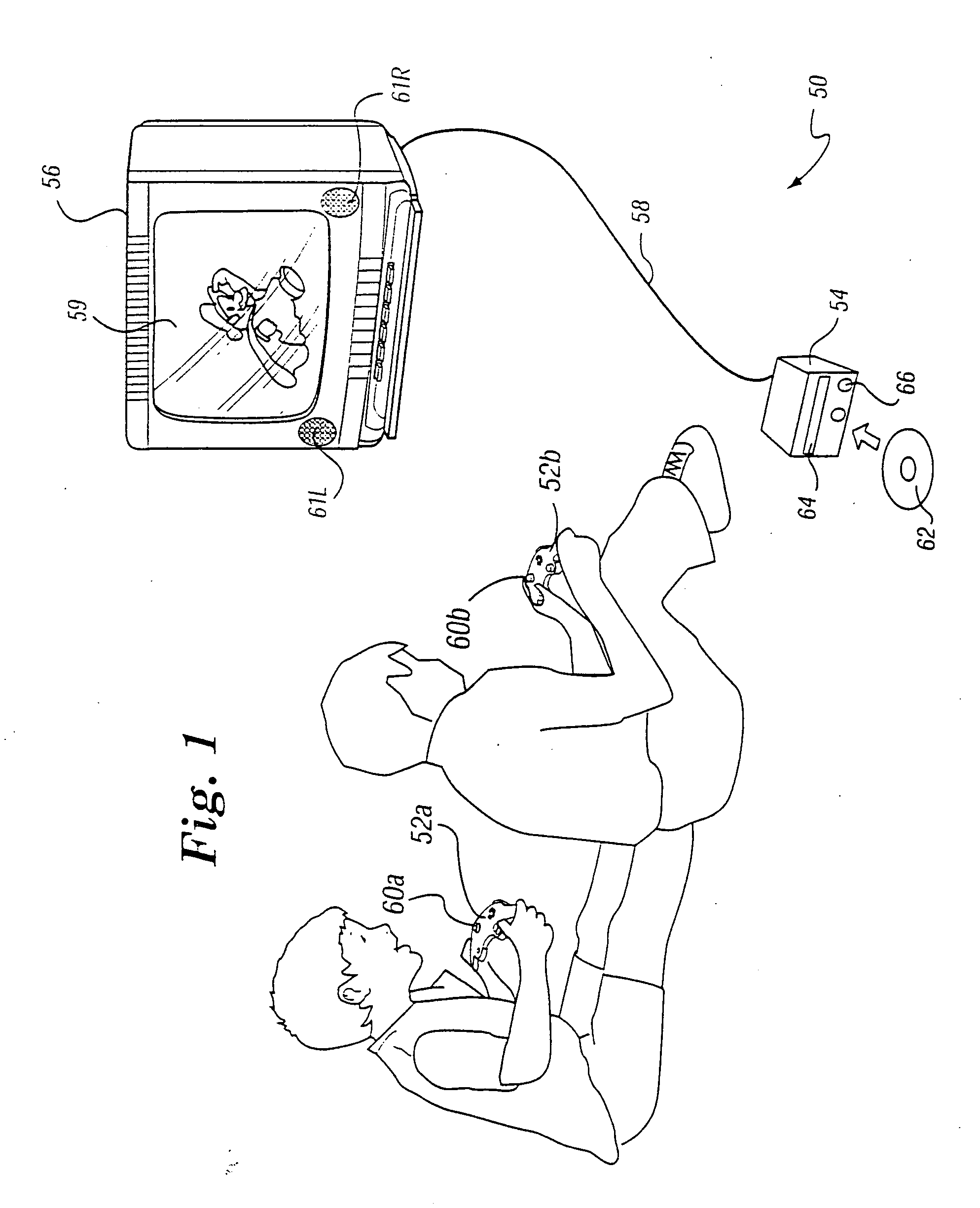

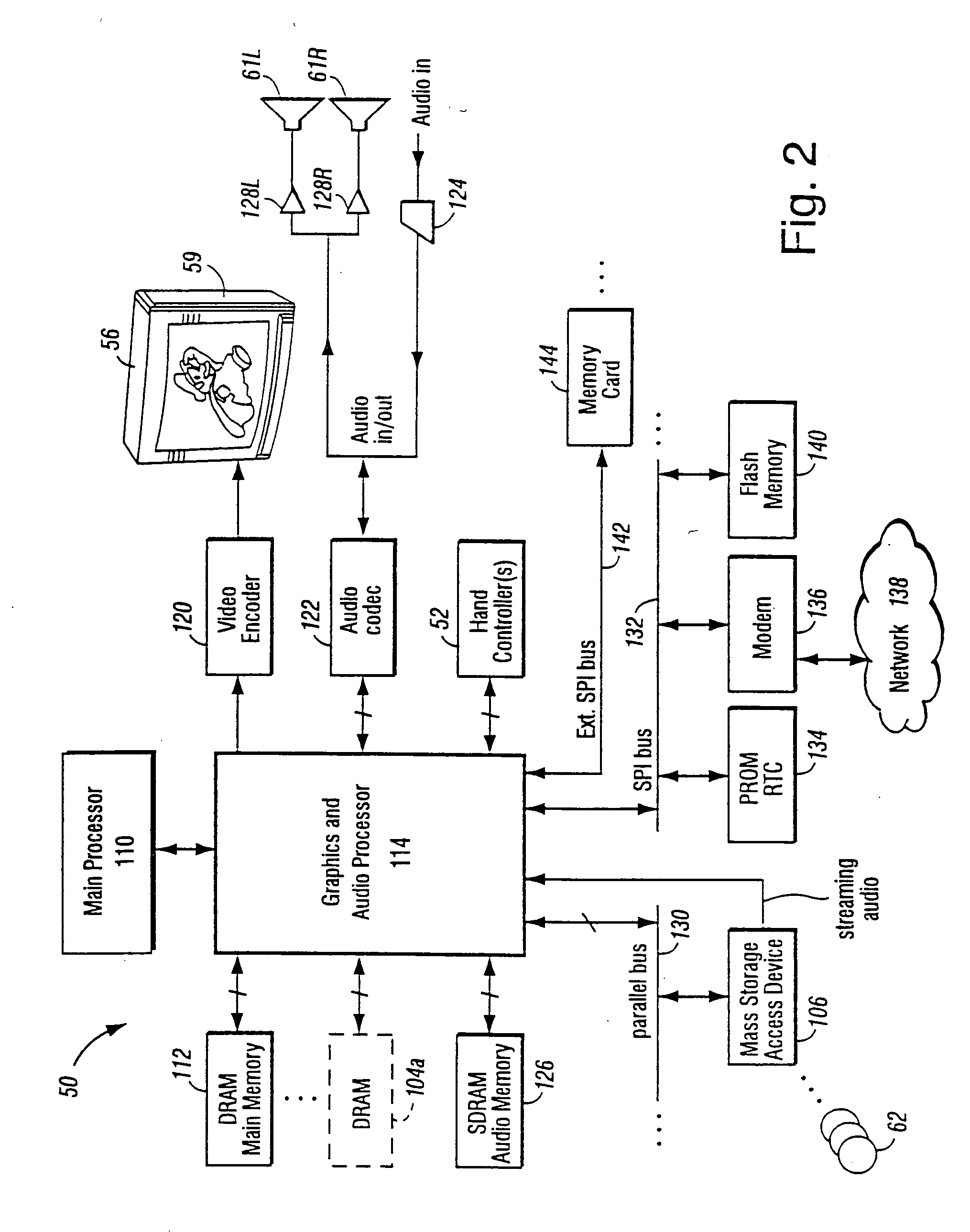

Method and apparatus for buffering graphics data in a graphics system

InactiveUS20070165043A1Effective bufferCreate efficientlyImage memory managementCathode-ray tube indicatorsTerm memoryWrite pointer

A graphics system including a custom graphics and audio processor produces exciting 2D and 3D graphics and surround sound. The system includes a graphics and audio processor including a 3D graphics pipeline and an audio digital signal processor. Techniques for efficiently buffering graphics data between a producer and a consumer within a low-cost graphics systems such as a 3D home video game overcome the problem that a small-sized FIFO buffer in the graphics hardware may not adequately load balance a producer and consumer—causing the producer to stall when the consumer renders bit primitives. One aspect of the invention solves this invention by allocating part of main memory to provide a variable number of variable sized graphics commands buffers. Applications can specify the number of buffers and the size of each. All writes to the graphics FIFO can be routed a buffer in main memory. The producer and consumer independently maintain their own read and write pointers, decoupling the producer from the consumer. The consumer does not write to the buffer, but uses its write pointer to keep track of data valid positions within the buffer. The producer can write a read command to a buffer that directs the consumer to read a string of graphics commands (e.g., display list) stored elsewhere in the memory, and to subsequently return to reading the rest of the buffer. Display lists can be created by simply writing a command that redirects the output of the producer to a display list buffer.

Owner:NINTENDO CO LTD

Non-intrusive processor tracing

Owner:APPLE INC

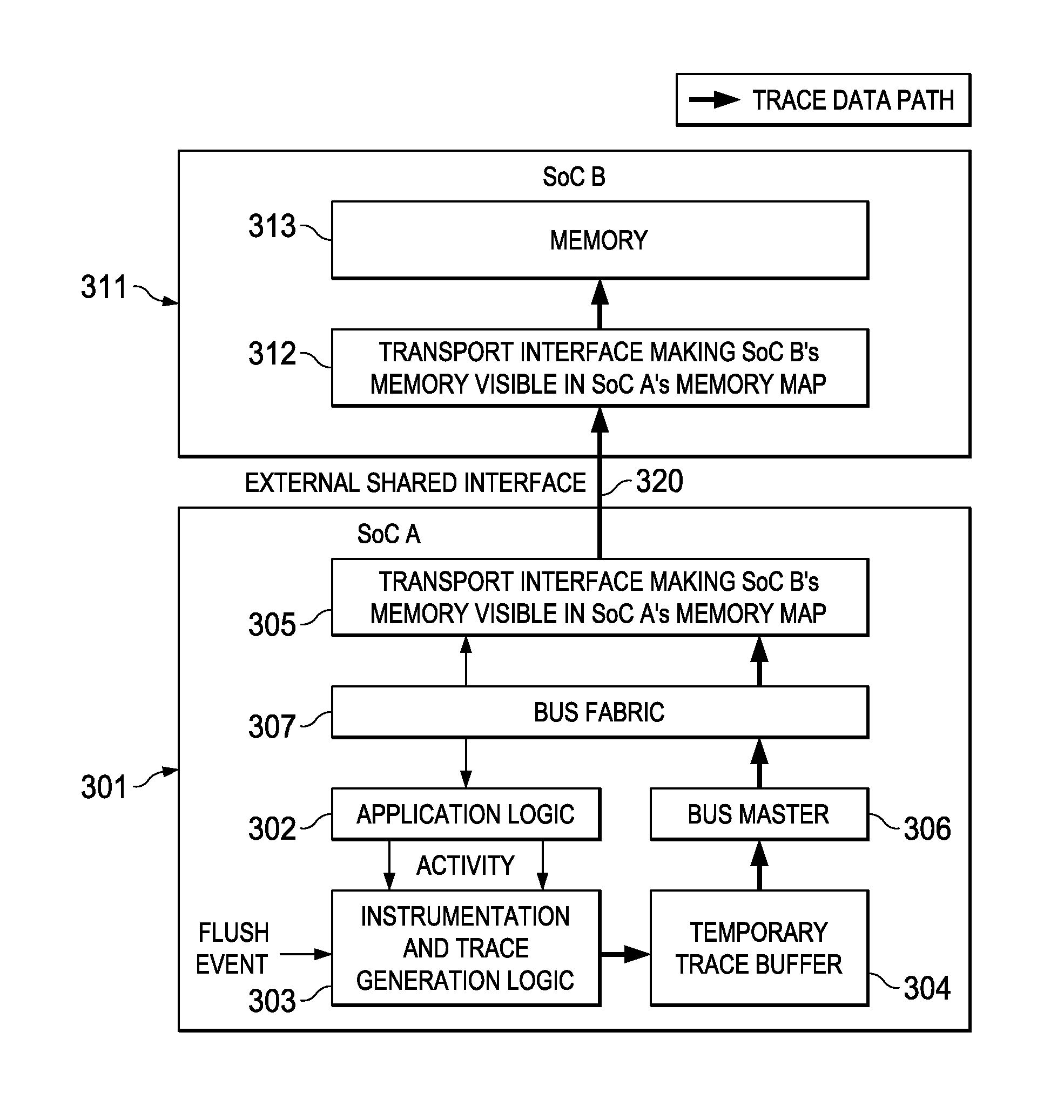

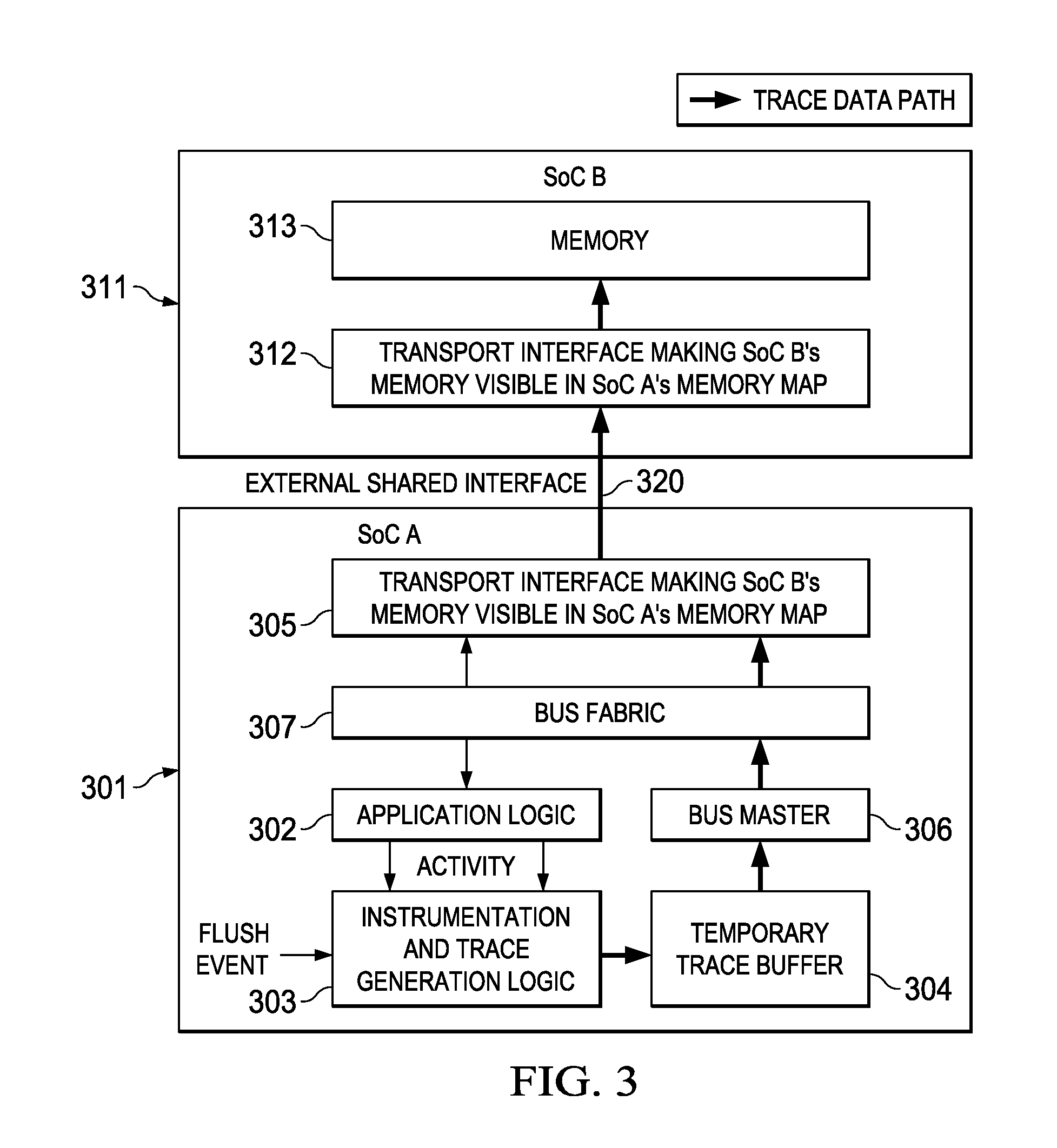

Trace Data Export to Remote Memory Using Memory Mapped Write Transactions

A method for easily tracing the execution of an application in a computer system having a plurality of computing nodes interconnected by high speed data links is disclosed. While executing the application on one or more of the computing nodes, trace data is collected into a separate temporary trace buffer coupled to each computing node. A trace transfer request event may be generated after collecting a portion of the trace data. The trace data is recorded on a designated recording and analysis computing node by transferring the trace data from each trace buffer to a recording buffer in the designated recording node in response to the transfer request by performing memory mapped write transfers initiated by each computing node that has collected trace data. The address of the recording buffer is memory mapped into an address space of each computing node that has collected trace data.

Owner:TEXAS INSTR INC

Adaptive next-executing-cycle trace selection for trace-driven code optimizers

ActiveUS8756581B2Compilation is improvedReduce the amount of solutionError detection/correctionSoftware engineeringDynamic compilationParallel computing

An apparatus includes a processor for executing instructions at runtime and instructions for dynamically compiling the set of instructions executing at runtime. A memory device stores the instructions to be executed and the dynamic compiling instructions. A memory device serves as a trace buffer used to store traces during formation during the dynamic compiling. The dynamic compiling instructions includes a next-executing-cycle (N-E-C) trace selection process for forming traces for the instructions executing at runtime. The N-E-C trace selection process continues through an existing trace-head when forming traces without terminating a recording of a current trace if an existing trace-head is encountered.

Owner:GLOBALFOUNDRIES US INC