Patents

Literature

398 results about "Write pointer" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

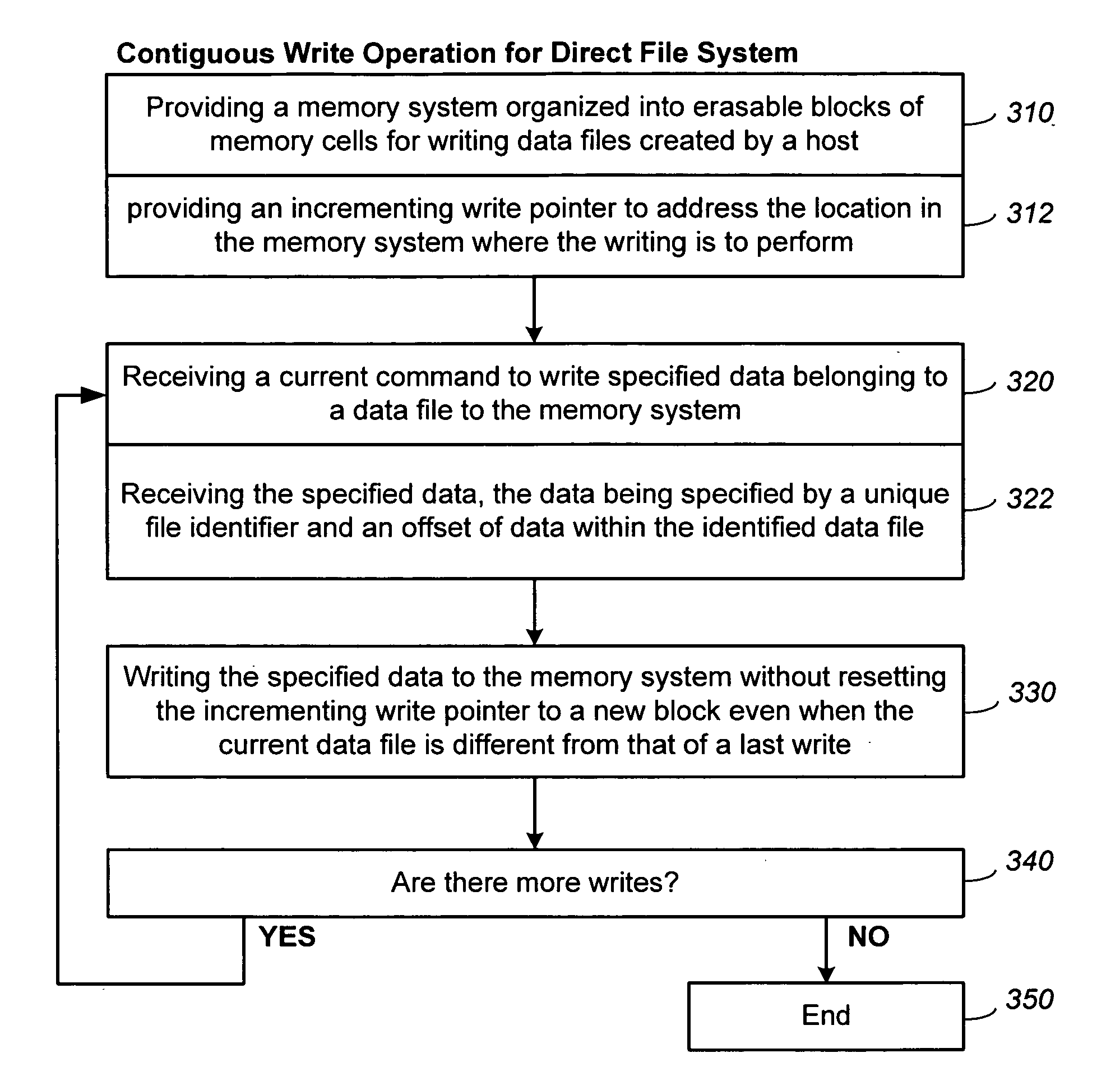

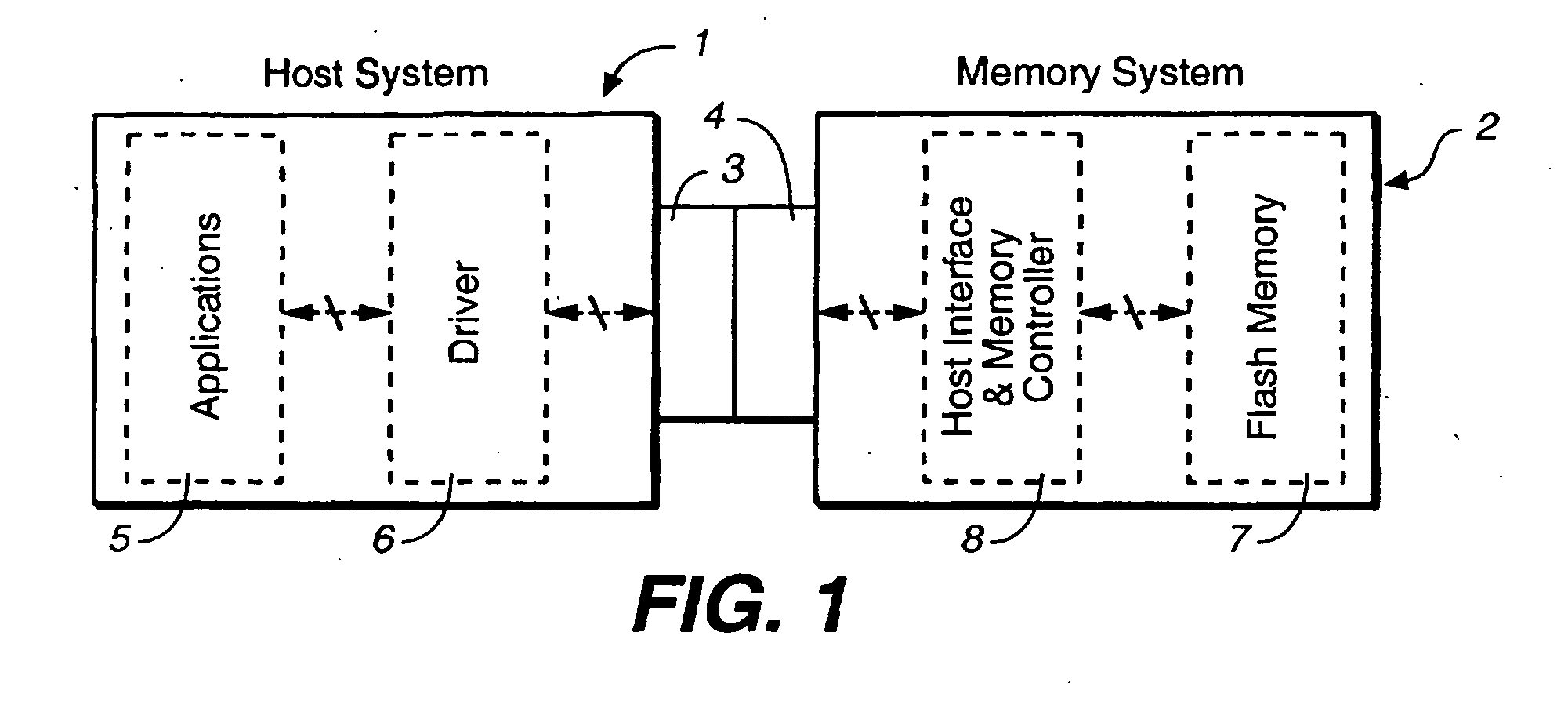

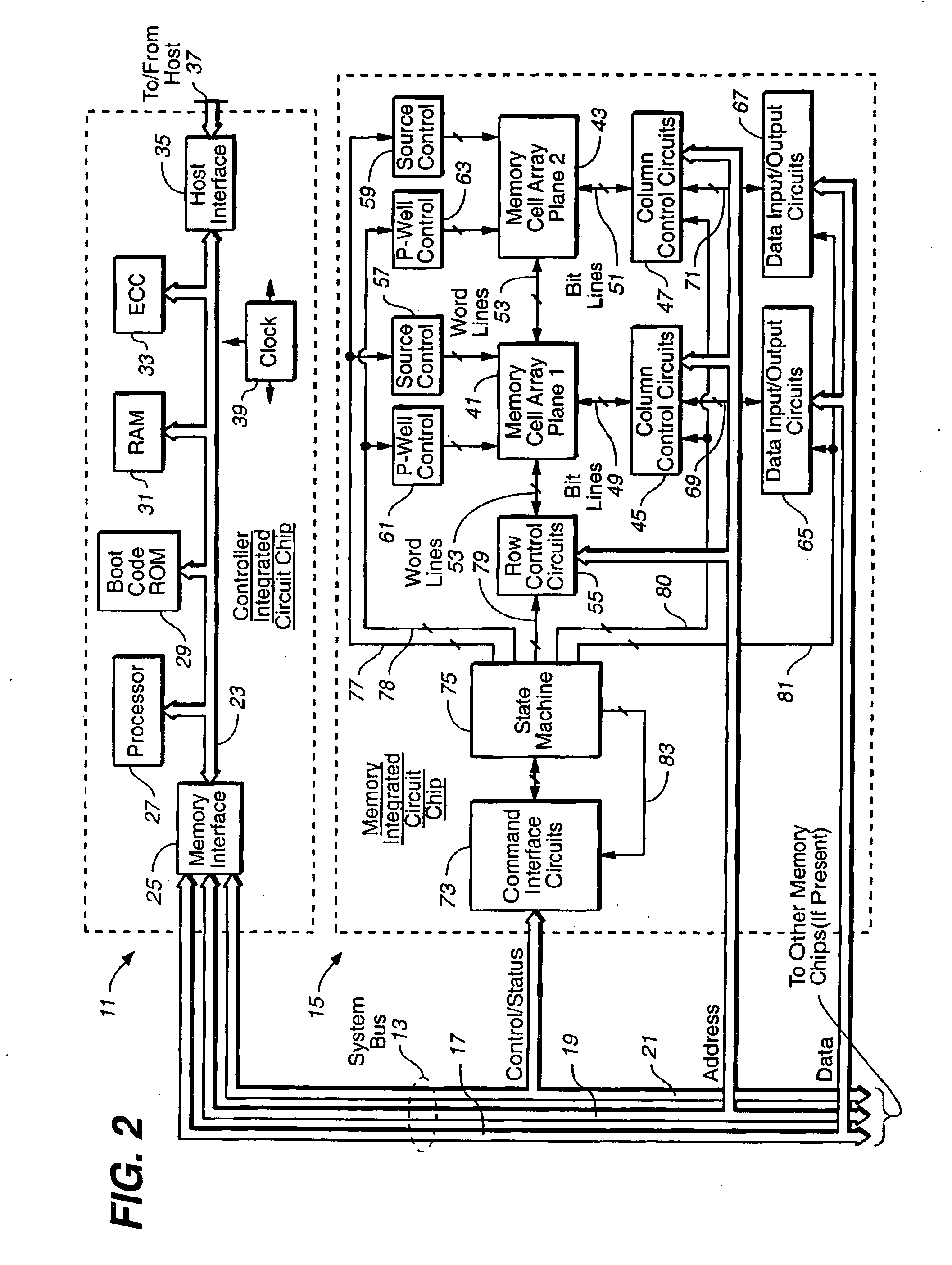

Methods for memory allocation in non-volatile memories with a directly mapped file storage system

InactiveUS20070156998A1Improve performanceEfficient packagingMemory architecture accessing/allocationMemory systemsData compressionWrite pointer

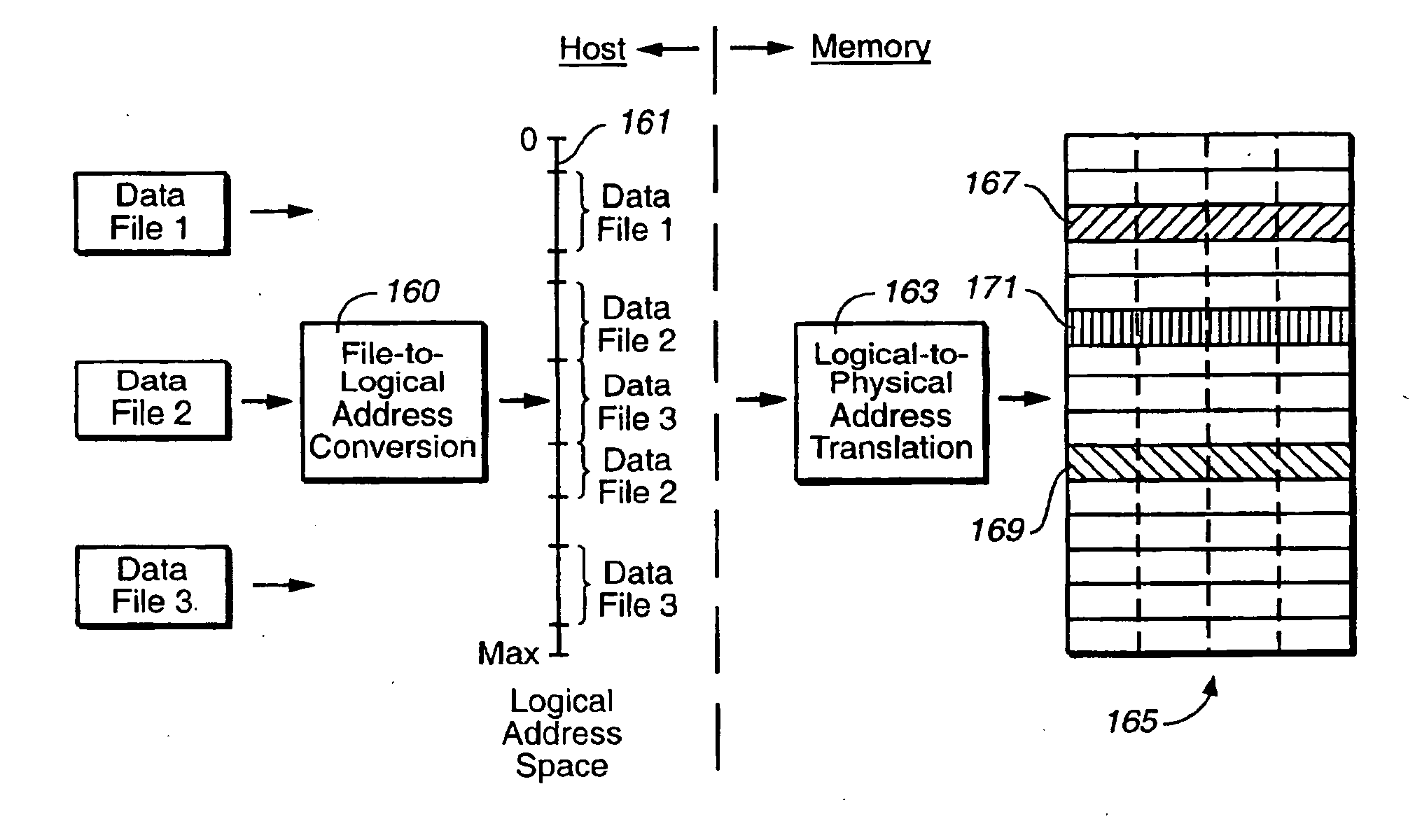

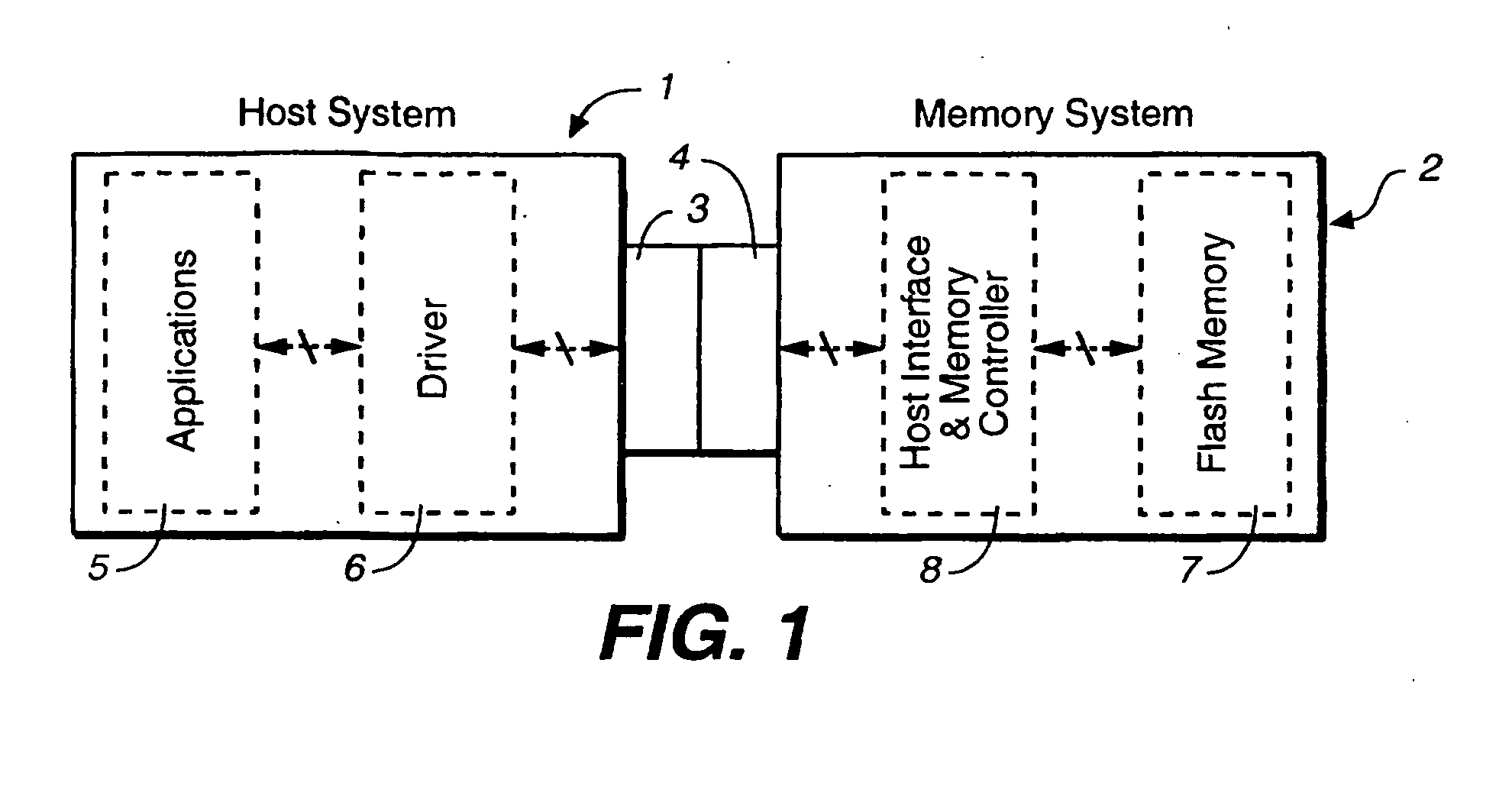

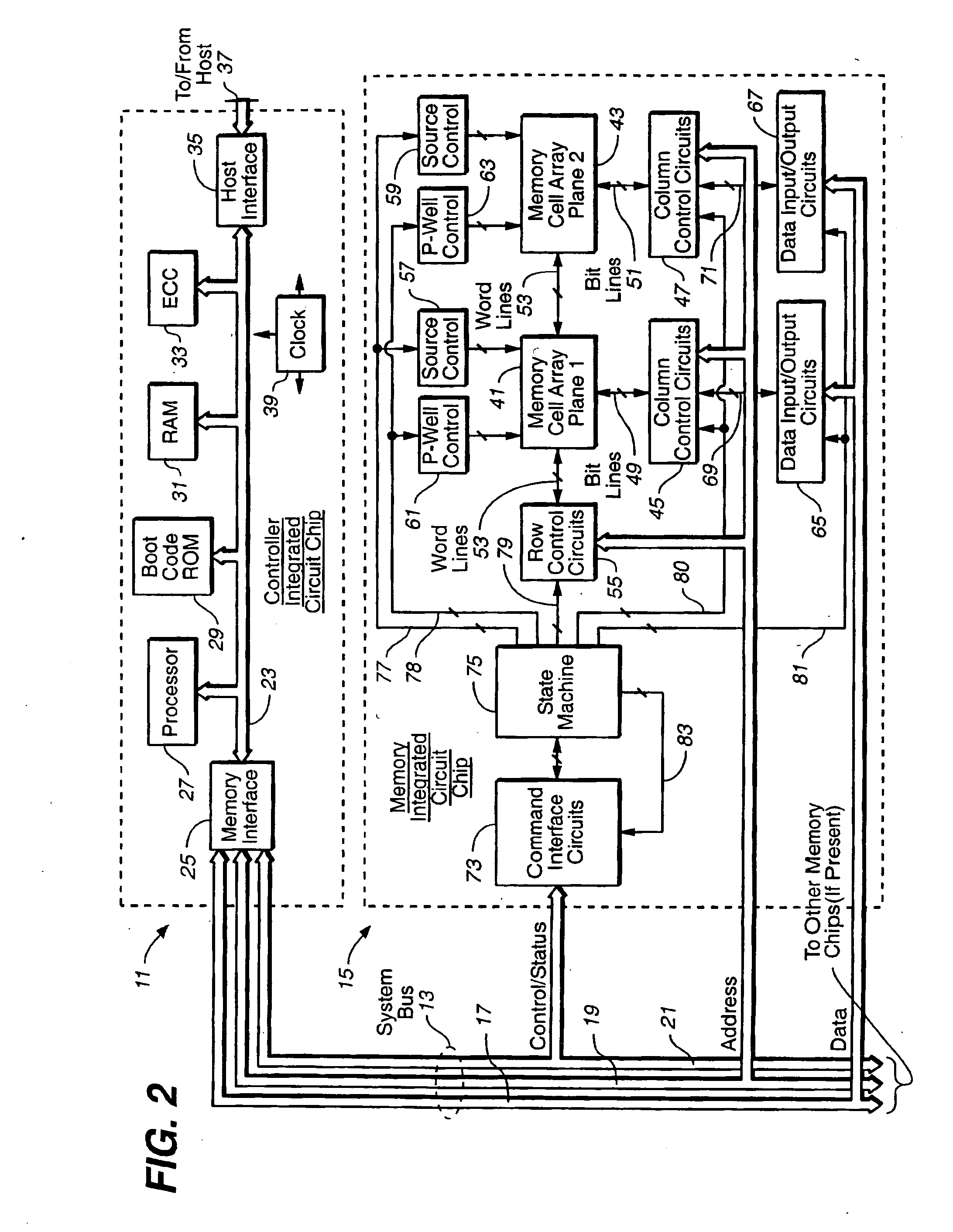

In a memory system with a file storage system, a scheme for allocating memory locations for a write operation is to write the files substantially contiguously in a memory block one after another rather than to start a new file in a new block. In this way, they are more efficiently packed into the blocks by being written contiguously one after another. In a preferred embodiment, an incrementing write pointer points to the write location in memory for the next data for a file, which is independent of the offset address of the data within the file. When a current write block becomes filled with file data, an erased block is allocated, and the write pointer is moved to this block. Similarly a relocation pointer is used for data relocation during garbage collection or data compaction operations.

Owner:SANDISK TECH LLC

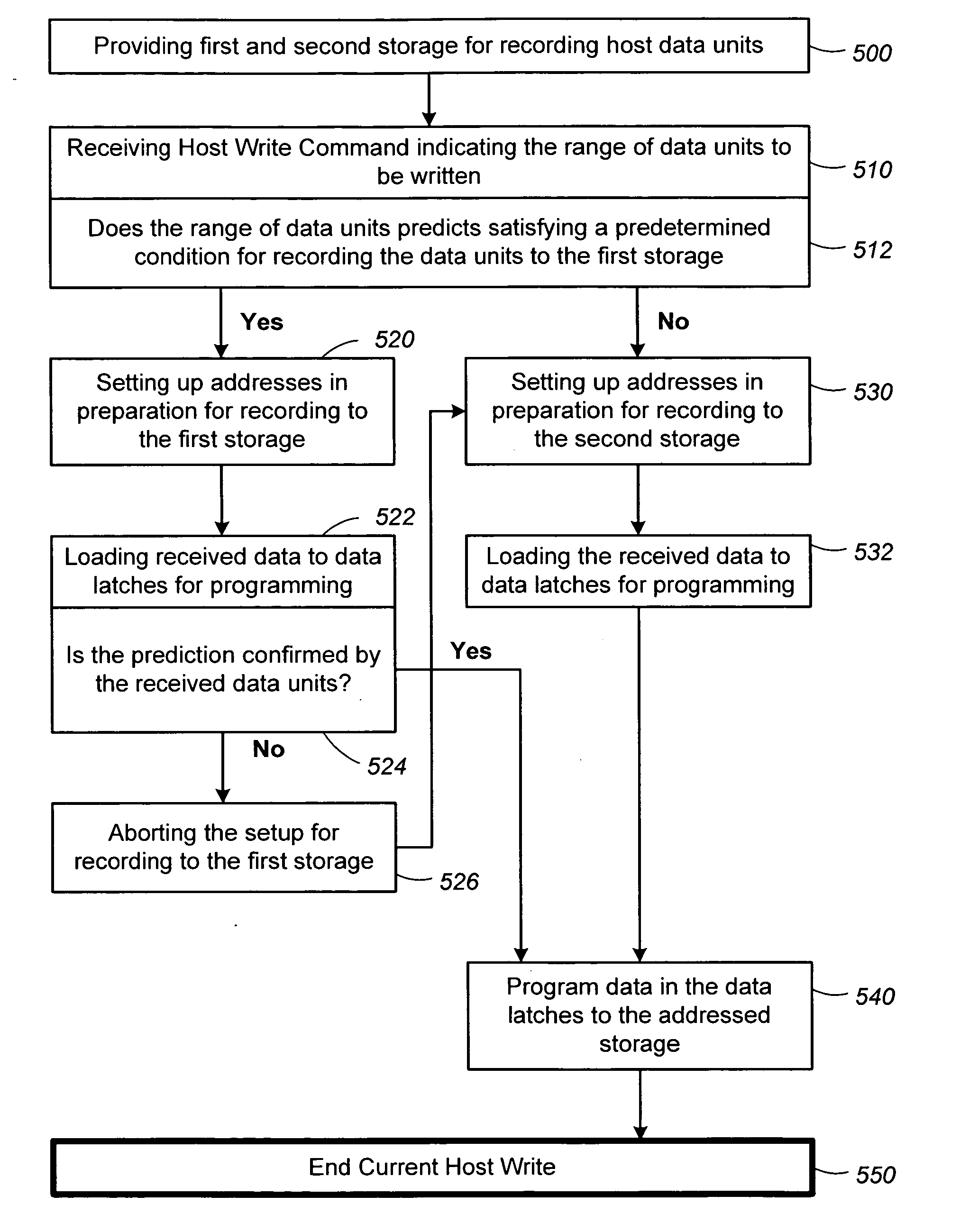

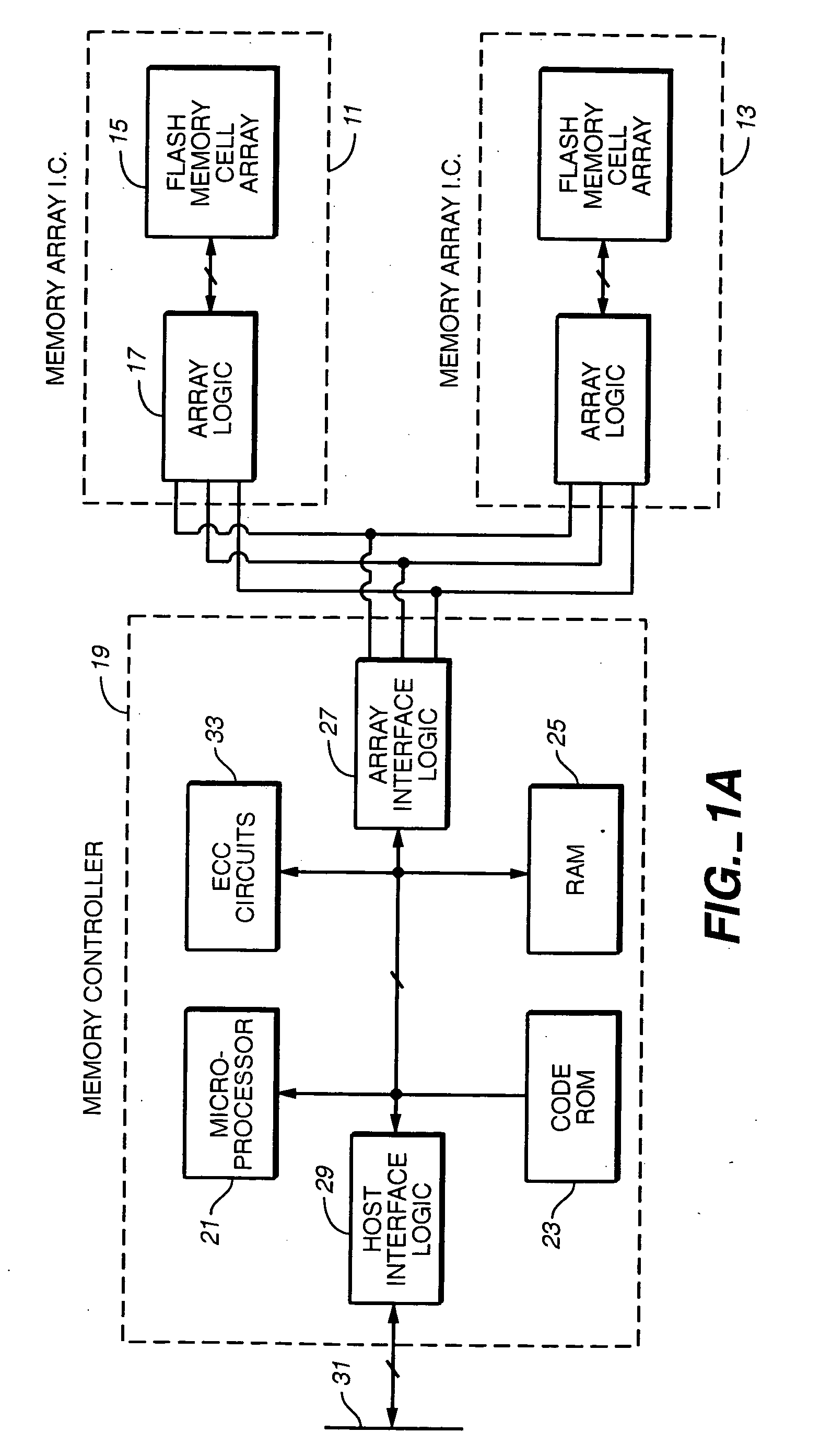

Non-volatile memory and method with multi-stream update tracking

ActiveUS20060155921A1Improve performanceWrite efficientlyMemory architecture accessing/allocationRead-only memoriesData streamMulti stream

Update data to a non-volatile memory may be recorded in at least two interleaving streams such as either into an update block or a scratch pad block depending on a predetermined condition. The scratch pad block is used to buffered update data that are ultimately destined for the update block. Synchronization information about the order recording of updates among the streams is saved with at least one of the streams. This will allow the most recently written version of data that may exist on multiple memory blocks to be identified. In one embodiment, the synchronization information is saved in a first block and is a write pointer that points to the next recording location in a second block. In another embodiment, the synchronization information is a time stamp.

Owner:SANDISK TECH LLC

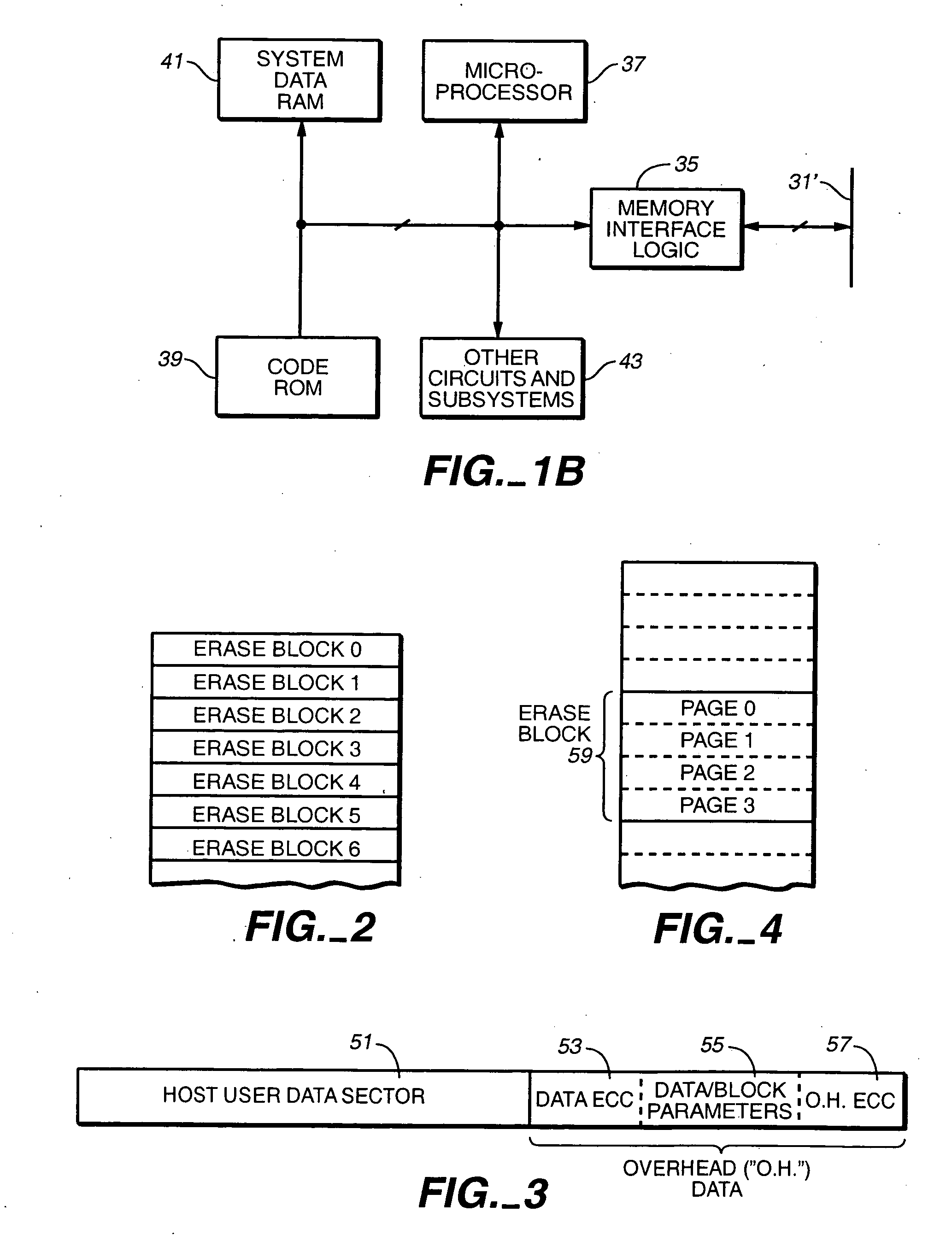

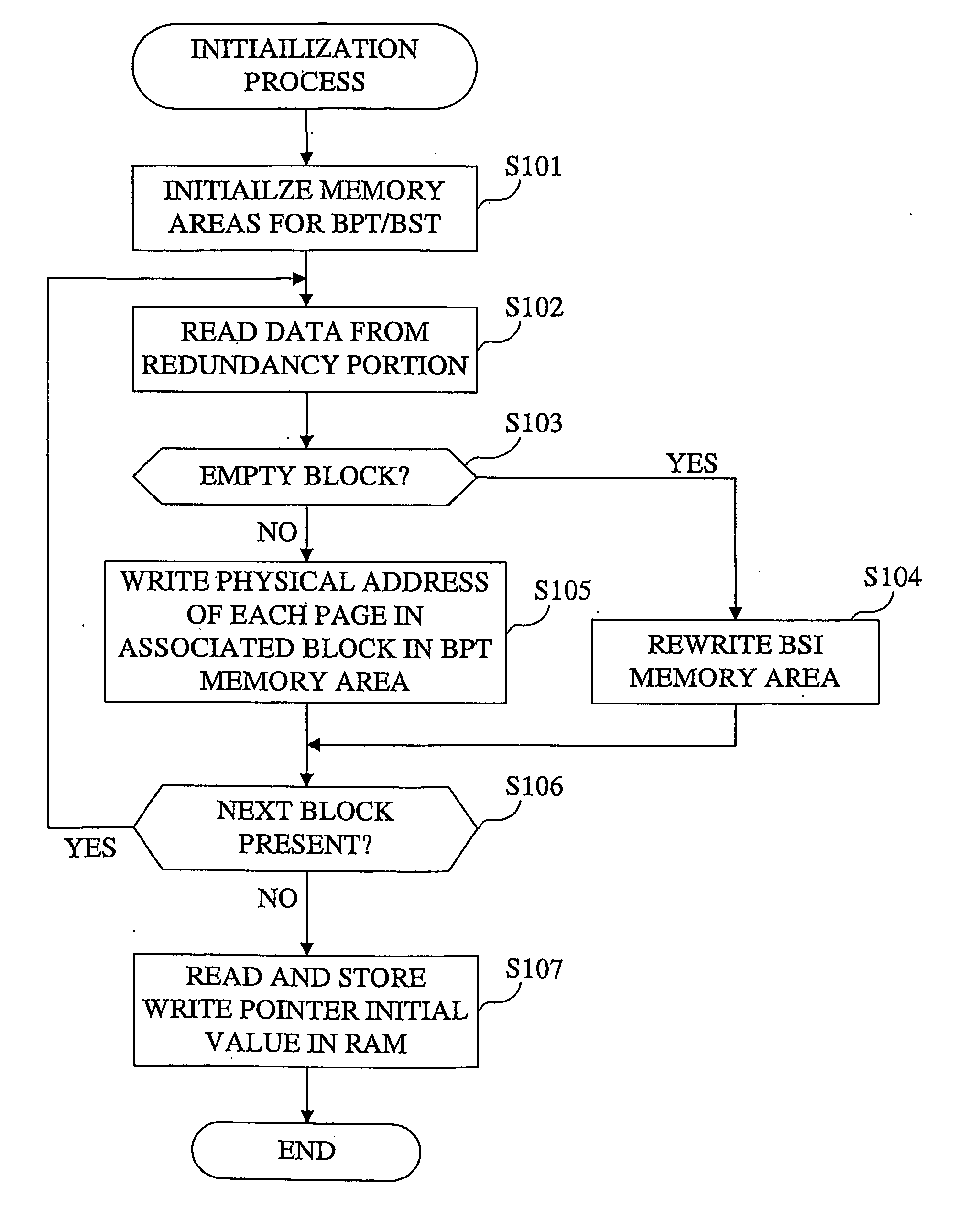

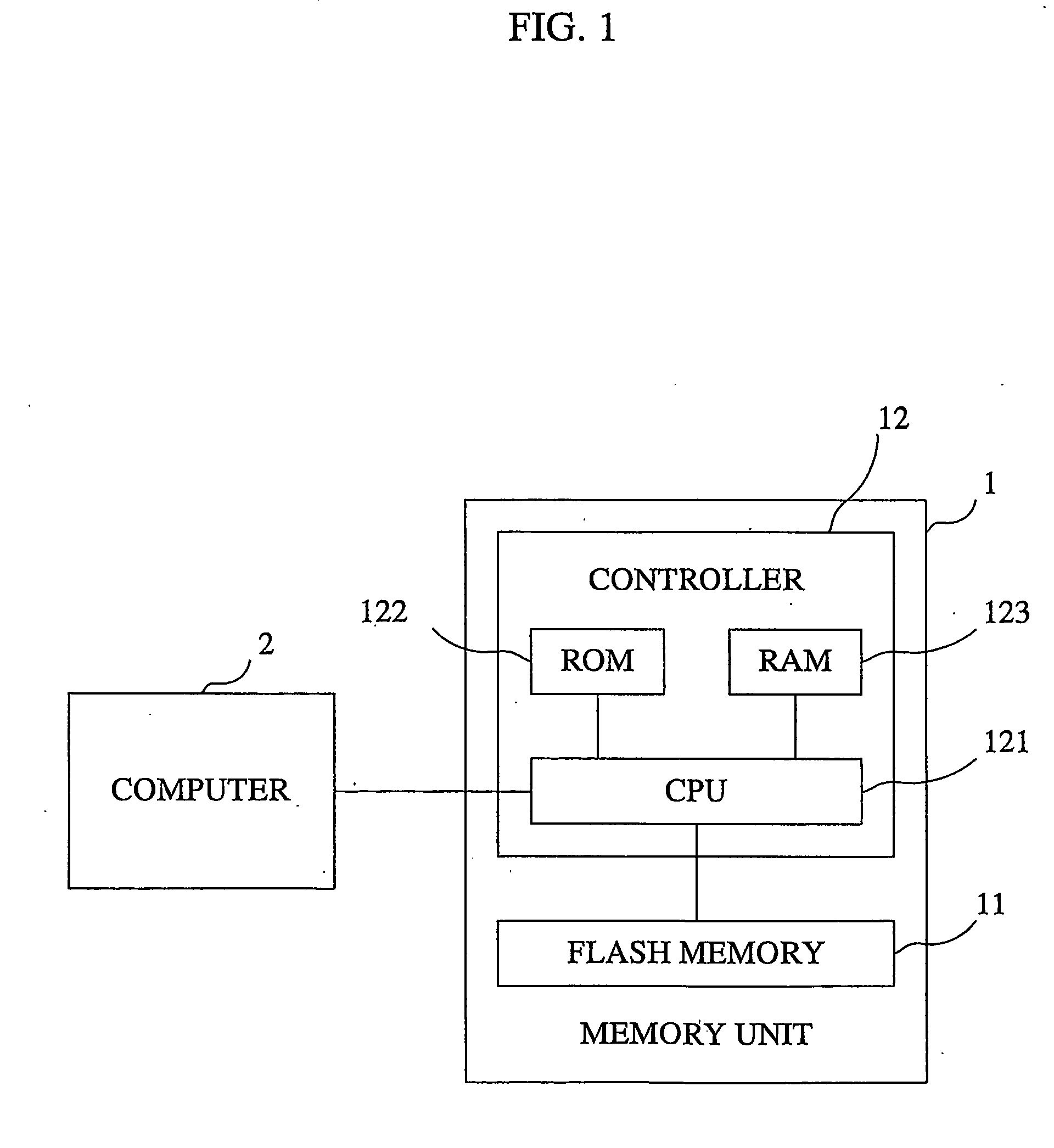

Memory device, memory managing method and program

InactiveUS20060143365A1Wasteful flash eraseDifficult to cause degradingInput/output to record carriersMemory adressing/allocation/relocationTerm memoryWrite pointer

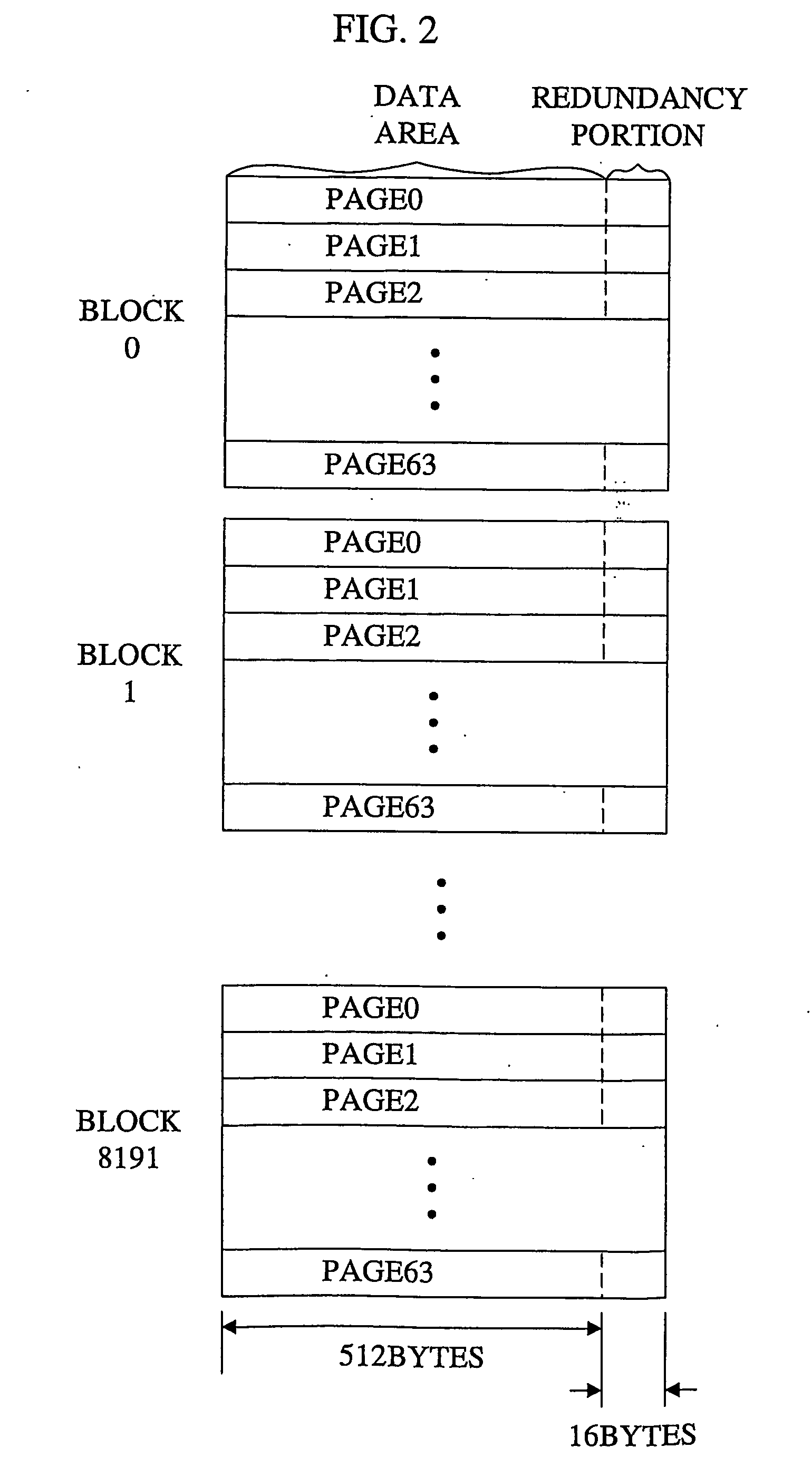

Disclosed is a memory device which is not easily deteriorated and a memory managing method which does not easily deteriorate a memory device. A physical address is given to a memory area of a flash memory (11) page by page. When supplied with to-bewritten data and a logical address where the data is to be written, a CPU (121) writes this data in a page indicated by a write pointer. The correlation between the physical address and the logical address of the page is stored in a RAM (123) in the form of BPT (Block Pointer Table). At the time of reading, the CPU (121) that has been supplied with the logical address searches the BPT to specify a physical address associated with that logical address and reads data from that page which is given the specified physical address. Flash erasing of a block is executed when the number of empty blocks becomes equal to or smaller than a predetermined number.

Owner:TOKYO ELECTRON DEVICE

Non-volatile memories with memory allocation for a directly mapped file storage system

InactiveUS20070143560A1Promote high performanceImprove performanceRead-only memoriesMemory systemsData compressionWrite pointer

In a memory system with a file storage system, a scheme for allocating memory locations for a write operation is to write the files substantially contiguously in a memory block one after another rather than to start a new file in a new block. In this way, they are more efficiently packed into the blocks by being written contiguously one after another. In a preferred embodiment, an incrementing write pointer points to the write location in memory for the next data for a file, which is independent of the offset address of the data within the file. When a current write block becomes filled with file data, an erased block is allocated, and the write pointer is moved to this block. Similarly a relocation pointer is used for data relocation during garbage collection or data compaction operations.

Owner:SANDISK TECH LLC

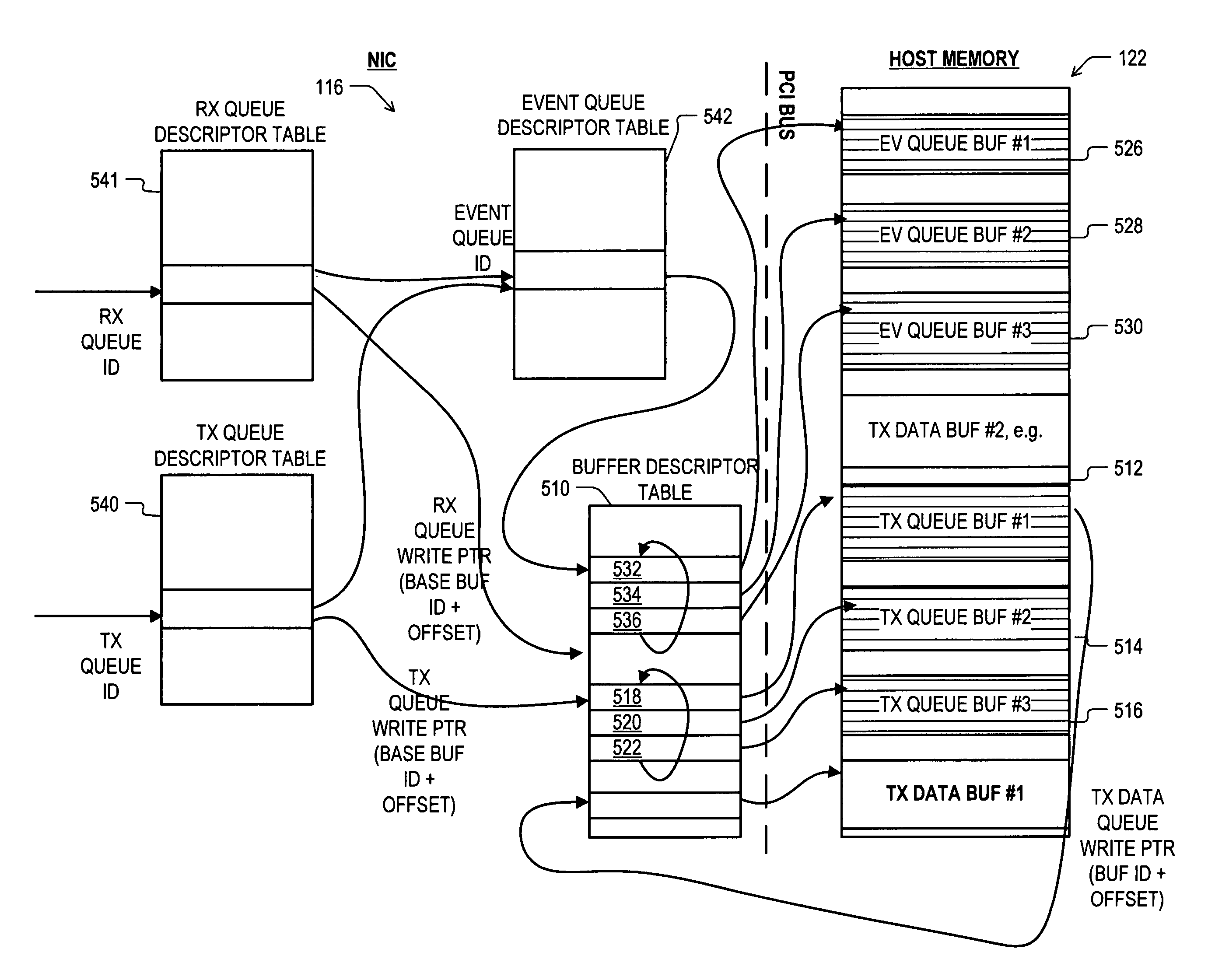

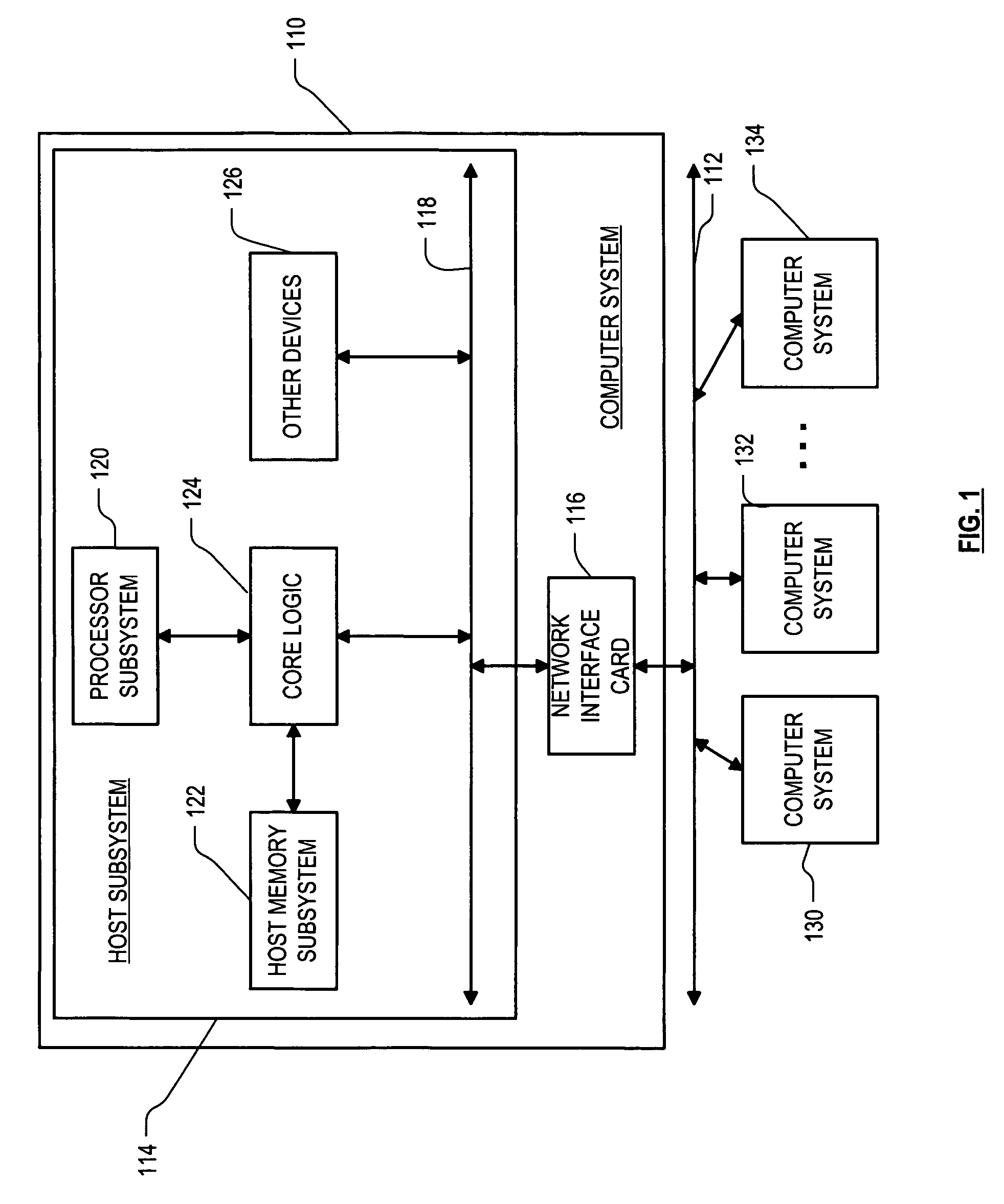

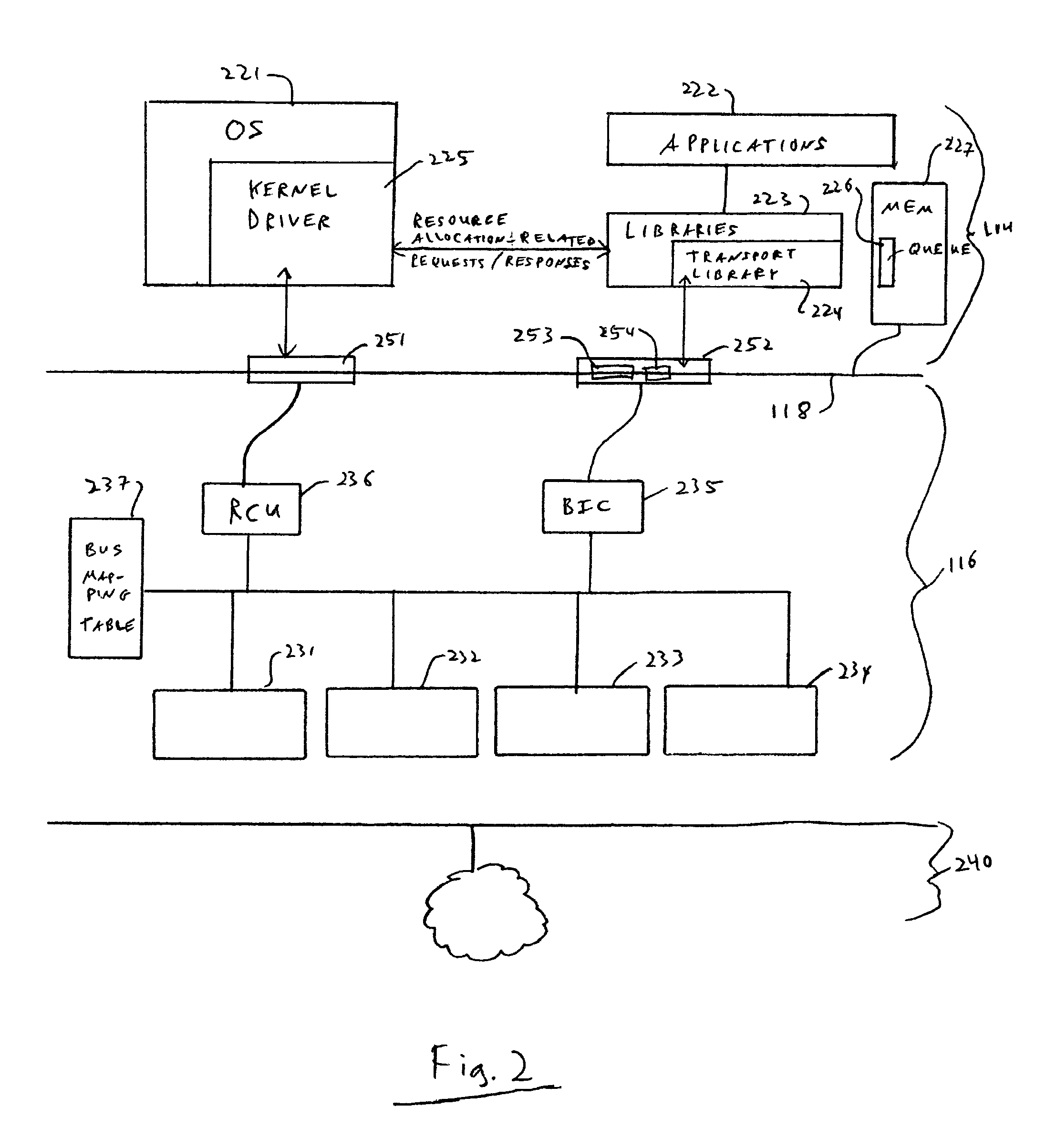

DMA descriptor queue read and cache write pointer arrangement

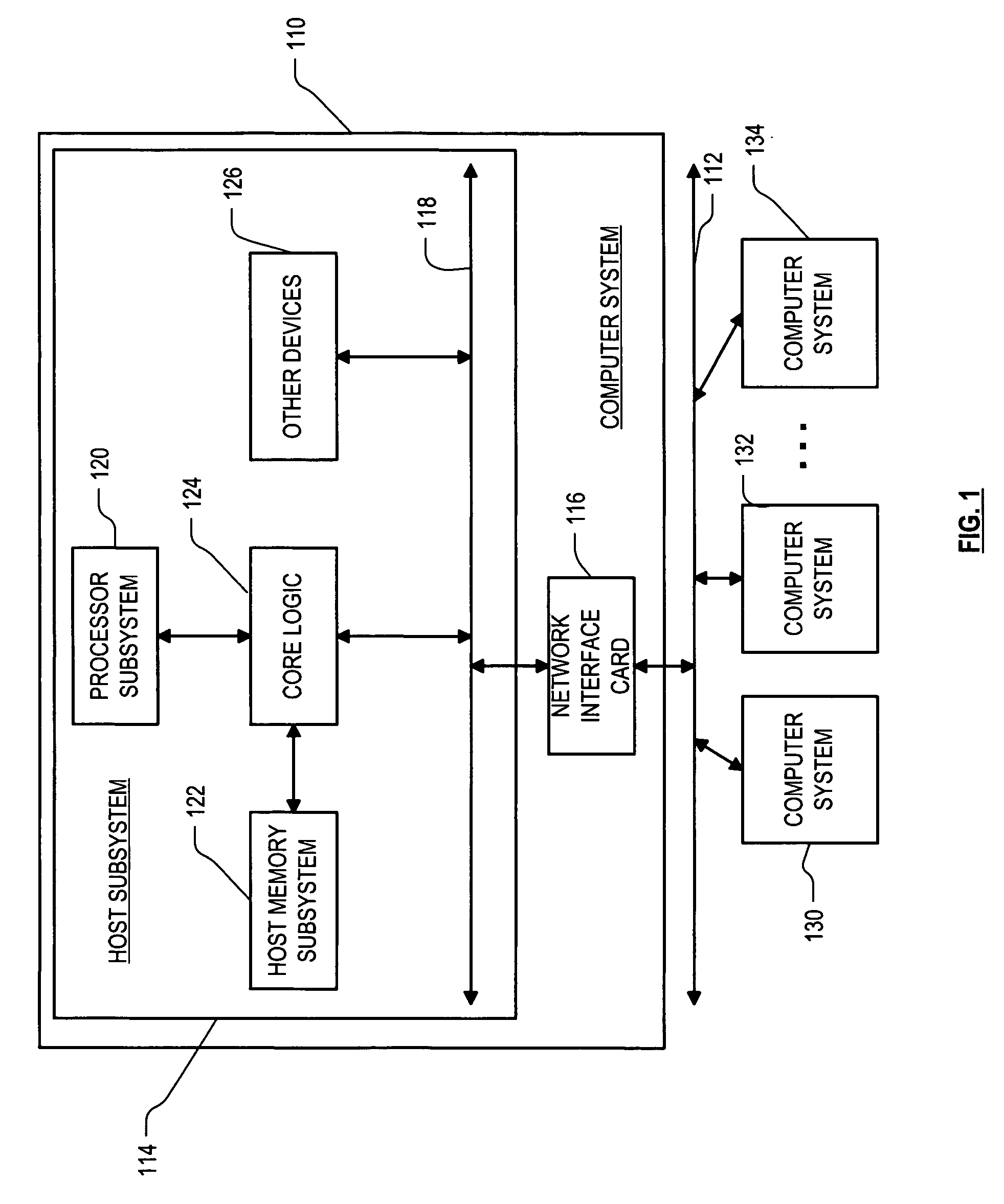

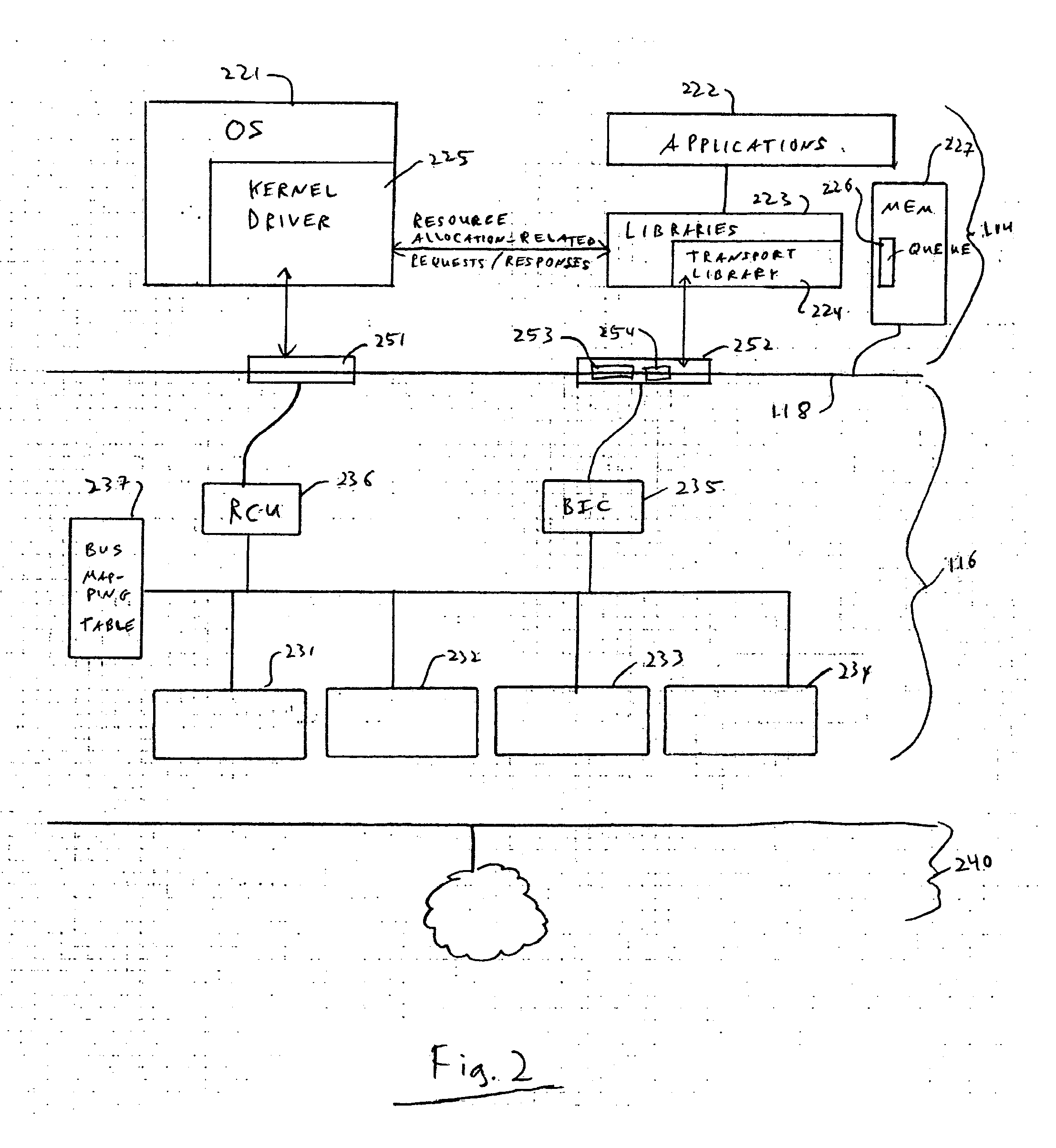

Method and apparatus for retrieving buffer descriptors from a host memory for use by a peripheral device. In an embodiment, a peripheral device such as a NIC includes a plurality of buffer descriptor caches each corresponding to a respective one of a plurality of host memory descriptor queues, and a plurality of queue descriptors each corresponding to a respective one of the host memory descriptor queues. Each of the queue descriptors includes a host memory read address pointer for the corresponding descriptor queue, and this same read pointer is used to derive algorithmically the descriptor cache write addresses at which to write buffer descriptors retrieved from the corresponding host memory descriptor queue.

Owner:XILINX INC

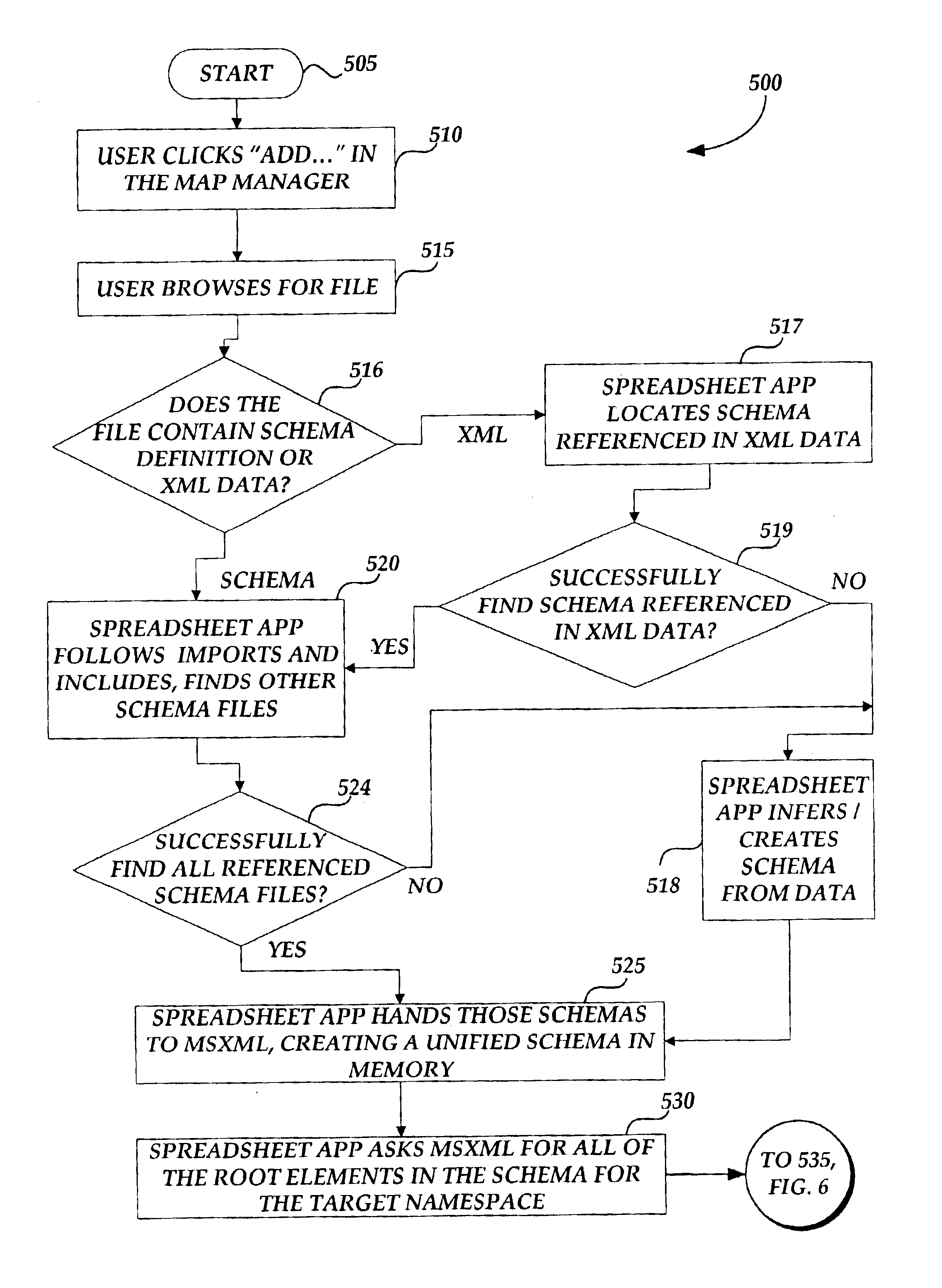

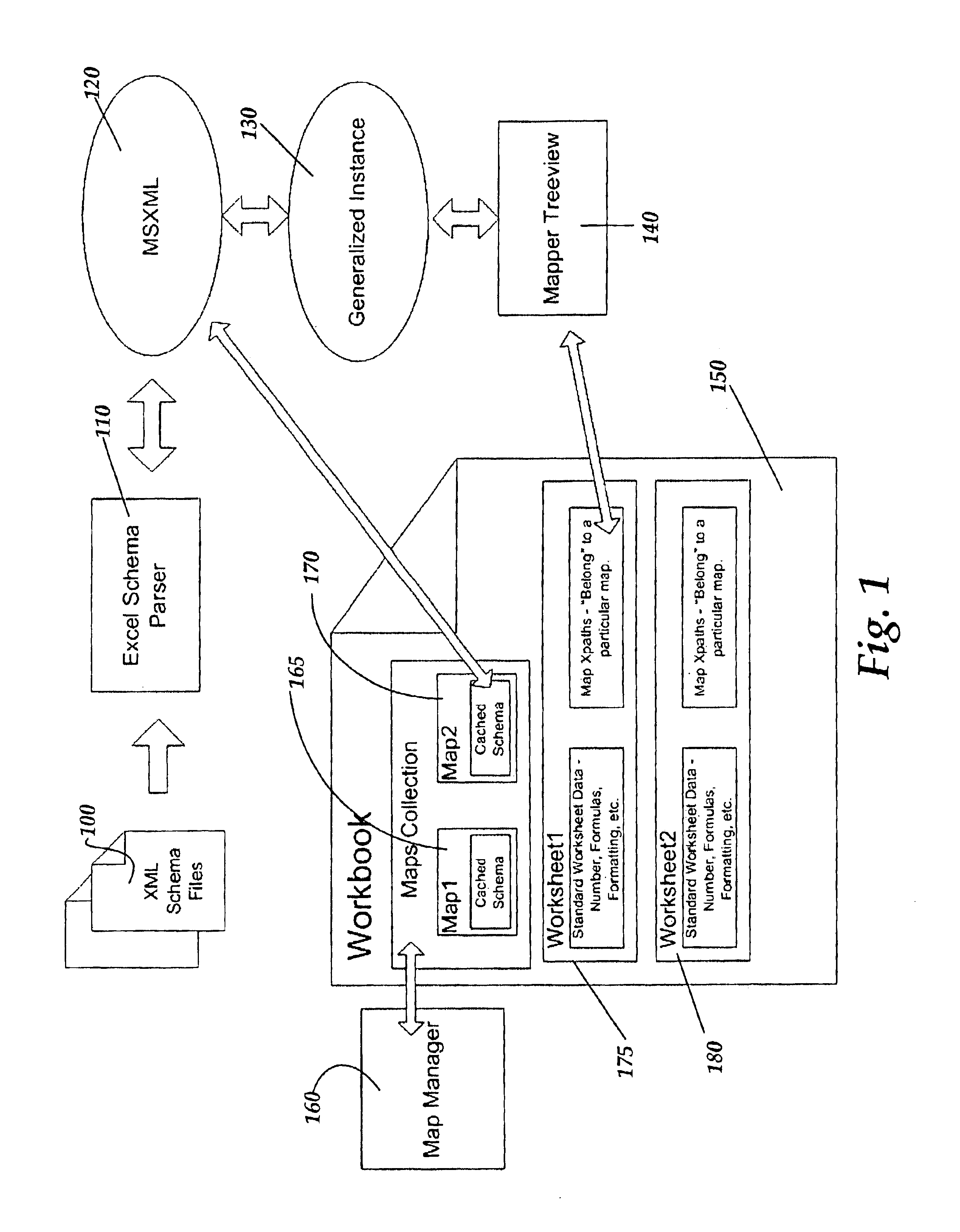

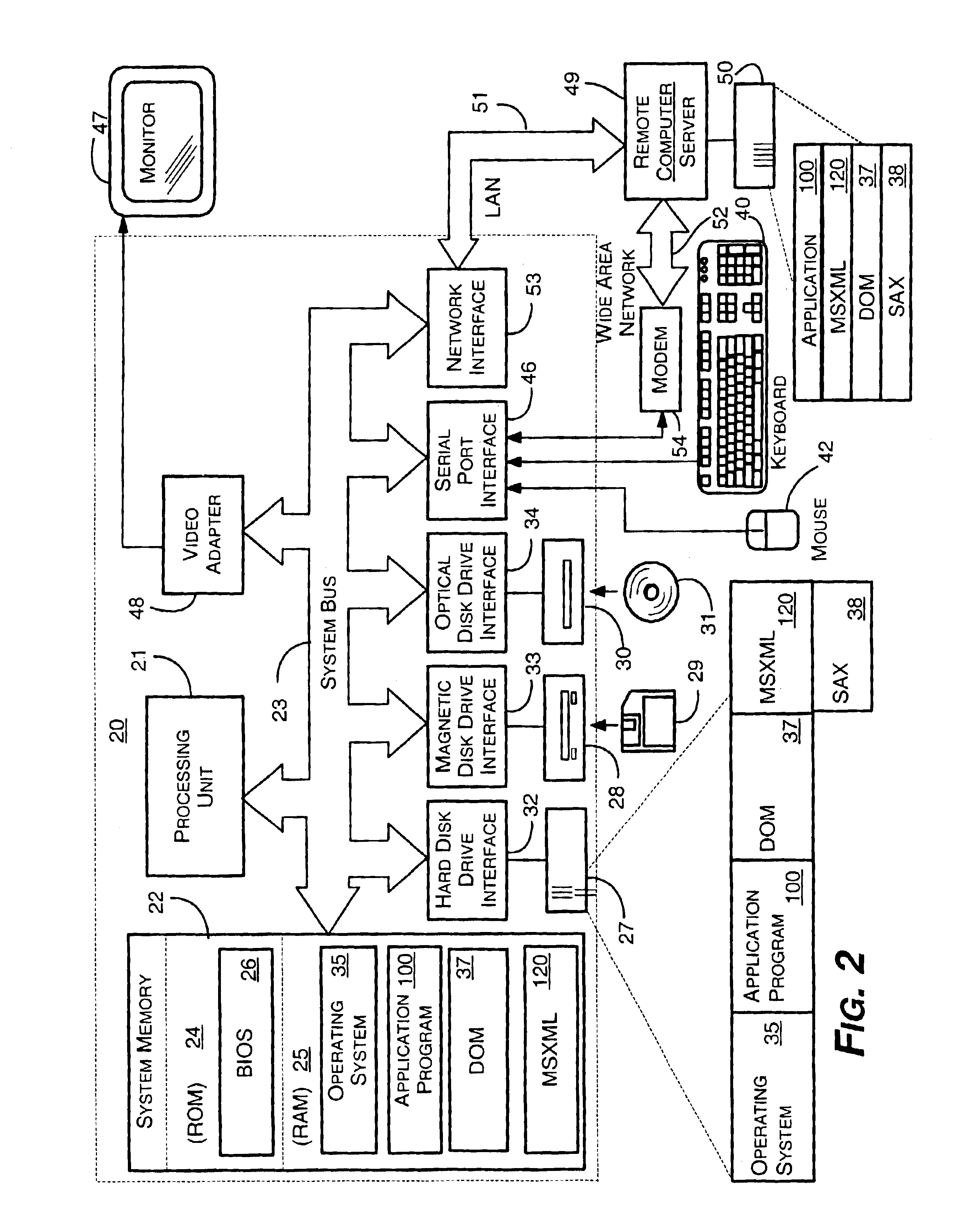

Management of markup language data mappings available to a spreadsheet application workbook

InactiveUS7007033B1Data processing applicationsDigital data processing detailsRoot elementXML schema

Owner:MICROSOFT TECH LICENSING LLC

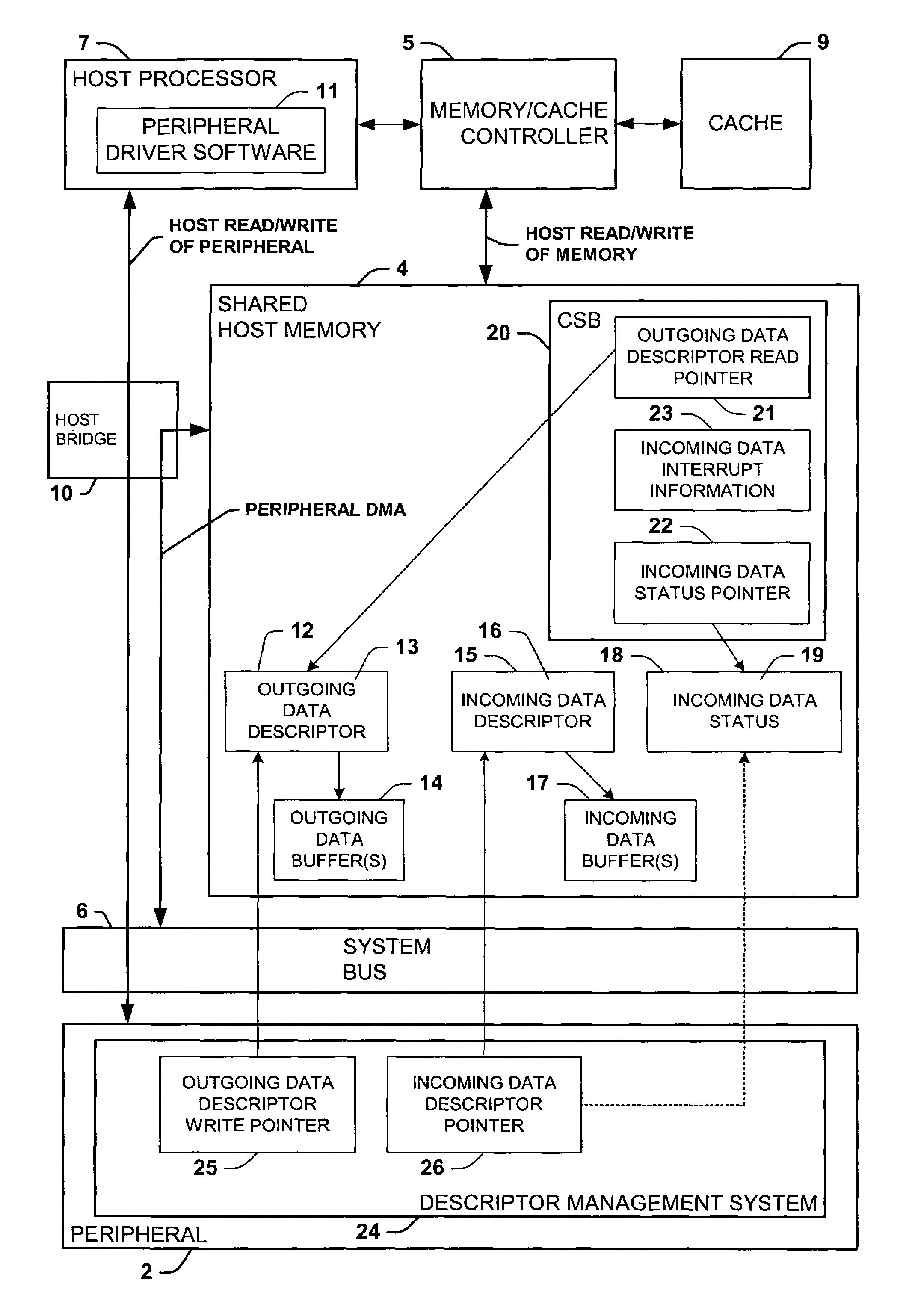

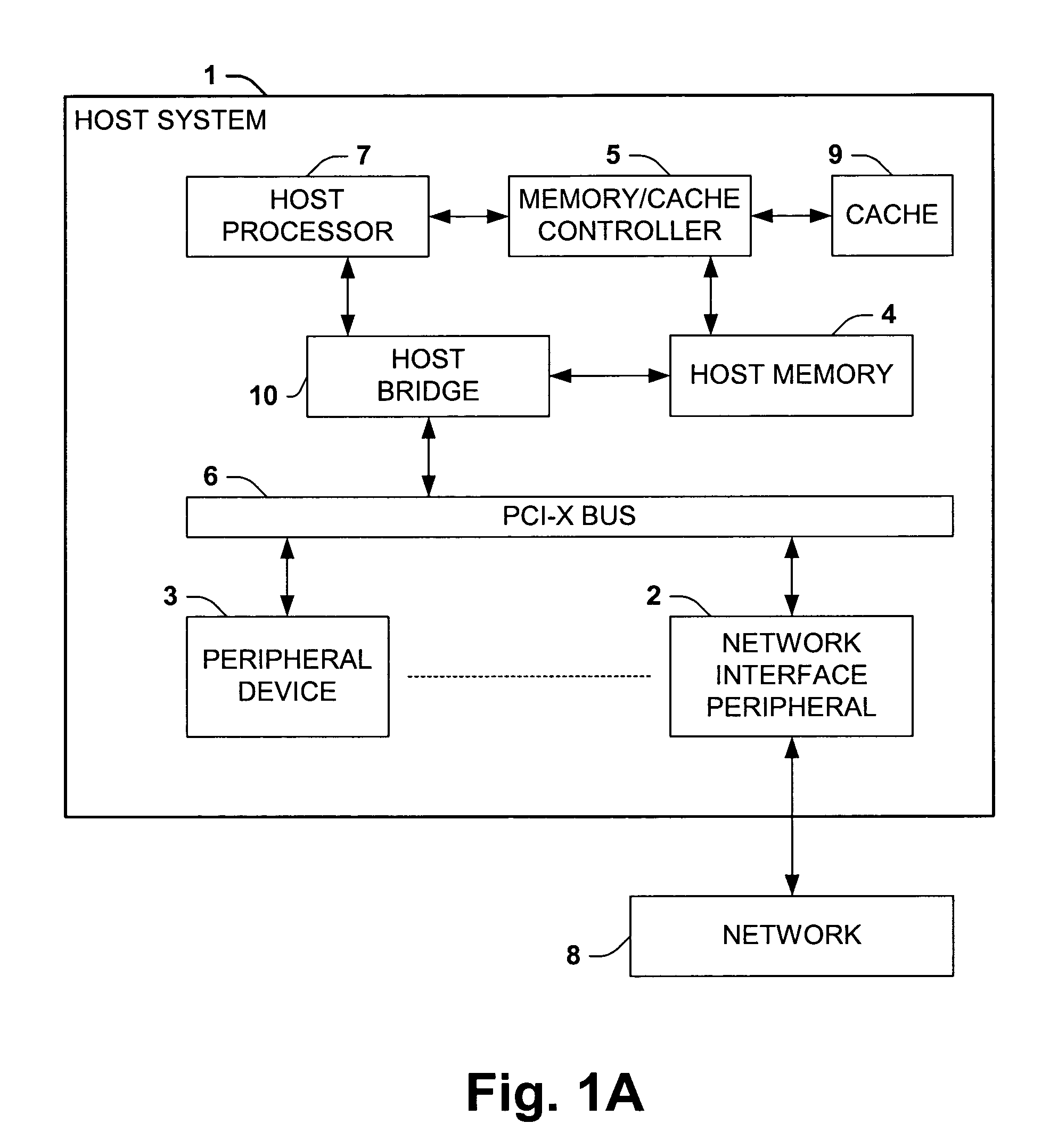

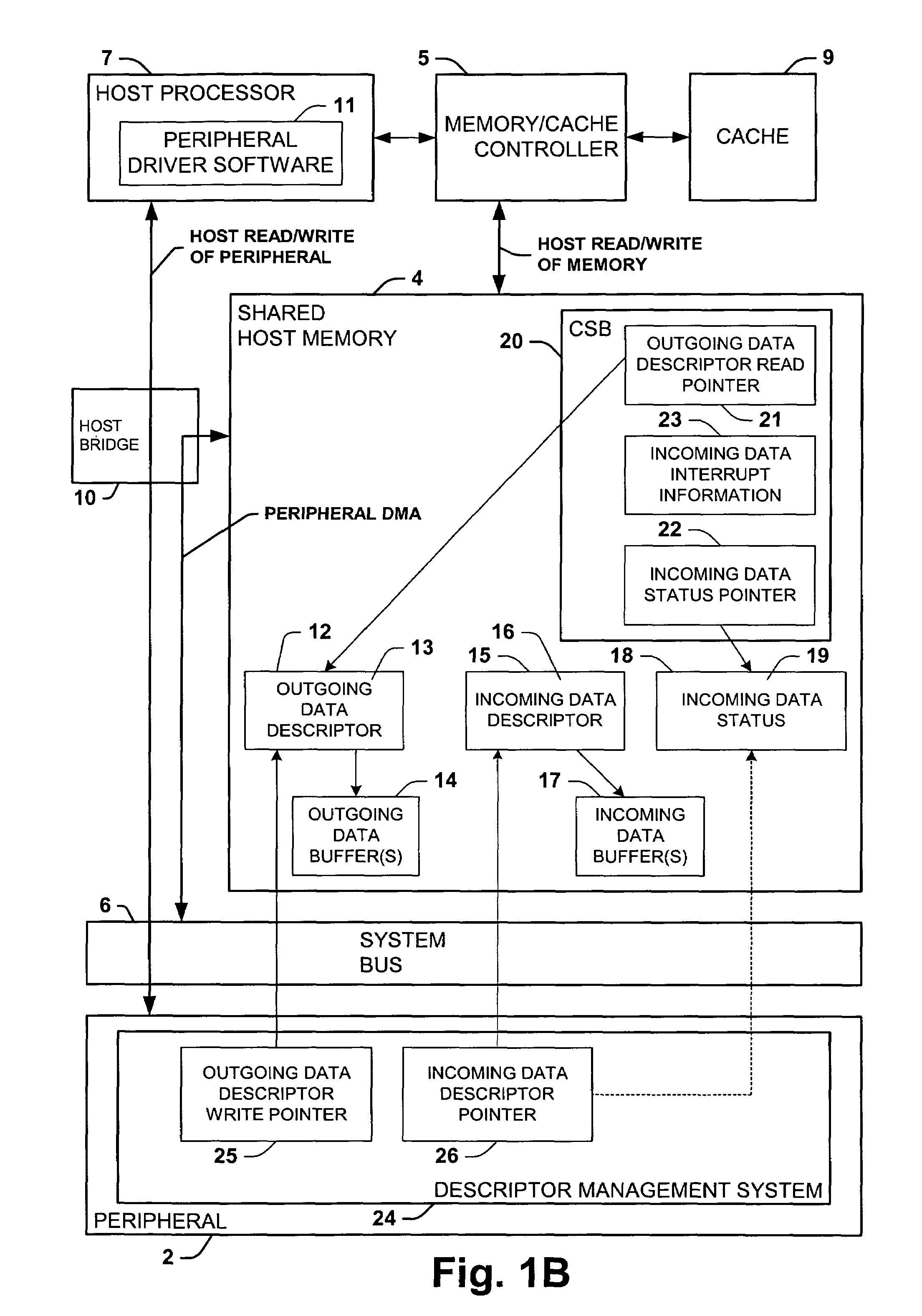

Descriptor management systems and methods for transferring data between a host and a peripheral

ActiveUS6963946B1Fast I/O write operationMitigate excessive cache partial cache line writesMultiple digital computer combinationsMemory systemsDescriptor systemsMaster processor

An improved descriptor system is provided in which read pointers indicate to a host and a peripheral the next location to read from a queue of descriptors, and write pointers indicate the next location to be written in a queue. The system also allows an incoming descriptor to point to a plurality of data frames for transfer to the host processor, wherein the peripheral need not read a new descriptor each time a frame is to be transferred to the host.

Owner:ADVANCED MICRO DEVICES INC

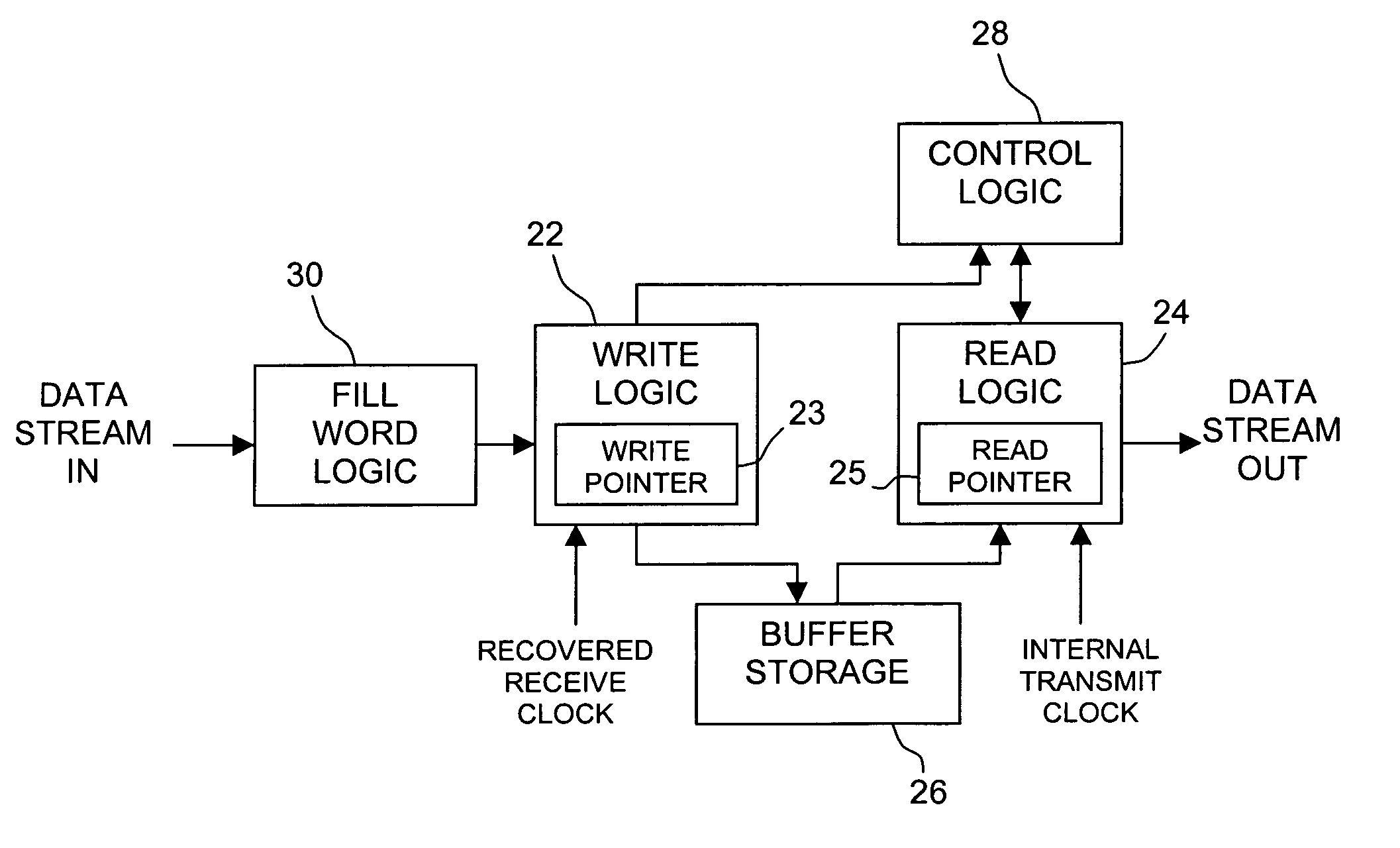

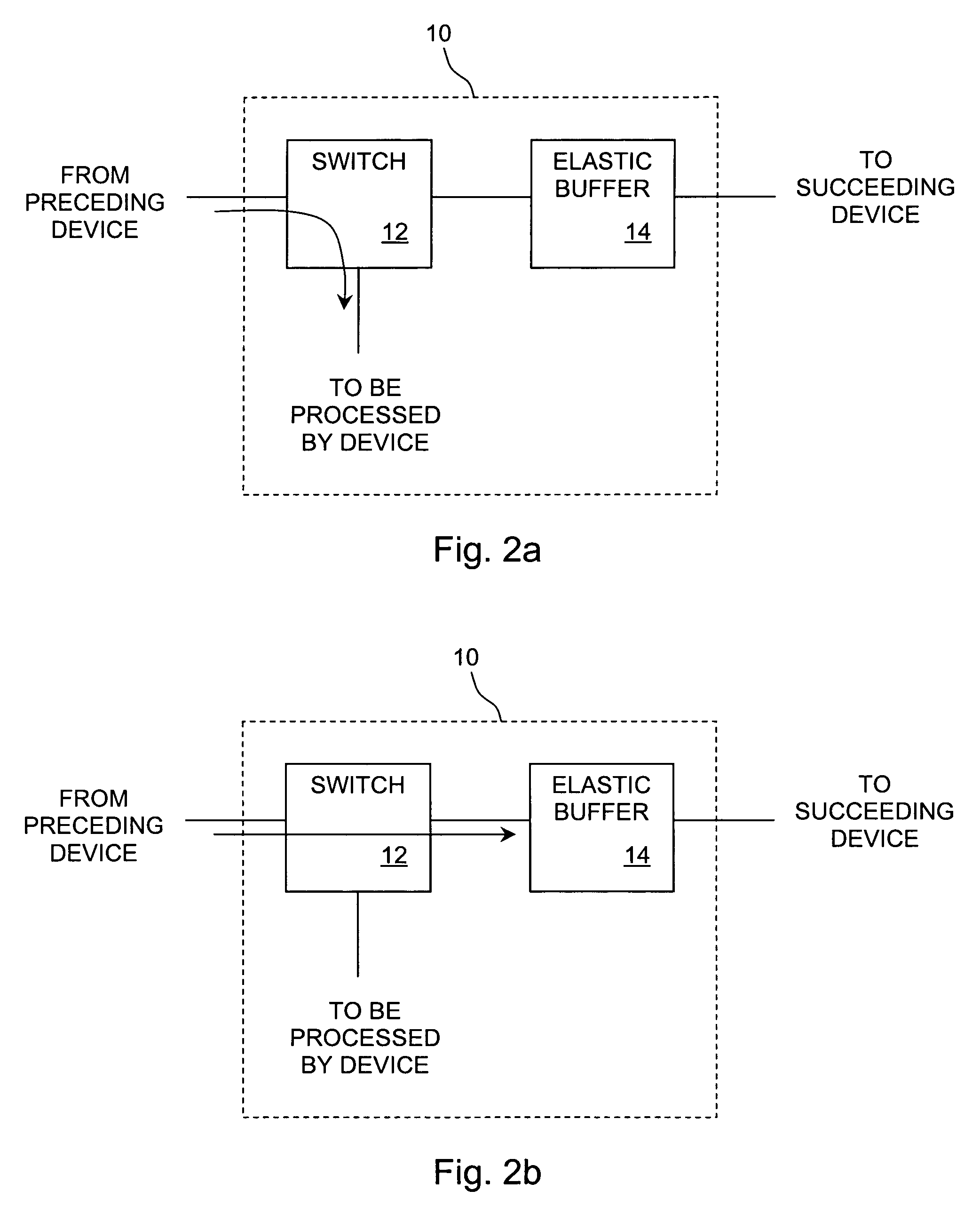

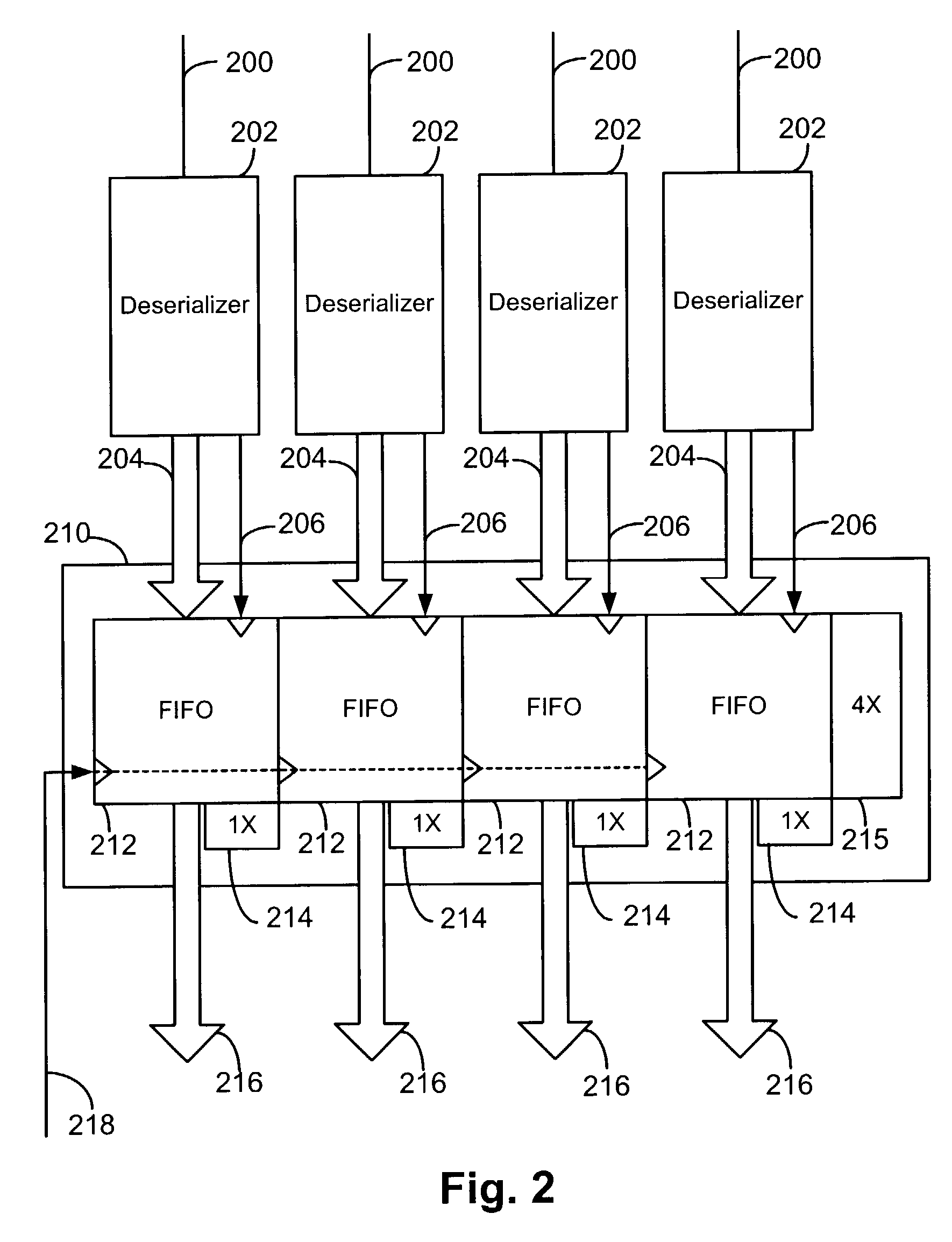

System and method for jitter compensation in data transfers

InactiveUS6977897B1Reduce in quantitySimplify comparison logicError preventionFrequency-division multiplex detailsCircular bufferData Corruption

A system and method for compensating for differences between a recovered receive clock and an internal transmit clock in an elastic buffer and thereby preventing corruption of data. In one embodiment, the system comprises a circularly accessed buffer coupled to read and write logic. The read and write logic read and write to locations within the circular buffer as indicated by respective read and write pointers. The system further comprises control logic which compares the pointers to determine whether the buffer is approaching an underflow or overflow condition and adds or deletes fill words between frames of data to compensate for the underflow or overflow condition. In one embodiment, the system includes fill word logic which is configured to add a fill word bit to each received word and to set or clear the fill word bit to indicate whether or not the corresponding word is a fill word.

Owner:CF DB EZ +1

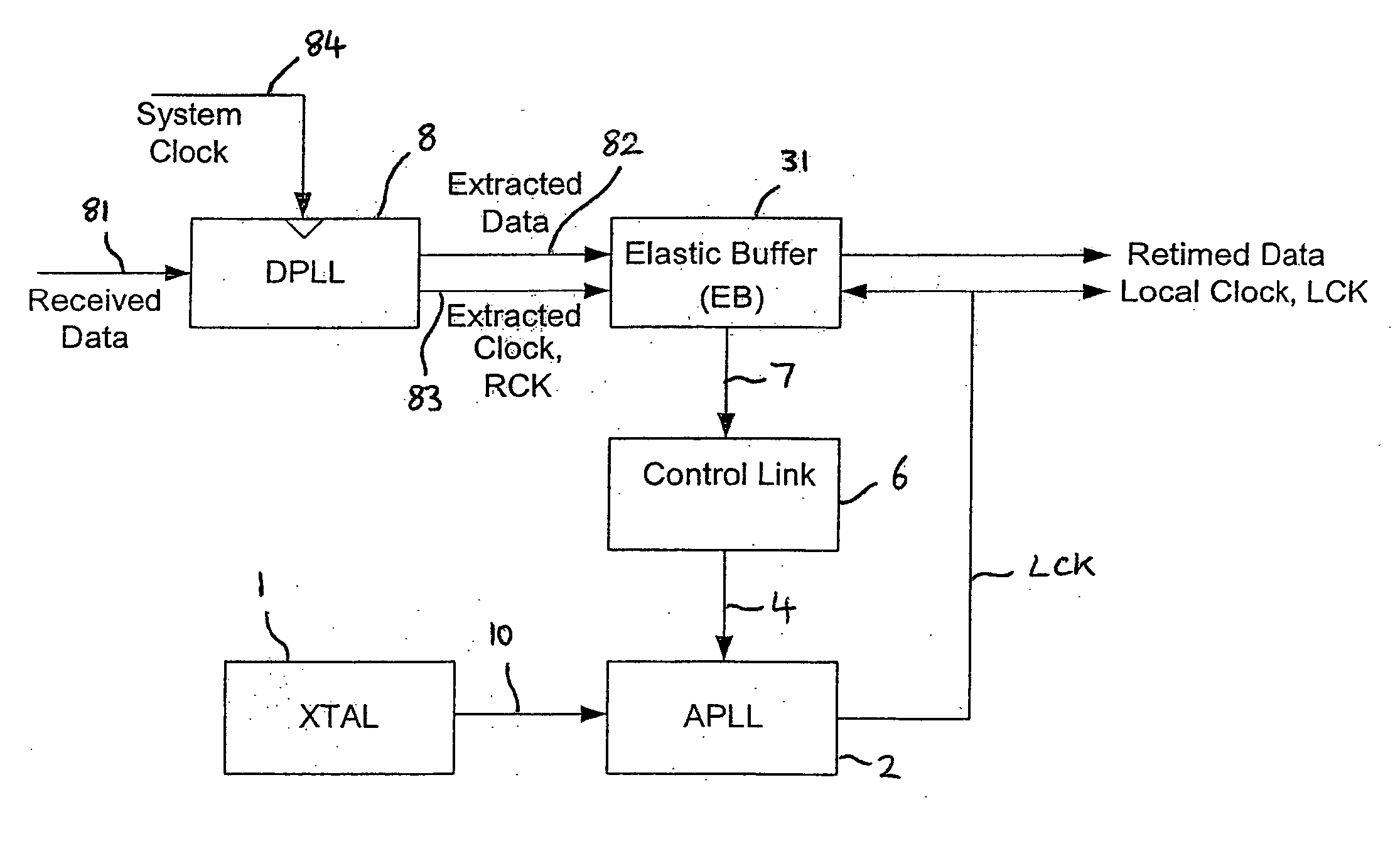

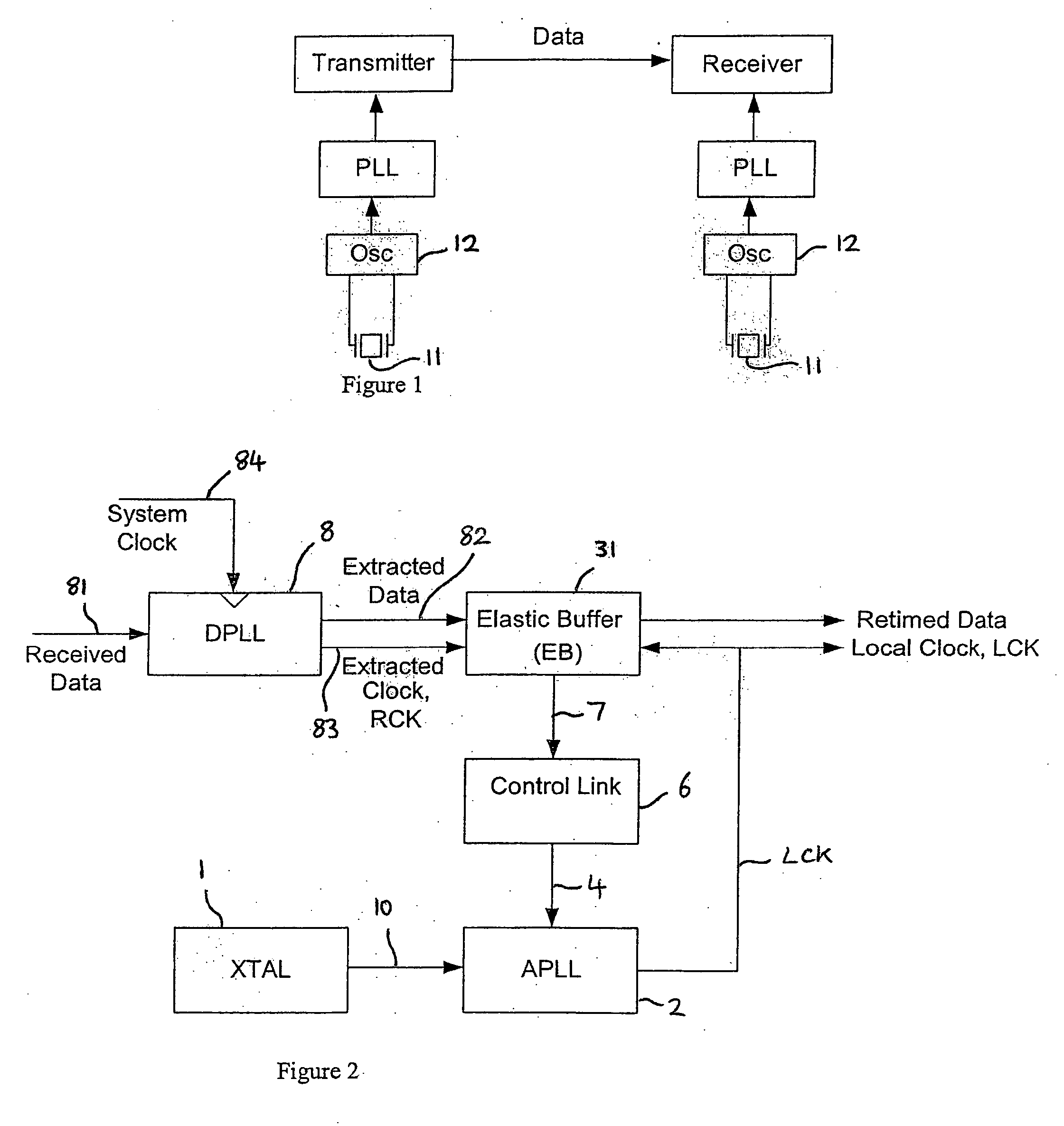

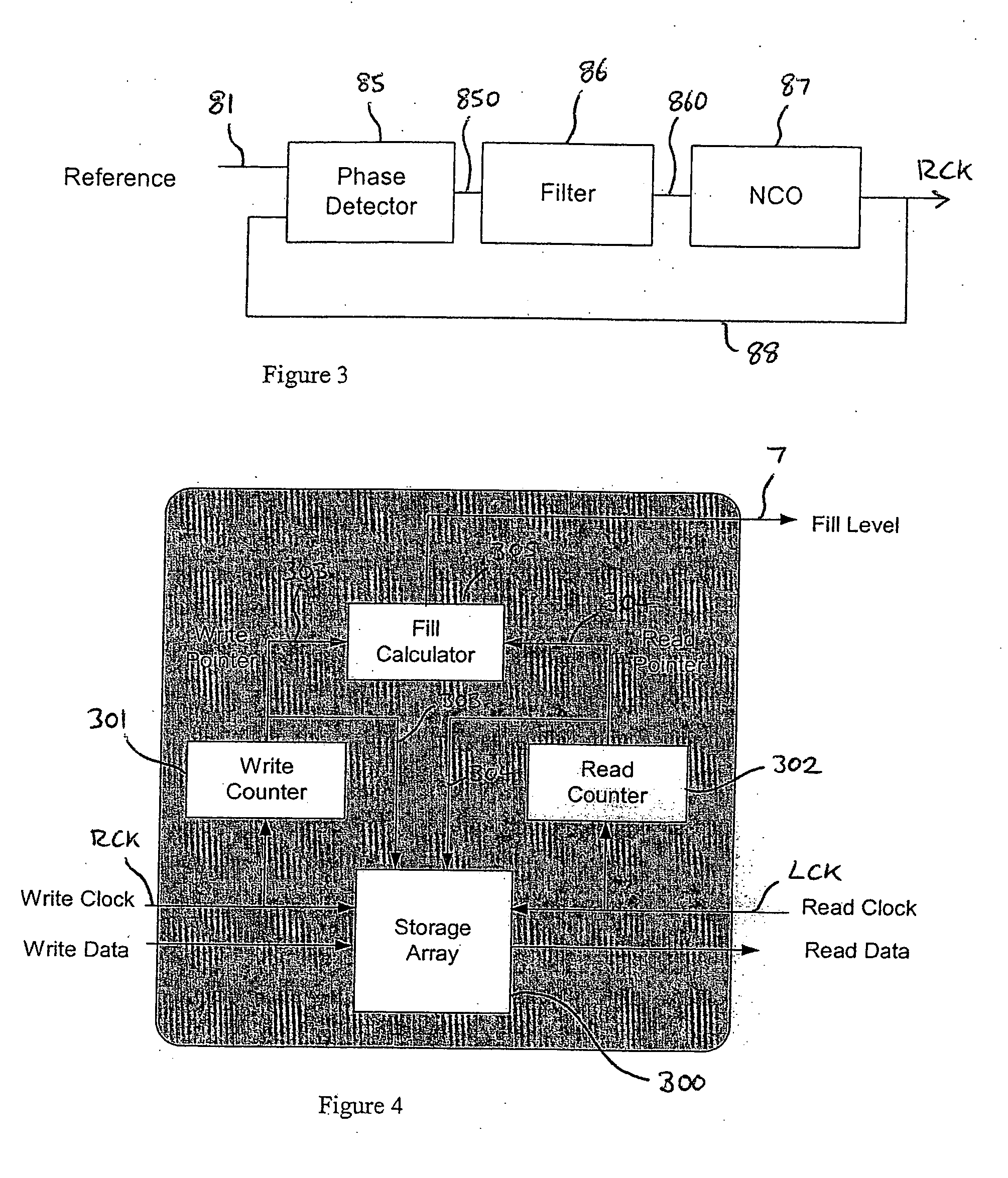

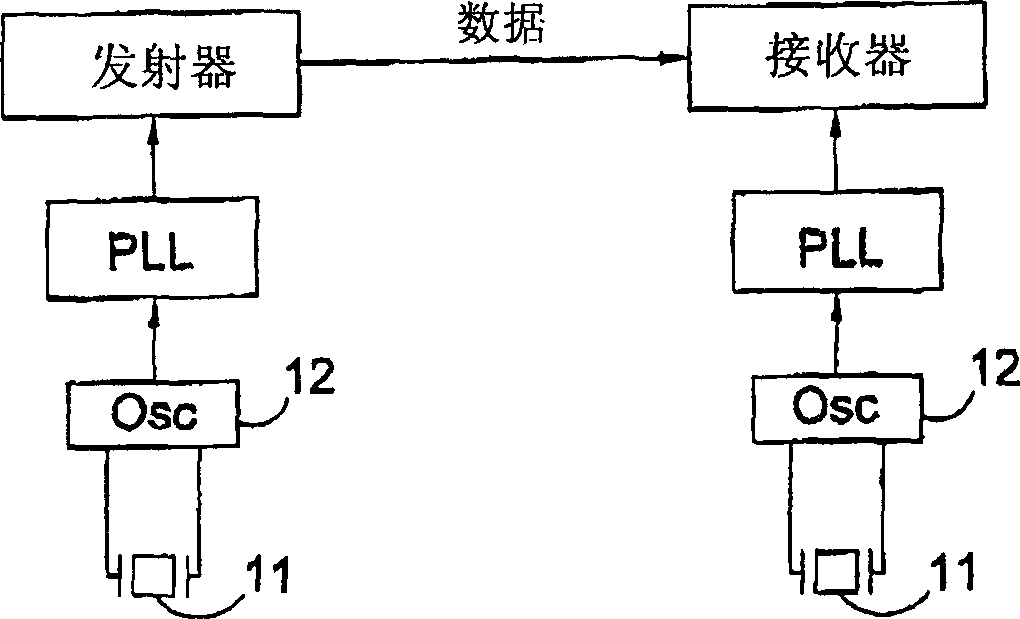

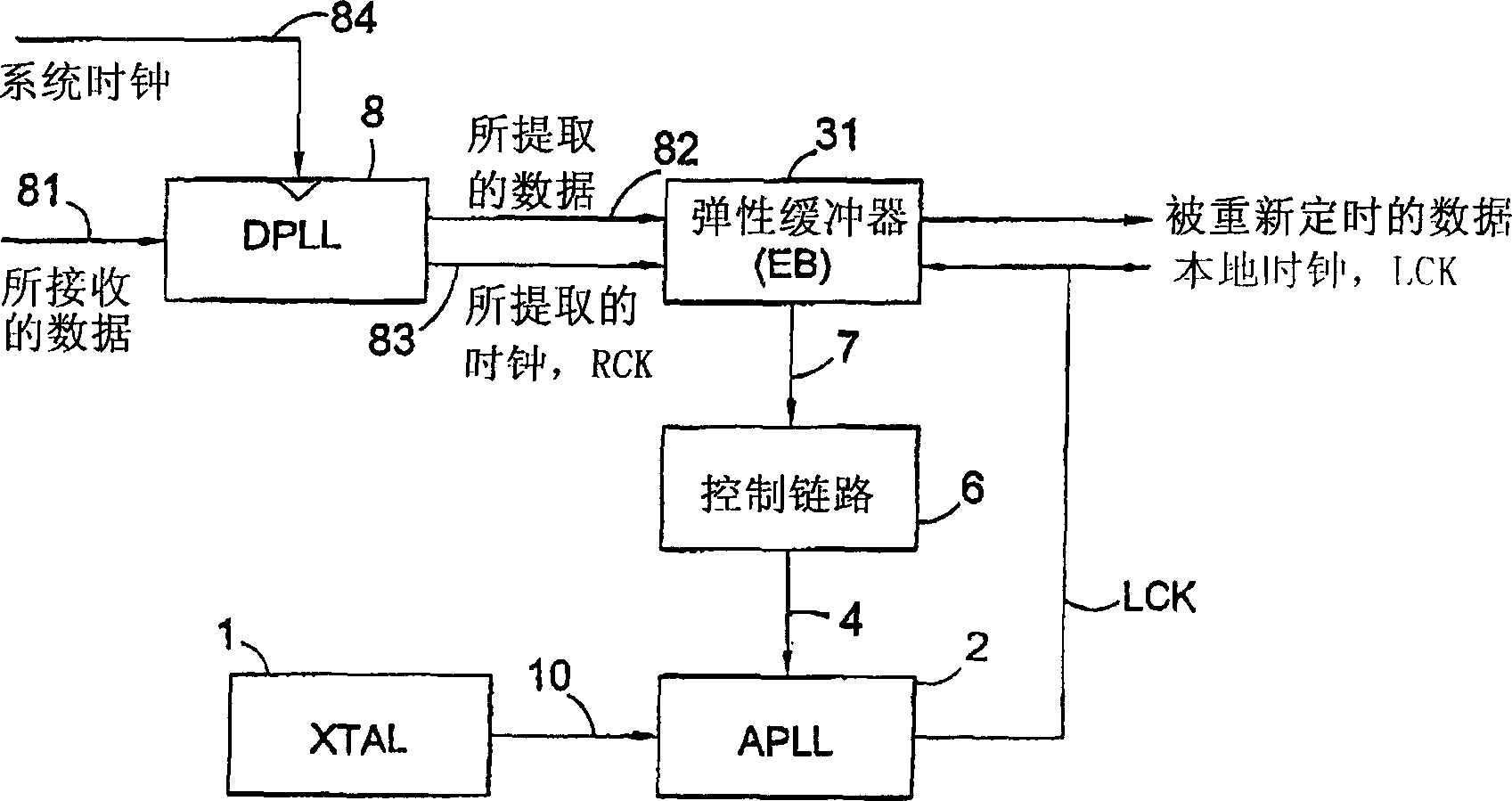

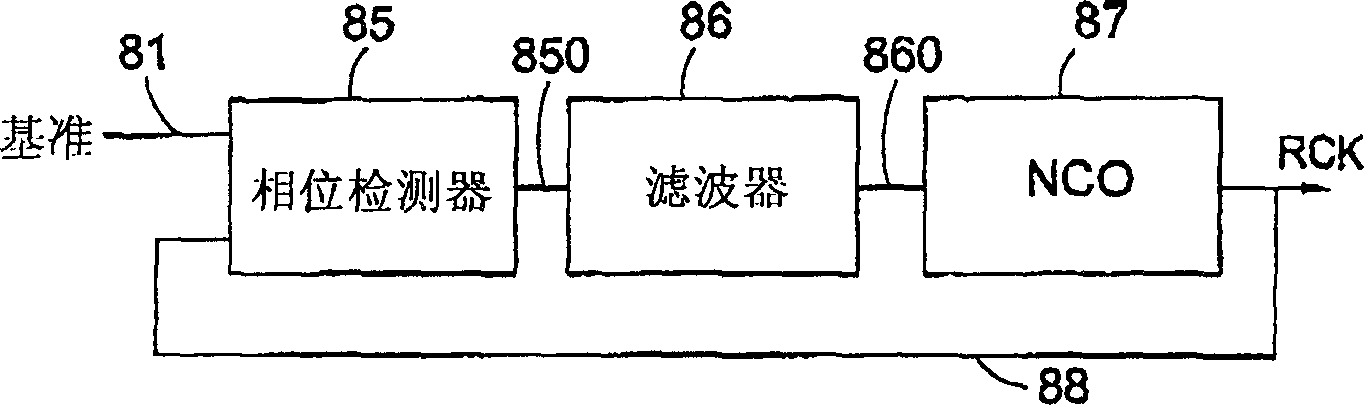

Clock synchroniser and clock and data recovery apparatus and method

InactiveUS20050220240A1Reduce jitterAvoid data lossPulse automatic controlElectric/magnetic signal storageLeast significant bitComputer science

A clock synchroniser, and clock and data recovery apparatus incorporating the clock synchroniser, are described, together with corresponding clock synchronisation methods. The clock synchroniser incorporates an elastic buffer. A received clock signal is used to clock data into the buffer, and a locally generated clock is used to clock data out of the buffer. The local clock is synthesised using a PLL, and a fill-level signal from the elastic buffer is used to control to local clock frequency to maintain a desired average quantity of data in the buffer, thereby achieving synchronisation of the received and local clocks. In preferred embodiments the fill-level signal is used to control a variable divider in the feedback path of the PLL, which is supplied with a highly stable reference signal. A synchronised, and low-jitter local clock is thus produced. Preferably, the elastic buffer employs counters of relatively wide word width, and a storage array of much reduced depth, read and write pointers being provided by just a few of the least significant bits of the words.

Owner:WOLFSON MICROELECTRONICS LTD

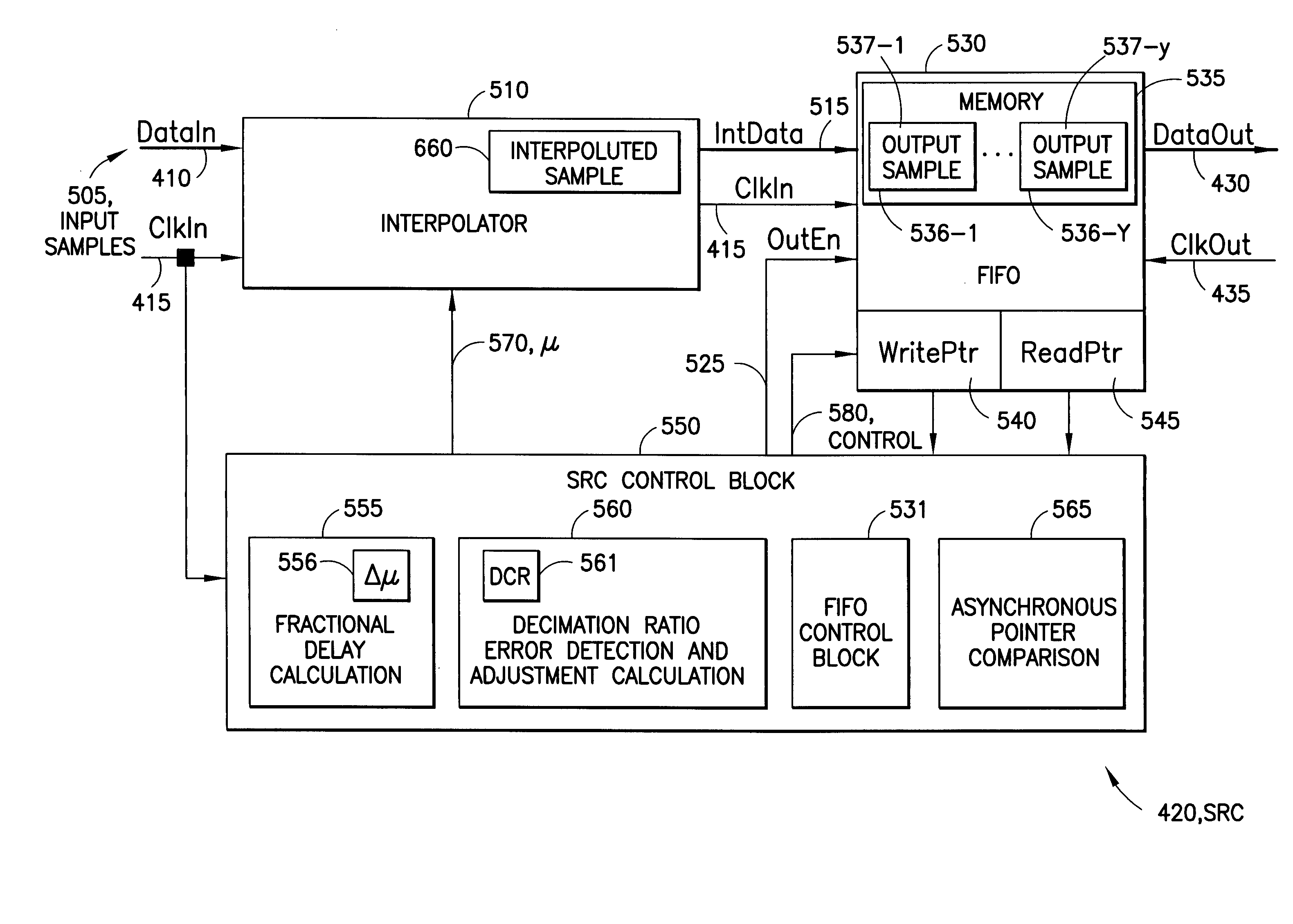

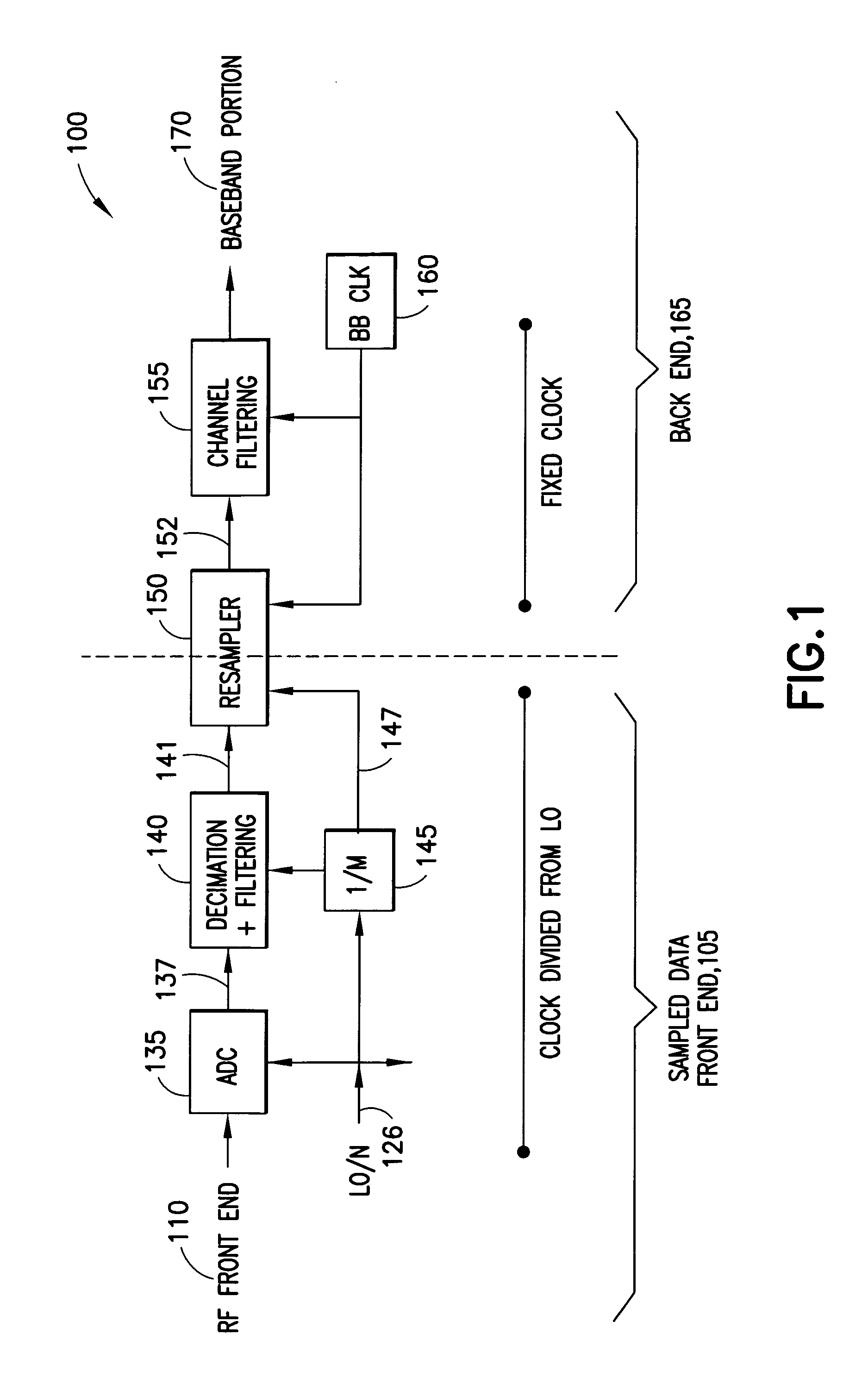

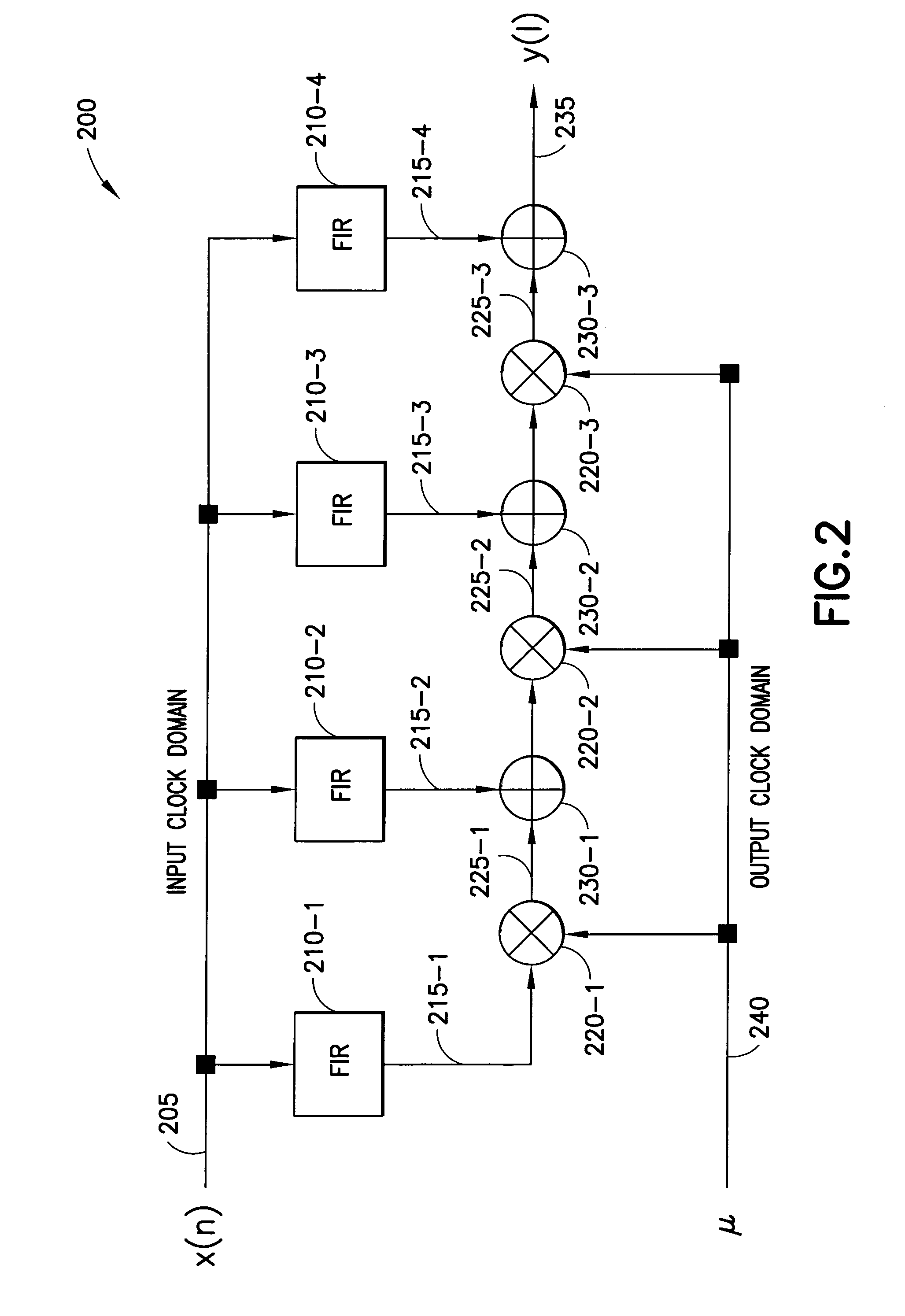

Techniques for sample rate conversion

Techniques for sample rate conversion are disclosed. In one exemplary embodiment, a sample rate conversion occurs between first samples having a sample rate defined by a first clock signal and second samples having a sample rate defined by a second clock signal. Using a conversion ratio and at a first rate defined by the first clock signal, a given second sample is determined from at least one first sample. A write pointer is updated for a buffer when second samples are written into the buffer. A read pointer is updated for the buffer when second samples are read from the buffer. The second samples are read from the buffer at a second rate defined by the second clock signal. The conversion ratio is modified based on the write and read pointers.

Owner:NOKIA TECHNOLOGLES OY

System and method for an asynchronous data buffer having buffer write and read pointers

ActiveUS20050286506A1Multiplex system selection arrangementsMemory adressing/allocation/relocationMemory controllerWrite pointer

A system and method for facilitating the adjustment of timing parameters between a memory controller operating in a first clock domain and a memory device operating in a second clock domain. A write pointer and a read pointer are monitored to provide a write-read pointer offset representing the timing between when read data is made available by the memory device and when the read data is retrieved by the memory controller. Based on the write-read pointer offset, adjustment to different timing parameters can be made.

Owner:MICRON TECH INC

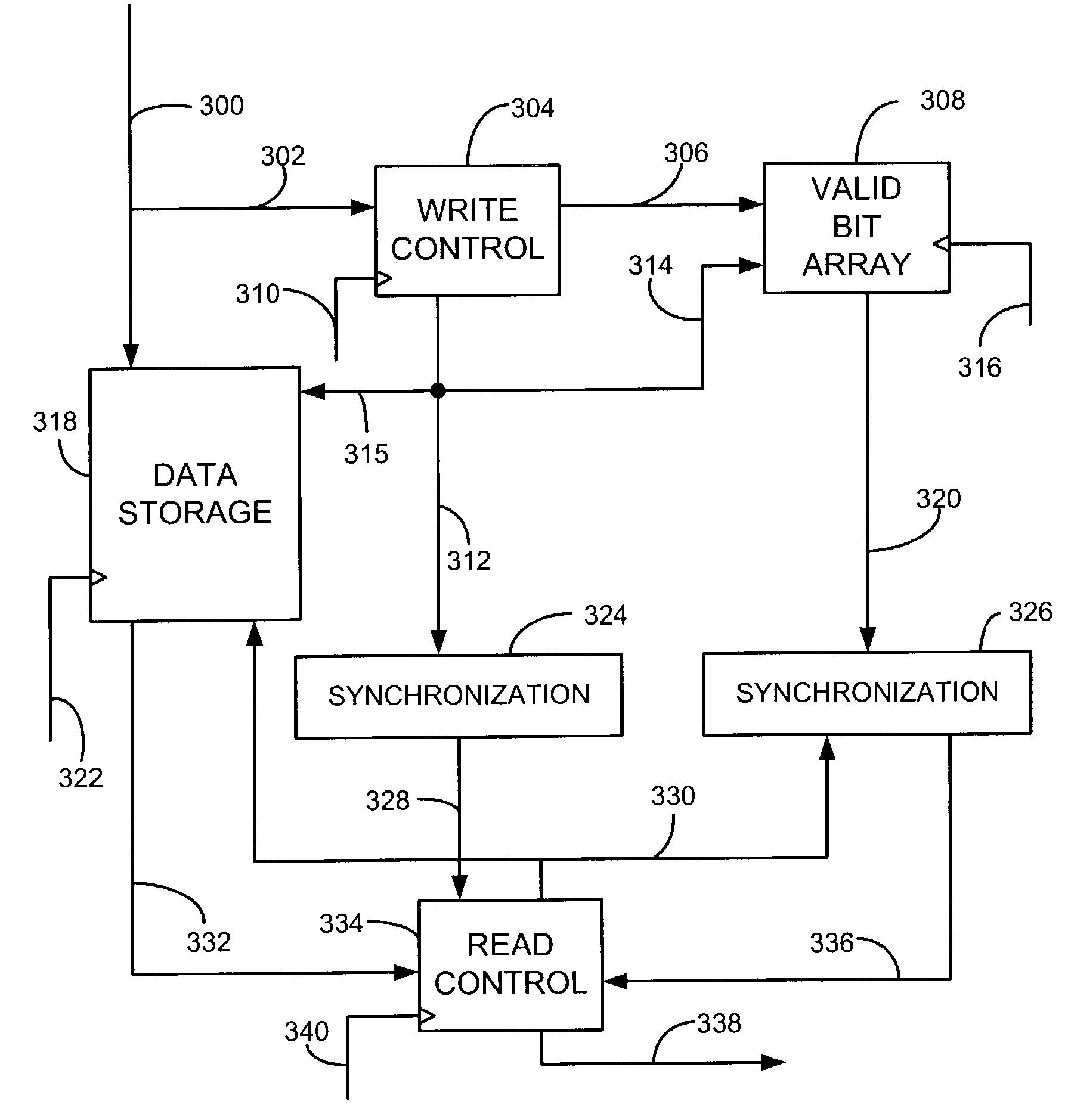

Method and apparatus for asynchronous read control

A method and apparatus for operating a memory is presented. Information is stored in the memory based on a first time domain and information is read from the memory based on a second time domain. A cooperative relationship is maintained between a write pointer which points to memory locations, where data will be stored and a read pointer which points to memory locations, from which data will be read. A FIFO memory is presented which has memory locations and a register array is presented which stores a bit array that has bit locations. Each bit location in the bit array corresponds to a memory location in the memory. As the write pointer points to a memory location and data is stored in the memory location, a bit (e.g. flag) is set in the bit array. The Flag designates whether the data stored in the memory location is available for reading. Prior to reading information from the memory location, a test is made of the bit location that corresponds to the memory location. The bit value denotes whether the data stored in the memory location is valid data and available for reading.

Owner:AVAGO TECH INT SALES PTE LTD

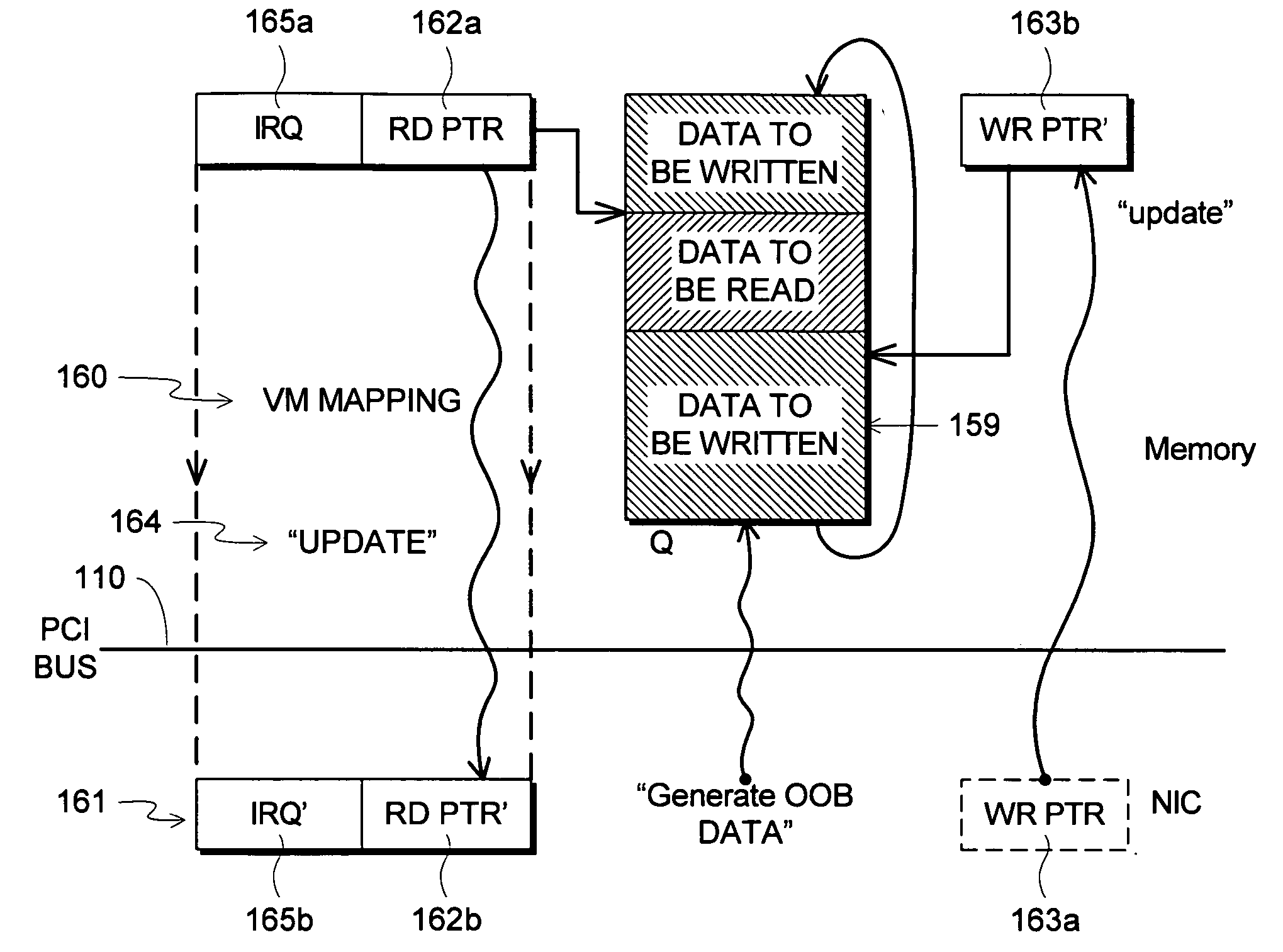

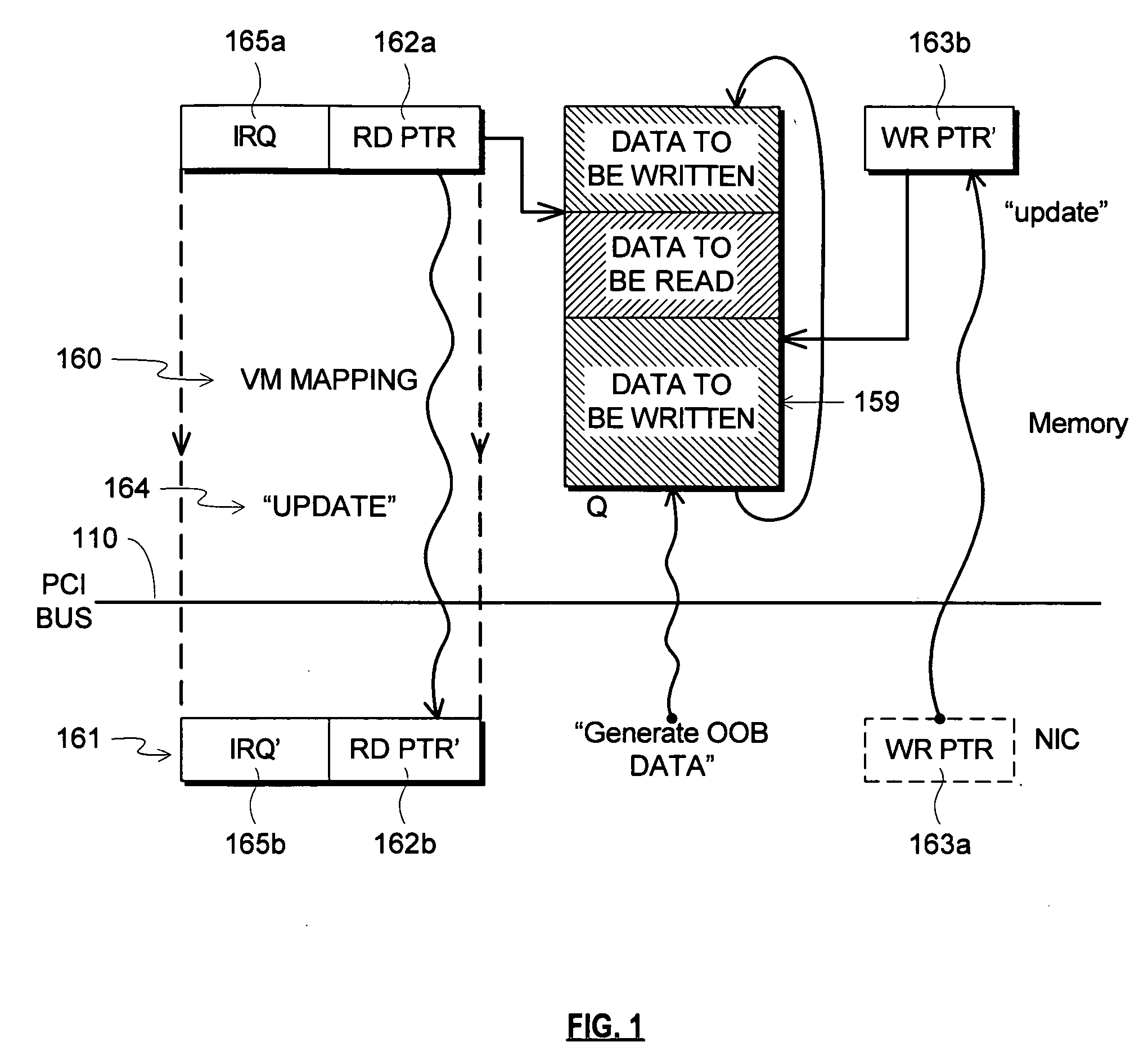

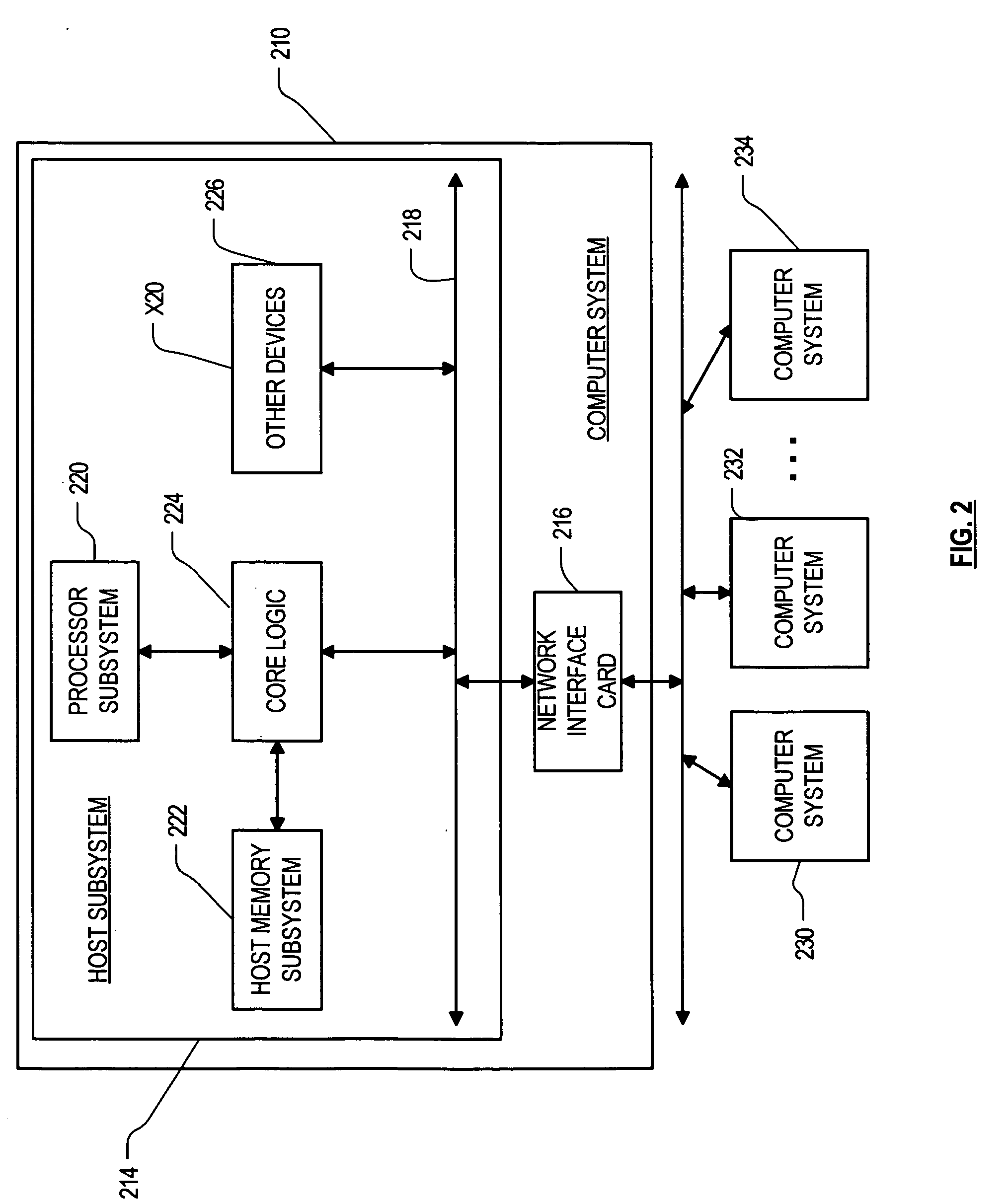

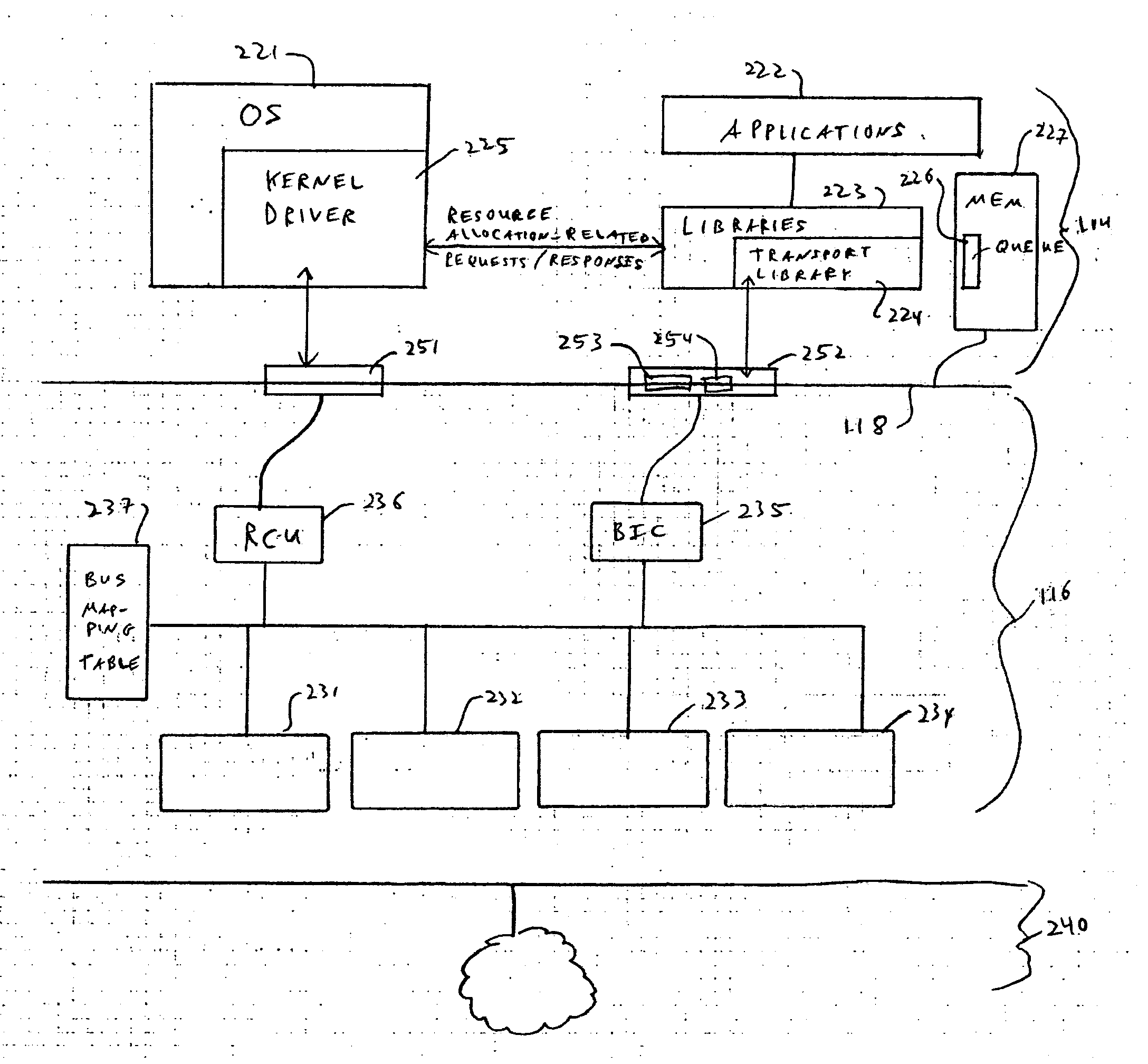

Queue depth management for communication between host and peripheral device

ActiveUS20050177657A1Easy maintenanceHigh trafficMultiprogramming arrangementsStatic storageHost memoryWrite pointer

Method for managing a queue in host memory for use with a peripheral device. Roughly described, the host makes a determination of the availability of space in the queue for writing new entries, in dependence upon historical knowledge of the number of queue entries that the host has authorized the device to write, and the number of entries that the host has consumed. In dependence on that determination, the host authorizes the device to write a limited number of new entries into the queue. The device writes entries into the queue dependence upon the number authorized. The host maintains a read pointer into the queue but does not need to maintain a write pointer, and the peripheral device maintains a write pointer into the queue but does not need to maintain a read pointer.

Owner:XILINX INC

DMA descriptor queue read and cache write pointer arrangement

Method and apparatus for retrieving buffer descriptors from a host memory for use by a peripheral device. In an embodiment, a peripheral device such as a NIC includes a plurality of buffer descriptor caches each corresponding to a respective one of a plurality of host memory descriptor queues, and a plurality of queue descriptors each corresponding to a respective one of the host memory descriptor queues. Each of the queue descriptors includes a host memory read address pointer for the corresponding descriptor queue, and this same read pointer is used to derive algorithmically the descriptor cache write addresses at which to write buffer descriptors retrieved from the corresponding host memory descriptor queue.

Owner:XILINX INC

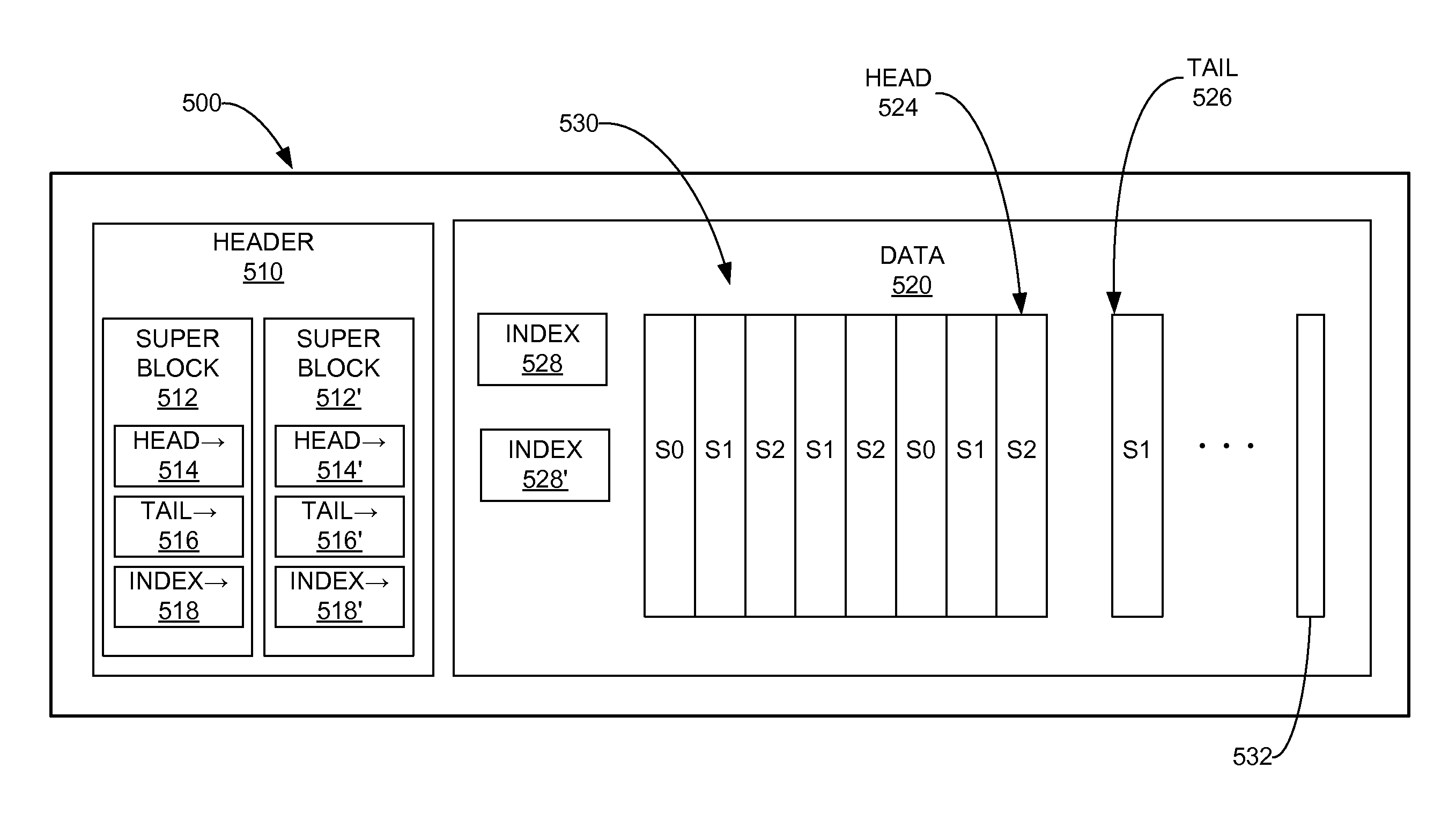

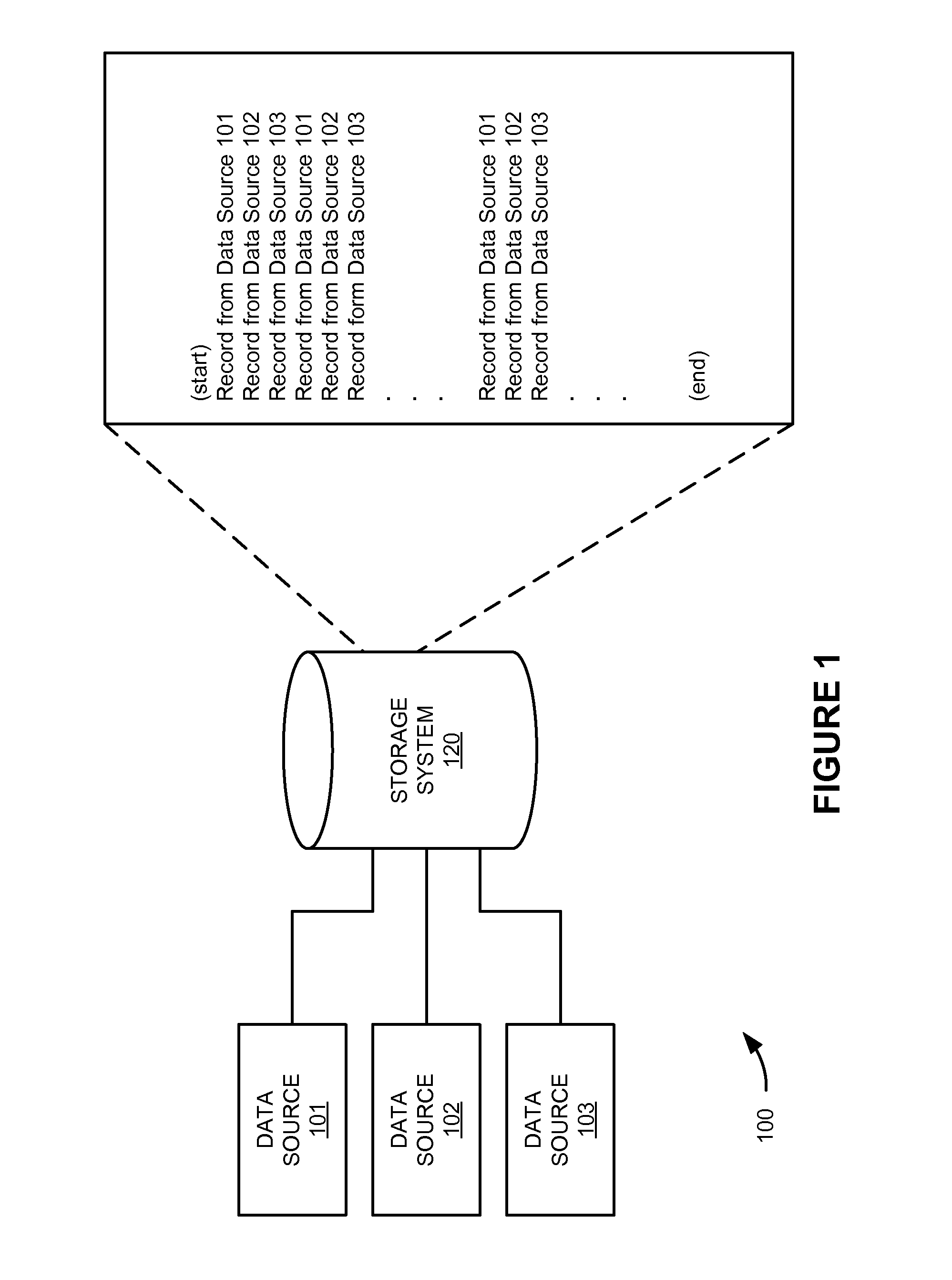

Systems, methods, and software for interleaved data stream storage

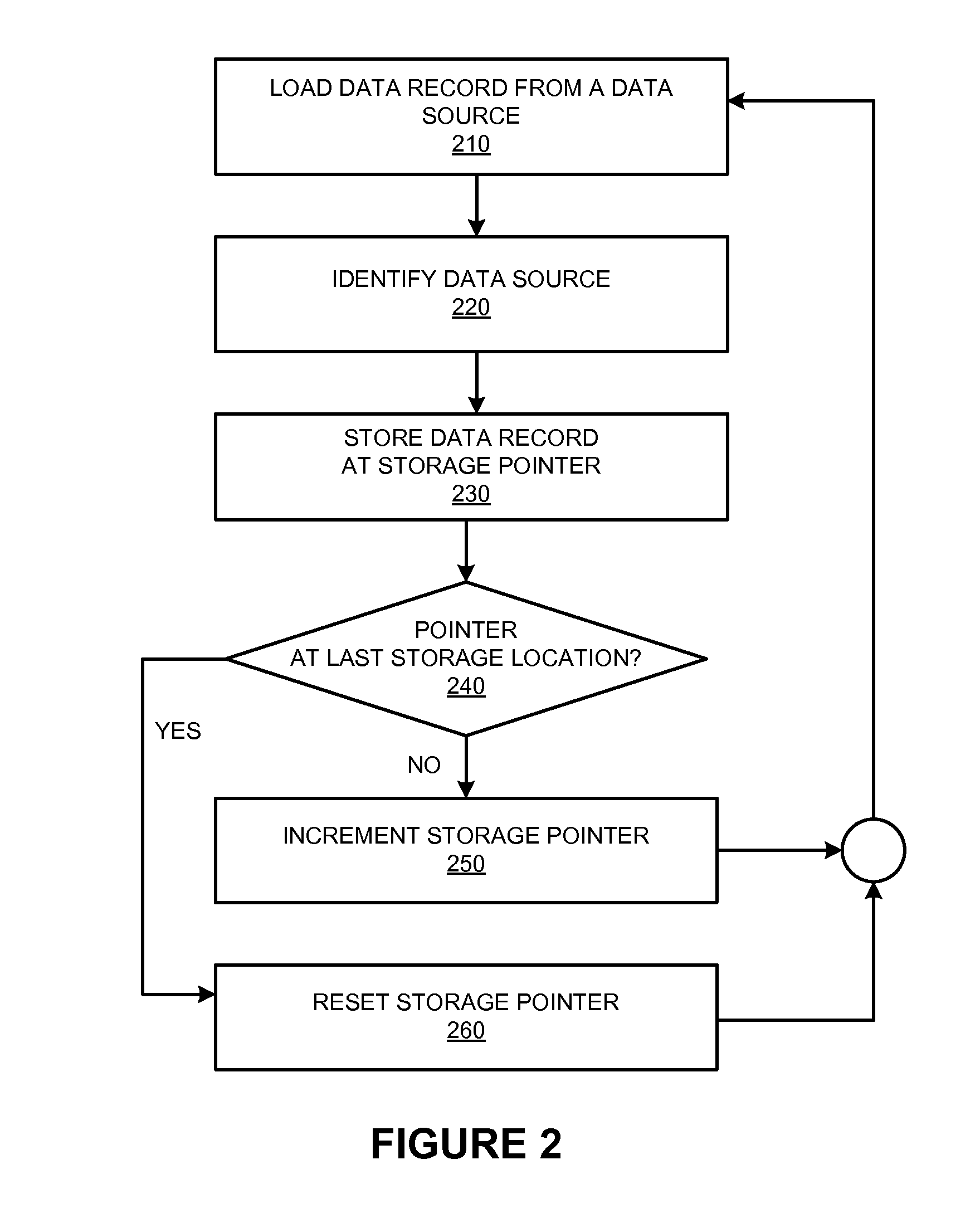

Methods, systems, and software are provided herein that allow a user to store and retrieve data records. In one example, a method of storing data records is provided. The method includes initializing a shared write pointer to a first location in a shared memory of a data storage system, and receiving a plurality of data records transferred by a plurality of data sources for storage in the shared memory. The method also includes, beginning with a first of the plurality of data sources, writing in a cyclic sequence one of the plurality of data records for each of the plurality of data sources based on the shared write pointer, and incrementing the shared write pointer after each writing, and updating at least a header portion of the shared memory with the shared write pointer responsive to each writing.

Owner:VERINT AMERICAS

Method and system for data placement in a hard disk drive based on access frequency for improved iops and utilization efficiency

ActiveUS20190391748A1Facilitates data placementEnhanced data placementMemory architecture accessing/allocationInput/output to record carriersShingled magnetic recordingHard disc drive

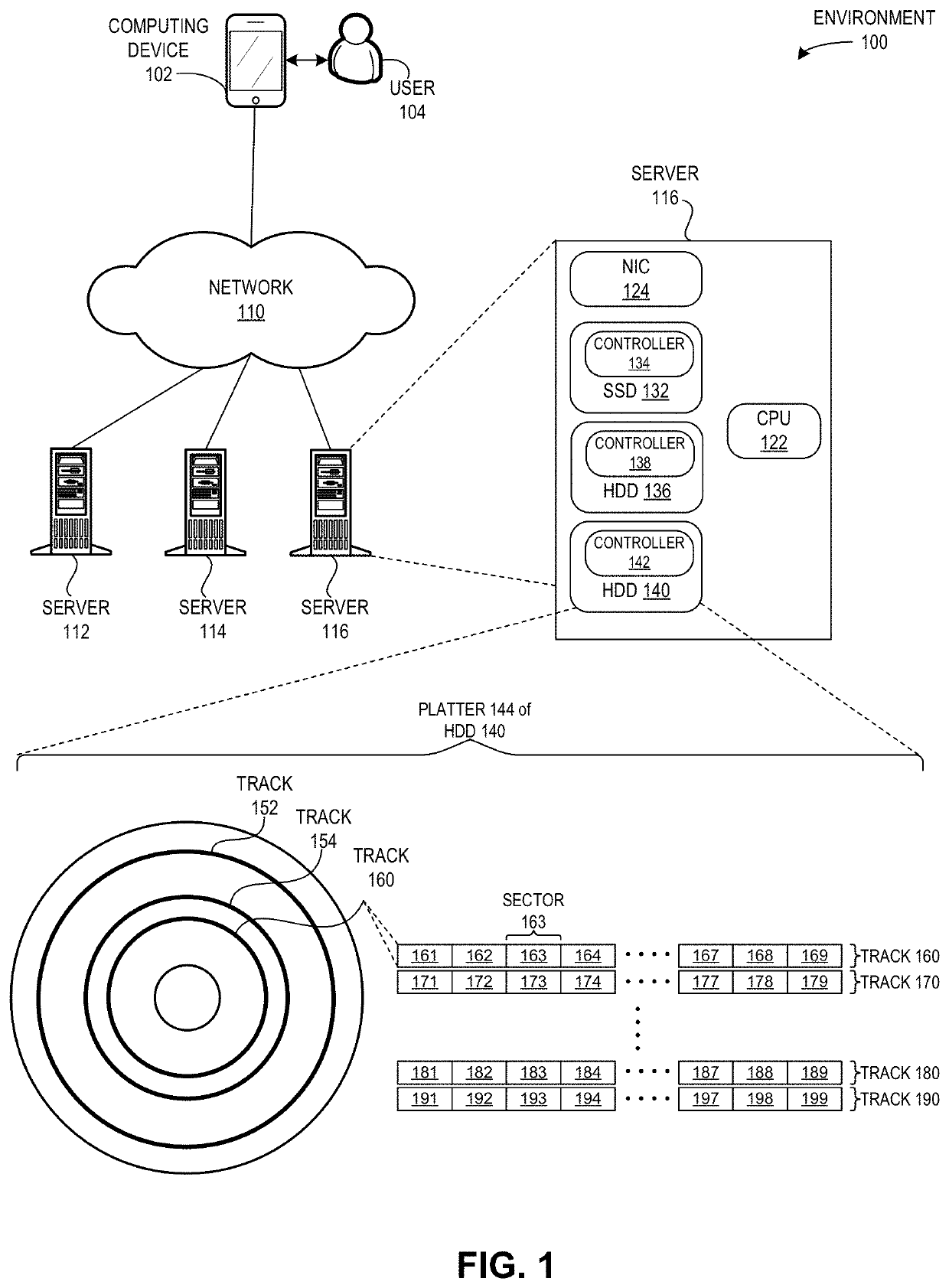

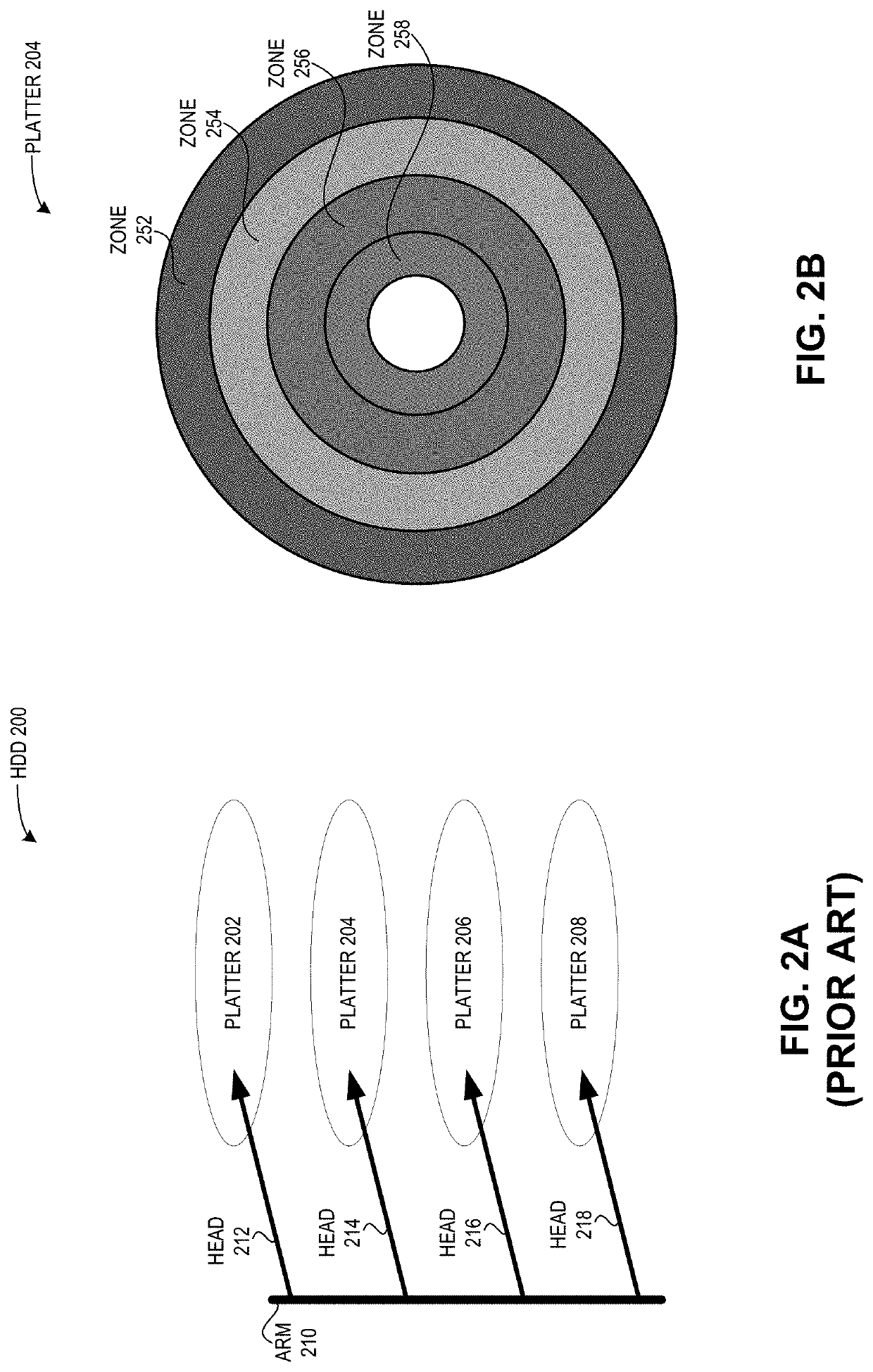

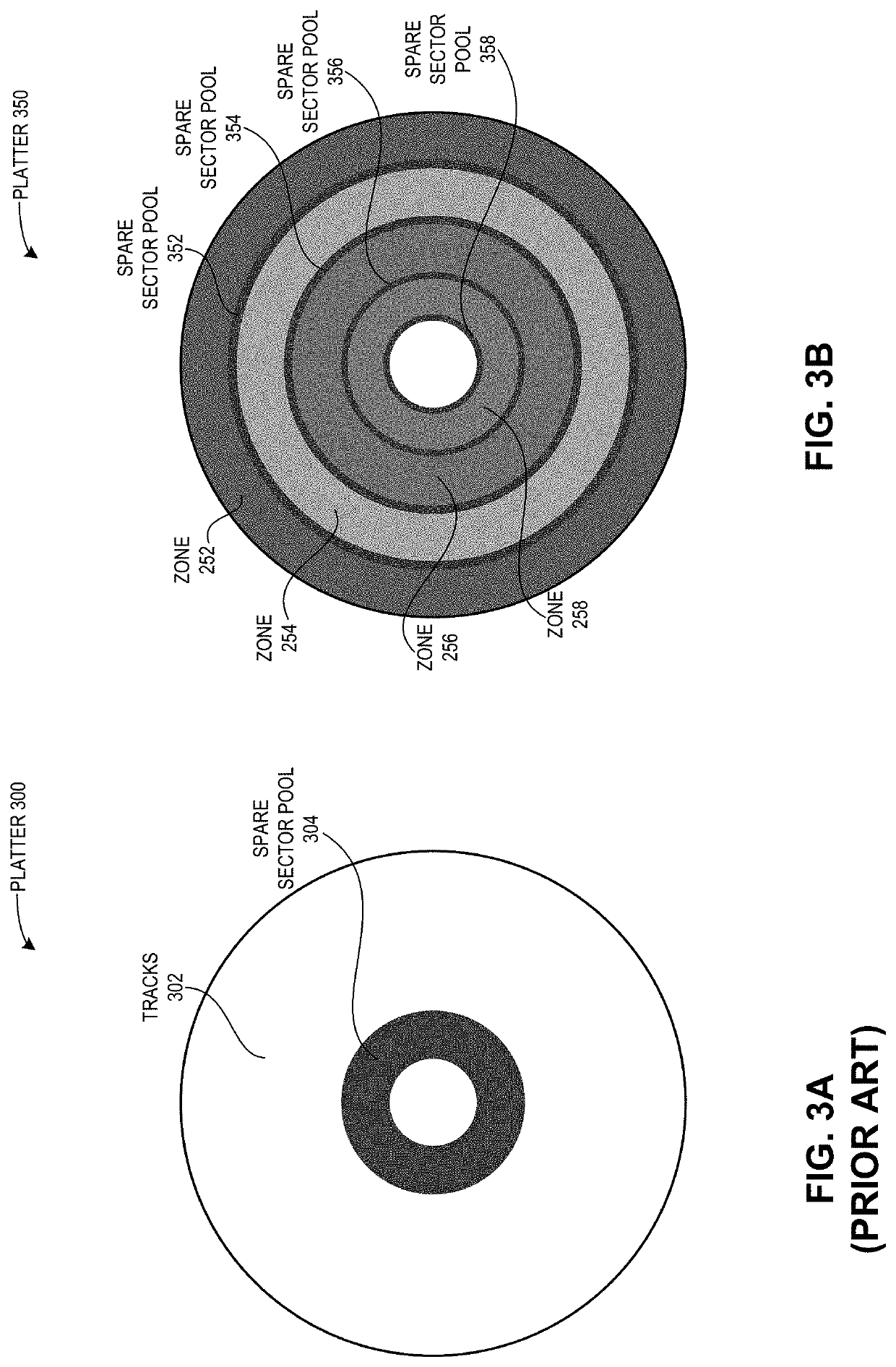

One embodiment facilitates a write operation in a shingled magnetic recording device. During operation, the system receives, by the storage device, data to be written to the storage device and access-frequency information associated with the data, wherein the storage device includes a plurality of concentric tracks. The system distributes a plurality of spare sector pools among the plurality of concentric tracks. The system selects a track onto which to write the data based on the access-frequency information, wherein data with a highest access-frequency is written to an outer track. The system appends the data at a current write pointer location of the selected track, thereby facilitating an enhanced data placement for subsequent access in the storage device.

Owner:ALIBABA GRP HLDG LTD

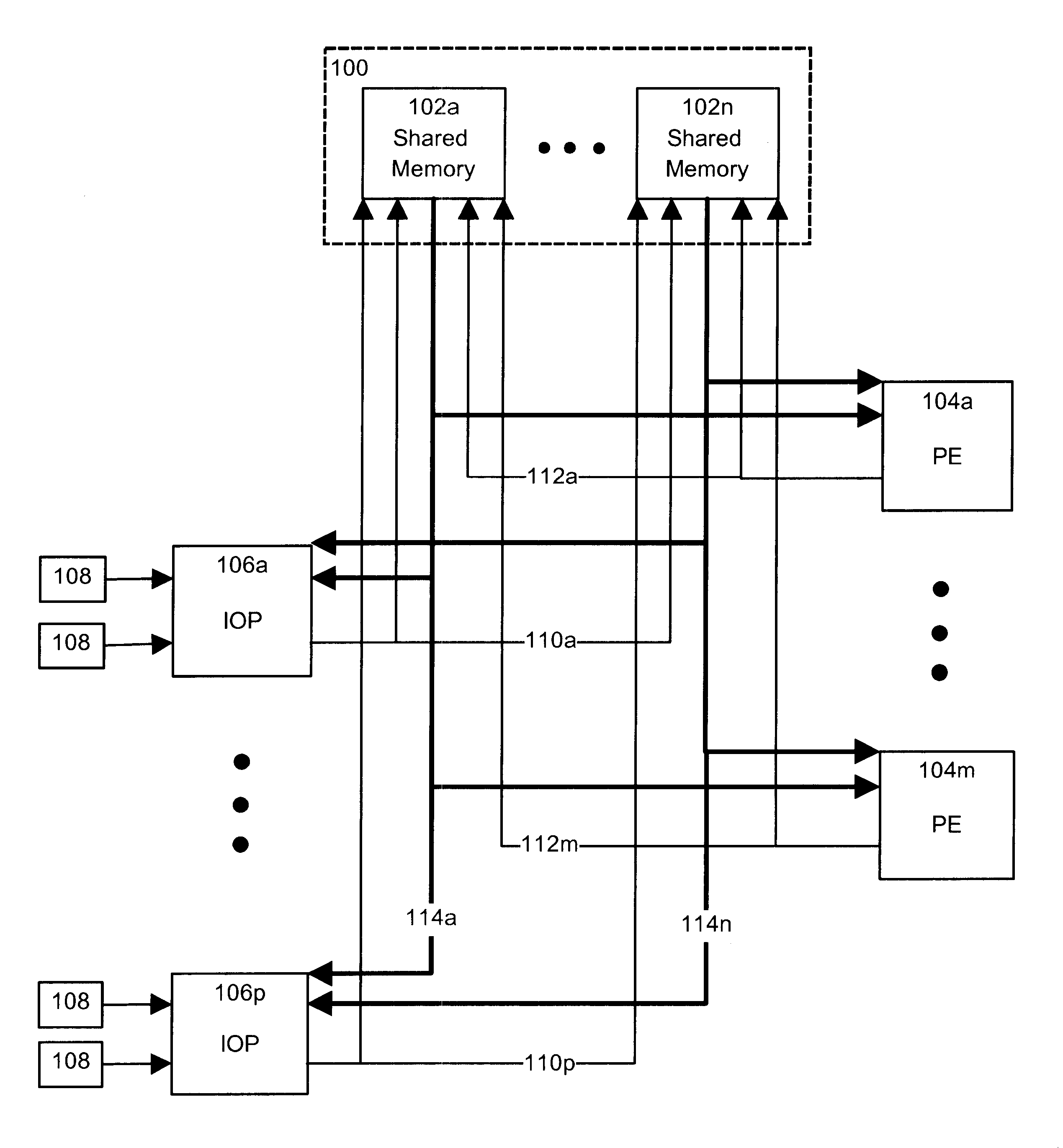

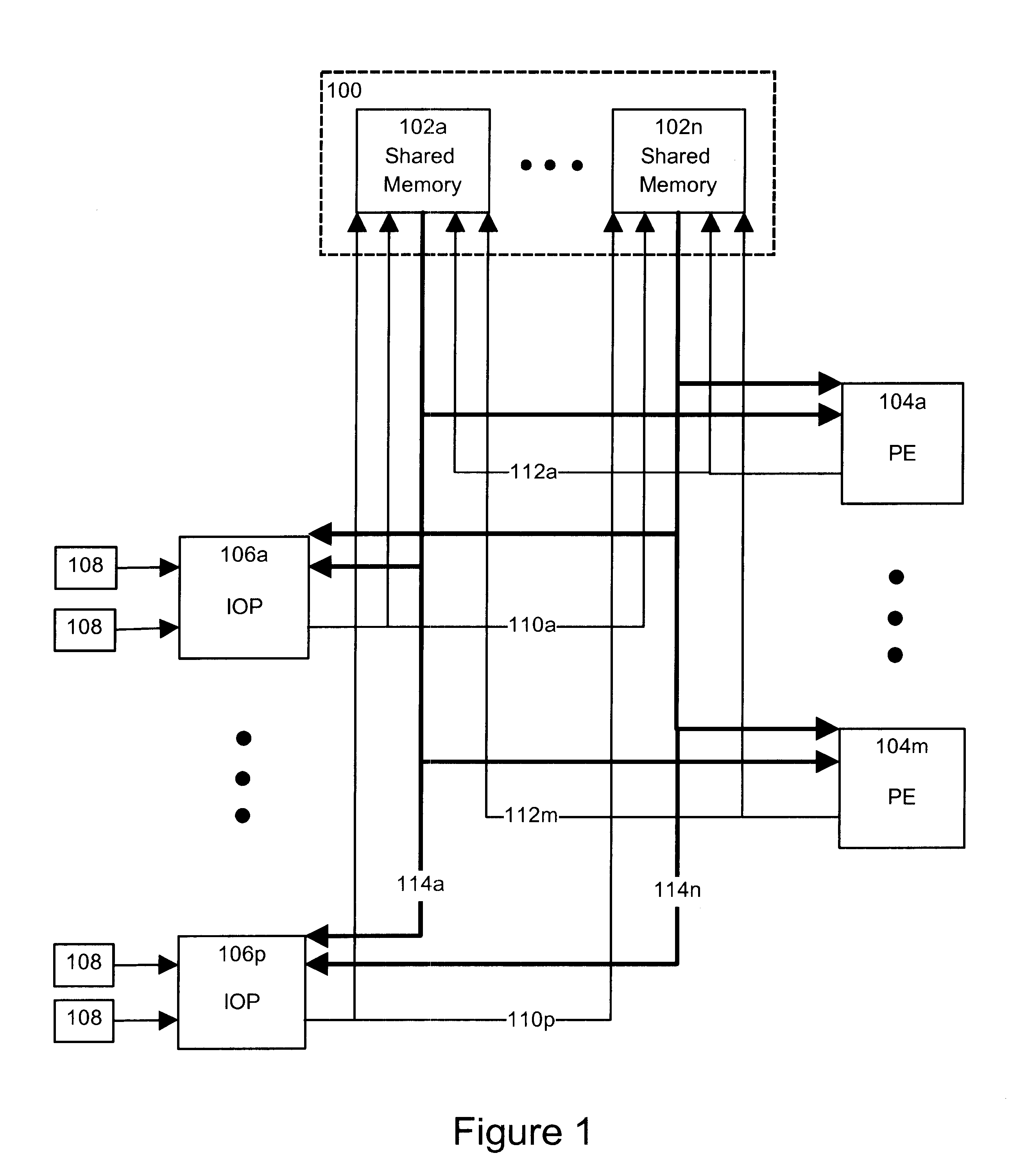

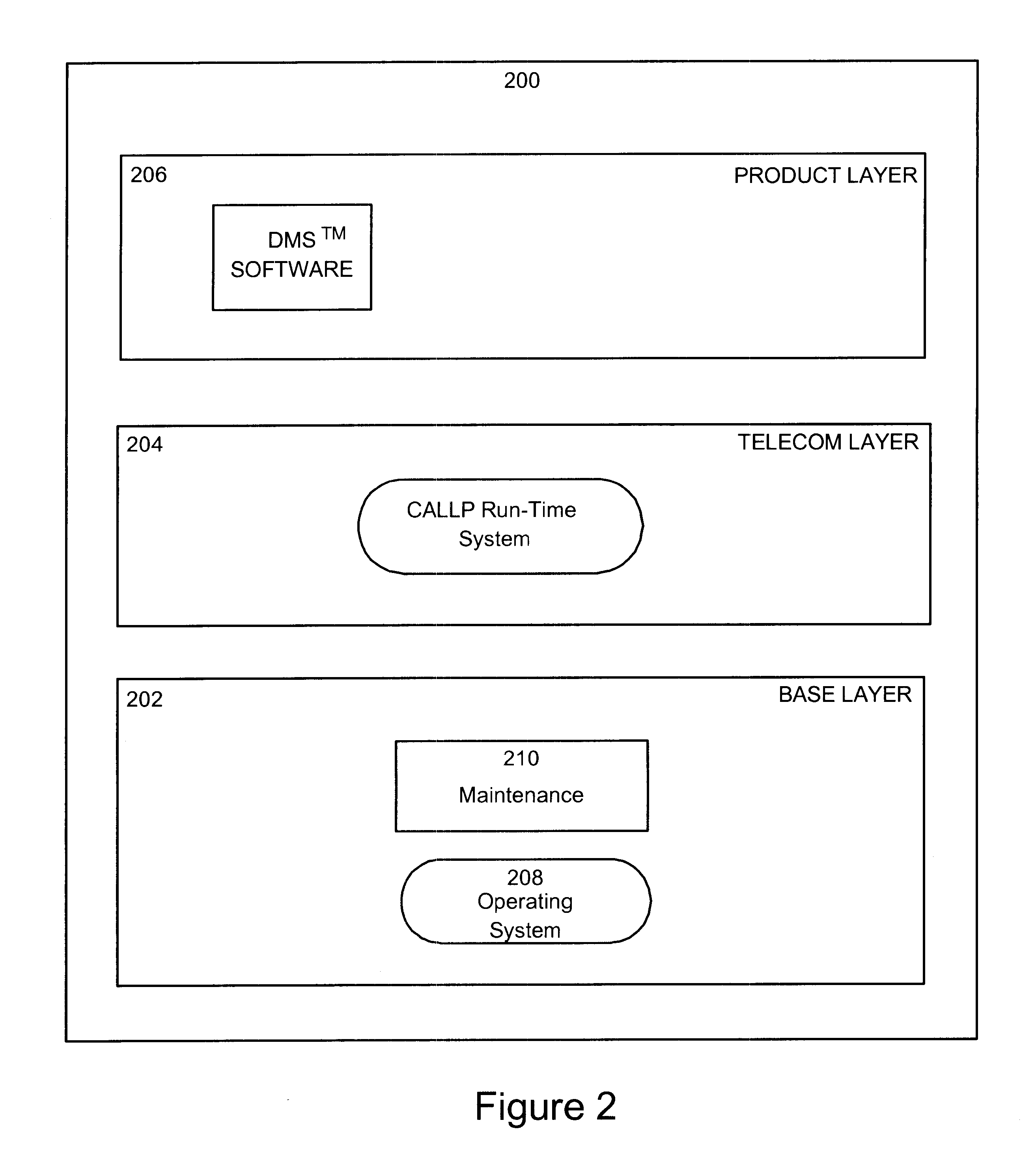

Method and apparatus for exchanging data between transactional and non-transactional input/output systems in a multi-processing, shared memory environment

InactiveUS6557056B1Memory adressing/allocation/relocationInput/output processes for data processingData elementComputer science

The present invention relates to a queuing system, implemented in the memory of a computer by the execution of a program element. The queuing system includes a queue with a plurality of memory slots, a write pointer and a read pointer. The write pointer permits to enqueue data elements in successive memory slots of the queue. The read pointer permits to dequeue data elements from the queue memory slots for processing, where these data elements are potentially non-dequeuable. Upon identifying a non-dequeuable data element in a particular memory slot of the queue, the read pointer is capable to skip over the particular memory slot and move on to a successive memory slot.

Owner:RPX CLEARINGHOUSE

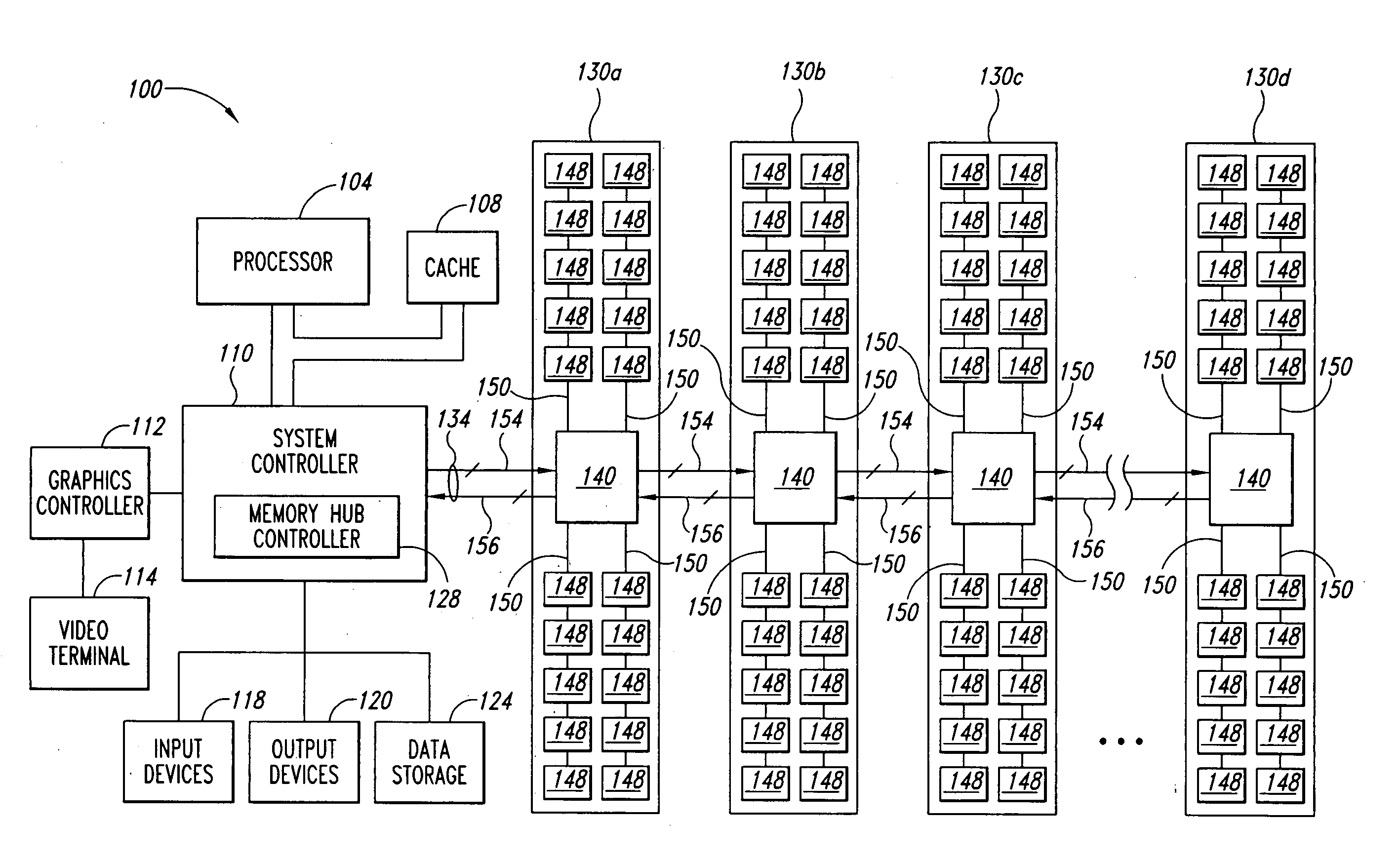

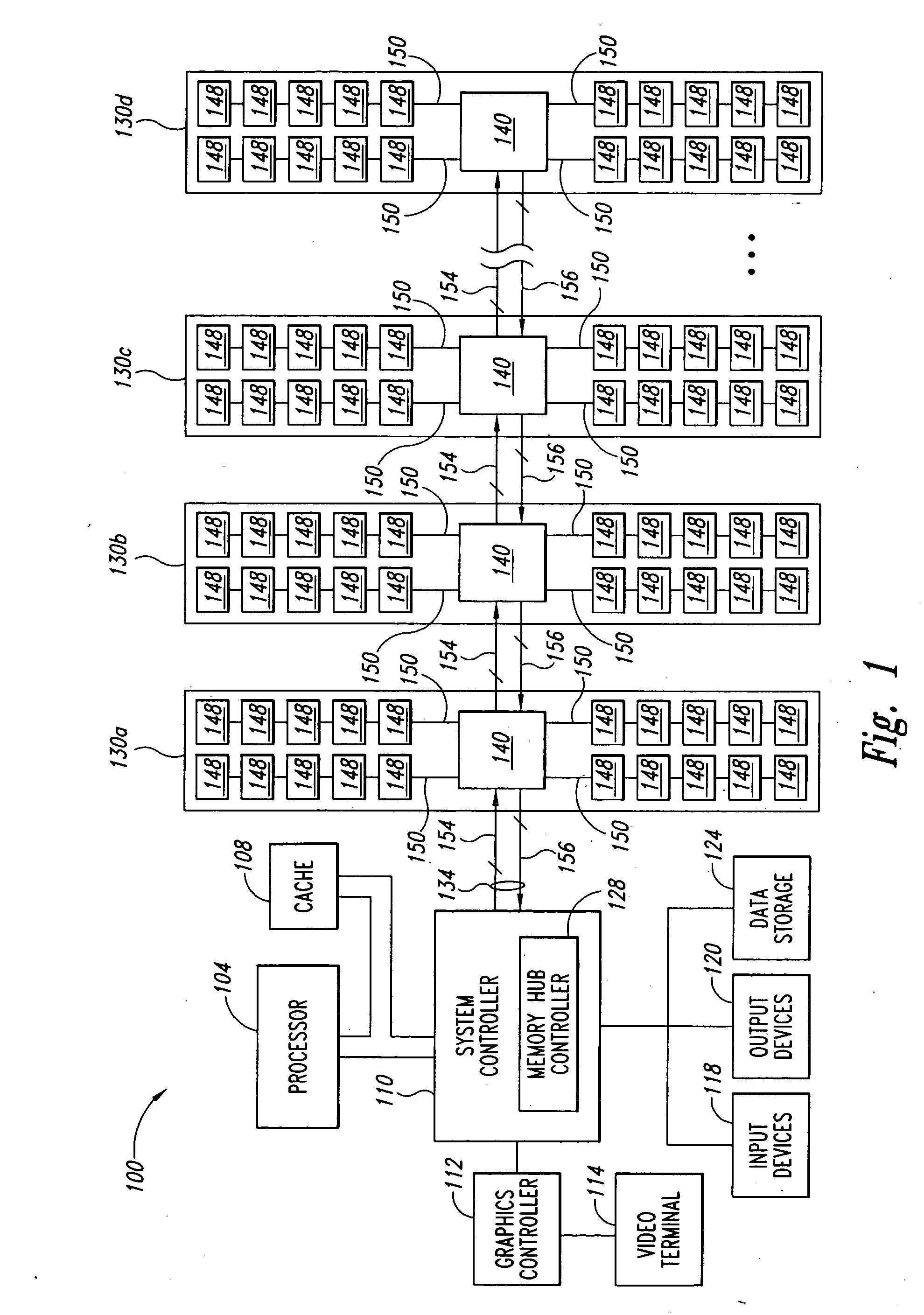

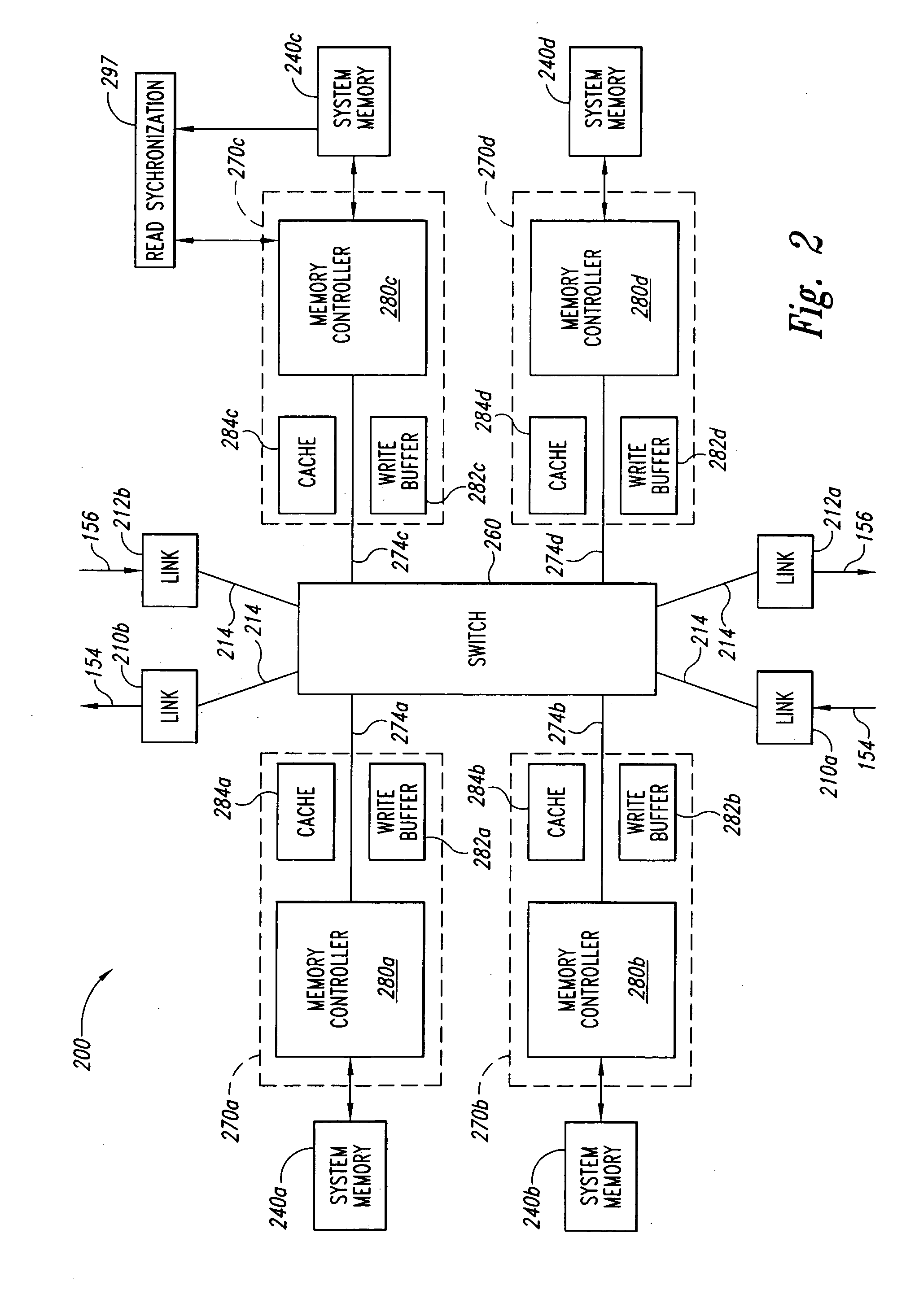

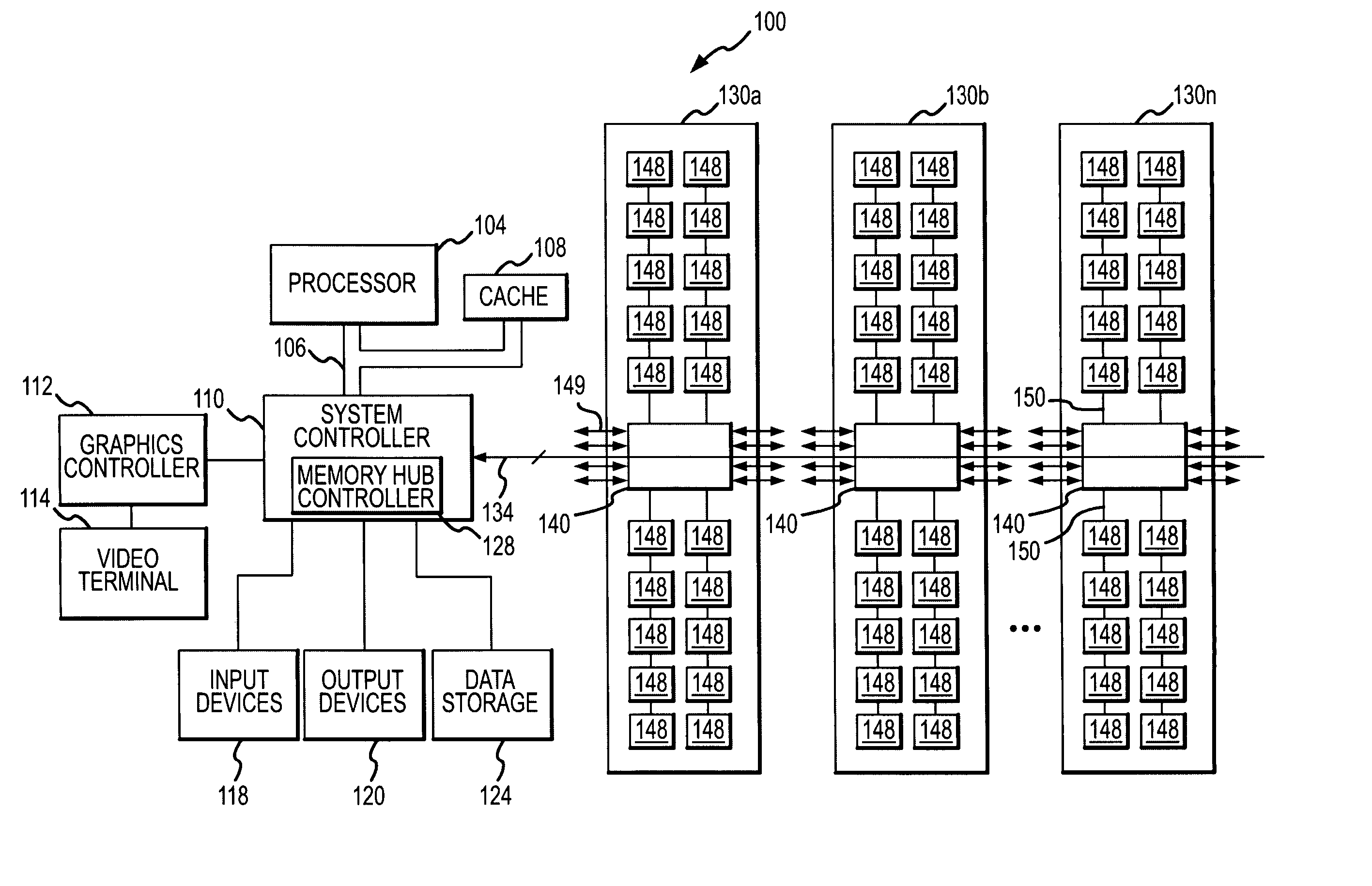

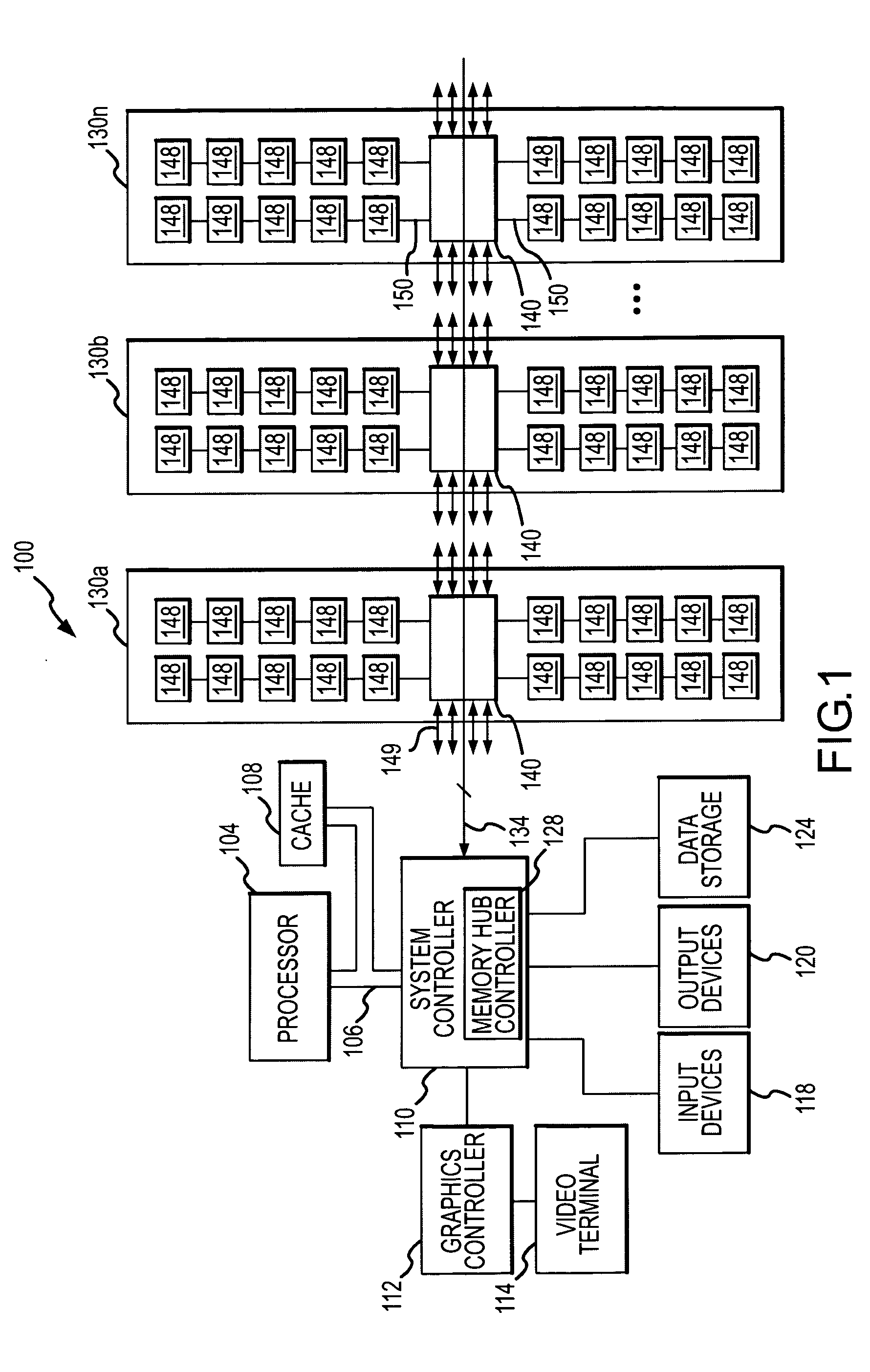

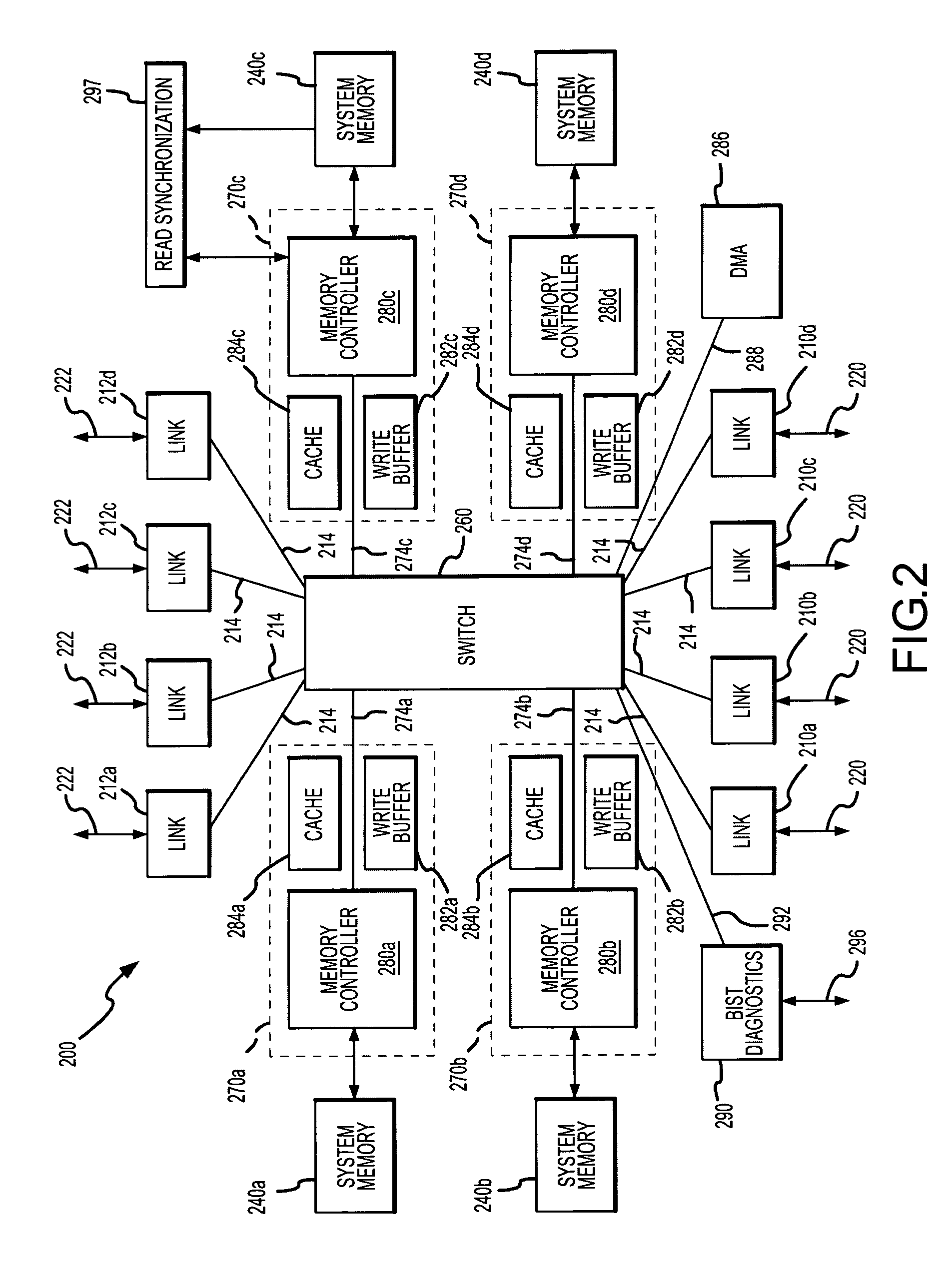

System and method for read synchronization of memory modules

A memory module includes several memory devices coupled to a memory hub. The memory hub includes several link interfaces coupled to respective processors, several memory controller coupled to respective memory devices, a cross-bar switch coupling any of the link interfaces to any of the memory controllers, a write buffer and read cache for each memory device and a read synchronization module. The read synchronization module includes a write pointer, a read pointer and a buffer. The write pointer is incremented in response to the receipt of read data. The read pointer increments in response to coupling of the read data from the memory hub. A comparator compares the read pointer an the write pointer, and the comparison is used to adjust the memory timing.

Owner:MICRON TECH INC

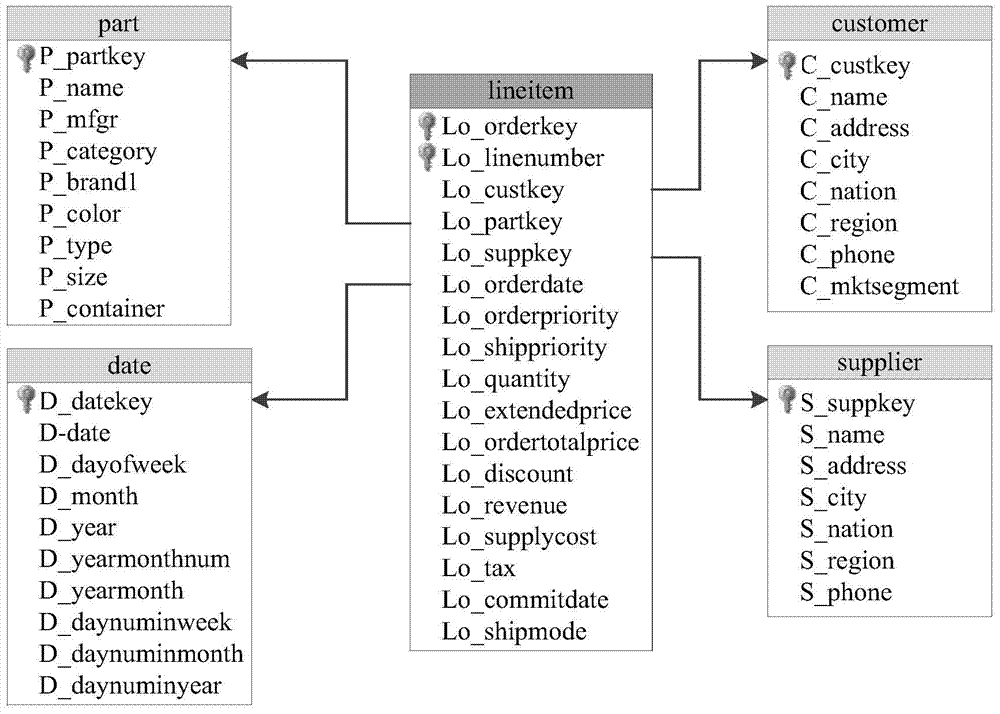

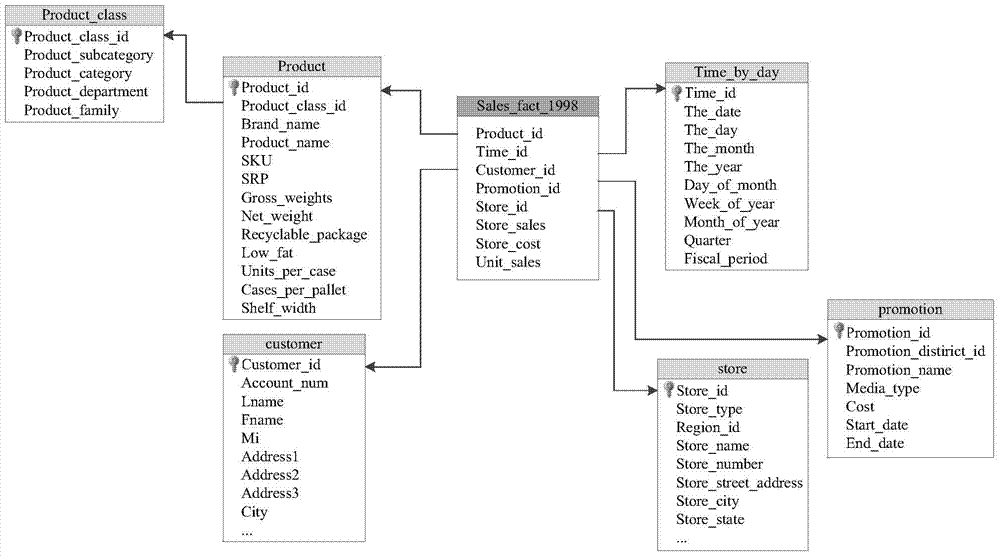

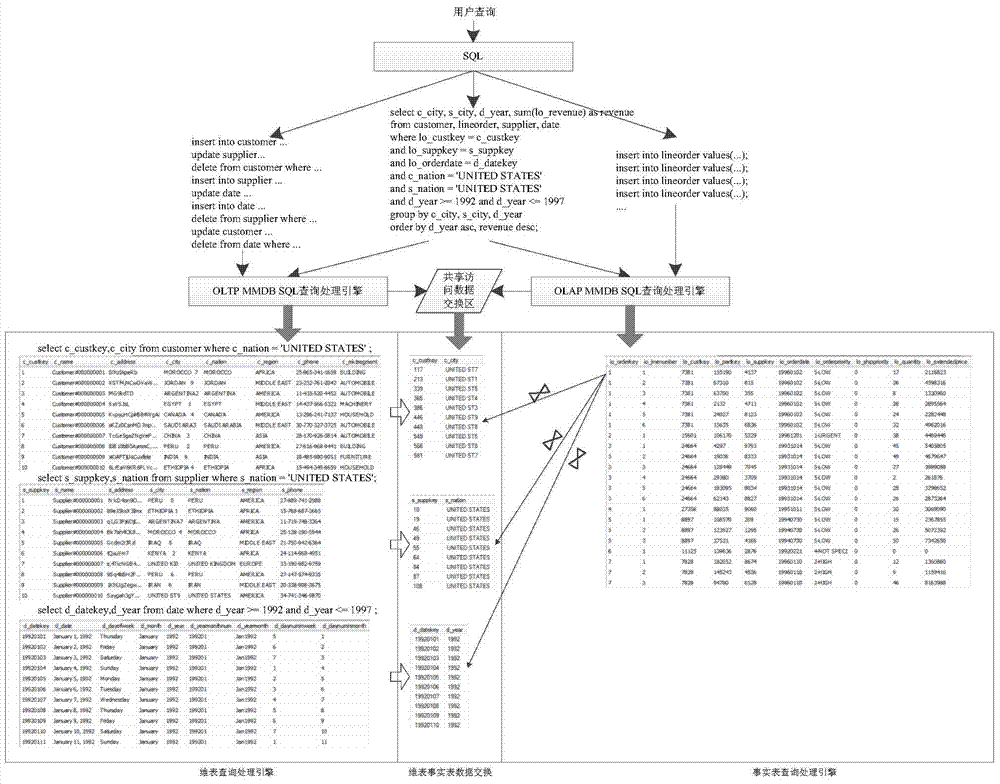

Memory database OLTP and OLAP concurrency query optimization method

ActiveCN103942342AIncrease the probability of concurrent access conflictsEasy to handleMulti-dimensional databasesSpecial data processing applicationsData compressionArray data structure

The invention relates to a memory database OLTP and OLAP concurrency query optimization method. The method includes the steps that (1) by means of two query processing engines, independent storage engines are adopted to a dimension table and a fact table; (2) the dimension table is updated through an embedded concurrency control mechanism of the independent storage engines, the fact table is equivalent to multiple continuous arrays in logic and maintains two dynamic data structures, namely a read record pointer and a write record pointer, the read record pointer records the position of the last record inquired through OLPA currently, and the write record pointer records the insert position of a new record; (3) an OLTP transactional queue and an OLAP transactional queue are independently executed with the read pointer and the write pointer as boundaries, the fact table adopts a column storage horizontal fragmentation model based on the fixed number of columns, N columns of storage records serve as an independent column storage container, and each column storage container adopts an independent data compression mechanism; (4) an access function on compressed data or non-compressed data is provided through access interfaces of the column storage containers when OLAP query has access to the column storage containers.

Owner:RENMIN UNIVERSITY OF CHINA

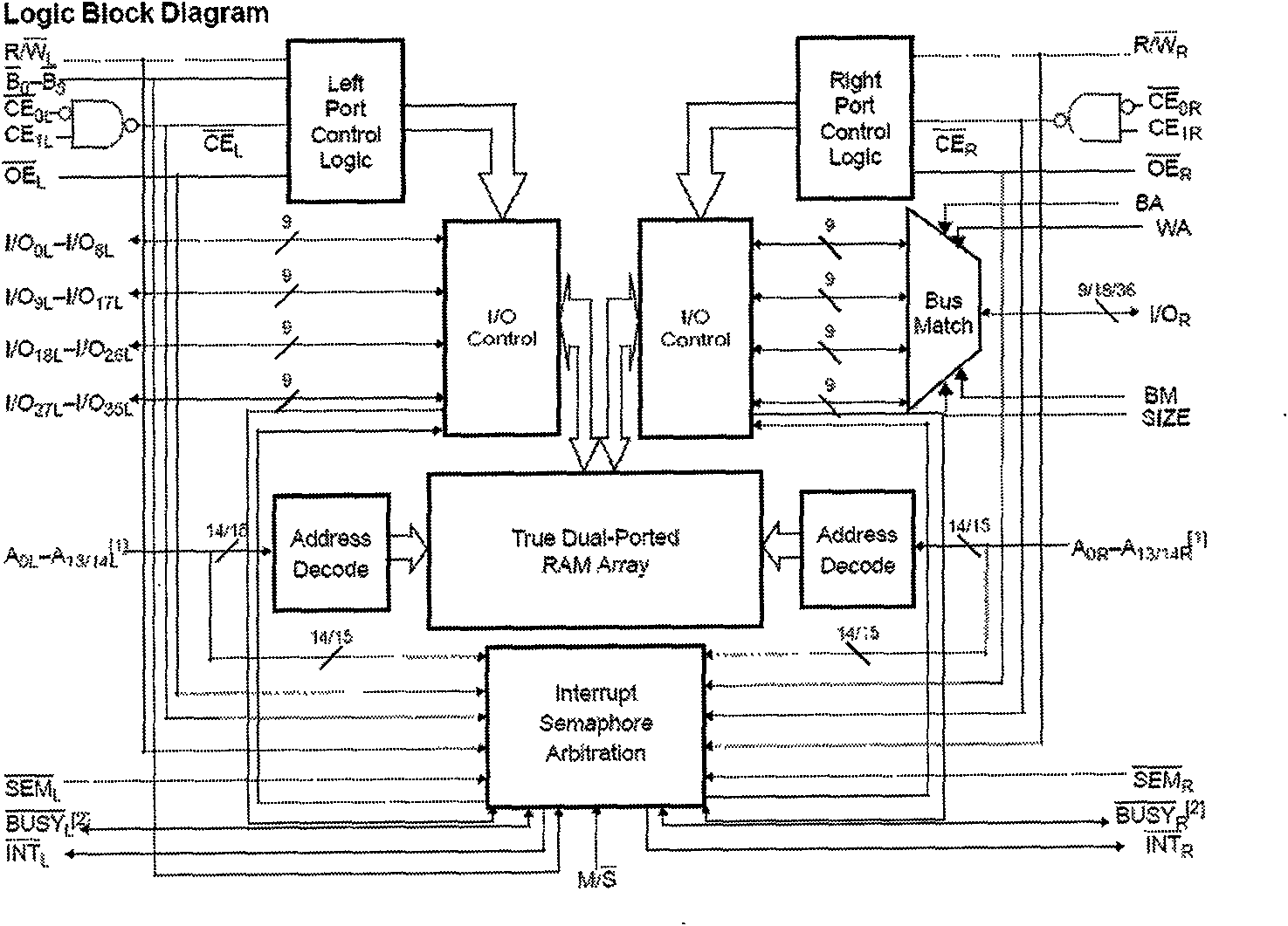

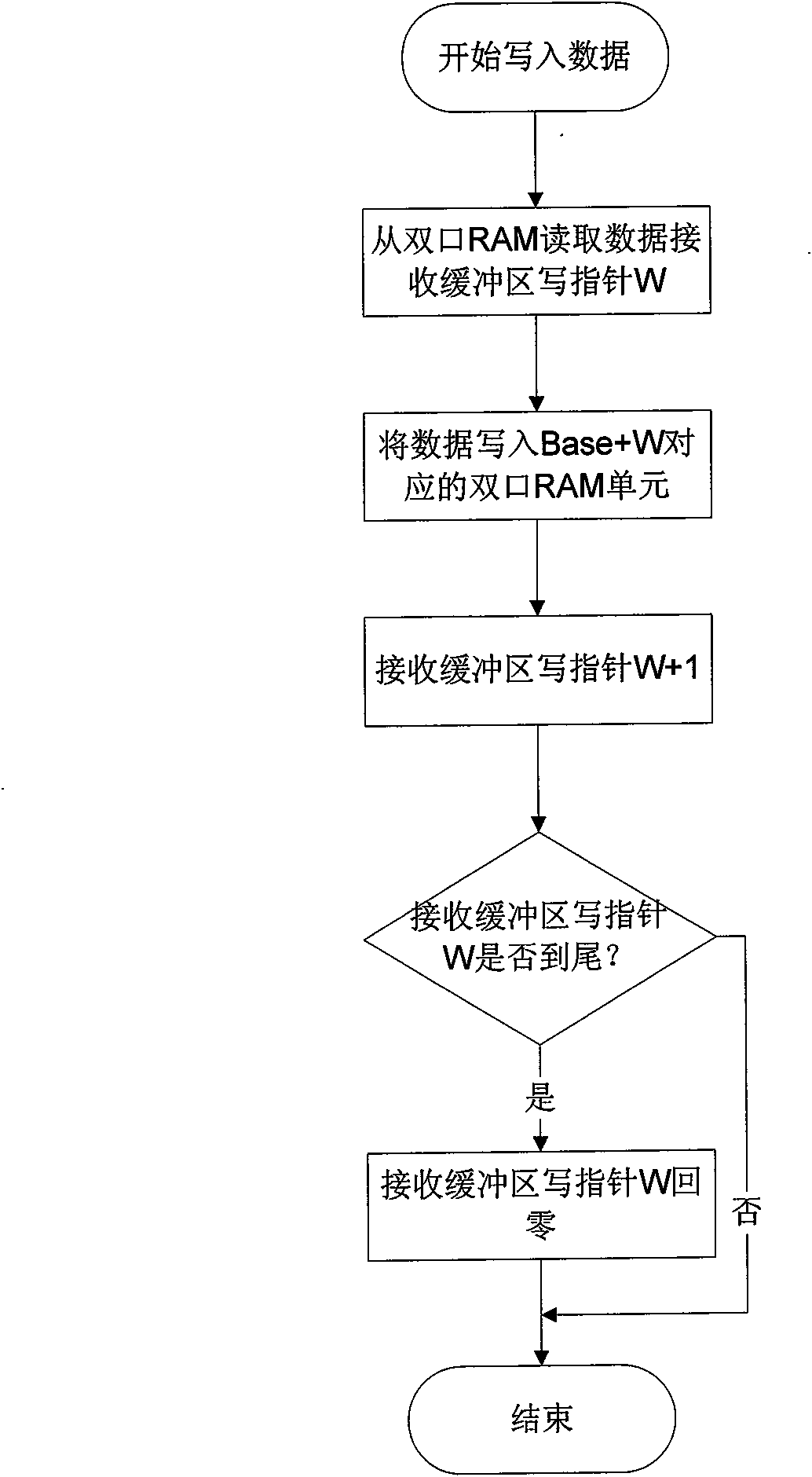

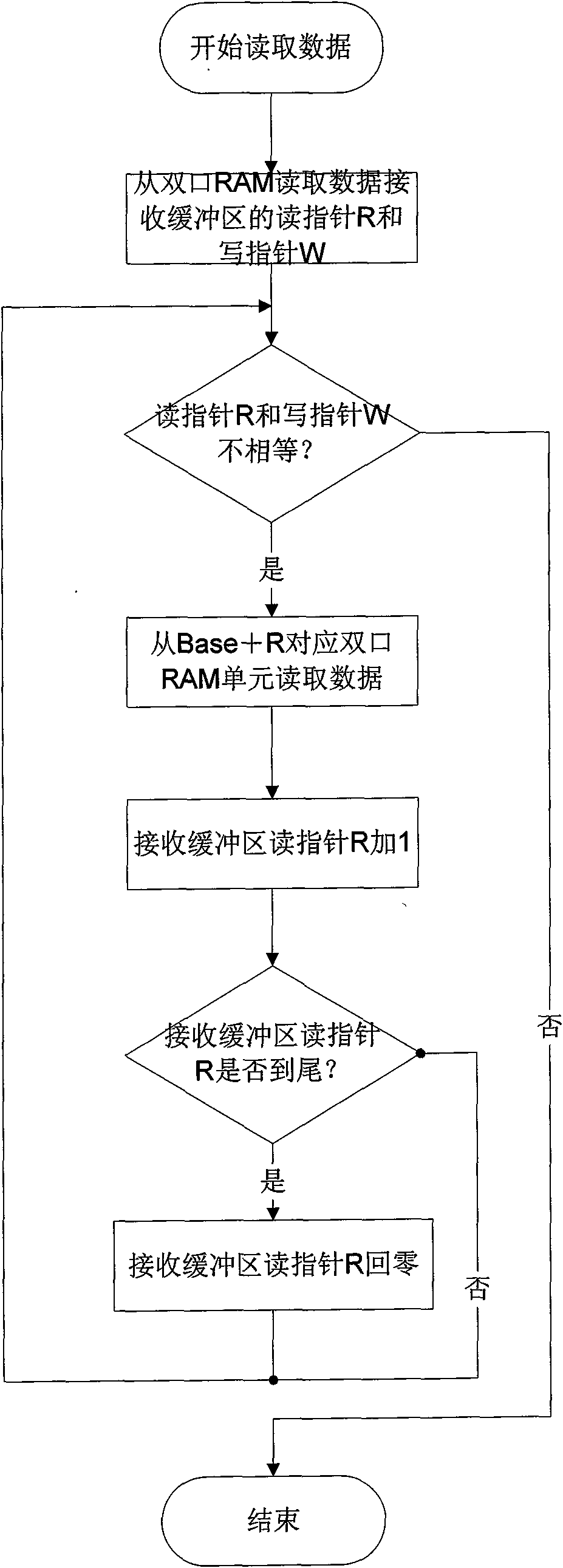

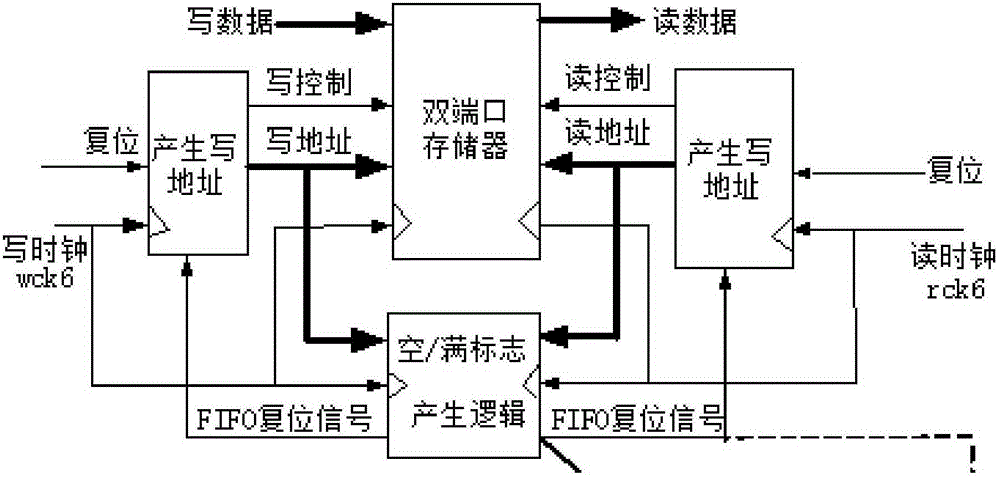

Implementation method of double-port RAM mutual exclusion access

InactiveCN101655824AAvoid competitionImprove real-time performanceElectric digital data processingData accessWrite pointer

The invention relates to an implementation method of double-port RAM mutual exclusion access. The method comprises the following operation steps: 1) dividing a shared data area into a plurality of data areas by an address partitioned mode, and establishing a corresponding software protocol; 2) dividing a shared storage area of a RAM into a plurality of large data areas starting from an initial unit according to the type of exchange data in software partition processing; determining size of the data areas based on practical transmission data; and subdividing the large data areas into a data receive buffer area and a data send buffer area, and defining each buffer area with corresponding data access base addresses and read-write pointers; and 3) in the system, all the communication work of an external system is completed by a slave, while a host is only required to write the date to be sent into the corresponding data buffer area in the double-port RAM or read the required data.

Owner:CHINA TECHENERGY

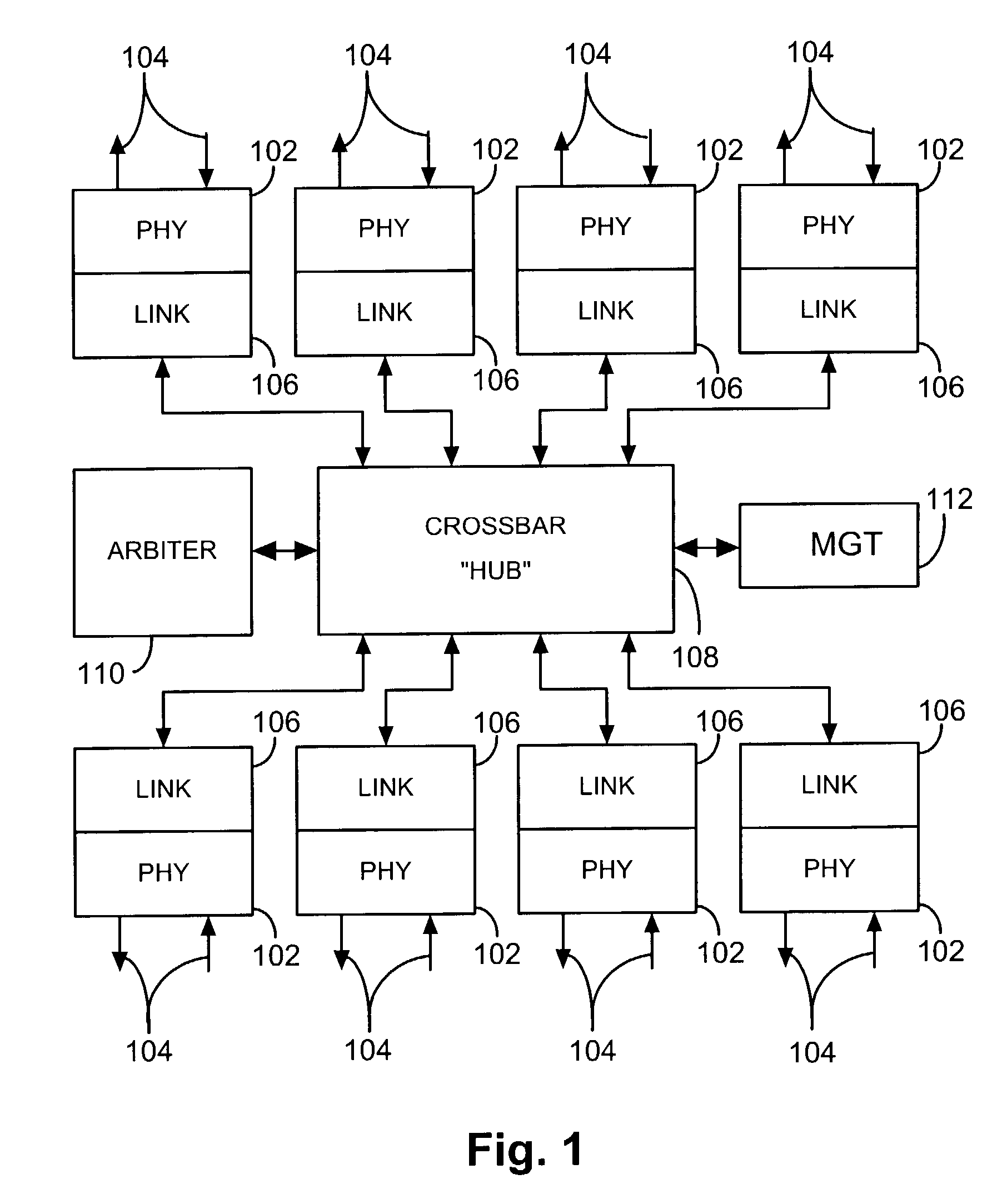

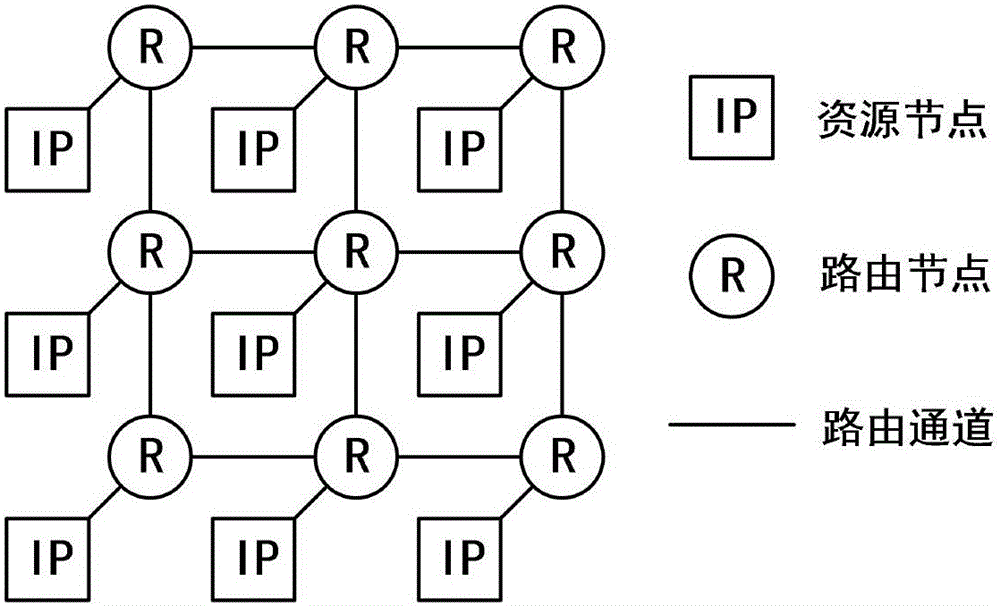

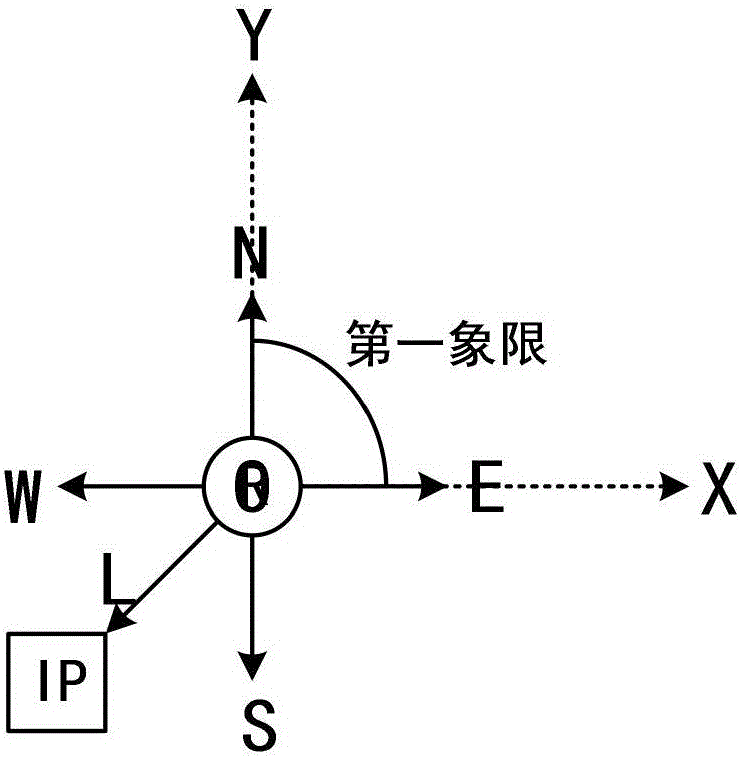

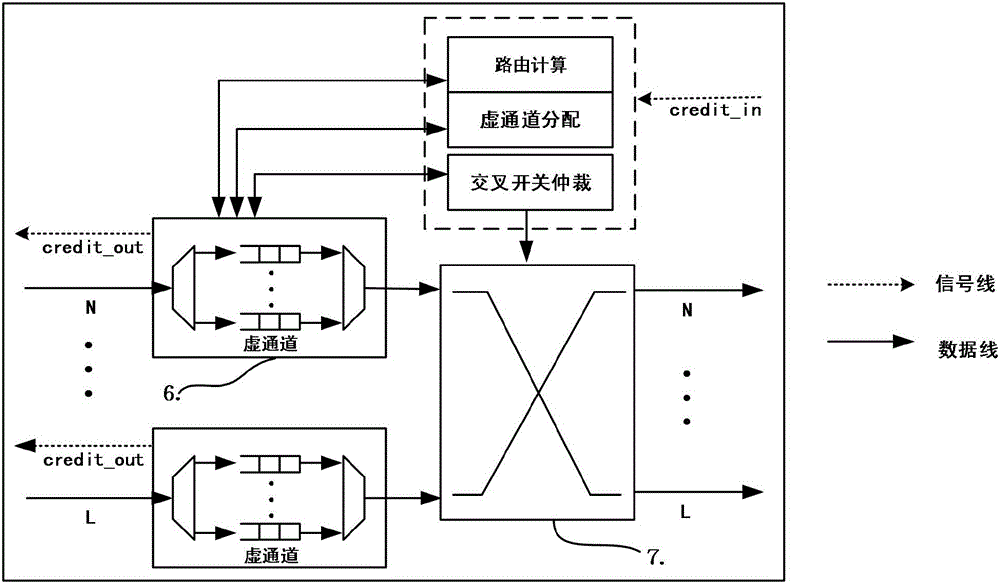

Adaptive router in NoC (network-on-chip) on basis of virtual output queue mechanism

InactiveCN105871742AReduce the possibilityEliminate the effects ofArchitecture with single central processing unitData switching networksCrossbar switchTraffic capacity

The invention discloses an adaptive router in an NoC (network-on-chip) on the basis of a virtual output queue mechanism. The adaptive router comprises five input ports, a port selection module, a valve judgment module, a storage module, an or-onward routing computation module, a header fit modification module, a crossbar switch judgment module, a crossbar switch and five output ports; the input ports partition an input buffer space according to output directions of data packets so as to form virtual output queues; an idle bit of a header fit of each data packet is used for parenthetically propagating congestion information of the network; any one virtual channel is equally divided into two storage spaces each of which is respectively provided with one set of read-write pointer; on a routing computation hierarchy, the output ports are adaptively selected; and in one single virtual channel, the data packet is adaptively read. According to the invention, by adaptation of two hierarchies, traffic distribution of the whole network is balanced and congestion is relieved, so that a possibility of generating HOL (head of line) blocking is reduced; and when the HOL blocking is generated, influence of the HOL blocking is eliminated, so that delay of the network is reduced and throughput of the network is improved.

Owner:HEFEI UNIV OF TECH

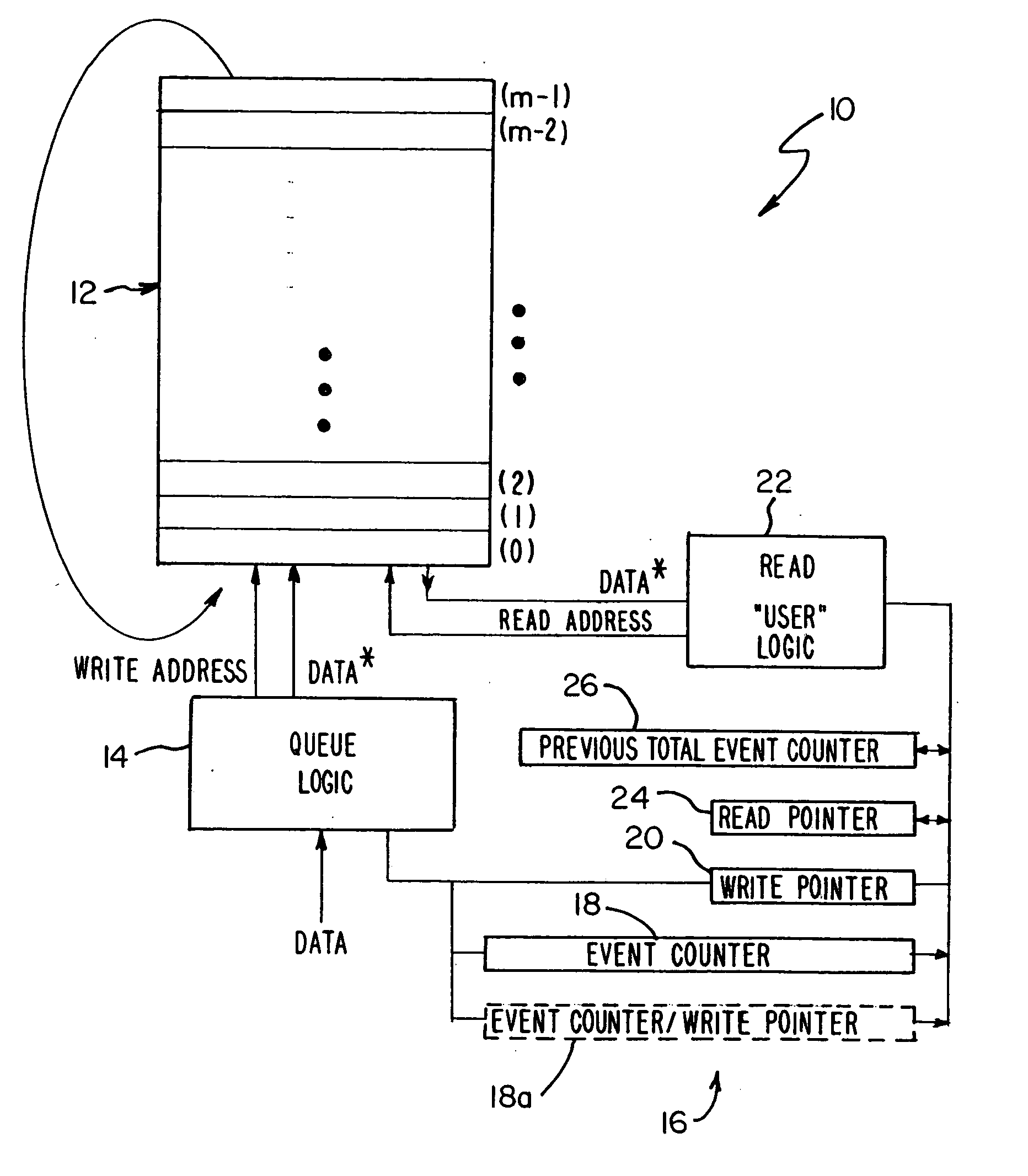

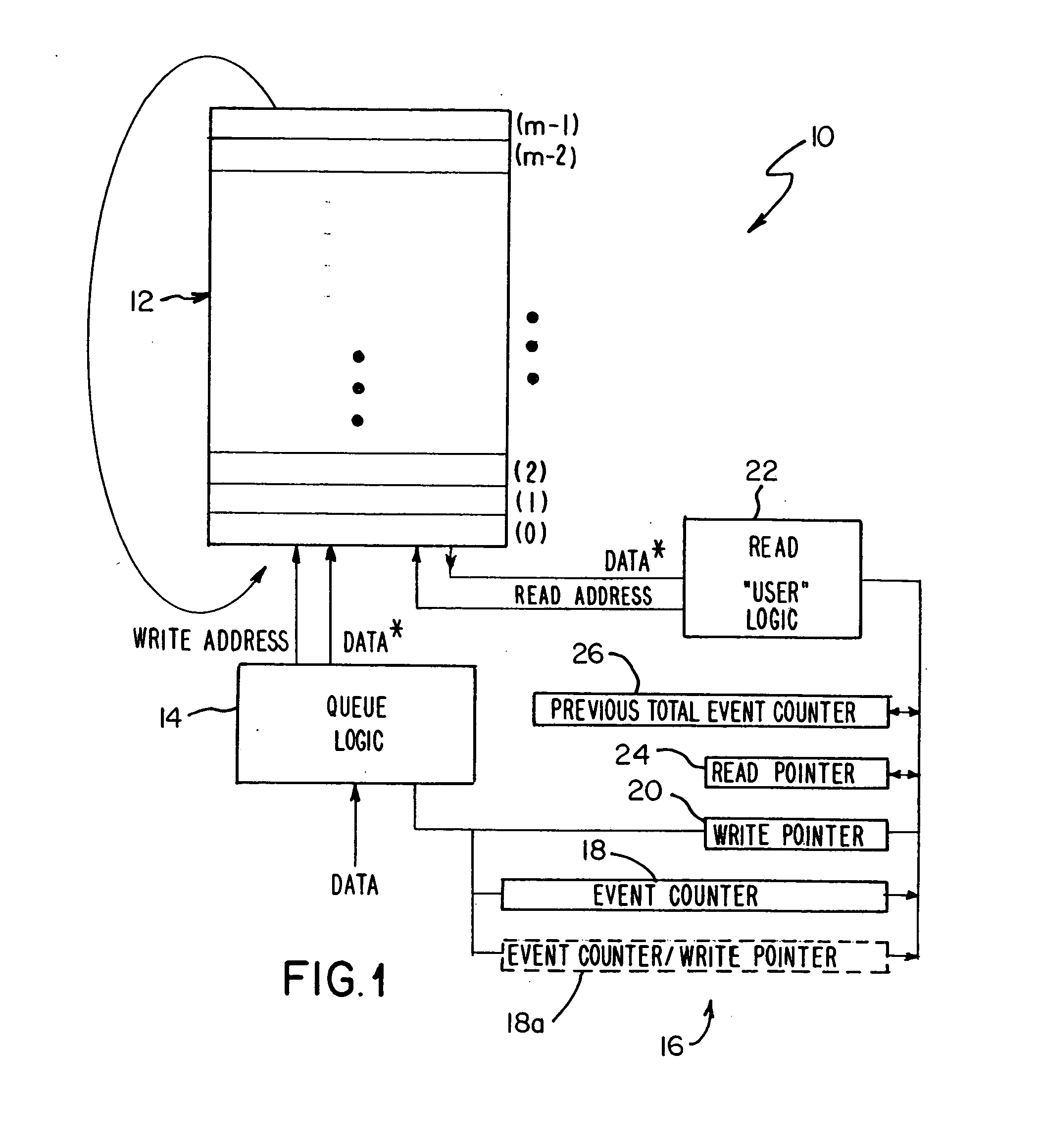

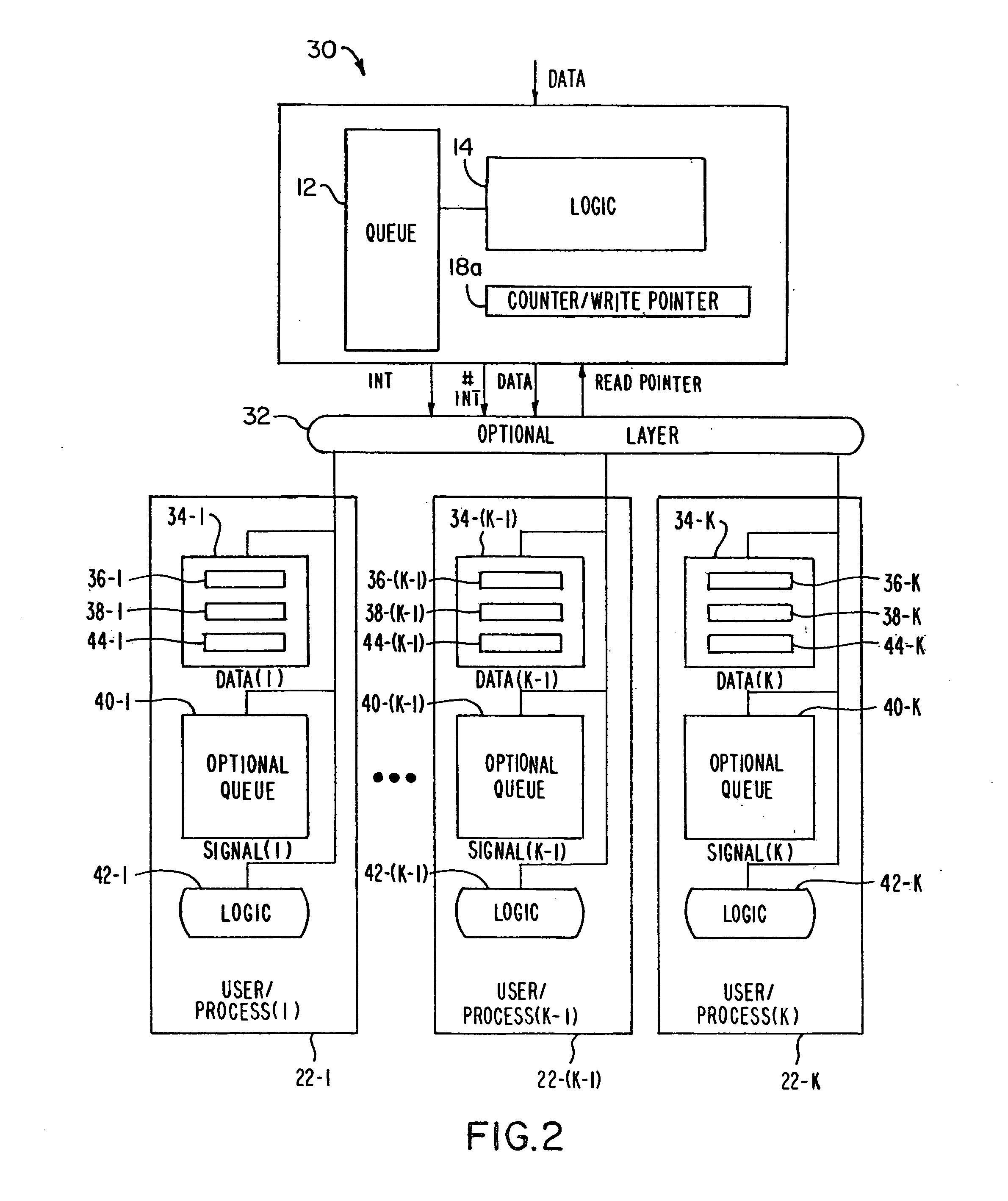

Queues for information processing and methods thereof

InactiveUS20070260777A1Overcome disadvantagesInput/output processes for data processingData conversionInformation processingDistributed computing

Systems and methods implement queues that perform write operations in a re-circulating sequential manner. The nature of the queue systems of the present invention allow writes to the queue to occur independently of read operations therefrom. A current event counter is updated by the queue logic to keep track of a count value that corresponds to the total number of data events written to the queue. Preferably, the current event counter is capable of counting an amount greater than the total number of addressable storage locations of the queue. A write pointer may be derived from the count value stored in the event counter from which a select addressable storage location of the queue can be determined for queuing each new data event. Read operations from the queue may be performed according to any prescribed manner, including random access thereto. Moreover, read operations can be performed in a first manner when no overflow is detected, and in a second manner in response to overflow.

Owner:SYSTRAN

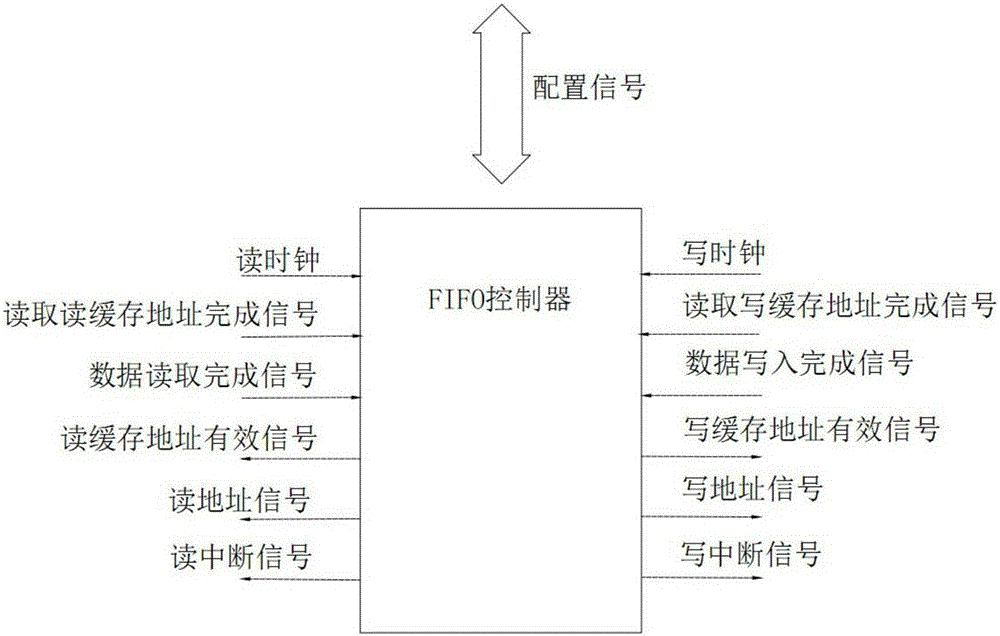

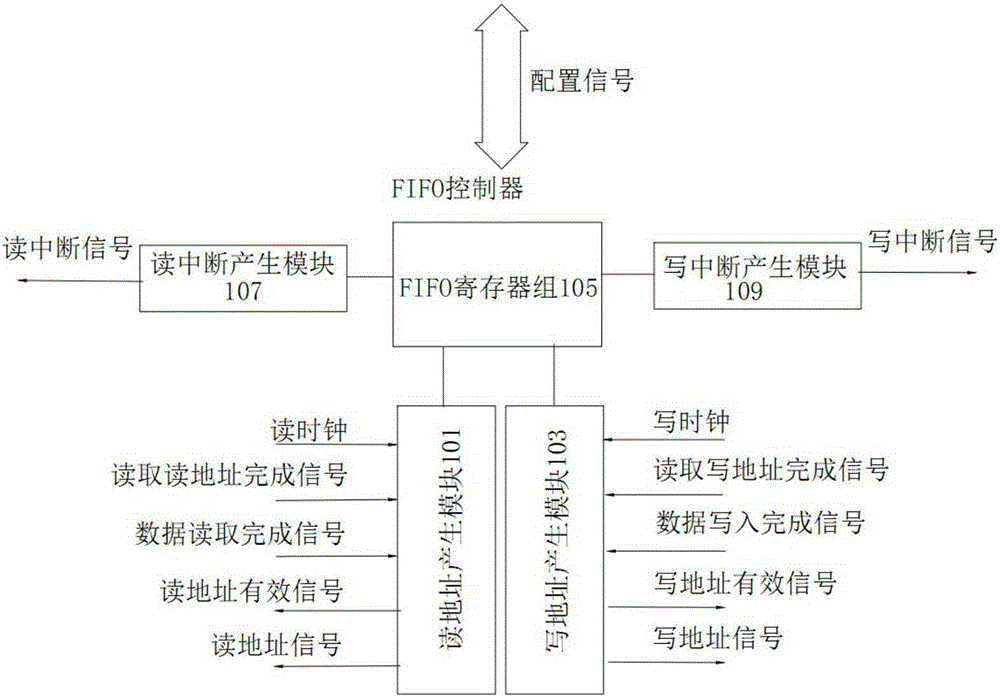

Data-caching access method and data-caching controller

ActiveCN105183665AAdapt to development needsAdapt to operational needsMemory adressing/allocation/relocationCache accessAccess method

The invention provides a data-caching access method and a data-caching controller and relates to the field of data processing, in particular to data caching. According to the data-caching access method and the data-caching controller, a segment of continuous storage space is distributed in a shared storer and used for conducting first-in-first-out data caching, a head address pointer of the controller points to a head address of the storage space, a tail address pointer points to a tail address of the storage space, the value of a write pointer is the value of the head address pointer, the value of a read pointer is the value of the head address pointer, and the storage space is initialized into a data-caching queue; read-write units are the minimal units of read-write operation of the storage space, and the length of the storage space is the number of the read-write units in the storage space. The controller can be well adapted to different program development and operation requirements, and storer resources can be utilized sufficiently.

Owner:FUZHOU ROCKCHIP SEMICON

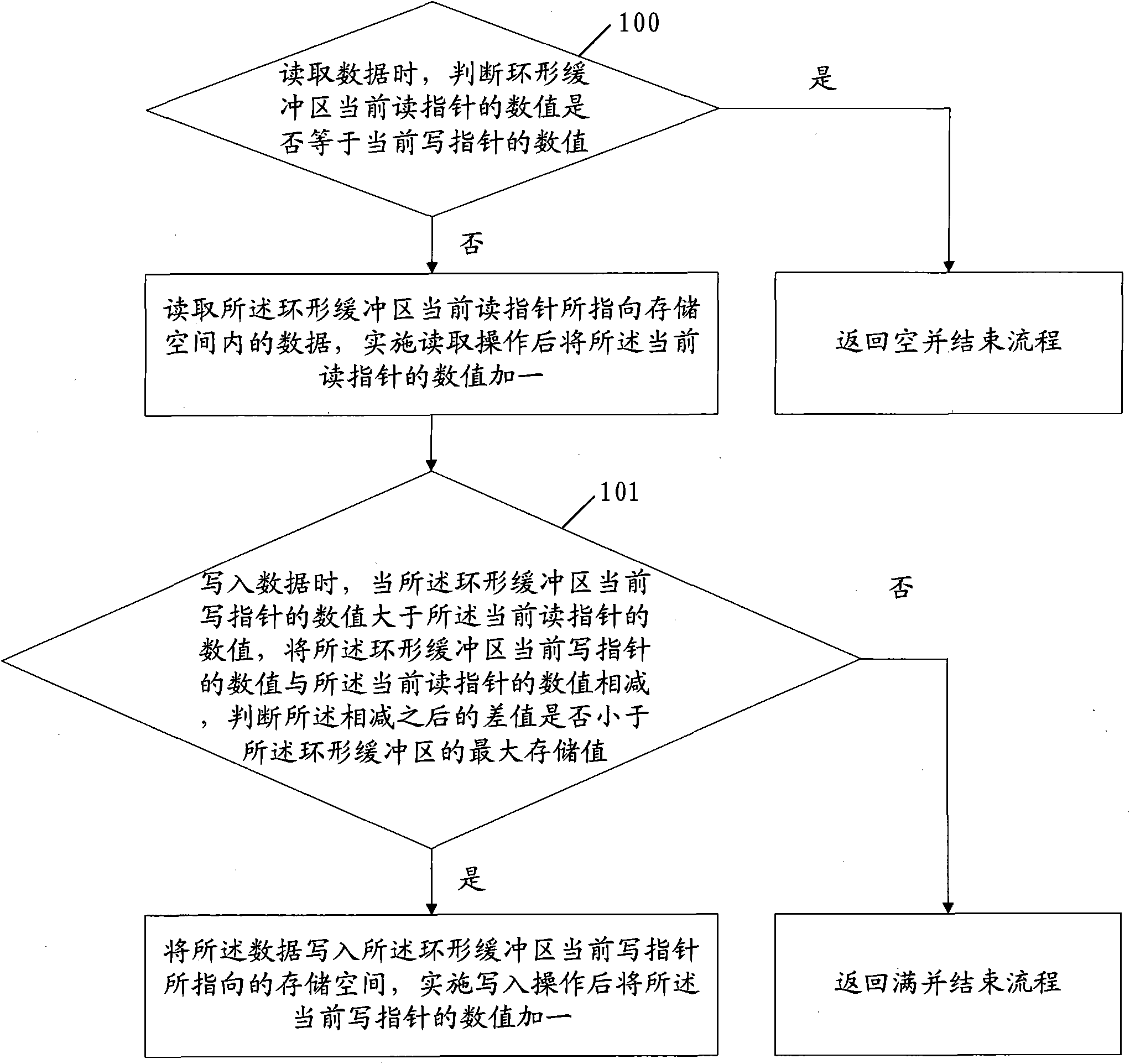

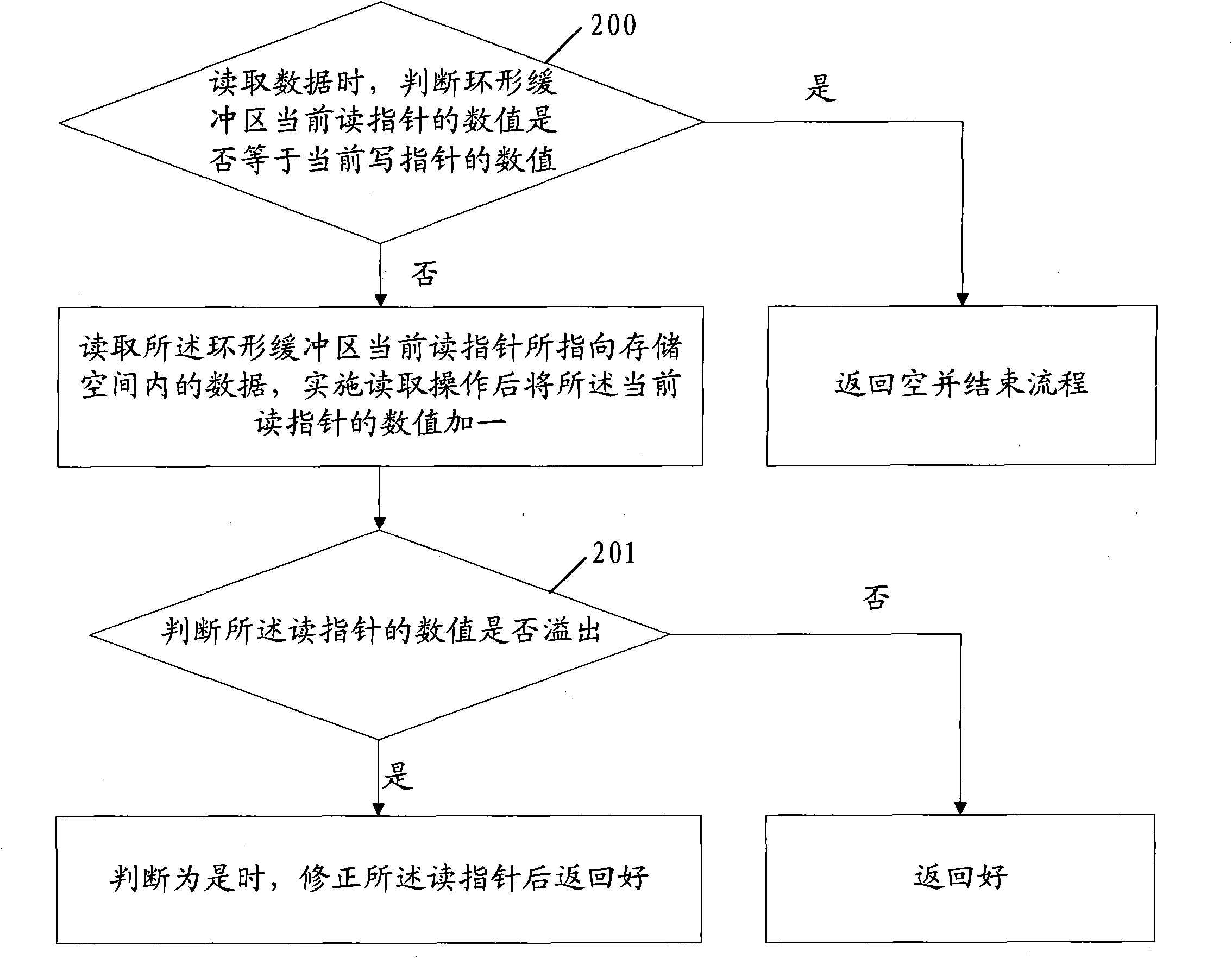

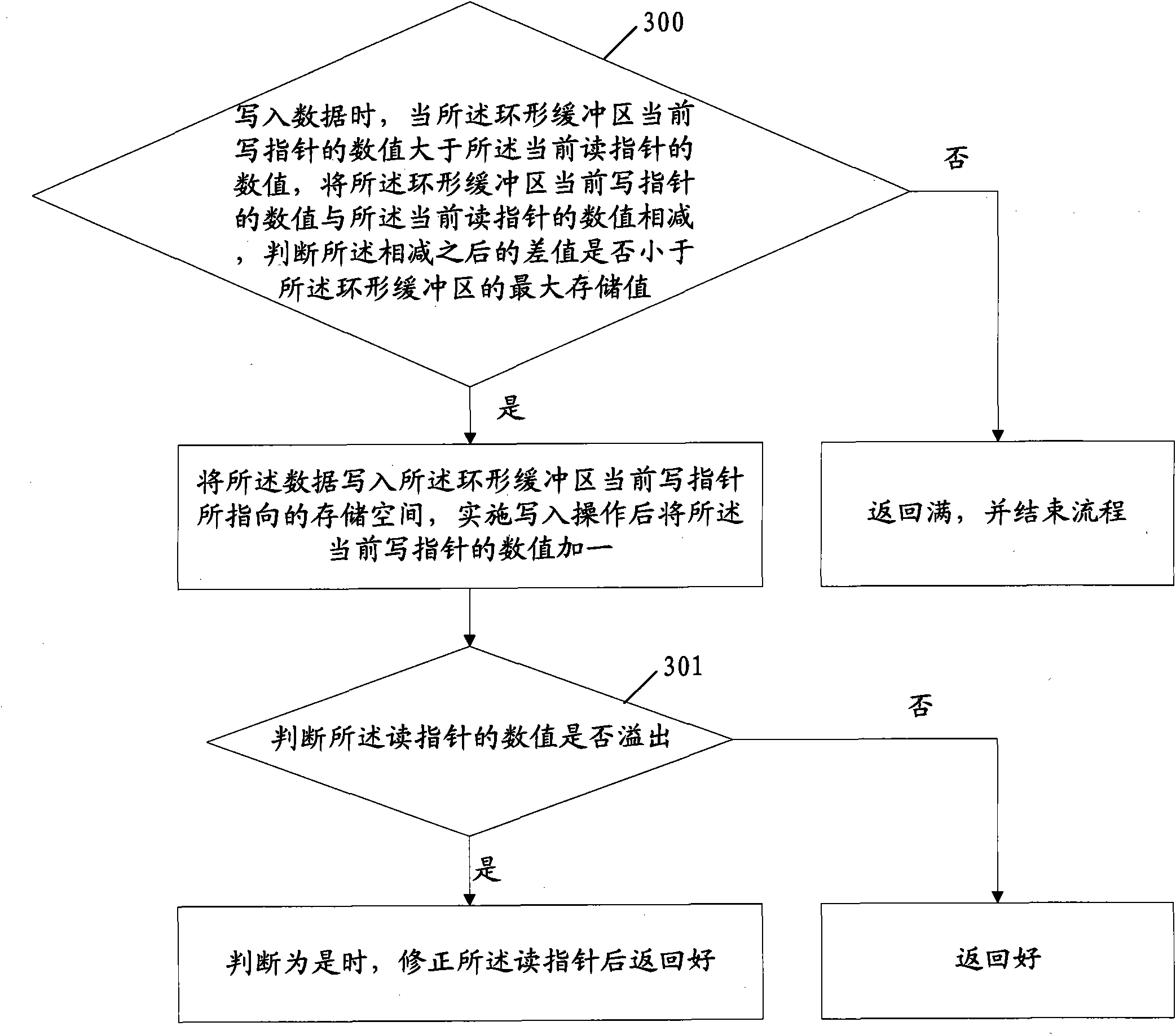

Method, device and digital-television receiving terminal for realizing ring buffer

InactiveCN101800867AAvoid performance degradationTelevision system detailsInput/output to record carriersComputer architectureWrite pointer

The embodiment of the invention discloses a method for realizing a ring buffer, which comprises the following steps: when reading data, judging whether the value of a current read pointer of the ring buffer is equal to the value of the current write pointer, if so, returning to null, otherwise reading data in the storage space pointed by the current read pointer of the ring buffer, and adding 1 to the value of the current read pointer after the read operation is carried out; and when writing data, subtracting the value of the current write pointer of the ring buffer from the value of the current read pointer, and judging whether the difference after the subtraction is less than the maximum storage value of the ring buffer, if so, writing the data into the storage space pointed by the current write pointer of the ring buffer and adding 1 to the value of the current write pointer after the write operation is carried out, otherwise returning to full. The invention can maximally utilize the message space of the ring buffer without degrading the system performance.

Owner:SHENZHEN COSHIP ELECTRONICS CO LTD

Clock synchronizer and clock and data recovery apparatus and method

A clock synchroniser, and clock and data recovery apparatus incorporating the clock synchroniser, are described, together with corresponding clock synchronisation methods. The clock synchroniser incorporates an elastic buffer. A received clock signal RCK is used to clock data into the buffer, and a locally generated clock LCK is used to clock data out of the buffer. The local clock is synthesised using a PLL, and a fill-level signal from the elastic buffer is used to control to local clock frequency to maintain a desired average quantity of data in the buffer, thereby achieving synchronisation of the received and local clocks. In preferred embodiments the fill-level signal is used to control a variable divider in the feedback path of the PLL, which is supplied with a highly stable reference signal. A synchronised, and low-jitter local clock is thus produced. Preferably, the elastic buffer employs counters of relatively wide word width, and a storage array of much reduced depth, read and write pointers being provided by just a few of the least significant bits of the words.

Owner:CIRRUS LOGIC INT SEMICON

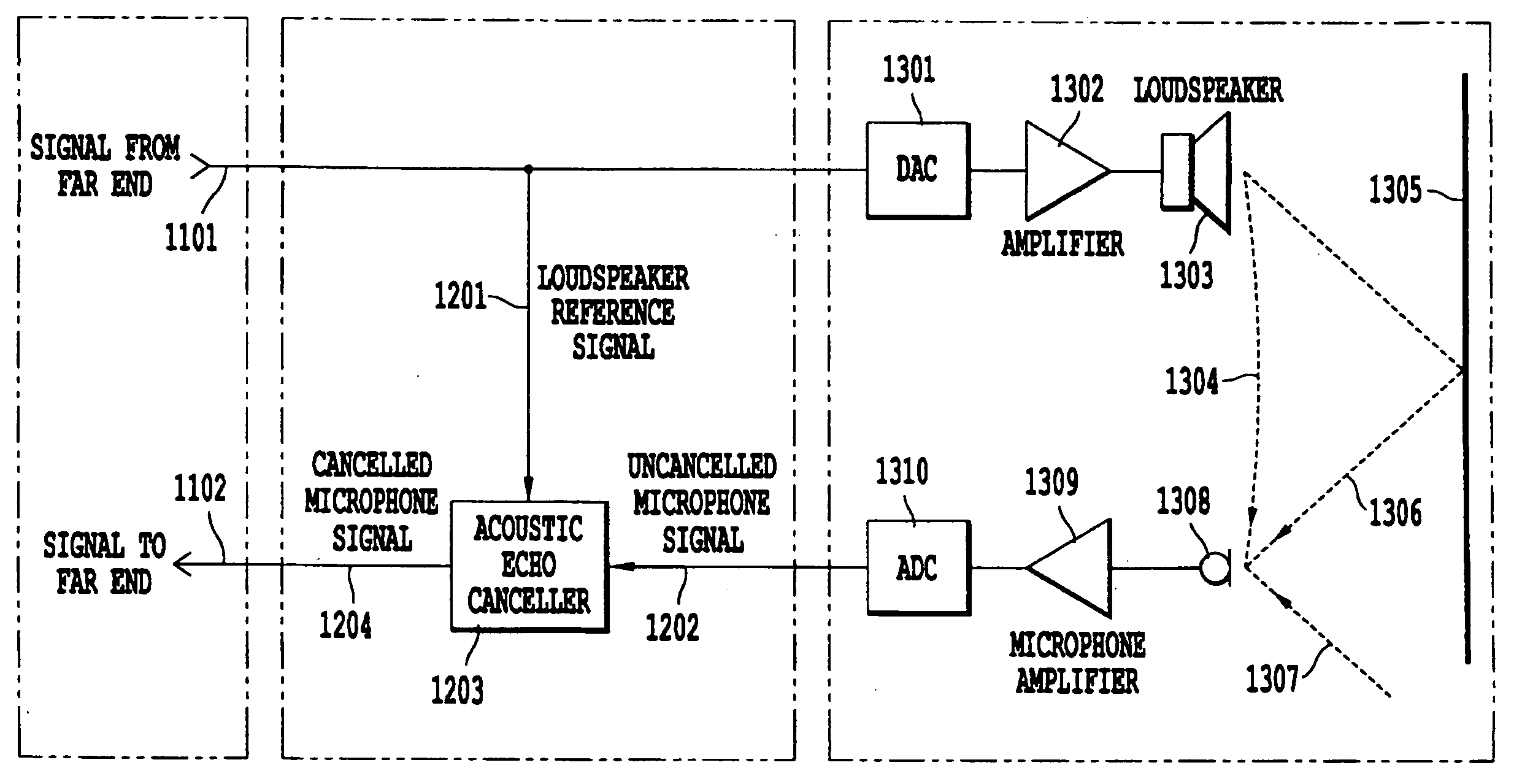

Method and system for clock drift compensation

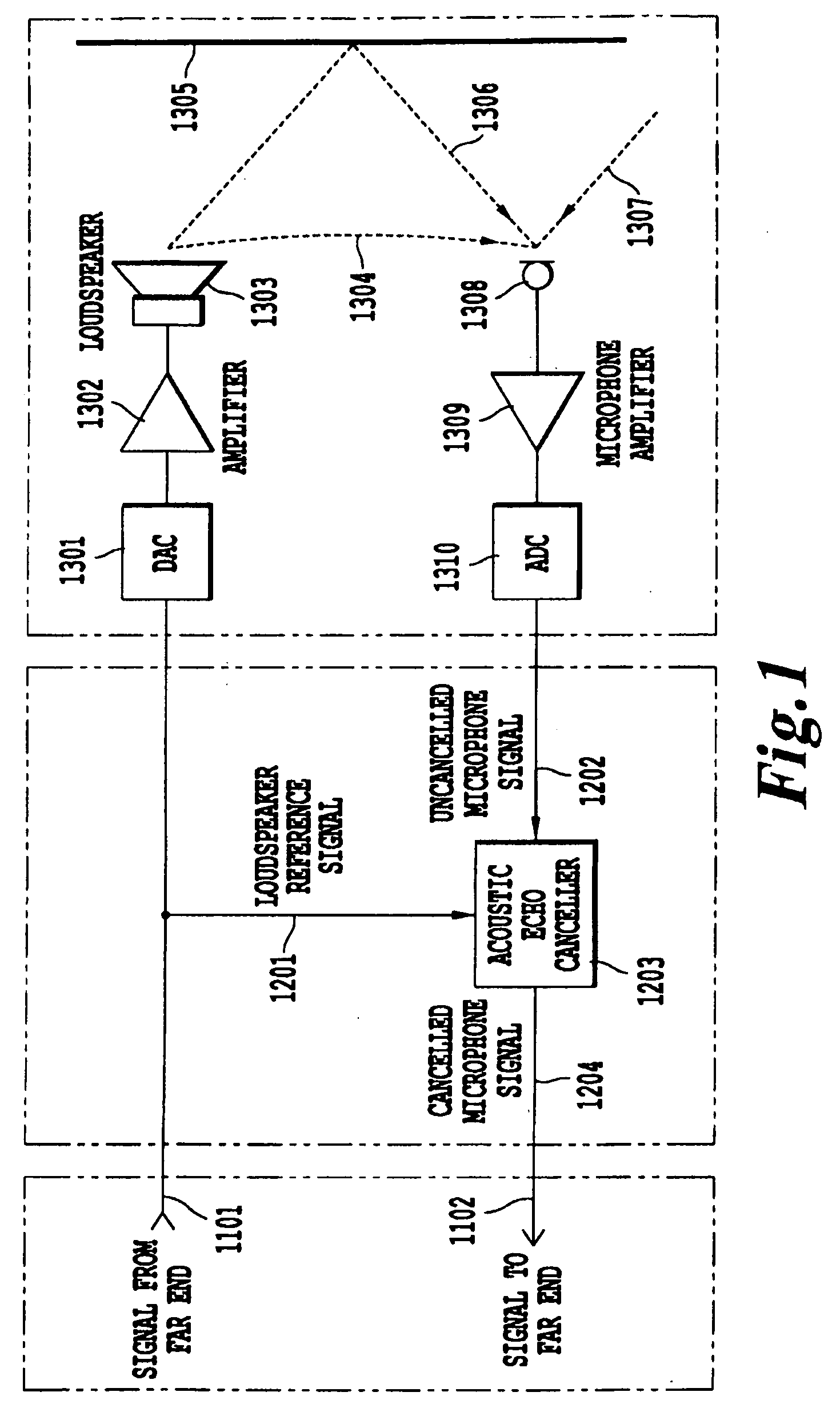

ActiveUS20090185695A1Solve problemsTwo-way loud-speaking telephone systemsEar treatmentClock timeTime domain

Different sampling rates between a playout unit and a capture unit are compensated for via a system, method and computer program product. The playout unit receives samples from a computational unit, and the capture unit sends samples to the computational unit. A playout FIFO buffer operates in a playout time domain, and a capture FIFO buffer operates in a capture time domain. The computational unit is synchronized to a common clock. A first relationship is calculated between the common clock and a playout fifo buffer read pointer, and a second relationship is calculated between the common clock and a capture FIFO buffer write pointer. For each sample in the playout time domain a corresponding sample in the samples from said computational unit is found and sent to the playout FIFO buffer. For each sample in the common clock time domain the corresponding sample in the capture time domain is found and sent to the computational unit.

Owner:CISCO TECH INC

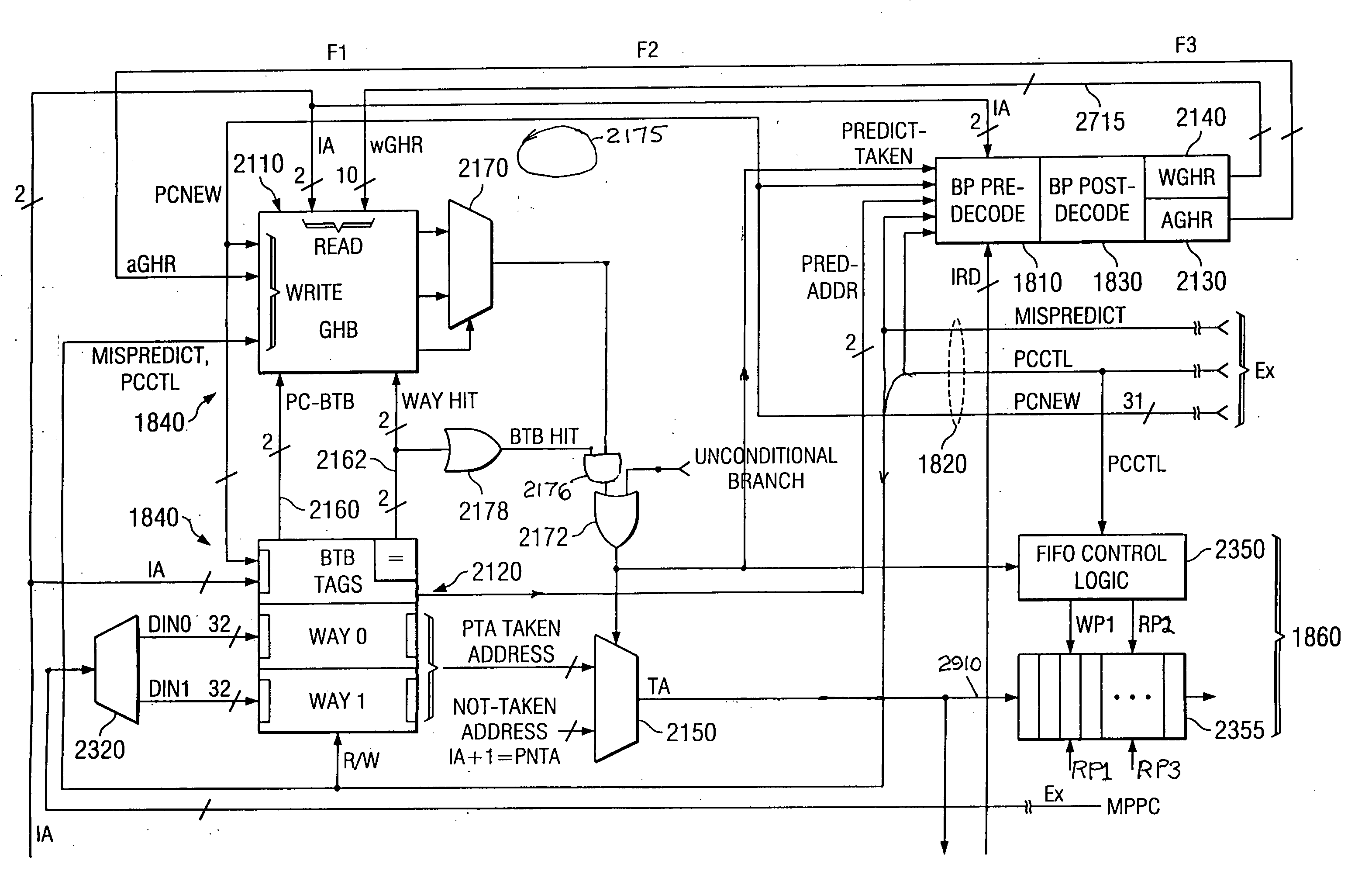

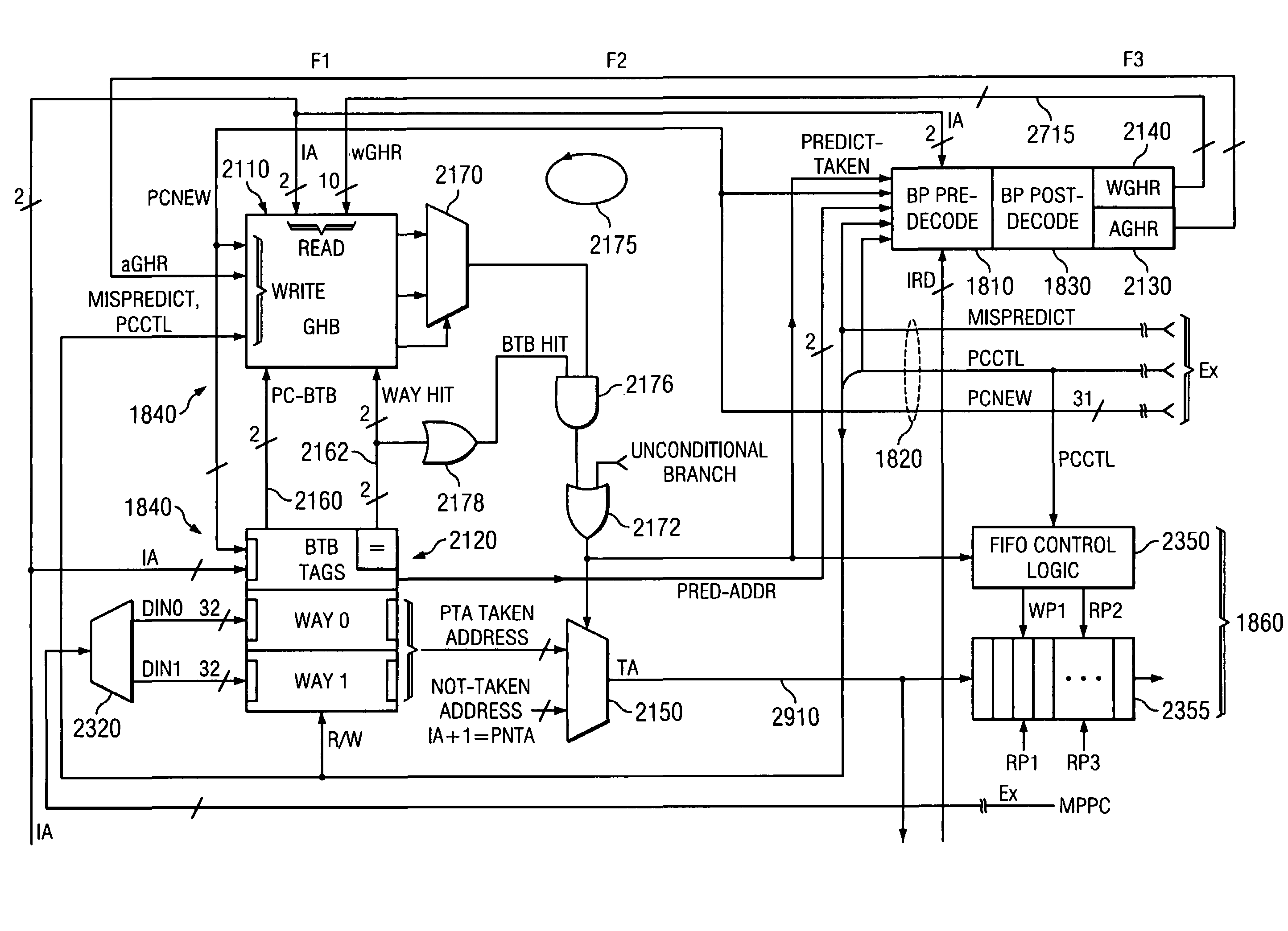

Processes, circuits, devices, and systems for branch prediction and other processor improvements

A processor (1700) including a pipeline (1710, 1740) having a fetch pipeline (1710) with branch prediction circuitry (1840) to supply respective predicted taken target addresses for branch instructions, an execution pipeline (1740) with a branch execution circuit (1870), and storage elements (in 1860) and control logic (2350) operable to establish a first-in-first-out (FIFO) circuit (1860) with a write pointer WP1 and a read pointer RP1. The control logic (2350) is responsive to the branch prediction circuitry (1840) to write a predicted taken target address to a storage element (in 1860) identified by the write pointer (WP1) and the predicted taken target address remains stationary therein. The FIFO circuit (1860) bypasses a plurality of pipestages between the branch prediction circuitry (1840) and the branch execution circuit (1870). The control logic (2350) is operable to read a predicted taken target address (PTTPCA) from a storage element (in 1860) identified by the read pointer RP1.

Owner:TEXAS INSTR INC

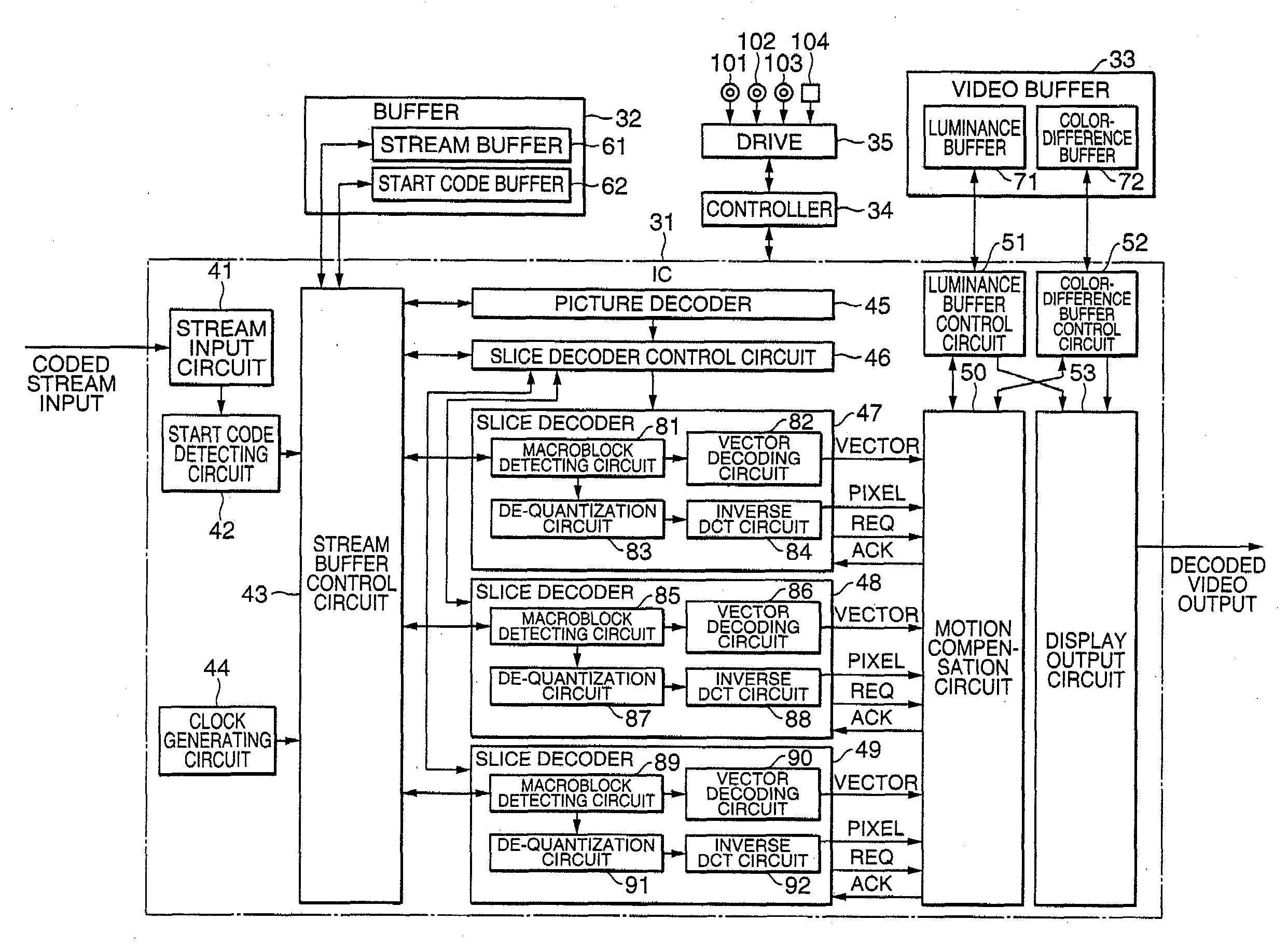

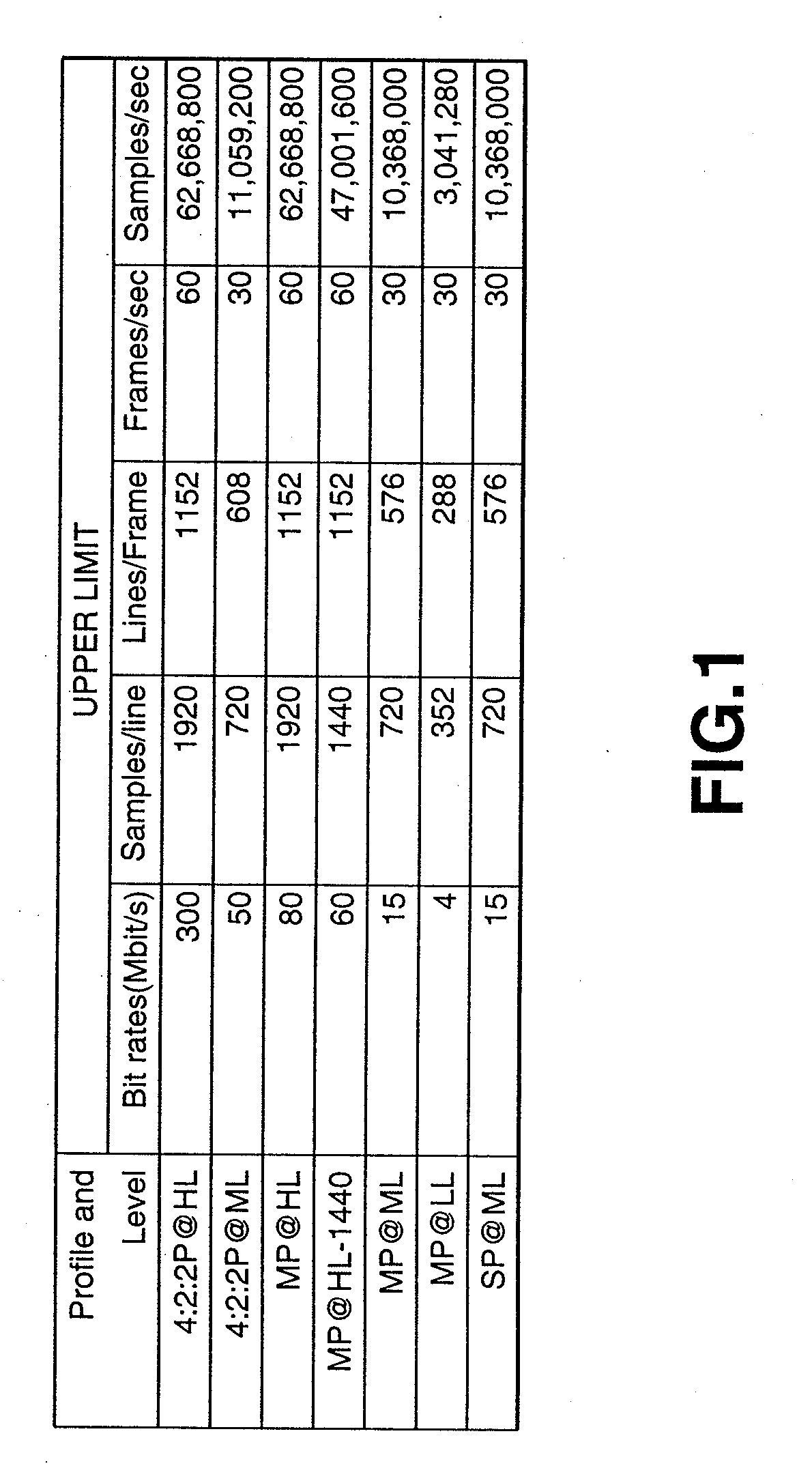

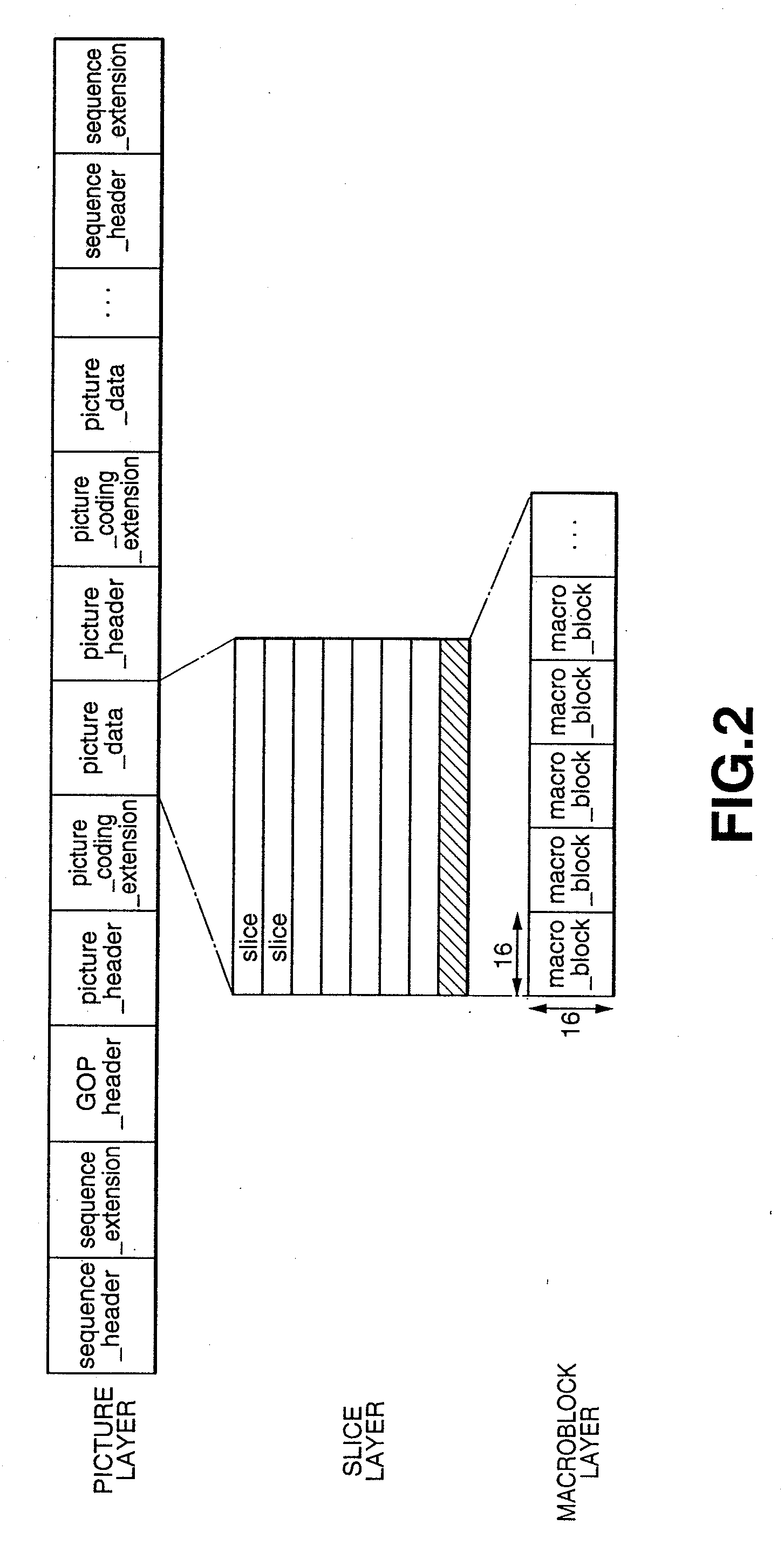

Decoding device, decoding method, recording medium, and program

InactiveUS20090010334A1Faster decoding processingTelevision system detailsPicture reproducers using cathode ray tubesDecoding methodsControl circuit

A slice decoder control circuit sequentially supplies the parameter of the picture layer and the write pointer of a first slice to a first slice decoder, the parameter of the picture layer and the write pointer of a second slice to a second slice decoder, and the parameter of the picture layer and the write pointer of a third slice to a third slice decoder, and causes the slice decoders to decode the respective parameters and write pointers. On the basis of the input of signals indicating the completion of decoding processing inputted from the slice decoders, the slice decoder control circuit supplies the write pointer of a fourth slice to the second decoder and causes the second slice decoder to decode the write pointer at timing A, and supplies the write pointer of a fifth slice to the third decoder and causes the third slice decoder to decode the write pointer at timing B. Subsequently, the similar processing is repeated until the last slice is decoded. The operations of a plurality of slice decoders are thus controlled.

Owner:UEDA MAMORU +5

Branch prediction and other processor improvements using FIFO for bypassing certain processor pipeline stages

A processor (1700) including a pipeline (1710, 1740) having a fetch pipeline (1710) with branch prediction circuitry (1840) to supply respective predicted taken target addresses for branch instructions, an execution pipeline (1740) with a branch execution circuit (1870), and storage elements (in 1860) and control logic (2350) operable to establish a first-in-first-out (FIFO) circuit (1860) with a write pointer WP1 and a read pointer RP1. The control logic (2350) is responsive to the branch prediction circuitry (1840) to write a predicted taken target address to a storage element (in 1860) identified by the write pointer (WP1) and the predicted taken target address remains stationary therein. The FIFO circuit (1860) bypasses a plurality of pipestages between the branch prediction circuitry (1840) and the branch execution circuit (1870). The control logic (2350) is operable to read a predicted taken target address (PTTPCA) from a storage element (in 1860) identified by the read pointer RP1.

Owner:TEXAS INSTR INC

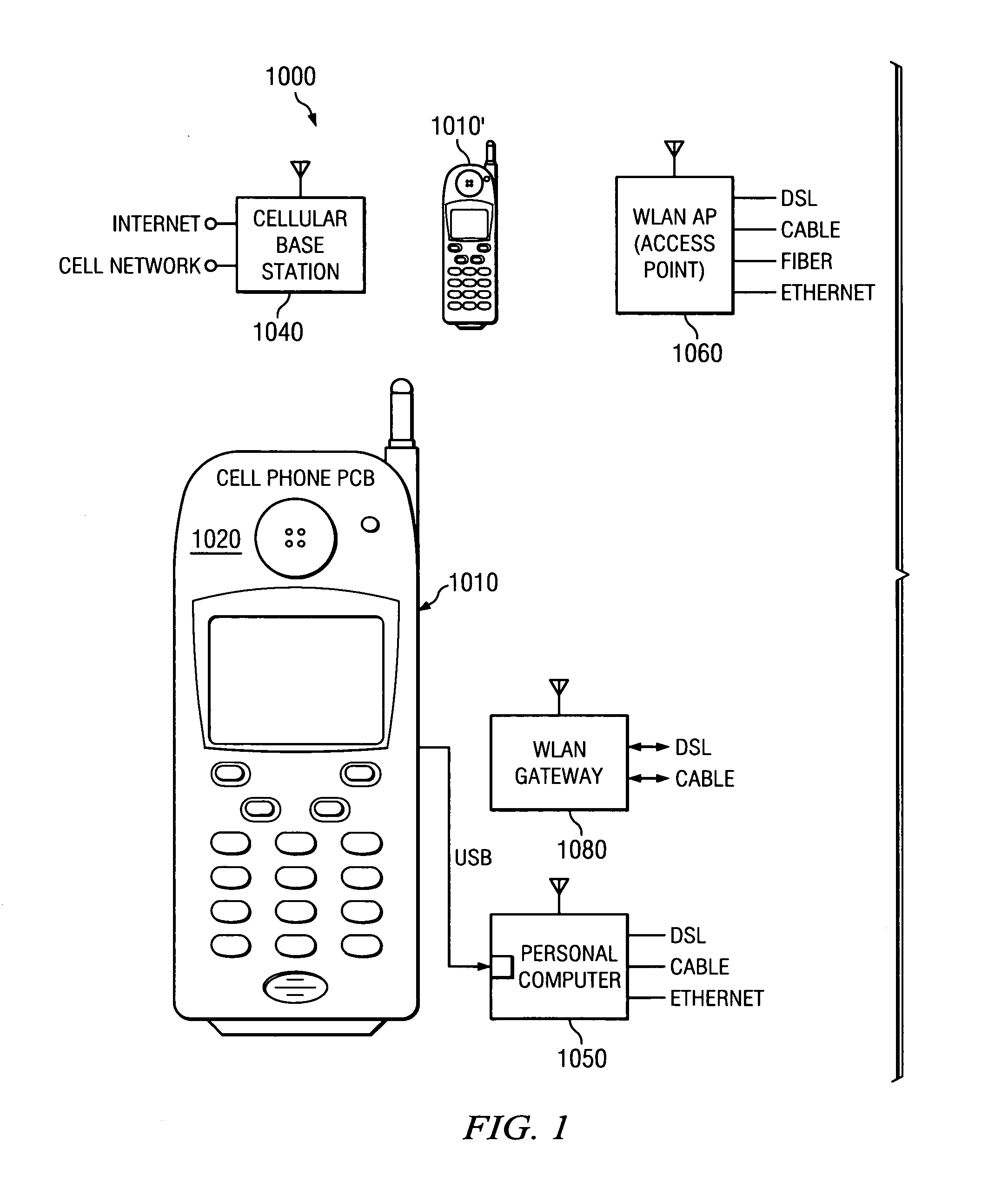

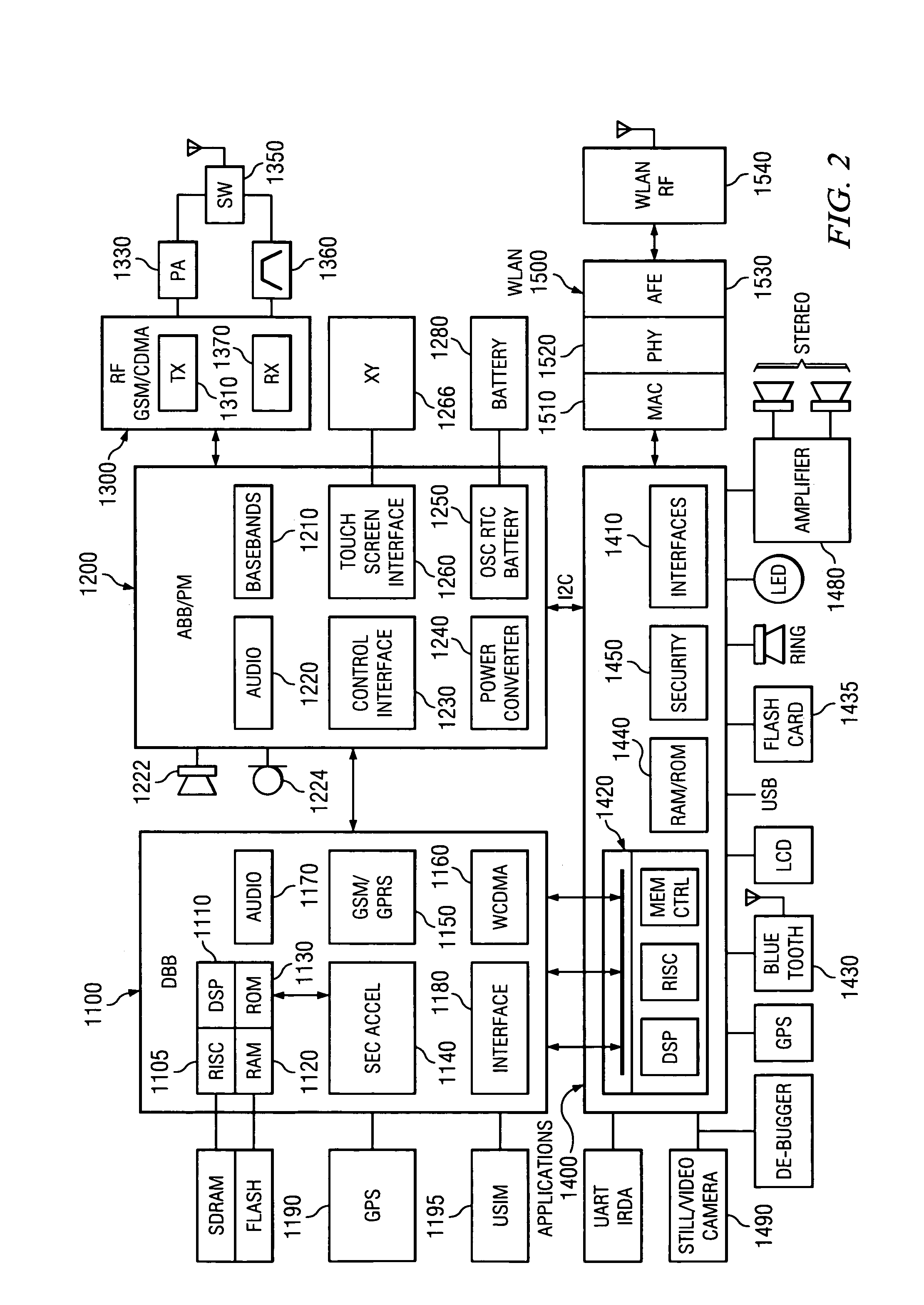

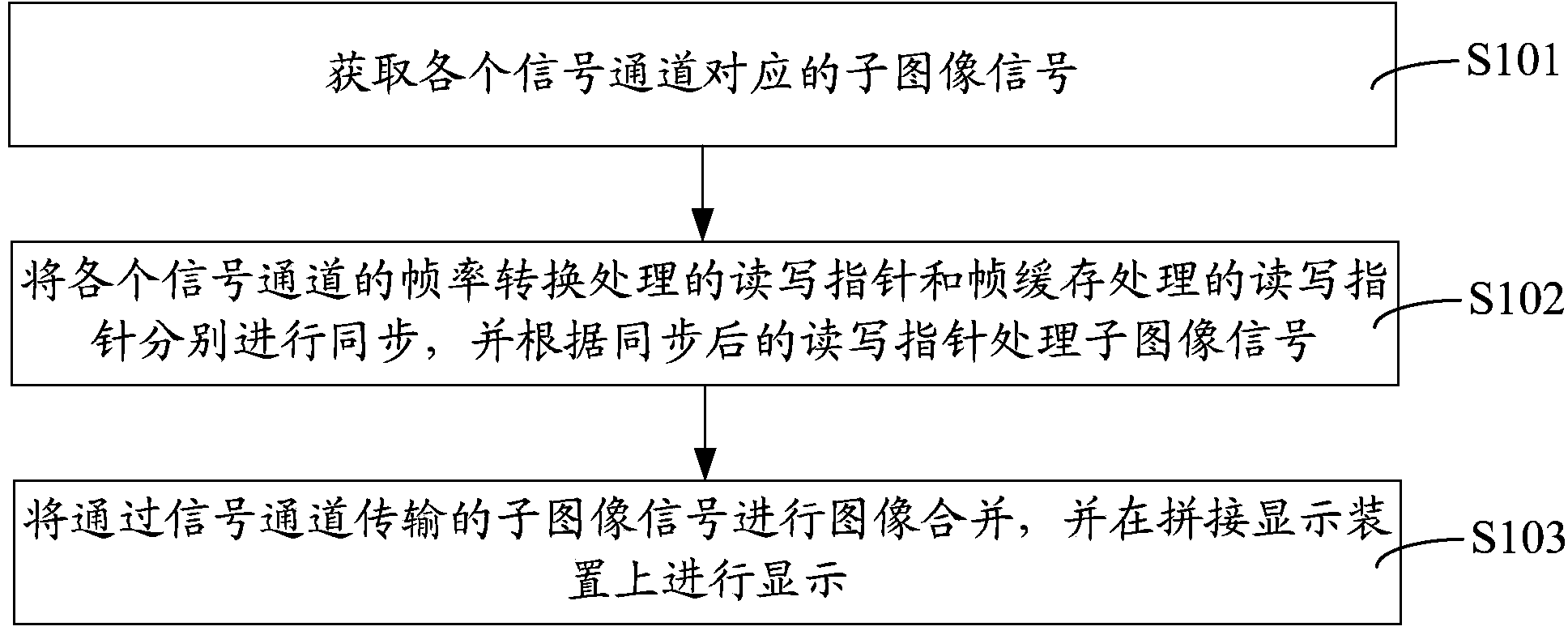

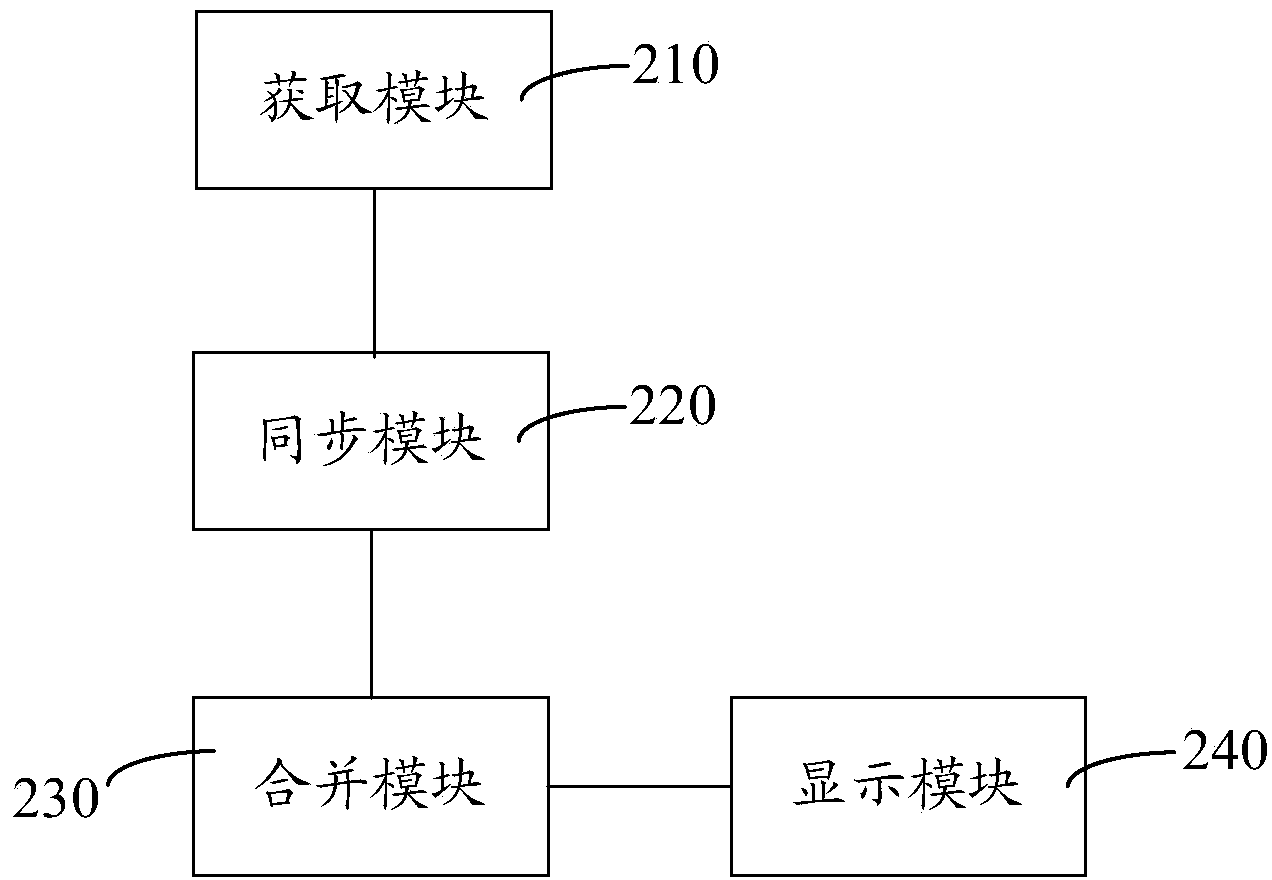

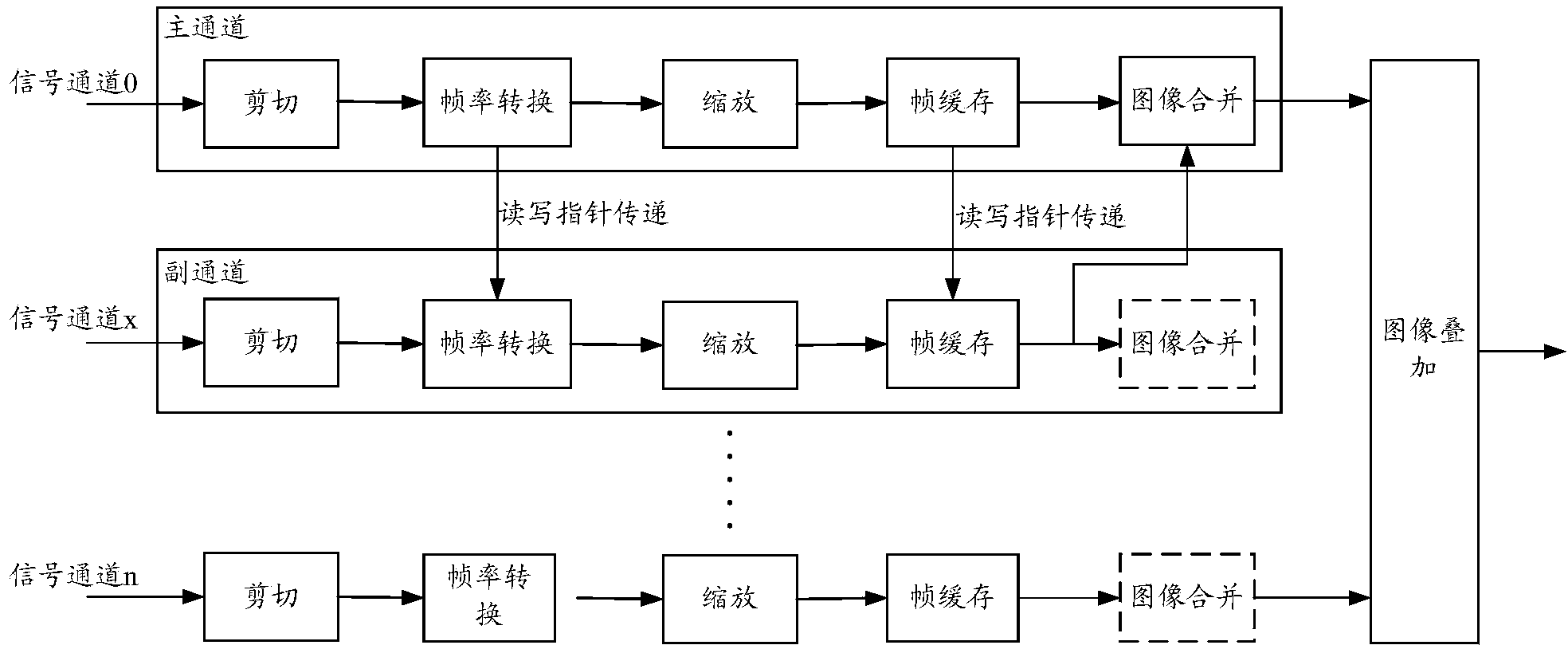

Method and system for synchronously displaying images with UHD resolution ratio

ActiveCN103595896ARealize synchronous displayTroubleshoot out-of-sync issuesTelevision system detailsColor television detailsImage resolutionDisplay device

The invention provides a method and system for synchronously displaying images with the UHD resolution ratio. The method includes the first step of obtaining subimage signals corresponding to signal channels, wherein the subimage signals are image signals obtained through segmentation of image signals, requiring to be displayed, with the UHD resolution ratio, the second step of carrying out synchronization on read-write pointers, subjected to frame rate conversion processing, of the signal channels and read-write pointers, subjected to frame buffer processing, of the signal channels, and processing the subimage signals according to the synchronized read-write pointers, and the third step of carrying out image merging on the processed subimage signals of the signal channels and carrying out display on a tiled display device. Through the method and system, the synchronous display of the images with the UHD resolution ratio is achieved, and cost is reduced.

Owner:GUANGDONG VTRON TECH CO LTD