Patents

Literature

154 results about "Scratch pad" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

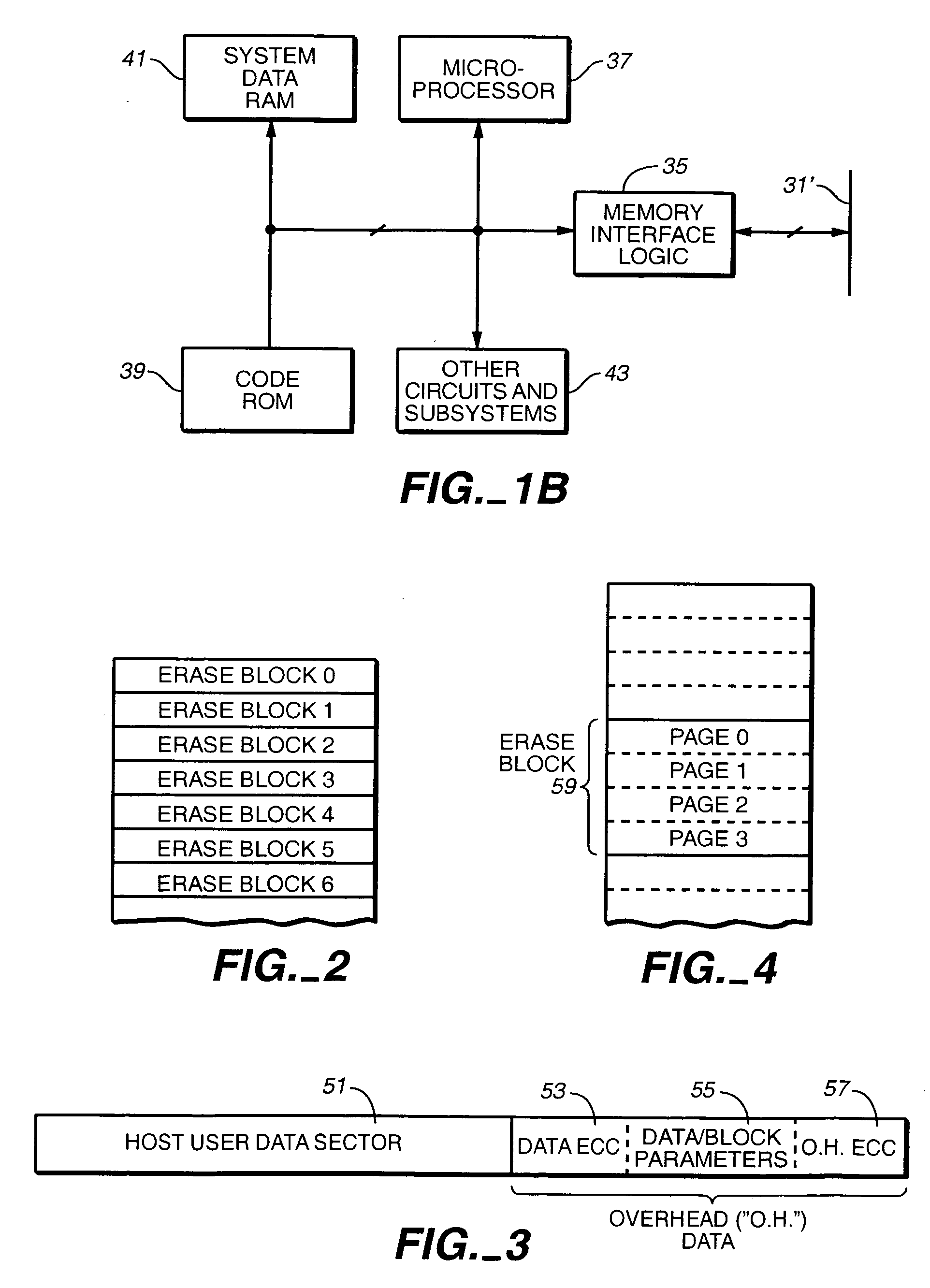

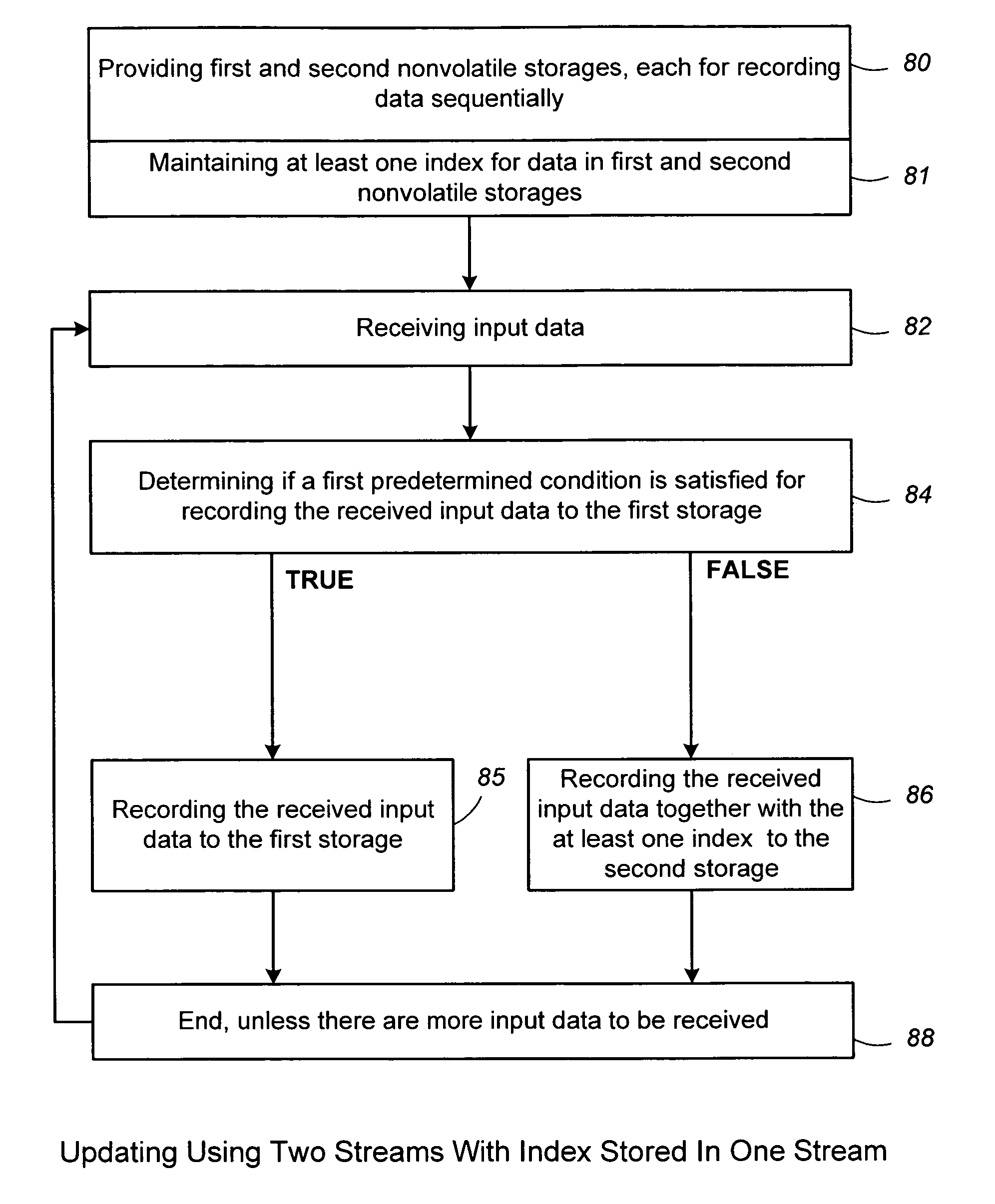

Non-volatile memory and method with improved indexing for scratch pad and update blocks

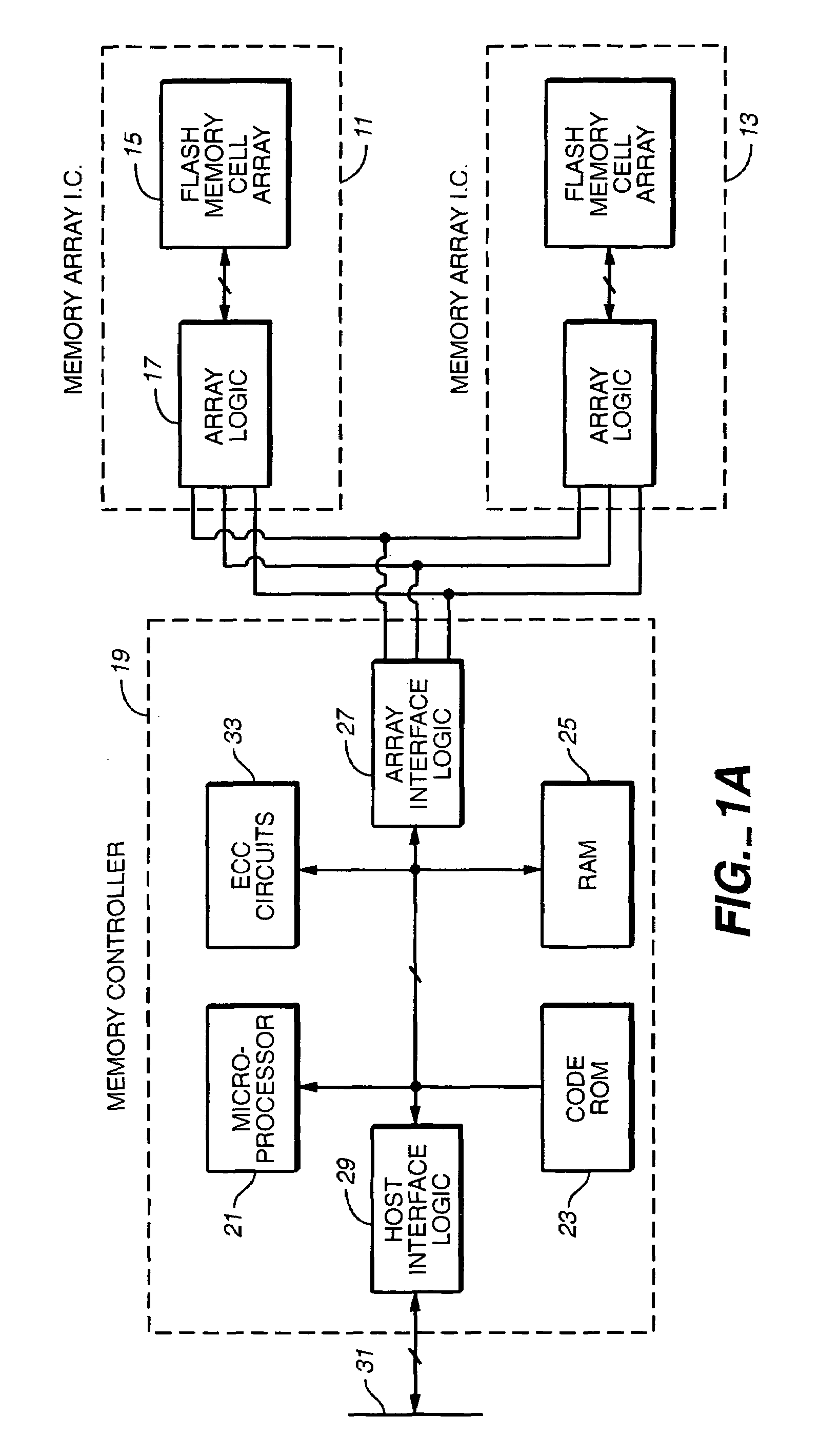

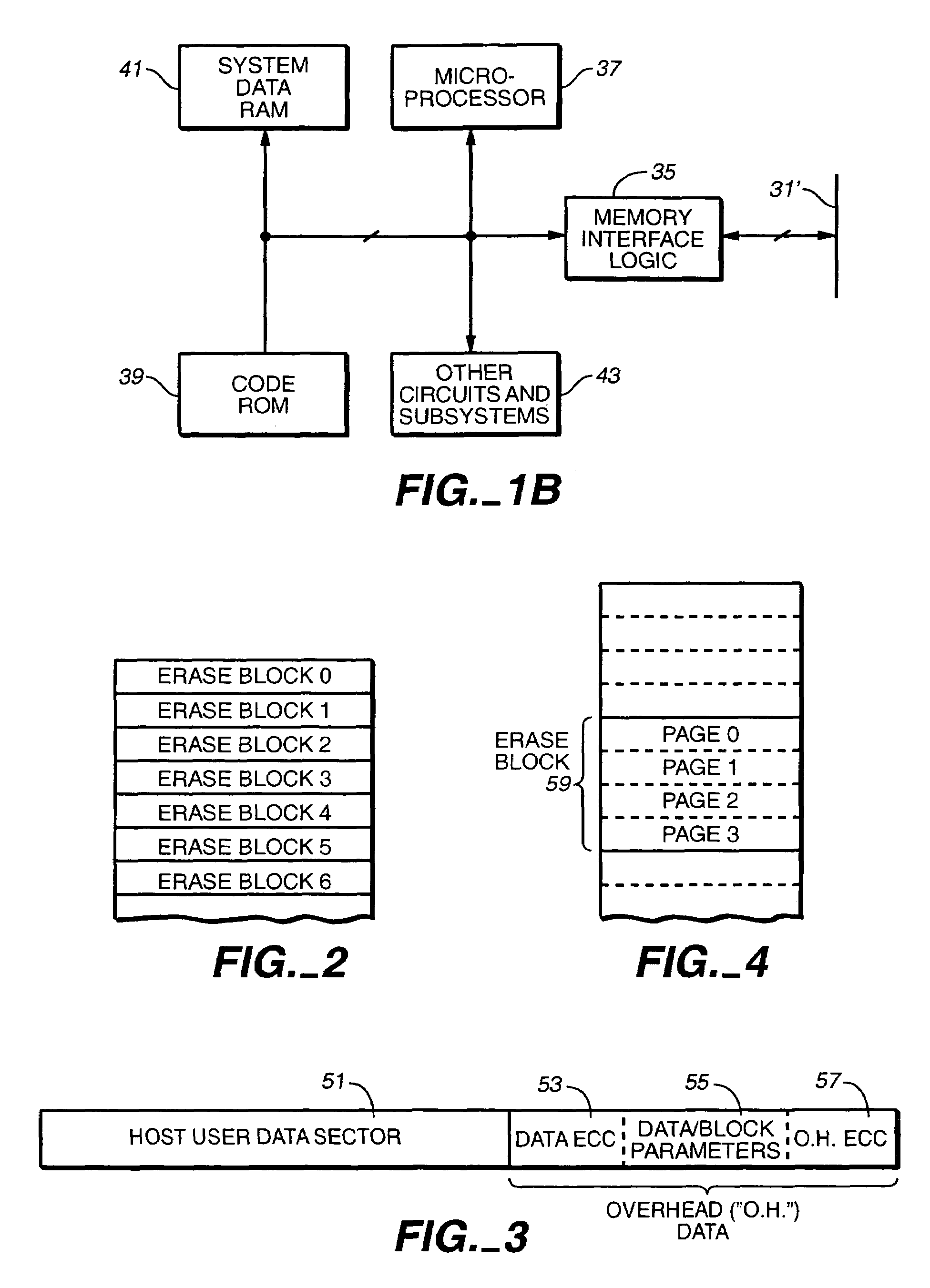

InactiveUS20060155922A1Efficient use ofMemory architecture accessing/allocationMemory adressing/allocation/relocationData storingData store

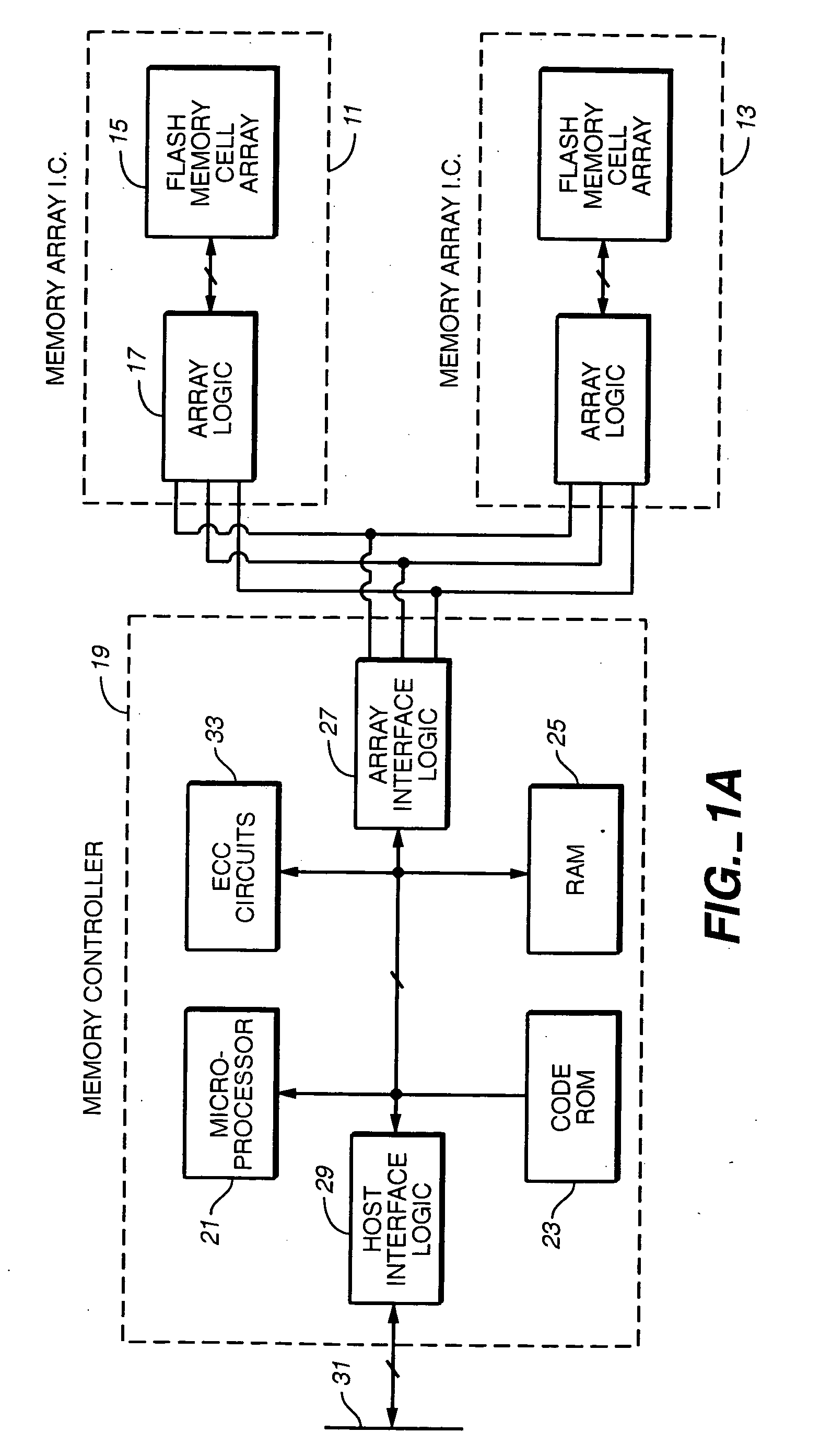

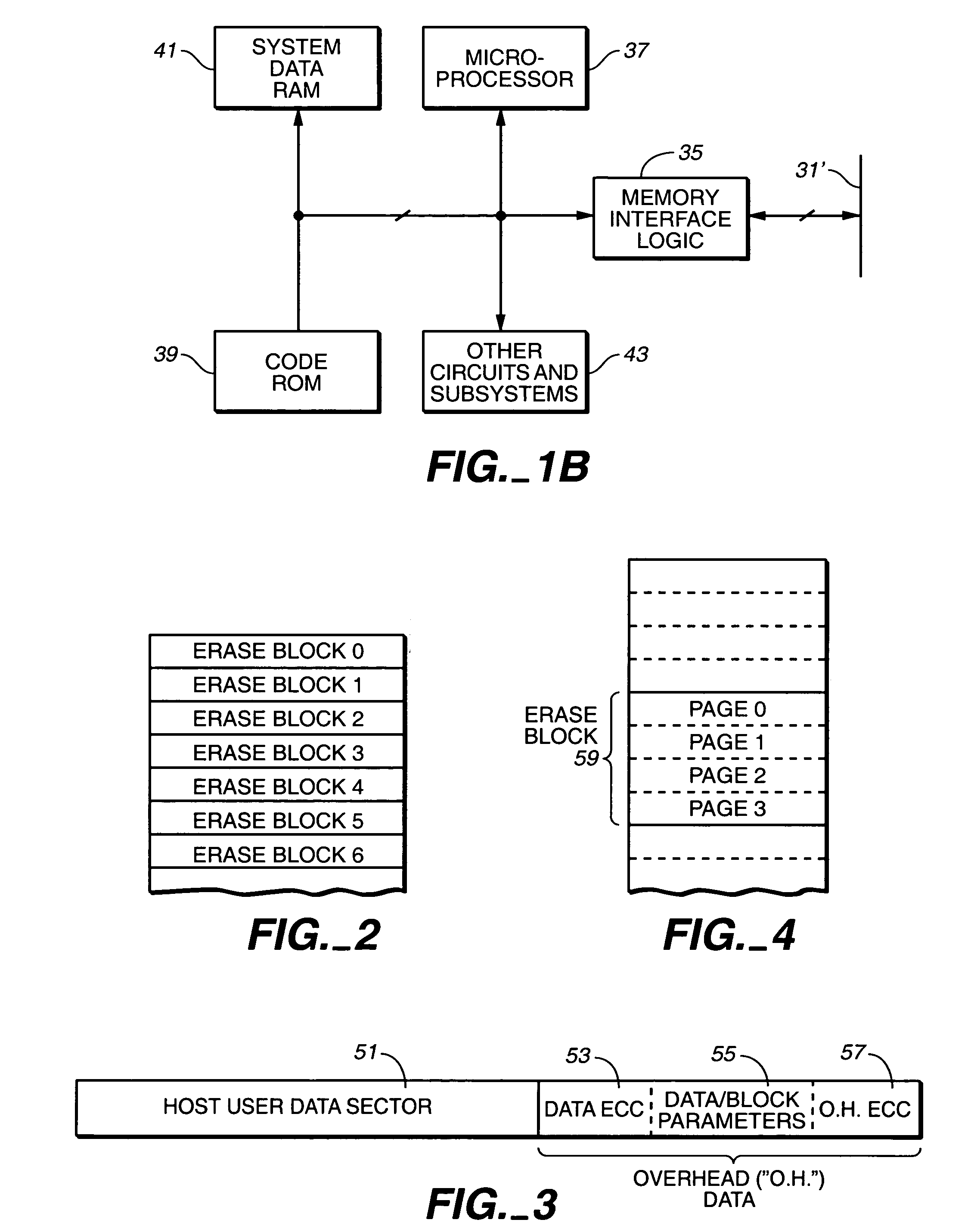

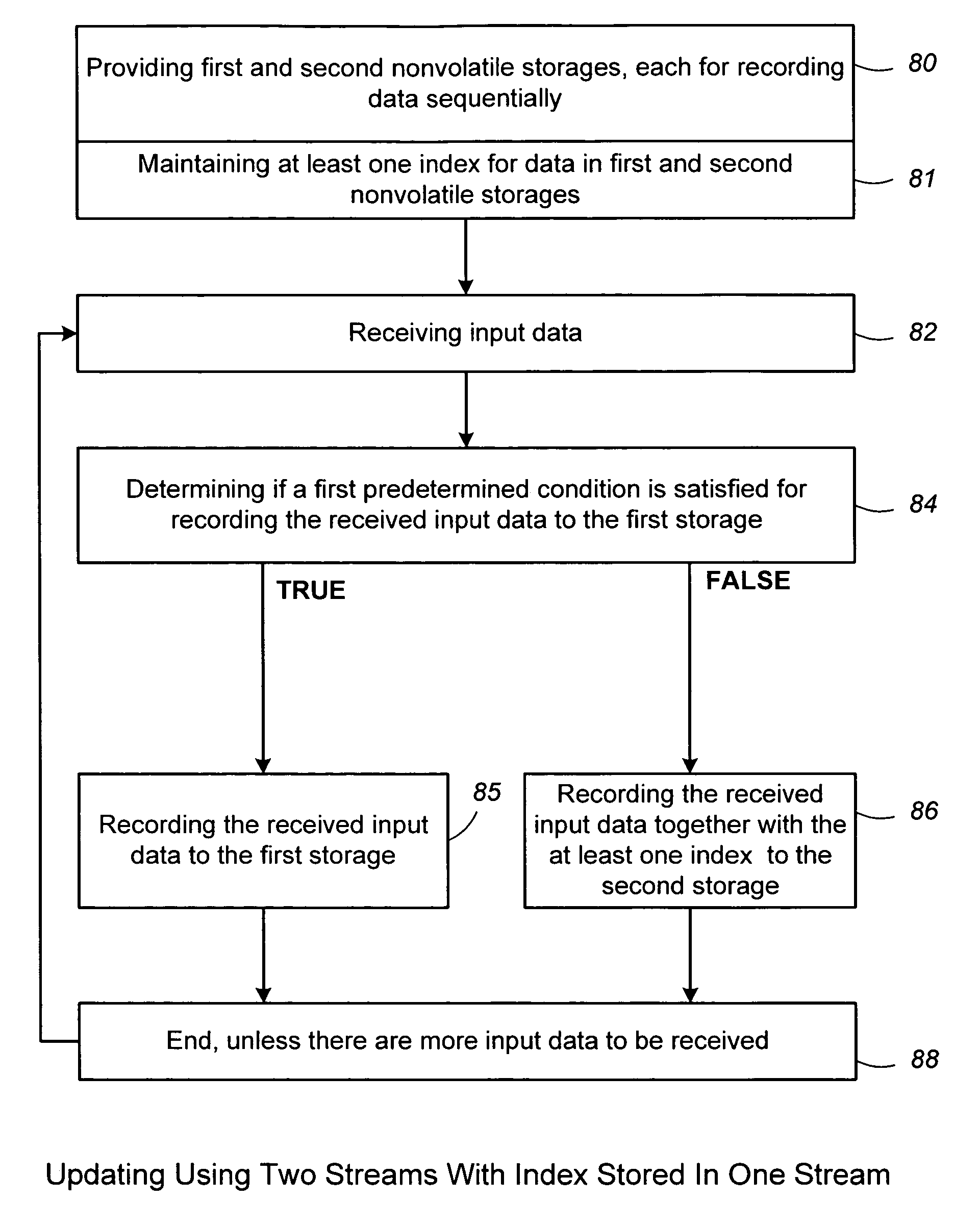

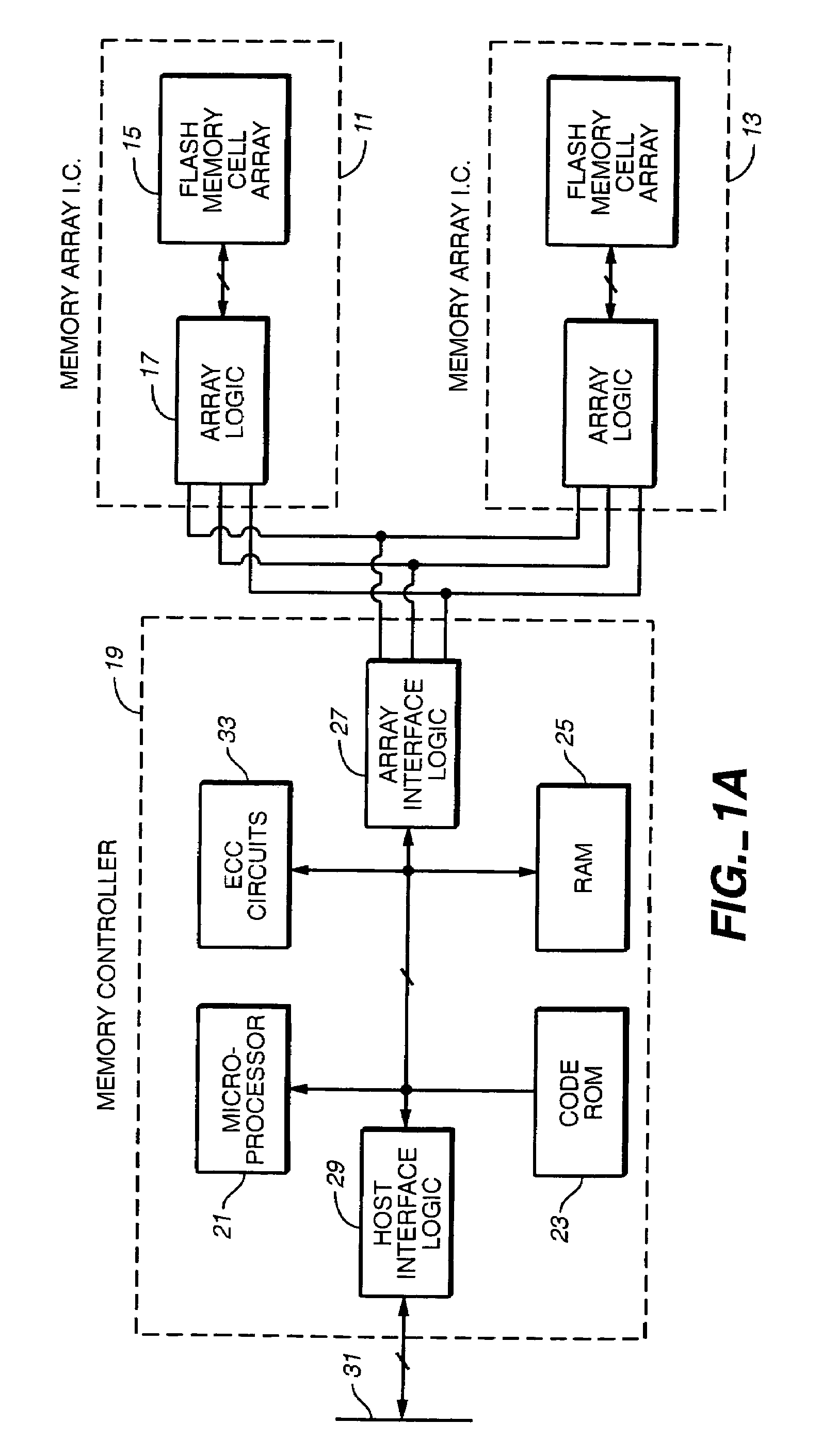

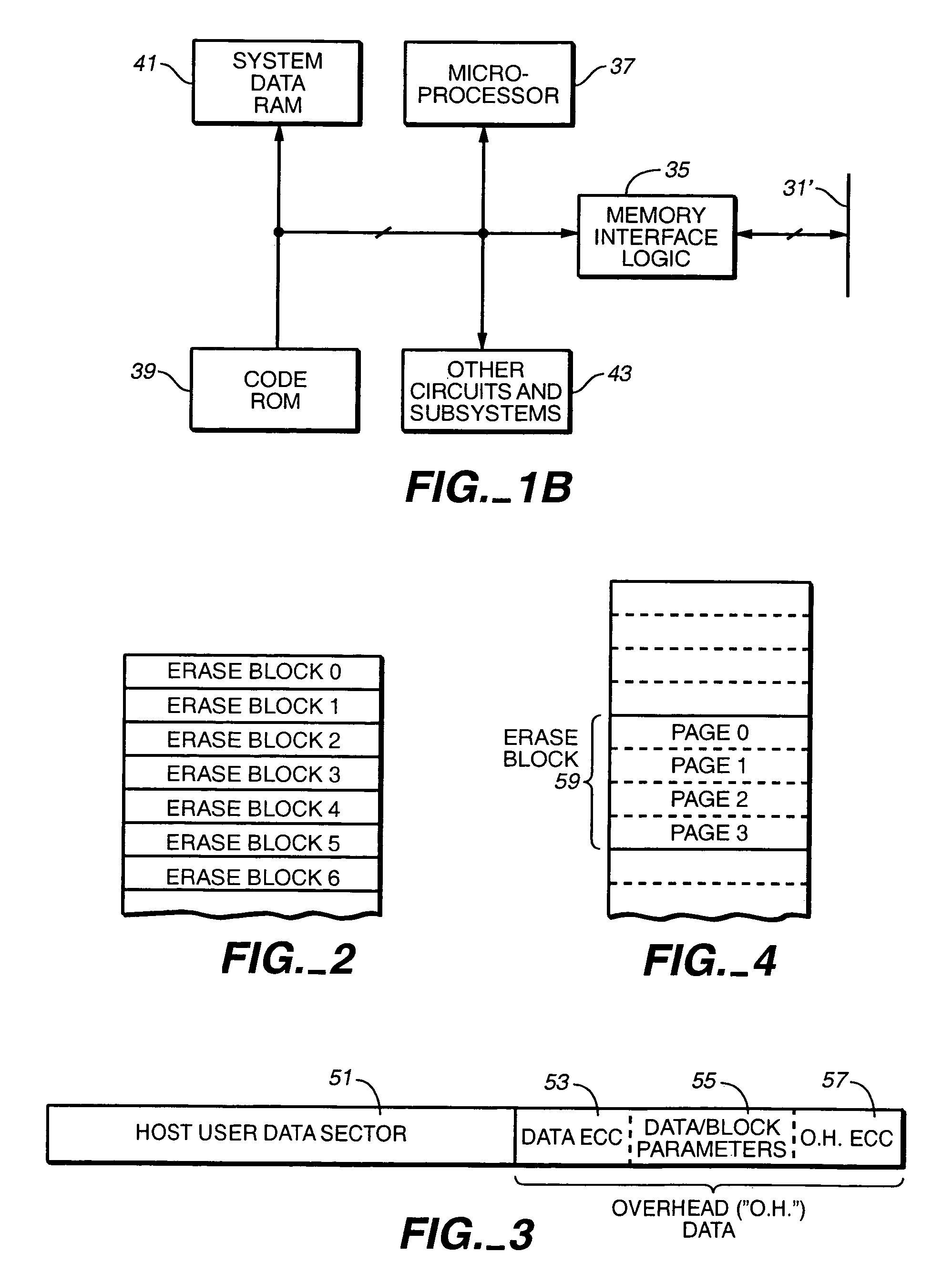

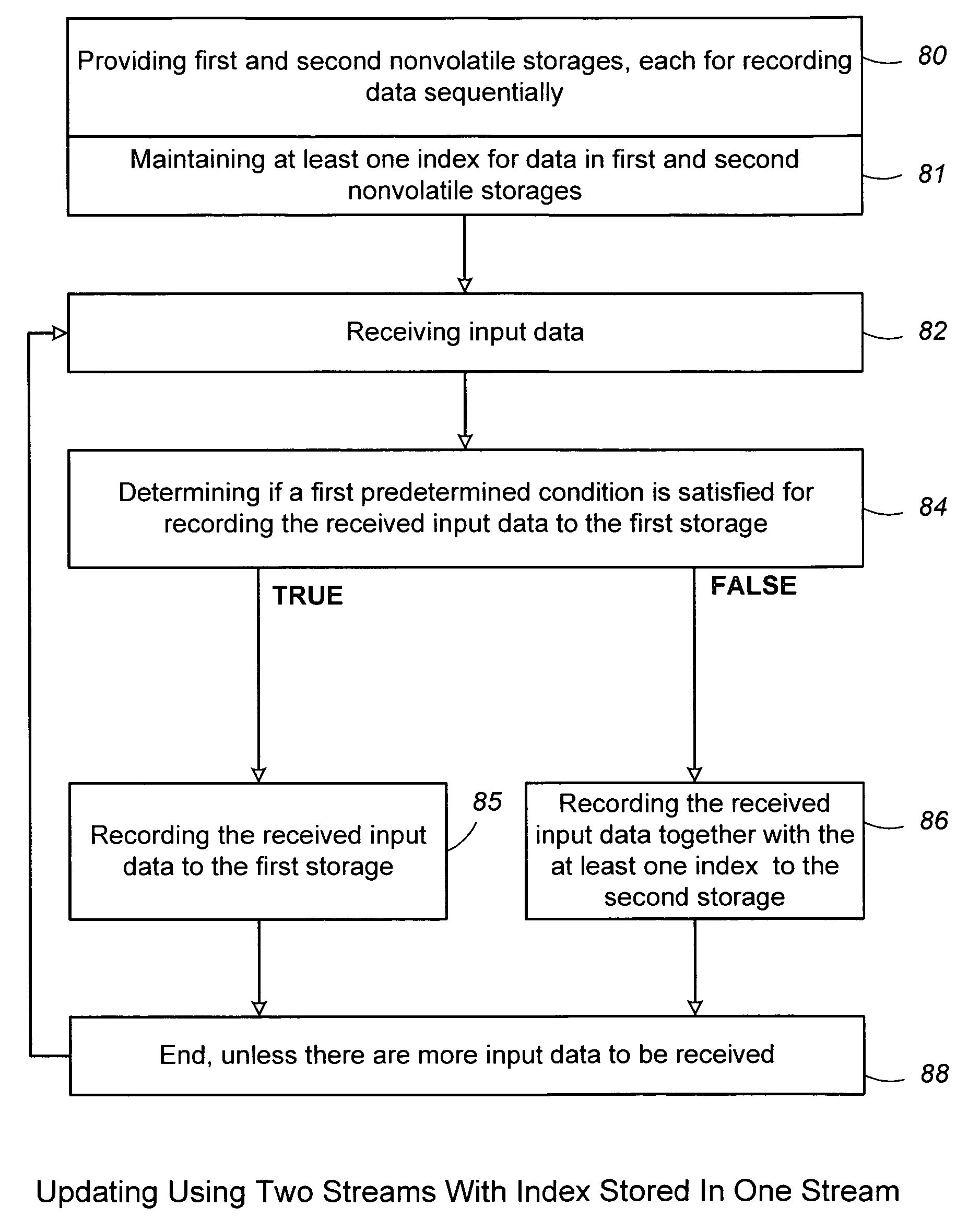

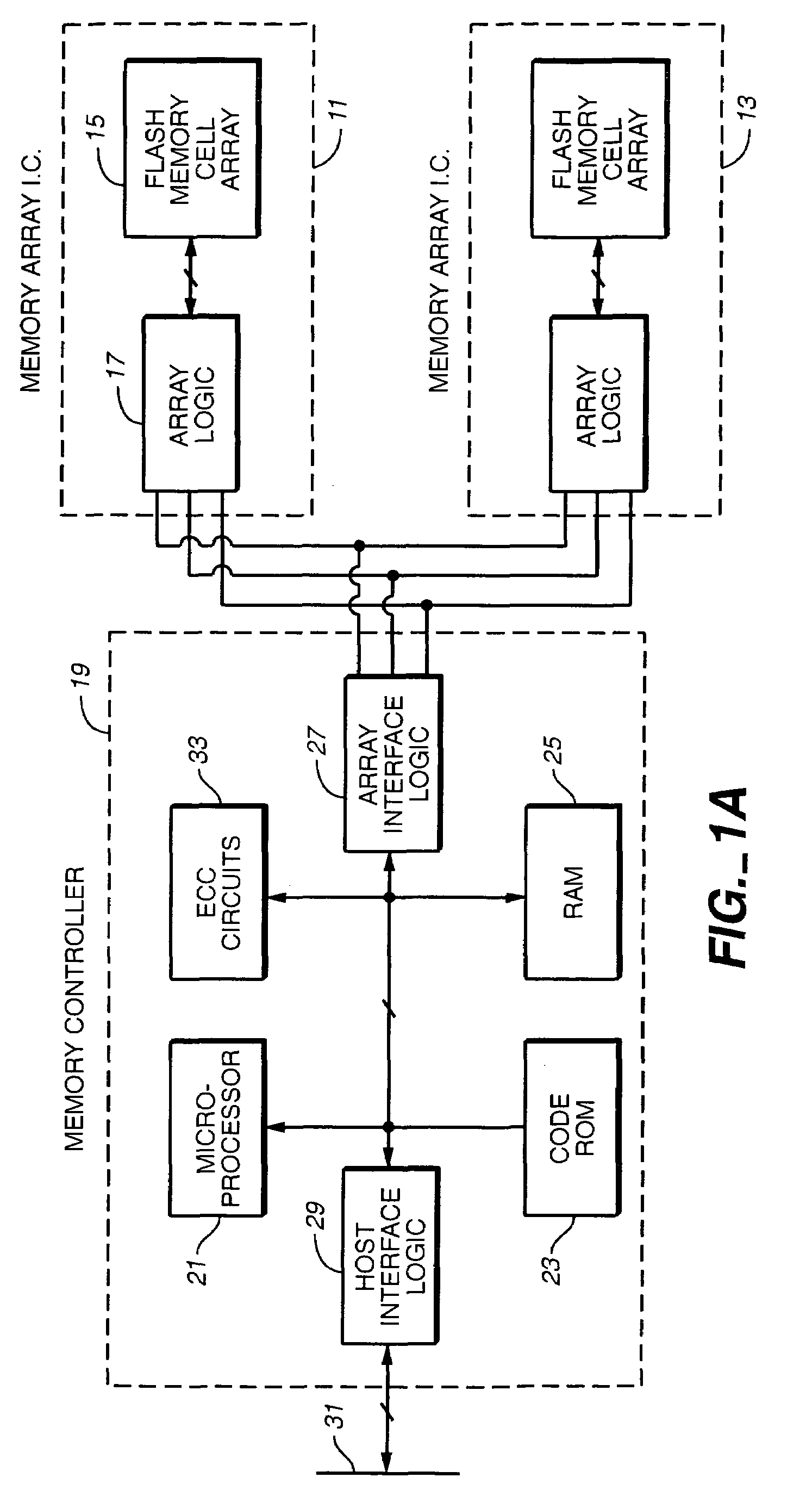

Update data to a non-volatile memory may be recorded in at least two interleaving streams such as either into an update block or a scratch pad block depending on a predetermined condition. The scratch pad block is used to buffered update data that are ultimately destined for the update block. In a preferred embodiment, an index of the data stored in the scratch pad block as well that stored in the update block is saved in an unused portion of the scratch pad block every time the scratch pad block is written to.

Owner:SANDISK TECH LLC

Non-volatile memory and method with multi-stream update tracking

ActiveUS20060155921A1Improve performanceWrite efficientlyMemory architecture accessing/allocationRead-only memoriesData streamMulti stream

Update data to a non-volatile memory may be recorded in at least two interleaving streams such as either into an update block or a scratch pad block depending on a predetermined condition. The scratch pad block is used to buffered update data that are ultimately destined for the update block. Synchronization information about the order recording of updates among the streams is saved with at least one of the streams. This will allow the most recently written version of data that may exist on multiple memory blocks to be identified. In one embodiment, the synchronization information is saved in a first block and is a write pointer that points to the next recording location in a second block. In another embodiment, the synchronization information is a time stamp.

Owner:SANDISK TECH LLC

Non-volatile memory and method with multi-stream updating

ActiveUS20060155920A1Improve performanceWrite efficientlyMemory architecture accessing/allocationRead-only memoriesMulti streamData recording

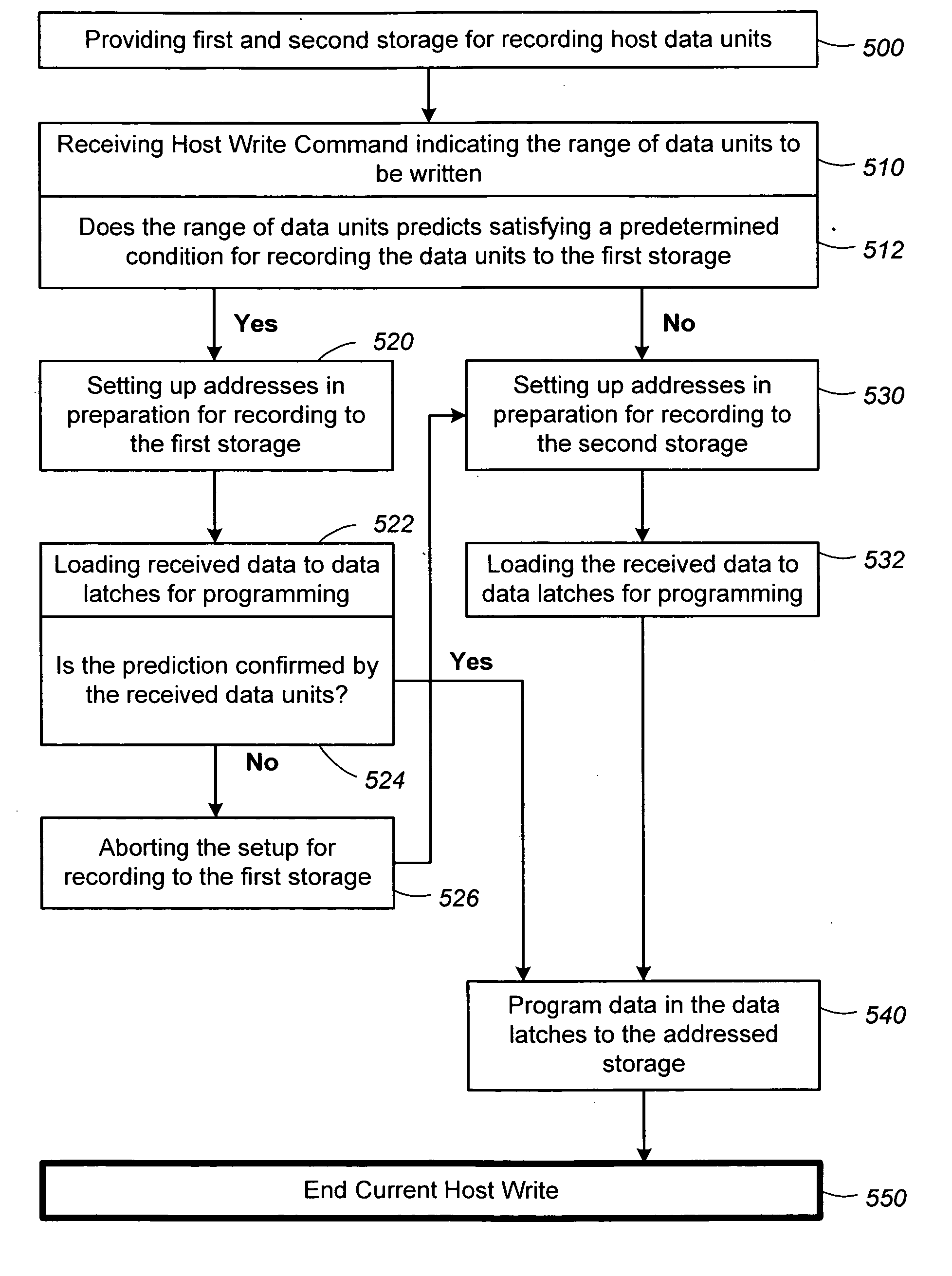

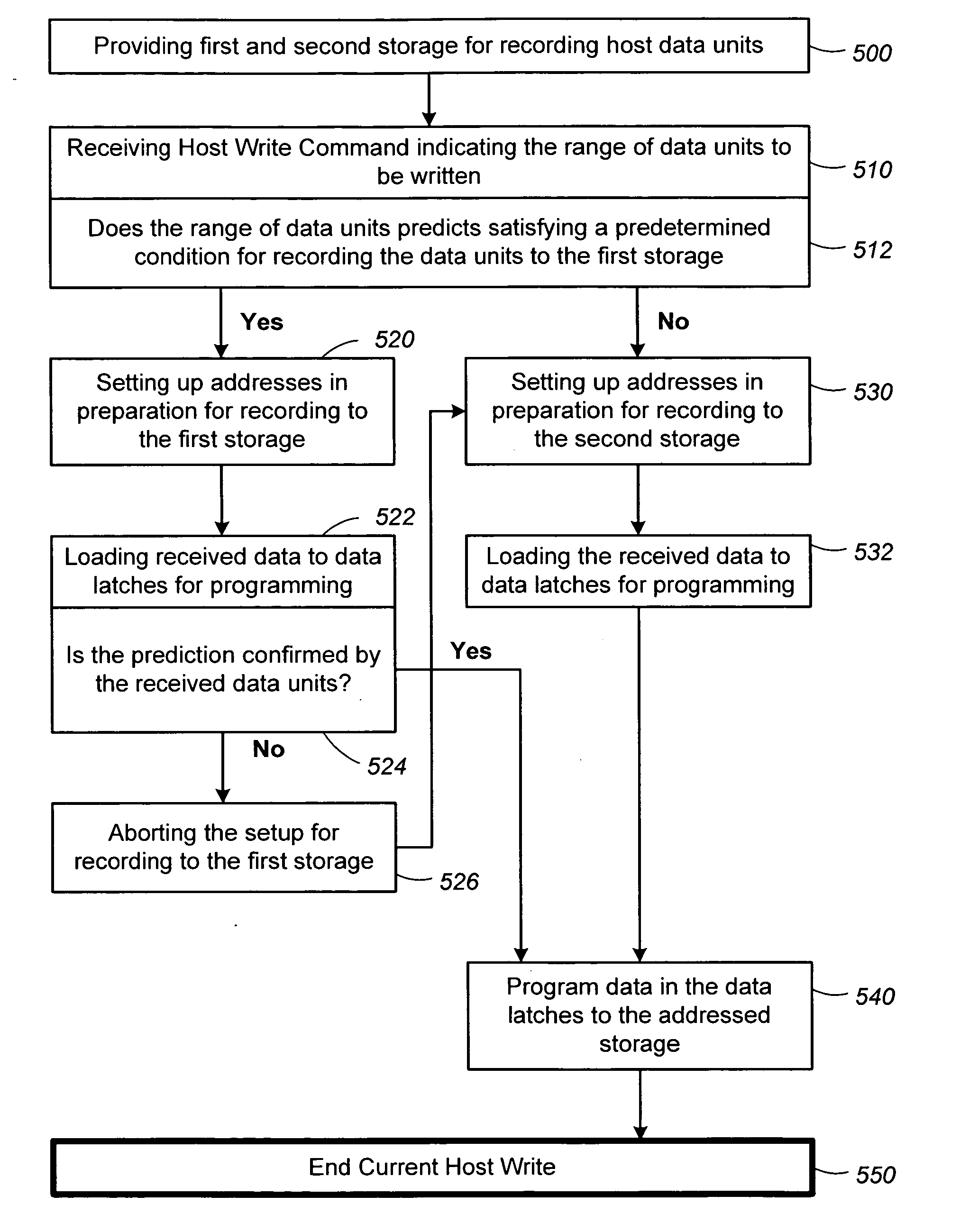

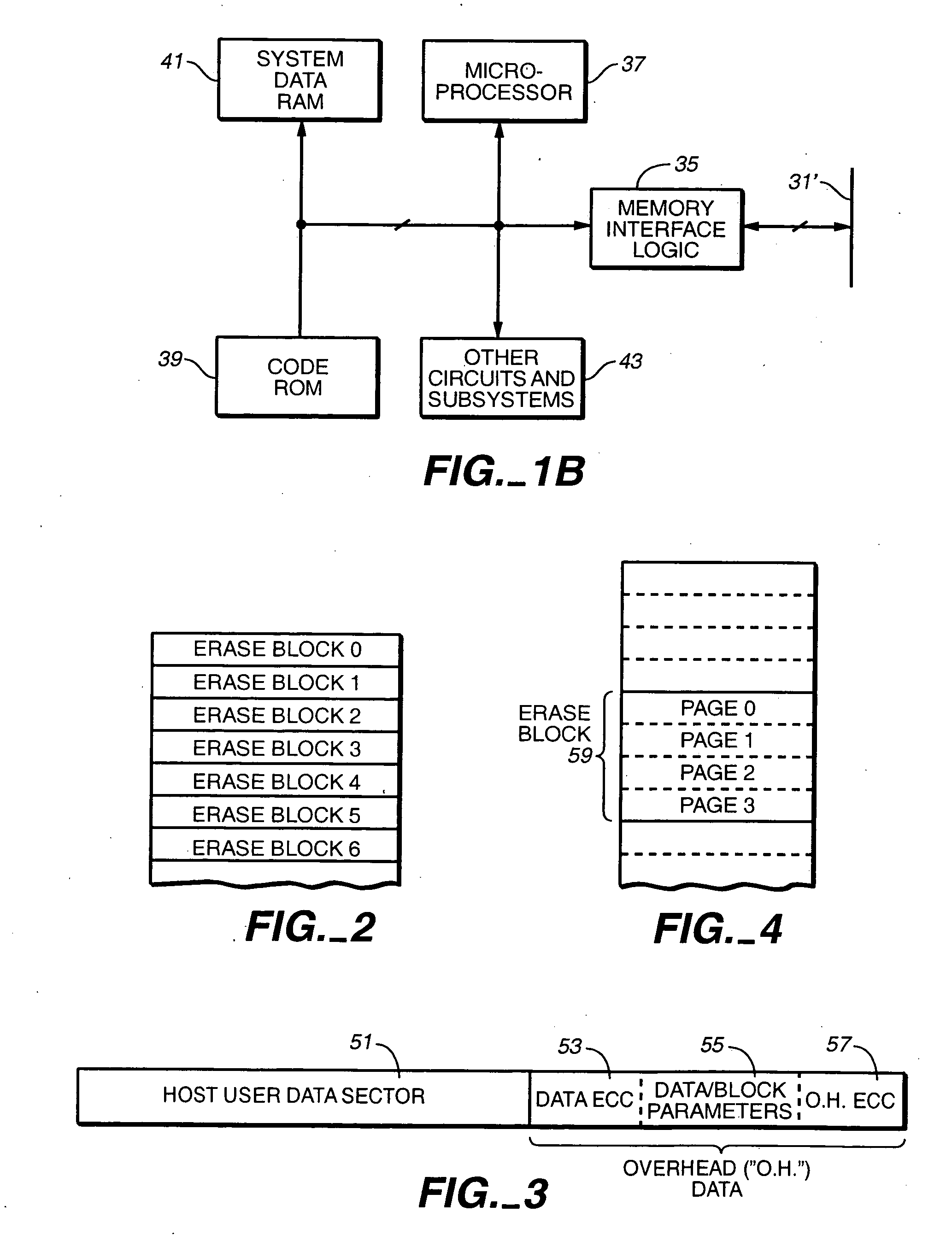

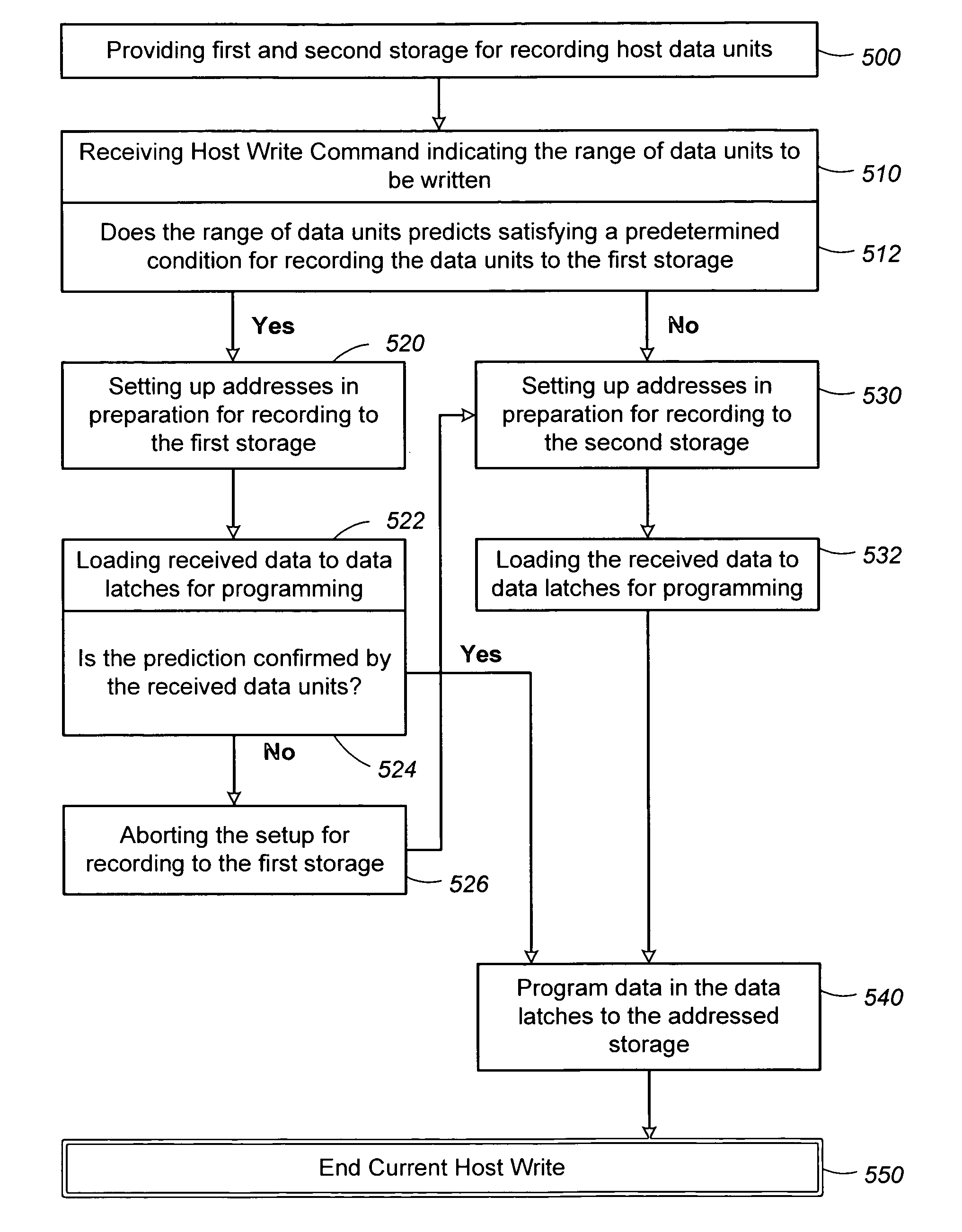

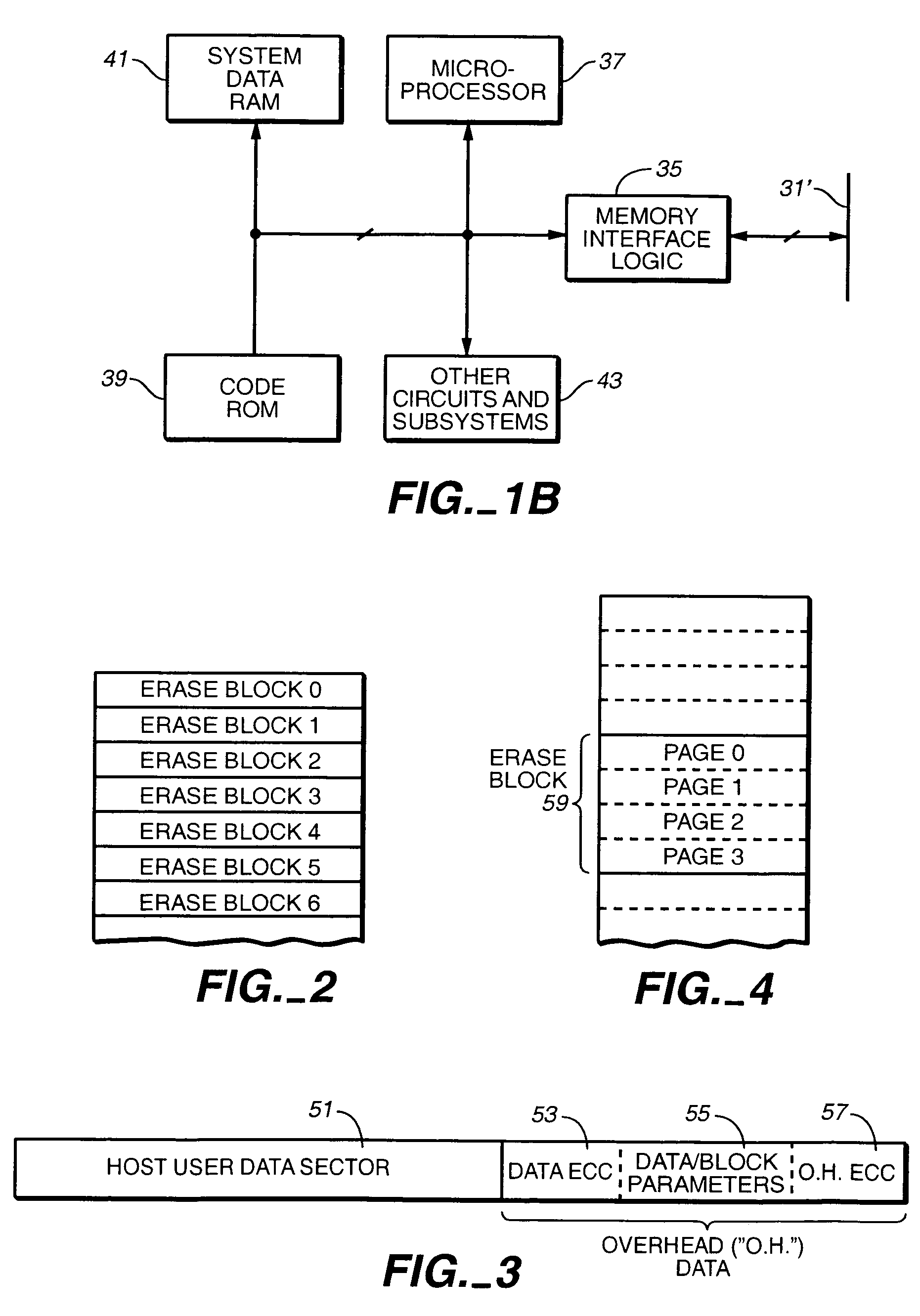

In a memory that is programmable page by page and each page having multiple sectors that are once-programmable, even if successive writes are sequential, the data recorded to an update block may be fragmented and non-sequential. Instead of recording update data to an update block, the data is being recorded in at least two interleaving streams. When a full page of data is available, it is recorded to the update block. Otherwise, it is temporarily recorded to the scratch pad block until a full page of data becomes available to be transferred to the update block. Preferably, a pipeline operation allows the recording to the update block to be set up as soon as the host write command indicates a full page could be written. If the actual write data is incomplete due to interruptions, the setup will be canceled and recording is made to the scratch pad block instead.

Owner:SANDISK TECH LLC

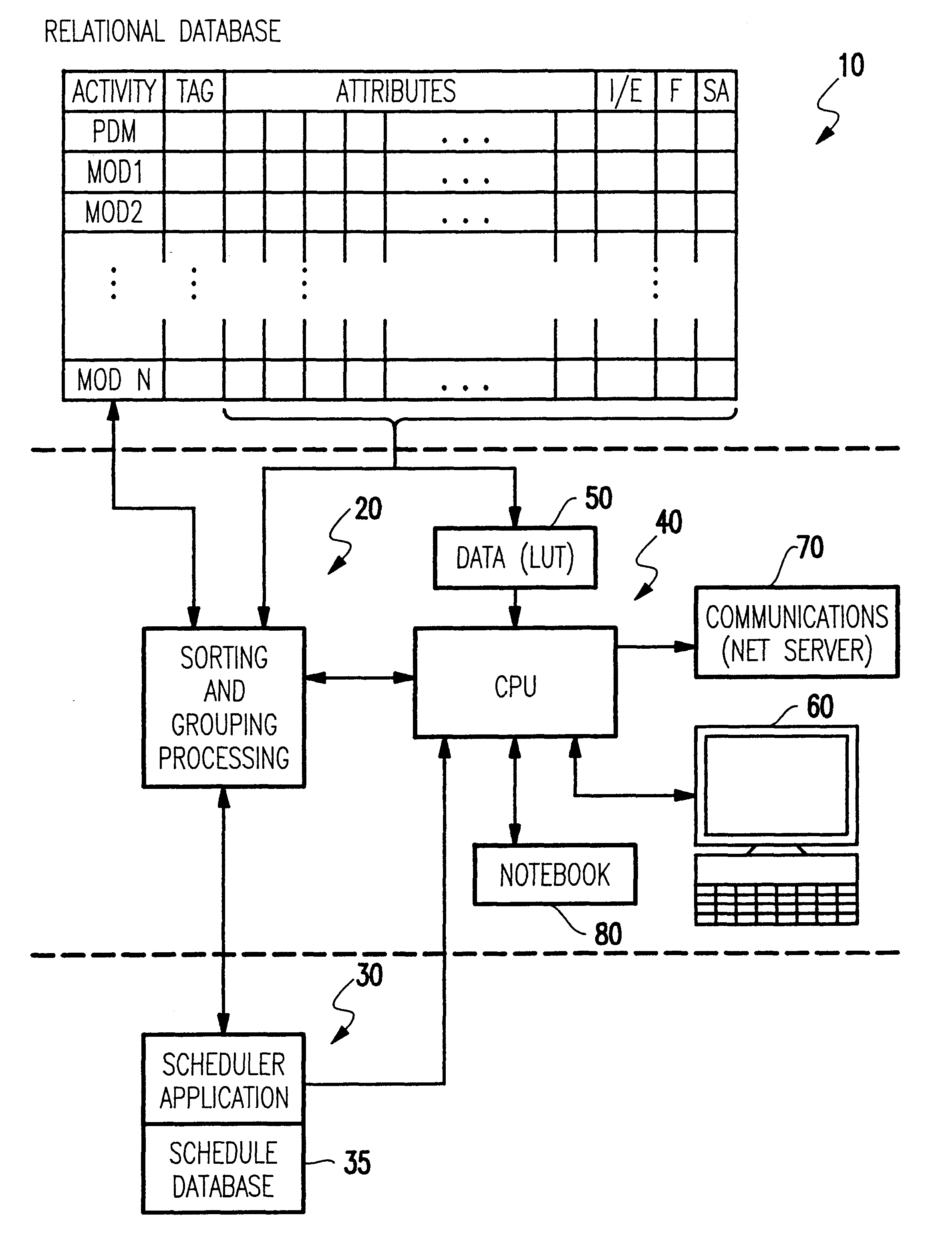

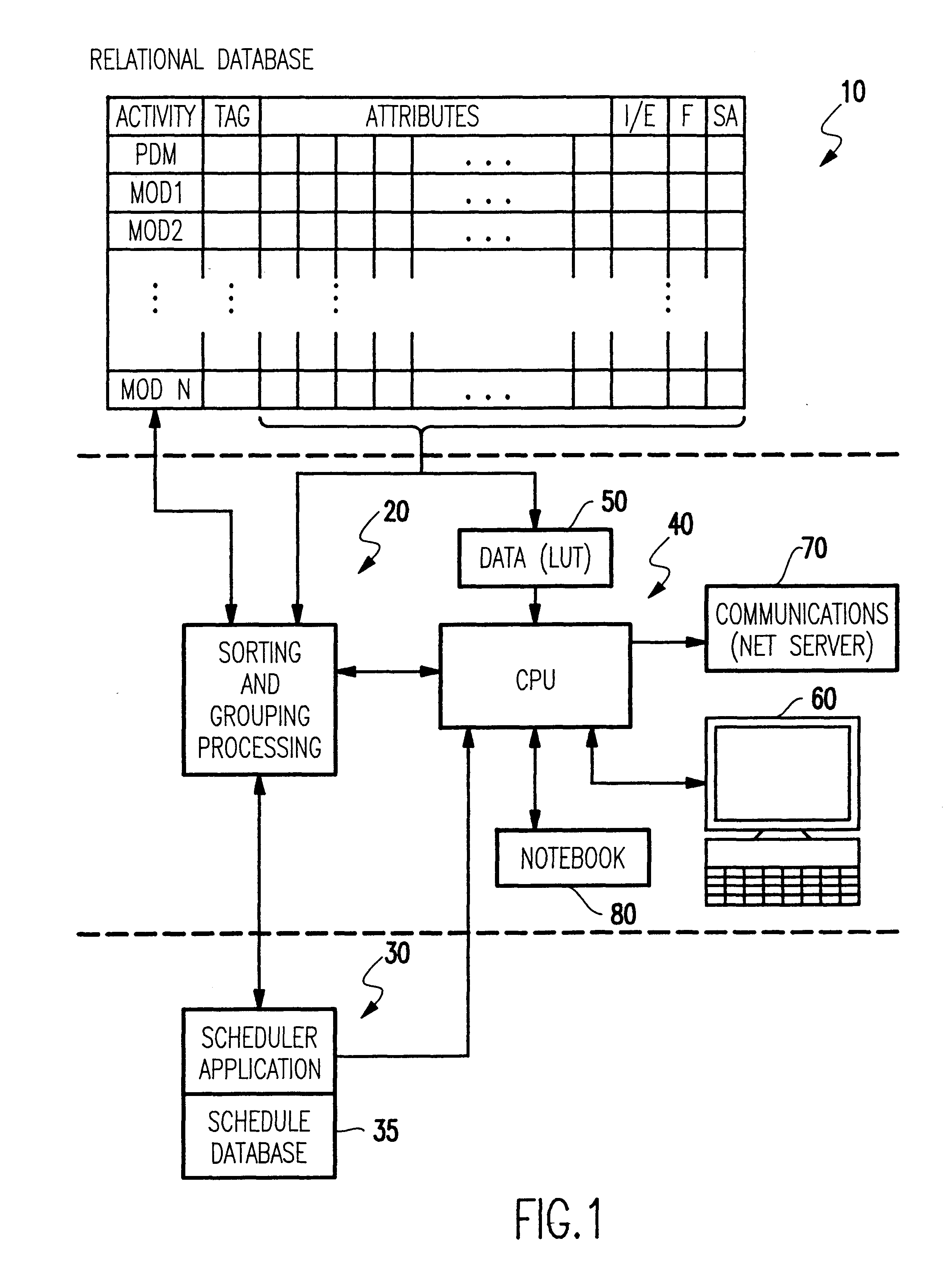

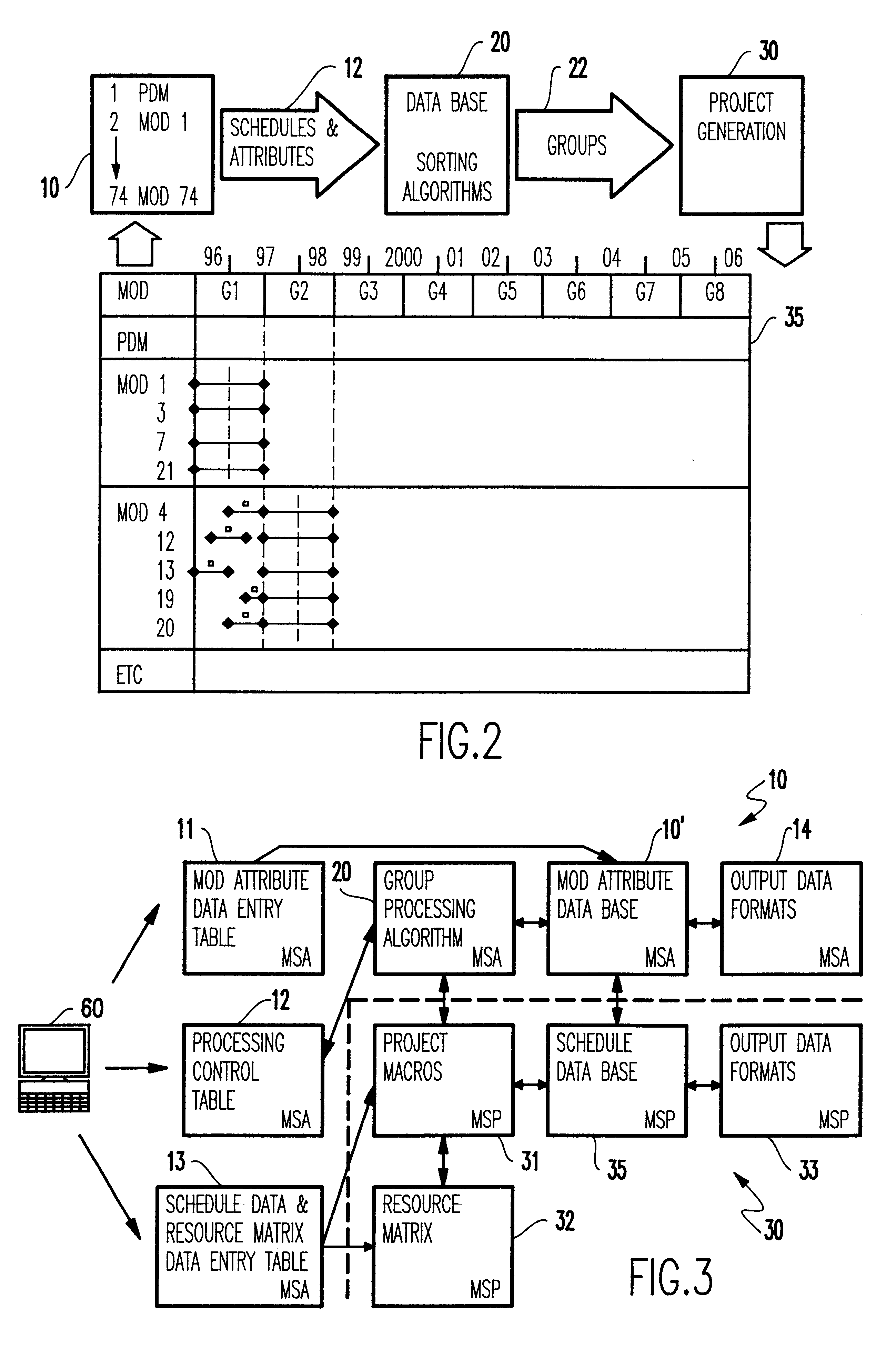

Program planning management system

InactiveUS6609100B2ResourcesSpecial data processing applicationsProgram managementRelational database

A data processing system provides development of complex schedule plans under user control by using sorting and grouping processing to interface between a relational database and a scheduler application. The sorting and grouping processing provides for user-interactive editing of data in the database by presentation of groupings of activities developed in accordance with attributes of the activities concurrently with activities which are not included in a group. Editing of the group based on the presentation of other activities allows the user to apply acquired knowledge and understanding of the subtleties and dynamics of the activities and to make business decisions which therefore do not need to be represented in the scheduler application. Changes to data in the database are logged in a notebook or scratch-pad store so that data may be returned to its original or any prior state.

Owner:LOCKHEED MARTIN CORP

Scratch pad block

ActiveUS7315916B2Improve performanceWrite efficientlyMemory architecture accessing/allocationRead-only memoriesHigh densityHigh velocity

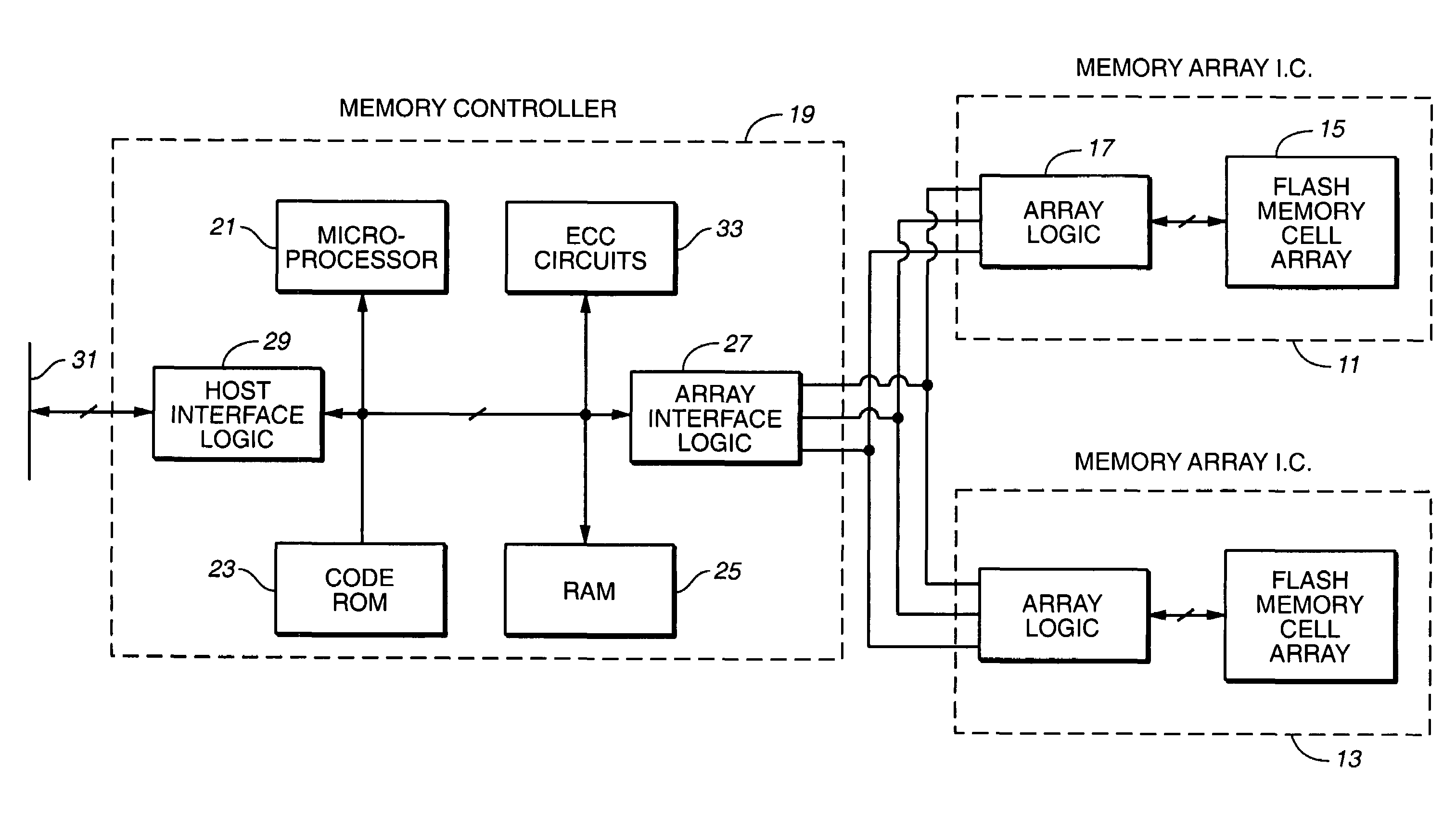

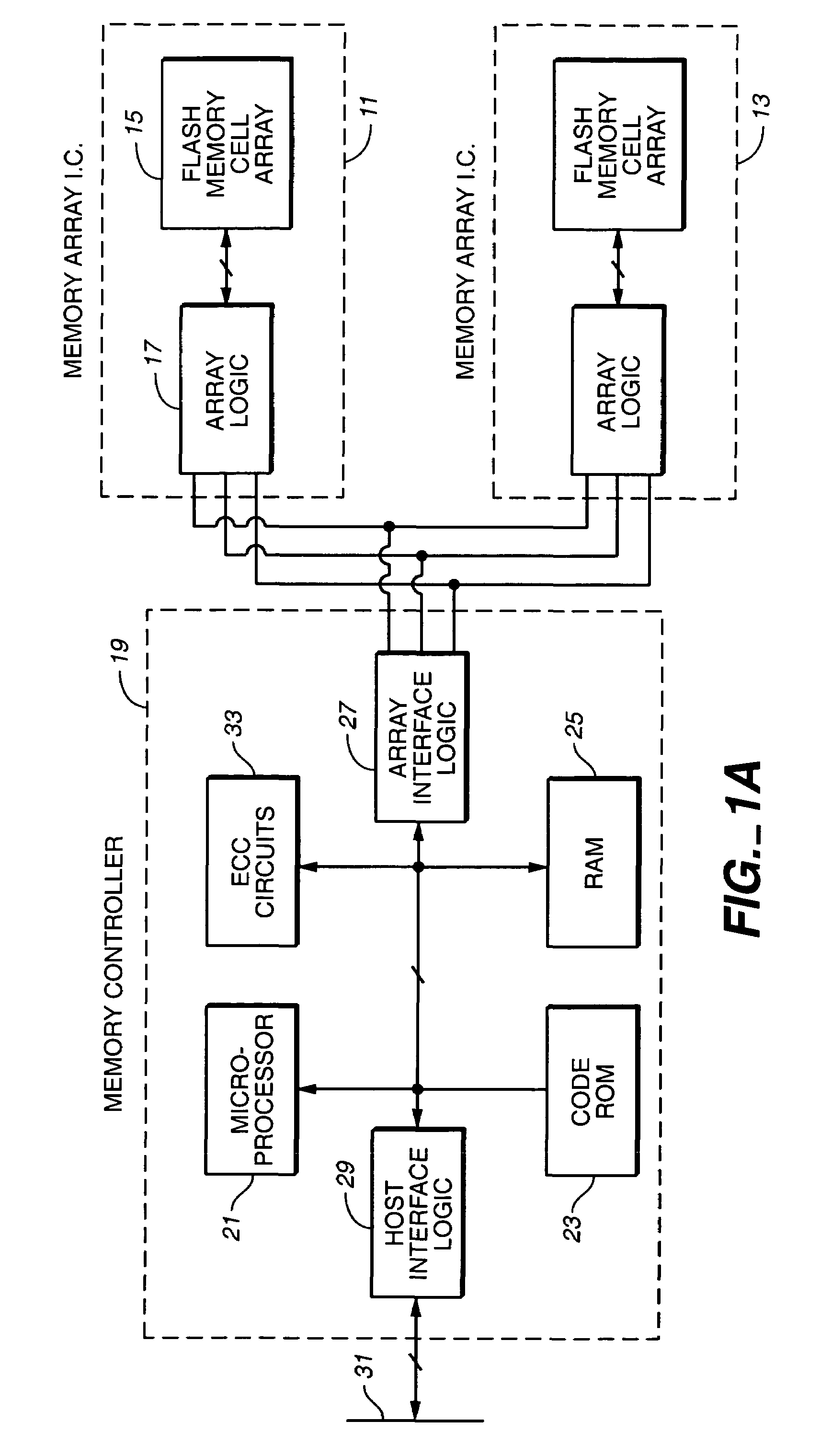

In a memory array having a minimum unit of erase of a block, a scratch pad block is used to store data that is later written to another block. The data may be written to the scratch pad block with a low degree of parallelism and later written to another location with a high degree of parallelism so that it is stored with high density. Data may be temporarily stored in the scratch pad block until it can be more efficiently stored elsewhere. This may be when some other data is received. Unrelated data may be stored in the same page of a scratch pad block.

Owner:SANDISK TECH LLC

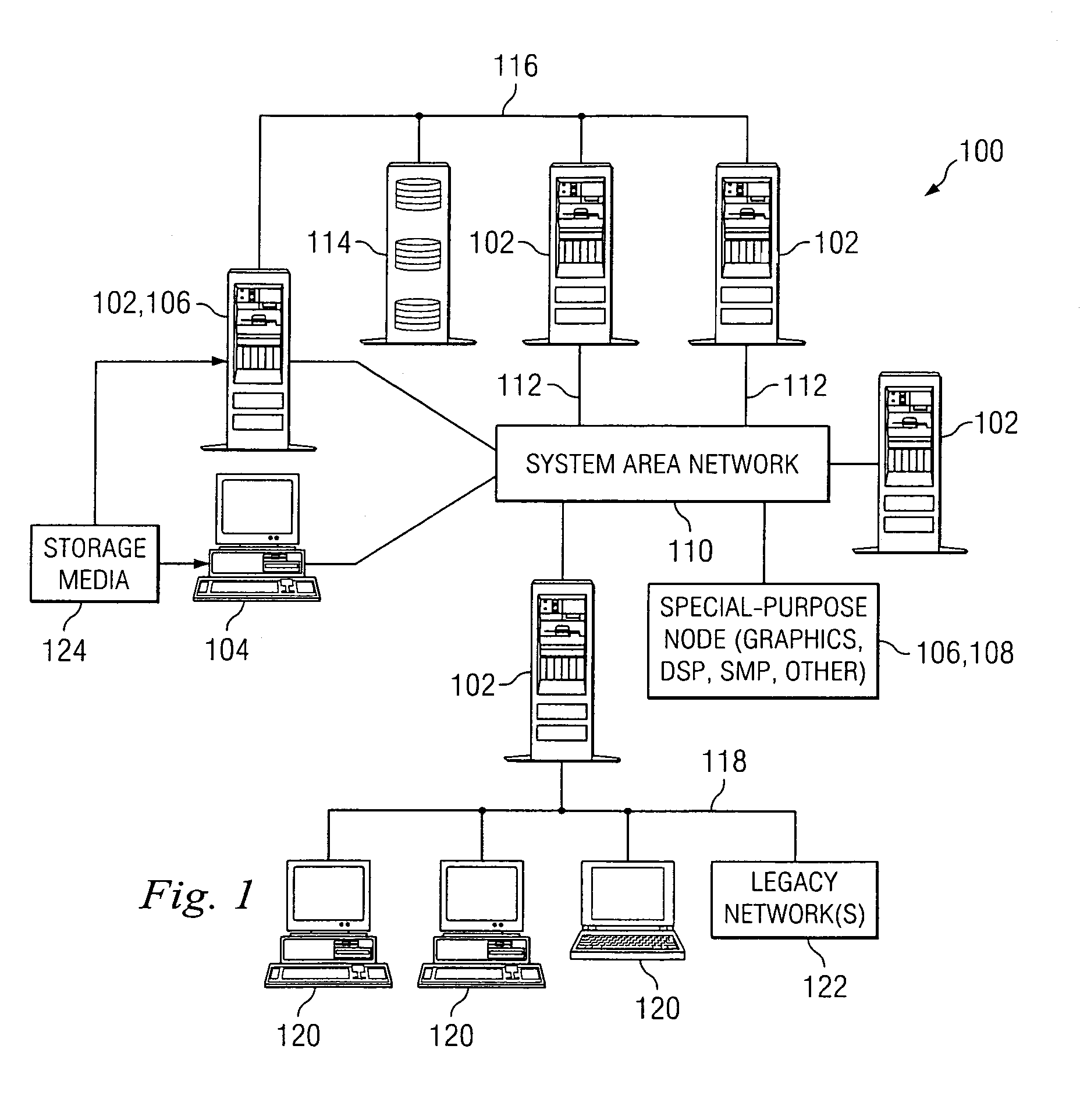

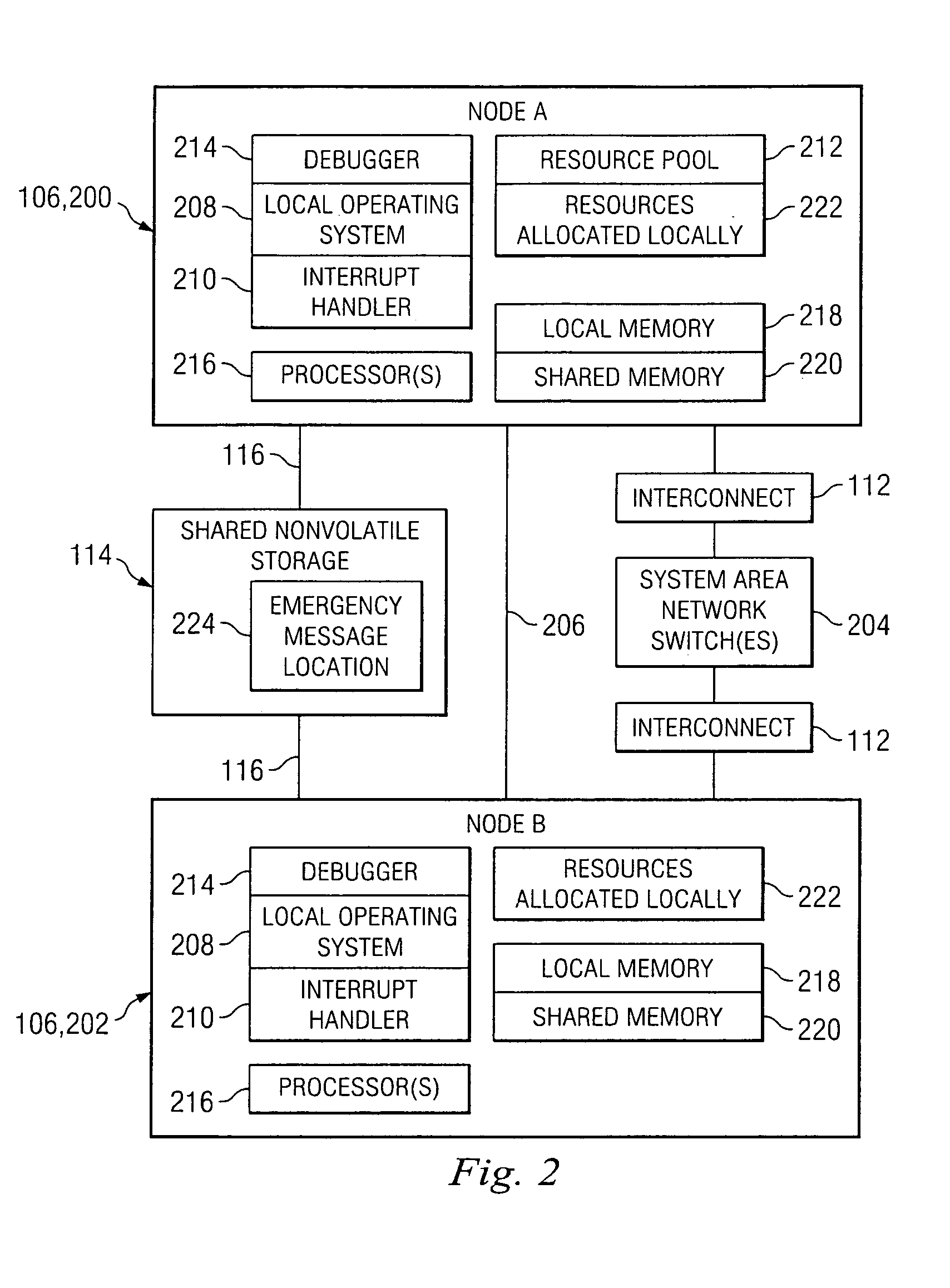

Method for detecting and resolving a partition condition in a cluster

InactiveUS6965936B1Error detection/correctionMultiple digital computer combinationsComputer clusterTheoretical computer science

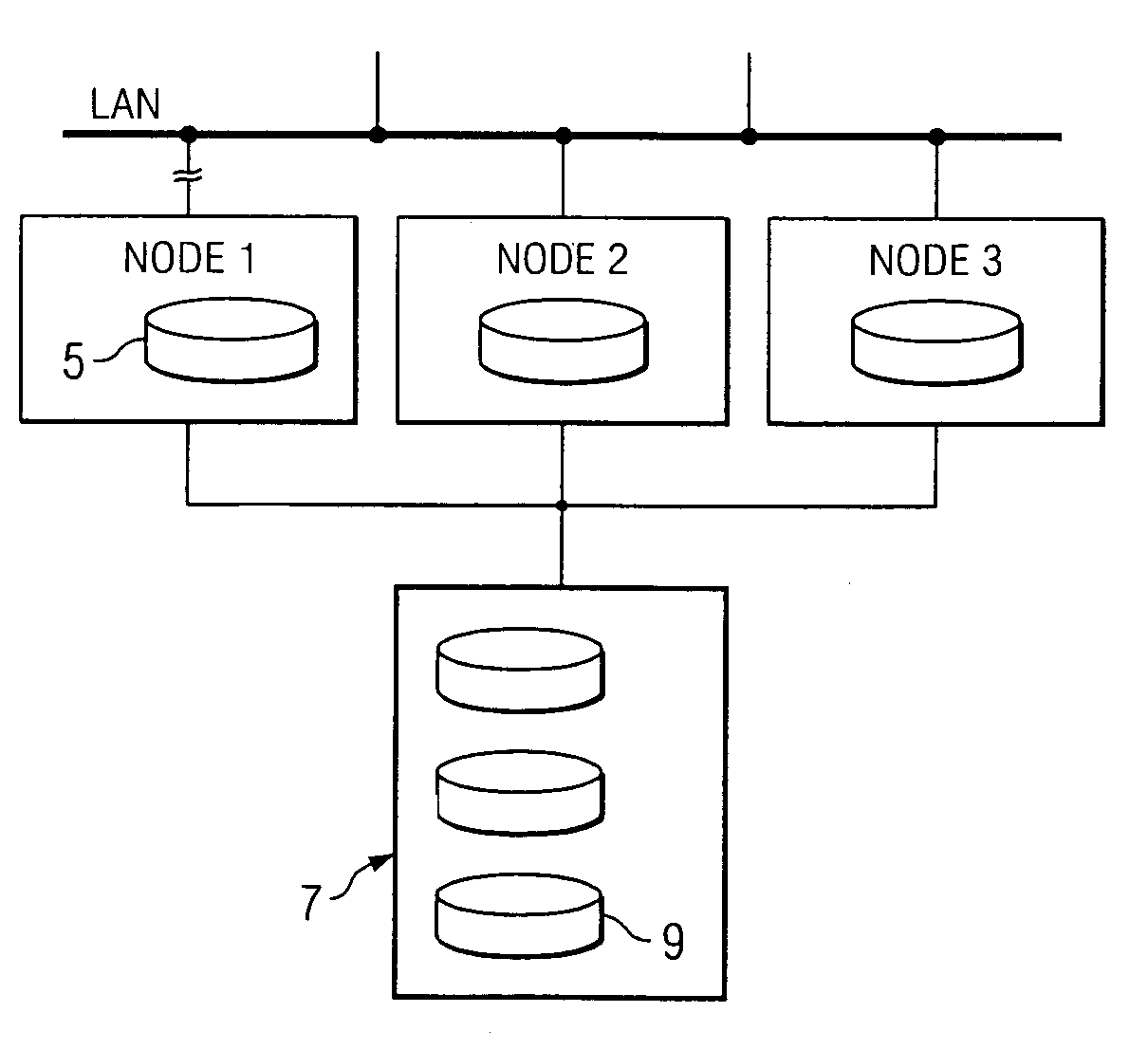

A method and system to detect and resolve a partition condition in a cluster of computers in a networked environment is described. The method can include: creating a scratch pad area accessible by the cluster of computers; dividing the scratch pad into a plurality of slots; recording in the plurality of slots, a generation number and a list of known nodes by each one of the plurality of notes, wherein an identifier is written in the list for each node that is known to a writing node; comparing each slot of the plurality of slots to ensure the generation number and the list of known nodes matches in each slot of the plurality of slots; and resolving the partition condition by creating a list of surviving nodes and re-allocating appropriate resources to each of the surviving nodes.

Owner:EMC IP HLDG CO LLC

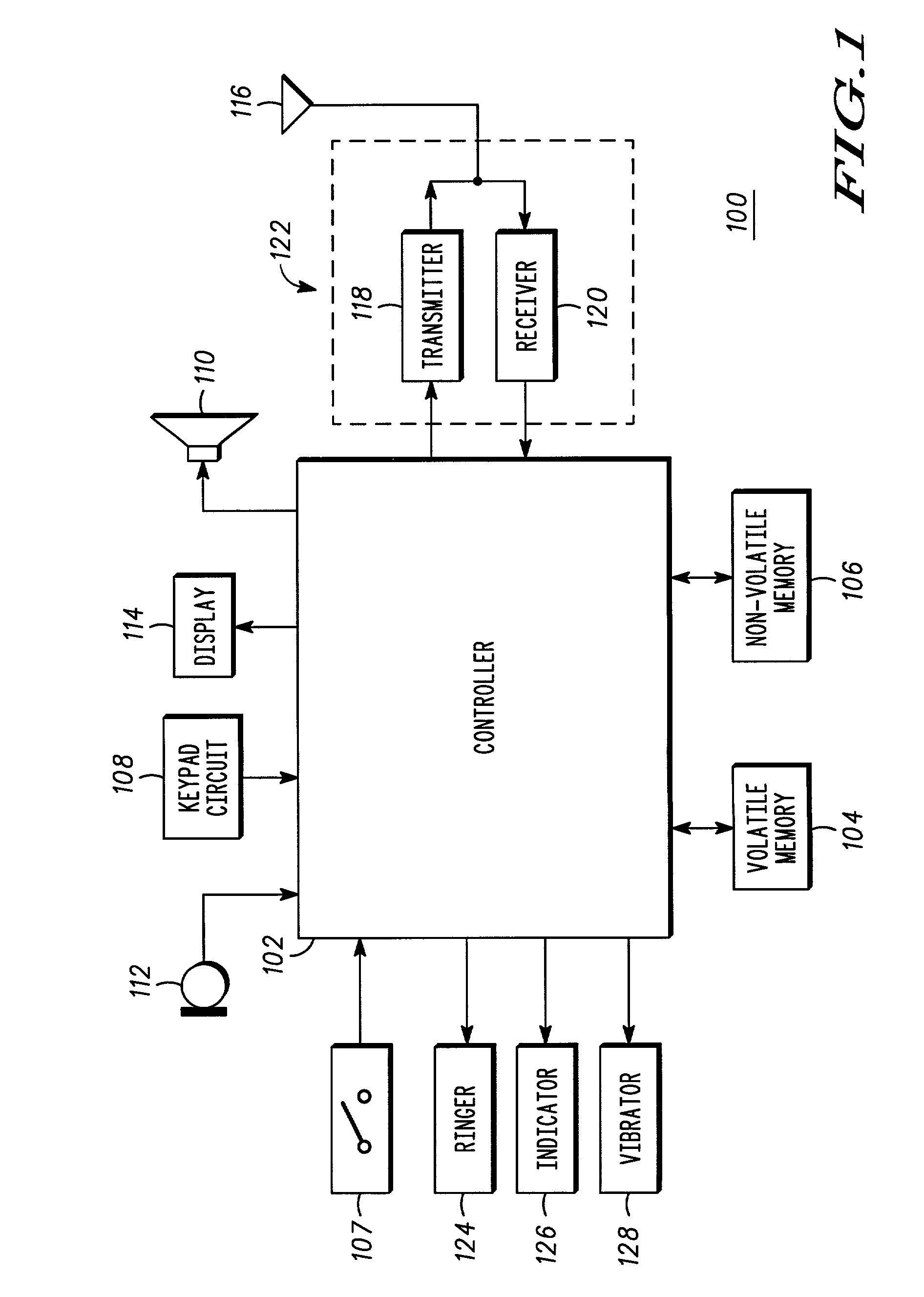

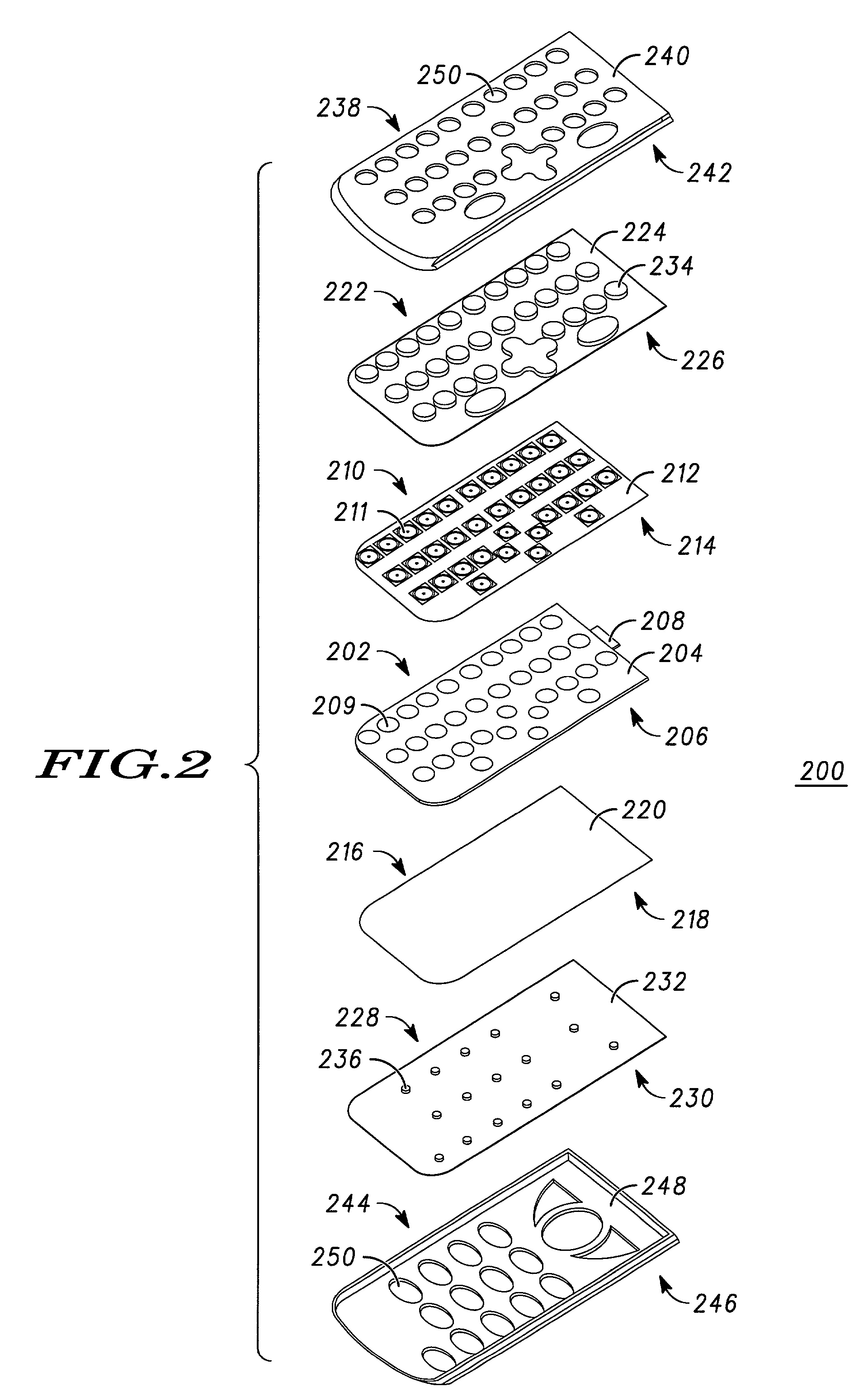

Portable communication device interchangeable user input module

The present invention is a portable communication device with an interchangeable user input module including two input devices, each disposed on one side of the module, opposite each other, to accommodate multiple functions, space limitations, and size reduction. Two or more features are often combined into one portable communication device to increase functionality. Input devices need to be interchangeable in order to facilitate the multiple features, for example, phone, messaging, personal data assistant, and gaming capabilities, of a portable communication device. The reduction in size of portable communication devices leads to space limitations for input devices. Each side of the interchangeable user input module includes a different input device, for example, QWERTY keyboard, numeric telephone input, touch sensitive panel, scratch pad, or gaming keypad. A user would flip the interchangeable user input module depending on which feature or function was needed.

Owner:MOTOROLA INC

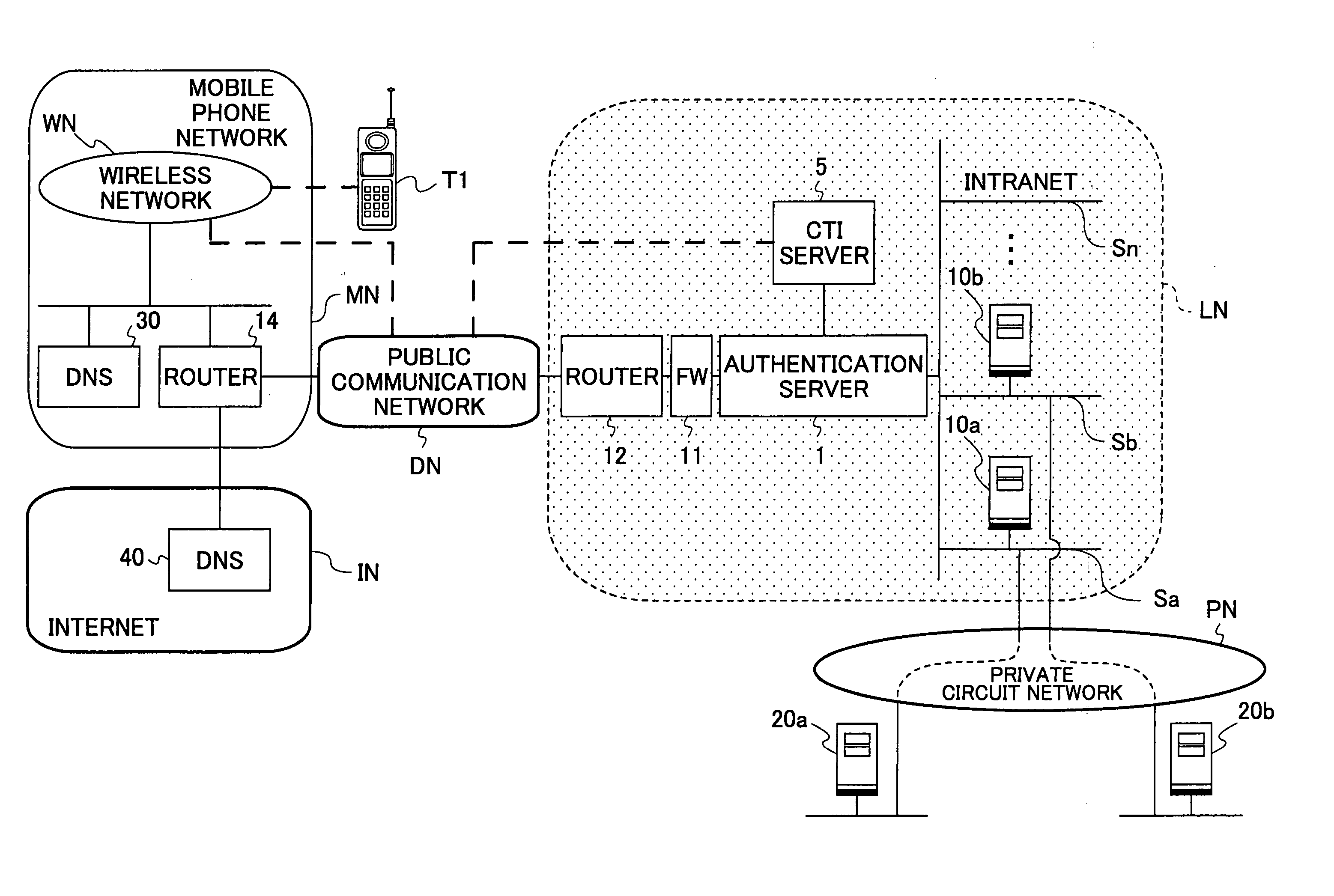

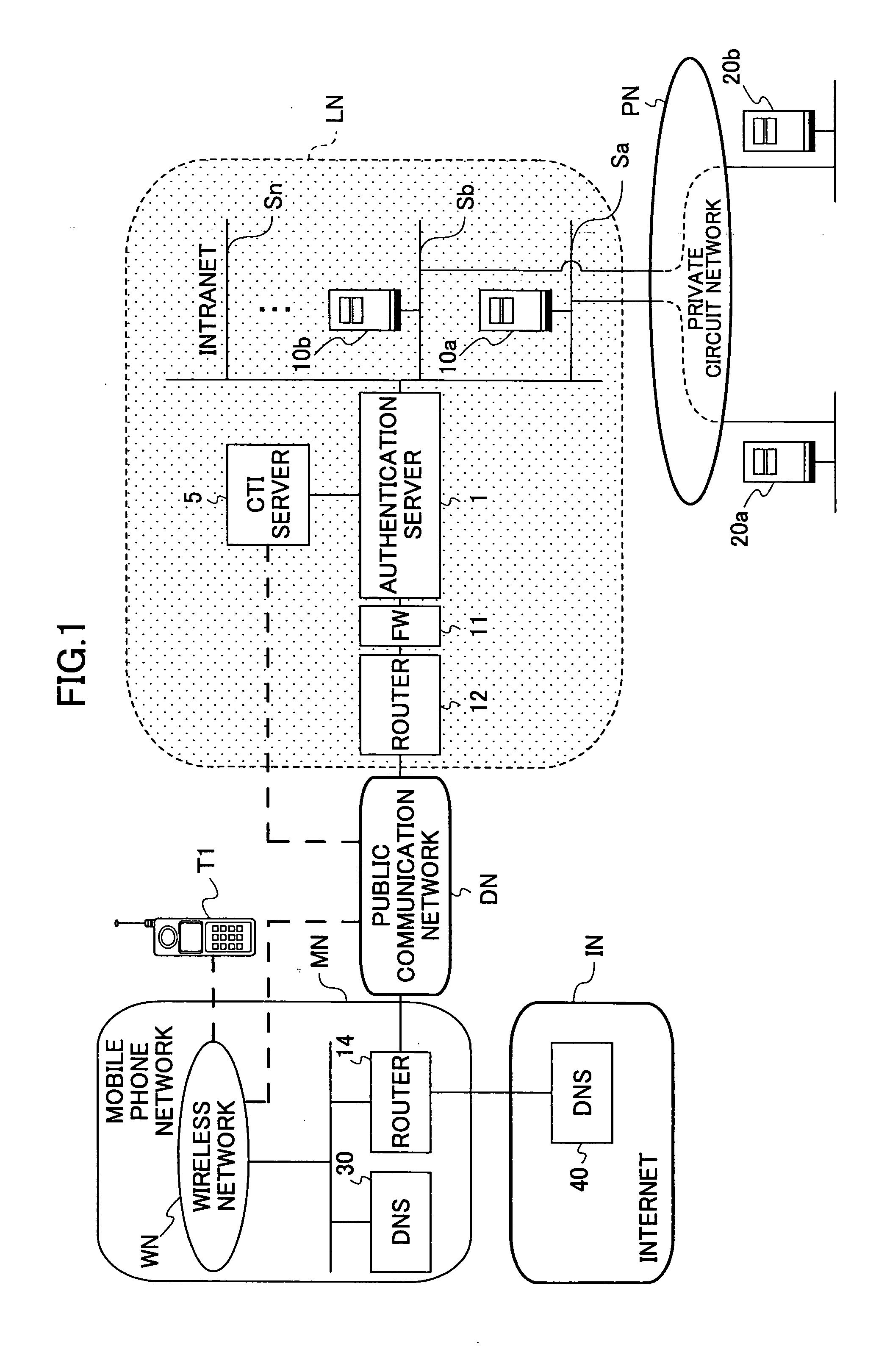

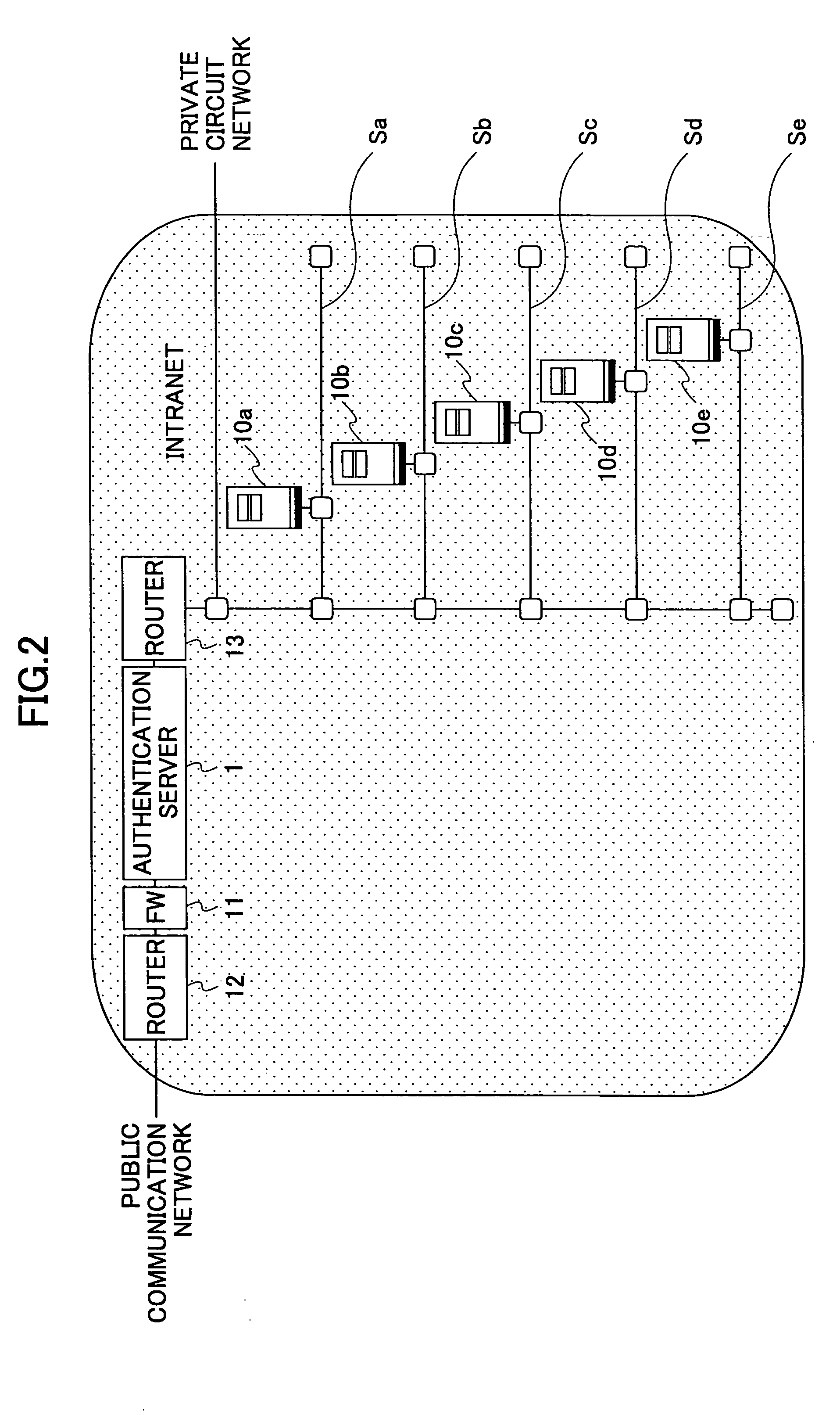

Authentication apparatus and method, network system, recording medium and computer program

InactiveUS20050108520A1Easy to displayEasy to buildDigital data processing detailsHardware monitoringNetworked systemAuthentication server

An authentication apparatus that makes it difficult to perform posing when accessing information is provided. When there is an access request from a mobile phone, an authentication server transmits a program to the mobile phone (S3202). The program is for reading data regarding an individual number (for example, serial number) recorded in a scratch pad of the mobile phone, and transmitting the data to the authentication server. The authentication server that receives the data regarding the serial number transmitted by activation of the program (S3202) compares the serial number with data regarding the identification number of each mobile phone, the data being maintained in the authentication server (S3203). When the serial number matches any of serial numbers maintained therein (S3203: Yes), the authentication server authenticates the access to be valid.

Owner:SUMITOMO HEAVY IND LTD

Non-volatile memory and method with improved indexing for scratch pad and update blocks

InactiveUS7386655B2Efficient use ofMemory architecture accessing/allocationMemory adressing/allocation/relocationData storingData store

Update data to a non-volatile memory may be recorded in at least two interleaving streams such as either into an update block or a scratch pad block depending on a predetermined condition. The scratch pad block is used to buffered update data that are ultimately destined for the update block. In a preferred embodiment, an index of the data stored in the scratch pad block as well that stored in the update block is saved in an unused portion of the scratch pad block every time the scratch pad block is written to.

Owner:SANDISK TECH LLC

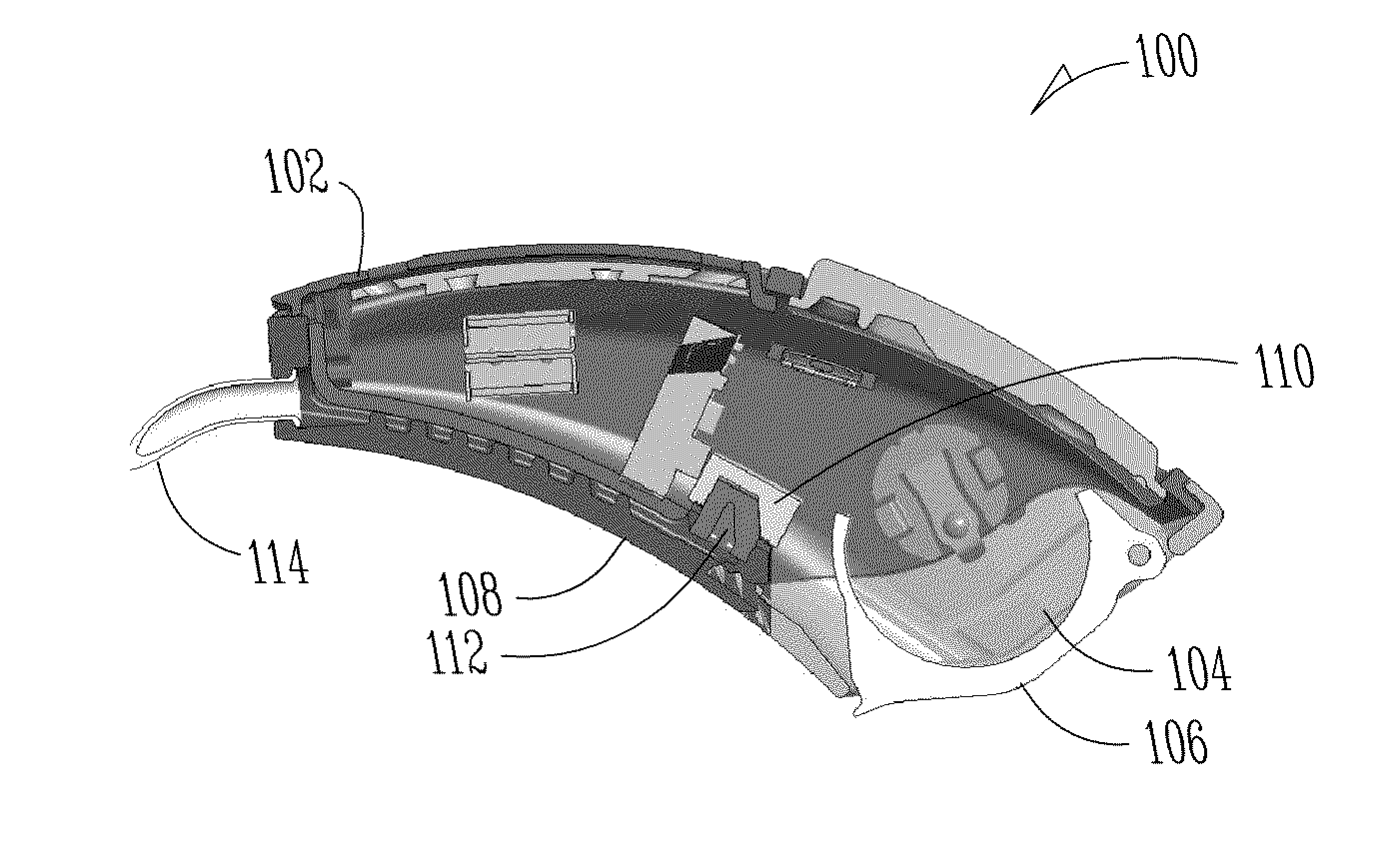

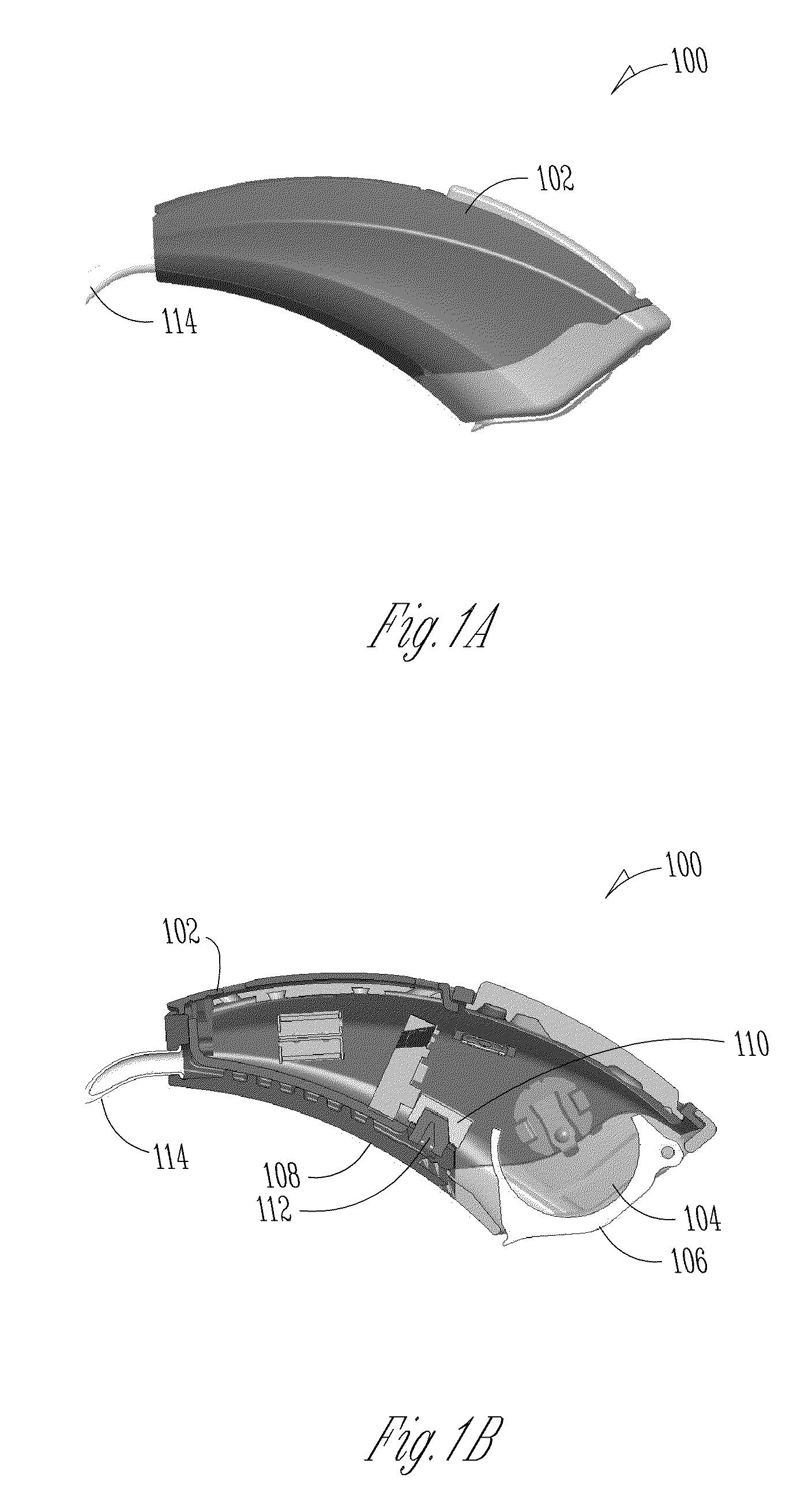

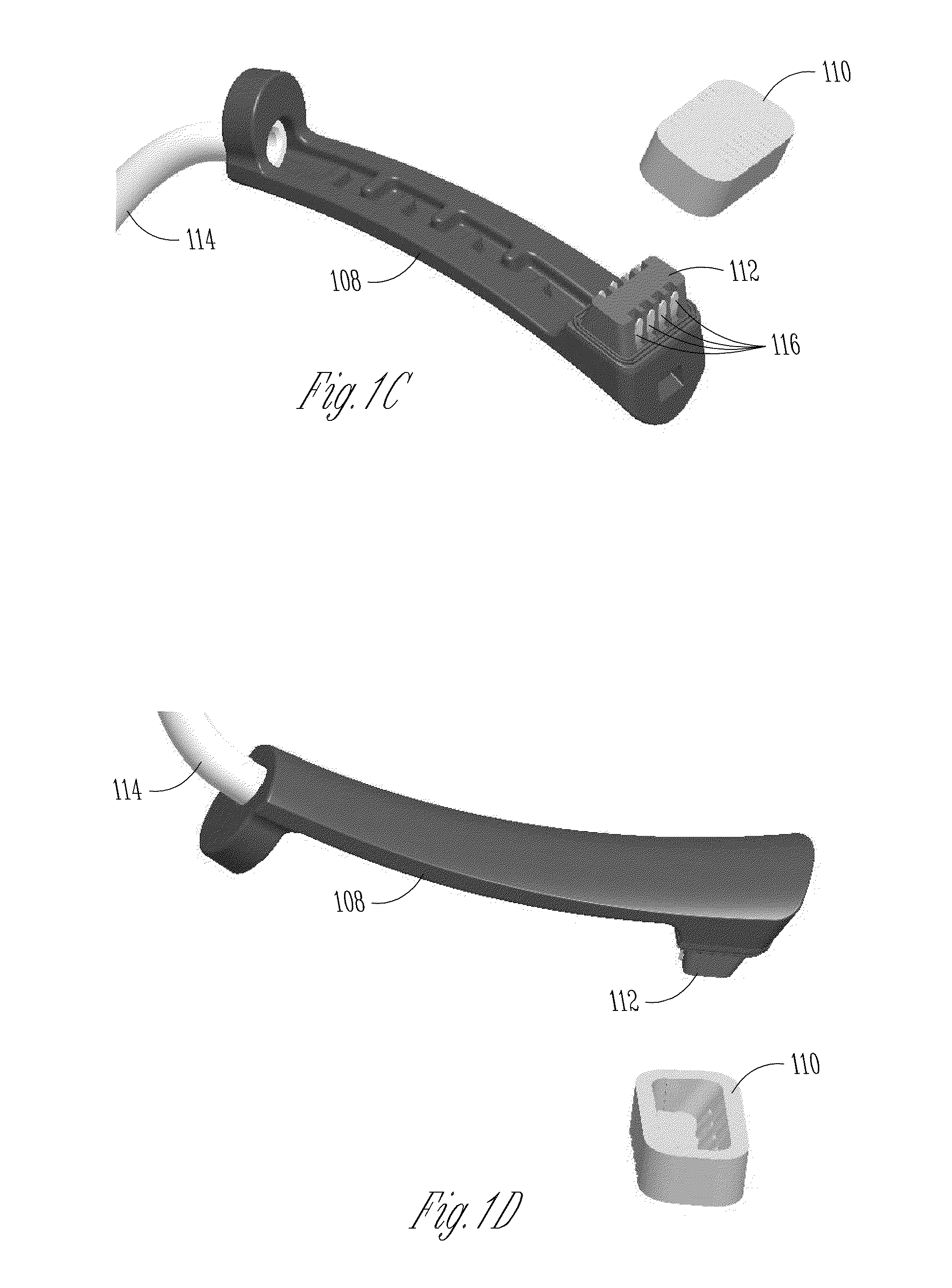

Receiver-in-canal hearing device cable connections

Disclosed herein, among other things, are methods and apparatus for hearing assistance devices, including, but not limited to connections for receiver-in-canal hearing devices. In various embodiments, a hearing device includes a hearing device component adapted to rest on or behind the ear and hearing assistance electronics disposed in the component. A first connector portion is disposed in the component, the first connector portion electrically connected to the hearing assistance electronics. A second connector portion is adapted to conform to a portion of the component and to electrically and physically connect a cable to the first connector portion. In various embodiments, at least one of the first connector portion and the second connector portion employ scratch pads for contacts. The first connector portion is top loading, in an embodiment.

Owner:STARKEY LAB INC

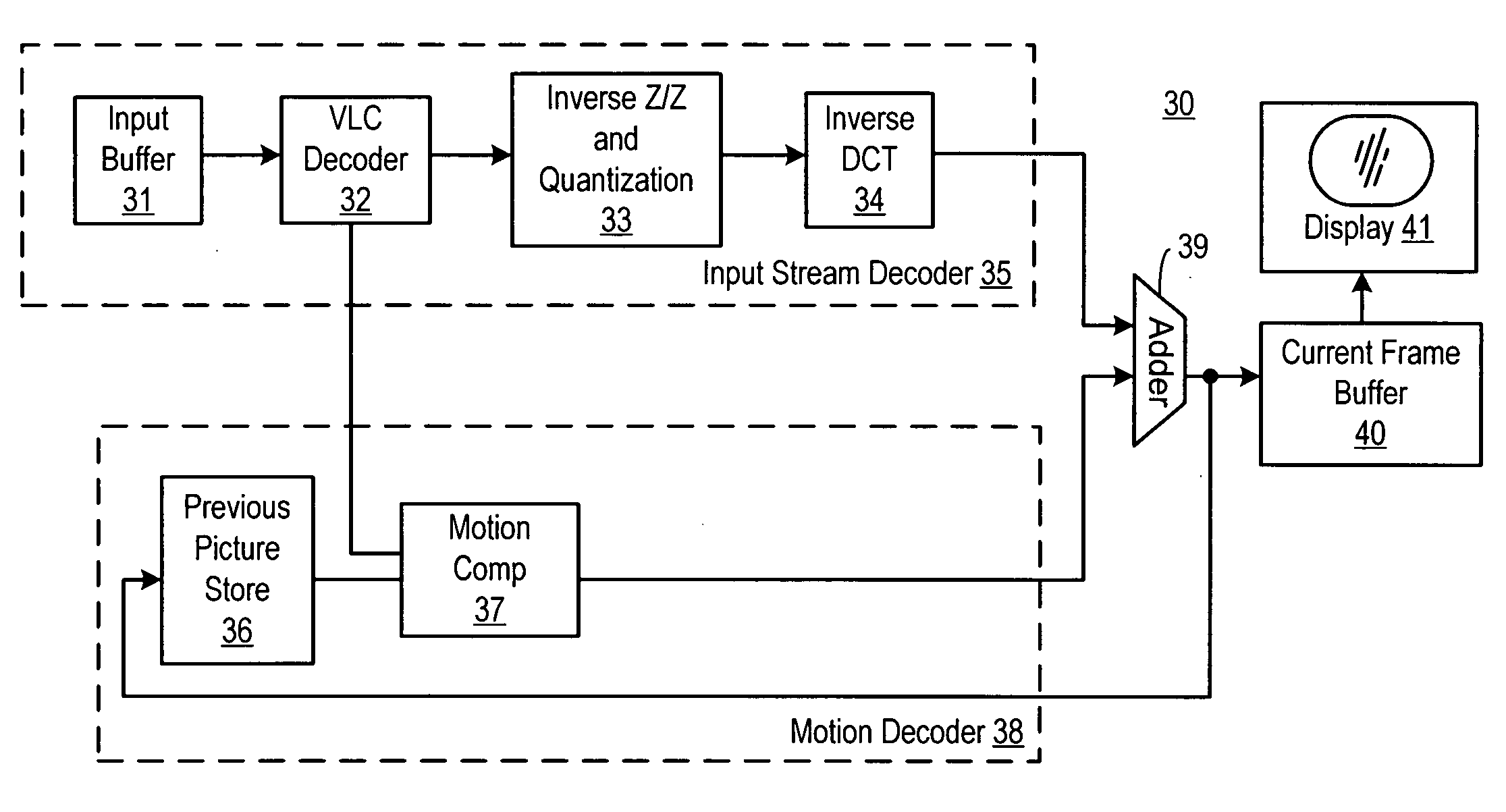

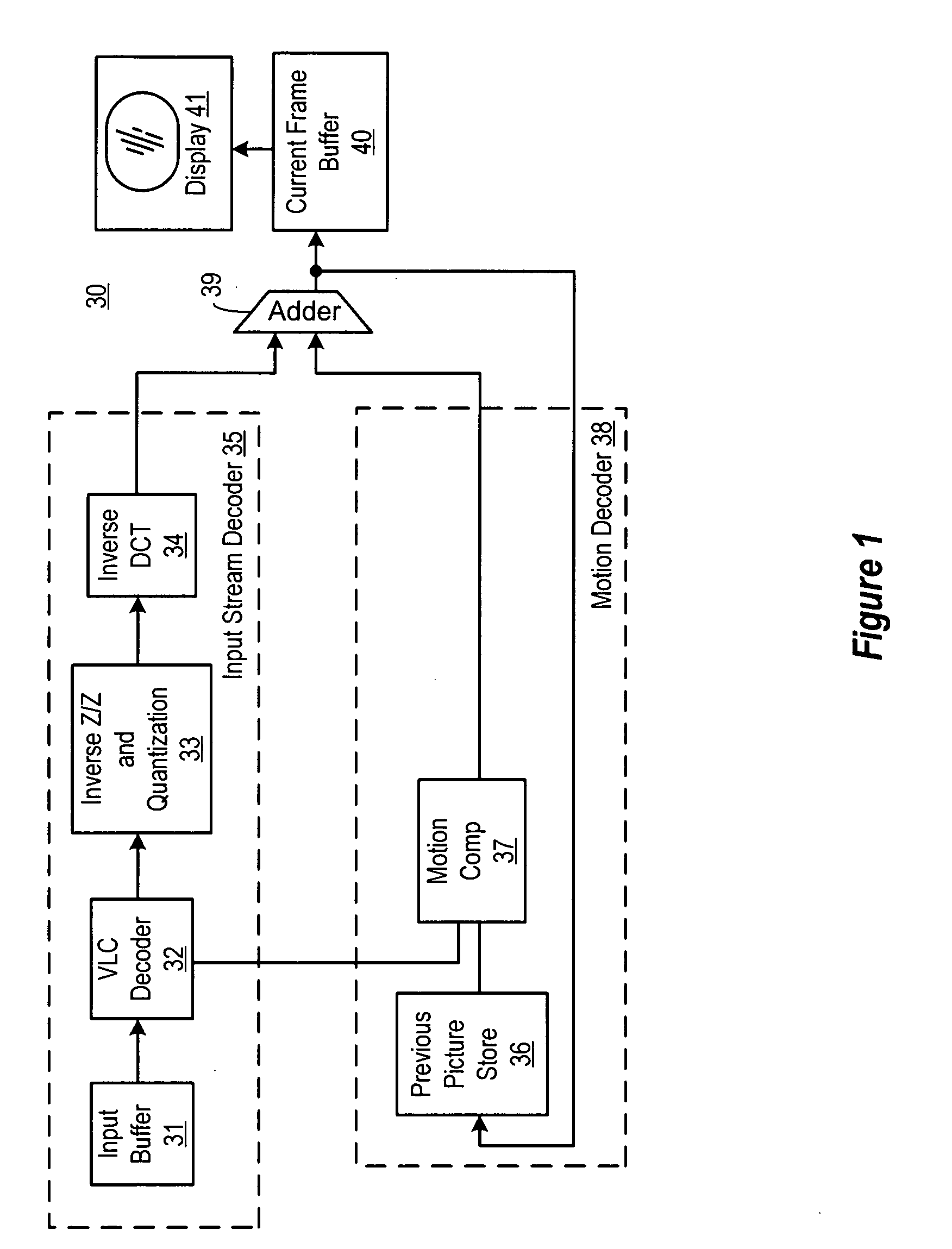

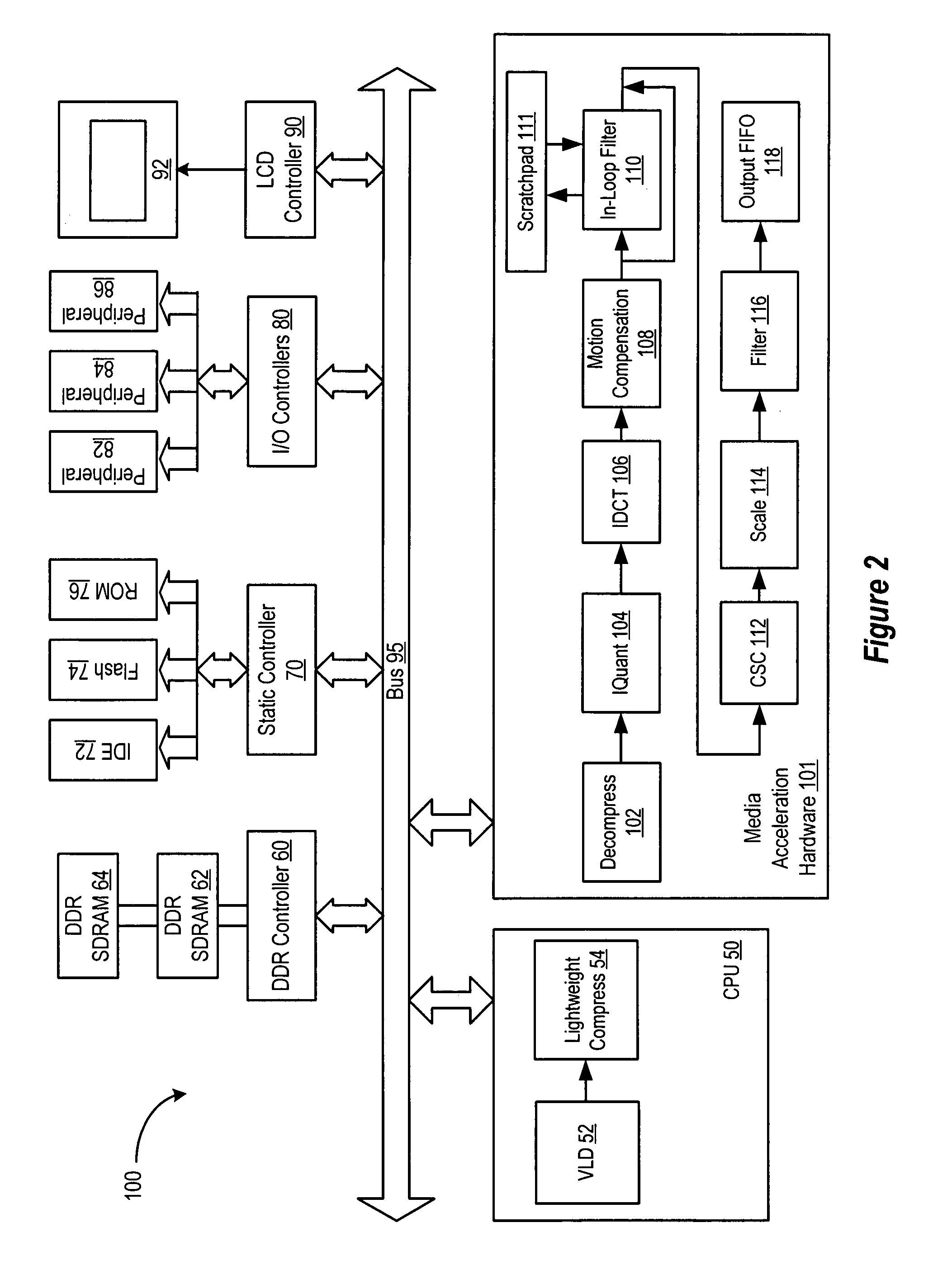

Scratch pad for storing intermediate loop filter data

ActiveUS20060165164A1Quickly and efficiently processMeet cutting requirementsColor television with pulse code modulationColor television with bandwidth reductionLoop filterFrame based

A video processing apparatus and methodology are implemented as a combination of a processor and a video decoding hardware block to decode video data by providing the video decoding block with an in-loop filter and a scratch pad memory, so that the in-loop filter may efficiently perform piecewise processing of overlap smoothing and in-loop deblocking in a macroblock-based fashion which is a much more efficient algorithm than the frame-based method.

Owner:MEDIATEK INC +1

Non-volatile memory and method with multi-stream update tracking

ActiveUS7366826B2Efficient use ofMemory architecture accessing/allocationRead-only memoriesMulti streamWrite pointer

Owner:SANDISK TECH LLC

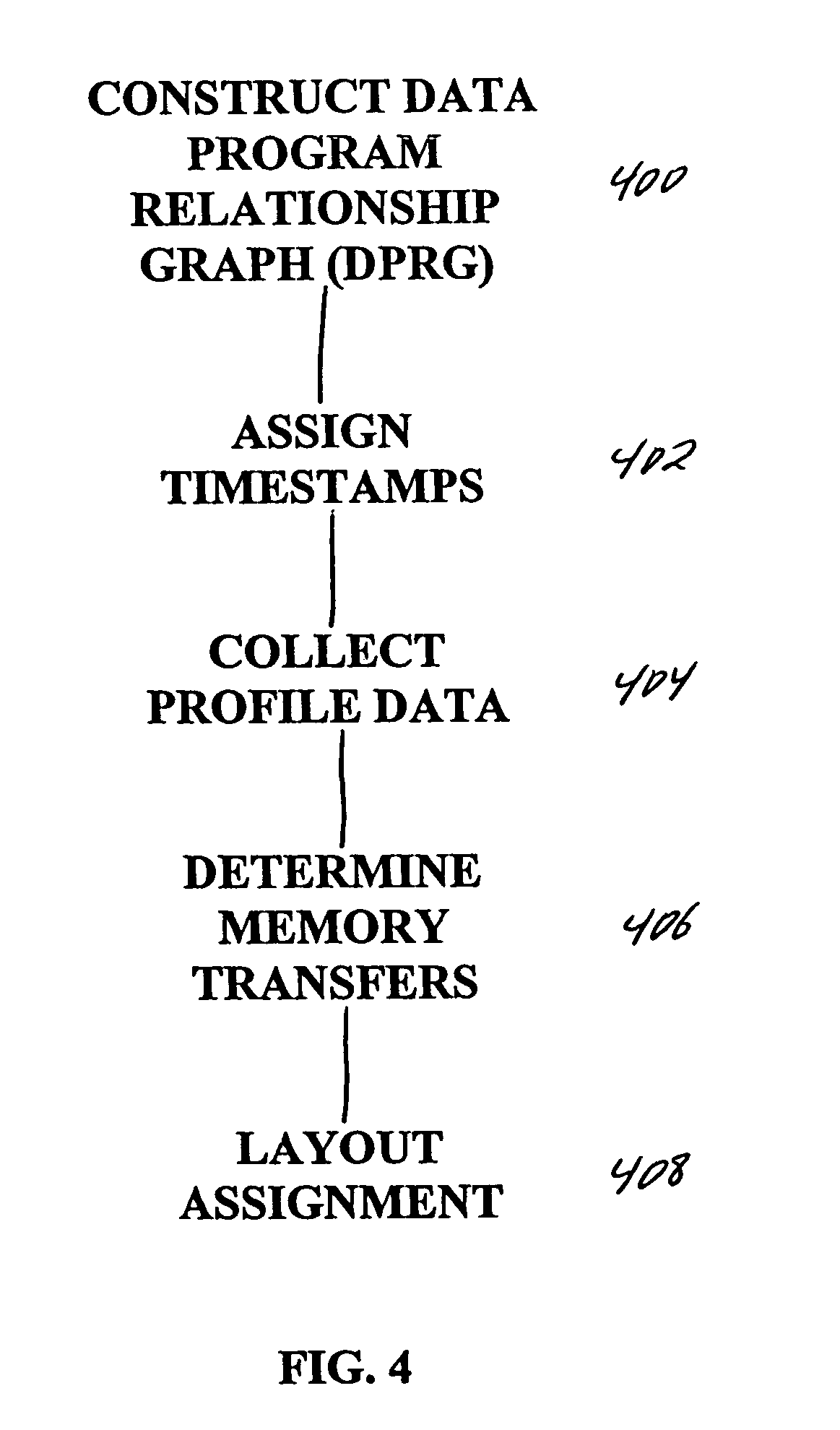

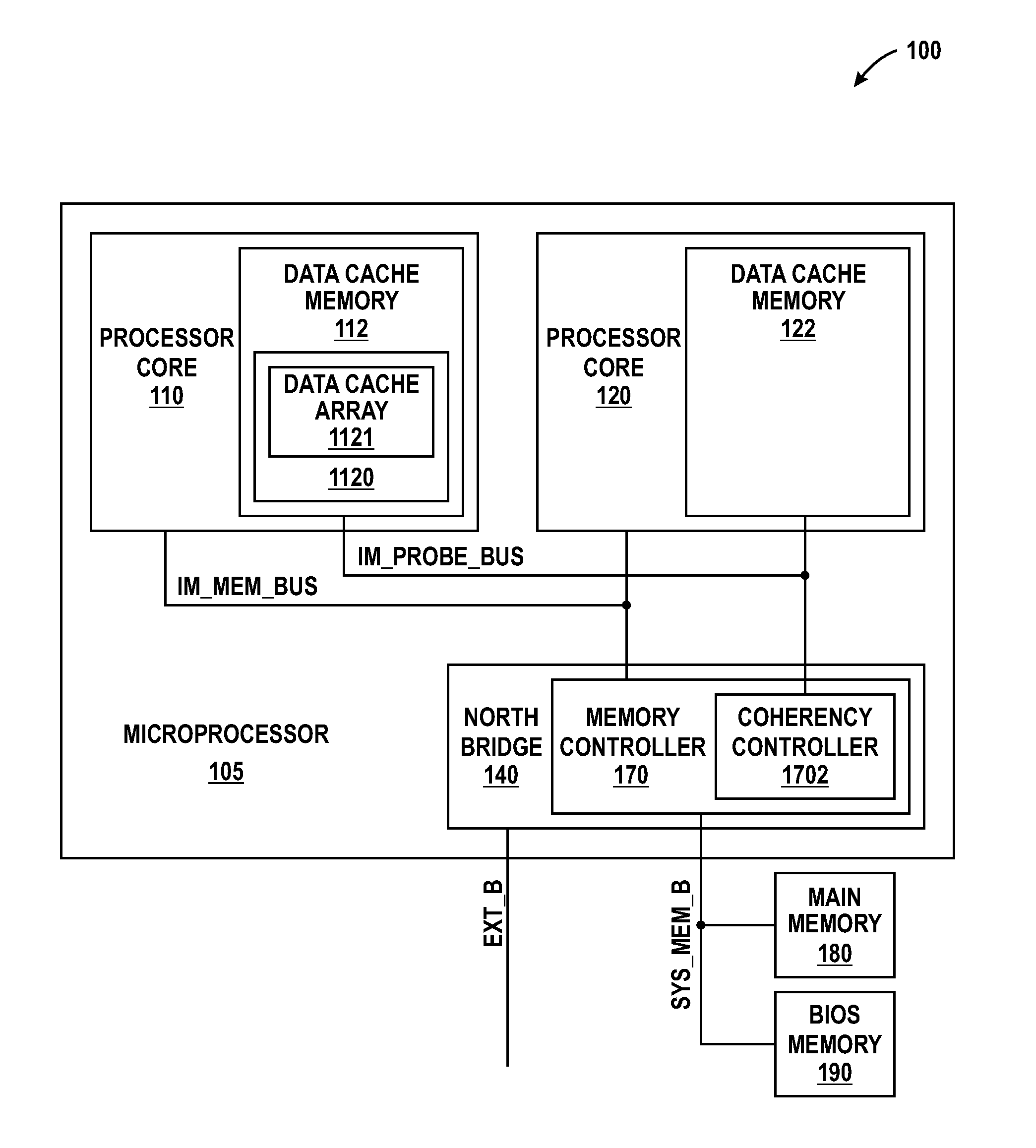

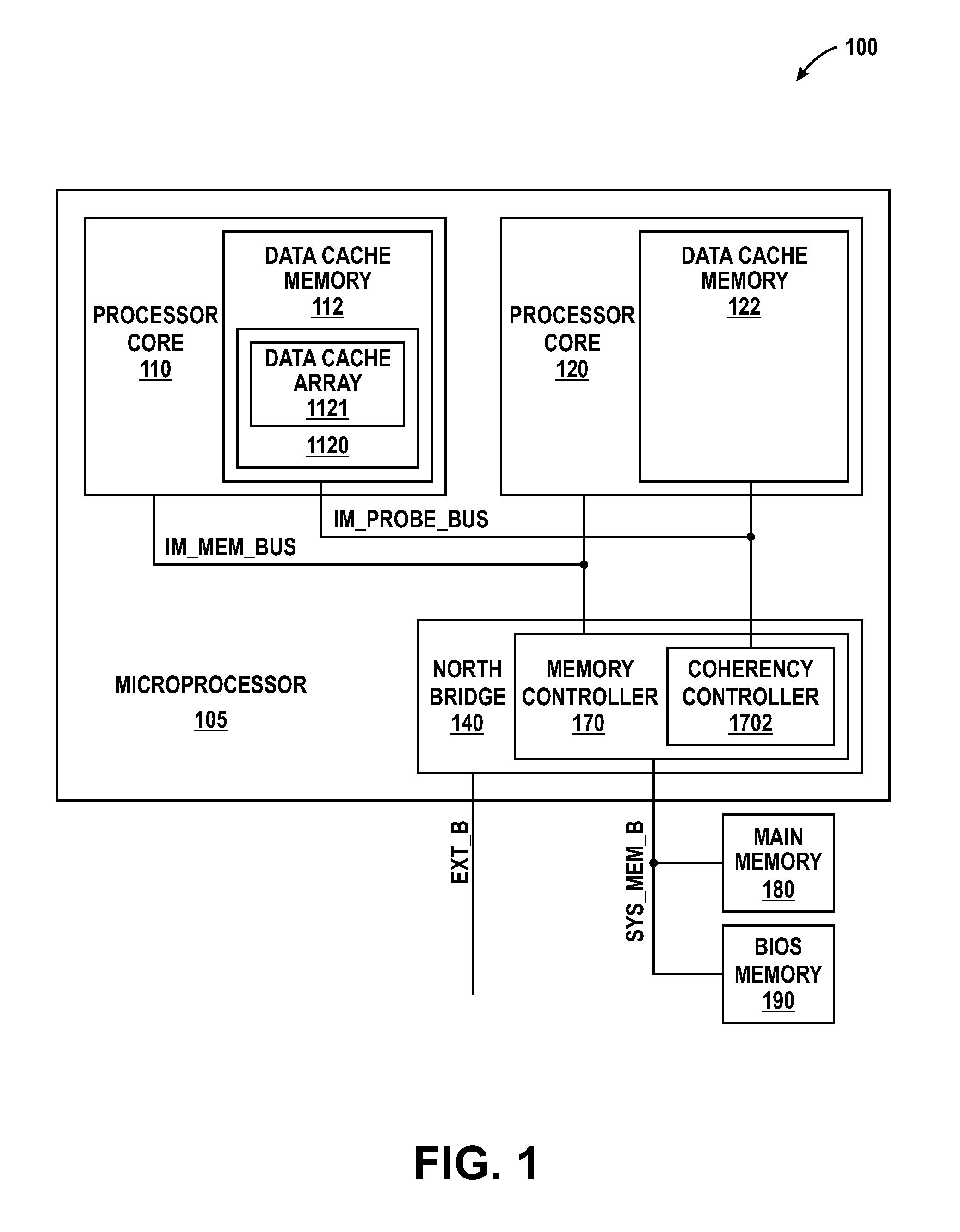

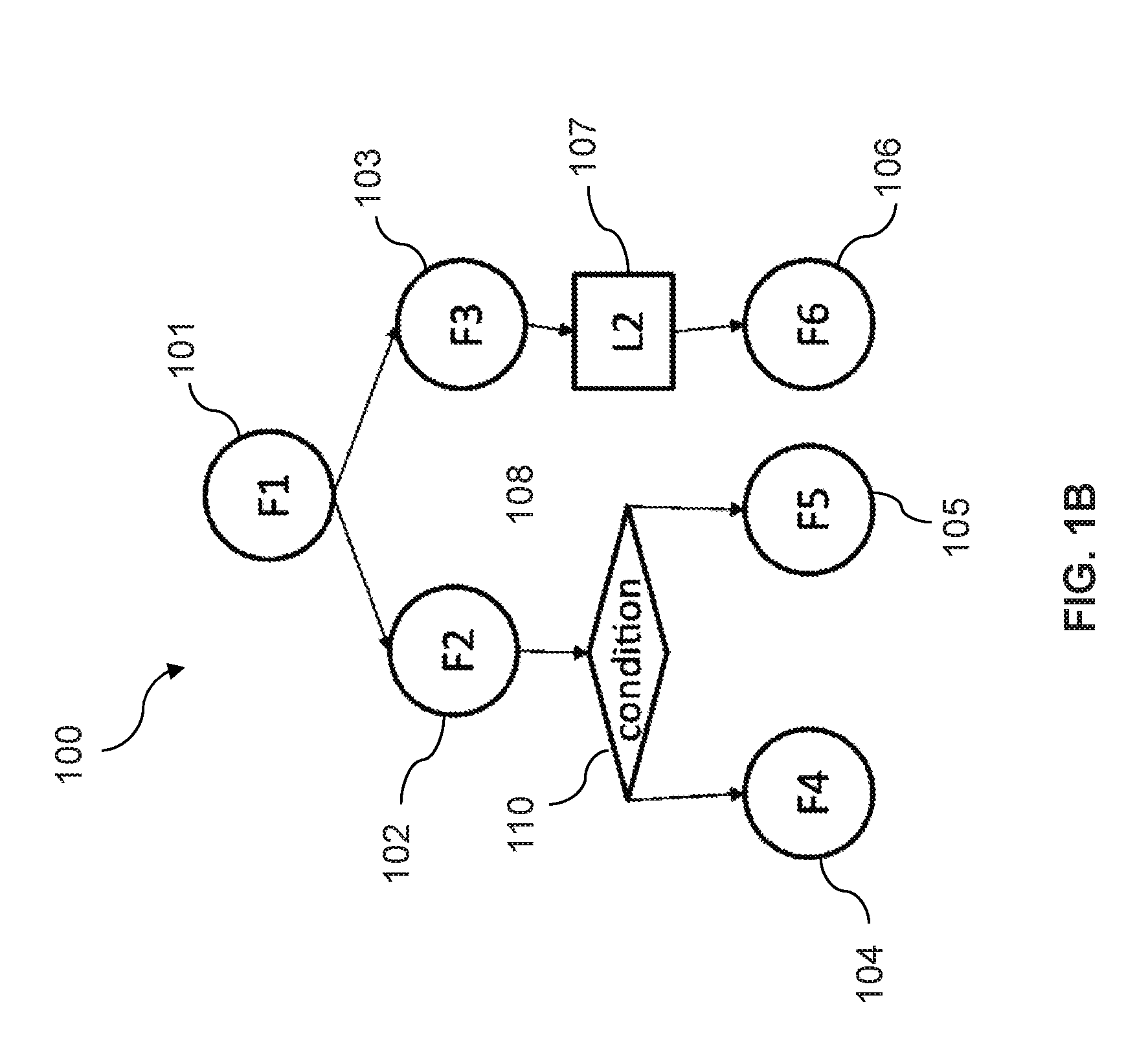

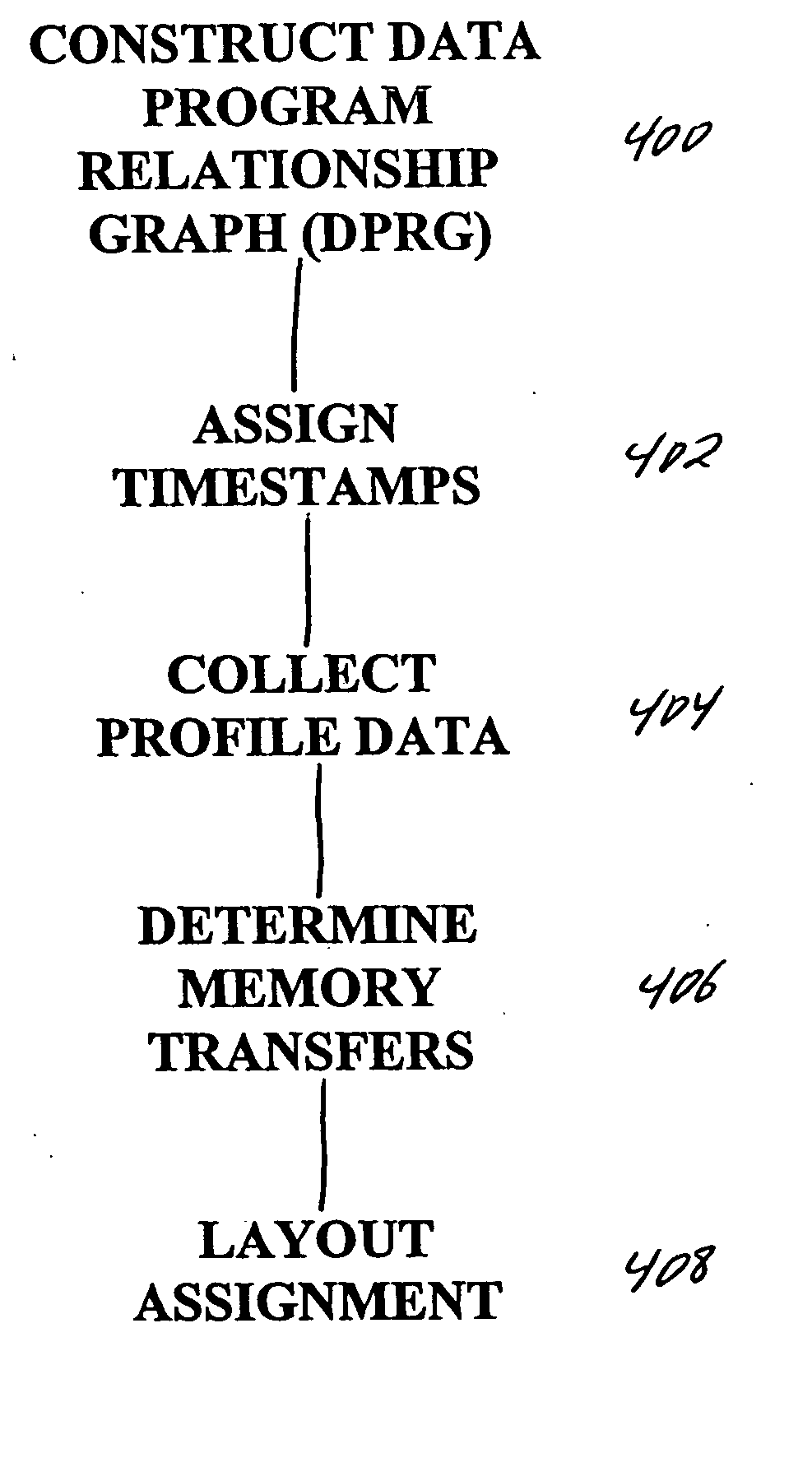

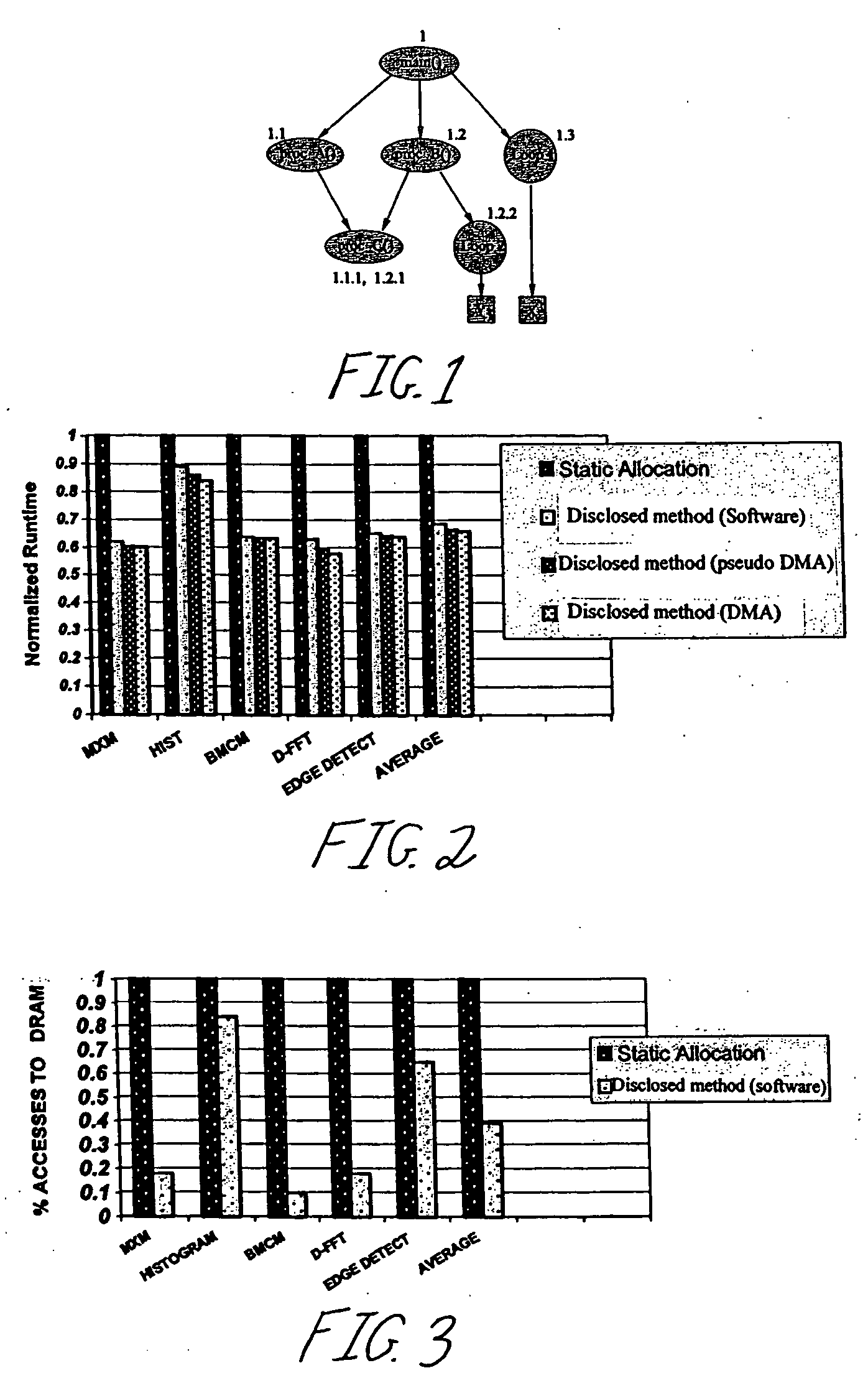

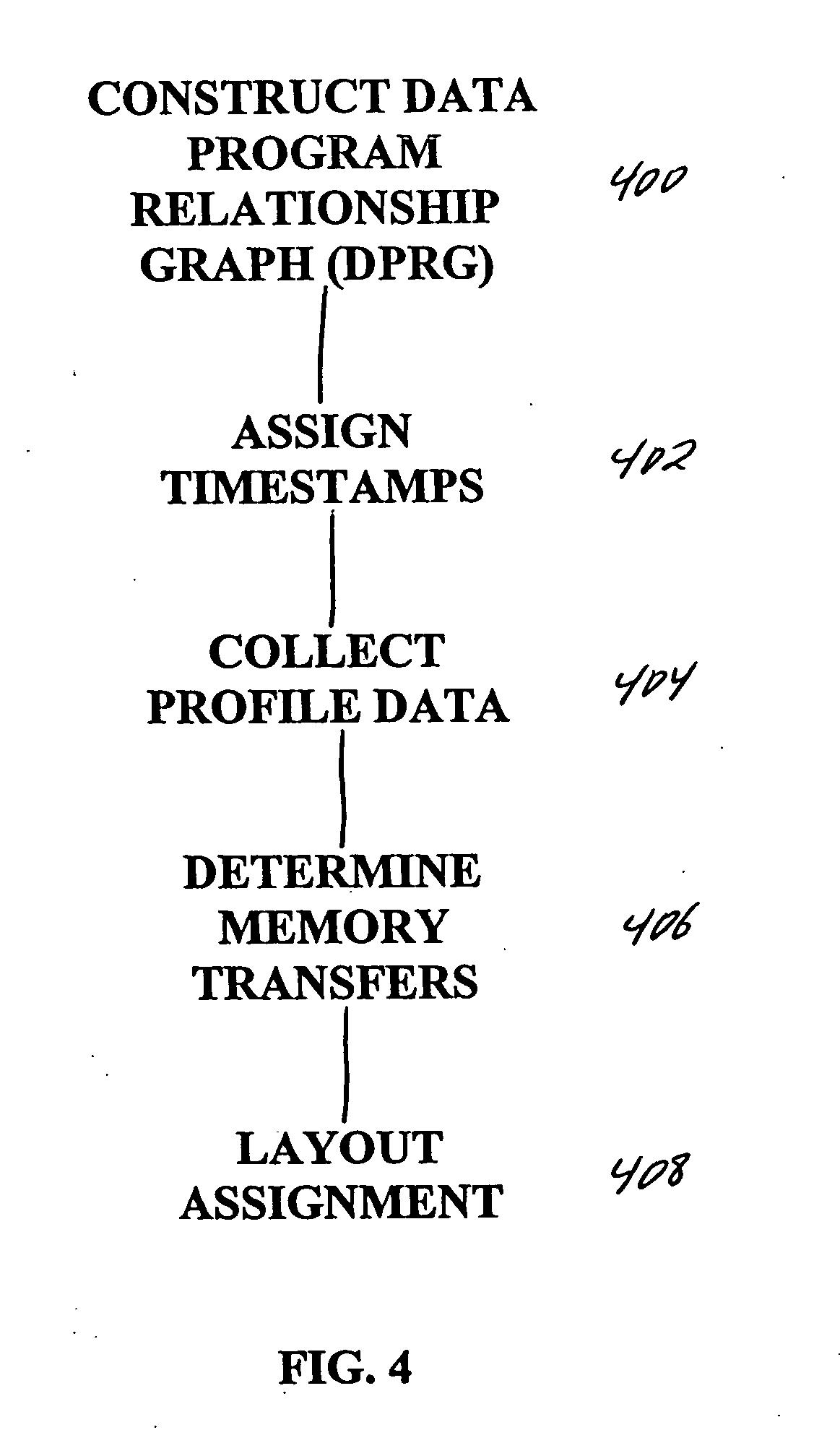

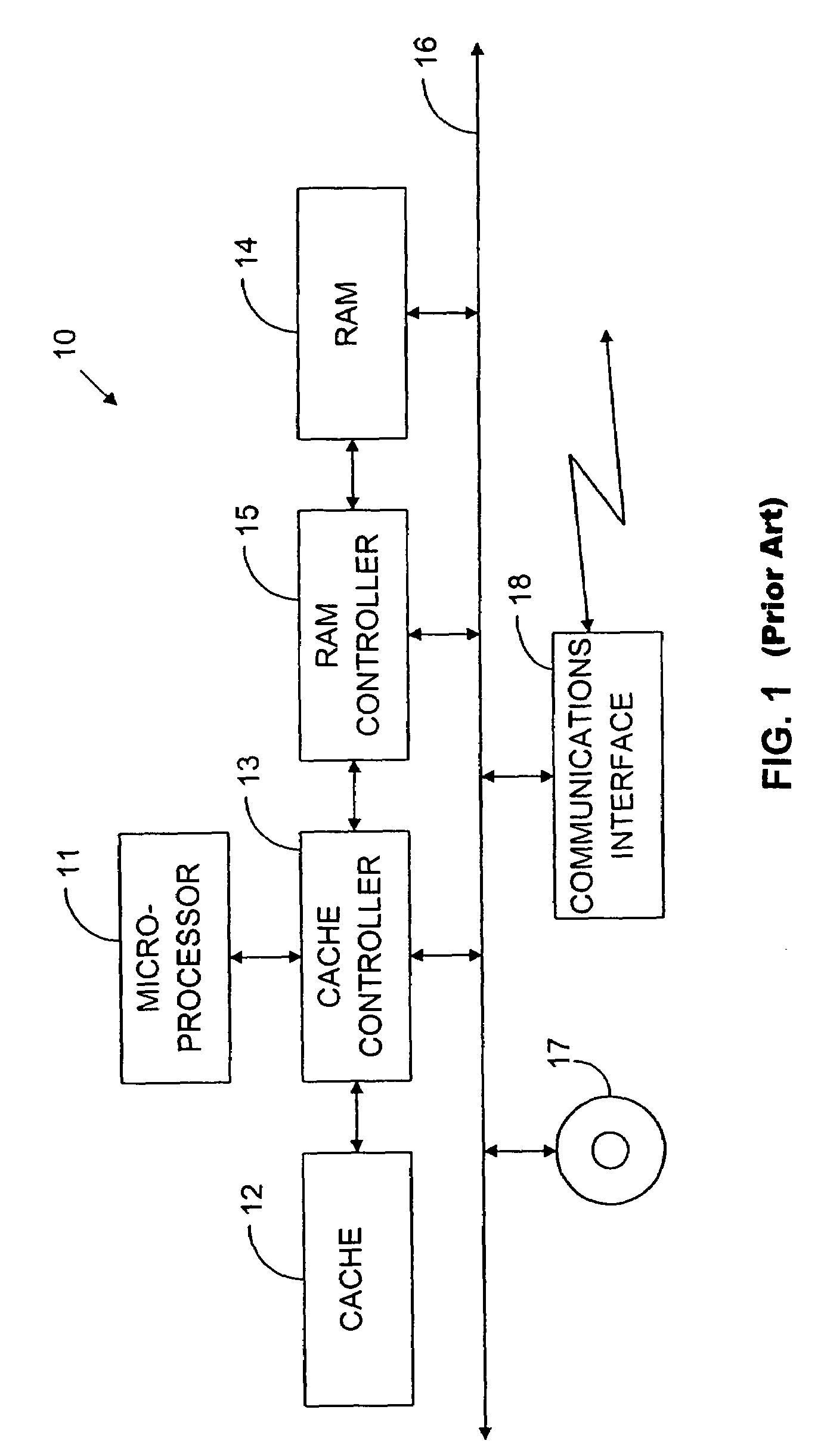

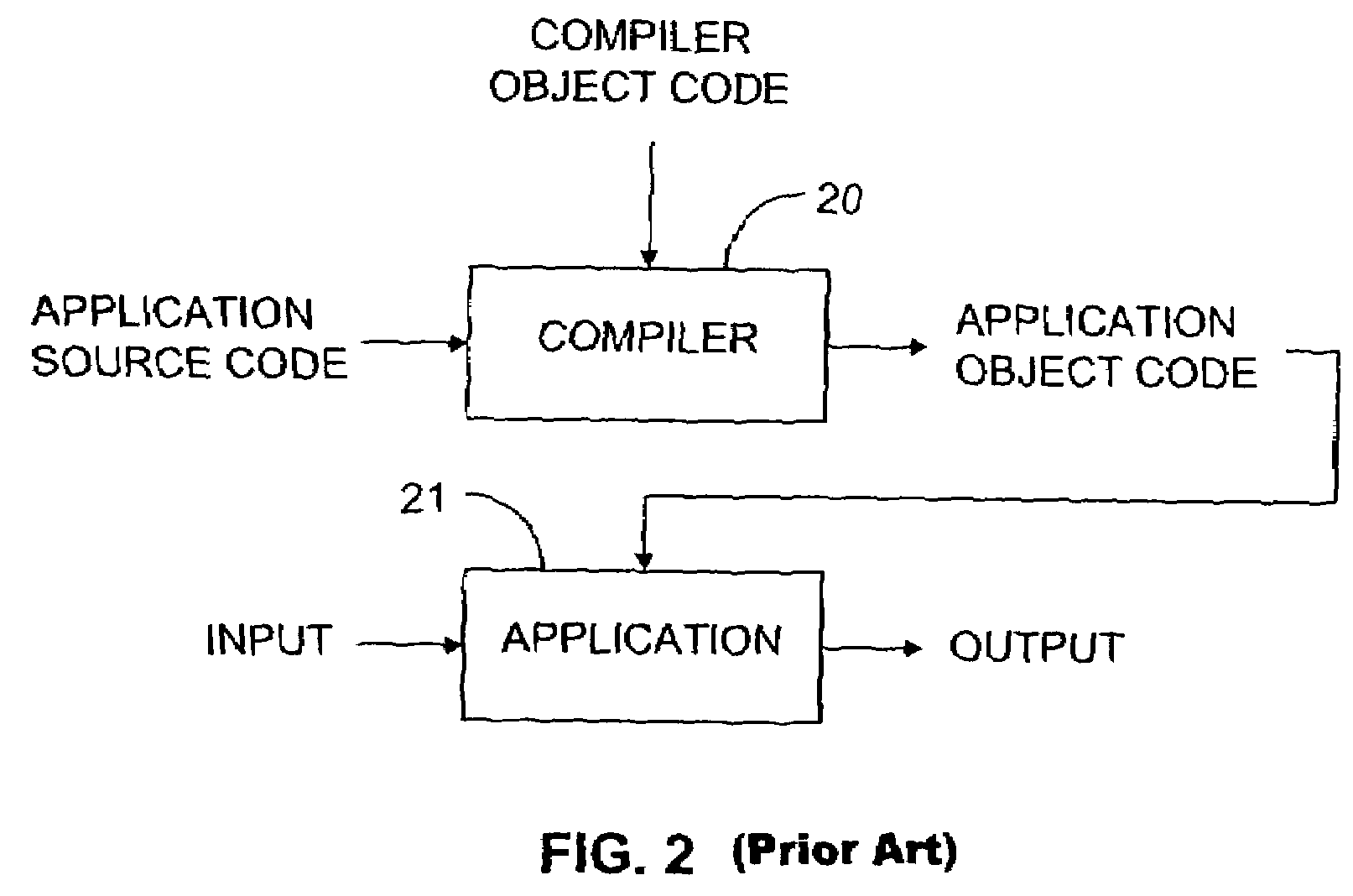

Compiler-driven dynamic memory allocation methodology for scratch-pad based embedded systems

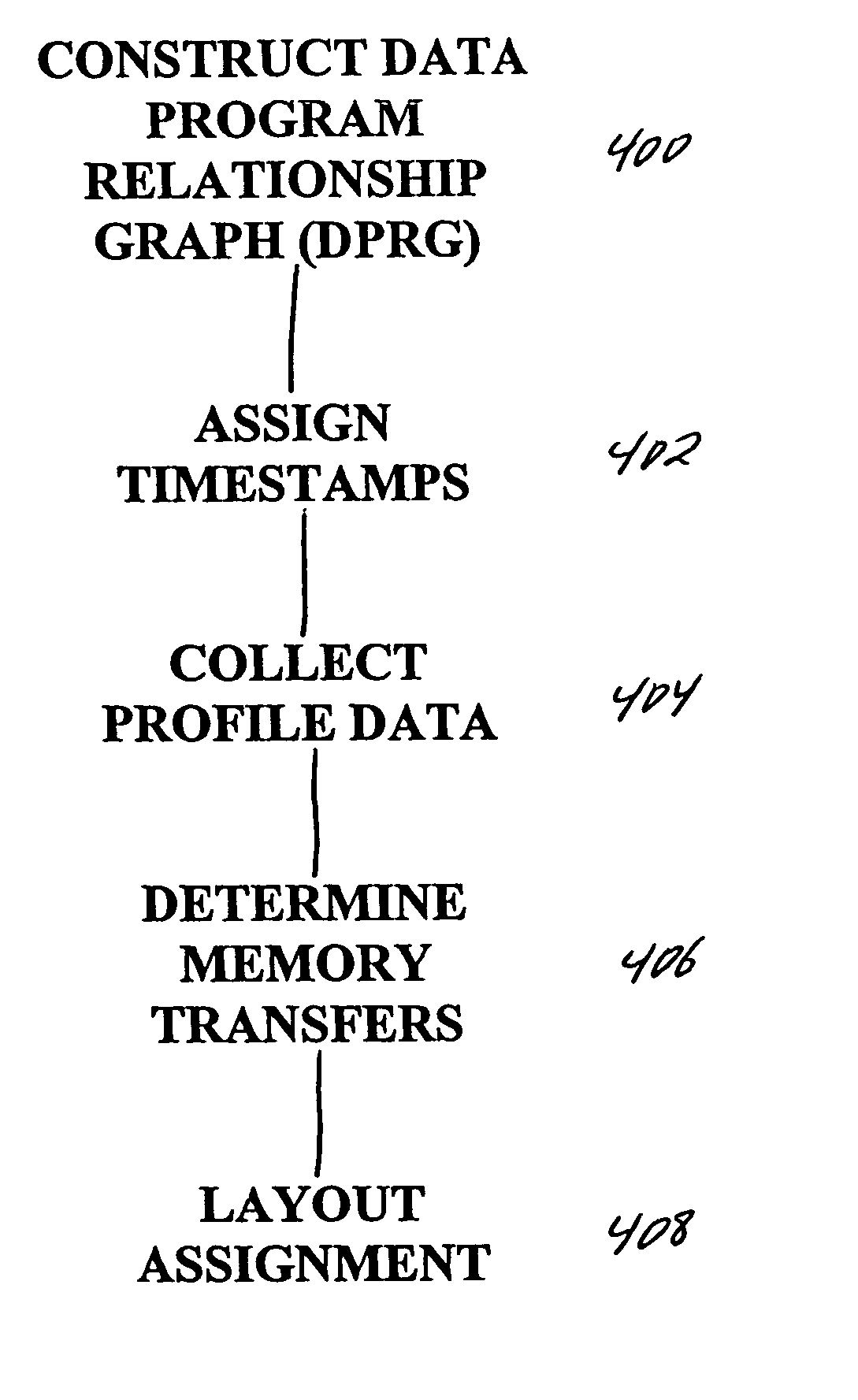

InactiveUS7367024B2Avoid overheadReduce overheadEnergy efficient ICTProgram controlAccess timeParallel computing

A highly predictable, low overhead and yet dynamic, memory allocation methodology for embedded systems with scratch-pad memory is presented. The dynamic memory allocation methodology for global and stack data (i) accounts for changing program requirements at runtime; (ii) has no software-caching tags; (iii) requires no run-time checks; (iv) has extremely low overheads; and (v) yields 100% predictable memory access times. The methodology provides that for data that is about to be accessed frequently is copied into the SRAM using compiler-inserted code at fixed and infrequent points in the program. Earlier data is evicted if necessary.

Owner:UNIV OF MARYLAND

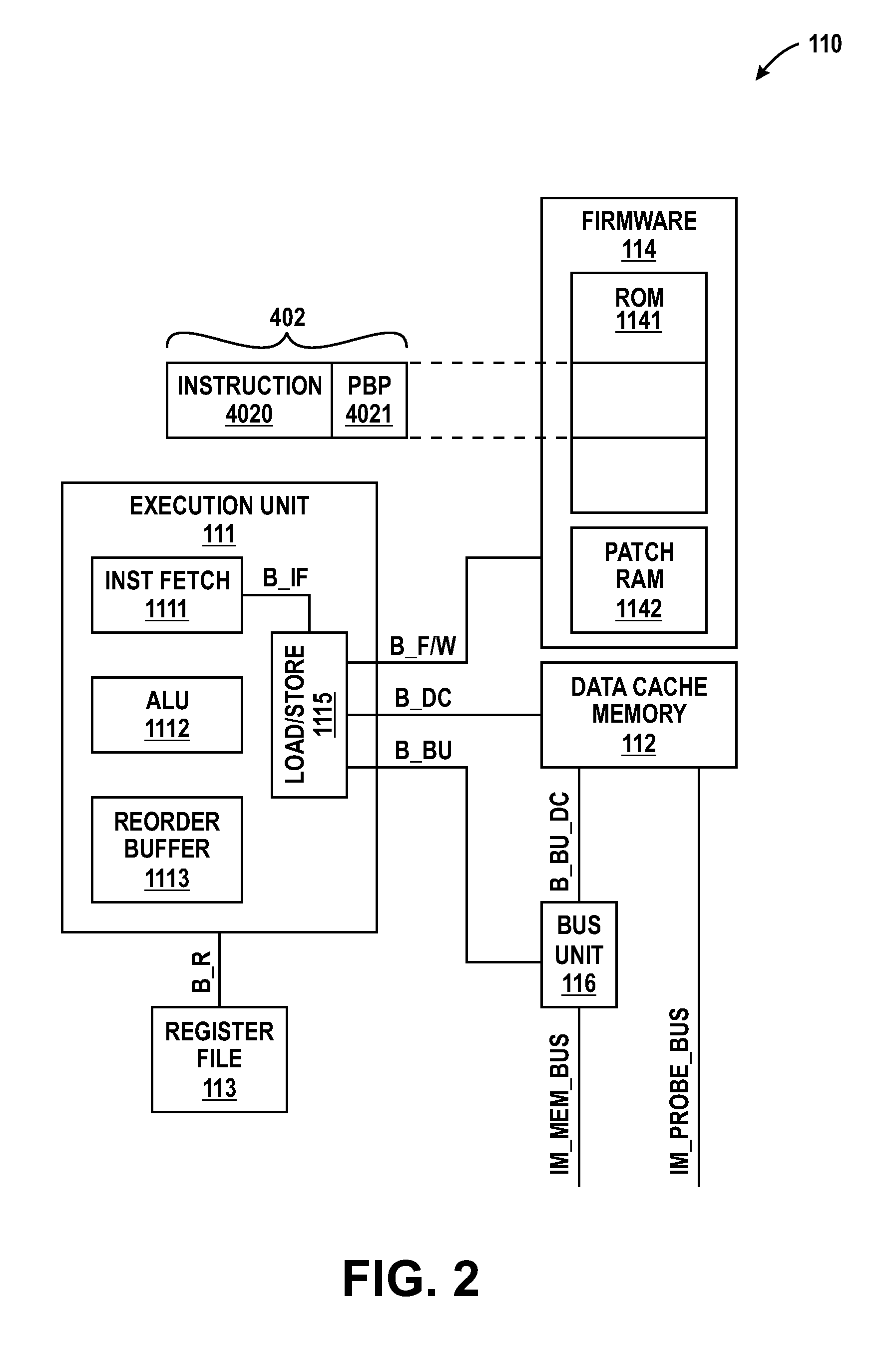

Cache scratch-pad and method therefor

InactiveUS20110131381A1Memory adressing/allocation/relocationUnauthorized memory use protectionParallel computingOperation mode

An address containing data to be accessed is determined in response to executing an instruction received at a processor core of a microprocessor. During a scratch-pad mode of operation, it is determined whether a set of cache lines of a data cache is accessible based upon the memory location from which the instruction was retrieved. The address space of the data cache during scratch-pad mode can be isolated from other address spaces.

Owner:ADVANCED MICRO DEVICES INC

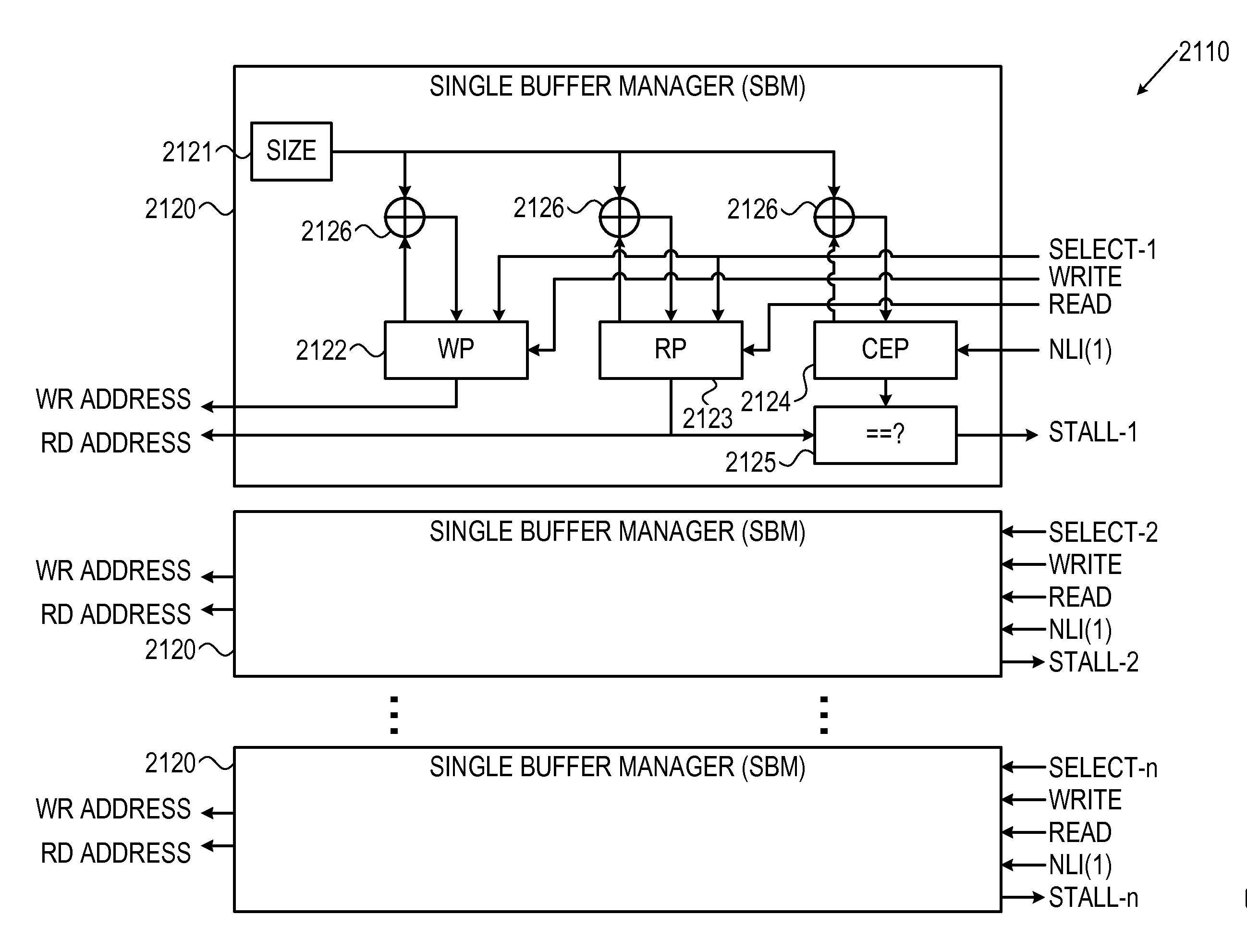

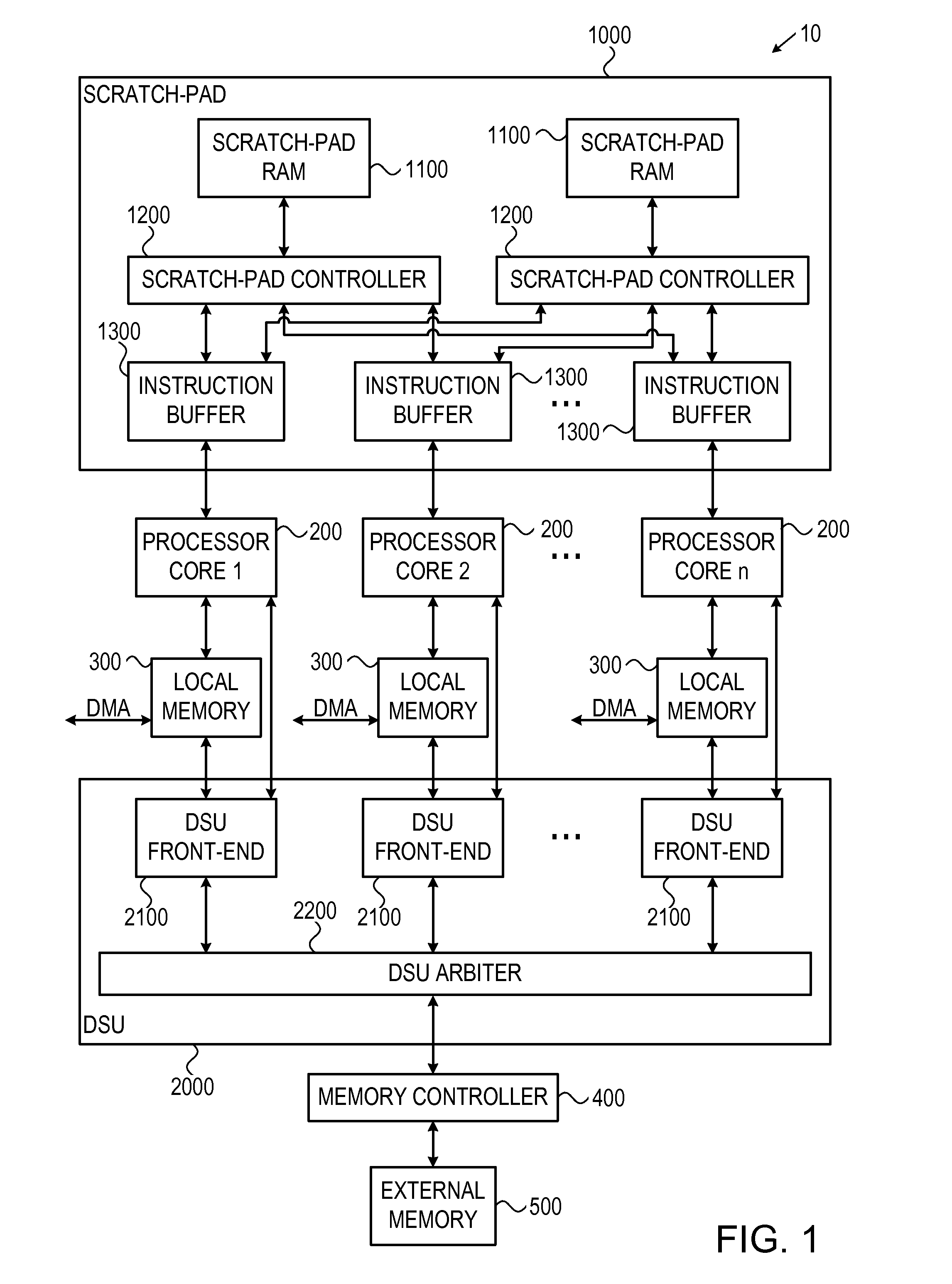

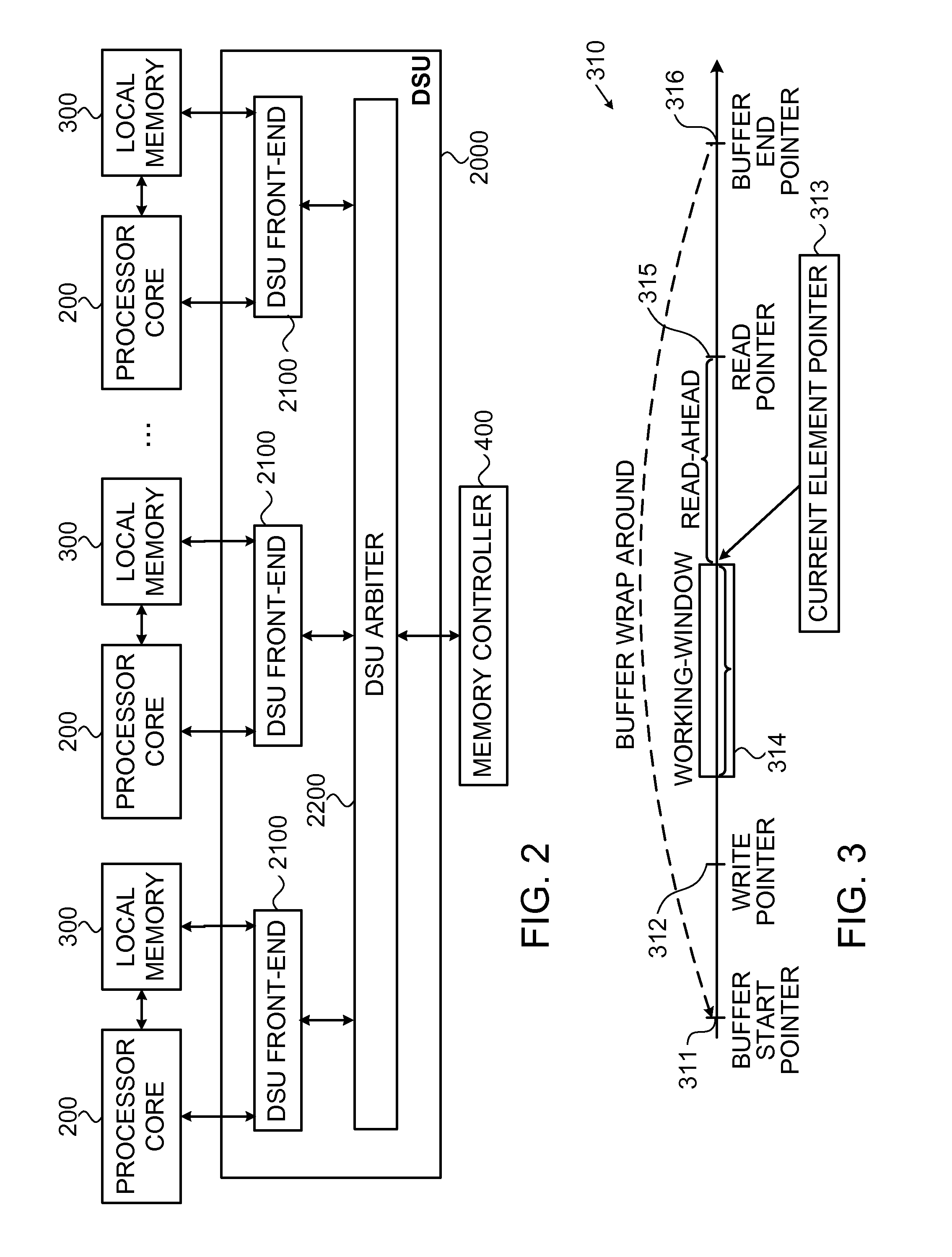

Multiprocessor system-on-a-chip for machine vision algorithms

ActiveUS20120042150A1Program control using stored programsGeneral purpose stored program computerMachine visionData stream

Owner:APPLE INC

Non-volatile memory and method with multi-stream updating

ActiveUS7412560B2Efficient use ofMemory architecture accessing/allocationRead-only memoriesMulti streamData recording

In a memory that is programmable page by page and each page having multiple sectors that are once-programmable, even if successive writes are sequential, the data recorded to an update block may be fragmented and non-sequential. Instead of recording update data to an update block, the data is being recorded in at least two interleaving streams. When a full page of data is available, it is recorded to the update block. Otherwise, it is temporarily recorded to the scratch pad block until a full page of data becomes available to be transferred to the update block. Preferably, a pipeline operation allows the recording to the update block to be set up as soon as the host write command indicates a full page could be written. If the actual write data is incomplete due to interruptions, the setup will be canceled and recording is made to the scratch pad block instead.

Owner:SANDISK TECH LLC

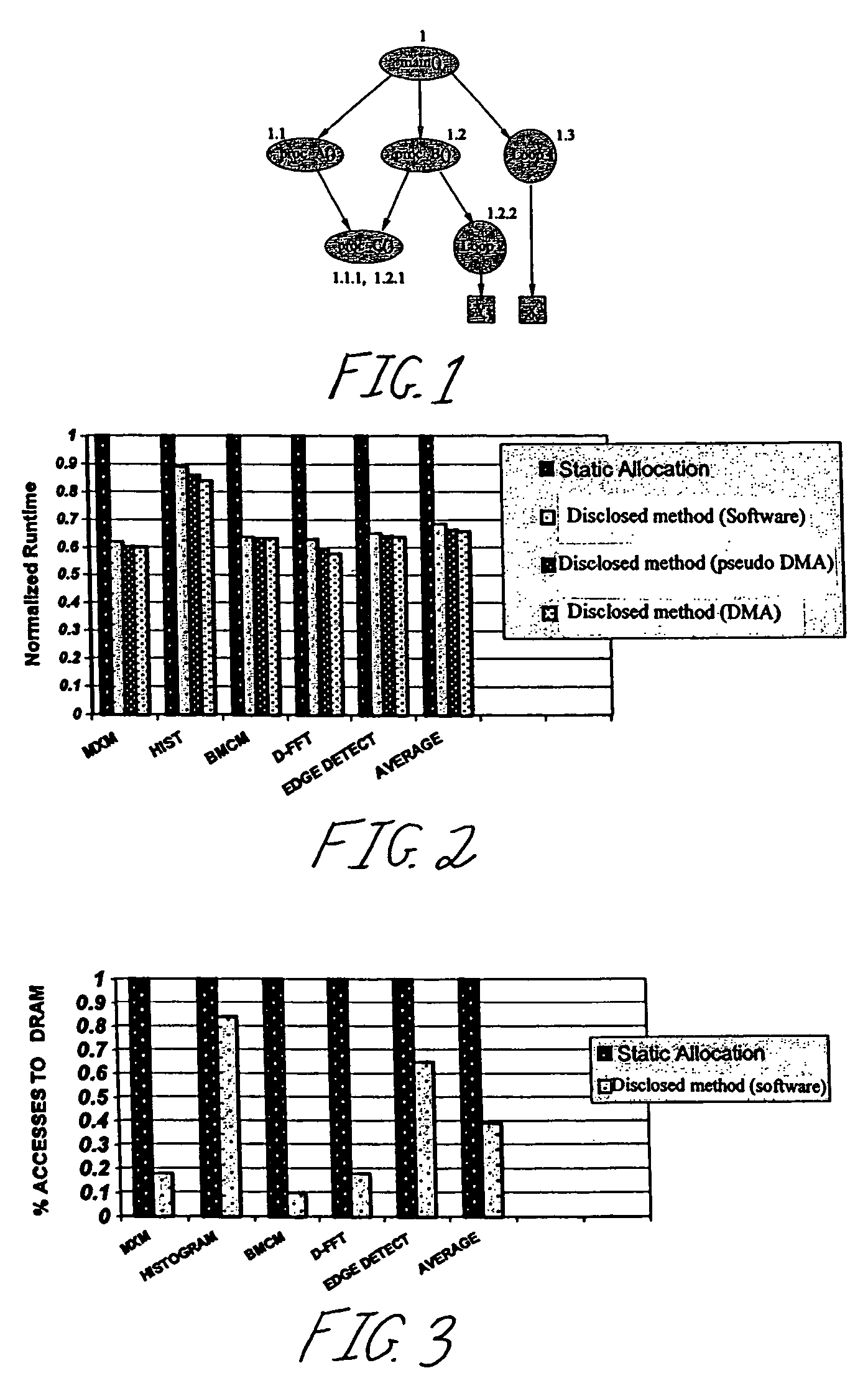

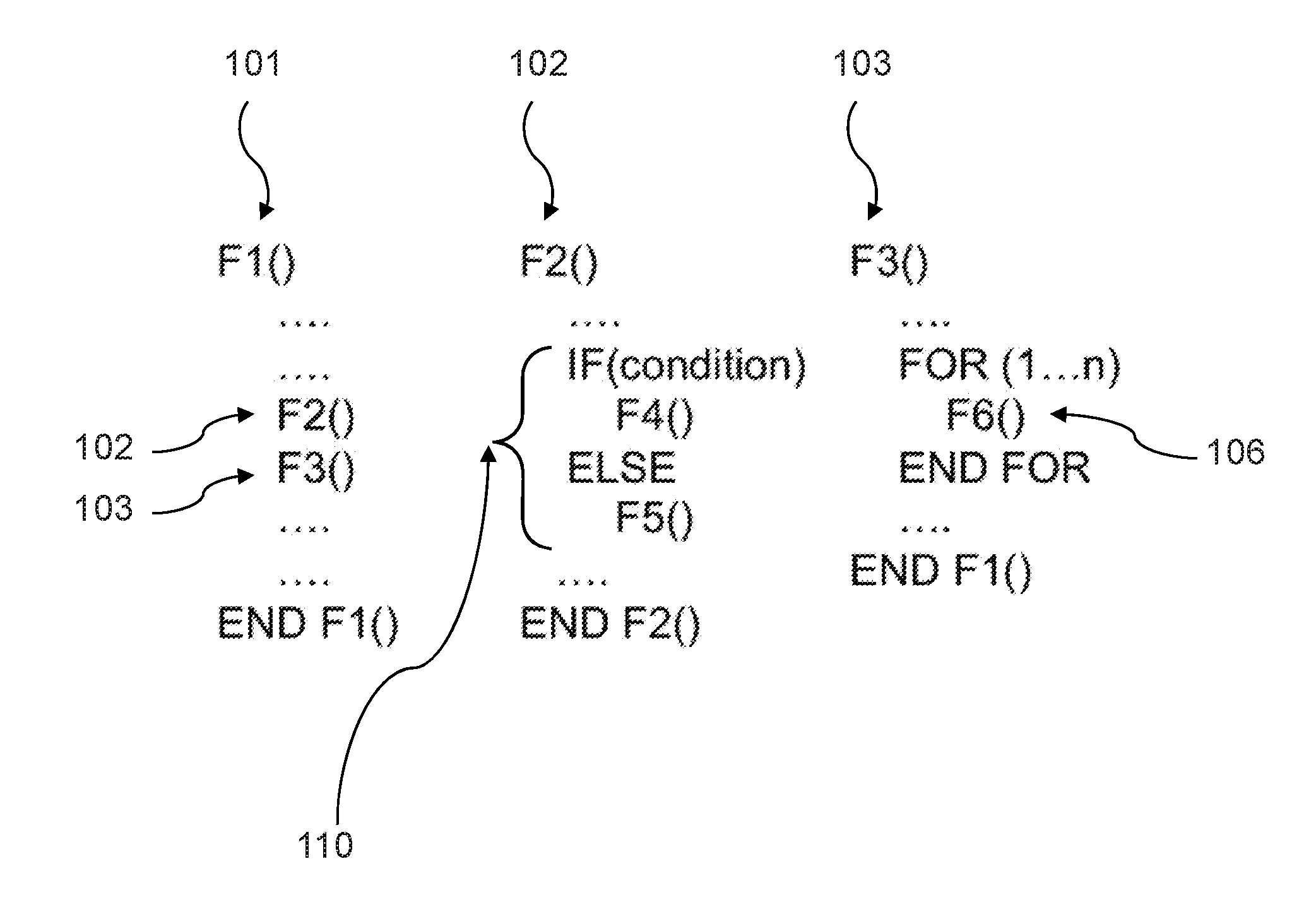

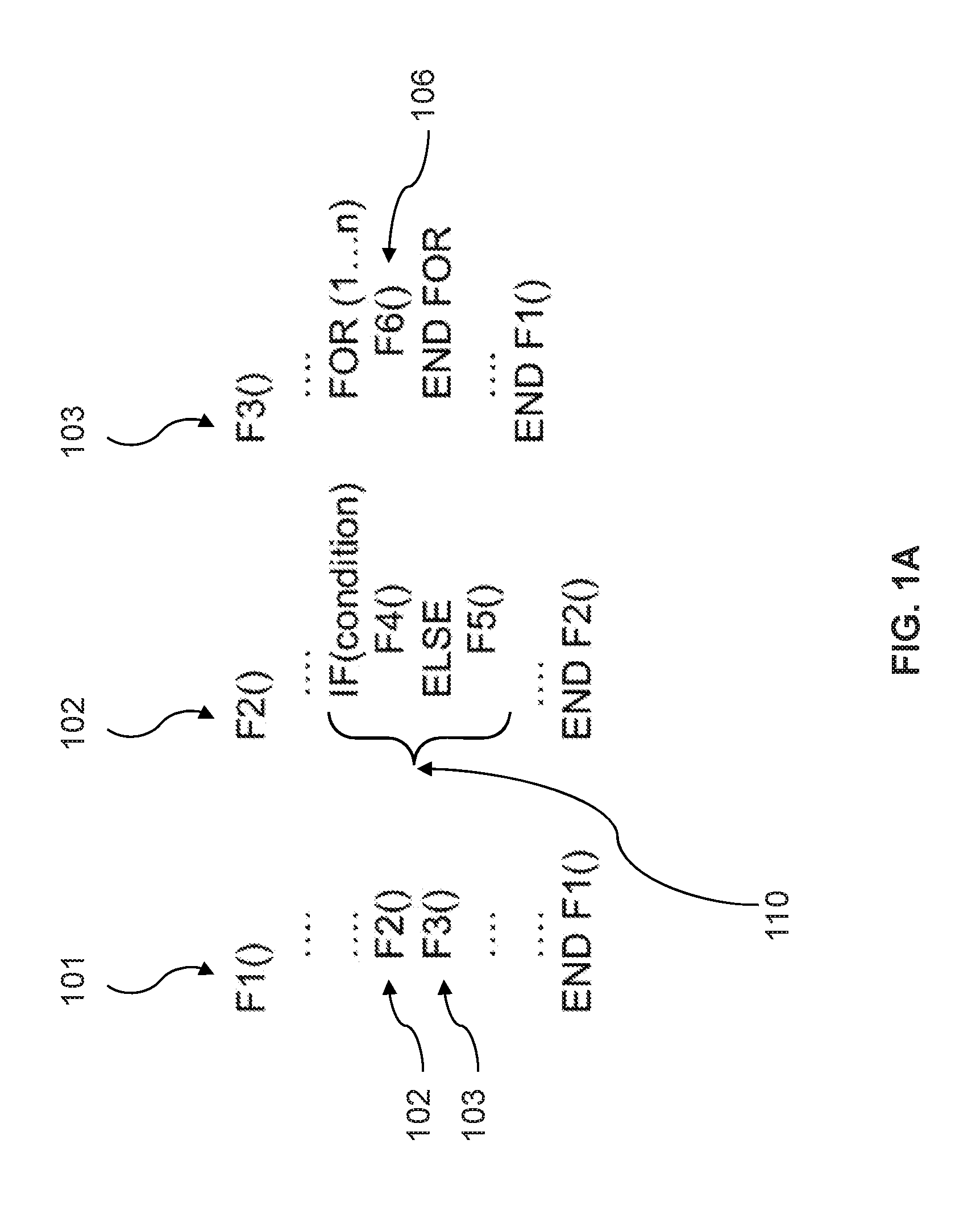

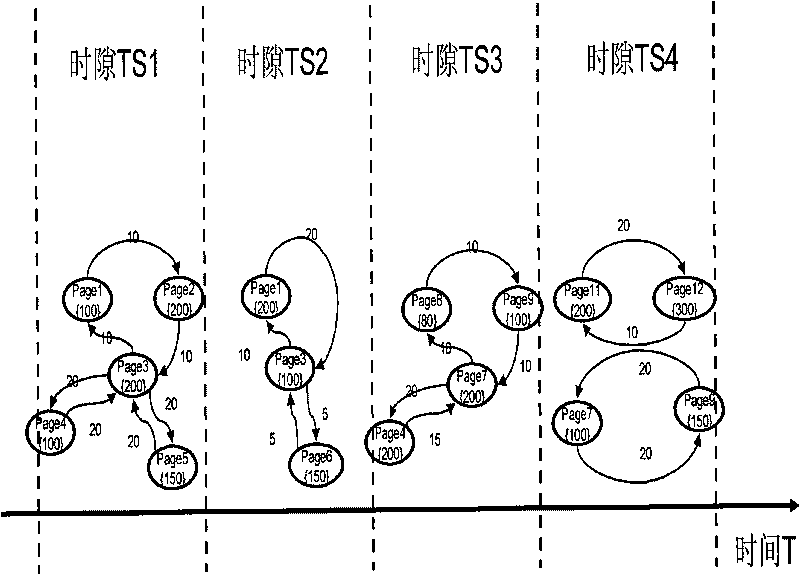

Global call control flow graph for optimizing software managed manycore architectures

InactiveUS20160170725A1Easy to useEfficient implementationSoftware engineeringProgram controlControl flowGraphics

Software Managed Manycore (SMM) architectures with scratch pad memory for reach core are a promising solution for scaling memory. In these architectures the code and data of the tasks mapped to the cores is explicitly managed by the compiler and often require inter-procedural information and analysis. But, a call graph of the program does not have enough information, and the Global CFG has too much information. Most new techniques informally define and use GCCFG (Global Call Control Flow Graph)—a whole program representation that succinctly captures the control-flow and function call information—to perform inter-procedural analysis. Constructing GCCFGs for several cases in common applications. The present disclosure provides unique graph transformations to formally and correctly construct GCCFGs for optimal compiler management of manycore systems.

Owner:ARIZONA STATE UNIVERSITY

Compiler-driven dynamic memory allocation methodology for scratch-pad based embedded systems

InactiveUS20060080372A1Avoid overheadReduce overheadEnergy efficient ICTProgram controlDistribution methodAccess time

A highly predictable, low overhead and yet dynamic, memory allocation methodology for embedded systems with scratch-pad memory is presented. The dynamic memory allocation methodology for global and stack data (i) accounts for changing program requirements at runtime; (ii) has no software-caching tags; (iii) requires no run-time checks; (iv) has extremely low overheads; and (v) yields 100% predictable memory access times. The methodology provides that for data that is about to be accessed frequently is copied into the SRAM using compiler-inserted code at fixed and infrequent points in the program. Earlier data is evicted if necessary.

Owner:UNIV OF MARYLAND

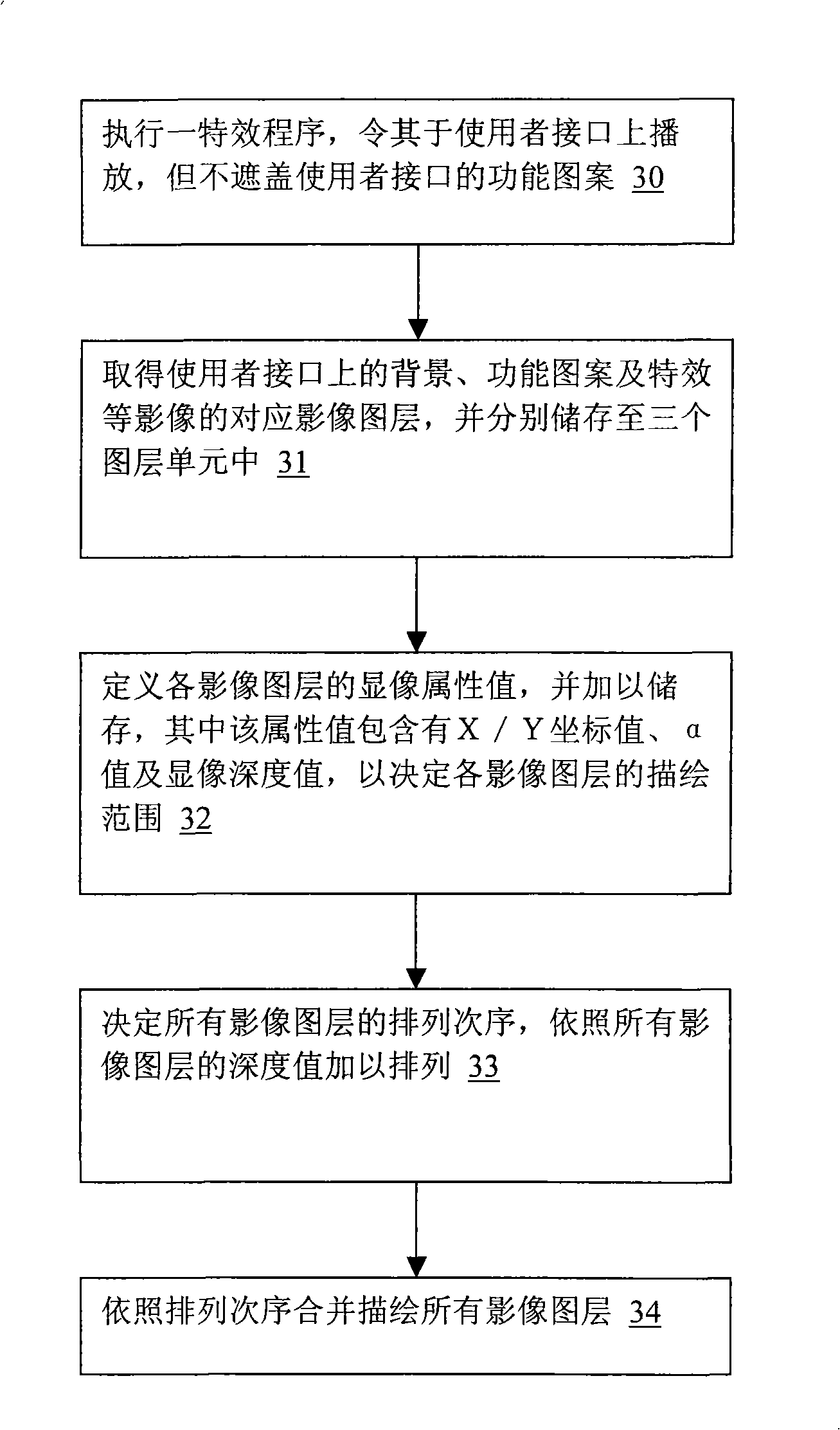

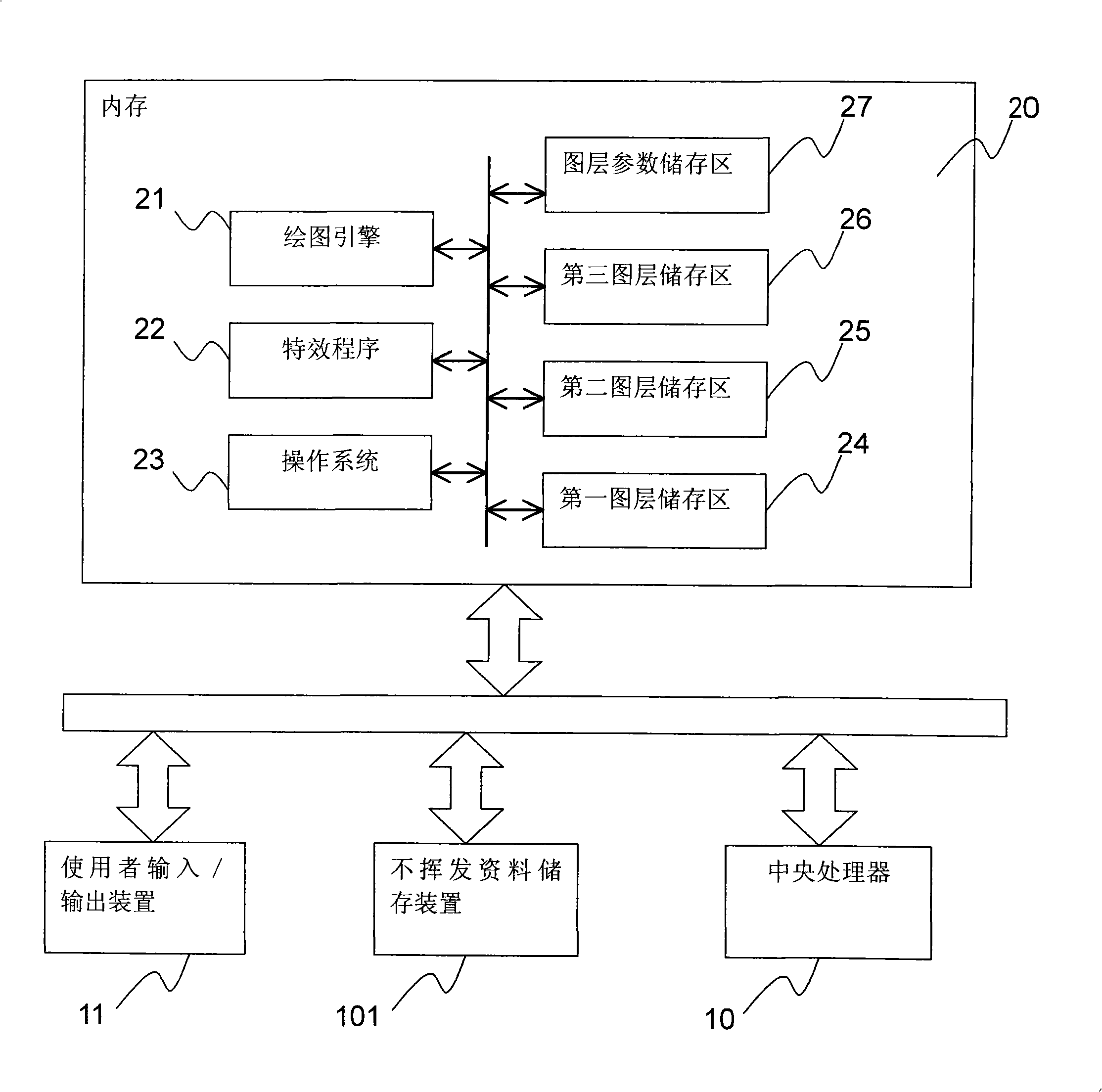

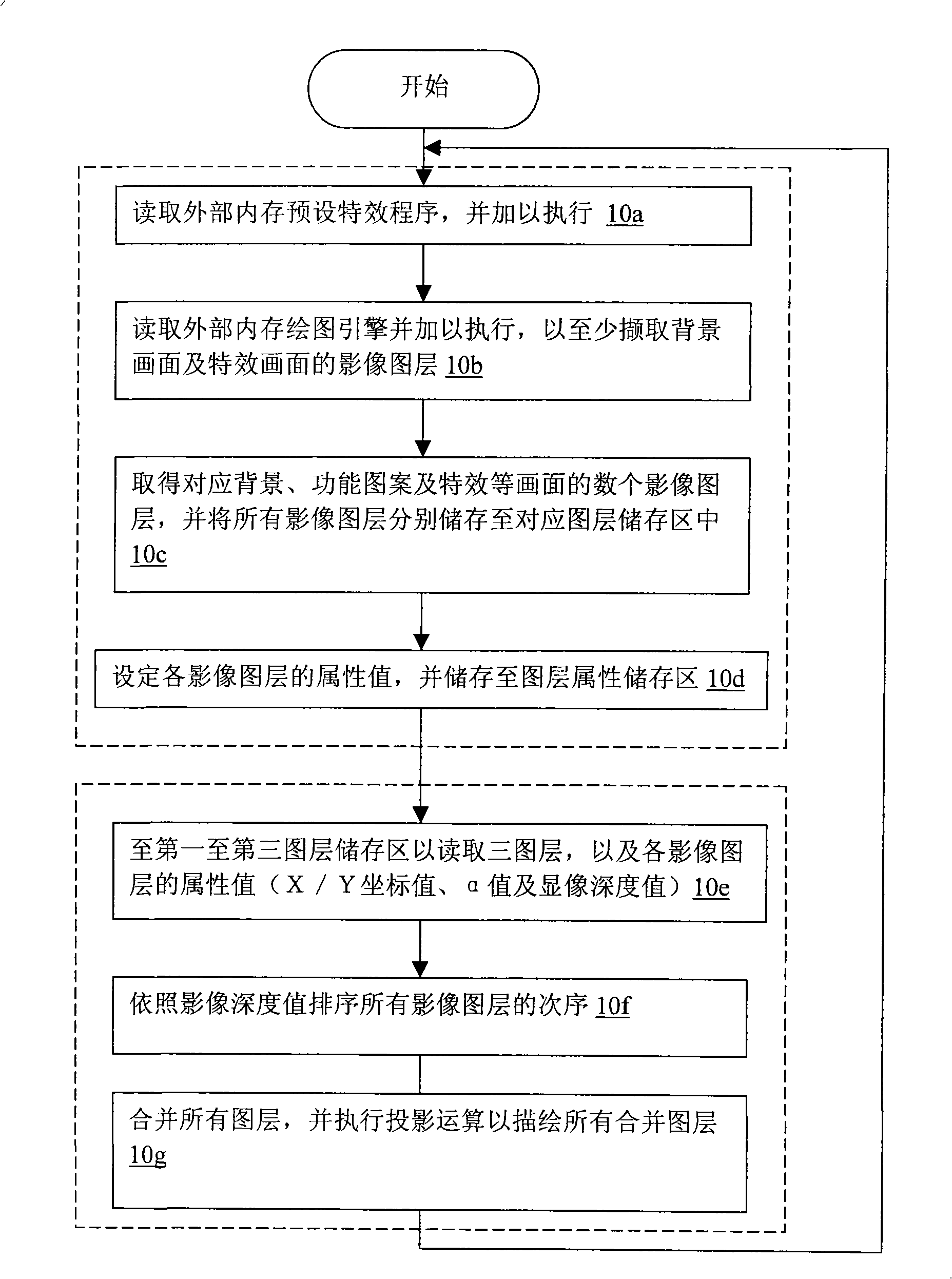

Dynamic display method and system for multi-layer plane graph layer

InactiveCN101315758AIncrease variabilityDazzling visual effectsCathode-ray tube indicatorsDigital output to display deviceComputer graphics (images)Dynamic imaging

The invention relates to a dynamic imaging method for multilayer flatten layers and a system thereof, wherein, the imaging system is mainly provided with a graphic engine, a special effect procedure, a plurality of layer storage areas and a scratch pad area for layer attributes in an external memory; first a special effect procedure is carried out before leading a user interface to assume a dynamic imaging method, then three types of image layers corresponding to a background picture, a functional picture and a special effect picture which are on the user interface are obtained, afterward imaging attribute values to which the image layers belong are defined for the following merged describing for a plurality of image layers; namely, the sequence of all the image layers is determined by the imaging depth value of each image layer, the merged describing of all the image layers is carried out according to the sequence; therefore, a plurality of functional patterns of the functional picture can be integrated into the user background and the special effect picture and present an unanticipated gorgeous user interface picture.

Owner:BROGENT TECH

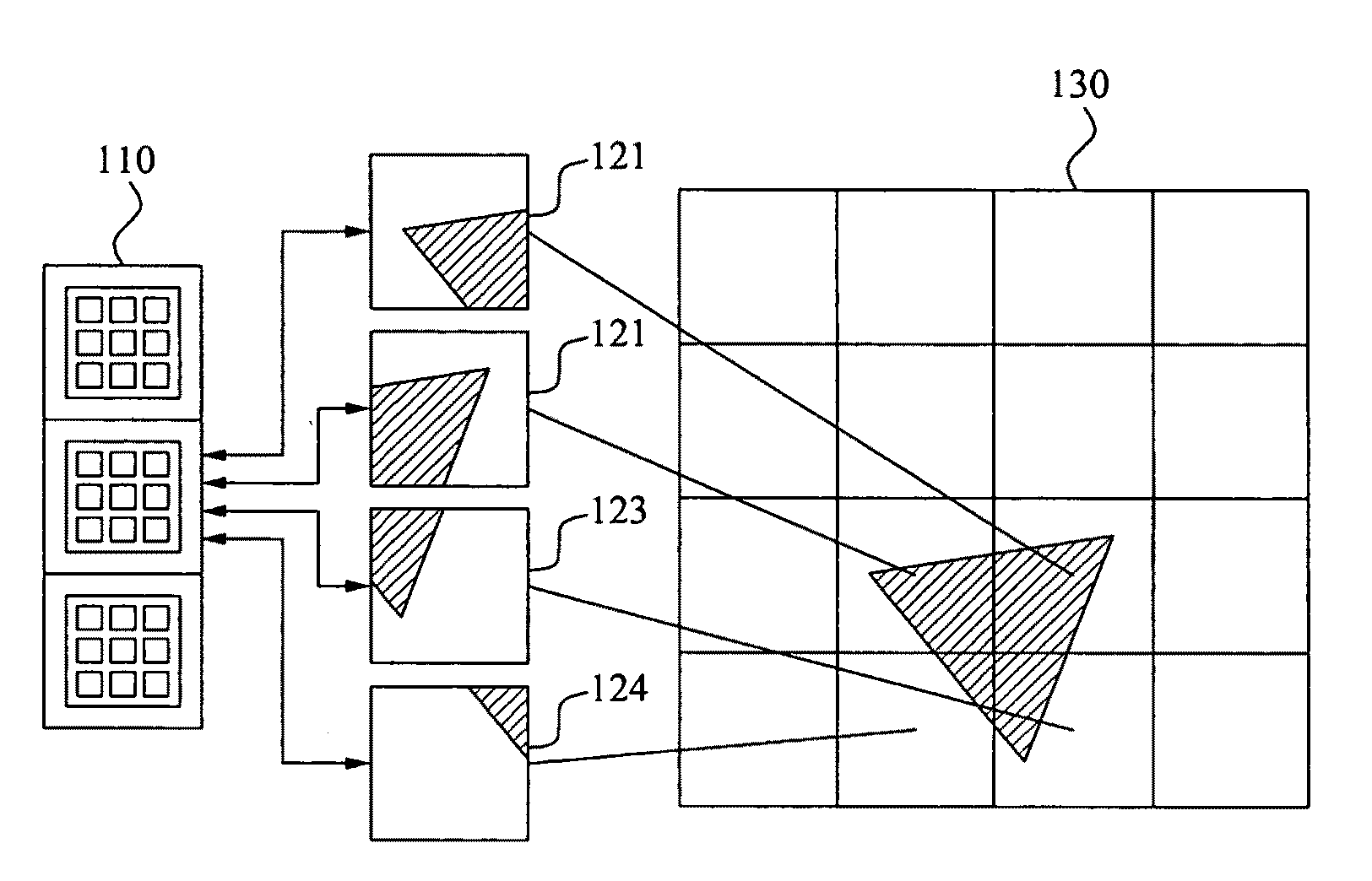

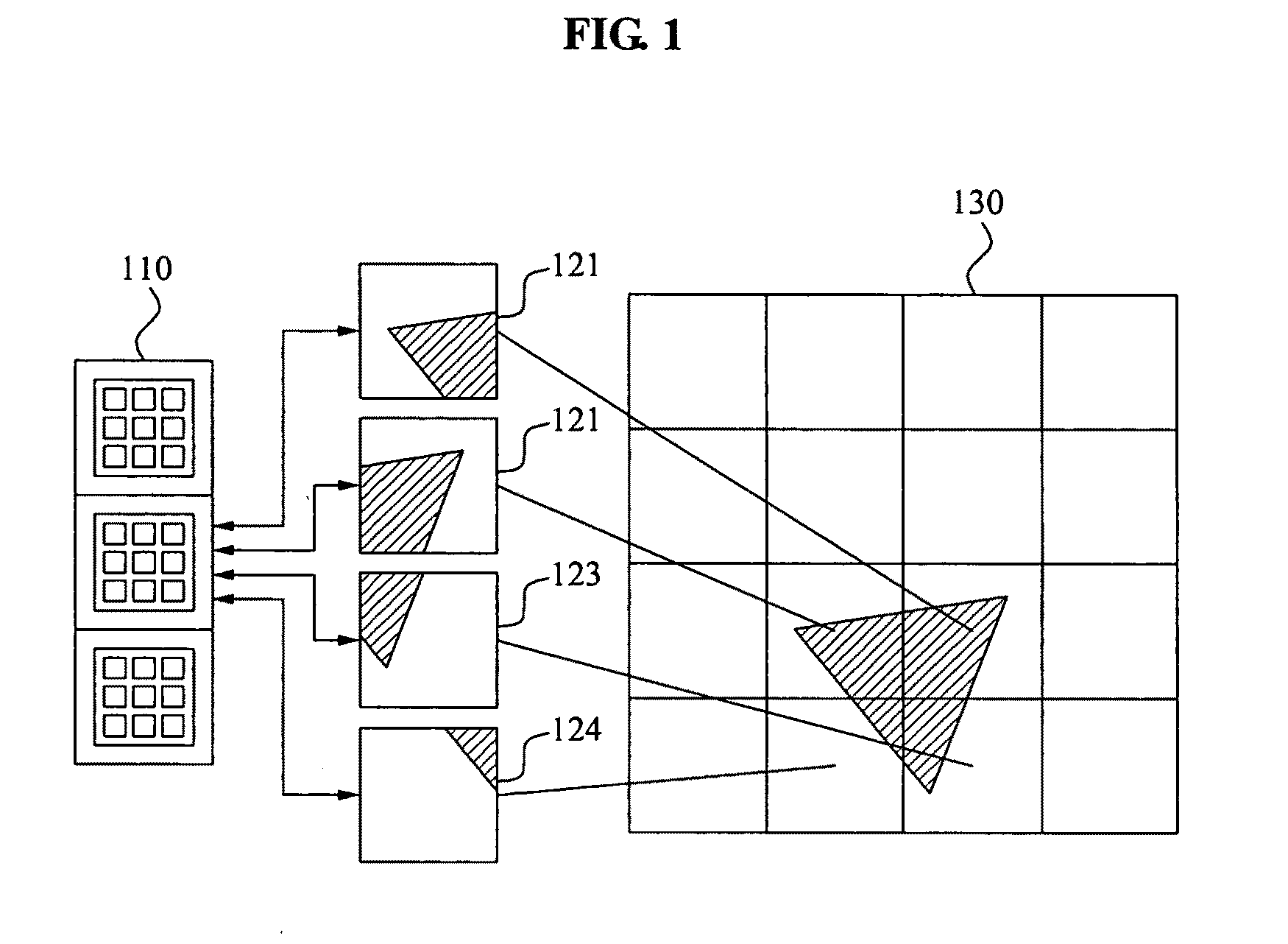

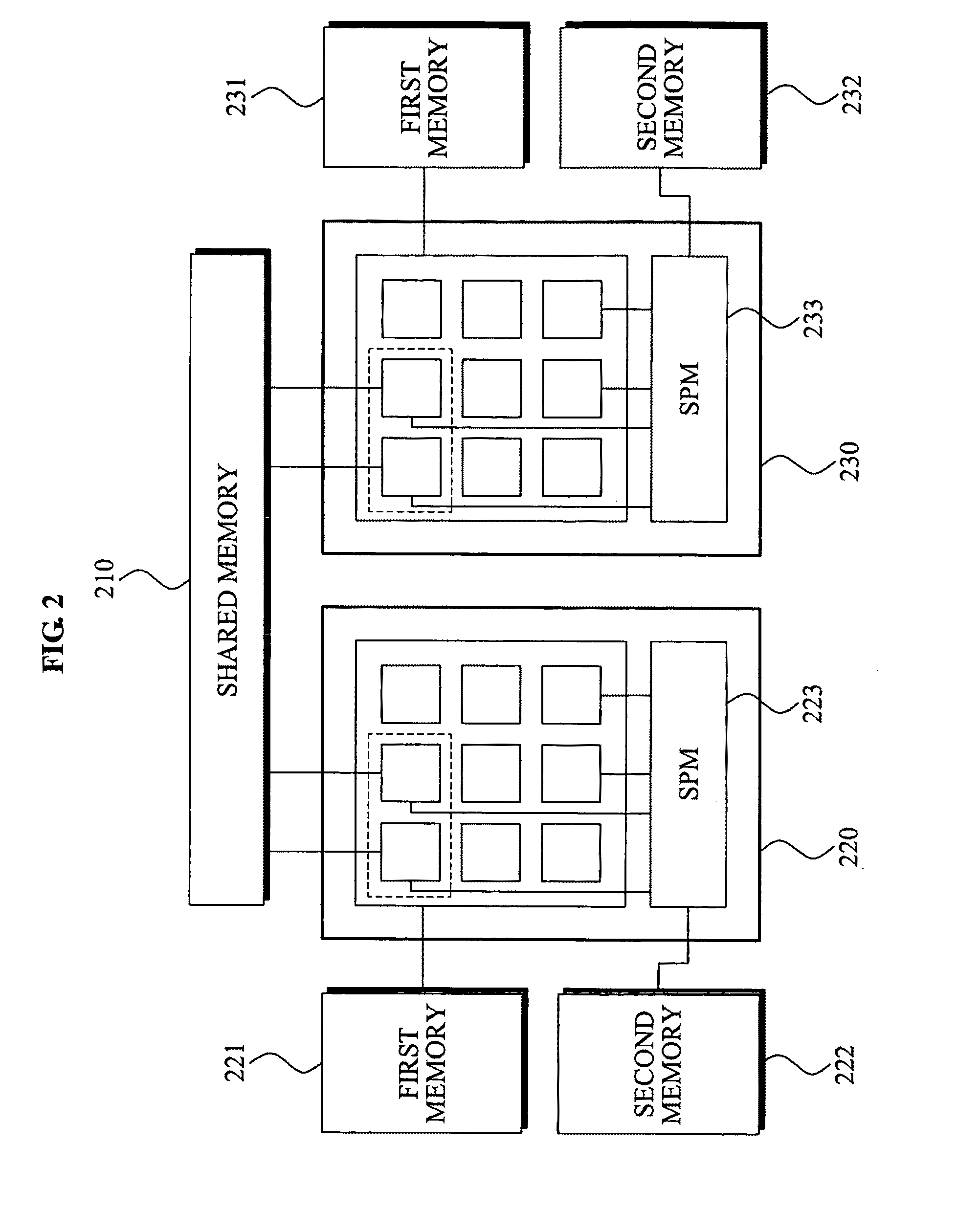

System and method of rendering 3D graphics

A system and method of rendering three-dimensional (3D) graphics. The system for rendering 3D graphics may include a plurality of cores including a scratch pad memory, a first memory to perform a control flow, a second memory for loop acceleration, and a shared memory to interpolate with the plurality of cores.

Owner:SAMSUNG ELECTRONICS CO LTD

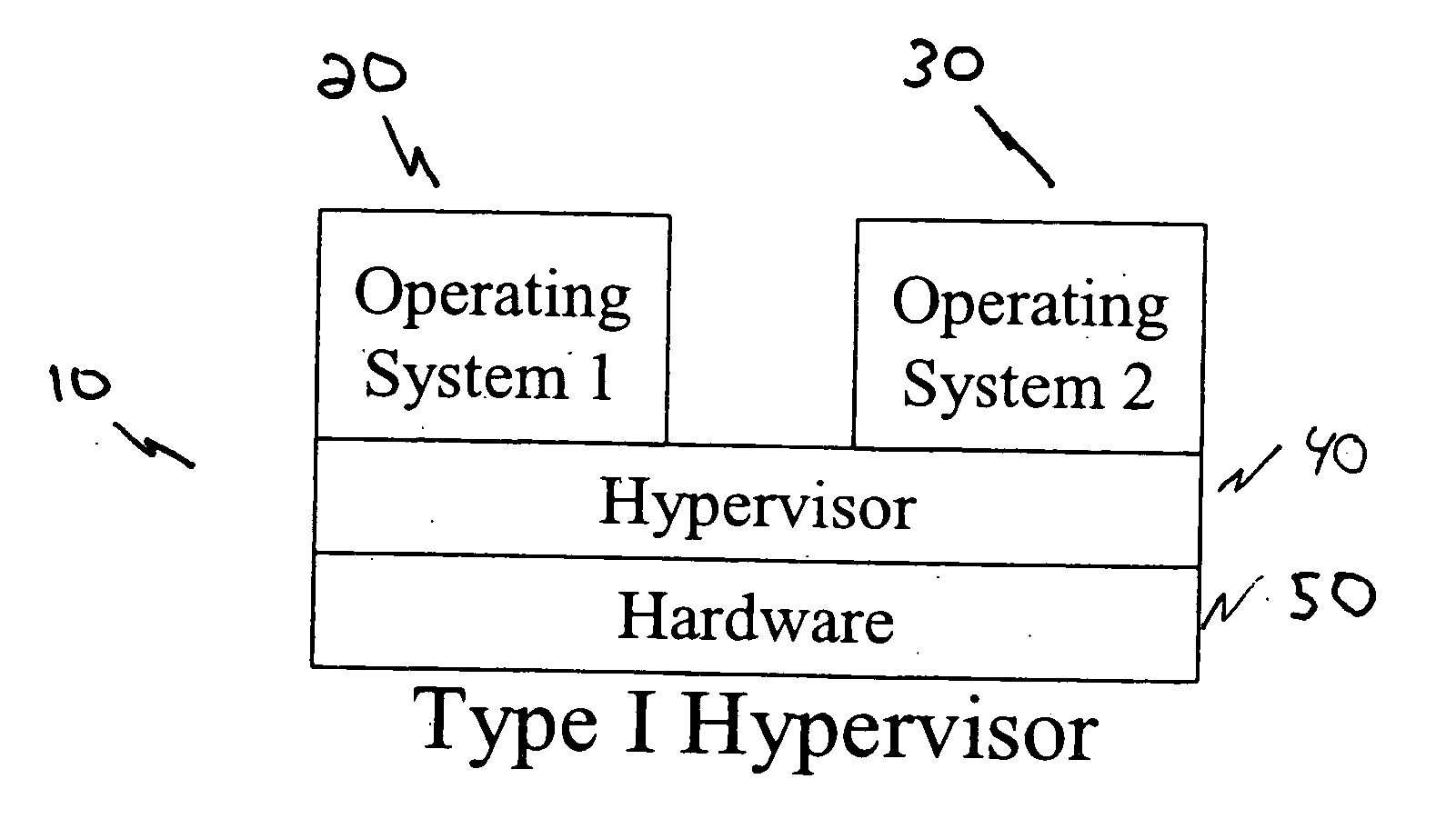

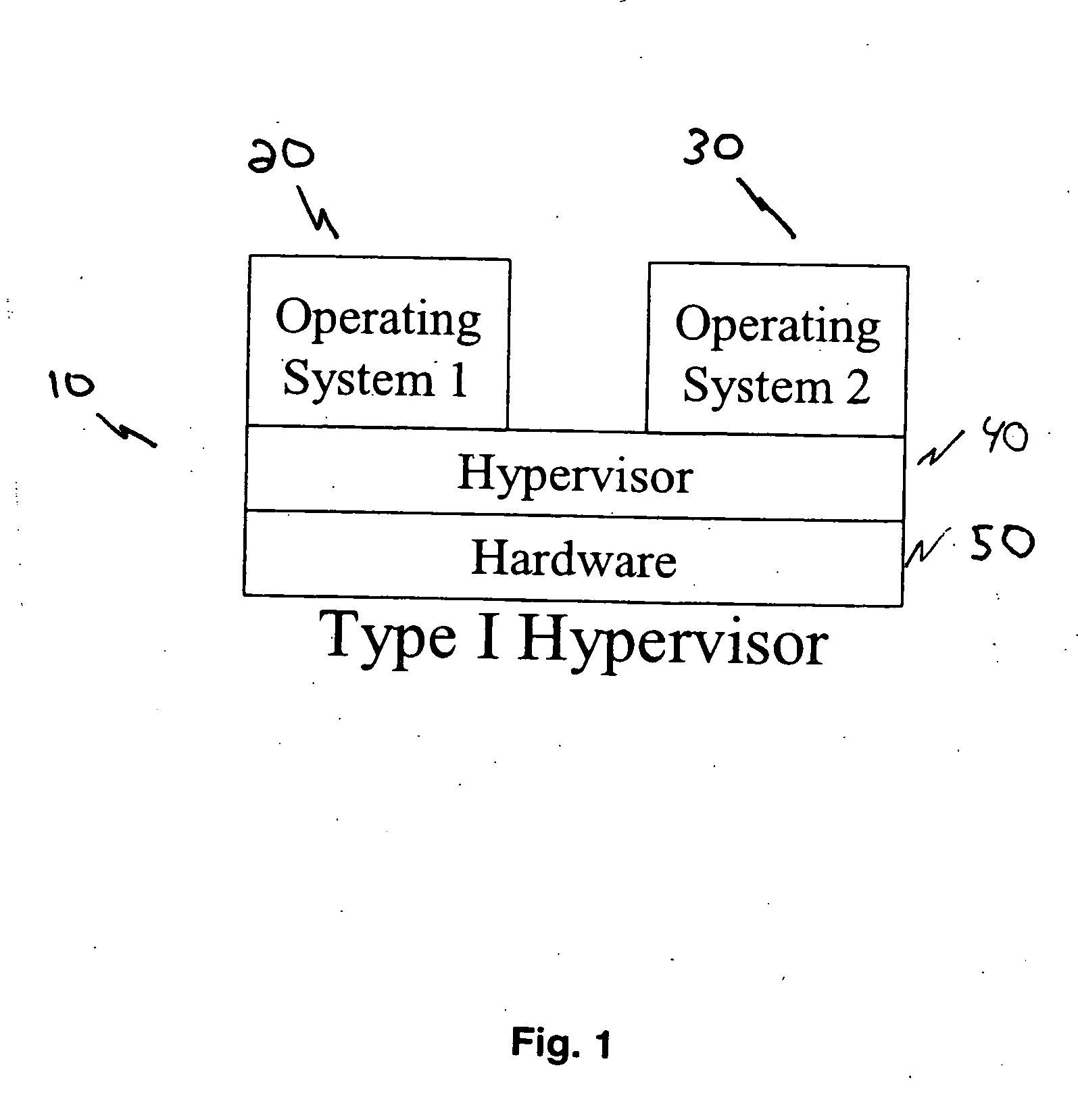

Hypervisor area for email virus testing

ActiveUS20070240216A1Improve performanceProvide protectionMemory loss protectionError detection/correctionOperational systemClient-side

Owner:LENOVO PC INT

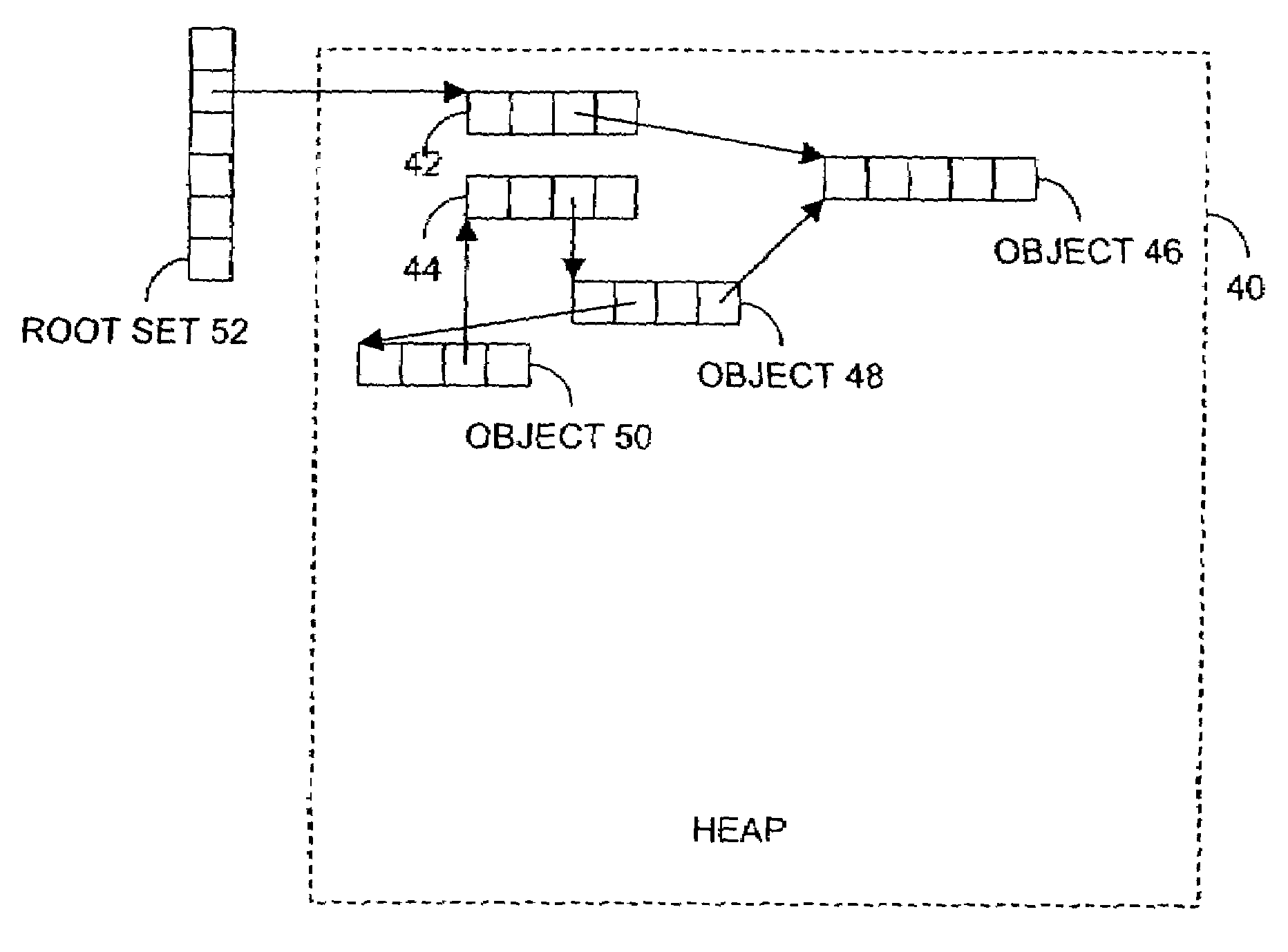

Avoiding remembered-set maintenance overhead for memory segments known to be in a collection set

ActiveUS7209935B2Reduce expensesData processing applicationsMemory adressing/allocation/relocationWaste collectionComputer science

A garbage collector that employs the train algorithm to manage a generation in a computer system's dynamically allocated heap maintains for each of the generation's cars a respective remembered set that identifies all locations where references to objects in that car have been found by scanning locations identified by the mutator as having been modified. To avoid some of the expense of remembered-set updating, the collector refrains from attempting to add to a remembered set any reference located in a car that will be collected during the next collection increment. Additionally, if no mutator operation will occur before a collection set of one or more cars will be collected, any reference located outside that collection set but referring to an object within the collection set is not recorded in a remembered set but is recorded instead in a scratch-pad list of entries that identify references to collection-set objects that need to be evacuated.

Owner:ORACLE INT CORP

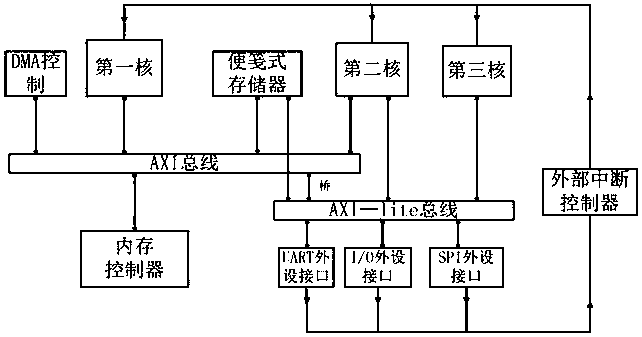

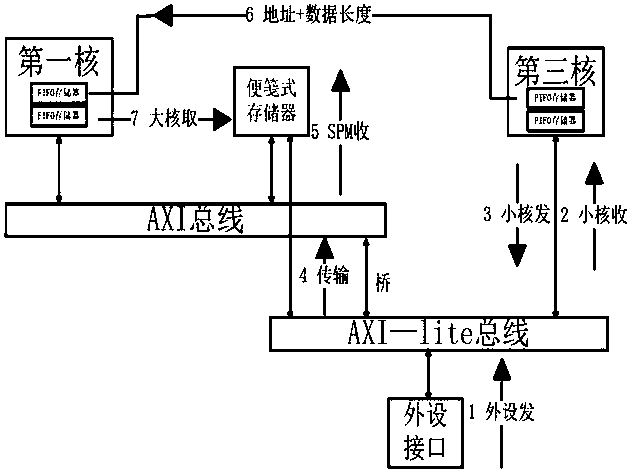

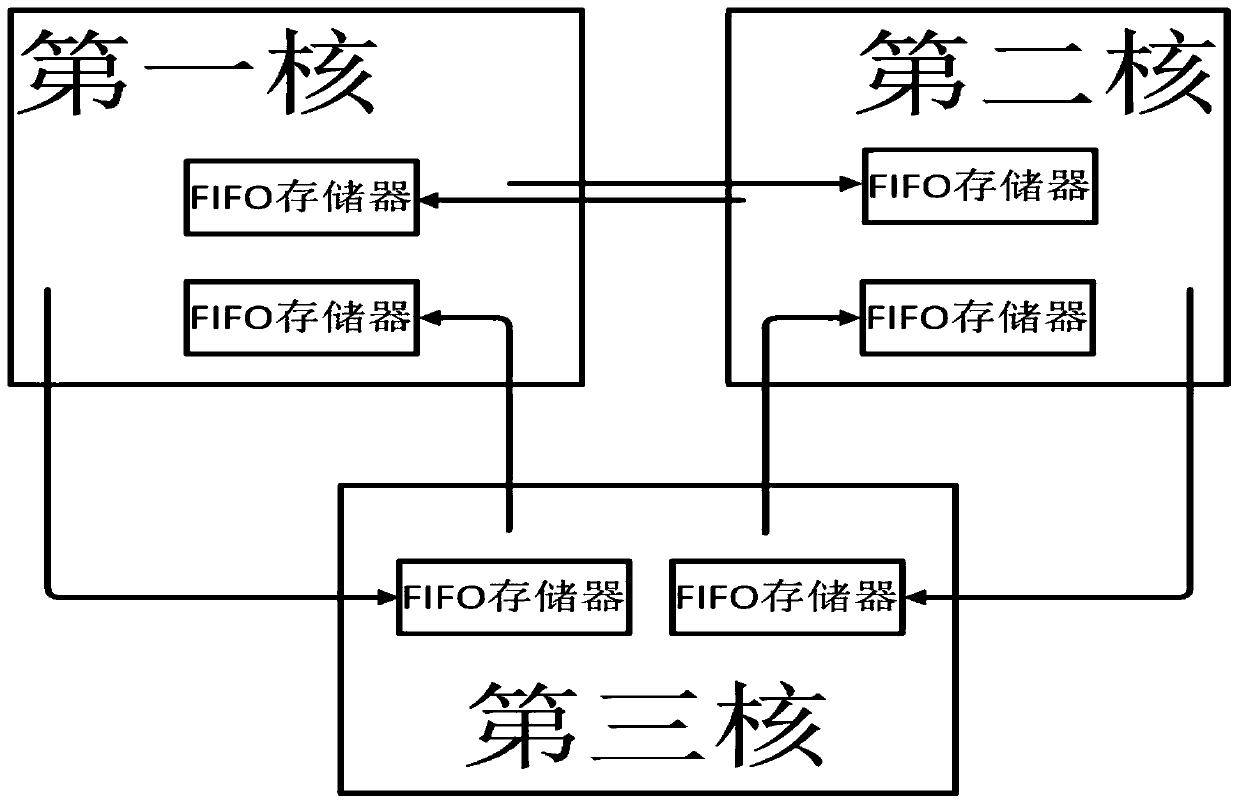

Heterogeneous multi-core microprocessor based on multi-layer bus

ActiveCN110347635AImprove processing efficiencyImprove computing powerDigital computer detailsElectric digital data processingProcessing coreNetwork packet

The invention discloses a heterogeneous multi-core microprocessor based on a multilayer bus. The heterogeneous multi-core microprocessor comprises a plurality of processing cores for uniform addressing, wherein the plurality of processing cores have different pipeline structures; the plurality of processing cores are connected through an AXI bus with bridge connection; the AXI bus with bridge connection is connected with a notepaper type memory; data packets are sent and read between every two processing cores through a scratch pad memory; a data packet head address and a data packet length are directly sent between every two processing cores so as to assist in completing the transmission of a data packet between the two processing cores; and the AXI bus with bridging is also connected with a peripheral interface, and the processing cores perform access control on external equipment through the peripheral interface. According to the heterogeneous multi-core microprocessor based on themulti-layer bus, disclosed by the invention, the communication delay can be reduced.

Owner:XIAN UNIV OF TECH

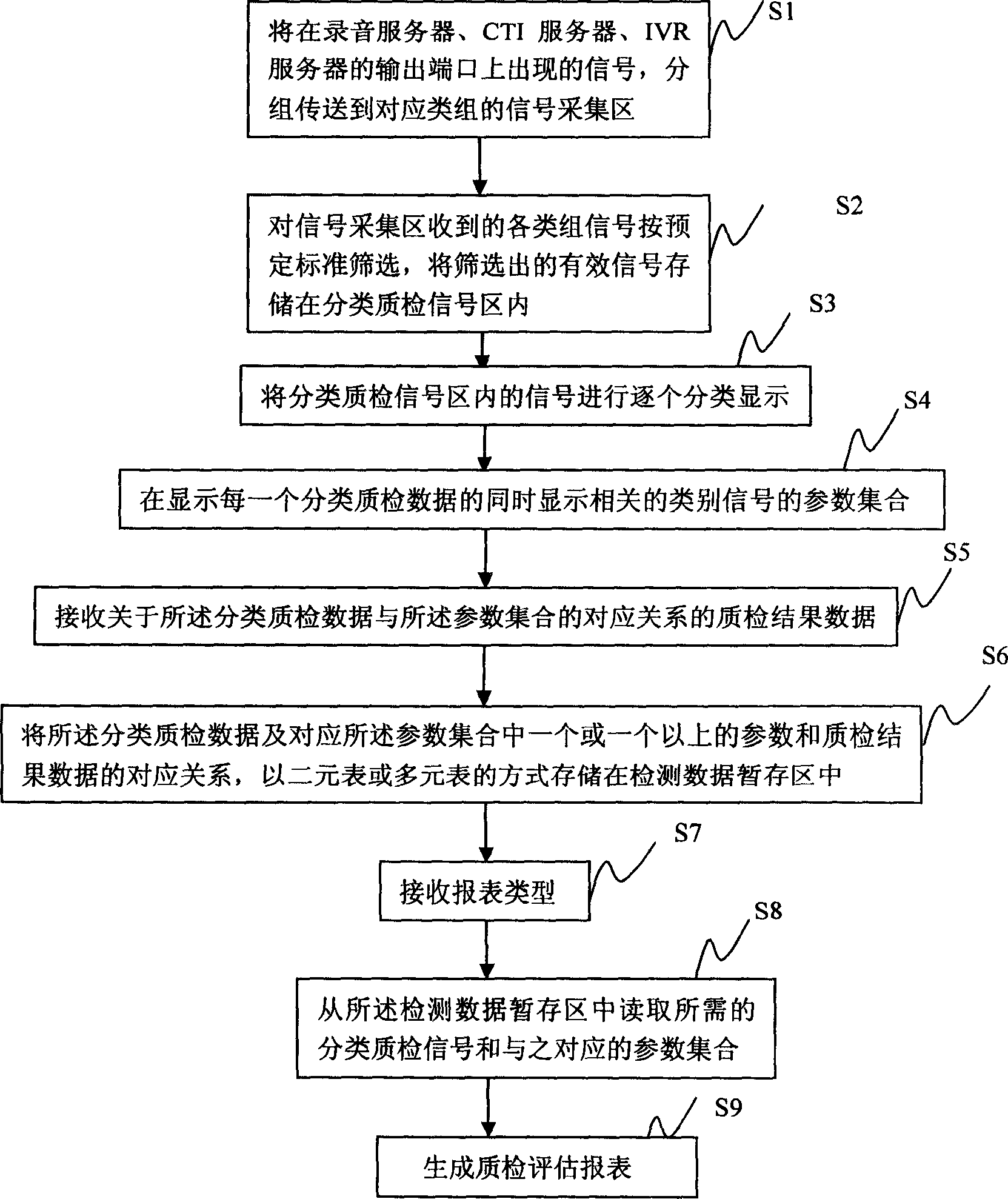

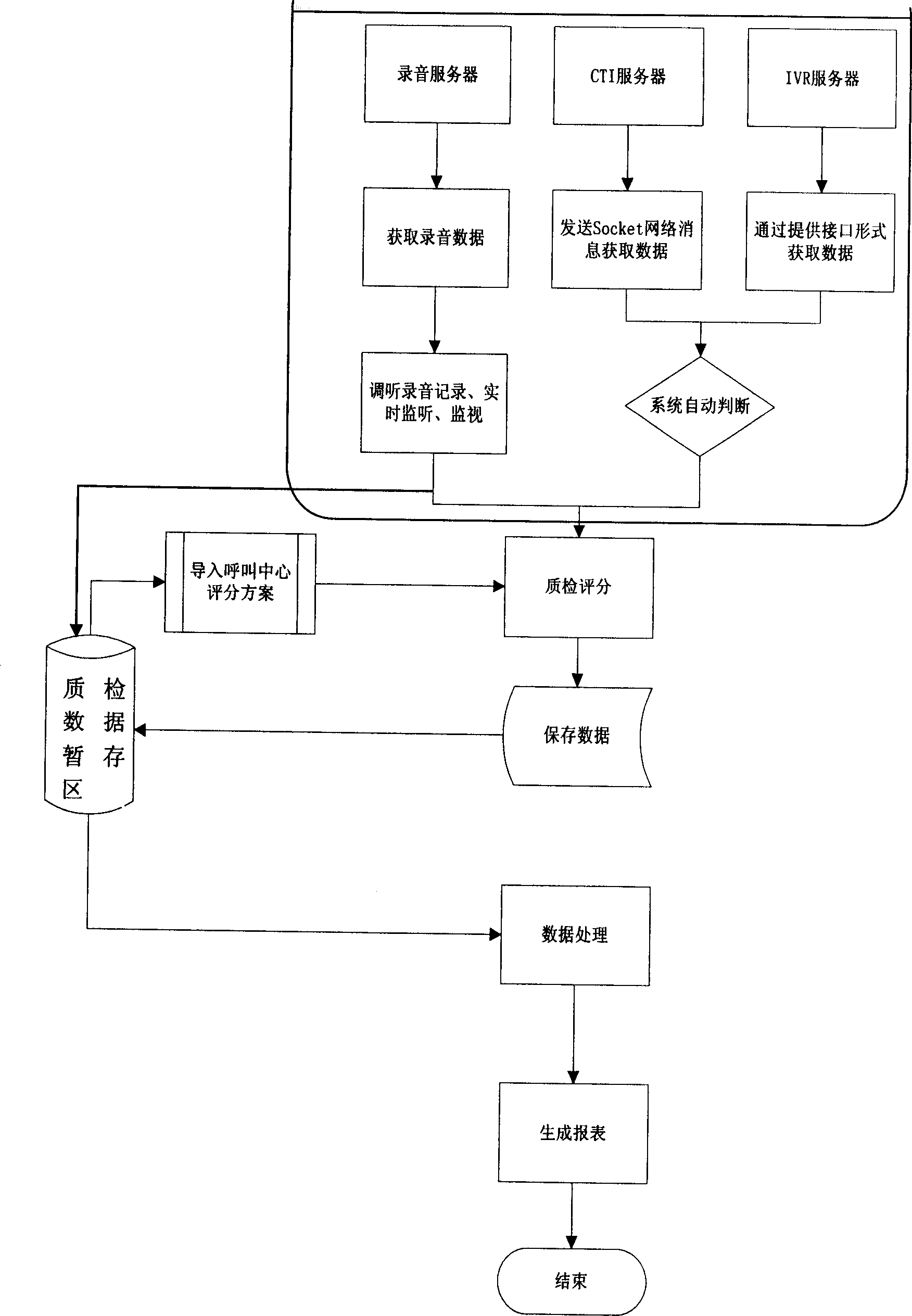

Method for generating quality detecting data of calling center

InactiveCN1859457AScoring objectiveImprove the quality of workSupervisory/monitoring/testing arrangementsPerformance indexComputer science

The present invention discloses calling centre quality testing data generation method, referring to signal detection technology. It contains screening signal collecting server output port signal, storing effective signal in classifying quality testing signal area; displaying signal in classifying quality testing signal area and relevant parameter congregation, generating quality testing result data, receiving quality testing result data and storing in quality testing data scratch pad area; reading corresponded parameter congregation and quality testing result data to generate quality testing evaluating report.

Owner:CALLRAY COMM

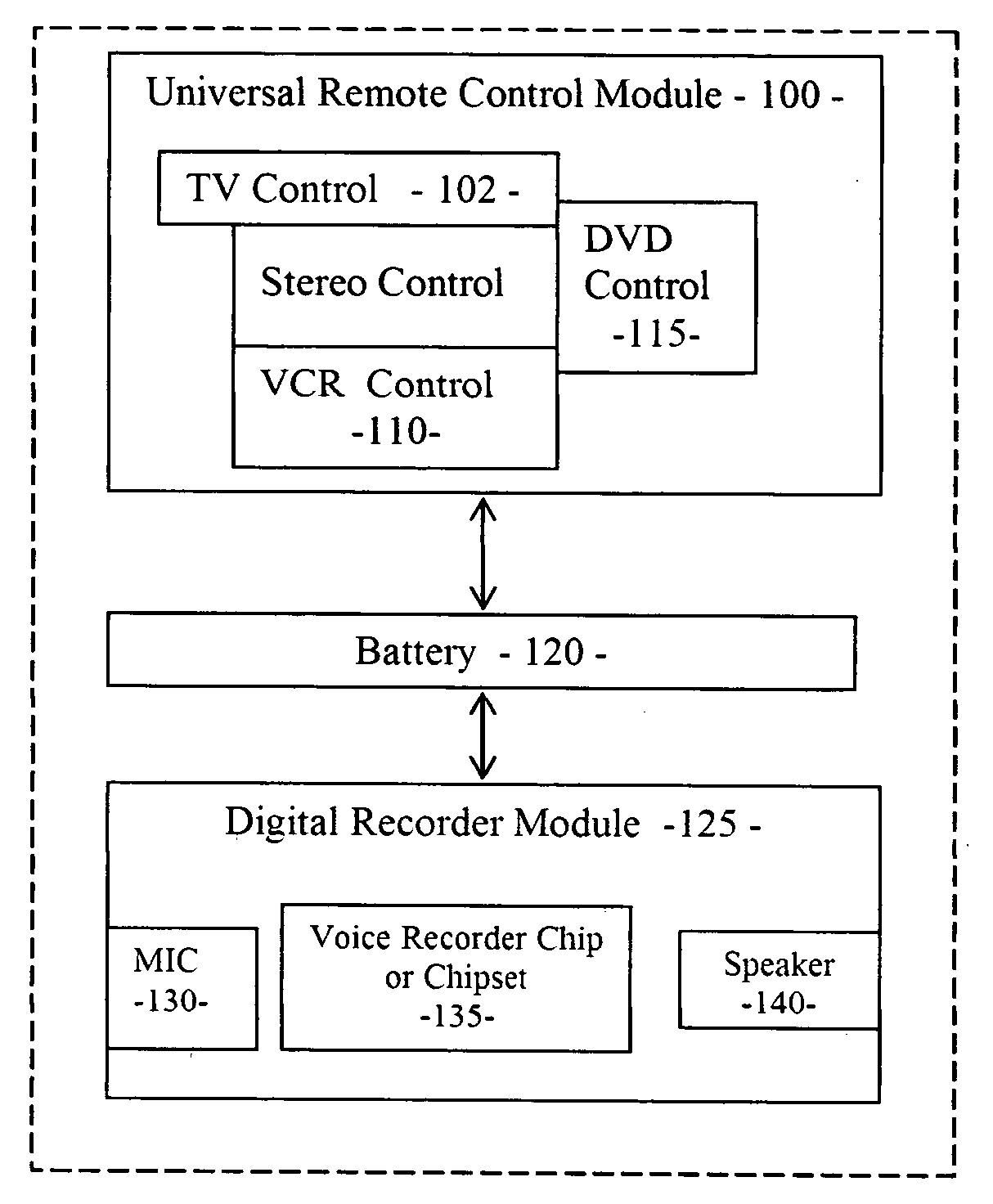

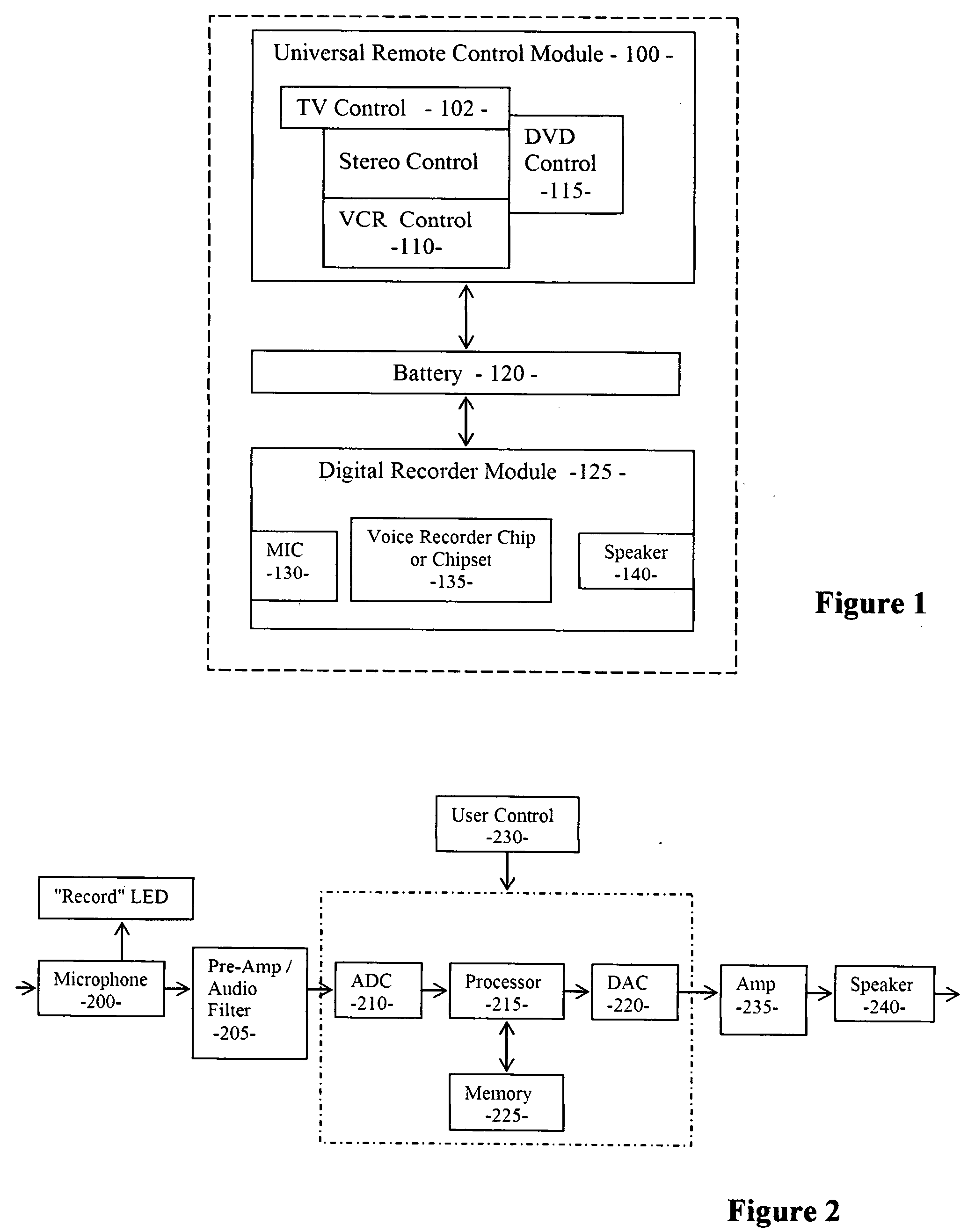

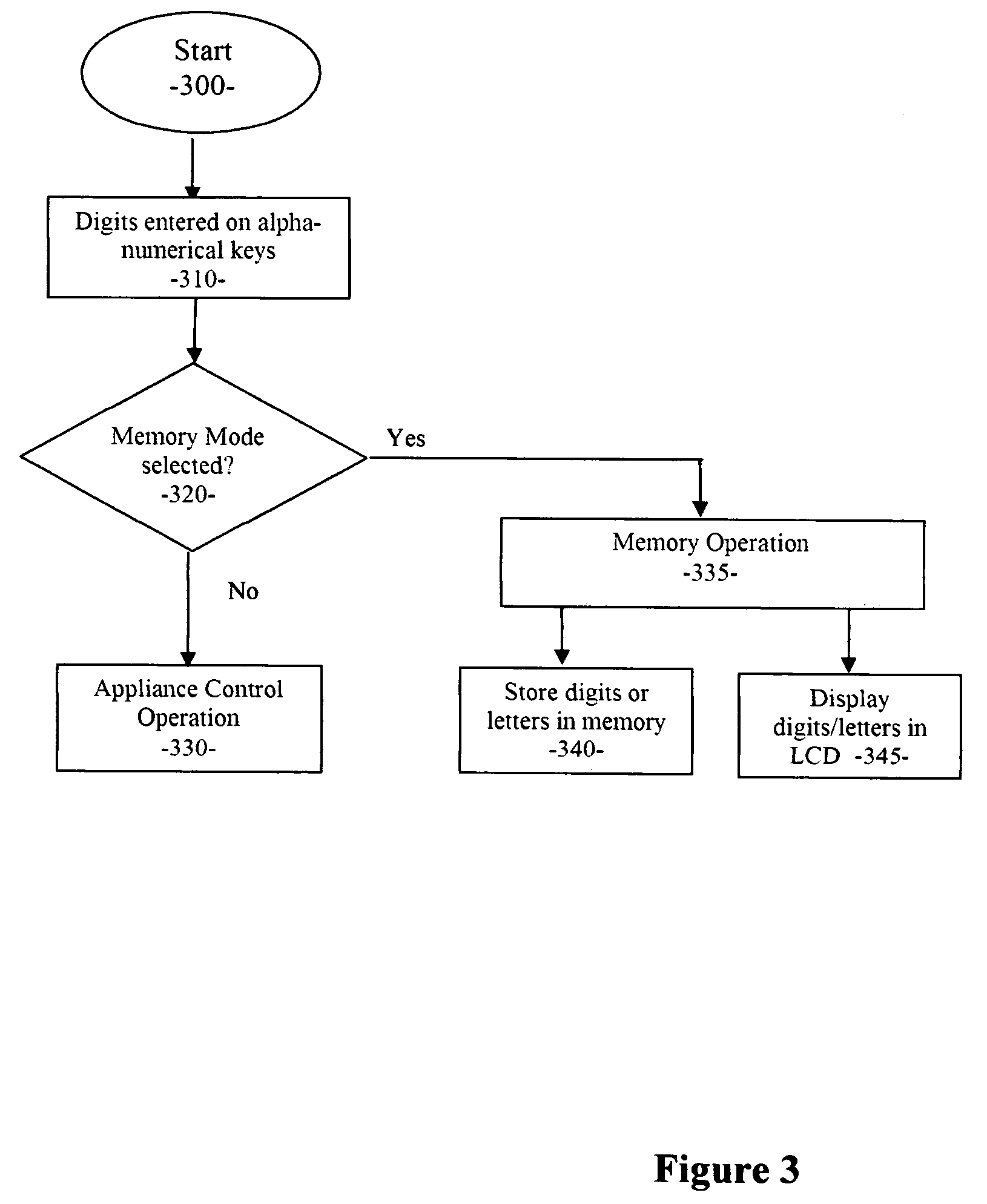

Universal remote controller with voice and digital memory

InactiveUS20060132326A1Television system detailsElectric signal transmission systemsWeb siteRemote control

An improved universal remote control unit (URC) for controlling electronic appliance units. The URC unit has the typical remote controller module for controlling appliances such as TV, stereo, VCR or DVD. Additionally, the URC has a scratch pad memory for storing telephone numbers and web site information entered through the URC unit's alphanumeric keys. When activated, the key pad entries are stored in the memory, instead of being used to control the appliance. The URC unit further has a digital recorder module that can be implemented with a microphone, a voice recorder chip and a speaker, all integrated with the URC unit. The digital recorder module can even use the battery that is typically used by the URC unit. The URC unit further has a display screen to display the information stored in and recalled from the memory.

Owner:FANG CALVIN C +1

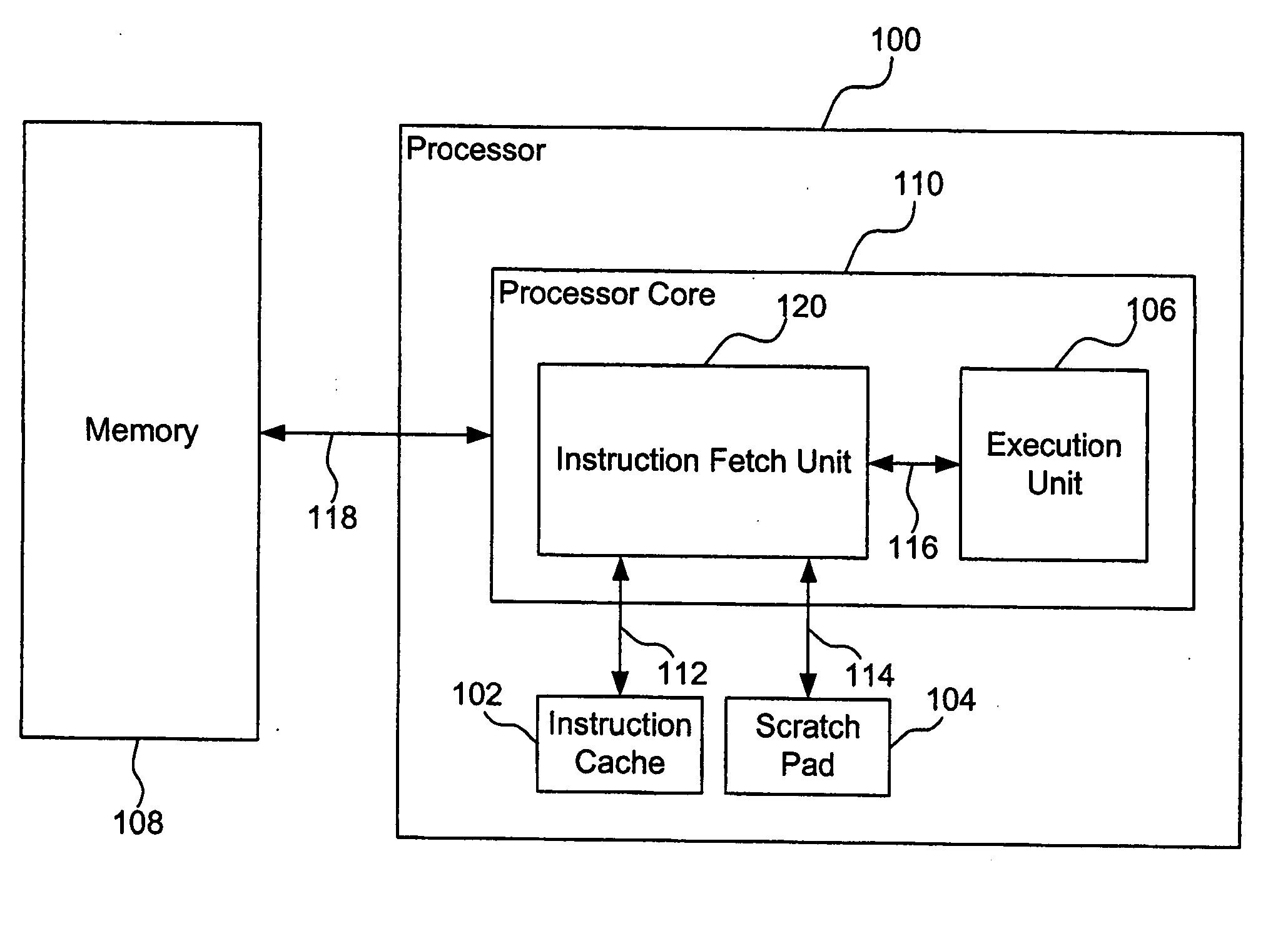

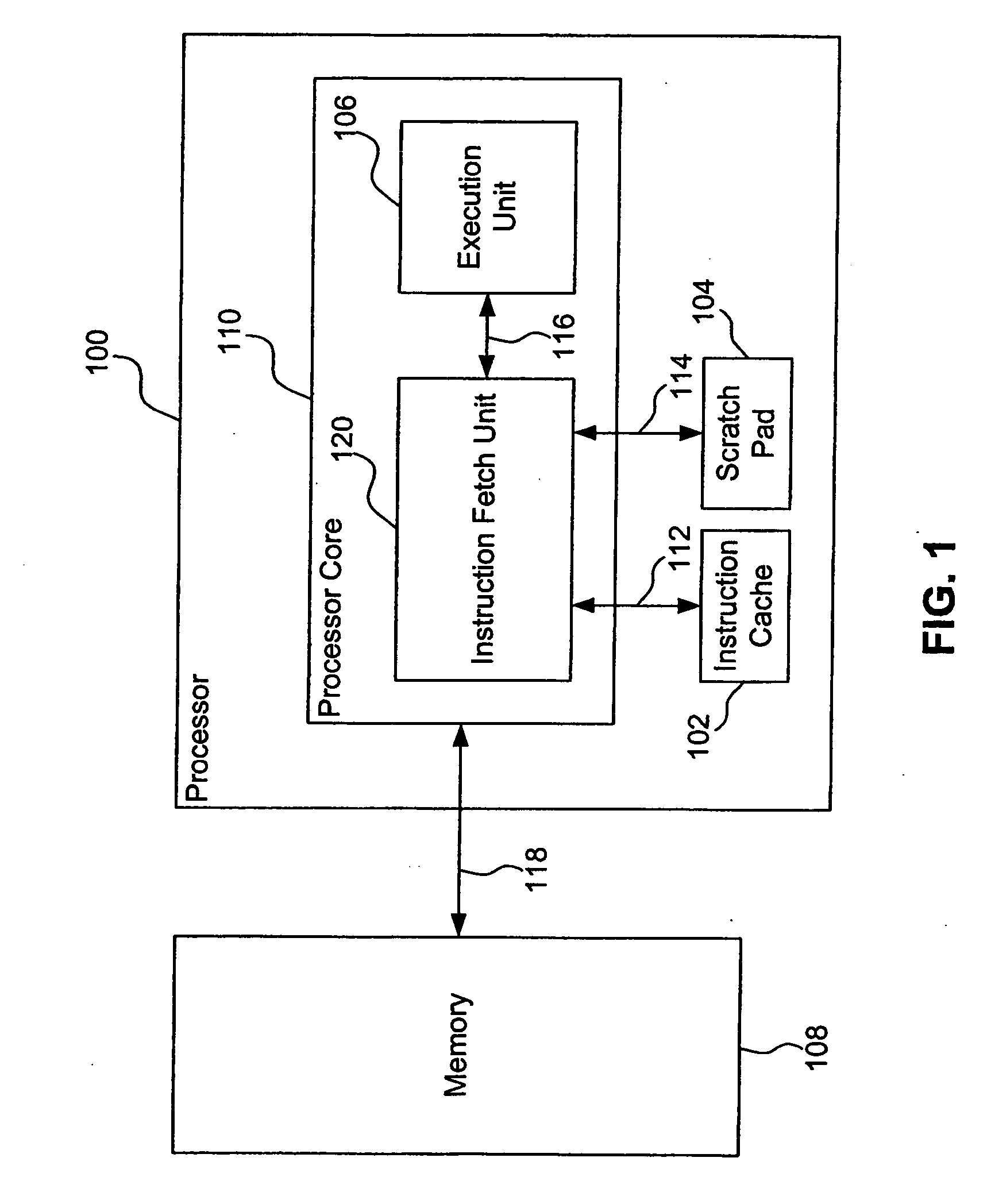

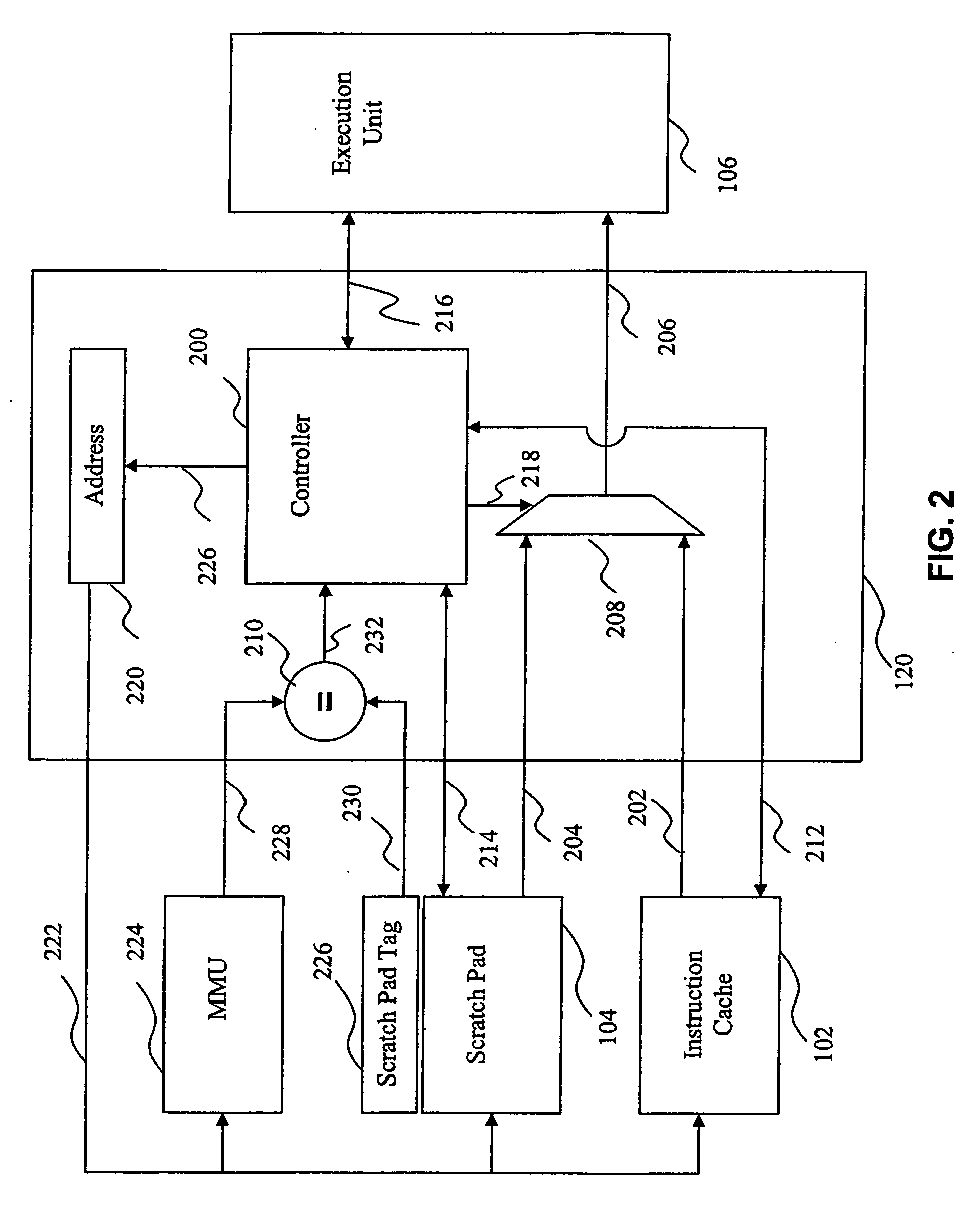

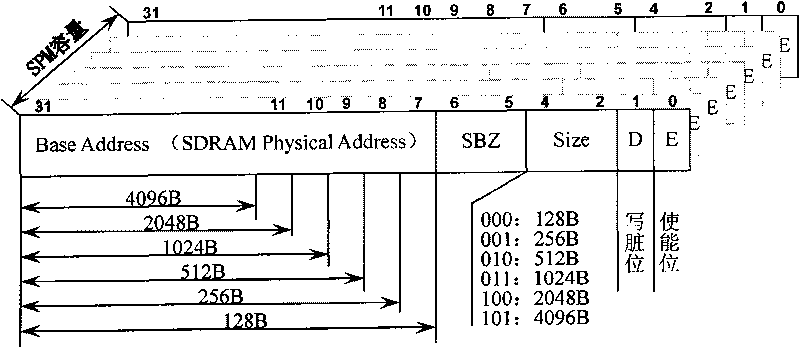

Processor accessing a scratch pad on-demand to reduce power consumption

ActiveUS20070113050A1Reduce power consumptionMemory architecture accessing/allocationEnergy efficient ICTParallel computingPhysical address

The present invention provides processing systems, apparatuses, and methods that access a scratch pad on-demand to reduce power consumption. In an embodiment, an instruction fetch unit initiates an instruction fetch. When a scratch pad is enabled, an instruction is retrieved from the scratch pad in parallel with a translation of a virtual address to a physical address. If the physical address is associated with the scratch pad, the retrieved instruction is provided to an execution unit. Otherwise, the scratch pad is disabled to reduce power consumption and the instruction fetch is re-initiated. When the scratch pad is disabled, an instruction is retrieved from another instruction source, such as an instruction cache, in parallel with the translation of the virtual address to the physical address. If the physical address is associated with the scratch pad, the scratch pad is enabled and the instruction fetch is re-initiated.

Owner:ARM FINANCE OVERSEAS LTD

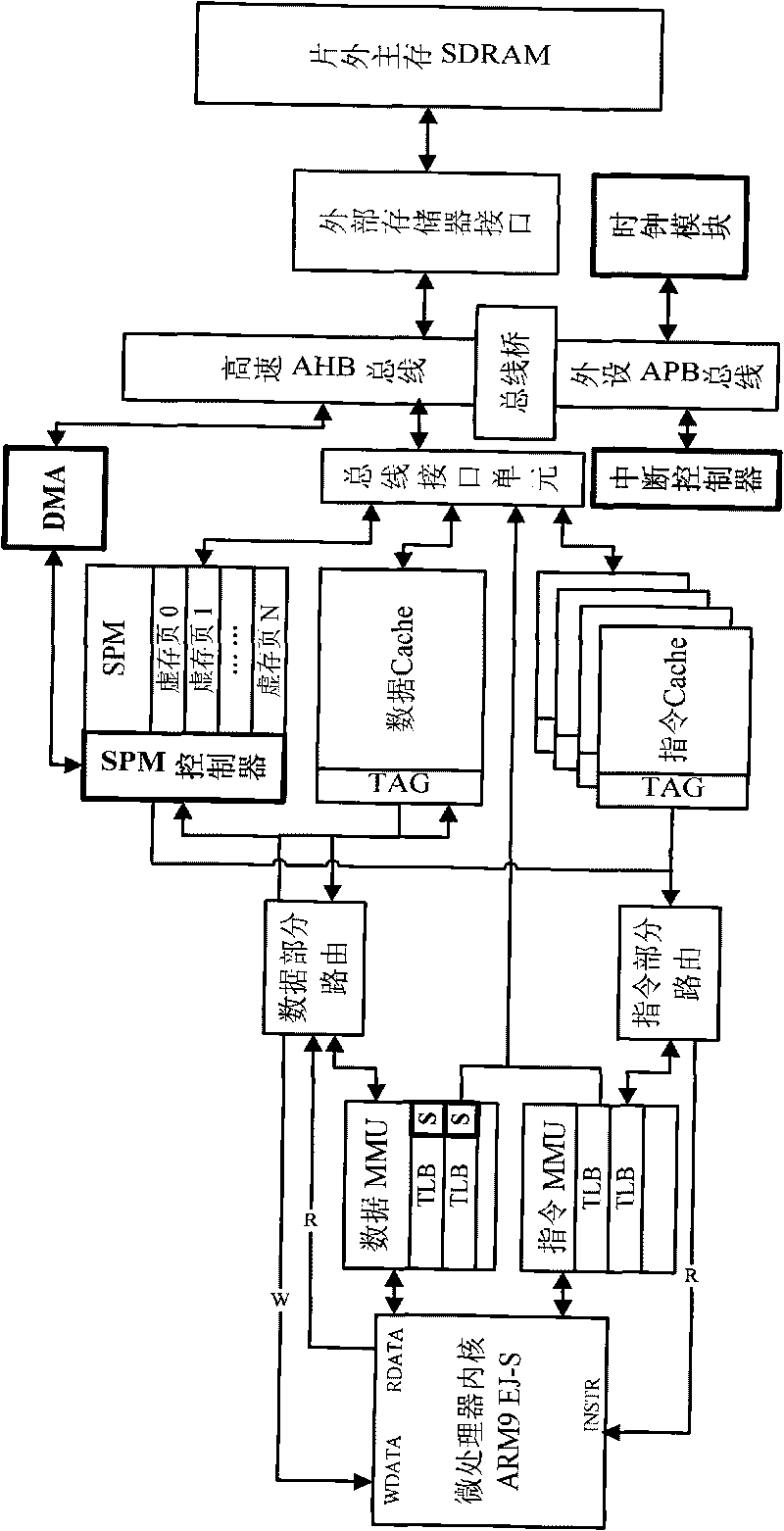

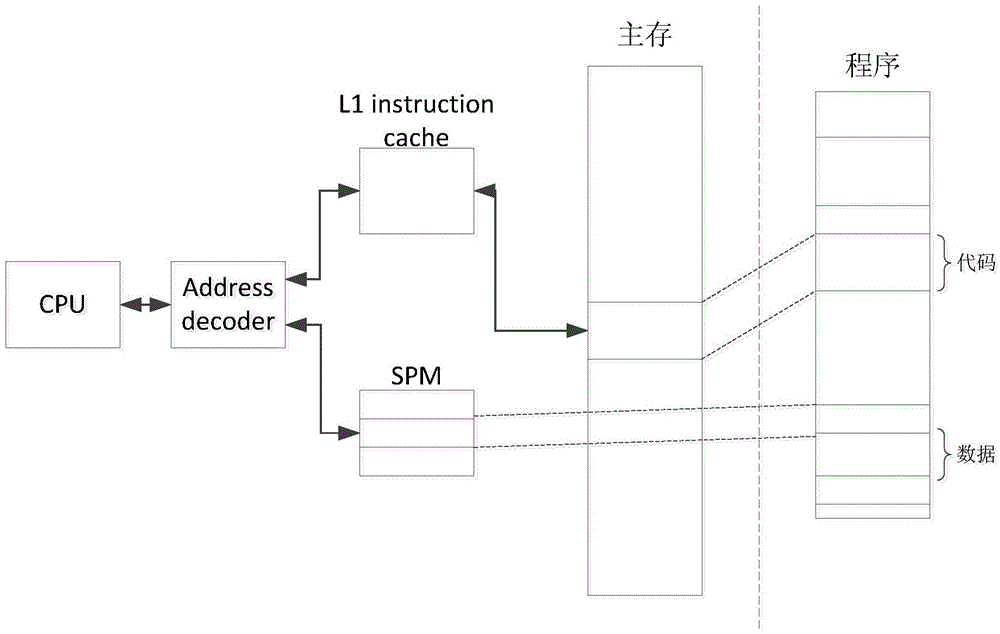

Method for dynamically allocating on-chip heterogeneous memory resources by utilizing virtual memory mechanism

InactiveCN101739358AReduce the number of cache conflictsReduce the number of conflictsEnergy efficient ICTMemory adressing/allocation/relocationInteger non linear programmingData segment

The invention discloses a method for dynamically allocating on-chip heterogeneous memory resources by utilizing a virtual memory mechanism, comprising the following steps of: analyzing the time and space distribution of data sections (comprising global data, stack data, pile data and constant pool data) with data Cache conflicts caused by high frequency by adopting a time slot analyzing method, then obtaining the time slot conflict diagram of the data Cache by the distribution and carrying out mathematical abstraction for the time slot conflict diagram. According to the target function of energy consumption and the target function of performance, a program part to be optimized is selected by using an integer nonlinear programming method and then is dynamically remapped in an on-chip data SPM (Scratch-pad Memory) by utilizing clock interrupt, and thereby, the extra memory access caused by the data Cache conflicts can be avoided. The method can reduce the energy consumption of a system and enhance the performance of the system due to the full utilization of on-chip heterogeneous memory.

Owner:SOUTHEAST UNIV

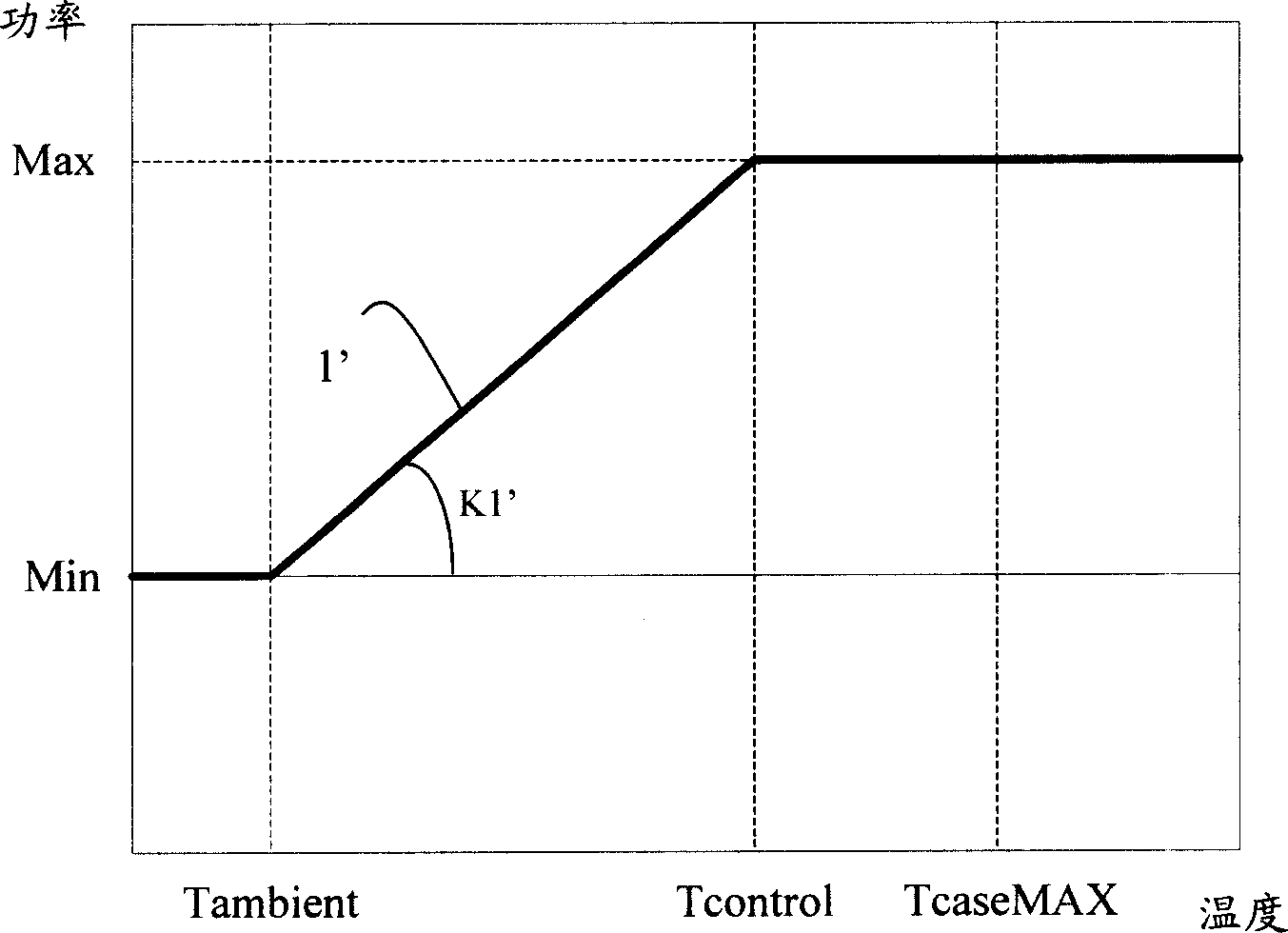

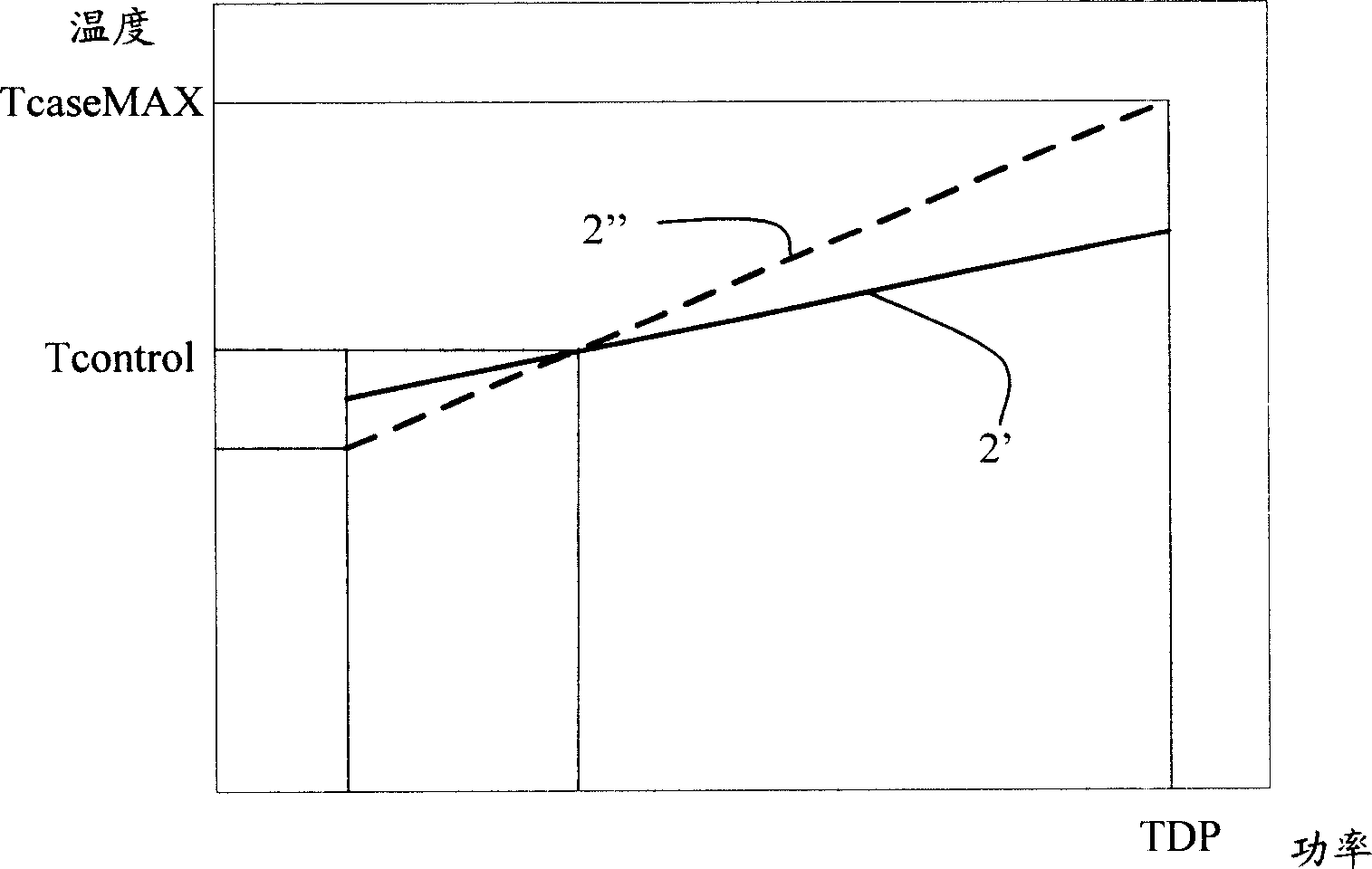

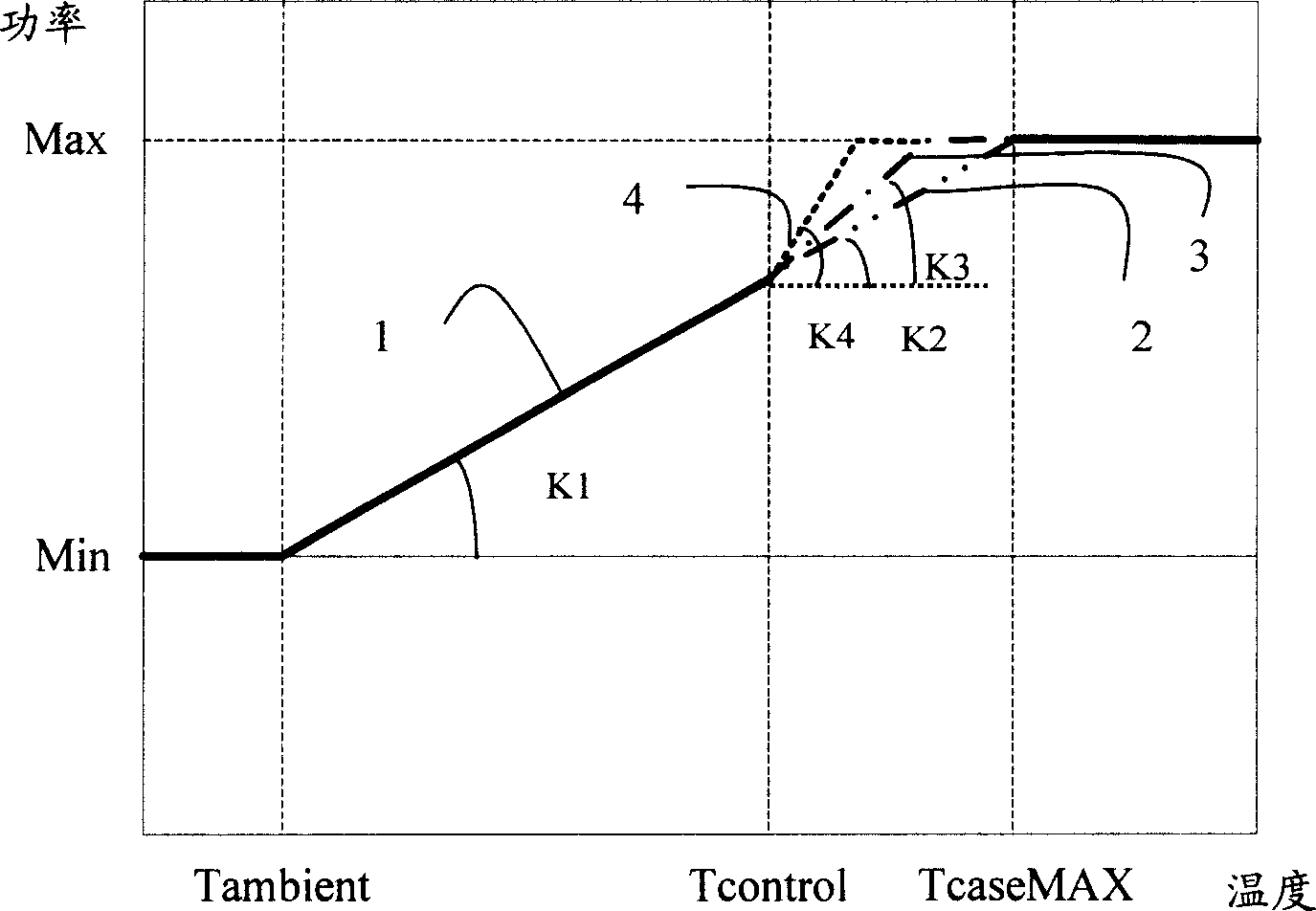

Automatic method for controlling rotate speed of fan

InactiveCN1916867AReduce noiseReduce power outputDigital data processing detailsHardware monitoringAutomatic controlSystems management

A method for automatically controlling rotary speed of fan includes setting different power-temperature slope parameter being stored in storage, confirming trigger value of system management interruption program (SMIP) by basic I / O system, deciding whether rotary speed of fan is necessary to be regulated or not according to said trigger value, using SMIP and a counter to commonly confirm temperature difference of central processor and calling up relevant power-temperature slope parameter to set rotary speed of fan then using SMIP to dynamically regulate scratch-pad storage of fan control loop to let SMIP be retriggered if it is necessary.

Owner:HONG FU JIN PRECISION IND (SHENZHEN) CO LTD +1

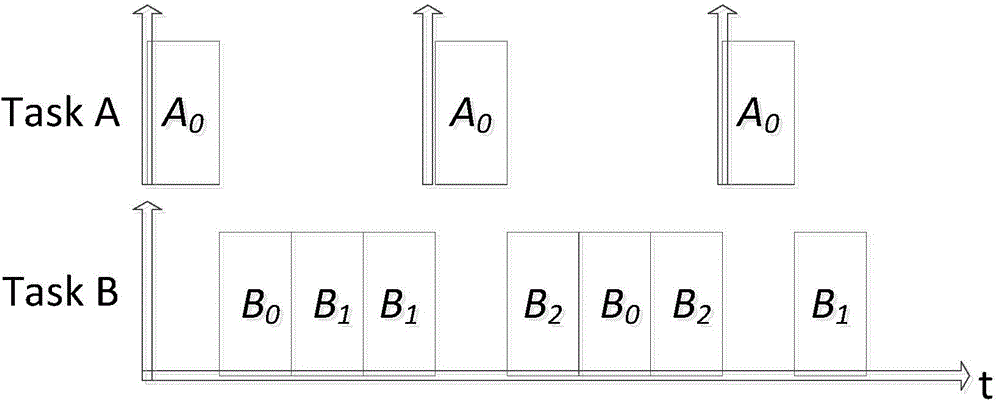

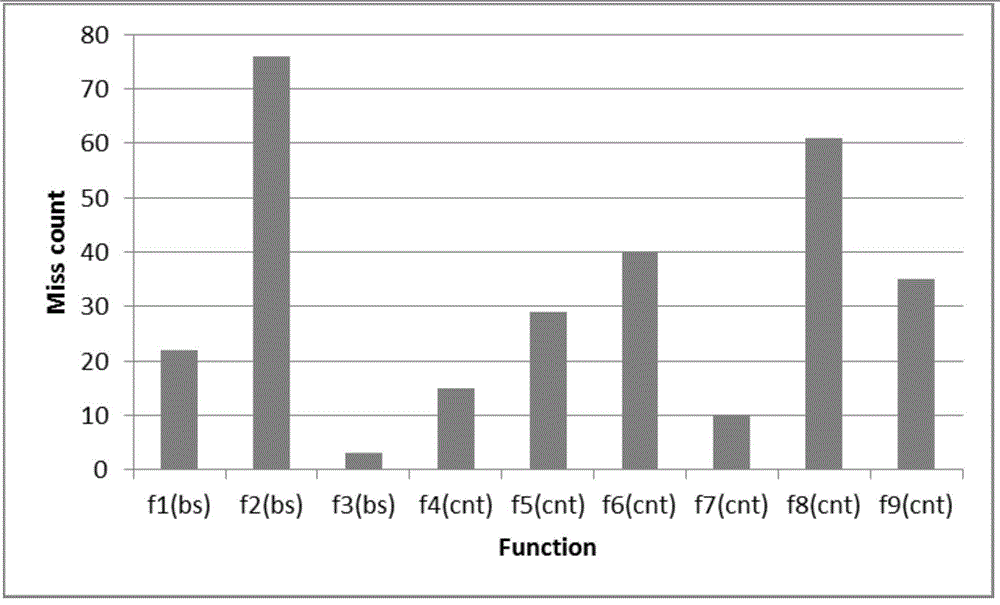

On-chip scratch-pad memory (SPM) management method facing multitasking embedded system

InactiveCN103559148AFast executionReduce energy consumptionEnergy efficient ICTResource allocationParallel computingCode segment

The invention discloses an on-chip scratch-pad memory (SPM) management method facing a multitasking embedded system. The on-chip scratch-pad memory management method comprises the steps as follows: pre-analyzing a program code segment; tracking a program to obtain an internal storage instruction accessing sequence of the program, so as to acquire the accessing times of an internal storage code block and Cache miss information, and accounting and recording a space-time conflict set of the internal storage code block under access of the Cache; selecting an algorithm as required to obtain an optimized SPM distribution scheme; generating a code distribution dispersion loading file, newly mapping and distributing the program code segment, and newly compiling codes to obtain an optimal execution result. Via comprehensive consideration of accessing frequency, cache miss frequency, intertask and intra-task conflict, the required optimal distribution is obtained, the utilization rate of the SPM is maximized, and finally under the premise of ensuring the real-time performance of the program, an optimal execution time scheme or an optimal energy conservation scheme is obtained.

Owner:SHANDONG UNIV

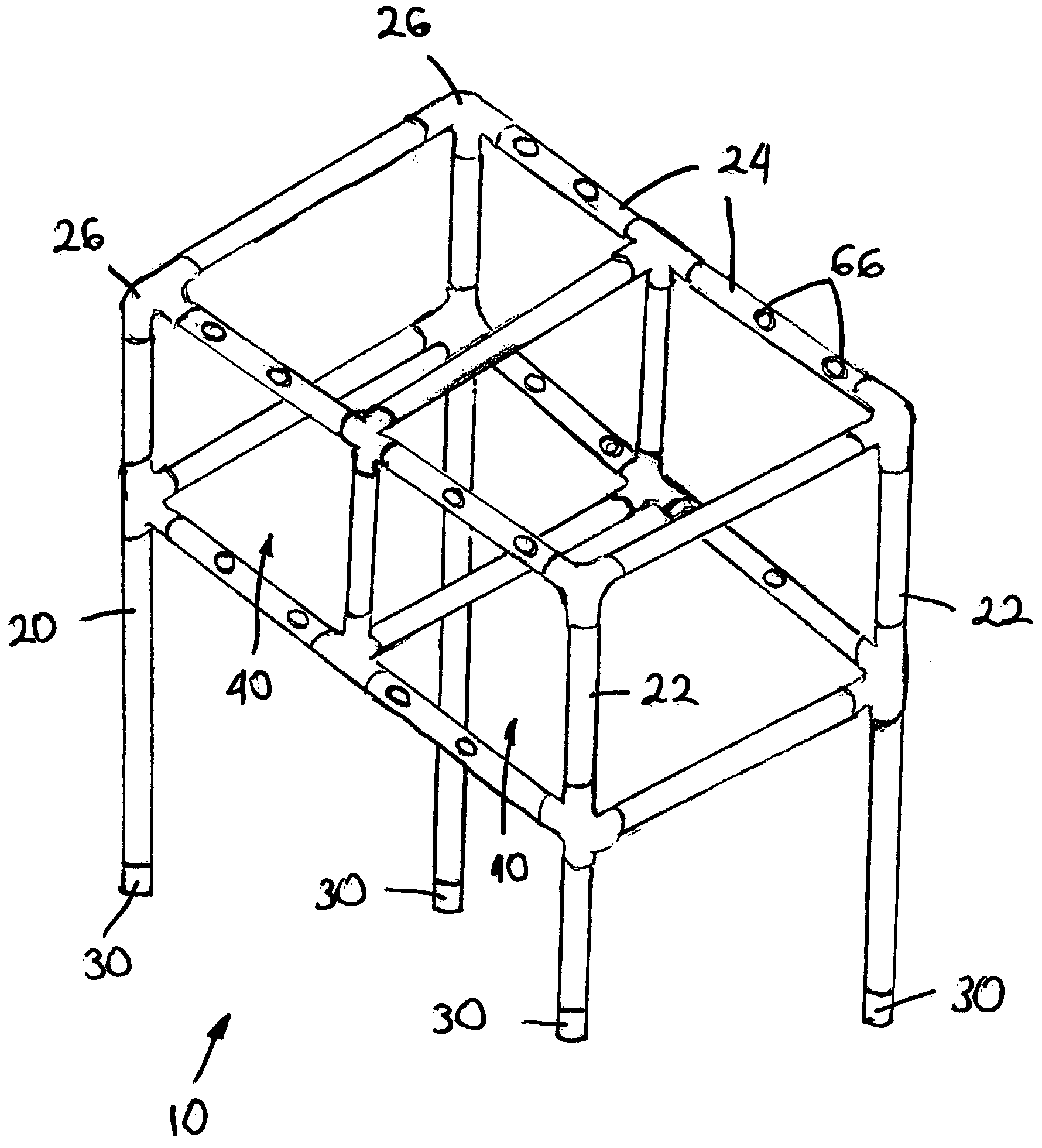

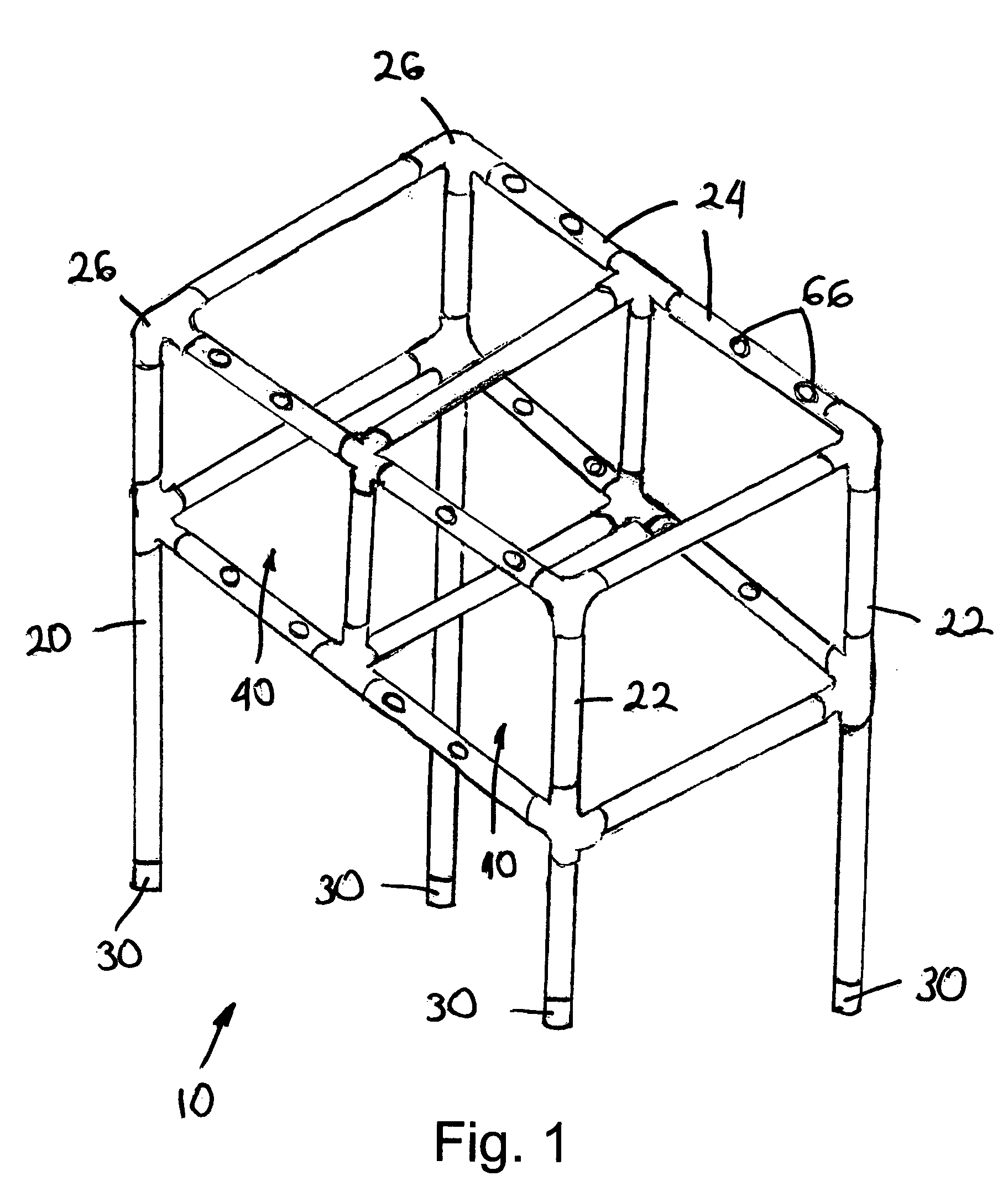

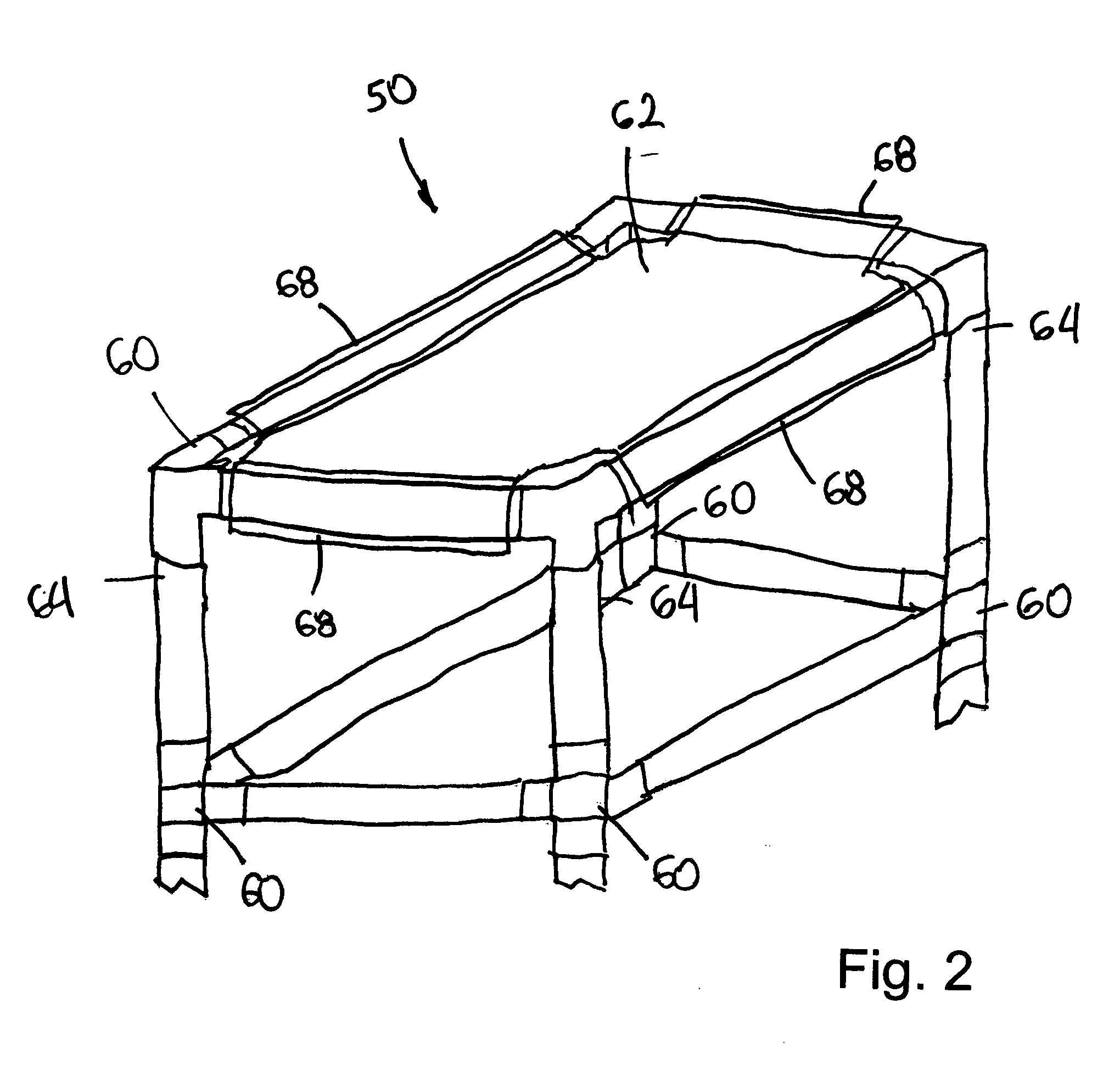

Modular pet furniture

Modular pet furniture providing a place for pets, in particular, cats, to rest, sleep and recreate, comprising a frame structure, a bed structure, a pet support and an attachment mechanism. The frame structure forms a single or a plurality of support regions or compartments that can accommodate different bed styles and different numbers of pets. The support regions also provide space for toys and other items of interest for pets, such as scratch pads. The modular pet furniture can be configured to contain a variable number of support regions in a number of different stacking configurations, to form pet furniture of a variety of shape and size.

Owner:ACCENTURE GLOBAL SERVICES GMBH