Patents

Literature

159results about "Electric/magnetic signal storage" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

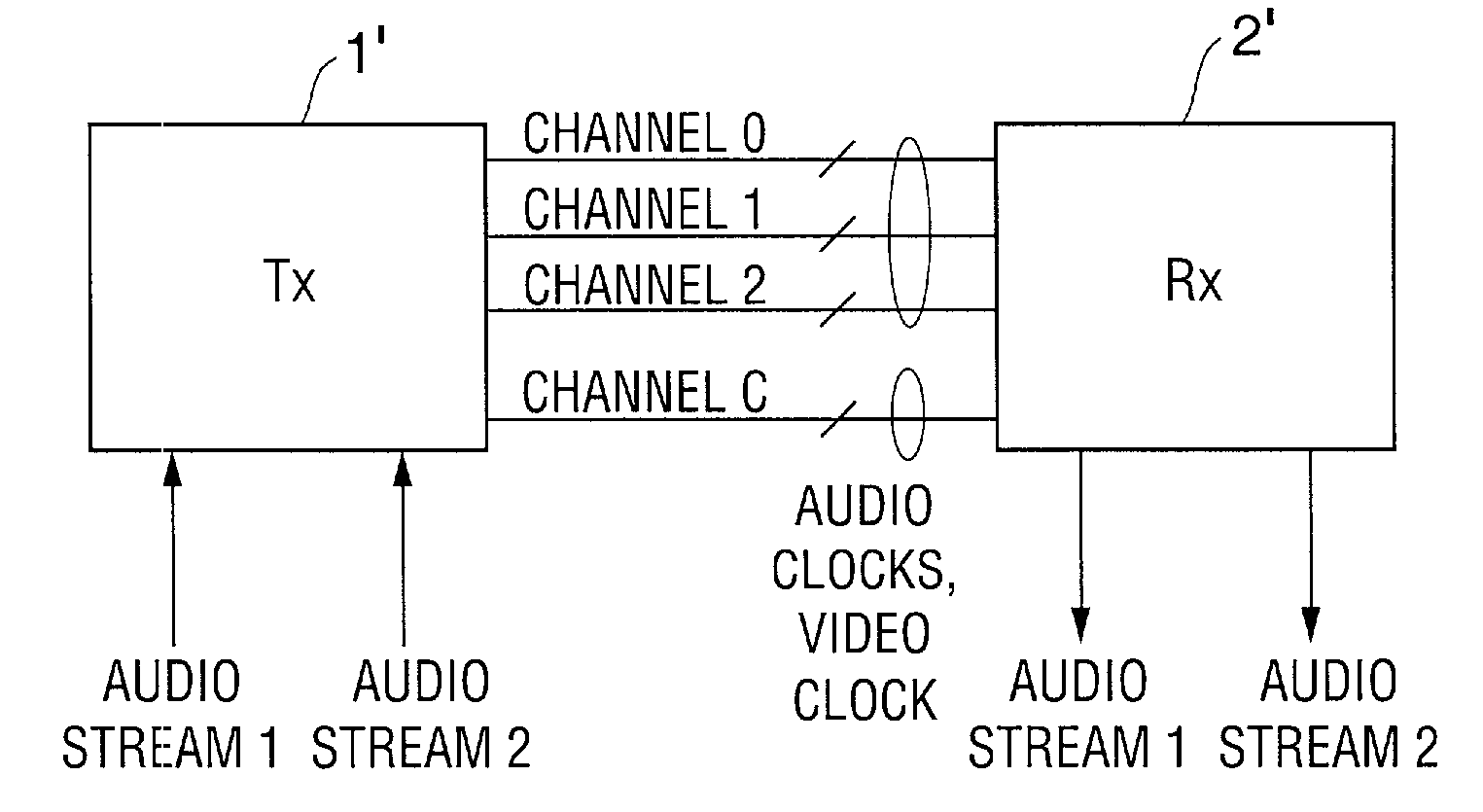

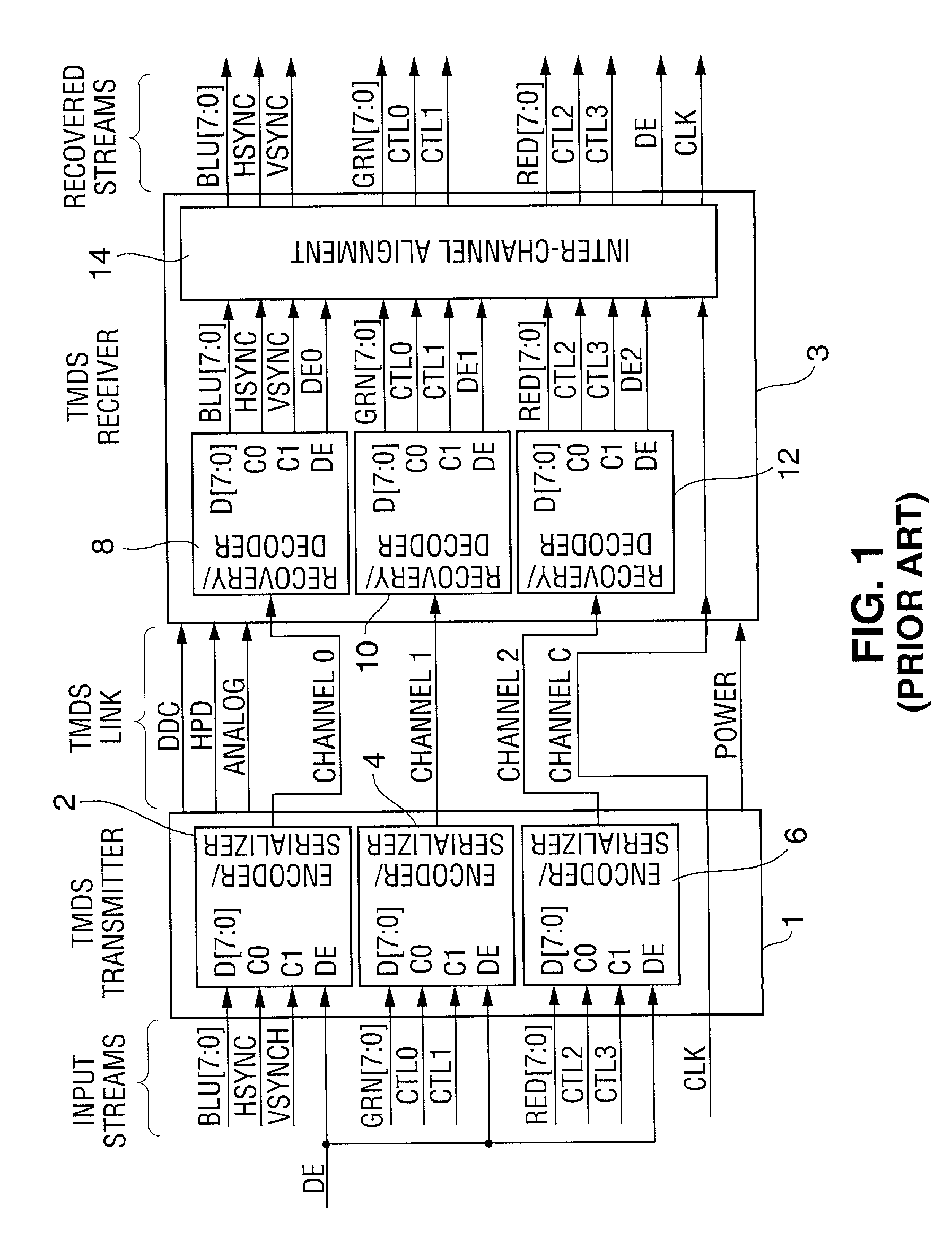

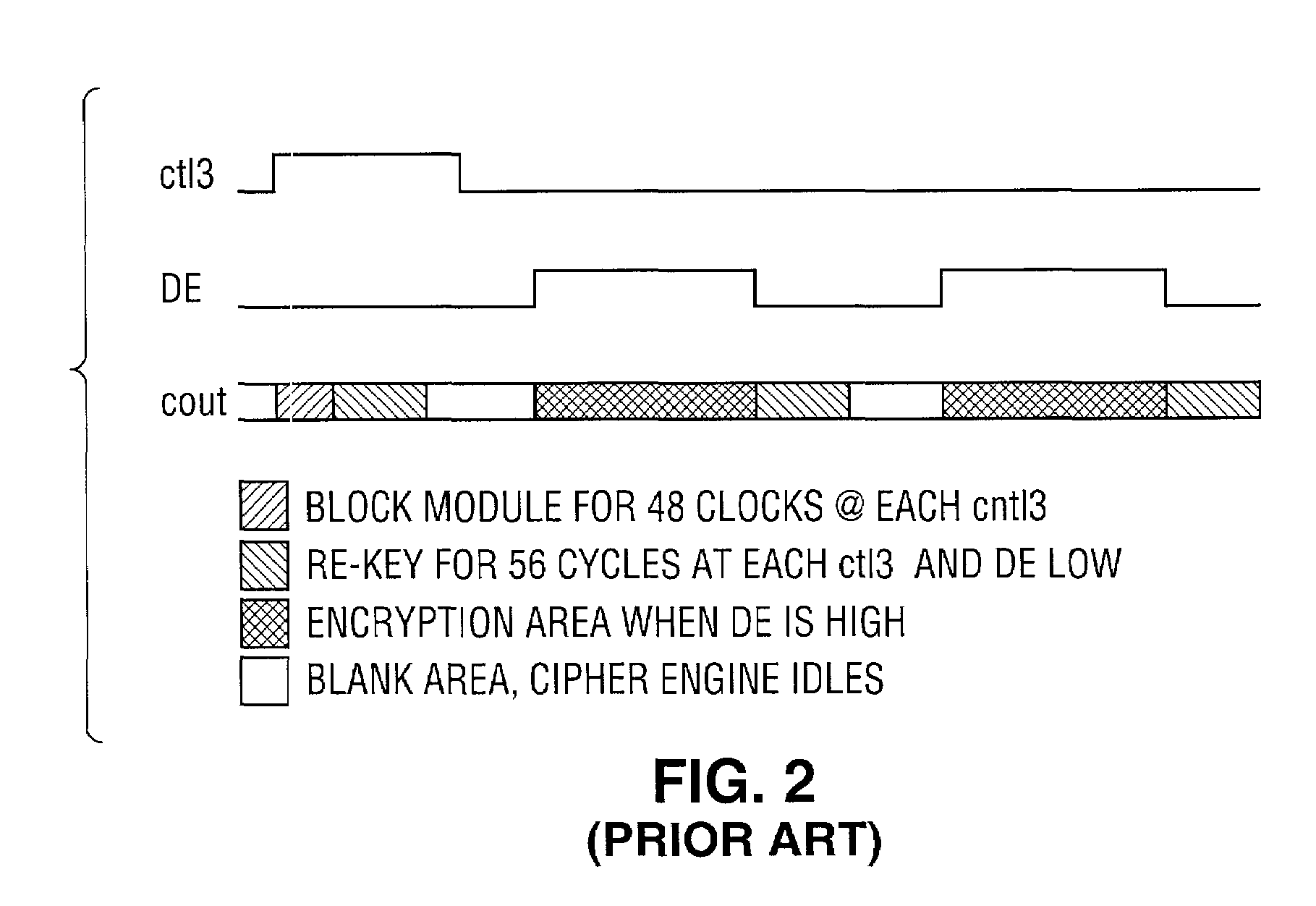

Method and apparatus for synchronizing auxiliary data and video data transmitted over a TMDS-like link

InactiveUS7295578B1Synchronisation information channelsPulse automatic controlData synchronizationCommunications system

A communication system including a transmitter, a receiver, and a TMDS-like link, in which video data and auxiliary data are transmitted from the transmitter to the receiver, or in which video data are transmitted over the link from the transmitter to the receiver and auxiliary data are transmitted from the receiver to the transmitter (or from the transmitter to the receiver and also from receiver to the transmitter), a transmitter or receiver for use in such a system, and methods for sending auxiliary data and video data over such a link, synchronizing such auxiliary data with such video data, and generating clocks having frequency closely matching the rate at which the auxiliary data are transmitted. Typically, the auxiliary data include one or more streams of audio data. In some embodiments the transmitter transmits a video clock to the receiver over a video clock channel, at least one of the transmitter and receiver transmits at least one stream of auxiliary data to the other one of the transmitter and the receiver, and at least one of the transmitter and the receiver transmits over the video clock channel at least one auxiliary clock for the auxiliary data.

Owner:LATTICE SEMICON CORP

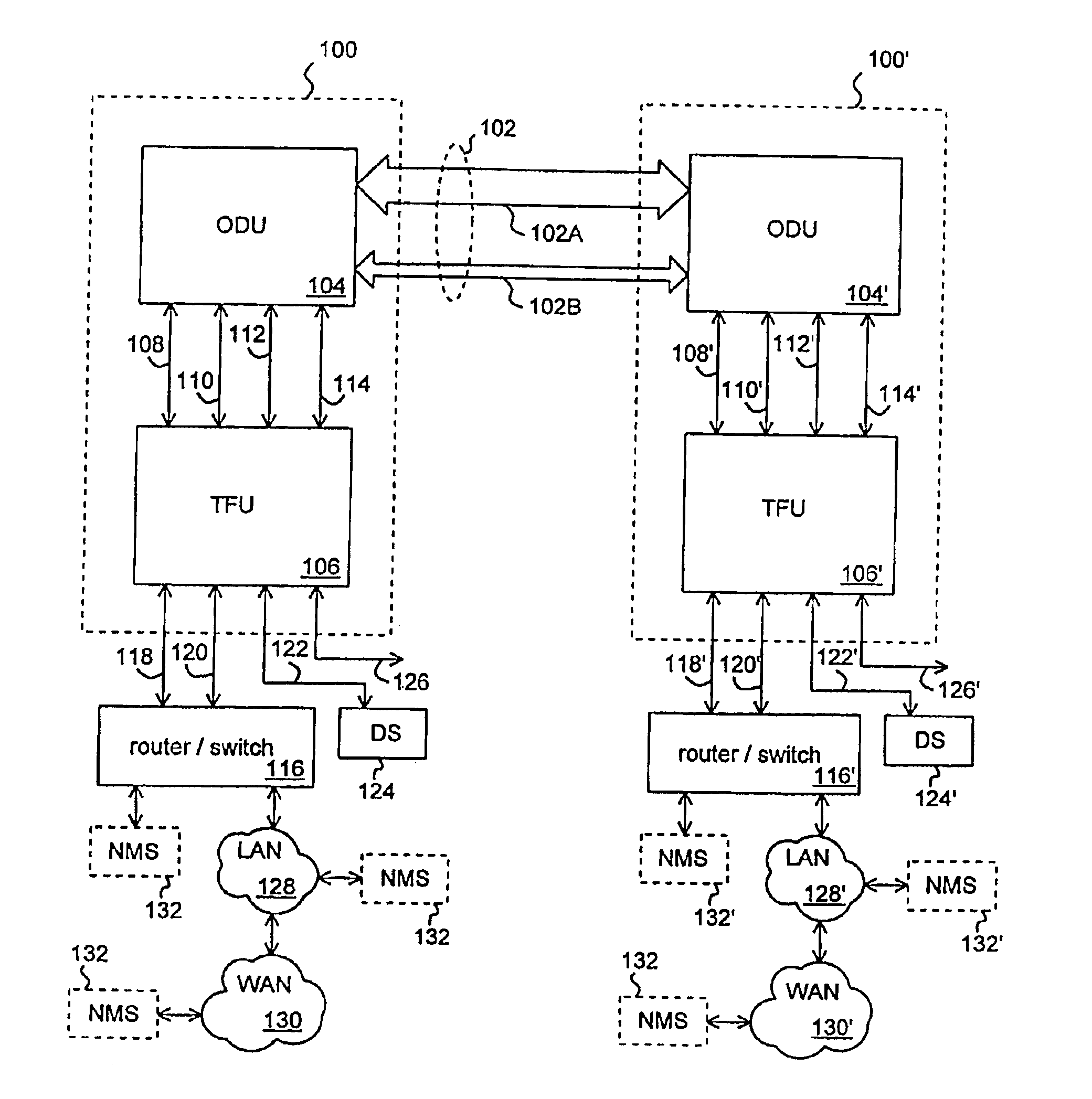

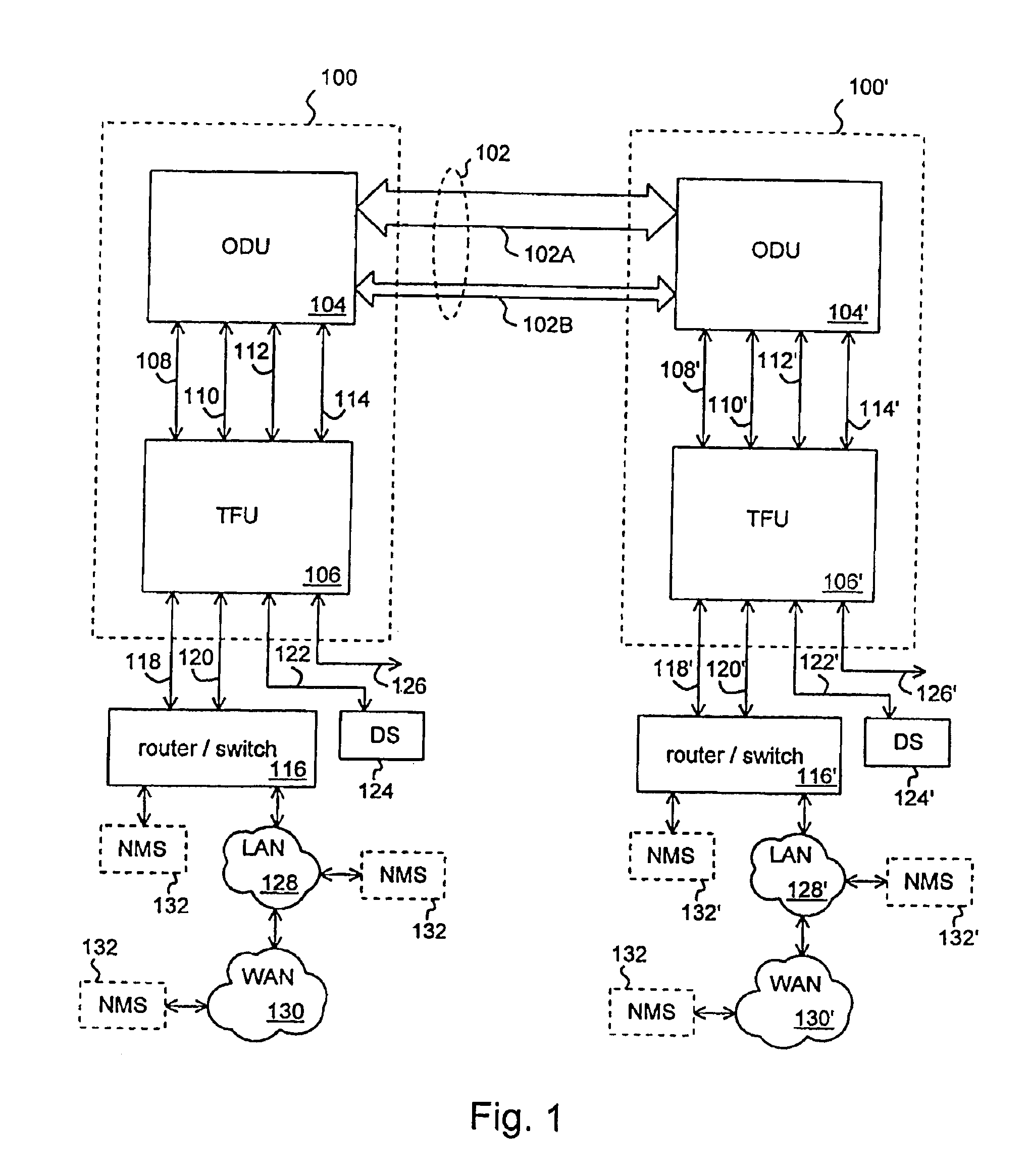

Method and apparatus for transporting ethernet data packets via radio frames in a wireless metropolitan area network

InactiveUS6907048B1Improve efficiencyElectric/magnetic signal storageRadio/inductive link selection arrangementsTransceiverWireless transceiver

Method and apparatus for transporting Ethernet data packets via radio frames in a wireless metropolitan area network. A terminal includes a data packet receiver for receiving data packets for communication over a wireless link wherein not every data packet has a same length; a data packet formatting apparatus for formatting the data packets according to radio frames wherein the radio frames each have a same length and wherein the data packets are formatted into the radio frames such that boundaries for the data packets are not necessarily aligned with boundaries for the radio frames; and a wireless transceiver for communicating the radio frames over the wireless link. The packets can be Fast Ethernet packets. The terminal does not convert the Ethernet data packets into a telephony communication protocol or into an asynchronous transfer mode (ATM) protocol prior to communication of the radio frames over the wireless link. The terminal can include a data packet synchronizer for synchronizing the data packets to a clock signal associated with the radio frames. The data packets can be time-division multiplexed into the radio frames. According to another aspect, a method of transporting Ethernet data packets via radio frames includes steps of receiving Ethernet data packets wherein each data packet includes a preamble and a start-of-frame delimiter, stripping off the preamble and start-of-frame delimiter, formatting the packet data according to radio frames, including appending a synch field to the packet data, and appending a length field to the packet data.

Owner:SAMSUNG ELECTRONICS CO LTD

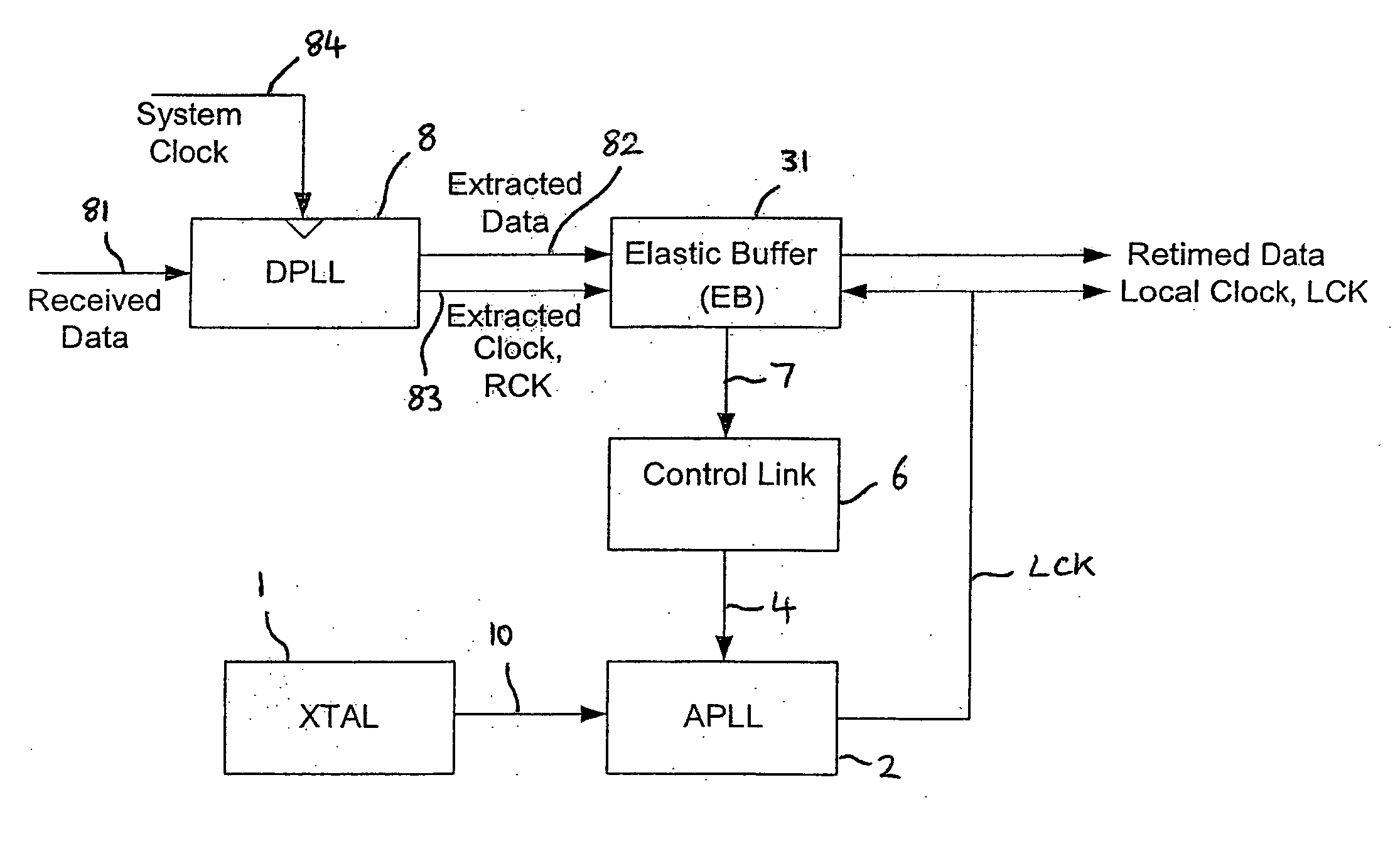

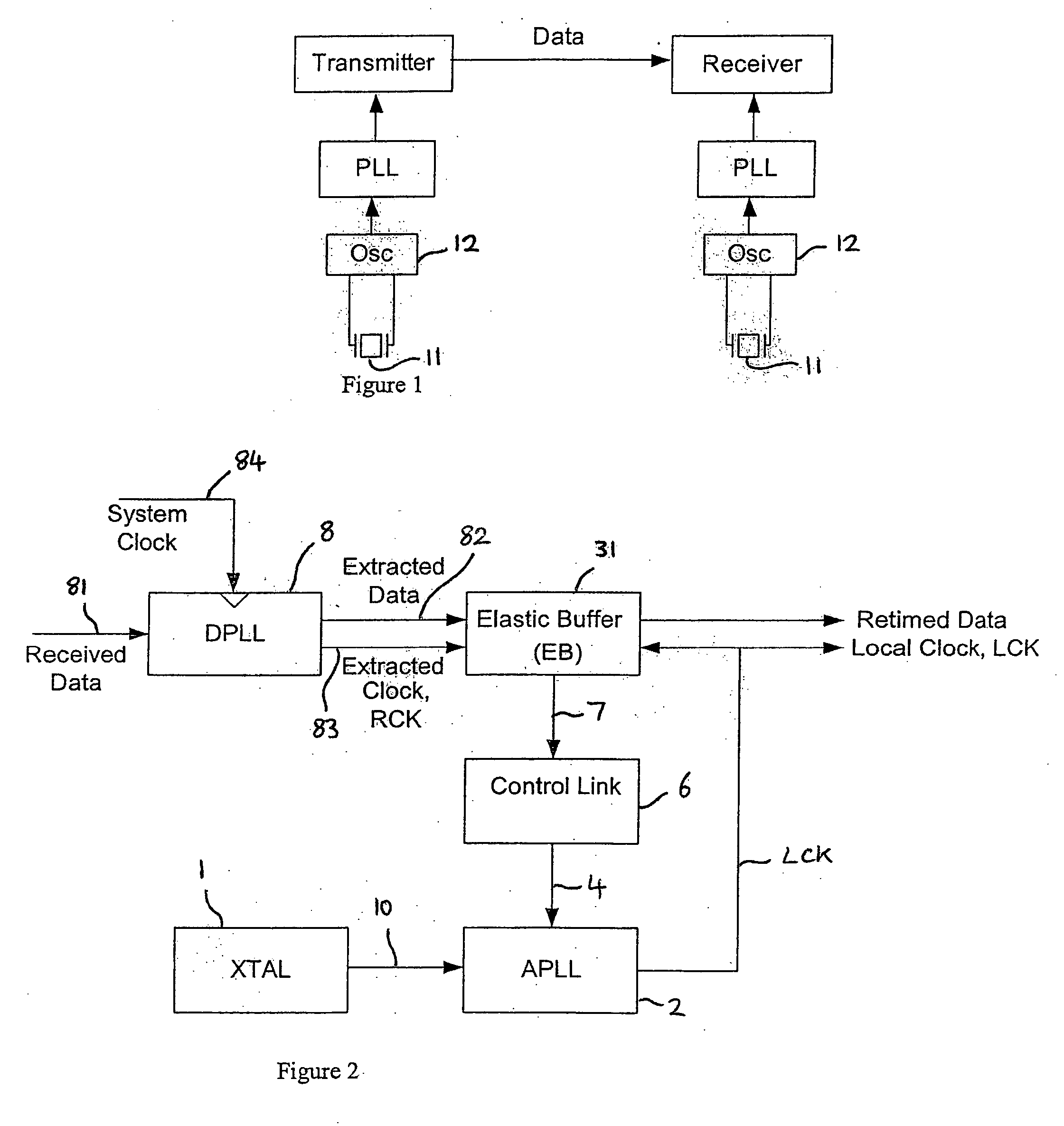

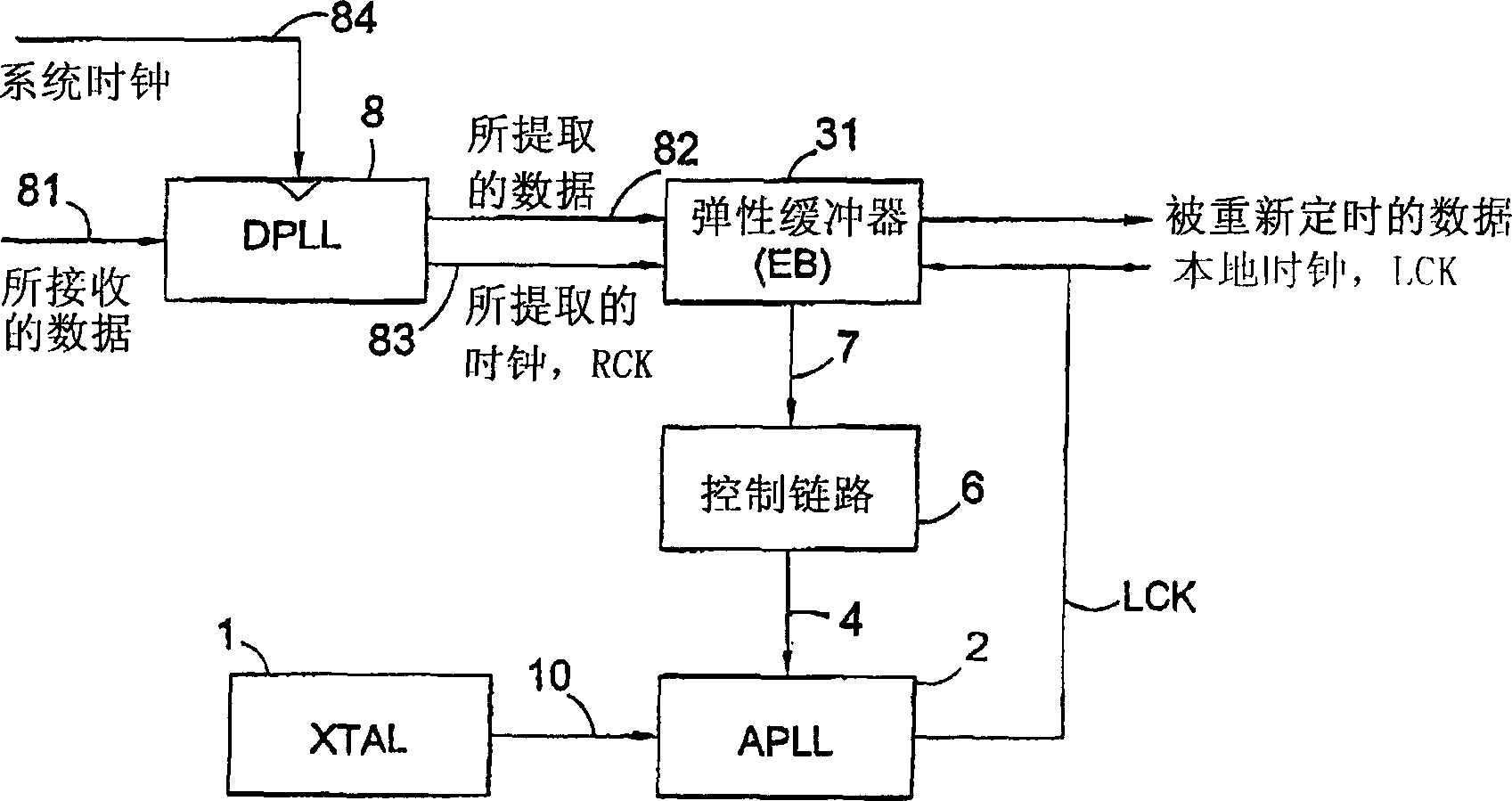

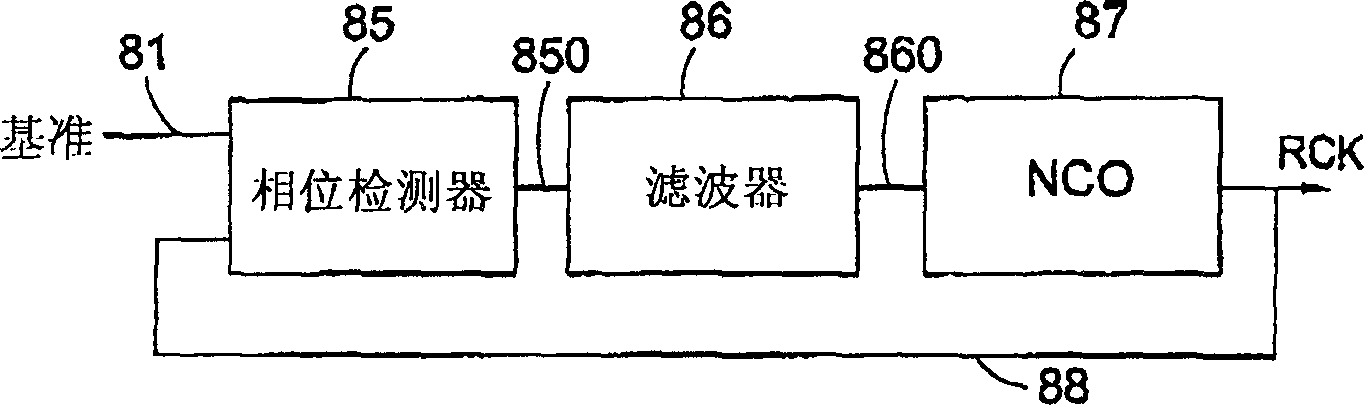

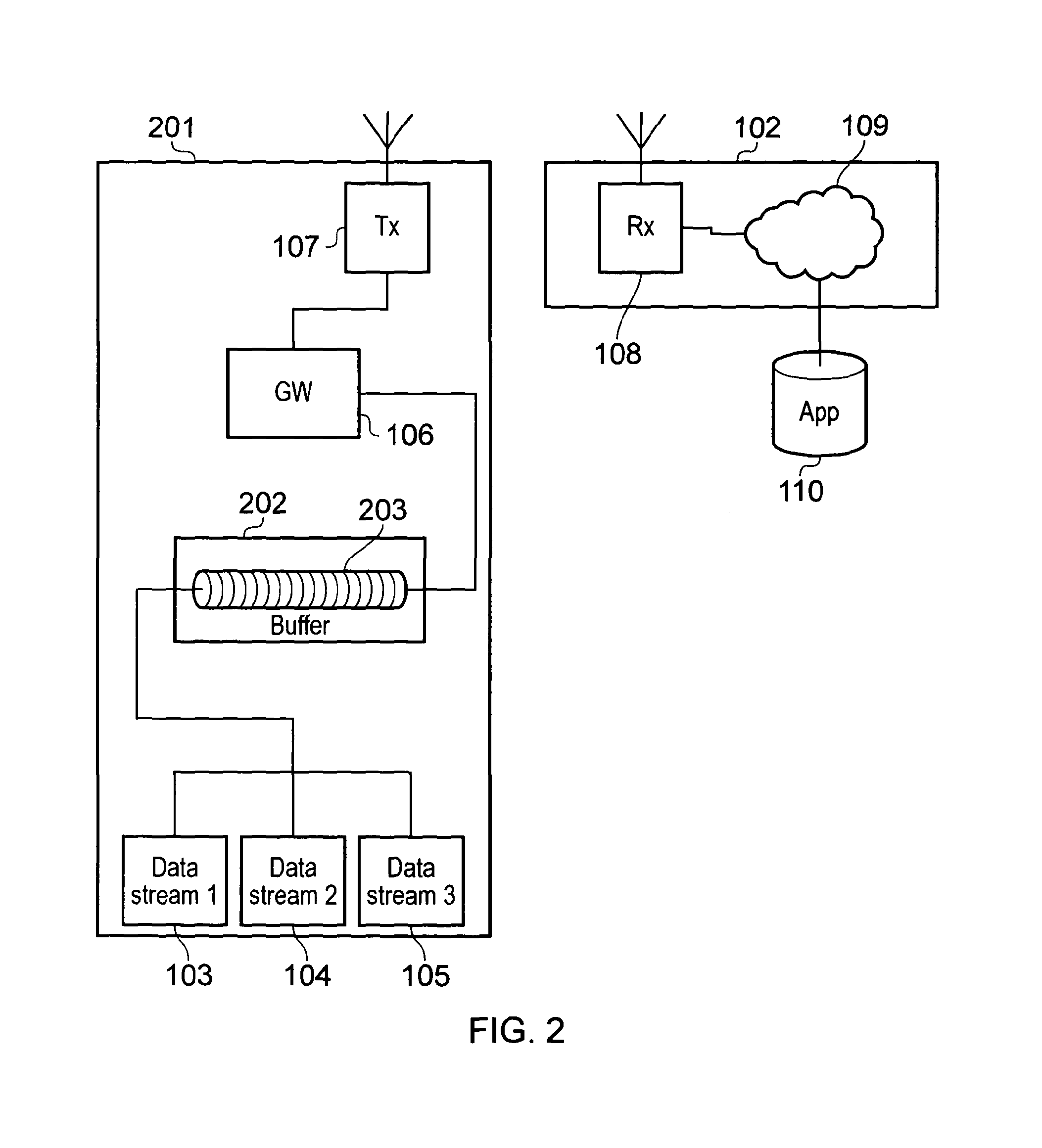

Clock synchroniser and clock and data recovery apparatus and method

InactiveUS20050220240A1Reduce jitterAvoid data lossPulse automatic controlElectric/magnetic signal storageLeast significant bitComputer science

A clock synchroniser, and clock and data recovery apparatus incorporating the clock synchroniser, are described, together with corresponding clock synchronisation methods. The clock synchroniser incorporates an elastic buffer. A received clock signal is used to clock data into the buffer, and a locally generated clock is used to clock data out of the buffer. The local clock is synthesised using a PLL, and a fill-level signal from the elastic buffer is used to control to local clock frequency to maintain a desired average quantity of data in the buffer, thereby achieving synchronisation of the received and local clocks. In preferred embodiments the fill-level signal is used to control a variable divider in the feedback path of the PLL, which is supplied with a highly stable reference signal. A synchronised, and low-jitter local clock is thus produced. Preferably, the elastic buffer employs counters of relatively wide word width, and a storage array of much reduced depth, read and write pointers being provided by just a few of the least significant bits of the words.

Owner:WOLFSON MICROELECTRONICS LTD

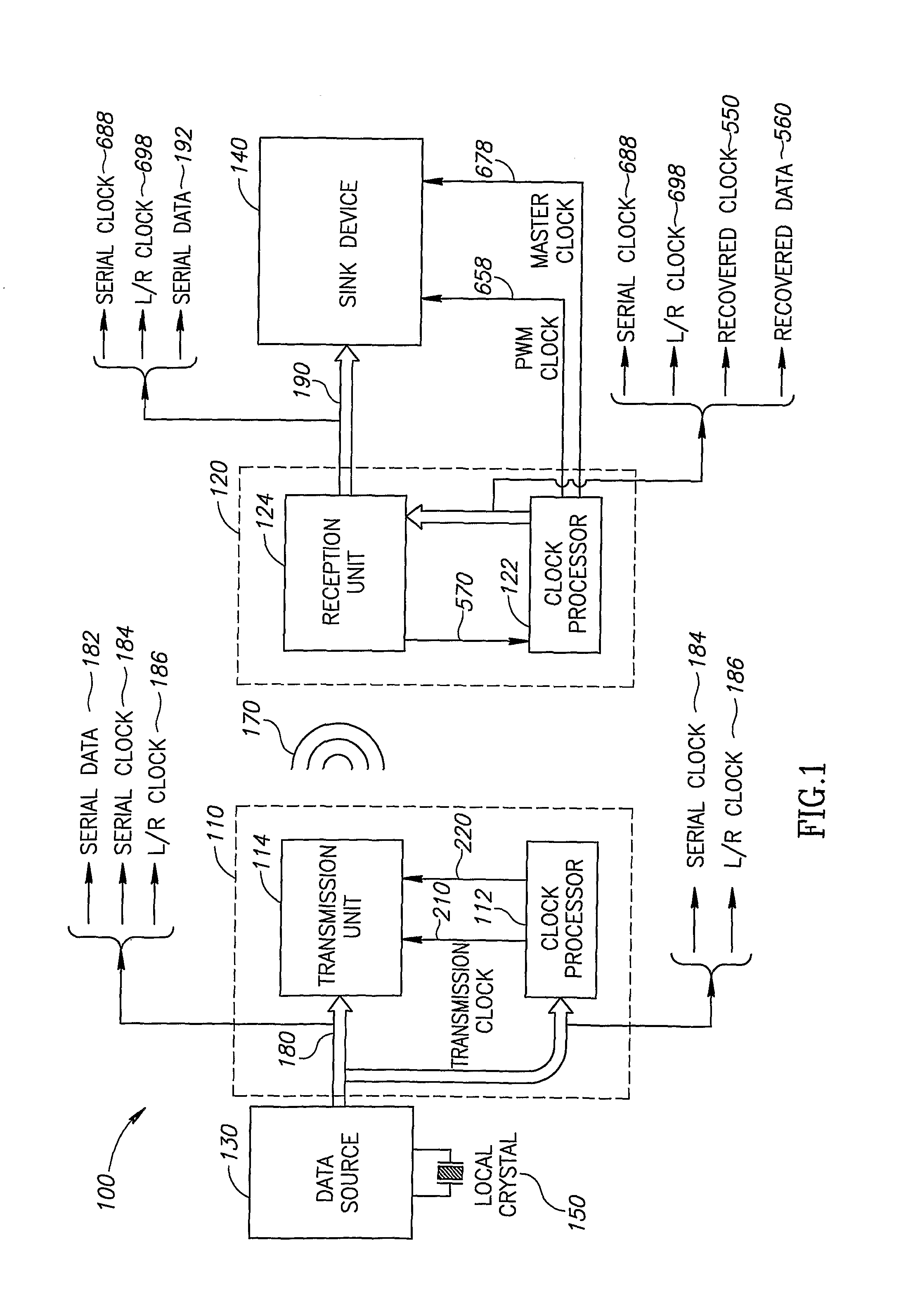

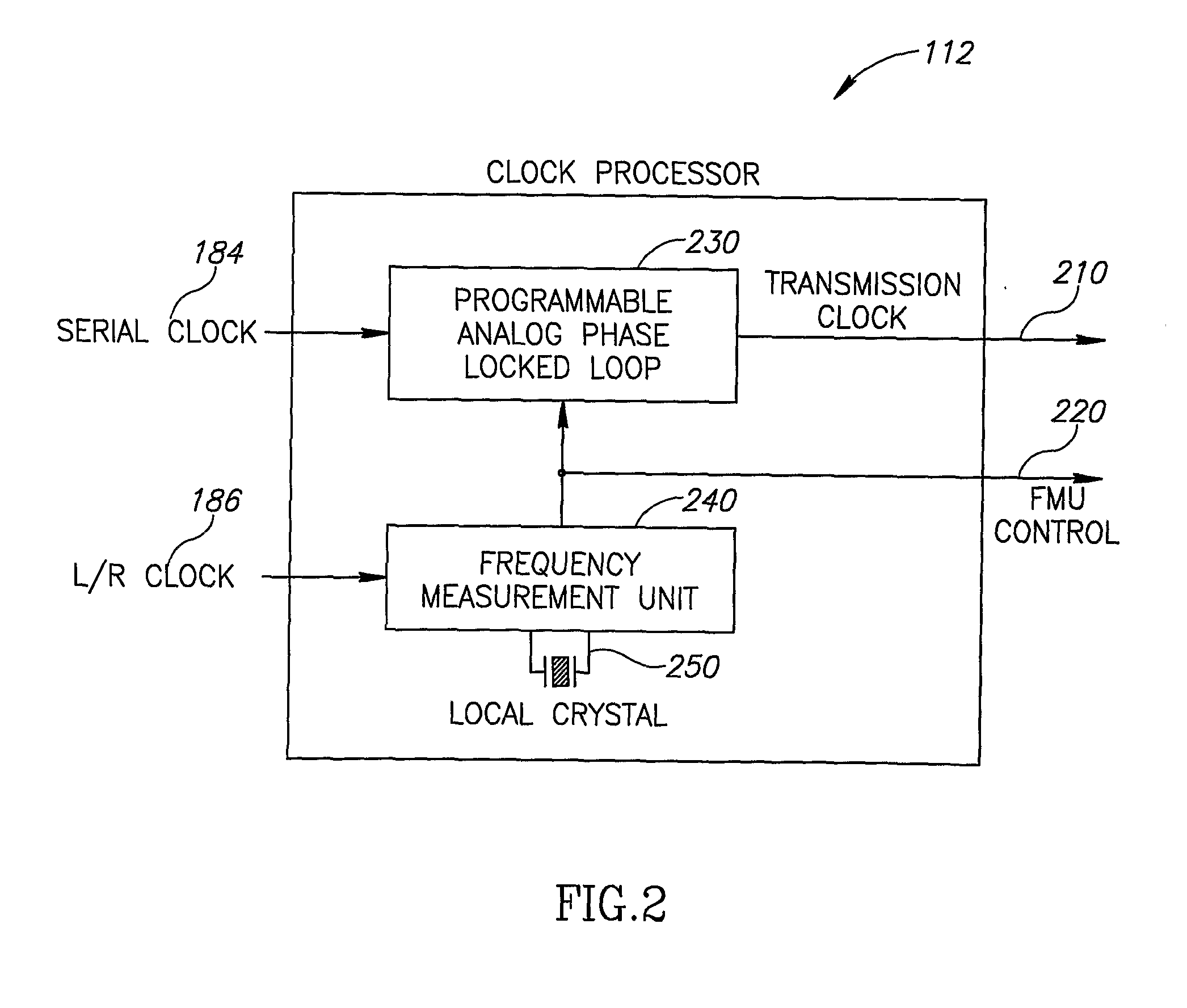

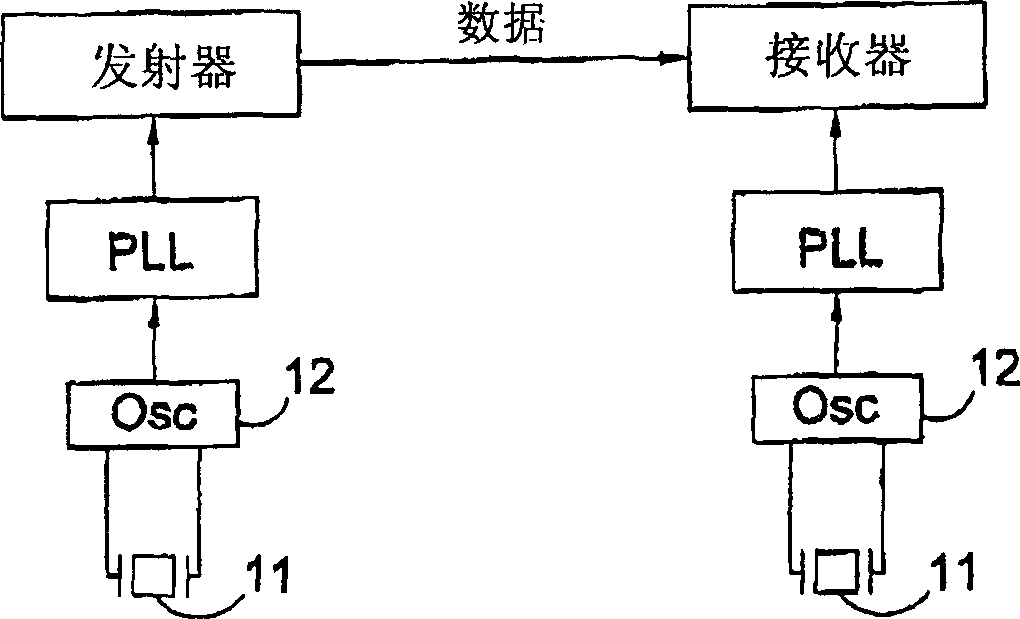

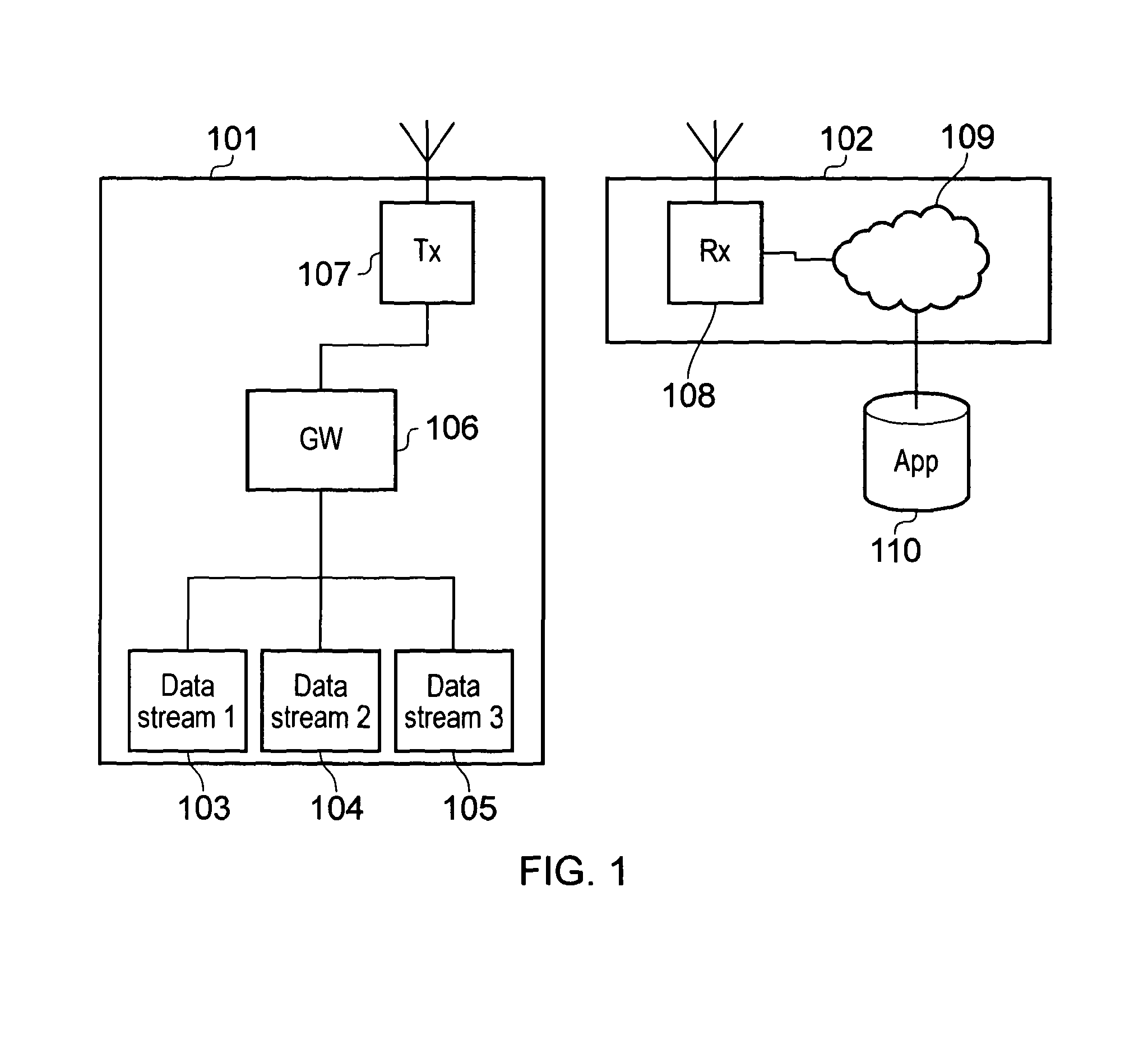

Low Jitter Clock Recovery from a Digital Baseband Data Signal Transmitted Over a Wireless Medium

InactiveUS20080212729A1Synchronisation error detectionCarrier regulationData streamWireless transmission

A system and method of transmitting a data stream from a data source over a baseband wireless communication system to one or more receivers. The receivers simultaneously recover the data and clock signals of the original data stream from the wireless transmitted data so that the data stream can be provided by the receivers to a data sink at the same rate as the original data stream, with low jitter performance.

Owner:INFRA

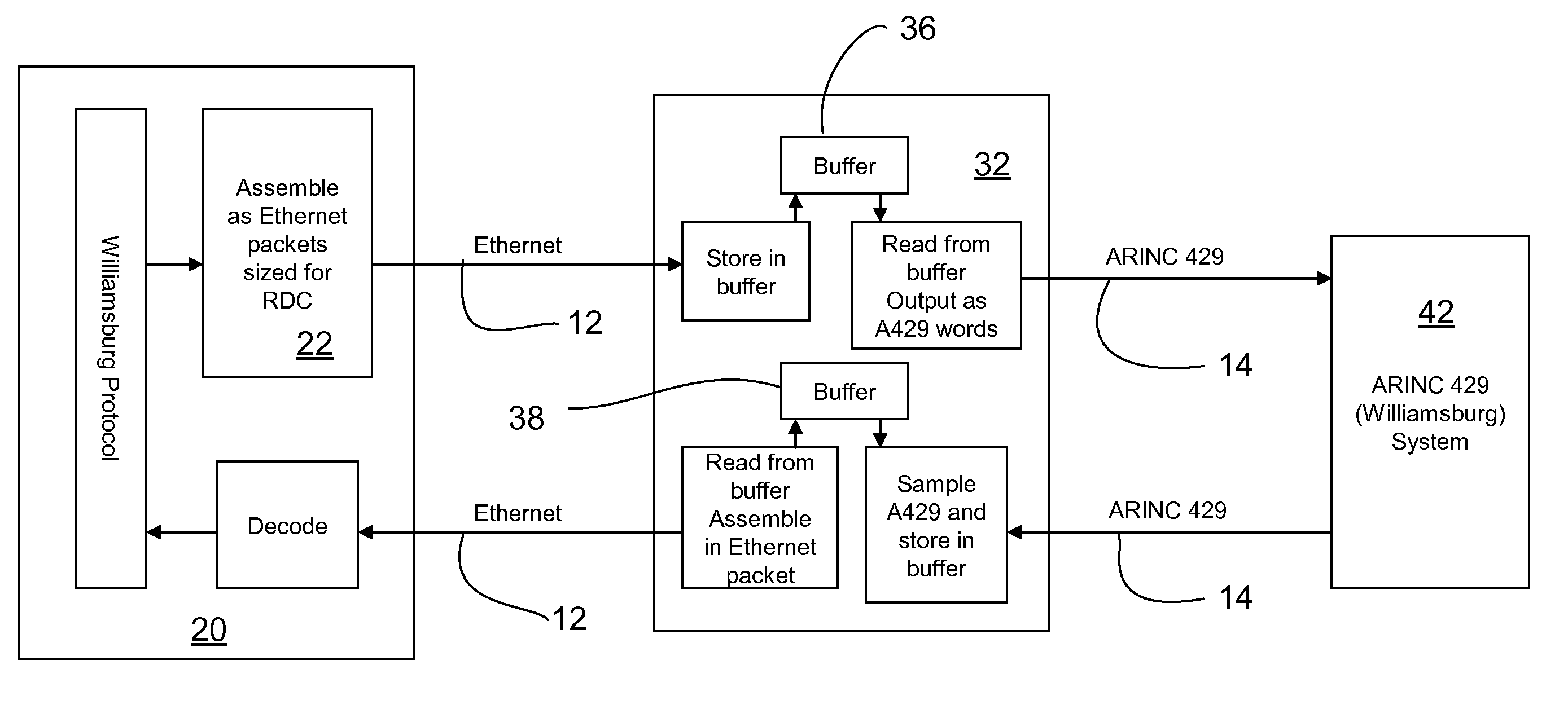

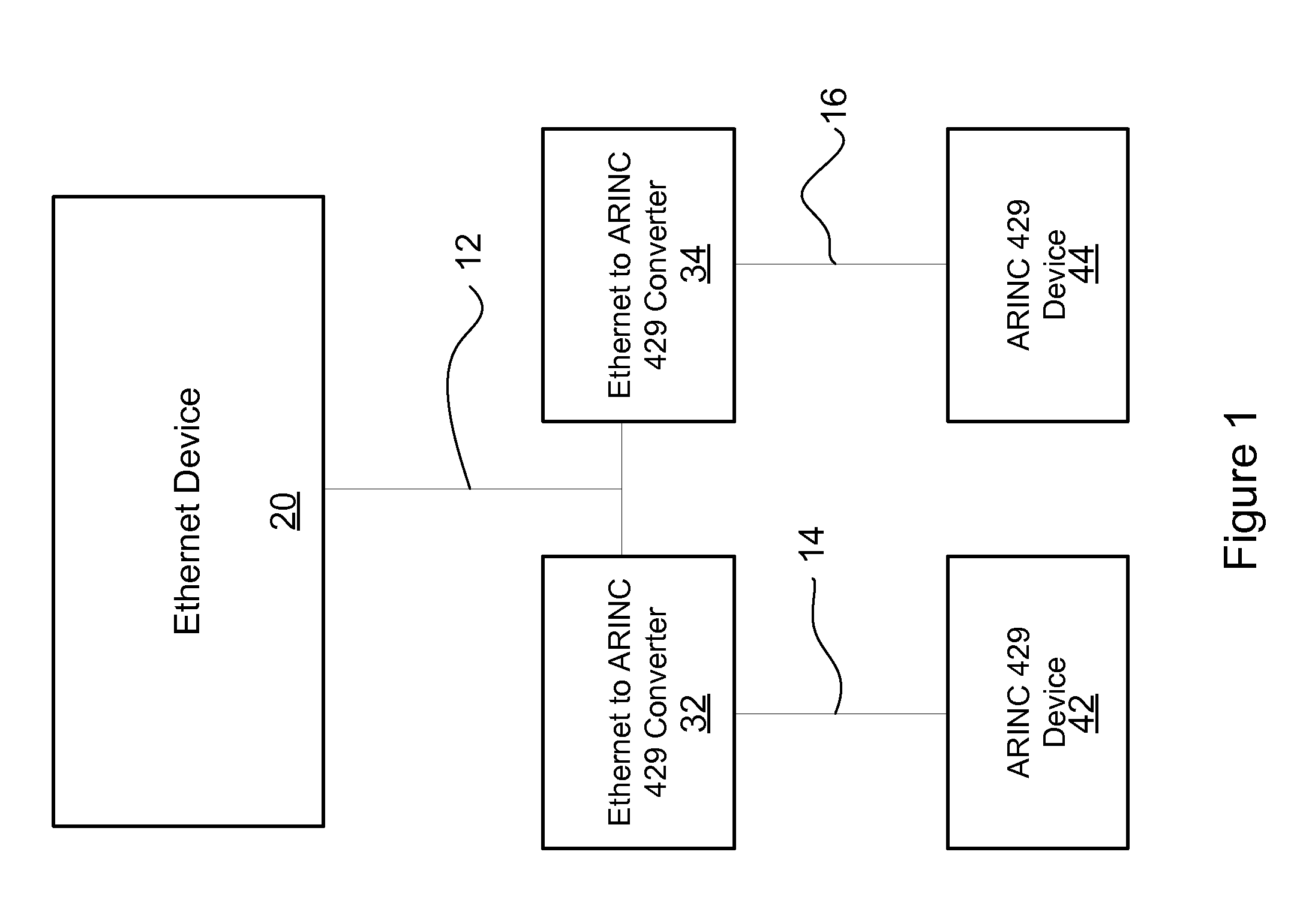

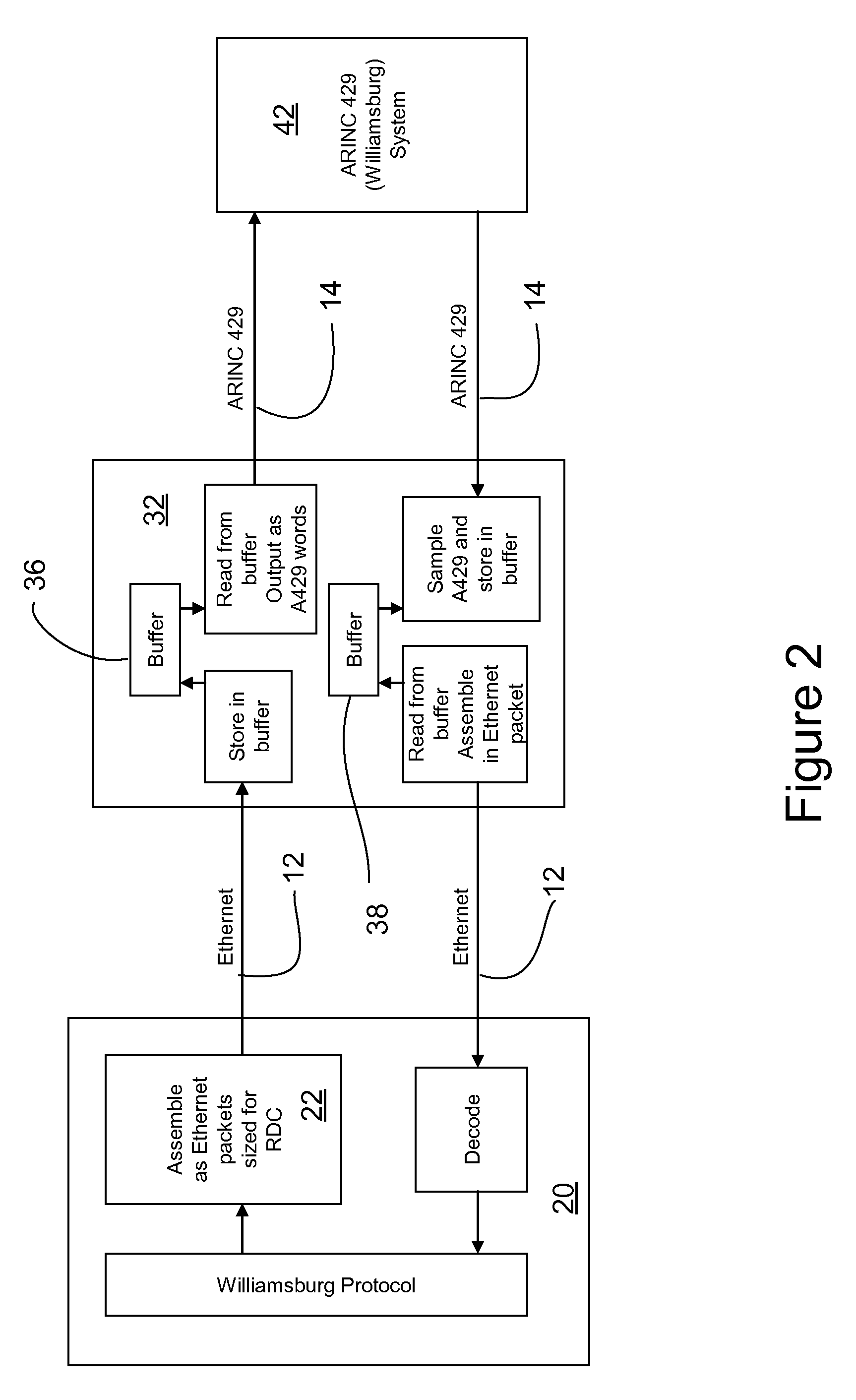

Interface between network data bus application and avionics data bus

InactiveUS20070127521A1Avoid expirationAvoid bufferingElectric/magnetic signal storageTime-division multiplexNetwork Communication ProtocolsNetwork data

A method for transmitting data between a first device and second device is disclosed. The method includes receiving a block of data; dividing the block of data into at least a first packet having a first size and a second packet having a second packet size; transmitting the first packet to a converter, the converter being configured to convert a packet from a first communication protocol to a second communication protocol; and transmitting the second packet to the converter after waiting a predetermined time. The first packet size, the second packet size, and the predetermined time are selected to prevent overflow of a memory of the converter. The second packet size, and the predetermined time are selected to prevent expiration of a timer at the second data bus. The time is associated with data transferred in the first and second packets.

Owner:THE BOEING CO

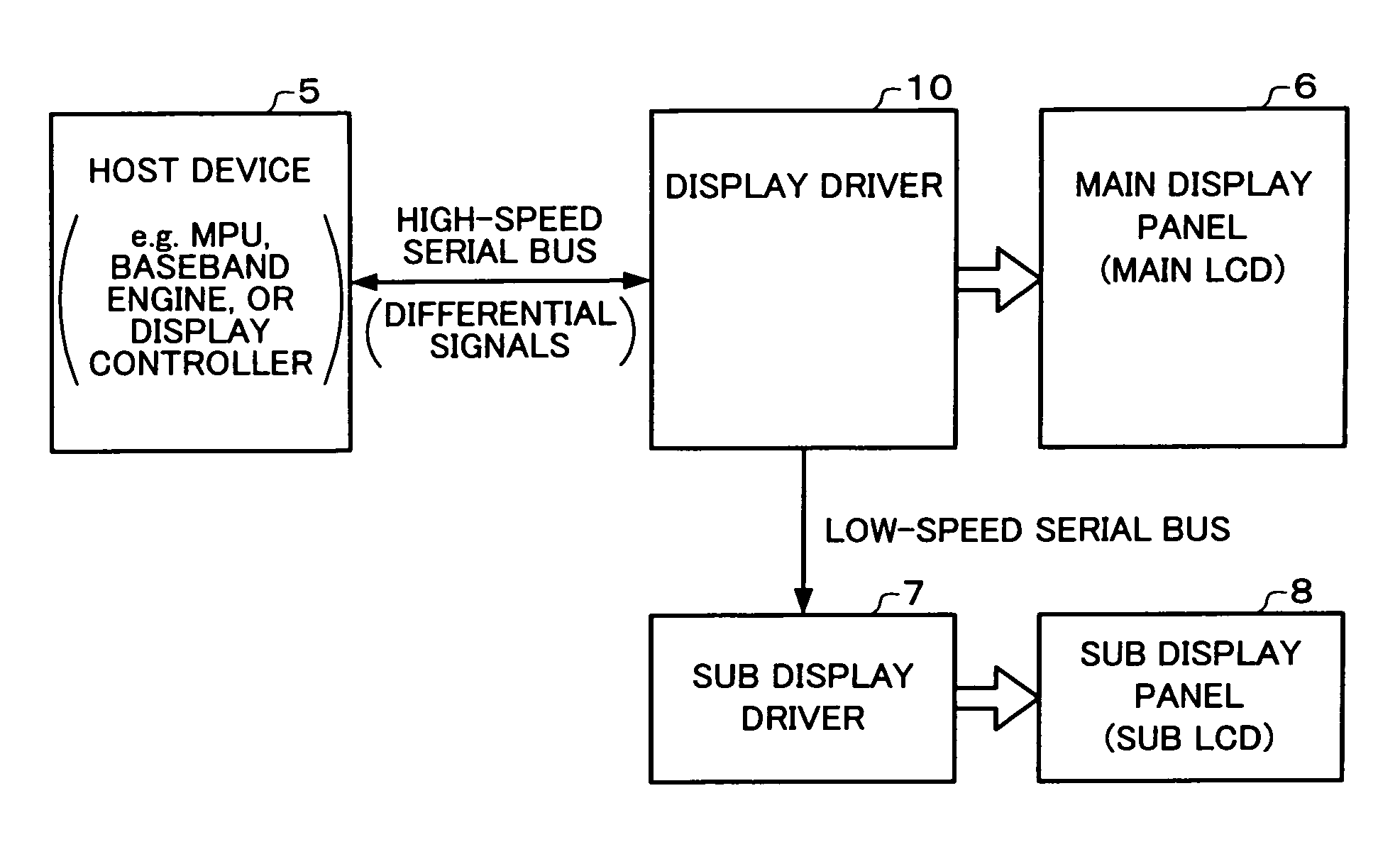

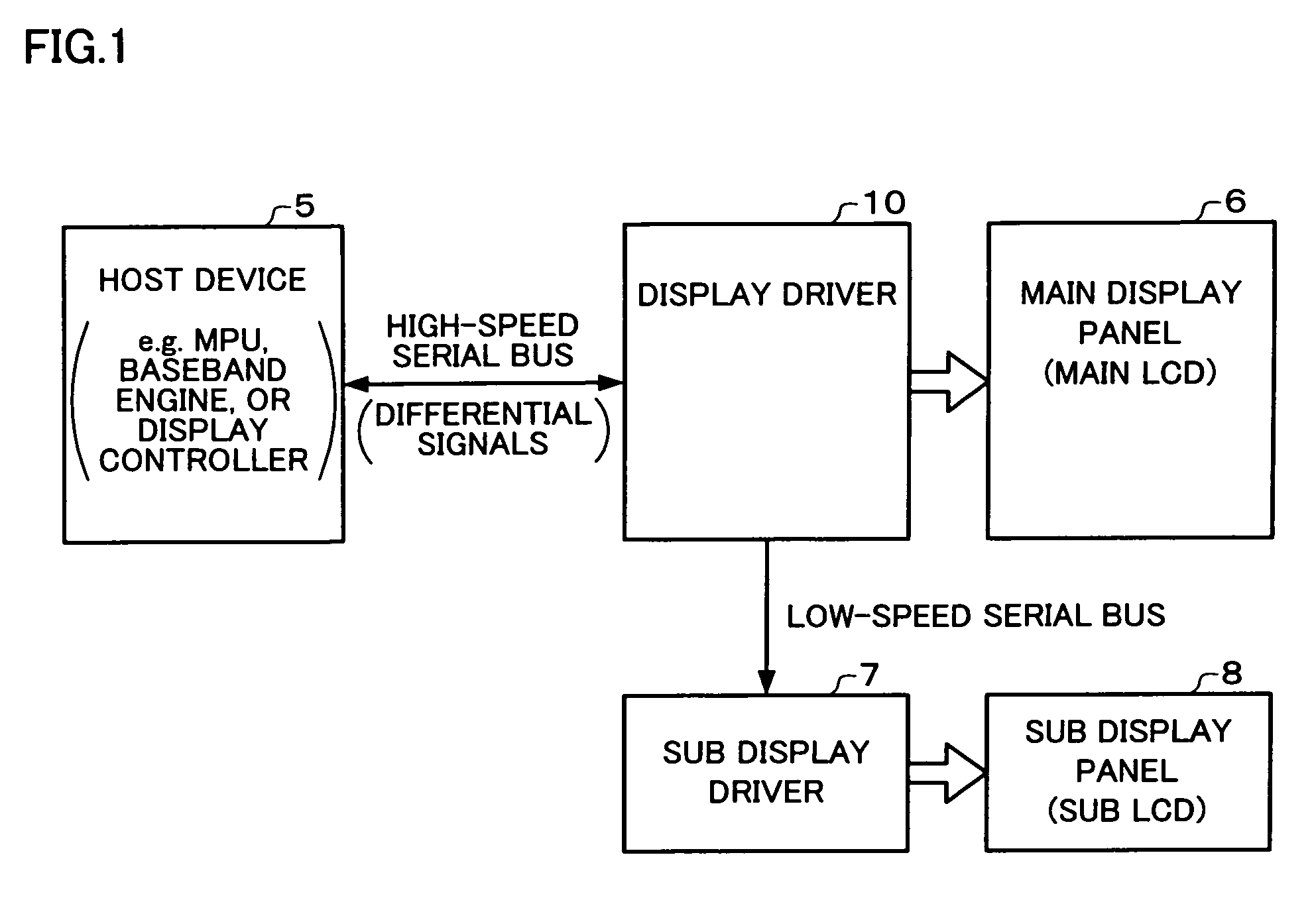

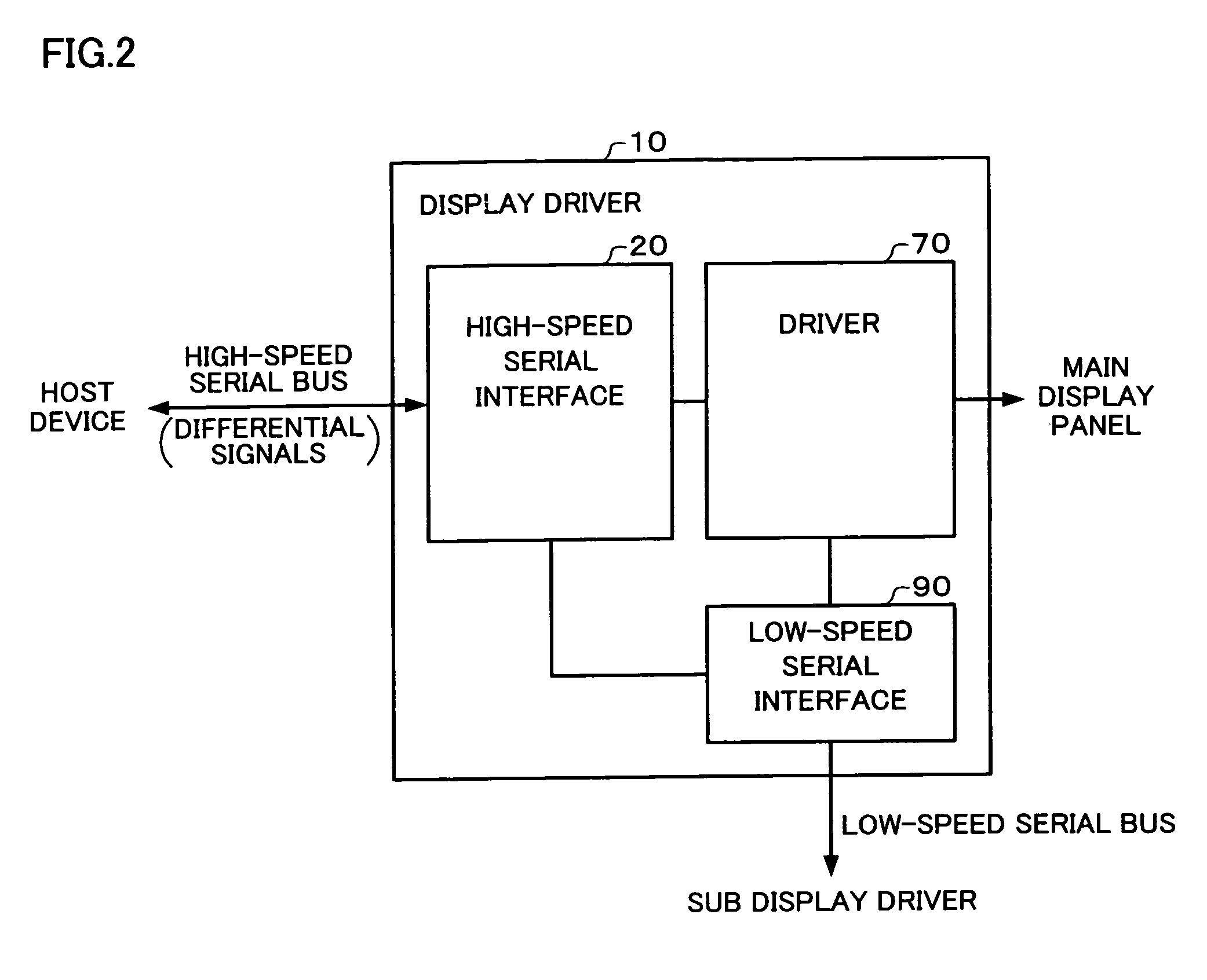

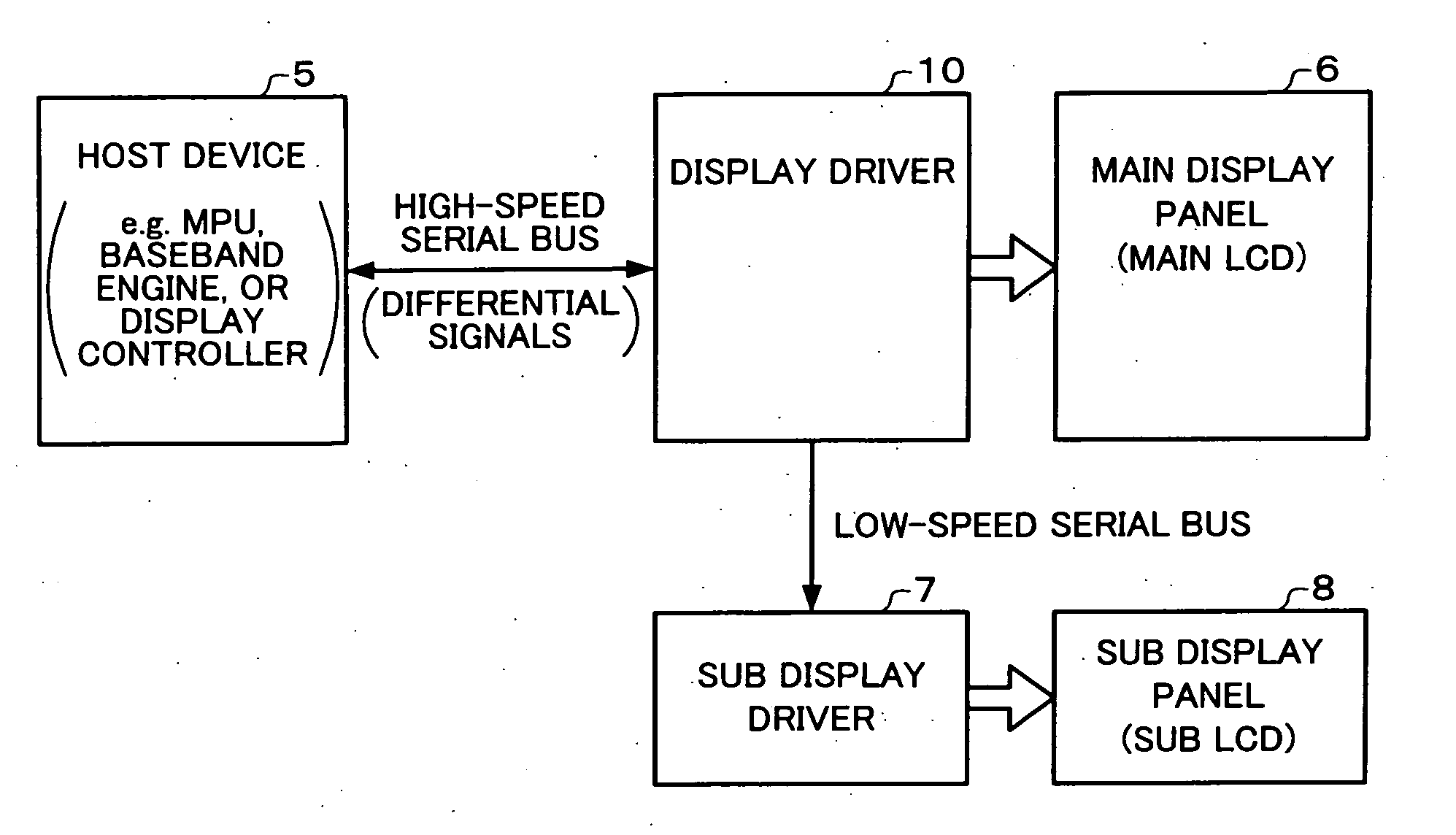

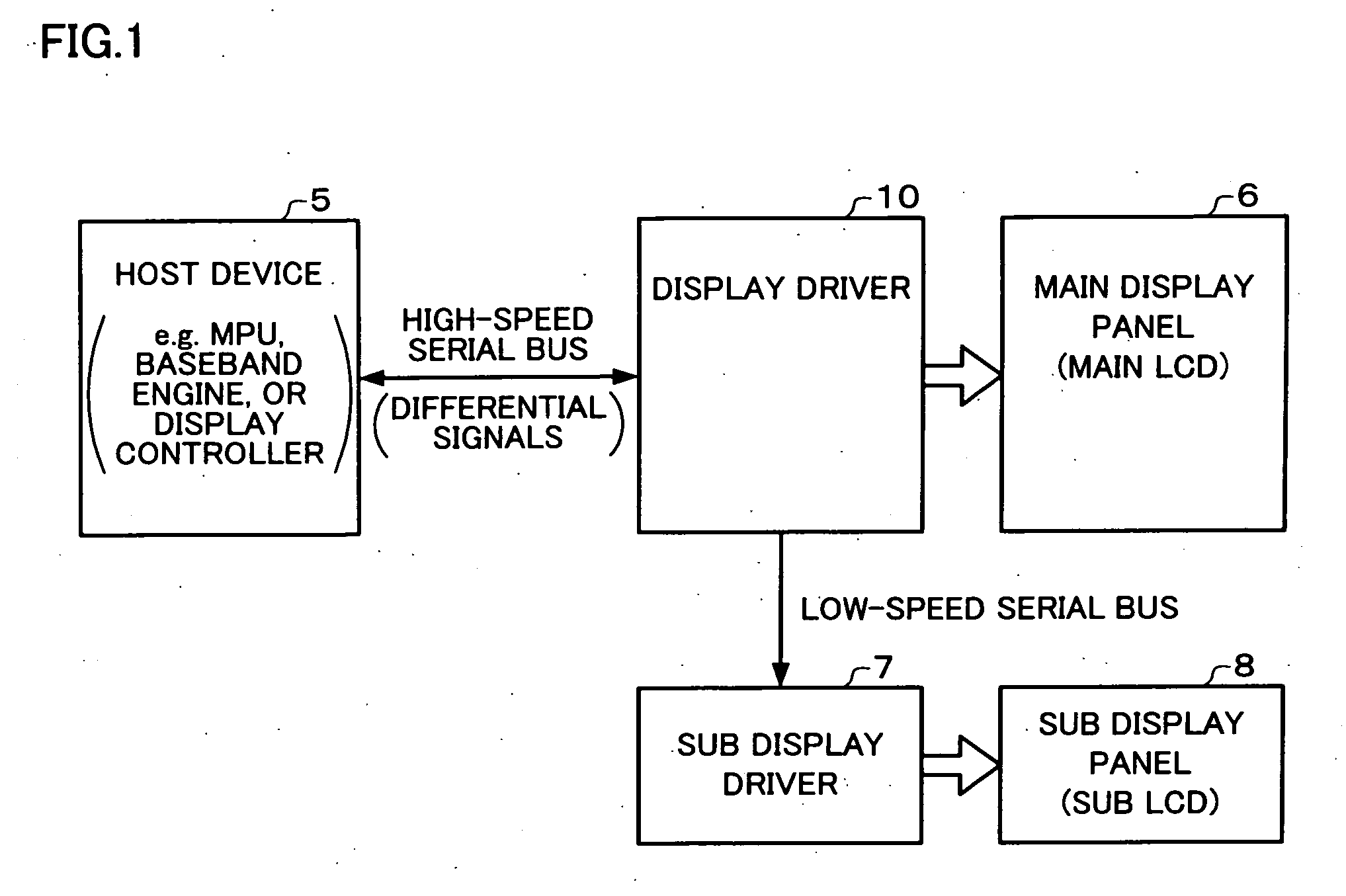

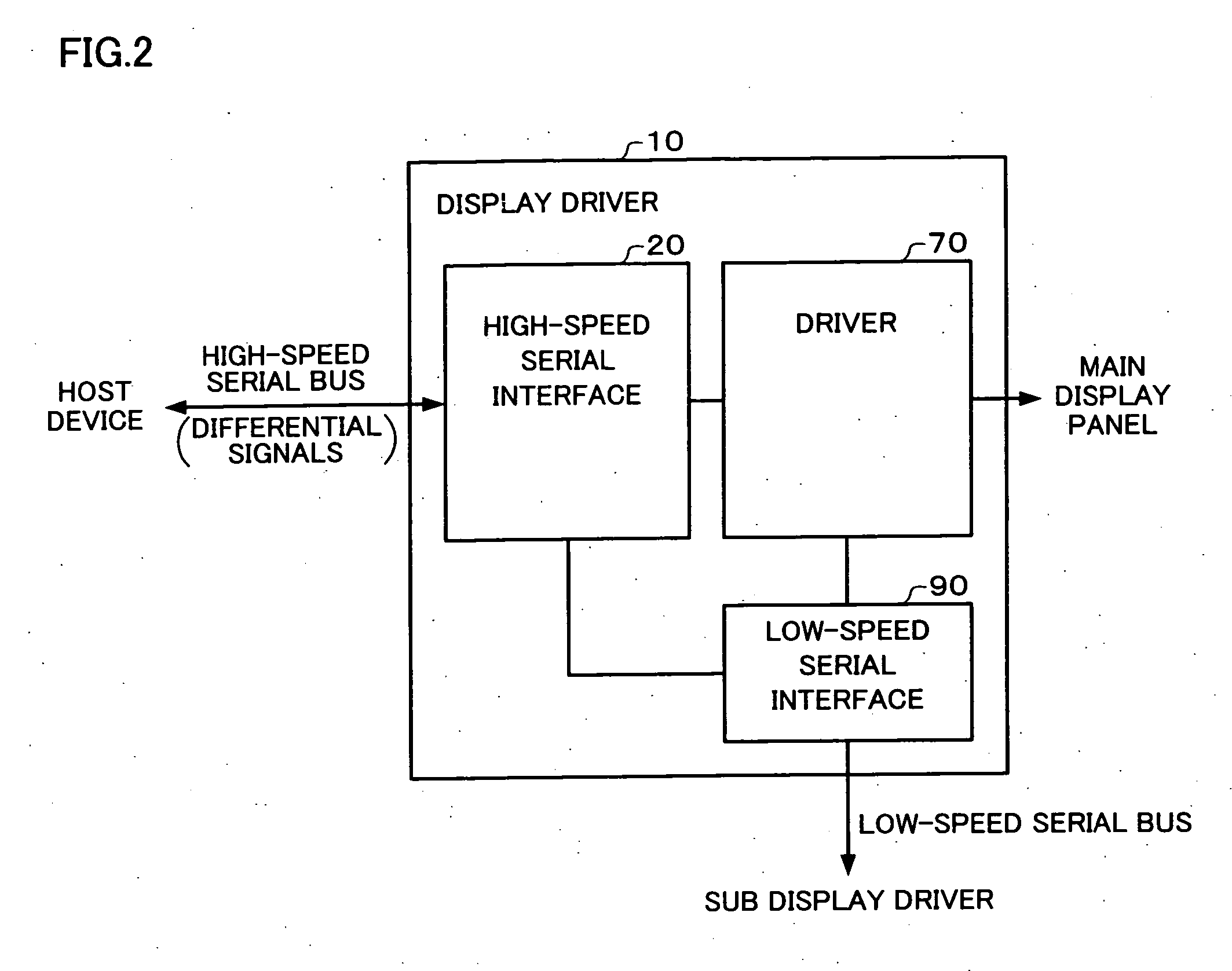

Display driver and electronic instrument

InactiveUS8031130B2Effective controlElectric/magnetic signal storageCathode-ray tube indicatorsDriver circuitLow speed

A display driver comprising: a high-speed serial interface circuit which receives a packet from a host device through a high-speed serial bus using differential signals, and outputs a command or data included in the received packet; a driver circuit which drives a main display panel based on the output command or data; and a low-speed serial interface circuit which outputs a command or data to a sub display driver through a low-speed serial bus when the packet received from the host device includes the sub display driver command or data. And the display driver inserts dummy data to the packet to adjust the difference of the transfer rate by inserting a dummy the dummy data. And the display driver adjust the difference of the transfer rate.

Owner:SEIKO EPSON CORP

Display driver and electronic instrument

InactiveUS20060214902A1Effective controlElectric/magnetic signal storageCathode-ray tube indicatorsInterface circuitsDummy data

A display driver comprising: a high-speed serial interface circuit which receives a packet from a host device through a high-speed serial bus using differential signals, and outputs a command or data included in the received packet; a driver circuit which drives a main display panel based on the output command or data; and a low-speed serial interface circuit which outputs a command or data to a sub display driver through a low-speed serial bus when the packet received from the host device includes the sub display driver command or data. And the display driver inserts dummy data to the packet to adjust the difference of the transfer rate by inserting a dummy the dummy data. And the display driver adjust the difference of the transfer rate

Owner:SEIKO EPSON CORP

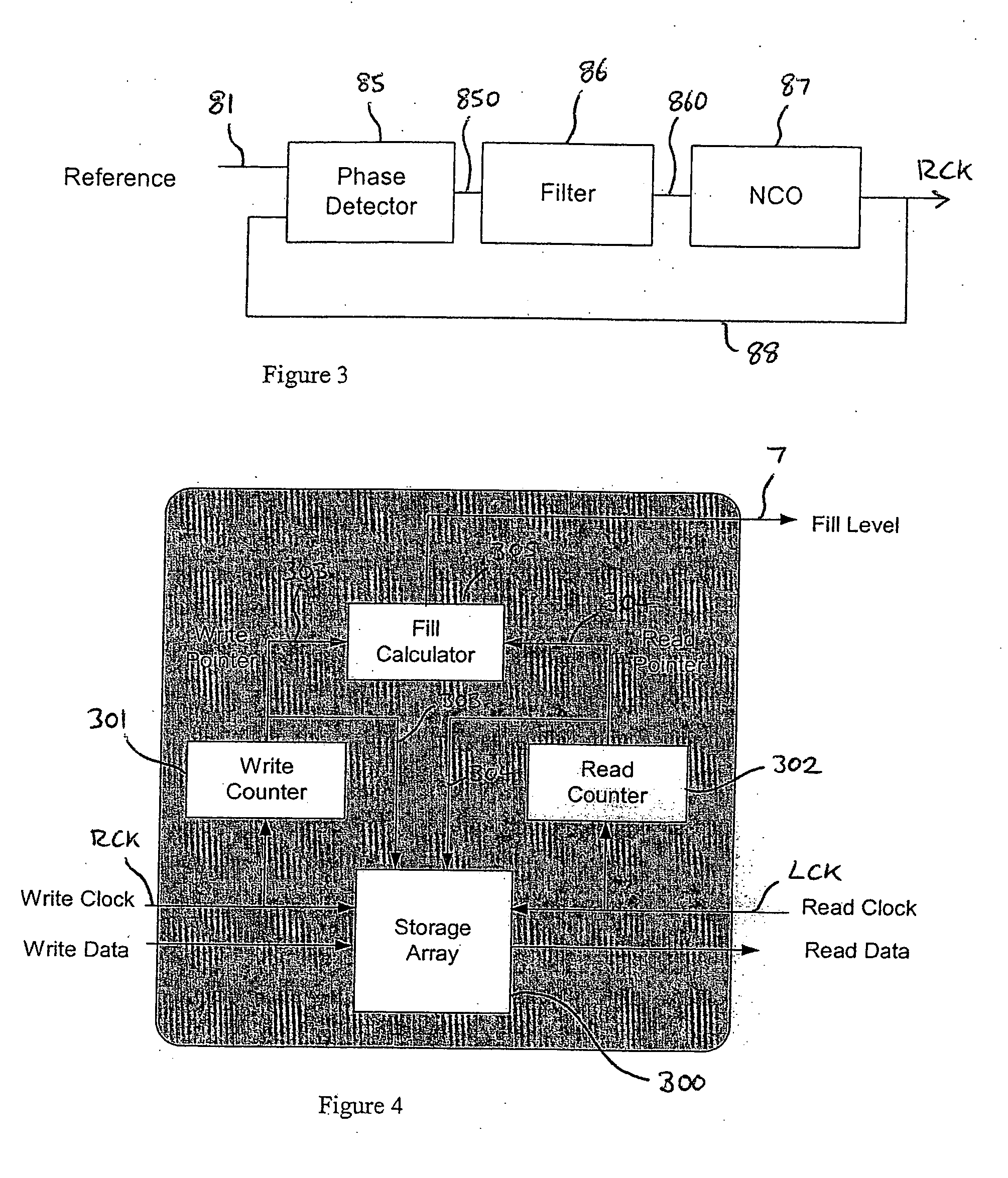

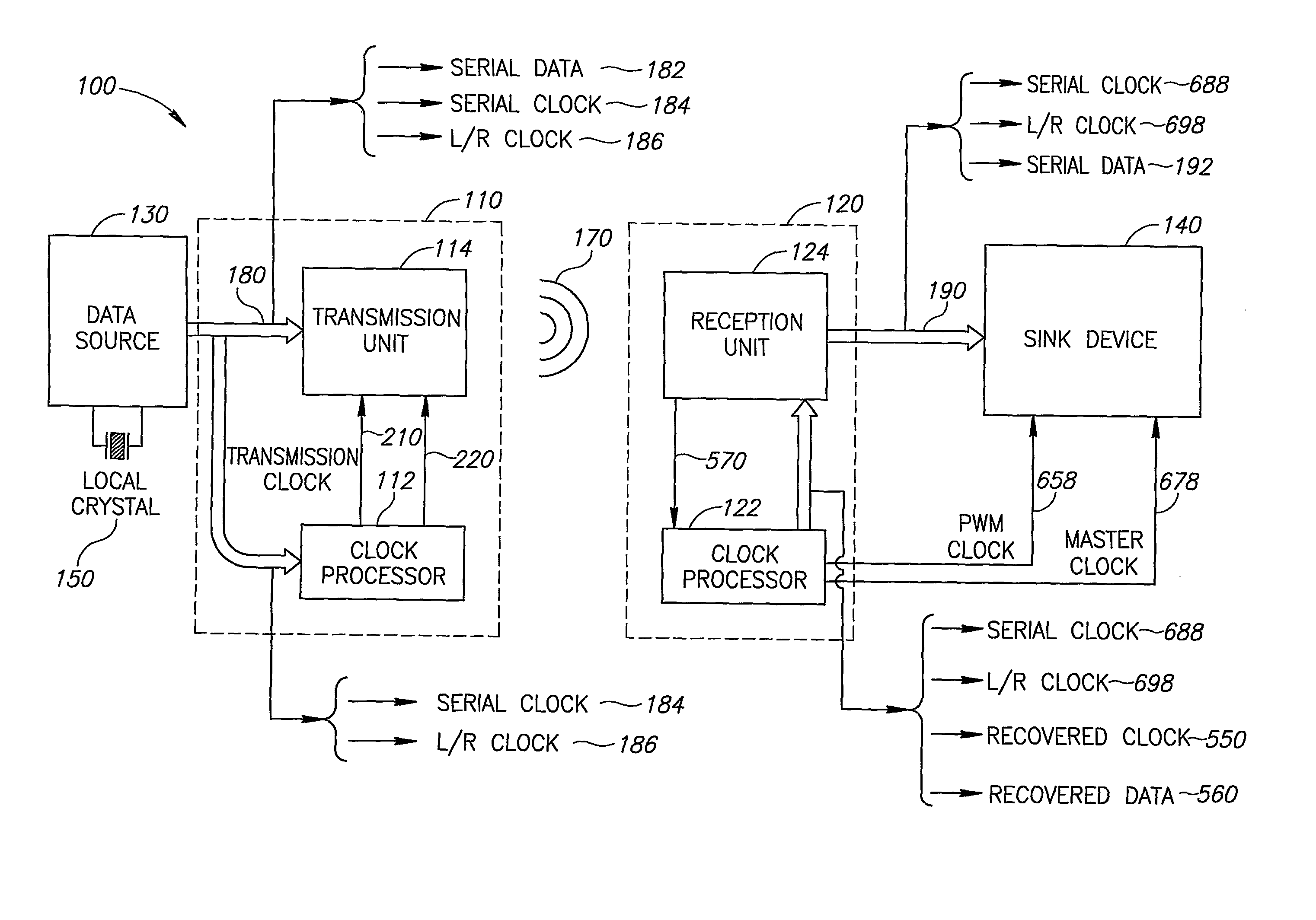

Clock synchronizer and clock and data recovery apparatus and method

A clock synchroniser, and clock and data recovery apparatus incorporating the clock synchroniser, are described, together with corresponding clock synchronisation methods. The clock synchroniser incorporates an elastic buffer. A received clock signal RCK is used to clock data into the buffer, and a locally generated clock LCK is used to clock data out of the buffer. The local clock is synthesised using a PLL, and a fill-level signal from the elastic buffer is used to control to local clock frequency to maintain a desired average quantity of data in the buffer, thereby achieving synchronisation of the received and local clocks. In preferred embodiments the fill-level signal is used to control a variable divider in the feedback path of the PLL, which is supplied with a highly stable reference signal. A synchronised, and low-jitter local clock is thus produced. Preferably, the elastic buffer employs counters of relatively wide word width, and a storage array of much reduced depth, read and write pointers being provided by just a few of the least significant bits of the words.

Owner:CIRRUS LOGIC INT SEMICON

Sample rate converter having distributed filtering

InactiveUS7280878B1Minimize artifactLower requirementDigital technique networkElectric/magnetic signal storageSample rate conversionSample sequence

A method and a computer program product for sample rate conversion that features distributive or hybrid filtering to reduce unwanted artifacts, such as aliasing and the computational requirements to avoid the aforementioned artifacts. The method includes receiving, at a first sample rate, a plurality of data points, associated with a first signal, operating on the plurality of data points to associate the signal with a predetermined set of parameters, with the set of parameters including a first transition band having an image associated therewith; and varying the sample rate associated with the first signal by interpolation with an interpolator having associated therewith a second transition band, with the width associated with the second transition band being a function of a spectral separation between the first transition band and its image, wherein a second signal is produced having a sequence of data samples approximating the first signal.

Owner:CREATIVE TECH CORP

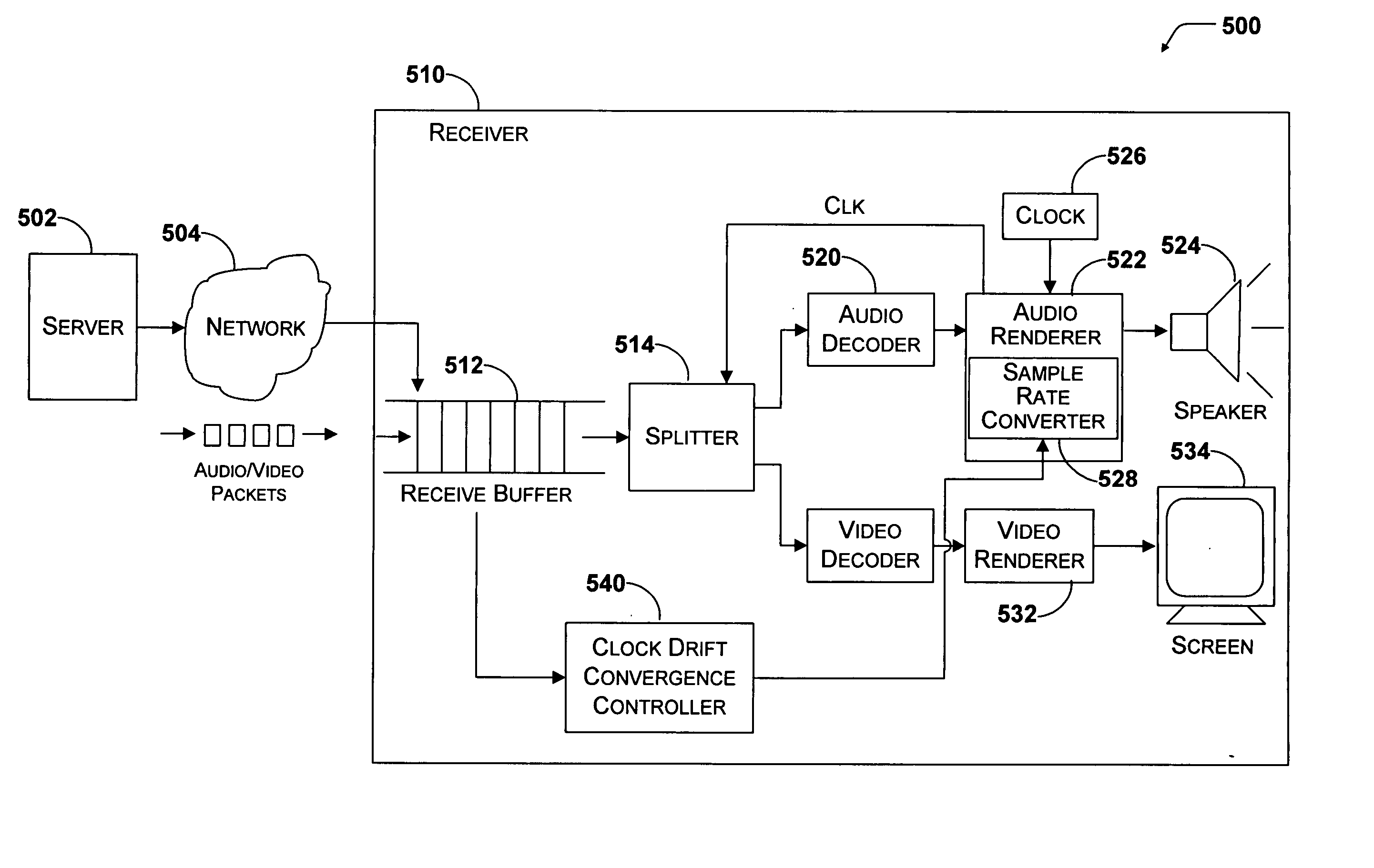

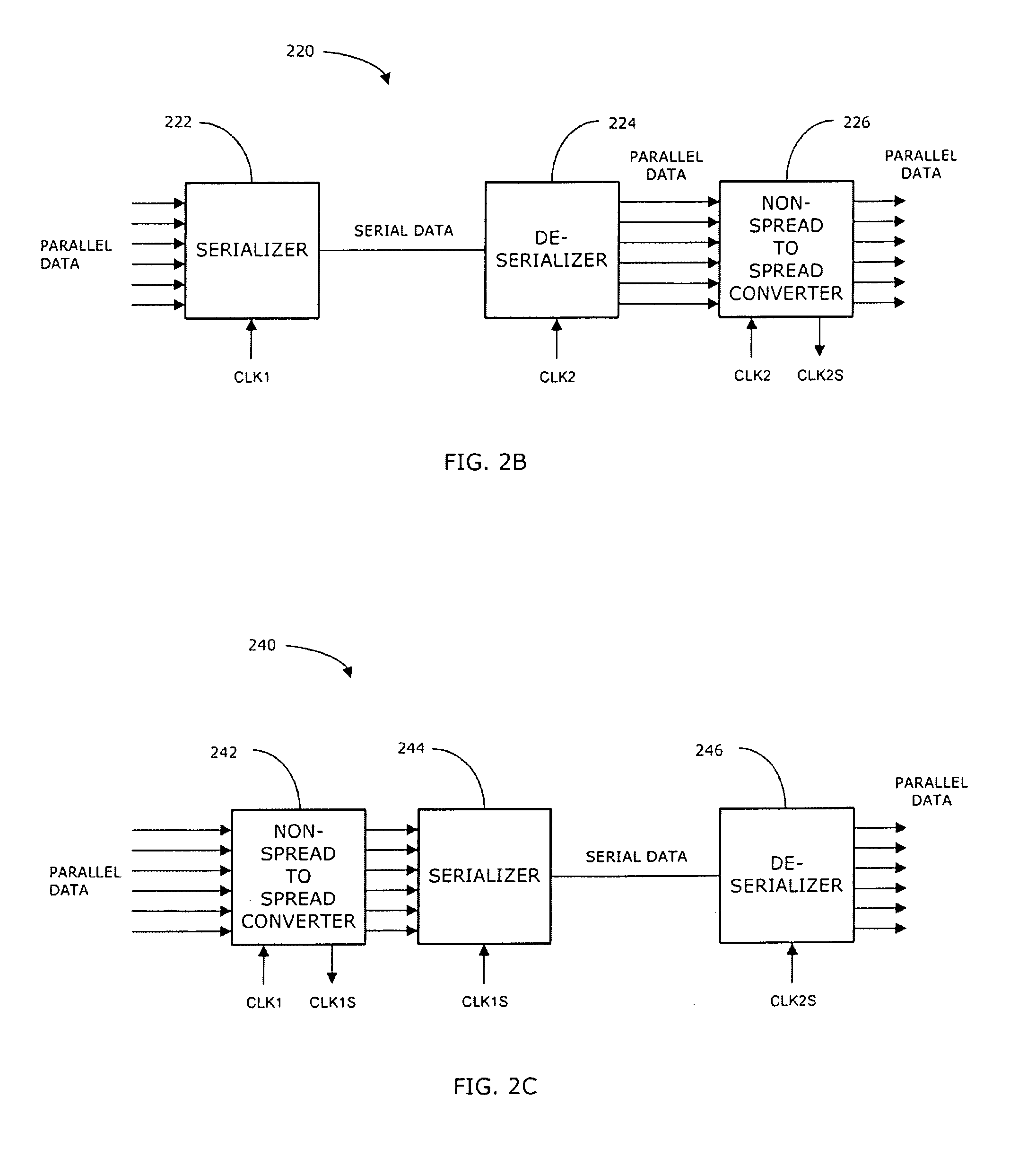

System and method for clock drift correction for broadcast audio/video streaming

InactiveUS20060104397A1Add depthError preventionFrequency-division multiplex detailsStreaming dataClock drift

A clock rate used in rendering broadcast streaming audio / video data is adjusted to converge on a clock rate associated with broadcasting the streaming data. The clock rate is adjusted by monitoring the buffer depth associated with a receive buffer that stores the incoming streaming data. The buffer depth provides an estimate of clock drift between the two clock rates. From the estimate of clock drift, the clock rate used in rendering broadcast streaming data is adjusted to avoid the clock drift causing skips or pauses in the rendered audio / video data.

Owner:MICROSOFT TECH LICENSING LLC

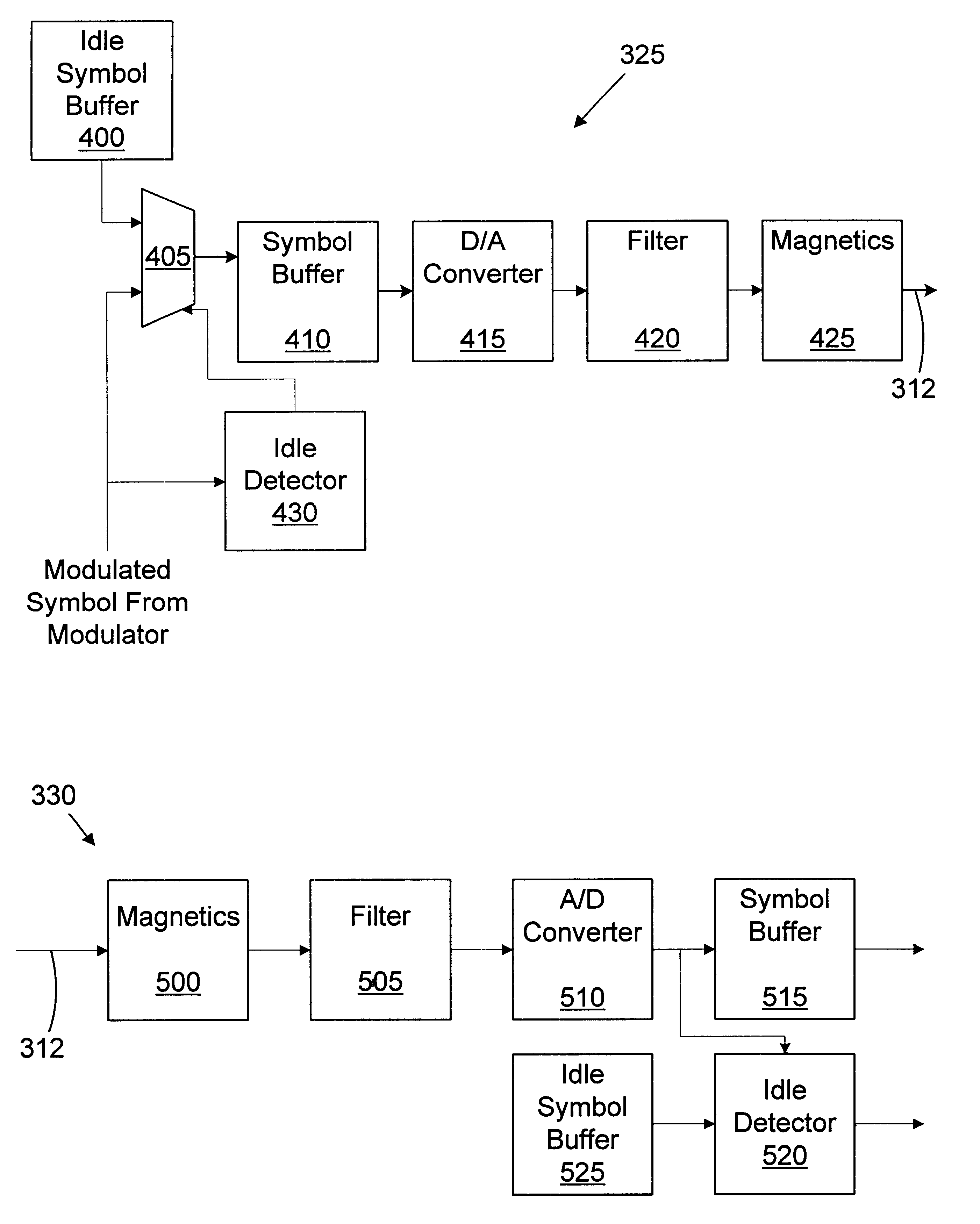

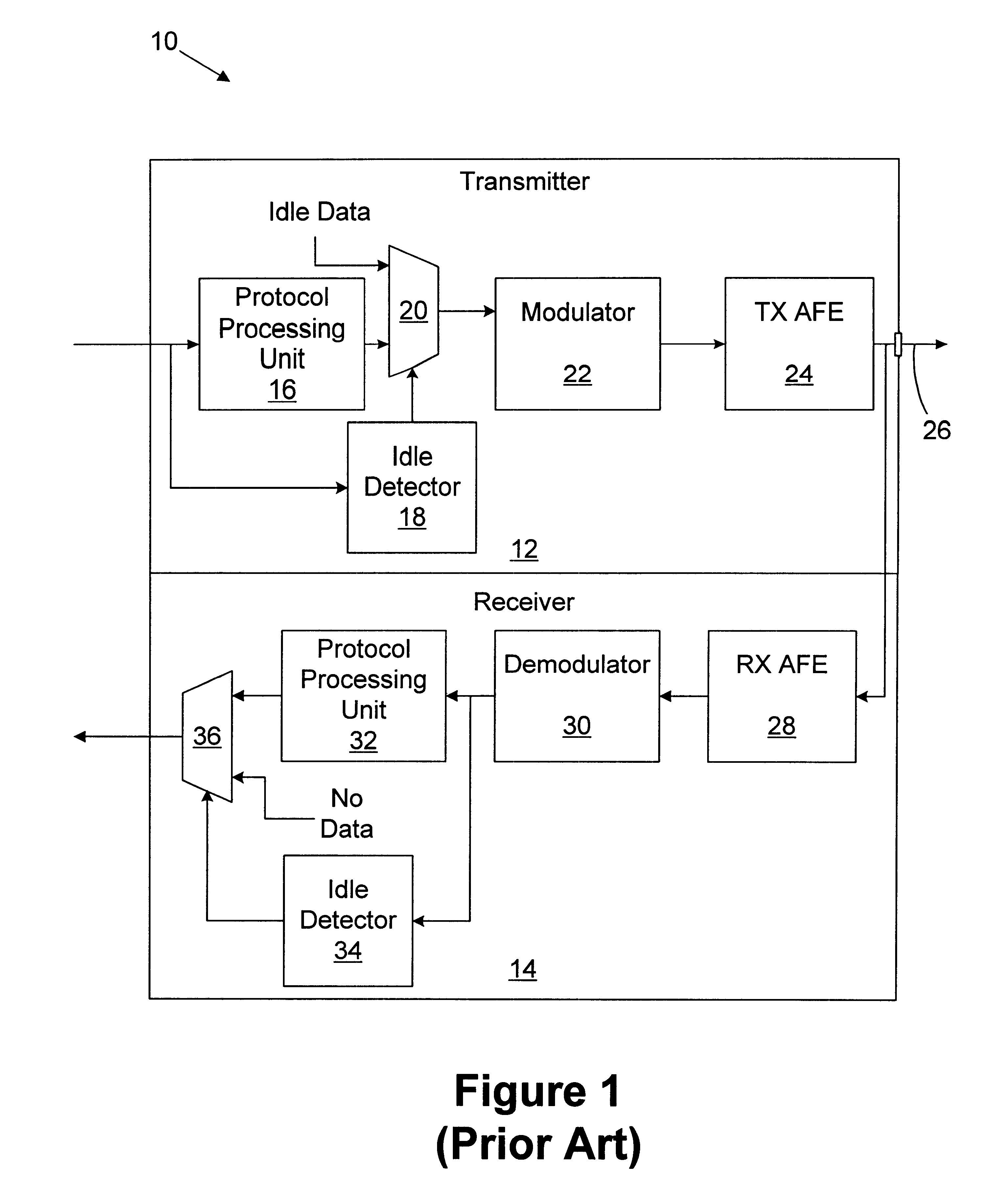

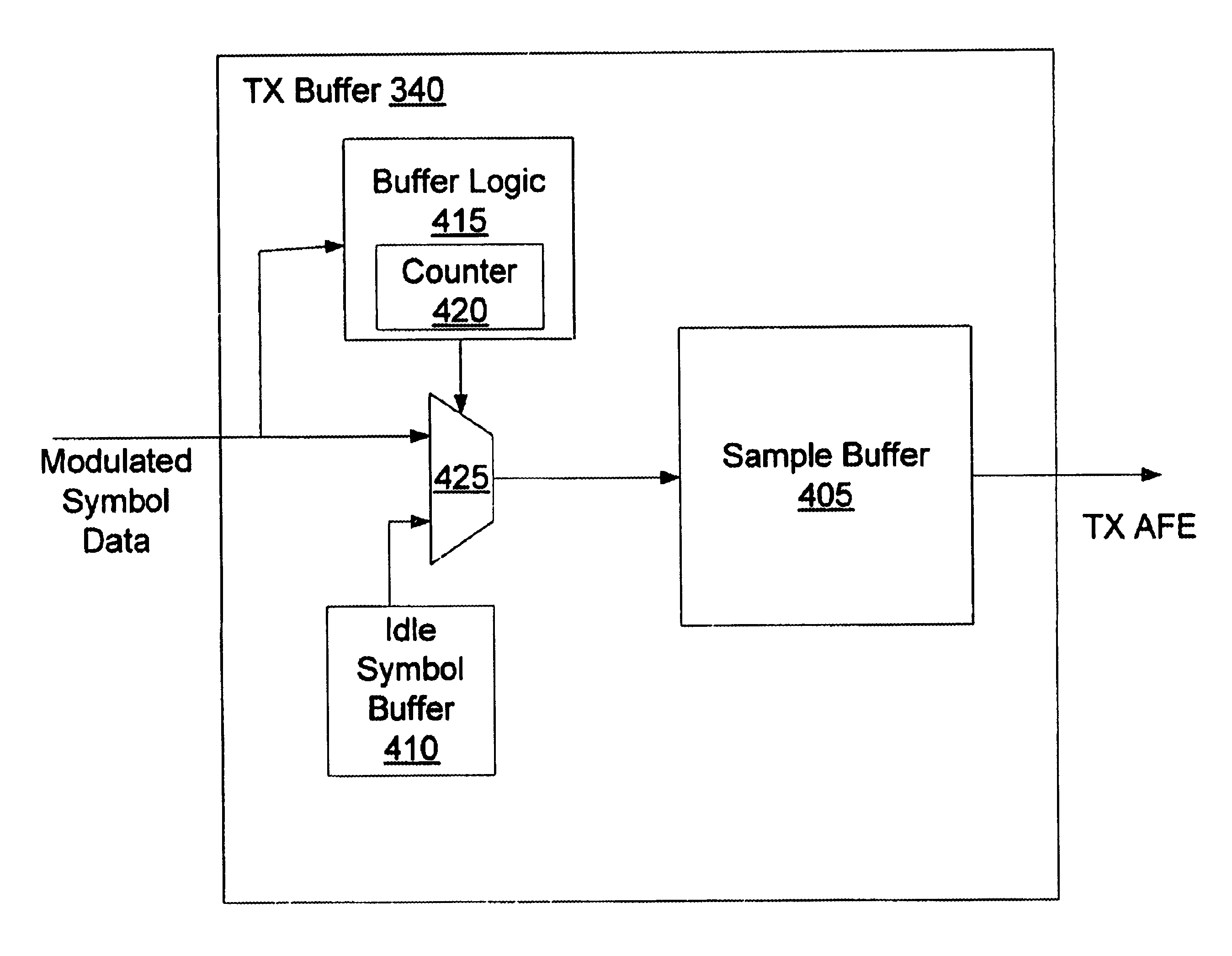

Method and apparatus for inserting idle symbols

A communication device includes a transmitter and a first idle detector. The transmitter is adapted to transmit digital data. The digital data includes user data. The transmitter includes a first idle symbol buffer for storing a first idle symbol. The first idle detector is adapted to detect an absence of user data. The transmitter is adapted to transmit the first idle symbol in response to detecting the absence of user data. A method for transmitting data includes defining a first idle symbol. The user data is stored in a buffer. The user data is modulated to generate a user symbol. An absence of user data in the buffer is detected, and the first idle symbol is transmitted in response to detecting the absence of user data.

Owner:MICROSEMI SEMICON U S

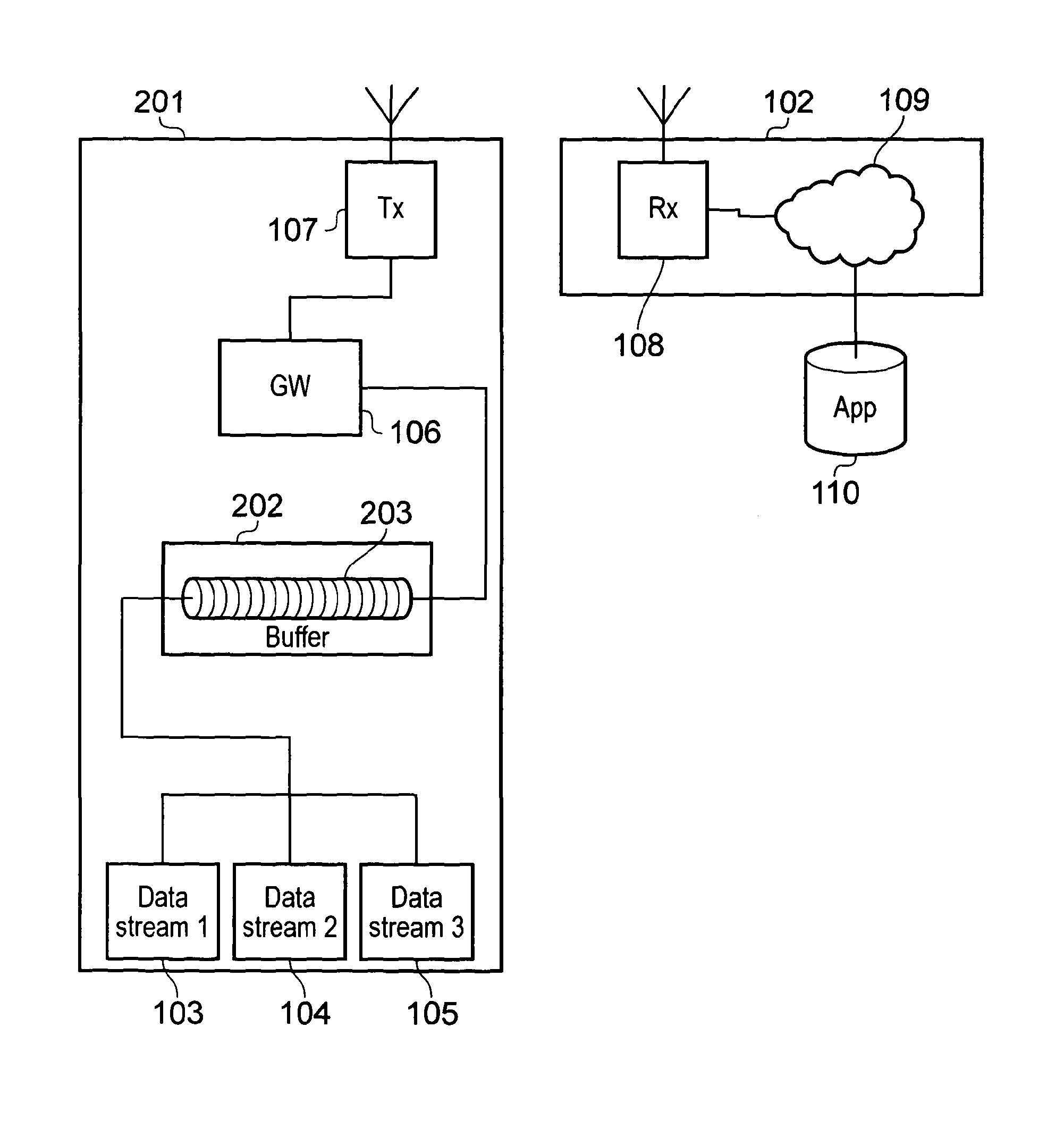

Apparatus, method and system for managing data transmission

InactiveUS20130215850A1Reduces efficiency of systemReduce capacityPower managementTransmission systemsData sourcePacket data transmission

An apparatus for managing data transmission in a telecommunications system, including a buffer unit arranged to receive data from one or more sources of data and to forward the data to a transmitter for transmission. The buffer unit is configured to delay the transmission of the data by storing the data for a time before forwarding it to the transmitter. The buffer unit is also configured to forward the stored data to the transmitter for transmission when an amount of data stored in the buffer unit reaches a predefined threshold.

Owner:IPLA HLDG

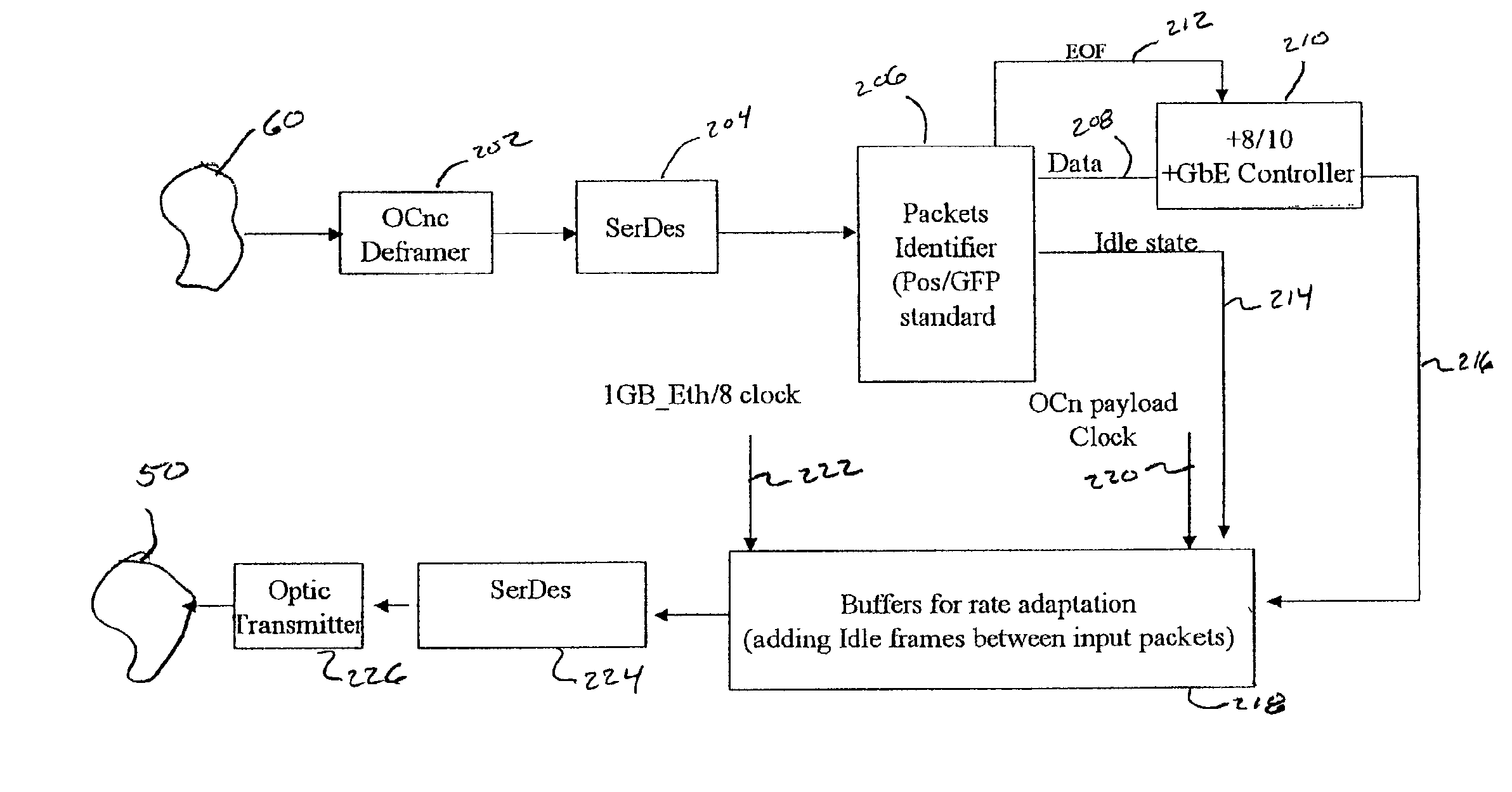

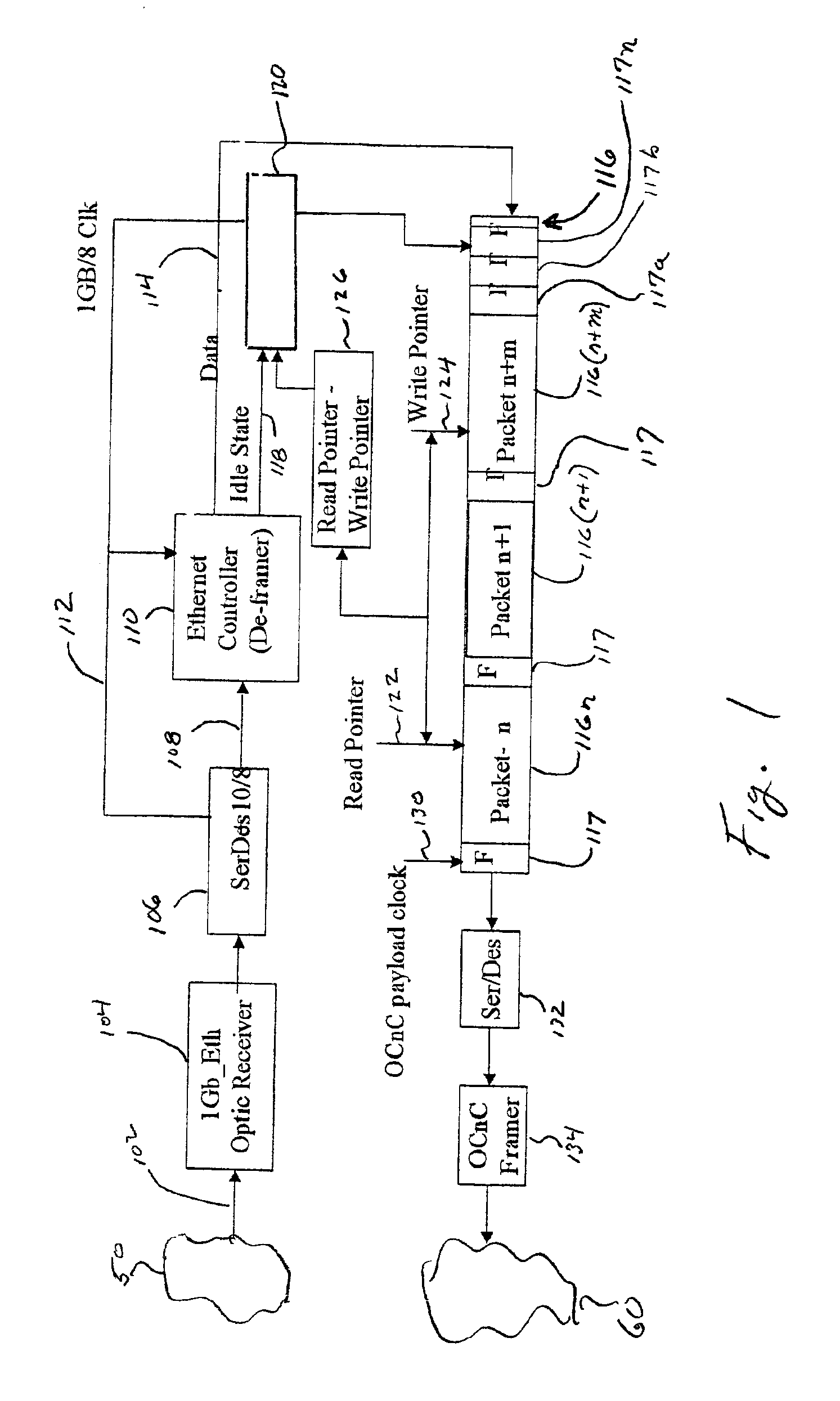

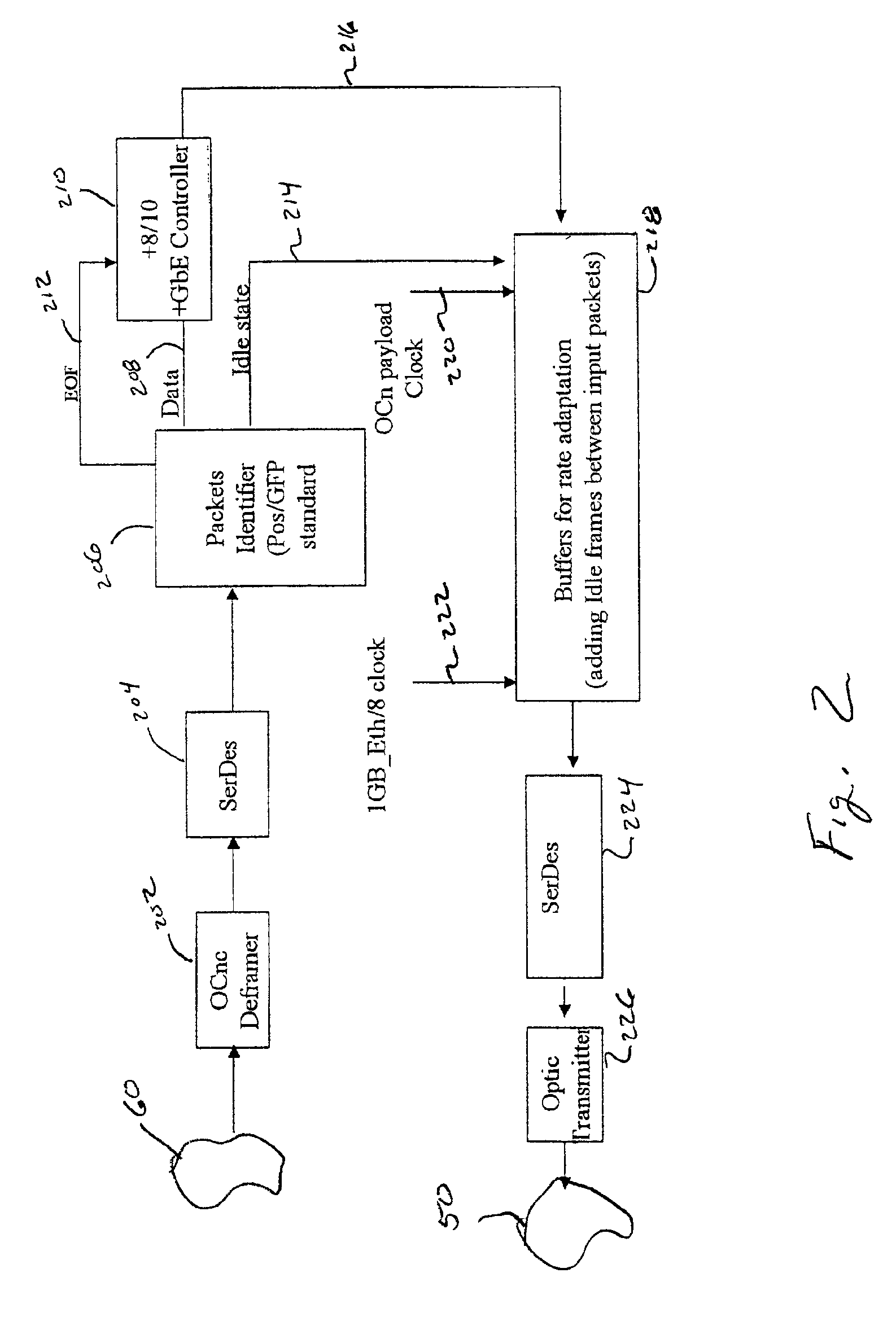

Method and apparatus for converting data packets between a higher bandwidth network and a lower bandwidth network

ActiveUS6934301B2Efficient communicationNo loss of data contentElectric/magnetic signal storageTime-division multiplexTraffic capacityHigh bandwidth

A method and apparatus for converting bursty, packetized data traffic from a wide bandwidth network to a constant, average rate traffic on a payload network having a narrower bandwidth is disclosed. The method includes converting a packet burst received from the wide bandwidth network to a serial stream having first and second pluralities of bytes, the second plurality of bytes having only idle bytes; substituting a place keeping flag for said second plurality of bytes thereby providing a reduced data; encapsulating the reduced data in a second packet; and providing the second packet to the narrower bandwidth network at a constant, average traffic rate. The method also includes converting the second packet received from the narrower bandwidth network to a second serial stream; substituting a plurality of idle bytes for the place keeping flags; converting the second serial stream and substituted idle bytes to a third packet; and providing the third packet to the wide bandwidth network.

Owner:ECE TELECOM LTD

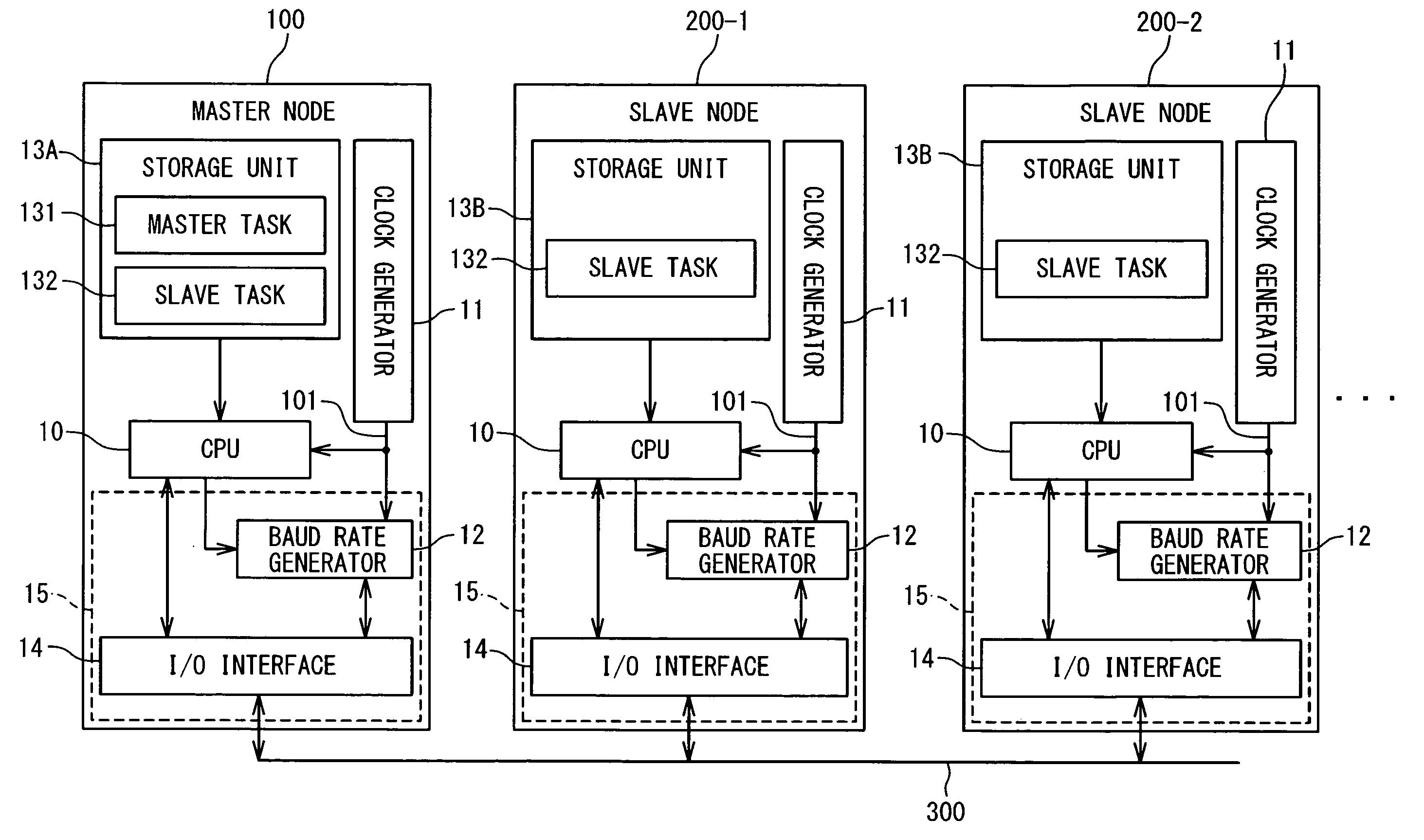

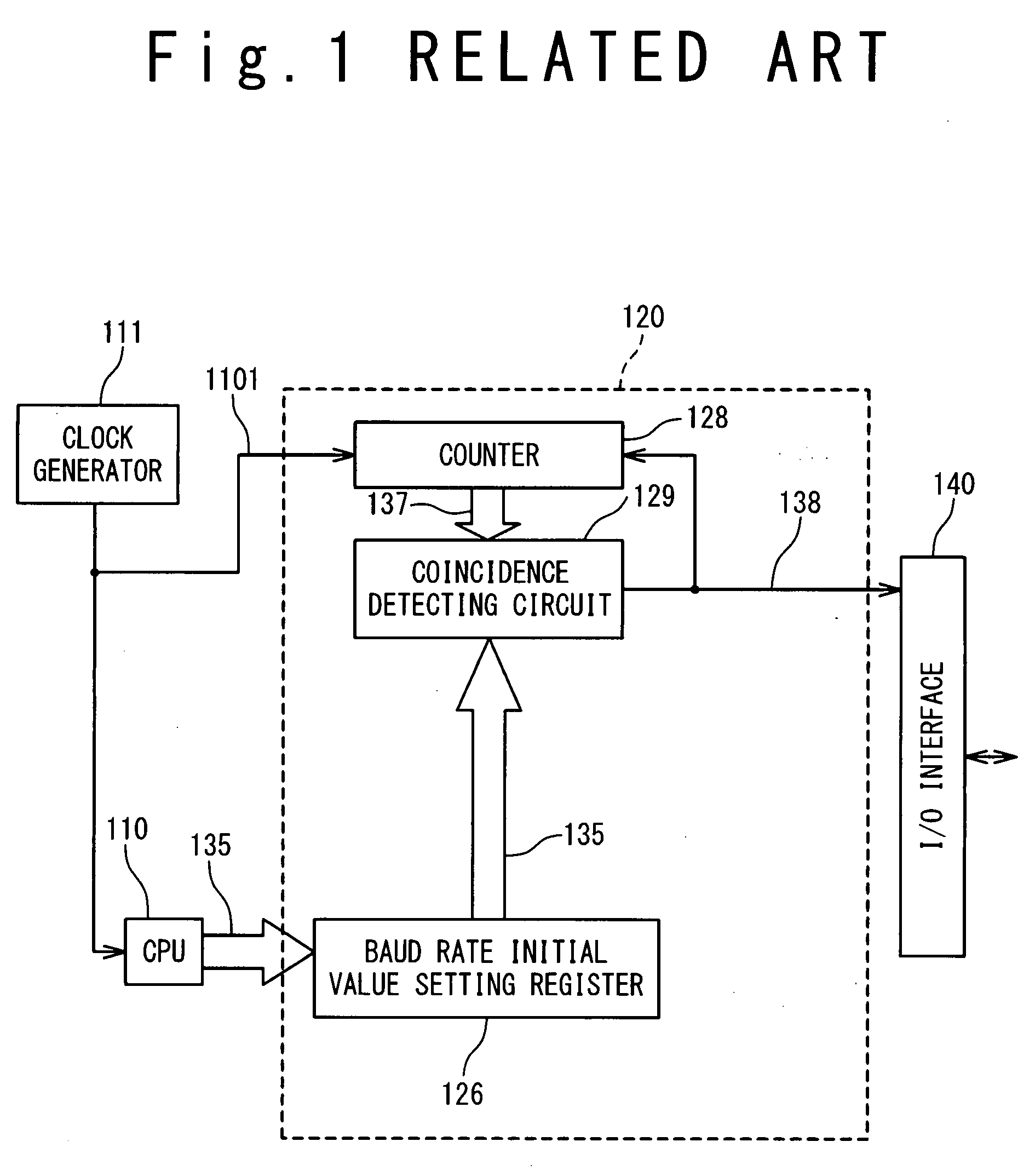

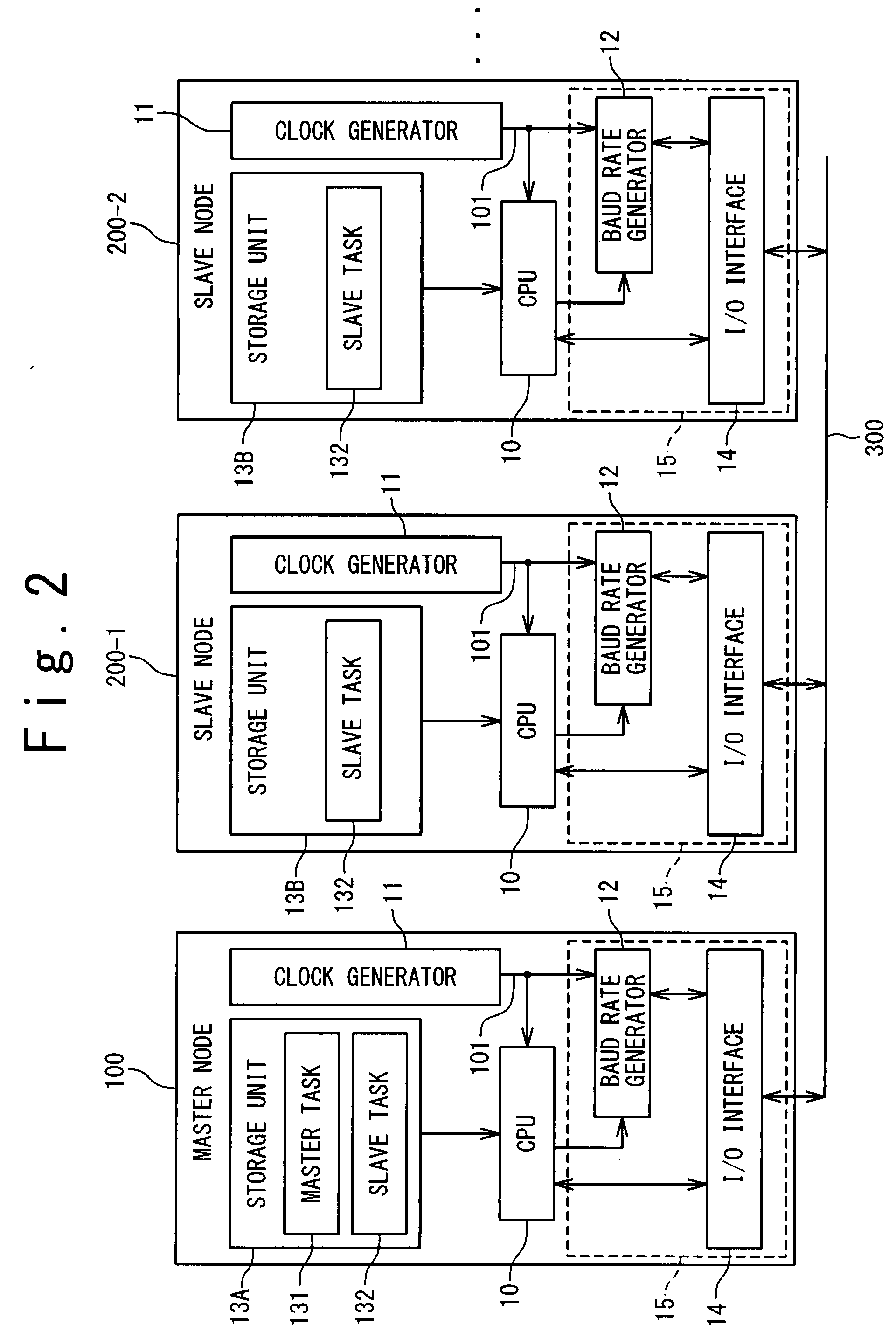

Serial communication system with baud rate generator

ActiveUS20070291887A1Reduce loadIncrease transfer speedError preventionTransmission systemsComputer scienceTimer

A baud rate generator includes a first counter, a timer and a baud rate correcting circuit. The first counter is configured to count bits of an inputted serial data. The timer is configured to measure a time for which the first counter counts a predetermined number of bits based on a reference clock signal. The baud rate correcting circuit is configured to output a baud rate correction value based on the measurement time by the timer such that a baud rate in a serial communication is corrected based on the baud rate correction value.

Owner:RENESAS ELECTRONICS CORP

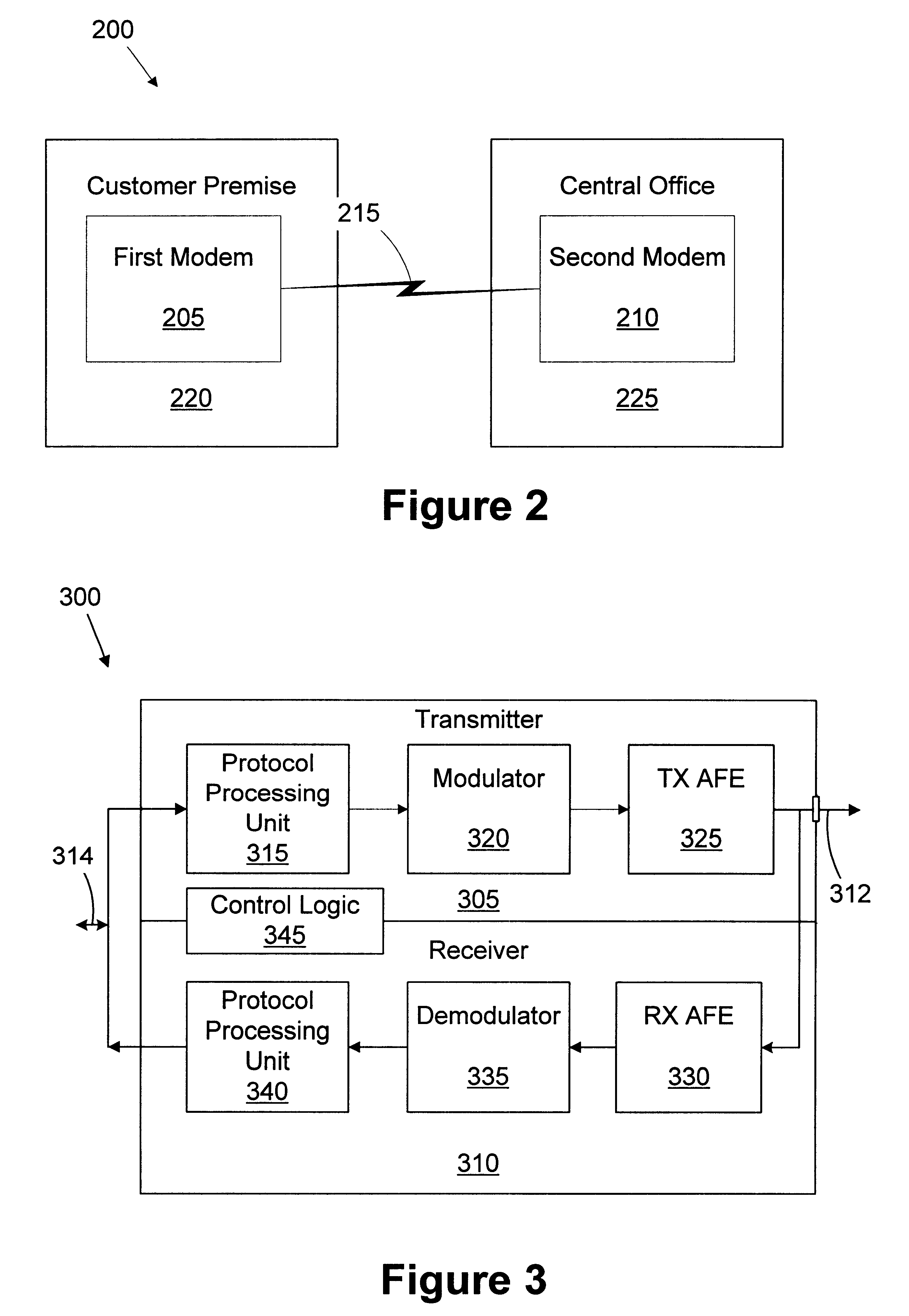

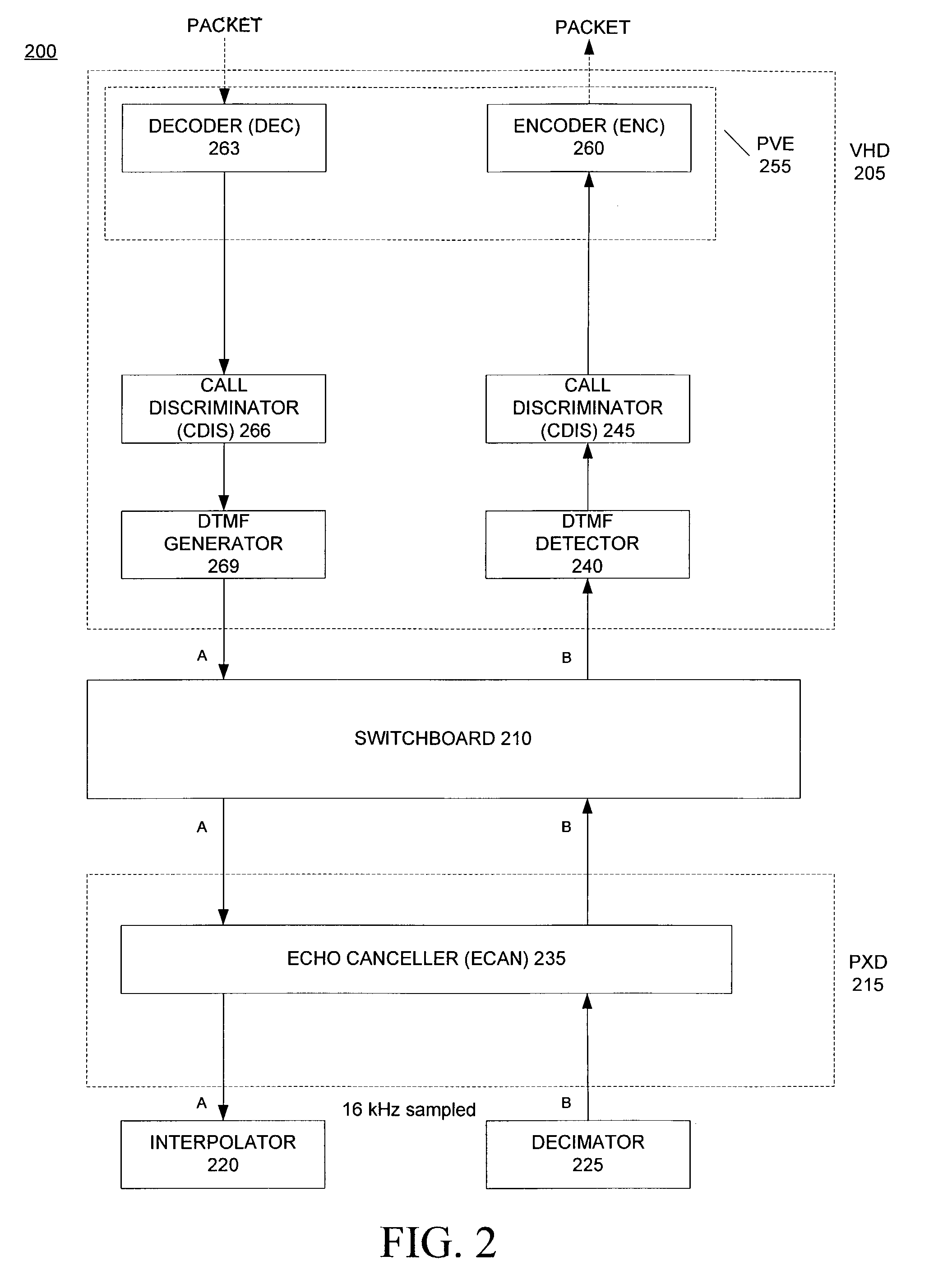

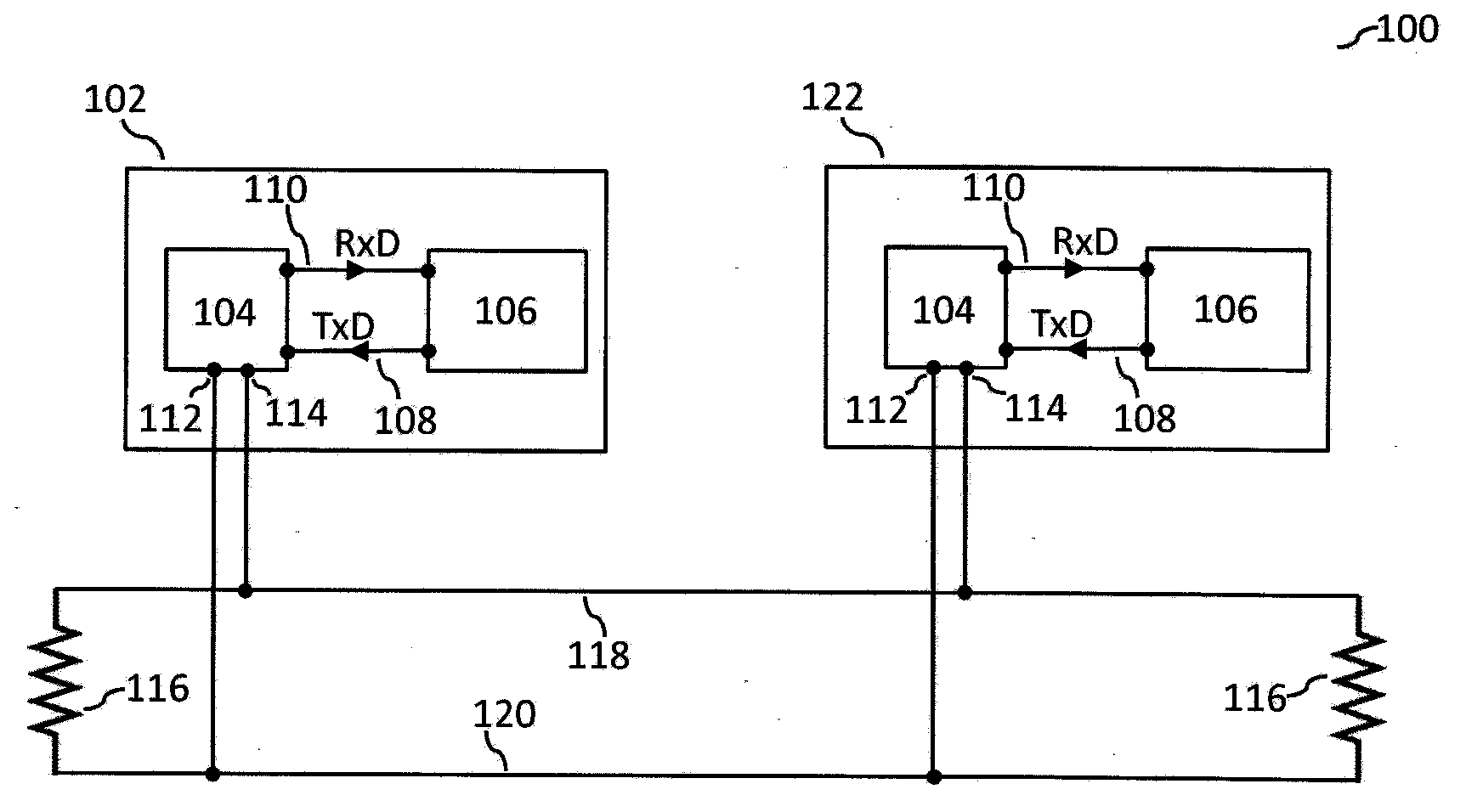

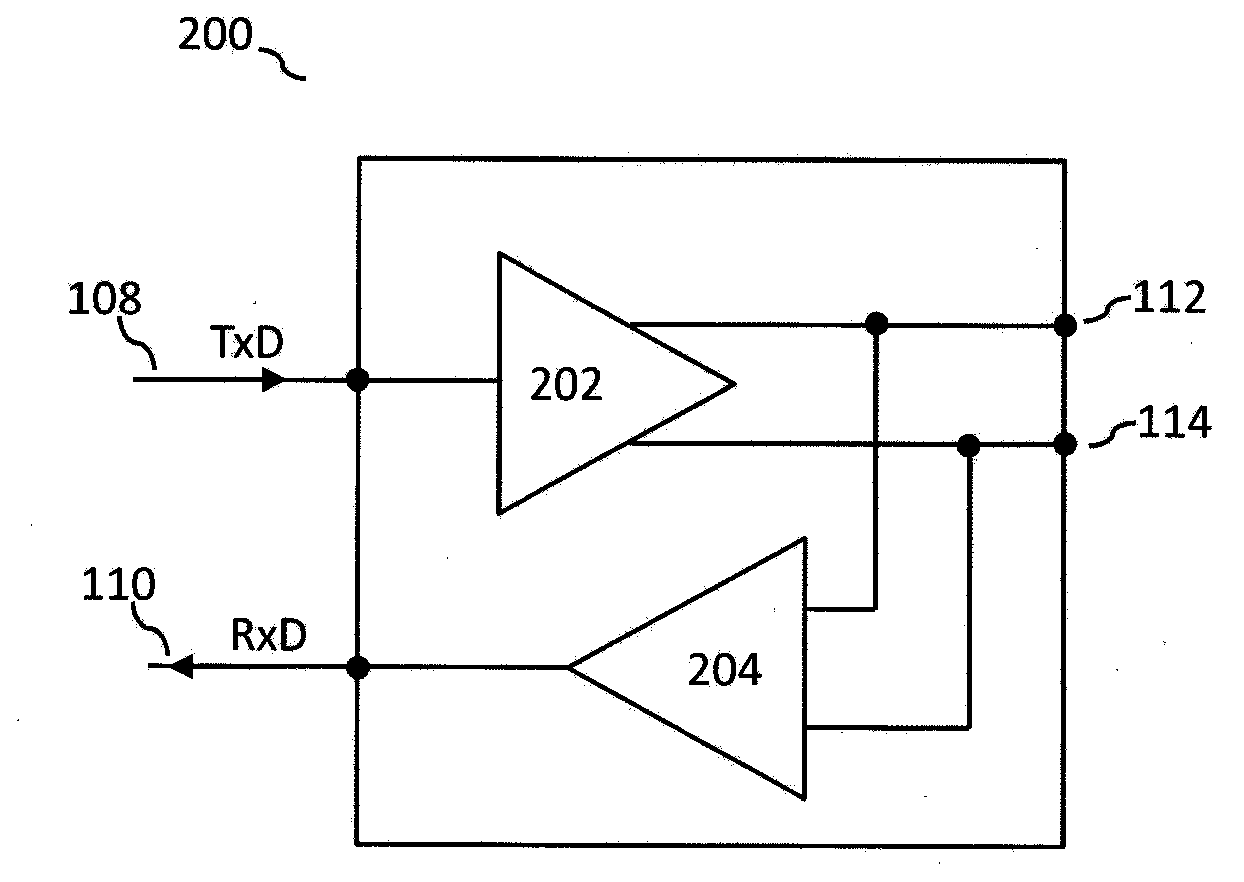

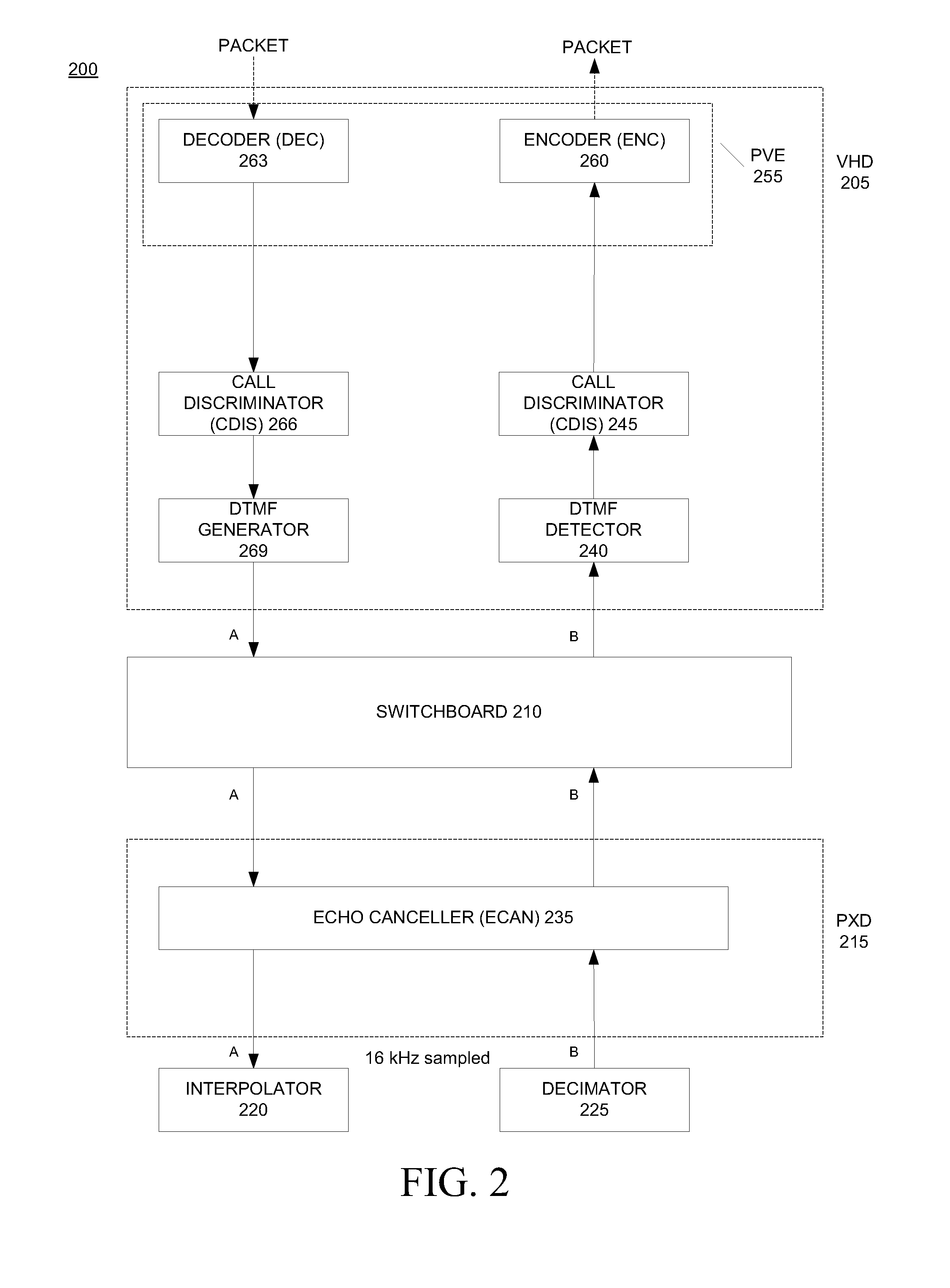

Switchboard for dual-rate single-band communication system

ActiveUS7409056B2Special service provision for substationInterconnection arrangementsCommunication interfaceCommunications system

Owner:AVAGO TECH INT SALES PTE LTD

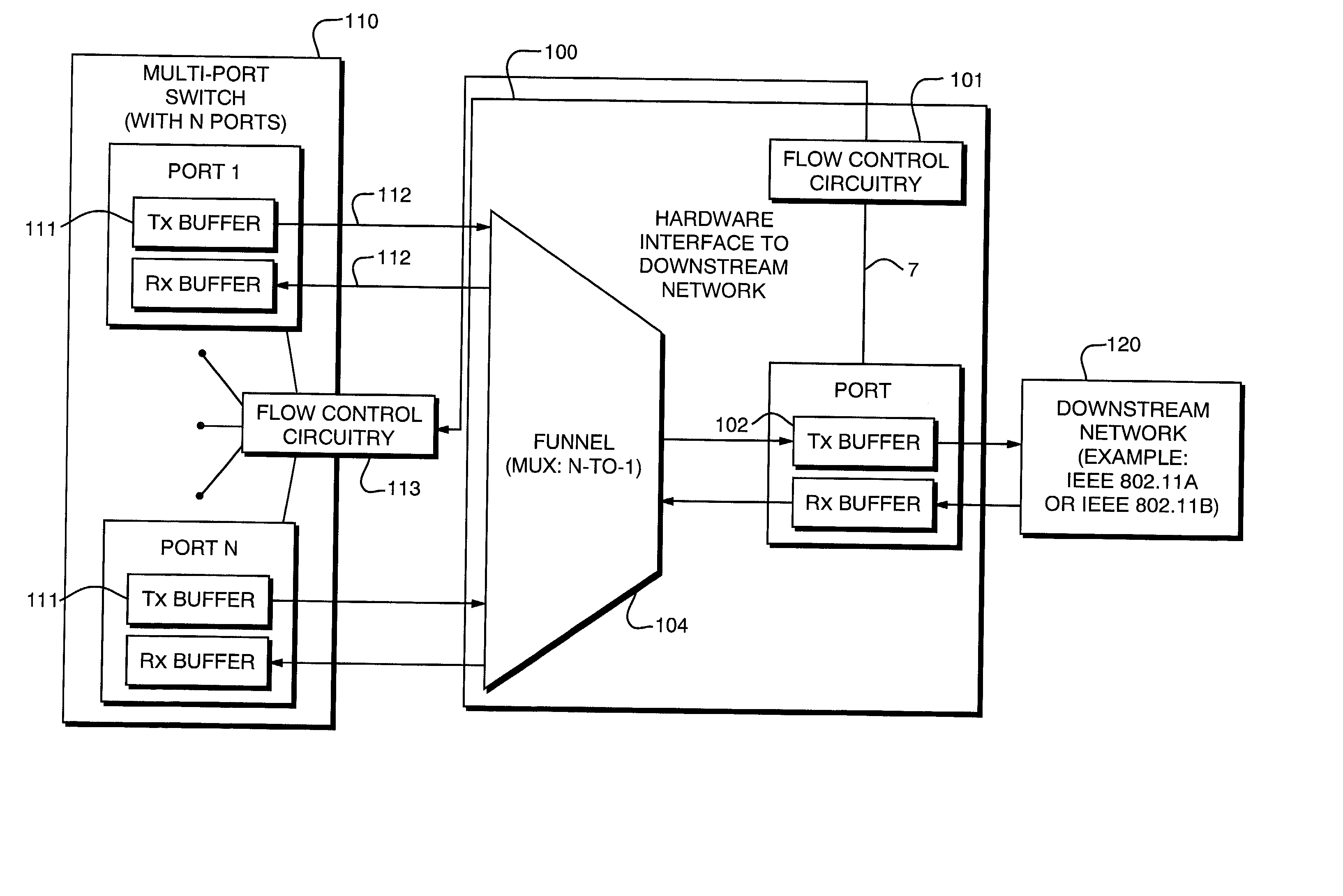

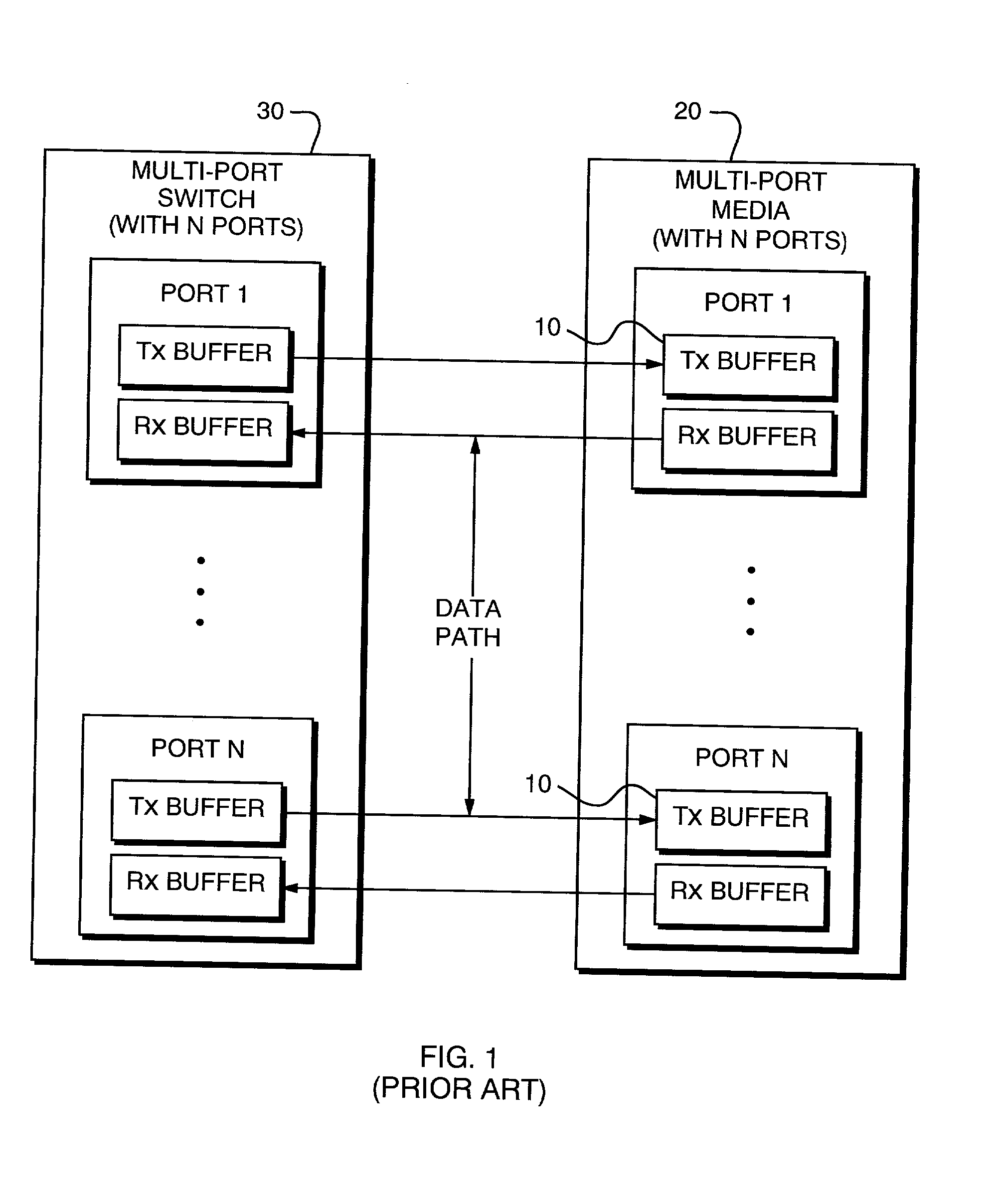

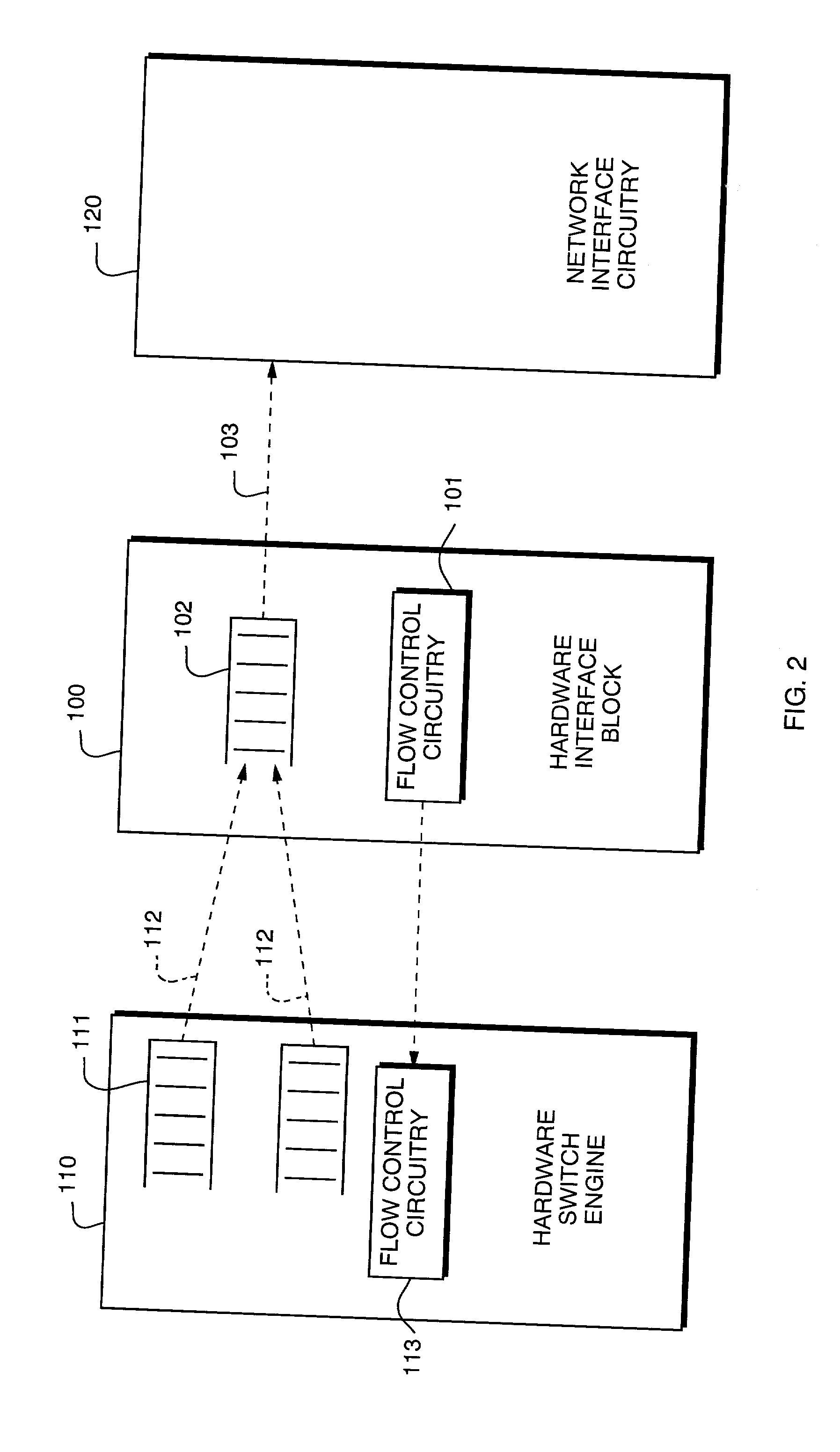

Flow control system to reduce memory buffer requirements and to establish priority servicing between networks

InactiveUS20020159460A1Network traffic/resource managementElectric/magnetic signal storageMultiplexingControl data

The invention is a system and method to allow precise control of the transmit packet rate between two different networks and to optionally introduce a priority servicing scheme across several related output ports of a switch engine. The invention employs flow control circuitry to regulate data packet flow across a local interface within a single device by asserting back-pressure. Specifically, flow control is used to prevent a switch port from transmitting a data packet until a subsequent processing stage is ready to accept a packet via that port. The downstream node only permits transmission of packets from the switch when its buffer is available. An interface block effectively multiplexes together multiple switch ports by maintaining constant back-pressure on all of the ports and then releasing the back-pressure, one port at a time, to see if a port has a packet to transmit. This use of back-pressure to control the flow of data packets also allows a priority servicing scheme to be implemented by controlling the sequence of releasing back-pressure to the ports and also the number of packets allowed out of a port when it is allowed to transmit.

Owner:ENTERASYS NETWORKS

Transmitter circuit and method for controlling operation thereof

In various embodiments, a method (900) for controlling the operation of a transmitter circuit is provided, the method (900) including: detecting (902) a state of a message field within a data message to be sent by the transmitter circuit indicating a bit rate to be used for transmission by the transmitter circuit and switching (904) the mode of operation of the transmitter circuit from a first data transmission mode to a second data transmission mode depending on the state of the message indication field, wherein in the first data transmission mode a first circuit configured to transmit data may be used and wherein in the second data transmission mode a second circuit configured to transmit data may be used. Further, a corresponding controlling circuit is provided.

Owner:INFINEON TECH AG

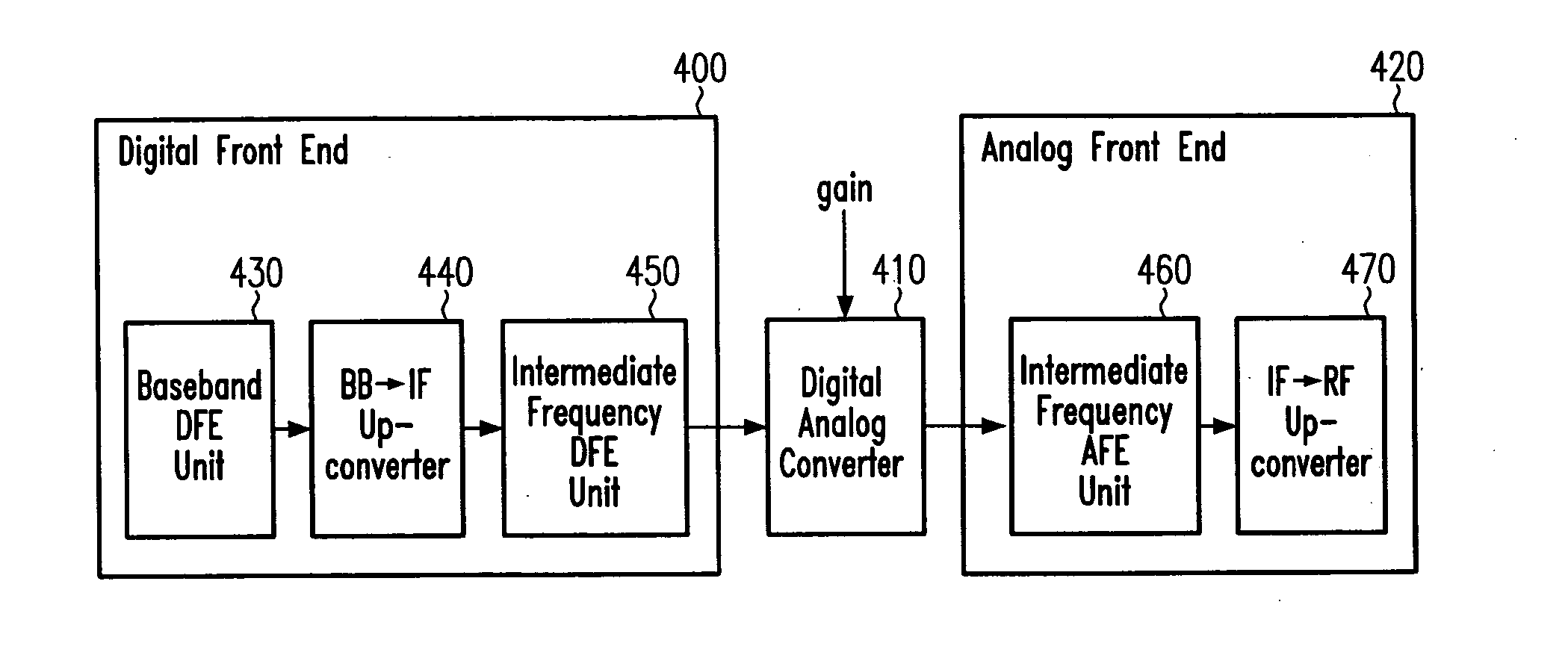

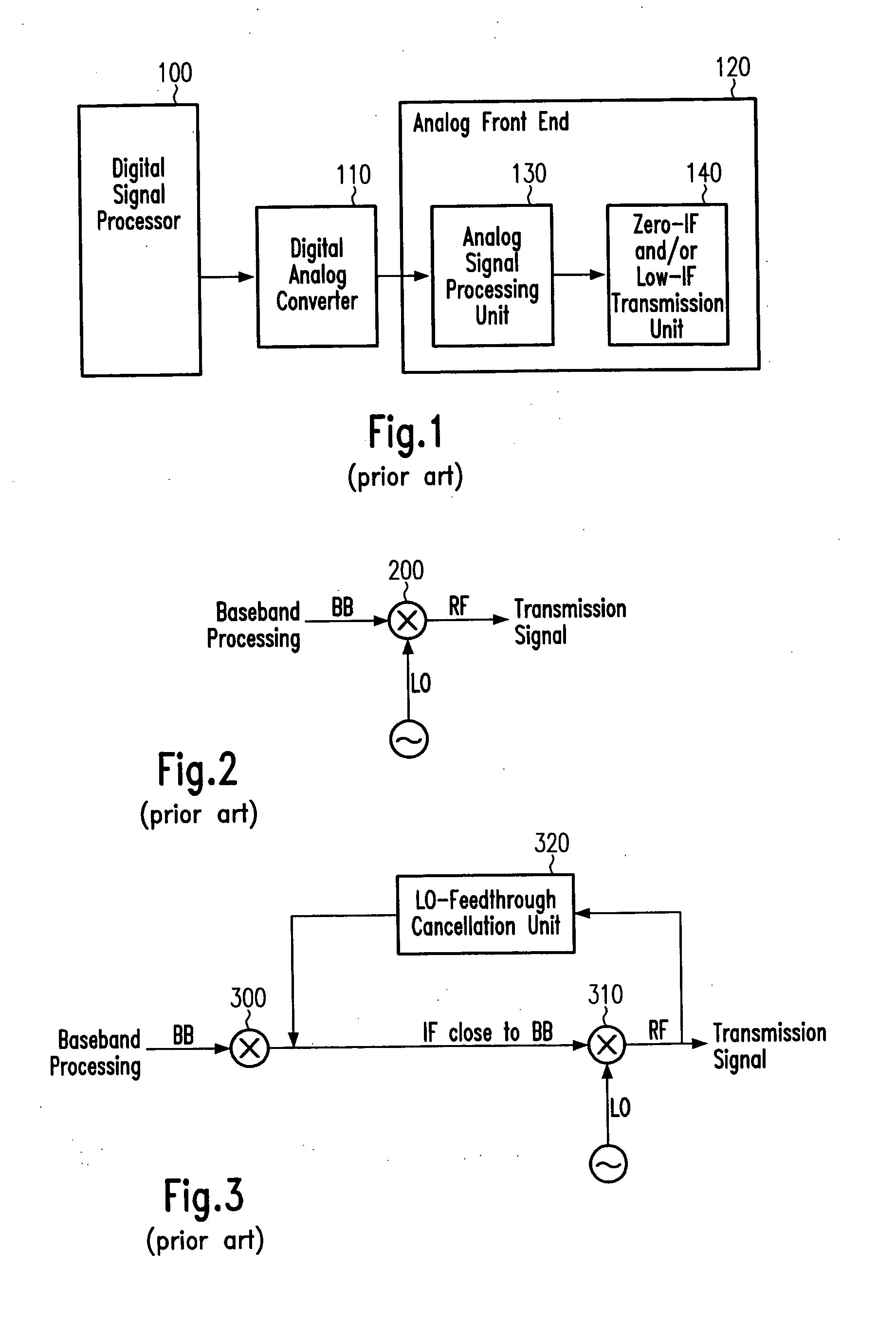

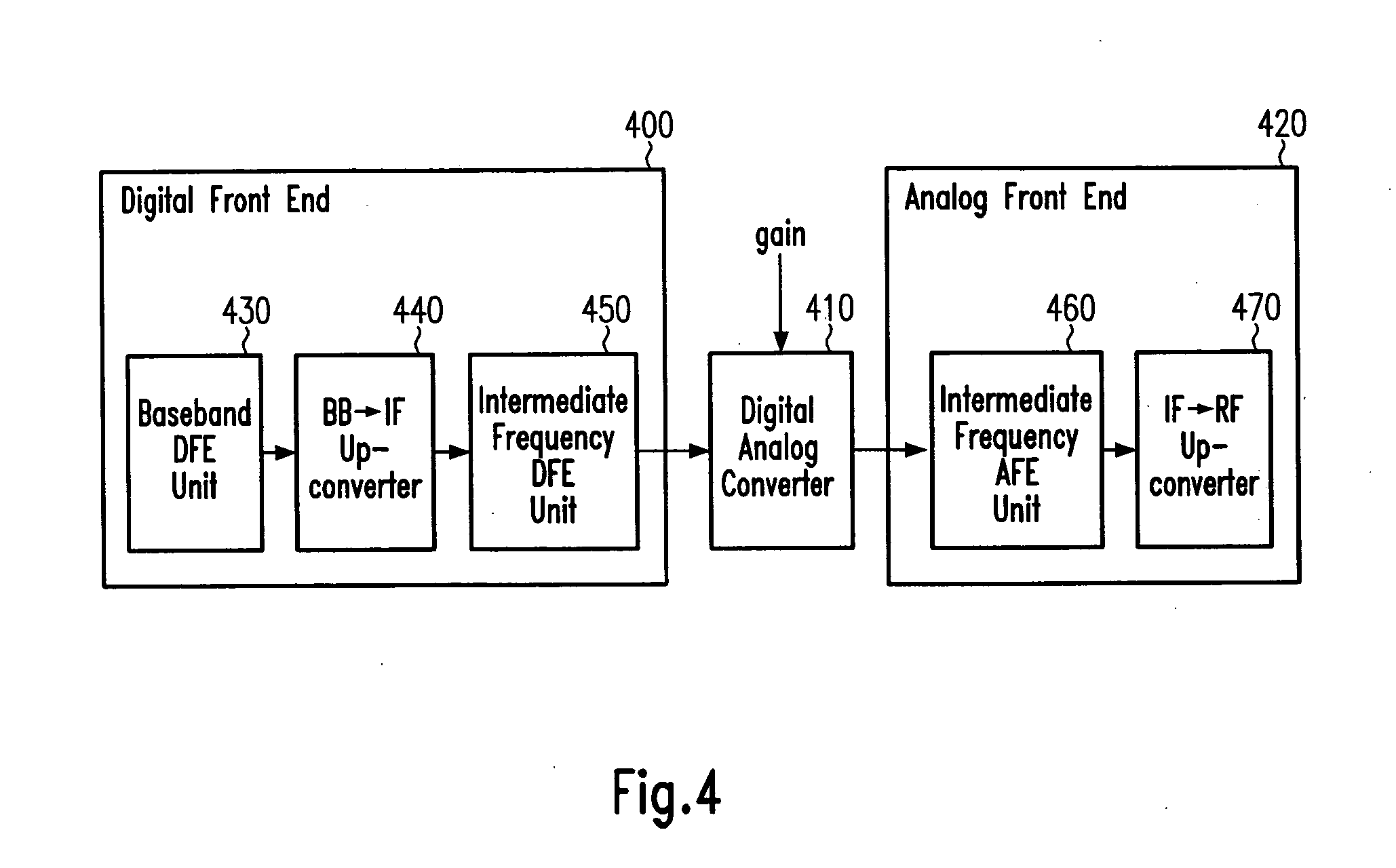

Low-if multiple mode transmitter front end and corresponding method

ActiveUS20060067429A1Reduce implementation complexityIncrease flexibilityMultiple modulation transmitter/receiver arrangementsNetwork topologiesData signalEngineering

A WLAN transmitter capable of transmitting data signals modulated in accordance with an individual one of at least two different modulation schemes and corresponding methods and integrated circuit chips are provided. The WLAN transmitter contains a front end section having a low-IF topology and including a digital front end unit and an analog front end unit. The digital front end unit contains a first signal processing branch for processing transmission data signals modulated in accordance with a first one of said at least two different modulation schemes. The digital front end unit further contains a second signal processing branch for processing transmission data signals modulated in accordance with a second one of said at least two different modulation schemes. The analog front end unit contains one single signal processing branch for processing transmission data signals modulated in accordance with any one of said at least two different modulation schemes.

Owner:GLOBALFOUNDRIES US INC

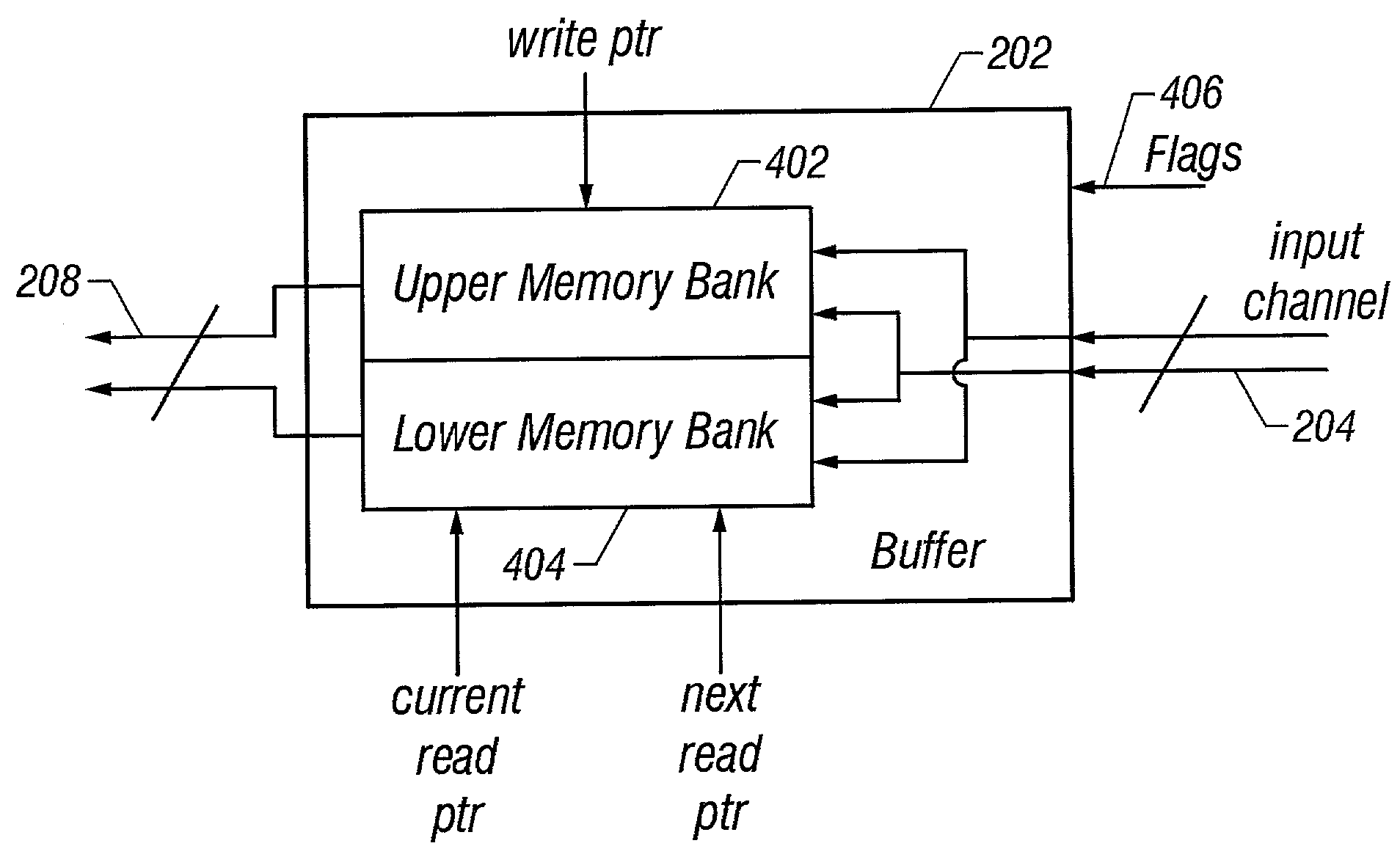

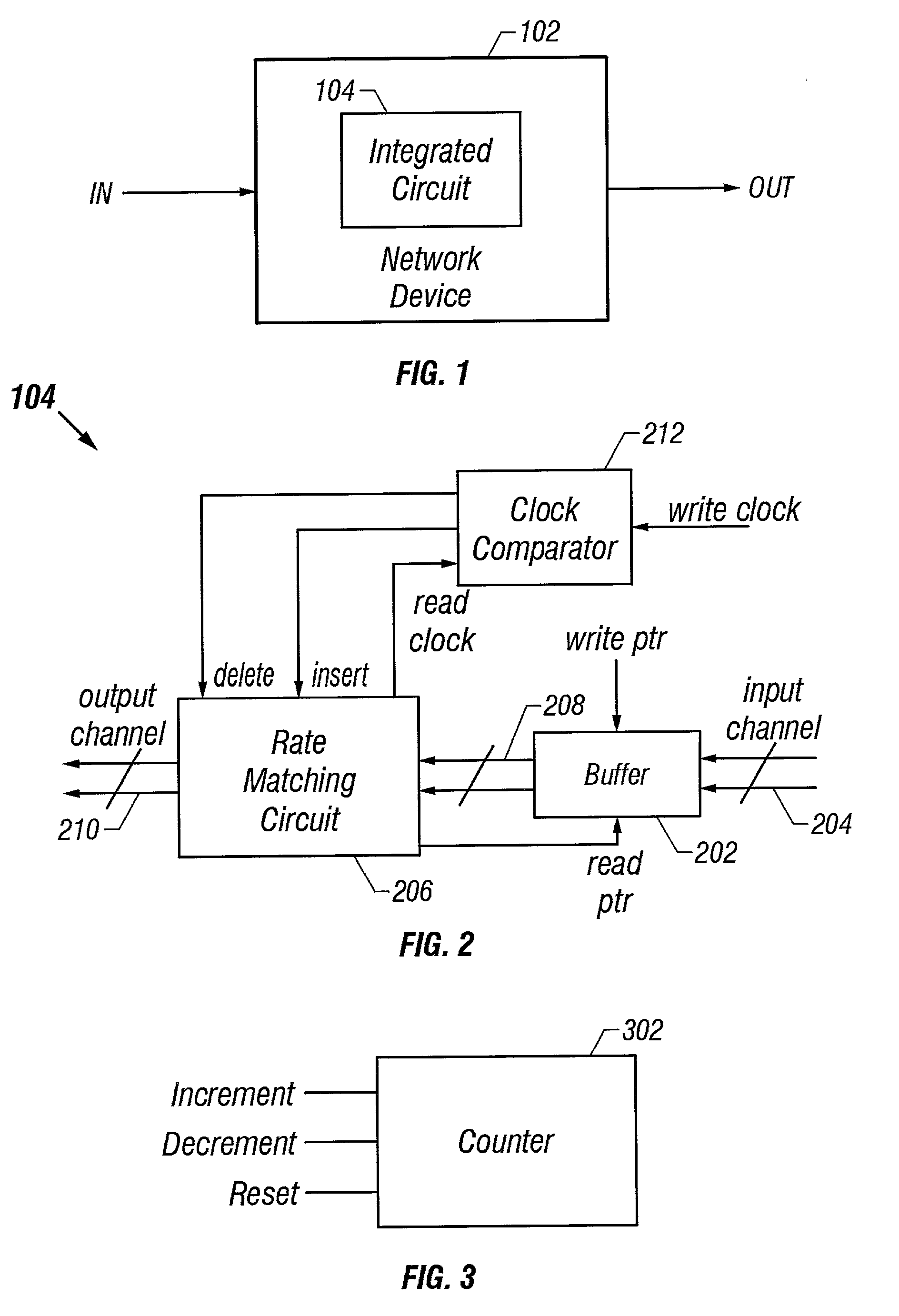

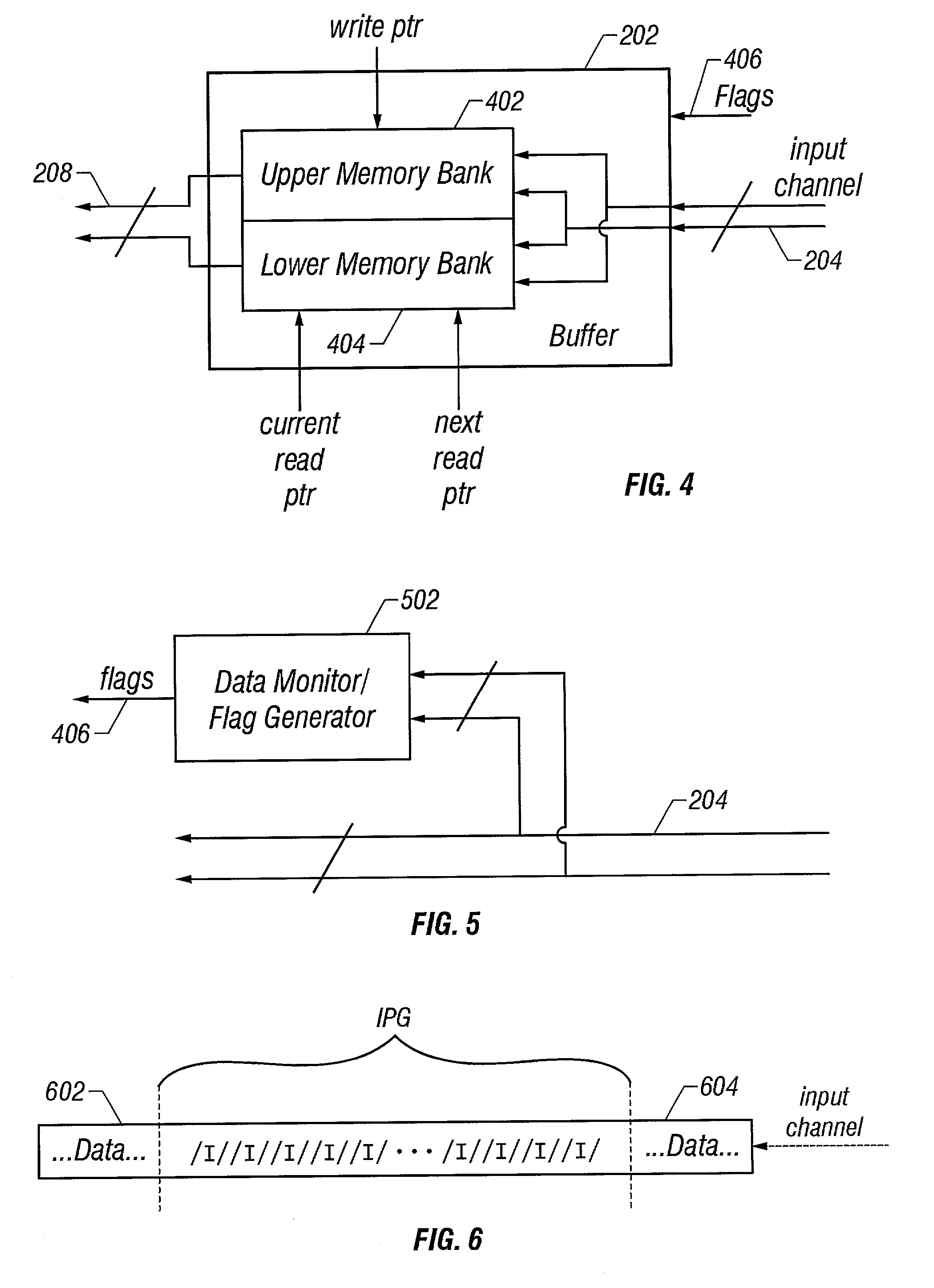

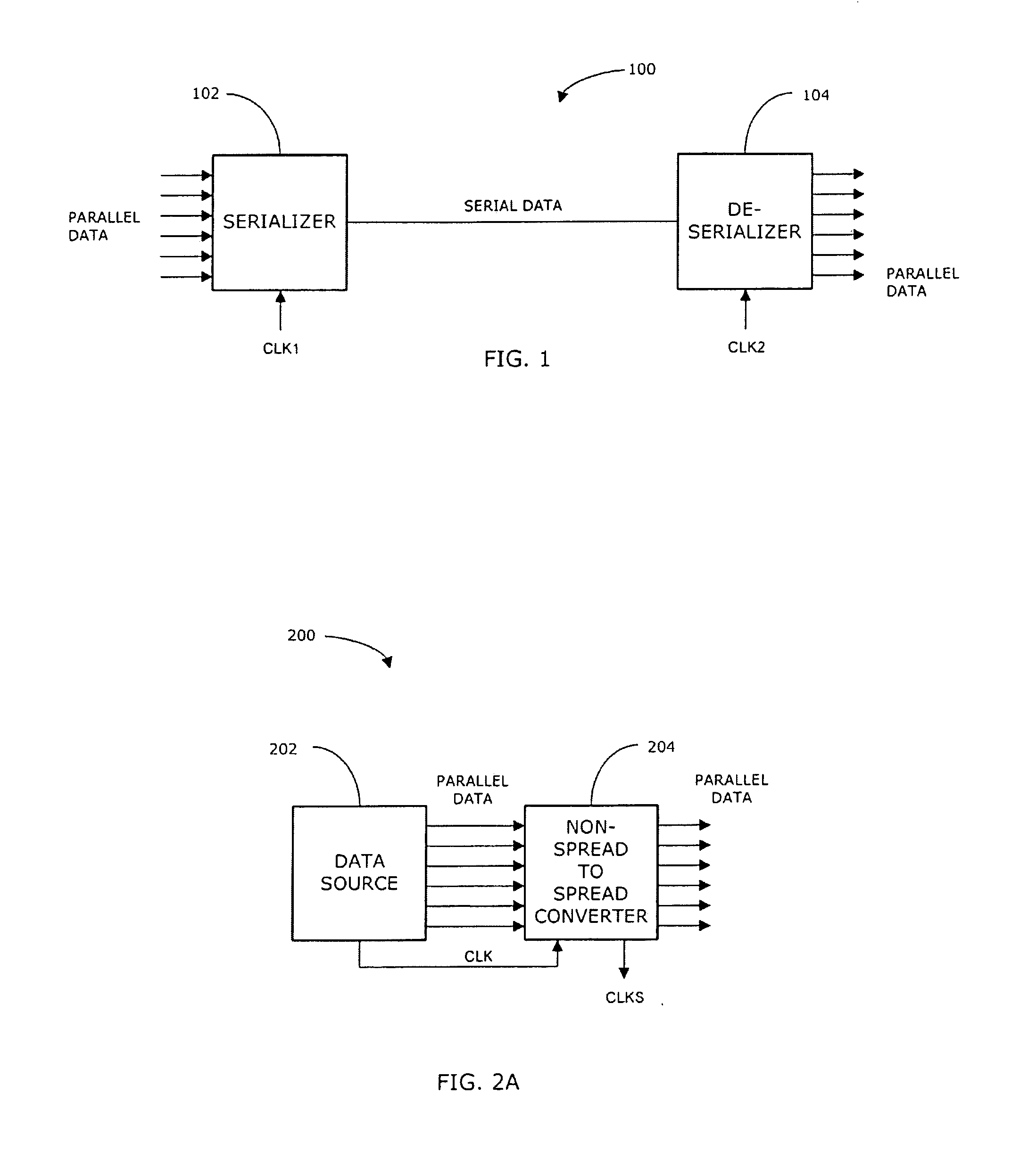

Method and apparatus for matching transmission rates across a single channel

InactiveUS7027547B1Electric/magnetic signal storageSynchronising arrangementClock rateTransmission channel

The invention provides a novel scheme to match the clock rates along a single transmission channel.The rate matching aspect of this invention receives a character stream synchronized by a first clock and buffers the character streams. Buffered characters are then transmitted over an output channel synchronized by a second clock. The rate matching system removes one or more filler or removable characters from the output channel if an overflow condition is detected and inserts one or more filler or removable characters in the output channel if an underflow condition is detected.

Owner:CREST MICROSYST

Wireless communication terminal and wireless communication method

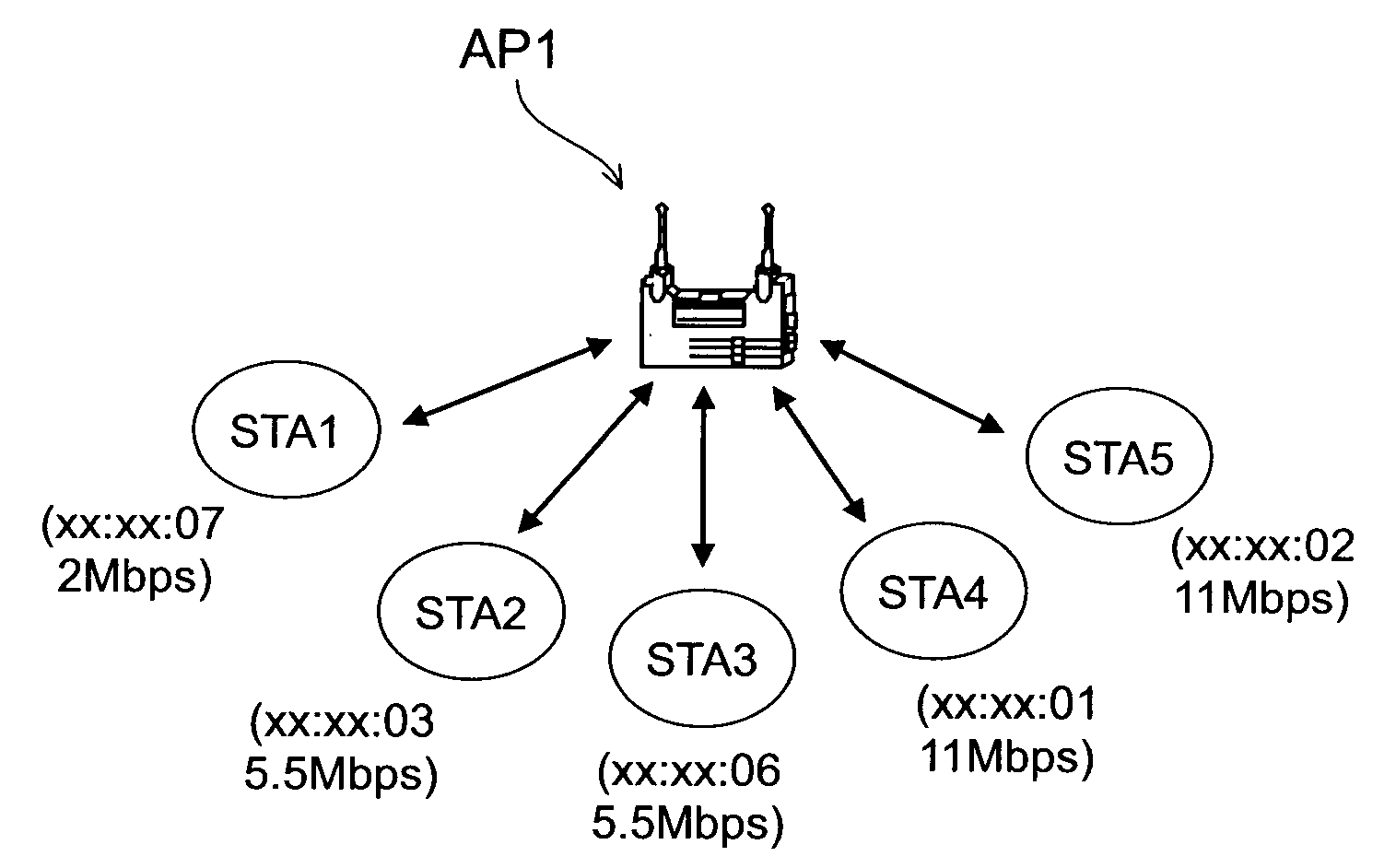

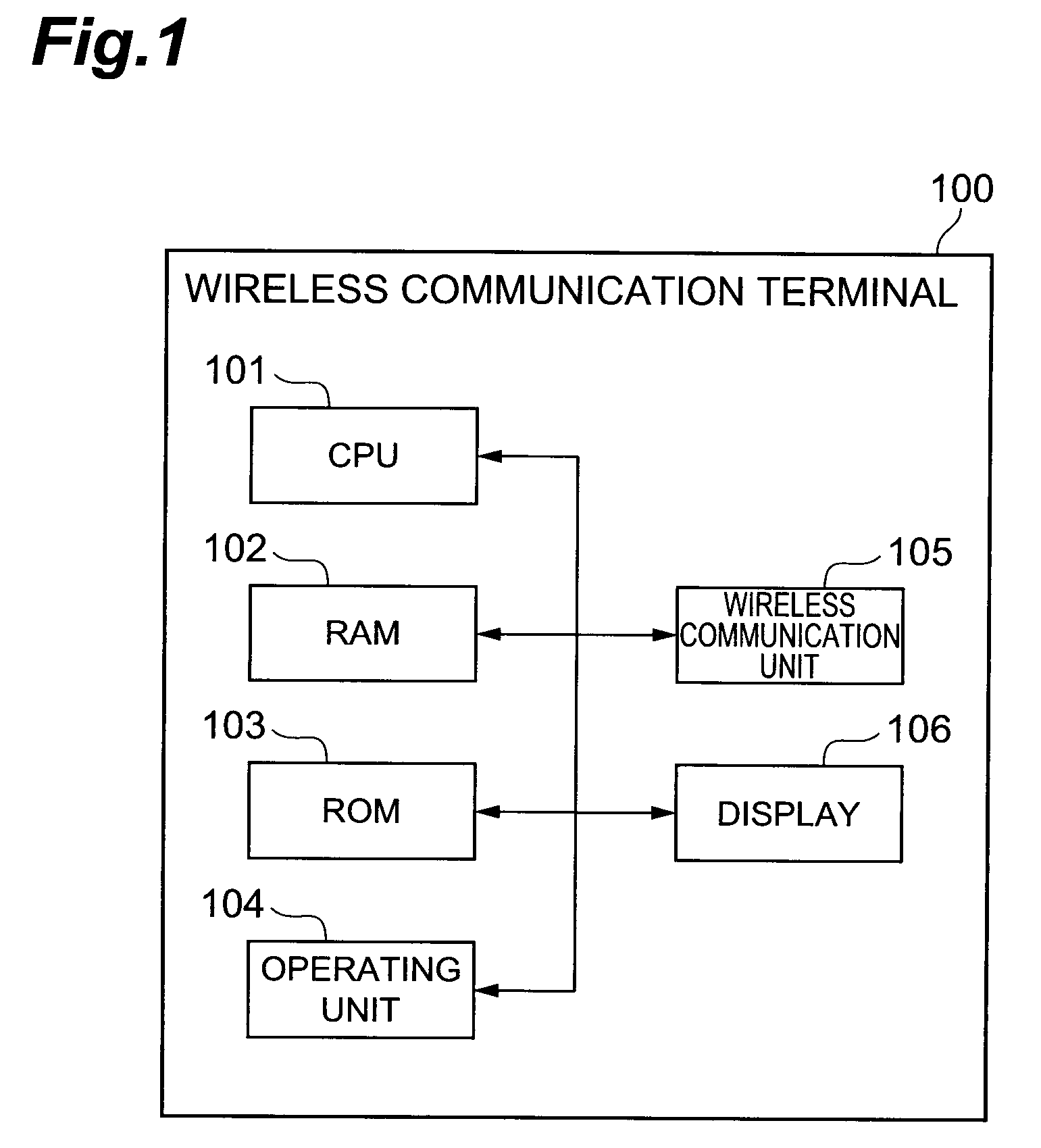

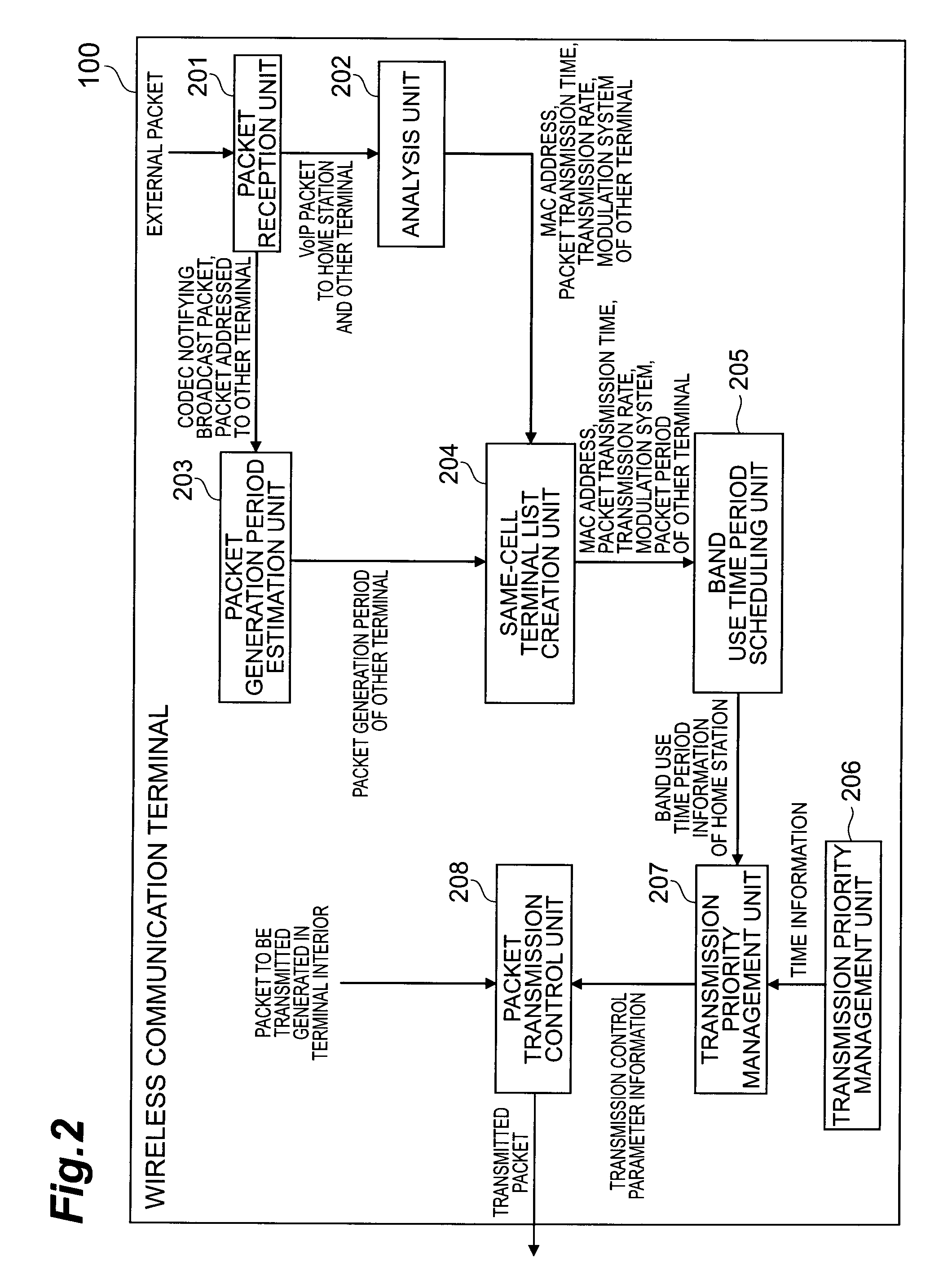

InactiveUS20080043688A1Improve communication qualitySuppress generationError preventionFrequency-division multiplex detailsMAC addressPacket transmission

A wireless communication terminal comprises: a packet receiving unit for receiving a packet from a wireless base station; module for obtaining a transmission rate and a required transmission time from the received packet; module for calculating a time required to perform a packet transmission / reception procedure on the basis of the required transmission time; an analysis unit that functions as module for recognizing the existence of other terminal by decoding a destination MAC address described in the packet when the obtained transmission rate is equal to or lower than a transmission rate used by the wireless communication terminal; and a same-cell terminal list creation unit and band use time period scheduling unit for setting a band use time period that is equal to or greater than the time required to perform the packet transmission / reception procedure, for a time period, within a predetermined period corresponding to a packet generation period, regarding the other terminal and the wireless communication terminal, in order from the terminal having the lowest transmission rate.

Owner:NTT DOCOMO INC

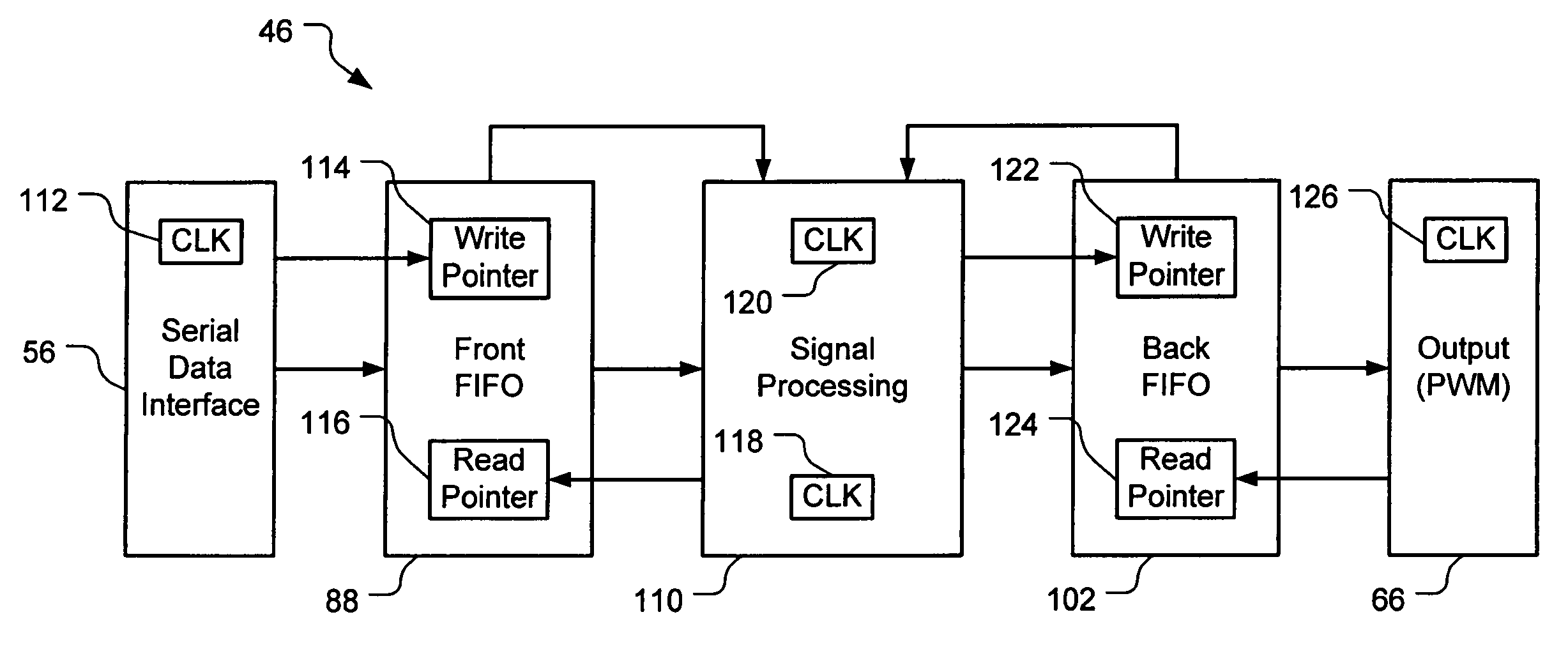

Input/output data rate synchronization using first in first out data buffers

An input / output data rate synchronization system includes a first data buffer that receives input data at a first rate, that temporarily stores the input data, and that outputs the input data at a second rate. A data processing module receives the input data from the first data buffer and outputs processed data at a third rate. A second data buffer receives the processed data from the data processing module at the third rate, temporarily stores the processed data, and outputs the processed data at a fourth rate. The data processing module temporarily stops receiving the input data and generating the processed data when the second data buffer exceeds a first predetermined capacity. The data processing module increases the second rate when the first data buffer exceeds a second predetermined capacity and decreases the second rate when a difference between the second and first rates is greater than a predetermined rate.

Owner:MARVELL ASIA PTE LTD

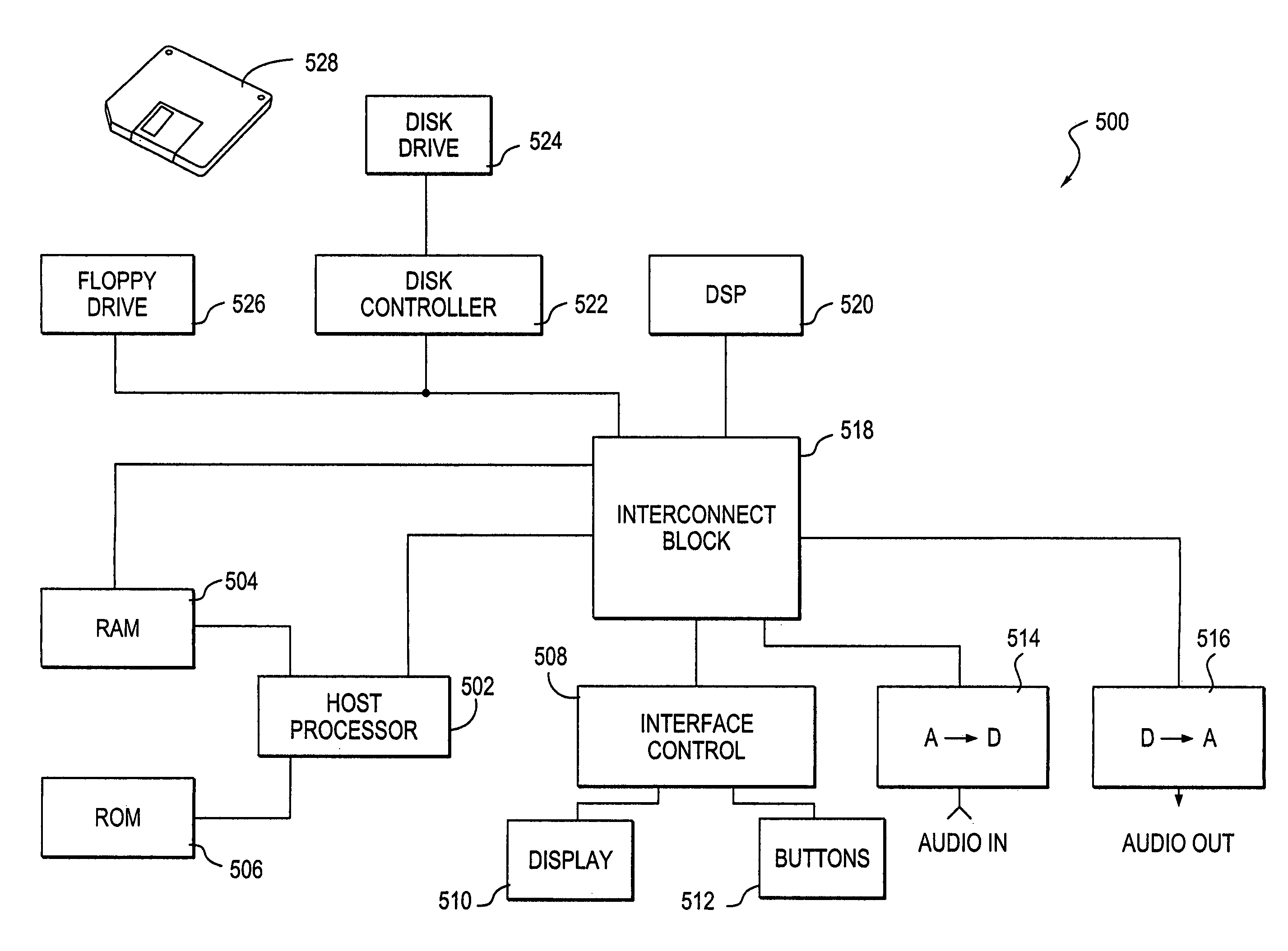

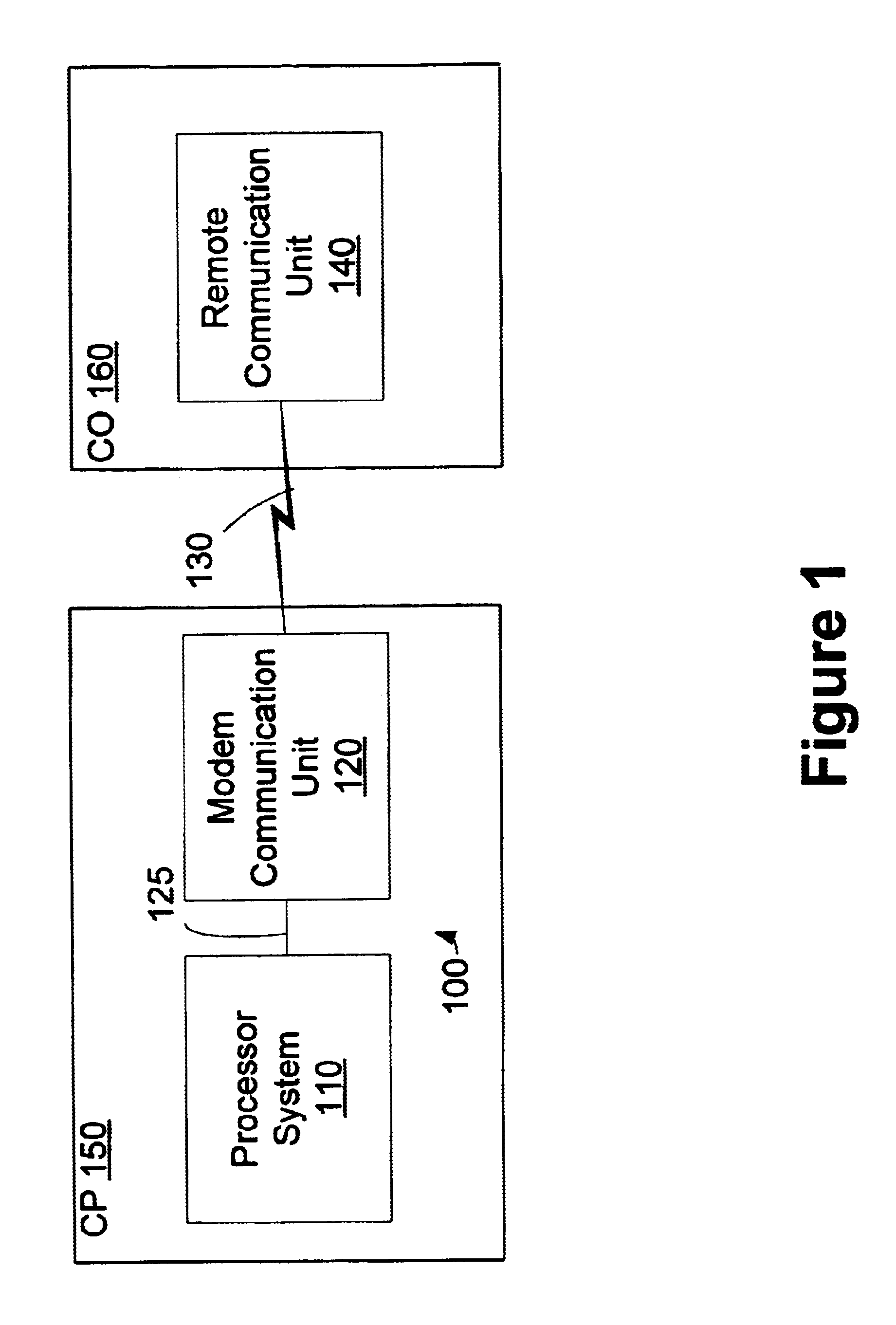

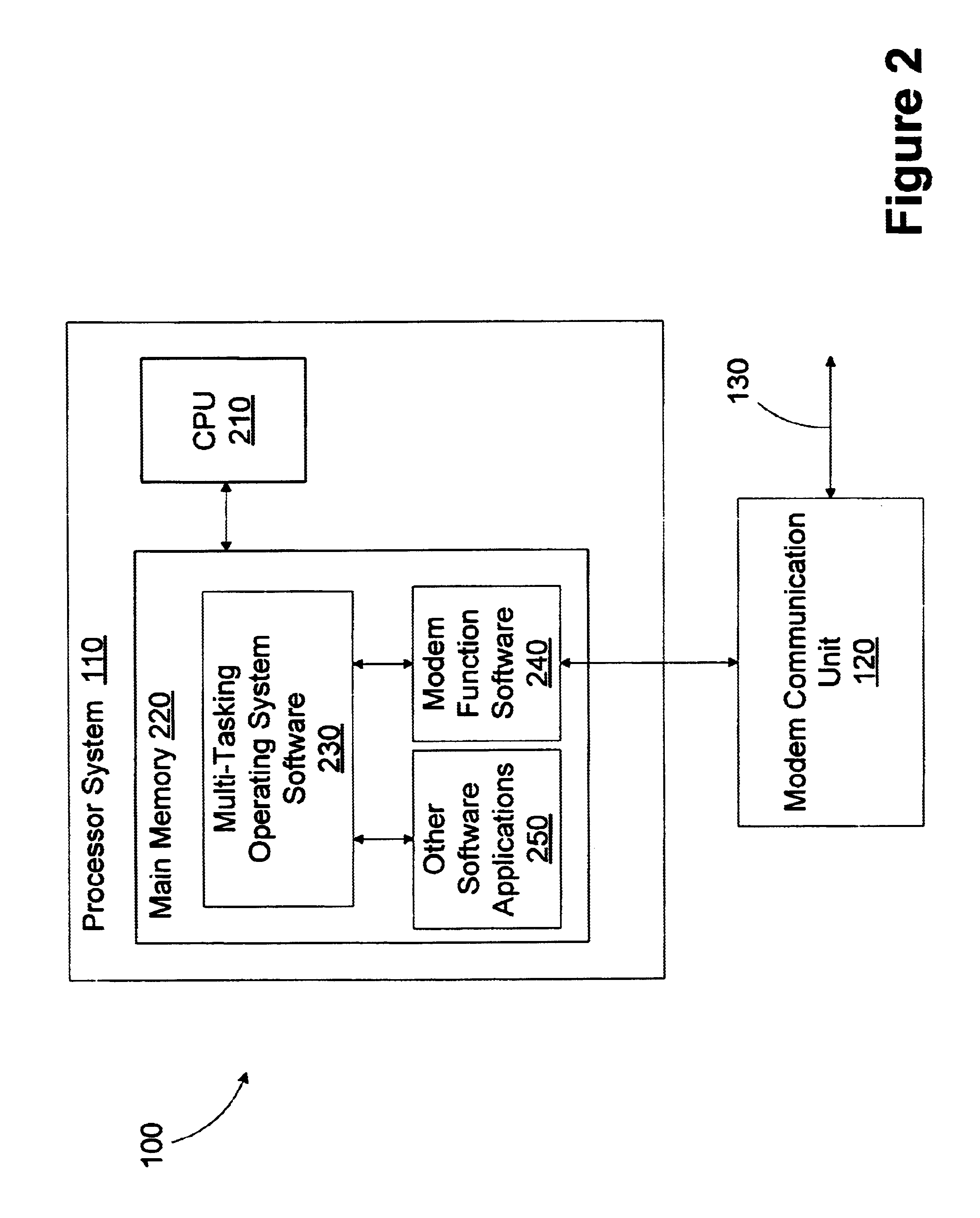

Method and apparatus for buffering data samples in a software based ADSL modem

A method and apparatus for buffering data samples in a software-based ADSL modem. The method includes generating data for transmission to a remote source and modulating the data to form a plurality of data symbols for transmission. The data symbols are stored in a buffer. An absence of a data symbol in the buffer is determined. In response to detecting an absence of a data symbol in the buffer, an idle data symbol is transmitted.

Owner:GLOBALFOUNDRIES INC

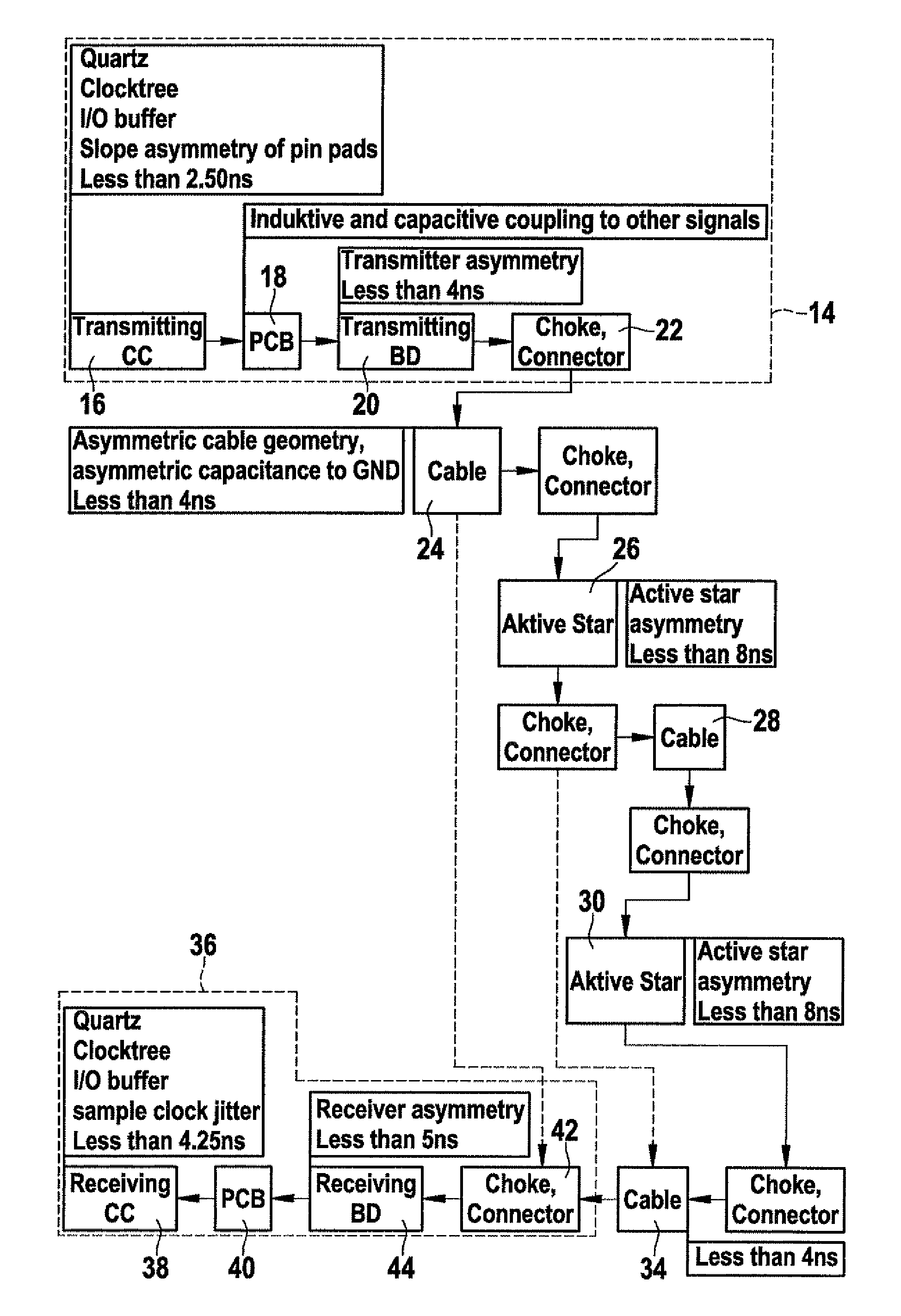

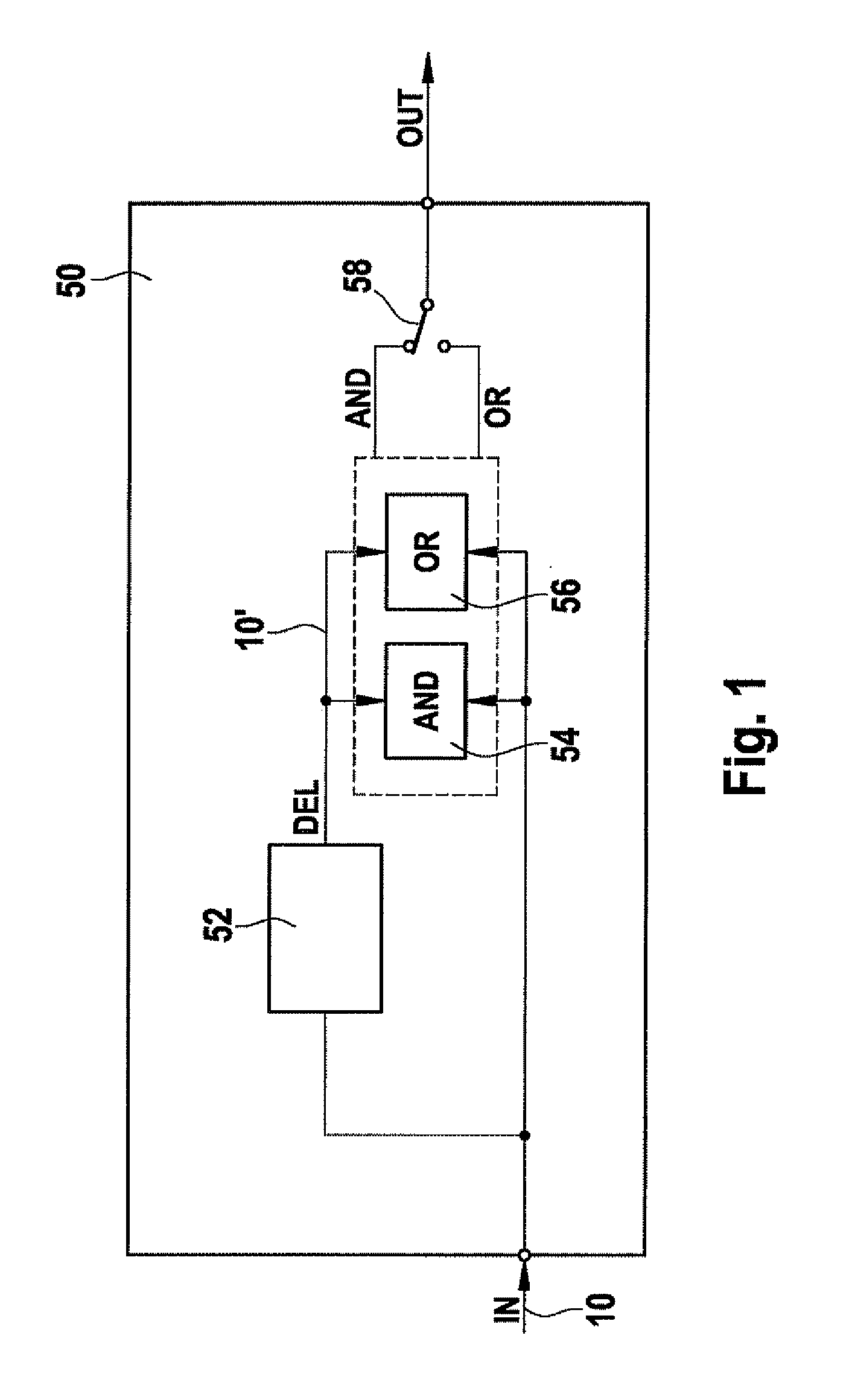

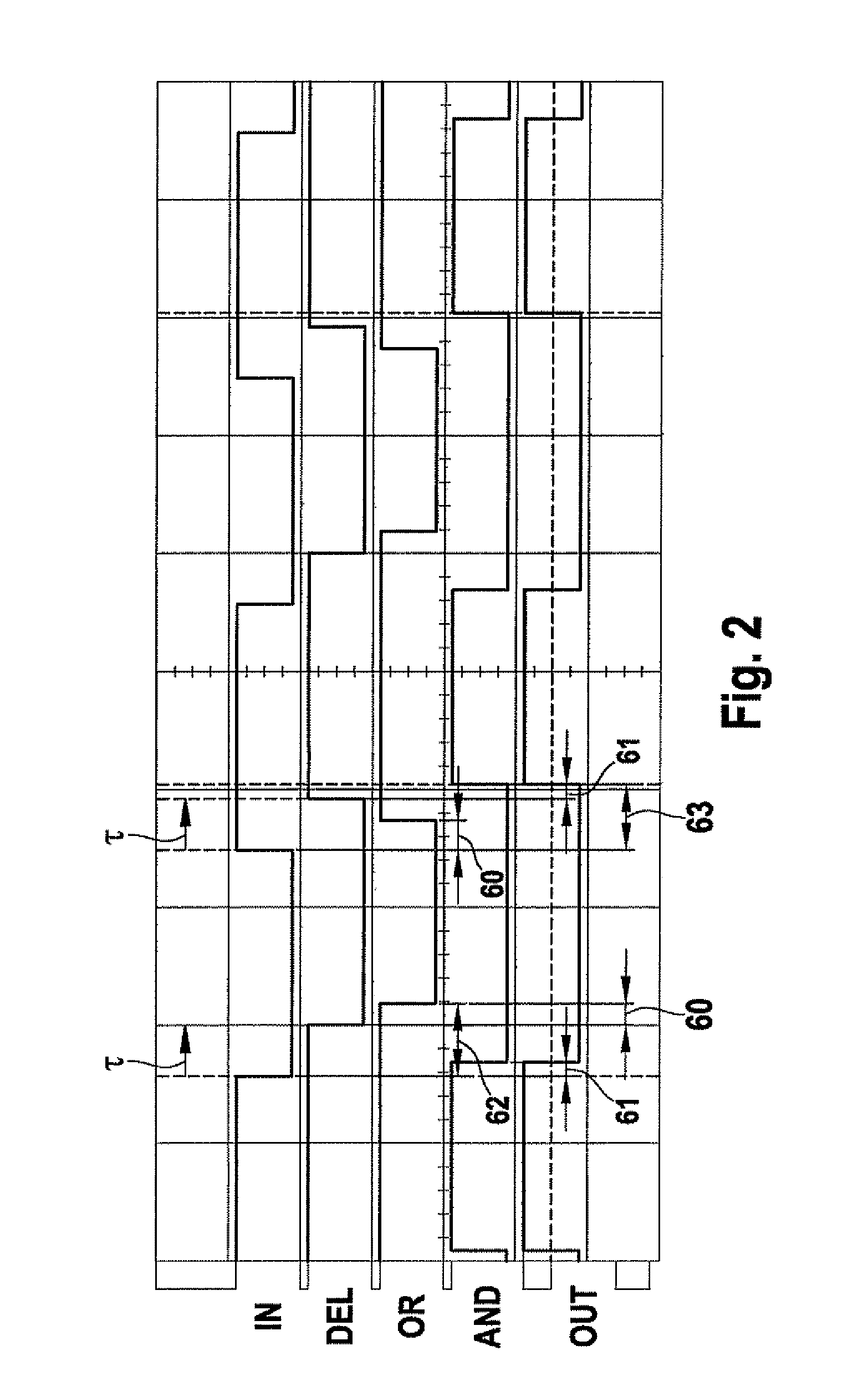

Method And System For Compensating Asymmetrical Delays

InactiveUS20100008456A1Improve immunityReduce quality problemsError preventionPulse automatic controlSerial transferNetwork structure

A method and a data-transmission system for transmitting data encoded in a signal between a transmitting user and a receiving user of the data-transmission system via a network structure of the data-transmission system. The data encoded in the signal are serially transmitted bit-by-bit in data frames having a defined structure. Each bit of the data encoded in the signal is sampled in the receiving user. Due to the transmission via the network structure, the signal is delayed asymmetrically. To compensate for the asymmetrical delay on the physical layer in the transmission channel, it is provided that the asymmetrical delay of the signal is determined at at least one point in the network structure, and is at least partially compensated prior to the receiving user sampling the bits of the data encoded in the signal. A measuring and compensating device is provided to measure and compensate for the asymmetrical delay.

Owner:ROBERT BOSCH GMBH

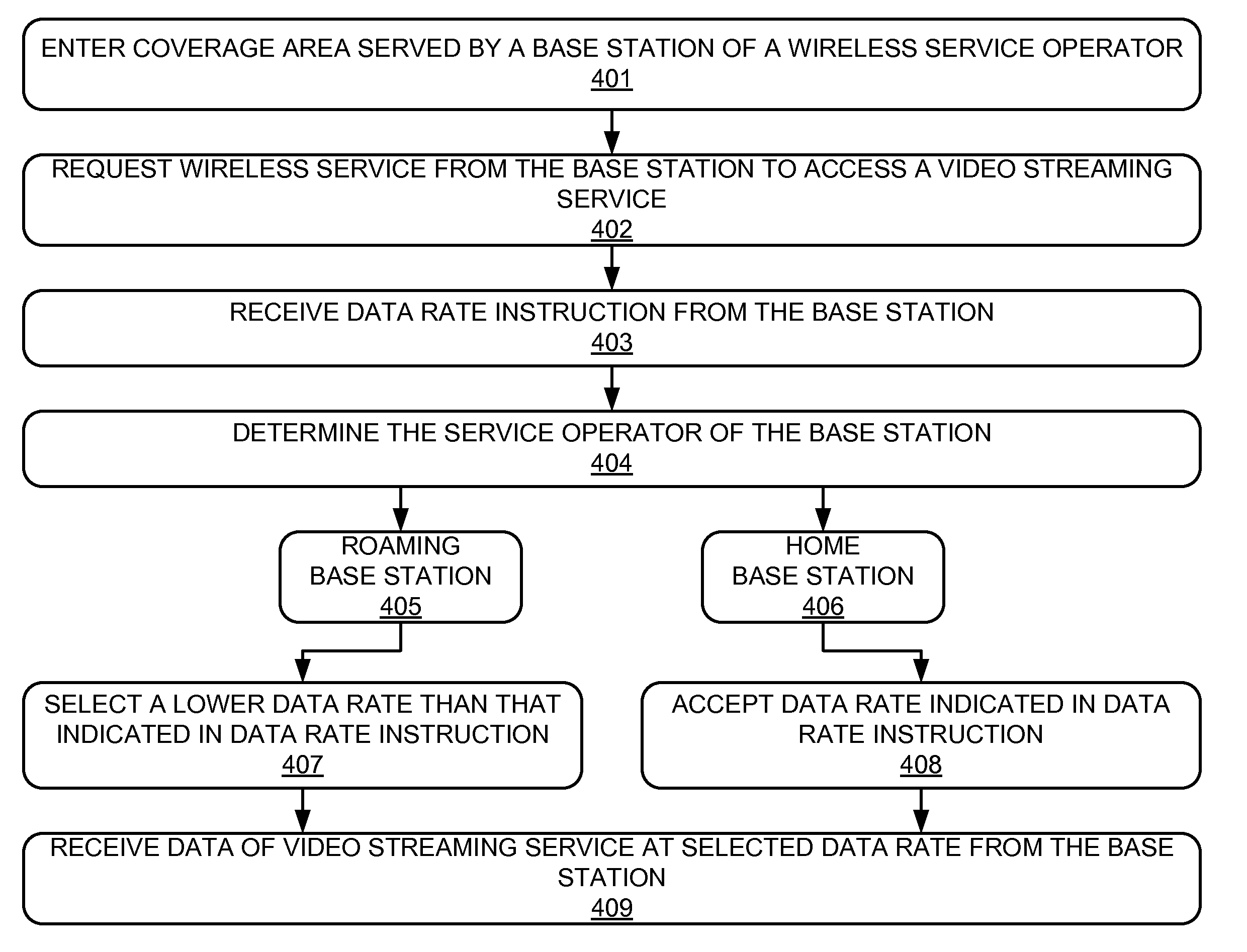

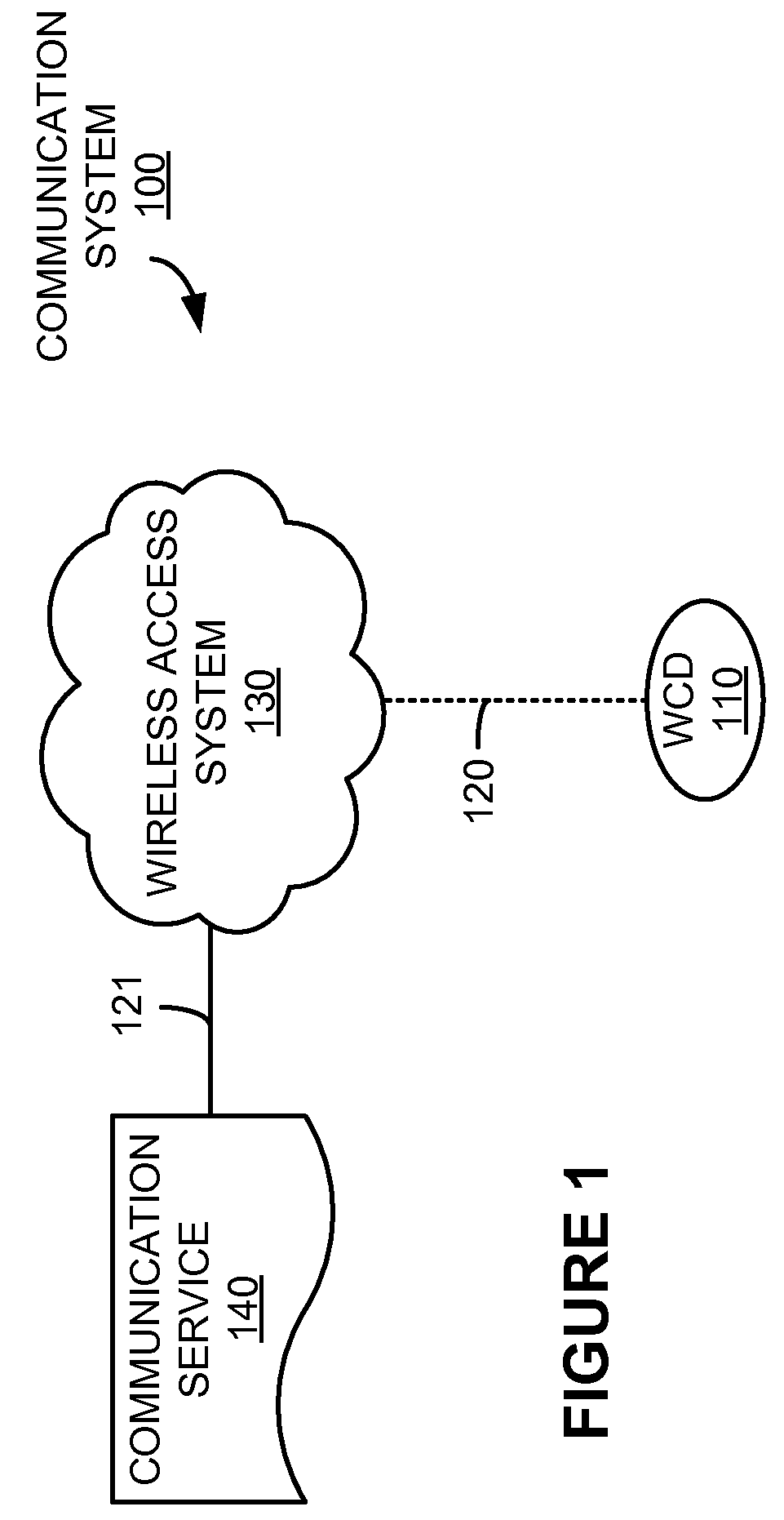

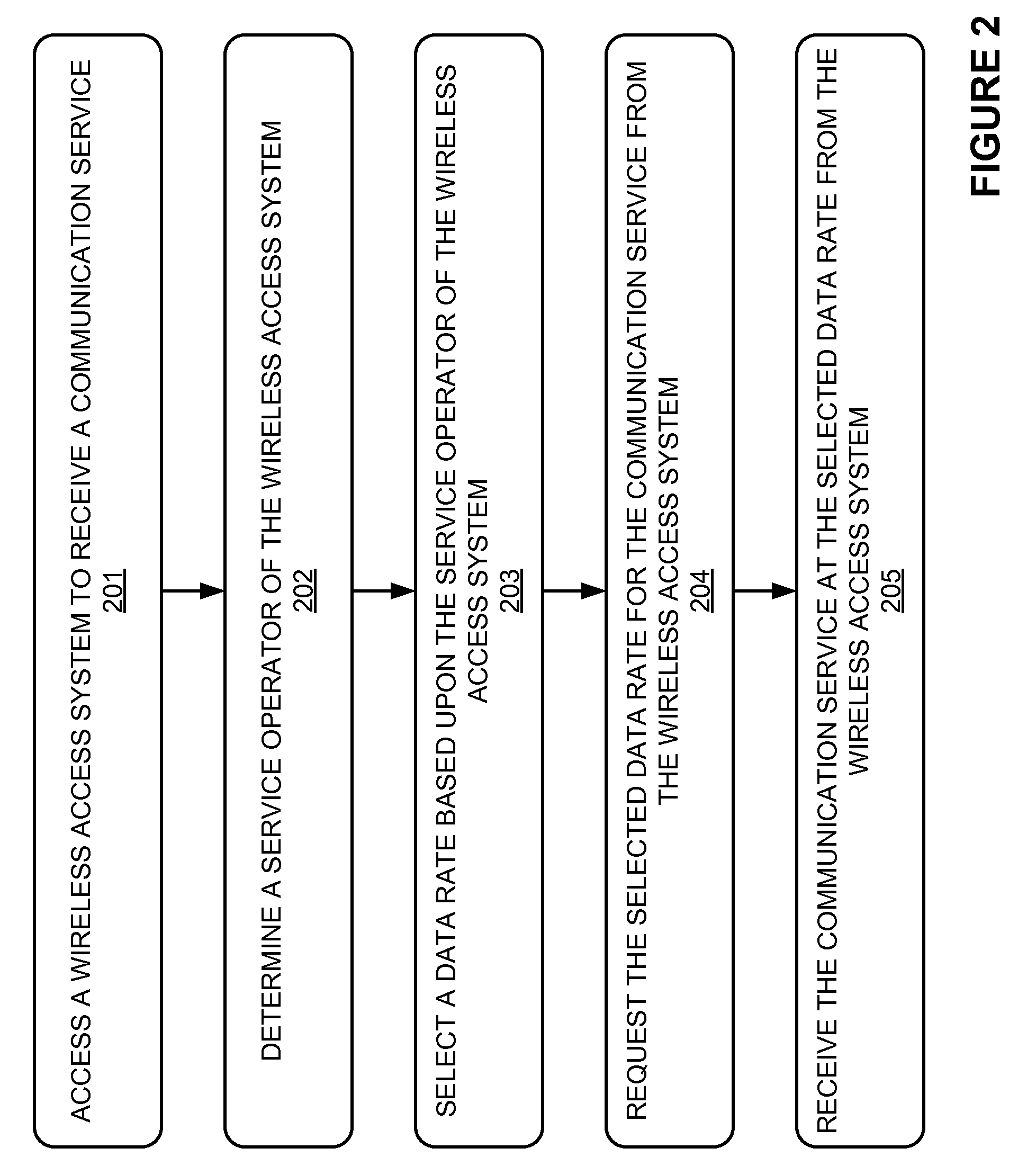

Data rate selection for wireless communication devices

What is disclosed is a method of operating a wireless communication device. The method includes accessing a wireless access system to receive a communication service, determining a service operator of the wireless access system, and selecting a data rate based on the service operator of the wireless access system. The method also includes requesting the selected data rate for the communication service from the wireless access system, and receiving the communication service at the selected data rate from the wireless access system.

Owner:T MOBILE INNOVATIONS LLC

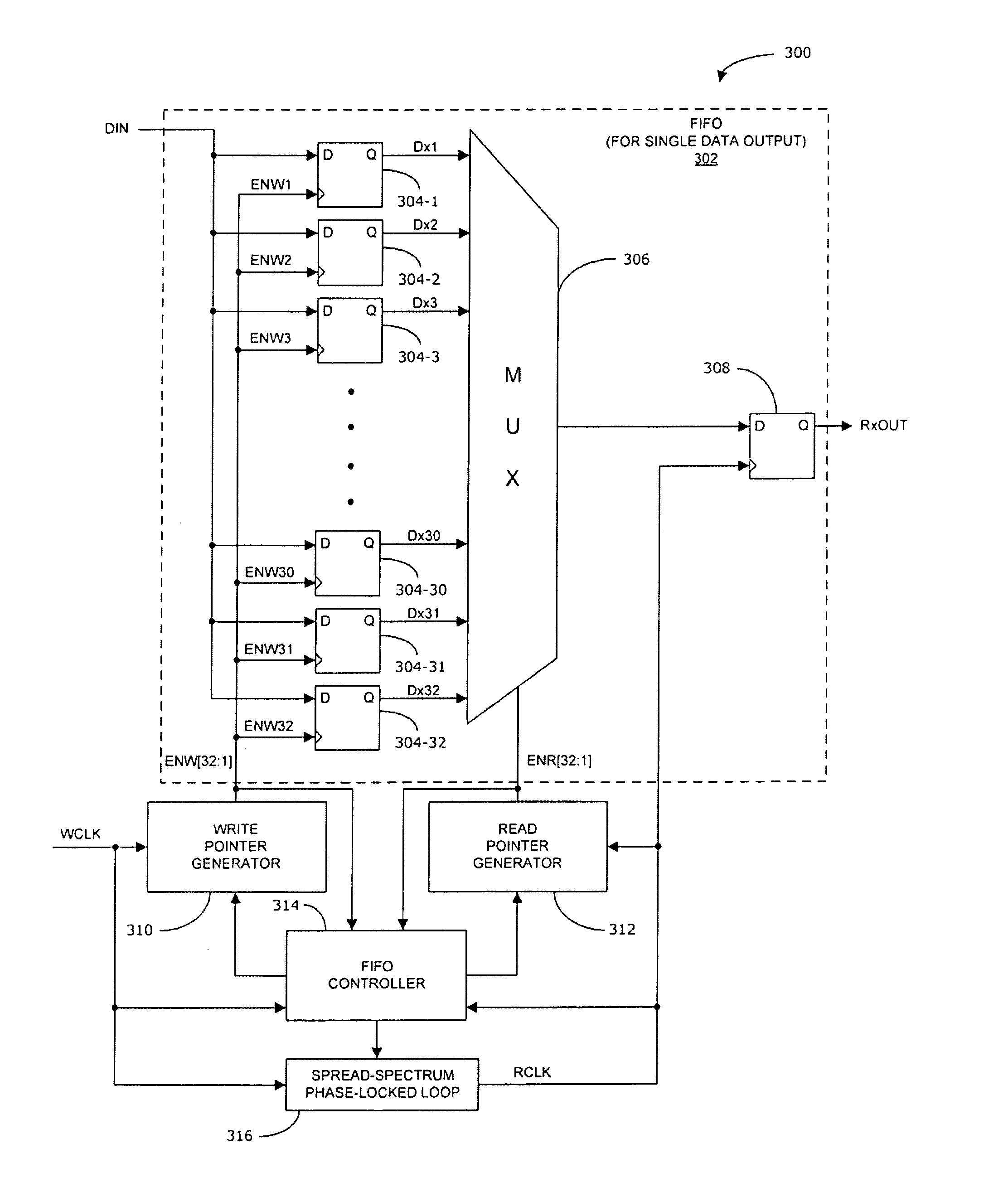

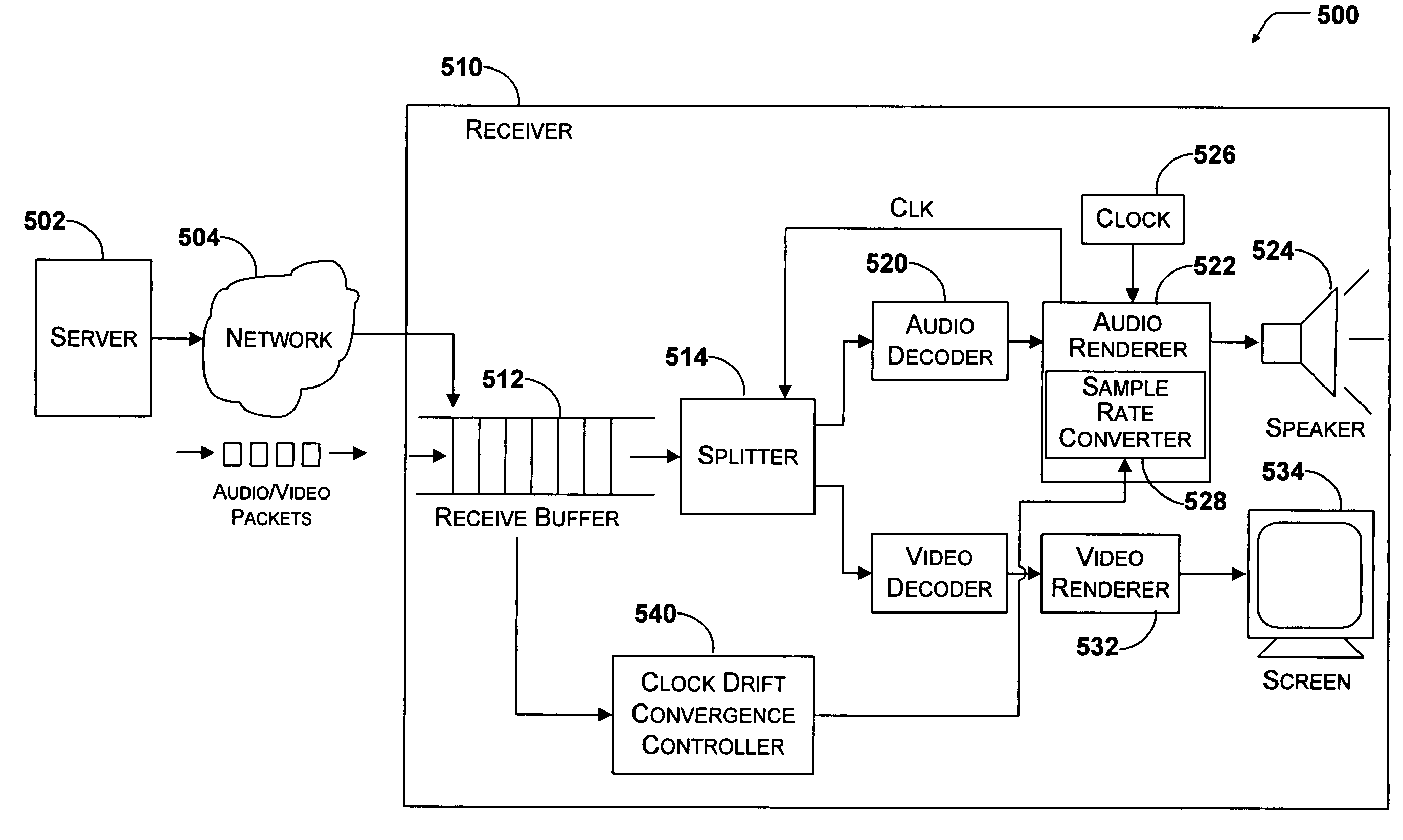

System and method for transferring data from non-spread clock domain to spread clock domain

An apparatus for transferring data in a non-spread domain to a spread domain. The apparatus comprises a first-in-first-out (FIFO) memory; a write pointer generator adapted to generate a write pointer for writing data into the FIFO memory in response to a non-spread clock signal; a spread-clock generator adapted to generate a spread clock signal based on the non-spread clock signal; a read pointer generator adapted to generate a read pointer for reading data from the FIFO memory in response to the spread clock signal; and a controller adapted to control the spread-clock generator in response to the read and write pointers indicating predetermined potential data overflow or underflow of the FIFO memory.

Owner:MAXIM INTEGRATED PROD INC

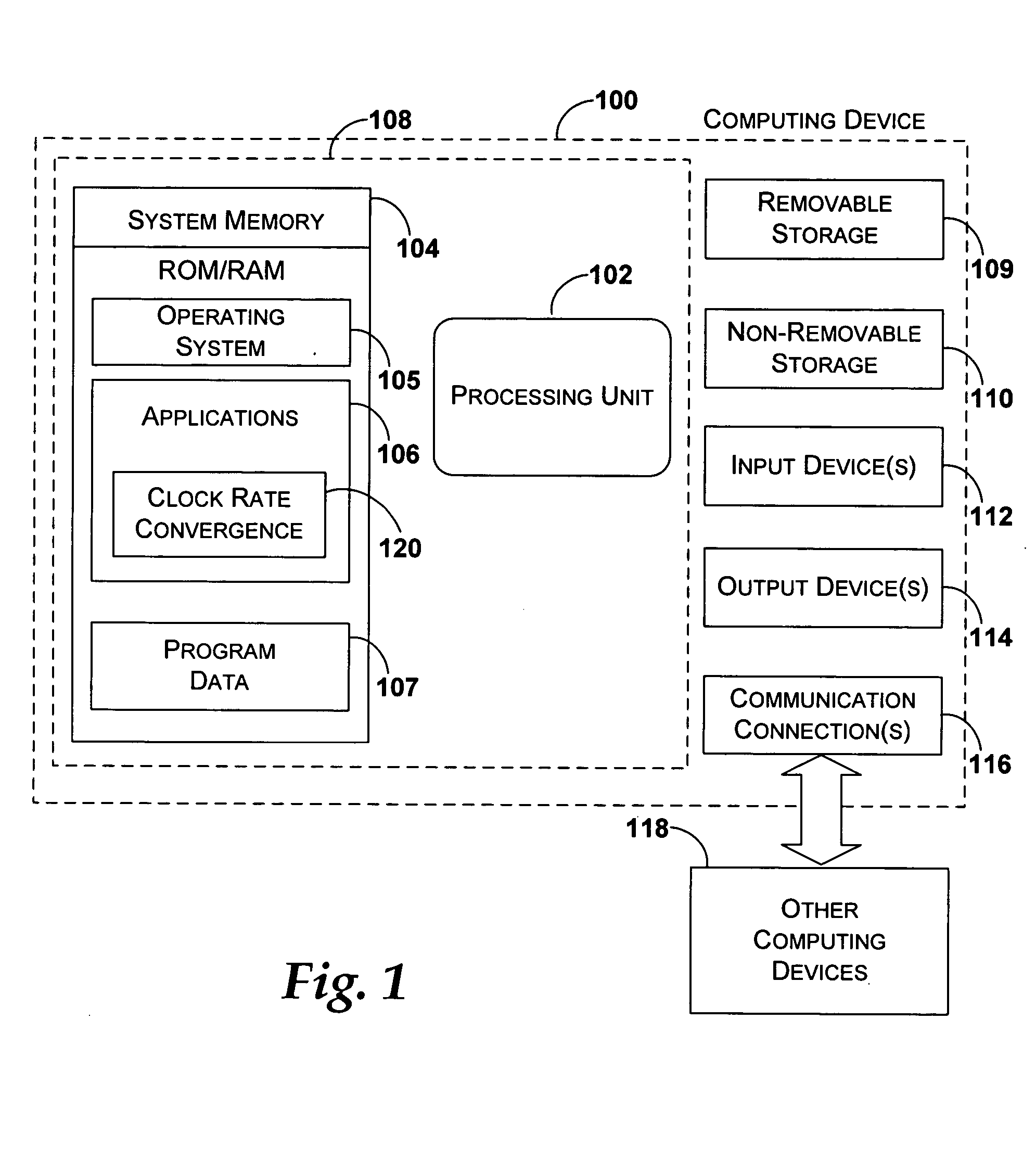

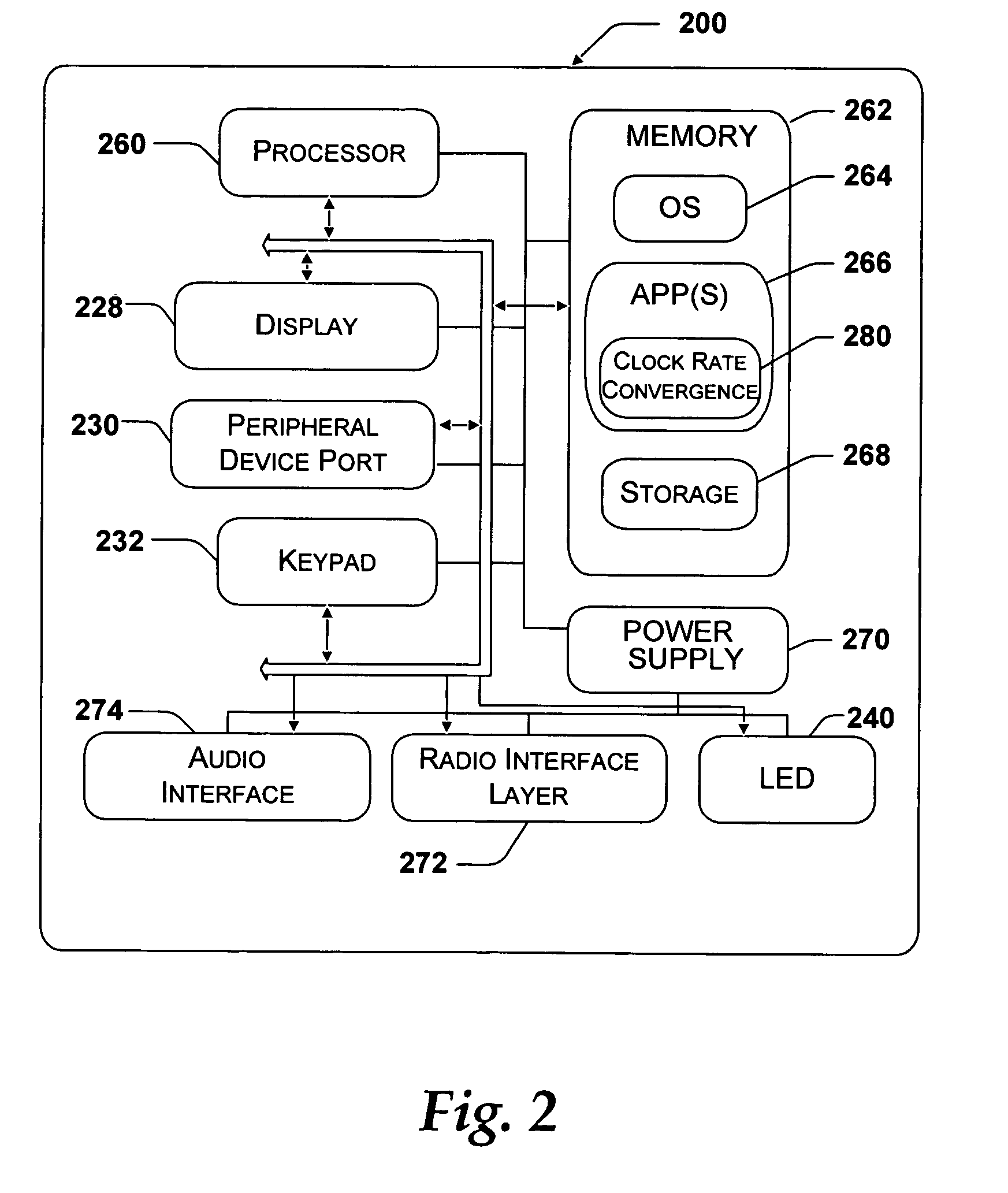

System and method for clock drift correction for broadcast audio/video streaming

A clock rate used in rendering broadcast streaming audio / video data is adjusted to converge on a clock rate associated with broadcasting the streaming data. The clock rate is adjusted by monitoring the buffer depth associated with a receive buffer that stores the incoming streaming data. The buffer depth provides an estimate of clock drift between the two clock rates. From the estimate of clock drift, the clock rate used in rendering broadcast streaming data is adjusted to avoid the clock drift causing skips or pauses in the rendered audio / video data.

Owner:MICROSOFT TECH LICENSING LLC

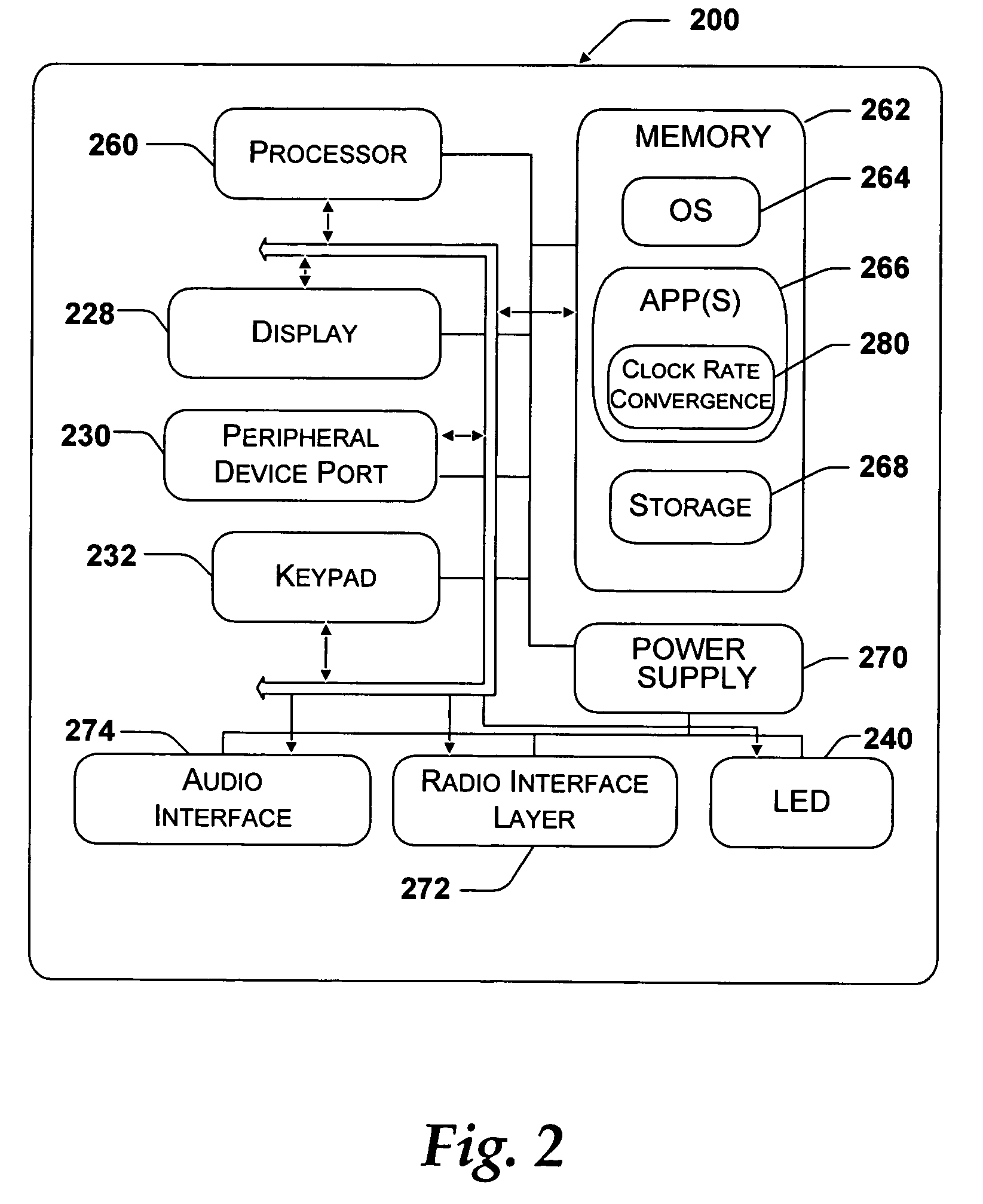

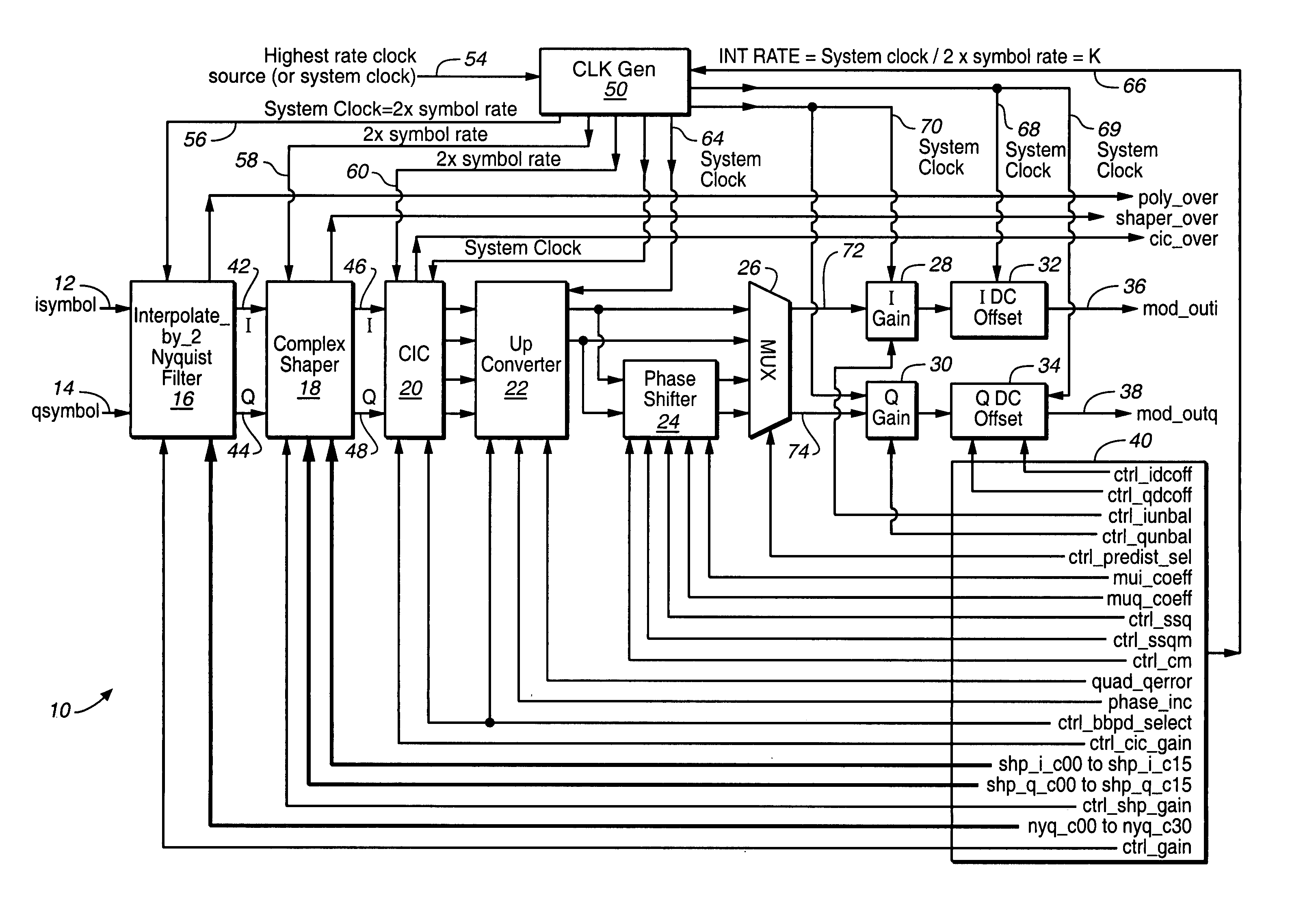

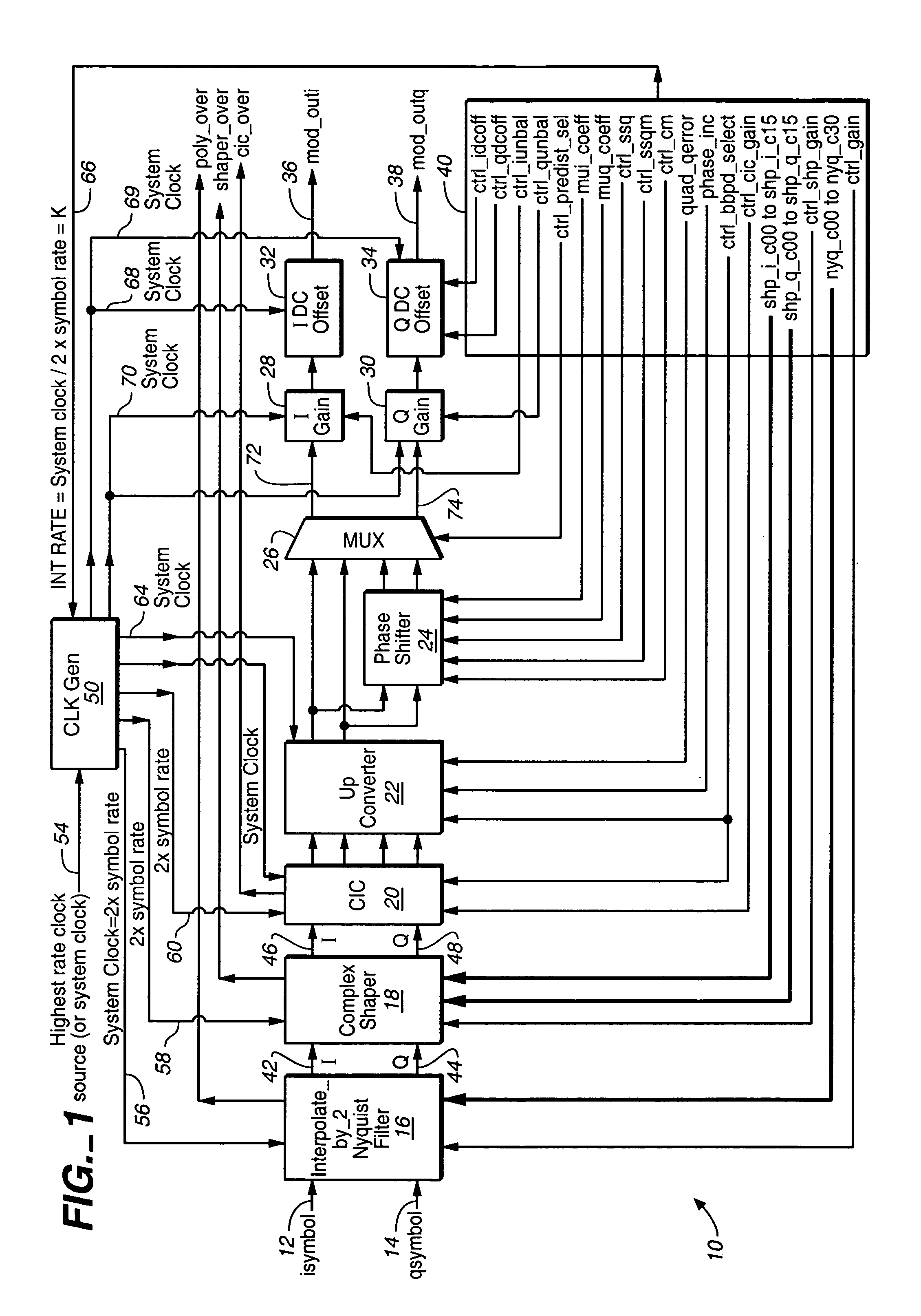

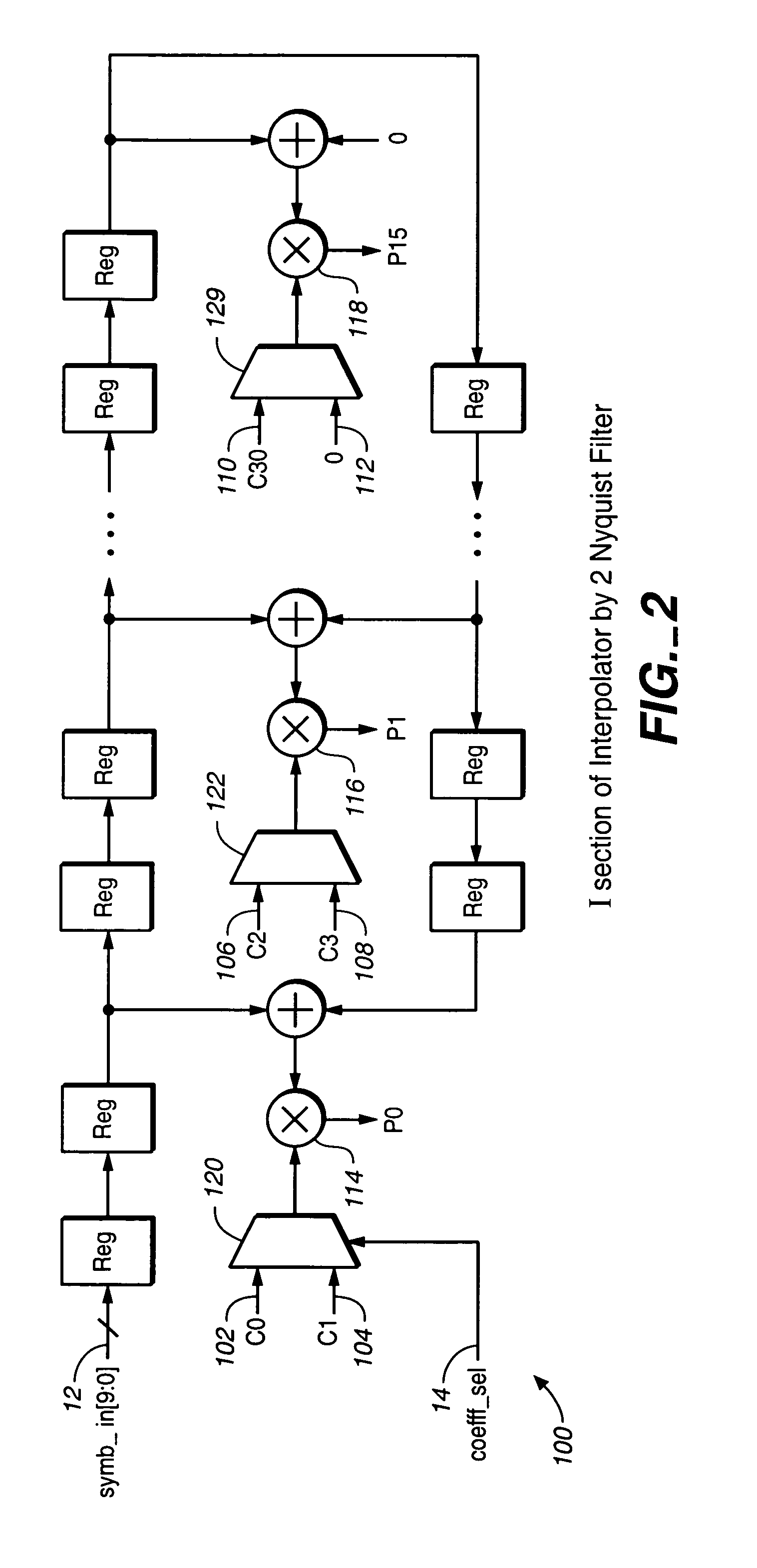

CIC qam modulator

InactiveUS7161989B1High speedElectric/magnetic signal storageAmplitude-modulated carrier systemsFrequency spectrumControl signal

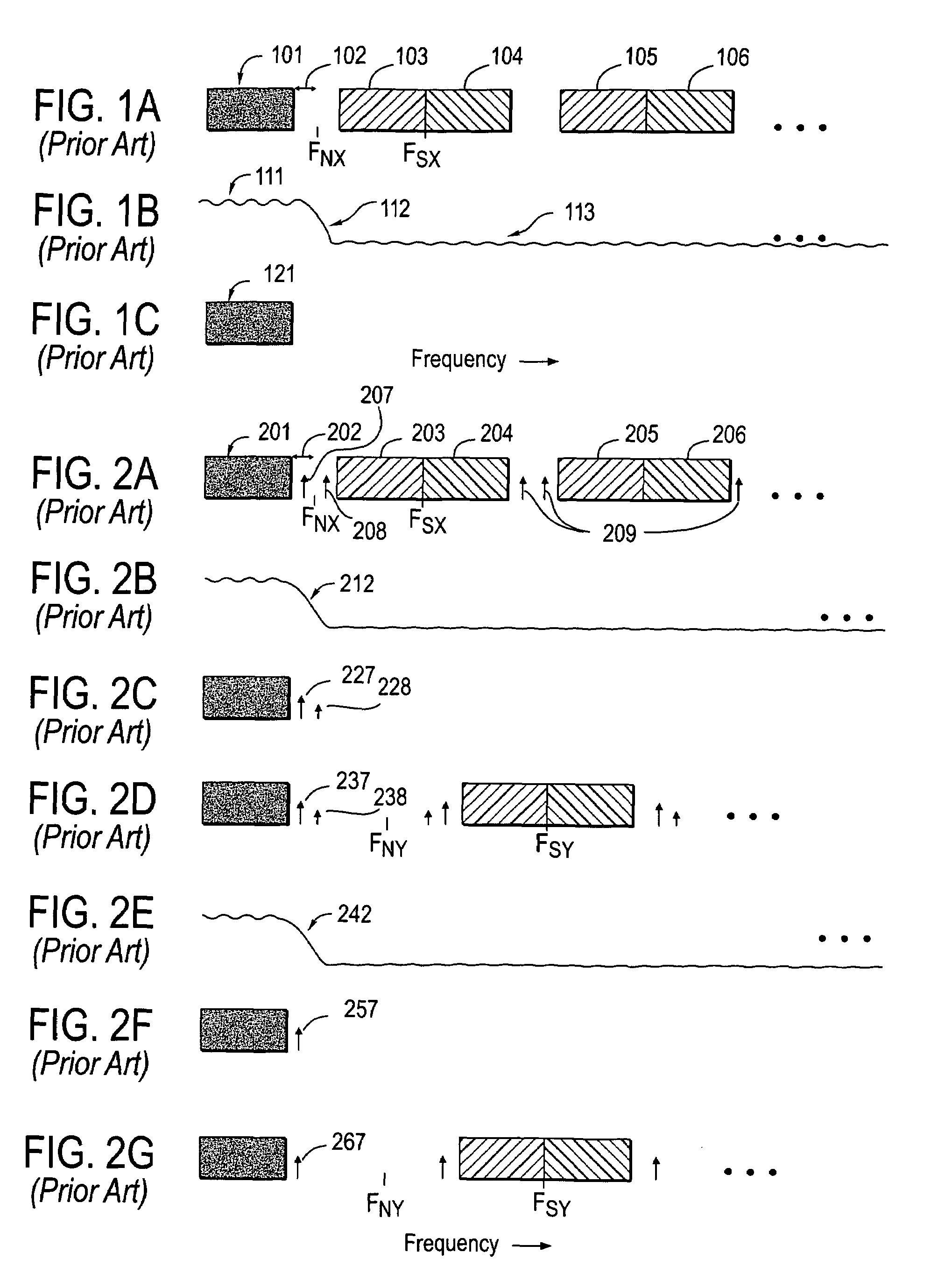

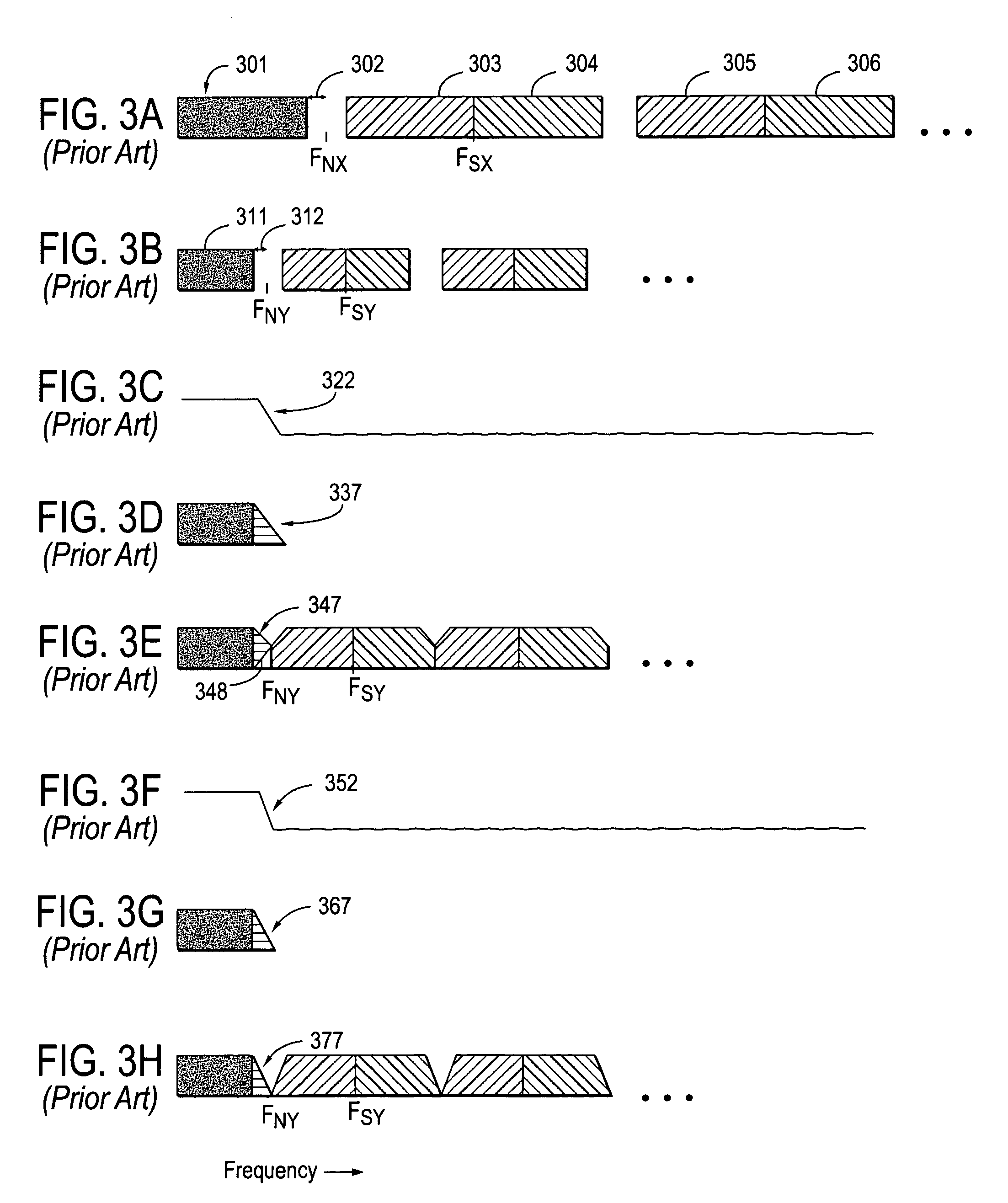

An apparatus for modulating a digital input signal having a pre-assigned symbol rate and having a baseband carrier frequency by using a single sample clock signal. The pre-assigned symbol rate is selected from the group consisting of a plurality of symbol rates. The apparatus in a baseband mode comprises: (a) an Interpolate_by_2_Nyquist Filter block configured to double the pre-assigned symbol rate, to perform Nyquist filtering operation, and configured to output an Inphase (I) and a Quadrature (Q) components of the pre-assigned signal having the double symbol rate; (b) a Complex Shaper block configured to pre-compensate the spectrum of I and Q components of the signal having the double symbol rate in advance for a spectrum distortion caused by the apparatus; ©) a Cascaded Integrated Comb (CIC) Interpolator filter configured to increase by an interpolation R factor the sample rate of the signal as compared with a sample rate of the baseband carrier; (d) a Phase Shifter configured to compensate a phase of interpolated by R signal for a known quadrature error; (e) an Inphase (I) channel and Quadrature (Q) channel Gain blocks configured to pre-compensate the I and Q components of the interpolated by R signal for a known gain difference circuit between the I and Q channel gains; (f) an I and Q channel DC offset blocks configured to pre-compensate I and Q components of the interpolated by R signal for a known DC offset difference circuit between I and Q channel DC offset blocks; and (g) a Controller block configured to supply a plurality of control signals to the apparatus. In the passband mode, I and Q channel Gains are set to one, and I and Q channel DC offsets are set to zero.

Owner:REMEC BROADBAND WIRELESS NETWORKS LLC

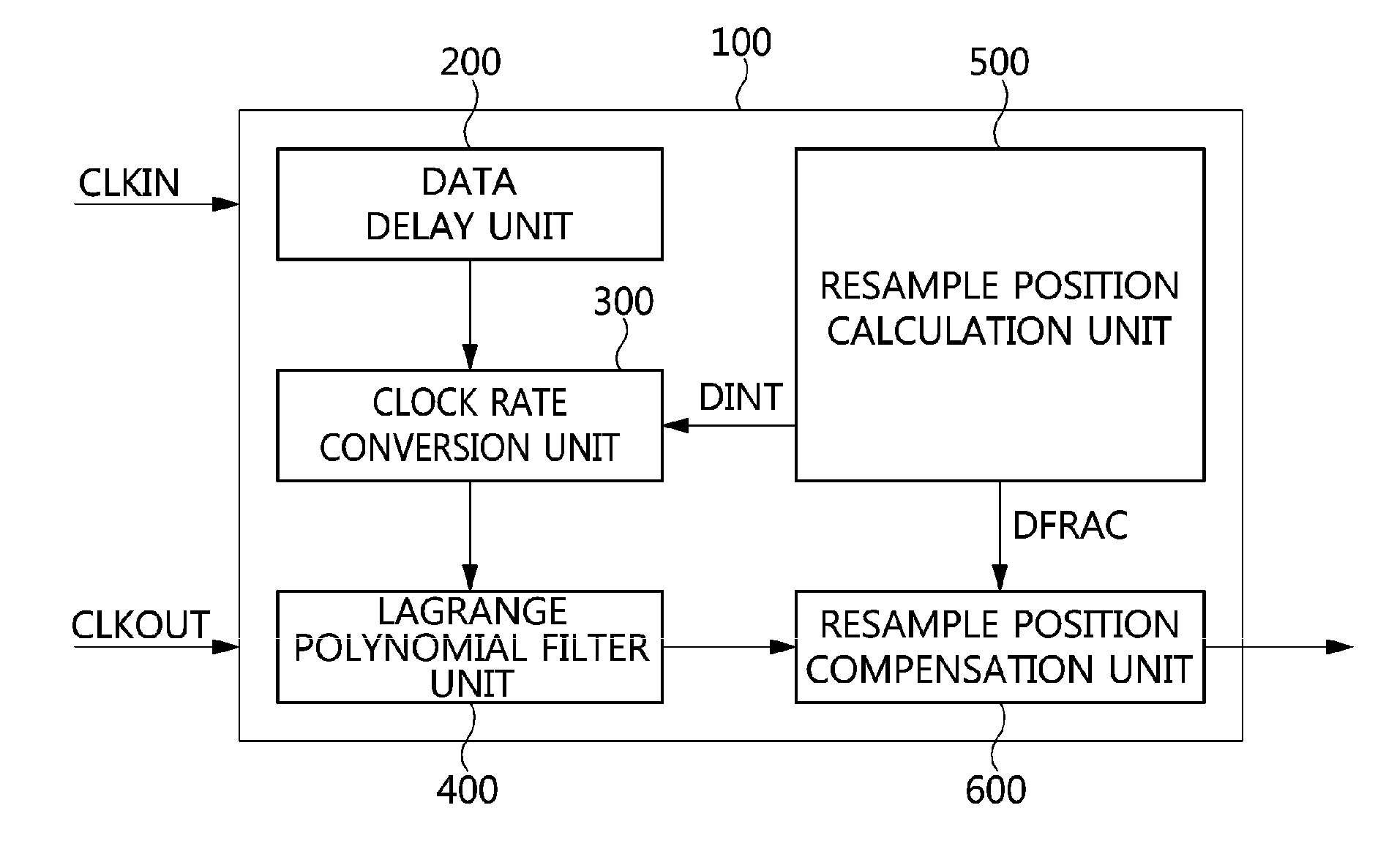

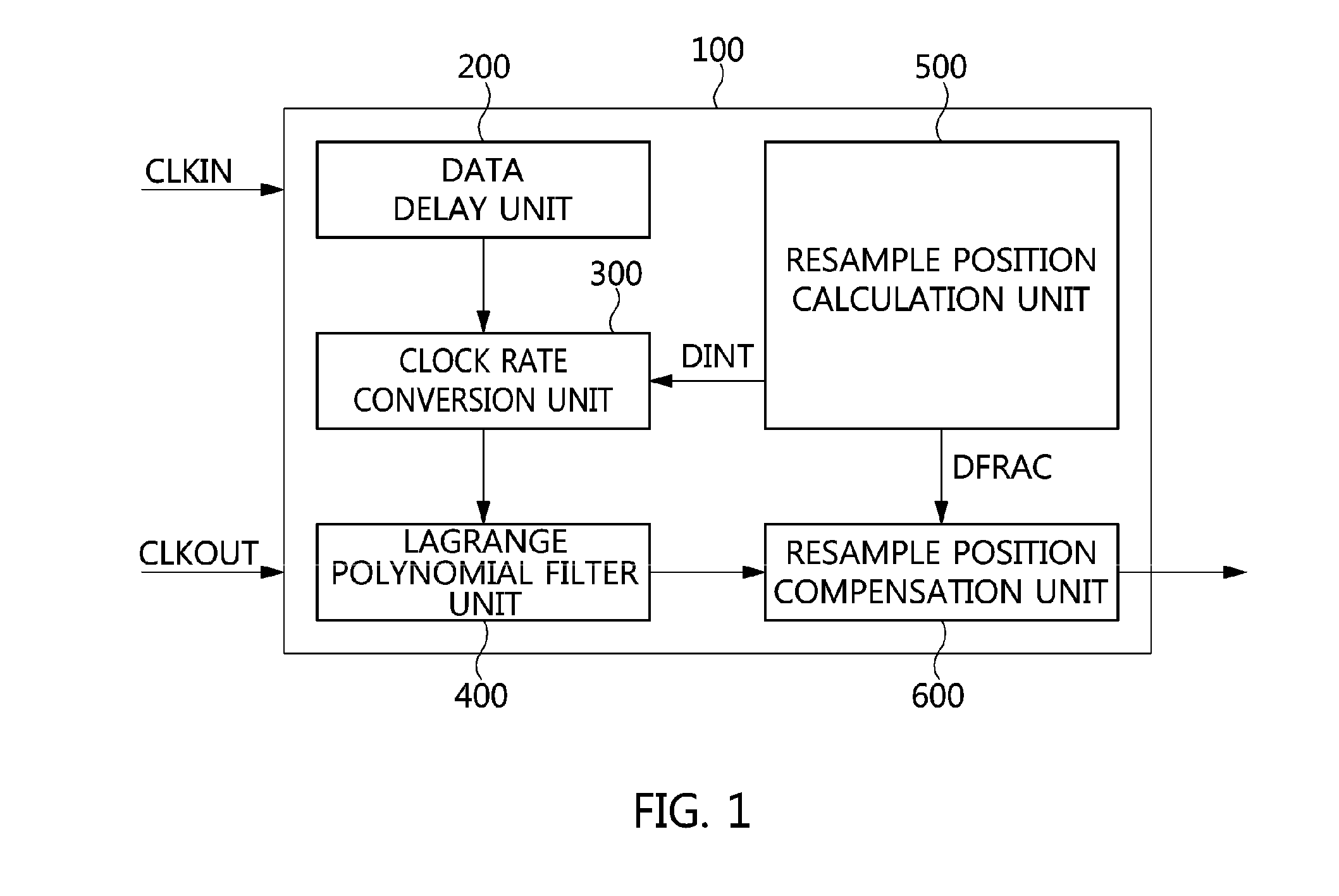

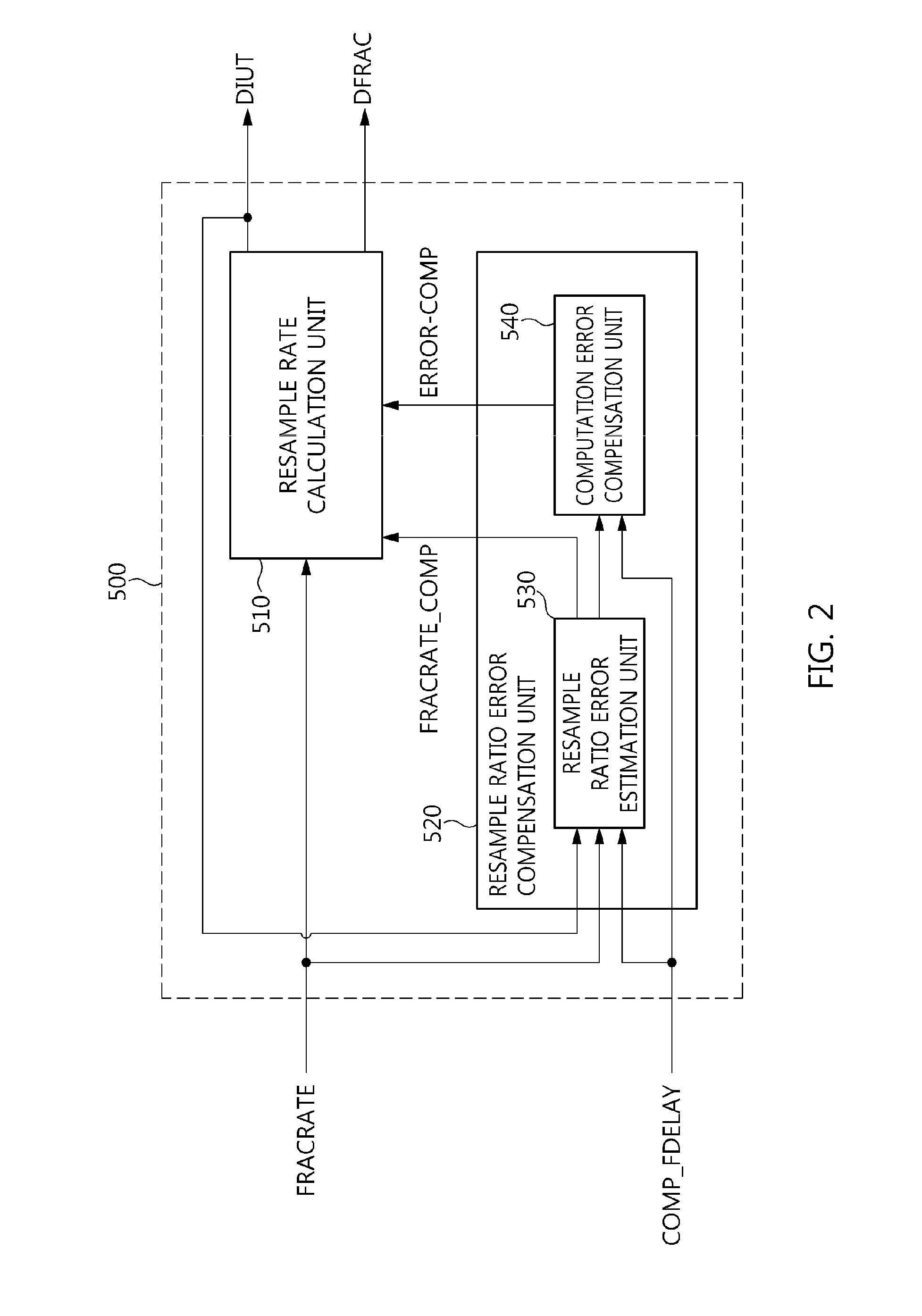

Sample rate converter and method of converting sample rate

ActiveUS20160087787A1Minimize impactDigital technique networkElectric/magnetic signal storageClock rateEngineering

A sample rate converter and a method of converting a sample rate are disclosed herein. The sample rate converter includes a data delay unit, a clock rate conversion unit, a Lagrange polynomial filter unit, a resample position calculation unit, and a resample position compensation unit. The data delay unit delays signals in response to an input clock signal. The clock rate conversion unit converts the sample rate of the signals. The Lagrange polynomial filter unit performs a filtering function on the signals whose rate has been converted. The resample position calculation unit outputs the value (Dint, dfrac) of the resample position of the signals based on a set resample ratio value. The resample position compensation unit corrects the error value of the signals by applying the value (Dint, dfrac) to the signals, and outputs a final signal.

Owner:ELECTRONICS & TELECOMM RES INST

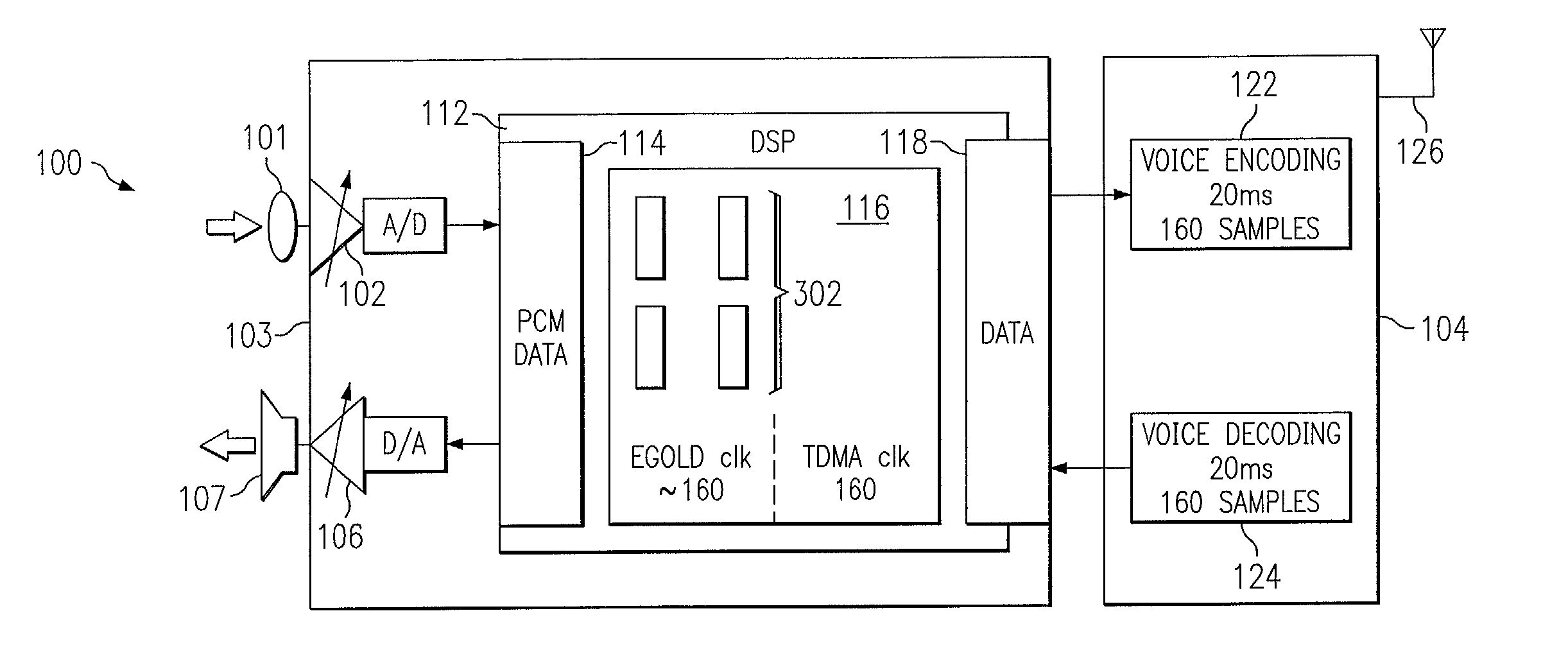

System and method for rate adaptation in a wireless communication system

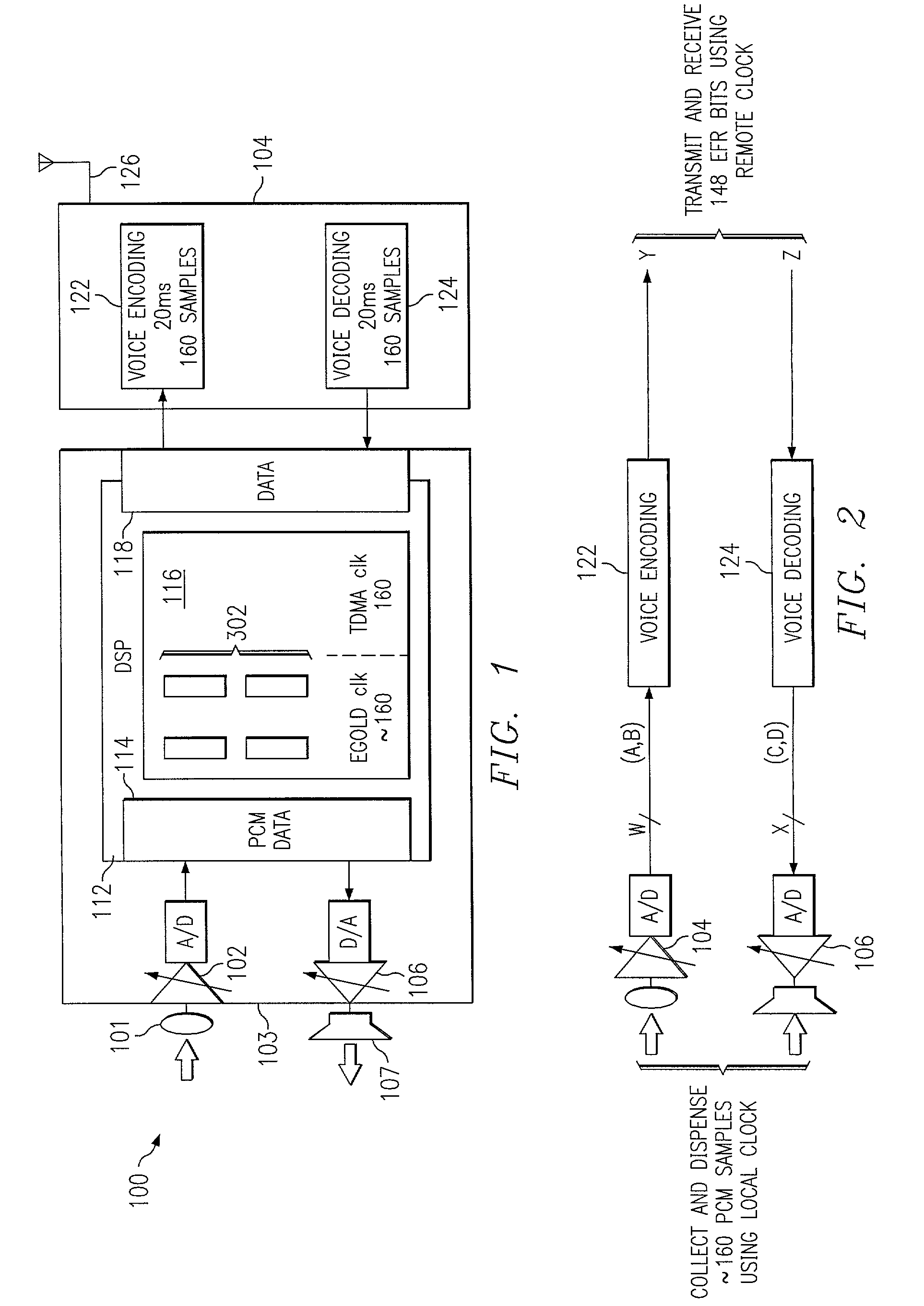

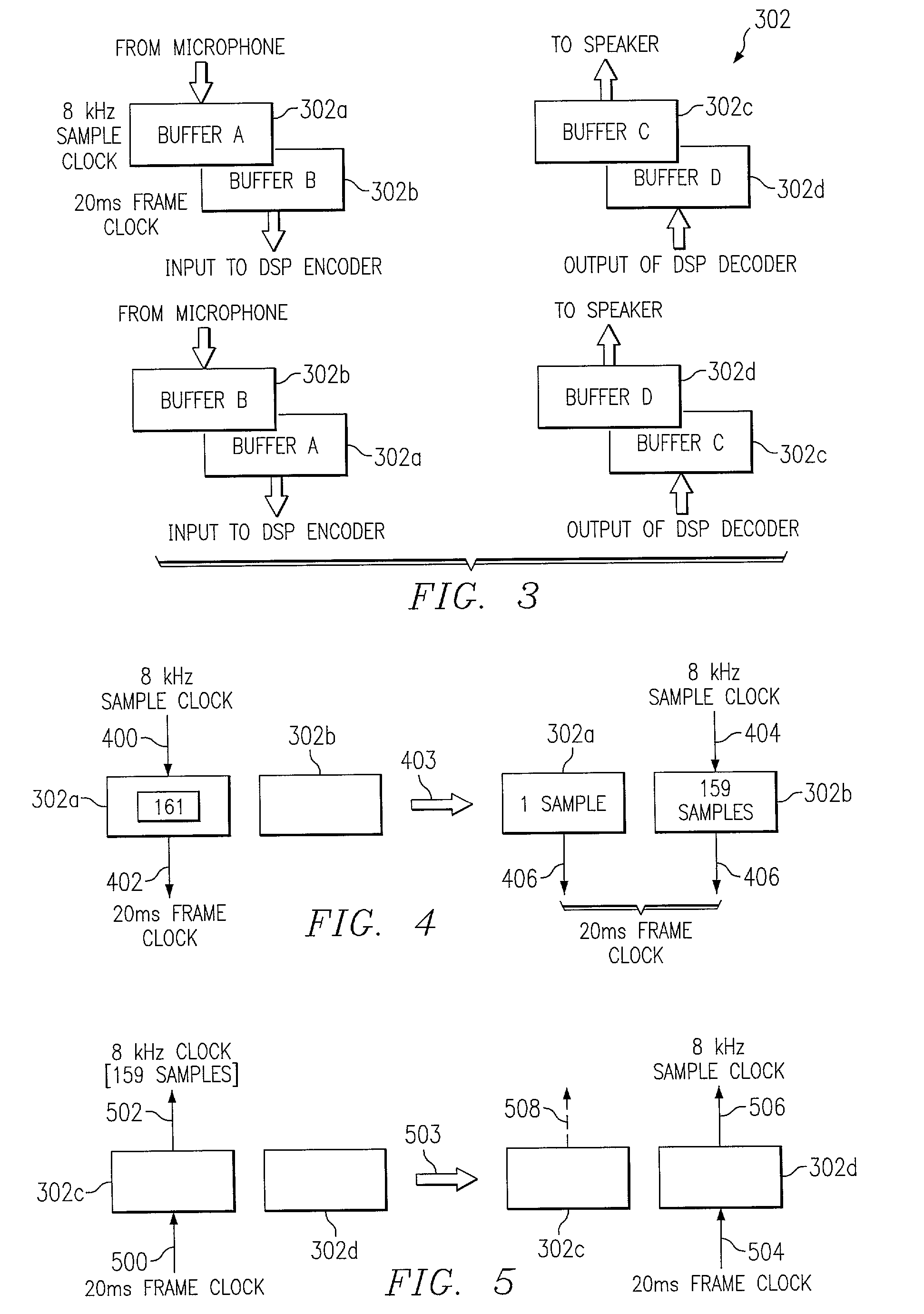

InactiveUS20020126707A1Overcomes drawbackElectric/magnetic signal storageTime-division multiplexComputer hardwareFrame based

A rate adjustment scheme. Two pairs of slightly oversized buffers are utilized as jitter buffers. While a pair of buffers are dispensing and gathering audio input and audio output samples, another pair of buffers function as encoder / decoder input and output buffers. The input and output sample buffers work in sample based time scale by accepting and discharging one sample at a time. The encoder / decoder buffers are utilized in frame based scale where an entire block of samples is read or written for encoding or decoding. On every frame clock derived from an external source, the uplink buffers (i.e., the audio input and the encoder input buffers) are swapped. The downlink buffers (i.e., the audio output and the decoder output buffers) are also swapped. The rate adjustment takes place seamlessly in the act of buffer swapping.

Owner:SIEMENS AG

Switchboard For Dual-Rate Single-Band Communication System

InactiveUS20080291940A1Special service provision for substationHybrid switching systemsCommunication interfaceData stream

A switchboard device and methods of operation of same are disclosed. Embodiments of the invention may provide a flexible means of interconnecting wideband and narrowband communications interfaces, where wideband communications interfaces may transfer wideband data sampled at a higher sampling rate, and narrowband communication interfaces may transfer narrowband data sampled at a lower sampling rate. Data streams sampled at different sampling rates can be combined and the sampling rate of the result adjusted as needed by the destination interface. Methods of operating embodiments of the present invention are included. An additional aspect of the present invention may include machine-readable storage having stored thereon a computer program having a plurality of code sections executable by a machine for causing the machine to perform the foregoing.

Owner:AVAGO TECH INT SALES PTE LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com