Patents

Literature

212 results about "Sample rate conversion" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

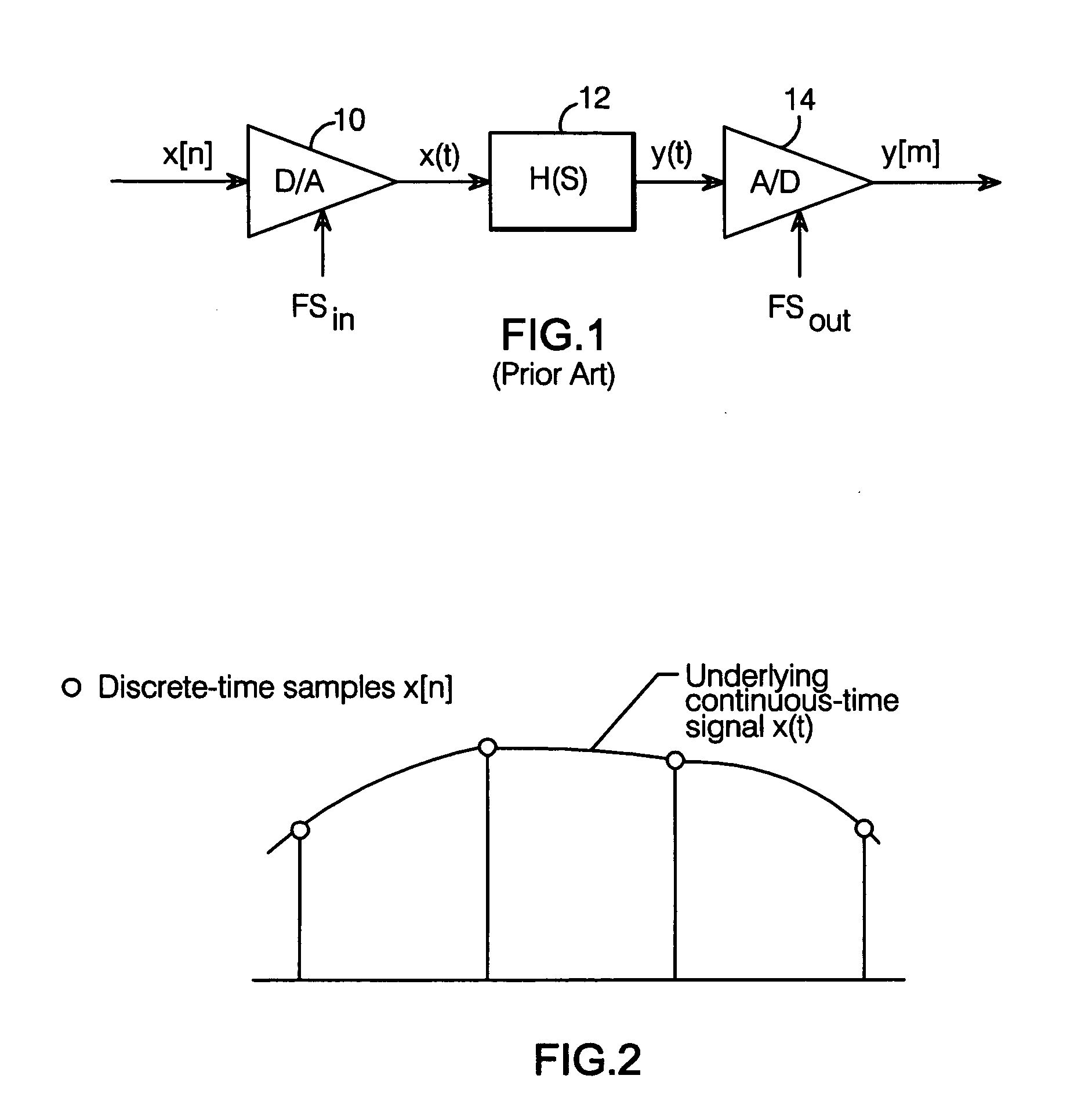

Sample-rate conversion is the process of changing the sampling rate of a discrete signal to obtain a new discrete representation of the underlying continuous signal. Application areas include image scaling and audio/visual systems, where different sampling rates may be used for engineering, economic, or historical reasons.

Communication system and method for sample rate converting data onto or from a network using a high speed frequency comparison technique

ActiveUS7106224B2High resolutionImprove accuracyTime-division multiplexIndividual digits conversionSample rate conversionPhase difference

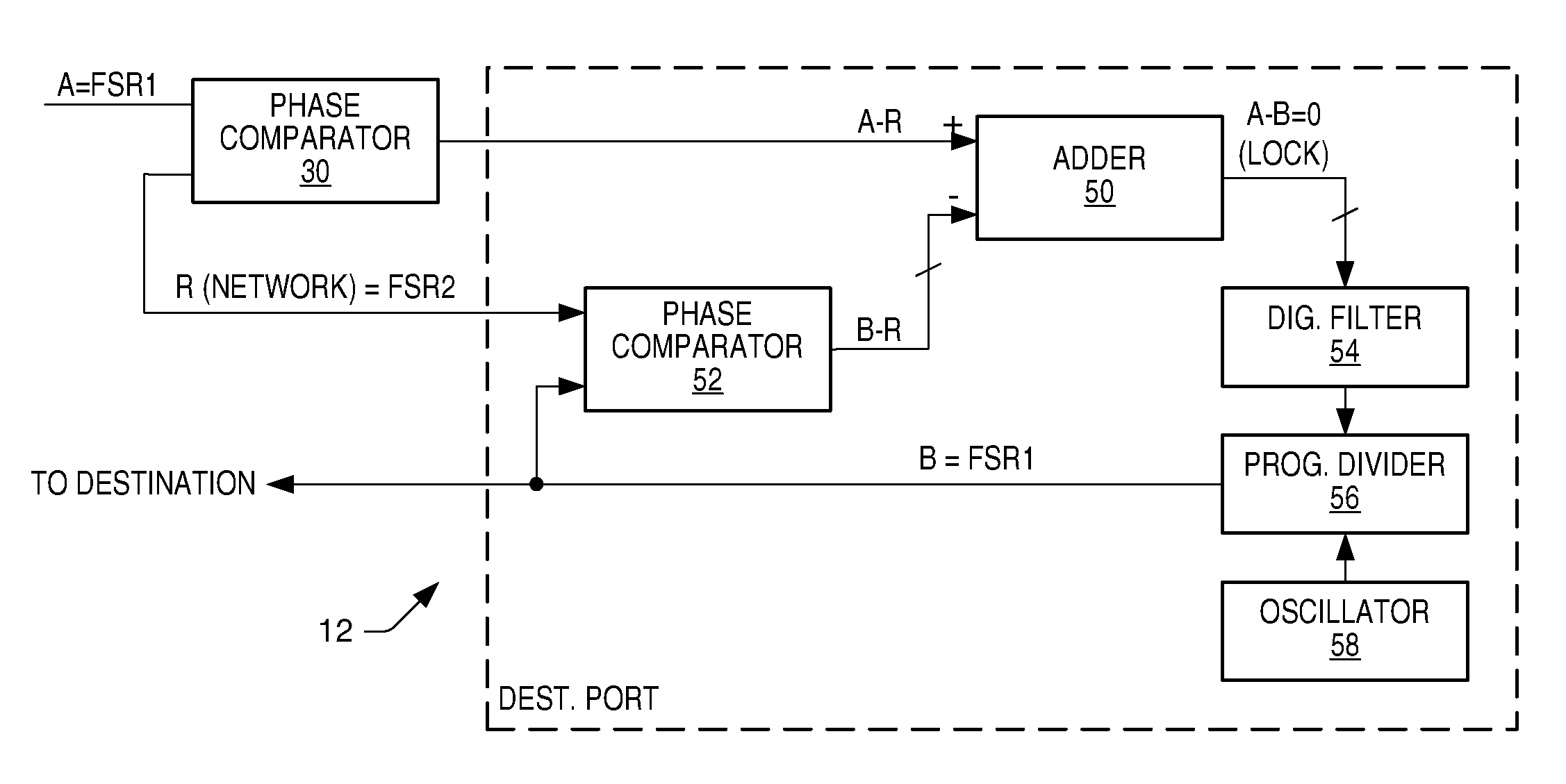

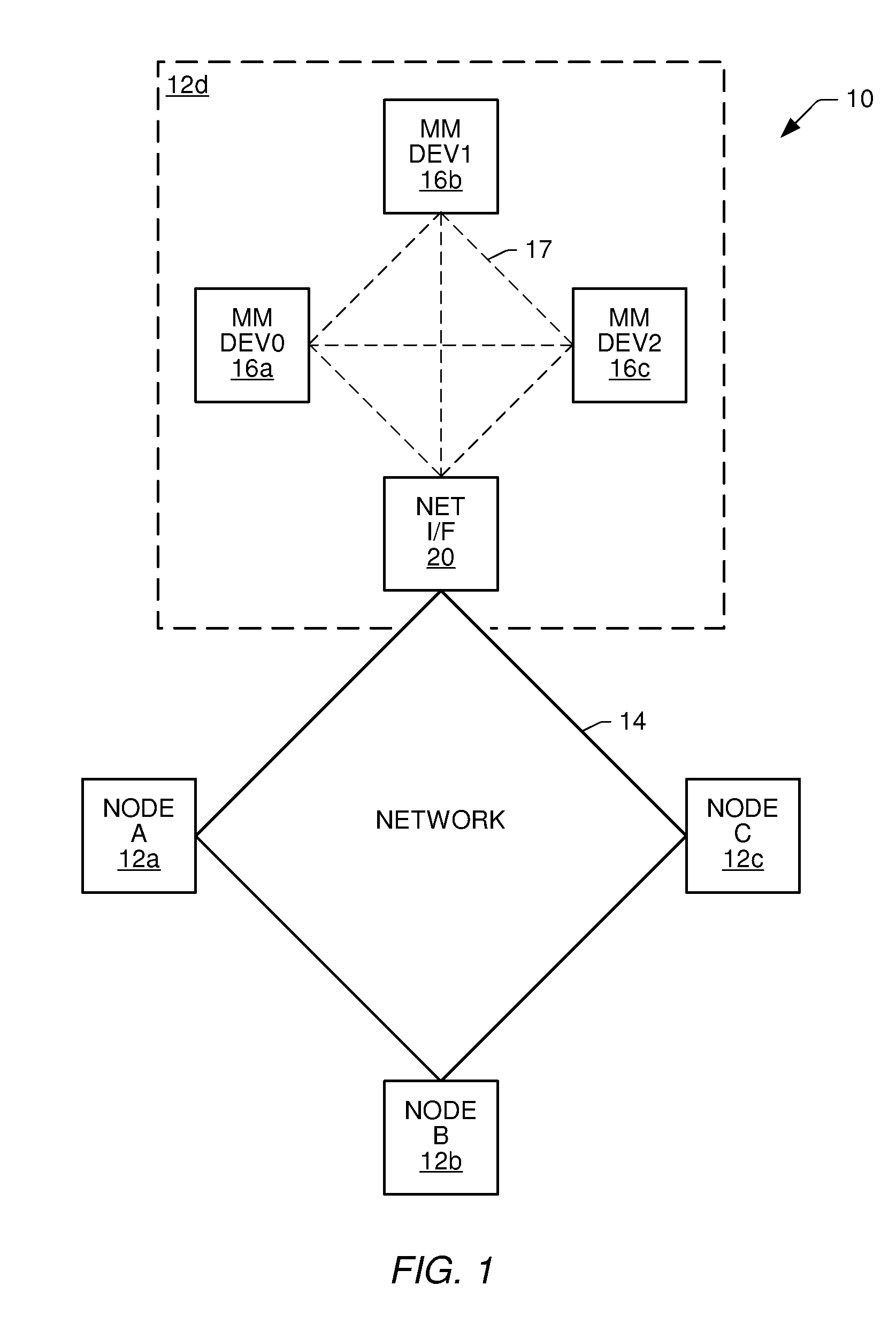

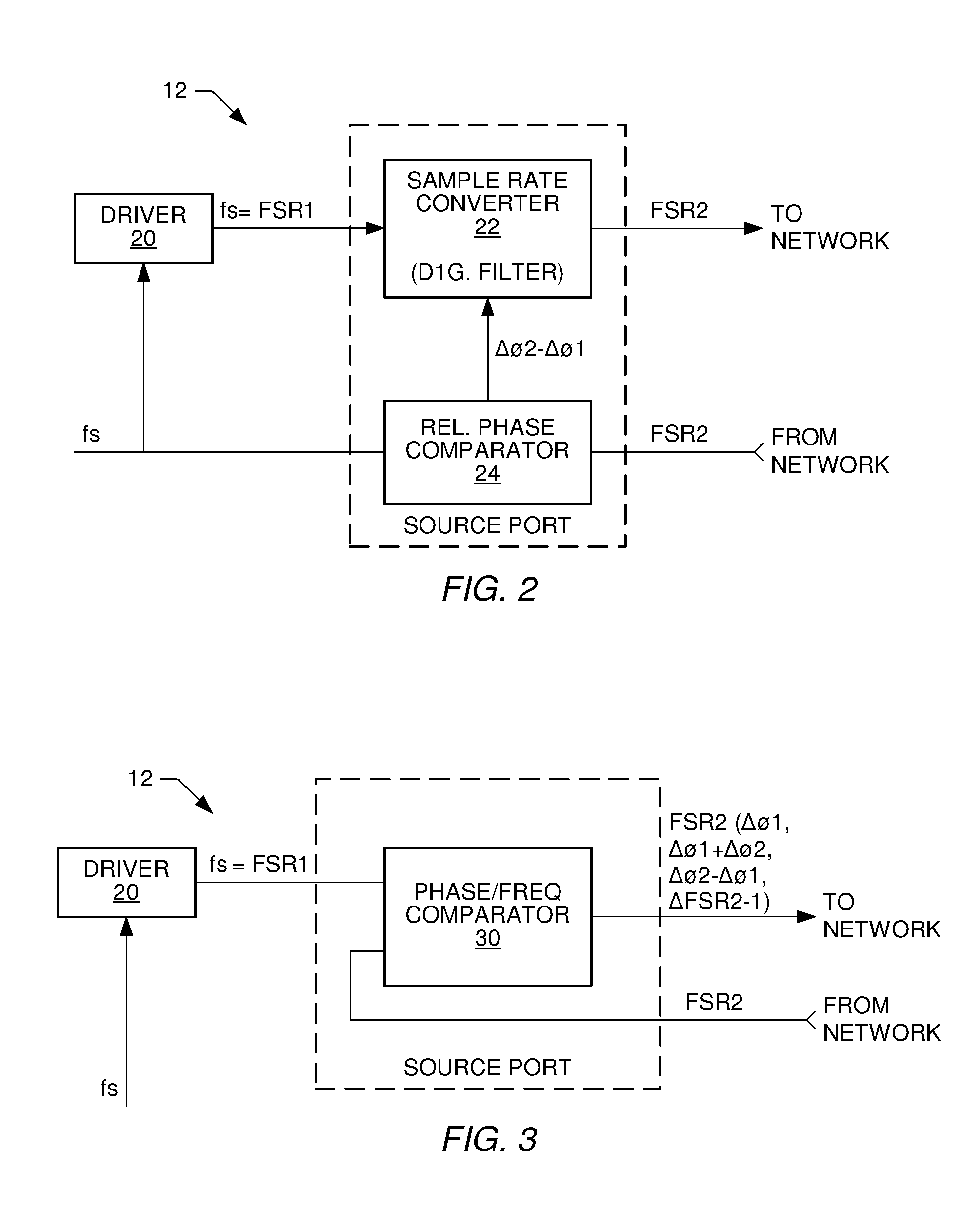

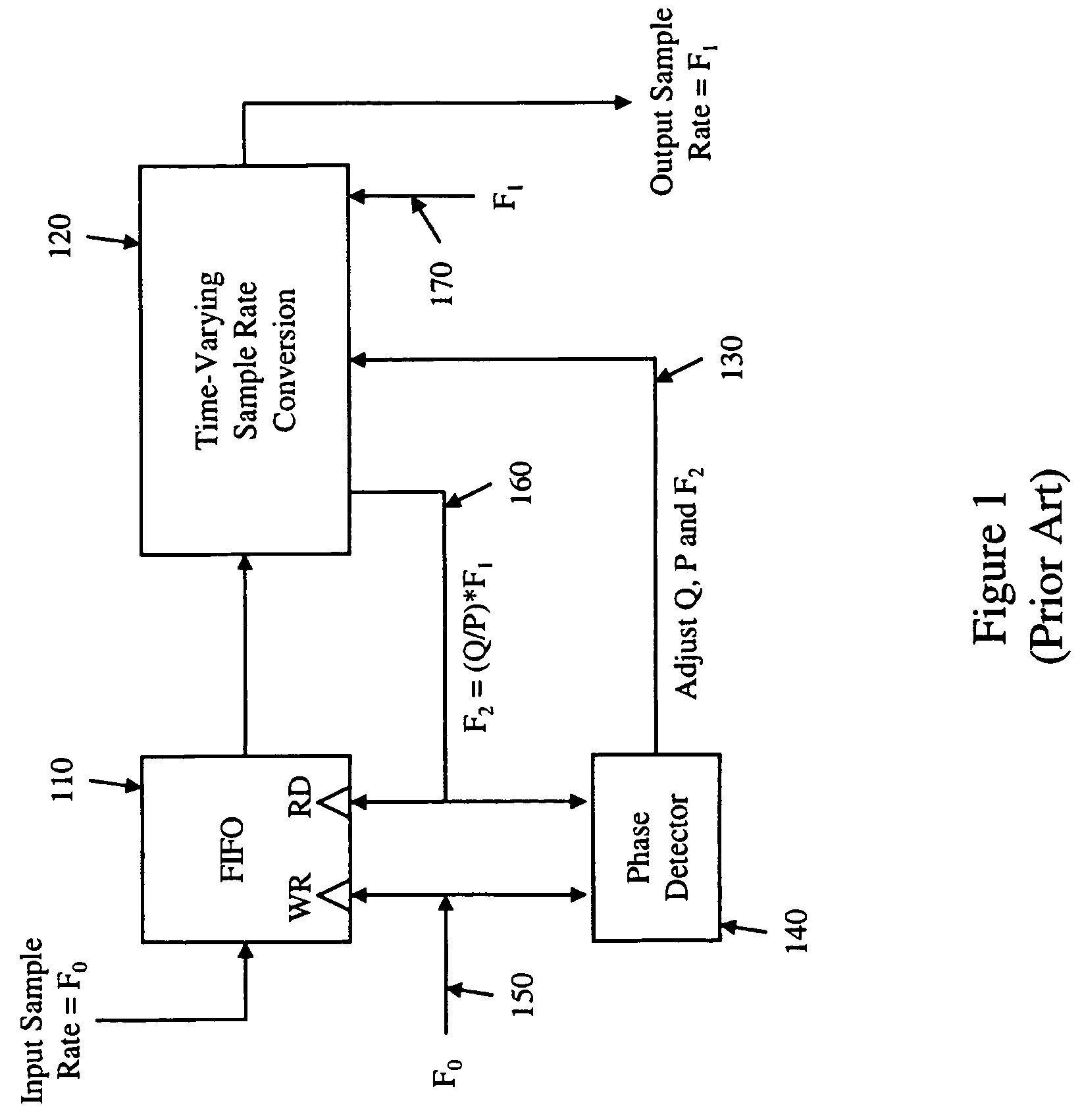

A communication system, source and destination ports of the communication system, and methodology is provided for transporting data in one of possibly three different ways. Data is transported across the network at a frame sample rate that can be the same as or different from the sample rate or master clock within the source port or the destination port. If the sample rate of the source port is known, the sample rate of the destination port can be created using a PLL within the destination port and simply employing a phase comparator in the source port. The phase comparator forwards the phase or frequency difference of the network transfer rate and the source sample rate to the destination port, which then generates a local clock equivalent to the source which then compiles audio data being played at the same rate in which it was sampled at the source. Where economically feasible, sample rate conversion can be used at the source. However, sample rate conversion at the destination is preferred if the source sample rate is forwarded across the network relative to the frame transfer rate of the synchronous network. The sample rate converter simply produces a play rate from the transmitted information at the destination. Again, however, sample rate conversion compares relative phase difference changes similar to the phase difference compared in the digital PLL mode. As a further alternative, sample rates within the source and destination ports can be derived from the network frame rate using fractional dividers in the source and destination ports.

Owner:STANDRD MICROSYSTEMS CORPORATION

Techniques for sample rate conversion

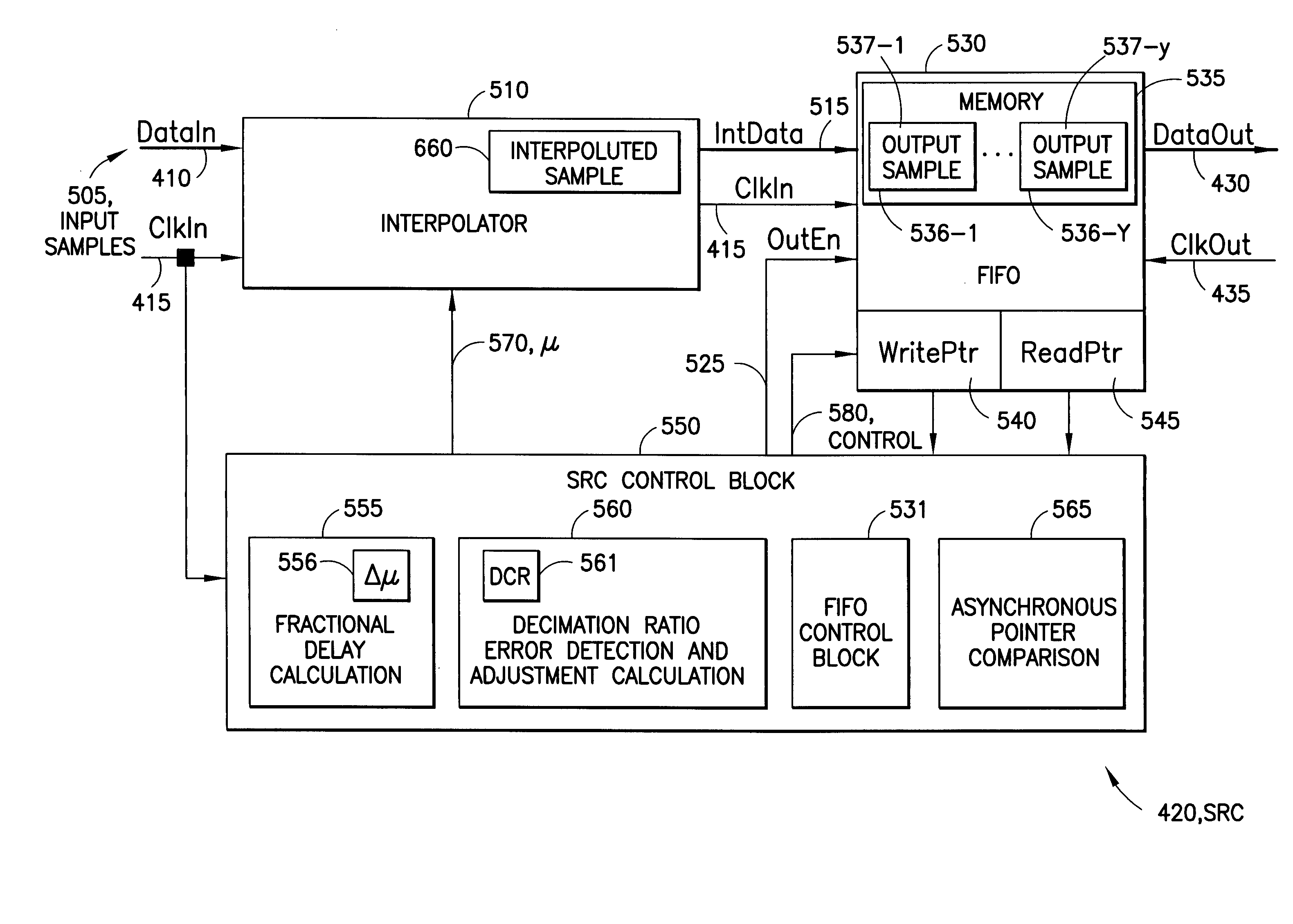

Techniques for sample rate conversion are disclosed. In one exemplary embodiment, a sample rate conversion occurs between first samples having a sample rate defined by a first clock signal and second samples having a sample rate defined by a second clock signal. Using a conversion ratio and at a first rate defined by the first clock signal, a given second sample is determined from at least one first sample. A write pointer is updated for a buffer when second samples are written into the buffer. A read pointer is updated for the buffer when second samples are read from the buffer. The second samples are read from the buffer at a second rate defined by the second clock signal. The conversion ratio is modified based on the write and read pointers.

Owner:NOKIA TECHNOLOGLES OY

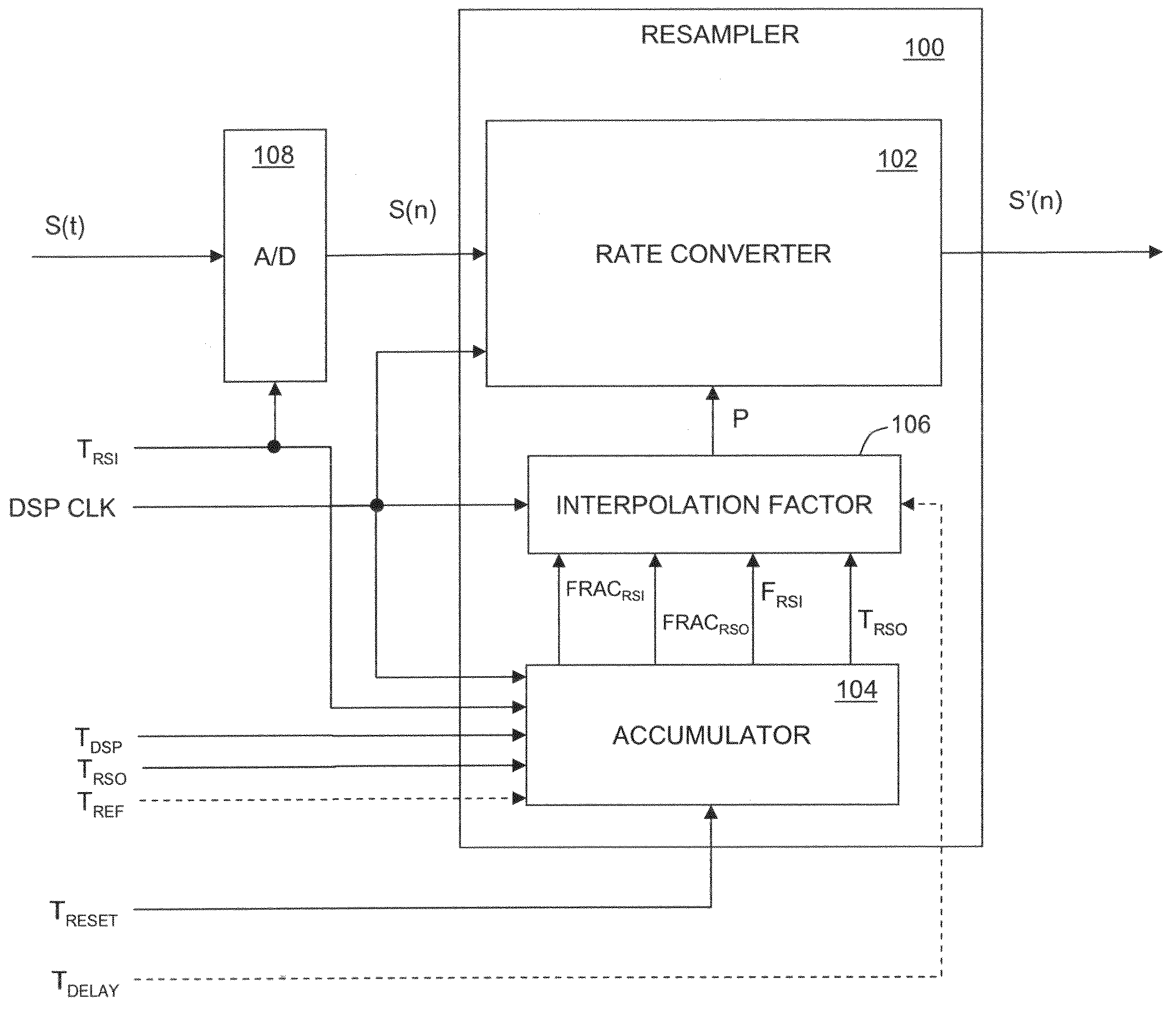

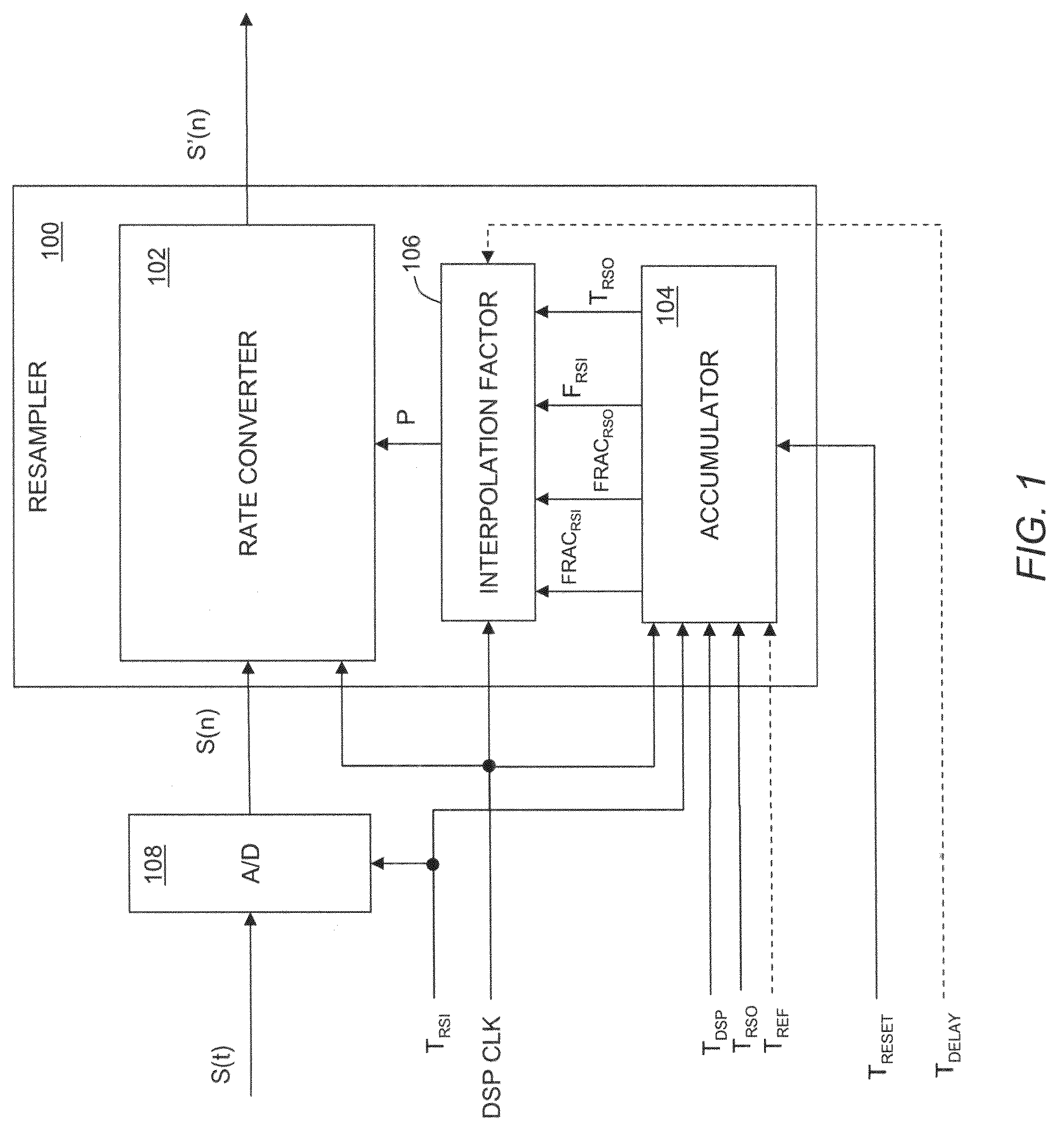

Method and apparatus for computing interpolation factors in sample rate conversion systems

ActiveUS7719446B2Simple requirementsGood flexibilityDigital technique networkCode conversionSample rate conversionClock rate

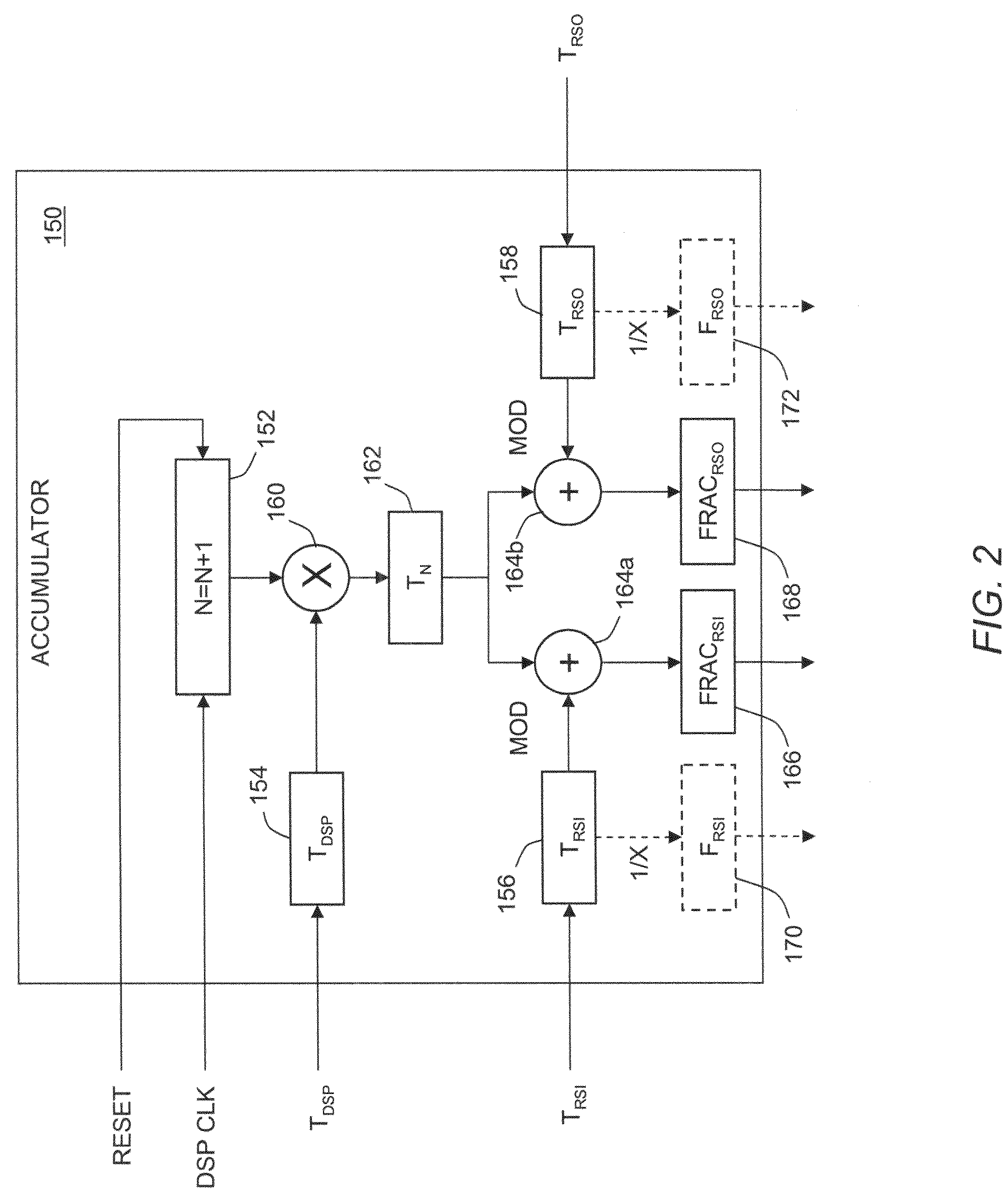

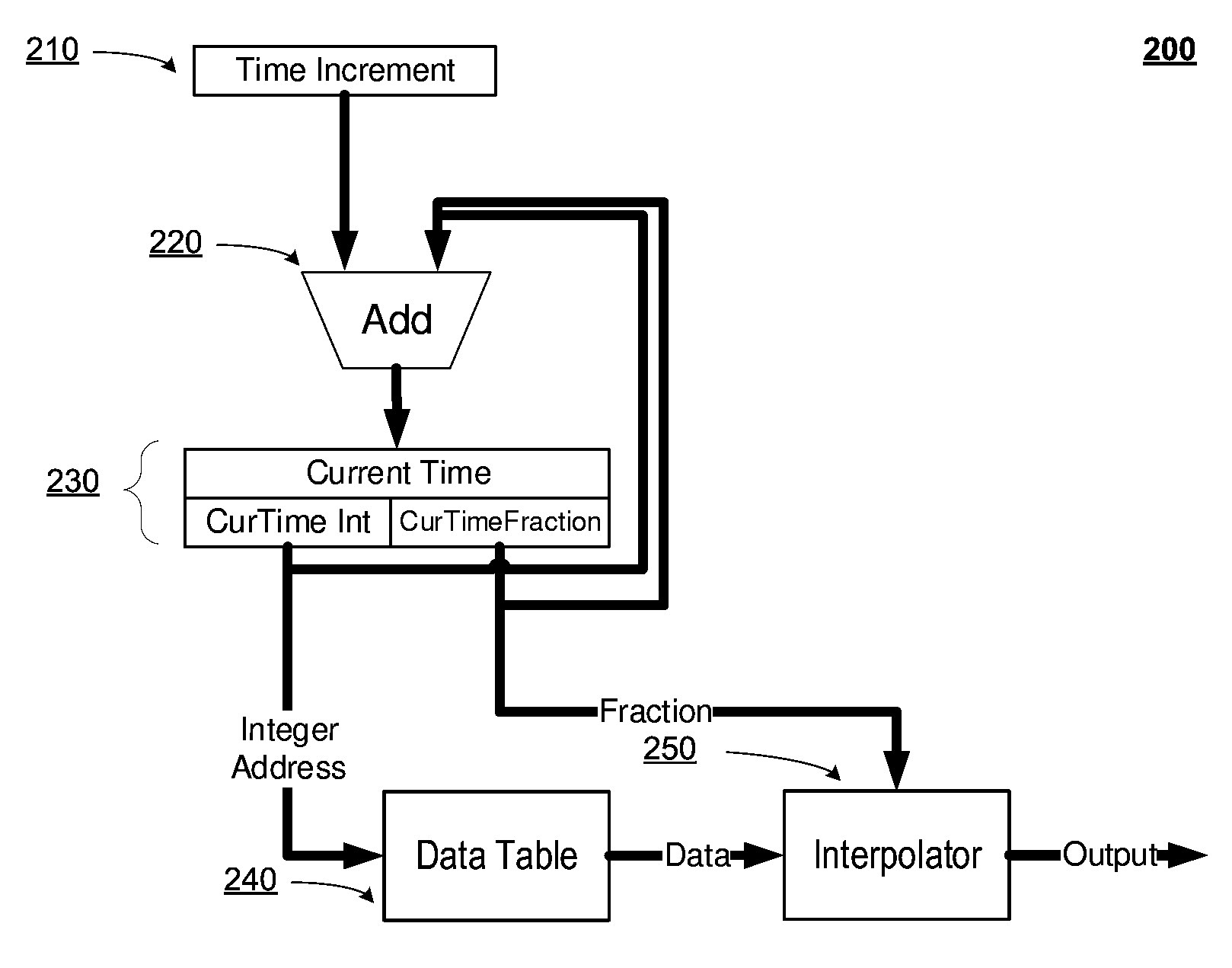

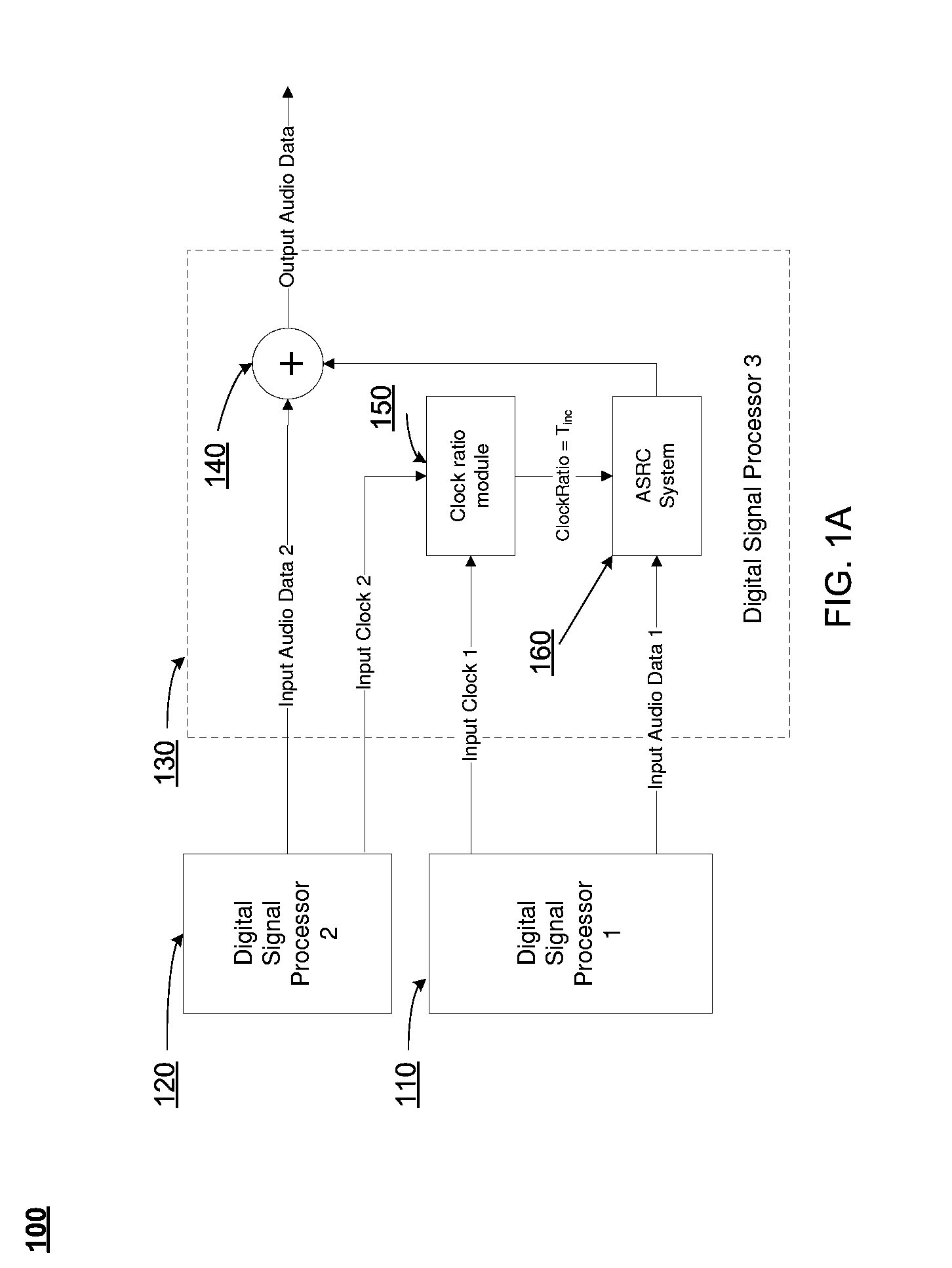

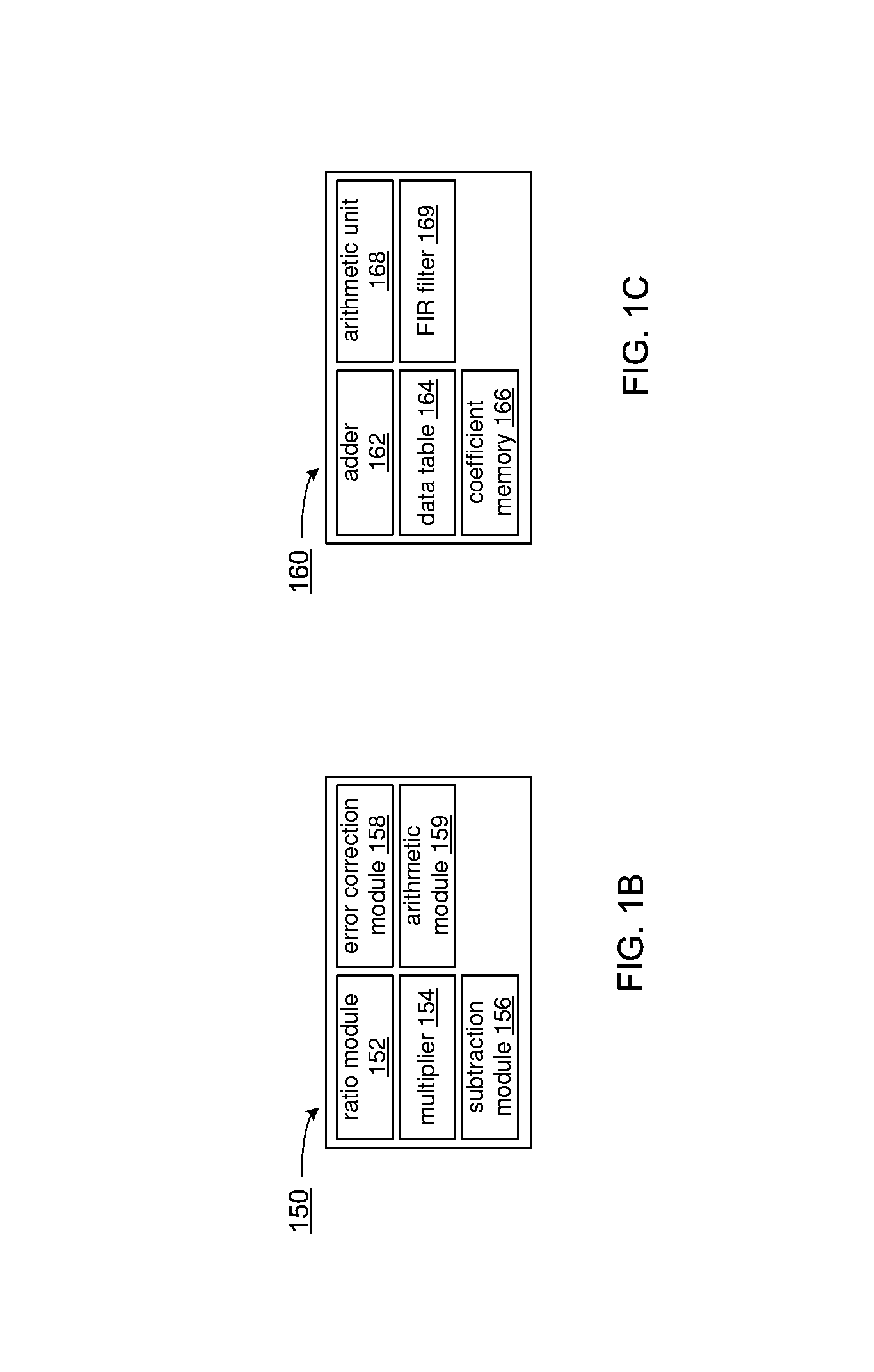

The invention allows the interpolation factor, a critical parameter in sample rate conversion systems, to be computed in a real-time system where there is a complex relationship between a DSP clock and the data clocks. Typically, two or three of the clocks in such a system will have simple relationships (such as CLOCK1=2*CLOCK2). This relationship leads to degenerate cases where, in fact, there are only one or two clocks to consider rather than three. Furthermore, the invention allows for input data rates that are higher than the DSP clock rate. The invention also provides for an arbitrary time delay to be applied to the output signal.

Owner:TERADYNE

Ultra-high bandwidth multi-port memory system for image scaling applications

InactiveUS6903733B1Improve reliabilityLow costGeometric image transformationCathode-ray tube indicatorsSample rate conversionParallel computing

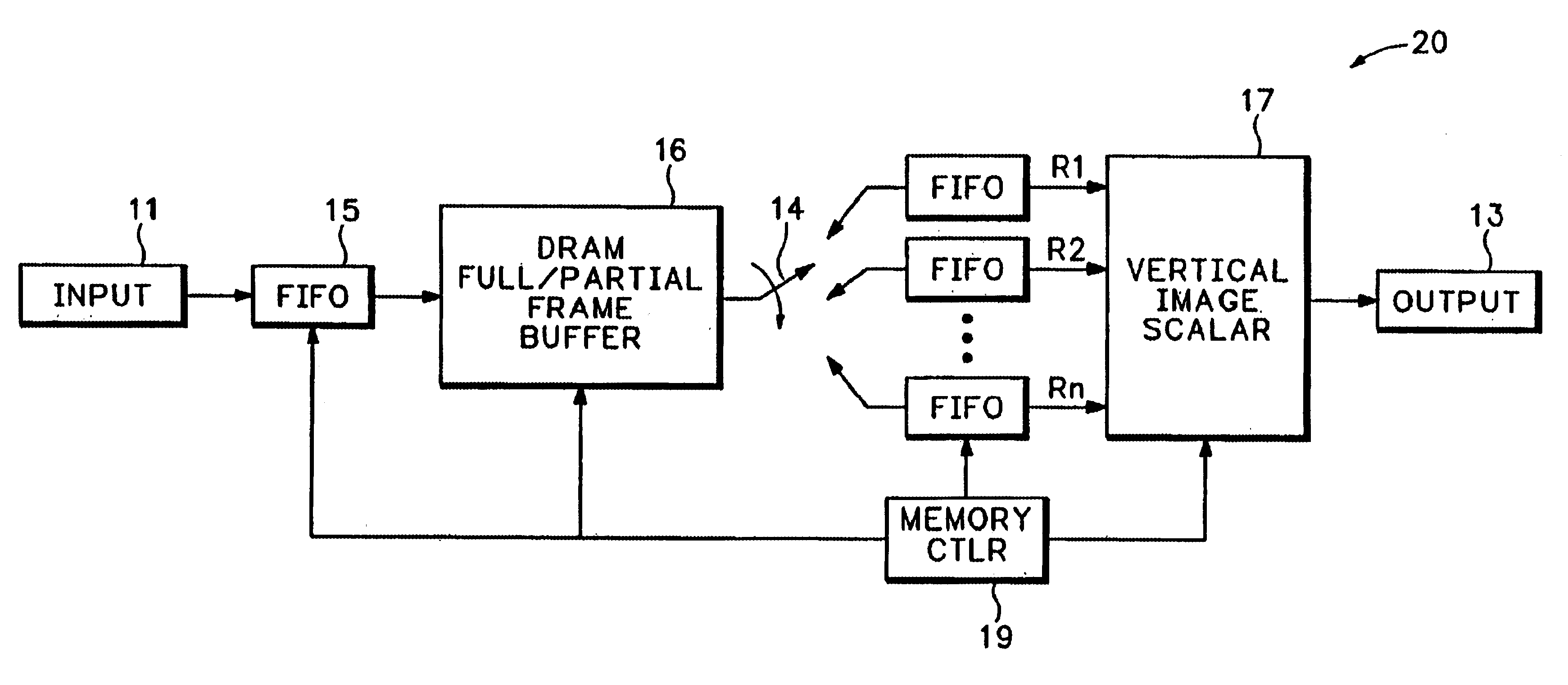

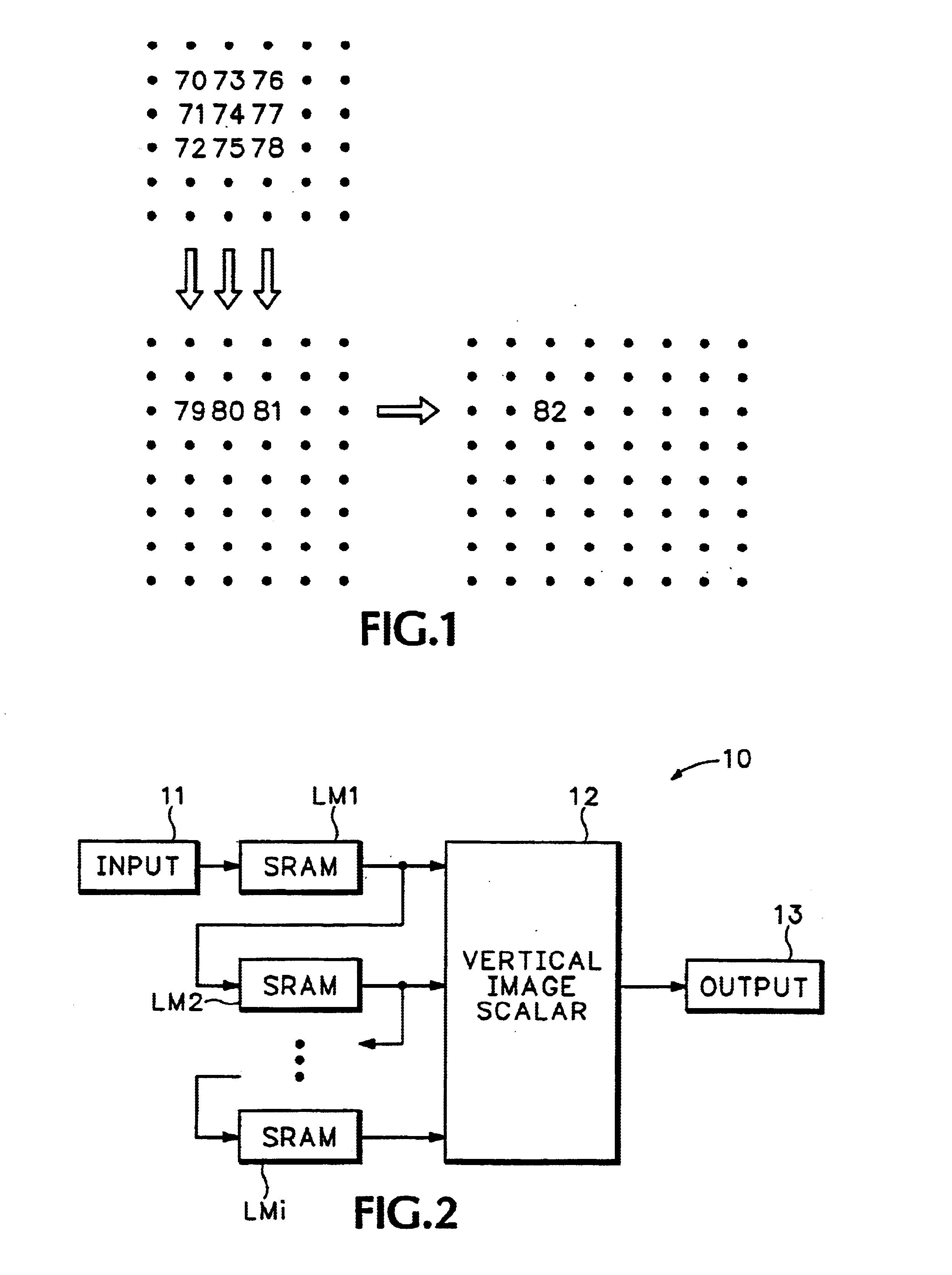

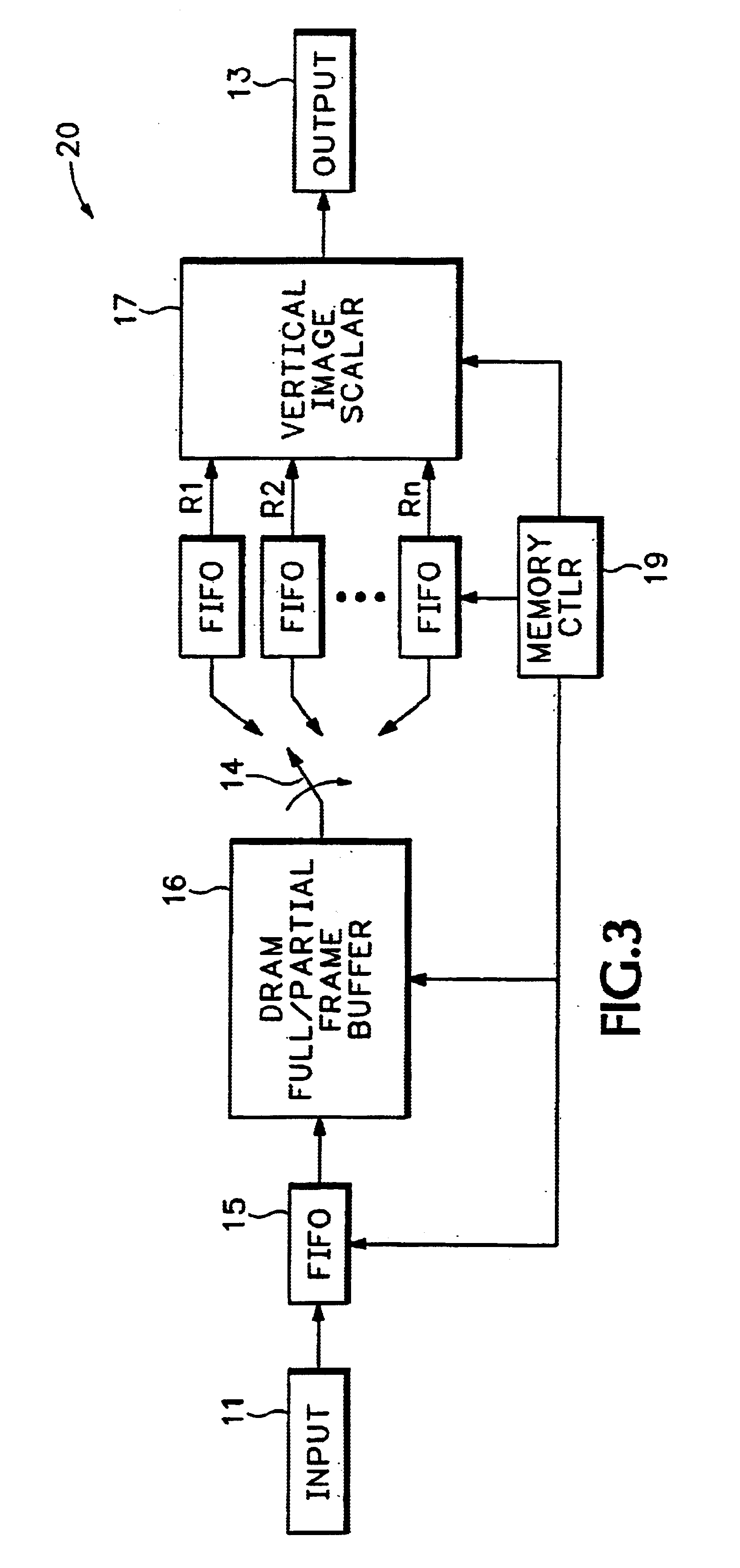

The image scaling memory system of the present invention eliminates the use of internal or external line memories by using an existing frame memory coupled with an input buffer and a plurality of output buffers for providing a vertical scalar with simultaneous parallel access to multiple lines of data. Additionally, the image scaling memory system of the present invention, including the frame memory, is embedded into an integrated circuit. Thus, the image scaling circuit of the present invention improves reliability, lowers cost, and improves silicon area usage. The frame memory is coupled to an input buffer at an input side and a plurality of output buffers at an output side. The plurality of output buffers is positioned between the frame memory and the vertical scalar. Each output buffer sequentially gains access to and transfers portions of image lines from the frame buffer. Each output buffer stores only a portion of an image line resulting in relatively small output buffers. The plurality of output buffers provides the vertical scalar with simultaneous parallel access to multiple lines of buffered digital image data. The frame memory preferably comprises DRAM that stores the image data such that row faults are minimized. The DRAM frame memory preferably includes at least two memory banks, each including a plurality of rows and a plurality of columns. The DRAM frame memory has multiple purposes including storing digital image data frames for sample rate conversion, as well as, storing bitmaps for access by an On Screen Display controller and storing microprocessor data for access by a microprocessor.

Owner:PIXELWORKS

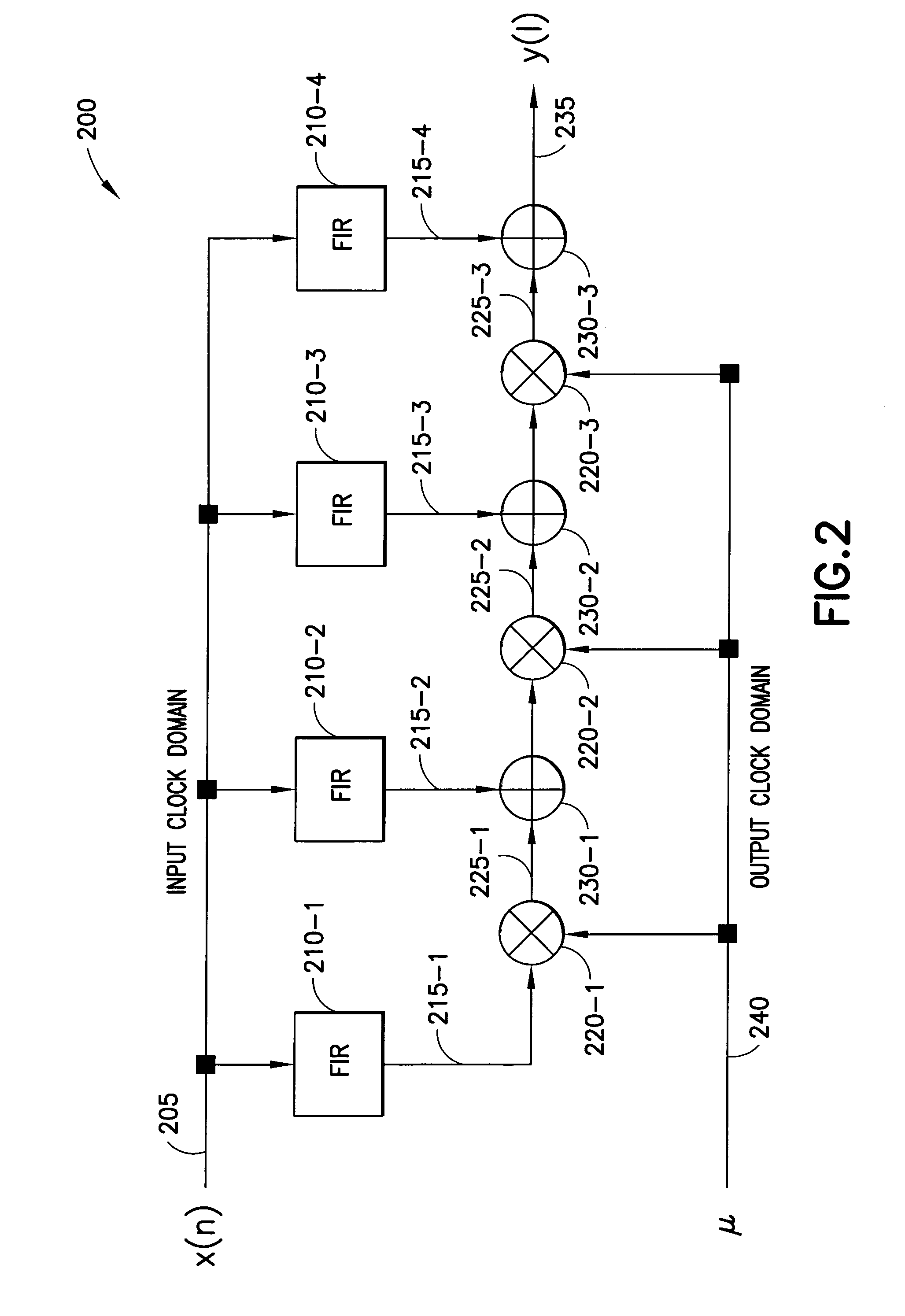

Asynchronous Sample Rate Conversion Using A Polynomial Interpolator With Minimax Stopband Attenuation

ActiveUS20120066280A1Digital technique networkComplex mathematical operationsUltrasound attenuationSample rate conversion

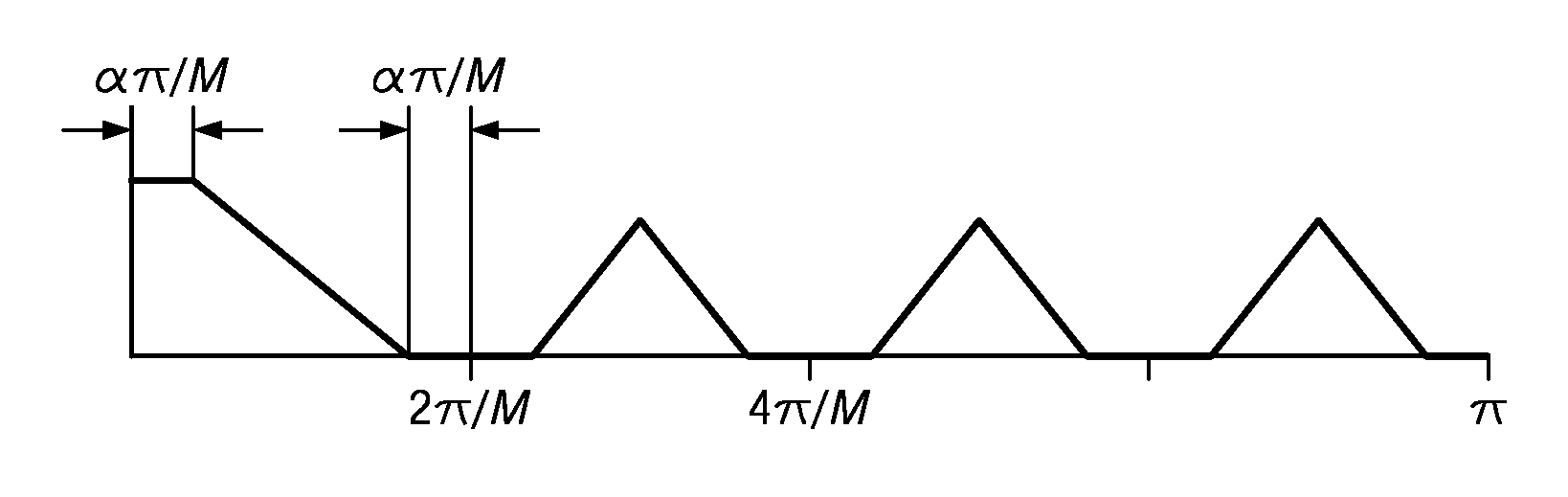

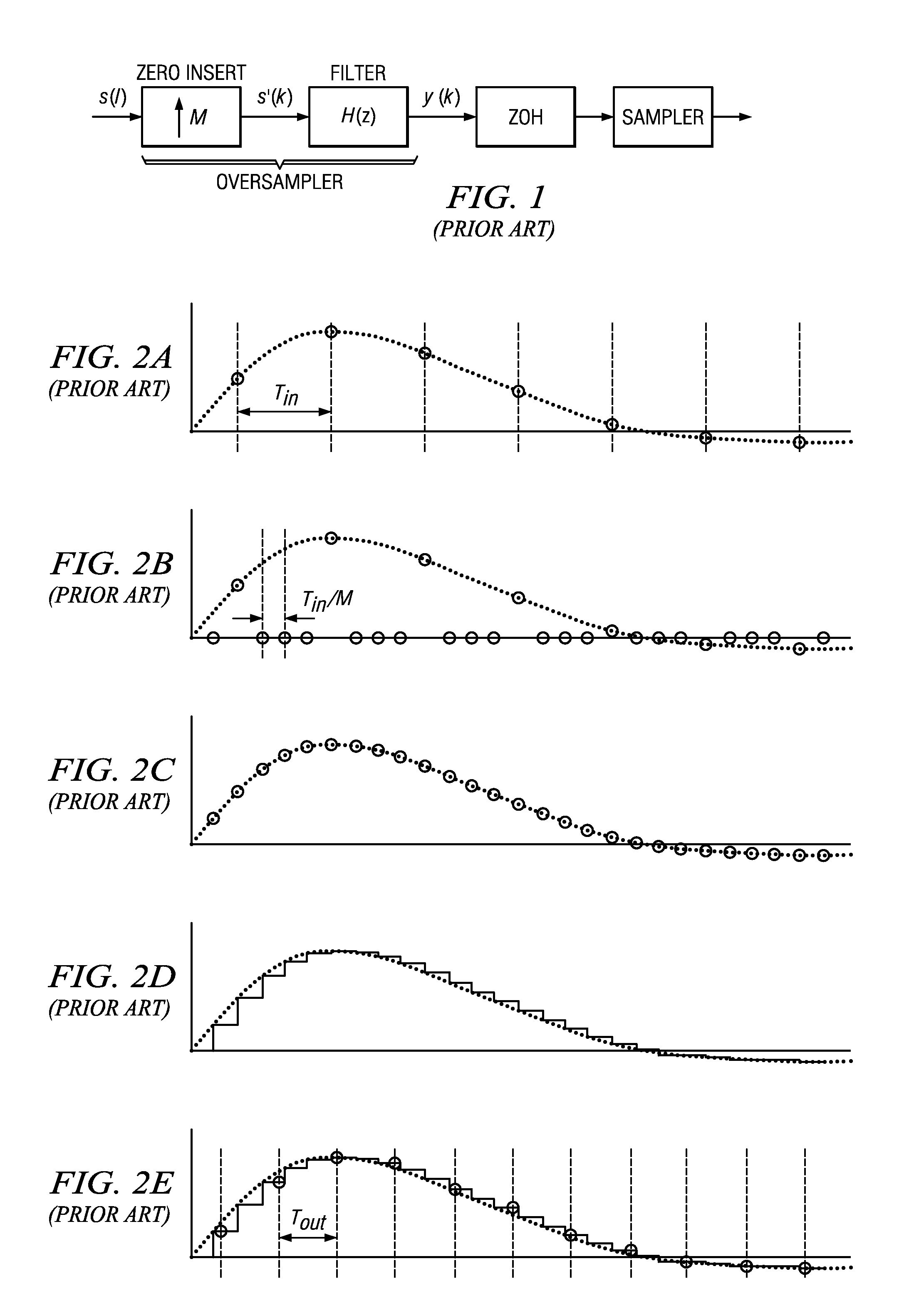

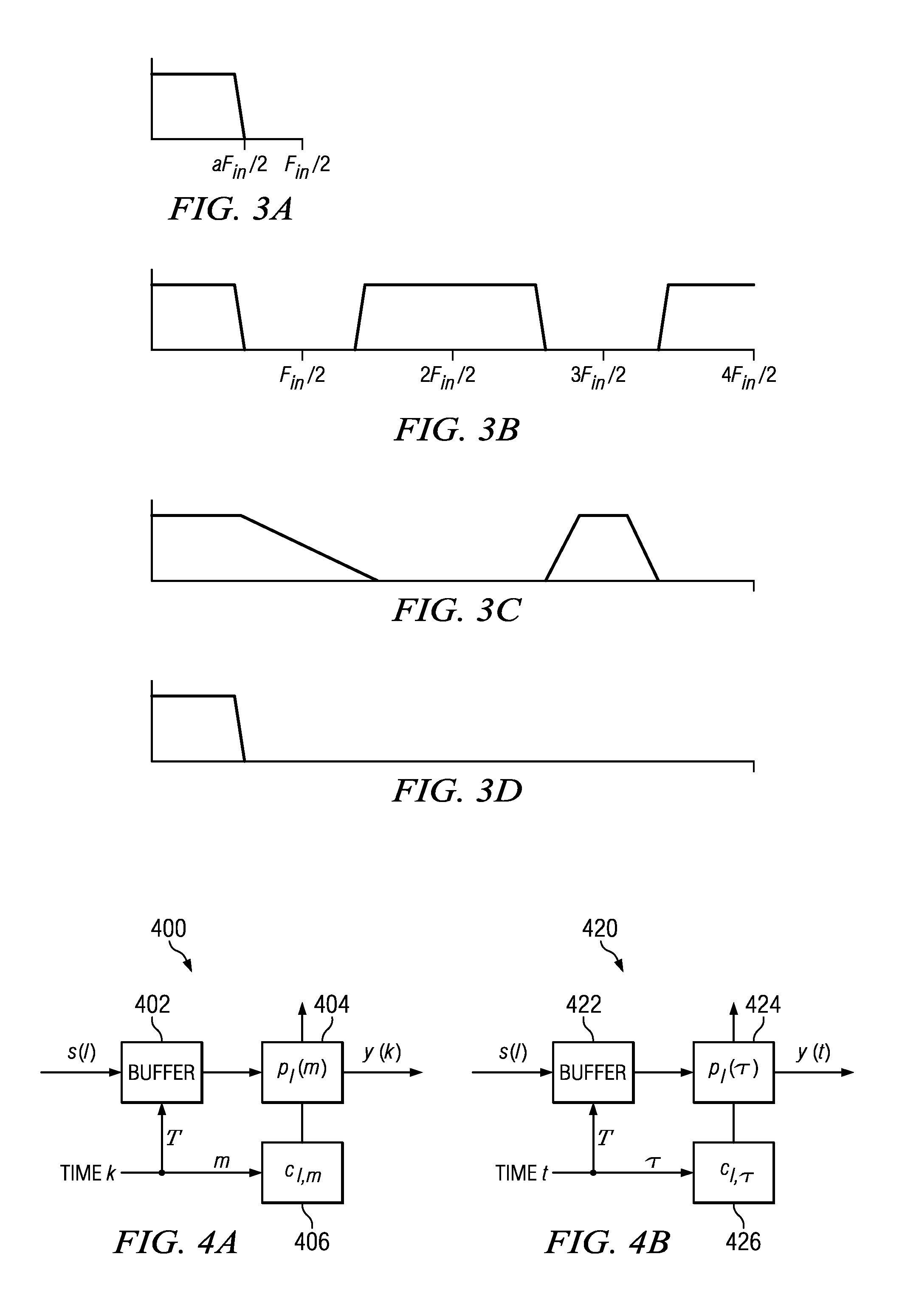

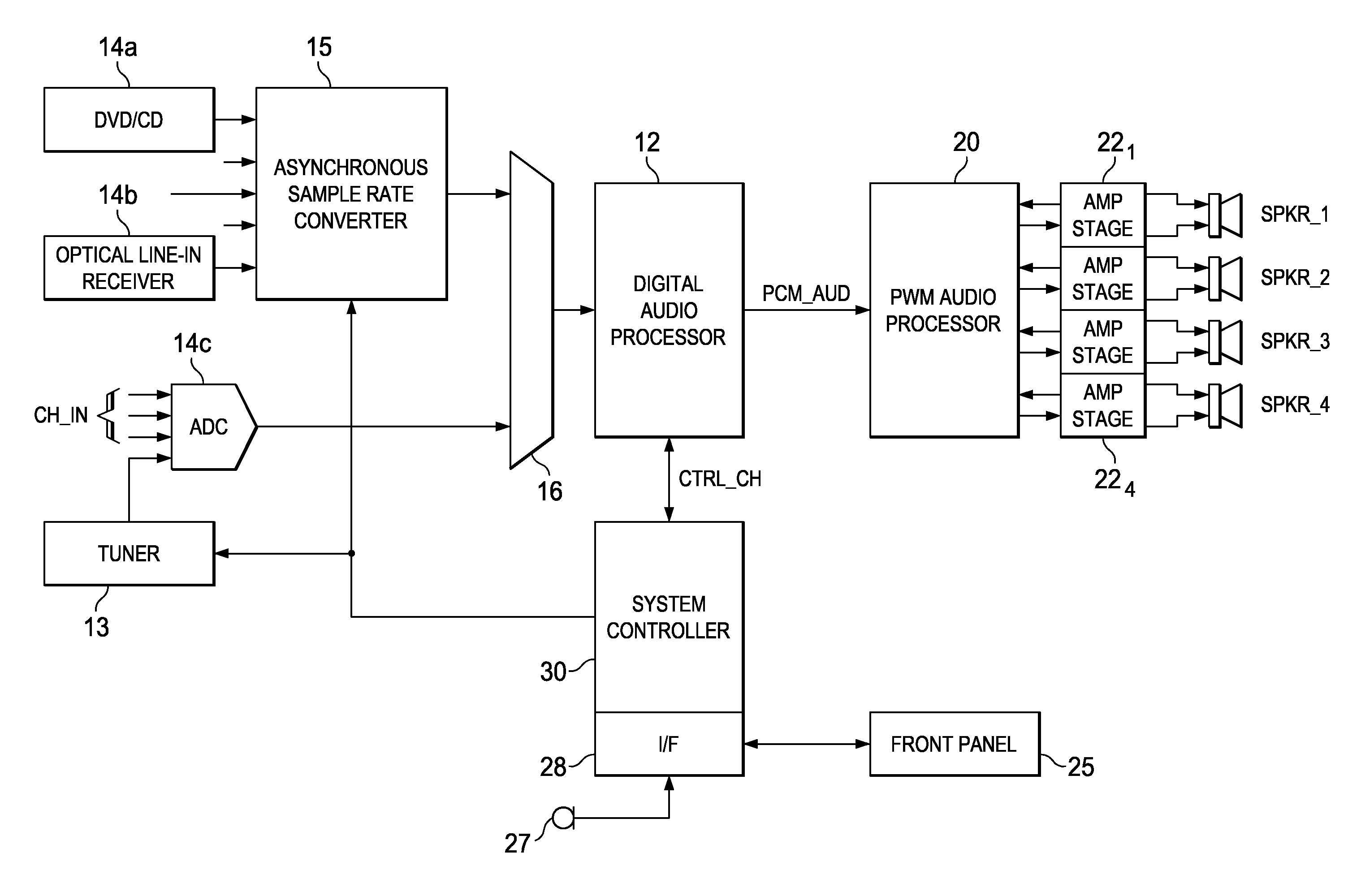

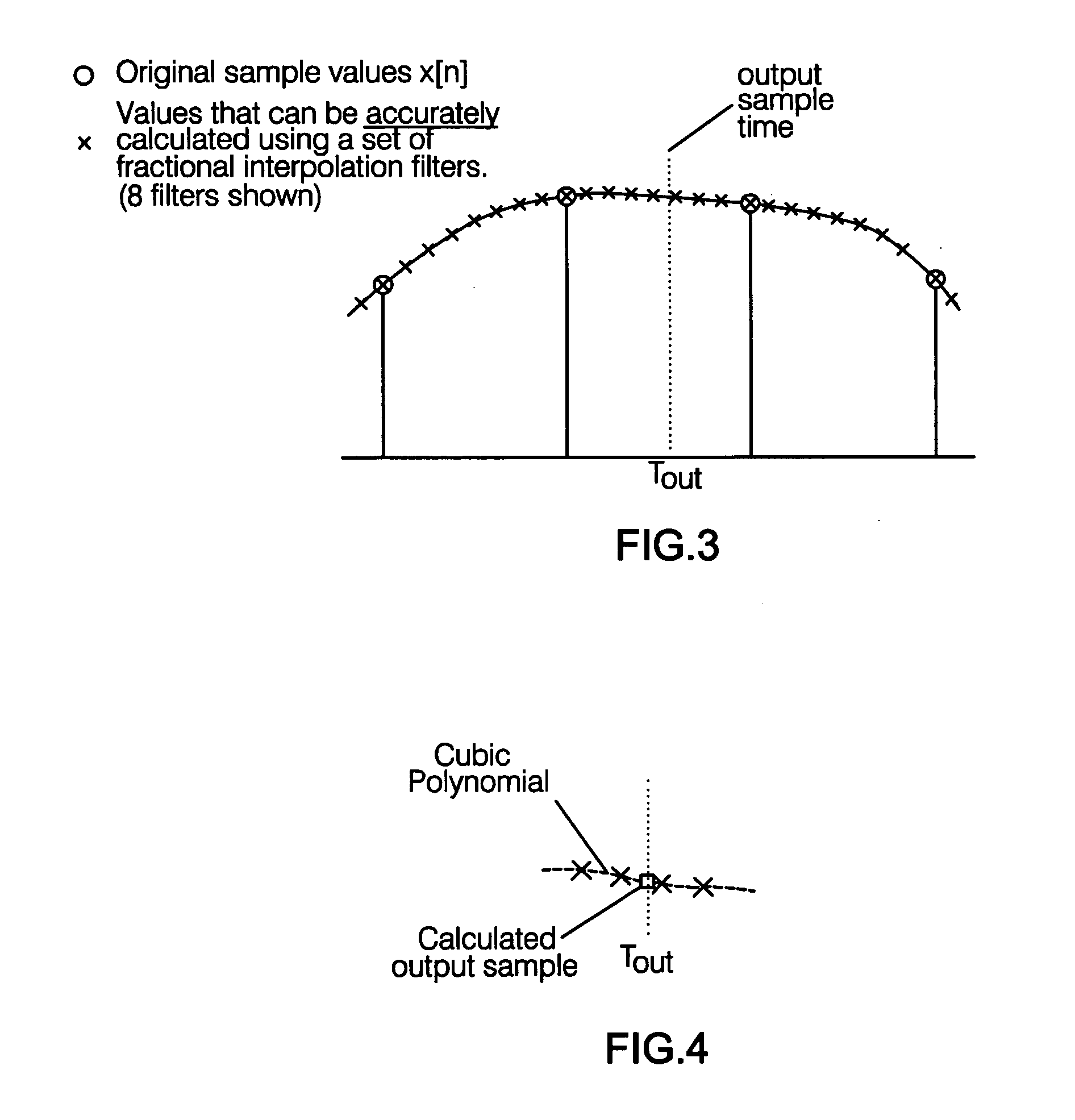

Methods for sample rate conversion are provided that use a polynomial interpolator with minimax stopband attenuation. A method for sample rate conversion of an input signal is provided that uses a time-varying polyphase filter having a discrete polyphase index m. Another method for sample rate conversion of an input signal is provided that uses a time-varying polyphase filter having a continuous polyphase index τ. In these methods, an output time index is mapped to an input sample index and the polyphase index, the polynomial coefficients of a polyphase filter are computed using the polyphase index, and the polyphase filter is applied to an input sample at the input sample index to generate the output sample at the output time index.

Owner:TEXAS INSTR INC

Efficient asynchronous sample rate conversion

ActiveUS8369973B2Improve efficiencyRecalculation of filter coefficients is minimizedDigital technique networkCode conversionSample rate conversionComputer science

Asynchronous sample rate conversion for use in a digital audio receiver is disclosed. Different algorithms are applied for the upsampling and downsampling cases. In the upsampling case, the input signal is upsampled and filtered, before the application of a finite impulse response (FIR) filter. In the downsampling case, the input signal is filtered by an FIR filter, and then filtered and downsampled. The FIR coefficients of the fractional delay FIR filter are calculated by evaluation of polynomial expressions over intervals of the filter impulse response, at times corresponding to the input sample points.

Owner:TEXAS INSTR INC

Method and apparatus for performing sample rate conversion

ActiveUS7227477B2Electric signal transmission systemsDigital technique networkSample rate conversionComputer science

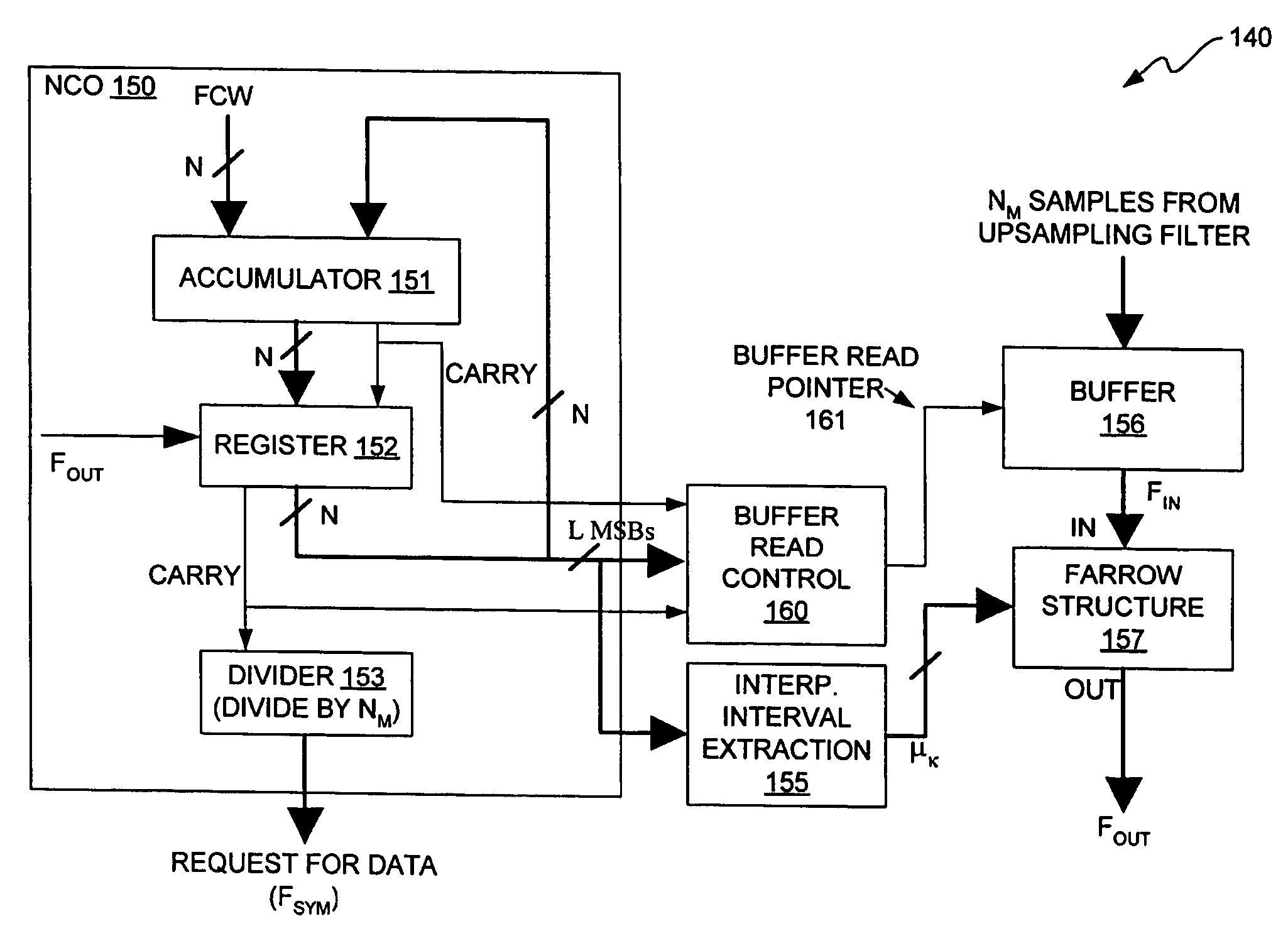

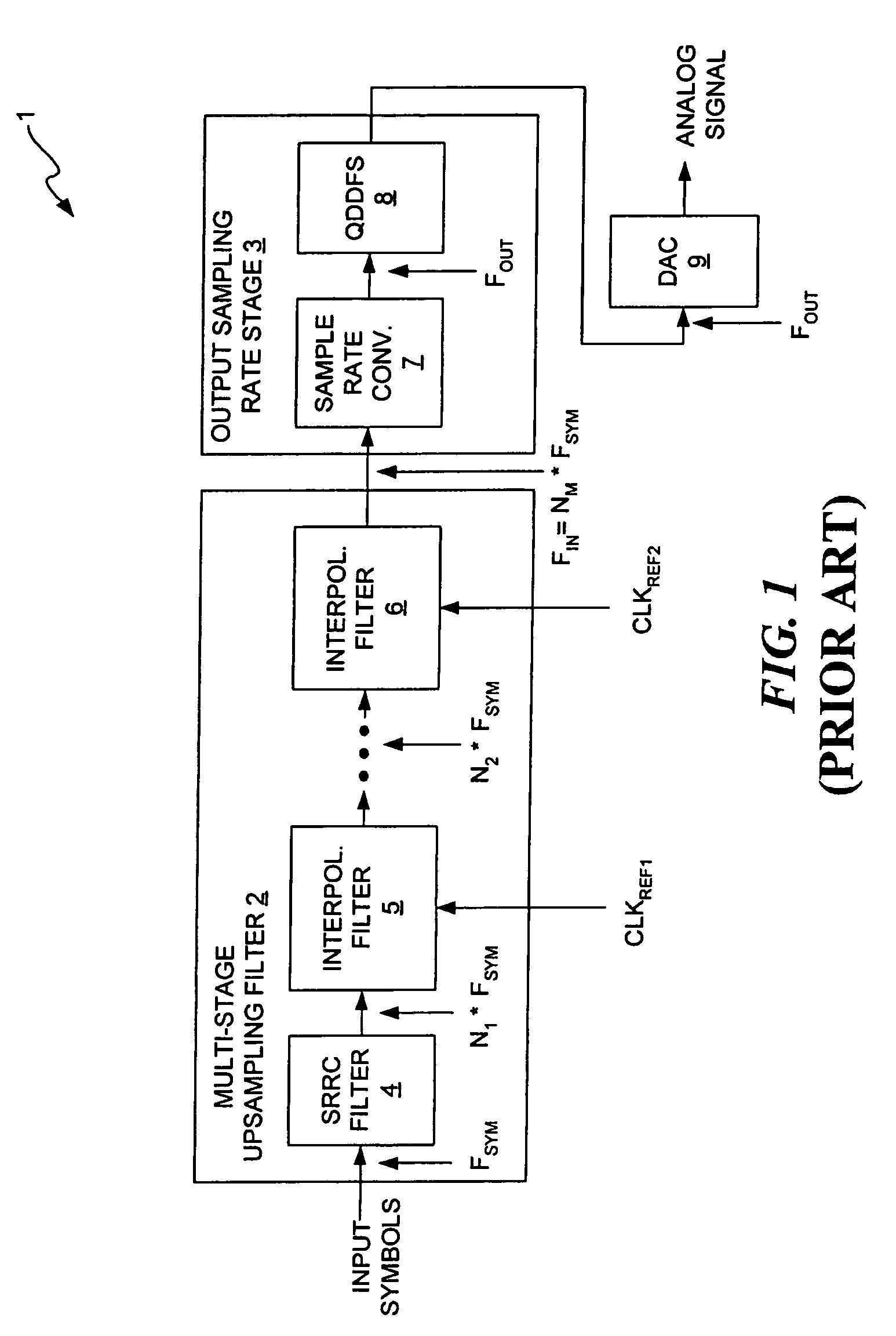

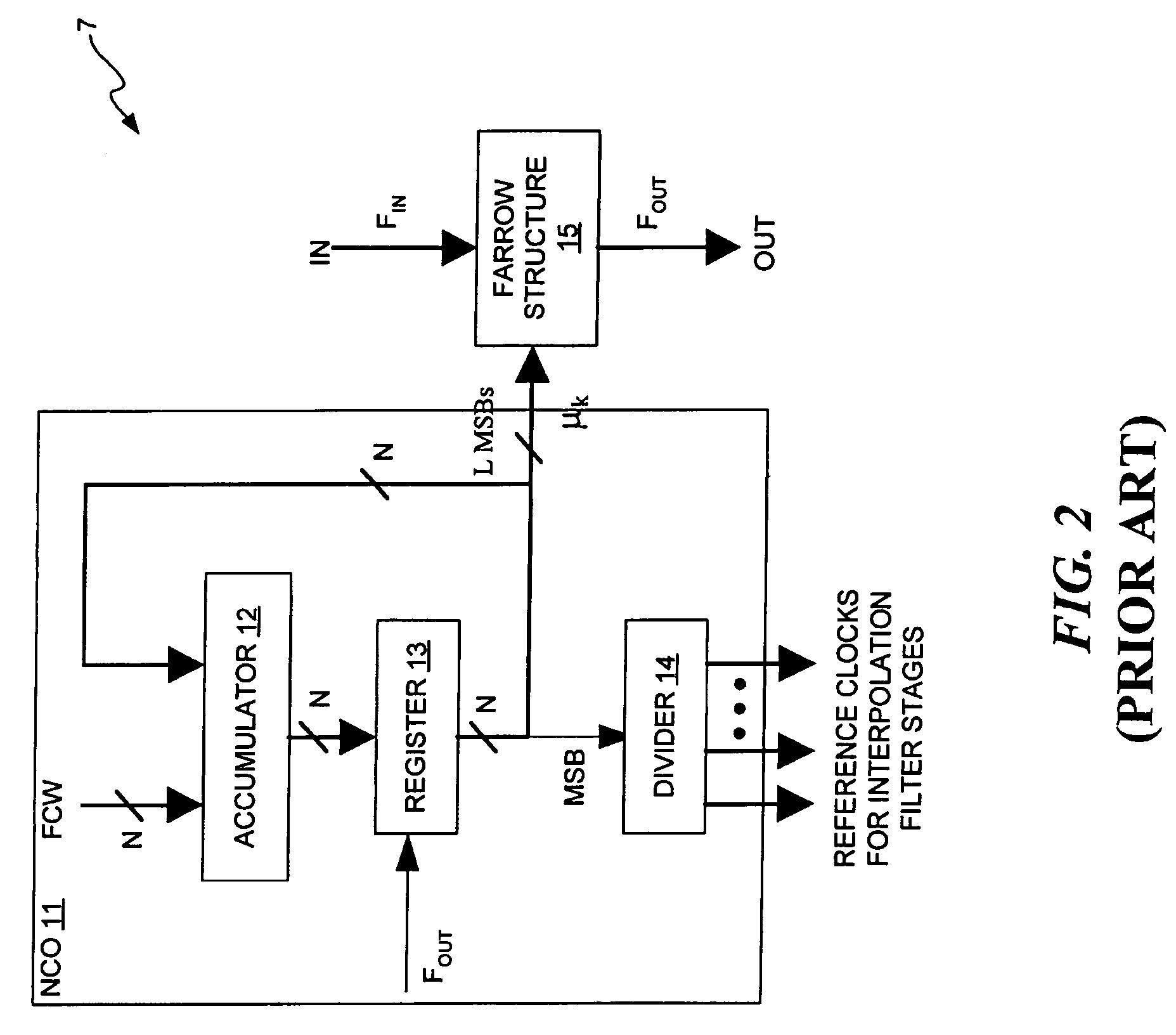

A digital modulator having a sample rate converter that does not require that the final output sampling rate, FOUT, of the sample rate converter be at least twice as great as the input sampling rate, FIN, of the sample rate converter. The upsampling interpolation filter stages of the sample rate converter of the invention do not require any reference clocks to be provided by the NCO of the sample rate converter. Therefore, the upsampling interpolation filter stages are decoupled from the final output sampling rate, FOUT. The interpolation algorithms may be implemented in software, hardware, or a combination of software and hardware. In addition, the polynomial-based interpolator of the Farrow Structure of the invention is capable of using an even or odd number of basepoints.

Owner:ARRIS ENTERPRISES LLC

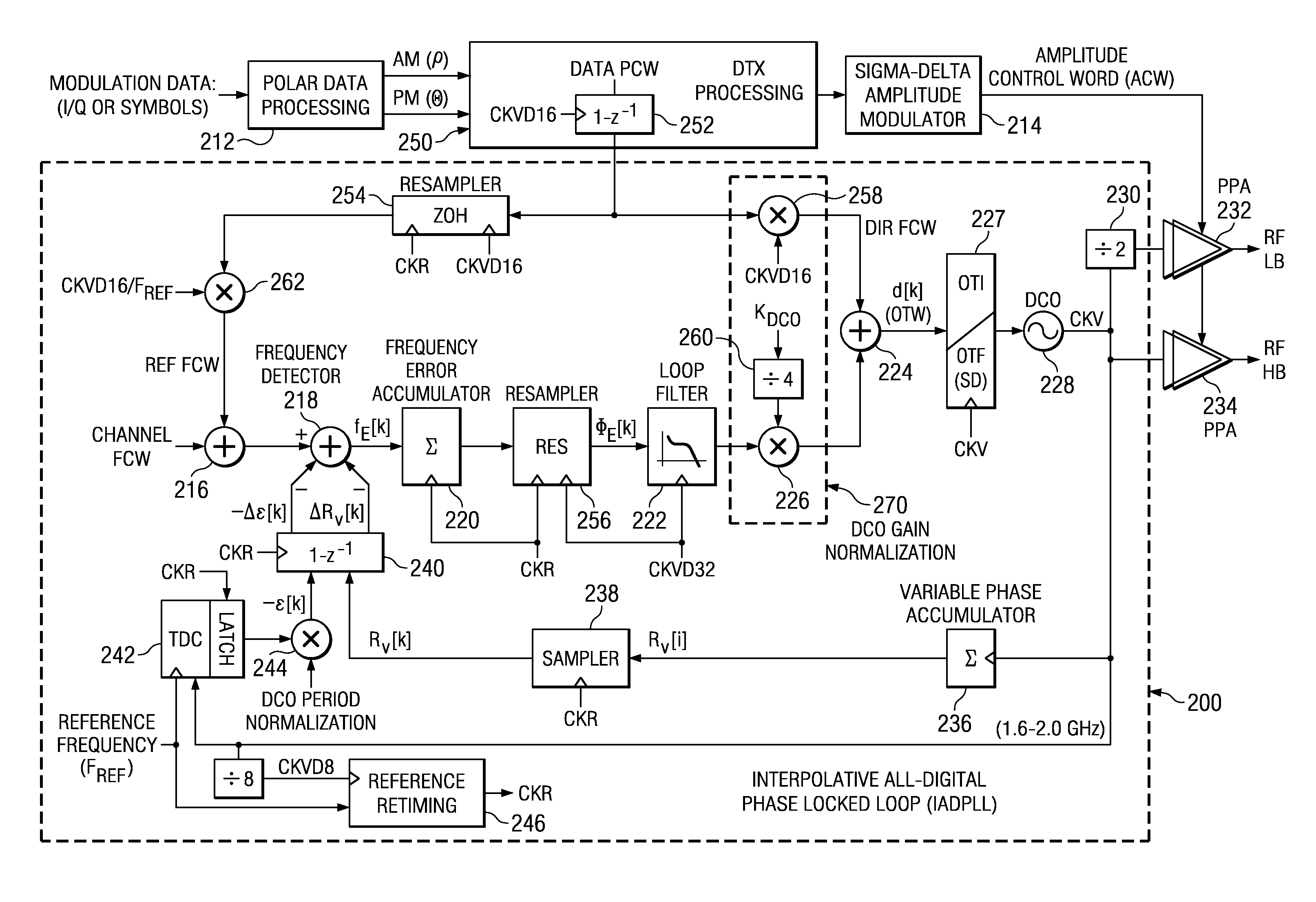

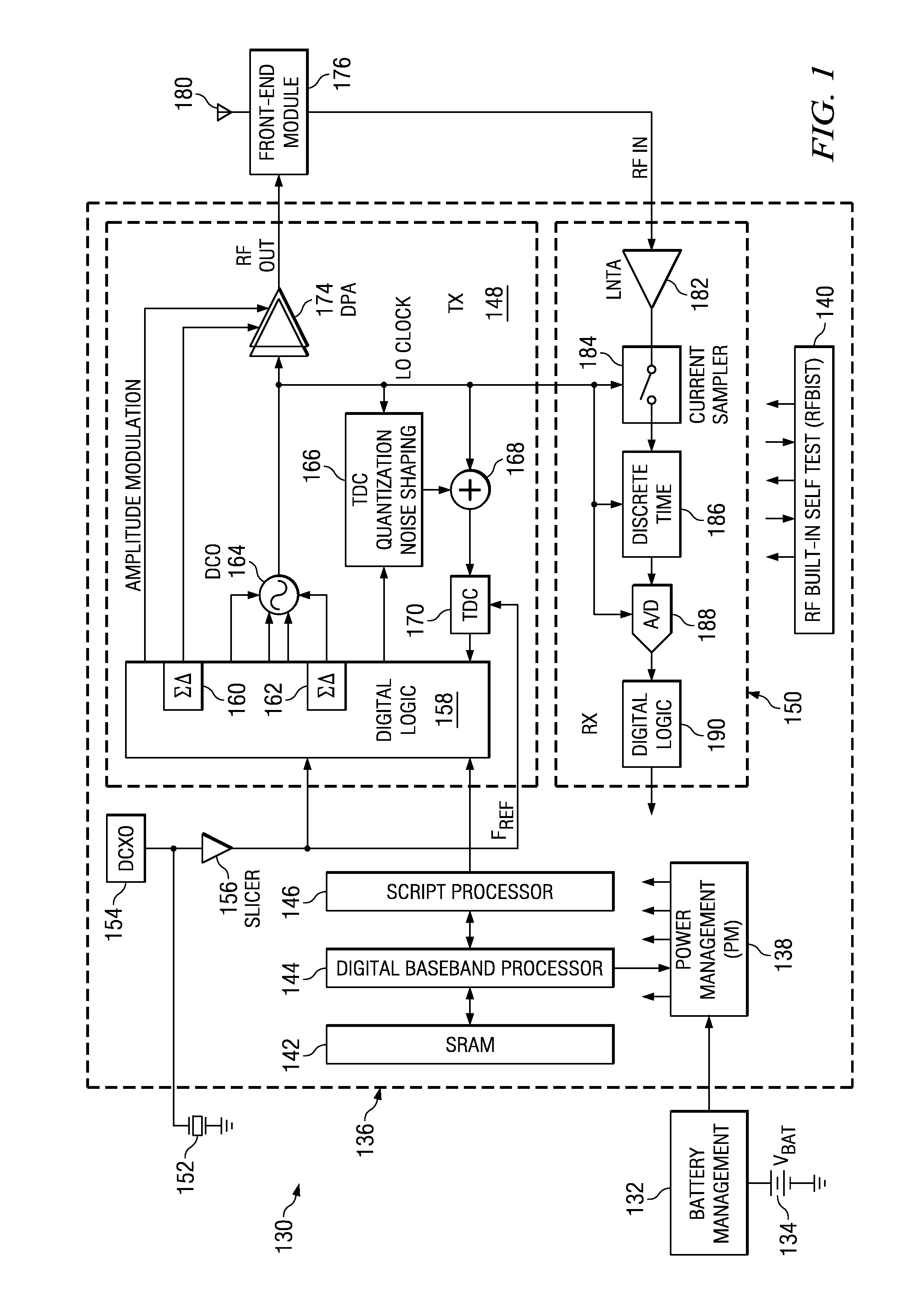

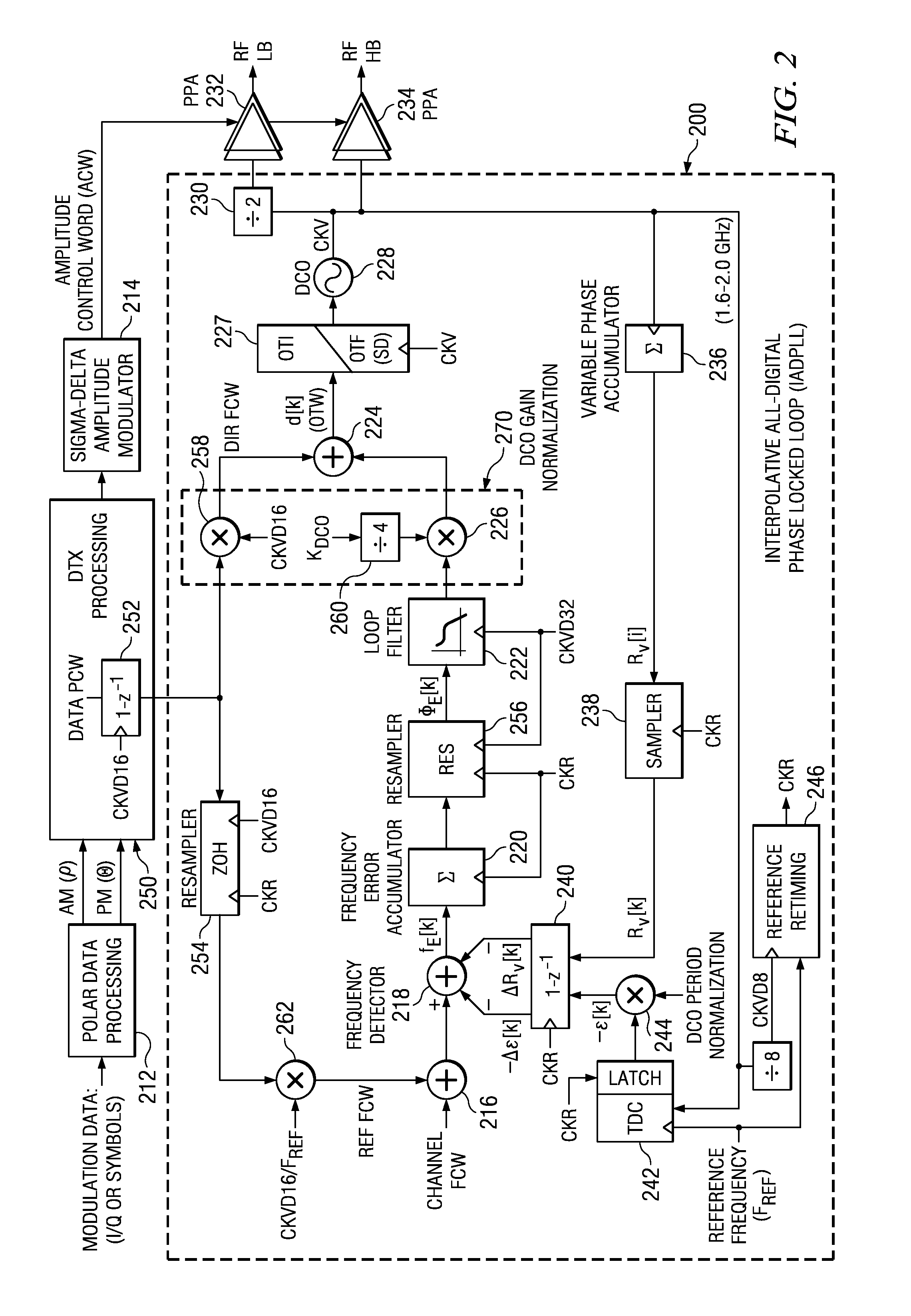

Interpolative All-Digital Phase Locked Loop

ActiveUS20080317187A1Pulse automatic controlTransmission path divisionSample rate conversionPhase difference

An embodiment of the present invention provides a phase locked loop that operates on clock signals derived from an RF clock signal generated by the phase locked loop. A frequency reference input provides a reference clock. A controllable oscillator generates the RF clock signal. A phase detection circuit operates on the reference clock to provide digital phase error samples indicative of a phase difference between the reference clock and the RF clock. An interpolator is coupled to the phase detection circuit for performing a sample rate conversion between the reference clock and the clock derived from the RF clock signal.

Owner:TEXAS INSTR INC

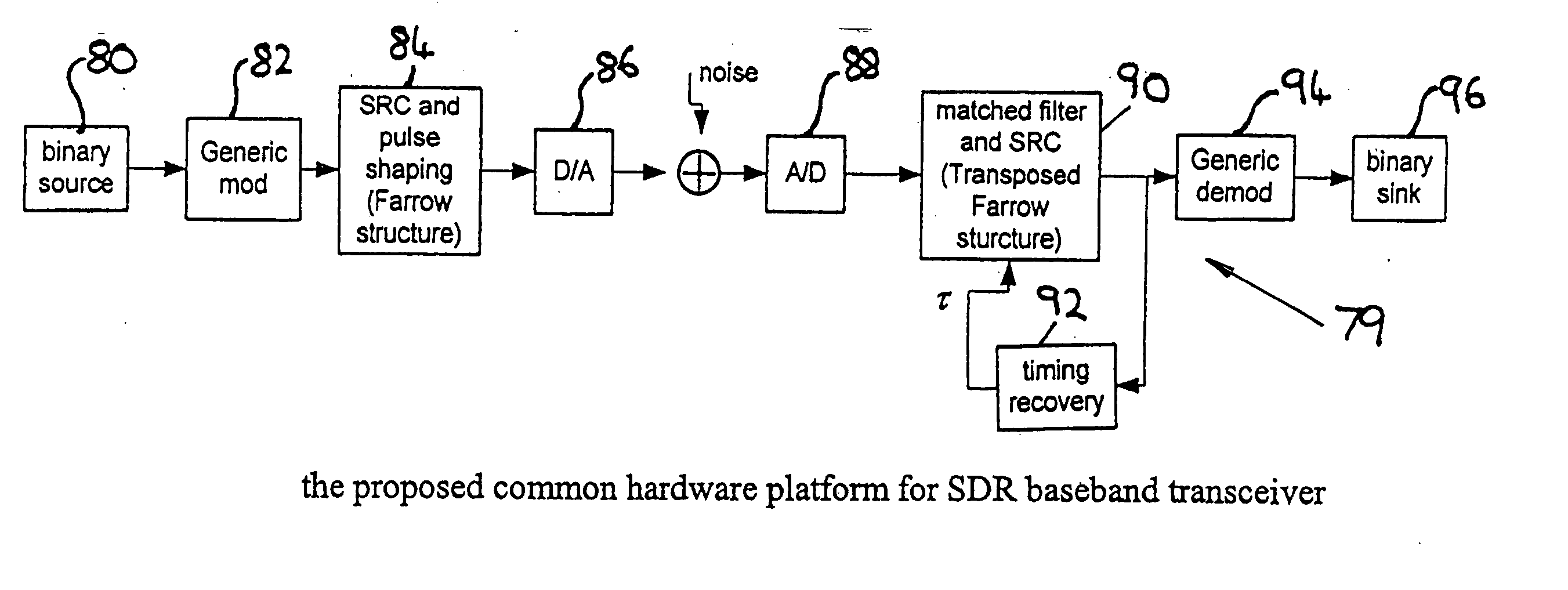

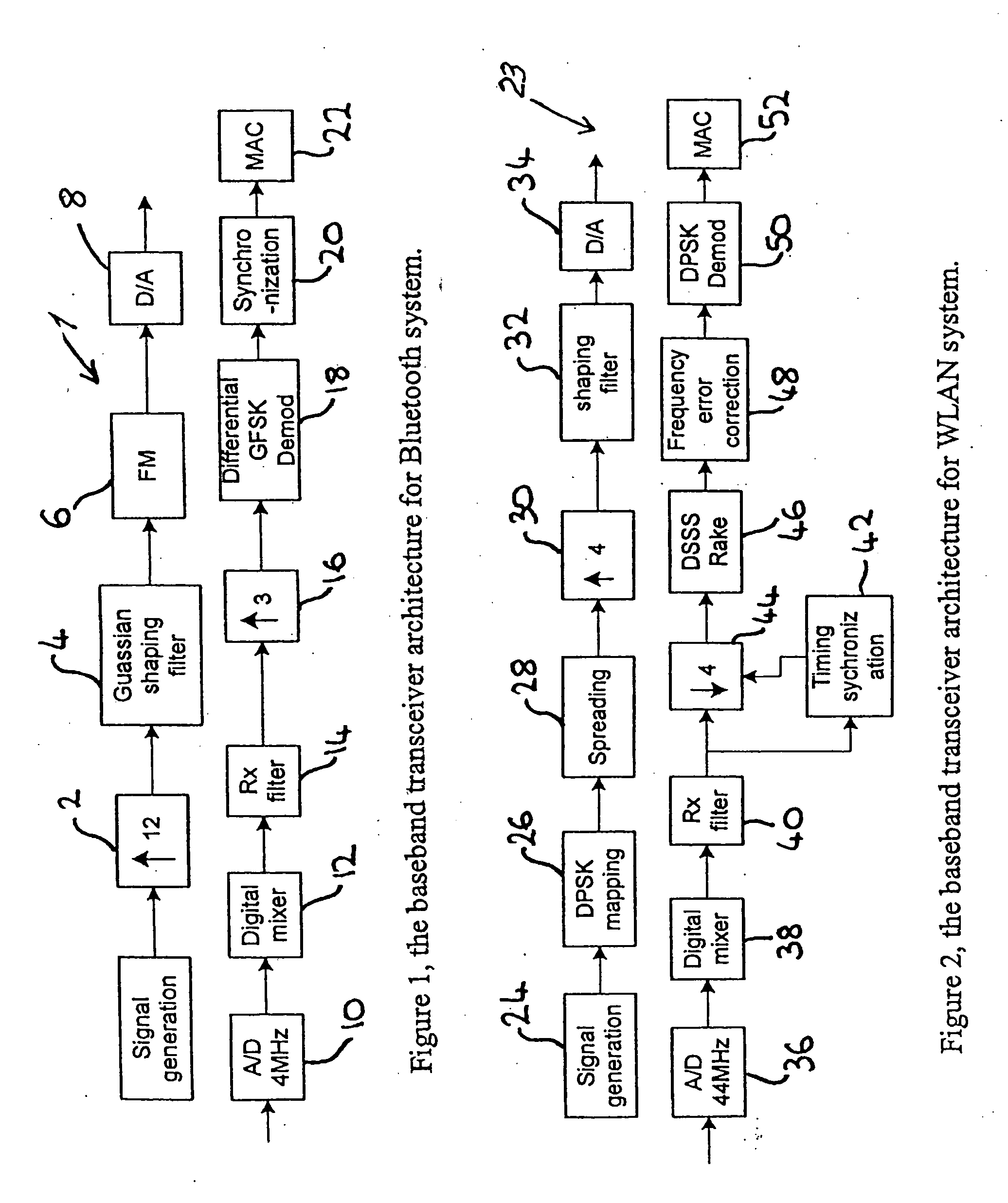

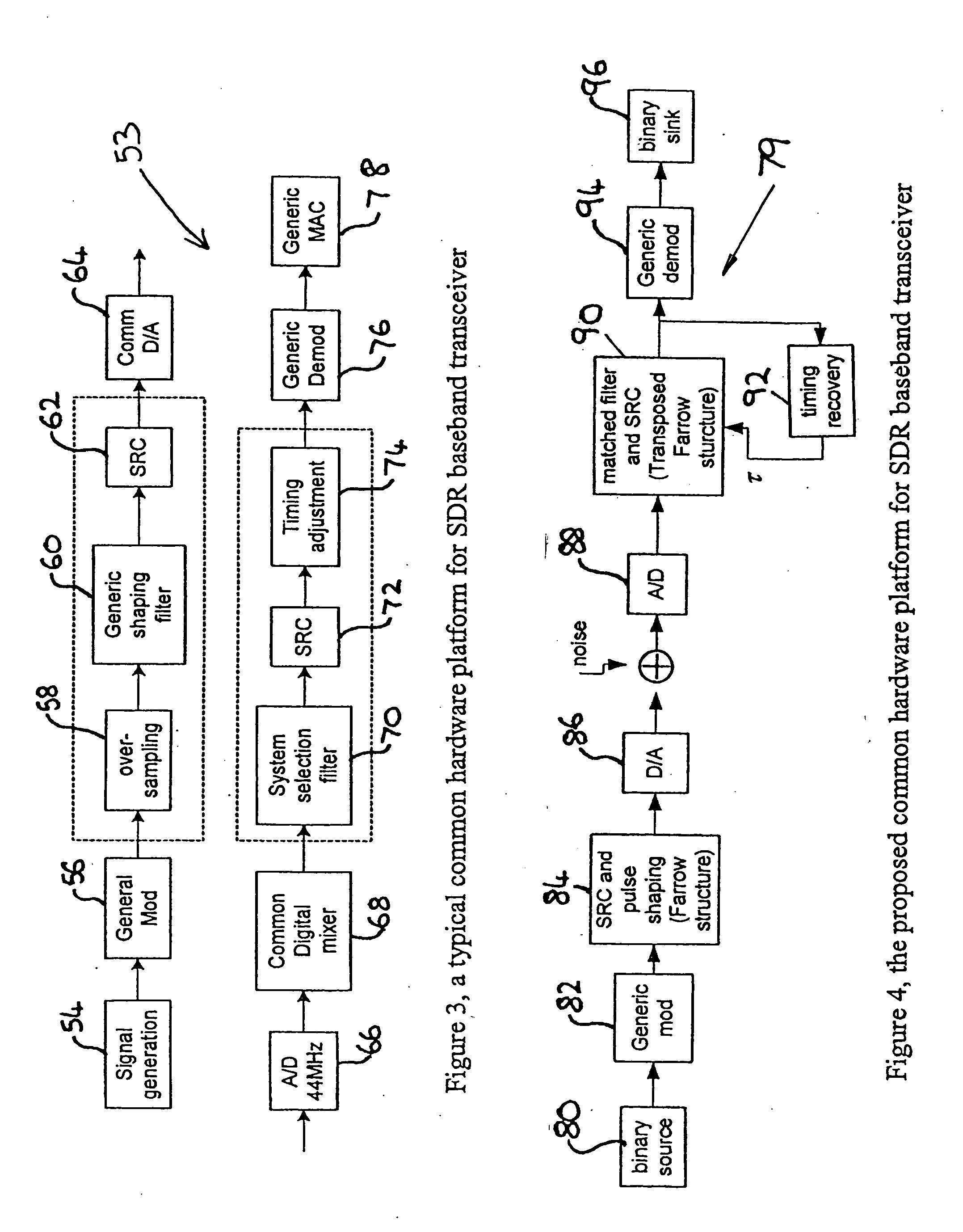

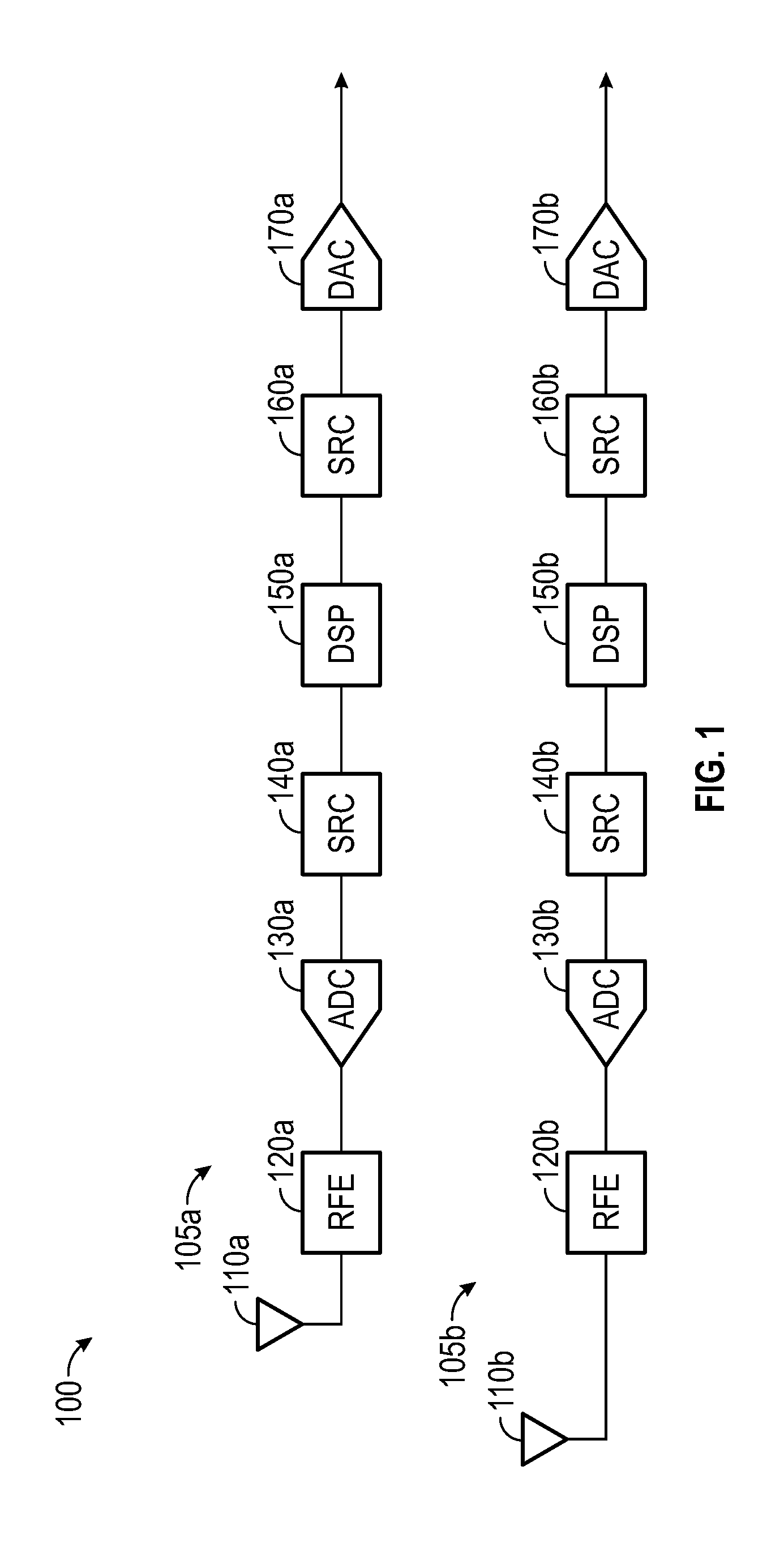

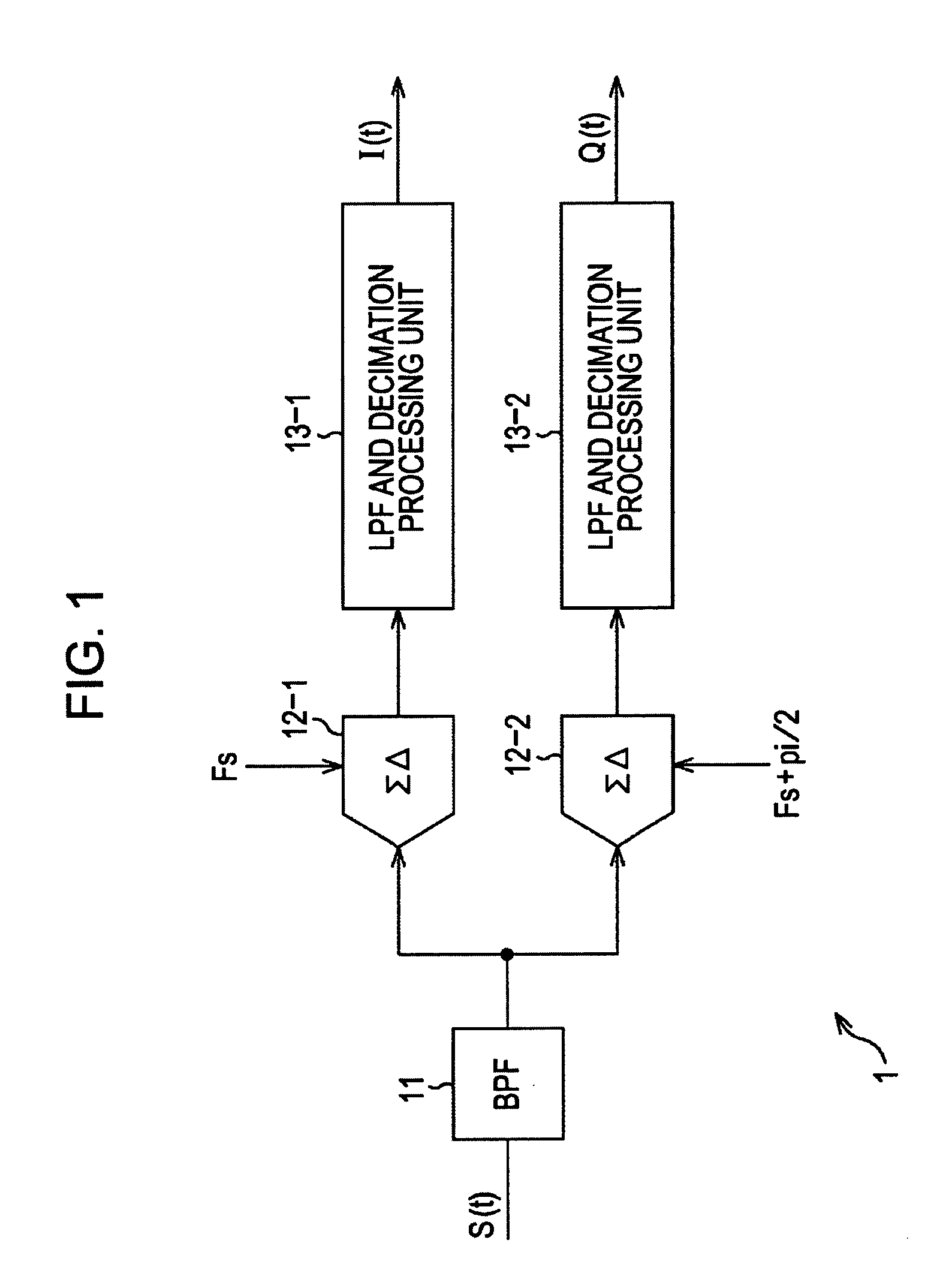

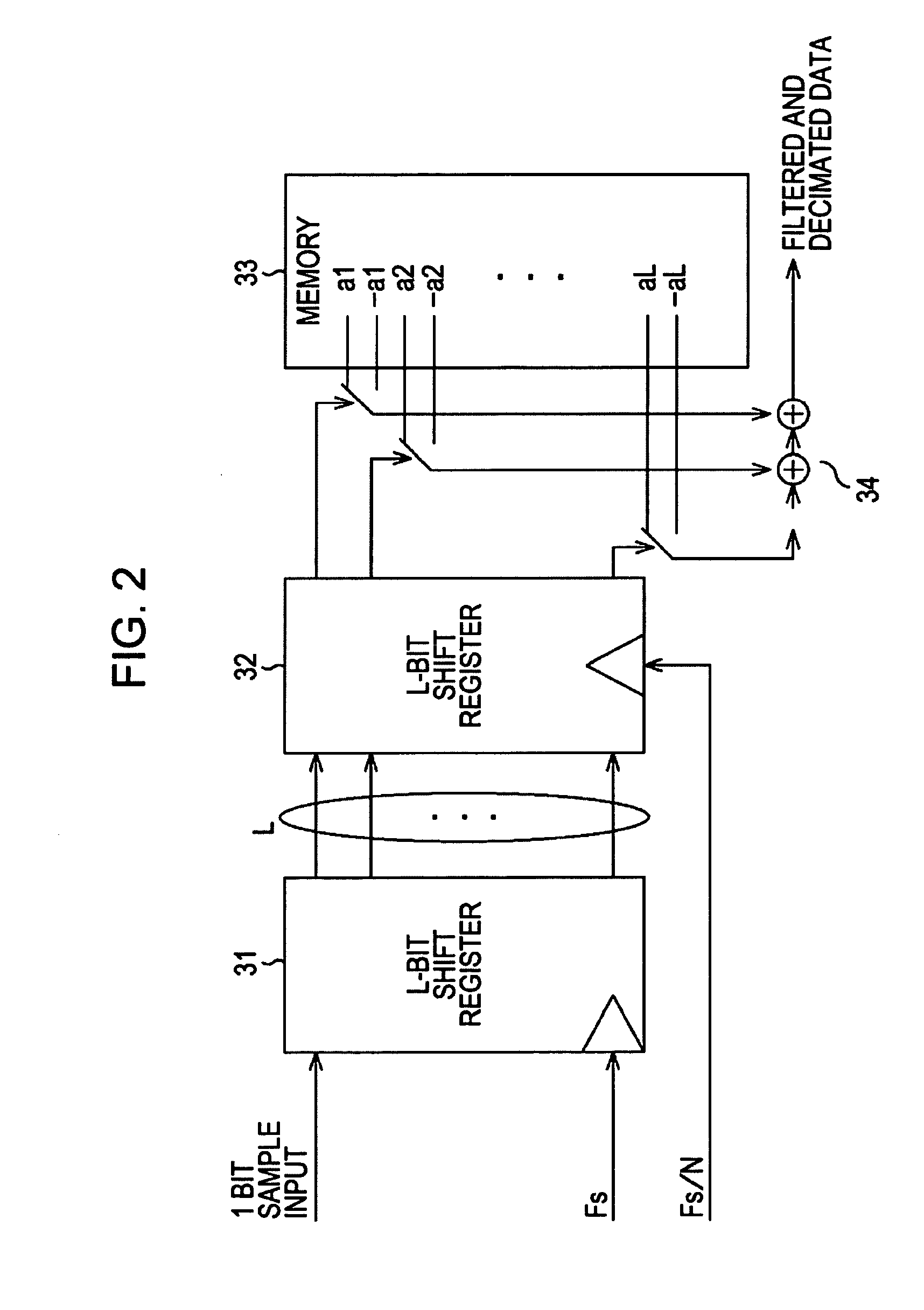

Methods for processing a received signal in a software defined radio (SDR) system, a transceiver for an SDR system and a receiver for an SDR system

InactiveUS20050243952A1Amplitude-modulated carrier systemsAmplitude demodulationFir systemTransceiver

A receiver for a software defined radio system comprises an input stage for receiving a transmitted signal, an analogue-to-digital converter having a sample rate, a filter matched to the received transmitted signal, and a sample rate converter for converting the digital signal output from the filter from an input sequence having the sample rate of the analogue-to-digital converter to an output sequence having an output sample rate defined by the received transmitted signal. The input and output sequences comprise respectively a number of input samples and a number of output samples. A controller controls the output sample rate and a demodulator coupled to the output of the sample rate converter recovers the transmitted signal. The sample rate converter is implemented by a transposed Farrow structure. The controller is arranged to reset the output sequence from the sample rate converter when any one of said number of input samples and any one of said number of output samples pass through coincidence in time.

Owner:OKI TECHNO CENT SINGAPORE PTE

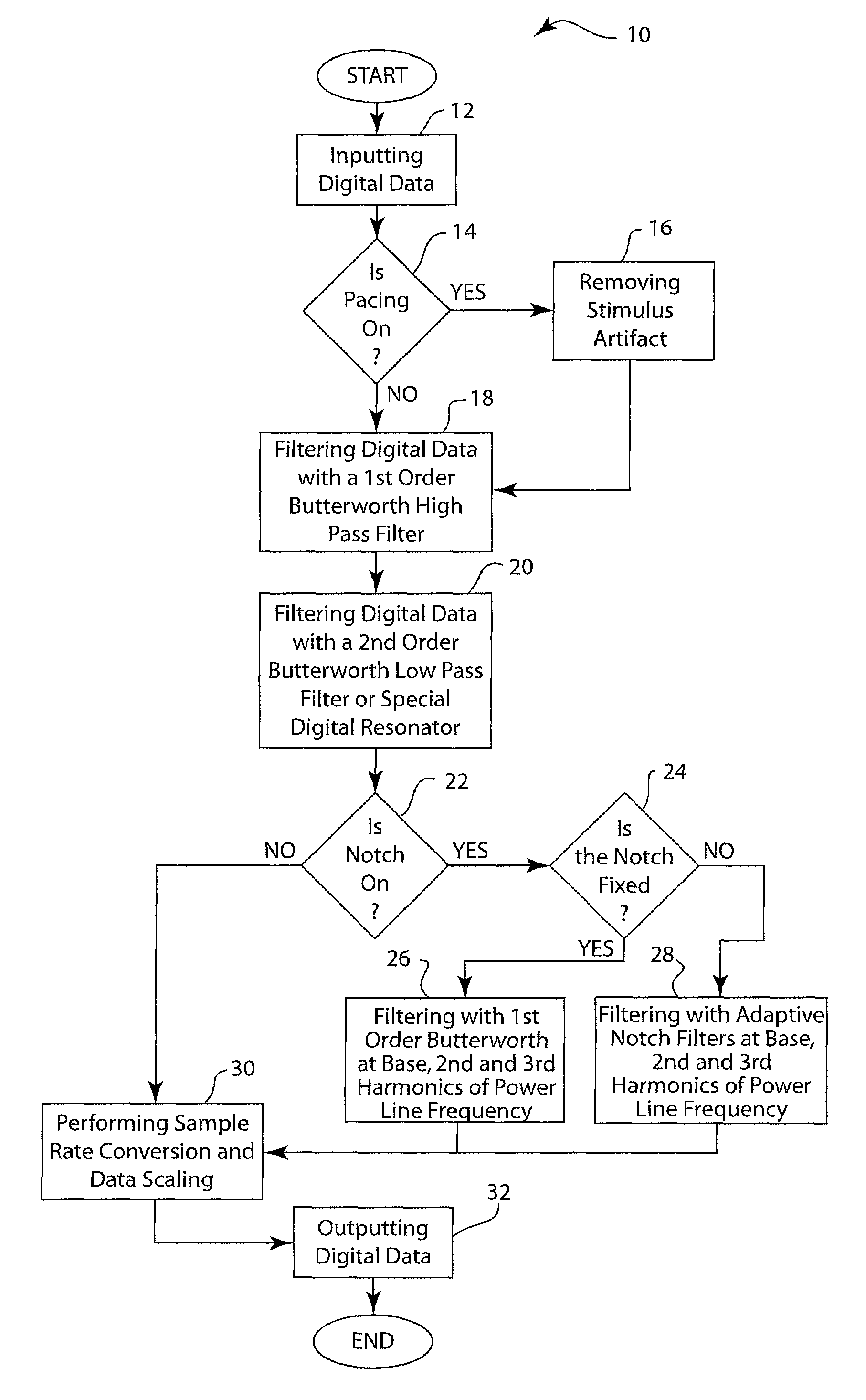

Method and system for real-time digital filtering for electrophysiological and hemodynamic amplifers

The present invention includes a method and system for real-time digital filtering for electrophysiological and hemodynamic amplifiers. The invention replaces the analog circuits currently used for signal filtering and conditioning in such systems with digital filters that may be implemented in a software application. The method and system includes digitizing the analog signal collected from the patient prior to performing the signal filtering and conditioning. The method and system also includes removing stimulus artifacts, as well as performing sample rate conversion and scaling on the digital signal. The processed digital signals may be used, displayed, saved and converted to analog signal thru digital-to-analog conversion.

Owner:GENERAL ELECTRIC CO

Sample rate converter having distributed filtering

InactiveUS7280878B1Minimize artifactLower requirementDigital technique networkElectric/magnetic signal storageSample rate conversionSample sequence

A method and a computer program product for sample rate conversion that features distributive or hybrid filtering to reduce unwanted artifacts, such as aliasing and the computational requirements to avoid the aforementioned artifacts. The method includes receiving, at a first sample rate, a plurality of data points, associated with a first signal, operating on the plurality of data points to associate the signal with a predetermined set of parameters, with the set of parameters including a first transition band having an image associated therewith; and varying the sample rate associated with the first signal by interpolation with an interpolator having associated therewith a second transition band, with the width associated with the second transition band being a function of a spectral separation between the first transition band and its image, wherein a second signal is produced having a sequence of data samples approximating the first signal.

Owner:CREATIVE TECH CORP

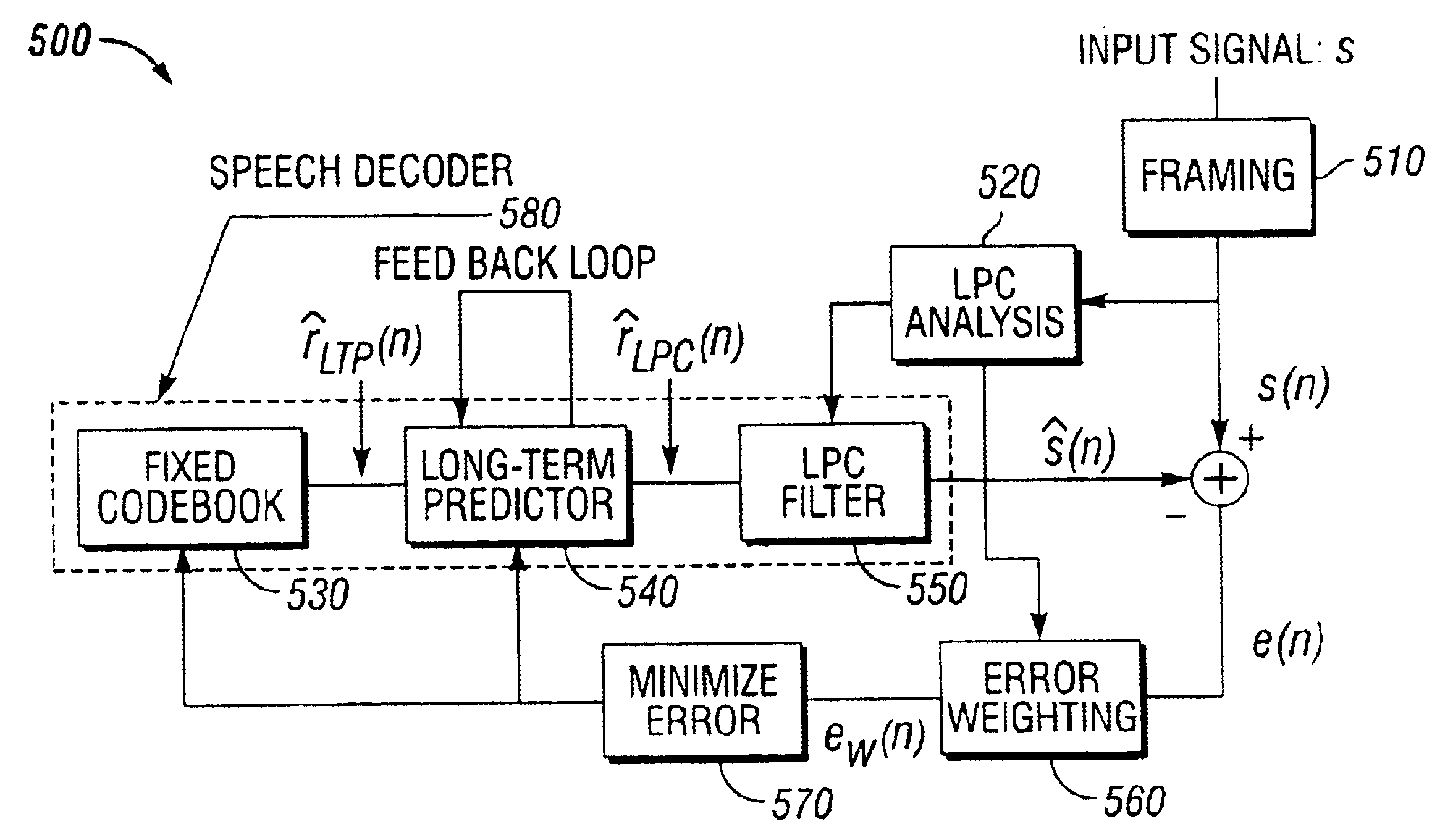

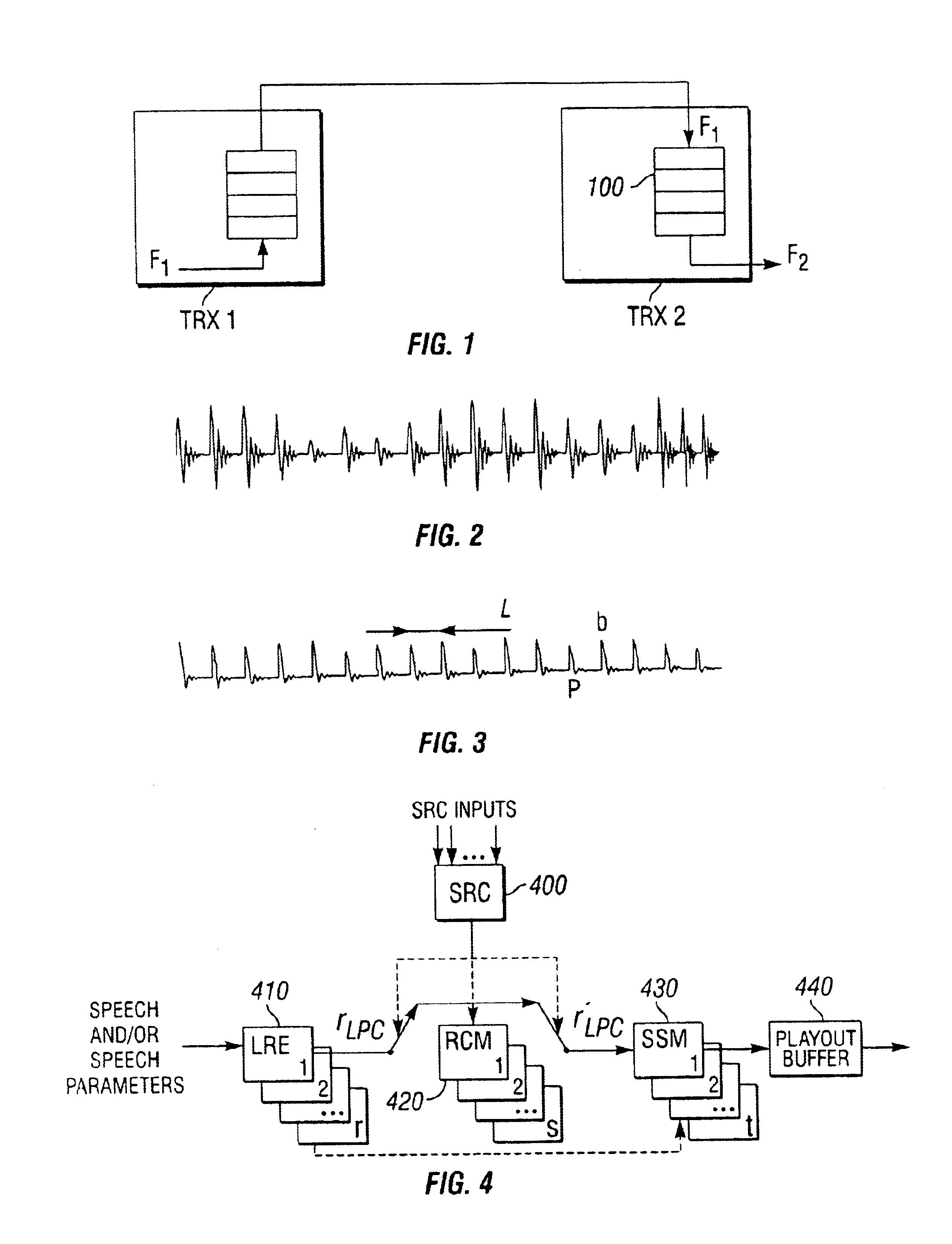

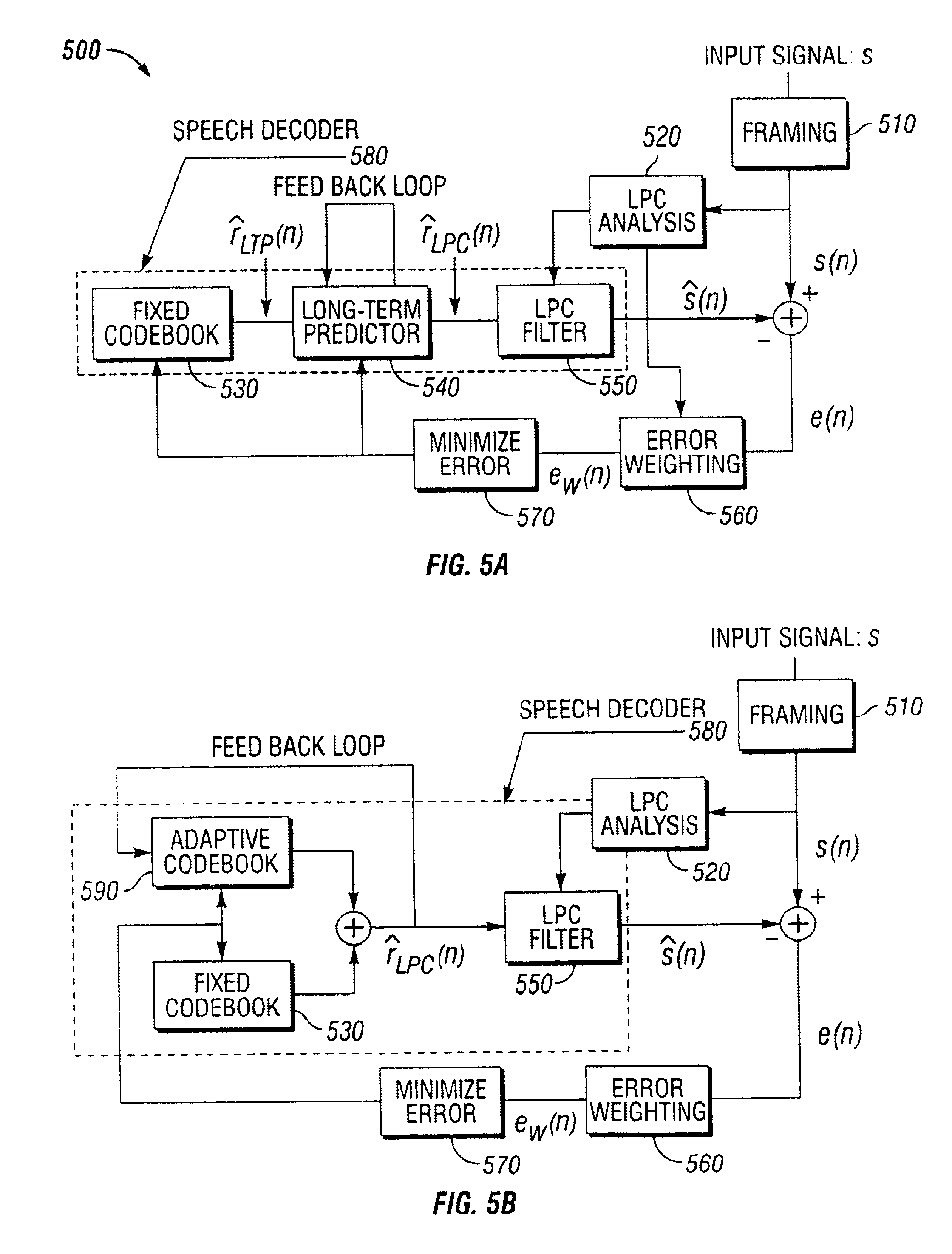

Method and apparatus in a telecommunications system

InactiveUS6873954B1Reducing audio artifactContinuously controlled with only small audio artifactsTime-division multiplexSpeech synthesisSample rate conversionSpeech synthesis

Audio artifacts due to overrun or underrun in a playout buffer caused by the sampling rates at a sending and receiving side not being at the same rate are reduced. An LPC-residual is modified on a sample-by-sample basis. The LPC-residual block, which includes N samples, is converted to a block comprising N+1 or N−1 samples. A sample rate controller decides whether samples should be added to or removed from the LPC-residual. The exact position at which to add respective remove samples is either chosen arbitrarily or found by searching for low energy segments in the LPC-residual. A speech synthesiser module then reproduces the speech. By using the proposed sample rate conversion method the playout buffer can be continuously controlled. Furthermore, since the method works on a sample-by-sample basis the buffer can be kept to a minimum and hence no extra delay is introduced.

Owner:TELEFON AB LM ERICSSON (PUBL)

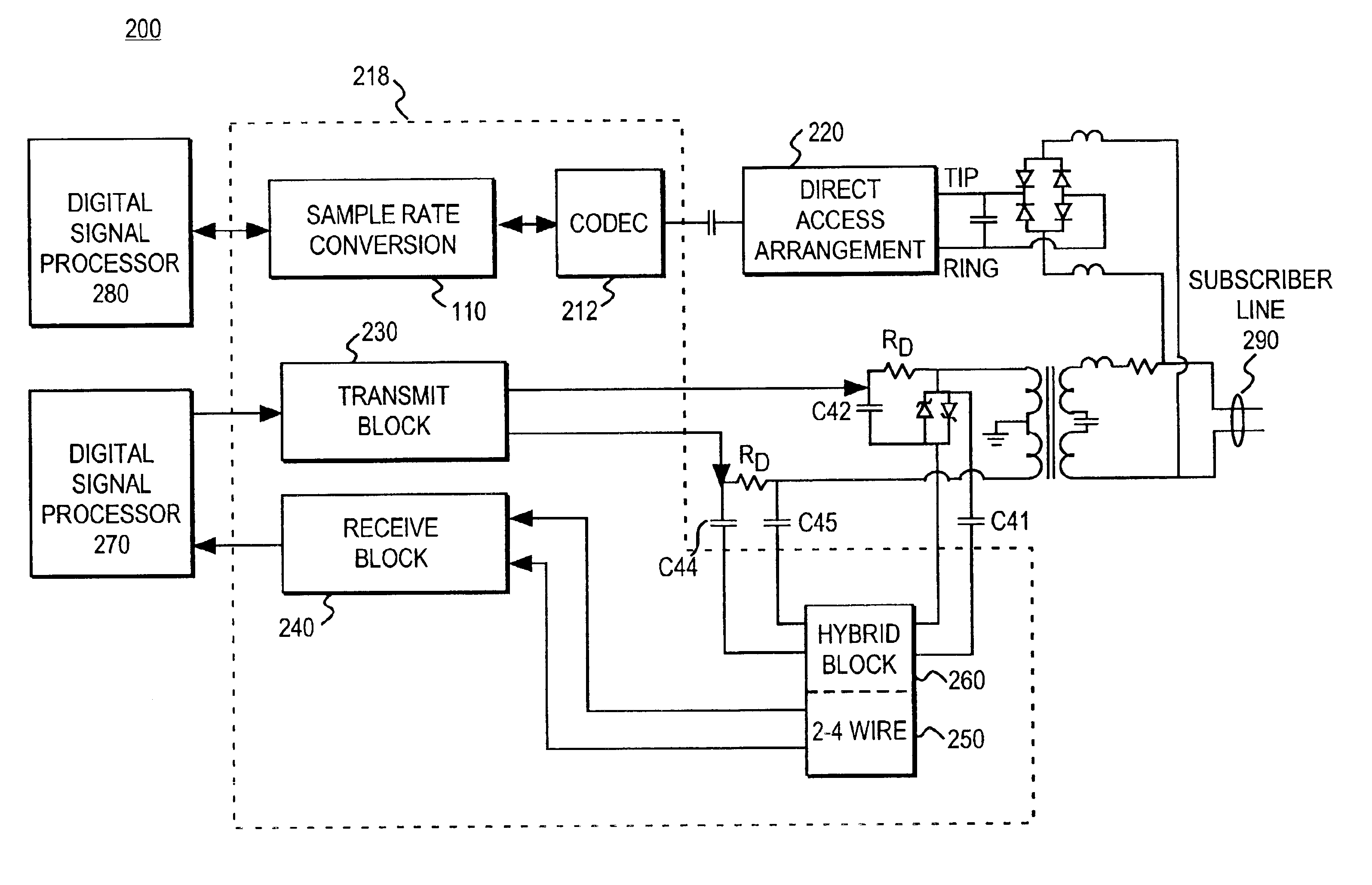

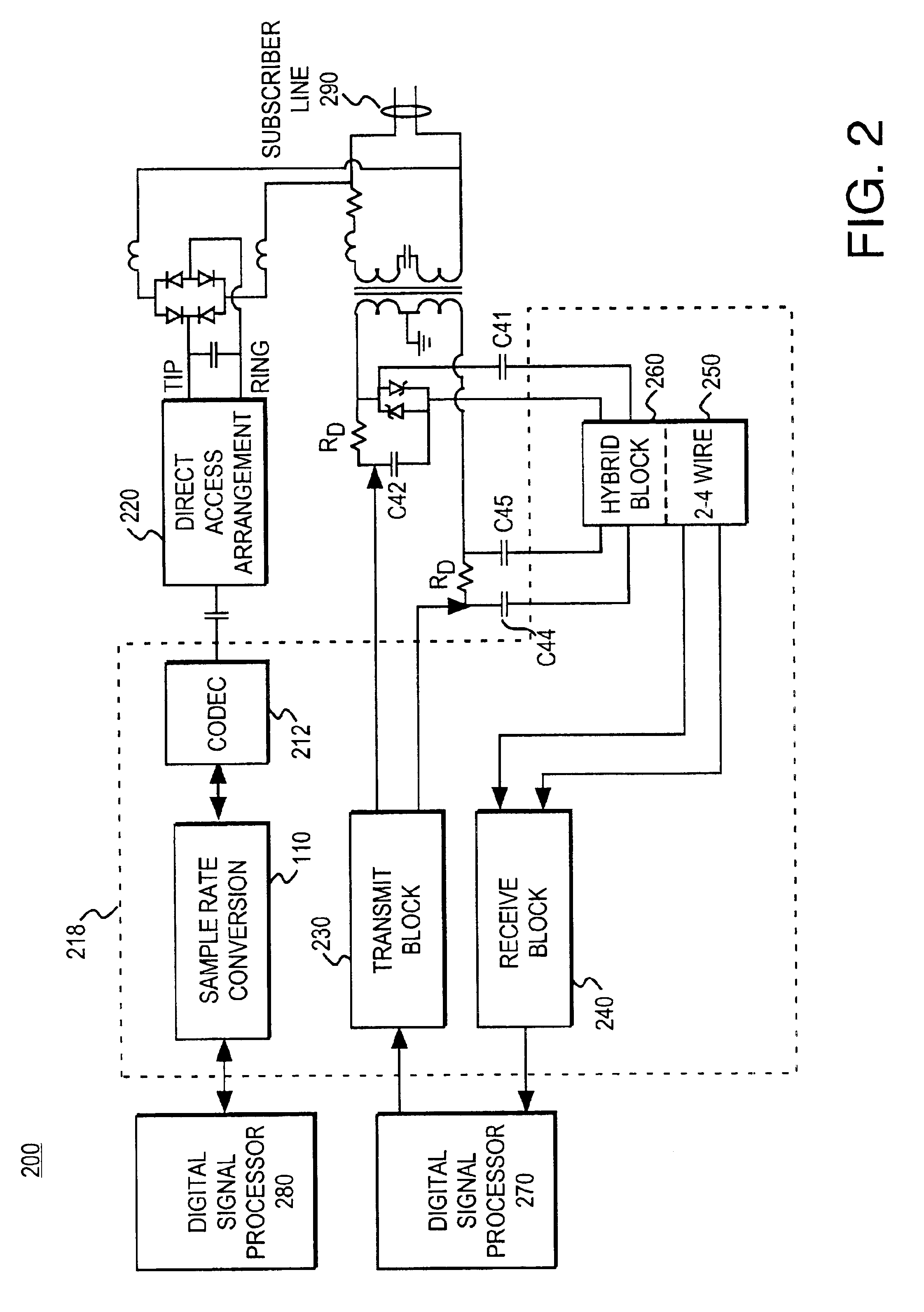

Architecture for a digital subscriber line analog front end

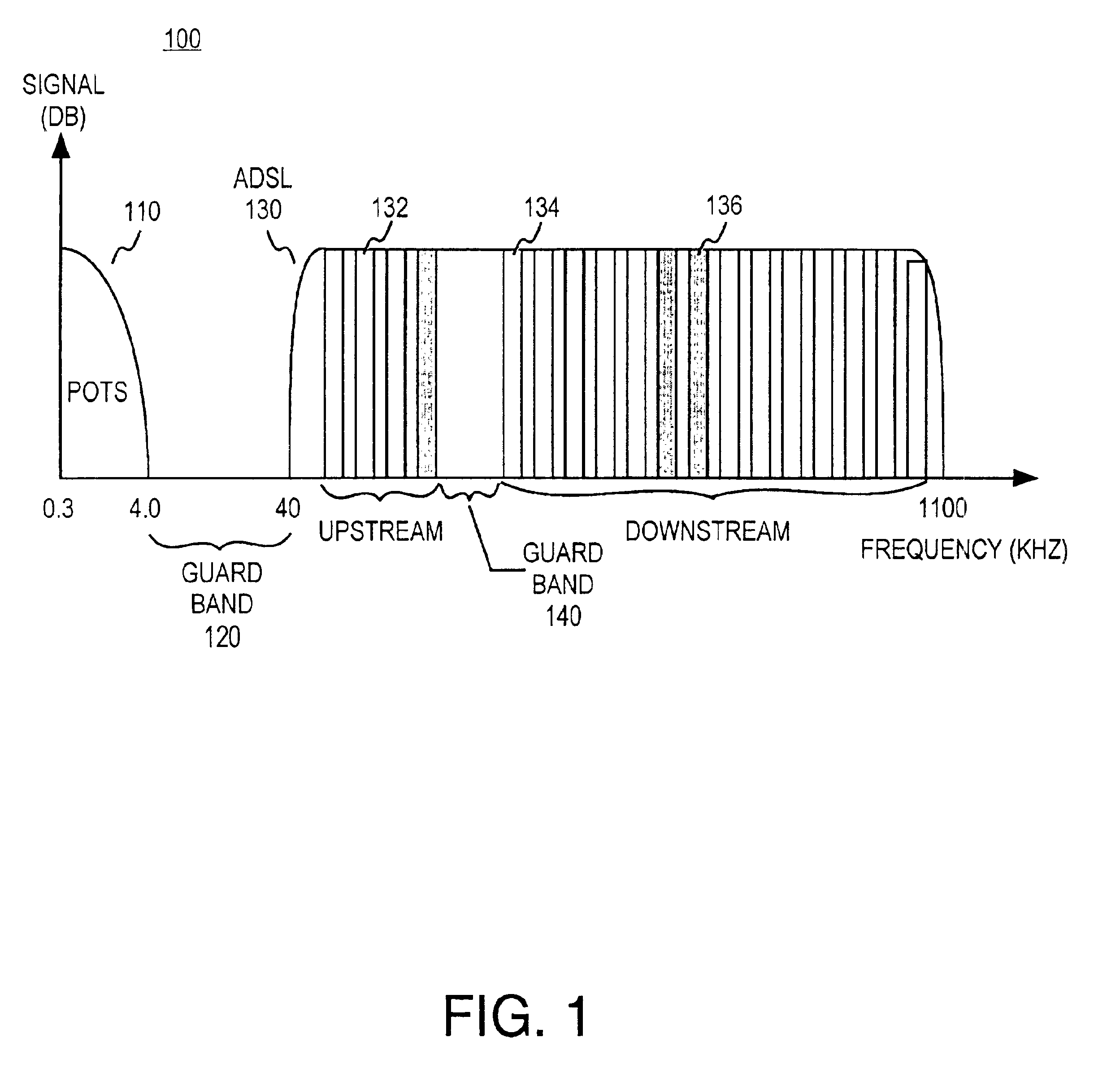

InactiveUS6895040B2Easy to integrateEliminates undesired energyInterconnection arrangementsError preventionDigital subscriber lineSample rate conversion

An analog front end for communicating discrete multitone modulated signals on a subscriber line includes a transmit block, a receive block, and a hybrid packaged within a same integrated circuit. Upstream data to be transmitted to the subscriber line is pre-processed to eliminate even images. A power spectral density shaping filter subsequently substantially eliminates undesired energy in the upstream data signal. A high pass filter further rejects upstream data from the downstream data signal. The power spectral density filter and the high pass filter enable the use of a first order hybrid network for extracting the downstream data. The analog front end may include an additional analog channel to enable voiceband (e.g., v.90) communication concurrent with non-voiceband (e.g., xDSL) operation. Sample rate conversion is utilized to avoid the use of multiple independent clocks for otherwise incompatible clocking requirements.

Owner:SILICON LAB INC

Wide-band multi-format audio/video production system with frame-rate conversion

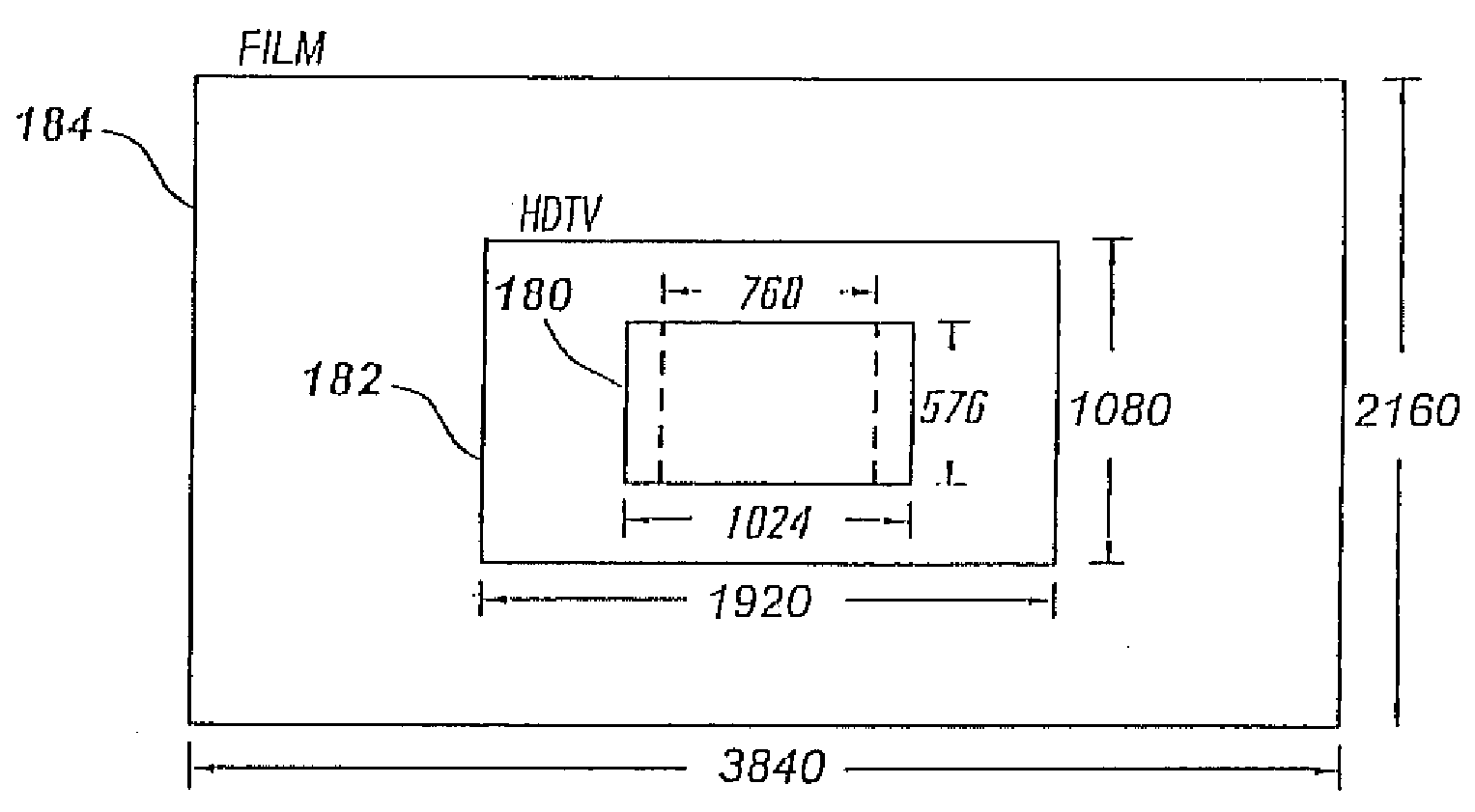

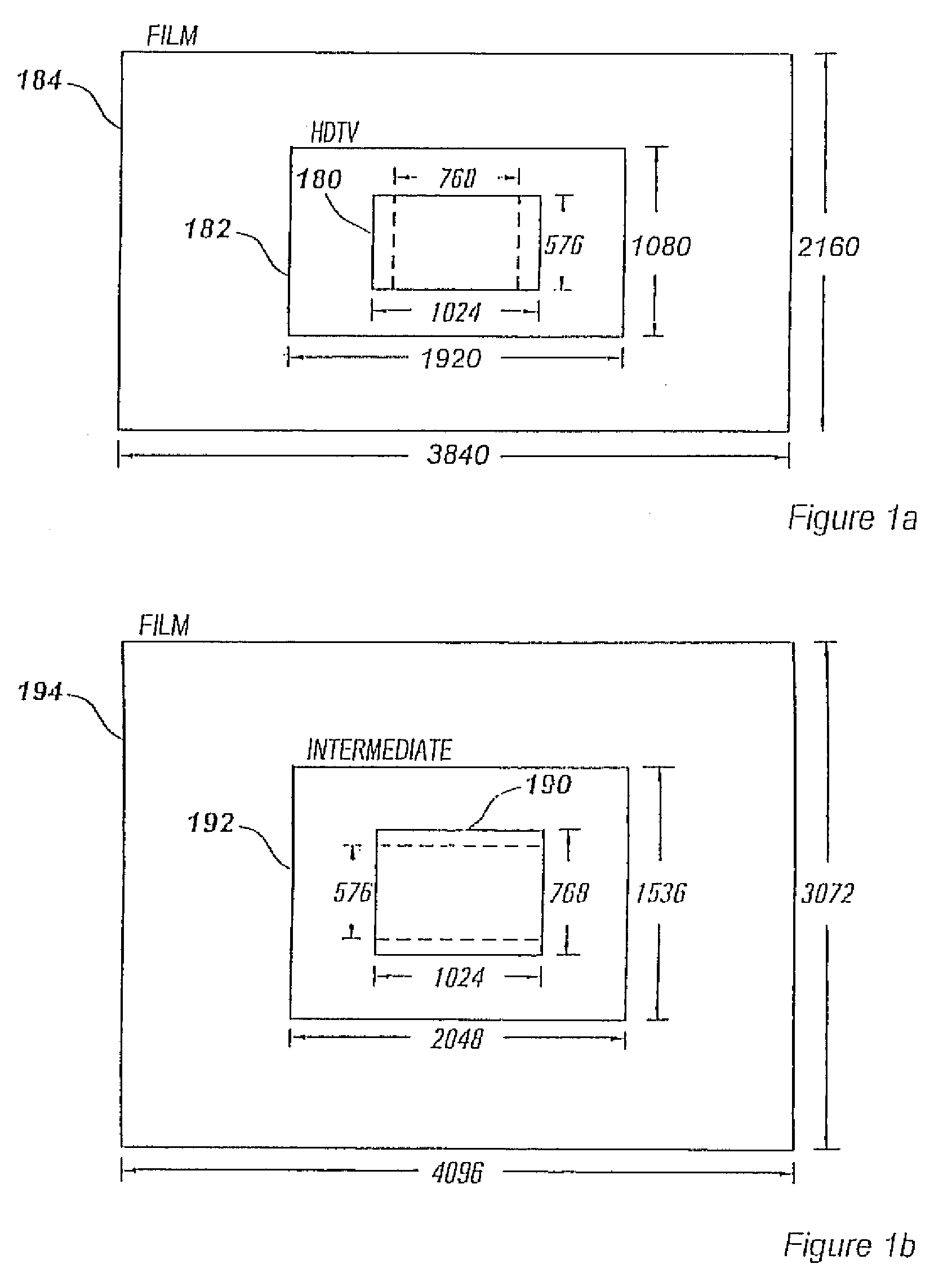

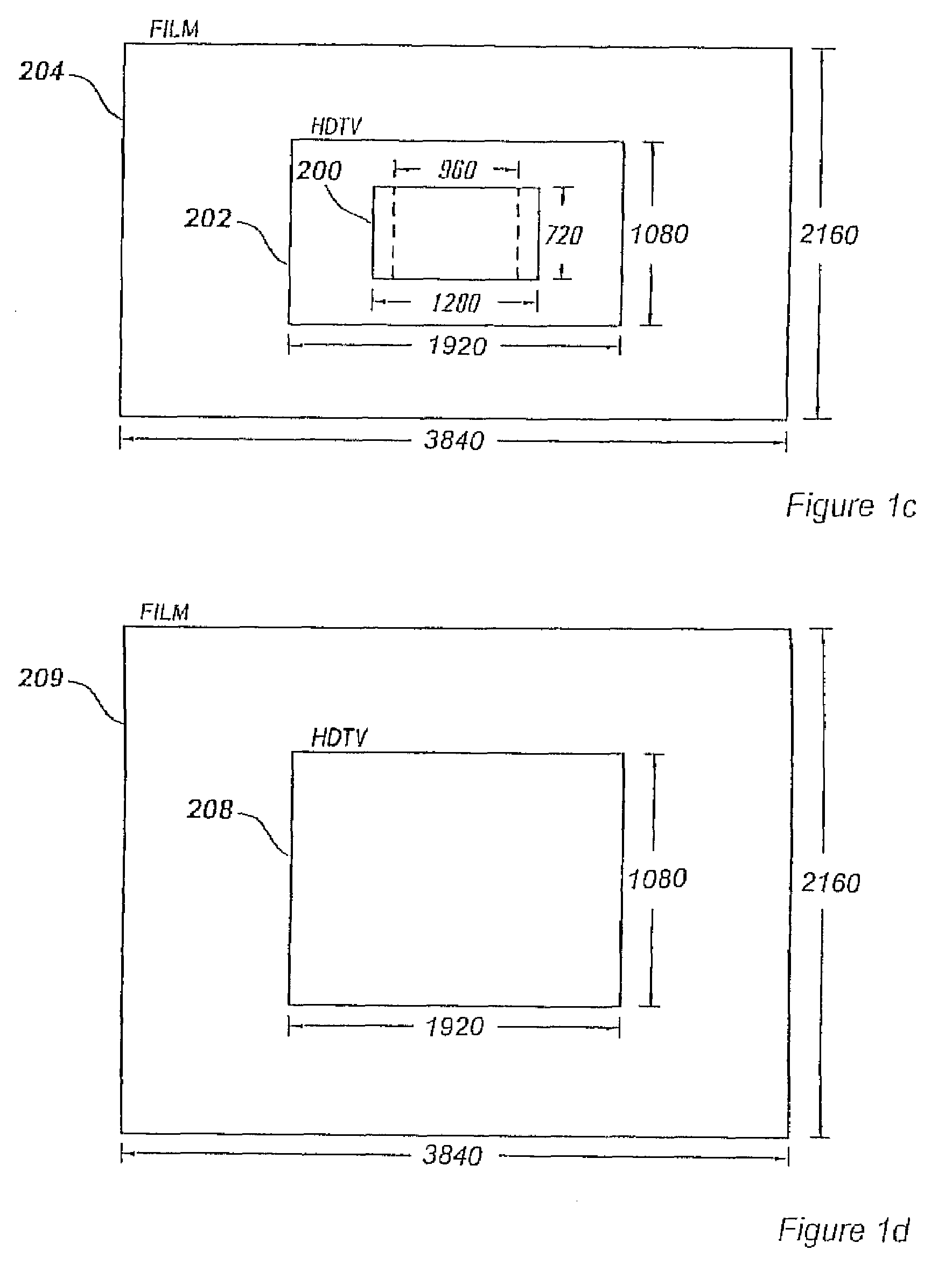

InactiveUS20090174813A1Improve signal-to-noise ratioExtensive controlTelevision system detailsTelevision system scanning detailsDigital videoSample rate conversion

A multi-format digital video production system enables a user to process an input video program to produce an output version of the program in a final format which may have a different frame rate, pixel dimensions, or both. An internal production format of 24 fps is preferably chosen to provide the greatest compatibility with existing and planned formats associated with HDTV standard 4:3 or widescreen 16:9 high-definition television, and film. Images are re-sized horizontally and vertically by pixel interpolation, thereby producing larger or smaller image dimensions so as to fill the particular needs of individual applications. Frame rates are adapted by inter-frame interpolation or by traditional schemes, including “3:2 pull-down” for 24-to-30 fps conversions. Simple speed-up (for 24-to-25 conversions) or slow-down (for 25-to-24 conversions) for playback, or by manipulating the frame rate itself using a program storage facility with asynchronous reading and writing capabilities. The step of converting the signal to a HDTV format is preferably performed using a modified upconversion process for wideband signals (utilizing a higher sampling clock frequency) and a resizing to HDTV format frame dimensions in pixels.

Owner:WASHINO KINYA +1

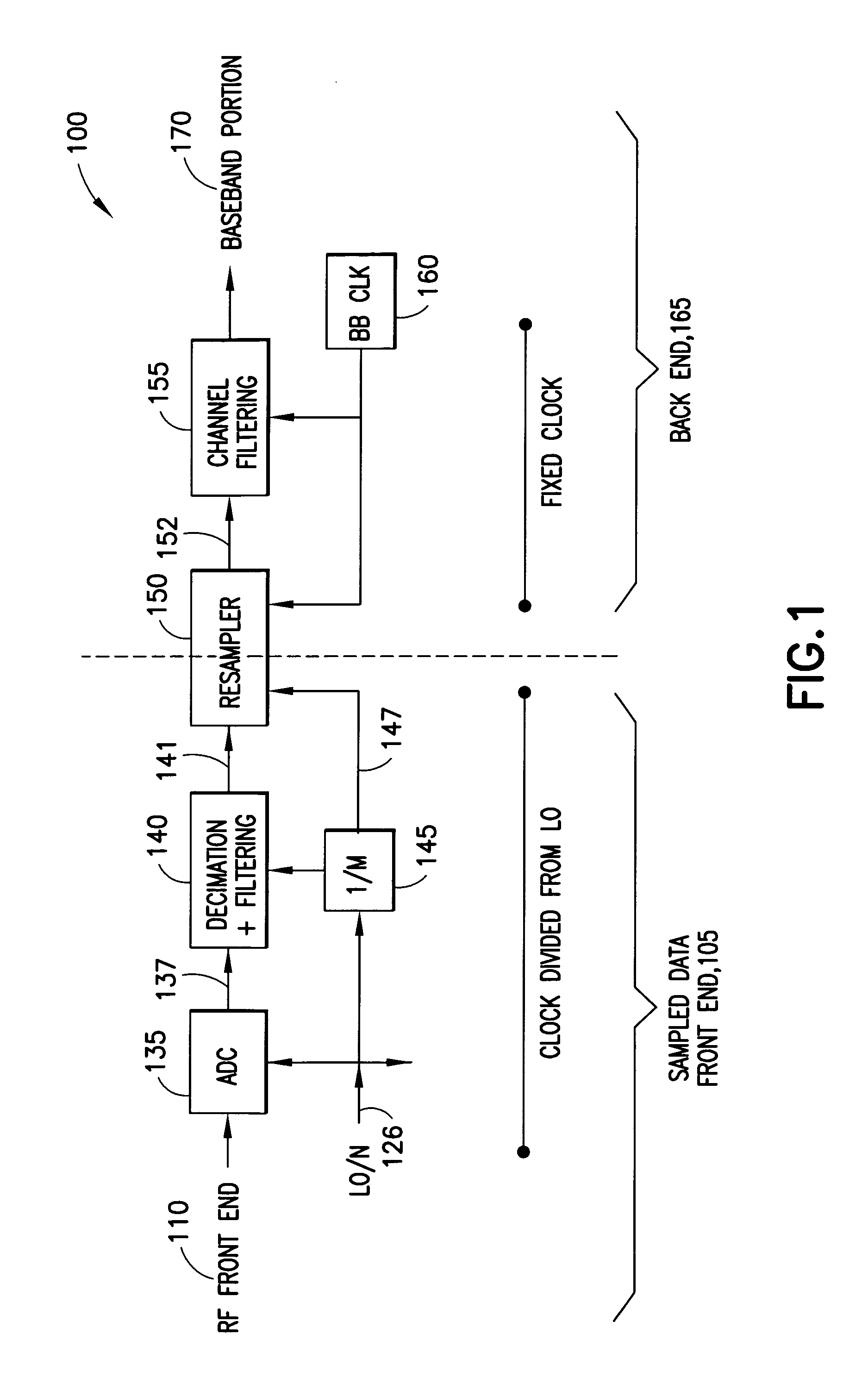

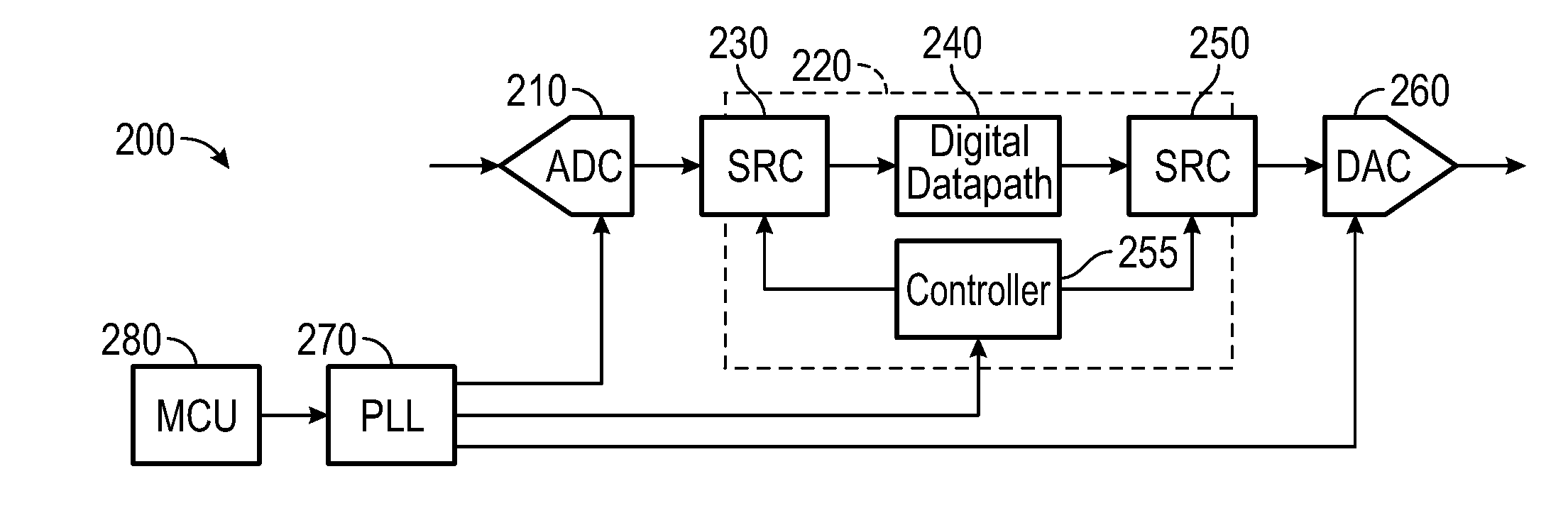

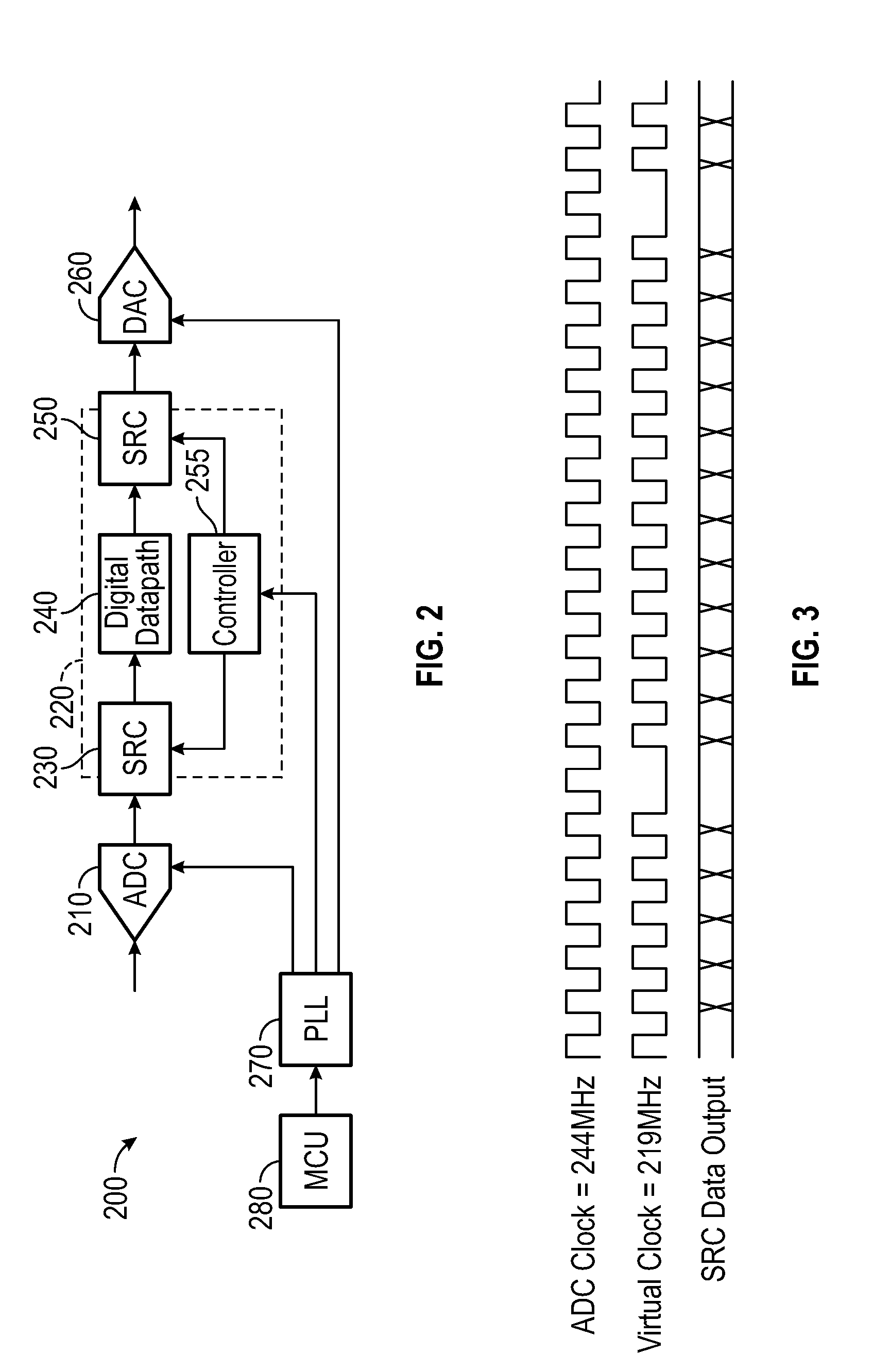

Frequency management using sample rate conversion

ActiveUS20150200649A1Digital technique networkAnalogue-digital convertersSample rate conversionRadio frequency signal

In one embodiment, an apparatus includes a first receiver path with a first digitizer to digitize an incoming signal obtained from a radio frequency signal including at least a first desired channel into samples, the first digitizer to operate at a first sampling frequency, a first sample rate converter coupled to an output of the first digitizer to receive the samples at the first sampling frequency and to output the samples at a fixed sampling frequency, and a first digital processor to receive and process the samples at the fixed sampling frequency. The apparatus may further include a controller to receive a frequency change indication and to dynamically control the first sample rate converter to accommodate a change in the first sampling frequency from a first rate to a second rate.

Owner:SILICON LAB INC

Adaptive sampling rate converter

InactiveUS7369637B1Compensation driftDigital technique networkMultiplex communicationClock driftSoftware define radio

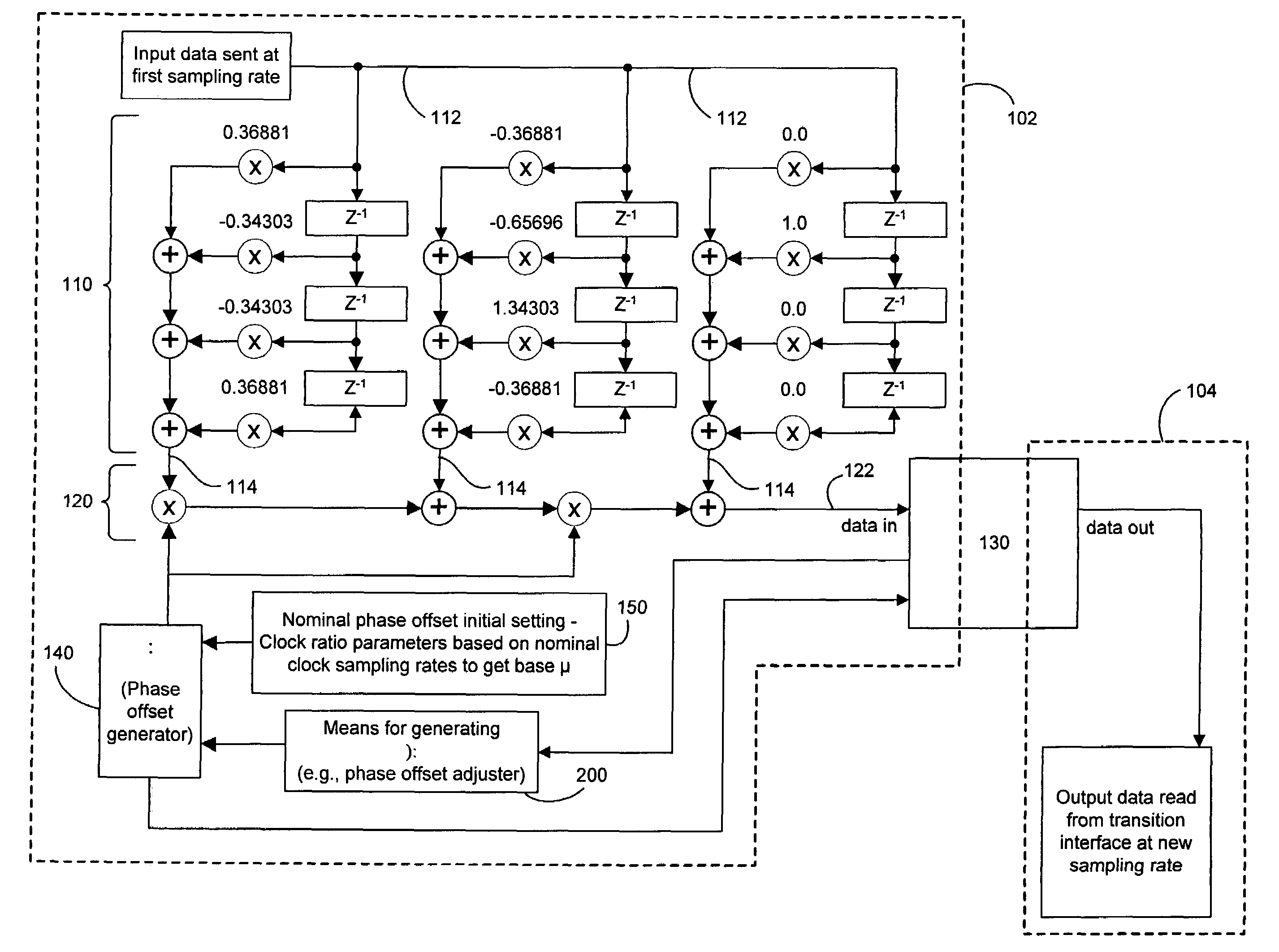

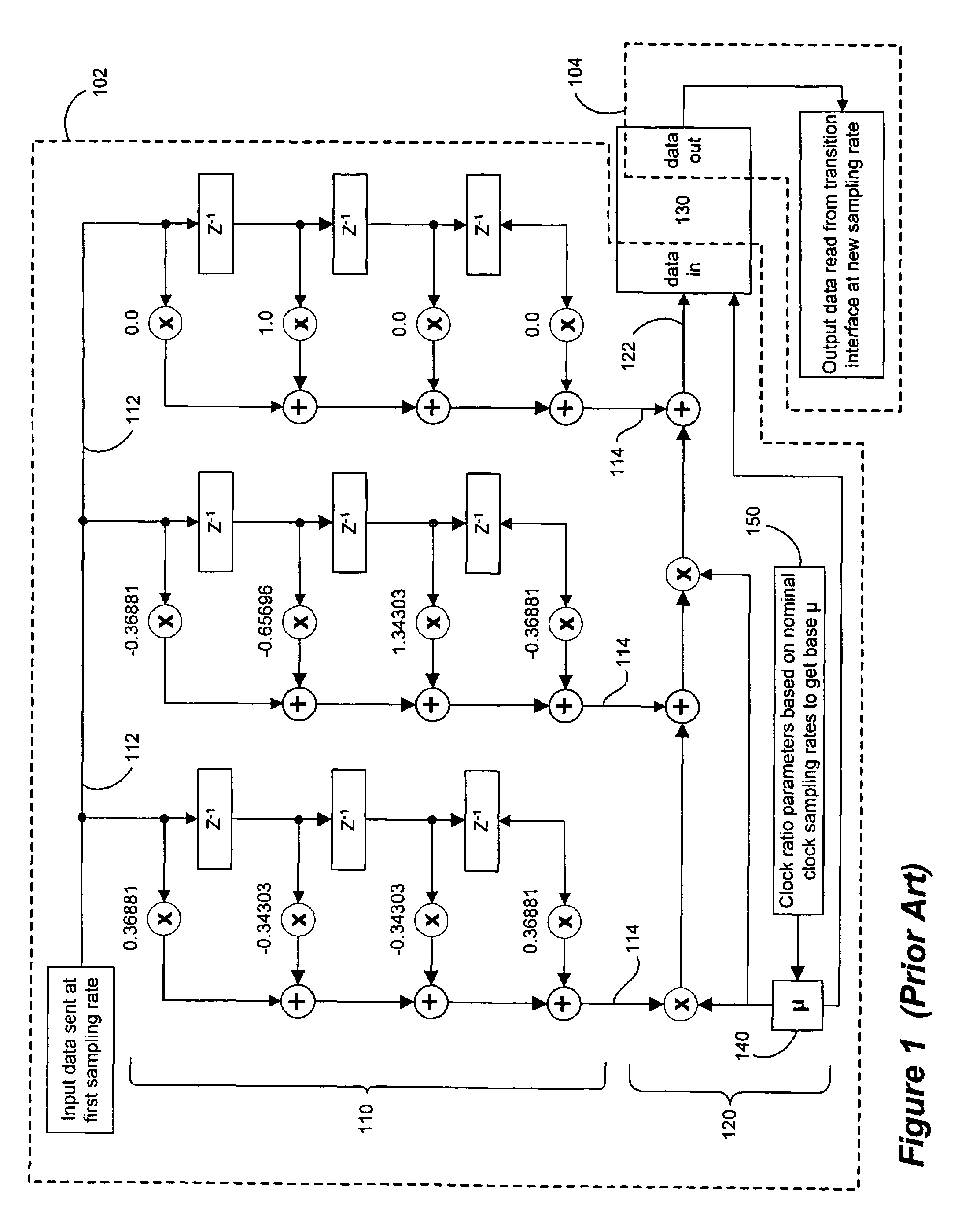

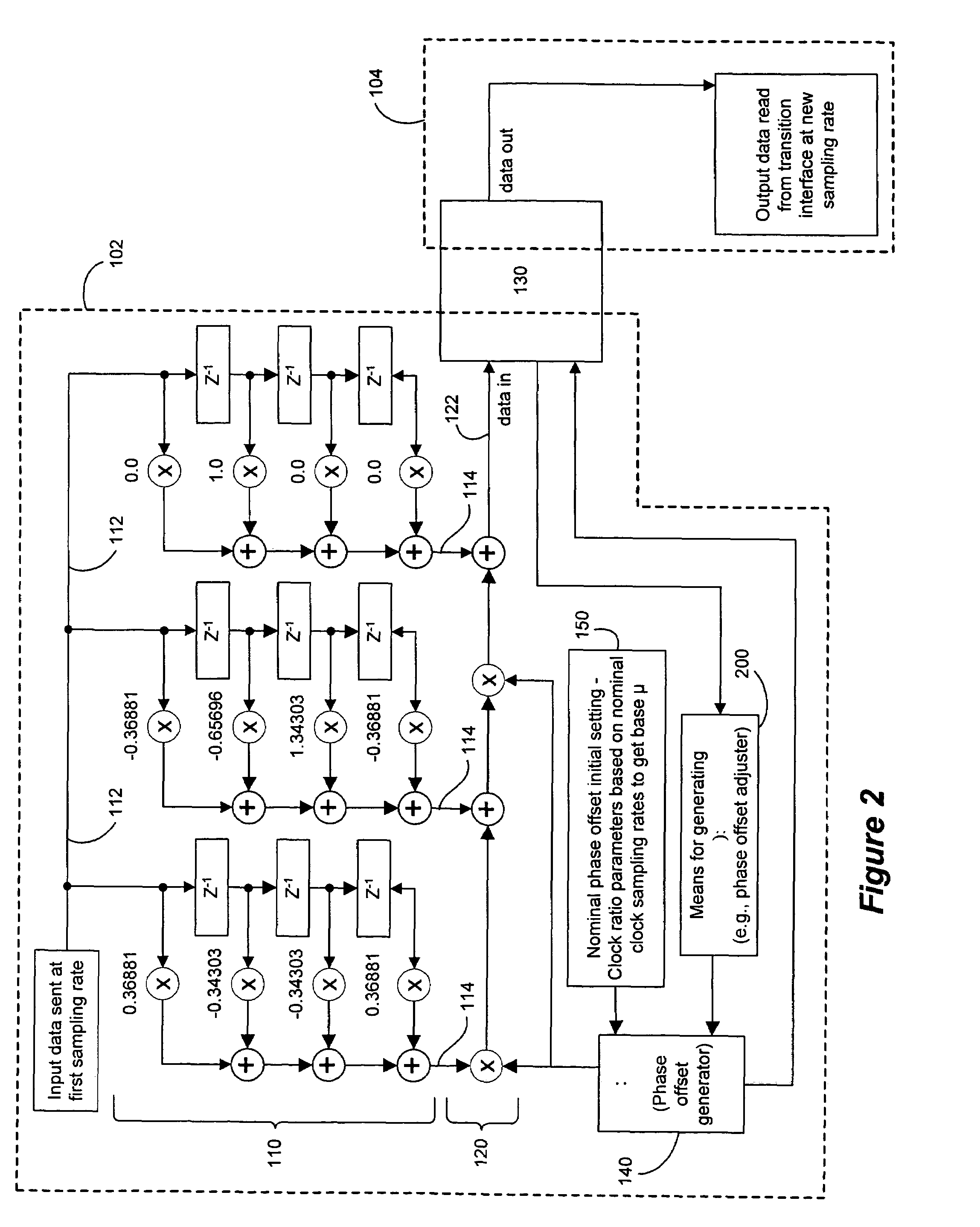

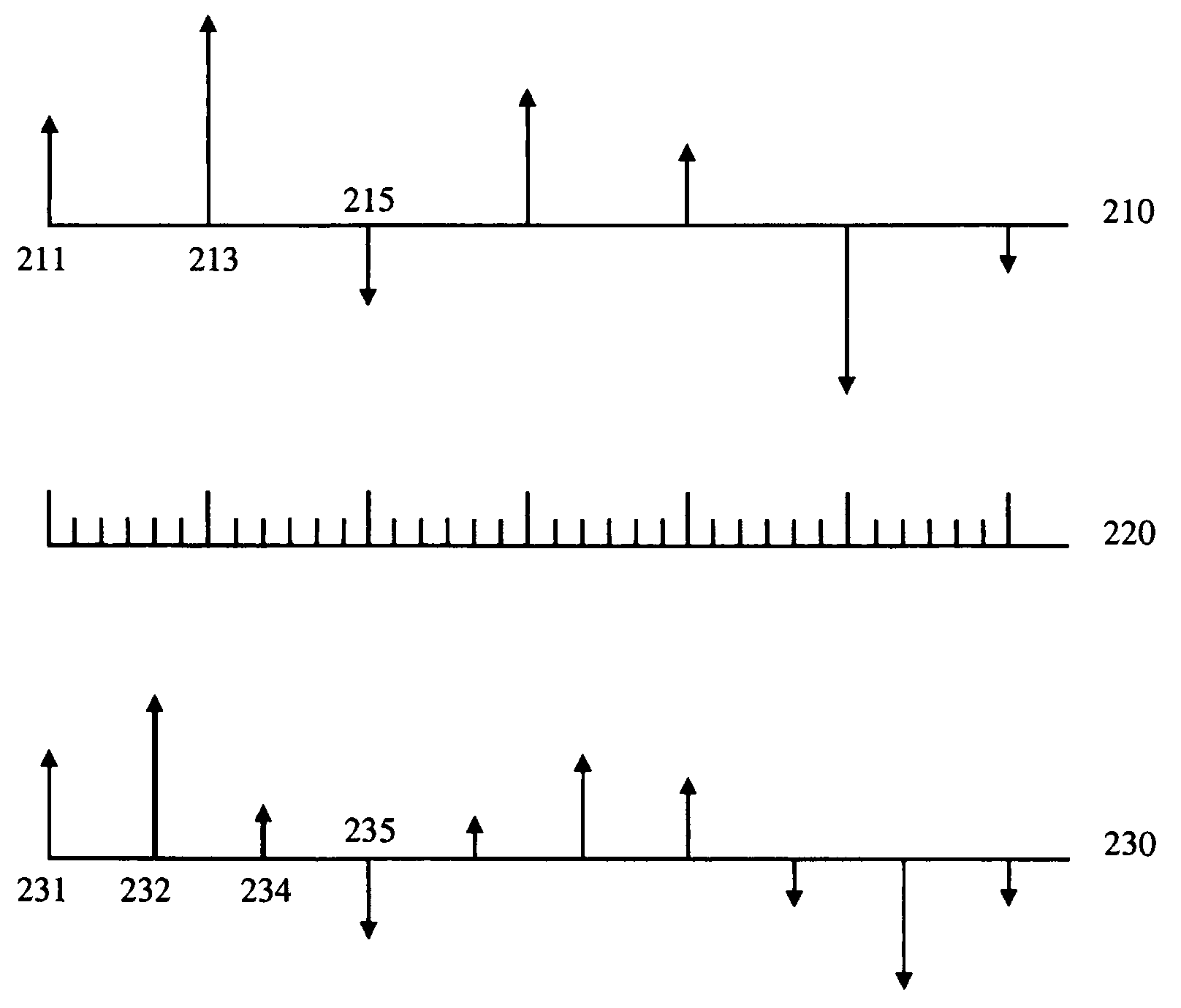

Apparatus, methods and techniques for adjusting the phase offset used in sampling rate conversion uses a Farrow structure or the like to compensate for clock problems such as “clock jitter” and / or “clock drift” effects, which typically arise where one clock is truly independent of the other. A phase offset adjustment value Δμ based on the measured data flow between clock domains across a transition interface and / or through a buffer is calculated. Where an output FIFO buffer is used, the measured data flow value represents the number of data words written to and read from the FIFO buffer, such as the current number of data words stored in the FIFO buffer or a counter value representing the net number of data words written to the FIFO buffer. The measured data flow value is compared to a target data flow value, which may be a range of values. The phase offset adjustment value may be updated and / or recalculated continuously and / or periodically and is added to or subtracted from the phase offset μ as necessary. Such systems are useful in software defined radio and the like and may be implemented on a variety of devices, including PLDs.

Owner:ALTERA CORP

Methods and systems for sample rate conversion and sample clock synchronization

ActiveUS7414550B1Electric signal transmission systemsDigital technique networkComputer hardwareSample rate conversion

The architecture for a combined universal sample rate converter and a sample clock synchronizer is presented. The universal sample rate converter can be applied, for example, to audio samples created or mixed using any of the standard audio frequencies in the set H={8, 11.025, 22.05, 44.1, 48, 96, and 192} kHz and played back using any other frequency from the set H. The synchronizer can be used where audio data are streamed or otherwise broadcast from, for example, the Internet, along with a system timestamp, and where this timestamp needs to be matched to the local audio clock for proper play-back. The same synchronizer can also be used for audio / video or video only synchronization.

Owner:NVIDIA CORP

Multi-channel sample rate conversion method

InactiveUS20060212503A1Valid conversionProvides computational efficiencyDigital technique networkComplex mathematical operationsSample rate conversionComputer science

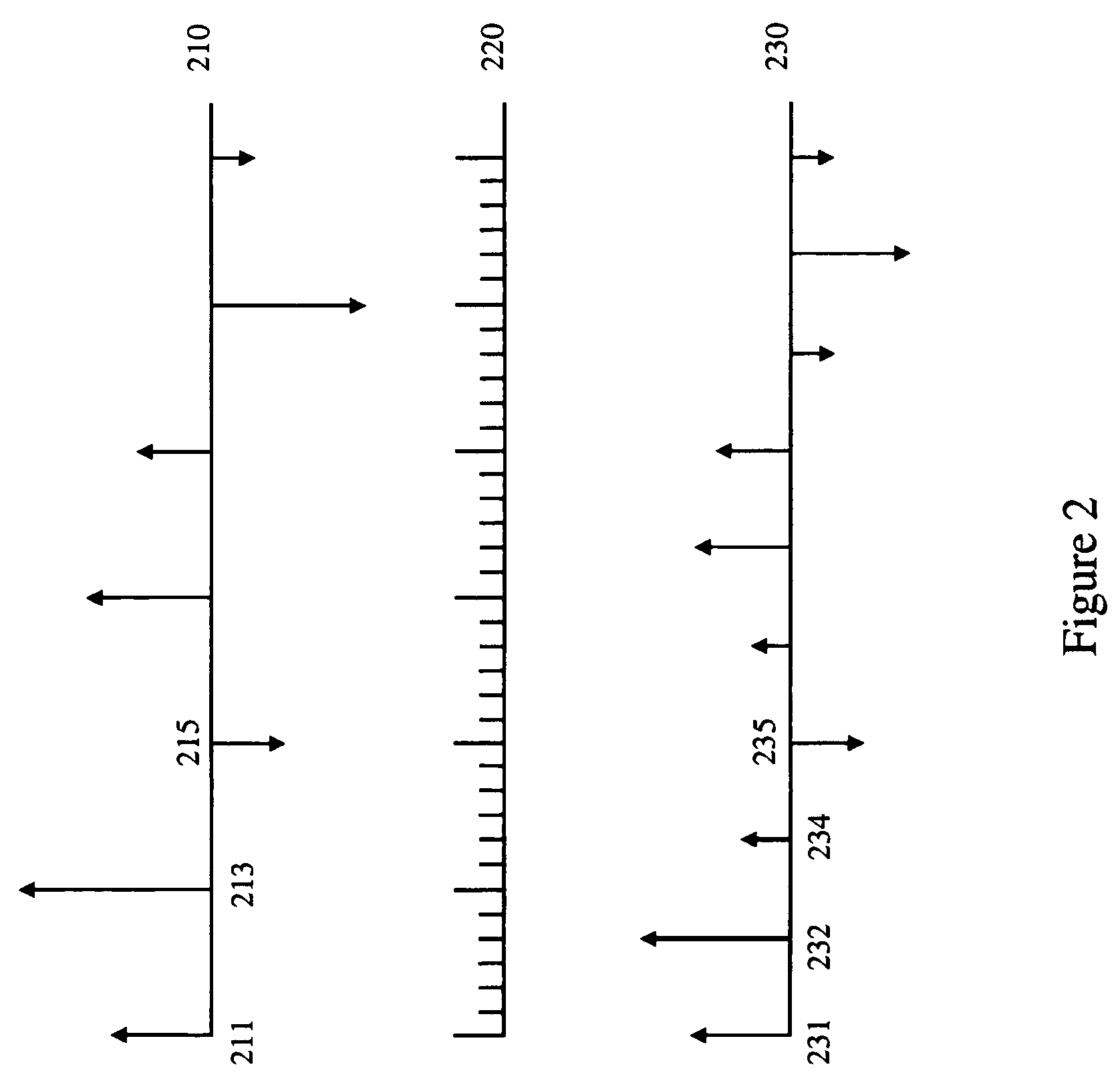

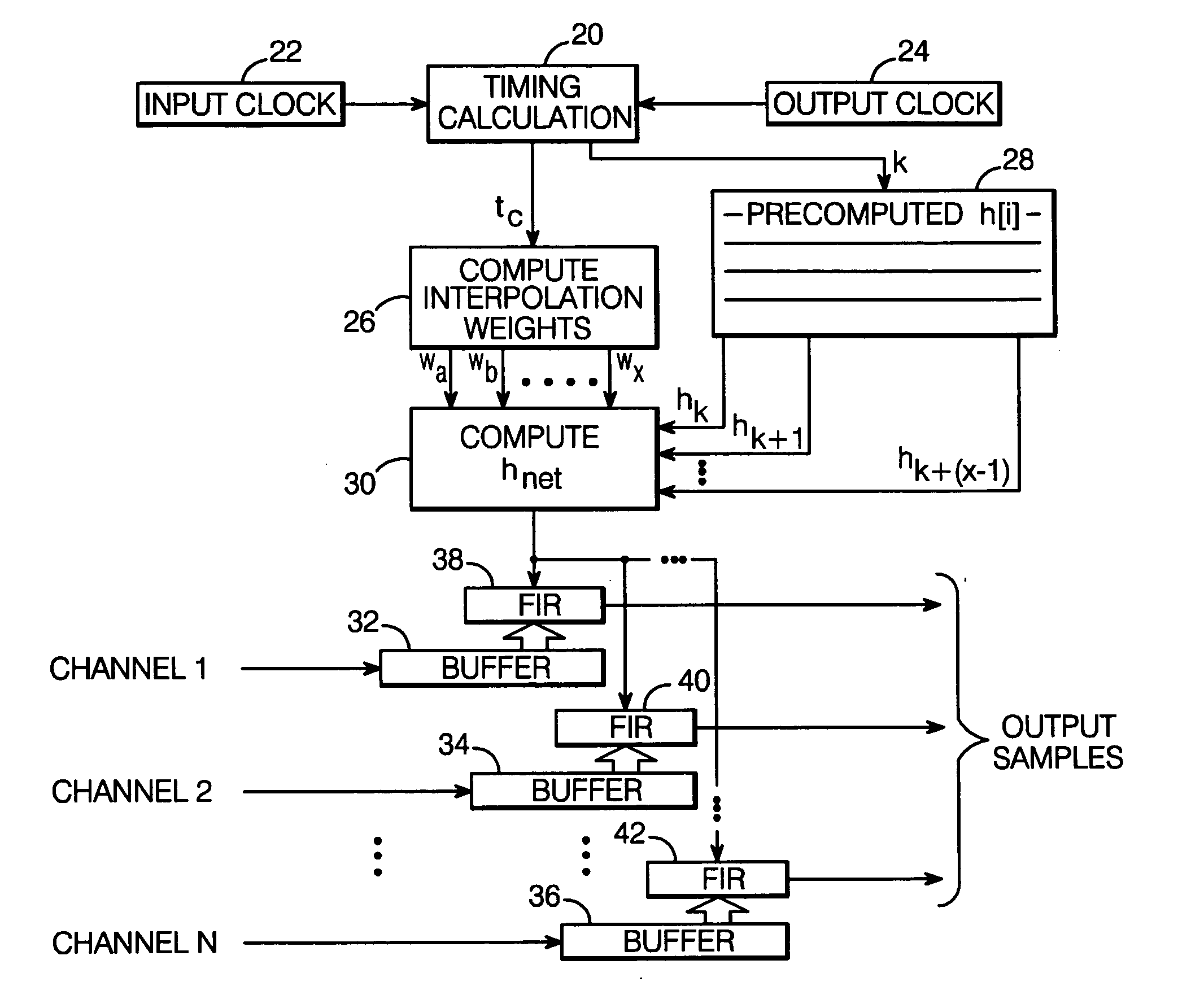

A sampling-rate conversion method receives N input channels which have been digitized at an input sampling rate, and converts the sampling rate of each input channel to produce N output channels at an output sampling rate. The method comprises computing a common FIR interpolating function which depends upon the input and output sample clocks and the instantaneous output time, and applying the common FIR interpolating function to all N input channels to compute all N output channels.

Owner:ANALOG DEVICES INC

Digital audio receiver with reduced AM interference

ActiveUS20060247810A1Eliminates audible noiseMinimum audible noiseAmplifier with semiconductor-devices/discharge-tubesTransmission monitoringDigital dataData stream

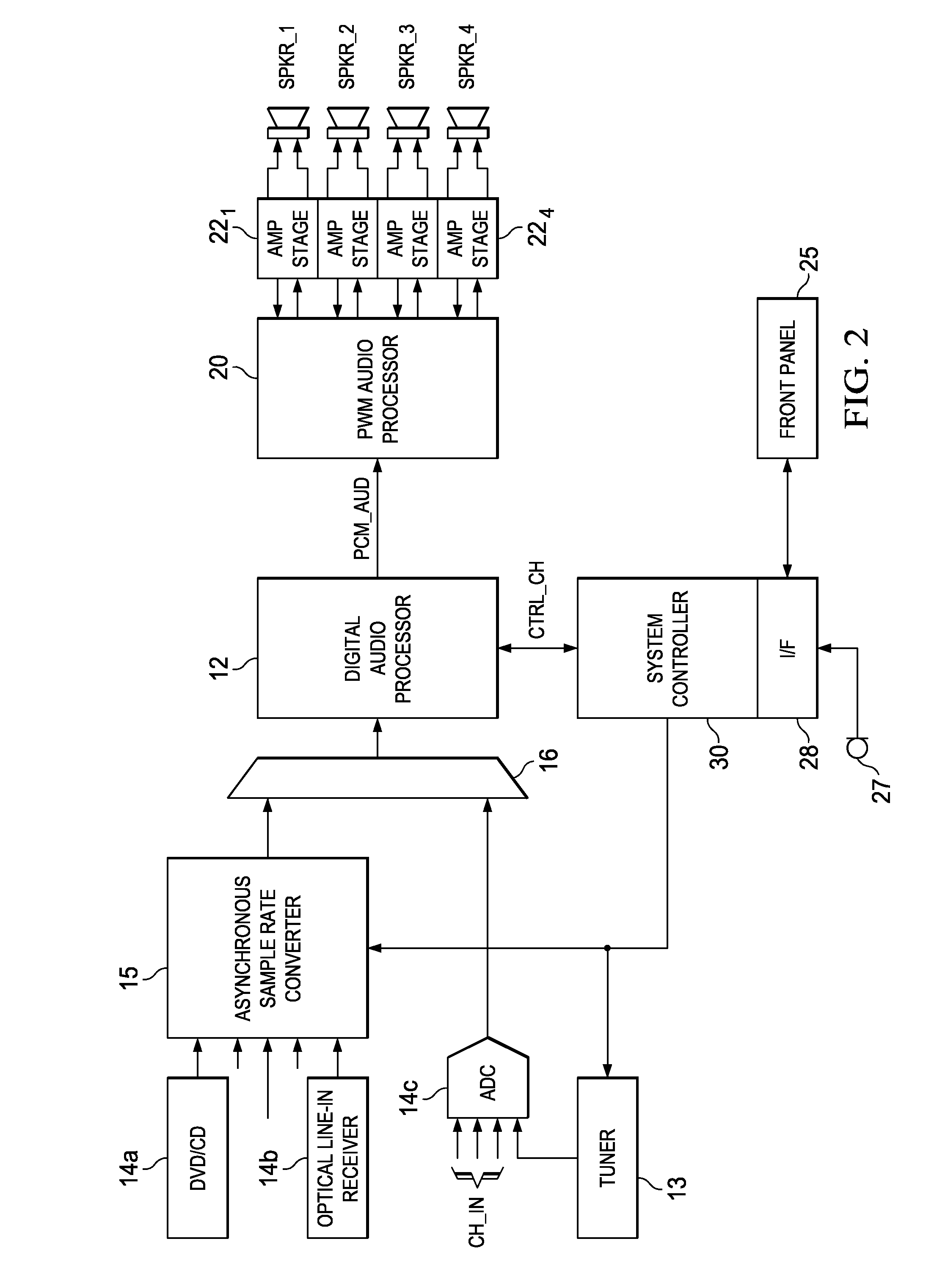

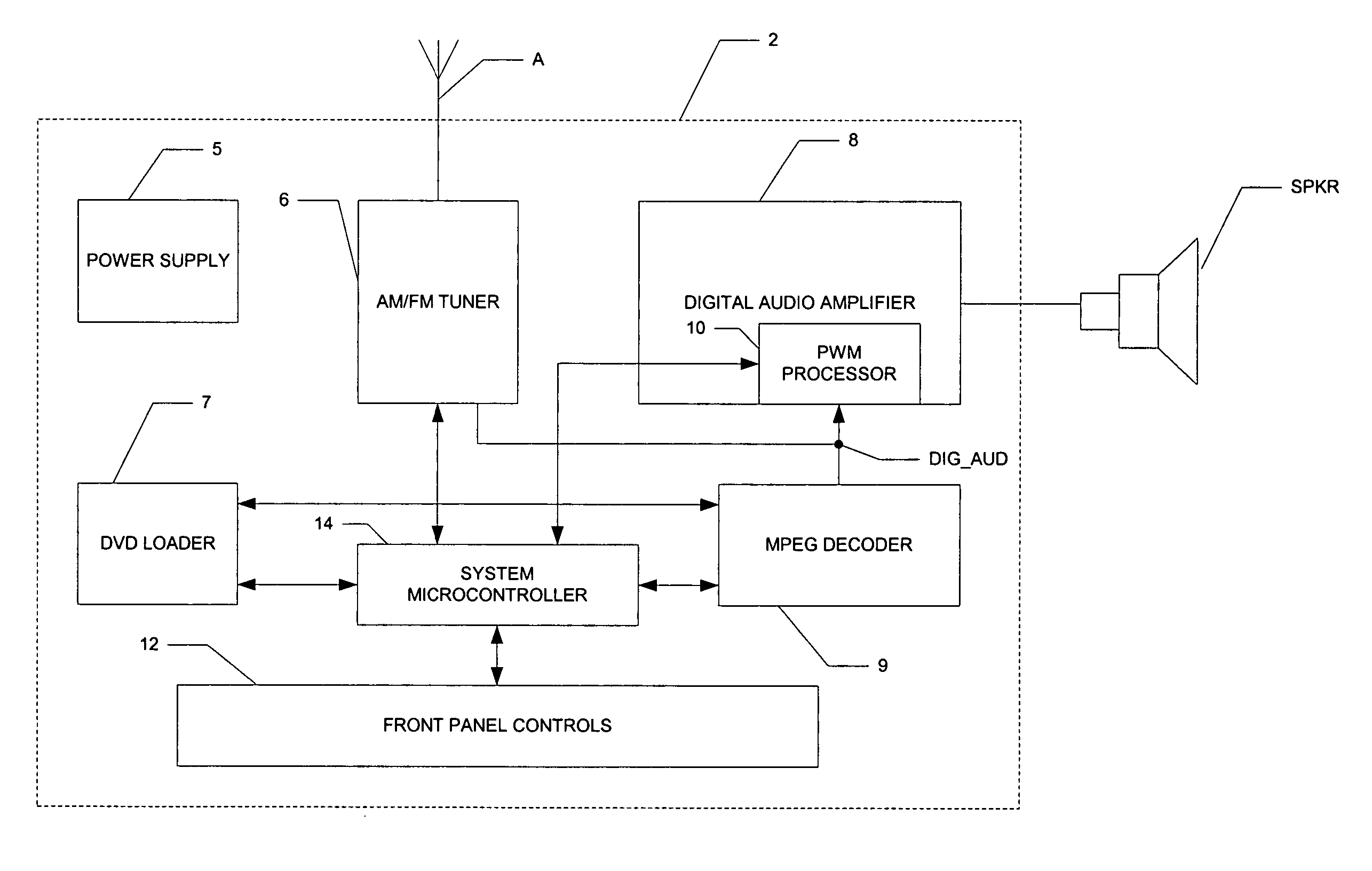

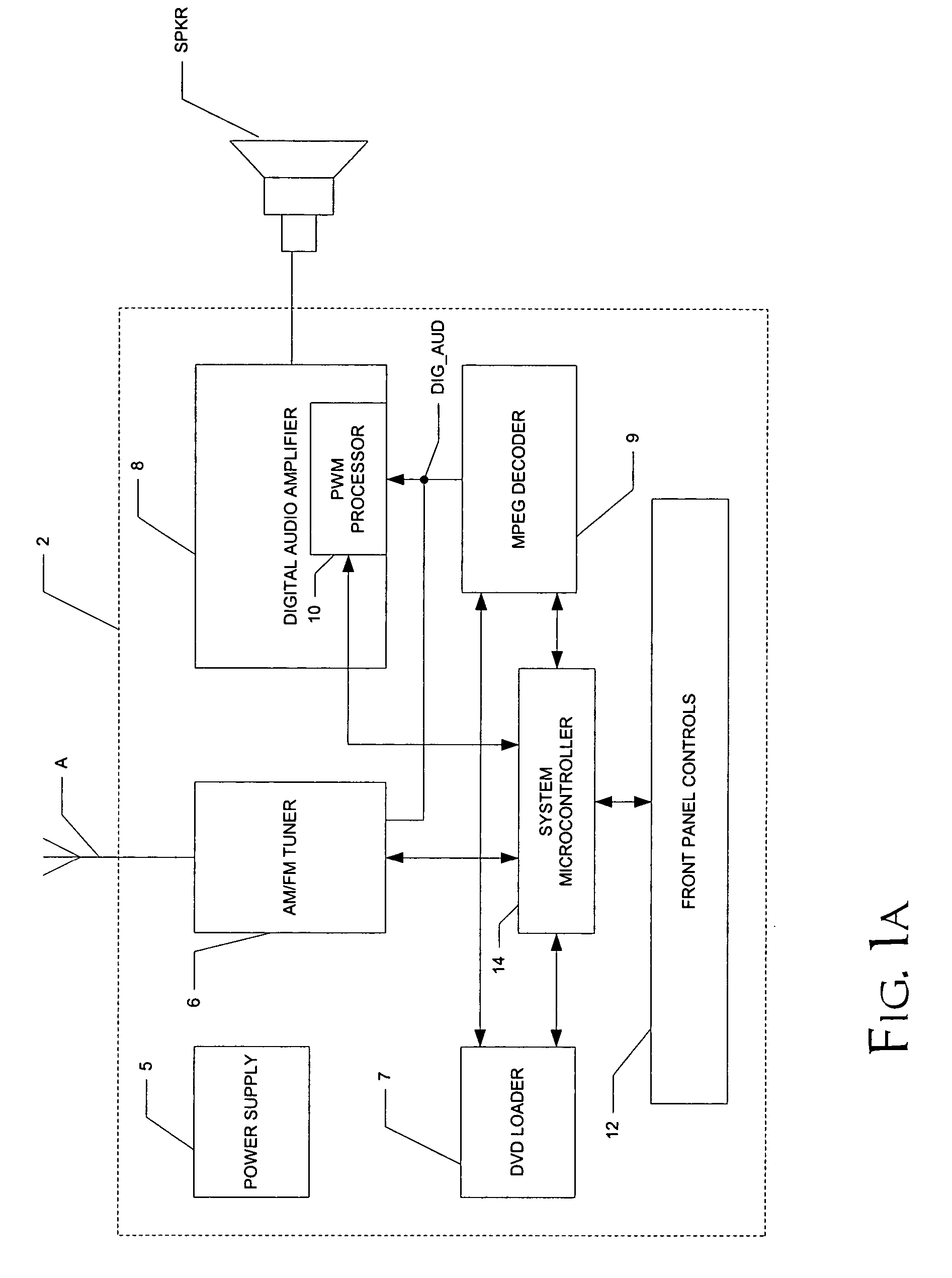

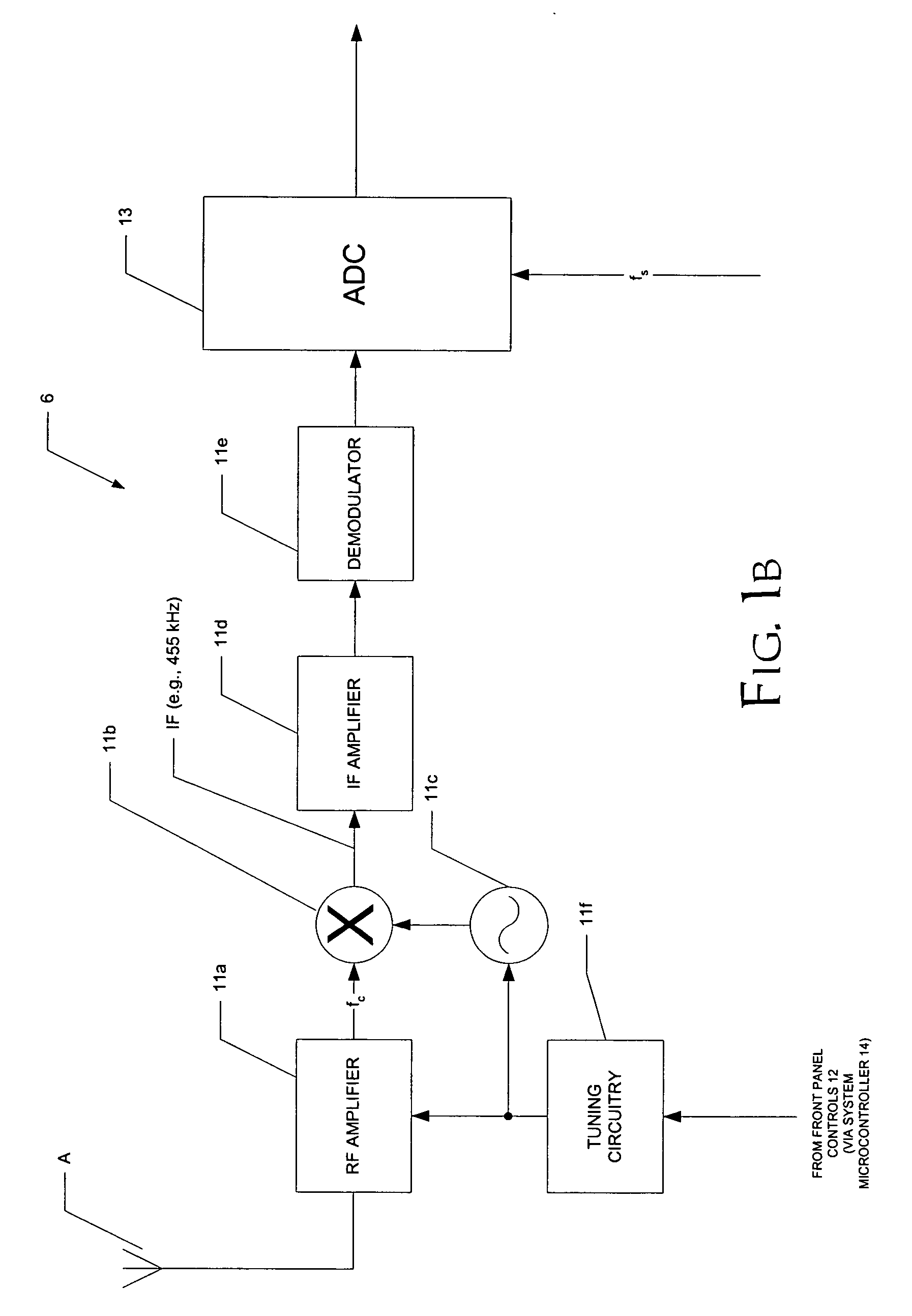

A digital audio system (2) including a digital audio amplifier (8) with reduced AM interference is disclosed. The digital audio amplifier (8) includes a pulse-width-modulation (PWM) processor (10) in which a digital datastream at a sampling frequency is upsampled by an interpolation filter (16) to a multiple of the sampling frequency. The upsampled datastream is applied to a sample rate converter (17) which resamples the upsampled datastream to produce a datastream at a converted sampling frequency, or PWM frame rate. The converted datastream is then applied to pulse-width-modulation circuitry (21) which generates a PWM signal at the PWM frame rate. Clock circuitry (25) generates clock signals, to the sample rate converter (17), responsive to a sample rate conversion ratio that is associated with the AM tuned frequency. For a given AM tuned frequency, the sample rate conversion ratio is selected so that the PWM frame rate and its lower harmonics avoid the AM tuned frequency, any intermediate frequency in the AM tuner (6), and also an image frequency in the tuner (6). The sample rate converter (17) can also be controlled to upsample digital audio from low sampling frequency sources.

Owner:TEXAS INSTR INC

Multi-carrier receiver for wireless communication

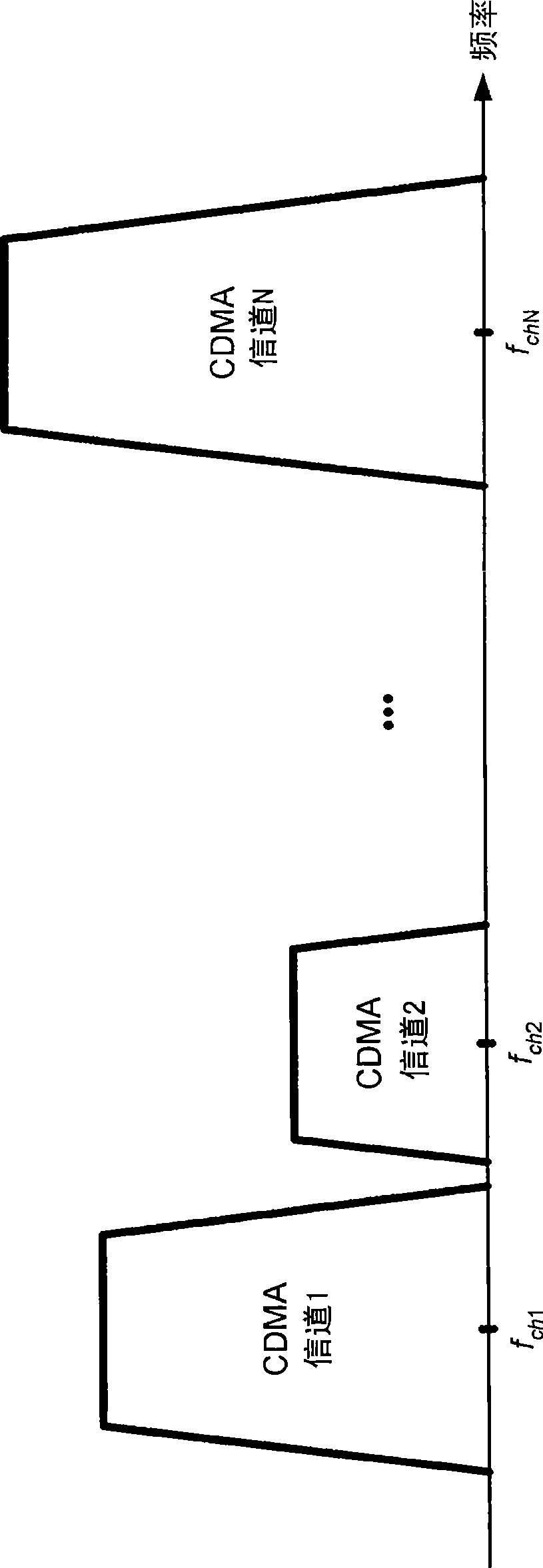

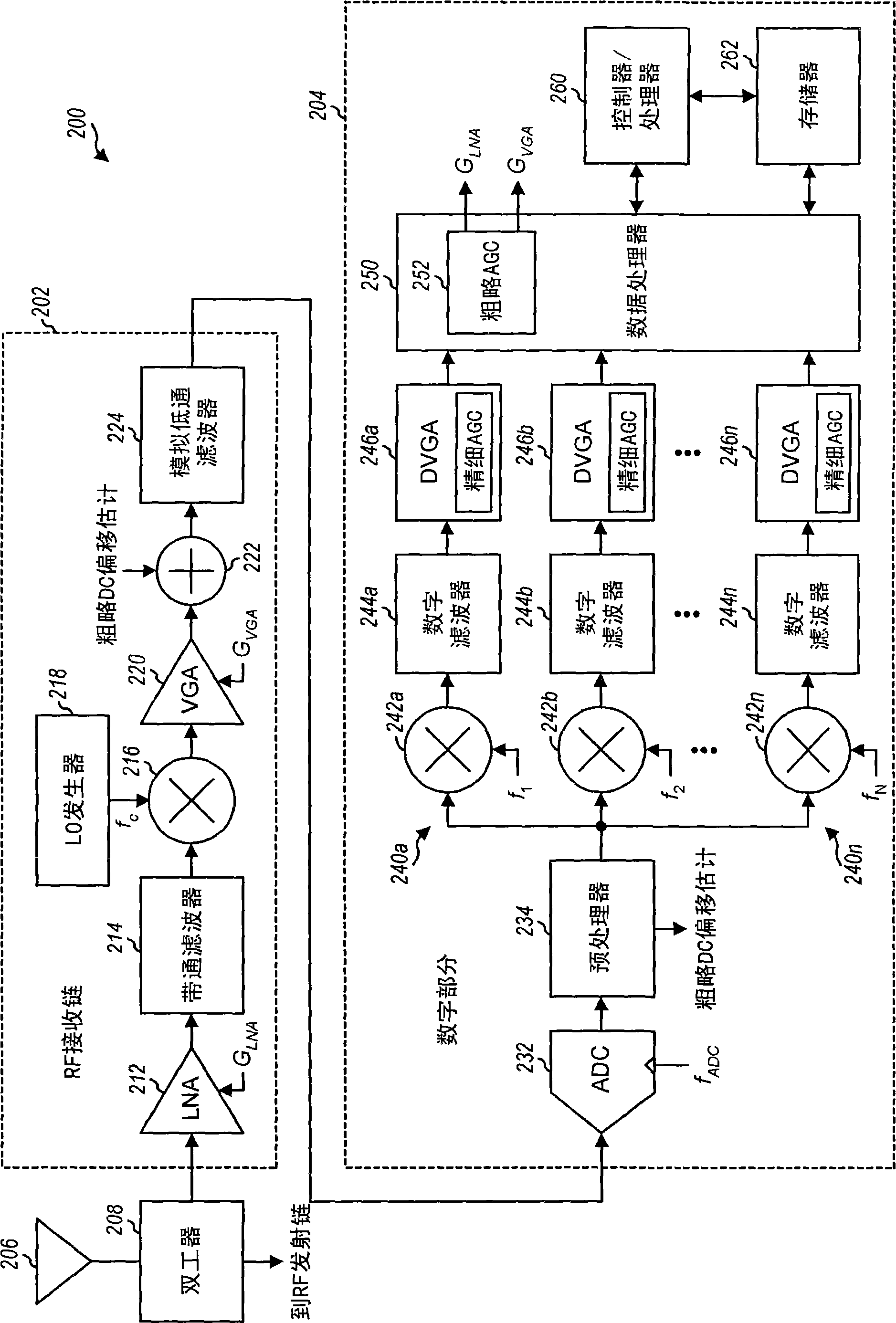

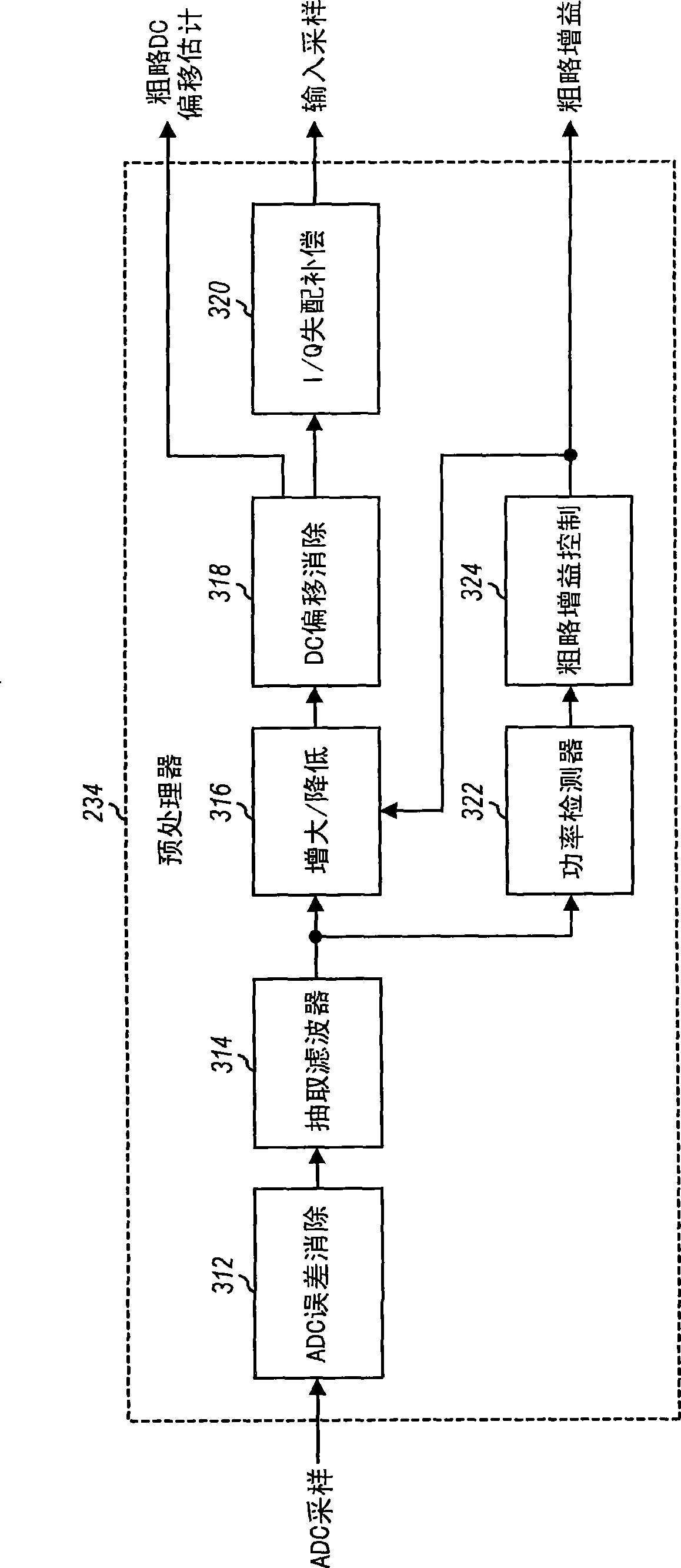

InactiveCN101490997AFrequency-division multiplex detailsGain controlSample rate conversionOffset cancellation

A multi-carrier receiver capable of receiving one or multiple frequency channels simultaneously is described. In one design, the multi-carrier receiver includes a single radio frequency (RF) receive chain, an analog-to-digital converter (ADC), and at least one processor. The RF receive chain processes a received RF signal and provides an analog baseband signal comprising multiple signals on multiple frequency channels. The ADC digitizes the analog baseband signal. The processor(s) digitally processes the samples from the ADC to obtain an input sample stream. This digital processing may include digital filtering, DC offset cancellation, I / Q mismatch compensation, coarse scaling, etc. The processor(s) digitally downconverts the input sample stream for each frequency channel to obtain a downconverted sample stream for that frequency channel. The processor(s) then digitally processes each downconverted sample stream to obtain a corresponding output sample stream. This digital processing may include digital filtering, downsampling, equalization filtering, upsampling, sample rate conversion, fine scaling, etc.

Owner:QUALCOMM INC

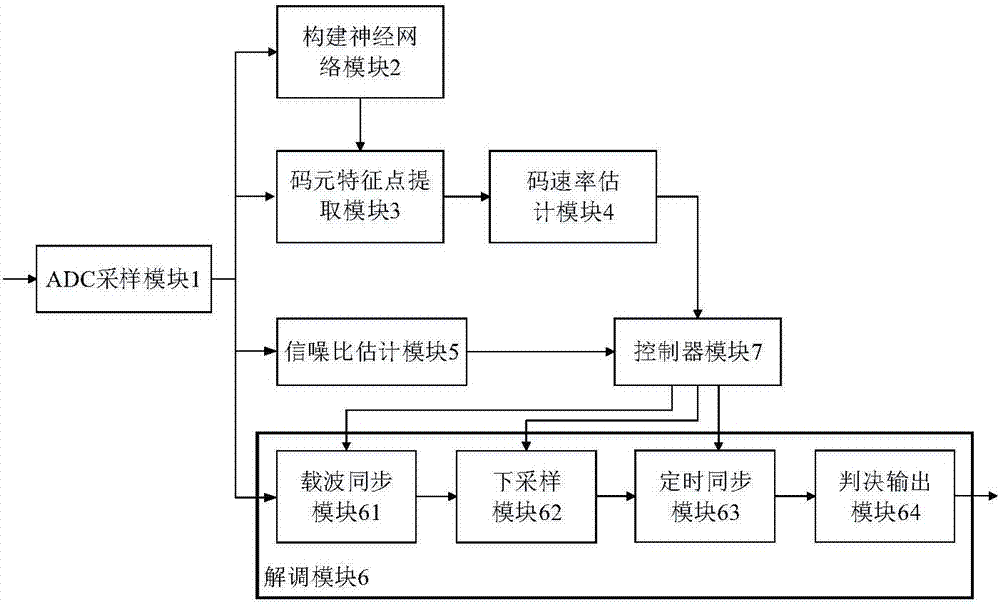

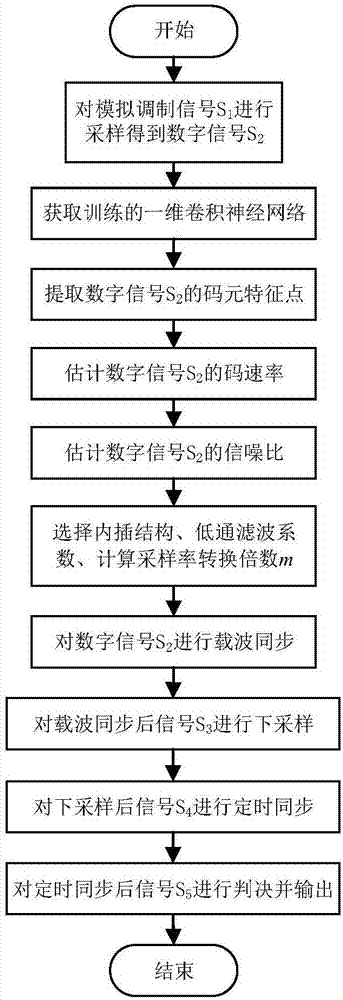

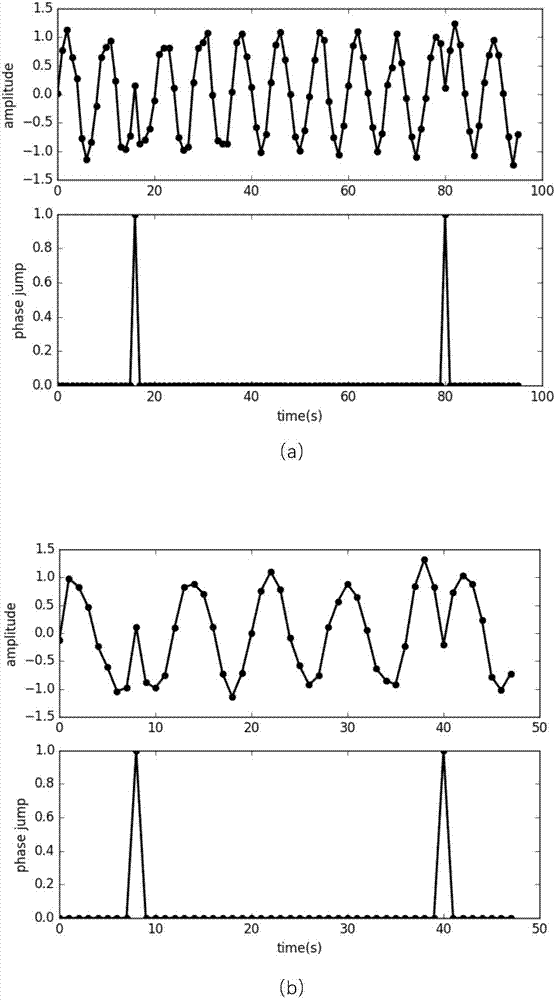

Multi-gear code rate adaptive demodulation system and method based on neural network

ActiveCN106936742AReduce complexityRealize adaptive demodulationCarrier regulationSynchronisation receiversSample rate conversionLow-pass filter

The invention provides a multi-gear code rate adaptive demodulation system and method based on a neural network so as to solve the technical problems of high complexity of realization of an existing multi-gear code rate adaptive demodulation system and large computation amount of a demodulation method. In the demodulation system, an ADC sampling module samples an analog modulation signal; a code element feature point extraction module carries out detection on phase jump points of the sampled signal by utilizing a one-dimensional convolution neural network trained by a neural network construction module; a code rate estimation module estimates code rate of the sampled signal according to the detection result; a signal-to-noise ratio estimation module estimates signal-to-noise ratio of the sampled signal; a controller module selects low-pass filter coefficients and an interpolation structure of a demodulation module according to the code rate estimation result and the signal-to-noise ratio estimation result, and calculates sampling rate conversion ratio of the demodulation module; and finally, the demodulation module carries out demodulation on the sampled signal according to the selected low-pass filter coefficients and the interpolation structure as well as the calculated sampling rate conversion ratio.

Owner:XIDIAN UNIV

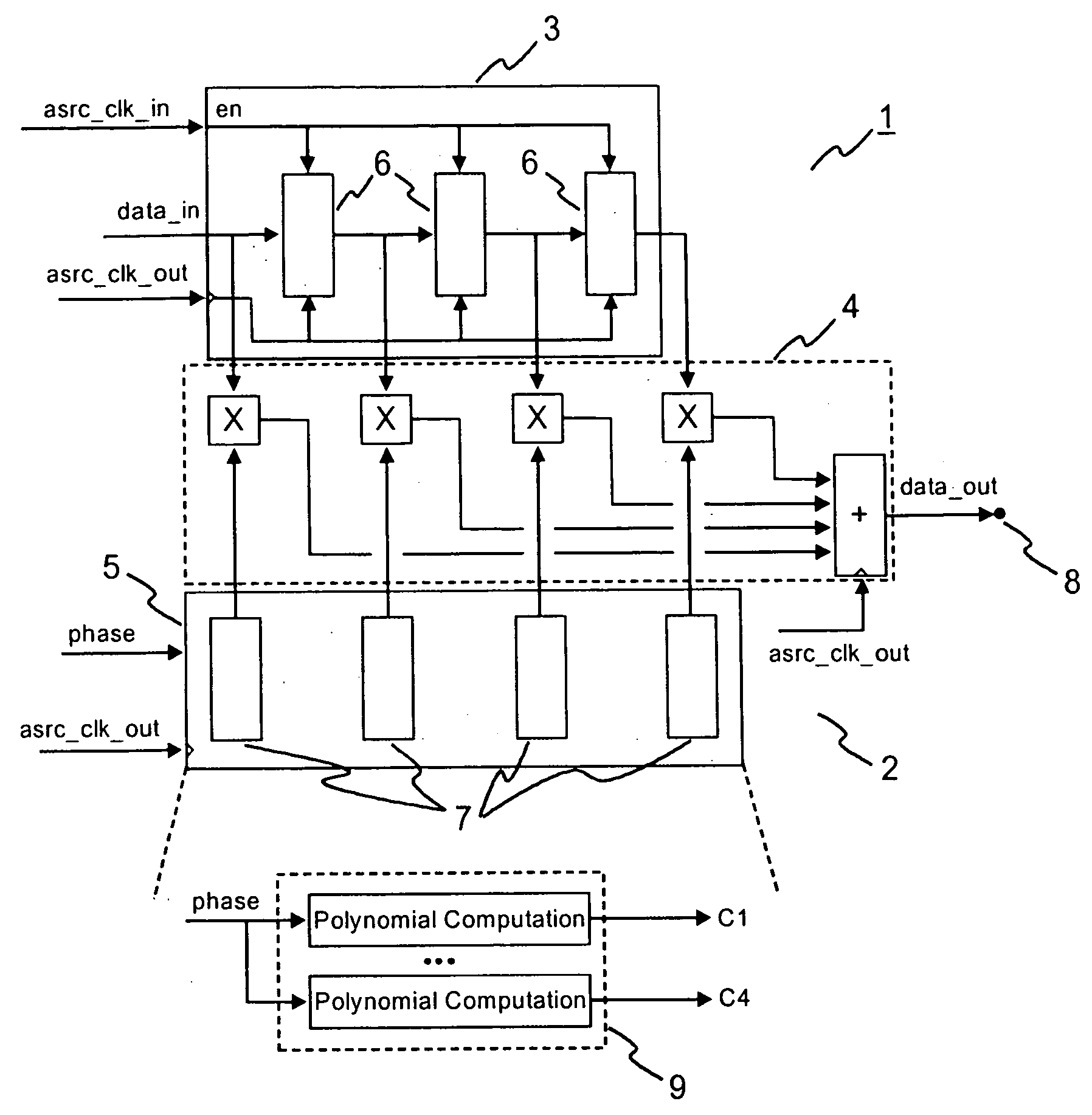

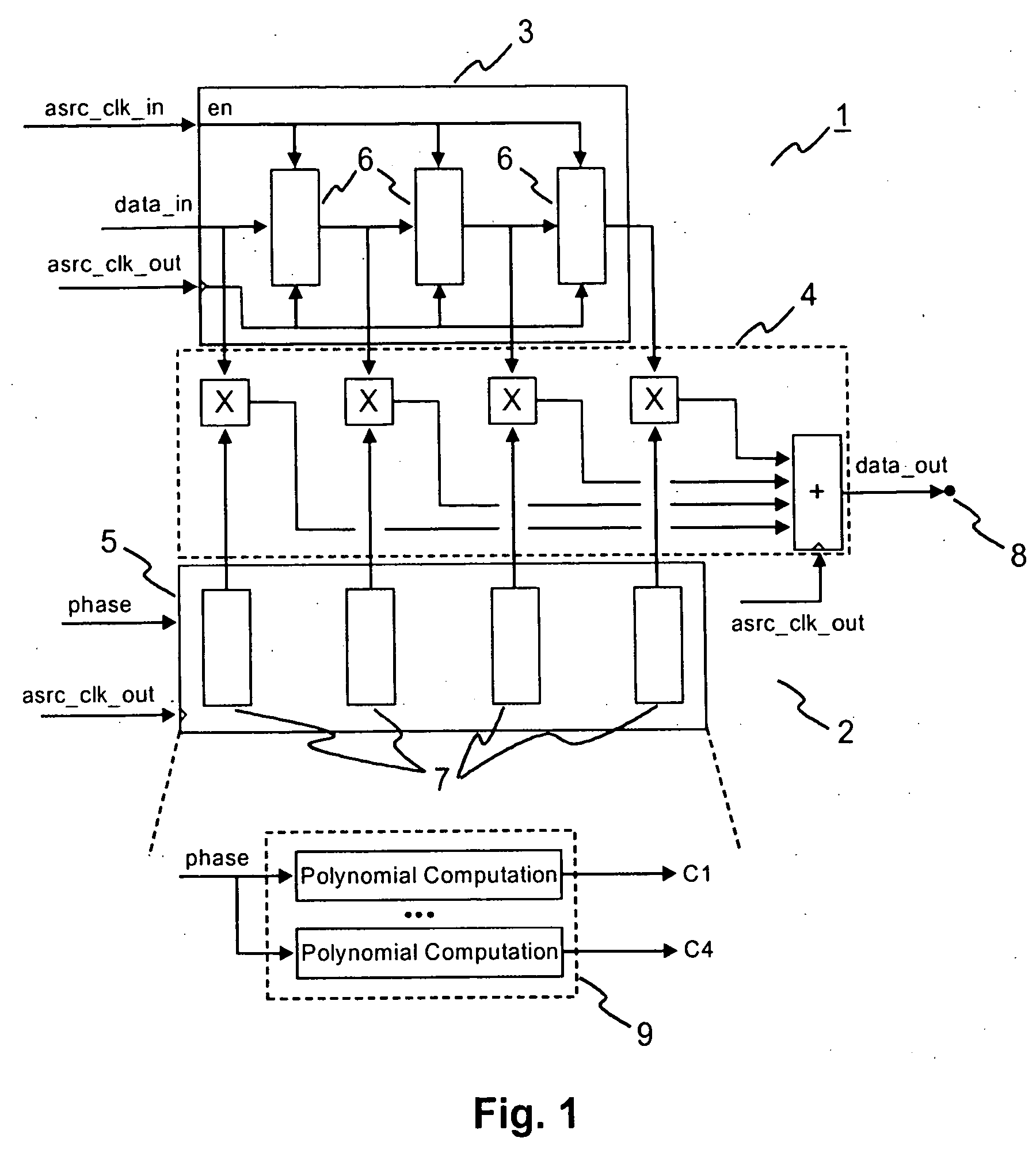

Sample rate converter

InactiveUS20060179095A1Digital technique networkApparatus for meter-controlled dispensingDigital dataUltrasound attenuation

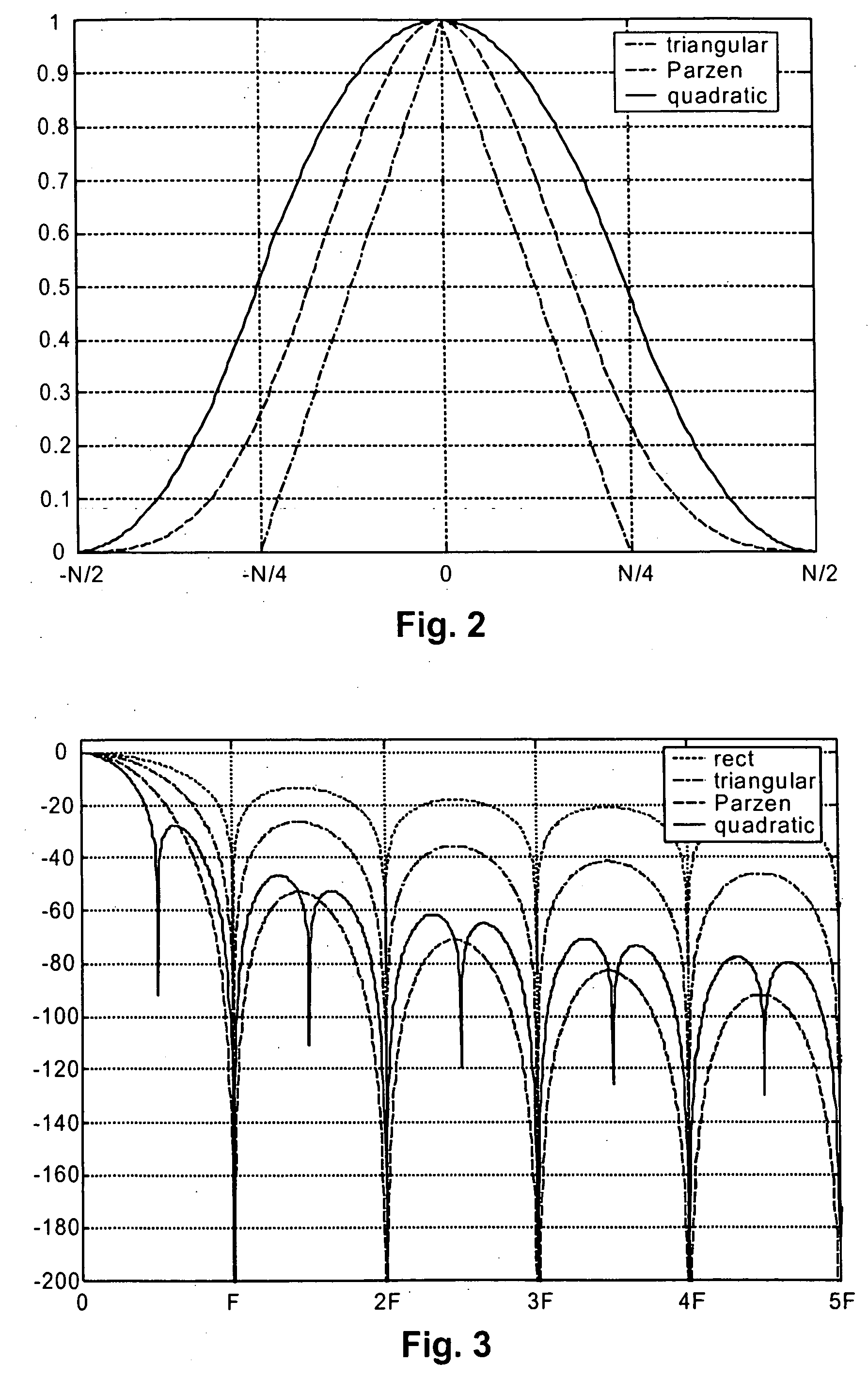

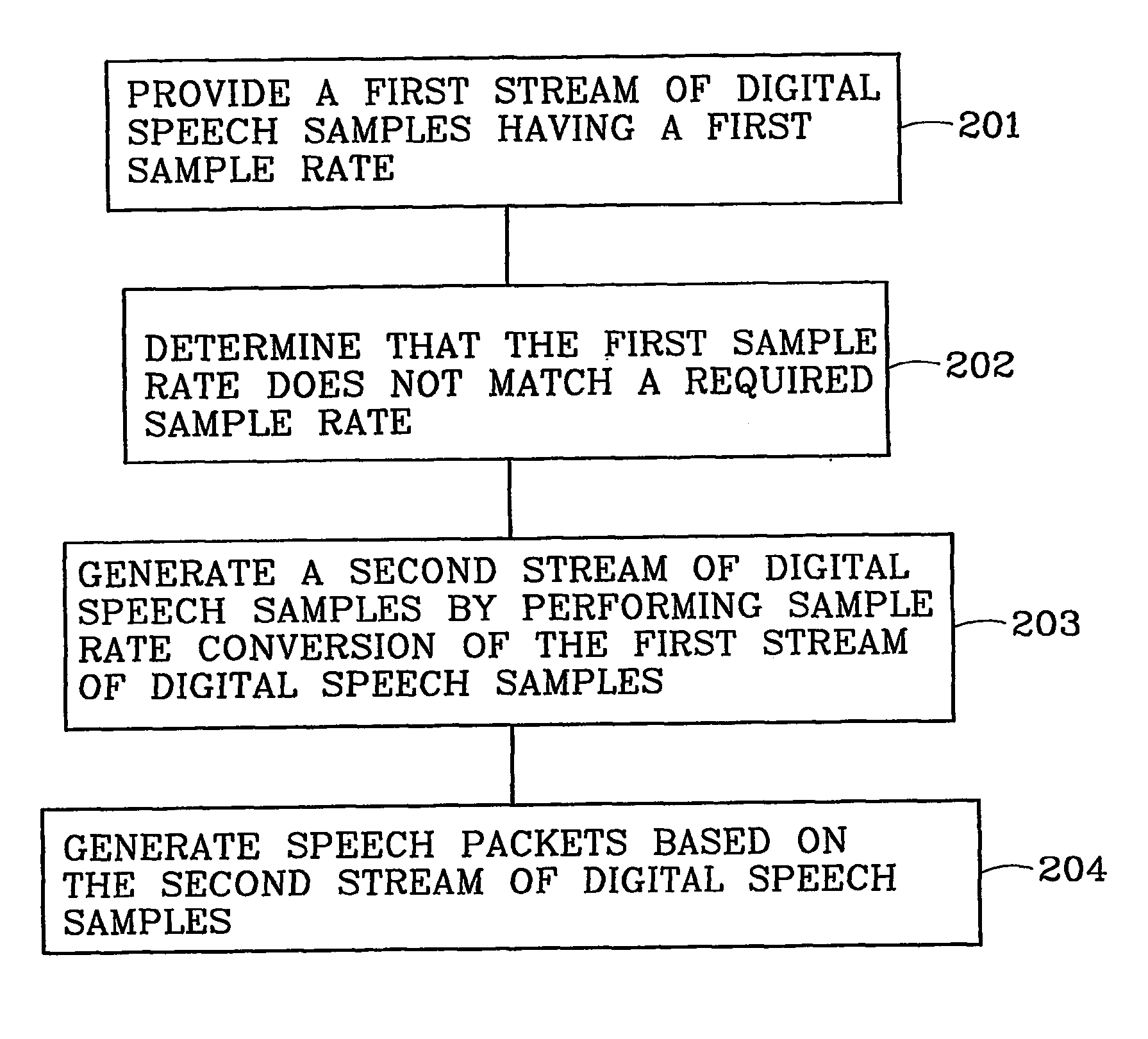

The invention relates to an asynchronous sample rate converter (ASRC) for the conversion of the sample rate of digital data such as audio data or video data. In the case of high over-sampling or sub-sampling factors an ASRC becomes quite complex. It is an object of the invention to provide an ASRC with a simplified design for such purposes. It is suggested to use an ASRC which has a n-tap polyphase filter, whereby a computational entity performs a polynomial computation of the filter coefficients. The attenuation at the notch frequencies is best when using a Parzen window or a quadratic window.

Owner:THOMSON LICENSING SA

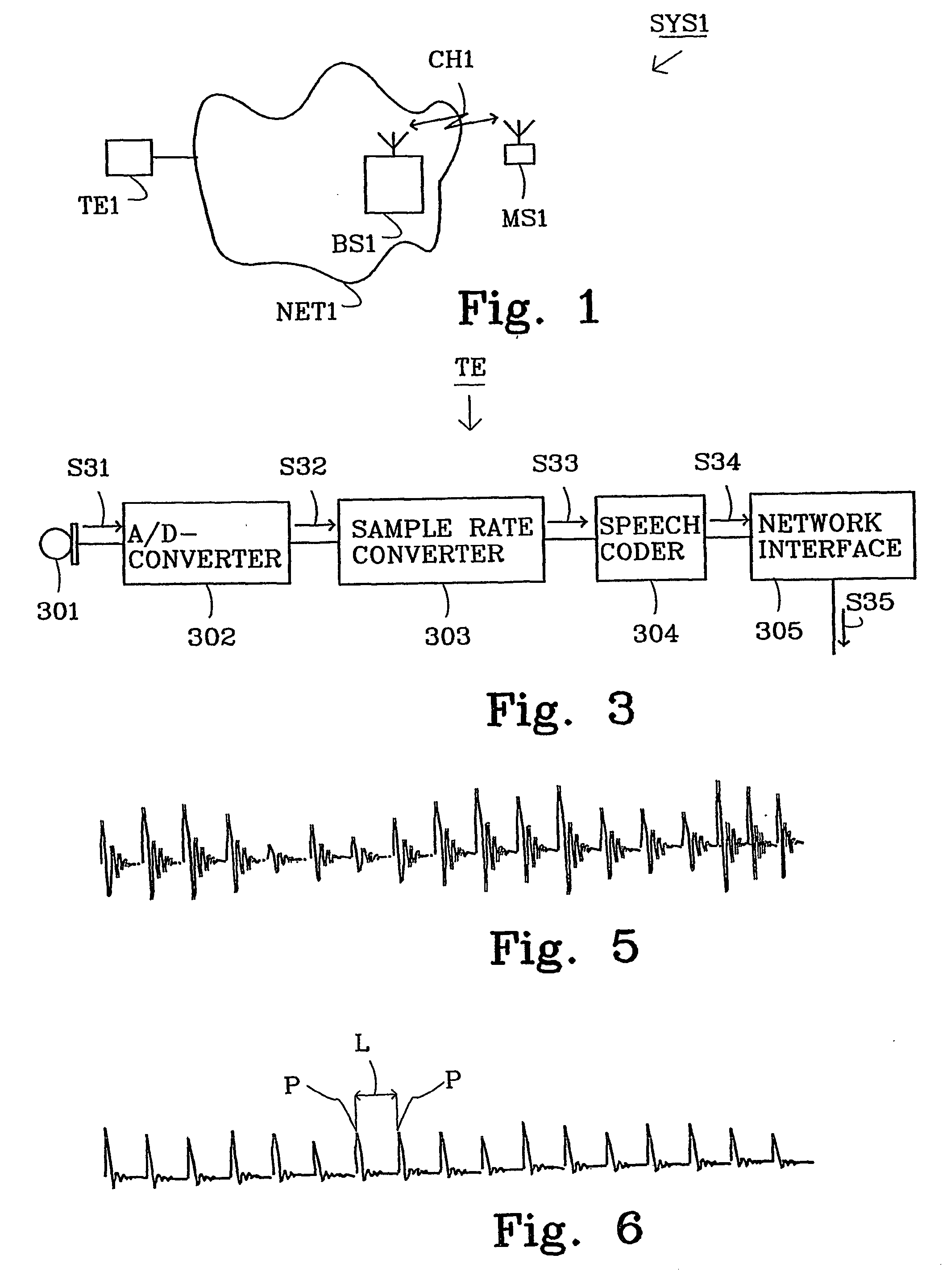

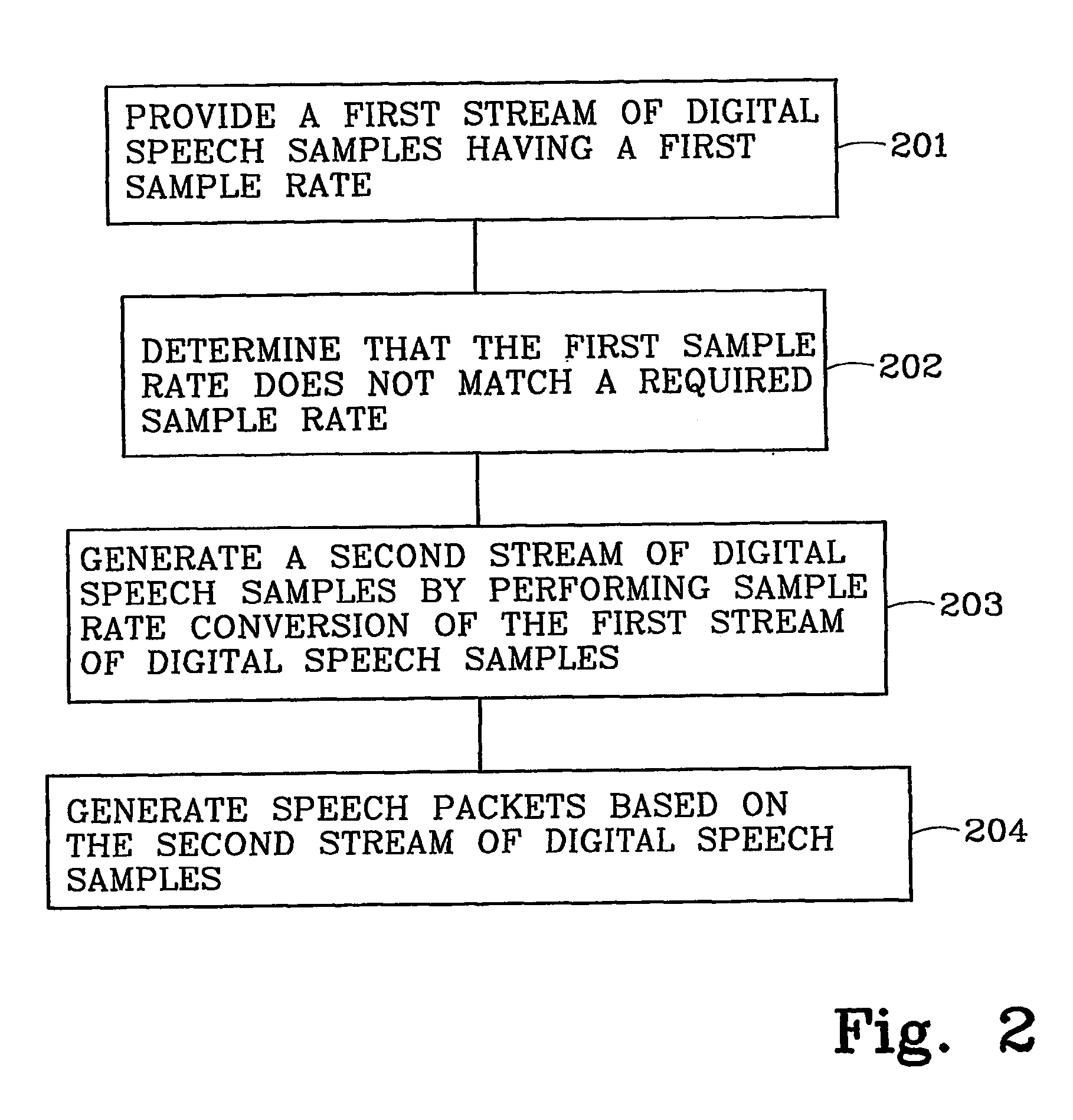

Method and a communication apparatus in a communication system

InactiveUS20040071132A1Improved control of rateEasy to controlSpeech analysisTime-division multiplexSample rate conversionCommunications system

A method for generating speech packets and a communication apparatus implementing the method and functioning as a first node of a communication system. A first stream of digital speech samples having a first sample rate is provided (201). If the first sample rate is determined (202) as not matching a required sample rate, said speech packets are generated (204) based on a second stream of digital speech samples generated (203) by performing sample rate conversion of the first stream of digital speech samples.

Owner:TELEFON AB LM ERICSSON (PUBL)

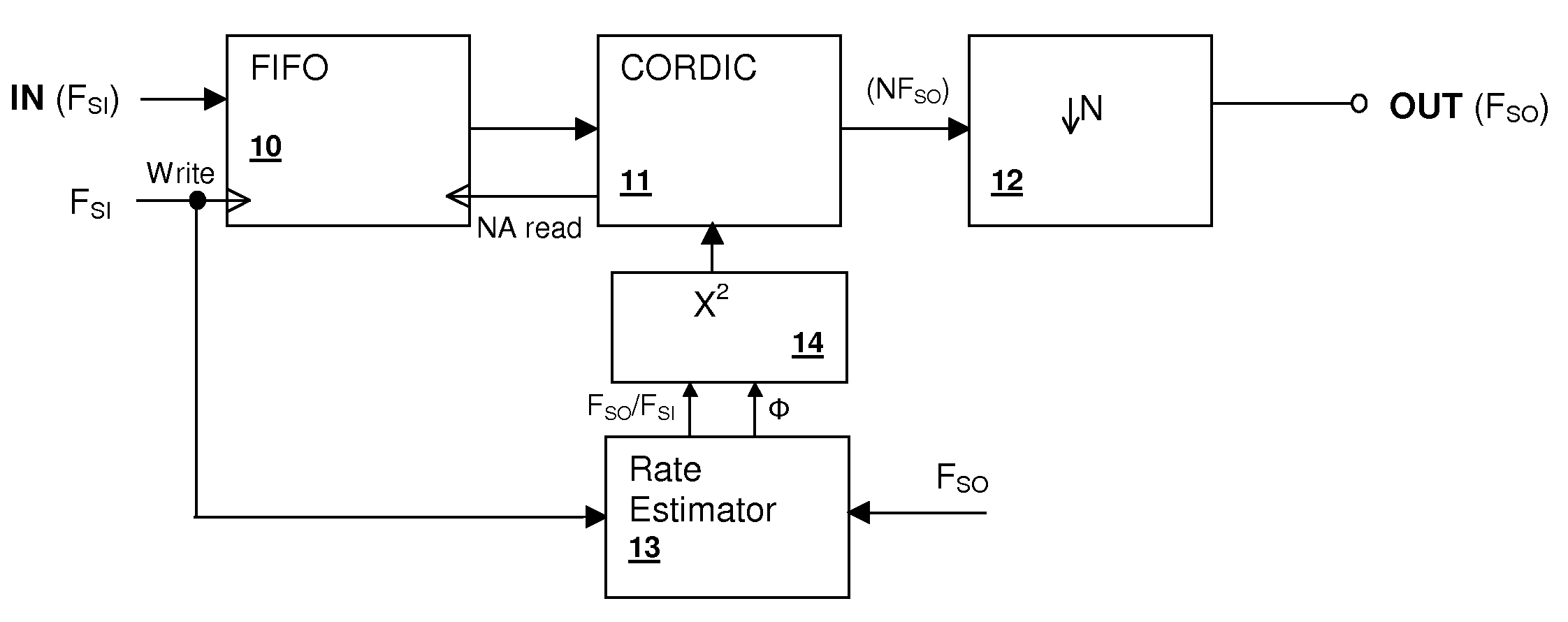

Asynchronous sample rate converter

Systems and methods for asynchronous sample rate conversion are provided that allow time-varying arbitrary sample ratios. An uncorrected ratio between two arbitrary sample rates is corrected and subsequently used to perform an efficient sample rate conversion on the samples in a data stream. Coefficients of a (polyphase) finite impulse response filter are interpolated based on a current time register value. Additional computational efficiency (and a smaller finite impulse response filter) may be used due to oversampling the input signal to the finite impulse response filter.

Owner:KNOWLES ELECTRONICS INC

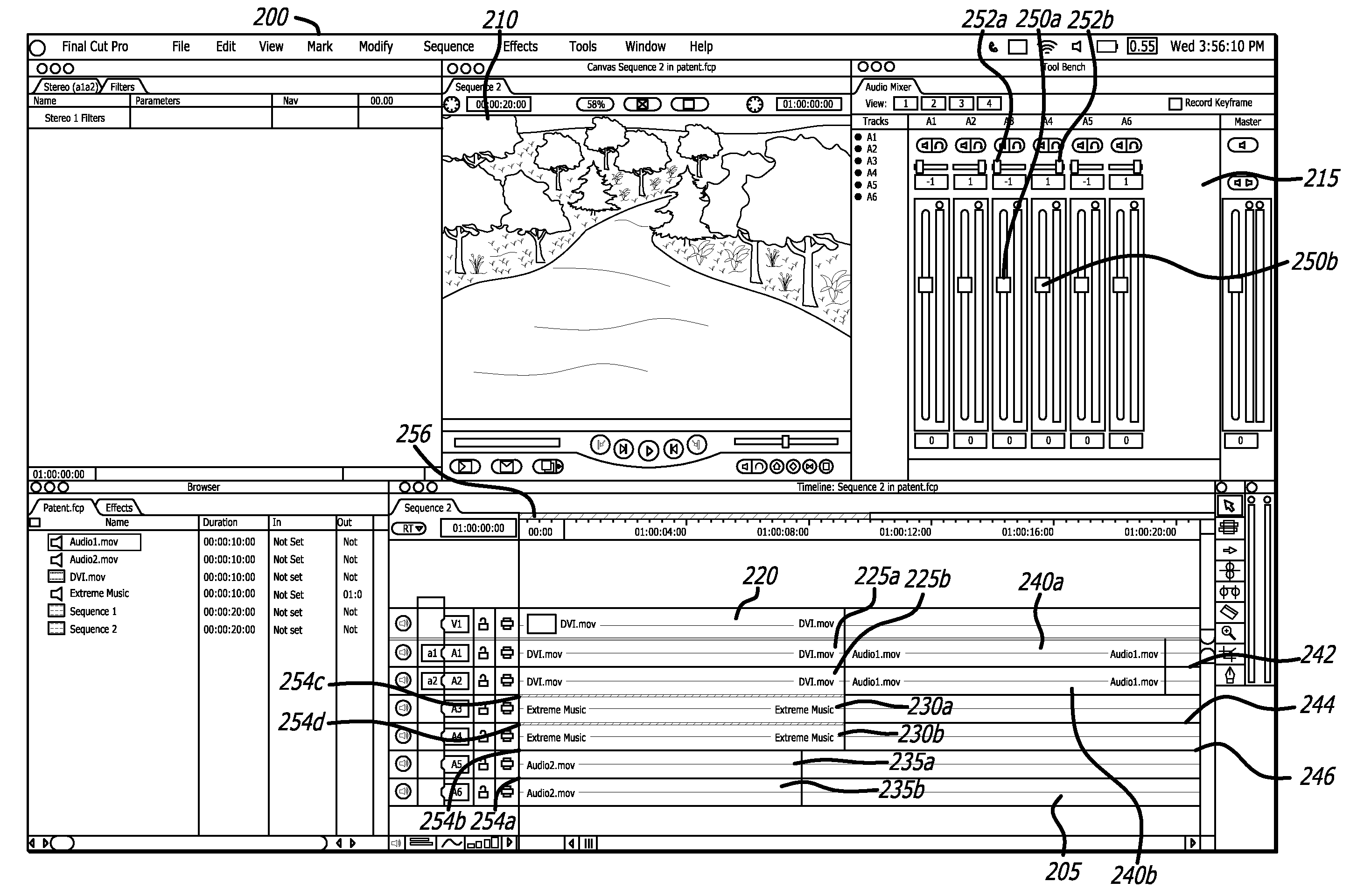

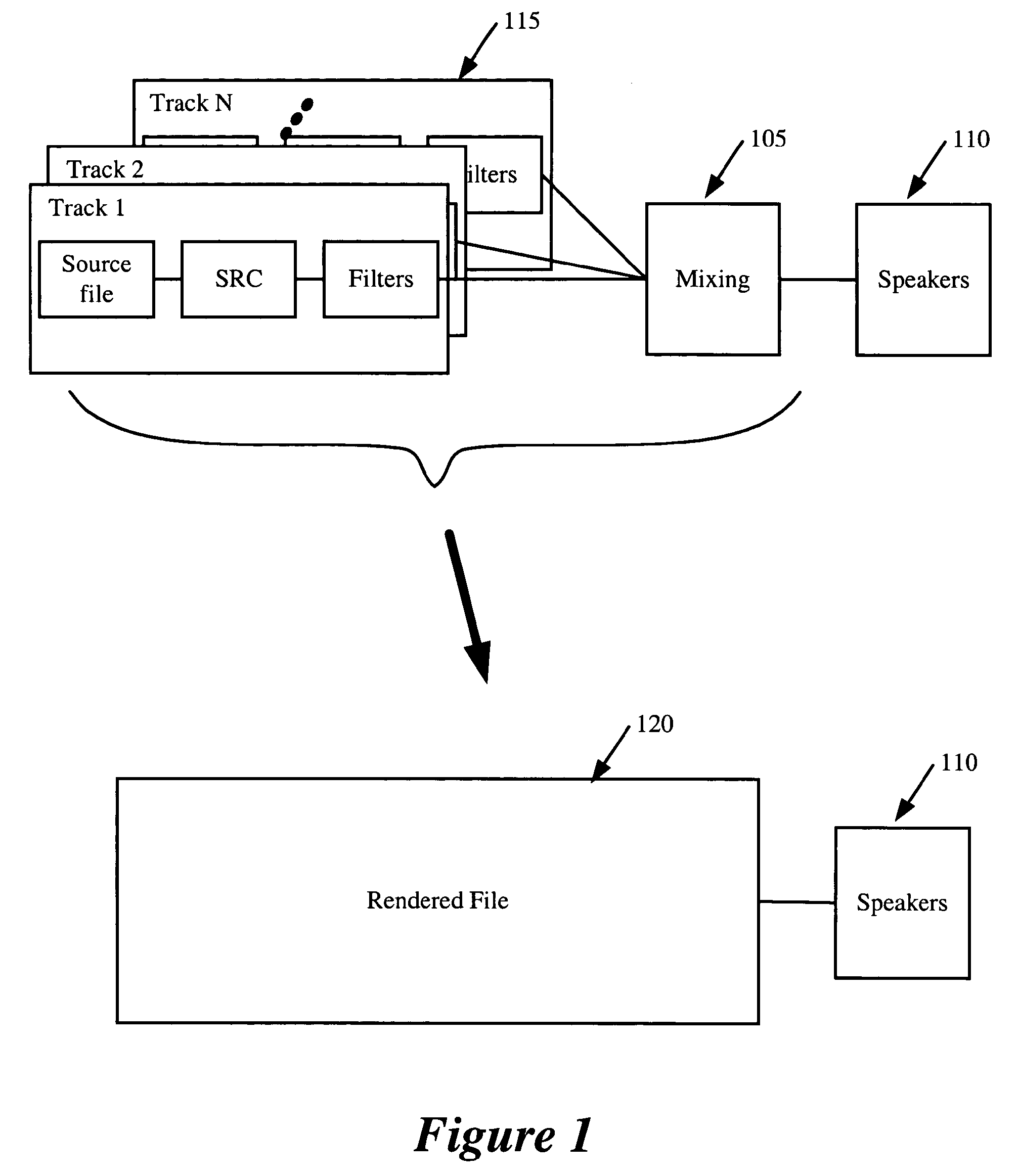

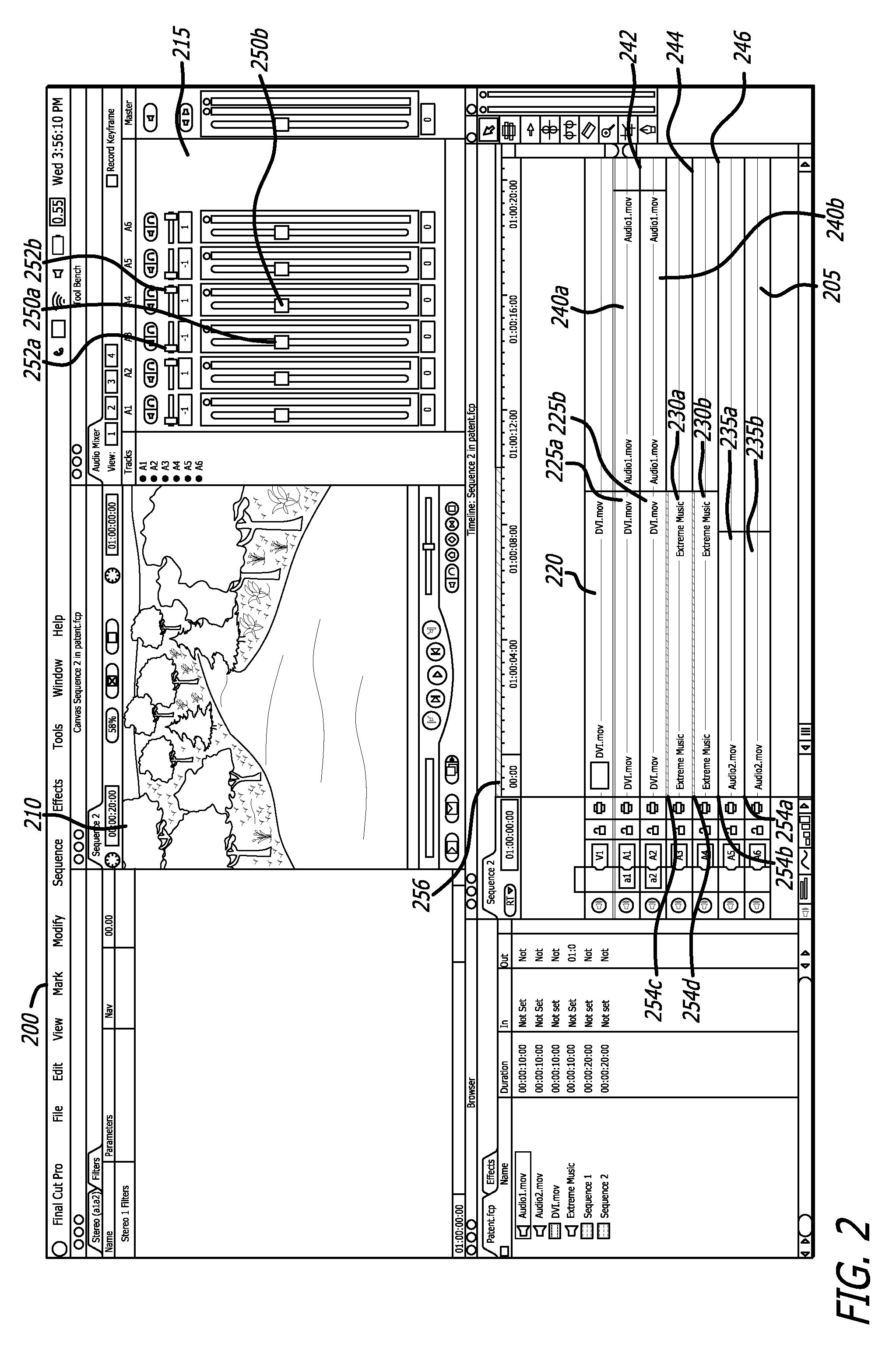

Pre-processing individual audio items in a media project in order to improve real-time processing of the media project

InactiveUS20080154407A1Electronic editing digitised analogue information signalsSpeech analysisSample rate conversionTime processing

Owner:APPLE INC

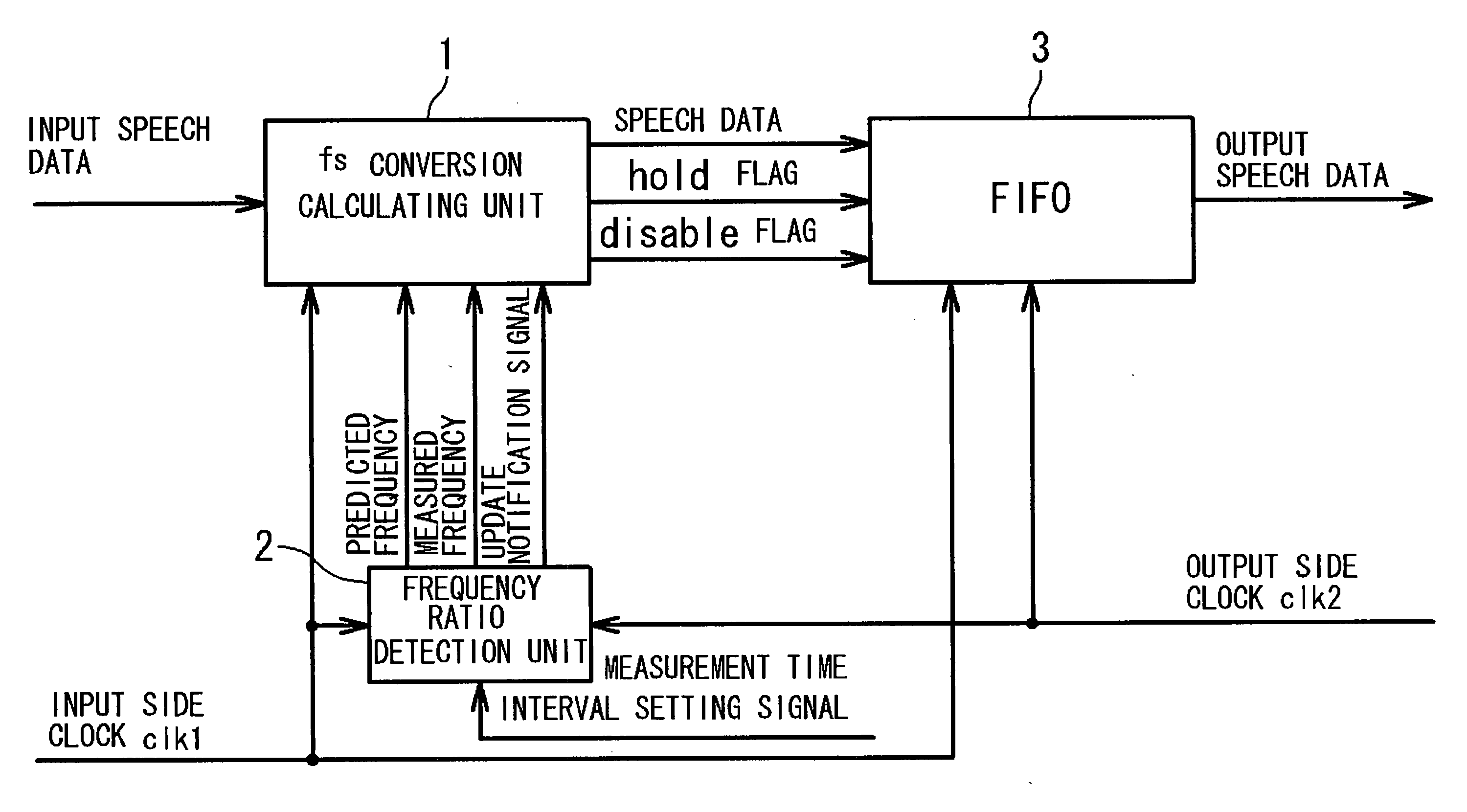

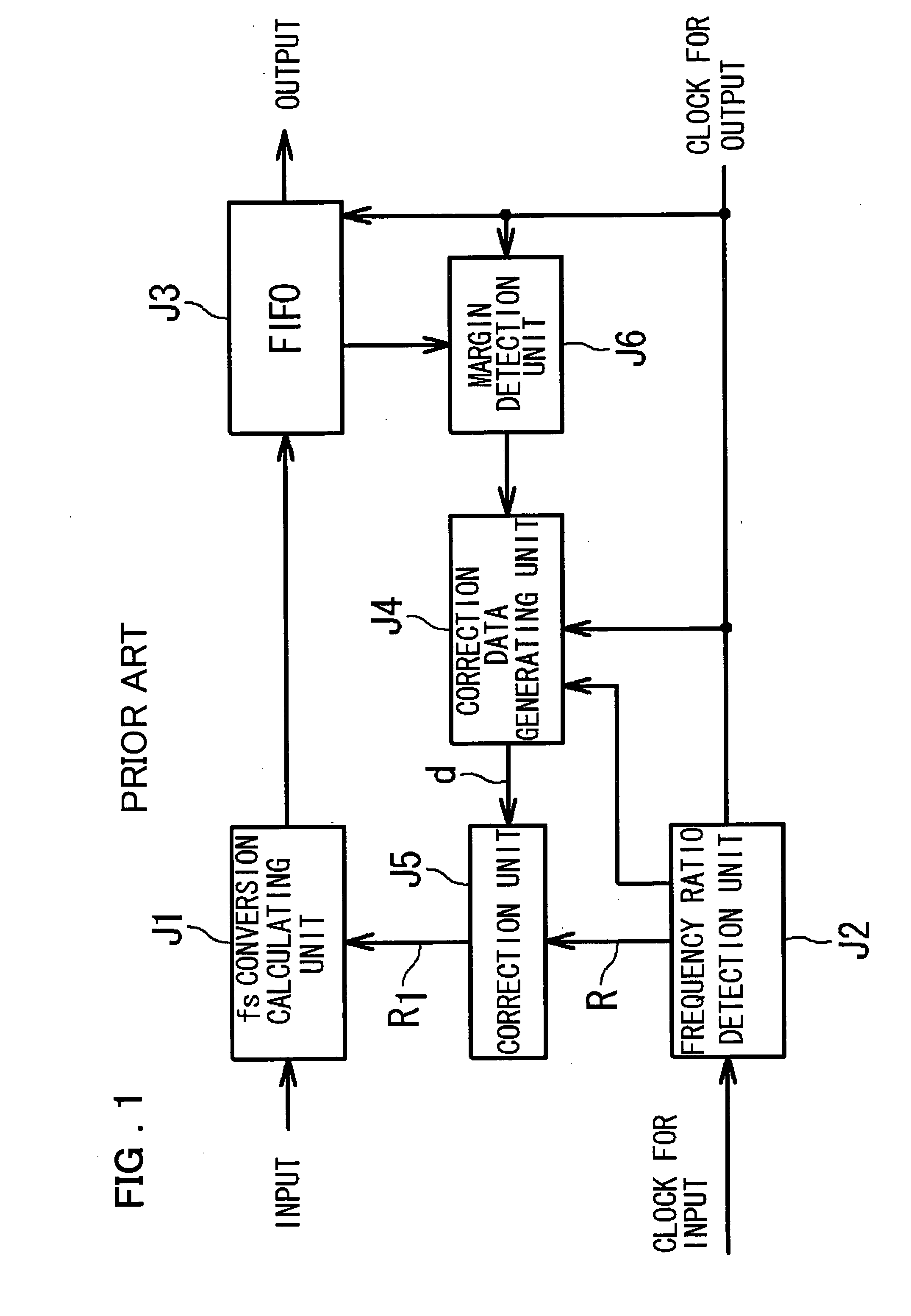

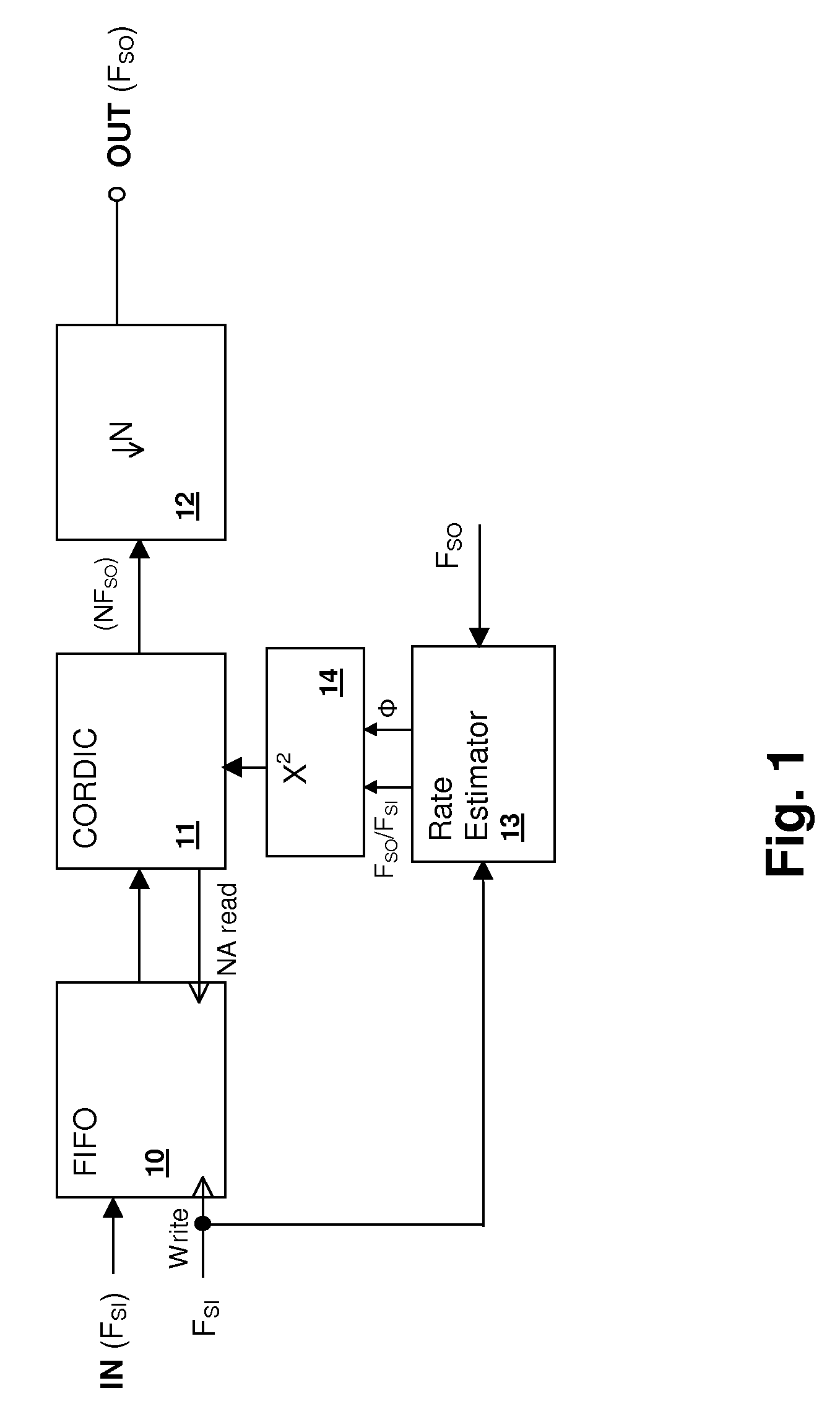

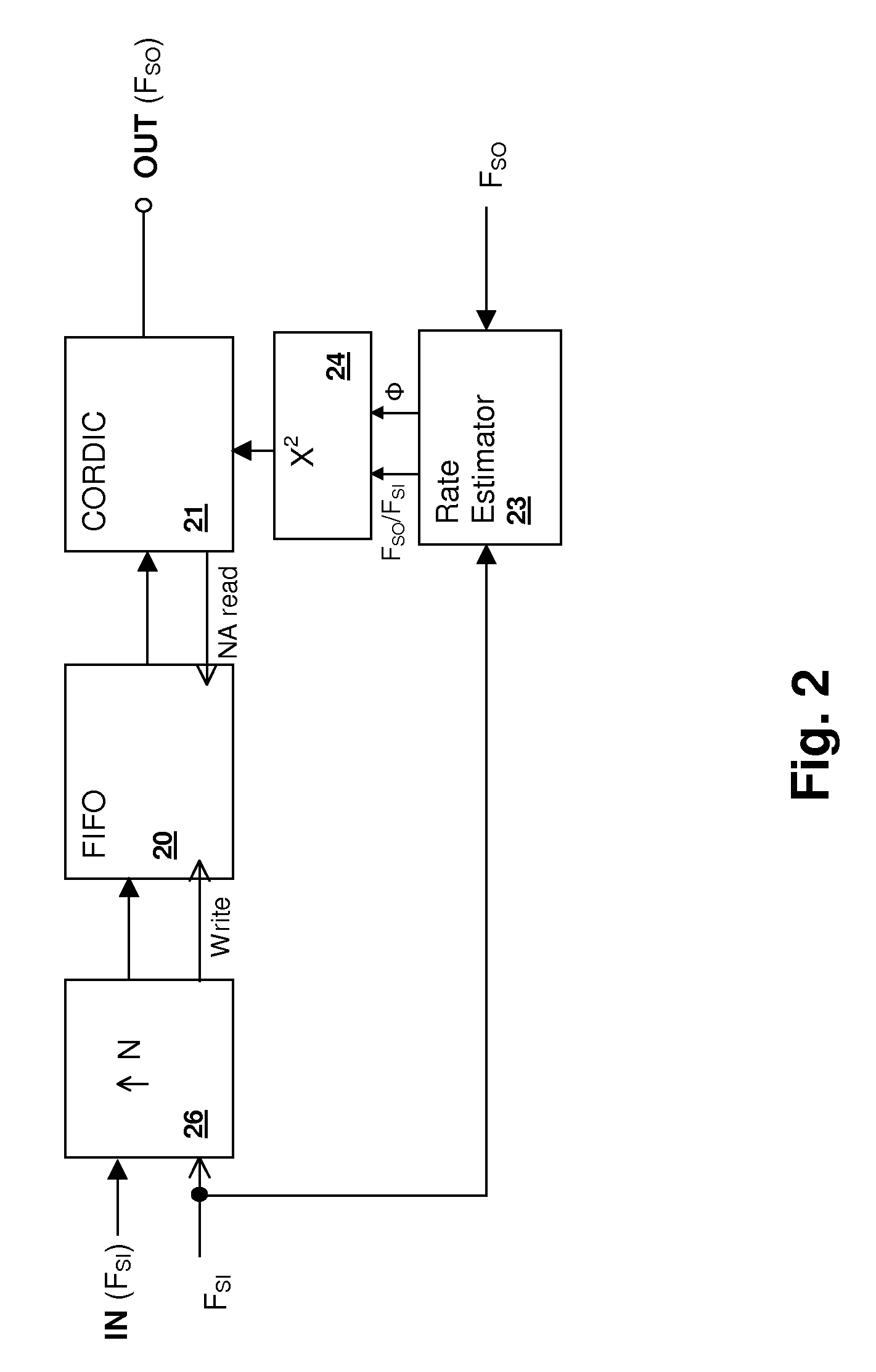

Sampling rate conversion method and apparatus

ActiveUS20050163276A1Improve accuracyOscillation suppressionDigital technique networkLocal circuitsSample rate conversionClock rate

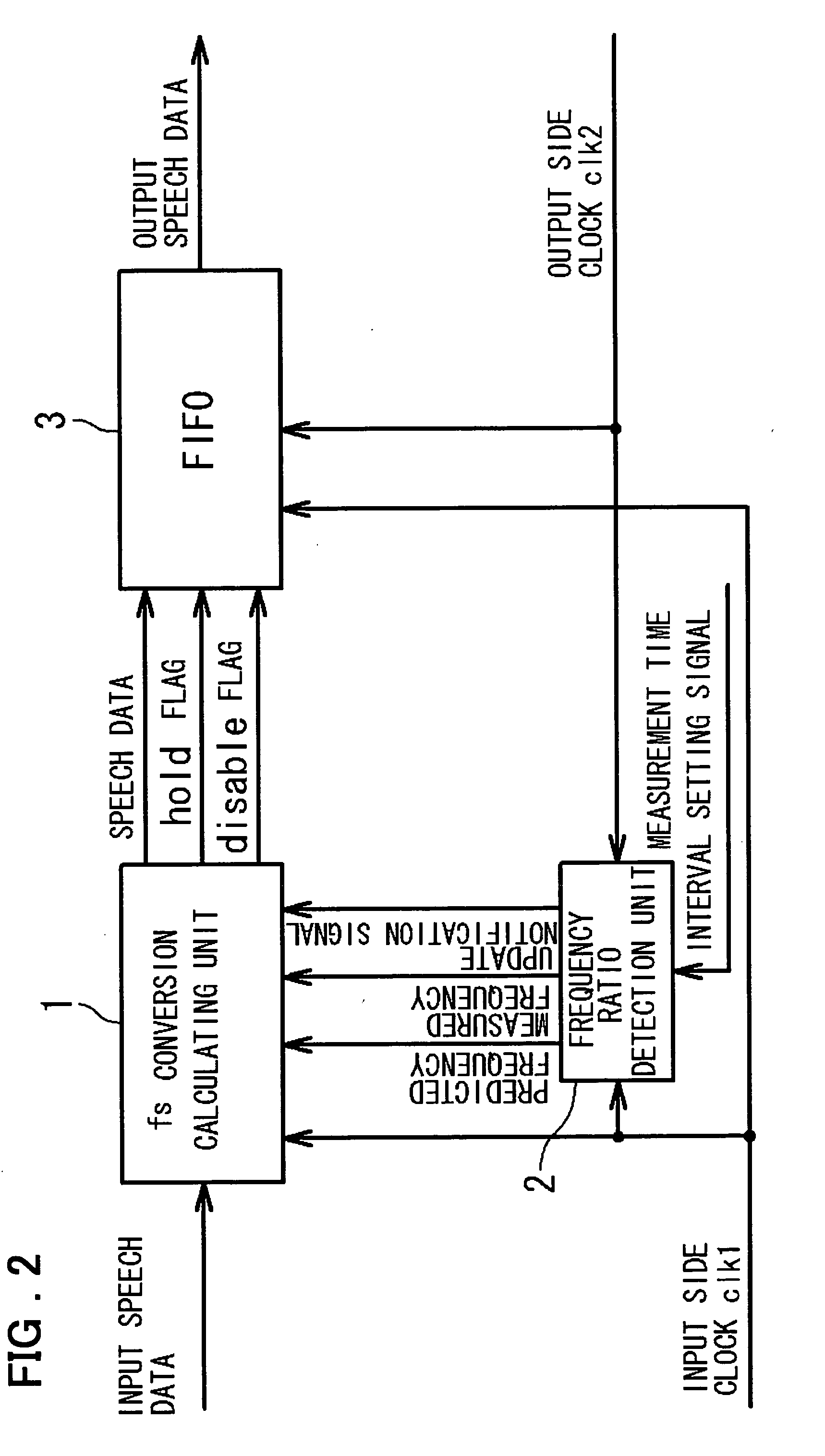

Disclosed is a sampling rate conversion apparatus for converting first data, sampled at a first sampling rate, into second data, sampled at a second sampling rate, includes a FIFO for storing the first data responsive to a first clock signal and for outputting the first data as second data responsive to the second clock signal. This FIFO stores the first data based on a write control signal indicating whether or not the first data written directly previously is to be updated to the first data, and outputs the second data read out based on a read control signal indicating whether or not the second data as read out is to be read out during the next time interval as well. The sampling rate conversion apparatus also includes a frequency detection unit for measuring the first clock signal during the current time interval to generate the value of the first current clock frequency, generating the value of a current predicted clock frequency from the value of the first current clock frequency and the value of the directly previously predicted clock frequency and for using the value of the current predicted clock frequency as the directly previously predicted clock frequency during the next time interval, and a calculating unit supplied with the first data to output the data to the FIFO. The calculating unit generates write control signal and read control signal from the value of a second current frequency, generated by measuring the second clock signal during the current time interval, and from the value of the current predicted clock frequency, to output the so generated write and read control signal to the FIFO.

Owner:RENESAS ELECTRONICS CORP

Information Processing Device and Information Processing Method

InactiveUS20080256157A1Low implementation costMinimize impactDigital technique networkComplex mathematical operationsInformation processingSample rate conversion

An information processing device for processing reception signals converted into digital signals, includes: a first conversion unit for executing sampling rate conversion of each of the digital signals to be computed with each tap coefficient of a K'th-order FIR filter; a filter computing unit for executing computation processing of the K'th order FIR filter on K digital signals each of which have been subjected to sampling rate conversion by the first conversion unit; and a control unit for controlling sampling rate conversion of the digital signals by the first conversion unit, and the computation processing of the K'th order FIR filter by the filter computing unit.

Owner:SONY CORP

Real-time sample rate converter having a non-polynomial convolution kernel

ActiveUS7298296B1Low costFast decayAnalogue/digital conversionElectric signal transmission systemsSample rate conversionConvolution

A real-time sample rate converter having a non-polynomial convolution kernel provides reduction in die area and power for performing sample rate conversion in real-time. A non-polynomial convolution kernel, which may be a gaussian operator, is used to determine output sample values from values of an incoming stream of values. If the input sample rate is higher than the output sample rate, the input sample stream is convolved with the gaussian kernel and then decimated to yield the output stream. If the input sample rate is lower than the output sample rate, the input stream is resampled to a small multiple of the output sample rate and convolved with the gaussian kernel to produce the output sample stream directly.

Owner:CIRRUS LOGIC INC

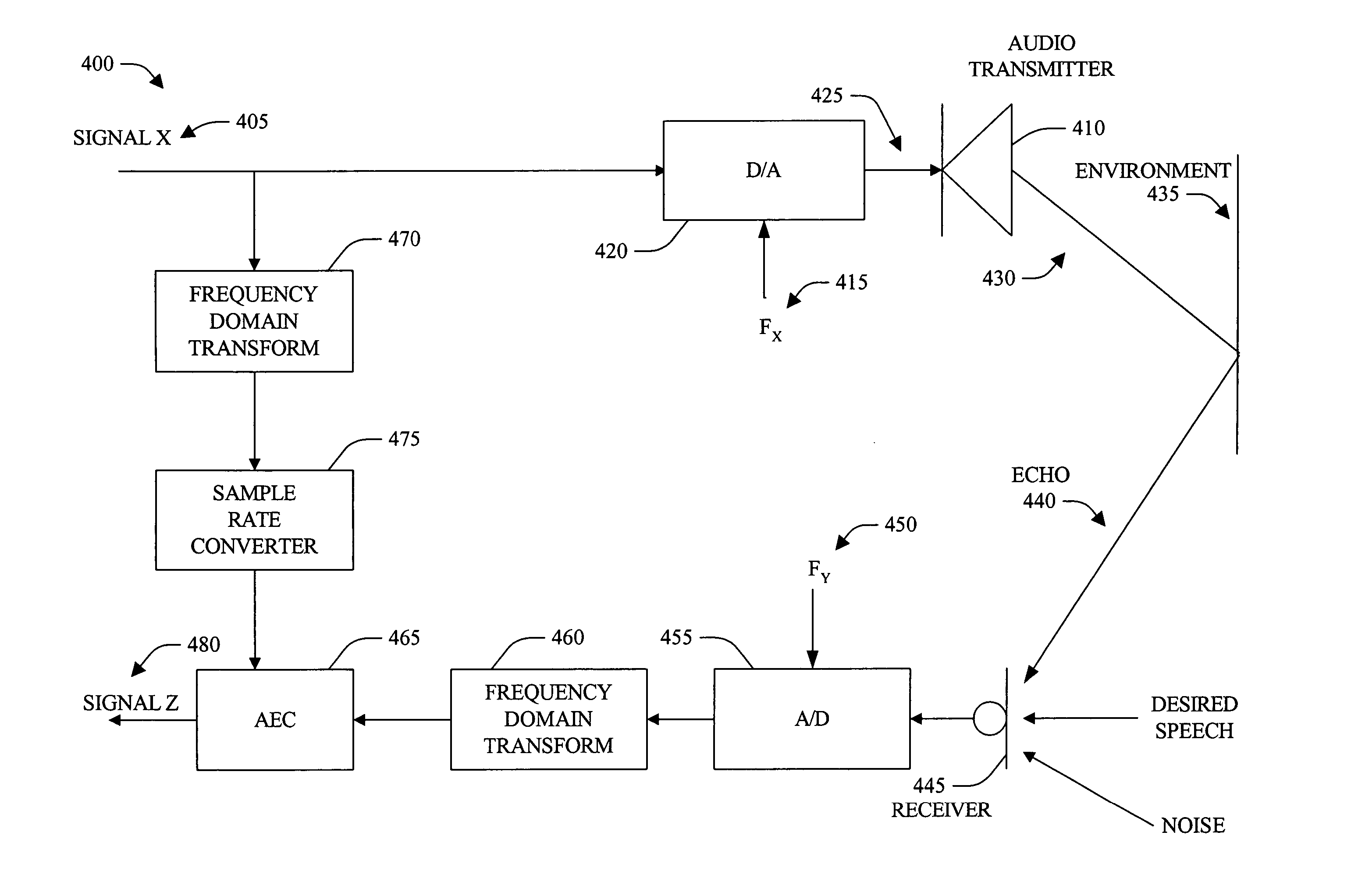

Systems and methods for echo cancellation with arbitrary playback sampling rates

InactiveUS20050089148A1Facilitate signal transformationQuality improvementTwo-way loud-speaking telephone systemsSpeech analysisSample rate conversionFrequency domain

The present invention relates to systems and methods that remove echo from a signal via a novel echo cancellation technique that supports arbitrary playback sampling rates. The novel echo cancellation technique transforms a playback signal to a frequency domain representation and converts its sampling rate to a sampling rate of a frequency domain transformed received signal for the appropriate number of frequency bins. This conversion is achieved via an exact or interpolated approached. The re-sampled playback signal transform is then utilized in connection with the received signal transform to remove echo associated with the playback signal from the received signal.

Owner:MICROSOFT TECH LICENSING LLC

Sample rate conversion combined with DSM

ActiveUS20070146185A1Reduce hardwareReduce computational complexityElectric signal transmission systemsDigital technique networkSample rate conversionDigital filter

Digital to Analog Conversion and sample conversion blocks are combined in order to reduce hardware and / or computational complexity. A novel DSM design is used to perform sample rate conversion. The DSM may also be used to perform other digital filtering functions, thus providing a single hardware / software technique to perform both functions. The invention includes a method and apparatus for converting input data samples provided at a first sample rate to an analog output signal. Input data samples are converted by a Delta Sigma Modulator (DSM) in a Digital to Analog Converter (DAC) to output data samples, where internal states of the DSM are updated at a second sample rate unequal to the first sample rate. At least one internal state of the DSM s modified to account for the time difference in response to a new input sample arriving at a time different from an update of the internal states of the DSM.

Owner:CIRRUS LOGIC INC