Patents

Literature

409 results about "Offset cancellation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

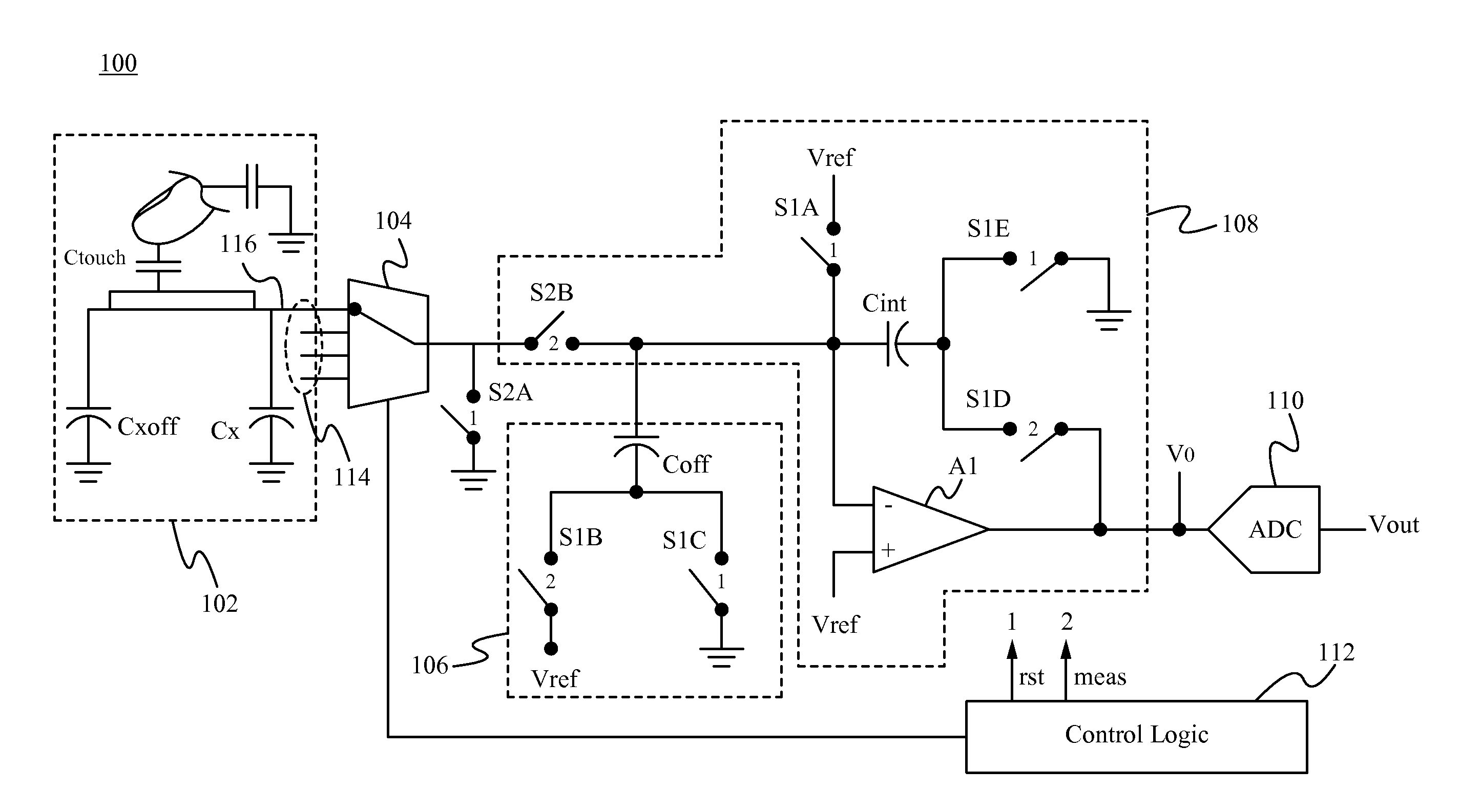

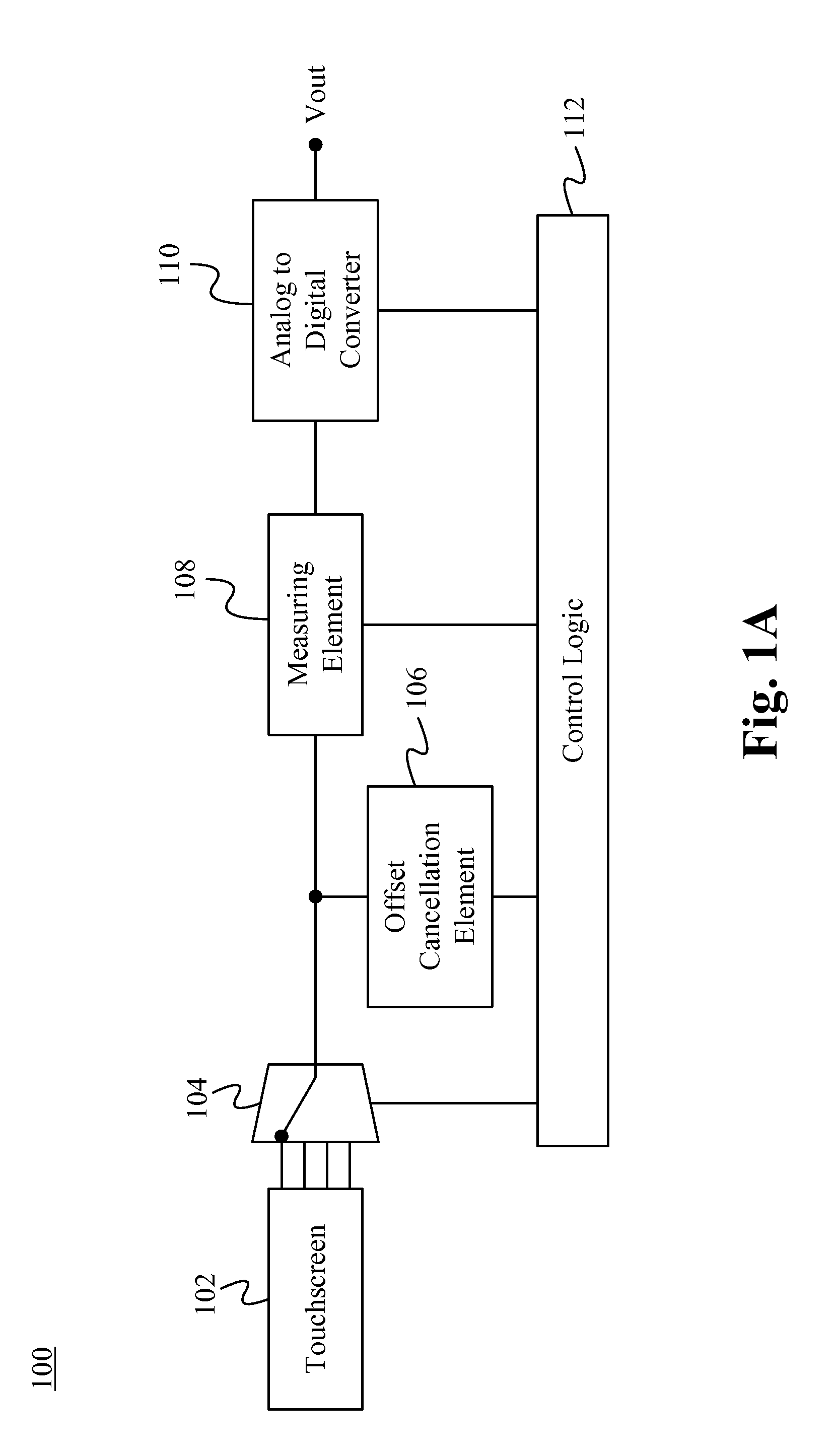

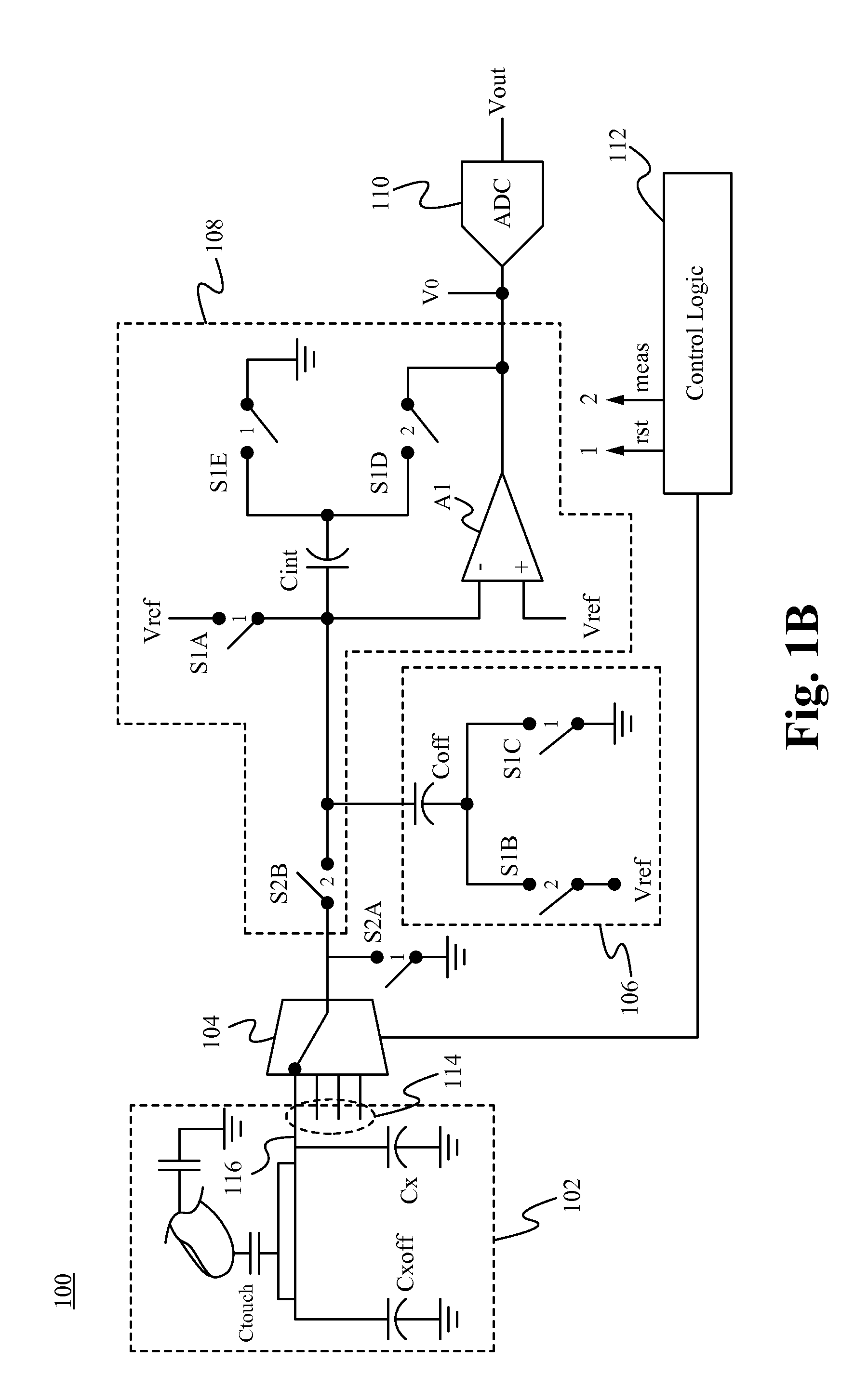

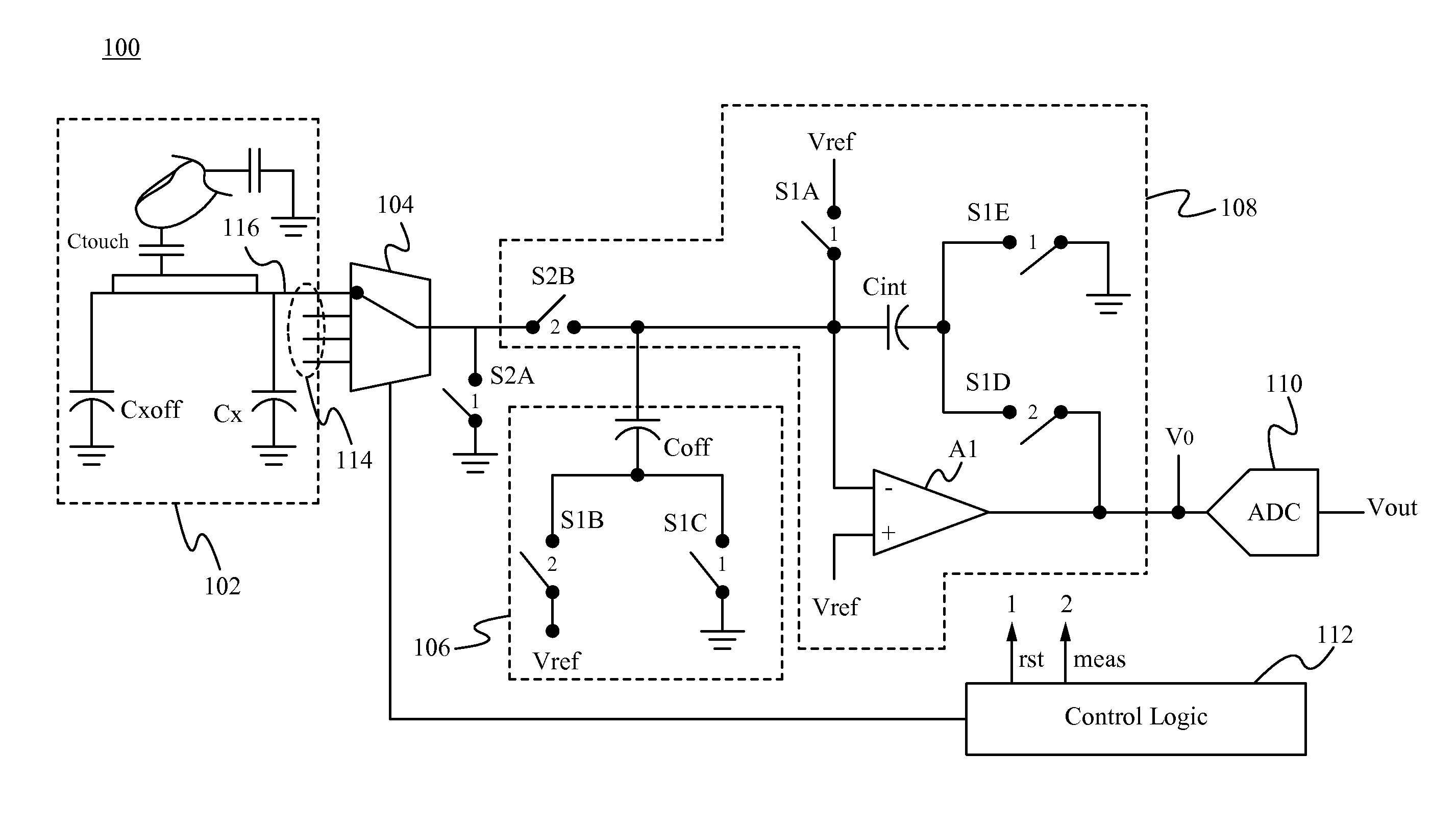

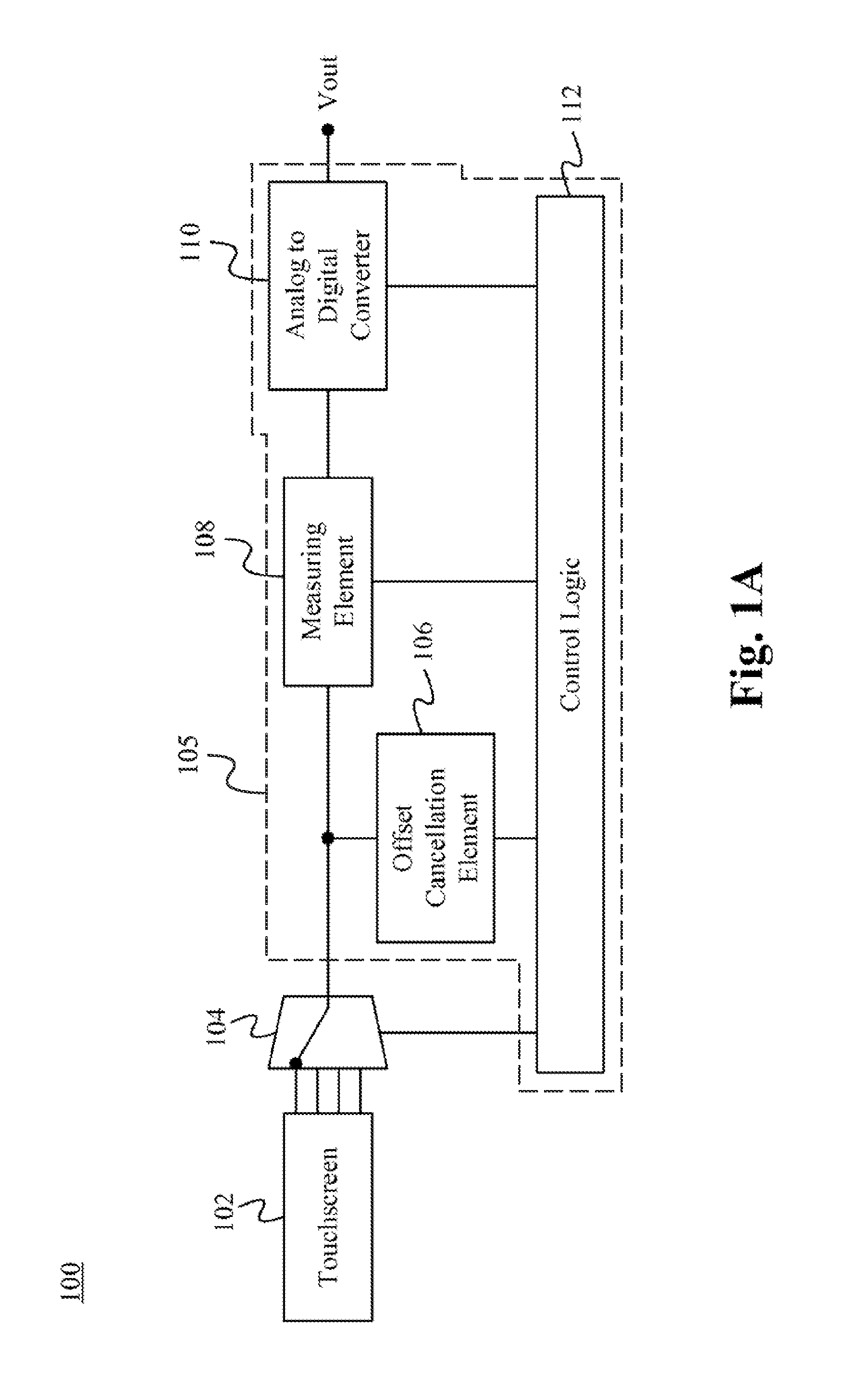

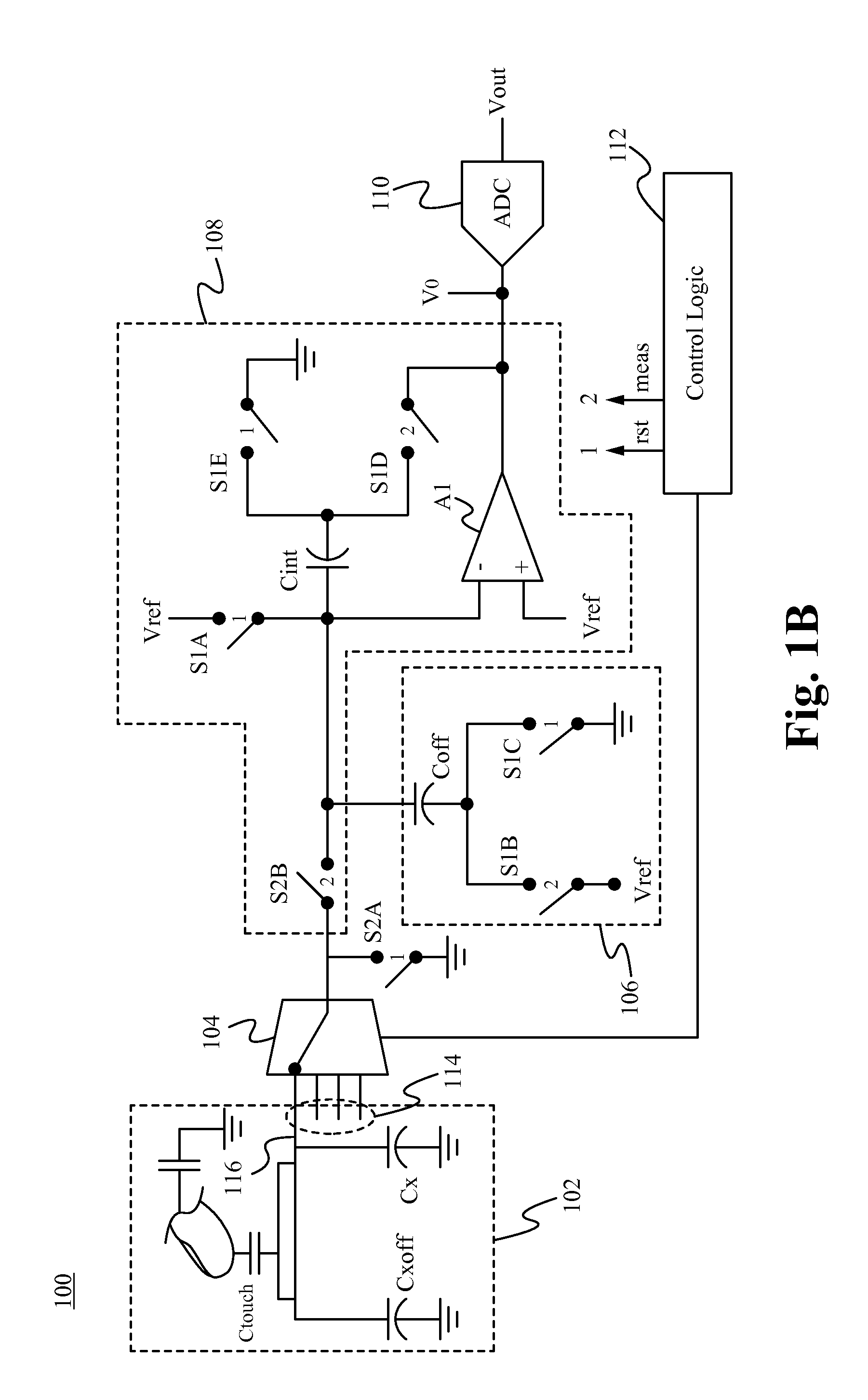

Method and apparatus for improving dynamic range of a touchscreen controller

ActiveUS20110261005A1Improve dynamic rangeLow costElectronic switchingInput/output processes for data processingOffset cancellationEngineering

A touchscreen system for increasing the dynamic range of the system comprising a touchscreen coupled to an offset cancellation element and a capacitance measuring element. The offset cancellation element is configured to be dynamically changed in capacitance such that it offsets parasitic and sensor capacitances of the touchscreen sensors thereby leaving only touch event capacitance to be measured by the measuring element. The offset cancellation element is able to adjust to the initial unwanted capacitances of each sensor as well as dynamically adjust to changes in the unwanted capacitance due to the environment. In some embodiments, the offset cancellation element is a capacitance digital-to-analog converter that is controlled by a controller for offsetting the unwanted capacitance. As a result, the touchscreen system is able to utilize a small integrating capacitor thereby lowering cost and improving the dynamic range of the system.

Owner:QUALCOMM INC

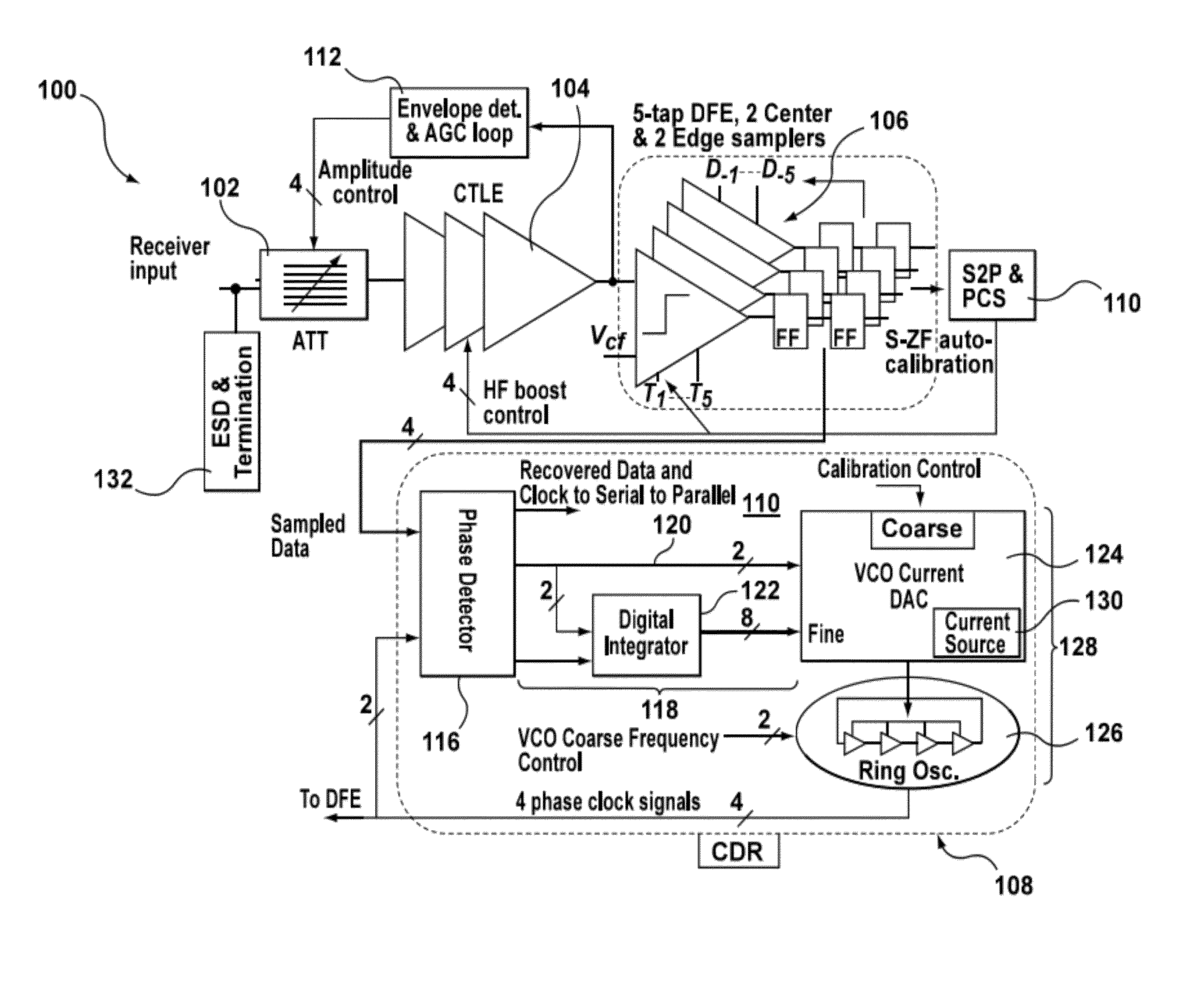

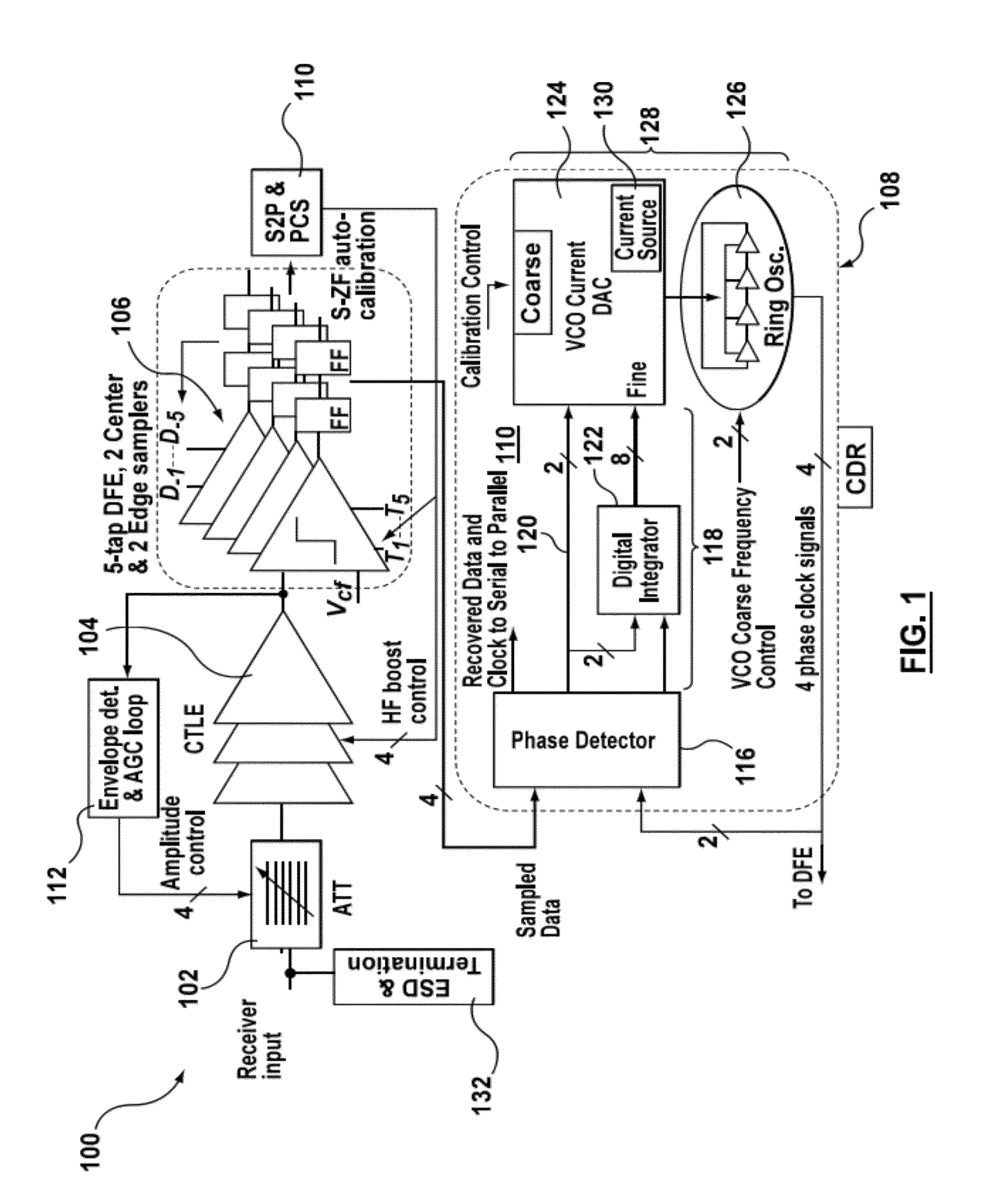

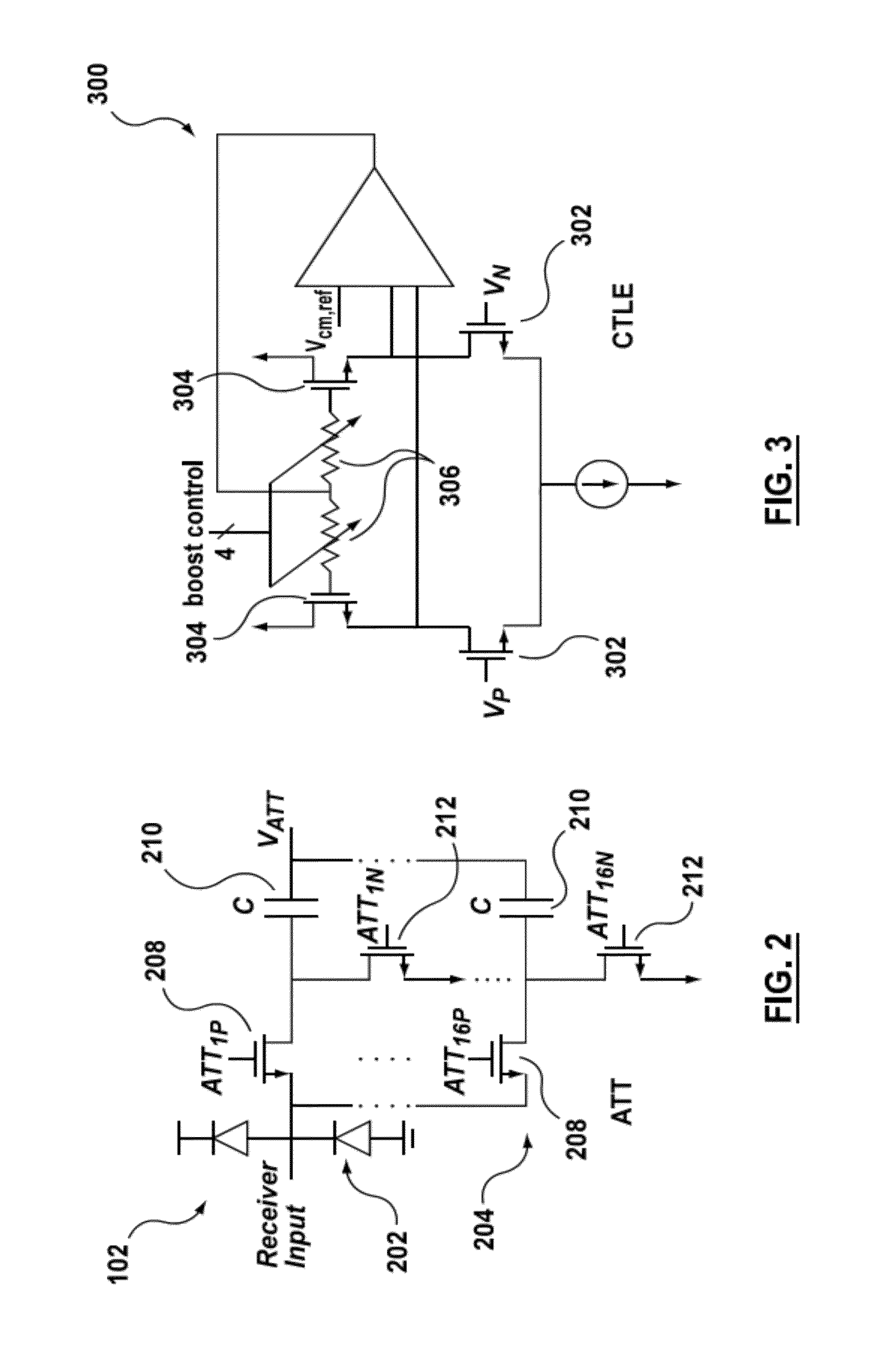

Decision feedback equalizer and transceiver

A decision feedback equalizer, transceiver, and method are provided, the equalizer having at least one comparator, the at least one comparator comprising a first stage, comprising a main branch having two track switches with a resistive load, an offset cancellation branch, a plurality of tap branches with transistor sizes smaller than the main branch, in which previous decisions of the equalizer are mixed with the tap weights using current-mode switching, and a cross coupled latch branch; and a second stage, comprising a comparator module for making decisions based on the outputs of the first stage and a clock input, and a plurality of flip-flops for storing the output of the comparator module.

Owner:RAMBUS INC

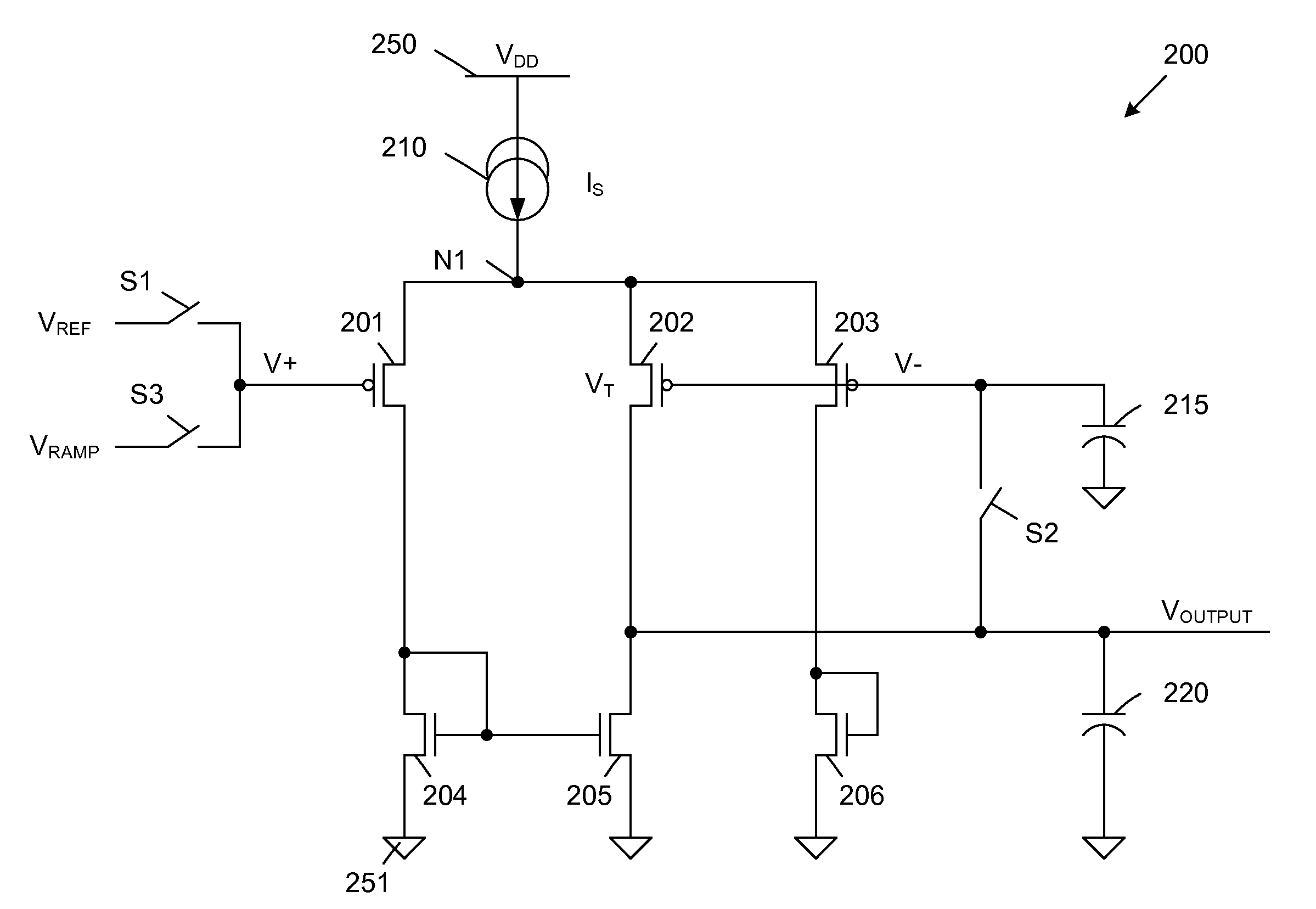

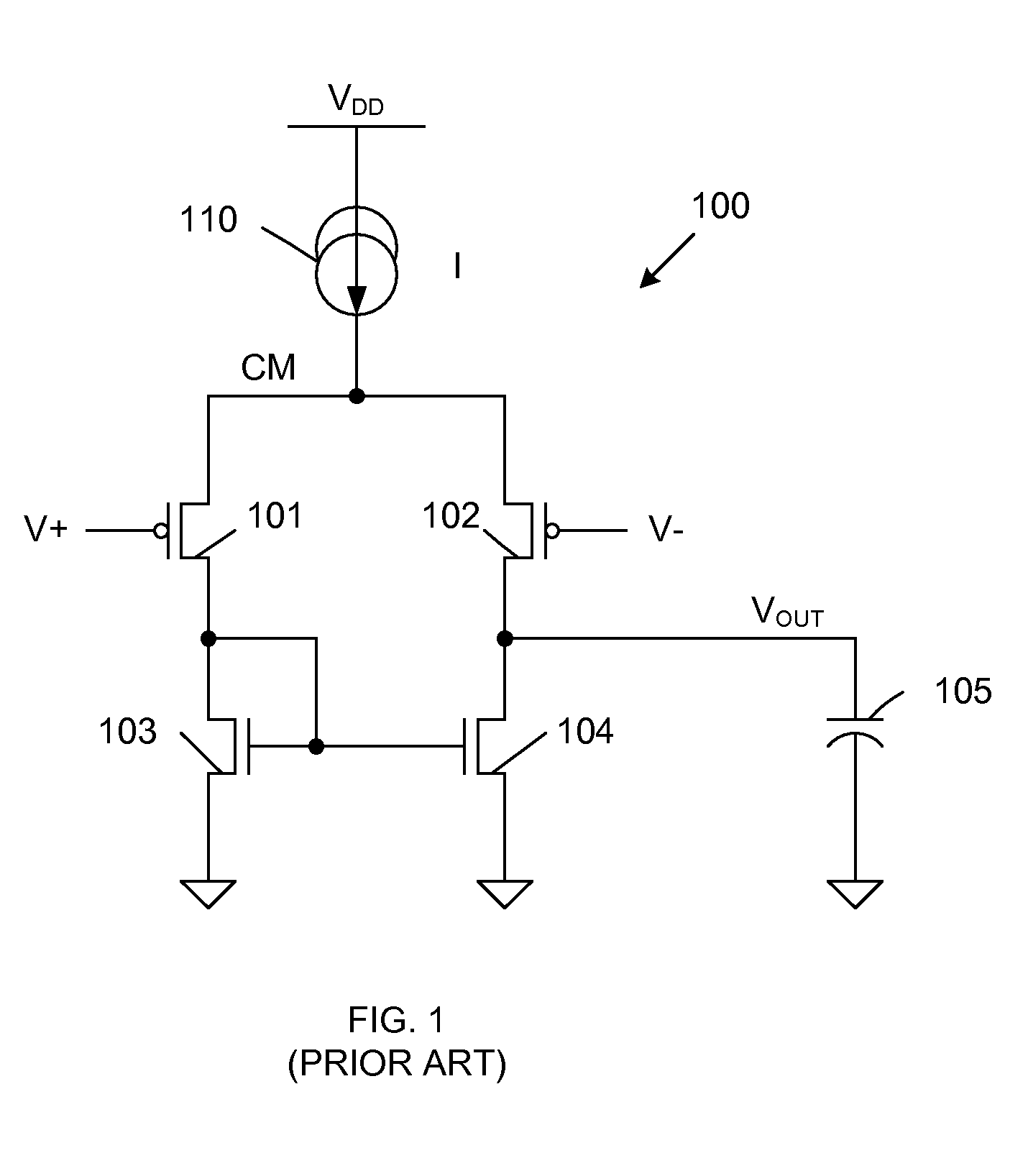

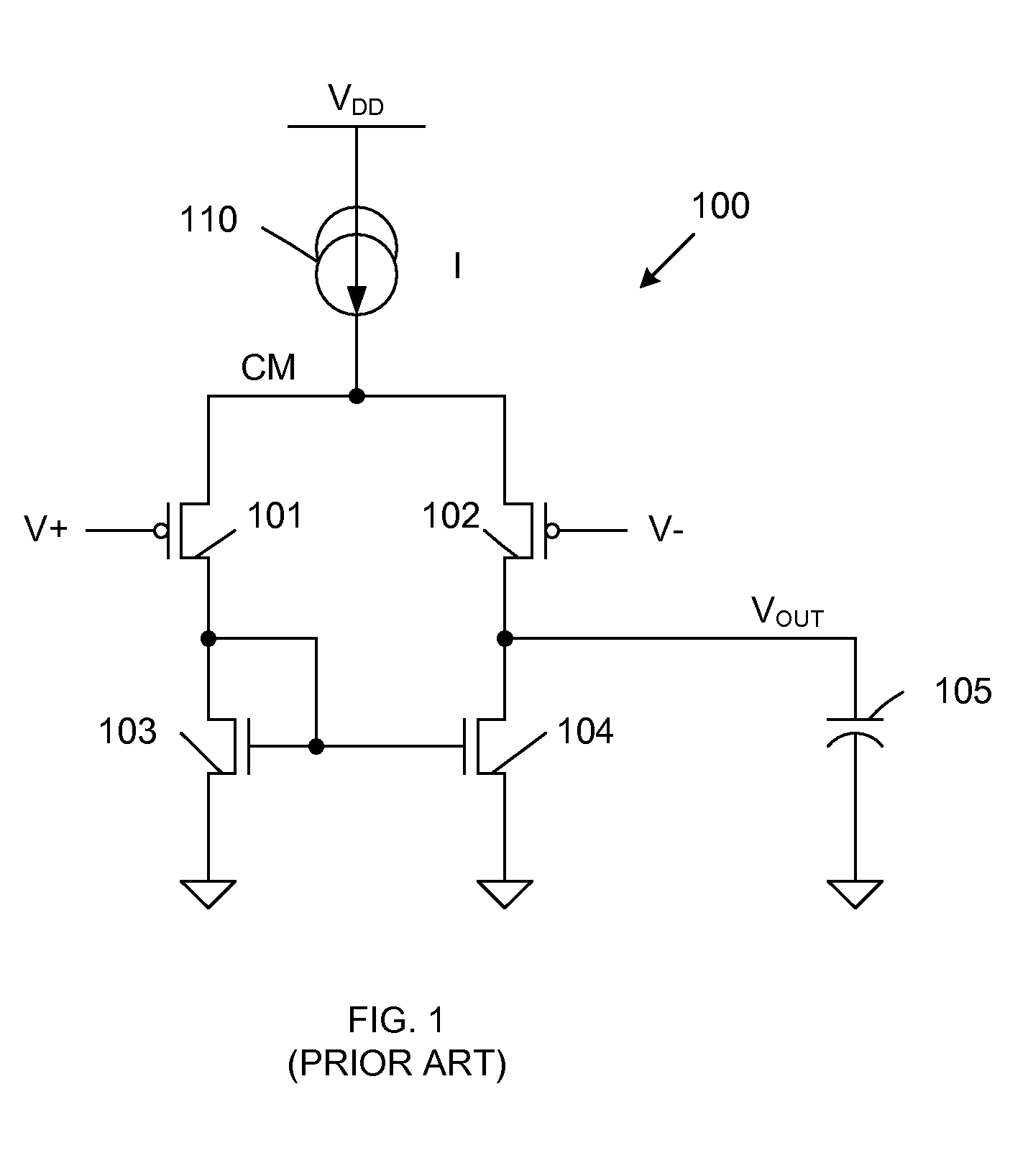

Comparator with low supply current spike and input offset cancellation

ActiveUS7609093B2Multiple input and output pulse circuitsInstant pulse delivery arrangementsOffset cancellationComparators circuits

A current control circuit is coupled in parallel with the current paths of a differential comparator circuit to ensure that a substantially constant current is drawn from a current source during all operating phases of a comparator. The current control circuit is biased by a reference voltage, which is also used to bias a V− input terminal of the differential comparator circuit. The reference voltage is stored by a sample capacitor, which is charged by applying the reference voltage to a V+ input terminal of the differential comparator circuit while coupling an output terminal of the differential comparator circuit to the sample capacitor in a unity feedback configuration.

Owner:TOWER SEMICONDUCTOR

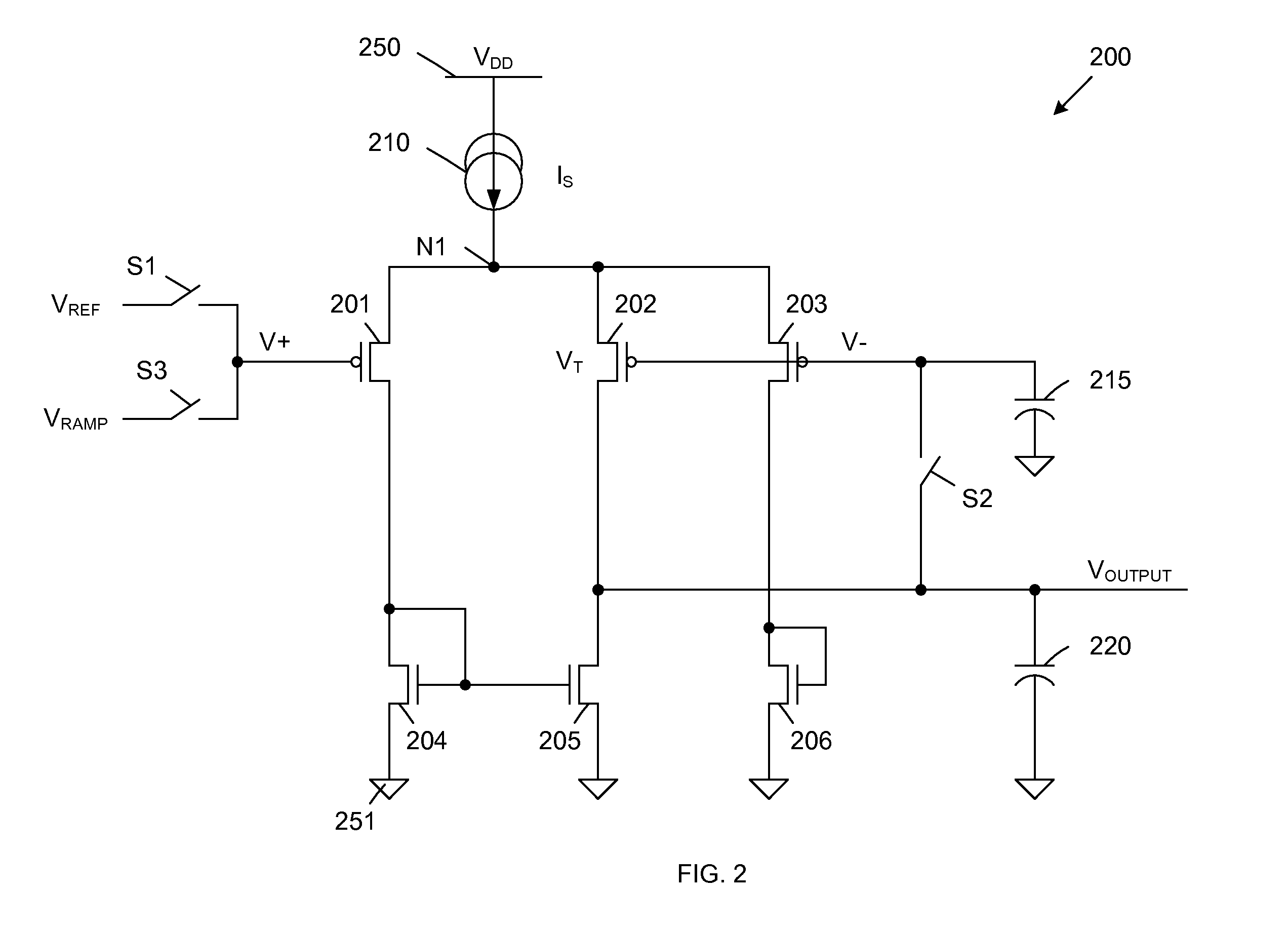

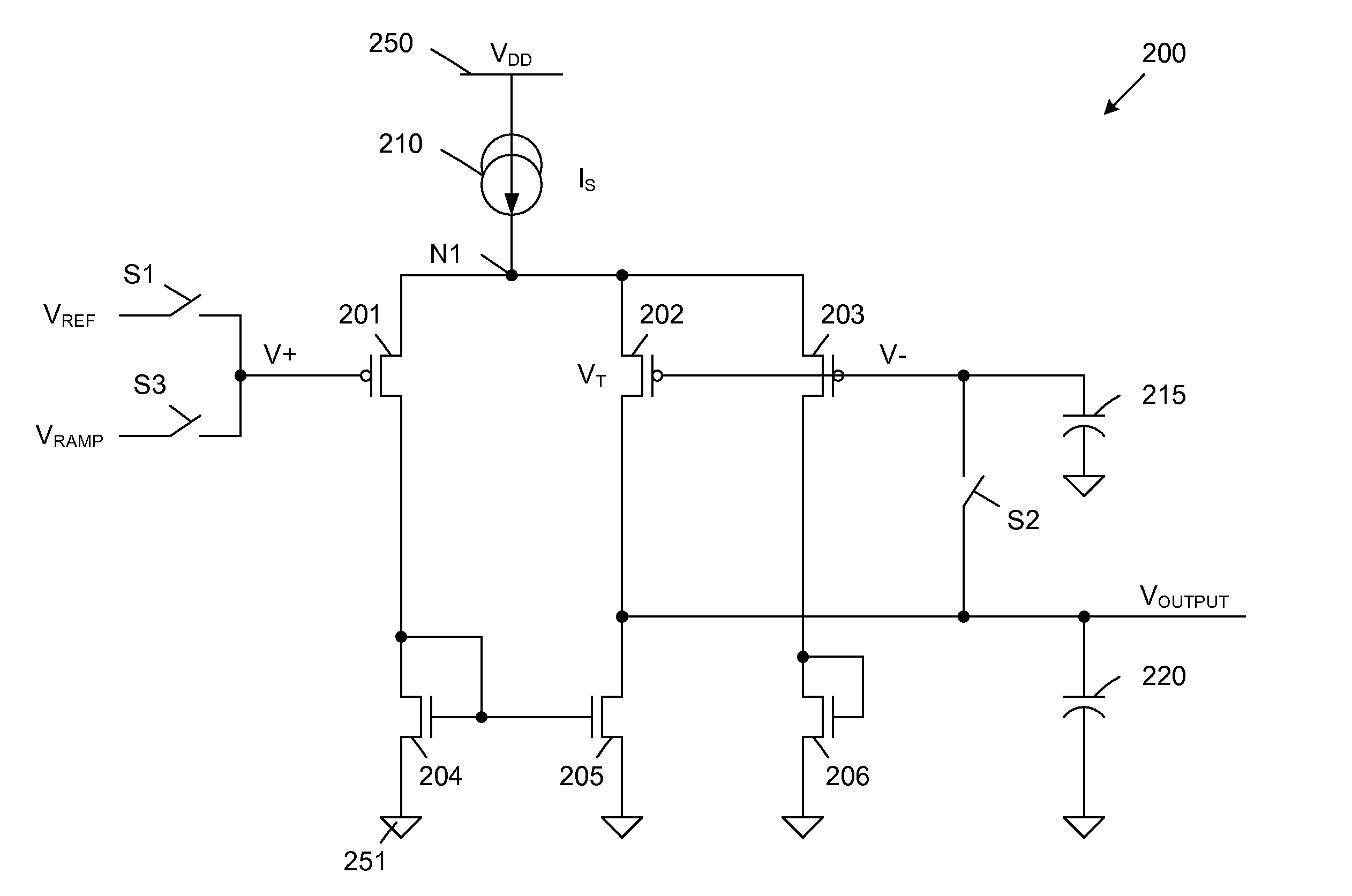

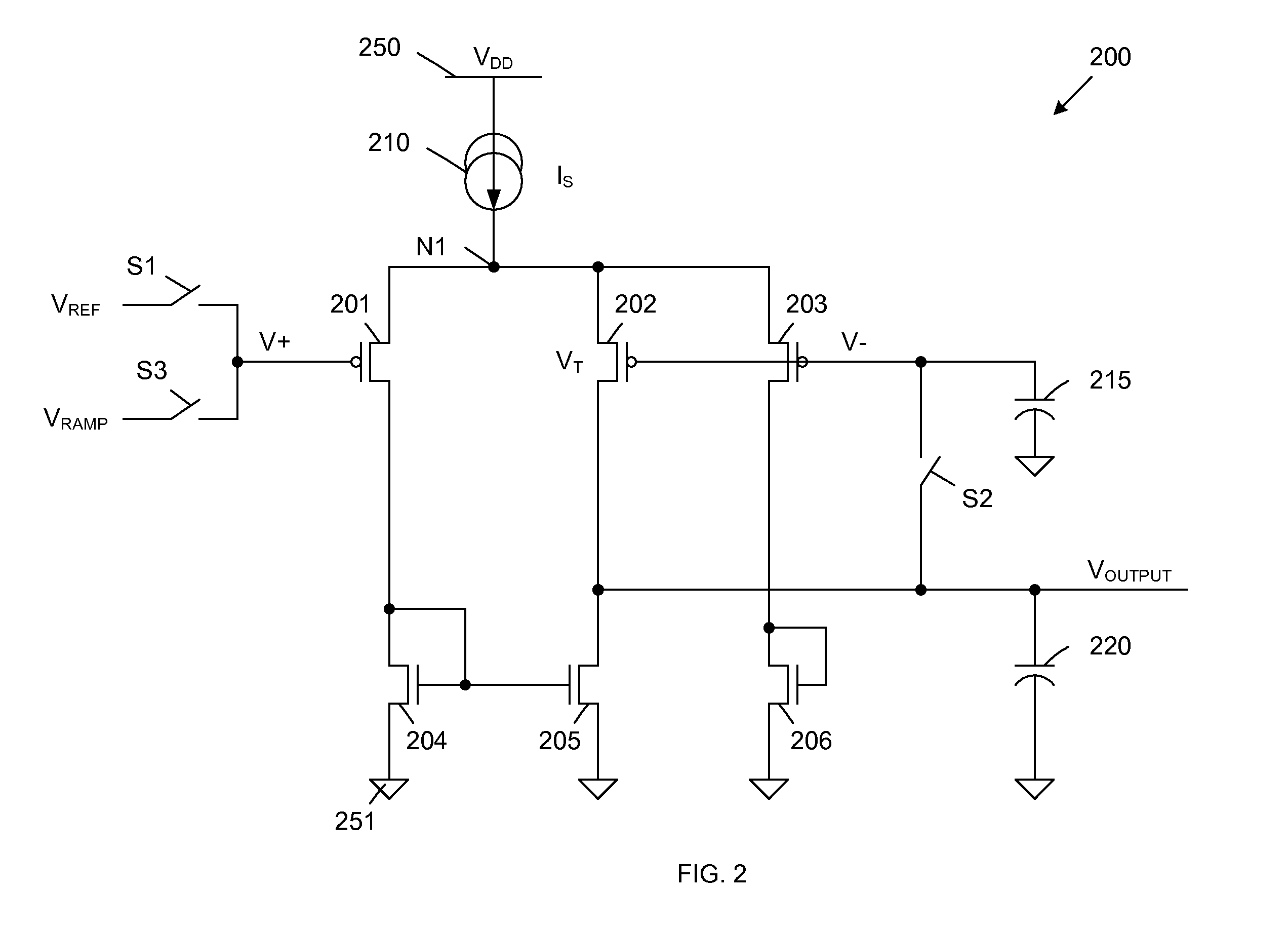

Comparator with low supplies current spike and input offset cancellation

ActiveUS20090033370A1Multiple input and output pulse circuitsInstant pulse delivery arrangementsOffset cancellationComparators circuits

A current control circuit is coupled in parallel with the current paths of a differential comparator circuit to ensure that a substantially constant current is drawn from a current source during all operating phases of a comparator. The current control circuit is biased by a reference voltage, which is also used to bias a V− input terminal of the differential comparator circuit. The reference voltage is stored by a sample capacitor, which is charged by applying the reference voltage to a V+ input terminal of the differential comparator circuit while coupling an output terminal of the differential comparator circuit to the sample capacitor in a unity feedback configuration.

Owner:TOWER SEMICONDUCTOR

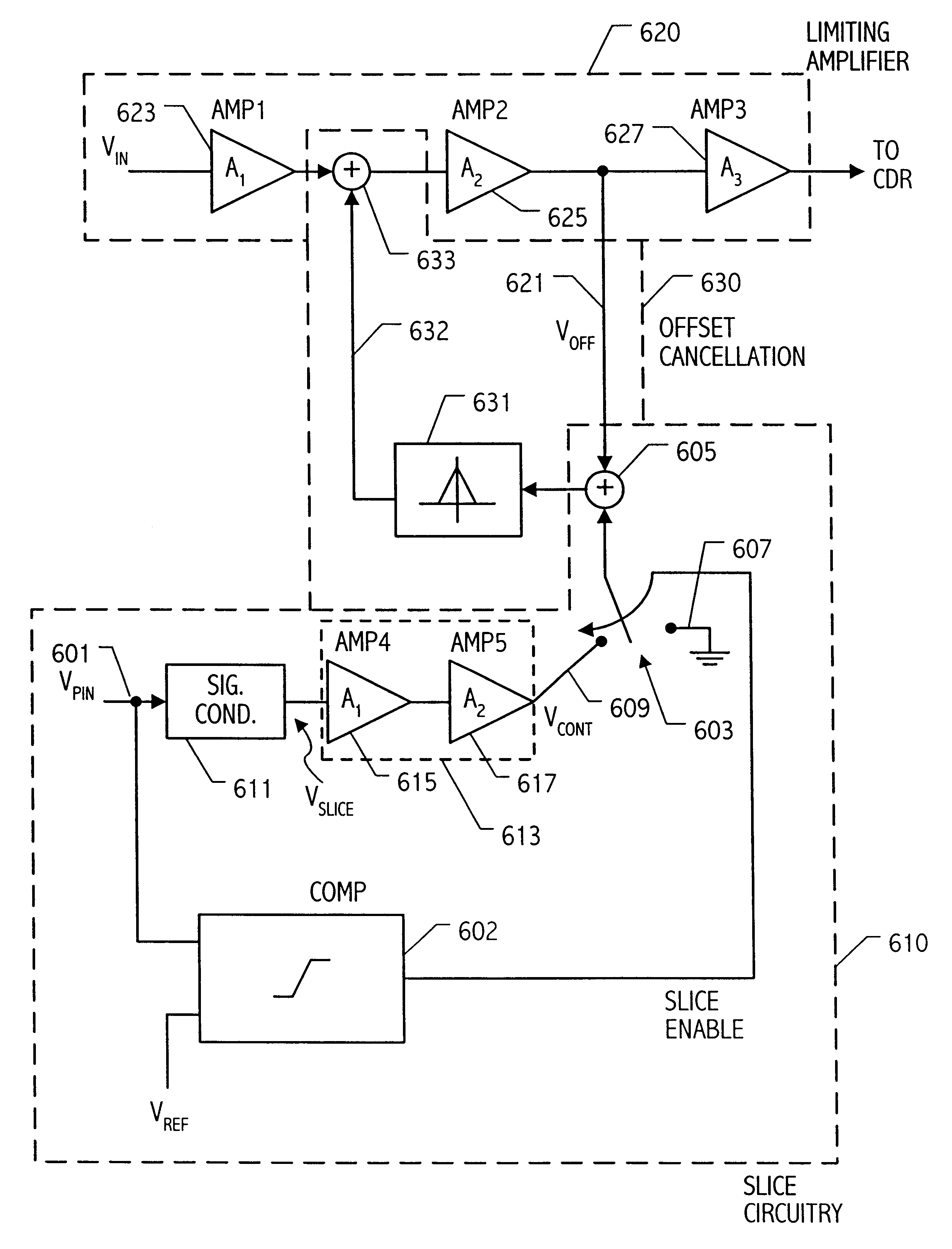

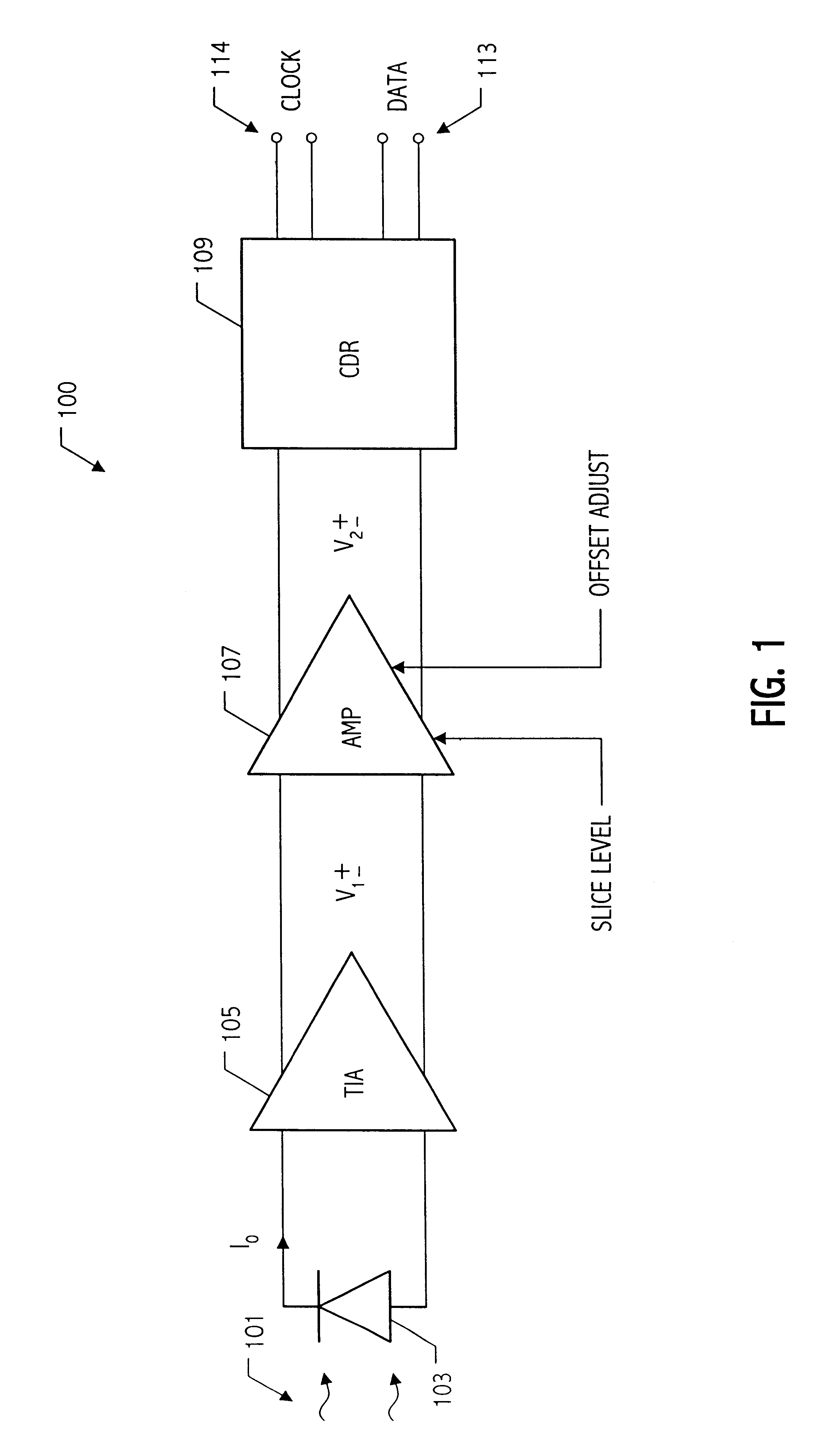

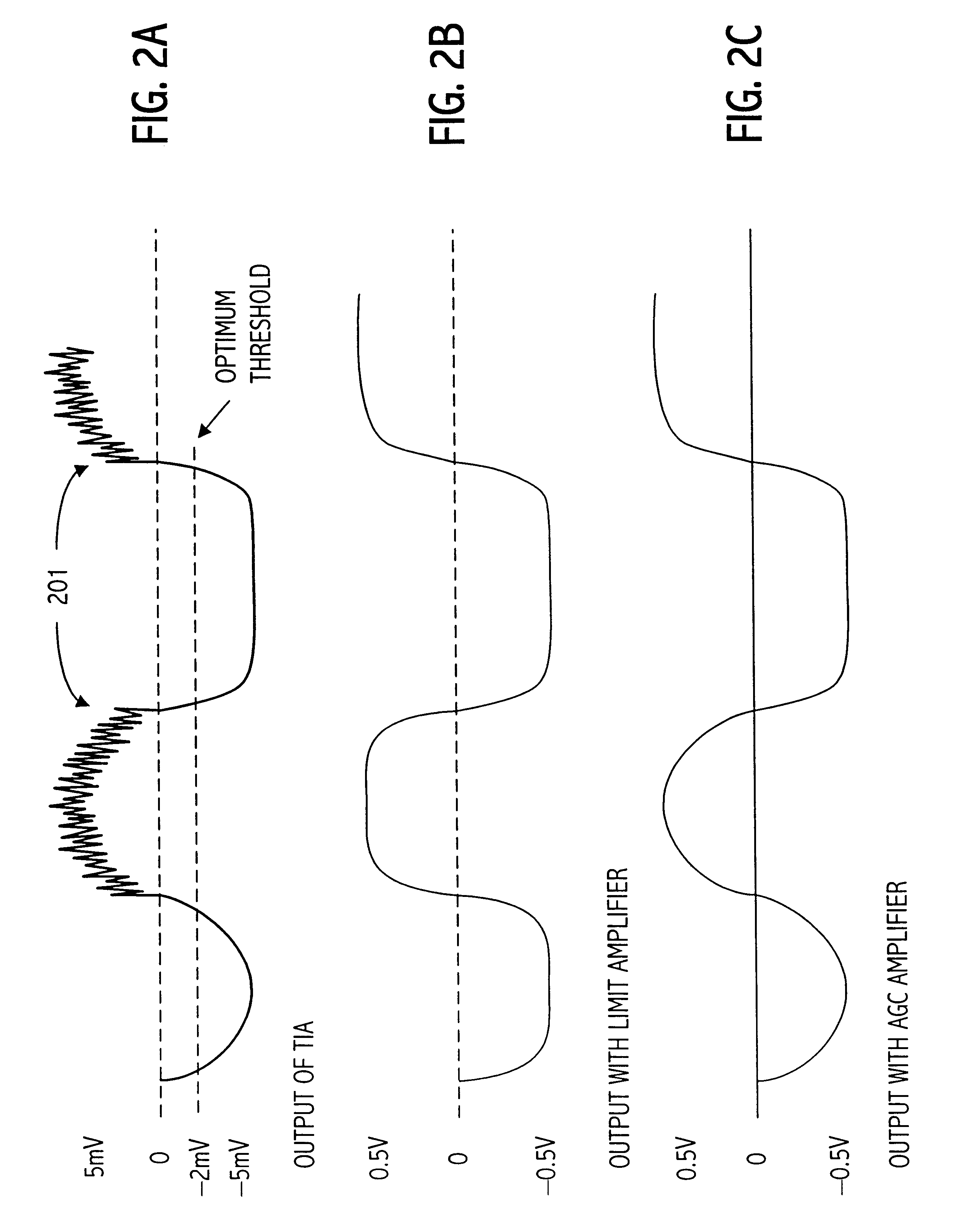

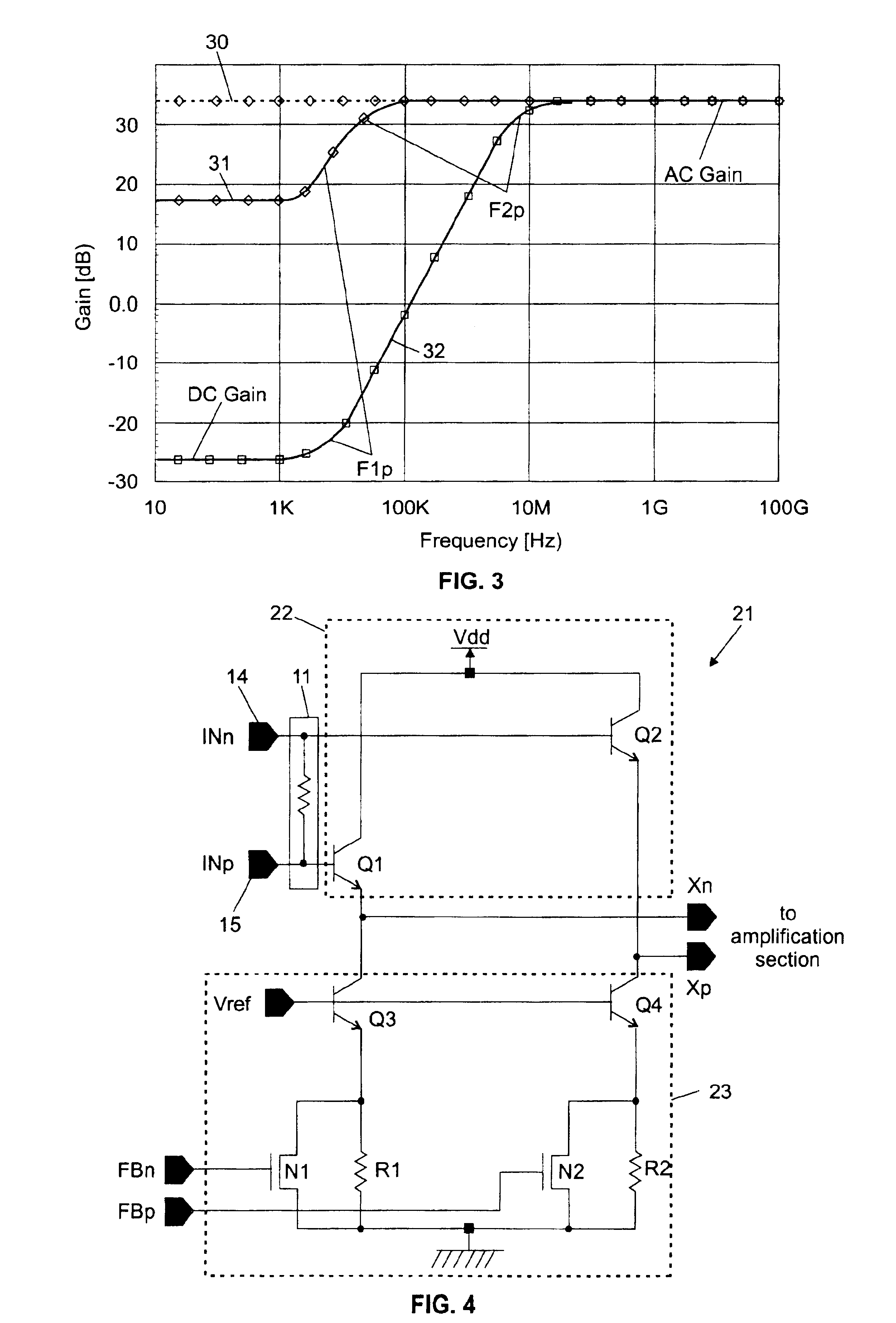

Offset correction and slicing level adjustment for amplifier circuits

InactiveUS6657488B1Pulse automatic controlAmplifier modifications to raise efficiencyIntegratorAudio power amplifier

A slice and offset circuit is provided that uses a digital integrator in the feedback loop of the offset cancellation circuitry. A slice circuit receives an indication of a desired slice voltage and supplies a signal to specify the slice level, which is combined with a sensed offset level of the amplifier. The feedback loop includes a low pass filter that receives the combined signal indicative of the offset and the slice level. The low pass filter includes the digital integrator circuit that includes an up / down counter that counts in a direction determined according to a digital signal having a ones-density indicative of a value of the combined signal with respect to a reference signal, thereby generating a feedback signal that cancels offset and adjusts for slice.

Owner:SKYWORKS SOLUTIONS INC

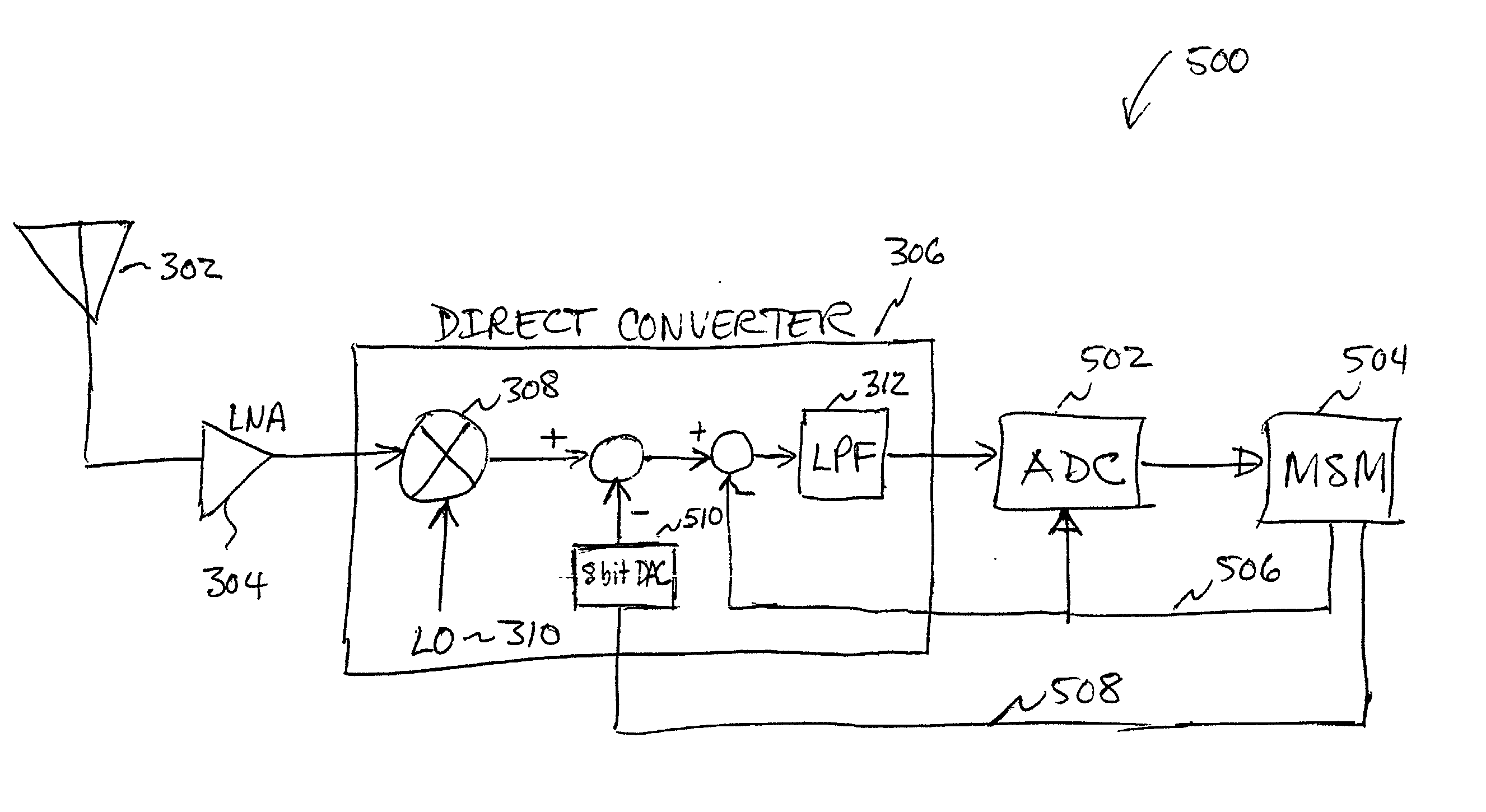

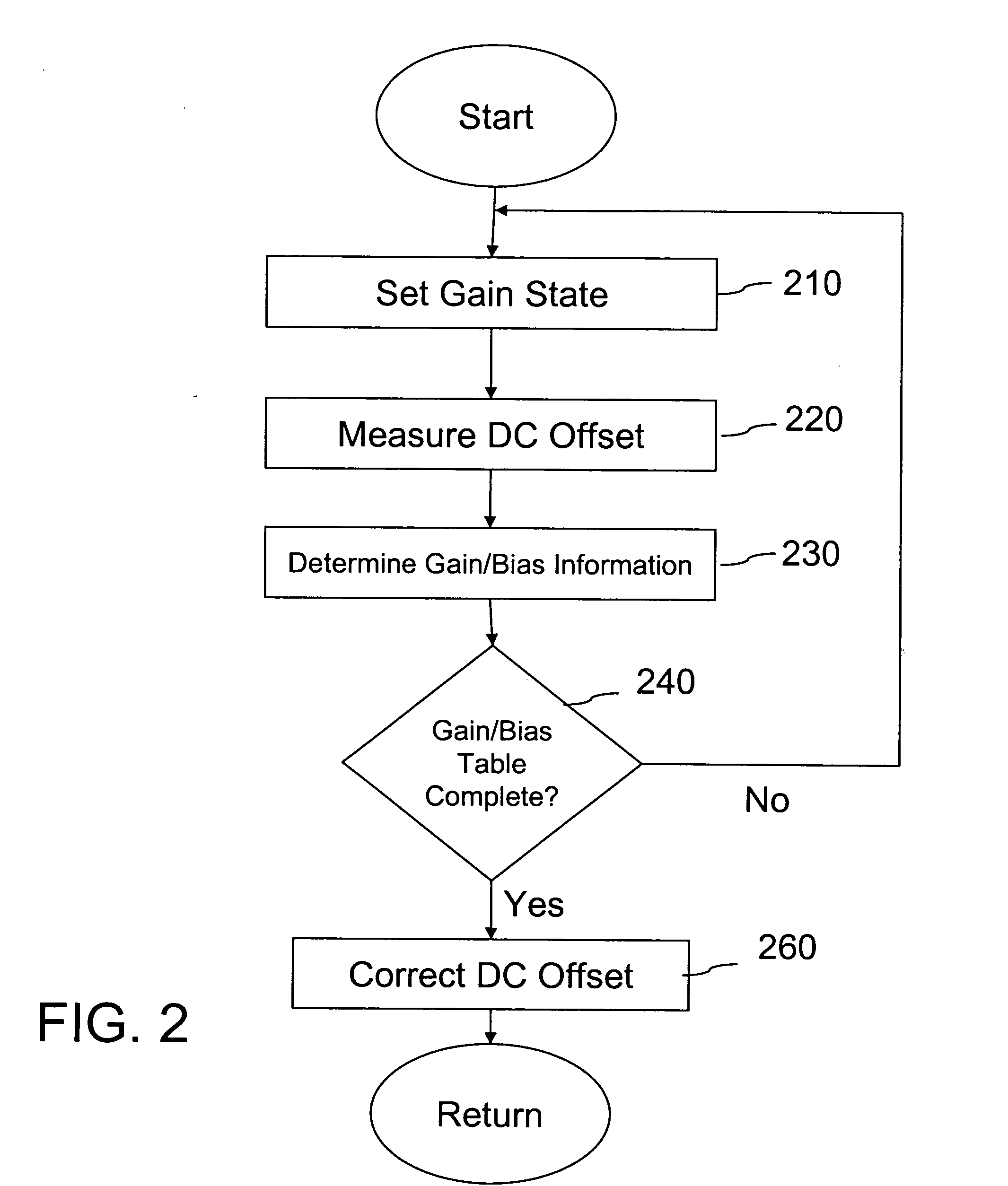

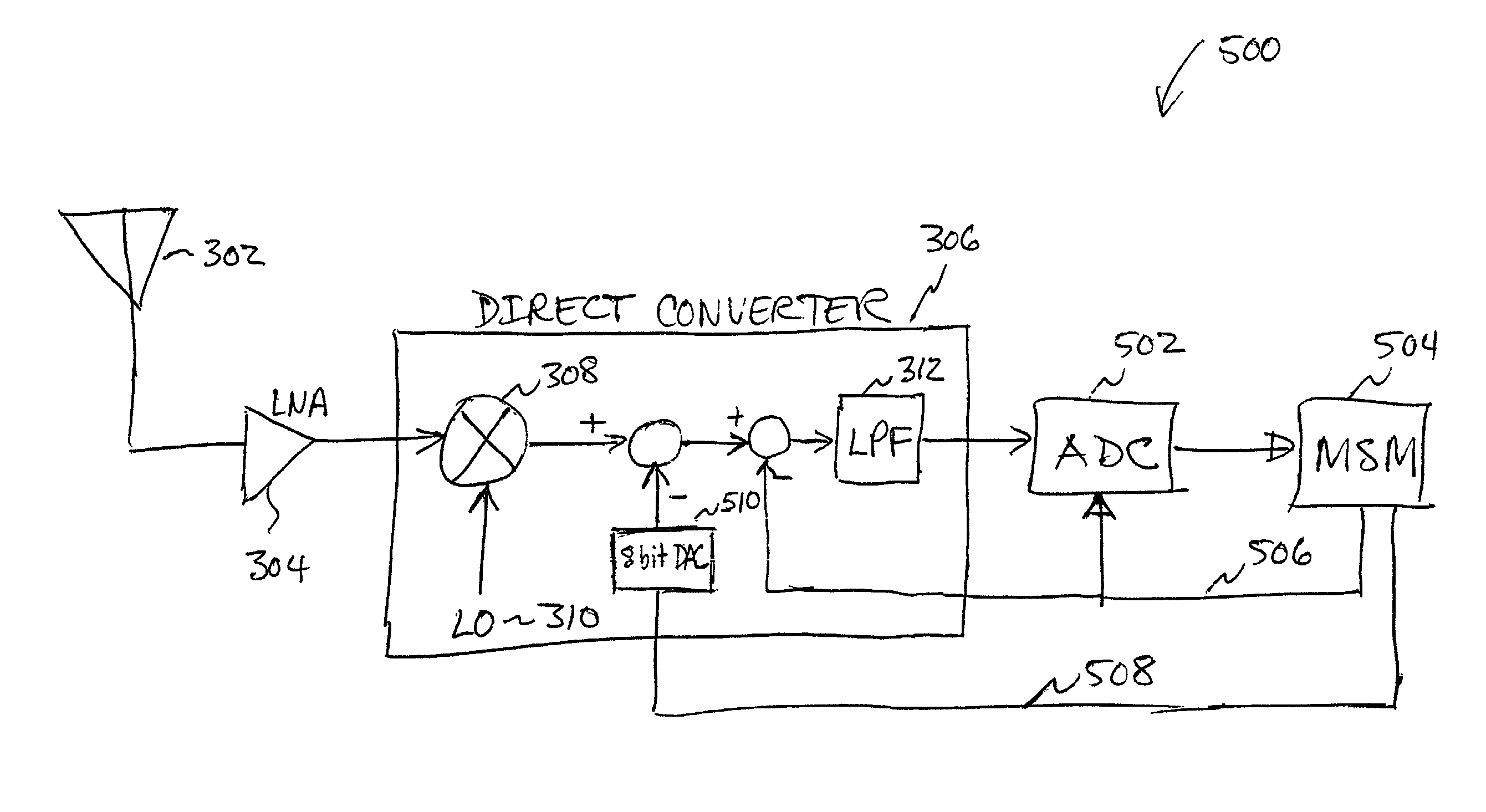

Direct current offset cancellation for mobile station modems using direct conversion

InactiveUS20030199264A1Dc level restoring means or bias distort correctionRadio transmissionModem deviceOffset cancellation

A system and method for canceling DC offset for Mobile Station Modems having direct conversion architectures. The present invention is a fast acquiring DC offset cancellation block that provides rapid and accurate DC offset estimates and cancellation techniques to support direct conversion architectures. The fast acquiring DC offset cancellation block combines four mechanisms to rapidly acquire and remove a DC offset estimate after power up, temperature changes, receiver frequency changes, and gain setting changes by increasing high pass loop bandwidth and adjusting DC offset levels at baseband. After removing the DC offset in large portions, the high pass loop bandwidth is decreased to fine tune the previous estimate and to remove any small variation in DC offset due to receiver self-mixing products.

Owner:QUALCOMM INC

Hybrid DC offset cancellation scheme for wireless receiver

ActiveUS20050258989A1Remove offsetElectric signal transmission systemsAnalogue-digital convertersNegative feedbackOffset cancellation

Systems and methods for canceling static and dynamic DC offsets by combining a digital DC offset correction scheme with an analog DC offset correction scheme. A feedback-based digital DC offset correction scheme provides different adjustment levels for a plurality of discrete gain states and the analog DC offset correction scheme operates in different cancellation modes dependent on a frame structure. A digital DC offset correction scheme collects DC offset control information and provides adjustment levels. In addition, a negative-feedback based switchable high pass filter has a plurality modes of operation, where one mode of operation includes an all-pass filter.

Owner:WIONICS RES +1

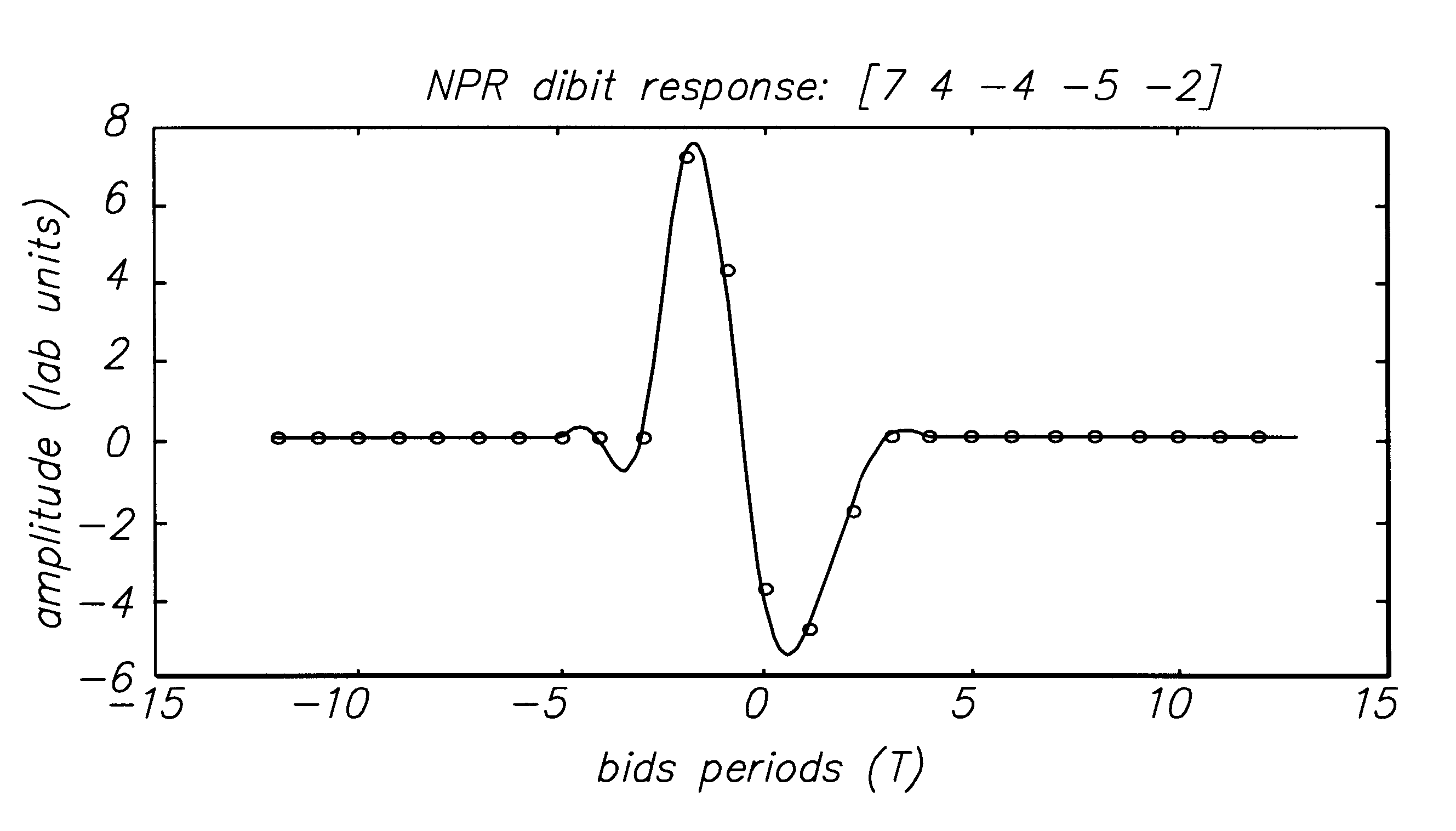

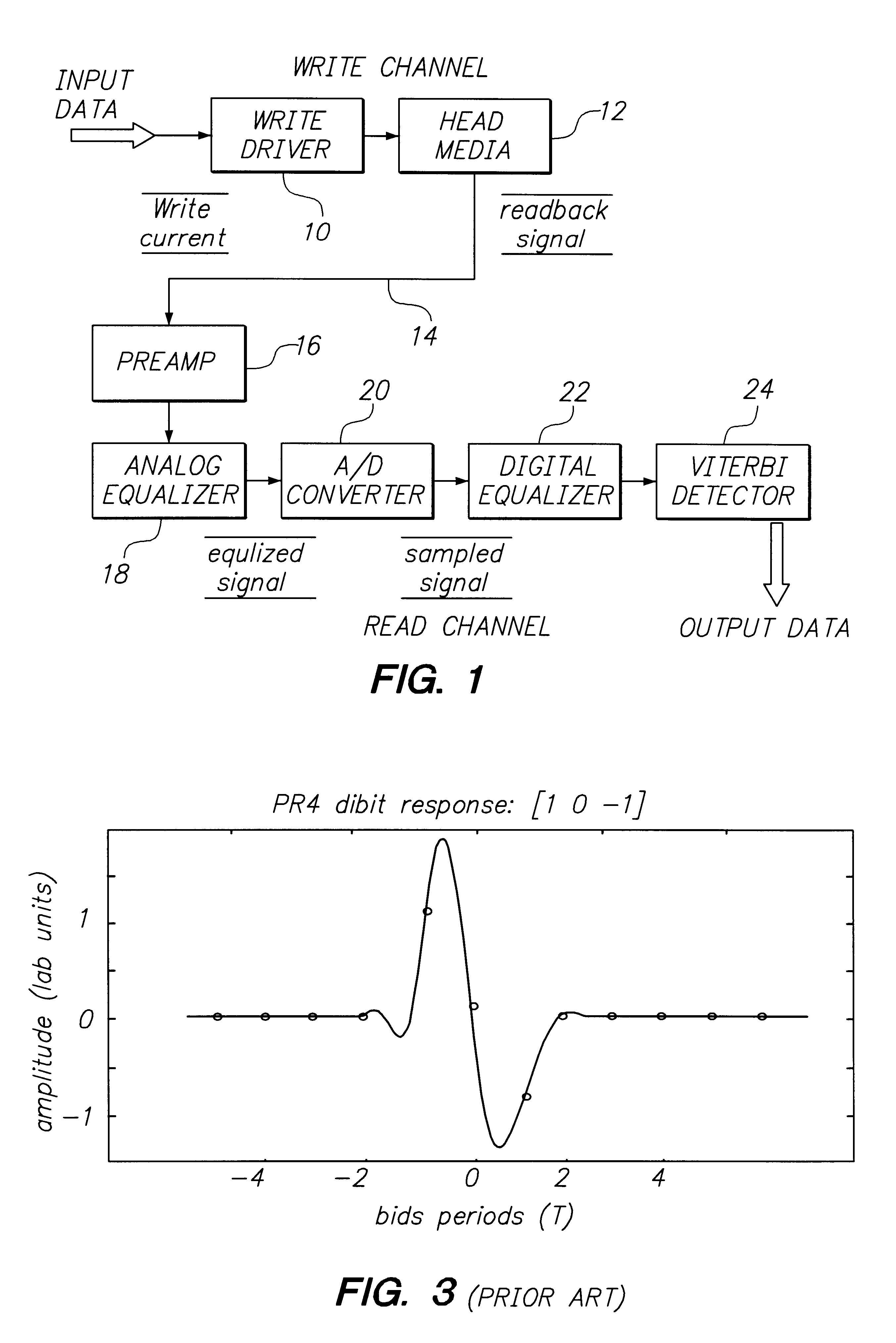

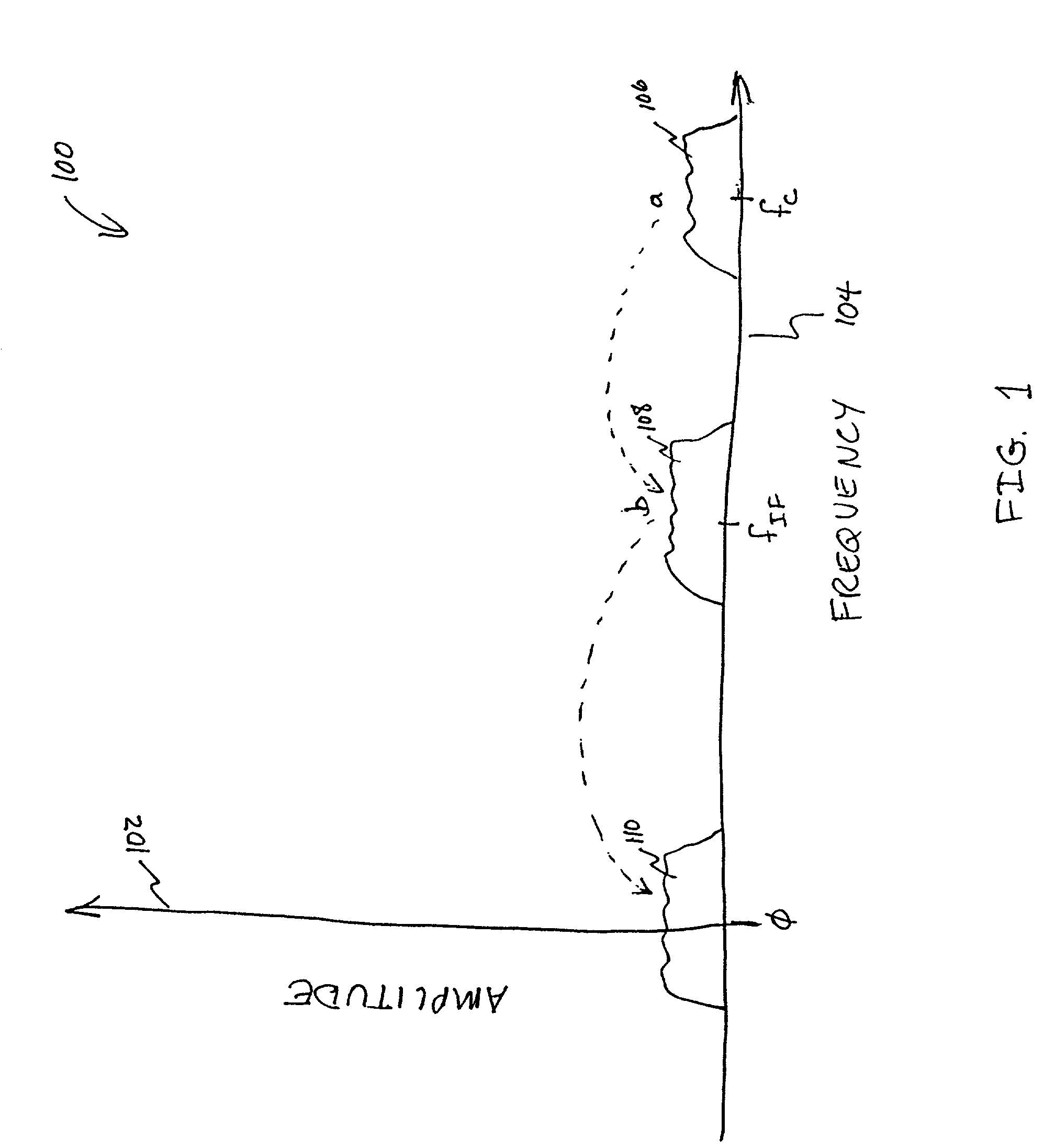

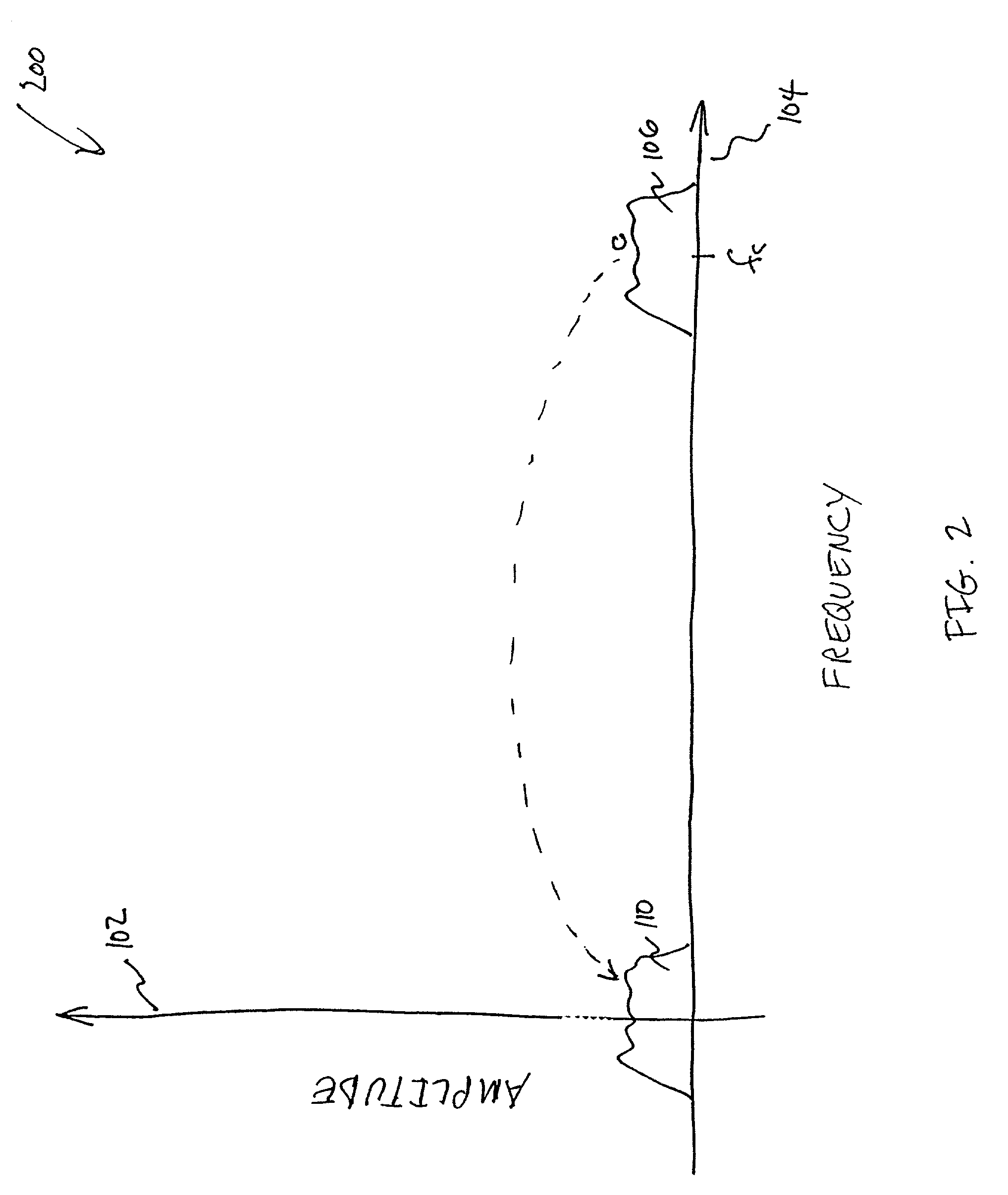

Class of fixed partial response targets in a PRML sampled data detection channel

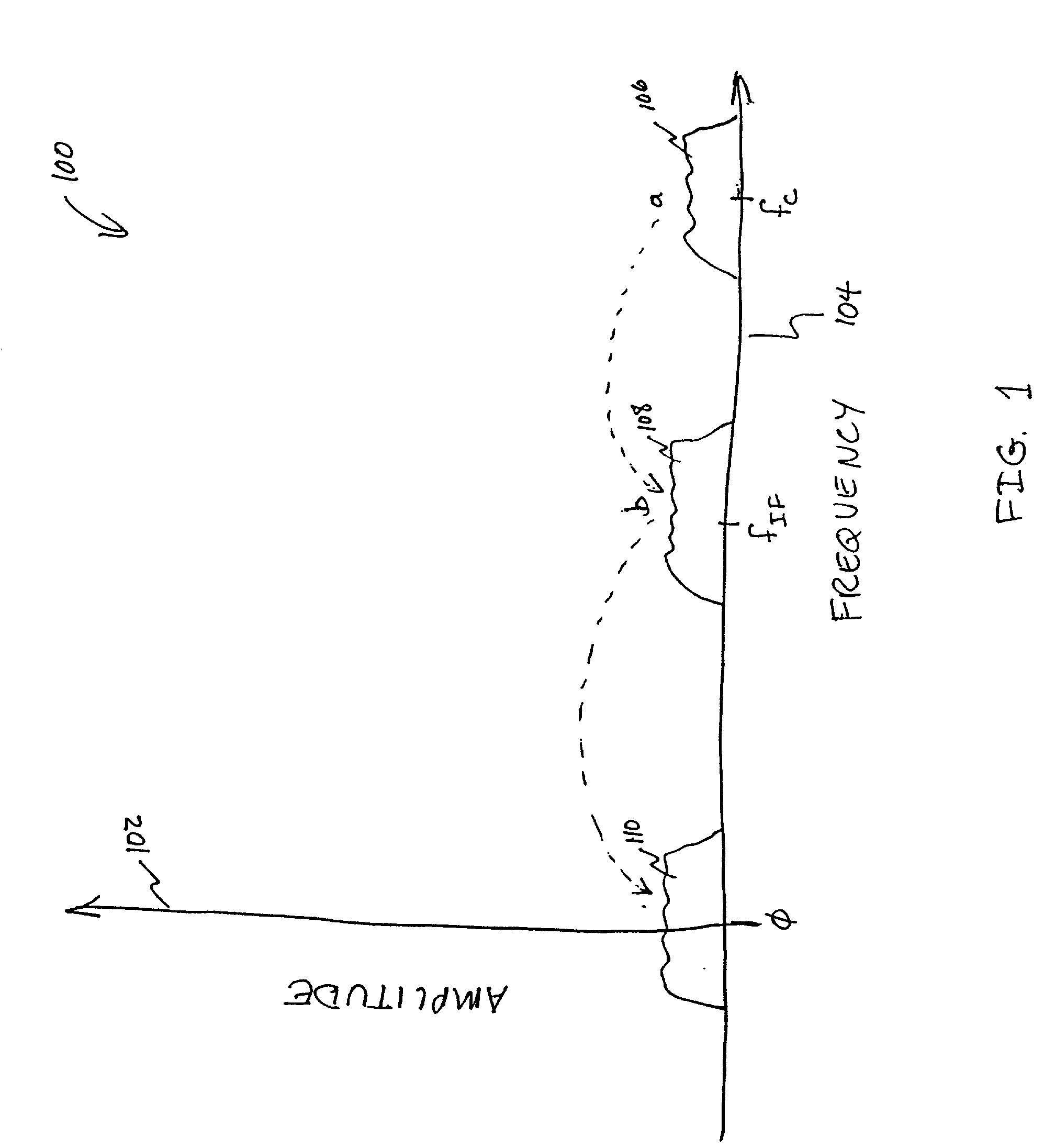

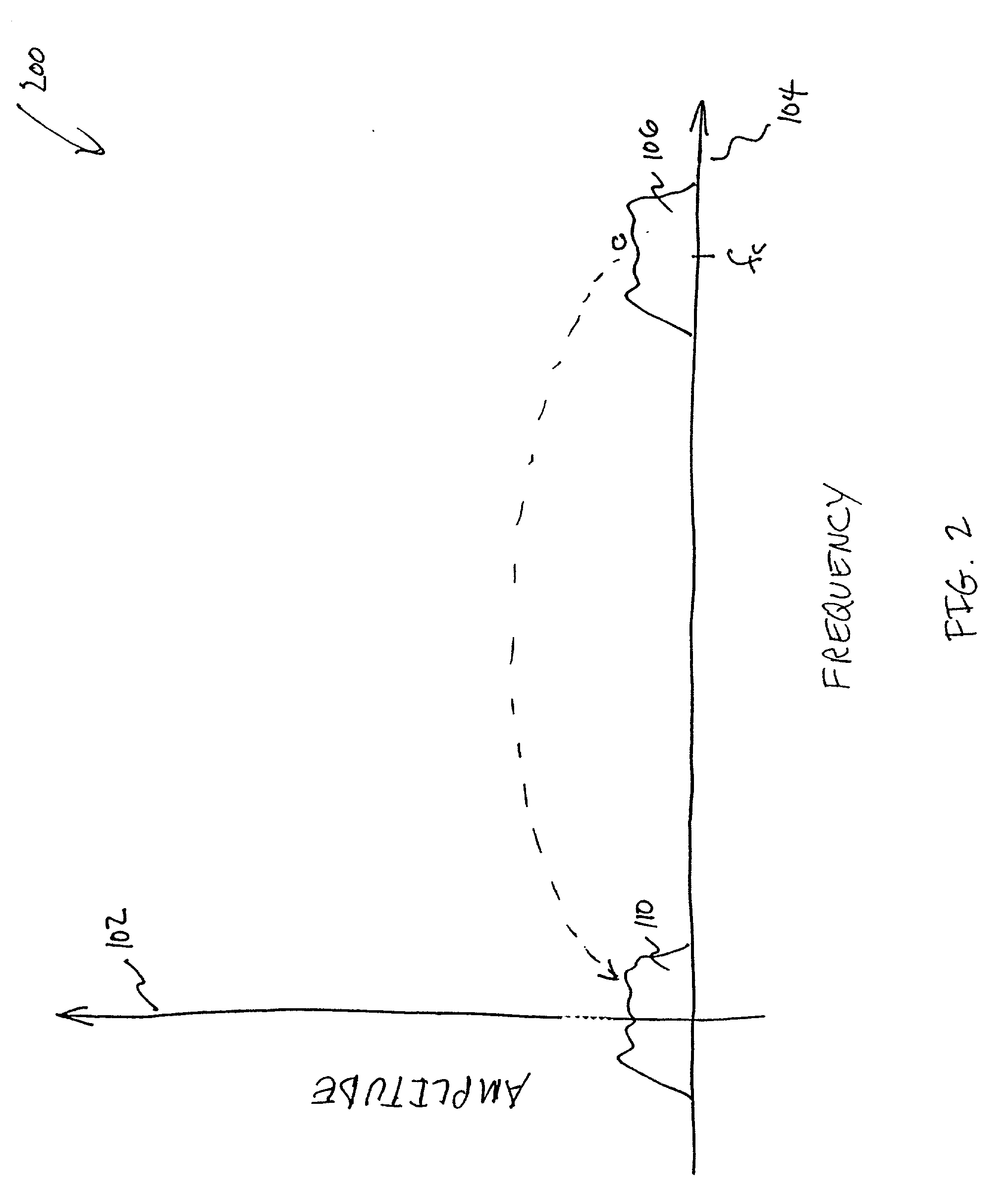

InactiveUS6249398B1Modification of read/write signalsRecord information storageFrequency spectrumMagnetic media

A new class of fixed partial response targets are disclosed for use in a PRML magnetic medium read channel. The preferred embodiment exhibits an equalization response characterized by the polynomial 7+4*D-4*D2-5*D3-2*D4, where D represents the unit delay operator. This read channel target provides improved matching to the inherent magnetic channel over the known canonical class of targets (1-D)(1+D){circumflex over ( )}N, and thereby reduces equalization losses. The improved spectral matching reduces amplification of noise in the channel, thereby reducing bit-error-rates. The new class of targets also exhibits a spectral null at DC, reducing problems for offset cancellation circuitry and making the disk drive less sensitive to thermal asperities. It also exhibits a spectral depression rather than a spectral null at the Nyquist frequency, making quasi-catastrophic error sequences virtually impossible. The new class of target simplifies coding and allows RLL code ratios that approach unity, improving effective recording densities, while significantly reducing BER.

Owner:LUCENT TECH INC +1

Amplifier with digital DC offset cancellation feature

InactiveUS6897700B1Increase speedLow amount of powerPulse automatic controlComputing operations for logarithmic/exponential functionsAudio power amplifierControl signal

A high speed, high sensitivity post amplifier as described herein includes a digitally-controlled DC offset cancellation feature. The amplifier circuit is configured to provide DC offset voltage levels in response to a digital control signal, where the digital control signal is generated based upon a data error metric such as bit error rate. The AC signal path and the DC offset adjustment signal path in the amplifier circuit are separated to facilitate operation with normal power supply voltages, and to achieve low power operation.

Owner:QUALCOMM INC

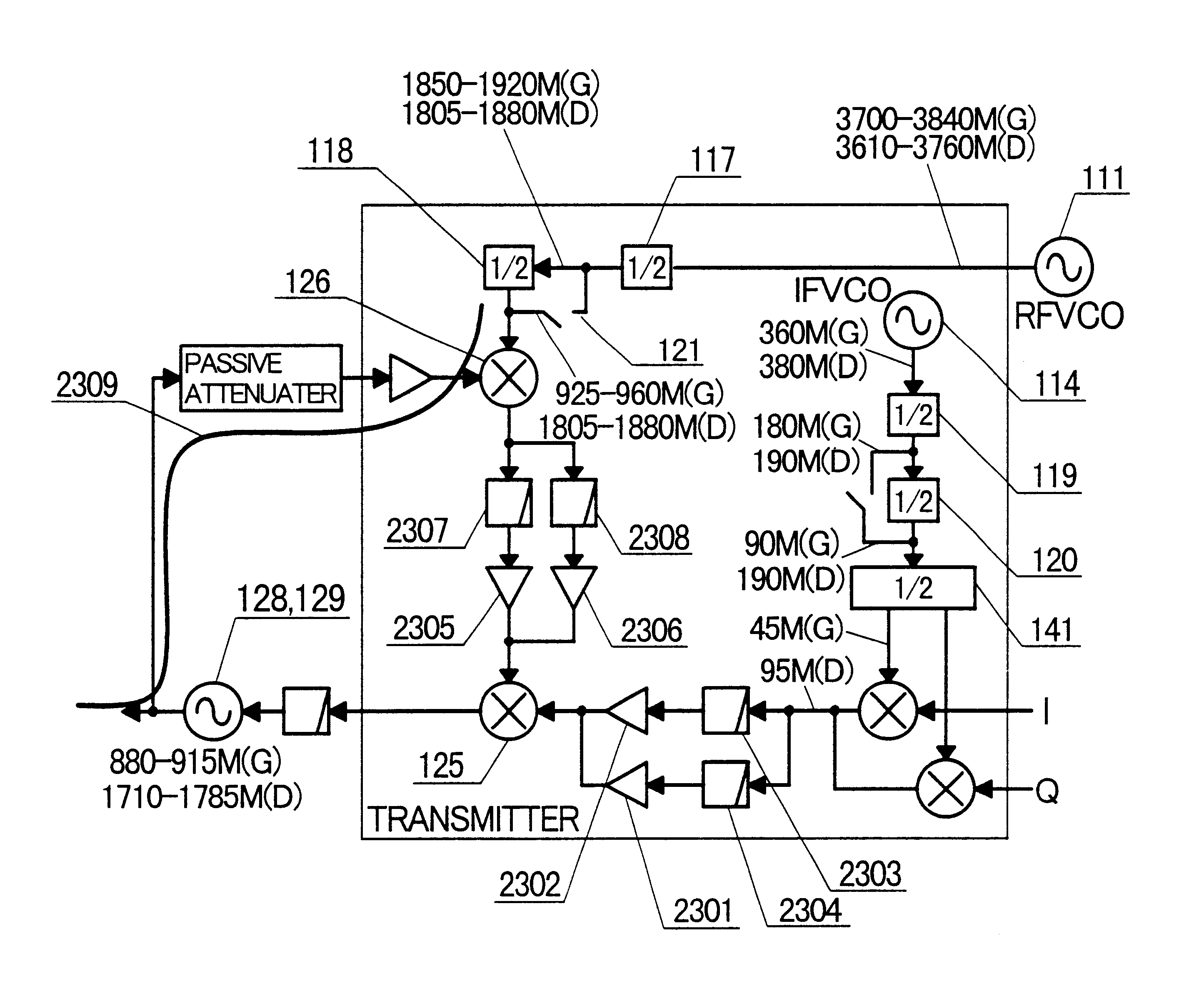

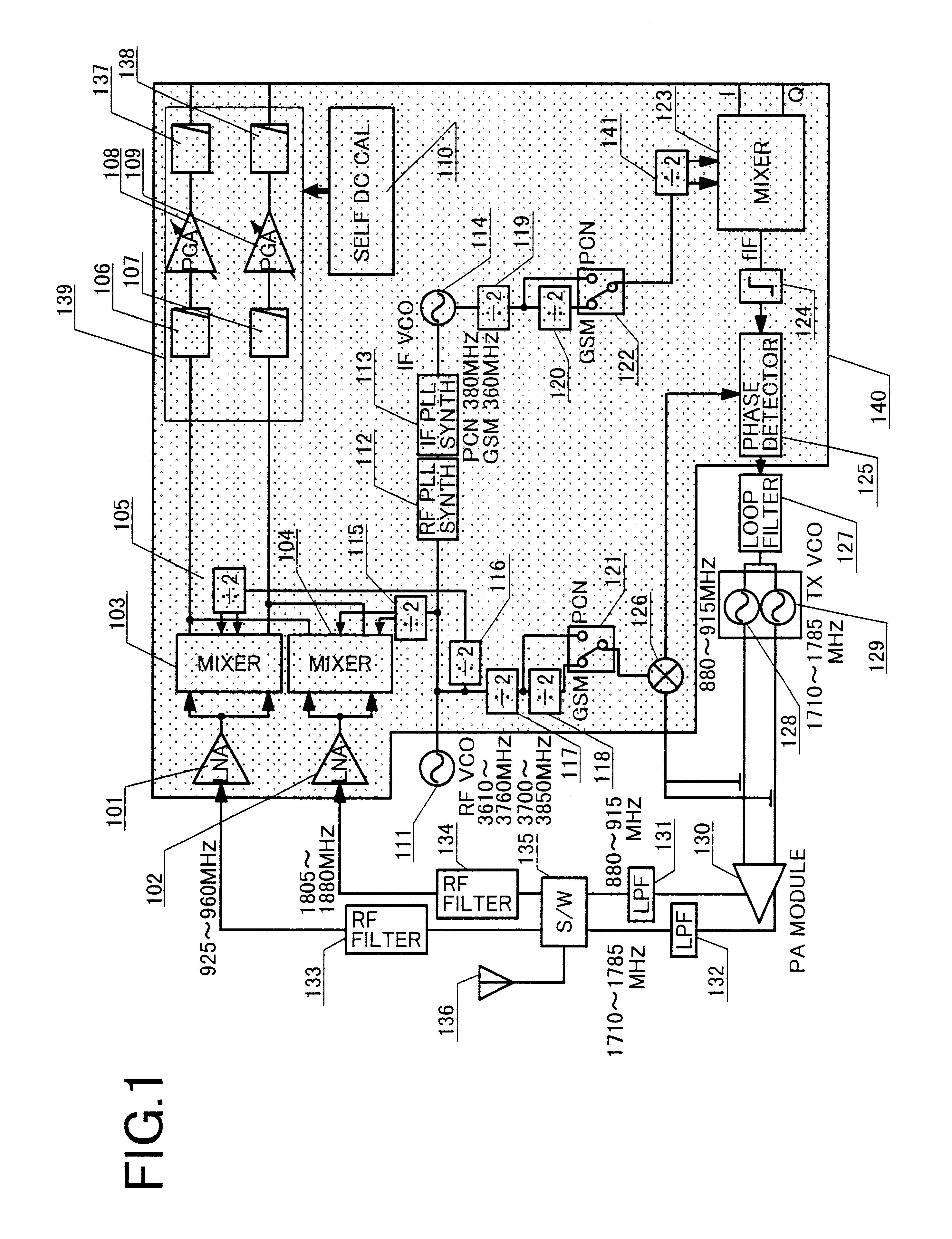

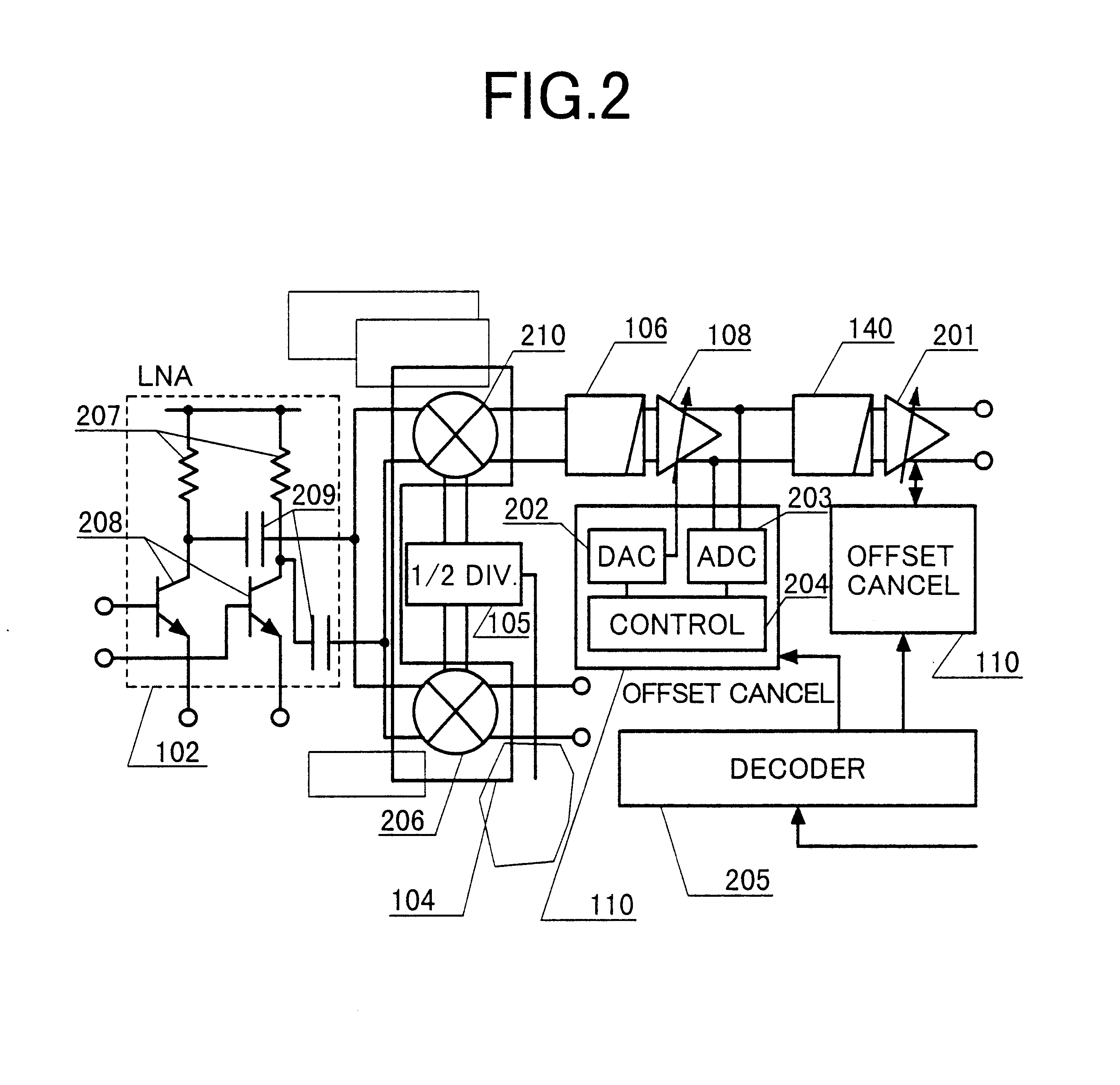

Mobile communication apparatus including dividers in transmitter and receiver

A transceiver suitable for larger scale of integration employs direct conversion reception for reducing the number of filters. Also, the number of VCOs is reduced by utilizing dividers to supply a receiver and a transmitter with locally oscillated signals at an RF band. Dividers each having a fixed division ratio are used for generating locally oscillated signals for the receiver, while a divider having a switchable division ratio are used for generating the locally oscillated signal for the transmitter. In addition, a variable gain amplifier for baseband signal is provided with a DC offset voltage detector and a DC offset canceling circuit for supporting high speed data communications to accomplish fast cancellation of a DC offset by eliminating intervention of a filter within a feedback loop for offset cancellation.

Owner:TTPCOM

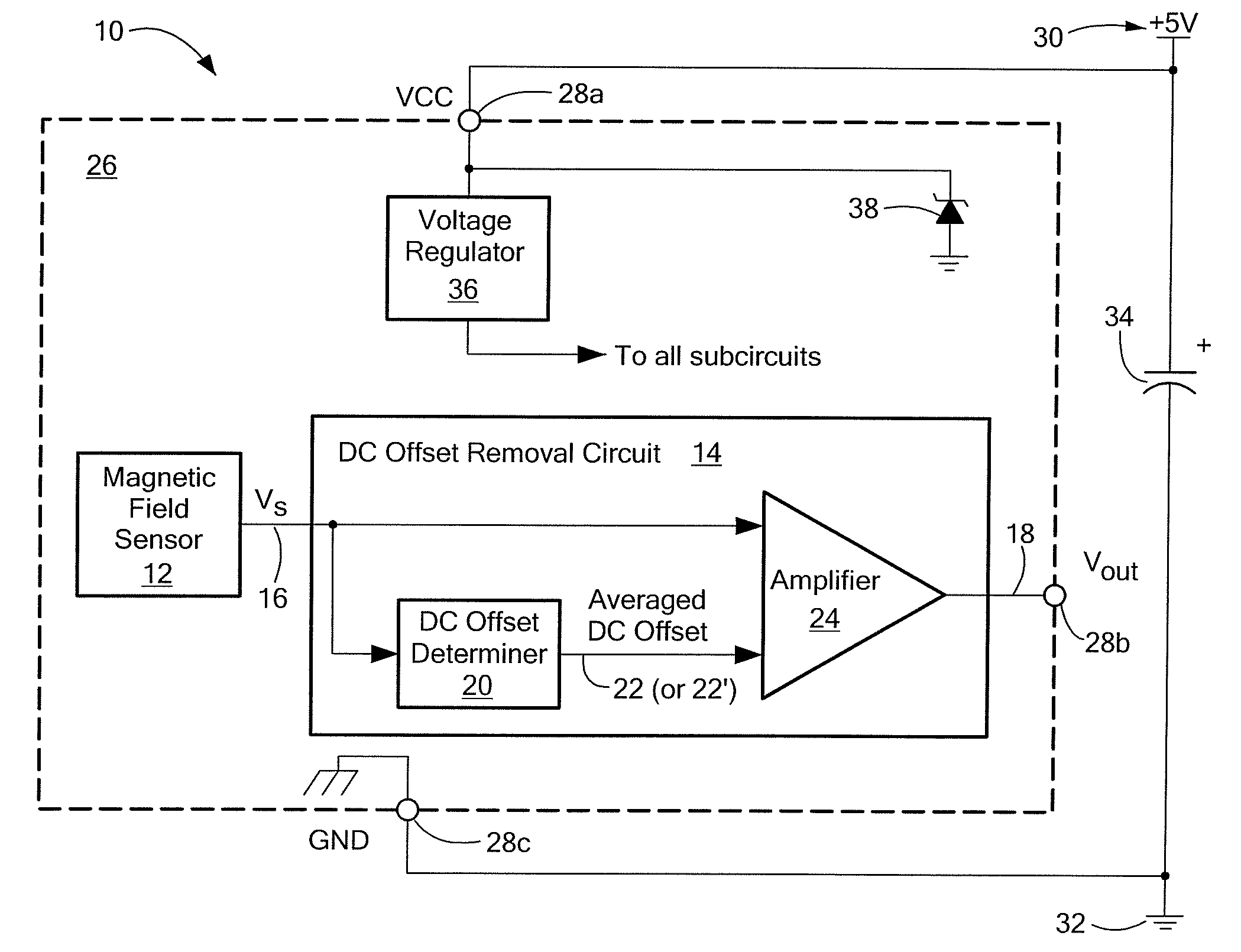

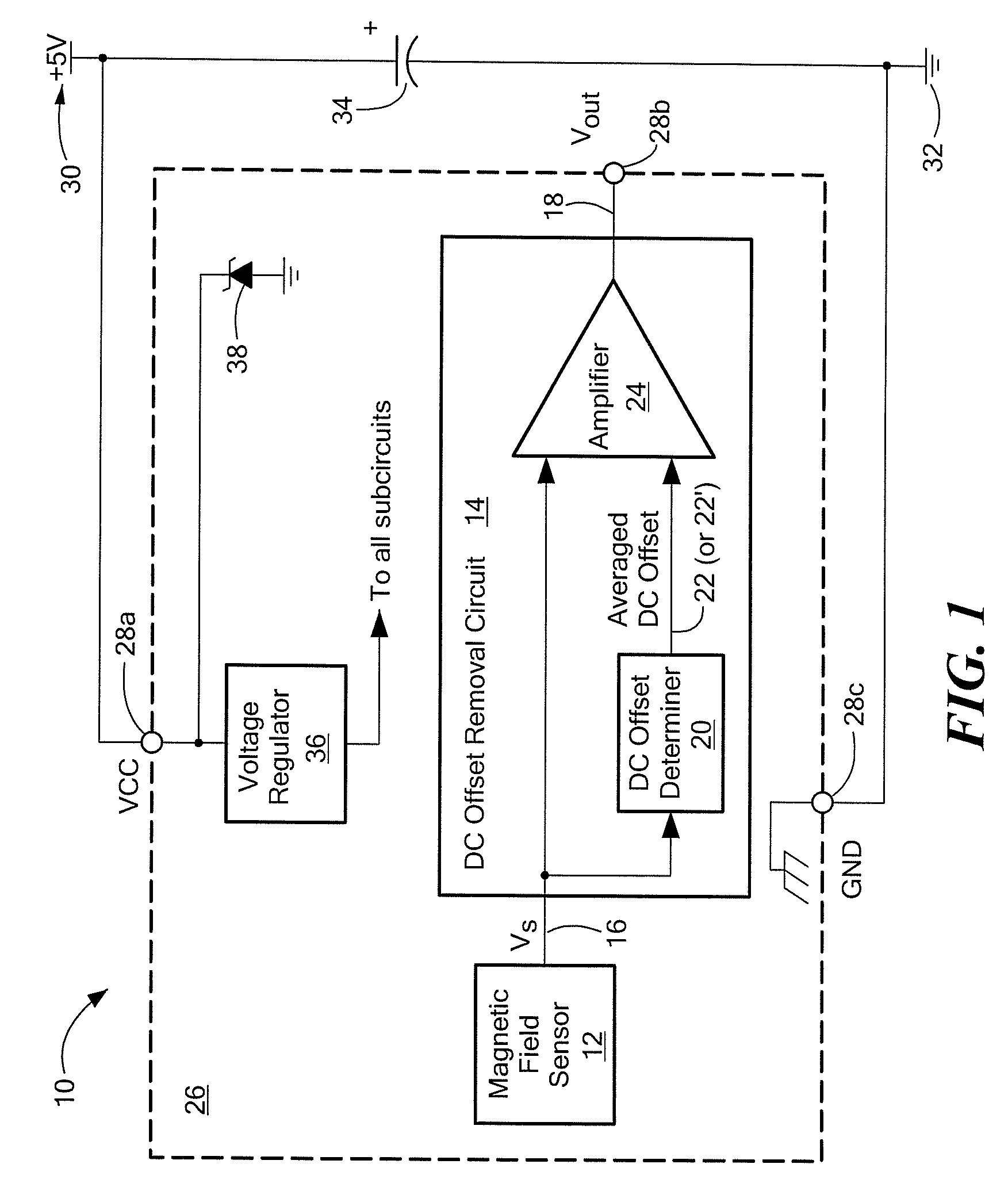

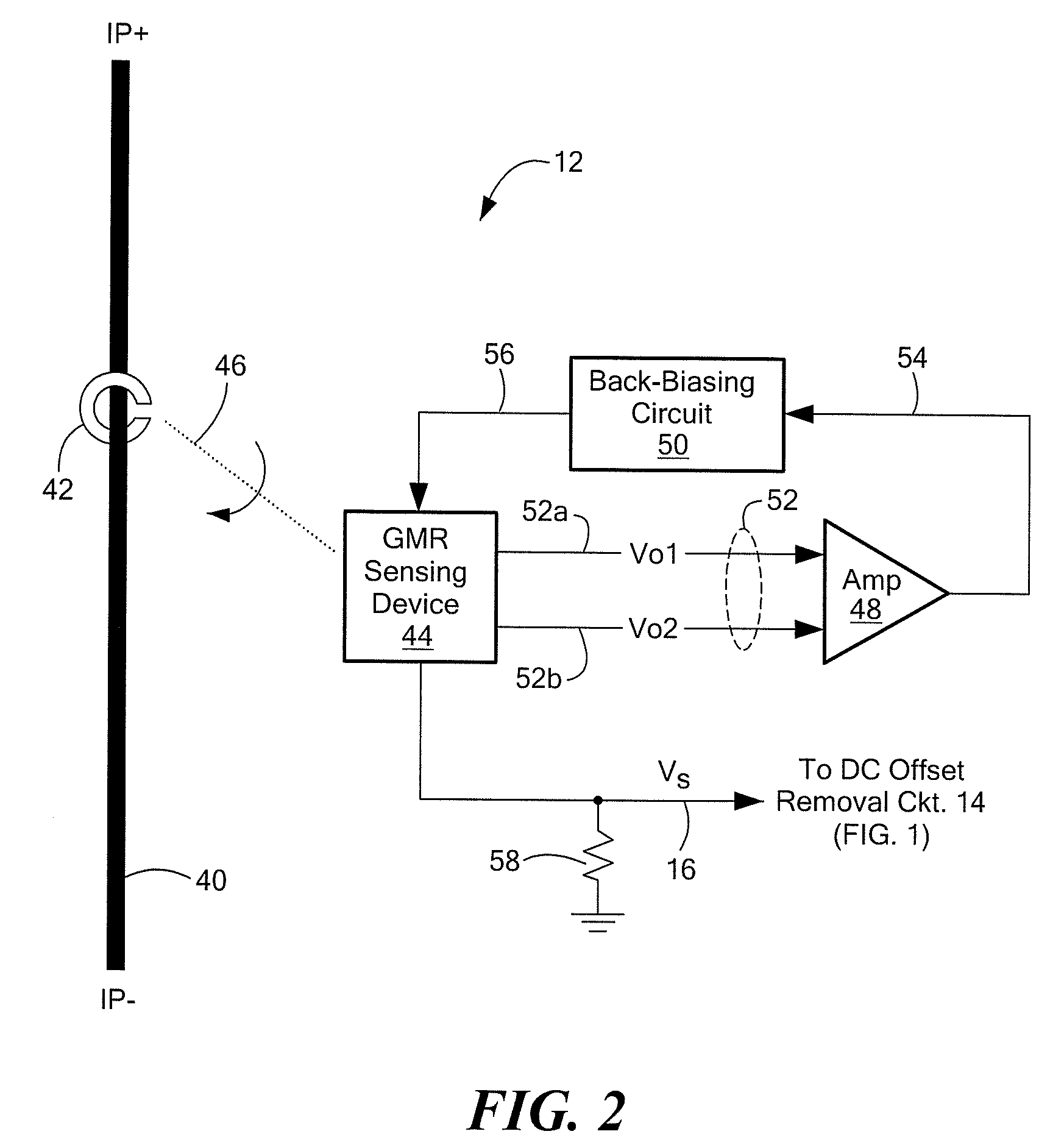

Hysteresis offset cancellation for magnetic sensors

ActiveUS20090212771A1Hysteresis characteristicElectrical measurementsMagnitude/direction of magnetic fieldsHysteresisOffset cancellation

Presented is a sensor that includes a magnetoresistive (MR) sensing device to sense a magnetic field and to produce an AC signal voltage proportional to the sensed magnetic field. The sensor also includes circuitry, coupled to the MR sensing device, to remove DC offset from the AC signal voltage. The DC offset may be related to the hysteresis characteristics of the MR sensing device. To remove DC offset, the circuitry may obtain an averaged DC offset and subtract the averaged DC offset from the AC signal voltage to produce a sensor output signal.

Owner:ALLEGRO MICROSYSTEMS INC

Direct current offset cancellation for mobile station modems using direct conversion

InactiveUS6985711B2Easy accessRapid and accurate DC offset estimates and cancellation techniquesDc level restoring means or bias distort correctionRadio transmissionModem deviceOffset cancellation

A system and method for canceling DC offset for Mobile Station Modems having direct conversion architectures. The present invention is a fast acquiring DC offset cancellation block that provides rapid and accurate DC offset estimates and cancellation techniques to support direct conversion architectures. The fast acquiring DC offset cancellation block combines four mechanisms to rapidly acquire and remove a DC offset estimate after power up, temperature changes, receiver frequency changes, and gain setting changes by increasing high pass loop bandwidth and adjusting DC offset levels at baseband. After removing the DC offset in large portions, the high pass loop bandwidth is decreased to fine tune the previous estimate and to remove any small variation in DC offset due to receiver self-mixing products.

Owner:QUALCOMM INC

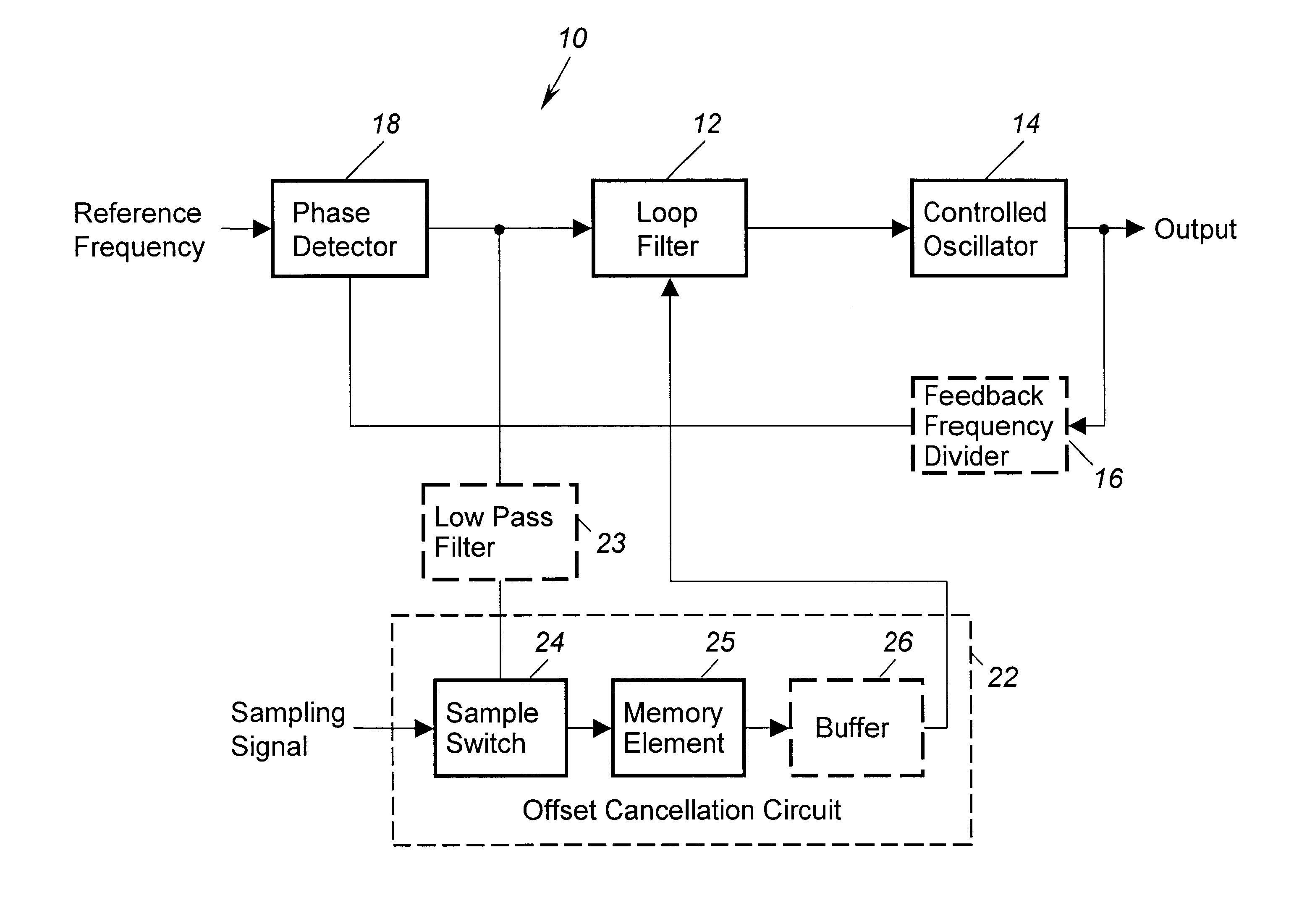

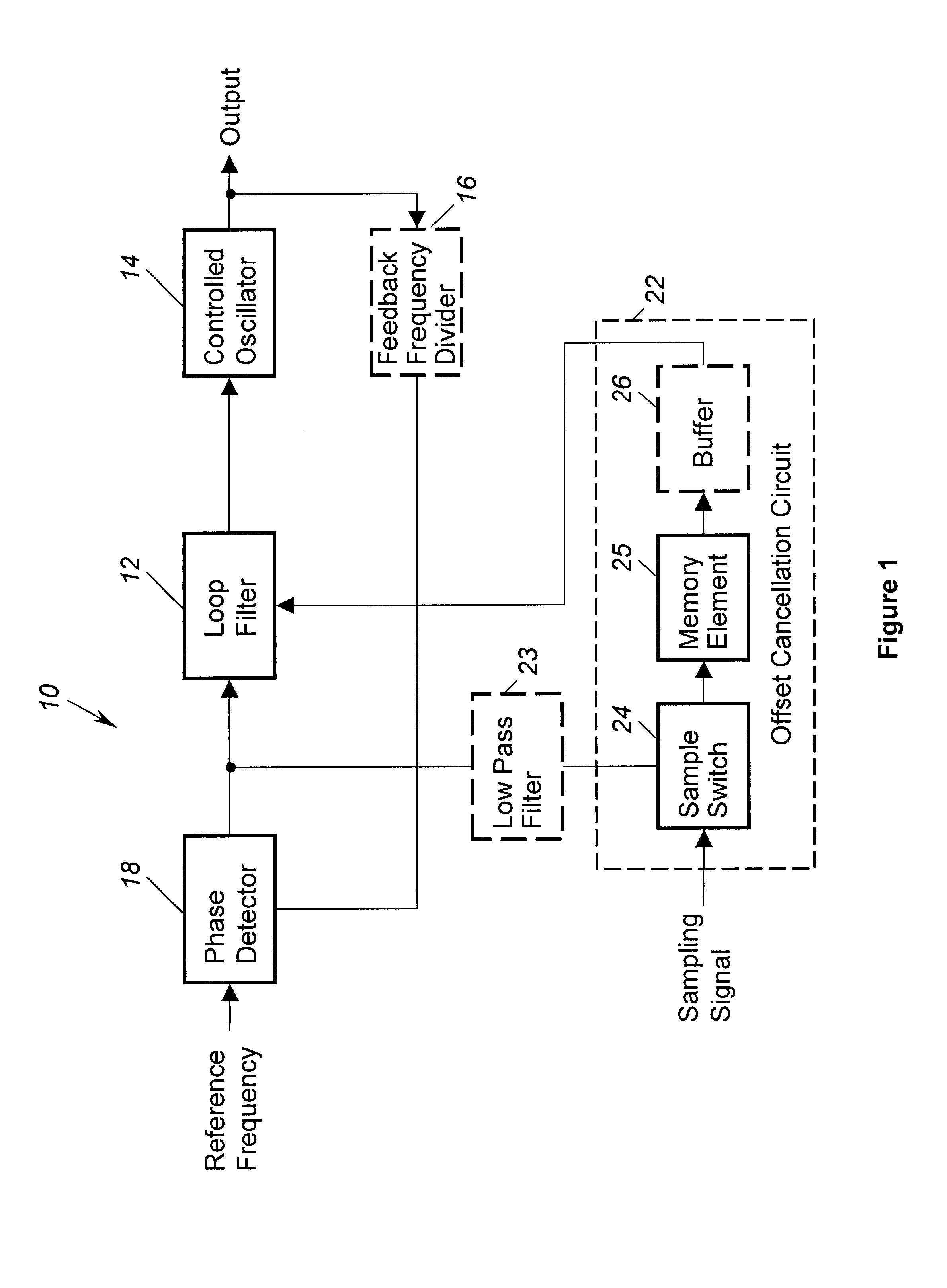

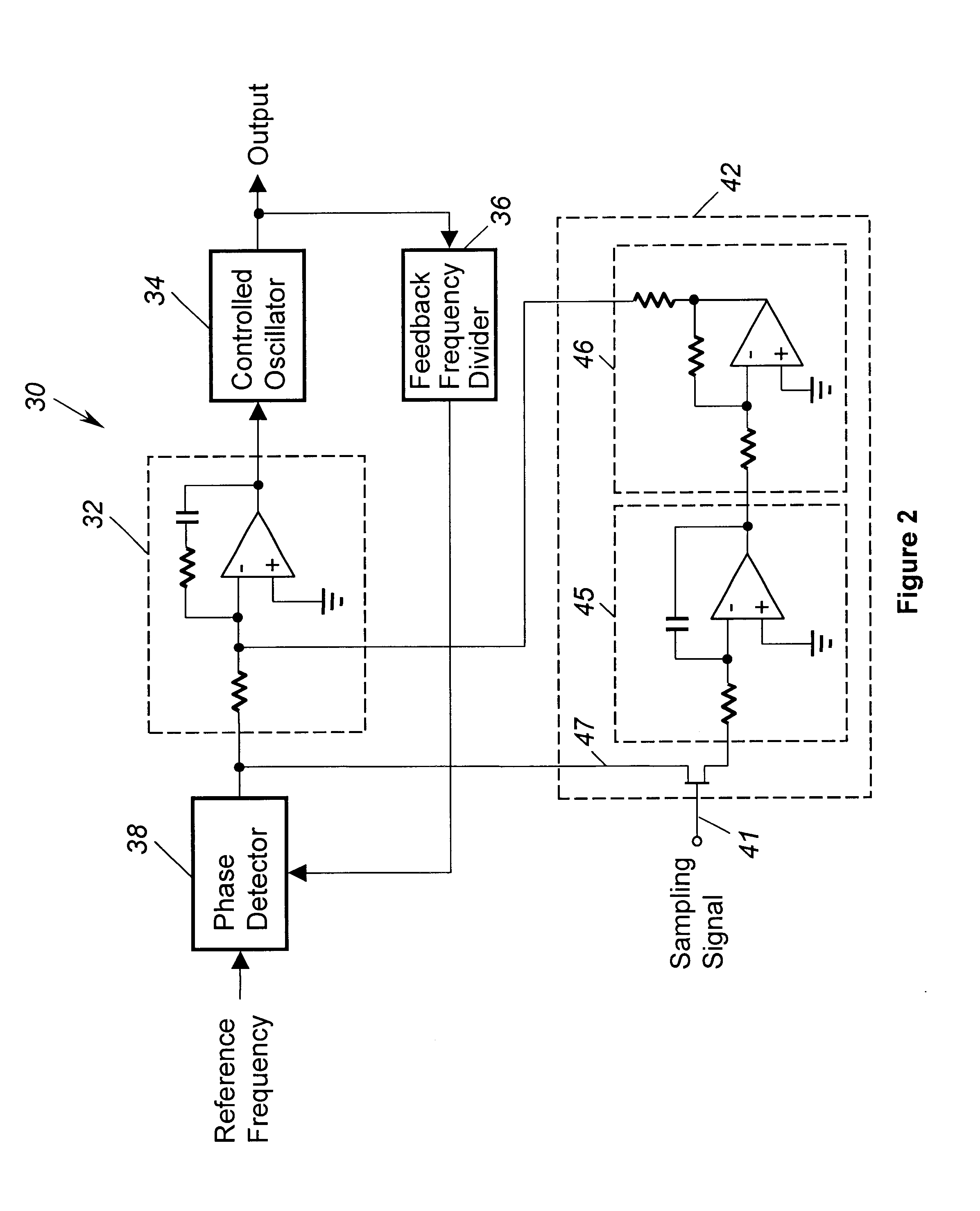

Phase locked loop with offset cancellation

A phase locked loop (10) for generating a variable output frequency signal. The phase locked loop (10) includes a controlled oscillator (14) to generate the variable output frequency signal in response to a tune signal. A phase detector (18) is activable in response to a gating signal (20) to generate an error signal representing a difference between a reference frequency signal and the variable output frequency signal. A loop filter (12) having a filter characteristic, filters the error signal and generates the tune signal. An offset cancellation circuit (22) is coupled to the loop filter (12). In response to an error signal representing phase offset of the phase locked loop (10), the offset cancellation circuit (22) supplies a compensating signal to reduce the phase offset.

Owner:NORTHROP GRUMMAN SYST CORP

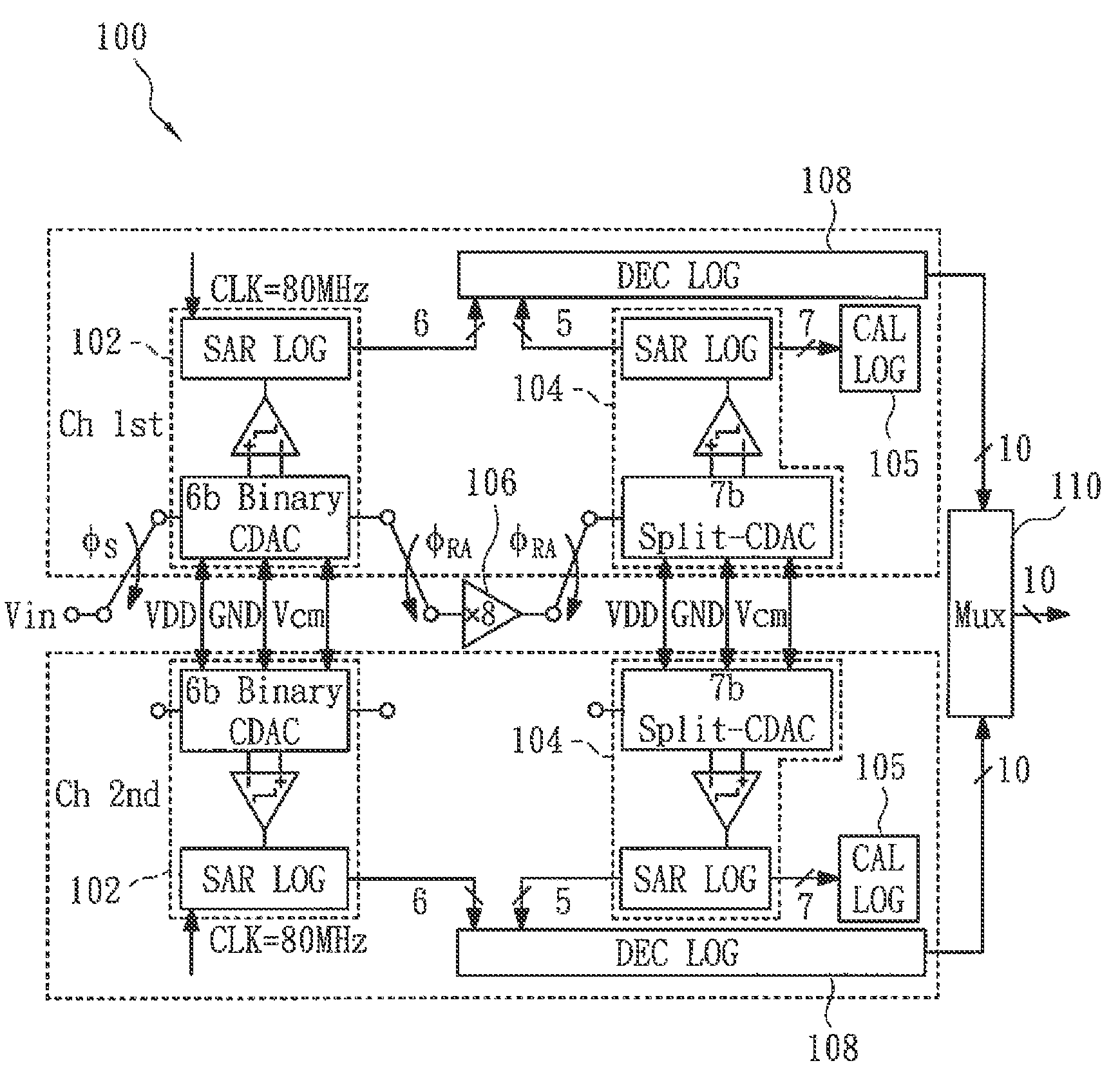

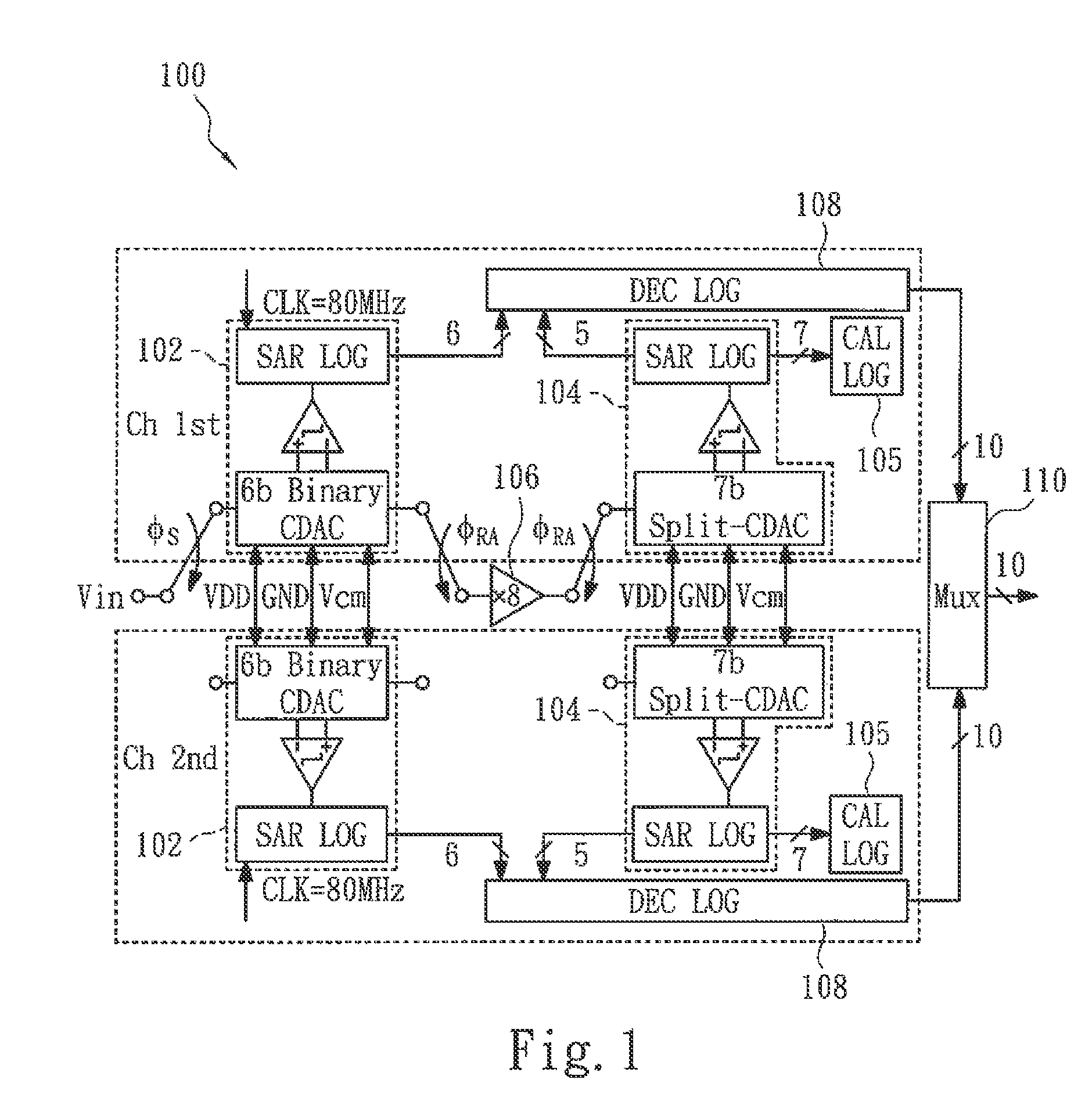

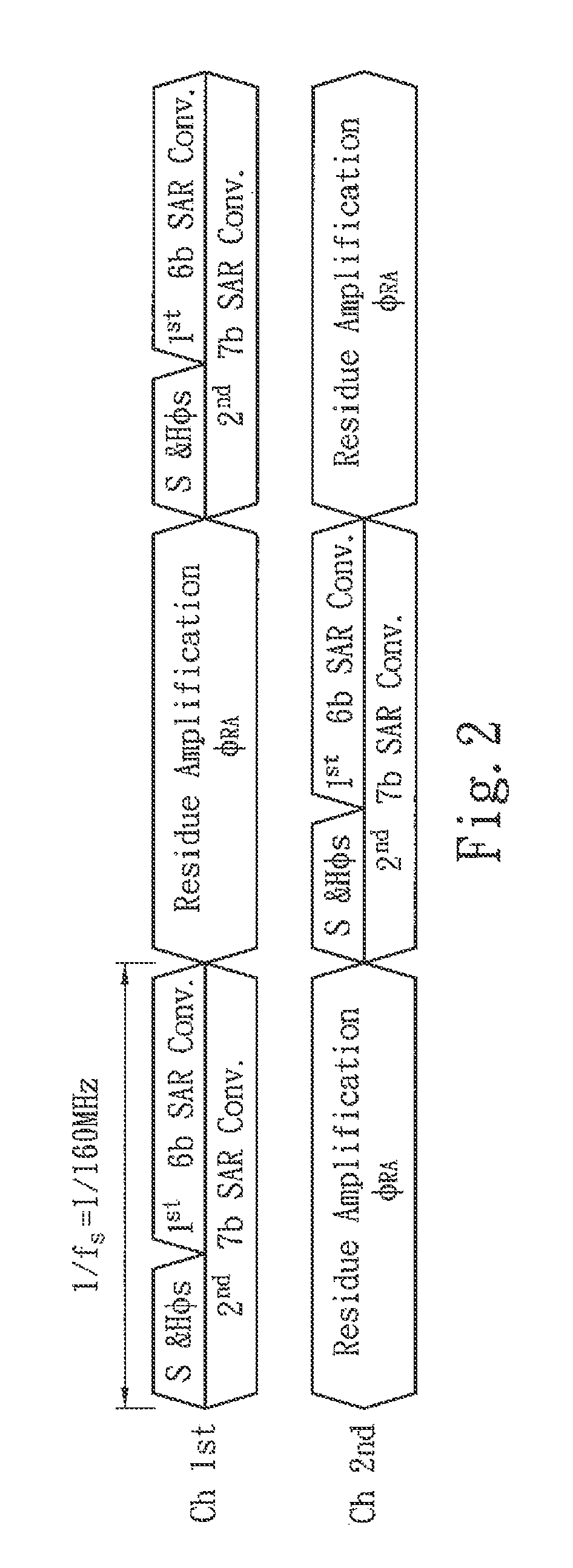

Analog to digital converter circuit

ActiveUS8659461B1Improving feedback factorLess powerElectric signal transmission systemsAnalogue-digital convertersCapacitanceUltrasound attenuation

The present invention provides a pipelined-successive approximation register (SAR) analog-to-digital converter (ADC) circuit with decoupled flip-around MDAC, capacitive attenuation solution and self-embedded offset cancellation. The flip-around MDAC architecture is built for low inter-stage gain implementation. A capacitive attenuation solution is provided for minimizing the power dissipation and optimizing conversion speed. The design reuses SAR ADC to perform offset cancellation, which significantly saves calibration area, power and time.

Owner:UNIVERSITY OF MACAU

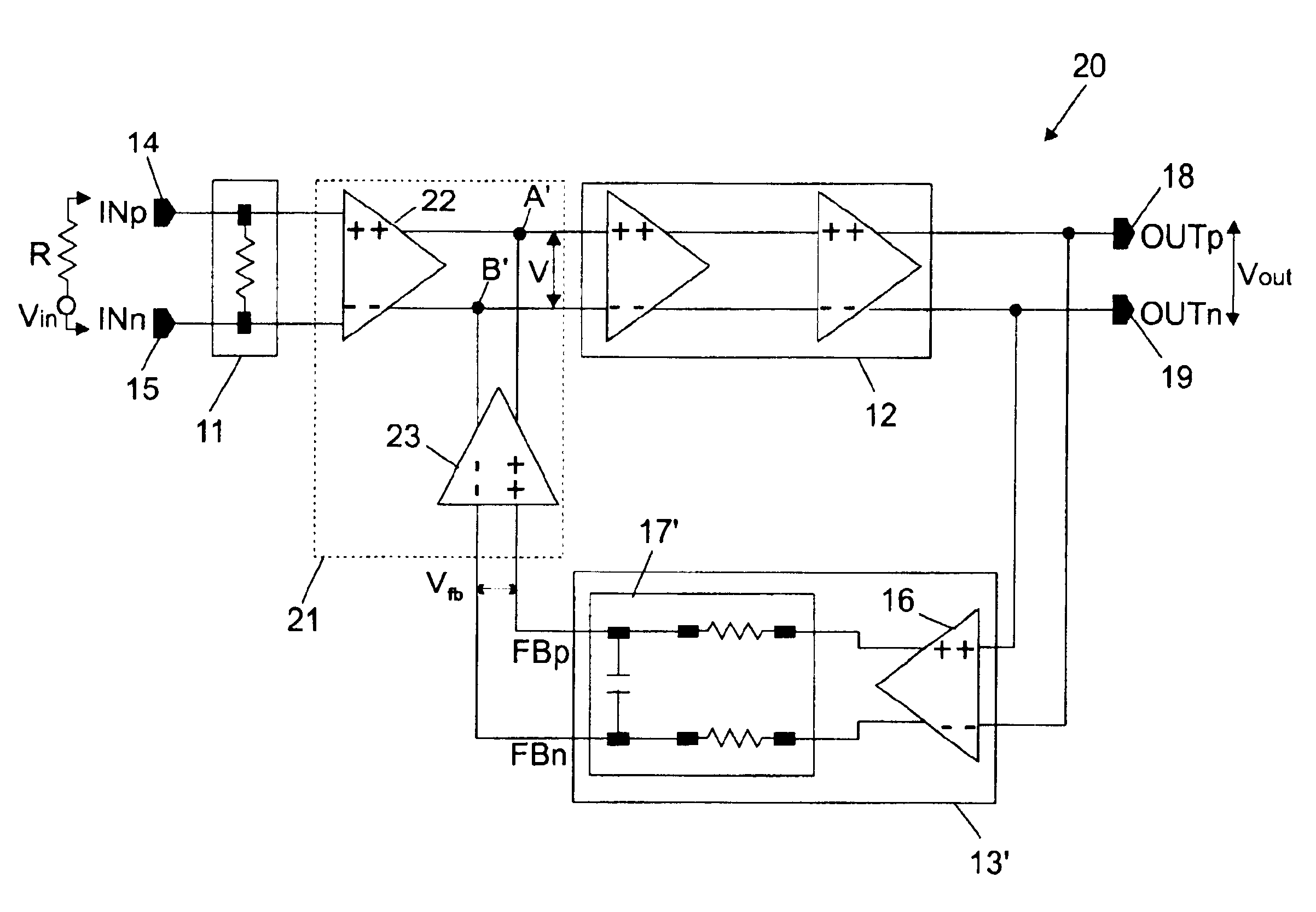

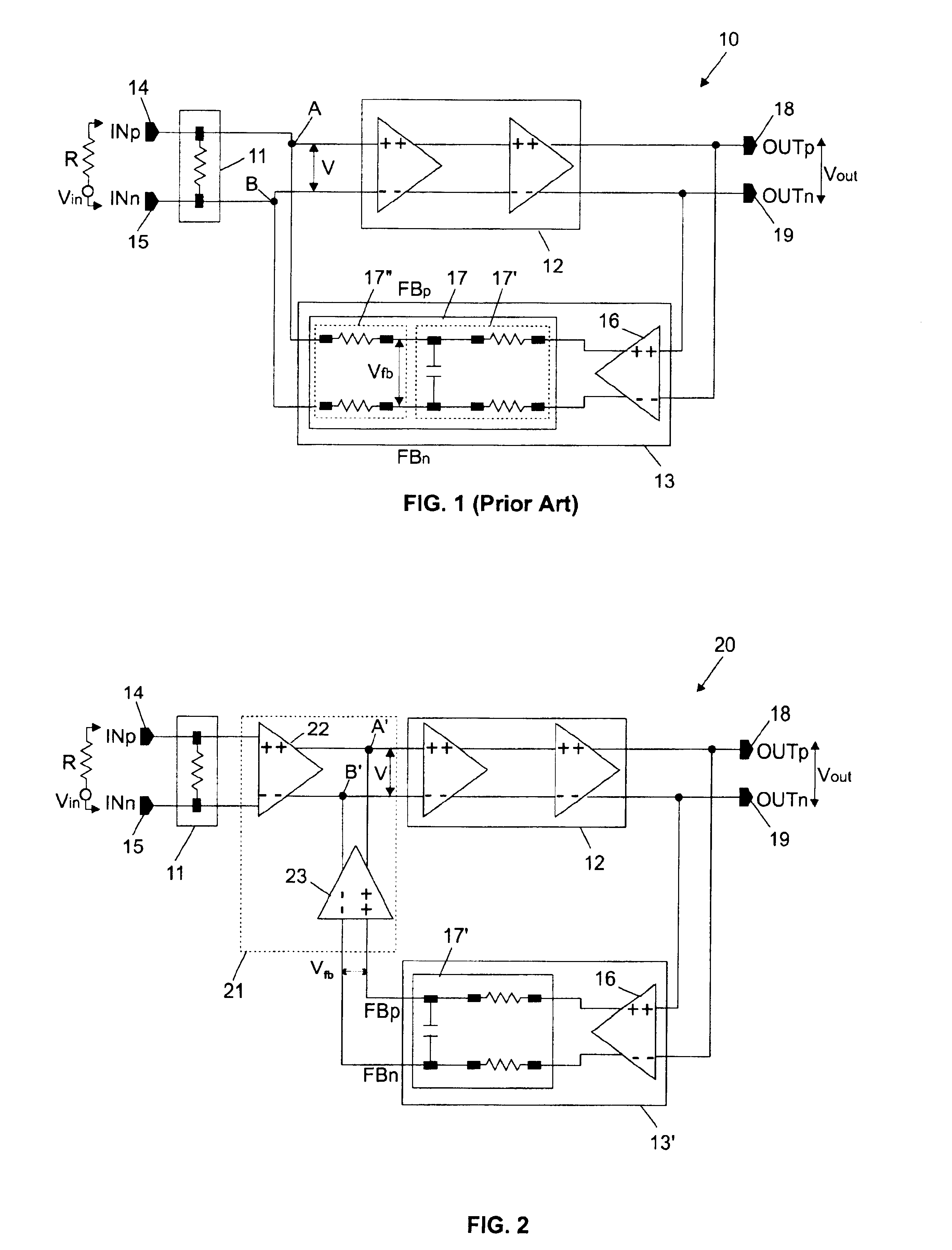

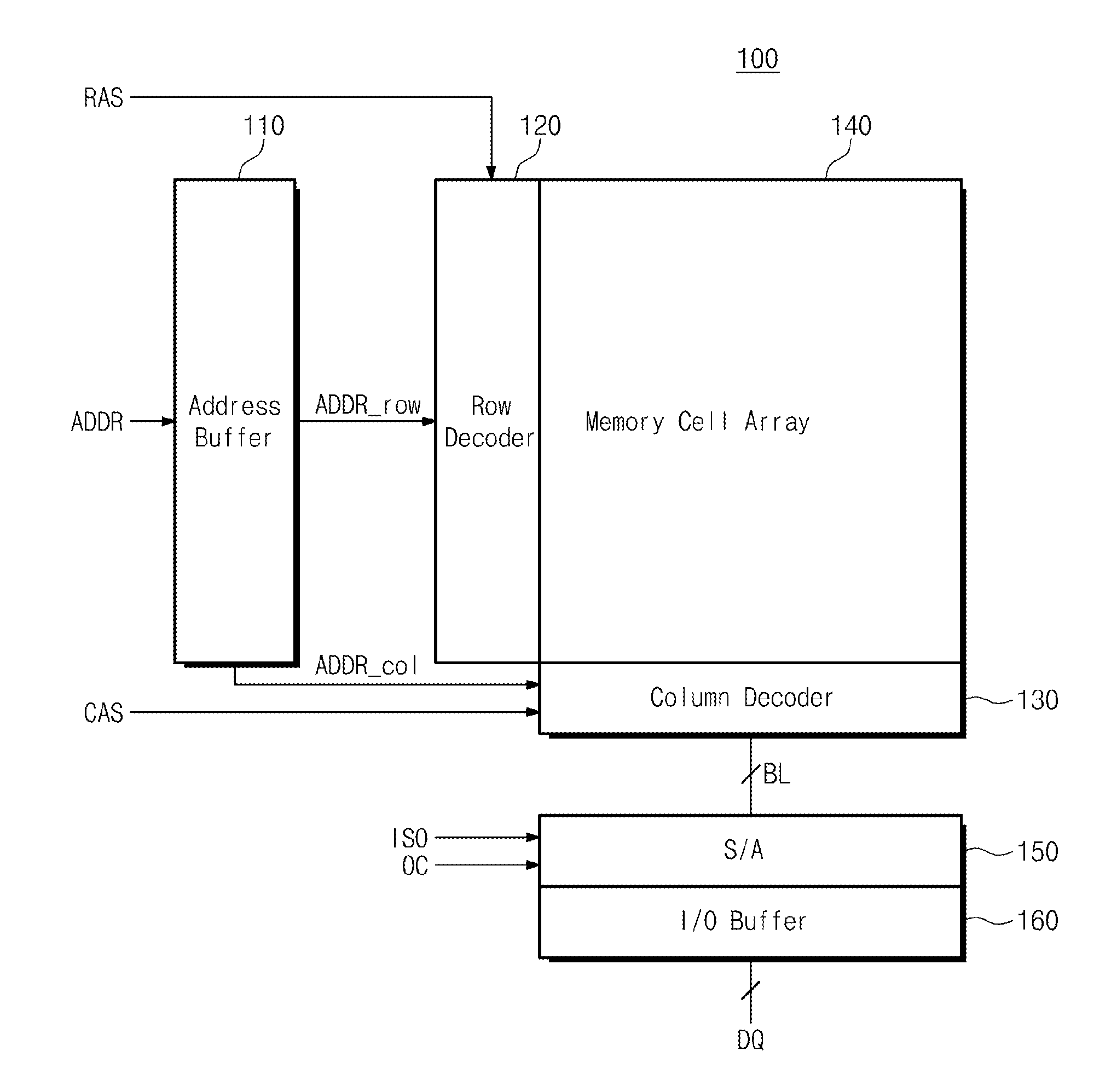

Differential amplifier with DC offset cancellation

InactiveUS6914479B1Excellent input impedance matchingLow eye-diagram closureDifferential amplifiersDc-amplifiers with dc-coupled stagesAudio power amplifierOffset cancellation

There is disclosed an improved differential amplifier (20) having a feedback loop that generates an amplified output signal (Vout) from an input signal (Vin) supplied by a preceding stage. It comprises an input matching circuit (11) connected to said preceding stage, a buffer (22) and an amplification section (12) connected in series in the direct amplification line, a first amplifier (16), a RC network (17′) and a second amplifier (23) connected in series in a parallel loop between the outputs and the inputs of the amplification section that generate the feedback signal. The role of said buffer and second amplifier associated in a dedicated direct and feedback signal combining block (21) is to respectively isolate the input signal and the feedback signal from the summing nodes (A′,B′) at the amplification section inputs. As a result, the summation of the input signal and the feedback signal is improved, the DC component of the output signal is filtered out in order to significantly reduce the DC offset. In addition, the input impedance matching represented by parameter S11 is considerably improved.

Owner:IBM CORP

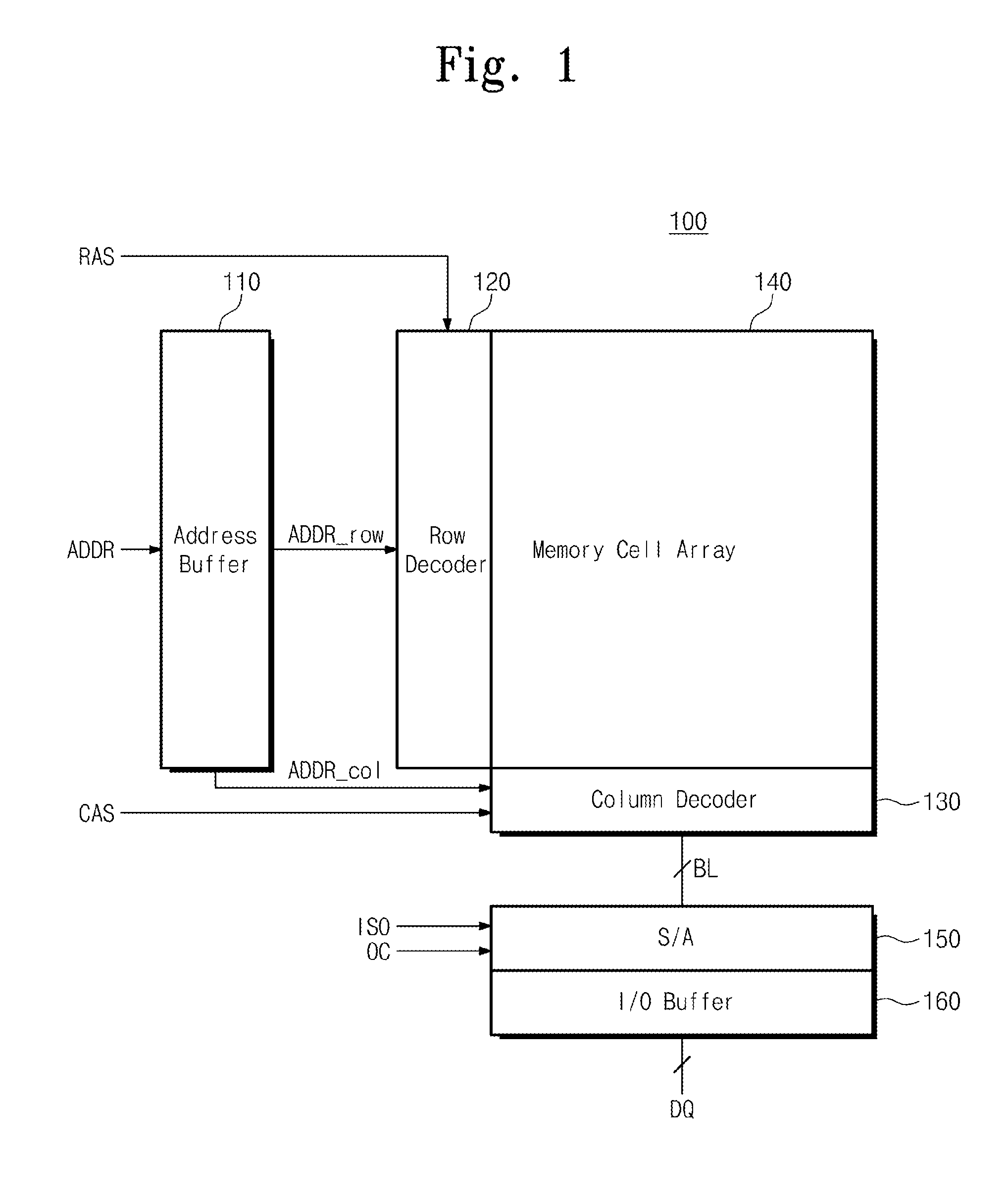

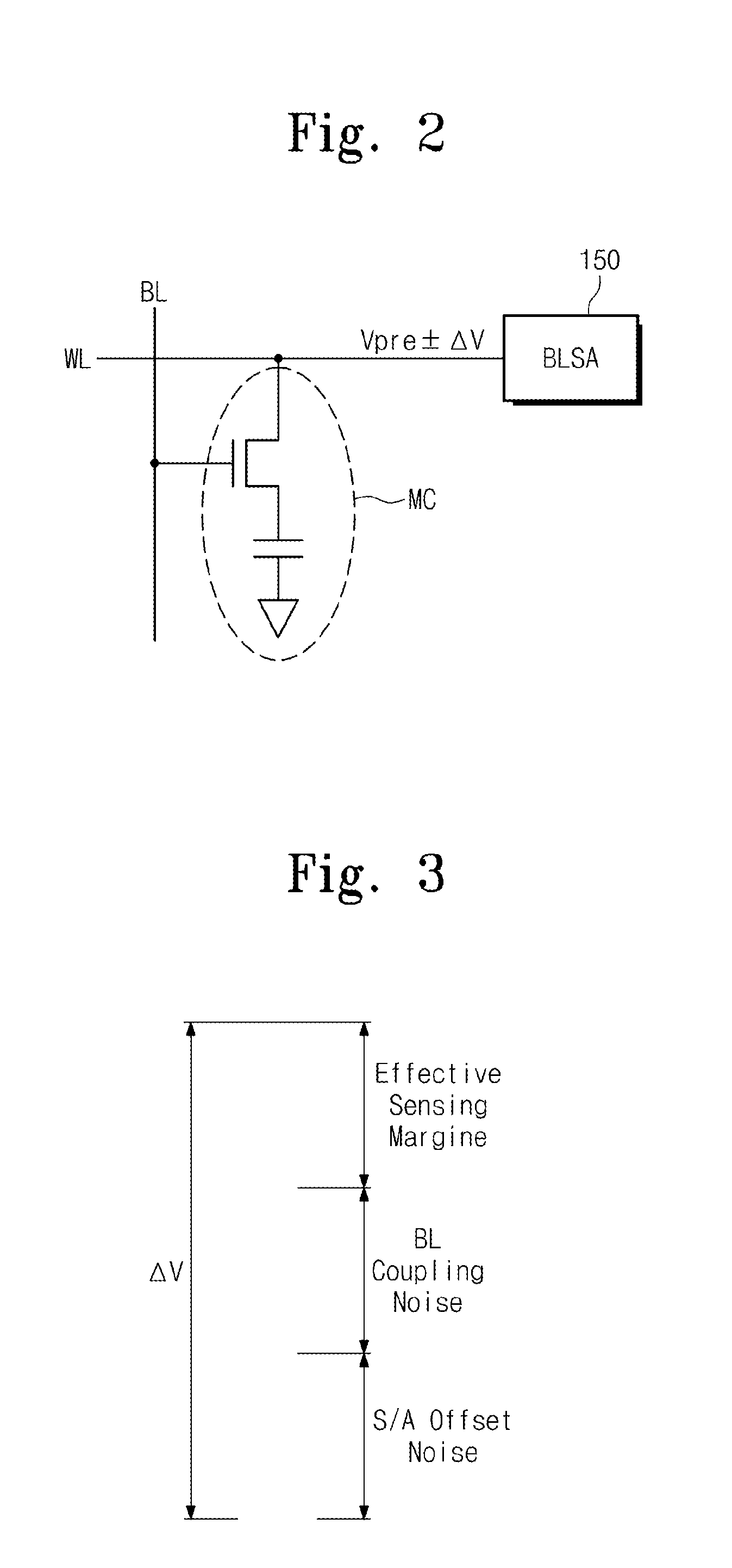

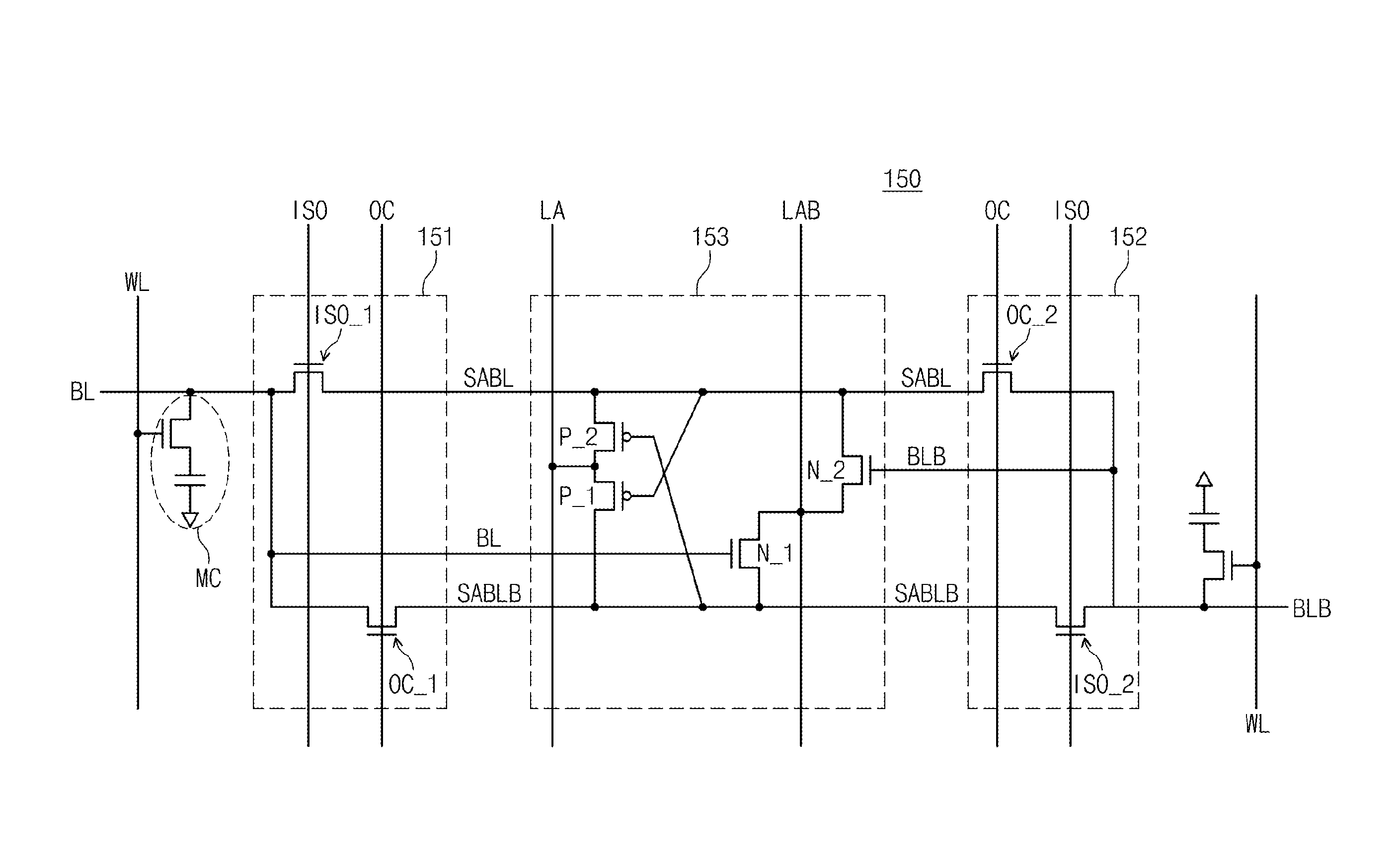

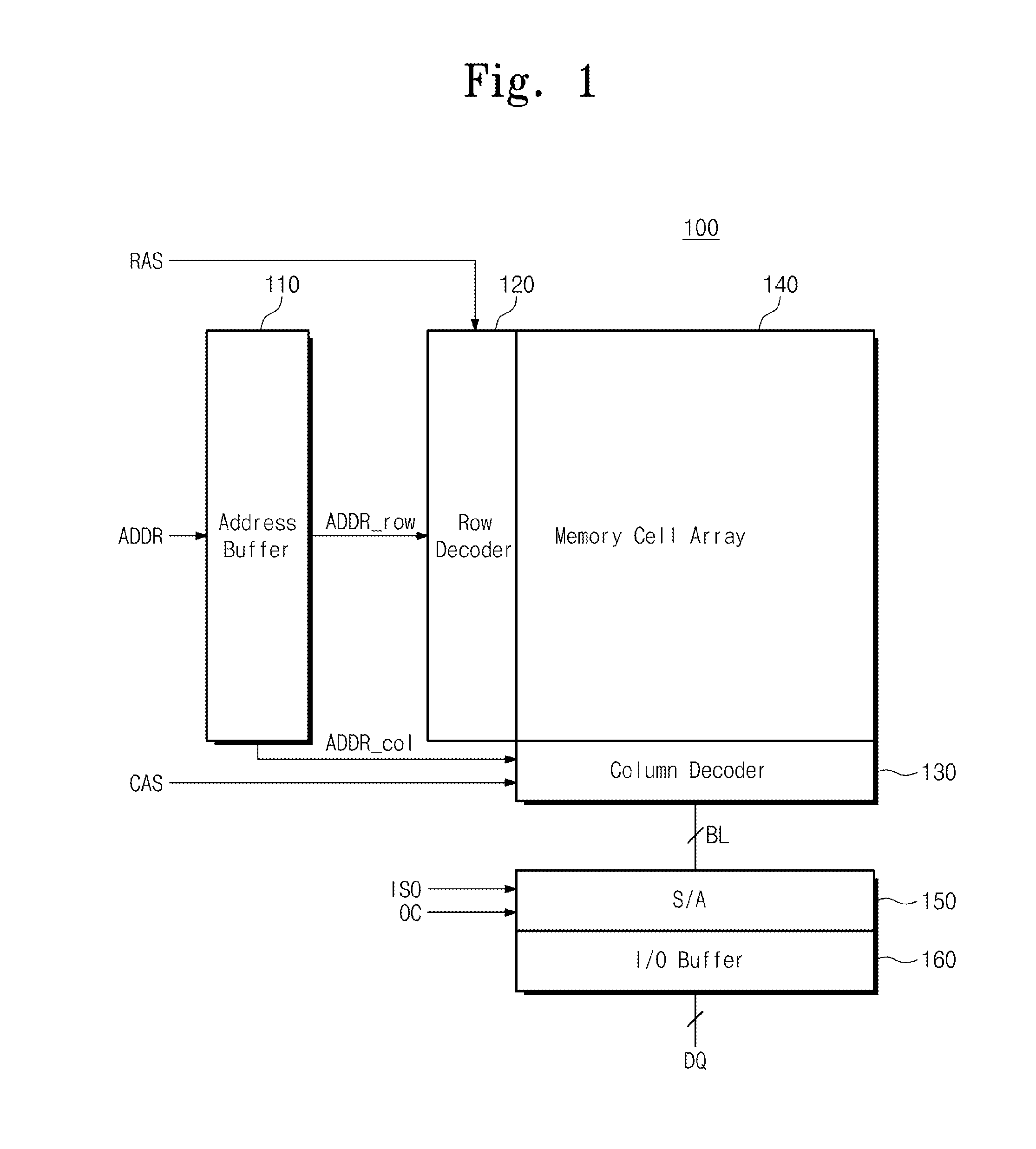

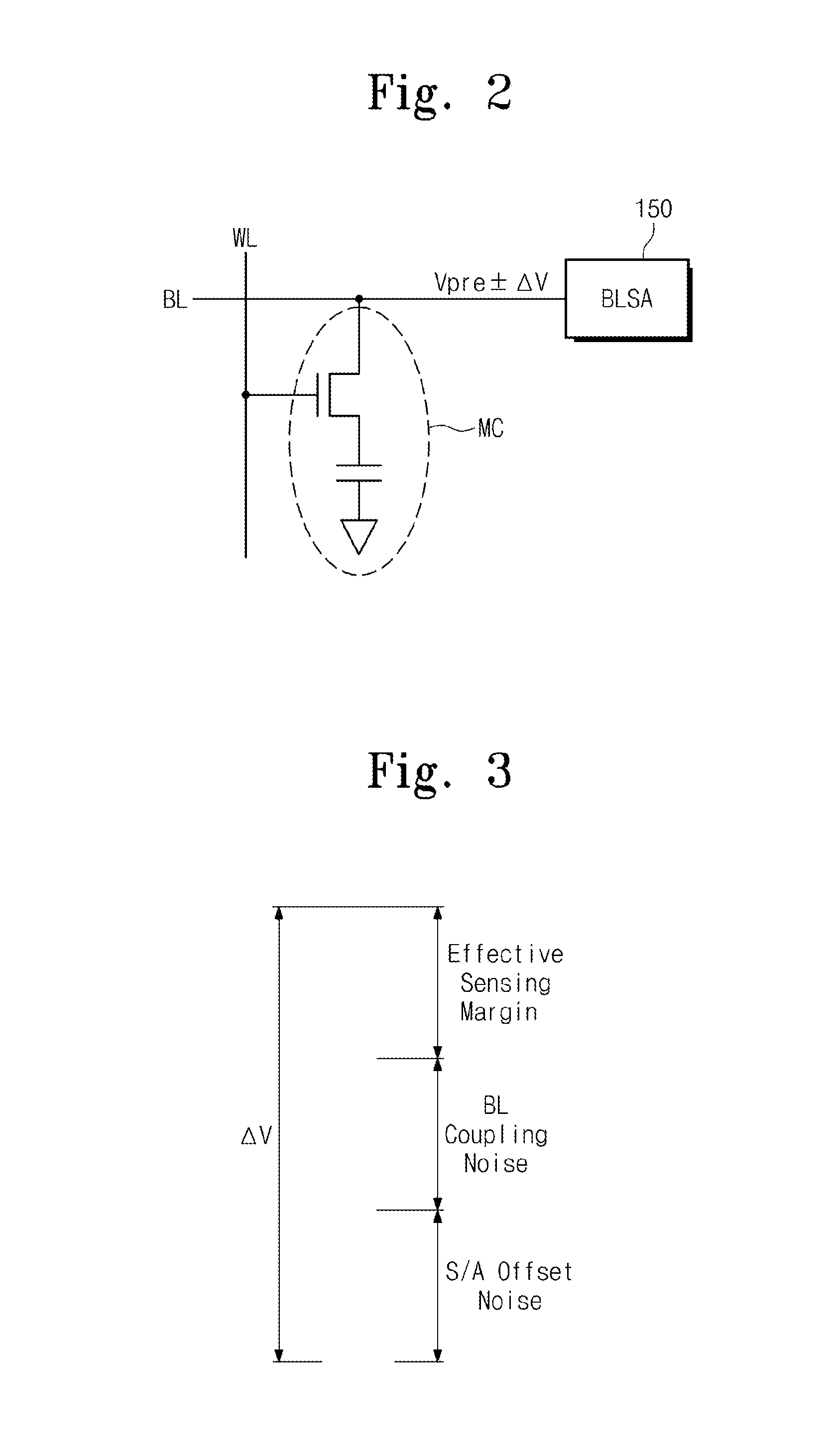

Sensor amplifier, memory device comprising same, and related method of operation

ActiveUS20150036444A1Reduces coupling efficiencyIncrease an effective sensing margin of a memory deviceDigital storageBit lineAudio power amplifier

A sense amplifier comprises a sense amplifying unit configured to be connected to a bitline and a complimentary bitline of a memory device, to sense a voltage change of the bitline in response to first and second control signals, and to control voltages of a sensing bitline and a complimentary sensing bitline based on the sensed voltage change. It further comprises a first isolation switch configured to connect the bitline with the sensing bitline in response to an isolation signal, a second isolation switch configured to connect the complimentary bitline with the complimentary sensing bitline in response to the isolation signal, a first offset cancellation switch configured to connect the bitline with the sensing bitline in response to an offset cancellation signal, and a second offset cancellation switch configured to connect the complimentary bitline with the complimentary sensing bitline in response to the offset cancellation signal.

Owner:SAMSUNG ELECTRONICS CO LTD

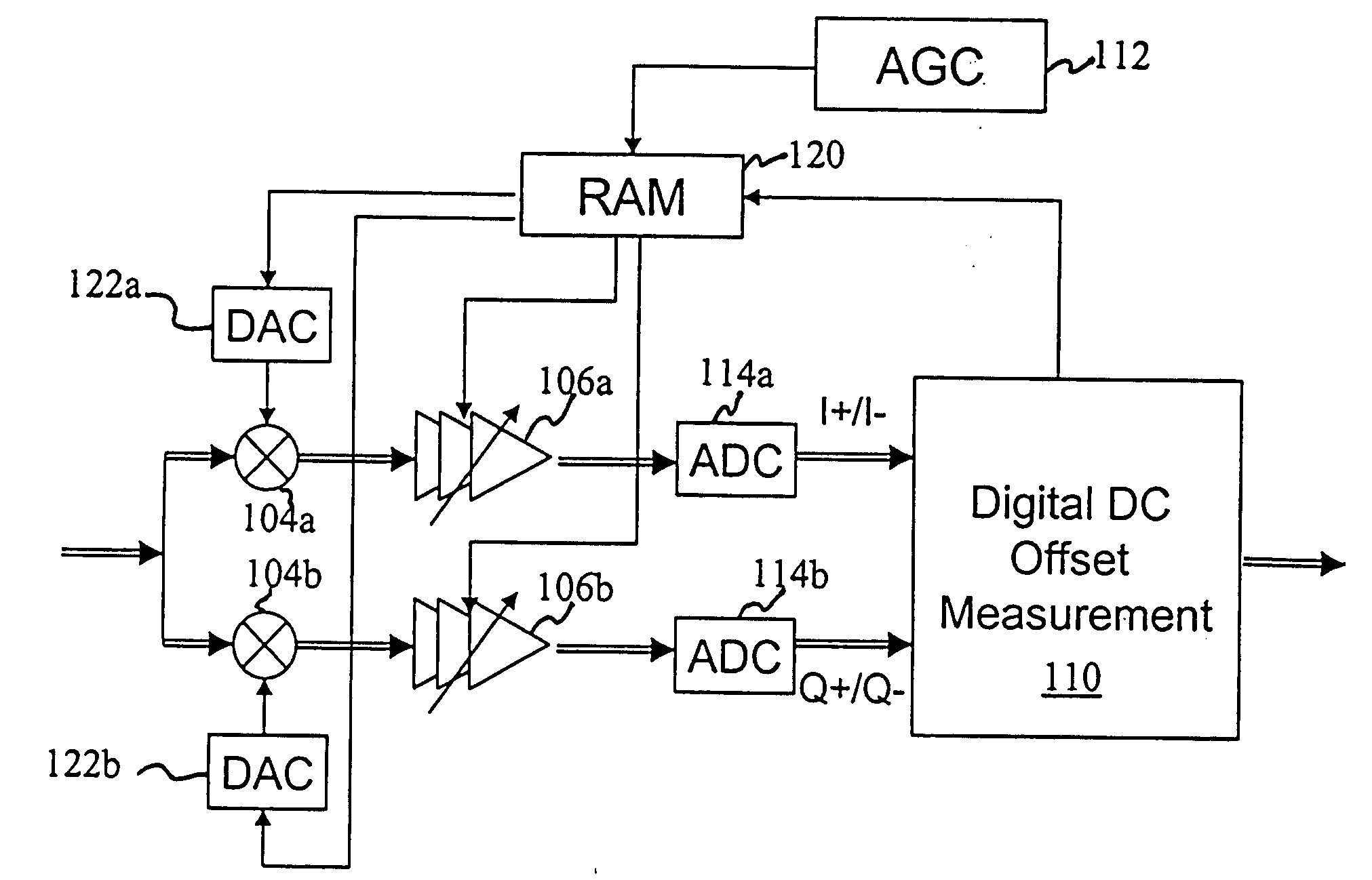

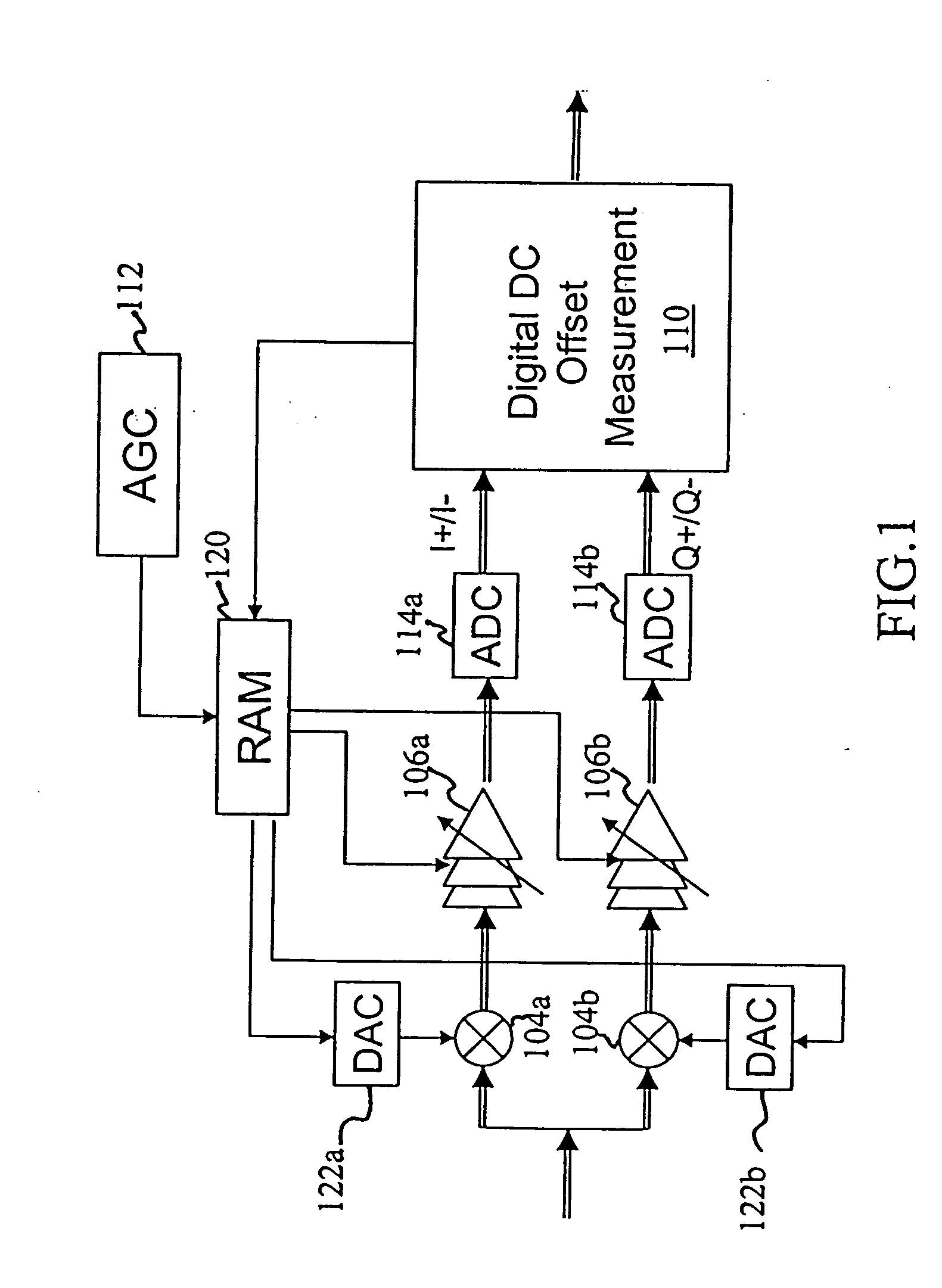

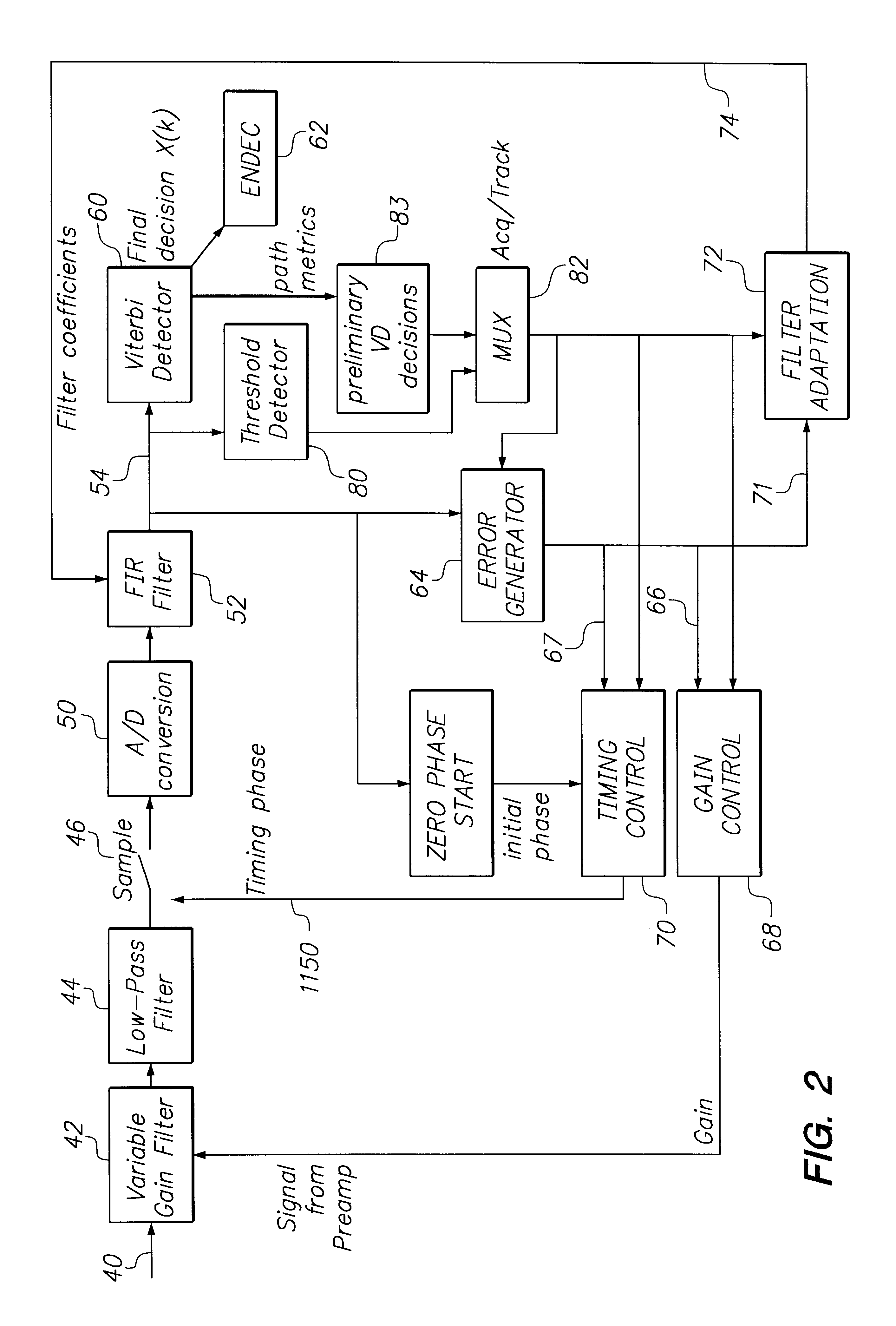

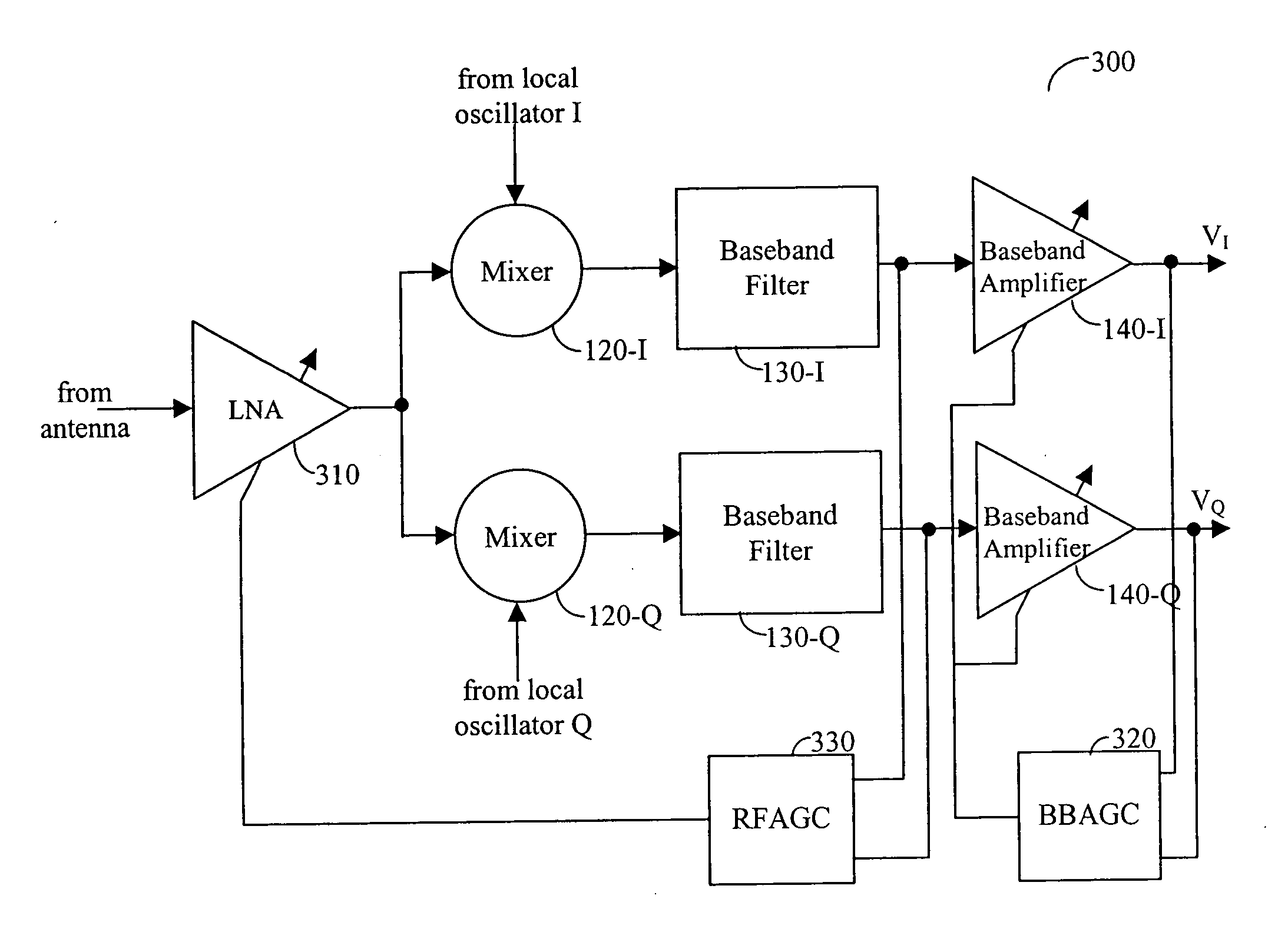

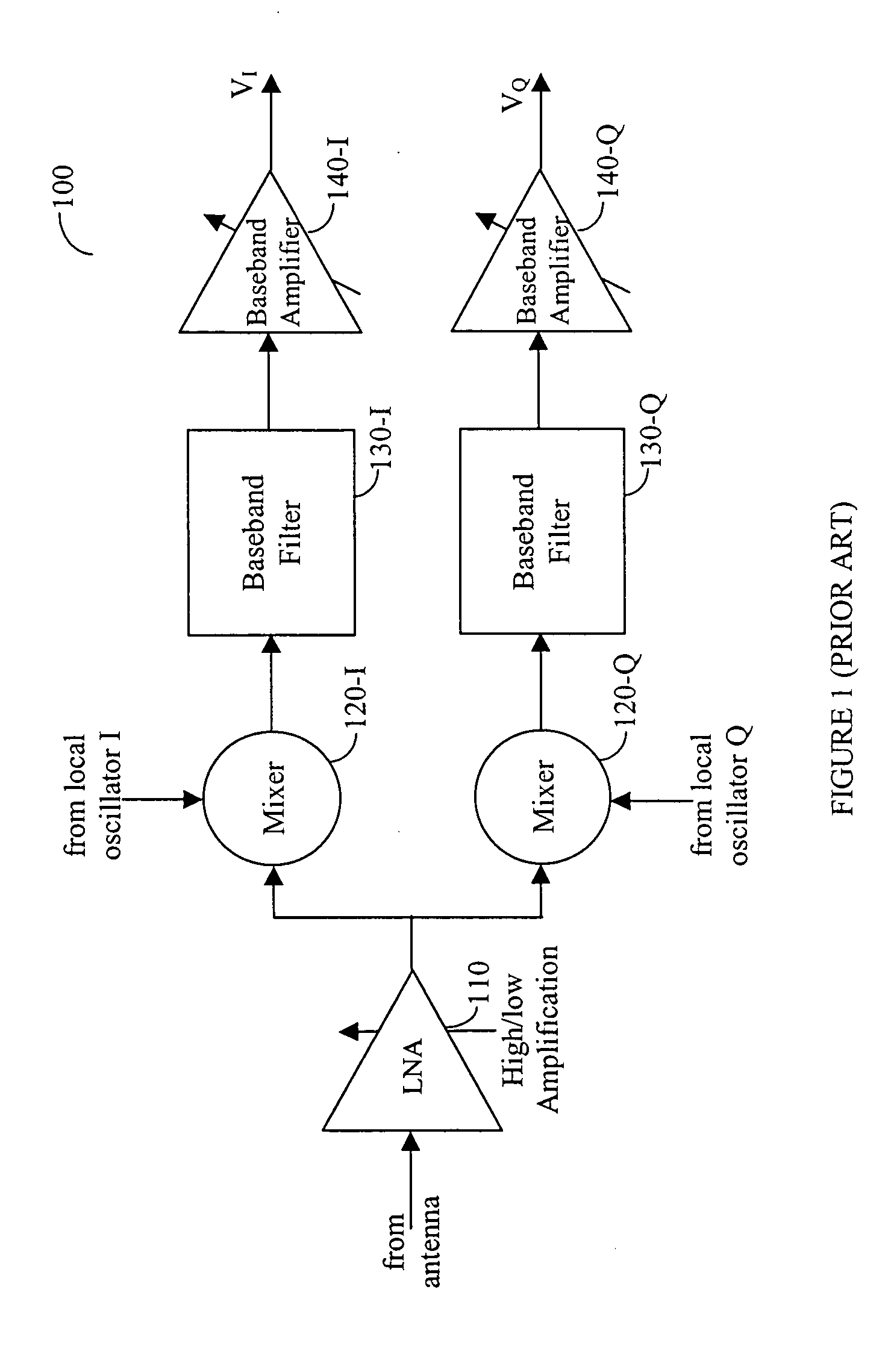

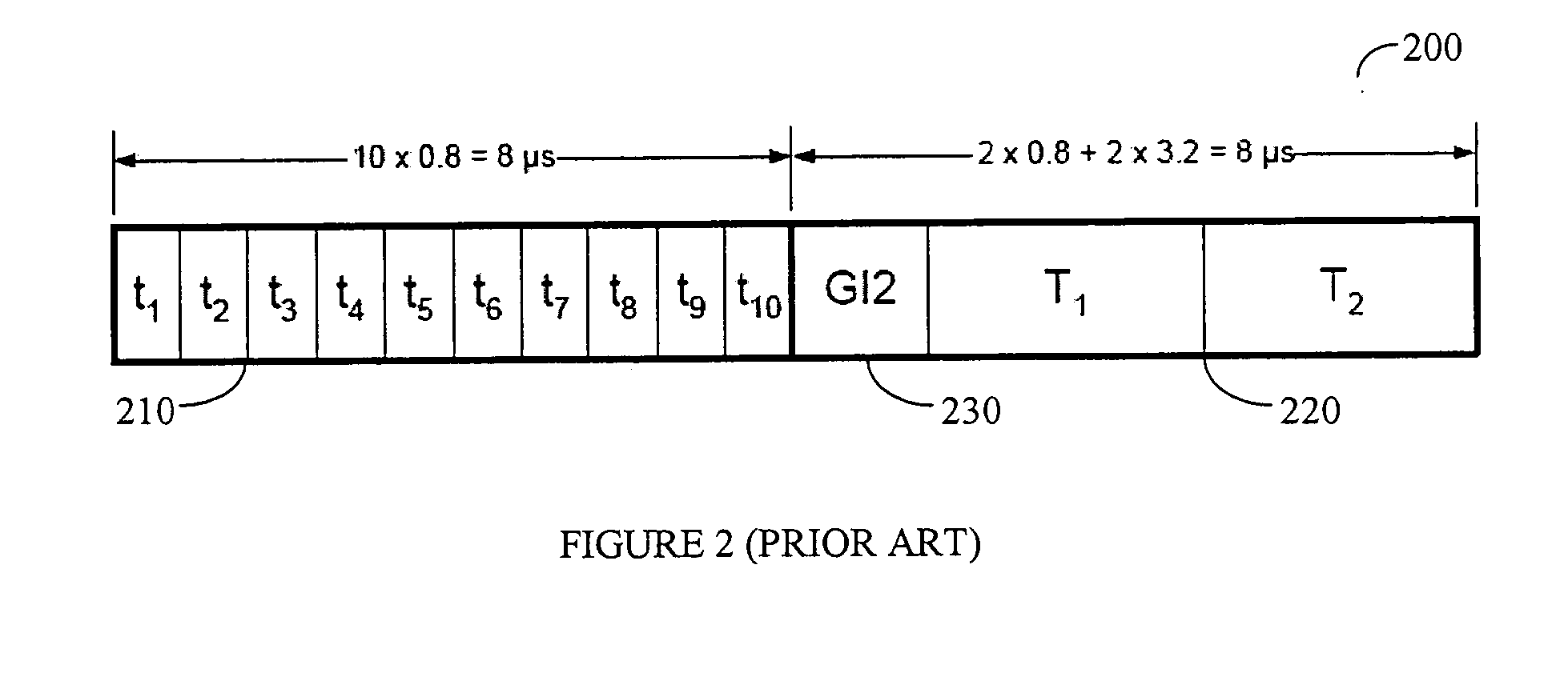

Wireless LAN receiver with I and Q RF and baseband AGC loops and DC offset cancellation

ActiveUS20050276358A1Quick controlOvercome limitationsGain controlAmplitude-modulated carrier systemsLoop controlOffset cancellation

A wireless local area network receiver having separate automatic gain control (AGC) loops for providing a radio frequency AGC and a baseband frequency AGC, as well as a DC offset cancellation circuit. The AGC loops control a low noise amplifier amplifying the received RF signal, and the baseband signal or signals from a mixer of I and Q mixers. The DC offset compensation loop is also responsive to the baseband AGC signal to maintain a substantially fixed gain in the DC offset compensation feedback. Details of various embodiments are disclosed, including embodiments for orthogonal frequency division multiplexing (OFDM) that provide the AGC operation and the DC offset cancellation to the desired levels within the relatively short period of a preamble that precedes the data transmission.

Owner:THETA IP

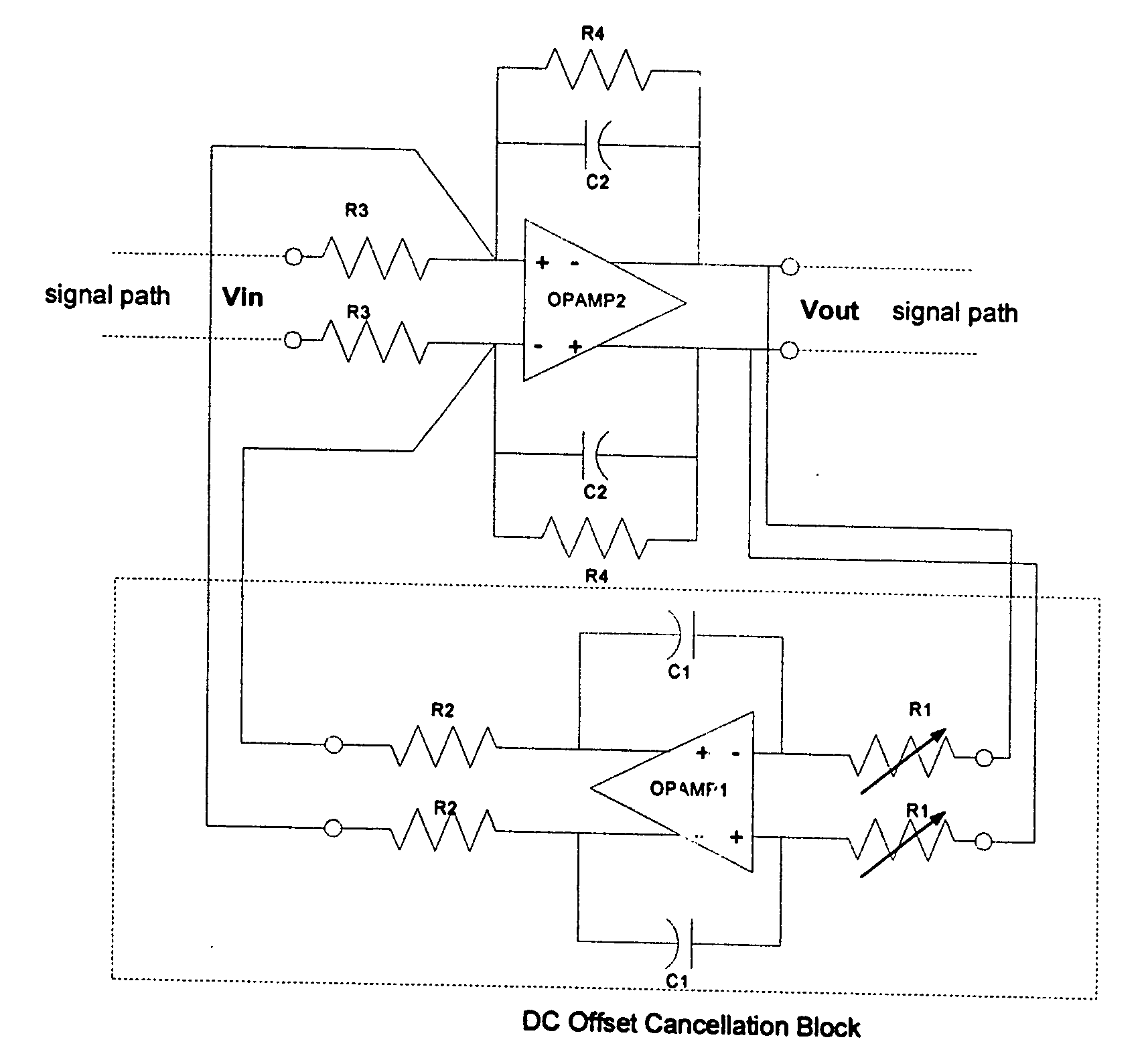

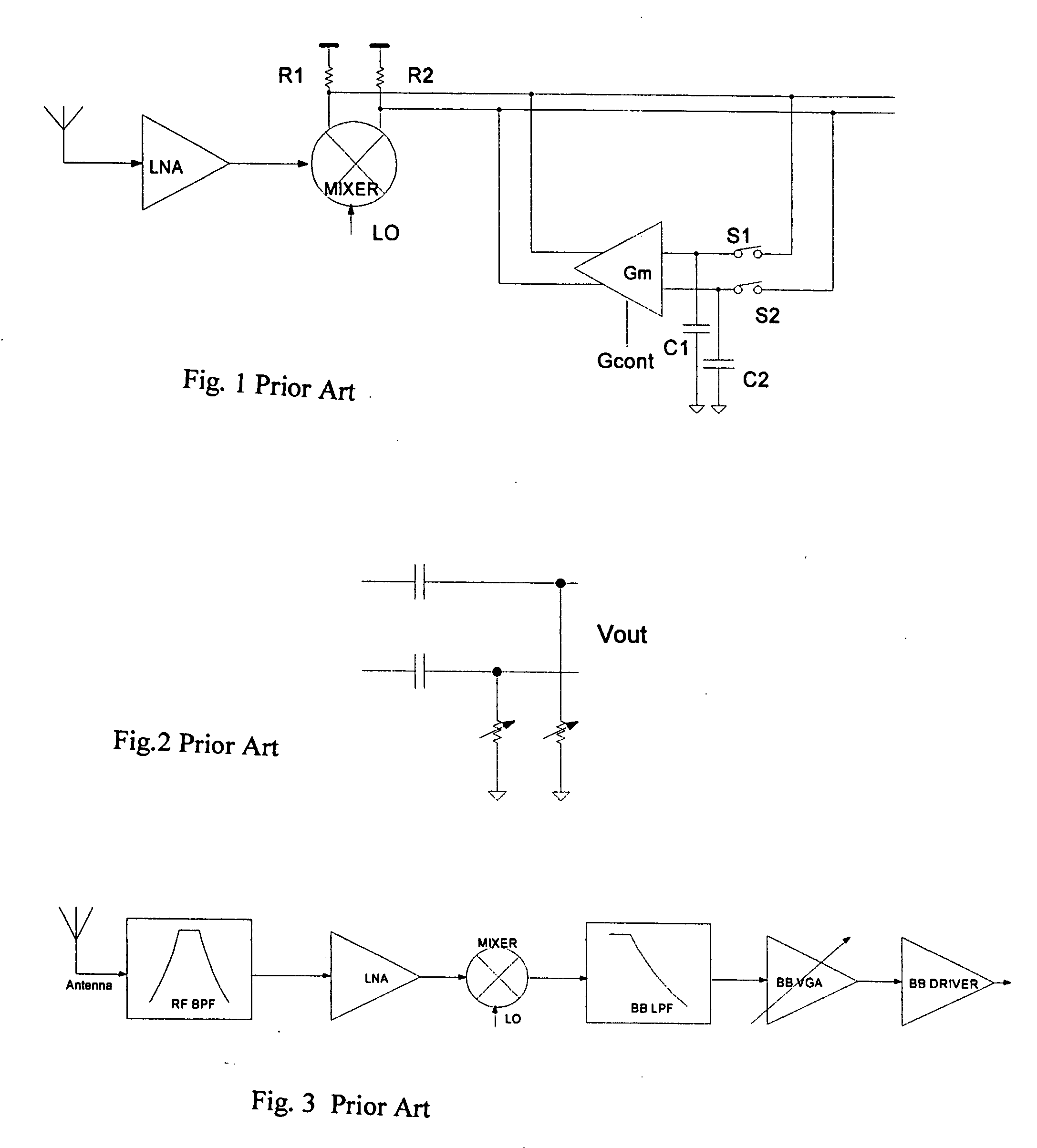

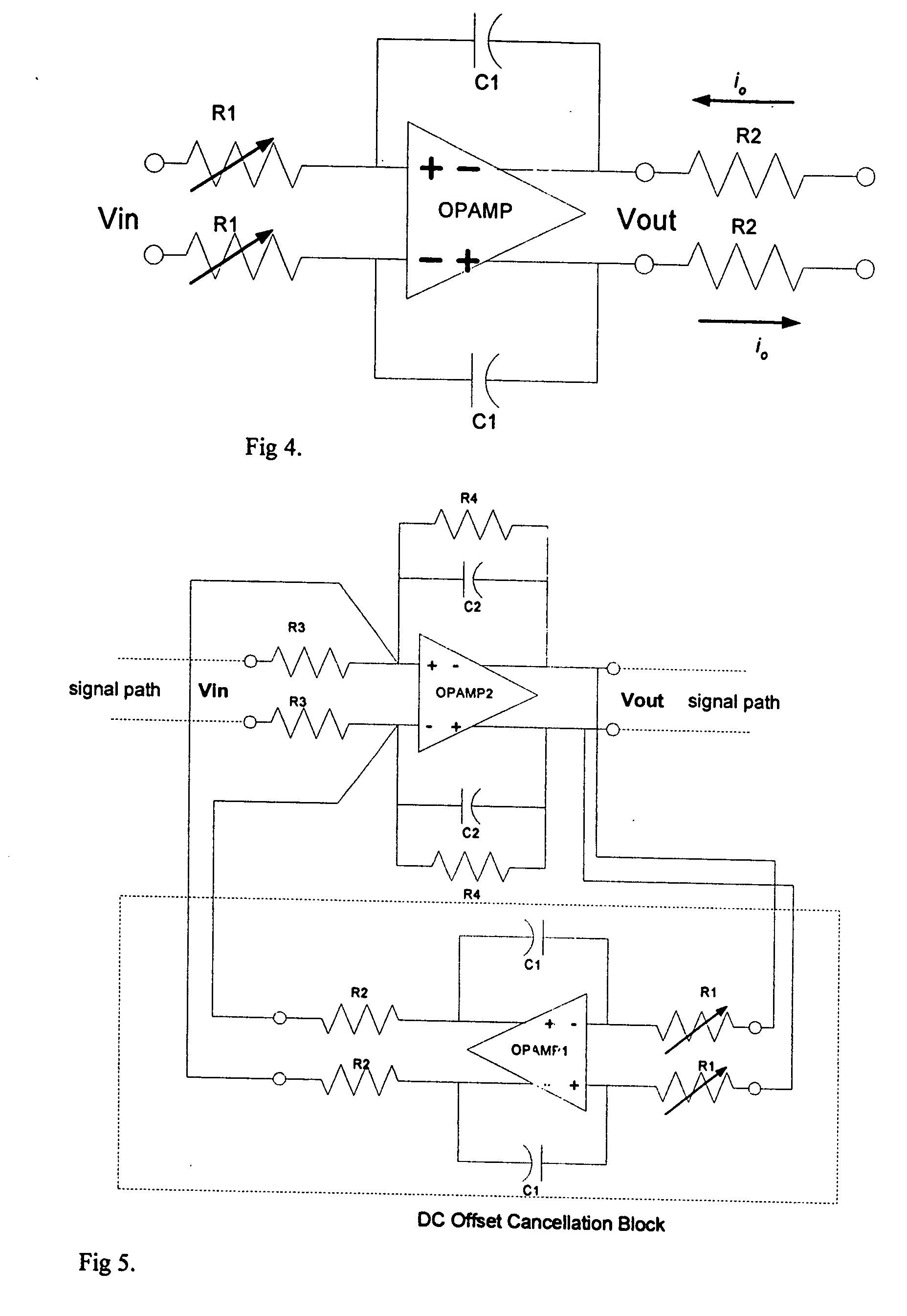

DC offset cancellation in a direct-conversion receiver

InactiveUS20050110550A1Reduce silicon areaSave powerPulse automatic controlDifferential amplifiersCapacitanceIntegrator

The DCOC block is used in ZIF BB to form HPF function to cancel dc offset with a penalty of small silicon area and low power consumption. It is a LPF plus a voltage to current conversion (VIC) resistor, and can hook up with any BB opamp used in signal path, to form a feedback loop, with or without signal gain stages in the loop. The BB opamp is used as a summing point. The summing method is input current summing. The cutoff frequency of the HPF function is thus defined by the integrator, the VIC resistor, and the feedback resistor in the summing opamp. The presence of the VIC resistor can drastically reduce the integrator capacitor and resistor values and thus save silicon area or improve receiver performance.

Owner:PROMINENT COMM

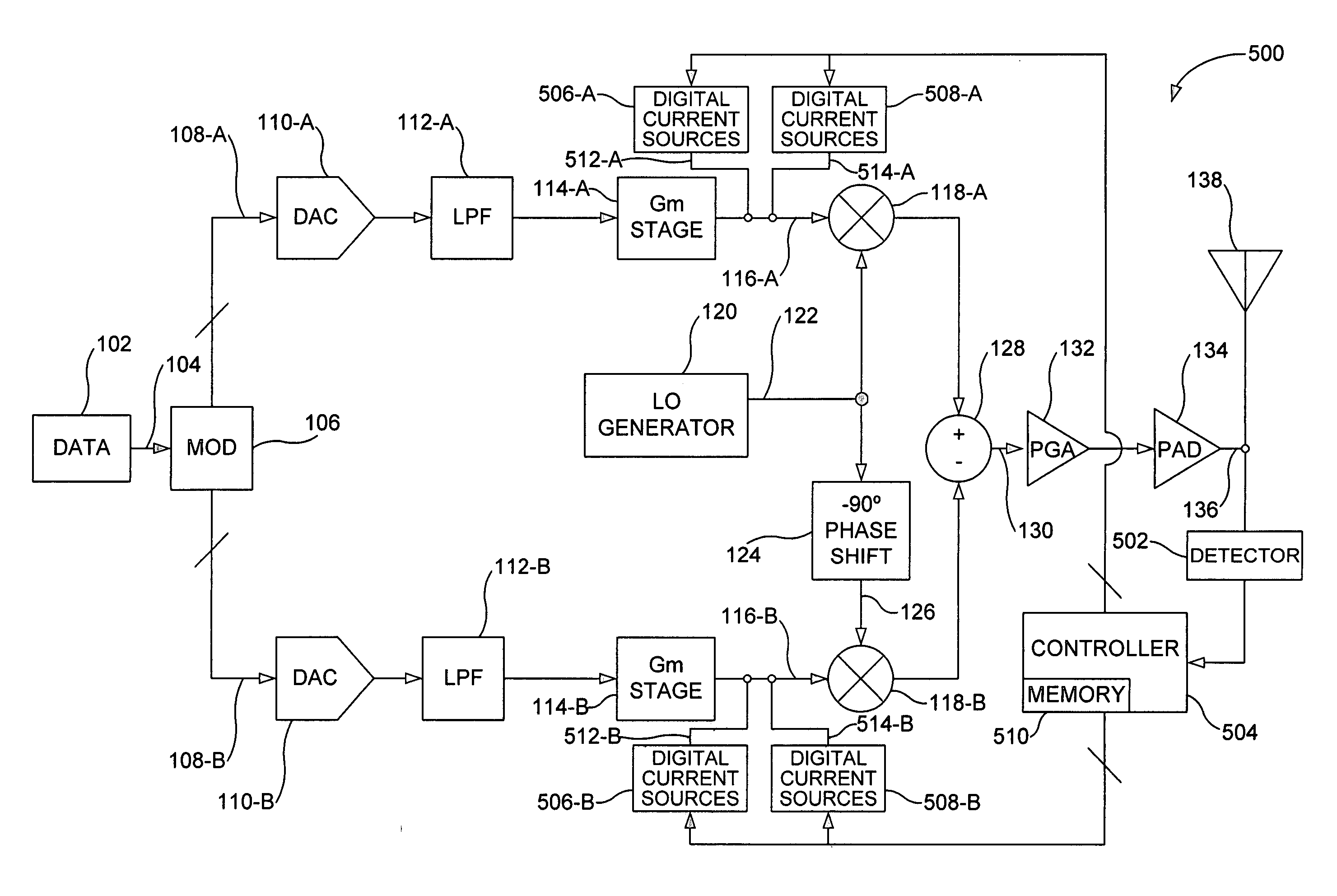

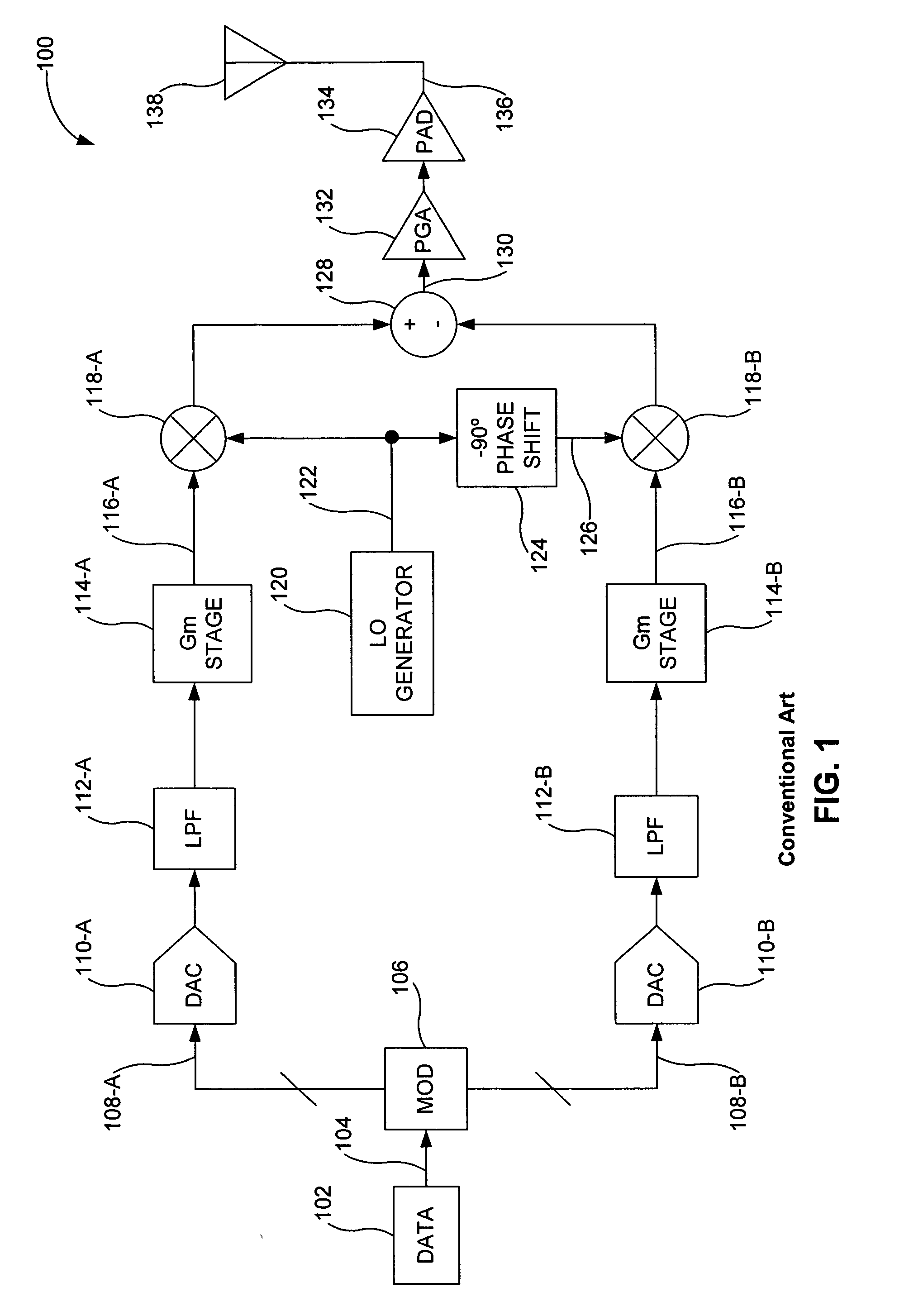

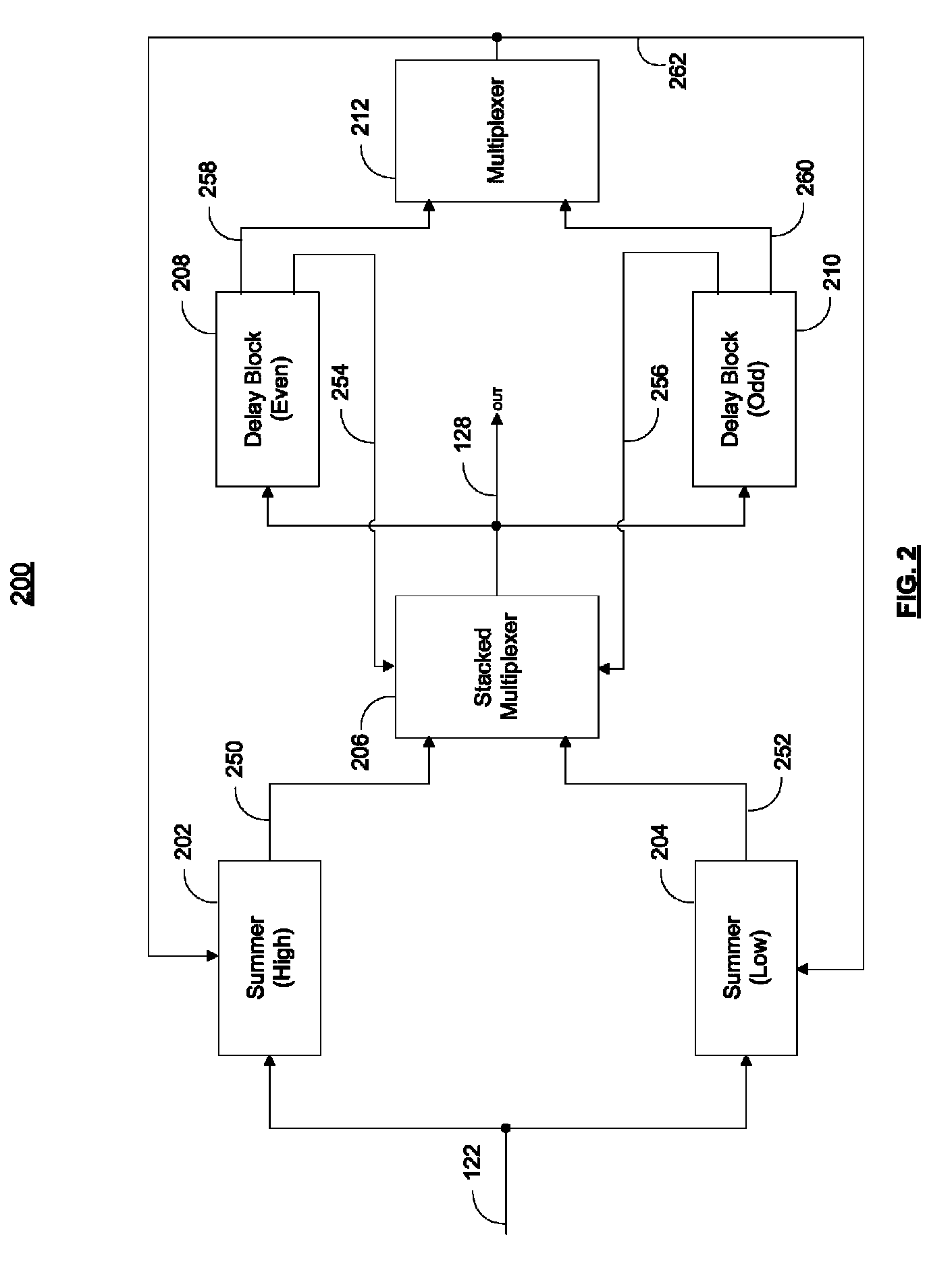

Transmitter having DC offset cancellation

ActiveUS20070042728A1Reduce direct LO coupling componentReduce the required powerResonant long antennasSecret communicationOffset cancellationLocal oscillator

A transmitter generates a transmitter output signal from first and second baseband signals. The transmitter includes a detector to detect a local oscillator (LO) leakage signal in the transmitter output signal. A controller coupled to the detector determines a direct LO coupling component and a baseband DC offset component of the LO leakage signal. First and second variable current sources are adjusted by the controller to provide first and second DC offsets to the first and second baseband signals, respectively. The first and second DC offsets reduce the direct LO coupling component. Third and fourth variable current sources are subsequently adjusted by the controller to provide third and fourth DC offsets to the first and second baseband signals, respectively. The third and fourth DC offsets reduce the baseband DC component. Overall, reducing the direct LO coupling component and the baseband DC component reduces a power of the LO leakage signal.

Owner:AVAGO TECH INT SALES PTE LTD

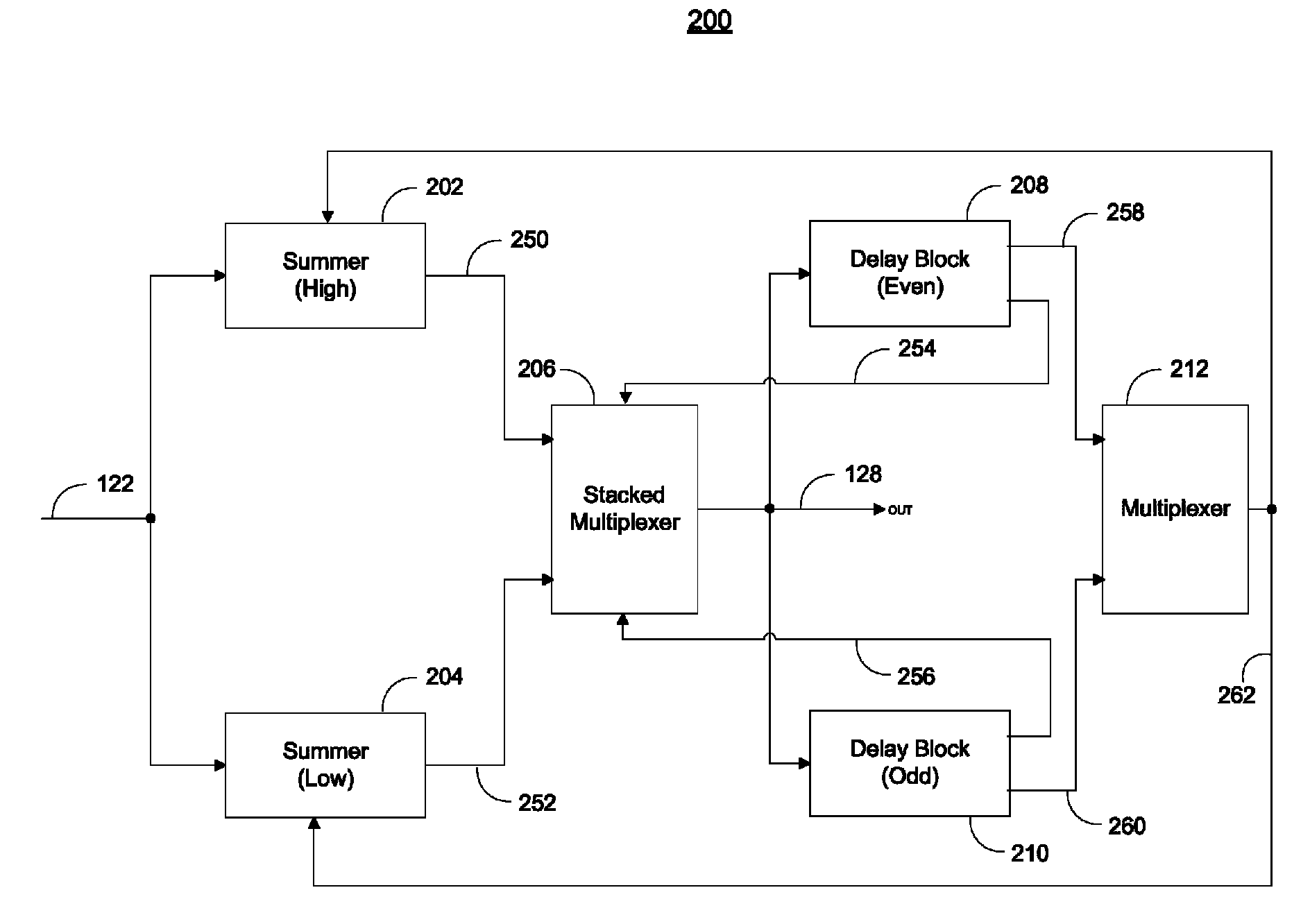

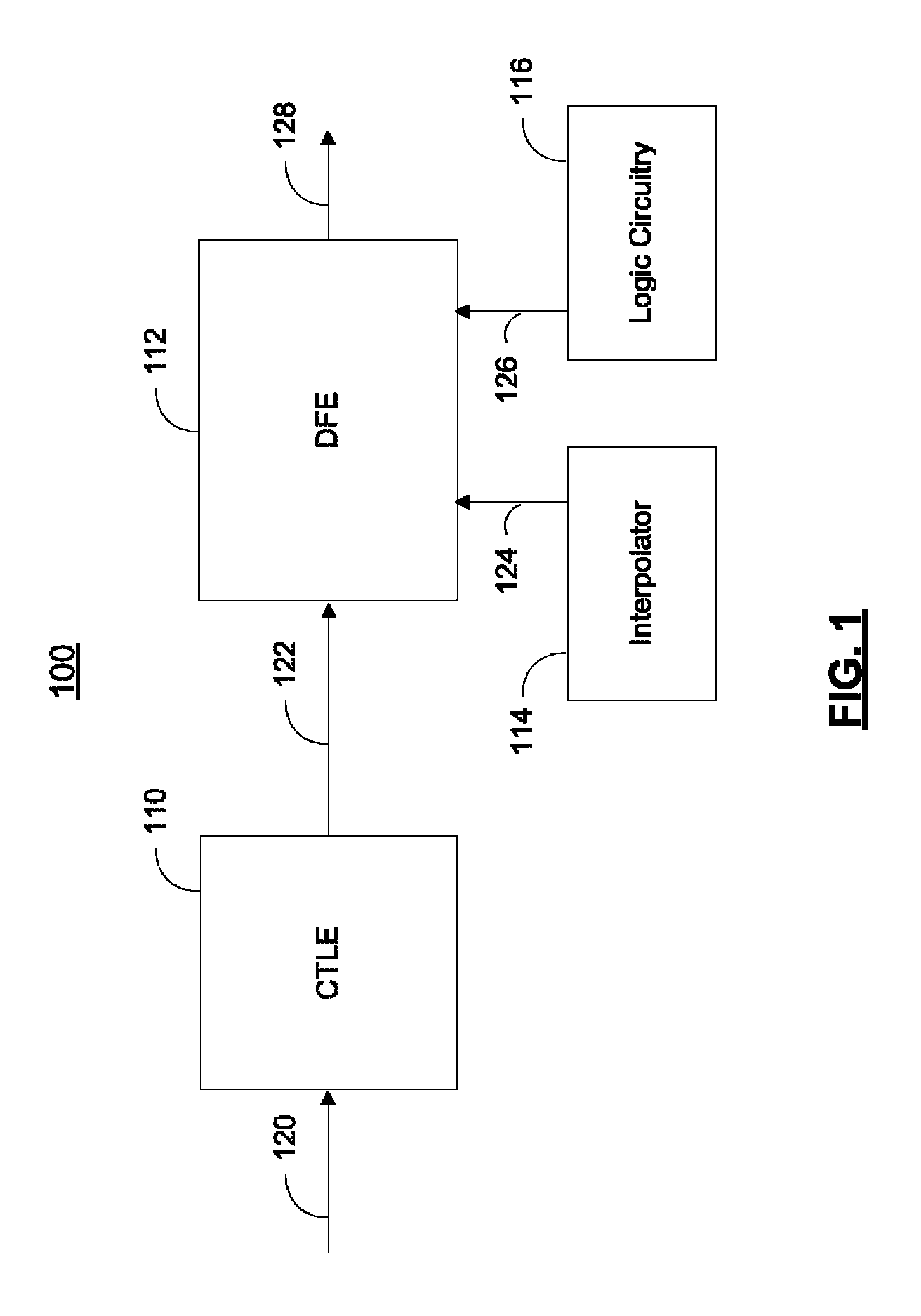

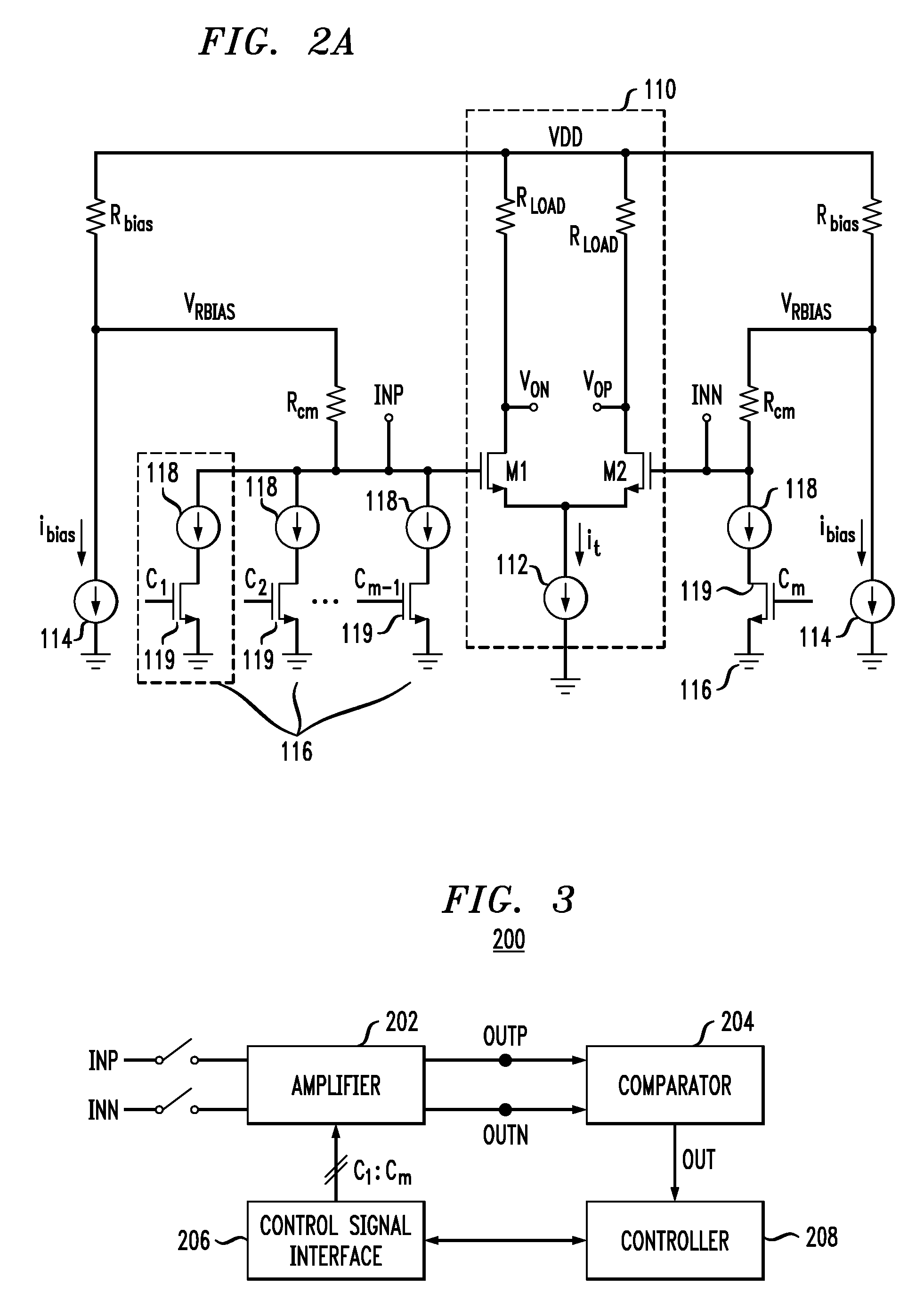

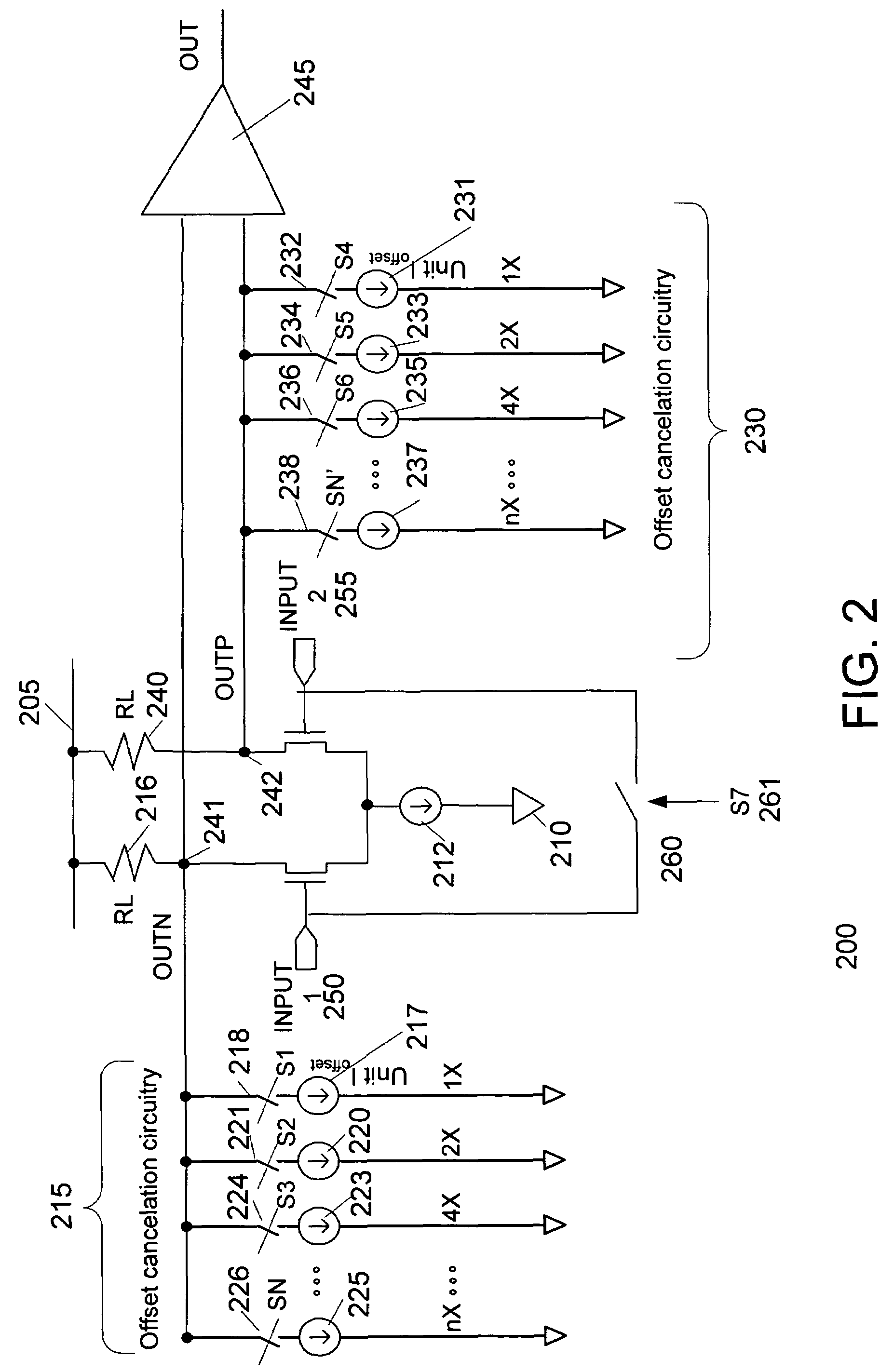

Reconfigurable equalization architecture for high-speed receivers

Systems and methods are disclosed for employing an equalization technique that improves equalizer input sensitivity and which reduces power consumption. In particular, an equalization architecture is described that includes a continuous-time linear equalizer and a decision feedback equalizer, each with offset cancellation that enables the equalizer to be used at high data rates. In addition, the equalization structure has a power-saving mode for bypassing the decision feedback equalizer. These offset cancellation and power-saving features are enabled and controlled using programmable logic on a programmable device.

Owner:ALTERA CORP

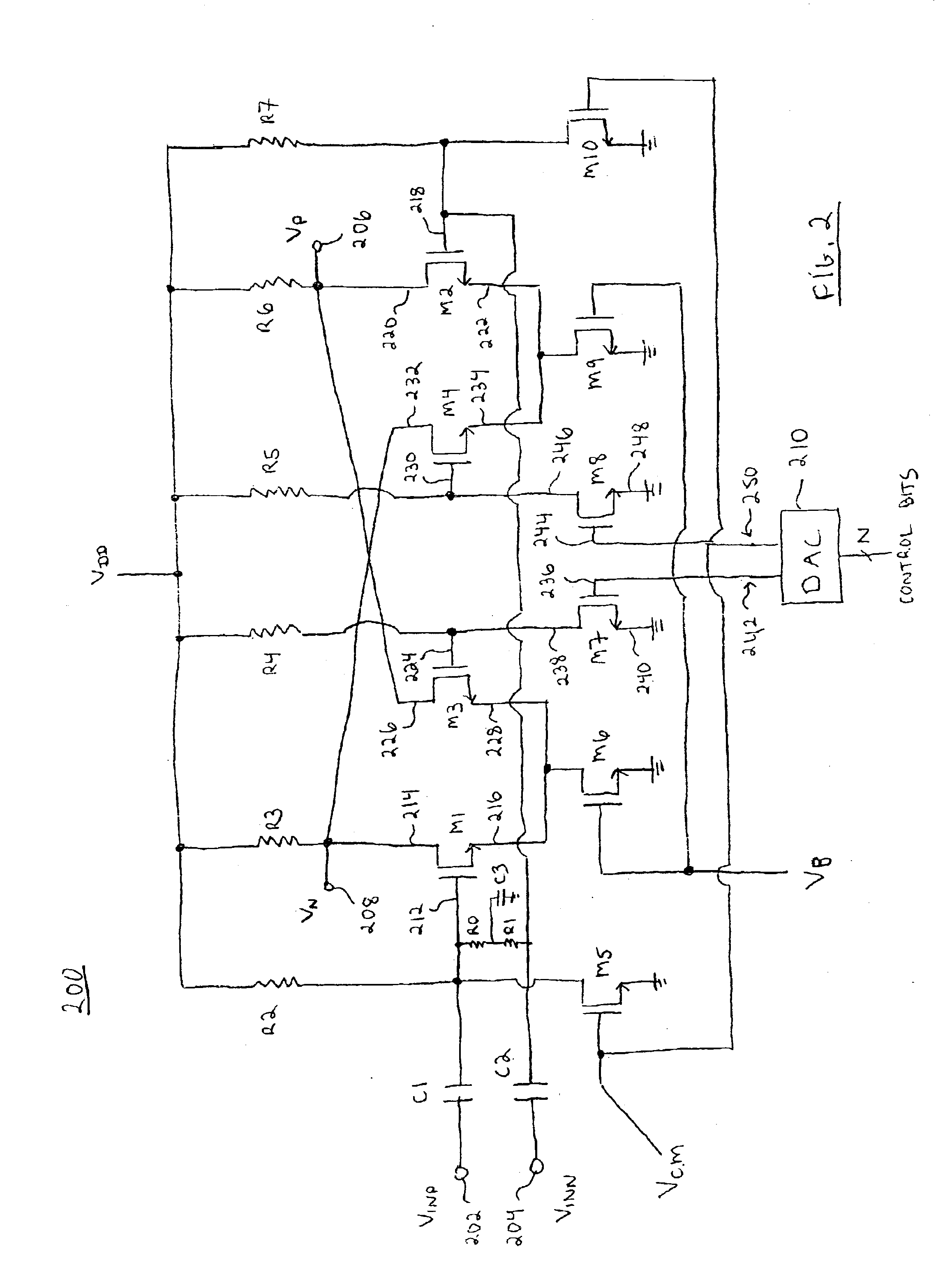

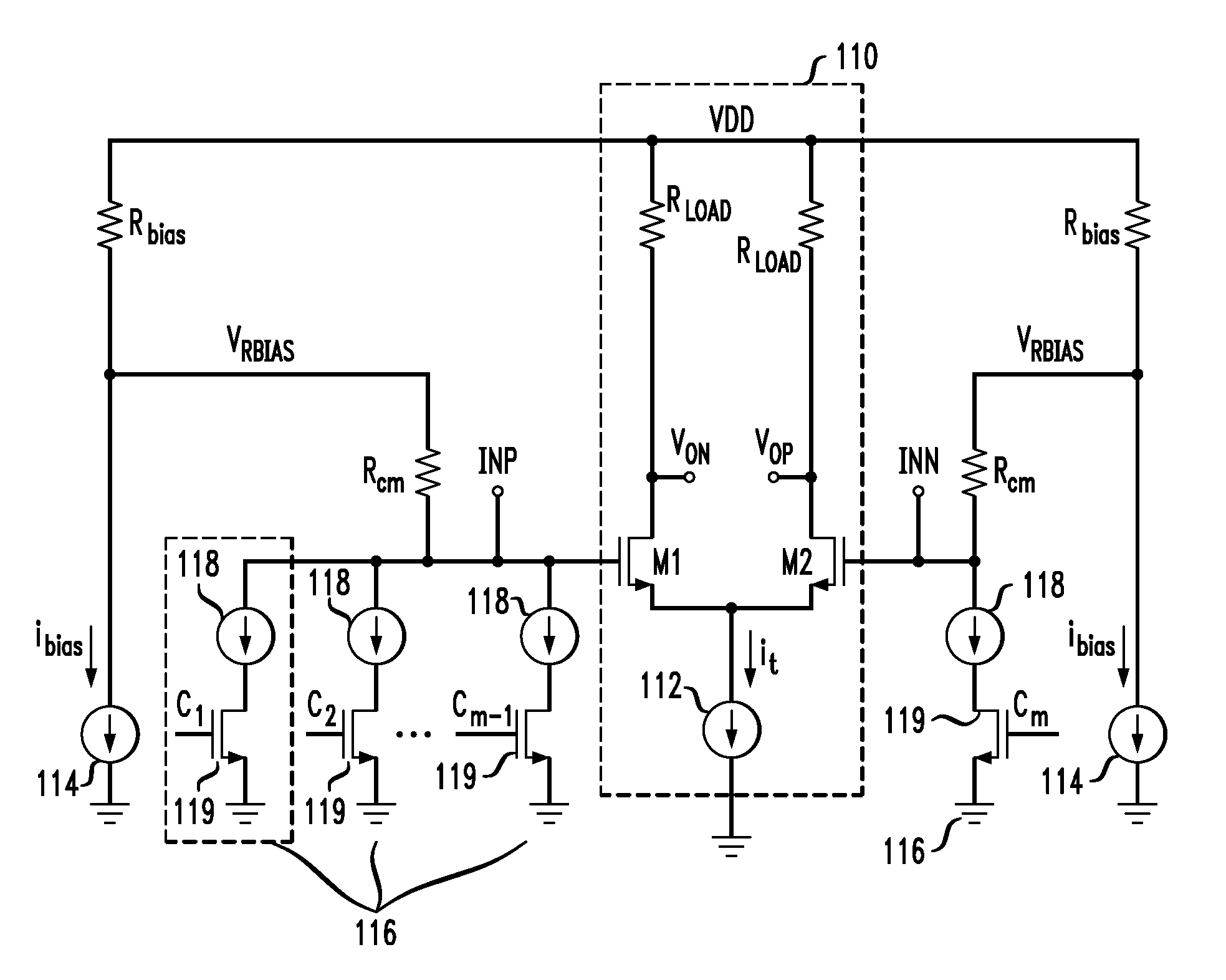

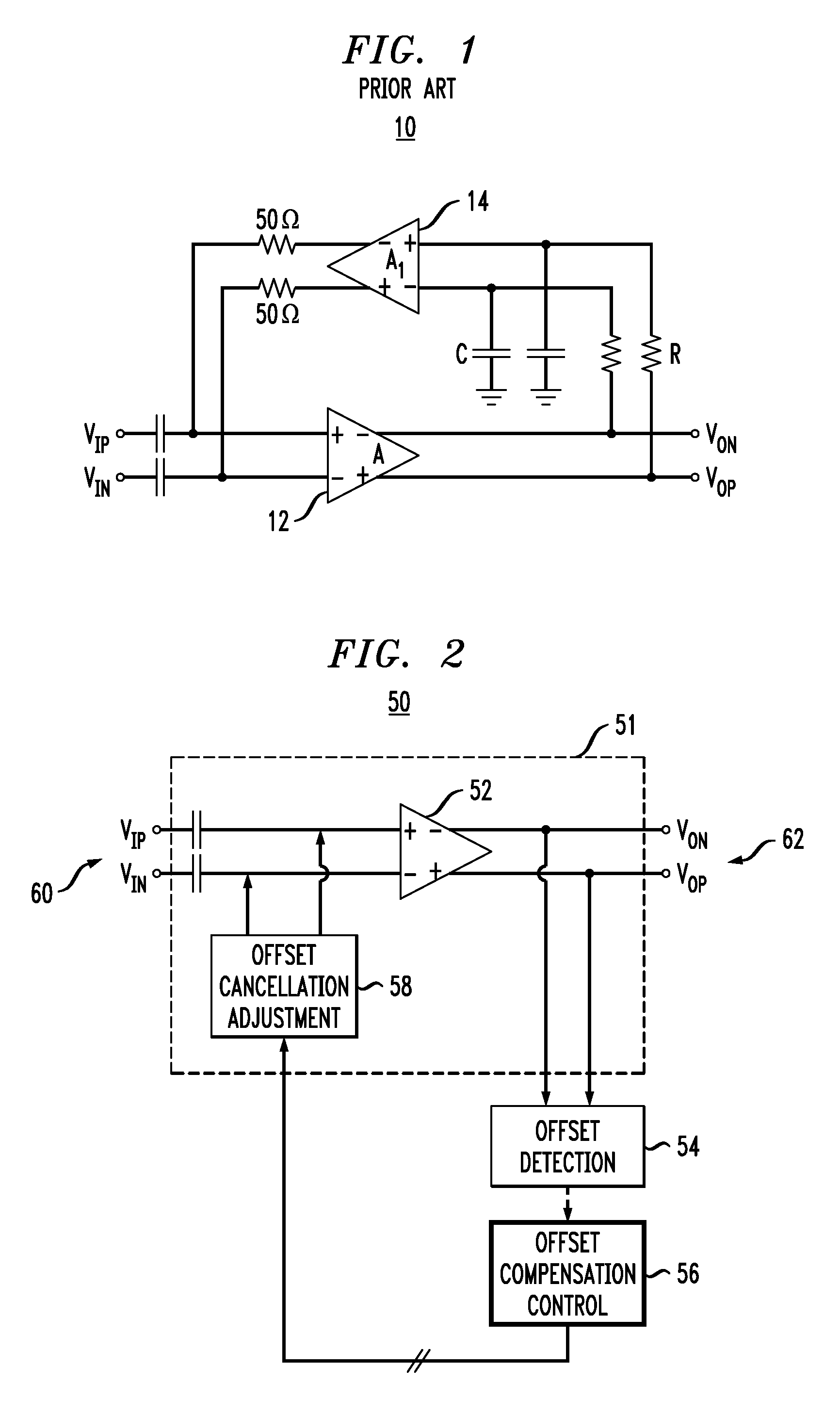

Analog amplifier having DC offset cancellation circuit and method of offset cancellation for analog amplifiers

ActiveUS20070013440A1Amplifier modifications to raise efficiencyAmplifier with semiconductor-devices/discharge-tubesAudio power amplifierOffset cancellation

An amplifier having DC offset compensation includes at least one input node and a pair of differential output nodes, a biasing circuit coupled to the input node; and a plurality of current sources. Selected ones of said current sources are coupled to the input node to adjust a DC voltage at the input node to provide DC offset compensation for the amplifier

Owner:AVAGO TECH INT SALES PTE LTD

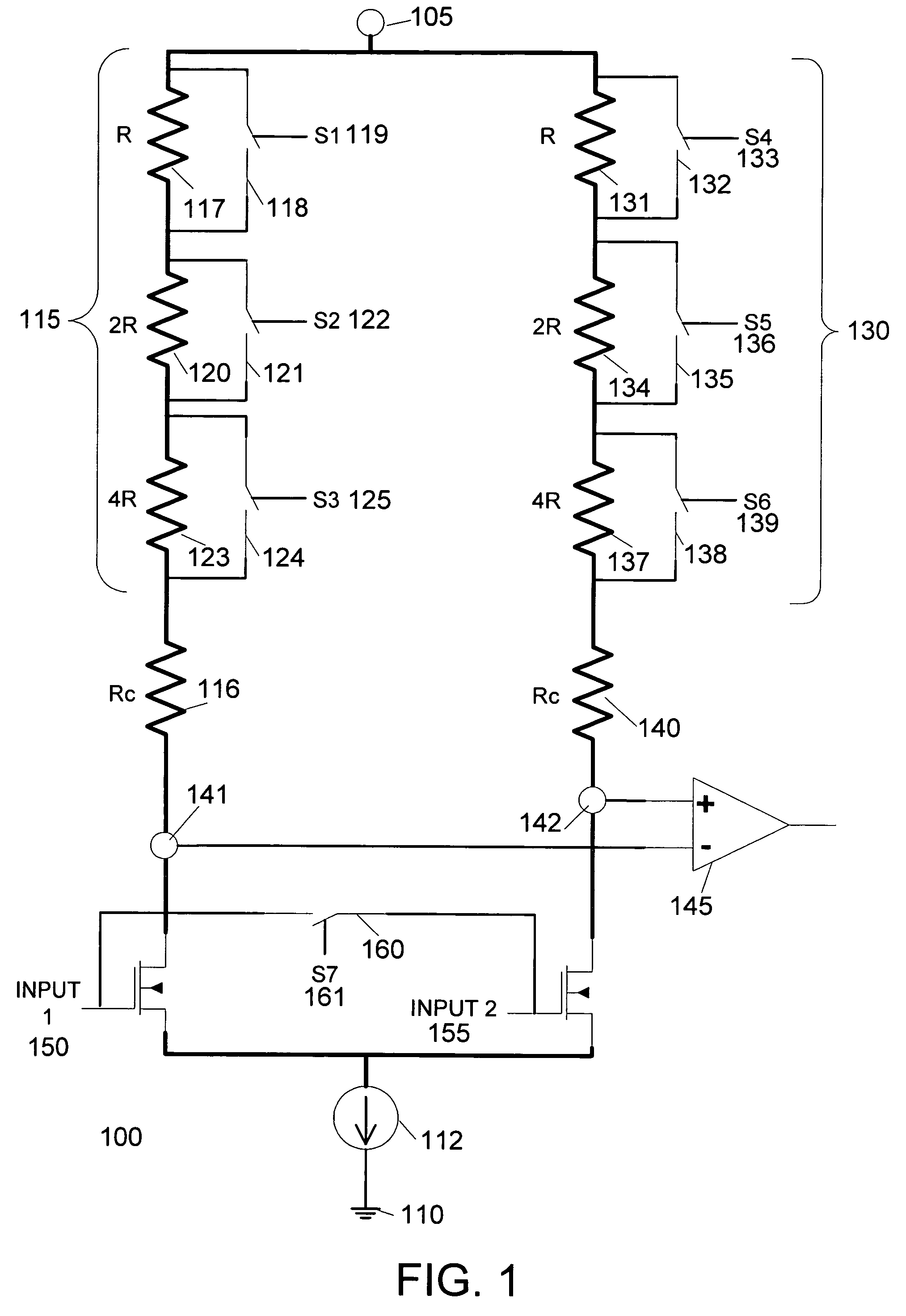

Comparator offset cancellation assisted by PLD resources

InactiveUS7541857B1Eliminate needPulse automatic controlCurrent/voltage measurementProgrammable logic deviceOffset cancellation

An impedance compensation circuit for inputs of a programmable device includes programmable impedance circuits connected with input nodes. The programmable impedance circuits can be configured to apply a compensating voltages to input nodes to reduce or eliminate unwanted offset voltages. An impedance compensation circuit may include resistors in series or current sources in parallel. A set of bypass switches selectively apply each resistor or current source to an input node, thereby changing the offset voltage of the node and compensating for impedance mismatches. Control logic provides signals to control the bypass switches. The control logic may be implemented using programmable device resources, enabling the control logic to be updated and improved after the manufacturing of the device is complete. The control logic can automatically evaluate offset voltages at any time and change compensating impedances accordingly. This reduces manufacturing costs and takes into account temperature and aging effects.

Owner:ALTERA CORP

Method and apparatus for improving dynamic range of a touchscreen controller

ActiveUS8599167B2Improve dynamic rangeLow costTransmission systemsElectronic switchingOffset cancellationEngineering

A touchscreen system for increasing the dynamic range of the system comprising a touchscreen coupled to an offset cancellation element and a capacitance measuring element. The offset cancellation element is configured to be dynamically changed in capacitance such that it offsets parasitic and sensor capacitances of the touchscreen sensors thereby leaving only touch event capacitance to be measured by the measuring element. The offset cancellation element is able to adjust to the initial unwanted capacitances of each sensor as well as dynamically adjust to changes in the unwanted capacitance due to the environment. In some embodiments, the offset cancellation element is a capacitance digital-to-analog converter that is controlled by a controller for offsetting the unwanted capacitance. As a result, the touchscreen system is able to utilize a small integrating capacitor thereby lowering cost and improving the dynamic range of the system.

Owner:QUALCOMM INC

Sensor amplifier, memory device comprising same, and related method of operation

ActiveUS9202531B2Increase an effective sensing margin of a memory deviceReduces coupling efficiencyDigital storageBit lineAudio power amplifier

A sense amplifier includes a sense amplifying unit configured to be connected to a bitline and a complimentary bitline of a memory device, to sense a voltage change of the bitline in response to first and second control signals, and to control voltages of a sensing bitline and a complimentary sensing bitline based on the sensed voltage change. The sense amplifier further includes a first isolation switch configured to connect the bitline with the sensing bitline in response to an isolation signal, a second isolation switch configured to connect the complimentary bitline with the complimentary sensing bitline in response to the isolation signal, a first offset cancellation switch configured to connect the bitline with the sensing bitline in response to an offset cancellation signal, and a second offset cancellation switch configured to connect the complimentary bitline with the complimentary sensing bitline in response to the offset cancellation signal.

Owner:SAMSUNG ELECTRONICS CO LTD

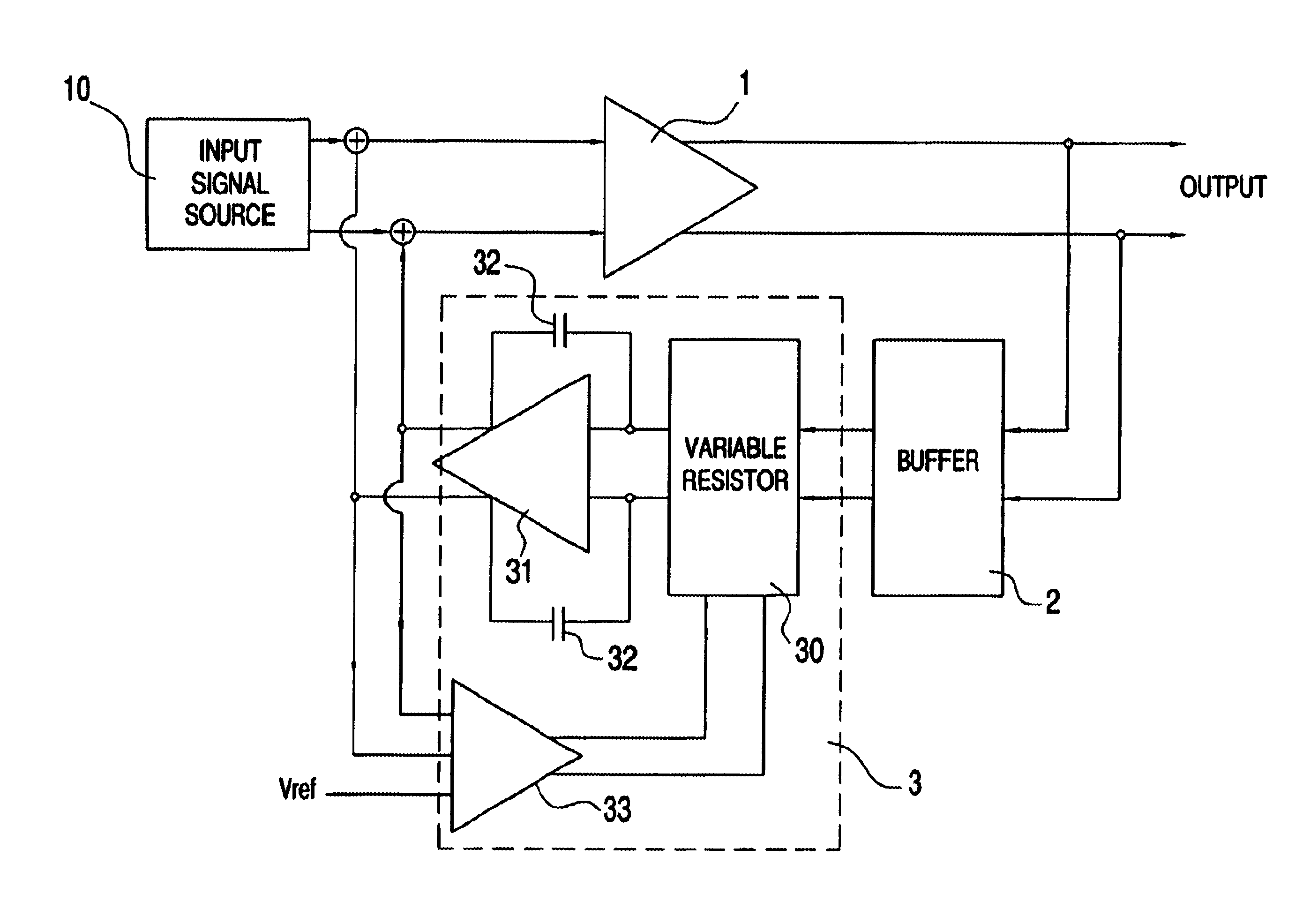

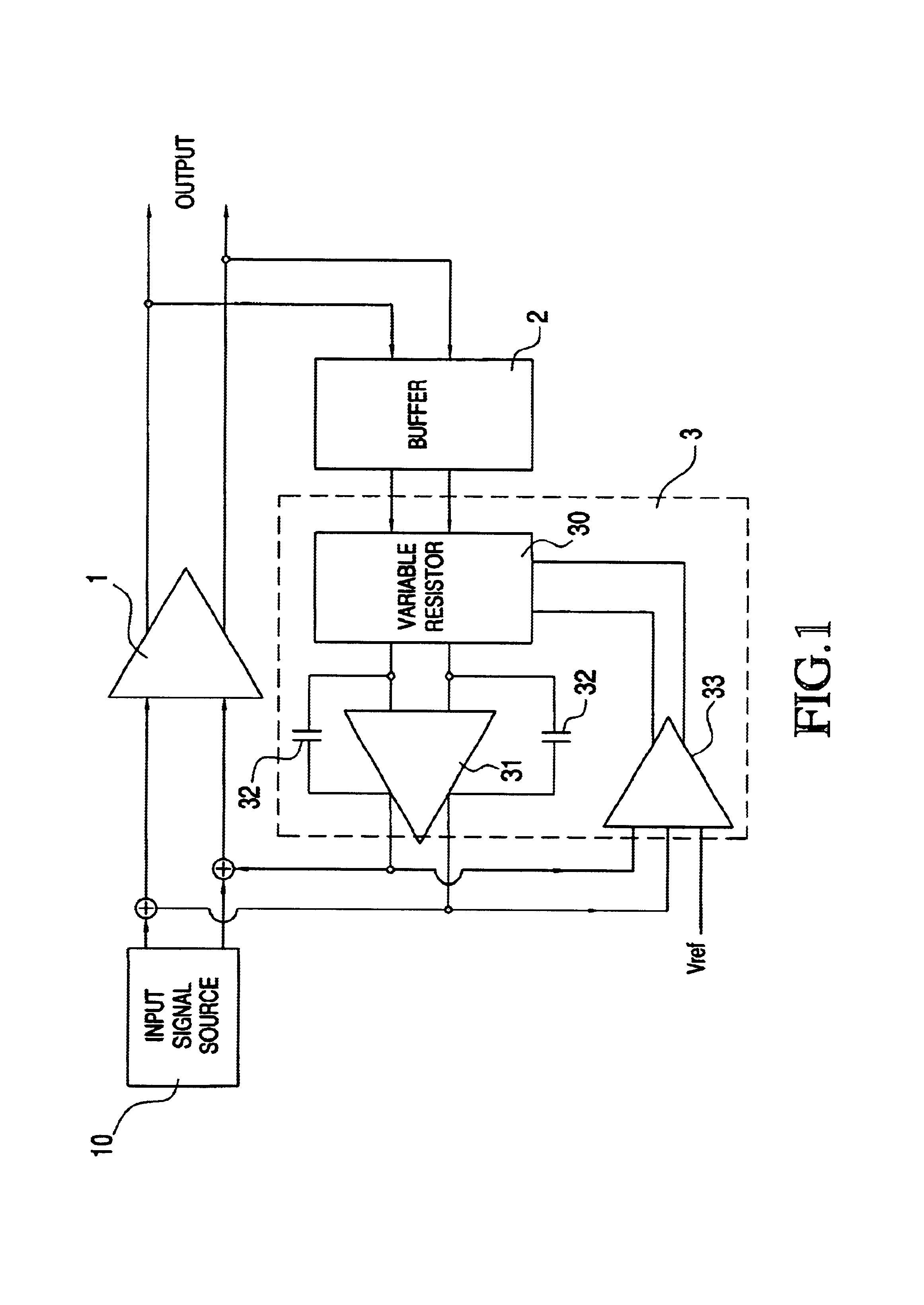

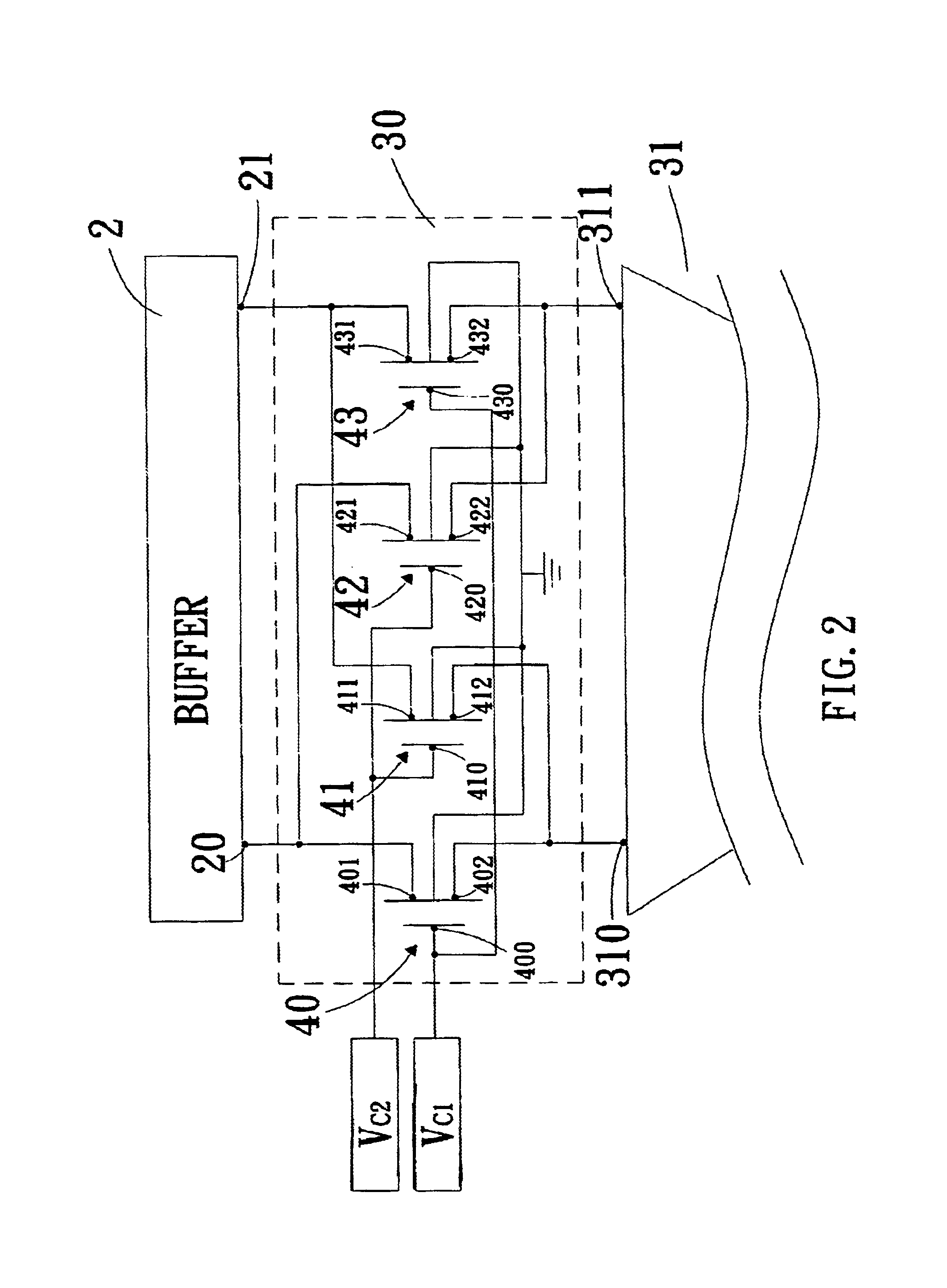

Gain amplifier with DC offset cancellation circuit

ActiveUS6903593B2Shorten convergence timePulse automatic controlComputing operation arrangementsNegative feedbackAudio power amplifier

A DC offset cancellation circuit employs multiple feedback factors for canceling DC offset by increasing convergence time. The DC offset cancellation circuit features an active low-pass analogue filter including a variable resistor, an amplifier, a capacitor pair and a comparator, the amplifier being coupled to an output of the variable resistor. Negative feedback is provided from the output of the variable resistor to the input signal source, the capacitor pair is coupled to the amplifier, one input of the comparator is coupled to an output of the amplifier, and a second input of the comparator is coupled to a reference voltage source such that a comparison signal is output by the comparator to the variable resistor after comparing the negative feedback signal with a reference voltage.

Owner:IND TECH RES INST

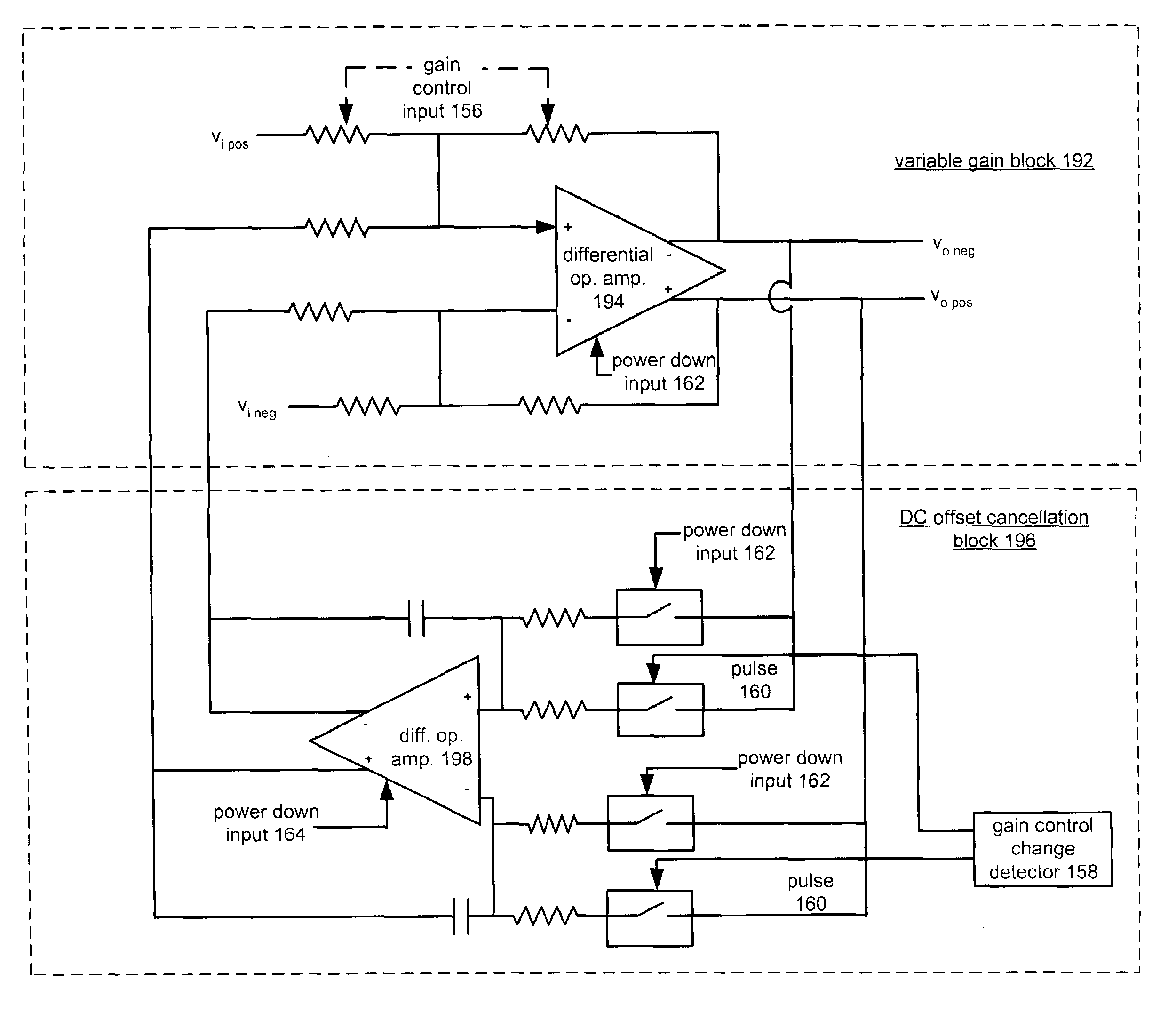

Fast settling variable gain amplifier with DC offset cancellation

ActiveUS7020449B2Minimize power consumptionReduce power consumptionEnergy efficient ICTGain controlTransceiverOffset cancellation

A variable gain amplifier includes circuit elements that may be partially powered down during transmit modes of operation and that may be powered back up whenever the radio transceiver receives a data packet within a specified settle time even for high throughput RF communications. The radio transceiver circuit may be powered down even in high throughput communications during a transmit mode to reduce power consumption. A DC offset cancellation block is operably coupled to the variable gain block to substantially remove any DC offset from the amplified output. The variable gain amplifier is further able to provide DC offset cancellation within the required settle time by holding the offset value during a dormant mode of operation. Further, the variable gain amplifier transitions from a first gain control value to a second gain control value and further modifies its internal settle time from a first value to a second value to enable the variable gain amplifier to reach a steady state within the required settle time whenever required. The settle time transitions from the second value back to the first value after a specified period of time.

Owner:AVAGO TECH INT SALES PTE LTD

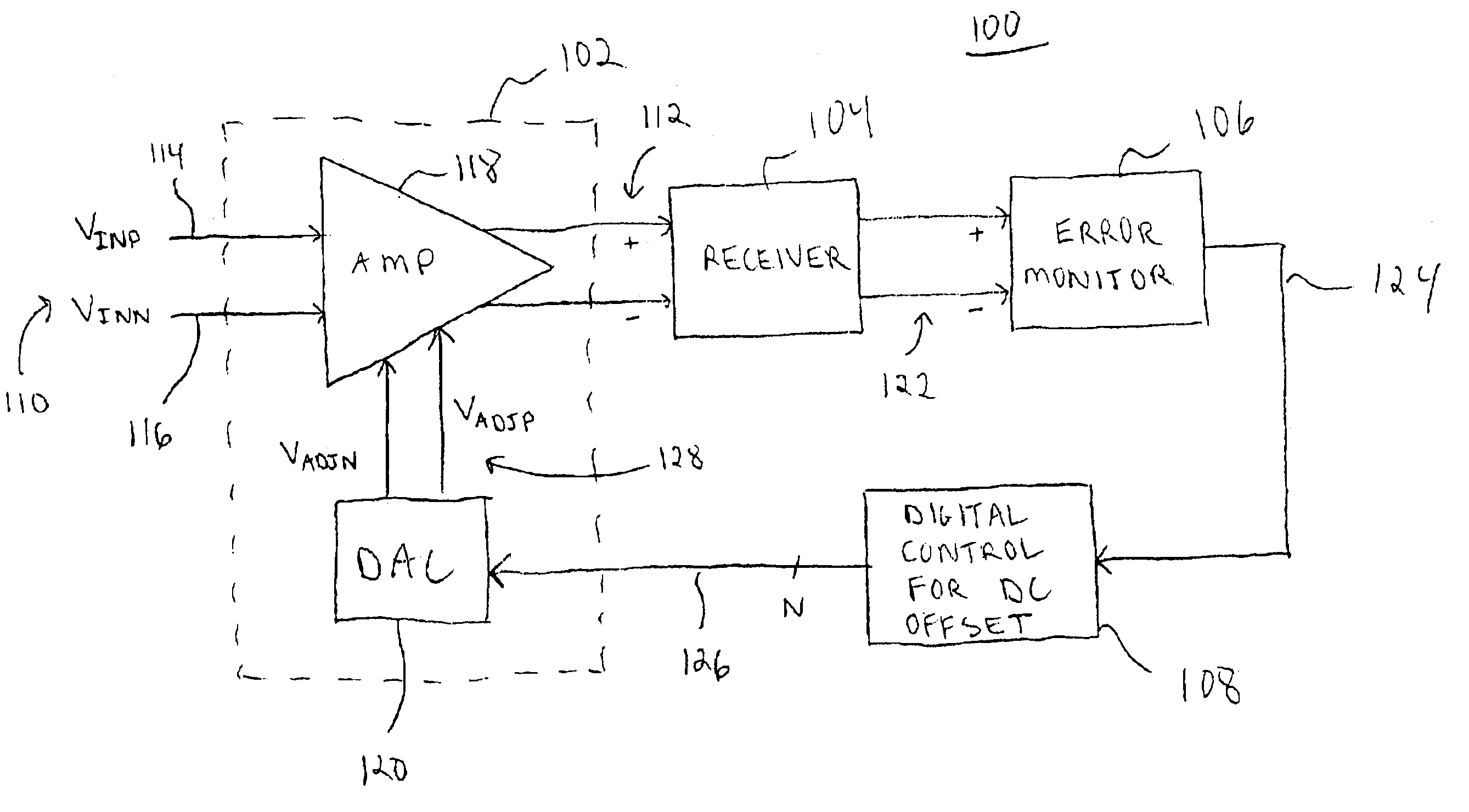

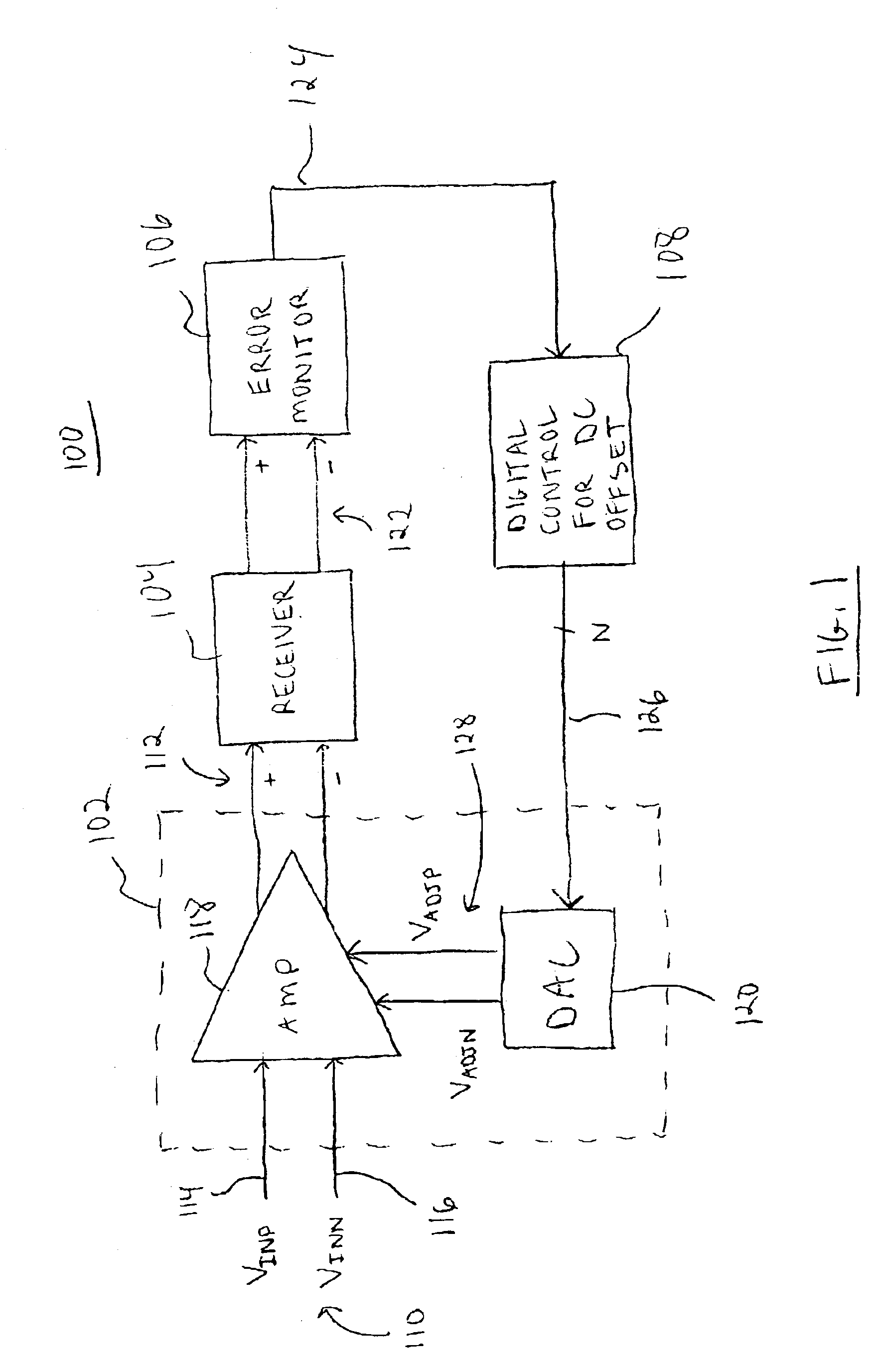

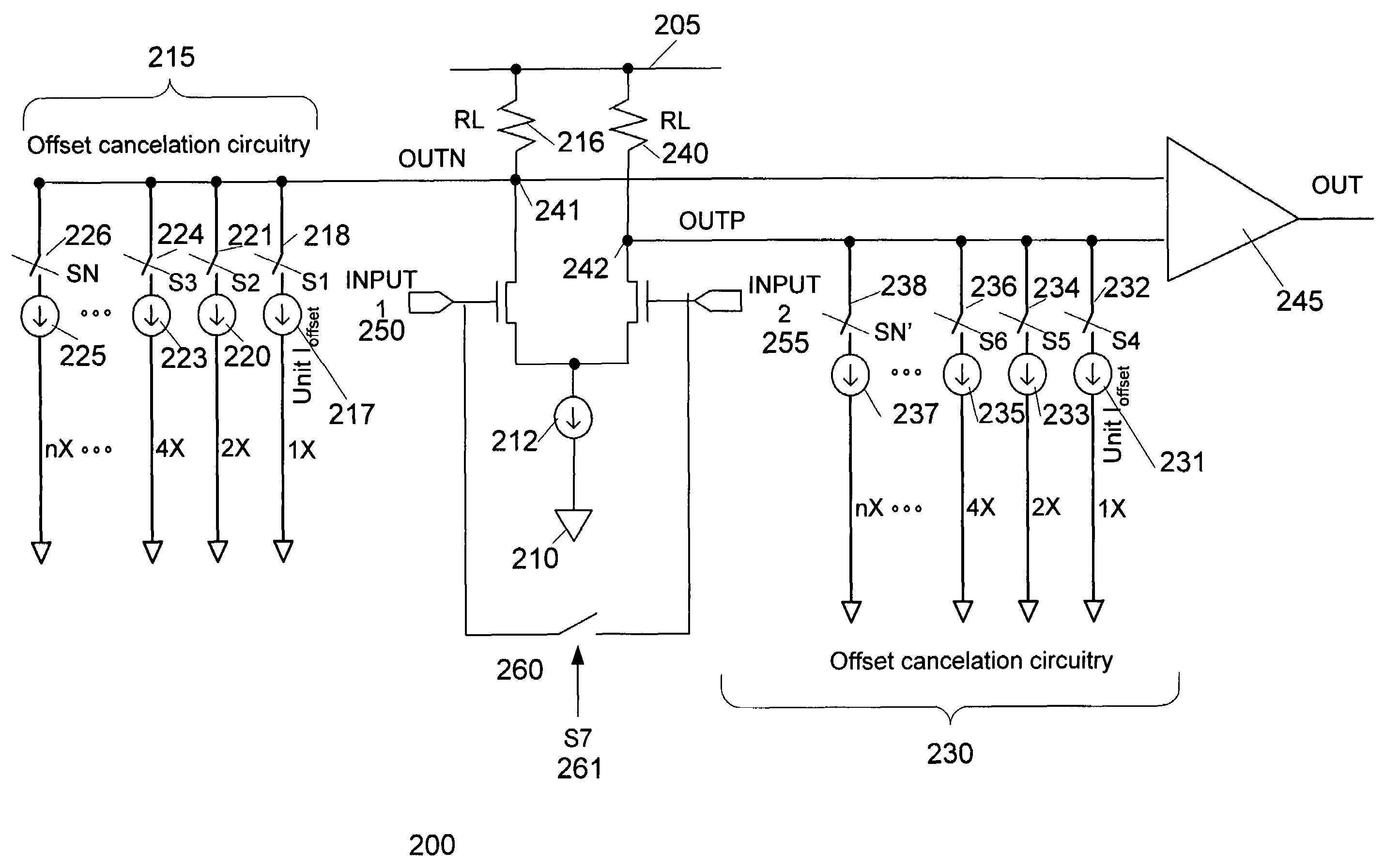

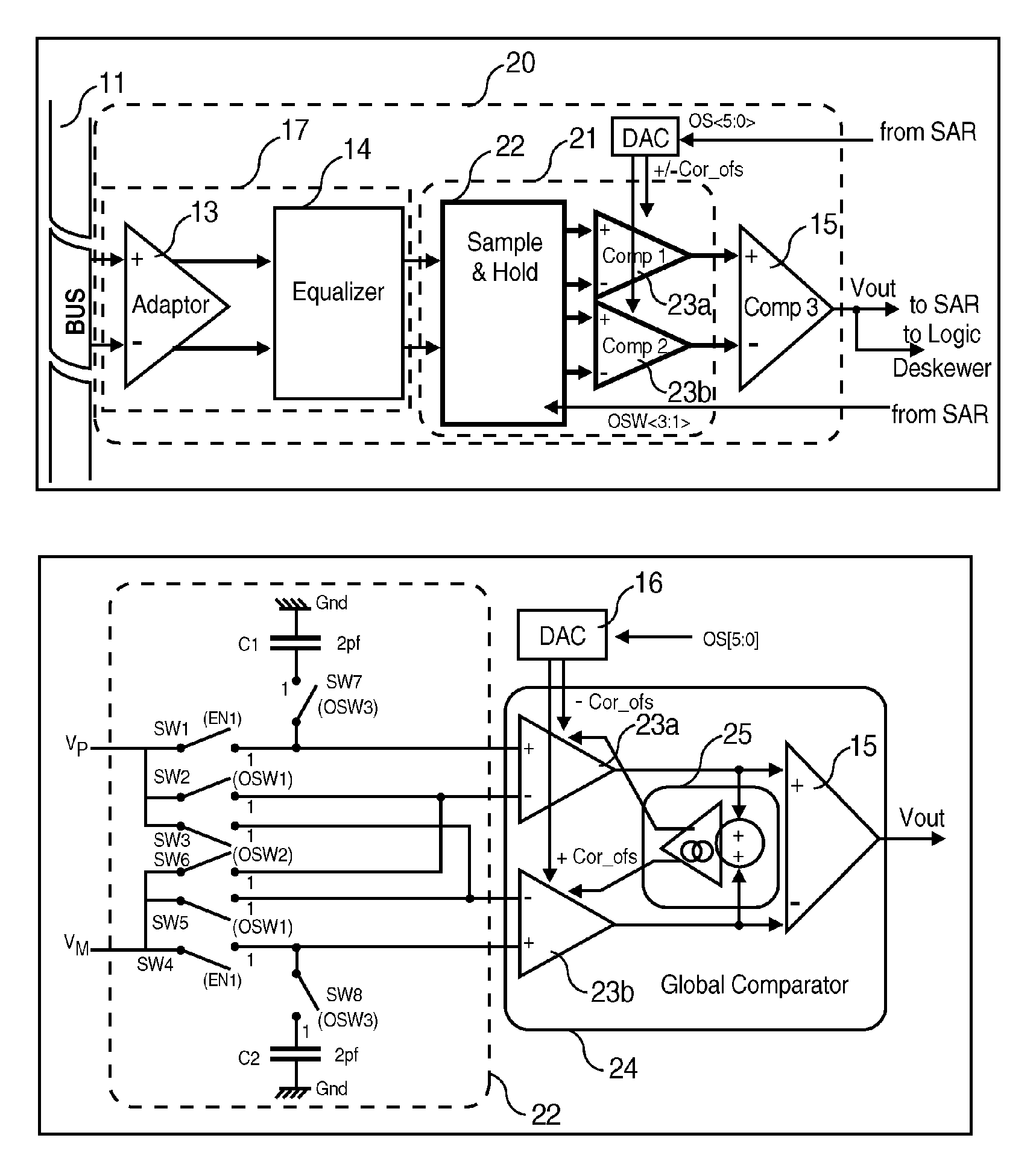

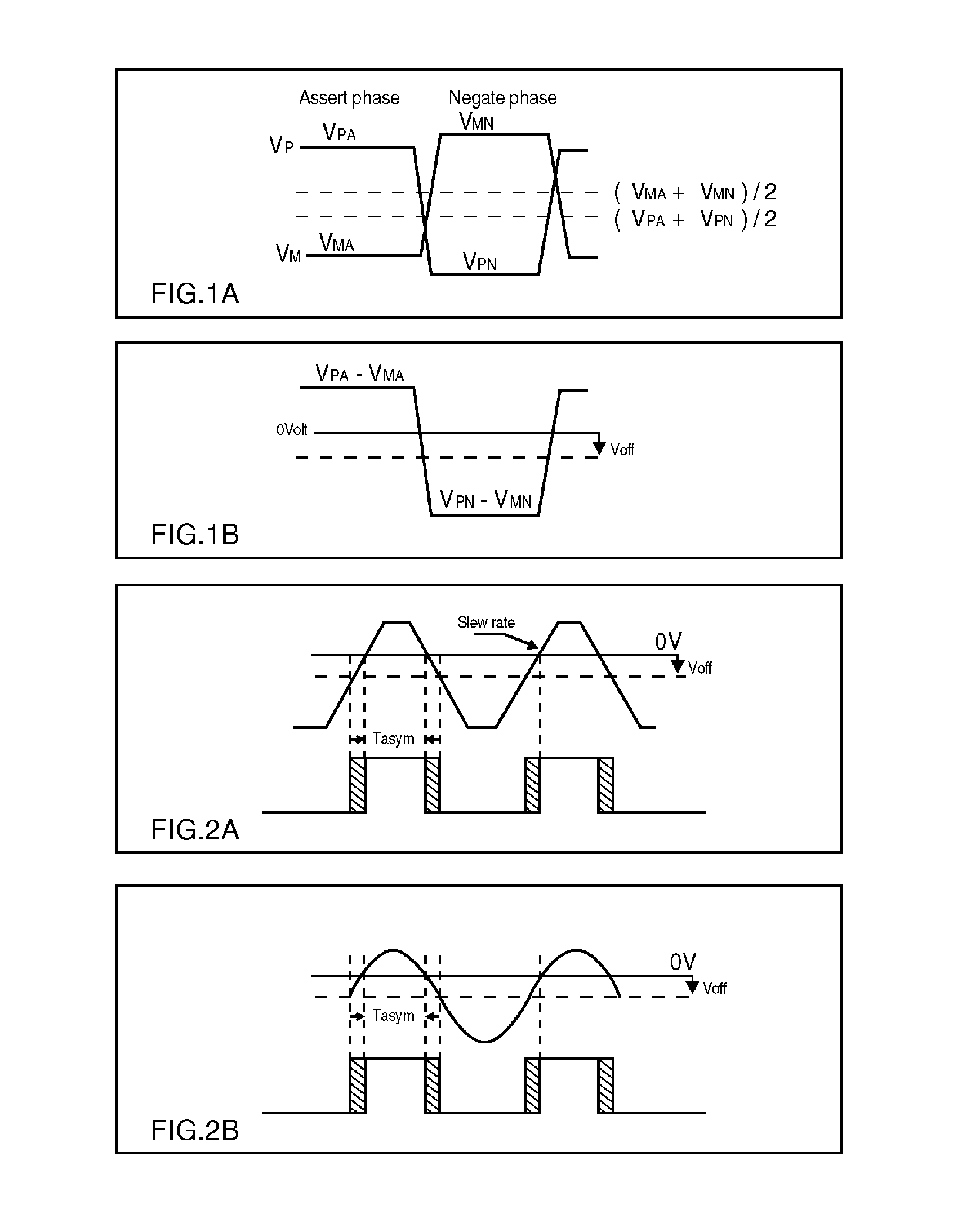

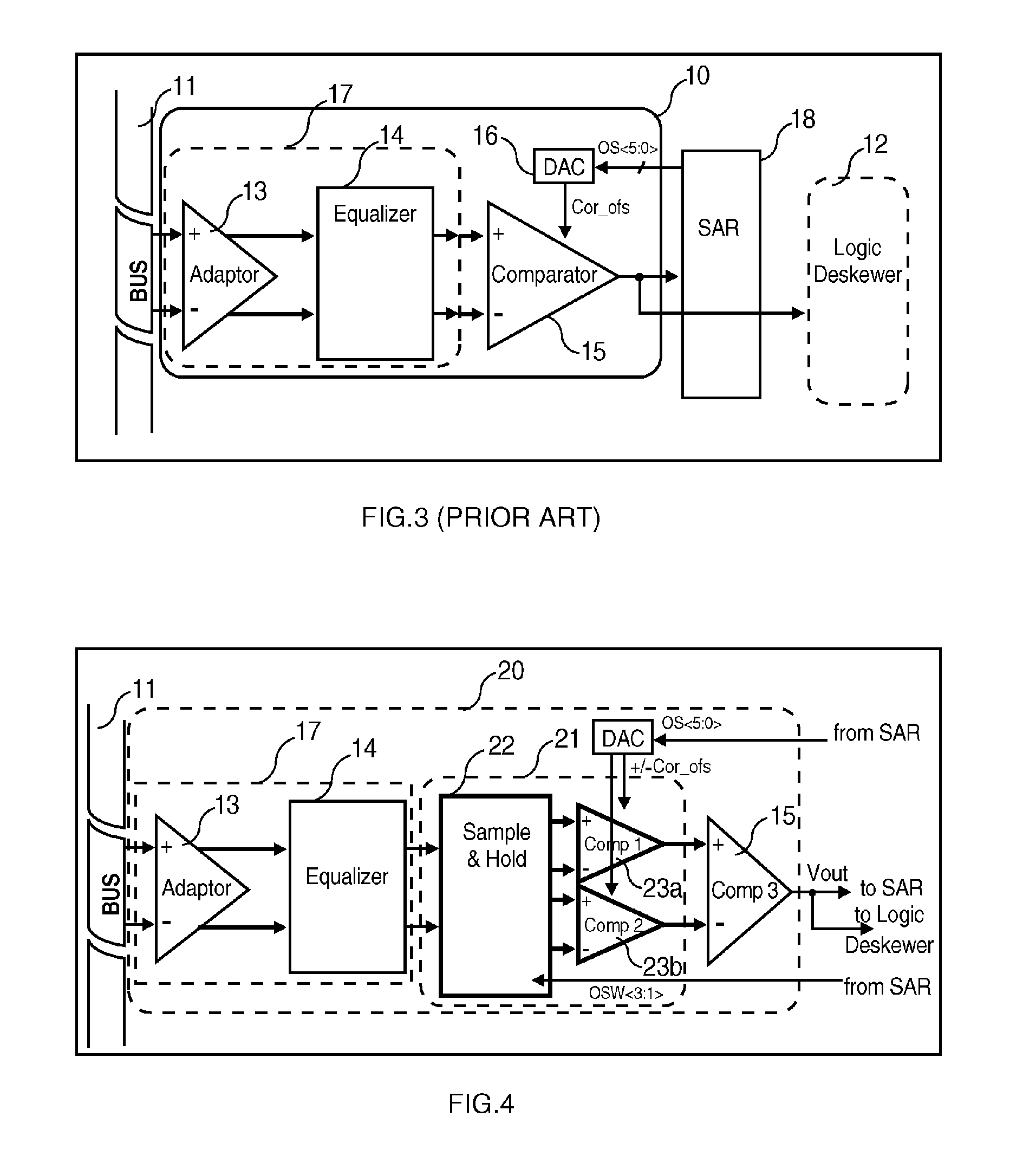

Receiver having full signal path differential offset cancellation capabilities

InactiveUS7180354B2Eliminates differential offsetPulse automatic controlAmplifier modifications to raise efficiencyDifferential signalingOffset cancellation

There is described an improved receiver which first comprises an analog input amplifier a sample and hold differential circuit and two stages of differential comparators that are connected in series, wherein the first stage consists of two comparators and the second stage of one comparator. By properly activating the switches with signals generated by a dedicated control logic, the input differential signal is sampled in the sample and hold circuit to generate first and second differential signals. The first differential signal holds a first state and the second differential signal propagates the second state. As result, the signal output by the second comparator stage reflects the differential offset minus the offset compensation.

Owner:IBM CORP

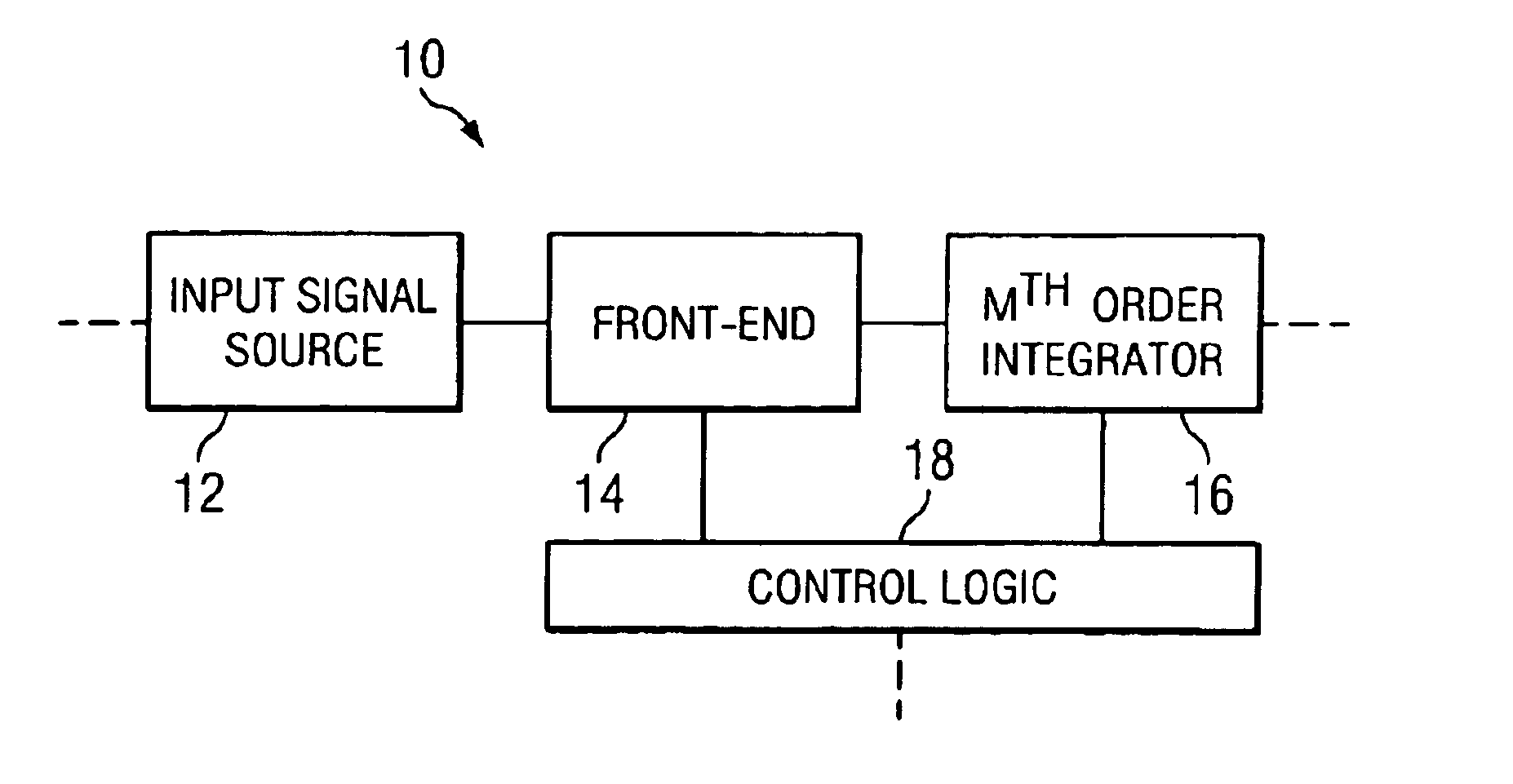

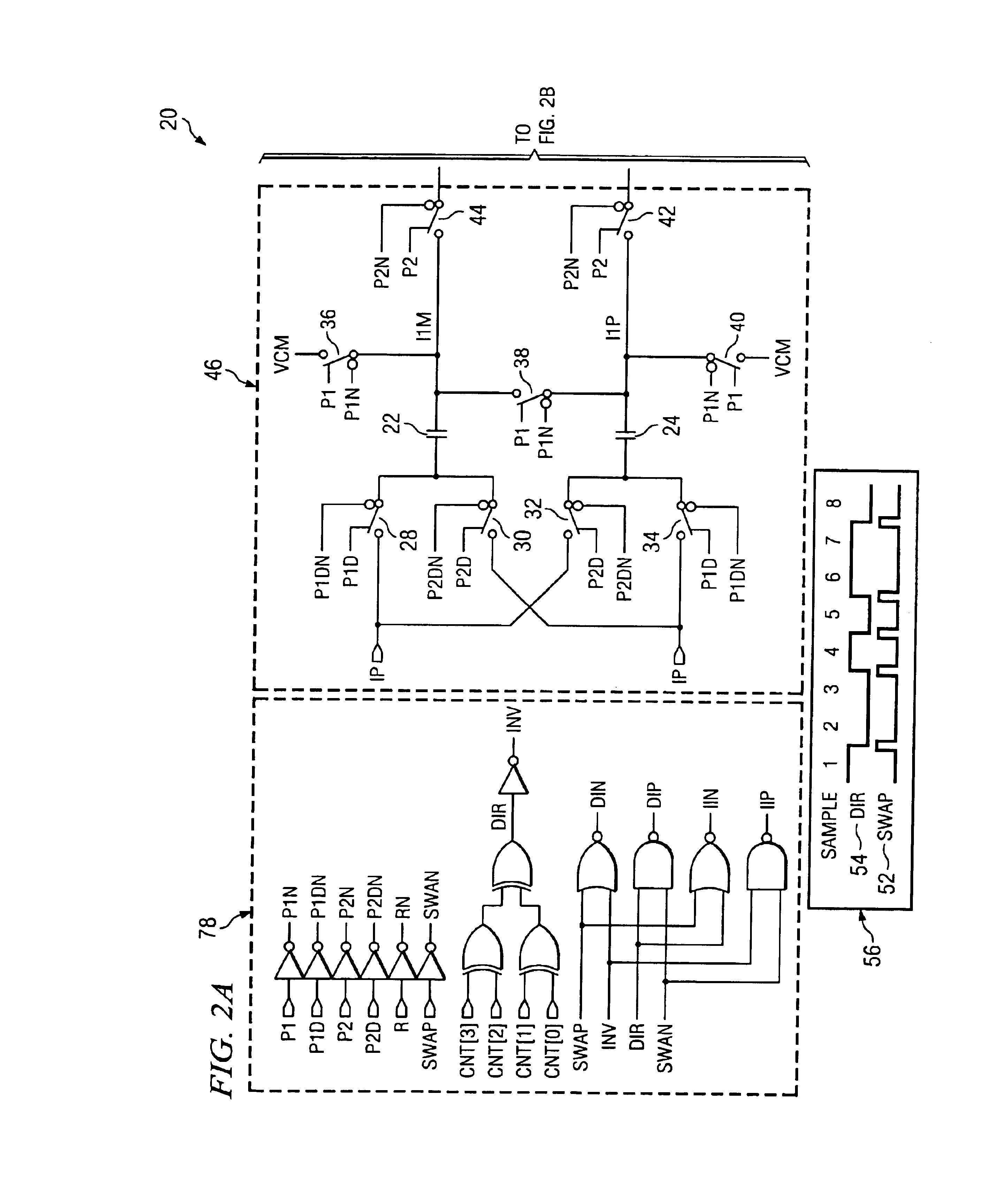

Fractal sequencing schemes for offset cancellation in sampled data acquisition systems

ActiveUS6909388B1Signal offsetReduce noiseElectric signal transmission systemsAnalogue conversionIntegratorData simulation

The present invention is directed to the isolation and cancellation of the offset voltage component typically experienced at the input of sampled-data analog systems. In an exemplary embodiment, offset isolation and cancellation may be performed during normal operation of the sampling circuitry. In an exemplary embodiment, the present invention combines a front-end switching topology with one or more differential integrator stages and a logic algorithm implemented in the differential integrator stages. In operation, the circuitry preferably performs a number of samples for each stage, applies an inversion factor to the samples in accordance with the algorithm and integrates the samples to effect the cancellation of the offset voltage without substantially affecting the sampled input.

Owner:MICROCHIP TECH INC

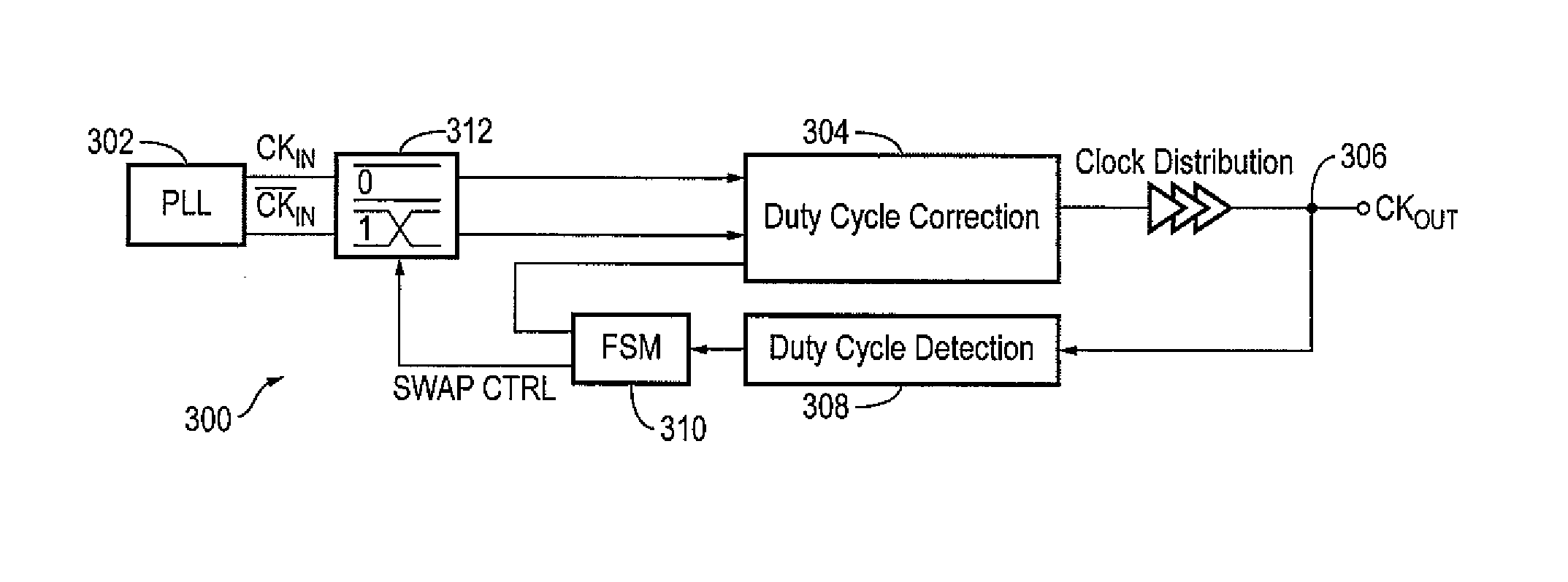

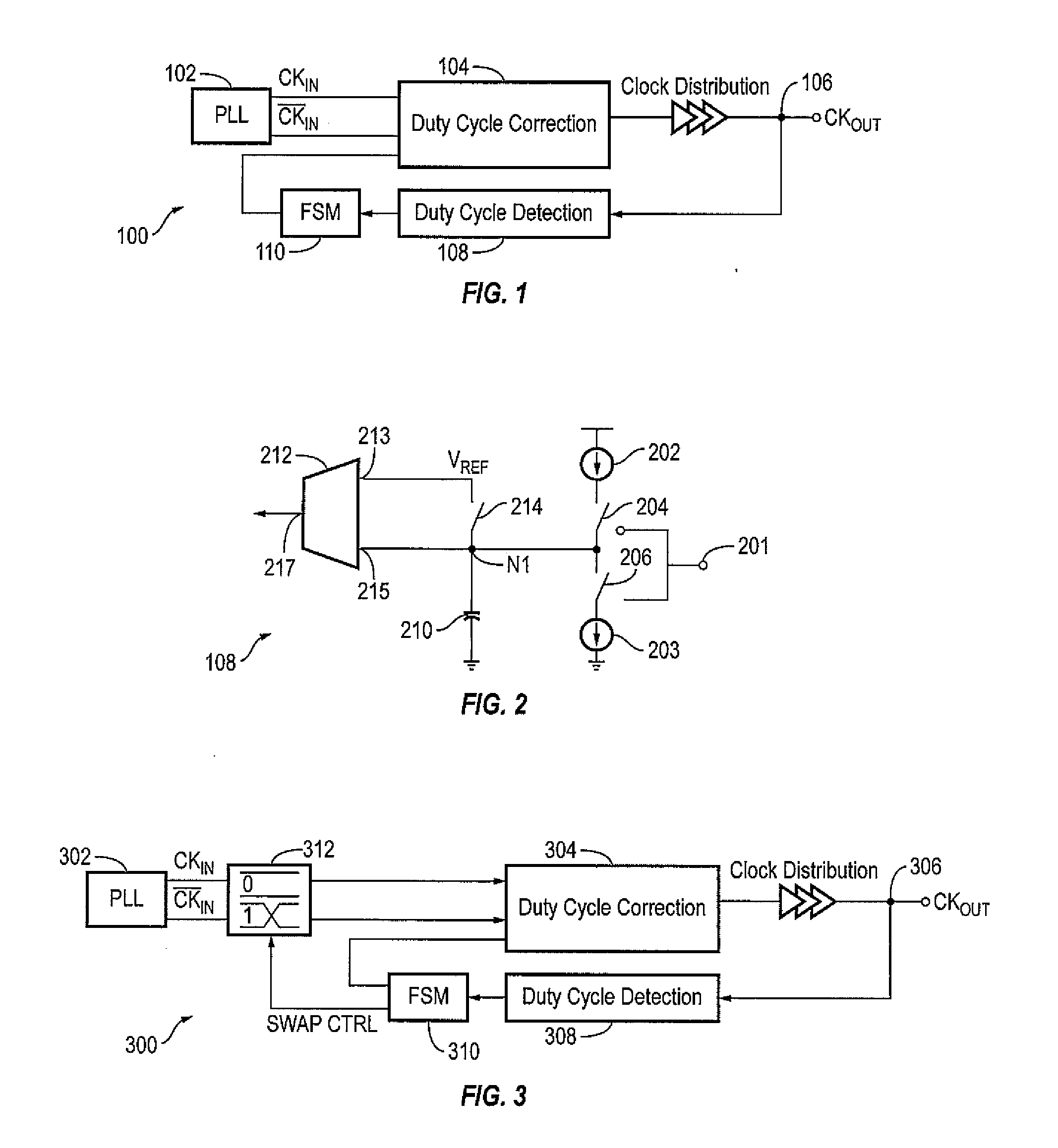

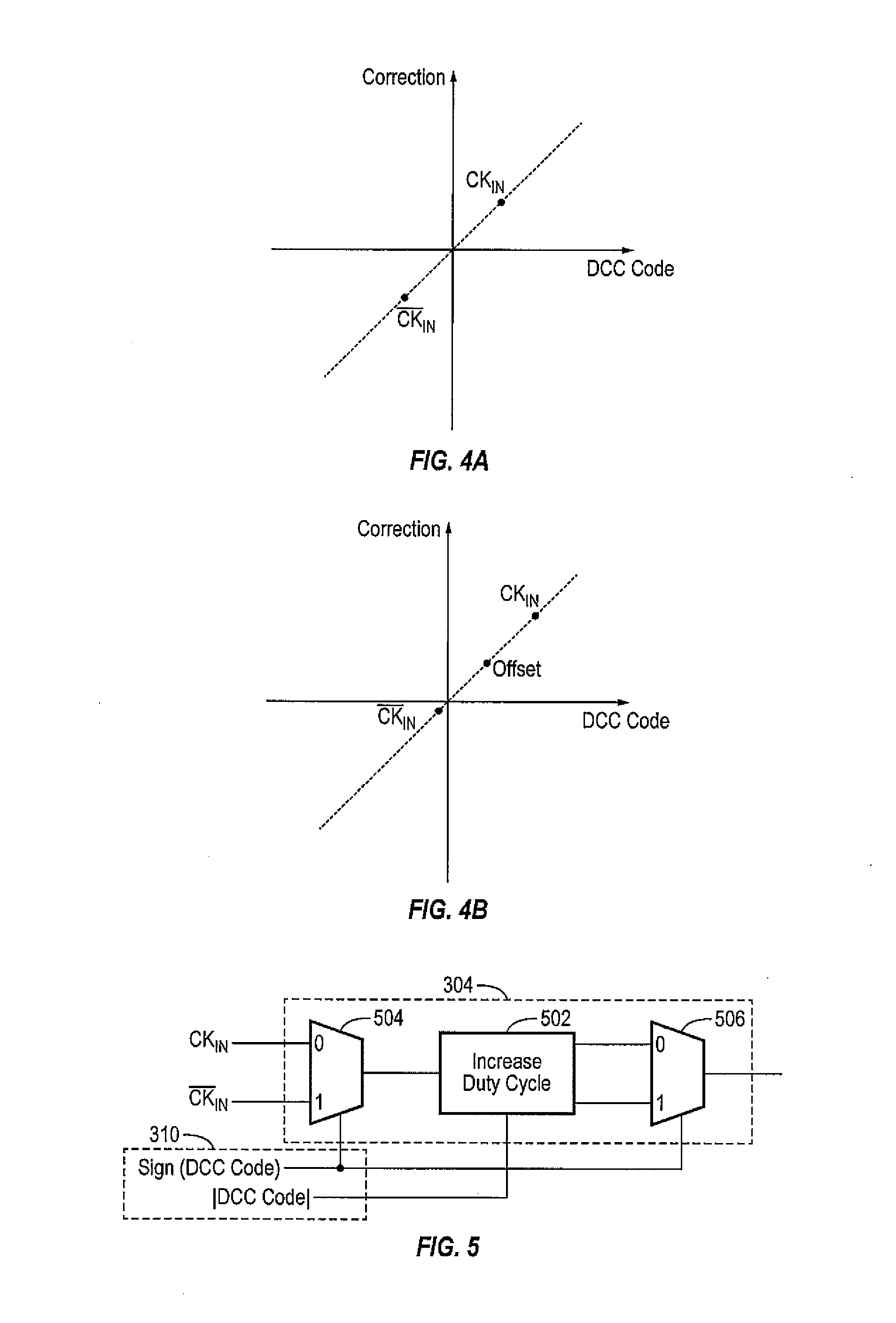

Apparatus and method for offset cancellation in duty cycle corrections

ActiveUS20150097603A1Increasing duty cycle correction circuit ' ability to duty cycleReduce errorsPulse automatic controlElectric pulse generatorOffset cancellationDuty cycle corrector

An electronic device includes a clock configured to transmit a first clock signal and a second clock signal for operation of the electronic device; a duty cycle corrector coupled to the clock to correct a duty cycle of the first and second clock signals, the duty cycle corrector being configured to: assign and store a first duty cycle correction code in response to the first clock signal; assign and store a second duty cycle correction code in response to the second clock signal; calculate an offset code based on the first and second duty cycle correction codes; and negate the offset code from results of duty cycle correction operations.

Owner:SAMSUNG DISPLAY CO LTD

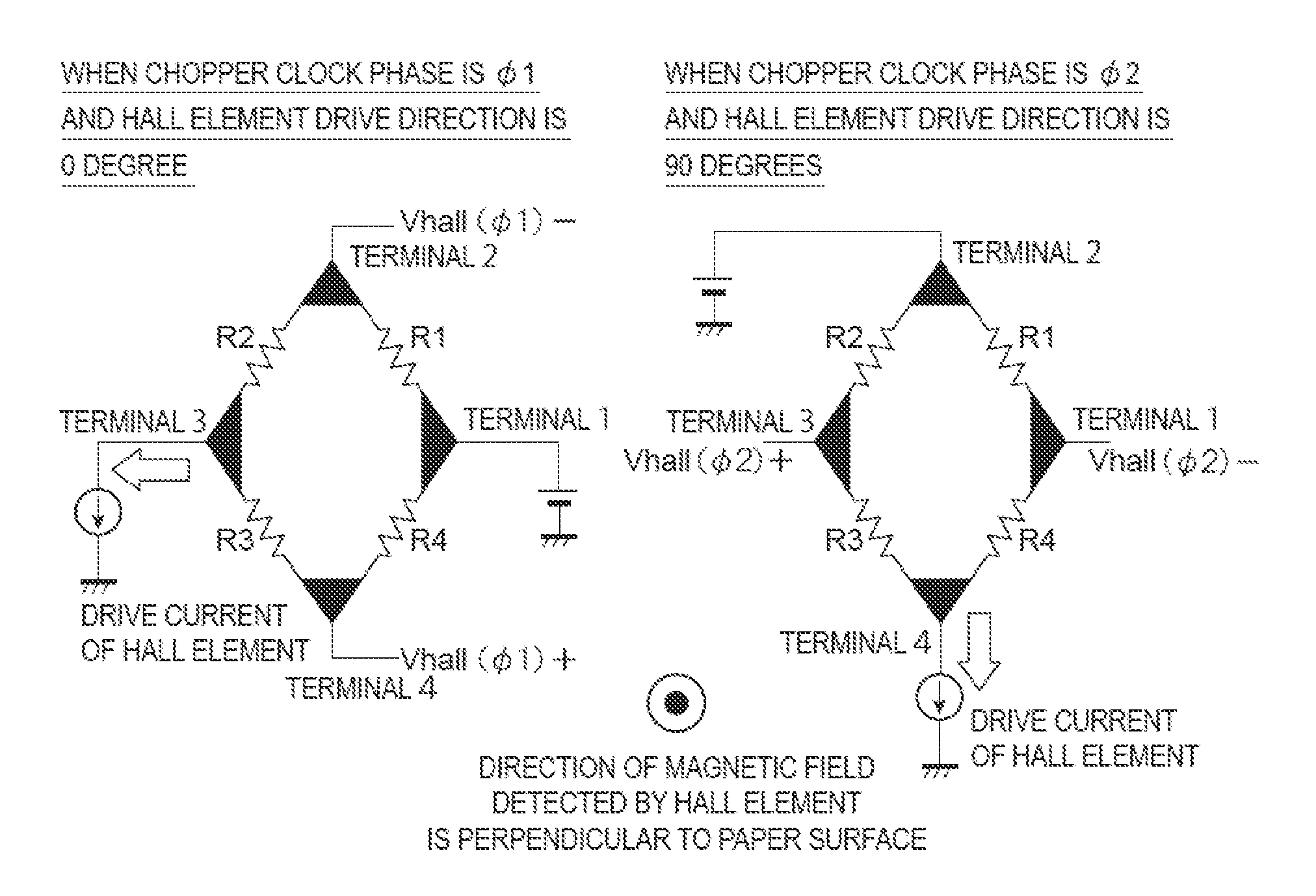

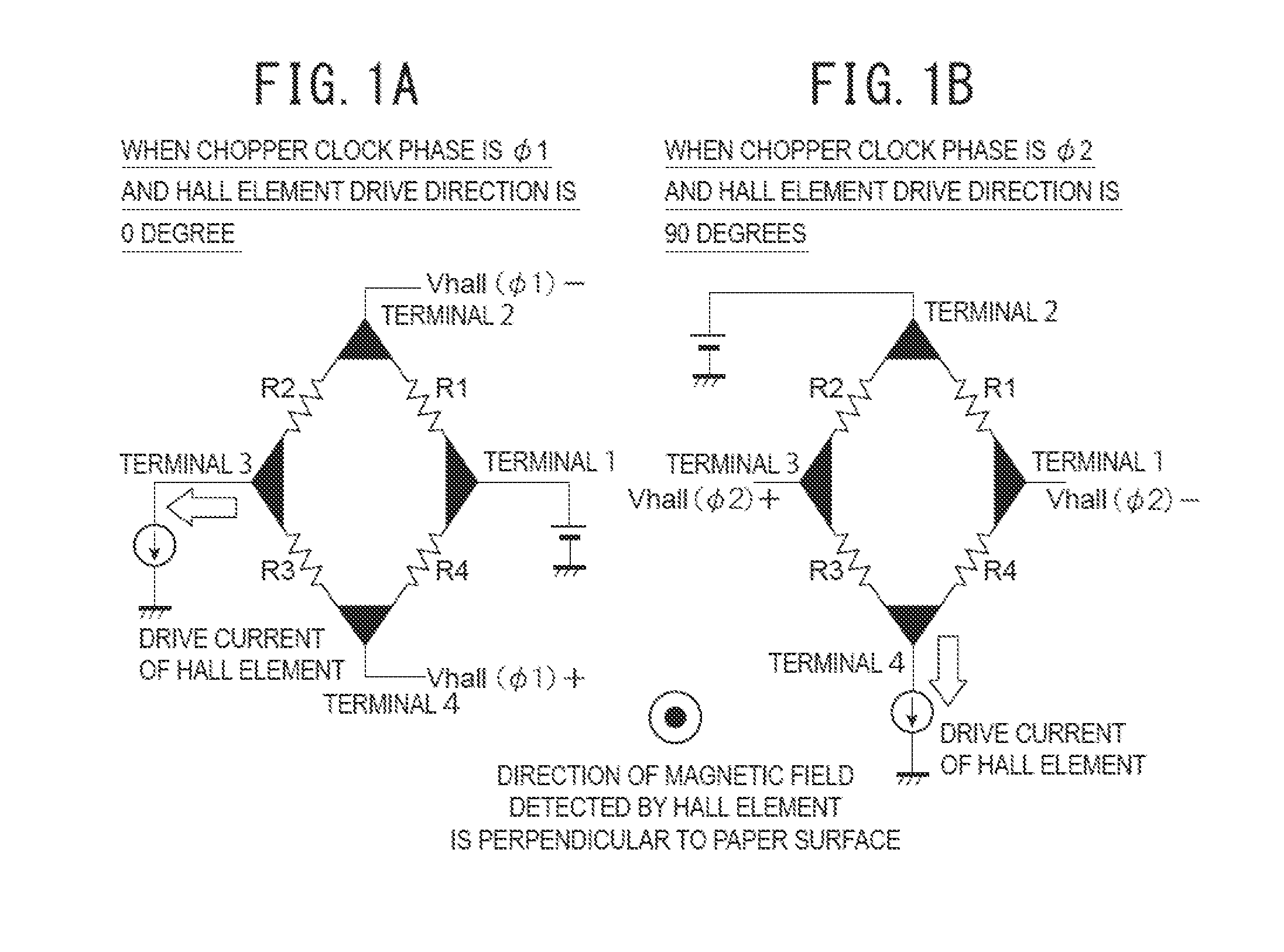

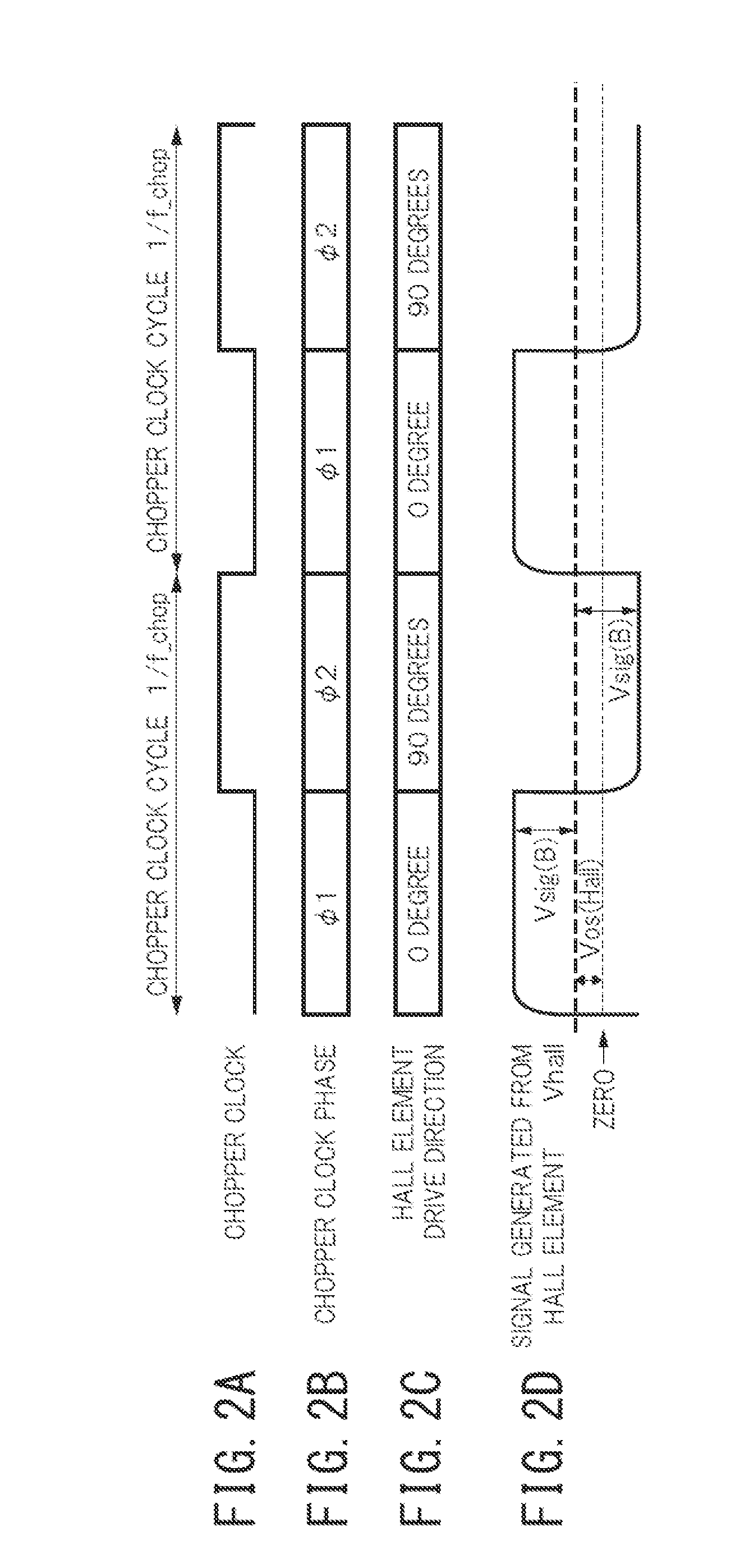

Hall electromotive force signal detection circuit and current sensor thereof

ActiveUS20130193962A1Reduce generationShort timeMagnetic field measurement using galvano-magnetic devicesPower supply testingDriving currentSignal processing circuits

A Hall electromotive force signal detection circuit combines offset cancellation means by a spinning current method of a Hall element with a continuous-time signal processing circuit. A first Hall element includes first to fourth terminals, and generates a Hall electromotive force signal voltage Vhall1. A third Hall element generates an other Hall electromotive force signal voltage Vhall3. A first switching circuit selects a terminal position for applying a drive current from the four terminals of the first Hall element. A third switching circuit selects a terminal position for applying a drive current from the four terminals of the third Hall element, which is different from the terminal position selected by the first switching circuit. A chopper clock generation circuit supplies a chopper clock signal φ1, φ2 having two different phases to the switching circuit, and also supplies the chopper clock signal φ1, φ2 to the switching circuit.

Owner:ASAHI KASEI ELECTRONICS CO LTD