Patents

Literature

402 results about "Analogue filter" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Analogue filters are a basic building block of signal processing much used in electronics. Amongst their many applications are the separation of an audio signal before application to bass, mid-range, and tweeter loudspeakers; the combining and later separation of multiple telephone conversations onto a single channel; the selection of a chosen radio station in a radio receiver and rejection of others.

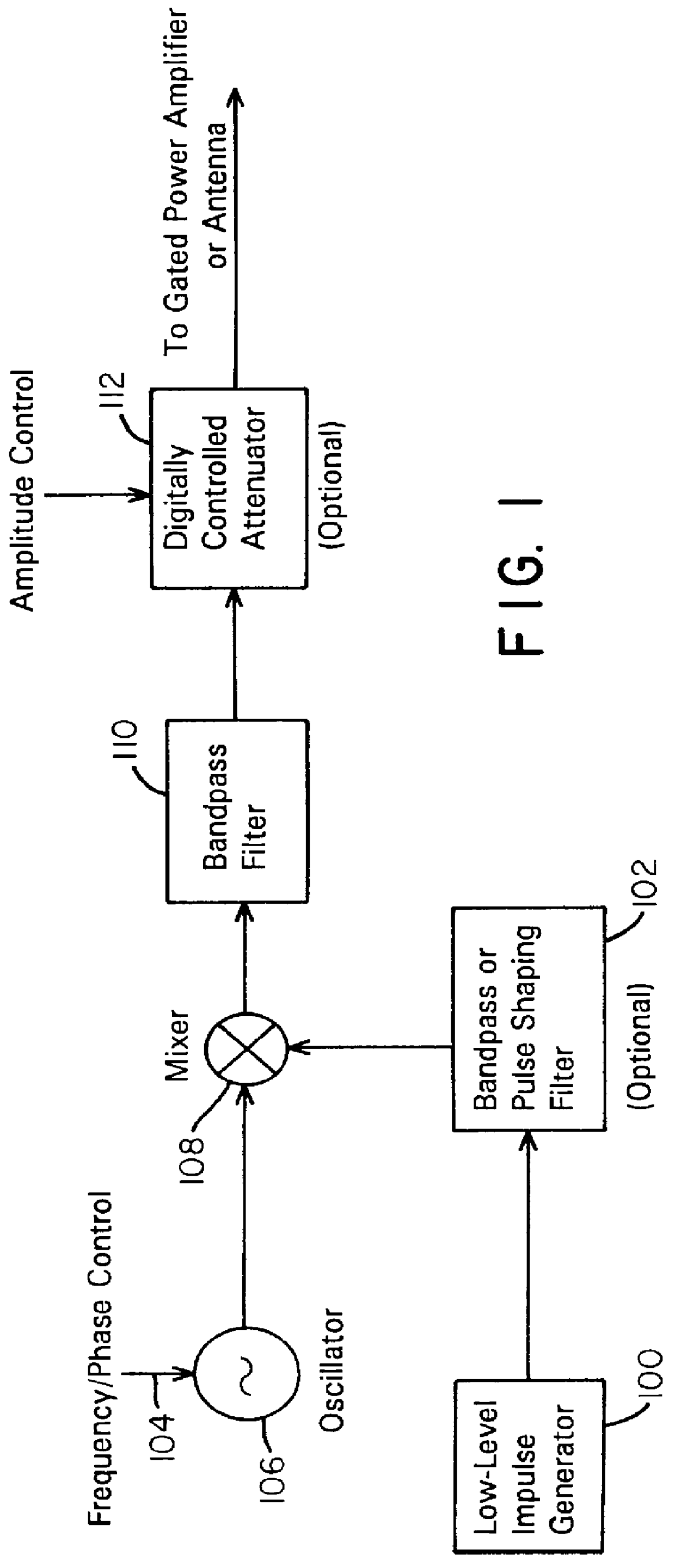

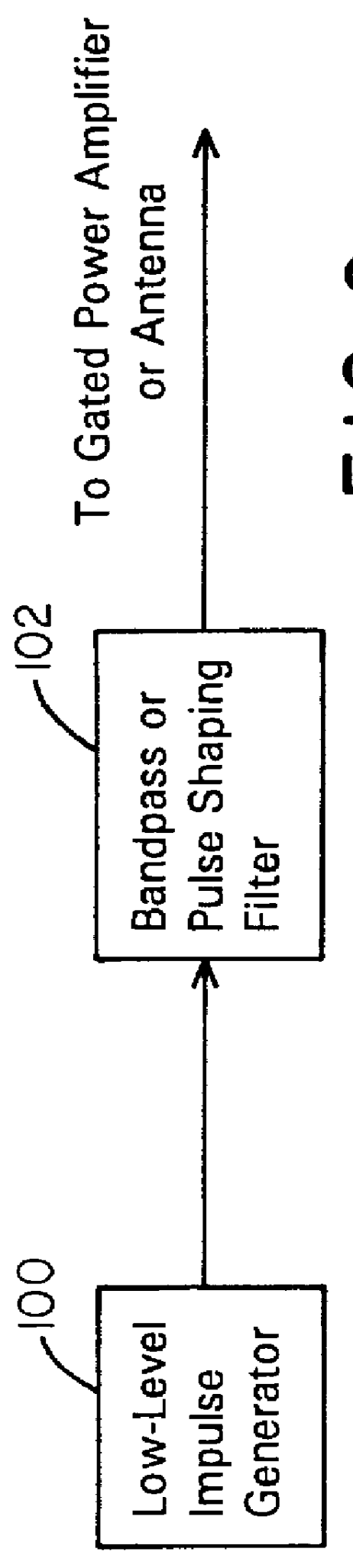

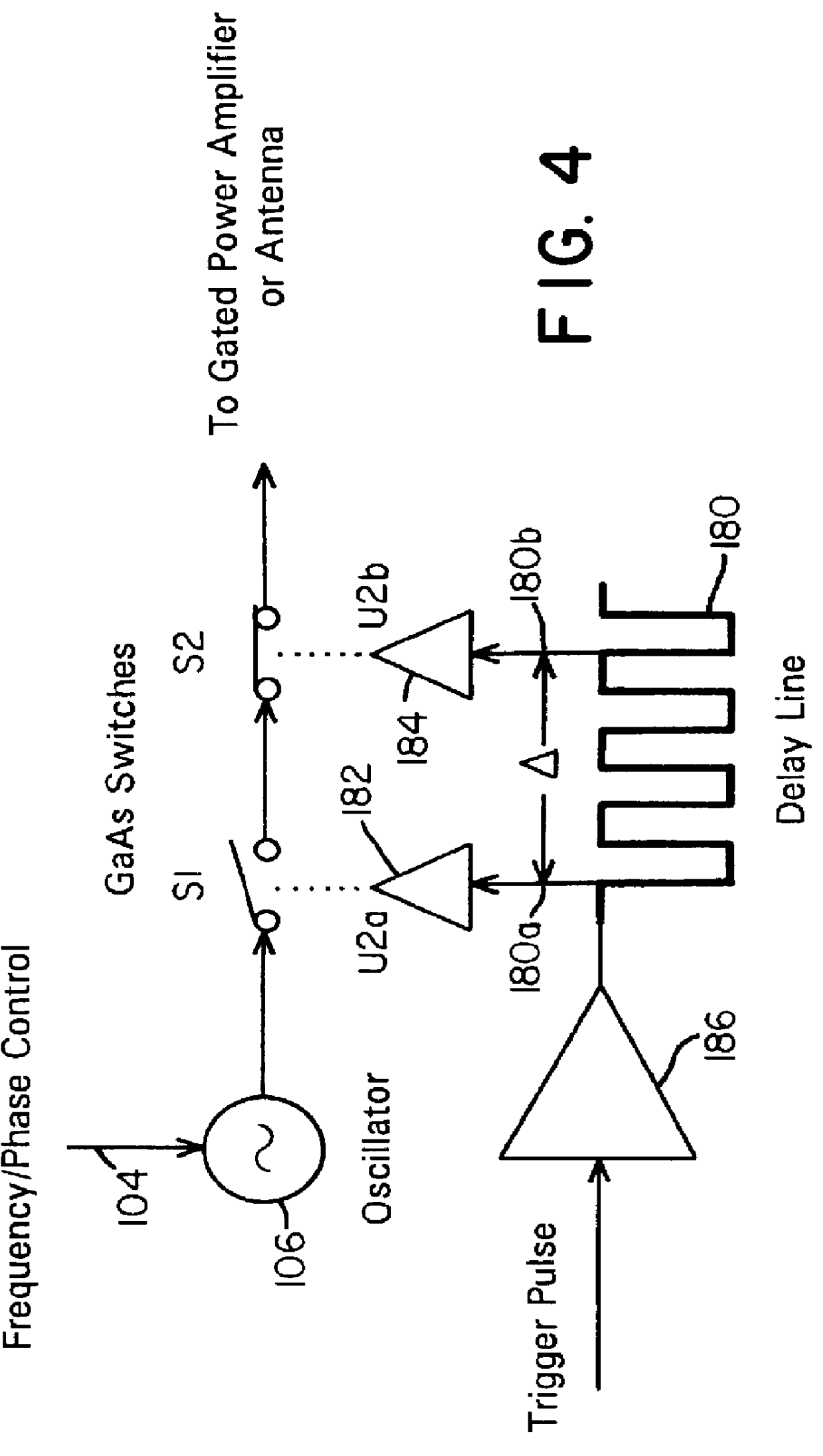

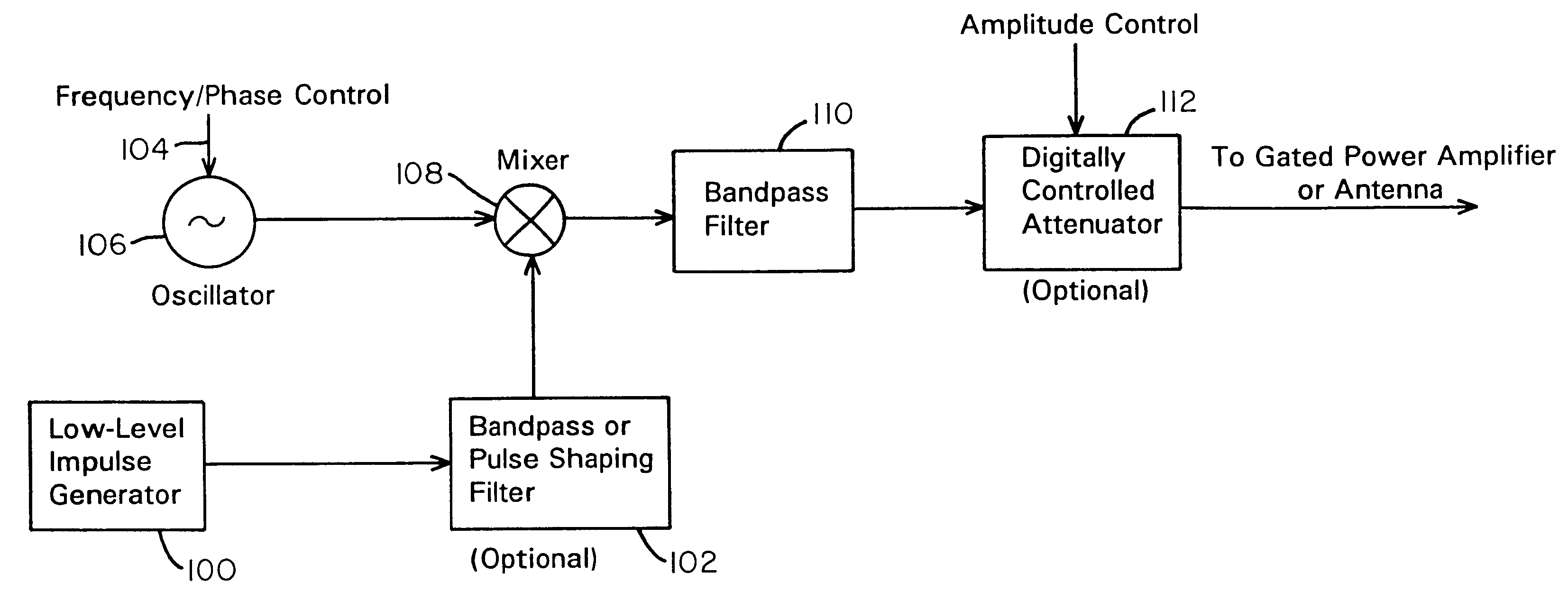

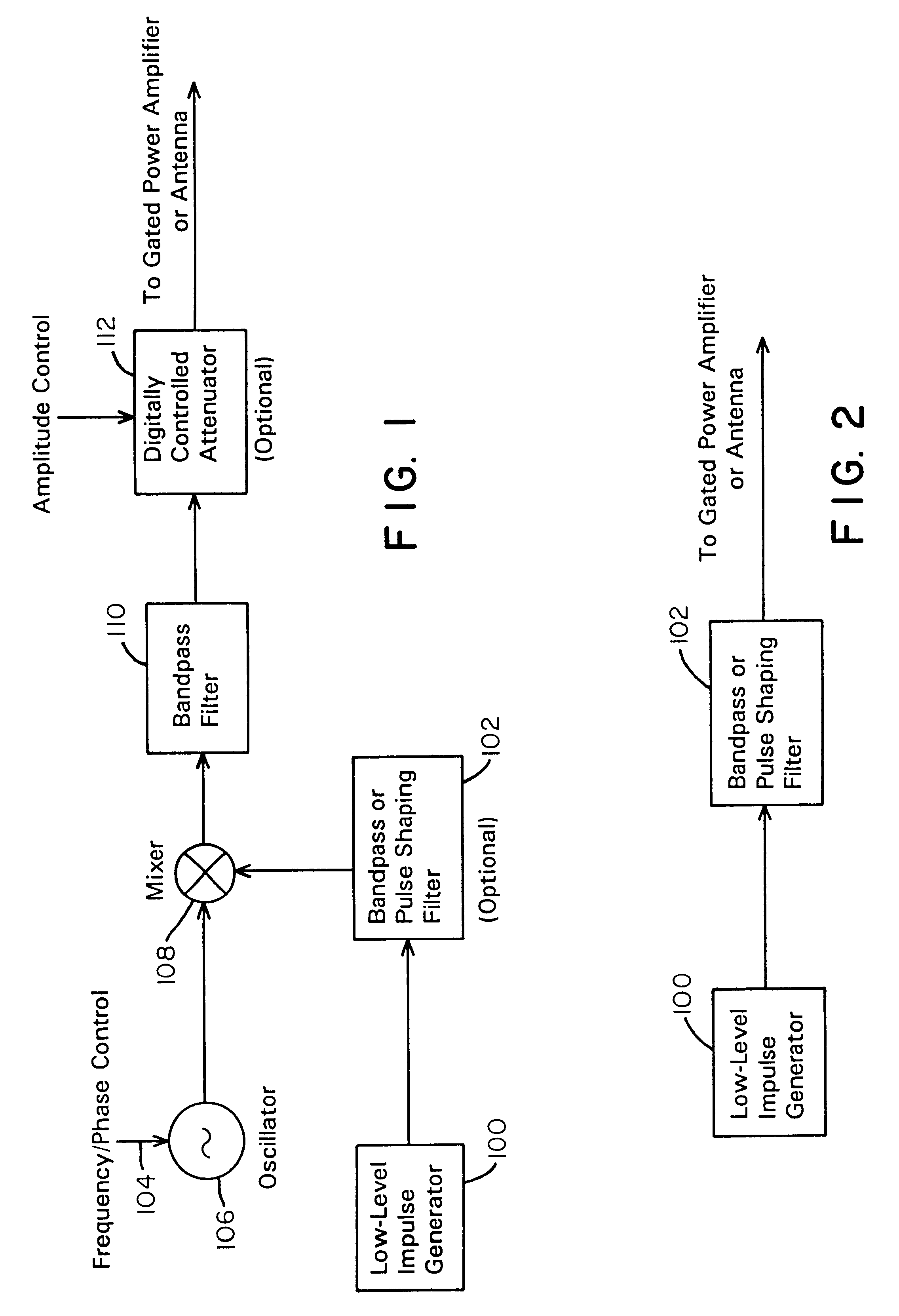

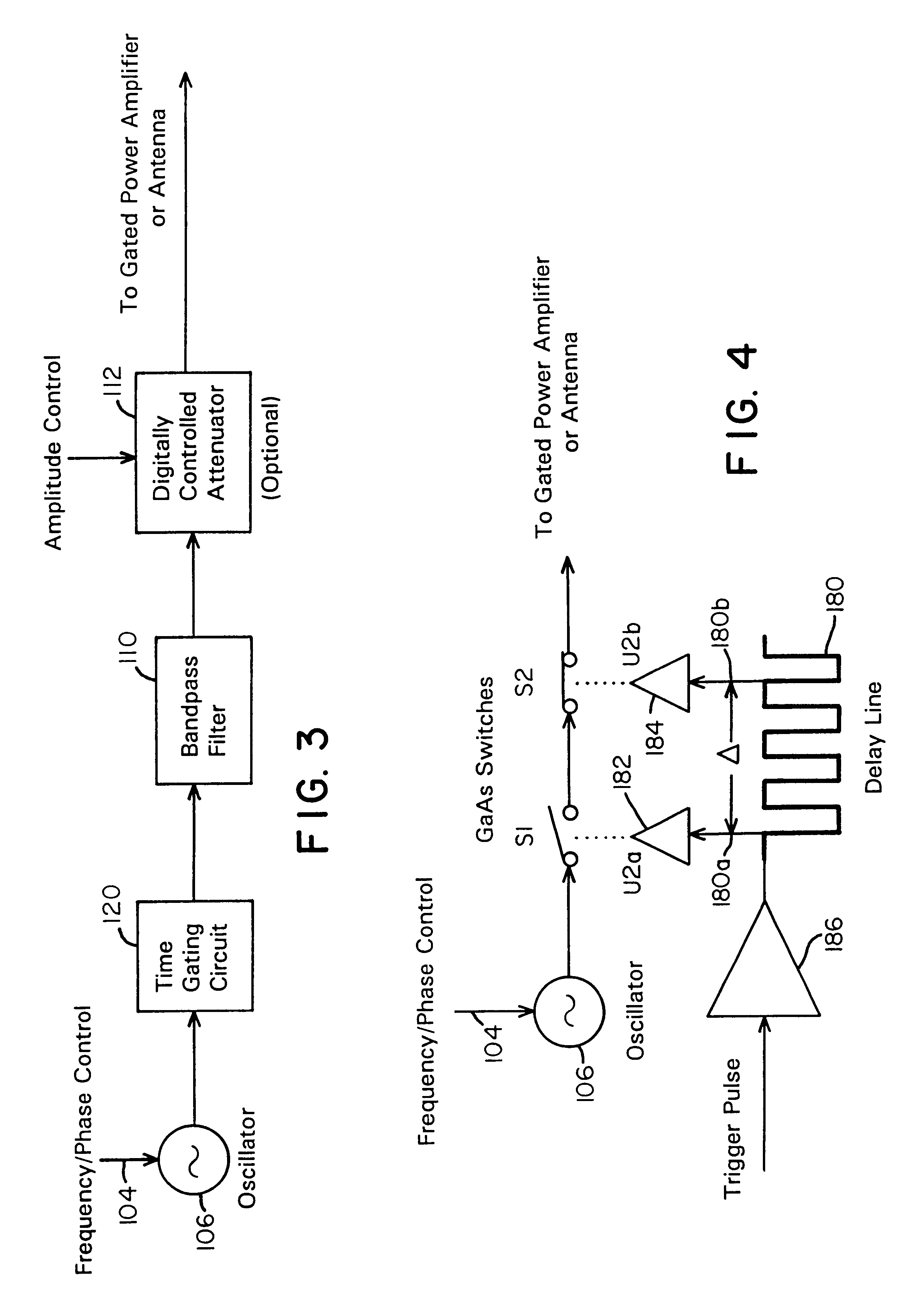

Waveform adaptive ultra-wideband transmitter

A waveform adaptive transmitter that conditions and / or modulates the phase, frequency, bandwidth, amplitude and / or attenuation of ultra-wideband (UWB) pulses. The transmitter confines or band-limits UWB signals within spectral limits for use in communication, positioning, and / or radar applications. One embodiment comprises a low-level UWB source (e.g., an impulse generator or time-gated oscillator (fixed or voltage-controlled)), a waveform adapter (e.g., digital or analog filter, pulse shaper, and / or voltage variable attenuator), a power amplifier, and an antenna to radiate a band-limited and / or modulated UWB or wideband signals. In a special case where the oscillator has zero frequency and outputs a DC bias, a low-level impulse generator impulse-excites a bandpass filter to produce an UWB signal having an adjustable center frequency and desired bandwidth based on a characteristic of the filter. In another embodiment, a low-level impulse signal is approximated by a time-gated continuous-wave oscillator to produce an extremely wide bandwidth pulse with deterministic center frequency and bandwidth characteristics. The UWB signal may be modulated to carry multi-megabit per second digital data, or may be used in object detection or for ranging applications. Activation of the power amplifier may be time-gated in cadence with the UWB source thereby to reduce inter-pulse power consumption. The UWB transmitter is capable of extremely high pulse repetition frequencies (PRFs) and data rates in the hundreds of megabits per second or more, frequency agility on a pulse-to-pulse basis allowing frequency hopping if desired, and extensibility from below HF to millimeter wave frequencies.

Owner:ZEBRA TECH CORP

Ultra wideband data transmission system and method

InactiveUS6690741B1Amplitude-modulated carrier systemsAngle modulationBandpass filteringExtensibility

A data-modulated ultra wideband transmitter that modulates the phase, frequency, bandwidth, amplitude and / or attenuation of ultra-wideband (UWB) pulses. The transmitter confines or band-limits UWB signals within spectral limits for use in communication, positioning, and / or radar applications. One embodiment comprises a low-level UWB source (e.g., an impulse generator or time-gated oscillator (fixed or voltage-controlled)), a waveform adapter (e.g., digital or analog filter, pulse shaper, and / or voltage variable attenuator), a power amplifier, and an antenna to radiate a band-limited and / or modulated UWB or wideband signals. In a special case where the oscillator has zero frequency and outputs a DC bias, a low-level impulse generator impulse-excites a bandpass filter to produce an UWB signal having an adjustable center frequency and desired bandwidth based on a characteristic of the filter. In another embodiment, a low-level impulse signal is approximated by a time-gated continuous-wave oscillator to produce an extremely wide bandwidth pulse with deterministic center frequency and bandwidth characteristics. The UWB signal may be modulated to carry multi-megabit per second digital data, or may be used in object detection or for ranging applications. Activation of the power amplifier may be time-gated in cadence with the UWB source thereby to reduce inter-pulse power consumption. The UWB transmitter is capable of extremely high pulse repetition frequencies (PRFs) and data rates in the hundreds of megabits per second or more, frequency agility on a pulse-to-pulse basis allowing frequency hopping if desired, and extensibility from below HF to millimeter wave frequencies.

Owner:ZEBRA TECH CORP

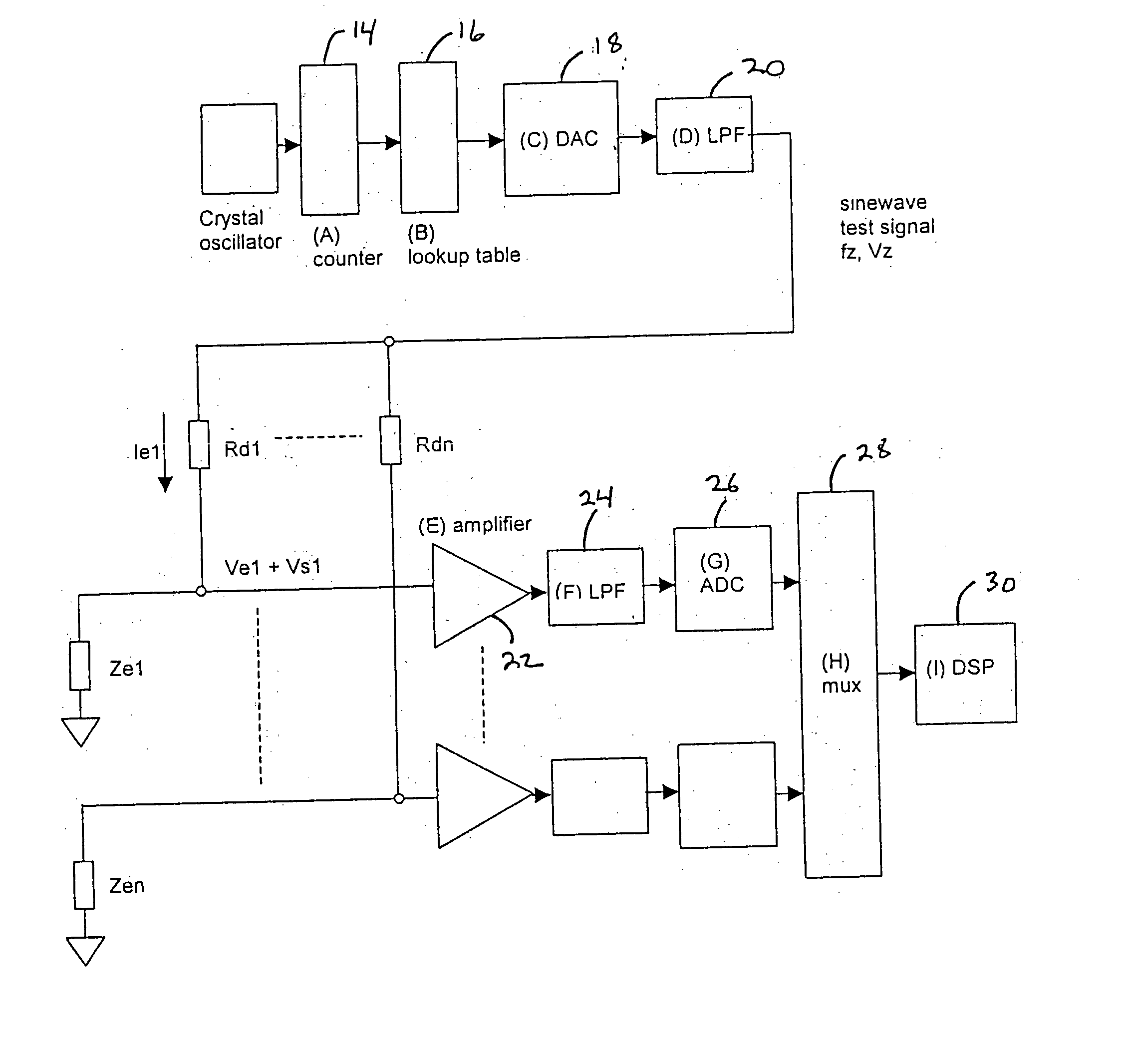

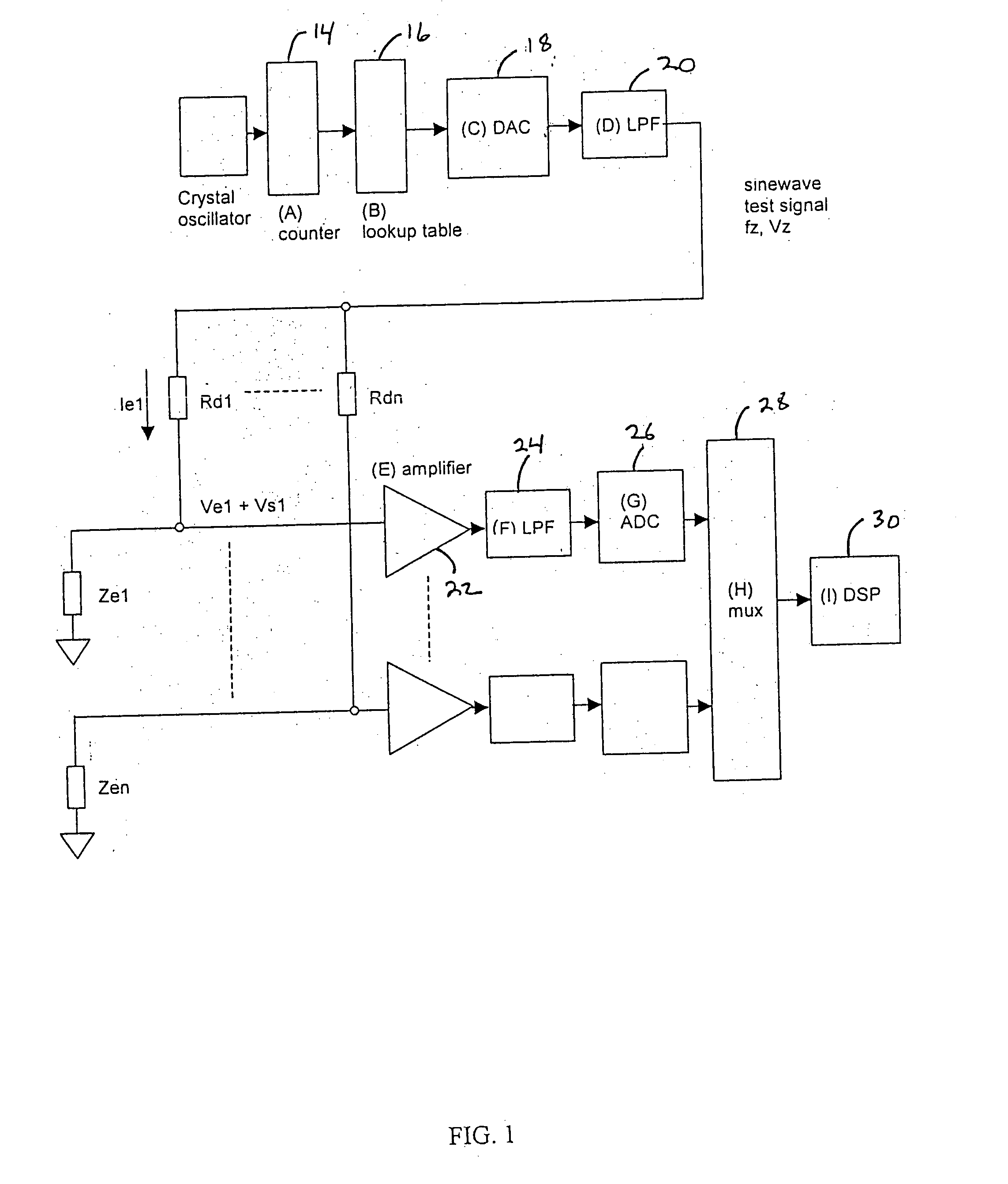

Method and apparatus for continuous electrode impedance monitoring

InactiveUS20060020218A1Continuous monitoringElectrocardiographyResistance/reactance/impedenceVoltage amplitudeBandpass filtering

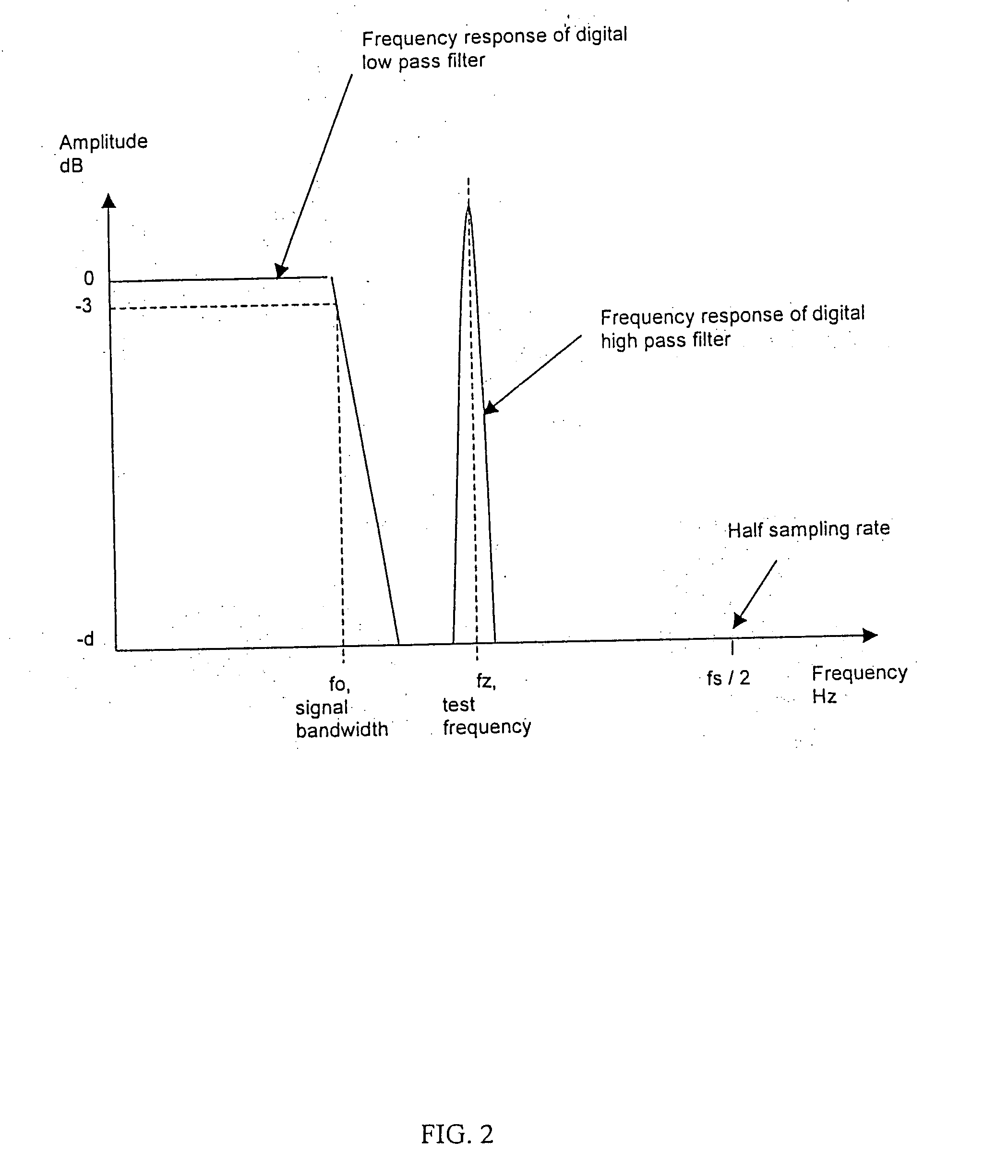

In one embodiment, the present invention includes a test signal generator capable of producing an impedance test signal comprising of a sine wave having a known frequency. The test signal generator may include a crystal oscillator, a counter, and a lookup table. The lookup table output is applied to a digital to analog converter and is then low pass filtered using a conventional analog filter to produce a sine wave of a known frequency and voltage amplitude. The test signal flows through the electrode and combines with an electrophysiological signal to form a combined signal. A signal processor is used to isolate the combined signal into the test signal component and the electrophysiological component. The signal processor digitally low pass filters the combined signal and the output of the low pass filter is the electrophysiological signal. The signal processor then digitally bandpass filters the combined signal using a filter with a center frequency which is the same as the test frequency. The output of this filter is then used to calculate the electrode impedance.

Owner:COMPUMEDICS

Digital to analog converter

ActiveUS7038608B1Reduce the amount of noiseImprove transient responseElectric signal transmission systemsDigital-analogue convertorsDigital feedbackClock rate

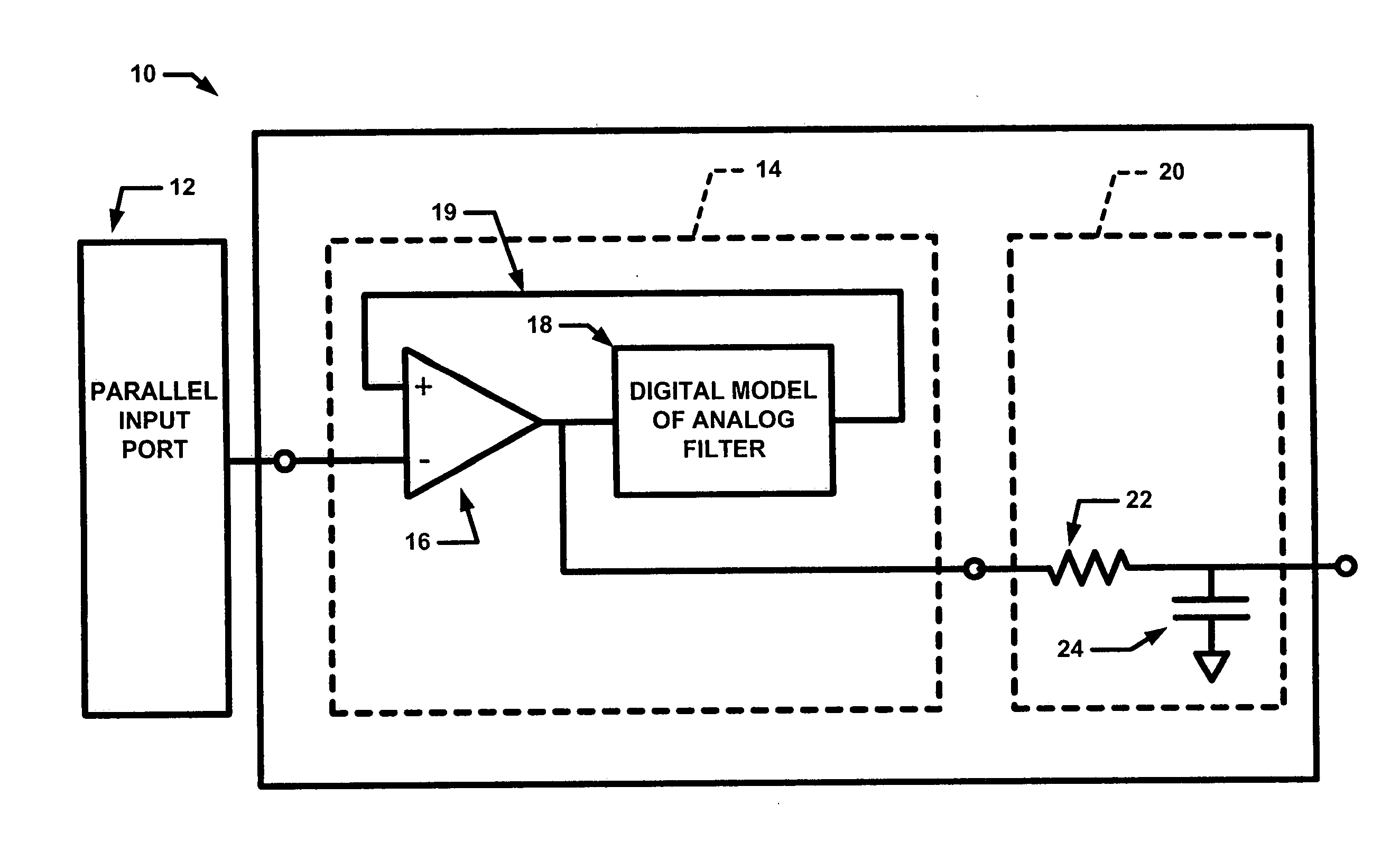

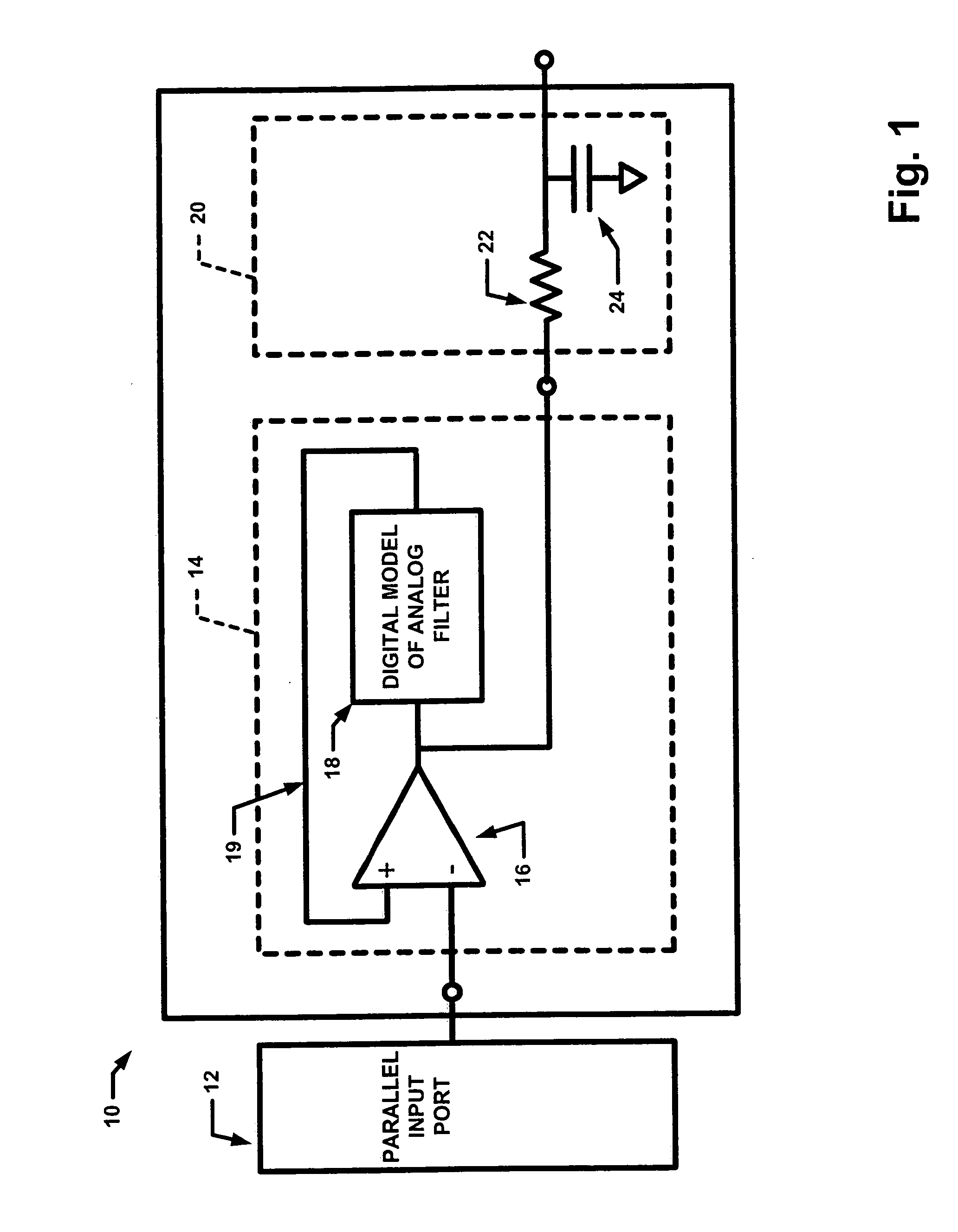

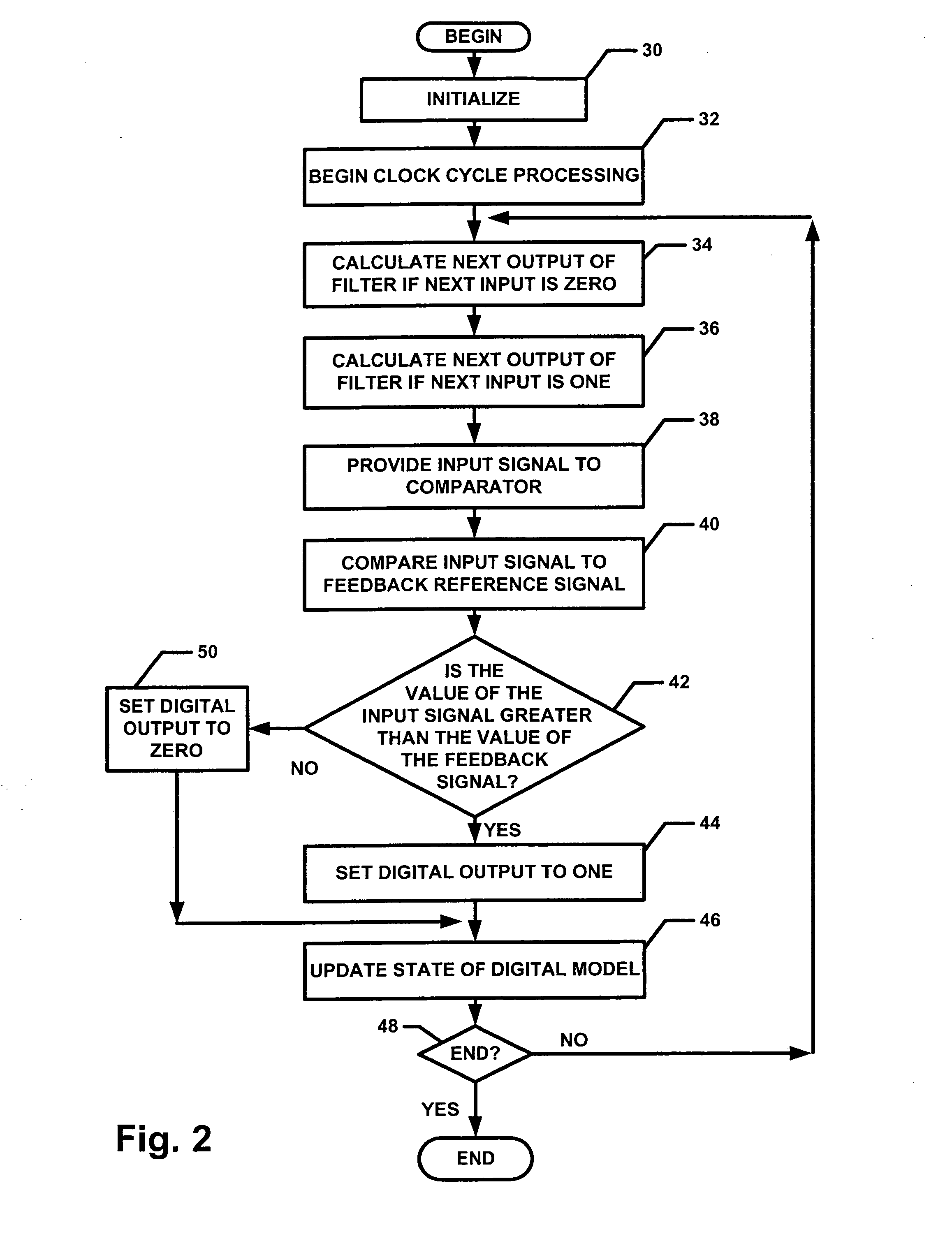

A digital to analog converter includes a digital processor having an input port adapted to receive an input signal and an output port coupled to an input port of an analog filter wherein the digital processor includes a digital feedback loop which compares a reference digital voltage with a digital voltage provided by a digital model of the analog filter. Using a completely digital feedback loop which compares an input digital voltage with the digital voltage from the digital model of the analog filter results in a single bit digital to analog converter having improved accuracy for a given clock rate and filter. The next digital state of the converter (i.e. ‘0’ or ‘1’) is selected based upon a comparison of the input (or reference) voltage with the digital voltage provided by the digital feedback loop. The digital converter output is then fed to the analog filter. If the analog filter matches the digital model, then the analog voltage will match the digital voltage, and therefore the reference voltage.

Owner:VALEO RADAR SYST

Systems and methods for semi-independent loop processing

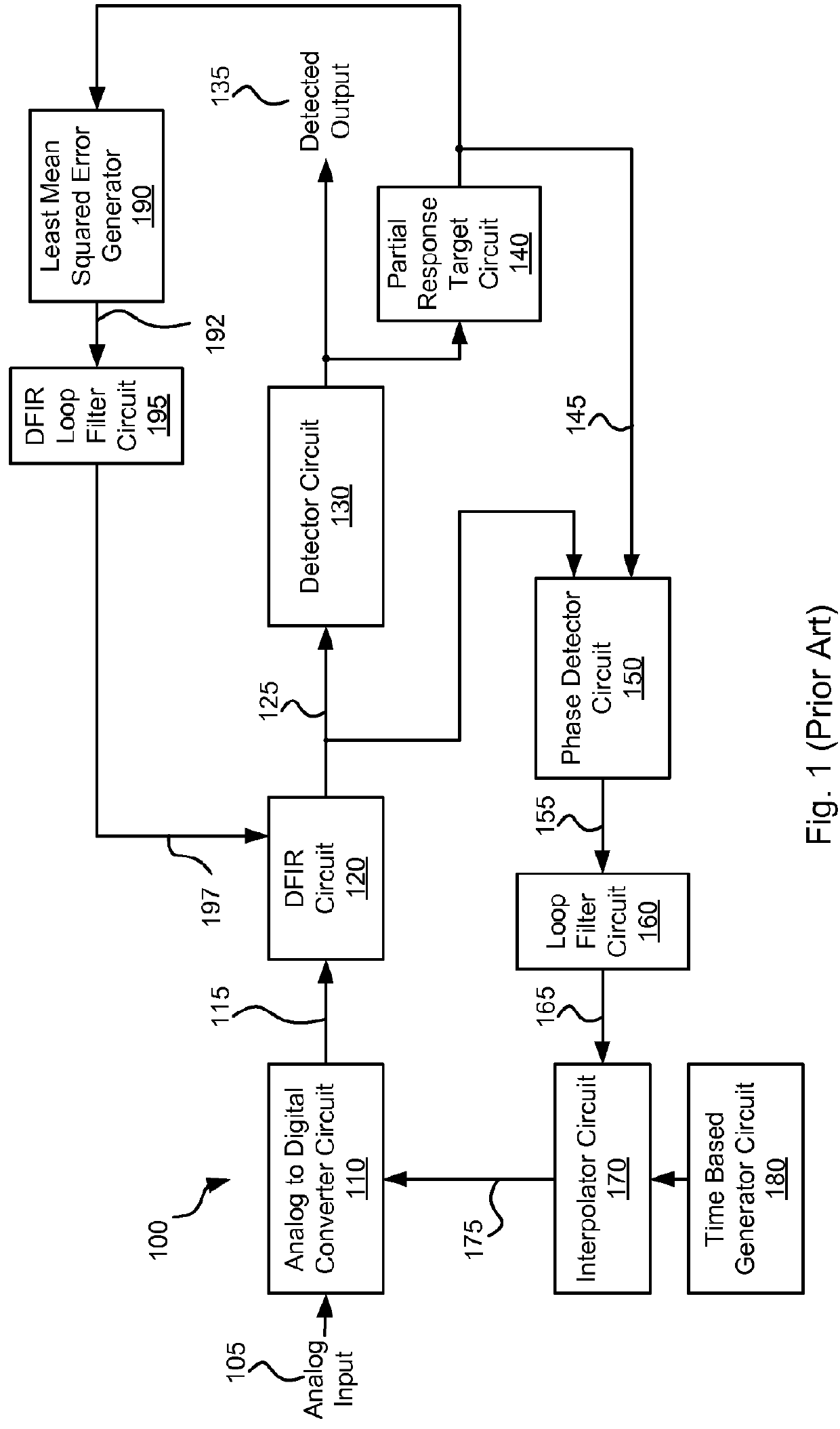

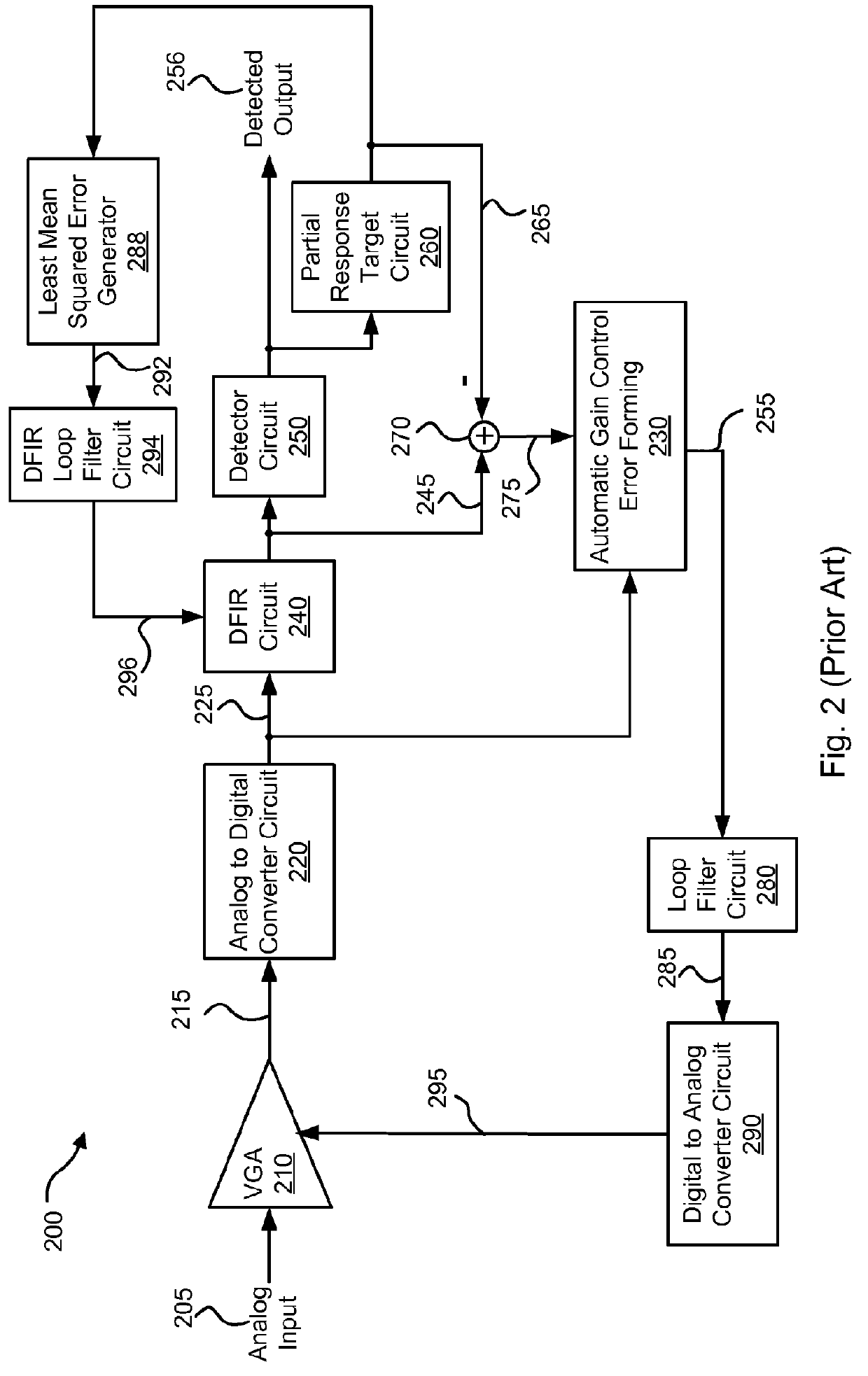

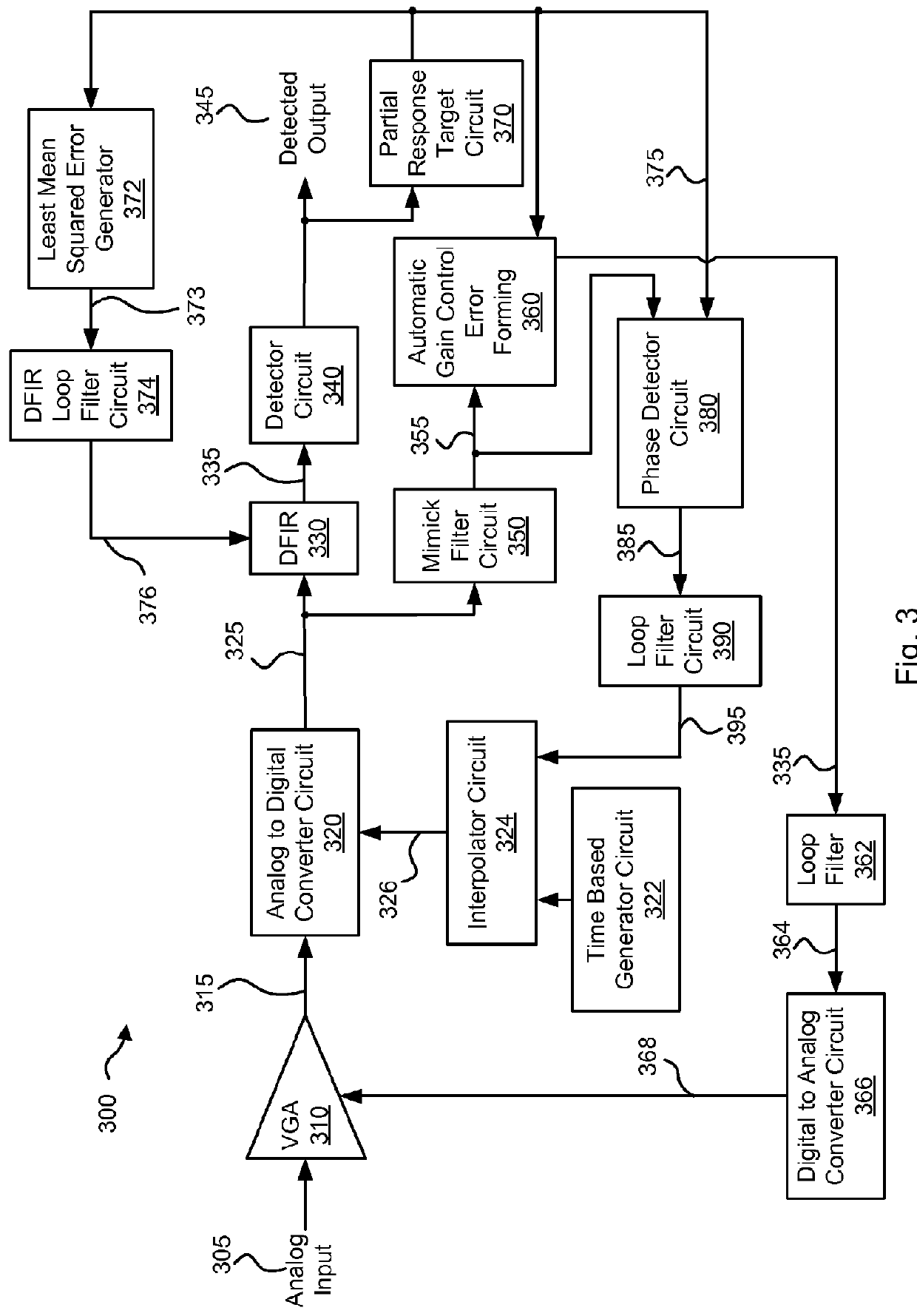

InactiveUS8237597B2Electric signal transmission systemsRecord information storageDetector circuitsAnalog-to-digital converter

Various embodiments of the present invention provide systems and methods for data processing. For example, a data processing circuit is discussed that includes an analog to digital converter circuit, a digital filter circuit, a data detector circuit, a mimic filter circuit, and a sample clock generation circuit. The analog to digital converter circuit is operable to receive a data input and to provide corresponding digital samples. The digital filter circuit is operable to receive the digital samples and to provide a filtered output. The data detector circuit is operable to perform a data detection process on the filtered output to yield a detected output. The mimic filter circuit is operable to receive the digital samples and to provide a mimicked output. The sample clock generation circuit is operable to provide a sample clock based at least in part on the detected output and the mimicked output.

Owner:AVAGO TECH INT SALES PTE LTD

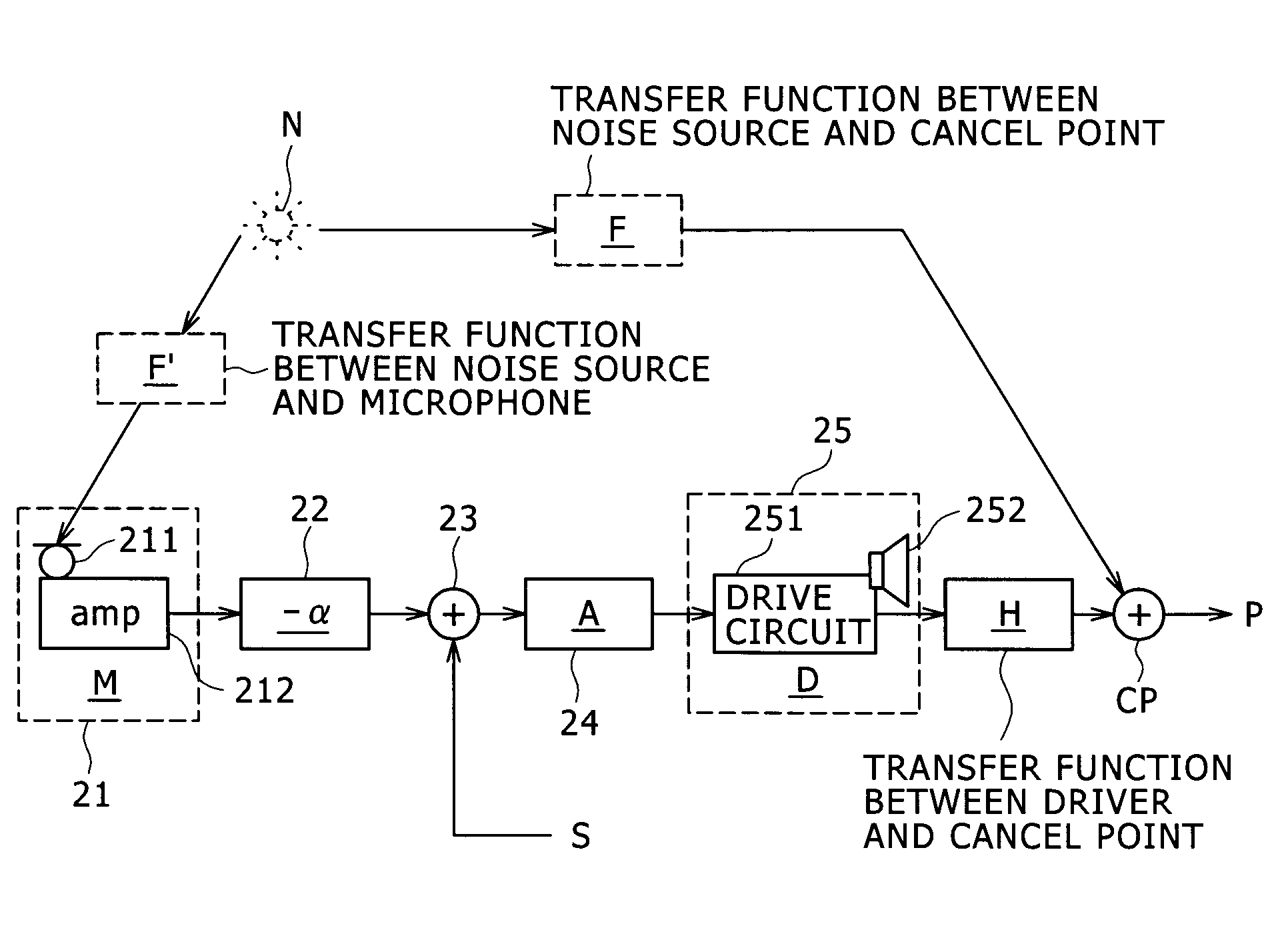

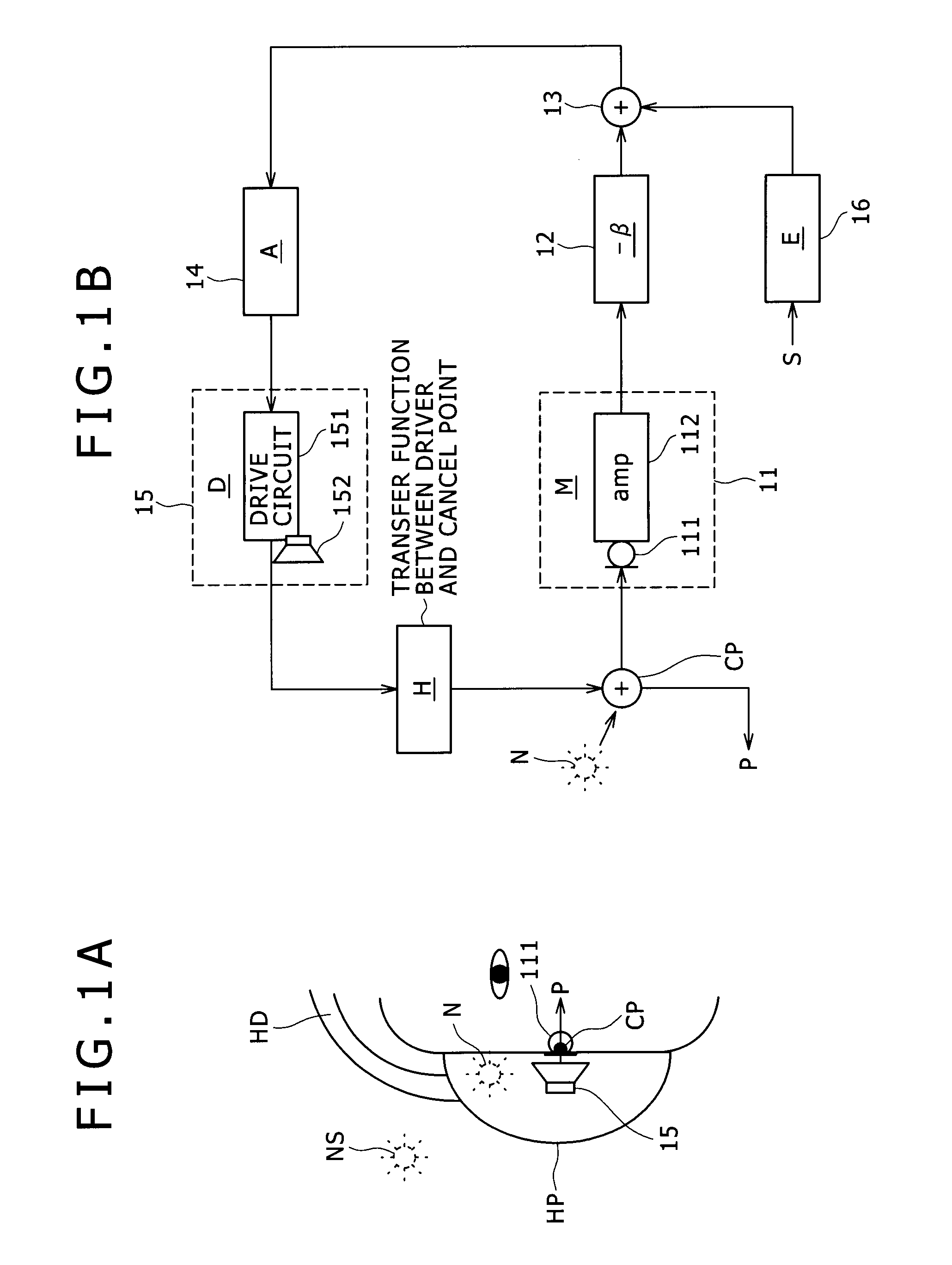

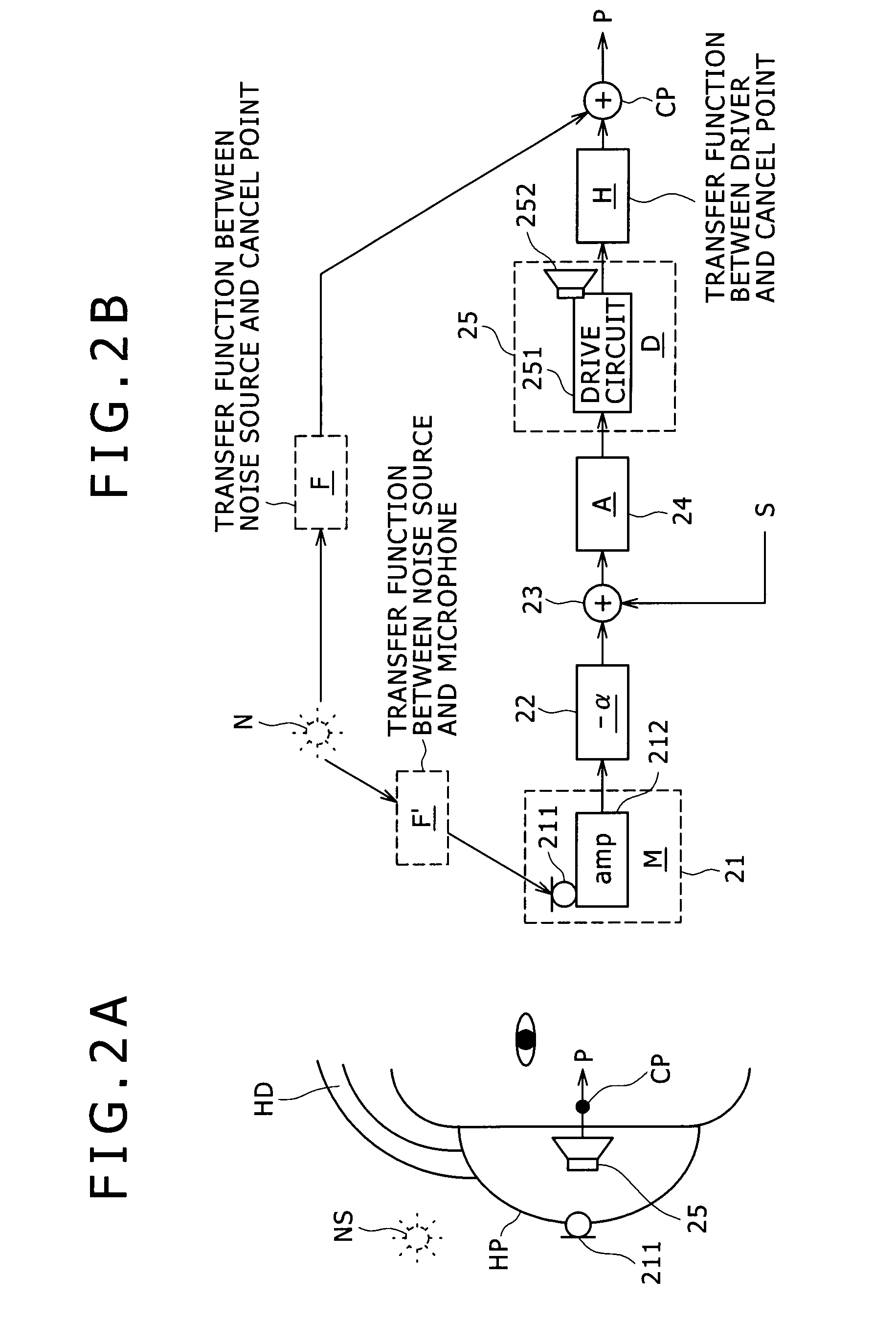

Filter circuit for noise cancellation, noise reduction signal production method and noise canceling system

There is provided a filter circuit for producing a noise reduction signal for reducing a noise signal collected by a microphone, including: a digital section including an analog / digital conversion section configured to convert the noise signal into a digital noise signal, a digital filter section configured to produce a digital noise reduction signal based on the digital noise signal, and a digital / analog conversion section configured to convert the digital noise reduction signal into an analog noise reduction signal; an analog path connected in parallel to said digital section and configured to output the noise signal as it is or after processed by an analog filter; and a synthesis section configured to synthesize the analog noise reduction signal outputted from said digital / analog conversion section of said digital section and the analog signal outputted from said analog path to produce a noise reduction signal to be used for noise reduction.

Owner:SONY CORP

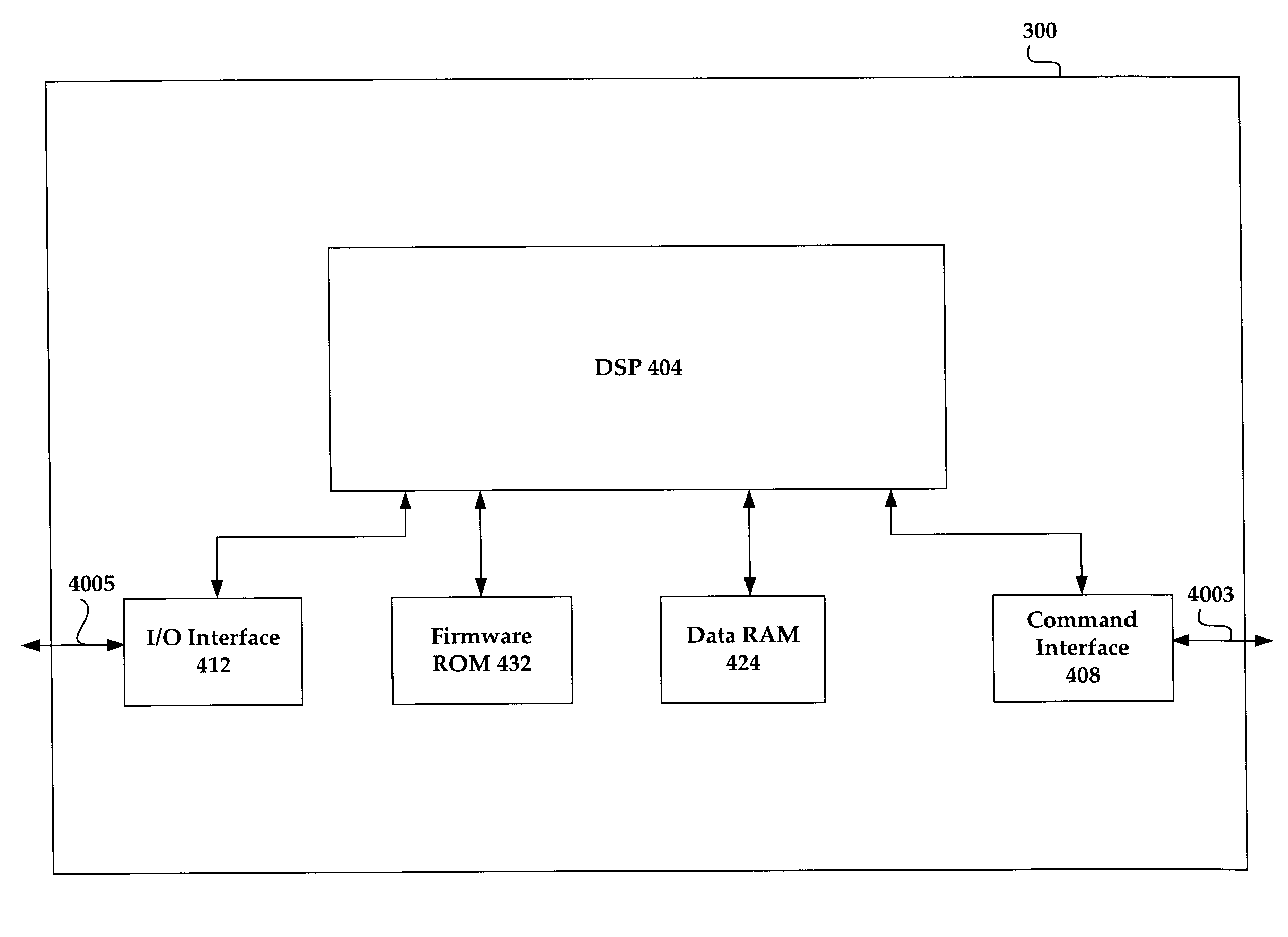

Digital crossover and parametric equalizer

InactiveUS6405227B1Digital technique networkComplex mathematical operationsBand-pass filterEqualization

A DSP-based and multi-channel digital filter chip providing crossover filtering and parametric equalization. Crossovers can be low-pass, high-pass, or band-pass filters with programmable cutoff frequencies. Each equalizer band has independently adjustable center frequency band, and levels over a -60 dB to +16 dB range. The chip can work either with a microprocessor controlling the chip or in a stand-alone mode having the filter settings downloaded automatically from an external EEPROM. The chip is ideal for applications that require precise digital filtering or software programmable filters, and is also an alternative to analog filters, eliminating passive components and reducing circuit size.

Owner:NJR CORP

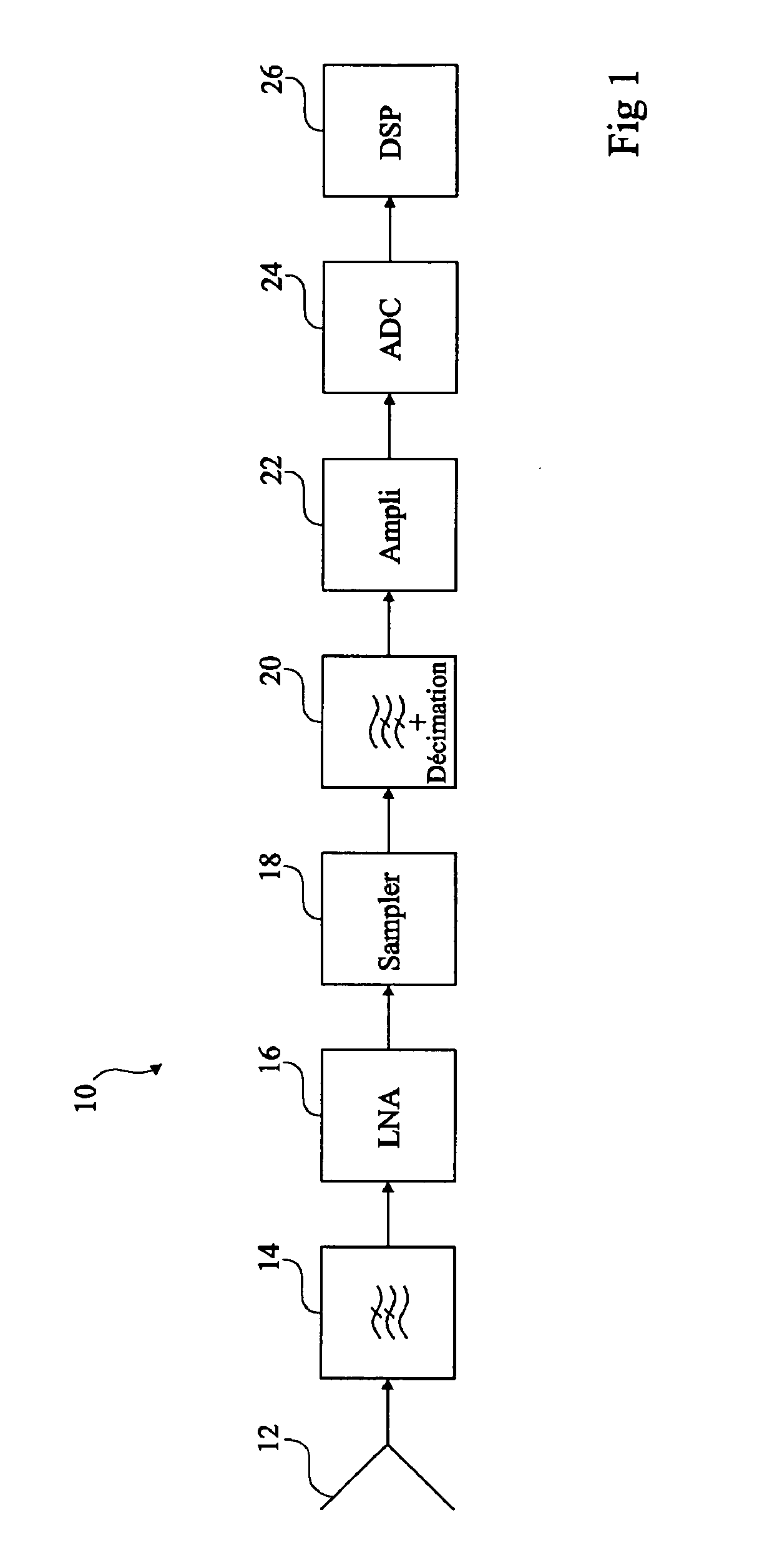

Filters for communication systems

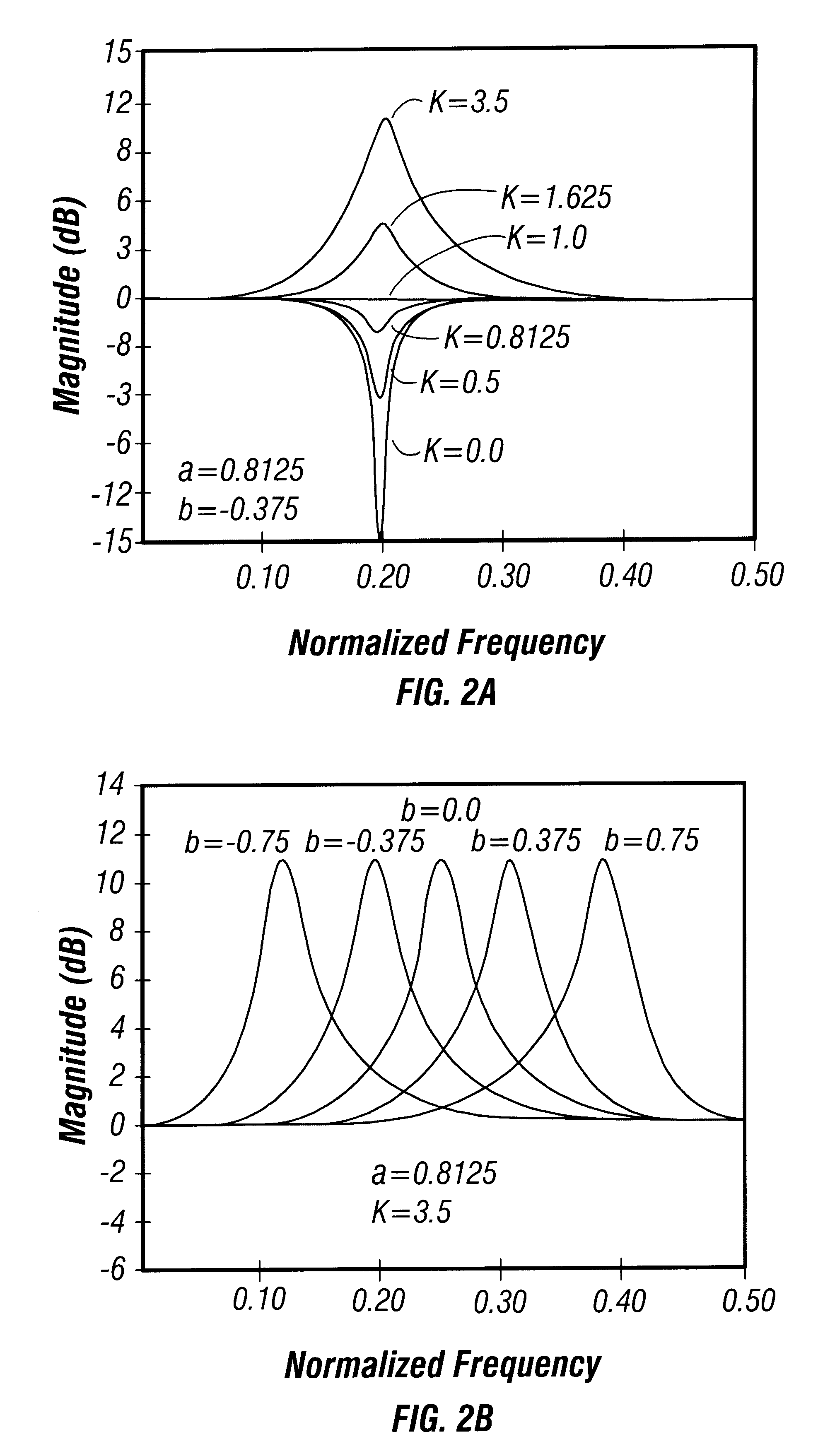

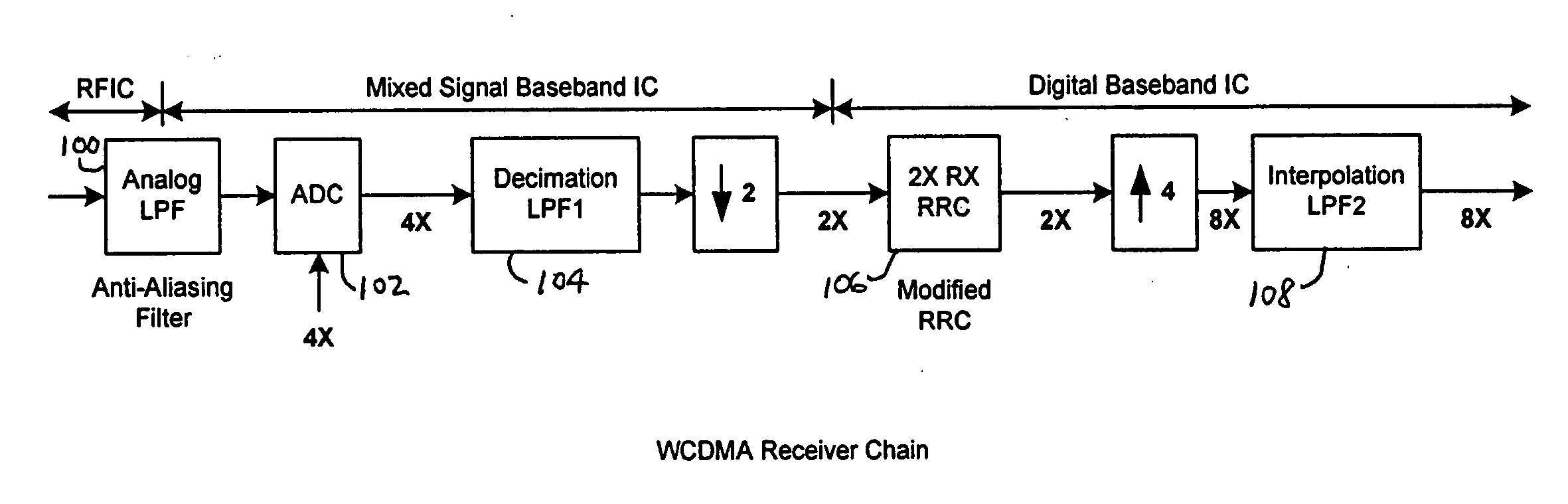

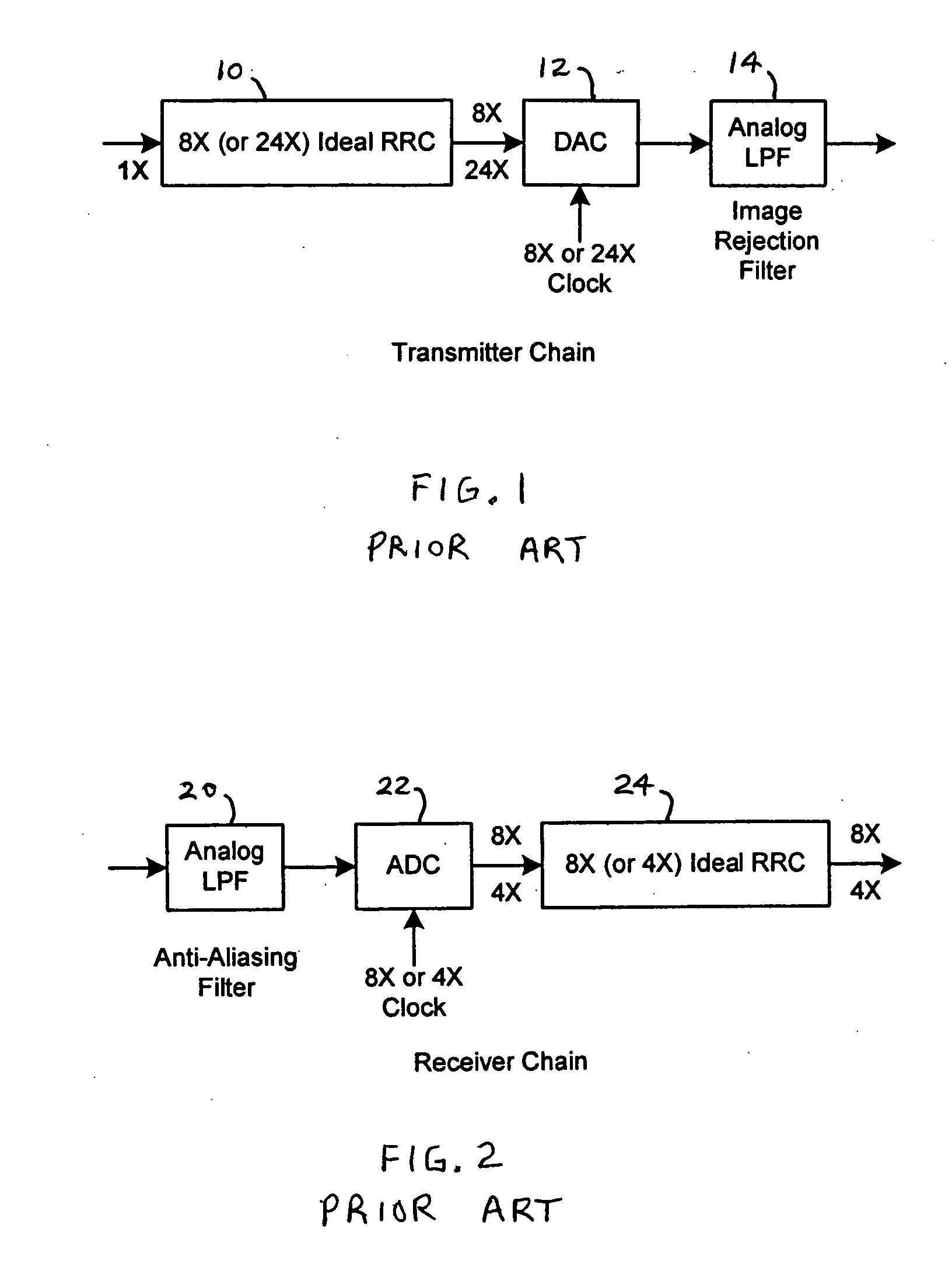

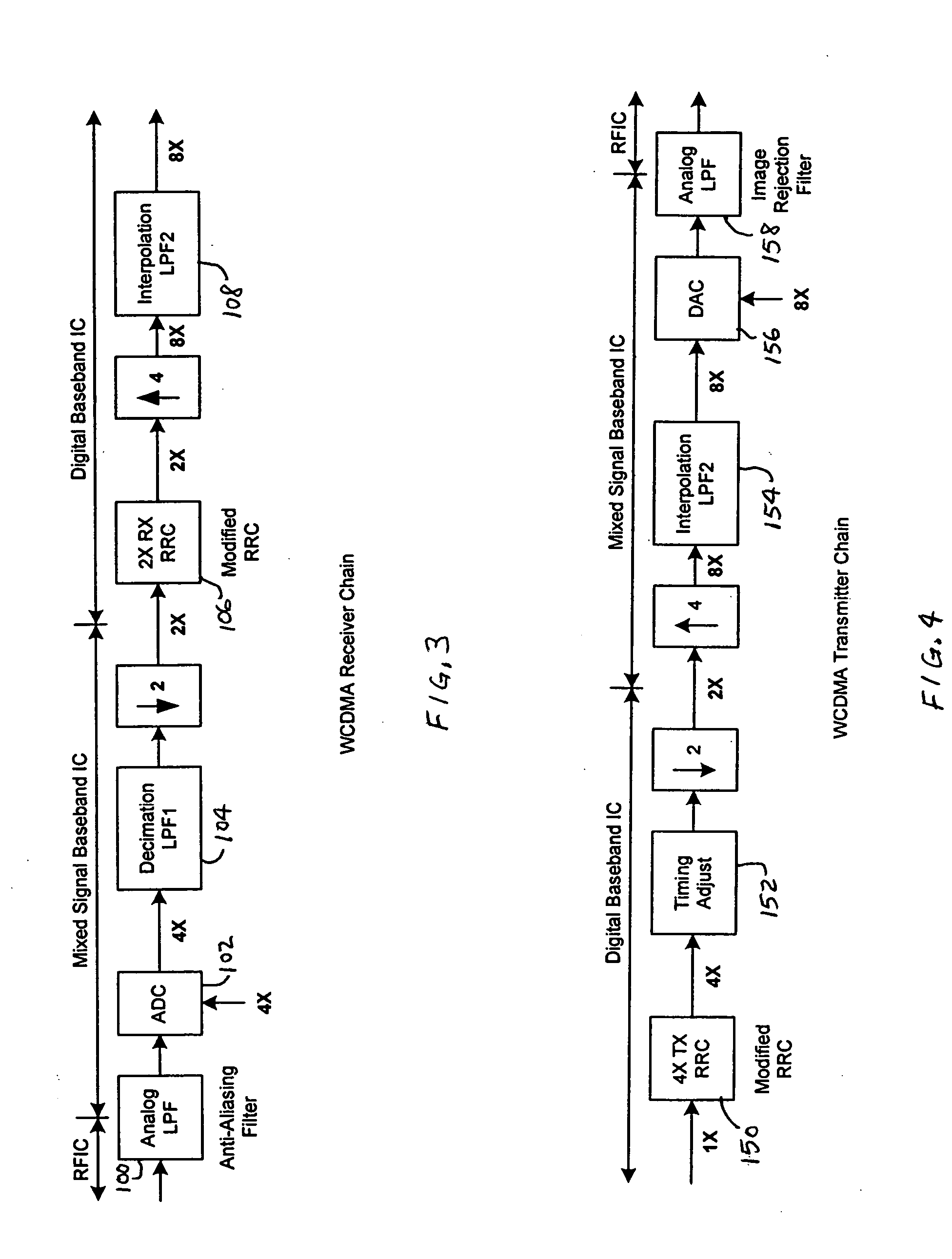

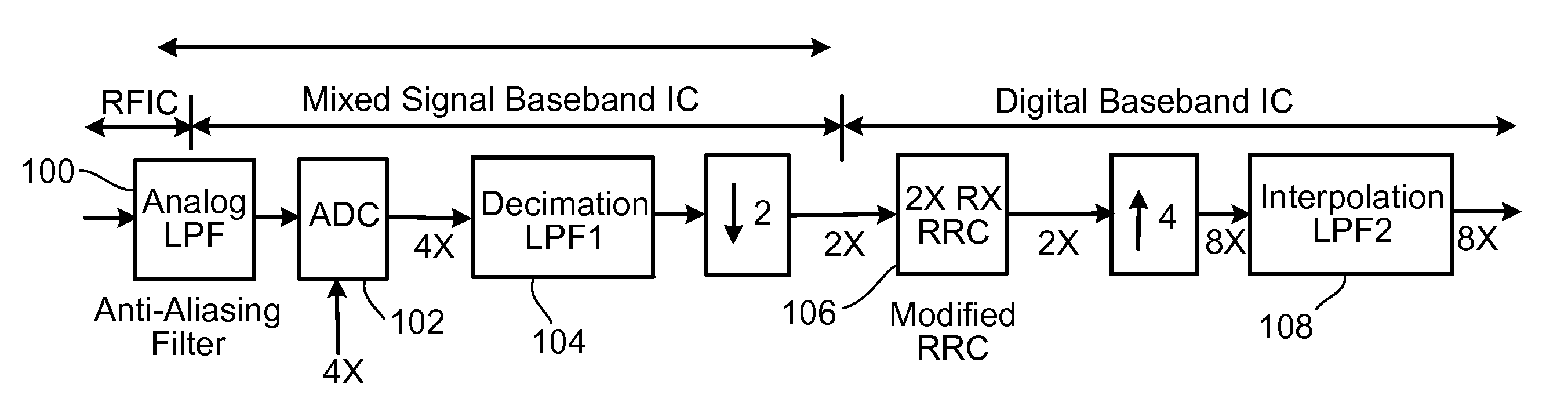

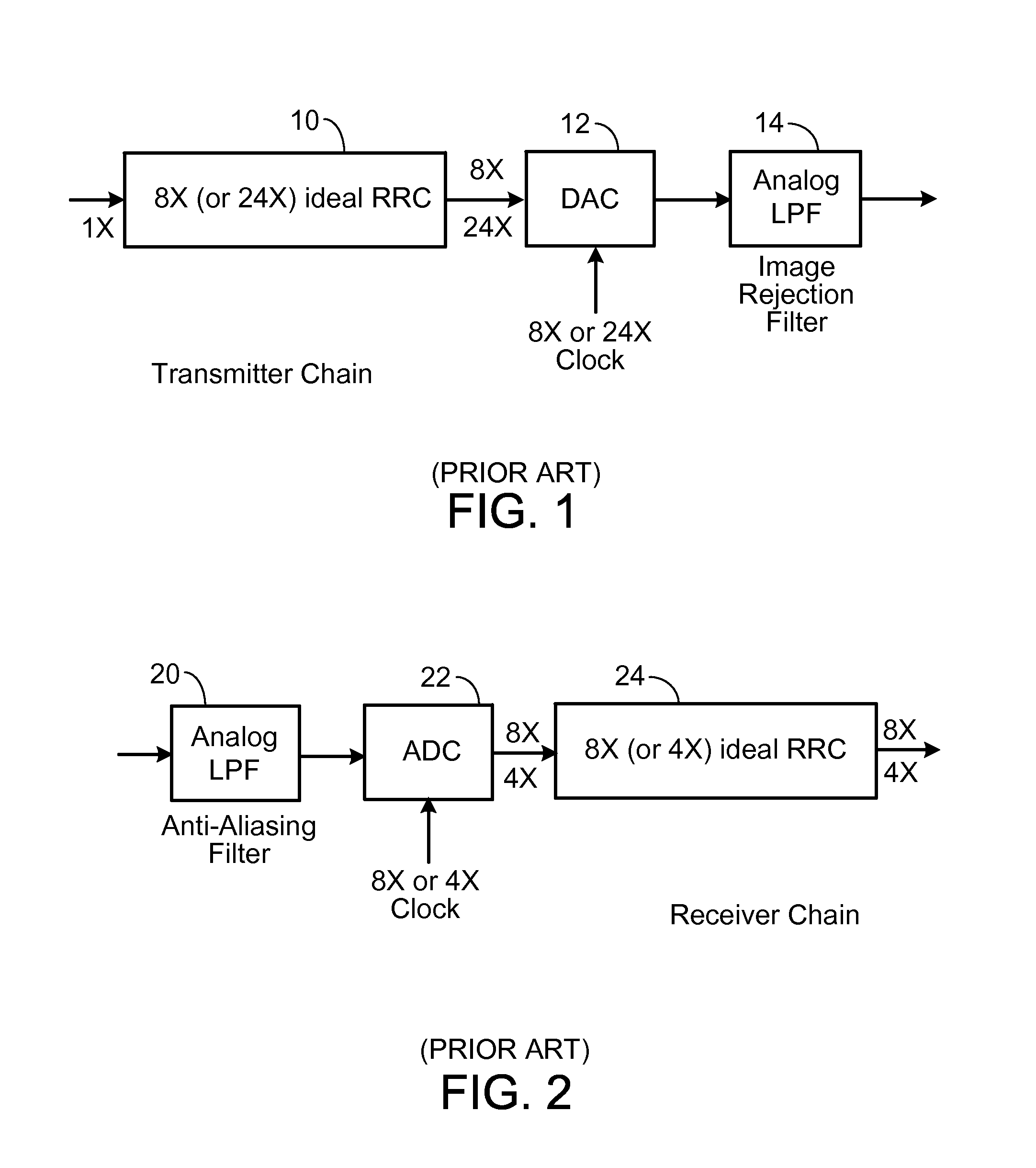

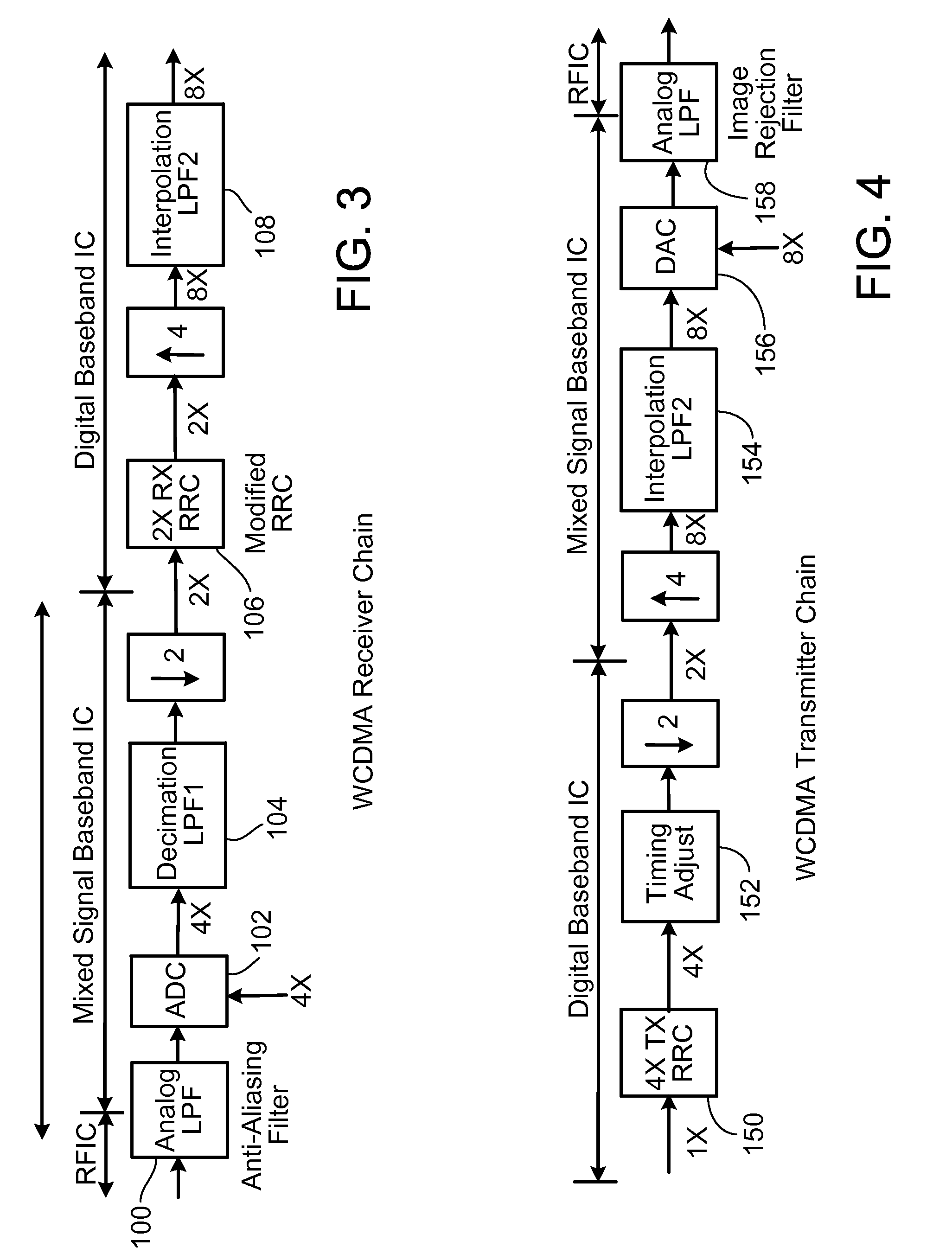

ActiveUS20060083297A1Low data rateMultiple-port networksDigital technique networkCommunications systemHigh rate

The invention relates to a cascaded scheme in which an RRC filter, a modified RRC filter or other digital filter is implemented at a relatively low data rate, such as twice the symbol or chip rate, or 2×. Interpolation filters are used to increase the data rate to a higher data rate, such as 8×. Decimation filters are used to reduce the data rate from a higher rate, such as 8×, to a lower rate, such as 2×. The coefficients of the digital filter may be adjusted to compensate for characteristics of other components across the entire filter chain. Most of the implementation complexity of the filter chain is consolidated into the relatively low rate (such as 2×) digital filter while interpolation or decimation filters can be implemented at very low cost. The compensation capability provided by the digital filter makes design of simple decimation or interpolation filters much easier. The compensation capability provided by the digital filter, along with the relatively high over-sampling rate for the output of the interpolation filter (or the input of the decimation filter), also makes the design of the preceding (or following) analog filters much easier.

Owner:MEDIATEK INC

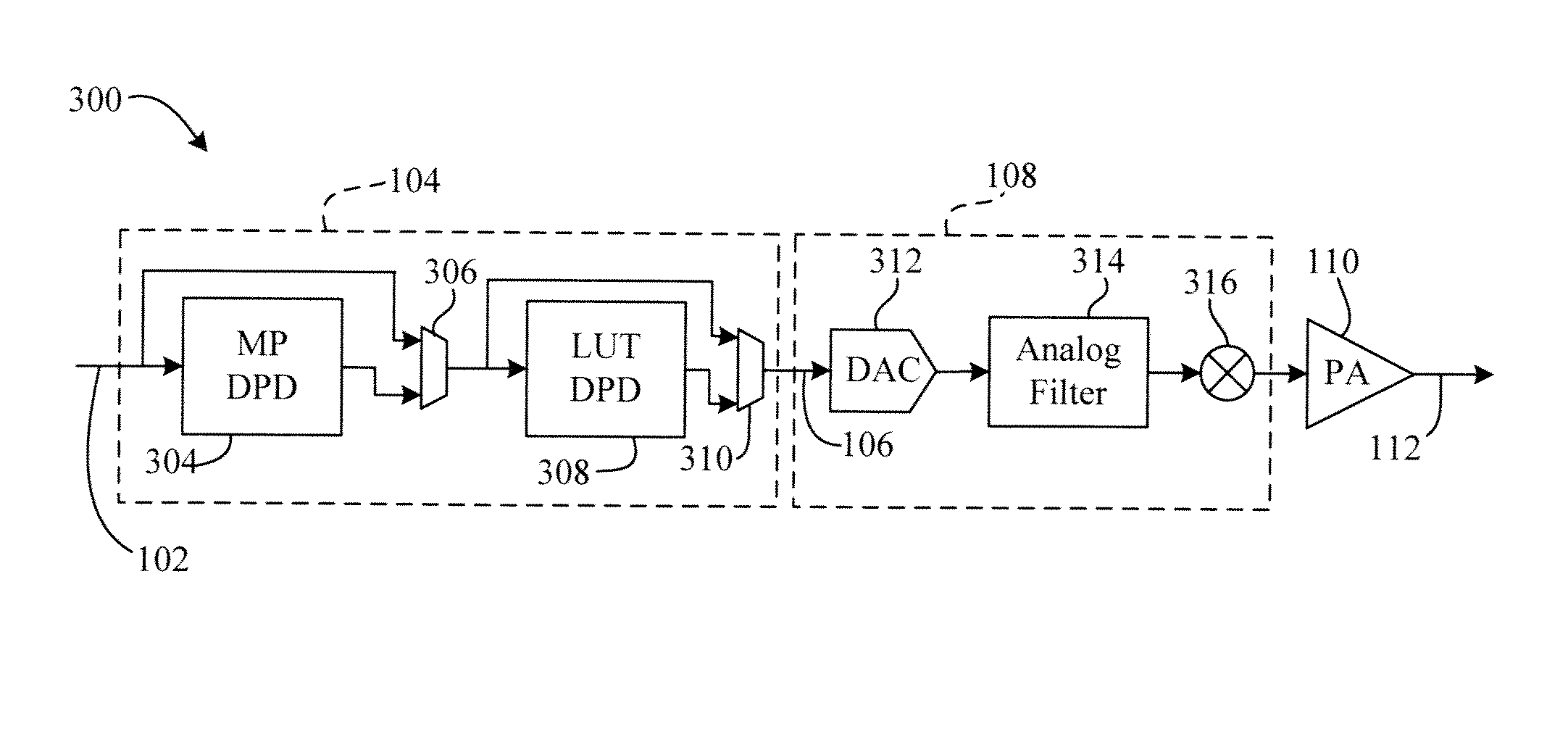

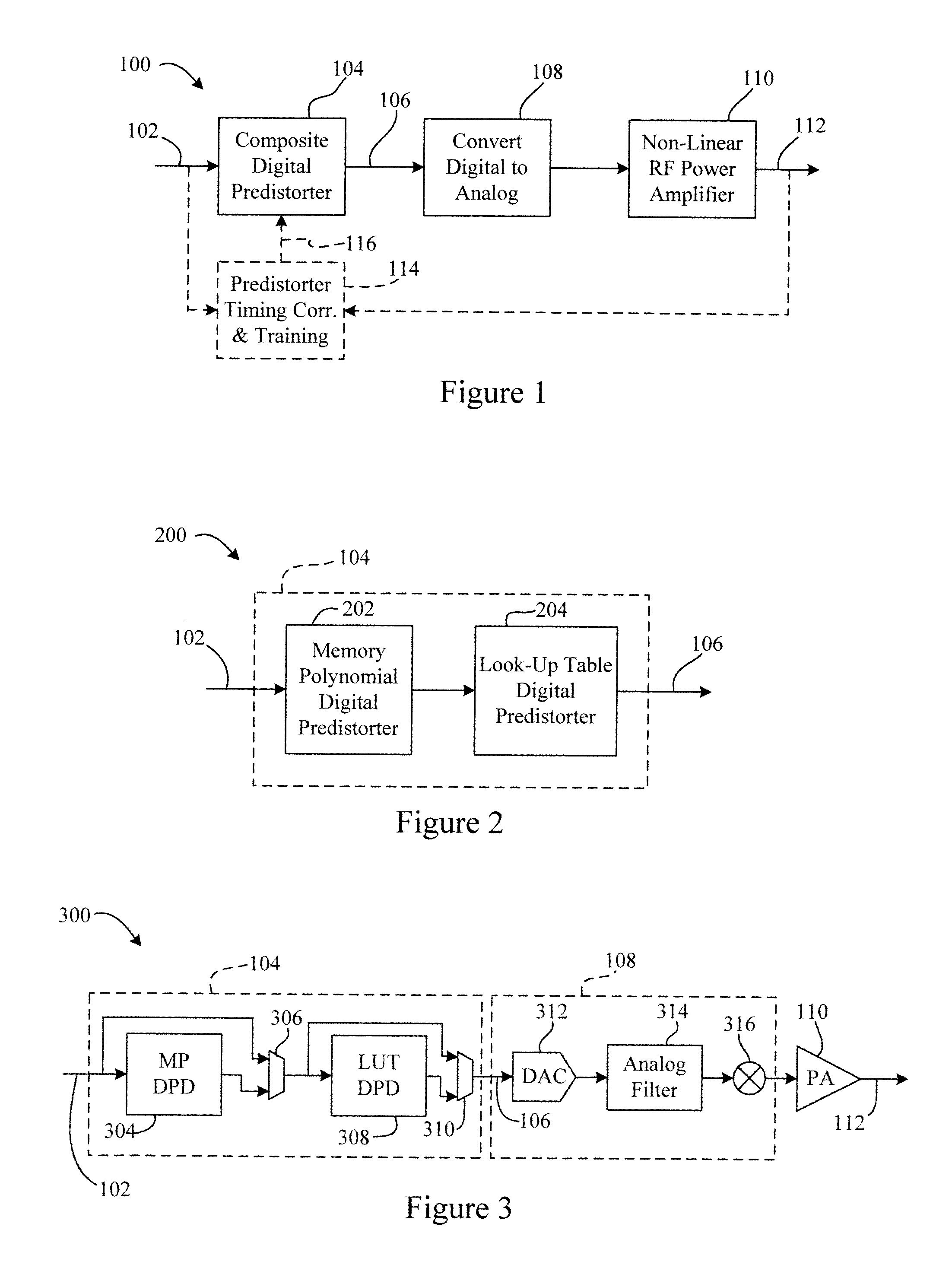

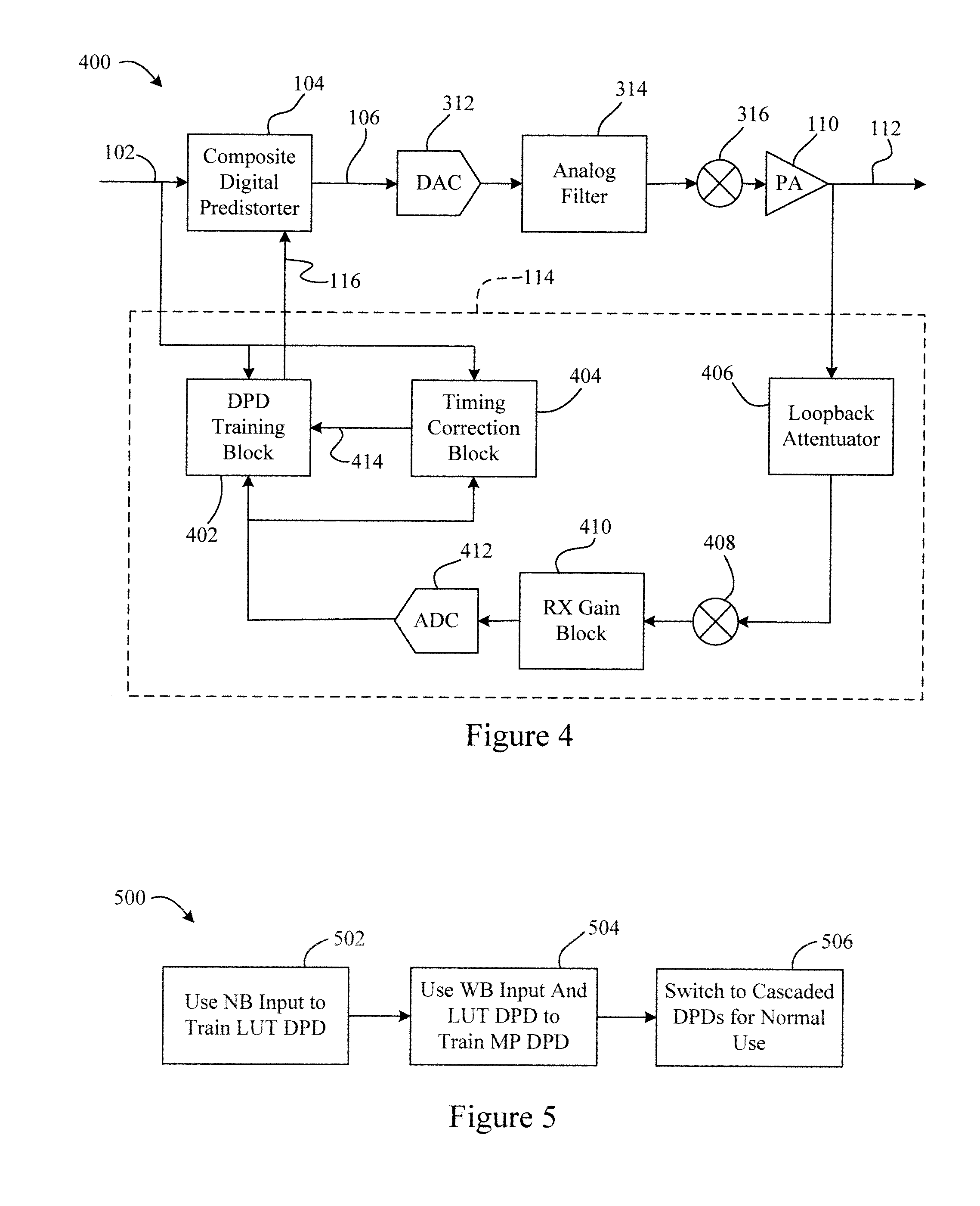

Power Amplifier System Including A Composite Digital Predistorter

InactiveUS20140254716A1Secret communicationTransmitter/receiver shaping networksAudio power amplifierMultiplexer

A power amplifier system including a composite digital predistorter (DPD) ensuring optimized linearity for the power amplifier is described. In this system, a digital-to-analog converter (DAC), an analog filter, a first mixer, and the power amplifier are serially coupled to the composite DPD. A second mixer, a receive gain block, and an analog-to-digital converter (ADC) are serially coupled to the output of the power amplifier. A DPD training component is coupled between the inputs of the composite DPD and the ADC. The composite DPD includes a memory-based DPD, e.g., a memory polynomial (MP) DPD, a memoryless-linearizing DPD, e.g., a look-up table (LUT) DPD, and two multiplexers.

Owner:QUALCOMM INC

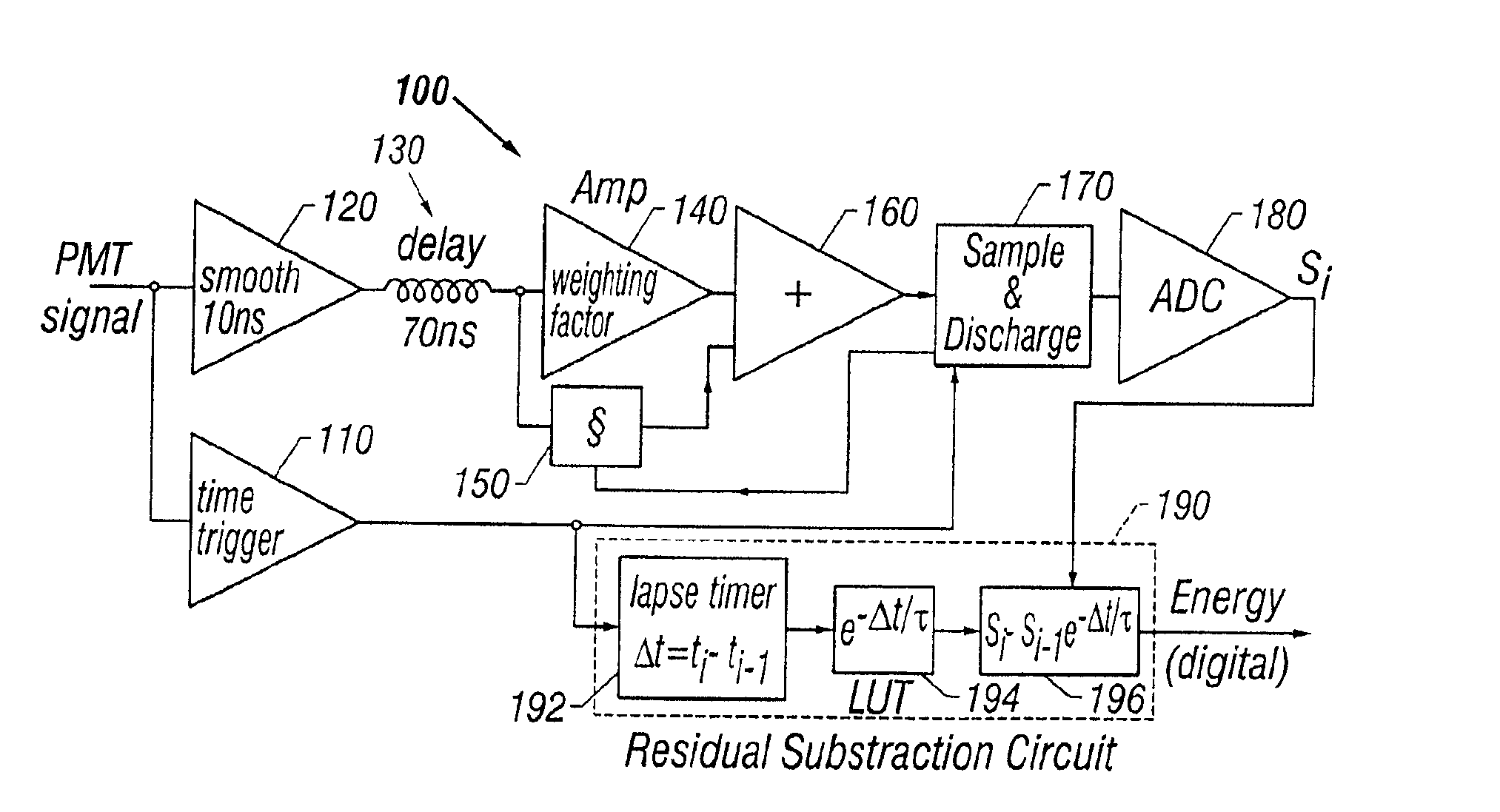

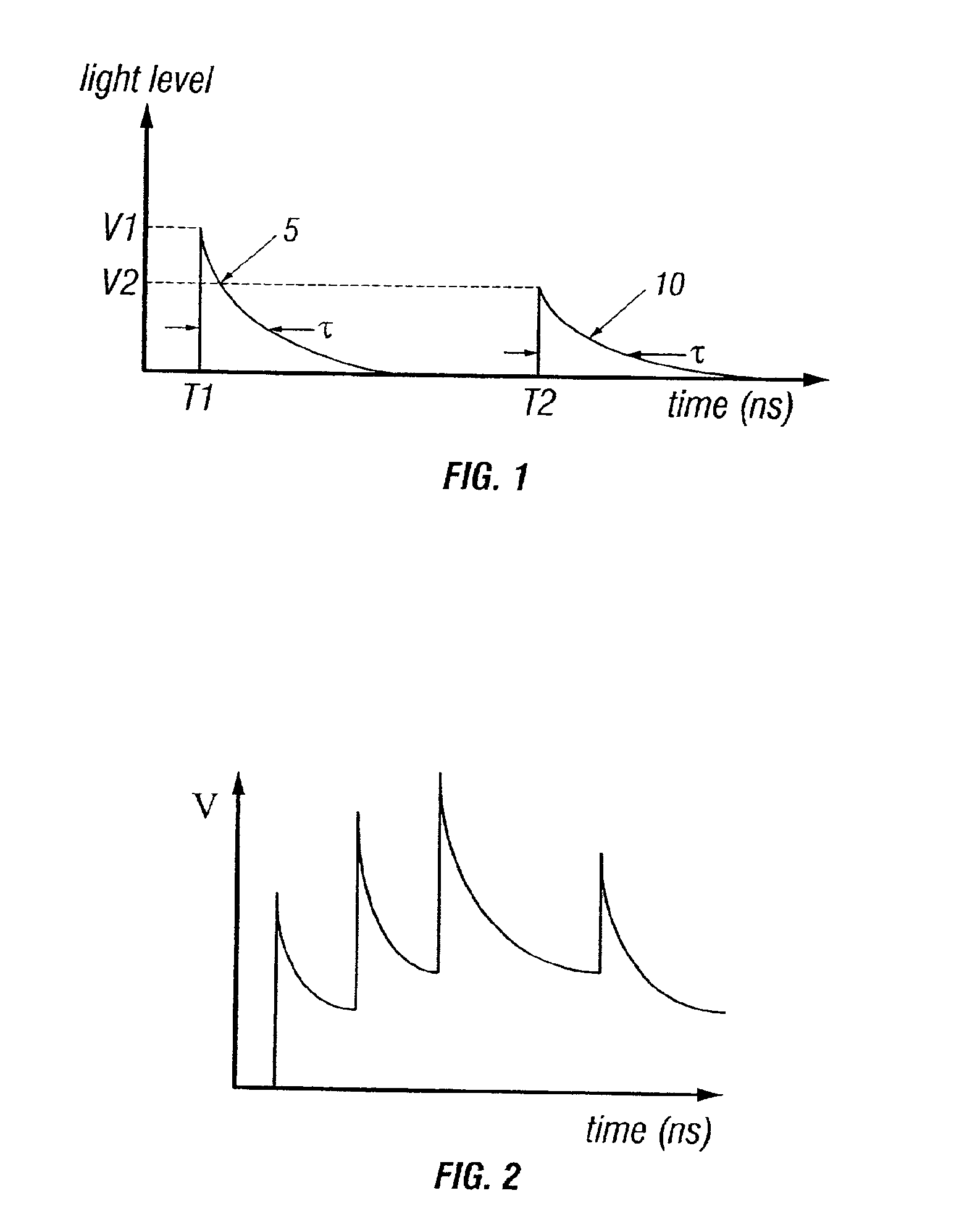

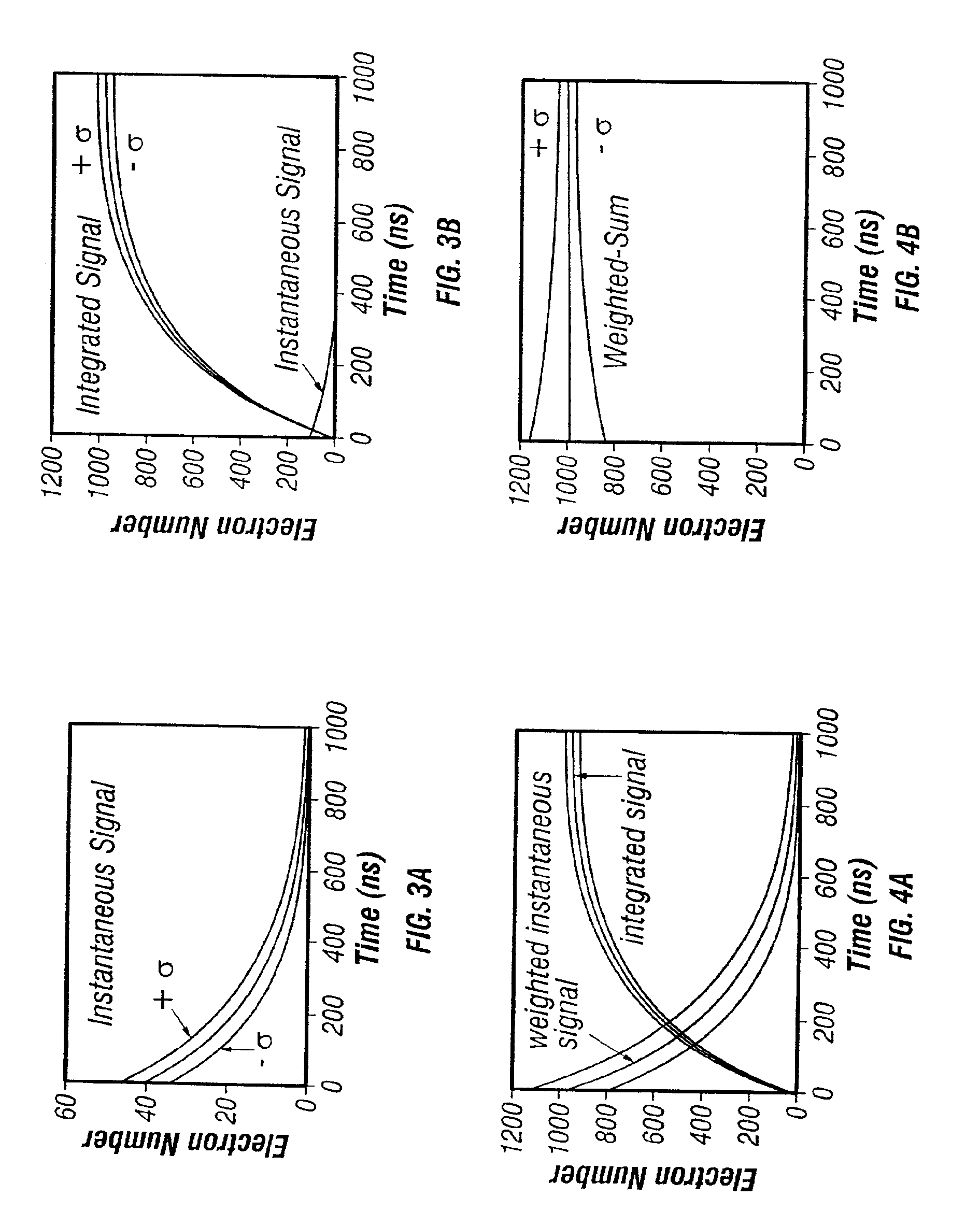

Method and apparatus to prevent signal pile-up

InactiveUS6936822B2Increase count-rate capabilityIncrease dose efficiencyMaterial analysis by optical meansTomographyFree energiesData treatment

Methods and apparatuses for obtaining position and energy information without pileup. Signal integration, which is triggered by a present event, stops when a subsequent event is detected. A weighted value for estimating the total energy in a scintillation is calculated, which includes the energy of the current event and a residual energy from previous events. Remnant correction is used to calculate a pile-up free energy from two consecutive weighted values. An analog filter may be applied to reduce noise. Dynamic digital weighting of integrated values, and / or digital integration may be used during data processing. Pileup can be avoided in conjunction with several types of applications, including multi-zone detector applications and coincidence detection applications. High-resolution timing techniques are also disclosed that facilitate one's ability to avoid pileup.

Owner:BOARD OF RGT THE UNIV OF TEXAS SYST

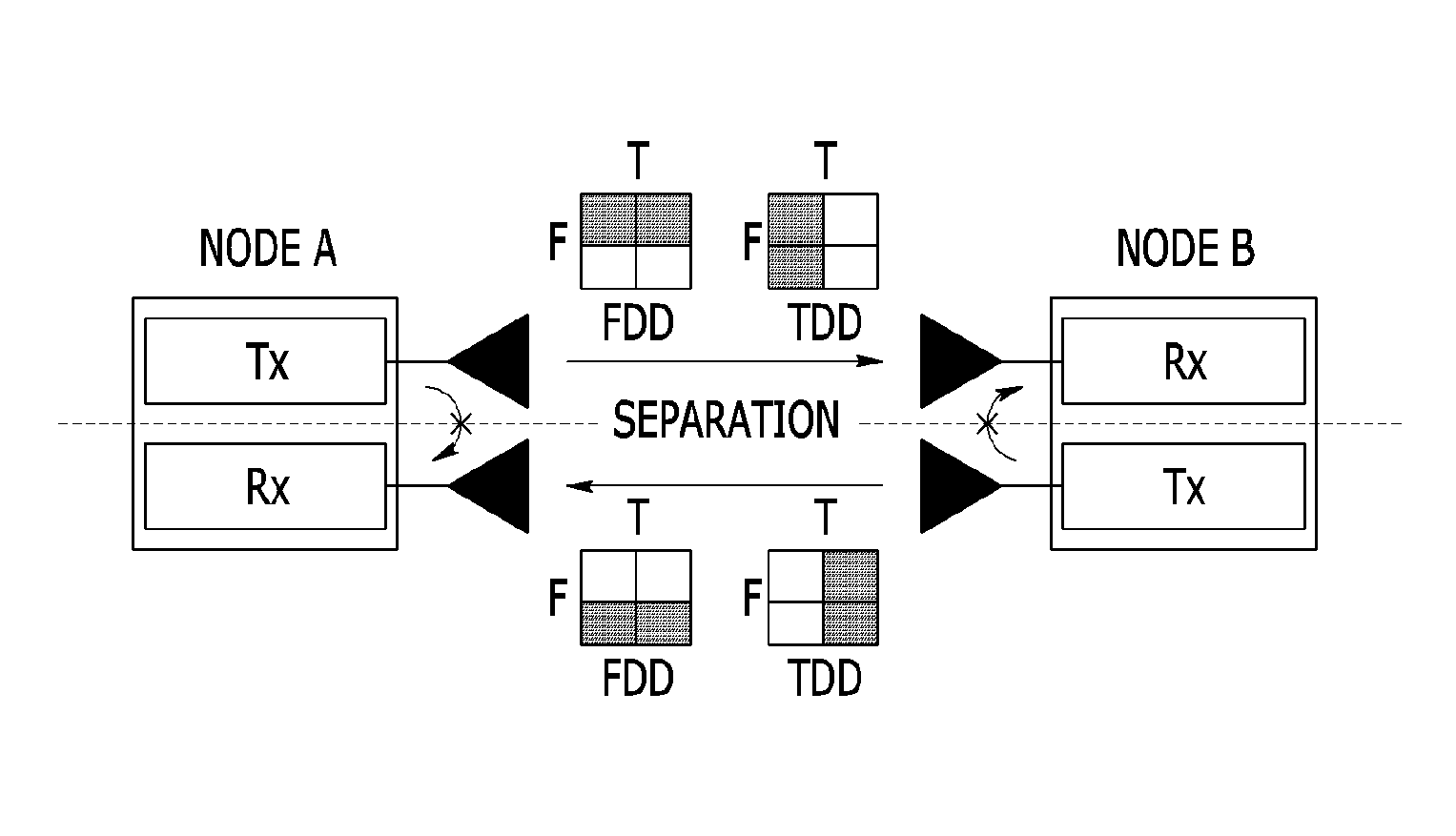

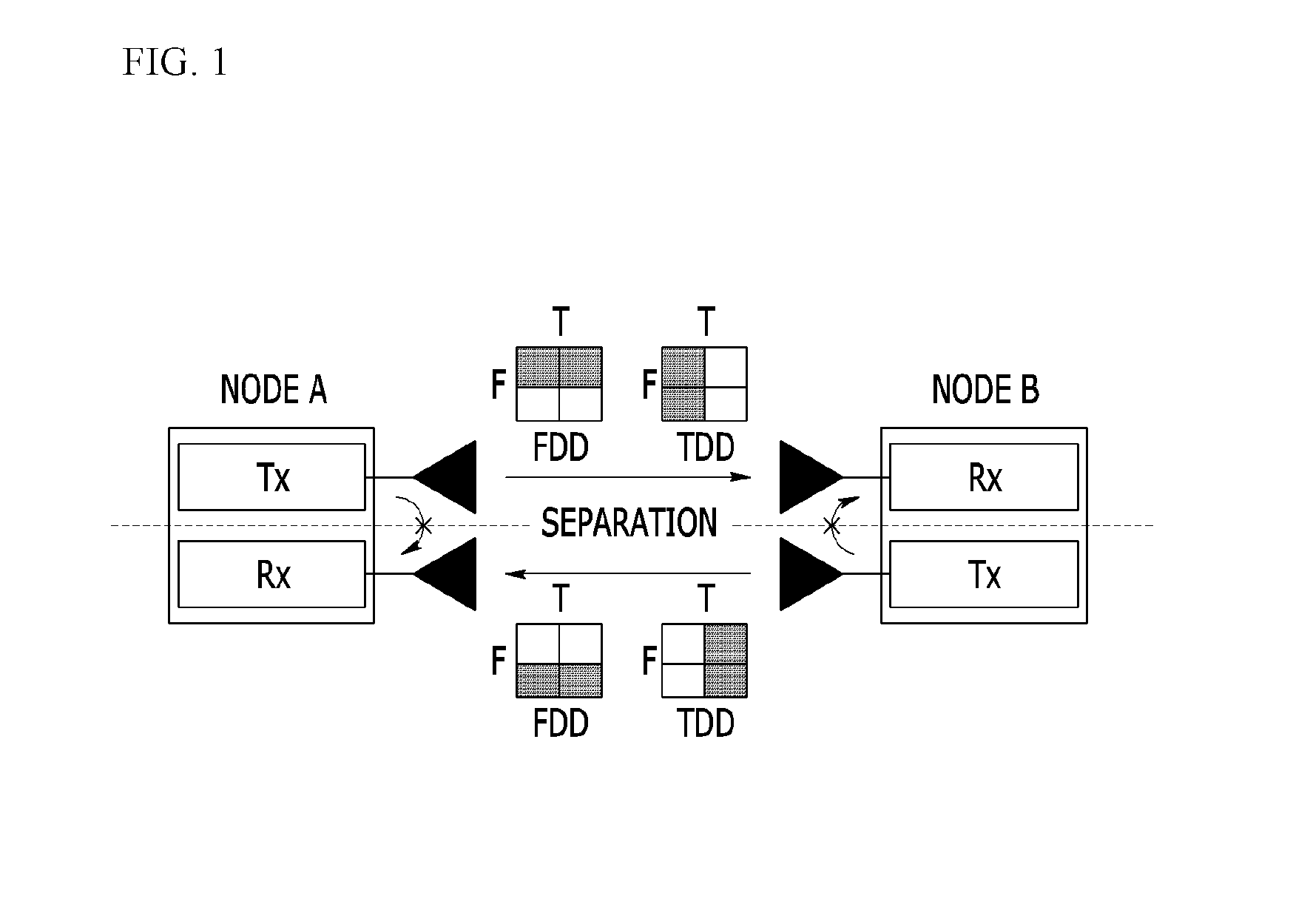

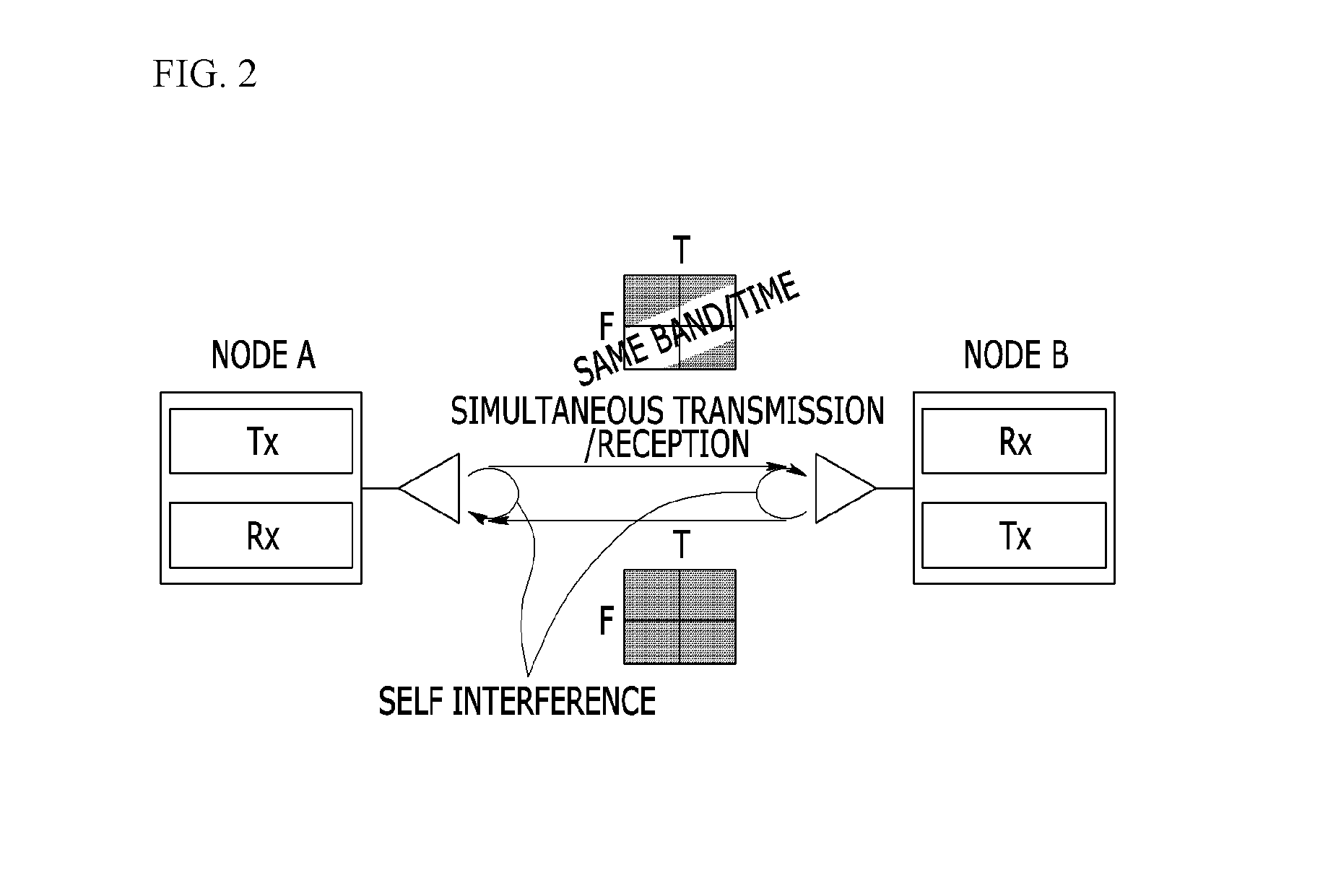

Method and apparatus for canceling self-interference

ActiveUS20160218769A1Low costReduce complexityDuplex signal operationSelf interferenceAnalogue filter

There are provided a method and an apparatus for performing a self-interference cancellation by determining a filter coefficient of an analog filter operated in an analog domain; and canceling self-interference generated in a received signal received by the node by a transmitted signal transmitted from the node, based on the filter coefficient.

Owner:ELECTRONICS & TELECOMM RES INST

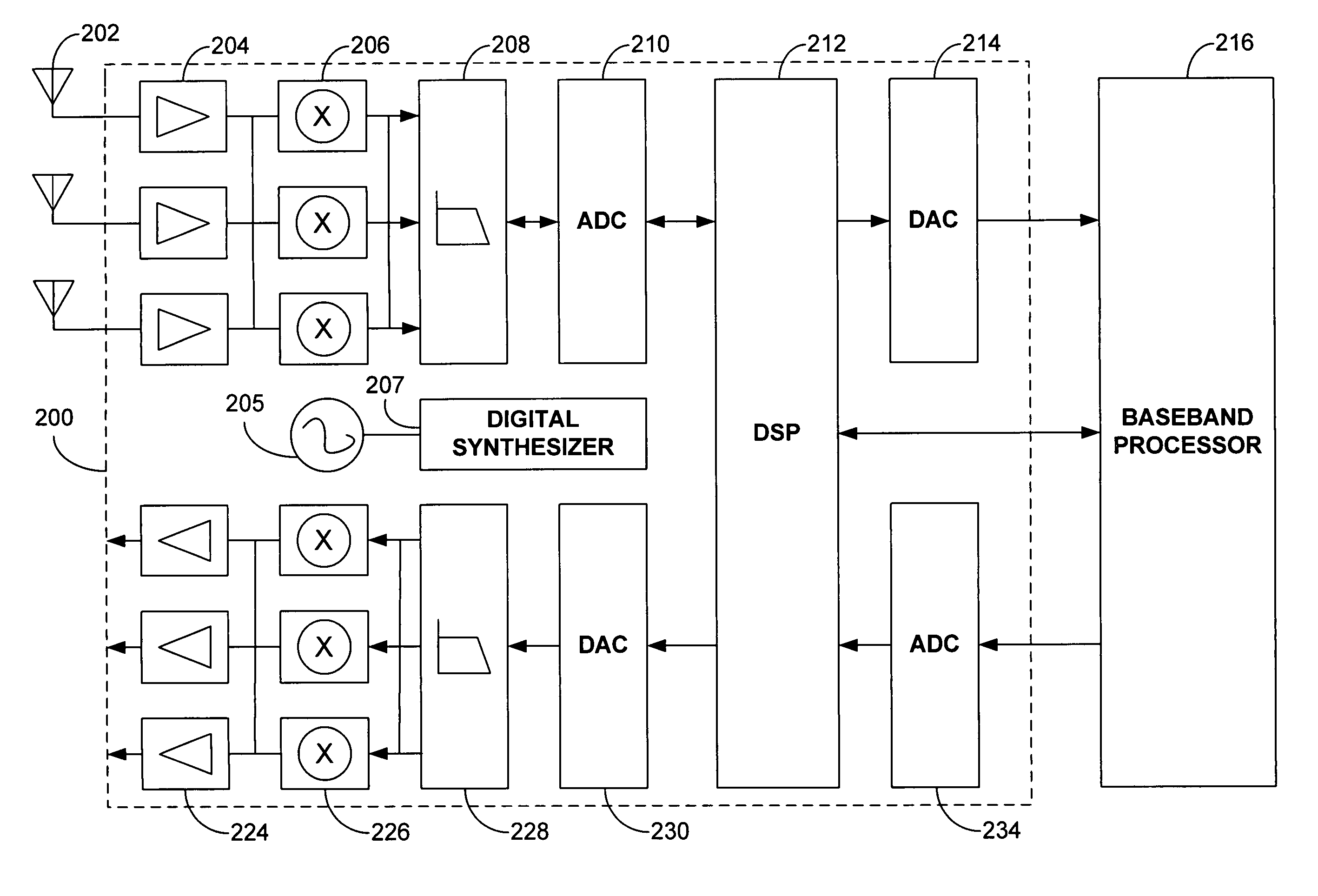

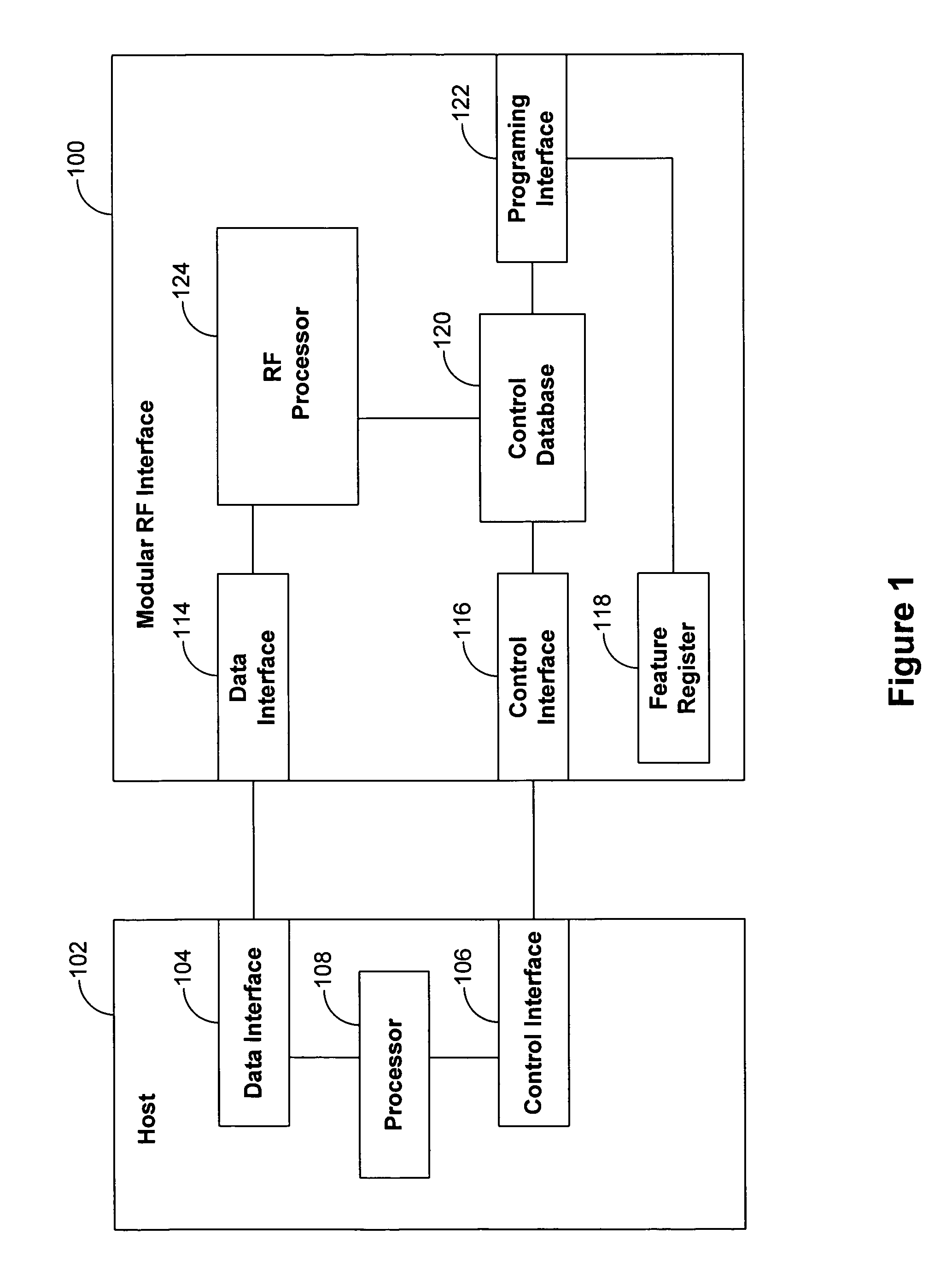

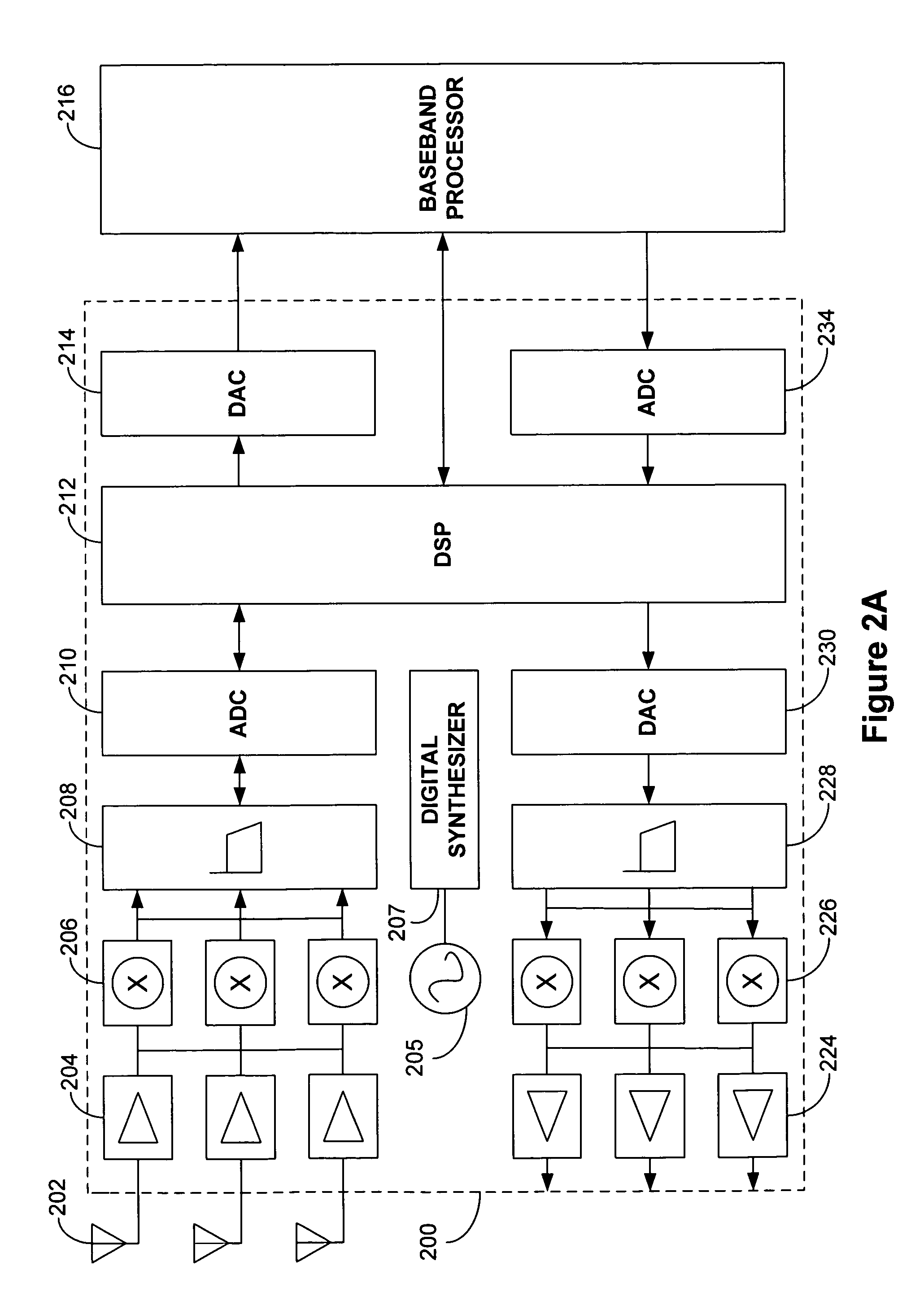

Configurable wireless interface

A multistandard RF transceiver is disclosed that may optionally include selectable mixers; selectable amplifiers; a configurable analog filter; and a configurable analog to digital converter. The multistandard RF transceiver may also include a data interface for sending data to a host controller and a control interface for receiving configuration commands from the host controller. The configuration commands identify a wireless standard that is to be implemented by the RF receiver. An RF processor processes an RF signal wherein the processed RF signal is output to the host controller on the data interface.

Owner:QUALCOMM INC

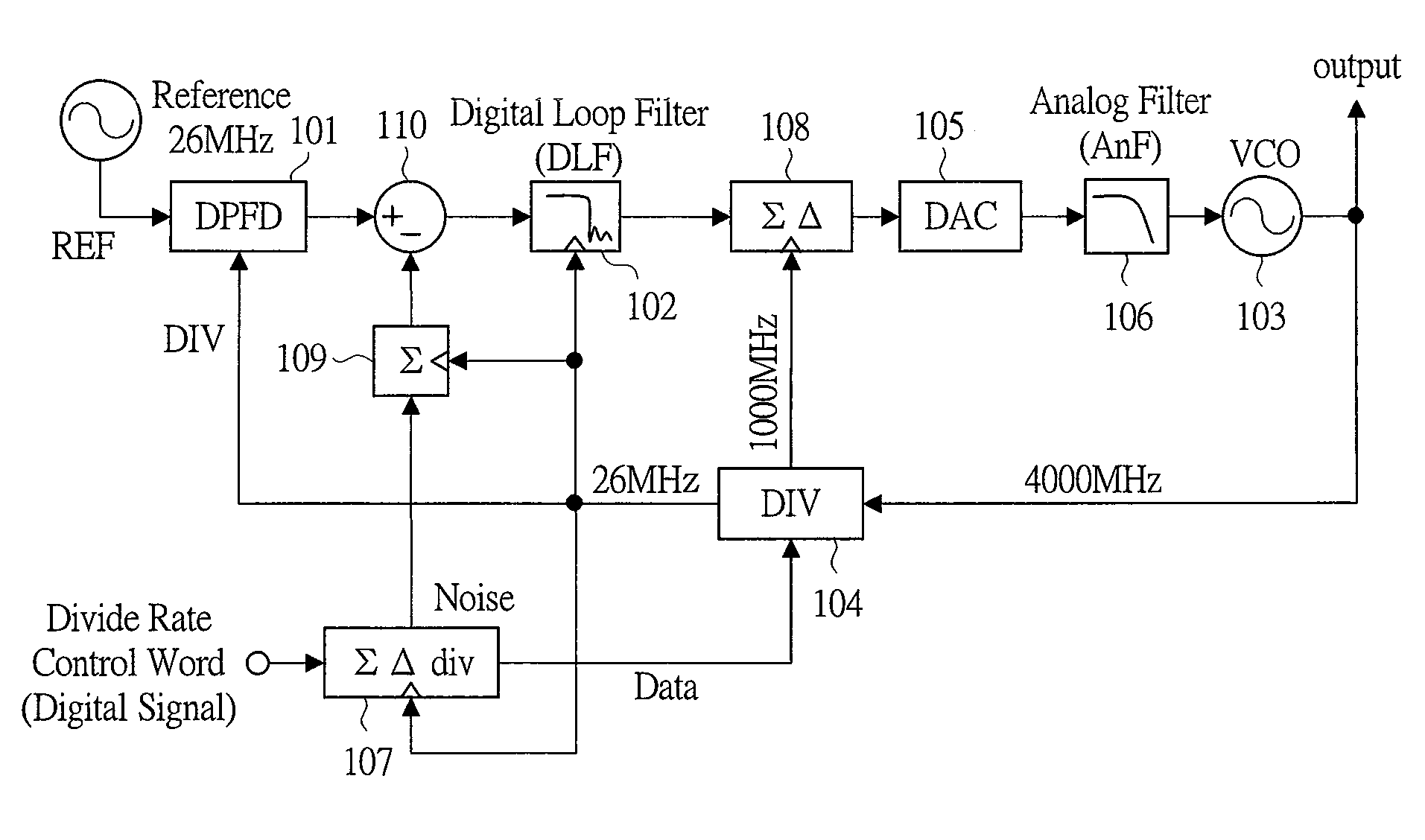

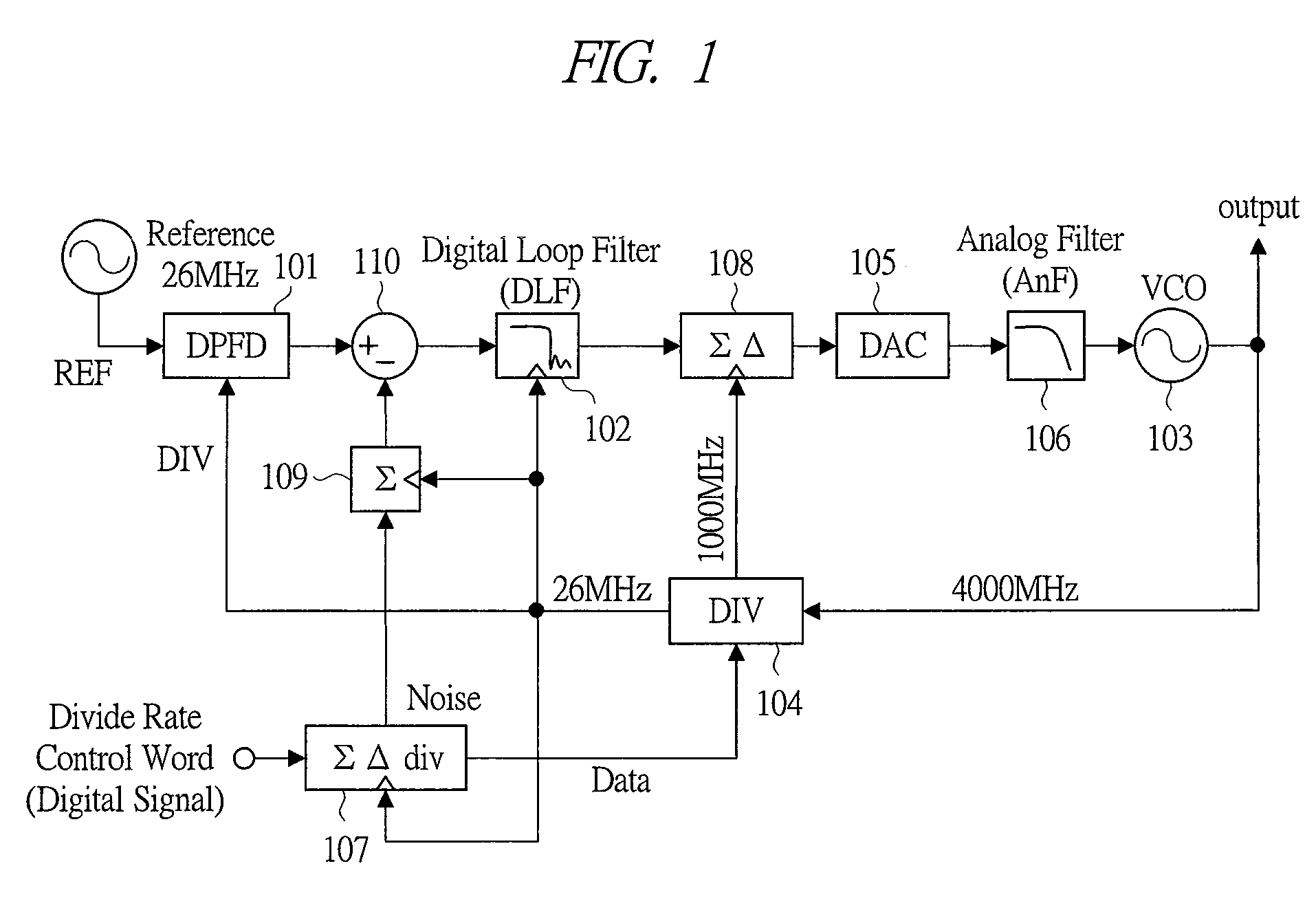

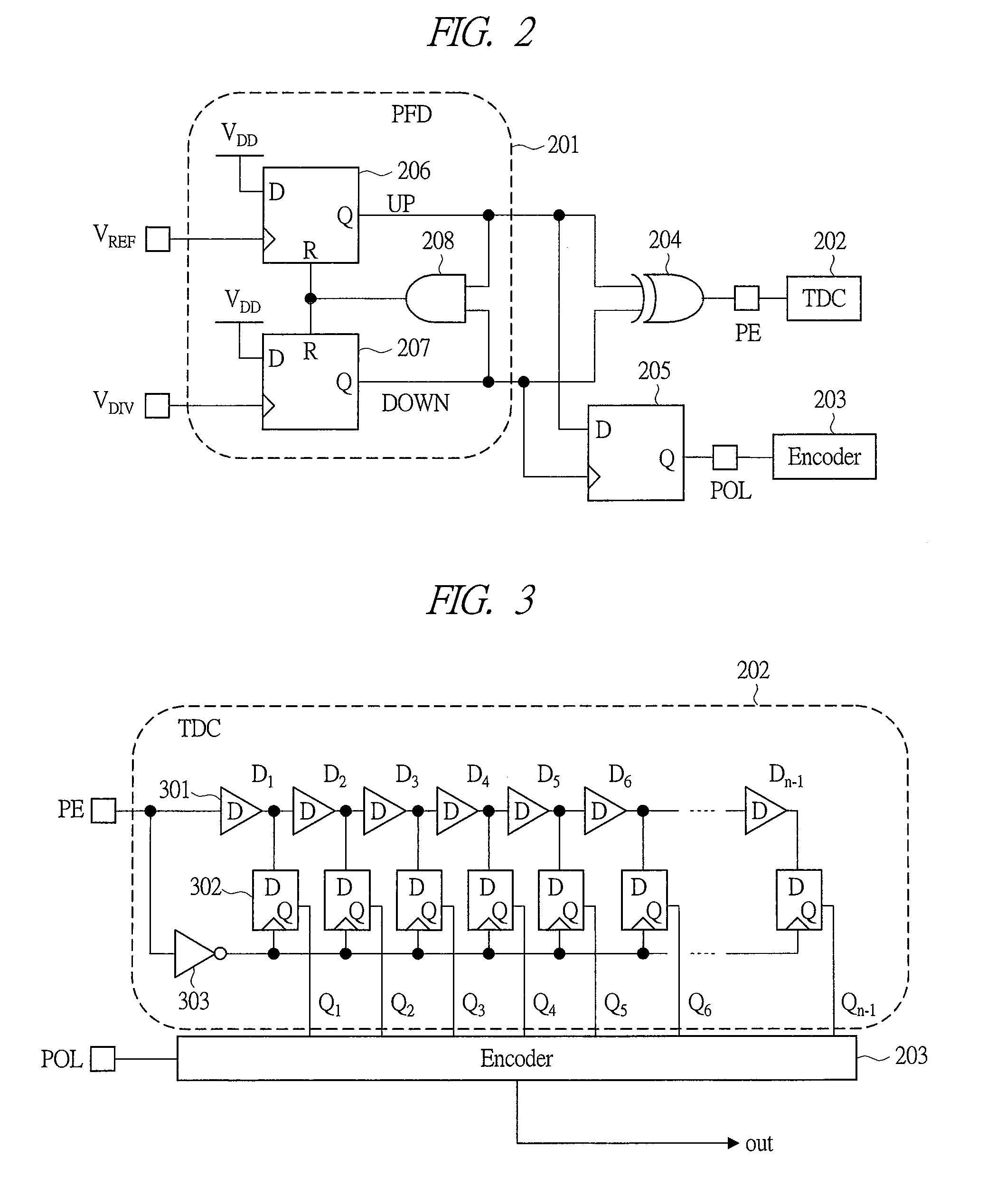

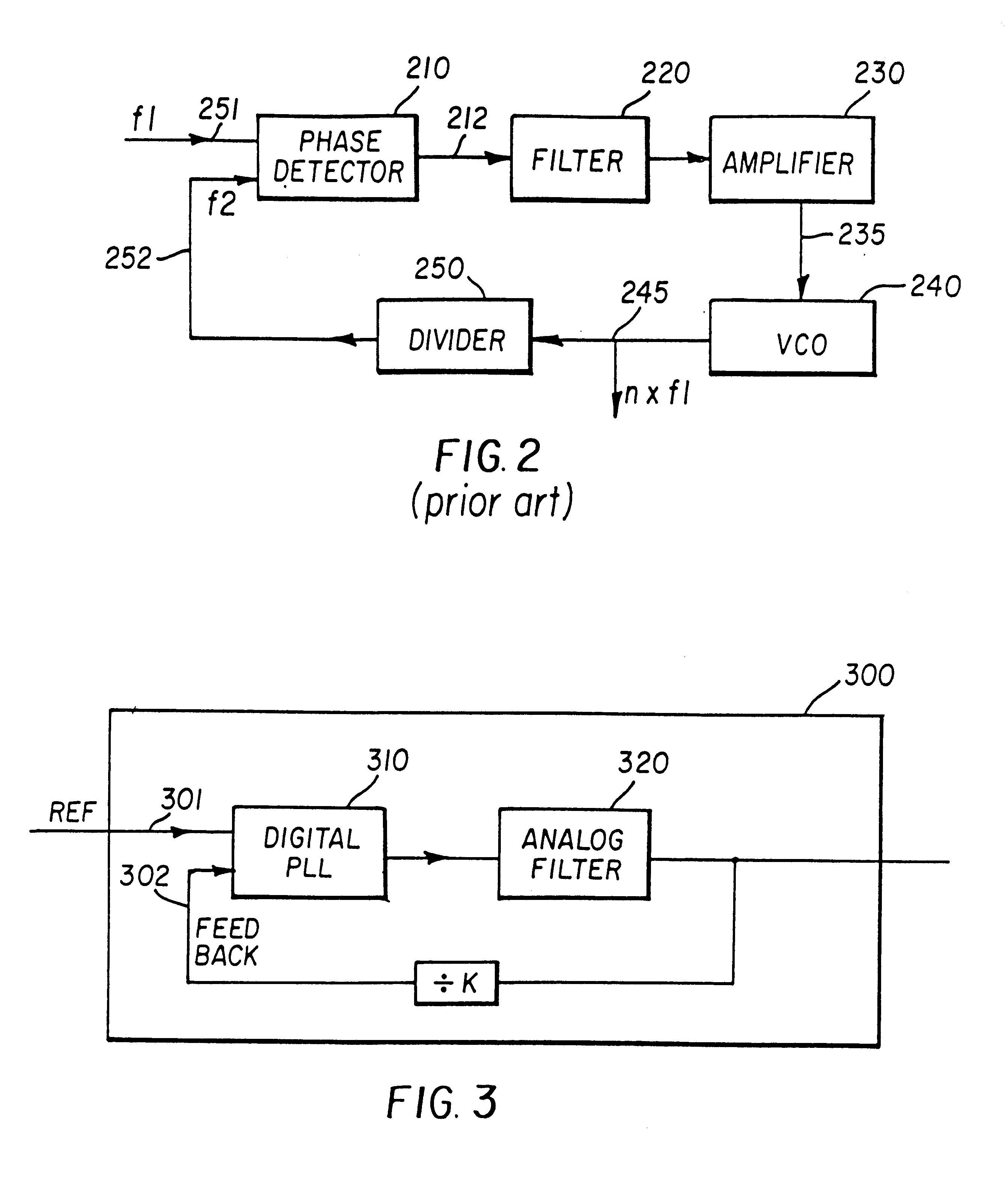

Pll circuit

InactiveUS20100097150A1Suppressing quantization noiseReduce areaPulse automatic controlLoop filterDigital analog converter

A technique for suppressing quantization noise generated due to digitizing an analog circuit in a PLL circuit is provided. The PLL circuit comprises: a digital phase frequency detector which detects (compares) phases and frequencies of a reference signal and a frequency-divided signal and converts the same to a digital value; a digital loop filter which eliminates high-frequency noise components from an output of the digital phase frequency comparator; a digital-analog converter which converts a digital value of an output of the digital loop filter to an analog value; an analog filter which eliminates a high-frequency noise component from an output of the digital-analog converter; a voltage controlled oscillator whose frequency is controlled based on an output of the analog filter; and a frequency divider which divides the frequency of the voltage controlled oscillator and outputs the frequency-divided signal.

Owner:RENESAS TECH CORP +1

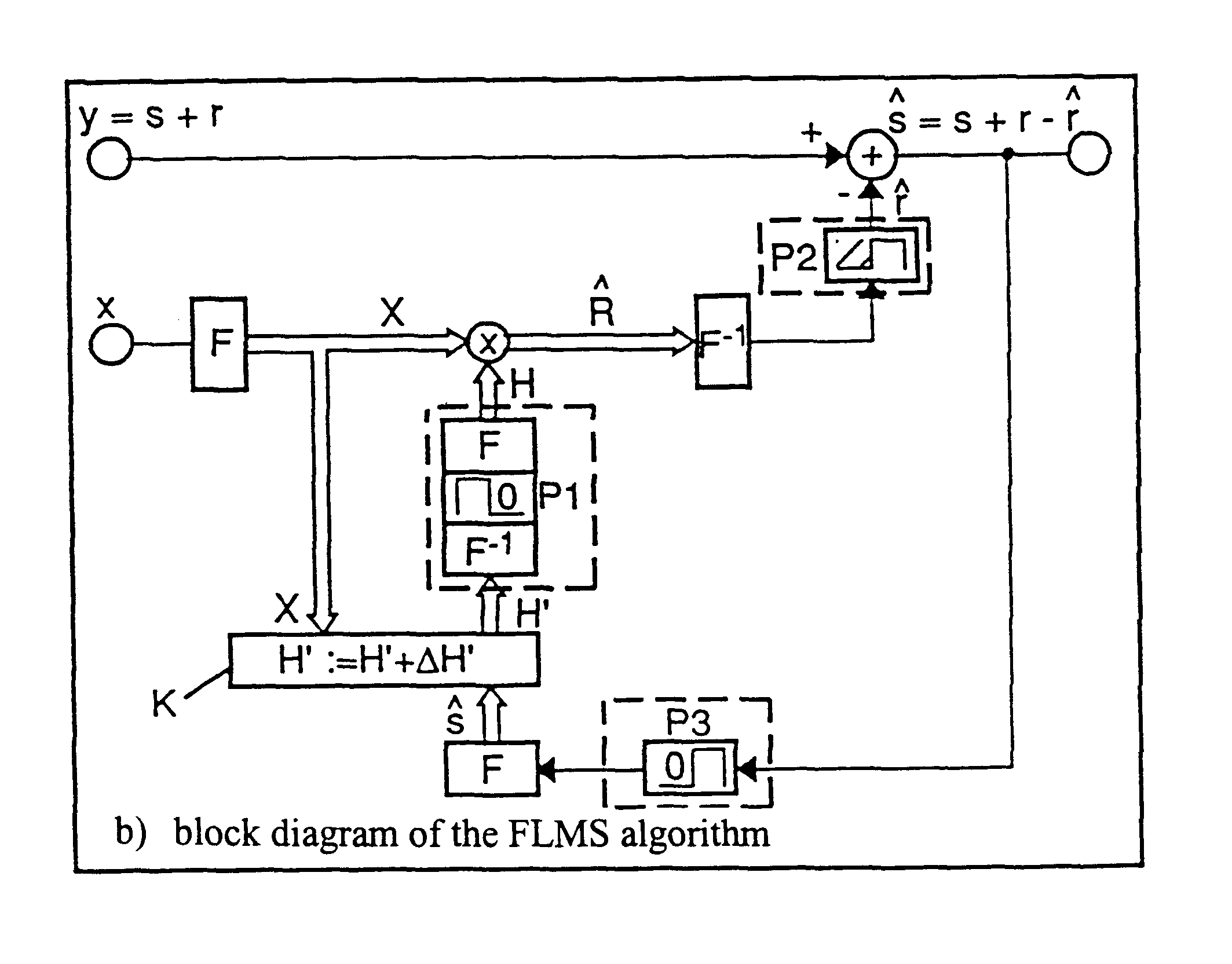

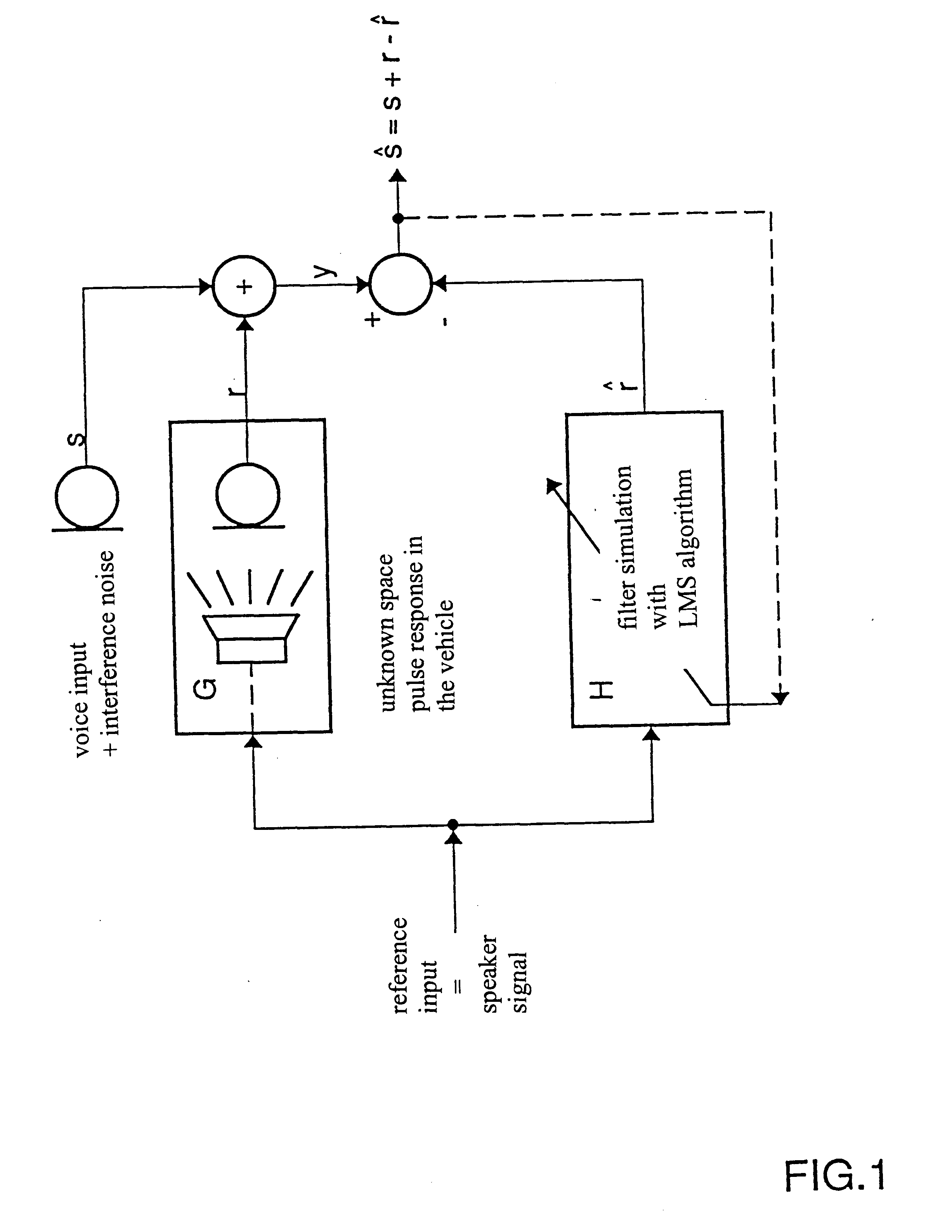

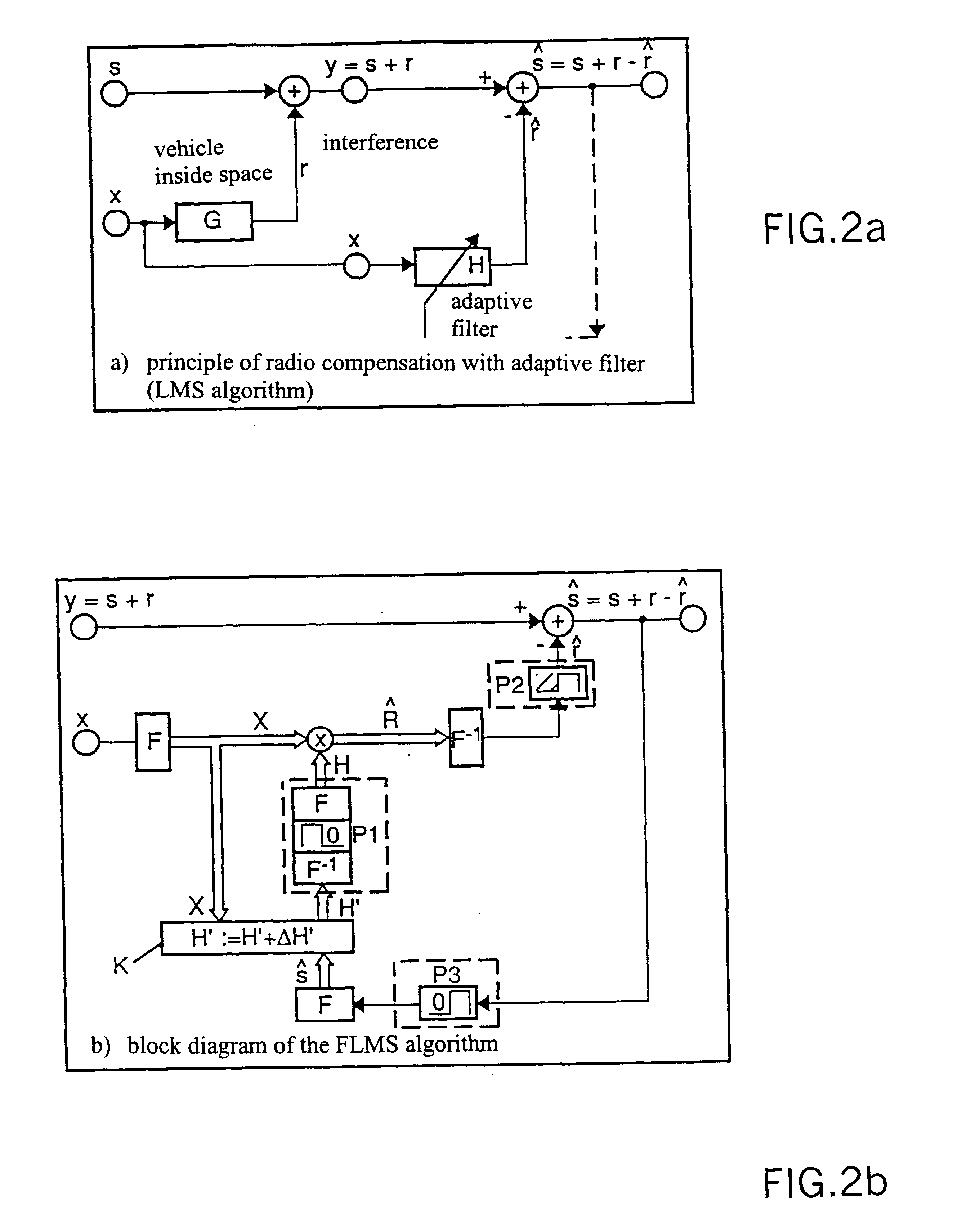

Method of eliminating interference in a microphone

InactiveUS6895095B1Low processing expenditureEliminate distractionsTwo-way loud-speaking telephone systemsSpeech analysisMicrophone signalEngineering

A method of eliminating interference components in a microphone signal by generating a compensation signal and subtracting the compensation signal from the microphone signal. The compensation occurs completely in the frequency domain and the output signal is processed in the frequency domain as well. Measures for reducing the expenditure during the signal processing are specified. For example, advantageous modifications provide that a filter setting, obtained during a preceding speech pause, be used for eliminating interference in a voice signal and / or that the simulation filter be divided into several partial filters for long pulse responses. In particular, the invention is suitable for eliminating interference signal components, e.g., caused by a radio or the like, from a voice input signal in a motor vehicle, the source signal of which is available as reference signal.

Owner:NUANCE COMM INC

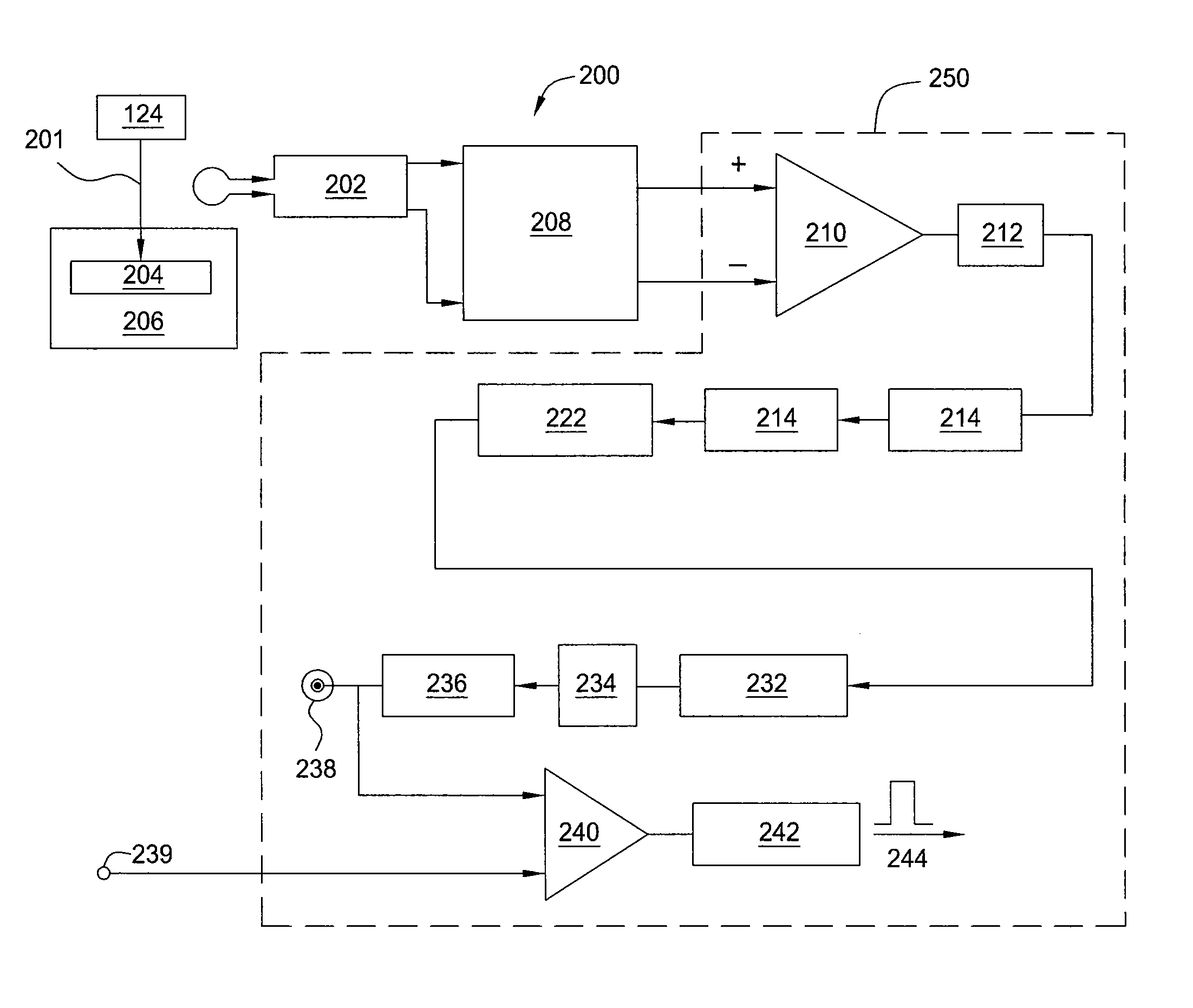

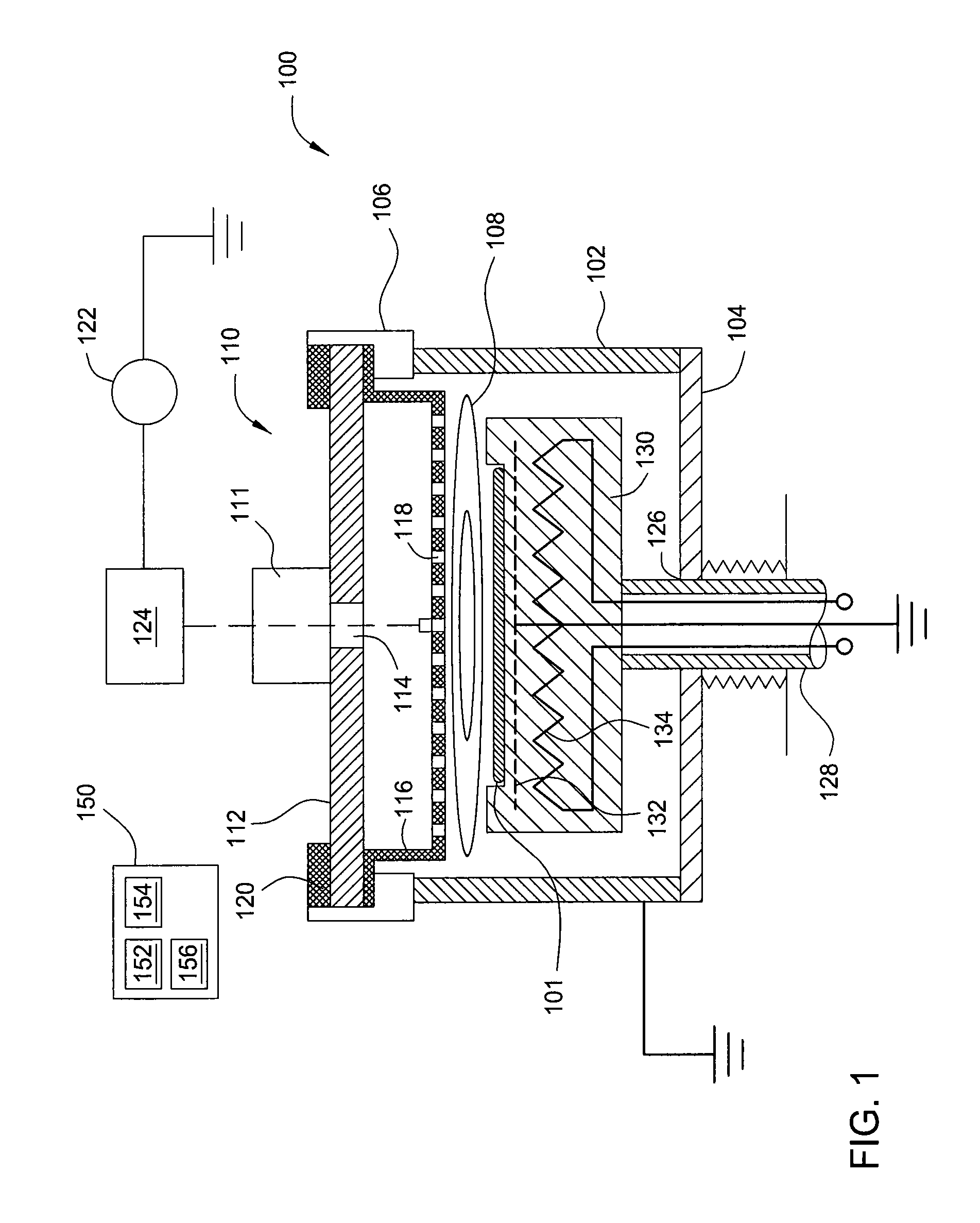

System and method for current-based plasma excursion detection

InactiveUS8587321B2Electric discharge tubesSemiconductor/solid-state device manufacturingPlasma instabilityEngineering

A system and method for the detection of plasma excursions, such as arcs, micro-arcs, or other plasma instability, during plasma processing by directly monitoring RF current just prior to reaching an RF power electrode of a plasma processing chamber is provided. The monitored RF current may be converted to an RF voltage and then passed through a succession of analog filters and amplifiers to provide a plasma excursion signal. The plasma excursion signal is compared to a preset value, and at points where the plasma excursion signal exceeds the preset value, an alarm signal is generated. The alarm signal is then fed back into a system controller so that an operator can be alerted and / or the processing system can be shut down. In one embodiment, the RF current amplified and converted to a digital signal for digital filtering and processing. In certain embodiments, multiple processing regions can be monitored by a single detection control unit.

Owner:APPLIED MATERIALS INC

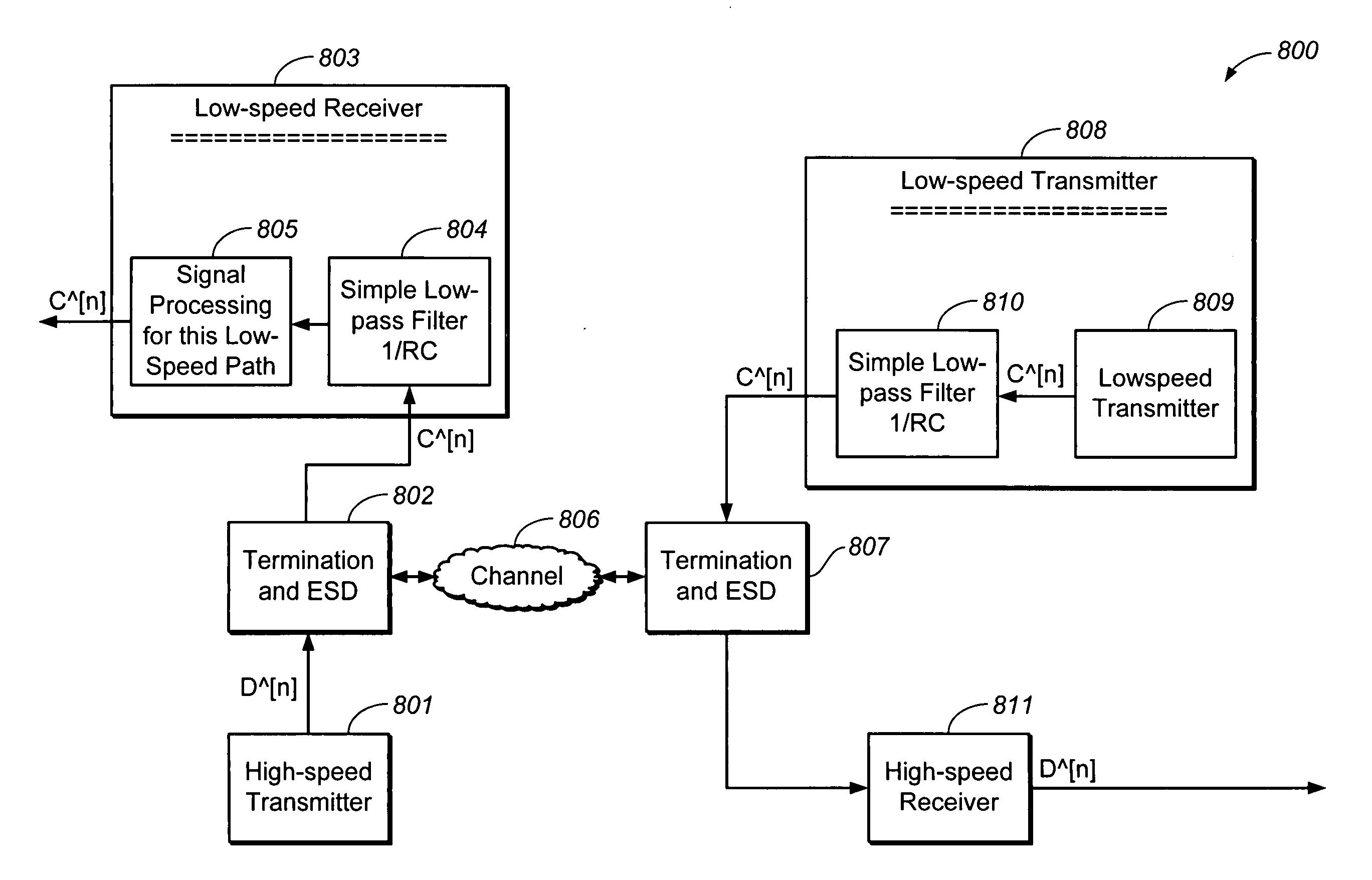

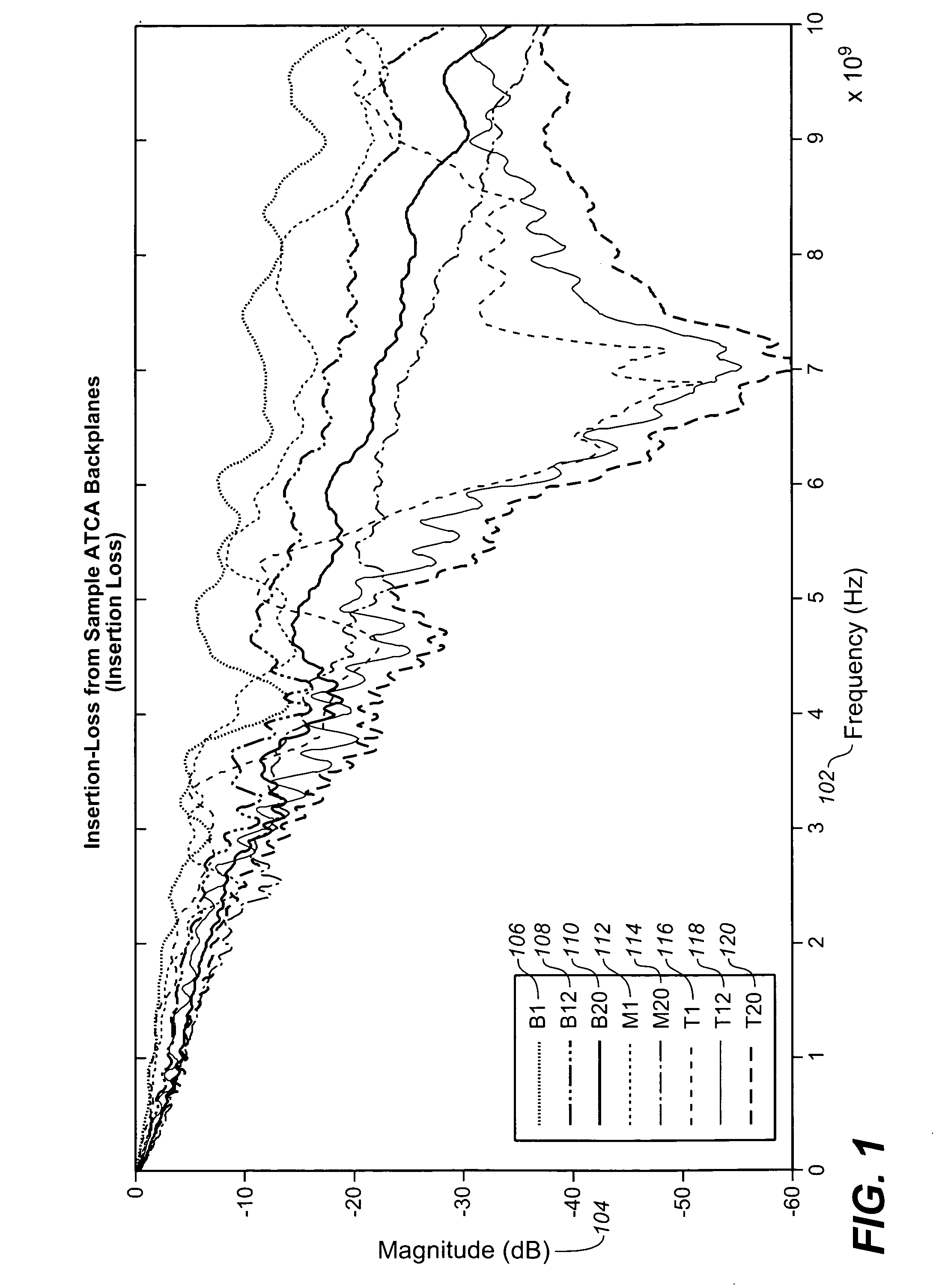

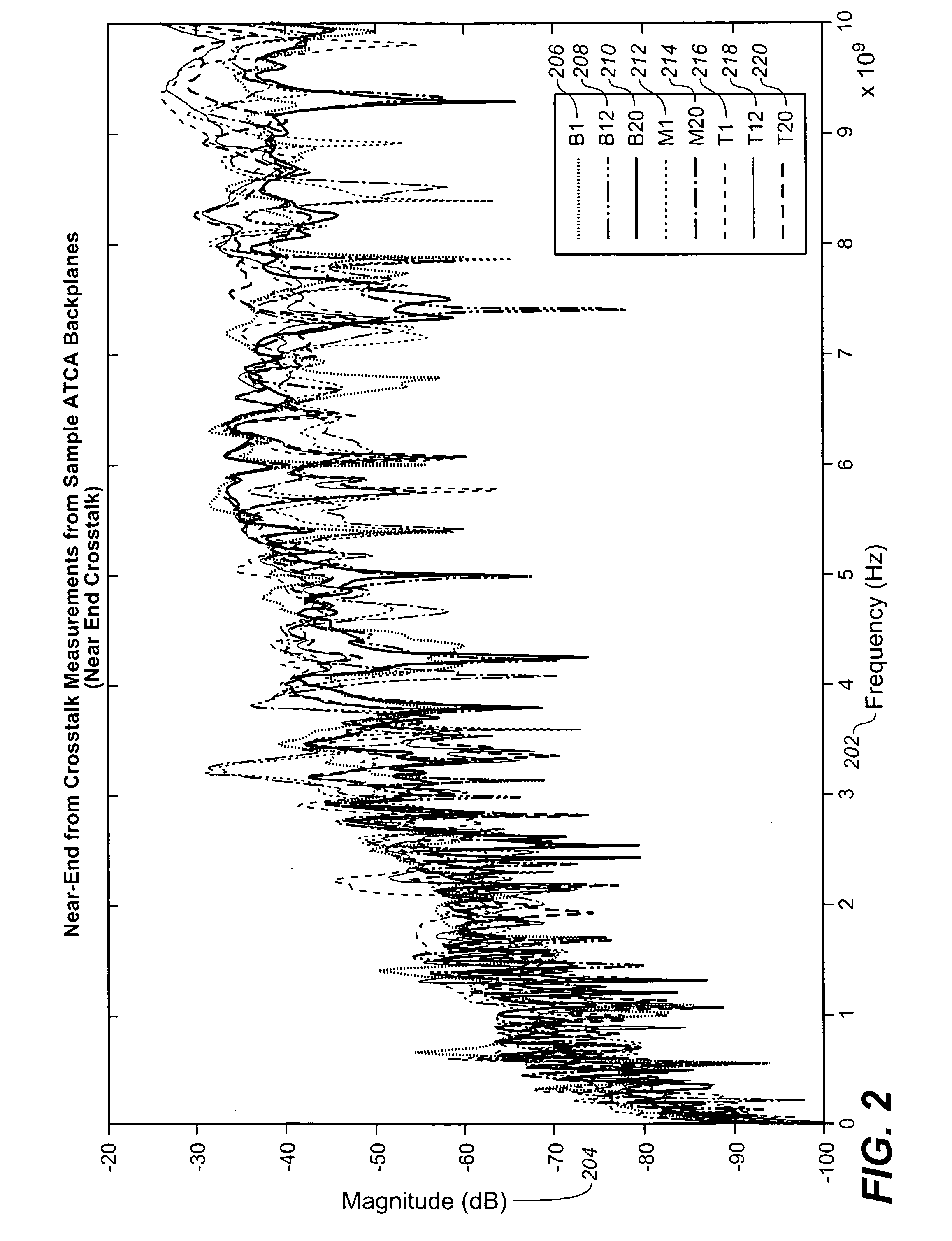

Band-pass high-order analog filter backed hybrid receiver equalization

InactiveUS20080069191A1Multiple-port networksDelay line applicationsTransceiverDifferential signaling

A system and a method for channel equalization are provided. A linear equalizer using a continuous-time linear equalization and a decision feedback equalizer using a discrete-time decision feedback equalization are integrated together from a hybrid receiver equalizer. The continuous-time linear equalization scheme and the discrete-time decision feedback equalization scheme are blended using a joint adaptation algorithm to form an equalization scheme for inter-symbol interference cancellation in the hybrid receiver equalizer. The hybrid receiver equalizer controls crosstalk while maintaining signal bandwidth and linearity of a signal by the high-order high frequency roll-off of the linear equalizer used. Using this configuration, the hybrid receiver equalizer eliminates the need for adaptive bandwidth controller used in conventional low-pass receiver equalization schemes. The hybrid receiver equalizer can be used in receivers for dual-speed simultaneous transmission on the same physical link. The hybrid receiver equalizer can also be used in receivers for simultaneous forward and back-channel transmission using differential-signaling in multi-Gbps transceivers.

Owner:AVAGO TECH INT SALES PTE LTD

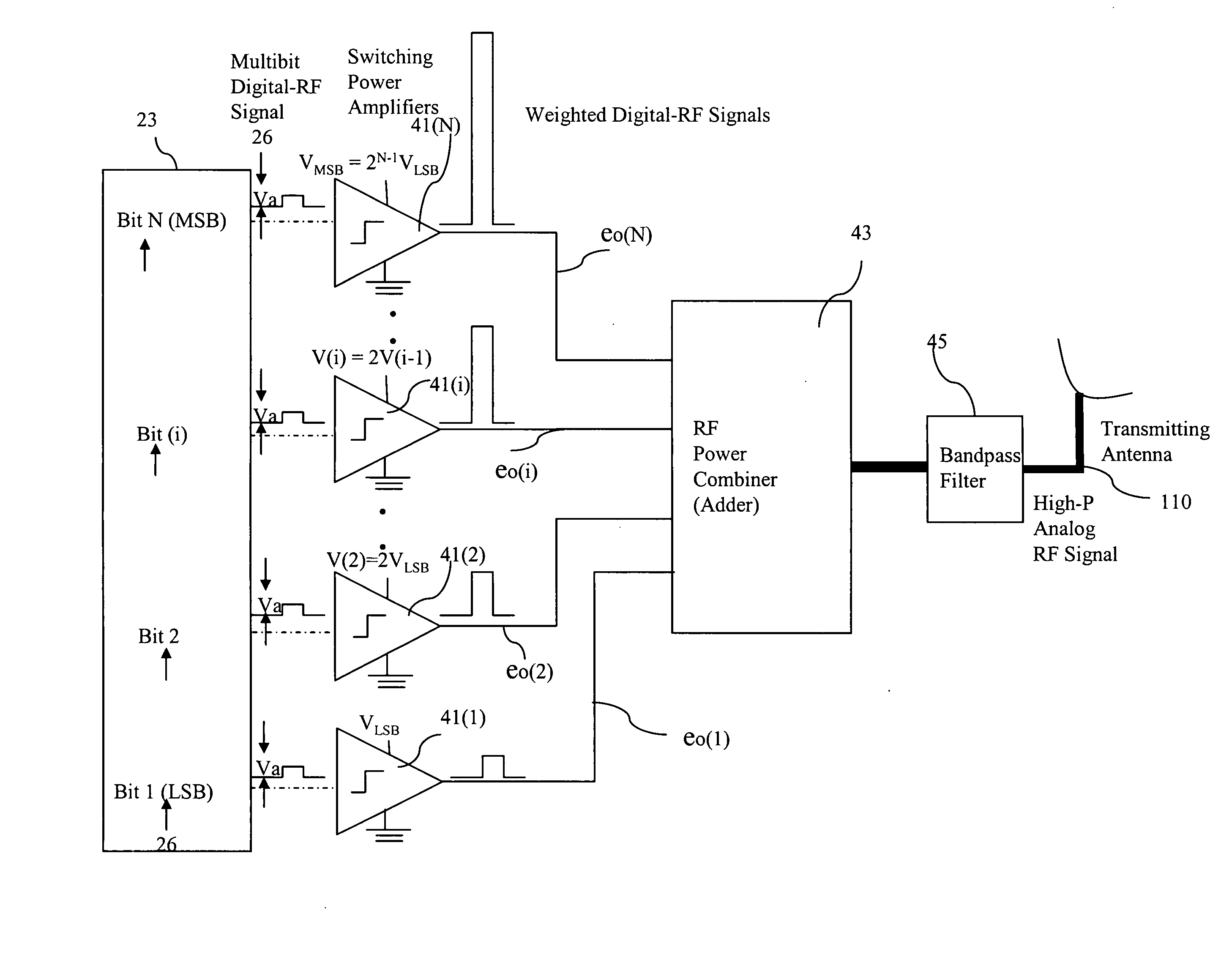

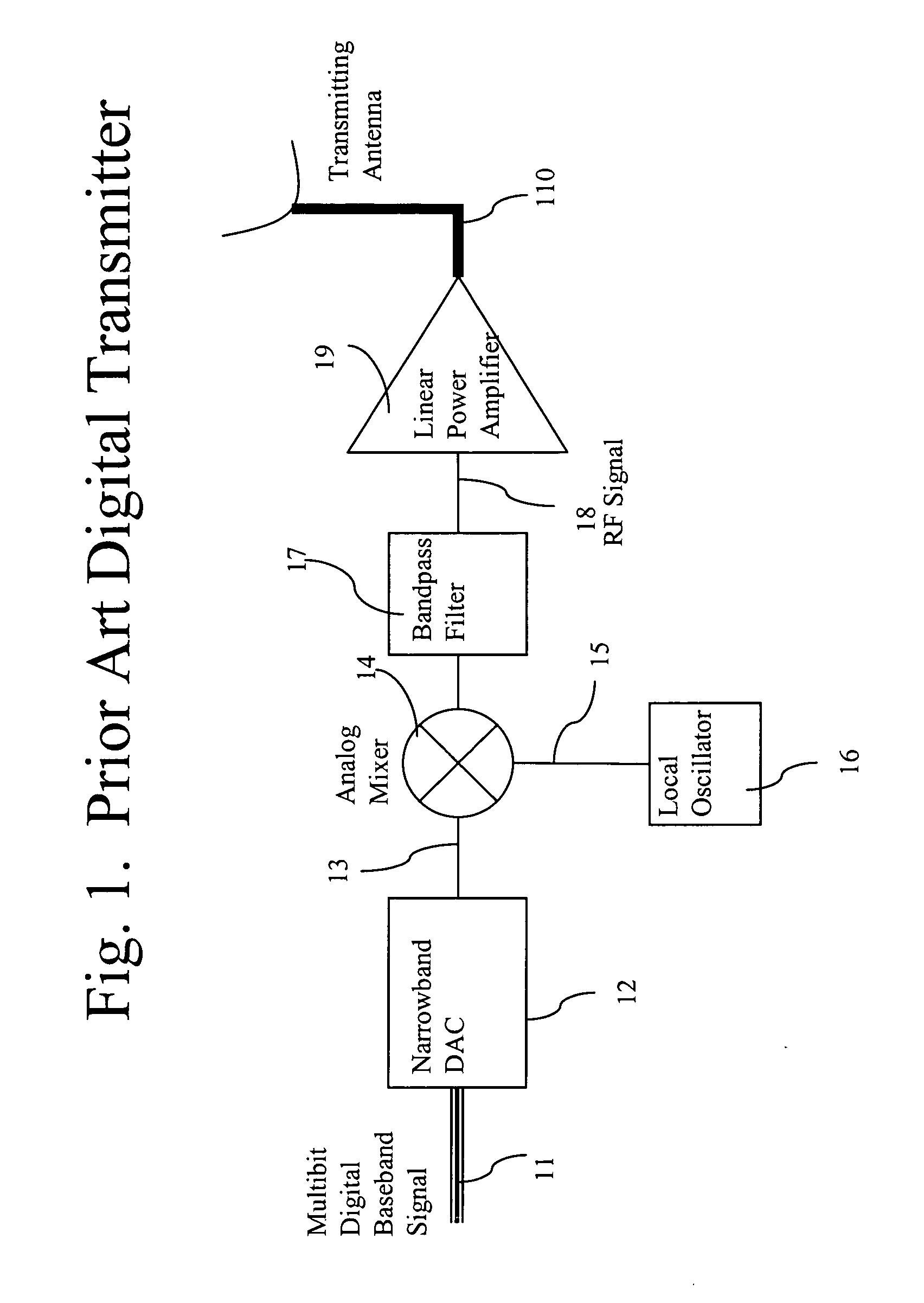

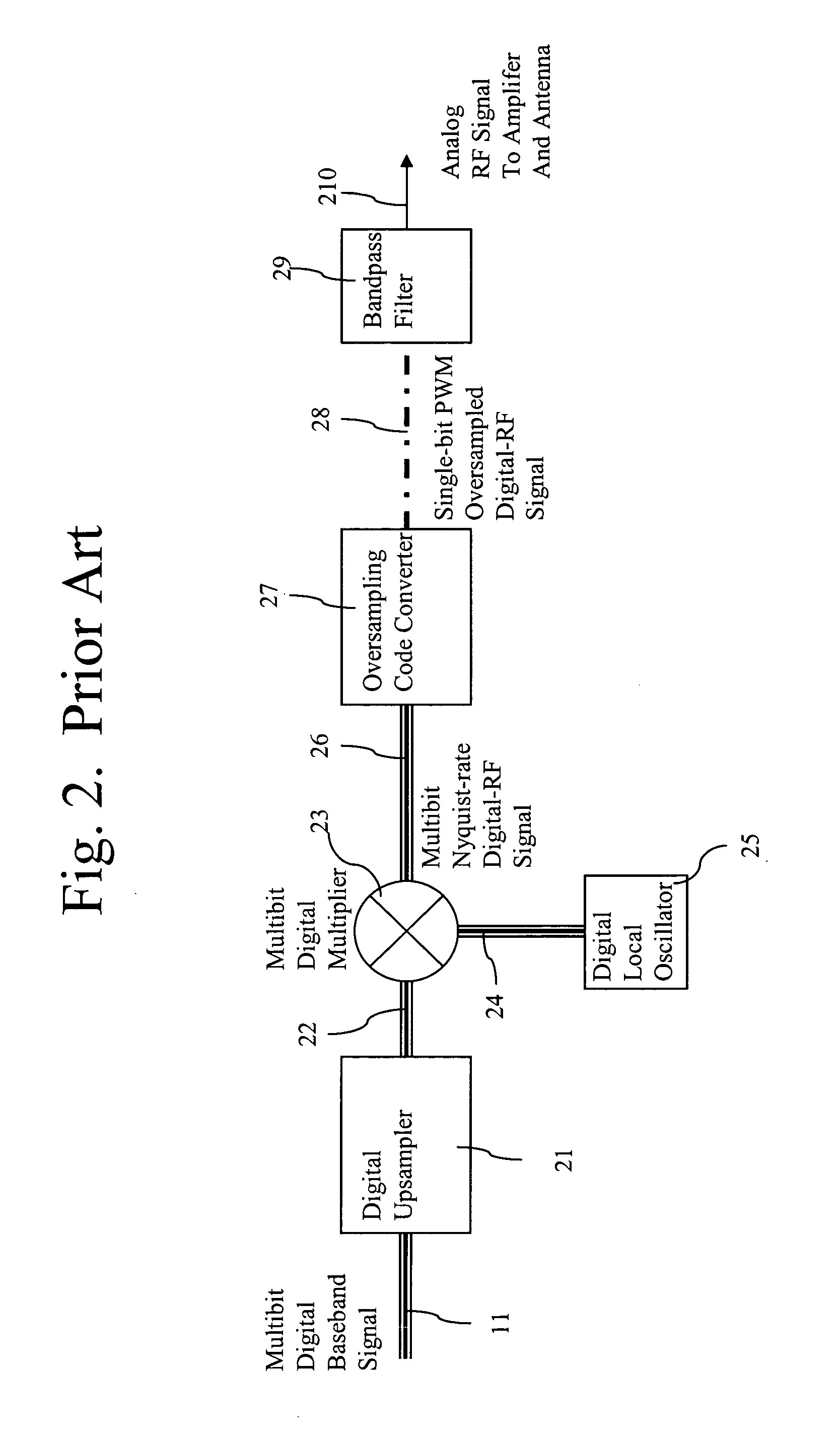

Multibit digital amplifier for radio-frequency transmission

InactiveUS20080290938A1Easy to useQuick switchPower amplifiersDigital/coded signal controlLow noiseLinearity

A broadband multibit digital radio-frequency (RF) signal is synthesized digitally. to convert the digital signal to a high-power analog signal for RF transmission. Each bit (or cluster of bits) of the digital signal is first separately amplified using a fast switching amplifier with a controlled dc power supply voltage. The DC voltages are weighted to match the significance of the bits, and controlled by a set of calibrated DC reference sources to maintain high precision. The amplified digital signals from the various bits are then combined and passed through an appropriate analog filter to generate the RF signal to be transmitted. Such a signal can exhibit broad bandwidth, high dynamic range, excellent linearity, and low noise. Preferred embodiments of this system can incorporate superconducting electronic elements. For ultimate precision, a set of primary or secondary DC voltage standards can be used to regulate the switching amplifier supply voltages.

Owner:HYPRES

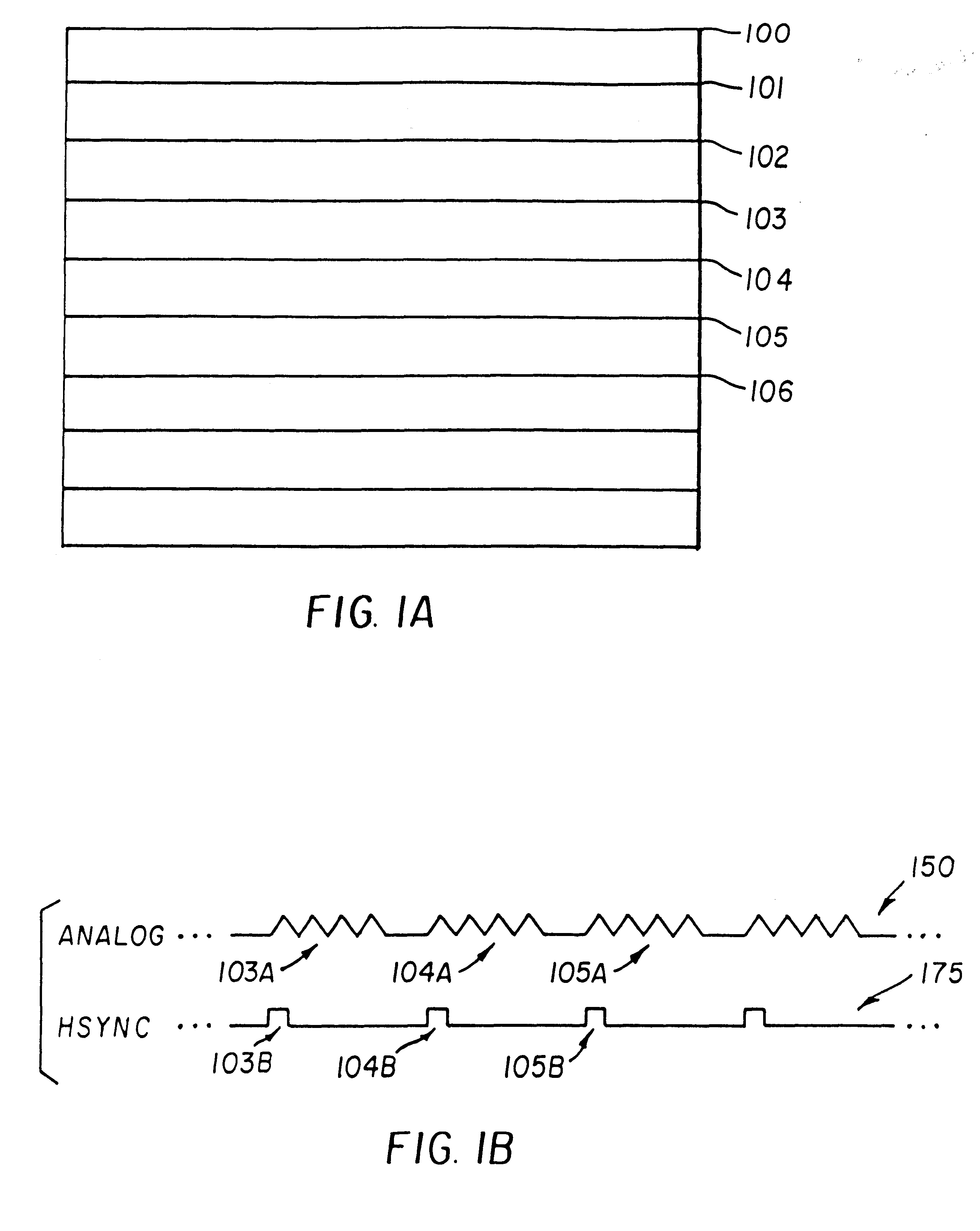

Circuit and method for generating pixel data elements from analog image data and associated synchronization signals

A clock recovery circuit in a digital display unit for recovering a time reference signal associated with analog display data. The clock recovery circuit includes a phase-locked loop (PLL) implemented in digital domain and an analog filter to eliminate any undesirable frequencies from the output signal of the PLL. The PLL includes independent control loops to track long term frequency drifts of the time reference signal and the transient phase differences respectively. By providing such independent control loops, the generated clock can be better synchronized with the time reference signal.

Owner:GENESIS MICROCHIP DELAWARE

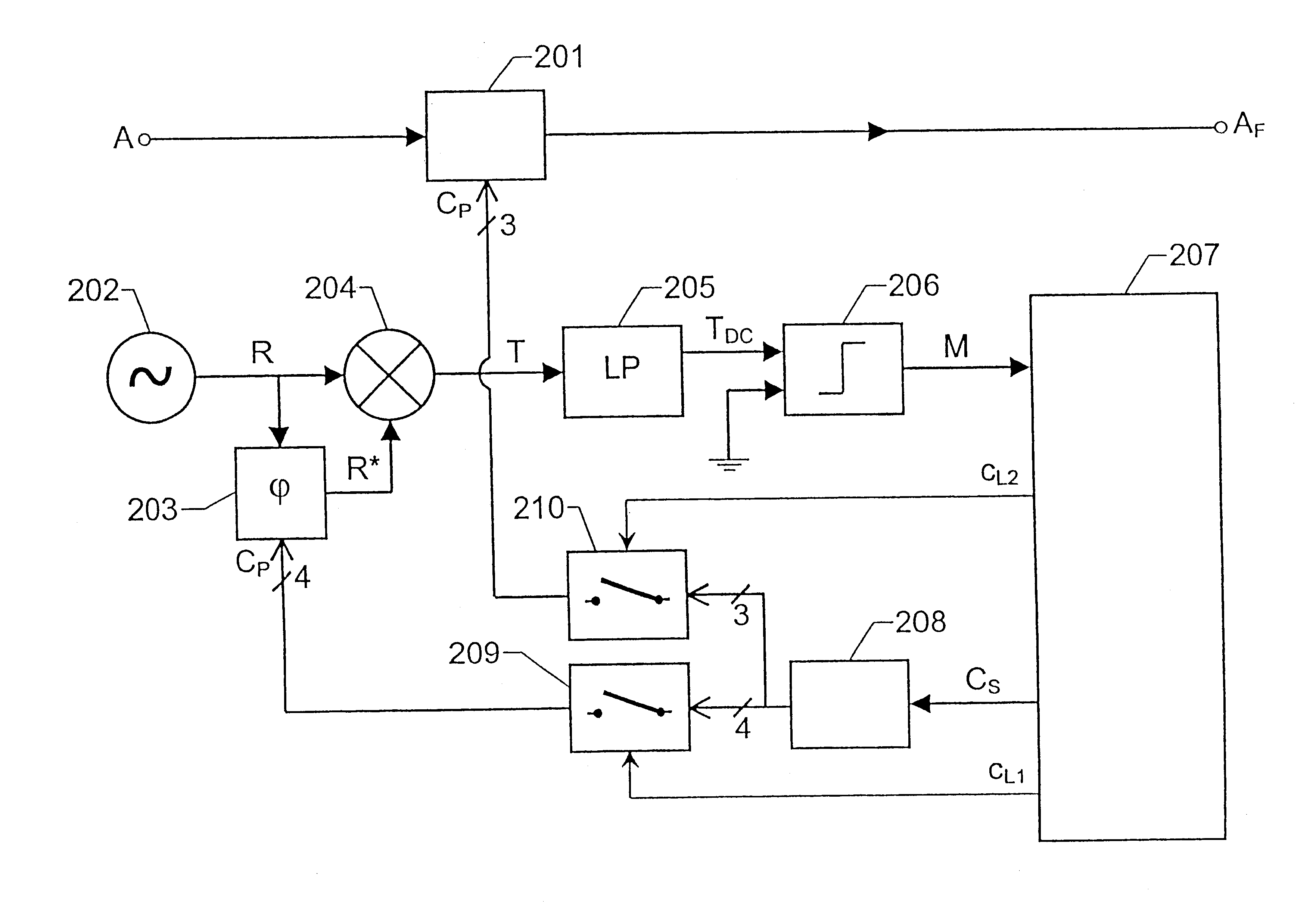

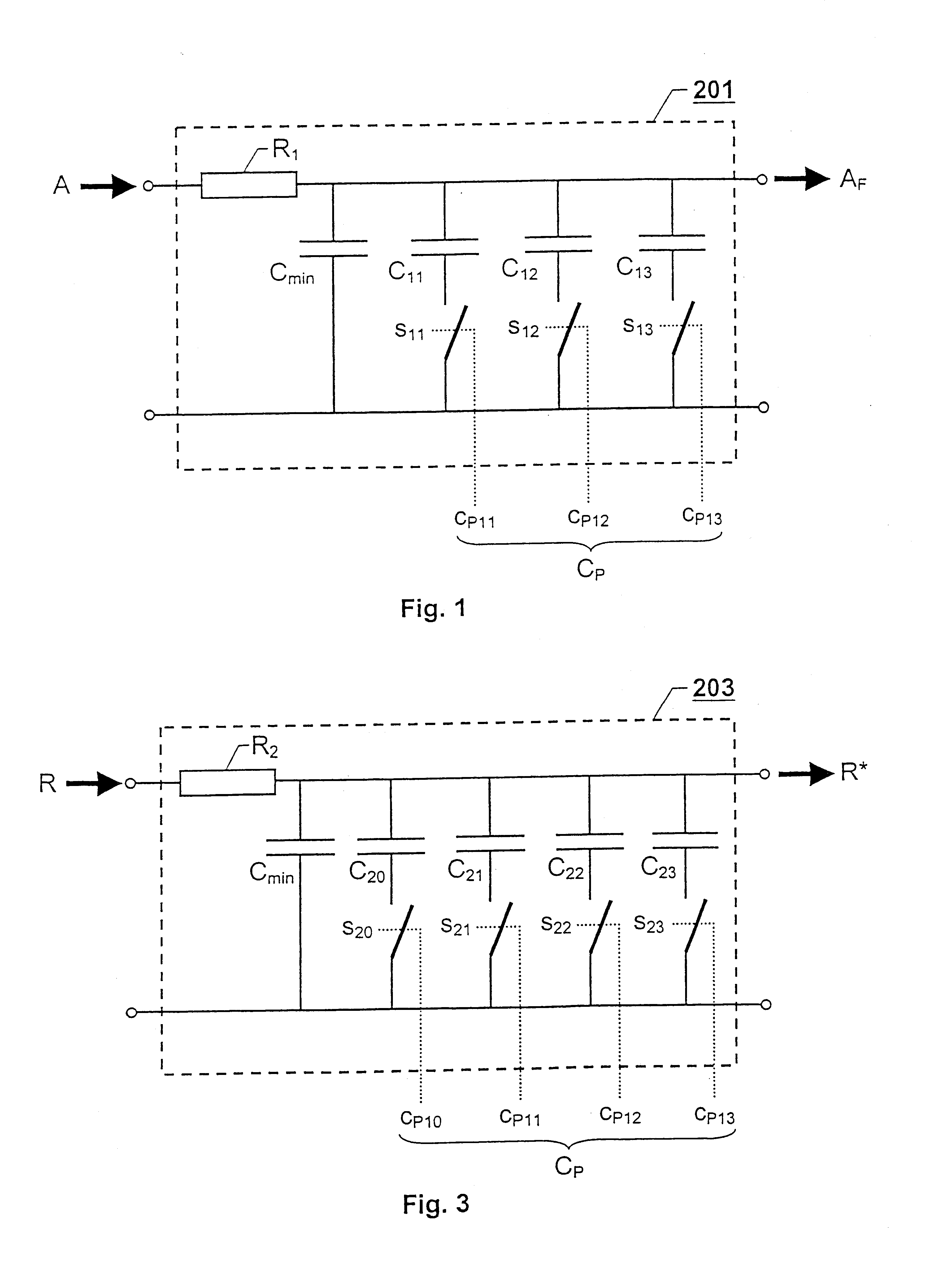

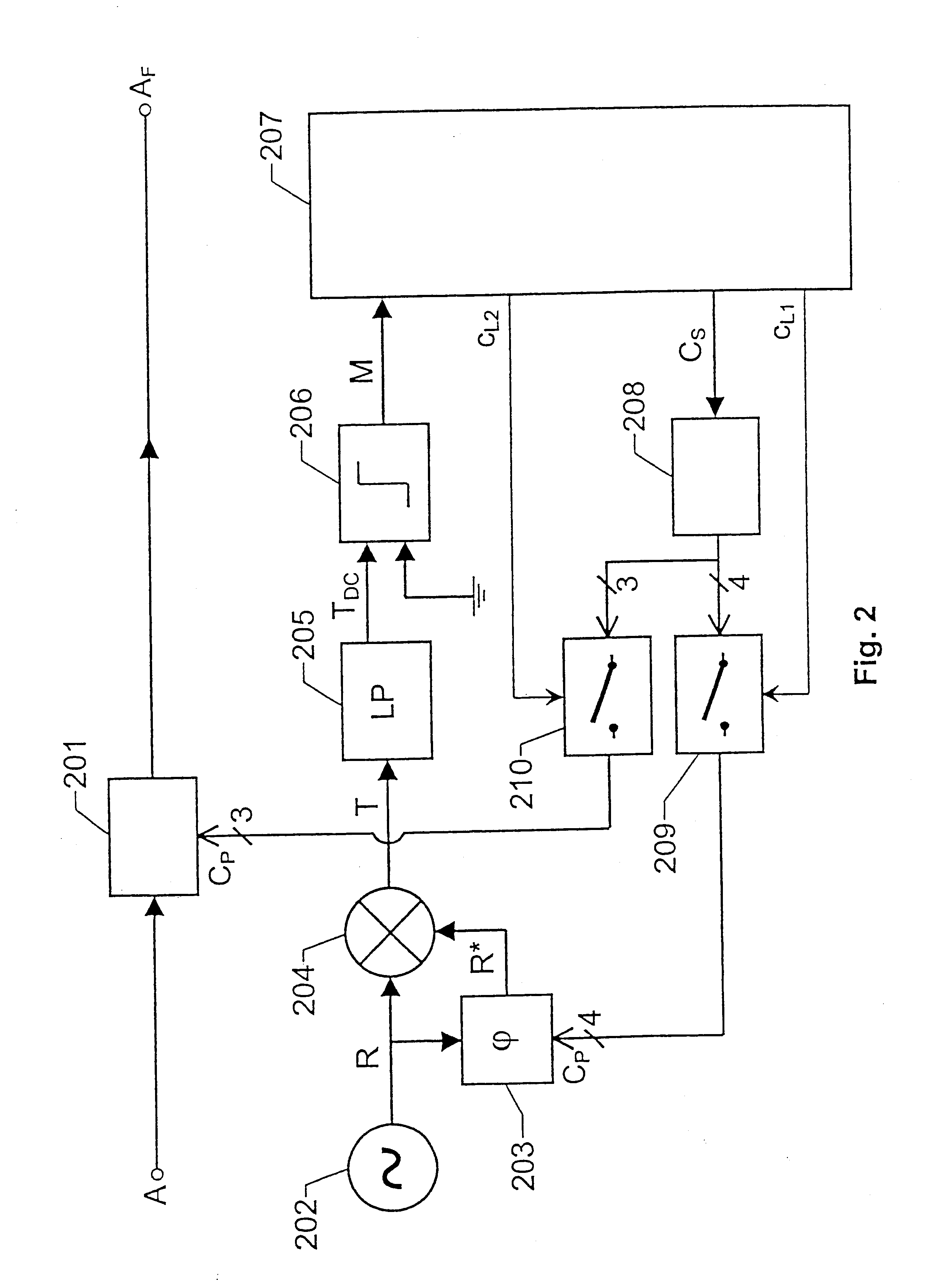

Filter trimming

InactiveUS6686809B2Multiple-port networksTransmission control/equlisationDigital signal processingPhase difference

The invention relates to trimming of analogue filters (201) in integrated circuits by means of an automatic adjusting circuit. A local oscillator (202) in the automatic adjusting circuit provides a periodic reference signal (R) to an adjustable phase shifter (203), which on basis thereof, produces a periodic phase shifted signal (R*). A phase detector (204) receives both the periodic reference signal (R) and the phase shifted period signal (R*) and produces a test signal (T) in response to a phase difference between the periodic reference signal (R) and the periodic phase shifted signal (R8). A lowpass filter (205) receives the test signal (T) and generates a level signal (TDC) relative a reference level, e.g. representing a zero voltage. A digital signal processor (207) produces a primary control signal (CS), having a serial format, on basis of the observation signal (M). A serial-to-parallel converter (208) converts the primary control signal (CS) into a control signal (CP) having a parallel signal format. The control signal (CP) influences a magnitude of at least one component value in the adjustable phase shift between the periodic reference signal (R) and the periodic phase shifted signal (R*) attains a calibrated value being as close as possible to a desired value. A latch (210) forwards at least one signal element of the control signal (CP) for setting of at least one component value in the analogue filter (201) in accordance with a setting of at least one component value in the adjustable phase shifter (203) which produces the calibrated value.

Owner:NAT SEMICON CORP

Filters for communication systems

The invention relates to a cascaded scheme in which an RRC filter, a modified RRC filter or other digital filter is implemented at a relatively low data rate, such as twice the symbol or chip rate, or 2×. Interpolation filters are used to increase the data rate to a higher data rate, such as 8×. Decimation filters are used to reduce the data rate from a higher rate, such as 8×, to a lower rate, such as 2×. The coefficients of the digital filter may be adjusted to compensate for characteristics of other components across the entire filter chain. Most of the implementation complexity of the filter chain is consolidated into the relatively low rate (such as 2×) digital filter while interpolation or decimation filters can be implemented at very low cost. The compensation capability provided by the digital filter makes design of simple decimation or interpolation filters much easier. The compensation capability provided by the digital filter, along with the relatively high over-sampling rate for the output of the interpolation filter (or the input of the decimation filter), also makes the design of the preceding (or following) analog filters much easier.

Owner:MEDIATEK INC

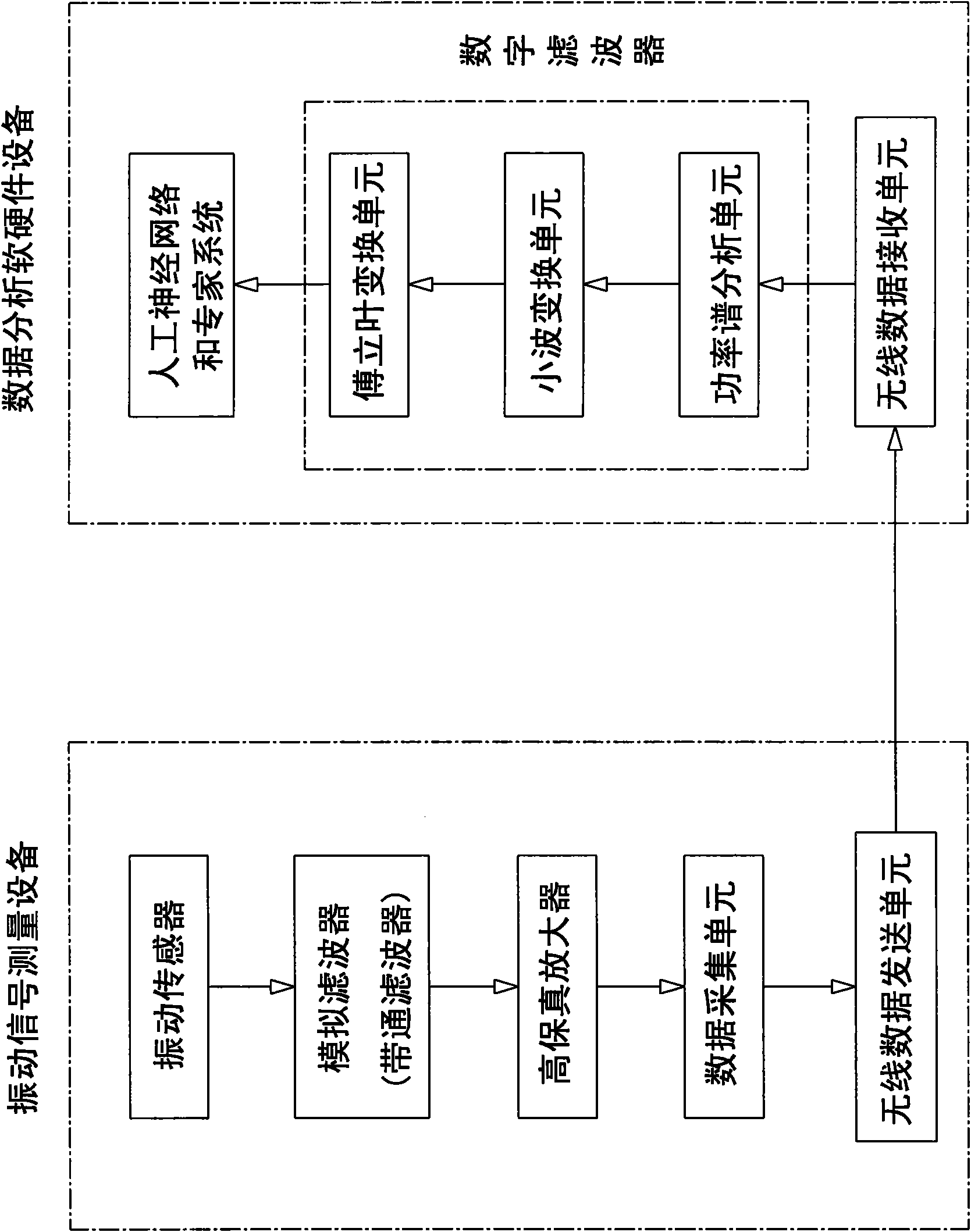

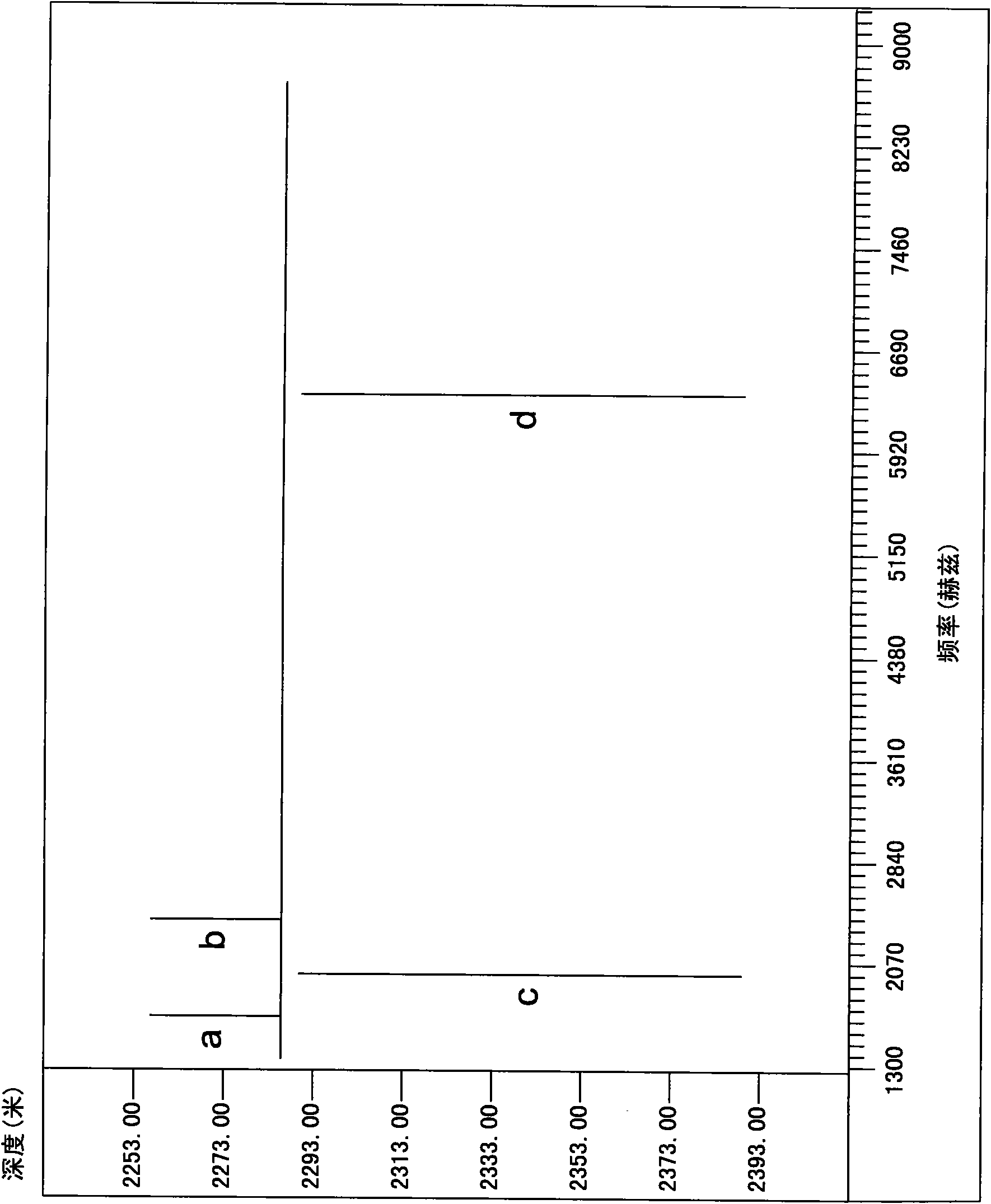

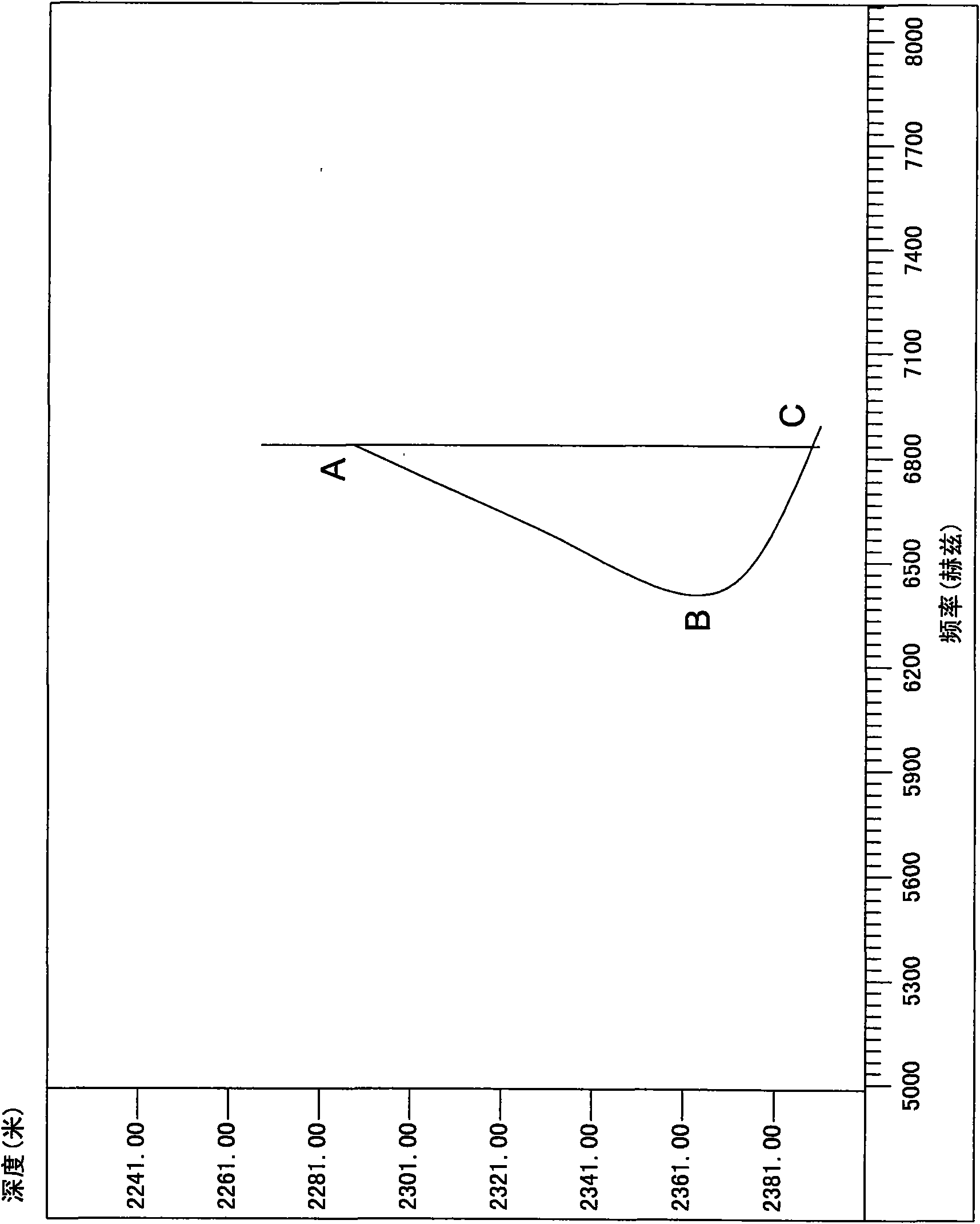

Lithology while drilling and reservoir characteristics recognizing method

InactiveCN101575970AMaintain stabilityConvergentBorehole/well accessoriesLithologyFrequency spectrum

A lithology while drilling and reservoir characteristics recognizing method comprises the following steps: (1), establishing data analysis software and hardware equipment; (2), mounting vibration signal measuring equipment; (3), transmitting vibration acoustic wave signals by a vibration transducer to an analog filter; (4), filtering useless frequency bands in the signals and transmitting useful frequency bands to a high fidelity amplifier by the analog filter; (5), amplifying, strengthening, and transmitting the signals to a digital filter by the high fidelity amplifier; (6), transmitting power spectral density of the signals to a wavelet transformation unit by a power spectrum analysis unit, (7), performing wavelet decomposition, reconstruction and noise elimination on the signals by the wavelet transformation unit; and (8), unfolding restored true signals in spectrographs and energy spectrum charts by a Fourier transformation unit, and determining multiple kinds of lithology and reservoir fluid characteristics by recognizing each group of spectrum lines. The method detects and filters the vibration acoustic wave signals, extracts stratum information, and obtains the lithology and the reservoir fluid characteristics through noise elimination and spectral analysis.

Owner:ZHIXIN COMM SCI & TECH SHANGHAI

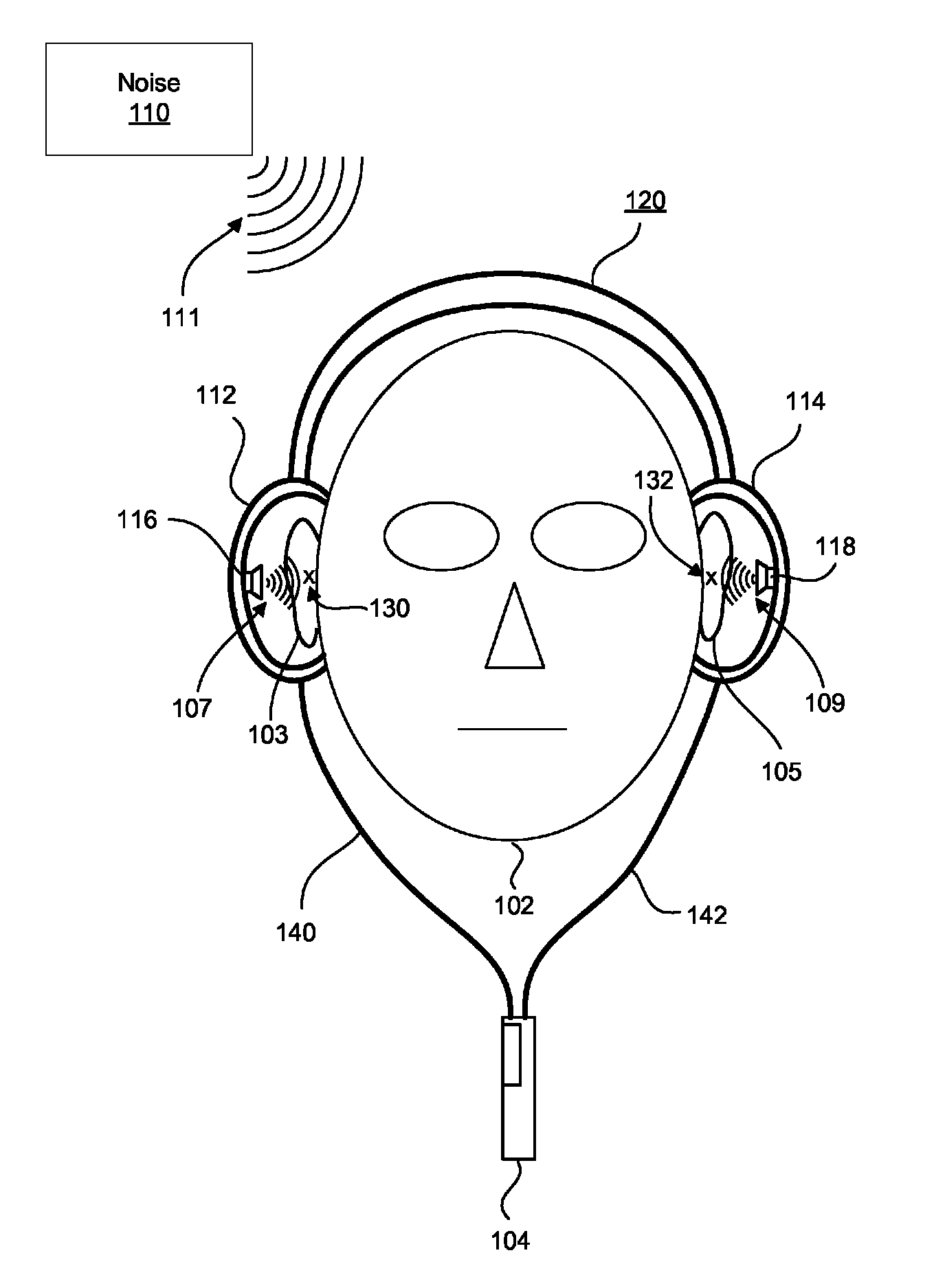

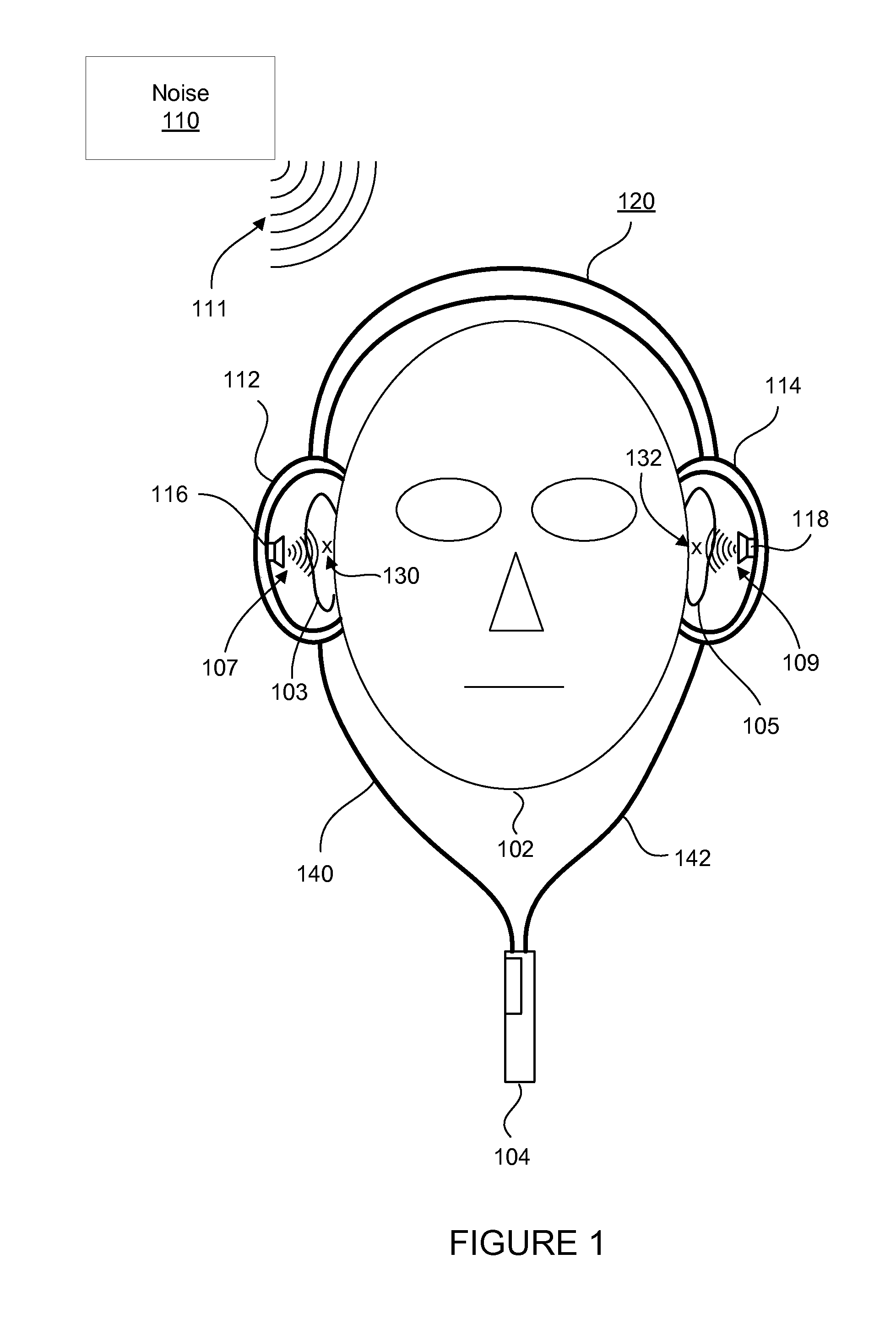

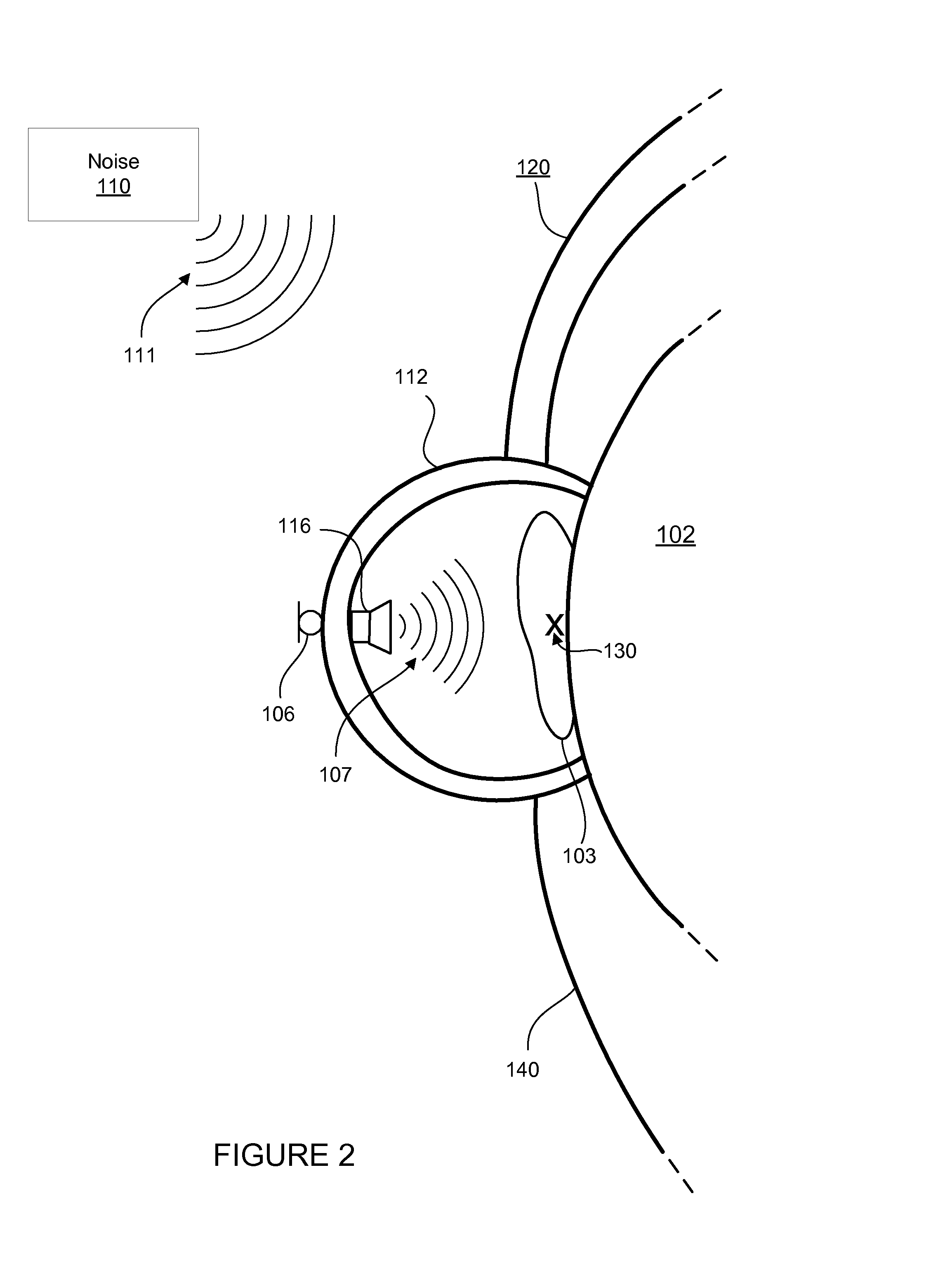

Low latency active noise cancellation system

ActiveUS8526628B1Reduce noiseLower latencyEar treatmentAnalogue conversionDigital signal processingComputer science

Systems and methods described herein provide for low latency active noise cancellation, which alleviates the problems associated with analog filter circuitry. The present technology utilizes low latency digital signal processing techniques that overcome the high latency conventionally associated with conversion between the analog and digital domains. As a result, low latency active noise cancellation is performed utilizing digital filter circuitry which is not subject to the inaccuracies and drift of analog filter components. In doing so, the present technology provides robust, high quality active noise cancellation.

Owner:KNOWLES ELECTRONICS INC

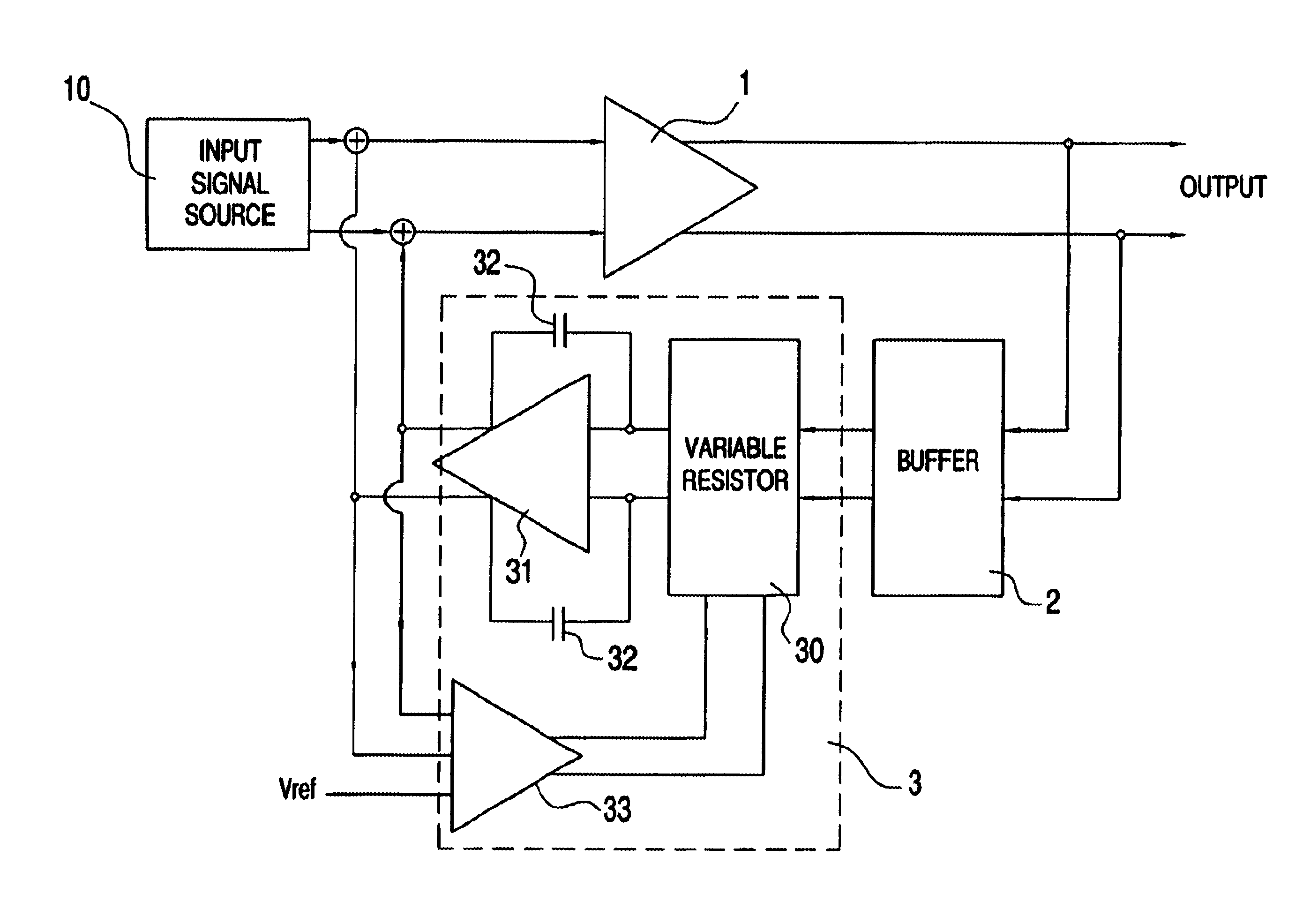

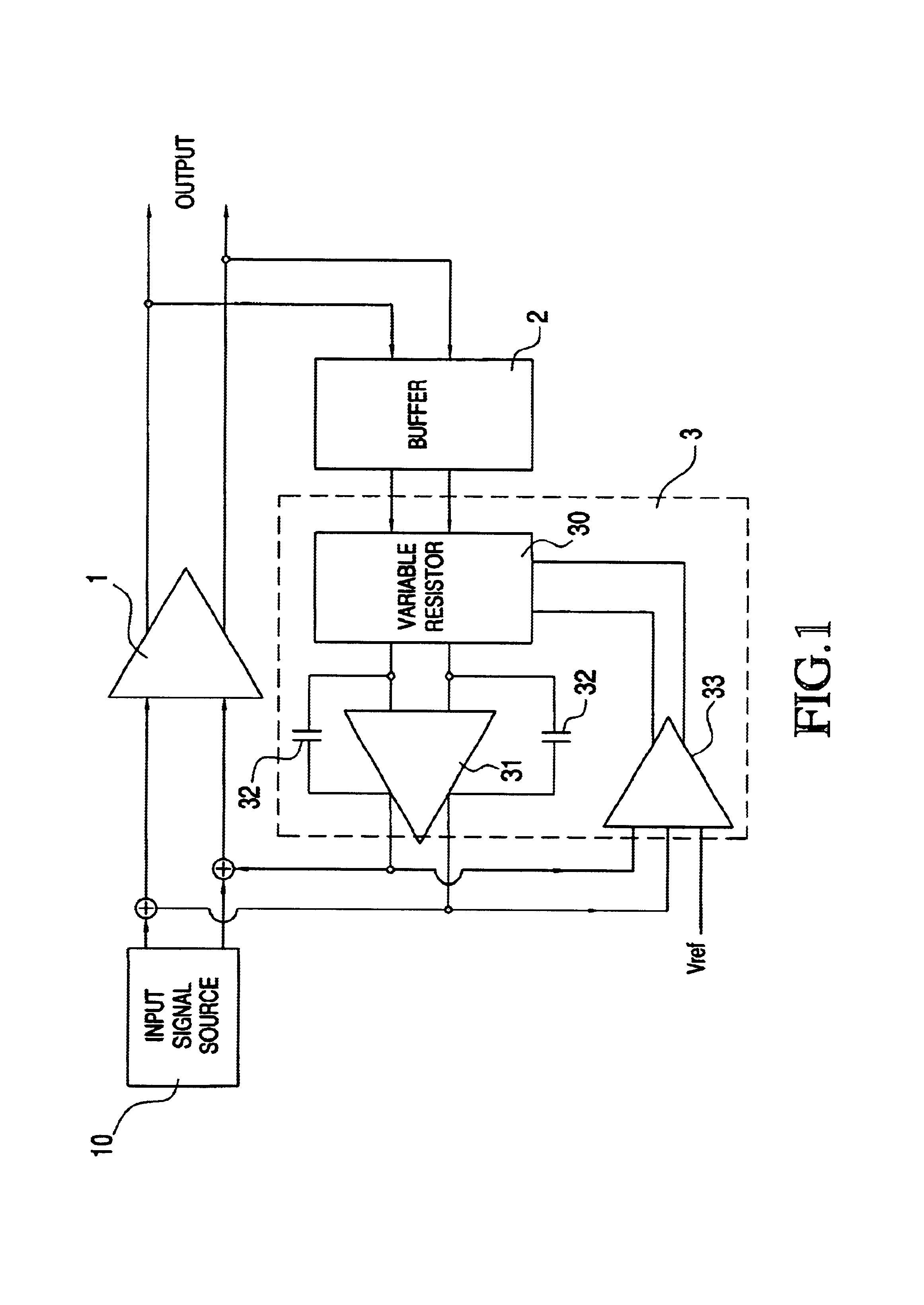

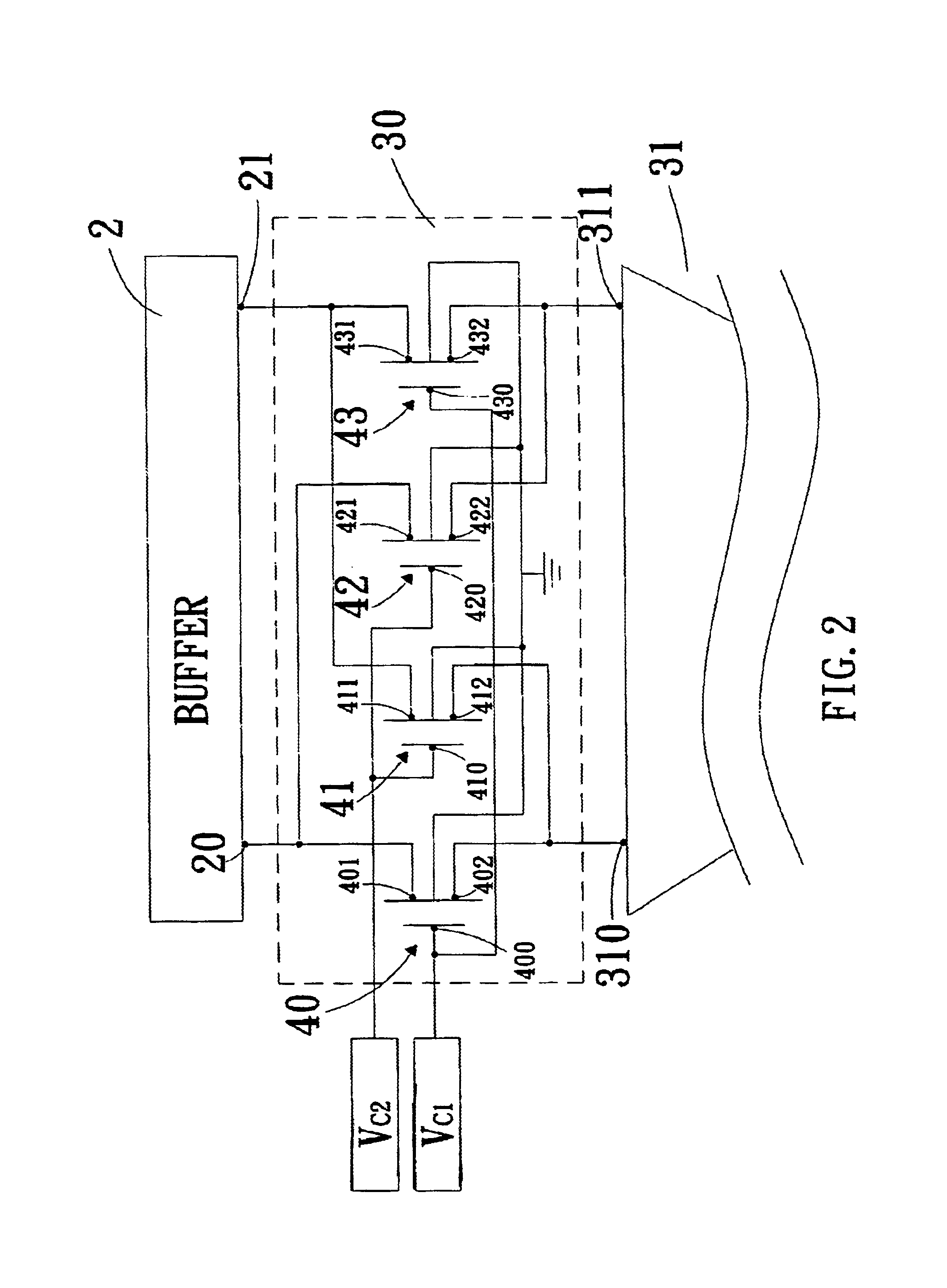

Gain amplifier with DC offset cancellation circuit

ActiveUS6903593B2Shorten convergence timePulse automatic controlComputing operation arrangementsNegative feedbackAudio power amplifier

A DC offset cancellation circuit employs multiple feedback factors for canceling DC offset by increasing convergence time. The DC offset cancellation circuit features an active low-pass analogue filter including a variable resistor, an amplifier, a capacitor pair and a comparator, the amplifier being coupled to an output of the variable resistor. Negative feedback is provided from the output of the variable resistor to the input signal source, the capacitor pair is coupled to the amplifier, one input of the comparator is coupled to an output of the amplifier, and a second input of the comparator is coupled to a reference voltage source such that a comparison signal is output by the comparator to the variable resistor after comparing the negative feedback signal with a reference voltage.

Owner:IND TECH RES INST

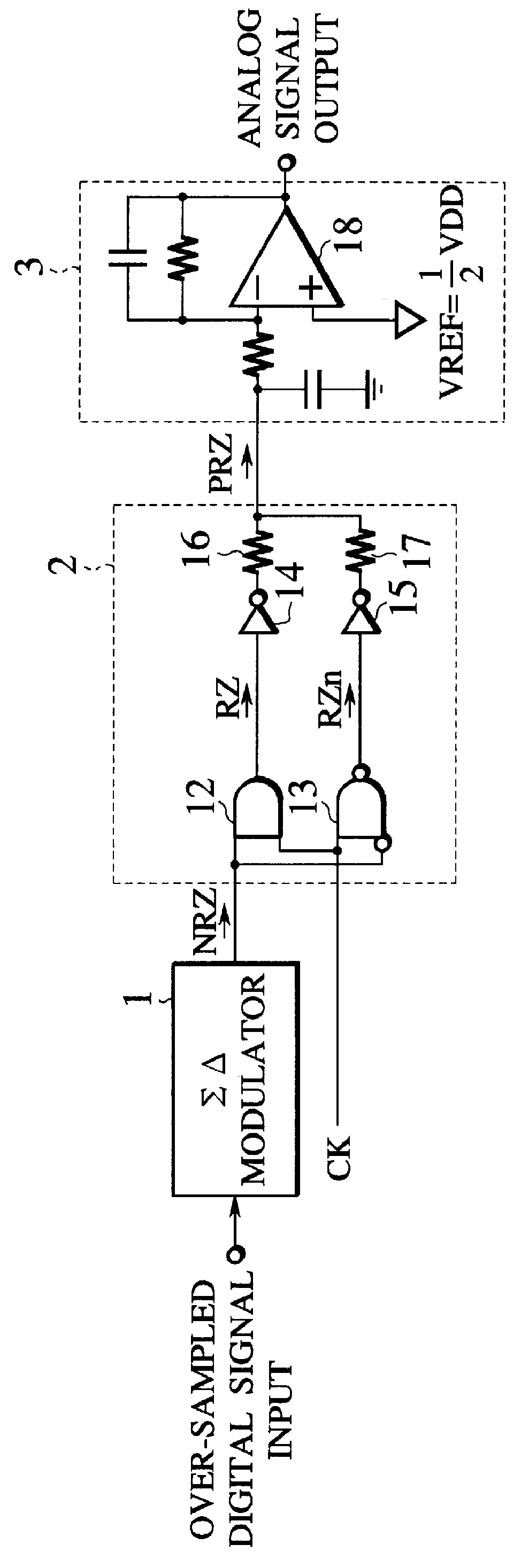

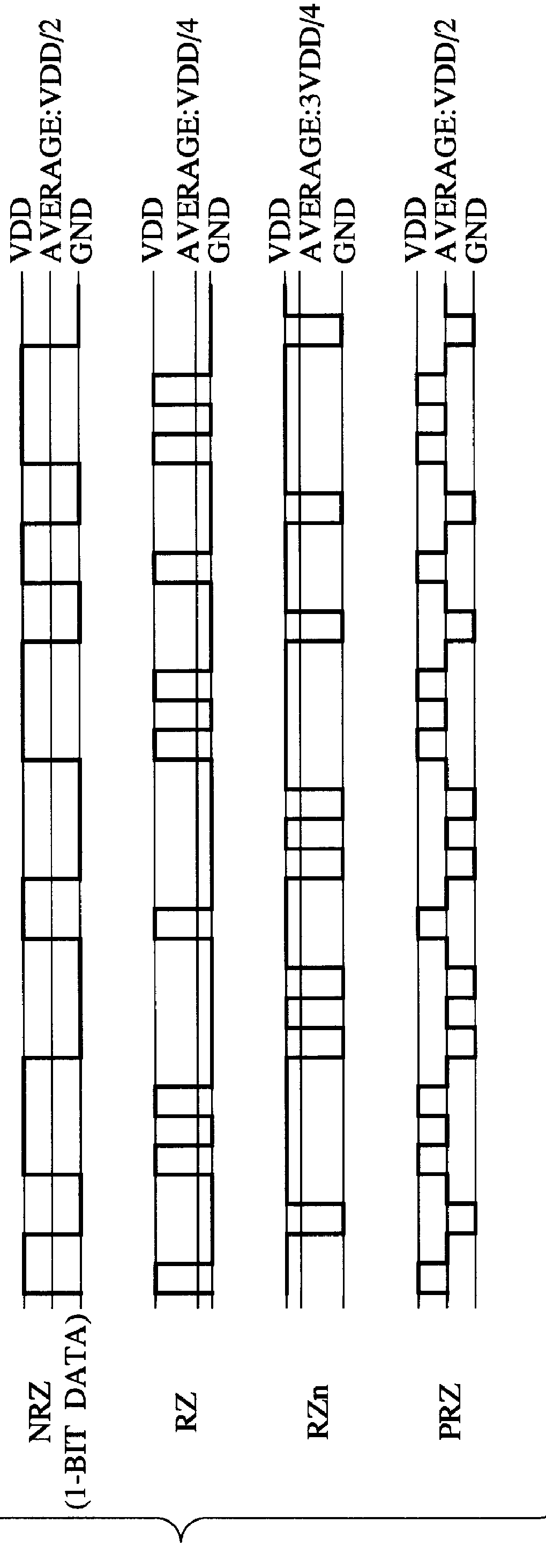

D/A converter

There is provided an over-sampling D / A converter which has a mute function for fixing an average DC potential of an analog output signal to a predetermined potential, and comprises a SIGMA DELTA modulator for receiving a multibit digital signal to which a DC offset value is added and then outputting a one-bit non-return-to-zero signal, a signal generator for receiving the non-return-to-zero signal and the clock signal, then generating a return-to-zero signal which is a logical multiplication of the non-return-to-zero signal and the clock signal and a complementary signal of the return-to-zero signal which is a logical addition of the non-return-to-zero signal and an inverted signal of the clock signal, and then adding the return-to-zero signal to the complementary signal of the return-to-zero signal to thus output a polar-return-to-zero signal, and an analog filter for receiving the polar-return-to-zero signal and then outputting an analog signal. Accordingly, because an average DC potential of an output signal at the time of the mute operation-ON is set substantially equal to the average DC potential of the output signal at the time of the mute operation-OFF, variation in the average DC potential in the output signal due to ON / OFF of the mute operation can be prevented. As a result, generation of audible click noises can be prevented.

Owner:KK TOSHIBA

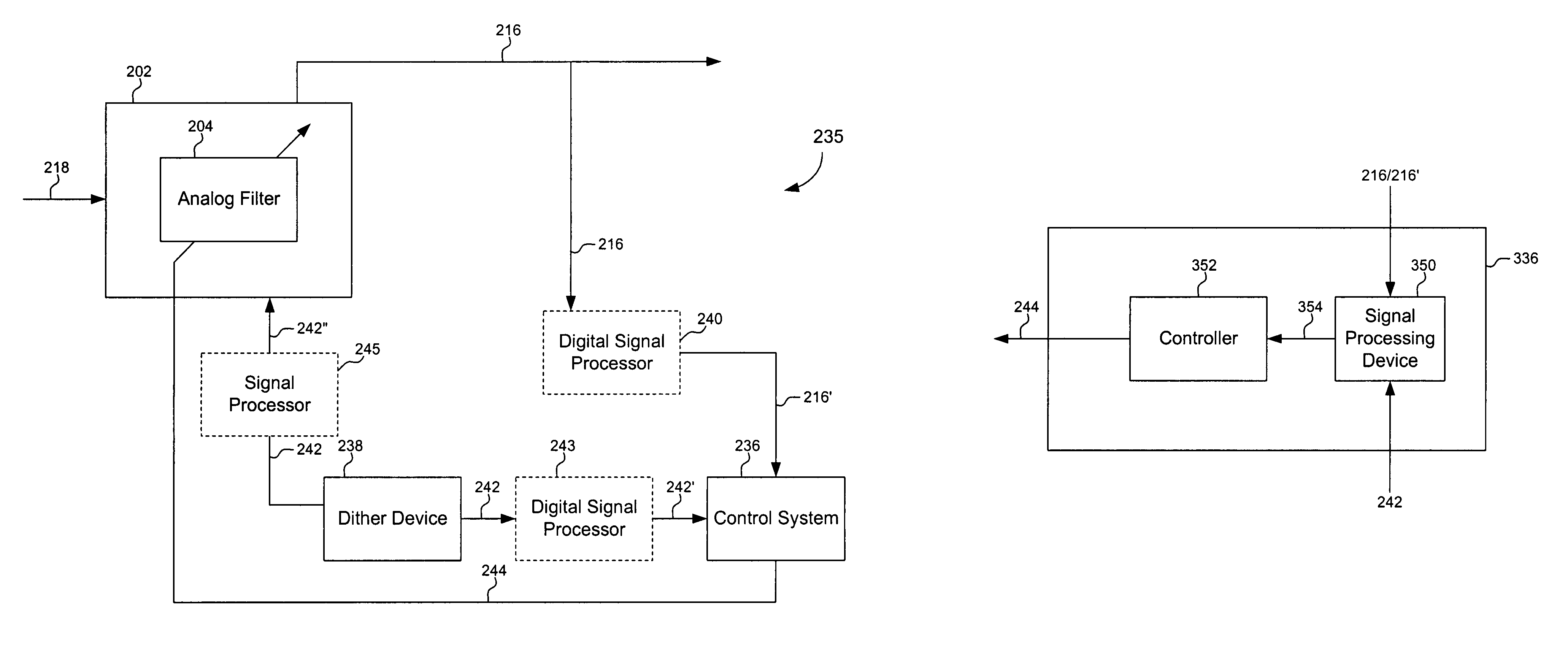

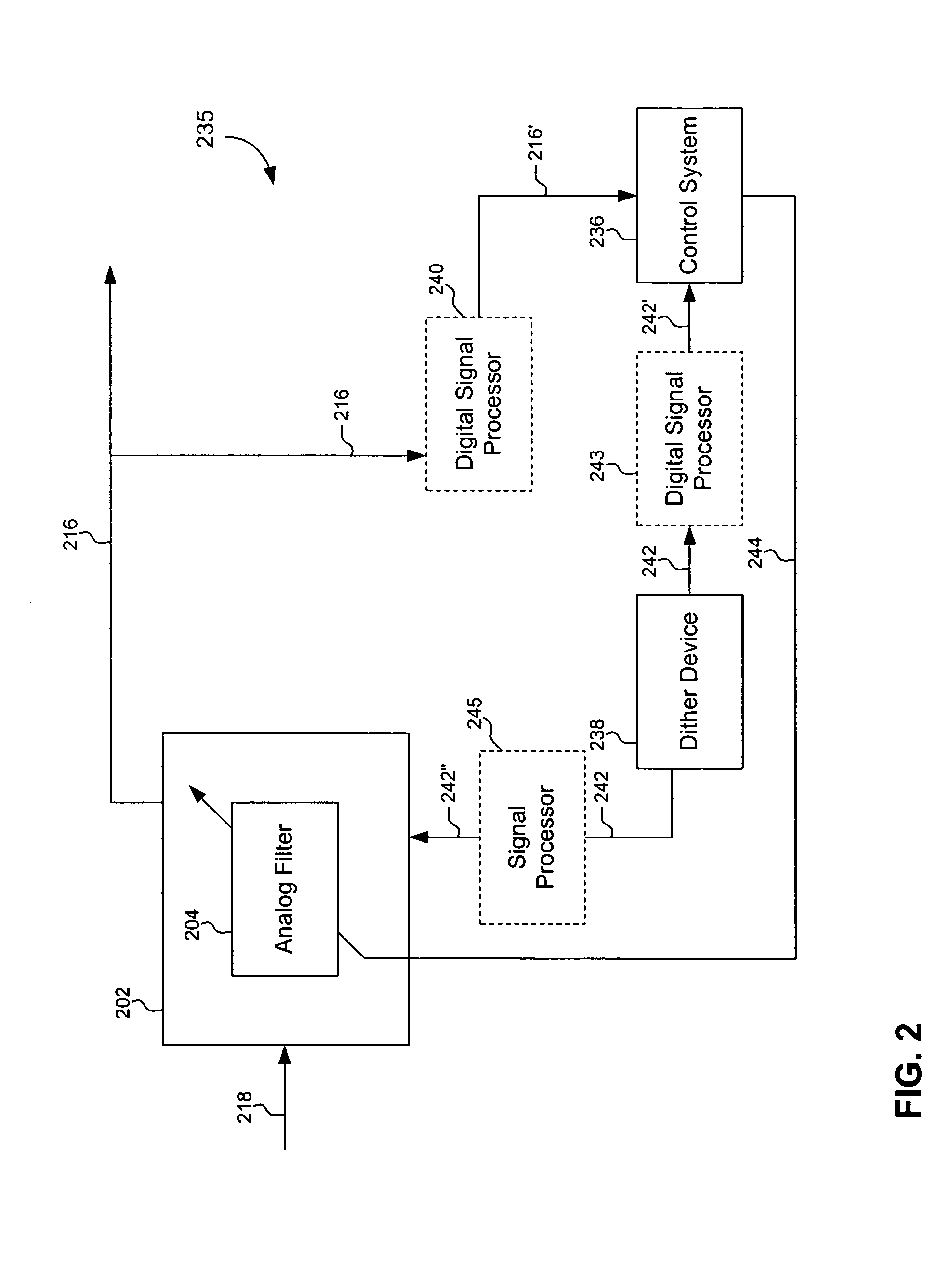

System and method using dither to tune a filter

A system and method is used to tune filters, for example, analog filters in a sigma-delta modulator ADC. A known dither signal is used, for example a digital dither signal. Through adding of the dither to the modulator loop, the digital output of the sigma delta modulator ADC contains a filtered version of the digital dither. This signal can be used to reveal characteristics of the modulator-loop, including characteristics of a continuous-time filter in the modulator. Therefore, using the known digital dither signal and the output signal of the modulator, the continuous-time loop filter can be tuned. The tuning can be done in multiple ways, for example, by using standard LMS adaptive filter techniques to estimate the actual response of the continuous-time loopfilter and adjust the continuous-time loopfilter to the desired response.

Owner:AVAGO TECH INT SALES PTE LTD

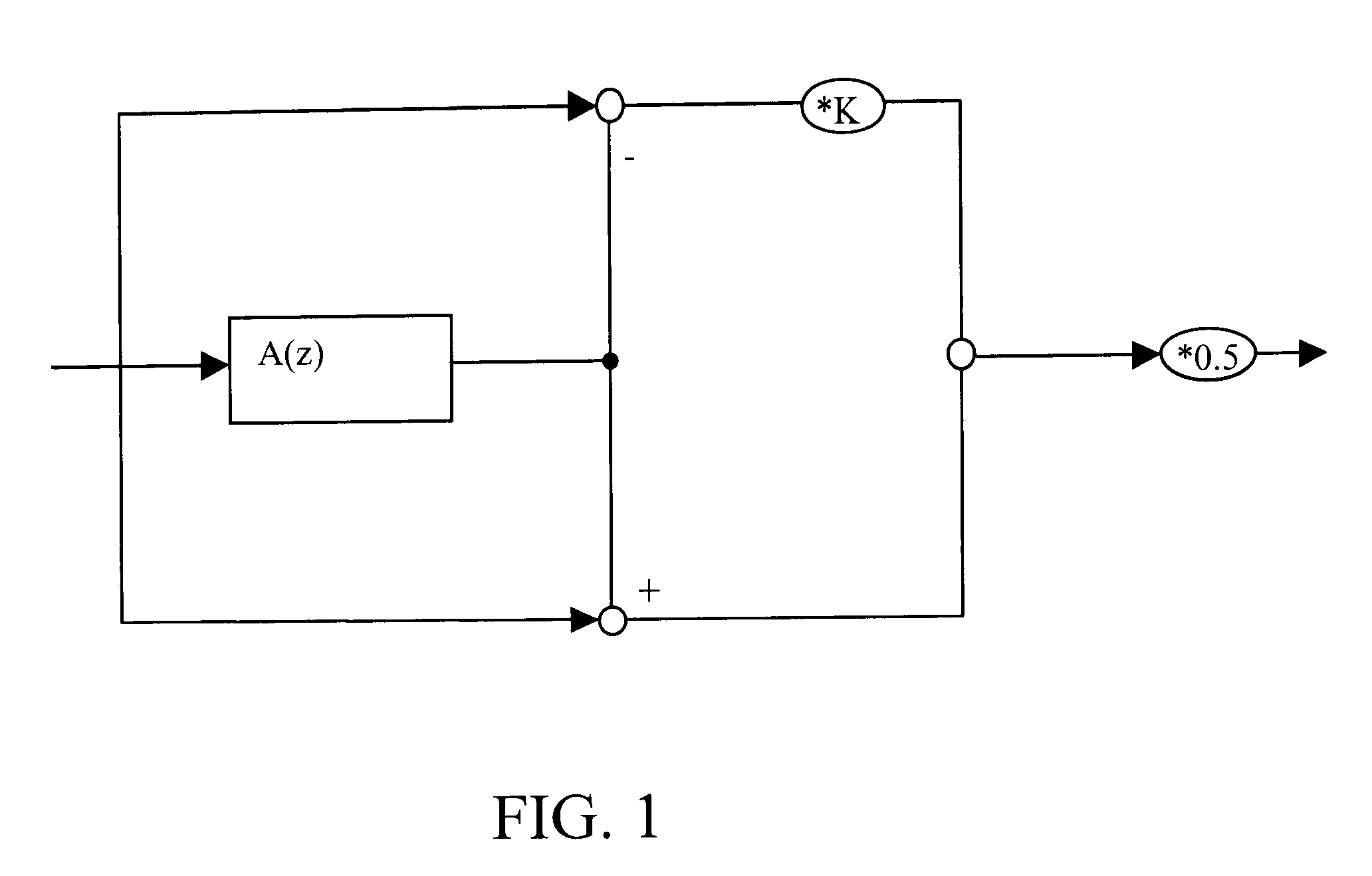

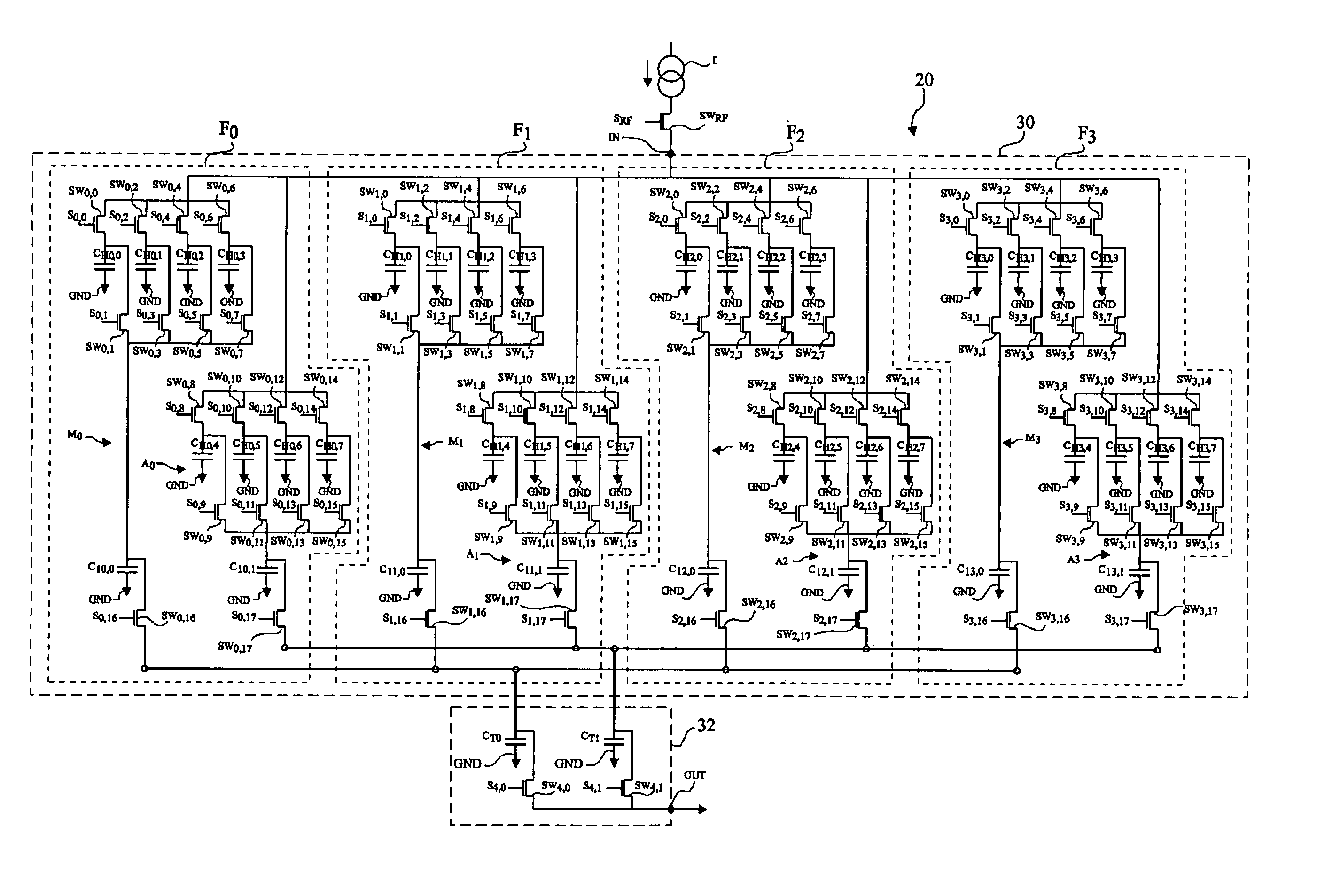

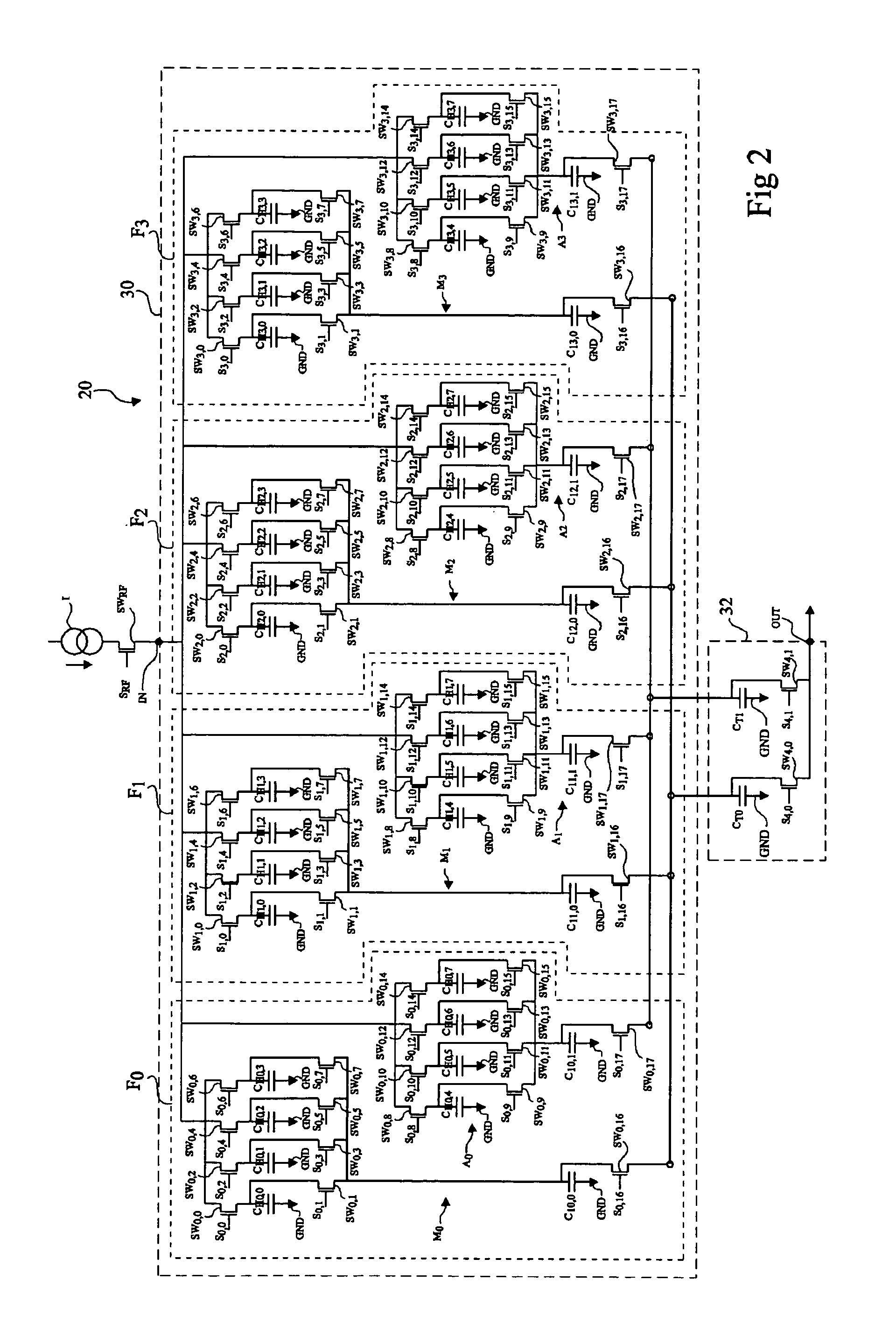

Analog filter with passive components for discrete time signals

InactiveUS7539721B2Well formedTransversal filtersOscillations generatorsClock rateDiscrete-time signal

A filter intended to receive a discrete time signal at a sampling clock frequency, comprising a determined number, greater than 2, of filtering units, each filtering unit comprising head capacitors in a number equal to the determined number, assembled in parallel between an input terminal and the terminal of an integration capacitor; and means for connecting, in successive clock cycles in a number equal to the determined number, successively each head capacitor to the input terminal, and for then simultaneously connecting the head capacitors to the integration capacitor, and in which the successive clock cycles during which the head capacitors of a filtering unit are connected to the input terminal are offset by one clock cycle from one filtering unit to the next one.

Owner:ST ERICSSON SA

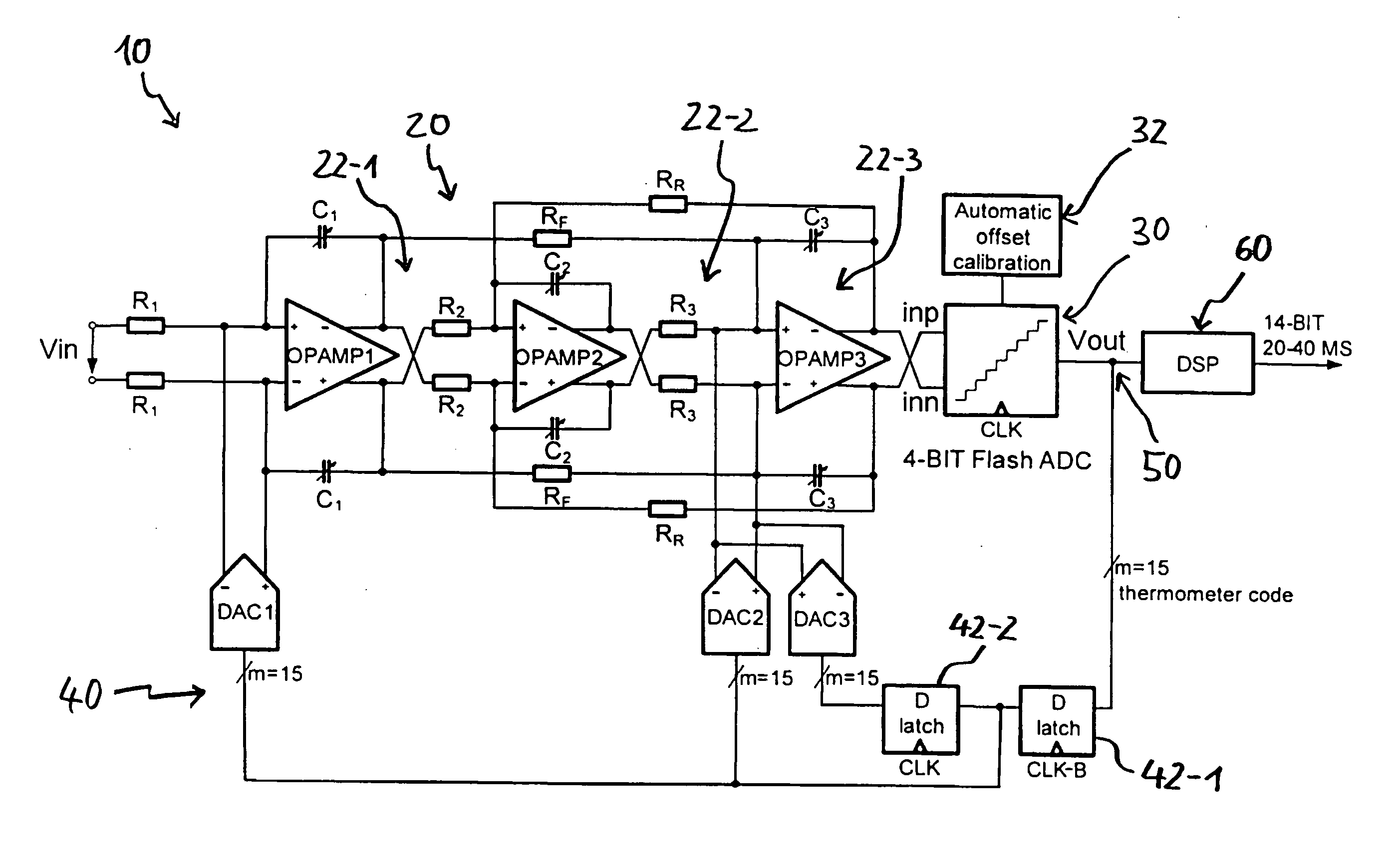

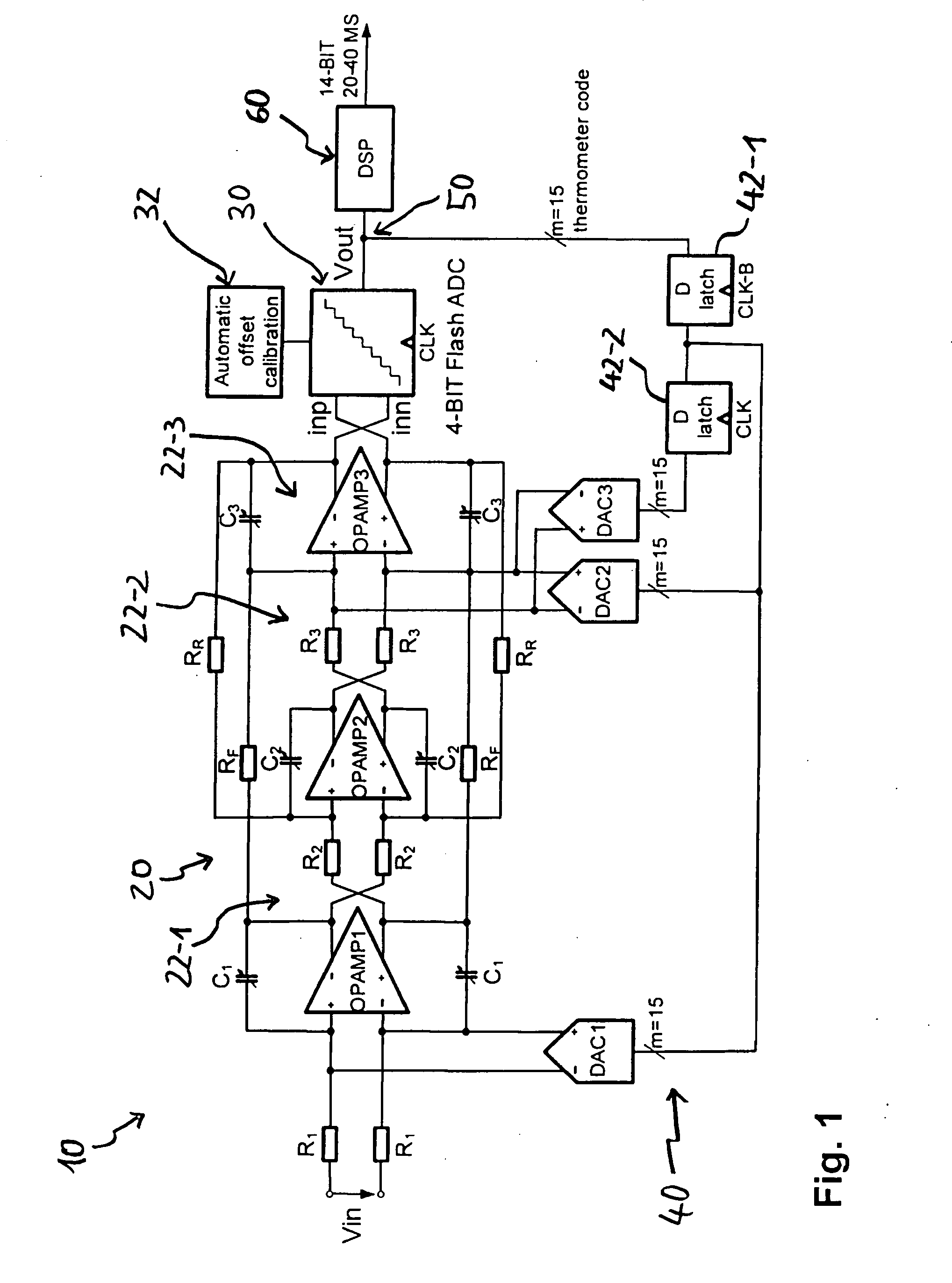

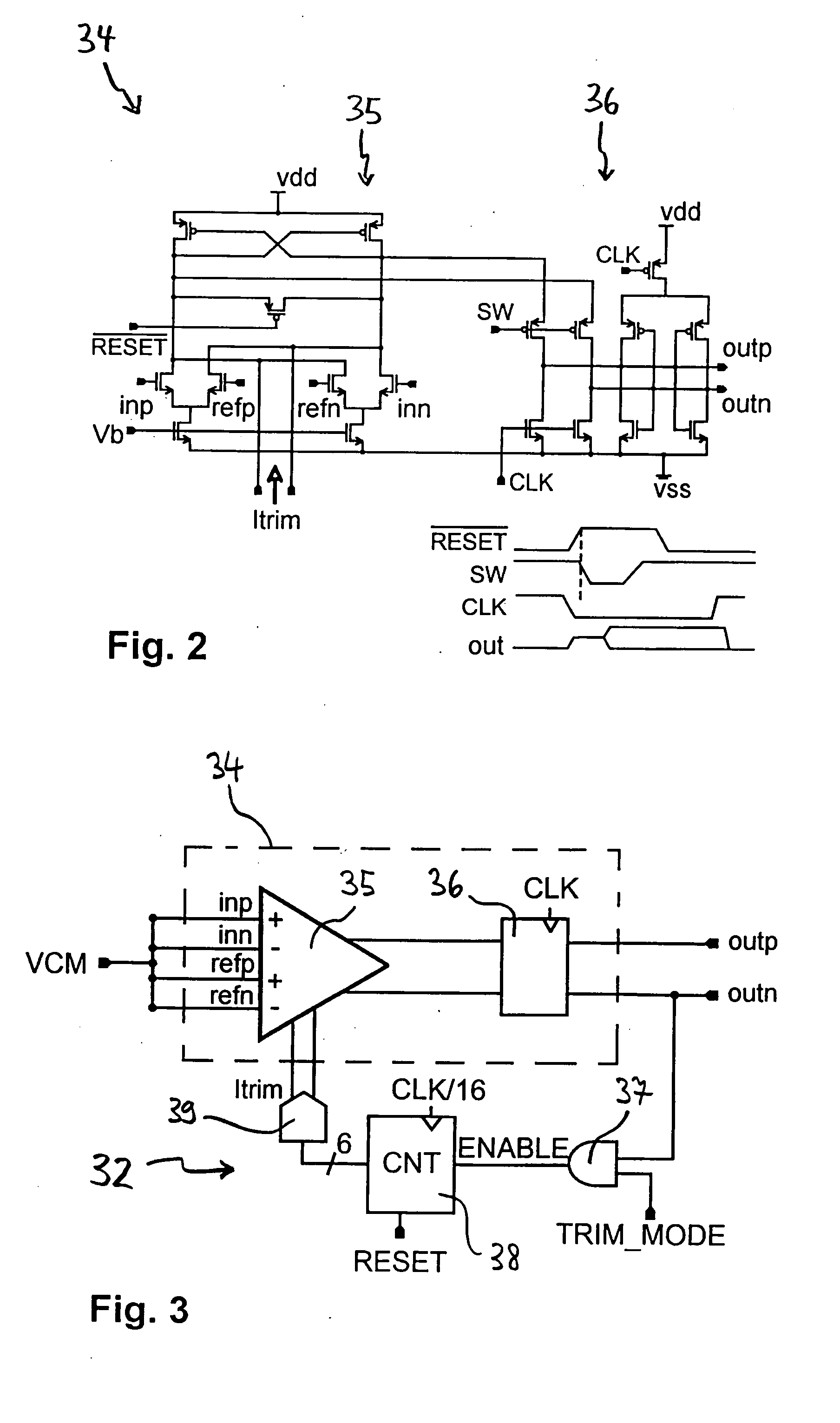

Delta-sigma analog digital converter with offset compensation

ActiveUS20070216557A1Improved performance characteristicsSimple configurationElectric signal transmission systemsAnalogue conversionSignal onA d converter

The invention concerns a time-continuous delta-sigma analog-digital converter for the conversion of an analog input signal into a digital output signal, comprising an analog filter for the filtering of the analog input signal, a clocked operated quantiser, which contains at least one comparator (34) and which quantises the filtered analog signal outputted through the analog filter for the generation of the digital output signal, and a feedback arrangement with at least one digital-analog converter, which supplies to the analog filter at least one feedback signal on the basis of the digital output signal. According to the invention a calibration device (32) linked with the quantiser is stipulated, which is designed to determine at a predetermined point in time an offset error of the comparator (34) and subsequently to compensate for this (Itrim).

Owner:NAT SEMICON GERMANY

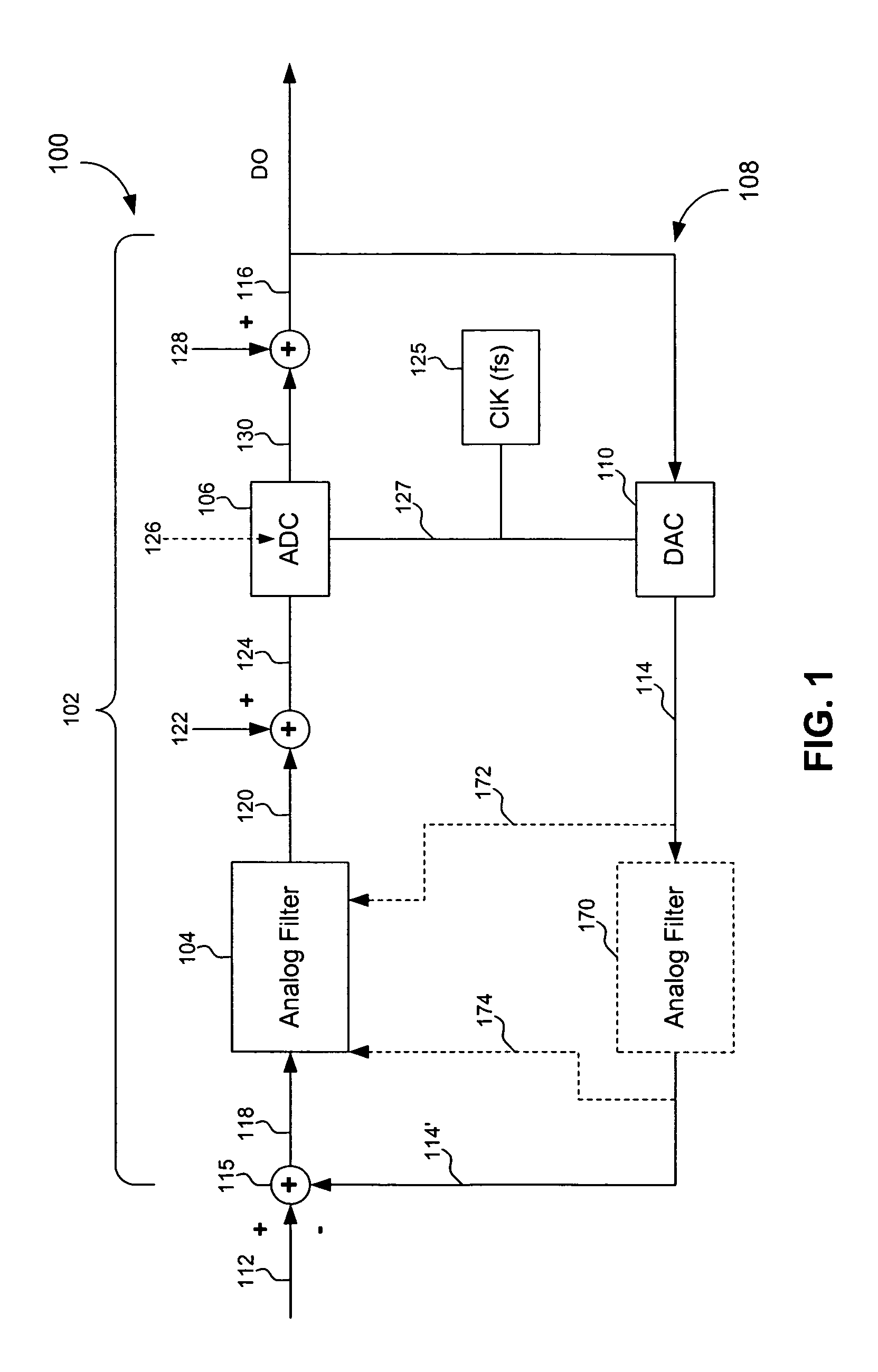

Continuous-time delta-sigma analog digital converter

ActiveUS7405687B2Rapid quantitationQuick conversionElectric signal transmission systemsAnalogue conversionAnalog feedbackAnalog signal

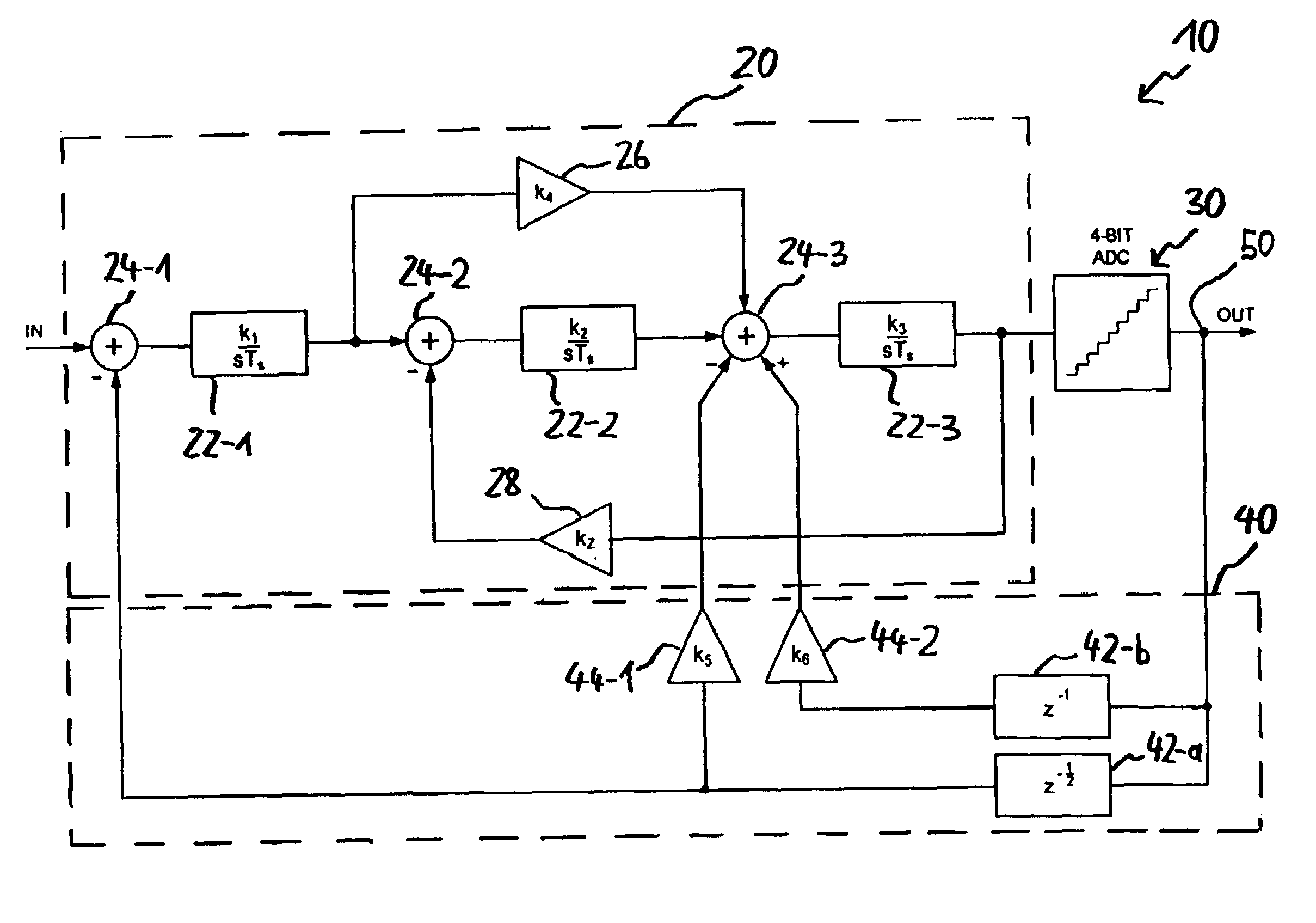

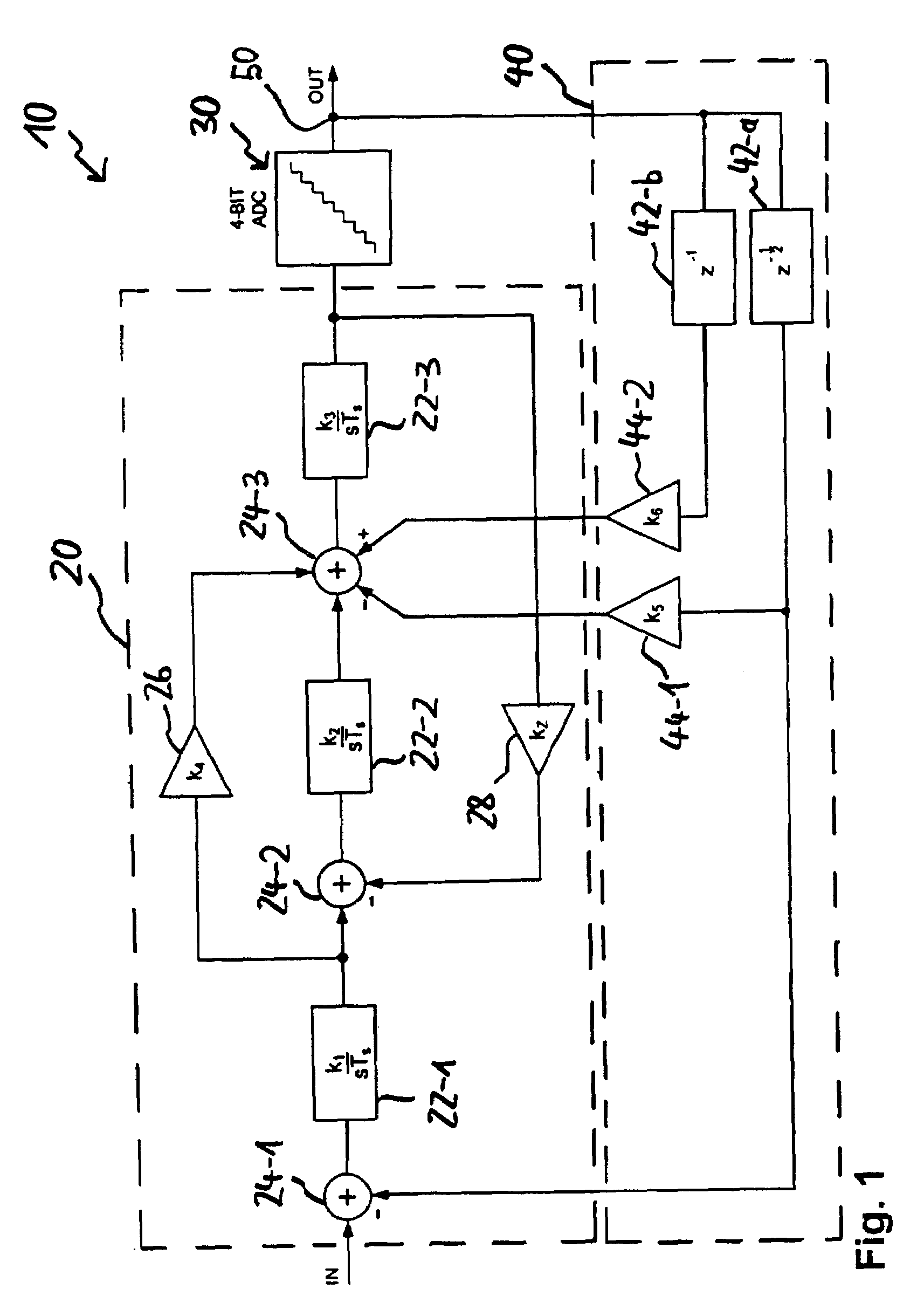

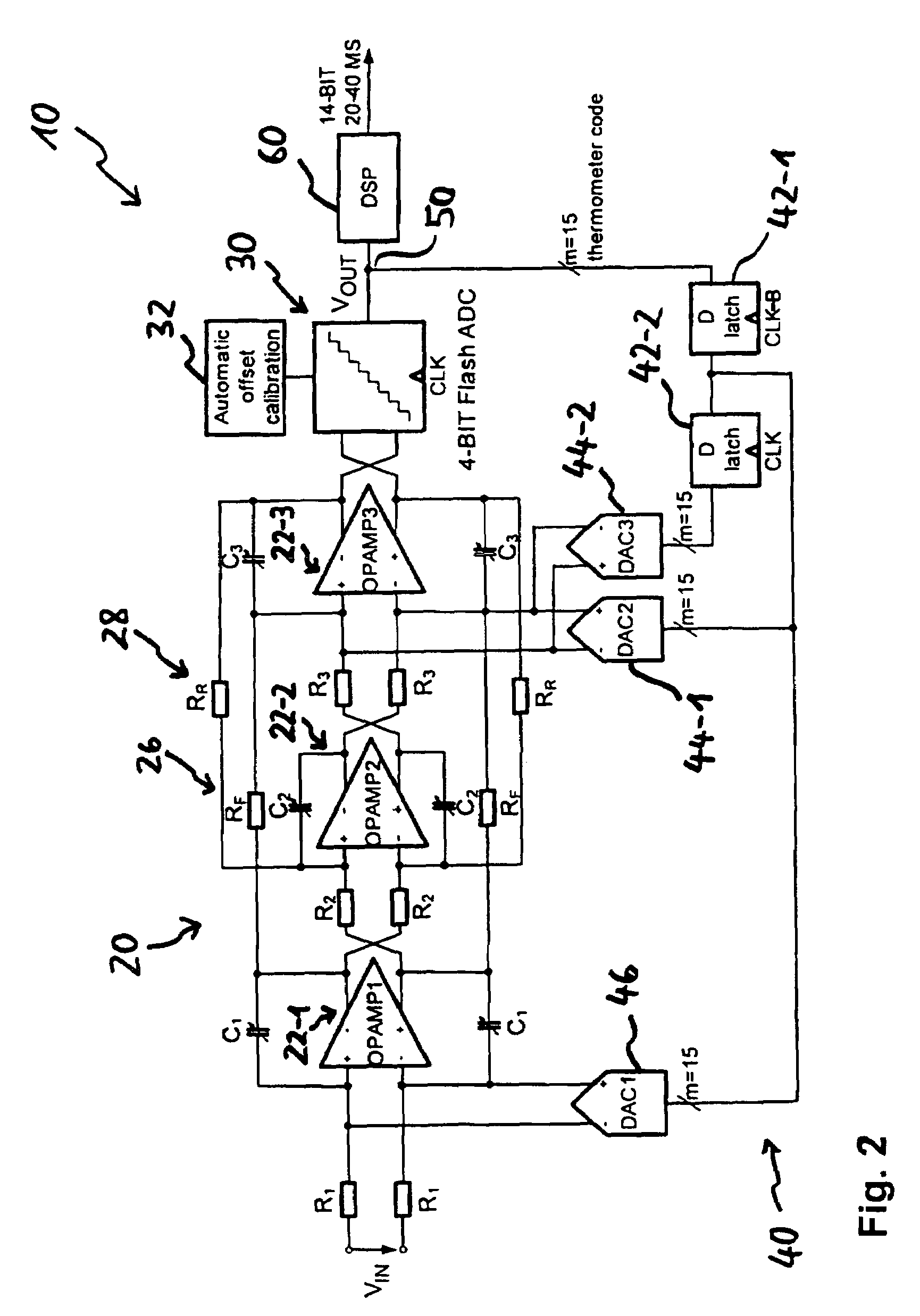

The invention relates to a continuous-time delta-sigma analog digital converter (10) for converting an analog input signal (IN) to a digital output signal (OUT), comprising an analog filter (20), which filters the analog input signal, a quantifier (30) cycled by a clock signal (CLK), which quantifier quantifies the filtered analog signal transmitted by the analog filter (20) to generate the digital output signal, and a feedback device (40) with at last one digital analog converter, which transmits at least one analog feedback signal based on the digital output signal (OUT) to the analog filter (20). To simplify the feedback without adversely affecting the converter stability and power consumption, provision is made, according to the invention, for the feedback device (40) for generating a feedback signal corresponding to the differentiated output signal of the quantifier, to comprise two digital analog converters (44-1, 44-2) to which the digital output signal (OUT) of the quantifier (30) is transmitted via a delay stage (42-1, 42-2) with different delays, and hose analog output signals are transmitted to an analog subtractor (24-3).

Owner:NAT SEMICON GERMANY

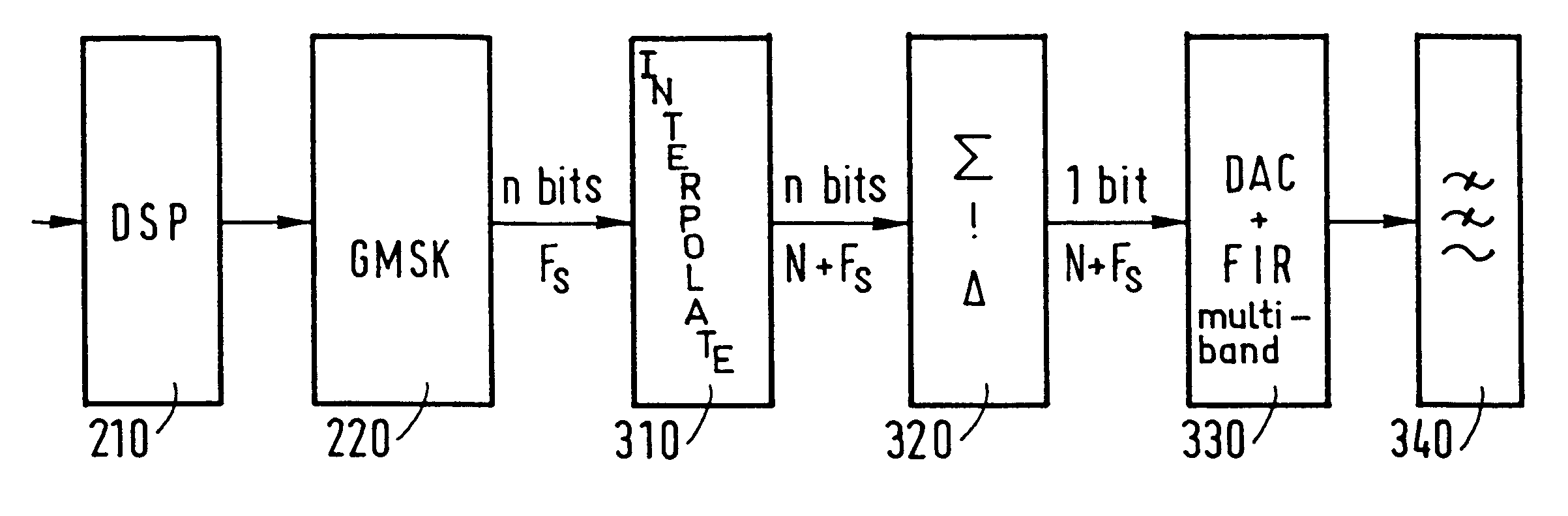

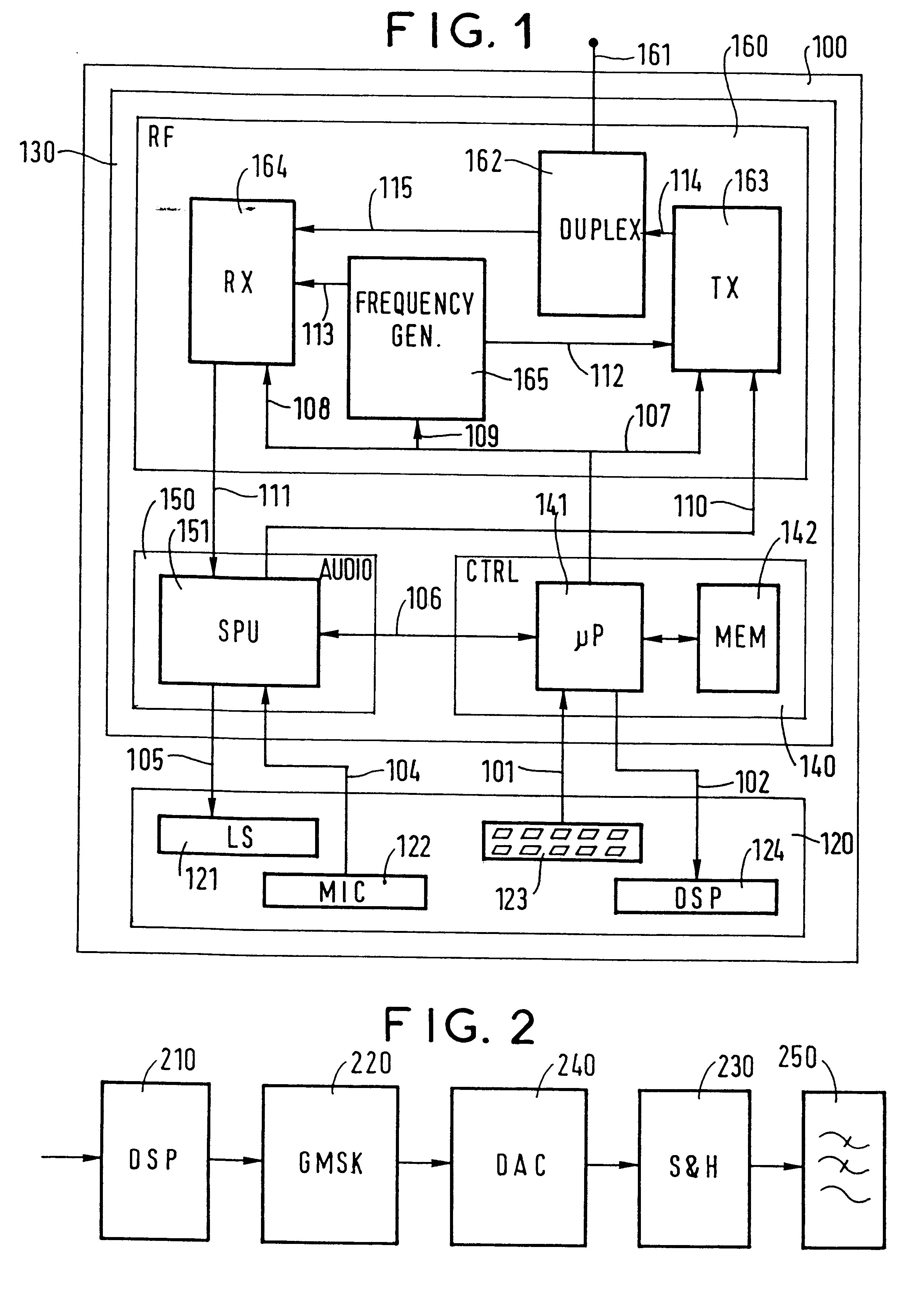

Electronic digital-to-analog converter circuit for a baseband transmission system

InactiveUS6323795B1Mitigate such drawbackElectric signal transmission systemsDelta modulationFinite impulse responseDigital analog converter

The invention relates to an electronic circuit for solving problems of phase linearity involved with transmitting a signal through a digital-to-analog converter module. By connecting the following in cascade: an interpolator; a sigma-delta modulator; a digital-to-analog converter block made up of a 1-bit digital-to-analog converter and a multiband finite impulse response filter; and an analog filter, it is possible to filter out quantization noise while providing a linear response at the output from the circuit.

Owner:DRNC HLDG INC

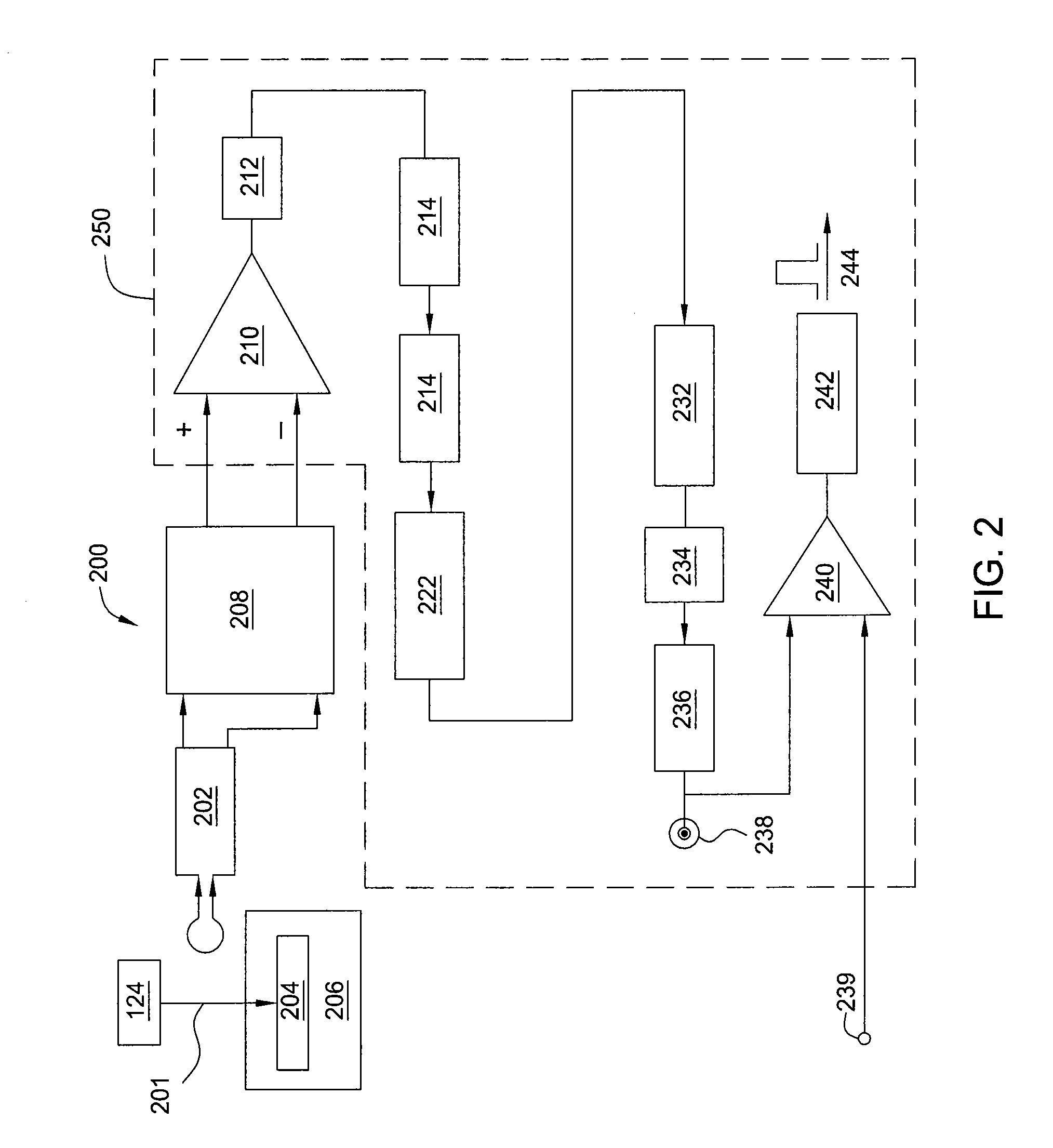

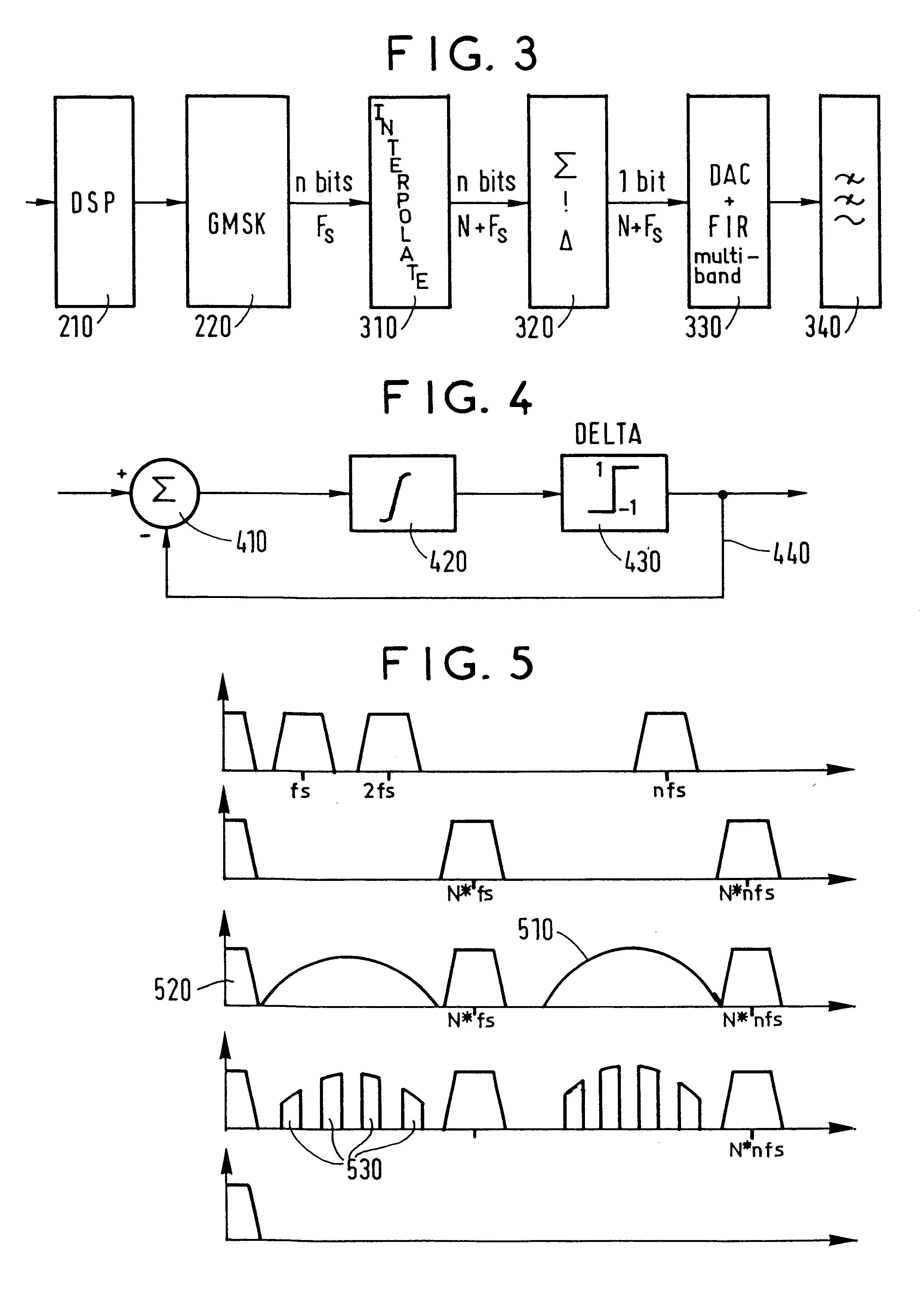

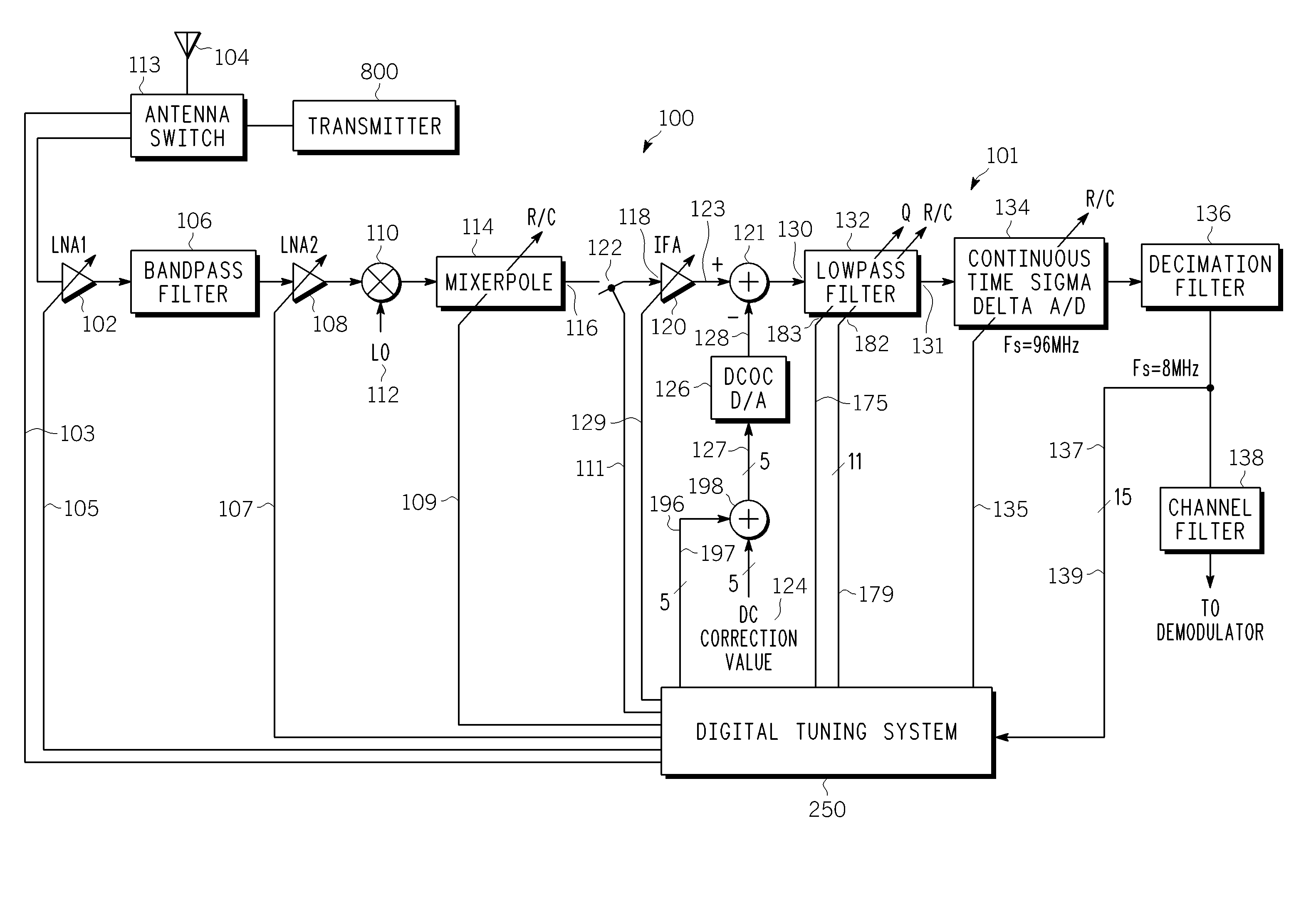

Controlling the bandwidth of an analog filter

ActiveUS20080096514A1Radio transmissionFrequency selective two-port networksDigital tuningCapacitance

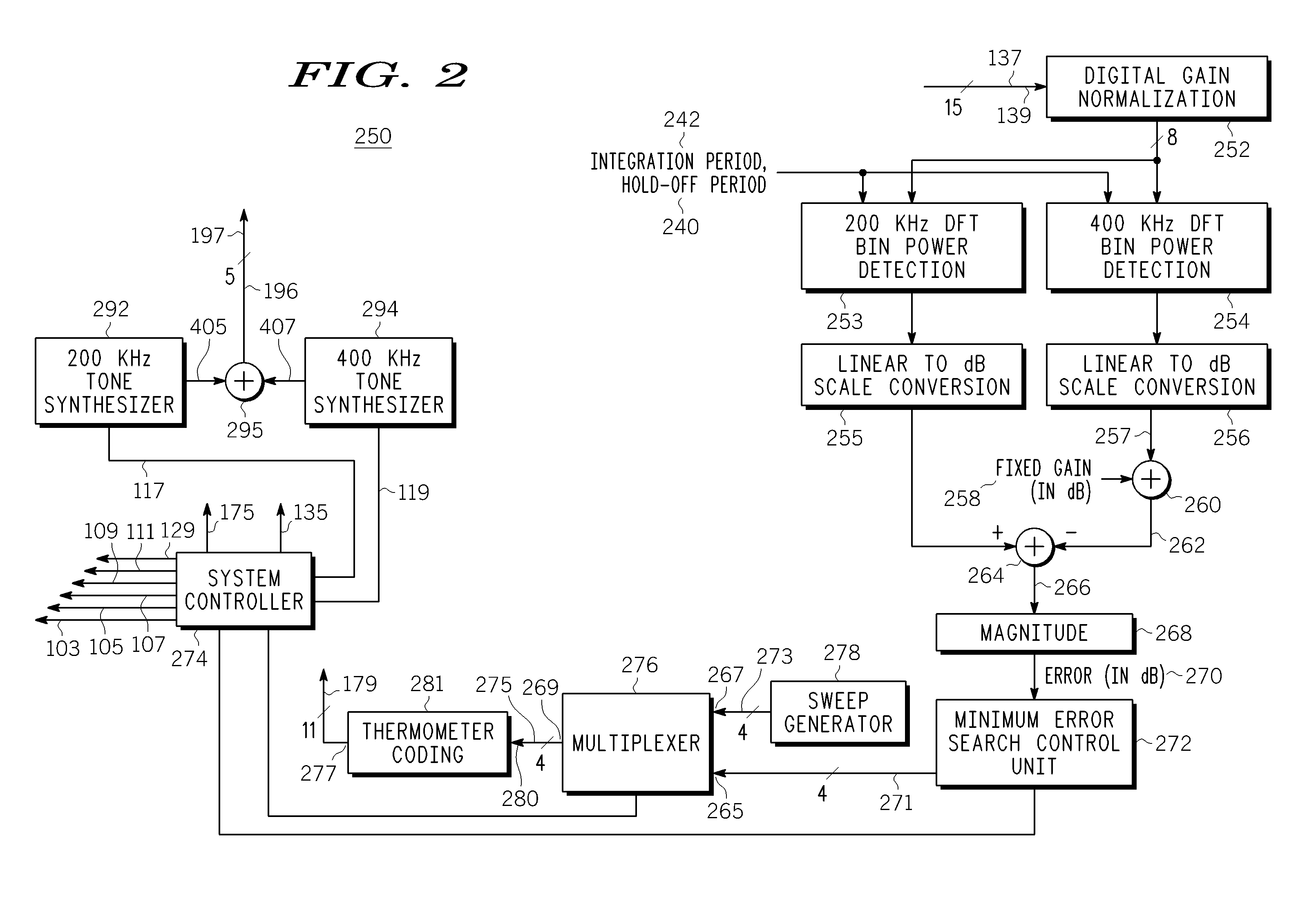

A digital tuning system (250) for changing a cutoff frequency of an analog filter (132) includes digital synthesizers (292 and 294) for producing a two-tone calibration signal (196) applied to an input of the filter after a quality factor of the filter is increased. The filter includes at least one R / C circuit with two resistors (304 and 306) for changing the quality factor and arrays (308 and 310) of capacitors for changing the cutoff frequency. The amplitude of the magnitude responses (409 and 411) of the filter to each tone (405 and 407) is measured by a two discrete Fourier transform single-frequency bin power detection circuits (253 and 254) while the filter is sequenced through a plurality of capacitance settings. An optimal capacitance for the R / C circuit is selected by comparing, to a pre-selected value, a difference between the responses of the filter to each tone, for each capacitance setting.

Owner:APPLE INC