Patents

Literature

1403 results about "Detector circuits" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

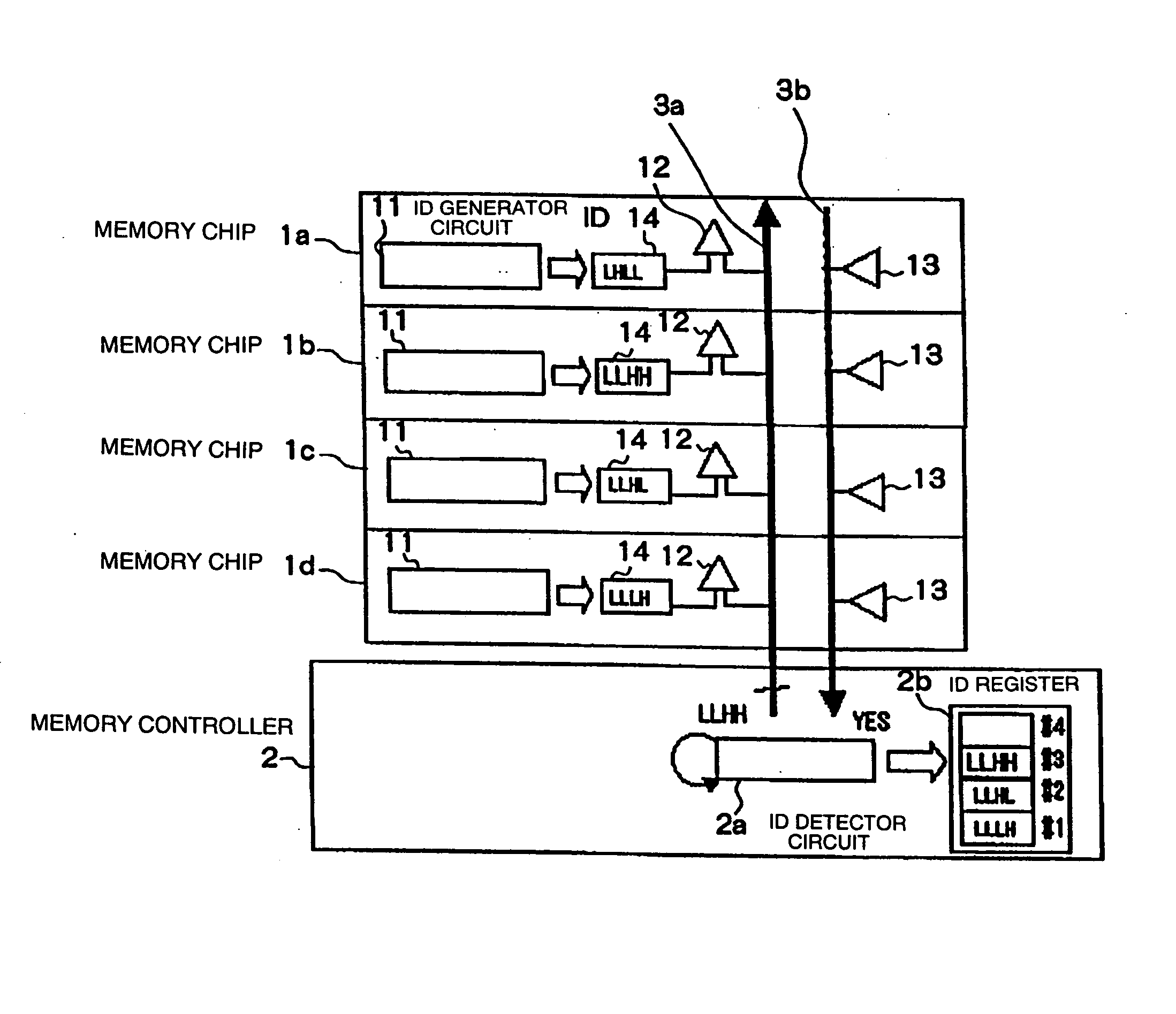

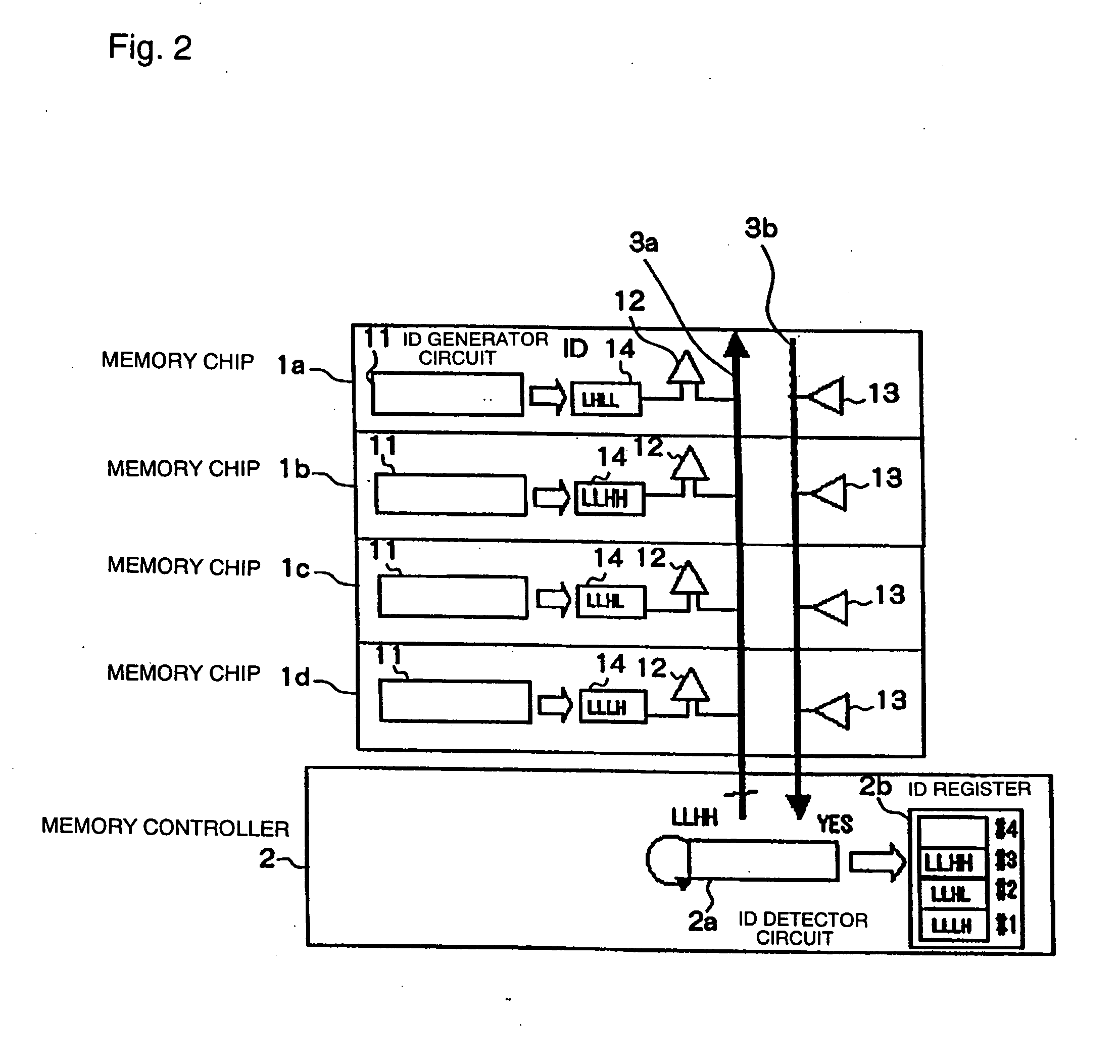

Stacked semiconductor device and semiconductor chip control method

InactiveUS20050082664A1Semiconductor/solid-state device detailsSolid-state devicesMemory chipDetector circuits

Each of stacked memory chips has an ID generator circuit for generating identification information in accordance with its manufacturing process. Since the memory chip manufacturing process implies process variations, the IDs generated by the respective ID generator circuits are different from one another even though the ID generator circuits are identical in design. A memory controller instructs an ID detector circuit to detect the IDs of the respective memory chips, and individually controls the respective memory chips based on the detected IDs.

Owner:ELPIDA MEMORY INC

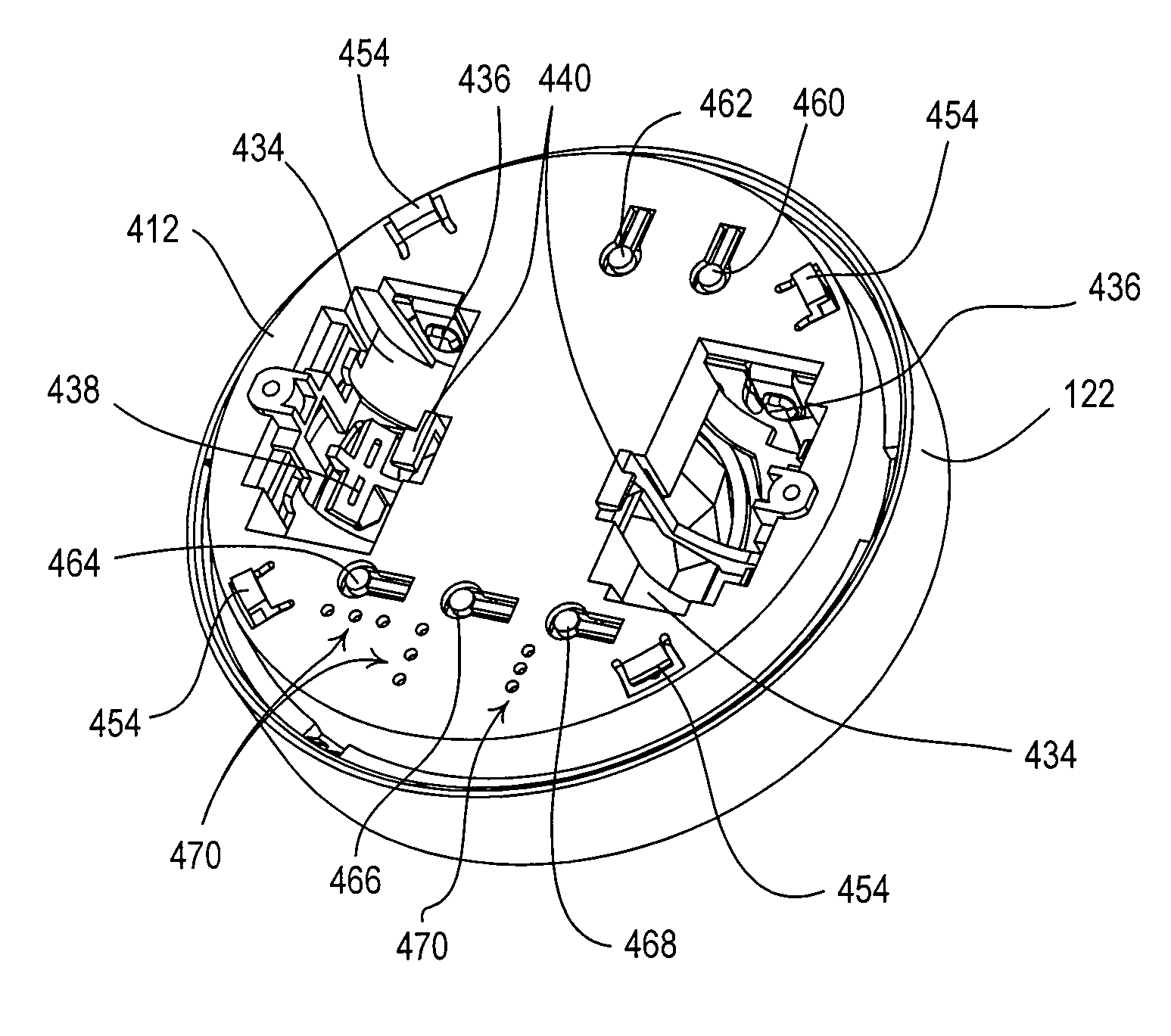

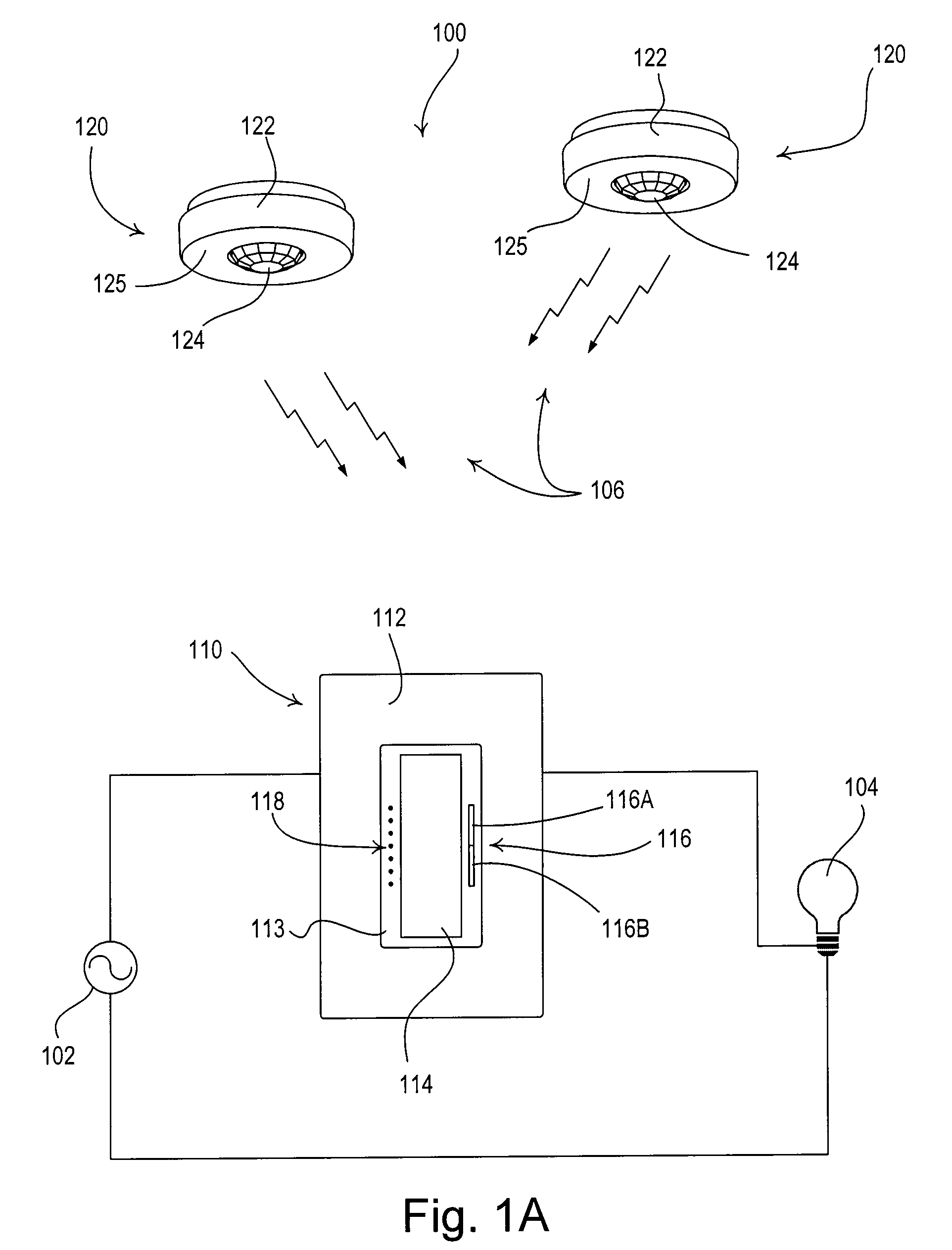

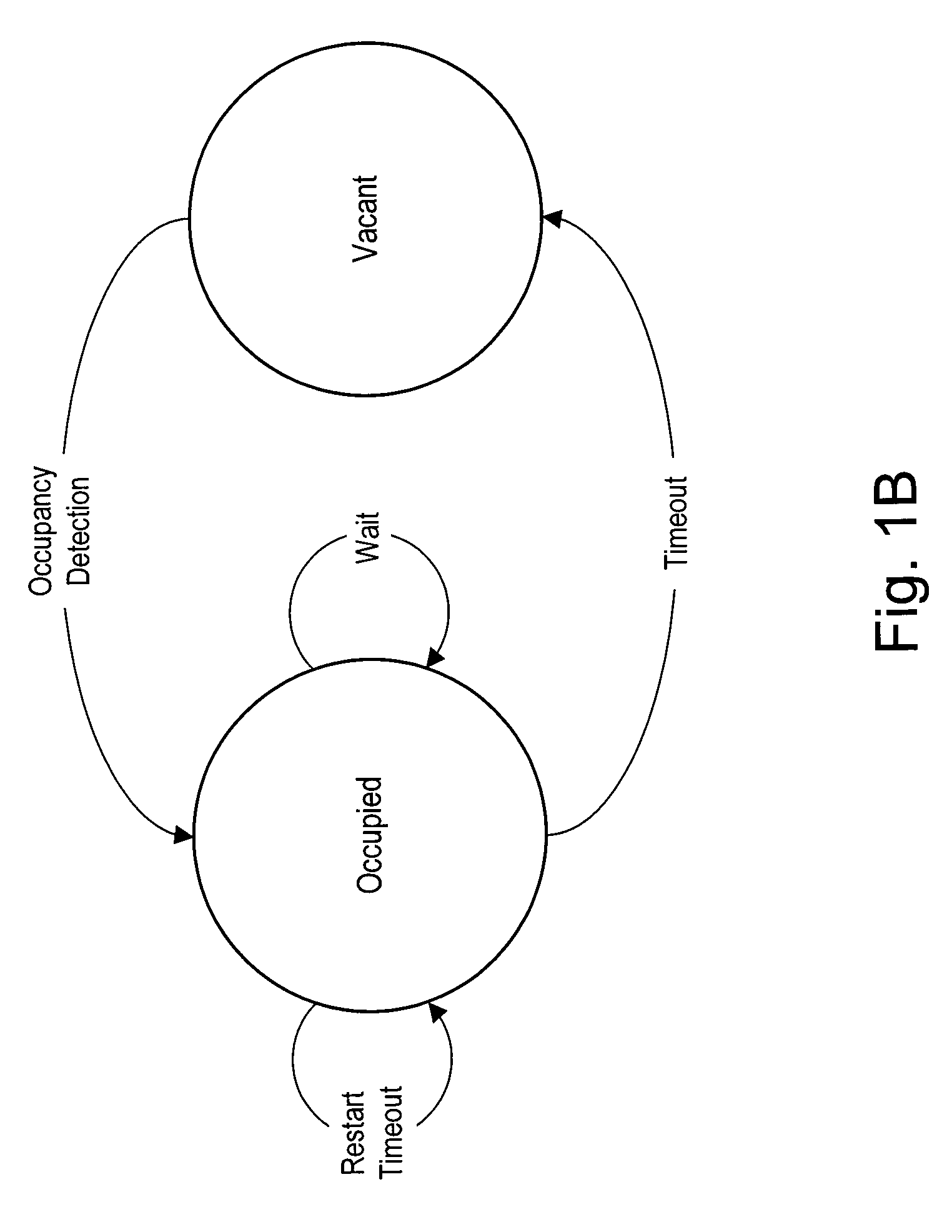

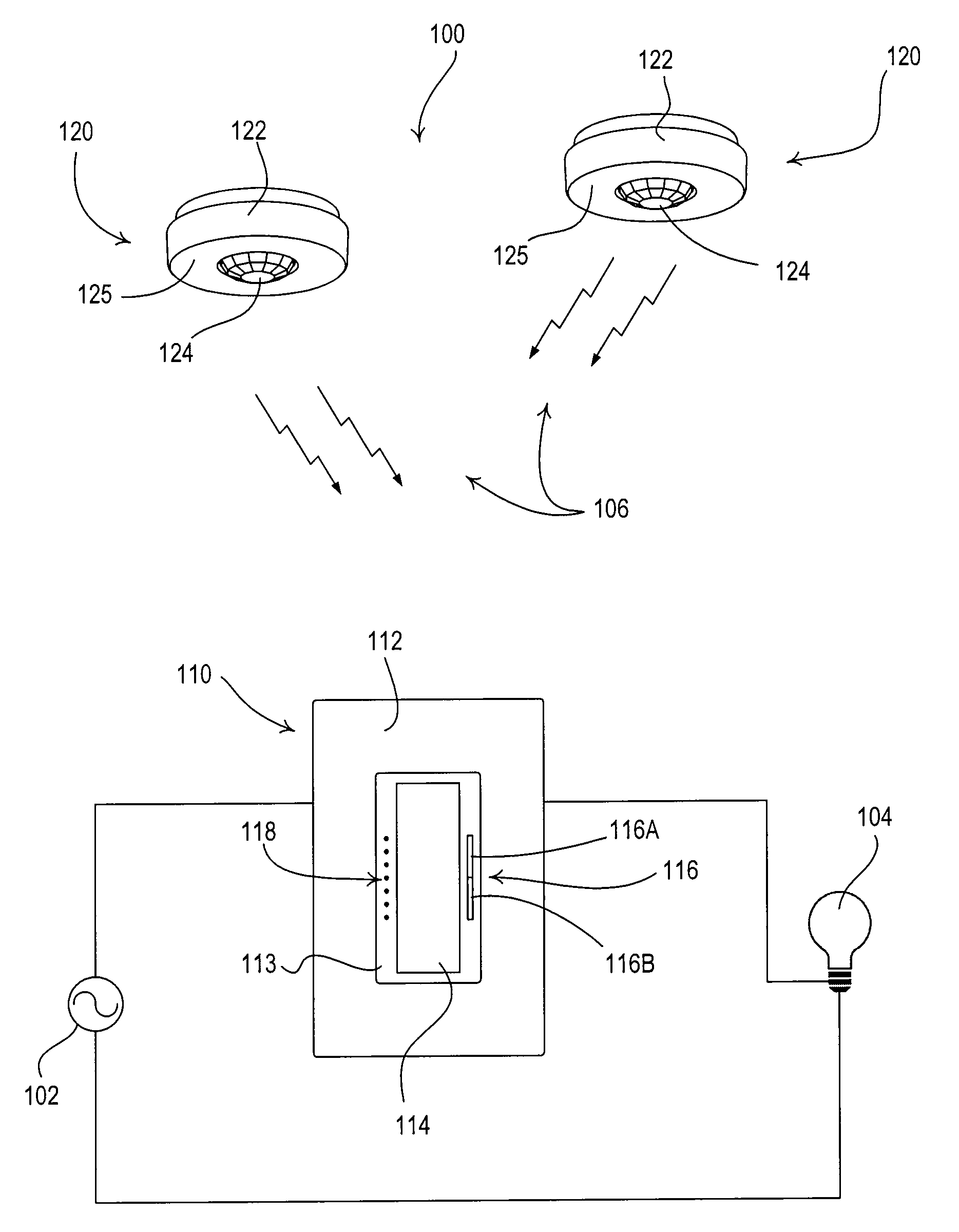

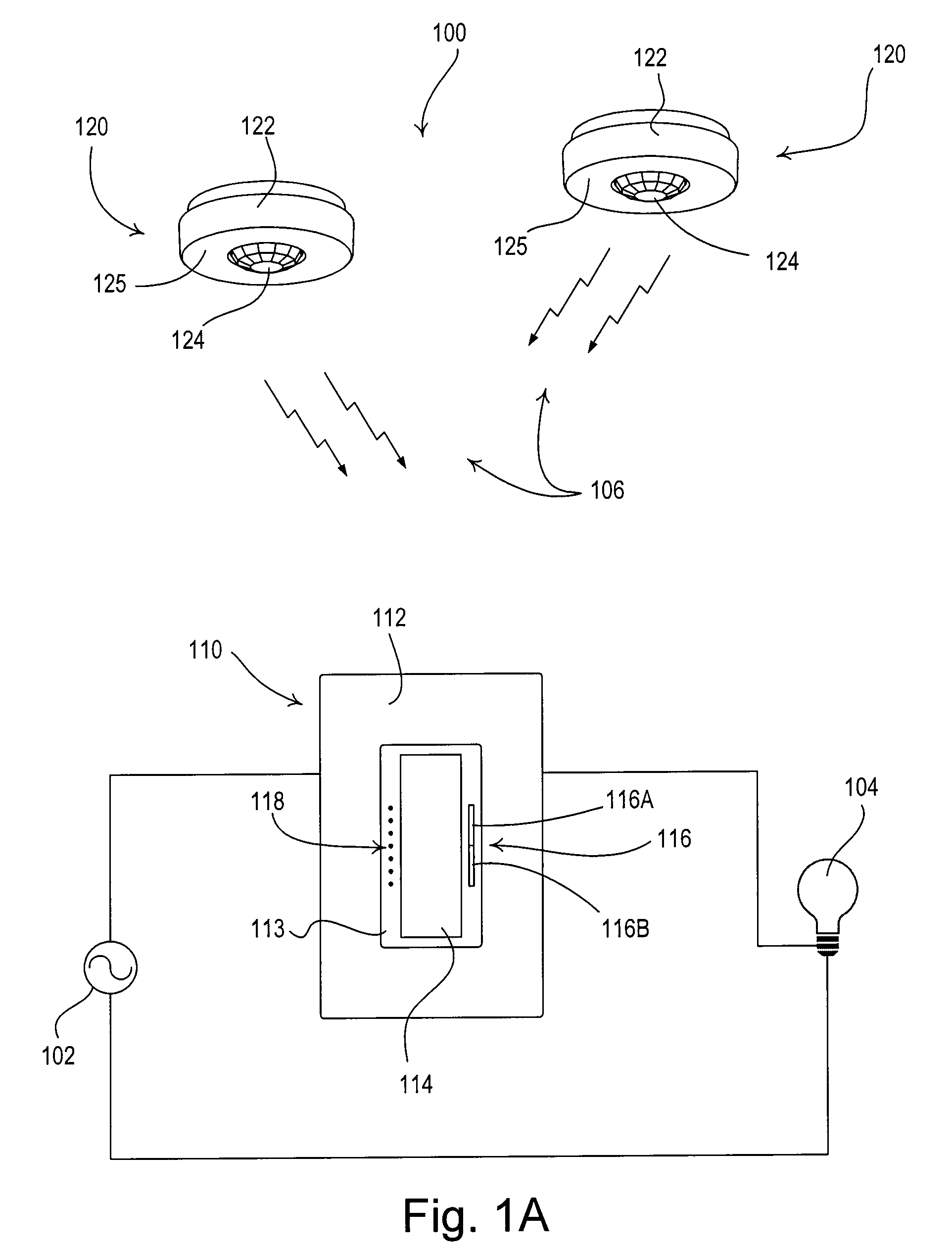

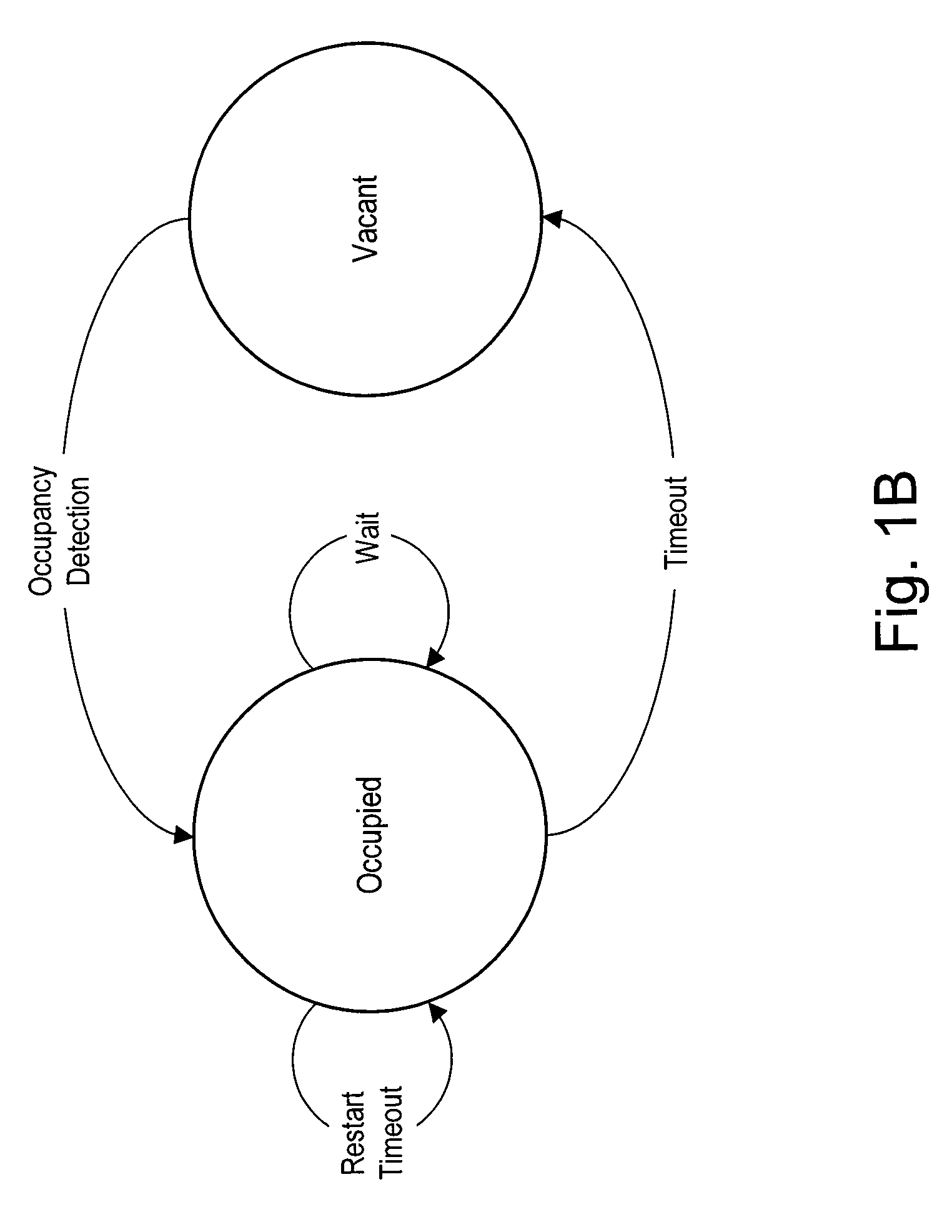

Battery-powered occupancy sensor

A battery-powered occupancy sensor for detecting an occupancy condition in a space comprises first and second batteries, an occupancy detector circuit, a controller, and a wireless transmitter for transmitting a first wireless signal in response to the occupancy detector circuit detecting the occupancy condition in the space. The controller and the wireless transmitter are powered by the first battery, while only the occupancy detector circuit is powered by the second battery, such that the occupancy detector circuit is isolated from noise generated by the controller and the wireless transmitter. The occupancy detector circuit draws a current having a magnitude of approximately 5 microamps or less from the second battery. The occupancy sensor transmits a second wireless signal is response to determining that the voltage of one of the batteries has dropped too low.

Owner:LUTRON TECH CO LLC

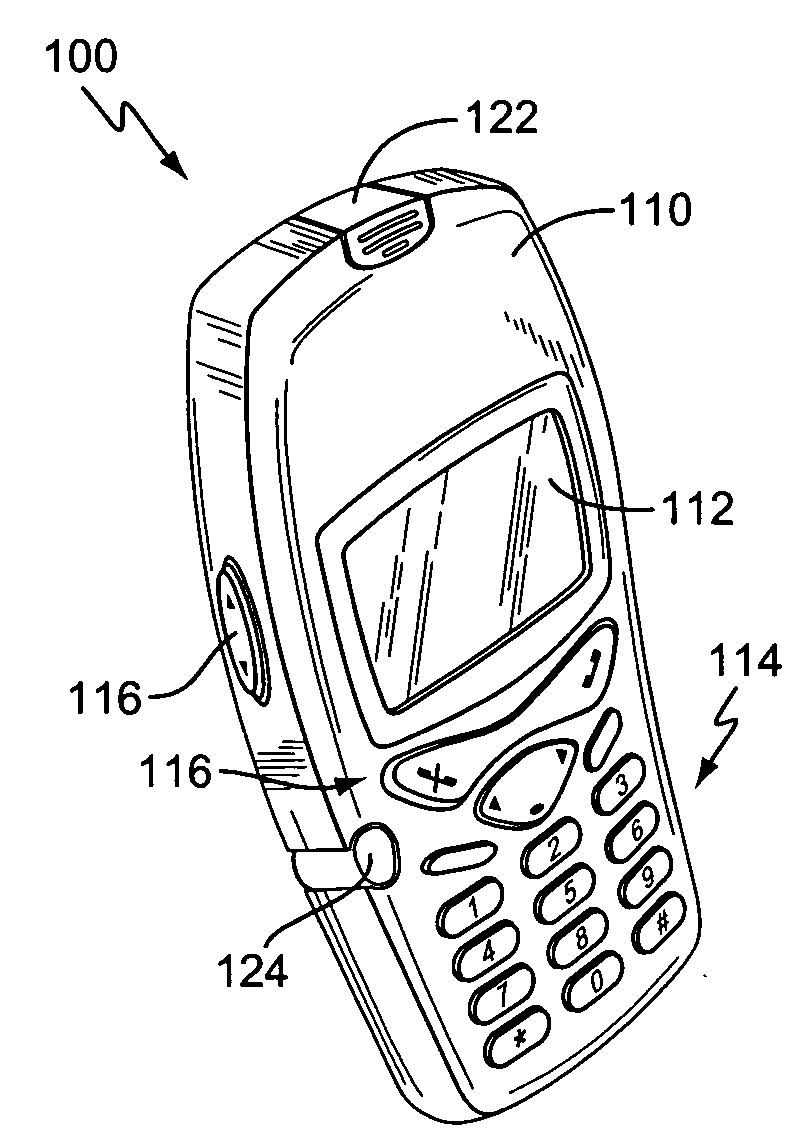

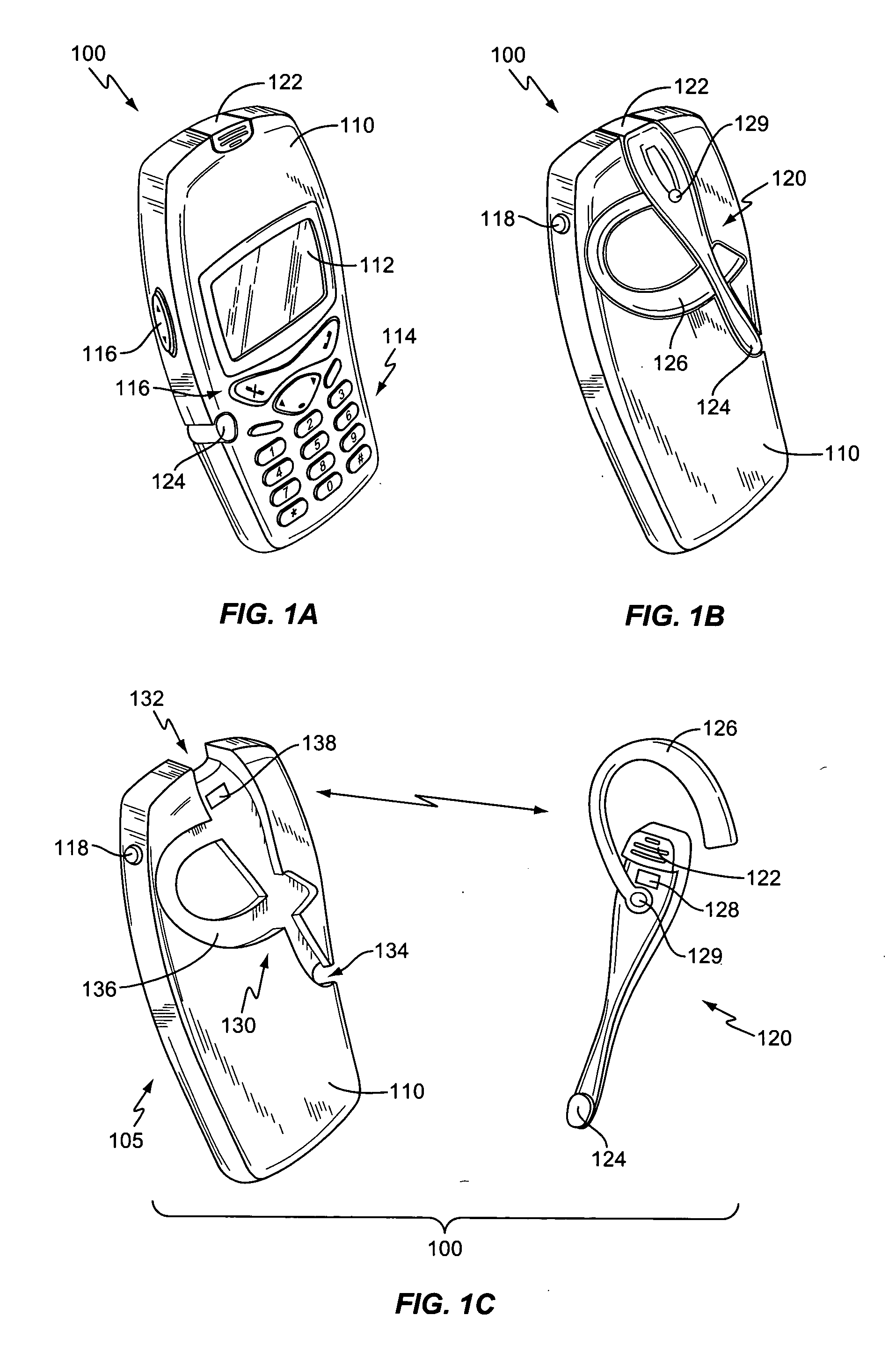

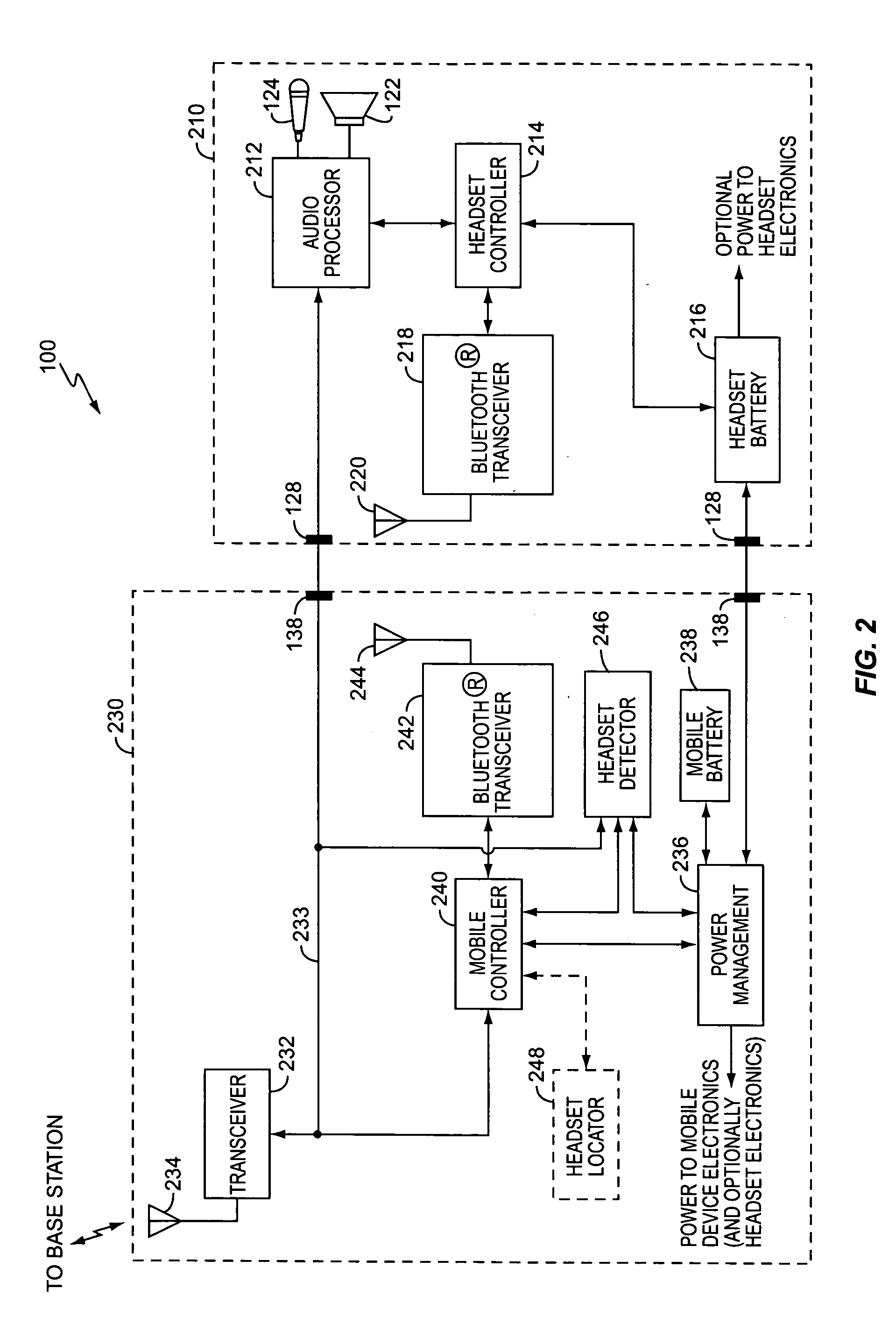

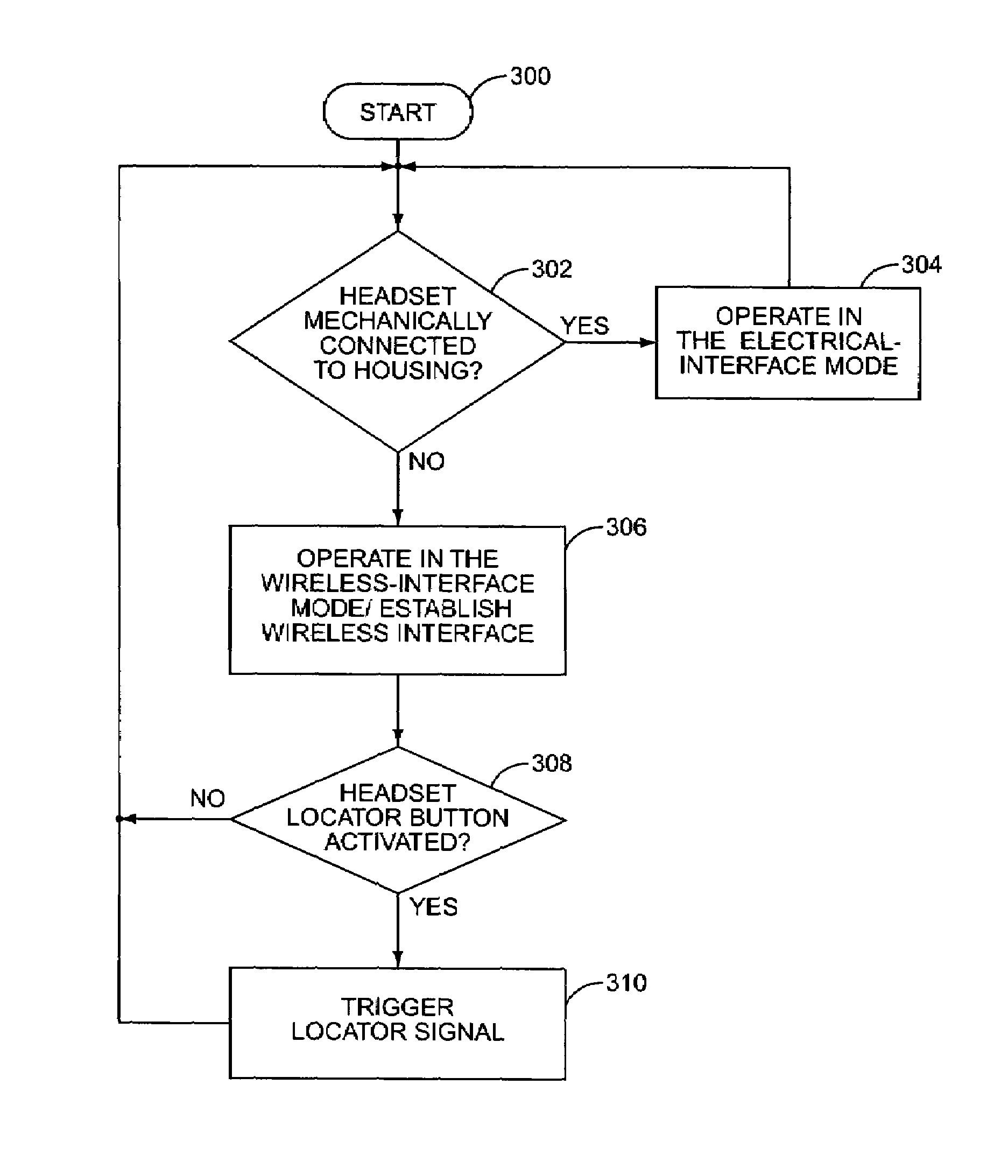

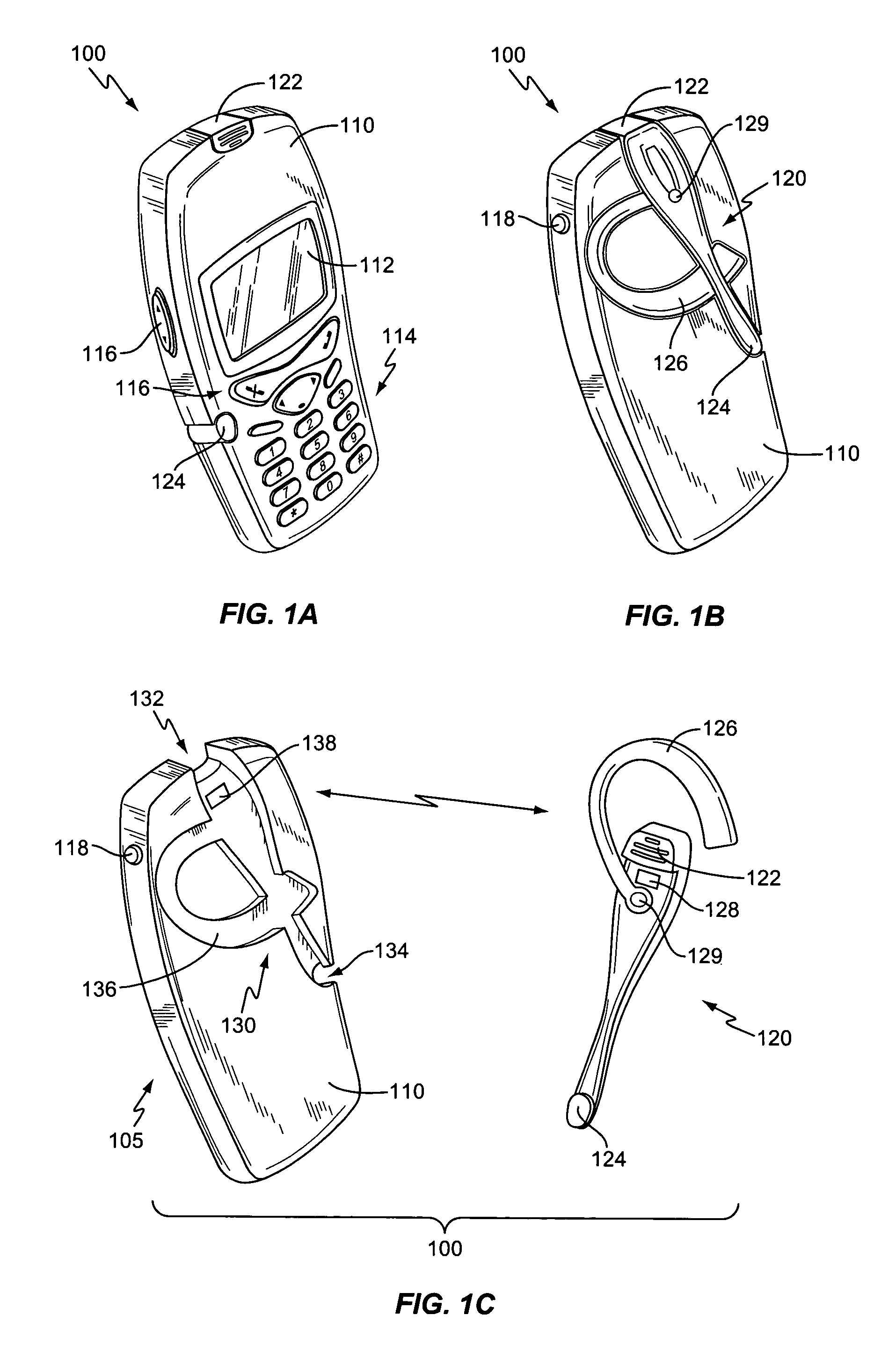

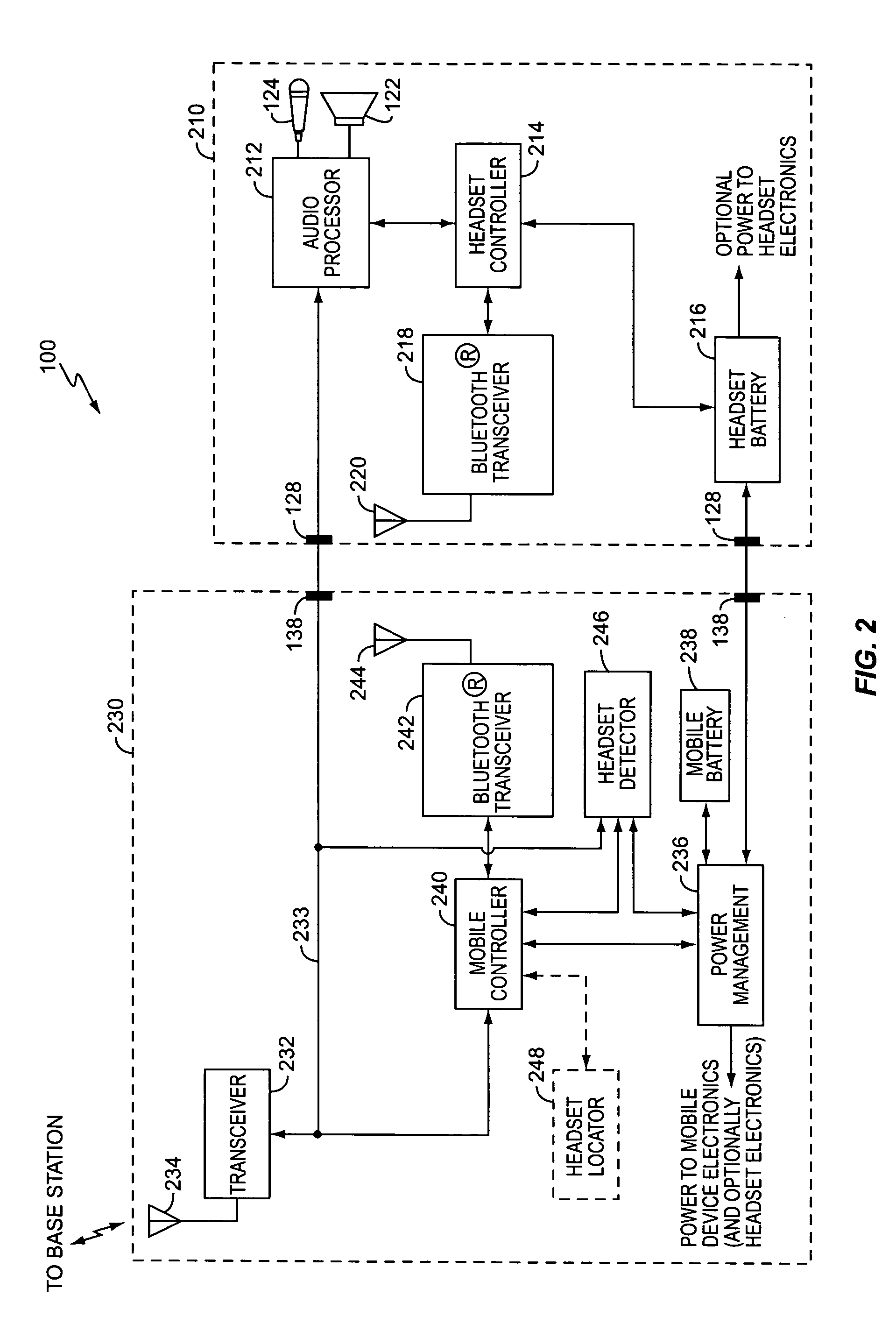

Integrated wireless headset

InactiveUS20050130593A1Interconnection arrangementsSubstation speech amplifiersDetector circuitsEngineering

A mobile device integrates a wireless headset with the housing of a mobile terminal. In an exemplary embodiment, the housing of the mobile terminal includes a fastener for mechanically connecting the wireless headset to the housing. When the wireless headset is mechanically disconnected from the housing, a speaker and microphone associated with the wireless headset interfaces with the mobile terminal via a wireless interface. However, when the wireless headset mechanically connects to the housing, the speaker and microphone associated with the wireless headset mechanically and electrically connect to the housing and operate as the speaker and microphone for the mobile terminal. A detector circuit included in the mobile device also determines the position of the wireless headset relative to the mobile terminal, and may automatically select a wireless or electrical interface between the wireless headset and the mobile terminal based on the determined position.

Owner:SONY ERICSSON MOBILE COMM AB

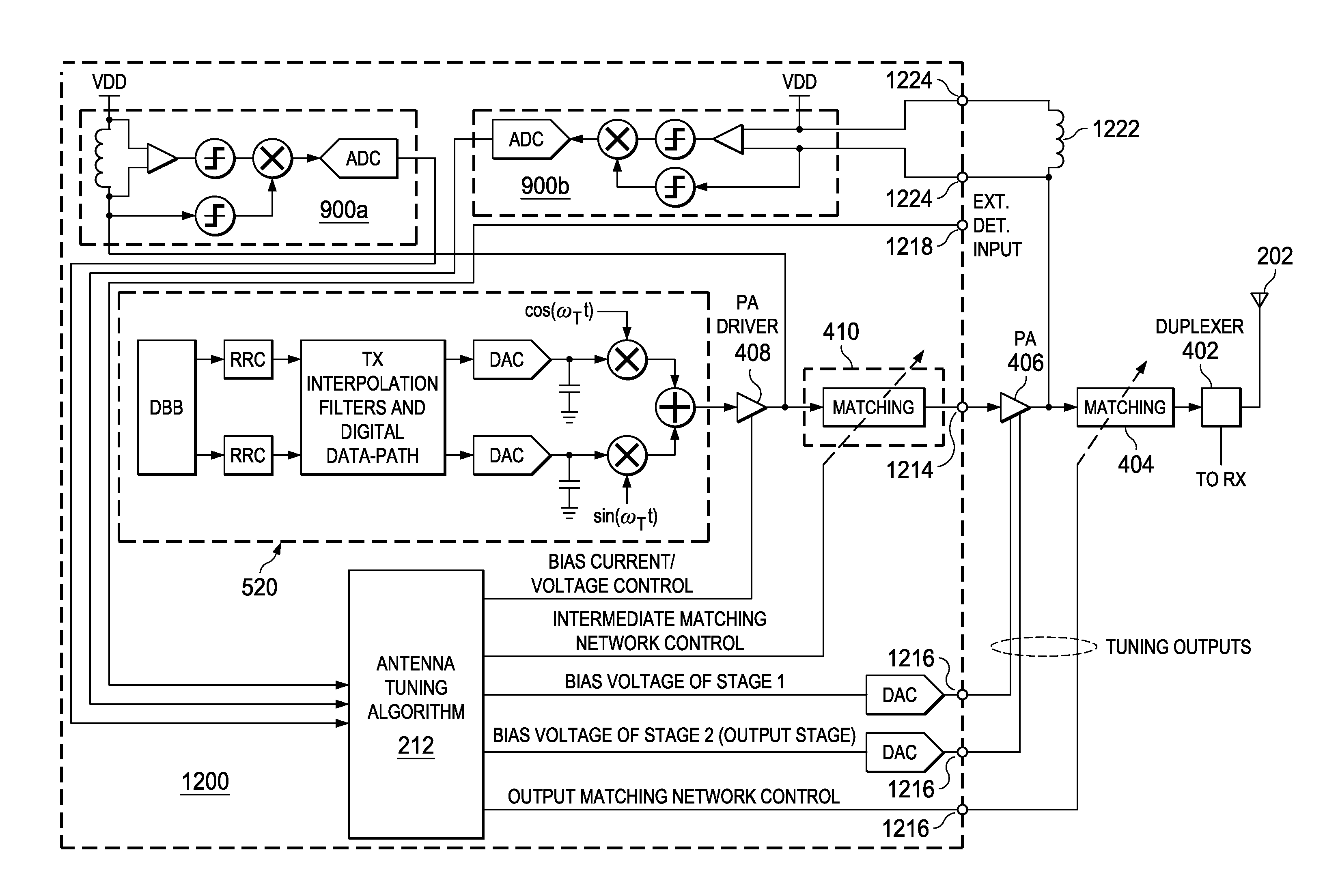

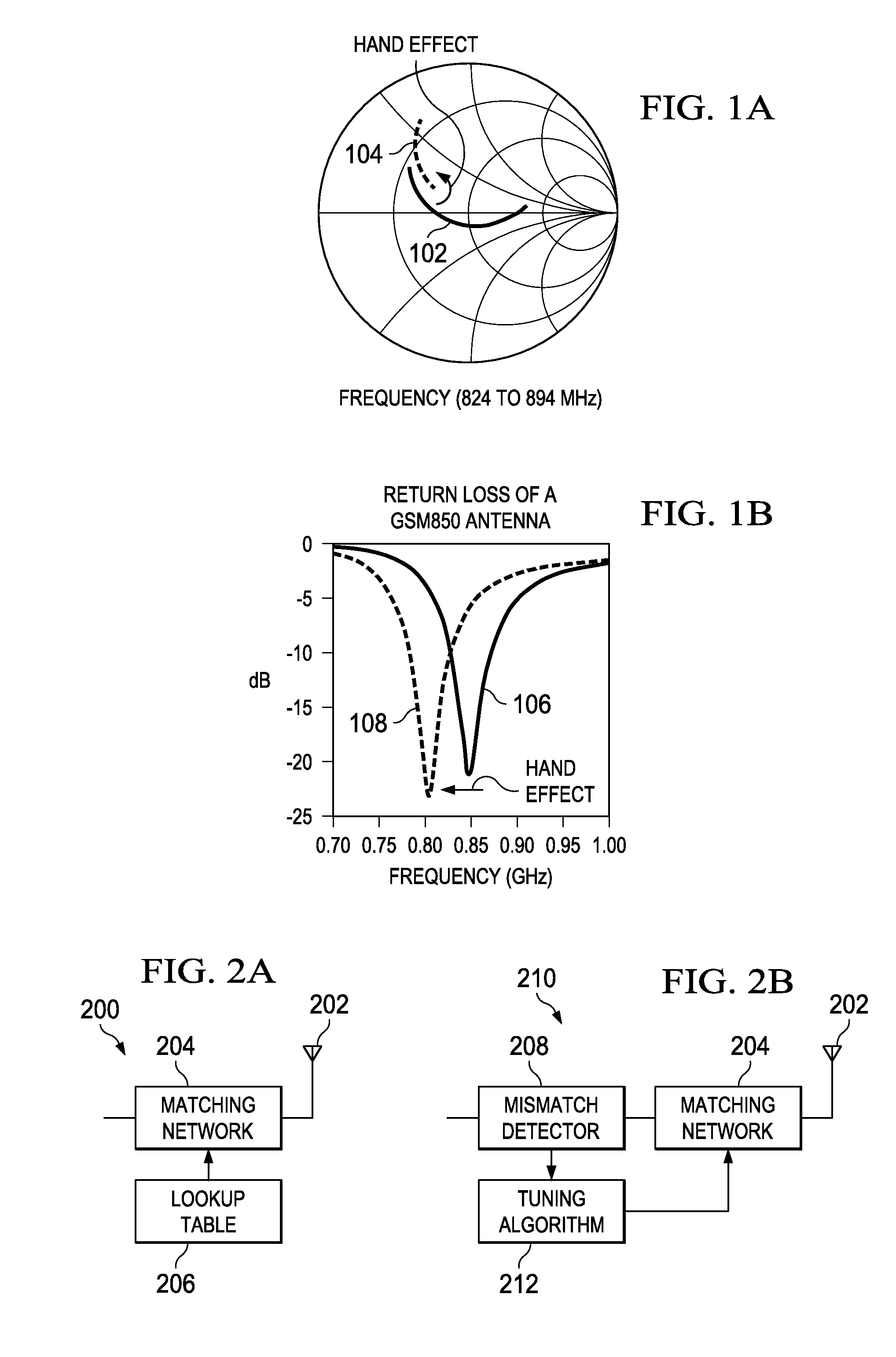

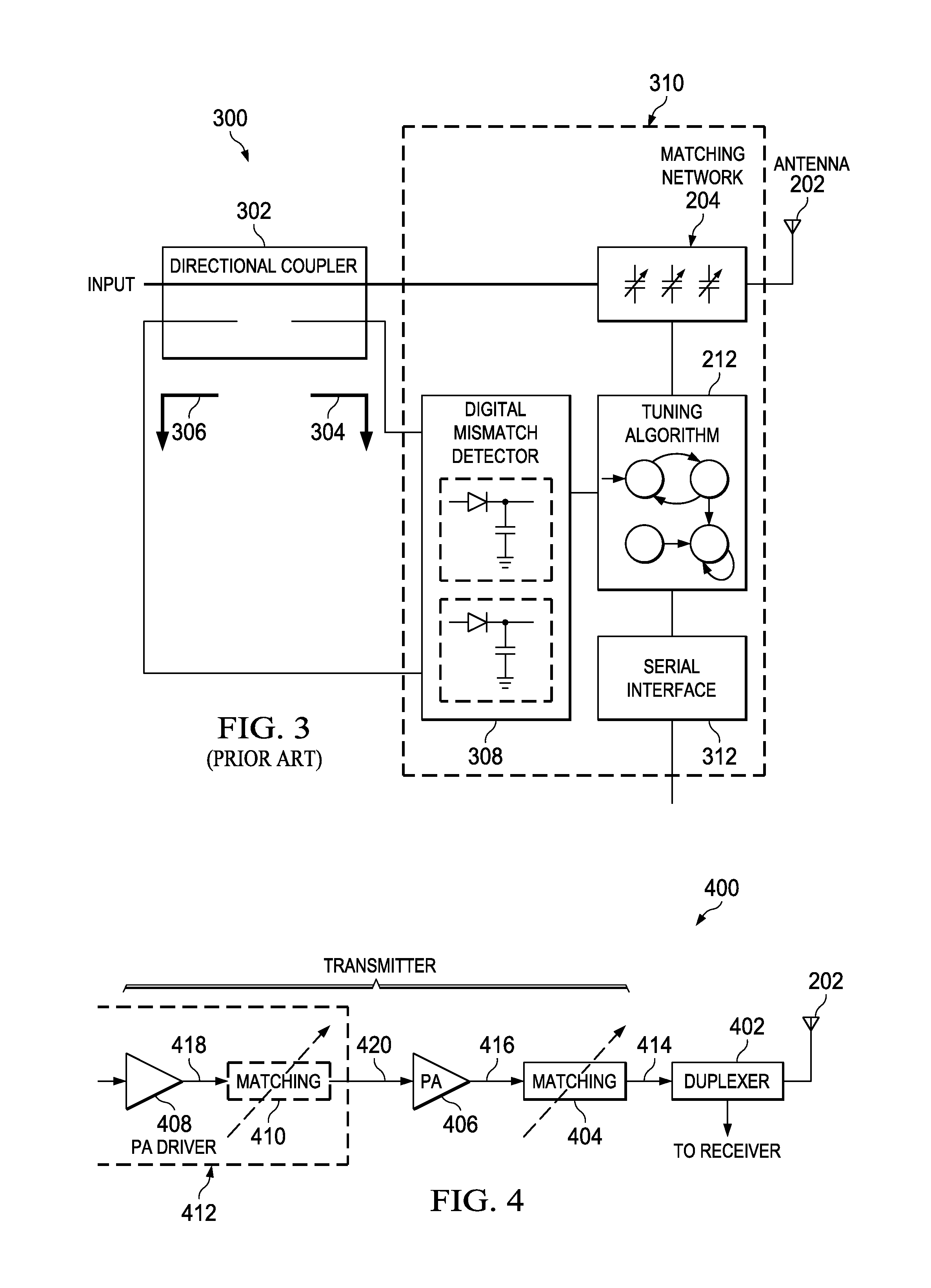

Method and apparatus for antenna tuning

ActiveUS20110086600A1Reduce Impedance MismatchReduce biasResonant long antennasNegative-feedback-circuit arrangementsTransceiverOperating point

A method for tuning a transmitter in order to improve impedance matching to an antenna or to intermediate radio frequency stages uses an error detector that senses a deviation of the amplitude or phase angle of a load current of a power amplifier driver or of a power amplifier. A controller calculates a correction and dynamically adjusts tunable transmitter parameters, which may include values of components in matching networks or bias voltages in the power amplifier or the power amplifier driver, so as to reduce the deviation and thereby improve the impedance matching. The load current of the power amplifier may alternatively be sensed by measuring the duty cycle of its switching mode power supply. A transmitter having a power amplifier and one or more tunable circuit elements incorporates an error detector that senses the amplitude or phase of a load current and a controller that adjusts one or more tunable parameters to reduce impedance mismatch. An integrated circuit device suitable for use in a transmitter includes a power amplifier driver circuit and a detector circuit capable of sensing a load current, and a controller circuit that can adjust tunable parameters either within or external to the integrated circuit. By eliminating directional couplers and integrating the detectors and power amplifier drivers, the size, complexity, and cost of wireless transceivers can be reduced, while efficiency and power consumption are improved through the dynamic adjustment of operating points and impedance matching.

Owner:TEXAS INSTR INC

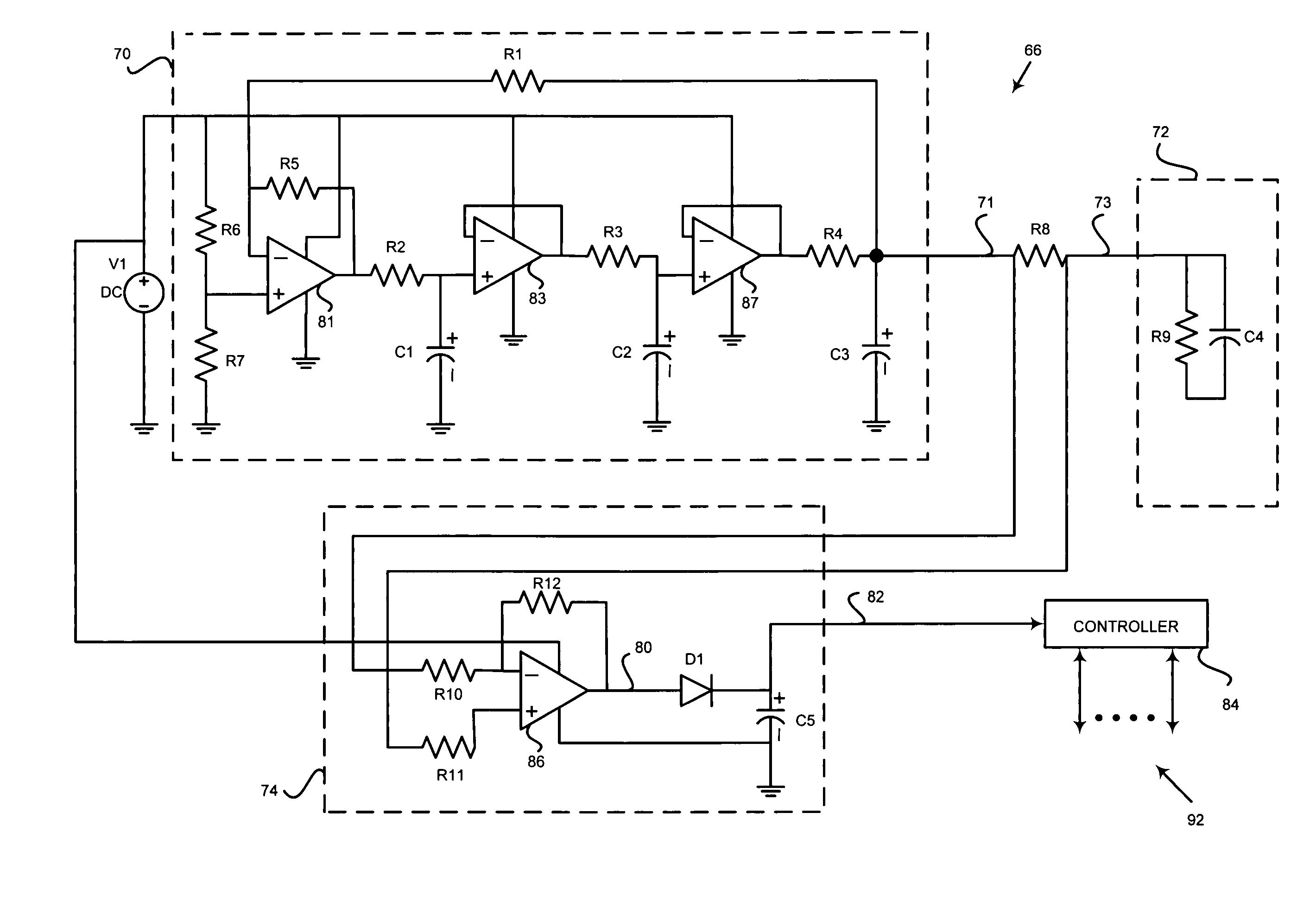

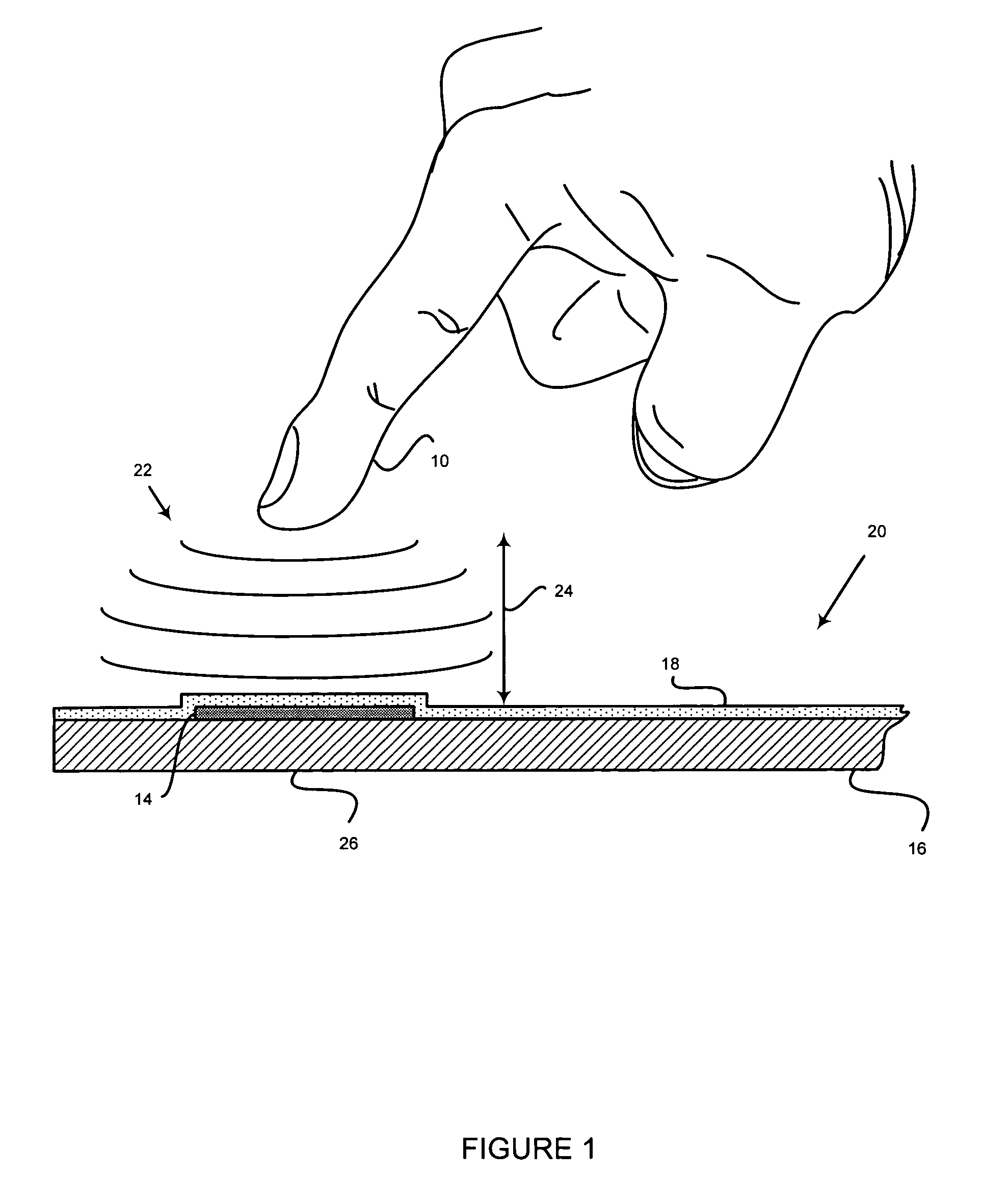

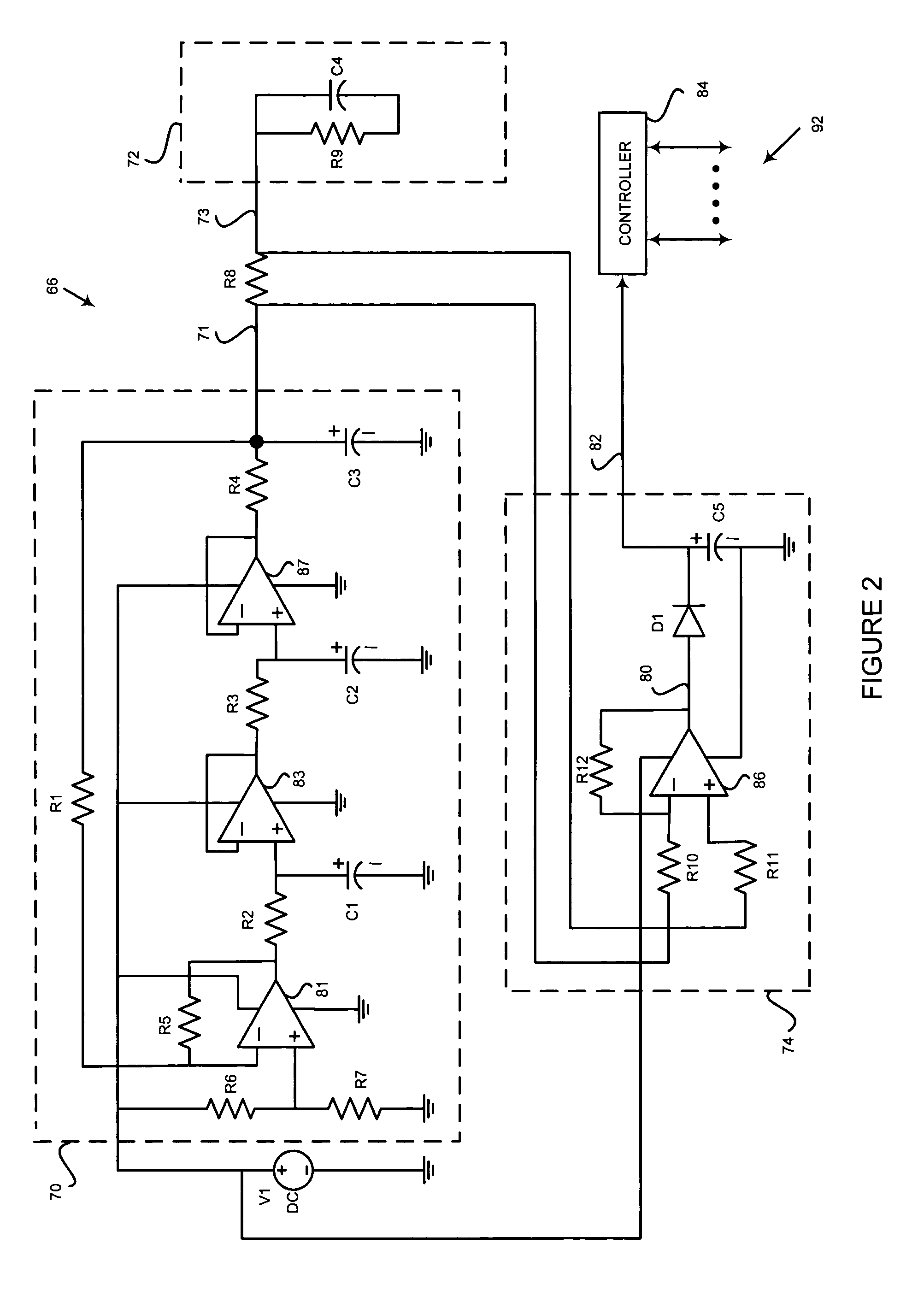

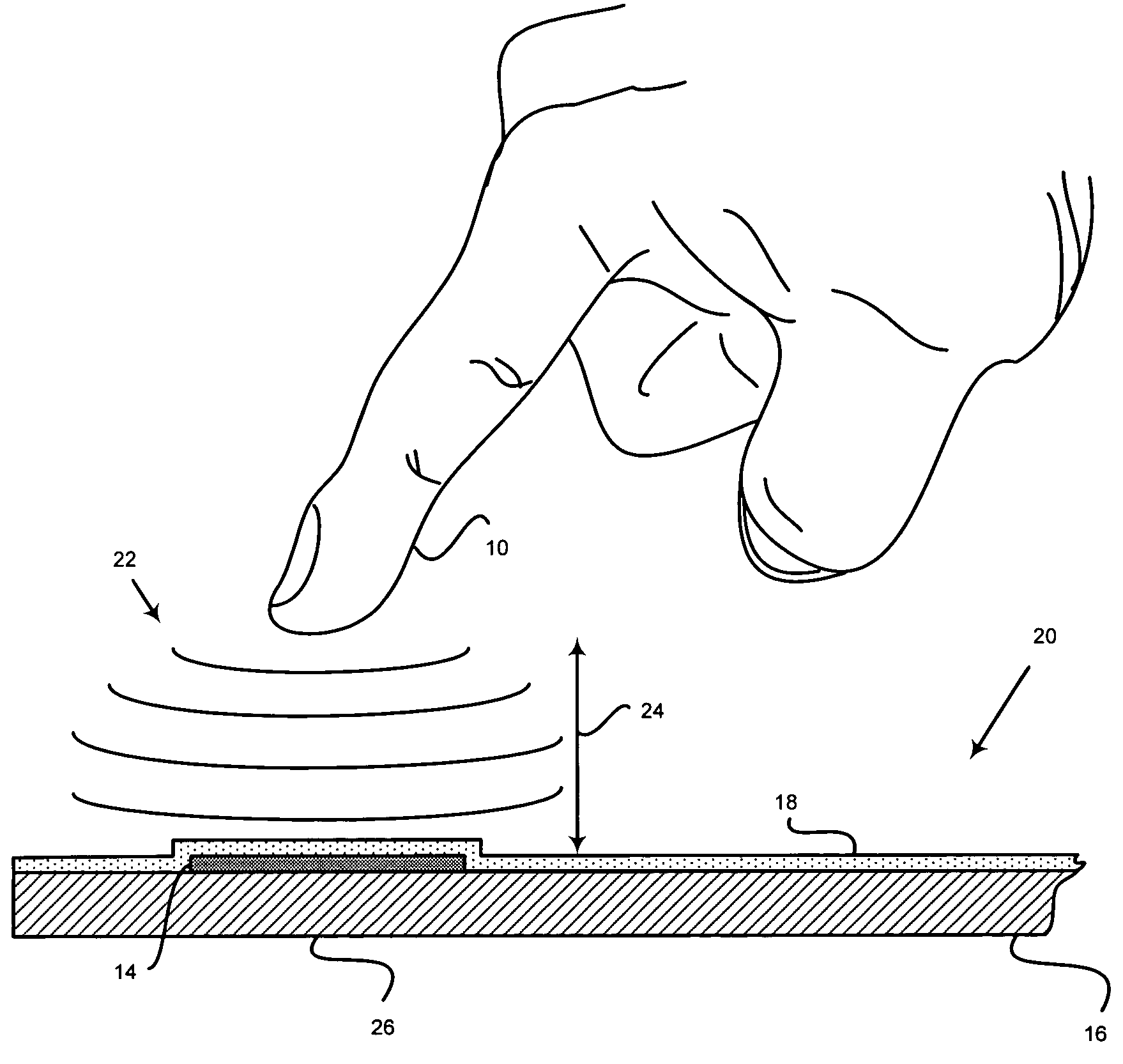

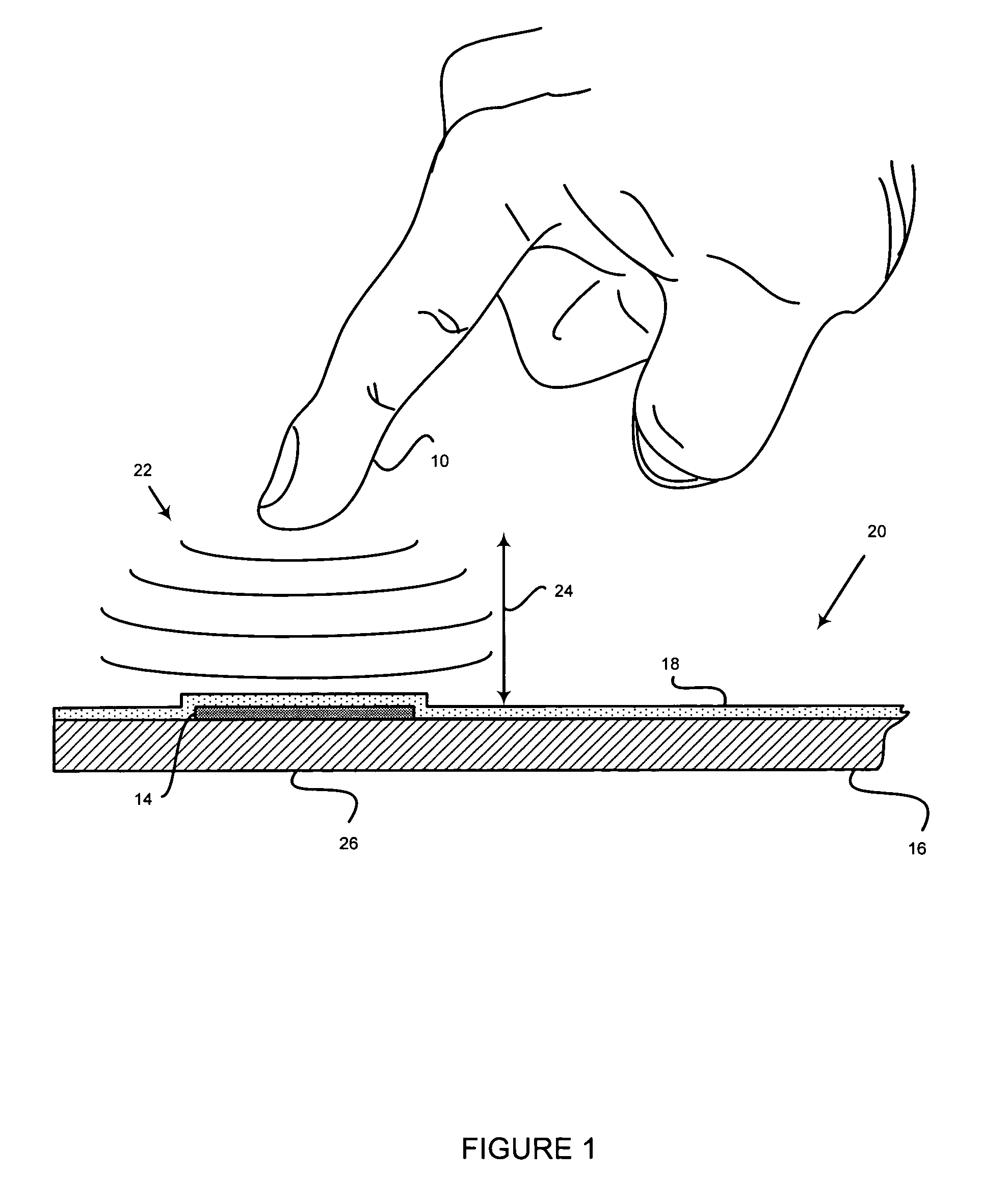

Electric field proximity keyboards and detection systems

ActiveUS7145552B2High resolutionReduce complexityInput/output for user-computer interactionElectronic switchingDetector circuitsImage resolution

Owner:SOLECTRON

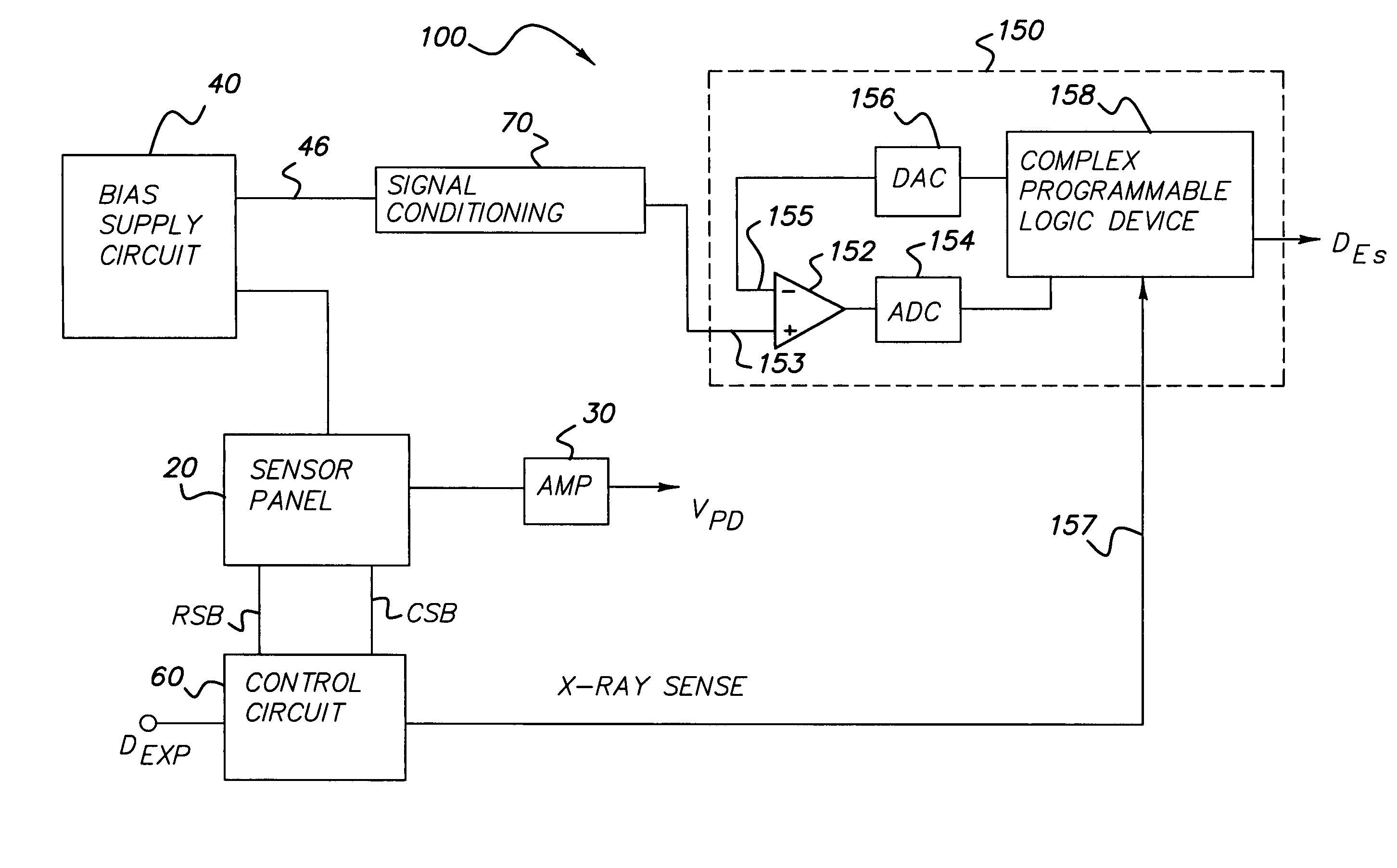

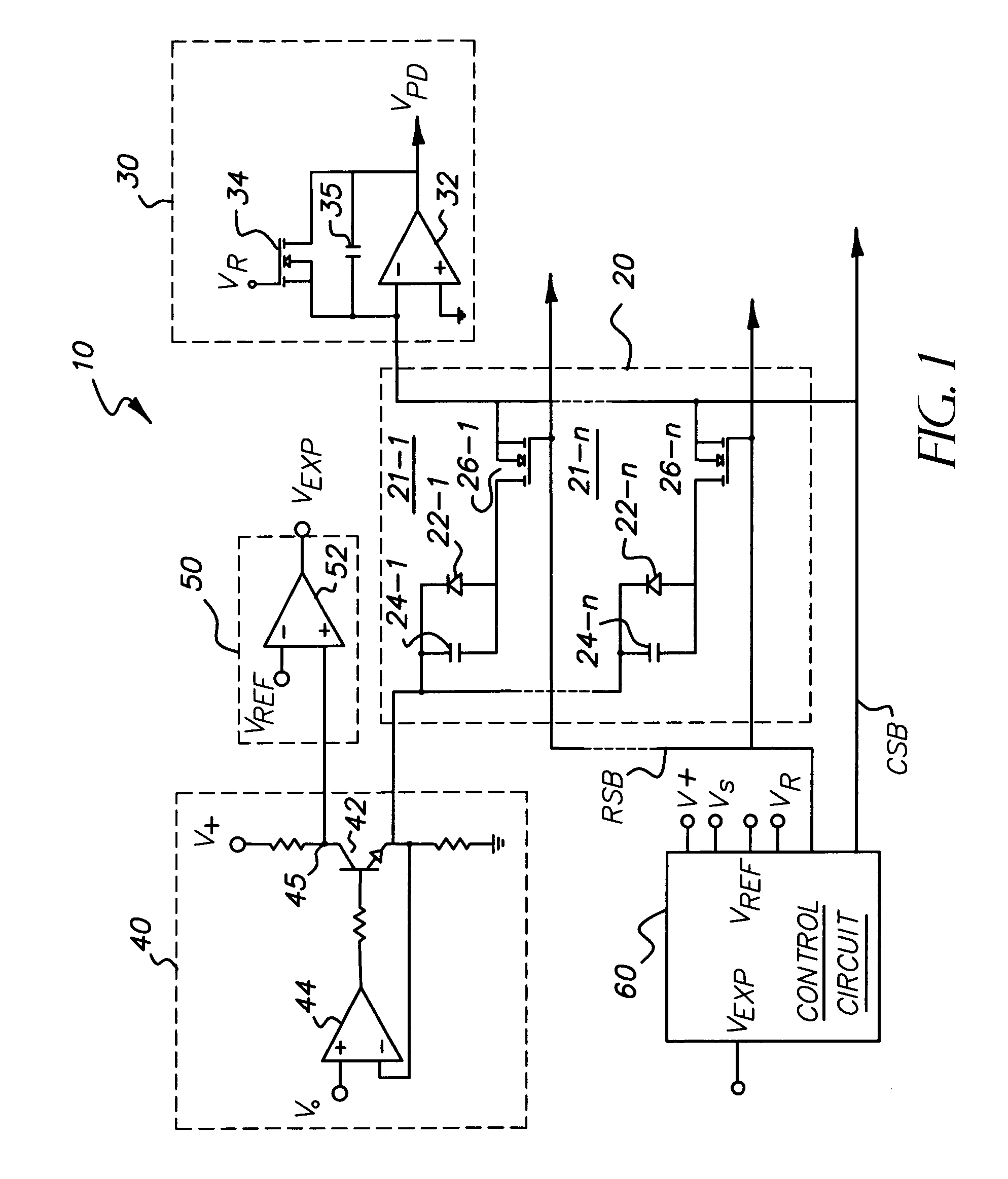

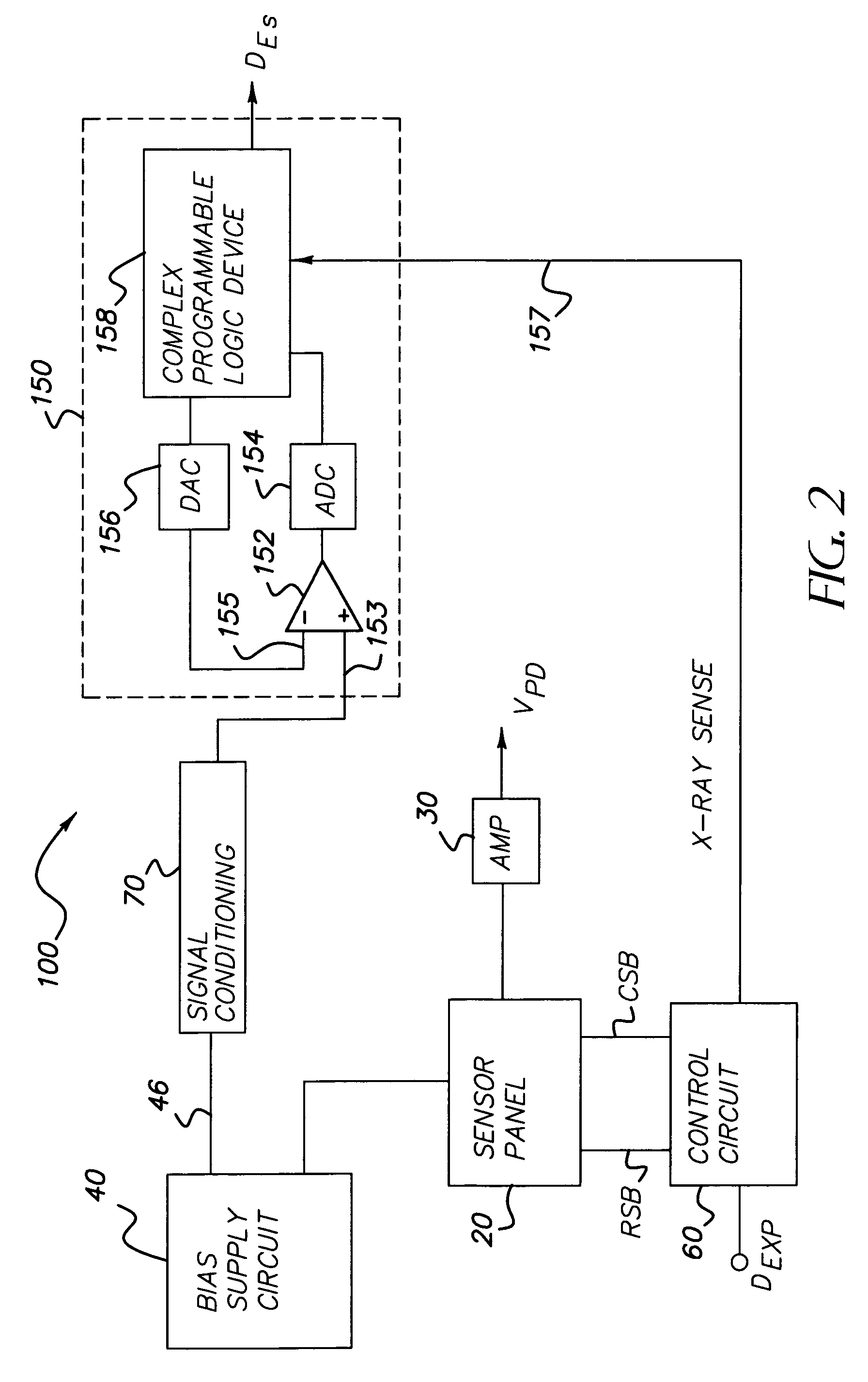

Wireless X-ray detector for a digital radiography system with remote X-ray event detection

ActiveUS7211803B1Improve signal-to-noise ratioQuick checkMaterial analysis using wave/particle radiationRadiation/particle handlingDetector circuitsX-ray

A wireless X-ray detector for a digital radiography system with remote detection of impinging radiation from the system X-ray source onto a sensor panel having amorphous or crystalline silicon photodiodes or metal insulated semiconductor (MIS) sensors. Changes in current in the photodiode bias supply circuit is sensed to generate a signal indicating presence of radiation. Improved detection of X-ray cessation is achieved either by leaving at least one line of sensors connected between the bias supply circuit to a virtual ground during charge accumulation or by using an X-ray presence detector circuit that increases the sensitivity of the detector circuit to bias circuit current changes occurring after onset of the radiation.

Owner:CARESTREAM HEALTH INC

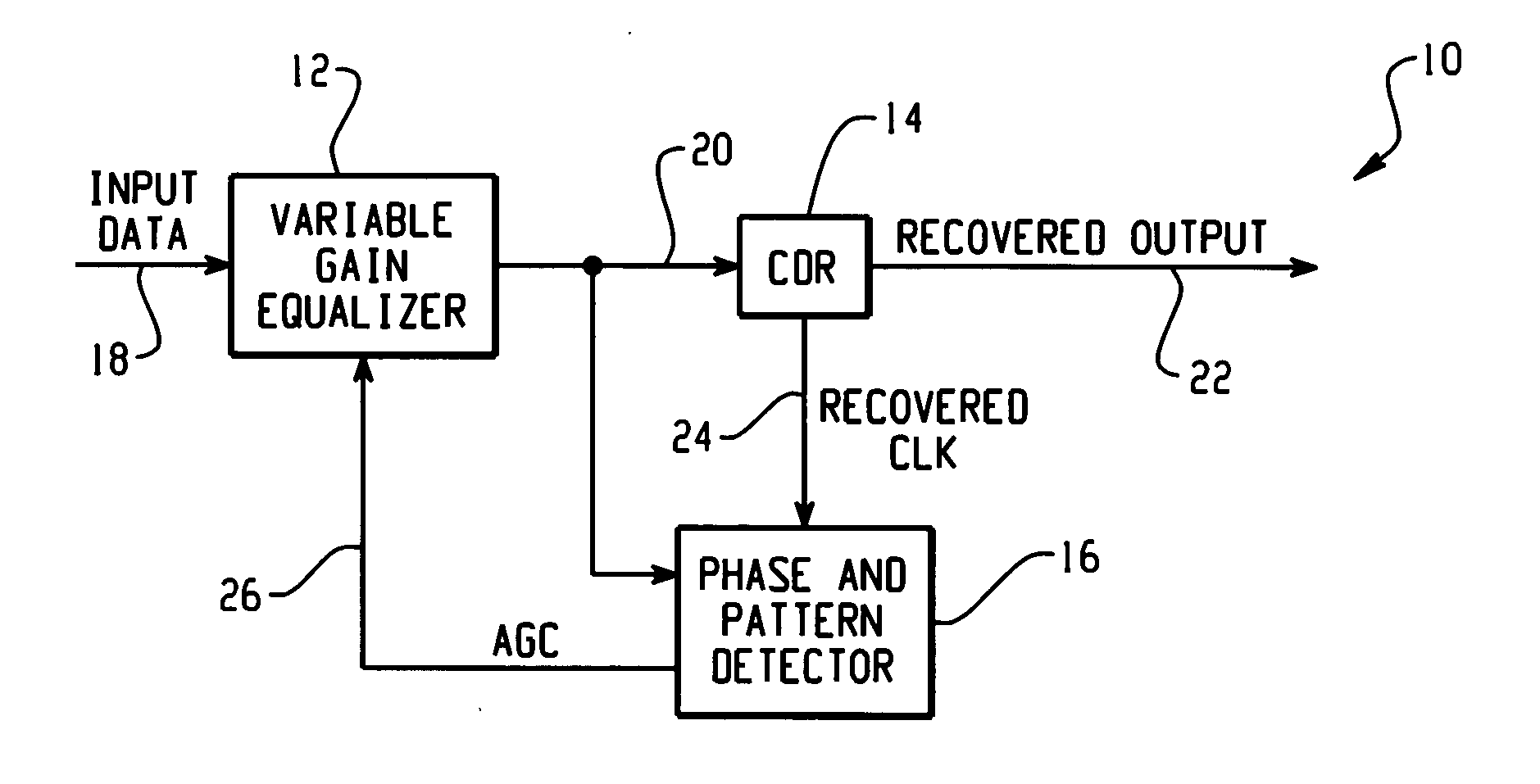

Precision adaptive equalizer

InactiveUS20050047500A1Multiple-port networksAdaptive networkDetector circuitsAutomatic gain control

In accordance with the teachings described herein, systems and methods are provided for a precision adaptive equalizer. A variable gain equalizer may be used to apply a variable gain to an input signal to generate an equalized output signal. A phase and pattern detector circuit may be coupled in a feedback loop with the variable gain equalizer. The phase and pattern detector circuit may be used to identify a high frequency data pattern in the equalized output signal and compare the high frequency data pattern with a clock signal to detect a high frequency phase error. The phase and pattern detector circuit may be further operable to generate an automatic gain control signal as a function of the high frequency phase error, the automatic gain control signal being fed back to the variable gain equalizer to control the variable gain applied to the input signal.

Owner:SEMTECH CANADA

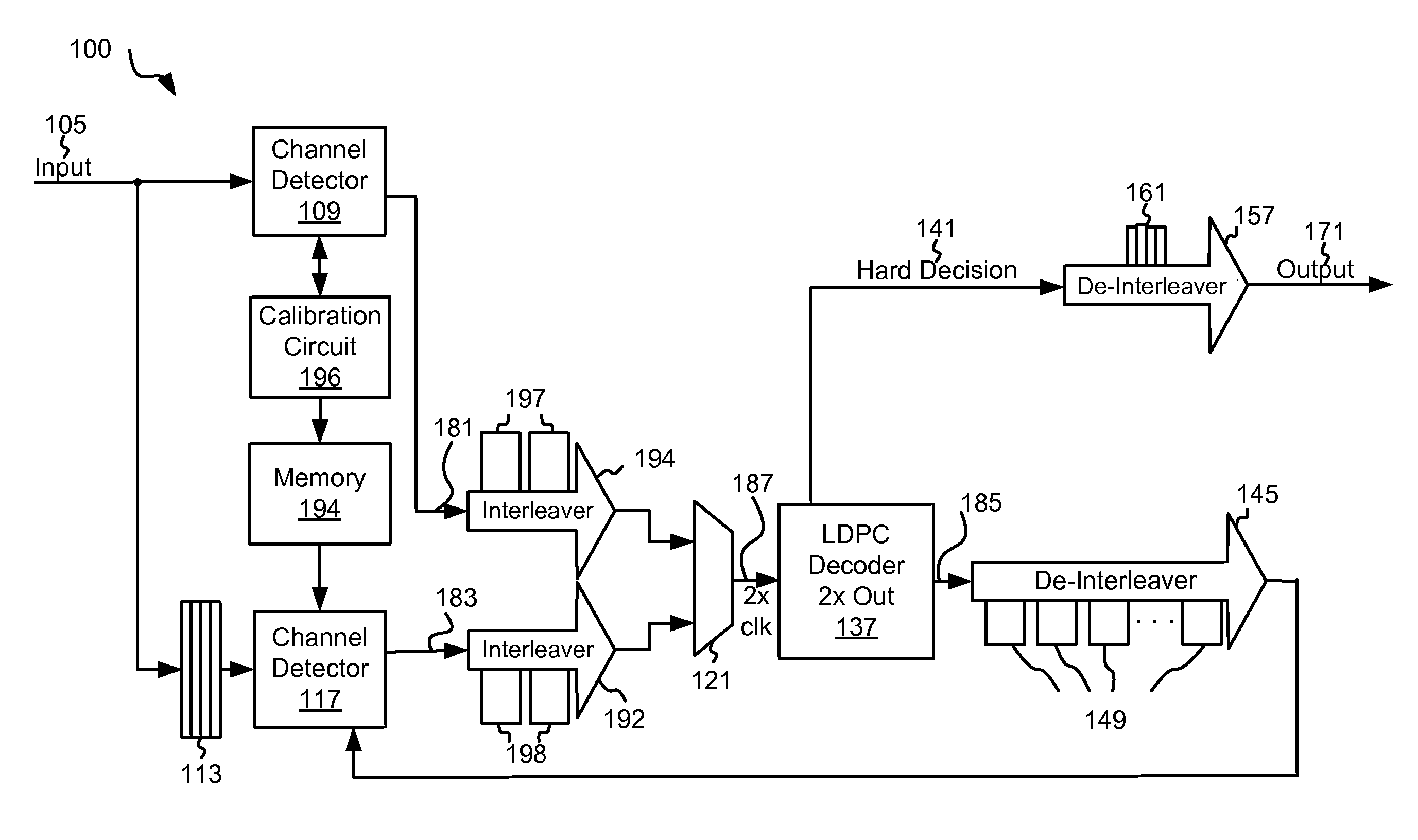

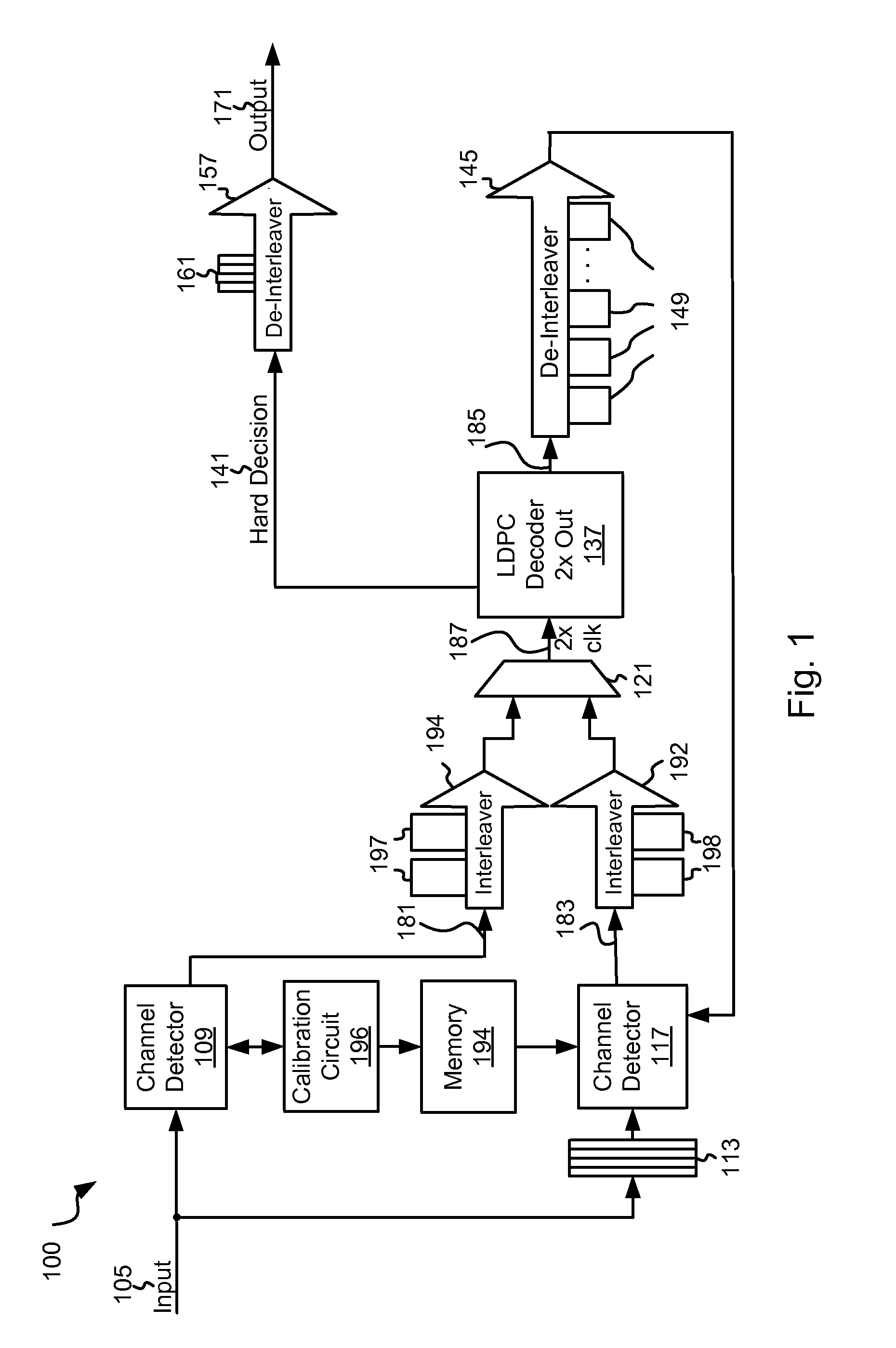

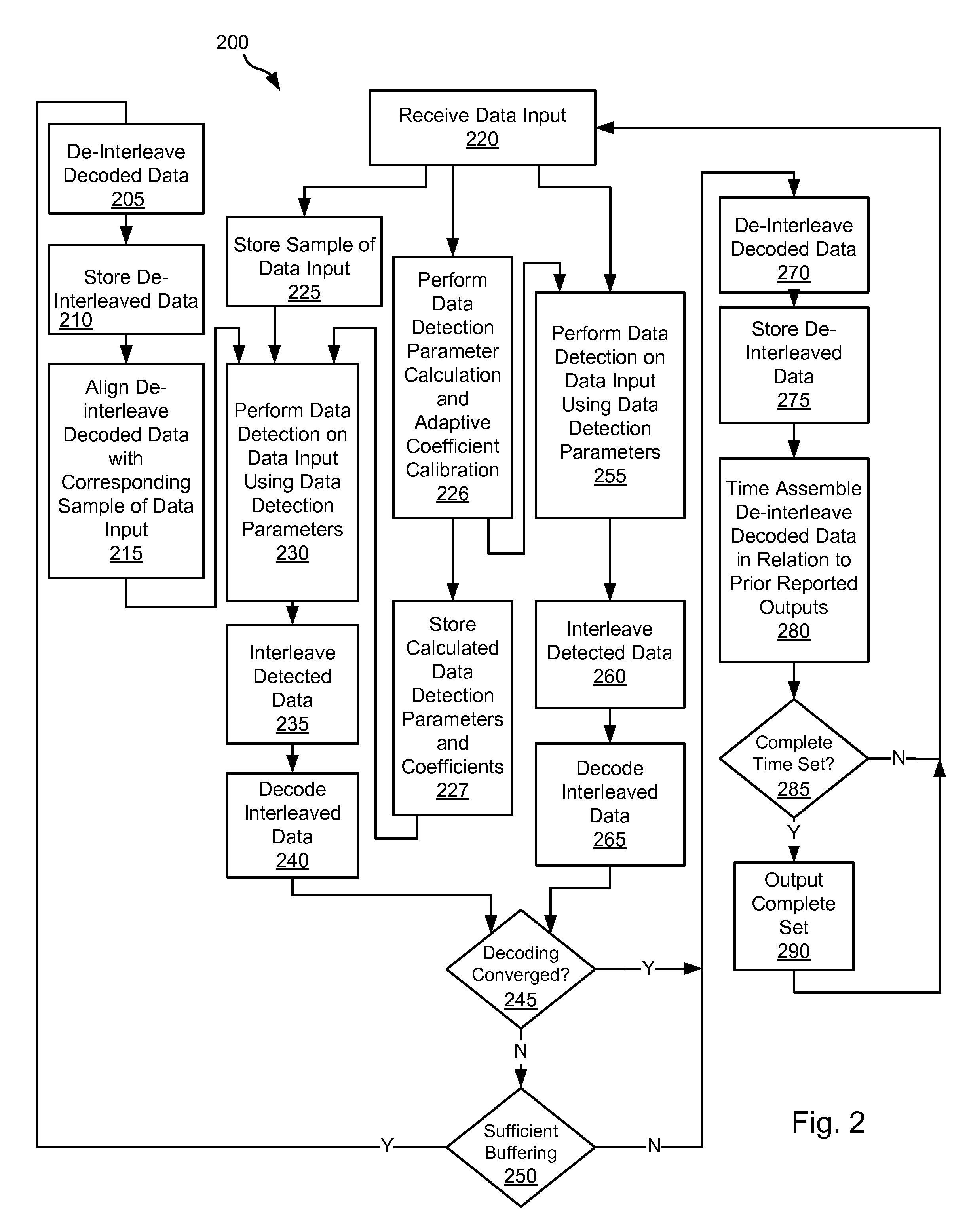

Systems and Methods for Updating Detector Parameters in a Data Processing Circuit

ActiveUS20110167227A1Data representation error detection/correctionError detection/correctionDetector circuitsData set

Various embodiments of the present invention provide systems and methods for updating detector parameters in a data processing circuit. For example, a data processing circuit is disclosed that includes a first detector circuit, a second detector circuit, and a calibration circuit. The first detector circuit is operable to receive a first data set and to apply a data detection algorithm to the first data set, and the second detector circuit is operable to receive a second data set and to apply the data detection algorithm to the second data set. The calibration circuit is operable to calculate a data detection parameter based upon a third data set. The data detection parameter is used by the first detector circuit in applying the data detection algorithm to the first data set during a period that the data detection parameter is used by the second detector circuit in applying the data detection algorithm to the second data set.

Owner:AVAGO TECH INT SALES PTE LTD

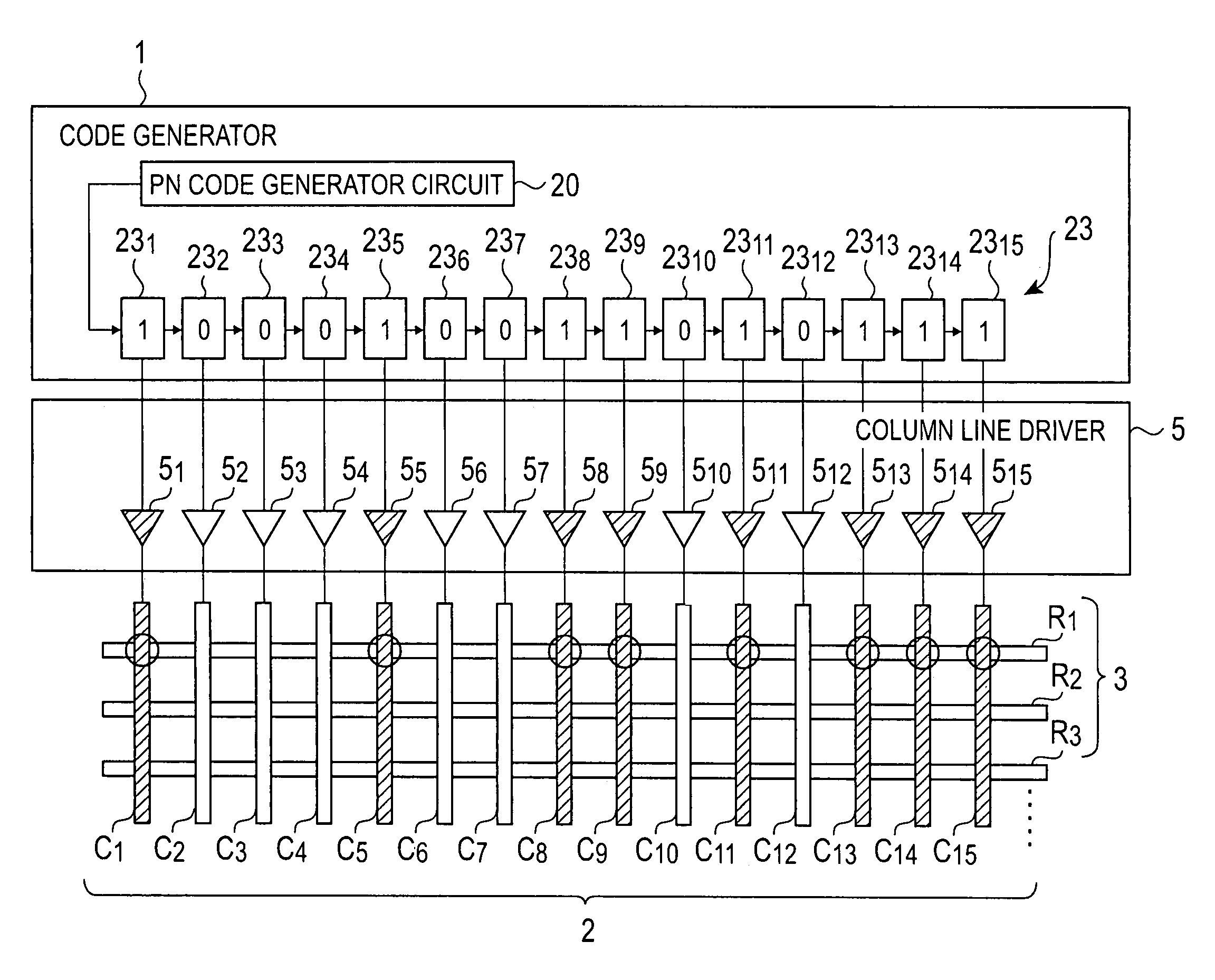

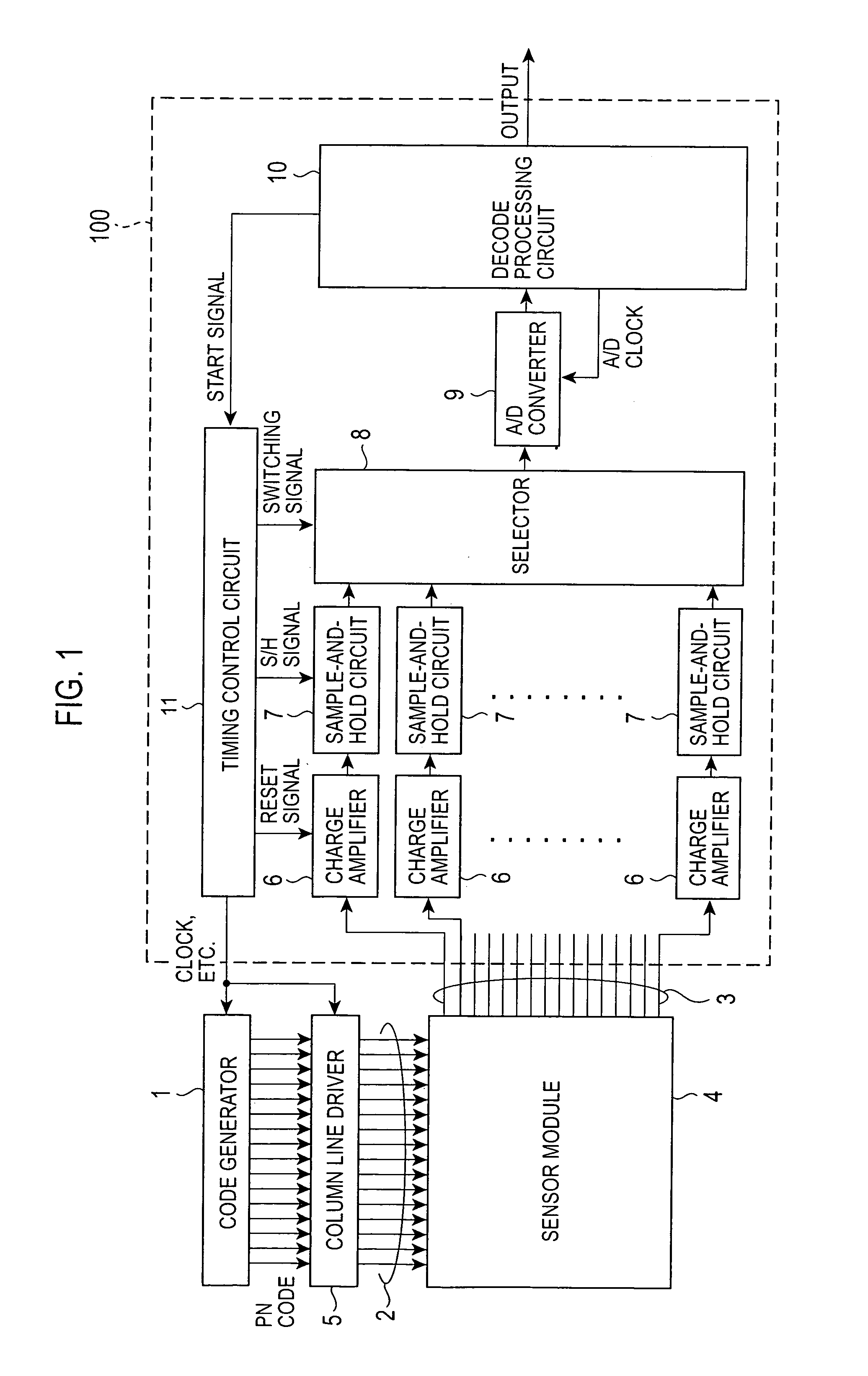

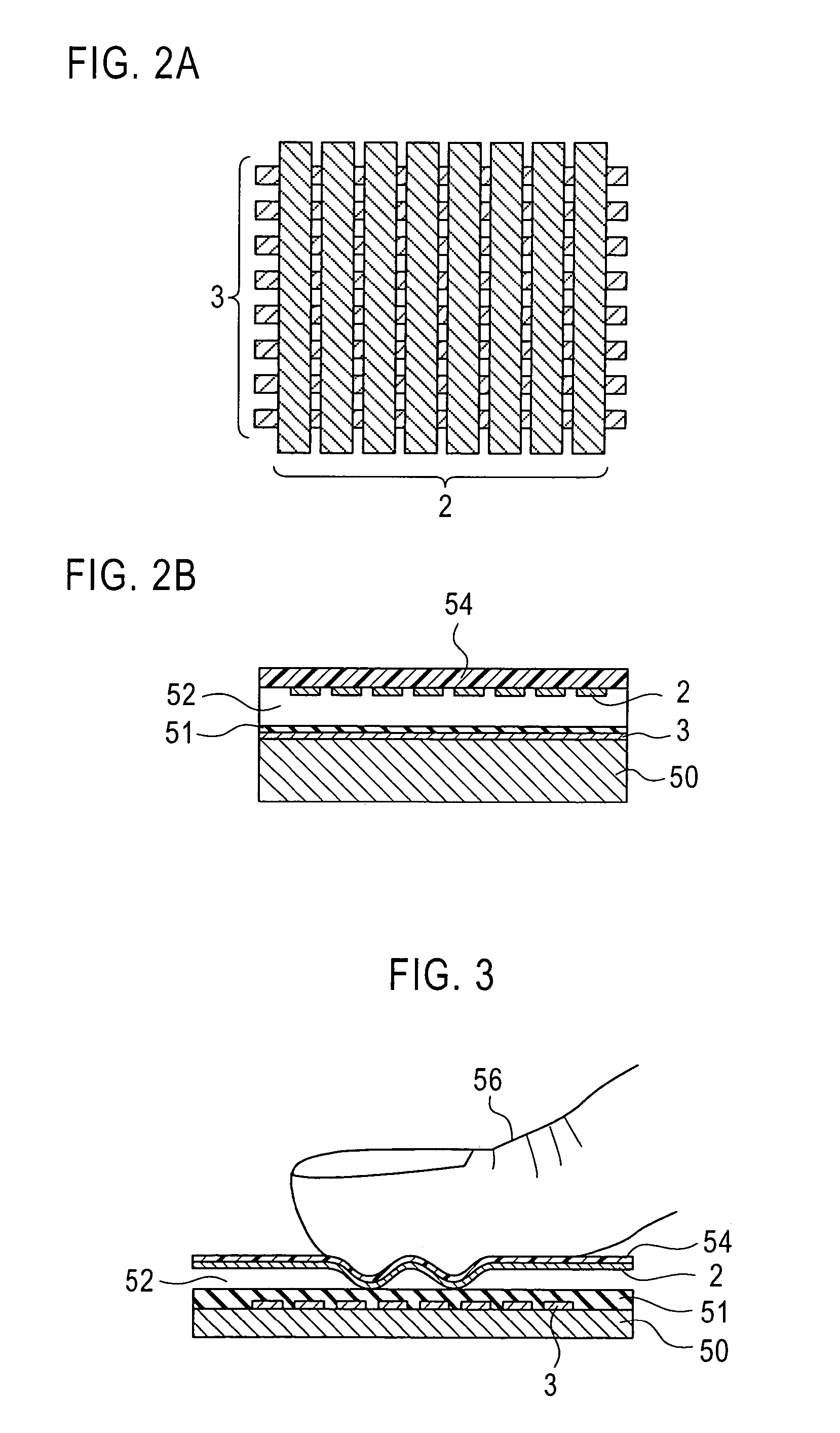

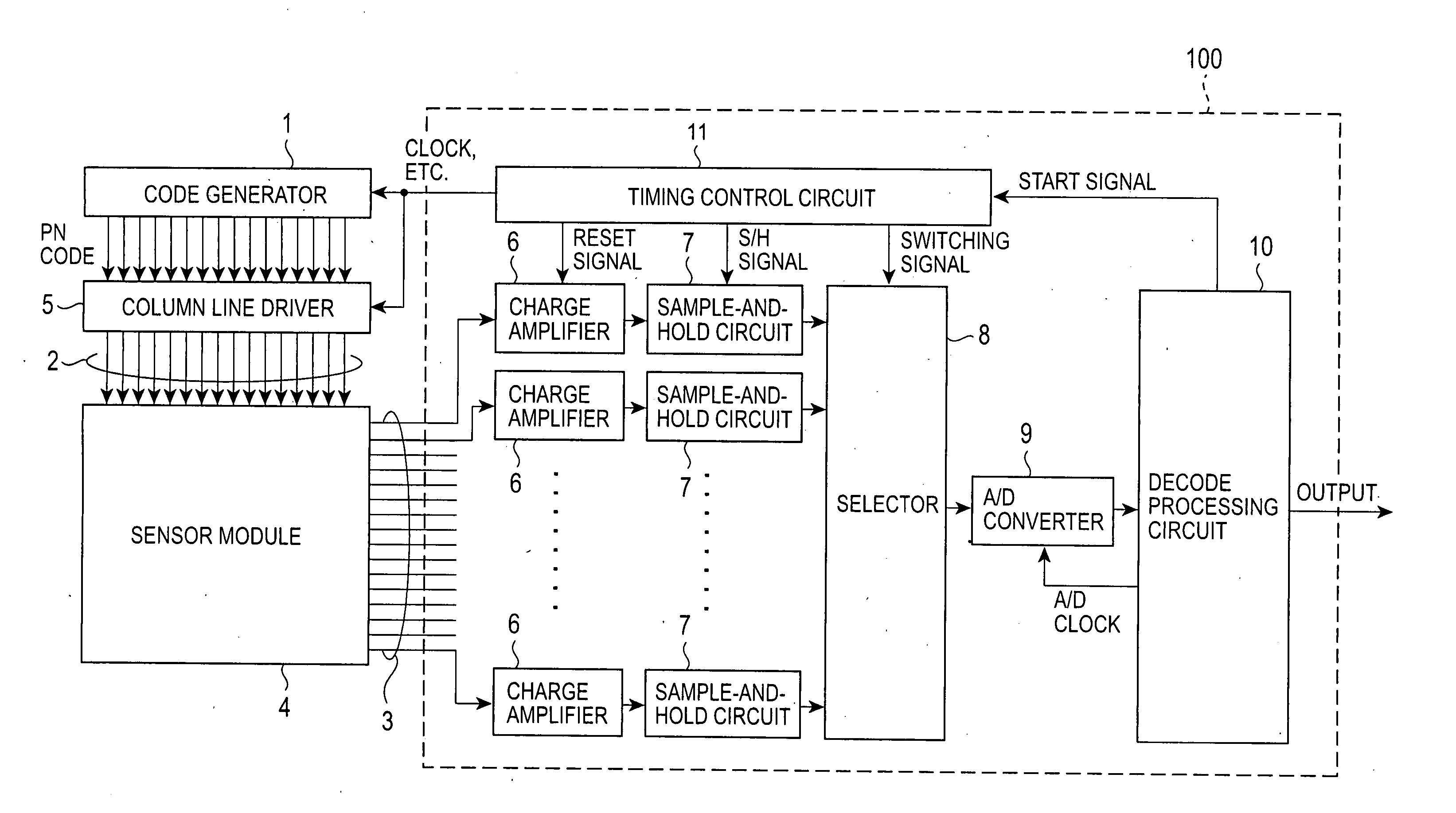

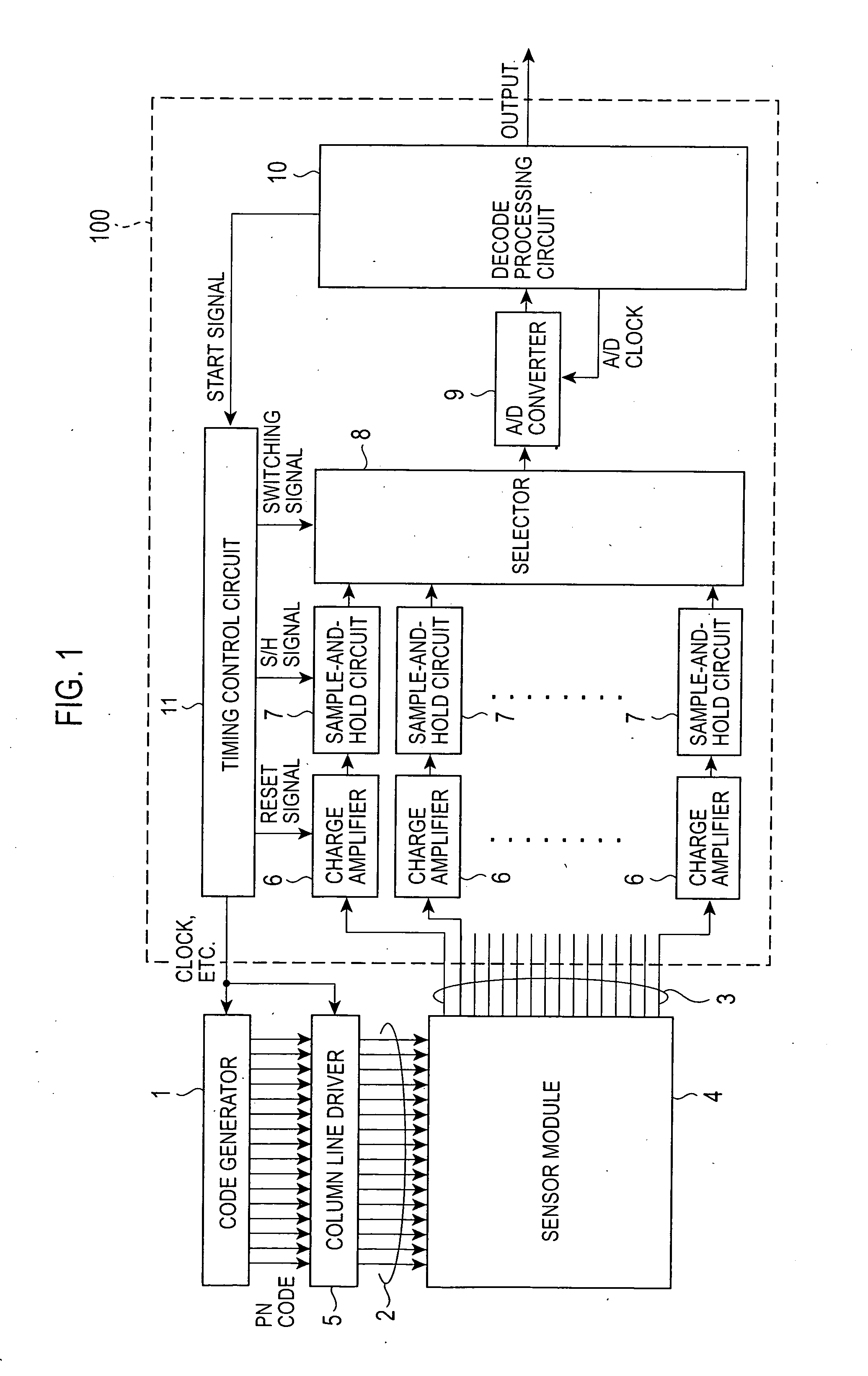

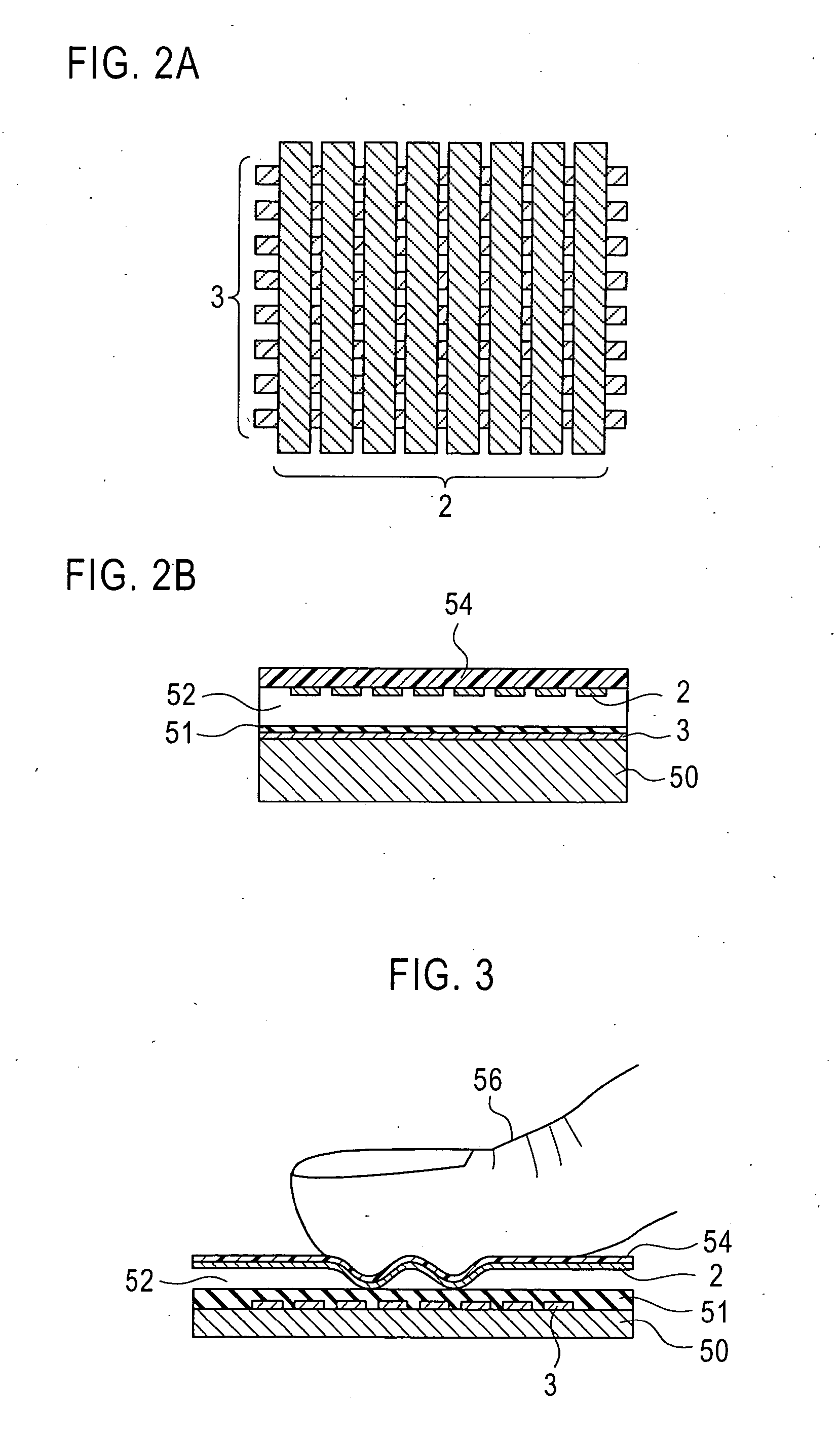

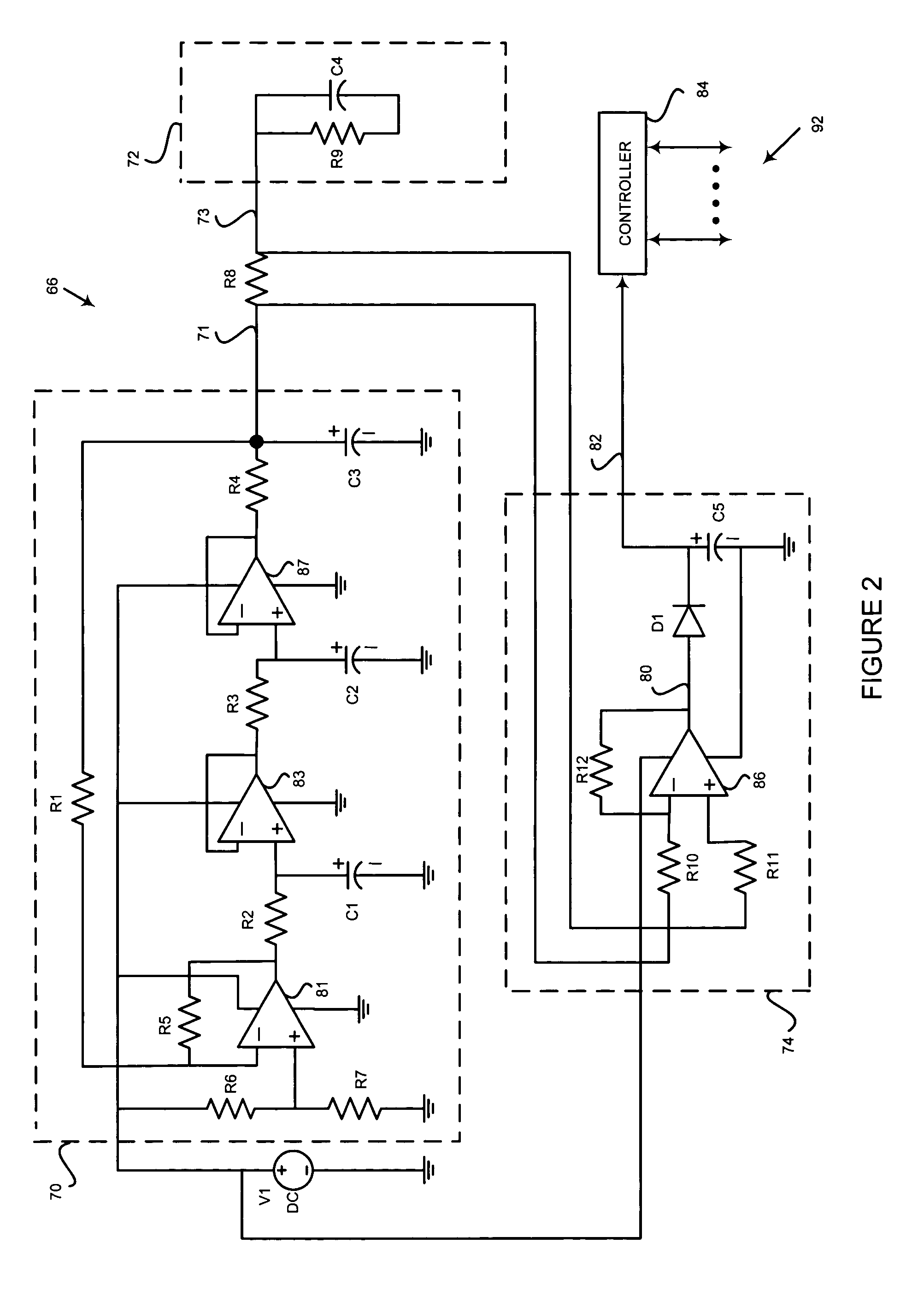

Capacitance detector circuit, capacitance detection method, and fingerprint sensor using the same

ActiveUS7075316B2Improve signal-to-noise ratioCapacitance measurementsElectric analogue storesDetector circuitsCapacitance transducer

A capacitance detecting circuit of a capacitive sensor having a plurality of column lines and a row line intersecting the column lines detects a change in capacitance at an intersection of a column line and a row line. The circuit includes a PN code generating unit for generating a code having orthogonality in time sequence to output the generated code as a column drive signal, a column line drive unit for driving a predetermined one of the column lines which are selected in response to the code, a capacitance detecting unit, connected to the row line, for detecting a voltage by converting a total sum of changes in capacitance at intersections of the selected column lines into the voltage to output the detected voltage, and a decode processing unit for performing a predetermined calculation on the detected voltage output from the capacitance detecting unit and the code to determine a voltage value responsive to the capacitance change at the intersection.

Owner:SYNAPTICS INC

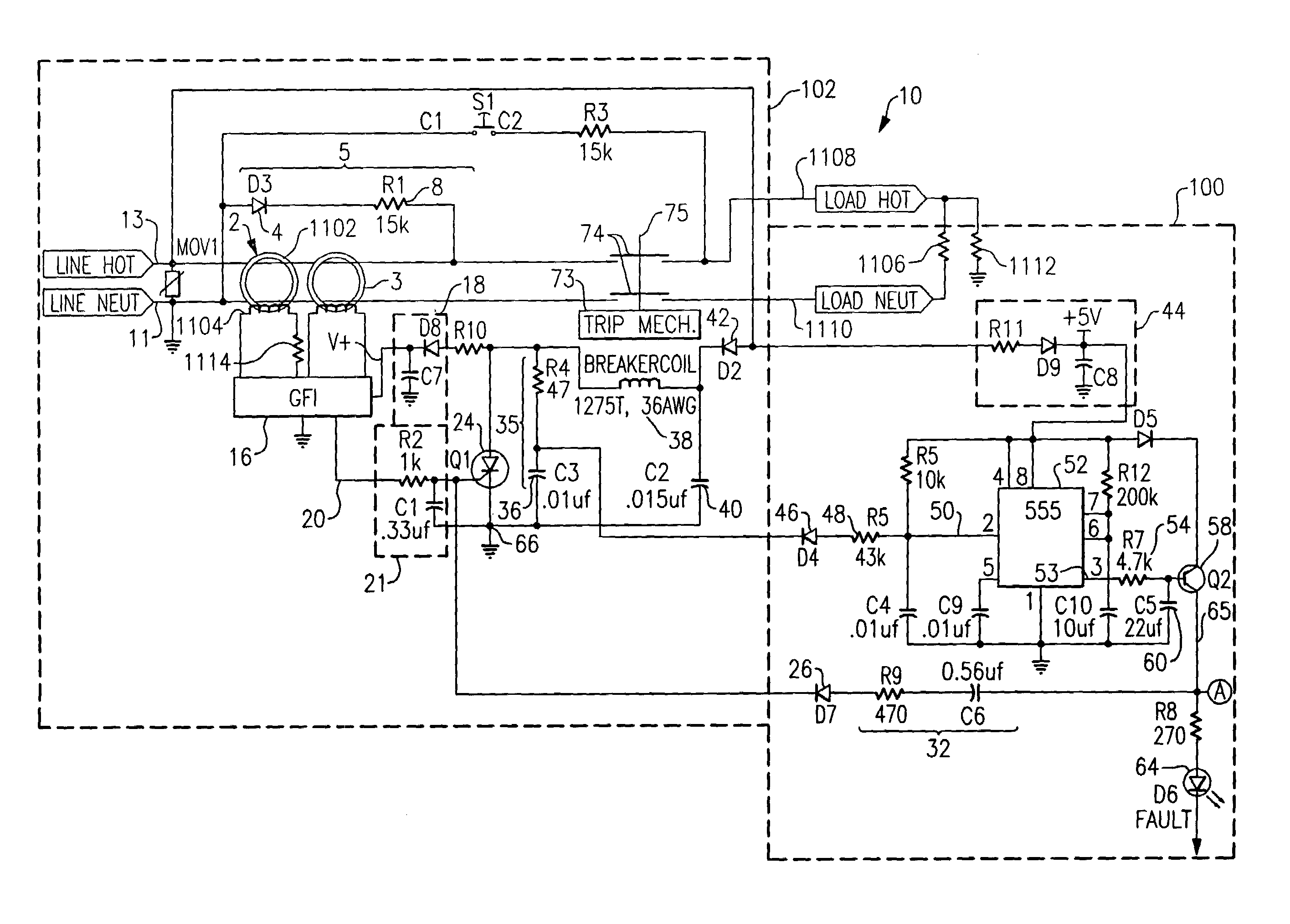

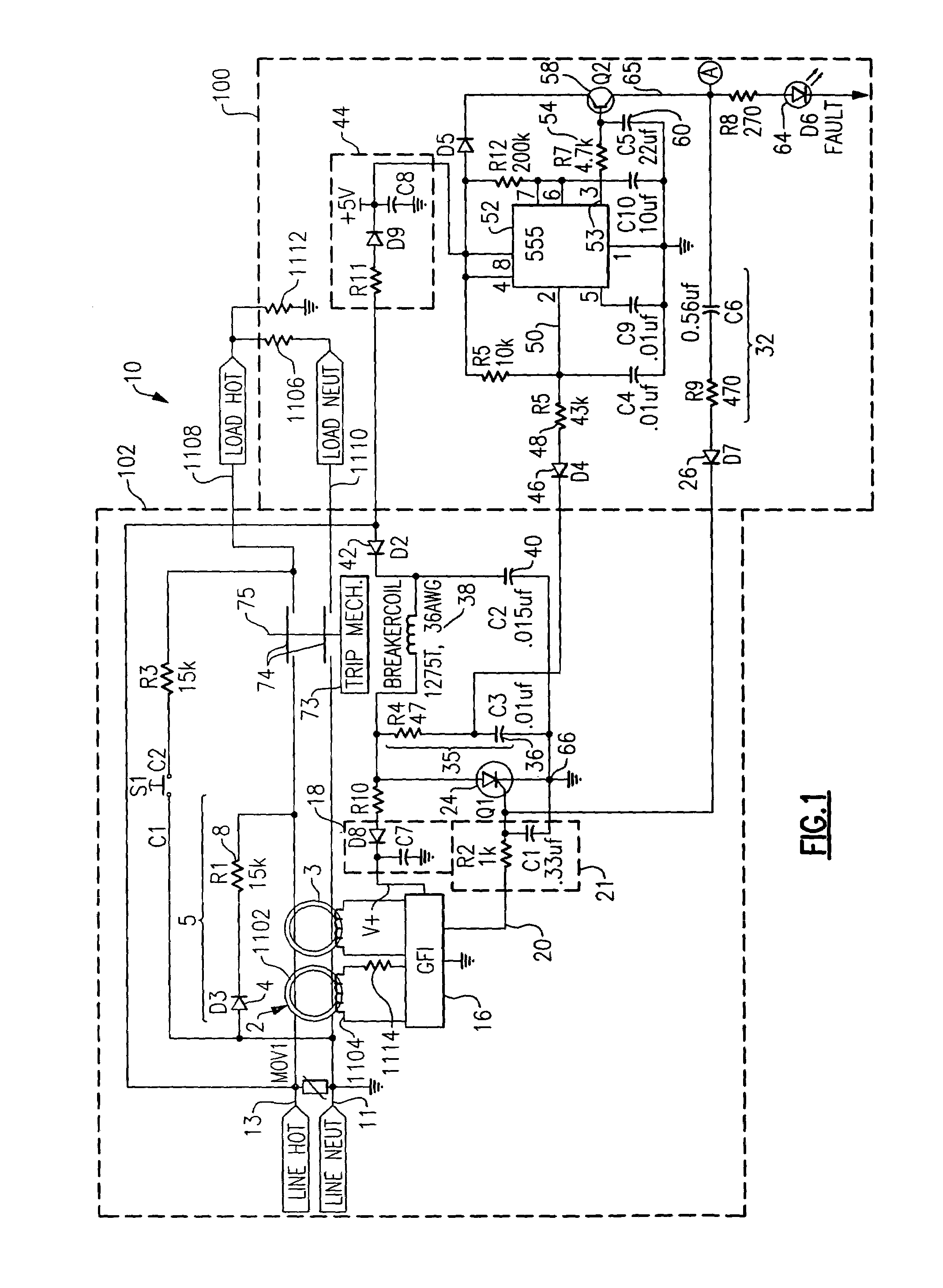

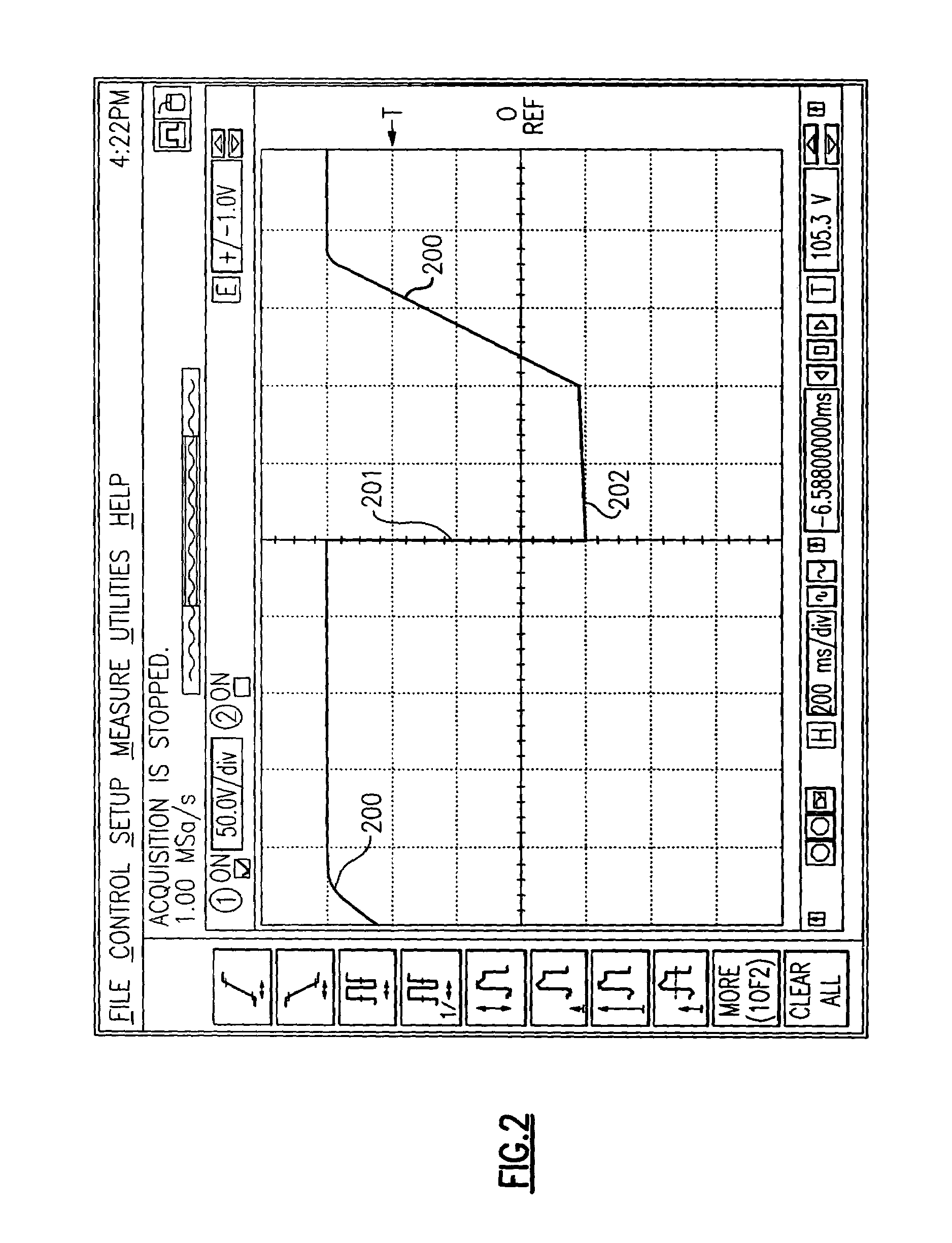

Circuit protection device with timed negative half-cycle self test

InactiveUS6980005B2Emergency protective arrangements for automatic disconnectionCircuit interrupters testingElectricityDetector circuits

The present invention is directed to an electrical wiring protection device for use in coupling an AC power distribution system to at least one electrical load. The device includes an automated self-test circuit coupled to the AC power distribution system. The automated self-test circuit is configured to generate at least one simulated fault signal during a first predetermined half-cycle of AC power. A detector circuit is coupled to the automated self-test circuit. The detector circuit generates a detection signal in response to the at least one simulated fault signal. An interval timing circuit is coupled to the test circuit. The interval timing circuit is configured to enable the automated self-test circuit to generate the at least one simulated fault signal during a first predetermined interval and not enable the test circuit during a subsequent second predetermined interval. The first predetermined interval and the second predetermined interval are recurring time intervals.

Owner:PASS SEYMOUR

Integrated wireless headset

InactiveUS7603148B2Interconnection arrangementsSubstation speech amplifiersDetector circuitsEngineering

A mobile device integrates a wireless headset with the housing of a mobile terminal. In an exemplary embodiment, the housing of the mobile terminal includes a fastener for mechanically connecting the wireless headset to the housing. When the wireless headset is mechanically disconnected from the housing, a speaker and microphone associated with the wireless headset interfaces with the mobile terminal via a wireless interface. However, when the wireless headset mechanically connects to the housing, the speaker and microphone associated with the wireless headset mechanically and electrically connect to the housing and operate as the speaker and microphone for the mobile terminal. A detector circuit included in the mobile device also determines the position of the wireless headset relative to the mobile terminal, and may automatically select a wireless or electrical interface between the wireless headset and the mobile terminal based on the determined position.

Owner:SONY ERICSSON MOBILE COMM AB

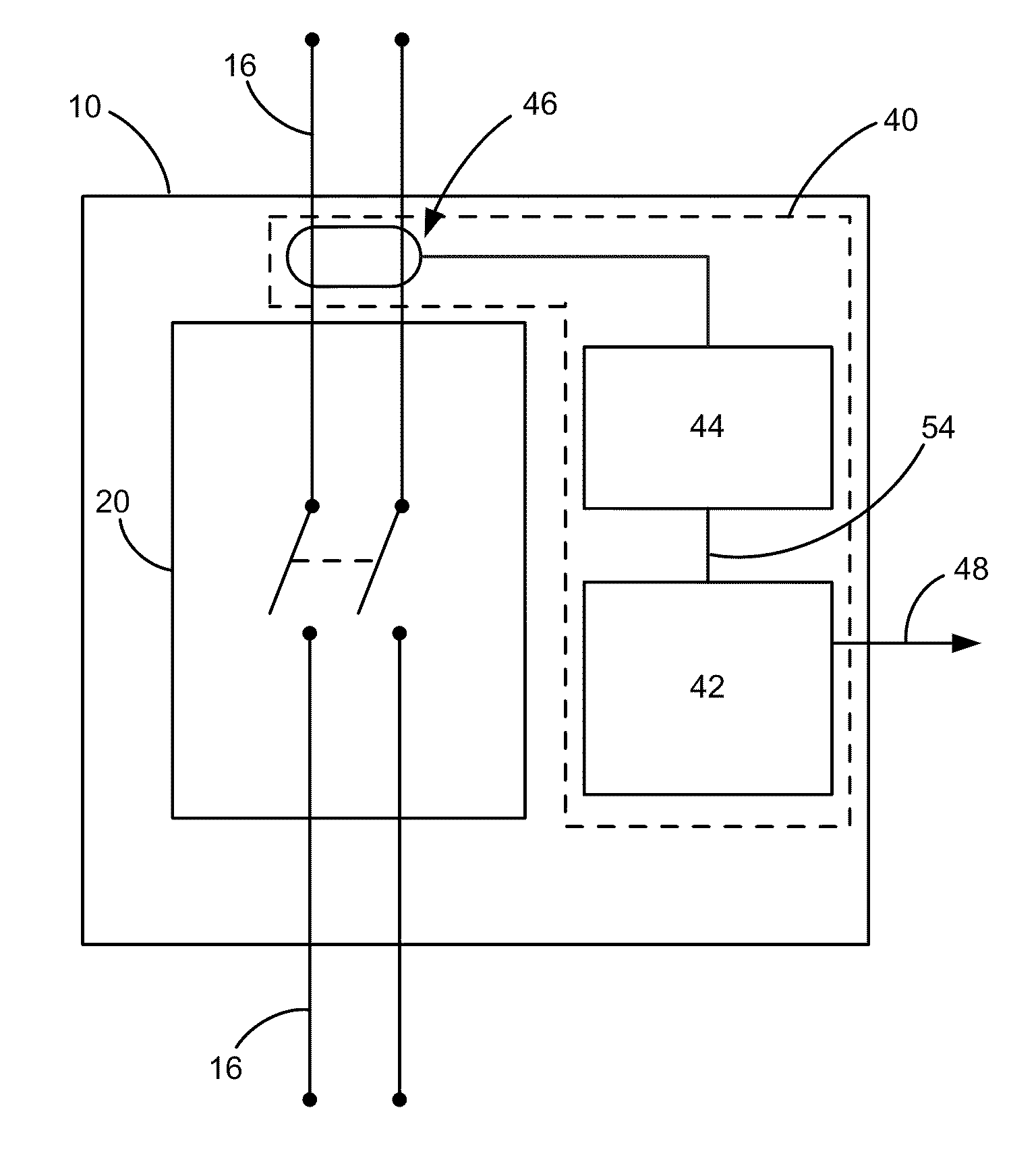

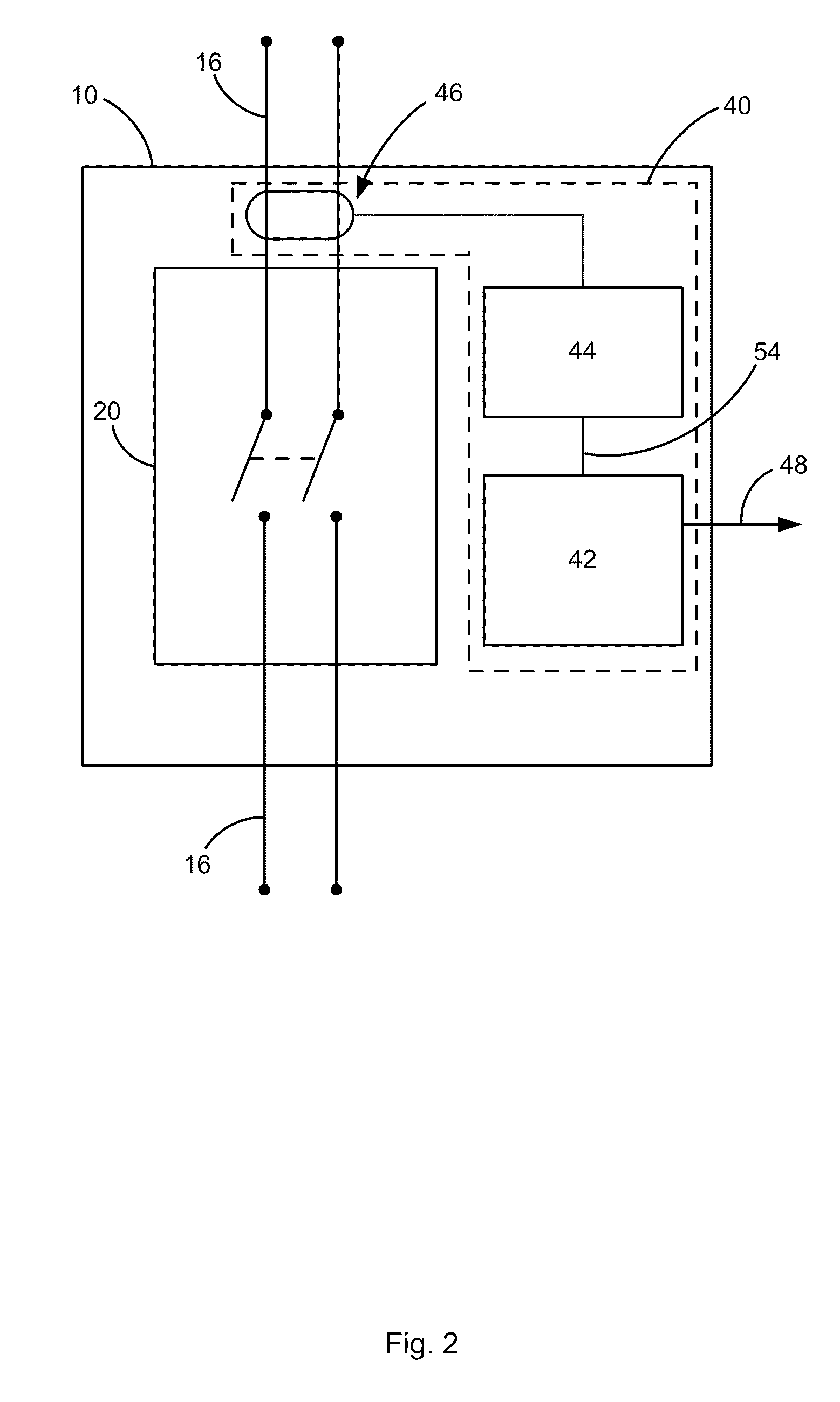

Smart Electrical Wire-Devices and Premises Power Management System

ActiveUS20100145536A1Maximize effectivenessMechanical power/torque controlLevel controlElectricityDetector circuits

Disclosed is power management system based on a “smart” wire-device installable in an electric power line (i.e., the “drop-grid” or “micro-grid”) at a premises, such as a business or residence. The “smart” wire-device includes a management node integrated into the form of a typical electrical power outlet, circuit breaker or switch as would be found in such a premises, and is installable in the power line in a manner similar to existing wire-device. The “smart” wire-device requires no special skill to install beyond that of an ordinary skilled electrician. The present wire-device is “smart” in that the node has a detector circuit that senses the electrical characteristic(s) of the power line at the point at which it is installed. The node's communications circuit signals what it detects to a spatially separated remote controller device, and receives instructions from one or more spatially separated remote controller devices. The node's control mechanism operates a remotely controllable maker / breaker means in response to the received instructions to alter the condition of the electrical power output of the wire-device.

Owner:DALCHEMY INC

Battery-powered occupancy sensor

InactiveUS20100052894A1Electric light circuit arrangementOther accessoriesDetector circuitsWireless transmitter

A battery-powered occupancy sensor for detecting an occupancy condition in a space comprises first and second batteries, an occupancy detector circuit, a controller, and a wireless transmitter for transmitting a first wireless signal in response to the occupancy detector circuit detecting the occupancy condition in the space. The controller and the wireless transmitter are powered by the first battery, while only the occupancy detector circuit is powered by the second battery, such that the occupancy detector circuit is isolated from noise generated by the controller and the wireless transmitter. The occupancy detector circuit draws a current having a magnitude of approximately 5 microamps or less from the second battery. The occupancy sensor transmits a second wireless signal is response to determining that the voltage of one of the batteries has dropped too low.

Owner:LUTRON TECH CO LLC

Capacitance detector circuit, capacitance detection method, and fingerprint sensor using the same

ActiveUS20050073324A1Reduce the impact of interferenceEasy to detectCapacitance measurementsElectric analogue storesDetector circuitsEngineering

A capacitance detecting circuit of a capacitive sensor having a plurality of column lines and a row line intersecting the column lines detects a change in capacitance at an intersection of a column line and a row line. The circuit includes a PN code generating unit for generating a code having orthogonality in time sequence to output the generated code as a column drive signal, a column line drive unit for driving a predetermined one of the column lines which are selected in response to the code, a capacitance detecting unit, connected to the row line, for detecting a voltage by converting a total sum of changes in capacitance at intersections of the selected column lines into the voltage to output the detected voltage, and a decode processing unit for performing a predetermined calculation on the detected voltage output from the capacitance detecting unit and the code to determine a voltage value responsive to the capacitance change at the intersection.

Owner:SYNAPTICS INC

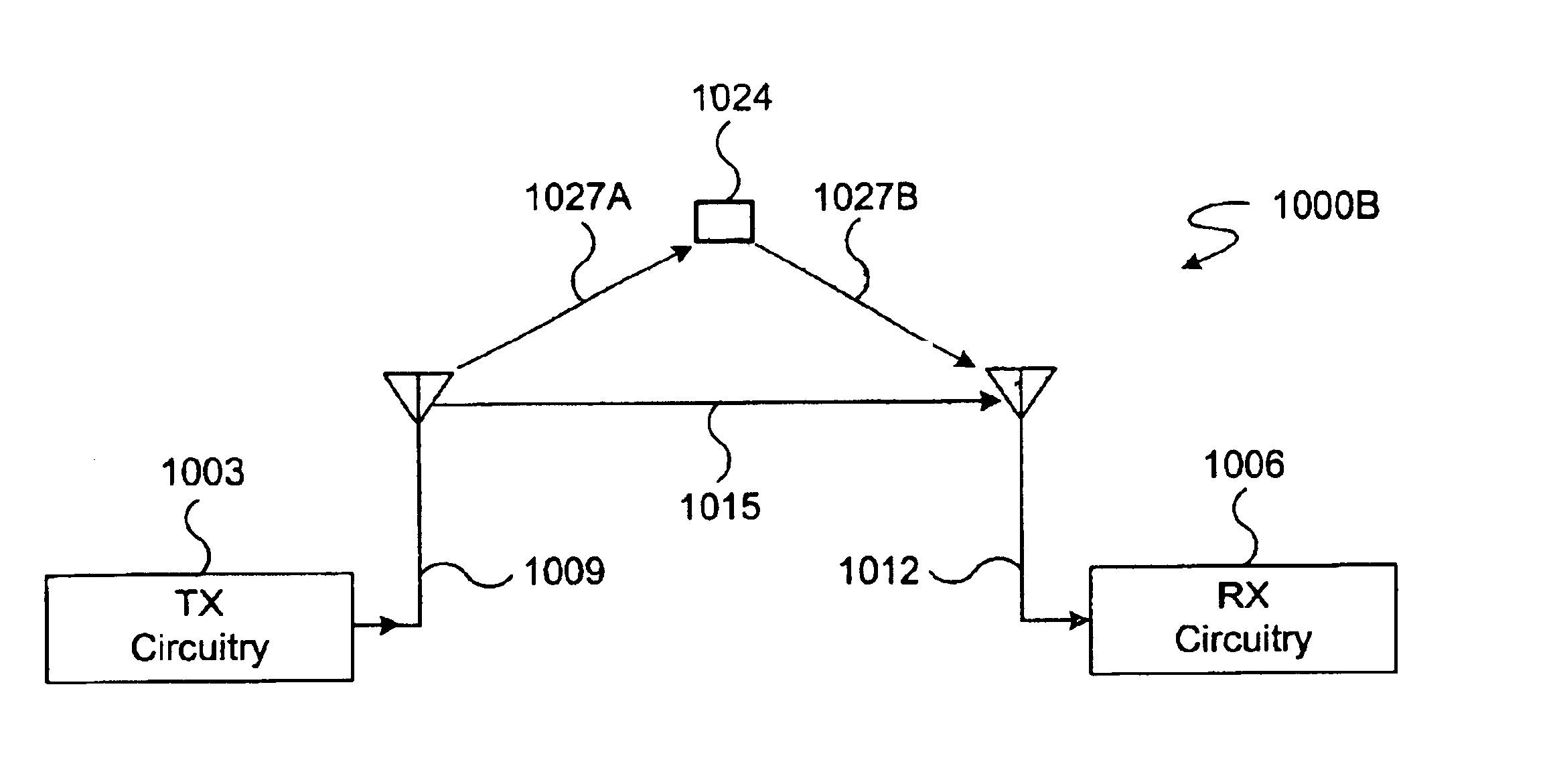

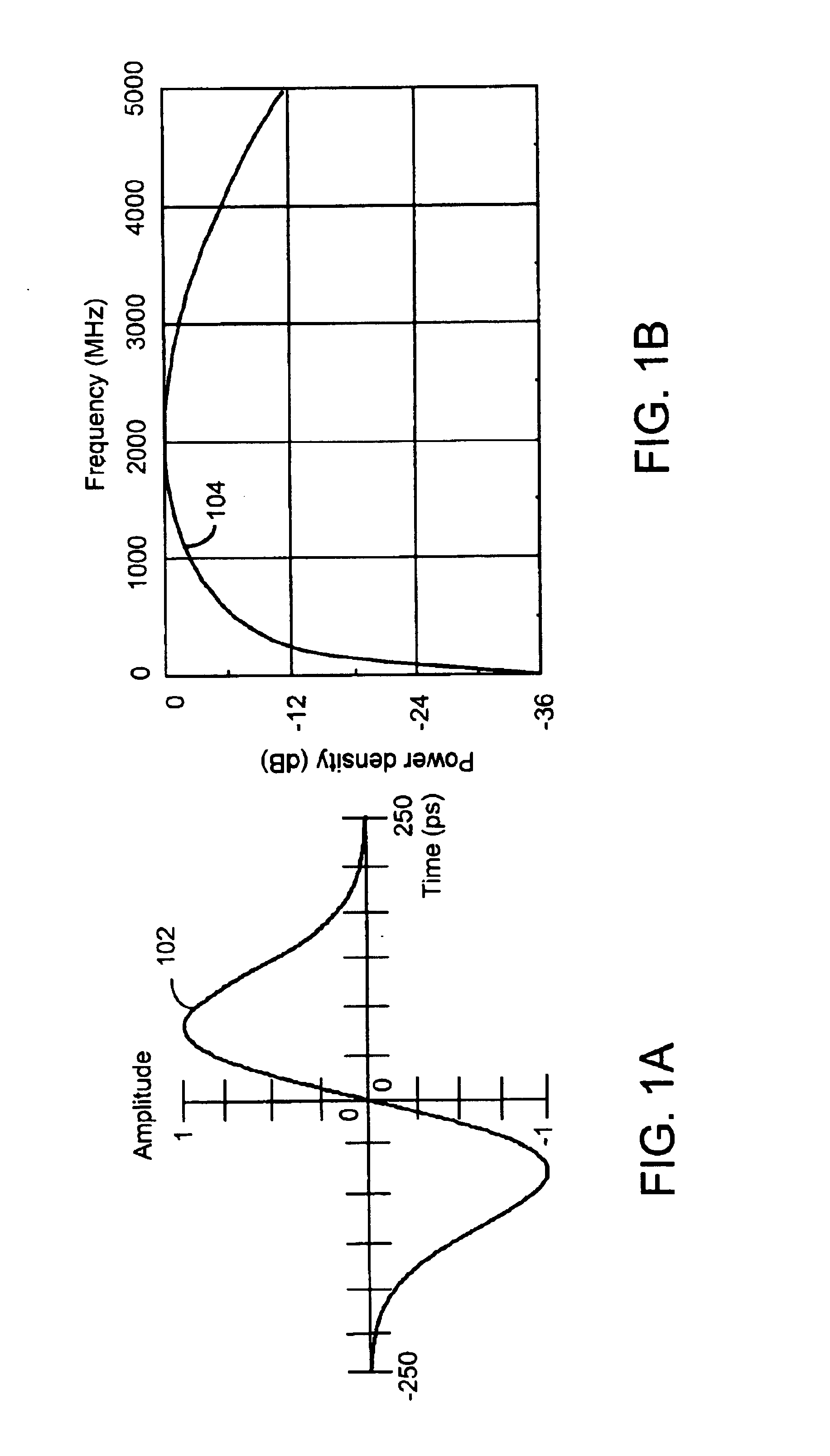

Direct-path-signal detection apparatus and associated methods

InactiveUS6963727B2Transmission control/equalisingRadio/inductive link selection arrangementsDetector circuitsTelecommunications link

Direct-path-signal (DPS) detector circuitry includes a standard deviation calculator circuitry configured to determine a standard deviation of a plurality of data values within a data frame. The data frame corresponds to a radio-frequency signal received via a communication link. The DPS detector circuitry also includes a threshold circuitry configured to detect a direct-path signal depending on the relative values of the standard deviation and a threshold signal.

Owner:HUMATICS CORP

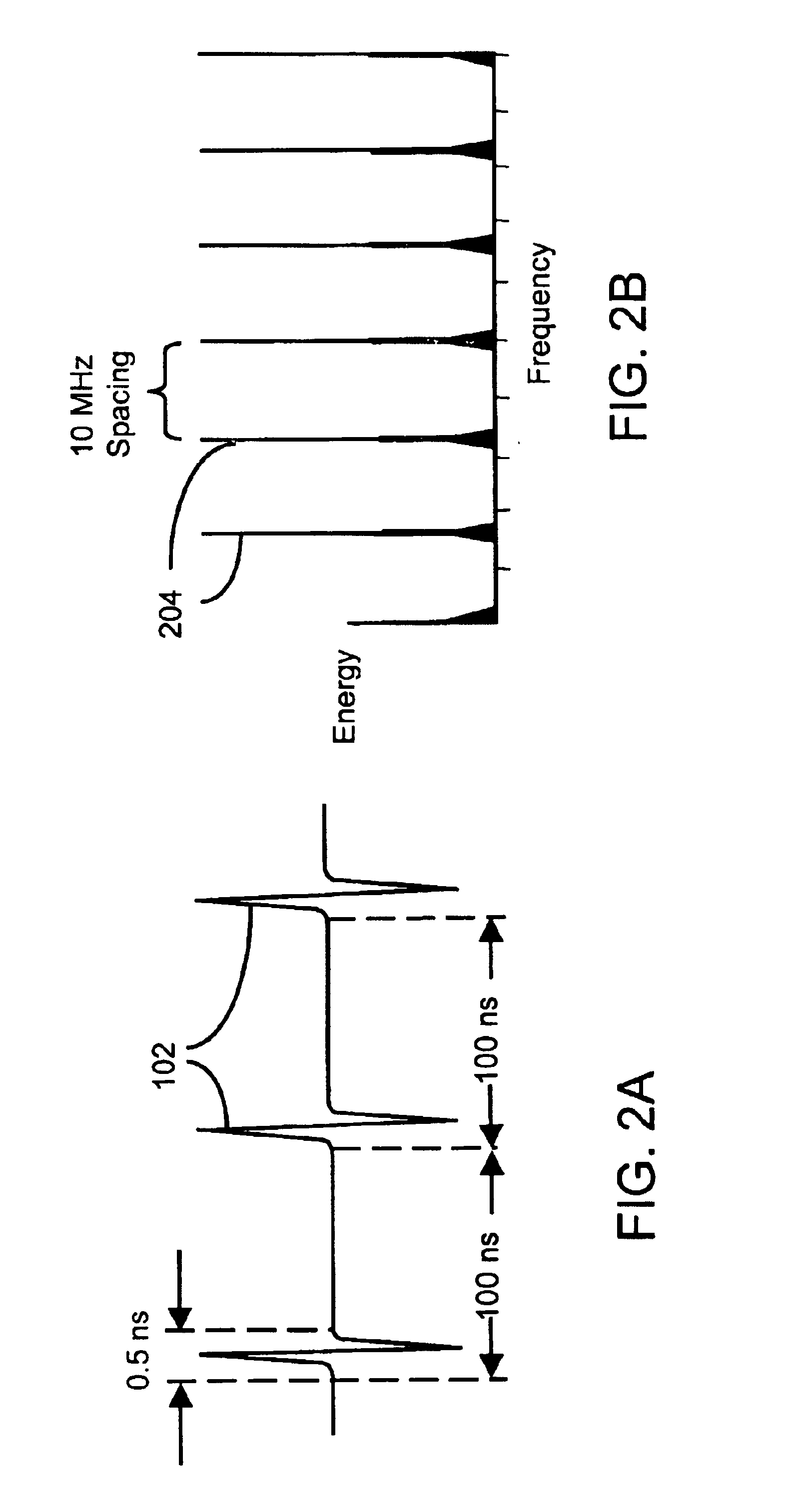

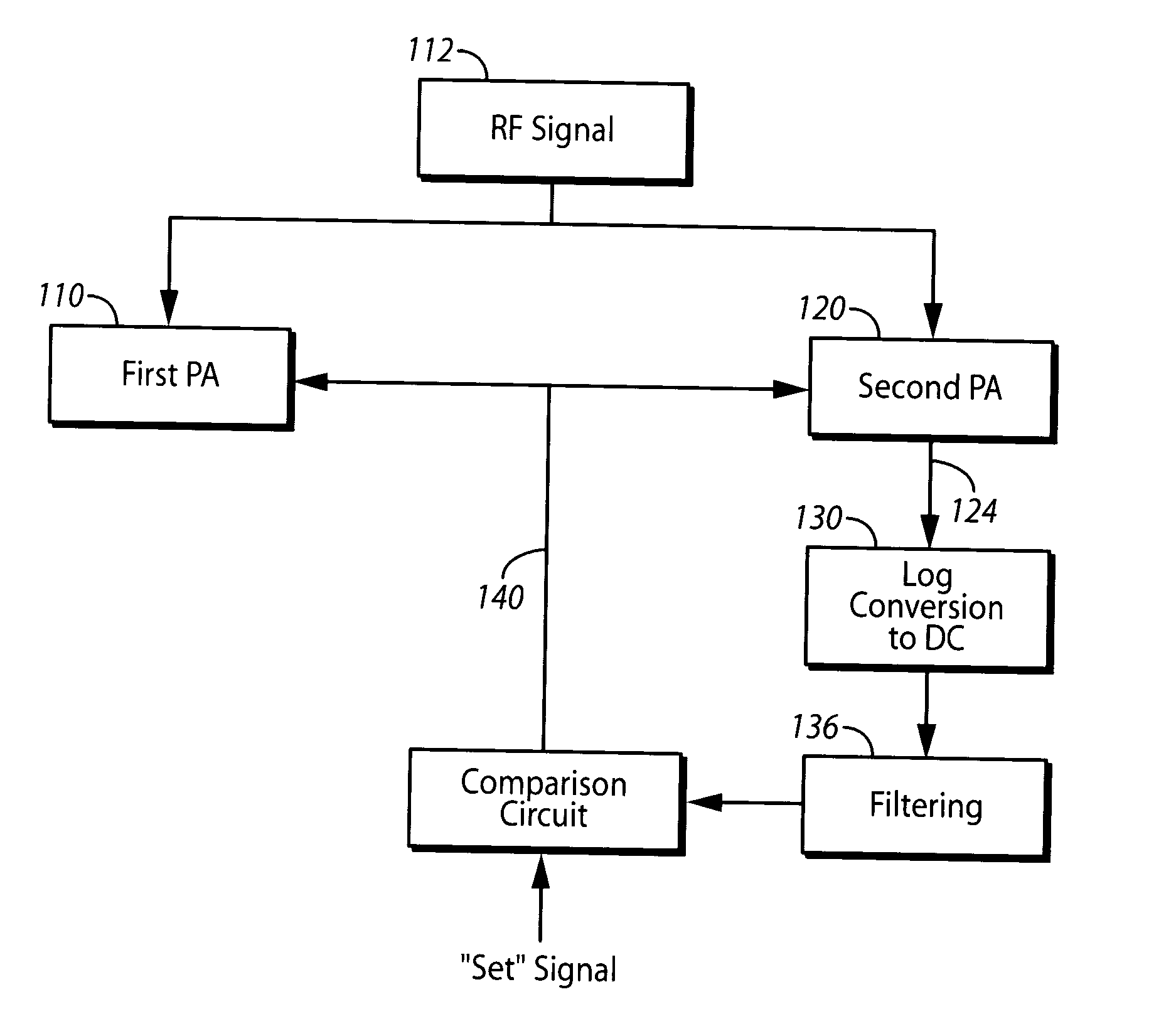

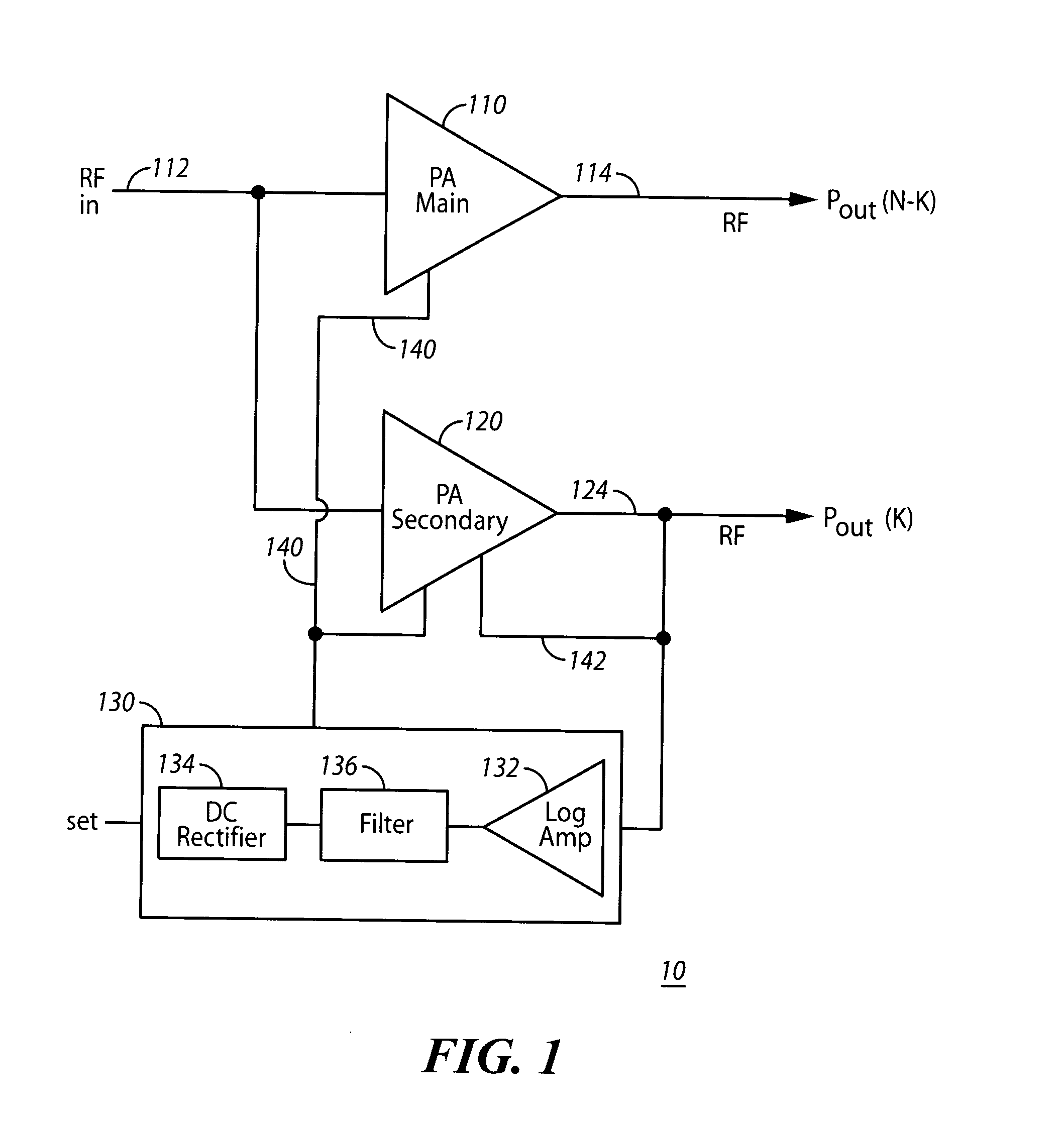

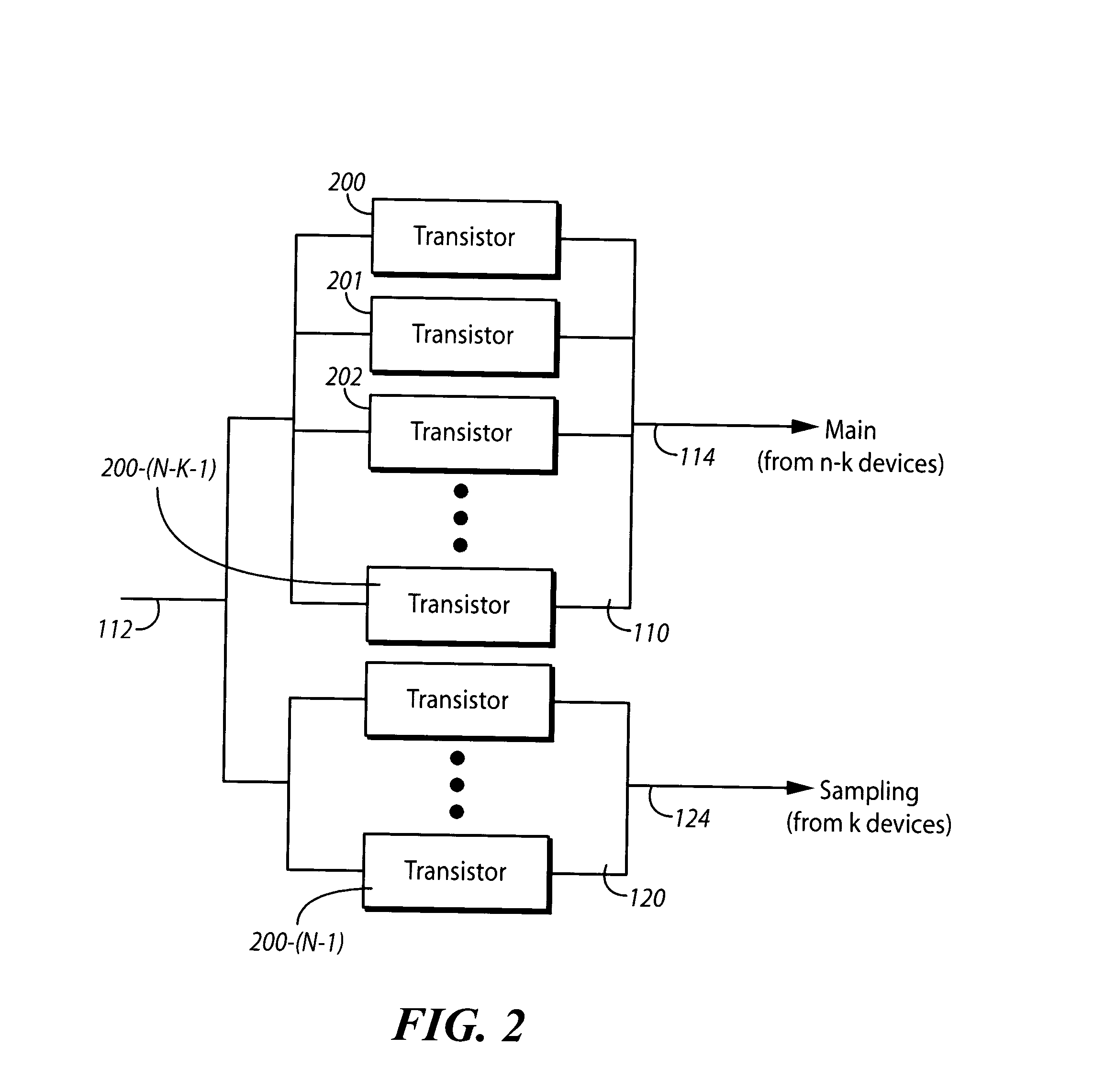

Radio frequency power detecting circuit and method therefor

A circuit for detecting the amount of radio frequency power provided by an amplifier. The circuit contains an array of coupled transistors in two power amplifiers, and a log-detector circuit, all resident on a single semiconductor die. The main power amplifier contains the larger array of transistors to amplify the radio frequency signal for feeding to an antenna, and a secondary power amplifier contains a smaller array of transistors to provide a scaled output that is proportional to the amplified radio frequency signal and is used to control the main power amplifier. The log-detector circuit converts the signal from the secondary power amplifier to a full-wave rectified log-linear DC signal that is logarithmically proportional to the controlling signal. The DC signal output from the log-detector circuit is fed to the main power amp to control it.

Owner:YUANTONIX

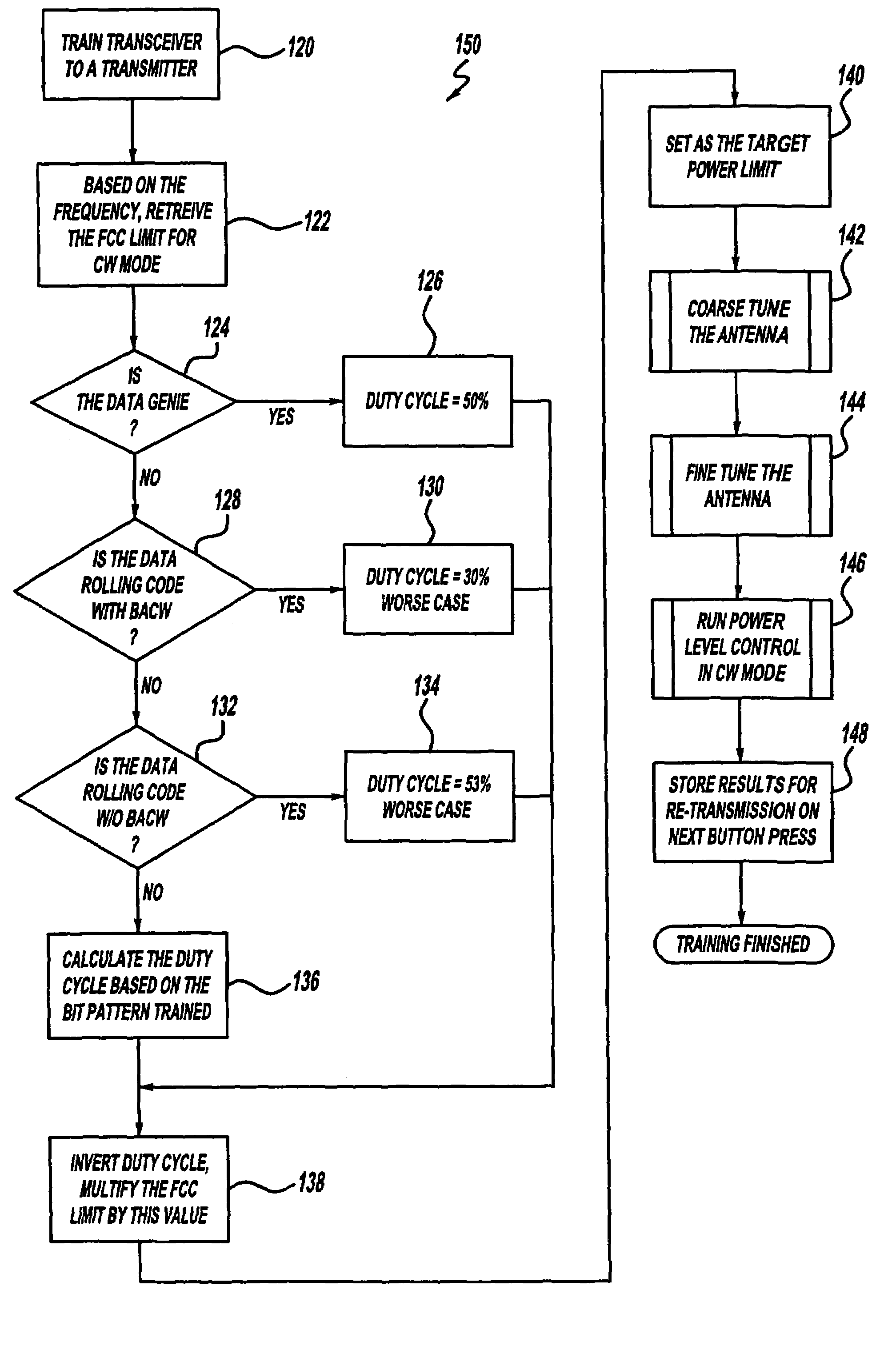

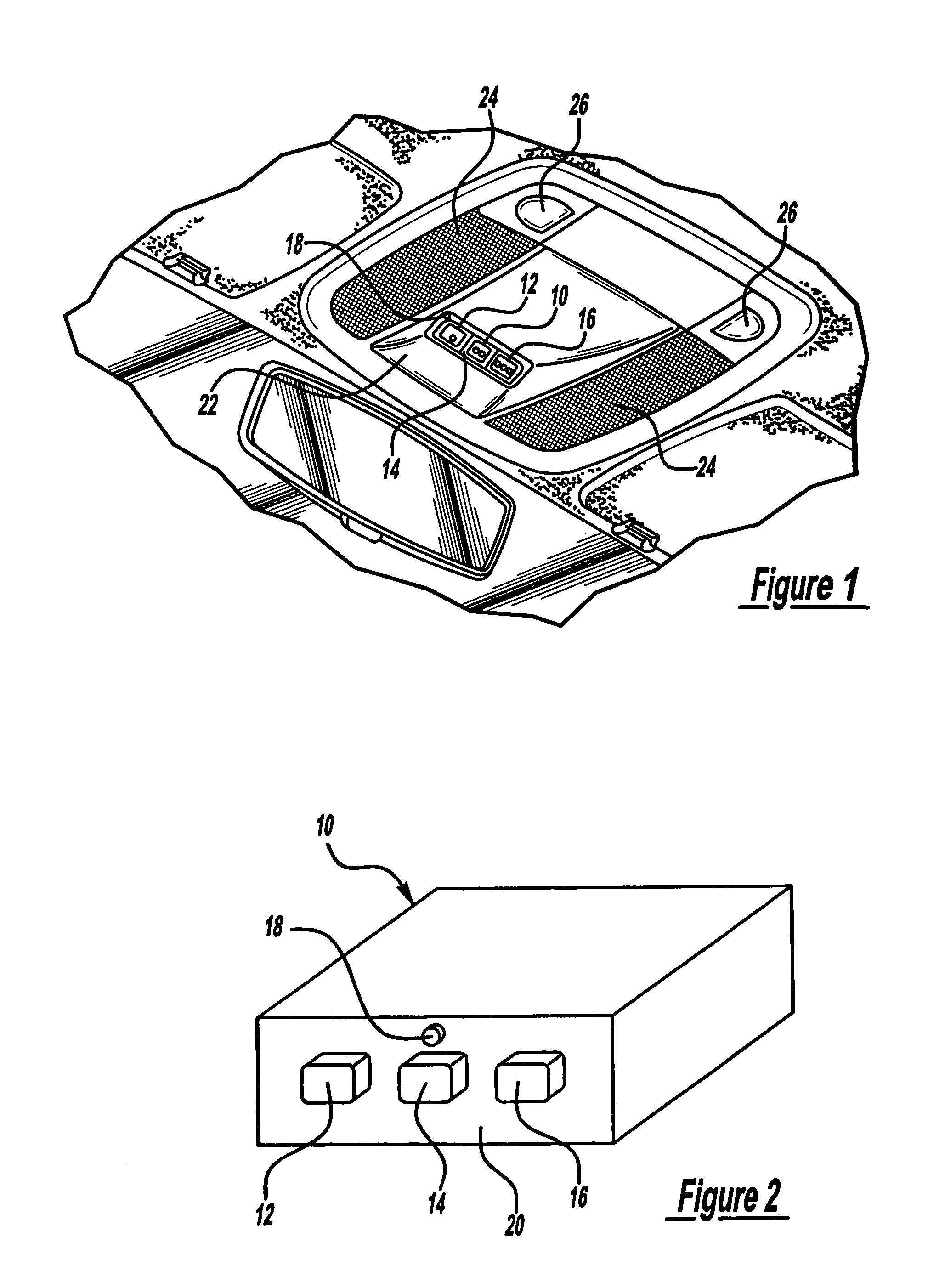

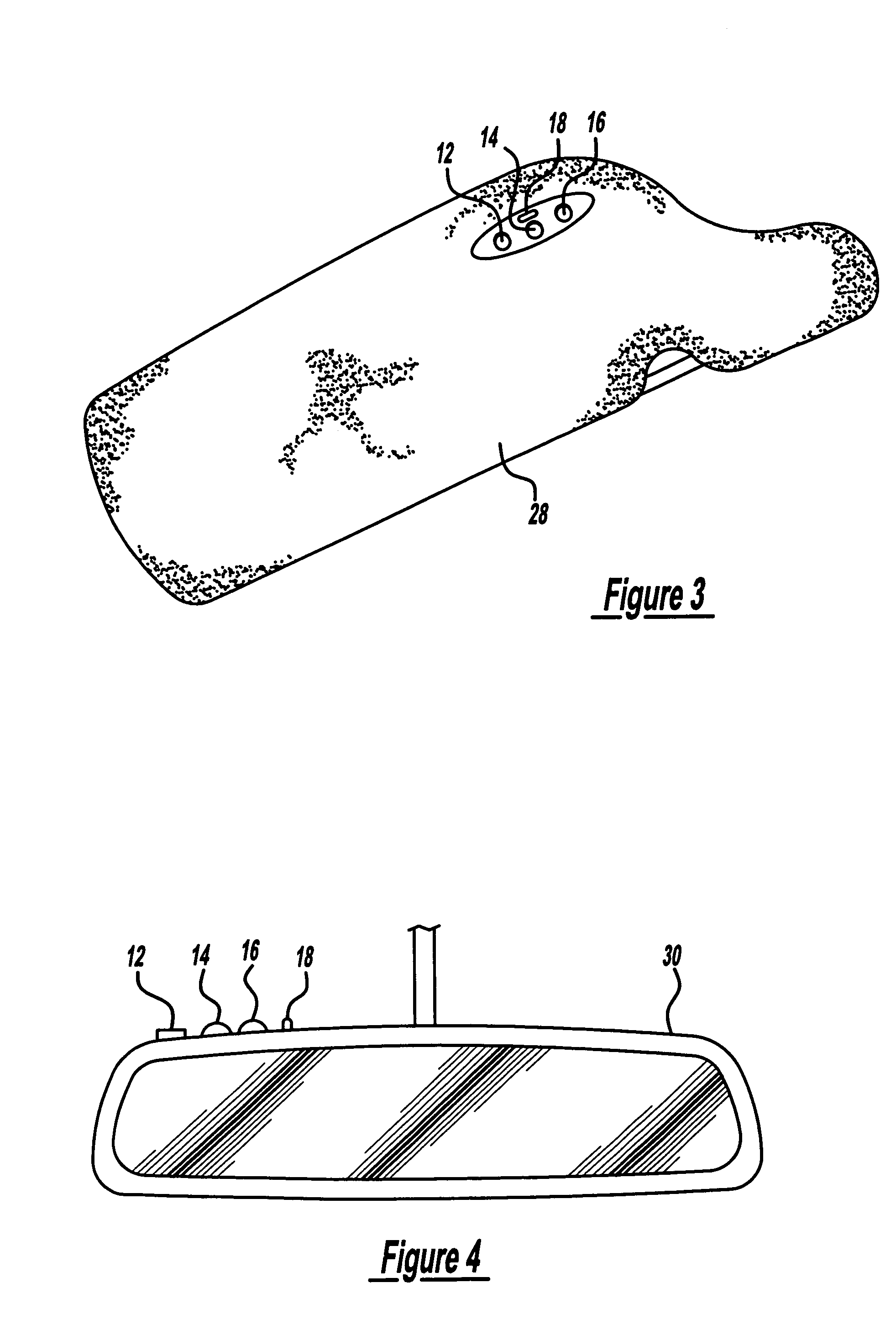

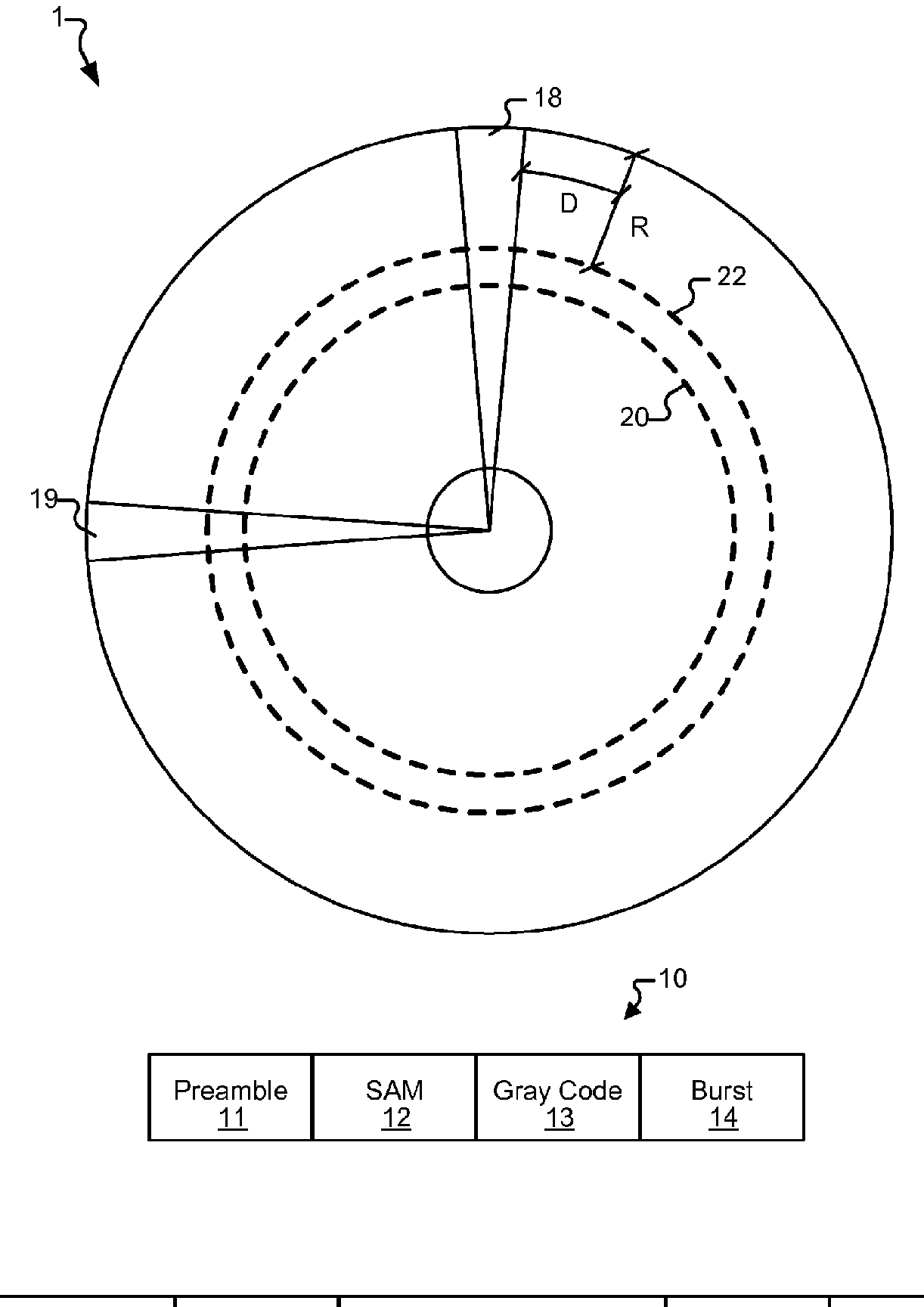

Transceiver with closed loop control of antenna tuning and power level

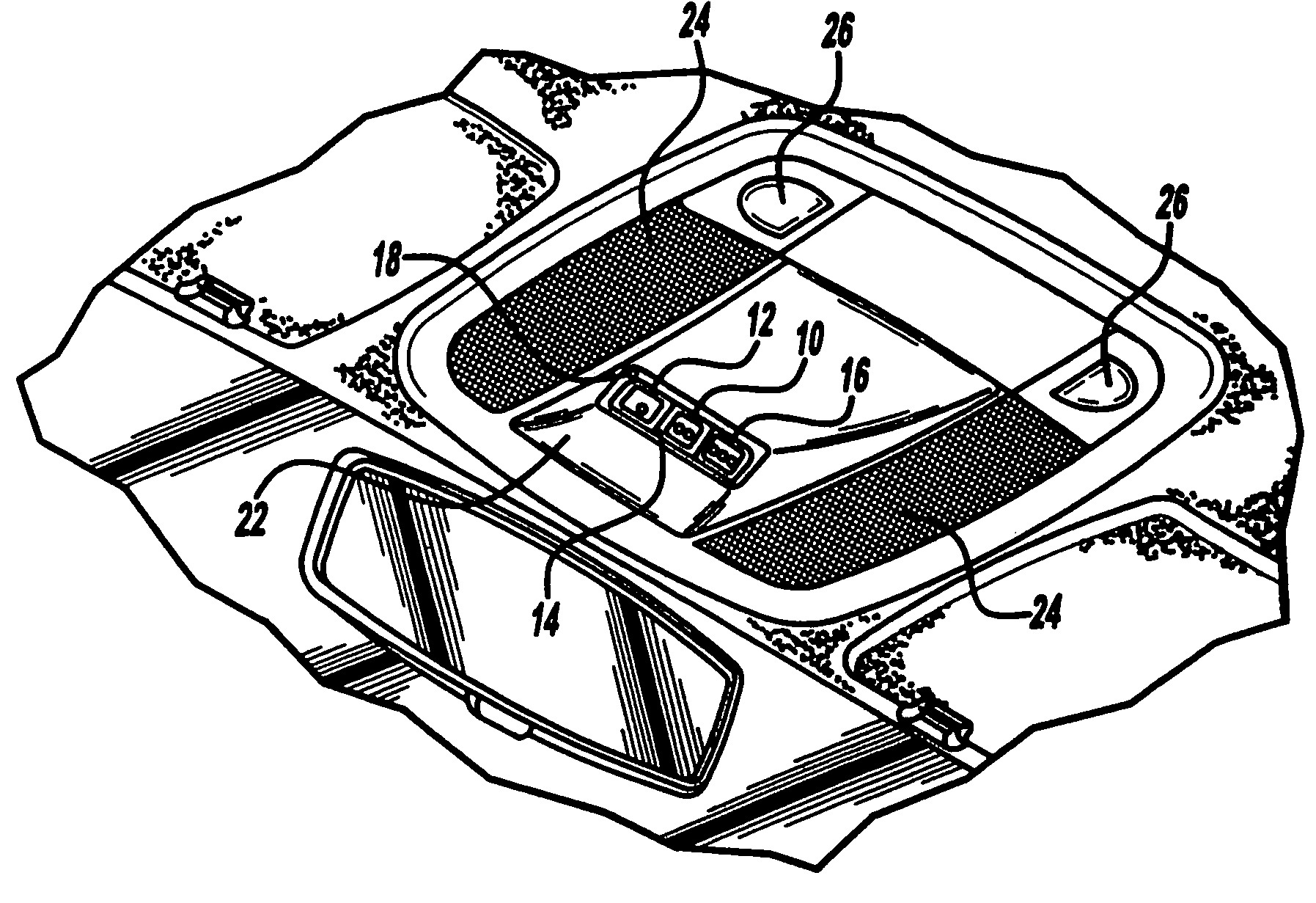

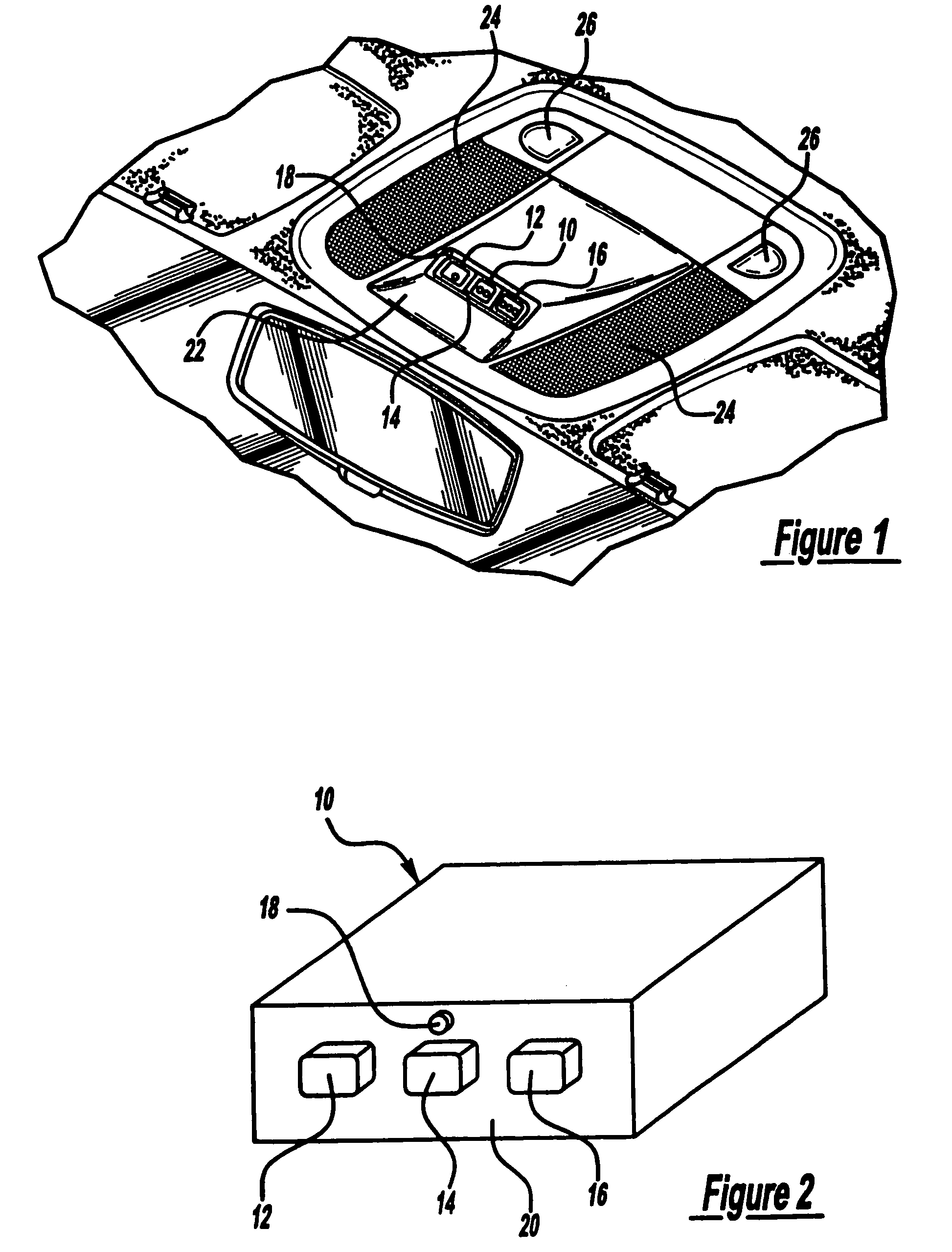

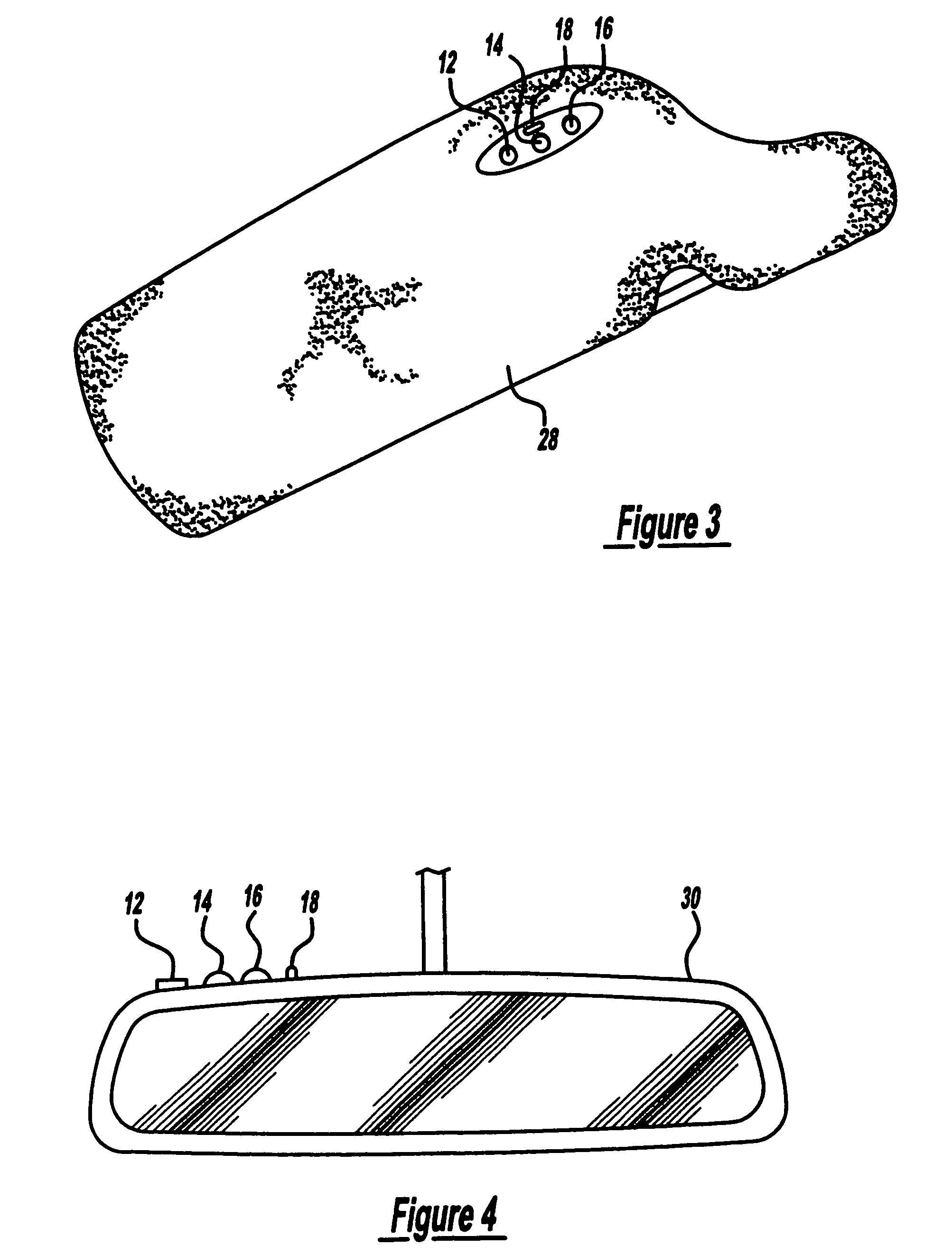

InactiveUS6978126B1Guaranteed normal transmissionEfficient receptionElectric signal transmission systemsDigital data processing detailsDetector circuitsTransceiver

A trainable transceiver for learning and transmitting an activation signal that includes an RF carrier frequency modulated with a code for remotely actuating a device, such as a garage door opener. The trainable transceiver preferably includes a controller, a signal generator, and a dynamically tunable antenna having a variable impedance that may be selectively controlled in accordance with a detector circuit signal. The detector circuit provides a measurement of the transmission power and is also used to vary the applied transmission power of the transceiver in response to operating and environmental parameters.

Owner:GENTEX CORP +1

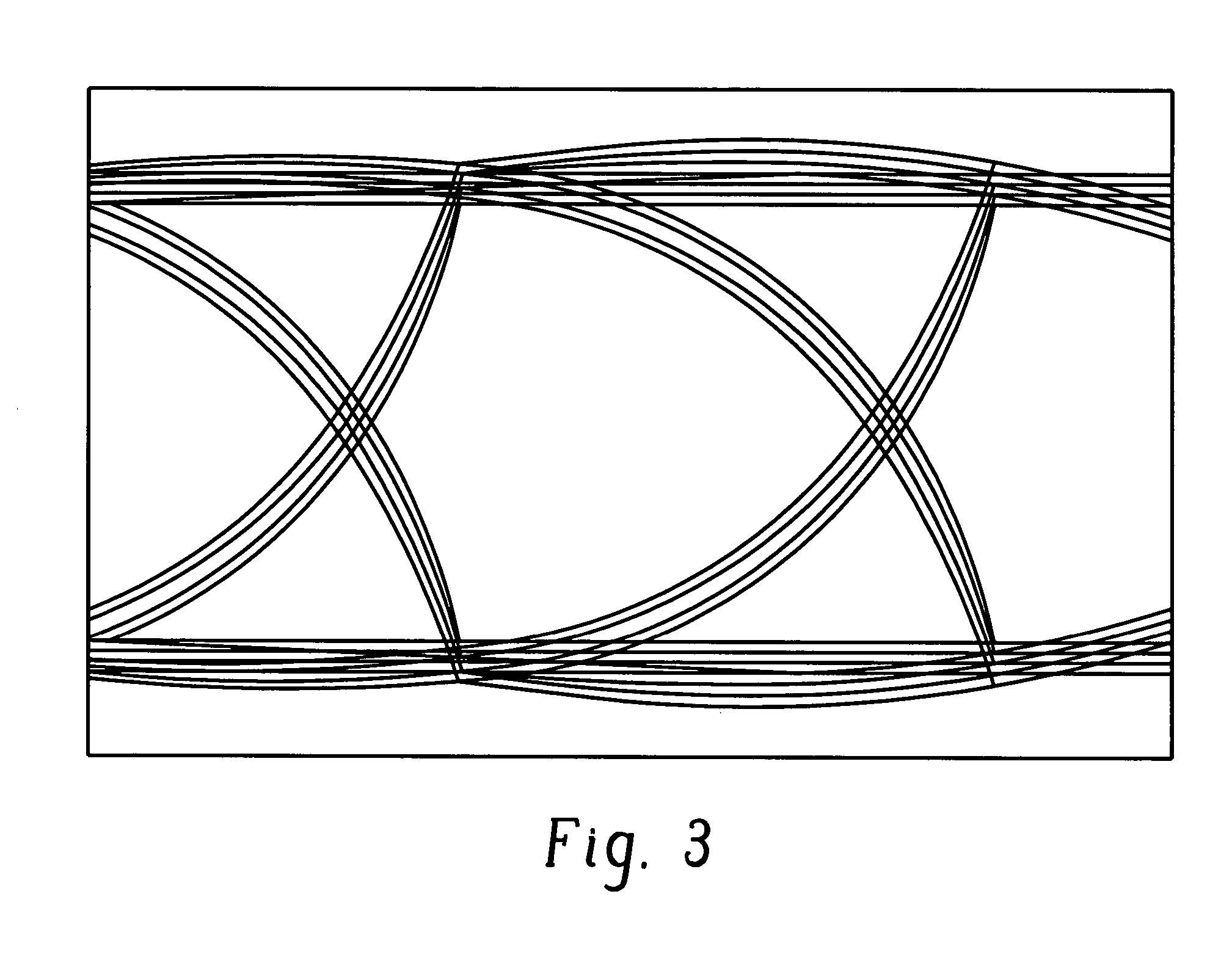

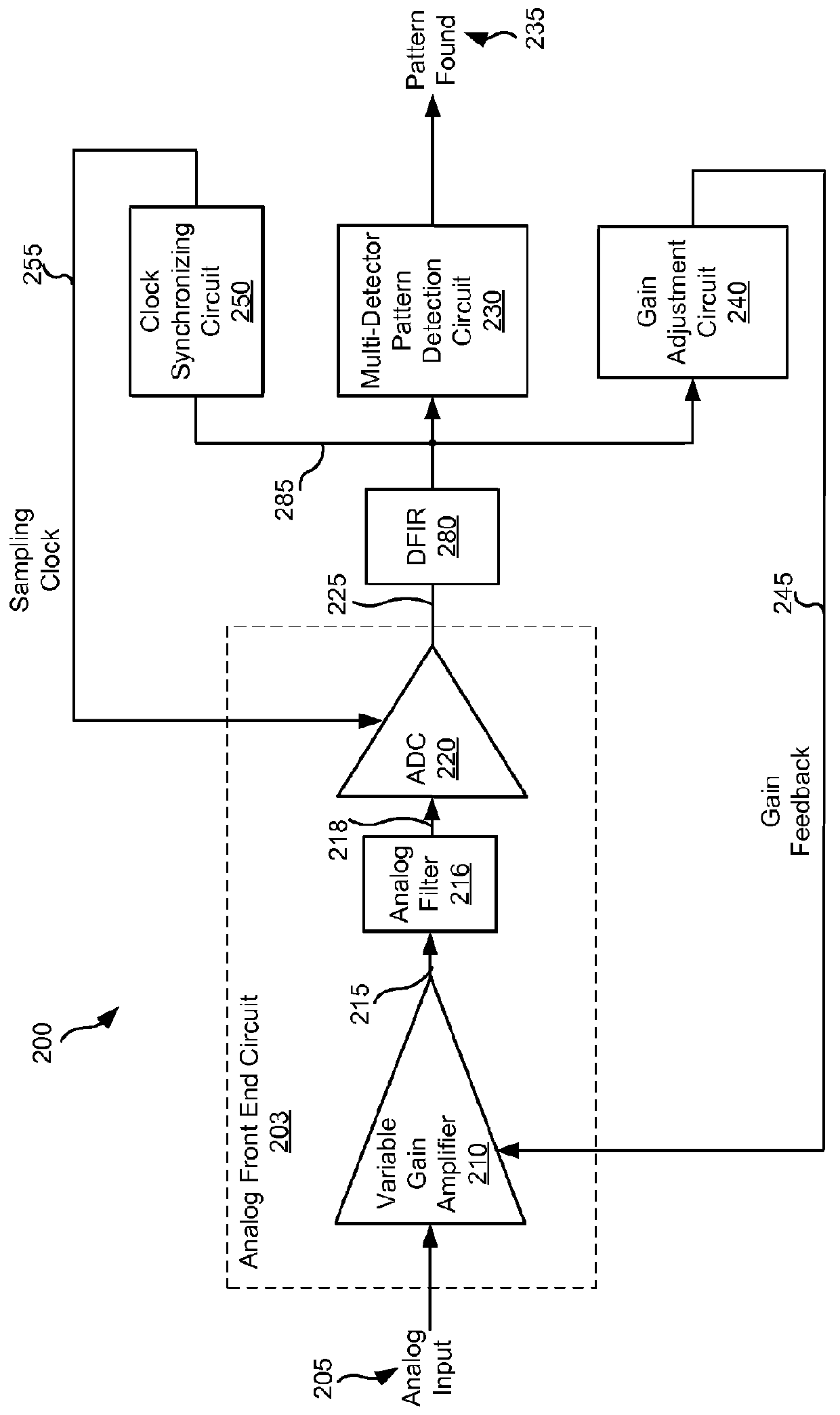

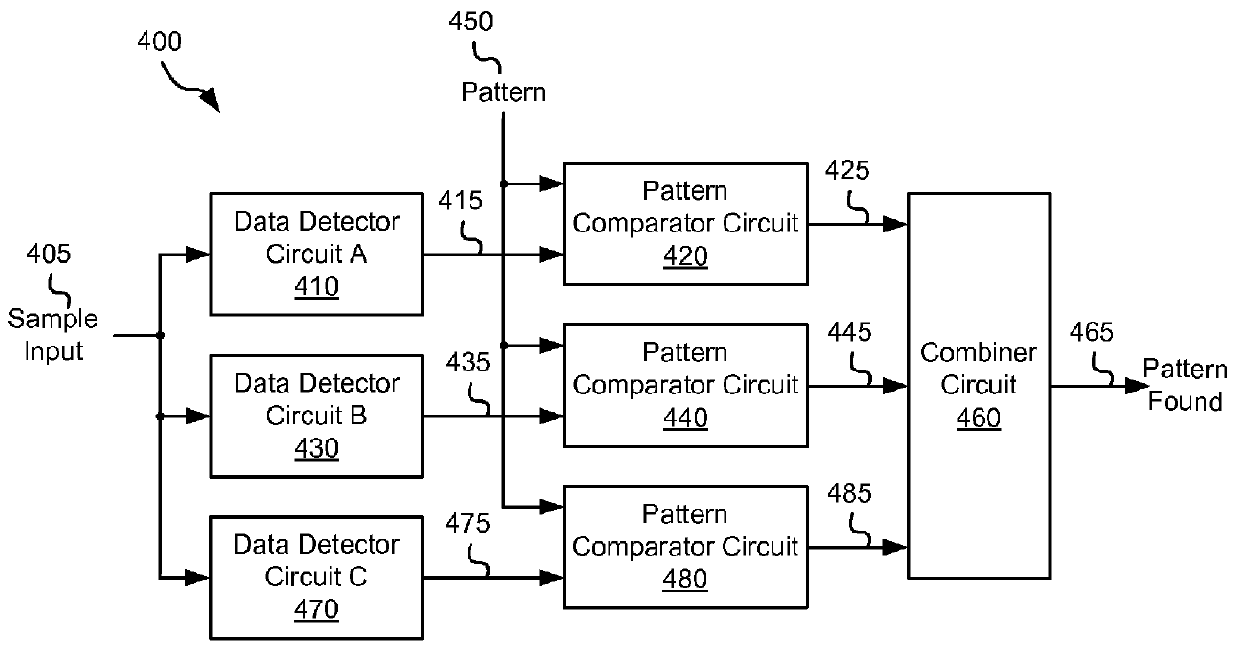

Systems and methods for diversity combined data detection

InactiveUS8261171B2Data representation error detection/correctionDigital data processing detailsDetector circuitsPattern detection

Various embodiments of the present invention provide systems and methods for data processing. For example, some embodiments of the present invention provide data processing circuits including a pattern detection circuit having at least two data detector circuits each operable to receive the same series of data samples and to provide a first detected data output and a second detected data output, respectively. In addition, the data pattern detection circuit includes a result combining circuit that is operable to assert a pattern found output based at least in part on the first detected data output and the second detected data output.

Owner:BROADCOM INT PTE LTD

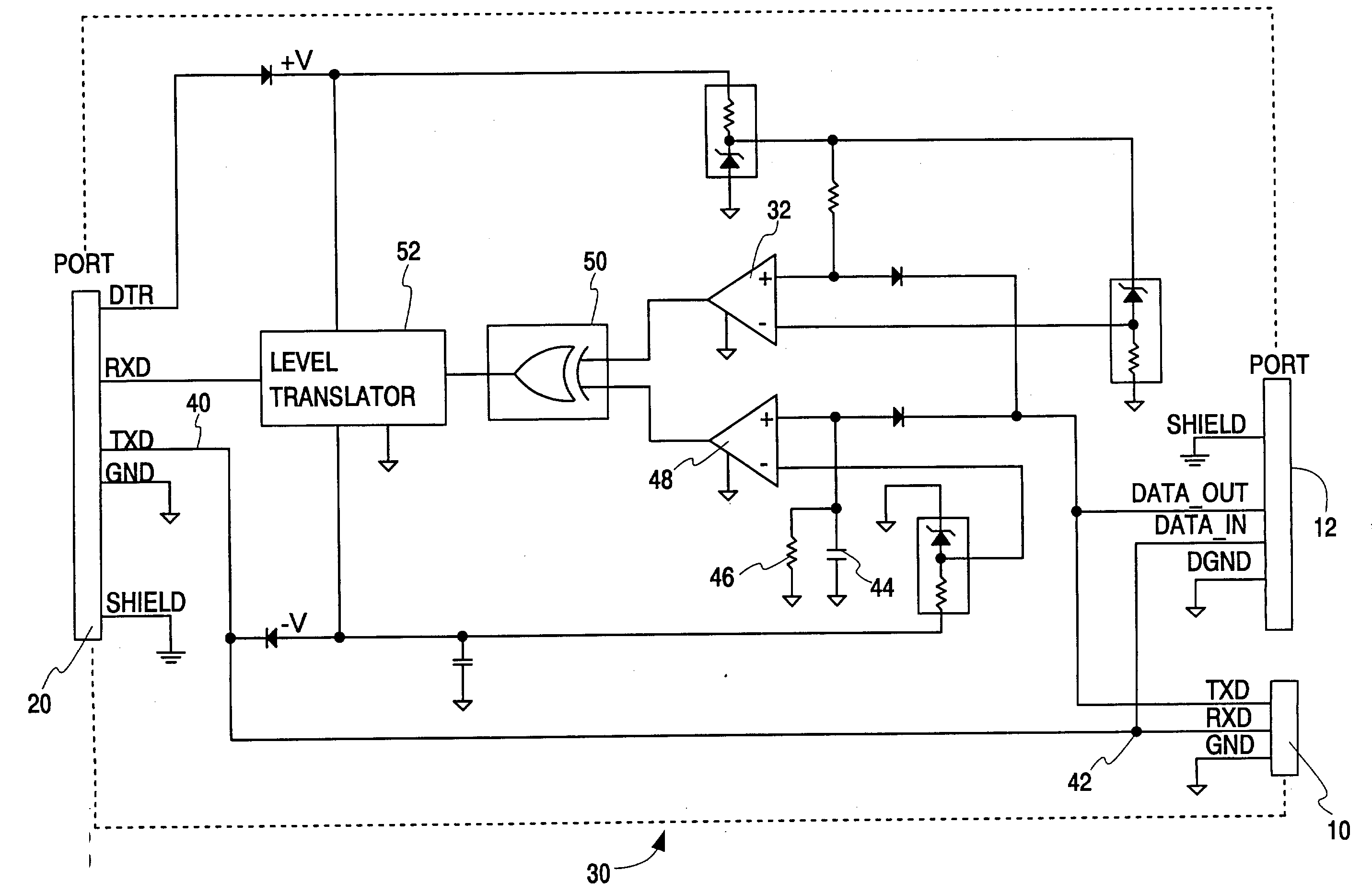

Interface system

ActiveUS20030225317A1Pulse automatic controlElectronic switchingDetector circuitsSignal characteristic

An interface system delivers an output signal having a first signal characteristic in response to first and second input signals having the first signal characteristic and a second, different signal characteristic. The interface system includes a signal input for receiving a first signal having a first signal characteristic and a second signal having a second signal characteristic which is different from the first signal characteristic, a detector circuit for detecting whether the signal at the input is the first signal or the second signal, and a translator circuit for translating either of the first signal or the second signal into the output signal.

Owner:ASCENSIA DIABETES CARE HLDG AG

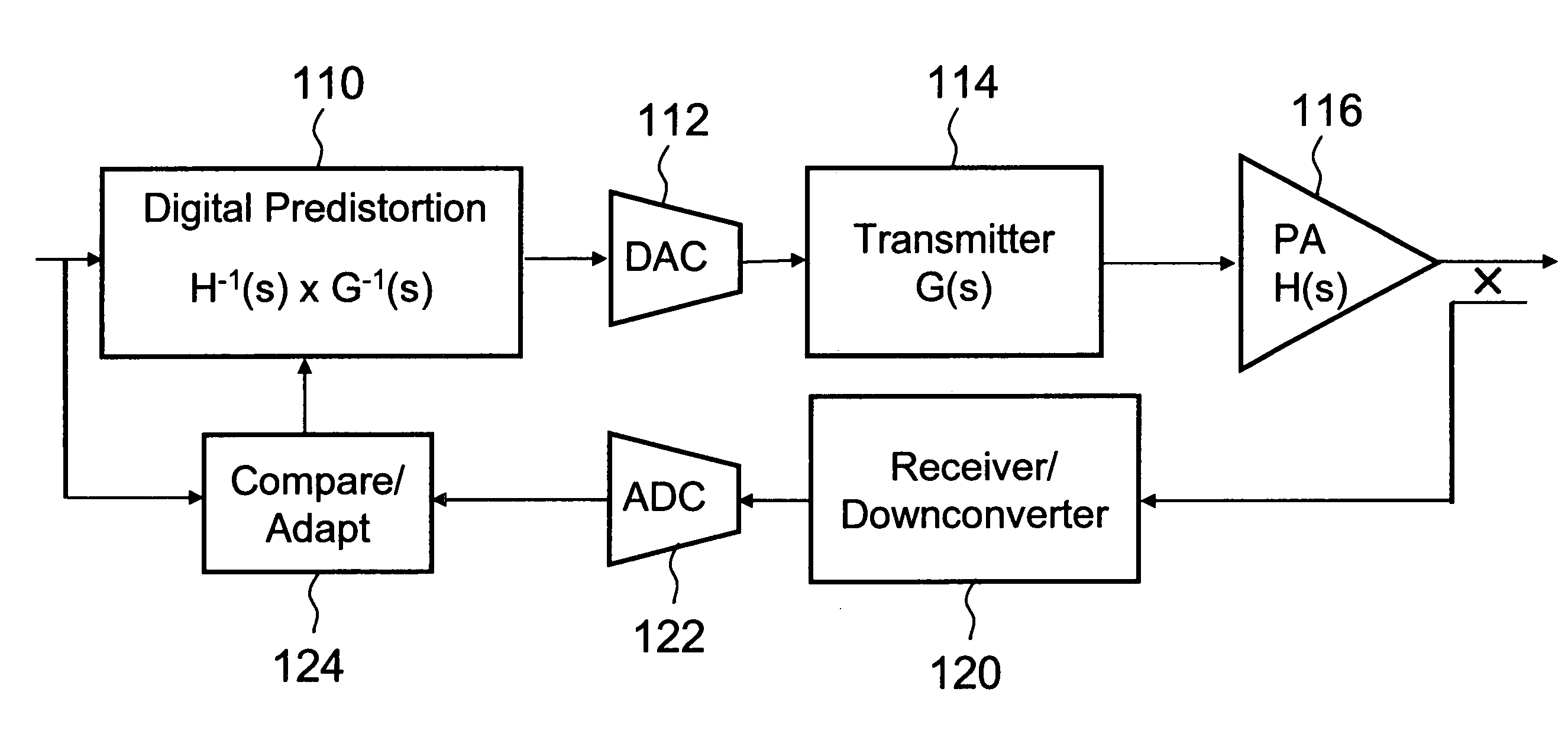

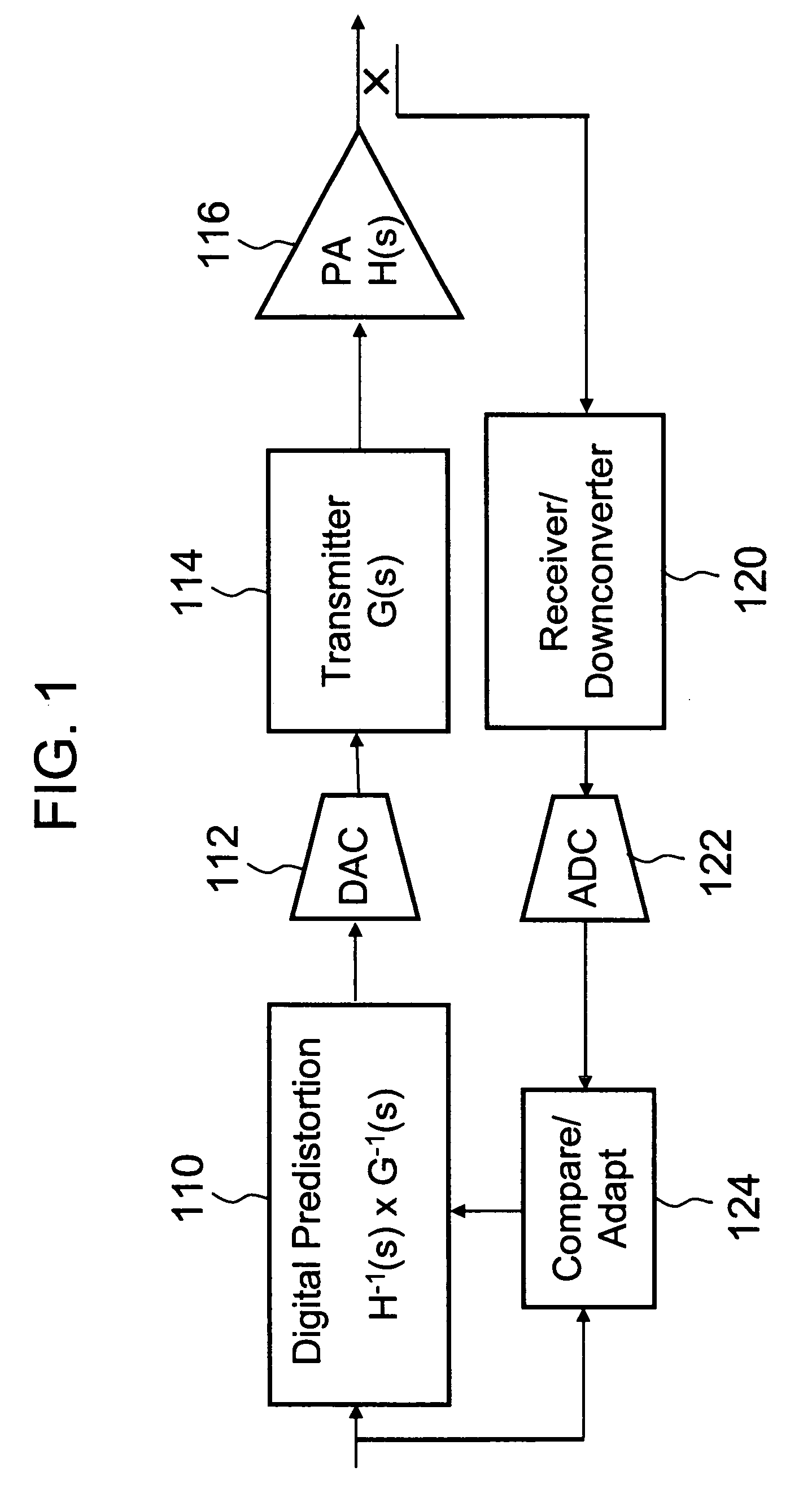

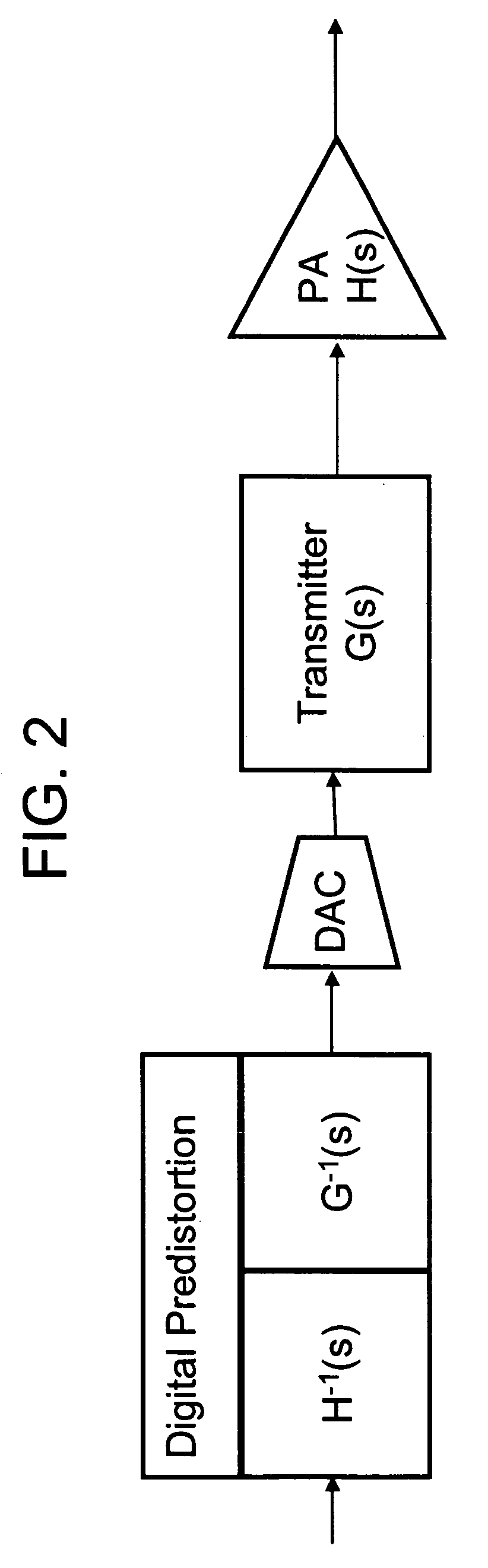

Method of power amplifier predistortion adaptation using compression detection

InactiveUS20090256630A1Reduce power consumptionNegative-feedback-circuit arrangementsElectric devicesAudio power amplifierDetector circuits

A method of power amplifier predistortion that makes use of a compression detector circuit in a feedback loop in order to adapt the channel gain for changing transmitter behavior. By monitoring the compression behavior of the amplifier, the signal is scaled to compensate for gain and compression point variations in the power amplifier and transmitter, while keeping a predistortion correction function constant.

Owner:SAMSUNG ELECTRONICS CO LTD

Transceiver with closed loop control of antenna tuning and power level

InactiveUS7469129B2Efficiently transmits and receivesMost efficientElectric signal transmission systemsResonant long antennasDetector circuitsTransceiver

A trainable transceiver for learning and transmitting an activation signal that includes an RF carrier frequency modulated with a code for remotely actuating a device, such as a garage door opener. The trainable transceiver preferably includes a controller, a signal generator, and a dynamically tunable antenna having a variable impedance that may be selectively controlled in accordance with a detector circuit signal. The detector circuit provides a measurement of the transmission power and is also used to vary the applied transmission power of the transceiver in response to operating and environmental parameters.

Owner:GENTEX CORP

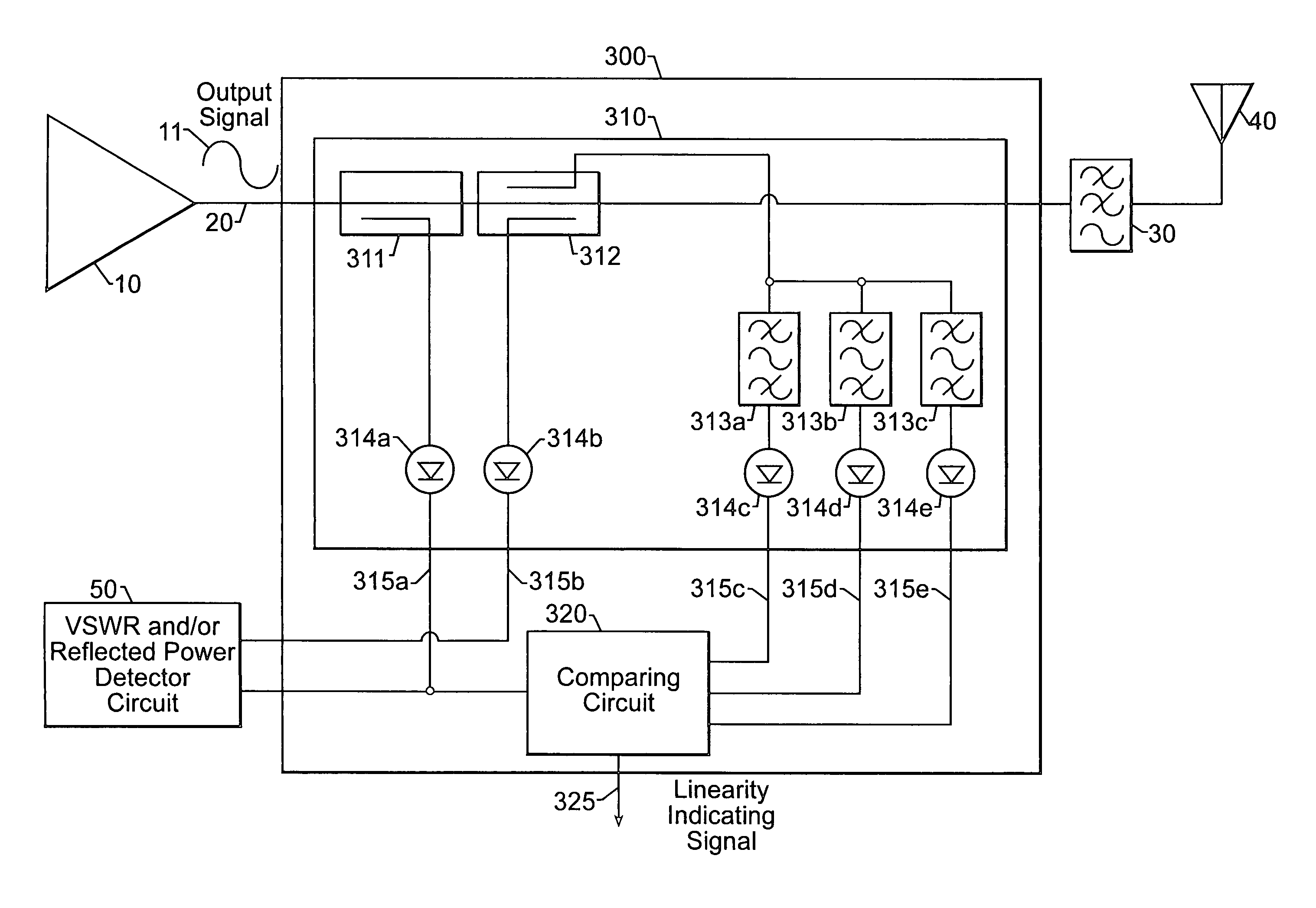

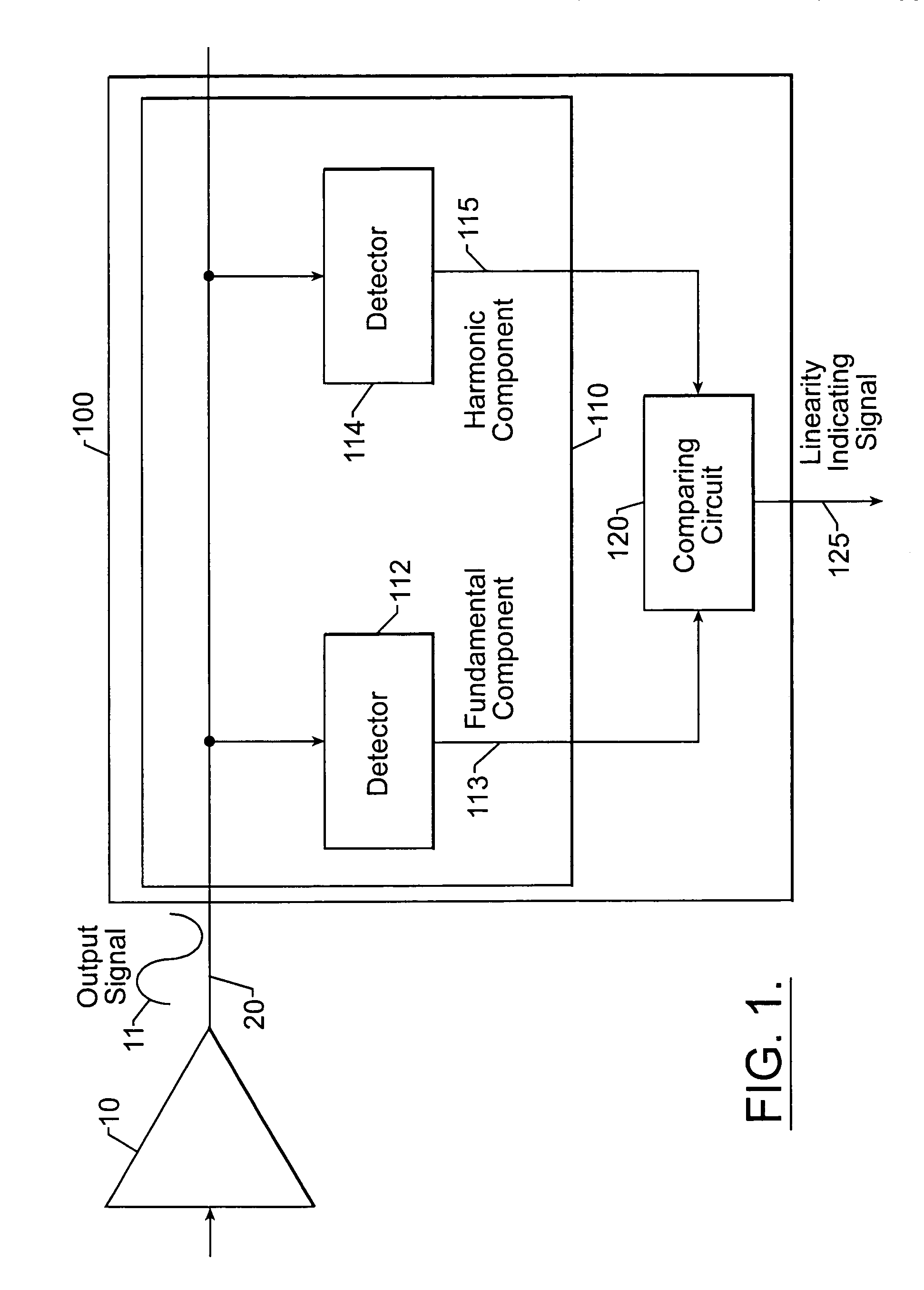

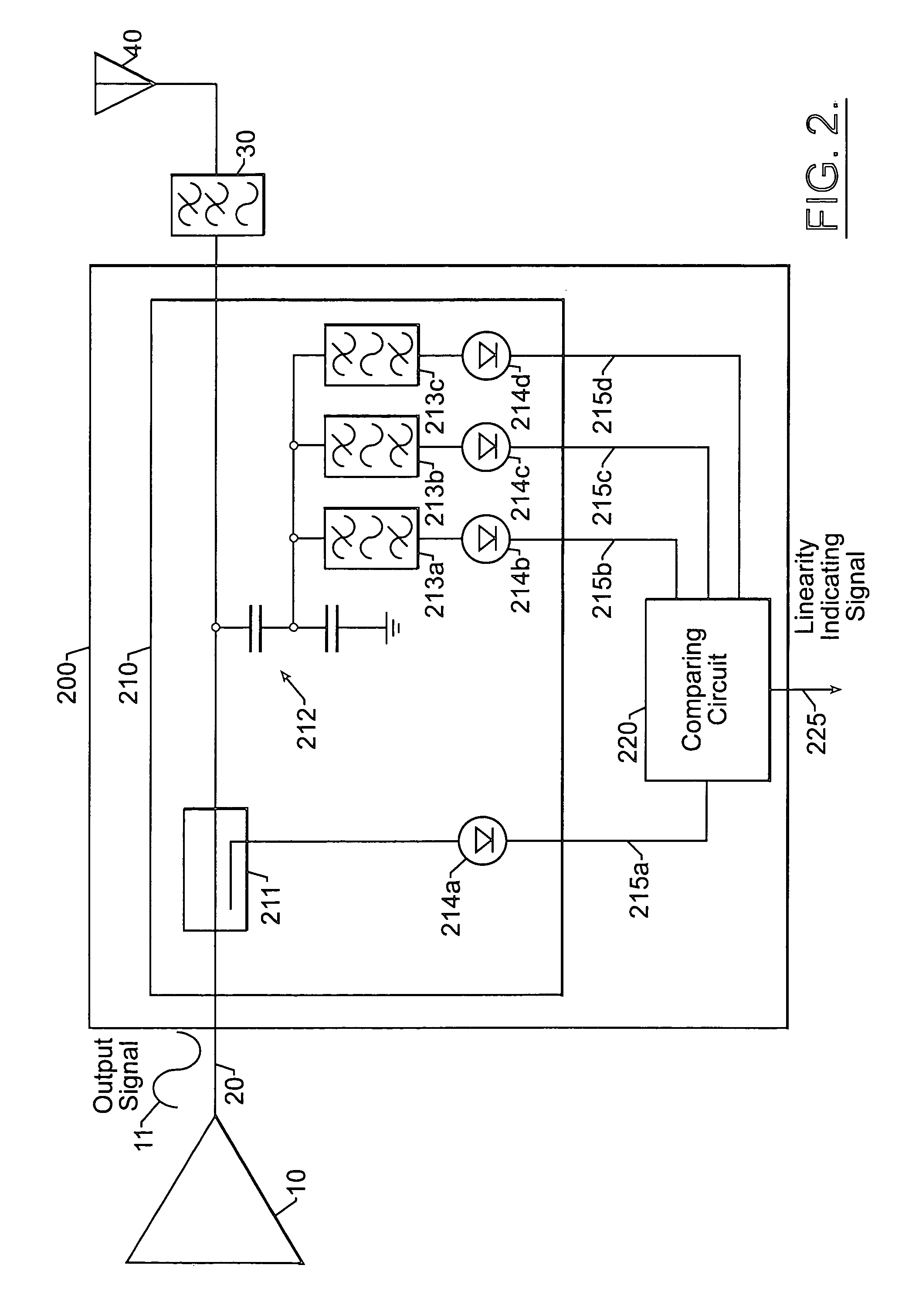

Apparatus and methods for monitoring and controlling power amplifier linearity using detected fundamental and harmonic components

InactiveUS6960956B2Amplifier modifications to reduce non-linear distortionResonant long antennasDetector circuitsAudio power amplifier

An apparatus for monitoring a power amplifier coupled to a transmission medium includes a detector circuit, coupled to the transmission medium, that generates first and second detector signals corresponding to respective fundamental and harmonic components of a power amplifier output signal produced by the power amplifier. A comparing circuit is coupled to the detector circuit and compares the first and second detector signals. The comparing circuit, responsive to a comparison of the first and second detector signals, may generate a signal that indicates linearity of the power amplifier. In some embodiments, the detector circuit may generate the second detector signal without requiring phase information for the harmonic component. In other embodiments, a control circuit controls linearity of the power amplifier responsive to comparison of the first and second detector signals, for example, by controlling power amplifier bias and / or input signal level based on the comparison. Related methods are also discussed.

Owner:TELEFON AB LM ERICSSON (PUBL)

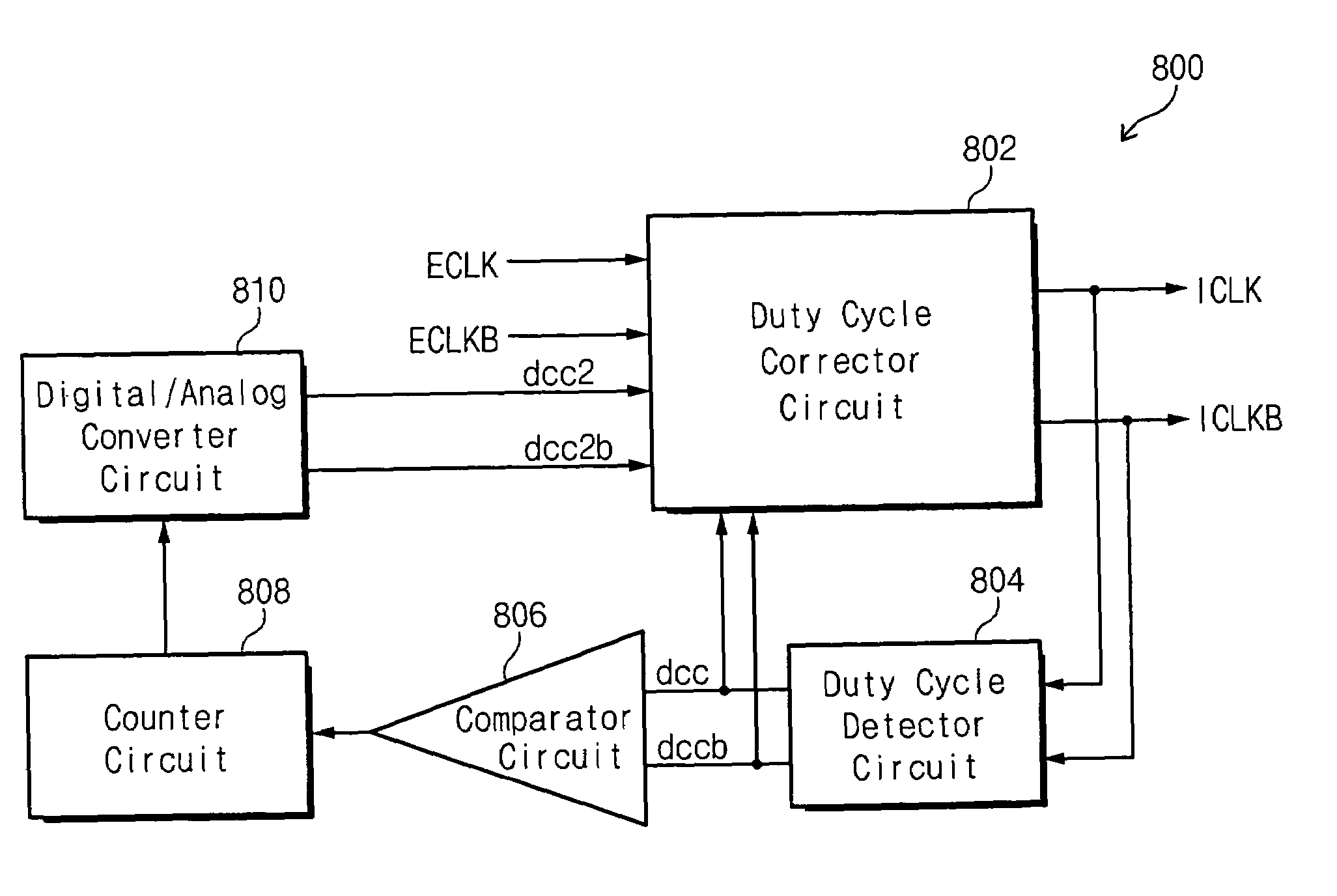

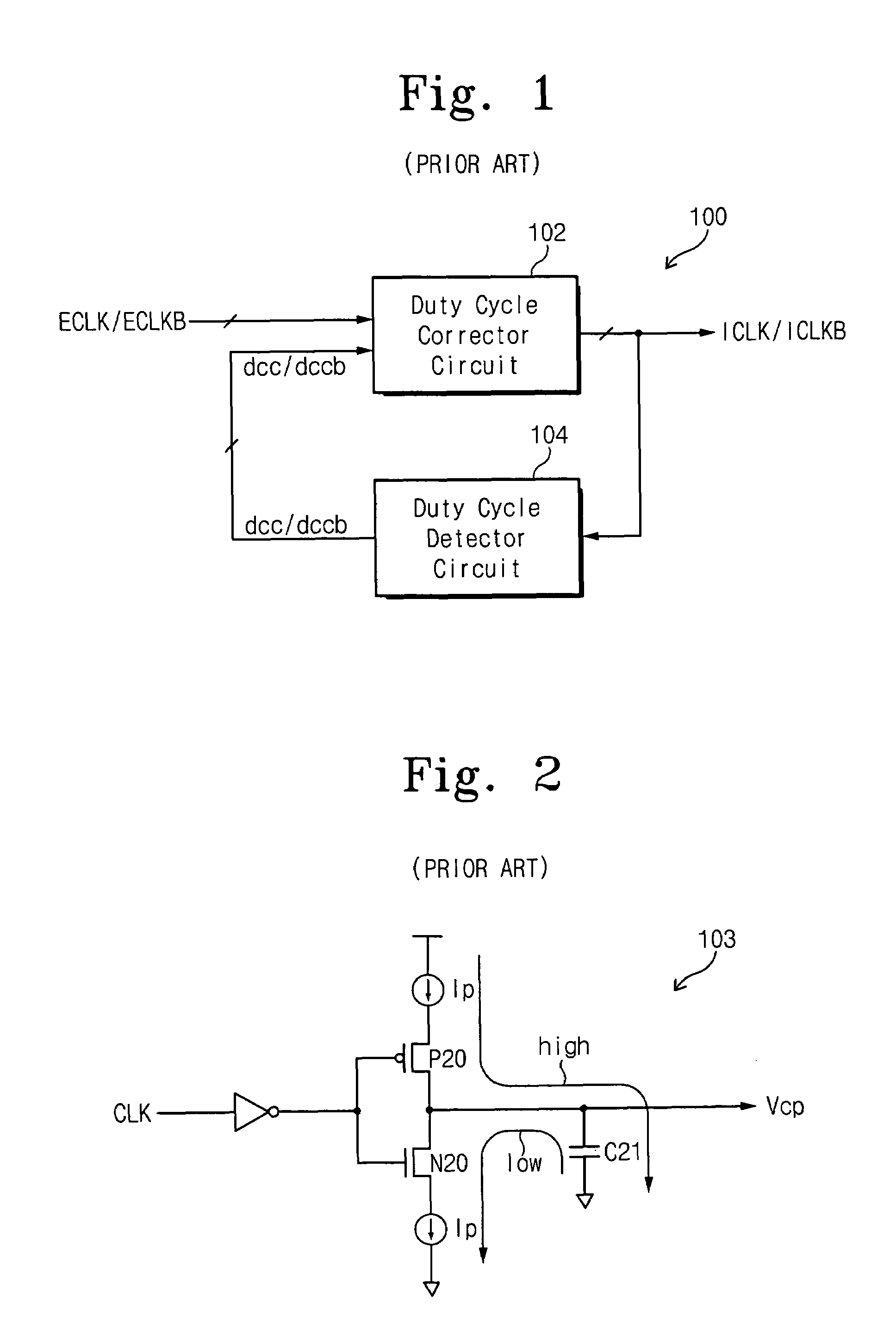

Integrated circuit devices having duty cycle correction circuits that receive control signals over first and second separate paths and methods of operating the same

InactiveUS7015739B2Pulse automatic controlContinuous to patterned pulse manipulationDigital analog converterDetector circuits

Digital duty cycle correction circuits are provided including a duty cycle detector circuit configured to generate first and second control values associated with a first internal clock signal and a second internal clock signal, respectively. A comparator circuit is also provided and is configured to compare the first control value to the second control value and provide a comparison result. A counter circuit is configured to perform an addition and / or a subtraction operation responsive to the comparison result to provide a digital code. A digital to analog converter is configured to generate third and fourth control values responsive to the digital code. Finally, a duty cycle corrector circuit is configured to receive first and second external clock signals and the first through fourth control values and generate the first and second internal clock signals having a corrected duty cycle. The first and second control values are received over a first path and the third and fourth control values are received over a second path, different from the first path. Related methods of operating duty cycle correction circuits are also provided.

Owner:SAMSUNG ELECTRONICS CO LTD

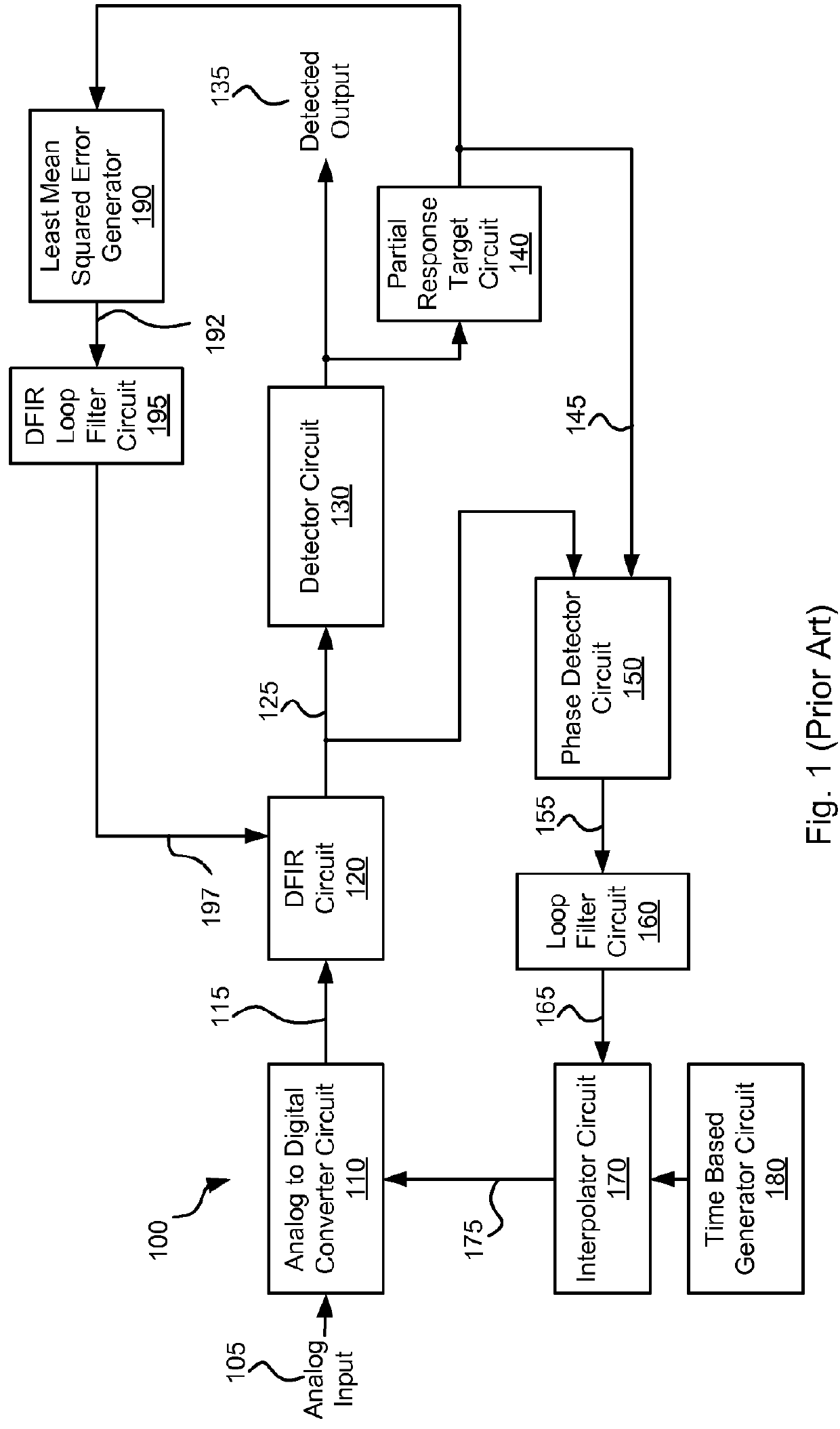

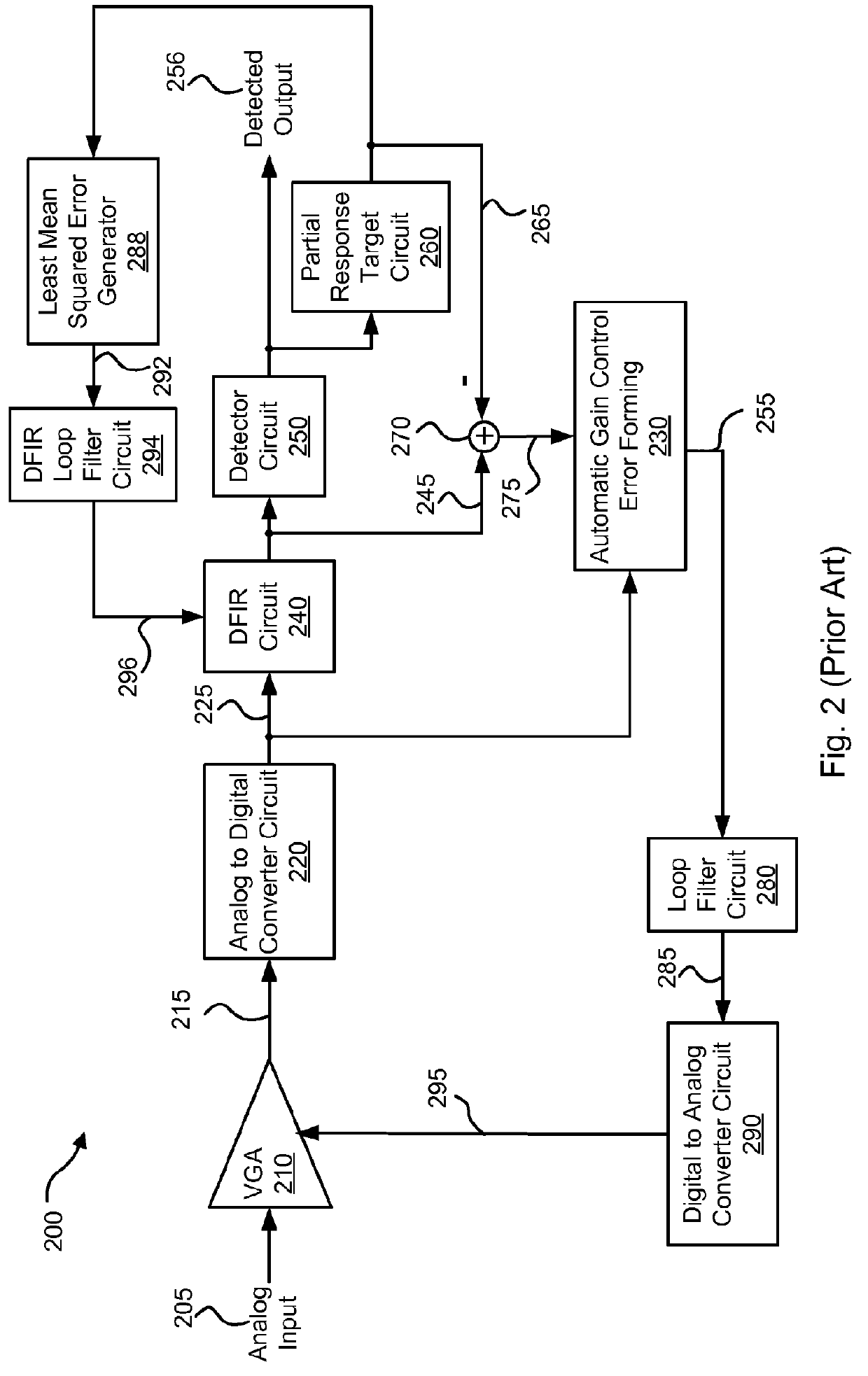

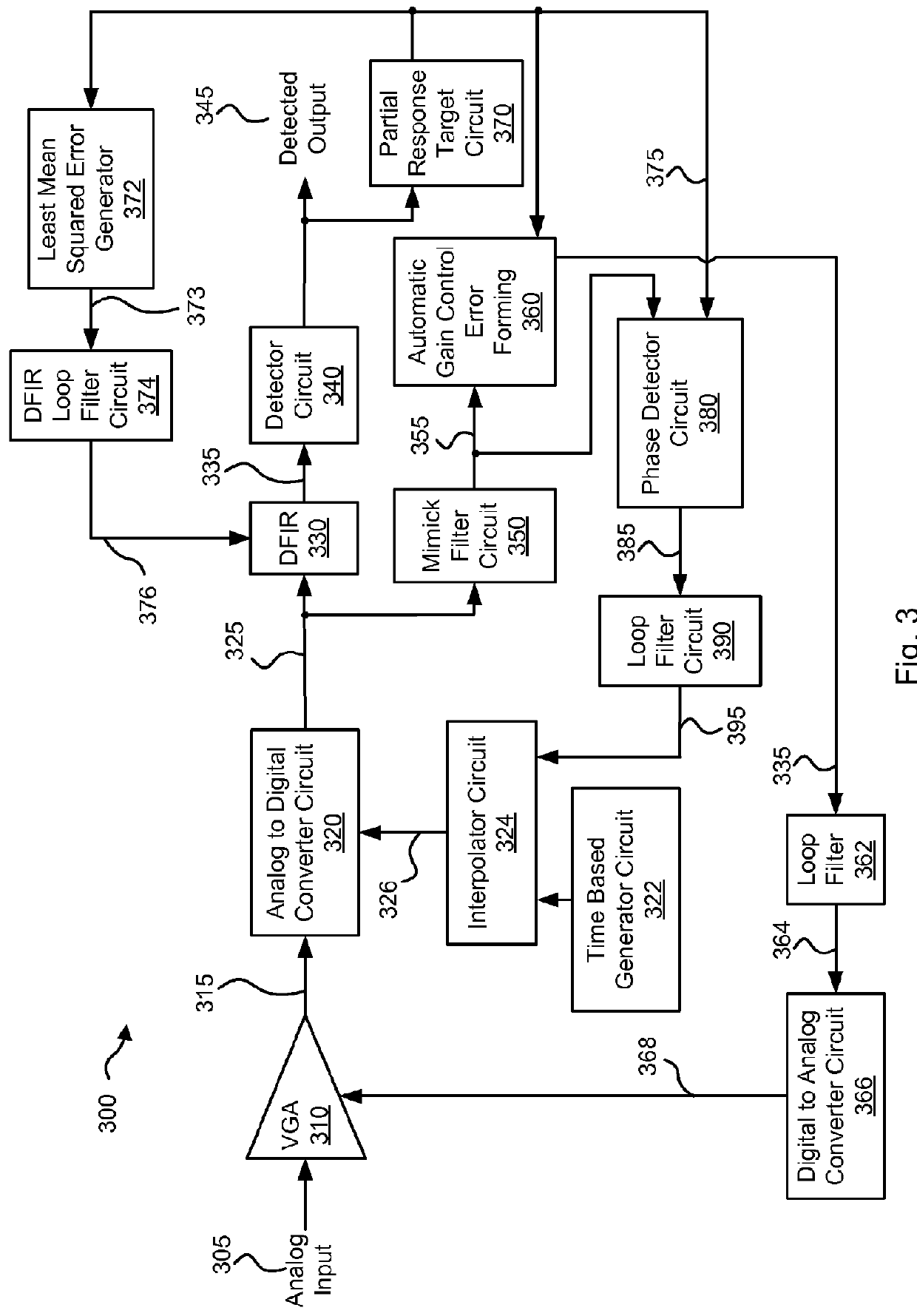

Systems and methods for semi-independent loop processing

InactiveUS8237597B2Electric signal transmission systemsRecord information storageDetector circuitsAnalog-to-digital converter

Various embodiments of the present invention provide systems and methods for data processing. For example, a data processing circuit is discussed that includes an analog to digital converter circuit, a digital filter circuit, a data detector circuit, a mimic filter circuit, and a sample clock generation circuit. The analog to digital converter circuit is operable to receive a data input and to provide corresponding digital samples. The digital filter circuit is operable to receive the digital samples and to provide a filtered output. The data detector circuit is operable to perform a data detection process on the filtered output to yield a detected output. The mimic filter circuit is operable to receive the digital samples and to provide a mimicked output. The sample clock generation circuit is operable to provide a sample clock based at least in part on the detected output and the mimicked output.

Owner:AVAGO TECH INT SALES PTE LTD

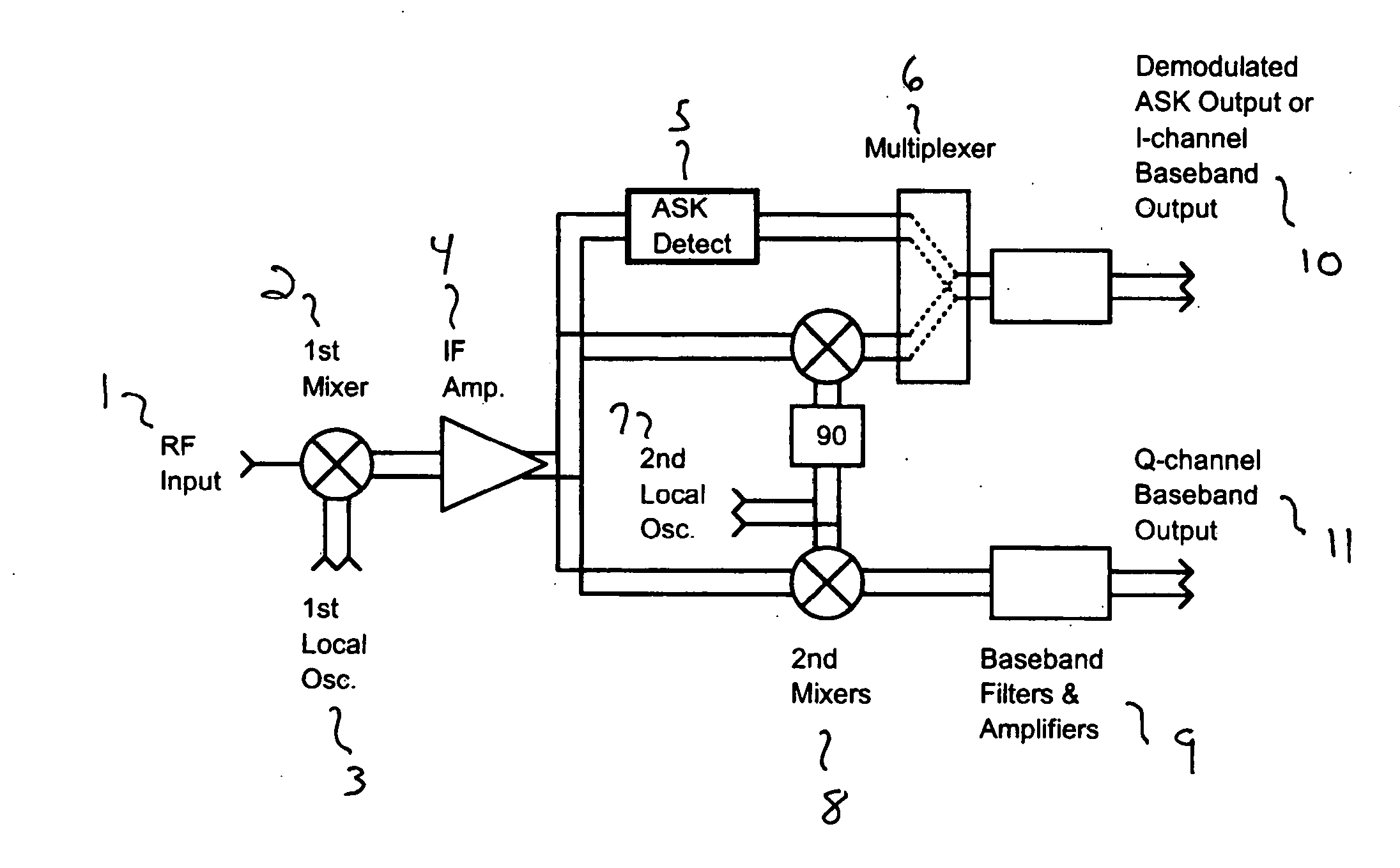

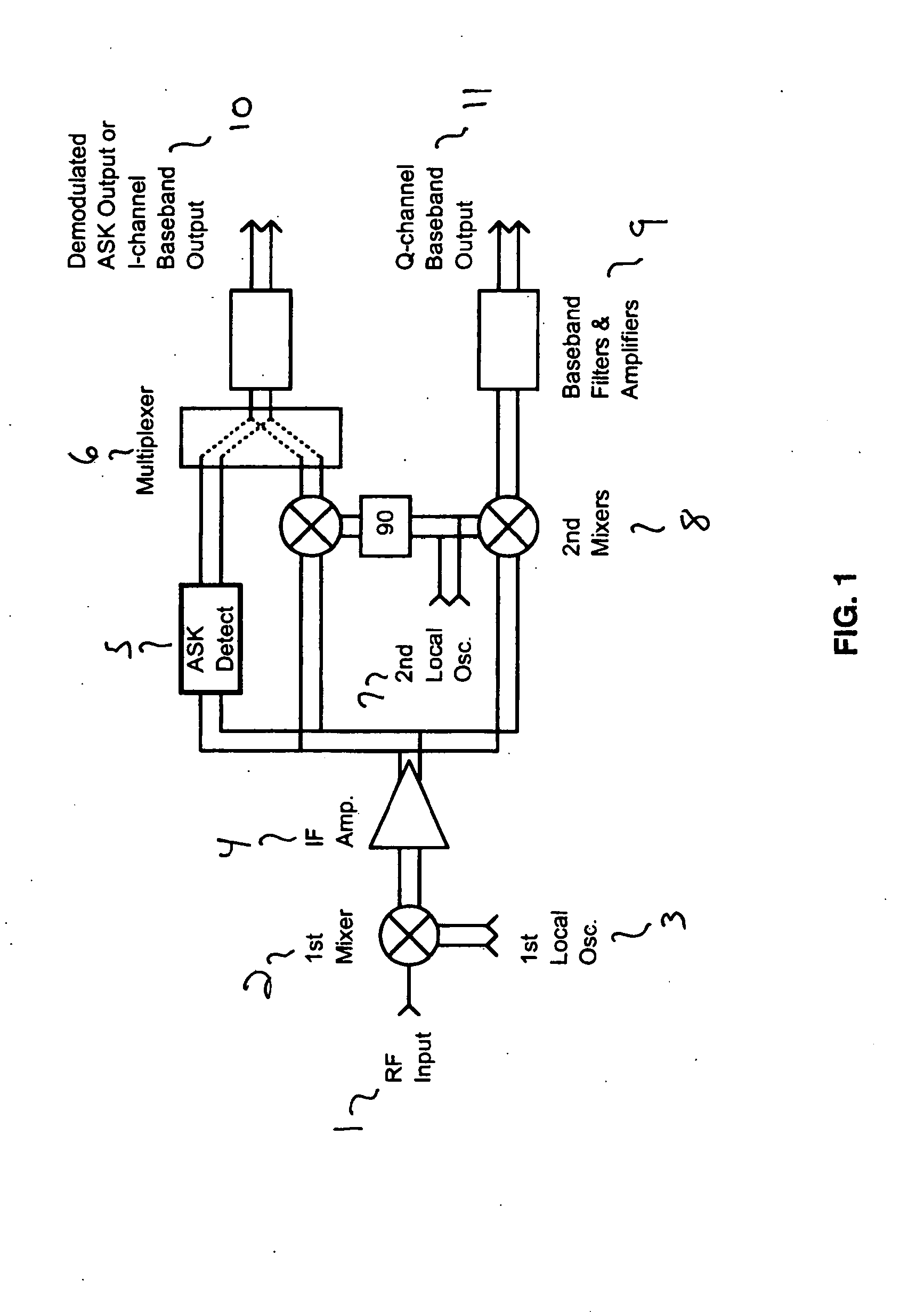

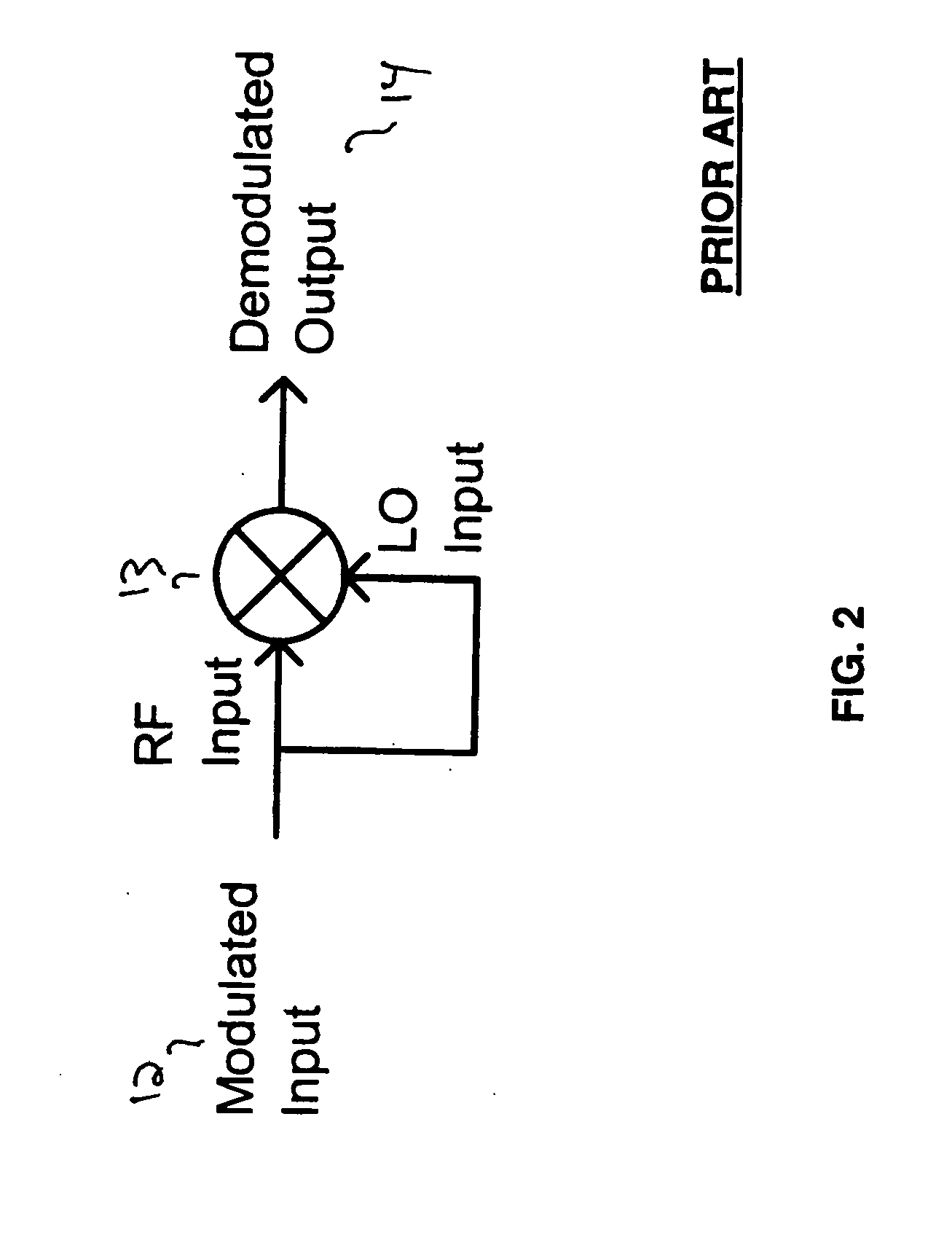

Receiver and integrated am-fm/iq demodulators for gigabit-rate data detection

ActiveUS20080280577A1Easily incorporated into integrated circuit receiver systemSimultaneous amplitude and angle demodulationAmplitude demodulationDiscriminatorDetector circuits

This disclosure addresses providing gigabit-rate data transmission over wireless radio links, using carrier frequencies in the millimeter-wave range (>30 GHz). More specifically, a circuit for detection of amplitude-shift keyed (ASK) or other amplitude modulations (AM) which can be easily incorporated into an integrated circuit receiver system is described, making the receiver capable of supporting both complex IQ modulation schemes and simpler, non-coherent on-off or multiple-level keying signals. Several novel radio architectures are also described which, with the addition of a frequency discriminator network, have the capability of handling frequency shift keyed (FSK) or other frequency modulations (FM), as well as AM and complex IQ modulation schemes. These radio architectures support this wide variety of modulations by efficiently sharing detector hardware components. The architecture for supporting both quadrature down-conversion and ASK / AM is described first, followed by the ASK / AM detector circuit details, then the AM-FM detector architecture, and finally the most general AM-FM / IQ demodulator system concept and the FSK / FM detector circuit details.

Owner:GLOBALFOUNDRIES US INC

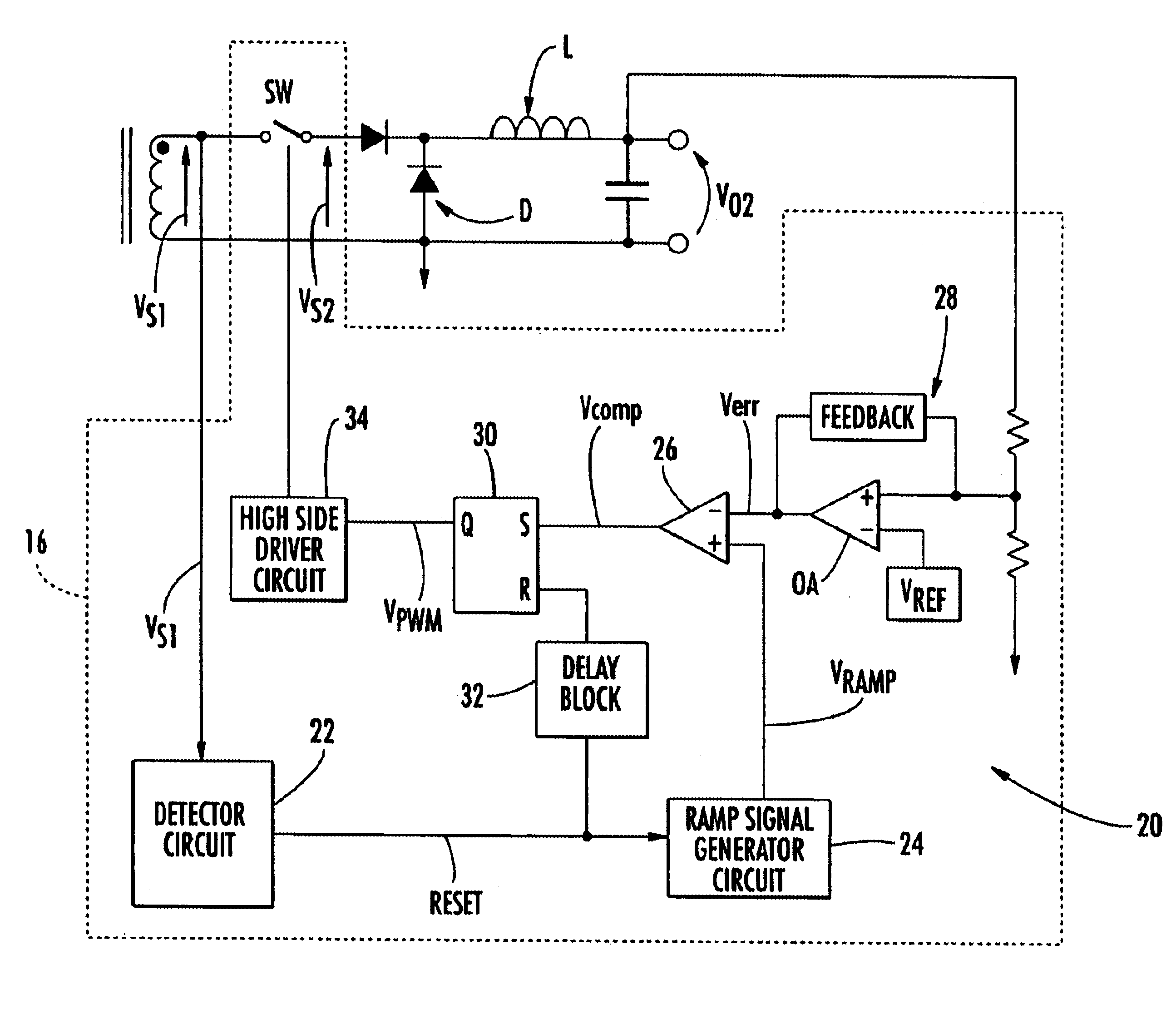

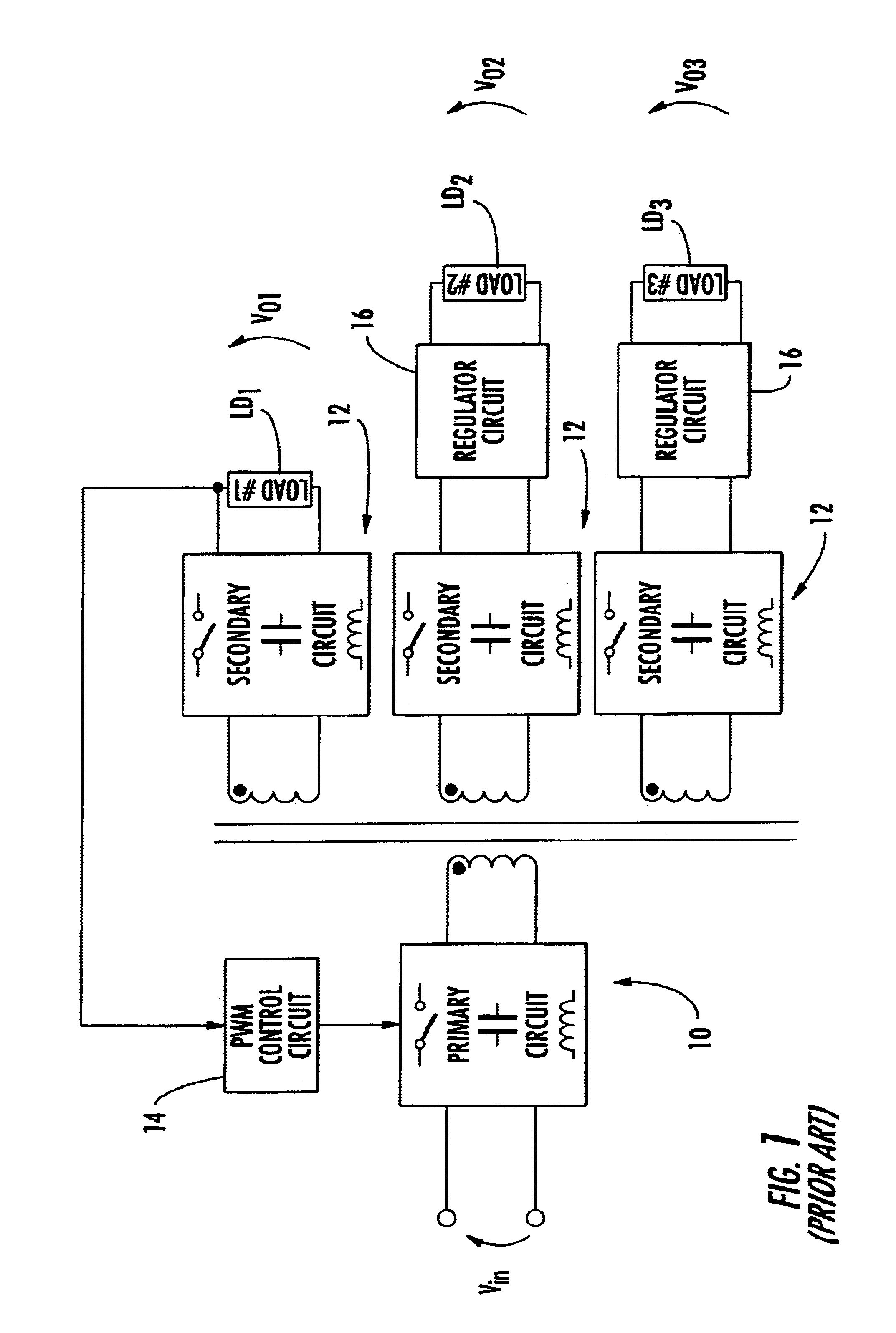

PWM control circuit for the post-adjustment of multi-output switching power supplies

InactiveUS6885176B2Simple and inexpensive circuit constructionAc-dc conversion without reversalConversion with intermediate conversion to dcDetector circuitsTrailing edge

A multi-output switching power supply may include a PWM regulator circuit arranged in cascade upstream of each output to receive, as an input, a square wave voltage signal with a predetermined duty cycle. The regulator circuit may include an auxiliary switching device for modulating the duty cycle of the input signal to supply, as an output, a regulated direct current voltage. A control circuit for the PWM regulator circuit may include a detector circuit for detecting the trailing edges of the voltage signal input to the regulator circuit which emits a pulse coinciding with each of the trailing edges. The control circuit may also include a ramp signal generator that is controlled by the emitted pulses. The ramp signal generator may be connected to the non-inverting input of a comparator having an inverting input for receiving a signal indicative of the error in the regulator output voltage.

Owner:STMICROELECTRONICS SRL

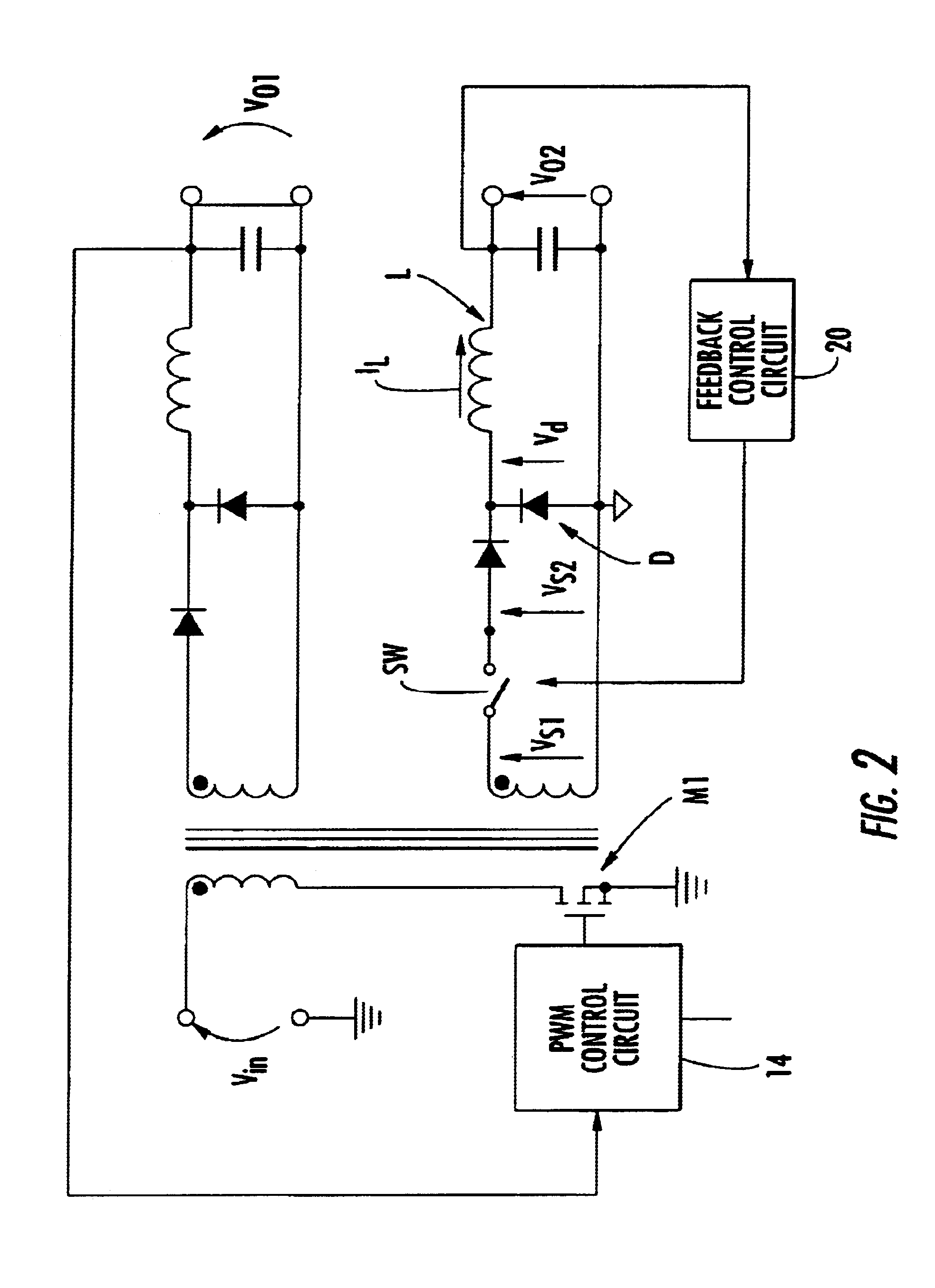

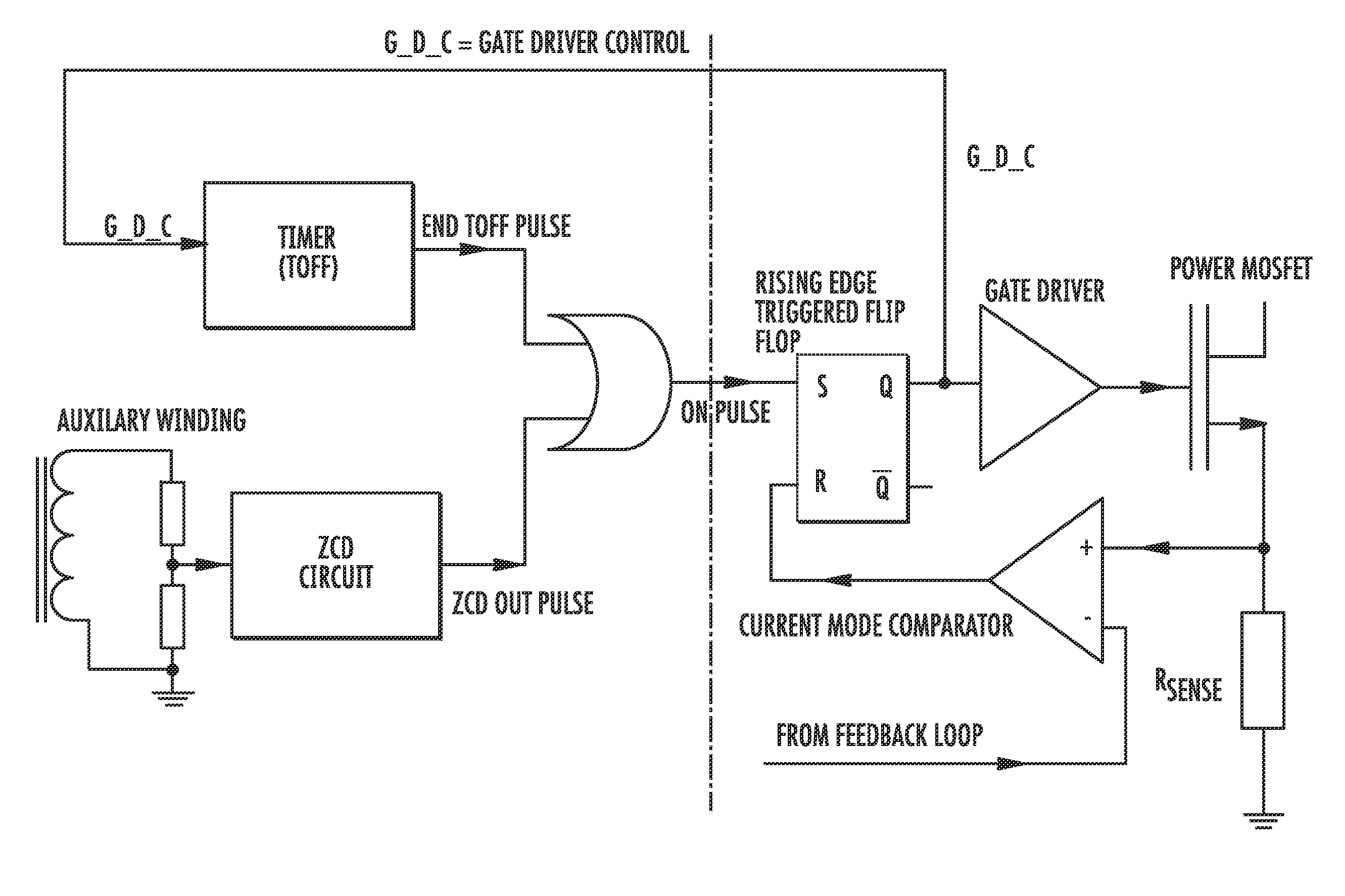

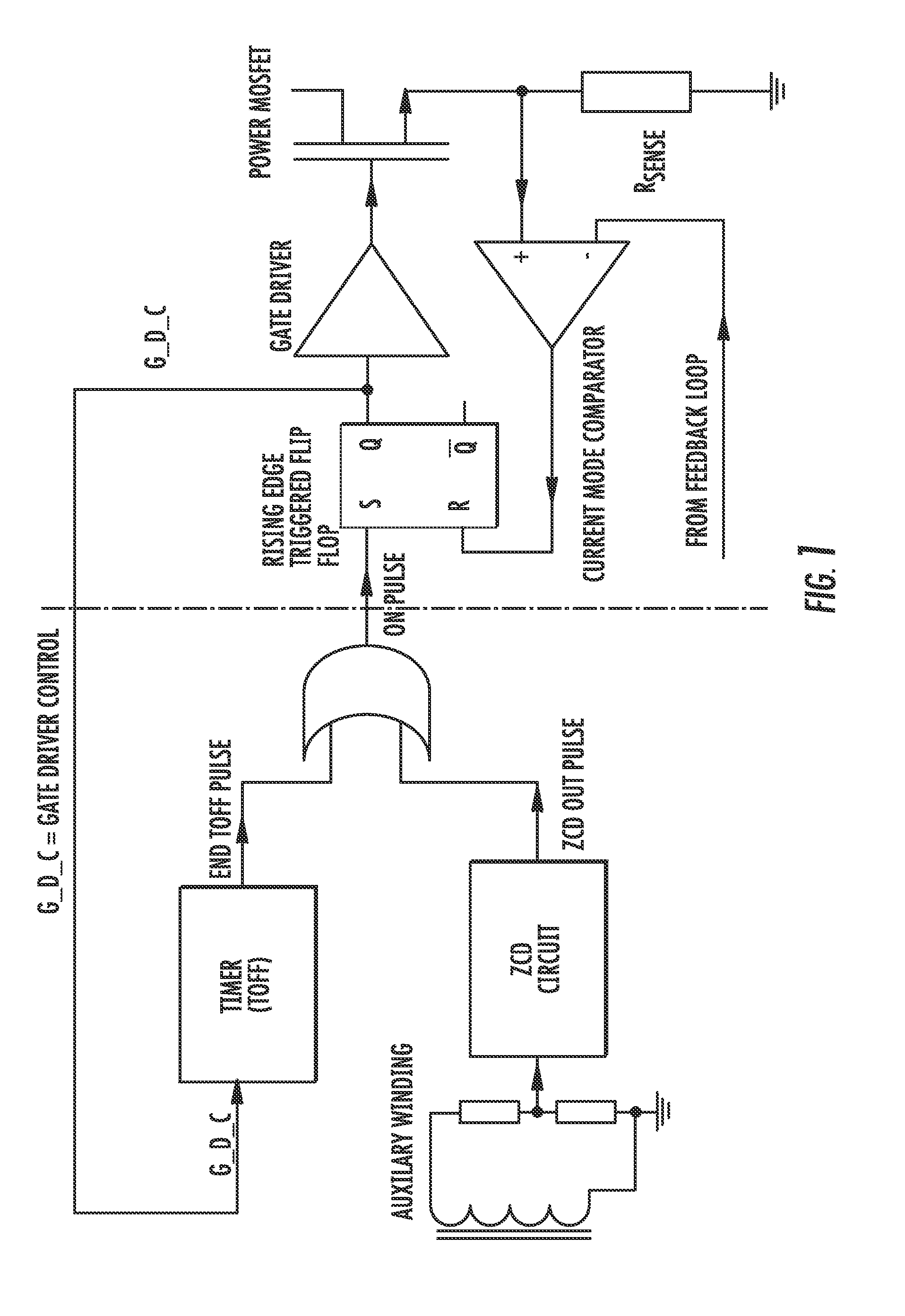

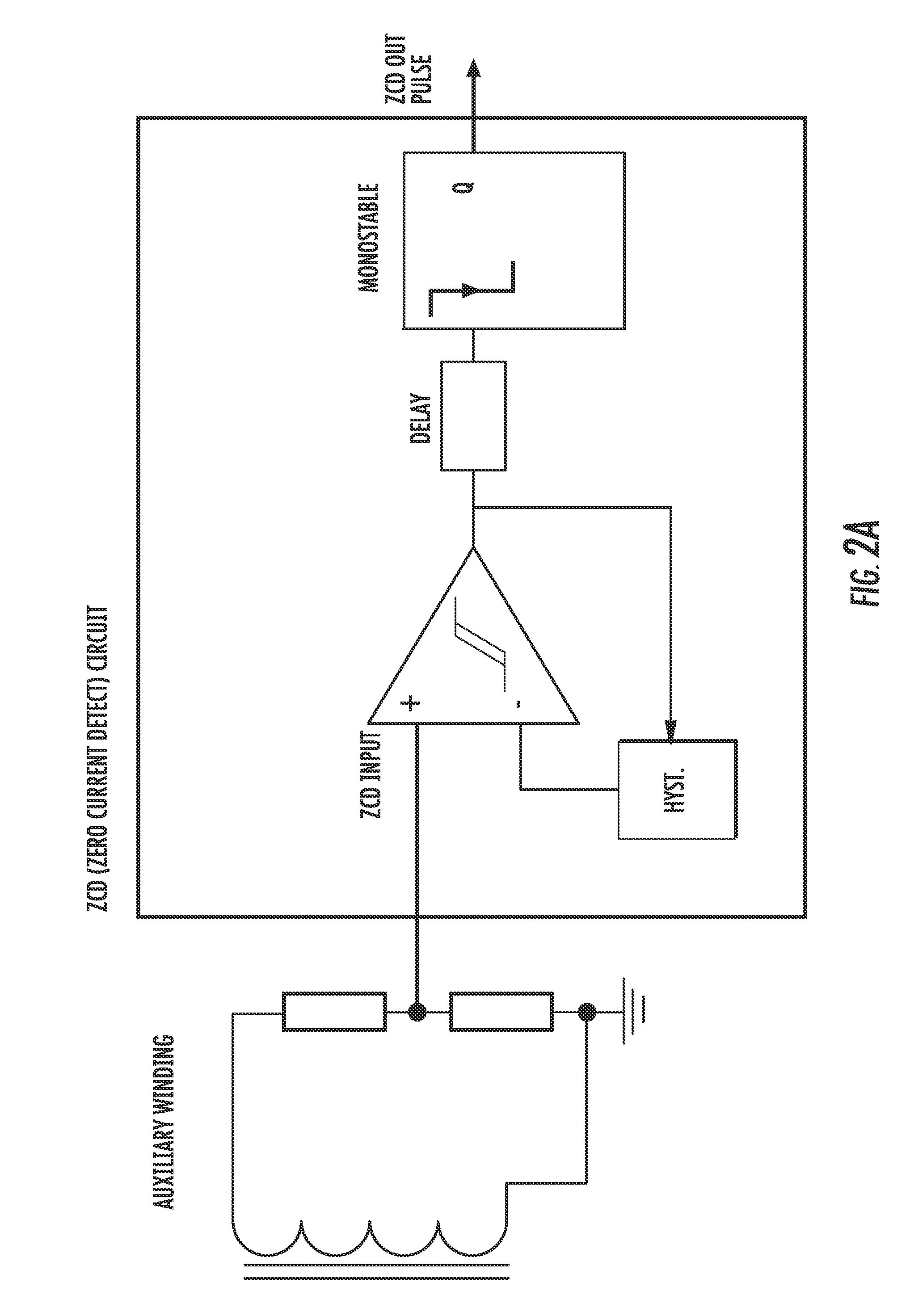

Dual mode flyback converter and method of operating it

ActiveUS20110149614A1Reduce lossesImprove efficiencyEfficient power electronics conversionDc-dc conversionDetector circuitsDual mode

A DC-DC converter includes a power switching device and a mode control logic circuit to control the power switching device and generate an ON-pulse. A flip-flop is configured to be set by the mode control logic circuit. A current mode comparator is configured to reset the flip-flop and to compare a signal based upon current flowing through the power switching device with a signal based upon an output voltage of the dual mode flyback DC-DC converter. A transformer is driven by the current mode comparator. The mode control logic circuit includes a timer starting when a gate driver control signal applied to the power switching device turns the power switching device off and configured to generate a pulse when an off time interval elapses, a zero current detector circuit configured to sense a voltage on the transformer and generate a pulse when the voltage drops below a trigger threshold, and a combinatory logic circuit configured to compare pulse signals generated by the timer and the zero current detector circuit and generate the ON-pulse based thereupon.

Owner:STMICROELECTRONICS SRL

Electric field proximity keyboards and detection systems

ActiveUS20050088416A1High resolutionReduce complexityInput/output for user-computer interactionElectronic switchingDetector circuitsSingle electrode

The invention is related to an electric field proximity detection system suitable for use as a touch sensitive keyboard or to be used in close proximity without direct contact. In an embodiment of a circuit useful in the system, an AC signal is coupled to a single electrode functioning as an antenna radiating an electric field through a high impedance circuit. A conductive object in close proximity disturbs the field causing a voltage change across nodes of the high impedance circuit that is compared by a detector circuit that generates a DC output indicating an object is close to the electrode. In another embodiment, the circuit couples to an analog multiplexer to control a plurality of electrodes. In another embodiment, a row and column address scheme coupling a plurality of electrodes and increases resolution without substantially increasing complexity. The circuits may be integrated in a semiconductor to reduce size and cost. The electric field proximity detection system extends to applications related to object detection such as remote sensing, motion detection and remote controls.

Owner:SOLECTRON

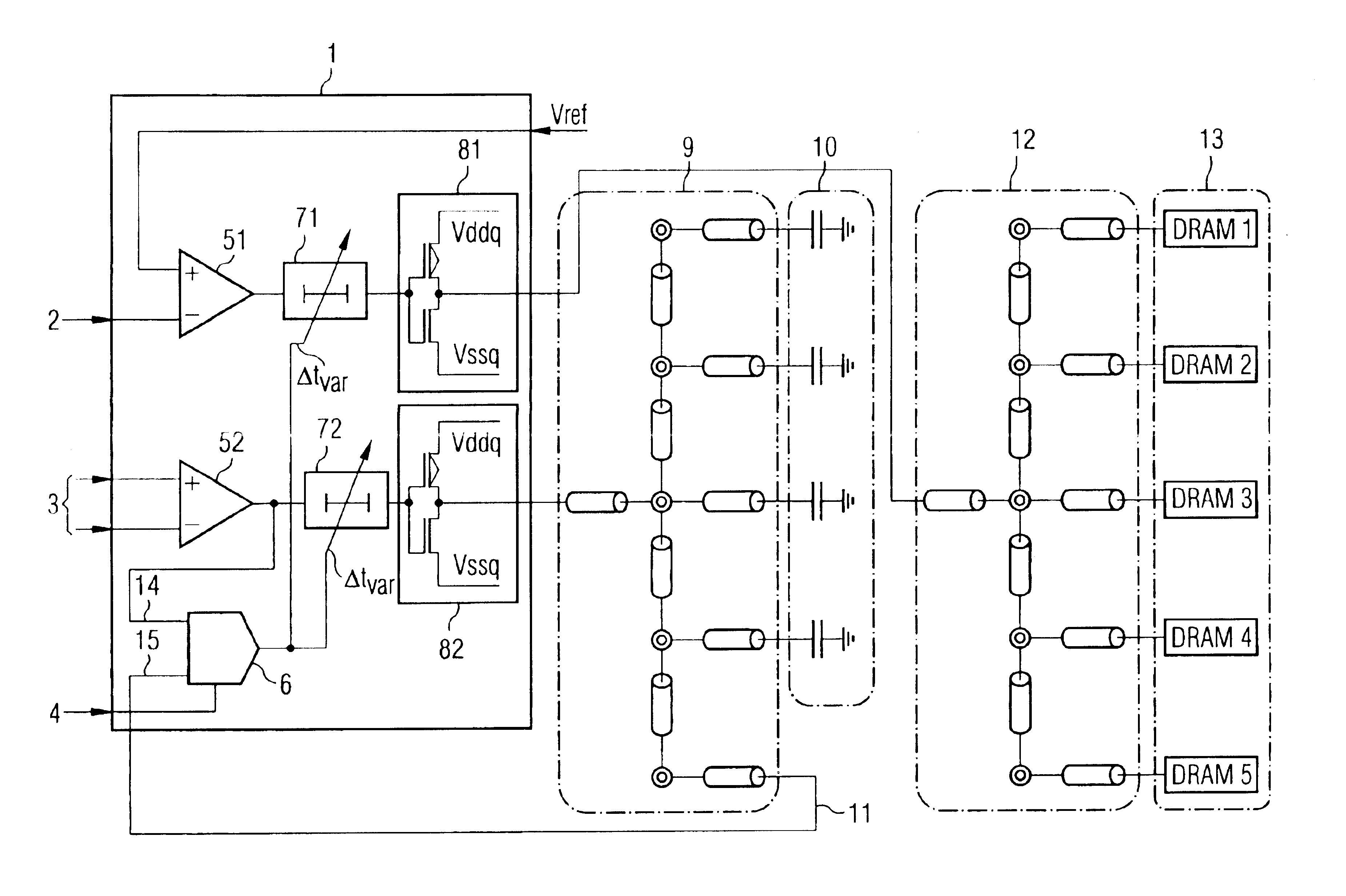

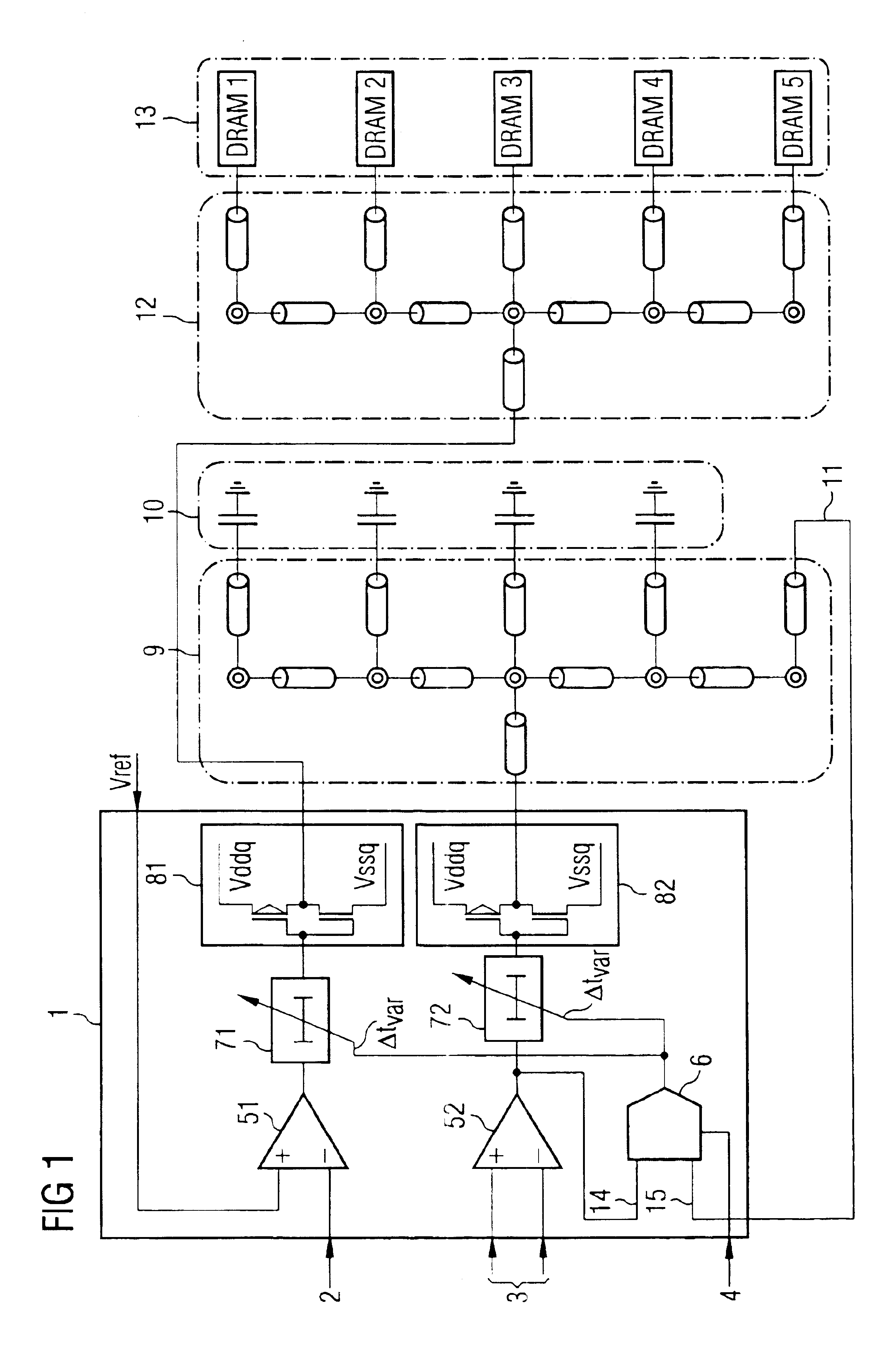

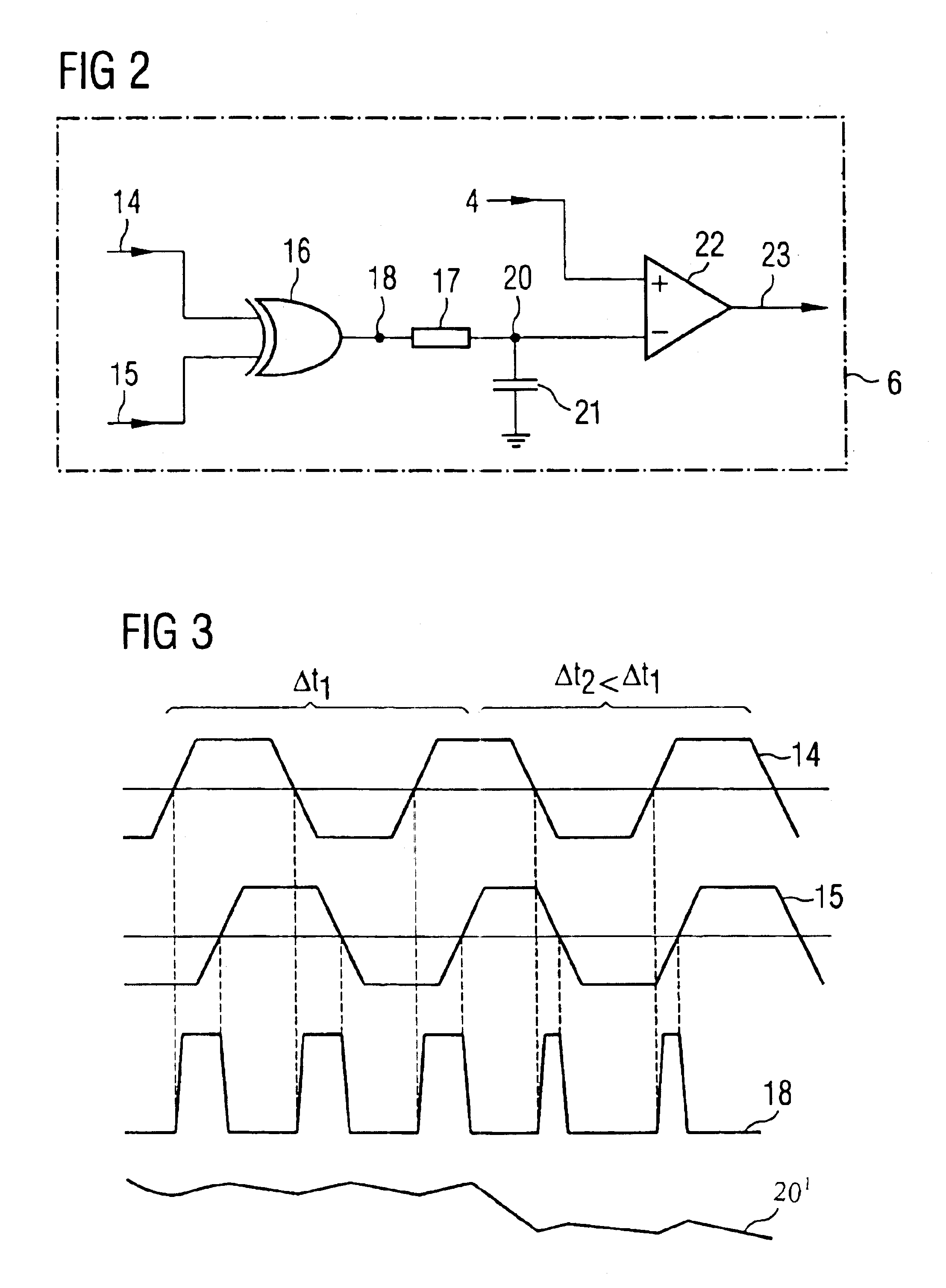

Buffer amplifier architecture for semiconductor memory circuits

A buffer amplifier architecture for buffering signals which are supplied in parallel to identical chips, particularly DRAM chips, on a semiconductor memory module, is disclosed. The architecture has adjustable delay circuits in each signal line and a delay detector circuit which receives a clock signal from the buffer amplifier architecture at the input and at the output of the buffer amplifier architecture, and takes the phase difference between the two signals to produce a control signal for setting the variable delay time of the delay circuits. To ensure that the delay time set by the delay detector circuit is independent of variations in parameters of the DRAM memory chips, the feedback path routed to the input of the delay detector circuit has a reference line network of the same structure and having the same electrical properties as capacitance elements which terminate the line network routed to the DRAM memory chips and the reference line network, and which have the same capacitances as the signal inputs on the DRAM memory chips.

Owner:POLARIS INNOVATIONS

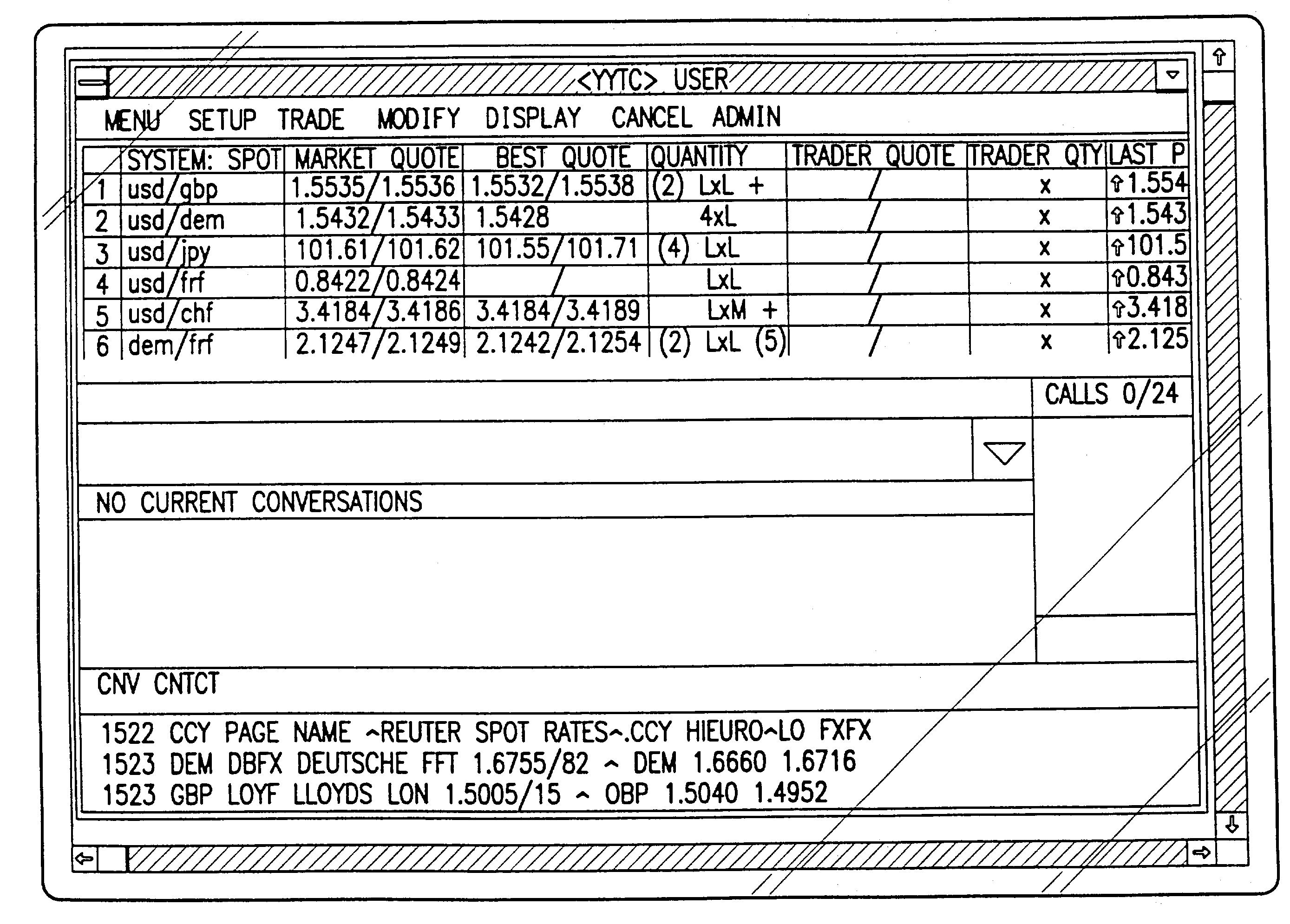

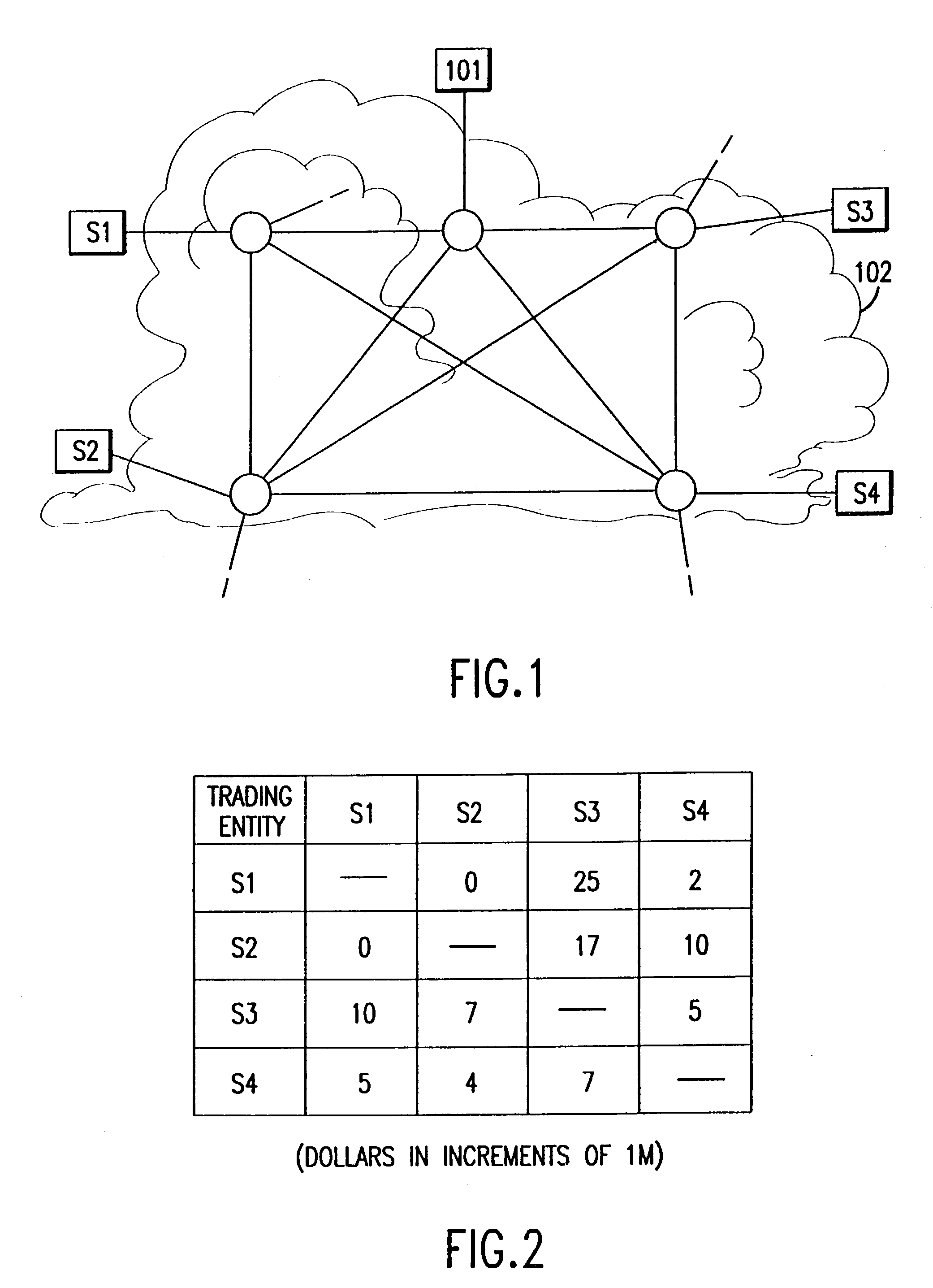

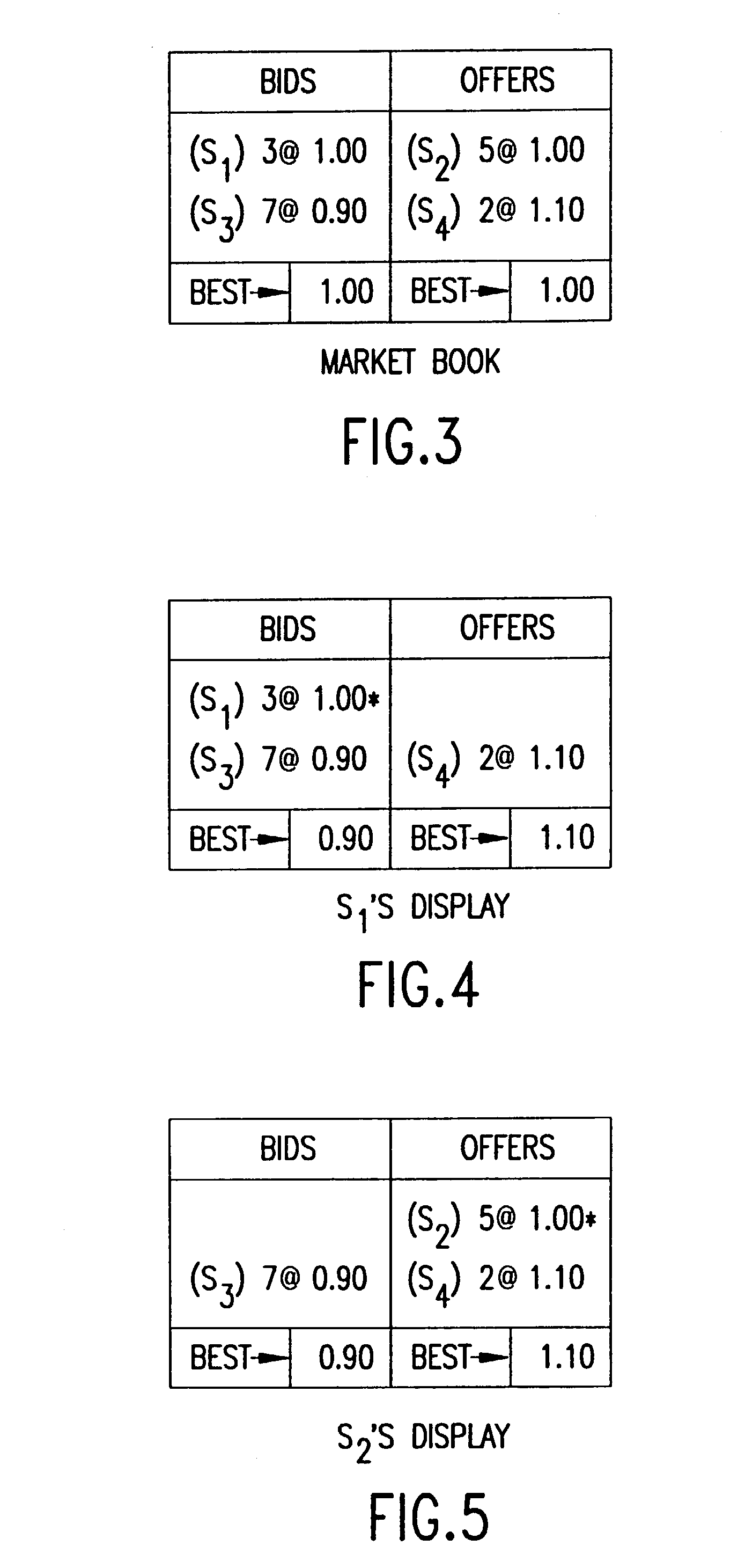

Electronic trading system including an auto-arbitrage feature or name switching feature

InactiveUS7080033B2Efficient executionEffectively avail itself of arbitrage opportunitiesFinanceCommerceDetector circuitsTransaction data

Owner:REUTERS LTD (GB)