Patents

Literature

493 results about "Buffer amplifier" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A buffer amplifier (sometimes simply called a buffer) is one that provides electrical impedance transformation from one circuit to another, with the aim of preventing the signal source from being affected by whatever currents (or voltages, for a current buffer) that the load may be produced with. The signal is 'buffered from' load currents. Two main types of buffer exist: the voltage buffer and the current buffer.

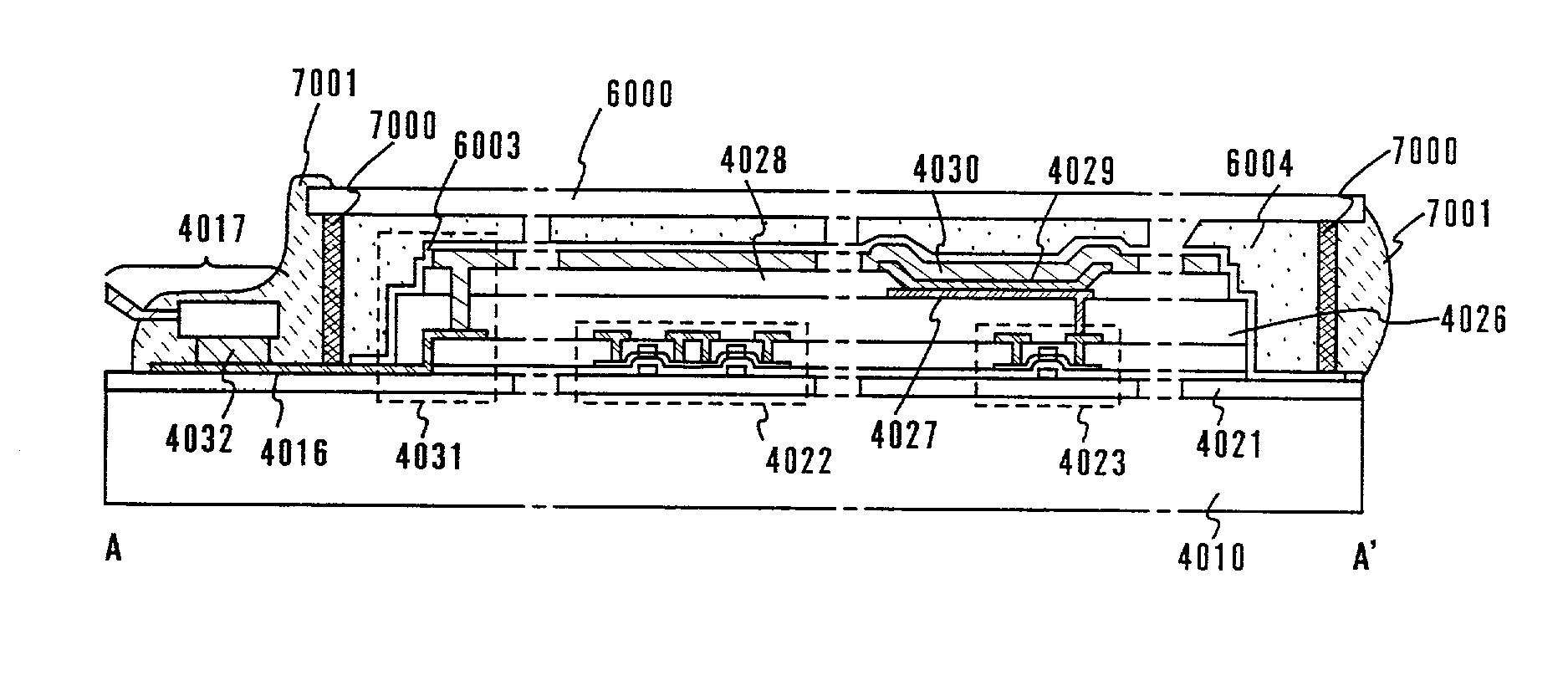

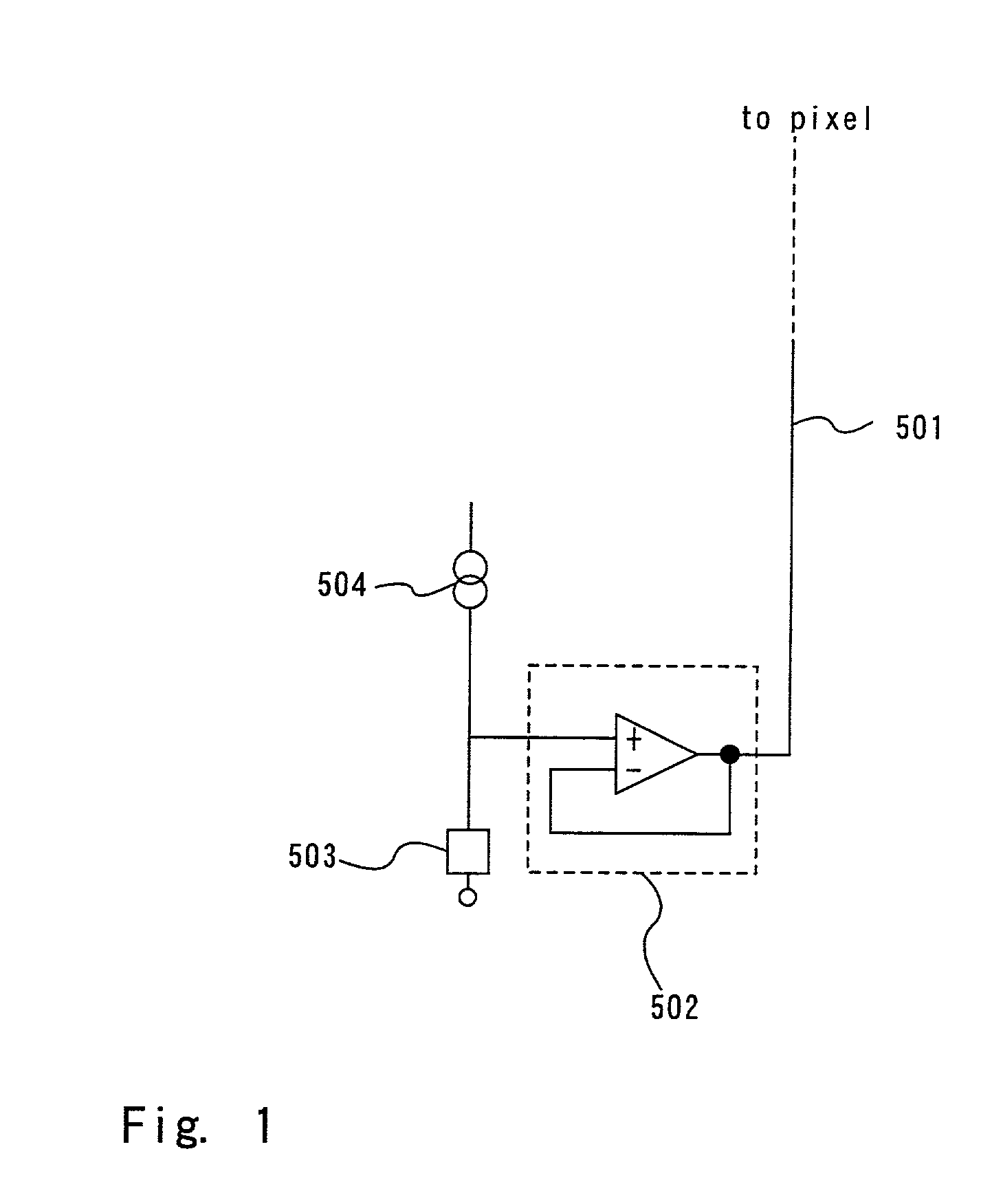

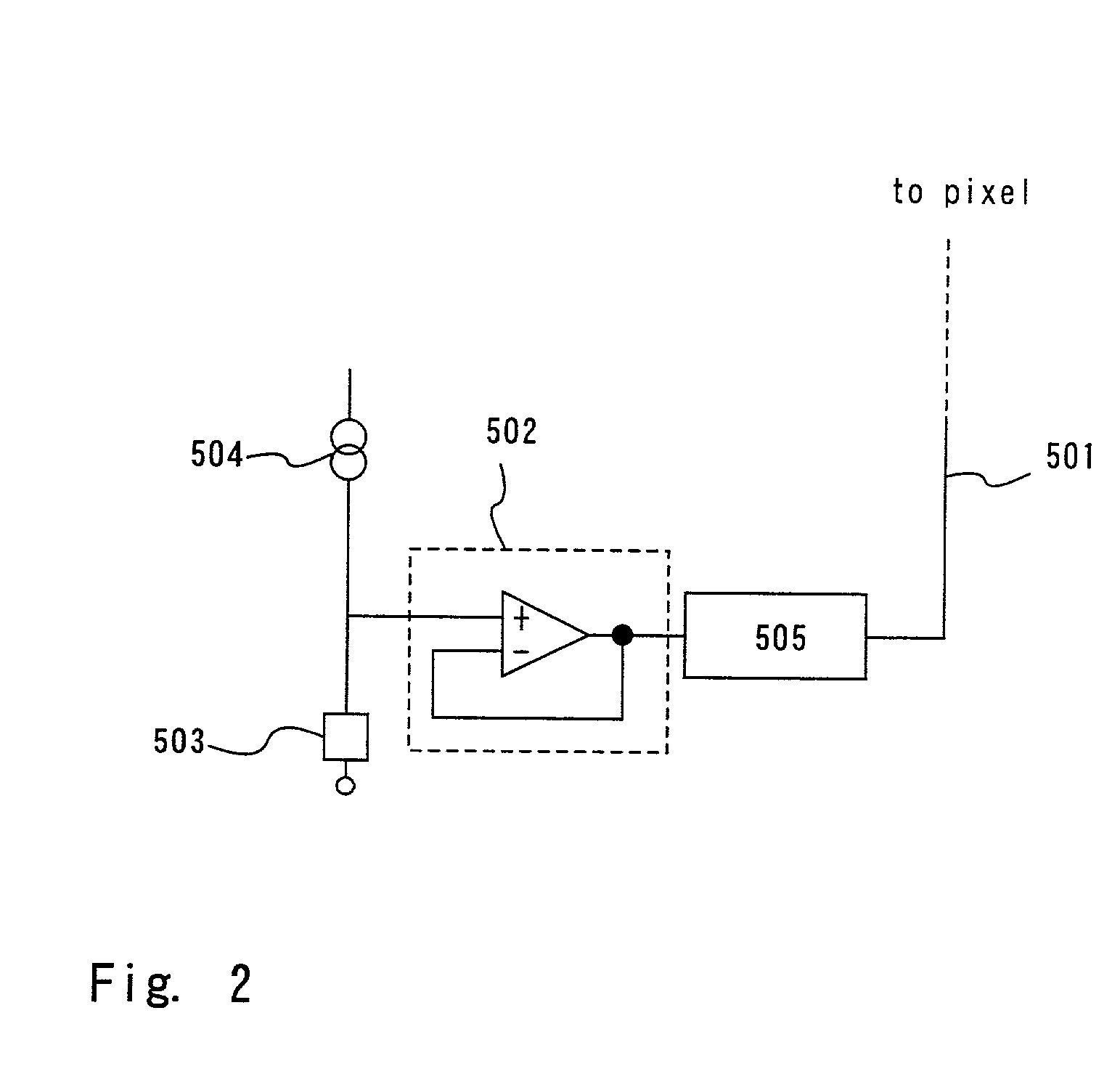

Display device

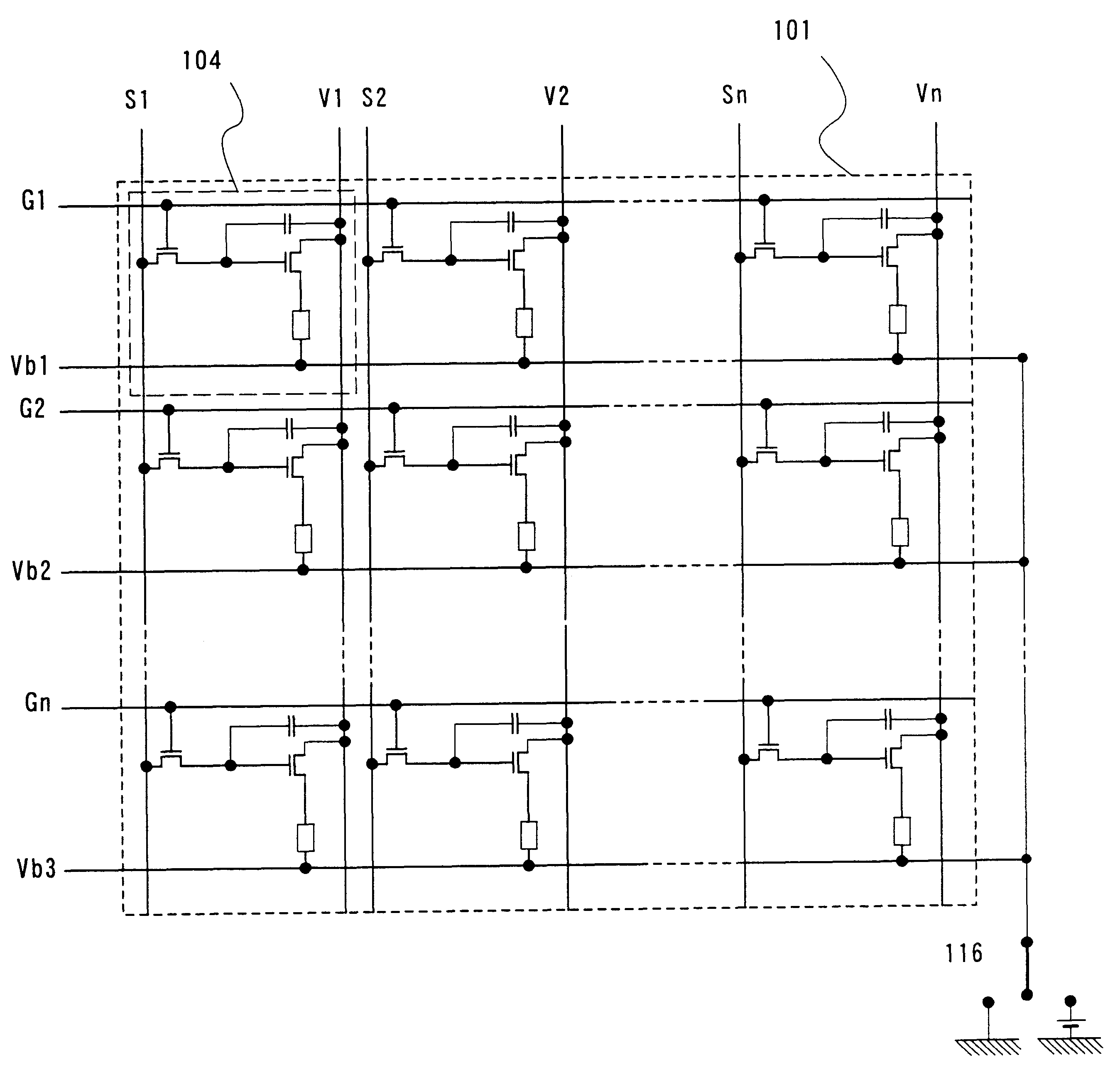

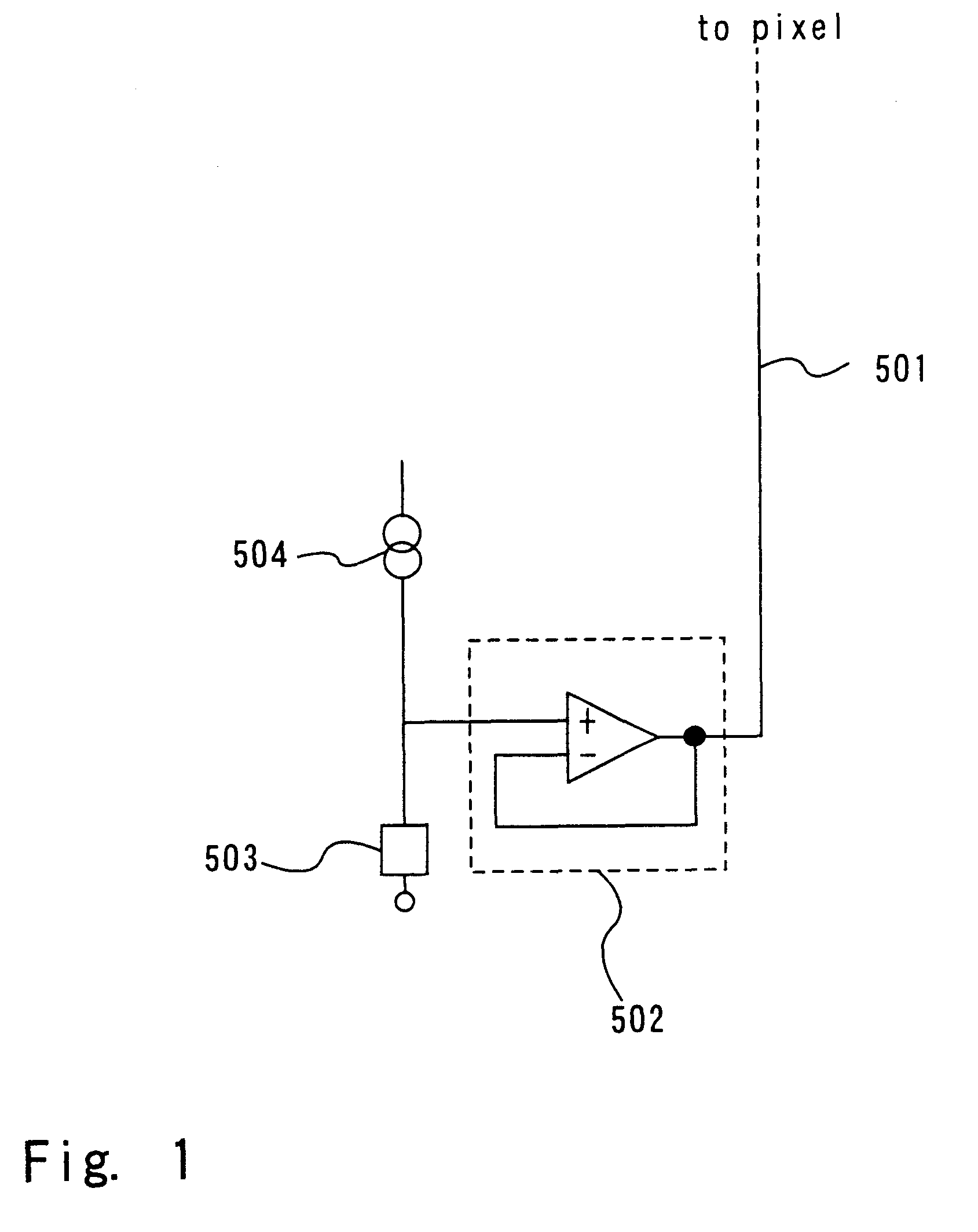

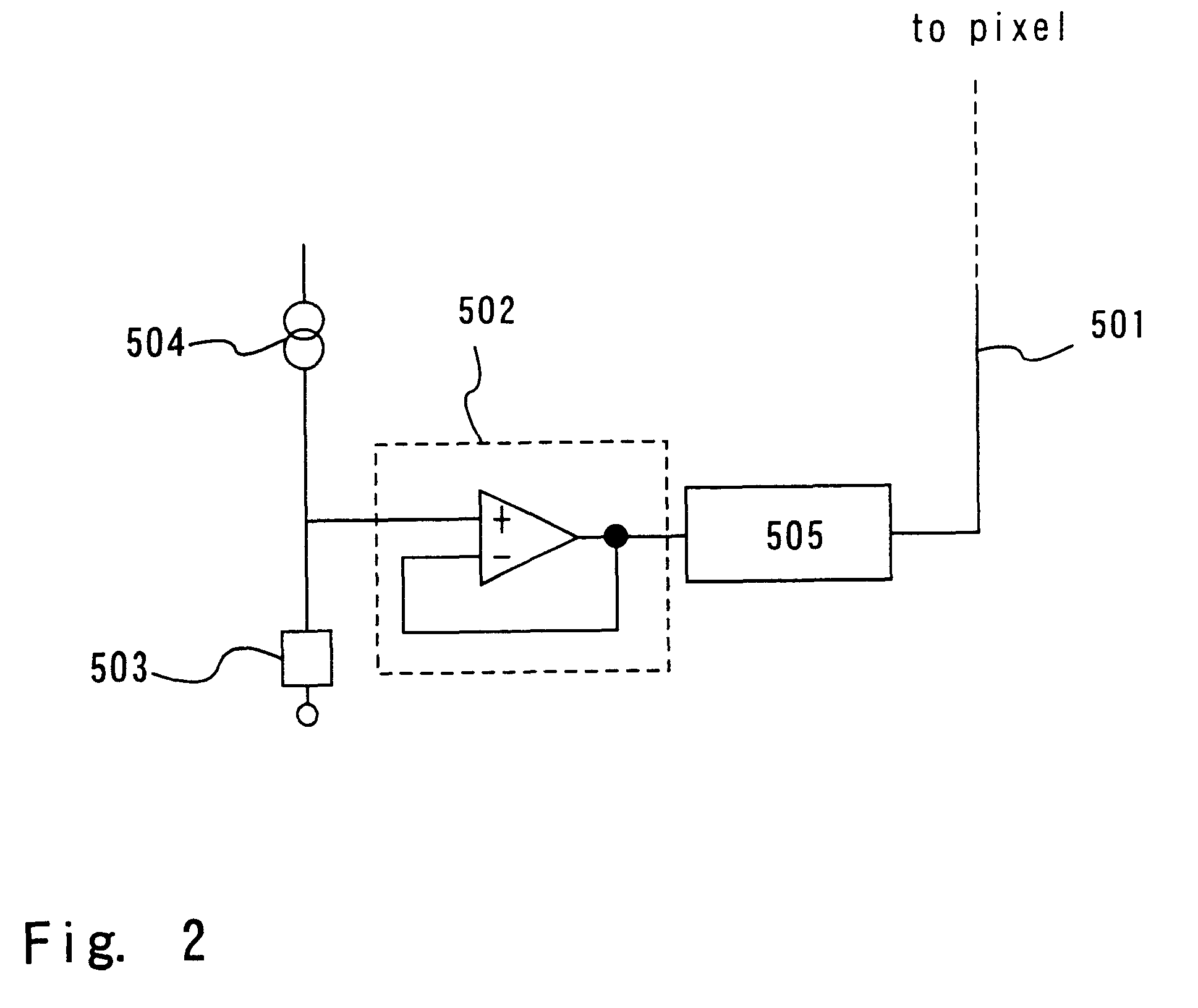

InactiveUS6528951B2Discharge tube luminescnet screensStatic indicating devicesDriver circuitImaging quality

The image quality of a display device using a bottom gate TFT is improved. In particular, fluctuation in luminance is controlled and the frequency characteristic of a driver circuit is compensated by suppressing a change in amount of current flowing through an EL element which is caused by a change in surrounding temperature while the device is in use. A monitoring EL element is provided in addition to a pixel portion EL element. The monitoring EL element constitutes a temperature compensation circuit together with a buffer amplifier and the like. A current is supplied to the pixel portion EL element through the temperature compensation circuit. This makes it possible to keep the amount of current flowing through the pixel portion EL element constant against a change in temperature, and to control the fluctuation in luminance. An input signal is subjected to time base expansion to perform sampling with accuracy.

Owner:SEMICON ENERGY LAB CO LTD

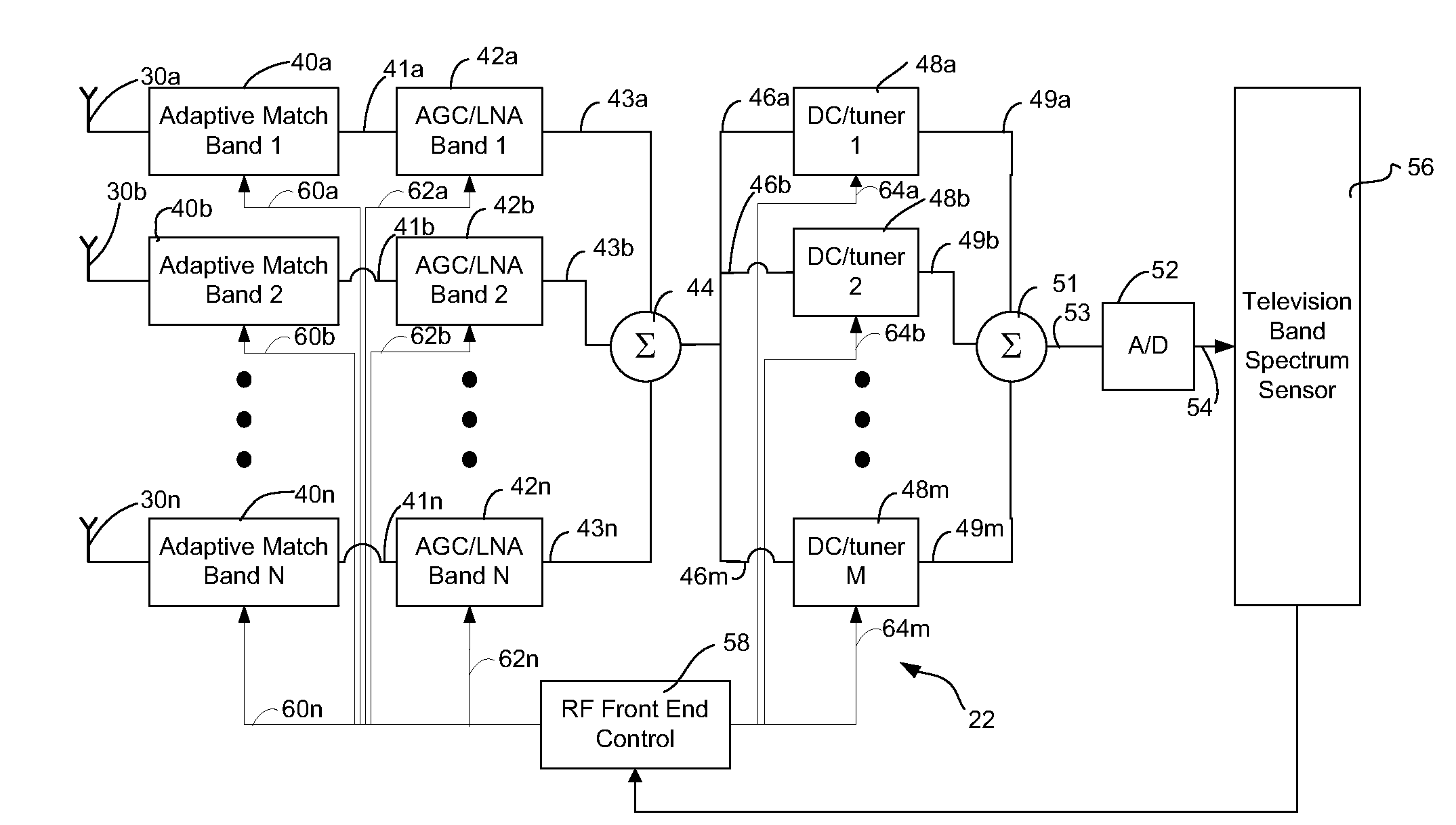

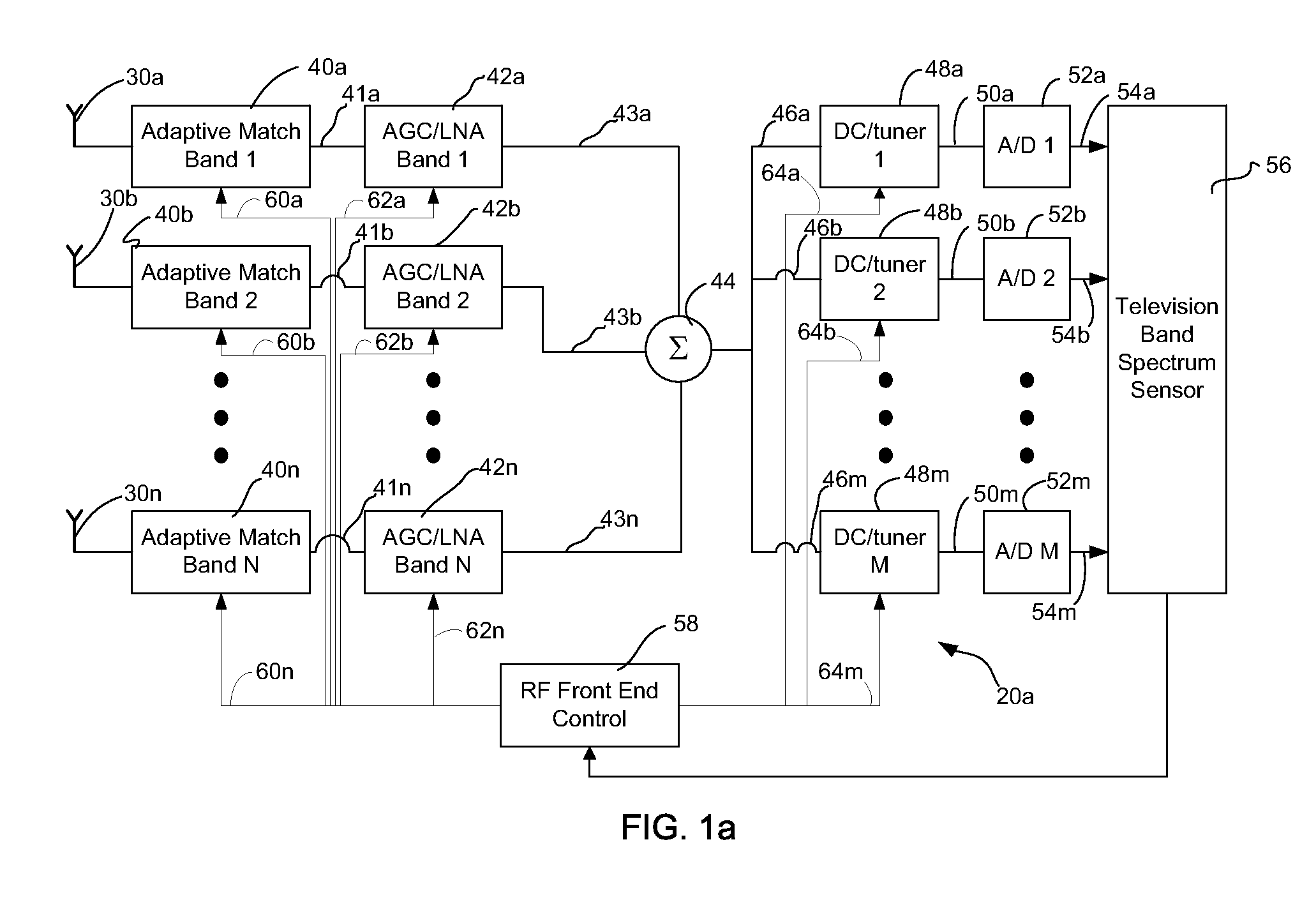

Radio frequency front end for television band receiver and spectrum sensor

InactiveUS20120182430A1Television system detailsElectric signal transmission systemsFrequency spectrumAudio power amplifier

A radio frequency front end for a television band receiver and spectrum sensor includes a low noise amplifier that amplifies a received signal output of a radio frequency antenna connected to the radio frequency front end, a pin diode attenuator circuit that selectively attenuates an output of the low noise amplifier, and a buffer amplifier that amplifies an output of the pin diode attenuator.

Owner:TAIWAN SEMICON MFG CO LTD

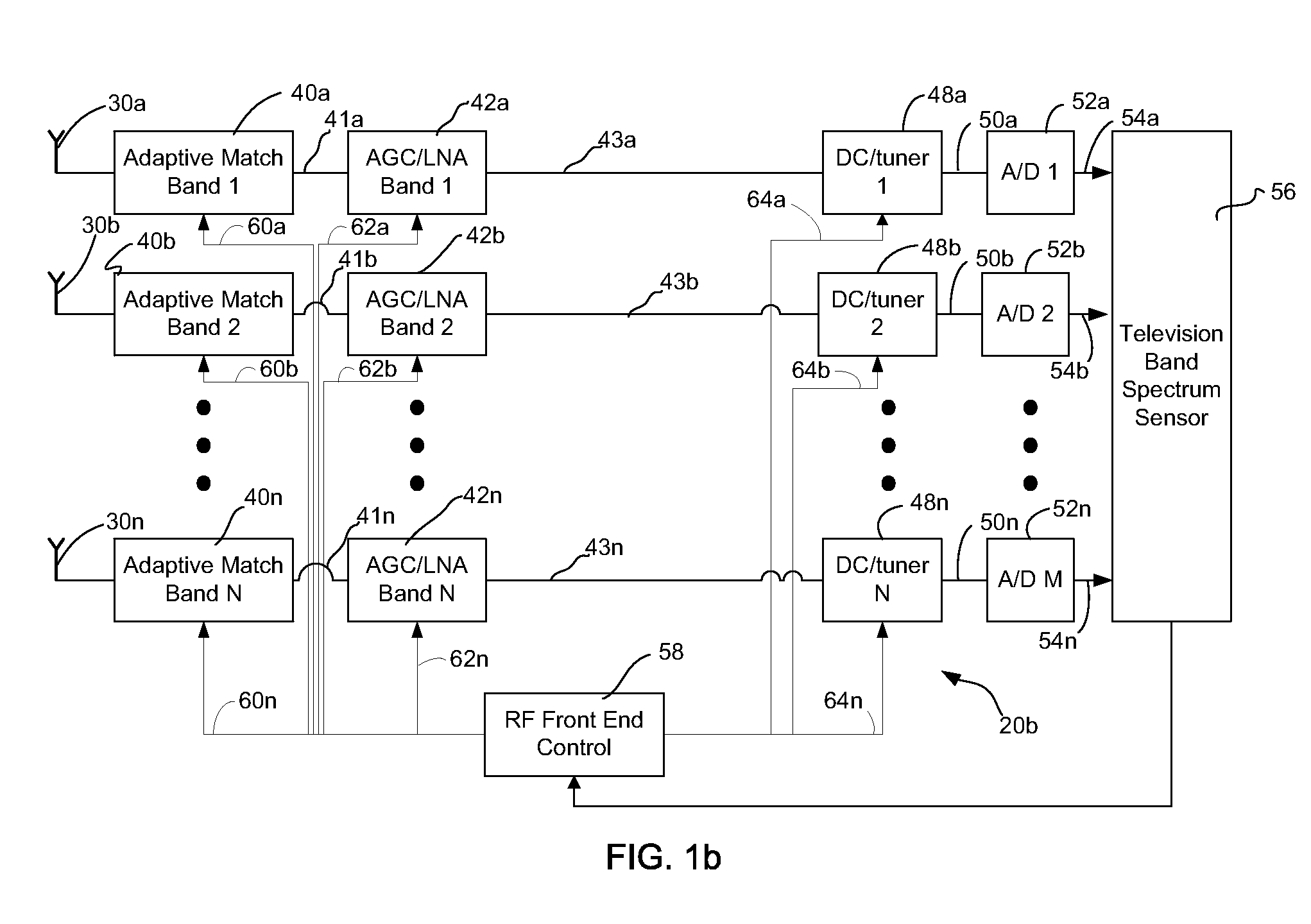

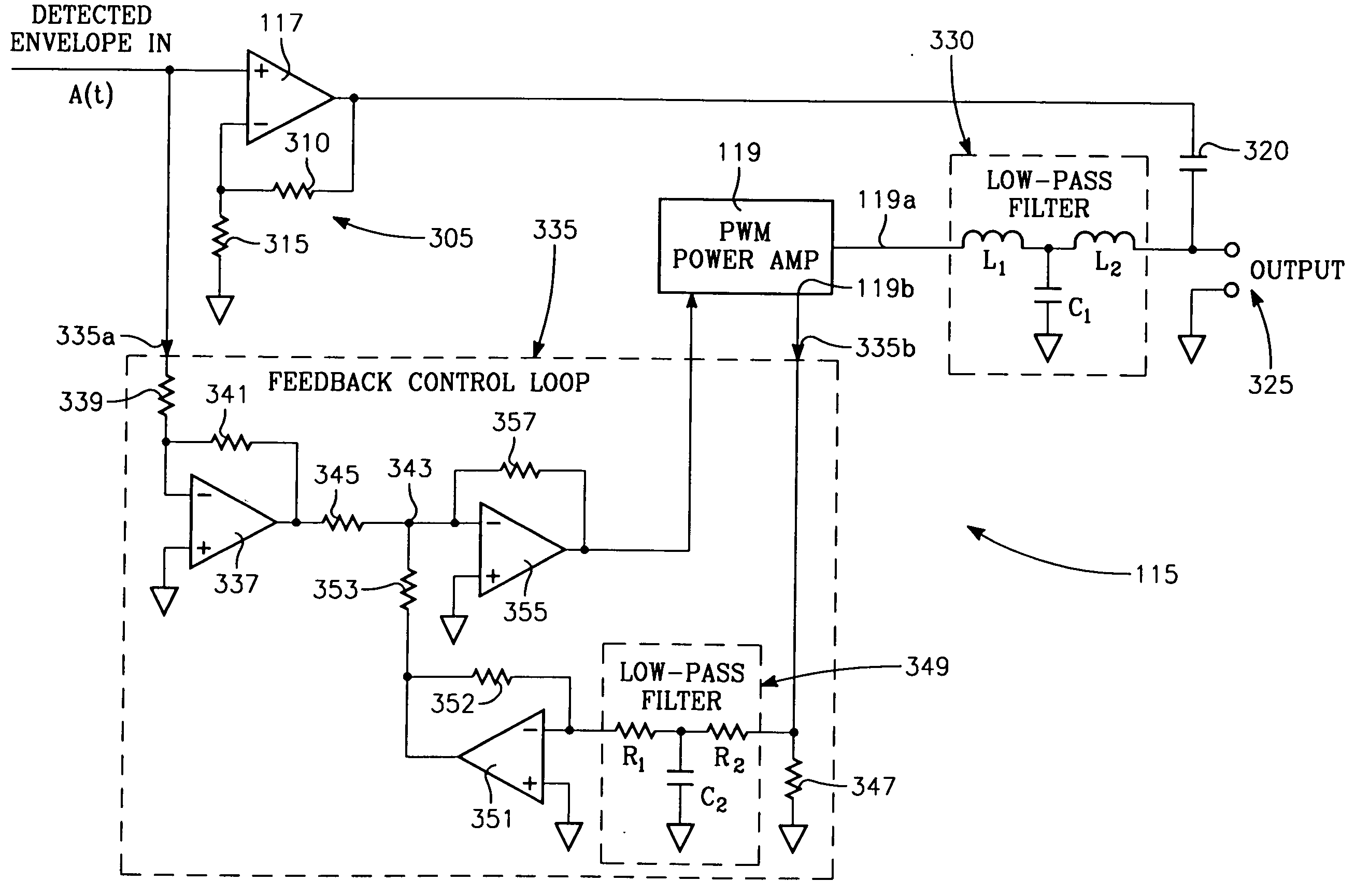

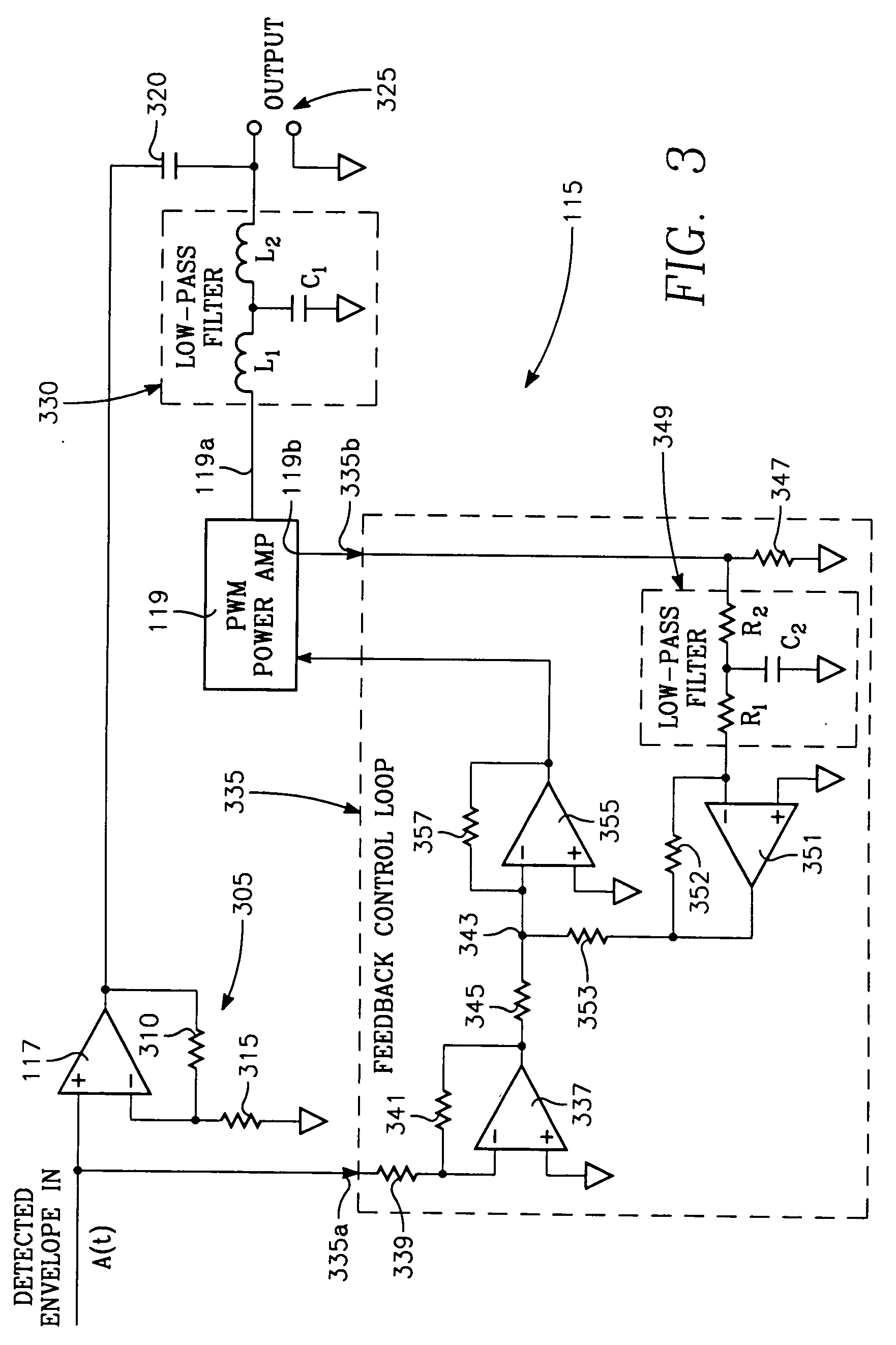

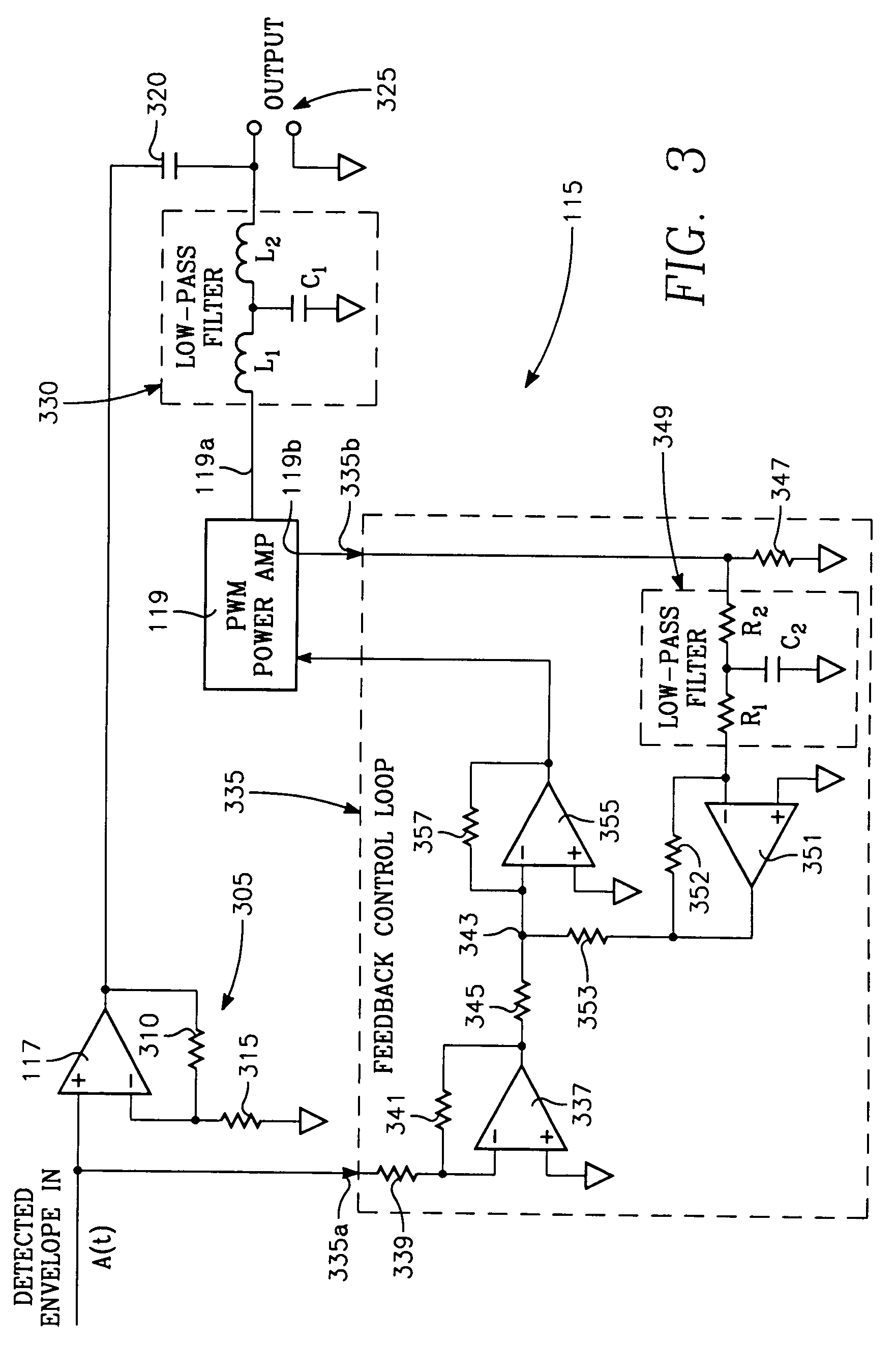

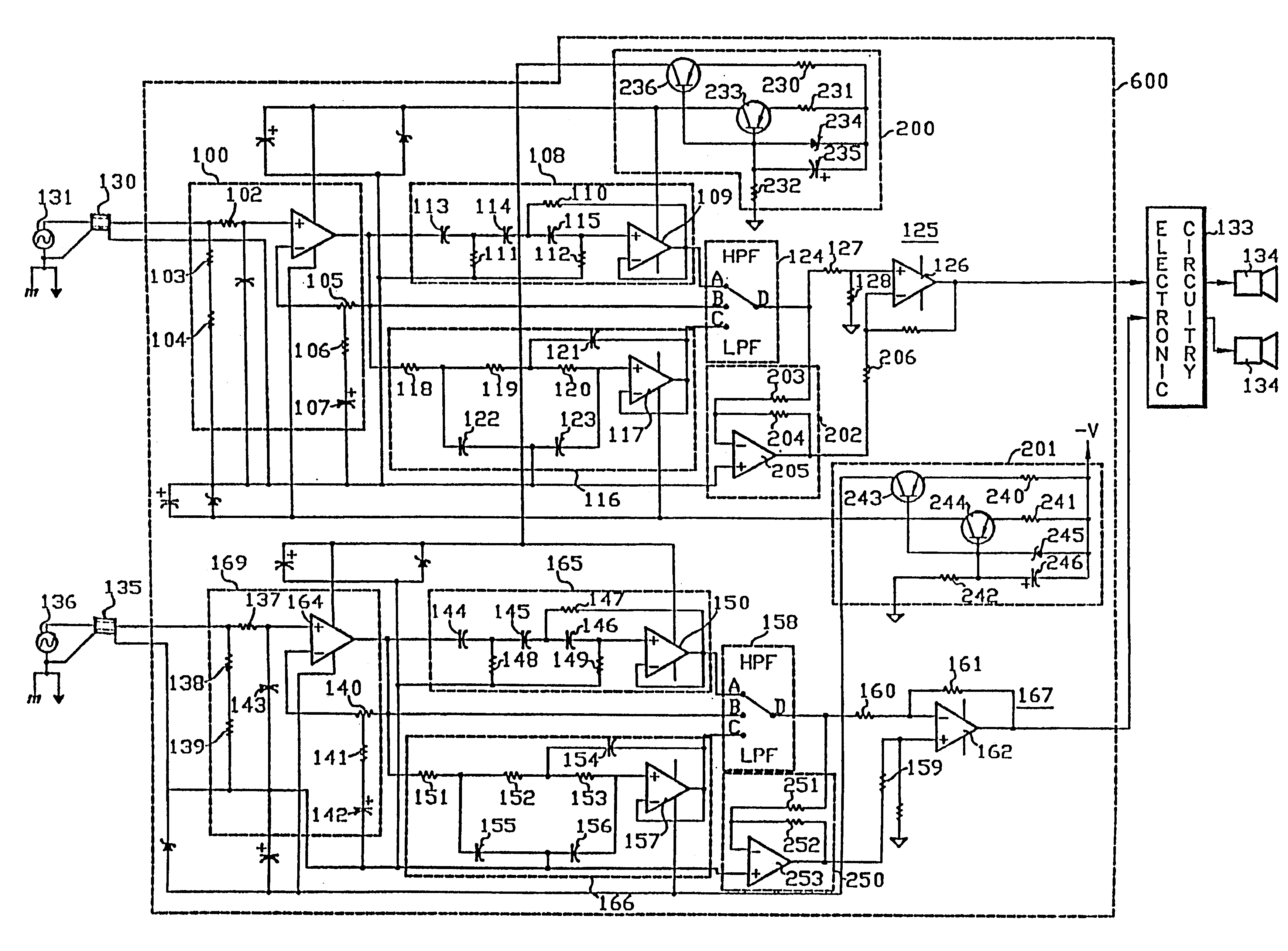

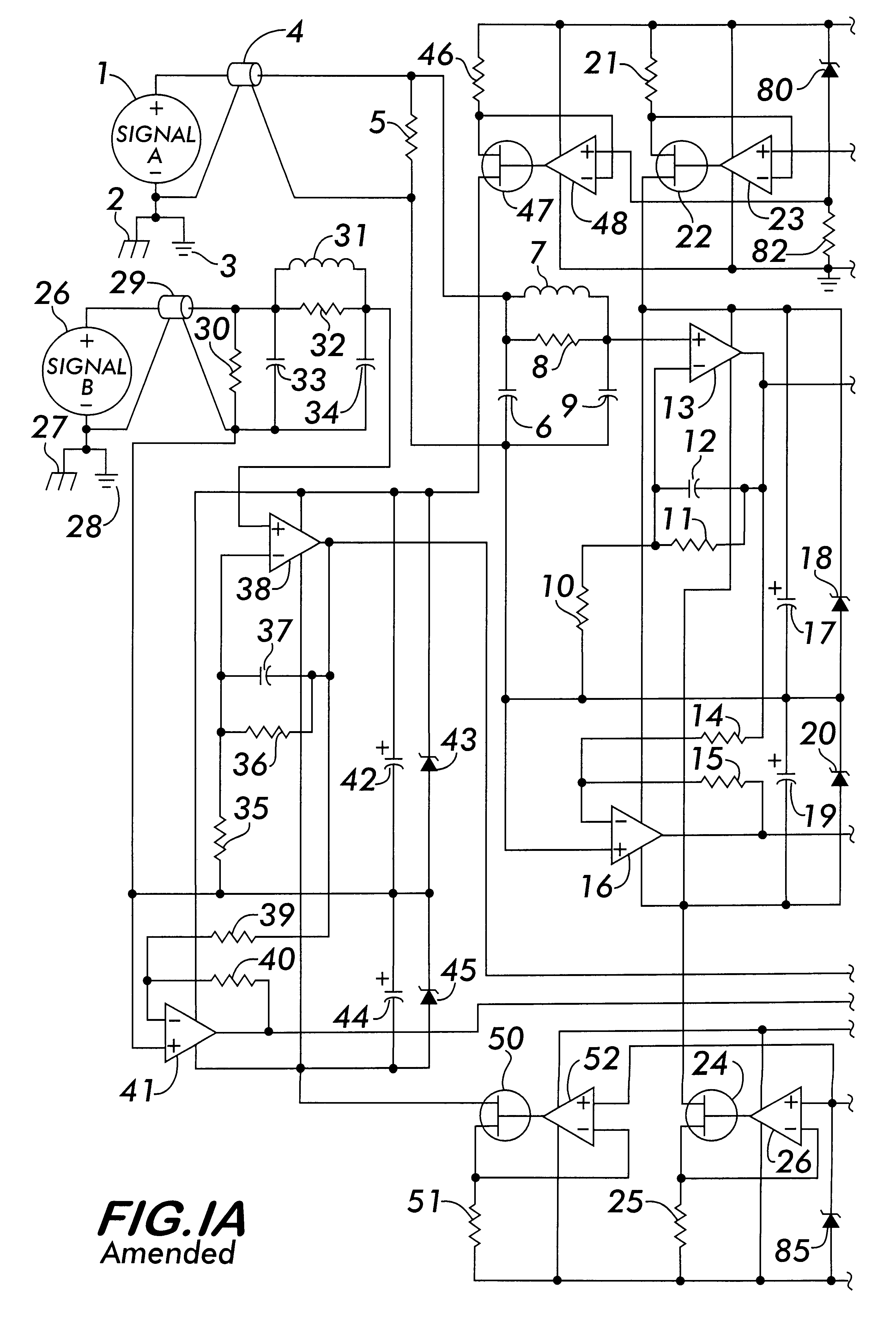

EER modulator with power amplifier having feedback loop providing soft output impedance

ActiveUS20050122163A1Efficient powerImprove efficiencyGain controlAmplifier modifications to raise efficiencyAudio power amplifierEngineering

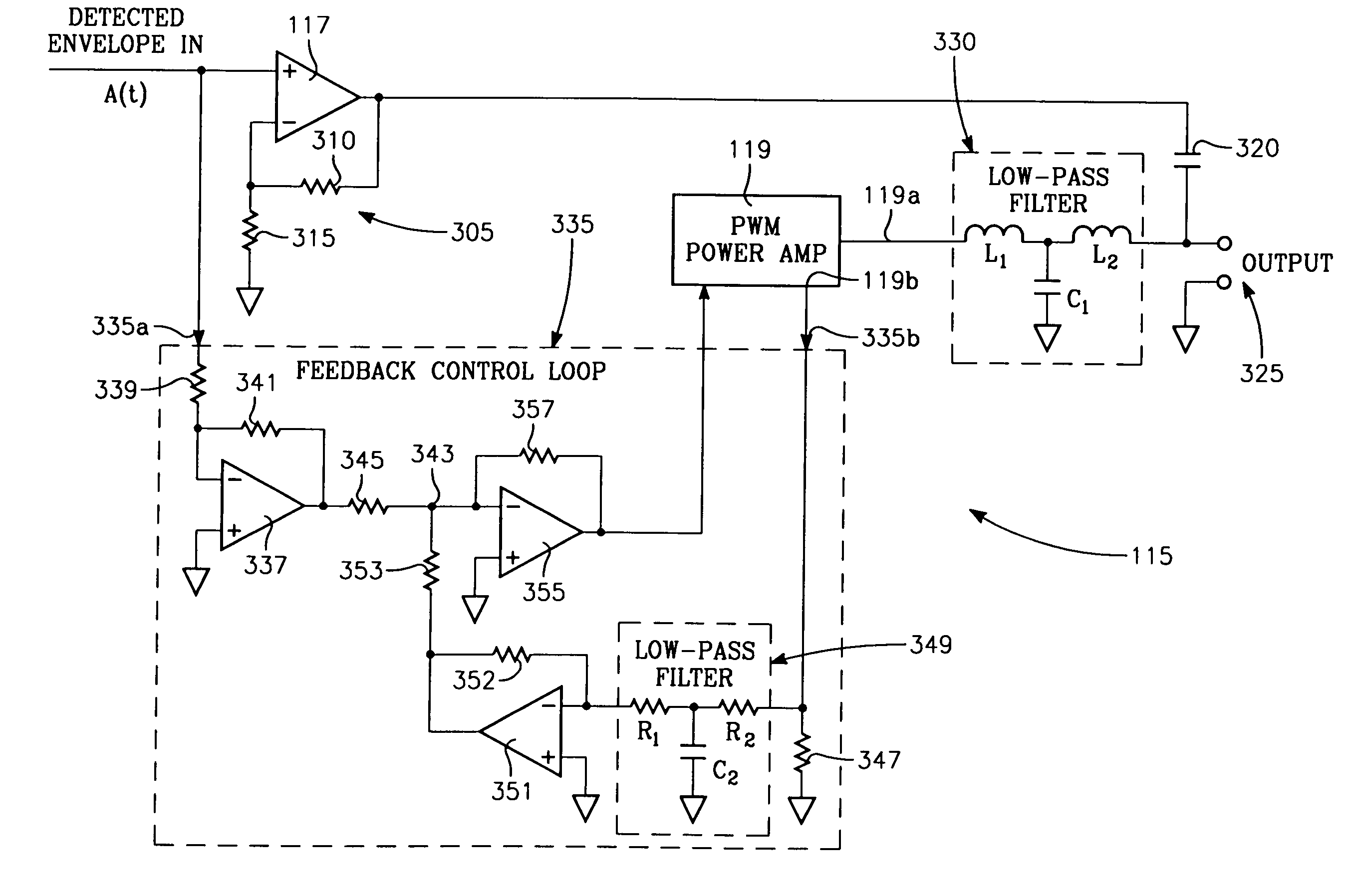

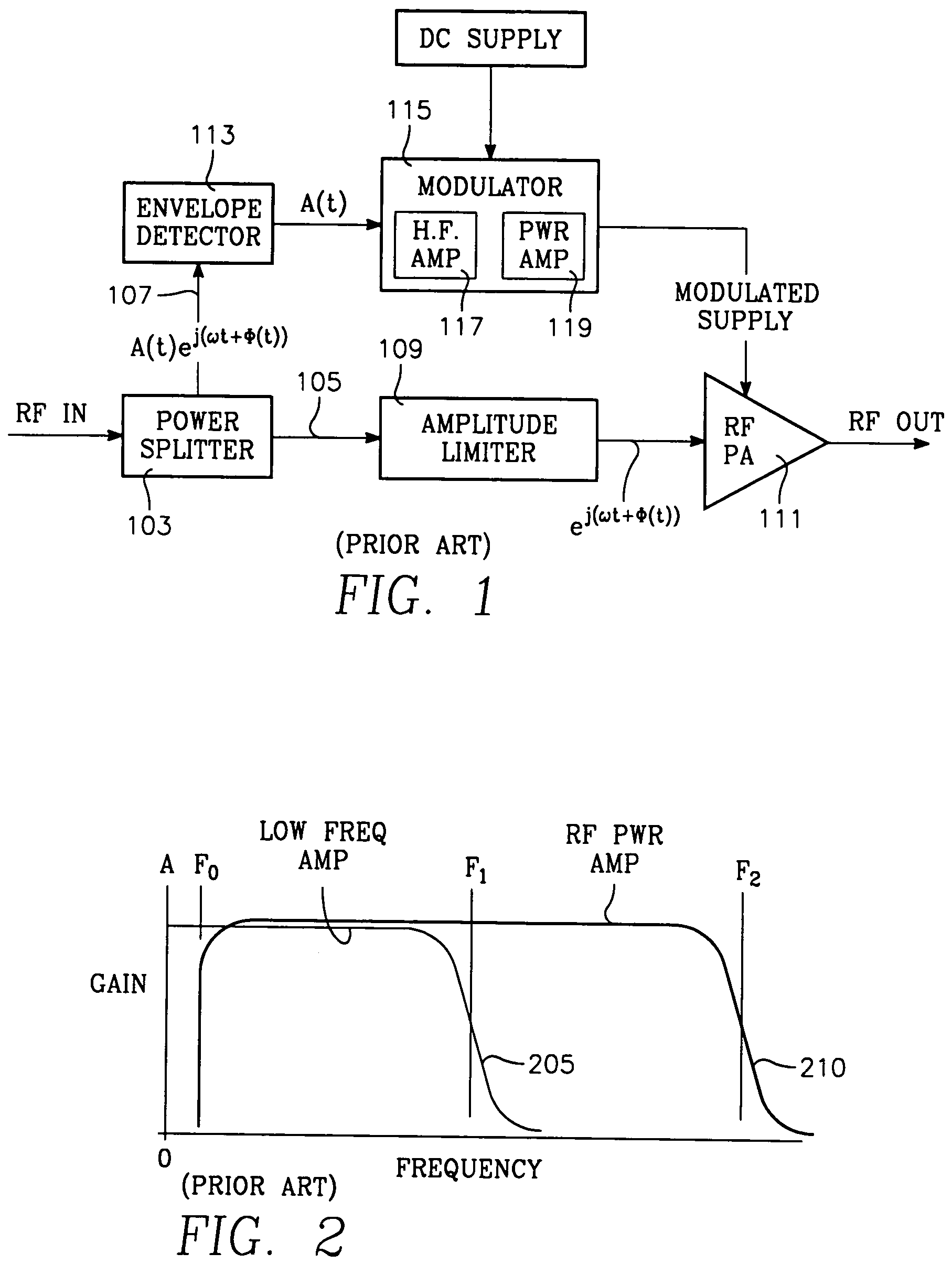

An EER amplifier for amplifying an RF signal includes: (II) a first RF amplifier for amplifying the phase portion of the signal; (III) an EER modulator for amplifying the envelope or baseband portion of the signal, including: A) a high frequency operational amplifier; B) a power amplifier; C) a feedback control loop including: (1) a current-to-voltage conversion amplifier having an input coupled to a current monitoring output of the power amplifier and an output, (2) an input buffer amplifier having an input coupled to receive the envelope signal and an output; (3) a summing amplifier having: (a) an input coupled to the outputs of: (a) the current-to-voltage conversion amplifier and (b) the input buffer amplifier, and (b) an output coupled to the current control input of the power amplifier.

Owner:NORTHROP GRUMMAN SYST CORP

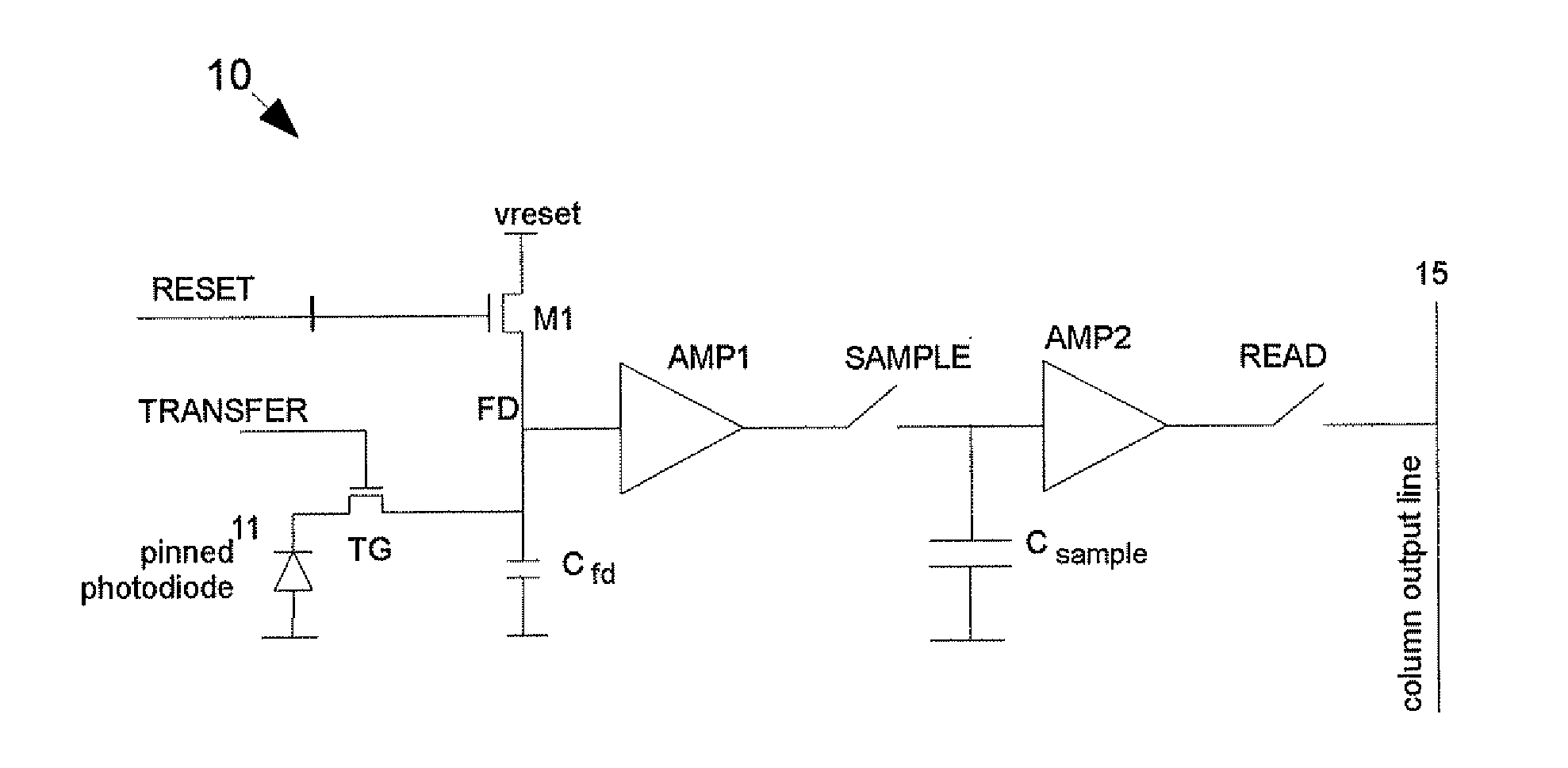

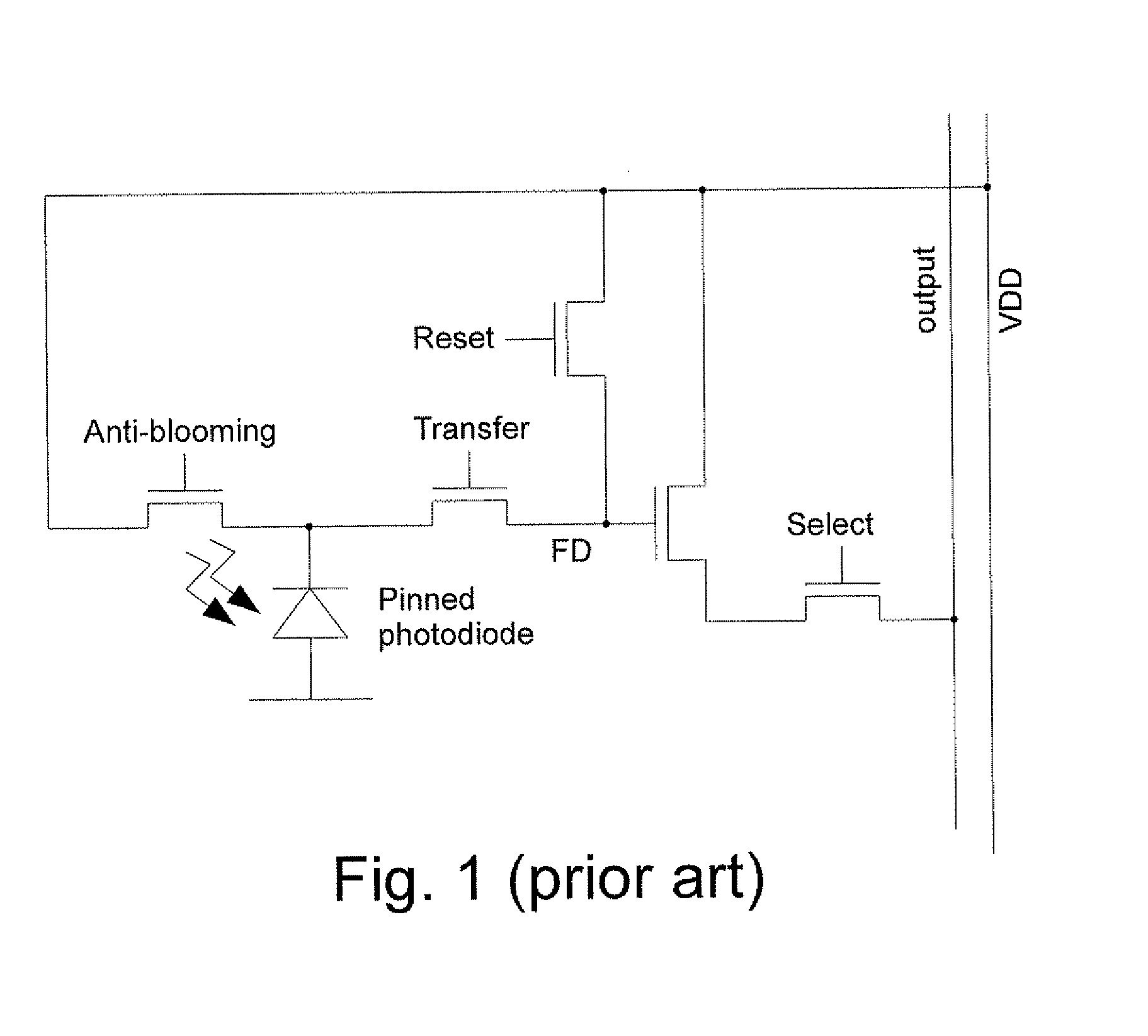

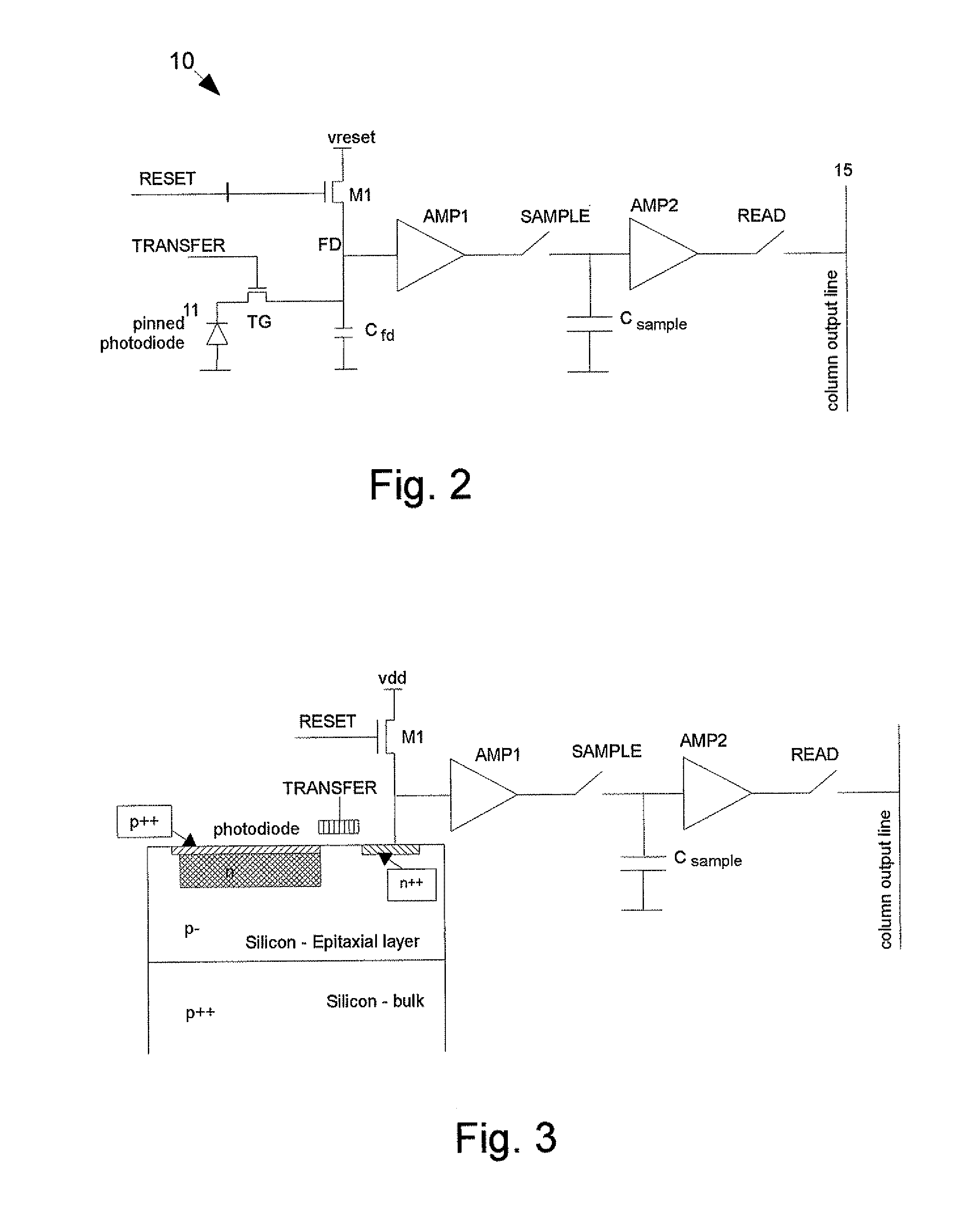

Pixel array with global shutter

ActiveUS20090256060A1Reduce in quantityOptimize layoutTransistorTelevision system detailsAudio power amplifierExposure period

A pixel comprises a photo-sensitive element for generating charges in response to incident radiation and a sense node. A transfer gate is positioned between the photo-sensitive element and the sense node for controlling transfer of charges to the sense node. A reset switch is connected to the sense node for resetting the sense node to a predetermined voltage. A first buffer amplifier has an input connected to the sense node. A sample stage is connected to the output of the first buffer amplifier and is operable to sample a value of the sense node. A second buffer amplifier has an input connected to the sample stage. Control circuitry operates the reset switch and causes the sample stage to sample the sense node while the photo-sensitive element is being exposed to radiation. An array of pixels is synchronously exposed to radiation. Sampled values for a first exposure period can be read while the photo-sensitive element is exposed for a second exposure period.

Owner:CMOSIS

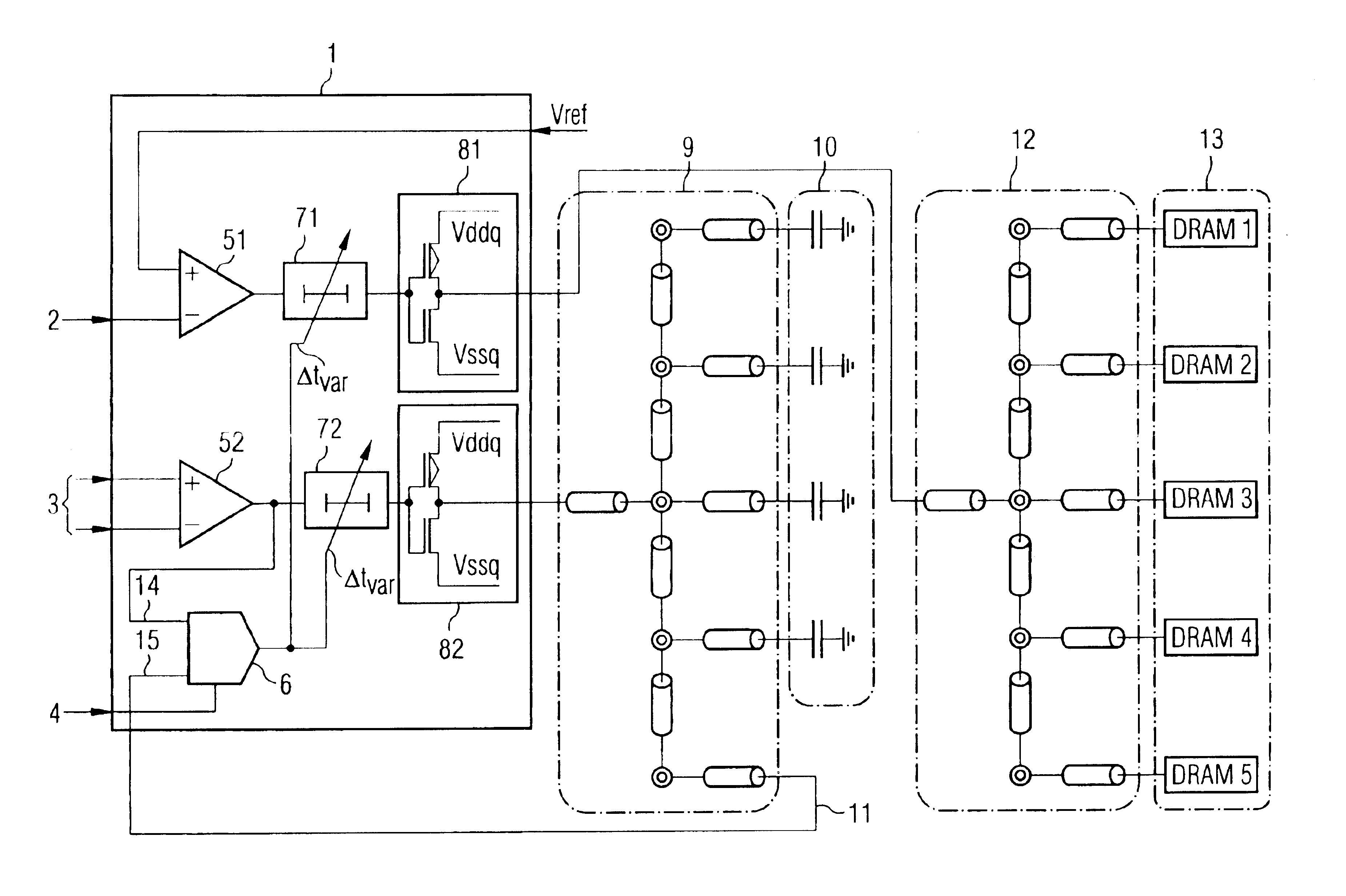

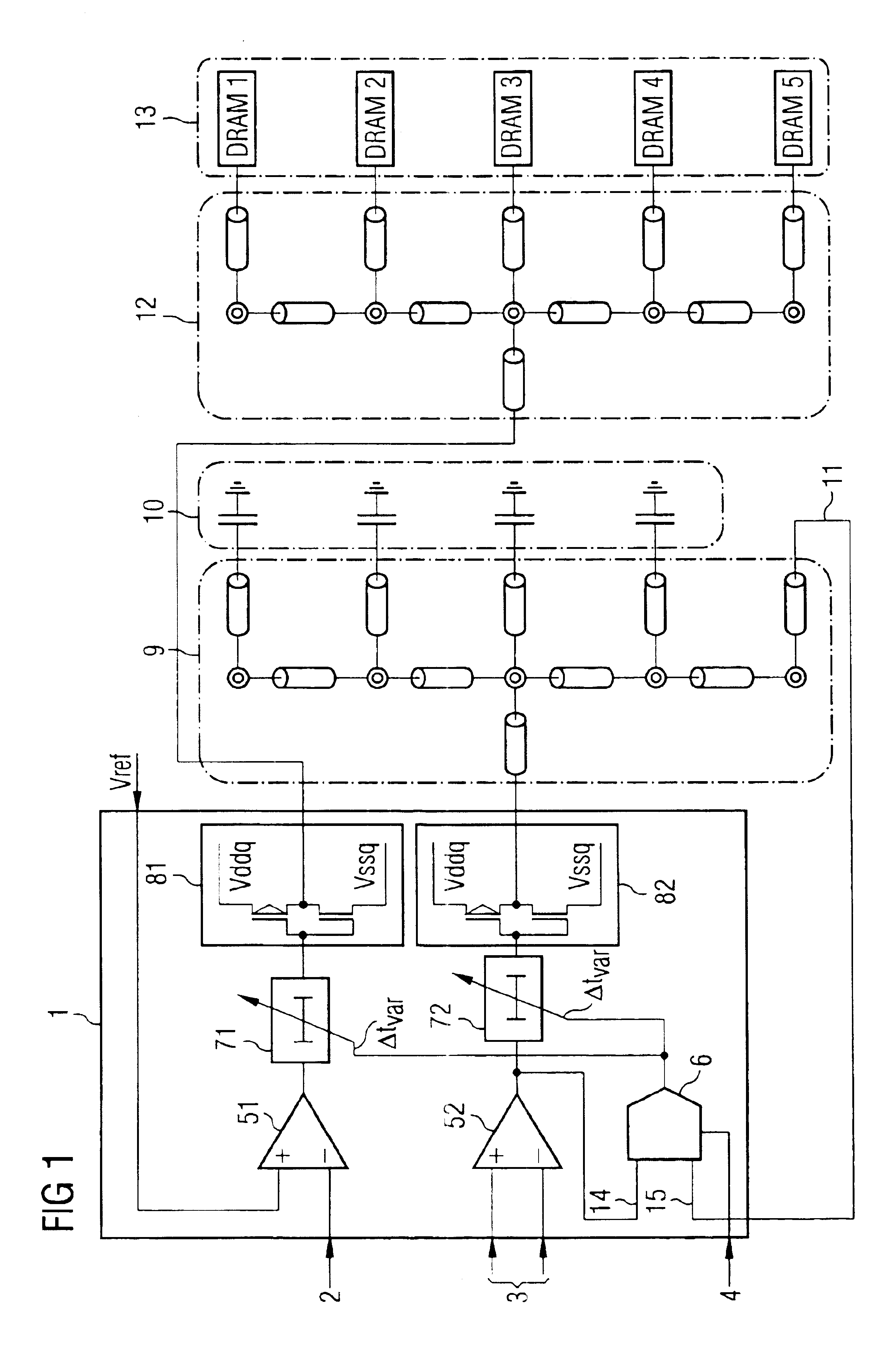

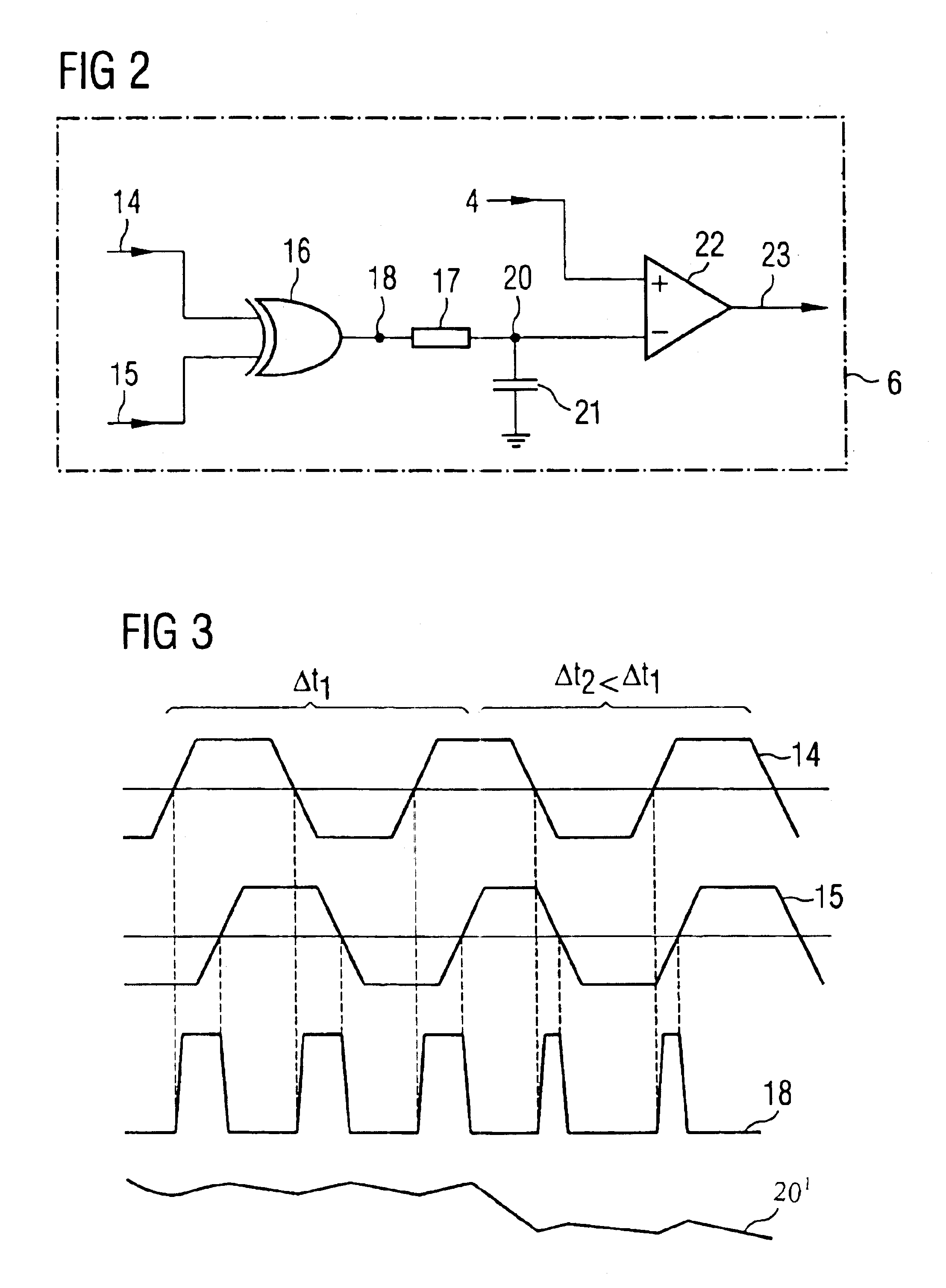

Buffer amplifier architecture for semiconductor memory circuits

A buffer amplifier architecture for buffering signals which are supplied in parallel to identical chips, particularly DRAM chips, on a semiconductor memory module, is disclosed. The architecture has adjustable delay circuits in each signal line and a delay detector circuit which receives a clock signal from the buffer amplifier architecture at the input and at the output of the buffer amplifier architecture, and takes the phase difference between the two signals to produce a control signal for setting the variable delay time of the delay circuits. To ensure that the delay time set by the delay detector circuit is independent of variations in parameters of the DRAM memory chips, the feedback path routed to the input of the delay detector circuit has a reference line network of the same structure and having the same electrical properties as capacitance elements which terminate the line network routed to the DRAM memory chips and the reference line network, and which have the same capacitances as the signal inputs on the DRAM memory chips.

Owner:POLARIS INNOVATIONS

Display device

InactiveUS20020005696A1Discharge tube luminescnet screensStatic indicating devicesDriver circuitImaging quality

The image quality of a display device using a bottom gate TFT is improved. In particular, fluctuation in luminance is controlled and the frequency characteristic of a driver circuit is compensated by suppressing a change in amount of current flowing through an EL element which is caused by a change in surrounding temperature while the device is in use. A monitoring EL element is provided in addition to a pixel portion EL element. The monitoring EL element constitutes a temperature compensation circuit together with a buffer amplifier and the like. A current is supplied to the pixel portion EL element through the temperature compensation circuit. This makes it possible to keep the amount of current flowing through the pixel portion EL element constant against a change in temperature, and to control the fluctuation in luminance. An input signal is subjected to time base expansion to perform sampling with accuracy.

Owner:SEMICON ENERGY LAB CO LTD

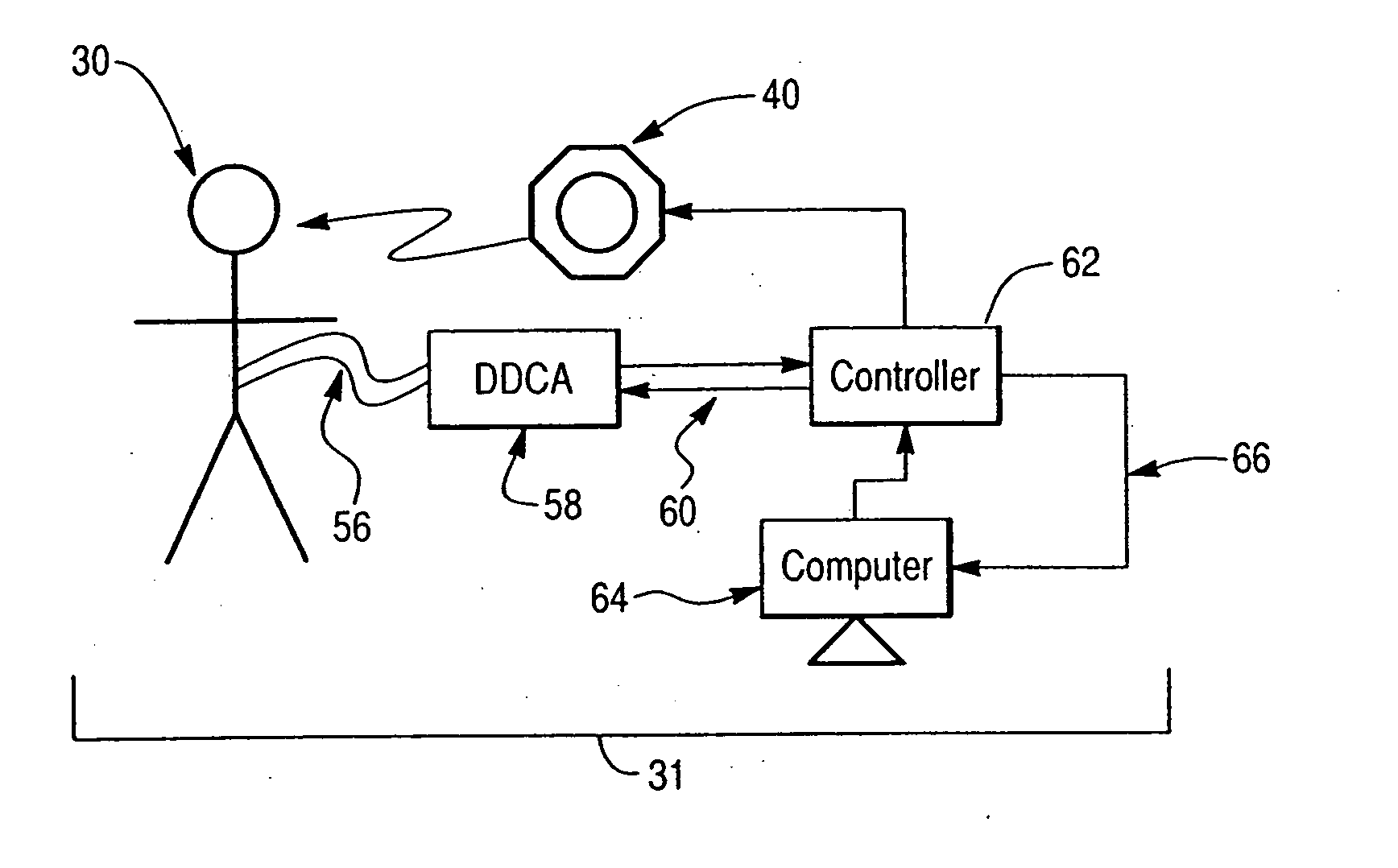

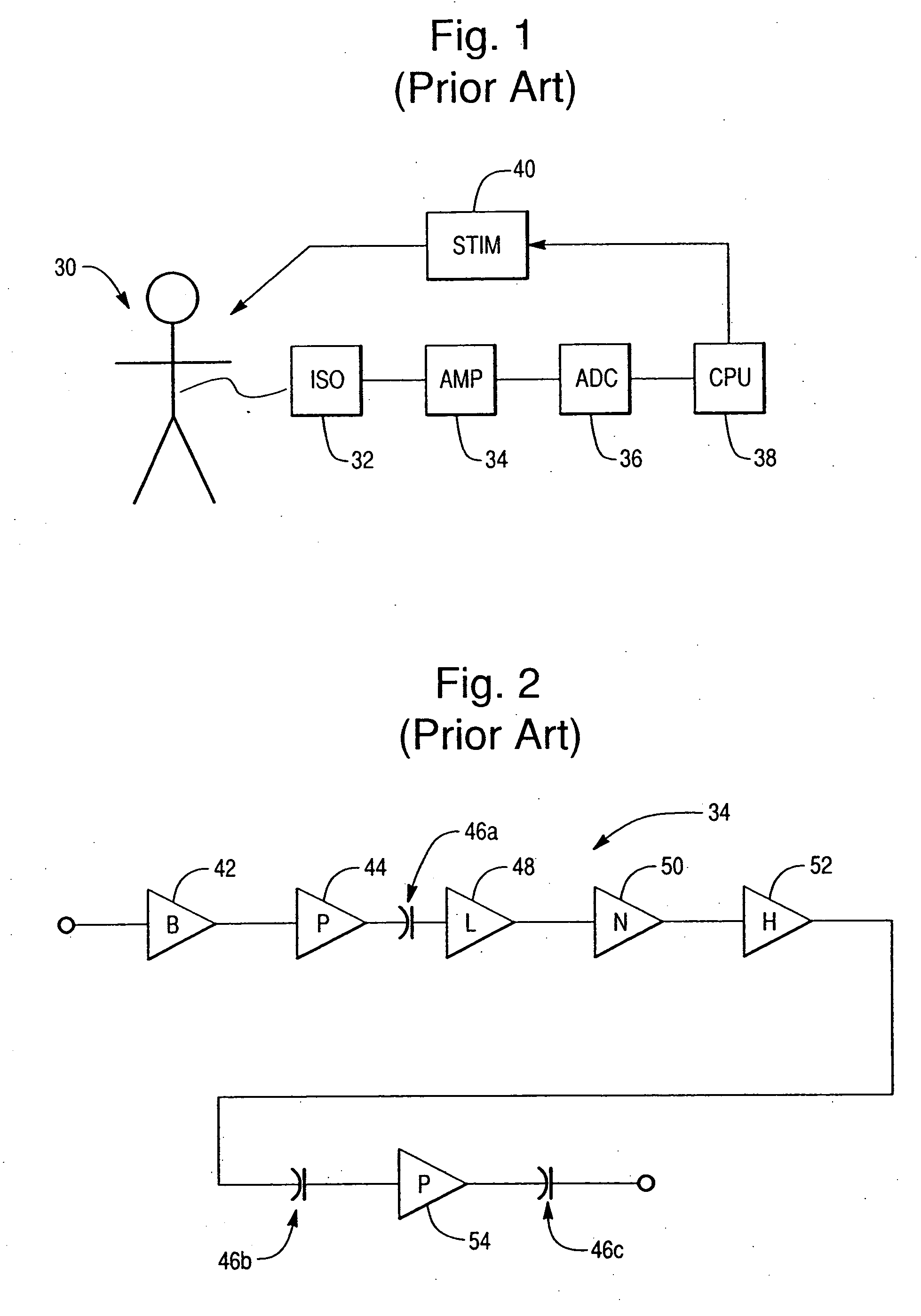

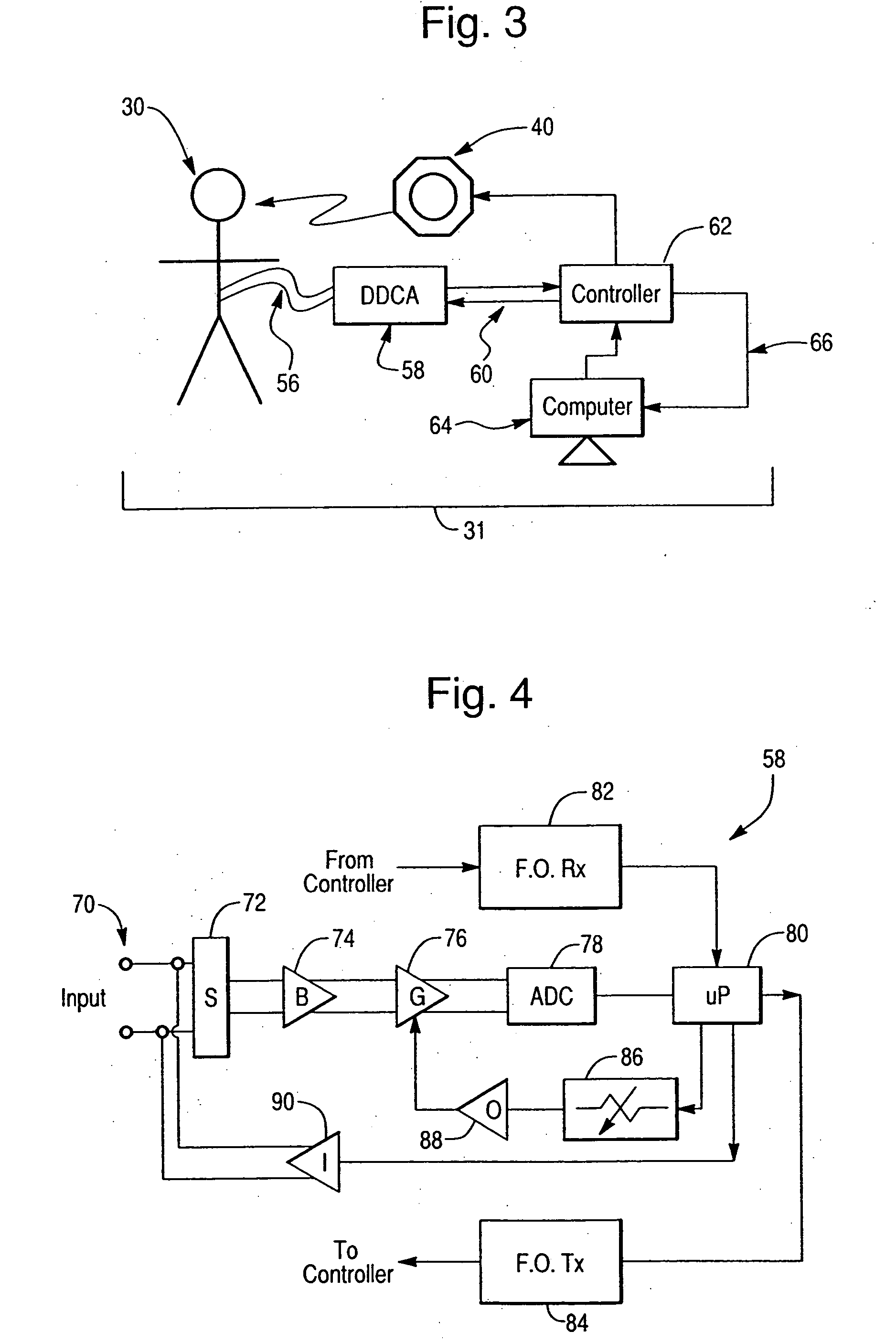

Low noise amplifier for electro-physiological signal sensing

InactiveUS20060122529A1Reduce noiseEnhanced response signalElectroencephalographySensorsLow noiseElectrical conductor

Owner:LKC TECH

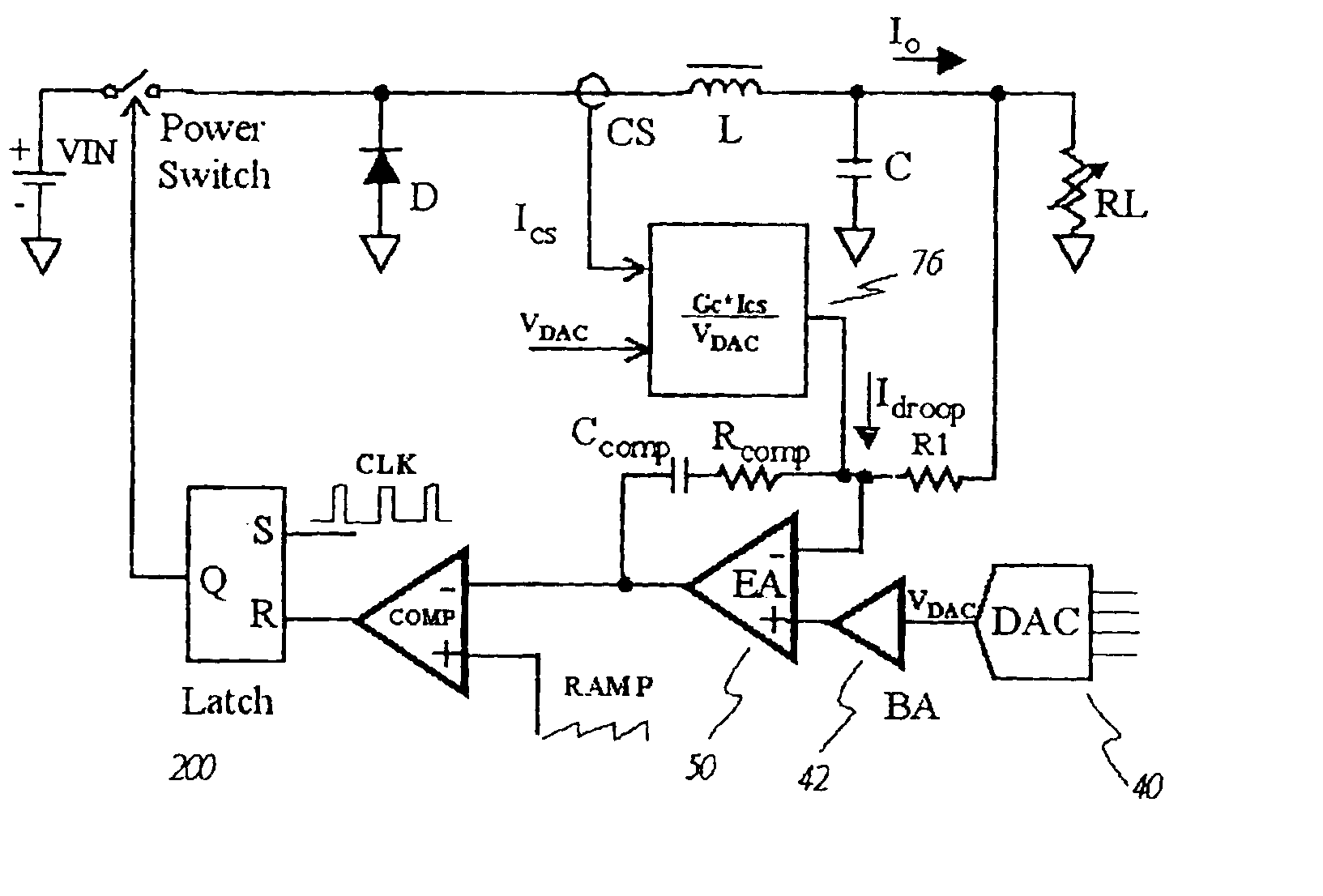

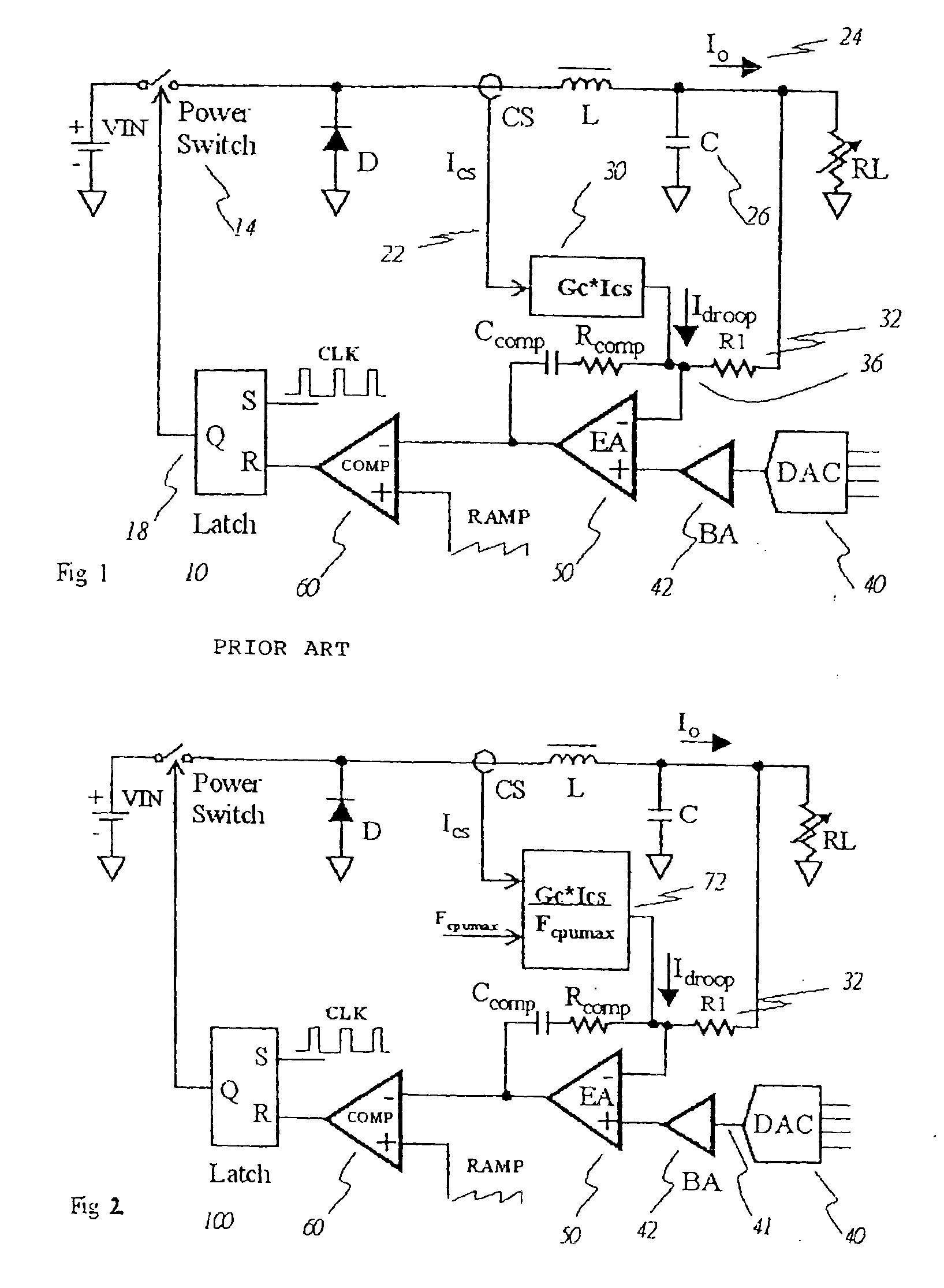

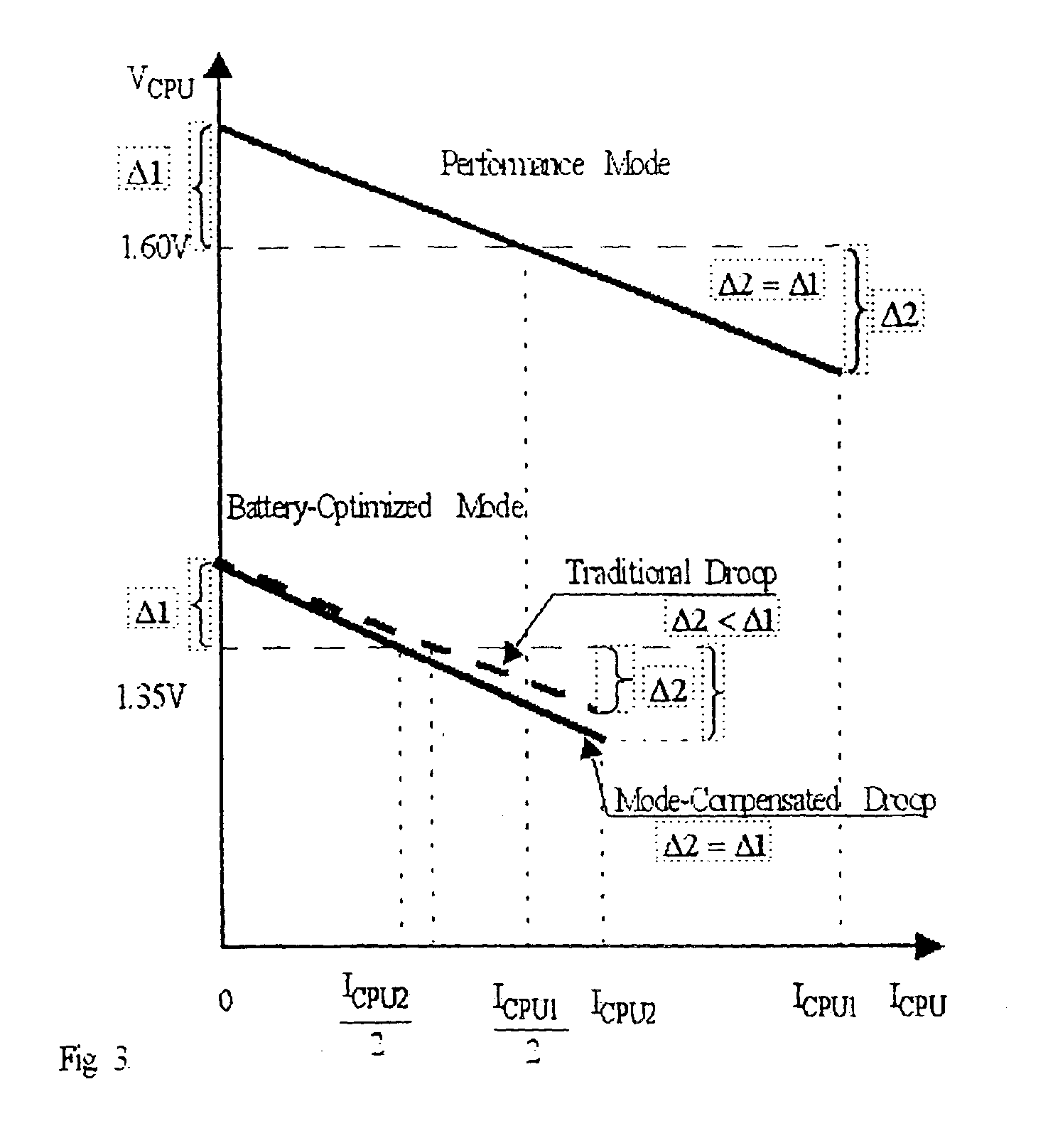

Methods to control the droop when powering dual mode processors and associated circuits

A DC / DC converter 100 has a DAC 40 that receives a code associated with desired processor operating voltage and sets the reference voltage on its output 41. The reference voltage (VDAC) is boosted by the buffer amplifier 42 to center the droop along the median load. A sensed current signal ICS 22 is proportional to the load current Io 24 and can be either inductor current, or switch current, or diode (or synchronous switch) current. In all cases it is scaled down by the factor of gain Gc. A droop control feedback circuit includes an error amplifier 50. It has two inputs. In one embodiment the gain of the converter is by a signal inversely proportional to the processor clock frequency FCPU max and transformed to the current IDROOP 32 that creates the voltage drop across the resistor R1. The other input is coupled to the buffer amplifier output. As a result, the output voltage of the converter 50 is inversely proportionally to the load current and is invariant to the processor clock frequency changes associated with the processor mode switchover. Other embodiments modify the gain of the error amplifier, or offset the gain and hold the amount of droop constant.

Owner:INTERSIL CORP

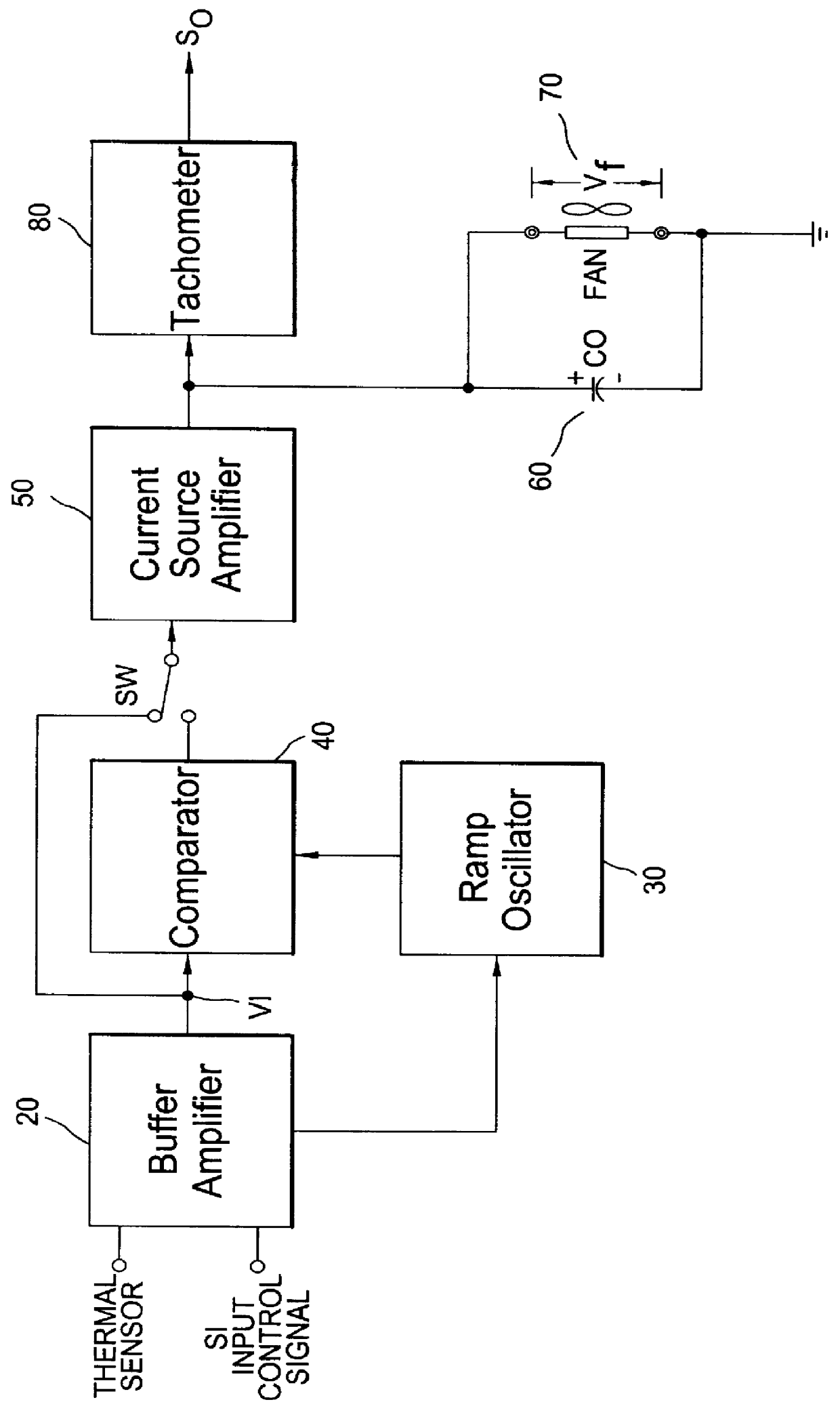

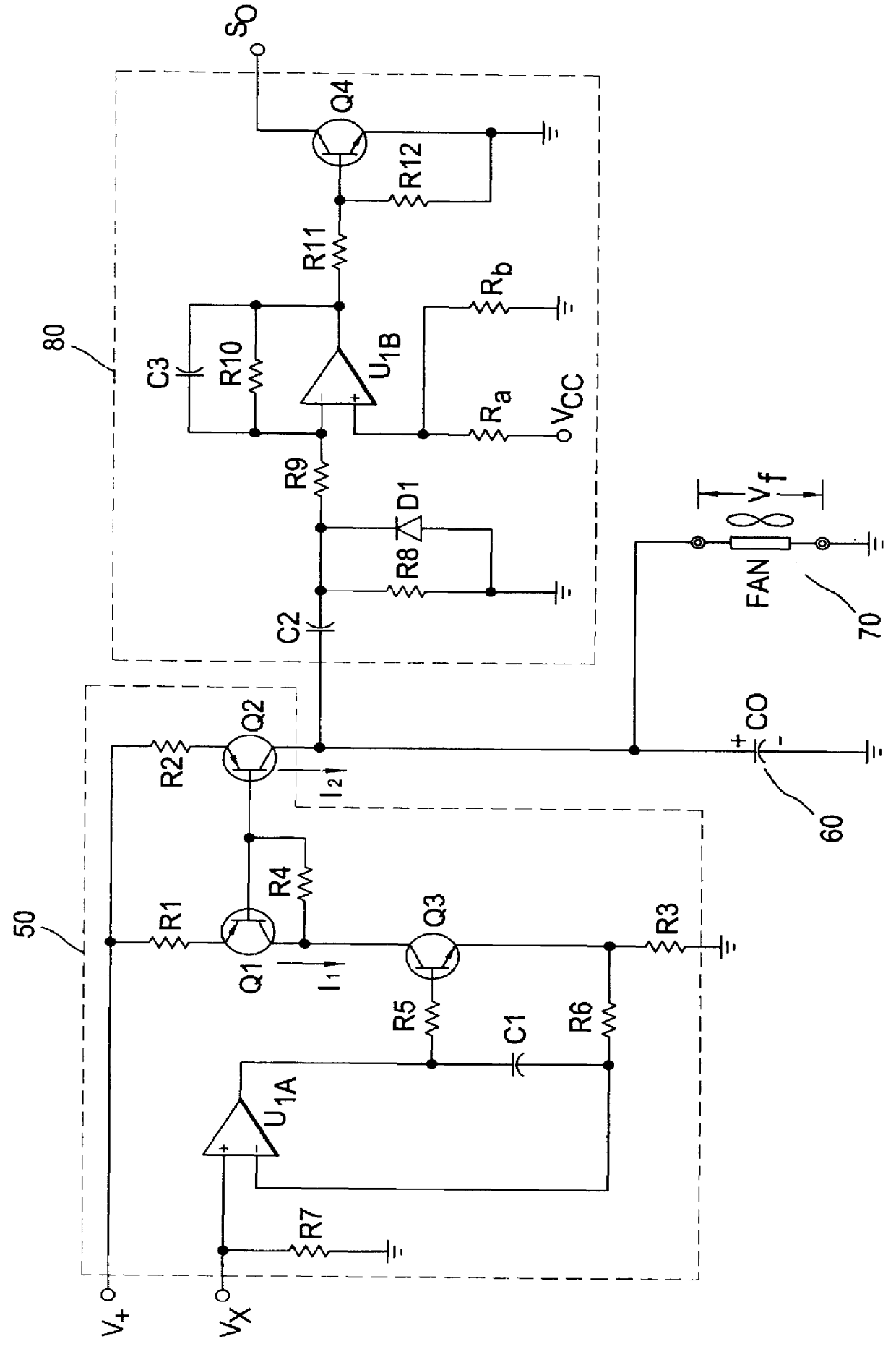

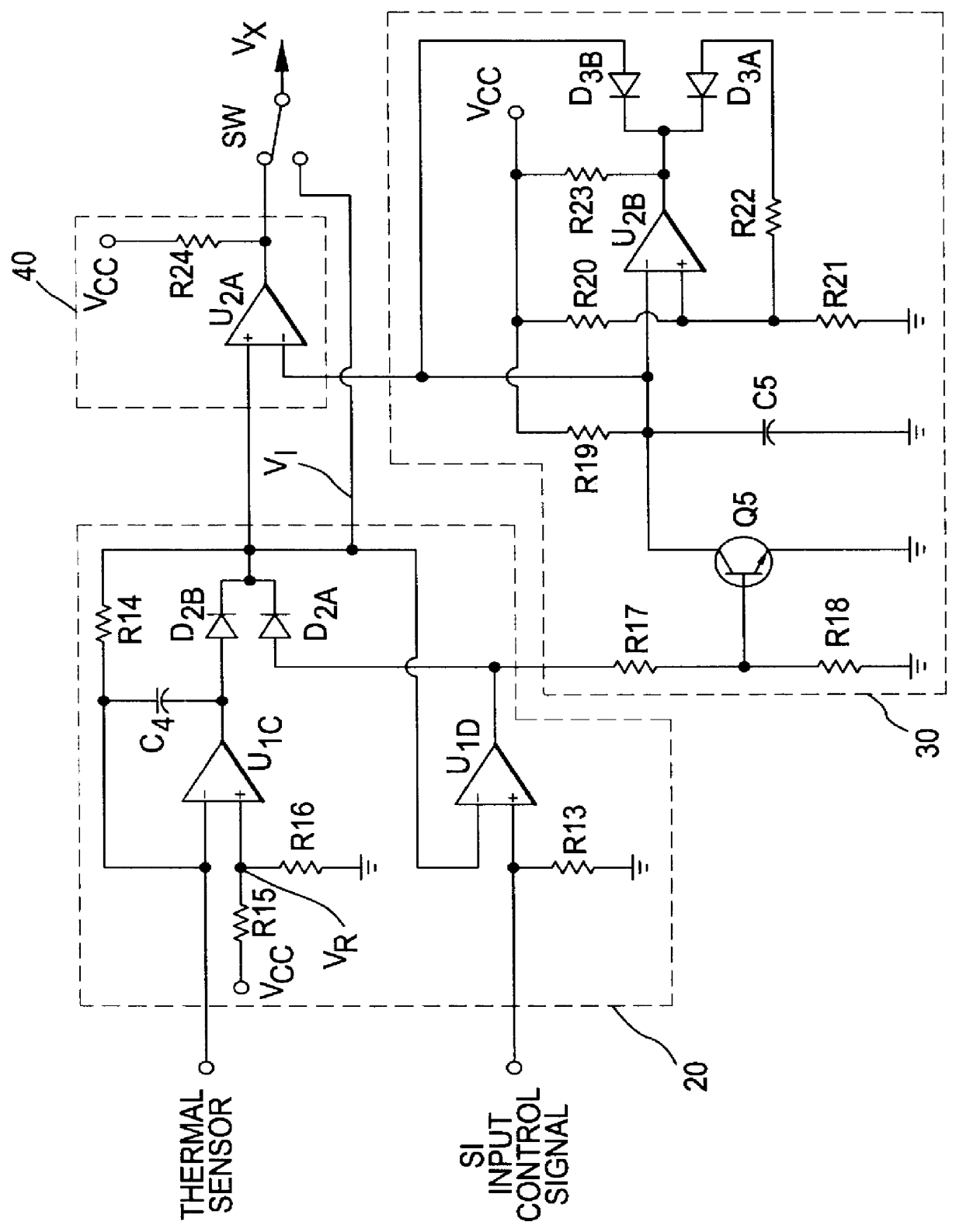

Interface apparatus for fan monitoring and control

InactiveUS6135718ADifficult to filterIncrease output impedancePump componentsTemperatue controlCapacitanceAudio power amplifier

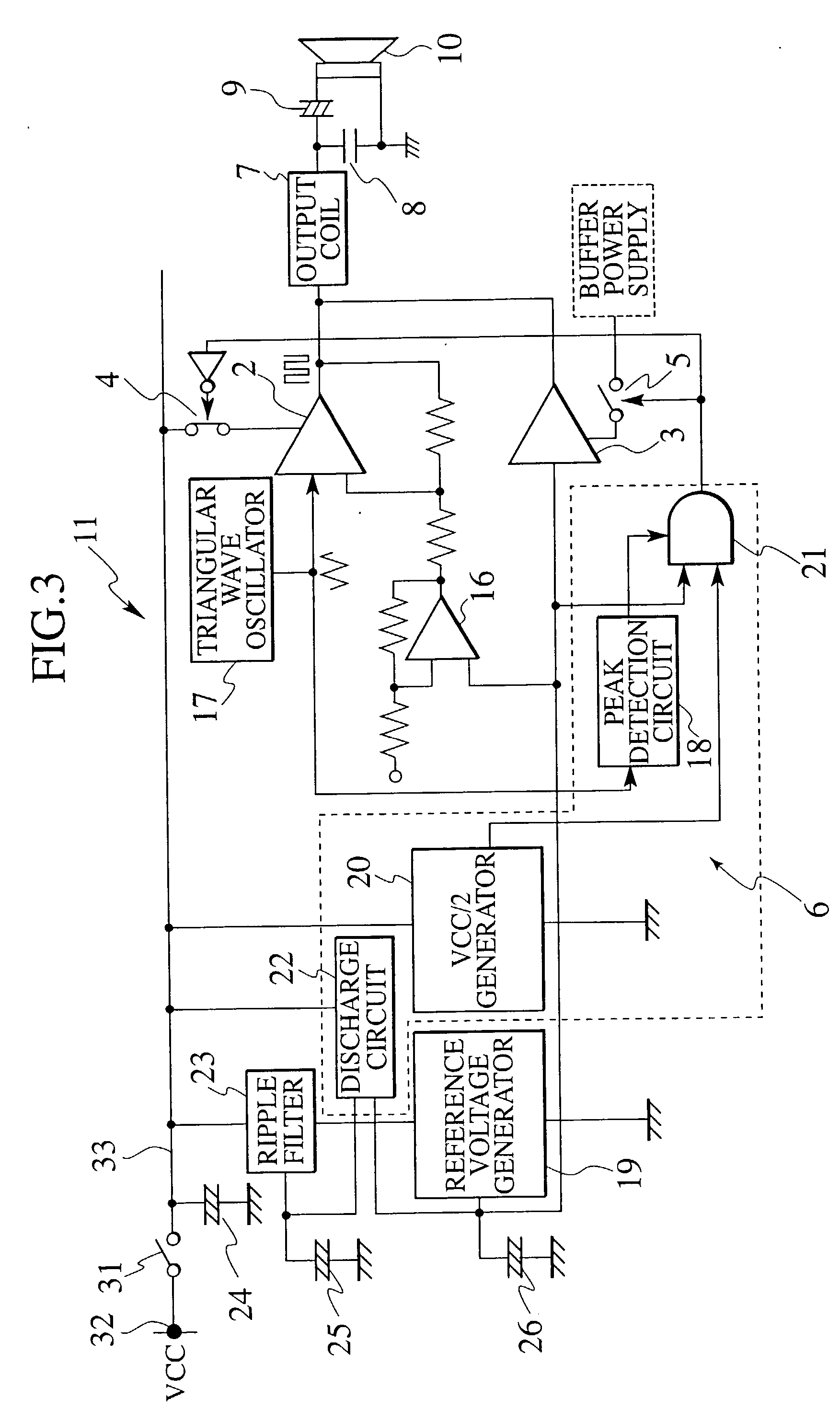

An interface apparatus for fan monitoring and control includes a current source amplifier that generates a programmable current in response to its input voltages. Associated with an output capacitor, which is able to reduce noise, the programmable current drives the fan at a desired speed. The rotating fan induces a ripple signal in the output capacitor, which is fed to a band-pass amplifier to produce a tachometer pulse. Through a buffer amplifier, an input control signal combined with a thermal sensor signal has direct control over the current source amplifier. Alternatively, a PWM circuit having a comparator, a ramp oscillator and the output of the buffer amplifier drives the current source amplifier in switching mode. Since the ramp oscillator can be synchronized by the input, both analog and pulse signals can function as the input control signals.

Owner:SEMICON COMPONENTS IND LLC

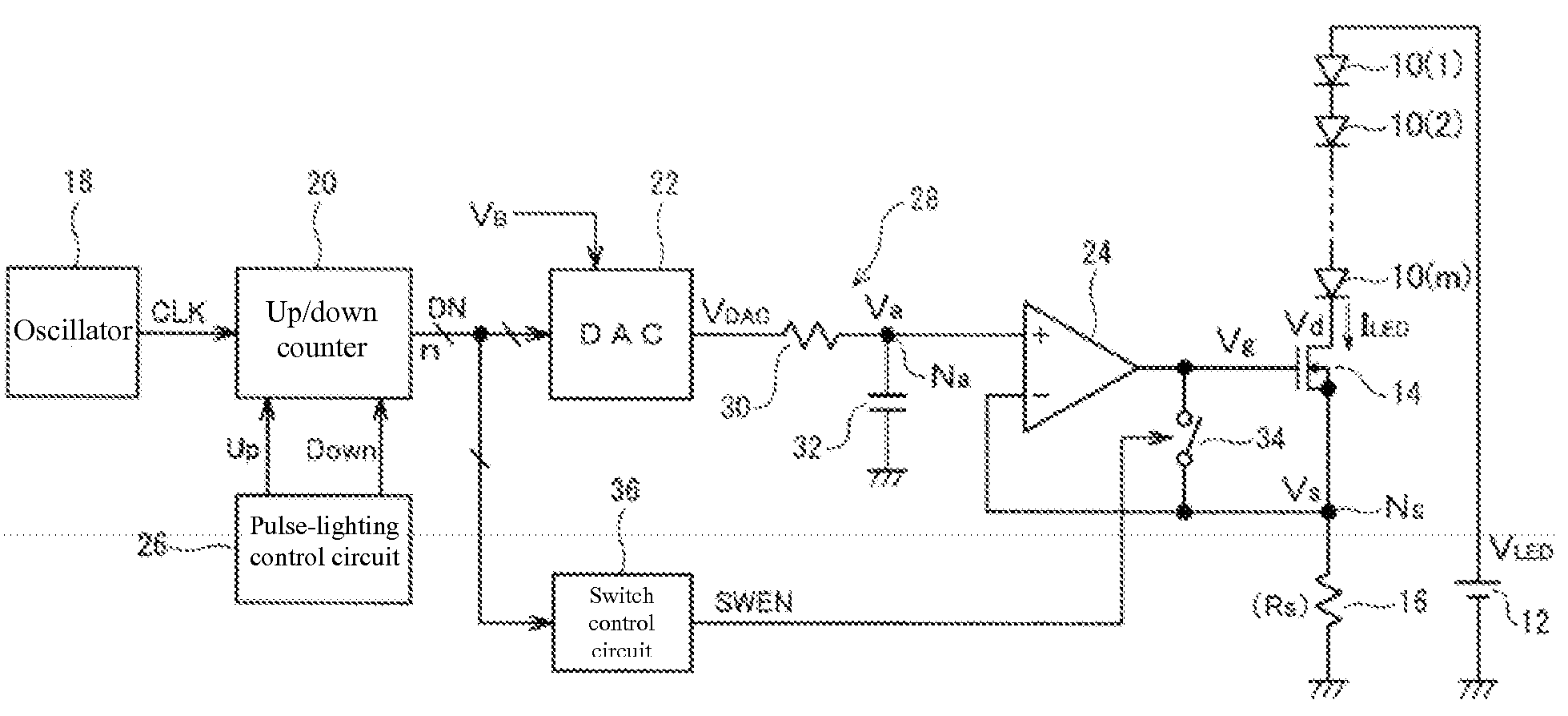

LED drive circuit

ActiveUS20090174338A1Low costEfficient workElectroluminescent light sourcesSemiconductor lamp usageAudio power amplifierLow-pass filter

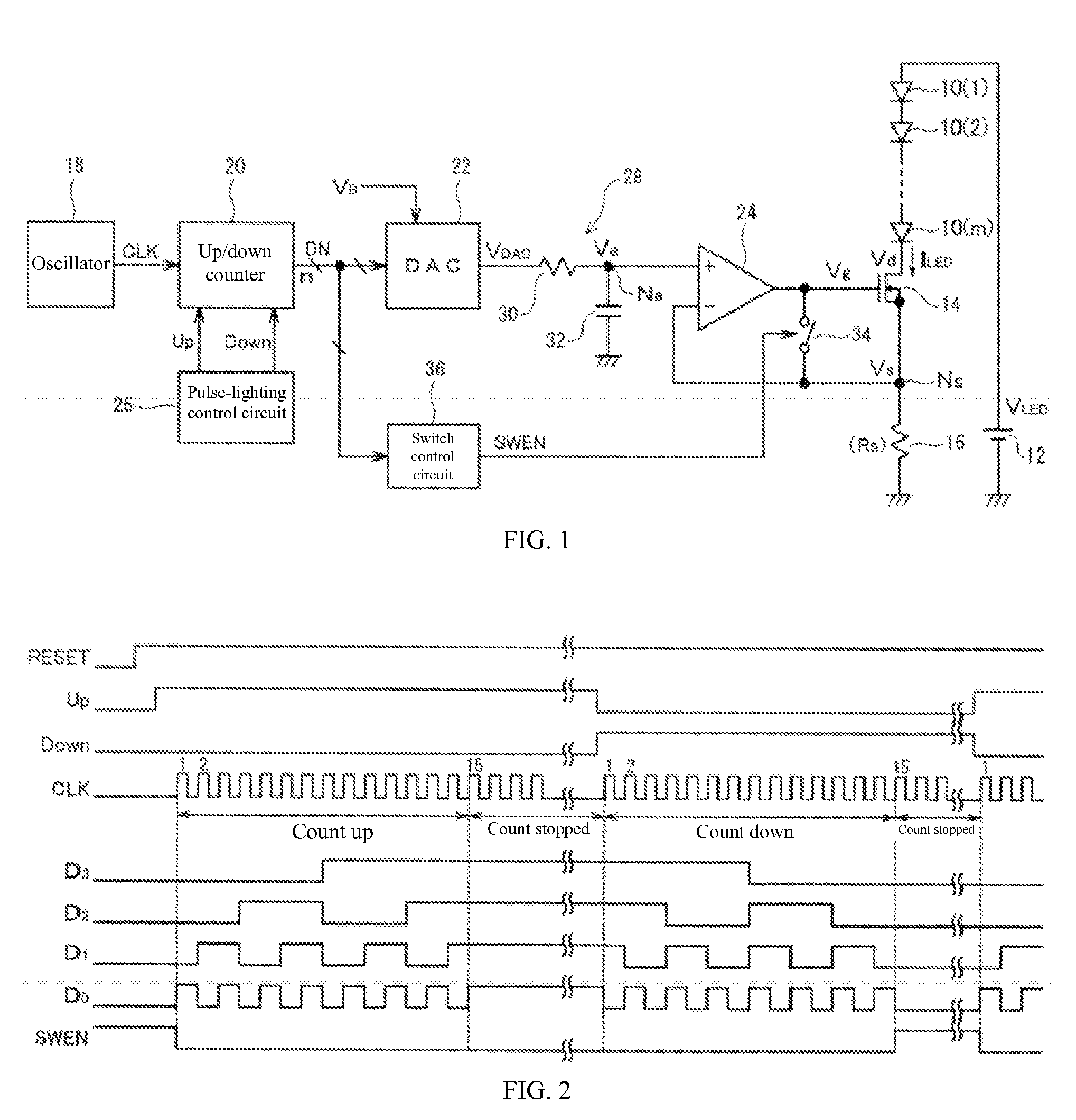

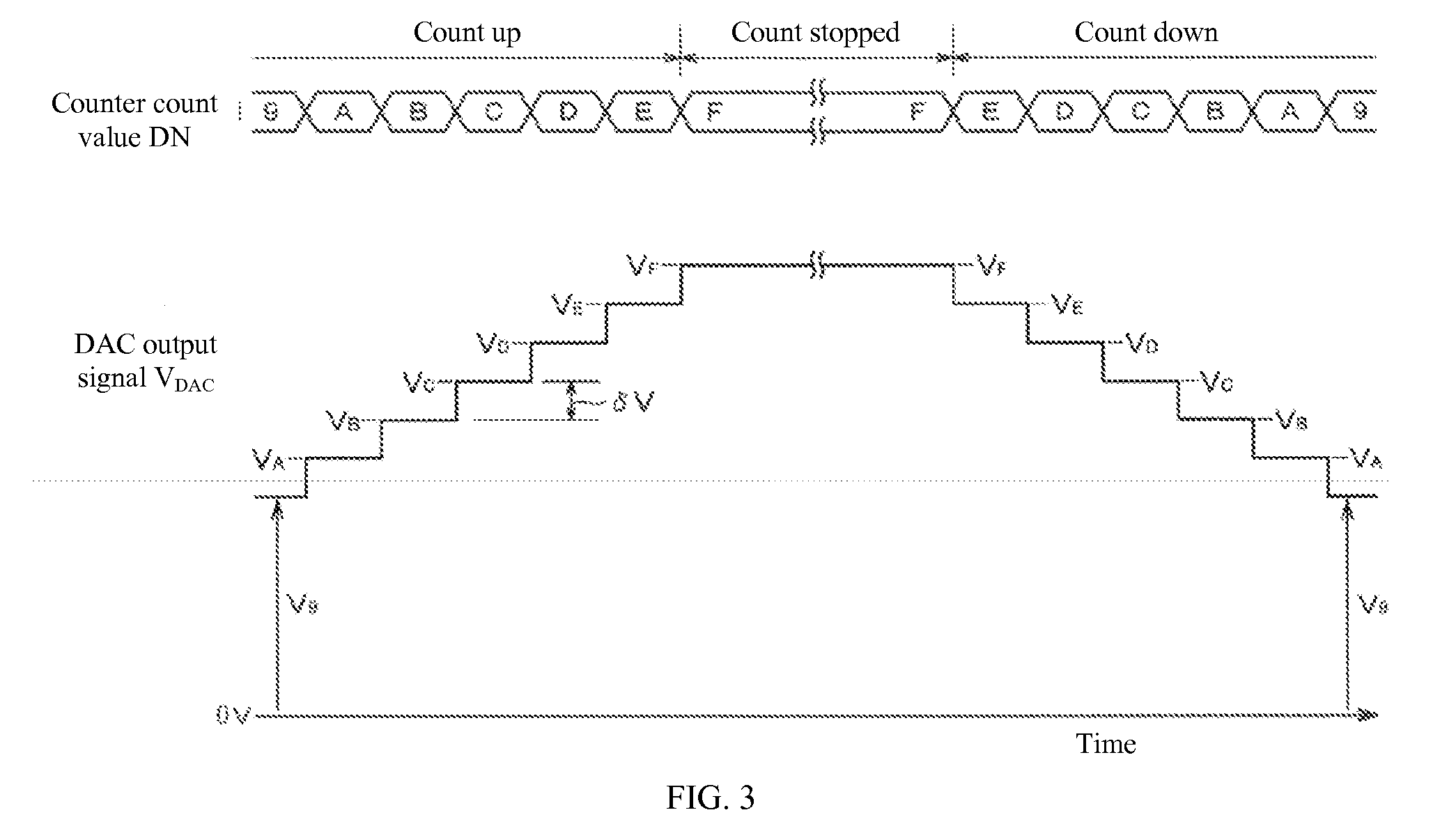

A LED drive circuit equipped with oscillator 18, up / down counter 20, and DAC 22 in order to drive multiple LEDs 10(1)-10(m) in a block. Up / down counter 20 carries out count-up / down operations in sync with clock CLK sent from oscillator 18 during the ramping up / down of pulse-lighting of the LEDs. DAC 22 converts counter count value DN into analog voltage signal VDAC and supplies it to the gate terminal of NMOS transistor 14 via low-pass filter 28 and buffer amplifier 24.

Owner:TEXAS INSTR INC

EER modulator with power amplifier having feedback loop providing soft output impedance

ActiveUS7068096B2Gain controlAmplifier modifications to raise efficiencyAudio power amplifierEngineering

An EER amplifier for amplifying an RF signal includes:(II) a first RF amplifier for amplifying the phase portion of the signal;(III) an EER modulator for amplifying the envelope or baseband portion of the signal, including:A) a high frequency operational amplifier;B) a power amplifier;C) a feedback control loop including:(1) a current-to-voltage conversion amplifier having an input coupled to a current monitoring output of the power amplifier and an output,(2) an input buffer amplifier having an input coupled to receive the envelope signal and an output;(3) a summing amplifier having:(a) an input coupled to the outputs of: (a) the current-to-voltage conversion amplifier and (b) the input buffer amplifier, and(b) an output coupled to the current control input of the power amplifier.

Owner:NORTHROP GRUMMAN SYST CORP

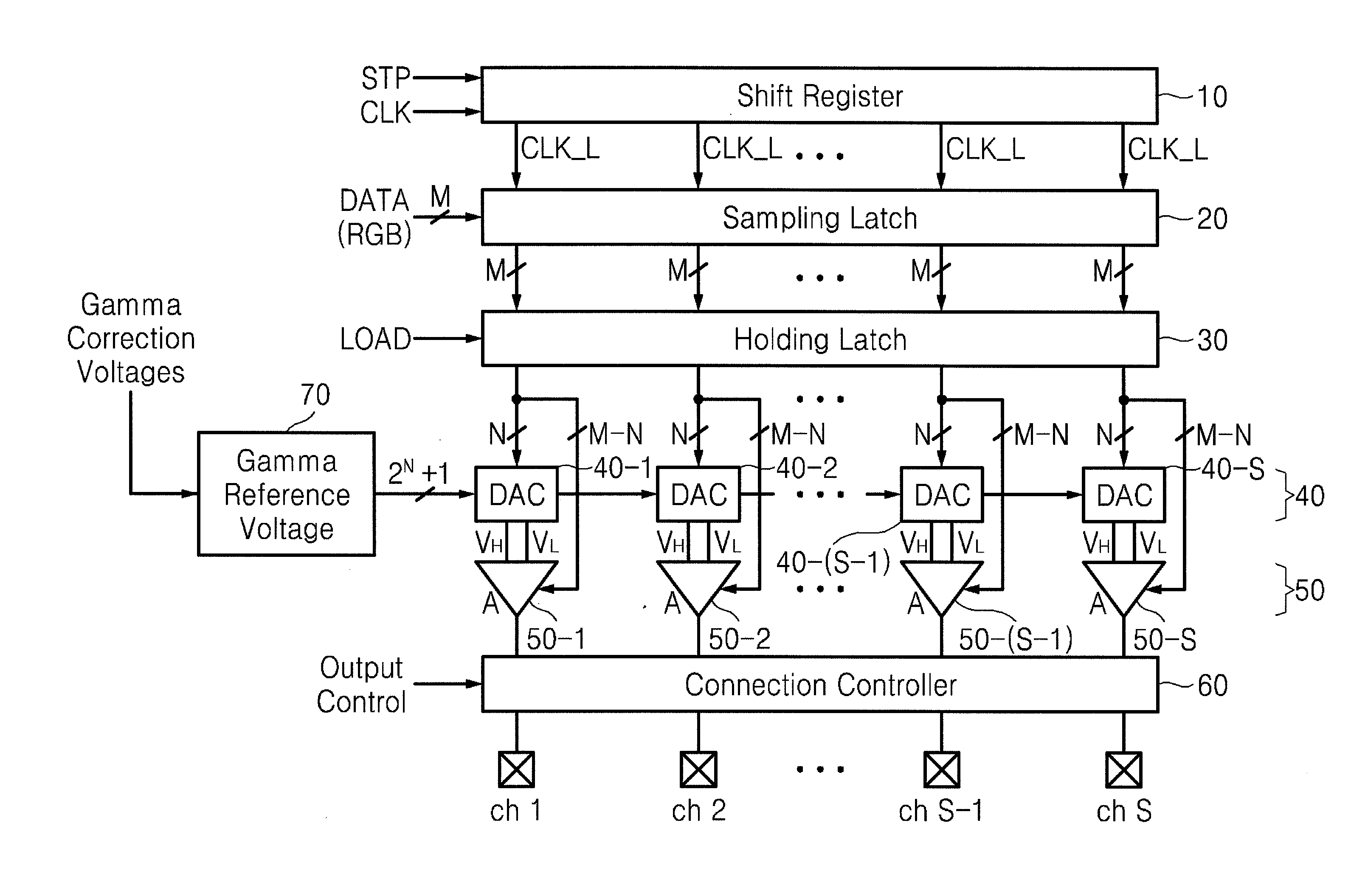

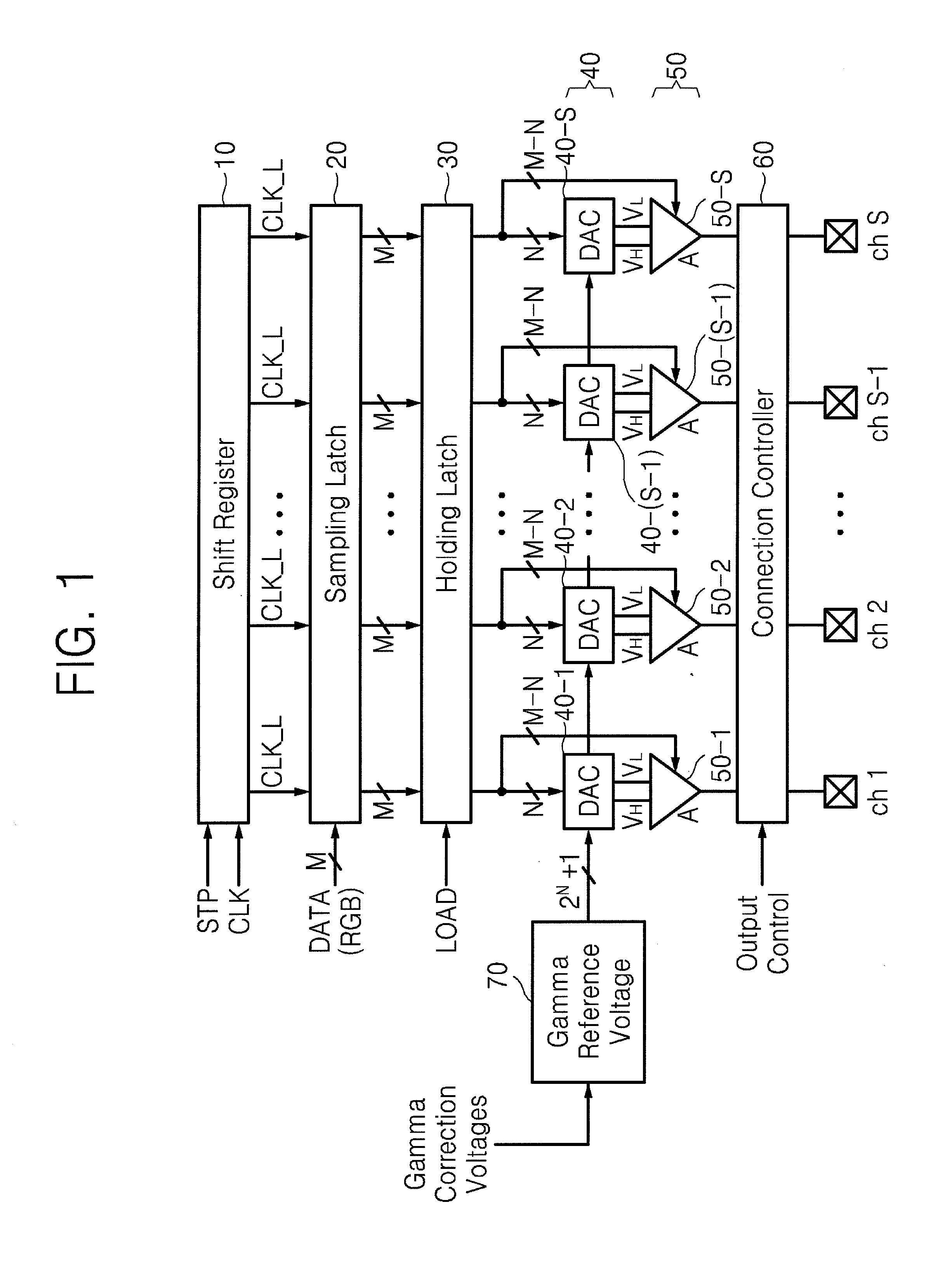

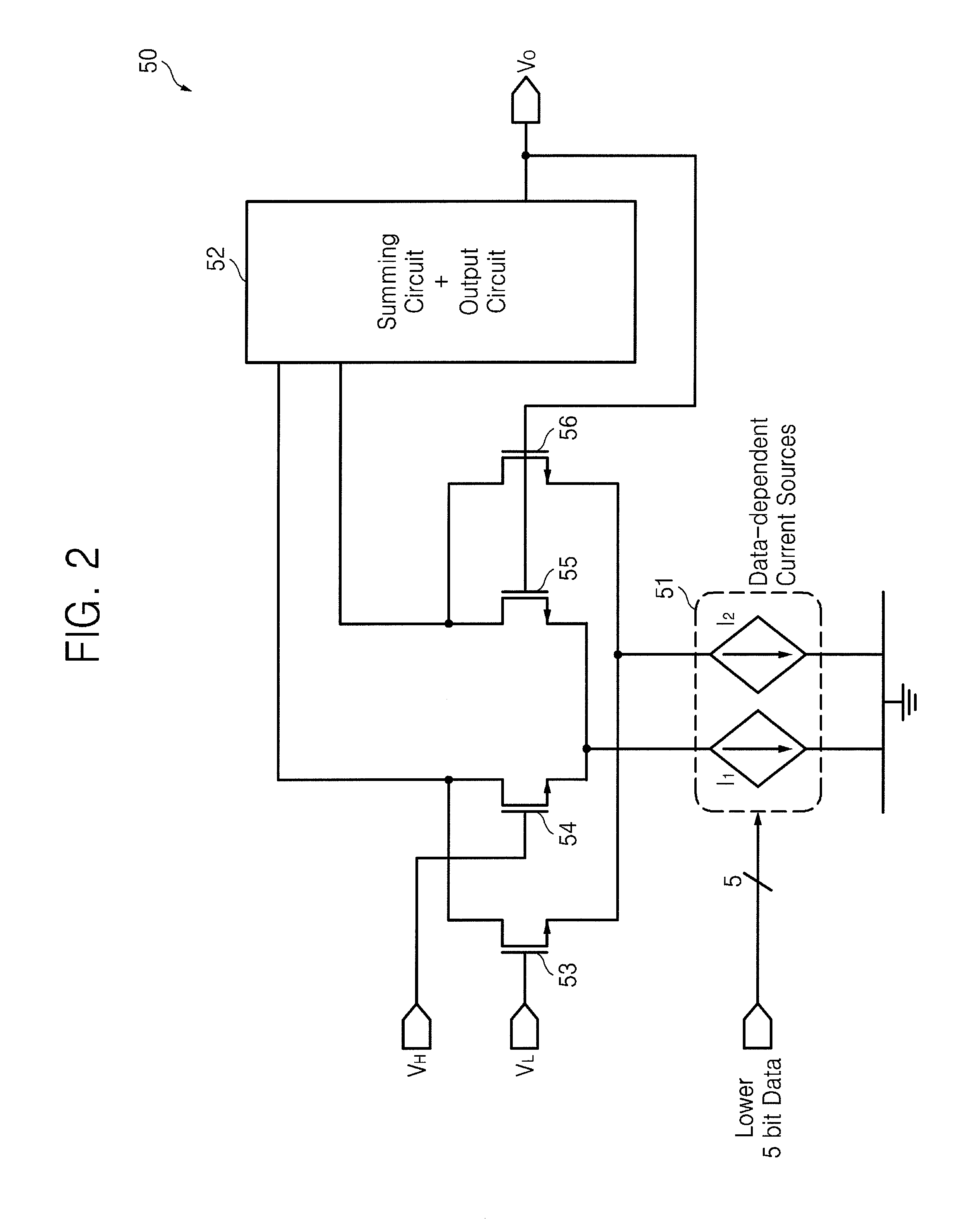

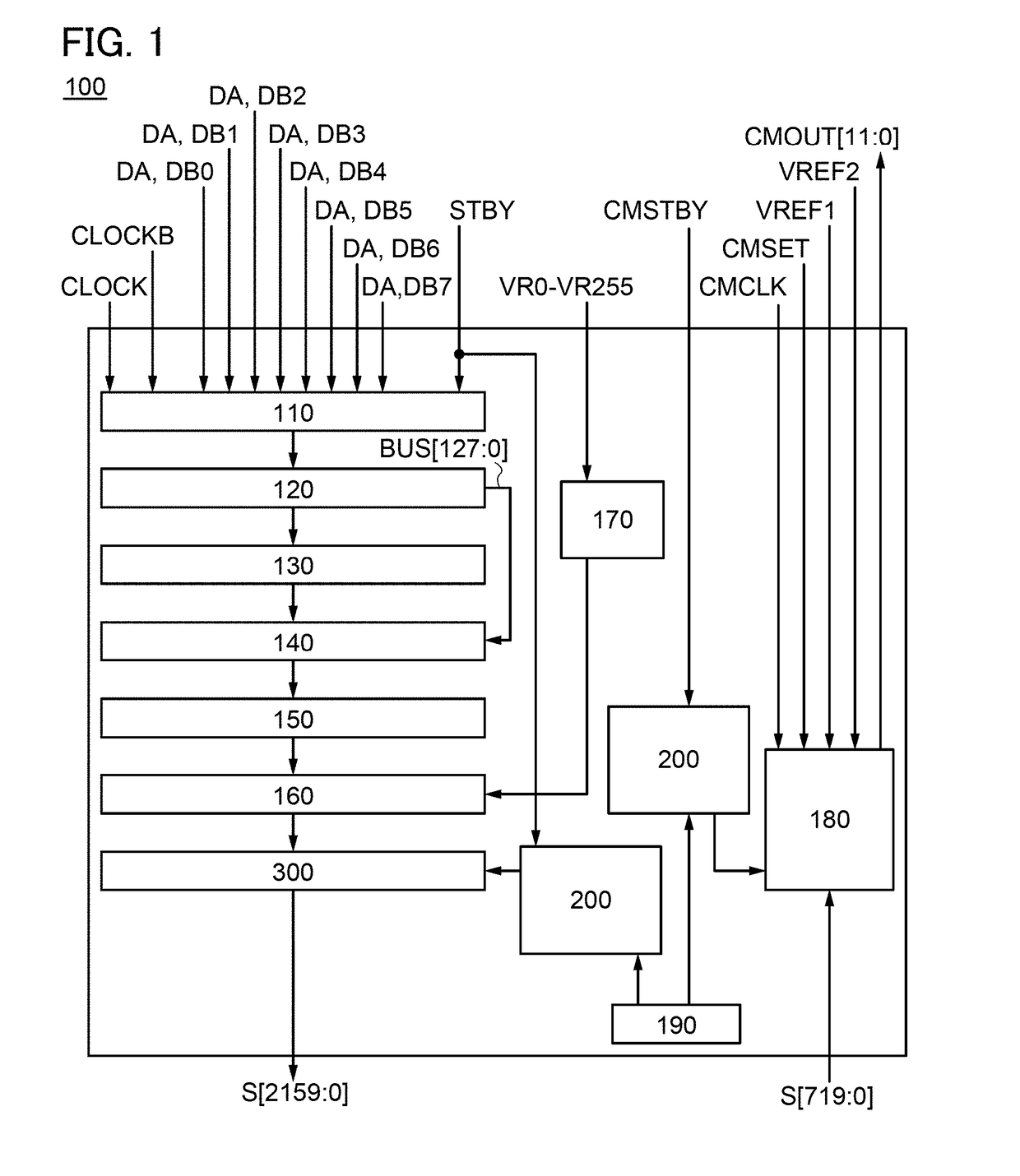

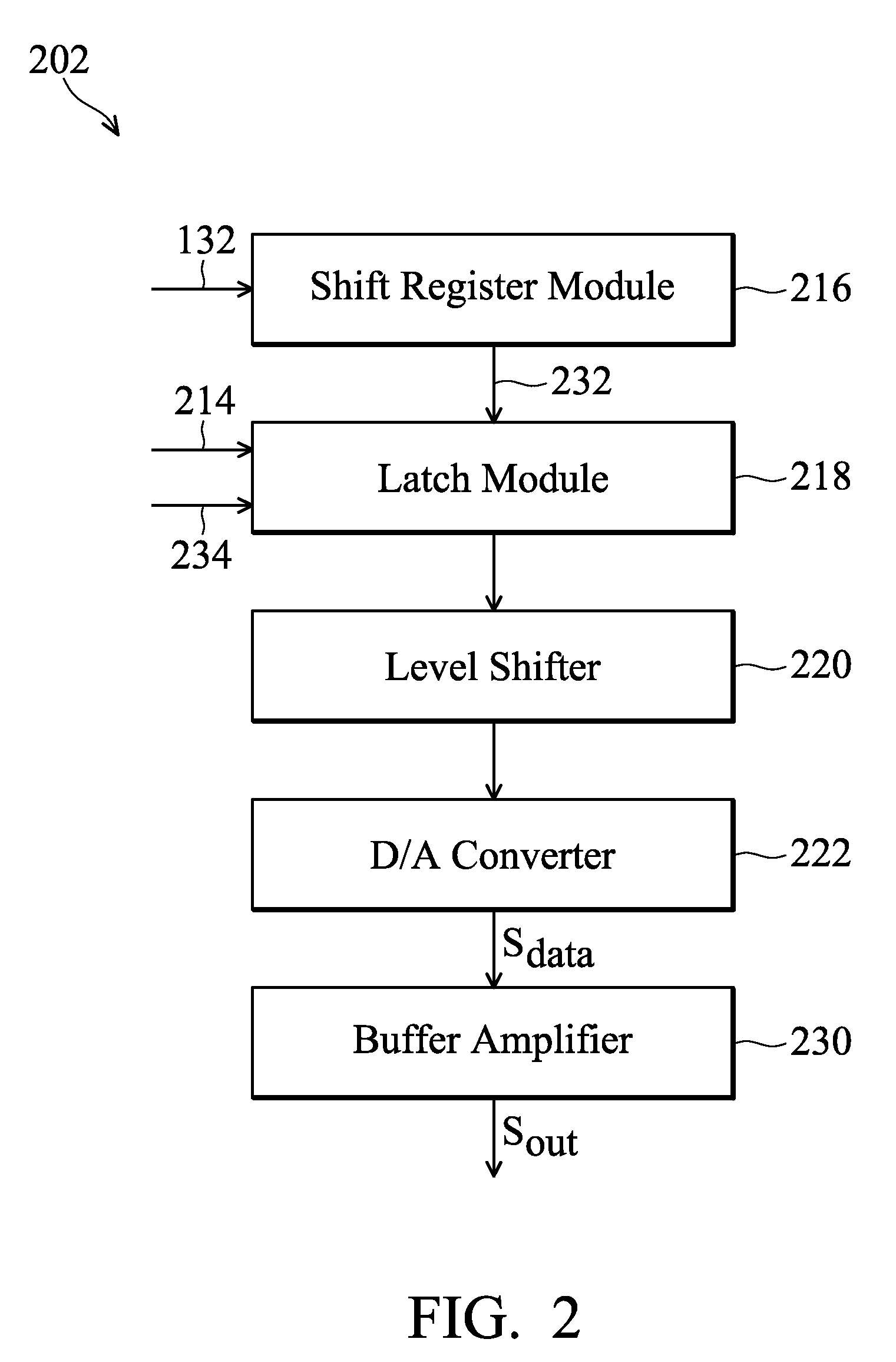

Digital-to-analog conversion circuit and column driver including the same

ActiveUS20100141493A1Electric signal transmission systemsStatic indicating devicesDigital dataDigital analog converter

A digital-to-analog conversion circuit includes a digital-to-analog converter and a buffer amplifier. The digital-to-analog converter receives upper bits of digital data and a plurality of analog voltages and is configured to output two adjacent analog voltages of the plurality of analog voltages based on the upper bits. The buffer amplifier includes two input terminals. One of the input terminals receives one of the two adjacent analog voltages and the other input terminal receives the other adjacent analog voltage. The buffer amplifier is configured to generate a current offset by controlling a current flowing into each of the two input terminals based on lower bits of the digital bits.

Owner:SAMSUNG ELECTRONICS CO LTD

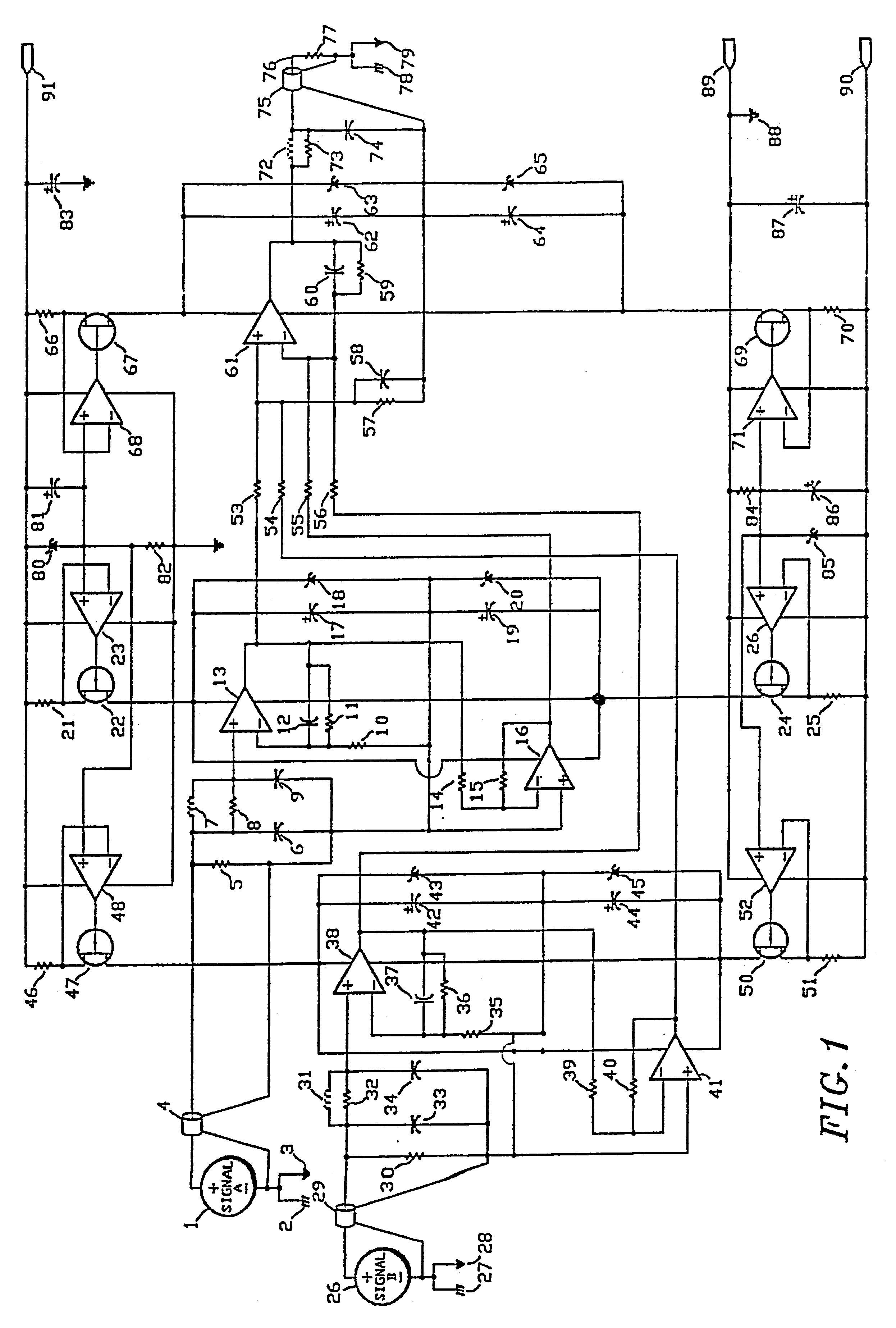

Linearized and balanced mixer apparatus and signal mixing method

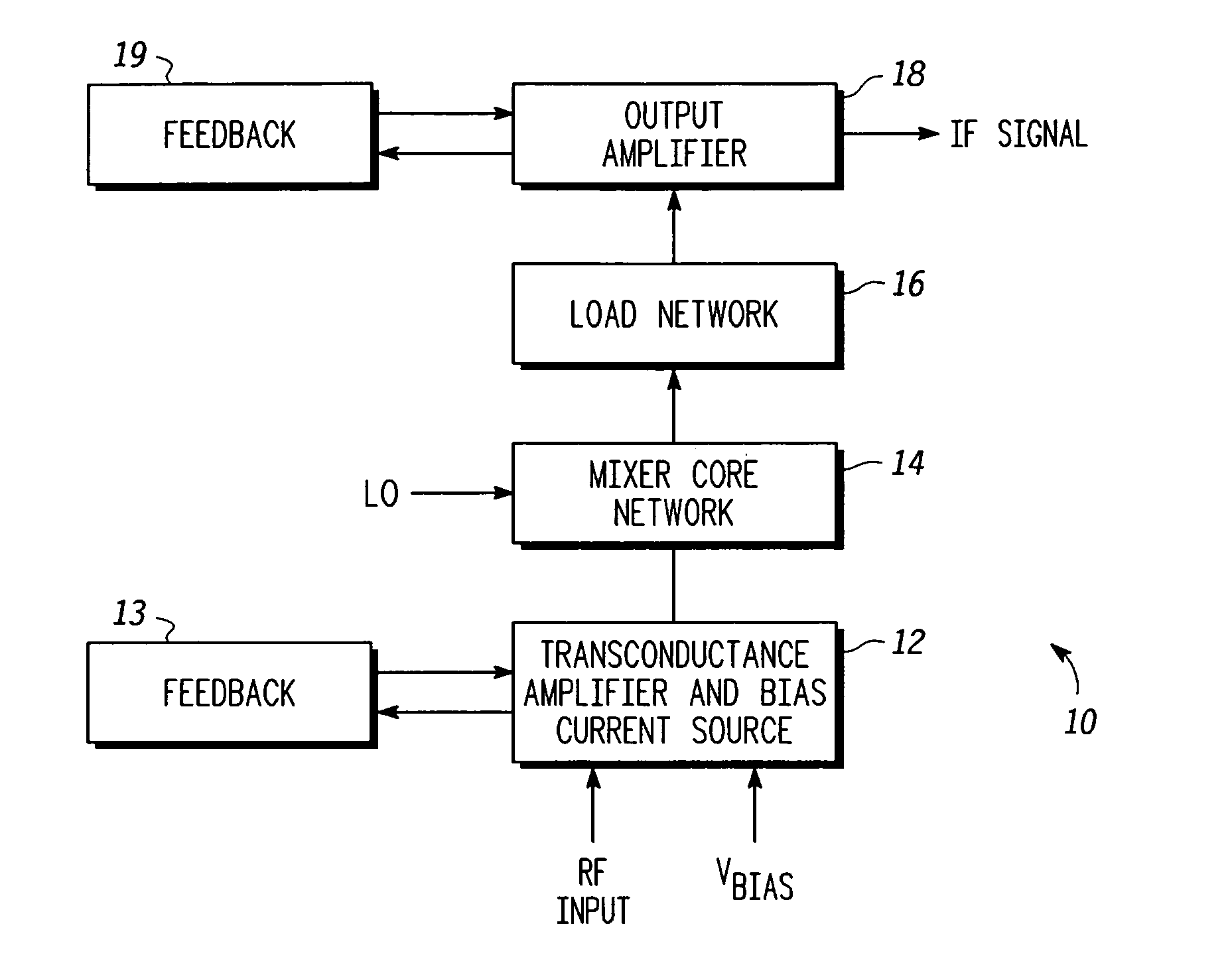

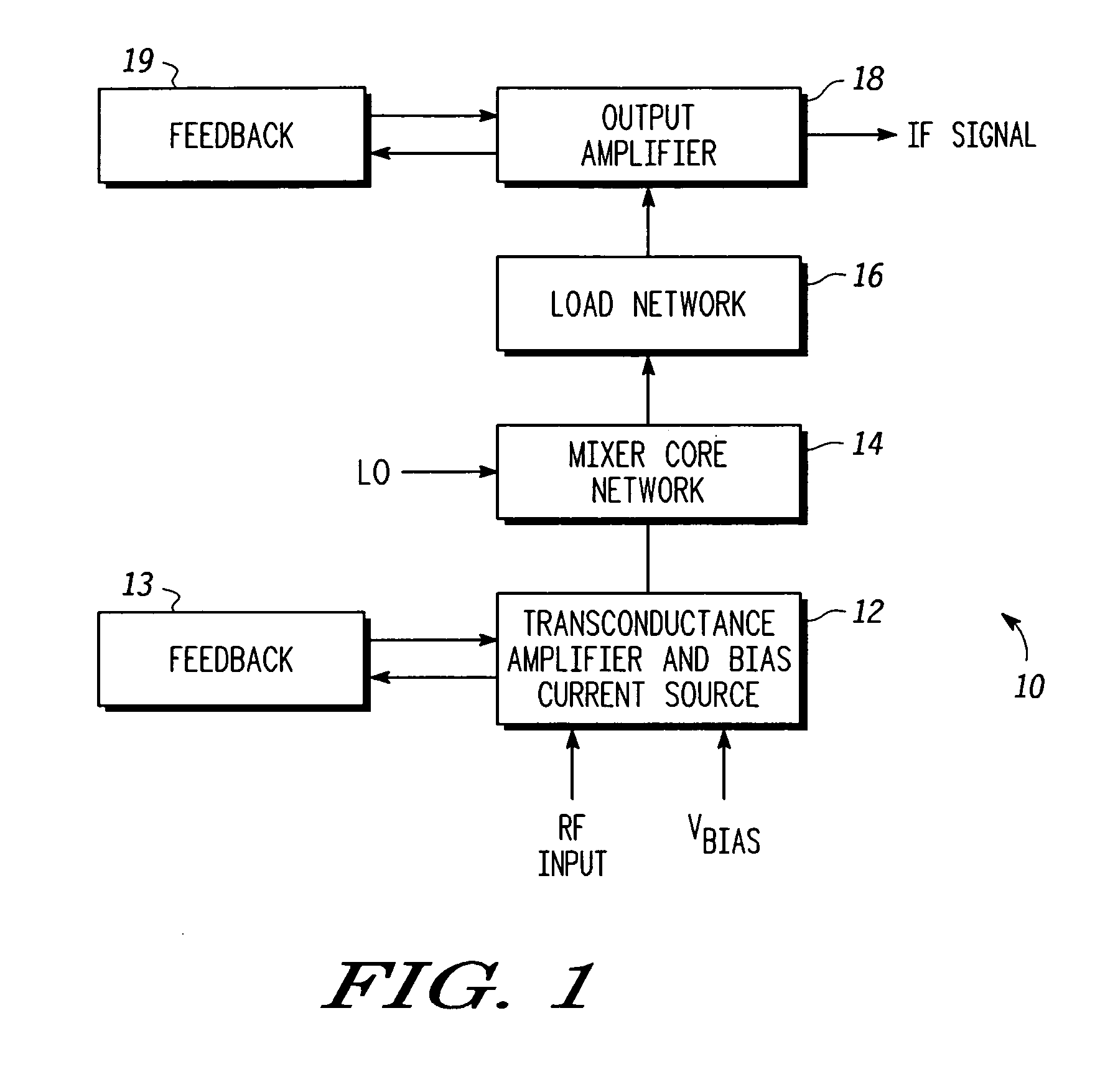

Method and apparatus are provided for linearized balanced signal mixing. A signal mixing circuit (10) for translating a radio frequency (RF) signal is provided comprising an input amplifier (12), a mixer network (14), and an output buffer amplifier (18). The input amplifier (12) is configured to produce an amplified RF signal and cancel an input third-order intermodulation (IM3) distortion in the amplified RF signal with a cross-coupled feedback amplifier (13). The mixer network (14) is configured to produce an intermediate frequency (IF) signal based on the amplified RF signal and a local oscillator signal. The output amplifier (18) is configured to buffer the IF signal and cancel an output IM3 distortion in the IF signal with a cross-coupled feedback amplifier (19). The input amplifier (12) and cross-coupled feedback amplifier (13) also serve as a bias current source for the mixer network (14), thus lowering the supply voltage required for the mixing circuit (10).

Owner:APPLE INC

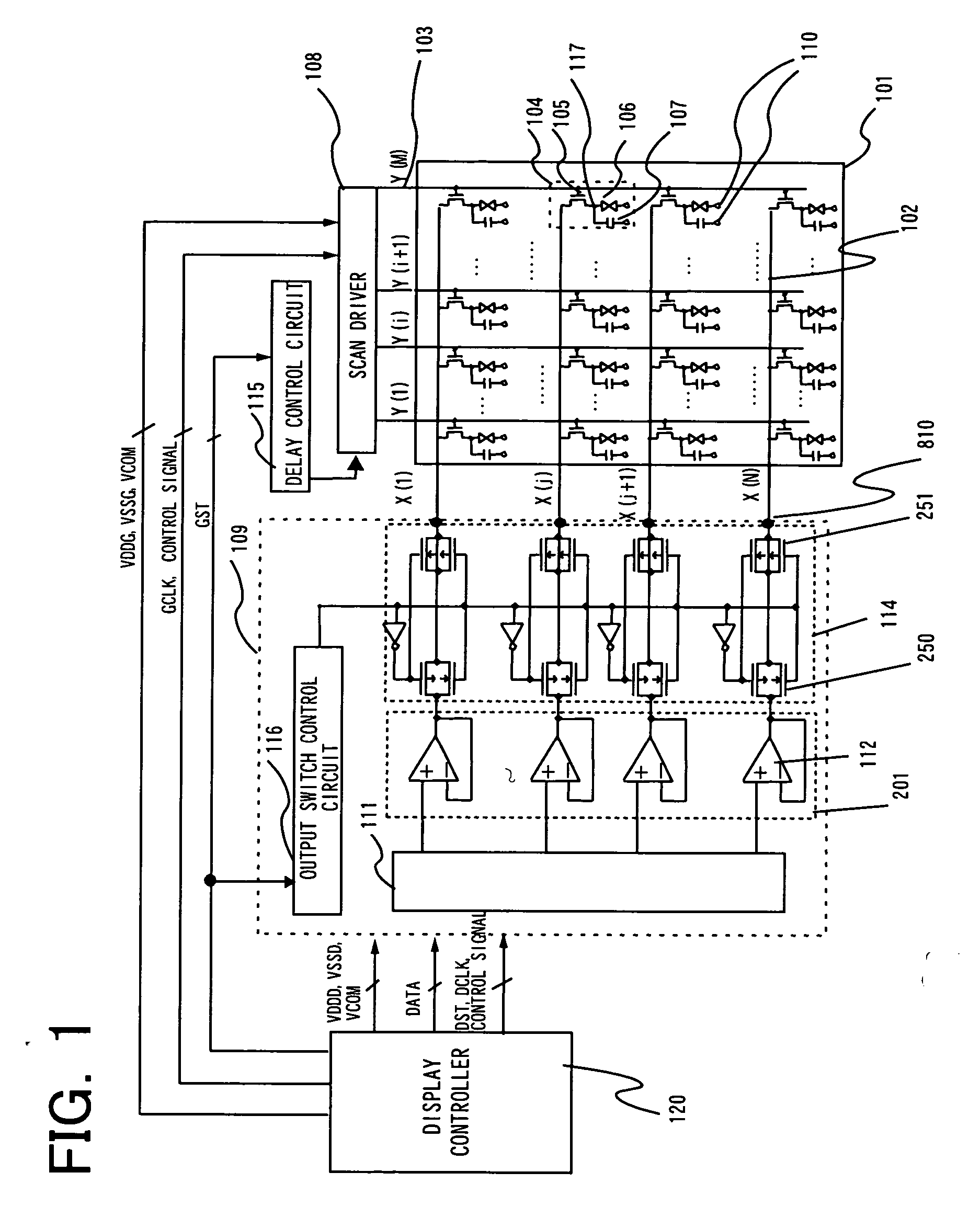

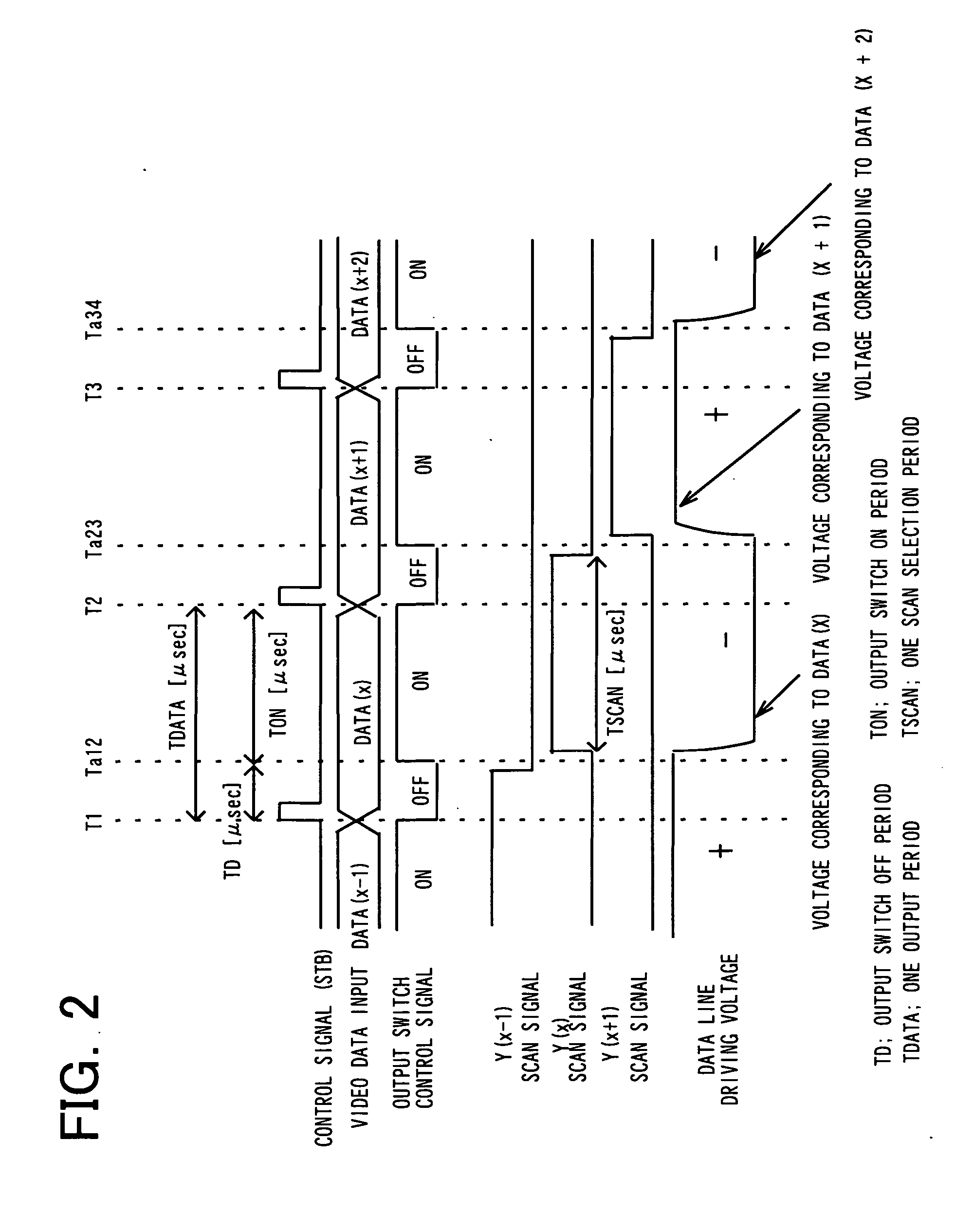

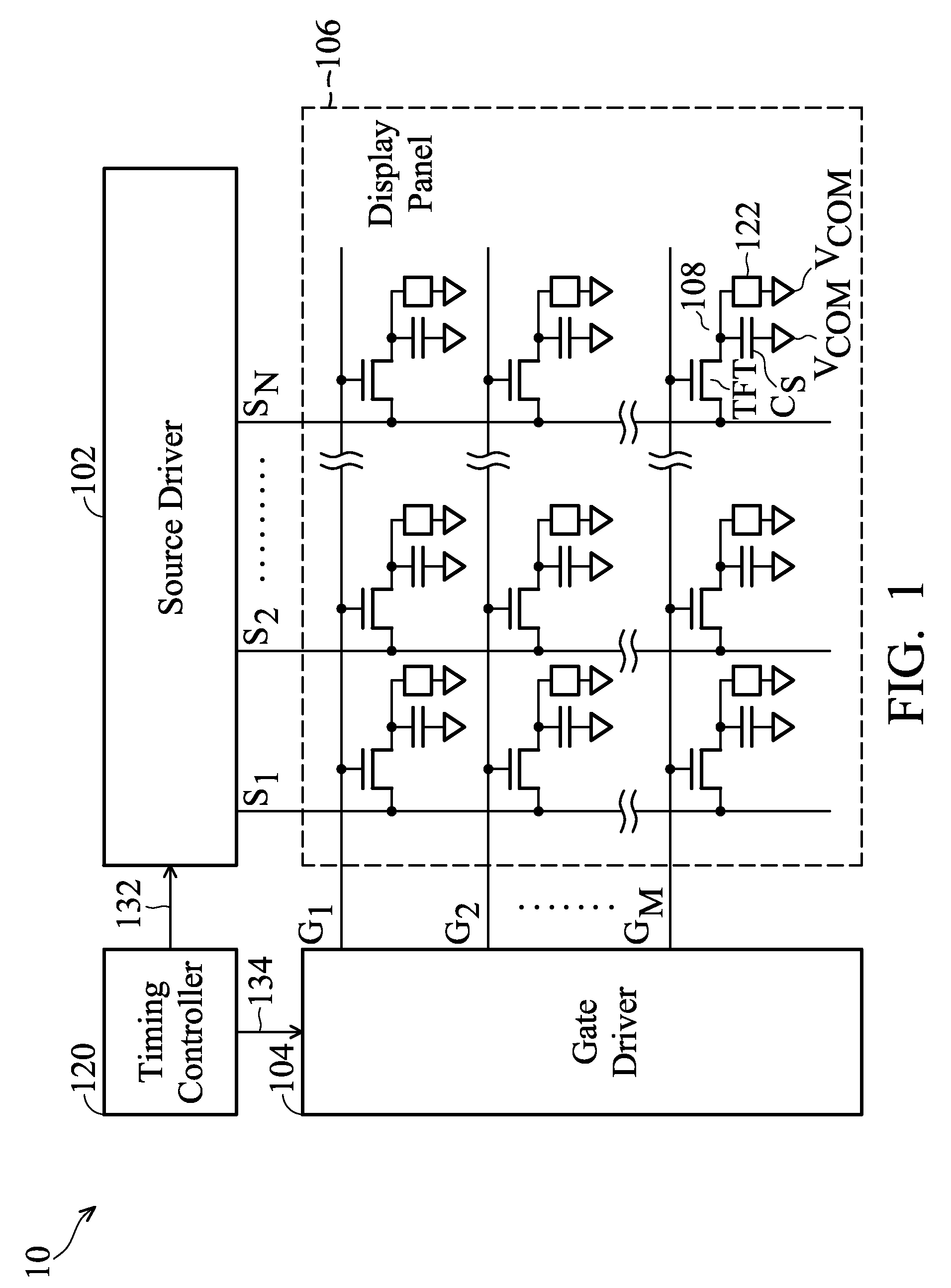

Active matrix type display device and driving method thereof

ActiveUS20060244710A1Improve rendering capabilitiesImprove display qualityCathode-ray tube indicatorsInput/output processes for data processingAudio power amplifierActive matrix

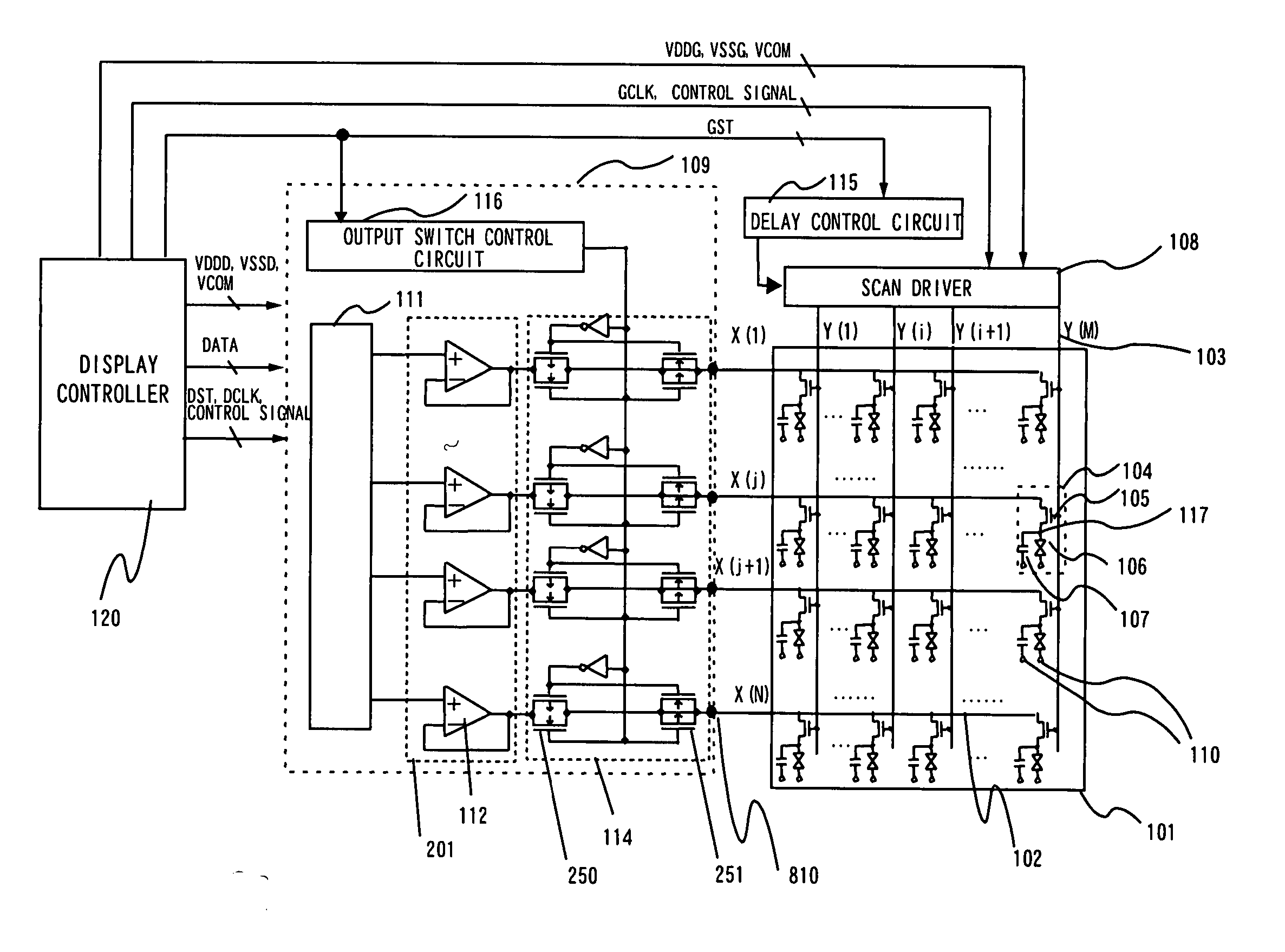

Disclosed is a display device including display unit, a column driver, a delay control circuit, an output switch control circuit, and a display controller. The display unit includes a plurality of pixel electrodes arranged at intersections between a plurality of data lines and a plurality of scan lines in a matrix form and TFTs. One of a drain and a source of each of the TFTs is connected to a corresponding one of the pixel electrodes. The other one of the drain and the source of each of the TFTs is connected to a corresponding one of the data lines, and a gate of each of the TFTs is connected to a corresponding one of the scan lines. The scan driver supplies a scan signal to each of the scan line in a preset scan cycle. The column driver includes D / A converter circuits for converting video data to gray scale signals, a plurality of buffer amplifiers for sequentially amplifying and outputting the gray scale signals in a preset output cycle, and an output switch circuit including a plurality of switches connected to output terminals of the buffer amplifiers and the data lines, respectively. The delay control circuit controls the scan driver so that the preset scan cycle is delayed from the preset output cycle just by a preset delay time. The output switch control circuit controls the output switch circuit to be kept off during the preset delay time. The display controller controls the video data, scan driver, column driver, delay control circuit, and output switch control circuit, respectively.

Owner:RENESAS ELECTRONICS CORP

Signal conditioning apparatus

InactiveUSRE37130E1Less-costly and efficientImprove the level ofHigh frequency amplifiersCurrent interference reductionElectrical conductorCoaxial cable

A signal conditioning system that receives inputs from at least one pair of conductors connected to its input. Each such input is processed by an input filter and presented to a buffer amplifier. Each such input filter and buffer amplifier refers to and is powered by independent power sources whose power return reference potentials are independently determined by the potential of the corresponding input signal potential reference conductor for the signal frequencies of interest. The outputs of all such buffer amplifiers, the power return reference potentials, and the power return reference potential of the conditioning circuit output are all appropriately added or subtracted in the next circuit stage. This circuit stage consists of an amplifier buffer having low output impedance which is powered by another independent power source whose power return reference potential is independently determined by the potential of the output signal reference conductor. The output of this circuit stage is connected to an output inductor circuit which in turn drives the output signal conductor. The output includes a filter, and is designed to decouple unstable loading conditions while rejecting external influences on the output signal. The invention also includes means that connect the reference potential of the destination of the output conductors to the system power ground potential. The present invention provides a relatively inexpensive and efficient way of reducing or eliminating interference caused by coax cabling in audio, power and video amplifiers, for example.

Owner:FIORI JR DAVID

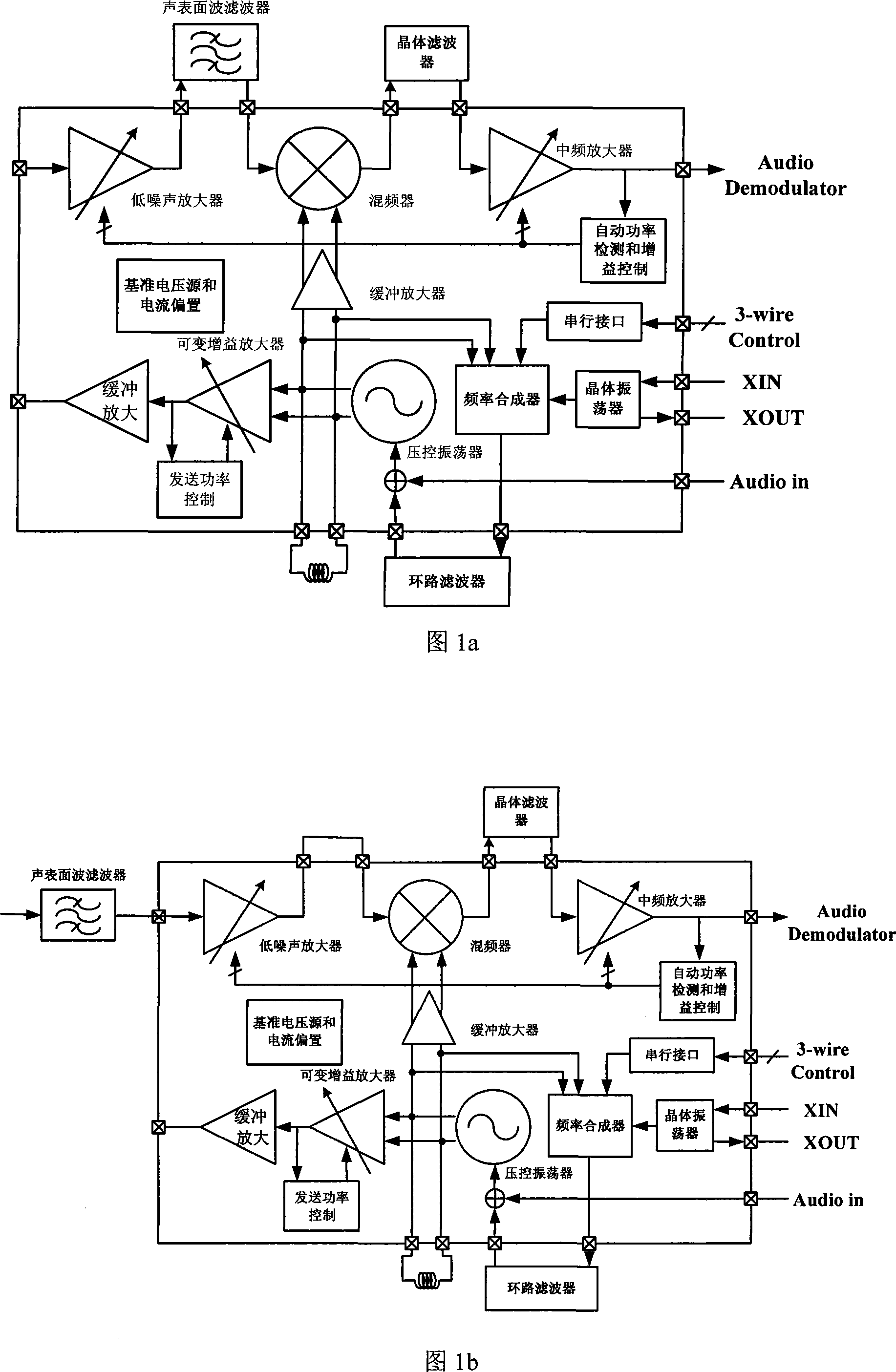

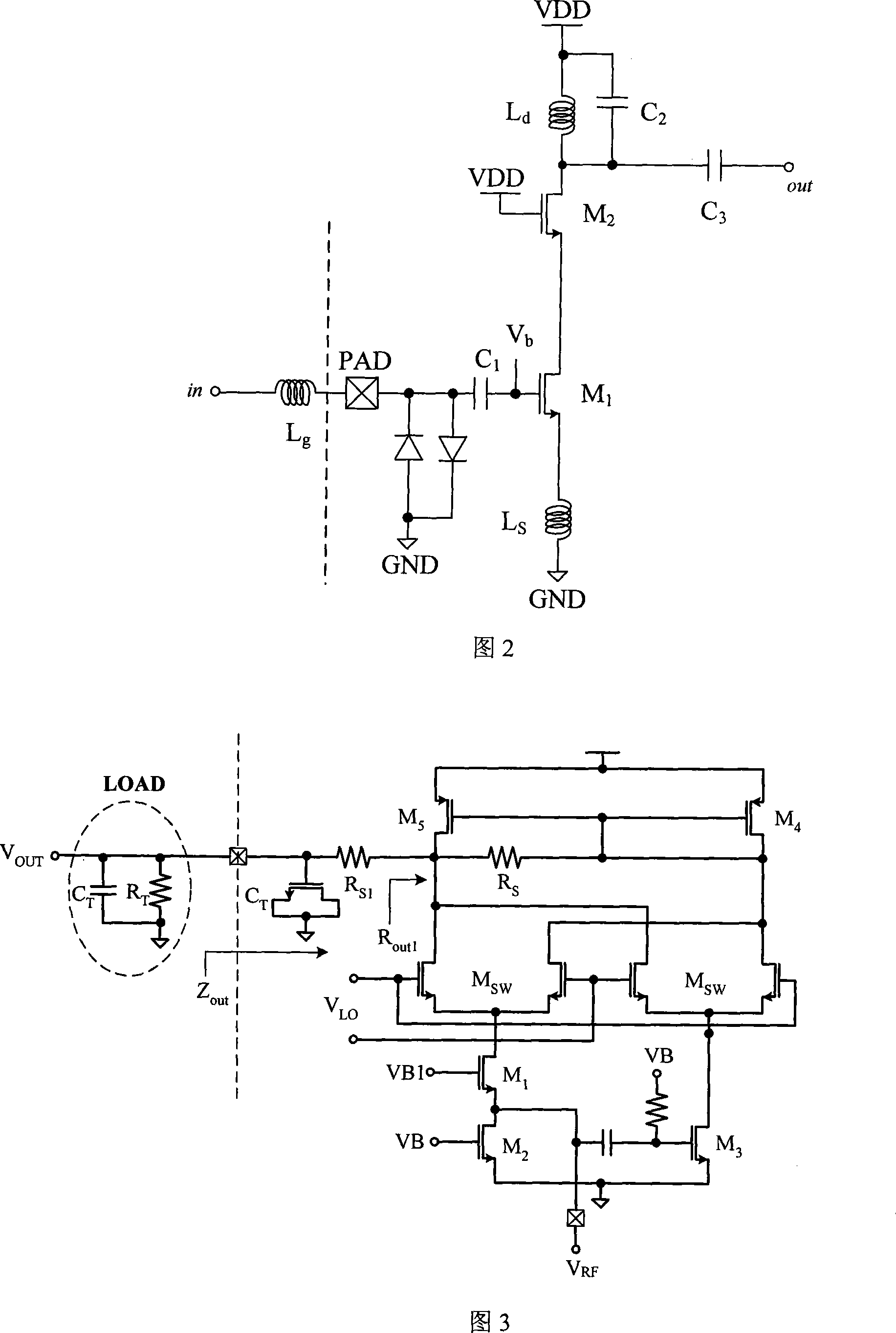

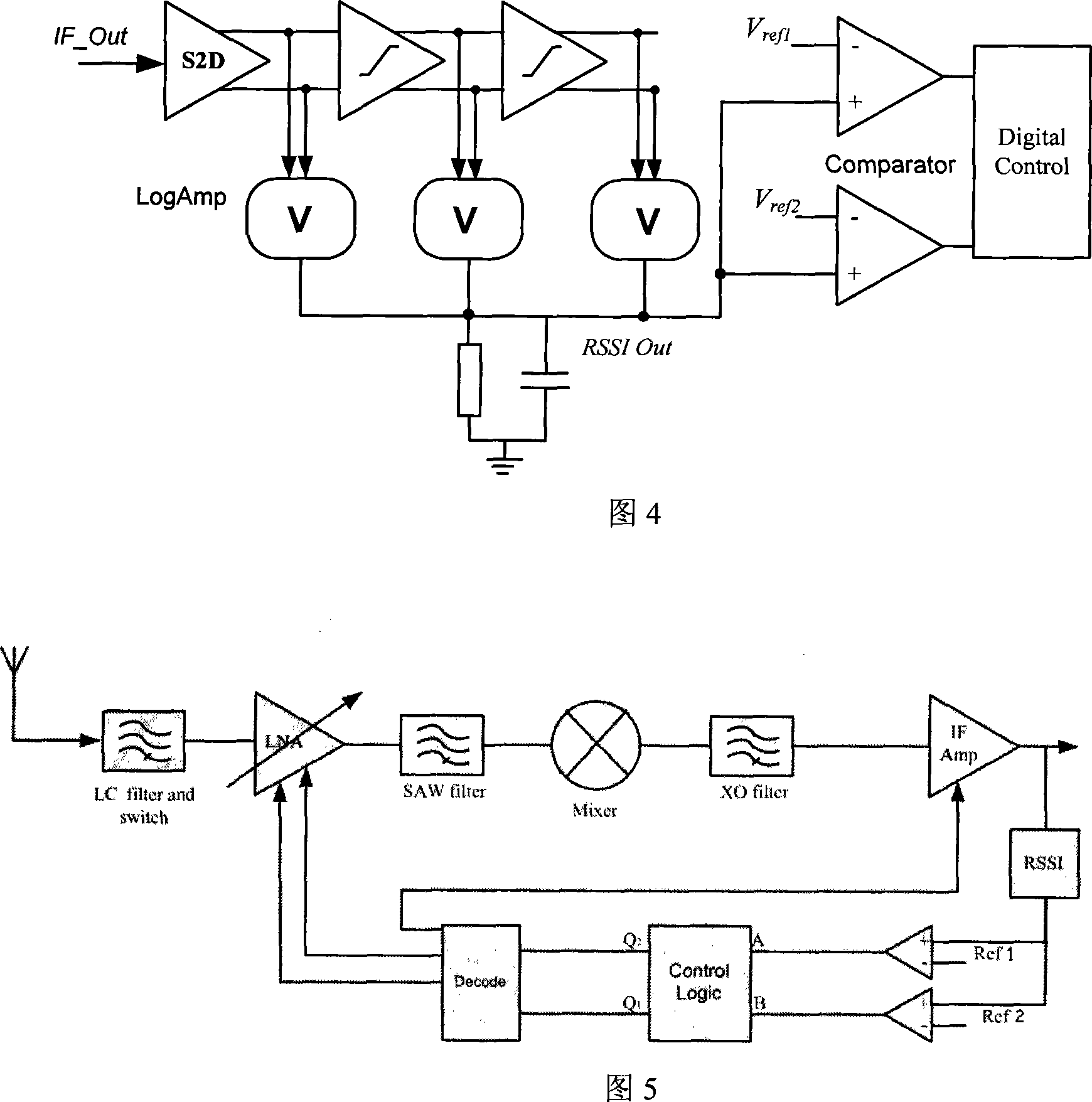

Single chip radio frequency transceiver

InactiveCN101162912AHighly integratedMeet performance index requirementsTransmissionTransceiverIntermediate frequency

A radio frequency transceiver of single chip includes a radio frequency receiving part, a radio frequency sending part, a local oscillation part, a reference voltage source and a current bias part. A low noise amplifier, a mixer and a intermediate frequency amplifier possessed by the radio frequency receiving part, an automatic gain regulator adjusting the gain of the radio frequency receiving part according to the intension of the received signal, a power adjuster and a buffer amplifier of a delivered power possessed by the radio frequency sending part, a voltage controlled oscillator, a frequency synthesizer and a crystal oscillator possessed by the local oscillation part, the reference voltage source and the current bias part are integrated to the single chip. The single chip has an input end and an output end of the received signal, which are connected with the receiving part, a filtering end connected with a filter at the outside, an input end and an output end of a signal to be emitted, which are connected with an emission part and a clock signal output end, a signal control end and an oscillation signal input end which are connected with the local oscillation part. In this way, the integration of the radio frequency transceiver is improved greatly.

Owner:上海富太克投资咨询有限公司

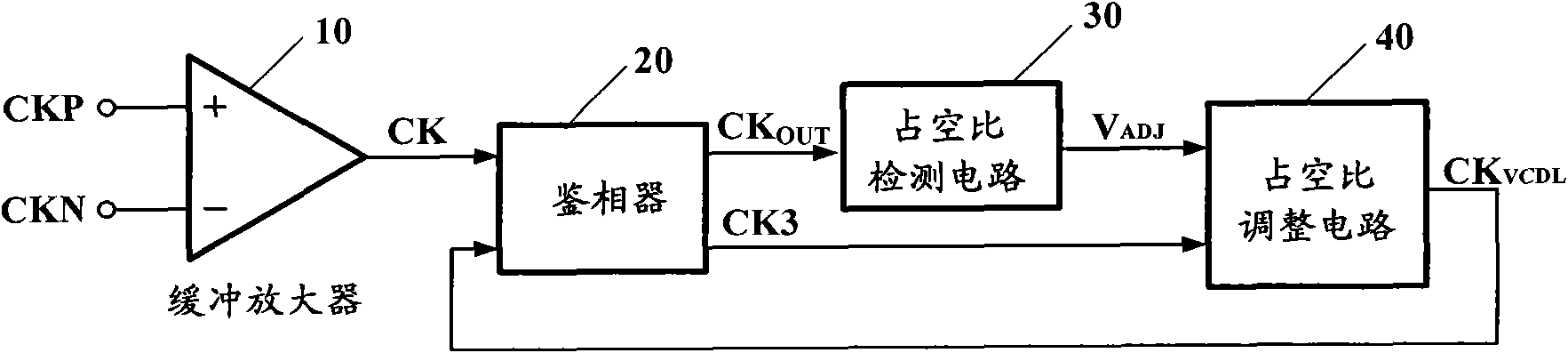

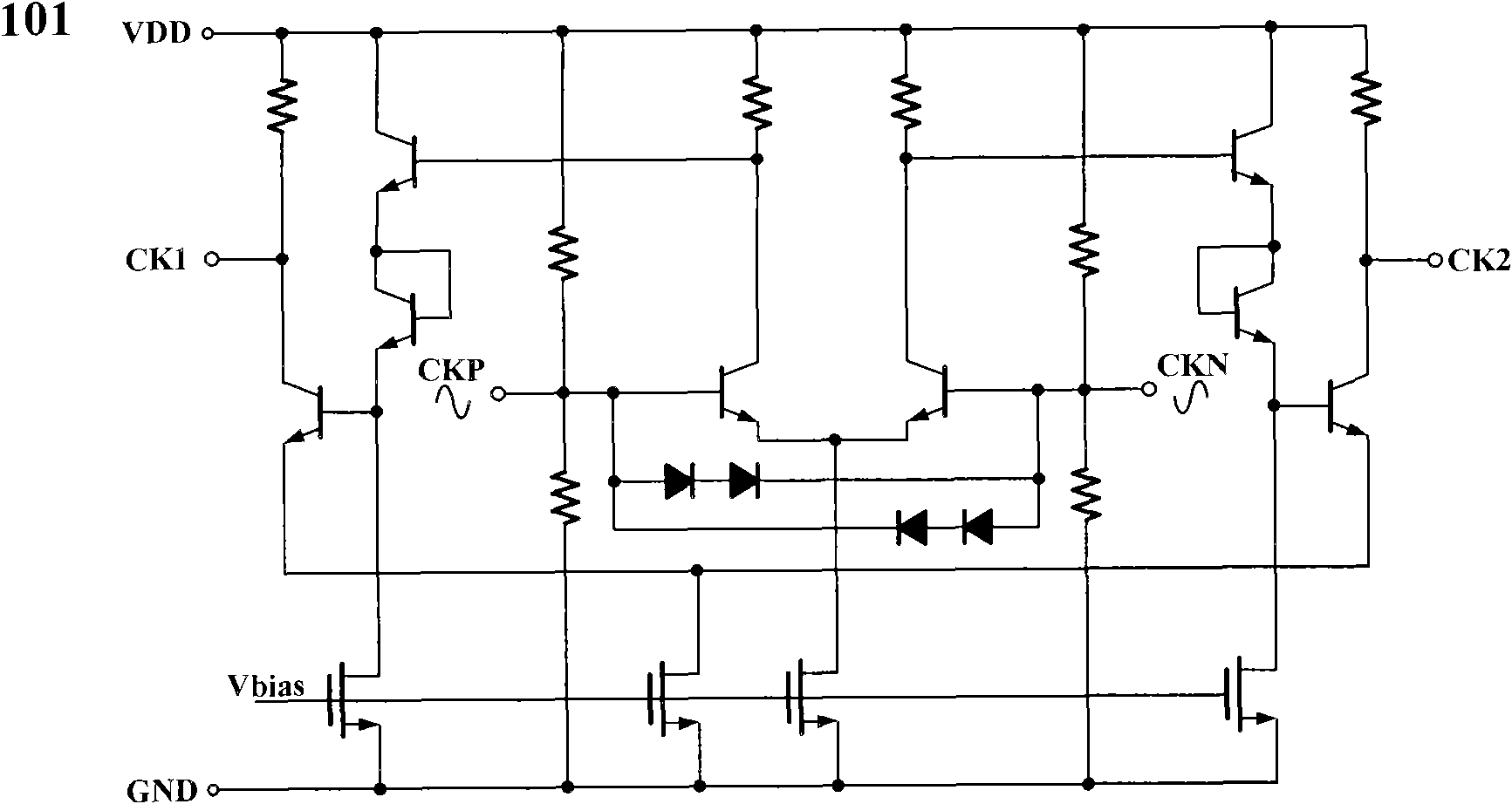

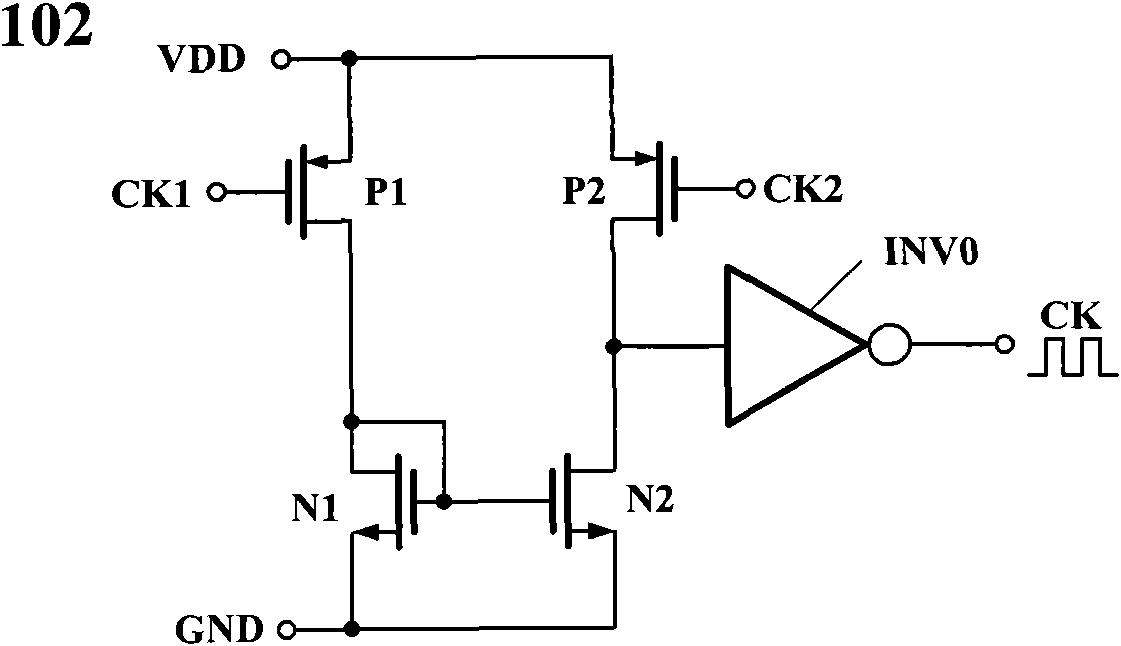

Clock adjustment circuit and adjustment method for clock circuit

InactiveCN102075167AReduce complexityFast adjustmentPulse train pattern monitoringDiscriminatorAudio power amplifier

The invention provides a clock adjustment circuit and an adjustment method for a clock circuit. The clock adjustment circuit comprises a clock buffer amplifier, a phase discriminator and a duty cycle adjustment circuit, wherein the clock buffer amplifier is used for receiving an external differential clock signal, shaping the differential clock signal into a single-end square wave clock signal and outputting the single-end square wave clock signal; the phase discriminator is used for receiving the single-end square wave clock signal from the clock buffer amplifier and a feedback signal from the duty cycle adjustment circuit, comparing the phase of the single-end square wave clock signal with the phase of the feedback signal to acquire a phase difference, and outputting the phase difference; and the duty cycle adjustment circuit is used for adjusting the duty cycle of the feedback signal by using the phase difference to acquire an adjusted feedback signal. The differential signal is shaped into the single-end square wave clock signal, the single-end square wave clock signal is compared with the feedback signal to acquire the phase difference, and the duty cycle is adjusted according to the phase difference, so that the complexity of duty cycle adjustment and hardware implementation can be effectively reduced, phase errors and the ripple waves of control voltage can be reduced, and adjustment accuracy is improved.

Owner:XIDIAN UNIV

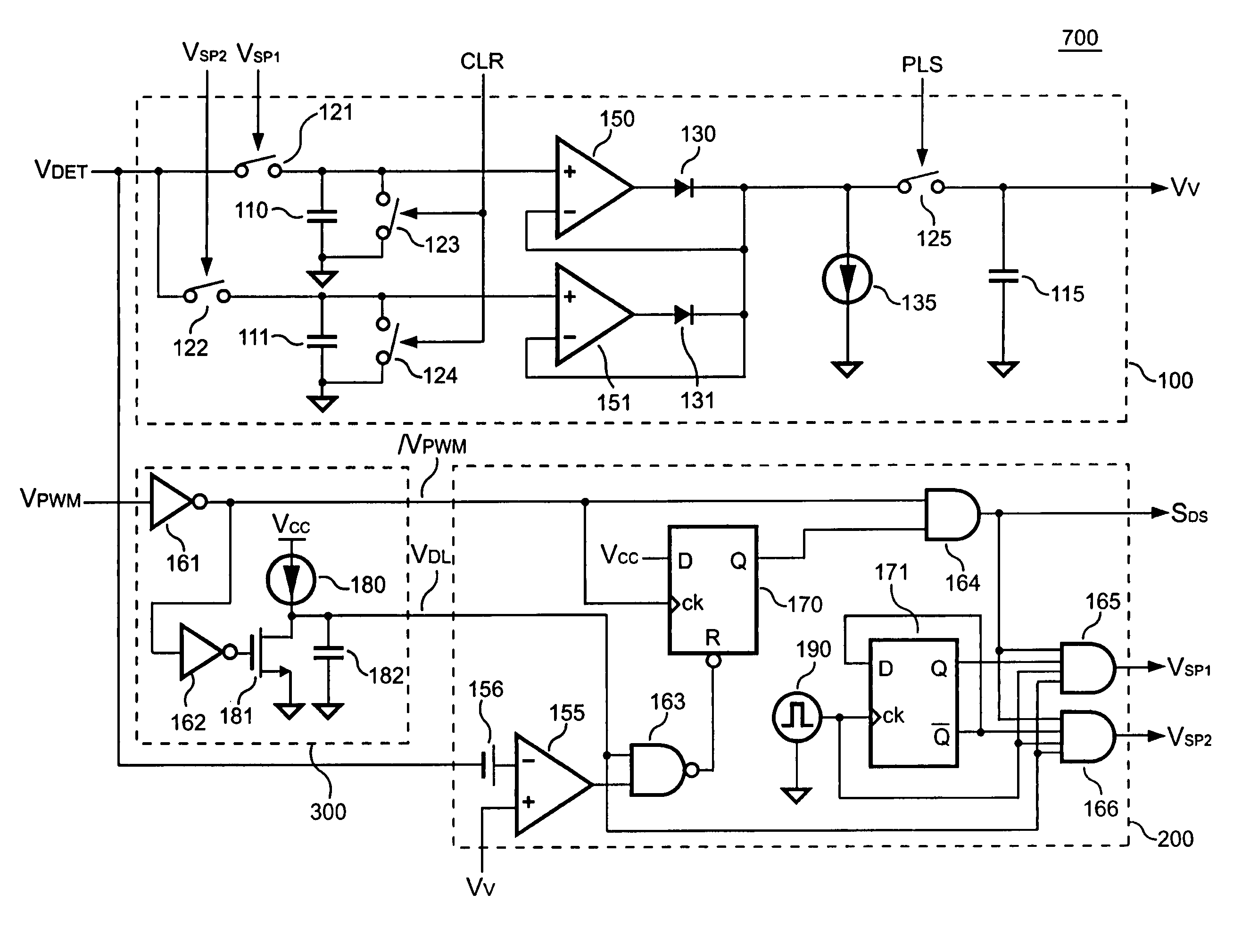

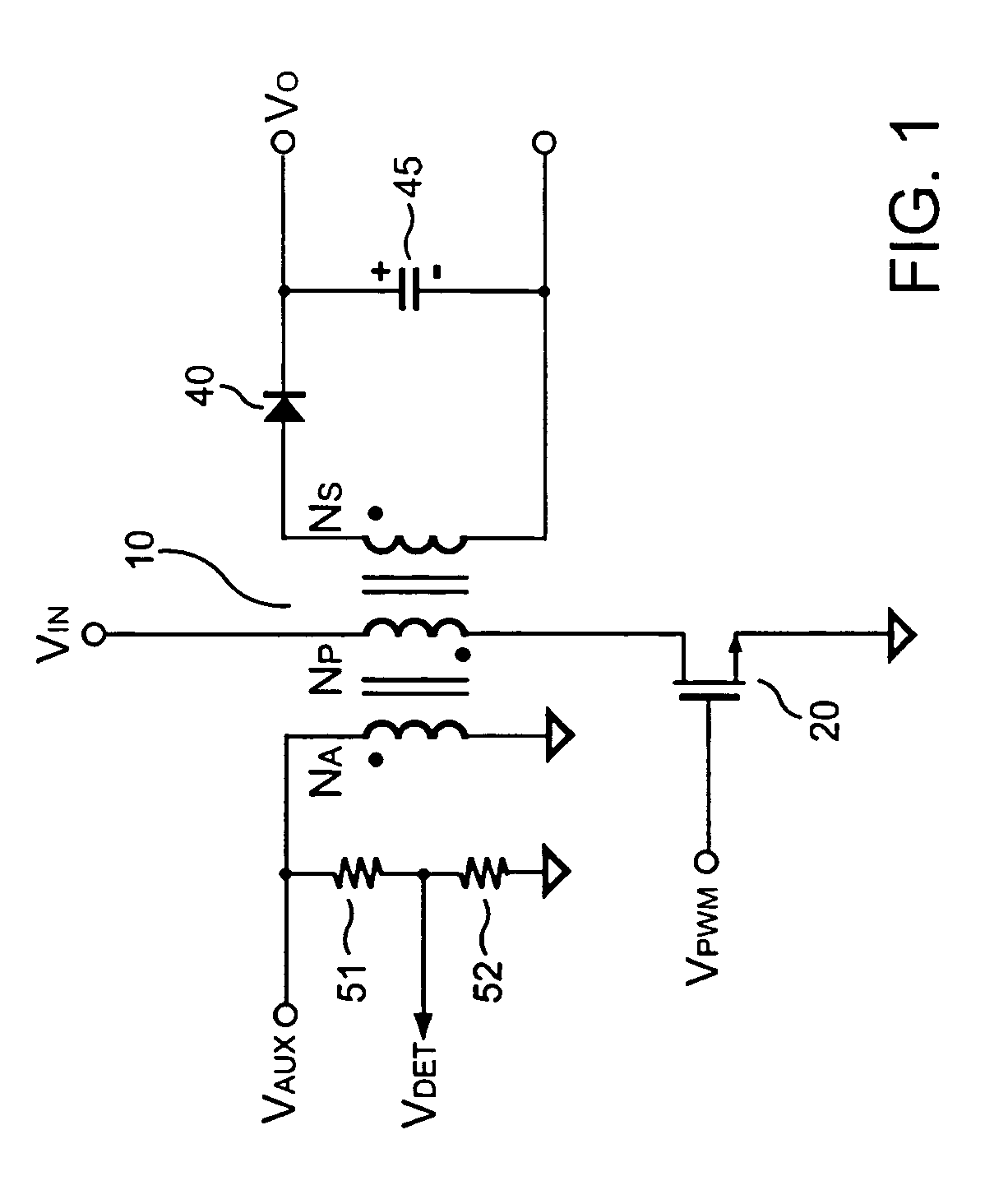

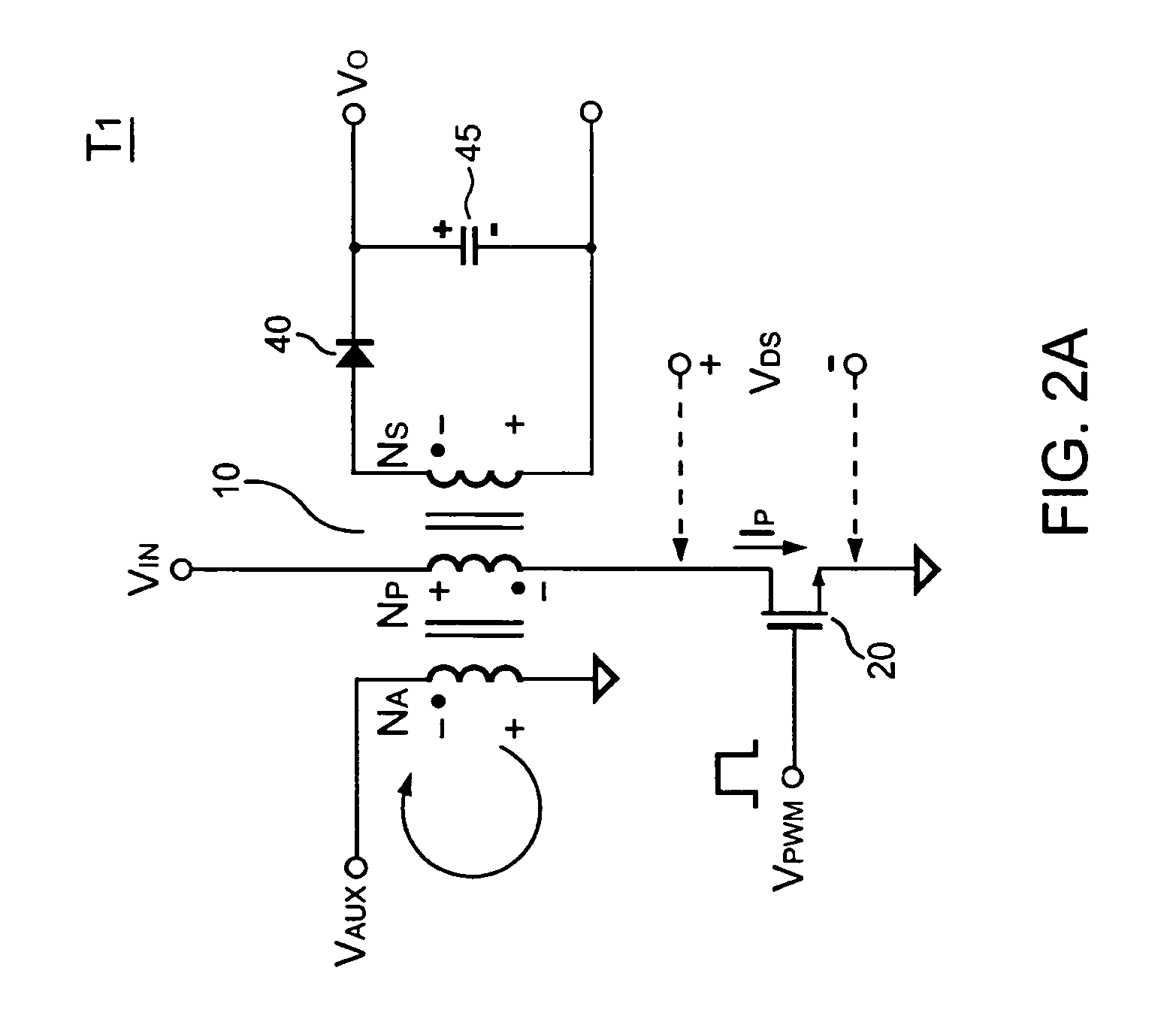

Multiple-sampling circuit for measuring reflected voltage and discharge time of a transformer

ActiveUS7151681B2Soft switchingDc-dc conversionElectric variable regulationTransformerSwitching signal

A multiple-sampling circuit is proposed for measuring a voltage signal and a discharge time of a transformer. Sampling signals are used for generating hold voltages by alternately sampling the reflected voltage from the transformer. A buffer amplifier generates a buffer voltage from the higher voltage of hold voltages. A sampling switch periodically conducts the buffer voltage to produce a voltage-feedback signal. The voltage-feedback signal is proportional to an output voltage of the switching circuit. A threshold signal added to the reflected voltage signal produces a level-shift reflected signal. A discharge-time signal is generated as the switching signal is disabled. The discharge-time signal is disabled once the level-shift signal is lower than the voltage-feedback signal. The pulse width of the discharge-time signal is therefore correlated to the discharge time of the transformer. The sampling signals are enabled to generate hold voltages only when the discharge-time signal is enabled.

Owner:FAIRCHILD SEMICON CORP

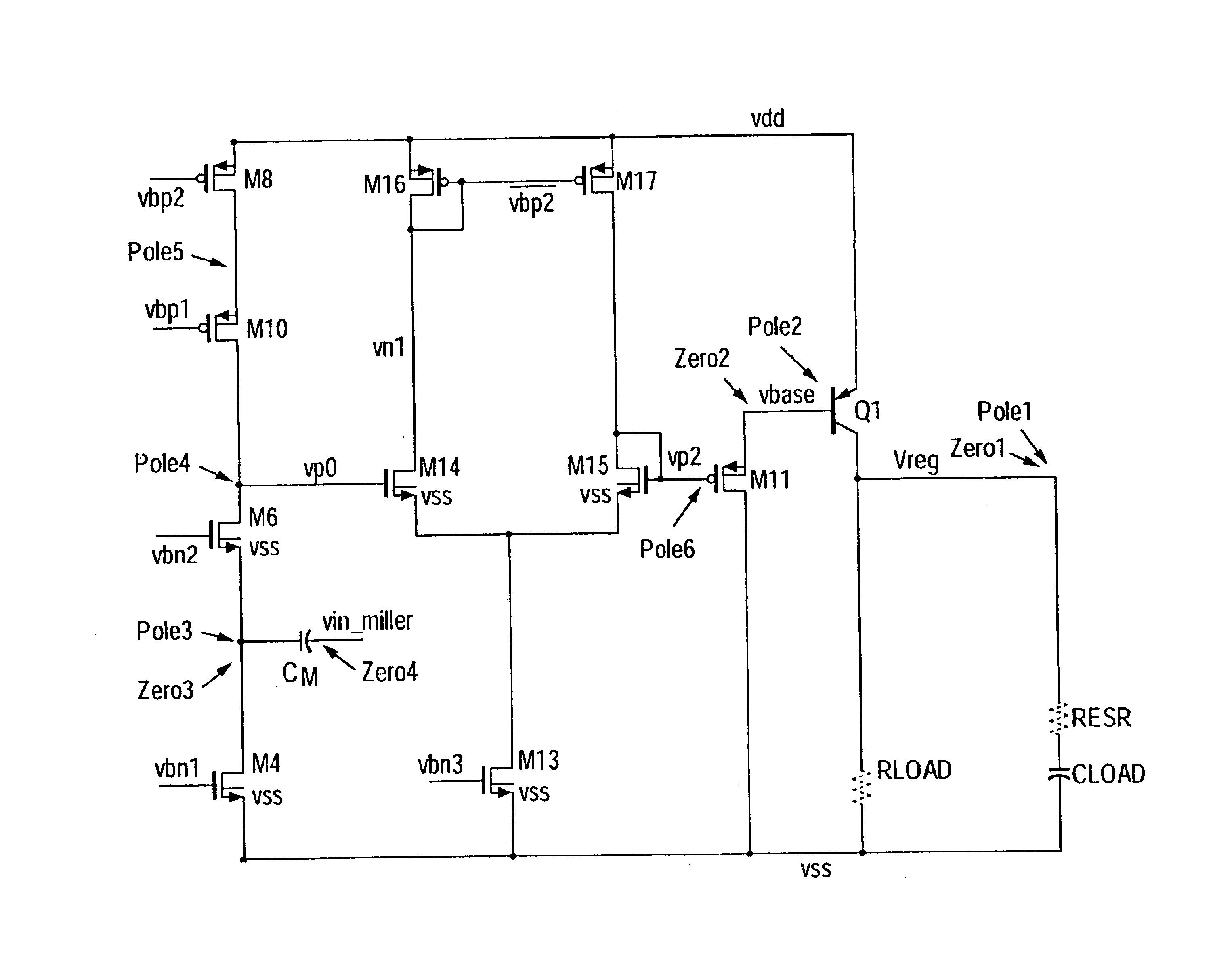

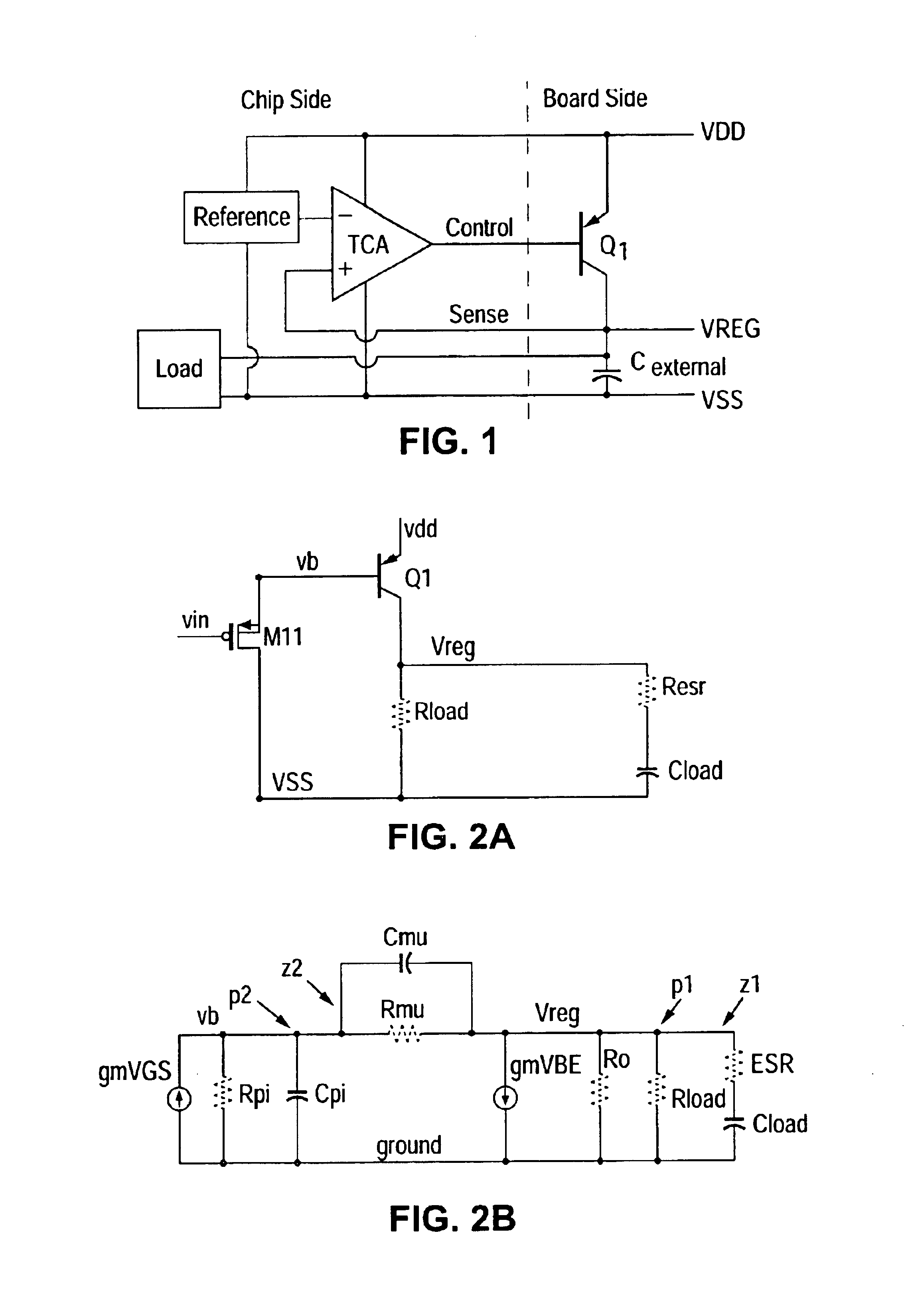

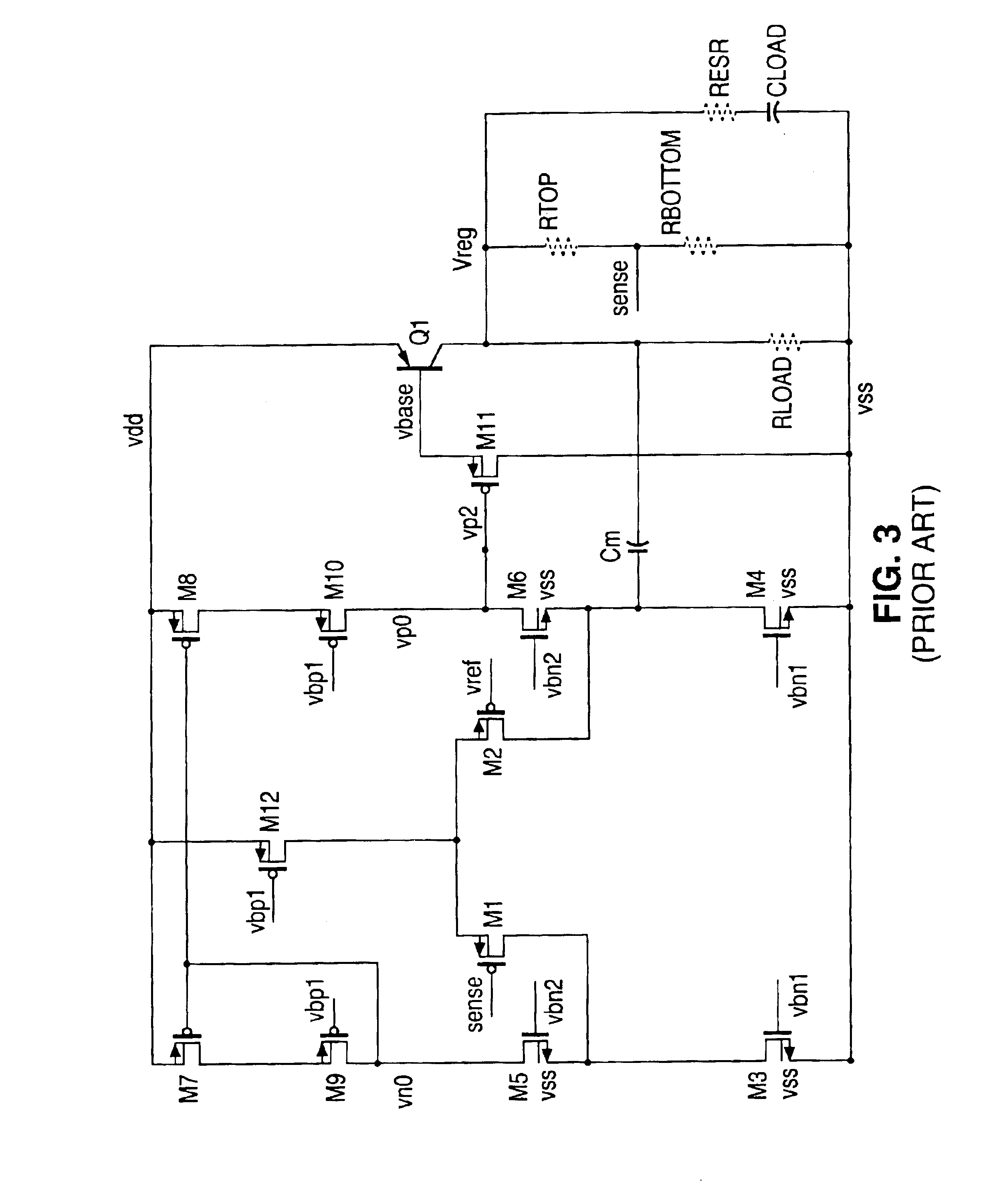

Amplifier with miller-effect compensation for use in closed loop system such as low dropout voltage regulator

InactiveUS6822514B1Amplifier modifications to reduce detrimental impedenceDifferential amplifiersLoad circuitAudio power amplifier

Circuitry including Miller-effect feedback for use as part of a closed loop system such as a low dropout voltage regulator that provides current to a load at a specified voltage close in value to the power supply voltage. Various aspects of the presently claimed invention include using, within the Miller-effect feedback loop: a buffer amplifier to reduce loading effects upon an internal high impedance circuit node, output compensation circuitry to introduce a transfer function pole for substantially canceling a transfer function zero associated with external load circuitry; and Miller-effect compensation circuitry to introduce a transfer function zero for substantially canceling a transfer function pole associated with the Miller-effect feedback.

Owner:NAT SEMICON CORP

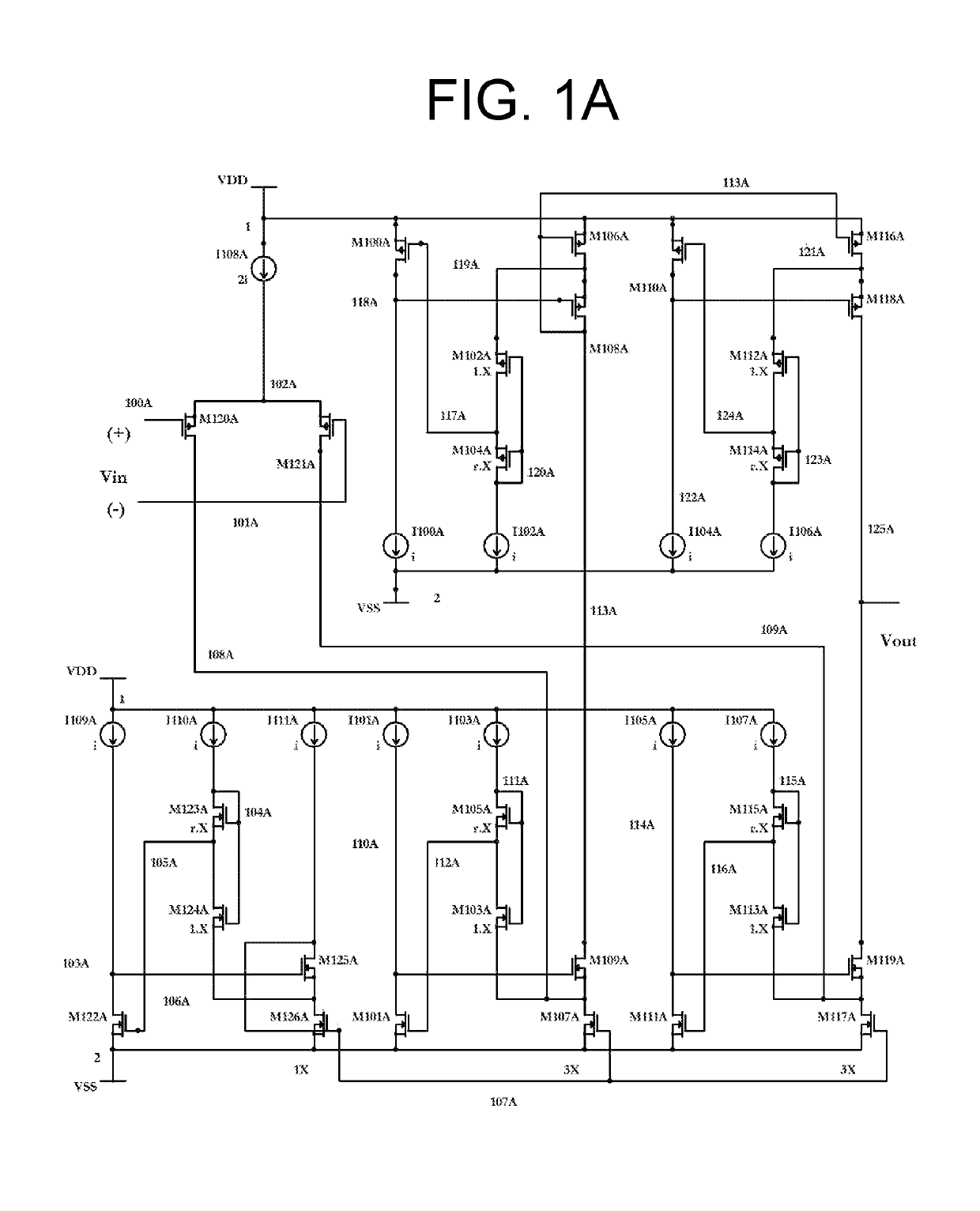

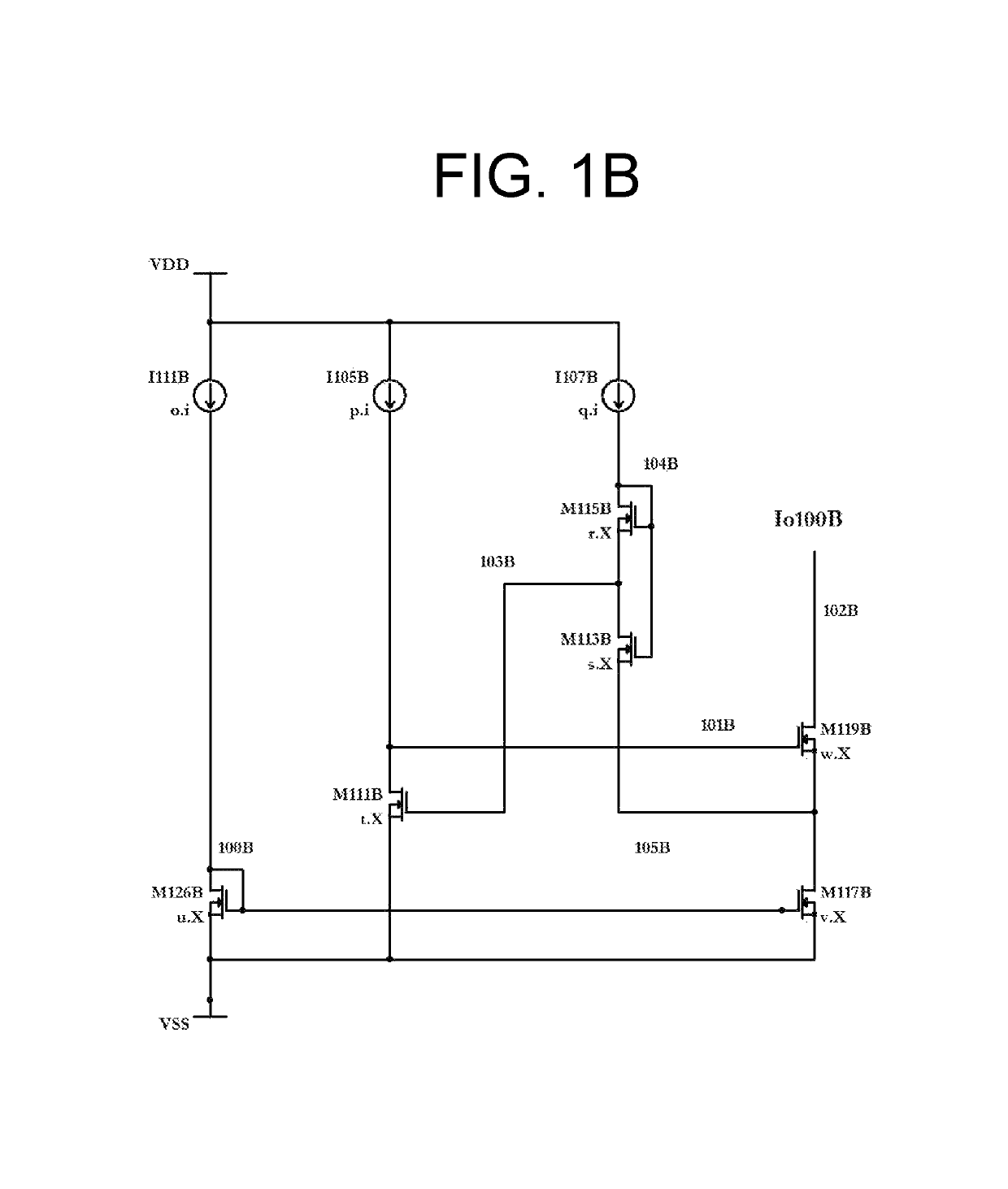

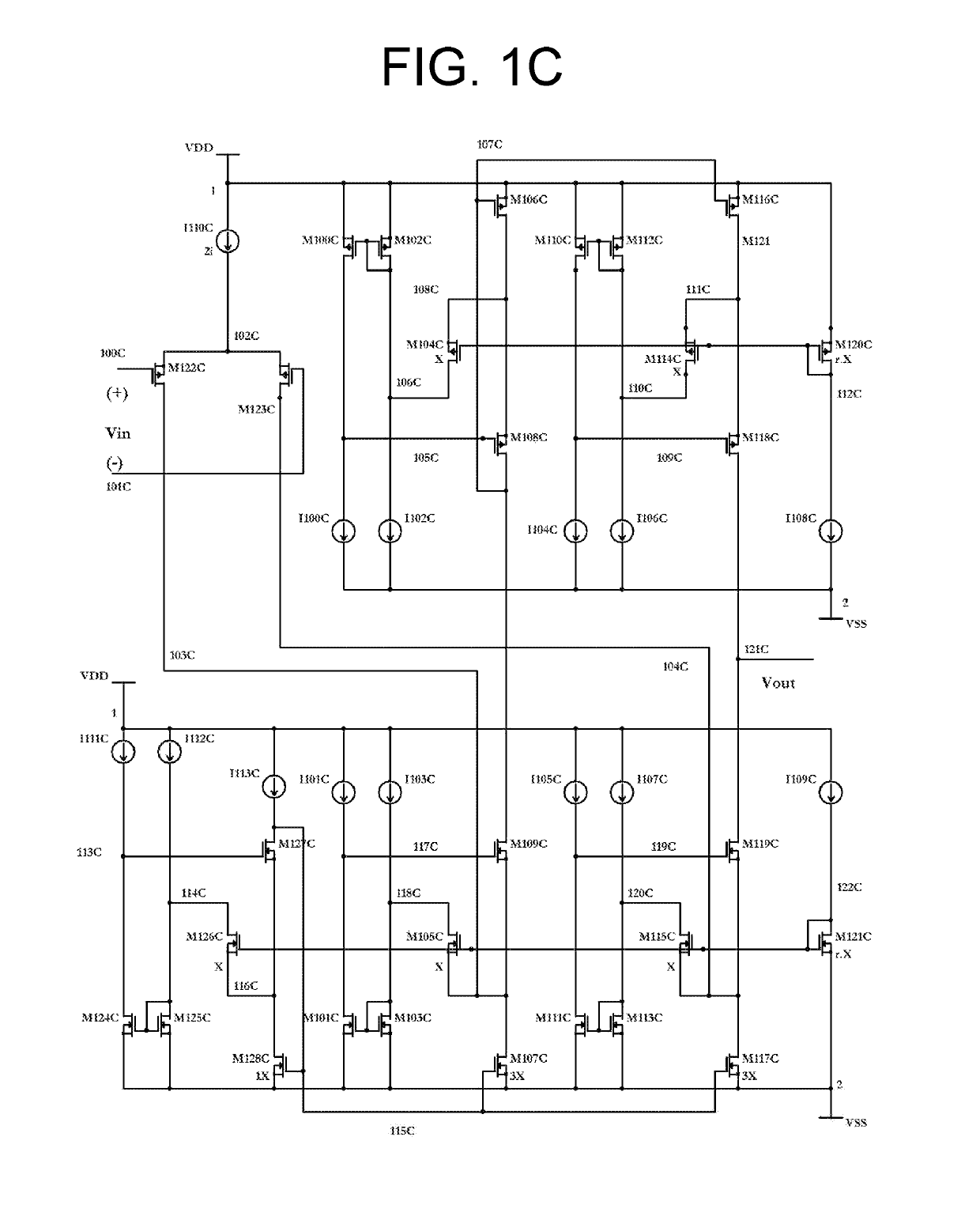

Low noise amplifier running fast at ultra low currents

ActiveUS10491167B1Lowering minimum operating power supplyReduce offsetAmplifier modifications to reduce noise influenceGain controlAudio power amplifierSlew rate

Methods, circuits, and apparatuses are disclosed that provide a buffer amplifier with lower output noise by narrow banding the amplifier. To reinvigorate the speed of the narrow-banded amplifier, a boost-on signal is initiated. The boost-on signal dynamically and rapidly injects a substantial current into the amplifier's bias current network to speed up its slew rate, when the amplifier's inputs get unbalanced when being subjected to a large transient differential input signal. Subsequently, after the amplifier regulate itself and as the amplifier's inputs approach substantial balance, a boost-off signal dynamically injects a slow and decaying current (that converges to the level of static steady-state bias current) into amplifier's bias circuitry, instead of turning off the boost current rapidly, which improves the amplifier's settling time.

Owner:FAR ALI TASDIGHI

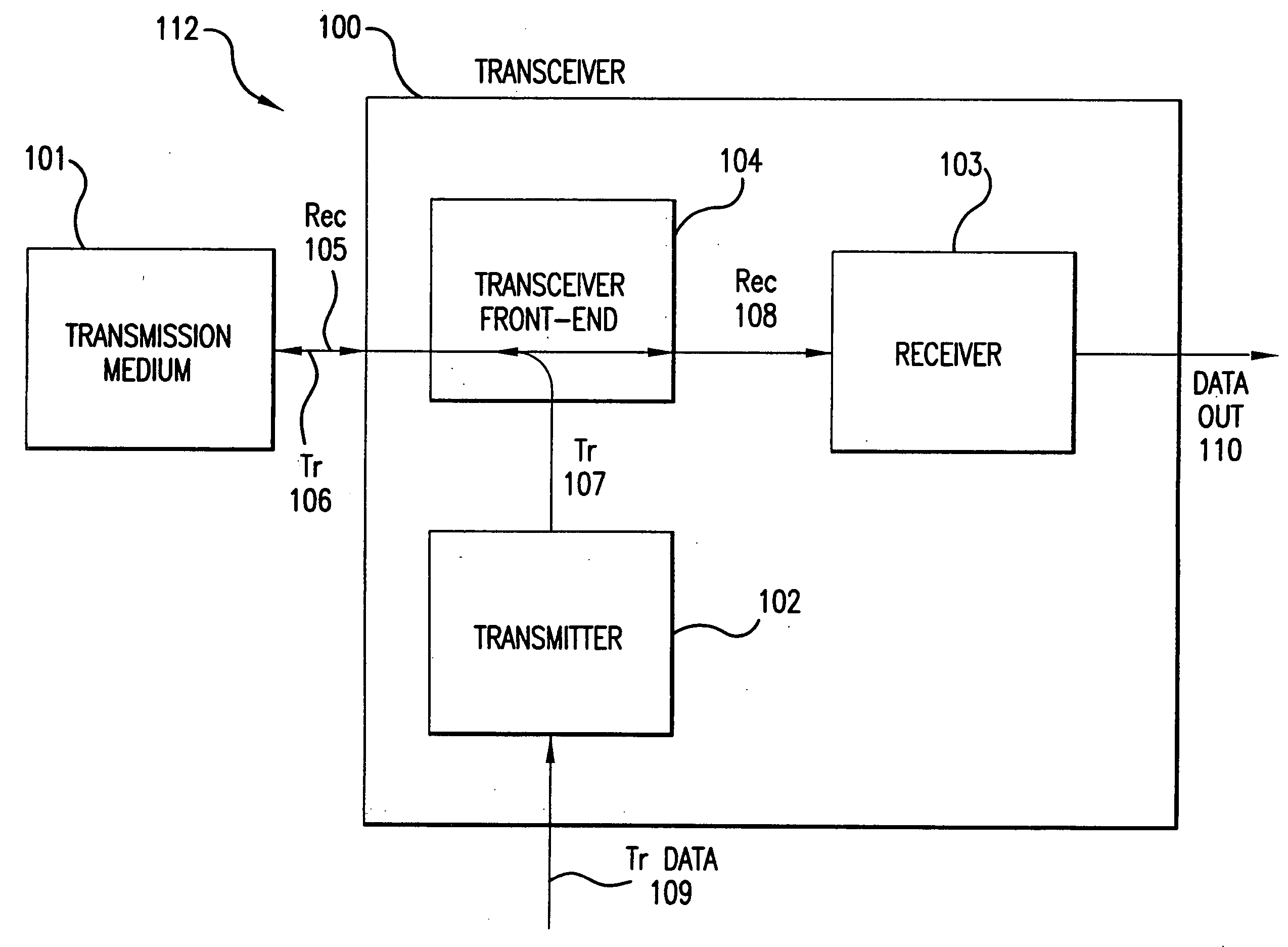

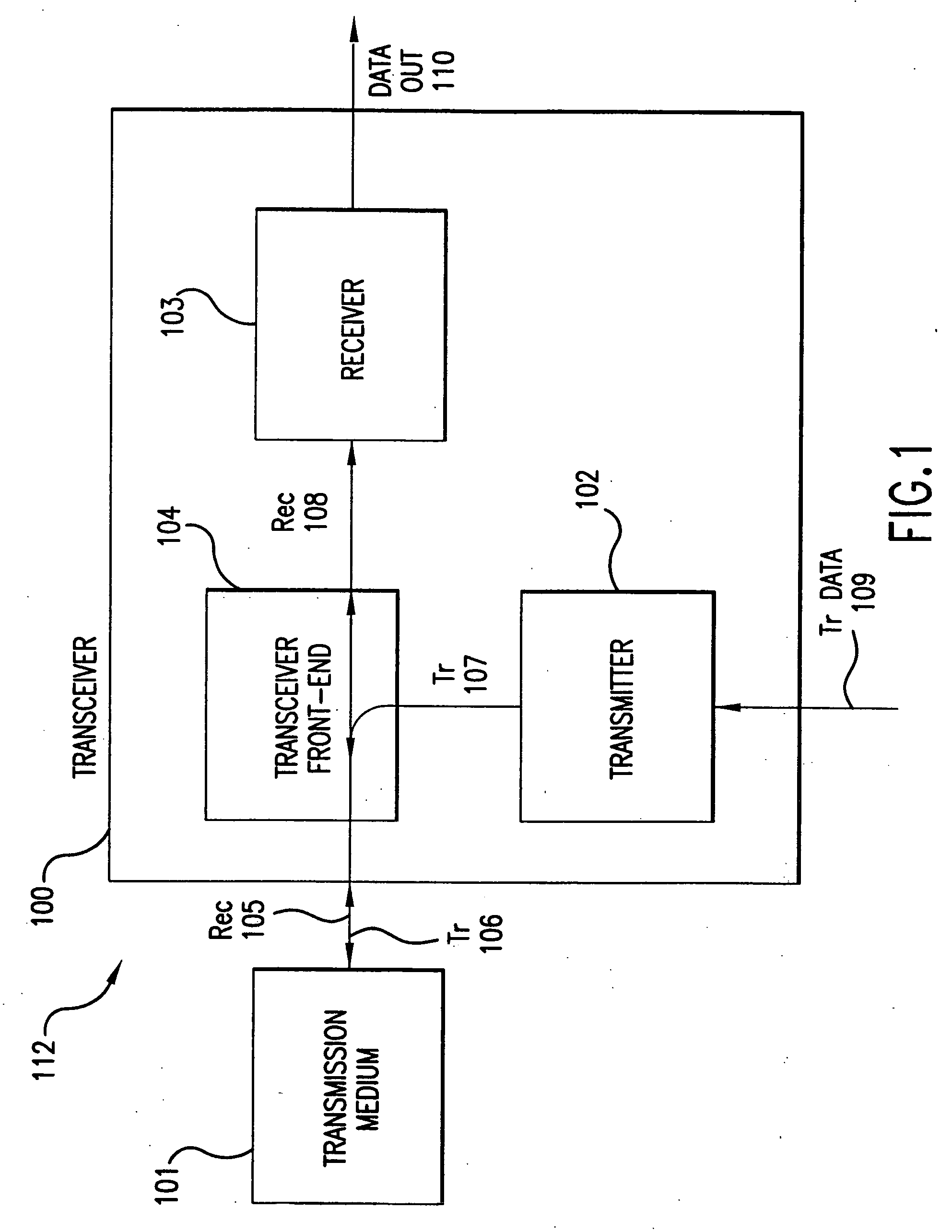

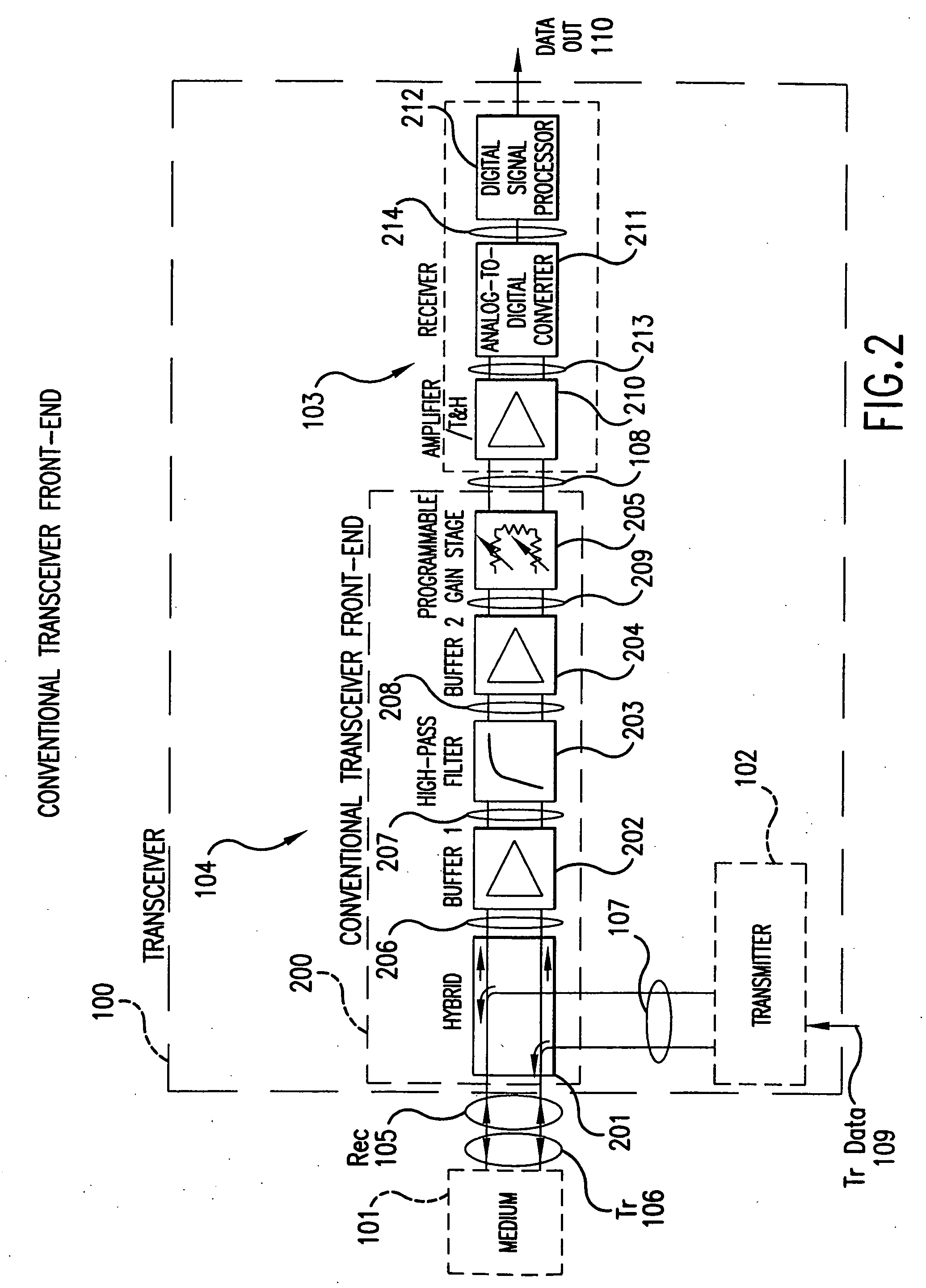

Transceiver front-end

A transceiver front-end provides an interface between a transmission medium and transmitter, and between a transmission medium and receiver. The transceiver front-end includes a hybrid circuit, a high-pass filter, and a gain stage, that permits the reduction or the complete elimination of buffer amplifiers. Buffer amplifiers can be eliminated because the hybrid circuit and / or the high-pass filter are adapted so that they can be directly connected to each other, without a loss in circuit performance. Furthermore, the high-pass filter and / or the gain stage are also adapted so they can be directly connected. As such, the transceiver front-end can be constructed using all passive components, reducing or eliminating excess heat generation.

Owner:AVAGO TECH INT SALES PTE LTD

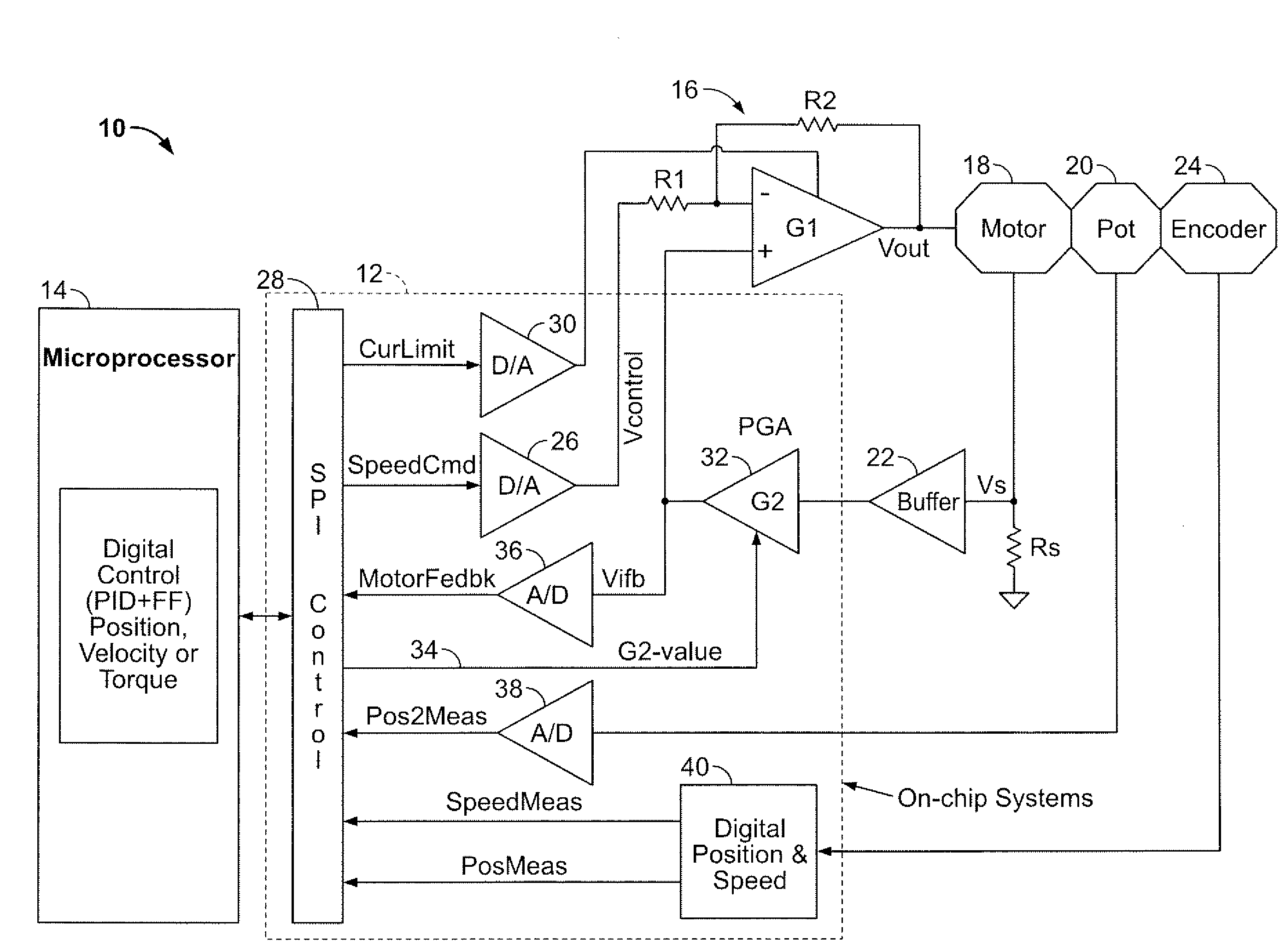

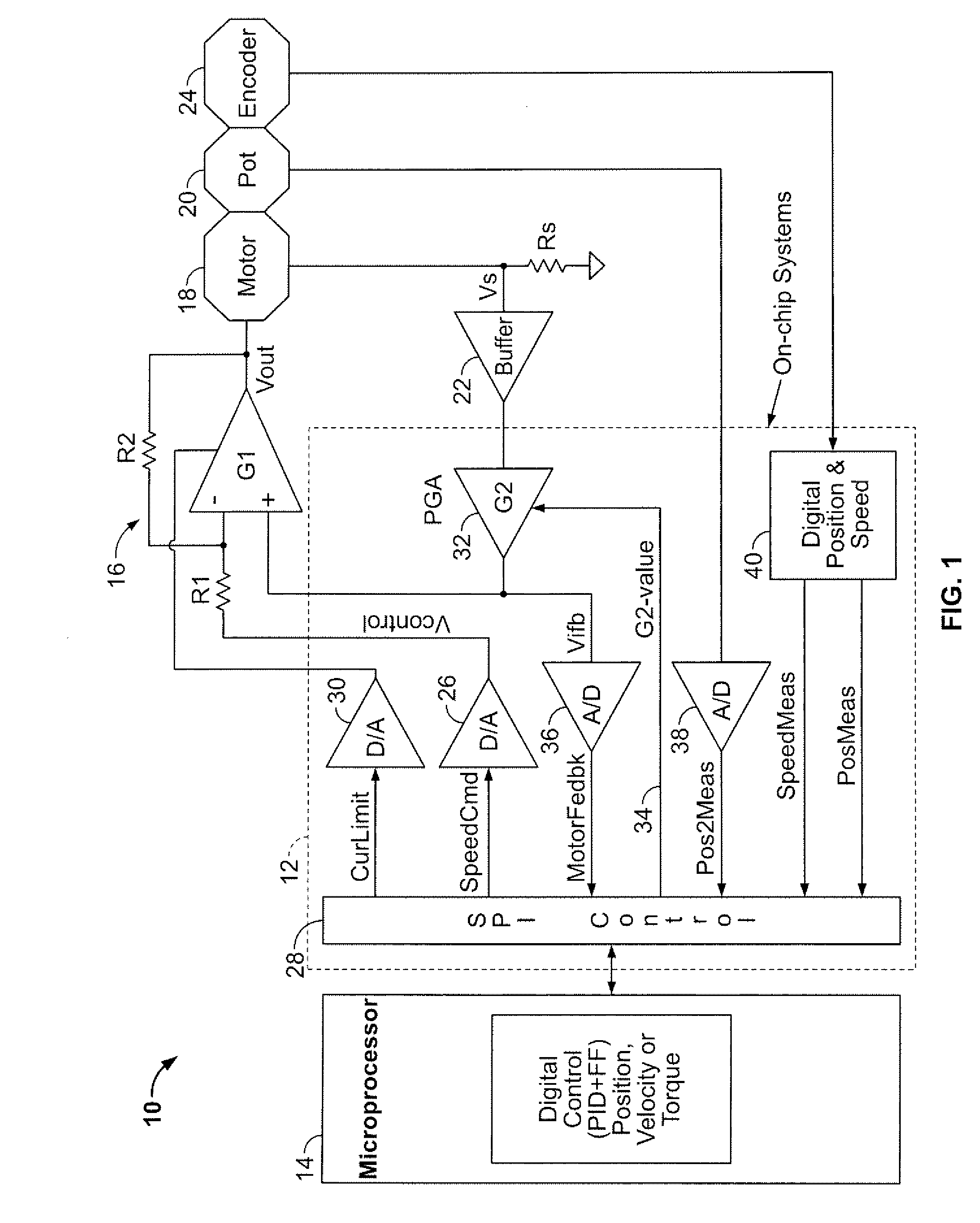

Adaptive and reconfigurable system for DC motor control

ActiveUS20080247735A1Digital variable displayAcceleration measurement using interia forcesDigital analog converterControl signal

An integrated circuit for controlling a DC motor is disclosed. The integrated circuit includes at least one digital position and speed circuit (DPS) for providing measurements of speed, position, and direction of the motor, the DPS being in signal communication with the motor for receiving a pair of signals having a quadrature relationship; and at least one programmable gain amplifier (PGA) electrically coupled to the motor, the PGA being configured to receive a feedback signal indicative of current flowing through the motor and to apply a second signal to the motor for adjusting the speed of the motor; and at least two analog-to-digital converters (A / D), one A / D being used to quantize the output of the PGA for an off-chip processor; and another A / D to provide motor reference position from an analog sensor, such as a potentiometer; and at least two digital-to-analog converters (D / A), one D / A used to set the motor voltage; and another D / A used to set the motor current limit. The integrated circuit can be incorporated into a larger motor control loop which further includes a summing amplifier for providing the feedback signal to the motor that is indicative of current flowing through the motor; a buffer amplifier electrically for sensing the output current of the motor, and a processor for providing control signals to the system monolithic module and for receiving the measurements of speed, position, and direction of the motor.

Owner:THE JOHN HOPKINS UNIV SCHOOL OF MEDICINE

Active balun circuit for single-ended to differential RF signal conversion with enhanced common-mode rejection

InactiveUS6922108B2Increased rejectBalance-unbalance networksDifferential amplifiersBalanced mixerDBc

An active balun circuit is provided for single-ended to differential RF signal conversion with enhanced common-mode rejection which suppresses common mode signal and which achieves phase and amplitude balance without sophisticated tuning or compensation methods. The circuit has a single-ended input and balanced output with phase and amplitude balance error less than 2° and 1.2 dB, respectively, measured from 1.5 GHz to 1.8 GHz at 5V supply. When supply voltage drops down to 1.5V, its phase and amplitude balance error remains within 5° and 2 dB, respectively. The circuit achieves a balanced output via an output network which behaves as an impedance matching network for differential mode signal and is grounded for common mode signal. As a result, common mode signal is suppressed and 180-degree phase balance at output is achieved. The circuit has high-linearity (P1 dBin=5 dBm, IIP3=16.6 dBm) and low residual phase noise (<−155 dBc / Hz at 100 kHz and above) which make it suitable as an active balun / buffer amplifier between LO and balanced mixer for base station receiver applications.

Owner:WSOU INVESTMENTS LLC +1

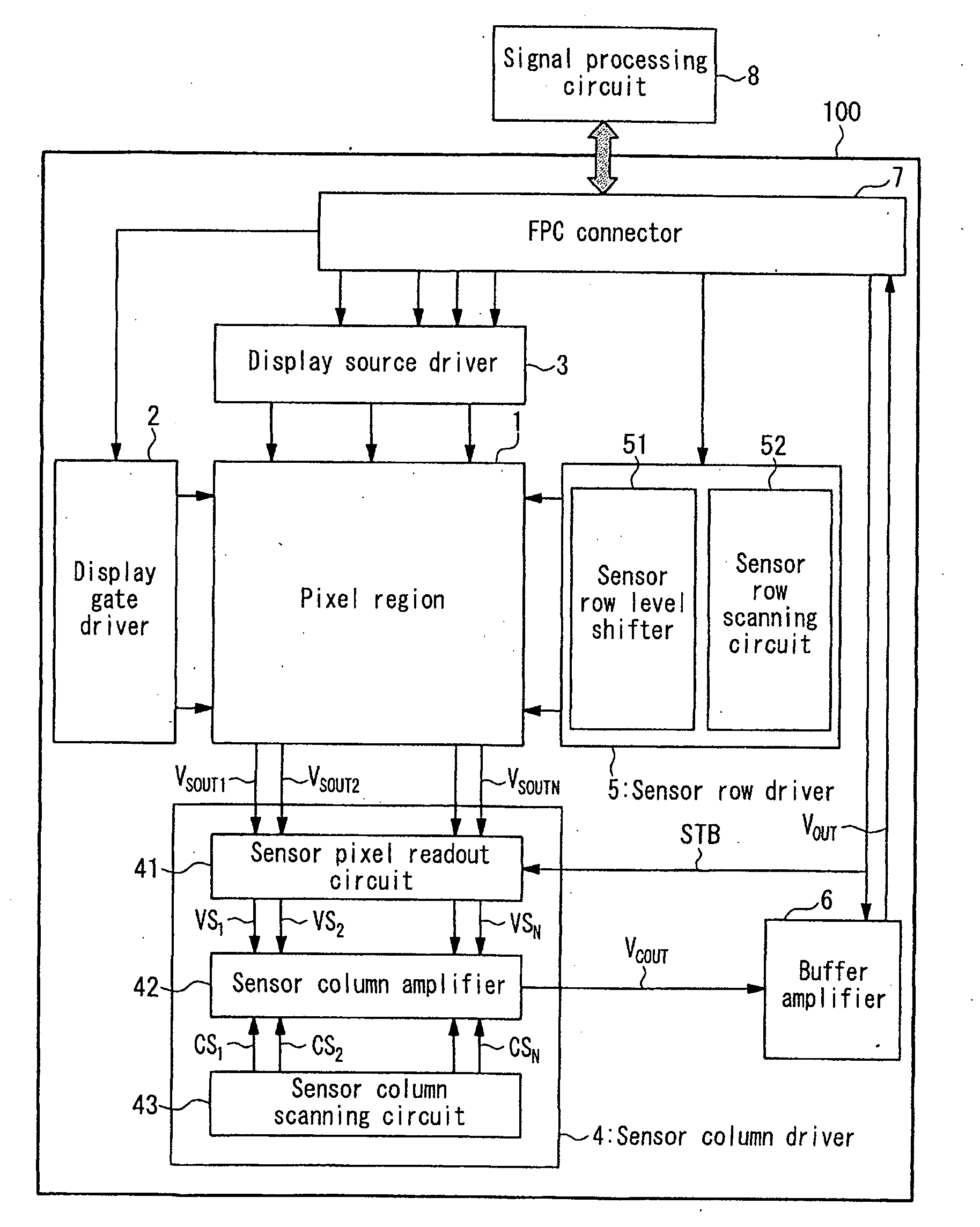

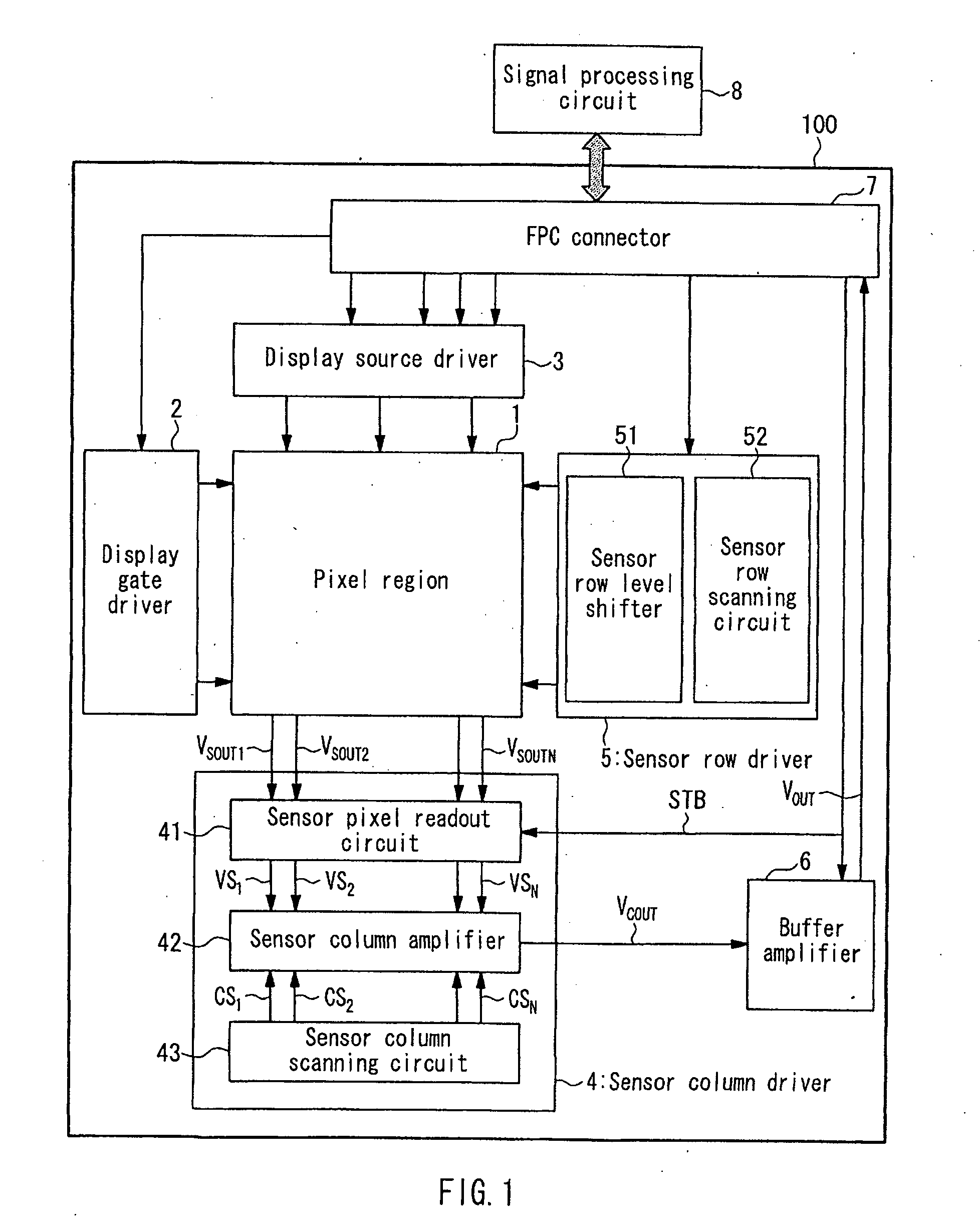

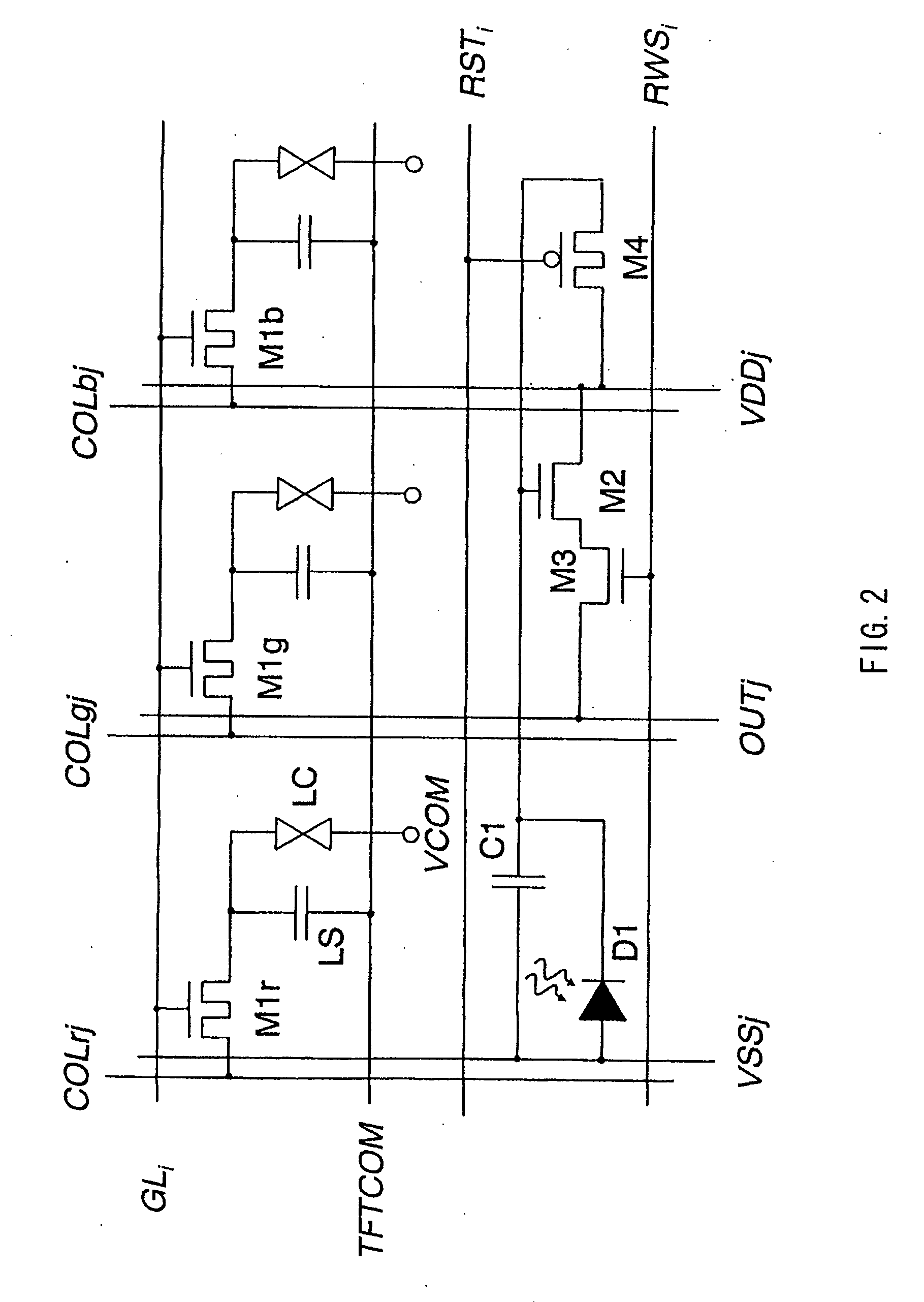

Display apparatus

InactiveUS20100315394A1Suppress power consumptionTelevision system detailsCathode-ray tube indicatorsAudio power amplifierActive matrix

The present invention provides a display apparatus with image capturing function including optical sensors in its pixels, particularly a display apparatus capable of capturing an image while suppressing the power consumption. The display apparatus includes: optical sensors and sensor wirings provided in a pixel region of an active matrix substrate; a sensor row driver for selecting the optical sensors row by row; a sensor pixel readout circuit for reading out signal charges from the optical sensors in the selected row; a sensor column amplifier including the number of amplifiers corresponding to the rows of the optical sensors for generating a sensor output voltage; a sensor column scanning circuit for selecting the signal charges readout by the sensor pixel readout circuit column by column so that the selected signal charges being outputted to the sensor column amplifier; and a buffer amplifier (6) provided subsequent to the sensor column amplifier (24). The sensor column amplifier (42) or the buffer amplifier (6) is provided with a standby switching circuit for suppressing an output to a subsequent stage of either of the amplifiers in accordance with a standby signal.

Owner:SHARP KK

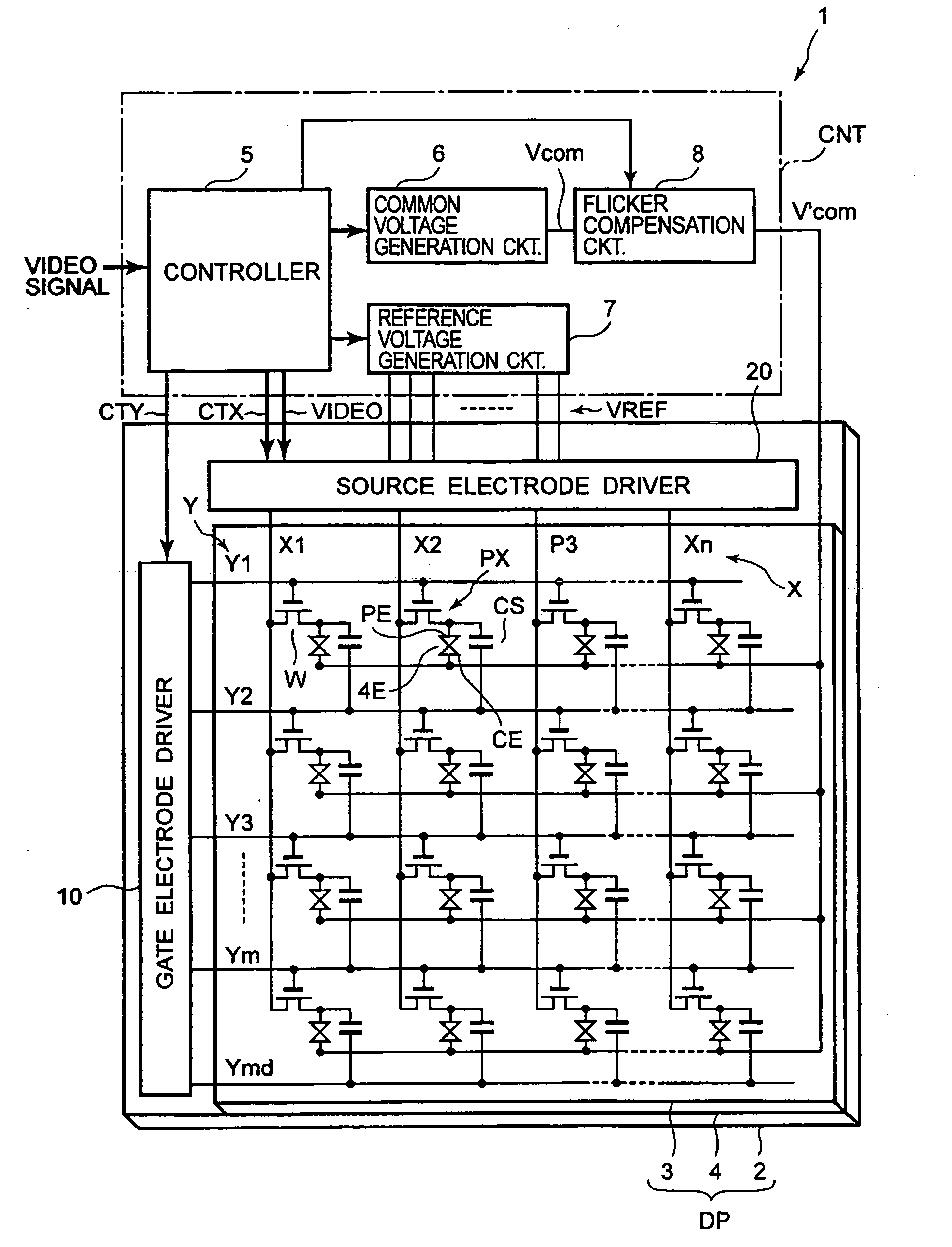

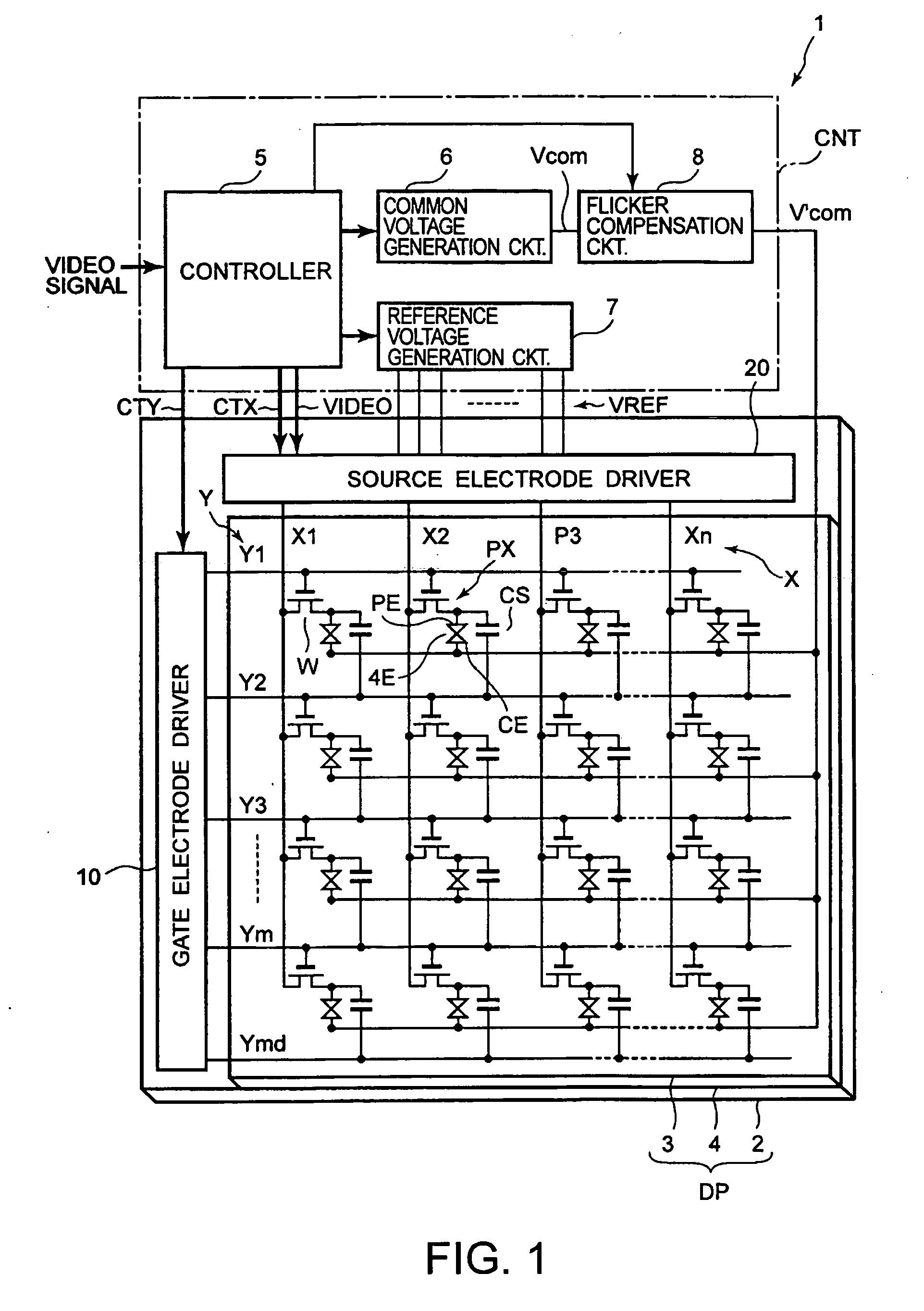

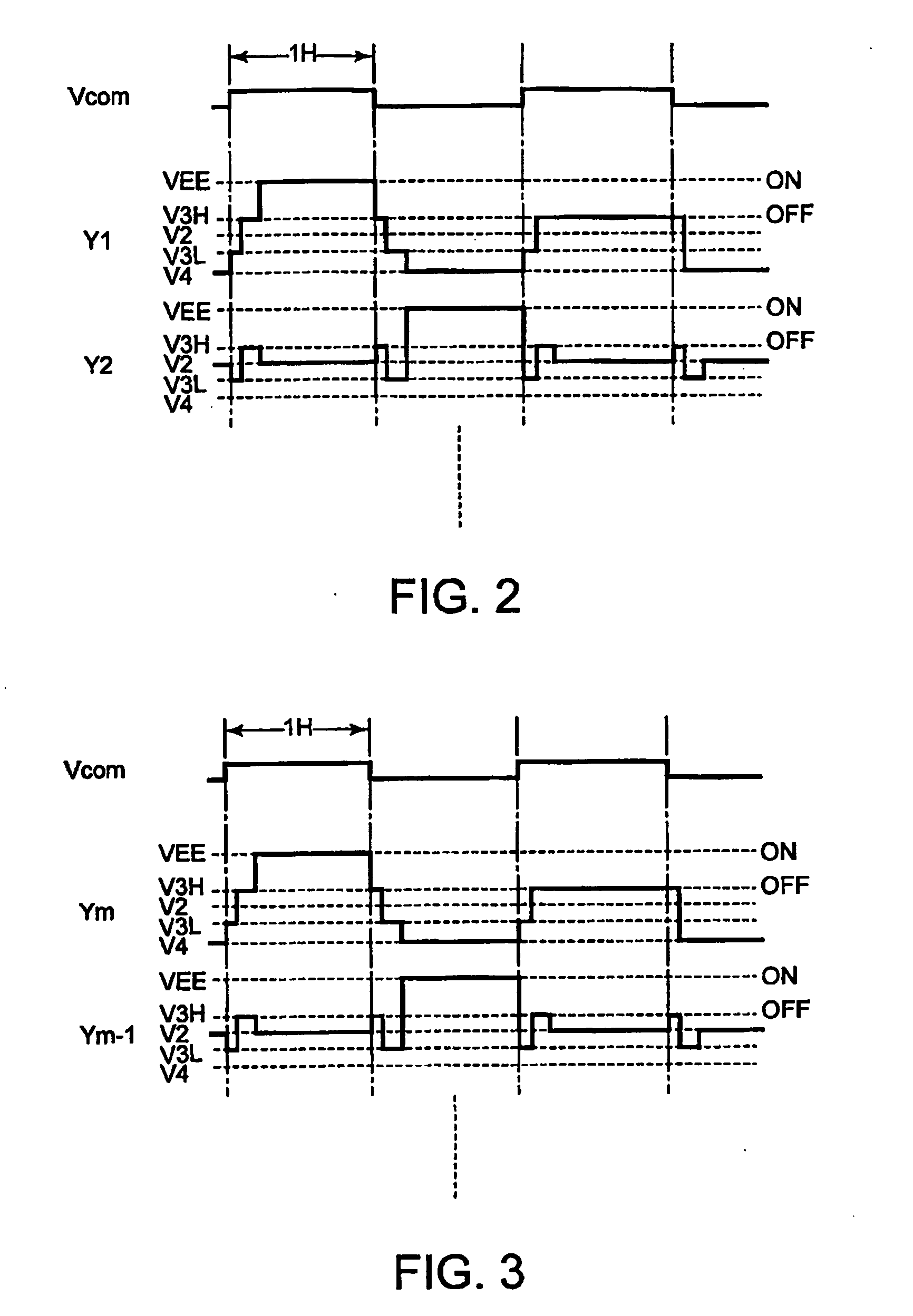

Liquid crystal display device

InactiveUS20050200588A1Short adjustment timeImprove productivityStatic indicating devicesLiquid-crystal displayCapacitor

Liquid crystal display device 1 includes pixels PX, individual and common electrodes PE and CE provided for pixels PX and flicker compensation circuit 8. Flicker compensation circuit 8 changes a central level of common voltage Vcom for common electrode CE. Flicker compensation circuit 8 is provided with capacitor 31, variable resistor 32, switch 34, arithmetic operation circuit 33 and buffer amplifier 35. Capacitor 31 supplies common voltages Vcom from common voltage generation circuit 6. Variable resistor 32 changes common voltages Vcom while switch 34 selects one of two different voltages VCC1 and VCC2. Arithmetic operation circuit 33 combines an output of variable resistor 32 with that of switch 34 and buffer amplifier 35 supplies thus combined outputs V'com to common electrode CE as compensated common voltages.

Owner:TOSHIBA MATSUSHITA DISPLAY TECH

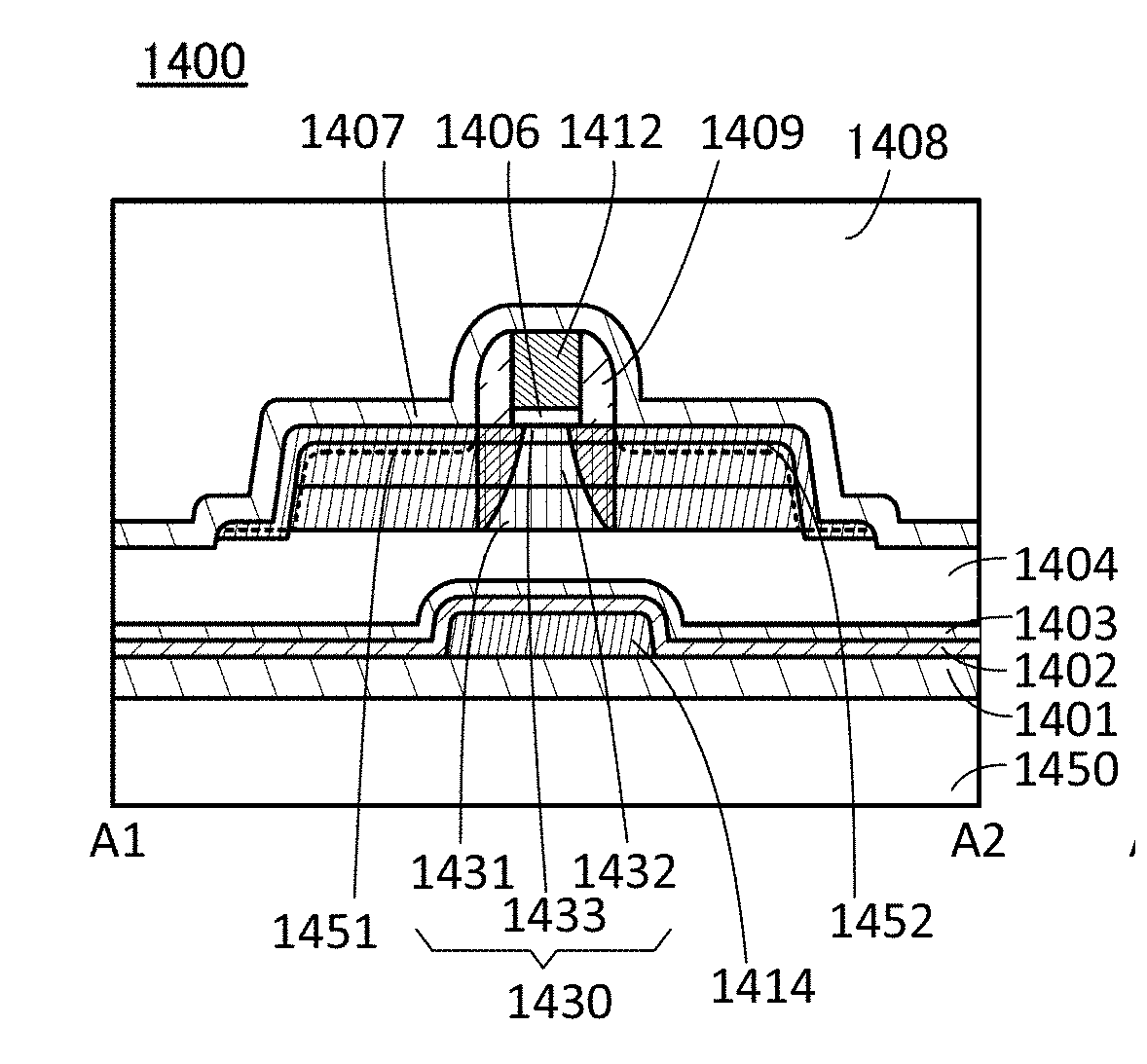

Semiconductor device and display device including the same

InactiveUS20170179160A1Reduce power consumptionImprove visibilityStatic indicating devicesSolid-state devicesAudio power amplifierDevice material

A semiconductor device with reduced power consumption and a display device including the semiconductor are provided. The semiconductor device generates a bias voltage that is to be supplied to a buffer amplifier. When the display device displays a still image, a data signal for updating the image need not be supplied from the buffer amplifier to a pixel array in the next frame; therefore, the circuit is configured so that the buffer amplifier is brought into a standby state (temporarily stopped). Specifically, input of a reference current from a BGR circuit to the semiconductor is stopped and a bias voltage is applied from the semiconductor device to the buffer amplifier to temporarily stop the operation of the buffer amplifier.

Owner:SEMICON ENERGY LAB CO LTD

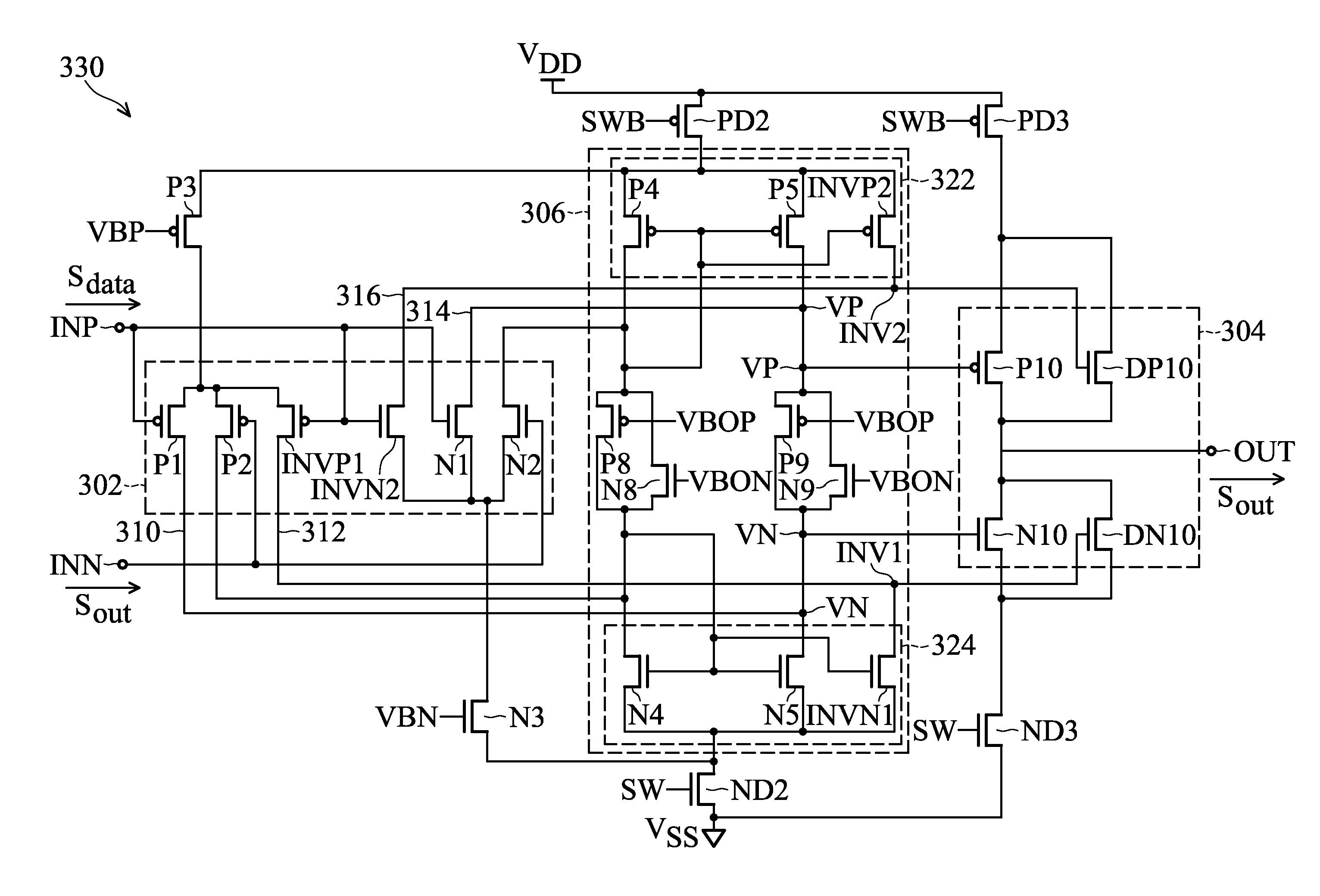

Buffer amplifier

A buffer amplifier includes an input stage circuit, an output stage circuit and a bias circuit, providing a buffered output signal at an output terminal according to an input signal applied to a first input terminal. The input stage circuit generates four control signals in response to the input signal when the logic level of the buffered output signal is opposite to that of the input signal. The output stage circuit includes four output transistors, wherein the first and second output transistor of a first type are provided for discharge in response to a first control signal and a second control signal, and the third and fourth output transistor of a second type are provided for charge in response to a third control signal and a fourth control signal. The bias circuit is used for determining the first, second, third and fourth control signal.

Owner:HIMAX TECH LTD

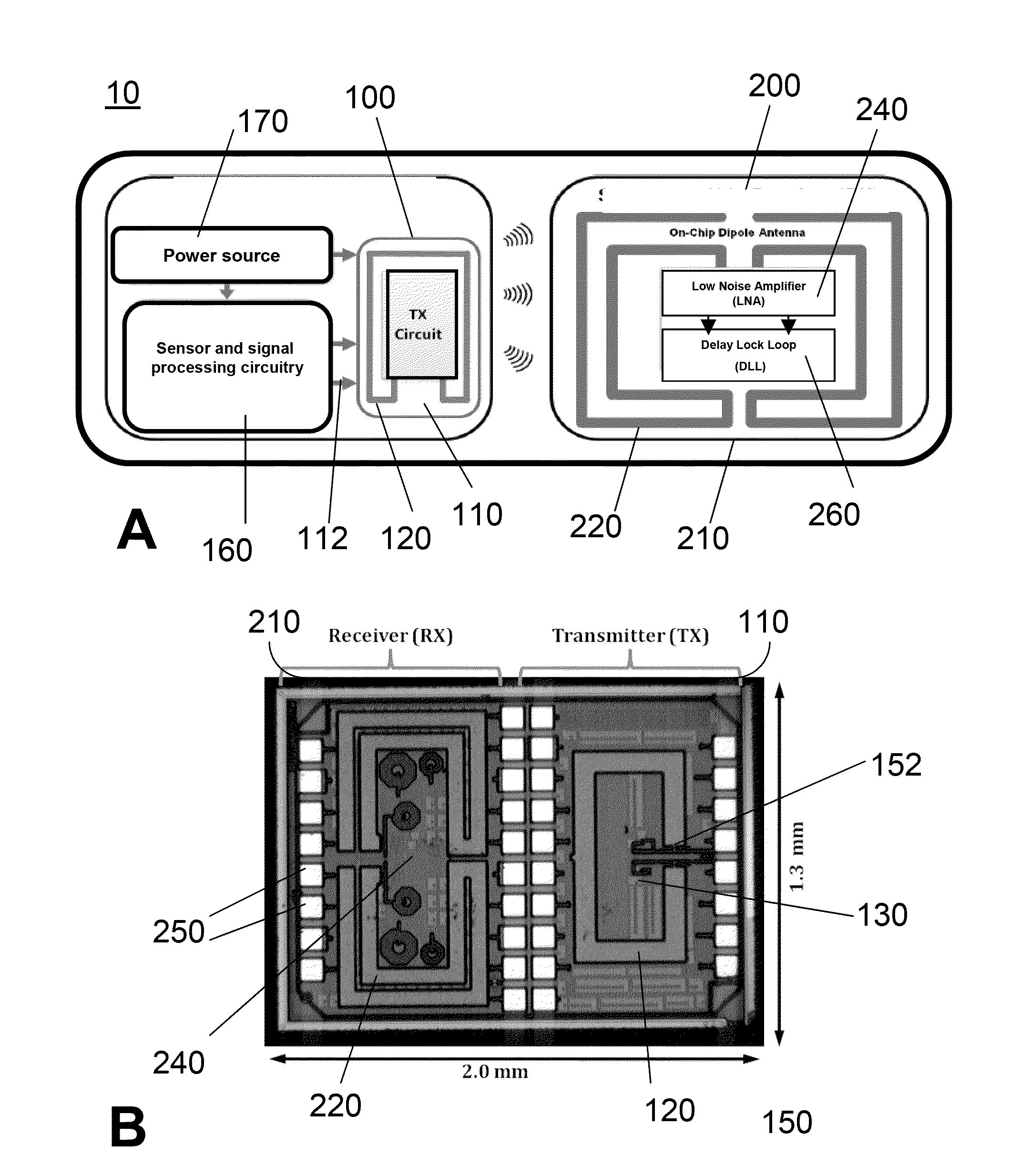

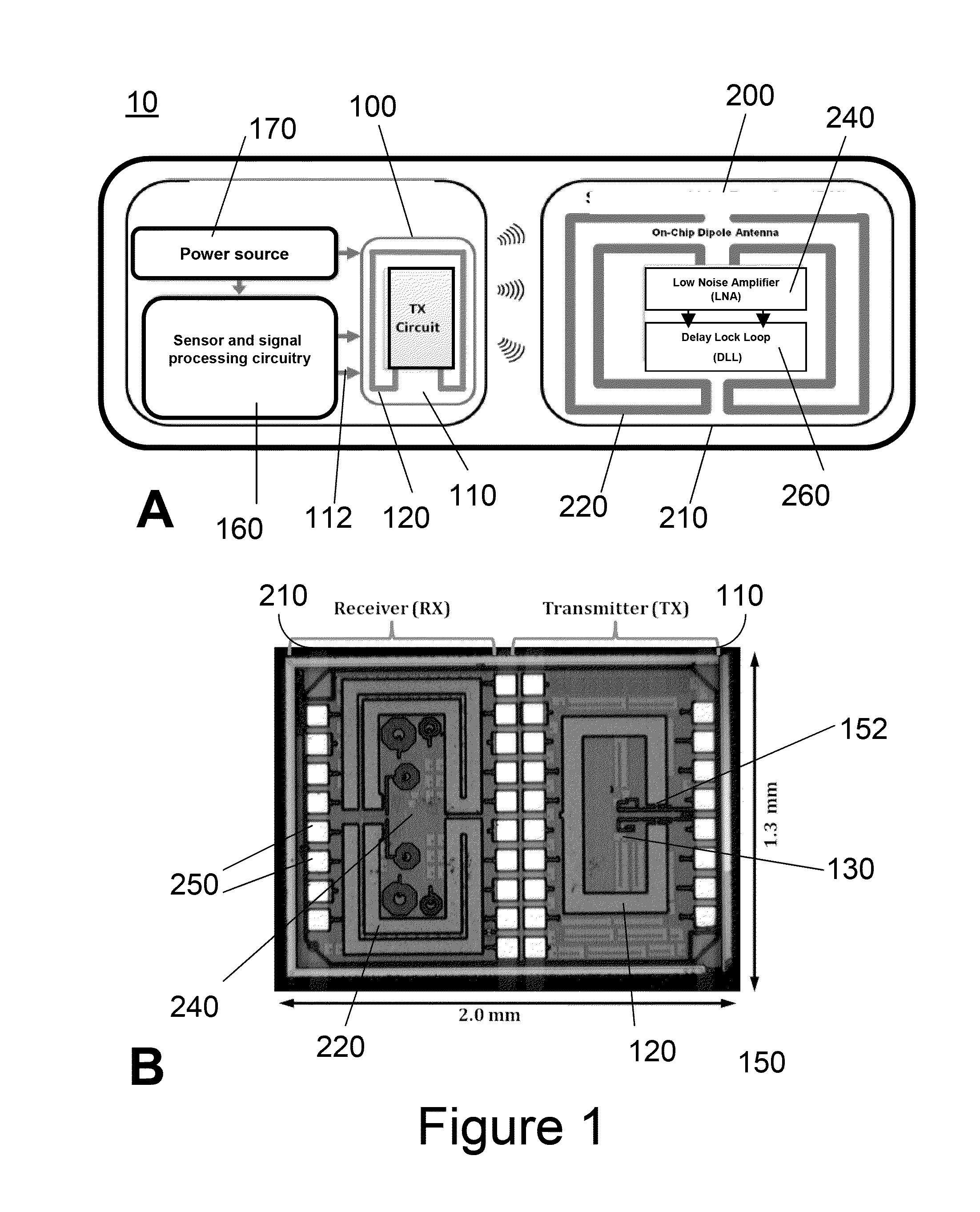

Miniaturized, low power, wireless transmitter and receiver with on-chip antenna, and wireless coupling of on-chip and off-chip antenna

ActiveUS20100099367A1High sensitivityLow resistivityAntenna arraysSolid-state devicesDual modeSoi cmos technology

A miniaturized, low power RF transmitter with a dual mode active on-chip antenna / inductor is disclosed in which antenna also serves as the oscillator inductor. Also disclosed is a miniaturized low power RF receiver with an on-chip antenna; and a RF transmitter system wherein an on-chip antenna is wirelessly coupled to an off chip patch antenna are disclosed. Advantageously, the TX chip is housed in a low loss, e.g. Low Temperature Co-fired Ceramic (LTCC) package with a patch antenna to provide a System-on-Package implementation comprising electromagnetic coupling between a RF TX chip comprising an integrated on-chip antenna and a package antenna. The on-chip antenna feeds the LTCC patch antenna through aperture coupling, thus negating the need for RF buffer amplifiers, matching elements, baluns, bond wires and package transmission lines, and significantly increases the gain and range of the module with respect to the on-chip antenna alone, without deterioration of the circuit performance and power consumption. Exemplary embodiments are disclosed which may be fabricated using standard CMOS technology, for operation in the 5 GHz U-NII band for applications such as miniaturized, low cost, low power wireless devices and sensor systems.

Owner:KING ABDULLAH UNIV OF SCI & TECH

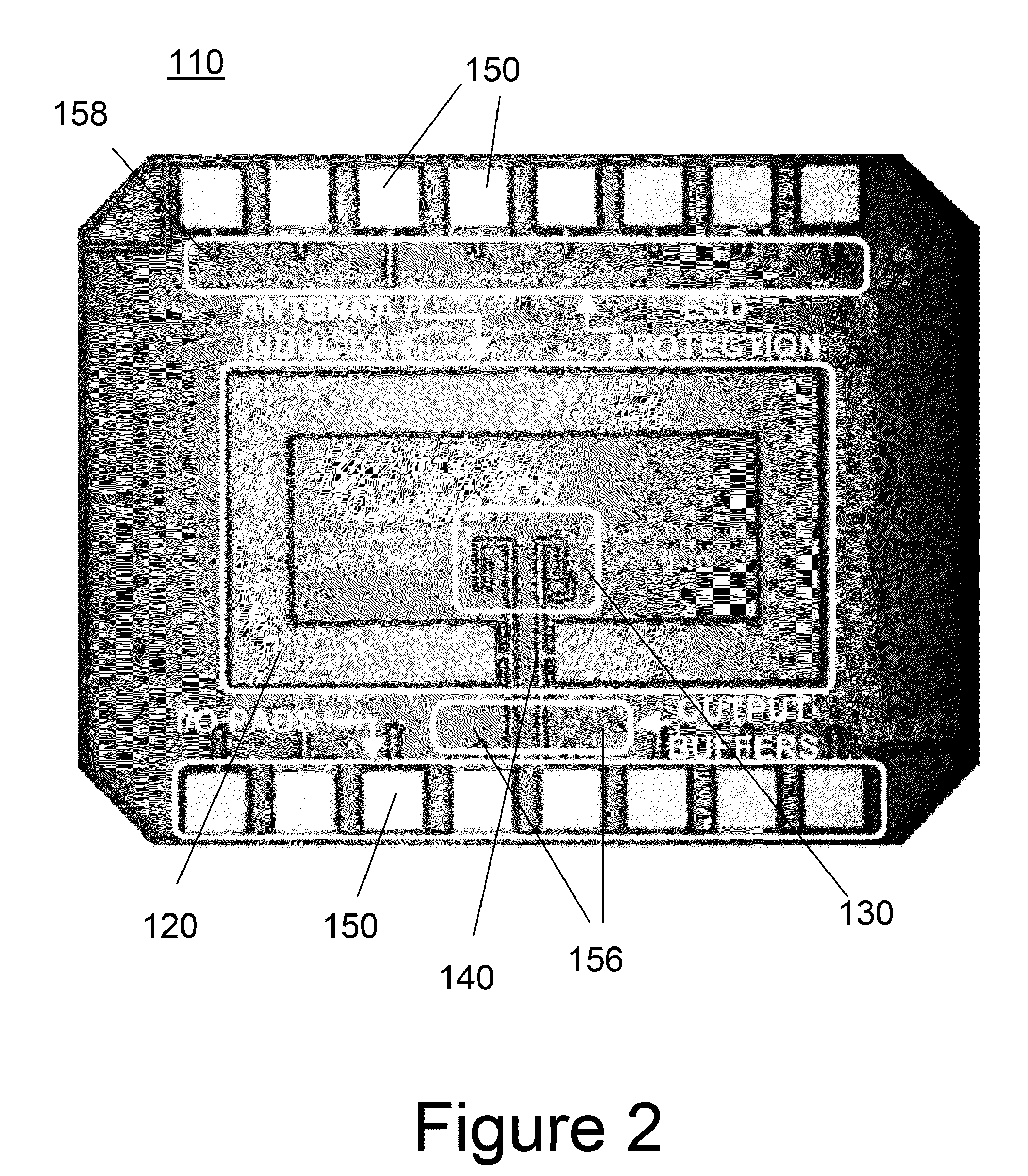

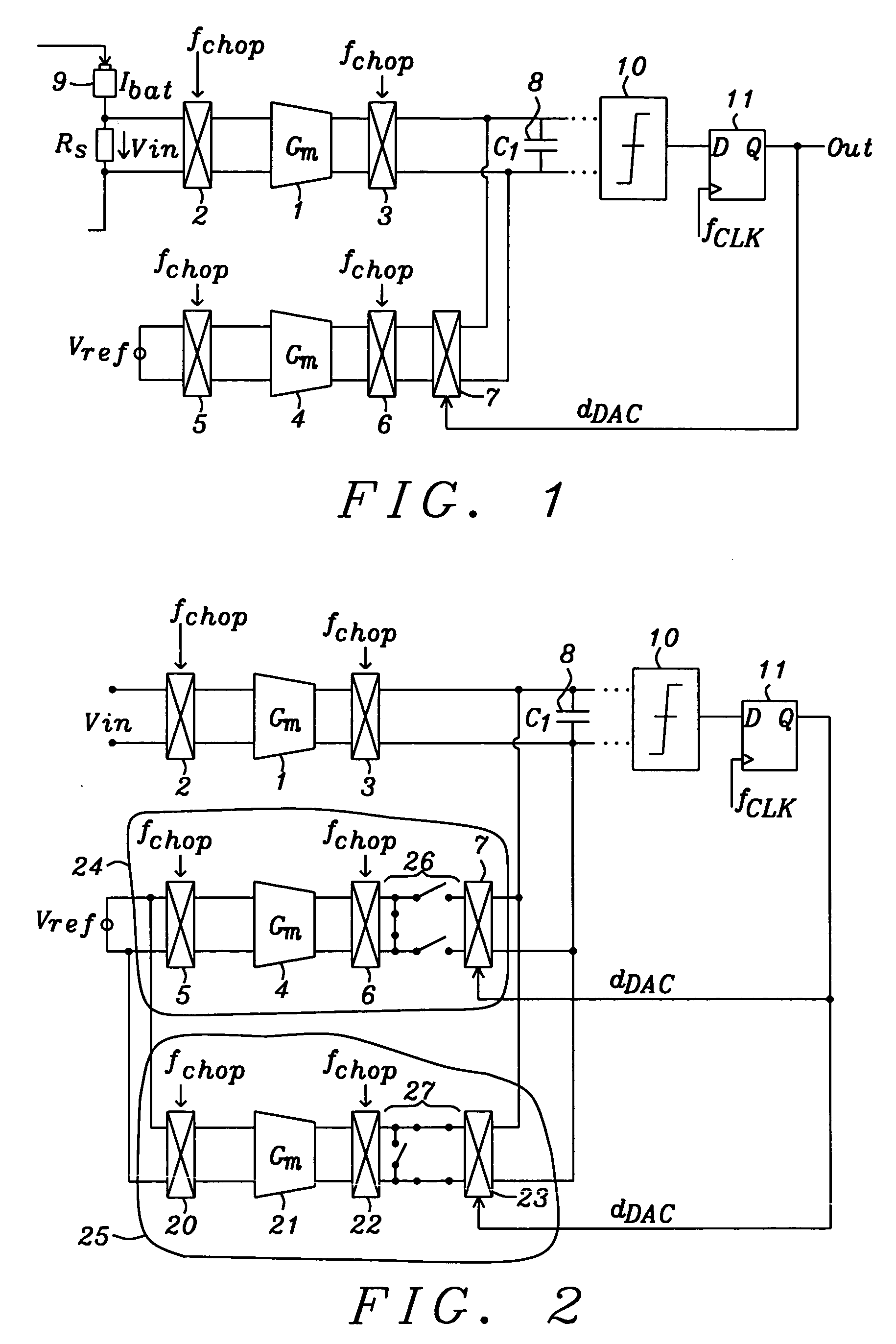

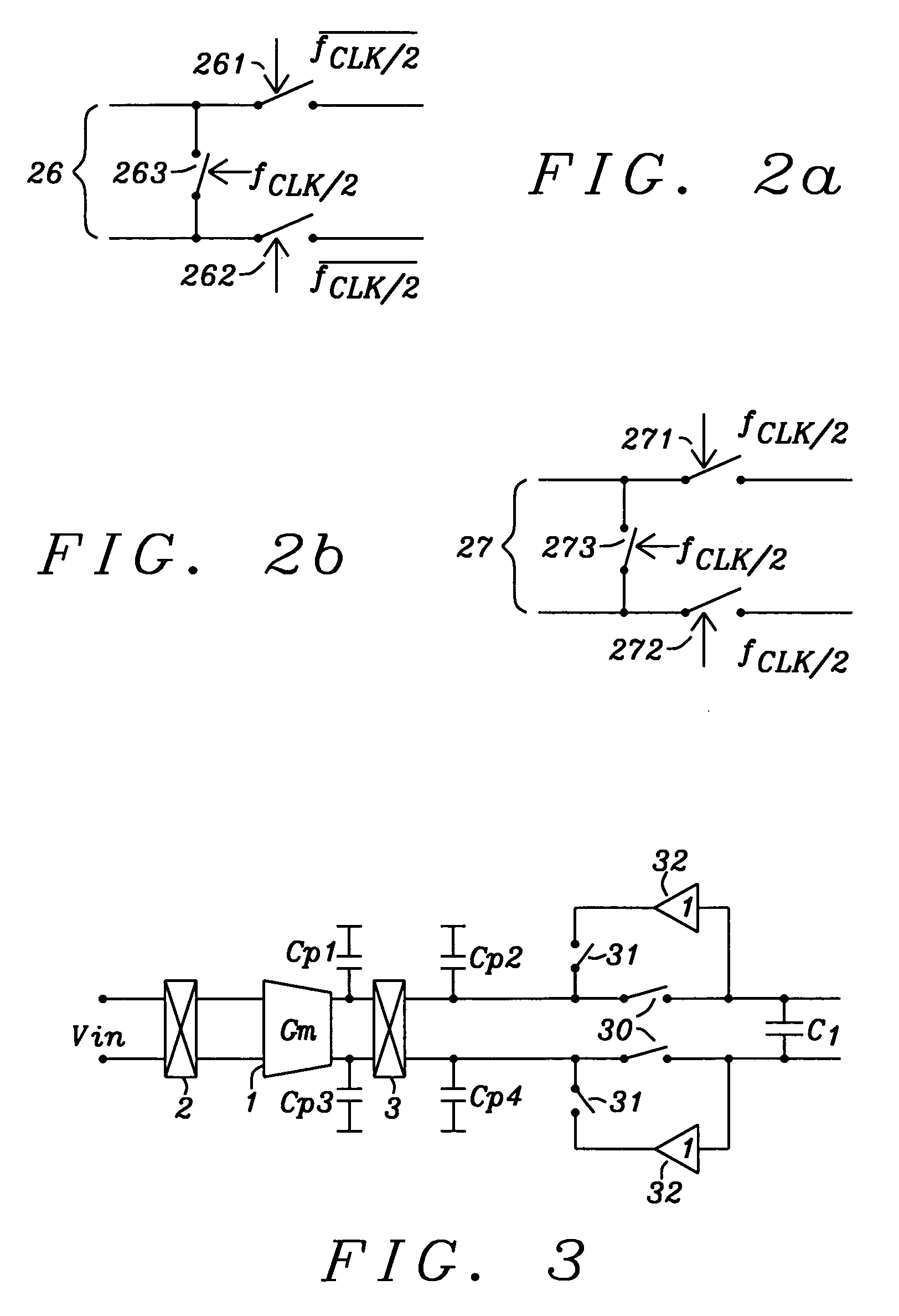

Sigma-delta modulator

ActiveUS7250886B1Reduce noiseReduce parasitic effectsElectric signal transmission systemsAnalogue conversionLow noiseIntegrator

Circuits and methods to achieve a low-noise and low offset continuous sigma-delta modulator used e.g. for battery management are disclosed. Continuous integration of input is enabled by special switching principle of three parallel integrators. Precharging of integrator output in so called pre-run mode minimizes integrator leakage and non-ideal effects by connecting a Gm in pre-run mode either to input voltage or to a reference voltage depending this Gm is being used in a following clock period. Parasitic effects due to switching at first integration capacitor are minimized by using buffer amplifiers tracking the voltage on integration capacitors.

Owner:DIALOG SEMICONDUCTOR GMBH

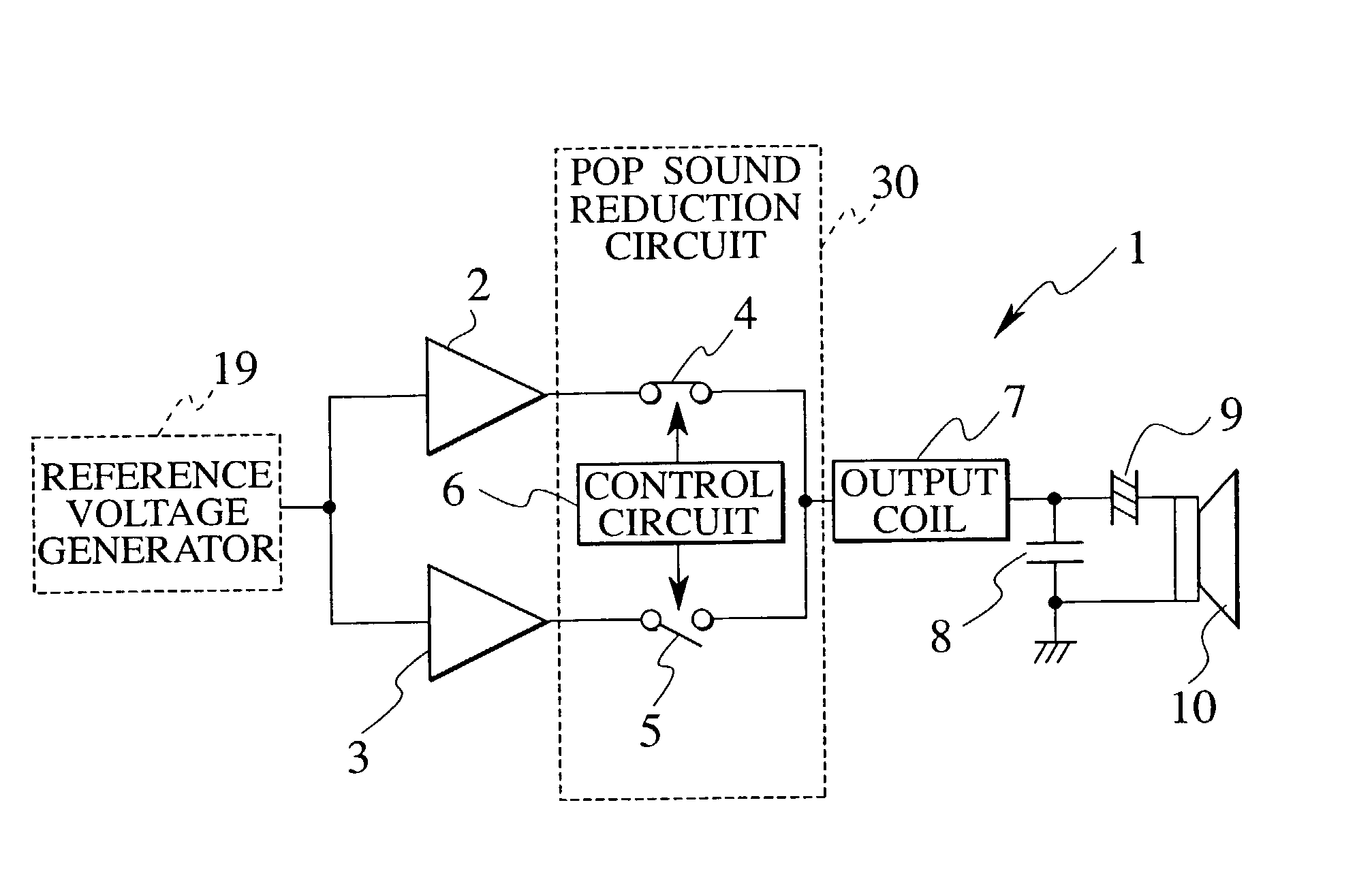

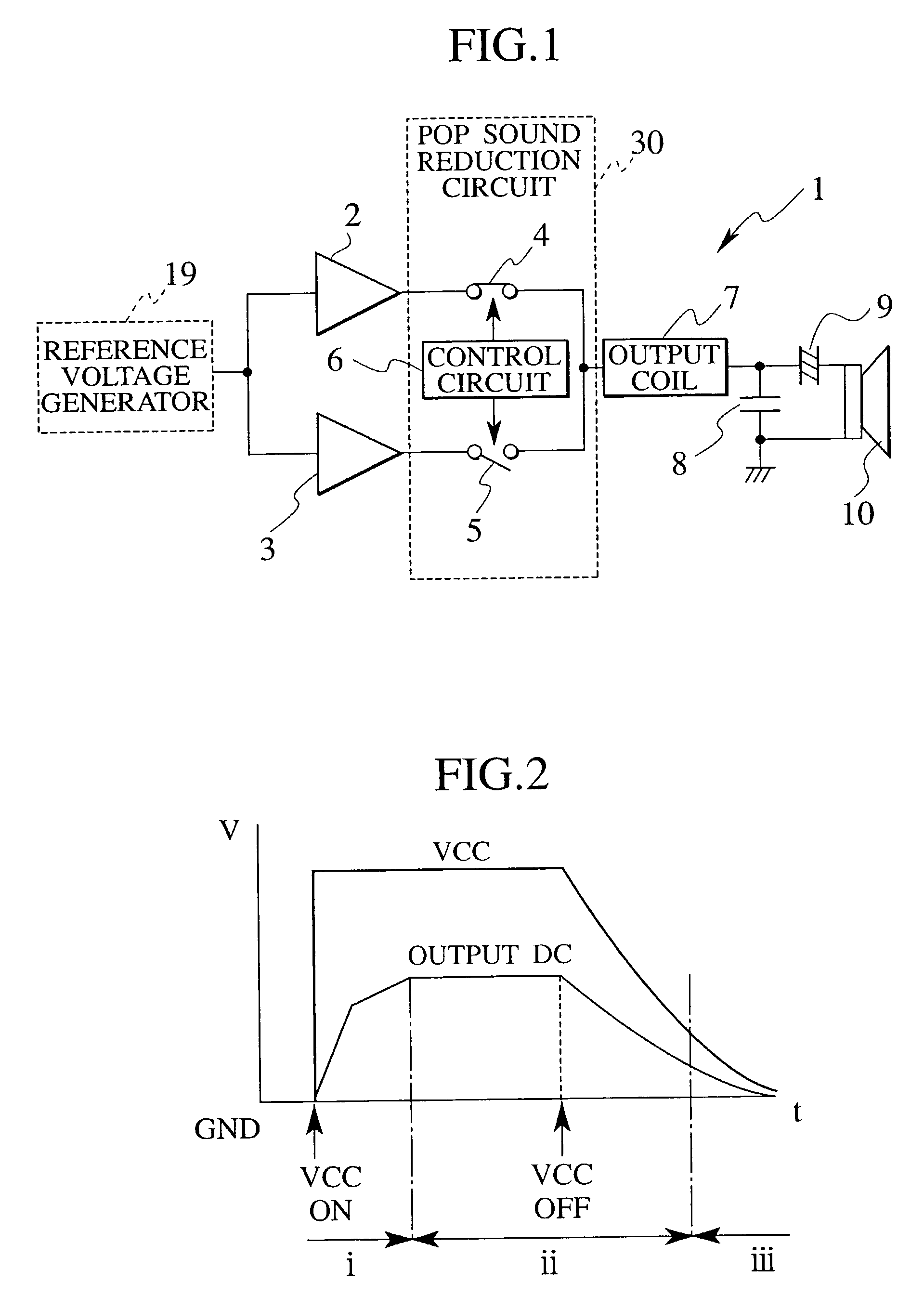

Pop sound reduction circuit and voice output amplification device

InactiveUS20030058040A1Gain controlAmplifier modifications to reduce temperature/voltage variationVoltage referenceControl circuit

A pop sound reduction circuit comprises a pulse width modulation amplifier configured to amplify a reference voltage to an intermediate amplitude of a pulse width modulated signal, a first switch configured to activate and deactivate the pulse width modulation amplifier, a buffer amplifier configured to generate a DC voltage equal to the reference voltage, a second switch configured to activate and deactivate the buffer amplifier, and a control circuit configured to close and open the first and second switches complementary, depending on a potential in a leading region of the reference voltage which rises from a time of turning-on of a power source as well as a potential in a trailing region of the reference voltage which falls from a time of turning-off of the power source.

Owner:KK TOSHIBA