Patents

Literature

306results about How to "Reduce parasitic effects" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

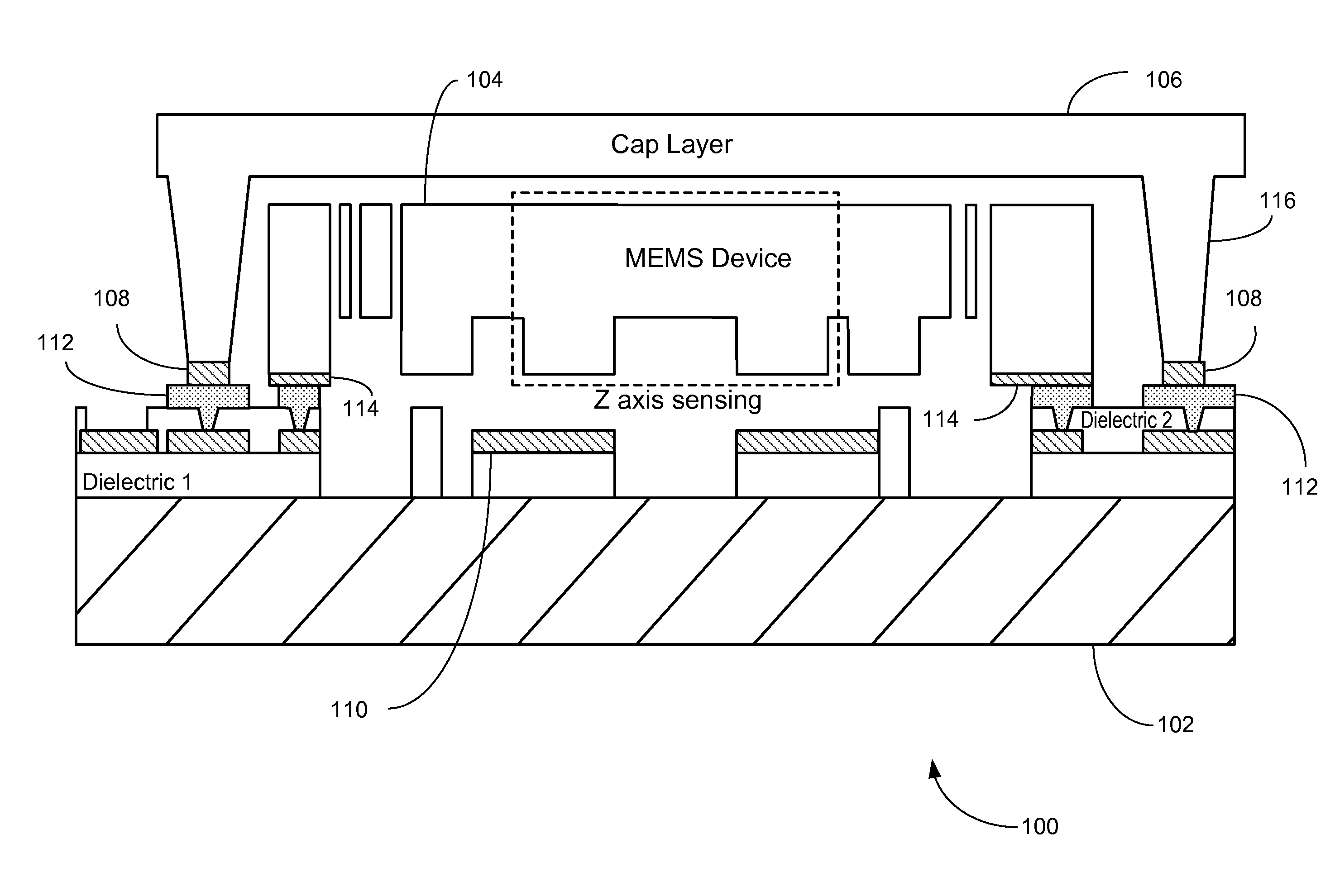

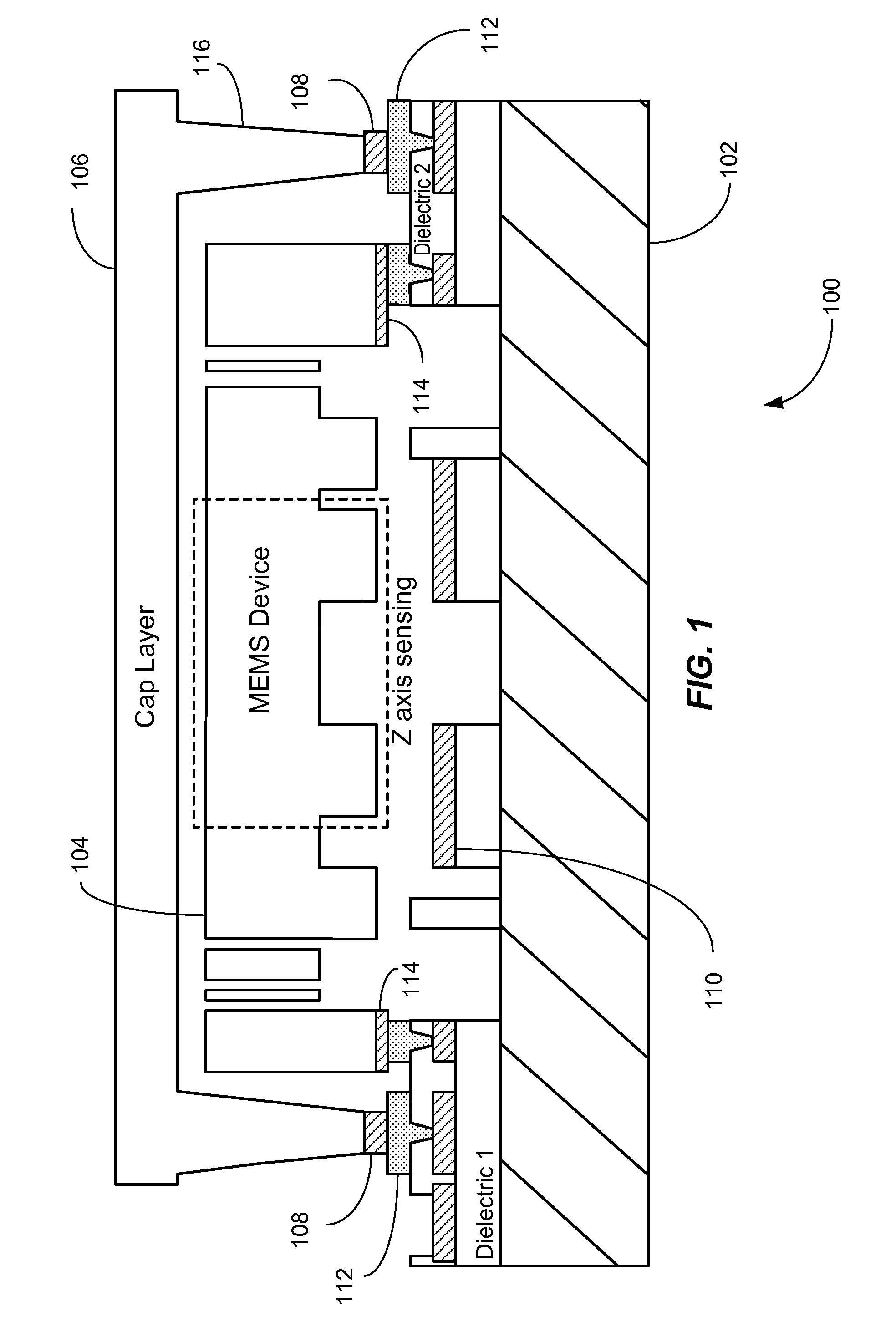

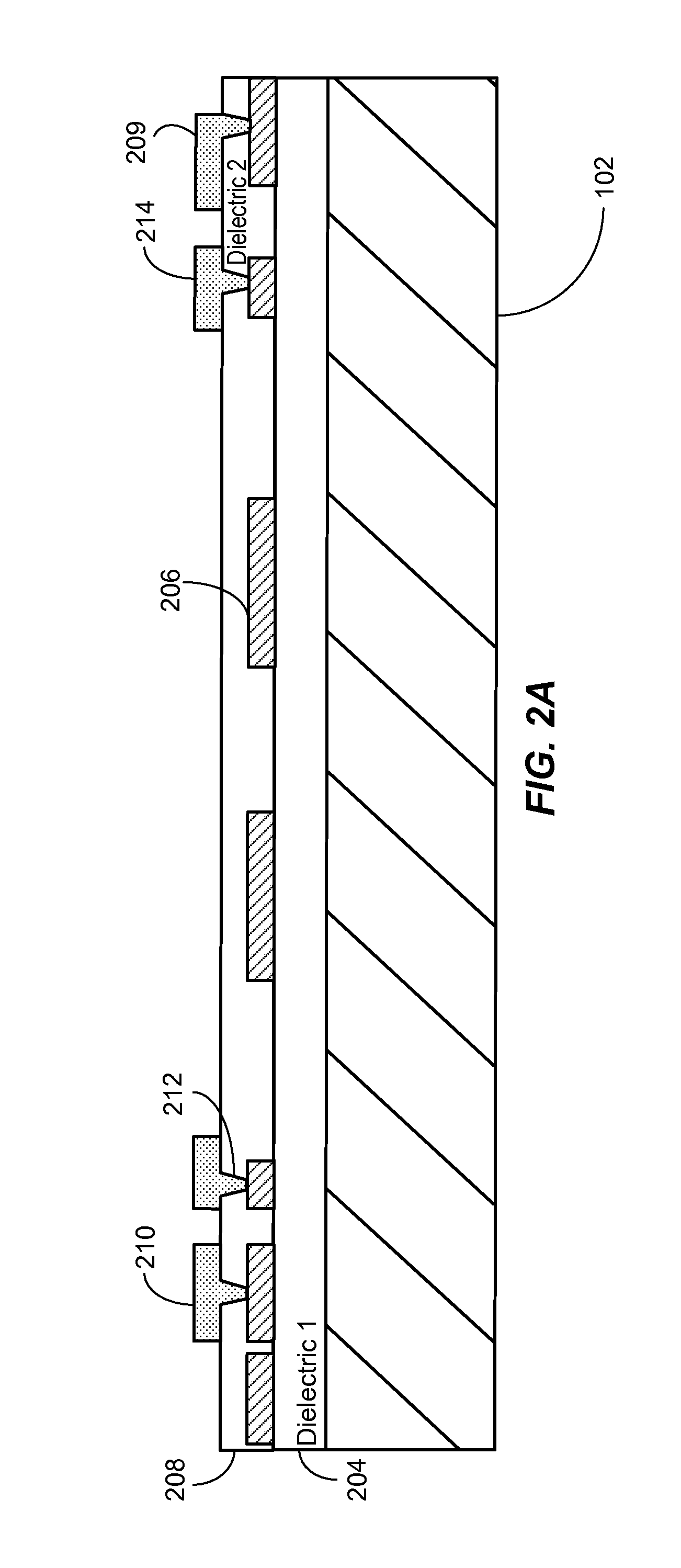

Method and system for MEMS devices

InactiveUS20110049652A1Accurately depositAccurately definedAcceleration measurement using interia forcesSemiconductor/solid-state device manufacturingEngineeringElectrical and Electronics engineering

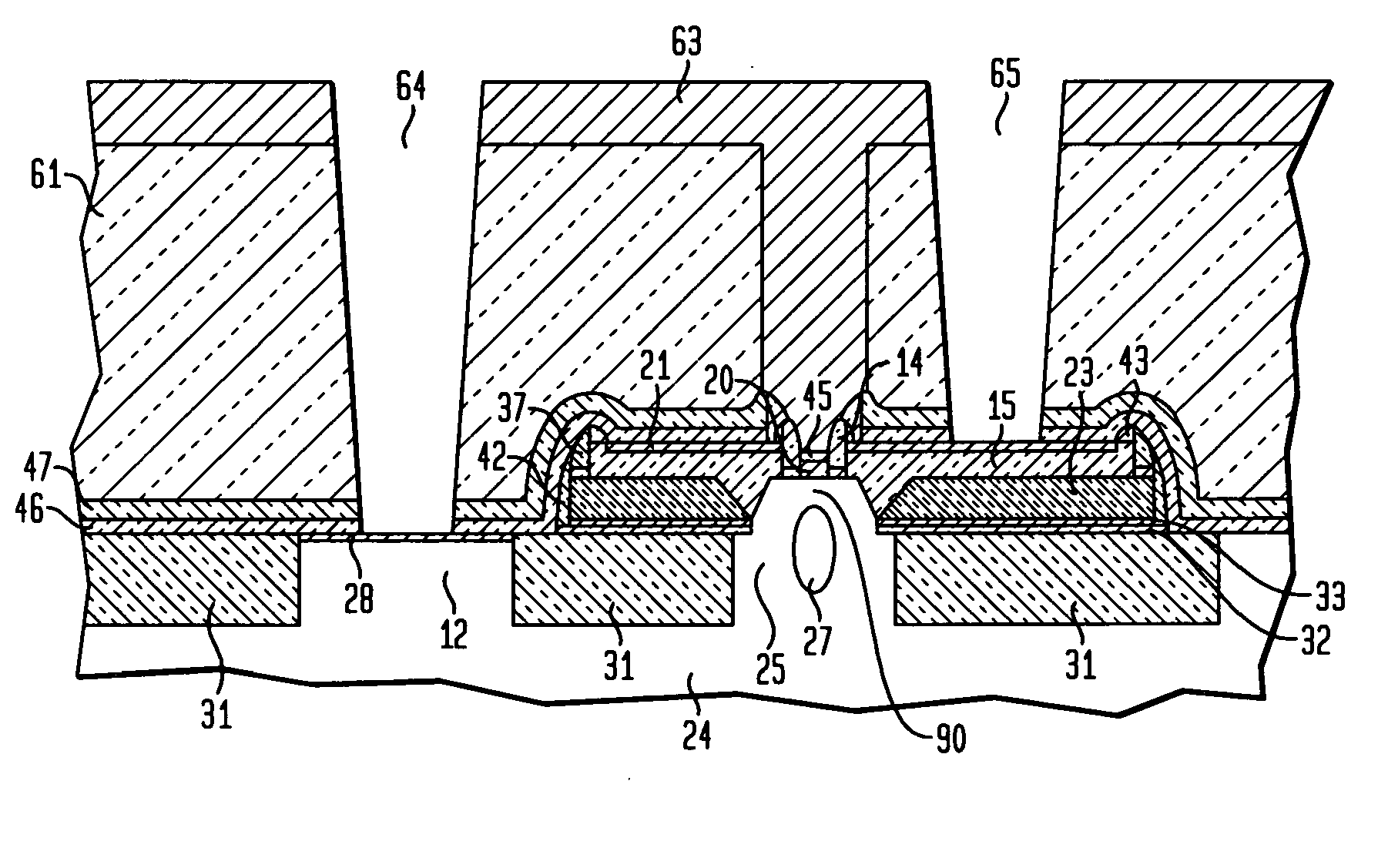

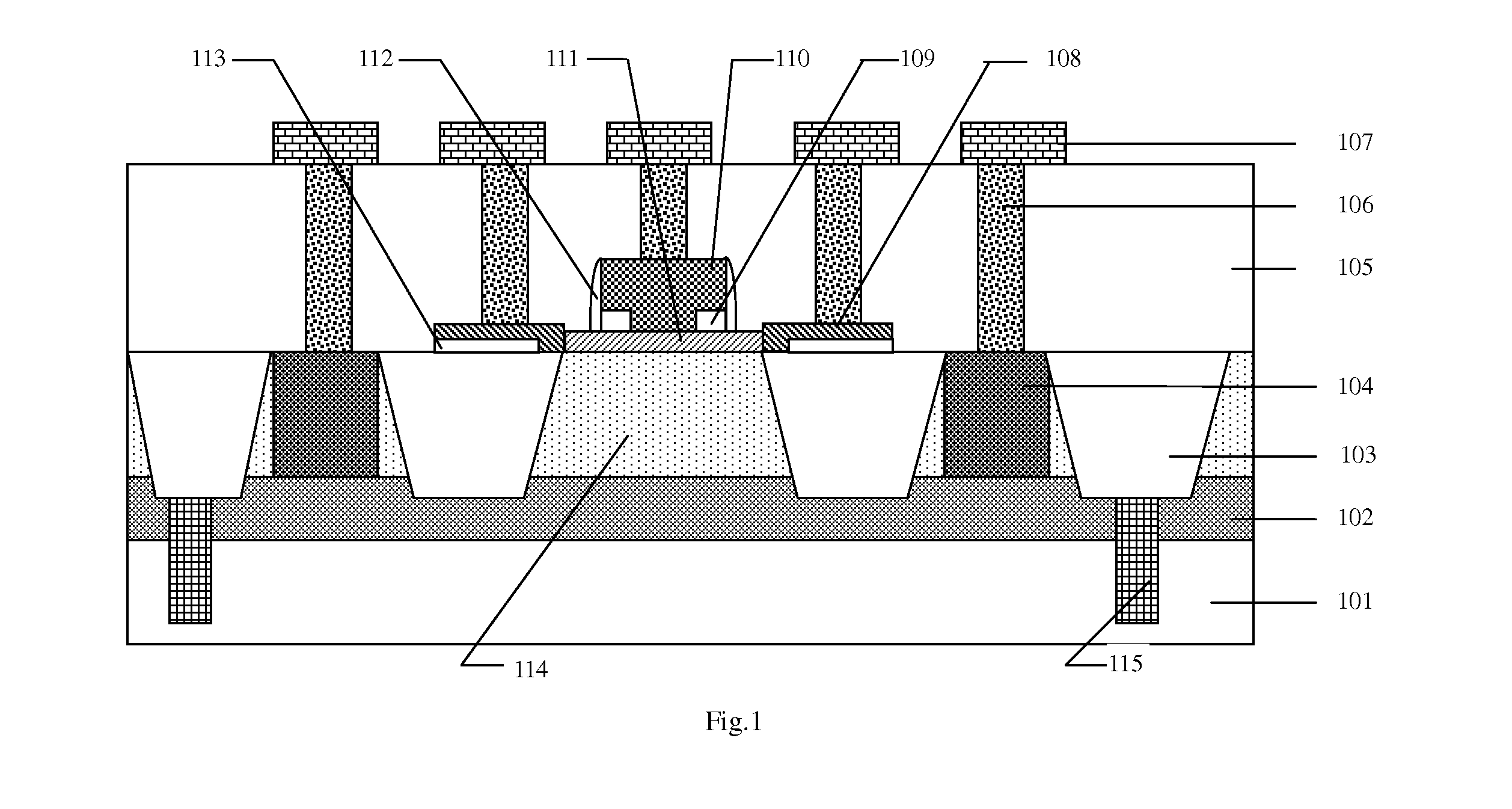

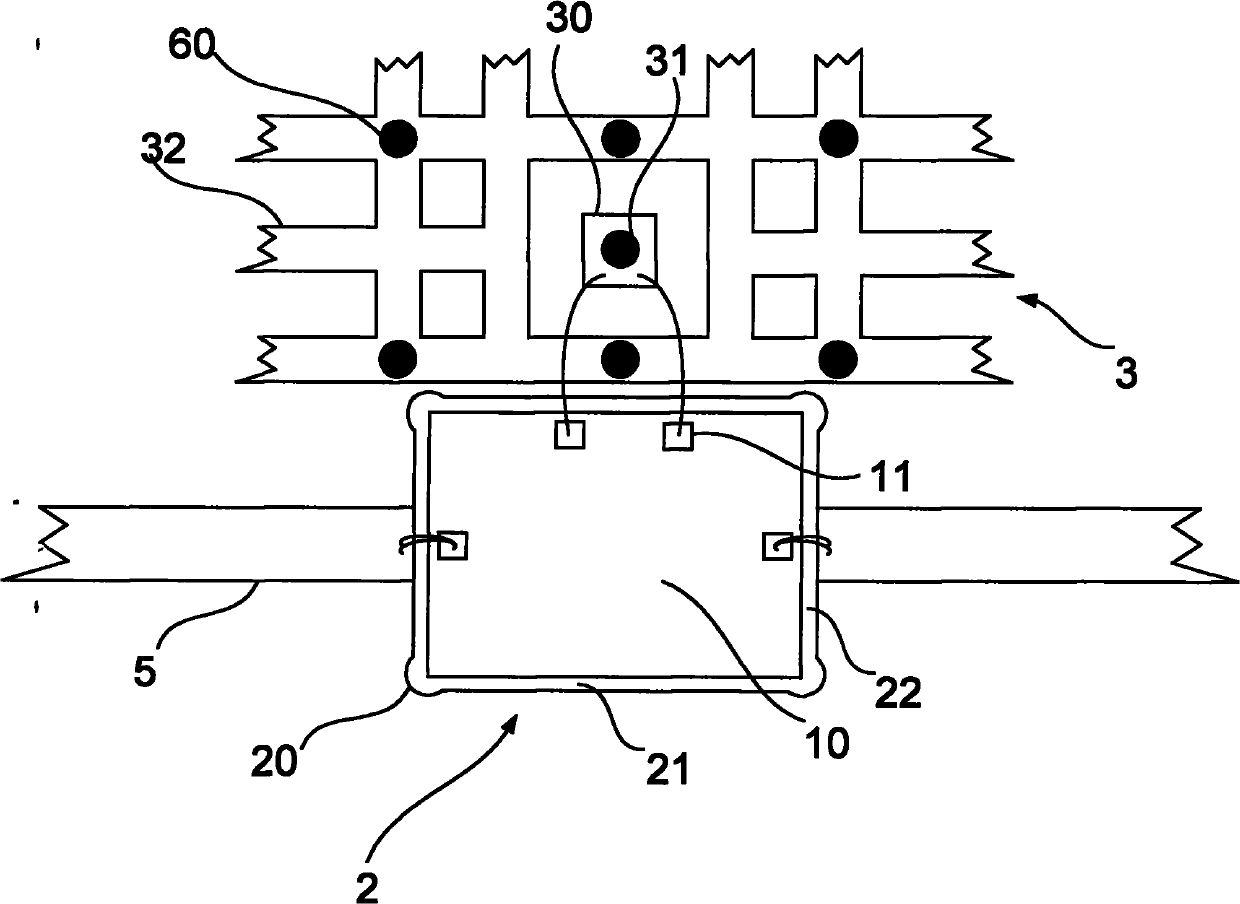

A micro electro-mechanical (MEMS) device assembly is provided. The MEMS device assembly includes a first substrate that has a plurality of electronic devices, a plurality of first bonding regions, and a plurality of second bonding regions. The MEMS device assembly also includes a second substrate that is bonded to the first substrate at the plurality of first bonding regions. A third substrate having a recessed region and a plurality of standoff structures is disposed over the second substrate and bonded to the first substrate at the plurality of second bonding regions. The plurality of first bonding regions provide a conductive path between the first substrate and the second substrate and the plurality of the second bonding regions provide a conductive path between the first substrate and the third substrate.

Owner:MIRADIA INC

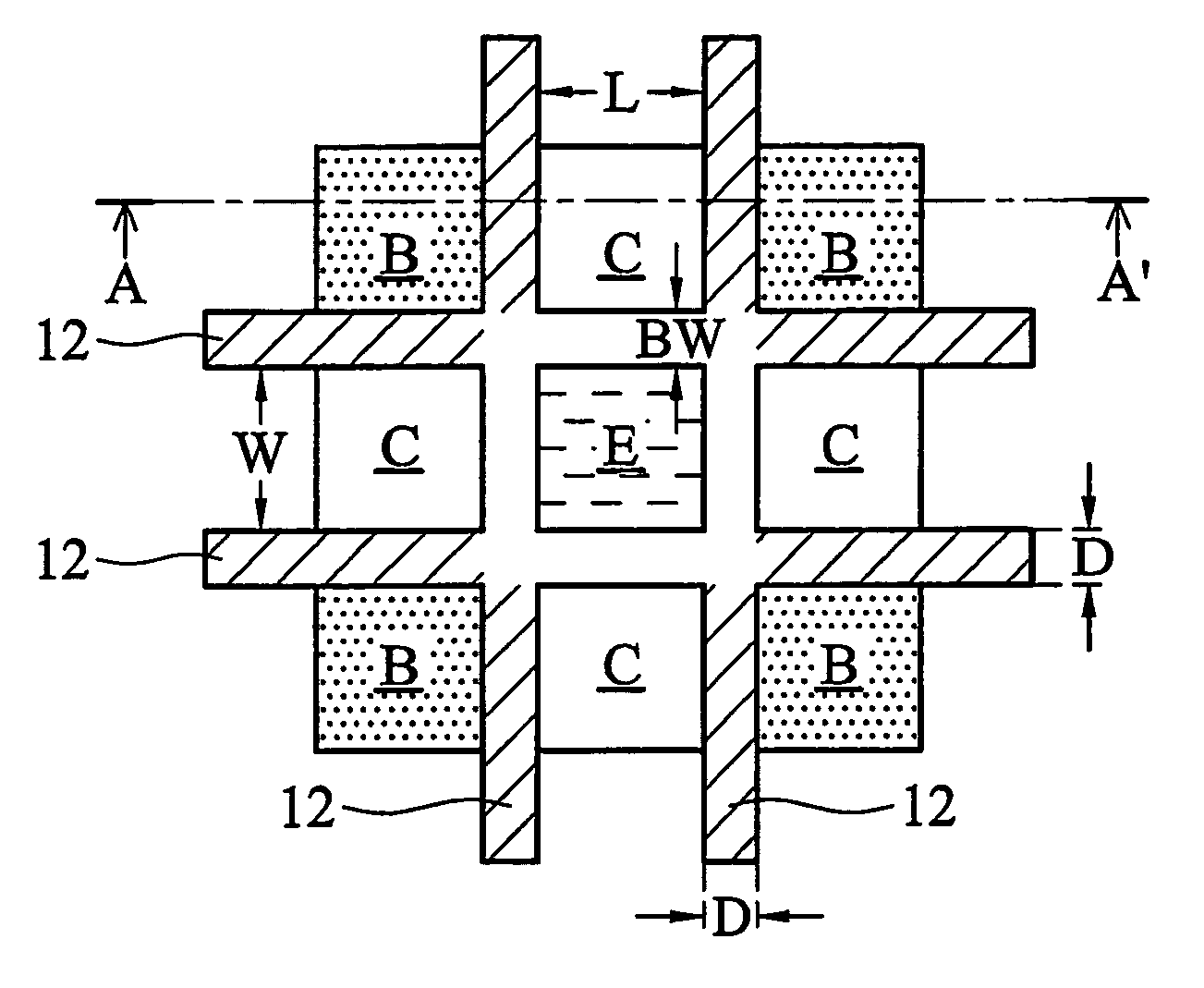

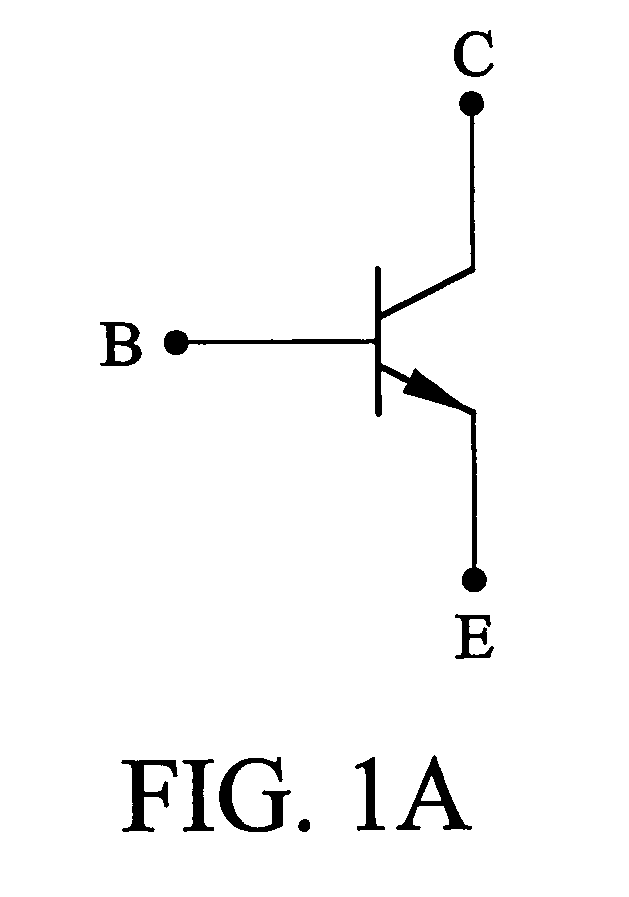

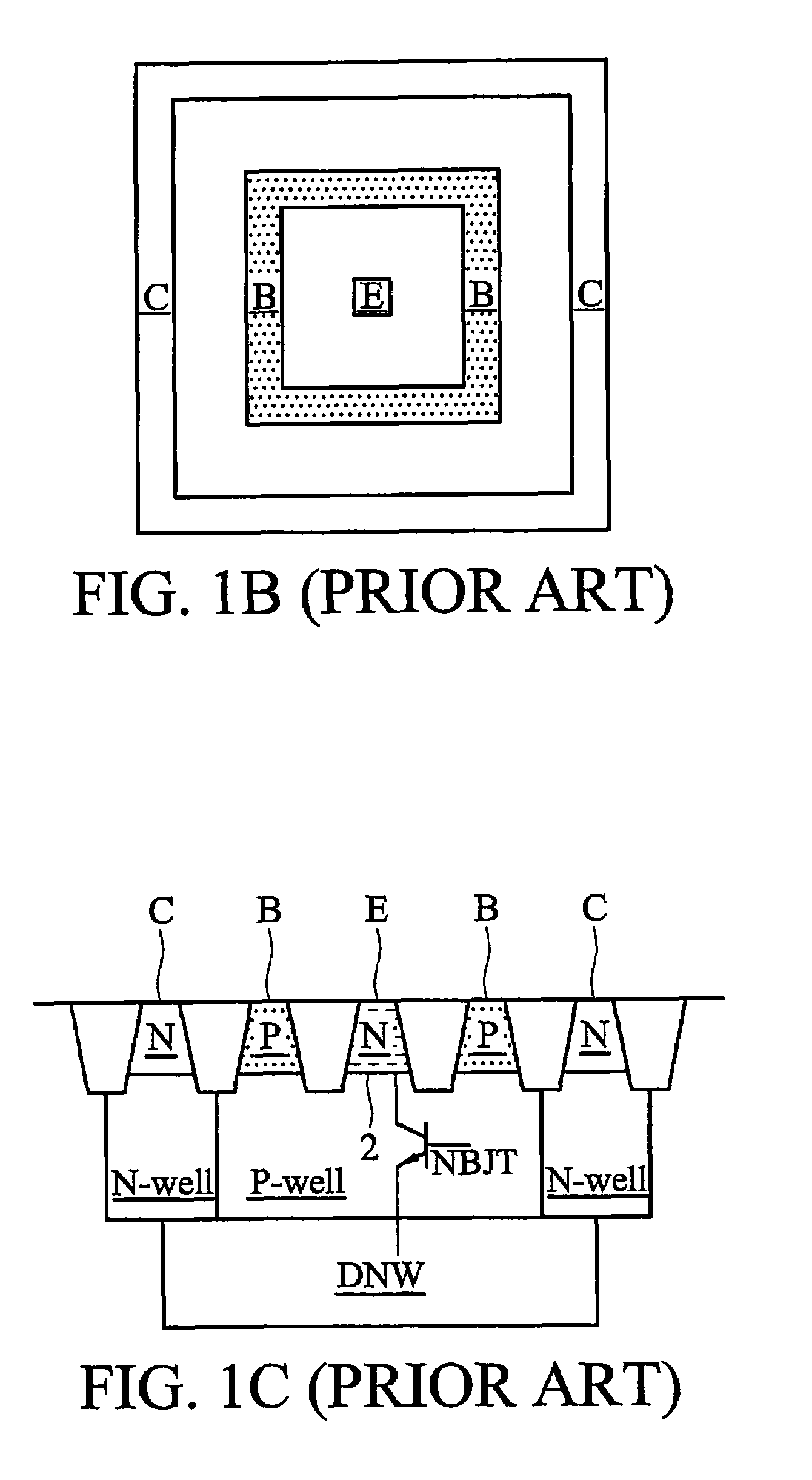

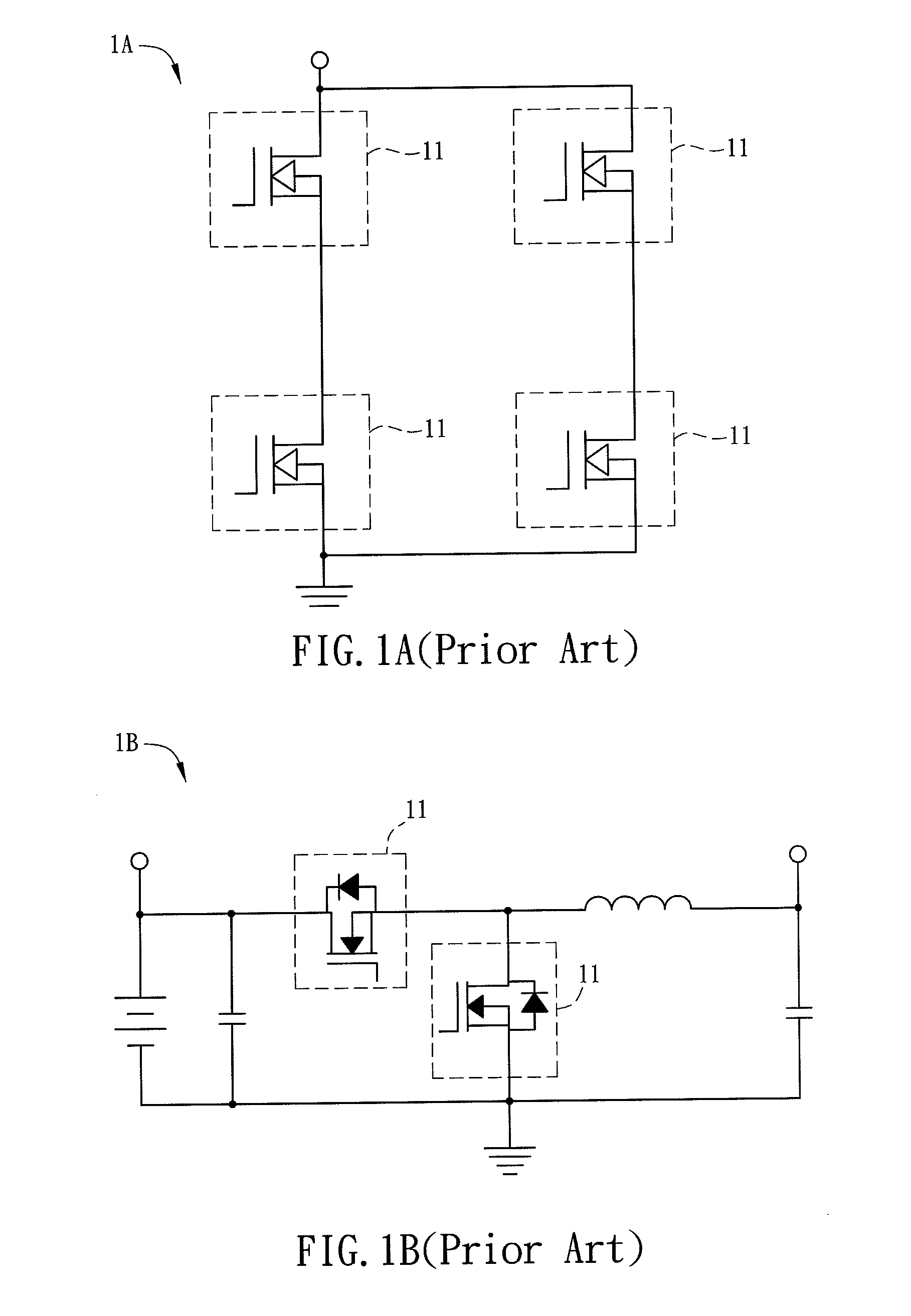

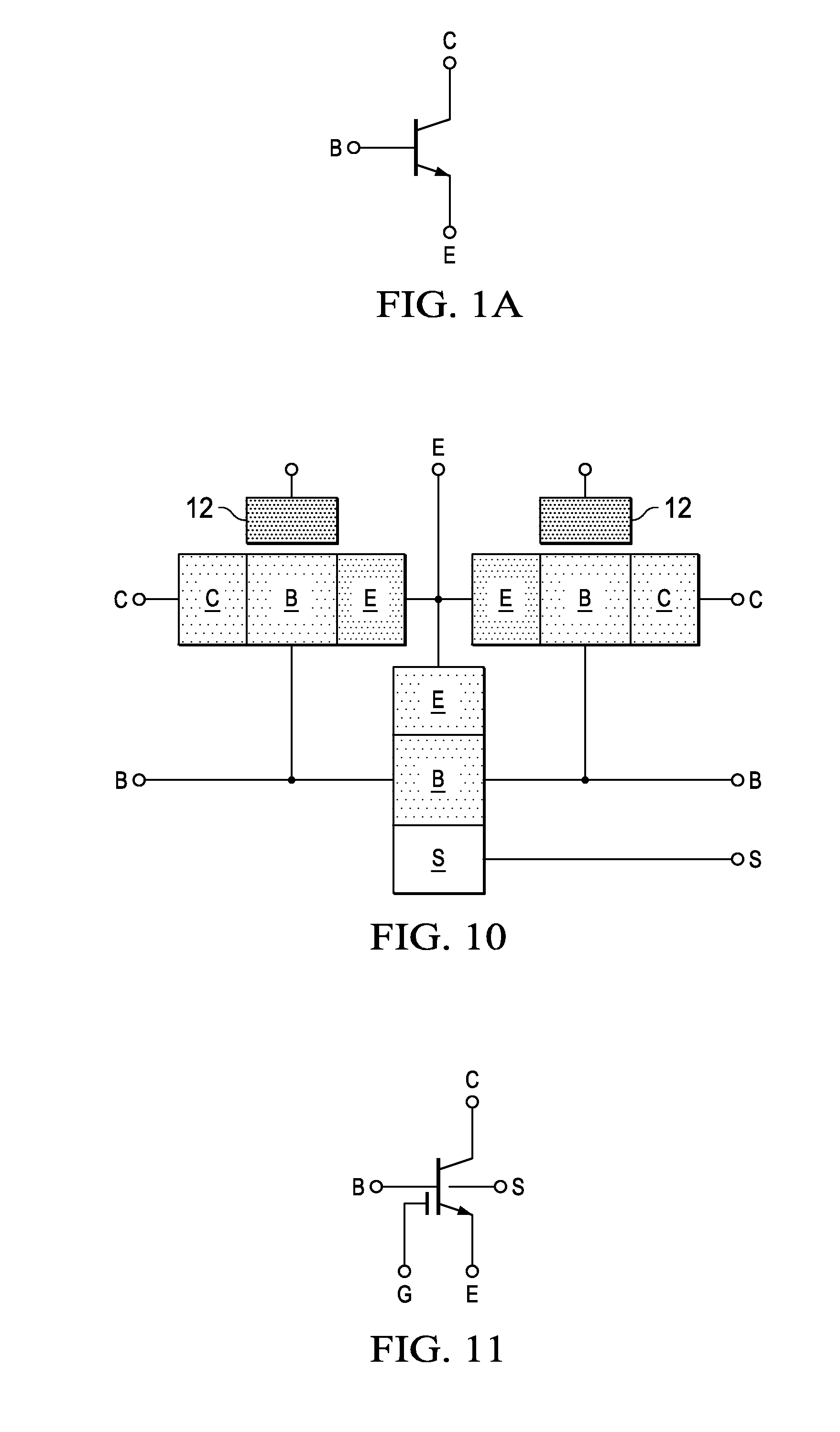

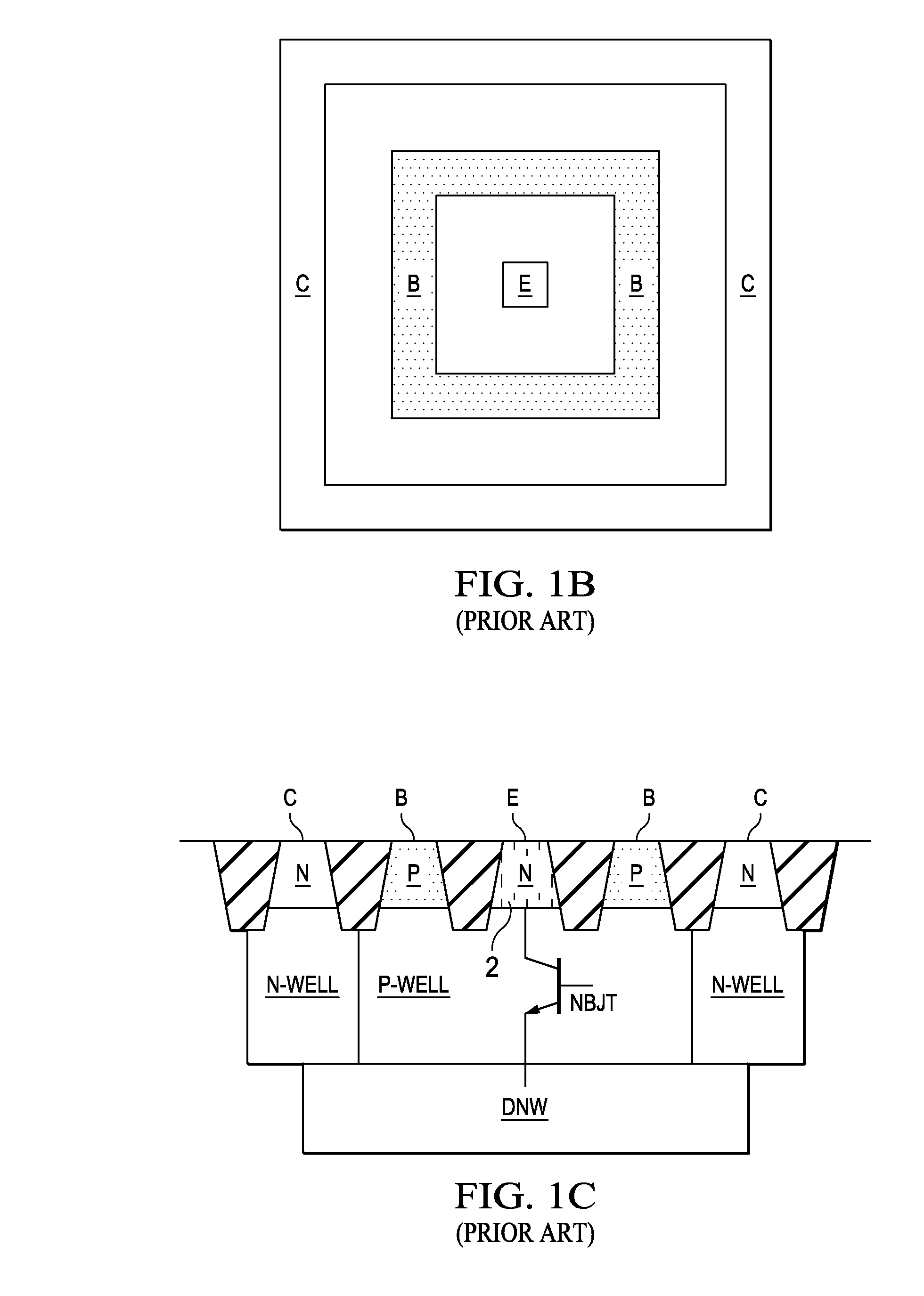

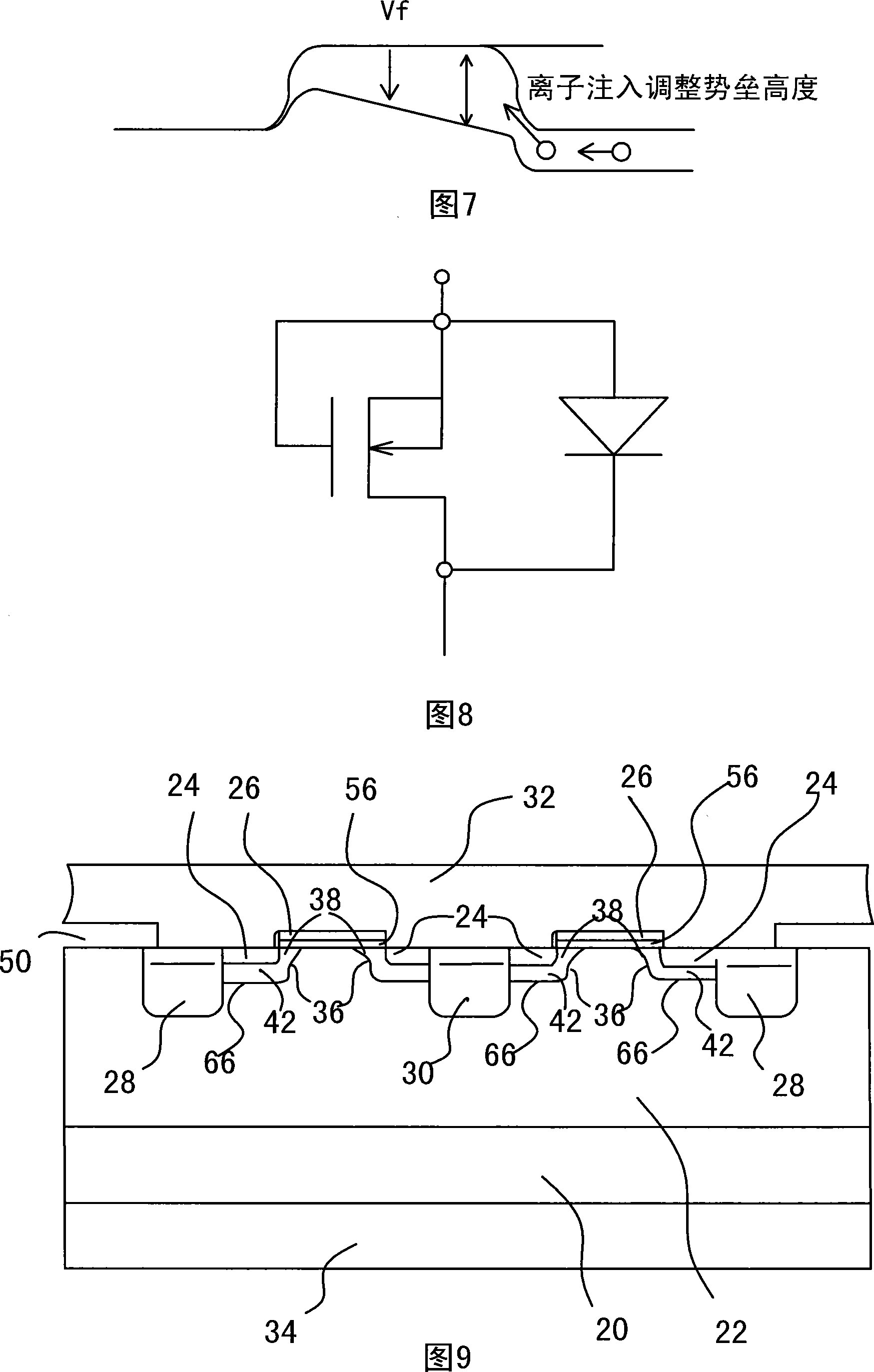

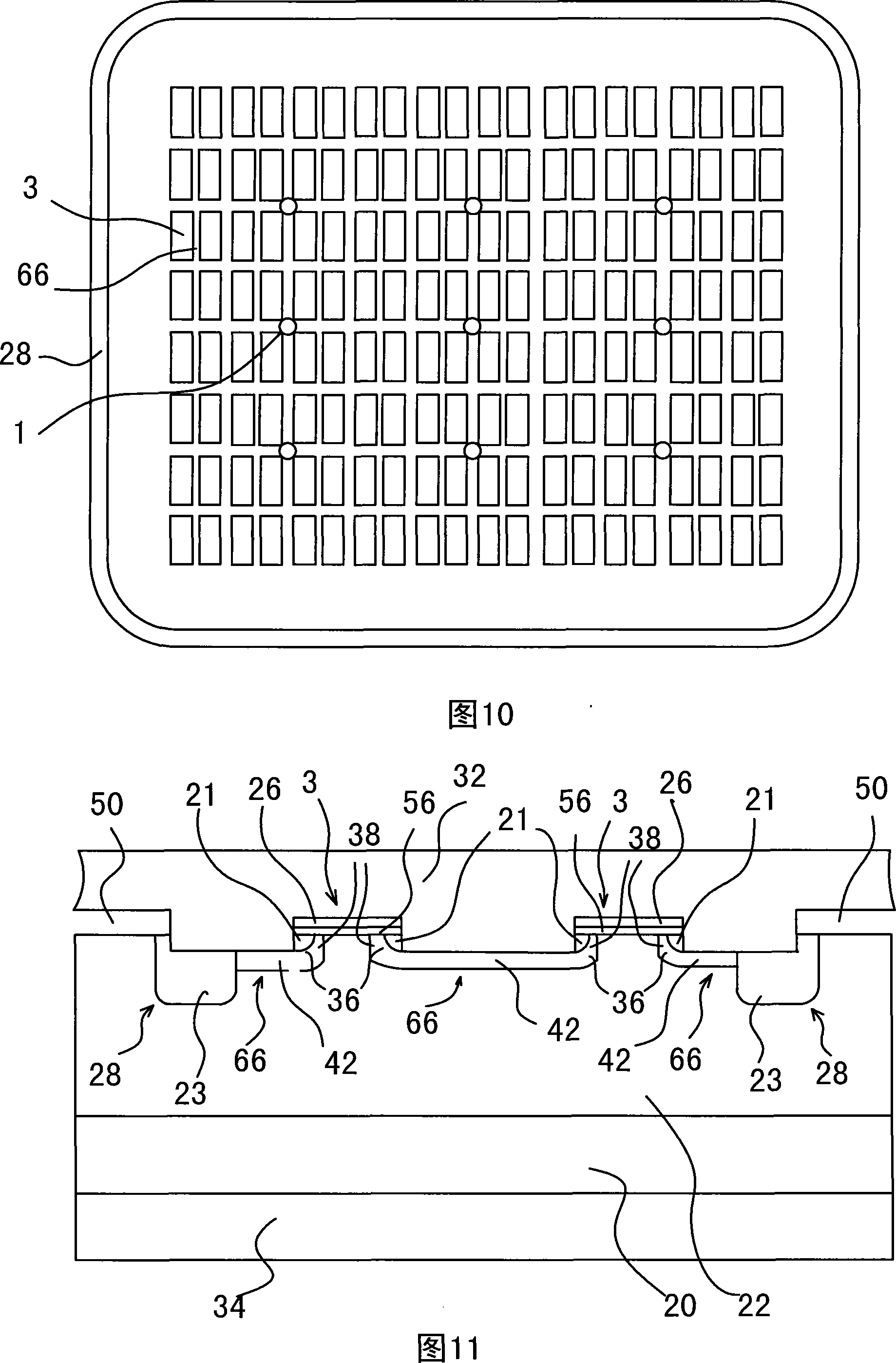

High-gain vertex lateral bipolar junction transistor

InactiveUS7701038B2Reduce parasitic effectsIncrease currentLogic circuits characterised by logic functionSemiconductor/solid-state device manufacturingPhysical chemistryEngineering

A lateral bipolar junction transistor having improved current gain and a method for forming the same are provided. The transistor includes a well region of a first conductivity type formed over a substrate, at least one emitter of a second conductivity type opposite the first conductivity type in the well region wherein each of the at least one emitters are interconnected, a plurality of collectors of the second conductivity type in the well region wherein the collectors are interconnected to each other, and a plurality of base contacts of the first conductivity type in the well region wherein the base contacts are interconnected to each other. Preferably, all sides of the at least one emitters are adjacent the collectors, and none of the base contacts are adjacent the sides of the emitters. The neighboring emitter, collectors and base contacts are separated by spacings in the well region.

Owner:TAIWAN SEMICON MFG CO LTD

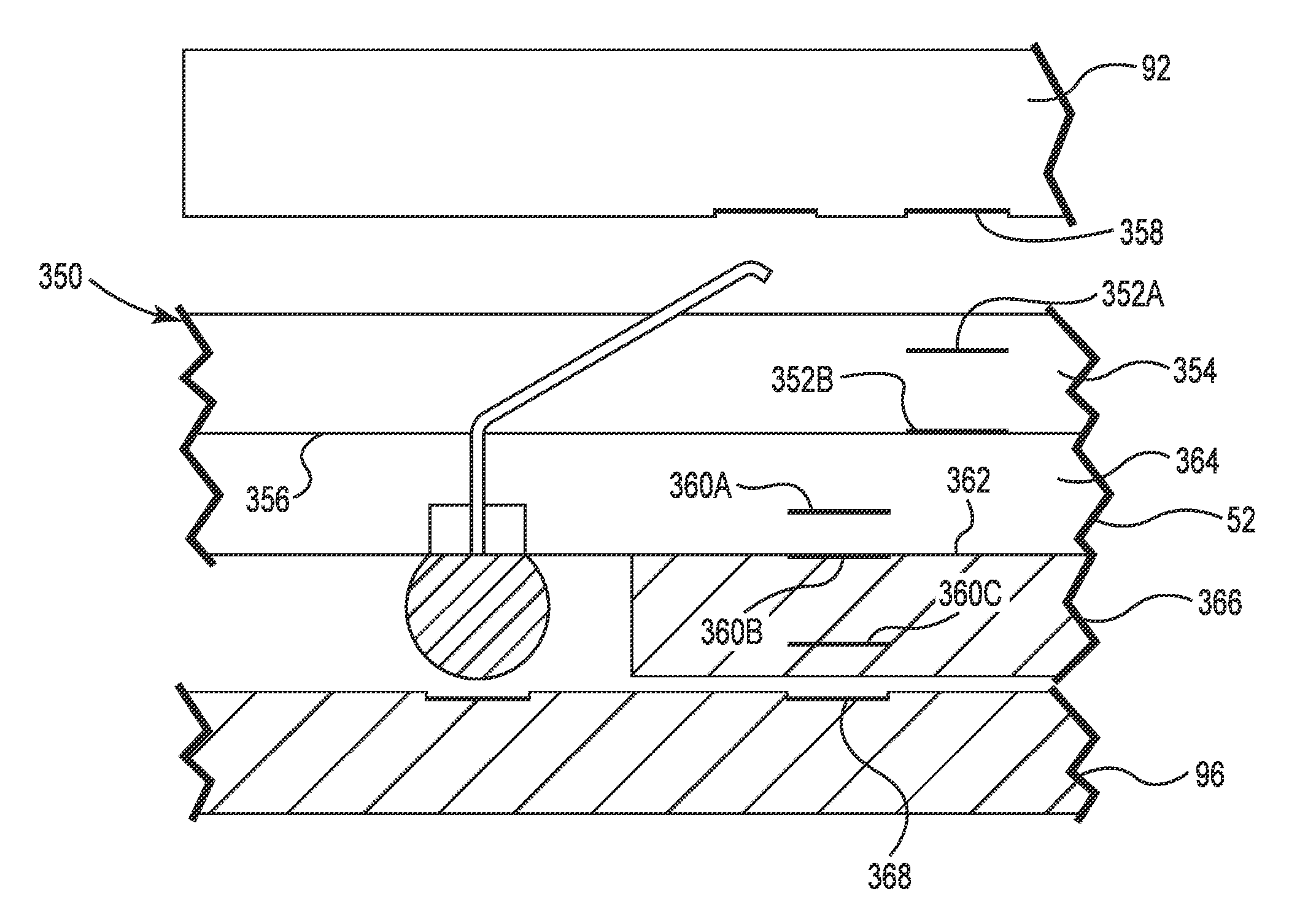

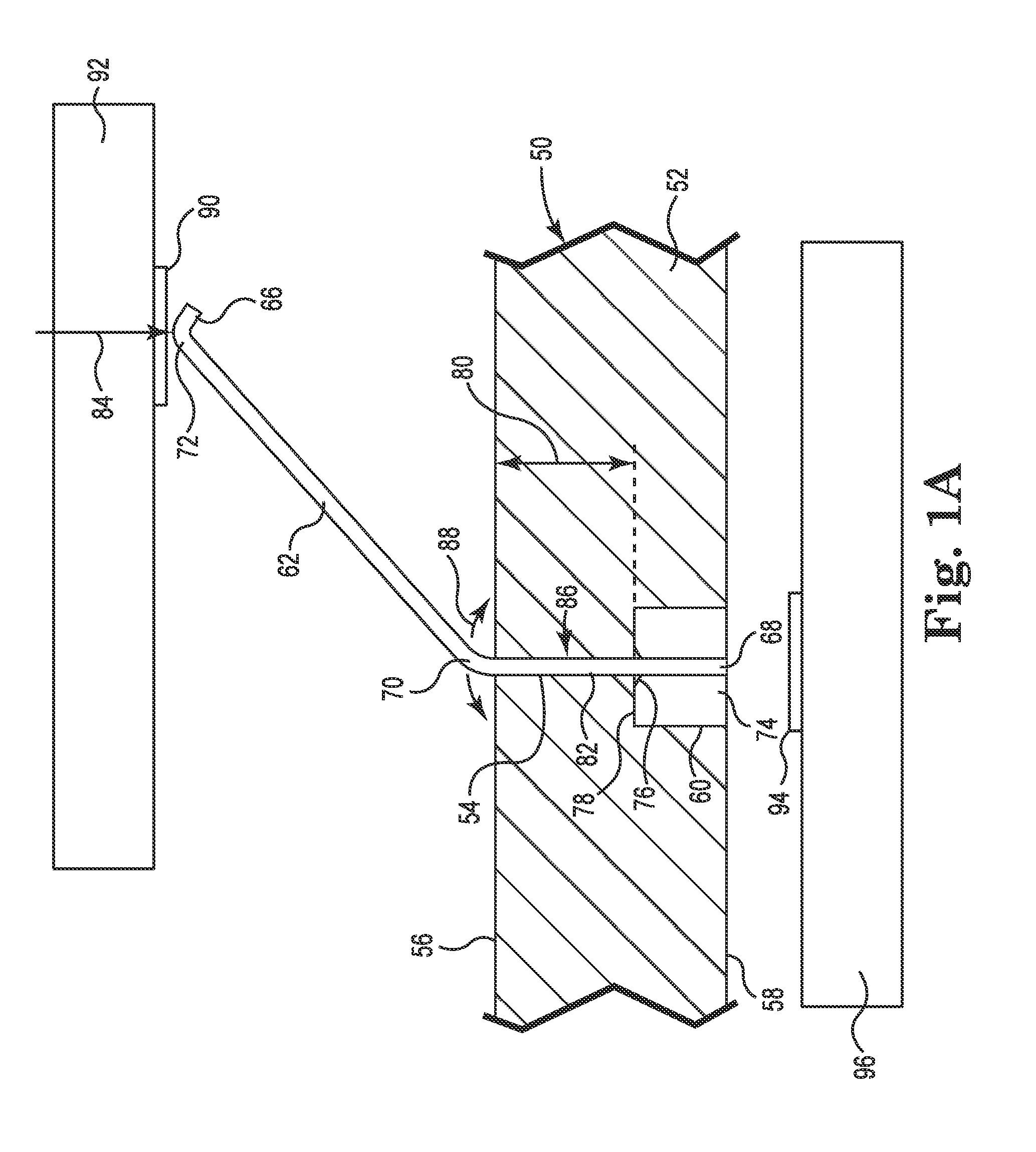

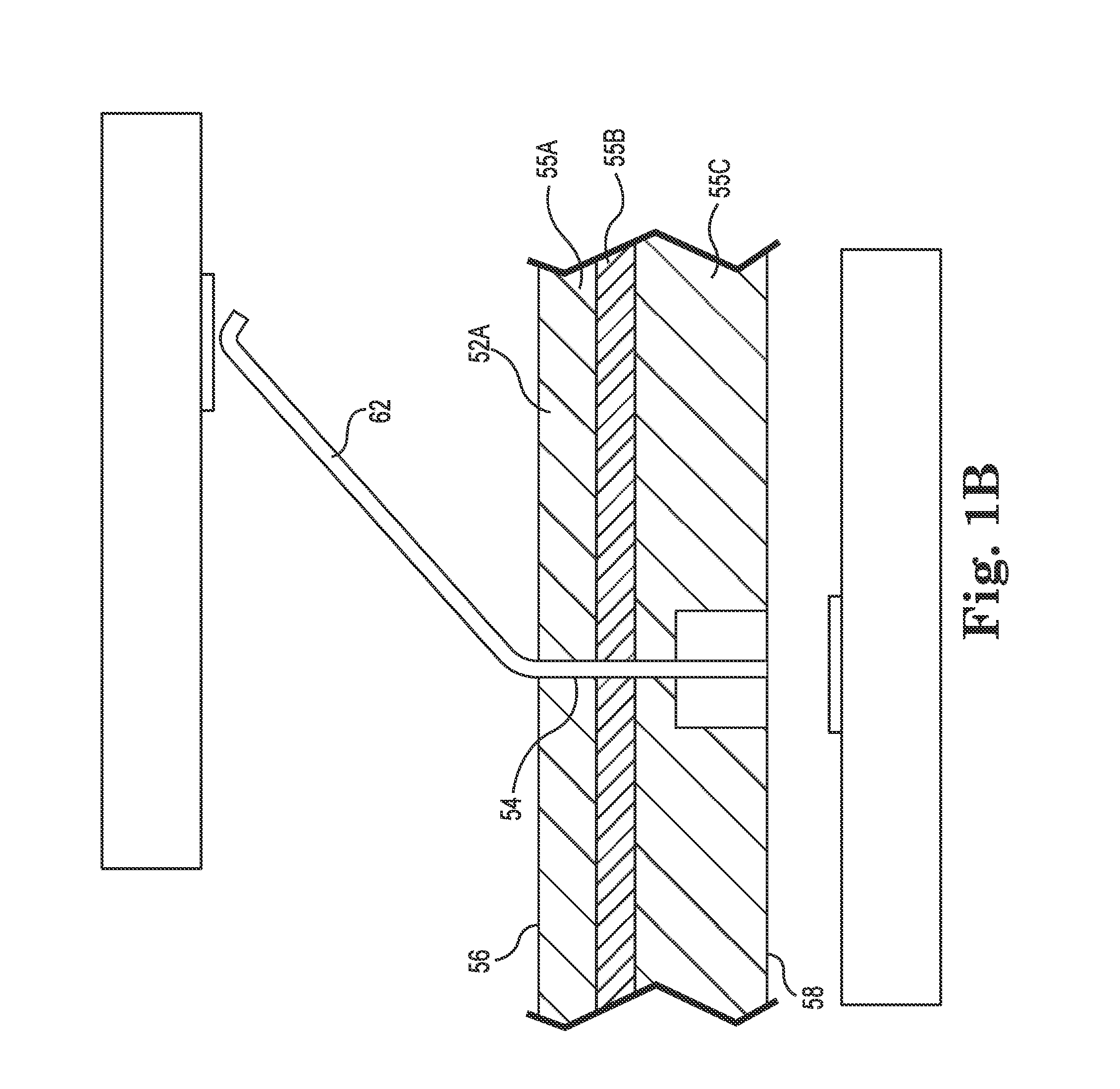

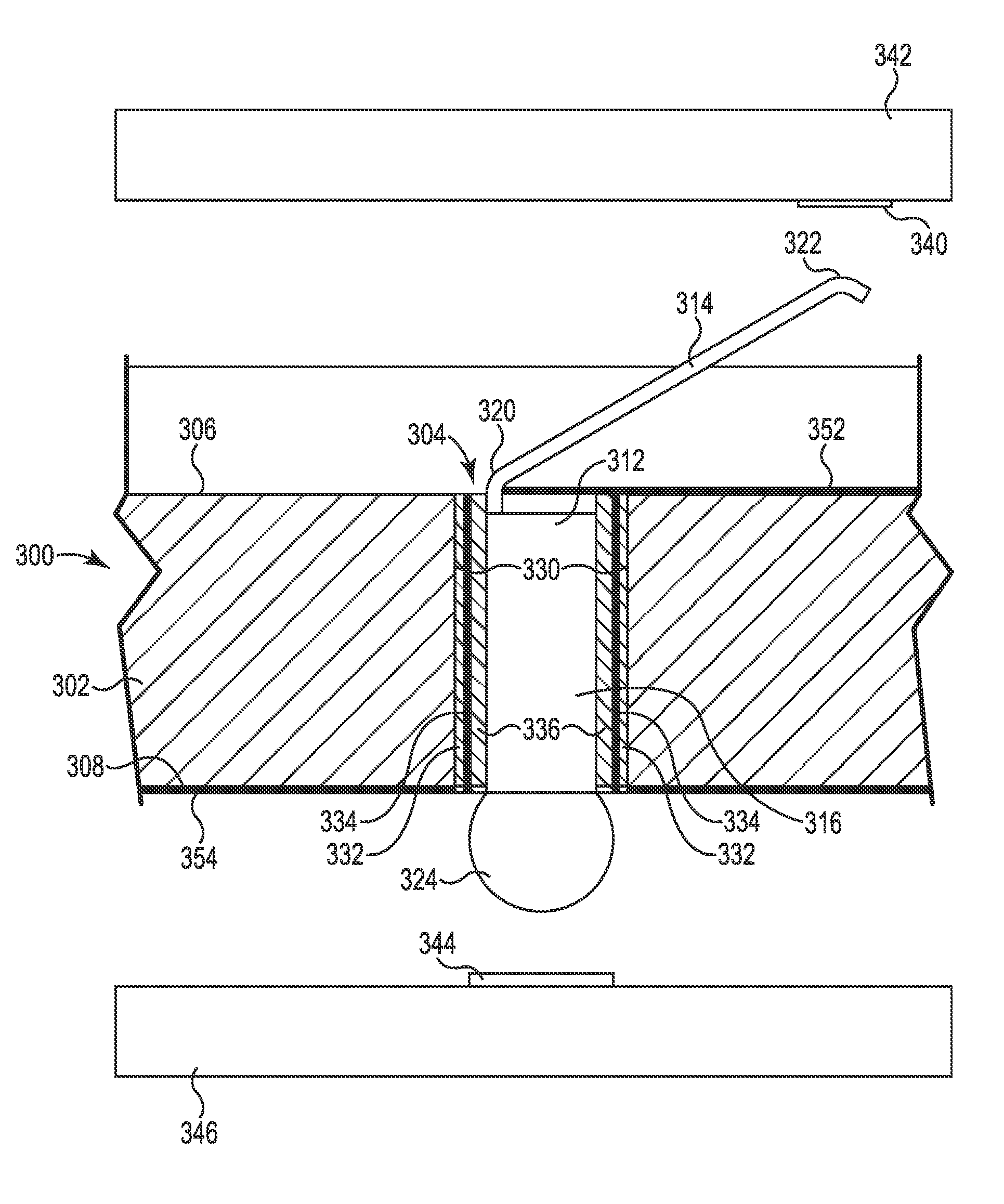

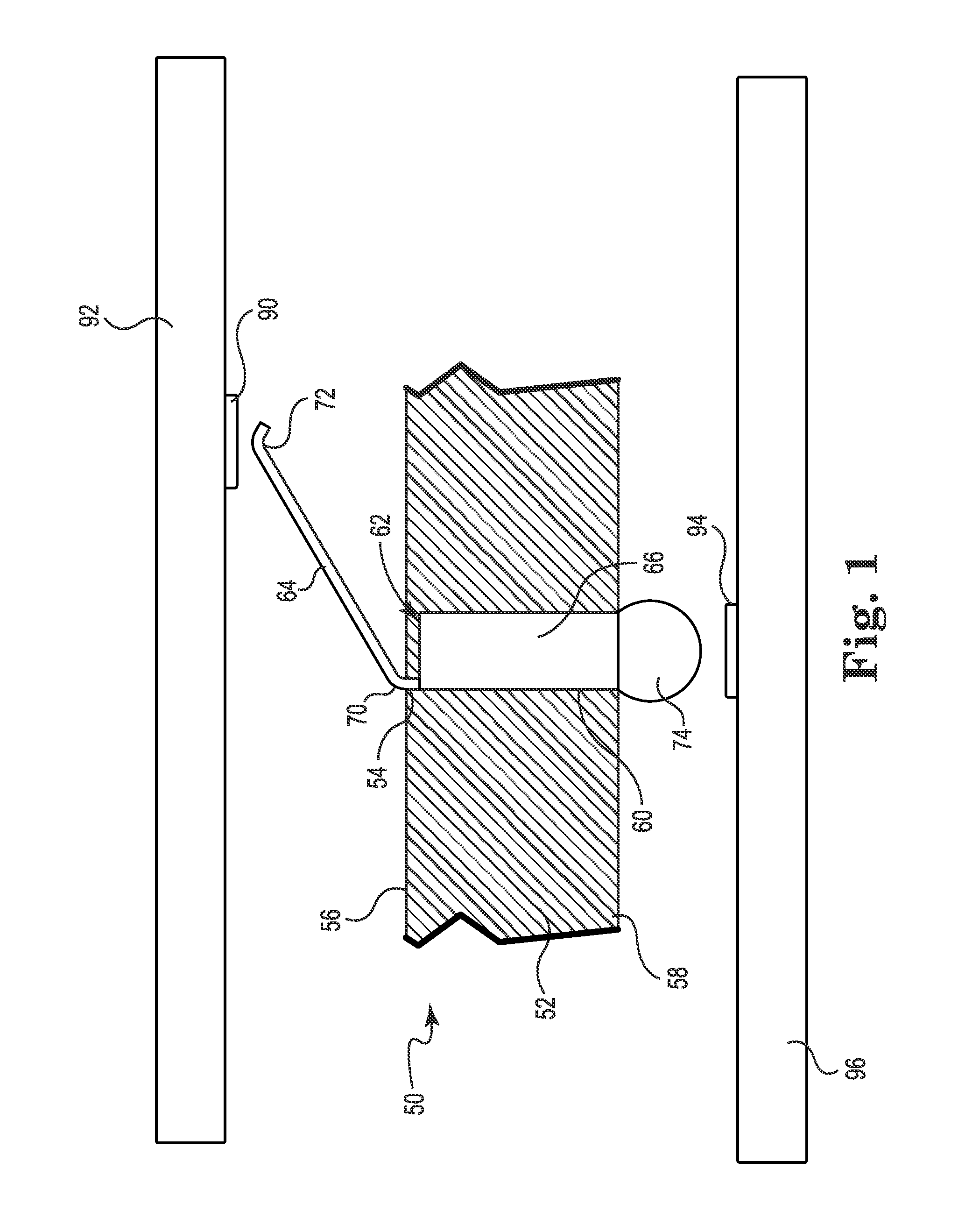

High performance surface mount electrical interconnect

ActiveUS20120055701A1Improve the substrateReduce complexityPrinted electric component incorporationFixed connectionsEngineeringMechanical engineering

An interconnect assembly including a substrate with a plurality of through holes extending from a first surface to a second surface. A plurality of discrete contact member are located in the plurality of through holes. The contact members include proximal ends that are accessible from the second surface, distal ends extending above the first surface, and intermediate portions engaged with an engagement region of the substrate located between the first surface and the recesses. Retention members are coupled with at least a portion of the proximal ends to retain the contact members in the through holes. The retention members can be made from a variety of materials with different levels of conductivity, ranging from highly conductive to non-conductive.

Owner:HSIO TECH

Patch antenna unit and antenna

ActiveCN105552550AIncrease the effective areaHigh bandwidthRadiating elements structural formsIndividually energised antenna arraysHigh bandwidthIntegrated circuit

The invention relates to the technical field of communication, and discloses a patch antenna unit, an antenna and communication equipment. The patch antenna unit comprises stacked first support layer, substrate, second support layer and integrated circuit, wherein radiation patches are attached to the first support layer and the second support layer respectively; ground layers are arranged on the second support layer and are provided with coupling gaps; a feeder line corresponding to the coupling gaps is arranged on the second support layer; and the integrated circuit is connected with the first ground layers and the feeder line respectively. In a specific technical scheme, fabrication is carried out by the four layer-substrate, so that a 57-66GHz full-band high-frequency signal can be effectively fed into upper two layers of antennas for radiation by the coupling gaps in the third layer; the parasitic effect is reduced; meanwhile, the effective area of the antenna is increased by the stacked structure; and the performance effects of a high bandwidth and a high gain are brought for the antenna by achieved low parasitic parameters and high effective area.

Owner:HUAWEI TECH CO LTD

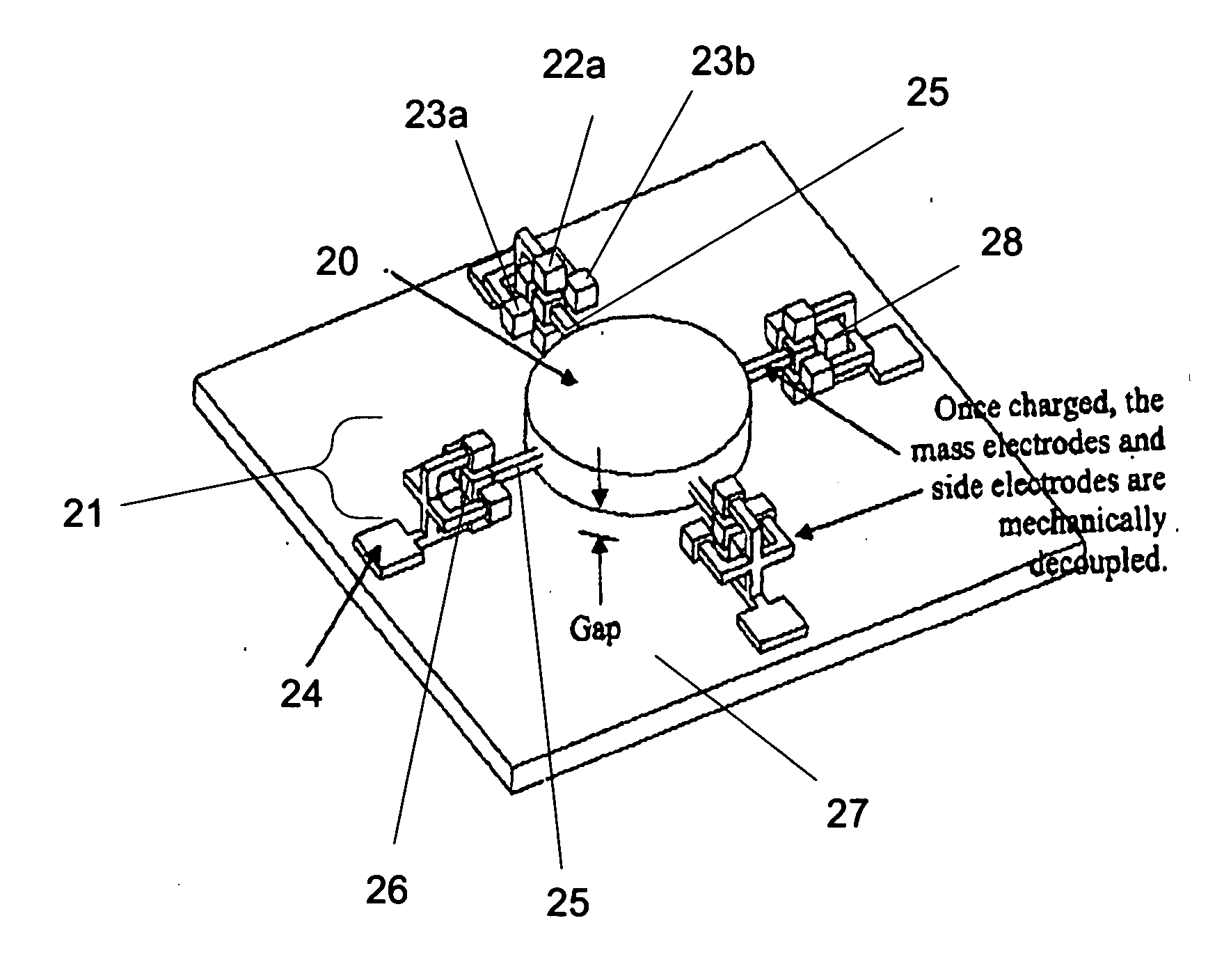

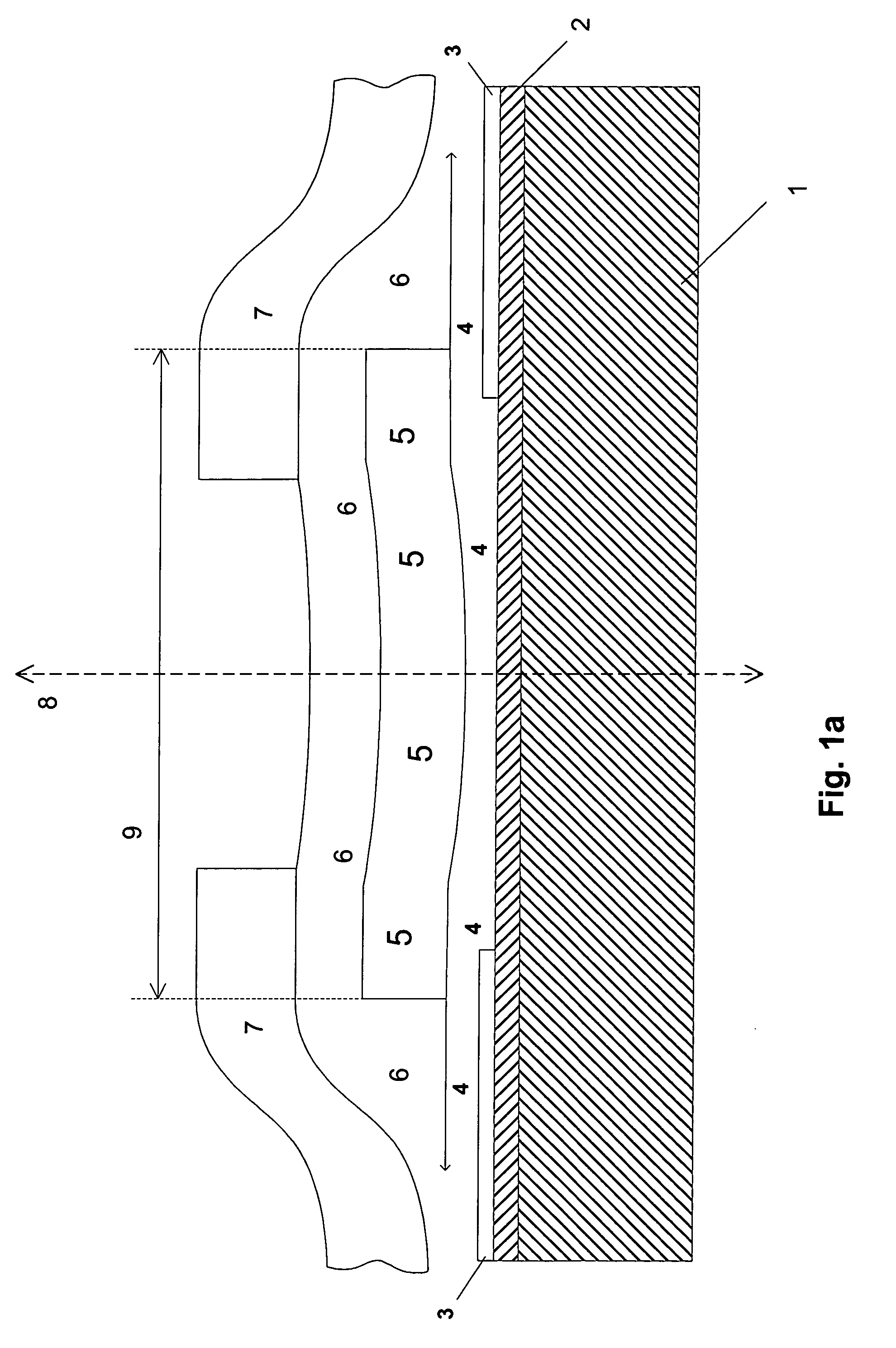

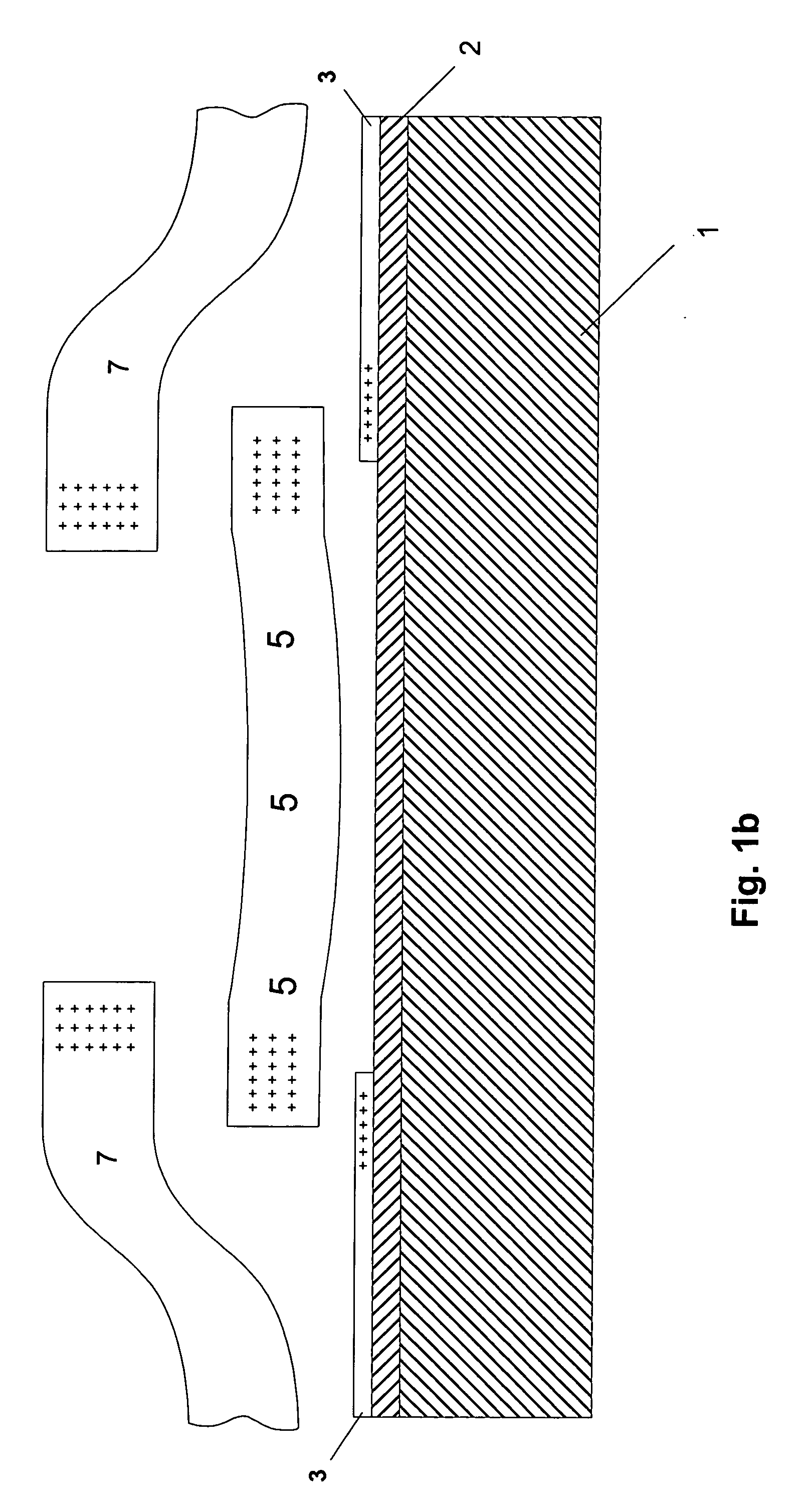

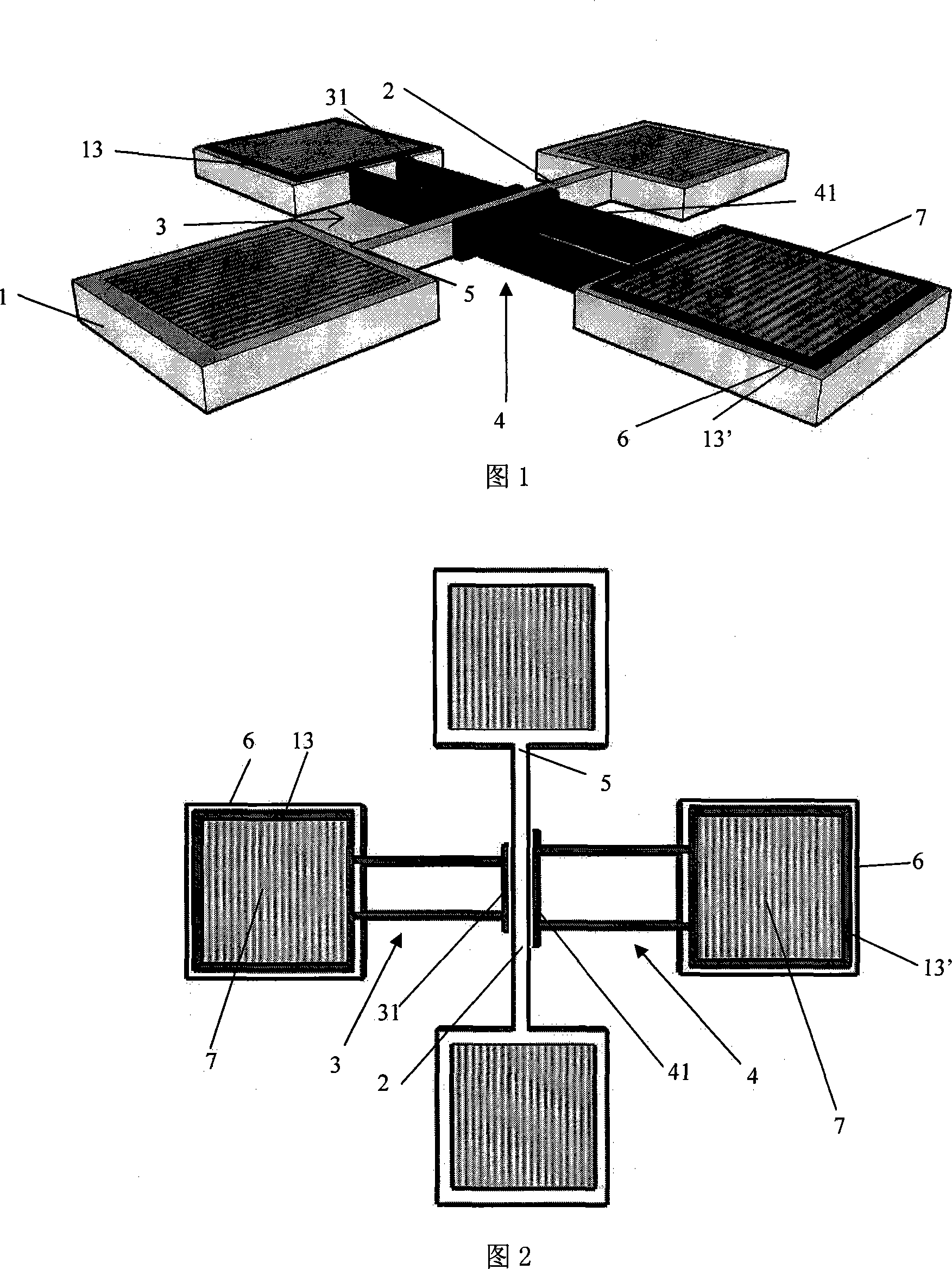

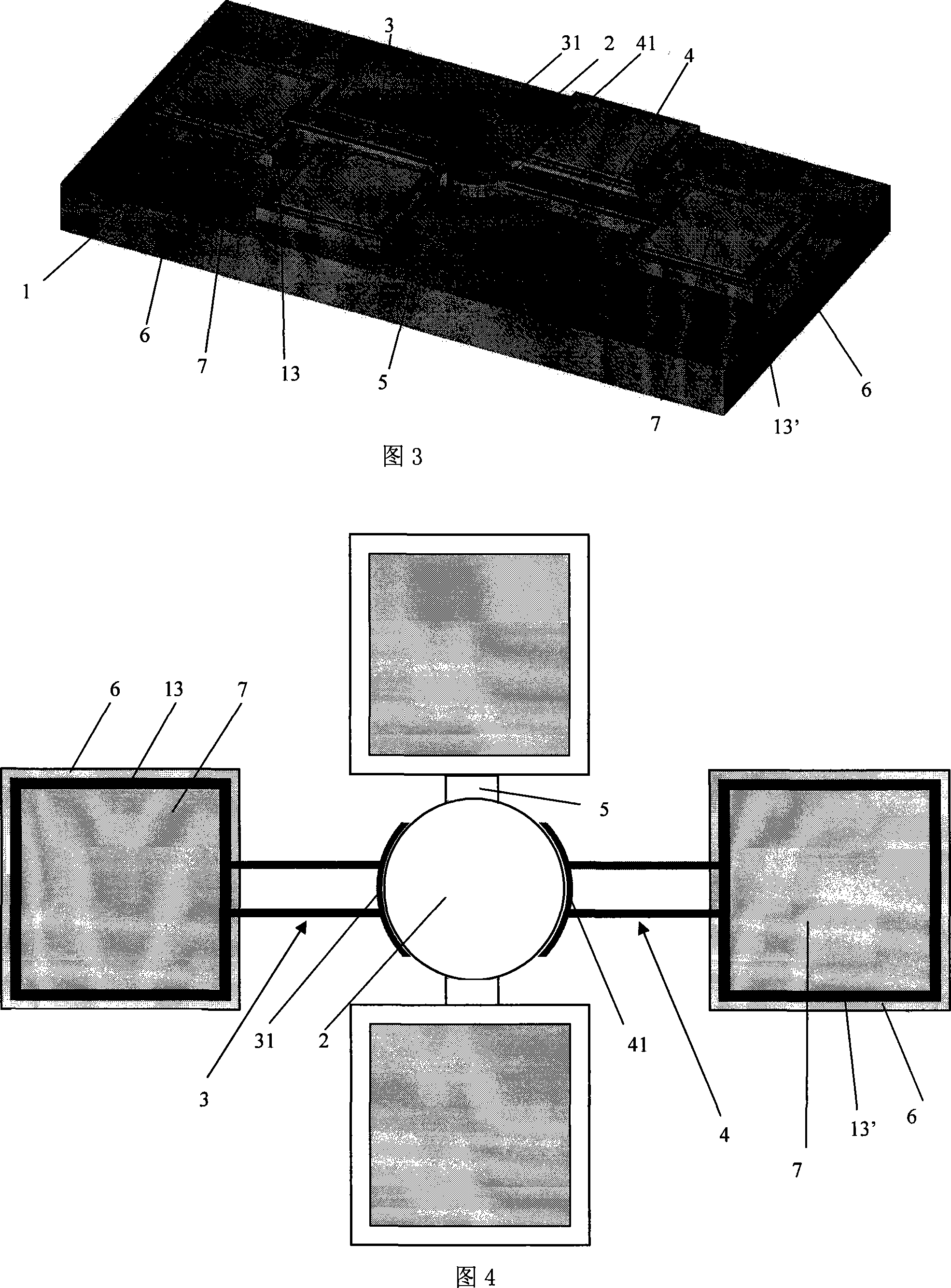

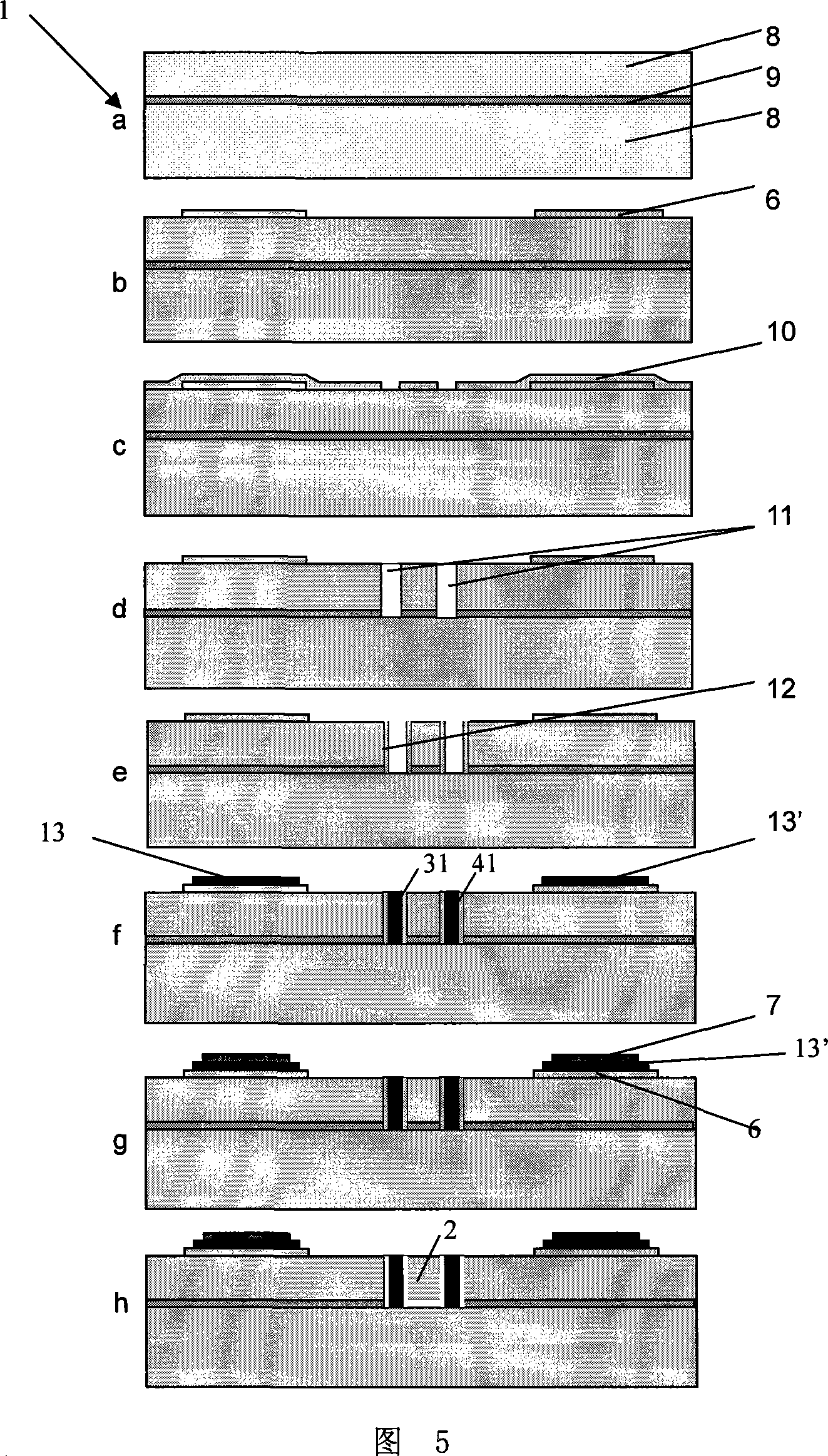

Self-stabilizing, floating microelectromechanical device

InactiveUS20050241394A1Eliminate mechanical wearReduce parasitic effectsAcceleration measurement using interia forcesPiezoelectric/electrostriction/magnetostriction machinesElectricityGyroscope

The present invention relates to MicroElectroMechanical Systems (MEMS), devices and applications thereof in which a proof mass is caused to levitate by electrostatic repulsion. Configurations of electrodes are described that result in self-stabilized floating of the proof mass. The electrical properties of the electrodes causing floating, such as currents and / or voltages, typically change in response to environmental perturbations affecting the proof mass. Measuring such currents and / or voltages allow immediate and accurate measurements to be performed related to those perturbations affecting the location and / or the orientation of the proof mass. Additional sensing electrodes can be included to further enhance sensing capabilities. Drive electrodes can also be included that allow forces to be applied to the charged proof mass resulting in a floating, electrically controllable MEMS device. Several applications are described including accelerometers, inertial sensors, resonators and filters for communication devices, gyros, one and two axis mirrors and scanners, among other devices. Several fabrication methods are also described.

Owner:RGT UNIV OF CALIFORNIA

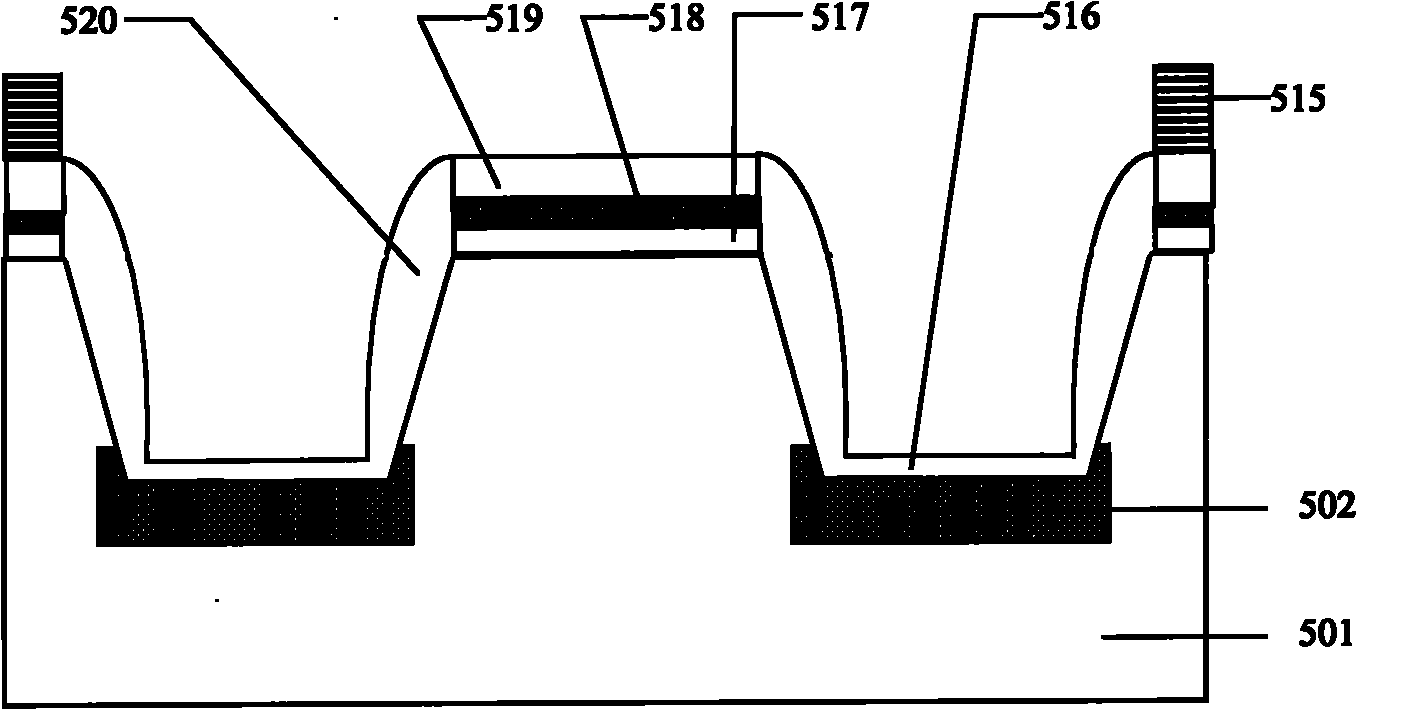

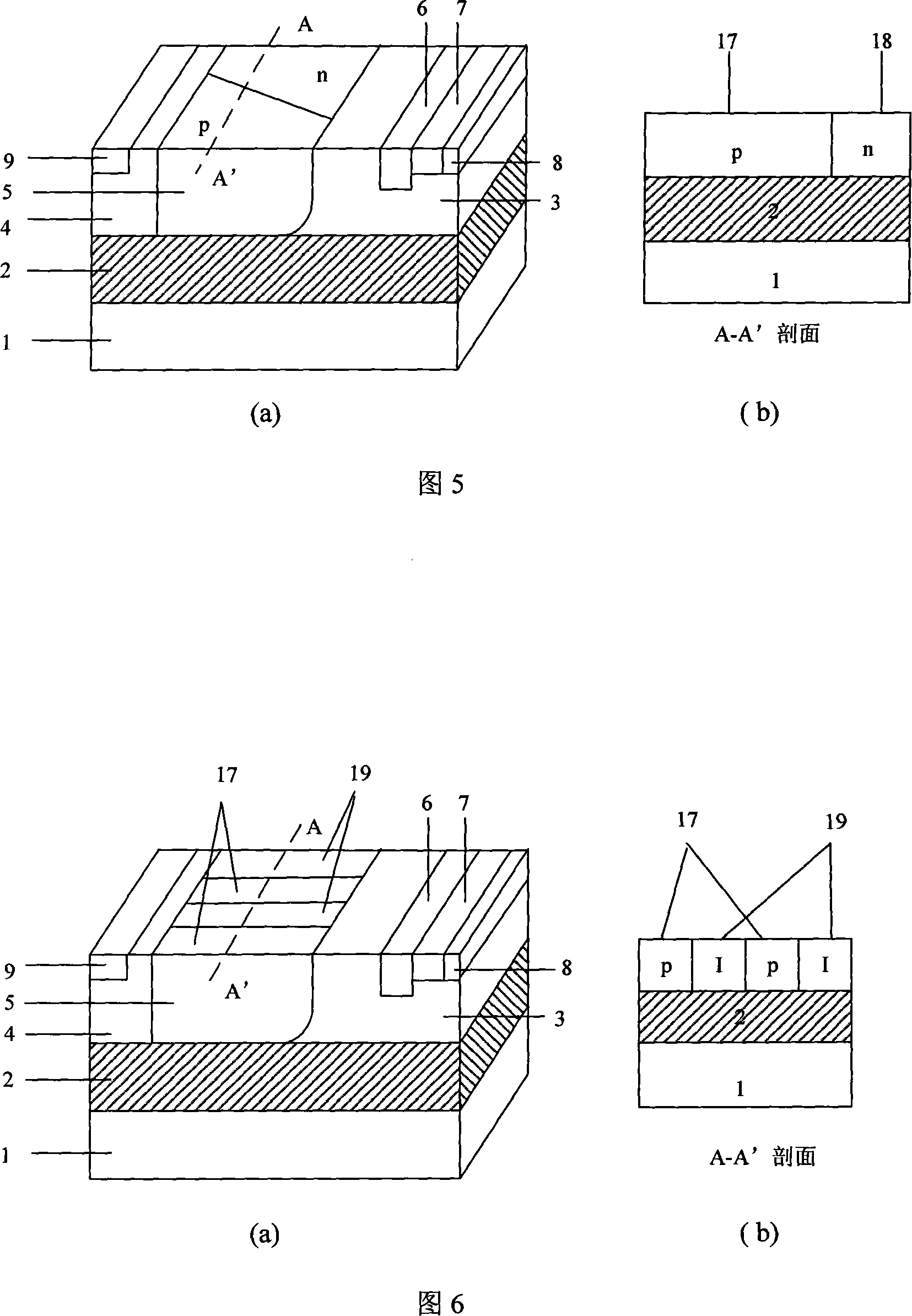

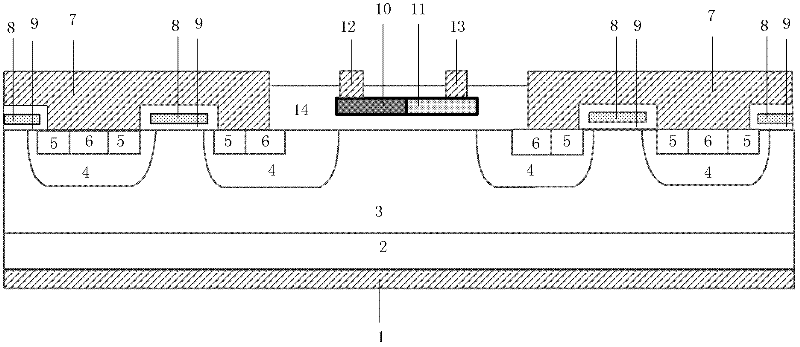

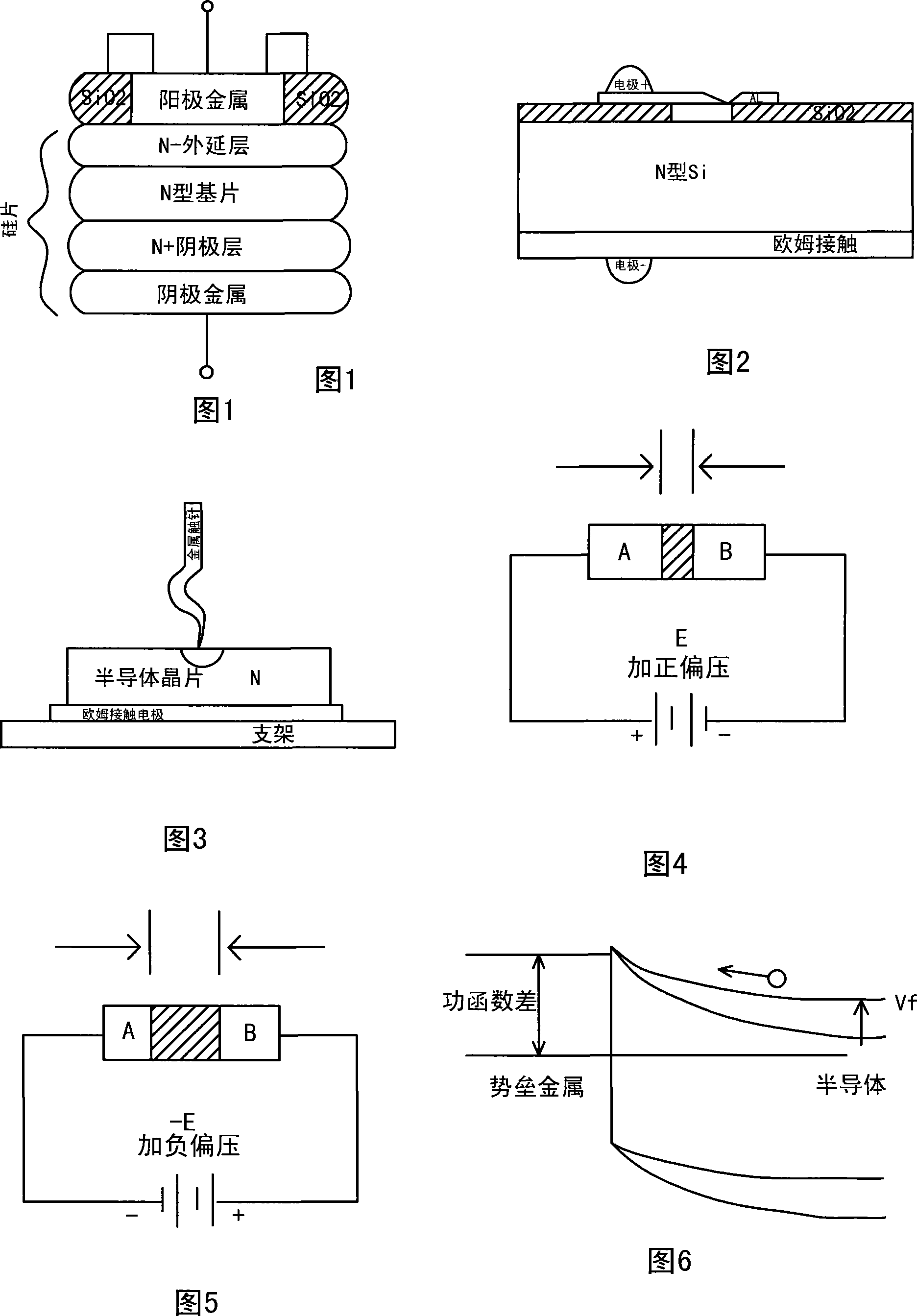

Bipolar transistor

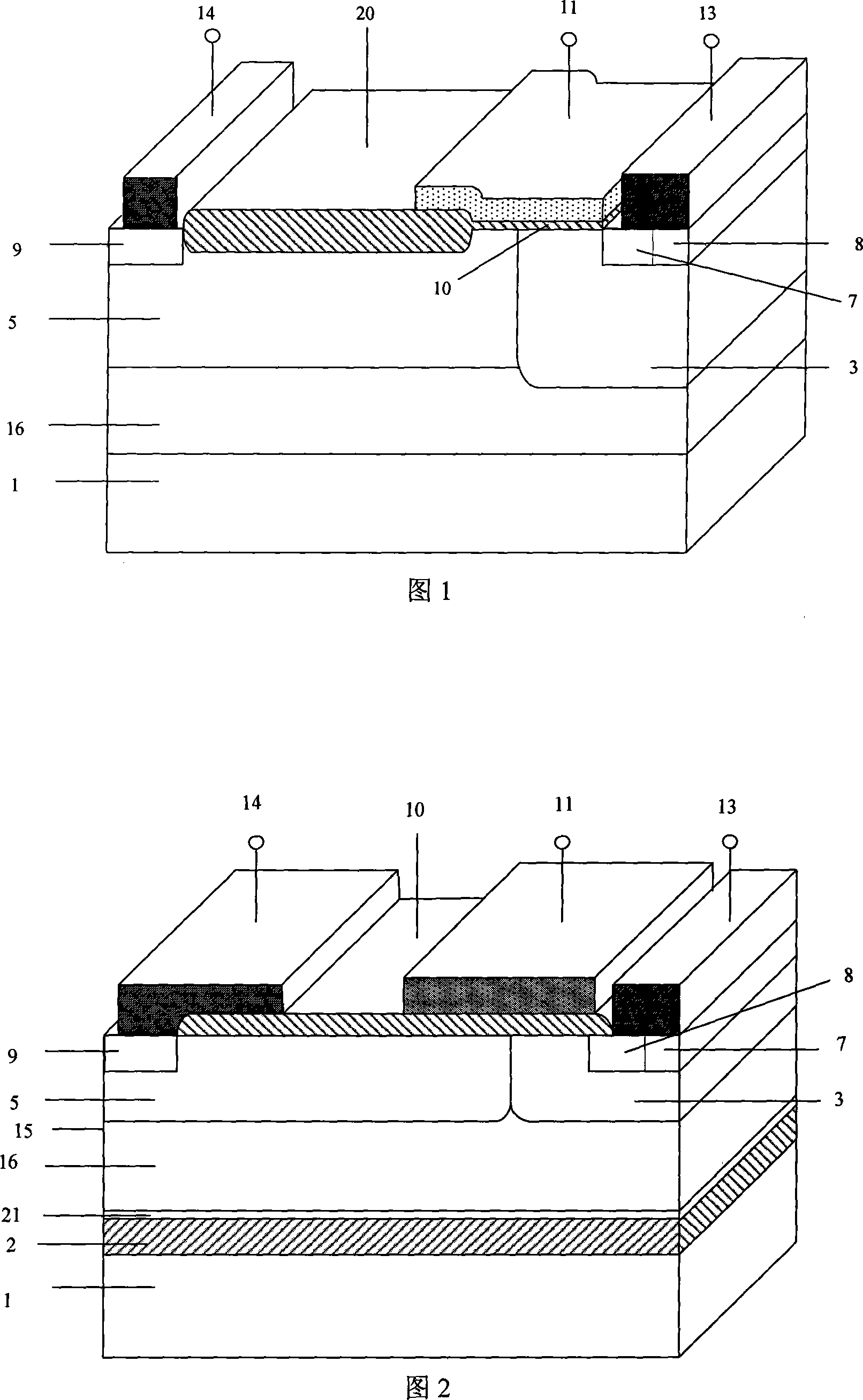

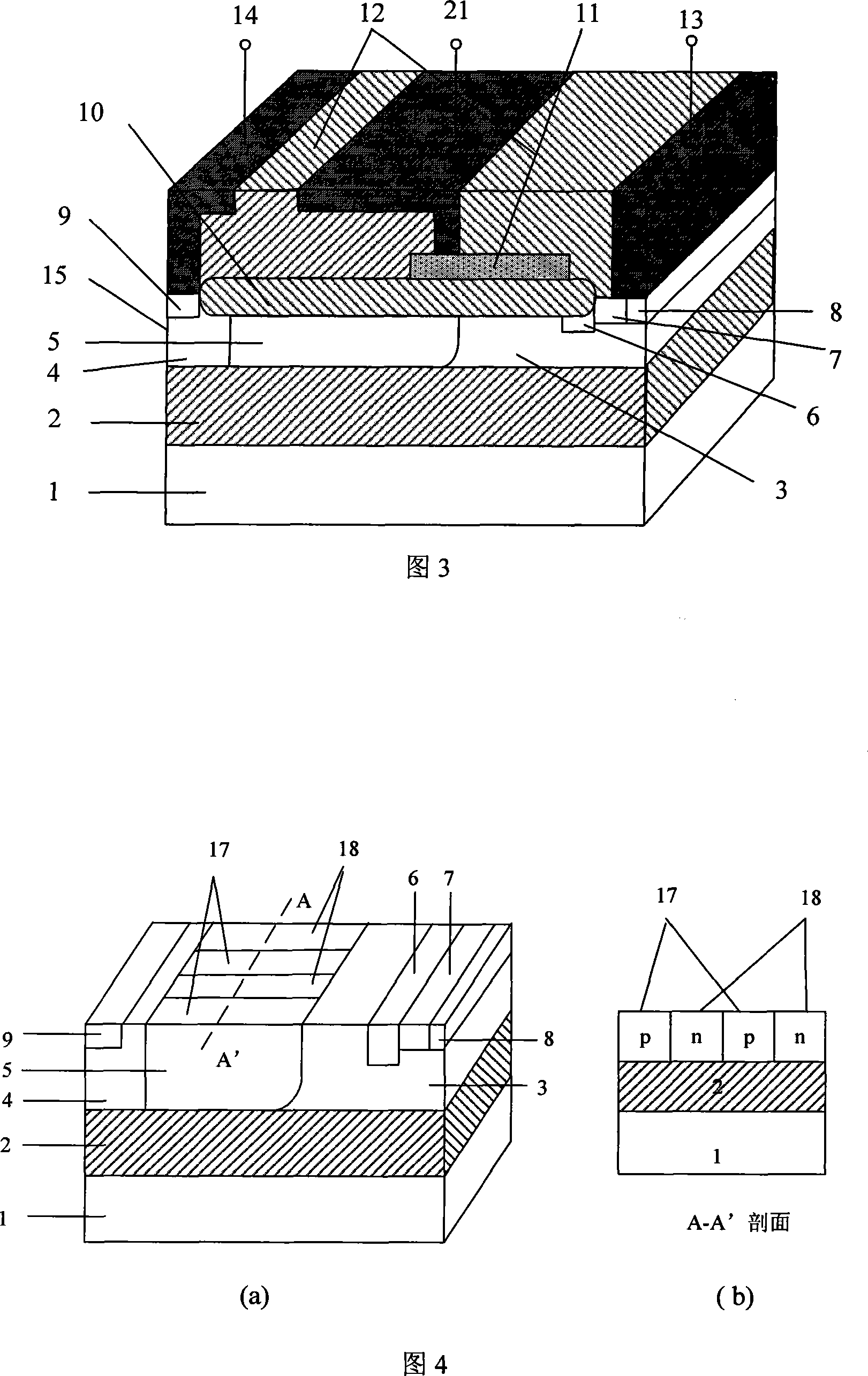

ActiveCN102104062AReduce areaReduce parasitic effectsTransistorSemiconductor/solid-state device manufacturingIon implantationImpurity

The invention discloses a bipolar transistor. An active area is isolated by shallow-trench field oxide. The bipolar transistor comprises a collector region, a base region and a transmission region, wherein the collector region is formed by a first conductive type foreign ion injection layer which are formed in the active area, and a buried layer formed by connection of two first conductive type pseudo-buried layers is connected to the bottom of the collector region, and the pseudo-buried layer is formed by injecting first conductive type foreign ions which are injected from the bottom of trenches at two sides of the active area; deep groove contact is manufactured in field oxide on the pseudo-buried layer to lead out a collector; the base region is formed by a second conductive type film which is formed on the collector region; and the transmission region is formed by first conductive type polycrystalline silicon which is formed on the base region. The bipolar transistor can reduce the device area, the parasitic effect, the number of photoetching layers and the process cost.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

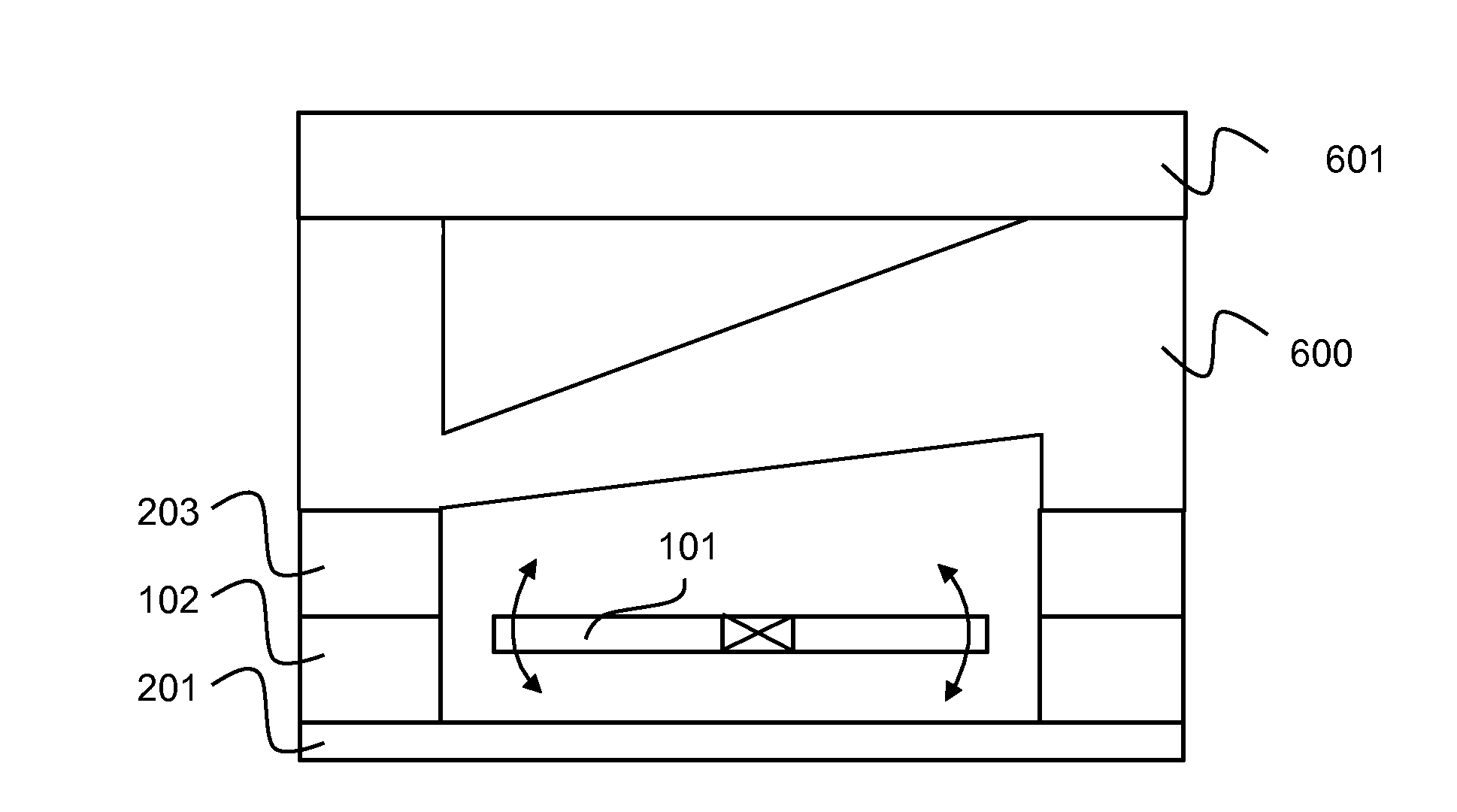

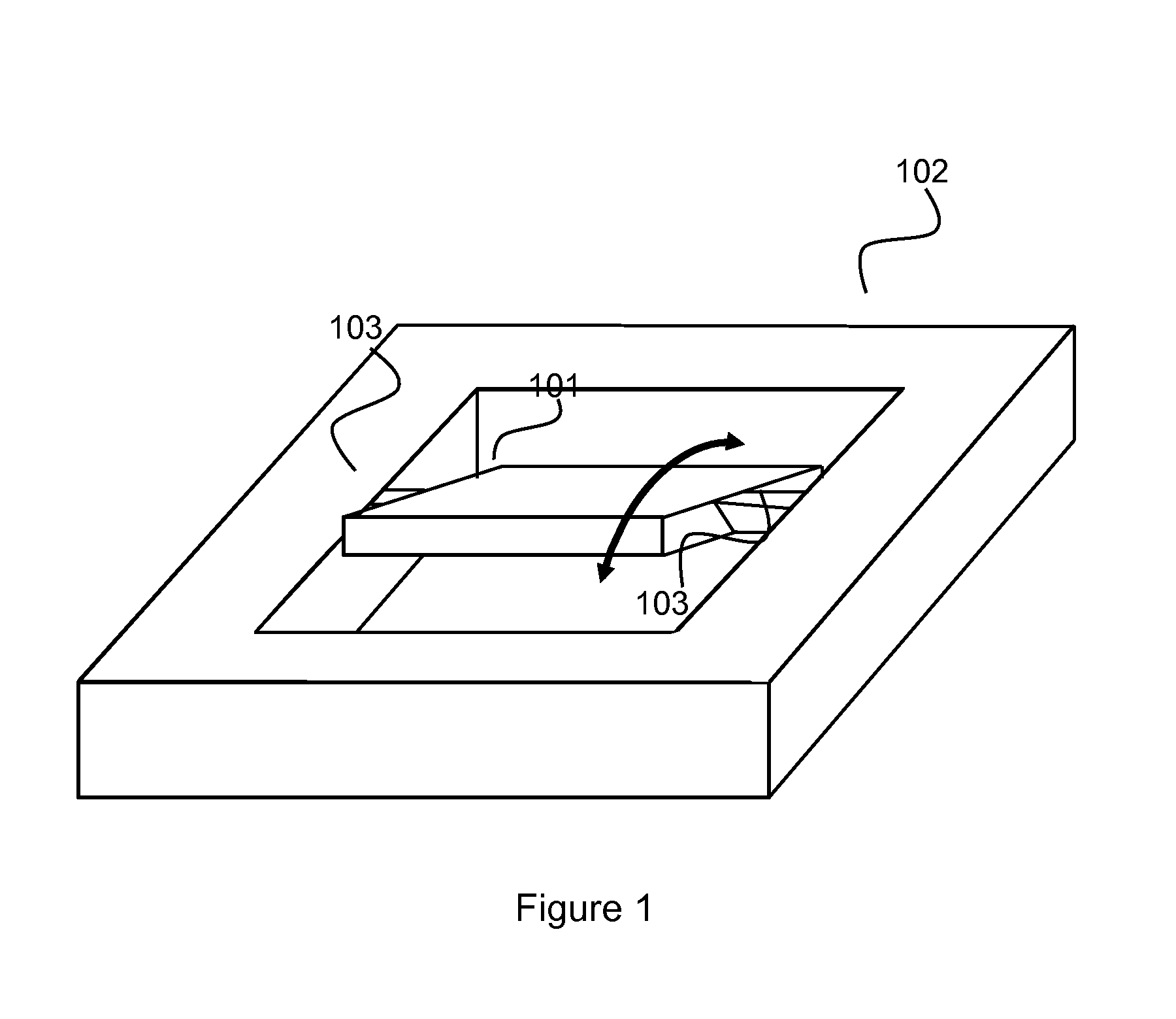

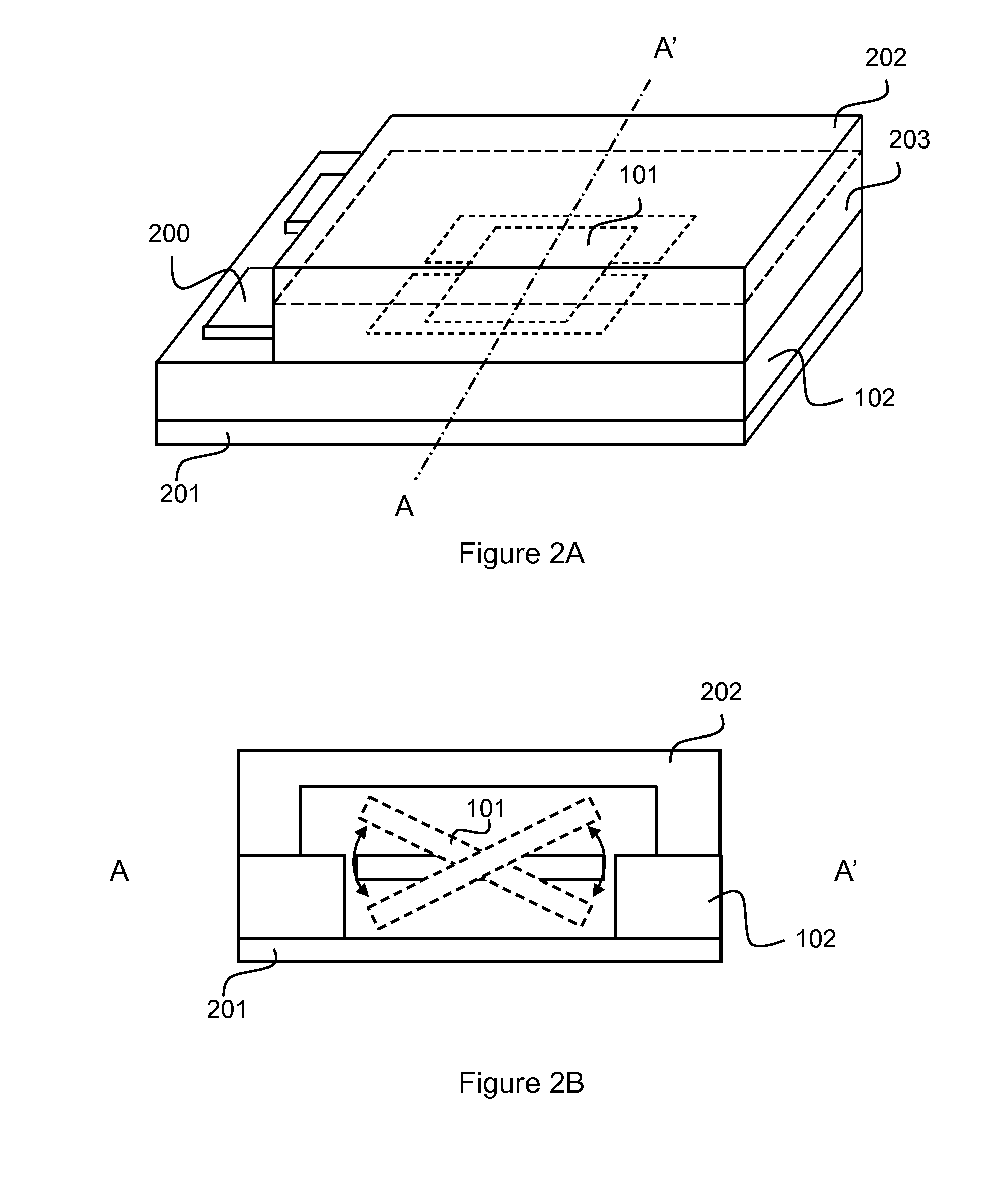

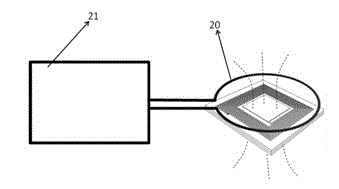

Optical MEMS scanning micro-mirror with speckle reduction

ActiveUS20130242275A1Reducing and suppressing speckleAvoid parasitic reflectionsProjectorsOptical elementsNeutral planePrism

Optical MEMS scanning micro-mirror comprising:—a movable scanning micro-mirror (101) pivotally connected to a MEMS body (102) substantially surrounding the lateral sides of the micro-mirror;—an transparent prism (500, 600) substantially covering the reflection side of the micro-mirror;—wherein said prism has its outer face non-parallel to the micro-mirror neutral plane N-N, thereby providing a dual anti-speckle and anti-reflection effect, namely against parasitic light. The invention also provides the corresponding micro-projection system and method for reducing speckle.

Owner:GOOGLE LLC

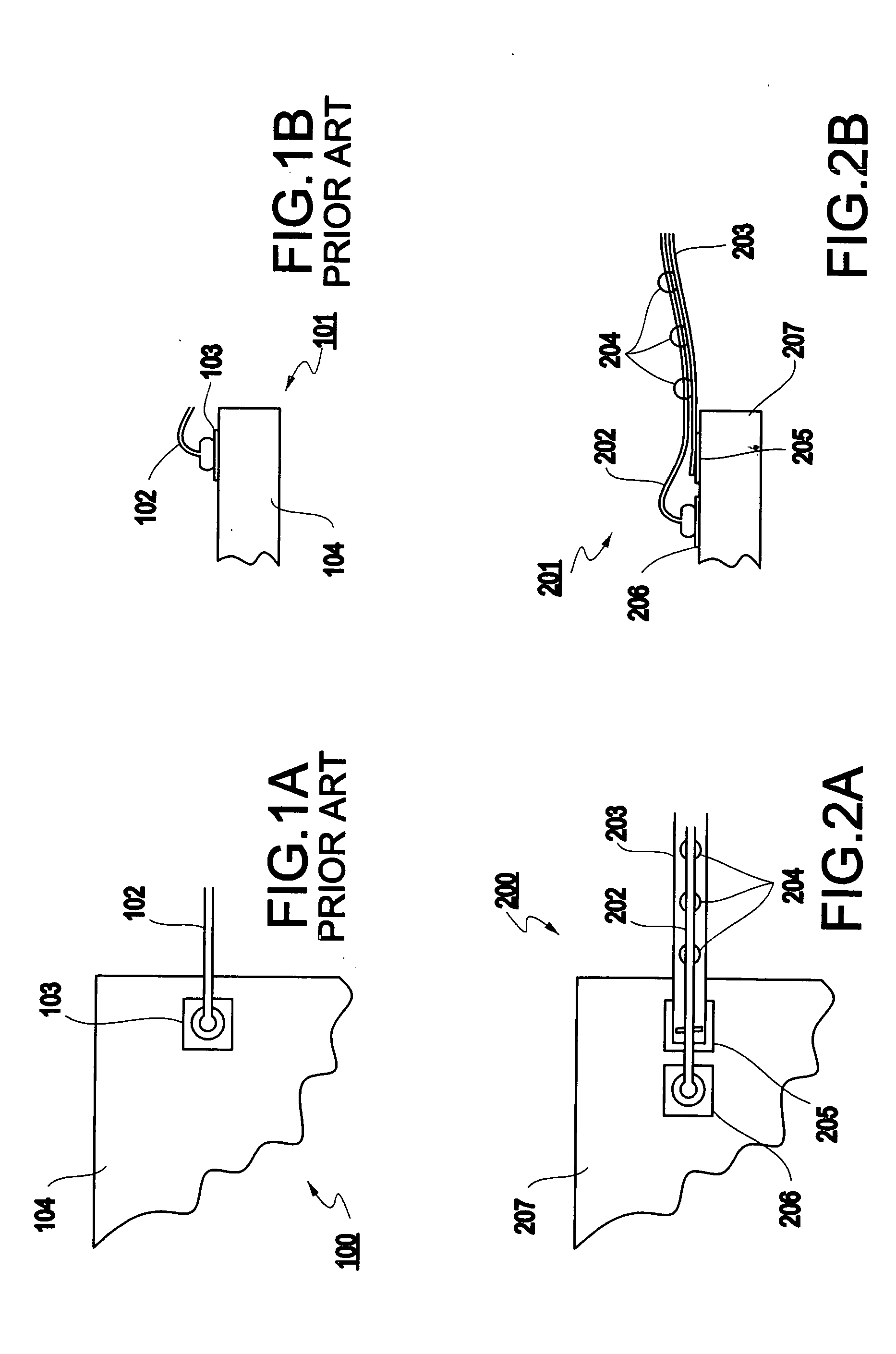

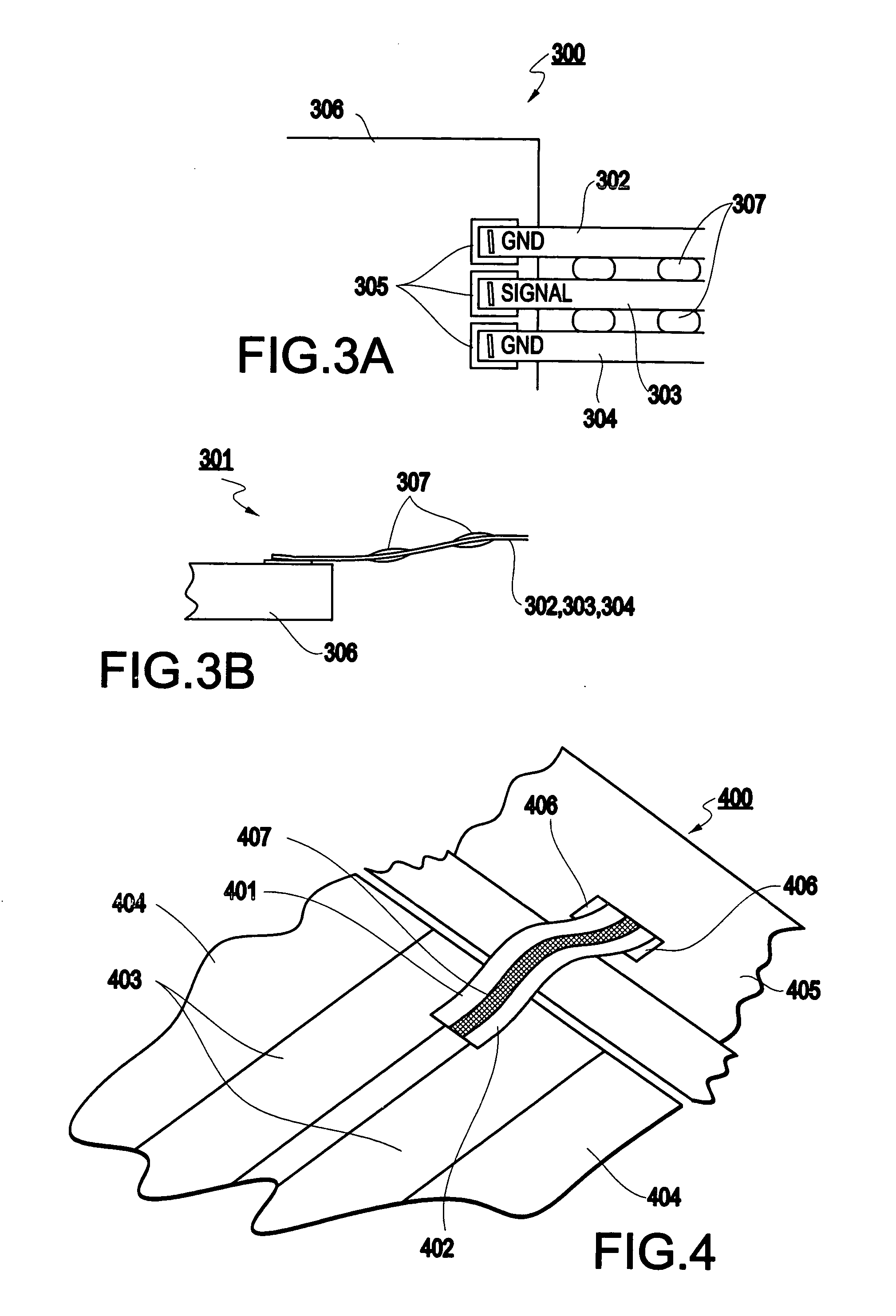

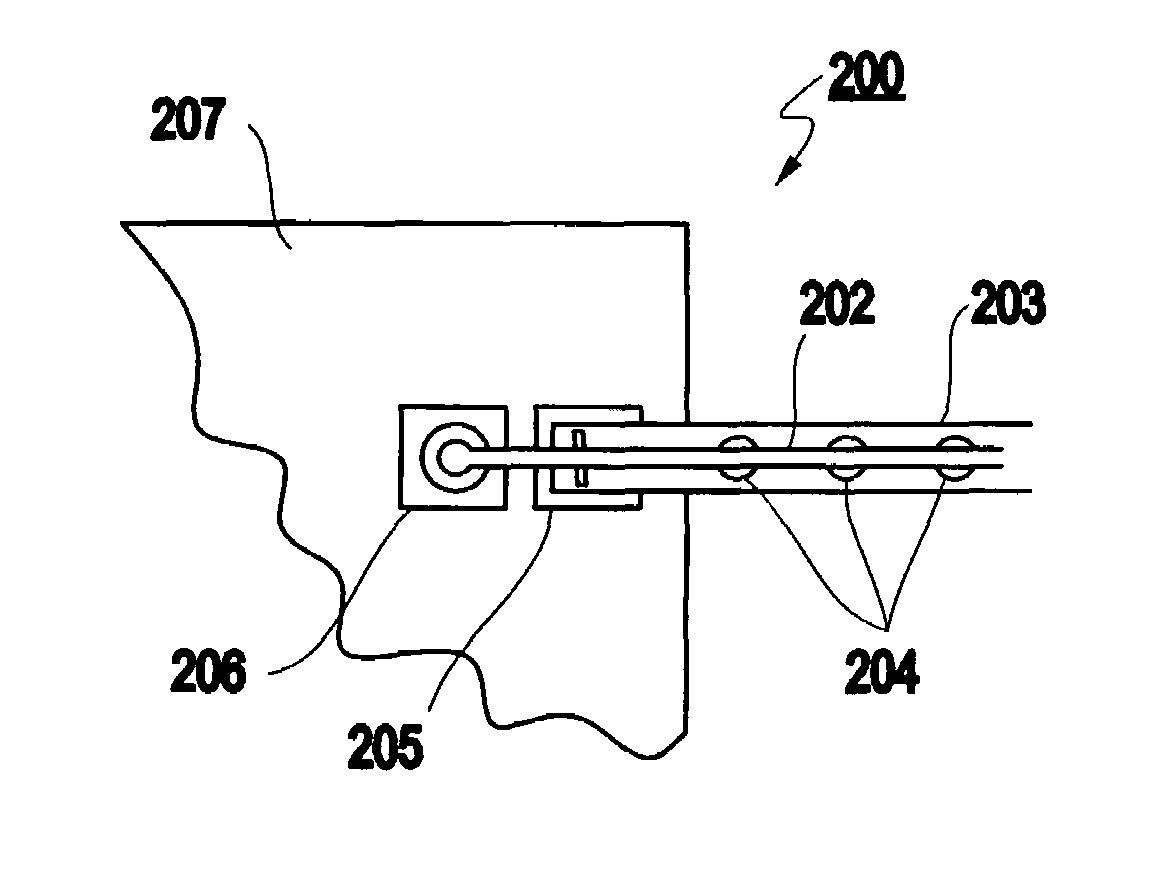

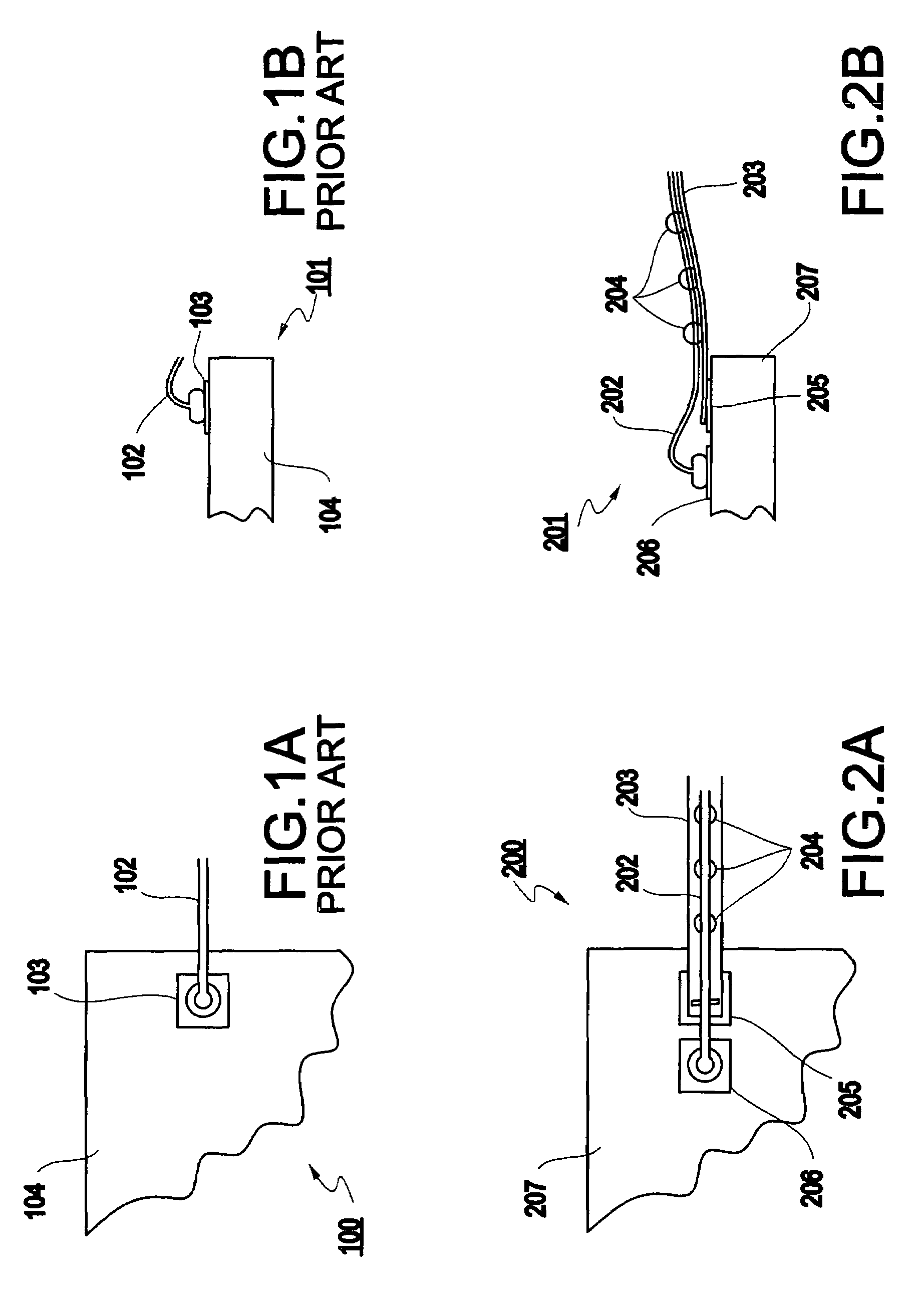

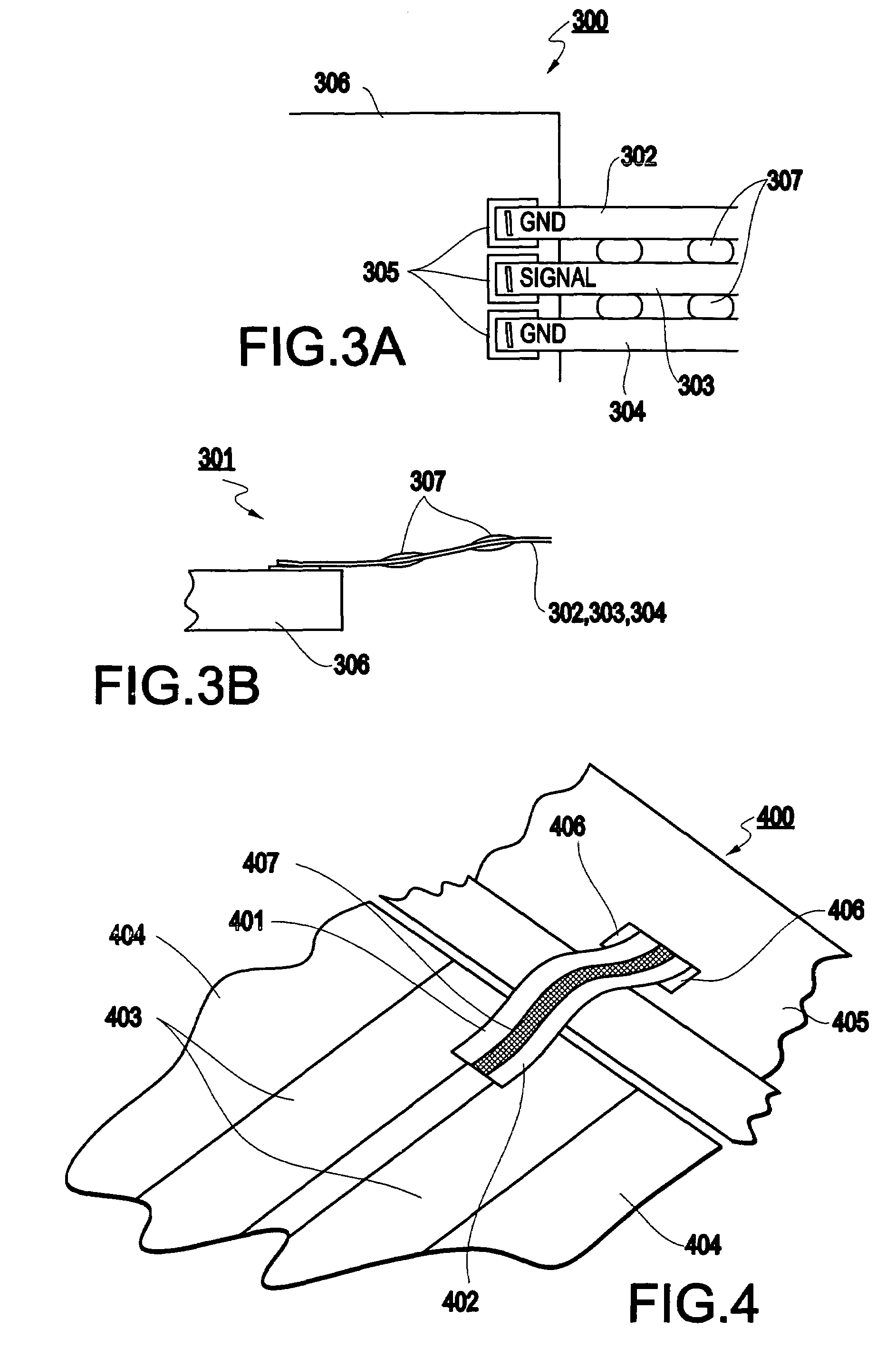

Method and structure for controlled impedance wire bonds using co-dispensing of dielectric spacers

InactiveUS20050116013A1Low costLow production costCross-talk/noise/interference reductionSemiconductor/solid-state device detailsEngineeringInterconnection

A method (and structure) of making an electronic interconnection, includes, for a signal line to be interconnected, using a plurality of bonding wires configured to provide a controlled impedance effect.

Owner:GLOBALFOUNDRIES INC

A plane capacitance resonator and its making method

InactiveCN101127514AReduce parasitic effectsReduce power consumptionTelevision system detailsImpedence networksCapacitanceMetal electrodes

The utility model discloses a planar capacitance resonator and the related preparation method, comprising a resonance body, a sensor electrode, a driving electrode and a related supporting substrate. The resonator is a suspended structure, and is fixed on the substrate through an anchor point; each of the sensor electrode and the driving electrode comprises an electrode plate and a solder pad, the electrode plates of the sensor electrode and the driving electrode are arranged on the two side of the resonance body separately and keep a clearance from the resonance body, the clearance between the plates performs as the media to form the capacitor structure; the solder pads of the sensor electrode and the driving electrode are fixed on the insulating medium layer, and the solder pads are provided with metal electrodes; the insulating medium layer are fixed on the substrate. The clearance between the any two electrodes of the capacitors is narrower than 100nm. The utility model has the advantages of extremely high dynamic performance, the harmonic resonance frequency exceeding 100 MHz, and the Q factor up to 105.

Owner:PEKING UNIV

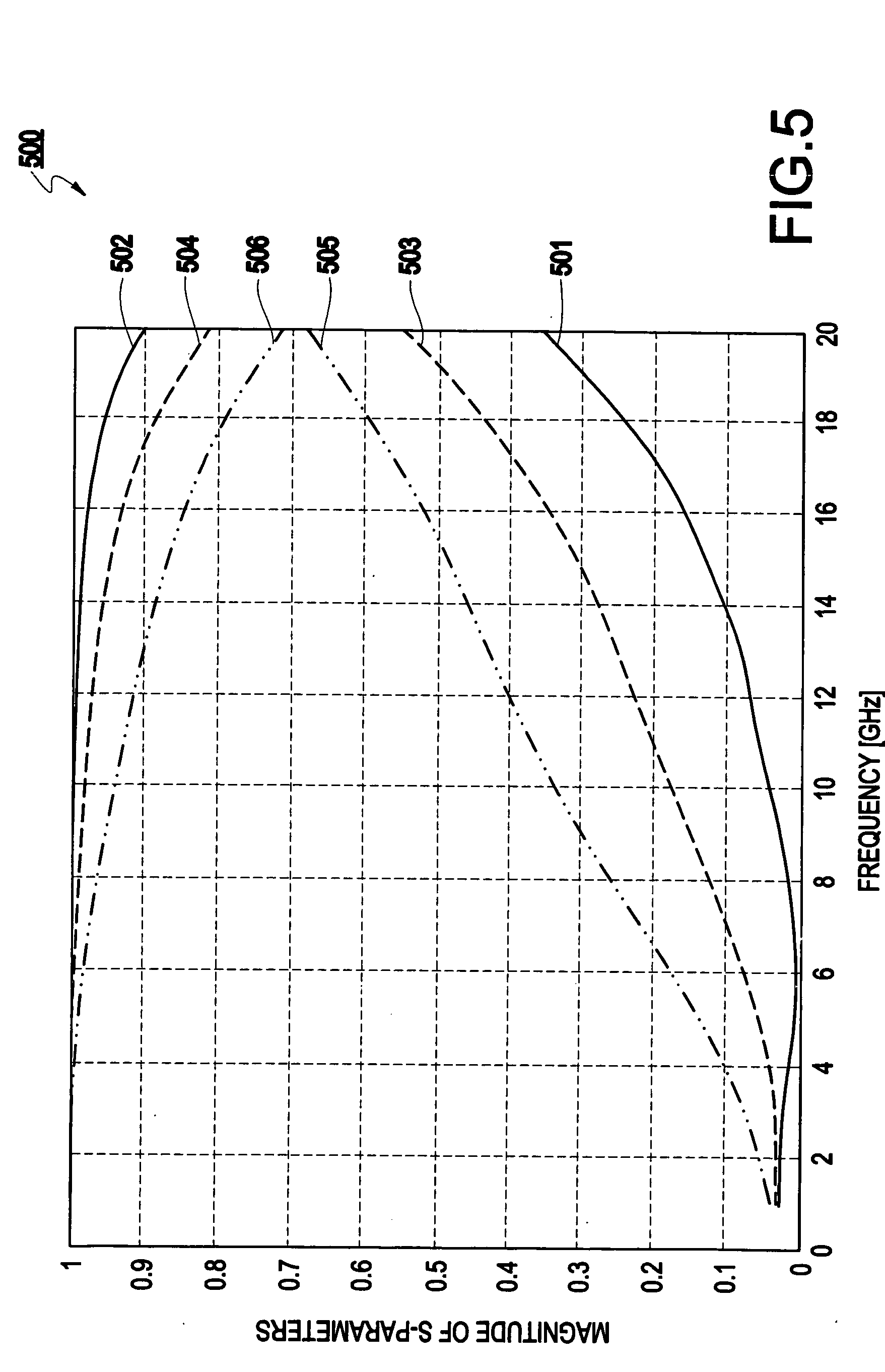

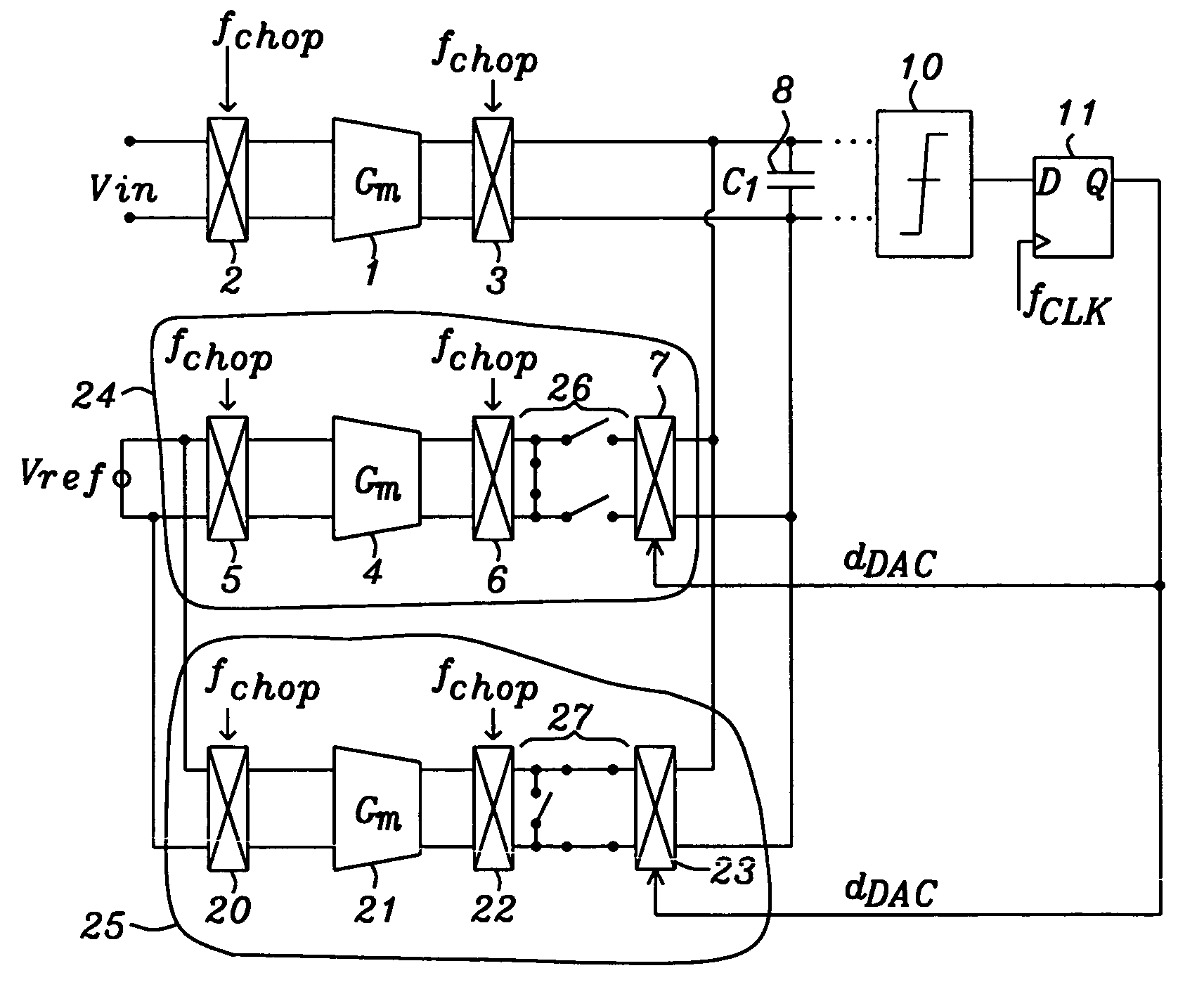

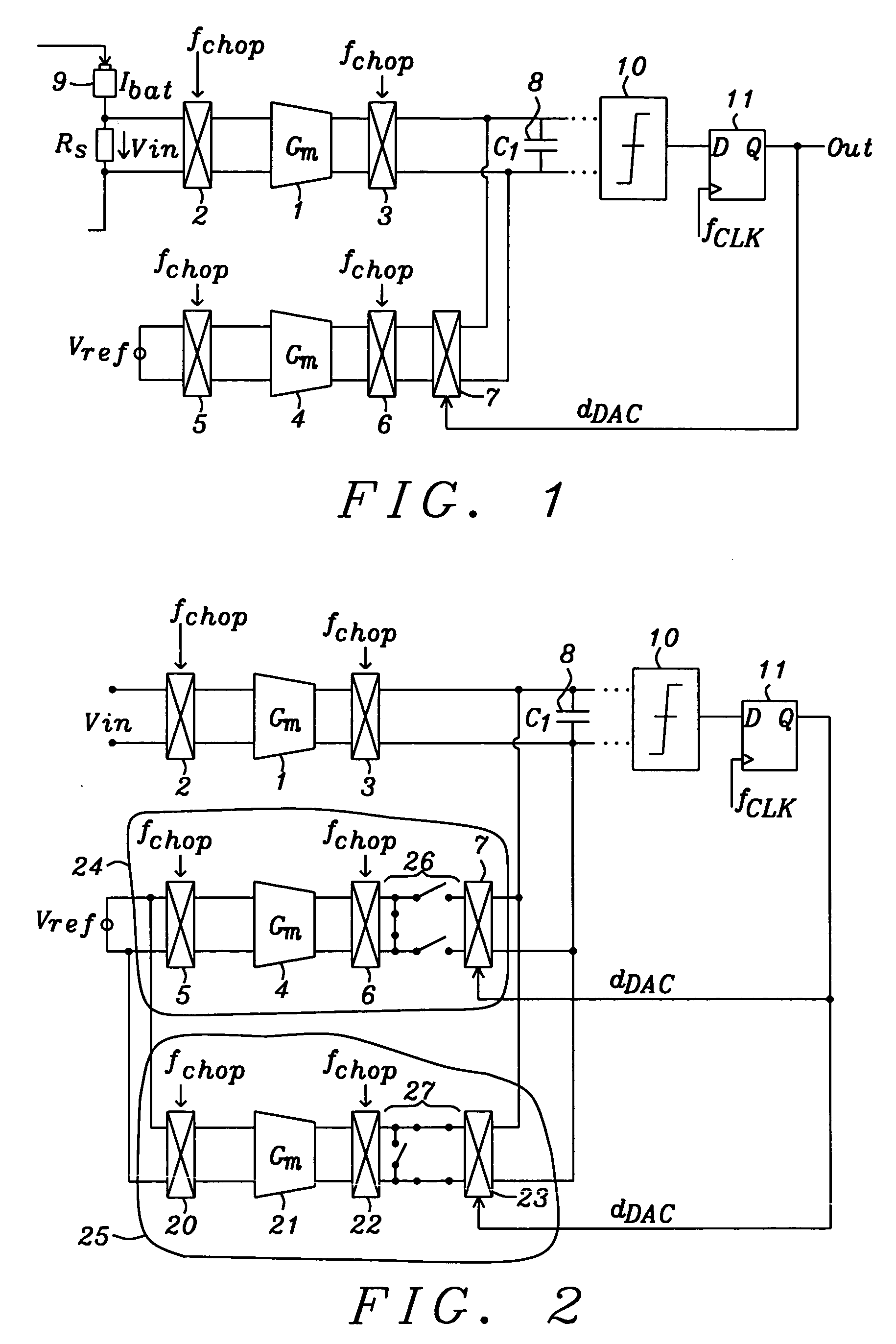

Sigma-delta modulator

ActiveUS7250886B1Reduce noiseReduce parasitic effectsElectric signal transmission systemsAnalogue conversionLow noiseIntegrator

Circuits and methods to achieve a low-noise and low offset continuous sigma-delta modulator used e.g. for battery management are disclosed. Continuous integration of input is enabled by special switching principle of three parallel integrators. Precharging of integrator output in so called pre-run mode minimizes integrator leakage and non-ideal effects by connecting a Gm in pre-run mode either to input voltage or to a reference voltage depending this Gm is being used in a following clock period. Parasitic effects due to switching at first integration capacitor are minimized by using buffer amplifiers tracking the voltage on integration capacitors.

Owner:DIALOG SEMICONDUCTOR GMBH

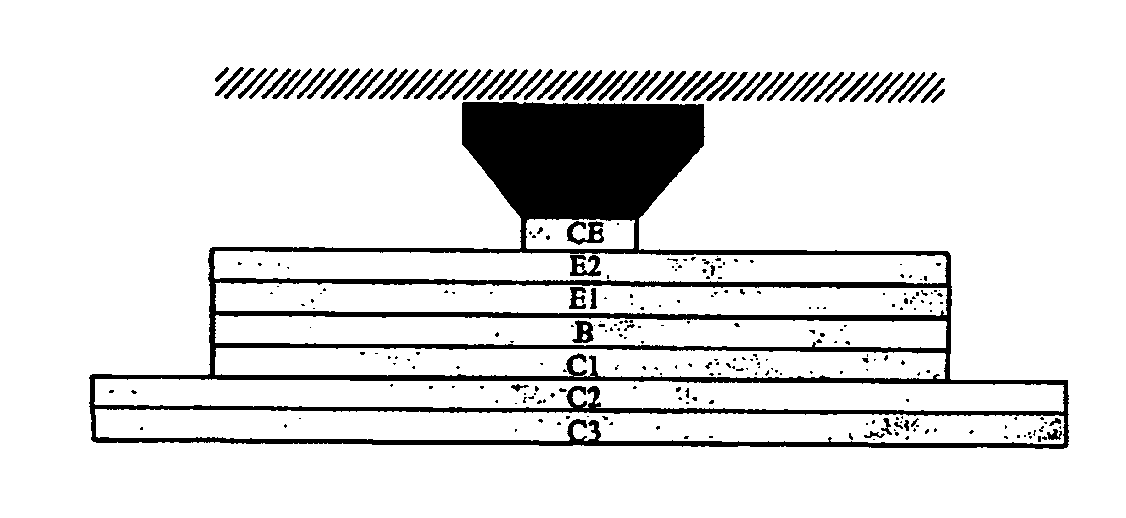

Method for Making a Heterojunction Bipolar Transistor

ActiveUS20100001319A1Reduce distortionGuaranteed CompatibilitySemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringHeterojunction bipolar transistor

The invention concerns a heterojunction bipolar transistor comprising a support, and epitaxially grown from said support, at least: one collecting, respectively emitting, layer; at least one base layer; and at least one emitting, respectively collecting, layer. The collecting, respectively emitting, layer comprises: at least one first undercoat contacted with said base layer, substantially of similar composition as said emitting, respectively collecting, layer; and at least one second undercoat on the side opposite said base layer relative to said first undercoat.

Owner:CENT NAT DE LA RECHERCHE SCI +1

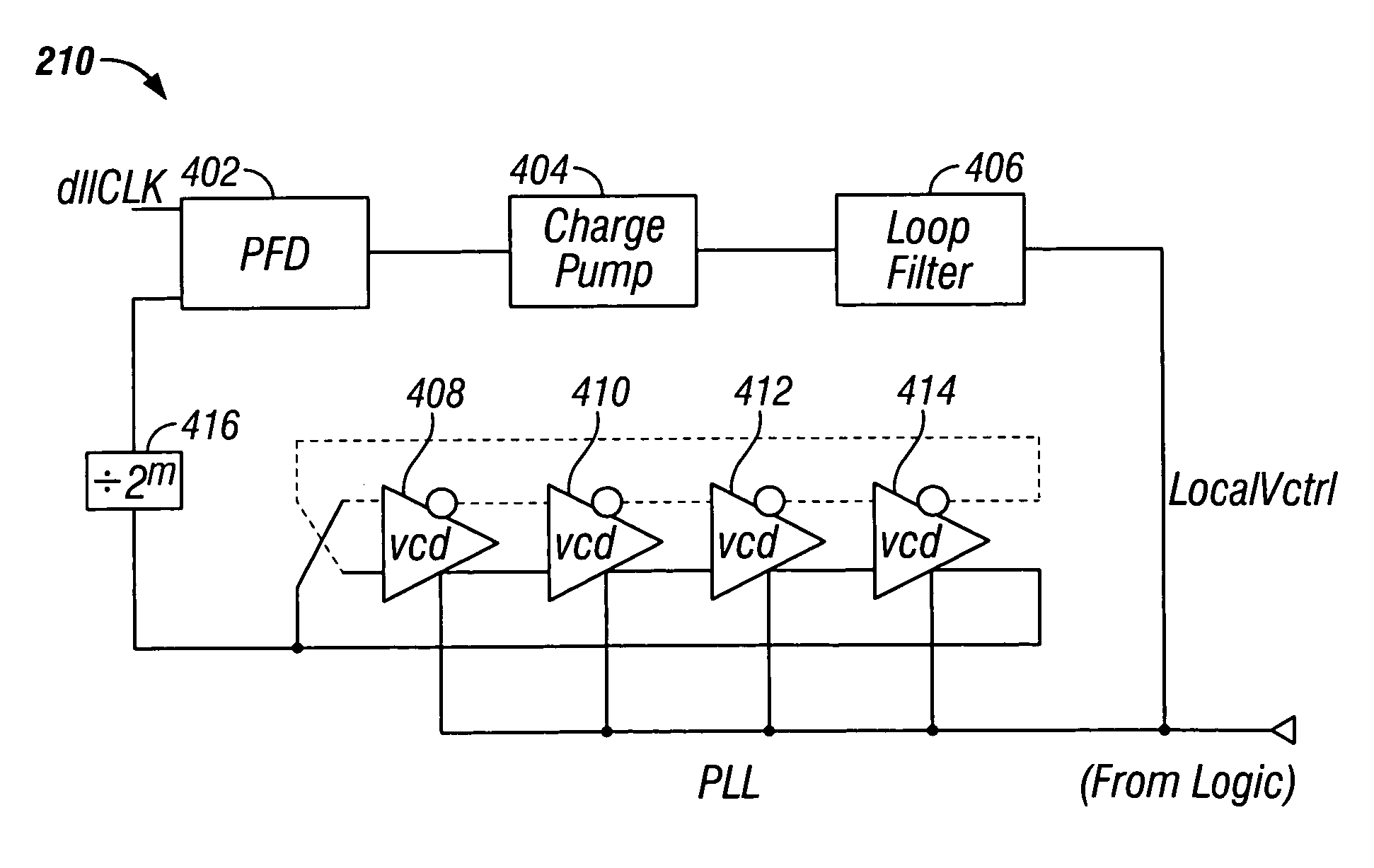

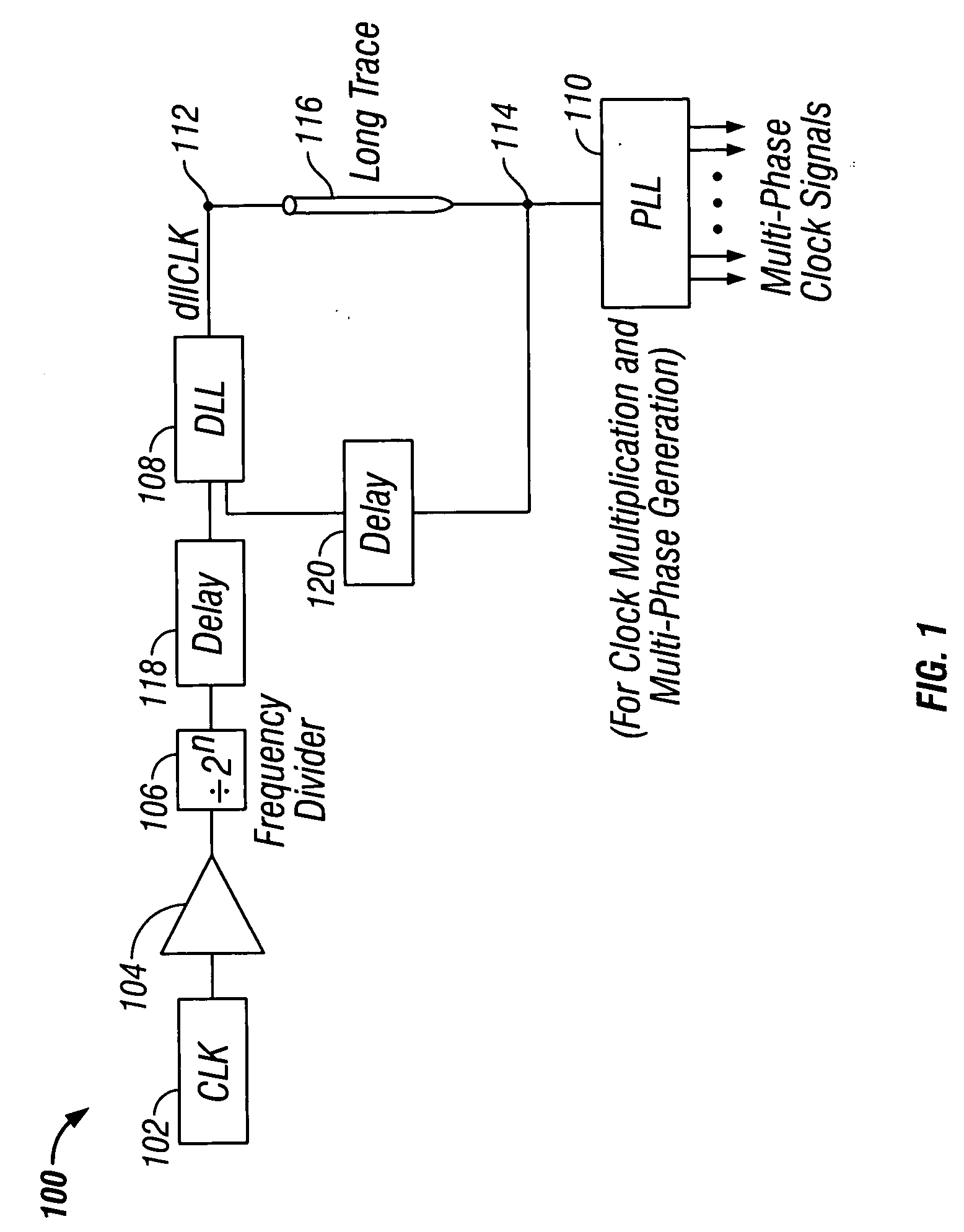

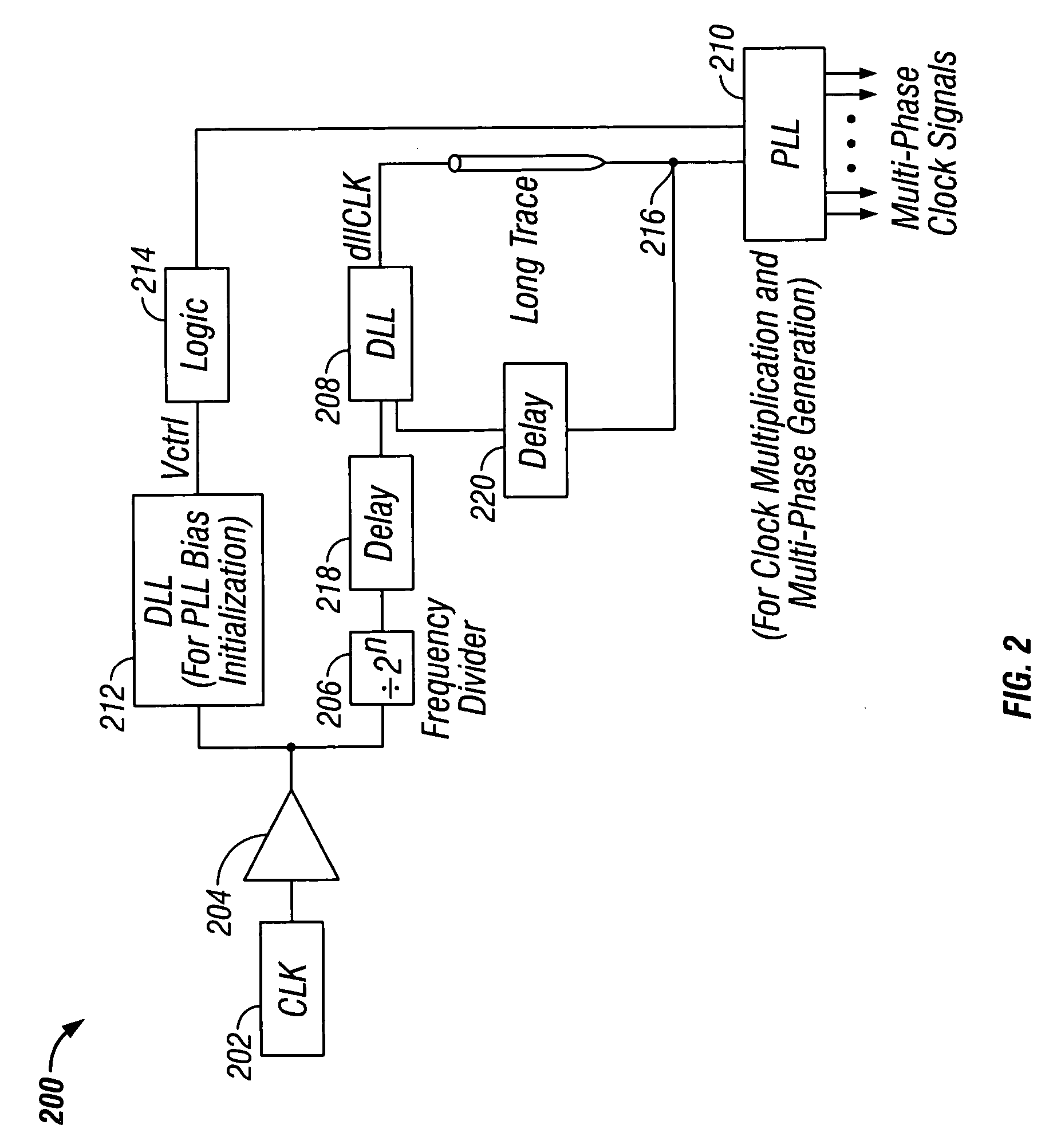

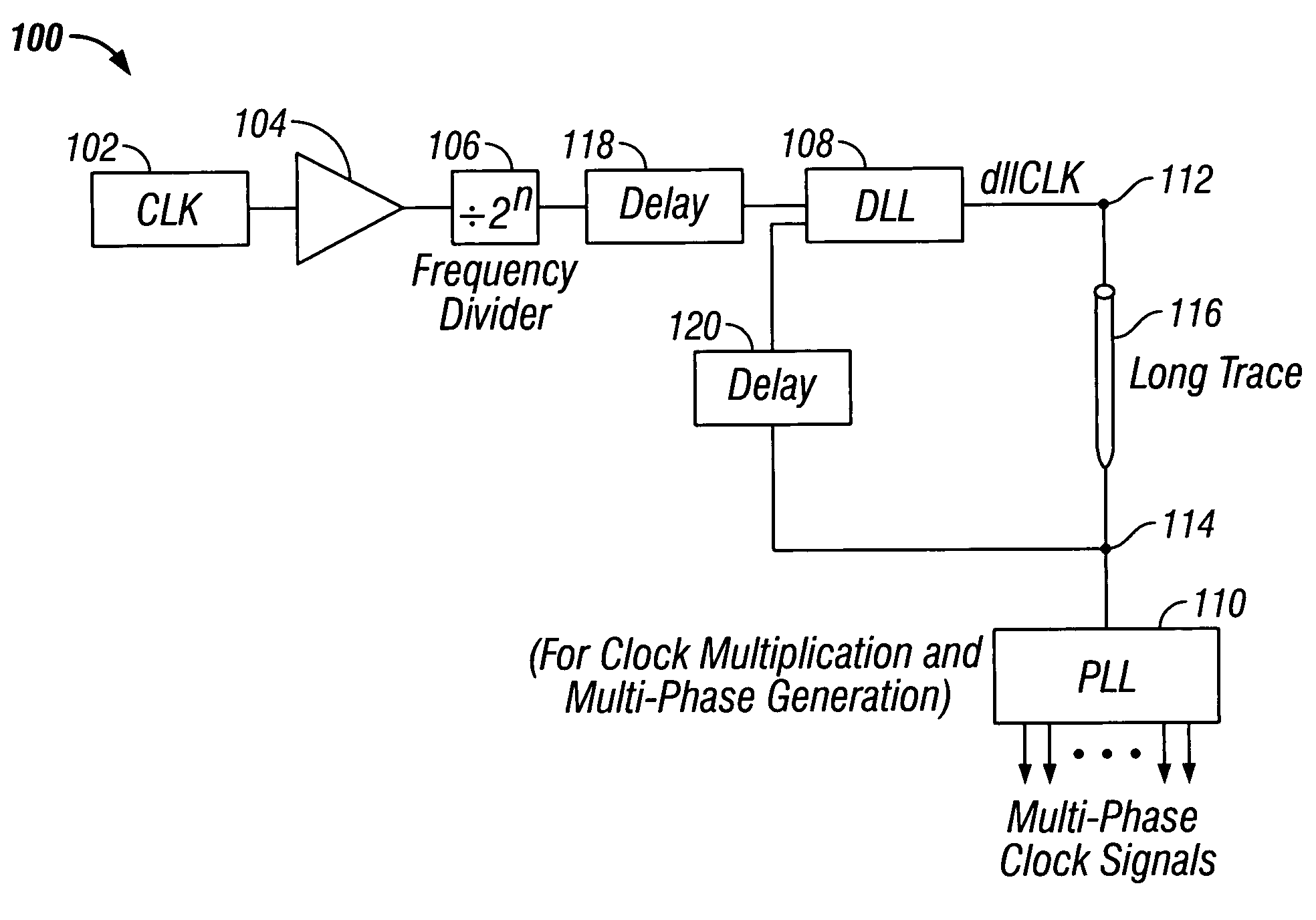

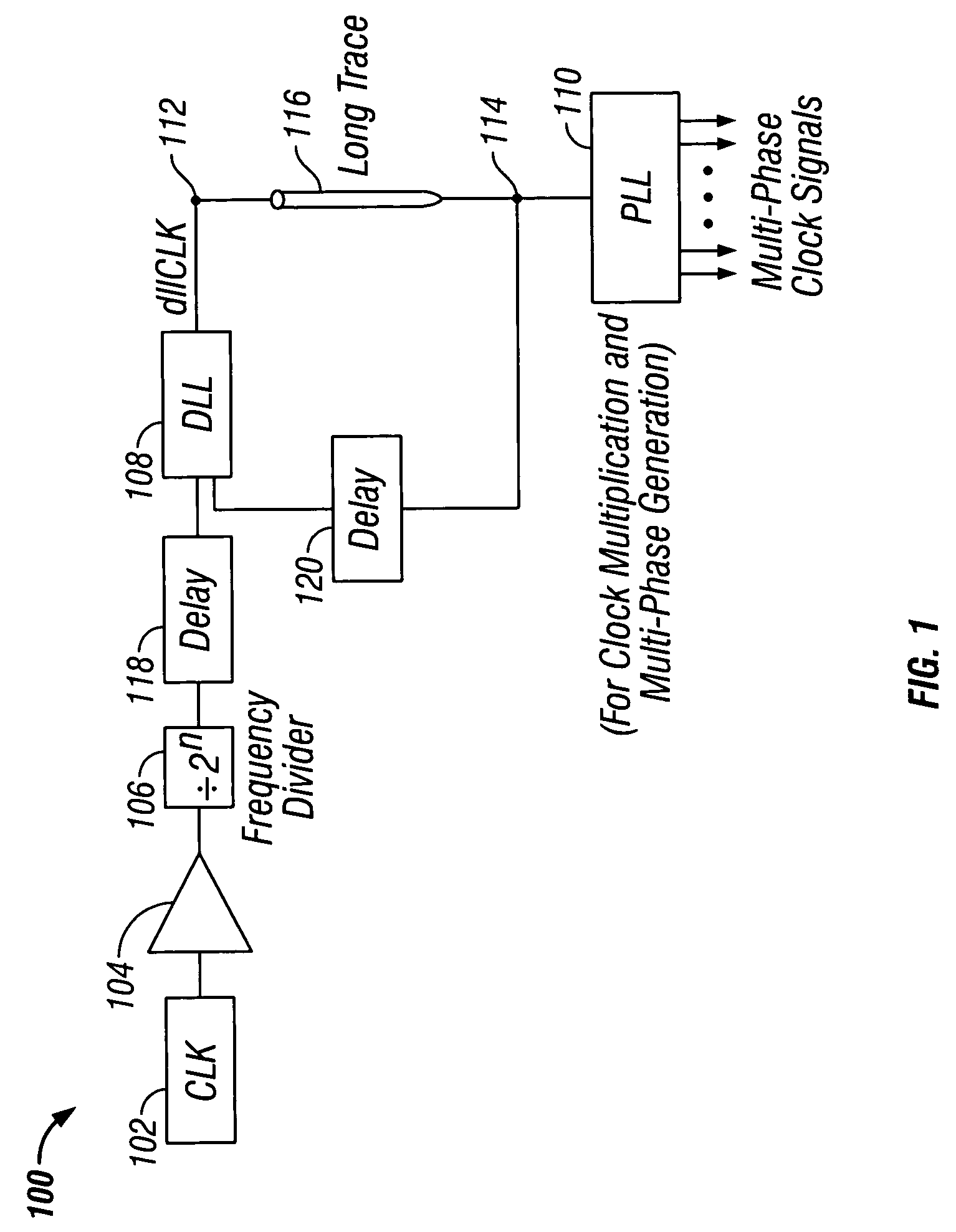

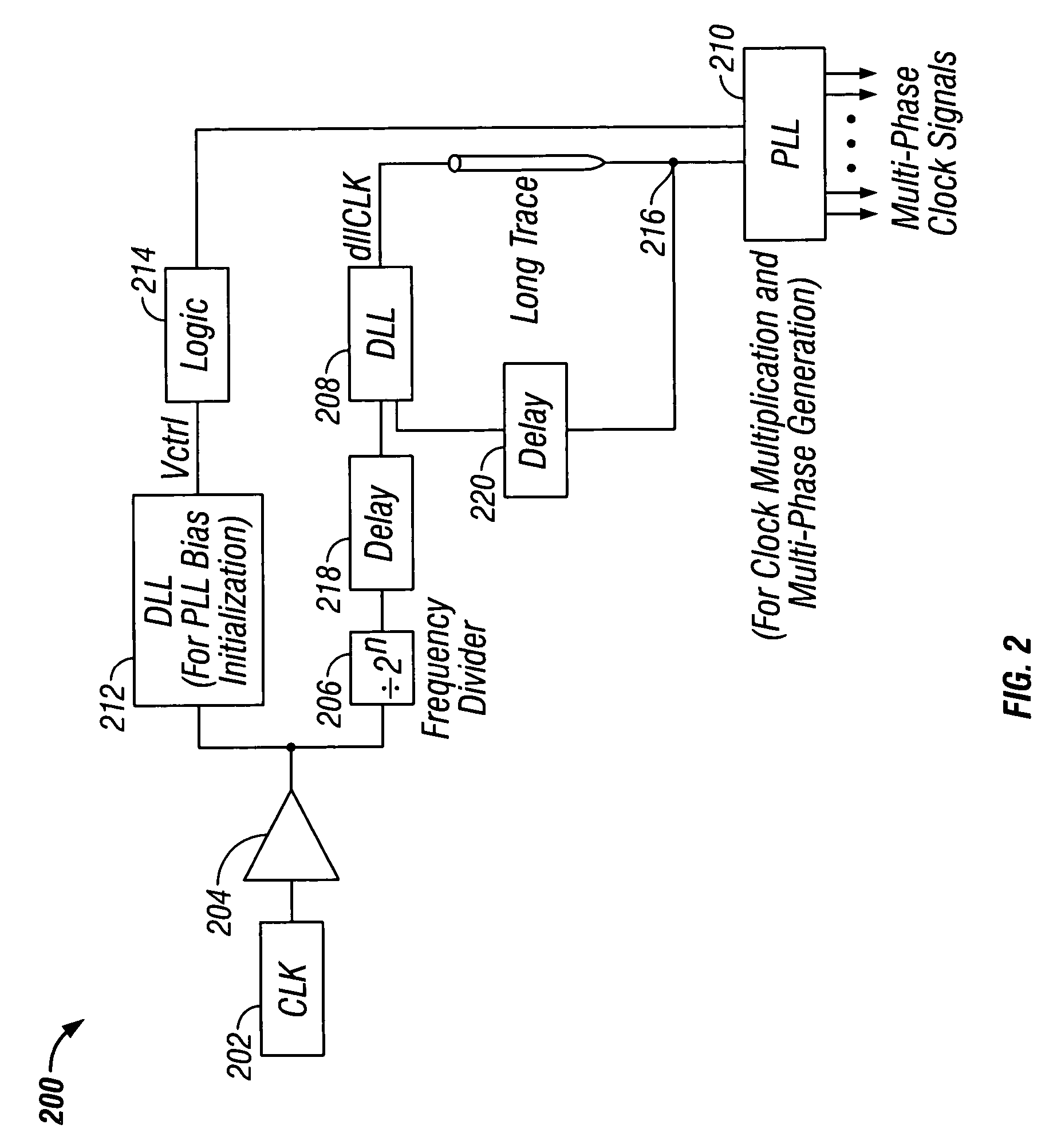

Clock signal distribution with reduced parasitic loading effects

ActiveUS20050134337A1Reduced parasitic loading effectReduce load effectPulse automatic controlGenerating/distributing signalsDelay-locked loopDistribution system

Clock signal distribution systems with reduced parasitic loading effects are provided. A reference clock is frequency-divided to produce a lower frequency clock signal. A delay-locked loop (DLL) circuit locks to the lower frequency clock signal, and outputs a corresponding lower frequency clock signal for distribution over a long trace. Power consumption caused by parasitic capacitance of the trace is thereby reduced. Parasitic effects associated with clock jitter are also reduced. A frequency multiplying phase-locked loop (PLL) circuit locks to the lower frequency clock signal, and outputs at least one clock signal having a higher frequency than the lower frequency signal.

Owner:MICRON TECH INC

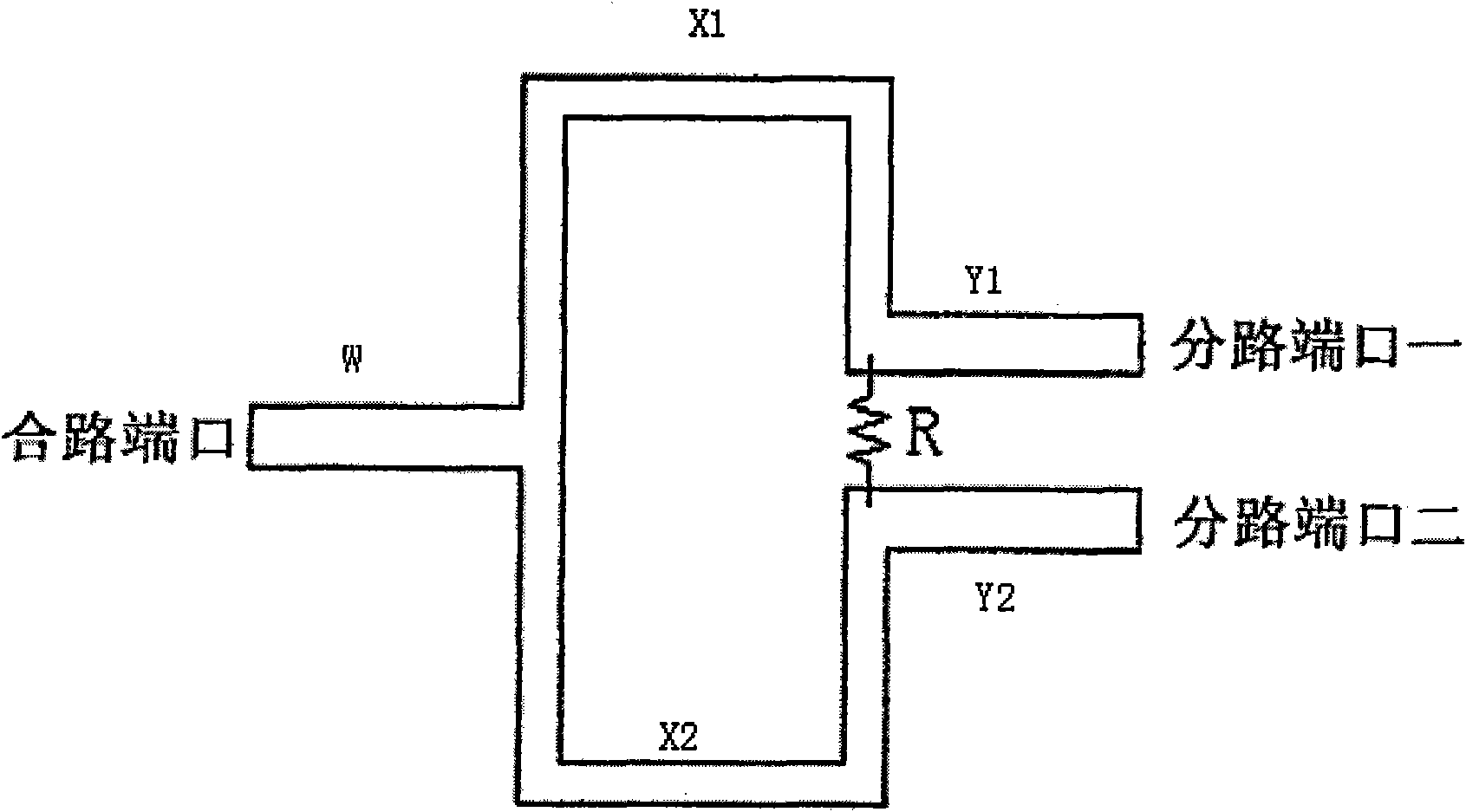

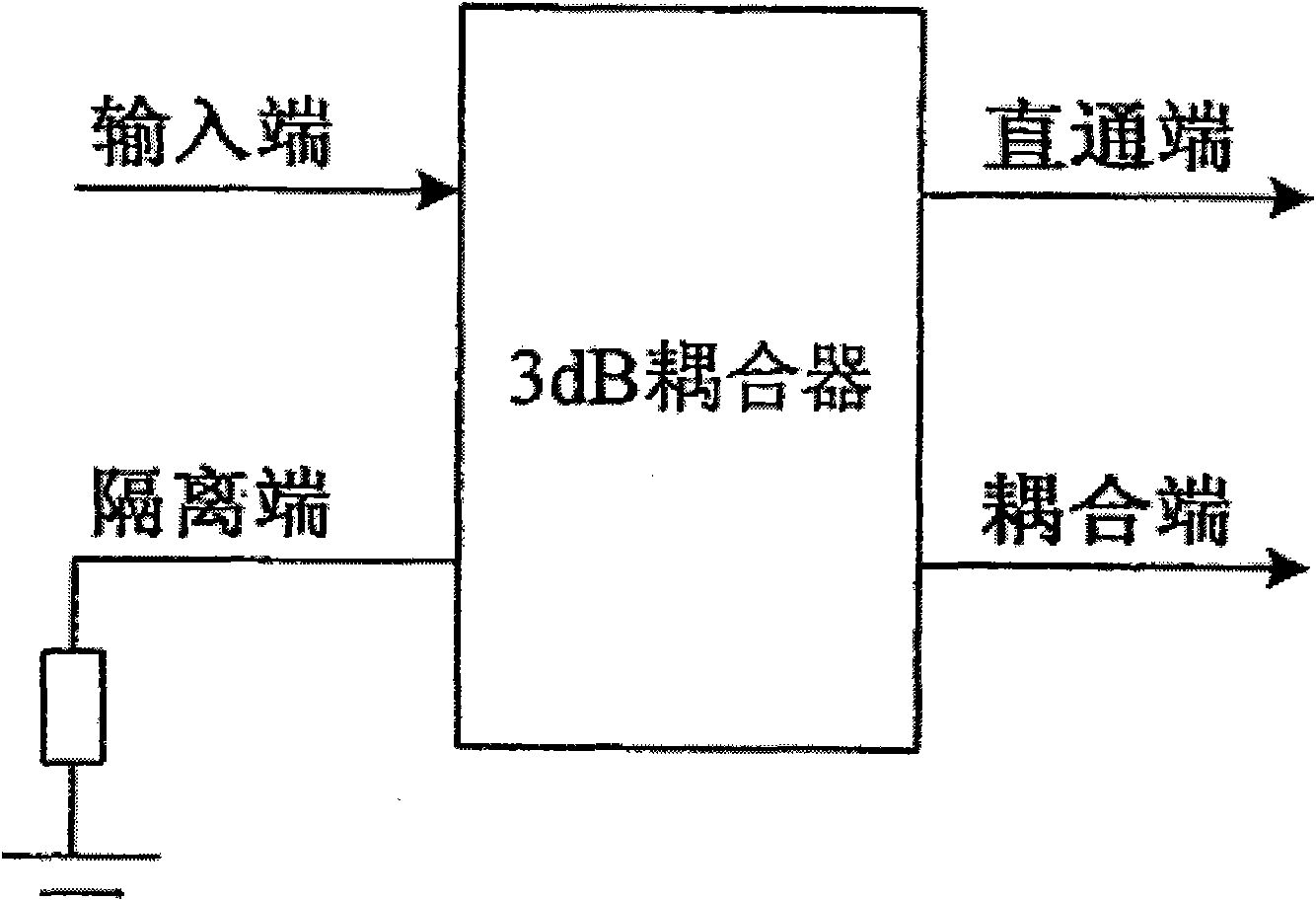

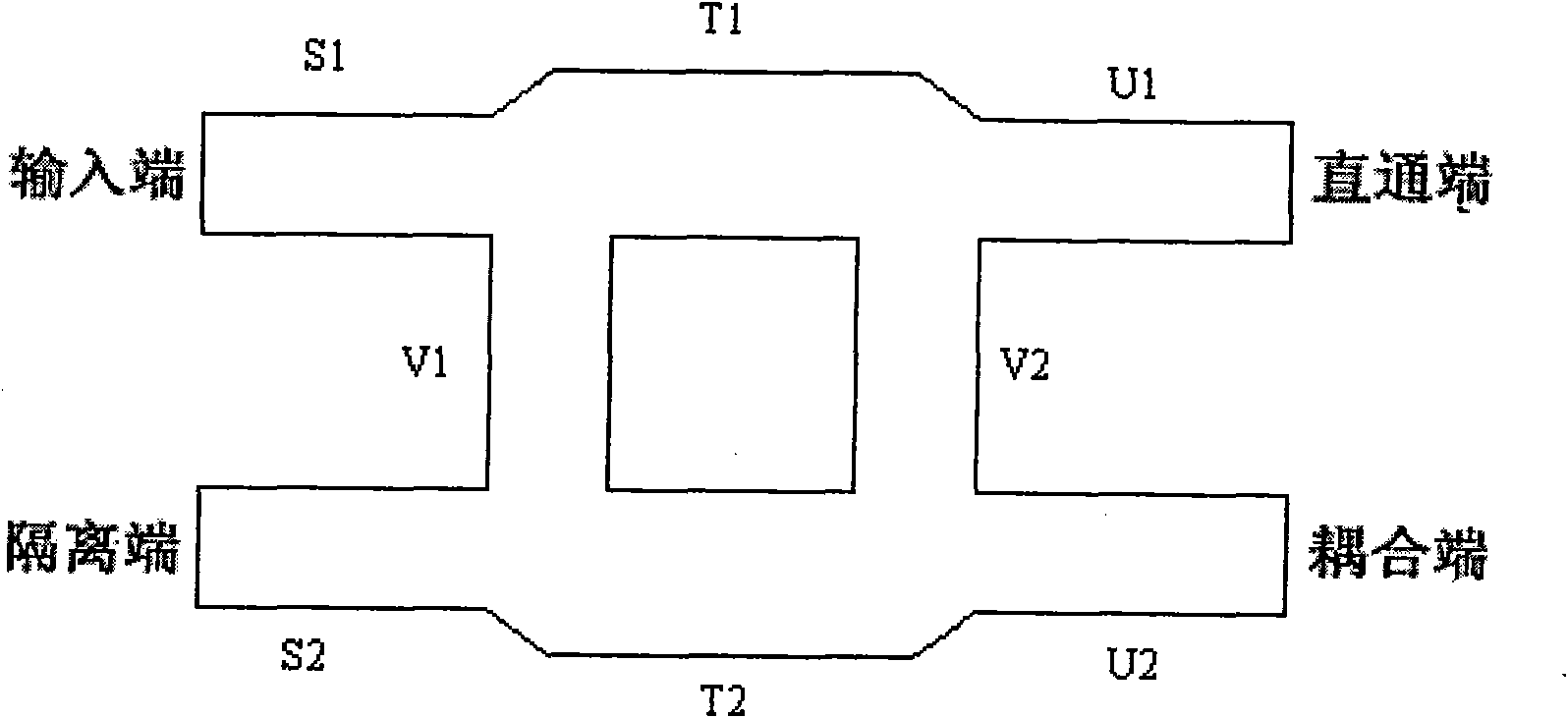

Power divider with new structure

InactiveCN101656343AImprove accuracyIncrease productivityCoupling devicesMain branchWilkinson power divider

The present invention discloses a power divider, wherein a transmission line includes a sub-2 connector, two branch ports of the connector are connected to two output main branches separately, more than two branch lines for communicating the two output main branches are arranged between two output main branches, the branches are designed so that a difference of a sum of a path from a node A to a node B11 and a path from the node A to a node B12, and a path from the node B11 to the node B12 is (Lambadaj / 2)*(2p +1) + (Lambadaj / 2)*Zeta, and the branches of other nodes are designed so that a difference of a sum of a path from a node Bk1 to a node B(k-1)1 and a path from the node B(k-1)1 to a node B(k-1)2 as well as a path from the node B(k-1)2 to a node Bk2, and a path from the node Bk1 to the node Bk2 is (Lambadai / 2)*(2m+1) + (Lambadai / 2) * Delta. The output and input of the invention are matched well, there is a good separation between two output ends, and overcomes autoeciousness effects of Wilkinson power divider caused by insulation electric resistances and a problem that a phase of a signal outputted from a directly-connecting end is inconsistent to that of a signal outputted from a coupling end of a branch line electric bridge power divider.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

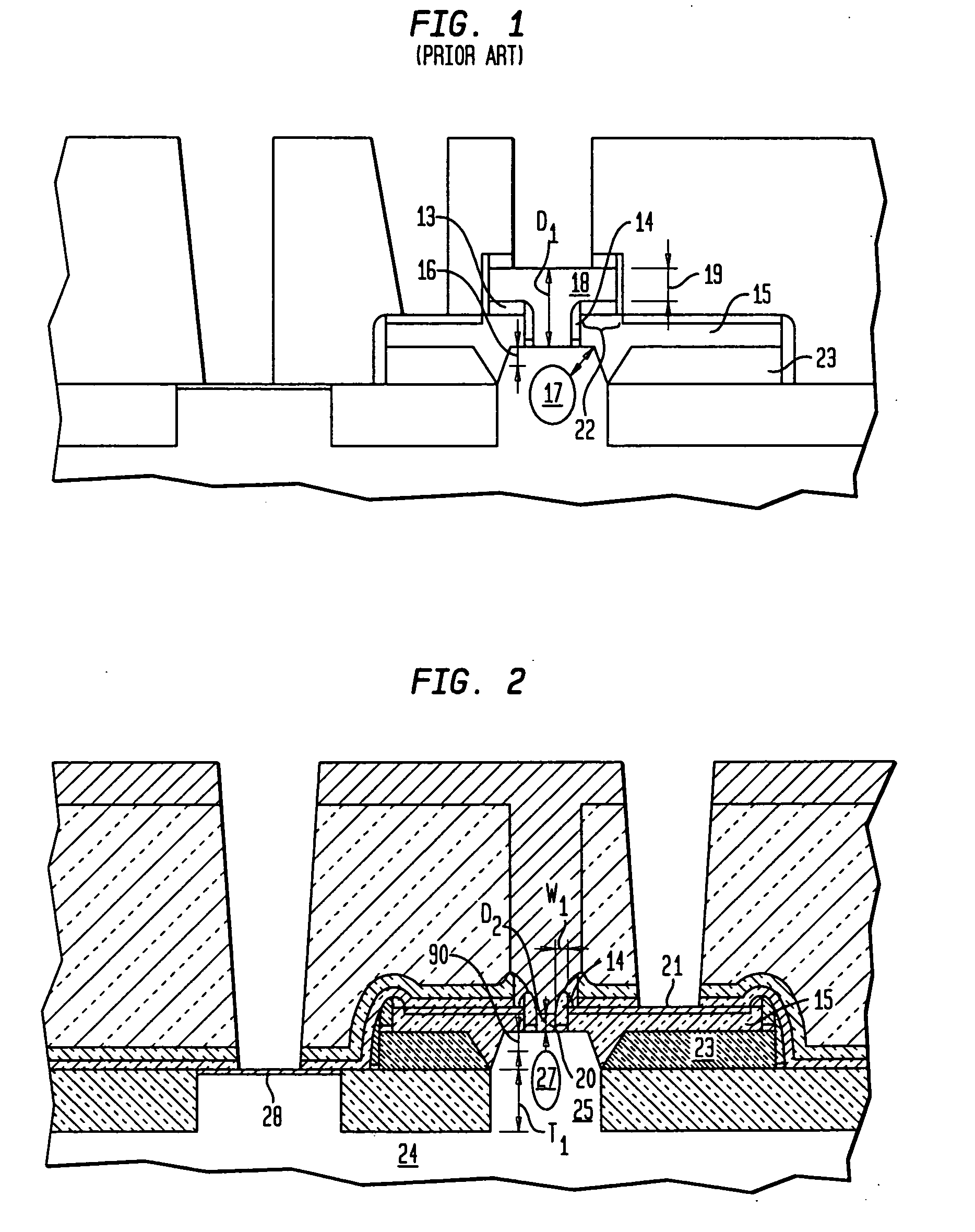

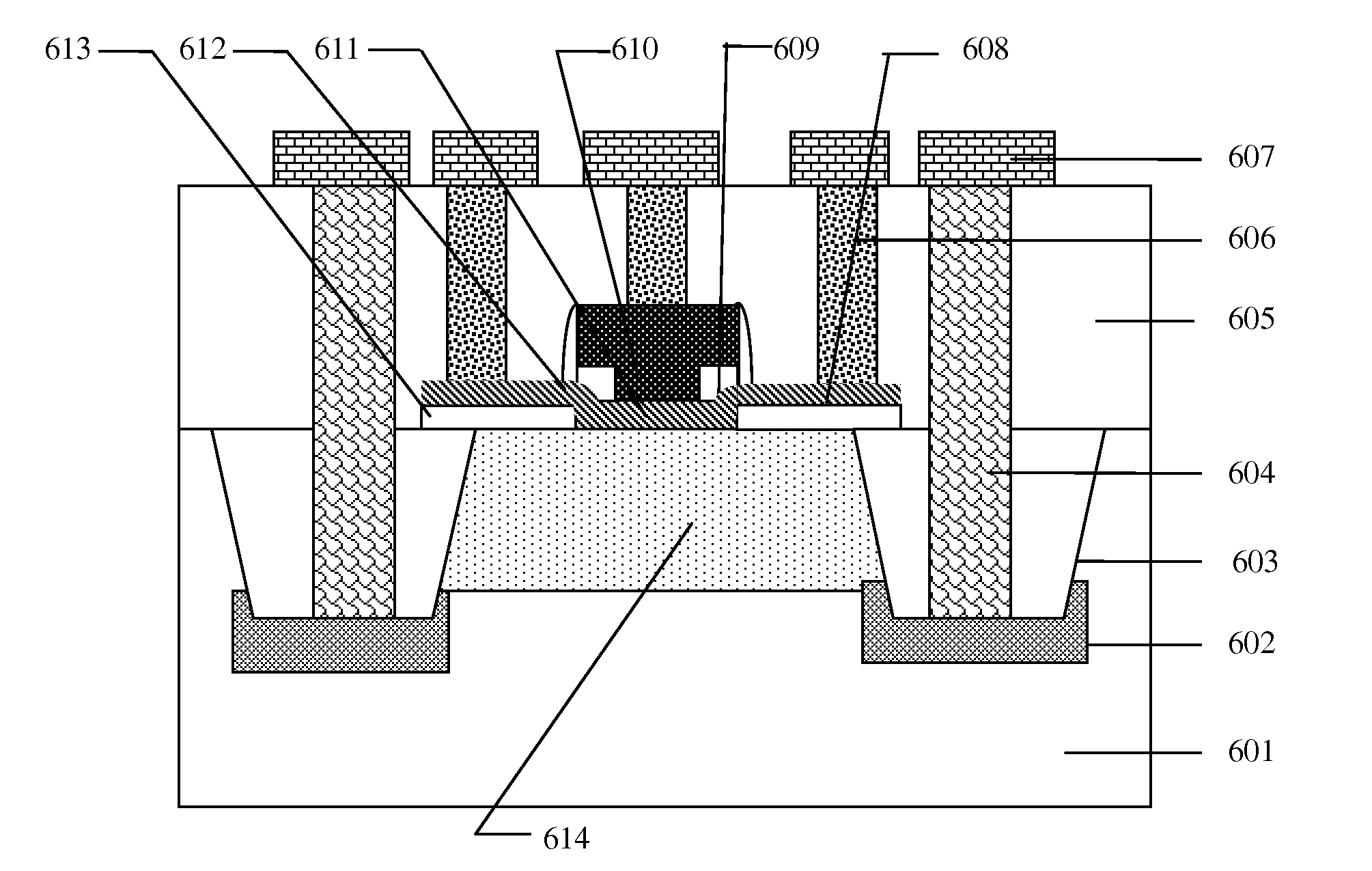

Transistor structure with minimized parasitics and method of fabricating the same

InactiveUS20050191911A1Reduce parasitic effectsImprove performanceTransistorThyristorIntrinsicsWindow opening

A transistor having minimized parasitics is provided including an emitter having a recessed extrinsic emitter portion atop an intrinsic emitter portion; a base including an intrinsic base portion in electrical contact with the intrinsic emitter portion and an extrinsic base portion in electrical contact with the intrinsic base portion and electrically isolated from the recessed extrinsic emitter portion by a set of emitter / base spacers; and a collector in electrical contact with the intrinsic base portion. The transistor may further include extrinsic base having top surfaces entirely silicided to the emitter / base spacer. Additionally, the transistor may include a base window opening within the transistor's active area. Methods of forming the above-described transistor are also provided.

Owner:GLOBALFOUNDRIES INC

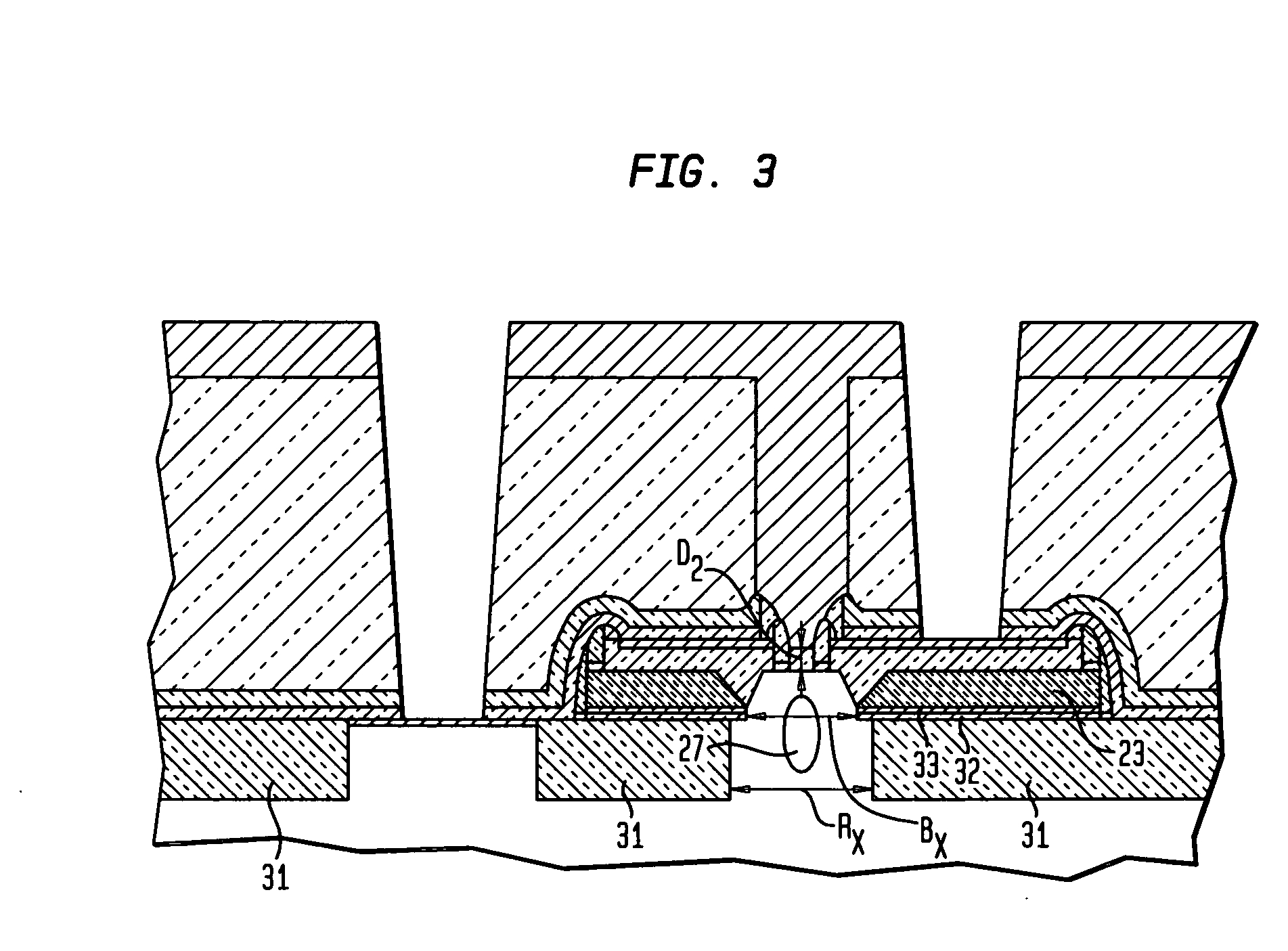

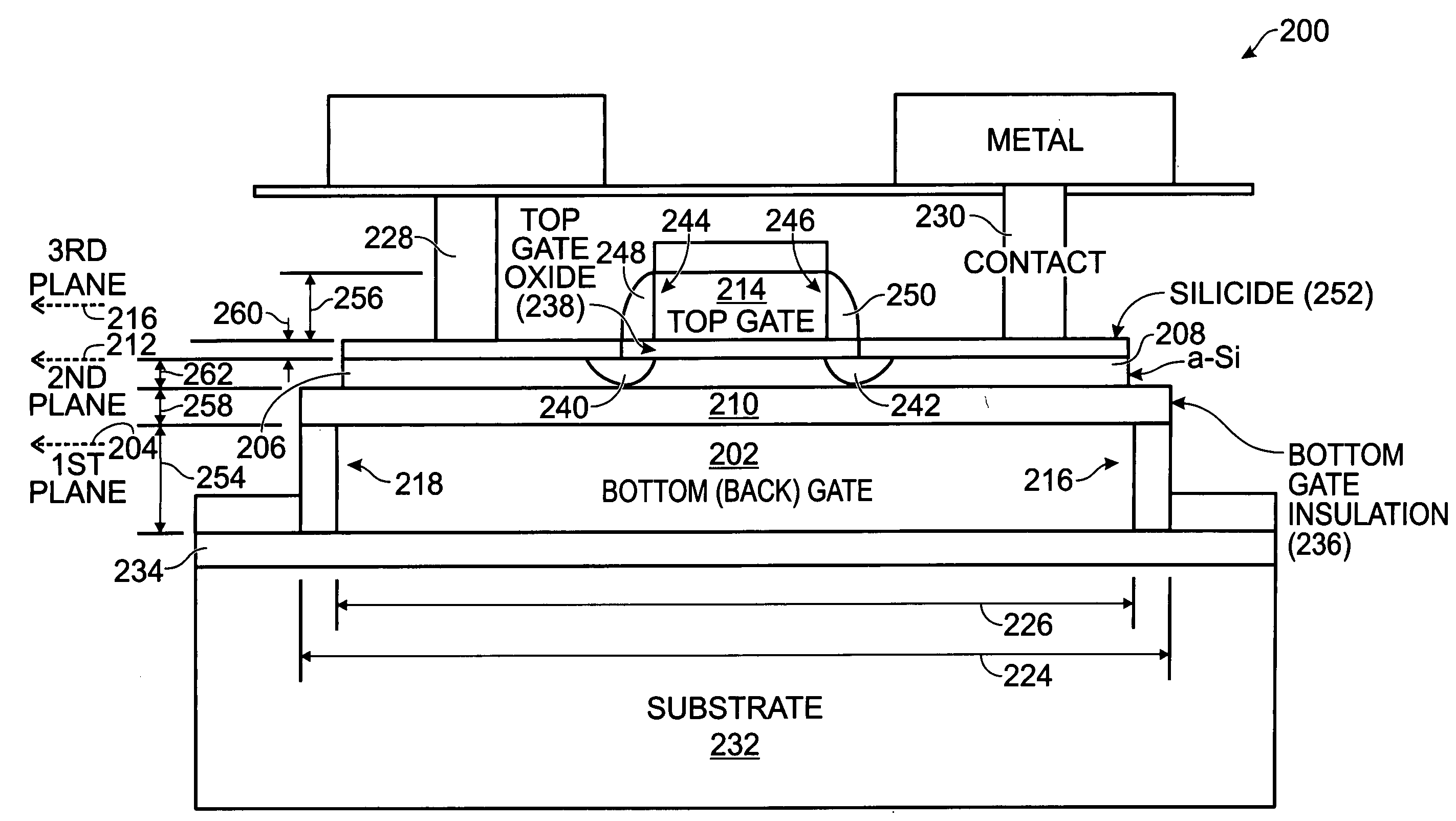

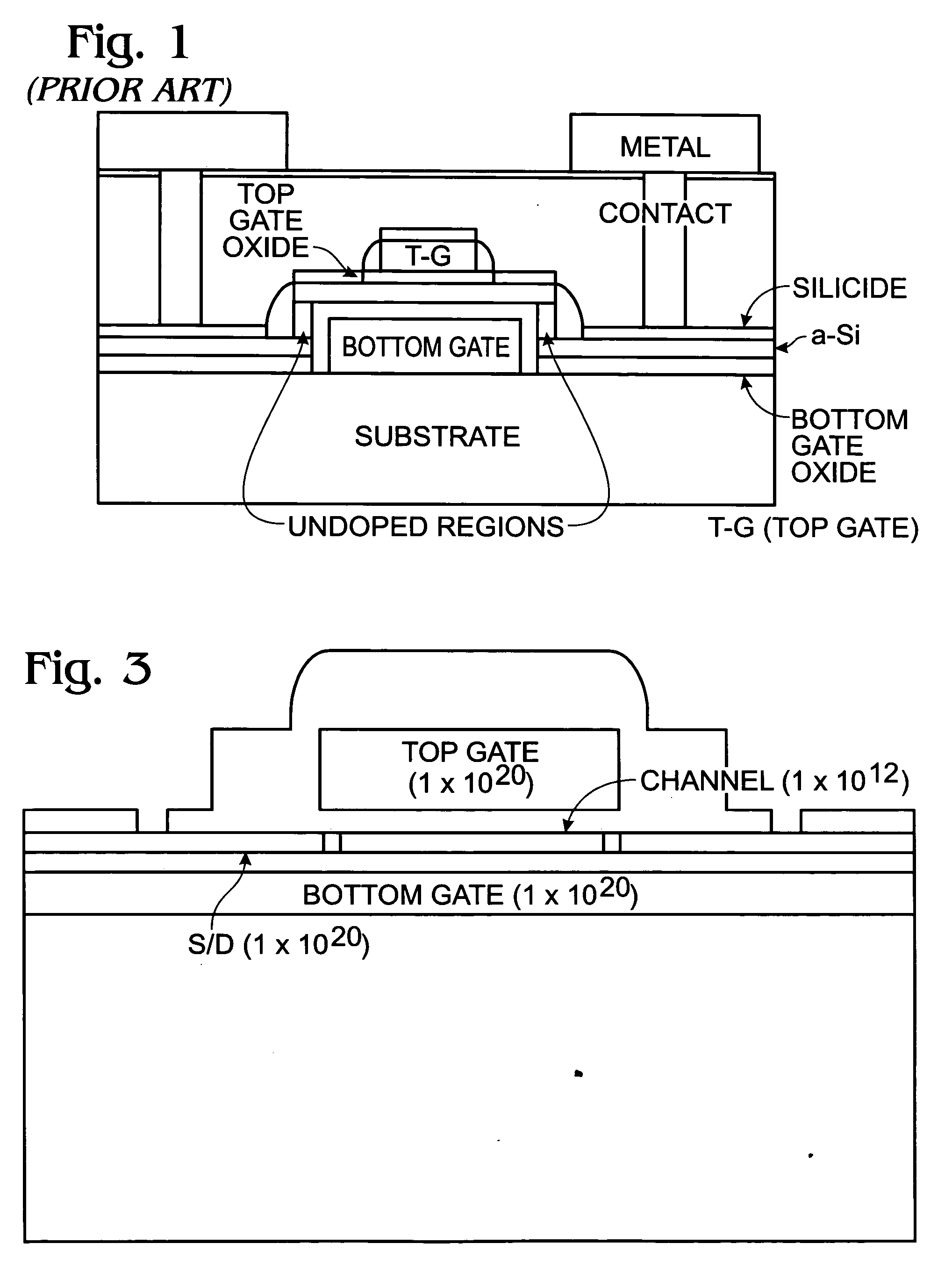

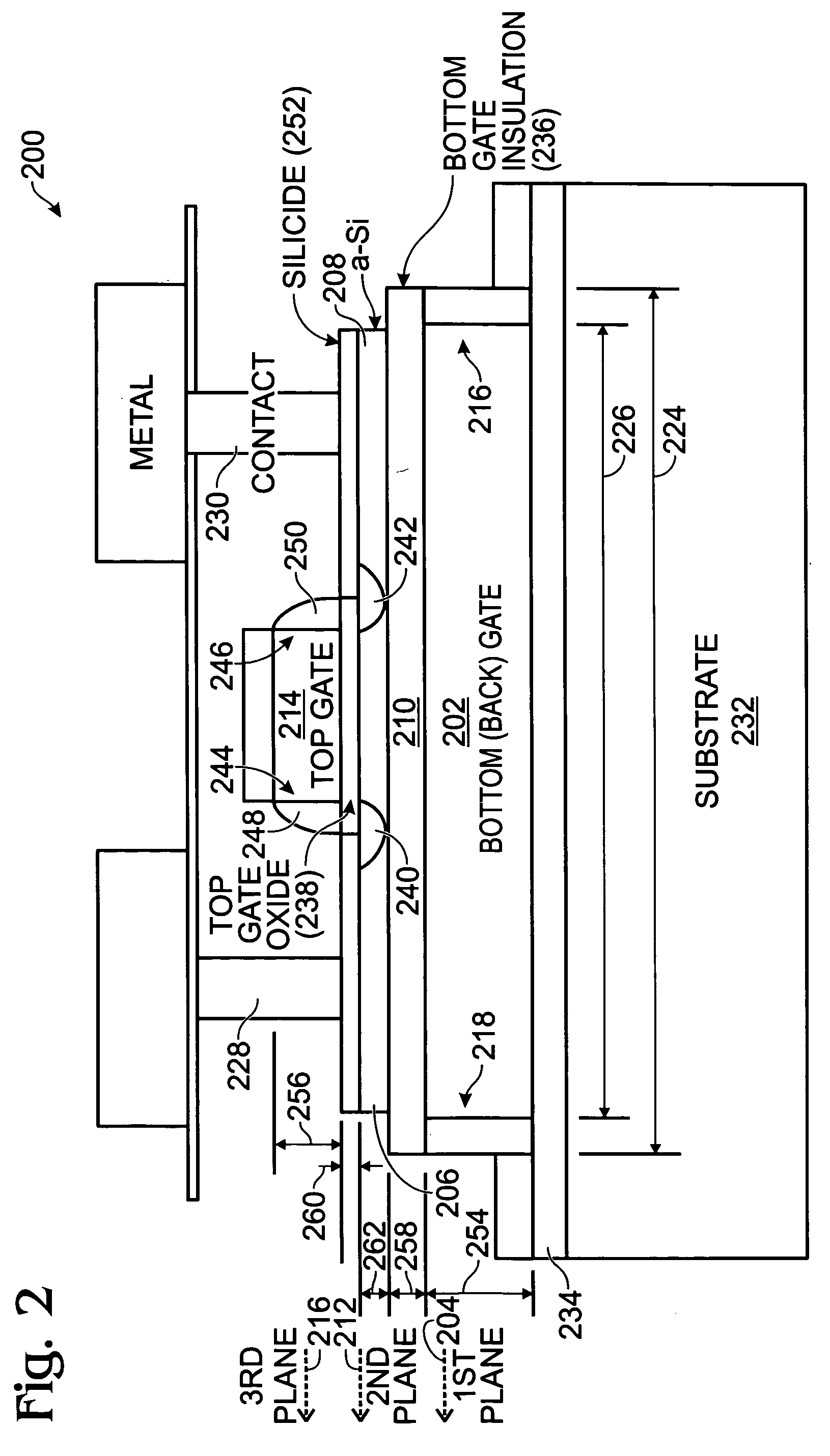

Dual-gate thin-film transistor

InactiveUS20060068532A1Alleviate parasitic effectReduce parasitic effectsStatic indicating devicesSemiconductor/solid-state device manufacturingPhysicsInsulation layer

A dual-gate thin film transistor (DG-TFT) and associated fabrication method are provided. The method comprises: forming a first (back) gate in a first horizontal plane; forming source / drain (S / D) regions and an intervening channel region in a second horizontal plane, overlying the first plane; and, forming a second (top) gate in a third horizontal plane, overlying the second plane. The S / D regions and intervening channel region have a combined length, smaller than the length of the first gate. A substrate insulating layer is formed over the substrate, made from a material such as SiO2. A first gate insulation layer is formed over the first gate. Amorphous silicon (a-Si) is deposited over the first gate insulation layer and crystallized. The S / D and channel regions are formed from the crystallized Si layer. A second gate oxide layer is formed over the channel region.

Owner:SHARP LAB OF AMERICA

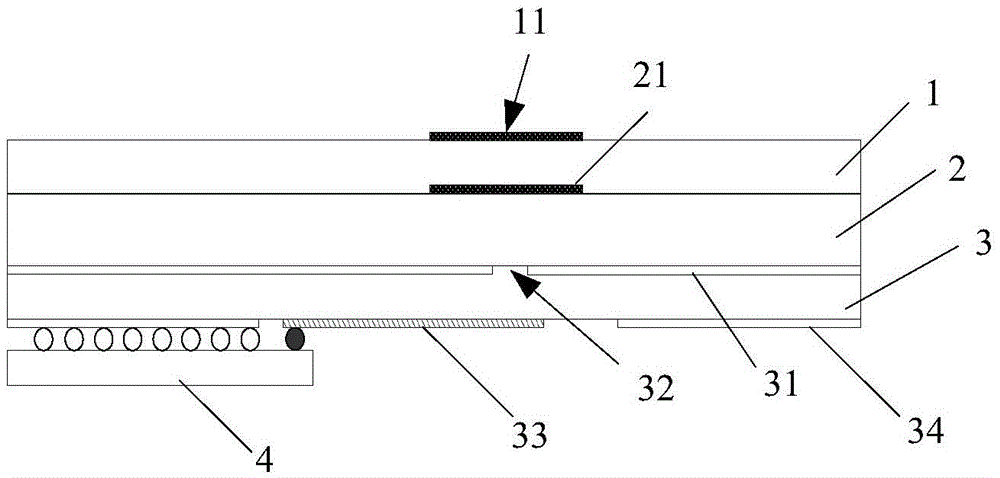

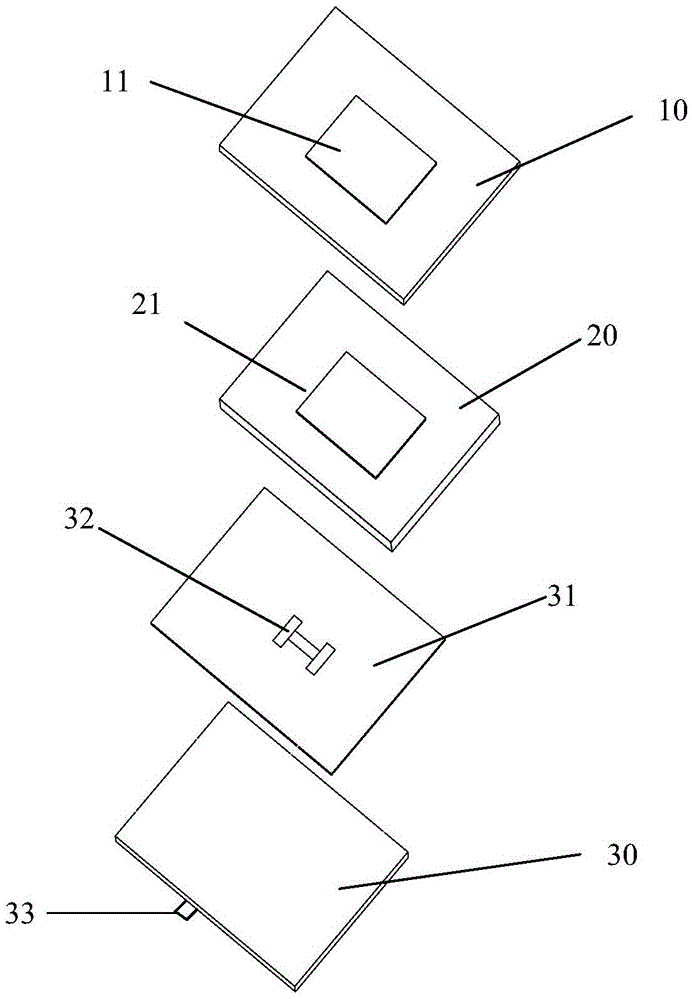

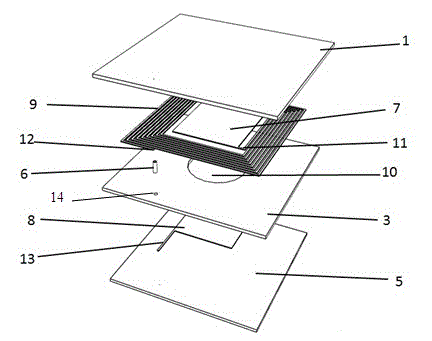

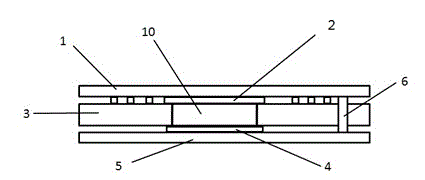

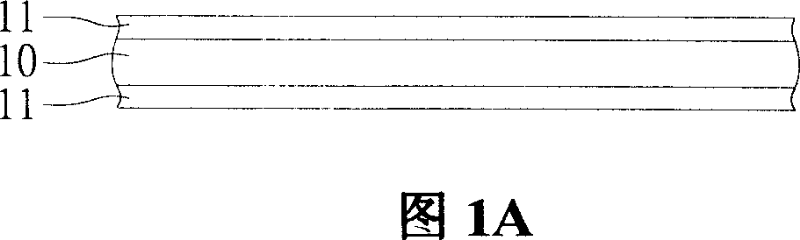

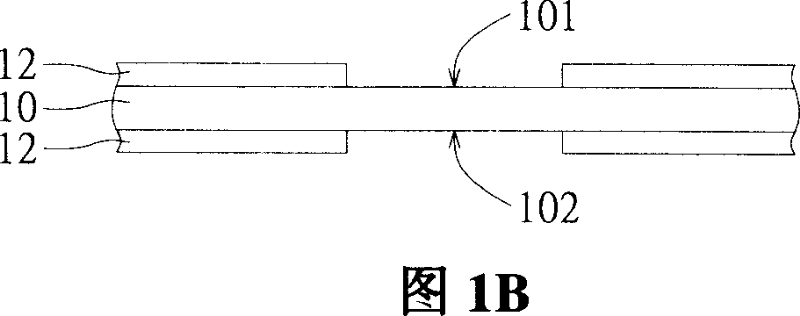

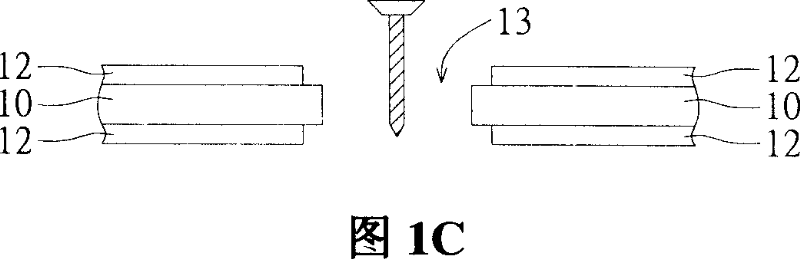

Flexible-substrate-based passive wireless pressure sensor with self-packaging function

InactiveCN103148977AProtection capacitorProtection inductanceFluid pressure measurement using capacitance variationCapacitanceEngineering

The invention discloses a flexible-substrate-based passive wireless pressure sensor with a self-packaging function. The pressure sensor comprises an upper flexible substrate, an upper metal layer, a middle flexible substrate, a lower metal layer and a lower flexible substrate, which are sequentially arranged from top to bottom and fixedly connected. An electric through hole and a cavity are formed in the middle flexible substrate. The upper metal layer comprises a planar inductance coil and a capacitor upper polar plate positioned on the middle part of the planar inductance coil. An inner connector of the planar inductance coil is connected with the capacitor upper polar plate. The lower metal layer comprises a capacitor lower polar plate opposite to the upper plate capacitor and an interconnecting wire connected with the capacitor upper polar plate. The sizes of the capacitor upper polar plate and capacitor lower polar plate are the same. An outer connector of the planar inductance coil of the upper metal layer is connected with the interconnecting wire of the lower metal layer through a conductive medium column in the electric through hole. The cavity of the middle flexible substrate is positioned between the capacitor upper polar plate and capacitor lower polar plate. The pressure sensor has the high performance of self packaging, non-contact, high sensitivity and high quality factor.

Owner:SOUTHEAST UNIV

Method and structure for controlled impedance wire bonds using co-dispensing of dielectric spacers

InactiveUS7303113B2Reduce signal transmissionReduce high frequency parasiticsCross-talk/noise/interference reductionSemiconductor/solid-state device detailsInterconnectionEngineering

Owner:GLOBALFOUNDRIES INC

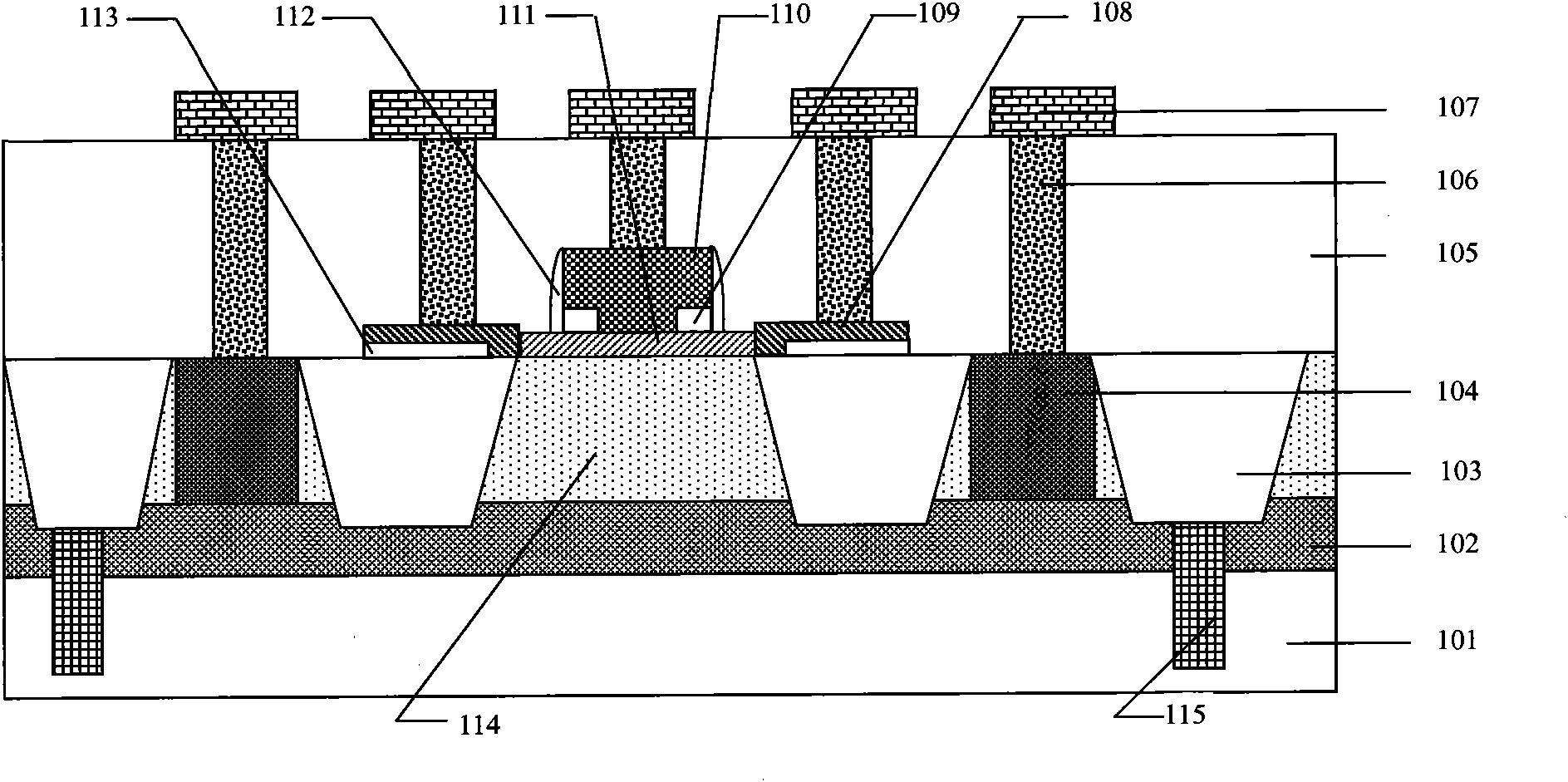

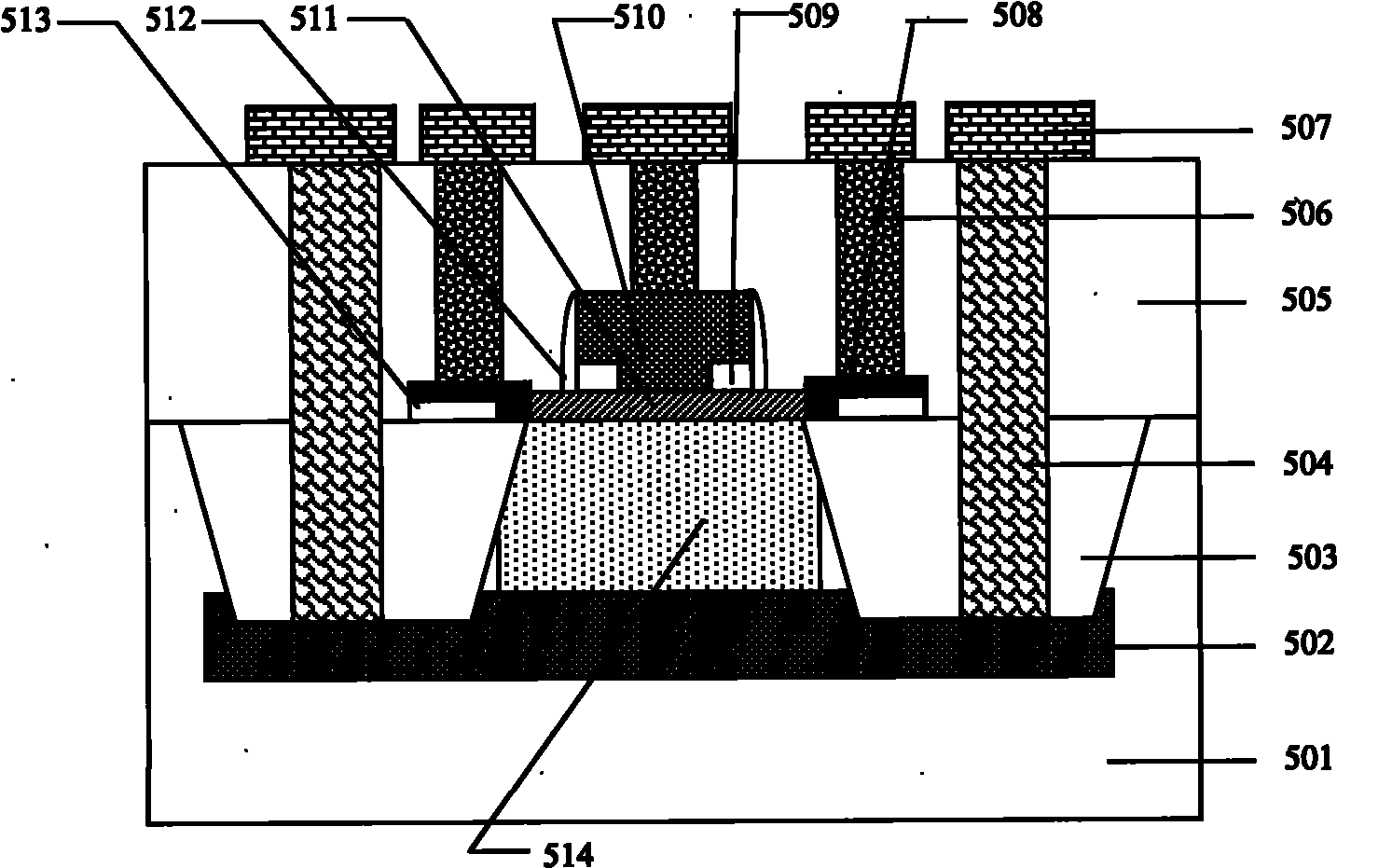

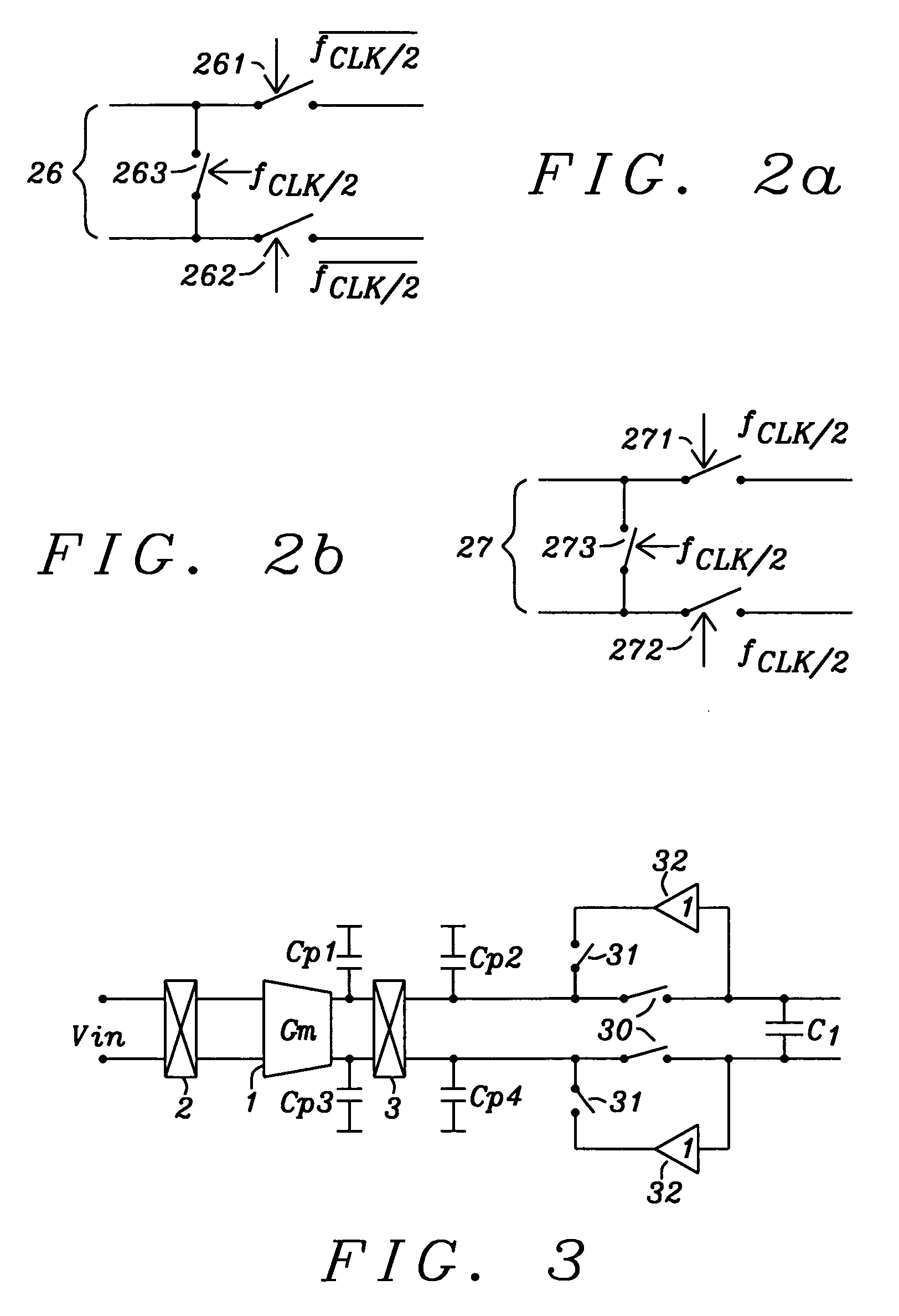

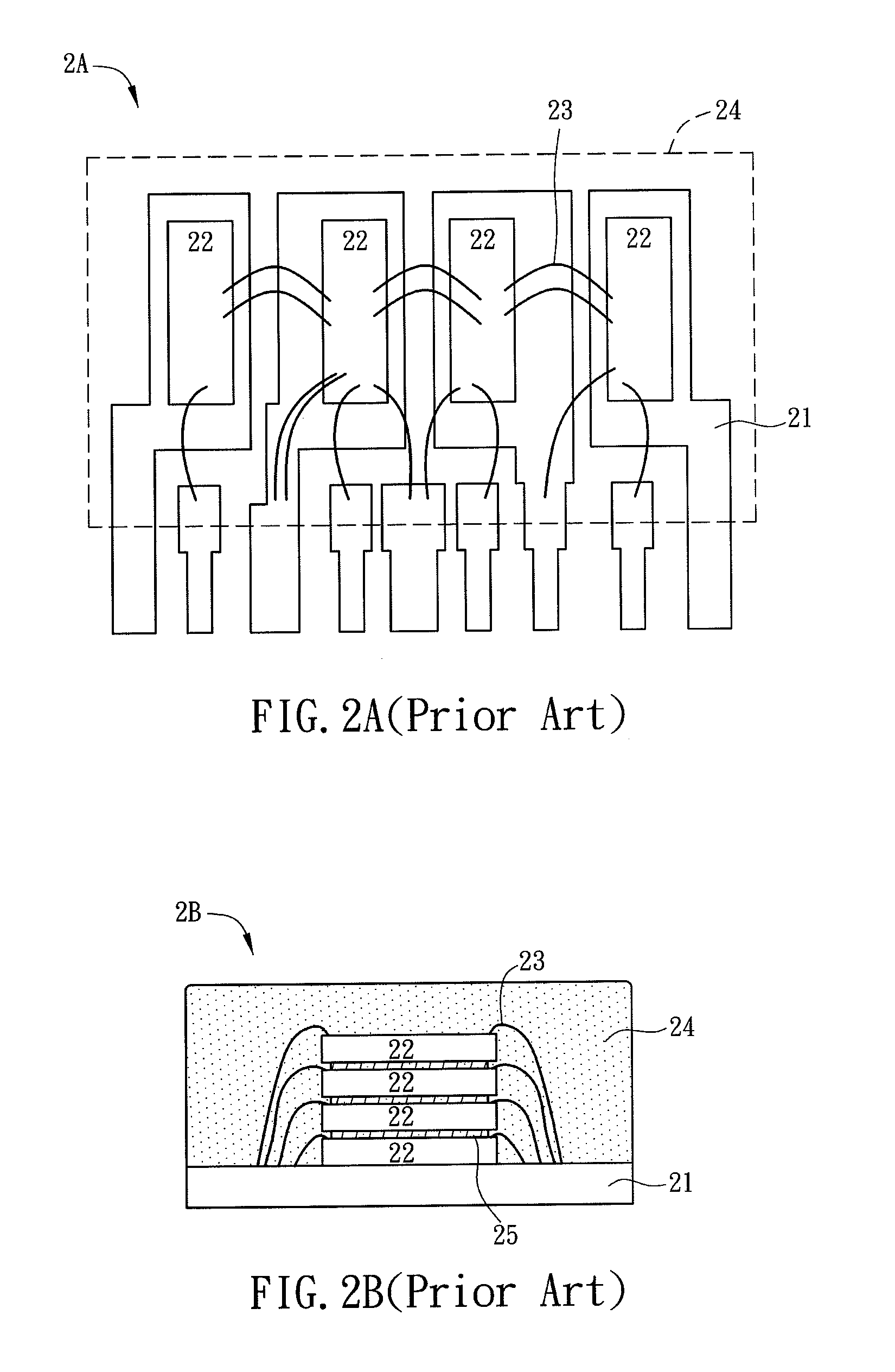

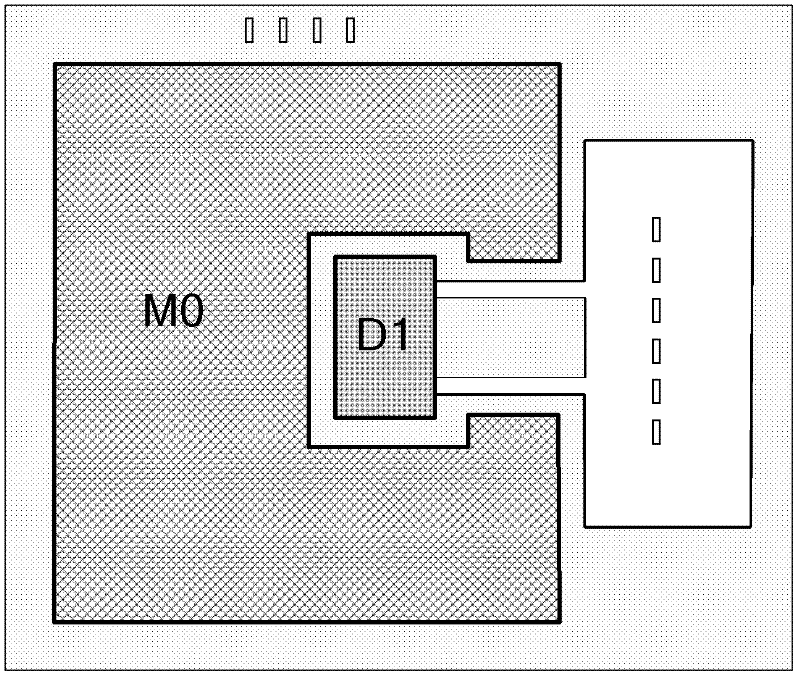

High Voltage Bipolar Transistor with Pseudo Buried Layers

ActiveUS20110140239A1Low costImprove breakdown voltageTransistorSemiconductor/solid-state device manufacturingHigh dosesEngineering

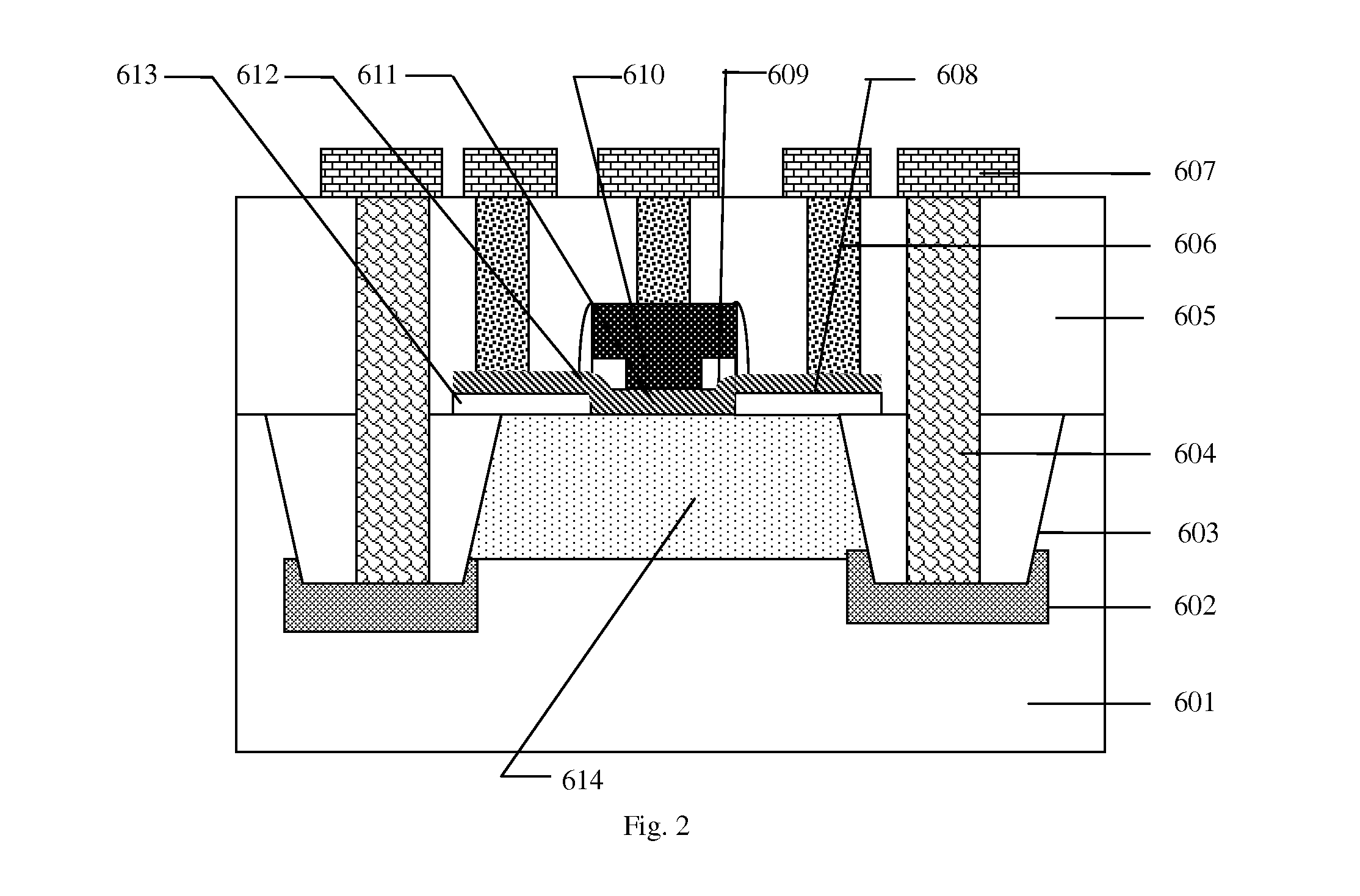

A high voltage bipolar transistor with shallow trench isolation (STI) comprises the areas of a collector formed by implanting first electric type impurities into active area and connected with pseudo buried layers at two sides; Pseudo buried layers which are formed by implanting high dose first type impurity through the bottoms of STI at two sides if active area, and do not touch directly; deep contact through field oxide to contact pseudo buried layers and pick up the collectors; a base deposited on the collector by epitaxial growth and in-situ doped by second electric type impurity, in which the intrinsic base touches local collector and extrinsic base is used for base pick-up; a emitter which is a polysilicon layer deposited on the intrinsic base and doped with first electric type impurities. This invention makes the depletion region of collector / base junction from 1D (vertical) distribution to 2D (vertical and lateral) distribution. The bipolar transistor's breakdown voltages are increased by only enlarge active critical dimension (CD). This is low-cost process.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Thin film SOI thick grid oxygen power device with grid field plate

InactiveCN101221986AFast switching speedImprove breakdown characteristicsSemiconductor devicesPeak valueOxygen

The invention belongs to the semi-conductor power device technical field. A SOI layer of the device is thinner (1to 2um); a grid oxide layer is thick (100 to 800nm); a grid field plate gets across a grid and extends above a drift region. An active expansion region positioned below the thick grid oxide layer and connected with a source region can be also arranged in the body of the device to assure the more effective formation of the whole device. The grid oxide layer of the invention is thicker, can bear high grid-source voltage and meet the need of a level displacement circuit; the SIO layer is thinner, can decrease the parasitic effect of the device and reduce consumption; through adding the grid field plate striding over the grid on the surface of the power device, the depletion of the drift region can be increased, the electric field peak value on the silicon surface at the tail end of the grid is decreased, the breakdown characteristic of the device is improved, further more the concentration of the drift region is helped to improve, and the on-state resistance of the device is decreased. The invention has the advantages of low parasitic effect, fast speed, low power consumption, strong radiation-resistant ability and so on, and is compatible with the standard process. By adopting the invention, various high-voltage, high-speed and low conducting loss devices of excellent performance can be produced.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

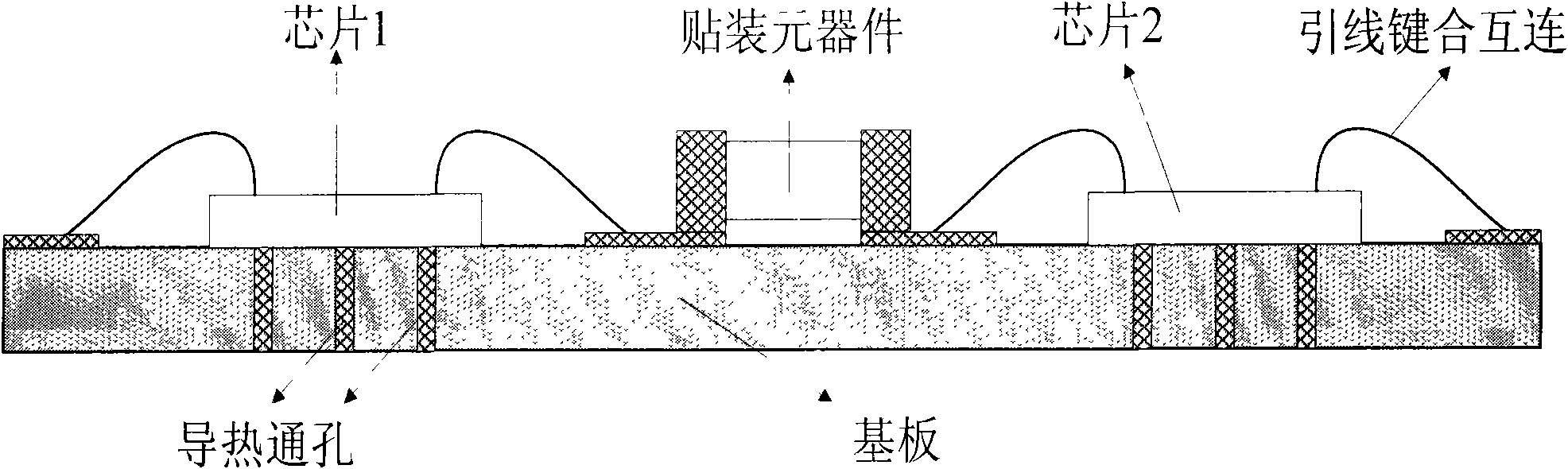

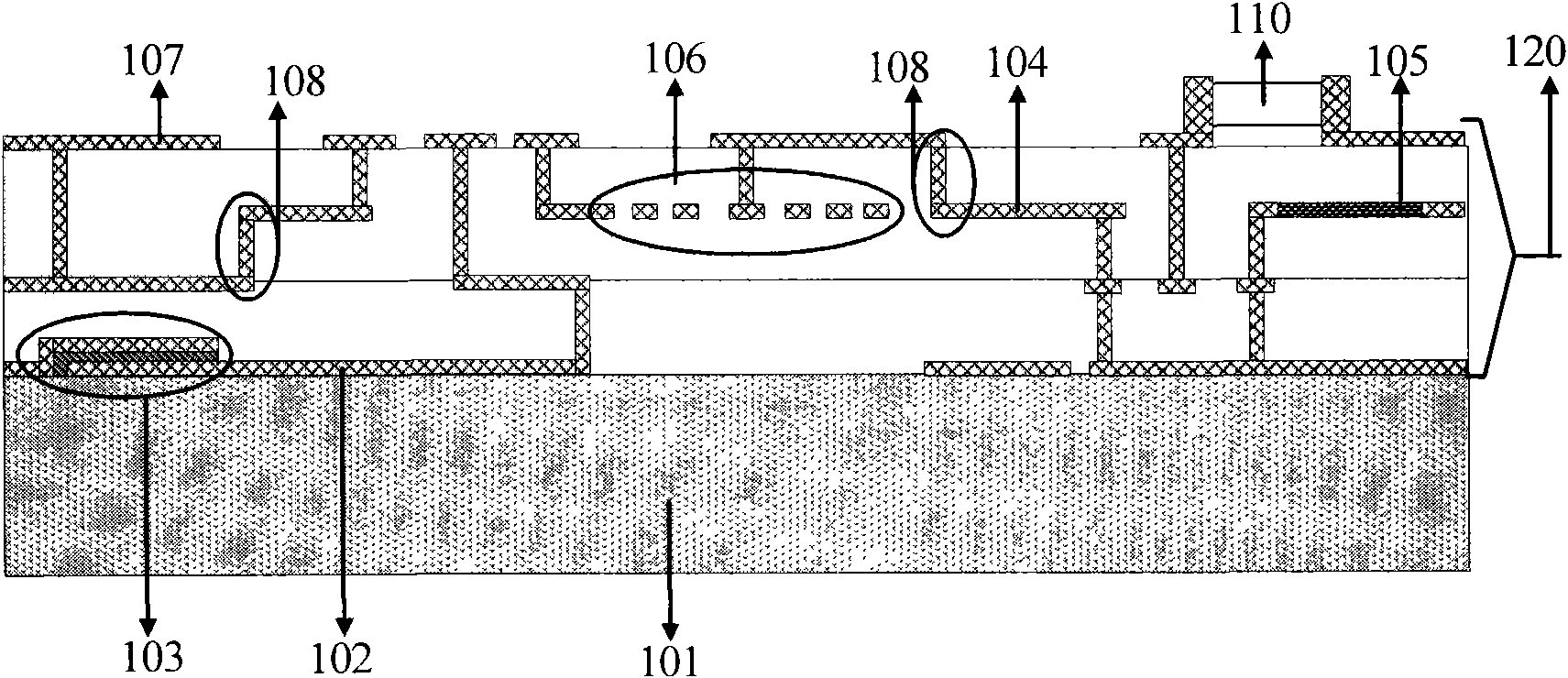

Multilayer interconnection structure of wafer level package, manufacturing method and application

InactiveCN101656249AImprove packing density and production efficiencyReduce parasitic effects and lossesSemiconductor/solid-state device detailsSolid-state devicesTransmission lineEngineering

The invention provides a multilayer interconnection structure of wafer level package, a manufacturing method and application thereof. The multilayer interconnection structure is used for microwave multi chip modules. The invention is characterized by using benzocyclobutene (BCB) as a dielectric layer, realizing the multilayer connection structure of a metal / organic polymer by combining wafer levelprocessing technics such as photoetching, electroplating, mechanical polishing and the like and embedding integrated varied passive devices and transmission lines for interconnection. The whole process is matched with IC process, is completed on the basis of wafer level and has higher integration of packaging and lower high-frequency transmission loss. The structure can effectively integrate varied function device units, reduce the interconnection loss among the devices and improve the properties of the whole module while improving the density and integration of packaging and reducing the cost of packaging.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

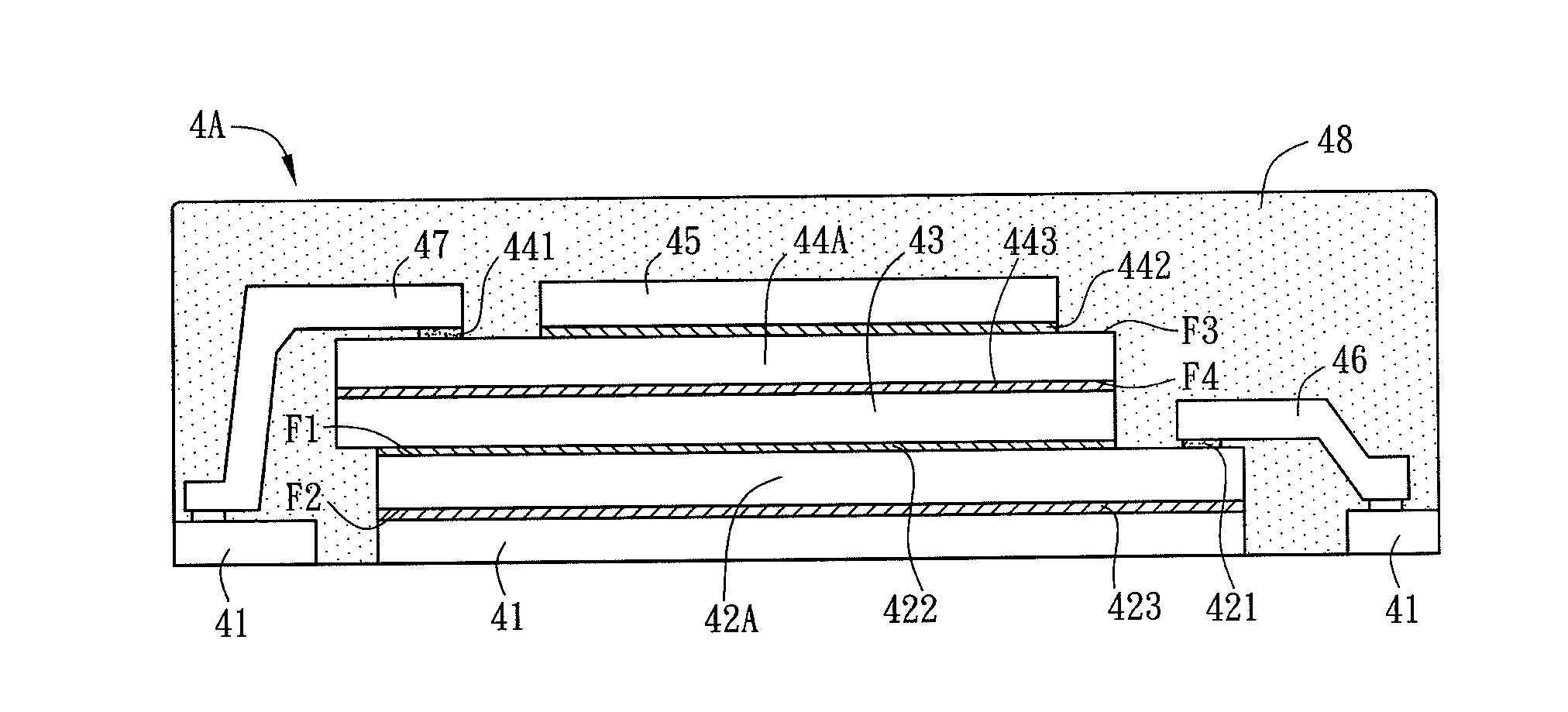

Power semiconductor package structure and manufacturing method thereof

ActiveUS20120181706A1Improve reliabilityReduce parasitic effectsSemiconductor/solid-state device detailsSolid-state devicesElectricitySemiconductor package

A power semiconductor package structure includes a carrier, a first power chip, a second power chip, a first conductive sheet, a second conductive sheet and a third conductive sheet. The first power chip has a first surface and a second surface opposing to the first surface. A first control electrode and a first main power electrode are disposed on the first surface, and a second main power electrode is disposed on the second surface. The second surface is disposed on the carrier, and electrically connected to the carrier through the second main power electrode. The second power chip has a third surface and a fourth surface opposing to the third surface. A third main power electrode is disposed on the third surface, and a fourth main power electrode is disposed on the fourth surface. The fourth surface is disposed on the first power chip. The first conductive sheet is electrically connected to the first main power electrode and the fourth main power electrode. The second conductive sheet is electrically connected to the third main power electrode. The third conductive sheet is electrically connected to the first control electrode. At least a part of the first control electrode is non-covered by the second power chip along a projection direction, which is perpendicular to the carrier.

Owner:DELTA ELECTRONICS INC

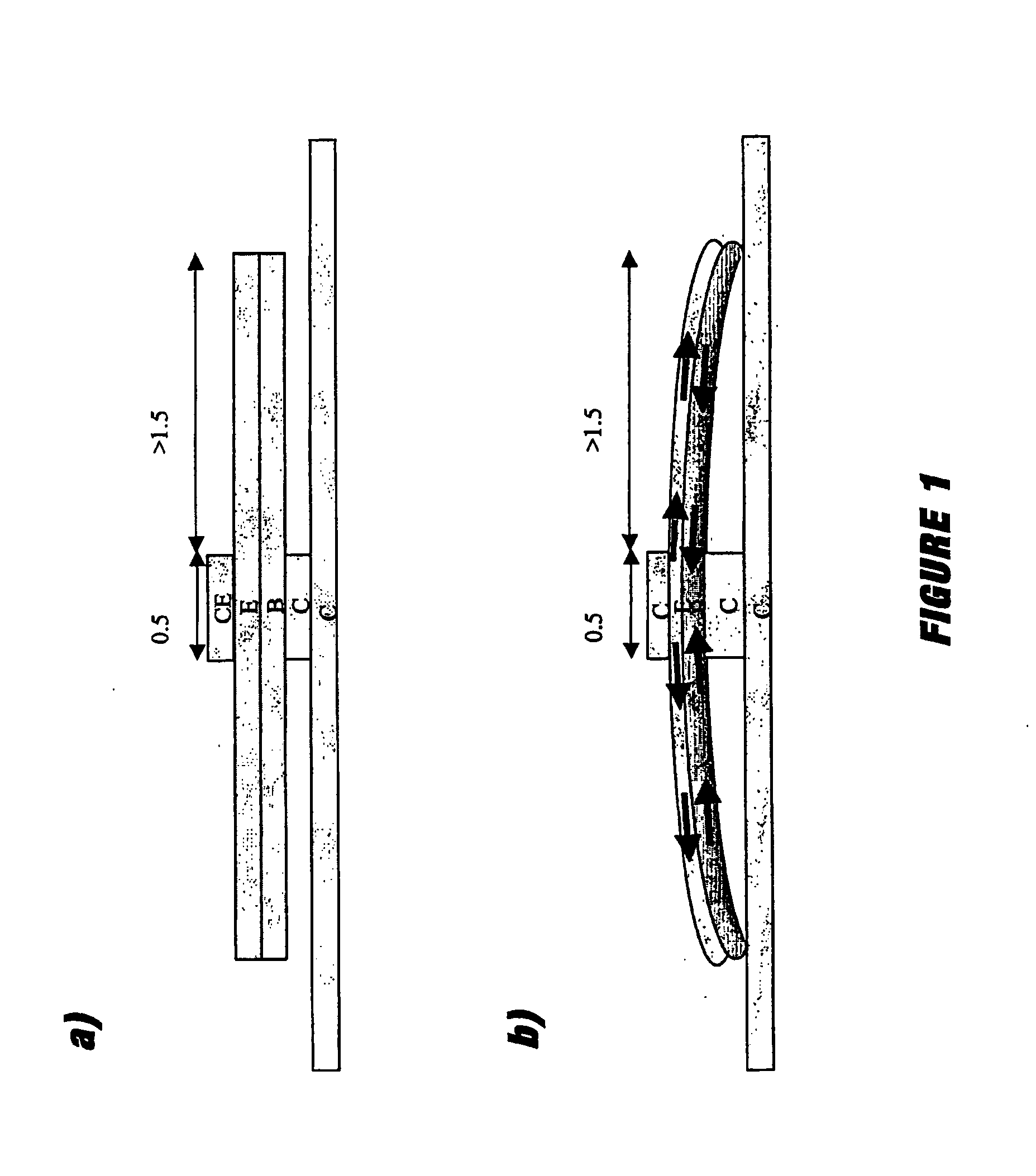

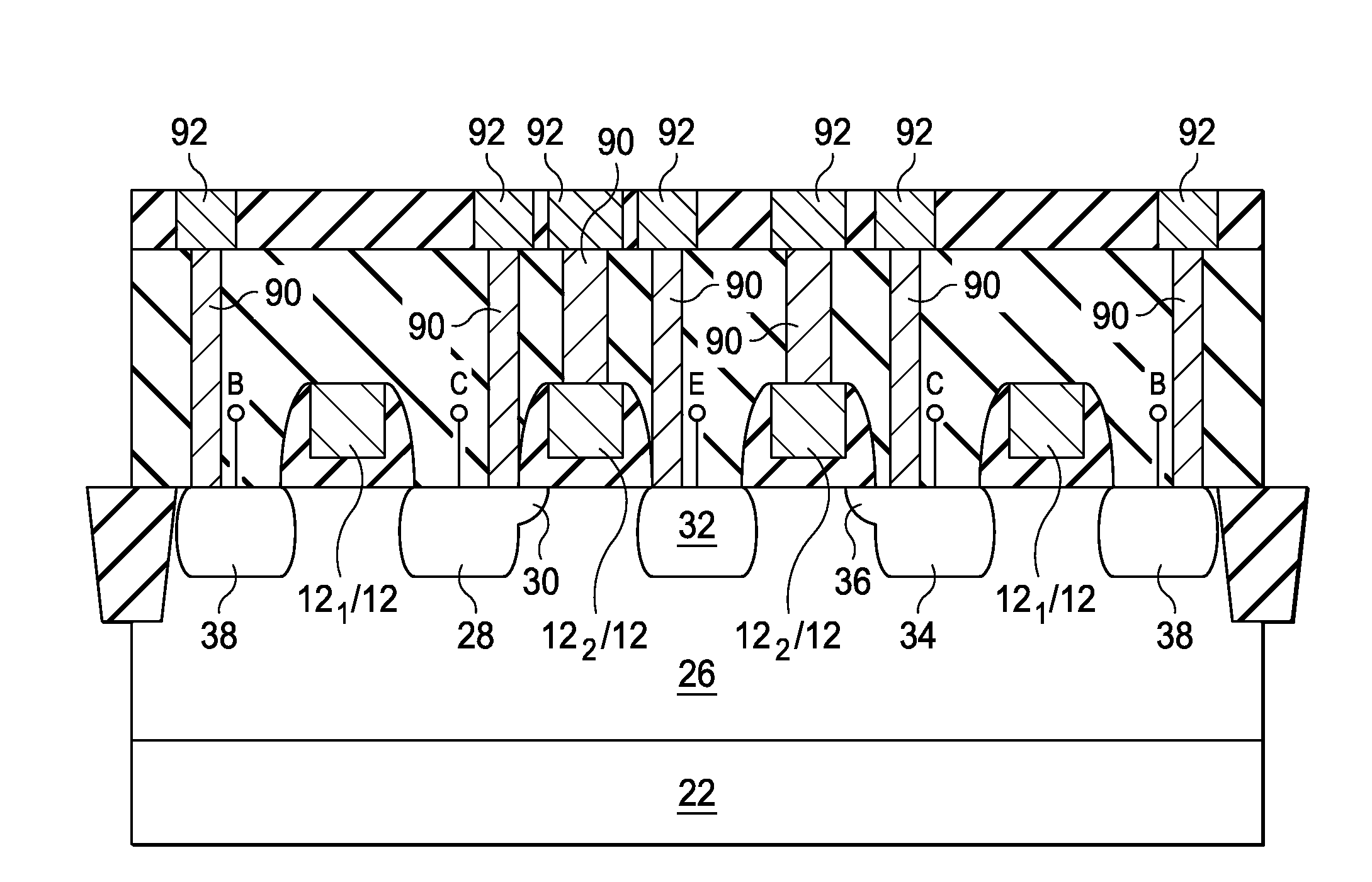

Profile Design for Lateral-Vertical Bipolar Junction Transistor

ActiveUS20100213575A1Improved current gainReduce parasitic effectsTransistorSolid-state devicesDielectricImpurity

A lateral-vertical bipolar junction transistor (LVBJT) includes a well region of a first conductivity type over a substrate; a first dielectric over the well region; and a first electrode over the first dielectric. A collector of a second conductivity type opposite the first conductivity type is in the well region and on a first side of the first electrode, and is adjacent the first electrode. An emitter of the second conductivity type is in the well region and on a second side of the first electrode, and is adjacent the first electrode, wherein the second side is opposite the first side. A collector extension region having a lower impurity concentration than the collector adjoins the collector and faces the emitter. The LVBJT does not have any emitter extension region facing the collector and adjoining the emitter.

Owner:TAIWAN SEMICON MFG CO LTD

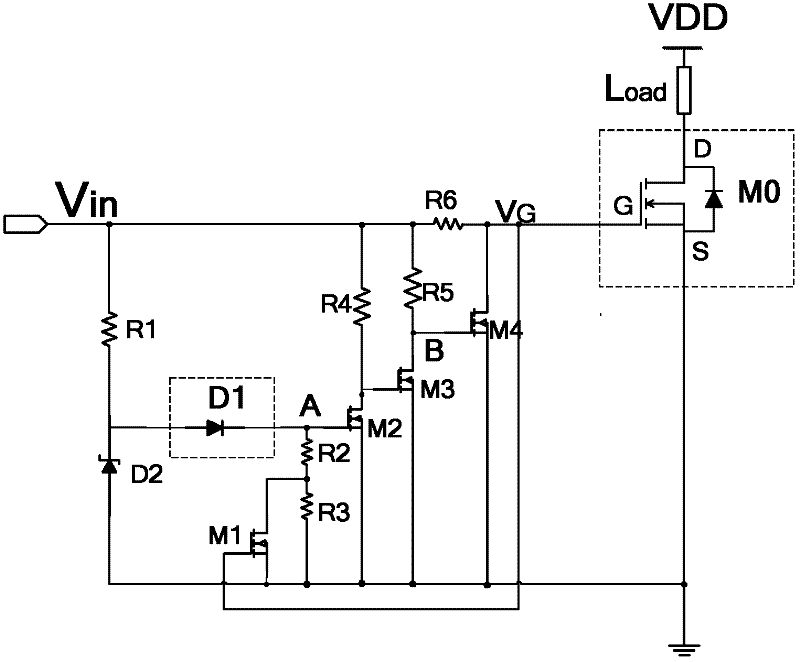

Composite VDMOS device possessing temperature sampling and over-temperature protection function

InactiveCN102394237AReduce failure rateAccurate samplingSolid-state devicesDiodePower semiconductor deviceNegative temperature

A composite VDMOS device possessing a temperature sampling and over-temperature protection function belongs to the power semiconductor device field. In the invention, a VDMOS device, a polysilicon thermal diode and an over-temperature protection circuit are integrated. Through using a negative temperature characteristic of forward voltage drop of the polysilicon thermal diode, the polysilicon thermal diode is made on an insulating layer of a VDMOS device surface so as to realize sampling of a VDMOS device operating temperature. Based on a temperature sampling signal of the polysilicon thermal diode, the over-temperature protection circuit carries out partial pressure to a gate input voltage Vin of the whole composite VDMOS device so as to obtain a gate control voltage VG of the VDMOS device. Therefore, the over-temperature protection can be performed to the VDMOS device, which is characterized by: when the operating temperature of the VDMOS device reaches TH, turning off the VDMOS device; when the internal temperature drops to TL after the VDMOS device is turned off, starting the VDMOS device, wherein temperature return difference can be represented as a following formula: Delta T=TH-TL. By using the composite VDMOS device of the invention, the accurate sampling and the over-temperature protection can be performed to the VDMOS device so that thermal failure of the device can be avoided and a service life of the device can be prolonged. A structure is simple and sampling accuracy is high. The device is compatible with a VDMOS device technology. The device is monolithic and has many other advantages.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA +1

Semiconductor rectifier device and manufacturing method thereof

InactiveCN101226883ASmall PN junction parasitic effectImprove junction characteristicsSemiconductor/solid-state device detailsSolid-state devicesEngineeringP–n junction

Disclosed are a semiconductor rectifier device and a method for preparation thereof. The device is composed of an equivalent PN junction and a vertical MOS pipe in parallel connection. And an upper source / drain area in the vertical MOS pipe is formed through the following procedures: a, performing N-type ion implantation for an area exposed from a first primary surface of silicon chips after procedures of photo-etching and corroding of a grid electrode, b, performing silicon controlled corrosion for the area exposed from the first primary surface of the silicon chips after implanted by N-type ions, rapidly annealing the N-type ions retained in an area bellow the lateral face of the grid electrode to form the upper source / drain area. The invention resolves the problems brought by the larger surface and unreasonable distribution of the upper source / drain N+ area of the existing vertical MOS pipe through the process of silicon controlled corrosion. For equivalent PN junction areas, a single PN junction is used to replace the original NPN pipe, and thereby the equivalent PN junction areas have fewer parasitic effect of the PN junction. For equivalent vertical MOS pipe areas, residual N-type ions are used to form the upper source / drain area via rapidly annealing, thereby largely reducing effective junction area of the upper source / drain area with smaller reverse leakage current.

Owner:SUZHOU SILIKRON SEMICON CO LTD

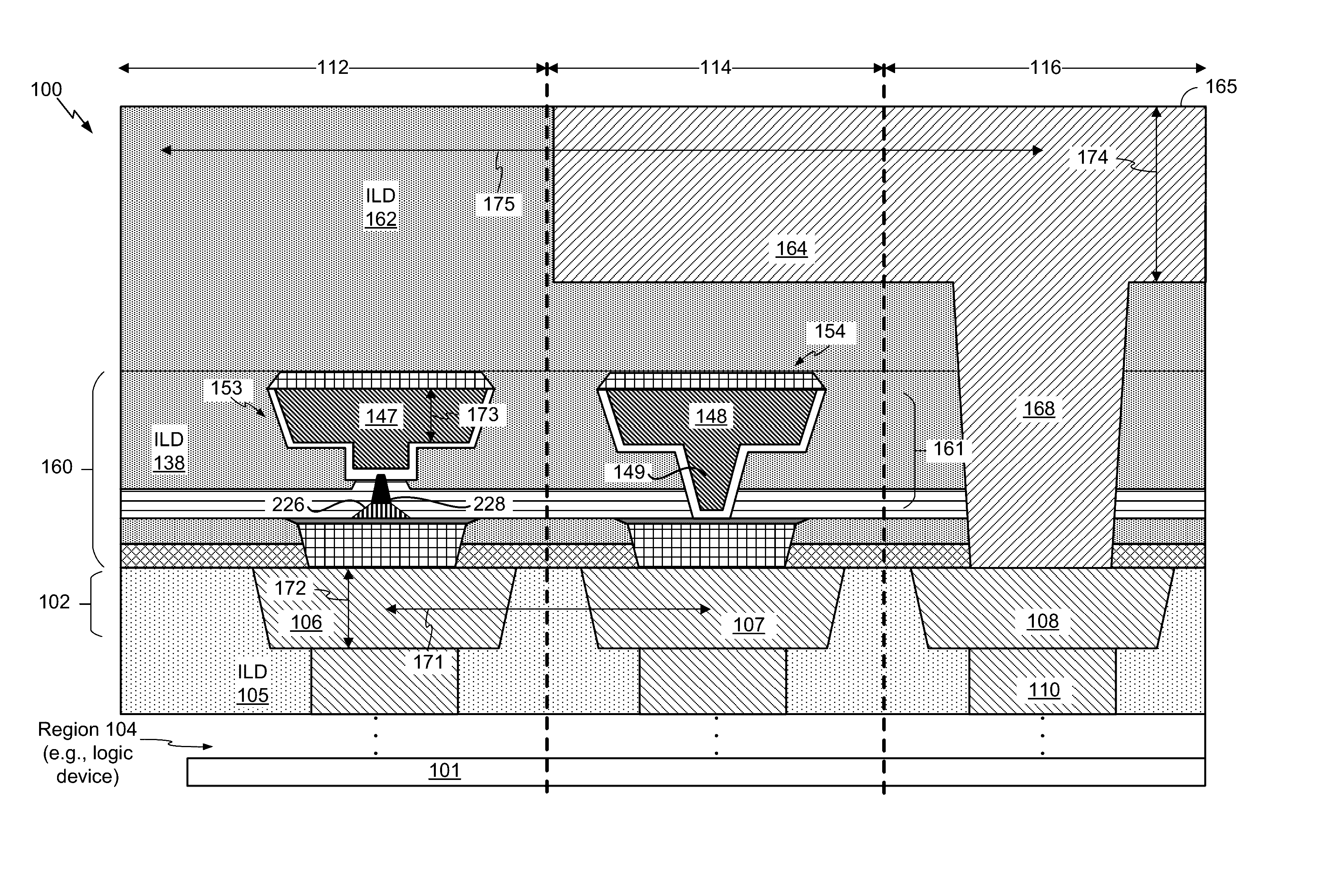

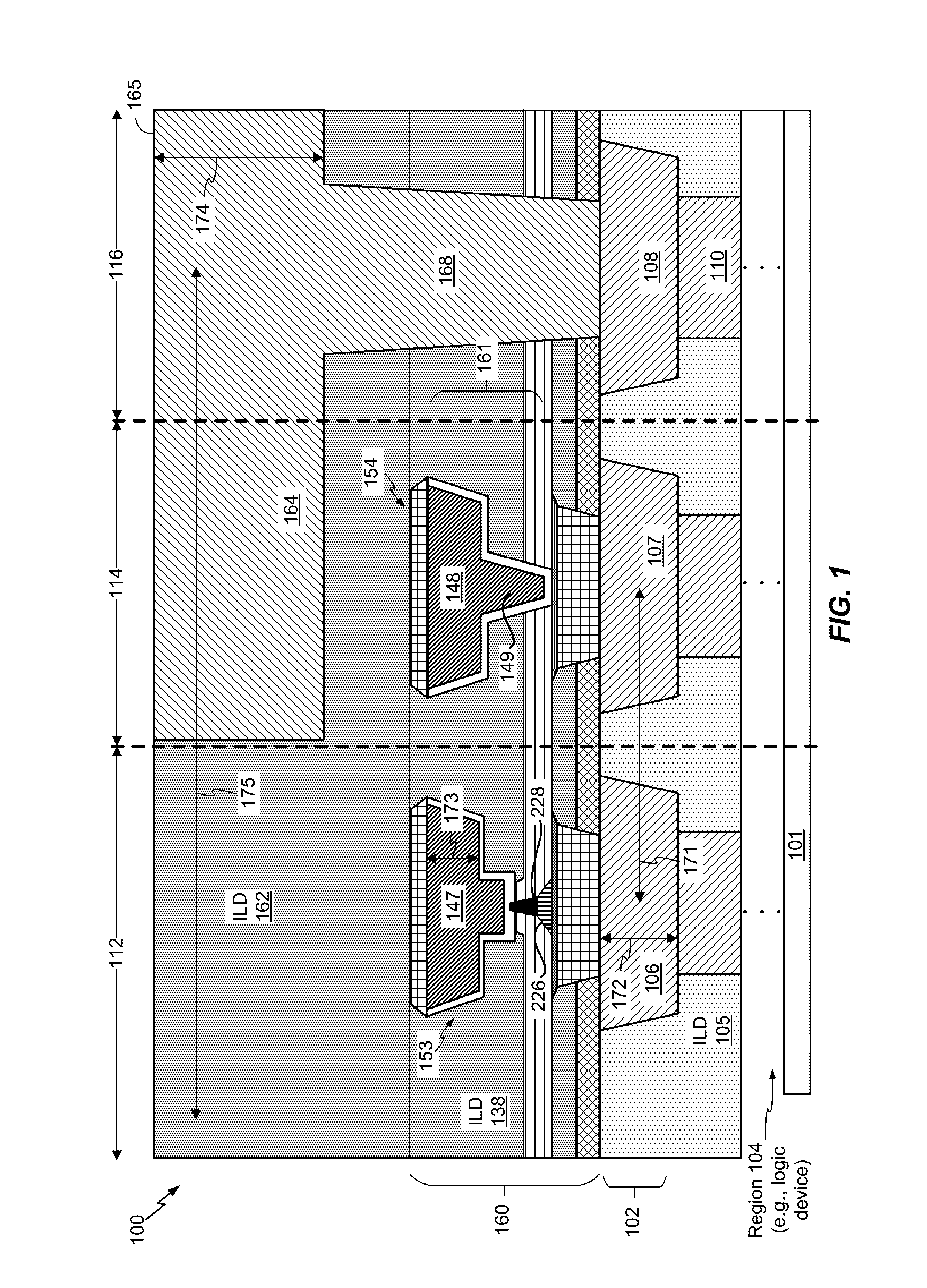

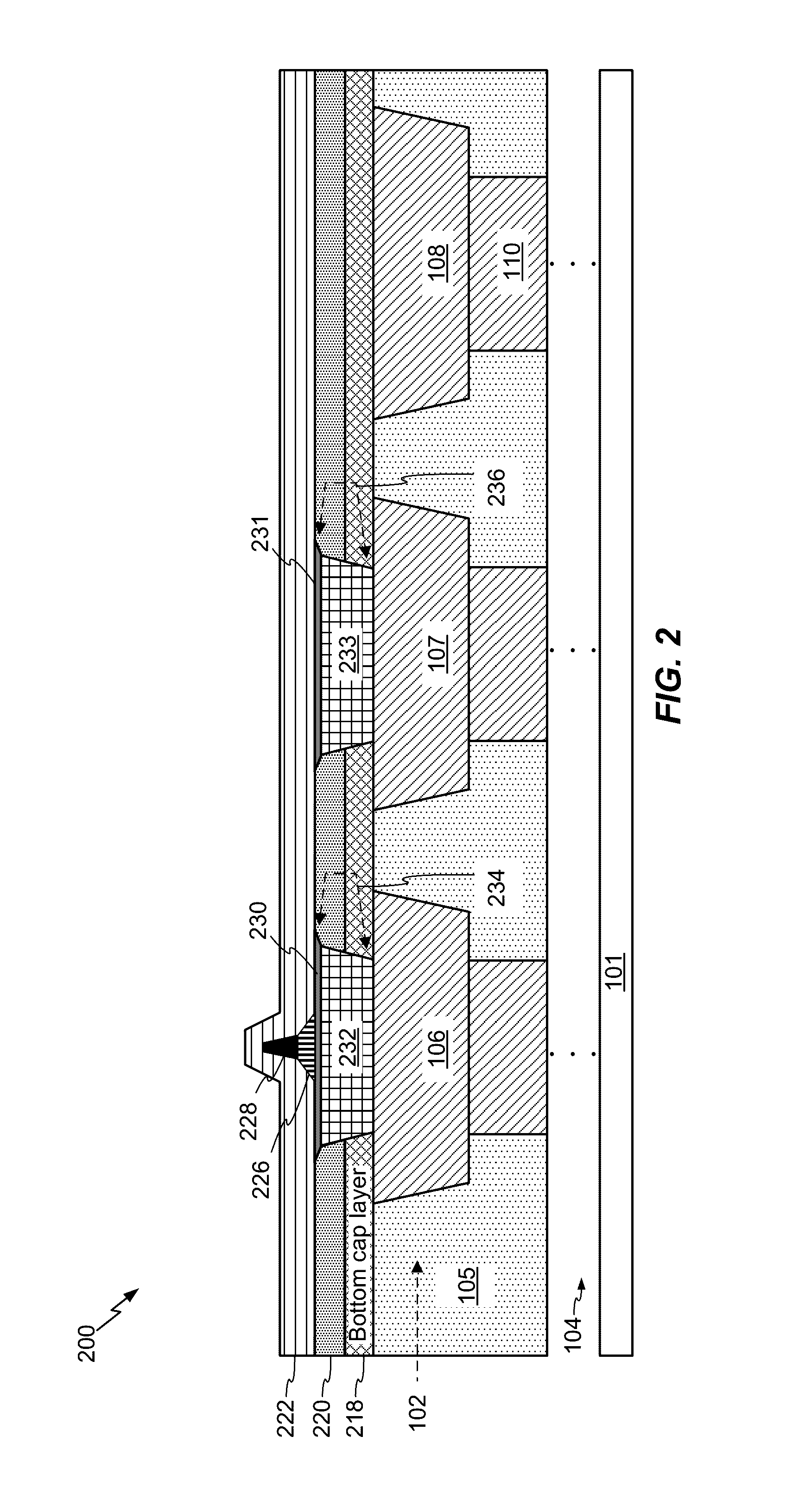

Metallization process for a memory device

ActiveUS20170047374A1High data storage densityIncrease fabrication costSemiconductor/solid-state device detailsMagnetic-field-controlled resistorsMagnetic reluctanceComputer science

A method of fabrication of a device includes forming a first metallization layer that is coupled to a logic device of the device. The method further includes forming a second metallization layer that is coupled to a magnetoresistive random access memory (MRAM) module of the device. The second metallization layer is independent of the first metallization layer.

Owner:QUALCOMM INC

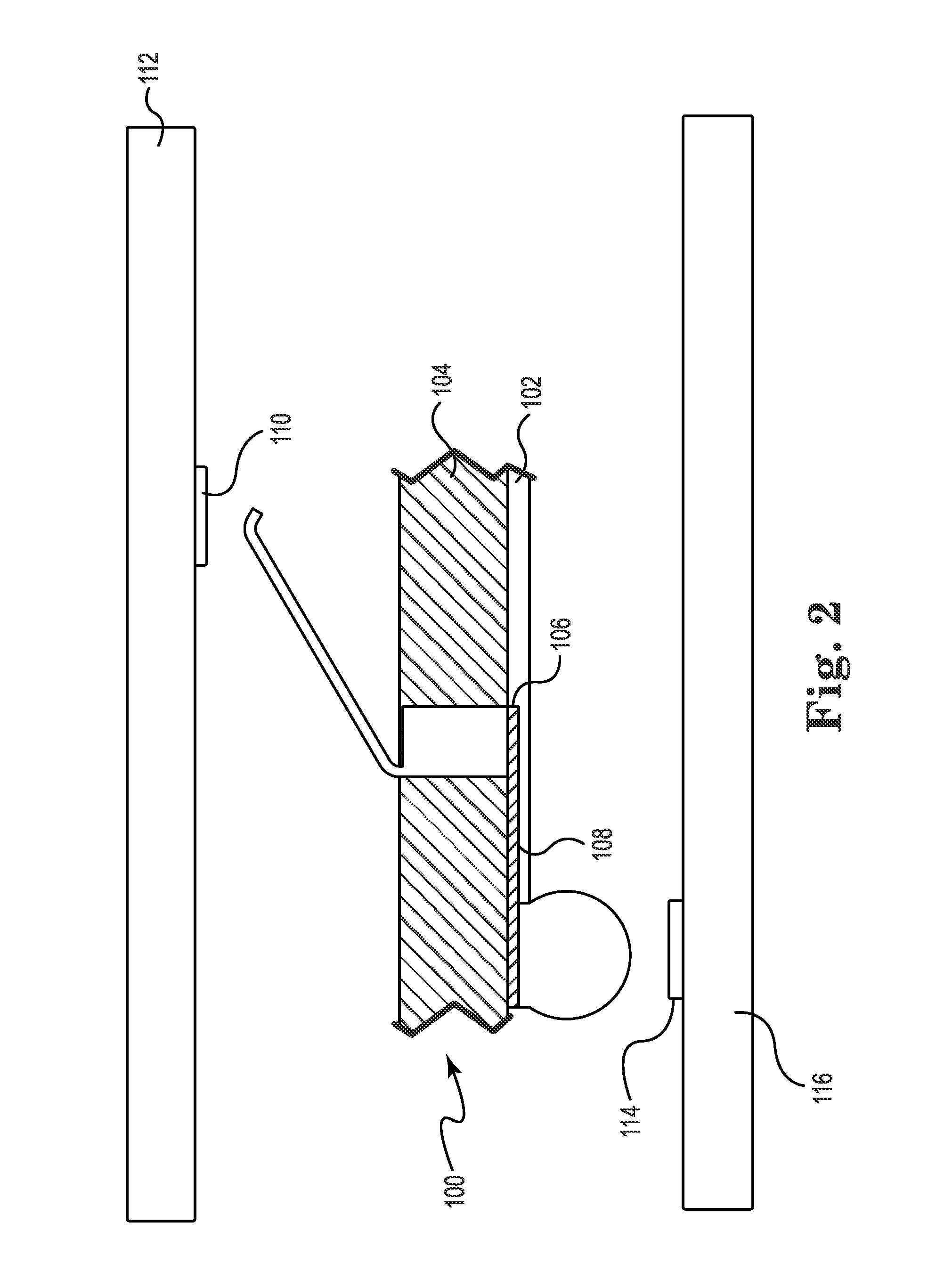

Semiconductor socket with direct selective metalization

ActiveUS20150279768A1Improve electrical performanceImprove intelligenceContact member manufacturingSemiconductor/solid-state device detailsEngineeringConductive materials

A semiconductor socket including a substrate with a plurality of through holes extending from a first surface to a second surface. A conductive structure is disposed within the through holes A plurality of discrete contact members are located in the plurality of the through holes, within the conductive structure. The plurality of contact members each include a proximal end accessible from the second surface, and a distal end extending above the first surface. The conductive structure can be electrically coupled to circuit geometry. At least one dielectric layer is bonded to the second surface of the substrate with recesses corresponding to desired circuit geometry. A conductive material deposited in at least a portion of the recesses to form conductive traces redistributing terminal pitch of the proximal ends of the contact members.

Owner:HSIO TECH

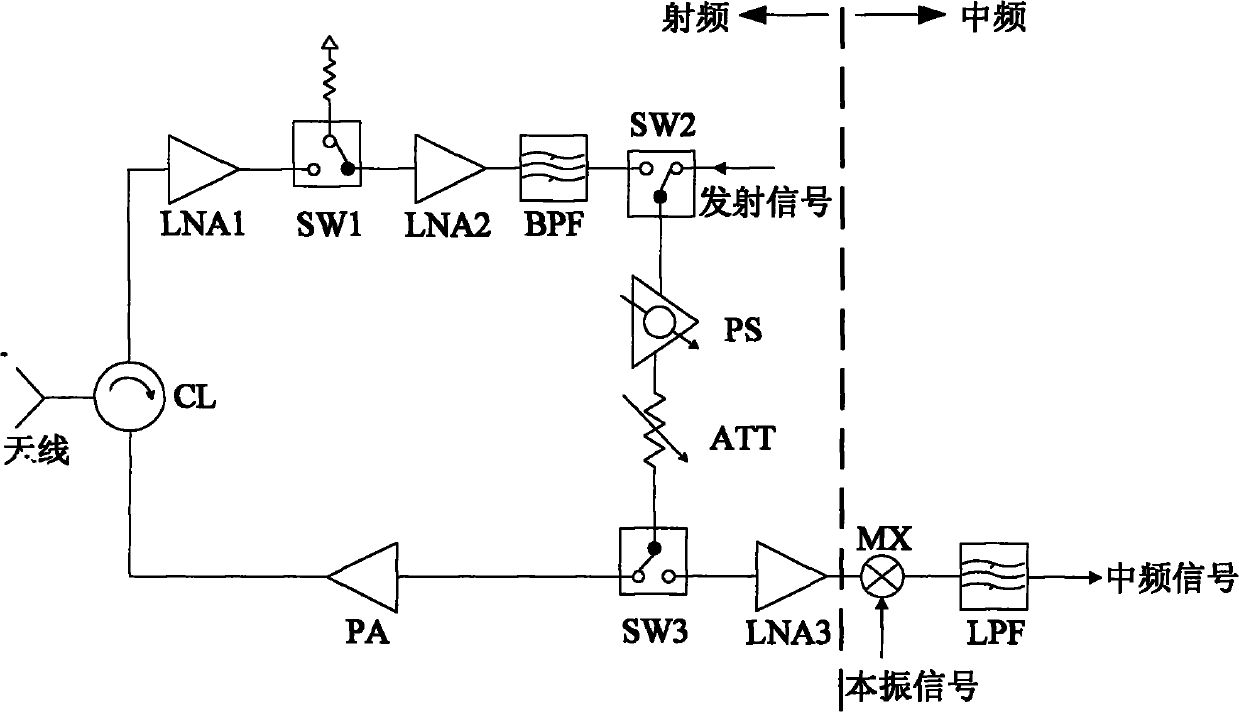

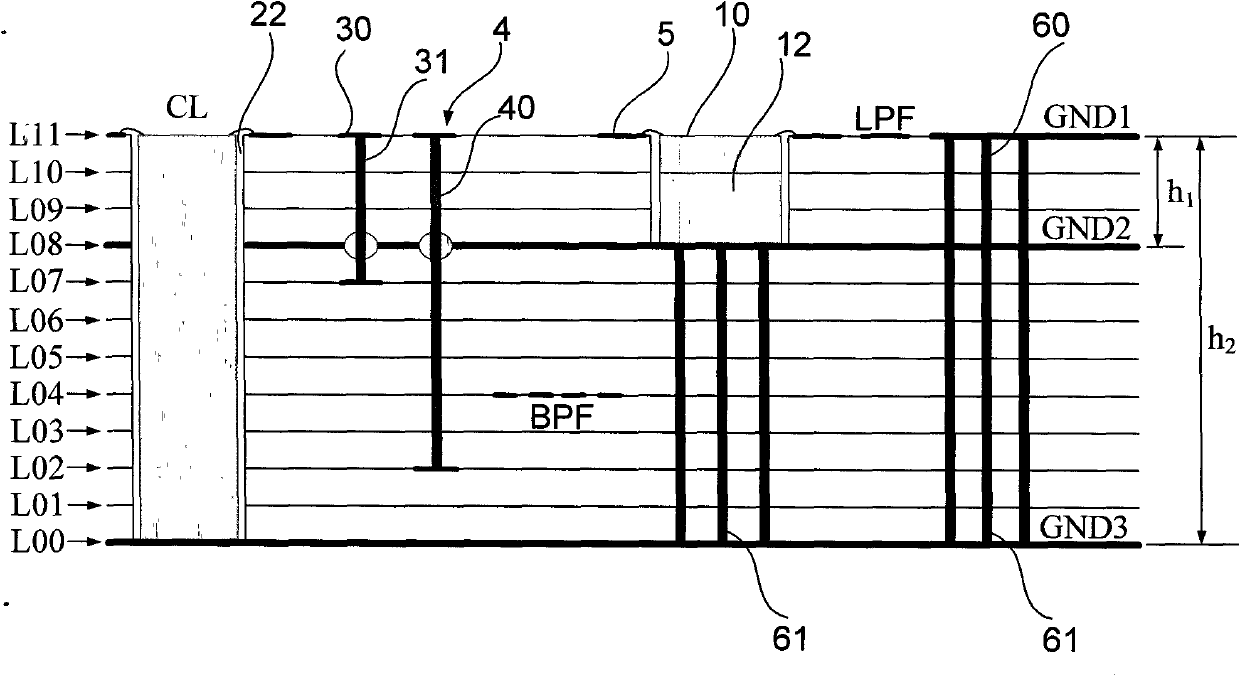

High-performance low-cost miniature low temperature co-fired ceramic (LTCC) transceiving component

InactiveCN102200574AWork lessShorten the lengthWave based measurement systemsLow-pass filterBand-pass filter

The invention relates to a microwave millimetre-wave transceiving component device, which consists of a transmitting branch, a receiving branch, a micro-strip line, a chip feeding network, a control network, an input / output interface and a metal box body, wherein functional circuit modules are integrated in low temperature co-fired ceramic (LTCC) multi-layer medium substrates to form a miniature microwave three-dimensional stereo structure; a band-pass filter, a low-pass filter, the micro-strip line, the chip feeding network, the control network and the input / output interface are formed by printing metal conduction bands with different shapes on different layers of LTCC substrates; and the functional modules, except a circulator, the band-pass filter and the low-pass filter, are realized by a monolithic microwave integrated circuit (MMIC) chip circuit. A near end of an MMIC chip feeding network consists of a feeder line pad and a grid-shaped metal conduction band; and the metal conduction band encloses the centre of the feeder line pad into a closed structure. The three-dimensional stereo structure at least comprises three layers of horizontal planes which are in short-circuited connection by metallized through holes. The device has the advantages of high performance, low cost and miniaturization.

Owner:费元春 +1

Clock signal distribution with reduced parasitic loading effects

ActiveUS7528638B2Reduce load effectReduce power lossPulse automatic controlGenerating/distributing signalsDelay-locked loopDistribution system

Clock signal distribution systems with reduced parasitic loading effects are provided. A reference clock is frequency-divided to produce a lower frequency clock signal. A delay-locked loop (DLL) circuit locks to the lower frequency clock signal, and outputs a corresponding lower frequency clock signal for distribution over a long trace. Power consumption caused by parasitic capacitance of the trace is thereby reduced. Parasitic effects associated with clock jitter are also reduced. A frequency multiplying phase-locked loop (PLL) circuit locks to the lower frequency clock signal, and outputs at least one clock signal having a higher frequency than the lower frequency signal.

Owner:MICRON TECH INC

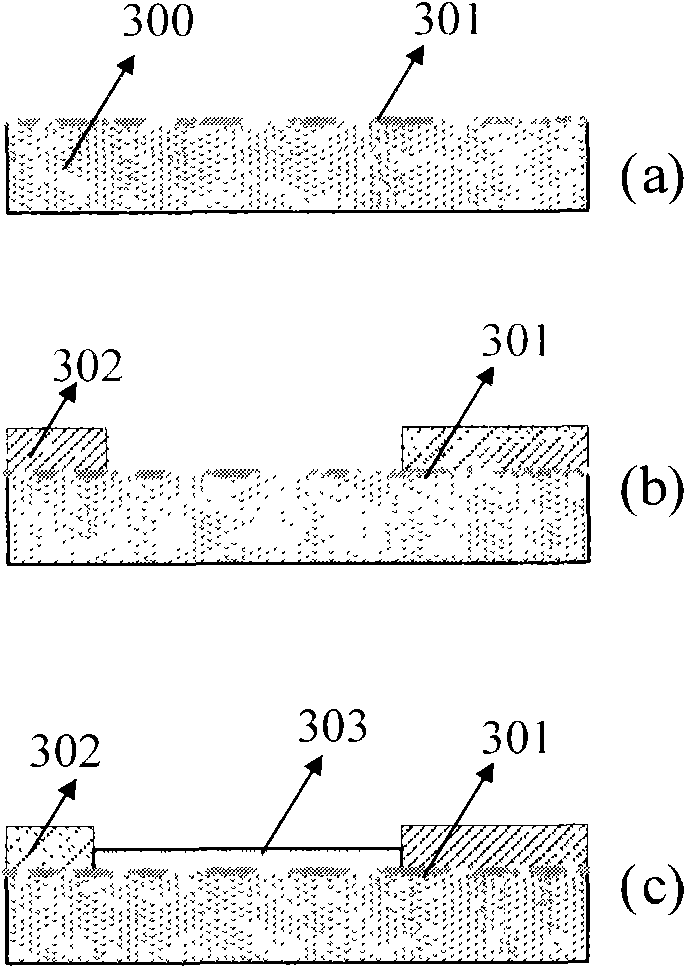

Method for manufacturing substrate

ActiveCN101038880AReduce thicknessIncreased versatilitySemiconductor/solid-state device manufacturingPrinted circuit manufactureEngineeringElectrical and Electronics engineering

The invention discloses a method for making substrate, which includes providing a core board having inner circuits on both upper and lower sides; forming a storage space on the core board; embedding an element in the storage space and forming an insulation layer to coat the element, core board and the inner circuit of upper and lower sides; forming plural holes on the insulation layer to expose plural electrodes of the elements; forming plural through holes to drill through the insulation layer and the core board; making conductive membrane on the surface of the insulation layer and the side walls of the through holes; forming conductive layer on the conductive membrane; patterning the conductive layer to form outer layer circuit; forming anti-welding layer on the outer layer circuit.

Owner:ADVANCED SEMICON ENG INC

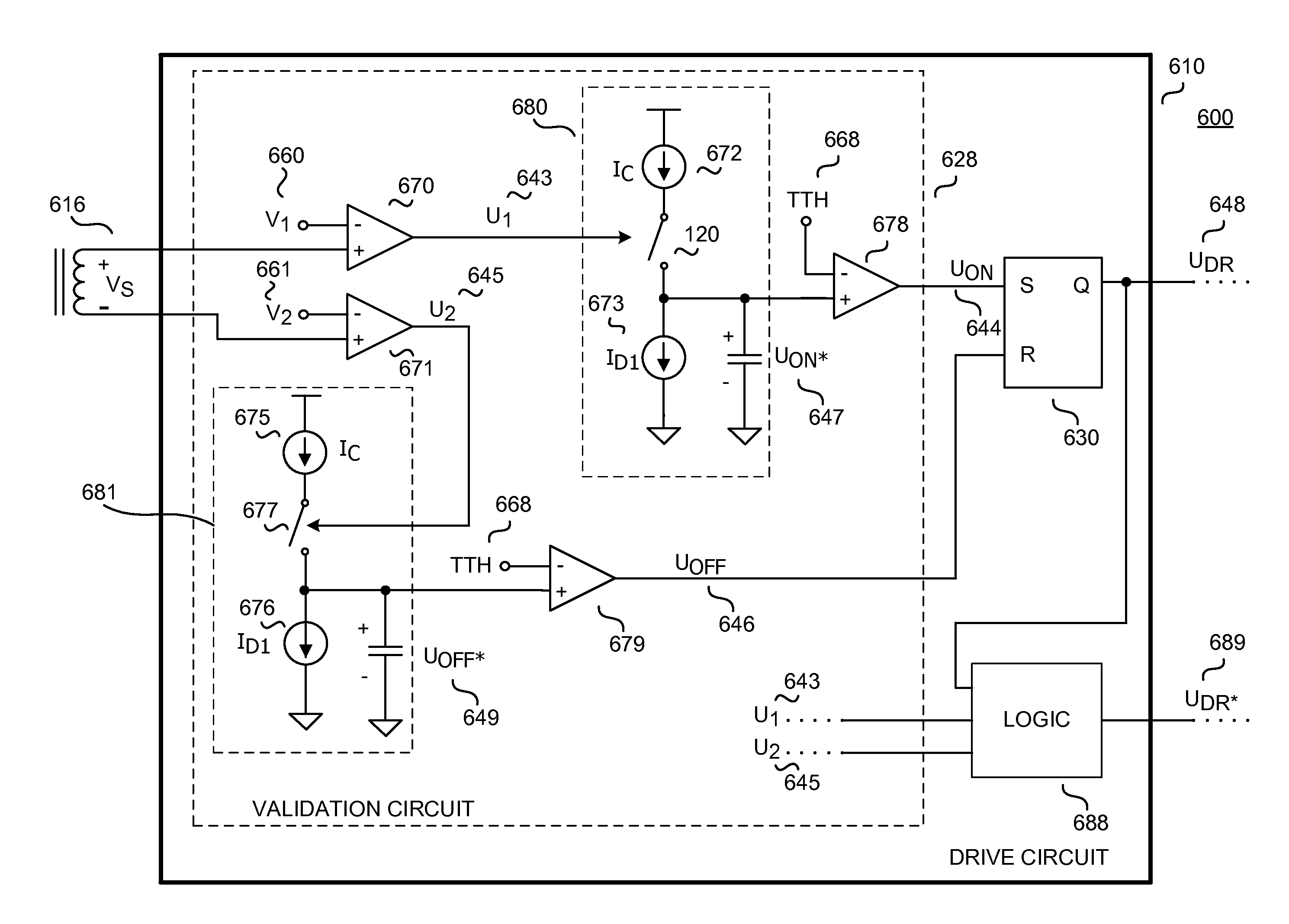

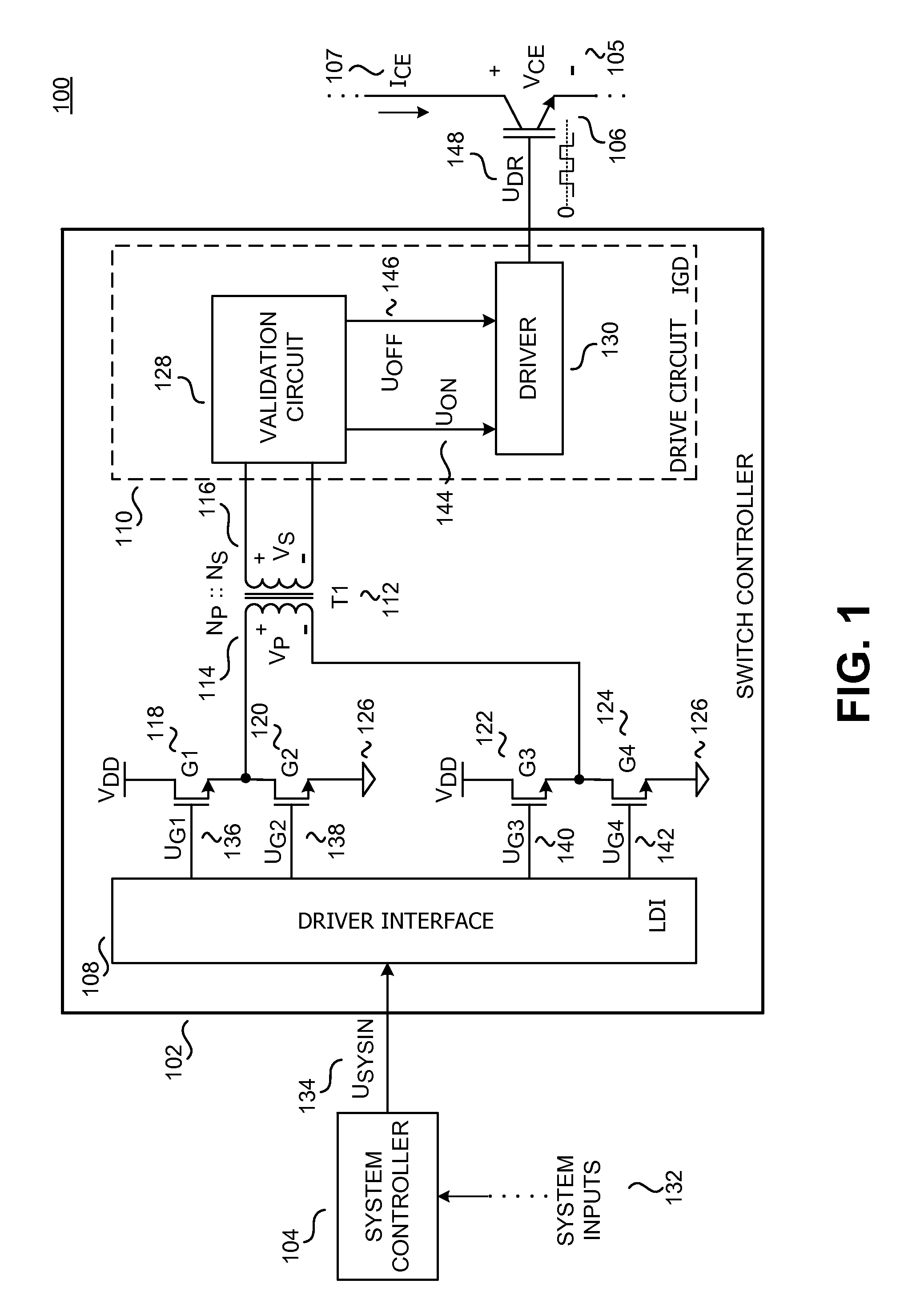

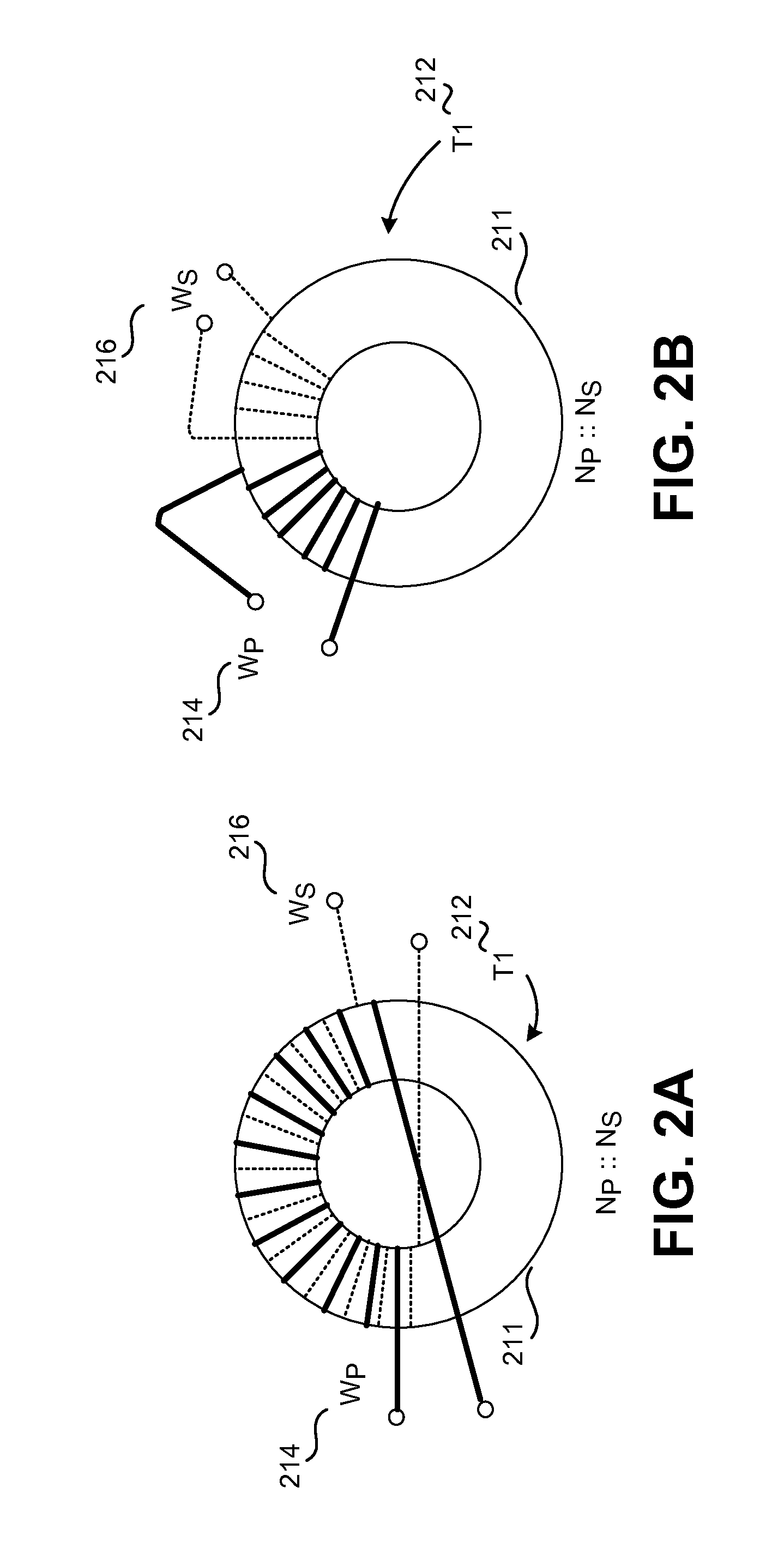

Switch controller with validation circuit for improved noise immunity

ActiveUS20160006337A1Improve shielding effectEnhanced couplingTransformersTransformers/inductances coils/windings/connectionsEngineeringSignal generator

A switch controller includes a primary side including signal transmission circuitry to transmit signals representative of desired transitions of a switch. A signal transformer galvanically isolates the primary side from a secondary side but inductively couples signal transmission circuitry to signal reception circuitry. A switch is coupled to switch a low impedance onto a primary side winding of the signal transformer during pauses between transmissions of the signals representative of the desired transition of the switch. The secondary side includes signal reception circuitry, a drive signal generator to generate a drive signal in response to valid signals received by the signal reception circuitry, and a validation circuit that includes a first comparator, a timer, and a second comparator to compare a timed duration with a threshold duration, and to output to the drive signal generator signals indicative of the validity of particular signals received by the signal reception circuitry.

Owner:POWER INTEGRATIONS INC