Patents

Literature

31results about How to "Protection capacitor" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

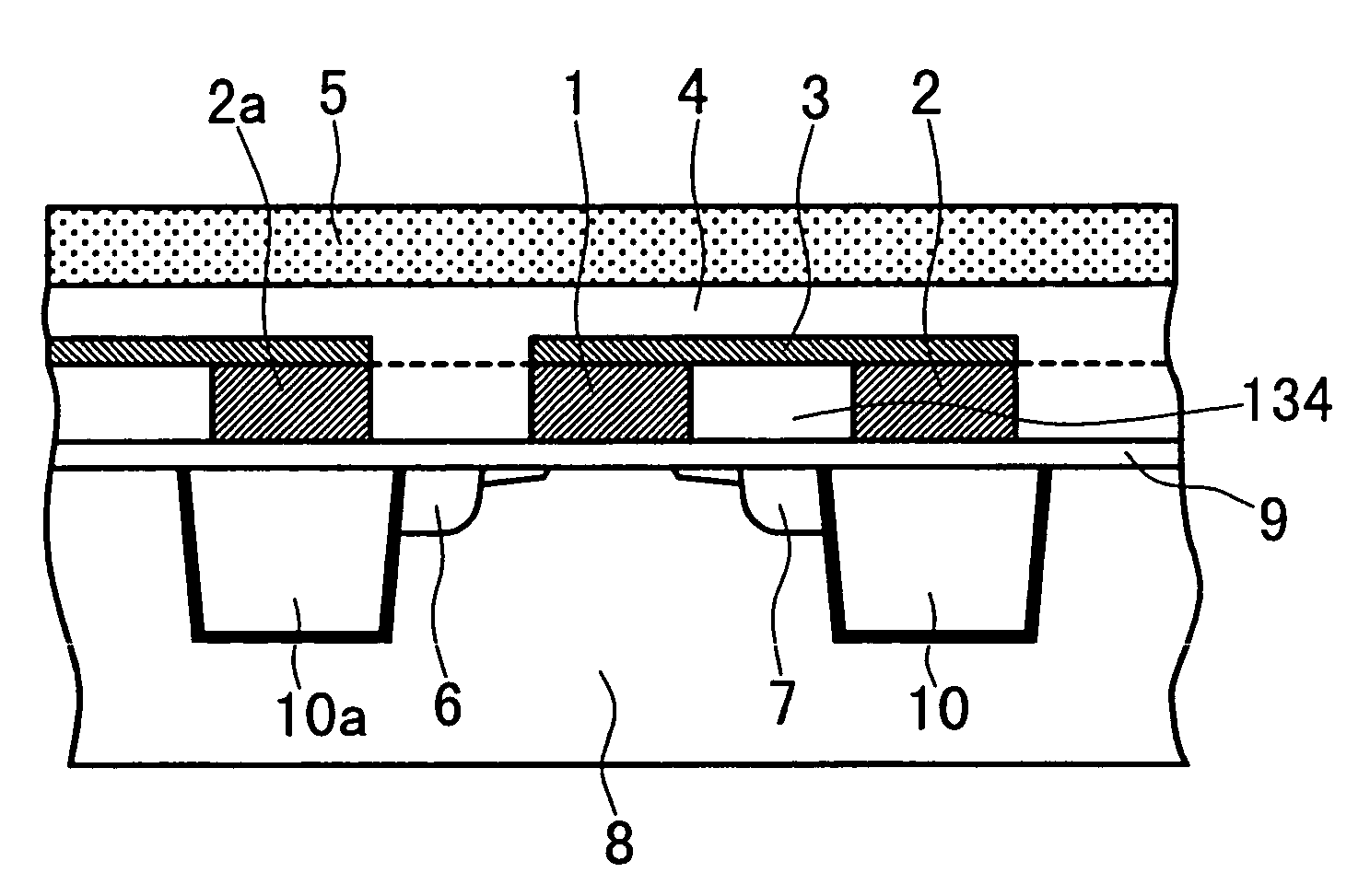

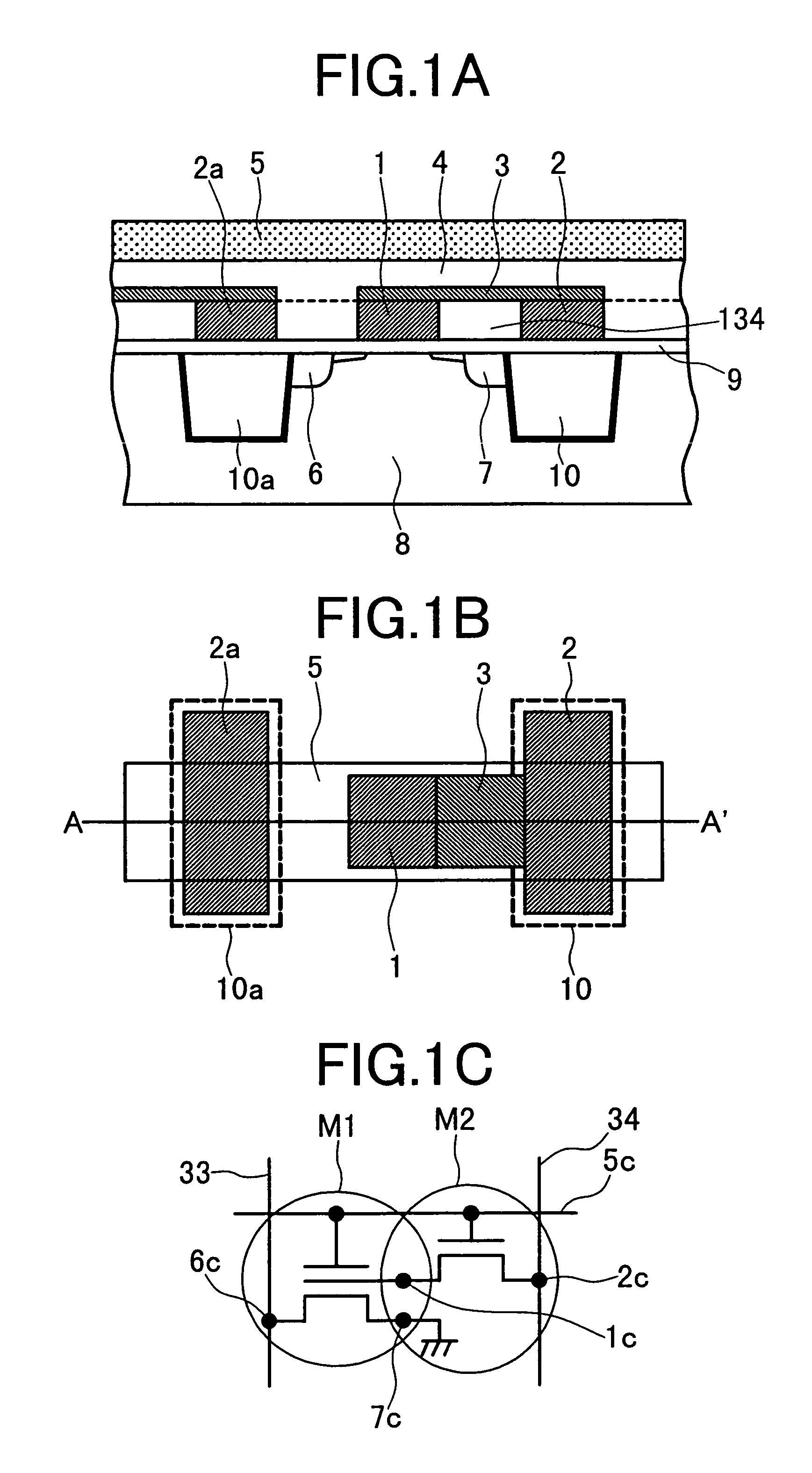

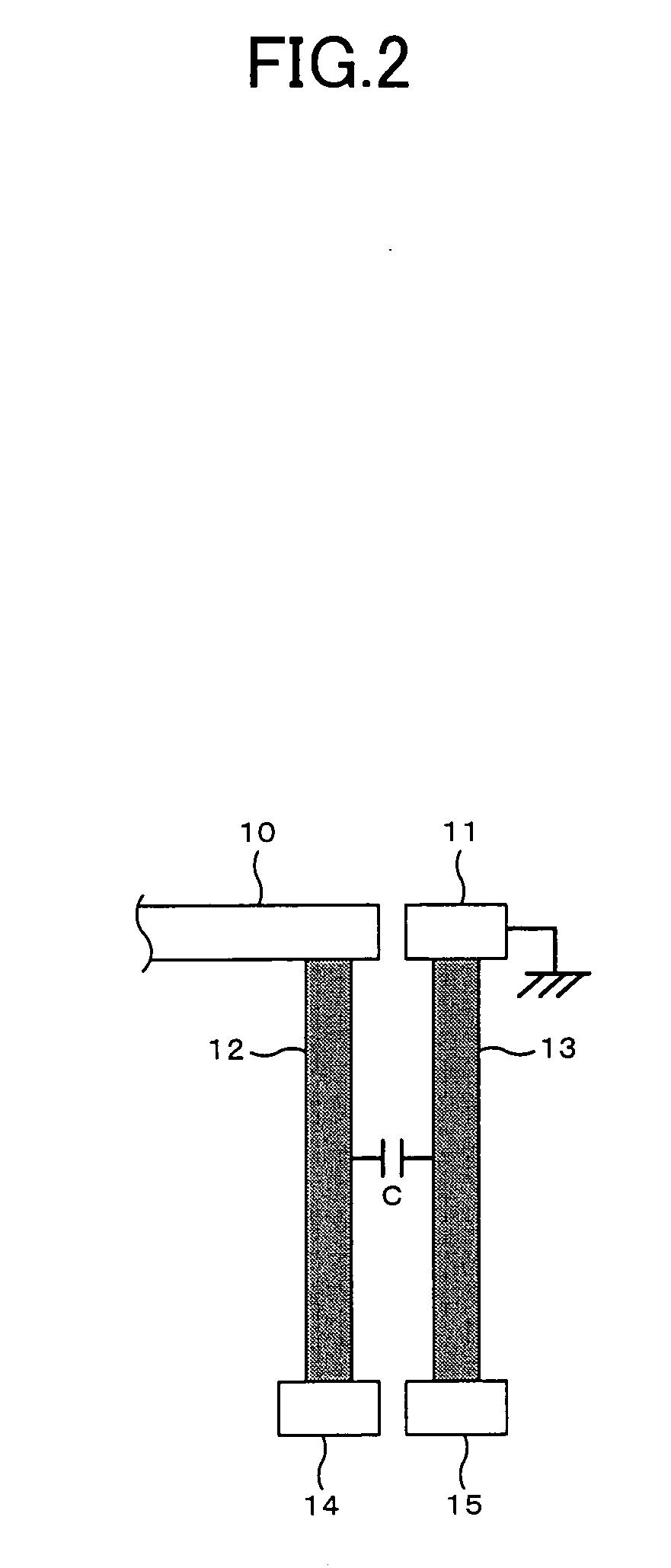

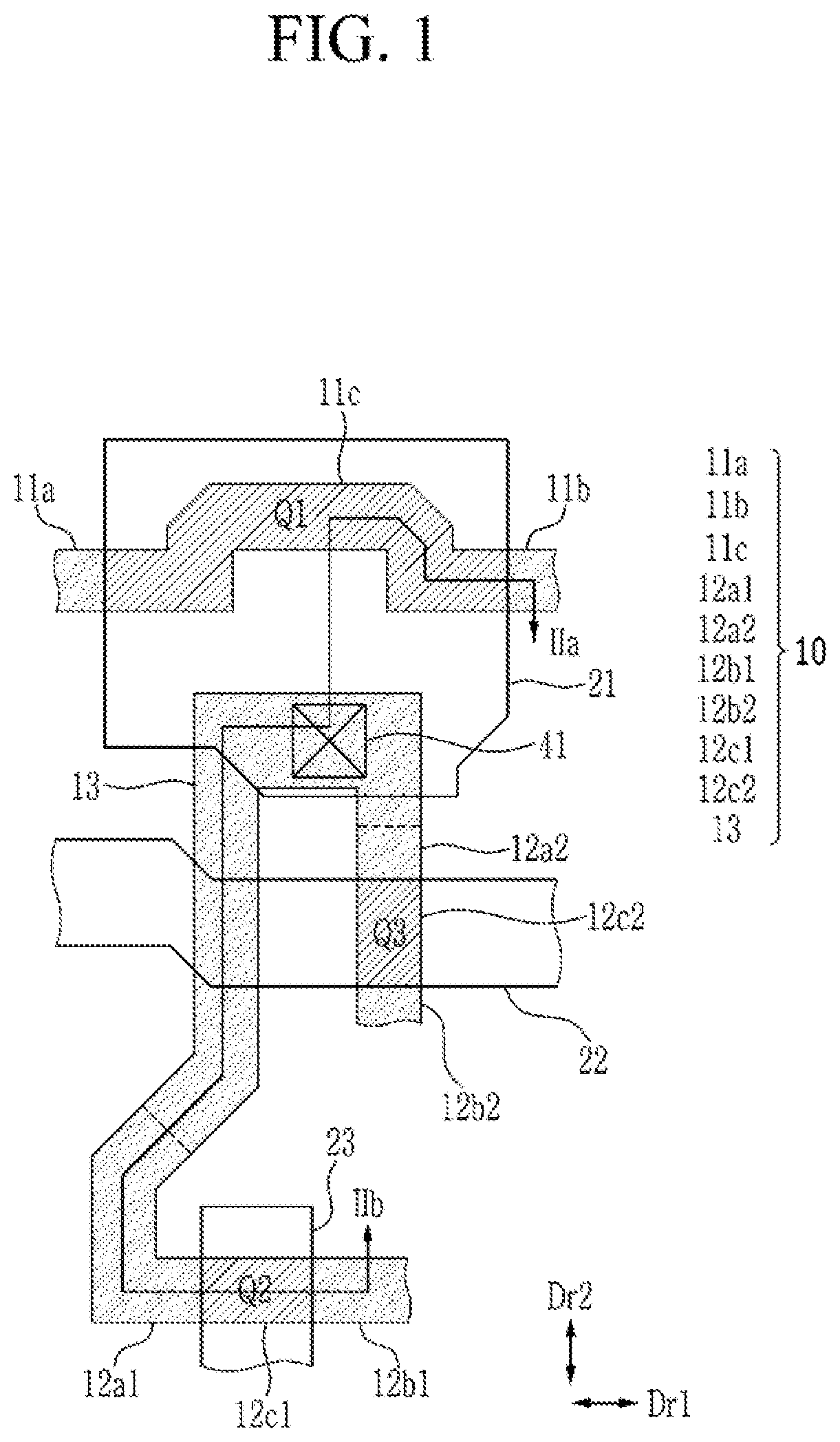

Semiconductor memory device

InactiveUS7009243B2Protection capacitorEasy to combineTransistorIndividual molecule manipulationSemiconductor materialsEngineering

Owner:HITACHI LTD

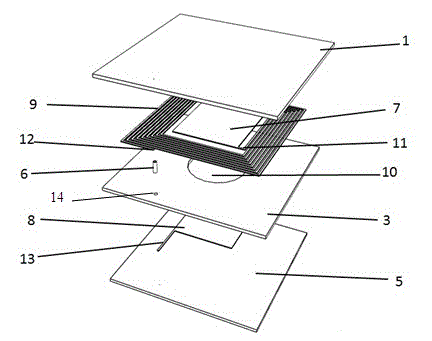

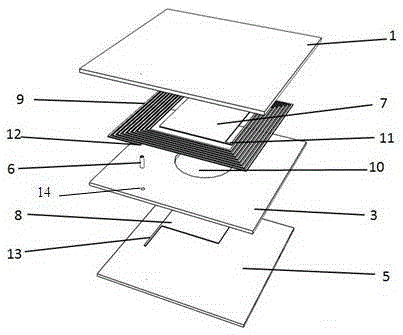

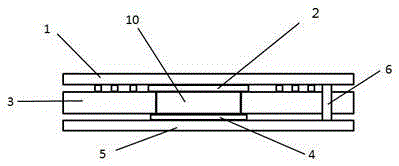

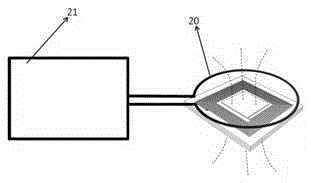

Flexible-substrate-based passive wireless pressure sensor with self-packaging function

InactiveCN103148977AProtection capacitorProtection inductanceFluid pressure measurement using capacitance variationCapacitanceEngineering

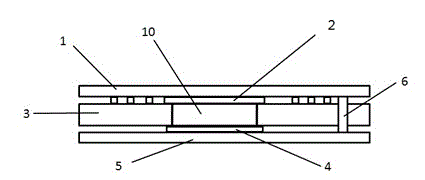

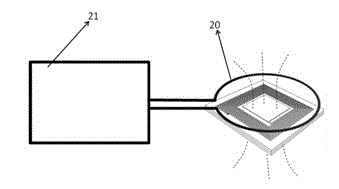

The invention discloses a flexible-substrate-based passive wireless pressure sensor with a self-packaging function. The pressure sensor comprises an upper flexible substrate, an upper metal layer, a middle flexible substrate, a lower metal layer and a lower flexible substrate, which are sequentially arranged from top to bottom and fixedly connected. An electric through hole and a cavity are formed in the middle flexible substrate. The upper metal layer comprises a planar inductance coil and a capacitor upper polar plate positioned on the middle part of the planar inductance coil. An inner connector of the planar inductance coil is connected with the capacitor upper polar plate. The lower metal layer comprises a capacitor lower polar plate opposite to the upper plate capacitor and an interconnecting wire connected with the capacitor upper polar plate. The sizes of the capacitor upper polar plate and capacitor lower polar plate are the same. An outer connector of the planar inductance coil of the upper metal layer is connected with the interconnecting wire of the lower metal layer through a conductive medium column in the electric through hole. The cavity of the middle flexible substrate is positioned between the capacitor upper polar plate and capacitor lower polar plate. The pressure sensor has the high performance of self packaging, non-contact, high sensitivity and high quality factor.

Owner:SOUTHEAST UNIV

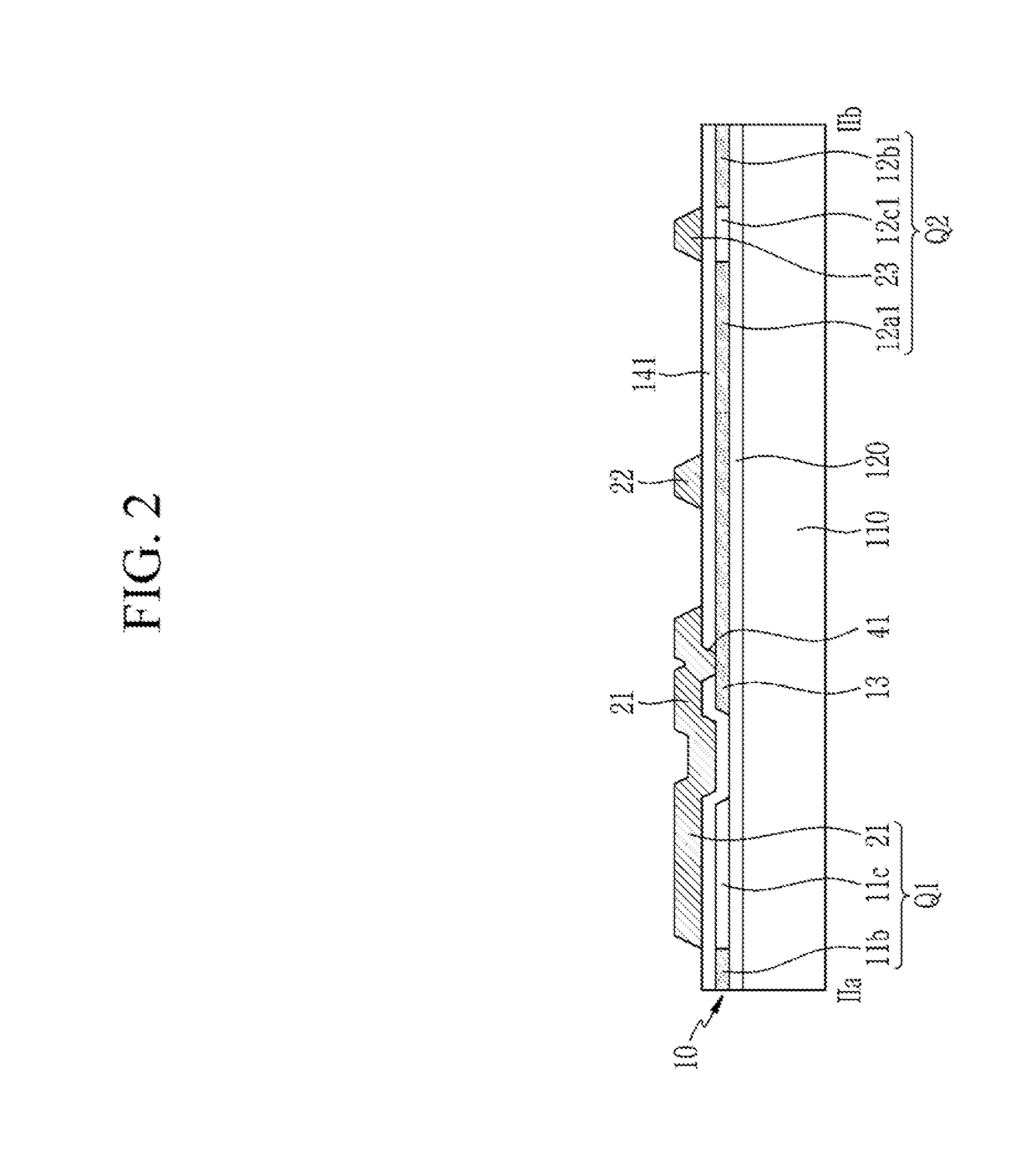

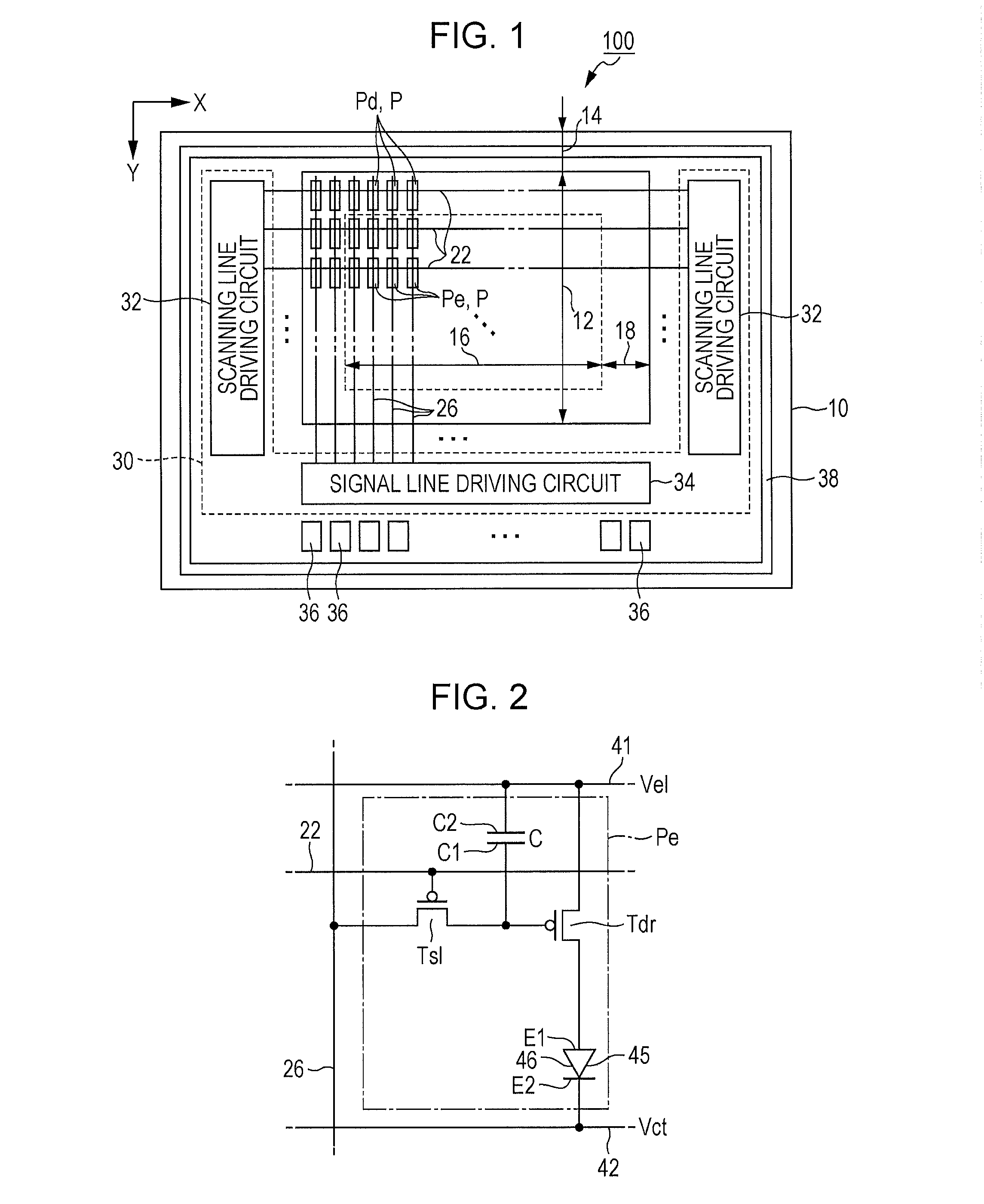

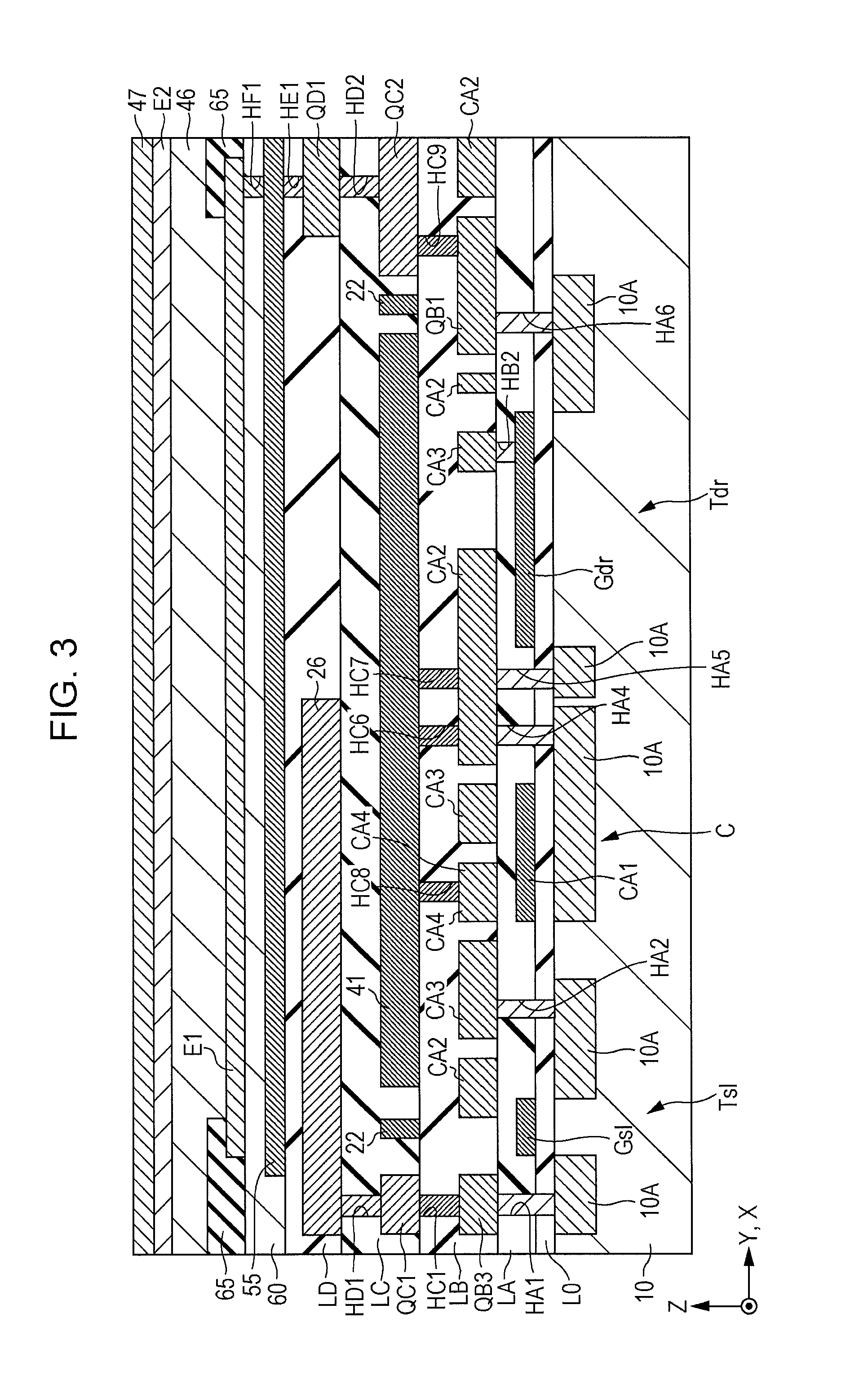

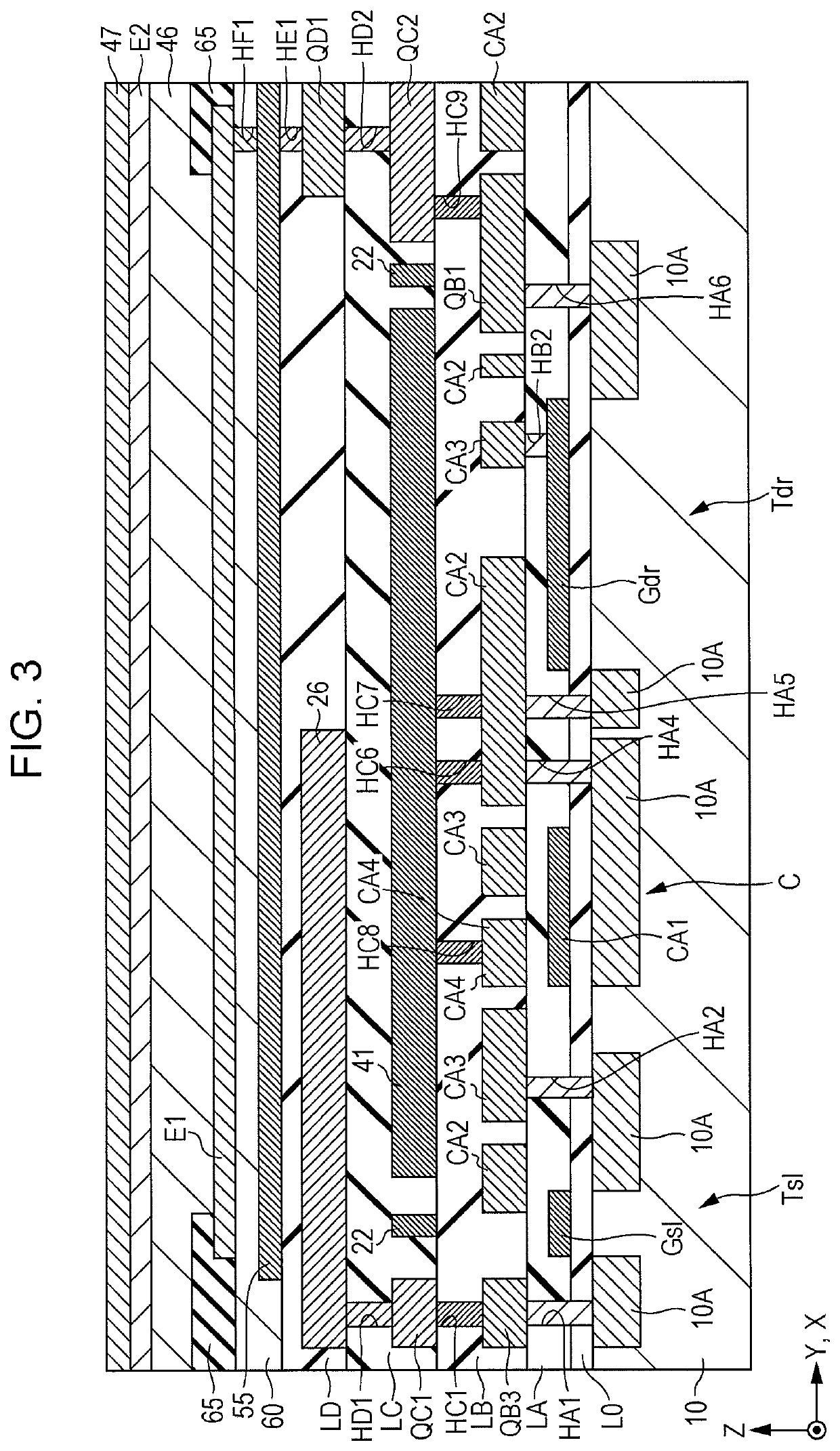

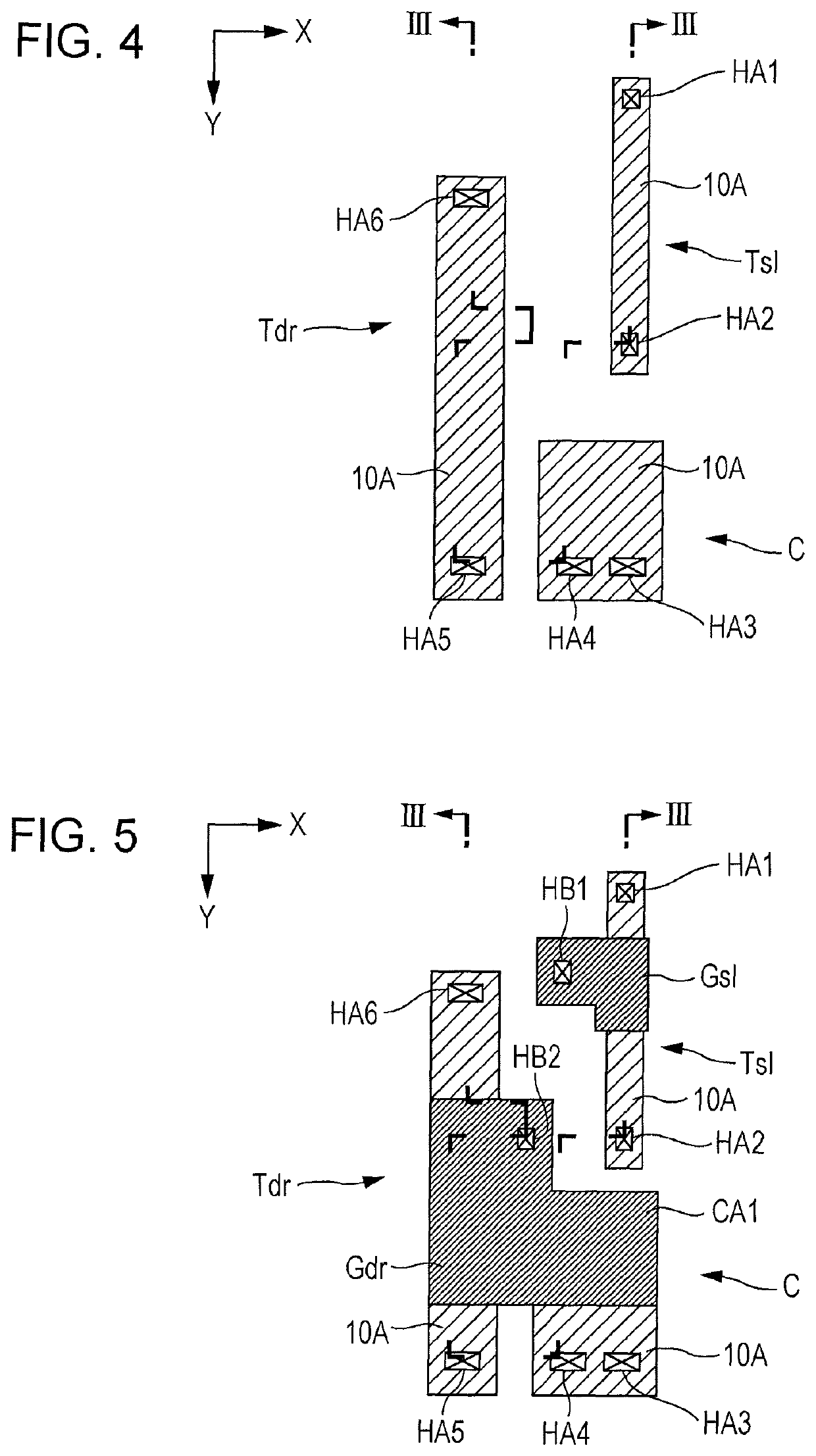

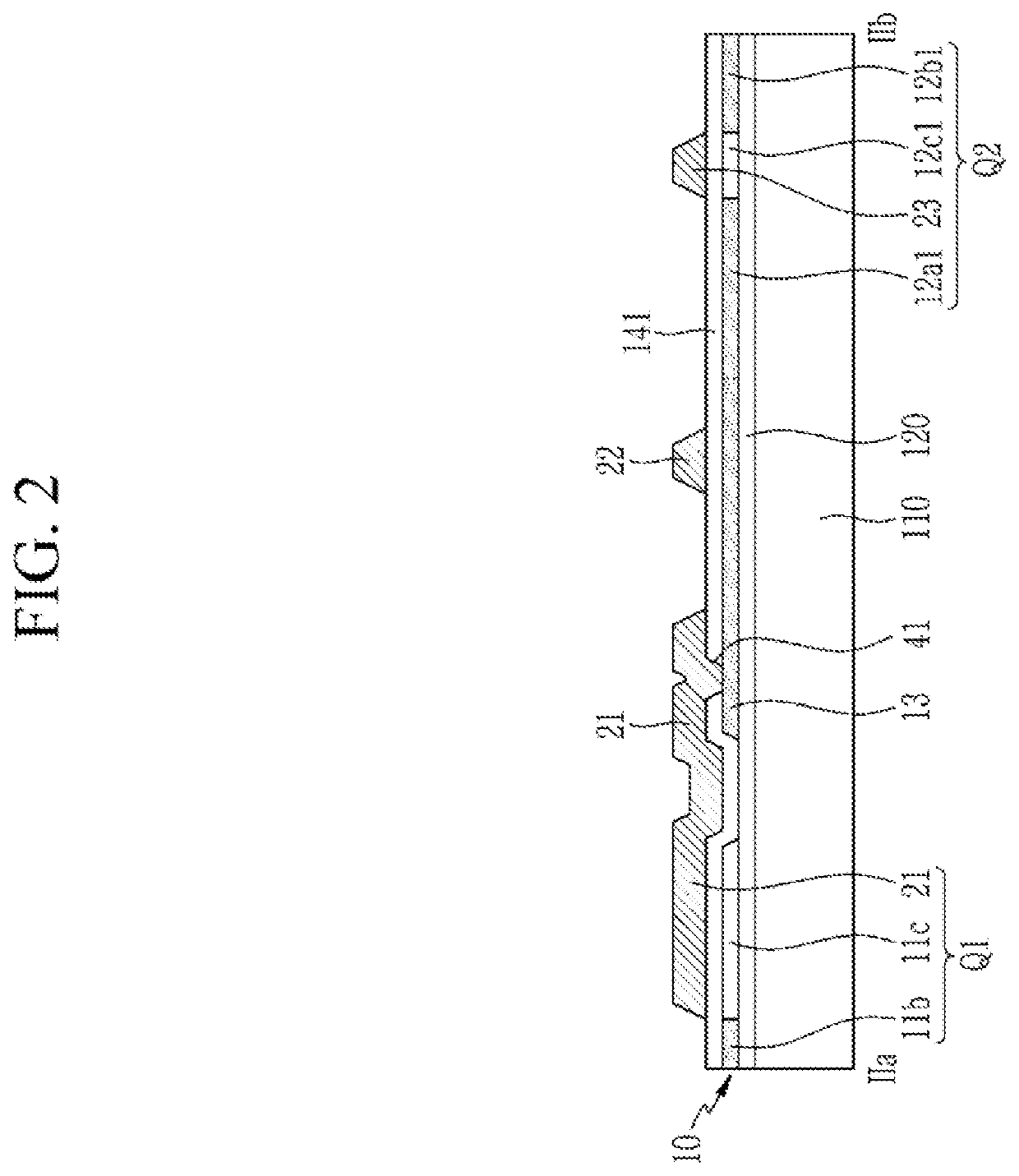

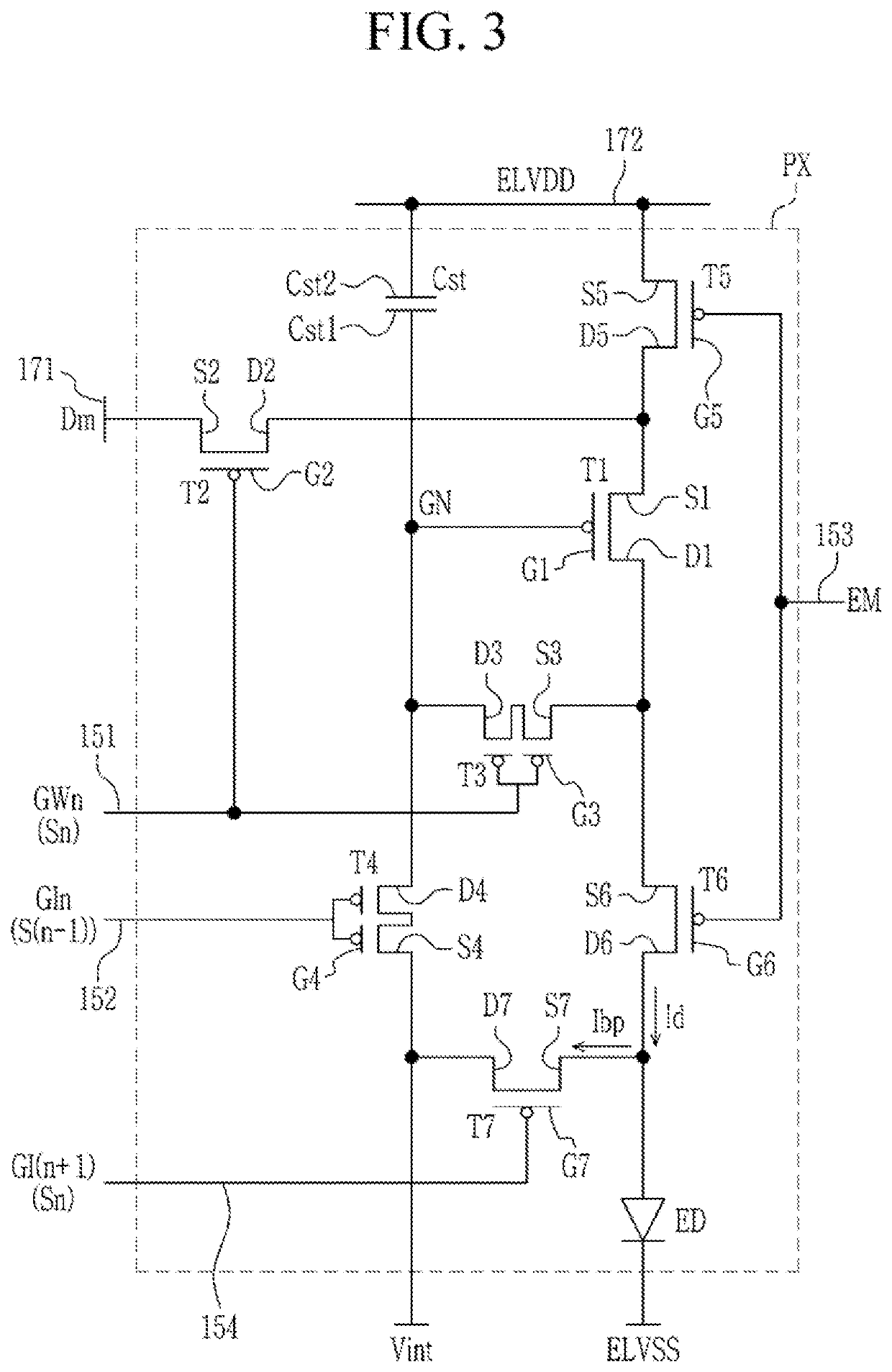

Display device and manufacturing method thereof

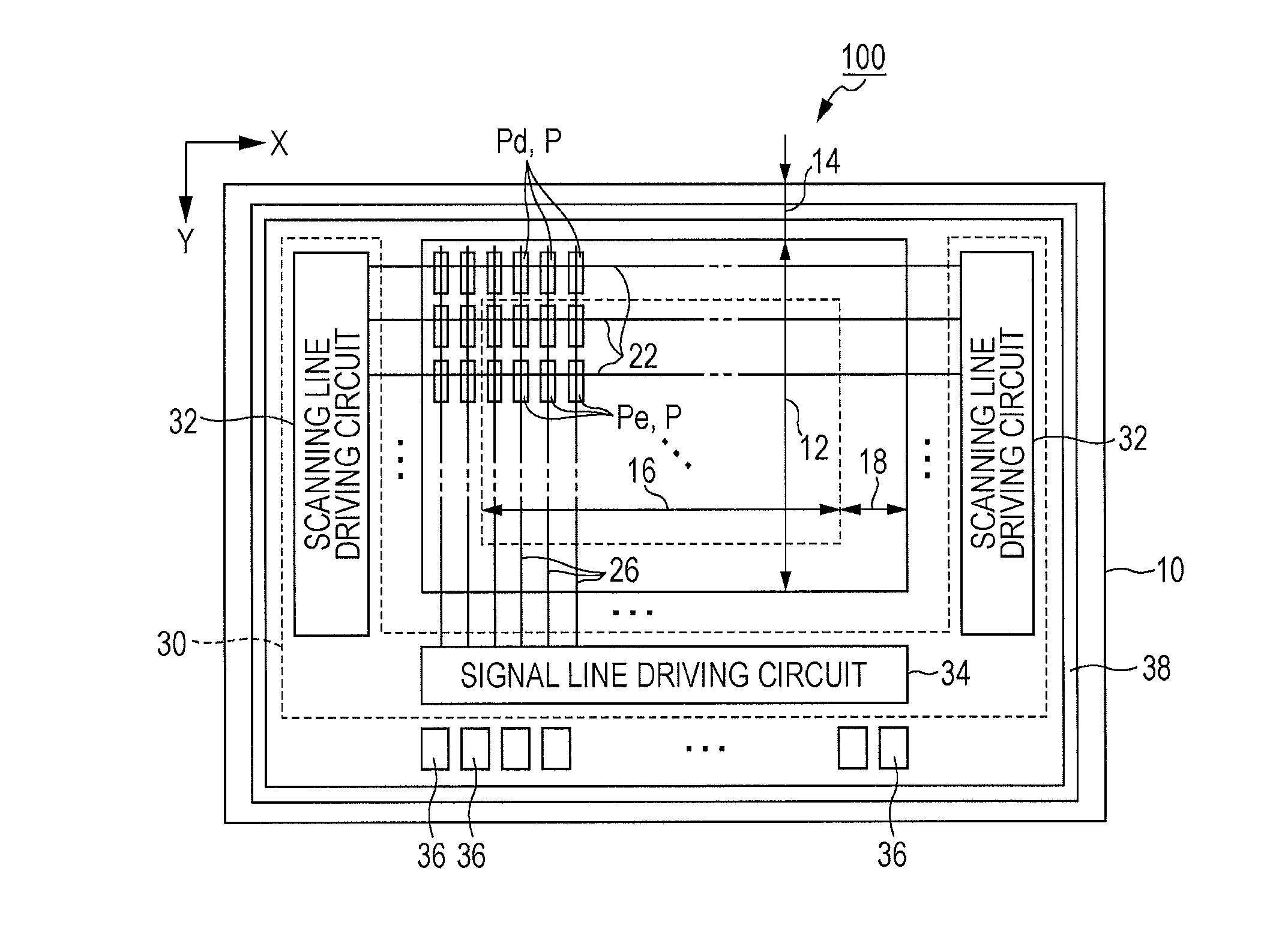

ActiveUS20180226459A1Protection capacitorReduce generationStatic indicating devicesSolid-state devicesElectrical conductorCharge carrier

The present disclosure relates to a display device. An exemplary embodiment of the present invention provides a display device including a substrate and an active pattern positioned above the substrate. to the active pattern includes a channel region and a conductive region having a higher carrier concentration than the channel region. A first insulating layer is disposed on the active pattern. A first conductive layer is disposed on the first insulating layer and includes a first conductor. The channel region of the active pattern includes a first channel region overlapping the first conductor along a direction orthogonal to an upper surface of the substrate. The conductive region of the active pattern includes a first conductive region overlapping the first conductor along the direction orthogonal to the upper surface of the substrate.

Owner:SAMSUNG DISPLAY CO LTD

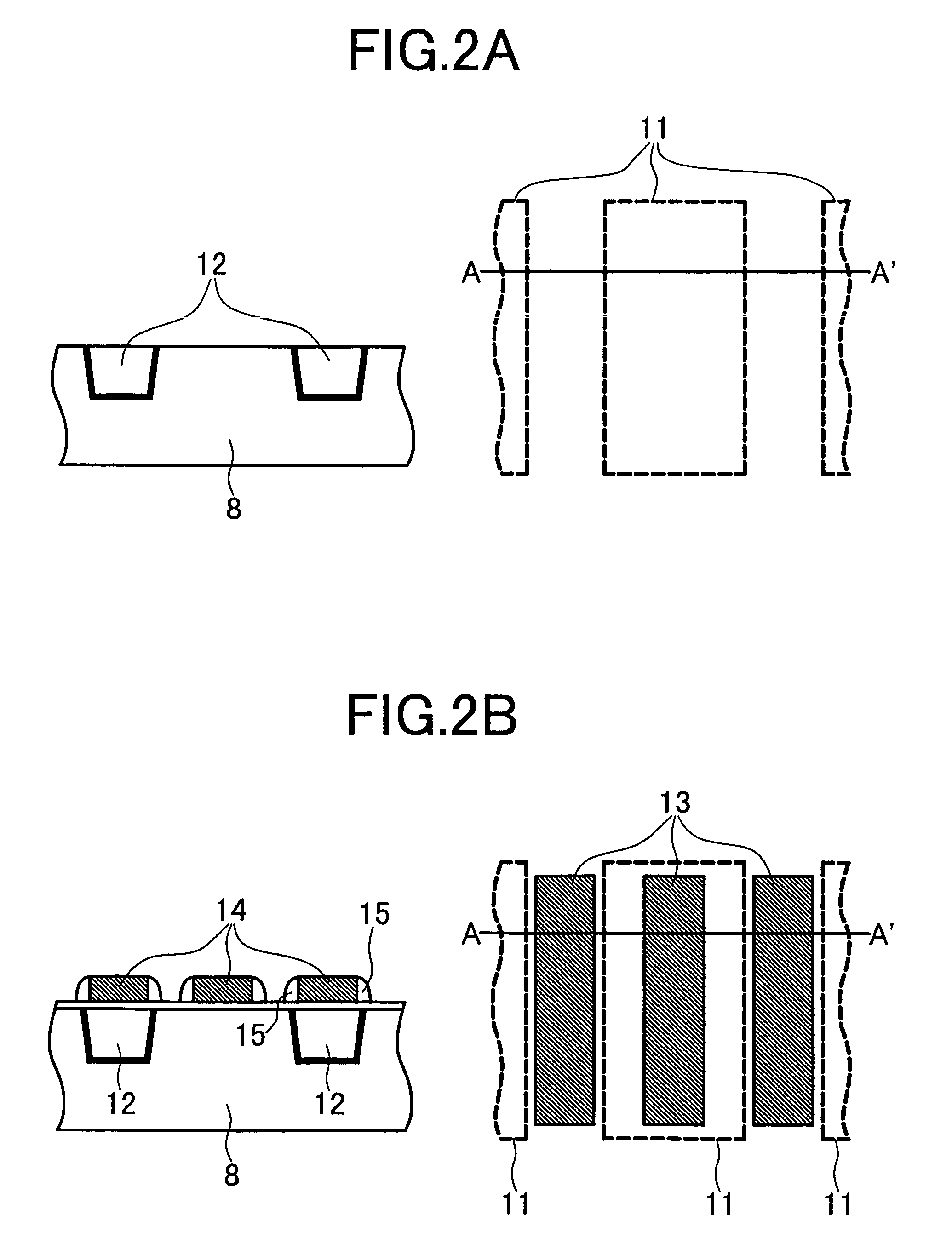

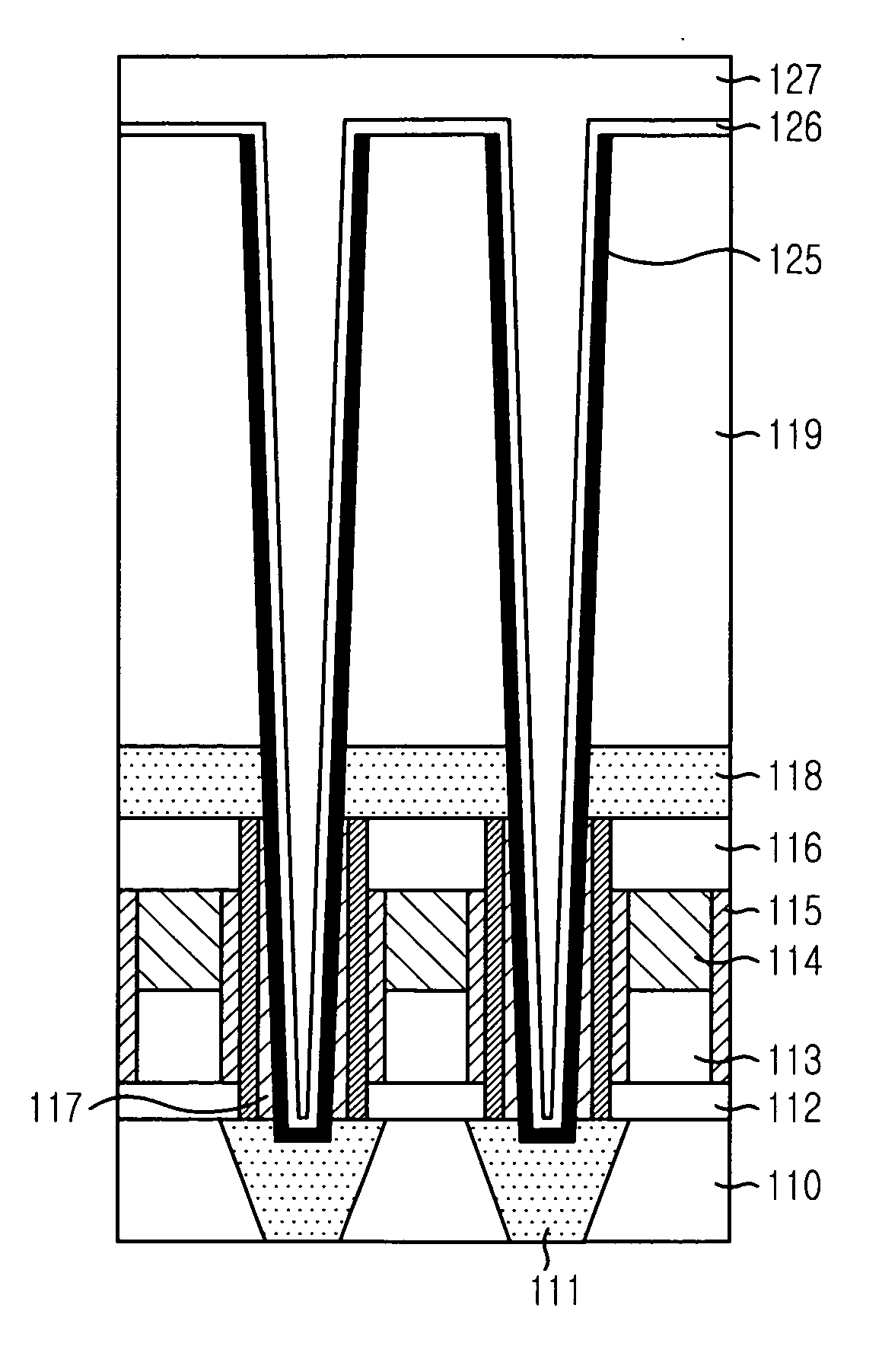

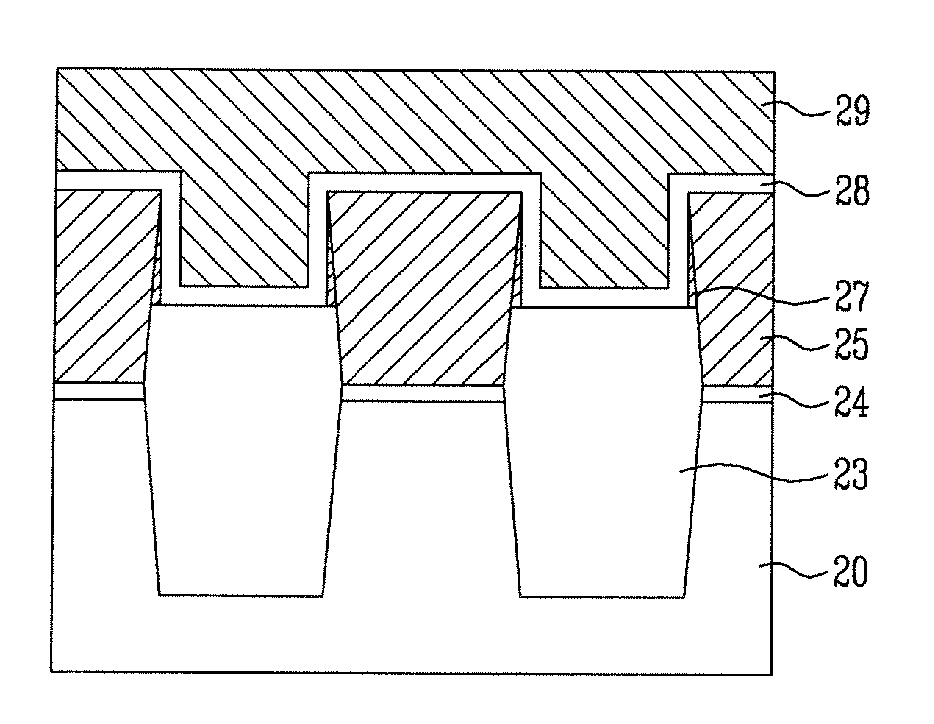

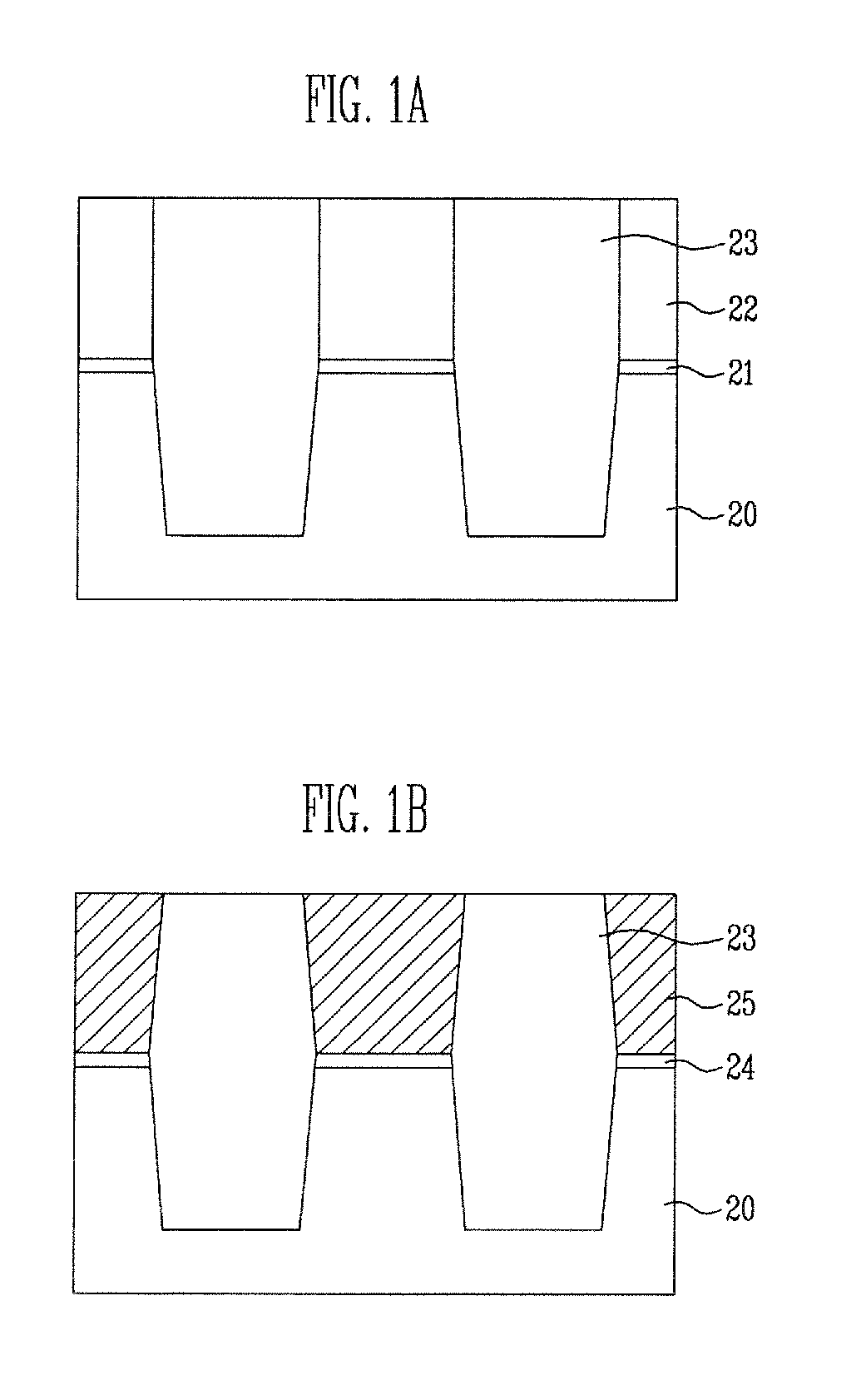

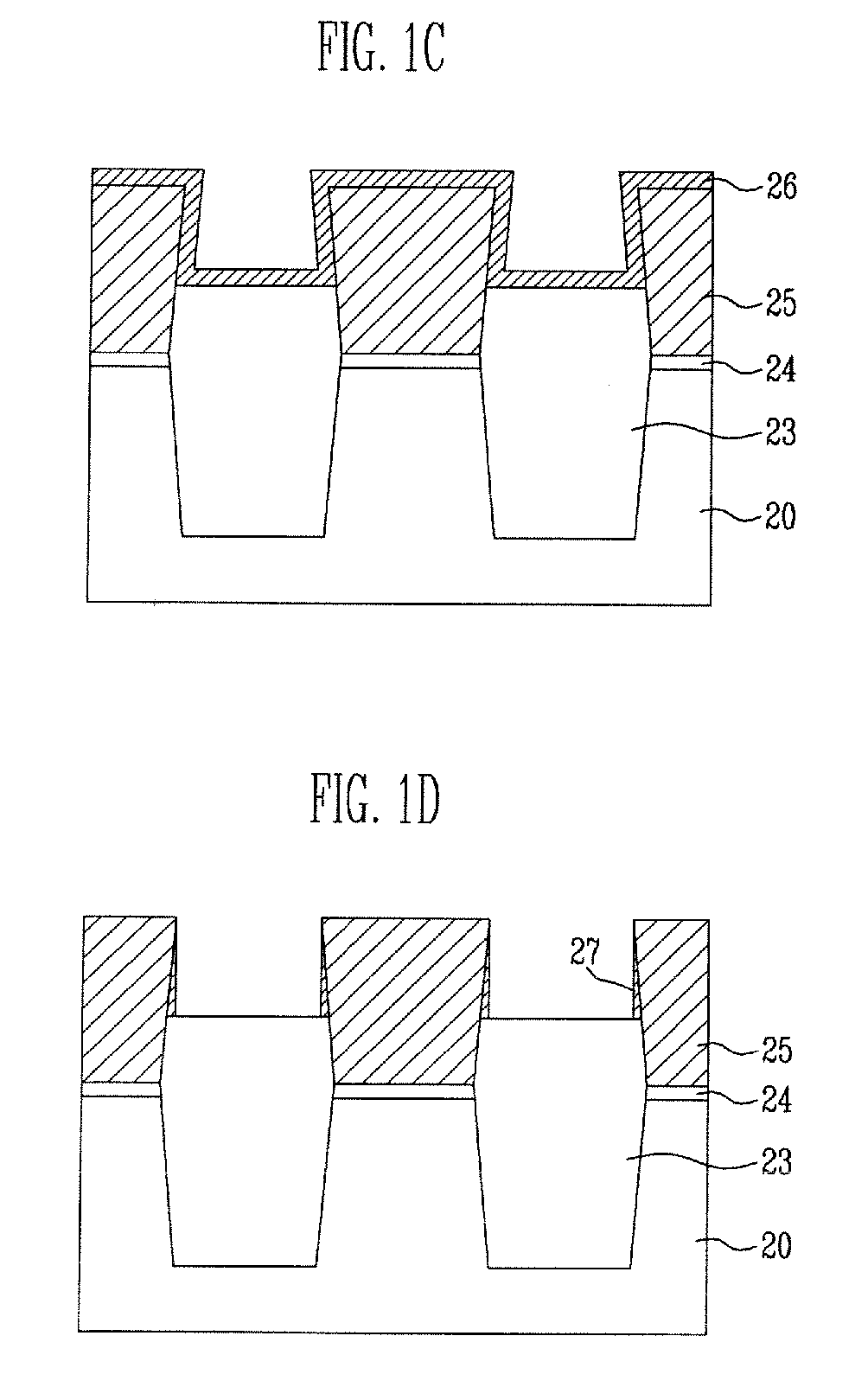

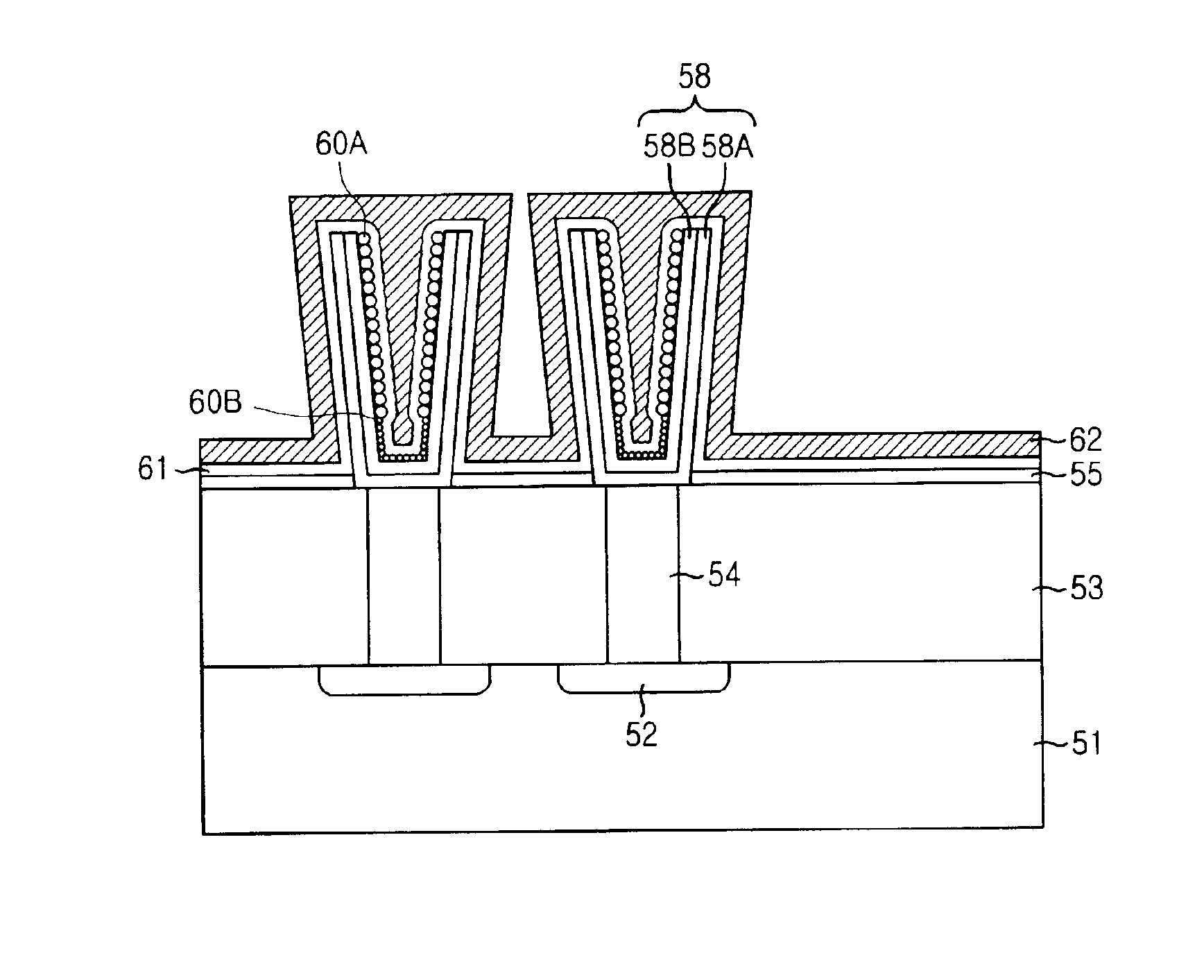

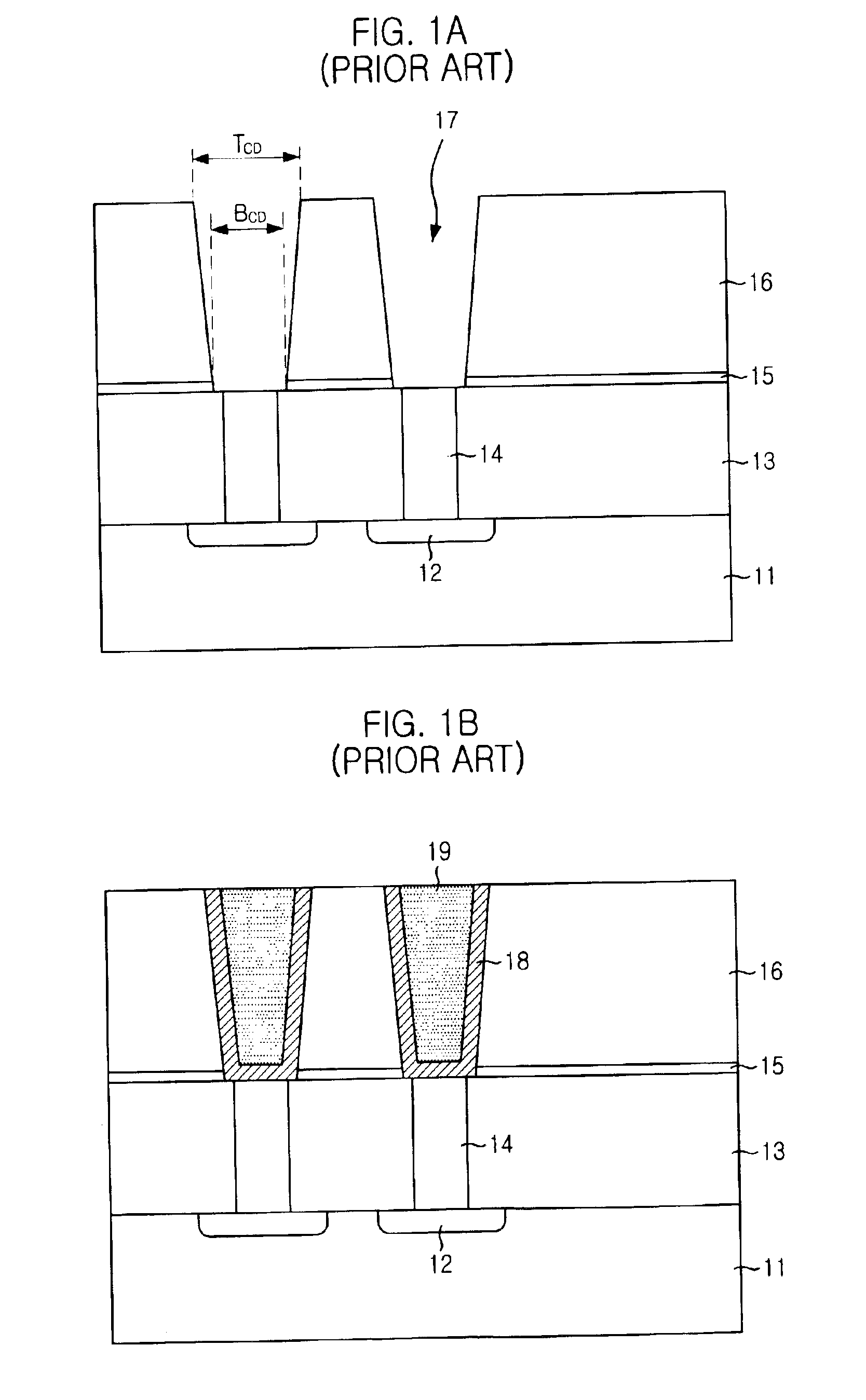

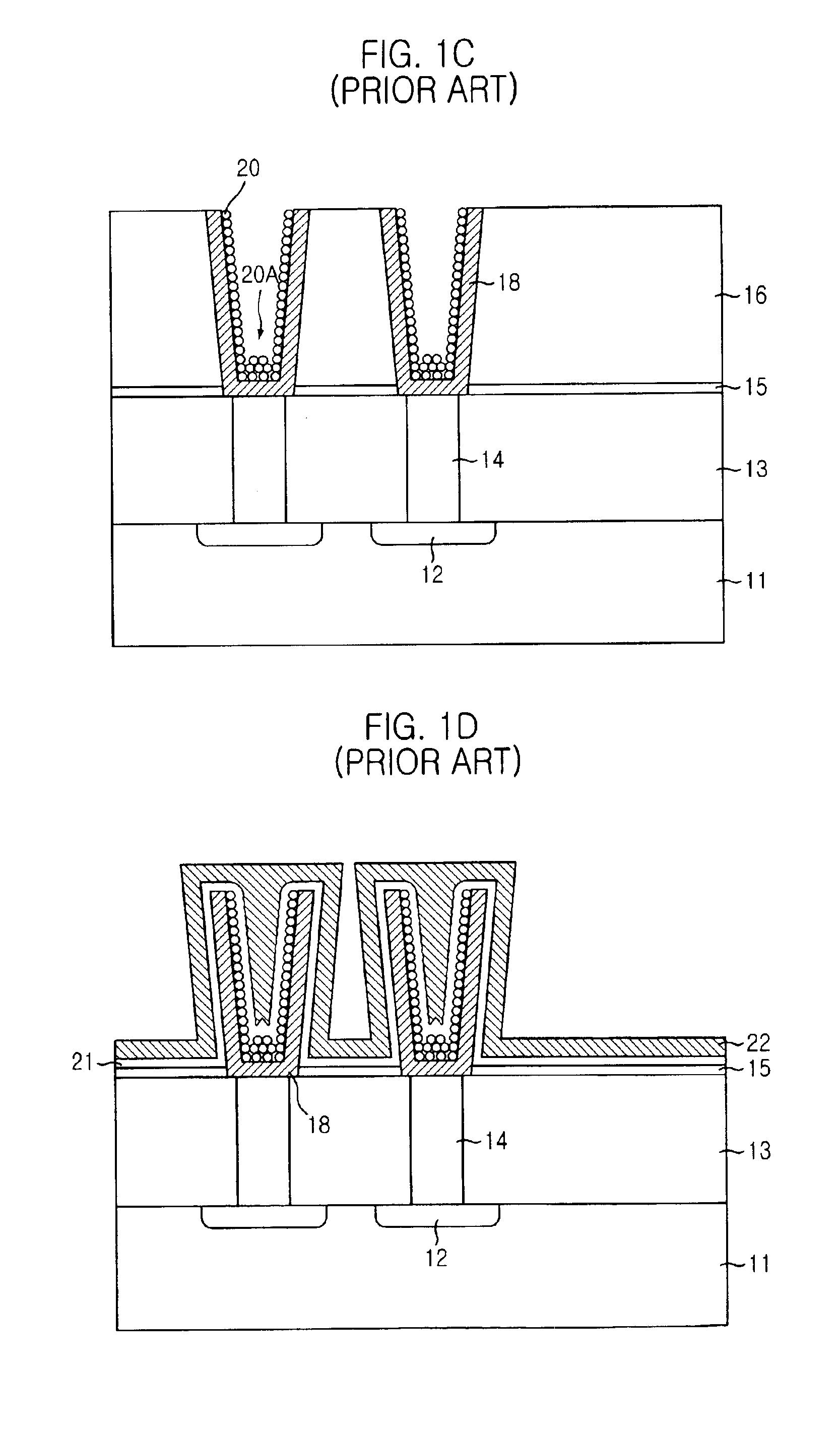

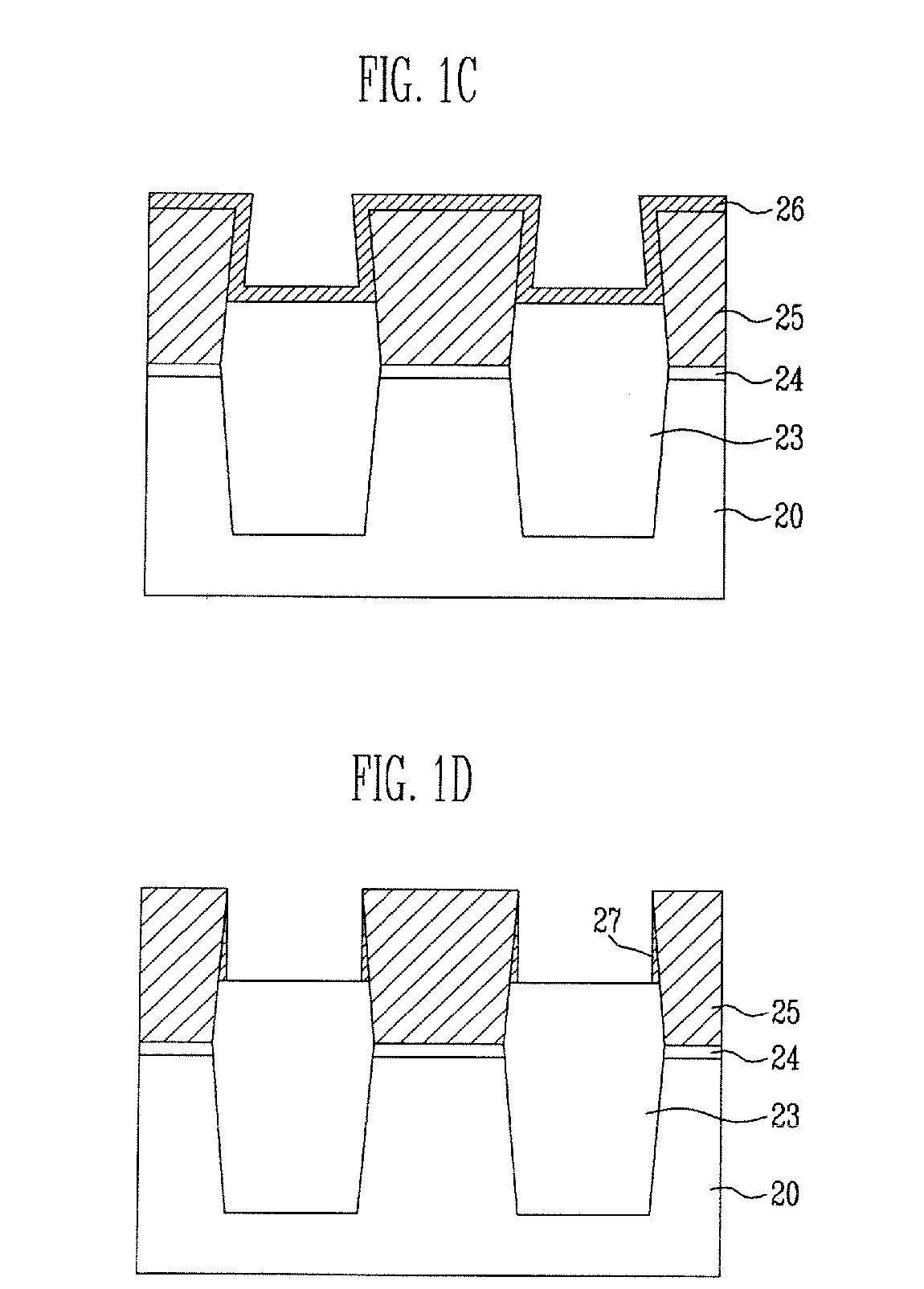

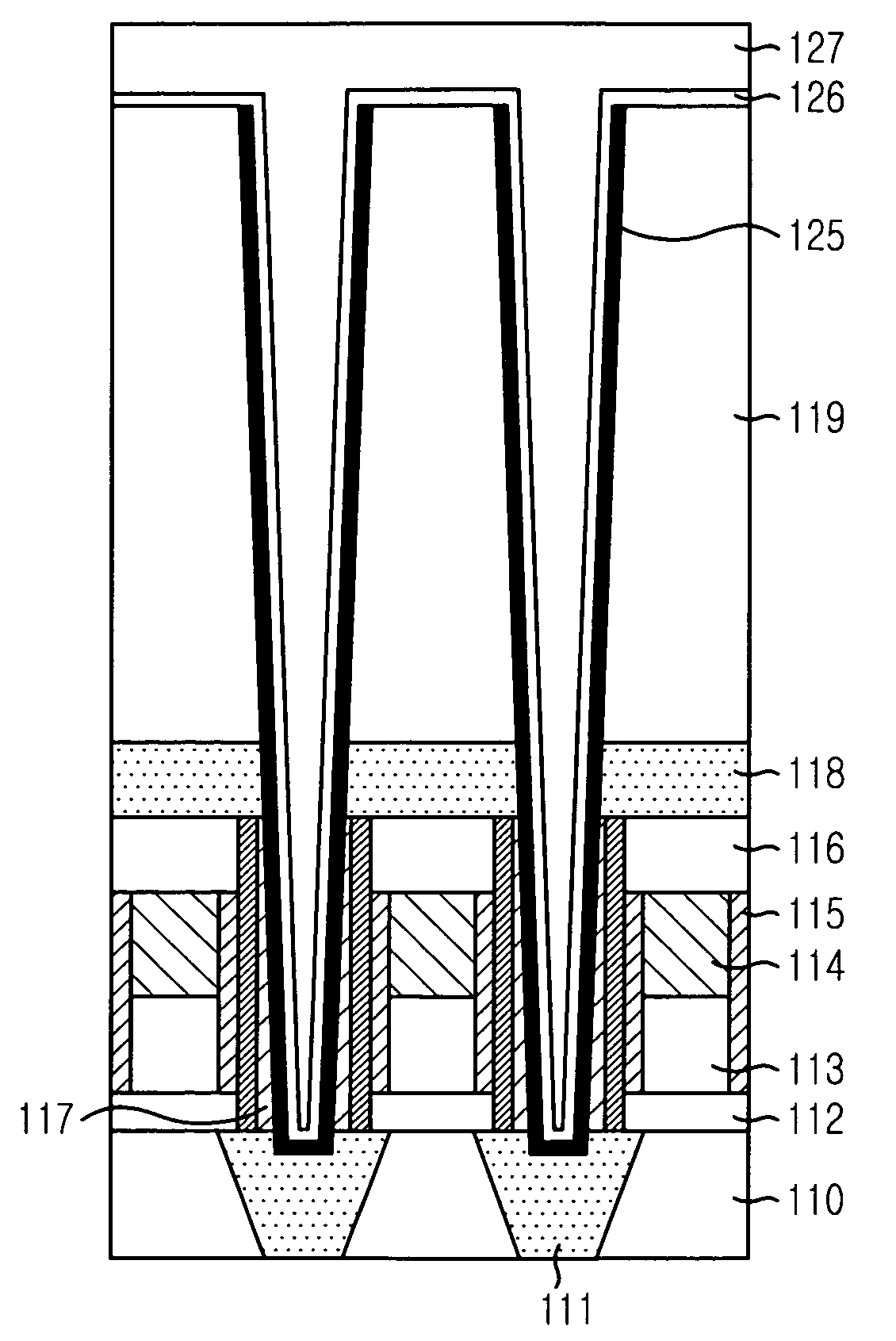

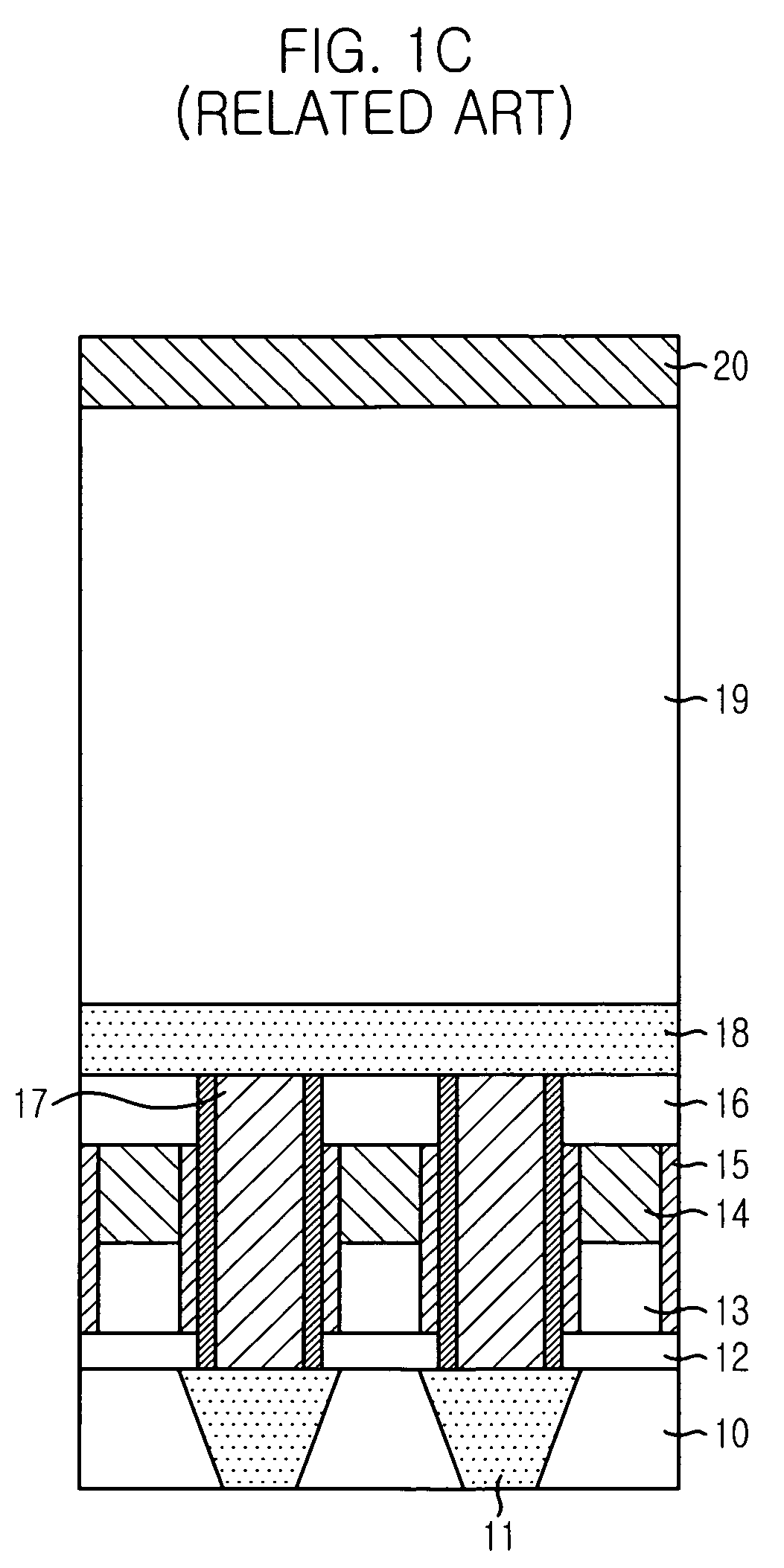

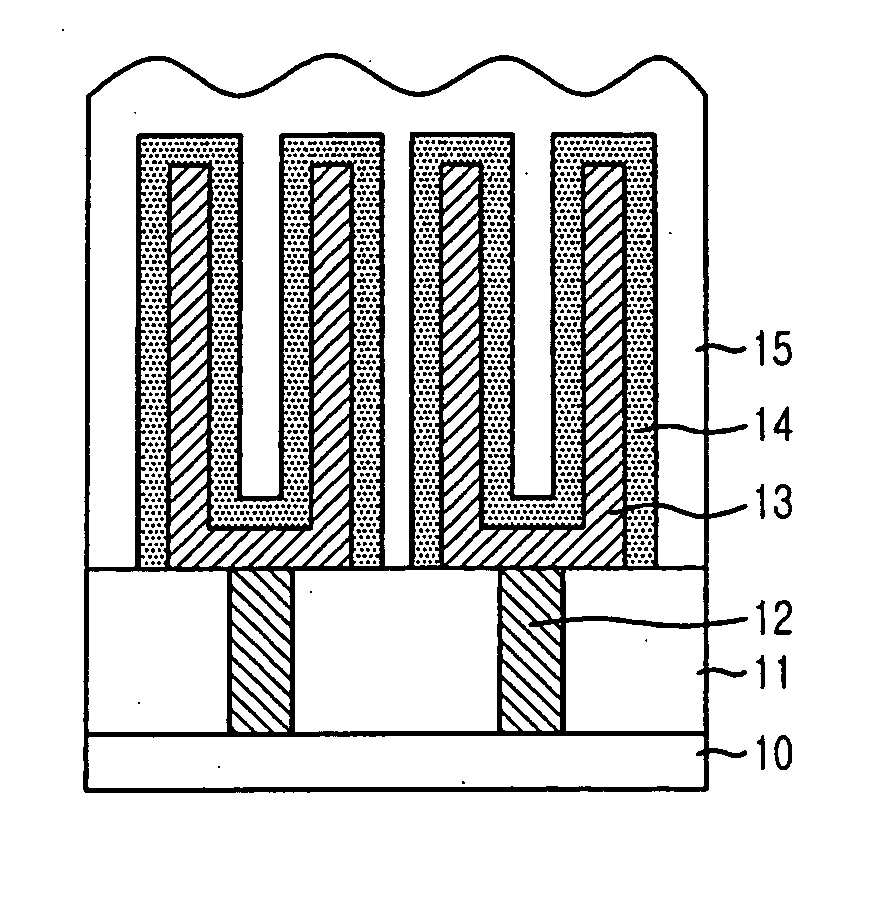

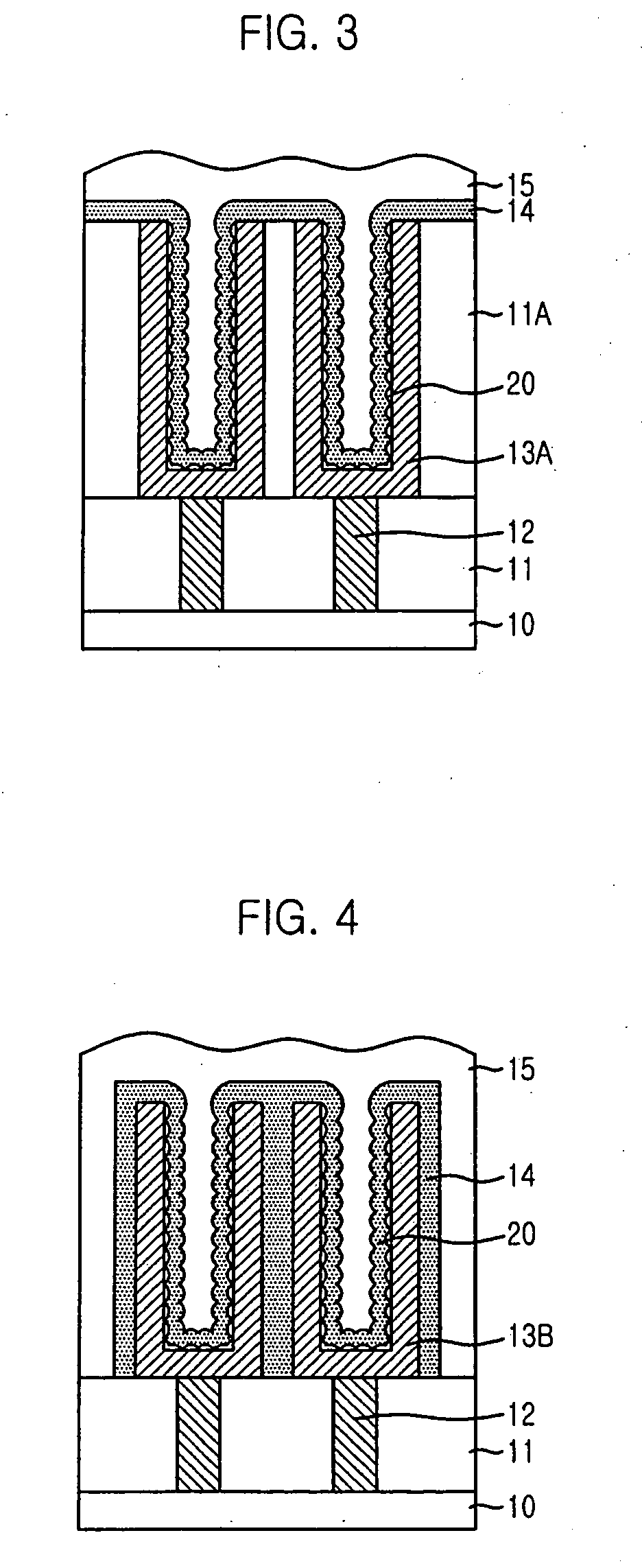

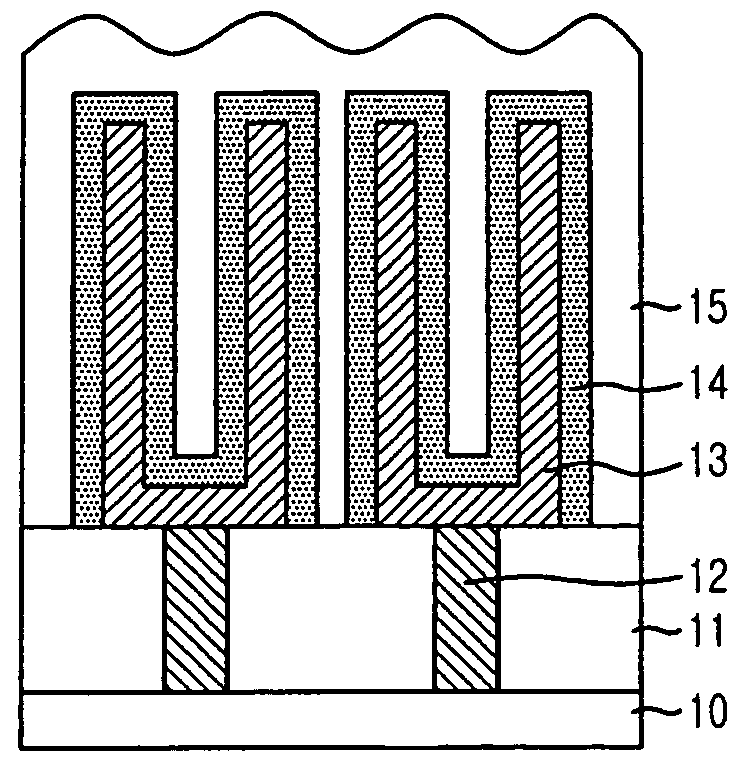

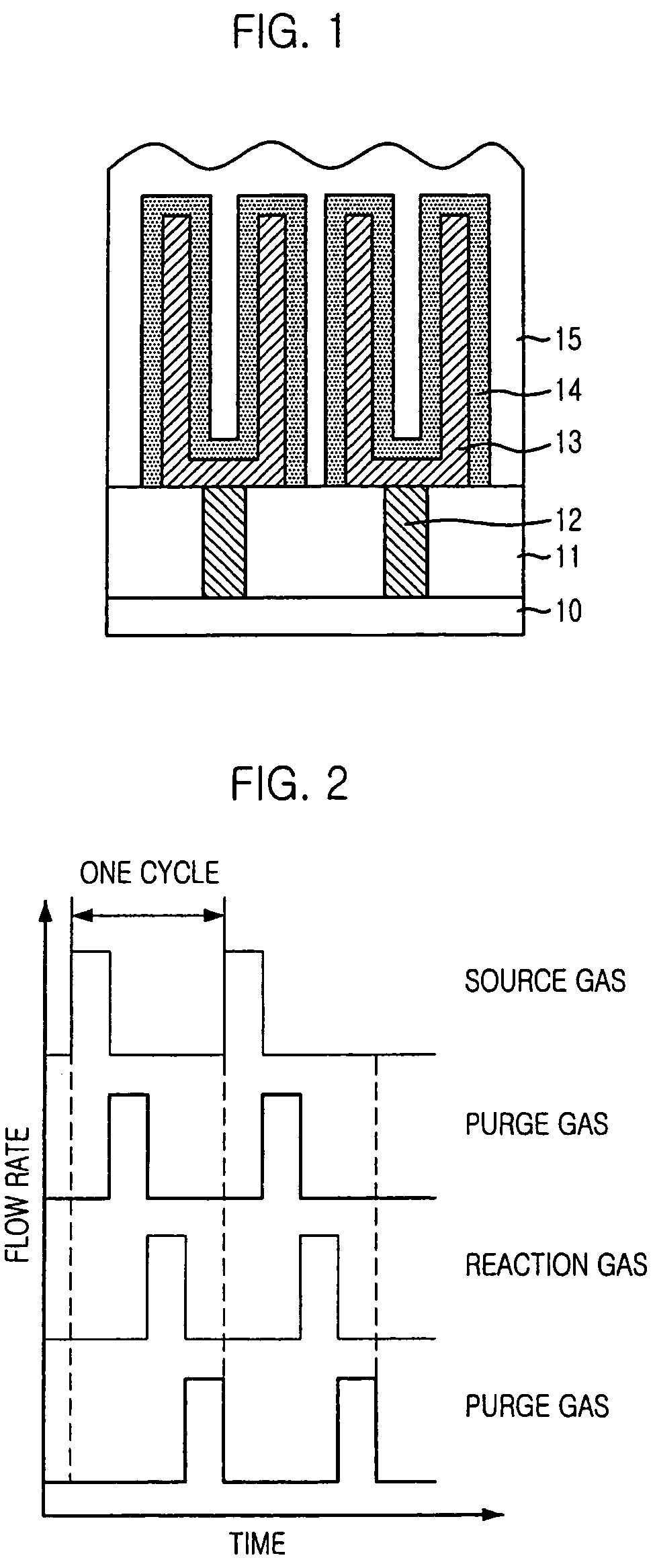

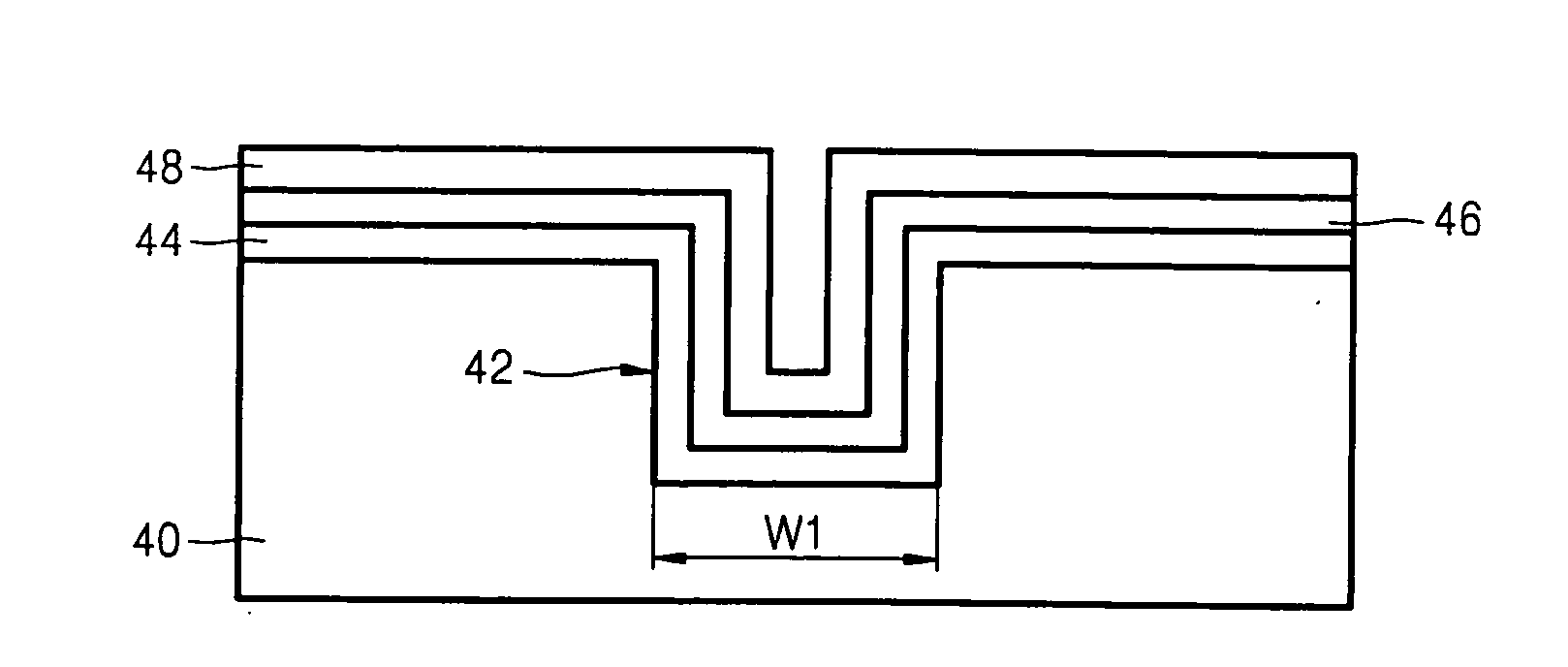

Semiconductor device and method for fabricating the same

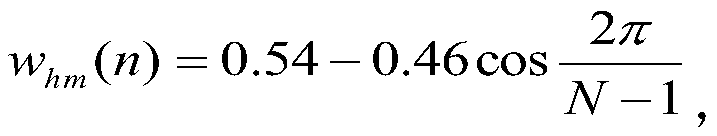

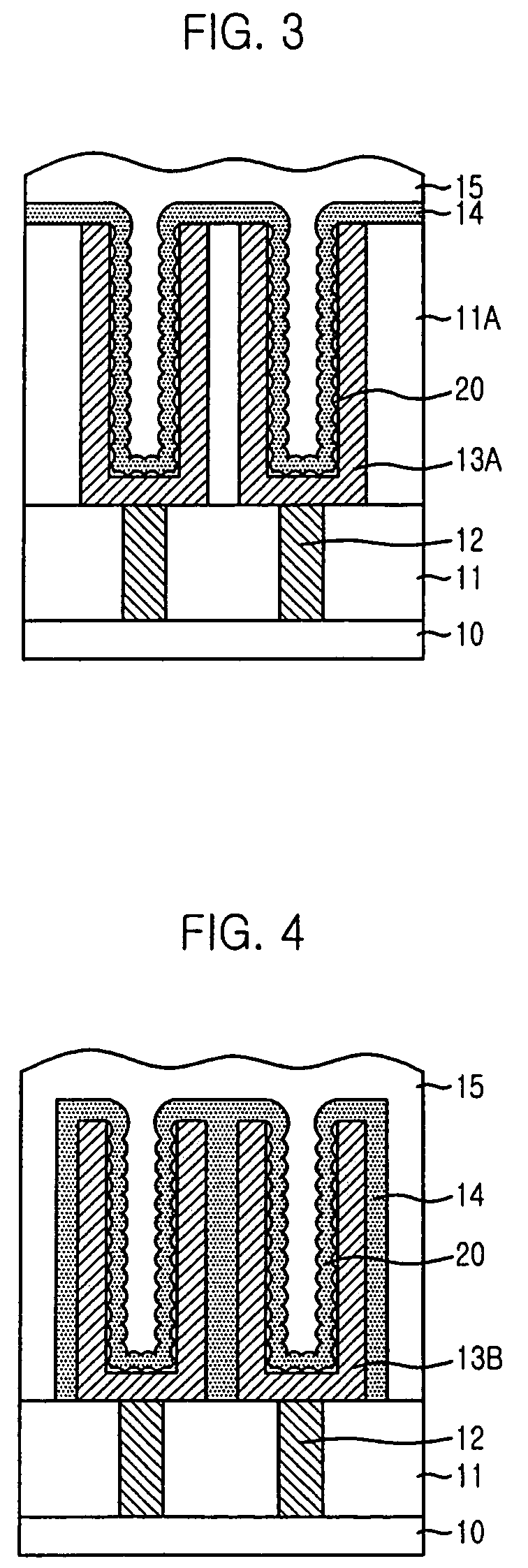

InactiveUS20060284228A1Increase the effective surface areaProtection capacitorTransistorSolid-state devicesInsulation layerEngineering

A method for fabricating a three dimensional type capacitor is provided. The method includes forming a first insulation layer including first contact layers over a substrate, forming a second insulation layer over the first insulation layer, forming second contact layers by using a material having an etch selectivity different from the first contact layers such that the second contact layers are connected with the first contact layers within the second insulation layer, forming an etch stop layer over the second insulation layer and the second contact layers, forming a third insulation layer over the etch stop layer, etching the third insulation layer and the etch stop layer to form first contact holes exposing the second contact layers, etching the exposed second contact layers to form second contact holes exposing the first contact holes, and forming bottom electrodes over the inner surface of the second contact holes.

Owner:SK HYNIX INC

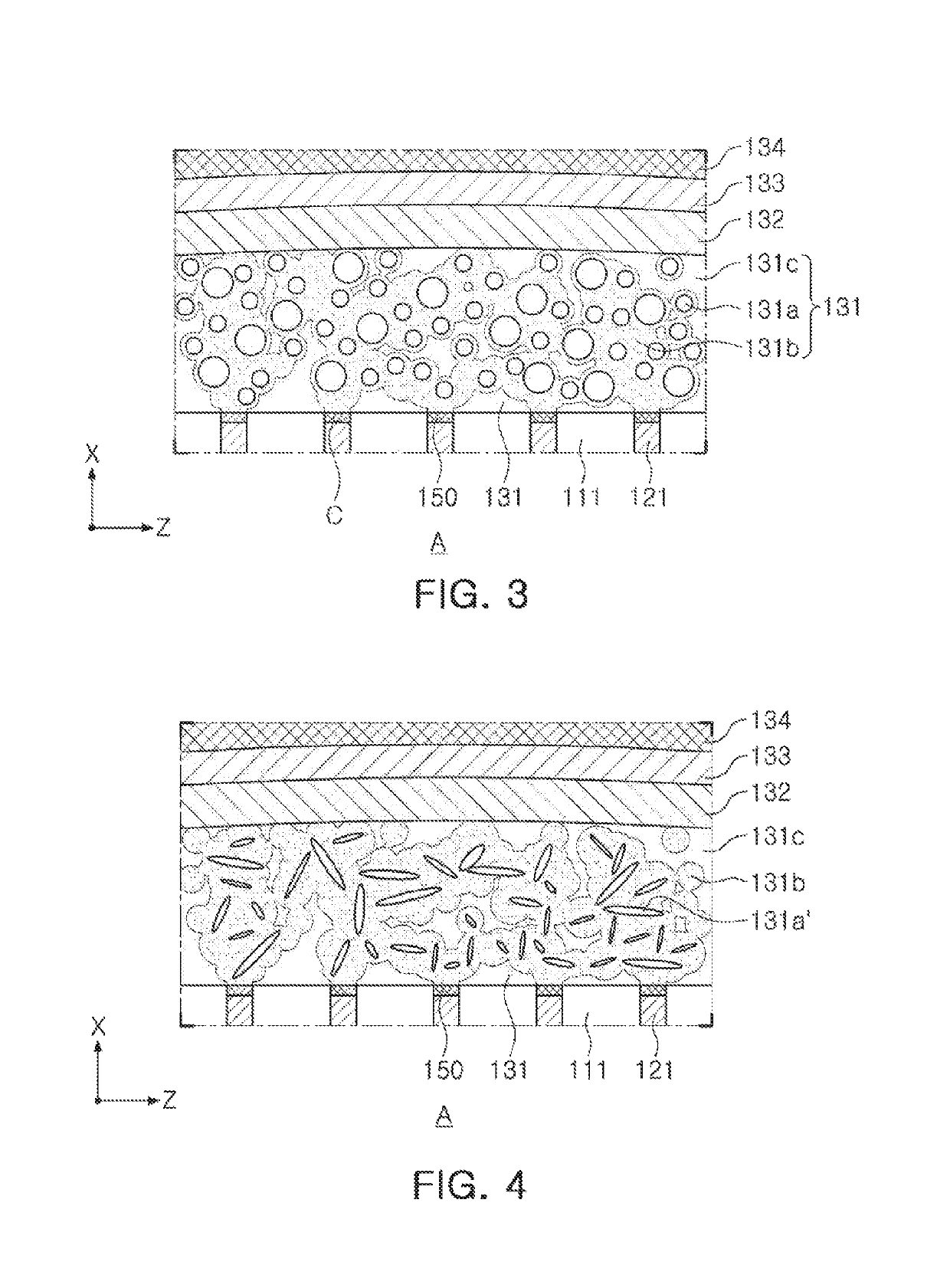

Electric chemical capacitor, and method and apparatus for manufacturing electrode for electric chemical capacitor

ActiveUS7251122B2Prevent peelingShort-circuit of preventedClosuresLiquid electrolytic capacitorsOptoelectronicsElectrochemistry

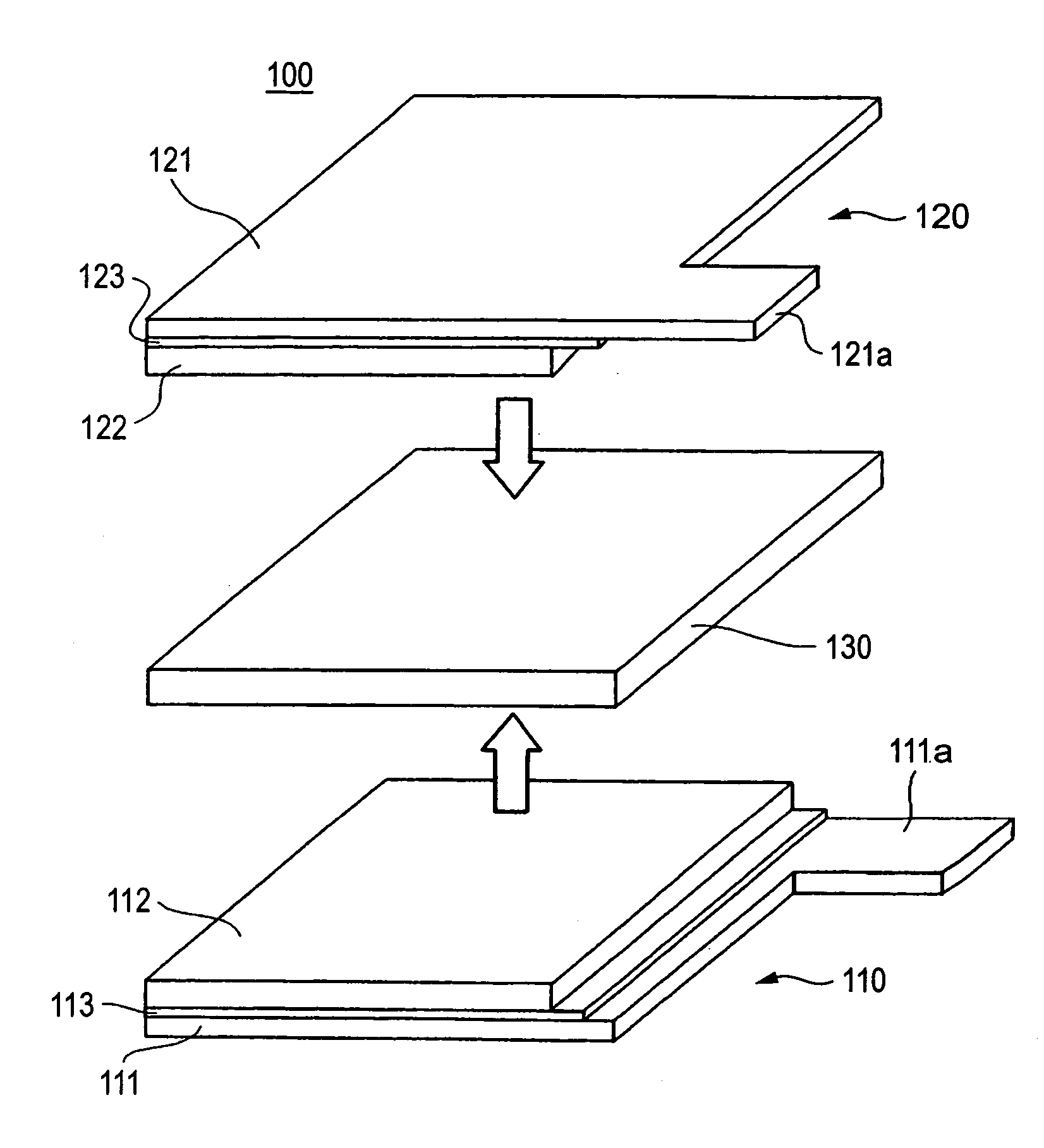

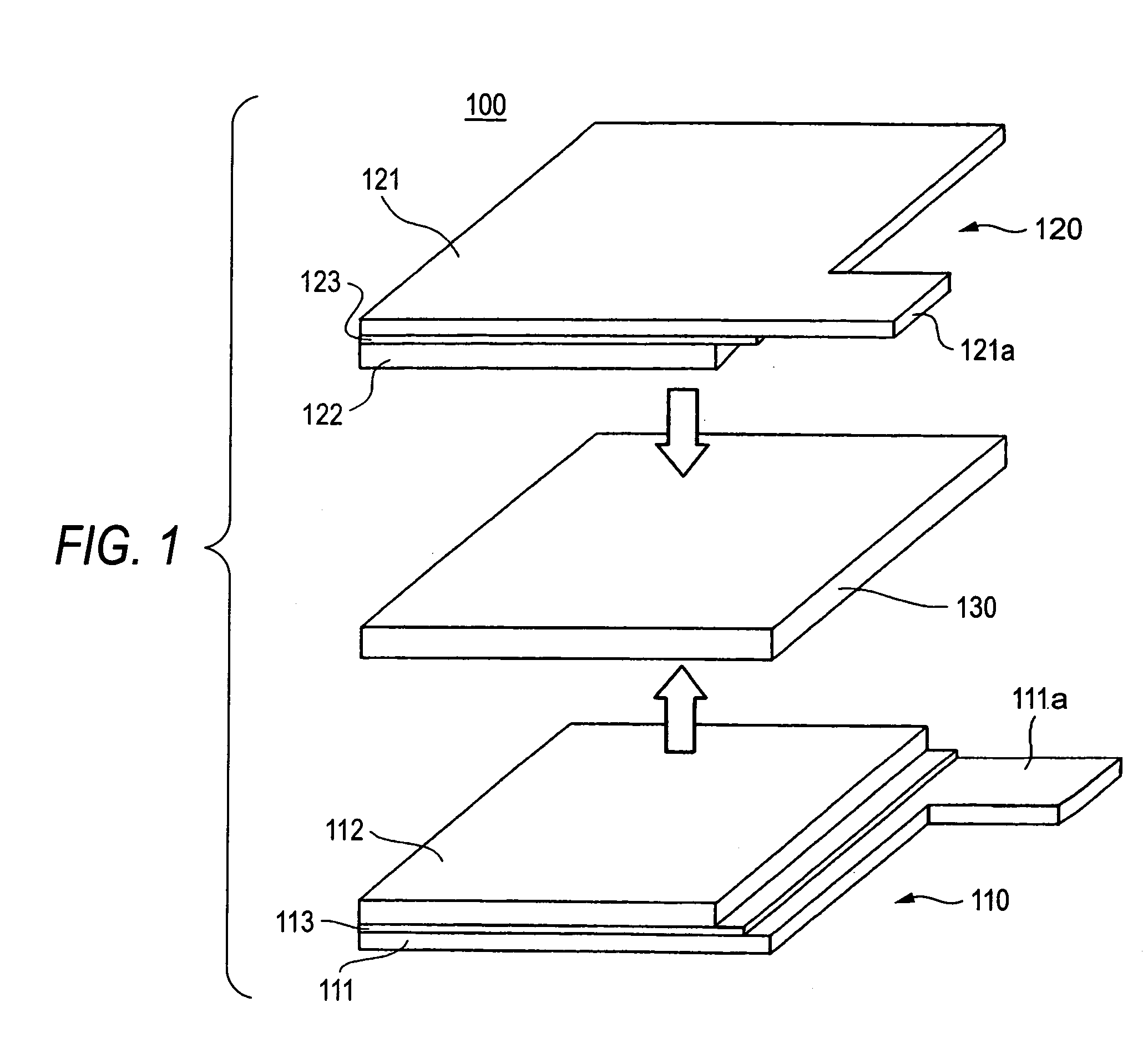

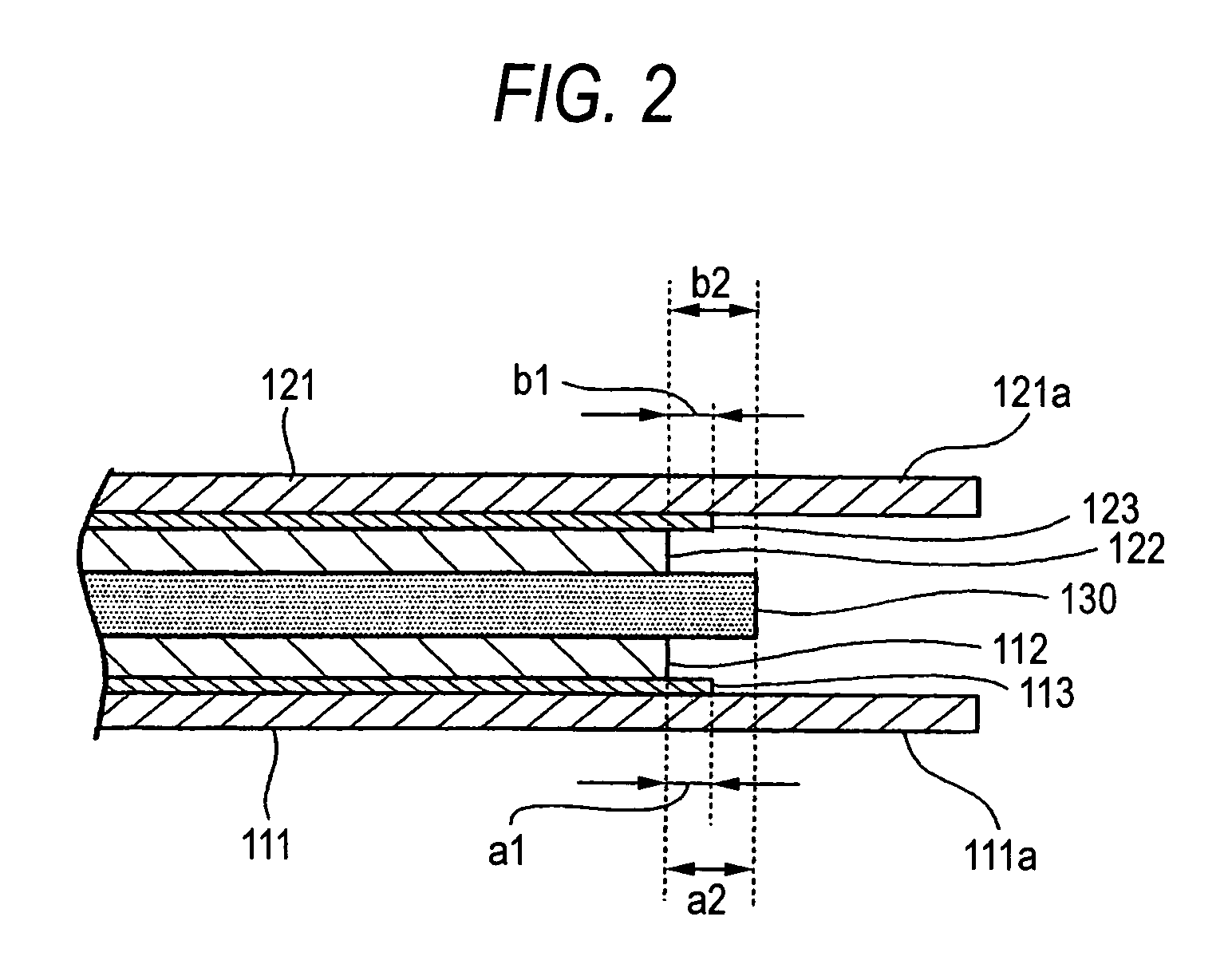

An electric chemical capacitor includes first and second electrodes each including a collector 111, 121, a polarized electrode layer 112, 122 and an undercoat layer 113, 123 for bonding the collector and the polarized electrode layer with each other, and a separator put between the first and second electrodes so that the polarized electrode layers 112 and 122 face each other, wherein an end portion of each undercoat layer 113, 123 is located in the same position as or on the outer side of an end portion of the corresponding polarized electrode layer 112, 122, and located on the inner side of an end portion of the separator 130. Thus, the polarized electrode layers can be prevented from peeling from the collector. Further, the undercoat layers can be prevented from abutting against each other, and the undercoat layer of one electrode and the collector of the other electrode can be prevented from abutting against each other.

Owner:TDK CORPARATION

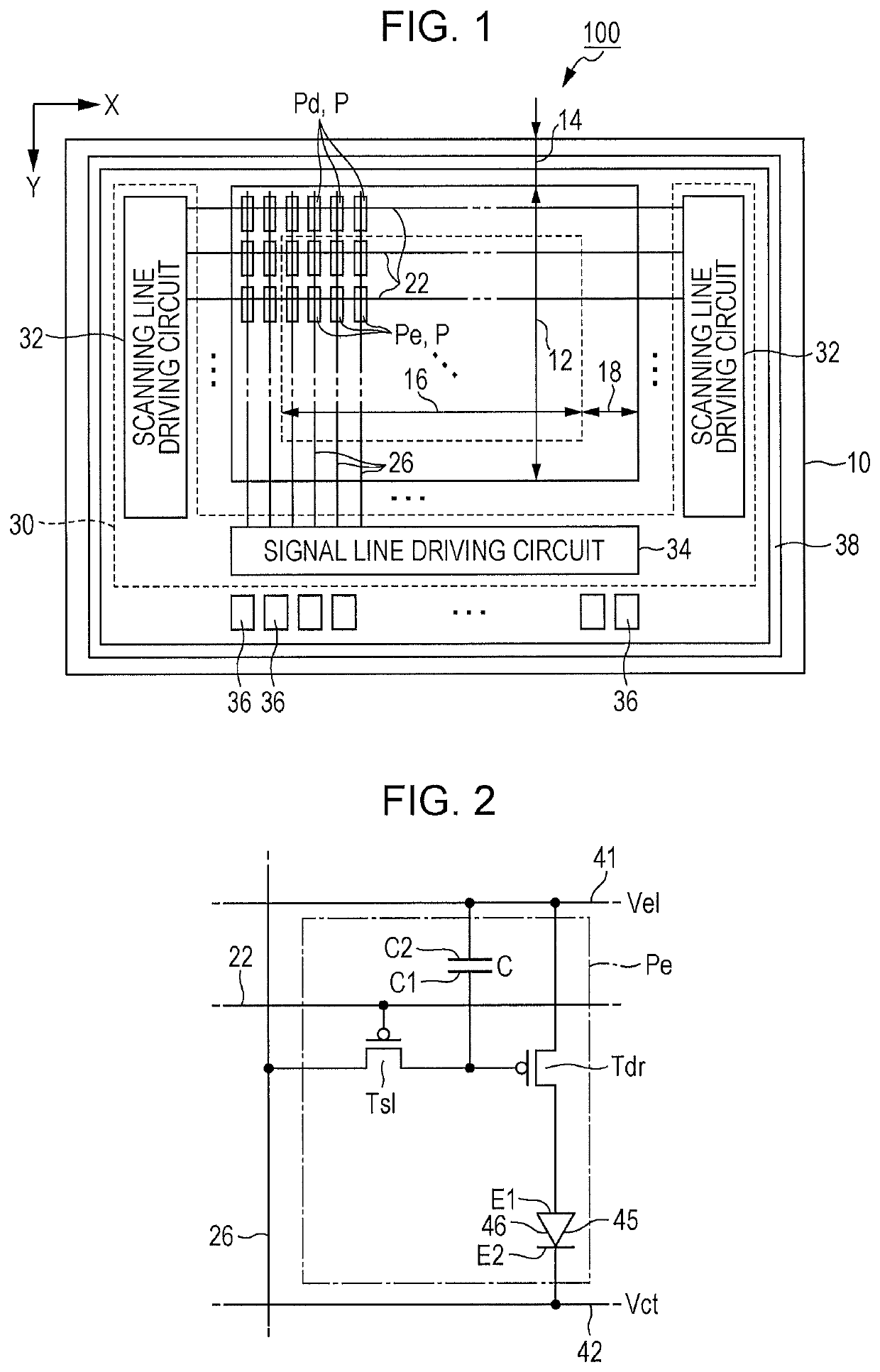

Organic electroluminescent device and electronic apparatus

ActiveUS20160063916A1Protection capacitorHigh densityCathode-ray tube indicatorsInput/output processes for data processingOrganic electroluminescenceCapacitance

An organic electroluminescent device includes a first transistor, an organic electroluminescent element that emits light with luminance corresponding to magnitude of a current supplied via the first transistor, and a capacitive element. The capacitive element includes a first electrode connected to a gate of the first transistor, a second electrode, and a dielectric film provided between the first electrode and the second electrode. The first electrode is formed on the same layer as the second electrode, and is arranged in a position away from the second electrode with the dielectric film interposed therebetween.

Owner:SEIKO EPSON CORP

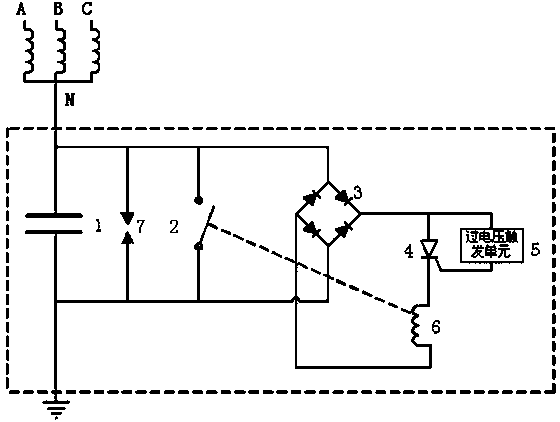

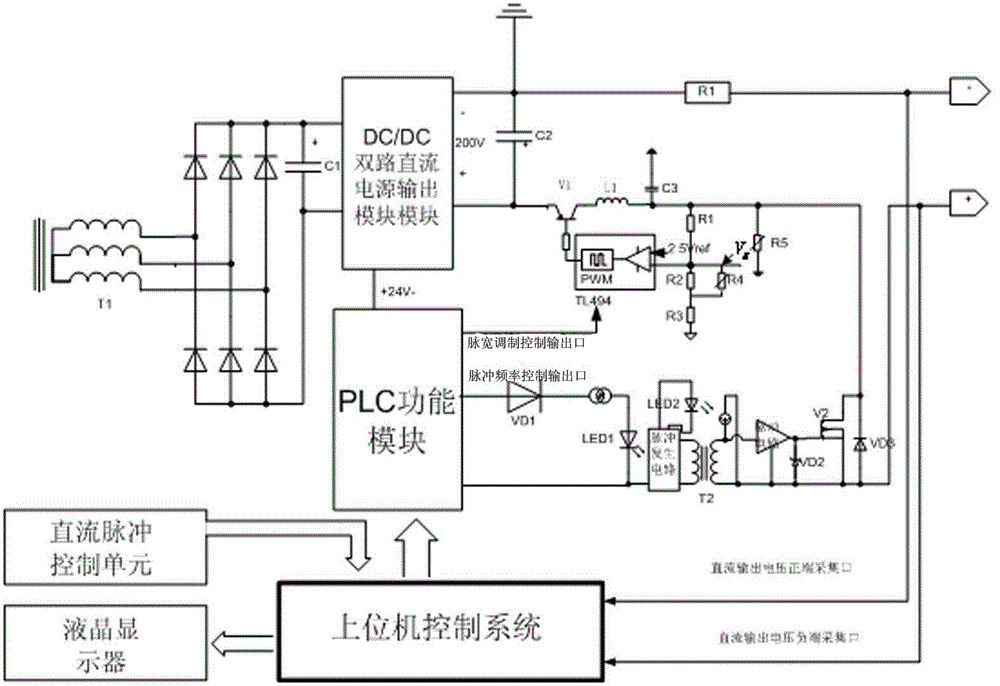

Transformer neutral point direct current suppression device

InactiveCN103683194AAct as a state transitionNeutral point protectionEmergency protective circuit arrangementsCapacitanceDc current

The invention discloses a transformer neutral point direct current suppression device. The transformer neutral point direct current suppression device comprises a blocking capacitor connected between a neutral point of a transformer and the ground, a rapid closing switch in parallel connection with the blocking capacitor, a rectifier bridge and a triggering module. The input end of the rectifier bridge is connected with the two ends of the blocking capacitor and enables an alternating current voltage of the neutral point of the transformer to be converted into a direct current voltage, and the direct current voltage is output to the triggering module. The output end of the triggering module is connected with a trip coil of the rapid closing switch and used for detecting the value of a voltage output by the rectifier bridge in time, when an over-voltage is detected, the triggering module is triggered and switched on so as to enable the trip coil to be powered on, the normally open contact of the rapid closing switch is closed rapidly, at the moment, the blocking capacitor is short-circuited by the rapid closing switch, and the neutral point of the transformer is connected with the ground through the rapid closing switch and retreats from the blocking capacitor automatically. The transformer neutral point direct current suppression device can prevent a direct current from flowing into the alternating current transformer, therefore, the neutral point of the transformer is protected, and the capacitor of the device is also protected; the reliability of the device is improved, and further expansion of power grid accidents is avoided.

Owner:STATE GRID CORP OF CHINA +2

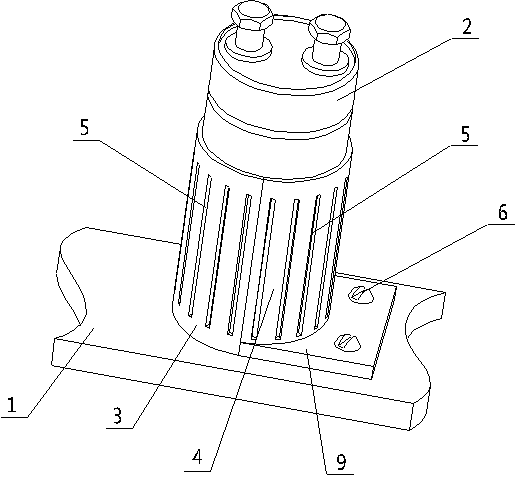

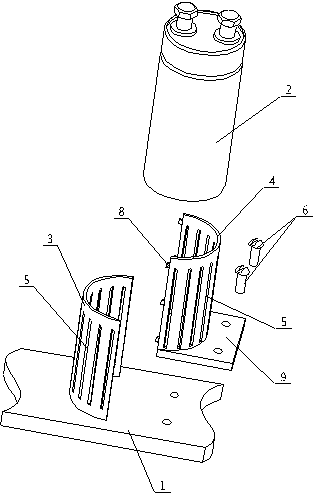

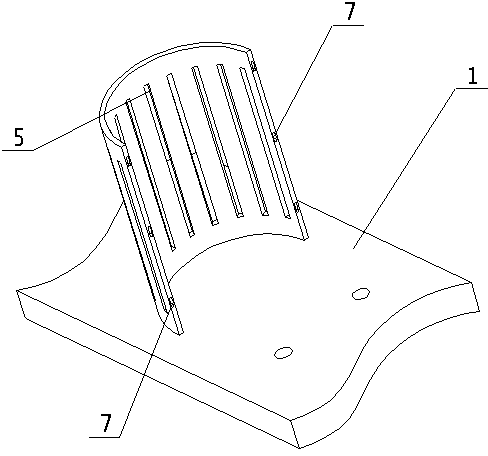

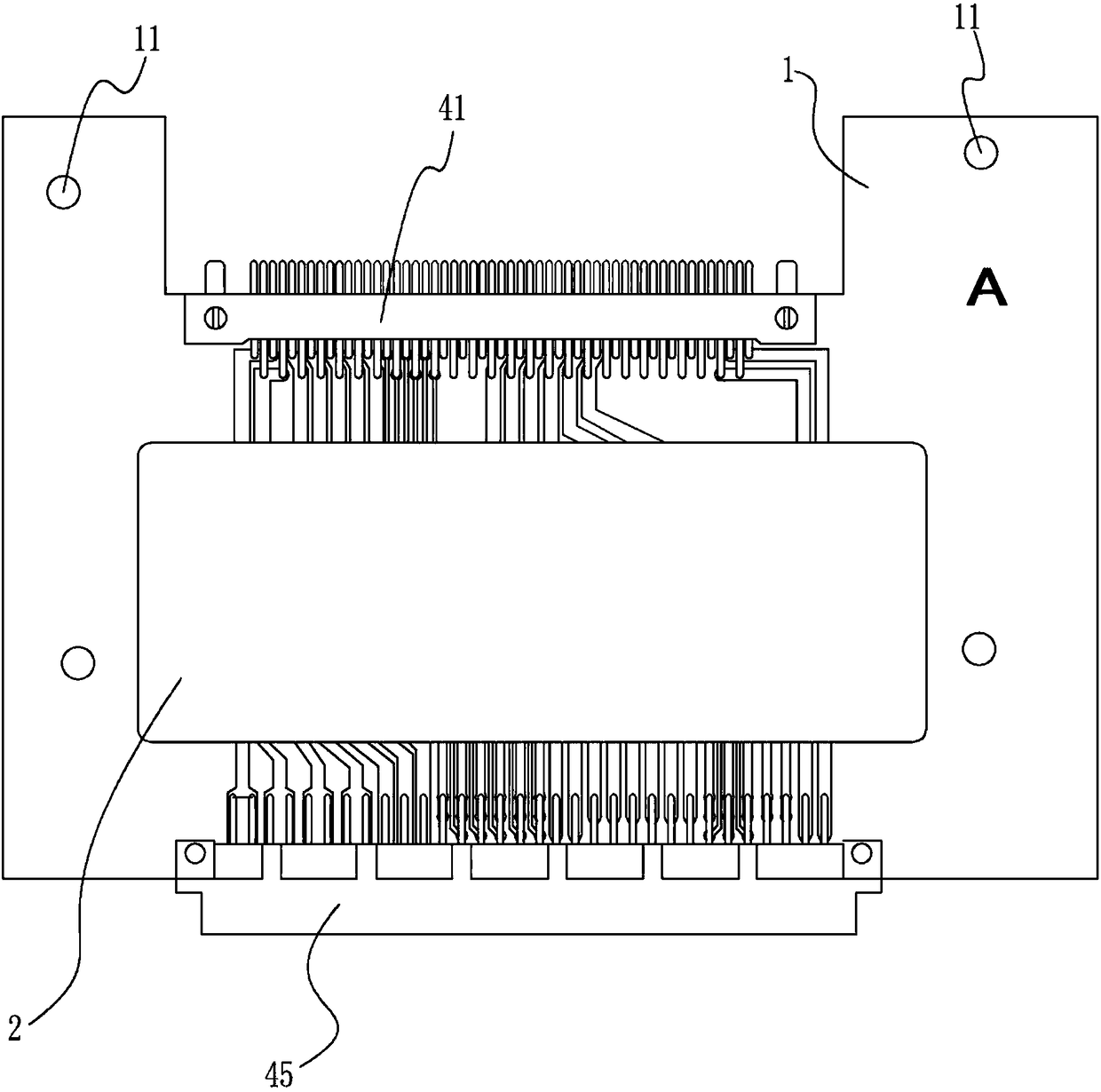

Installation structure for capacitor

The invention discloses an installation structure for a capacitor, which comprises an installation bottom plate, the capacitor, a left fixing plate, a right fixing plate and a movable plate, wherein the left fixing plate is welded on the installation bottom plate; the section of the left fixing plate is semi-annular; the internal diameter of the left fixing plate is the same as the external diameter of the capacitor; the left fixing plate and the right fixing plate have the same appearance, and are provided with opposite openings and matched with each other; the heights of both the left fixing plate and the right fixing plate are as 3 / 4 time as the height of the capacitor; a fixing groove is formed at the opening end of the left fixing plate; a bump matched with the fixing groove is arranged at the opening end of the right fixing plate; the movable plate welded at the bottom of the right fixing plate is located on the right side of the right fixing plate; the movable plate is fixed on the installation bottom plate by screws; and heat dissipation grooves are uniformly formed on the left fixing plate and the right fixing plate. The installation structure can protect the capacitor very well, adapt to different severe working environments and ensure the stability of the capacitor, is simple in structure and convenient to install, and facilitates promotion and using.

Owner:SUZHOU TANGFENG ELECTRICAL APPLIANCE

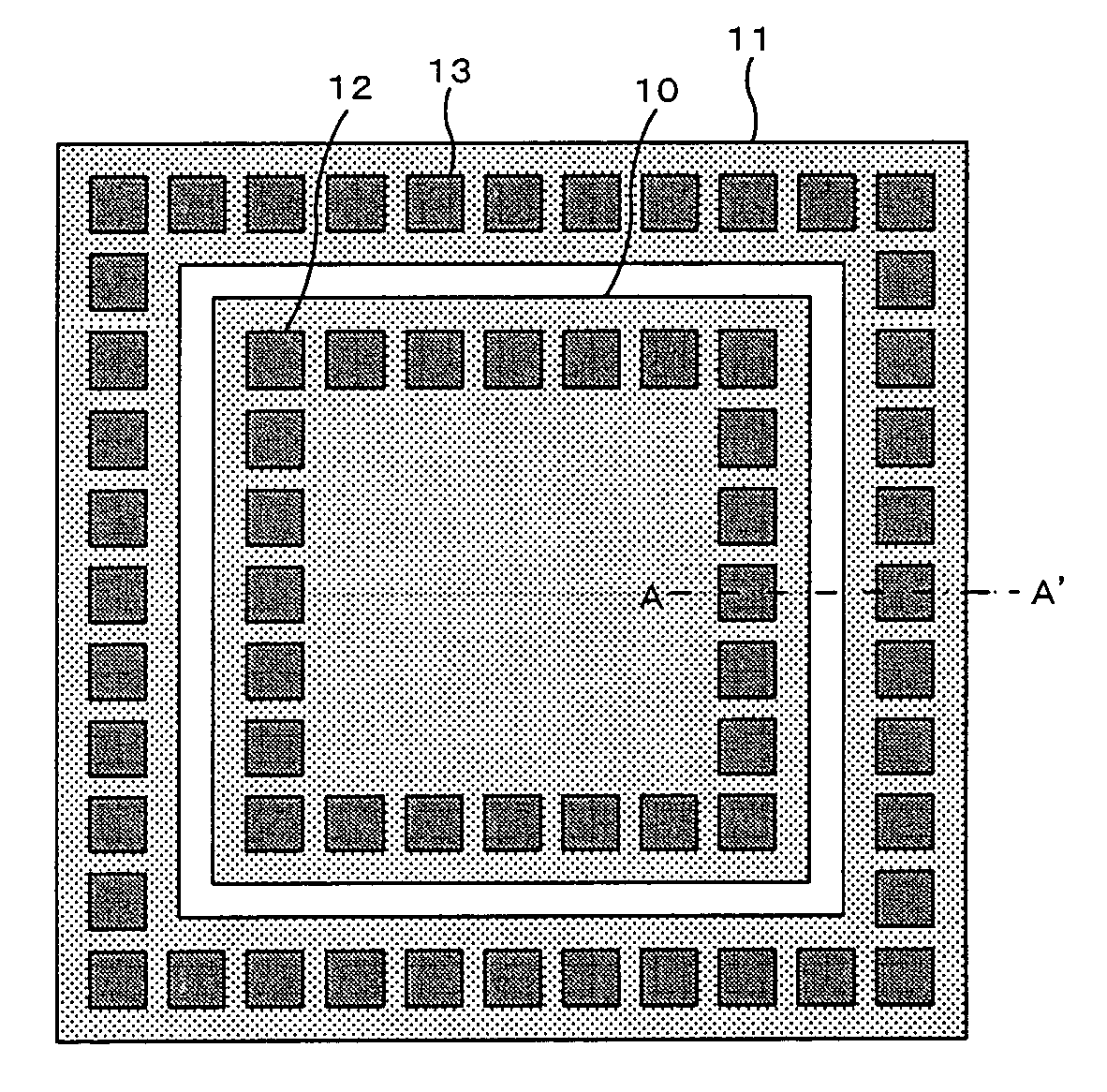

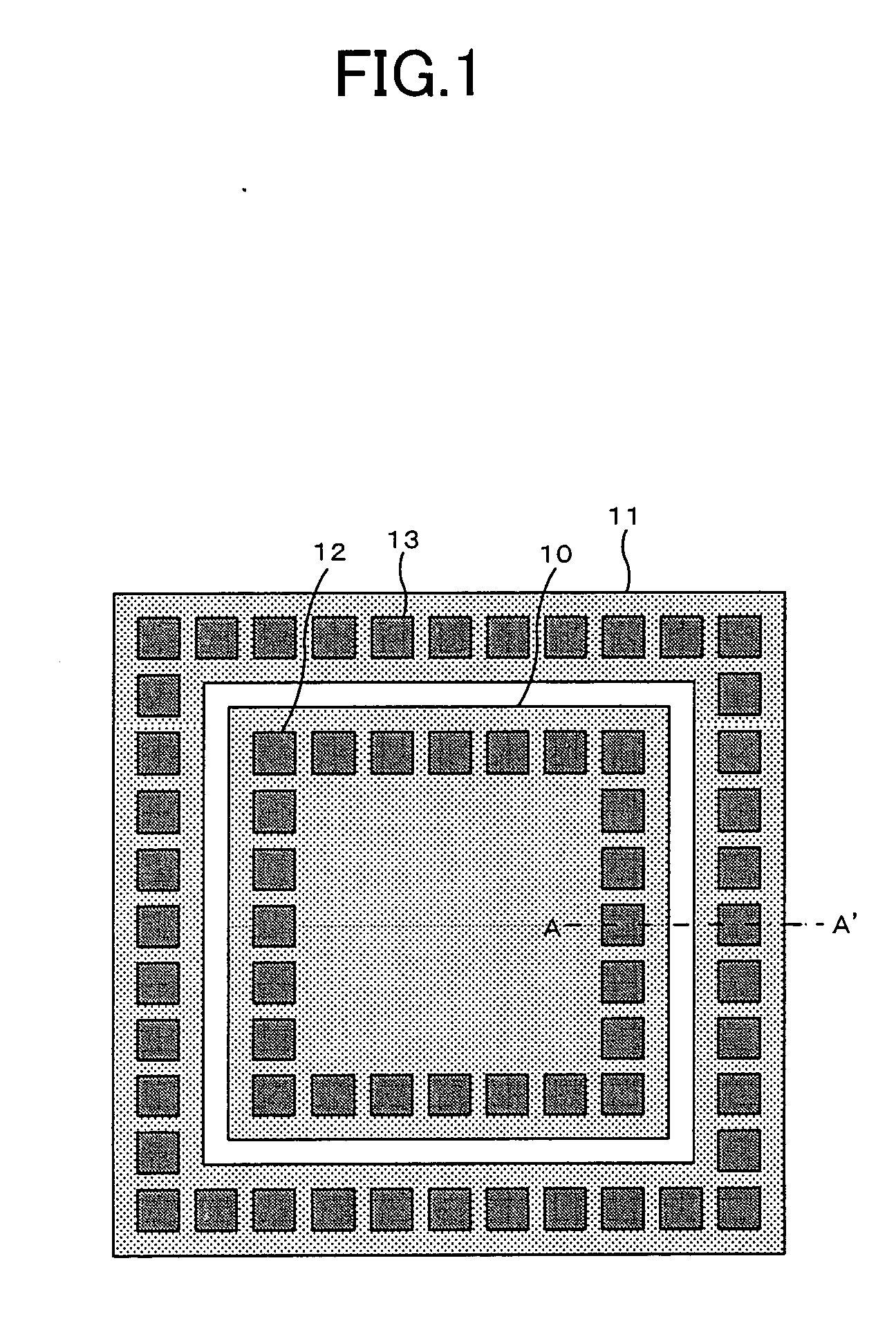

Capacitor device, semiconductor devioce, and setting method of terminal capacitance of pad electrode thereof

InactiveUS20060267142A1Improve accuracyImprove space efficiencySemiconductor/solid-state device detailsSolid-state devicesCapacitanceConductive materials

A capacitor device comprising: a first wiring region disposed at a predetermined location in a wiring layer on a semiconductor substrate, a second wiring region disposed in a vicinity of the first wiring region and insulated from the first wiring region, at least one first via formed by embedding conductive material in an opening of the first wiring region and electrically connected to the first wiring region; and at least one second via formed by embedding conductive material in an opening of the second wiring region and electrically connected to the second wiring region, wherein the first via and the second via are disposed so that side surfaces thereof are opposed to each other with an insulating film therebetween to form a capacitor.

Owner:ELPIDA MEMORY INC

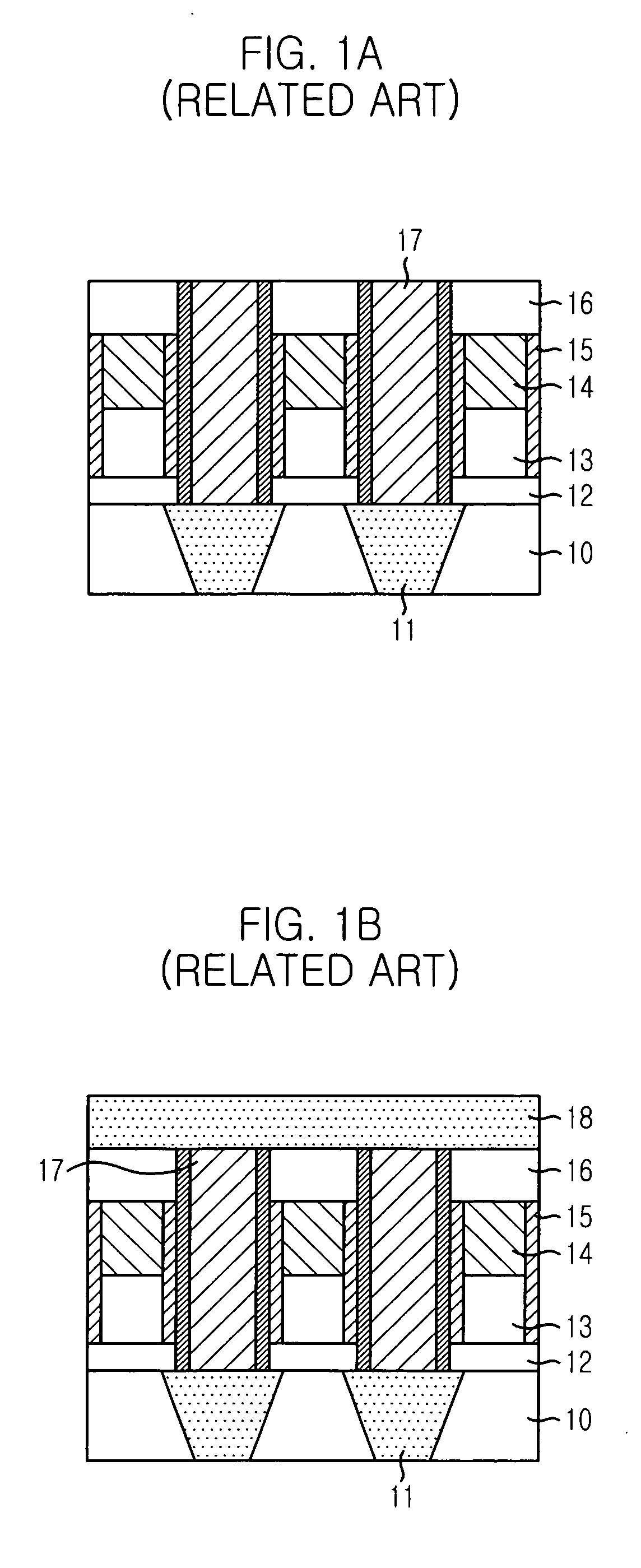

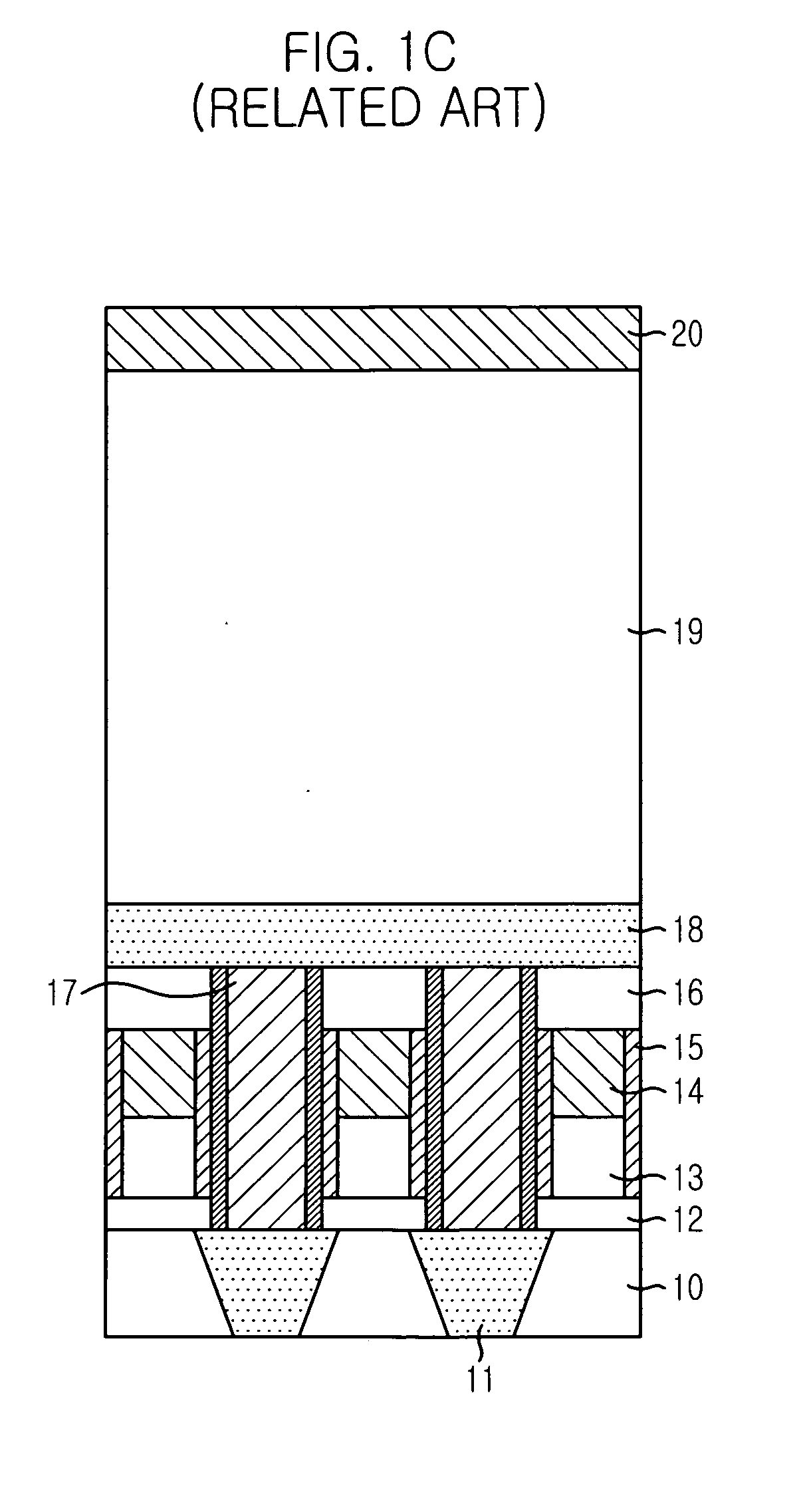

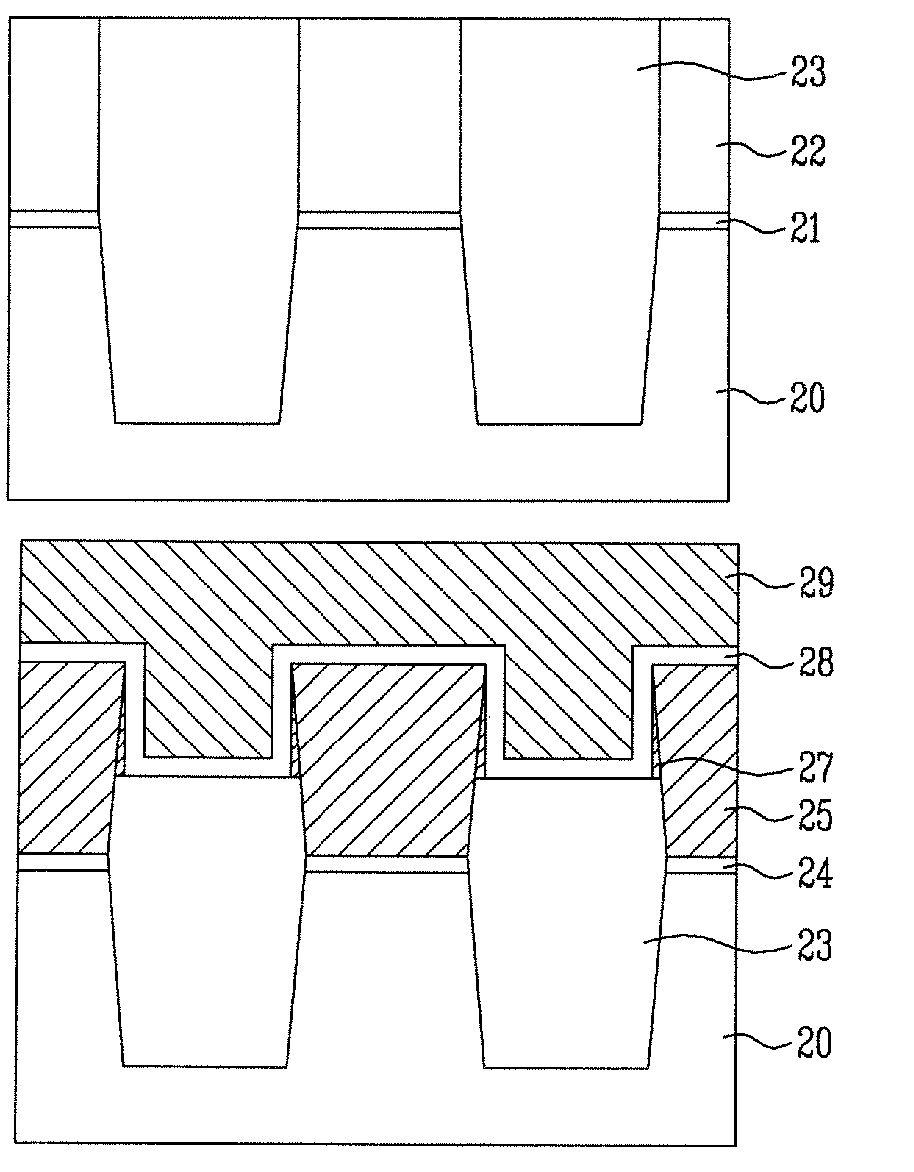

Method of fabricating flash memory device

ActiveUS7300843B2Preventing stringerProtection capacitorSolid-state devicesSemiconductor/solid-state device manufacturingCoupling ratioEngineering

A method of fabricating a flash memory device is disclosed wherein, electrode spacers are formed on sides of self-aligned floating gates having a negative slope. Thus, upon etching of a stack gate after an interlayer dielectric film and a control gate are formed, a stringer of a control gate, which is formed by the negative slope of the self-aligned floating gates, can be prevented. Furthermore, because an isotropic etch process is used to remove element isolation films between the floating gates, the element isolation films do not remain on the sides of the floating gates. It is thus possible to prevent loss of the coupling ratio. Accordingly, failure of devices can be reduced and decreasing the program speed can be prevented.

Owner:SK HYNIX INC

Capacitor and method for fabricating the same

A method for manufacturing a capacitor in a semiconductor device for securing capacitance without a merging phenomenon during a MPS grain growth process. The manufacturing step begins with a preparation of a substrate. The interlayer dielectric (ILD) layer is formed on the substrate and is etched to form conductive plug. Then, an etch barrier layer and a sacrifice insulating layer are formed on entire surface subsequently. A cylinder typed first electrode is formed over the conductive plug using the sacrifice insulating layer. Thereafter, first meta-stable poly silicon (MPS) grains are formed on inner wall of the first electrode except a bottom region thereof. However, second MPS grains with small sizes can be formed in the bottom region for increasing a storage area of the first electrode. Finally, a dielectric layer and a second electrode are formed on the first electrode subsequently.

Owner:SK HYNIX INC

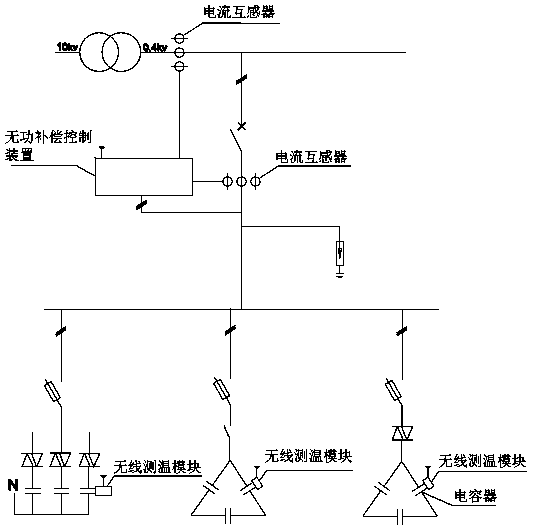

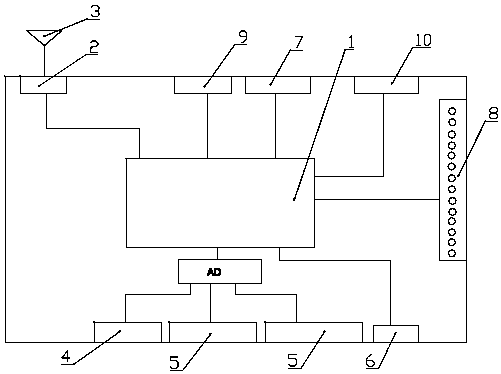

Reactive power compensation control device and capacitor switching method

PendingCN110071511AProtection capacitorExtended service lifeMeasurement devicesReactive power adjustment/elimination/compensationRadio frequencyCapacitance

The invention relates to the field of power equipment, in particular to a reactive power compensation control device comprising a radio frequency module, an antenna, an MCU controller, a three-phase voltage collecting circuit, two sets of three-phase current collecting circuits, a capacitor switching circuit, an alarm output circuit and a temperature control circuit, wherein the MCU controller isrespectively connected to the three-phase voltage collecting circuit, the three-phase current collecting circuits, the capacitor switching circuit, the alarm output circuit and the temperature controlcircuit. A capacitor switching method sets the capacity of the capacitor and an over-temperature protection value of the capacitor. The MCU controller controls the corresponding capacitor to be put into operation, and cuts off the capacitor loop and outputs an alarm when the temperature of the capacitor exceeds the set upper limit. The reactive power compensation controller and the capacitor switching method obtained by the invention have the function of wireless temperature measurement and capacitance detection of the capacitor.

Owner:浙江朗松智能电力设备有限公司

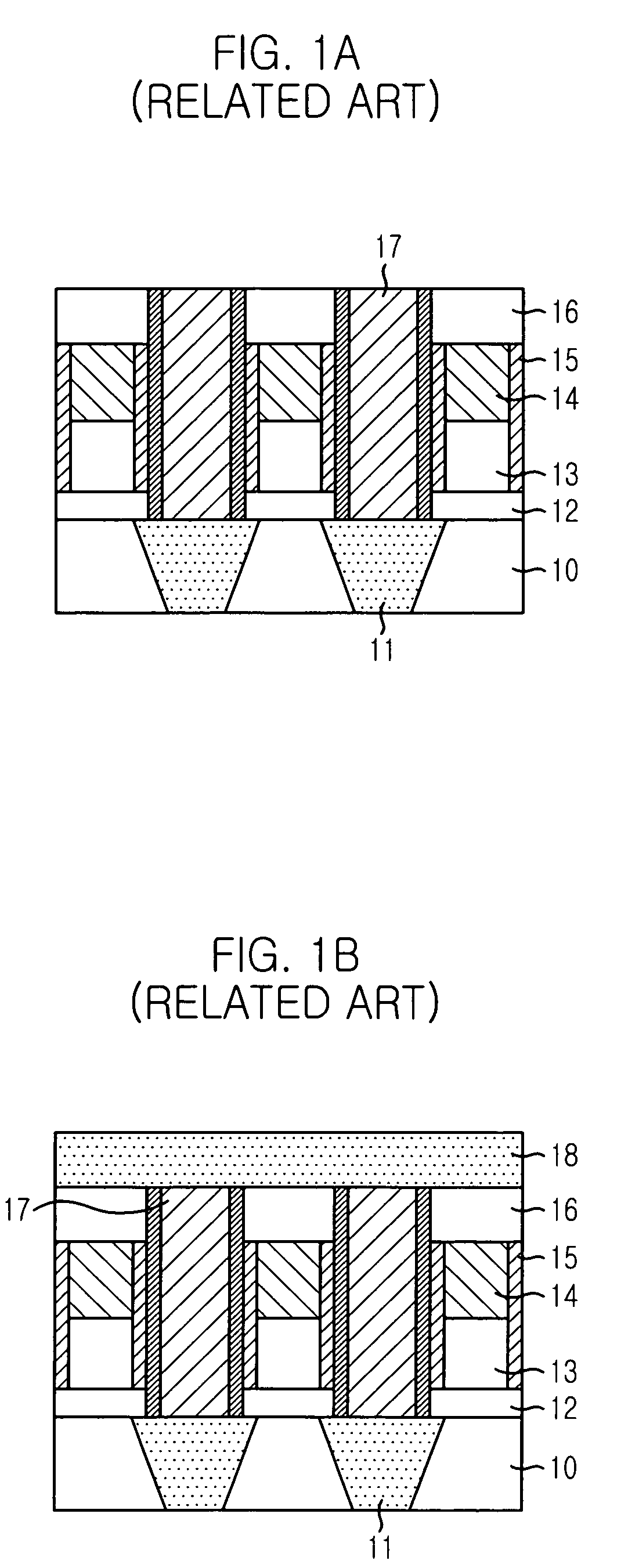

Method of fabricating flash memory device

ActiveUS20060205151A1Preventing stringerProtection capacitorSolid-state devicesSemiconductor/solid-state device manufacturingCoupling ratioElectrical and Electronics engineering

A method of fabricating a flash memory device is disclosed wherein, electrode spacers are formed on sides of self-aligned floating gates having a negative slope. Thus, upon etching of a stack gate after an interlayer dielectric film and a control gate are formed, a stringer of a control gate, which is formed by the negative slope of the self-aligned floating gates, can be prevented. Furthermore, because an isotropic etch process is used to remove element isolation films between the floating gates, the element isolation films do not remain on the sides of the floating gates. It is thus possible to prevent loss of the coupling ratio. Accordingly, failure of devices can be reduced and decreasing the program speed can be prevented.

Owner:SK HYNIX INC

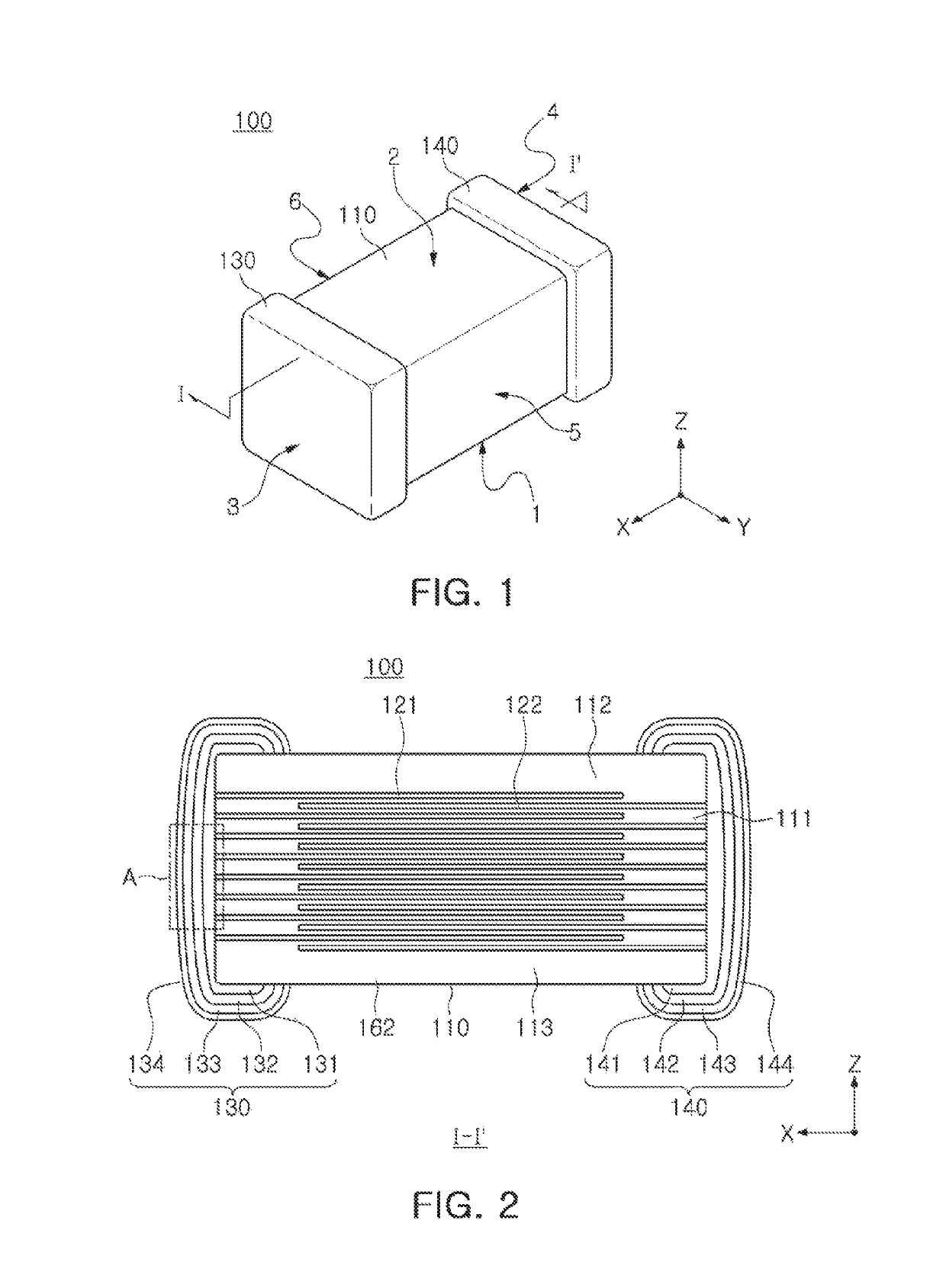

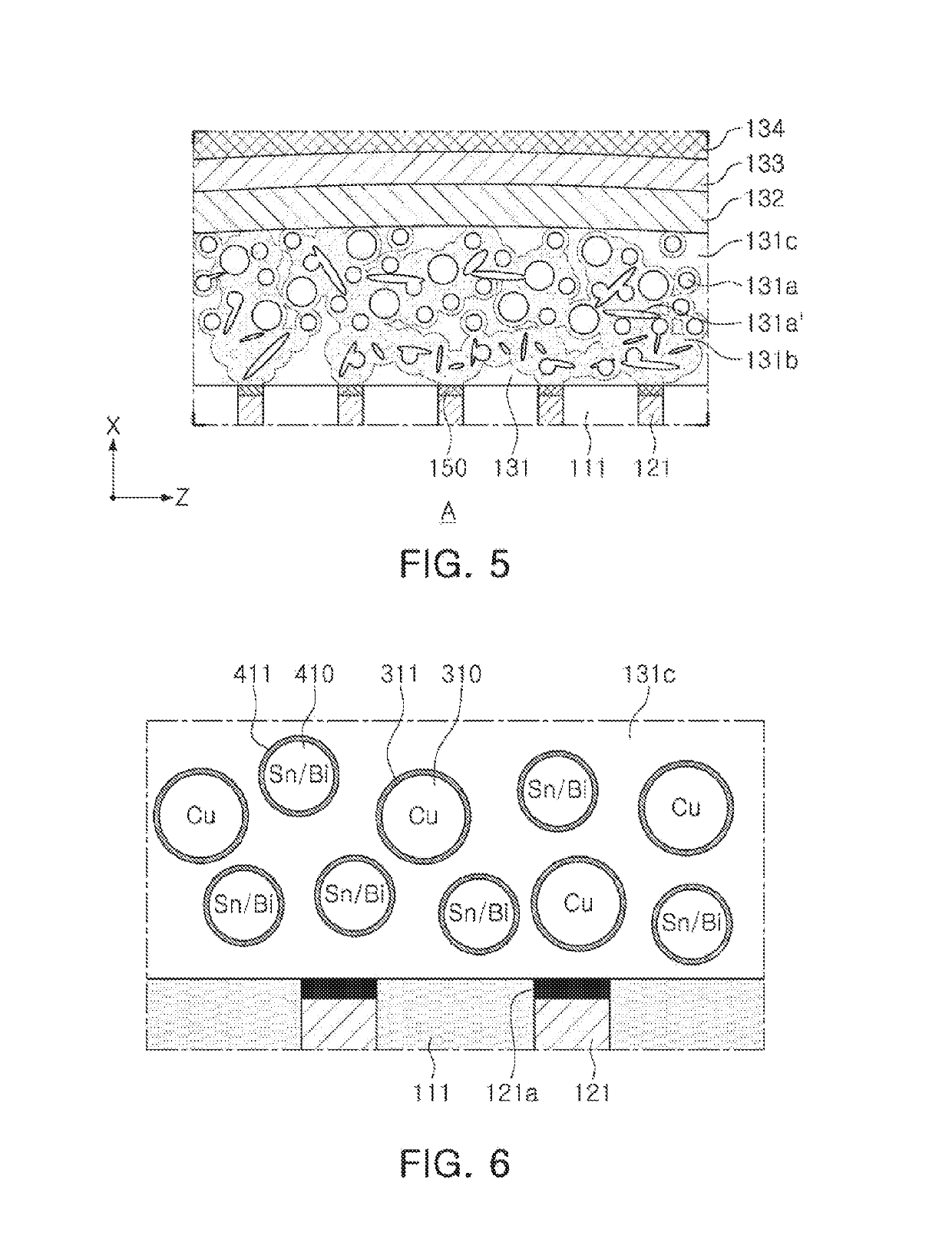

Multilayer capacitor

ActiveUS10319527B2Lower equivalent series resistanceImprove reliabilityThin/thick film capacitorFixed capacitor electrodesMetal particleUltimate tensile strength

A multilayer capacitor may have a decreased equivalent series resistance (ESR) and improved warpage strength and reliability with conductive resin layers of external electrodes on surfaces where internal electrodes are exposed from a body, intermetallic compounds are in contact with conductive connecting portions of the conductive resin layers and the internal electrodes, and conductive connecting portions are in contact with a plurality of metal particles and second electrode layers.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

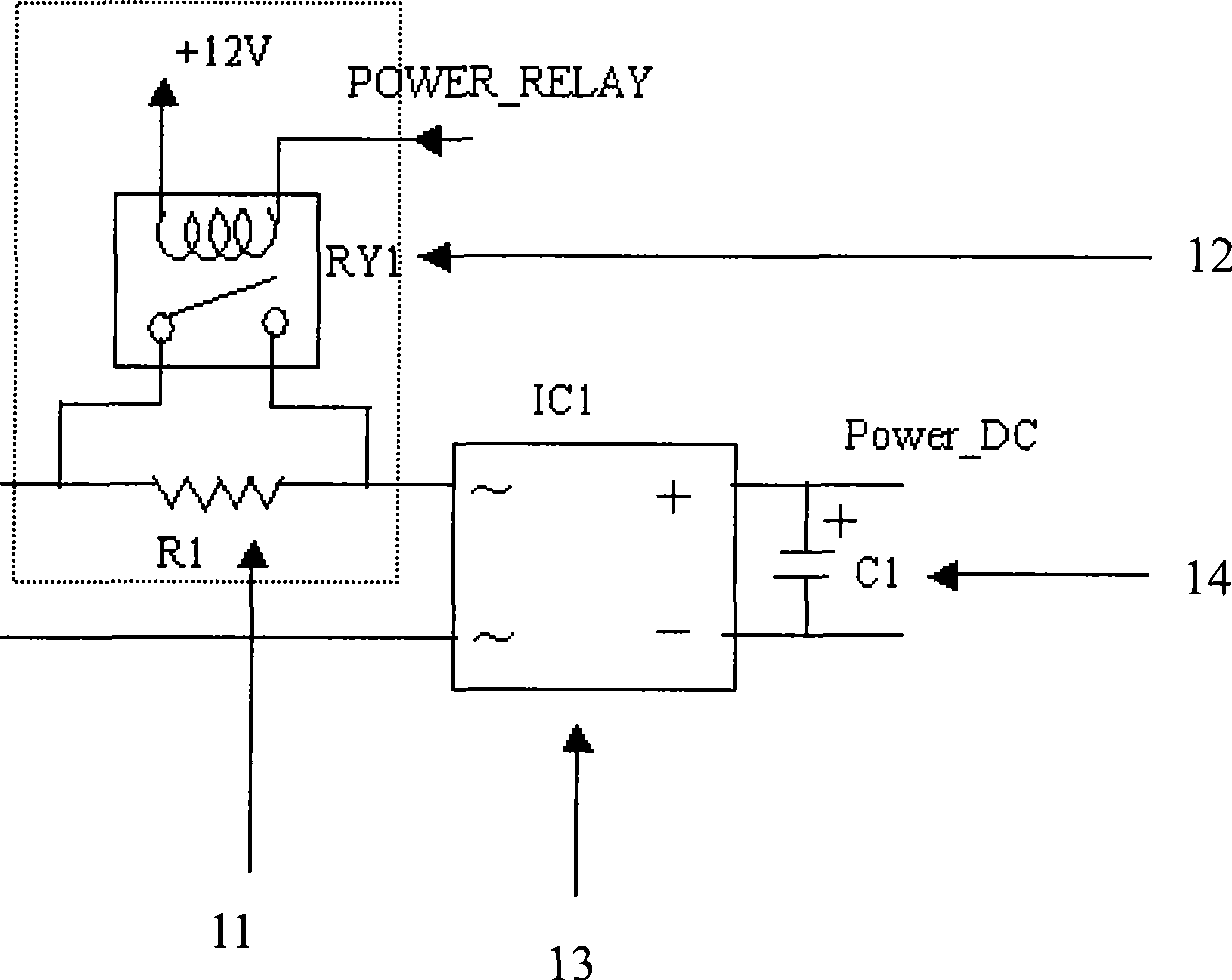

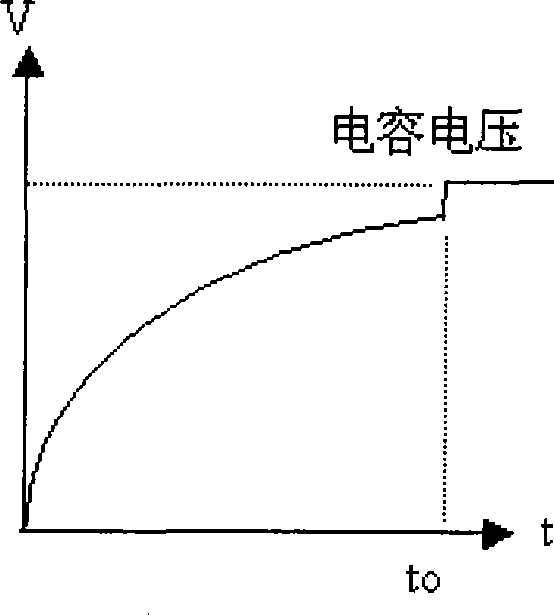

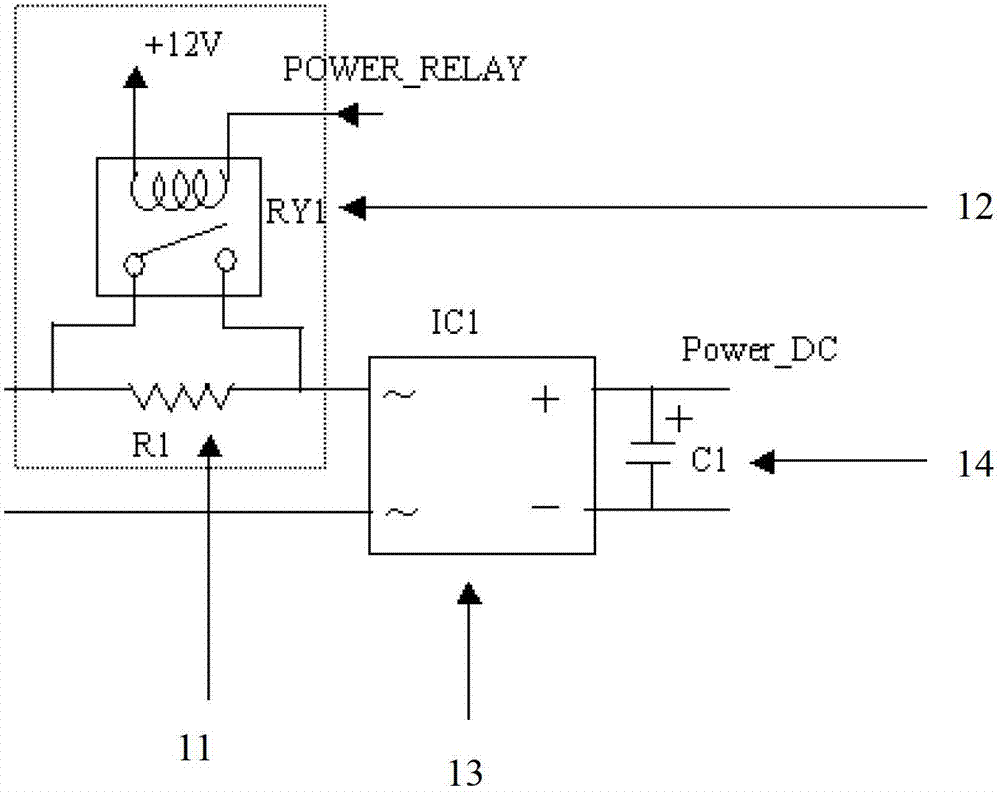

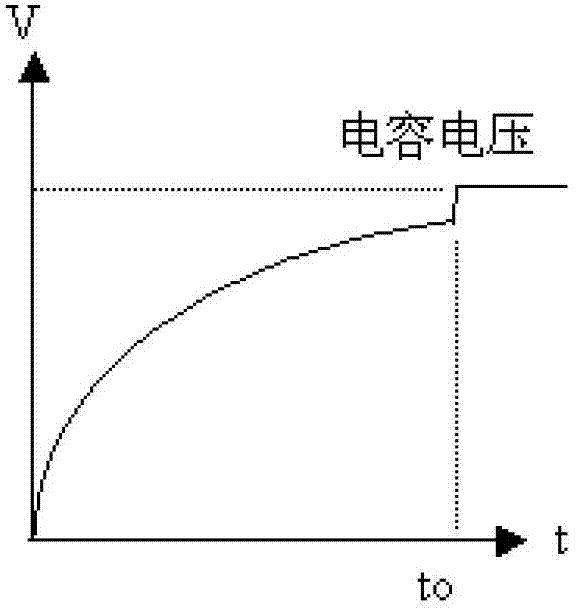

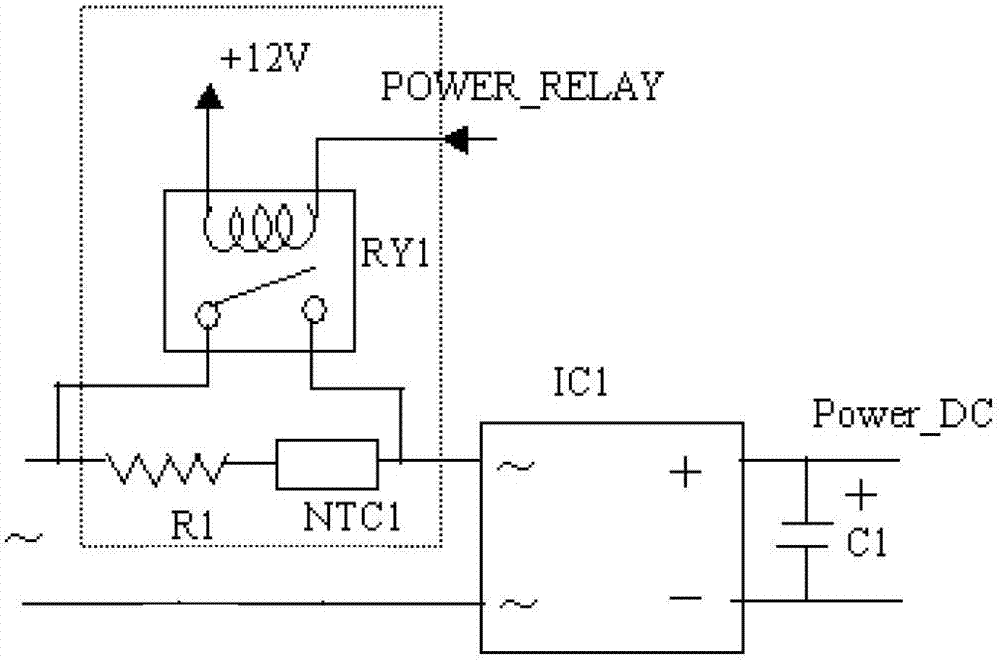

Novel frequency conversion power source protecting device

ActiveCN101394079AAvoid overvoltage and overcurrentProtection capacitorEmergency protective circuit arrangementsIntegrated circuitThermistor

A protective device for a variable-frequency power supply comprises a power resistor, a relay and a negative temperature coefficient thermistor, wherein the power resistor and the negative temperature coefficient thermistor are connected in series between the power supply and an integrated circuit; the relay is connected in parallel with the power resistor and both ends of the negative temperature coefficient thermistor; and a capacitor is connected in parallel with the integrated circuit. The invention includes the resistor satisfying the requirements of a rectification circuit, thereby effectively preventing overvoltage and overcurrent, protecting the capacitor and shortening the charge time.

Owner:SUZHOU SAMSUNG ELECTRONICS CO LTD

Semiconductor device and method for fabricating the same

InactiveUS7491606B2Increase the effective surface areaProtection capacitorTransistorSolid-state devicesInsulation layerContact layer

Owner:SK HYNIX INC

Organic electroluminescent device and electronic apparatus

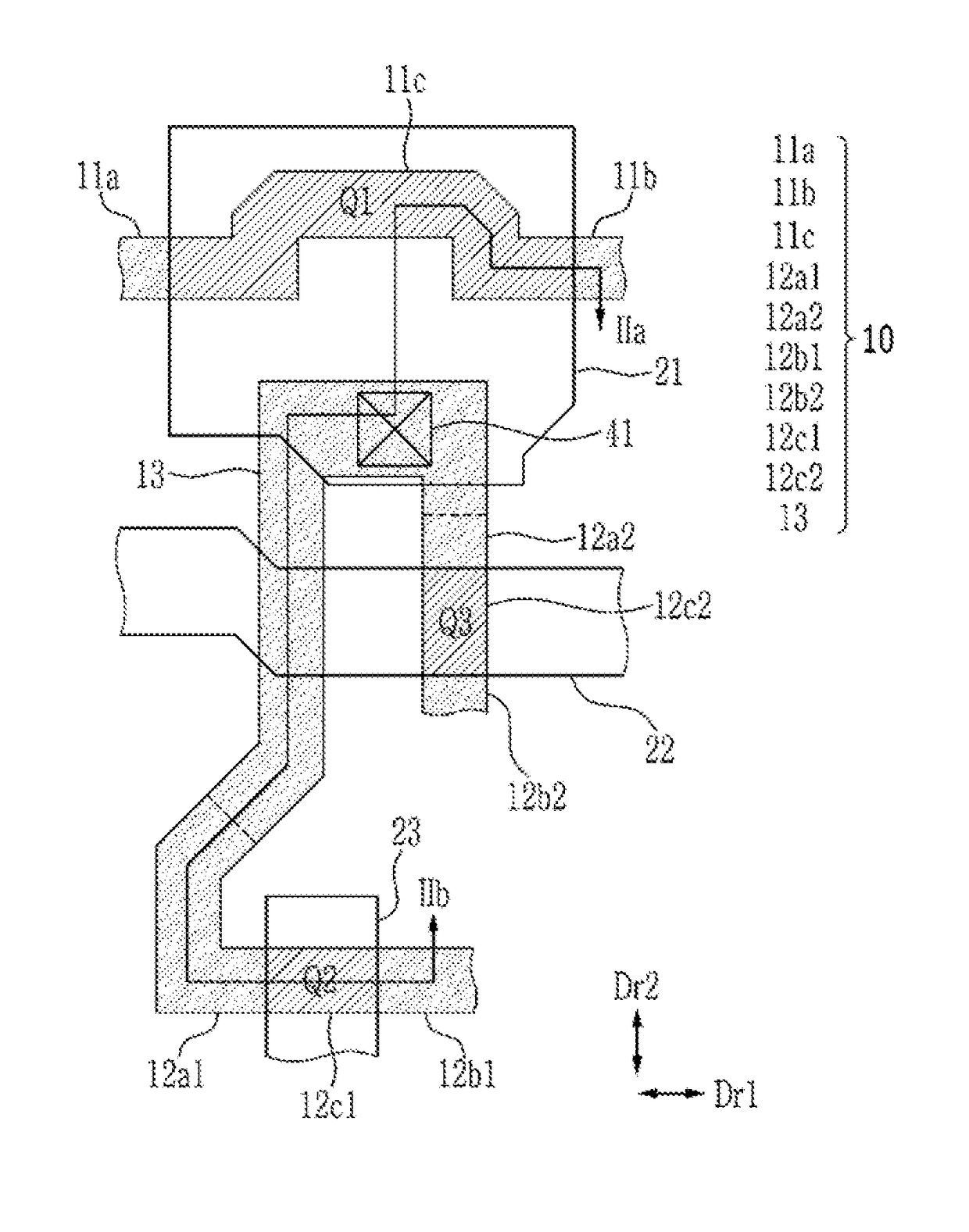

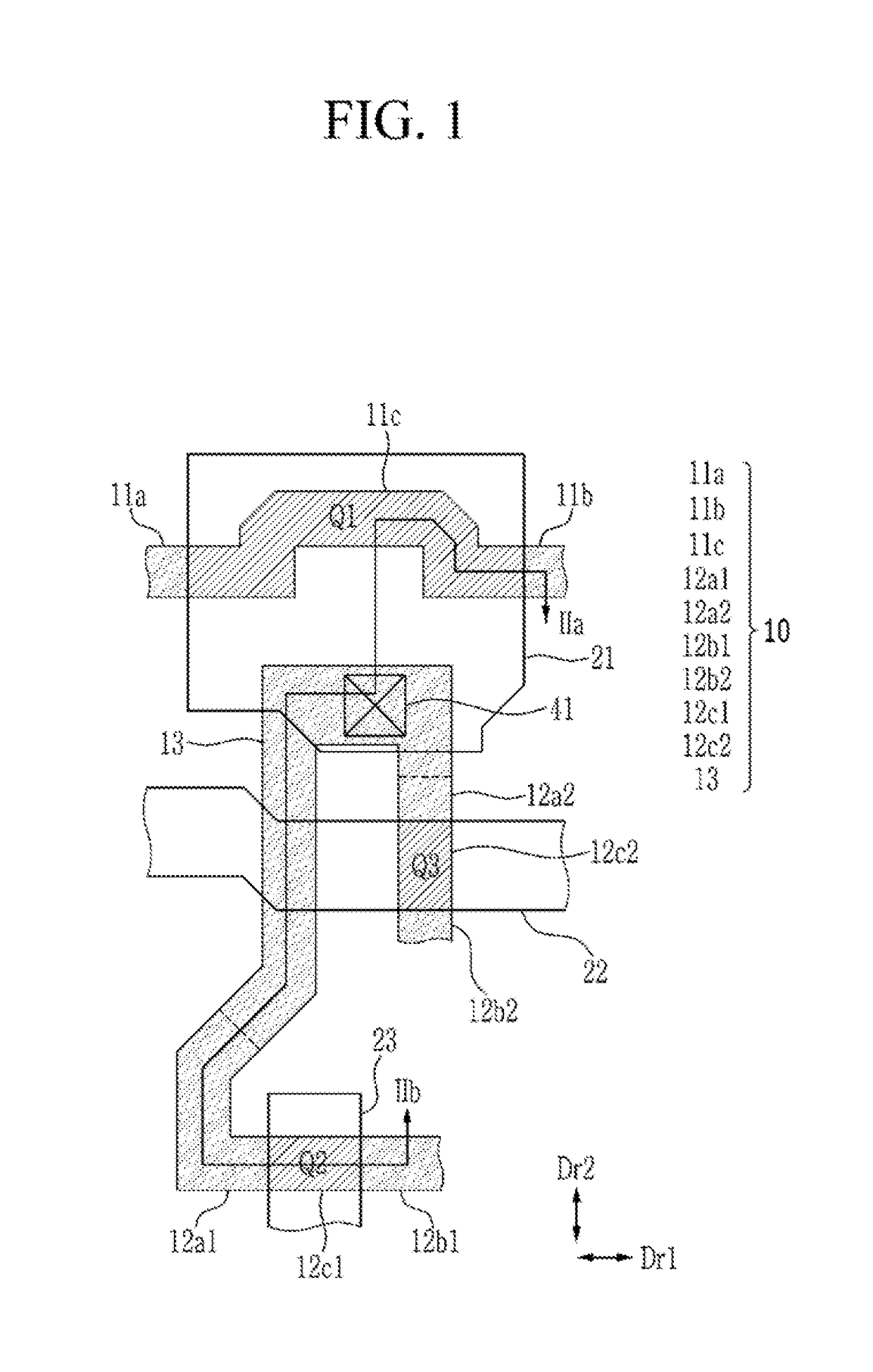

ActiveUS10777130B2Protection capacitorHigh densityStatic indicating devicesSolid-state devicesCapacitanceEngineering

An organic electroluminescent device includes a first transistor, an organic electroluminescent element that emits light with luminance corresponding to magnitude of a current supplied via the first transistor, and a capacitive element. The capacitive element includes a first electrode connected to a gate of the first transistor, a second electrode, and a dielectric film provided between the first electrode and the second electrode. The first electrode is formed on the same layer as the second electrode, and is arranged in a position away from the second electrode with the dielectric film interposed therebetween.

Owner:LUMITEK DISPLAY TECH LTD

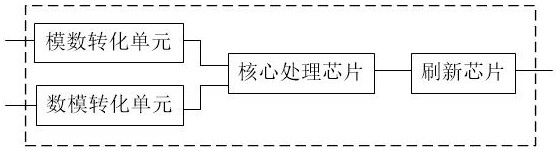

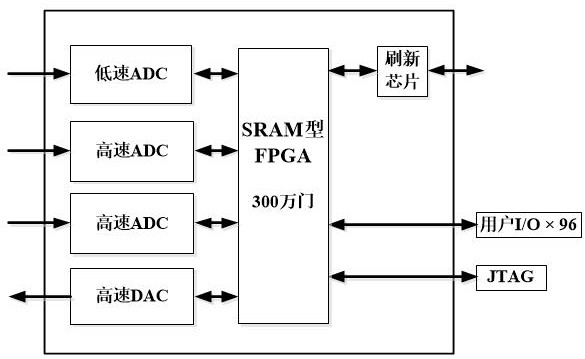

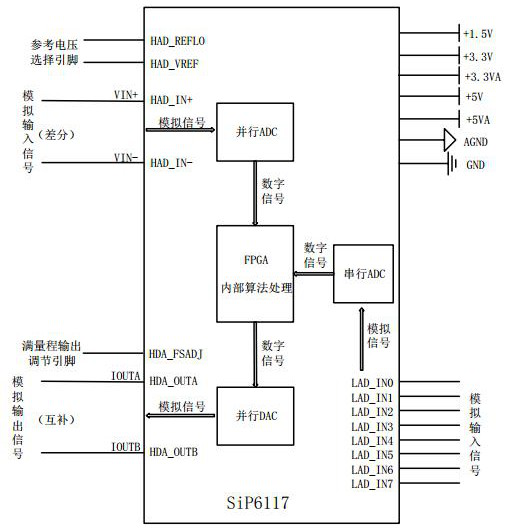

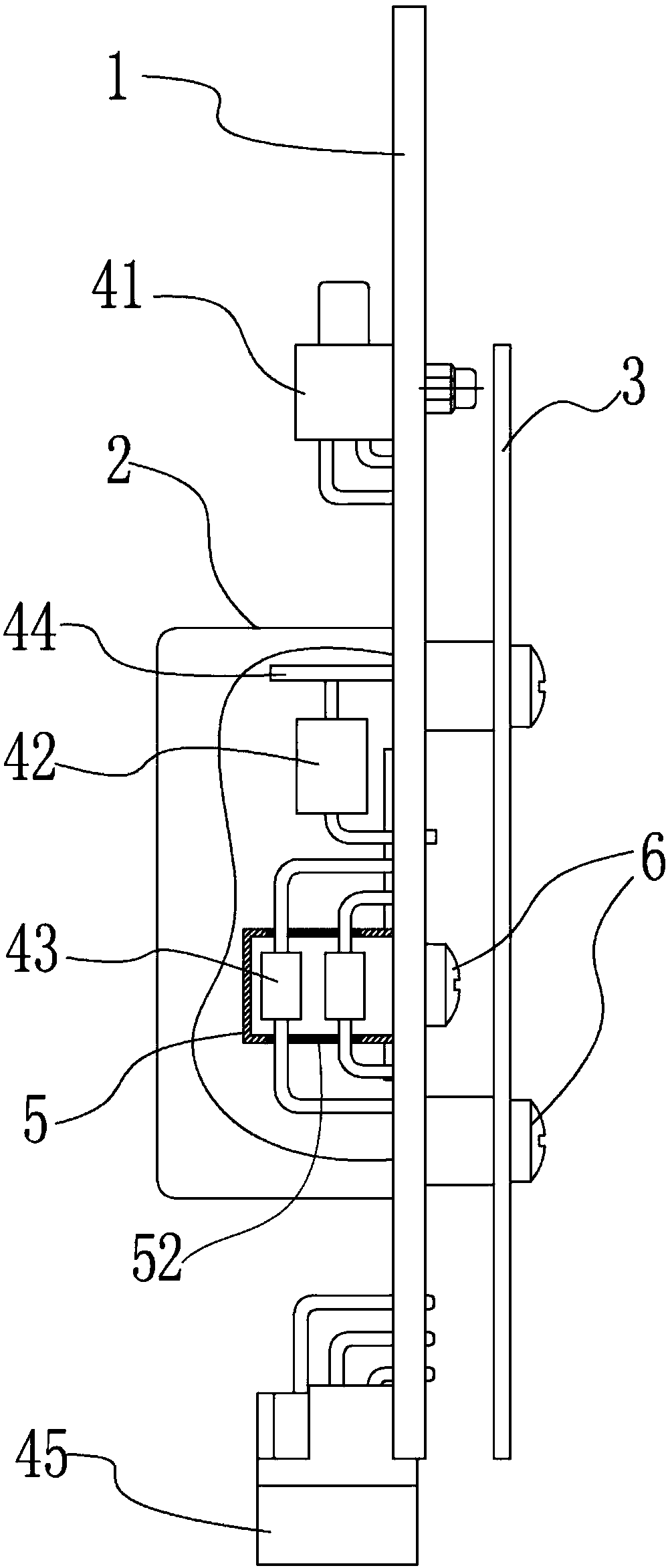

Programmable signal processing module based on SiP

PendingCN113126878AHighly integratedImprove performanceArchitecture with single central processing unitInput/output processes for data processingComputer hardwareSystem integration

A programmable signal processing module based on SiP comprises an analog-to-digital conversion unit used for converting collected analog quantity into digital quantity to be calculated and processed by a core processing chip, and the analog-to-digital conversion unit comprises a high-speed parallel ADC chip and a low-speed serial ADC chip; a core processing chip which comprises an FPGA chip and is used for completing the generation of a time sequence signal and the design of a closed-loop algorithm, calculating and processing the digital quantity converted by the analog-to-digital conversion unit and inputting the processed digital quantity into the digital-to-analog conversion unit; a digital-to-analog conversion unit which comprises a high-speed parallel DAC chip and is used for converting the digital quantity input by the core processing chip into analog quantity and outputting the analog quantity outwards; and a refreshing chip which is used for refreshing the core processing chip in real time when the single event upset occurs on the core processing chip so as to enable the core processing chip to quickly recover operation. System integration is achieved through the SIP technology, an FPGA + ADC + DAC architecture is adopted, the system is high in flexibility and integration degree, and miniaturization is achieved.

Owner:北京轩宇空间科技有限公司

Display device and manufacturing method thereof

ActiveUS10586836B2Change in luminanceQuality improvementStatic indicating devicesSolid-state devicesElectrical conductorDisplay device

The present disclosure relates to a display device. An exemplary embodiment of the present invention provides a display device including a substrate and an active pattern positioned above the substrate. to the active pattern includes a channel region and a conductive region having a higher carrier concentration than the channel region. A first insulating layer is disposed on the active pattern. A first conductive layer is disposed on the first insulating layer and includes a first conductor. The channel region of the active pattern includes a first channel region overlapping the first conductor along a direction orthogonal to an upper surface of the substrate. The conductive region of the active pattern includes a first conductive region overlapping the first conductor along the direction orthogonal to the upper surface of the substrate.

Owner:SAMSUNG DISPLAY CO LTD

Method for fabricating capacitor in semiconductor device

InactiveUS20070117309A1Improve reliabilityProtection capacitorTransistorSolid-state devicesDevice materialHafnium

The present invention relates to a method for fabricating a capacitor in a semiconductor device through the use of hafnium-terbium oxide (Hf1-xTbxO) as a dielectric layer. The method includes the steps of: forming a lower electrode on a substrate; forming an amorphous hafnium-terbium oxide (Hf1-xTbxO) dielectric layer on the lower electrode; crystallizing the Hf1-xTbxO dielectric layer by performing a thermal process; and forming an upper electrode on the Hf1-xTbxO dielectric layer.

Owner:SK HYNIX INC

A method for frequency modulation and voltage regulation of poultry electric hemp machine

ActiveCN103796406BReduce congestionEnsure hygiene and safetyElectric shock equipmentsElectric current slaughtering/stunningLow voltageAssembly line

Owner:NANJING AGRICULTURAL UNIVERSITY

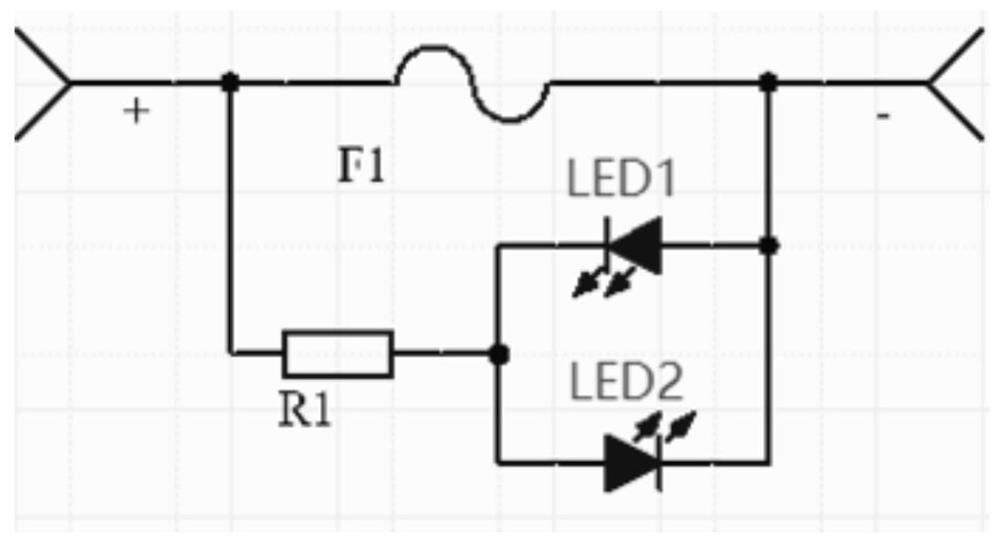

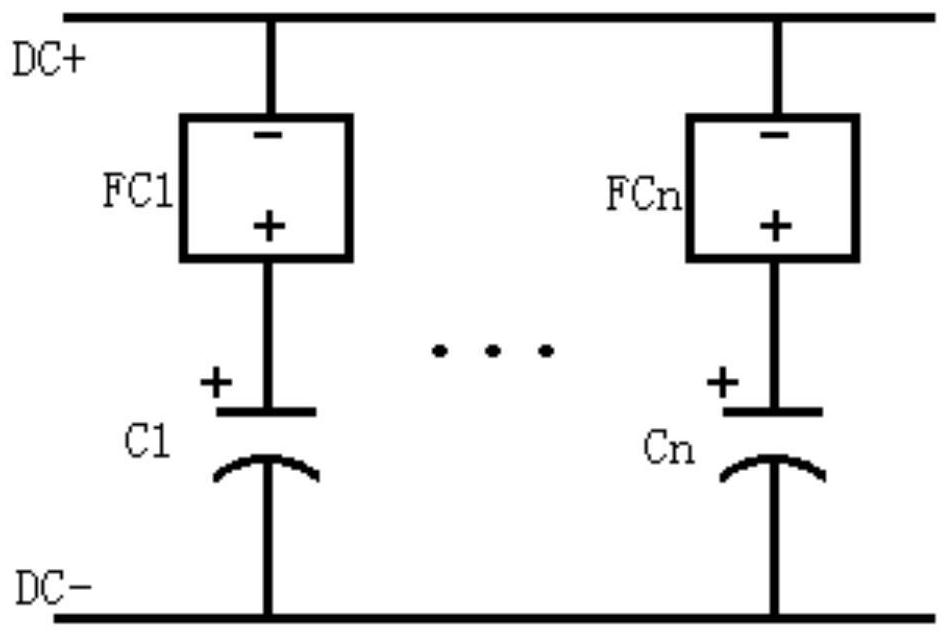

Real-time indicating circuit for overcurrent fault of single capacitor in large number of capacitors connected in parallel

InactiveCN113514715ATimely repair and maintenanceProtection capacitorCurrent/voltage measurementElectrical testingCapacitanceHemt circuits

The invention discloses a real-time indicating circuit for an overcurrent fault of a single capacitor in a large number of capacitors connected in parallel. The circuit comprises a plurality of capacitors which are connected in parallel, and each capacitor is connected in series with a corresponding capacitor overcurrent fault real-time indicating circuit; the positive electrode of each capacitor is connected with the first end of the corresponding capacitor overcurrent fault real-time indicating circuit, and the second end of each capacitor overcurrent fault real-time indicating circuit is connected with the positive electrode of a direct-current power supply; the negative electrode of each capacitor is connected with the negative electrode of the direct-current power supply; each capacitor overcurrent fault real-time indicating circuit comprises a fuse F, a resistor R and a parallel indication circuit, and the parallel indication circuit comprises a forward indication lamp and a reverse indication lamp. The circuit is simple and reasonable, is suitable for occasions with fuses, and is used for indicating whether the fuses are fused or not; based on a large number of capacitors connected in parallel, the circuit is easy to find the position of the capacitor with the overcurrent fault in a large number of capacitors connected in parallel, and is convenient to repair and maintain in time to protect normal capacitors.

Owner:SOUTHWESTERN INST OF PHYSICS

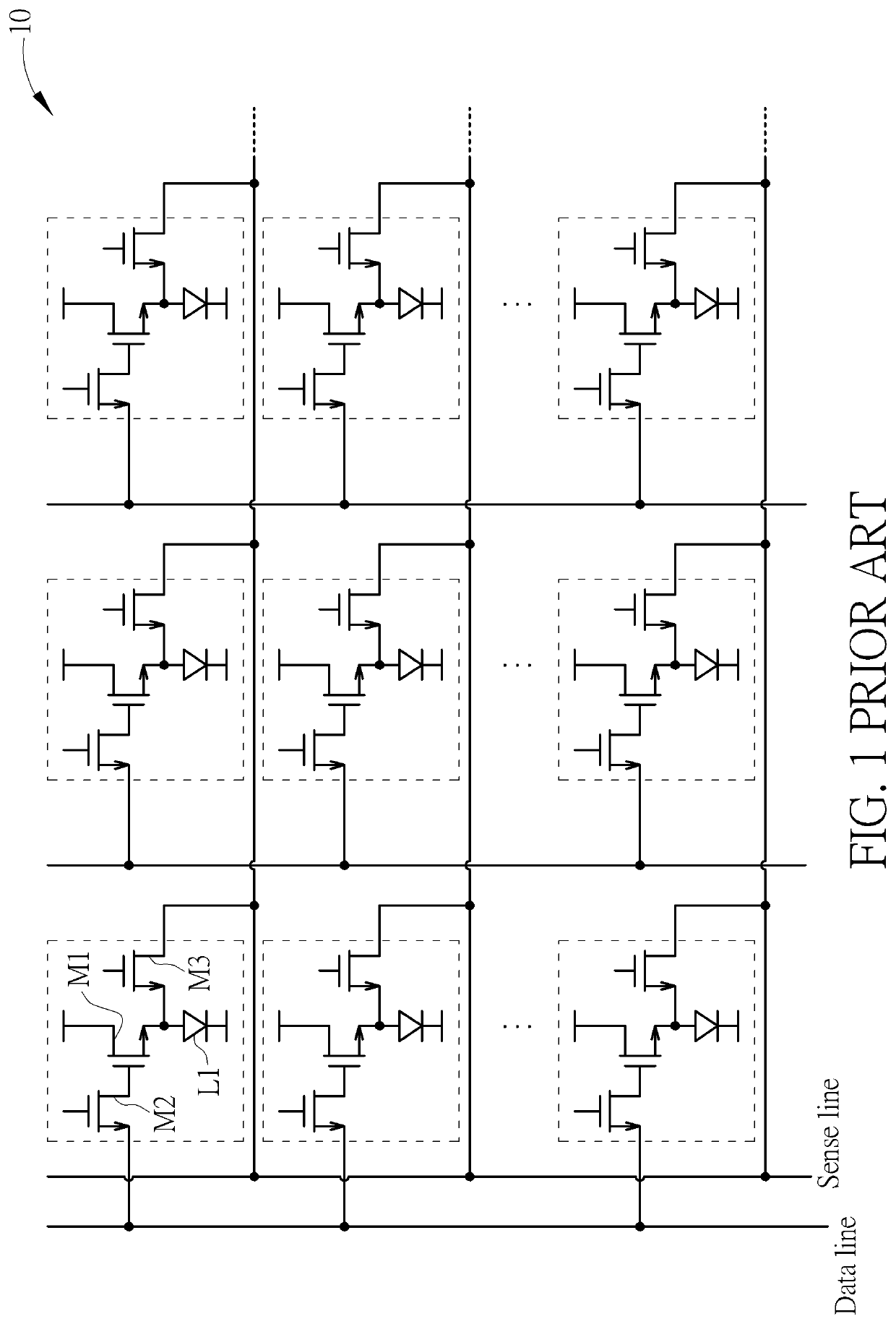

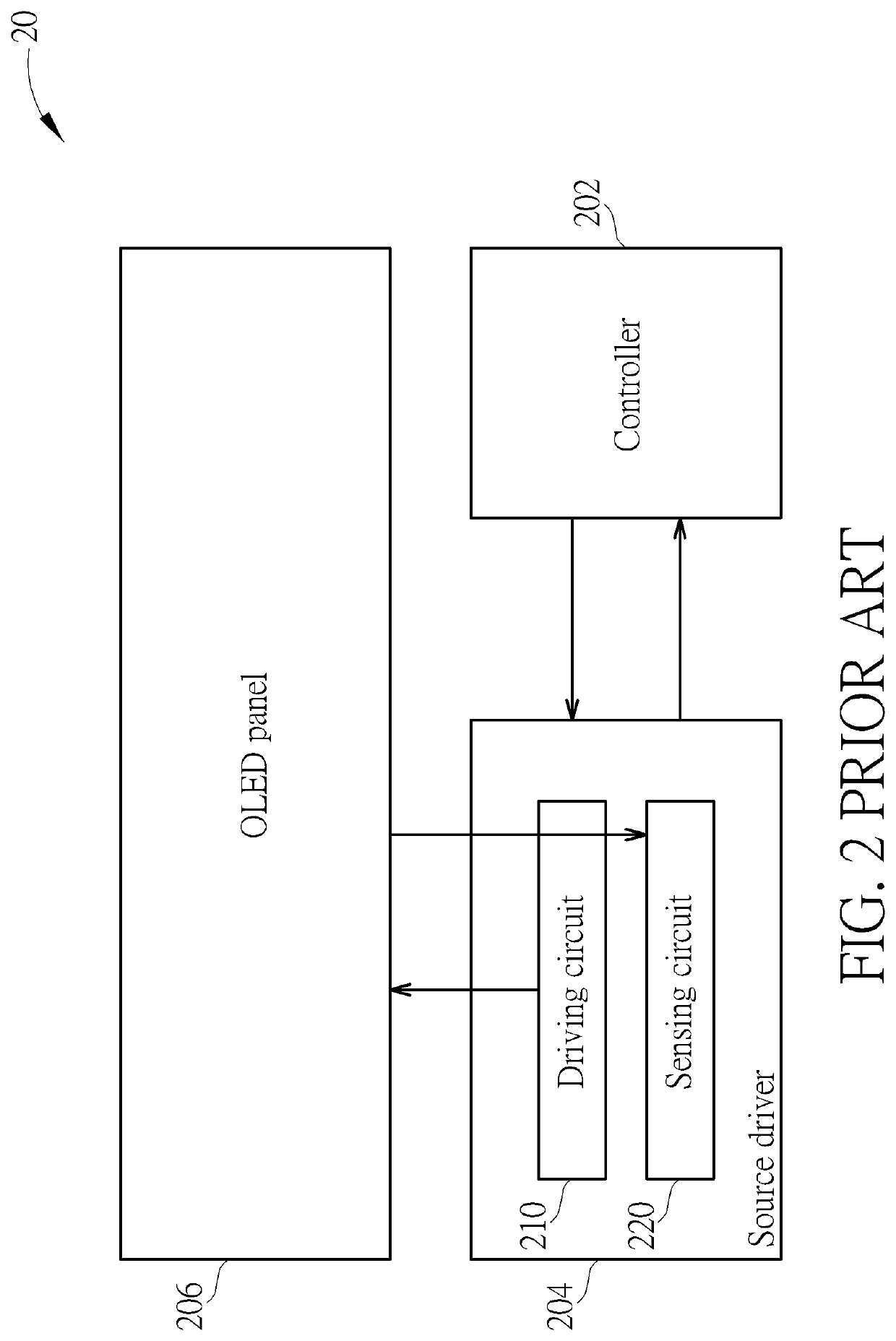

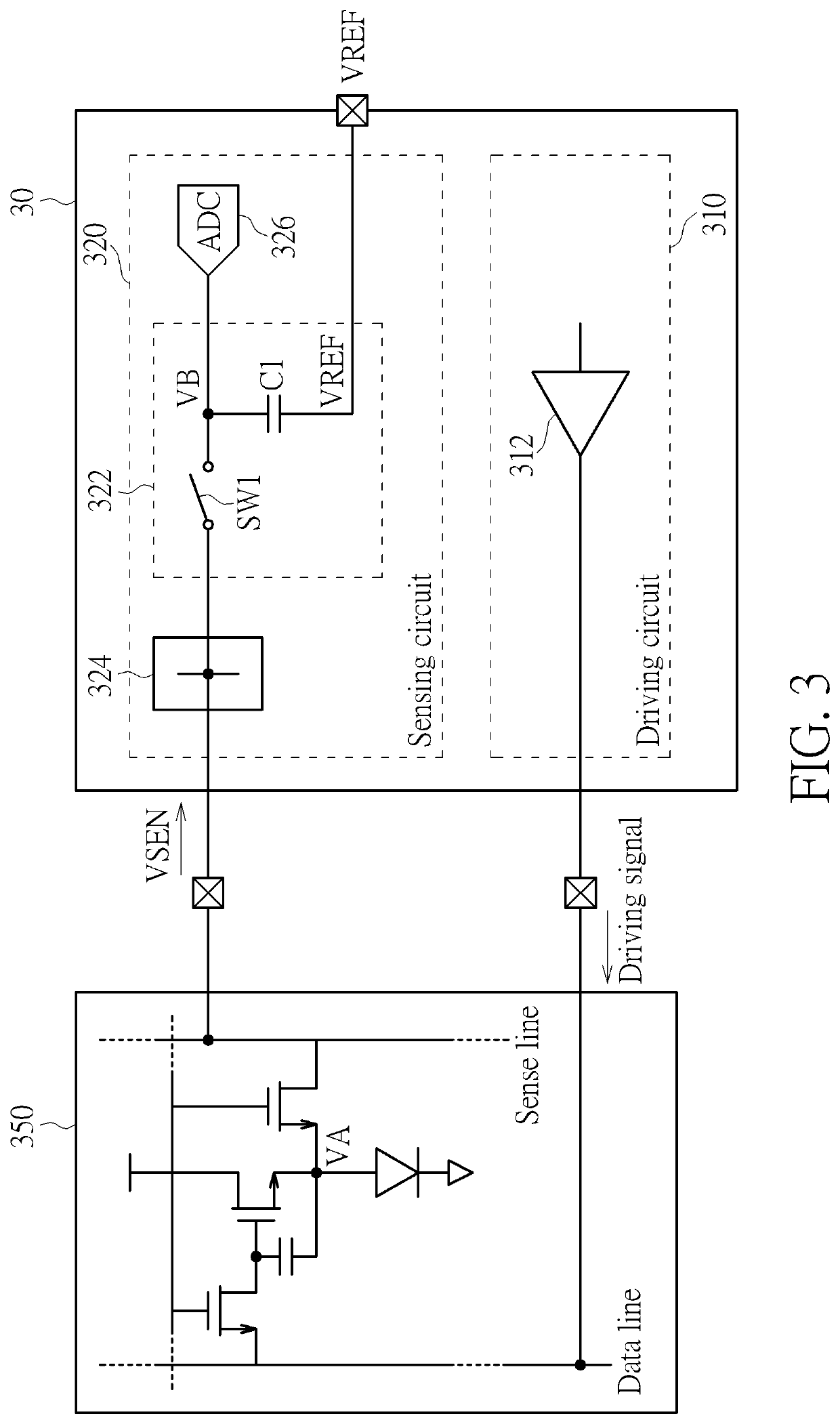

Sensing circuit for OLED driver and OLED driver using the same

ActiveUS11205382B2Protection capacitorStatic indicating devicesSolid-state devicesCapacitanceHemt circuits

A sensing circuit for an organic light-emitting diode (OLED) driver includes a sample and hold circuit and a clamping circuit. The sample and hold circuit includes a capacitor. The clamping circuit, coupled to the sample and hold circuit, is configured to clamp a sensing voltage received by the sample and hold circuit to conform to a withstand voltage of the capacitor.

Owner:NOVATEK MICROELECTRONICS CORP

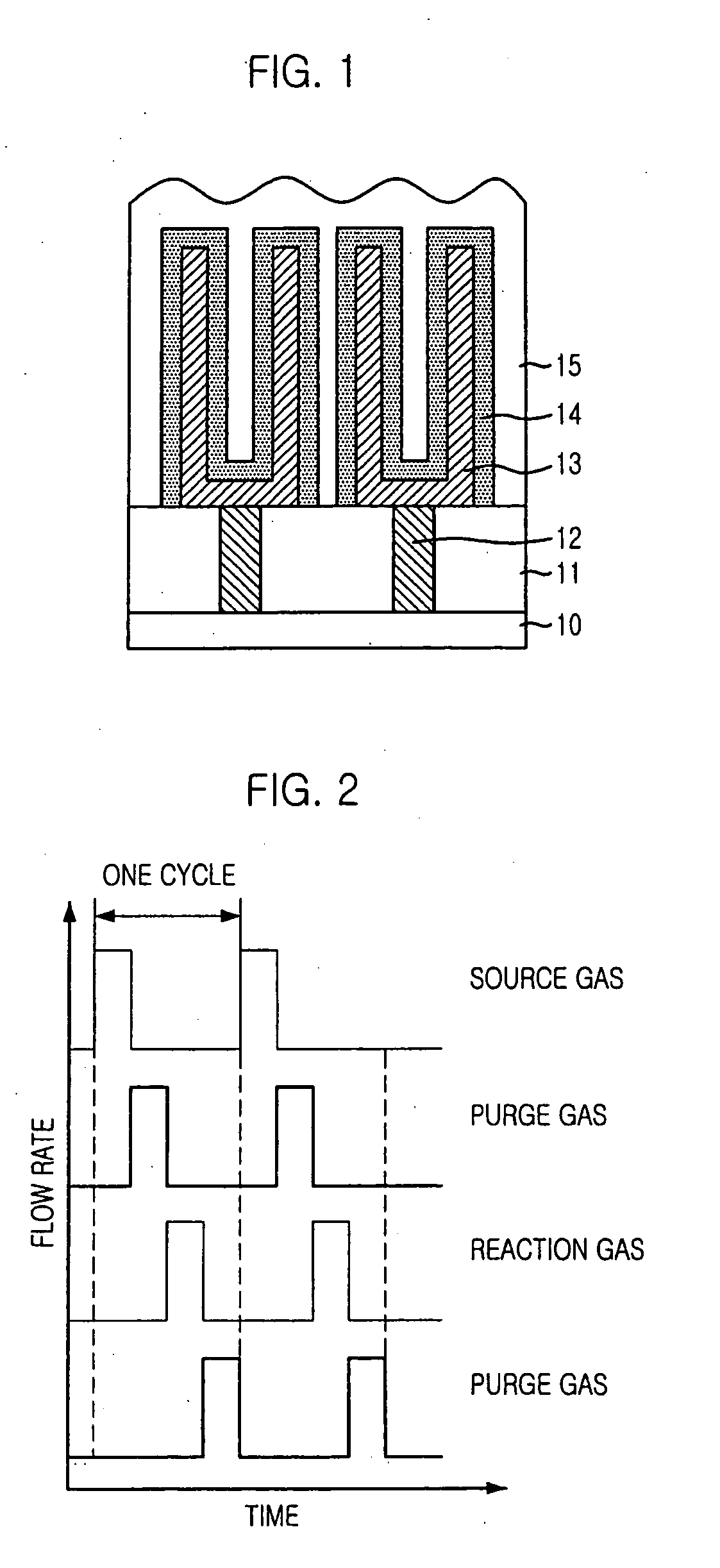

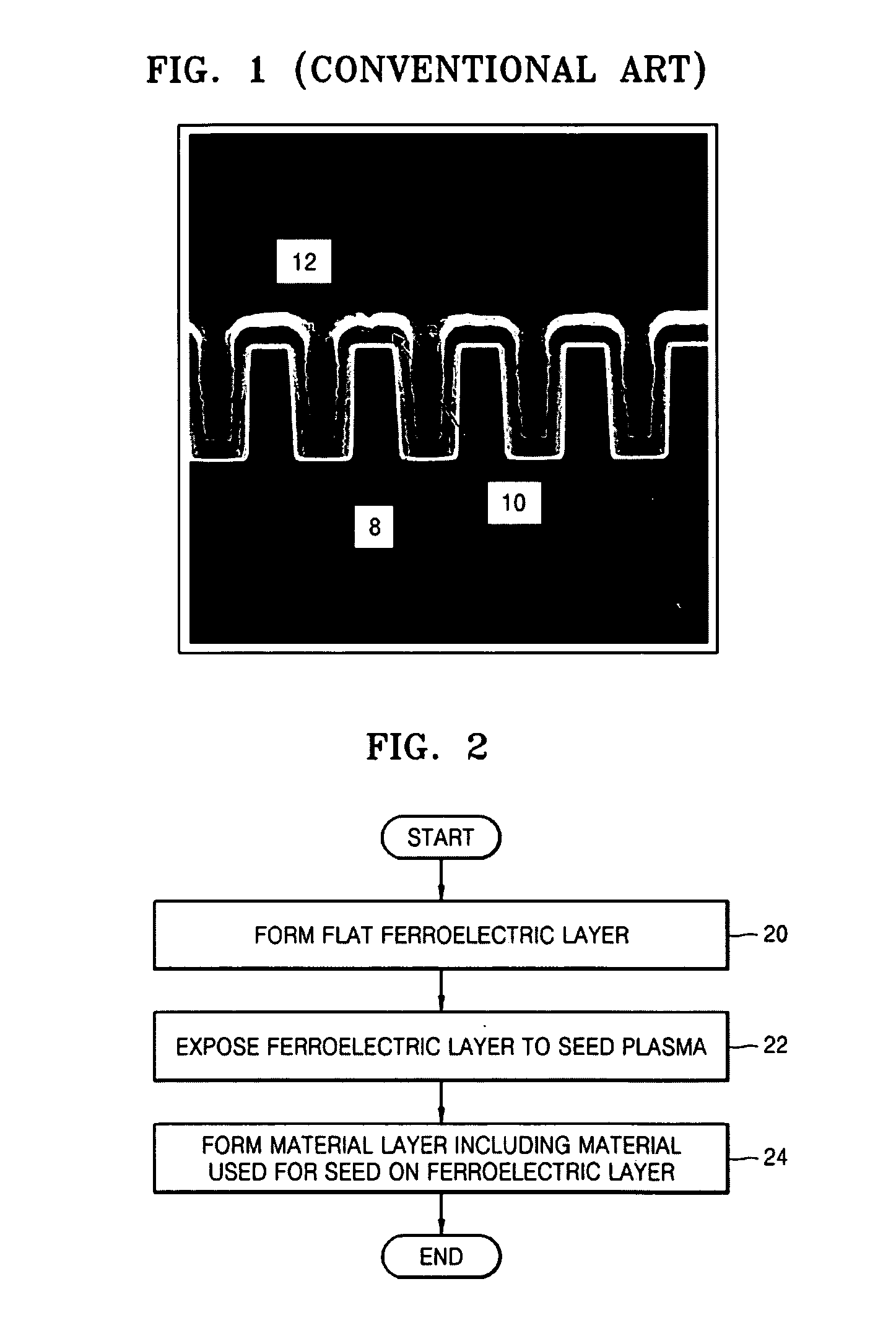

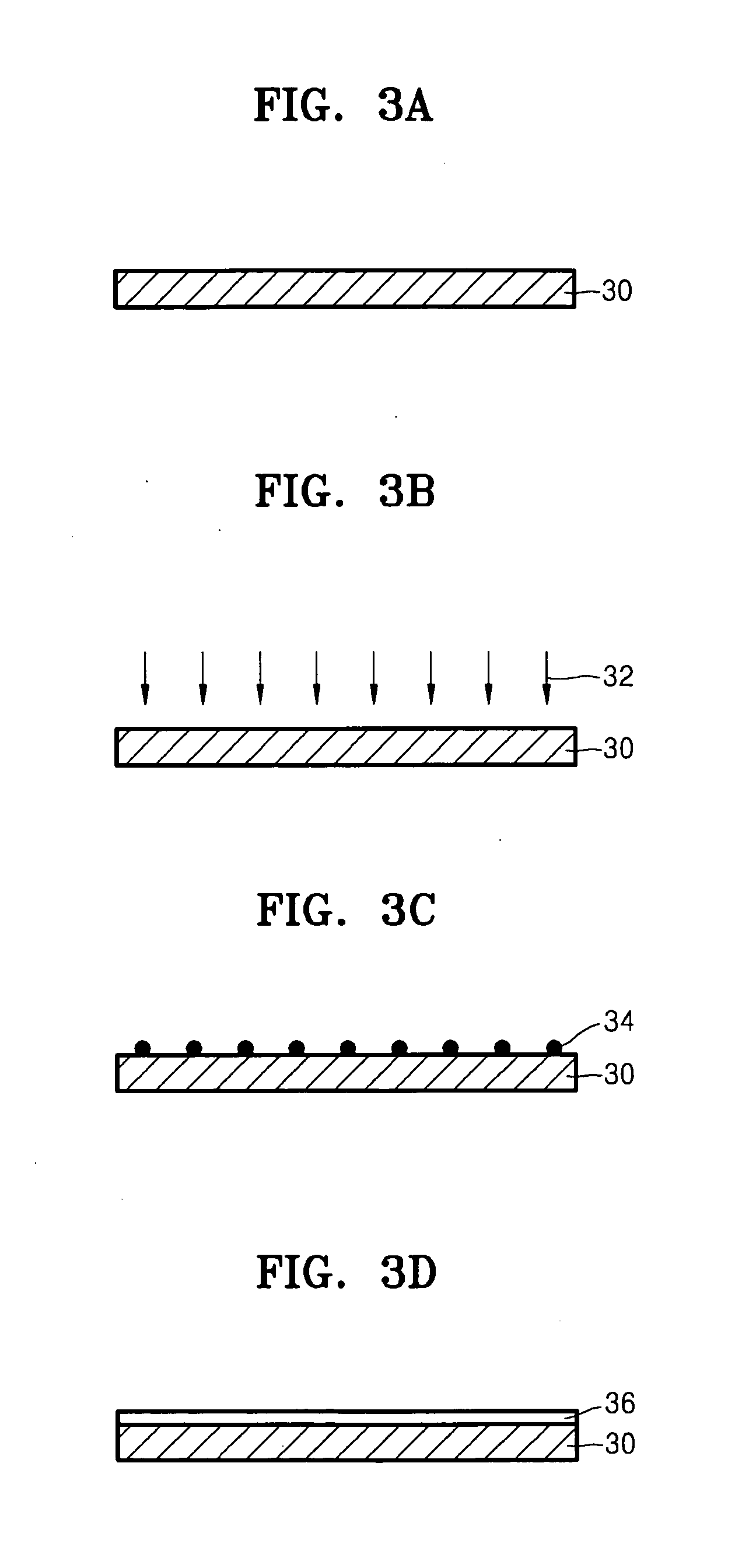

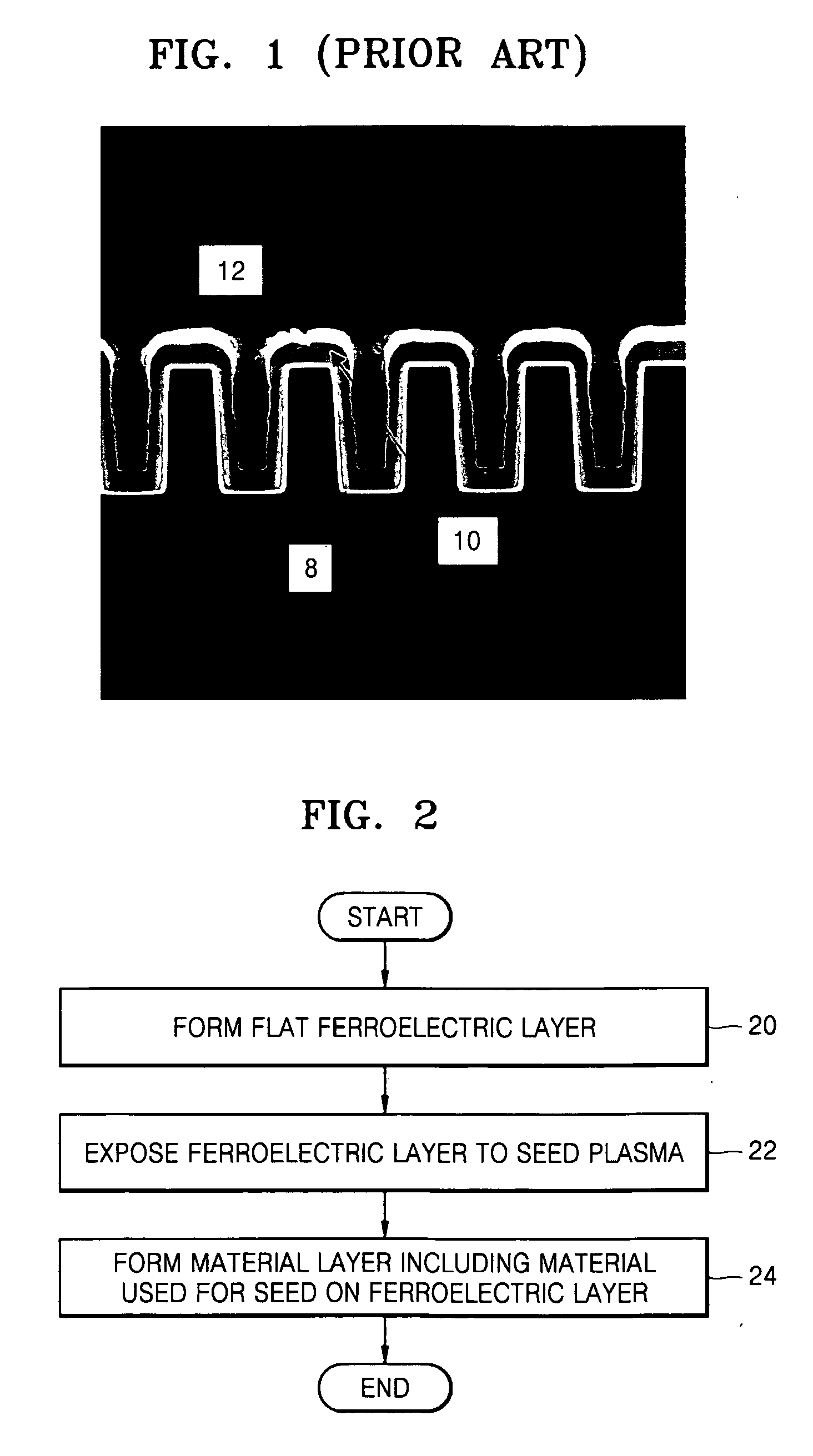

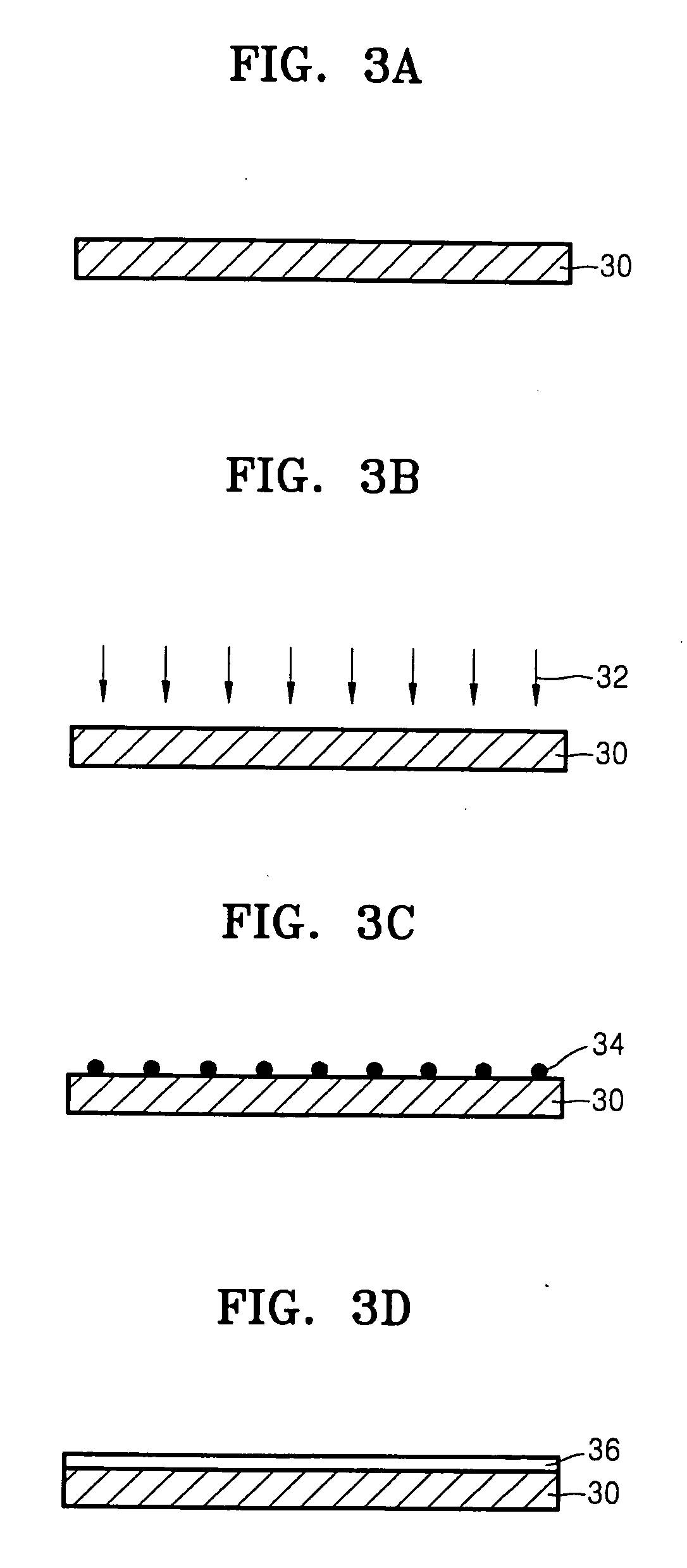

Method for manufacturing material layer, method for manufacturing ferroelectric capacitor using the same, ferroelectric capacitor manufactured by the same method, semiconductor memory device having ferroelectric capacitor and manufacturing method thereof

InactiveUS20070012974A1Sufficient capacitanceGuaranteed uptimeSolid-state devicesSemiconductor/solid-state device manufacturingSource materialManufactured material

Provided is a method for manufacturing a material layer capable of increasing the deposition rate of a noble metal layer on a ferroelectric layer, a method for manufacturing a ferroelectric capacitor using the same, a ferroelectric capacitor manufactured by the same method, and a semiconductor memory device having the ferroelectric capacitor and a manufacturing method thereof. According to a method for manufacturing the material layer, a ferroelectric layer is formed. The ferroelectric layer may be exposed to seed plasma, and a material layer including a source material of the seed plasma may be formed on a region of the ferroelectric layer exposed to the seed plasma.

Owner:SAMSUNG ELECTRONICS CO LTD

Method for fabricating capacitor in semiconductor device using hafnium terbium oxide dielectric layer

InactiveUS7531422B2Improve reliabilityProtection capacitorTransistorSolid-state devicesHafniumDielectric layer

The present invention relates to a method for fabricating a capacitor in a semiconductor device through the use of hafnium-terbium oxide (Hf1-xTbxO) as a dielectric layer. The method includes the steps of: forming a lower electrode on a substrate; forming an amorphous hafnium-terbium oxide (Hf1-xTbxO) dielectric layer on the lower electrode; crystallizing the Hf1-xTbxO dielectric layer by performing a thermal process; and forming an upper electrode on the Hf1-xTbxO dielectric layer.

Owner:SK HYNIX INC

Novel frequency conversion power source protecting device

ActiveCN101394079BAvoid overvoltage and overcurrentProtection capacitorEmergency protective circuit arrangementsOvervoltageElectrical resistance and conductance

A protective device for a variable-frequency power supply comprises a power resistor, a relay and a negative temperature coefficient thermistor, wherein the power resistor and the negative temperature coefficient thermistor are connected in series between the power supply and an integrated circuit; the relay is connected in parallel with the power resistor and both ends of the negative temperature coefficient thermistor; and a capacitor is connected in parallel with the integrated circuit. The invention includes the resistor satisfying the requirements of a rectification circuit, thereby effectively preventing overvoltage and overcurrent, protecting the capacitor and shortening the charge time.

Owner:SUZHOU SAMSUNG ELECTRONICS CO LTD

Self-encapsulating passive wireless pressure sensor based on flexible substrate

InactiveCN103148977BProtection capacitorSelf-encapsulatingFluid pressure measurement using capacitance variationCapacitanceEngineering

Owner:SOUTHEAST UNIV

Method for manufacturing material layer, method for manufacturing ferroelectric capacitor using the same, ferroelectric capacitor manufactured by the same method, semiconductor memory device having ferroelectric capacitor and manufacturing method thereof

InactiveUS20080210998A1Increase deposition rateGood step coverageTransistorSolid-state devicesSource materialManufactured material

Provided is a method for manufacturing a material layer capable of increasing the deposition rate of a noble metal layer on a ferroelectric layer, a method for manufacturing a ferroelectric capacitor using the same, a ferroelectric capacitor manufactured by the same method, and a semiconductor memory device having the ferroelectric capacitor and a manufacturing method thereof. According to a method for manufacturing the material layer, a ferroelectric layer is formed. The ferroelectric layer may be exposed to seed plasma, and a material layer including a source material of the seed plasma may be formed on a region of the ferroelectric layer exposed to the seed plasma.

Owner:KOO JUNE MO +5

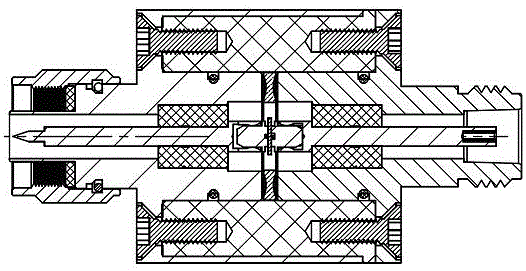

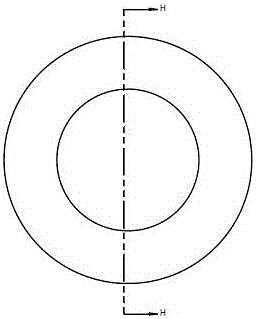

Elastic contact structure for 4G direct current blocking device

InactiveCN106602289ANo problem of insufficient elasticityIncrease elasticityClamped/spring connectionsCapacitanceEngineering

The invention discloses an elastic contact structure for a 4G direct current blocking device. The elastic contact structure comprises a circular ring, an inner side wall of the circular ring is provided with 4-8 petal elastic sheets, and one end of each petal elastic sheet is fixed on a circular ring in a spacing manner. The elastic contact structure disclosed in the invention can well contact with a capacitor, the capacitor can be therefore protected, and qualified rates of capacitor products can be improved.

Owner:CHANGZHOU AMPHENOL FUYANG COMM EQUIP CO LTD

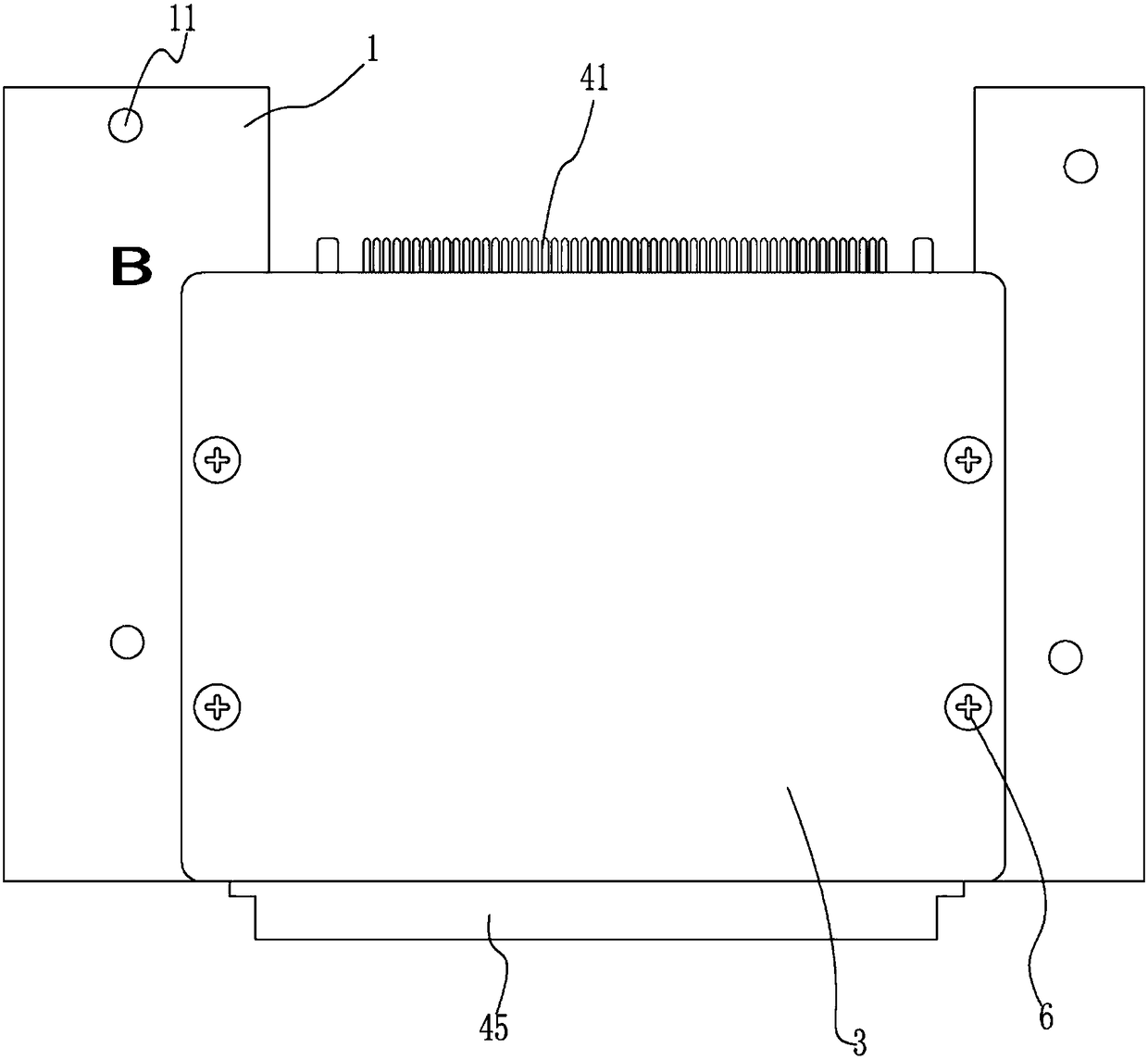

An integrated chassis filter board structure

ActiveCN106129671BEnables modular installationNot easy to make mistakesMultiple-port networksCoupling device detailsCapacitanceEngineering

The invention provides an integrated chassis filter plate structure, comprising a PCB (Printed Circuit Board) substrate, a screen, a protective plate and a filter, wherein the PCB substrate is provided with mounting holes and a fixed column; the screen and the protective plate are fixed on the PCB substrate and located on two opposite sides of the PCB substrate respectively, the screen is installed on the PCB substrate in an inverted mode, and the protective plate is located at the top of the fixed column and is parallel to the PCB substrate; the filter comprises an input connector, a two-way TVS (Transient Voltage Suppressor) diode, a capacitor, an earth plate and an output connector which are integrated on the PCB substrate and located on the same side as the screen, the input connector and the output connector are rectangular connectors and are located at the edge of the PCB substrate, the two-way TVS diode, the capacitor and the earth plate are located within a cavity encircled by the screen and the PCB substrate, one end of the two-way TVS diode is welded on the PCB substrate, and the other end of the two-way TVS diode is connected with the earth plate. The integrated chassis filter plate structure realizes modularized installation of the filter, reduces the assembly difficulty, improves the installation efficiency, and is more convenient to detach and replace.

Owner:CHONGQING DAJI ELECTRONICS TECH