Patents

Literature

2991 results about "Fpga chip" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

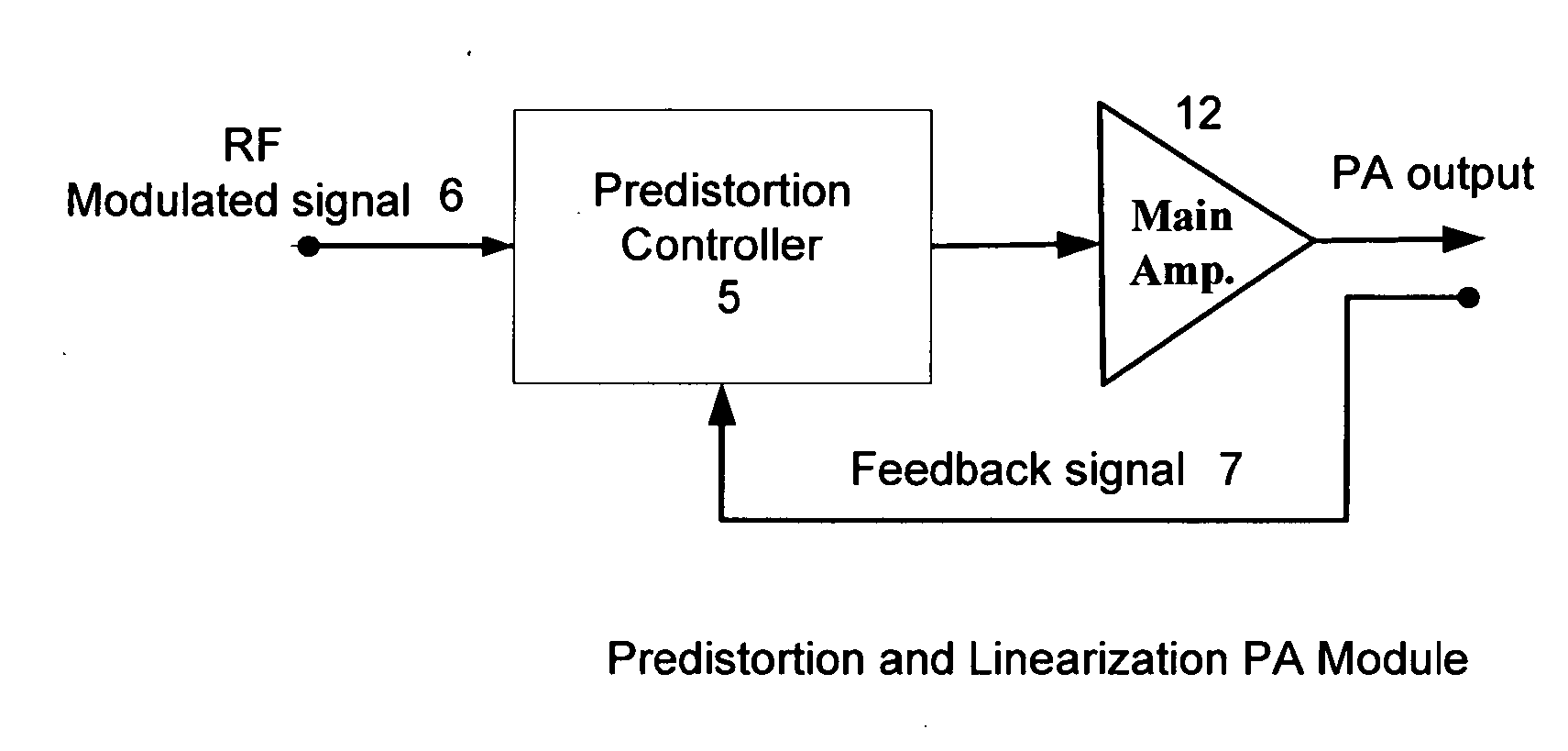

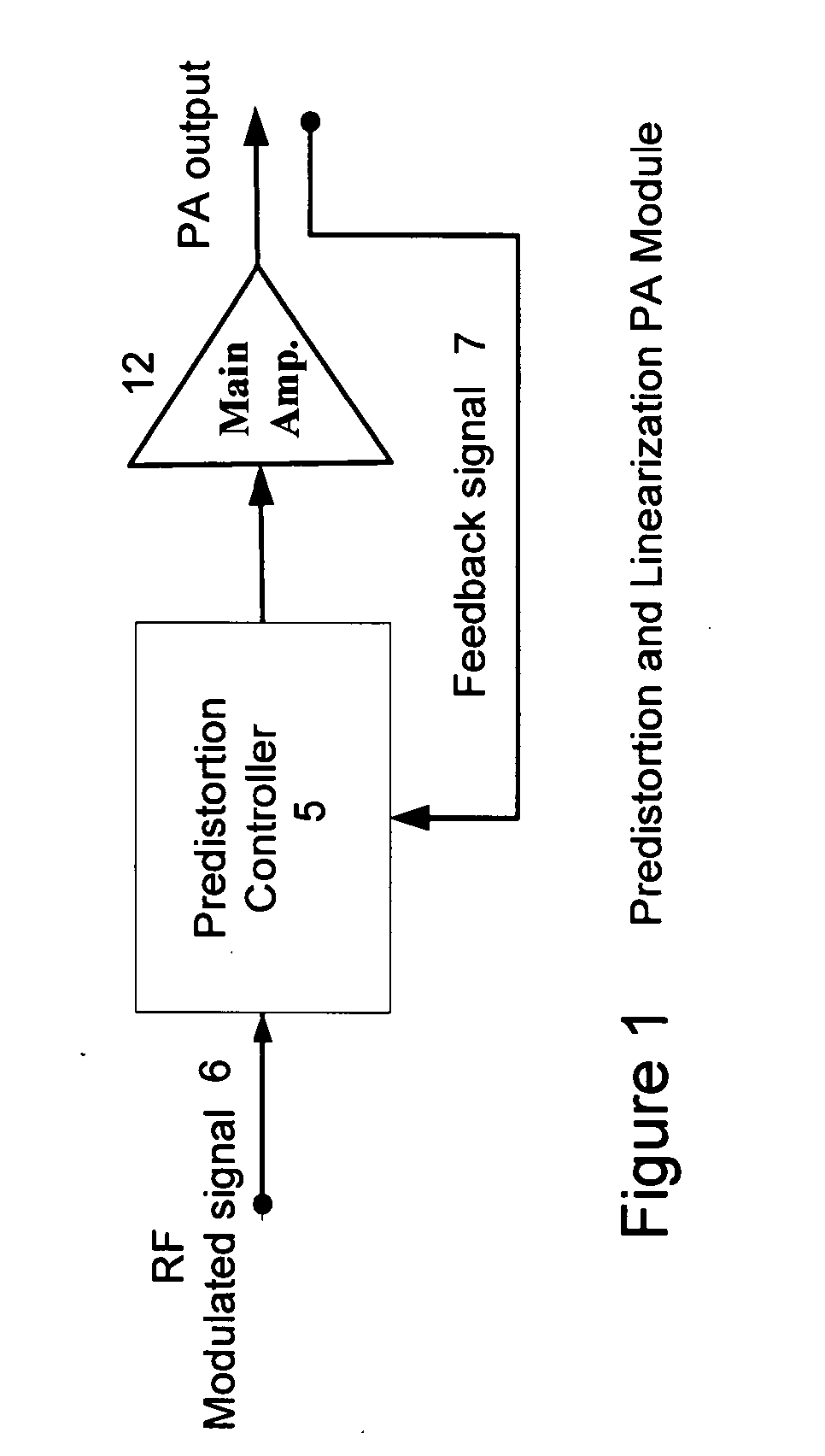

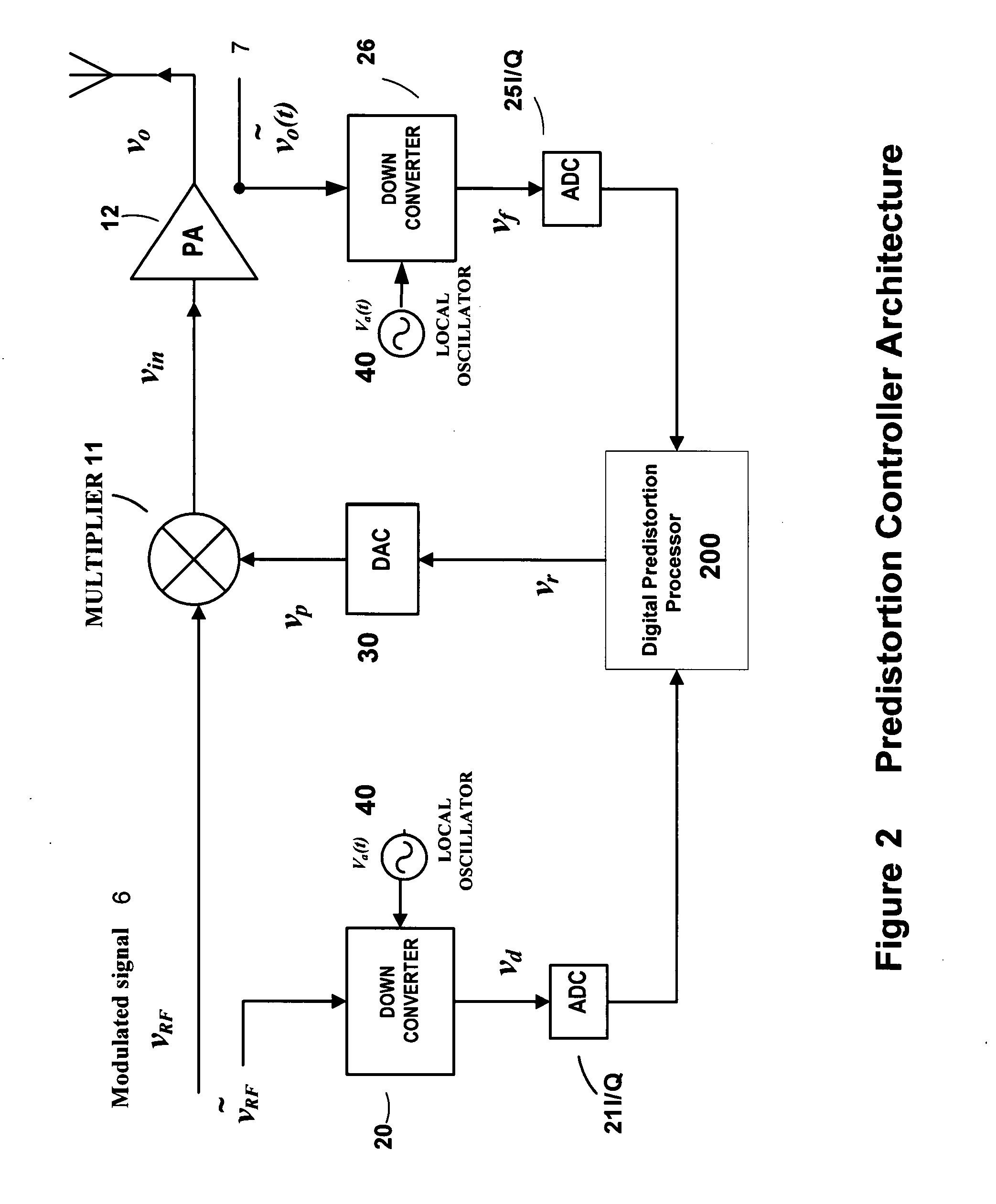

High efficiency linearization power amplifier for wireless communication

ActiveUS20070241812A1Improve efficiencyImprove linearityEnergy efficient ICTAmplifier details to increase power/efficiencyFrequency changerControl signal

An embodiment of the invention uses a predistortion correction signal to combination the modulated RF signal by an analog multiplier for linearization of power amplifiers having nonlinear characteristics such as those used in wireless RF transmitters. A predistortion controller comprises a plurality of down converters for retrieving both the ideal non-distorted information and the feedback distorted information, together with pre-stored digitally-indexed predistortion information stored, for example, in a look-up table. The digitally-indexed information models nonlinear characteristics of the high power amplifier, and is stored prior to processing of pre-compensation in the power amplifier. When the predistortion information is combined with the modulated RF signal in the analog multiplier, the result is a substantially linear information transmission from the power amplifier. In an embodiment of the system, the modulated RF input signal and the feedback signal from PA output are down-converted, respectively, by analog devices, such as mixers, after which the analog intermediate frequency (IF) signals are digitized by analog-to-digital converters for digital predistortion correction processing, followed by predistortion processing performed by, for example, a DSP or FPGA chip to generate a digital correction control signal, which is then converted to an analog signal by a digital-to-analog converter, followed by combining the analog correction signal with the RF modulated input signal to yield the input to the power amplifier.

Owner:DALI WIRELESS

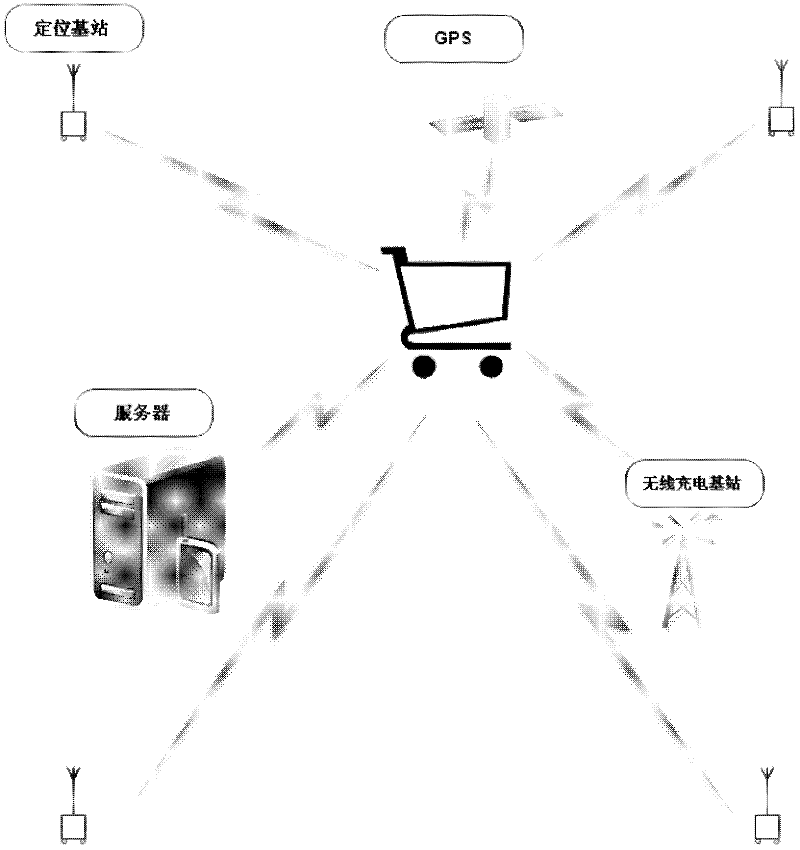

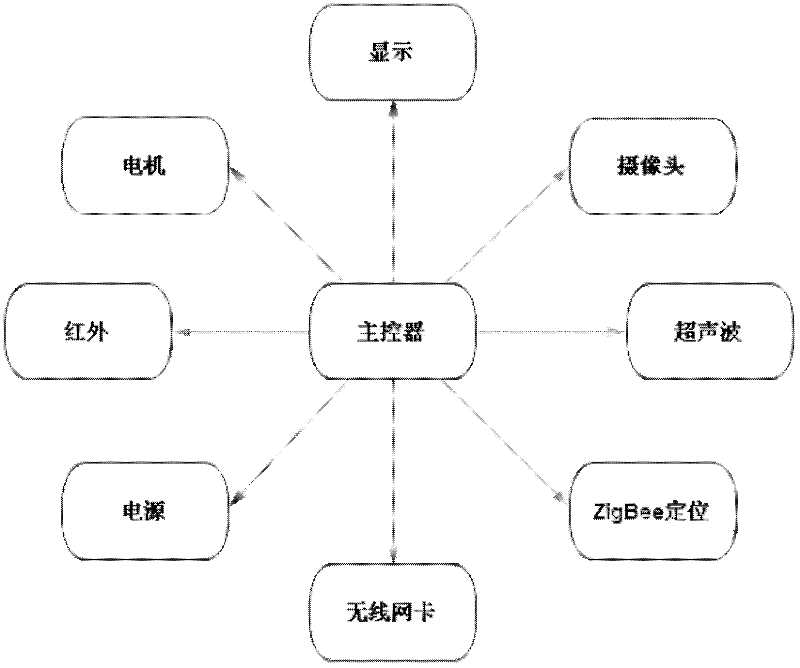

Intelligent trolley and application method thereof

ActiveCN102393739AImplement IntelliSenseAuto-adaptPosition/course control in two dimensionsHand cart accessoriesDigital signal processingAutomatic control

The invention discloses an intelligent trolley and belongs to the field of embedded type application and automatic control. Most trolleys used in the supermarkets at present are traditional manual trolley, and only certain additional functions are added at most. The intelligent trolley is hereinafter referred to as the trolley; the trolley comprises a main controller, a wireless module, a power supply, at least two anticollision sensors, a motor, a touch screen, an electronic label card reader and a camera, wherein the wireless module, the power supply, the at least two anticollision sensors, the motor, the touch screen, the electronic label card reader and the camera are respectively connected with the main controller; the main controller adopts one or the combination of two of an ARM (Advanced RISC Machines) processor, an FPGA (Field Programmable Gate Array) chip and a DSP (Digital Signal Processing) chip; the position of a handle of the trolley is defined to be at the rear end; the bottom part of a basket of the trolley is provided with the main controller, the wireless module and the power supply; the power supply is a pluggable or wireless charging battery module; and two wheels at the rear end of the trolley are directional wheels driven by the motor, and two wheels at the front end of the trolley are universal wheels. The intelligent trolley is a trolley with functions of intelligent sensing and automatic tracking.

Owner:广东微科商用机器有限公司

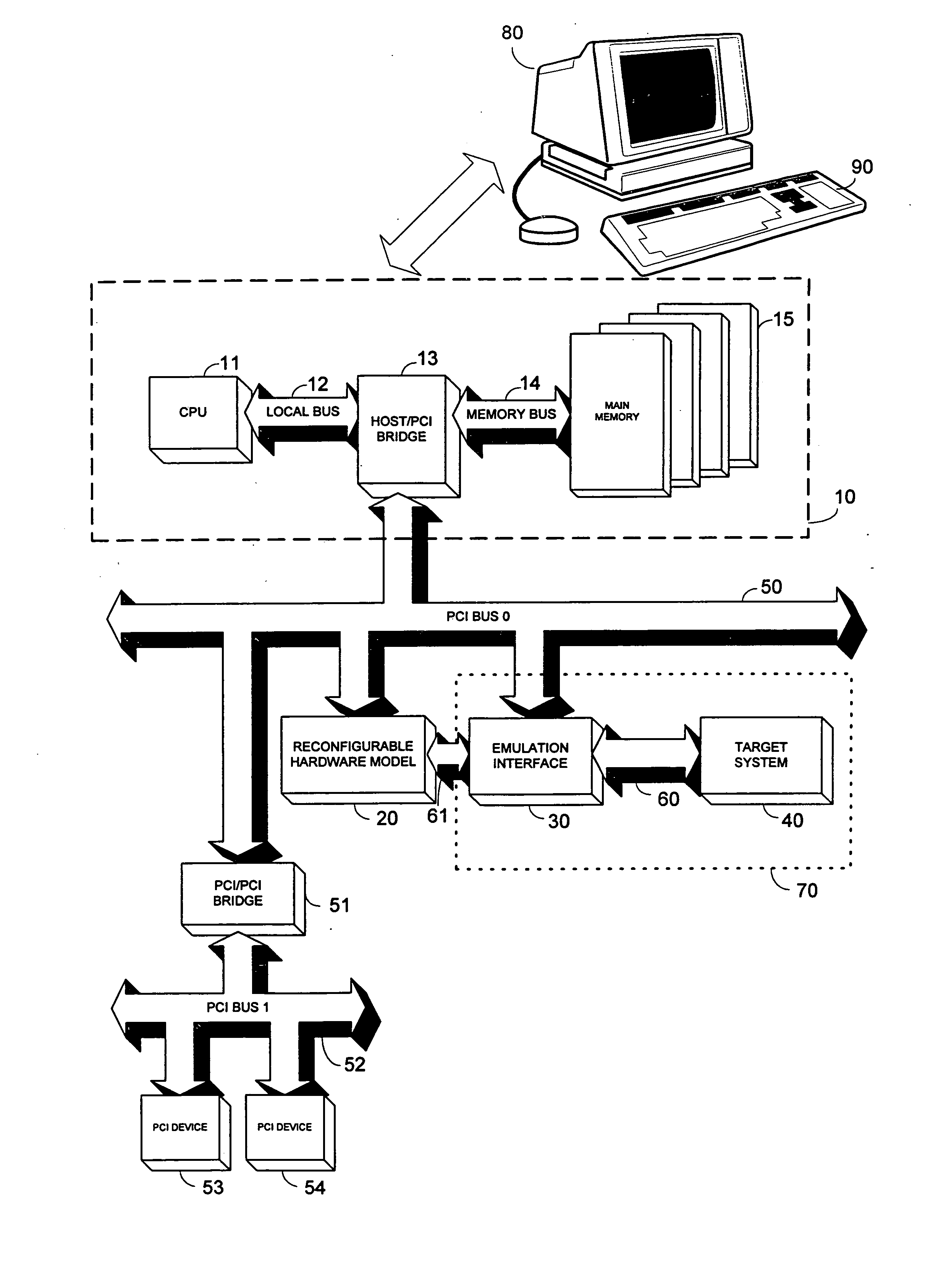

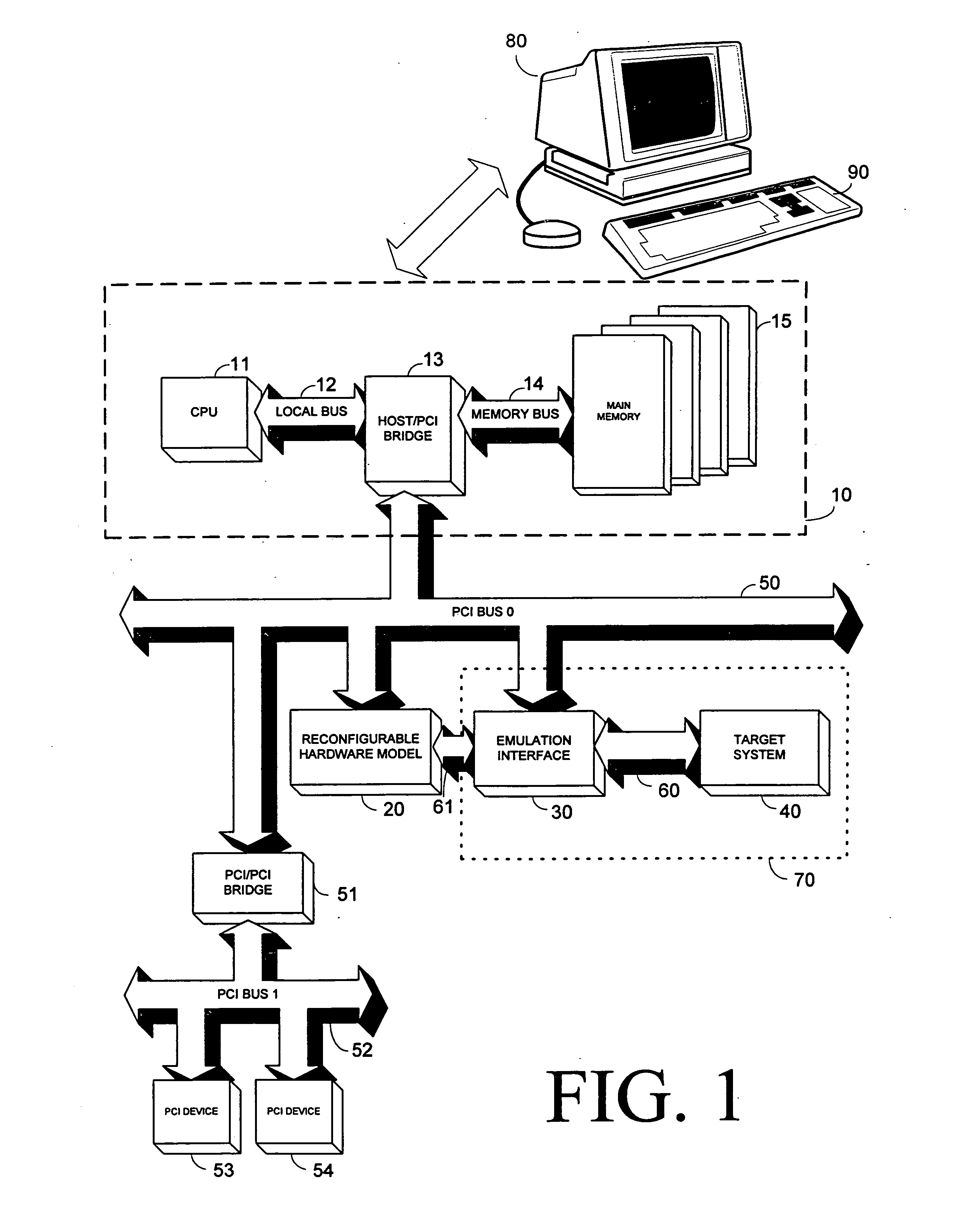

Inter-chip communication system

InactiveUS20050102125A1Decrease in performanceMultiple digital computer combinationsCAD circuit designData packCommunications system

Owner:CADENCE DESIGN SYST INC

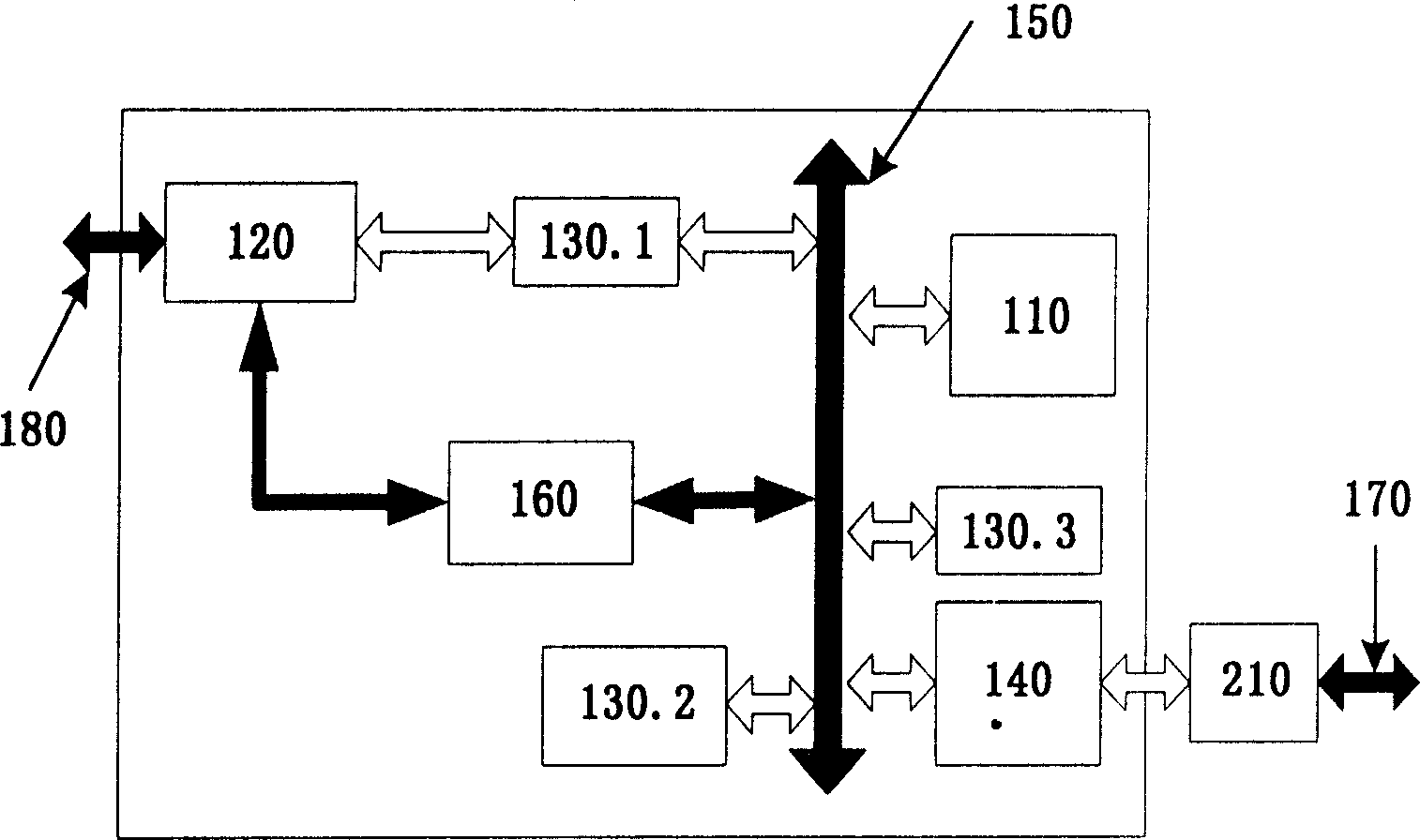

Inter-chip communication system

InactiveUS7512728B2Decrease in performanceMultiple digital computer combinationsCAD circuit designCommunications systemPacket scheduling

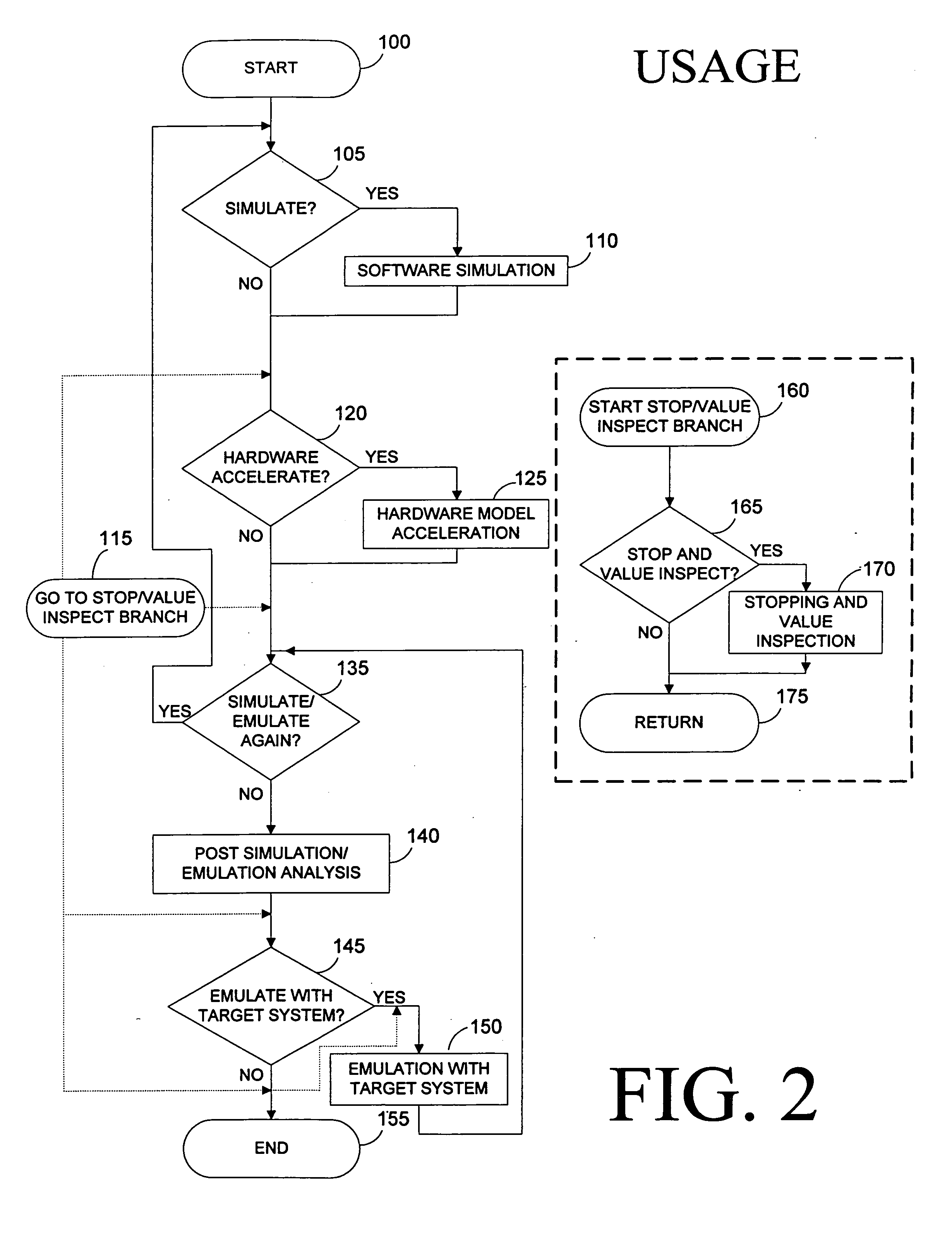

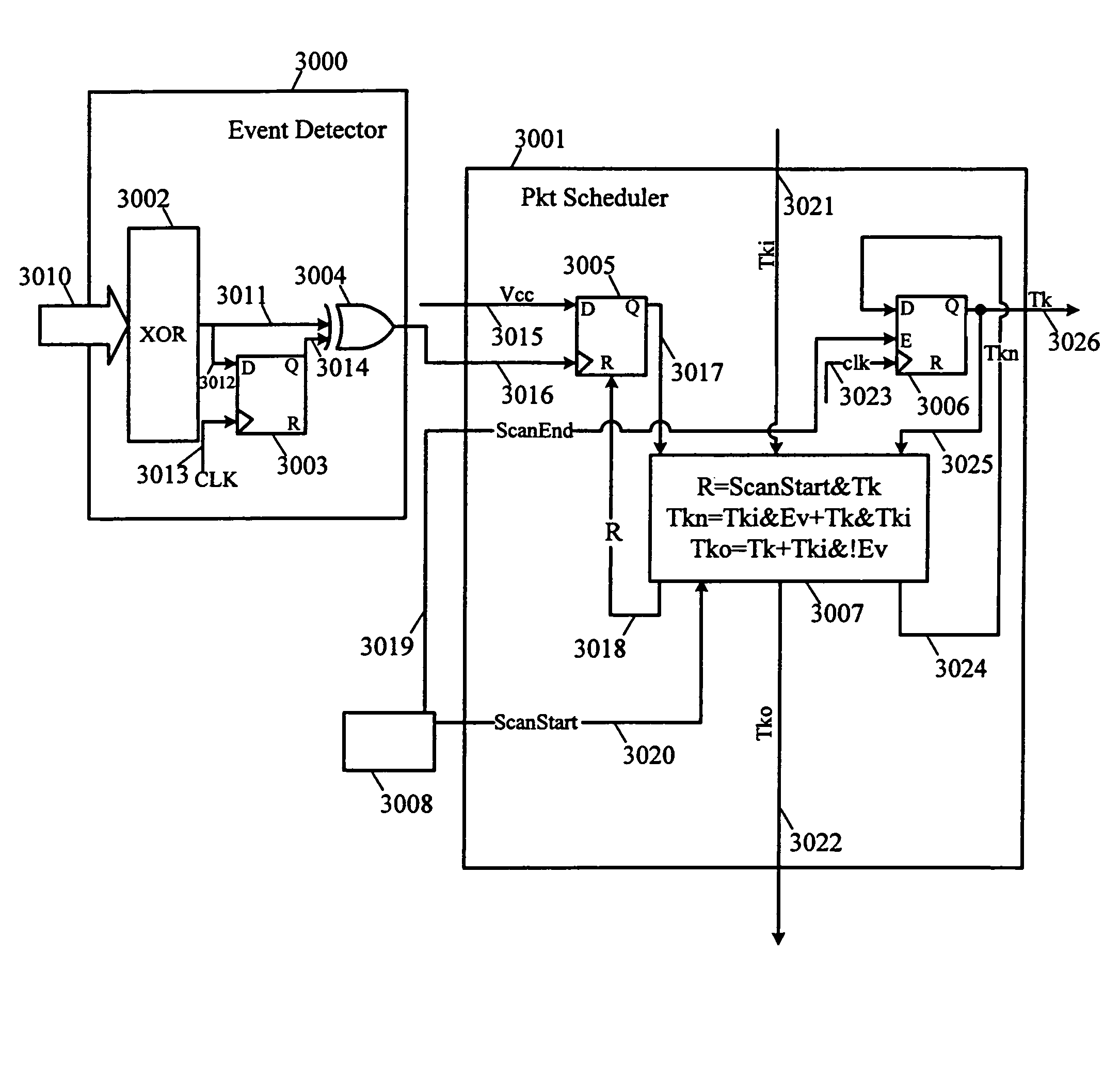

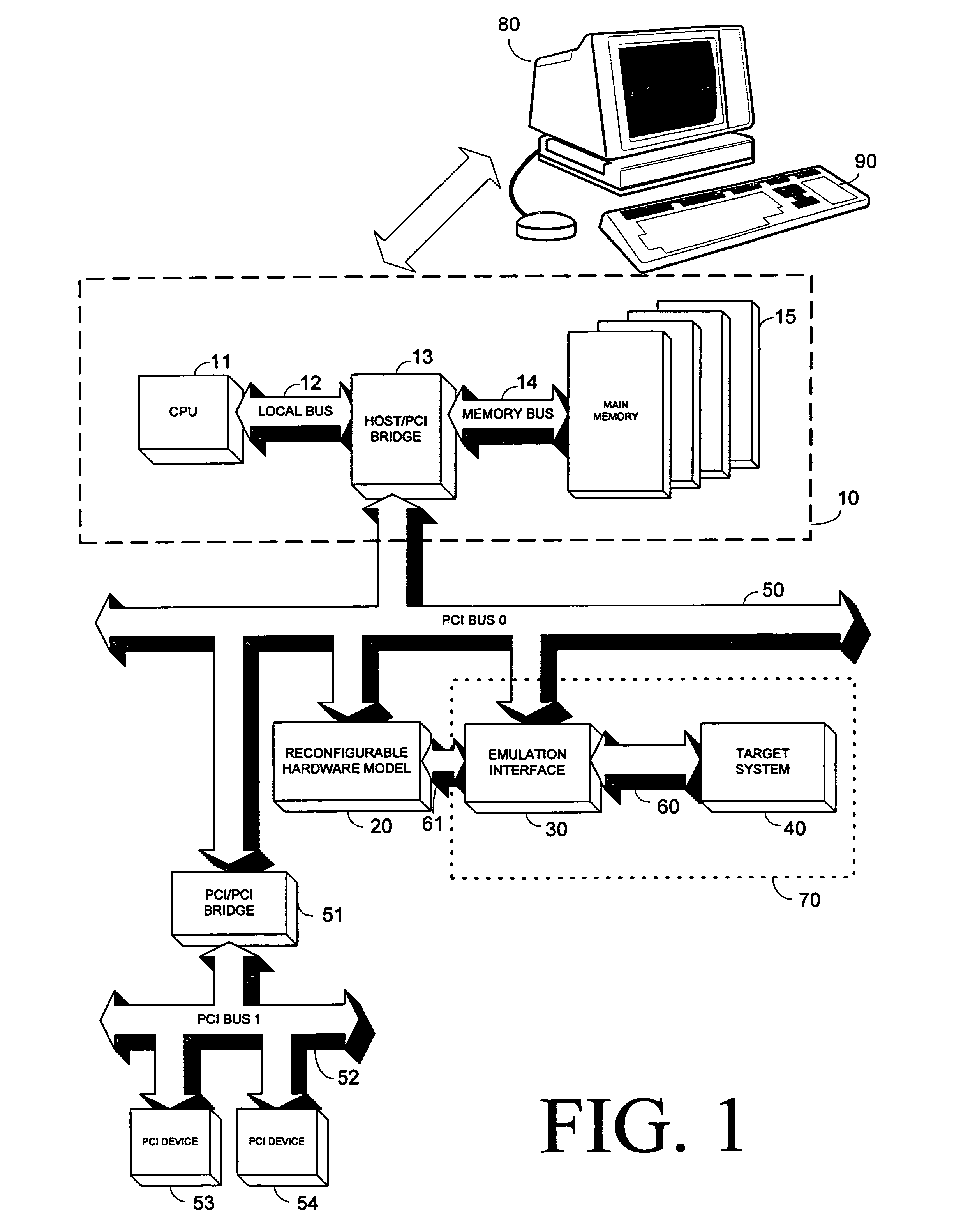

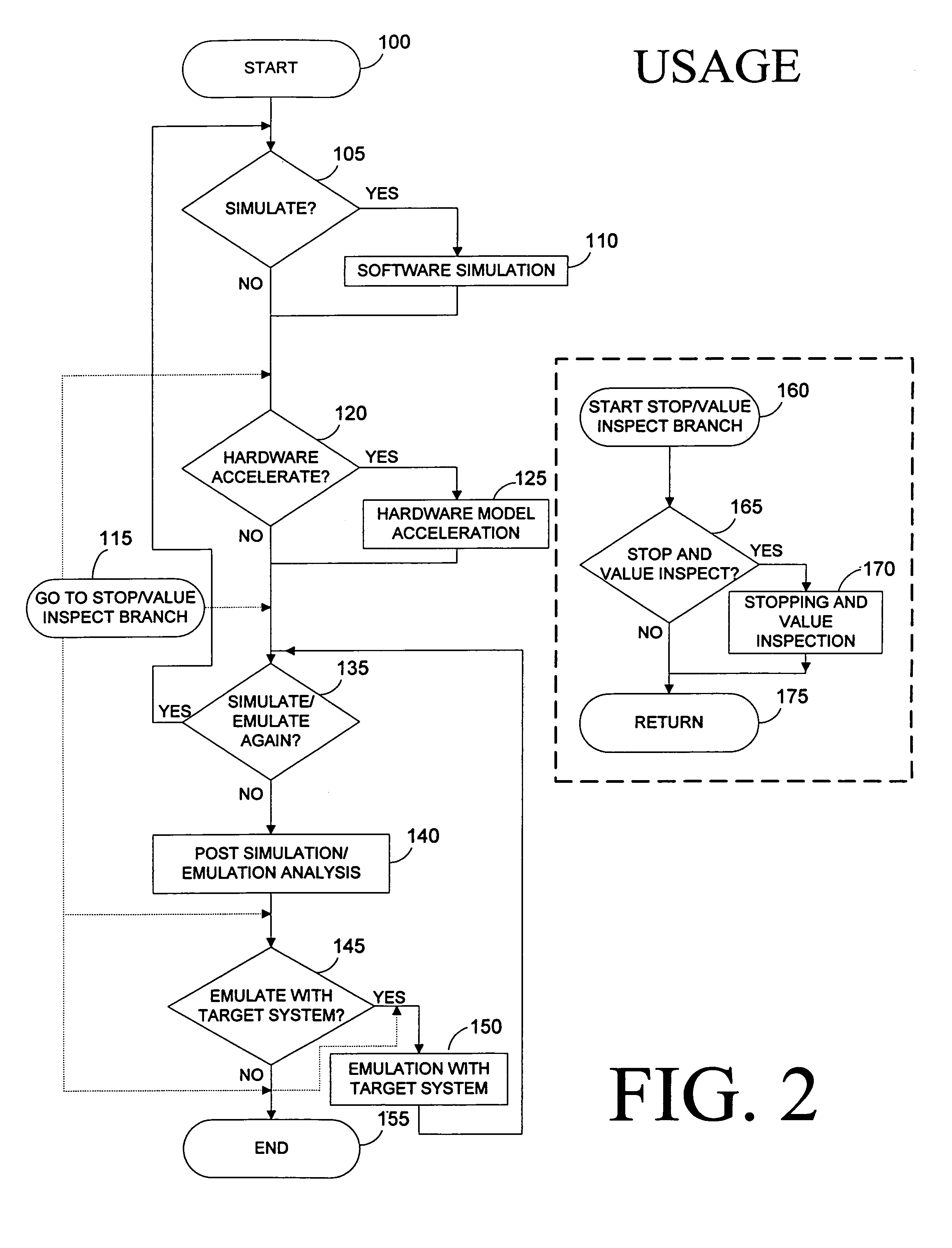

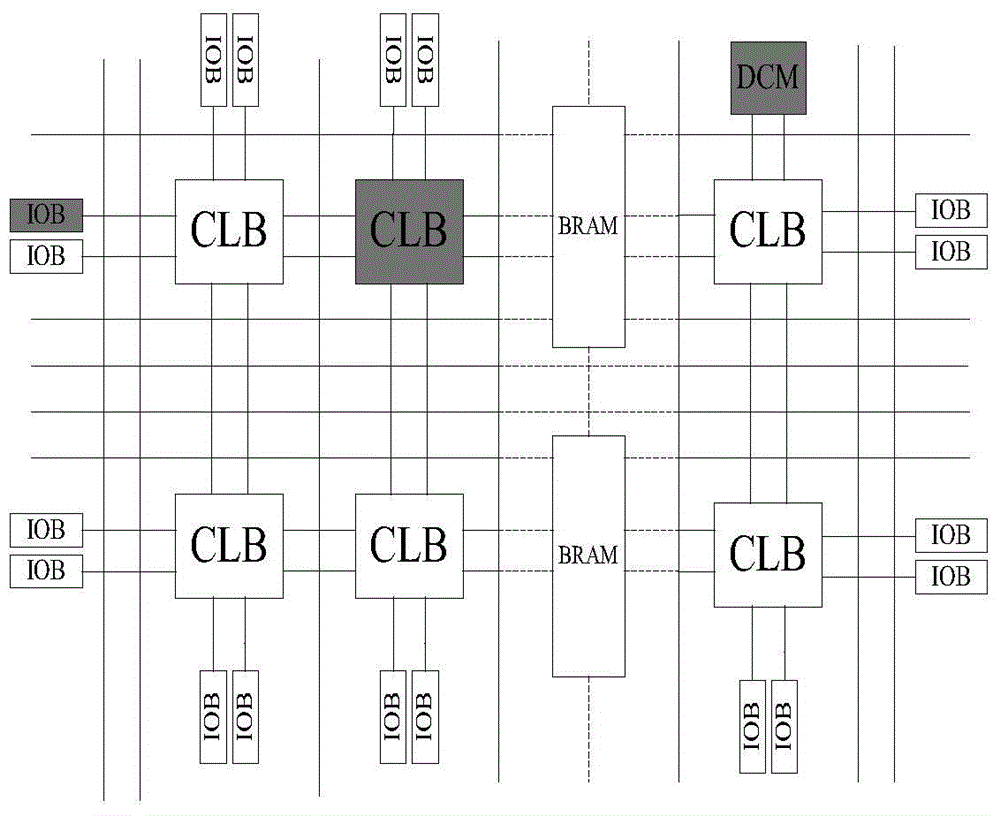

The complexity of user designs, the limited capacity of FPGA chips, and the limited number of chip pinouts have resulted in the development of inter-chip communication technology that necessitates the transfer of a large amount of data across a limited number of pins in the shortest amount of time. The inter-chip communication system transfers signals across FPGA chip boundaries only when these signals change values. Thus, no cycles are wasted and every event signal has a fair chance of achieving communication across chip boundaries. The inter-chip communication system includes a series of event detectors that detect changes in signal values and packet schedulers which can then schedule the transfer of these changed signal values to another designated chip. Working with a plurality of signal groups that represents signals at the separated connections, the event detector detects events (or changes in signal values). When an event has been detected, the event detector alerts the packet scheduler. The packet scheduler employs a token ring scheme as follows. When the packet scheduler receives a token and detects an event, the packet scheduler “grabs” the token and schedules the transmission of this packet in the next packet cycle. If, however, the packet scheduler receives the token but does not detect an event, it will pass the token to the next packet scheduler. At the end of each packet cycle, the packet scheduler that grabbed the token will pass the token to the next logic associated with another packet.

Owner:CADENCE DESIGN SYST INC

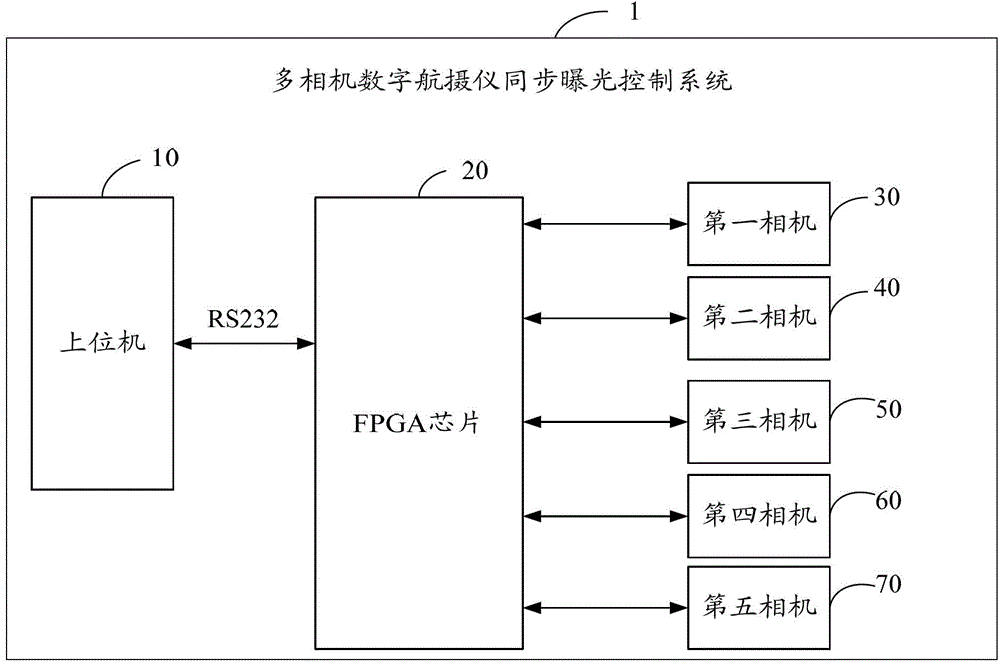

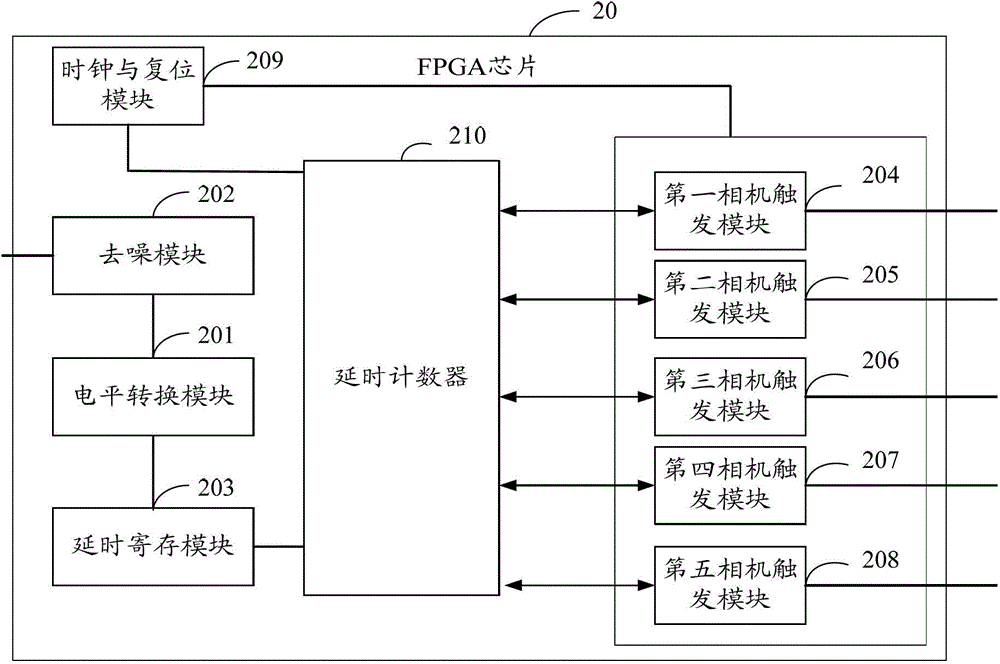

System and method for controlling multi-cameral digital aerial photographic camera synchronous exposure

InactiveCN103338334ALower trigger asyncSynchronized Exposure ControlAircraft componentsTelevision system detailsElectricityPhotographic camera

The invention discloses a system and a method for controlling a multi-cameral digital aerial photographic camera synchronous exposure. The system comprises an upper computer, an FPGA (Field-programmable Gate Array) chip as well as a first cameral, a second cameral, a third camera, a fourth camera and a fifth camera which are electrically connected with the FPGA chip, and the upper computer is in communication connection with the series port of the FPGA chip. The method comprises the steps as follows: receiving and pre-treating exposure signals; analyzing the exposure characteristics of different cameras and obtaining time sequence relation; regulating the time sequence of exposure signals according to the time sequence relation; outputting five types of controllable pulse triggering signals in a counting delay triggering way; triggering and controlling the first camera, the second camera, the third camera, the fourth camera and the fifth camera to synchronously execute exposure operation. The system and the method, provided by the invention, ensure the image synchronization precision of the exposure time of the multiple cameras.

Owner:CHINA TOPRS TECH

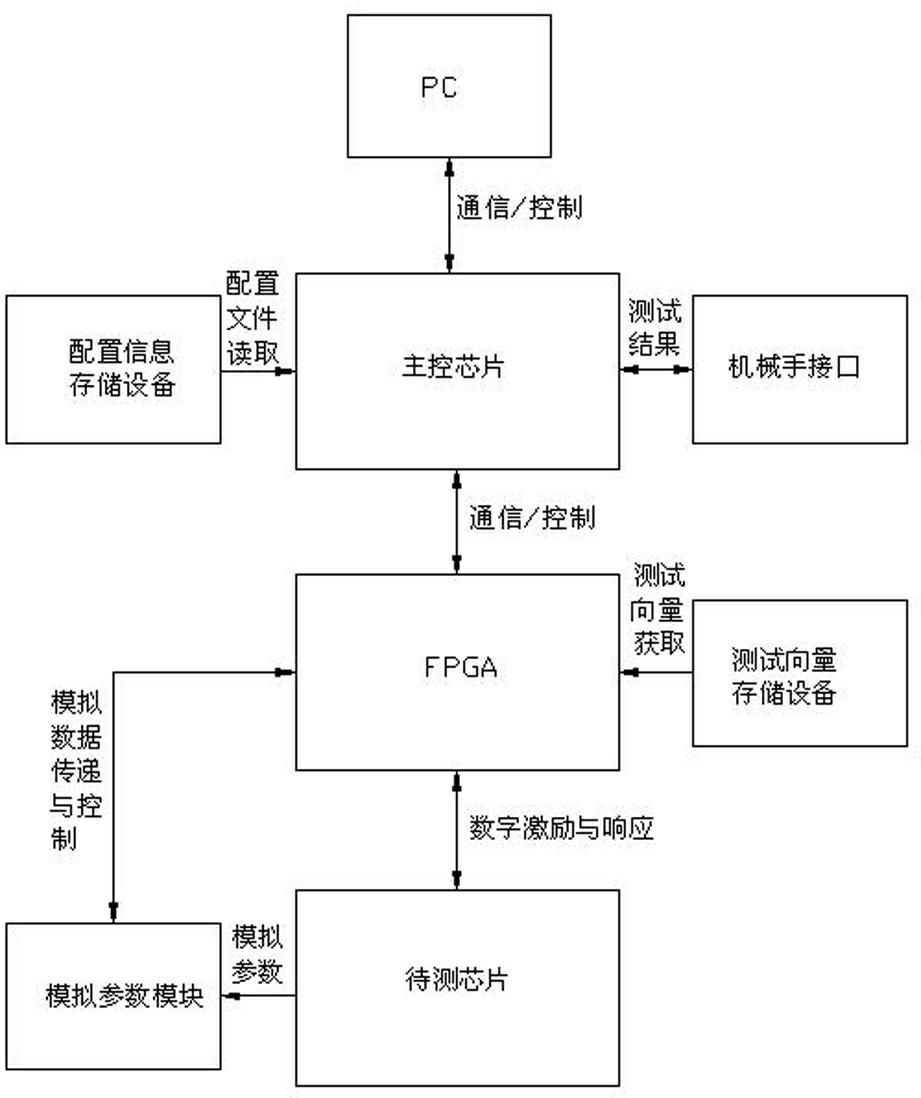

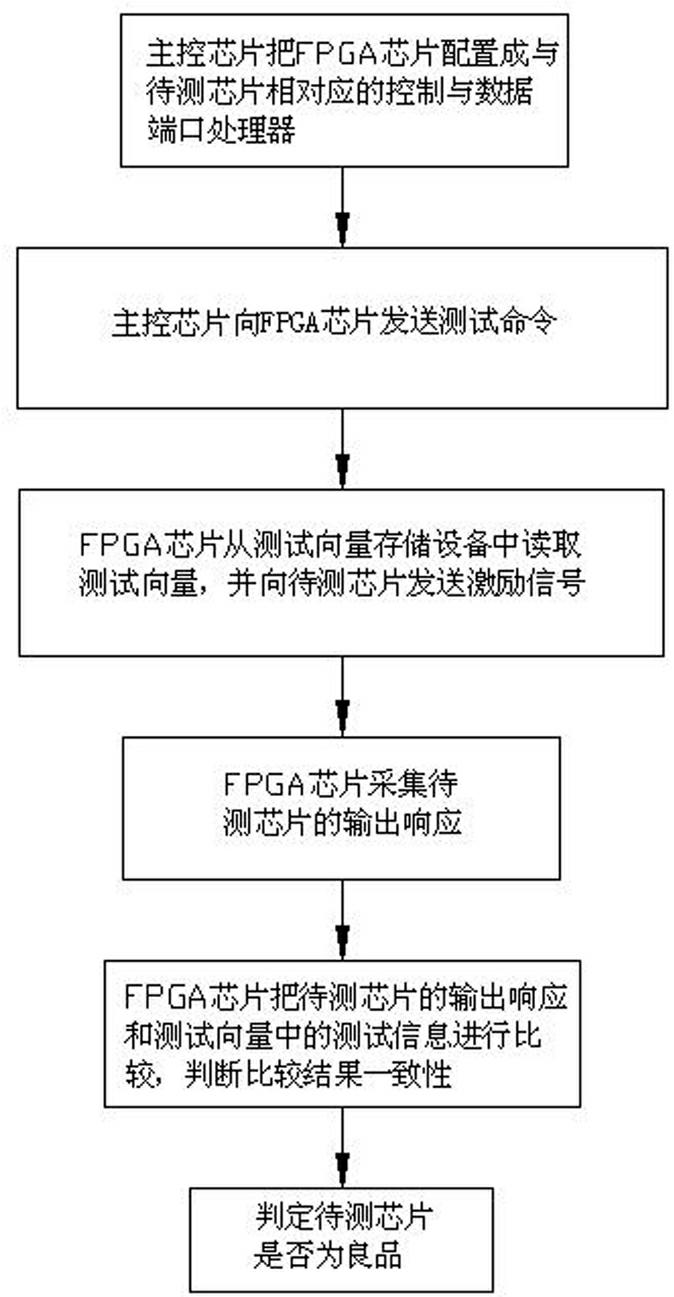

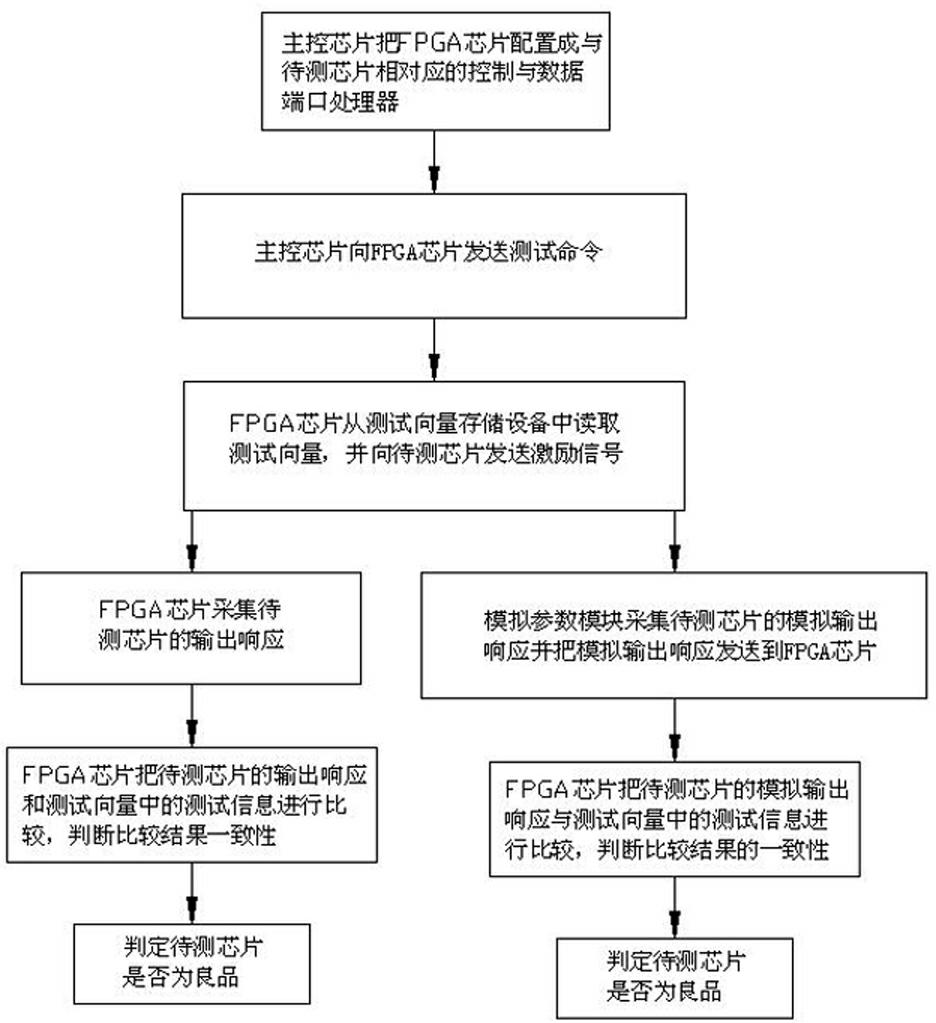

Field programmable gate array (FPGA)-based integrated circuit chip testing system and method

The invention discloses a field programmable gate array (FPGA)-based integrated circuit testing system, and a method for testing a digital-analog hybrid integrated circuit chip provided with a digital module or using a digital module as a main module and provided with a few analog modules by using the testing system. The system mainly comprises a personal computer (PC) machine, a main control chip, a FPGA chip, configuration information storage equipment and testing vector storage equipment. The testing method is implemented by the following steps that: the main control chip configures the FPGA chip, the main control chip sends a testing command to the FPGA chip, the FPGA chip sends an excitation signal to a chip to be tested and acquires the output response of the chip to be tested, or the analog parameter module acquires analog output response, the FPGA chip compares the output response or the analog output response of the chip to be tested with the testing information and judges the consistency of the output response and the testing information, and the chip to be tested is an accepted product or a defective product is judged. The system and the method can be widely applied in the field of integrated circuit chip test.

Owner:建荣集成电路科技(珠海)有限公司

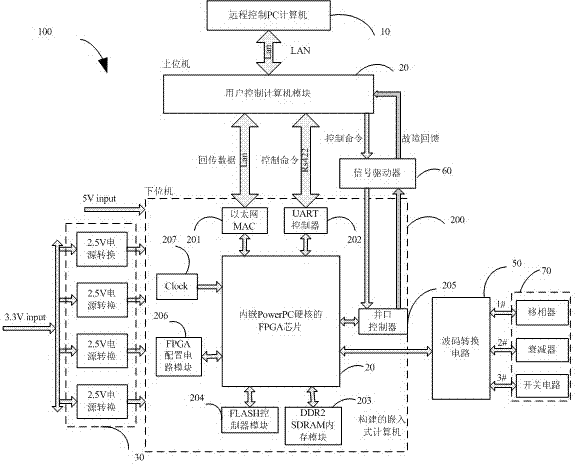

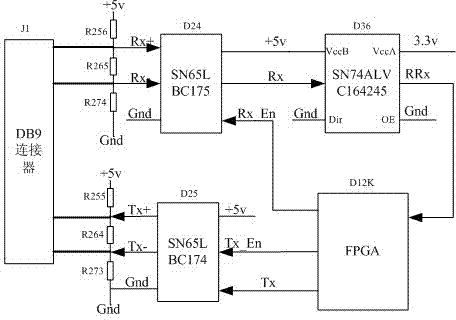

Phased array radar antenna beam control device

ActiveCN102495565AImprove reliabilityMeet developmentProgramme controlWave based measurement systemsDouble data rateUniversal asynchronous receiver/transmitter

The invention relates to a phased array radar antenna beam control device. The phased array radar antenna beam control device comprises a remote control PC (Personal Computer) computer, a user control computer module, a power supply management module, a FPGA (Field Programmable Gate Array) chip, a signal driver, a wave control conversion circuit and a controlled device which is electrically connected with the wave control conversion circuit, wherein the user control computer module remotely communicates with the remote control PC computer and are electrically connected with the FPGA chip, thepower supply management module and the wave control conversion circuit, respectively. The FPGA chip is embedded with a PowerPC hardcore and used for constructing an embedded computer; the embedded computer also comprises an Ethernet (Media Access Control), a UART (Universal Asynchronous Receiver Transmitter) controller, a DDR2SDRAM (Double Data Rate 2 Synchronous Dynamic Random Access Memory) memory module, a FLASH controller module, a parallel controller, a FPGA configuration circuit module and a clock generating circuit module. The phased array radar antenna beam control device provided by the invention has the advantage of high reliability.

Owner:CHINA ELECTRONIC TECH GRP CORP NO 38 RES INST

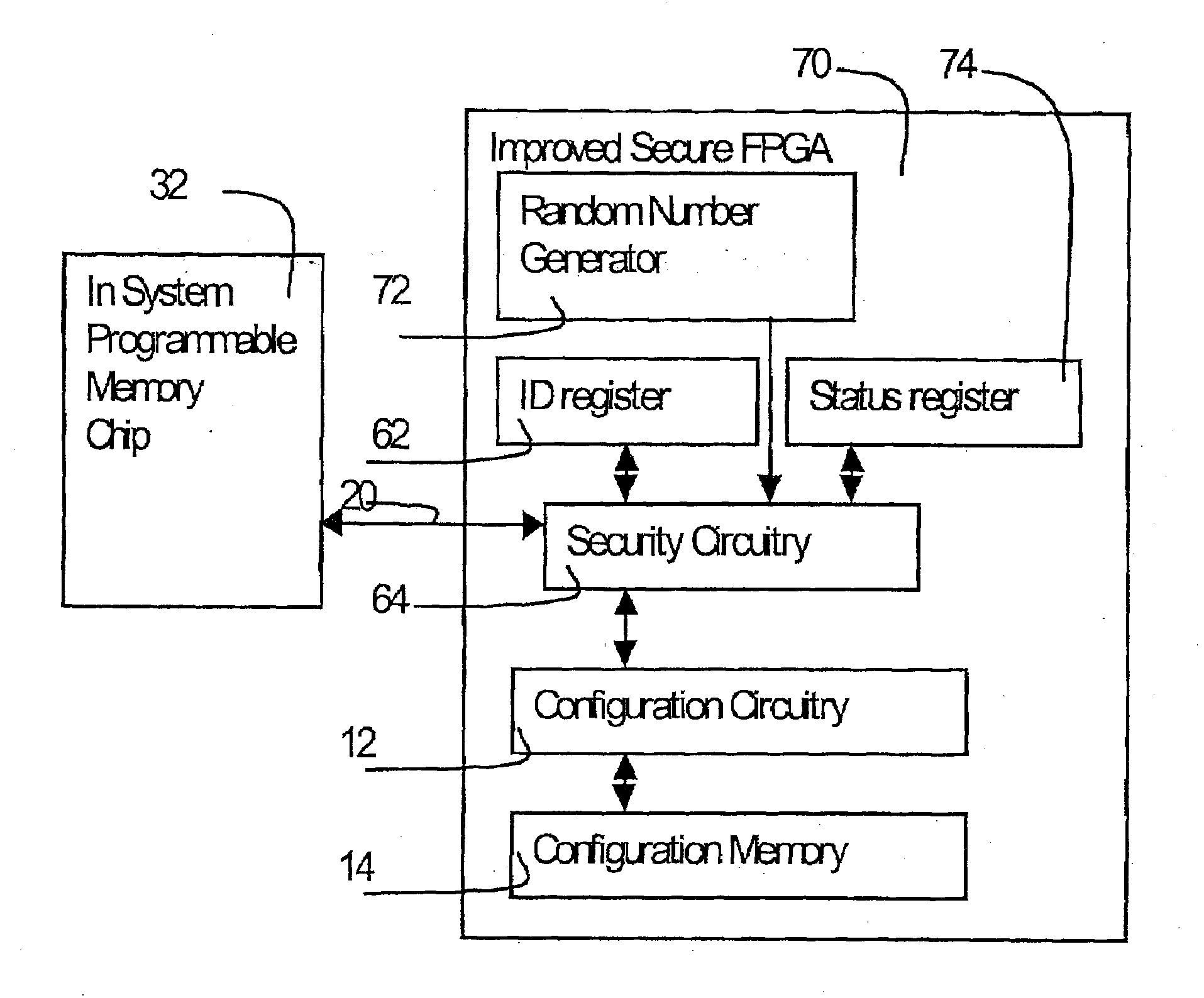

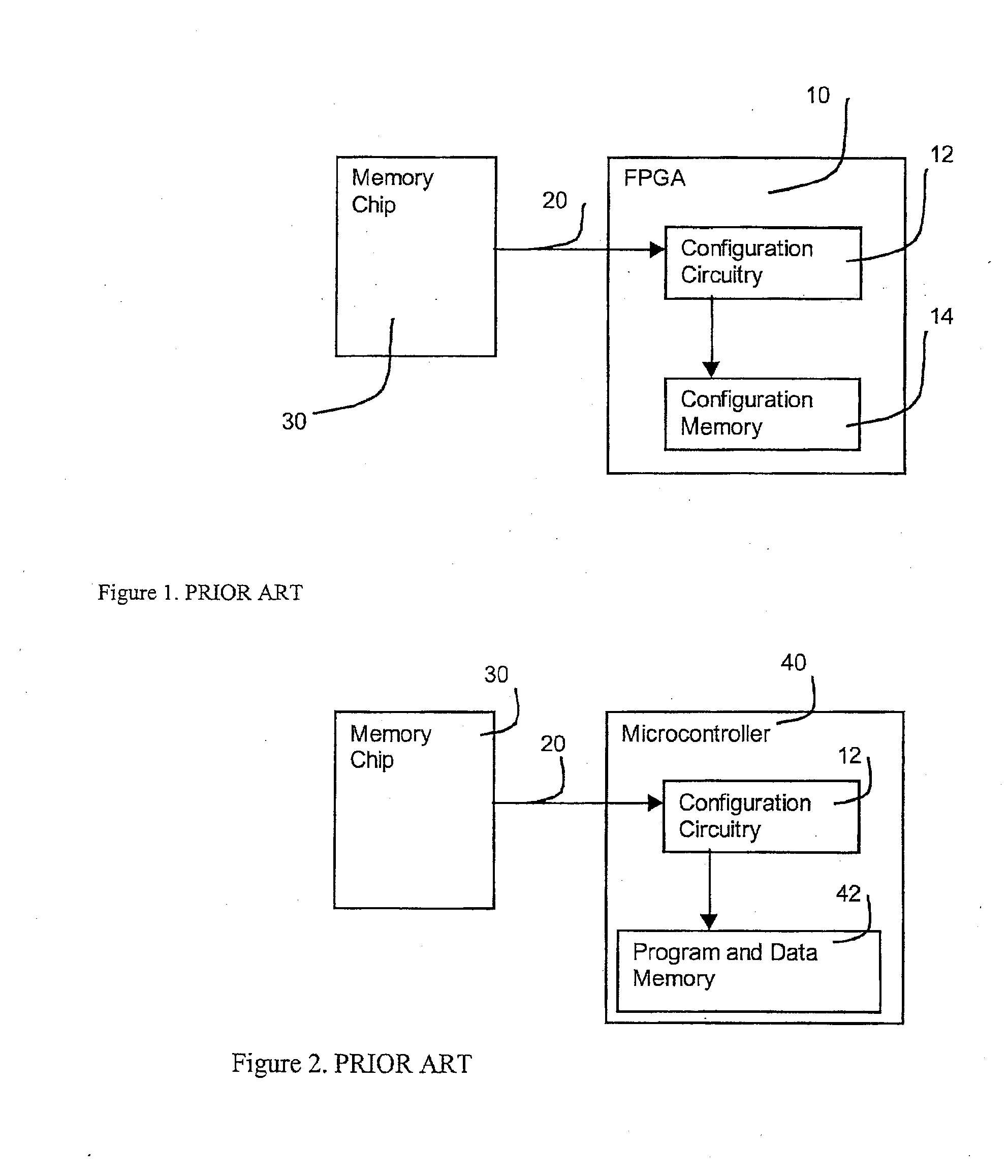

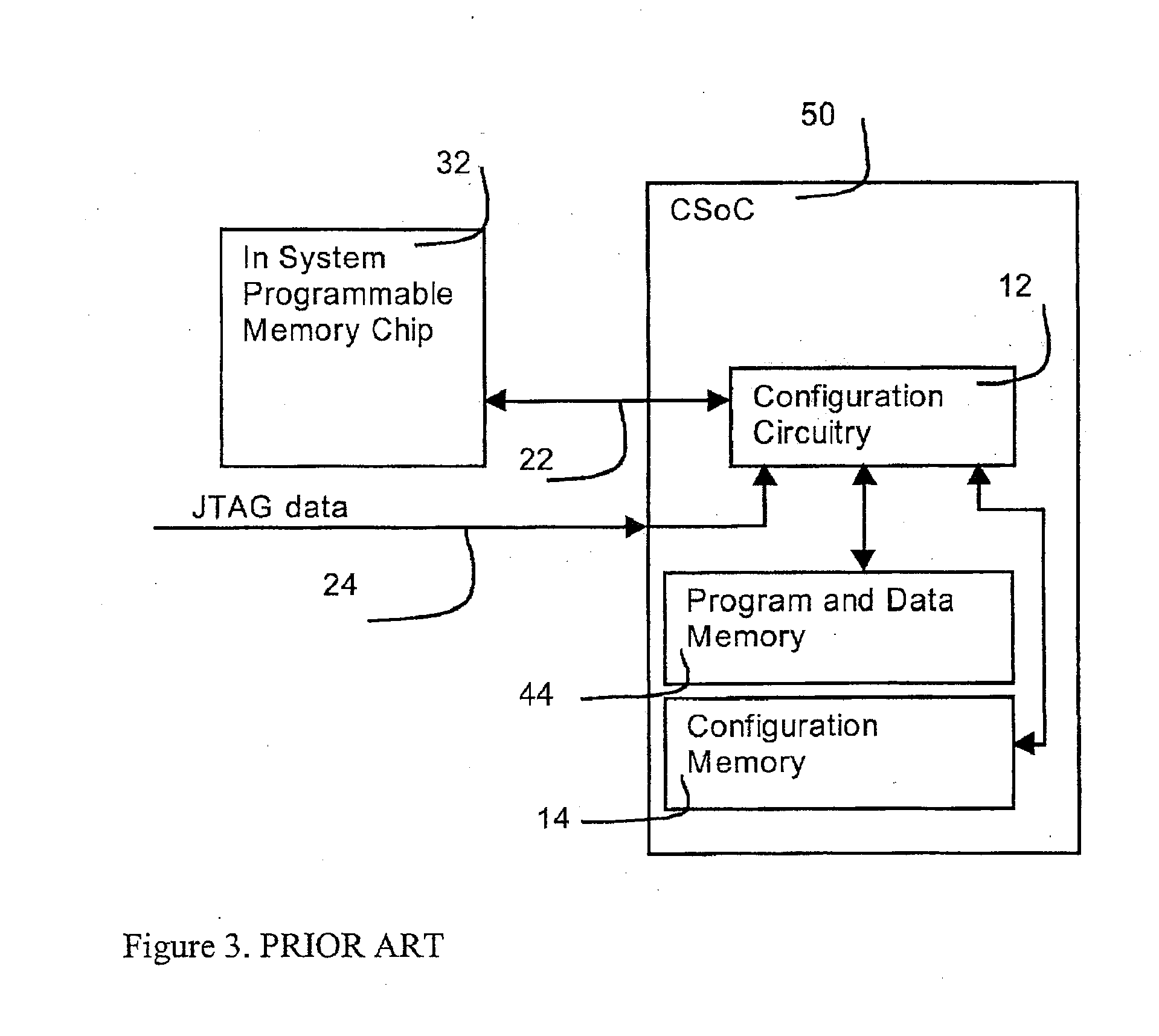

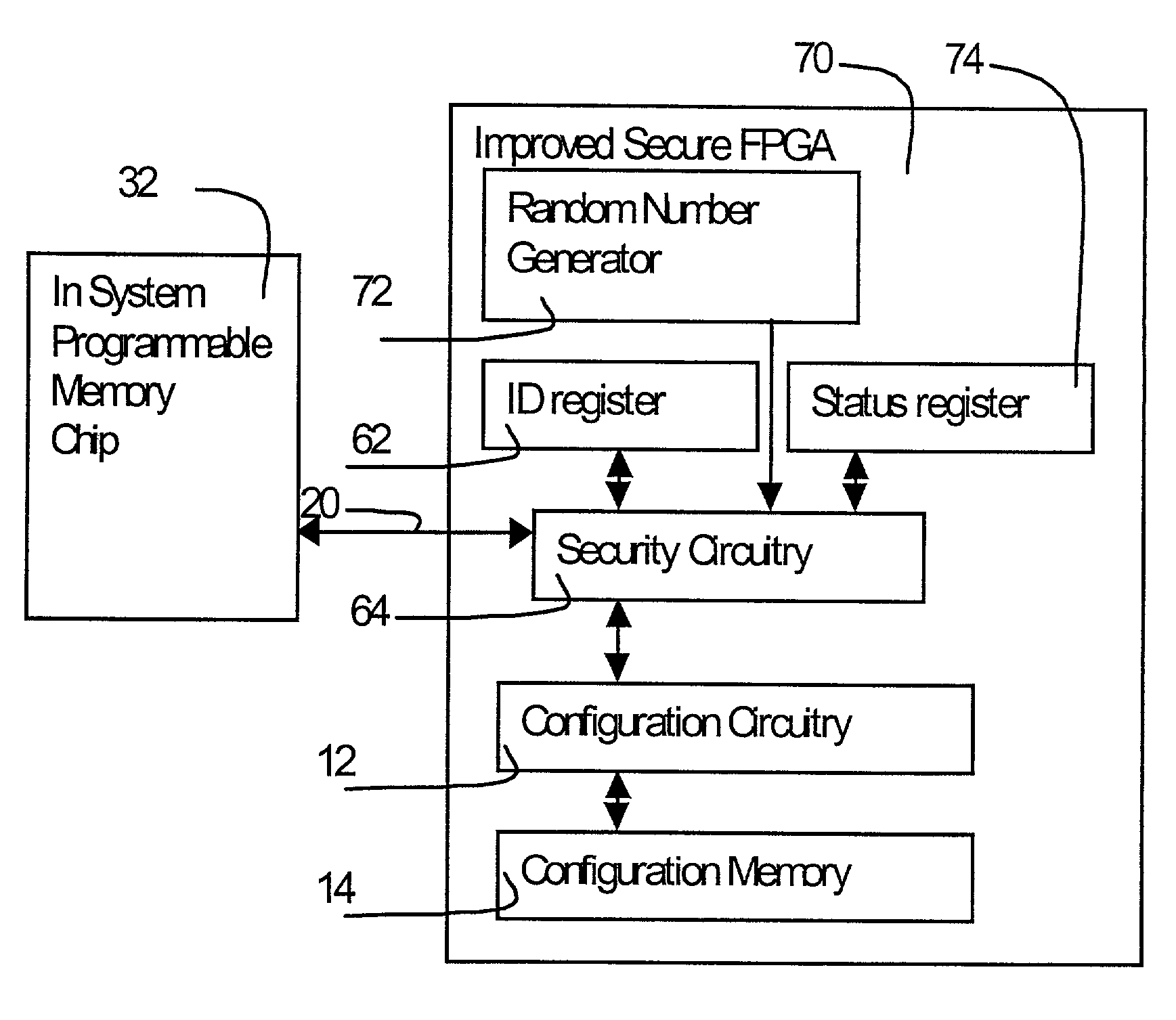

Method and Apparatus for Secure Configuration of a Field Programmable Gate Array

InactiveUS20070288765A1Provide securityPrevent removalUser identity/authority verificationUnauthorized memory use protectionFpga chipPhotomask

A field programmable gate array has security configuration features to prevent monitoring of the configuration data for the field programmable gate array. The configuration data is encrypted by a security circuit of the field programmable gate array using a security key. This encrypted configuration data is stored in an external nonvolatile memory. To configure the field programmable gate array, the encrypted configuration data is decrypted by the security circuit of the field programmable gate array using the security key stored in the artwork of the field programmable gate array. The secret key comprises a number of bits of key information that are embedded within the photomasks used in manufacture the FPGA chip.

Owner:ALGOTRONIX

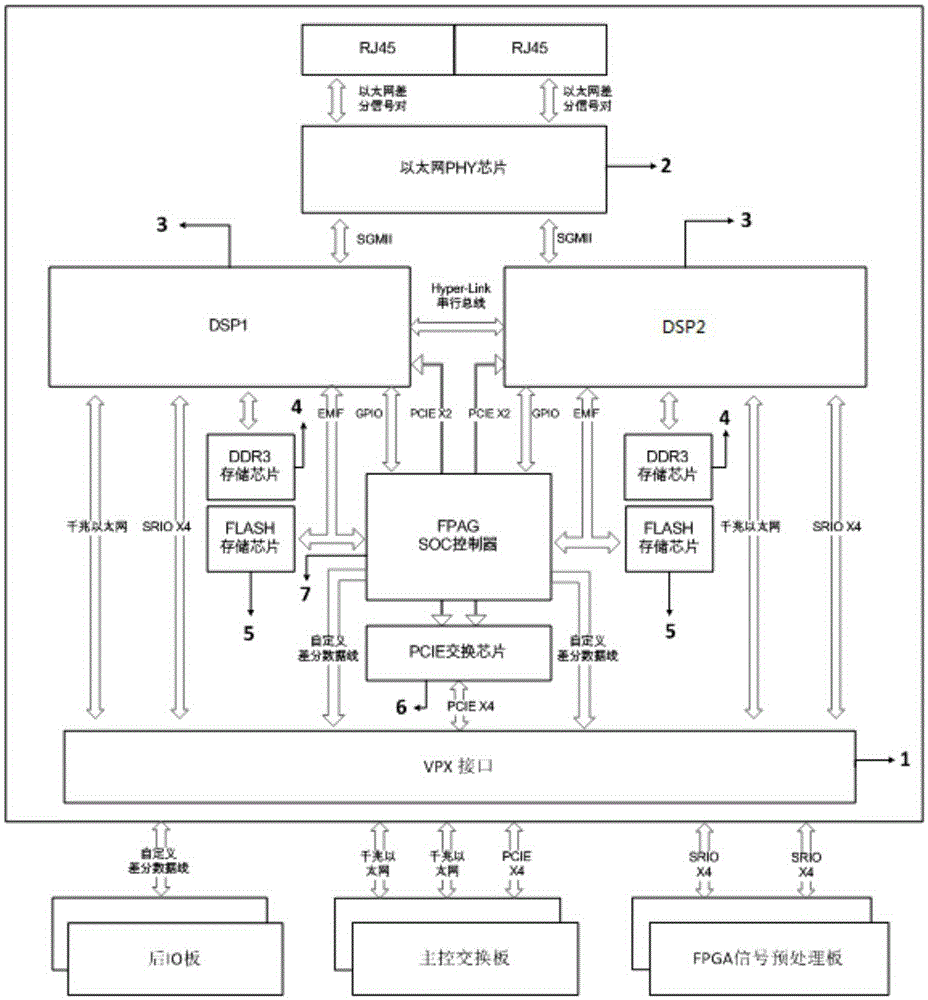

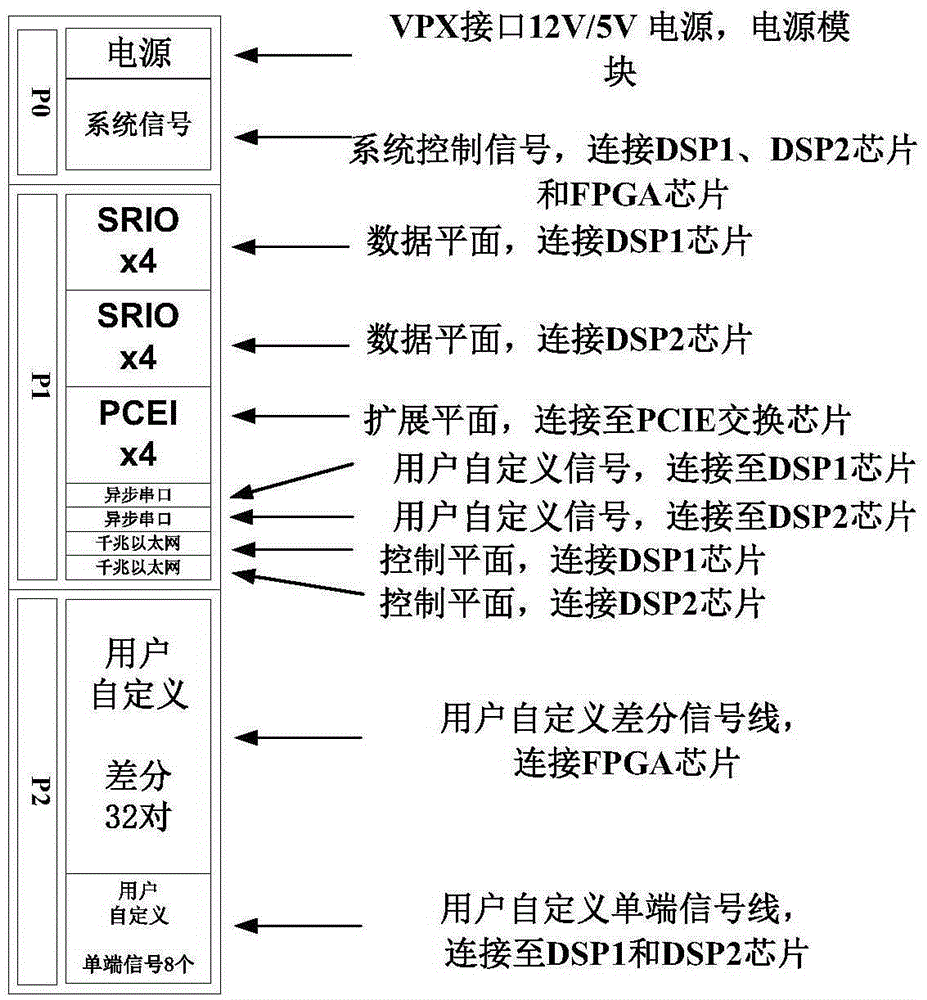

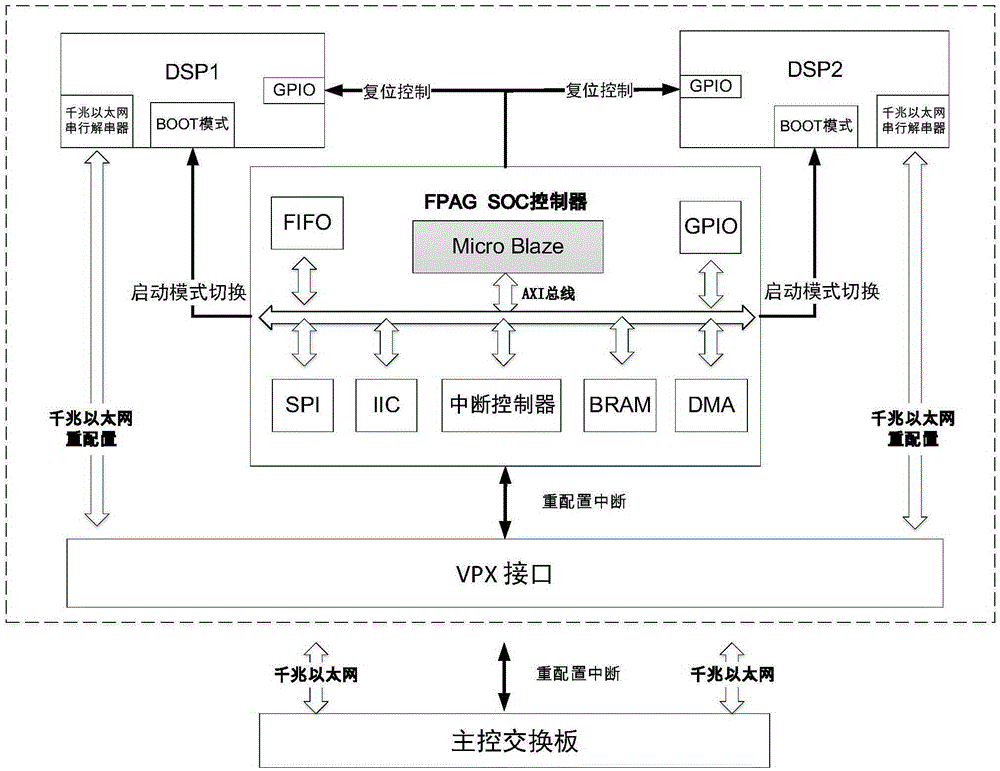

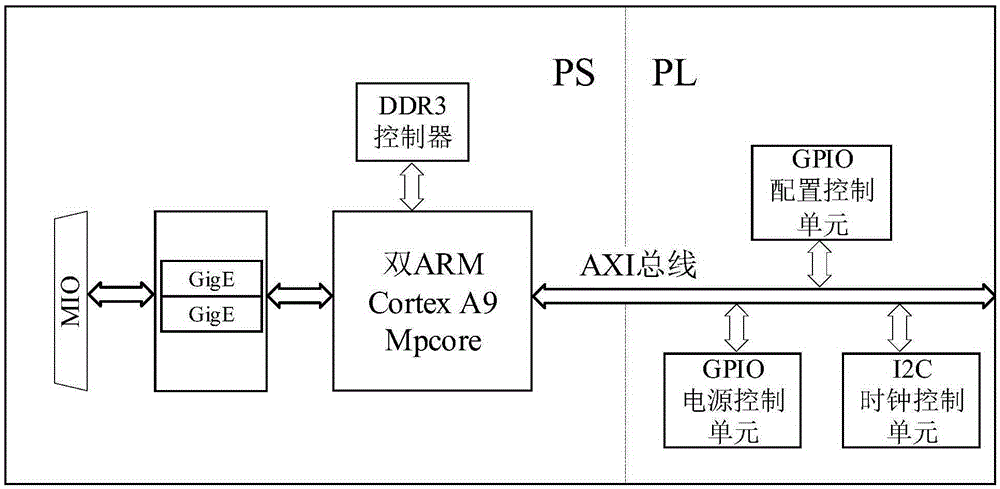

VPX parallel DSP signal processing board card based on SoC online reconstruction

InactiveCN105279133AIncrease flexibilityImprove real-time performanceDigital computer detailsElectric digital data processingDigital signal processingData signal

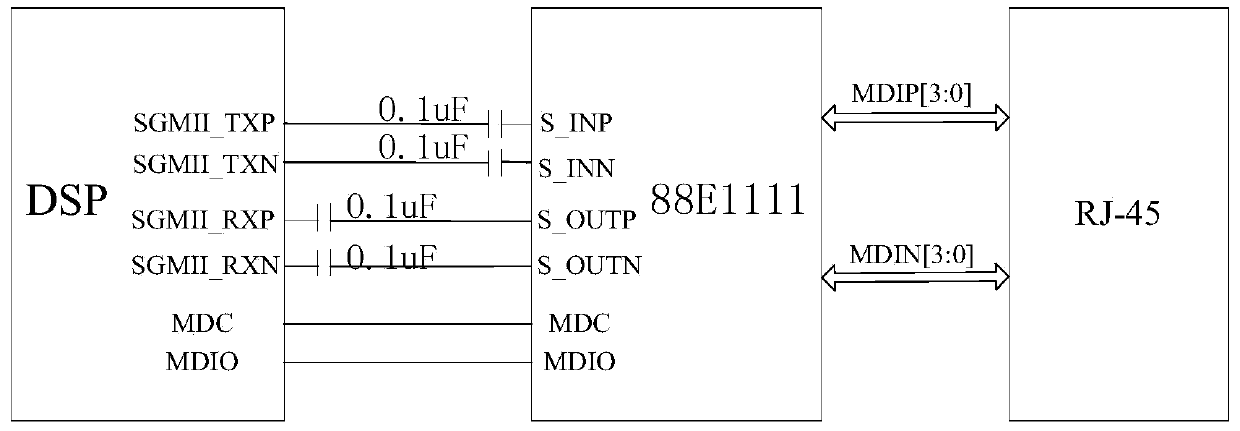

The invention discloses a VPX parallel DSP (Digital Signal Processing) board card based on SoC (System on a Chip) online reconstruction. An FPGA (Field Programmable Gate Array) chip is used as a board stage SoC controller; and two DSP chips are used as core operation chips of a DSP board card. During the practical configuration of the DSP chips, the FPGA chip used as the SoC controller can complete the dynamic re-configuration of work code by GE (Gigabit Ethernet) through the hardware resetting on the DSP and the switching on the starting mode; and the flexibility and the real-time performance during the DSP are greatly improved. The DSP chips receive two kinds of high-speed serial bus signals of SRIO (Serial Rapid Input Output) X4 and the GE transmitted through a VPX interface, repacking the transferred PCIE (Peripheral Component Interface Express) X2 high-speed serial bus signal through a PCIE exchange chip, and receives a data signal to be processed and a control instruction; or the DSP chips receive the GE protocol signal of a peripheral component through an RJ45 net port.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

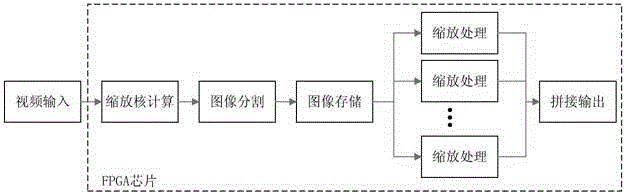

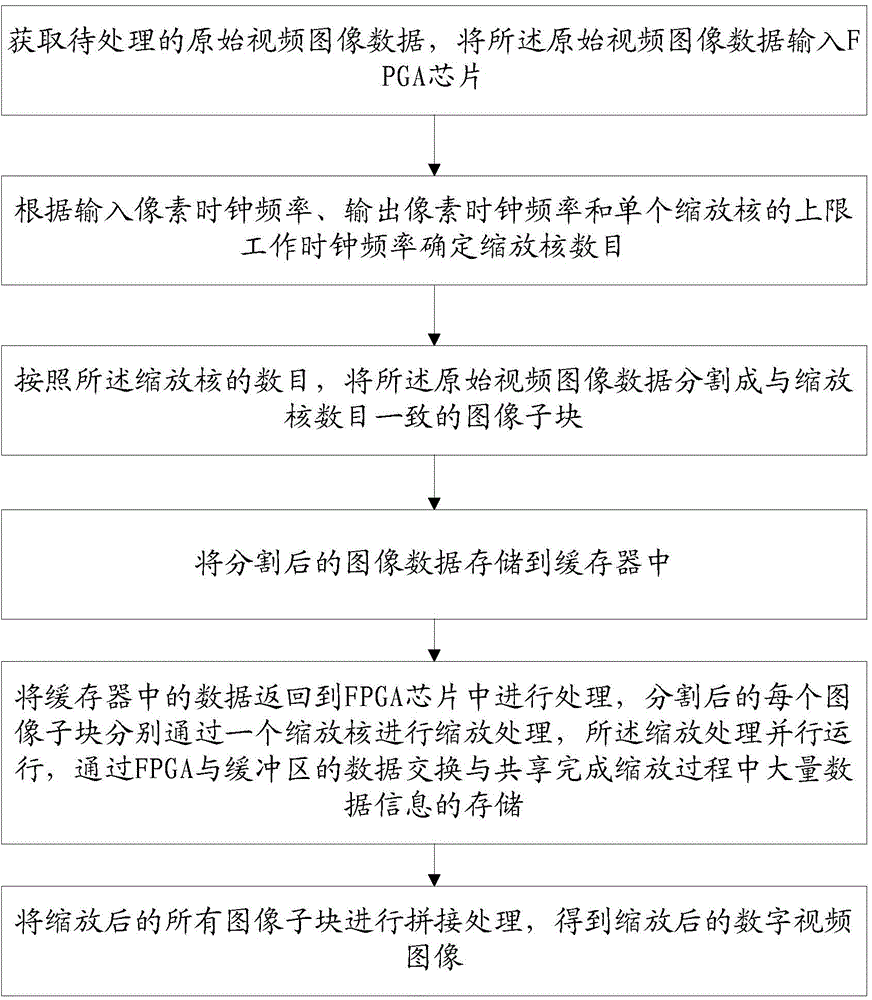

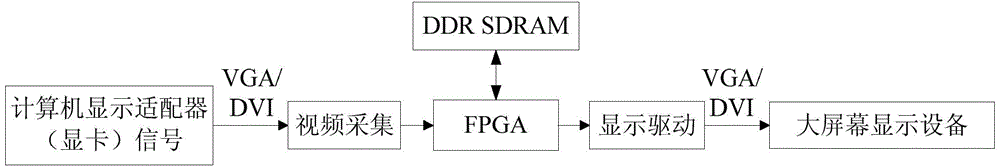

Parallel multi-core FPGA digital image real-time zooming processing method and device

InactiveCN104104888AReduce complexityGuaranteed uptimeTelevision system detailsColor television detailsDigital videoComputer graphics (images)

Provided is a parallel multi-core FPGA digital image real-time zooming processing method and device. The method comprises the steps that original video image data to be processed are acquired firstly. The original video image data are inputted to an FPGA chip and the number of zooming cores is confirmed, and the original video image data are divided into image sub-blocks having the same number with that of the zooming cores. Then the divided data are stored in a buffer, the data in the buffer are returned to the FPGA and parallel zooming processing is performed on each image sub-block via one zooming core respectively so that zooming is completed. All the image sub-blocks after zooming are displayed after splicing processing. The method has certain guiding effect on high throughput and high real-time application of digital video images.

Owner:DALIAN NATIONALITIES UNIVERSITY

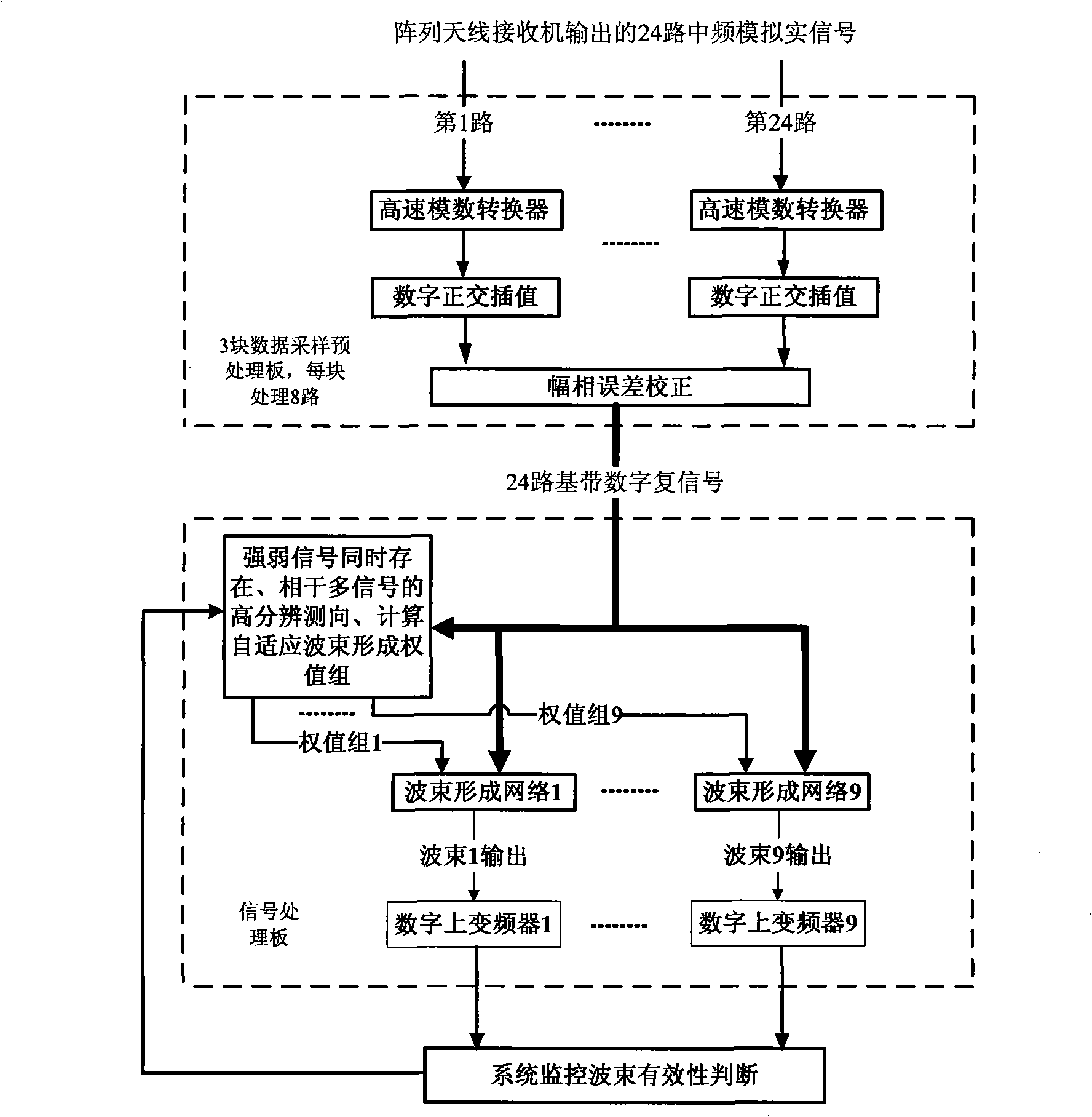

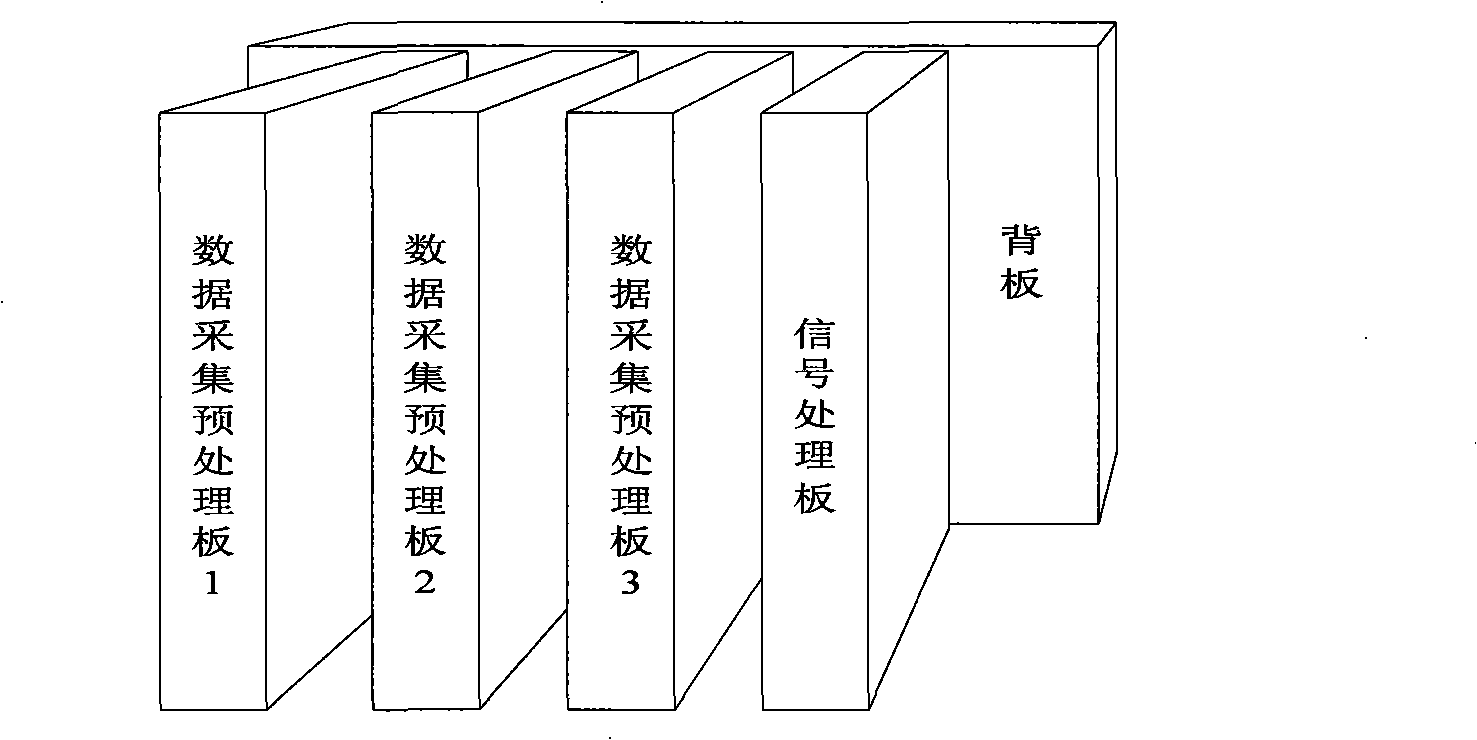

Phased array digital multi-beam forming machine for electron reconnaissance

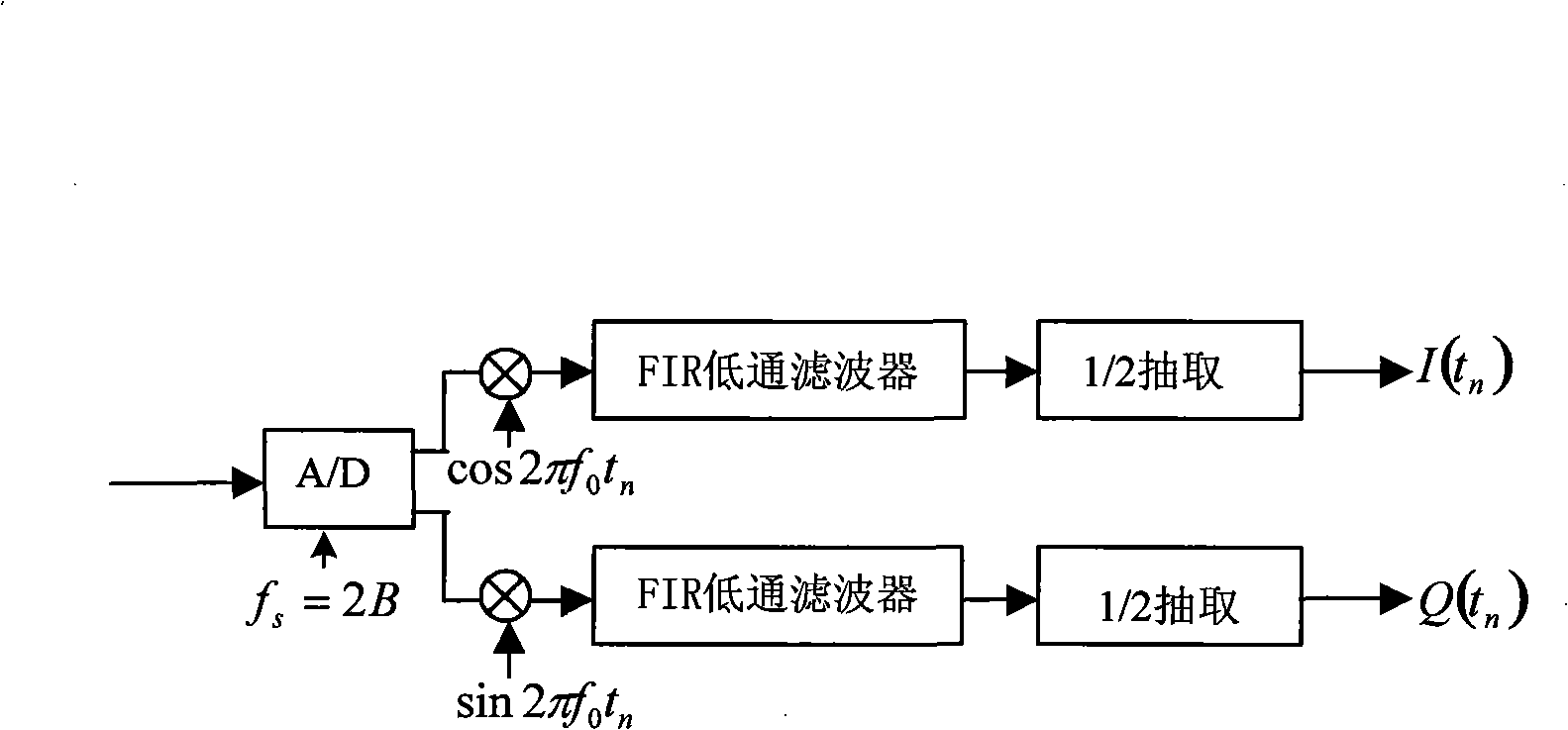

InactiveCN101349741AGuaranteed median alignmentGuaranteed bit alignmentRadio wave finder detailsRadio wave direction/deviation determination systemsIntermediate frequencyData acquisition

The invention discloses a phased array digital multi-beam generator for electronic reconnaissance, for the high resolution direction measurement having strong and weak signals or coherent multi signals, and forming the multi-target signal into anti-interference digital multi-beam to form a multi-beam process: first, in a data acquisition pretreatment board, an AD samples intermediate frequency analogue real signals output by each array antenna receiver, a DPS and a FPGA chip are cooperated to complete quadrate sampling and amplitude phase error correction; the intermediate frequency analogue actual signals are converted into a baseband digital complex signal and the amplitude phase error between the multi channels is corrected; a LVDS channel transmits the baseband digital complex signal to a signal processing board, the DPS completes the high resolution direction measurement having strong and weak signals or coherent multi signals and calculates the weight value group formed by the adaptive beam; the weight value group is added into the wave beam in the signal processing board FPGA to form a network; completing forming anti-interference digital multi-beam of the multi-target signal; an up frequency converter converts the output of the anti-interference digital multi-beam into needed intermediate frequency analogue signal.

Owner:XIDIAN UNIV

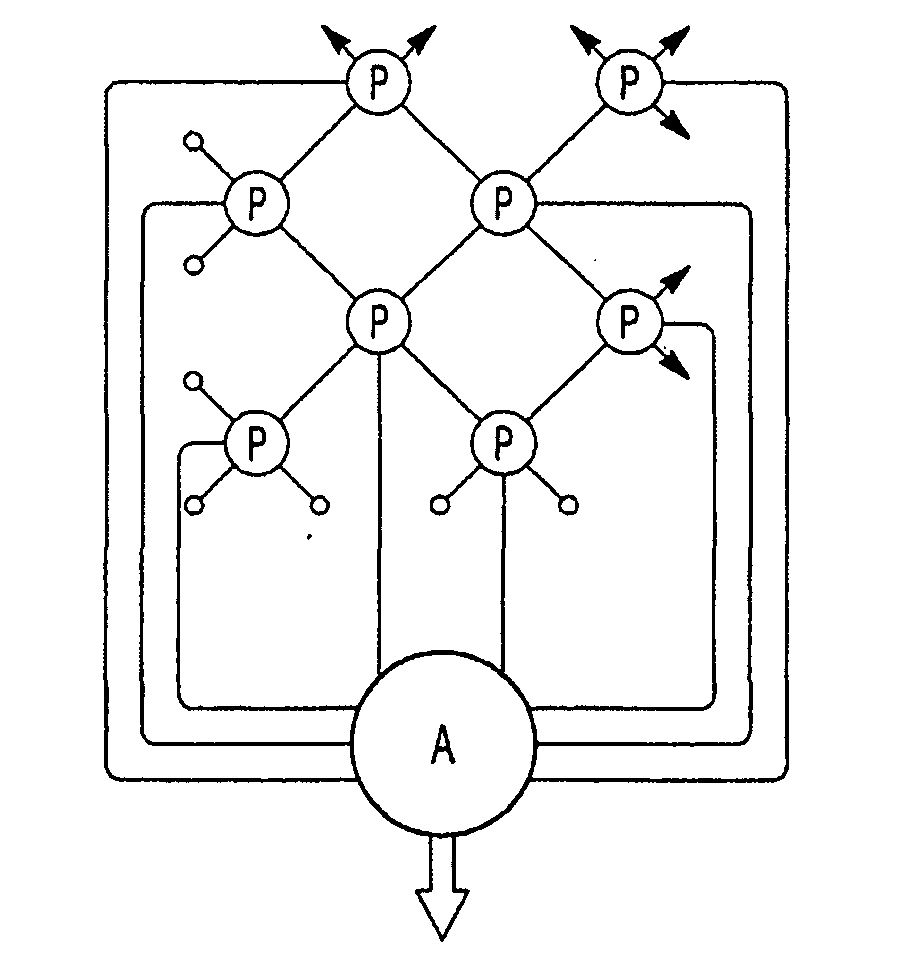

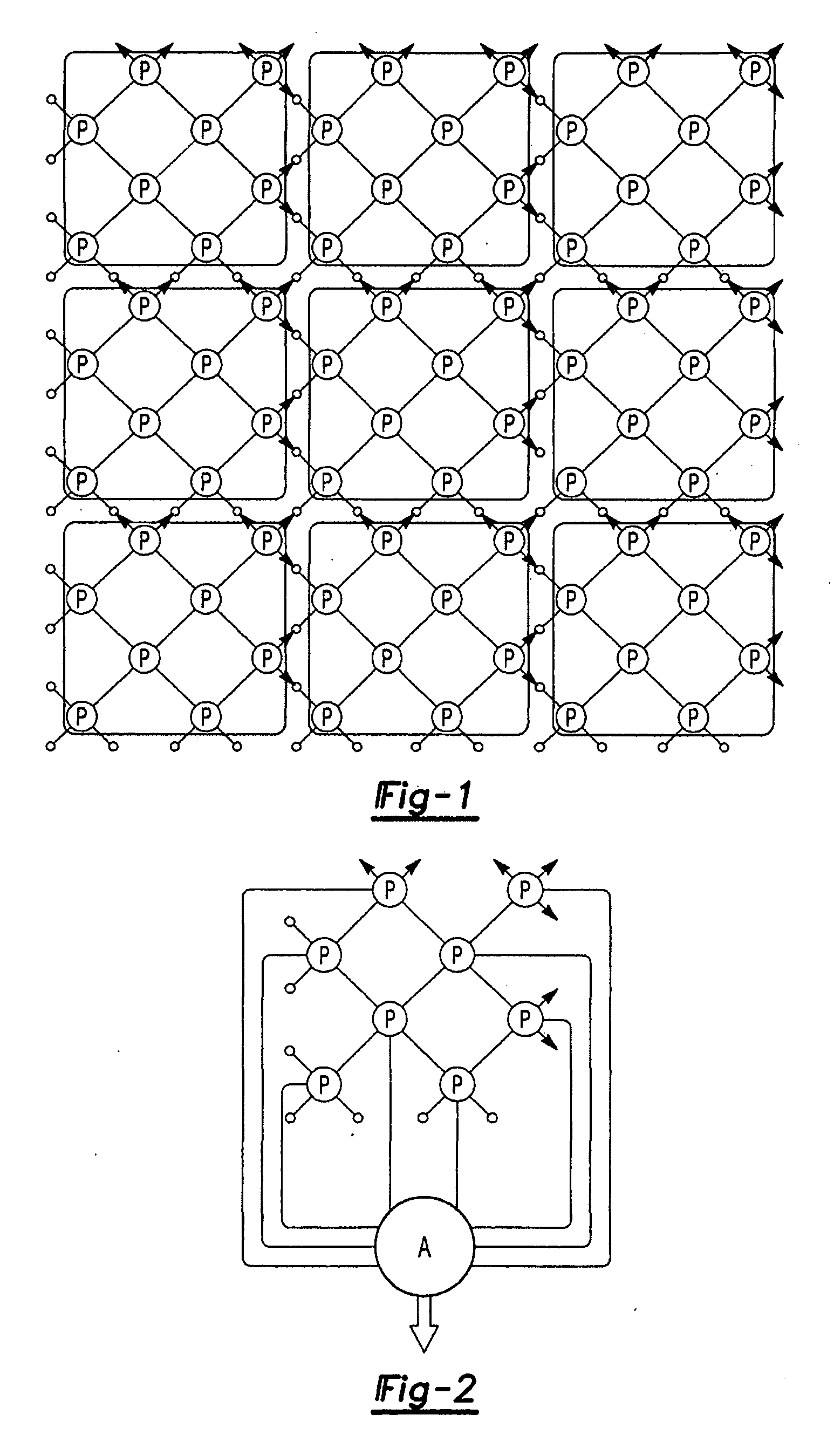

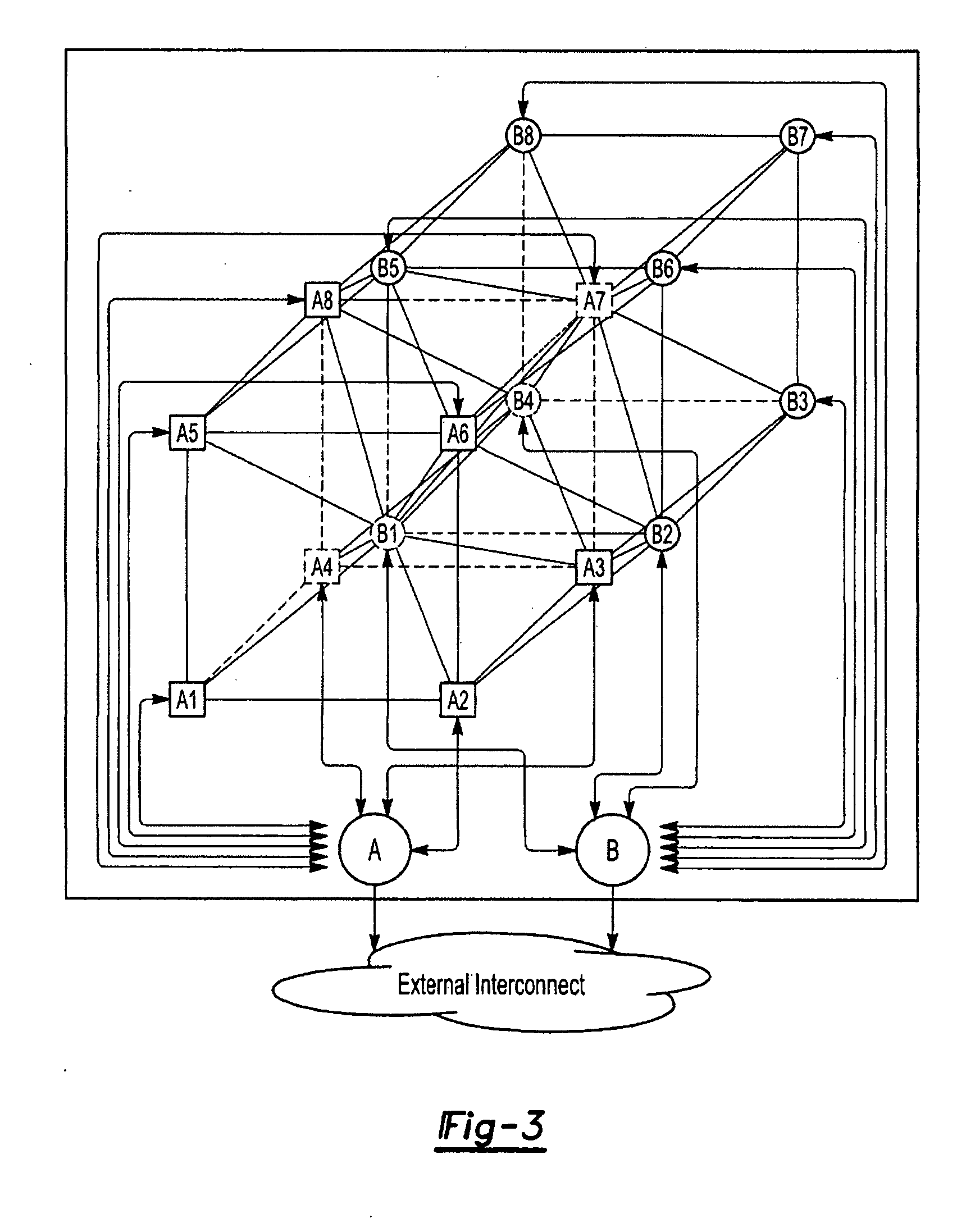

Ultra-scalable supercomputer based on mpu architecture

InactiveUS20090094436A1High-performance and sustained computing resourceHigh-performance and sustained computing resourcesProgram control using stored programsData switching by path configurationSupercomputerTraffic capacity

The invention provides an ultra-scalable supercomputer based on MPU architecture in achieving the well-balanced performance of hundreds of TFLOPS or PFLOPS range in applications. The supercomputer system design includes the interconnect topology and its corresponding routing strategies, the communication subsystem design and implementation, the software and hardware schematic implementations. The supercomputer comprises a plurality of processing nodes powering the parallel processing and Axon nodes connecting computing nodes while implementing the external interconnections. The interconnect topology can be based on MPU architecture and the communication routing logic as required by switching logics is implemented in the FPGA chips while some modular designs for accelerating particular traffic patterns from applications and meliorating the communication overhead are able to be deployed as well.

Owner:SHANGHAI REDNEURONS

Compact smart antenna for mobile wireless communications

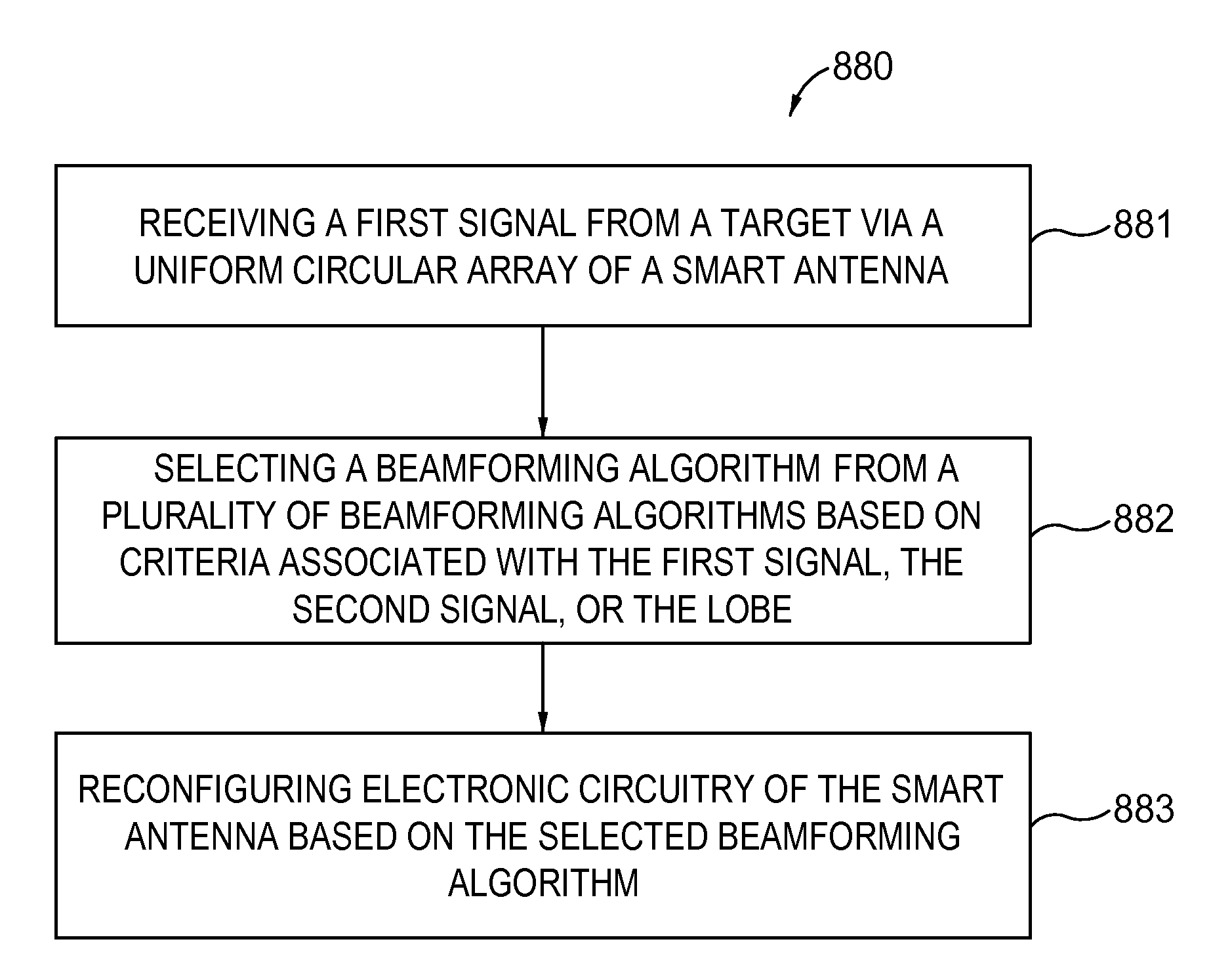

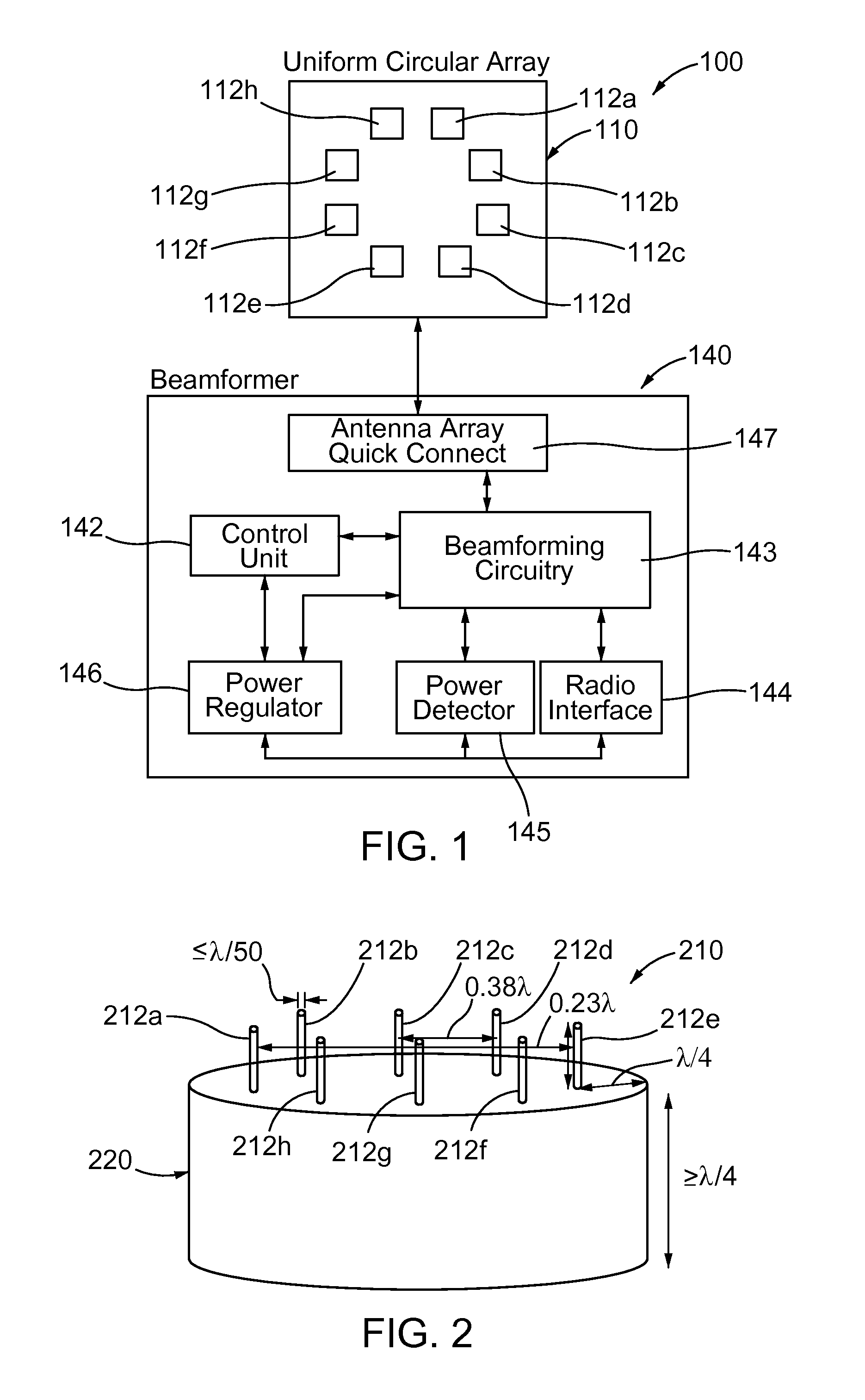

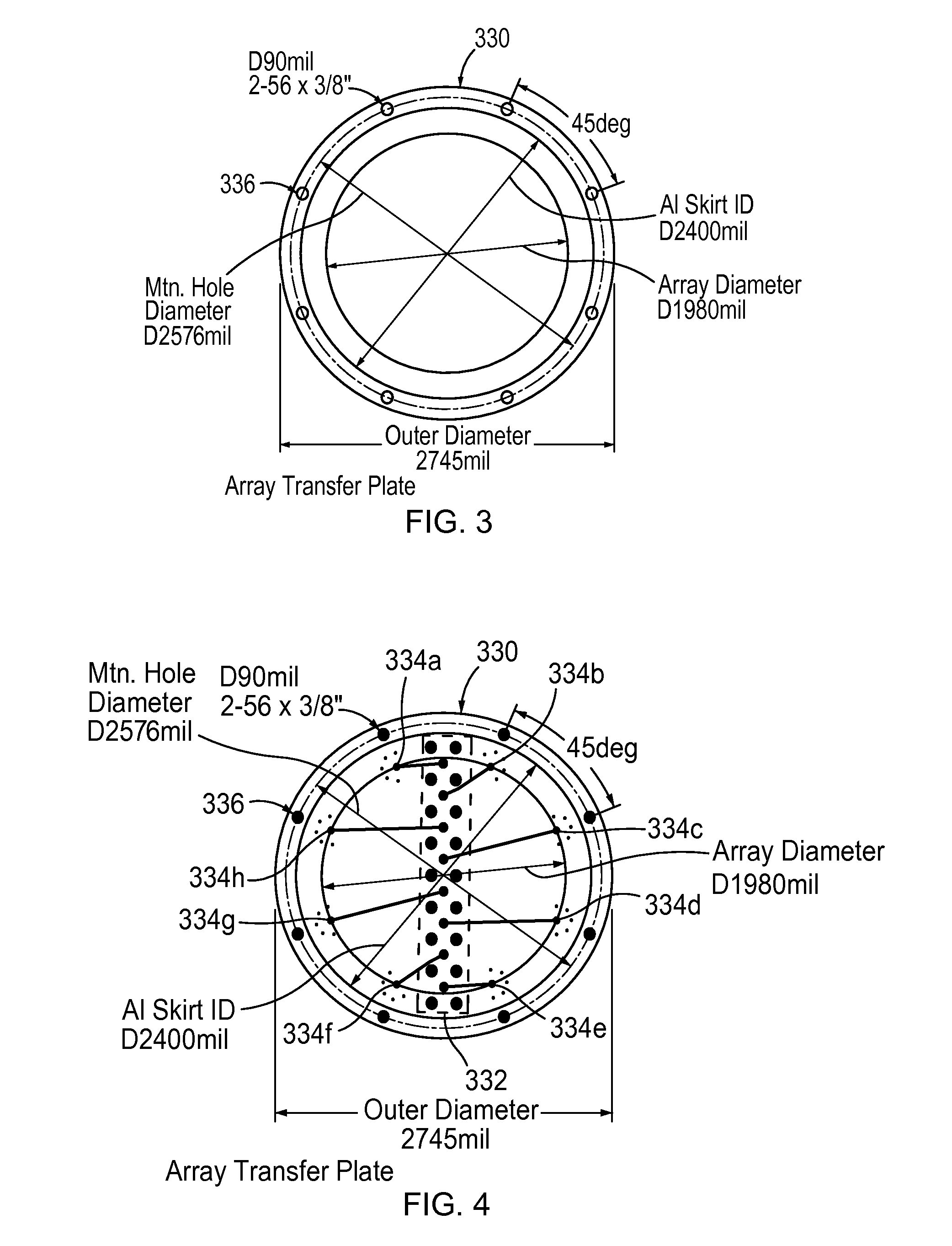

InactiveUS20120299765A1Suppress interferenceJam suppressionRadio transmissionIndividually energised antenna arraysLow noiseBand-pass filter

A compact, high gain 8-element circular smart antenna is able to scan a beam azimuthally through 360°. The 8-element array is placed on a ground skirt and connected to an 8-channel beamforning board via a transfer plate. Each channel has two T / R switches, one band pass filer, one power amplifier, two low noise amplifiers, one phase shifter, and one attenuator. The 8-channel-signal is combined through power splitters / combiners and then sent to a connected radio. An FPGA chip controls the digital phase shifters, attenuators and switches for signal searching, beamforming and tracking. The smart antenna can be operated as a compact switched beam system or with an additional processor as an adaptive array system. The smart antenna is capable of tracking mobile targets, directionally communicating with desired users, suppressing interference and jamming, and enabling long range communications with high throughput and reliable connection because of its high antenna gain.

Owner:MONTANA STATE UNIVERSITY +1

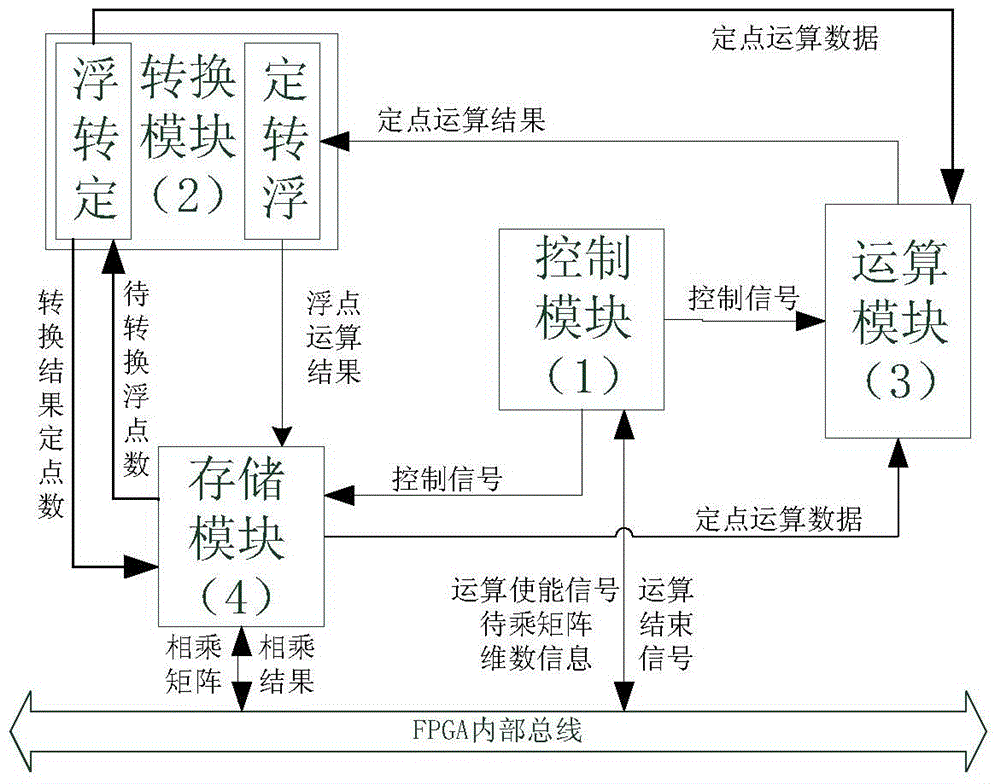

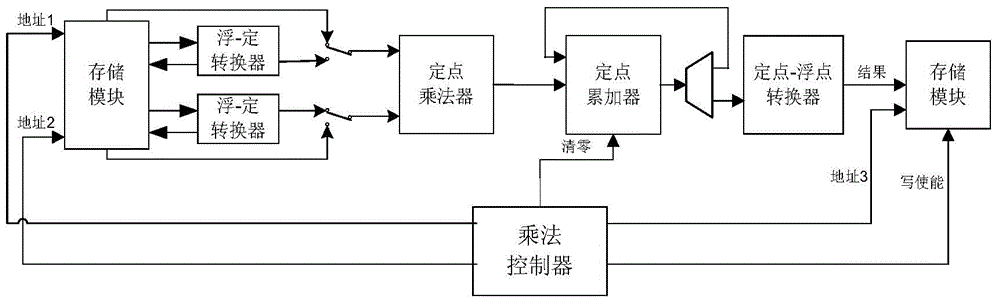

FPGA (Field Programmable Gate Array)-based general matrix fixed-point multiplier and calculation method thereof

ActiveCN104572011AImprove computing efficiencyImprove performanceComputation using non-contact making devicesGeneral matrixControl signal

The invention discloses an FPGA (Field Programmable Gate Array)-based general matrix fixed-point multiplier. An internal structure of the multiplier consists of a control module, a conversion module, an operation module and a storage module. The control module is used for generating a control signal according to dimension of a to-be-operated matrix. The conversion module is responsible for performing conversion between a fixed-point number and a floating-point number during operation. The operation module is used for reading operation data from the storage module and the conversion module, performing fixed-point multiplication and fixed-point accumulating operation and storing a result in the storage module. The storage module is used for caching to-be-operated matrix data and result matrix data, providing an interface compatible with a bus signal and allowing access of other components on a bus. The characteristic of high fixed-point calculation efficiency in hardware is fully utilized; by using a unique operation structure, simultaneous conversion and operation of the data are realized to improve the overall operation speed, and a plurality of matrix fixed-point multipliers can be simultaneously used to perform parallel calculation; thus the fixed-point multiplication of an arbitrary dimension matrix can be supported, and meanwhile extremely high calculation efficiency is guaranteed. Compared with matrix multiplication performed by using the floating-point number, the multiplier has the advantage that the calculation efficiency is greatly improved.

Owner:上海碧帝数据科技有限公司

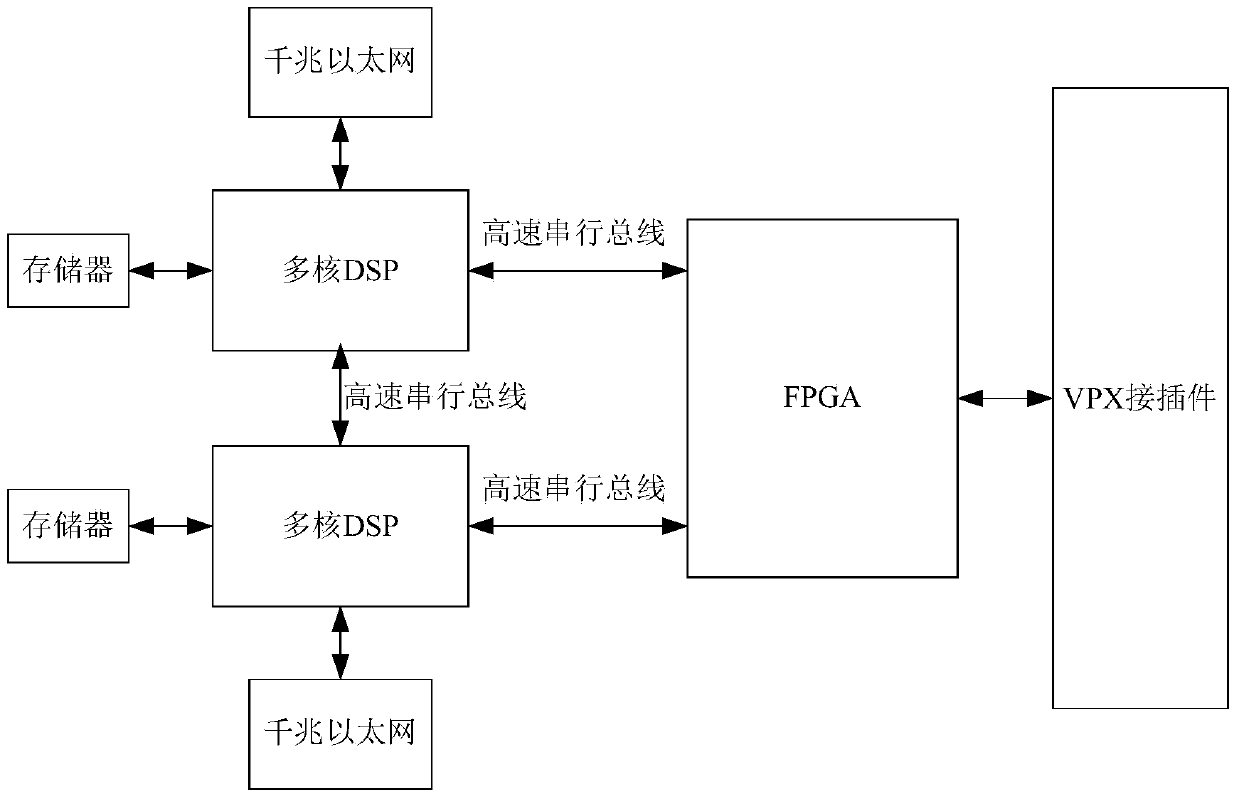

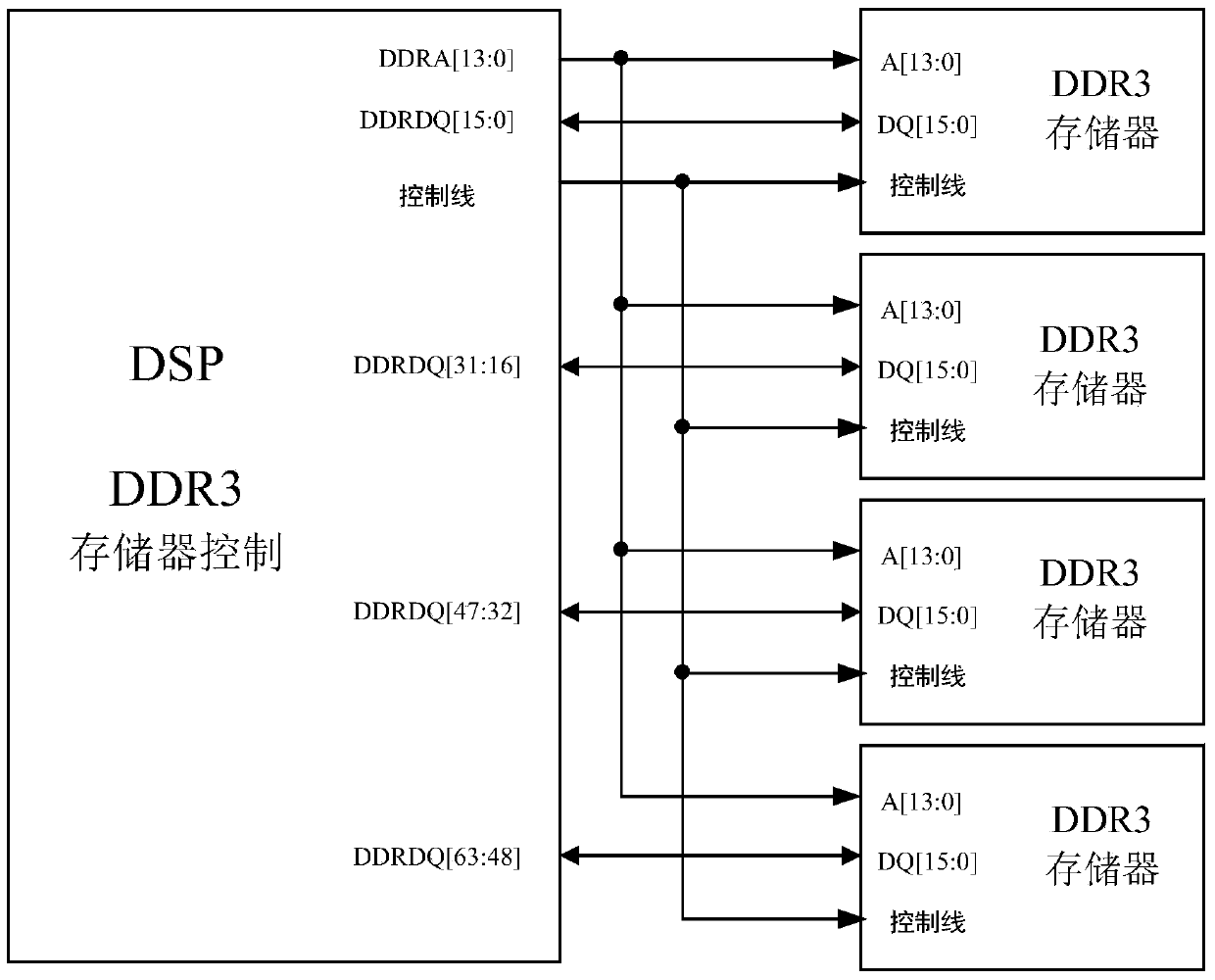

General signal processing board card based on multi-core DSP (digital signal processor)

InactiveCN103793355ASimple structureReduce volumeElectric digital data processingDigital signal processingTransceiver

The invention discloses a general signal processing board card based on a multi-core DSP (digital signal processor). An FPGA (field programmable gate array) serves as a master control core, and two multi-core DSP chips are connected through a high-speed serial bus and supportable to SRIO (serial rapid input / output) and PCIE (peripheral component interconnect express) protocols. Each DSP is connected with an expandable external memory and a gigabit Ethernet interface, and the DSPs are connected mutually through the high-speed serial bus and supportable to Hyperlink, SRIO and PCIE protocols. The FPGA and a VPX connector are mutually connected through a gigabit transceiver and supportable to SRIO, PCIE and Ethernet protocols. Mounting positions of an external memory chip, a DSP chip and an FPGA chip on a printed board of the general signal processing board card are compatible positions allowing placement of other chips in the series respectively and accord with 6U standards in size. The problems of poor universality, small data throughput, low storing rate and low processing speed of existing signal processing board cards are solved, and the general signal processing board card has the advantages of quickness in processing, high storing rate, large data throughput and high universality and can be widely applied to fields of communication, radar, guided missiles, remote sensing, image processing and the like.

Owner:XIDIAN UNIV

Embedded type combined navigation system and method thereof

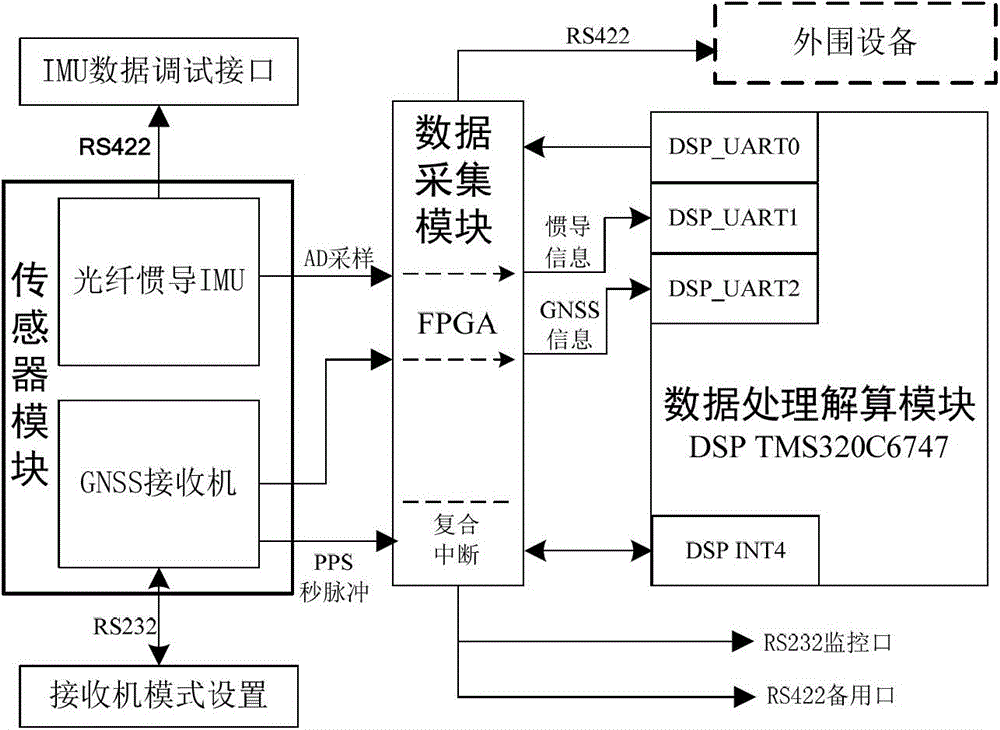

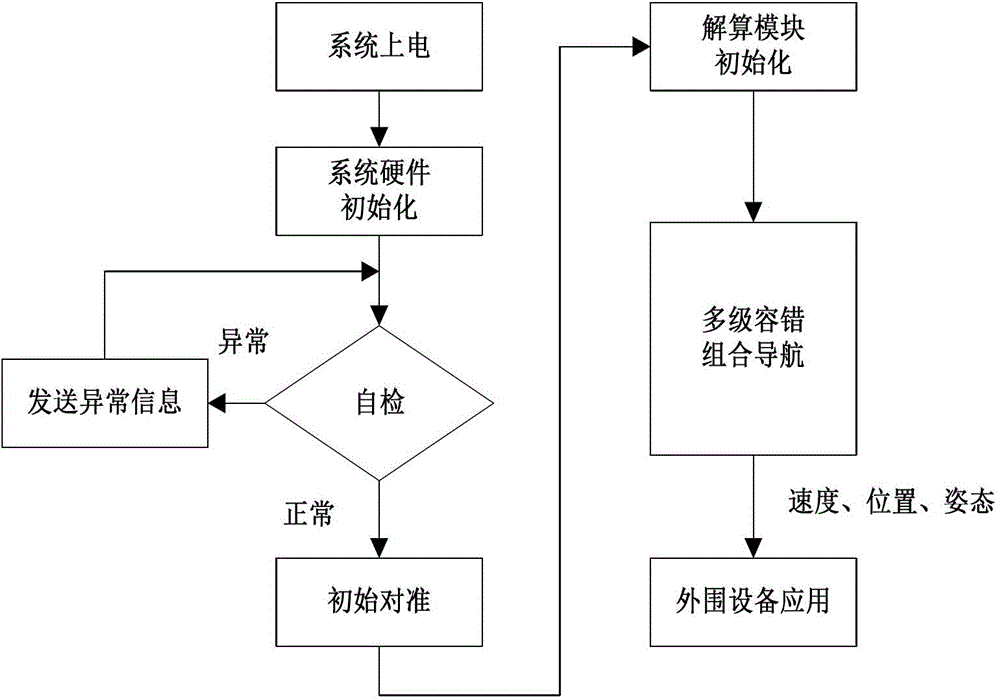

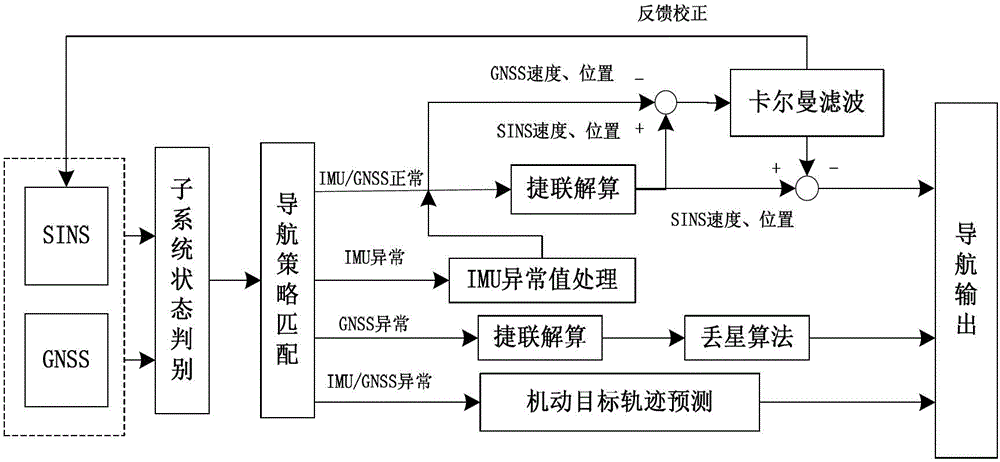

InactiveCN104422948AEfficient collectionEfficient handlingNavigational calculation instrumentsNavigation by speed/acceleration measurementsFault toleranceCommunication interface

The invention discloses an embedded type combined navigation system and a method thereof. The system comprises a sensor module, a data acquisition module, a data processing and calculating module and a peripheral communication interface module, wherein the sensor module comprises an optical fiber inertial navigation IMU and GNSS receiver; the data acquisition module is an FPGA module; the data processing and calculating module is a DSP chip; the sensor module and the data processing and calculating module are connected by a high-speed bus of the data acquisition module. The combined navigation method comprises the following steps: transmitting measurement data of the optical fiber inertial navigation IMU and GNSS receiver to a DSP for data processing and calculating by a bus of an FPGA; establishing an SINS / GNSS combined navigation system mathematical model for multi-level fault-tolerant combined navigation; judging according to the state of a sub system, carrying out navigation decision-making matching; and transmitting the obtained real-time speed, position and posture information to peripheral equipment by the peripheral communication interface module. The system has the advantages of high integration, abundant interfaces, high precision and good fault tolerance.

Owner:NANJING UNIV OF SCI & TECH

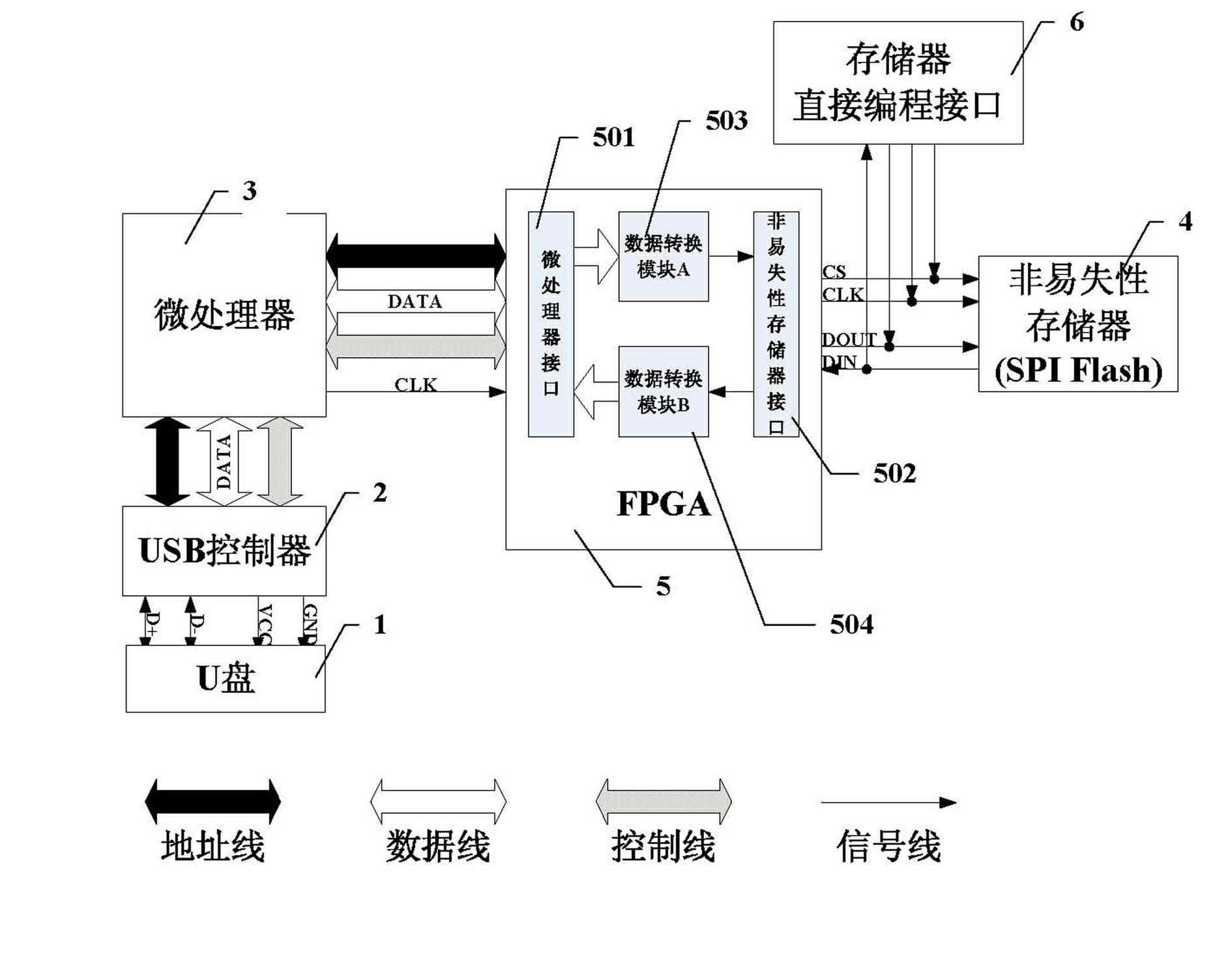

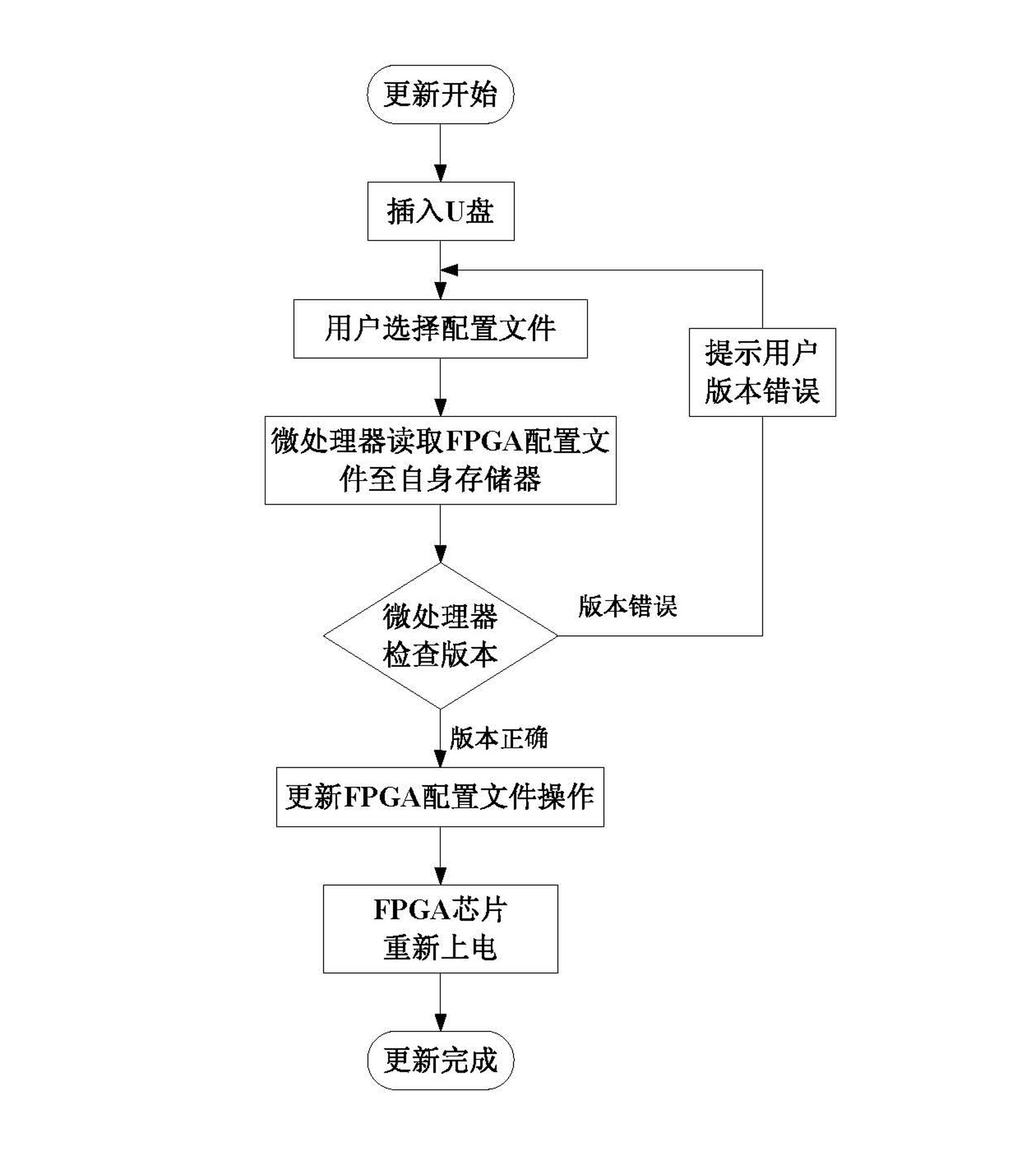

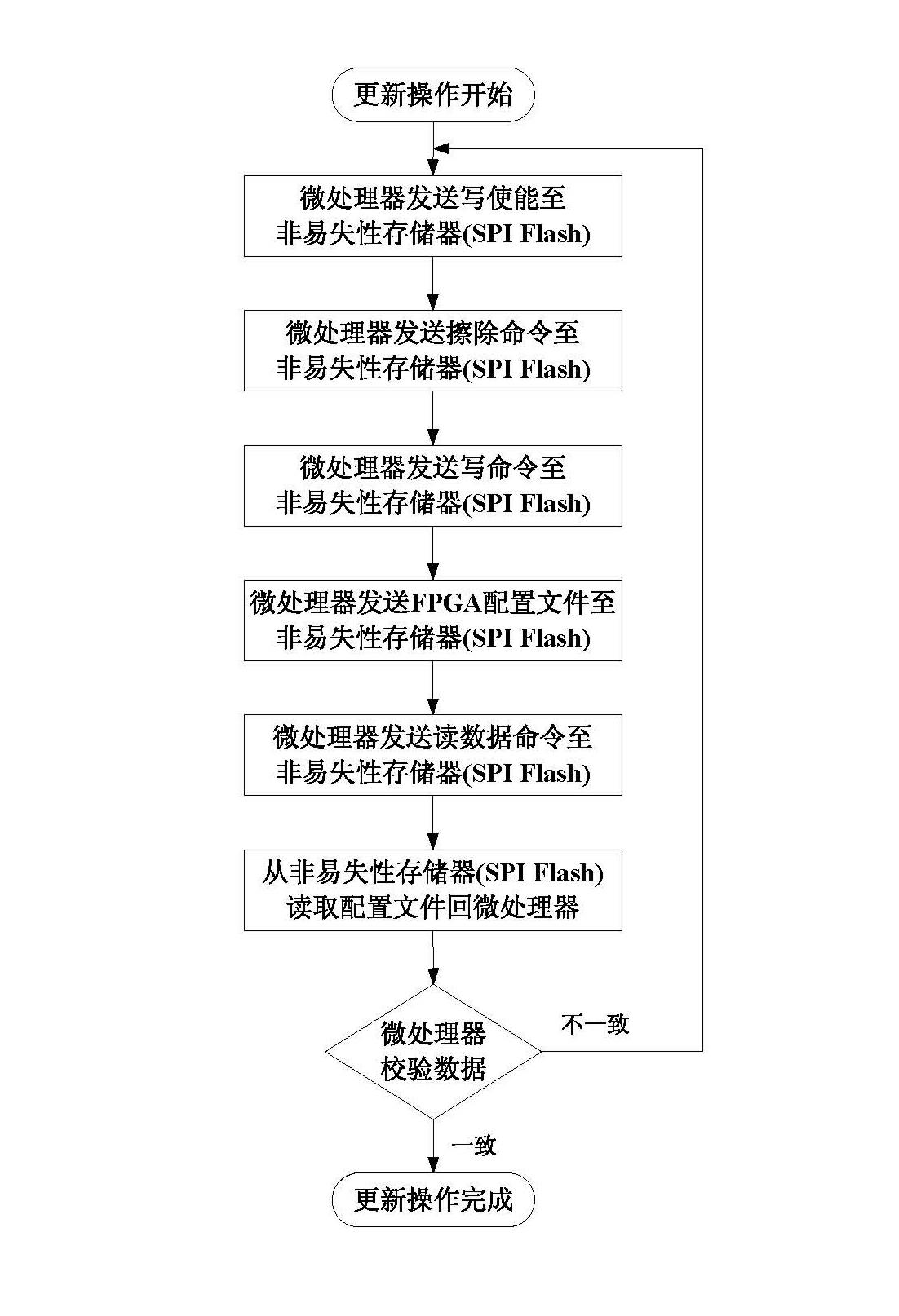

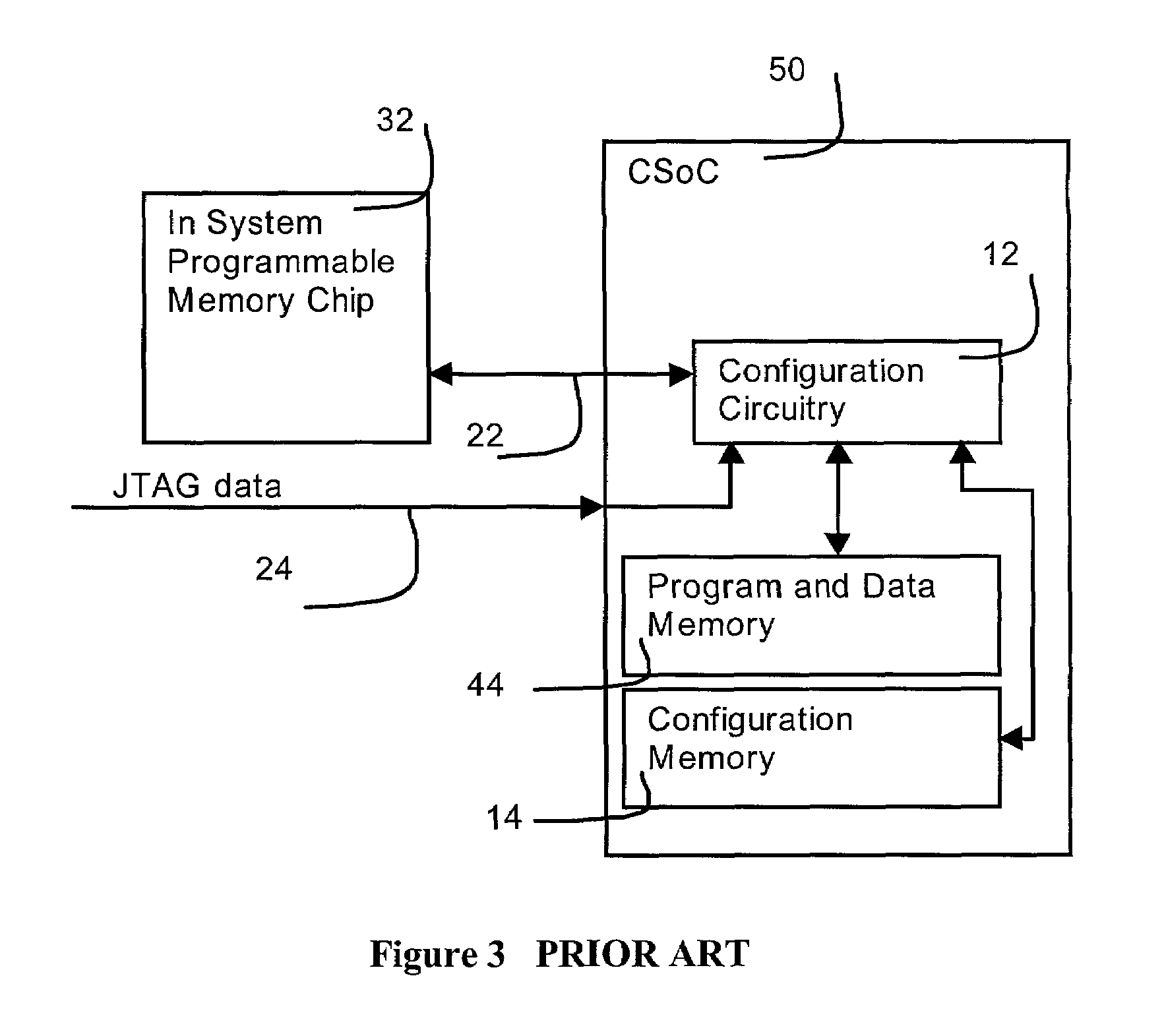

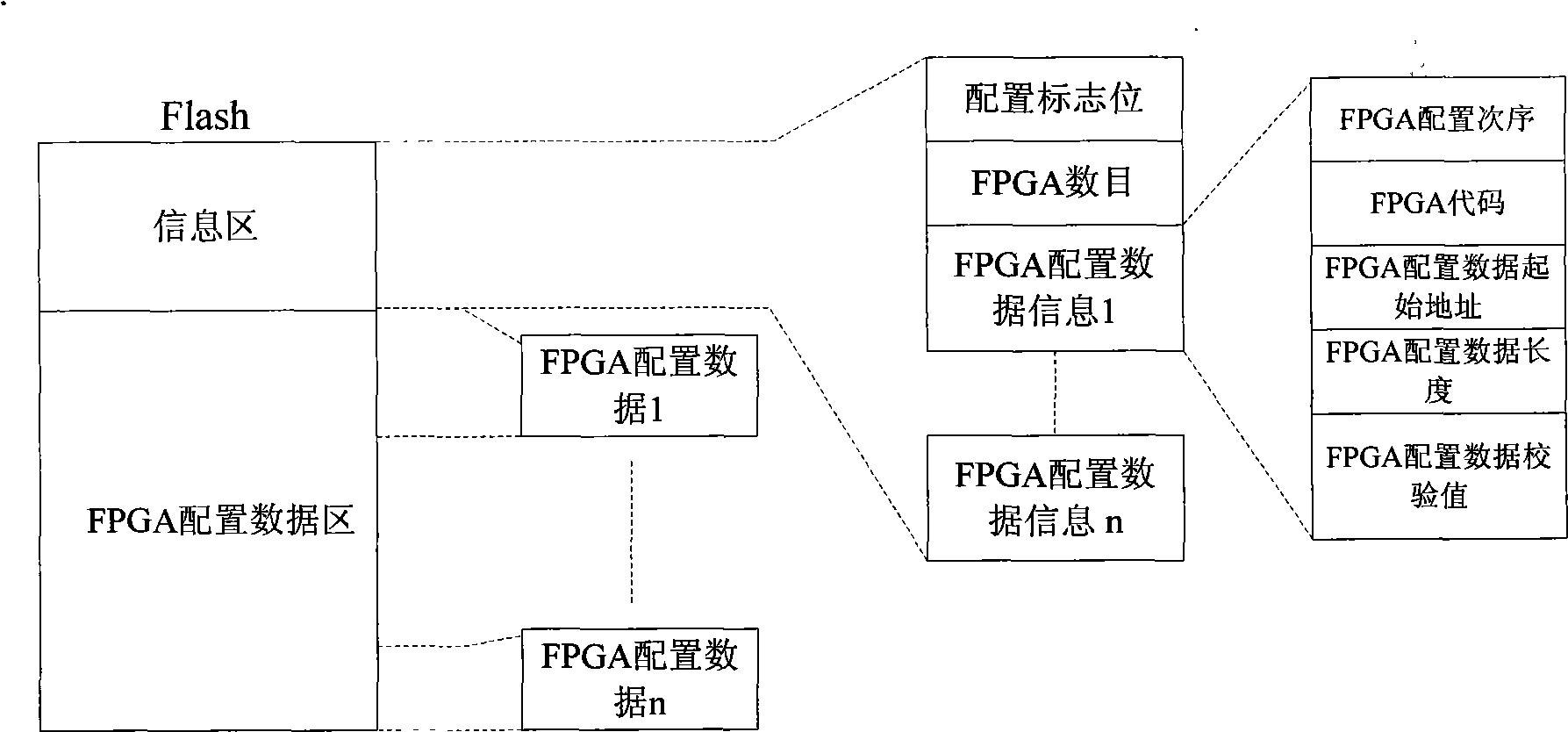

FPGA configuration file update device

InactiveCN102087606AMeet the needs of online configurationProgram loading/initiatingMicrocontrollerExternal storage

The invention discloses a field-programmable gate array (FPGA) configuration file update device. A microprocessor / microcontroller imports an FPGA configuration file from an external memory through a universal plug and play interface, and transmits the FPGA configuration file to an FPGA chip; the FPGA chip converts the FPGA configuration file into a data format capable of being identified by a nonvolatile memory, transmits the converted FPGA configuration file to the nonvolatile memory for storage, and updates the FPGA configuration file; and after a digital system is electrified again, the FPGA chip automatically reads the updated configuration file stored in the nonvolatile memory to realize automatic loading and normal operation. In the device, only when the FPGA configuration file needs to be updated, a new FPGA configuration file is written into the nonvolatile memory so as to realize the requirement of online configuration; and meanwhile, the microprocessor / microcontroller provides the interface for the external memory and reads the FPGA configuration file into the personal memory, and then the FPGA configuration file is written into the nonvolatile memory so as to realize the update of the FPGA configuration file and avoid the limitation of a special downloading line.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA

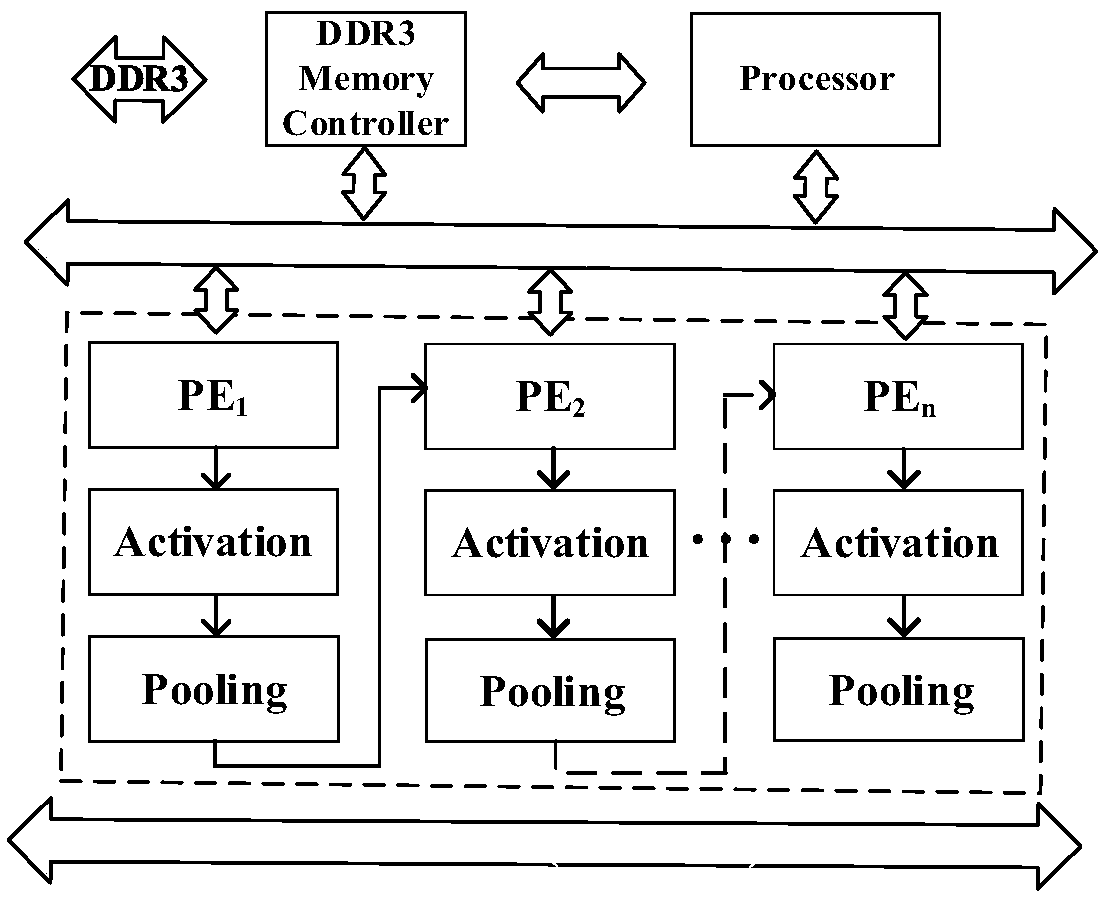

Convolutional-neural-network accelerating system based on field-programmable gate array

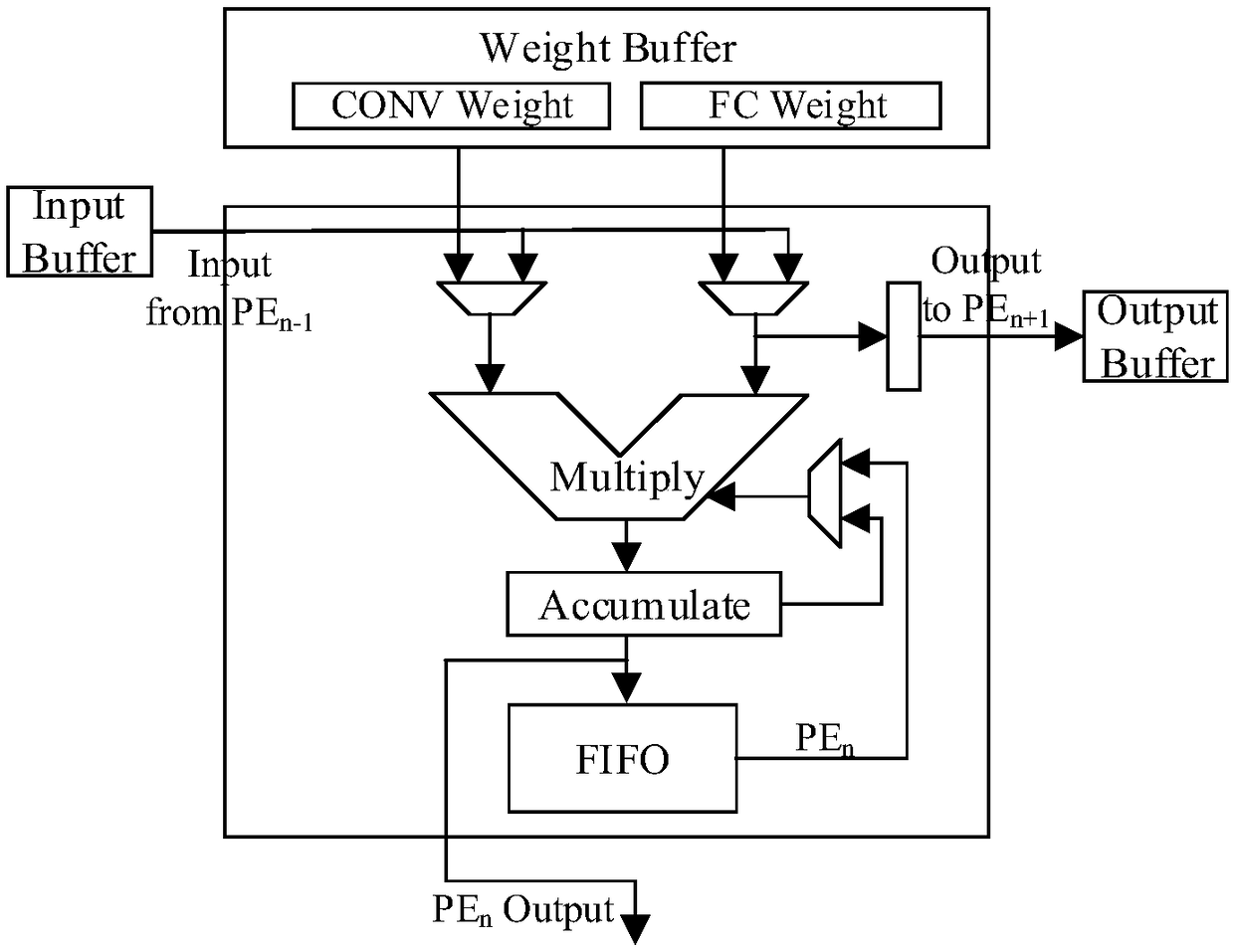

InactiveCN108665059AImprove resource utilizationImprove performanceNeural architecturesProduction lineExternal storage

The invention discloses a convolutional-neural-network accelerating system based on a field-programmable gate array. The convolutional-neural-network accelerating system comprises a general processor,the field-programmable gate array, a storage module, a data bus and a control bus, wherein the general processor is a soft core of a reduced instruction set, and is responsible for starting an accelerator, being in communication with a host terminal, conducting time measurement and the like; a DDR3 DRAM serves as an external storage of the accelerator system; an AXI4-Lite bus is used for demand transmission, and an AXI4 bus is used for data transmission; the field-programmable gate array comprises multiple processing engines (PE), and each processing engine adopts a most-suitable fragment unfolding strategy to correspond to calculation of one layer in the convolutional neural network; all the processing engines are mapped onto a same FPGA chip, and therefore different layers can simultaneously work in a production line mode. Compared with an existing convolutional-neural-network accelerating system, the convolutional-neural-network accelerating system based on the field-programmable gate array can obtain higher energy efficiency benefit.

Owner:SUZHOU INST FOR ADVANCED STUDY USTC

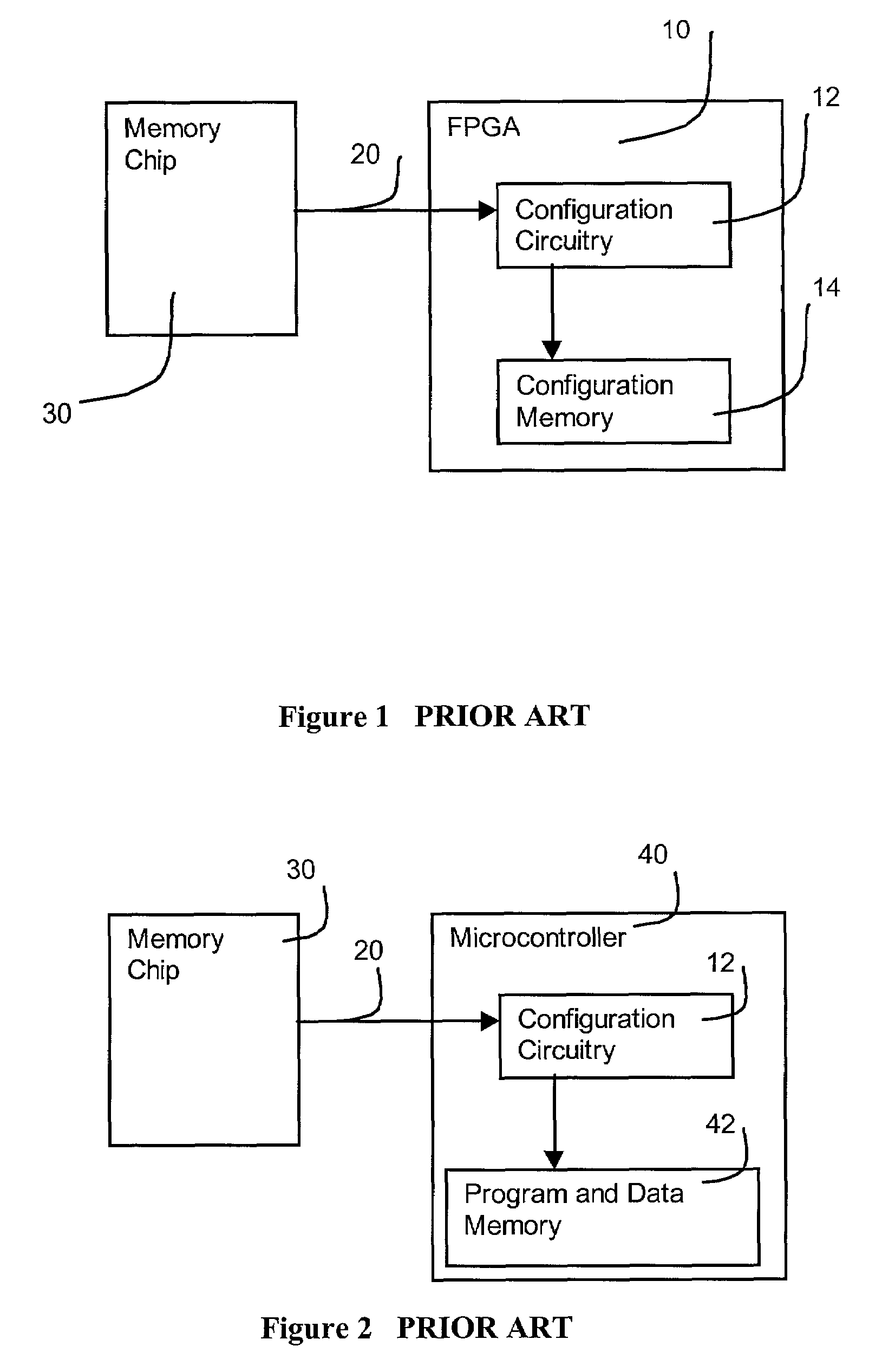

Method of using a mask programmed key to securely configure a field programmable gate array

InactiveUS7240218B2Provide securityPrevent removalDigital data processing detailsUser identity/authority verificationGraphicsFpga chip

A field programmable gate array has security configuration features to prevent monitoring of the configuration data for the field programmable gate array. The configuration data is encrypted by a security circuit of the field programmable gate array using a security key. This encrypted configuration data is stored in an external nonvolatile memory. To configure the field programmable gate array, the encrypted configuration data is decrypted by the security circuit of the field programmable gate array using the security key stored in the artwork of the field programmable gate array. The secret key consists of a number of bits of key information that are embedded within the photomasks used in manufacture the FPGA chip.

Owner:ALGOTRONIX

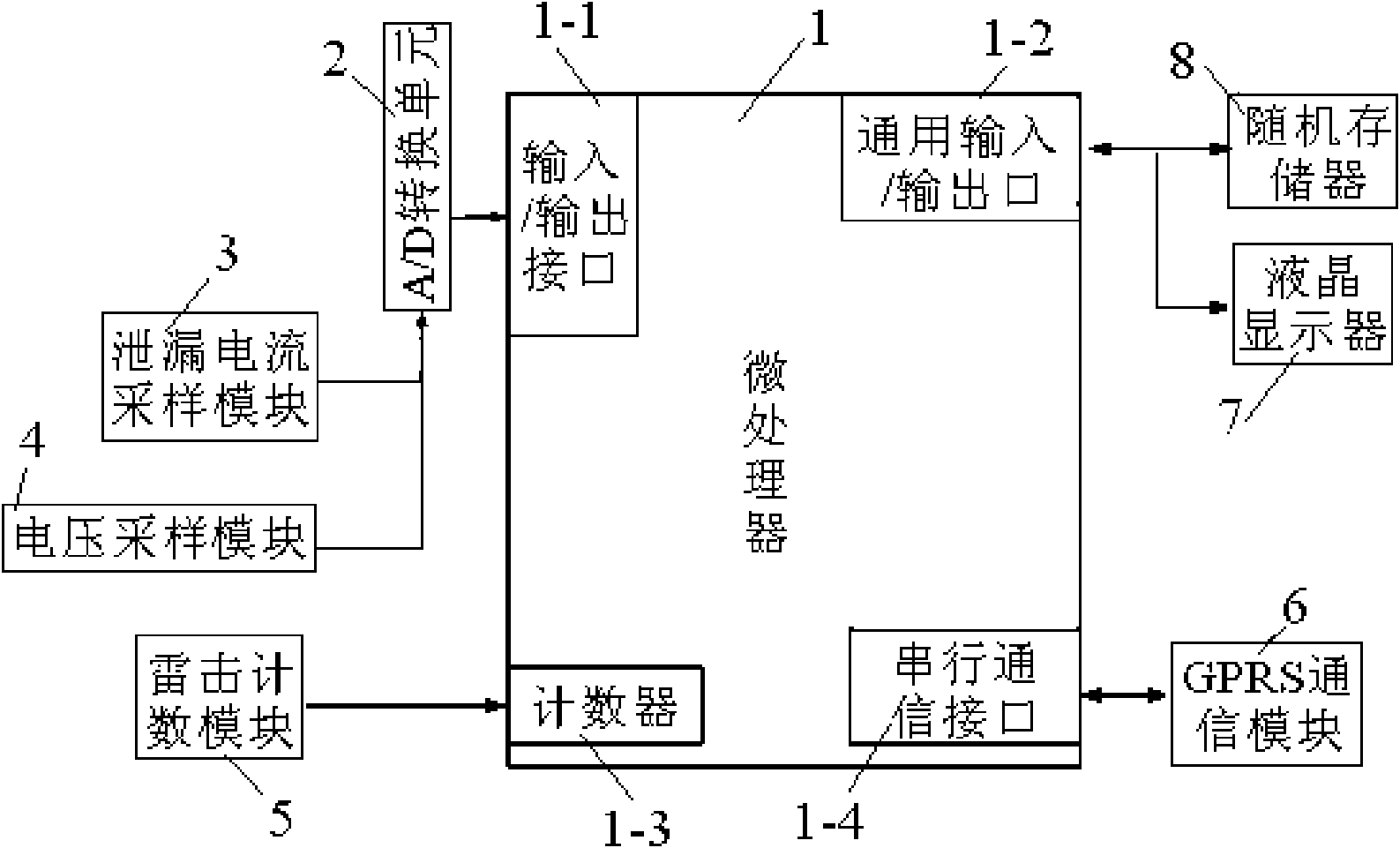

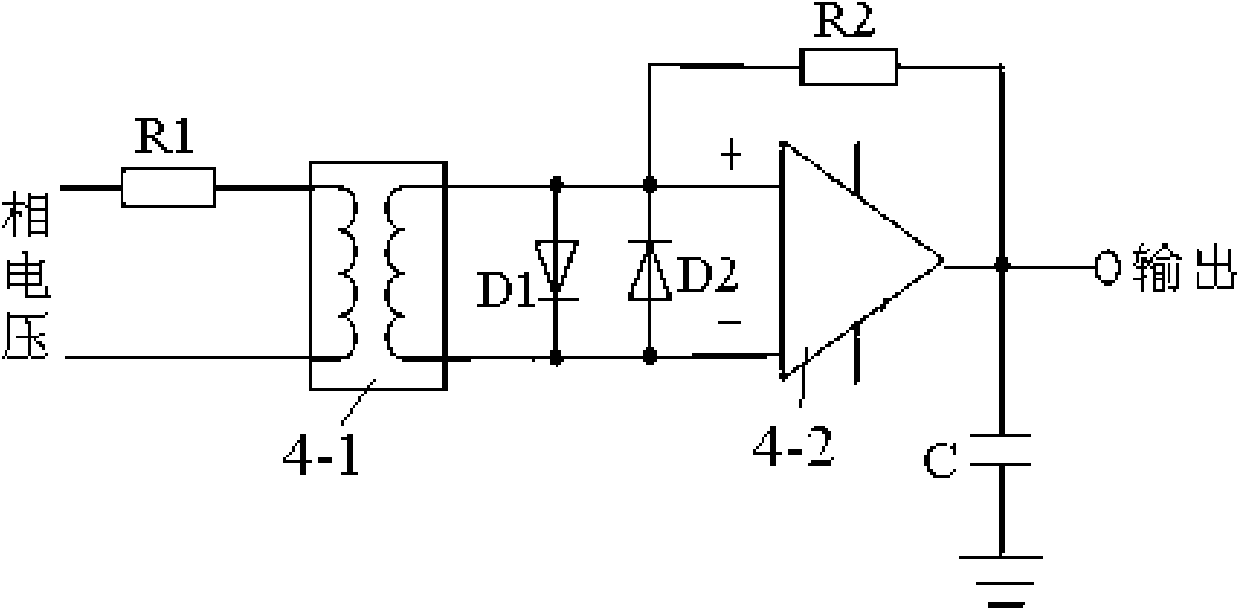

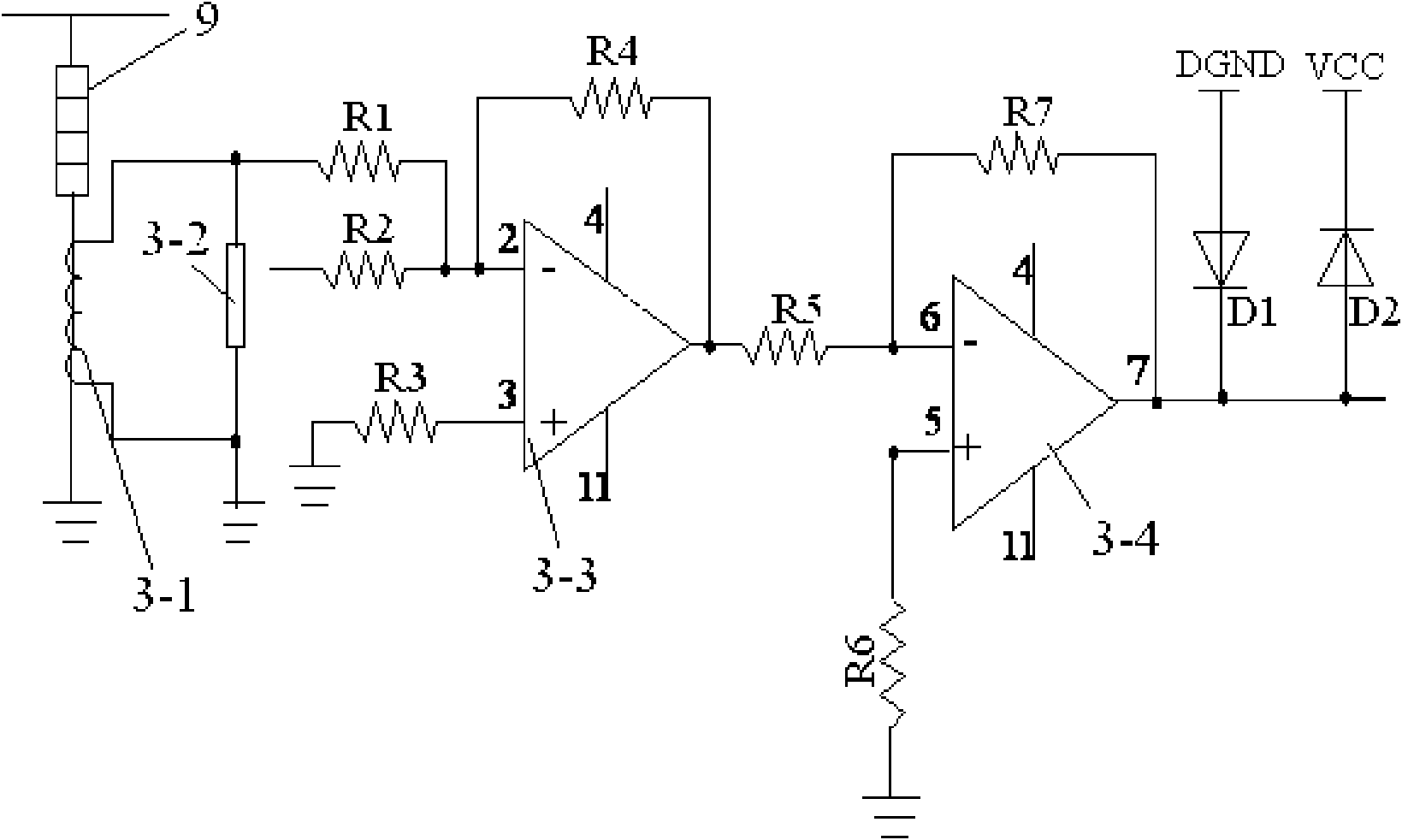

Zinc oxide arrester on-line monitoring system

InactiveCN101581748ALearn about running status informationConvenient queryElectrical testingMeasurement using digital techniquesLong term dataLightning strokes

The invention relates to a zinc oxide arrestor on-line monitoring system which comprises a microprocessor which is respectively connected with an A / D converting unit, a lightning stroke counting module and a GPRS communication module; the A / D converting unit is respectively connected with a leakage current sampling module and a voltage sampling module; the structure of the microprocessor comprises input / output interfaces, a counter and a serial communication interface; the input / output interfaces are connected with the A / D converting unit; the counter is connected with the lightning stroke counting module; the microprocessor is connected with the GPRS communication module; the microprocessor adopts a FPGA chip EPIC6Q240C8. The monitoring system dynamically monitors the insulating property of the zinc oxide arrestor under the operating voltage; the test results are accurate and reliable; the testing process is simple; and the test period is short; the zinc oxide arrestor on-line monitoring system is not easy to be affected by artificial and external factors, can provide long term data information of operation and performance deterioration of the zinc oxide arrestor, and has better practical value.

Owner:邱辰辰

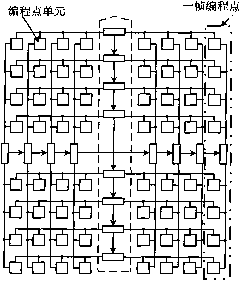

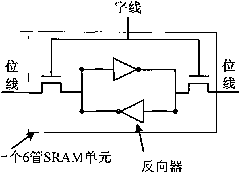

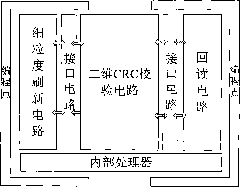

Circuit and method for resisting SEU of SRAM FPGA device

ActiveCN101826038AImprove mean time between failuresLong trouble-free timeRedundant data error correctionMachine controlFpga chip

The invention belongs to the technical field of field programmable gate array (FPGA), and particularly relates to a circuit and a method having the function of resisting the single event upset (SEU) effect for an SRAM FPGA device. The SEU-resisting circuit comprises a read-back circuit, a fine-grained refresh circuit and a two-dimensional CRC calibration circuit. A bus state machine controls the read-back circuit to read information stored in a programming point in a read-back register in the read-back circuit, and then, the two-dimensional CRC calibration circuit calibrates the information and writes the address of the programming point generating the SEU effect in an SEU register; and an internal processor generates a fine-grained refreshing bit stream via the fine-grained refresh circuit based on the output of the SEU register, and the refreshing bit stream is written in an internal programming point of the FPGA chip via a self-configuration interface. The programming point generating the SEU error in the FPGA is refreshed again, thereby realizing the SEU-resistant function. Meanwhile, the invention also reduces the time and power consumption for reconstructing the FPGA after the SEU generation.

Owner:FUDAN UNIV

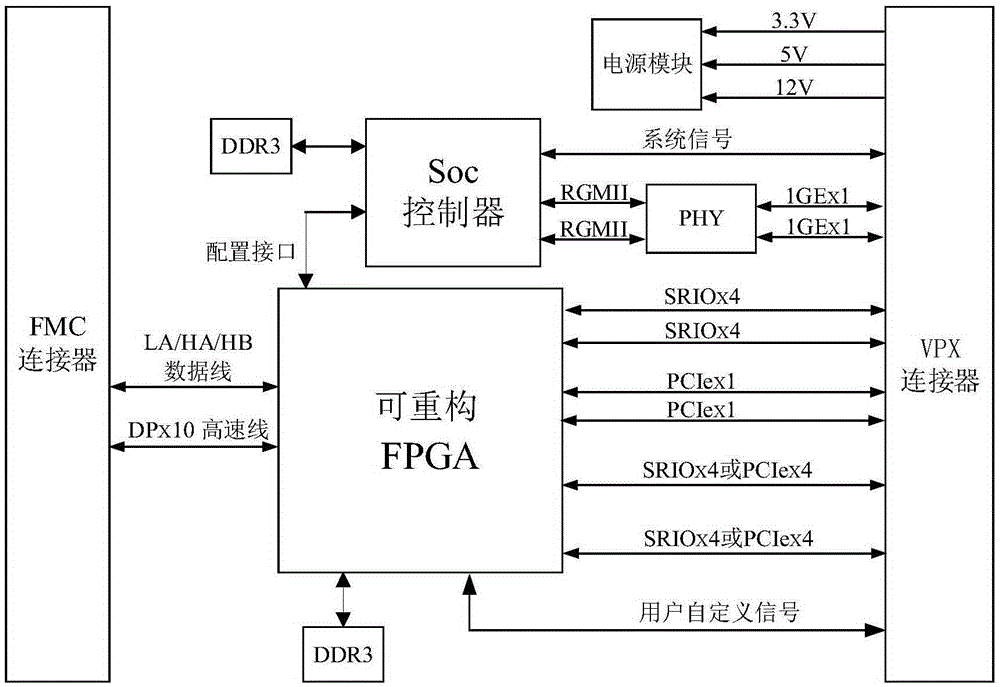

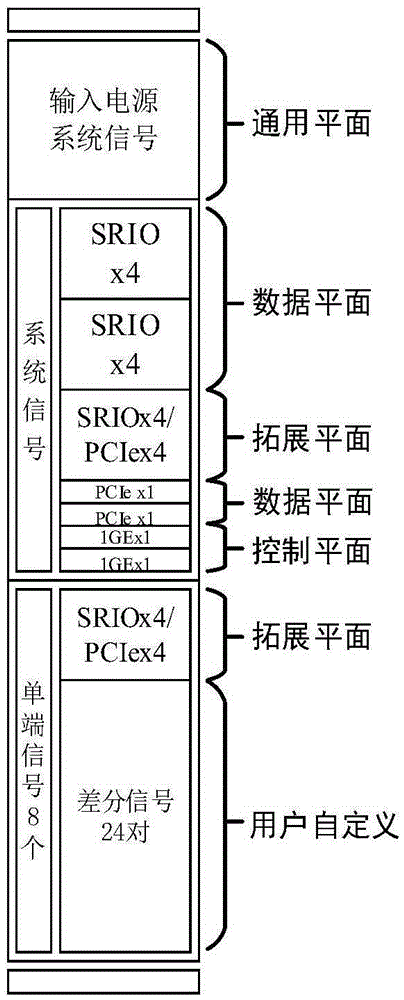

Reconfigurable/dual redundancy VPX3U signal processing carrier board based on Soc

InactiveCN105335327AIncrease flexibilityImprove versatilityElectric digital data processingDigital signal processingBus interface

The invention discloses a reconfigurable / dual redundancy VPX3U signal processing carrier board based on Soc, under VPX control surface 1GEx1 signalization, a carrier board Soc controller can perform control command dynamic loading and logical function on-line reorganization on a high-performance reconfigurable FPGA (Field Programmable Gate Array), and board-level power and timer management and condition monitoring are completed; a reconfigurable FPGA chip is in interaction with front-end received signals through a standard FMC interface, and multi-function real-time digital signal processing is realized according to a loading program. Meanwhile, a dual-redundancy data bus interface is designed in a VPX connector, and a signal processing carrier board can be in data interaction with other board cards such as a master control switch card, an adjacent board card and the like in the system by a VPX dual redundancy data bus interface.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

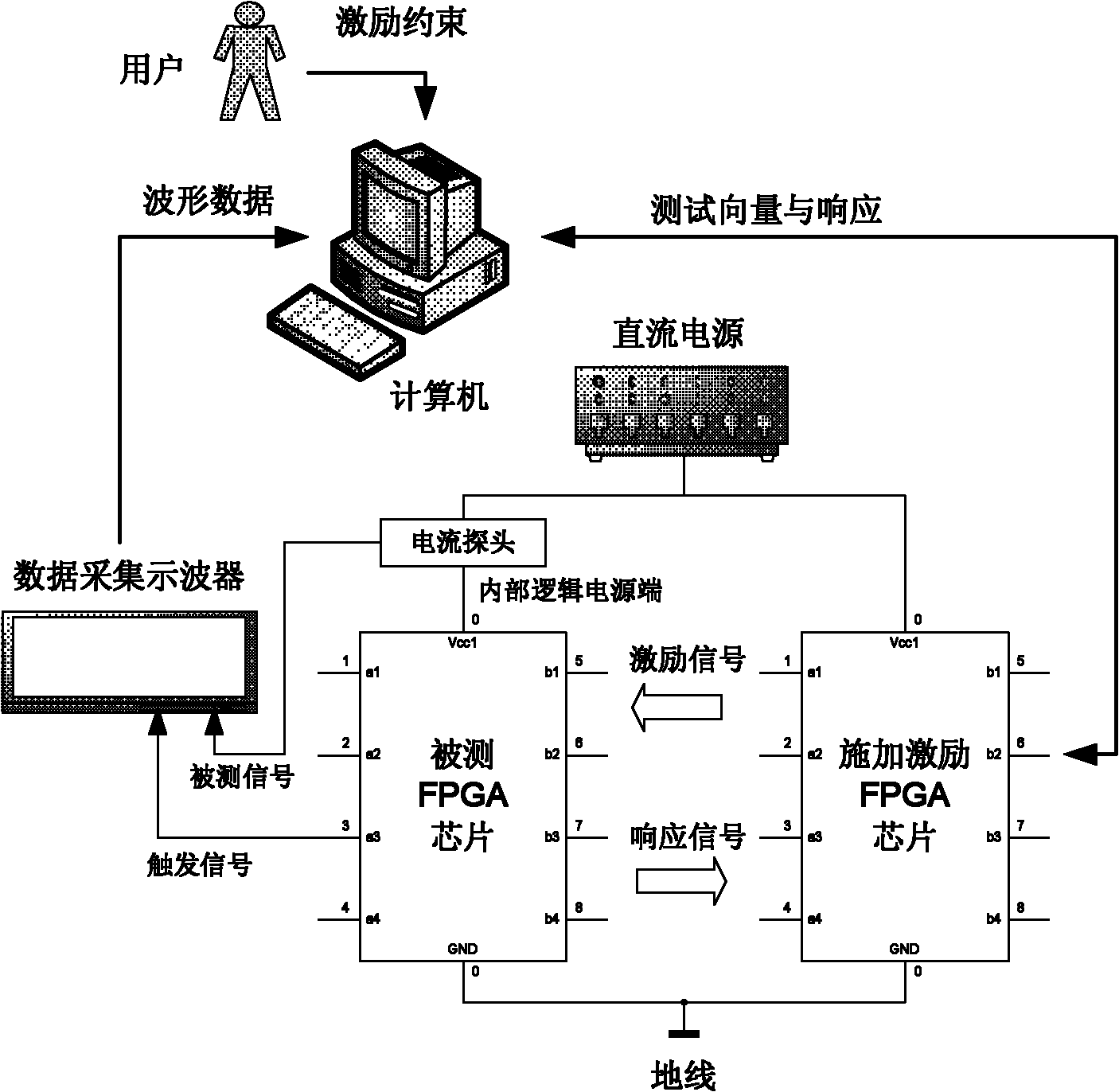

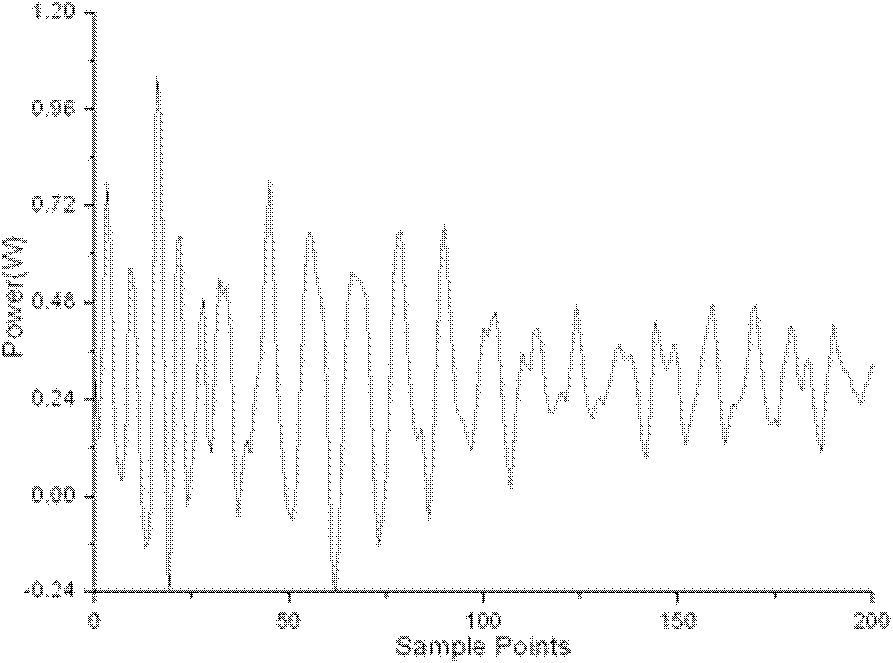

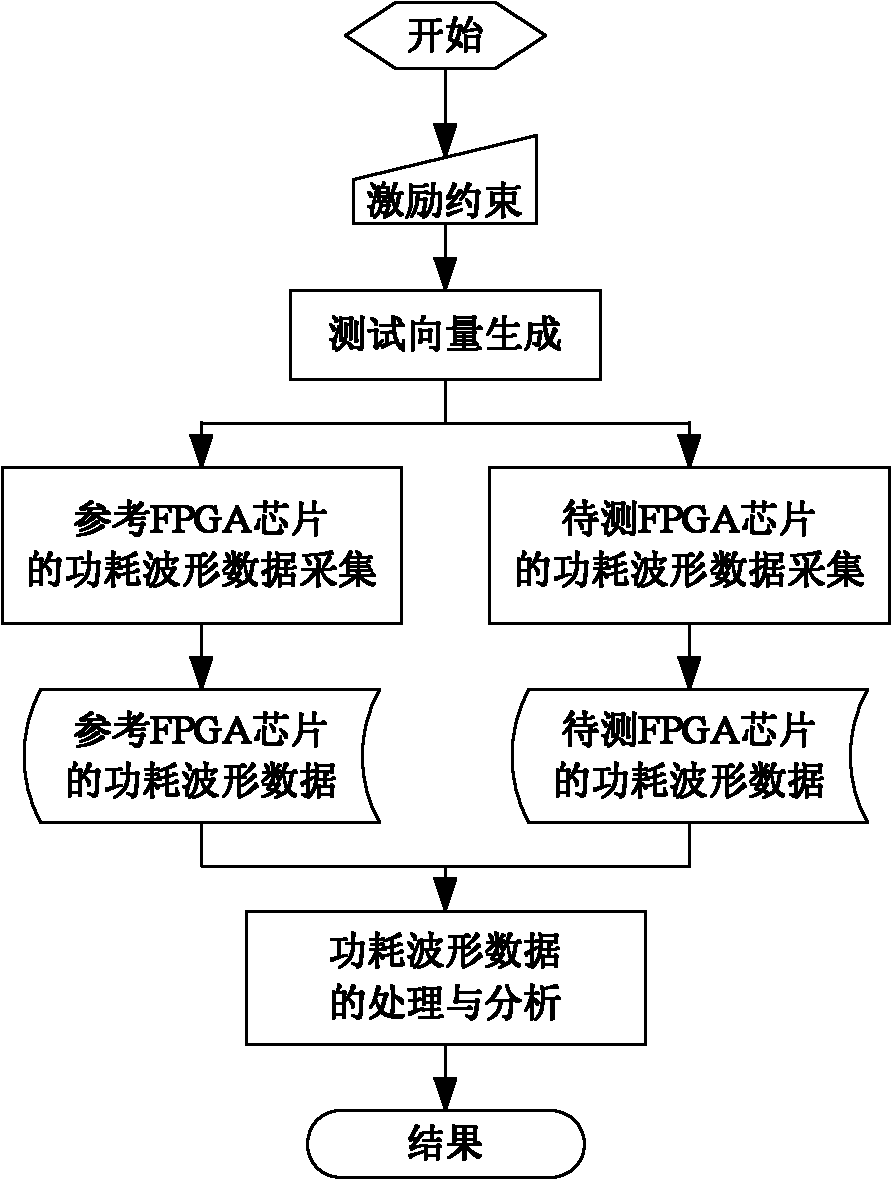

Method for detecting malicious circuit in FPGA (field programmable gate array) chip by power consumption analysis and system thereof

ActiveCN102592068AHigh measurement accuracyAchieve installationInternal/peripheral component protectionVoltage sourceFpga chip

The invention discloses a system for detecting malicious circuits in an FPGA (field programmable gate array) chip by power consumption analysis. The system comprises a DC (direct current) stabilized voltage source for supplying DC power to a to-be-detected FPGA chip and an excitation applying FPGA chip; a current probe for measuring a transient current at the power end of the to-be-detected FPGA chip; an oscilloscope triggered by a trigger signal generated by the to-be-detected FPGA chip to collect the current signal measured by the current probe; the excitation applying FPGA chip for applying an excitation signal to the to-be-detected FPGA chip, and transmitting the response signal of the to-be-detected FPGA chip to a computer for further verification and comparison with an expected response value; and the computer for receiving excitation restraint compiled by a user, generating a test vector, and completing response verification, oscilloscope setting, waveform data collection, data analysis and treatment. The invention also discloses a method for detecting malicious circuits in the FPGA chip by using the above system.

Owner:CHINA ELECTRONICS PROD RELIABILITY & ENVIRONMENTAL TESTING RES INST

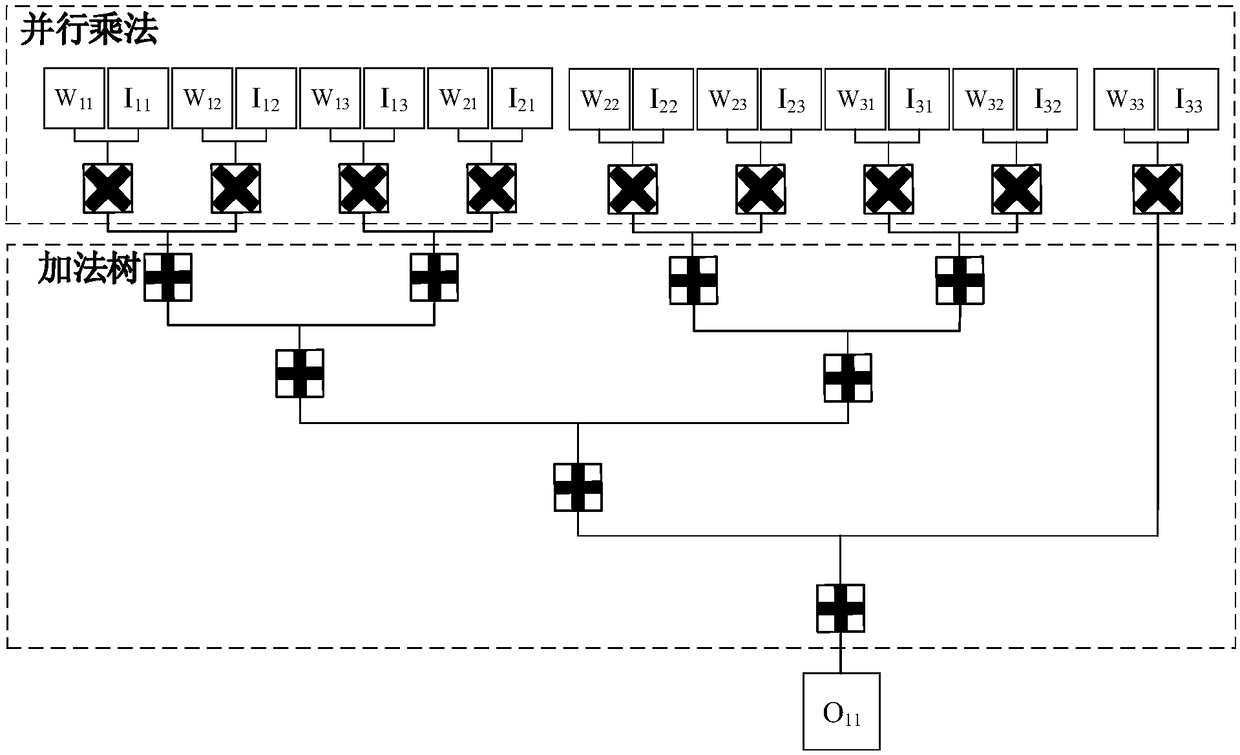

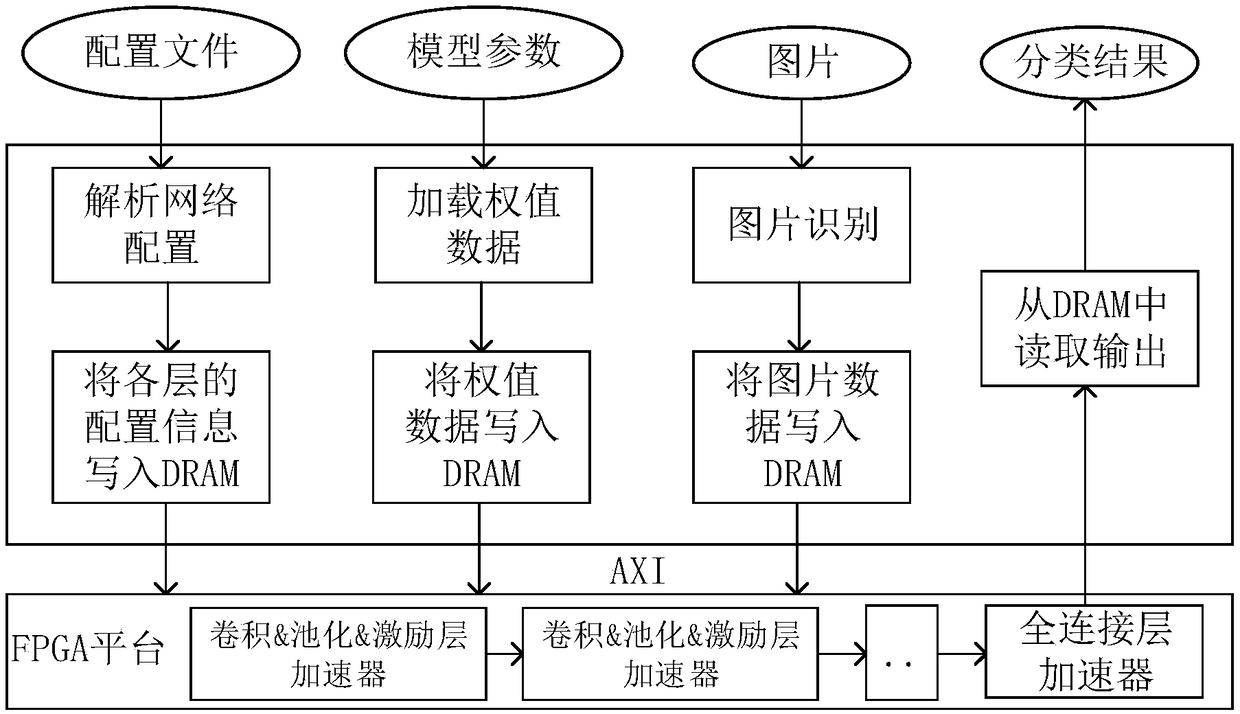

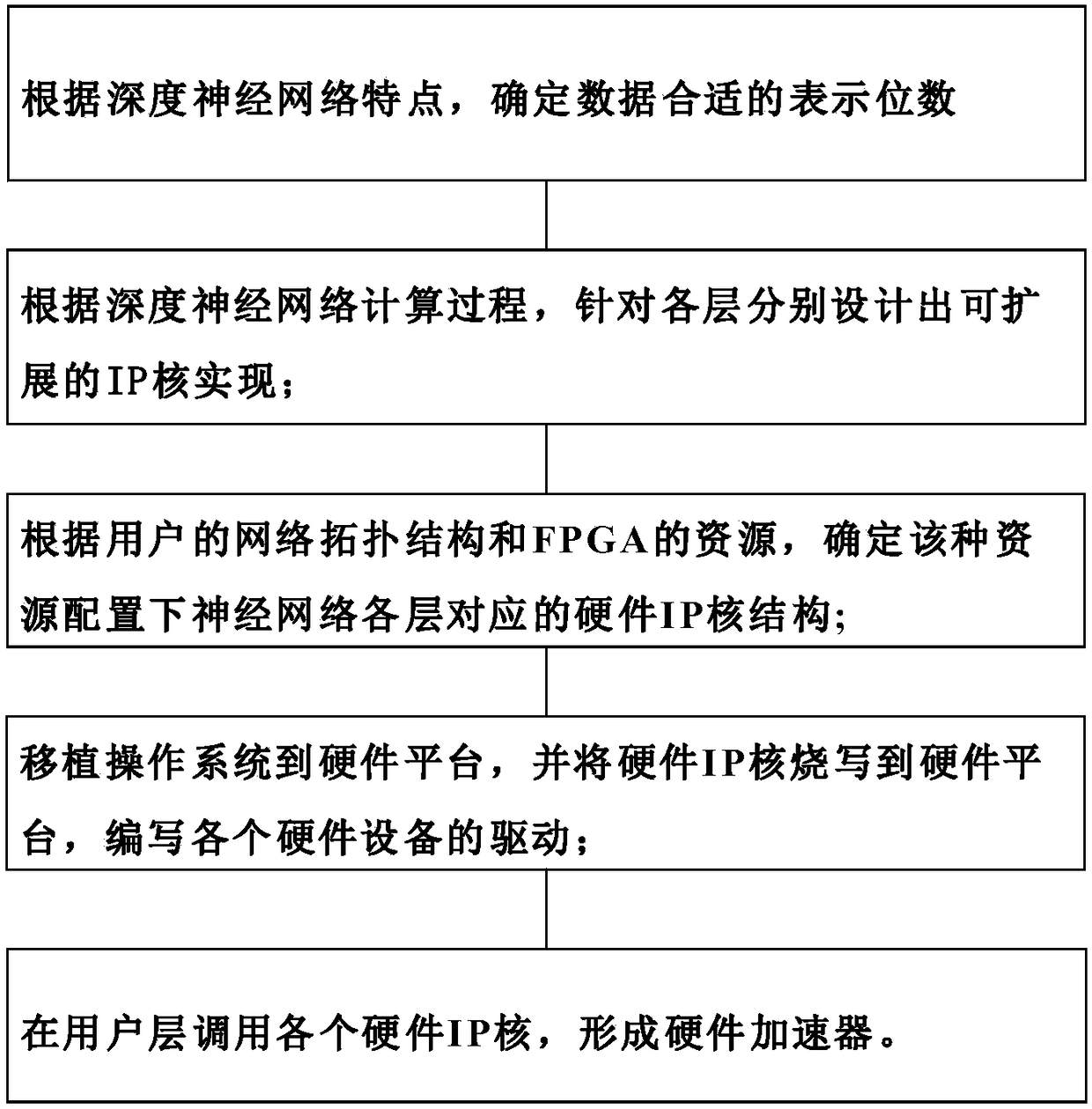

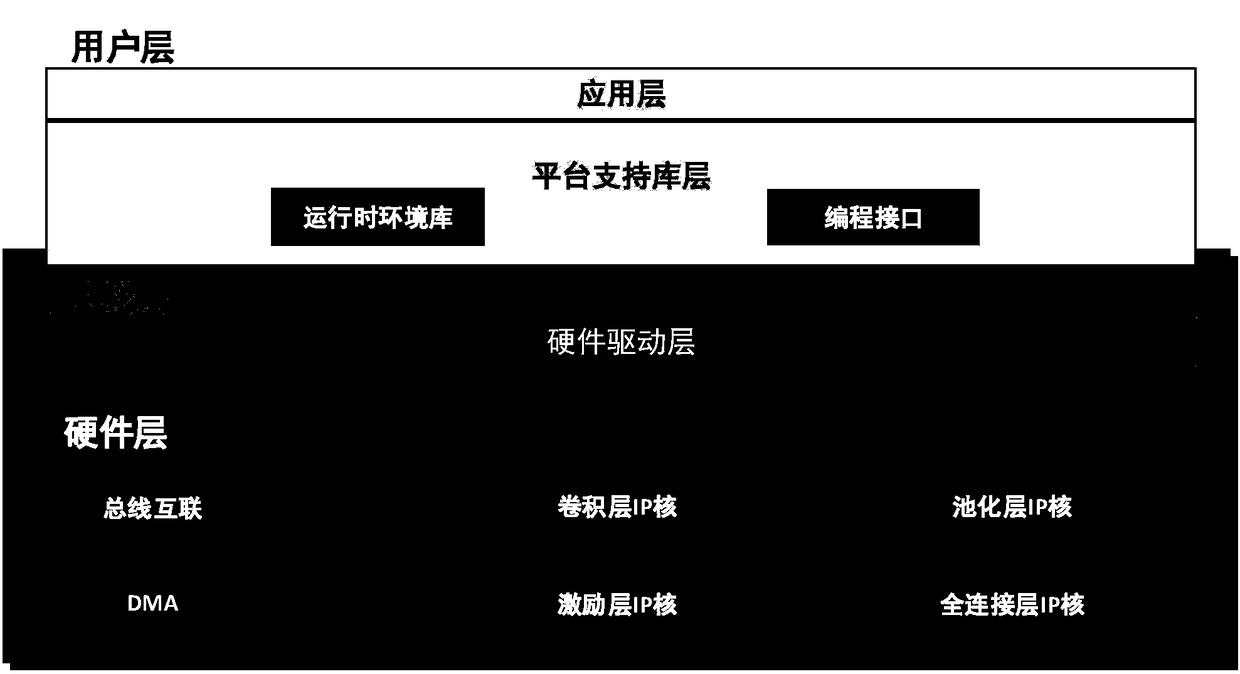

Deep neural network acceleration platform based on FPGA

The present invention discloses a deep neural network acceleration platform based on an FPGA. The platform comprises a general-purpose processor, an FPGA and a DRAM. The general-purpose processor is configured to analyze neural network configuration information and weight data and write the neural network configuration information and the weight data into the DRAM, the FPGA reads the configurationinformation from the DRAM to generate an FPGA accelerator, the general-purpose processor is configured to read in image information and write the image information into the DRAM, the FPGA acceleratorreads the image data from the DRAM and starts to calculate and writes a calculation result into the DRAM, and finally, the general-purpose processor reads a classification result from the DRAM. The accelerator allows each layer to be deployed on a FPGA chip at the same time, allows each layer to operate in a streamline mode, allows programmers having no hardware knowledge to utilize existing FPGAresources to easily obtain good performances.

Owner:苏州中科瀚海高工科技有限公司

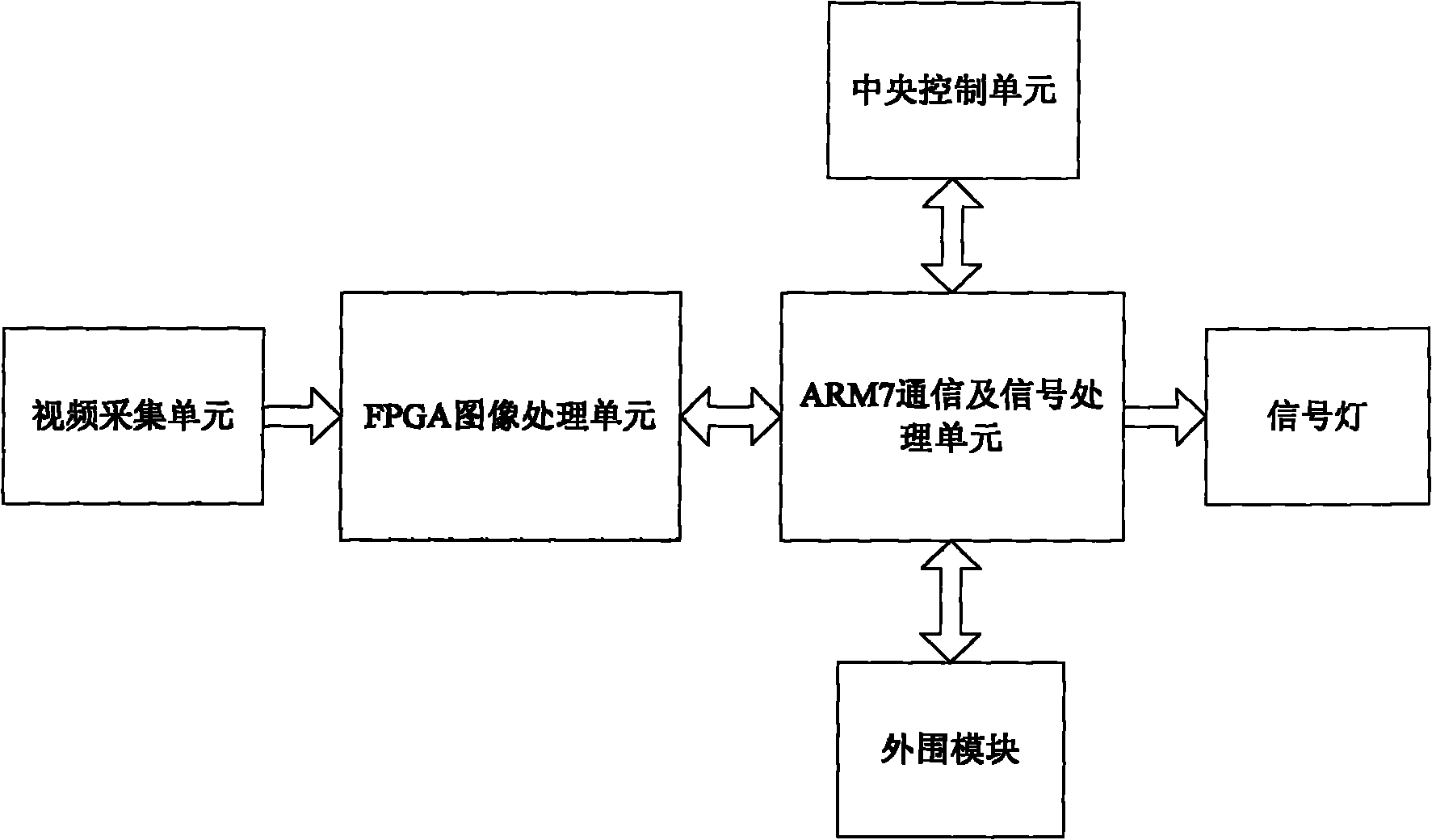

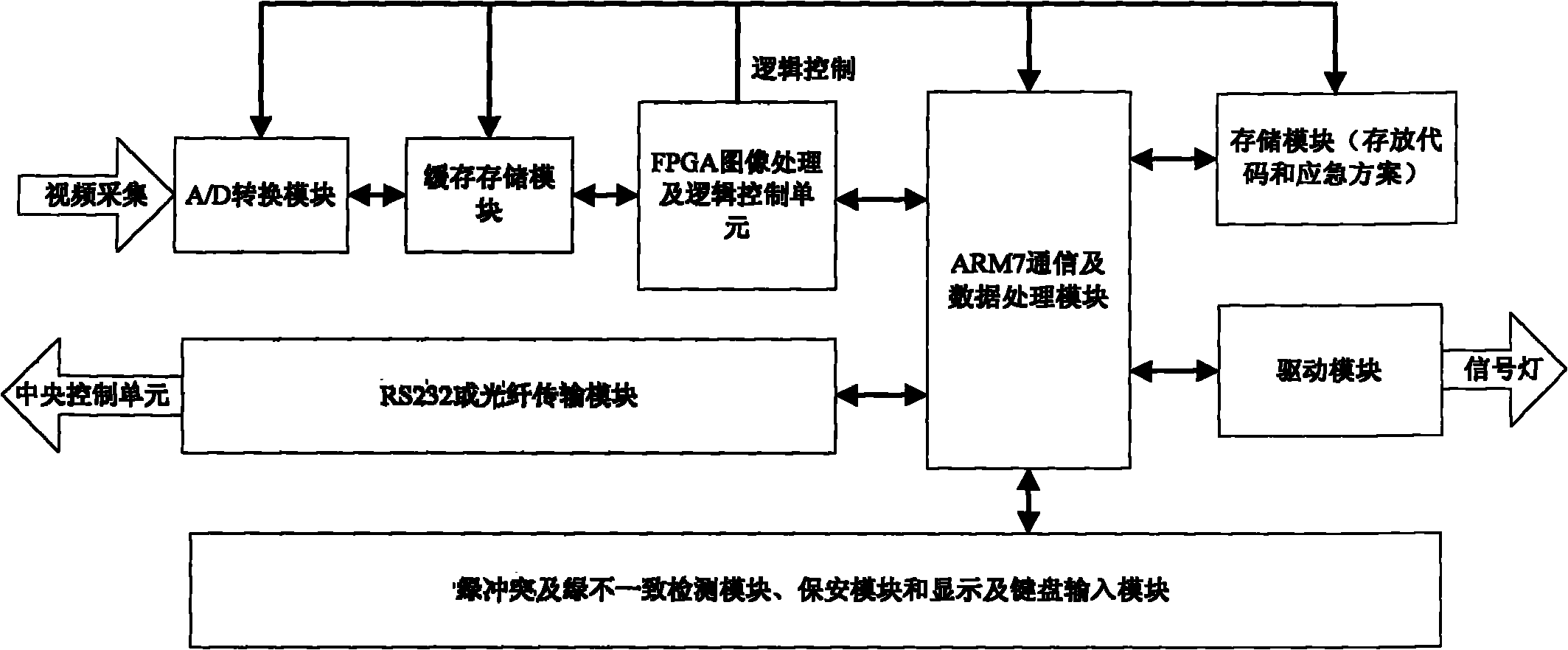

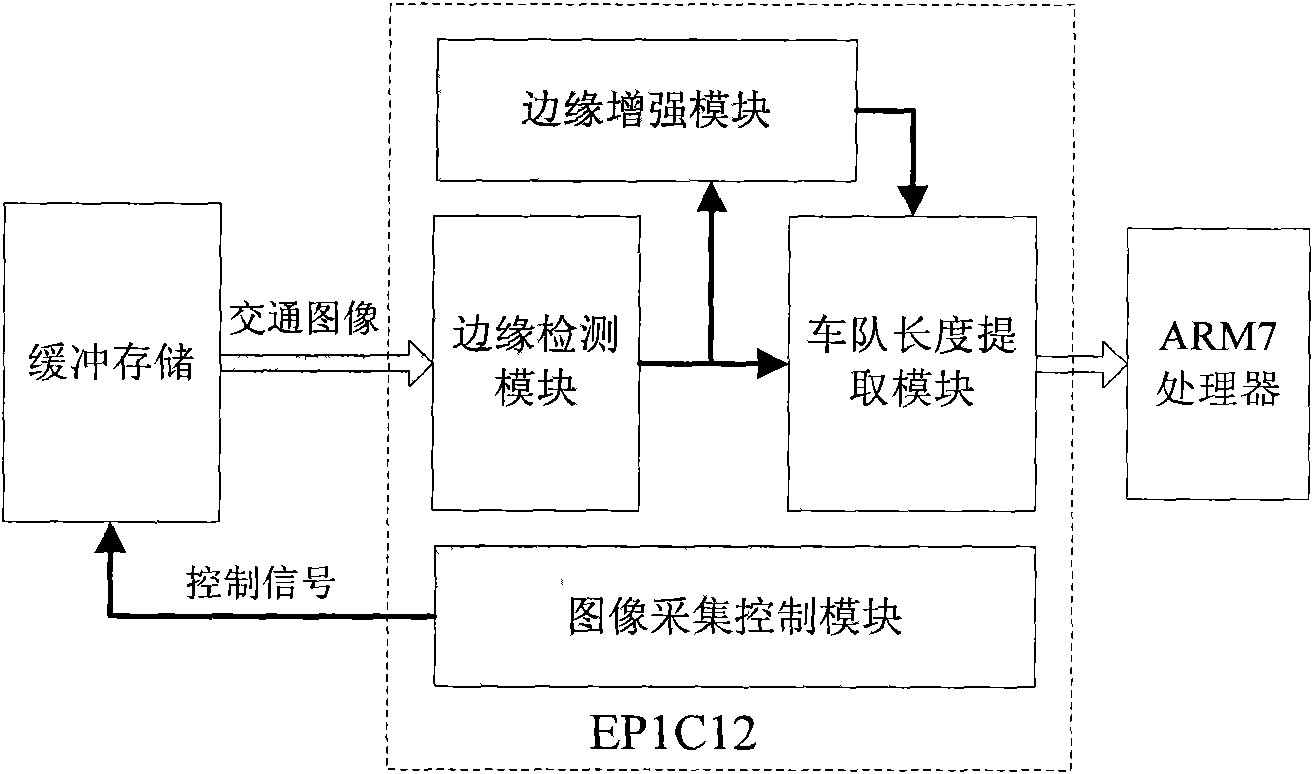

FPGA-based traffic signal control machine for intersection queue length image detection

InactiveCN102044159AImprove real-time performanceImprove scalabilityControlling traffic signalsDetection of traffic movementImaging processingImage detection

The invention relates to field programmable gate array (FPGA)-based intersection queue length image detection and traffic signal control implementation, and belongs to signal processing technology, communication technology and traffic signal control technology. A digital image interested region is detected by using an FPGA chip on the basis of the conventional signal machine, and the queue length at a traffic intersection is extracted and a signal machine mainboard is communicated with an ARM7 processor so as to control a traffic signal lamp. The invention is characterized in that: an image processing algorithm circuit constructed by FPGA hardware logic analyzes and processes the acquired image signal, calculates the split green ratio according to the result and makes an image processing algorithm become hardware without a computer or a digital signal processor (DSP) and other core processors.

Owner:XIAN FEISIDA AUTOMATION ENG

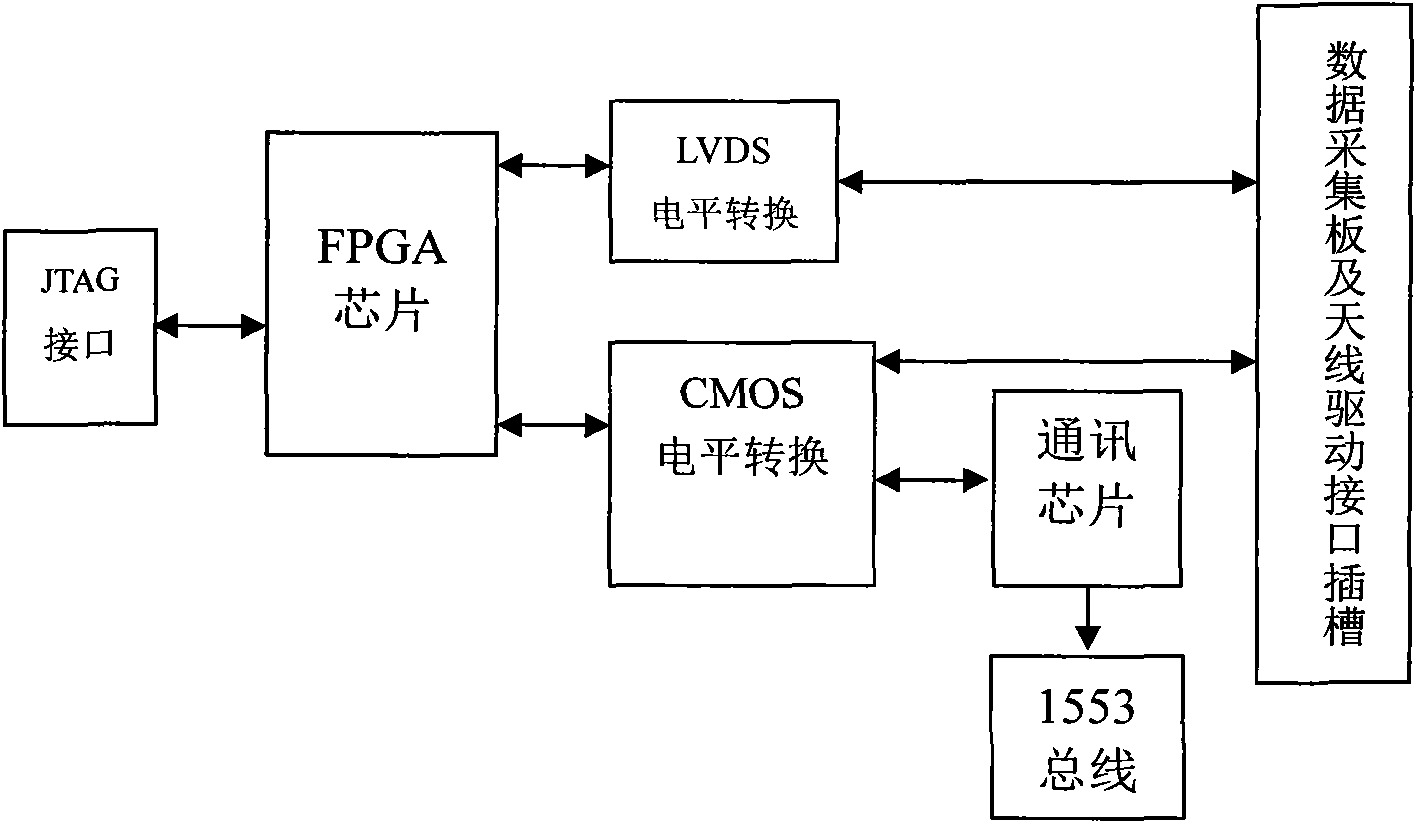

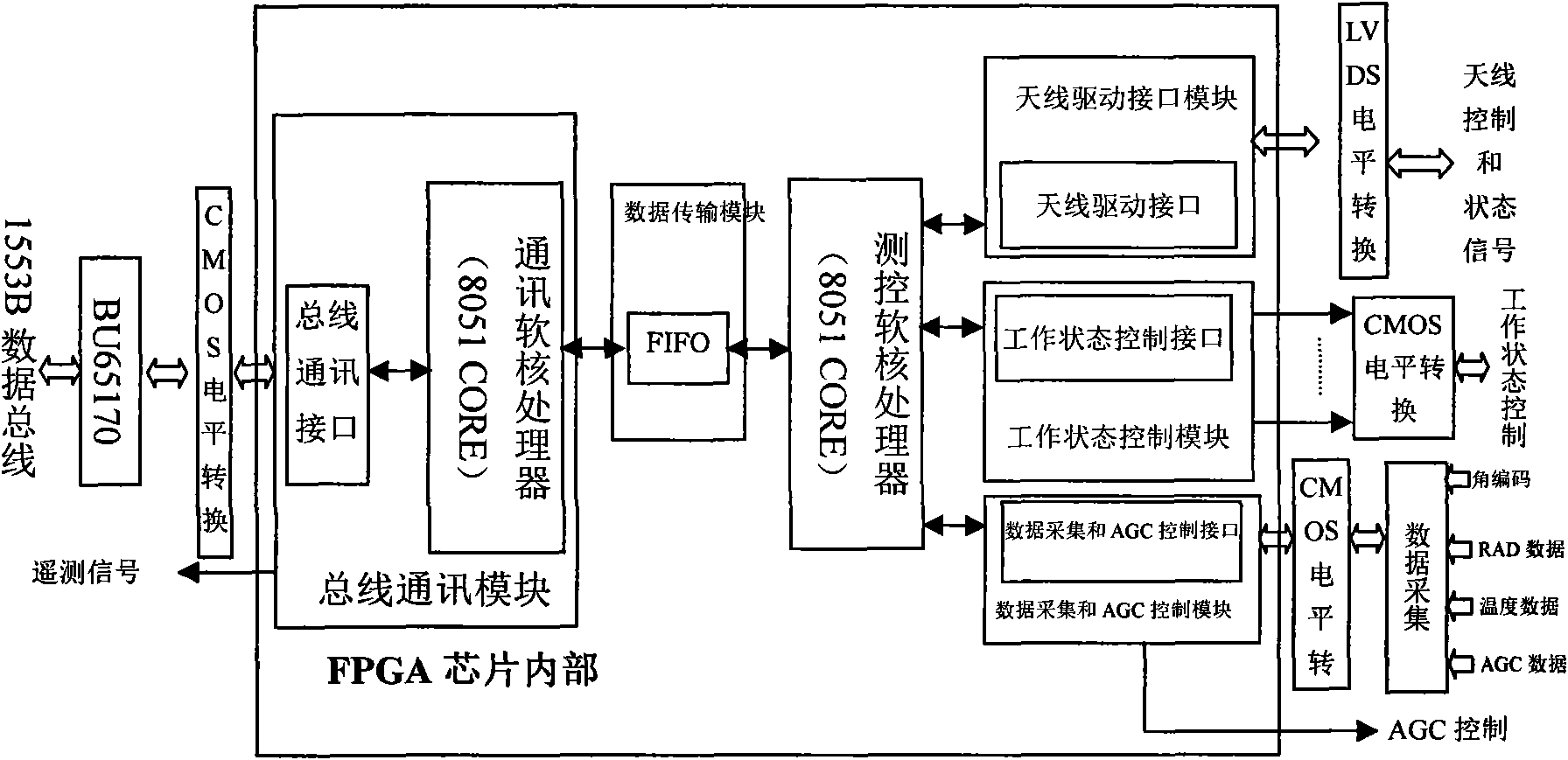

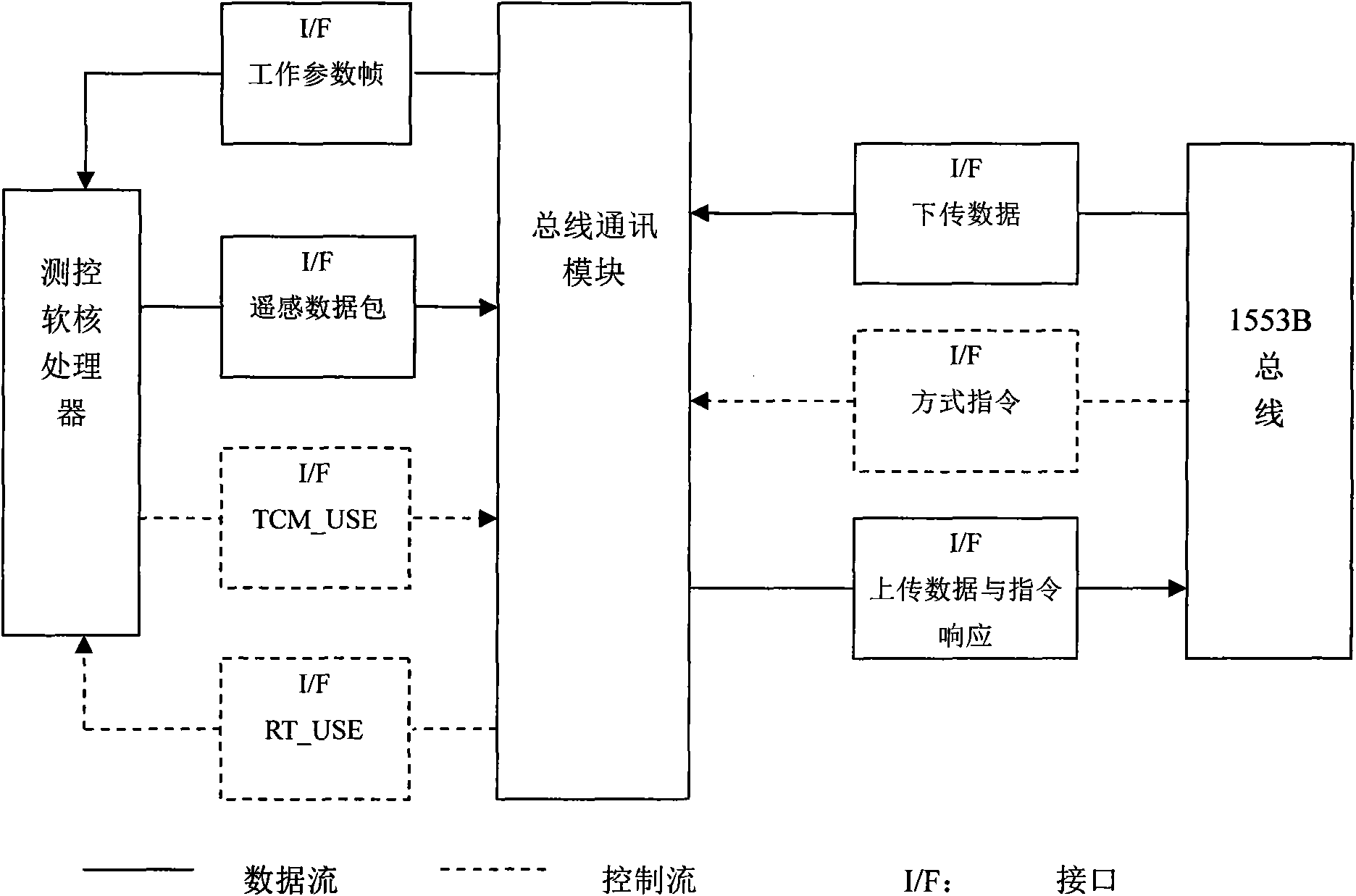

Control system and control method of satellite-borne microwave radiometer

InactiveCN101876699AHigh speedImprove reliabilityWave based measurement systemsControl systemData acquisition

The invention provides a control system and a control method of an FPGA soft-core processor technique-based satellite-borne microwave radiometer. The control system comprises an FPGA chip, a communication chip, a level switching circuit, a data acquisition board interface and an antenna driving interface slot, wherein the FPGA chip is matched with the communication chip, the level switching circuit and a data acquisition board to realize the system control of the satellite-borne microwave radiometer and finish the system functions, such as data acquisition, remote measurement, RAD control, antenna control and bus communication, of the microwave radiometer. The control system adopts the FPGA chip to realize a control circuit of the satellite-borne microwave radiometer and increase the integration of the control circuit, and the formed system has a small volume and low power consumption, is suitable for data processing with a higher speed requirement, and has high reliability. Besides, because the programmability of an FPGA is high, only a program inside the FPGA is changed to ensure that the FPGA can be suitable for the control system of the microwave radiometer with different requirements.

Owner:CENT FOR SPACE SCI & APPLIED RES

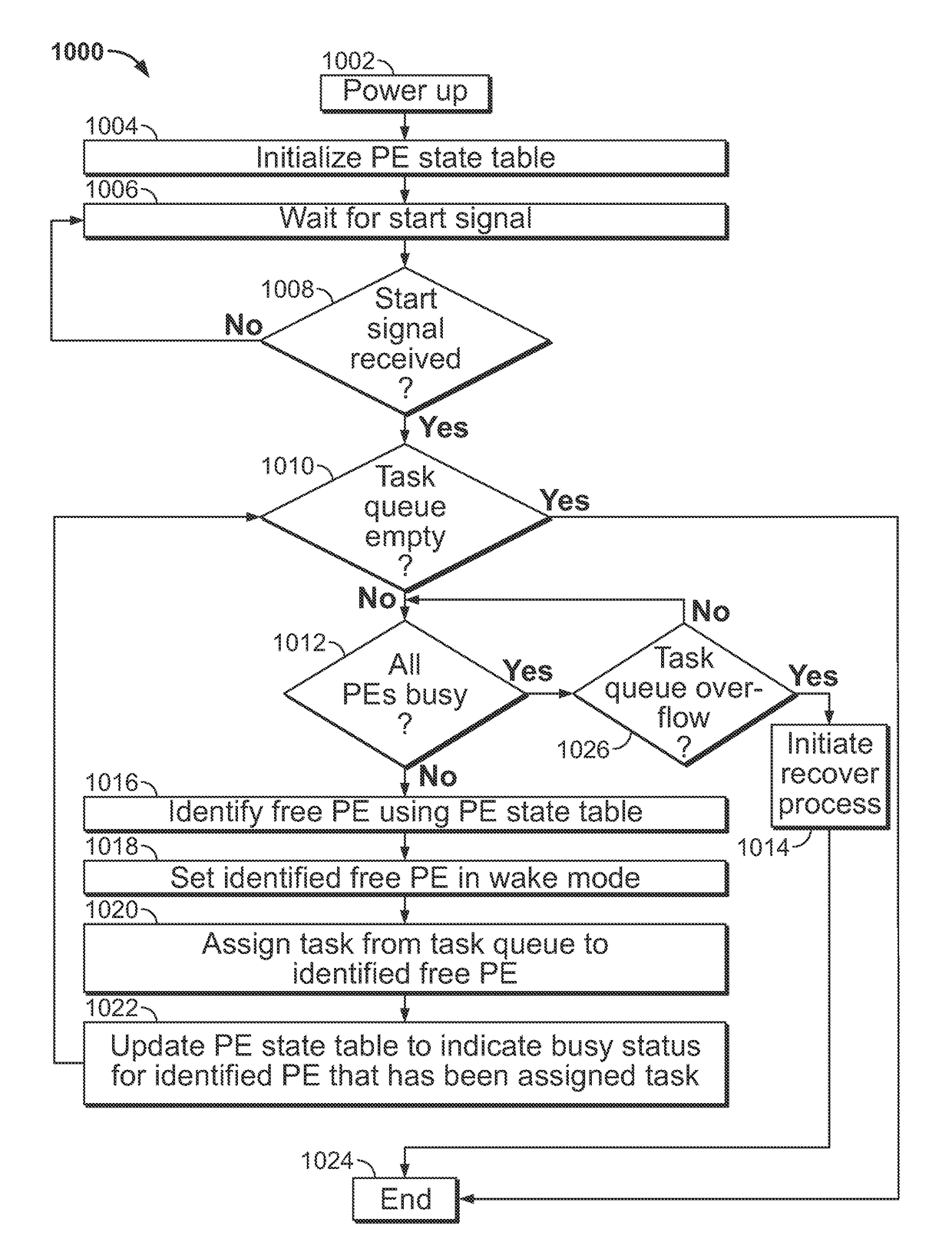

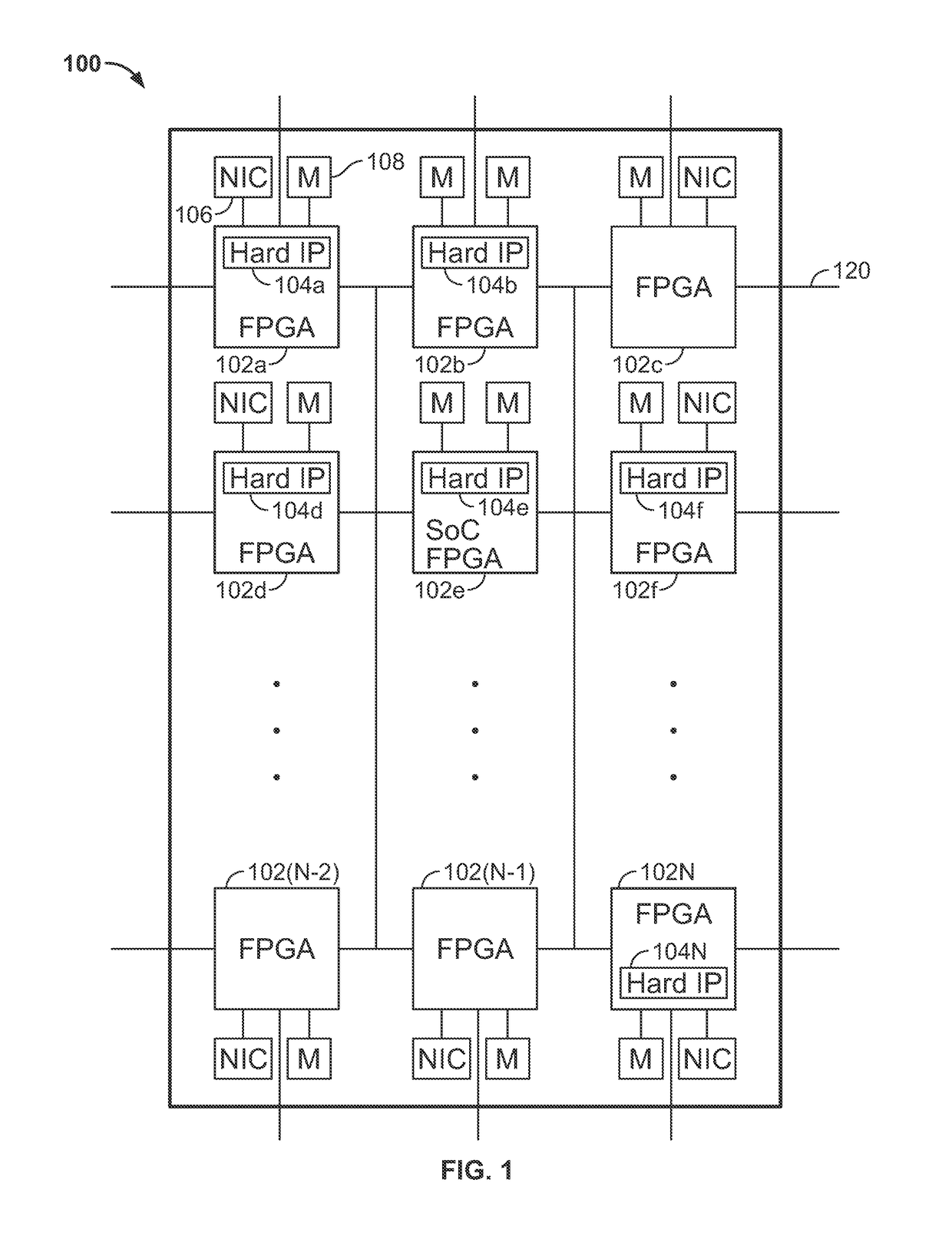

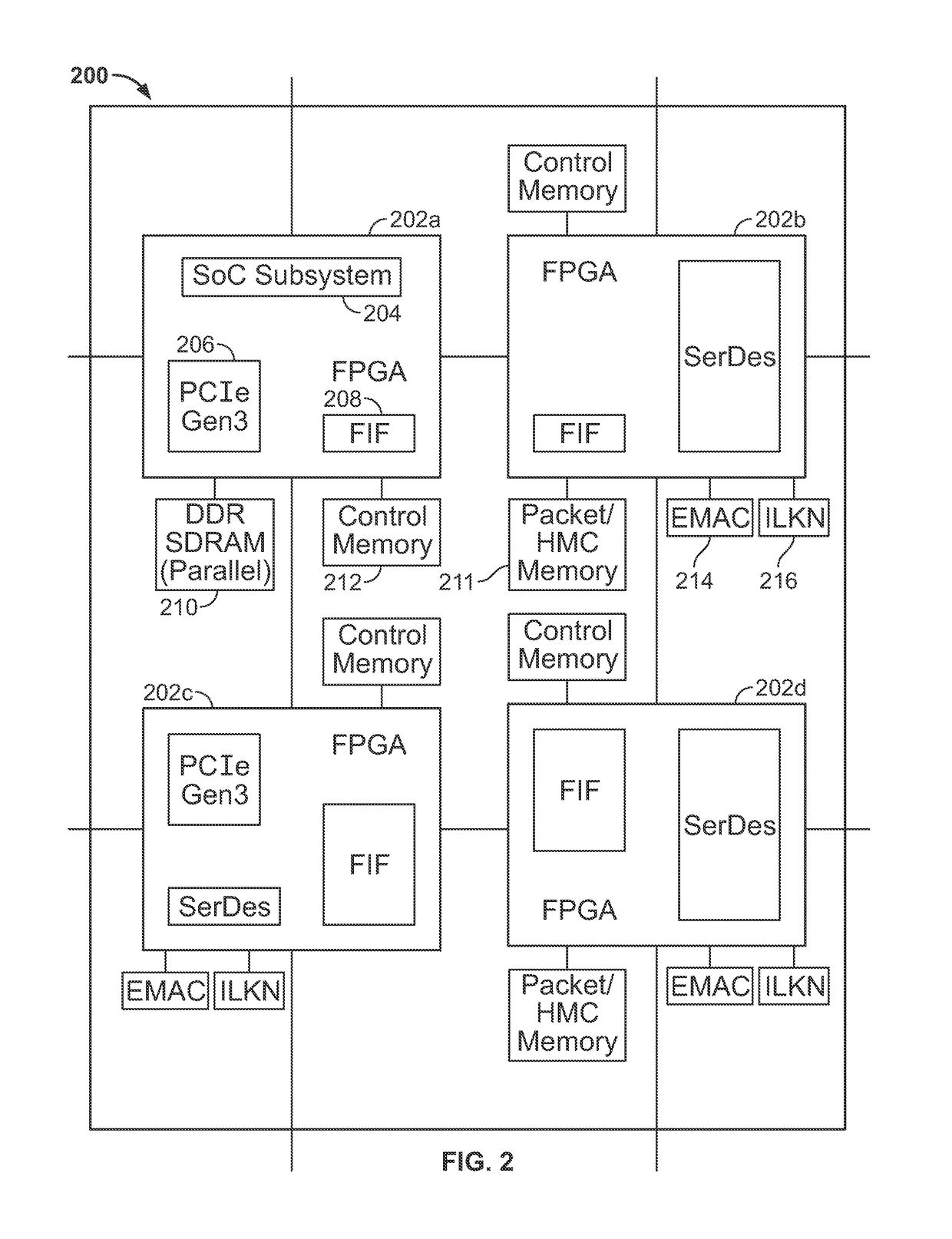

Network processor FPGA (npFPGA): multi-die FPGA chip for scalable multi-gigabit network processing

ActiveUS9886072B1Reduce power consumptionMonitor progressPower supply for data processingEnergy efficient computingGigabitProcessing element

Systems and methods are provided for reducing power consumption of a multi-die device, such as a network processor FPGA (npFPGA). The multi-die device may include hardware resources such as FPGA dies, which may be coupled to NIC dies and / or memory dies. Power consumption of the multi-die device may be reduced by monitoring usage of hardware resources in the multi-die device, identifying hardware resources that are not in use, and gating power to the identified hardware resources. The status of processing elements (PEs) in the multi-die device may be tracked in a PE state table. Based on the PE state table, tasks from a task queue may be assigned to one or more processing elements.

Owner:ALTERA CORP

Storage network adapter of supporting virtual interface

InactiveCN1761222AIncrease flexibilityHigh bandwidthData switching by path configurationMemory systemsInteroperability ProblemSoftware

Thorough mode of combining software with hardware in FPGA chip, the invention realizes protocol of virtual interface. The invention includes host interface, system on chip, Ethernet interface, and dedicated logic circuit for virtual interface. Through bus of system on chip, the system on chip is connected to Ethernet interface each other. Using communication mechanism sharing memory between host interface and system on chip realizes interlinkage and communication. Advantages are: reducing communication overhead of communication, obtaining more high transmission performance; using communication protocol in VIA lightweight level, the invention reduces data copy in communication process, shortens key path of storing data; Ethernet as transmission media is adopted at bottom layer so as to guarantee interlinkage and interoperability to current network; collaborative work between software and hardware speeds up procedure for processing protocol.

Owner:HUAZHONG UNIV OF SCI & TECH

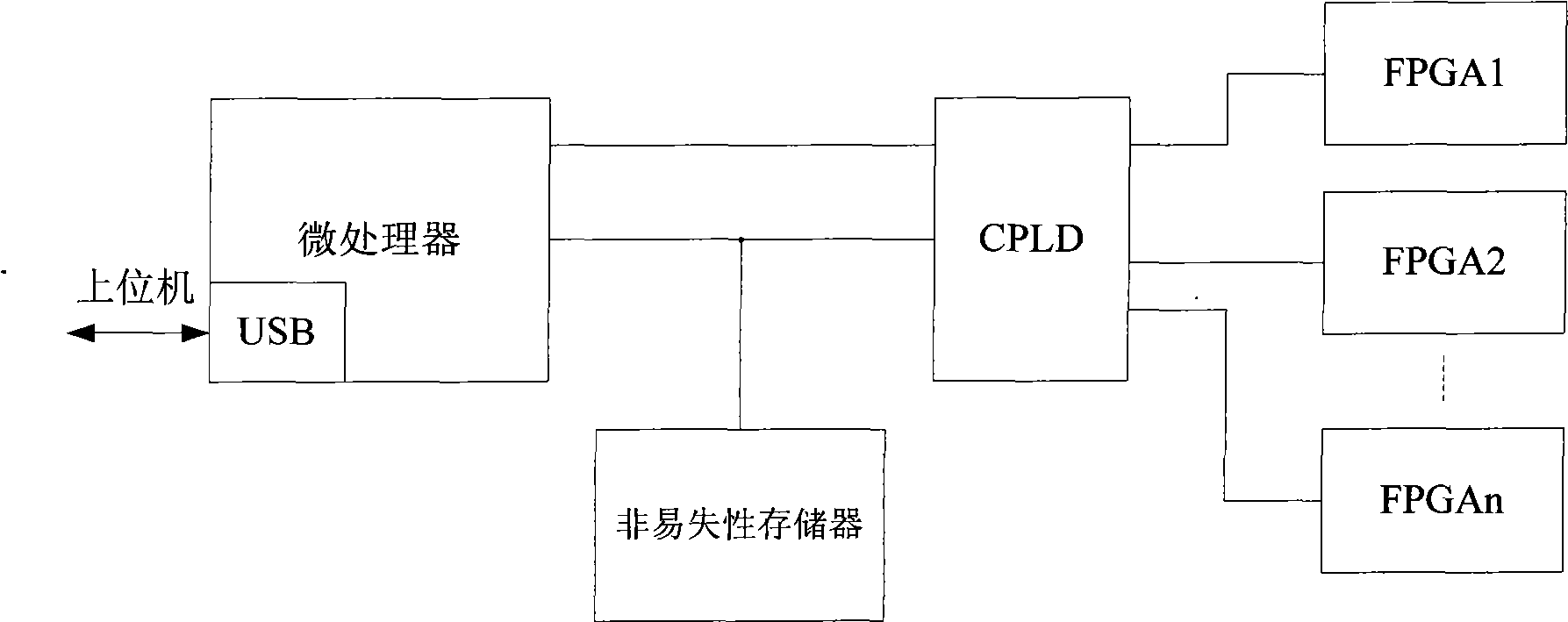

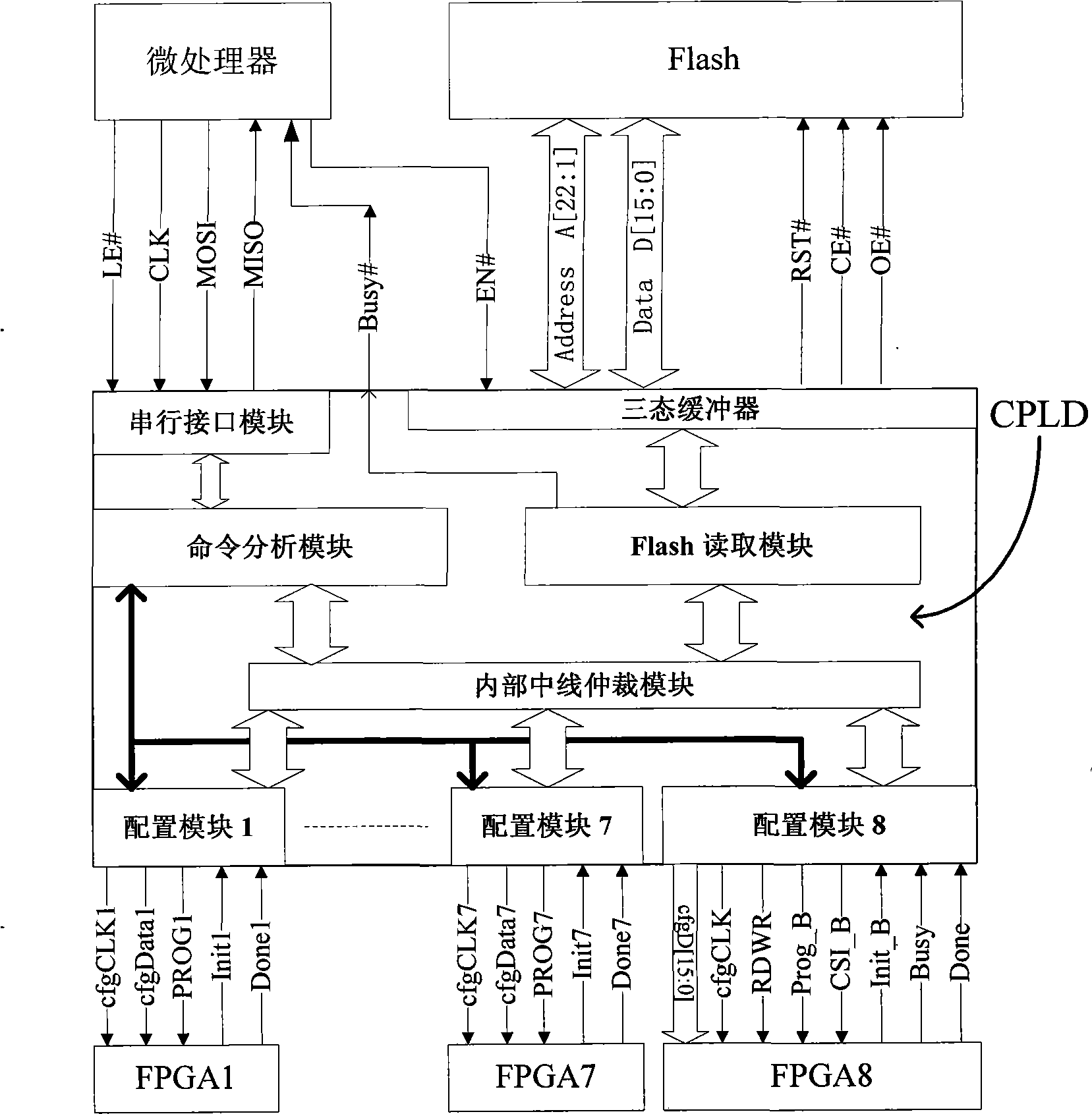

System for unified configuration and management of FPGA chip in equipment

InactiveCN101485576ARealize unified configurationRealize managementUltrasonic/sonic/infrasonic diagnosticsInfrasonic diagnosticsComplex programmable logic deviceFpga chip

The invention discloses a system for unified configuration and management of FPGA chips inside equipment. The system comprises a configuration and management logic component and at least one field programmable gate array (FPGA) chip, wherein the configuration and management logic component is connected with the FPGA, and comprises a microprocessor, a nonvolatile memory and a complex programmable logic device (CPLD) which are connected with each another; the CPLD is connected with the FPGA; and the configuration and management logic component is used to realize the configuration of one or more pieces of the FPGA in a serial mode or a parallel mode. The system realizes unified configuration and management of the FPGA chips inside the equipment and greatly increases the configuration efficiency of the FPGA chips inside the equipment, thereby increasing equipment efficiency during use and maintenance.

Owner:SHENZHEN LANDWIND IND

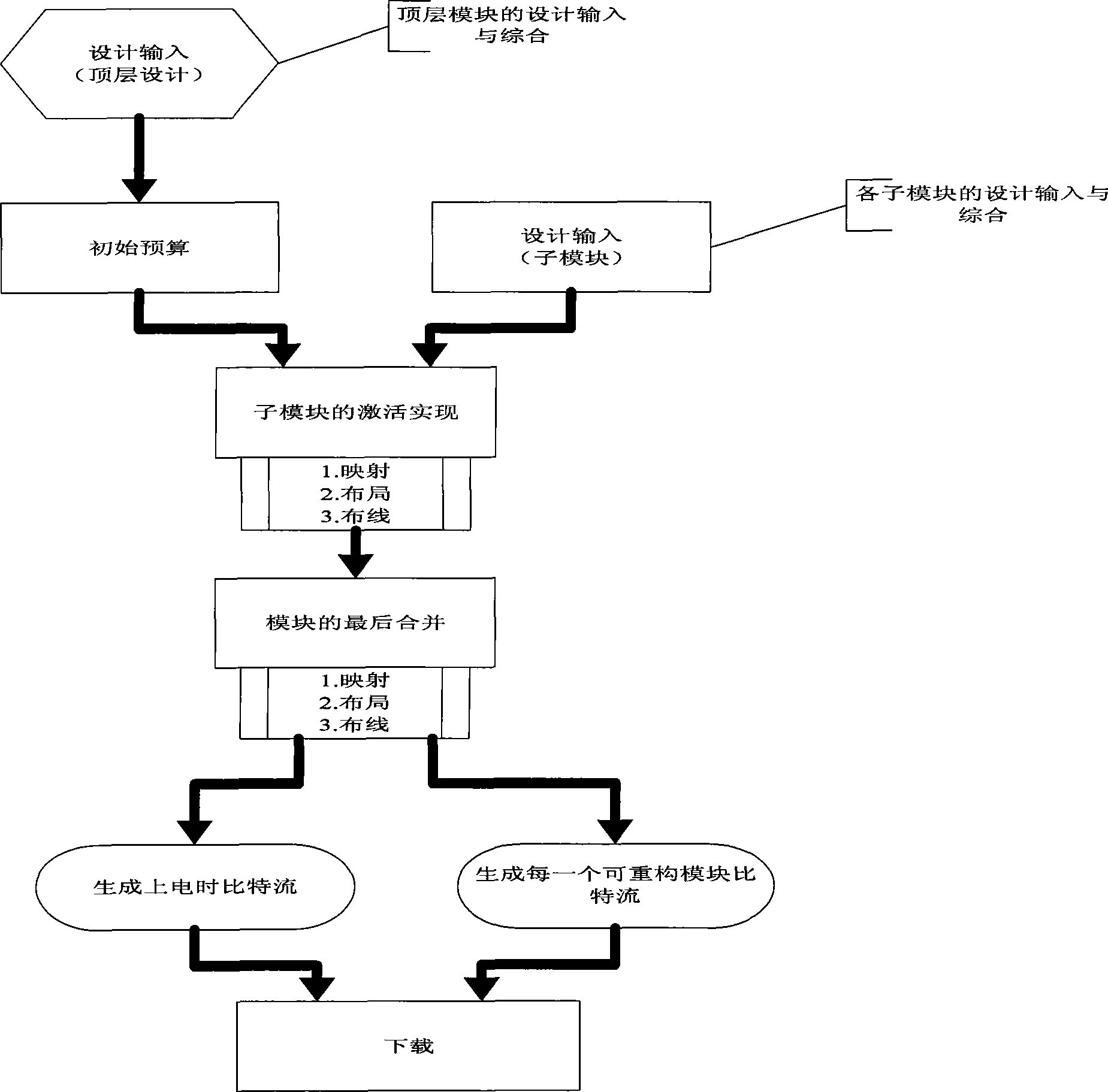

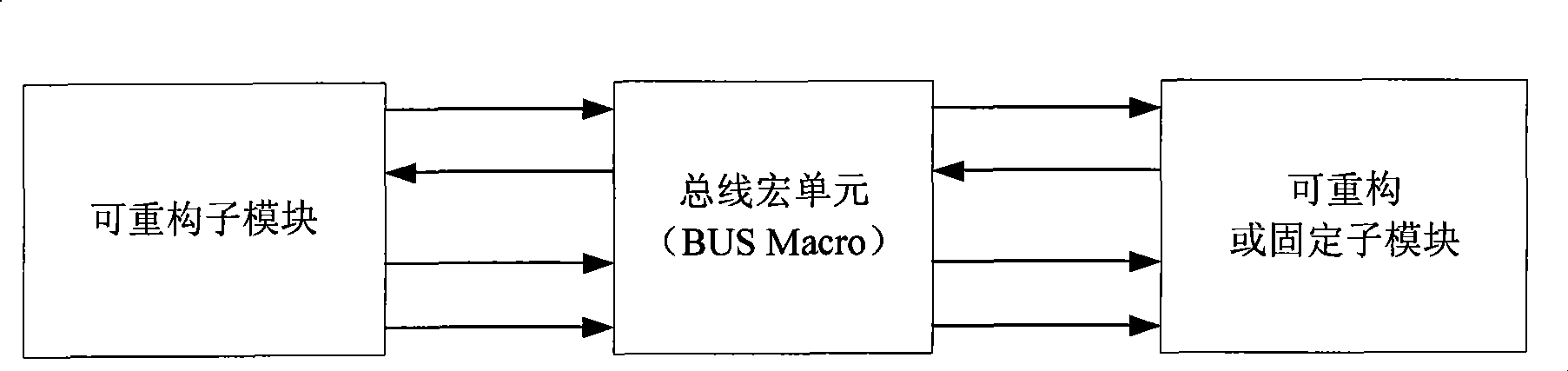

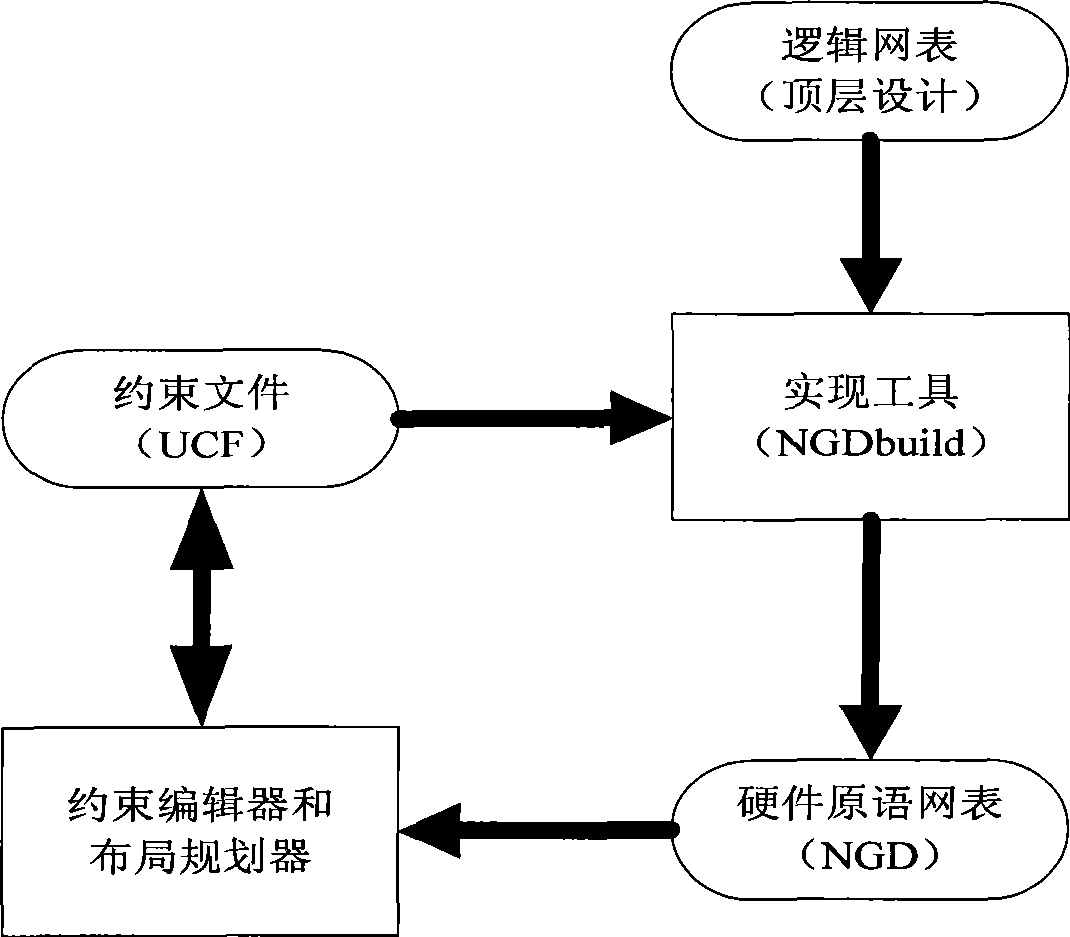

Implementing method of dynamic local reconstructing embedded type data controller chip

ActiveCN101436225AExtend the life cycleShorter time to marketSpecial data processing applicationsInternal memoryData control

The invention discloses a method for implementing a dynamic partial reconfiguration embedded data controller chip. In the controller chip, an FPGA chip is used to implement the dynamic partial reconfiguration embedded data controller chip; the CoreConnect bus standard supporting IBM development is adopted; the CoreConnect technique can make a plurality of chip cores(IP core) mutually connected to form a new whole chip; the dynamic partial reconfiguration embedded data controller chip adopts the CoreConnect bus frame, and a PLB bus to be connected with a high-performance processor core, an internal memory controller and basic peripheral chip cores, and the reconfiguration parts are connected by an OPB bus; the reconfiguration parts can be the chip cores of the peripheral equipment as well as bottom layer arithmetic cores, and logic parts are kept unchanged; all device resources in the width occupied by a reconfiguration module belong to the reconfiguration module, and the border of the reconstructed module is determined and constant; and when communication is established between the modules, Bus Macro is used on the border.

Owner:STATE GRID ELECTRIC POWER RES INST +1