Implementing method of dynamic local reconstructing embedded type data controller chip

A technology of a data controller and an implementation method, which is applied in the fields of electrical digital data processing, special data processing applications, instruments, etc., and can solve the problems that the system functions cannot be dynamically continuous.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0047] The present invention will be further described below in conjunction with the accompanying drawings and embodiments.

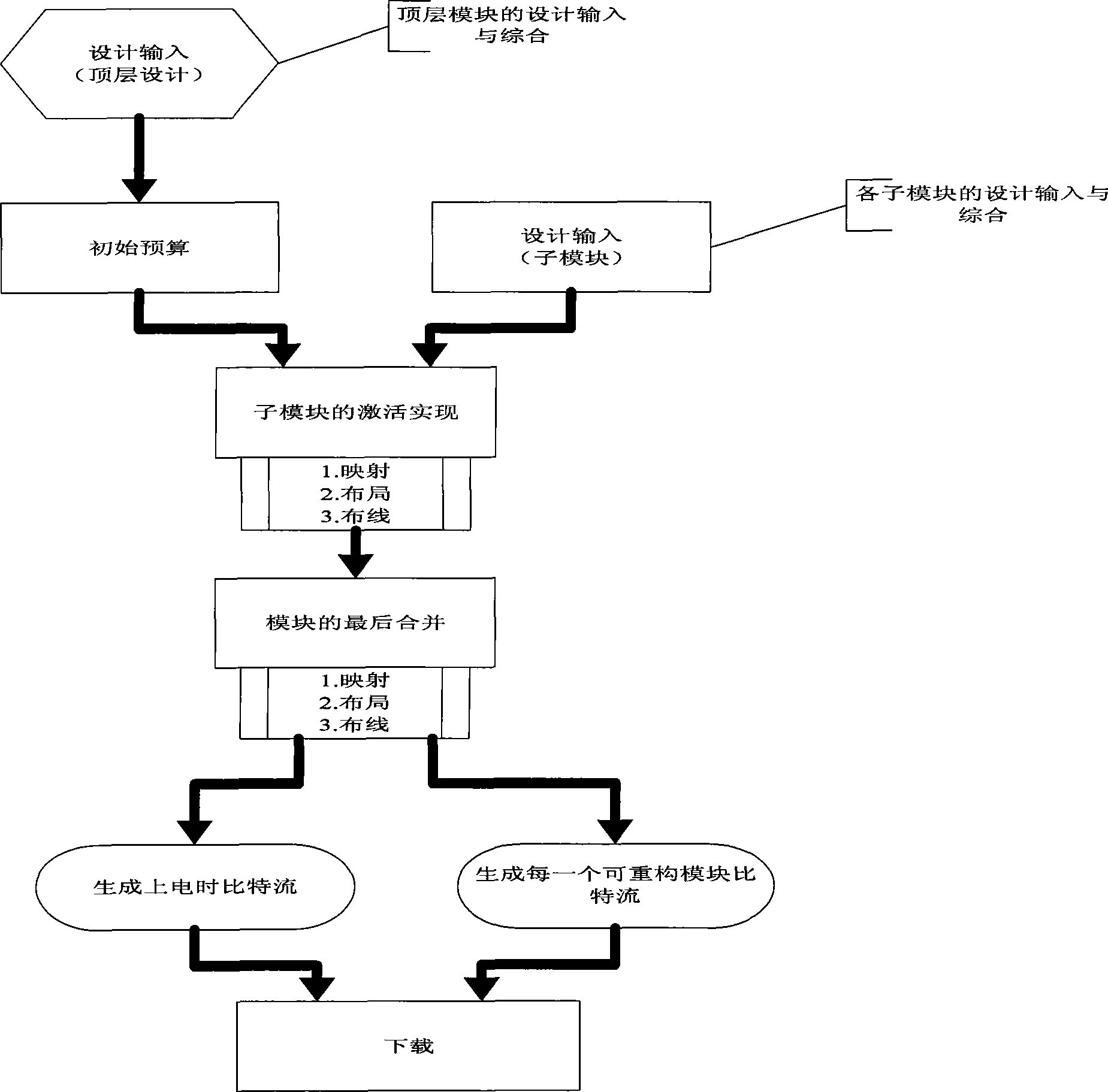

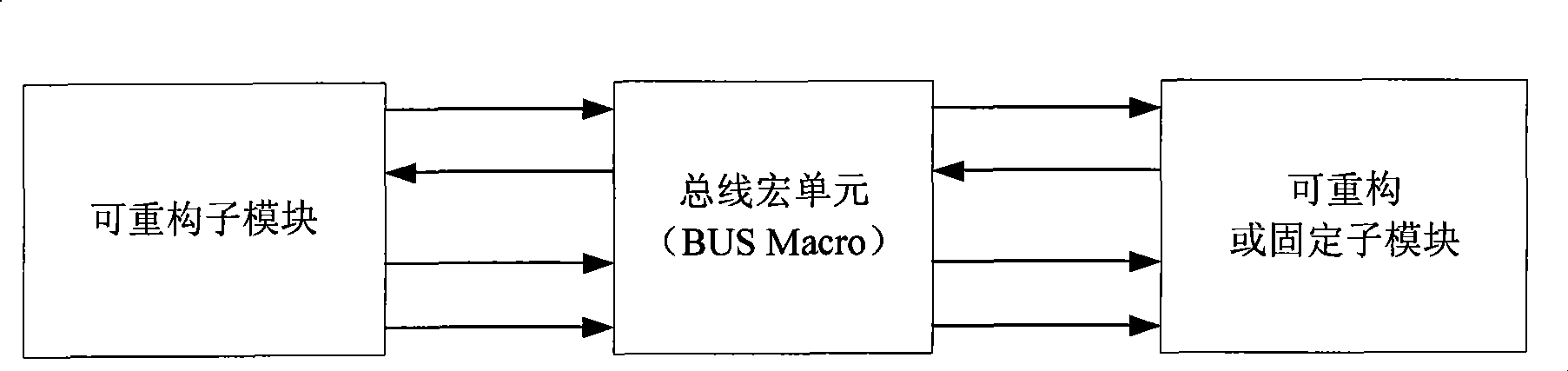

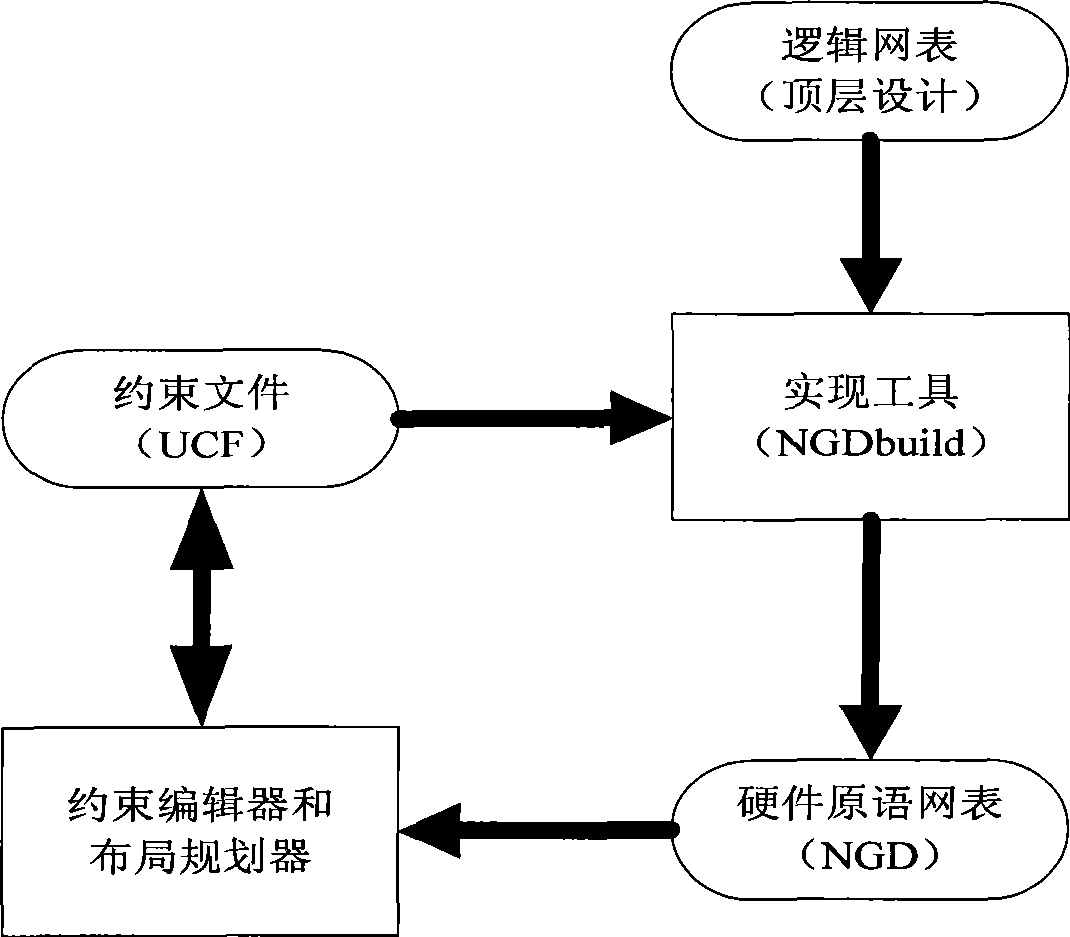

[0048] The invention adopts the Virtex-II Pro FPGA chip of Xilinx Company to realize the dynamic partial reconfigurable embedded data controller chip. Virtex-II Pro FPGA chip is embedded with PPC405 hard CPU core and supports the CoreConnect bus standard developed by IBM. CoreConnect technology makes it possible to connect multiple chip cores (IP Core) to each other to form a complete new chip. CoreConnect technology makes integration easier, and the processor, system and peripheral cores in a standard product platform design can be reused to achieve overall higher system performance. The CoreConnect bus specification designs a total of three buses and a bridge connecting the high-performance bus and the low-performance bus, namely PLB (Processor Local Bus), OPB (On-chip Peripheral BUS), DCR (Device Control Register Bus) and OPB bridge. The reconfigur...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More